Patents

Literature

17221 results about "Threshold voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The threshold voltage, commonly abbreviated as Vₜₕ, of a field-effect transistor (FET) is the minimum gate-to-source voltage VGS (th) that is needed to create a conducting path between the source and drain terminals. It is an important scaling factor to maintain power efficiency.

Semiconductor device, manufacturing method, and electronic device

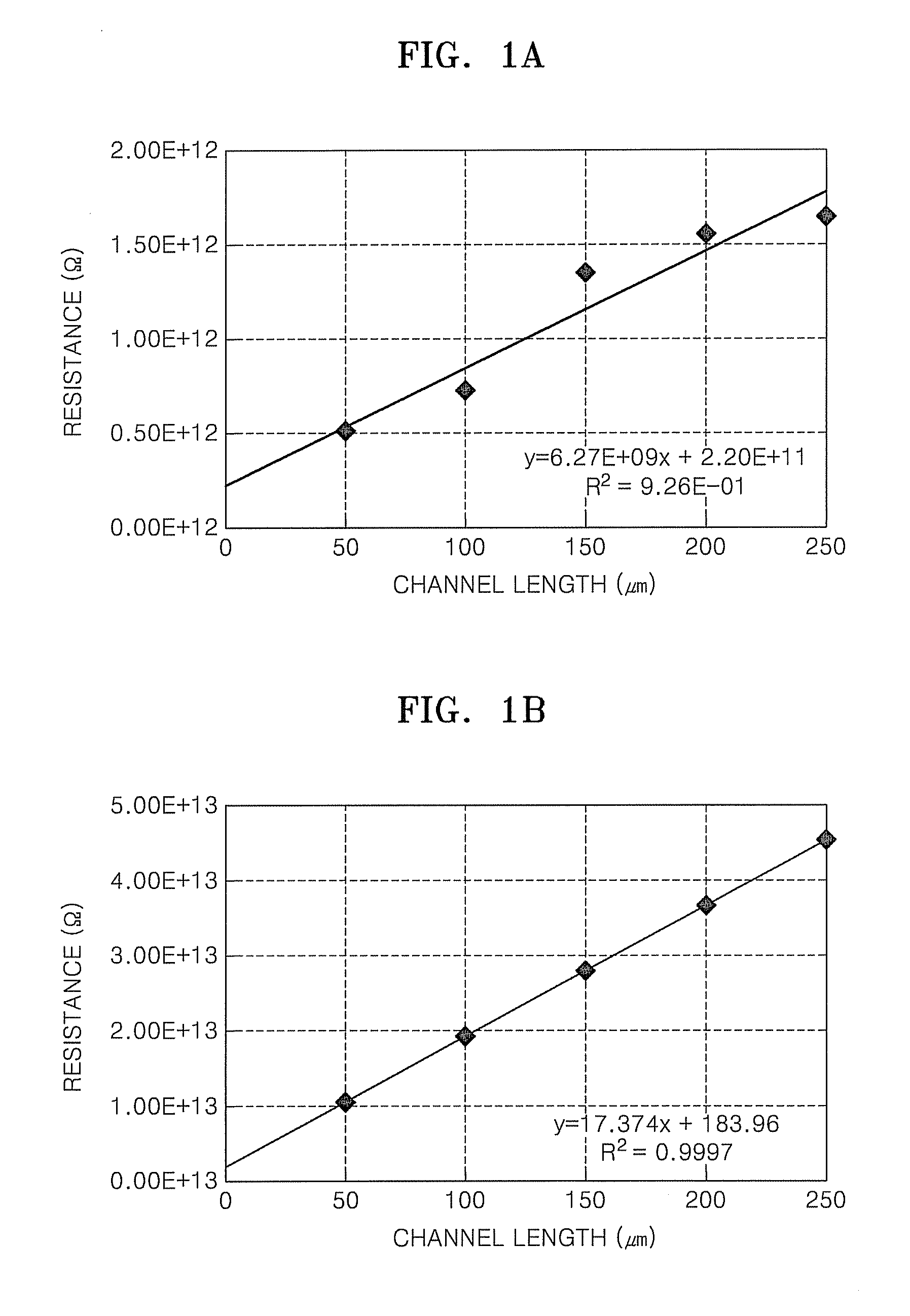

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

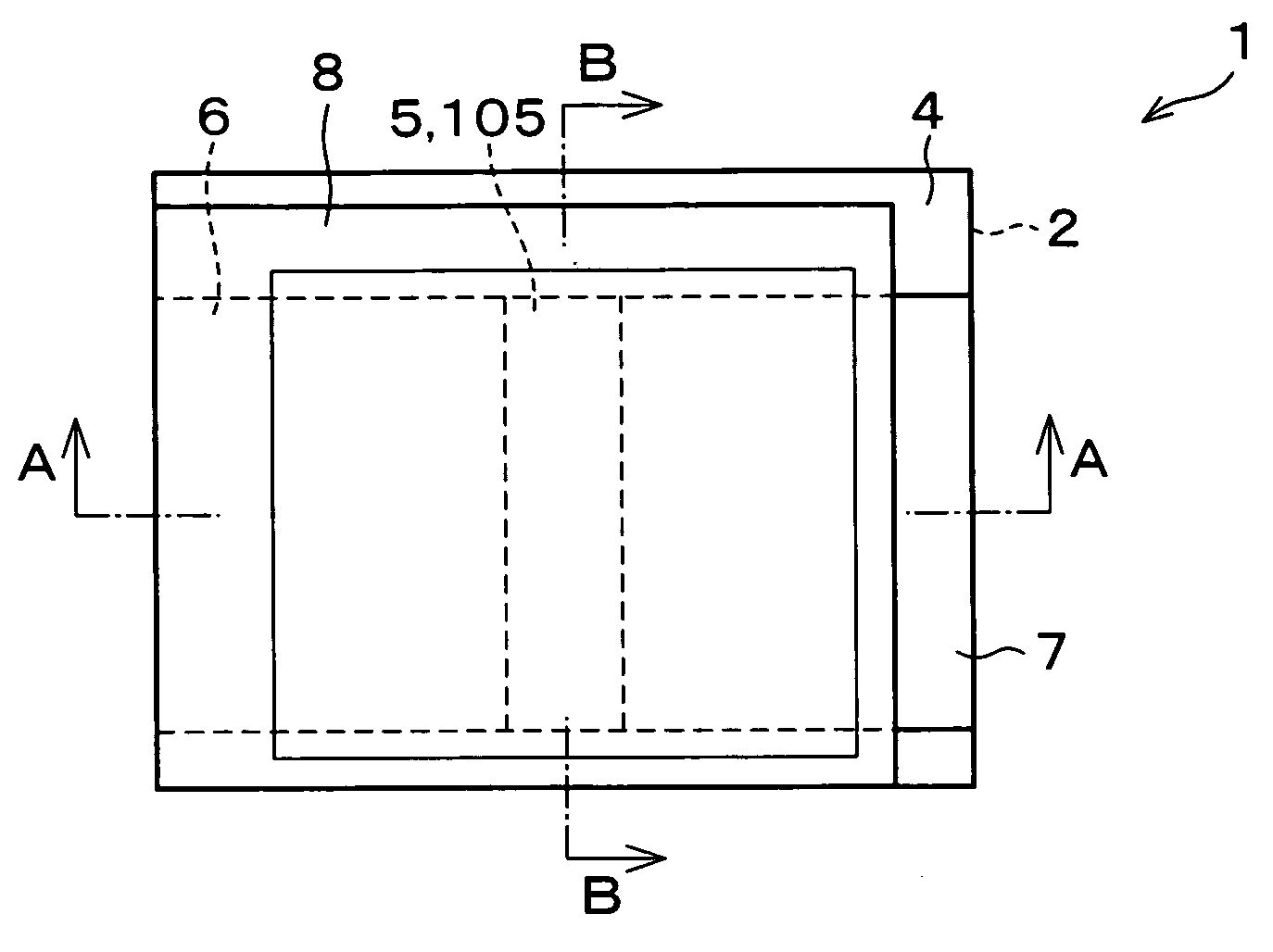

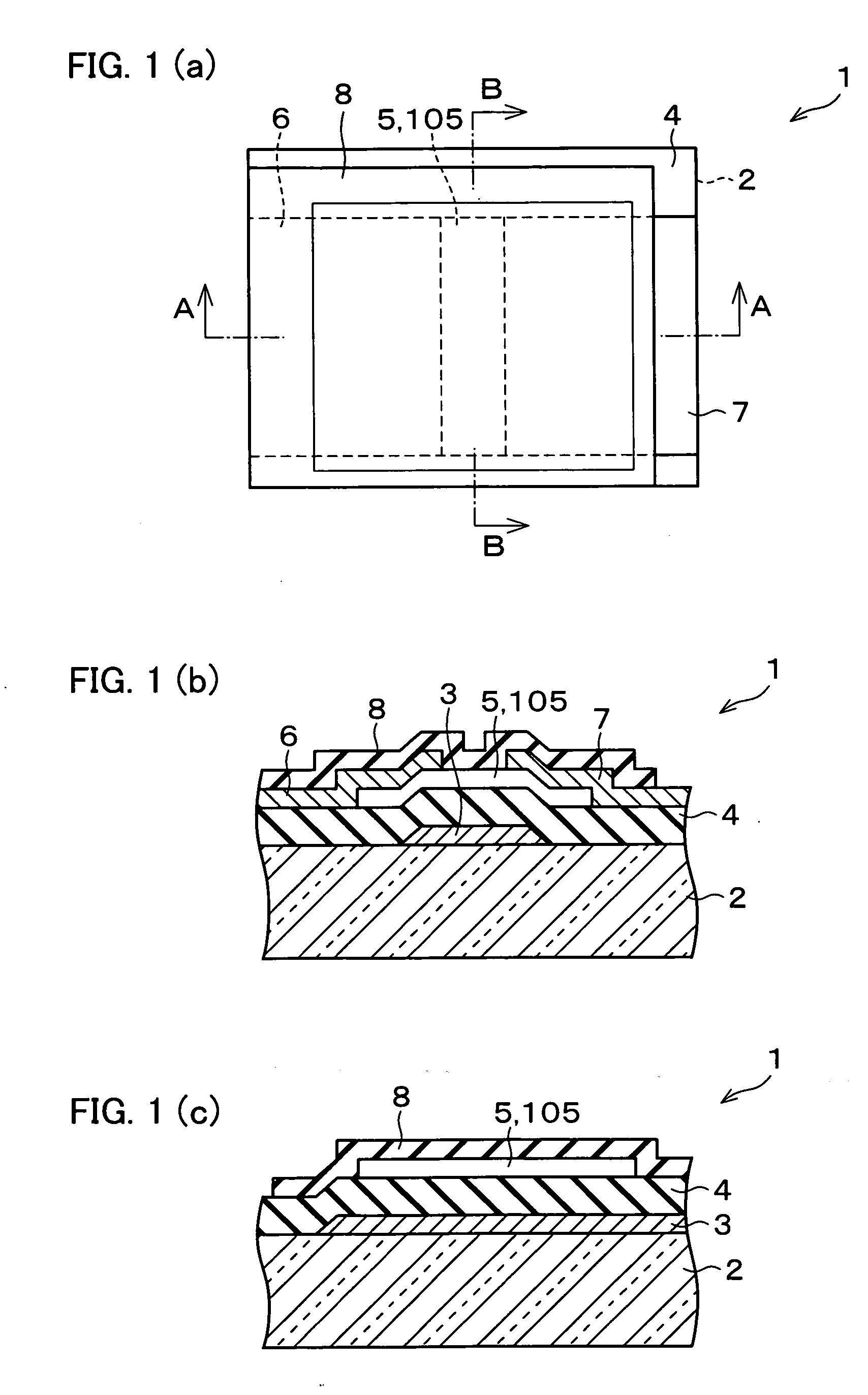

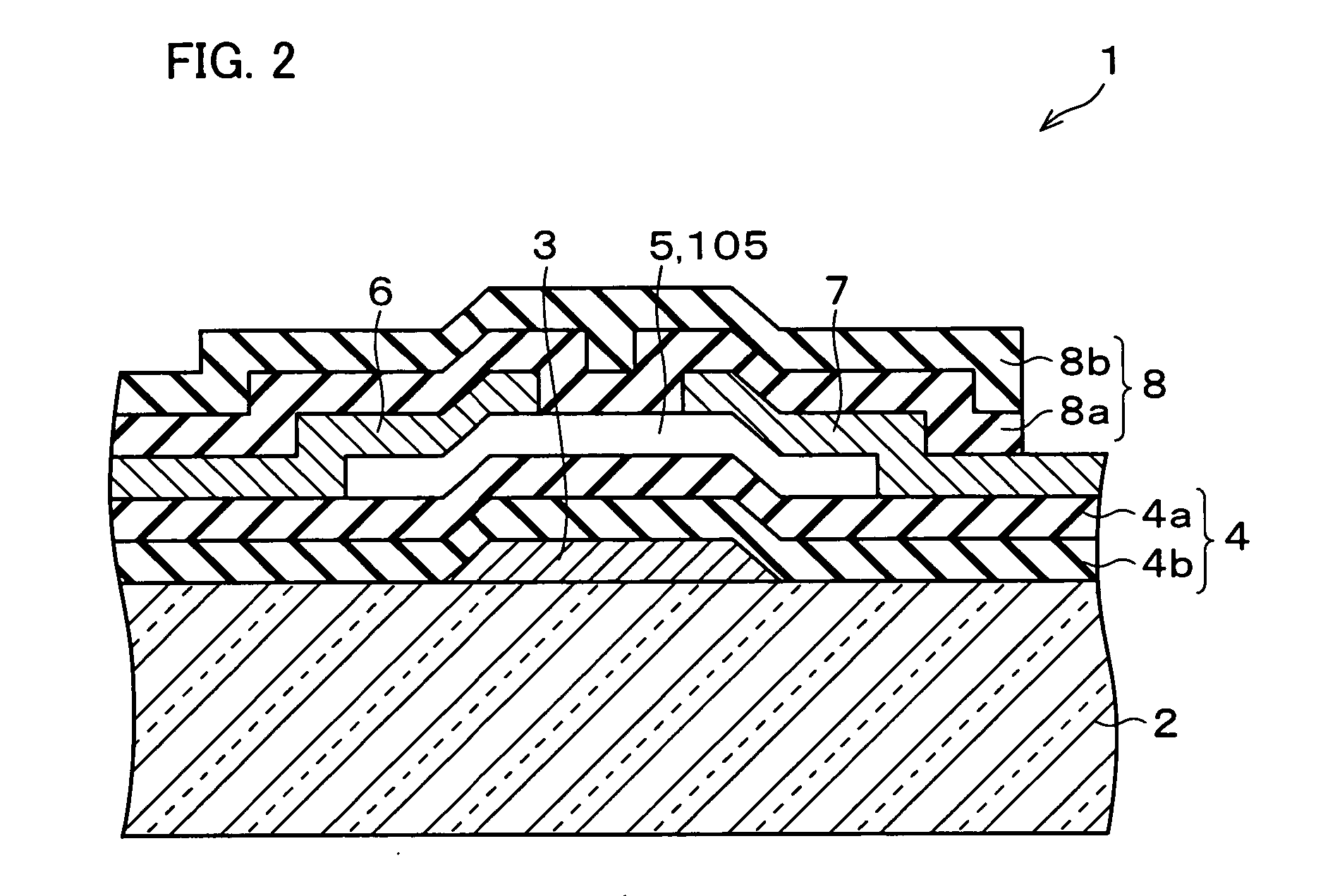

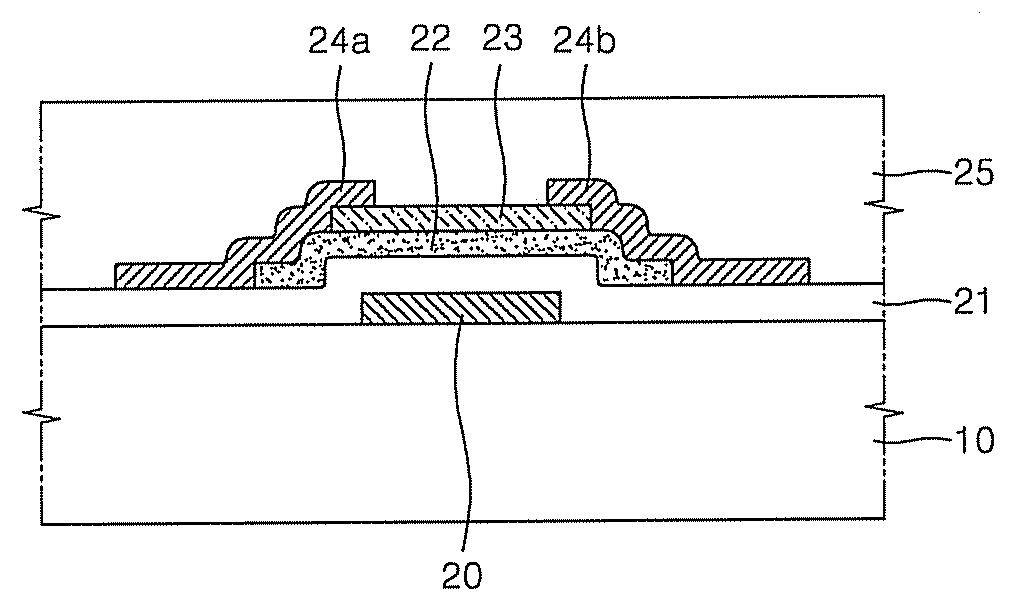

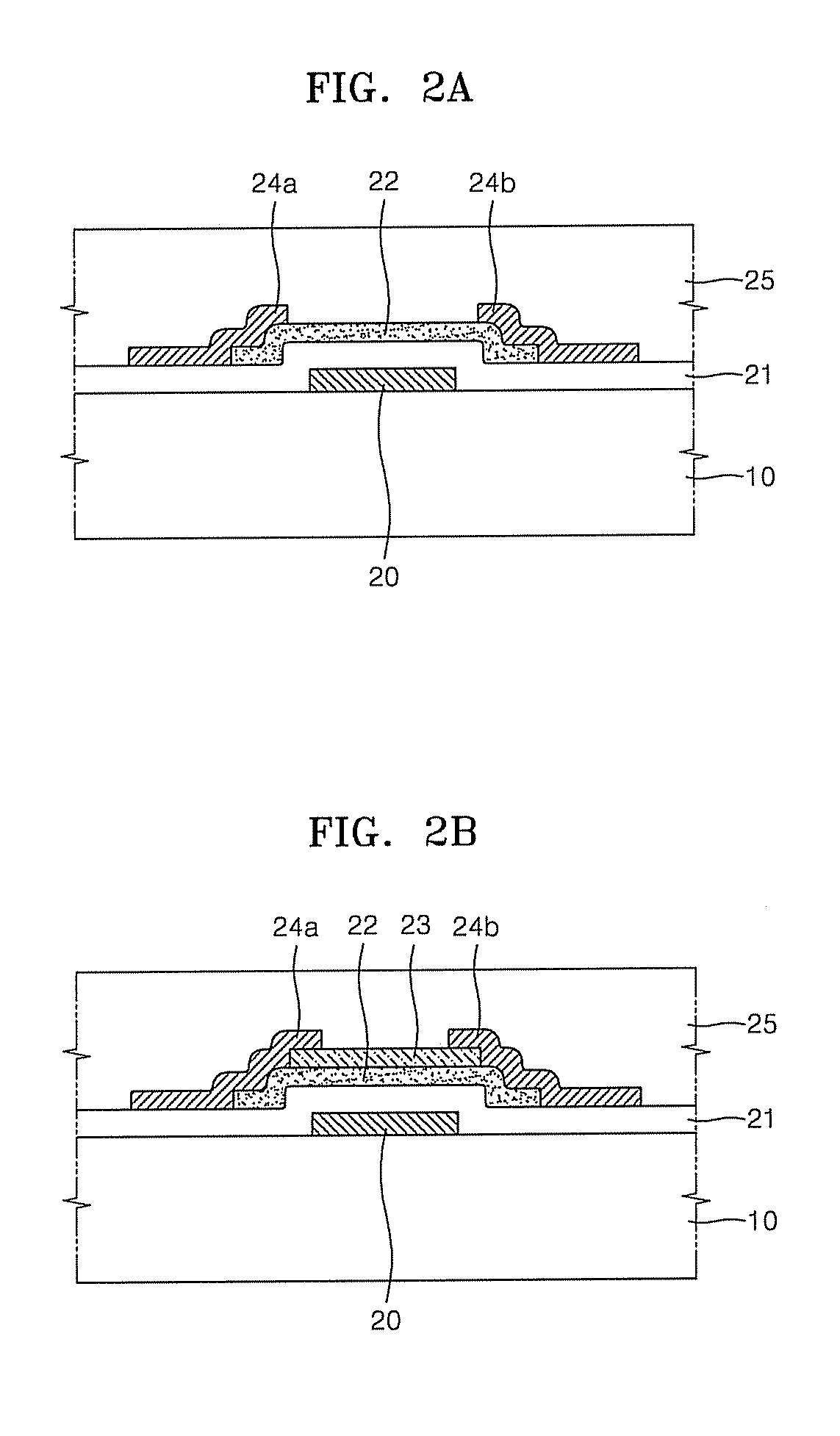

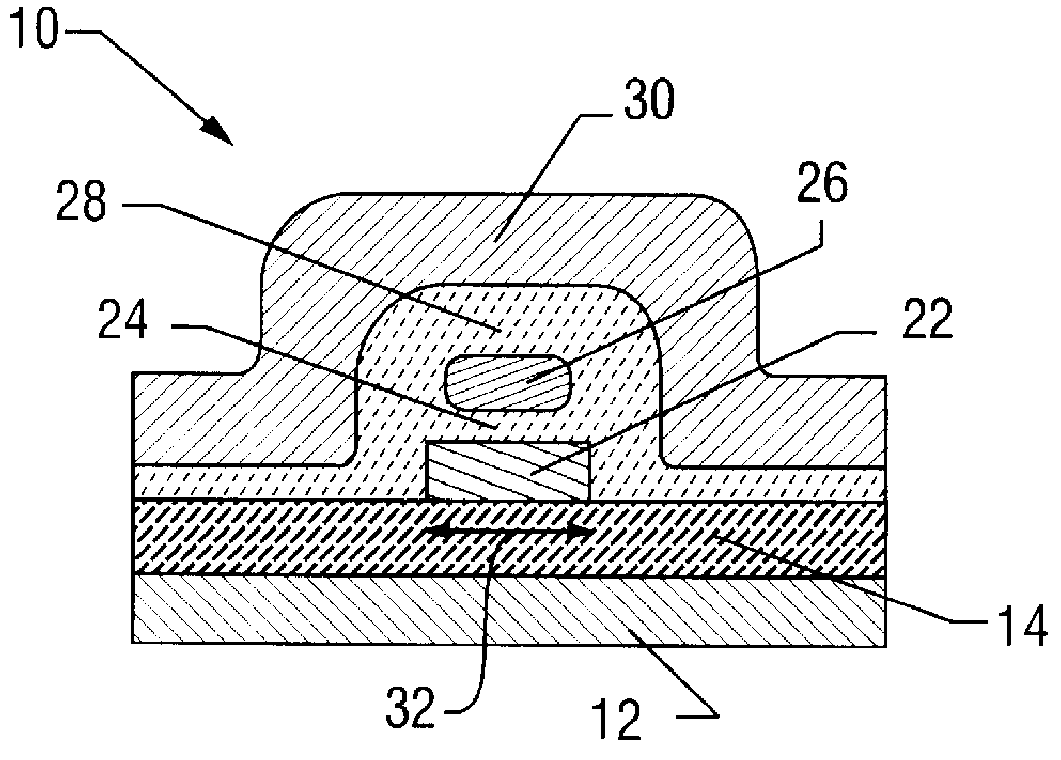

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

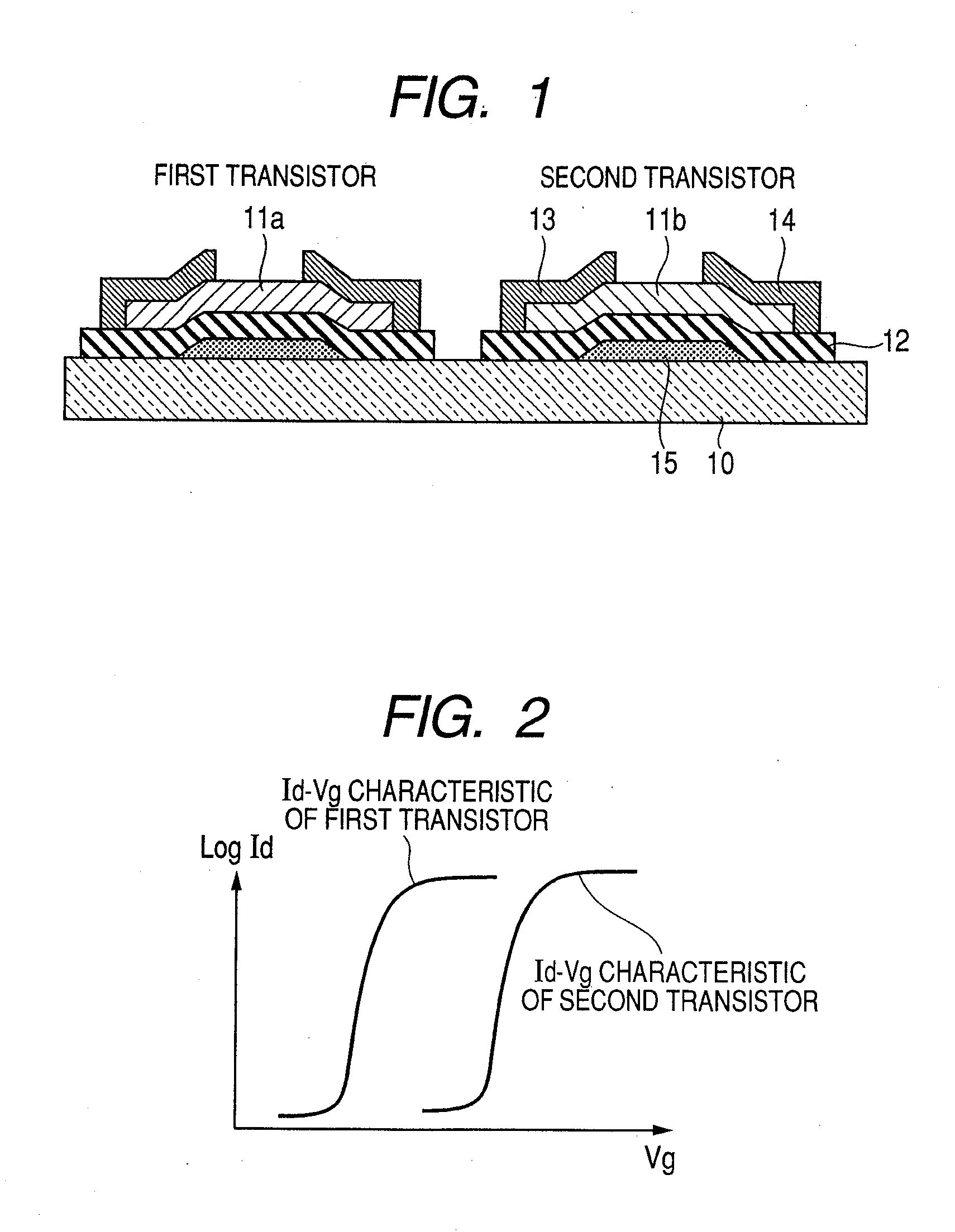

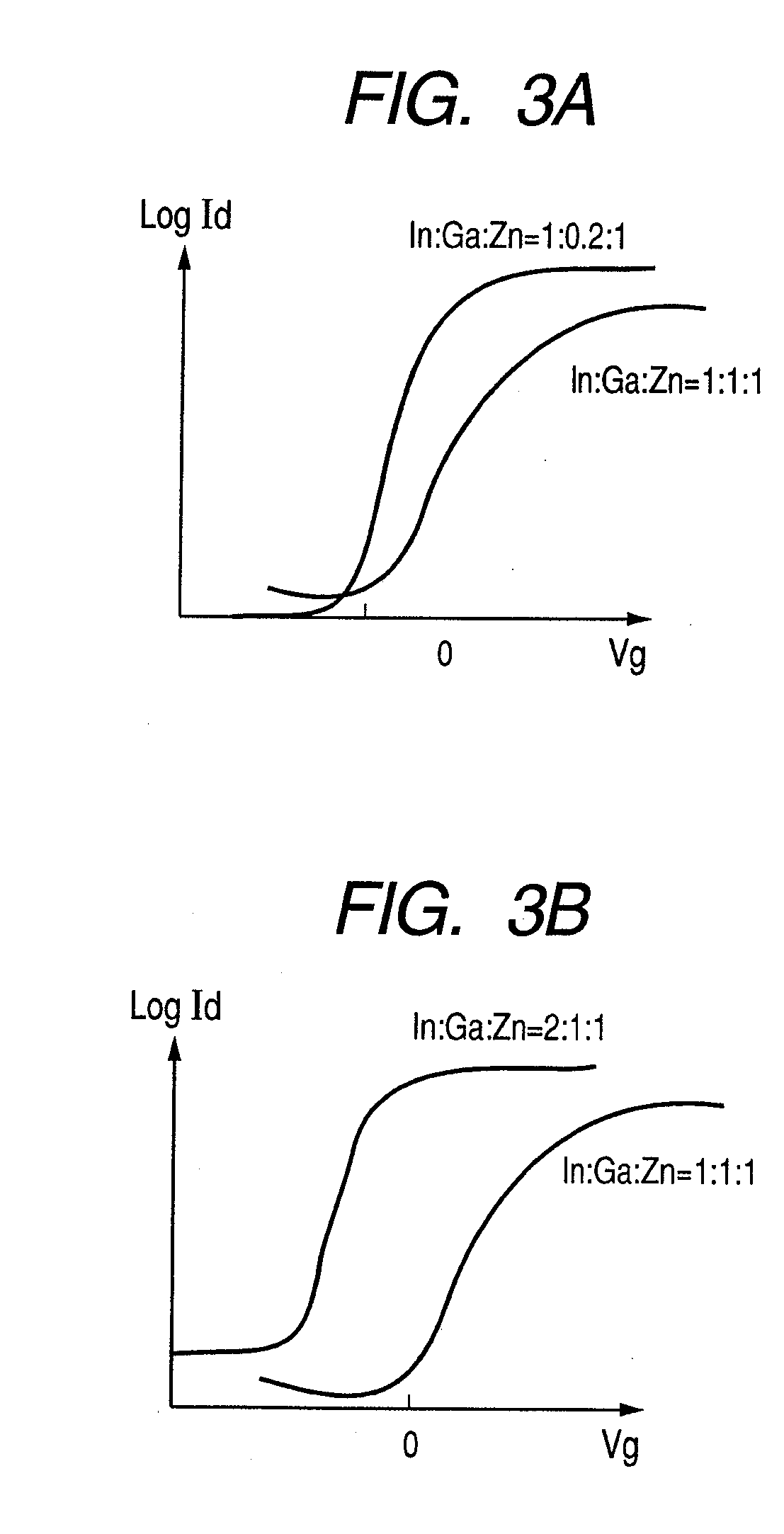

Semiconductor apparatus and method of manufacturing the same

InactiveUS20080073653A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

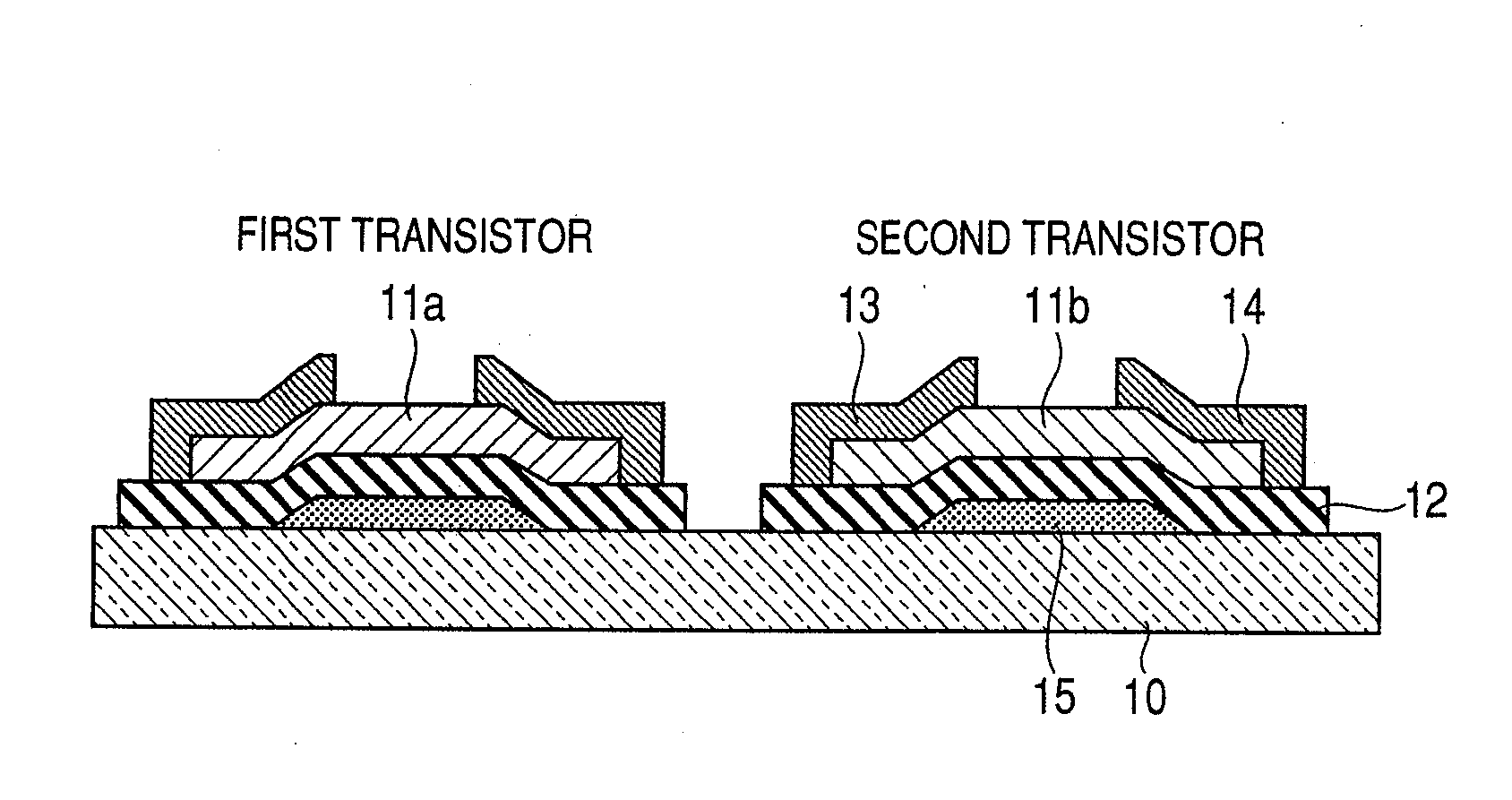

It is an object of the present invention to provide a technology of controlling a threshold voltage of a thin film transistor in which an amorphous oxide film is applied to a channel layer. There is provided a semiconductor apparatus including a plurality of kinds of transistors, each of the plurality of kinds of transistors including a channel layer made of an amorphous oxide containing a plurality of kinds of metal elements; and threshold voltages of the plurality of kinds of transistors are different from one another by changing an element ratio of the amorphous oxide.

Owner:CANON KK

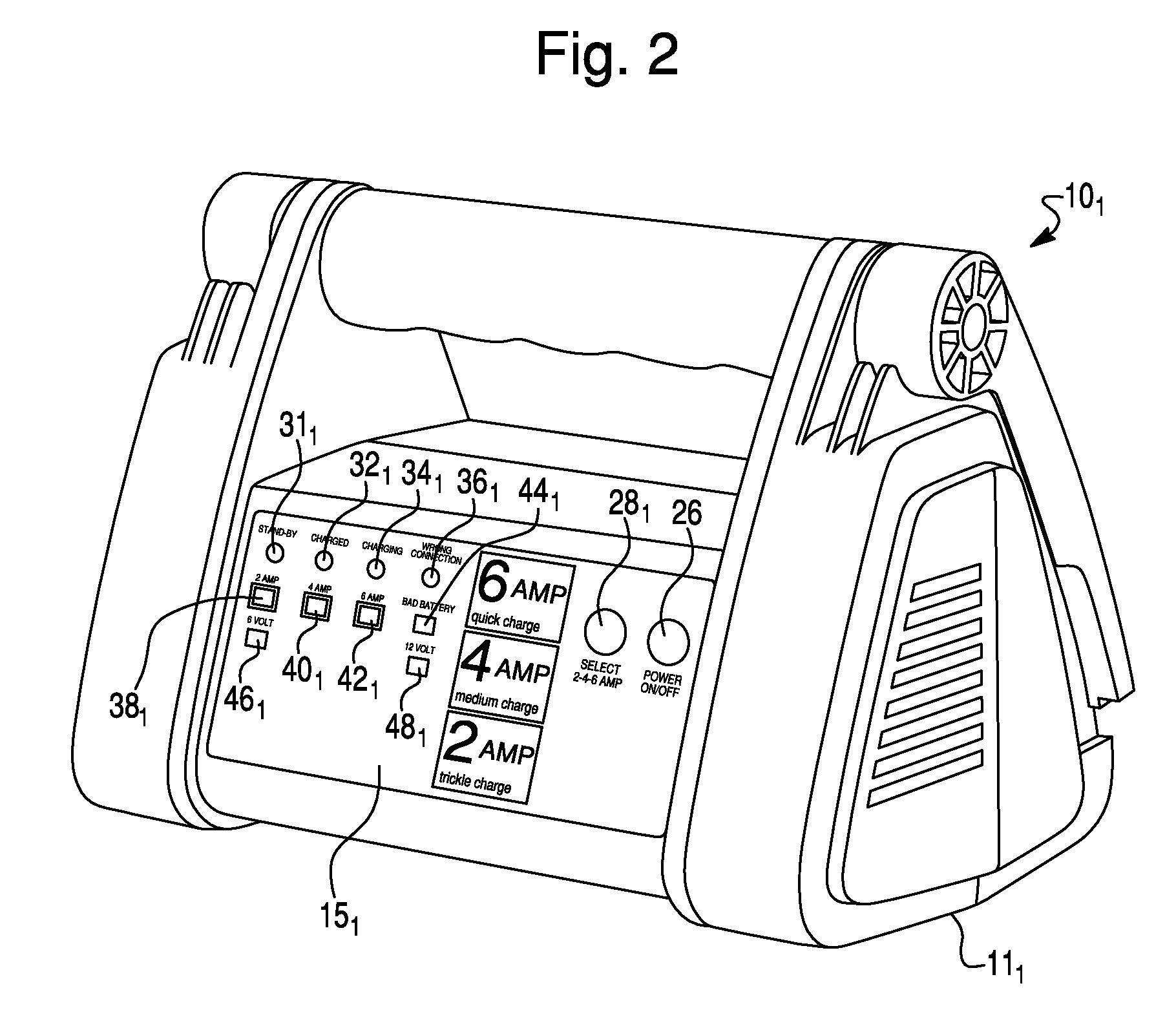

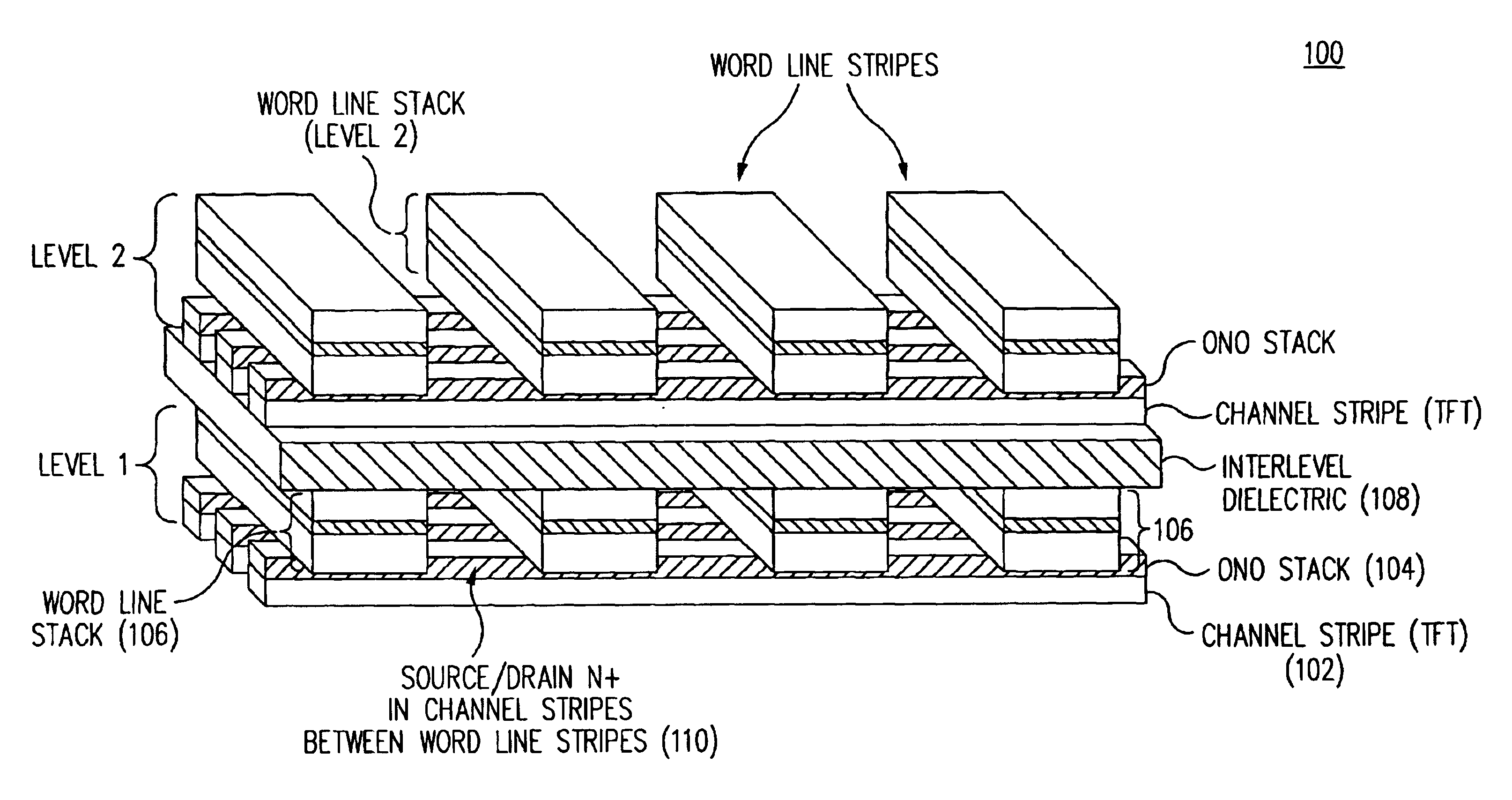

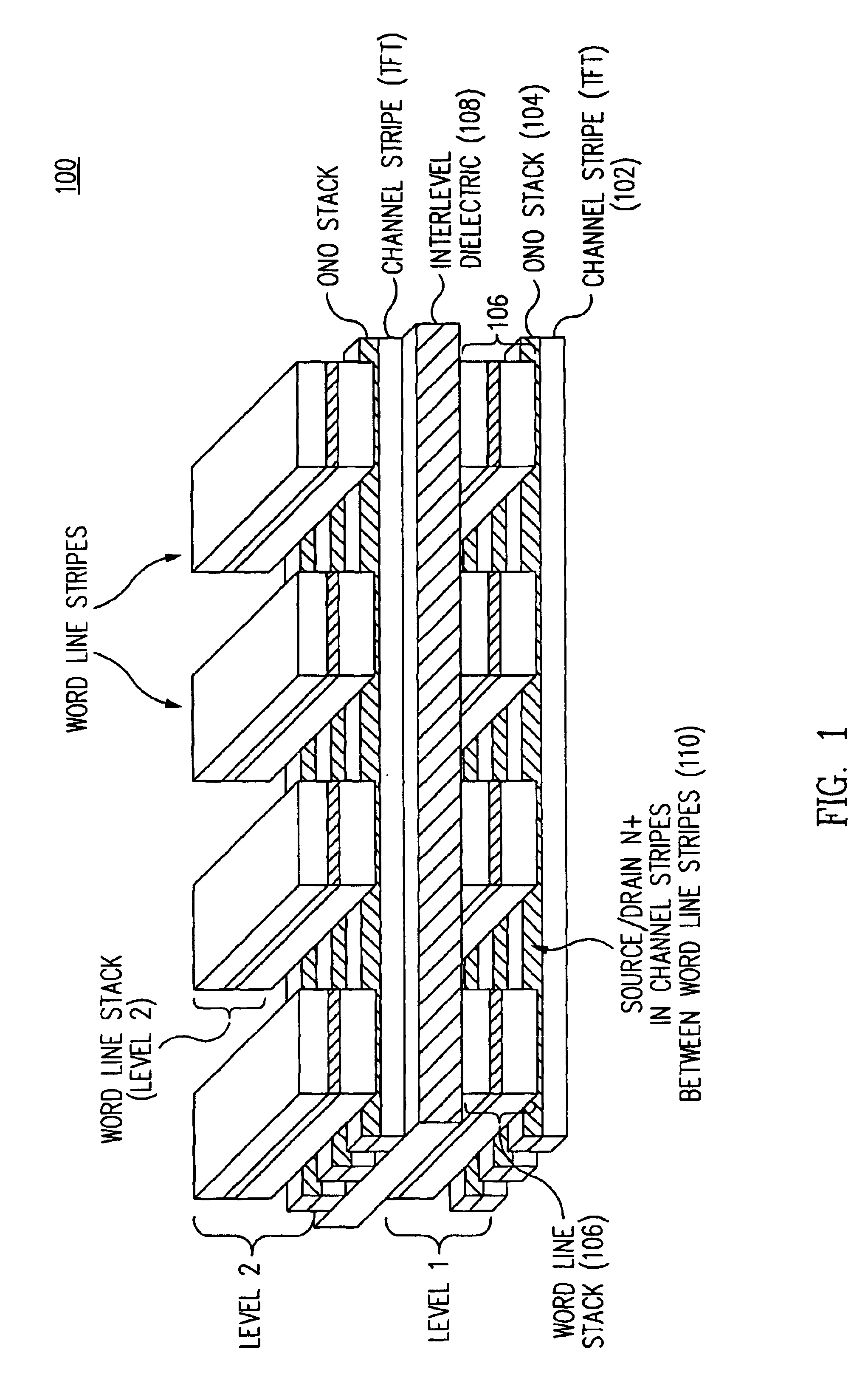

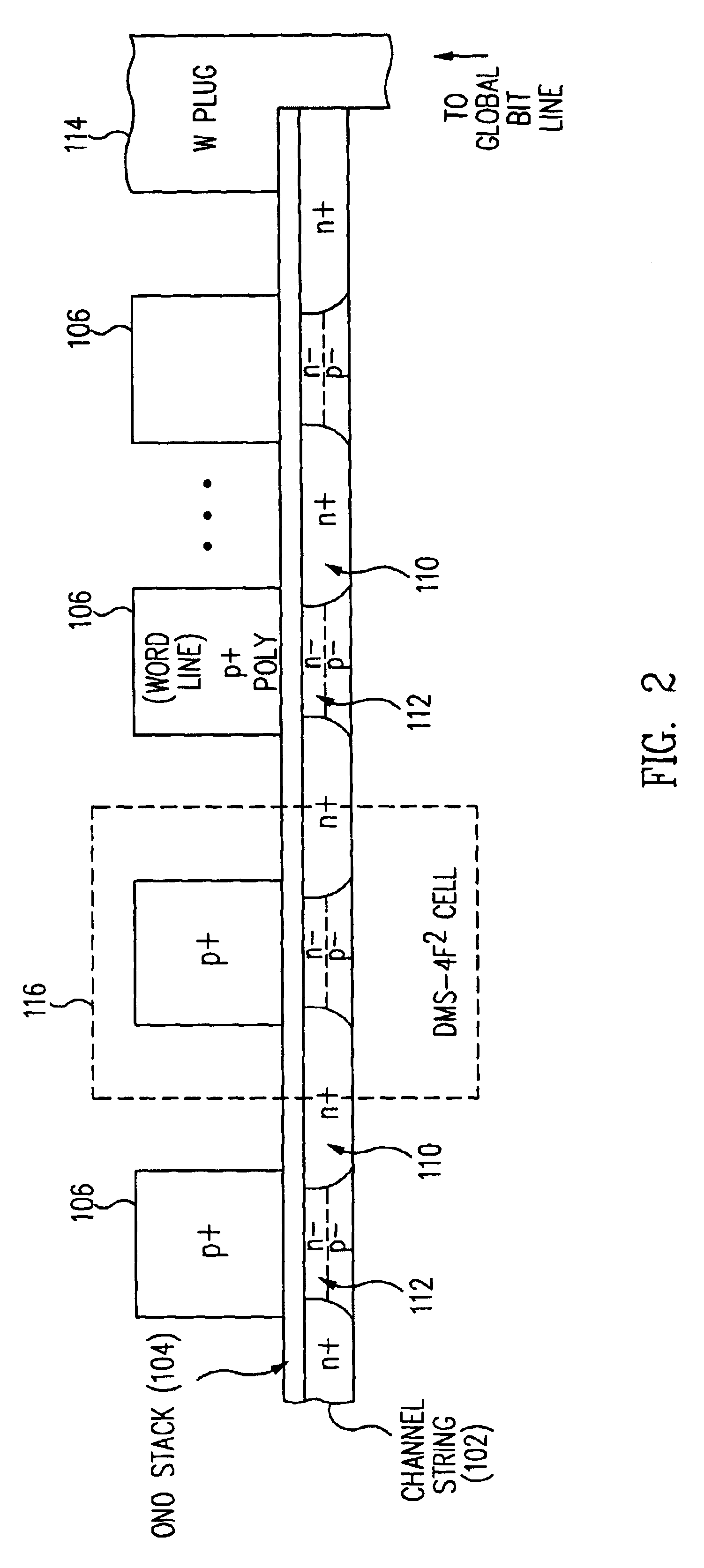

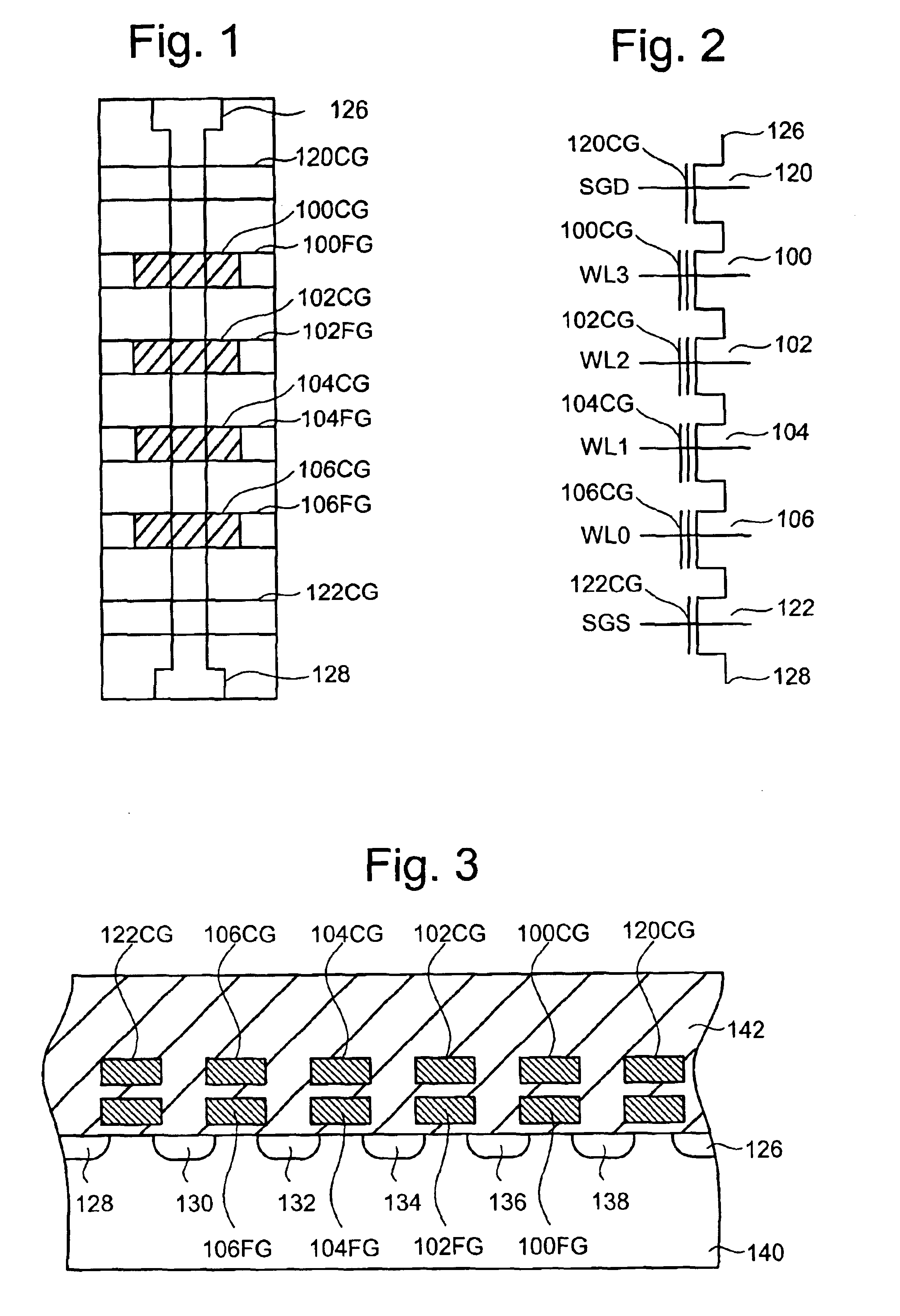

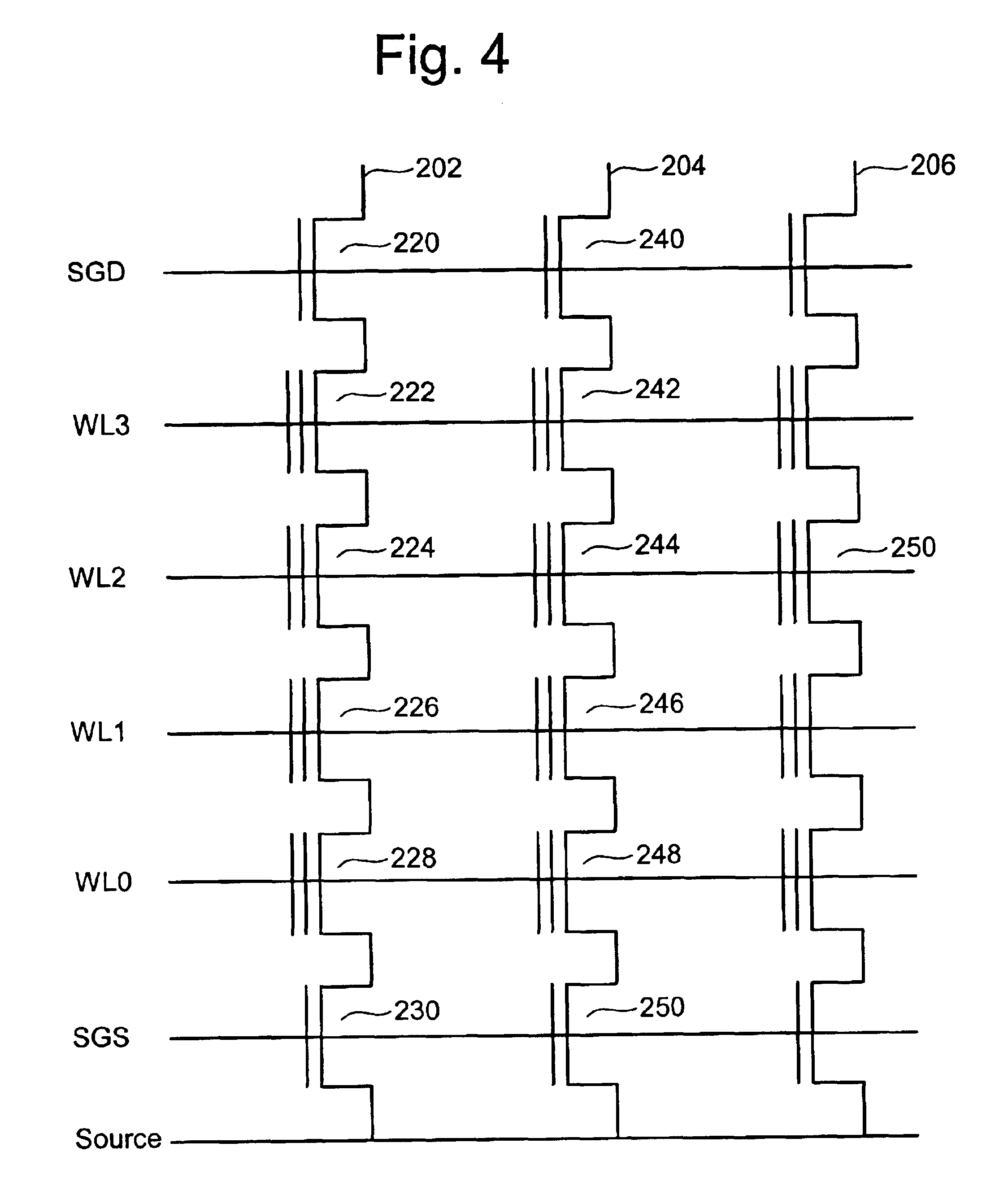

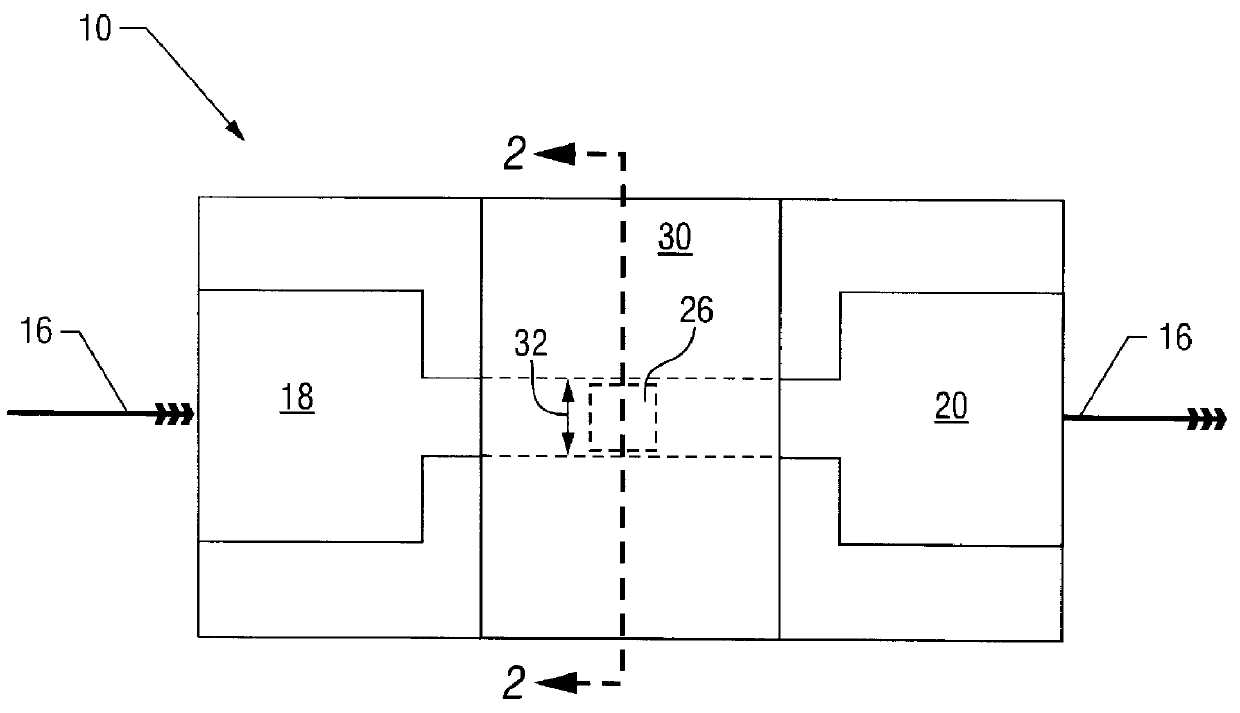

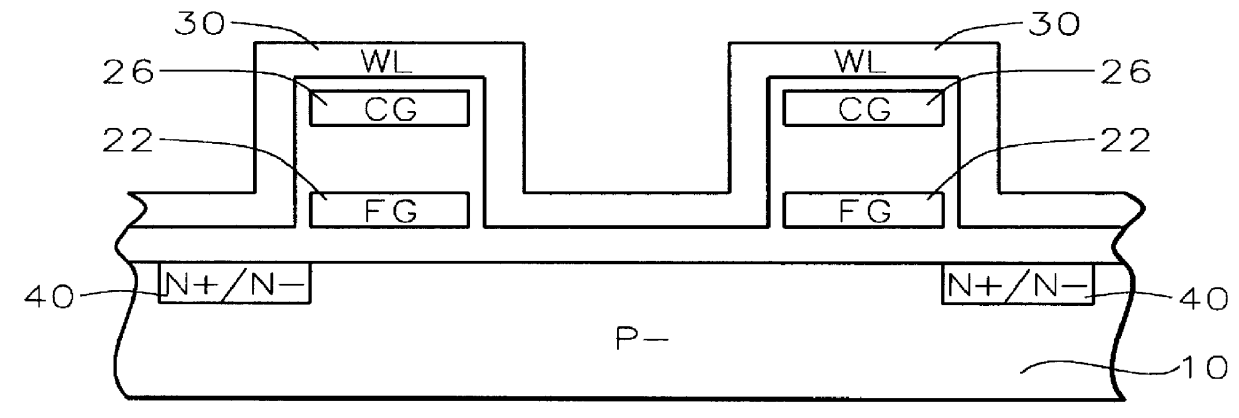

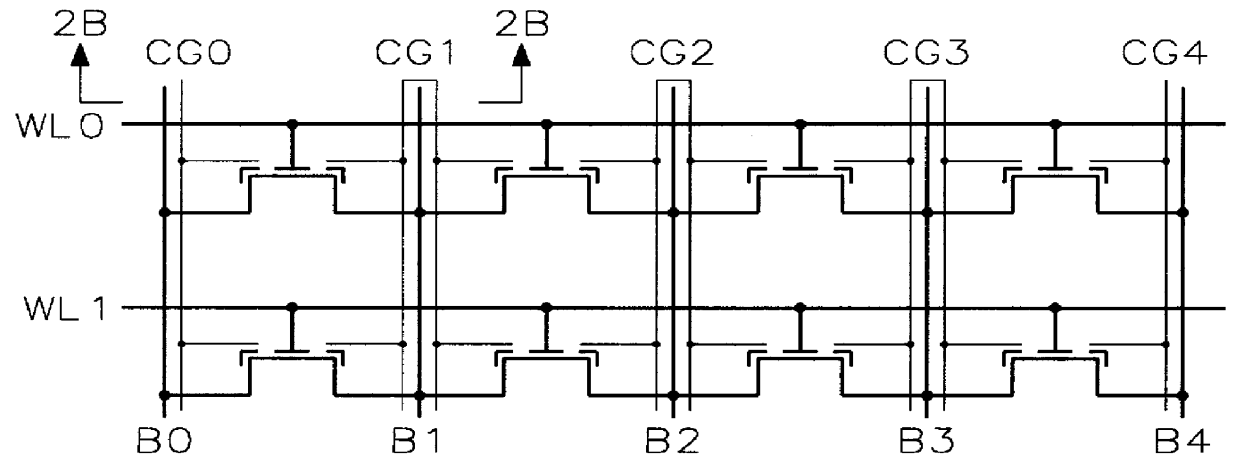

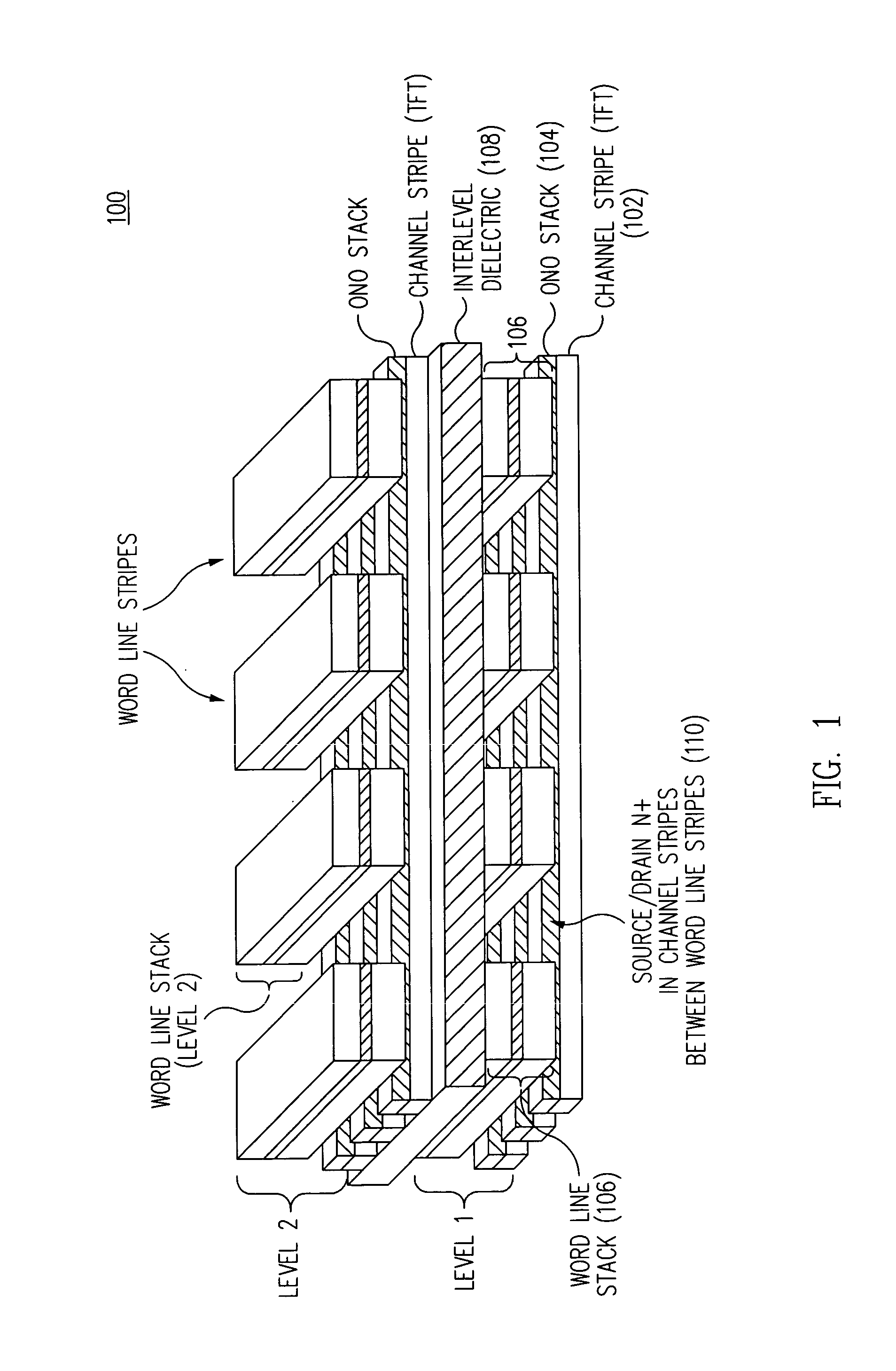

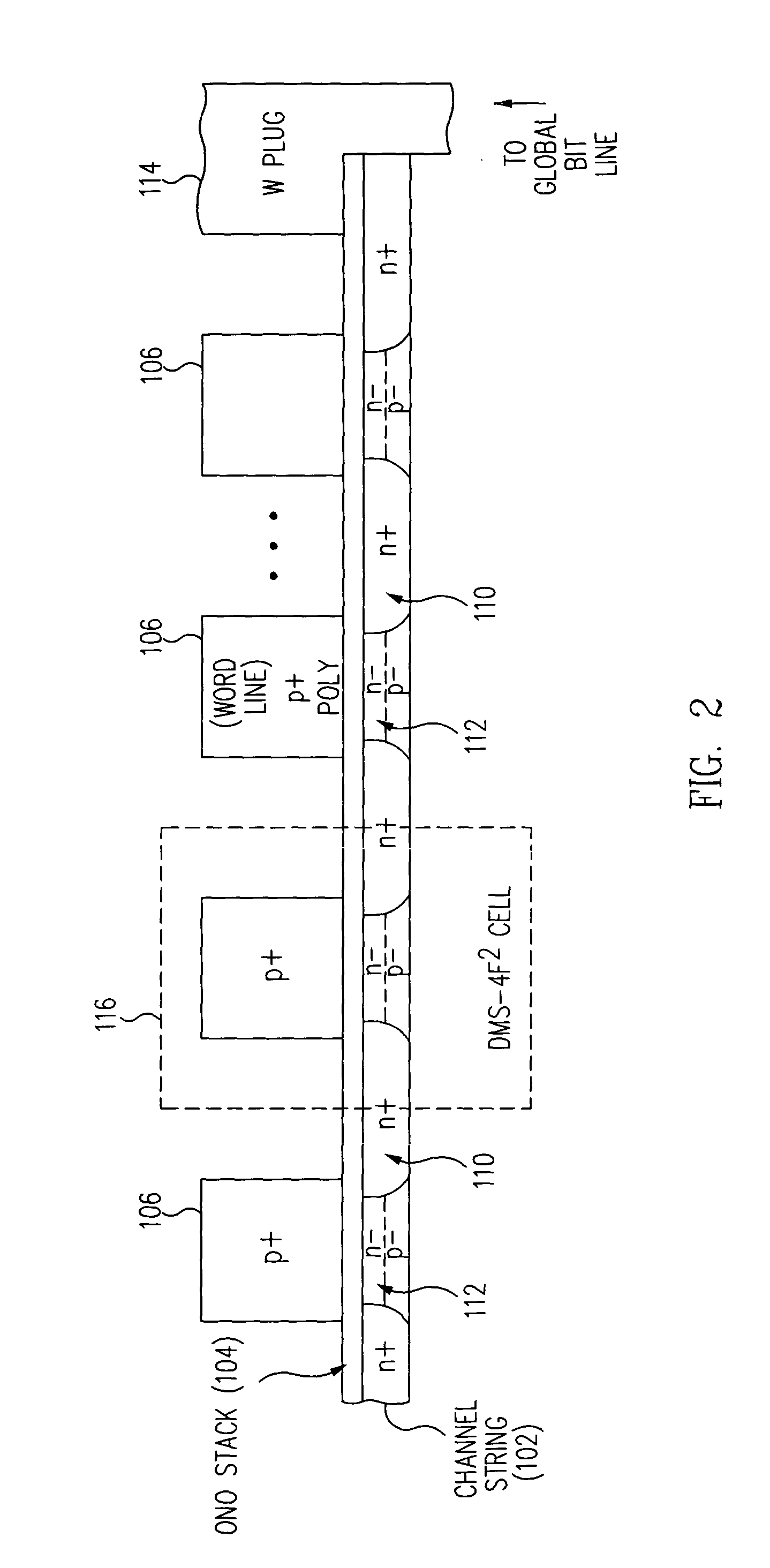

Method for fabricating programmable memory array structures incorporating series-connected transistor strings

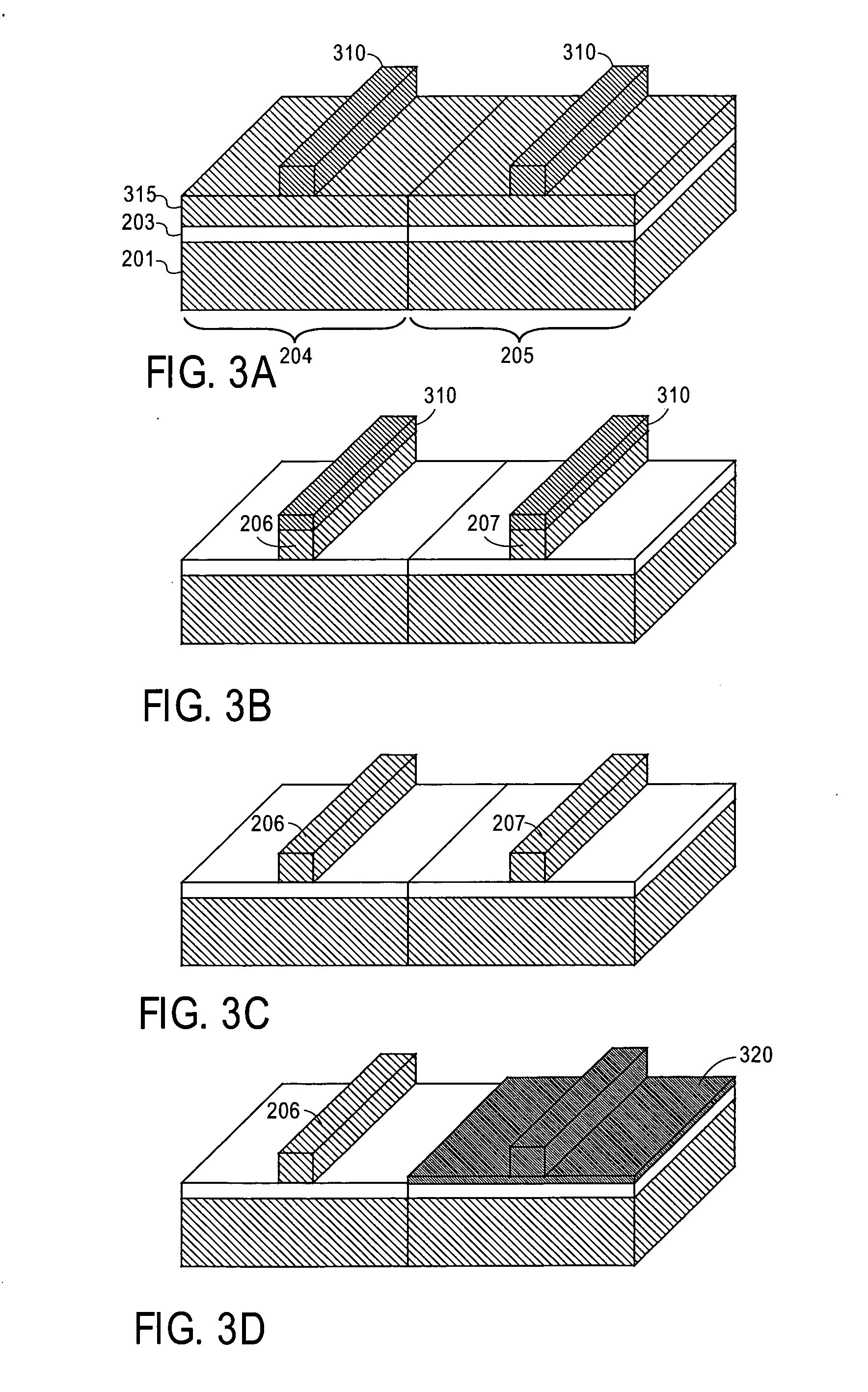

InactiveUS7005350B2Reduce in quantityDense memory arraySolid-state devicesRead-only memoriesBit lineComputer architecture

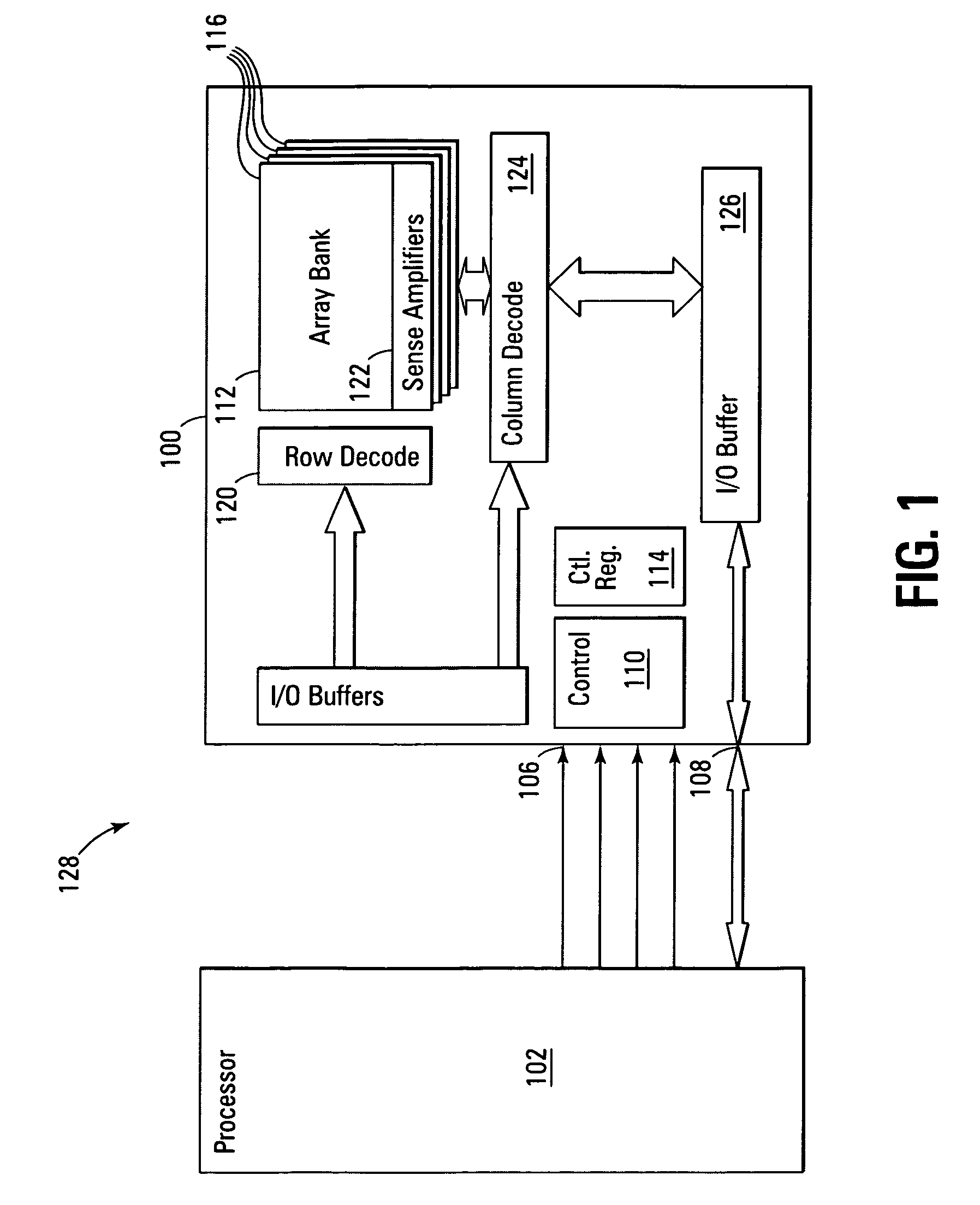

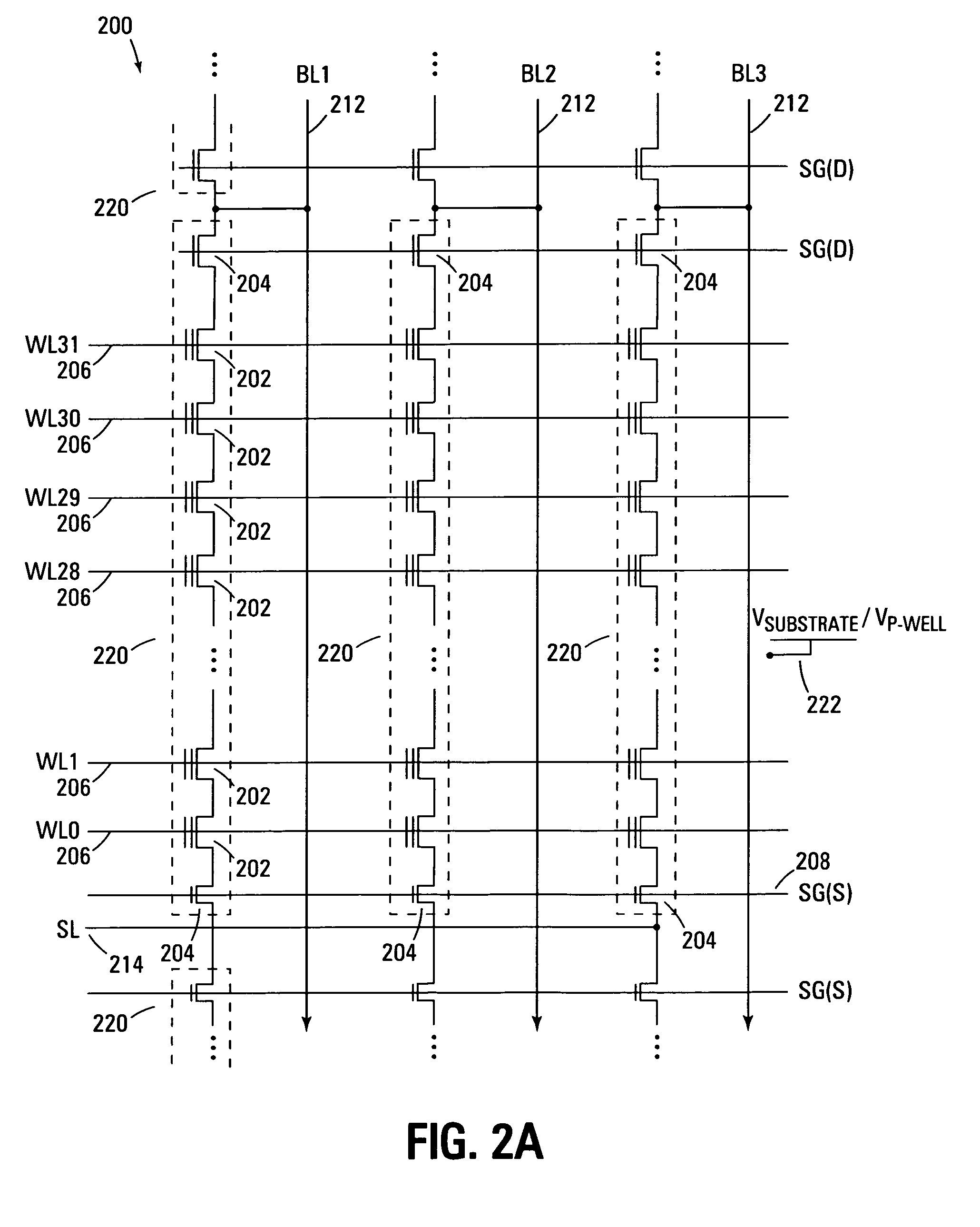

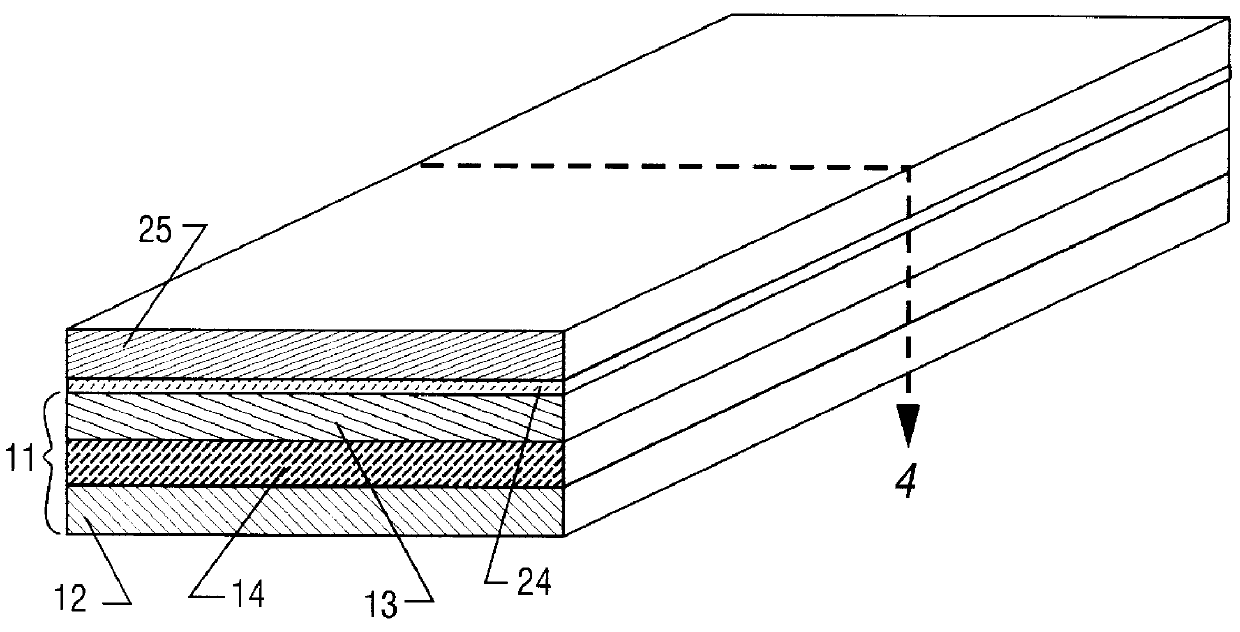

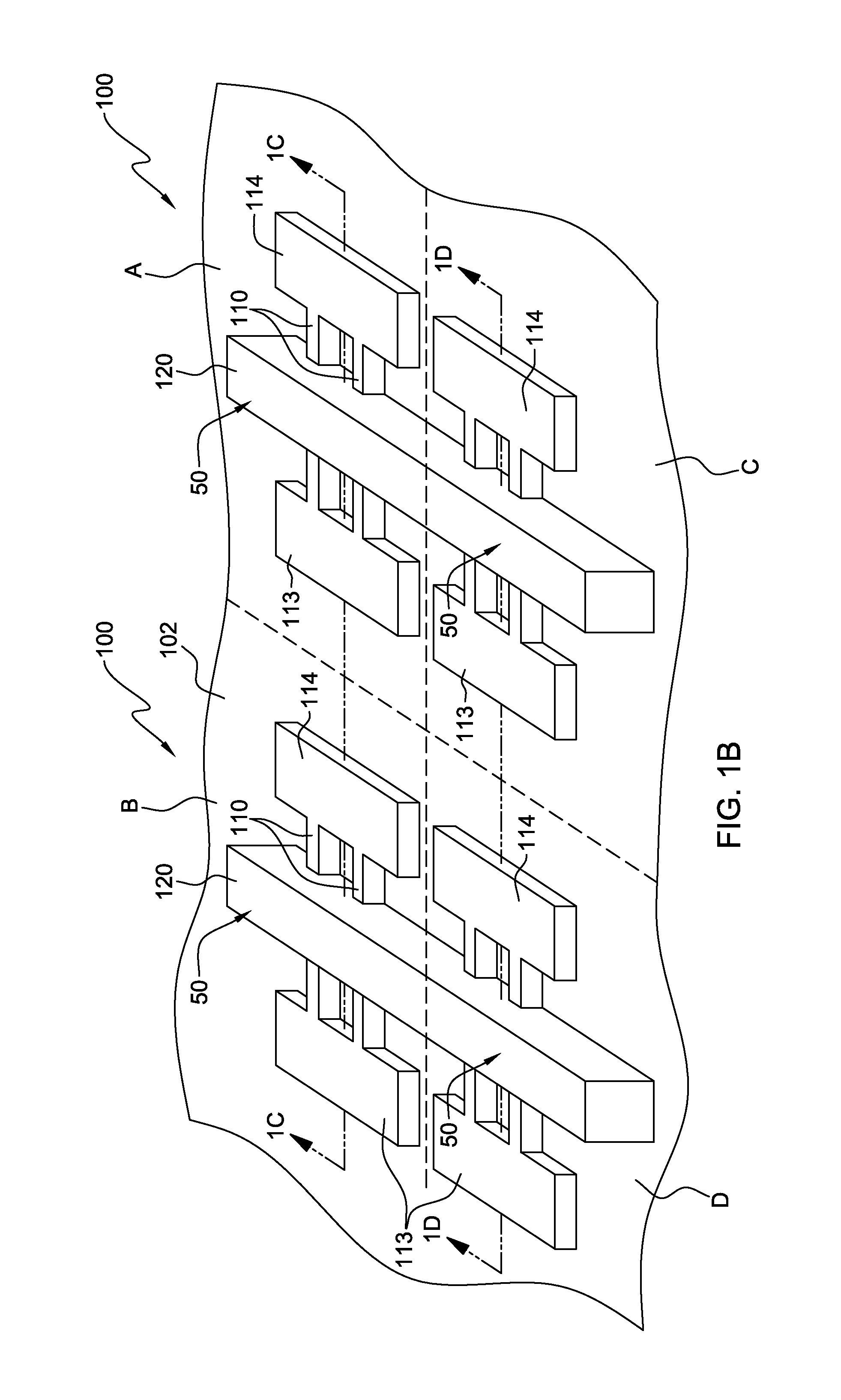

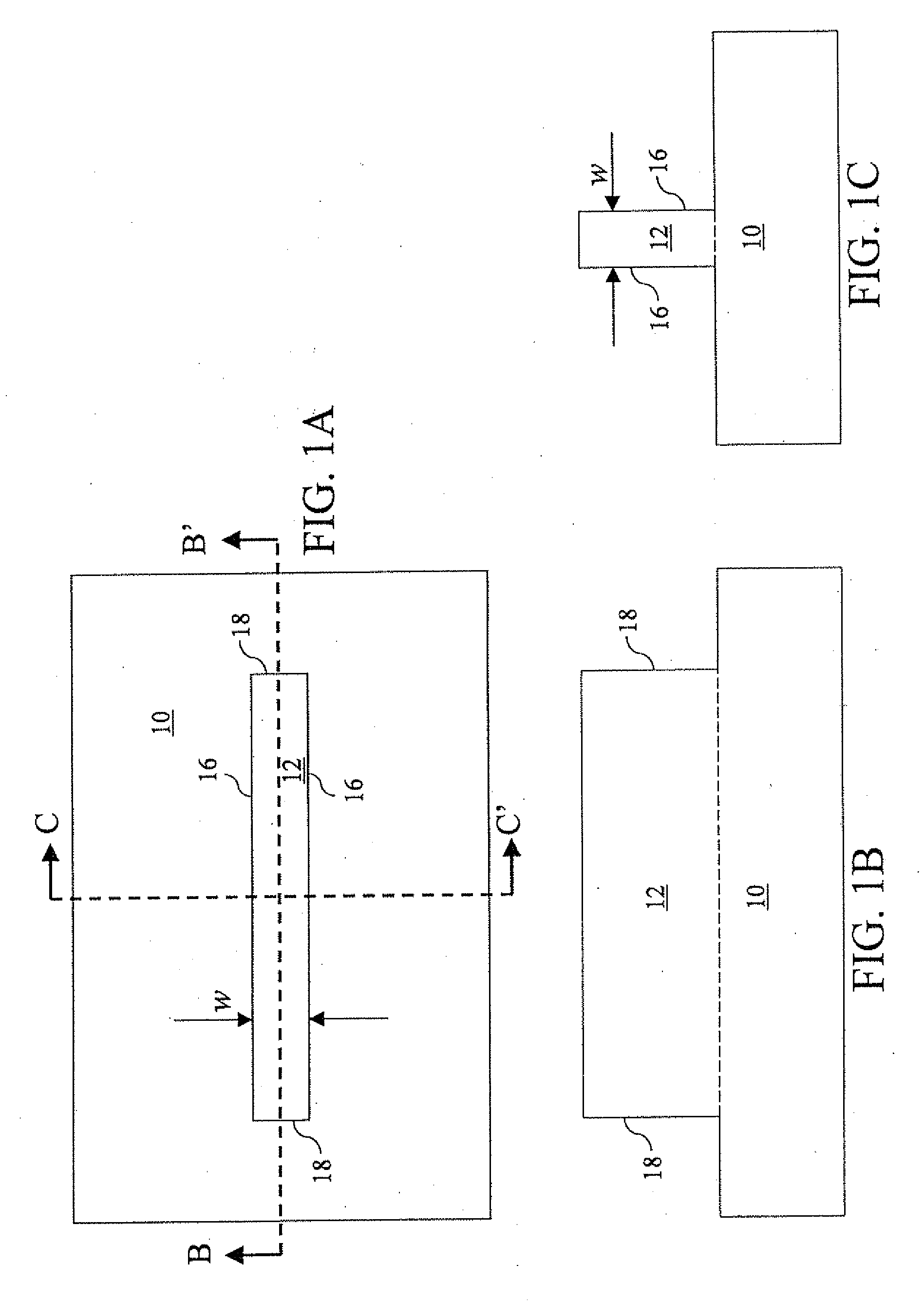

A three-dimensional flash memory array incorporates thin film transistors having a charge storage dielectric arranged in series-connected NAND strings to achieve a 4F2 memory cell layout. The memory array may be programmed and erased using only tunneling currents, and no leakage paths are formed through non-selected memory cells. Each NAND string includes two block select devices for respectively coupling one end of the NAND string to a global bit line, and the other end to a shared bias node. Pairs of NAND strings within a block share the same global bit line. The memory cells are preferably depletion mode SONOS devices, as are the block select devices. The memory cells may be programmed to a near depletion threshold voltage, and the block select devices are maintained in a programmed state having a near depletion mode threshold voltage. NAND strings on more than one layer may be connected to global bit lines on a single layer. By interleaving the NAND strings on each memory level and using two shared bias nodes per block, very little additional overhead is required for the switch devices at each end of the NAND strings. The NAND strings on different memory levels are preferably connected together by way of vertical stacked vias, each preferably connecting to more than one memory level. Each memory level may be produced with less than three masks per level.

Owner:SANDISK TECH LLC

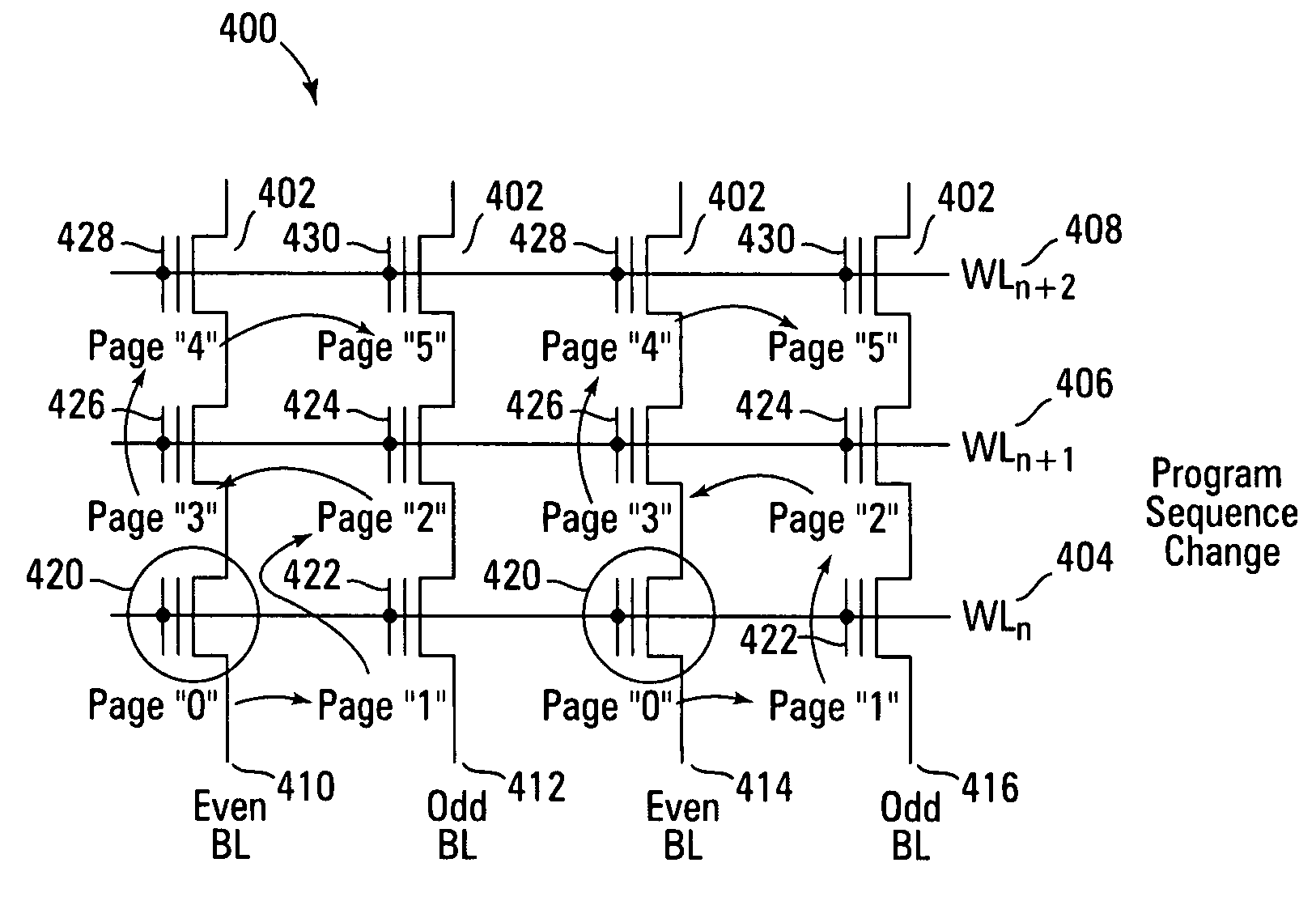

Programming method to reduce gate coupling interference for non-volatile memory

Owner:MICRON TECH INC

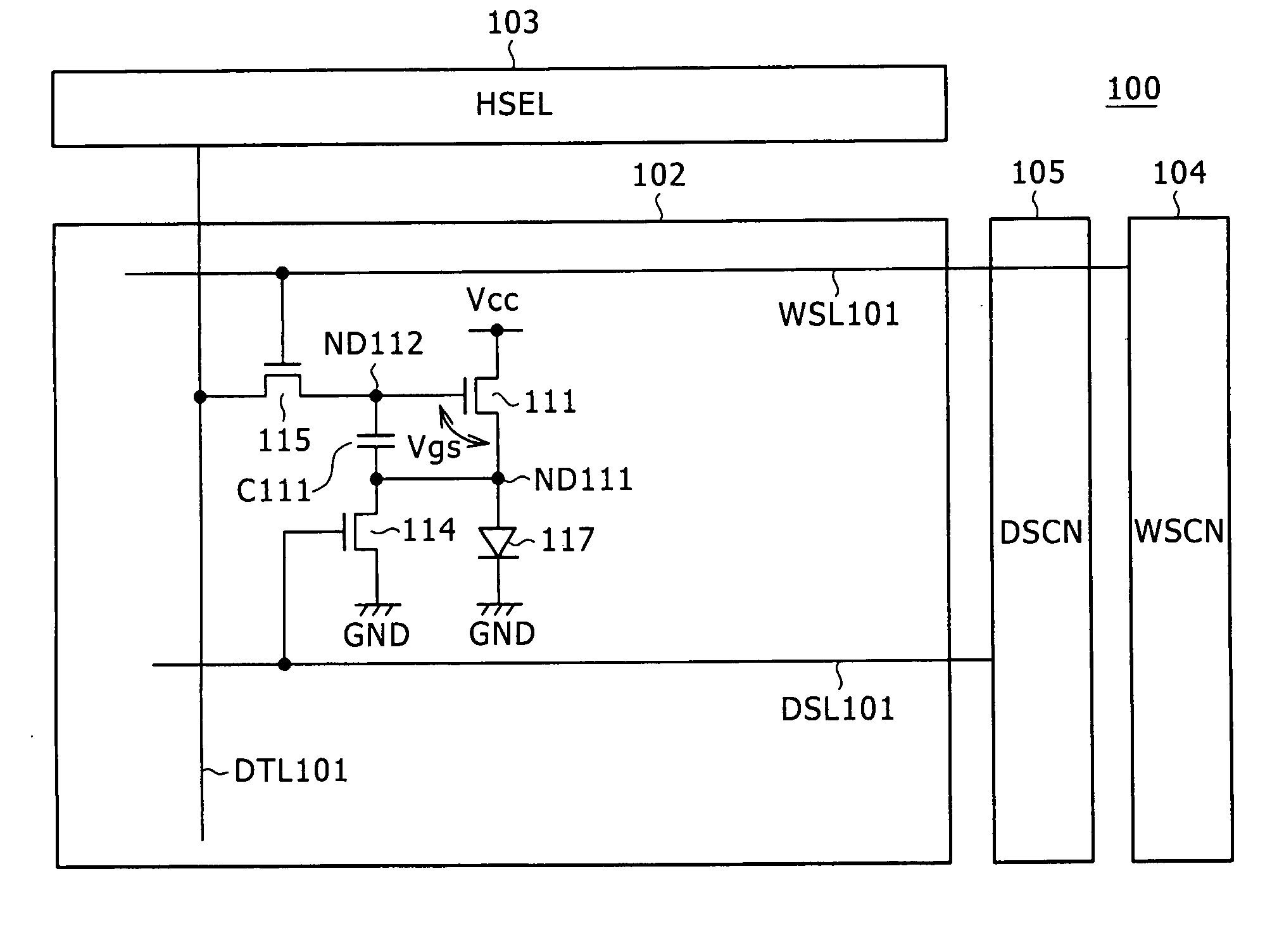

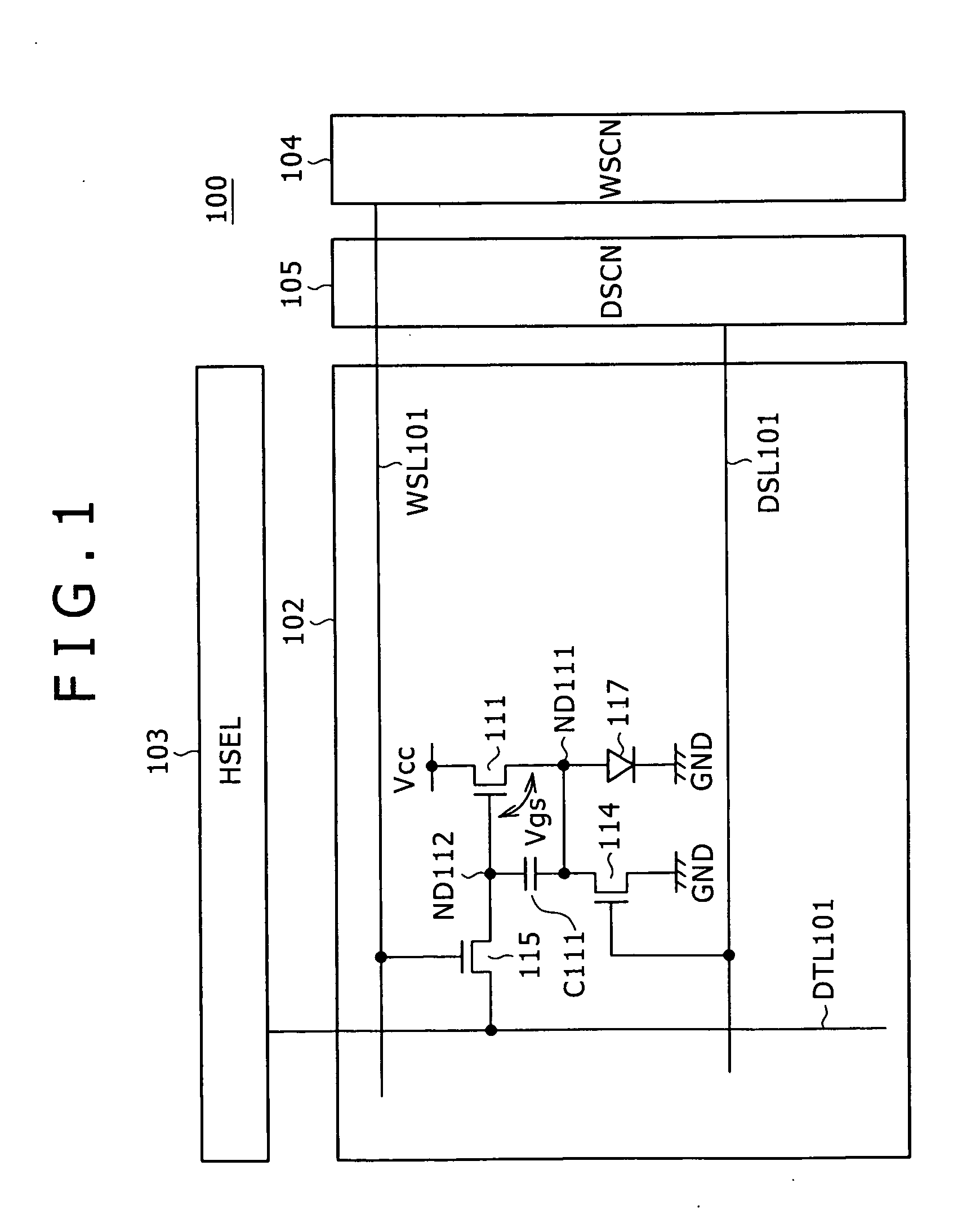

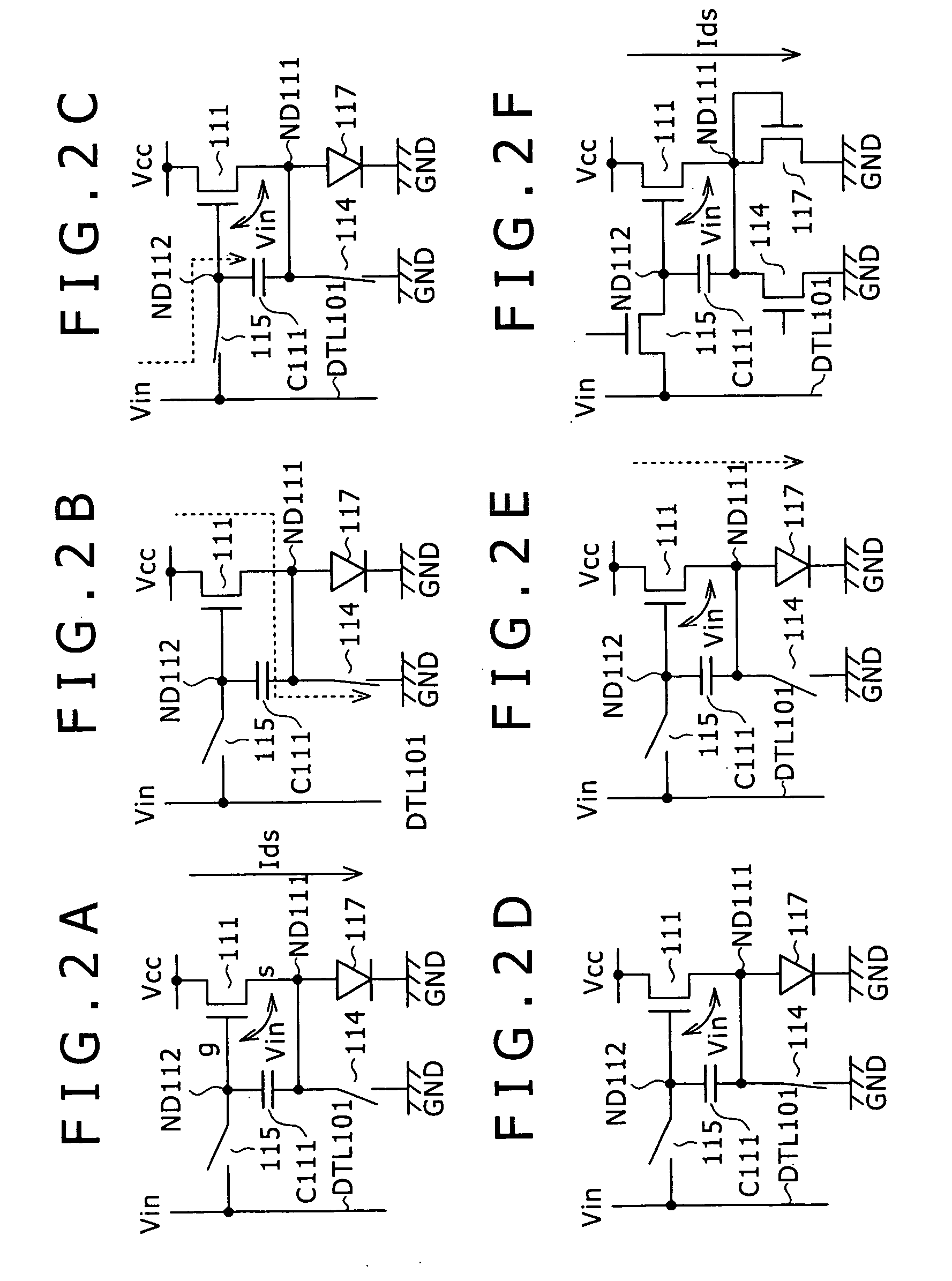

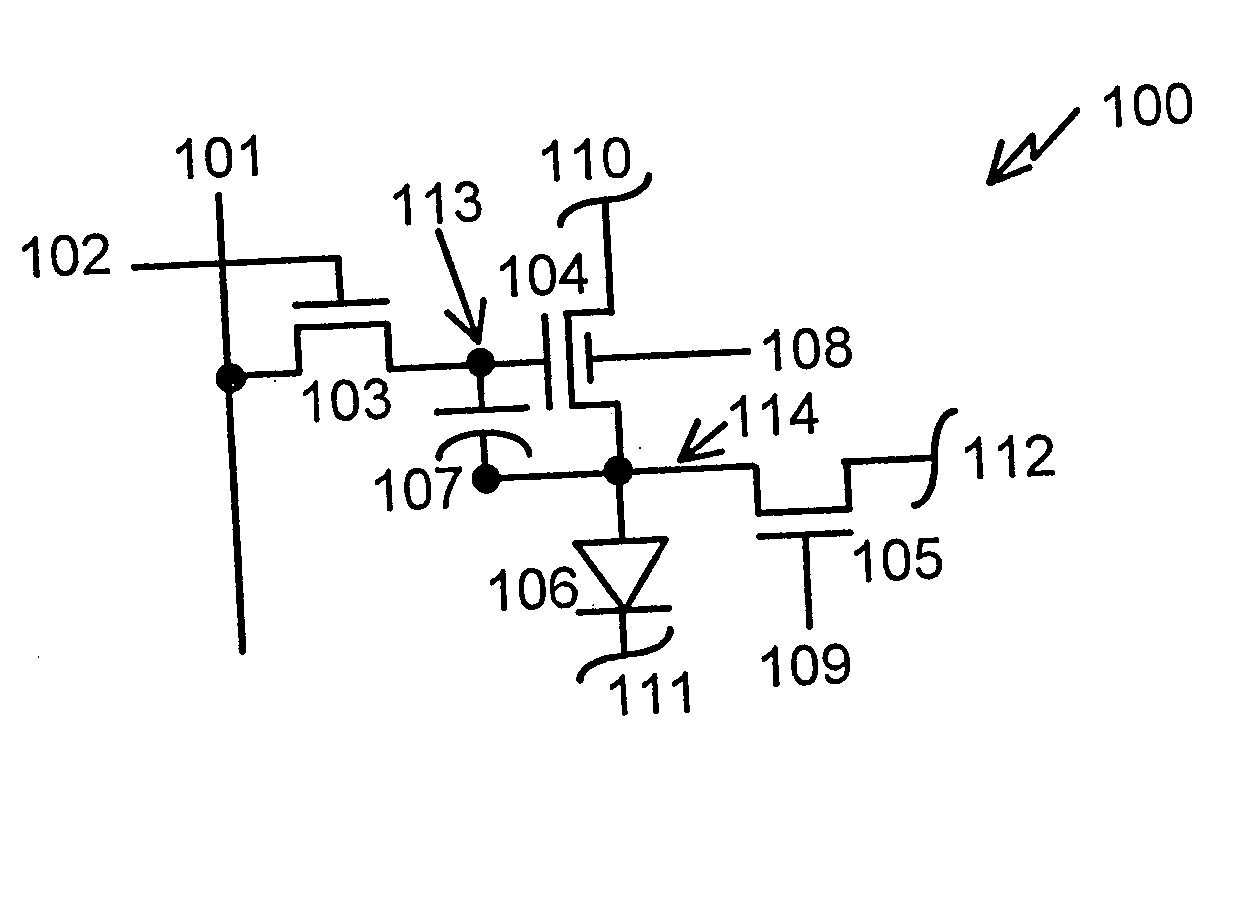

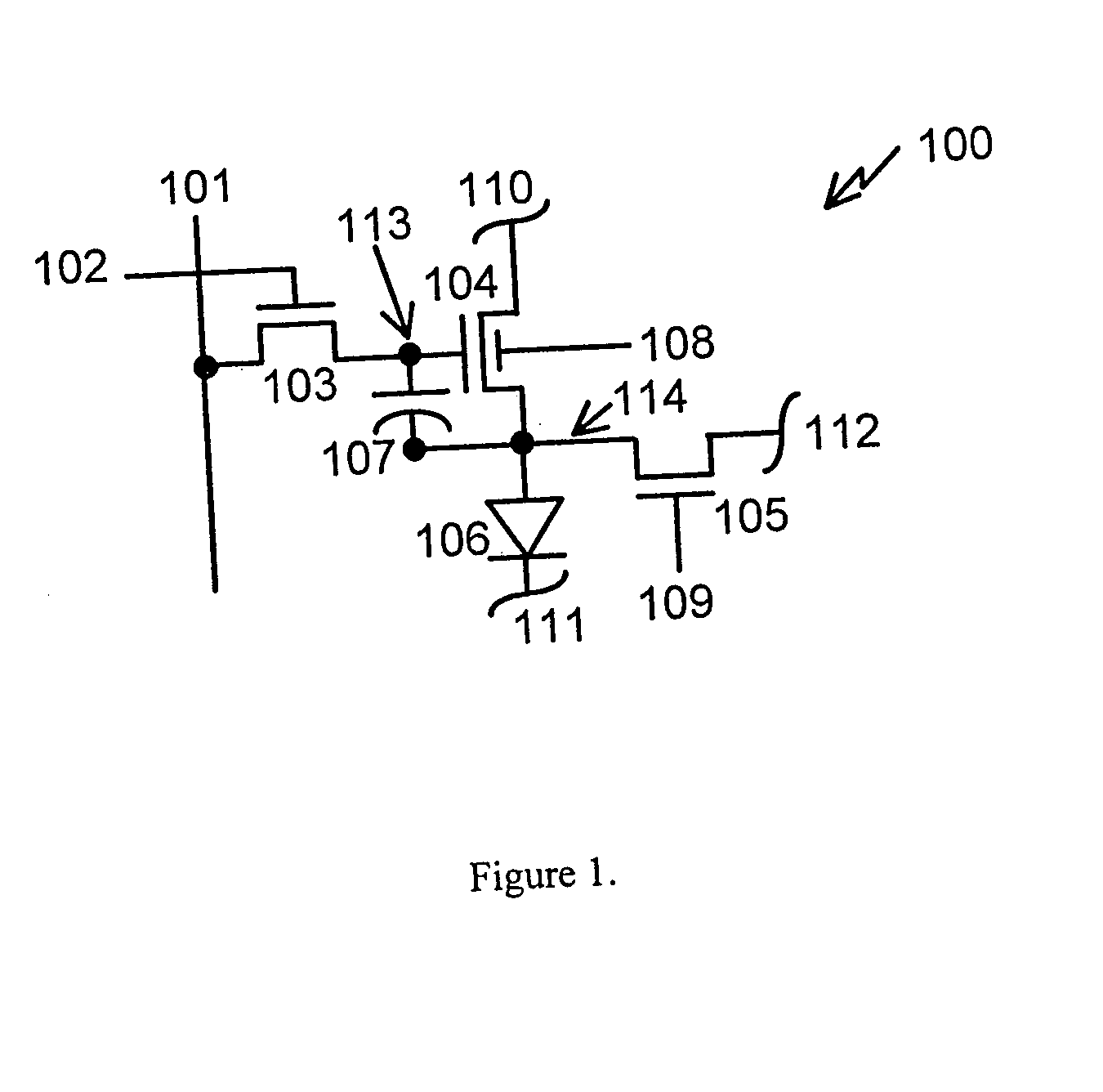

Pixel circuit, active matrix apparatus and display apparatus

ActiveUS20050269959A1Low costLuminance of light emission can be fixedStatic indicating devicesSolid-state devicesElectricityActive matrix

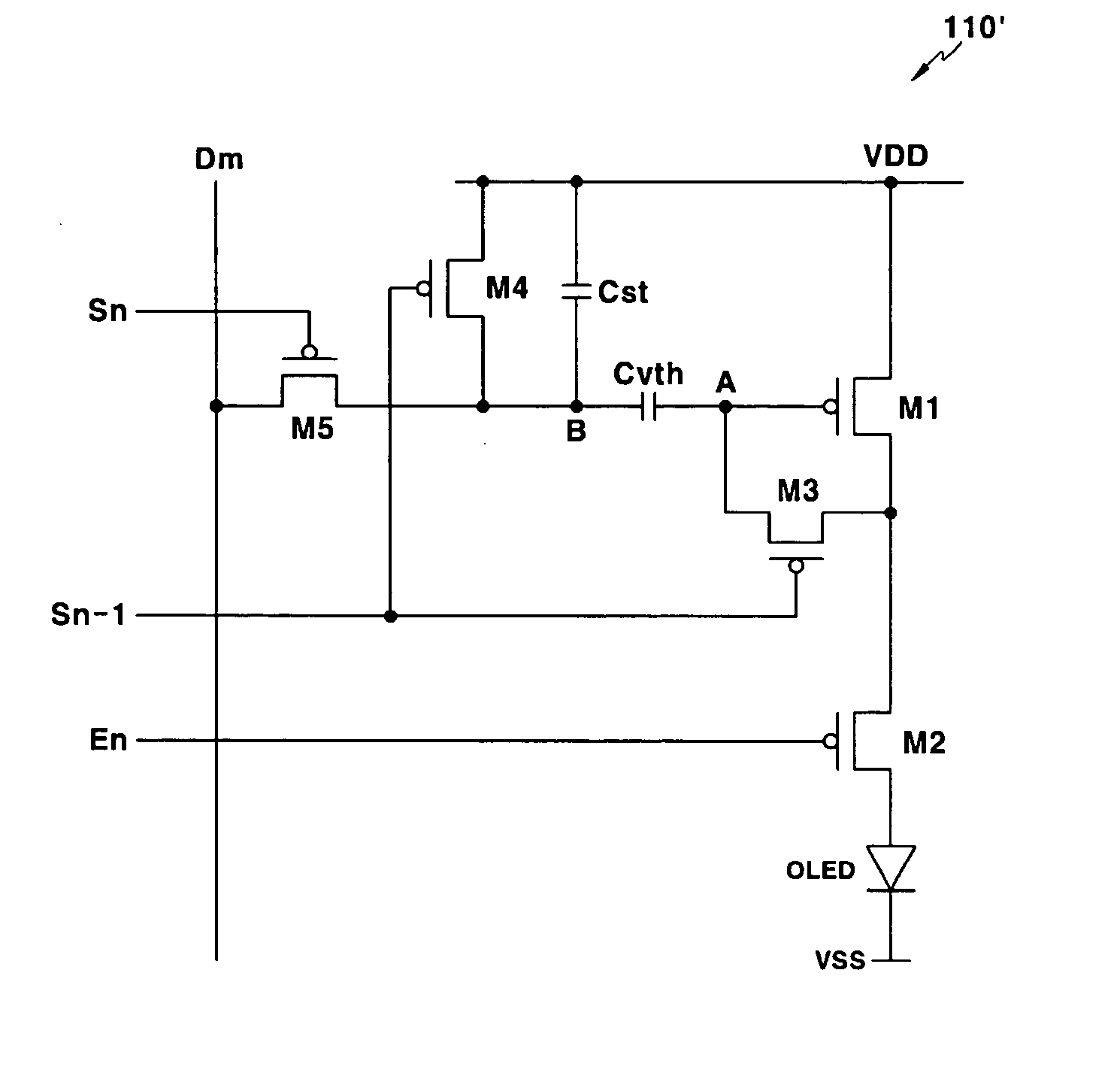

A pixel circuit having a function of compensating for characteristic variation of an electro-optical element and threshold voltage variation of a transistor is formed from a reduced number of component elements. The pixel circuit includes an electro-optical element, a holding capacitor, and five N-channel thin film transistors including a sampling transistor, a drive transistor, a switching transistor, and first and second detection transistors. The sampling transistor samples and supplies an input signal from a signal line so as to be held into the holding capacitor. The driving transistor drives the electro-optical element with current in response to the held signal potential. The first and second detection transistors detect a threshold voltage of the drive transistor and supply the detected voltage into the holding capacitor in order to cancel an influence of the threshold voltage in advance.

Owner:SONY CORP

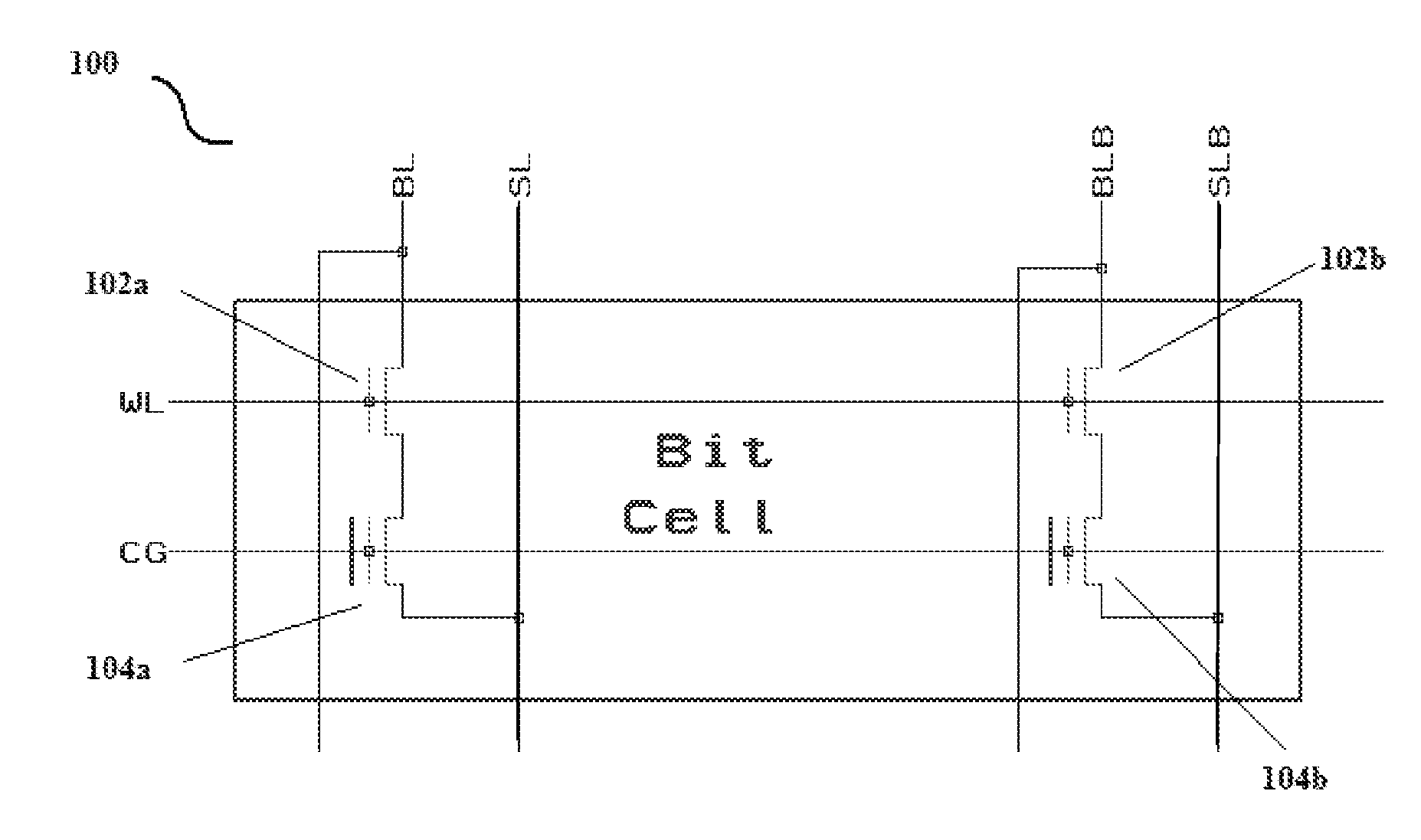

Dram-like nvm memory array and sense amplifier design for high temperature and high endurance operation

InactiveUS20110267883A1Improve threshold voltage sensing marginLarge silicon areaRead-only memoriesDigital storageBit lineAudio power amplifier

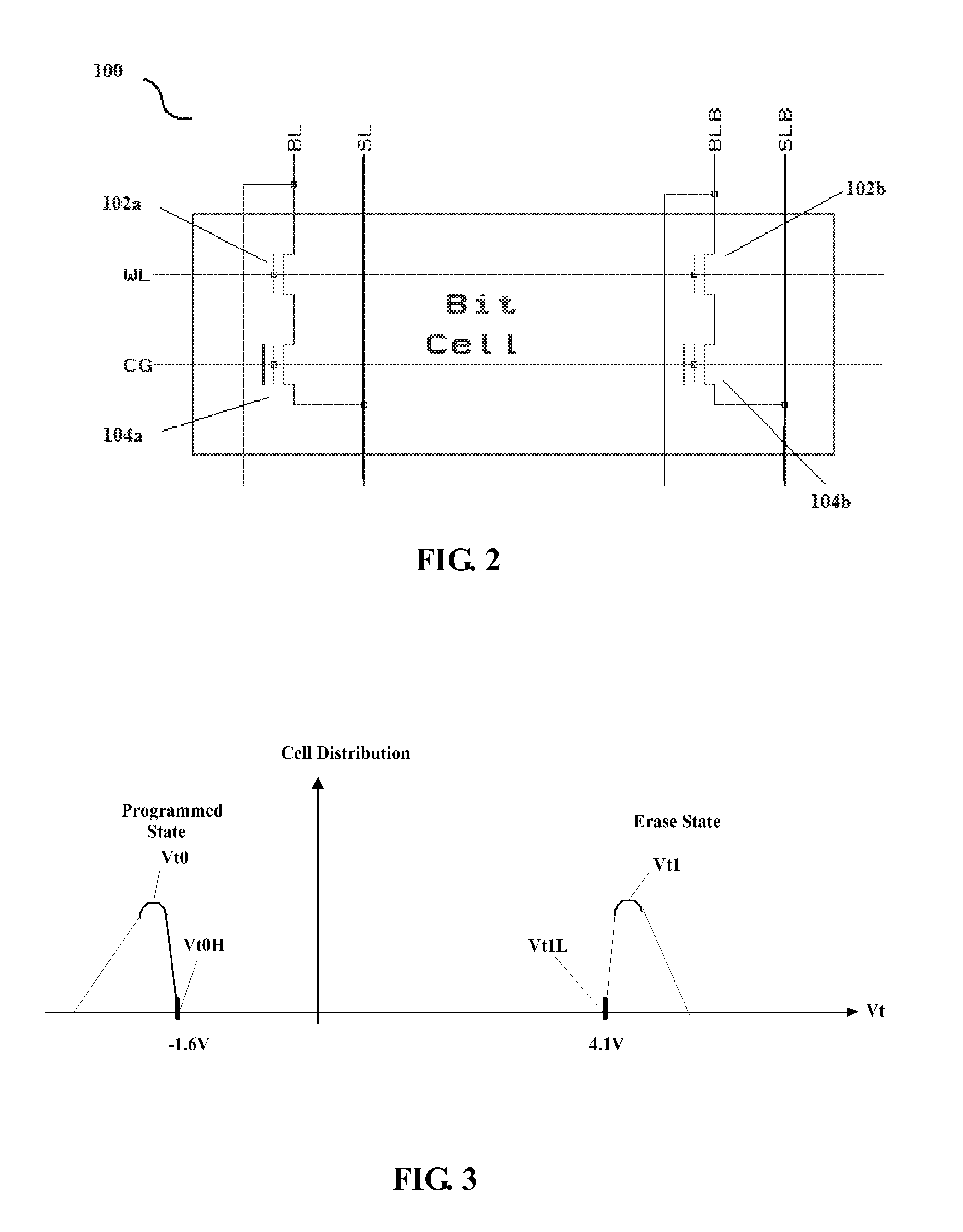

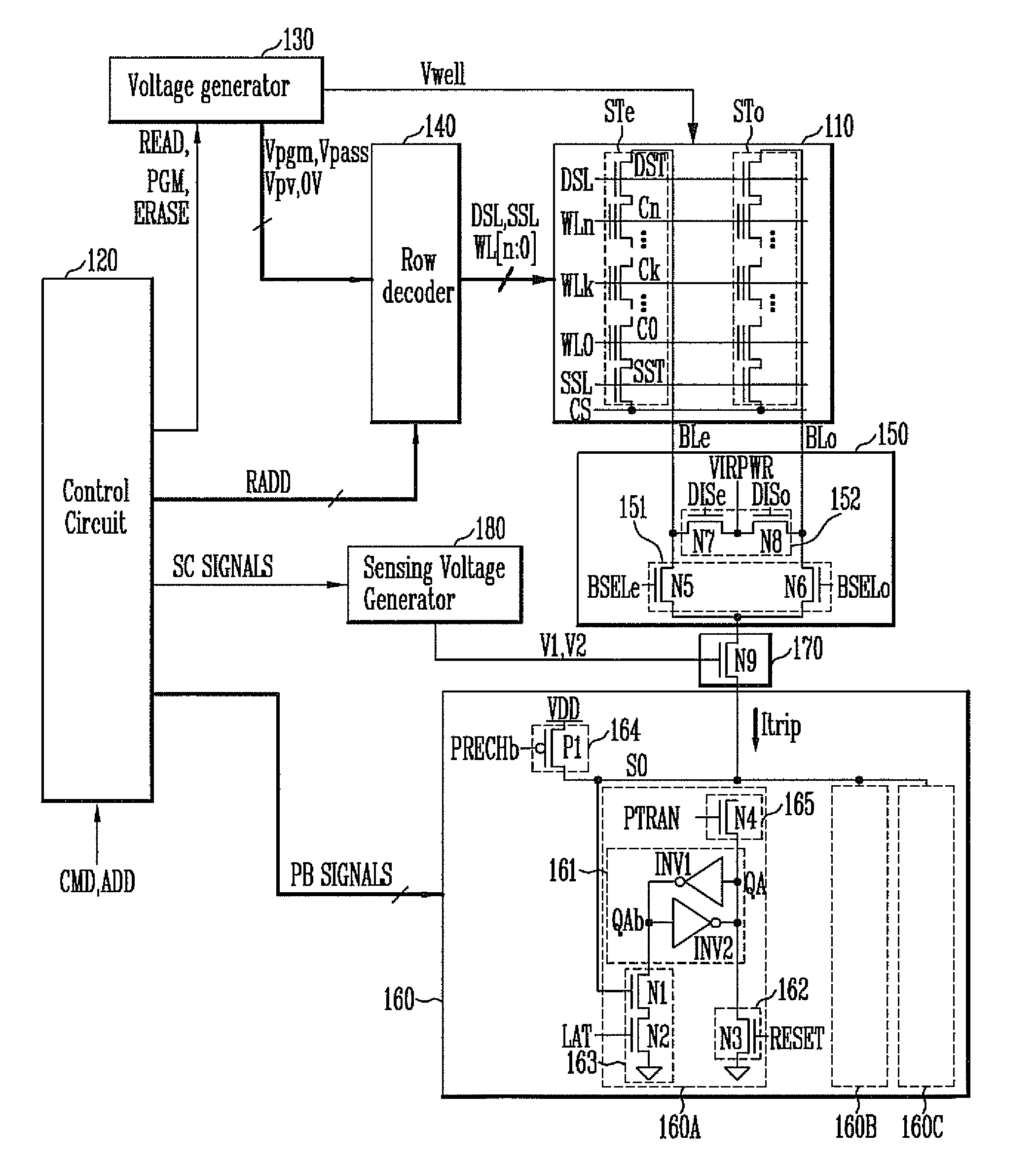

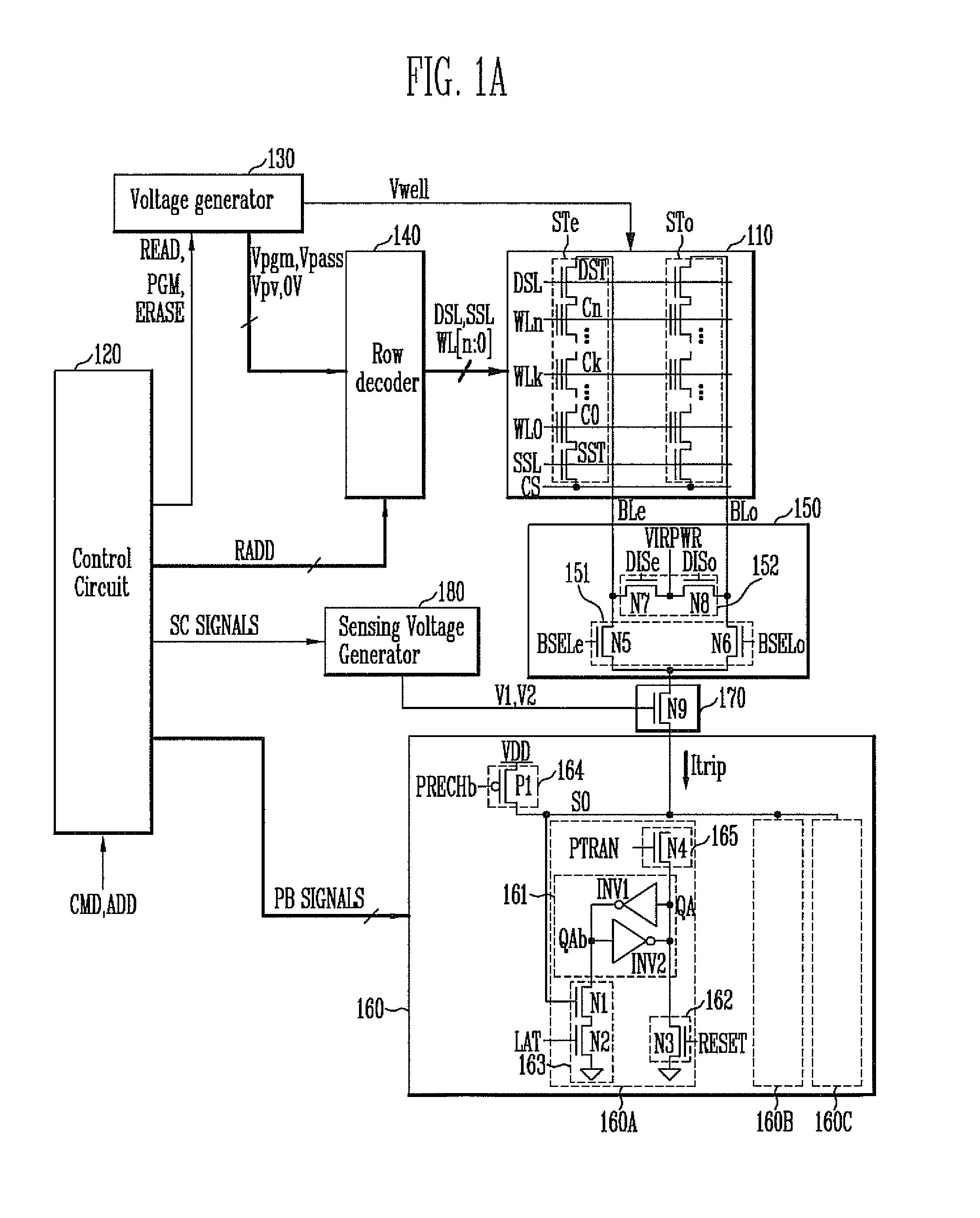

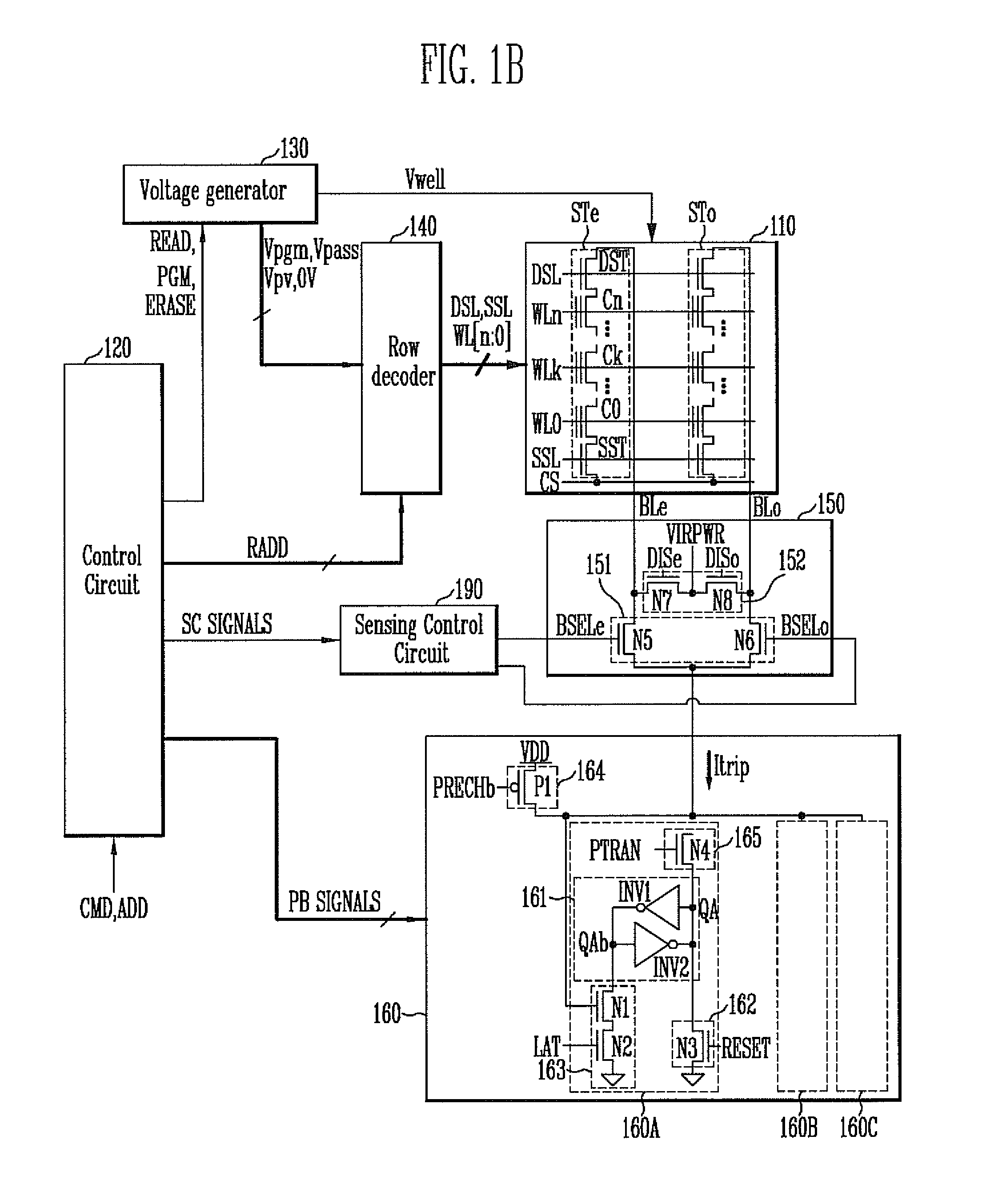

A DRAM-like non-volatile memory array includes a cell array of non-volatile cell units with a DRAM-like cross-coupled latch-type sense amplifier. Each non-volatile cell unit has two non-volatile cell devices with respective bit lines and source lines running in parallel and laid out perpendicular to the word line associated with the non-volatile cell unit. The two non-volatile cell devices are programmed with erased and programmed threshold voltages as a pair for storing a single bit of binary data. The two bit lines of each non-volatile cell unit are coupled through a Y-decoder and a latch device to the two respective inputs of the latch-type sense amplifier which provides a large sensing margin for the cell array to operate properly even with a narrowed threshold voltage gap. Each non-volatile cell device may be a 2 T FLOTOX-based EEPROM cell, a 2 T flash cell, 11 T flash cell or a 1.5 T split-gate flash cell.

Owner:APLUS FLASH TECH

Semiconductor memory device and method of operating the same

ActiveUS8526239B2Minimizing deteriorationImprove reliabilityRead-only memoriesDigital storageComputer architectureControl circuit

A semiconductor memory device includes a memory string coupled to a bit line, a page buffer configured to sense a sensing current of the bit line in an erase verification operation or a program verification operation, and a sensing control circuit configured to differently set a level of the sensing current in the erase verification operation and the program verification operation in order to sense the threshold voltage level of a selected memory cell of the memory string.

Owner:SK HYNIX INC

Flash memory cell and methods for programming and erasing

ActiveUS20060291282A1Facilitate device scaling effortsMitigates and avoids interface damageRead-only memoriesSemiconductor/solid-state device manufacturingElectricityElectrical battery

Owner:MONTEREY RES LLC

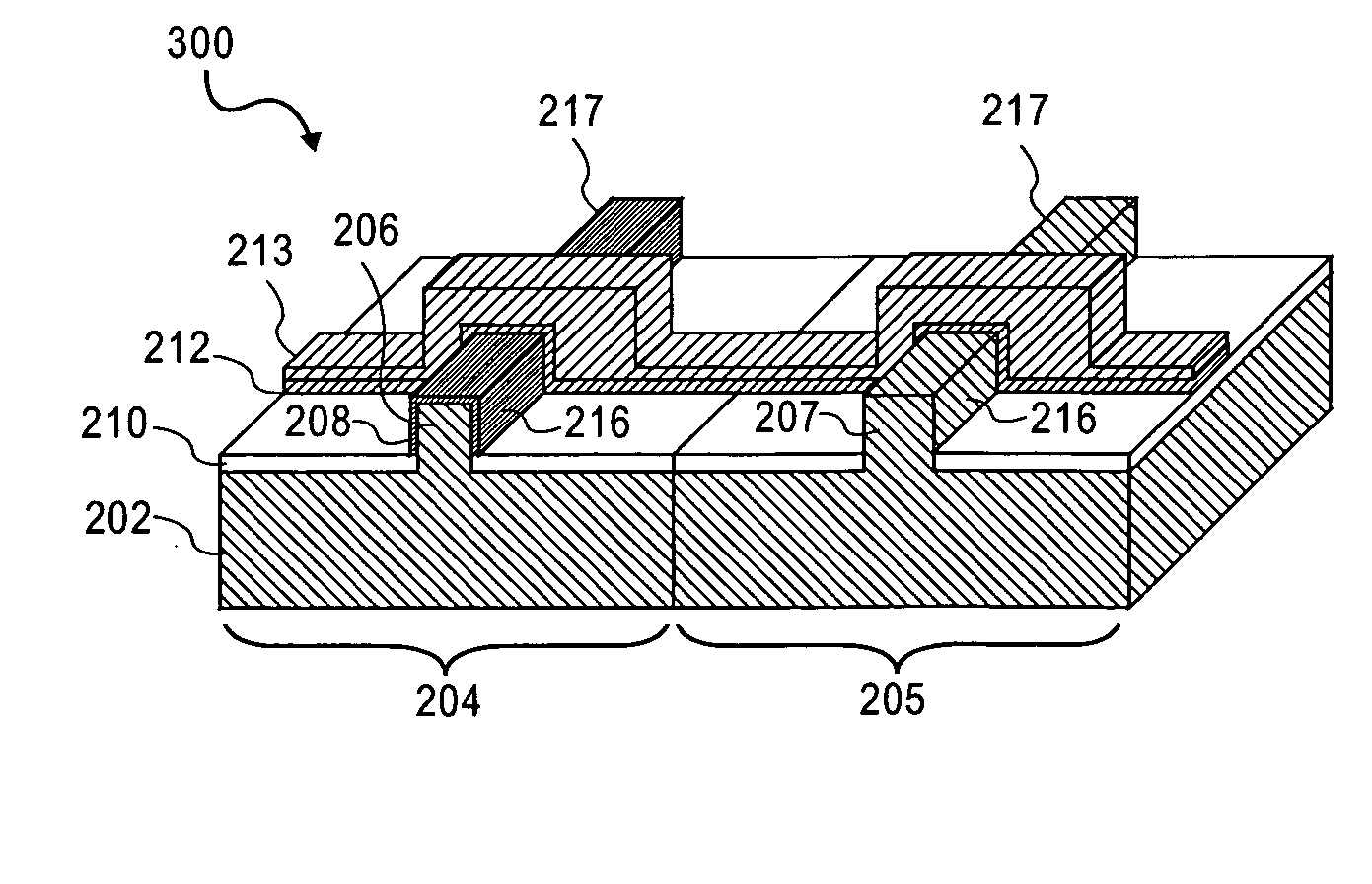

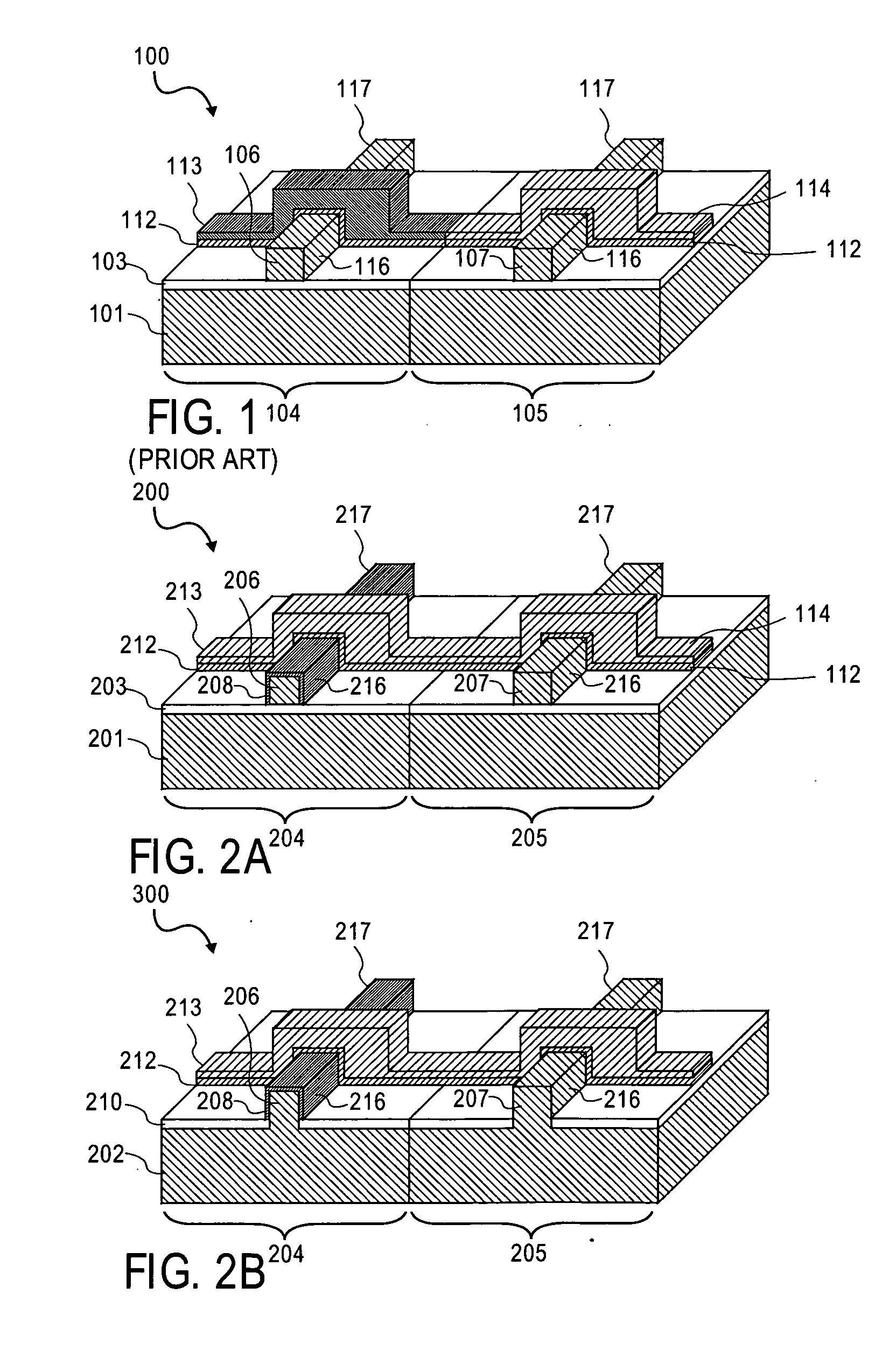

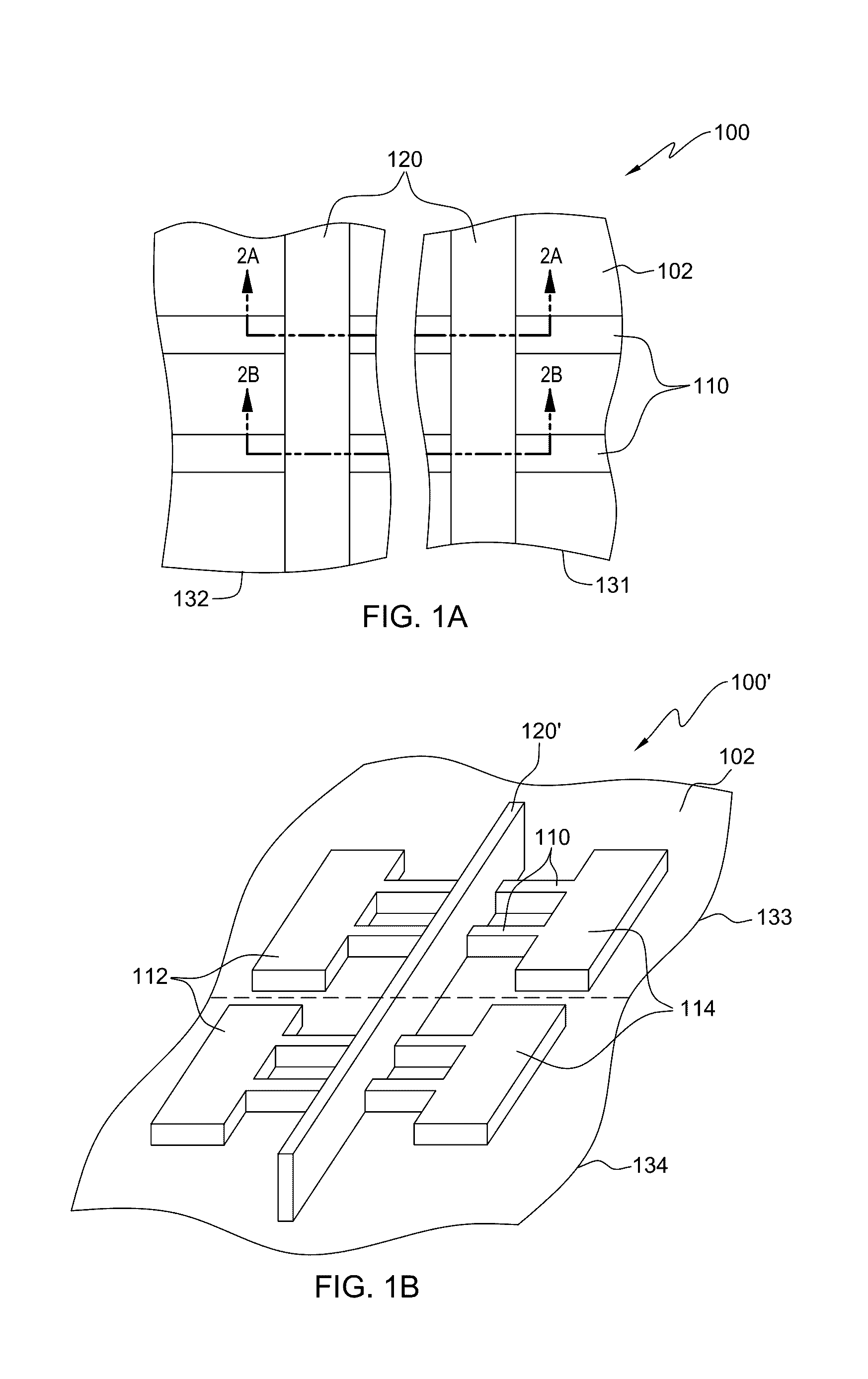

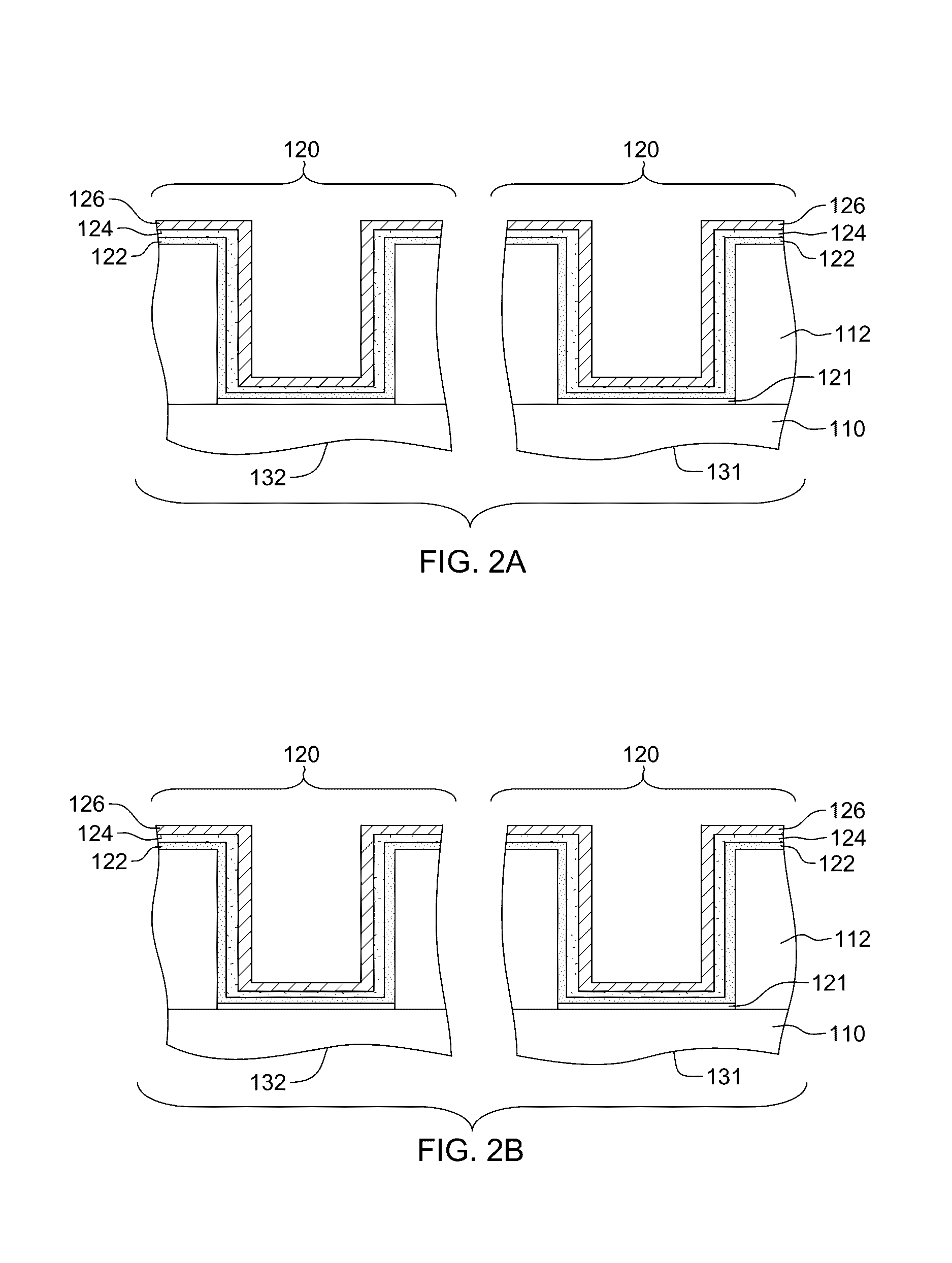

Integrated circuits with varying gate structures and fabrication methods

ActiveUS20150243658A1Overcomes shortcomingEnhanced advantageTransistorSolid-state devicesGate stackField-effect transistor

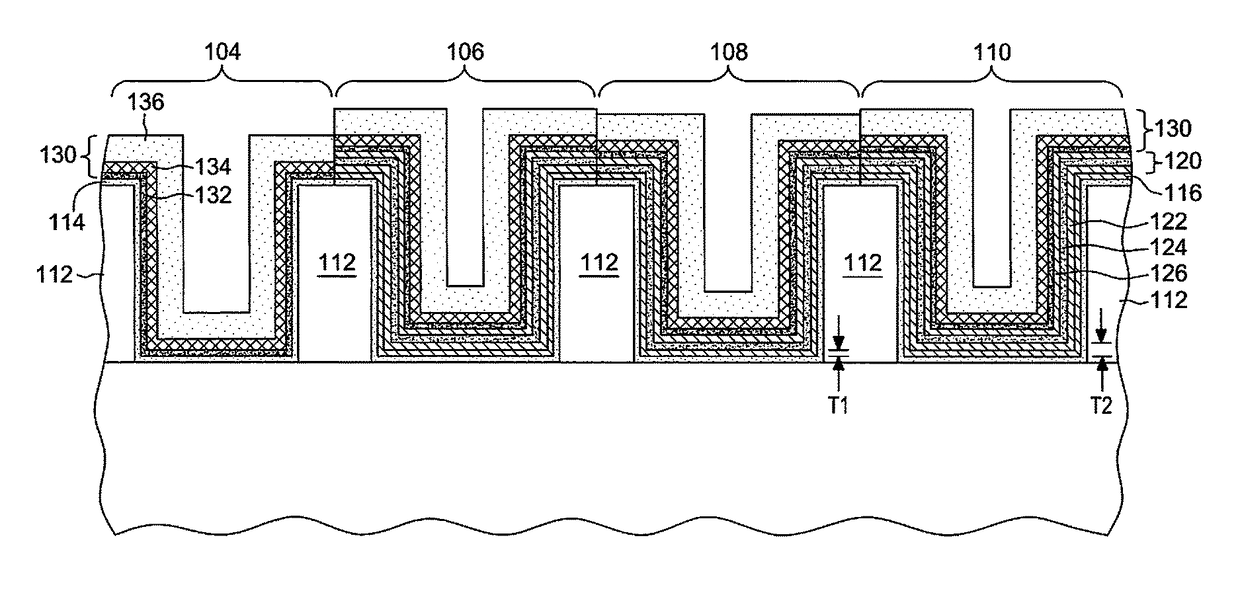

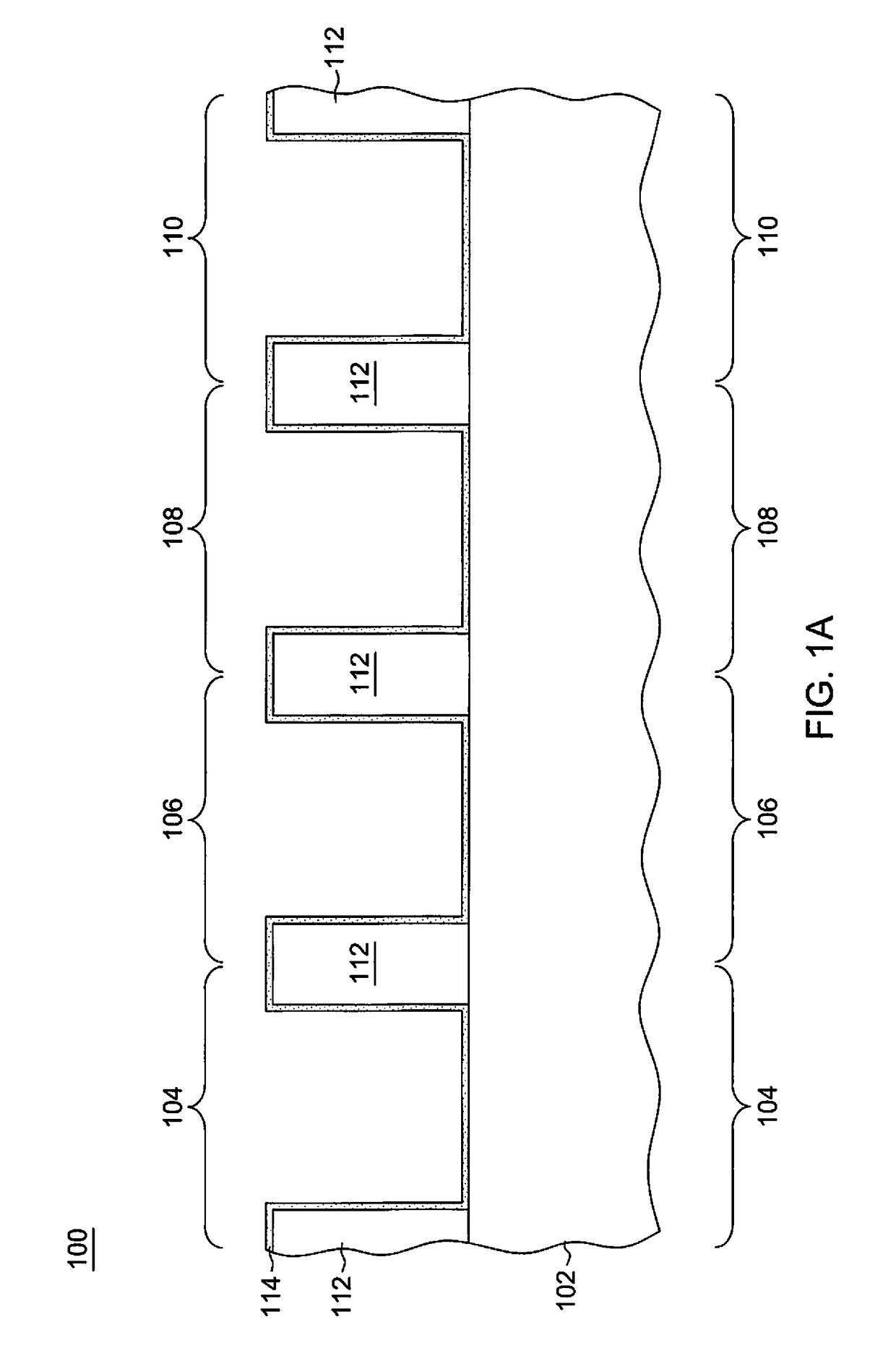

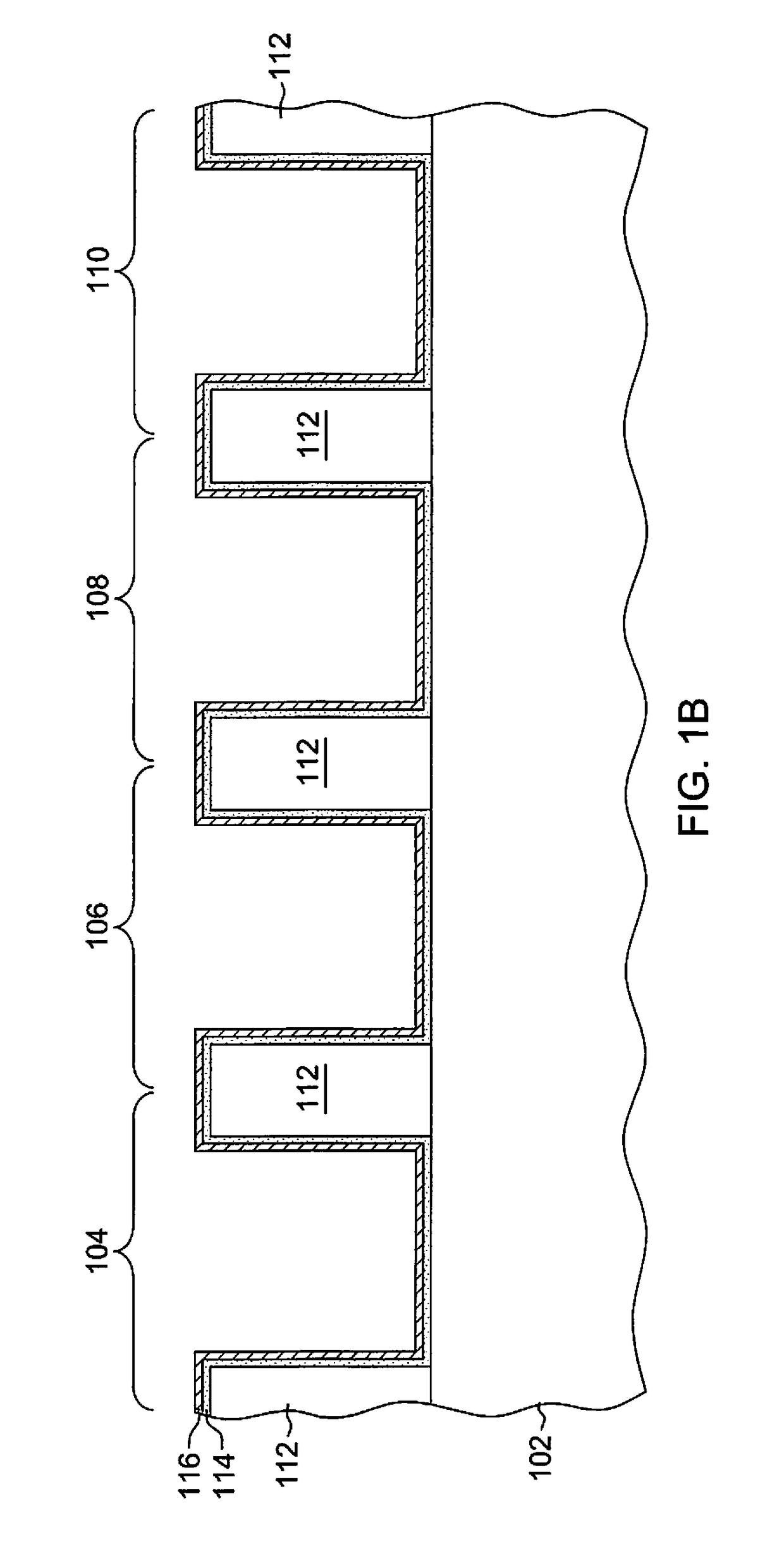

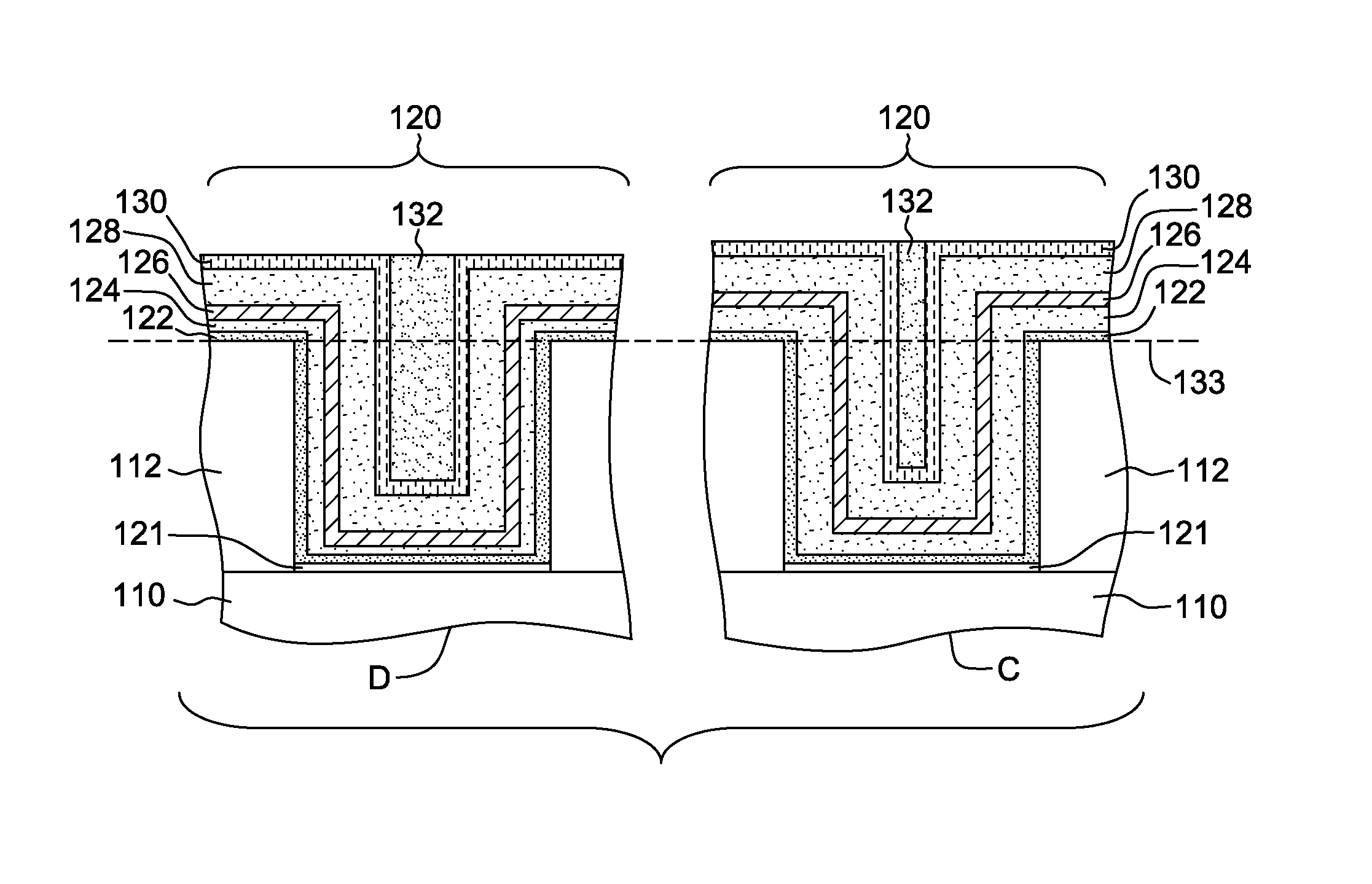

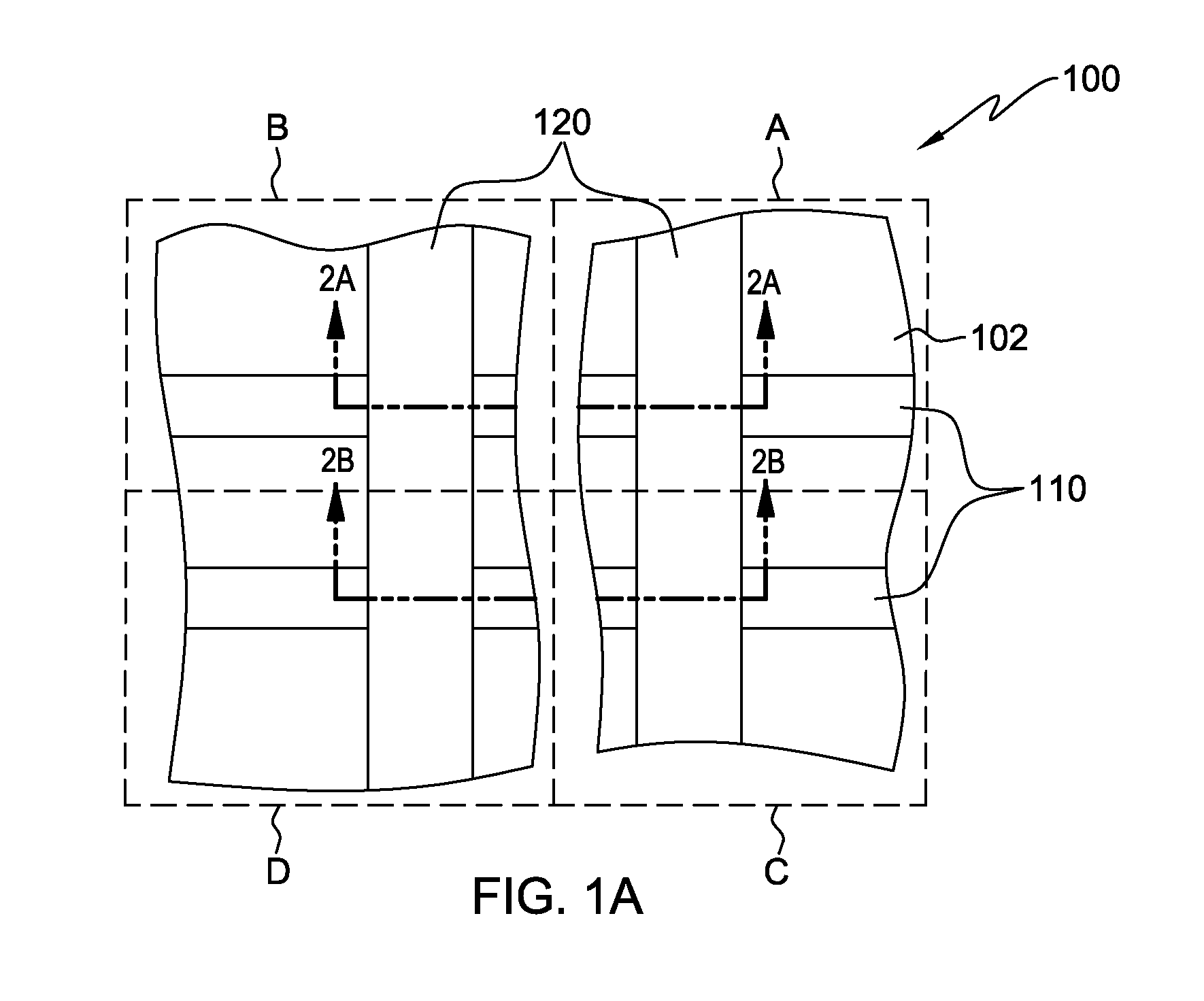

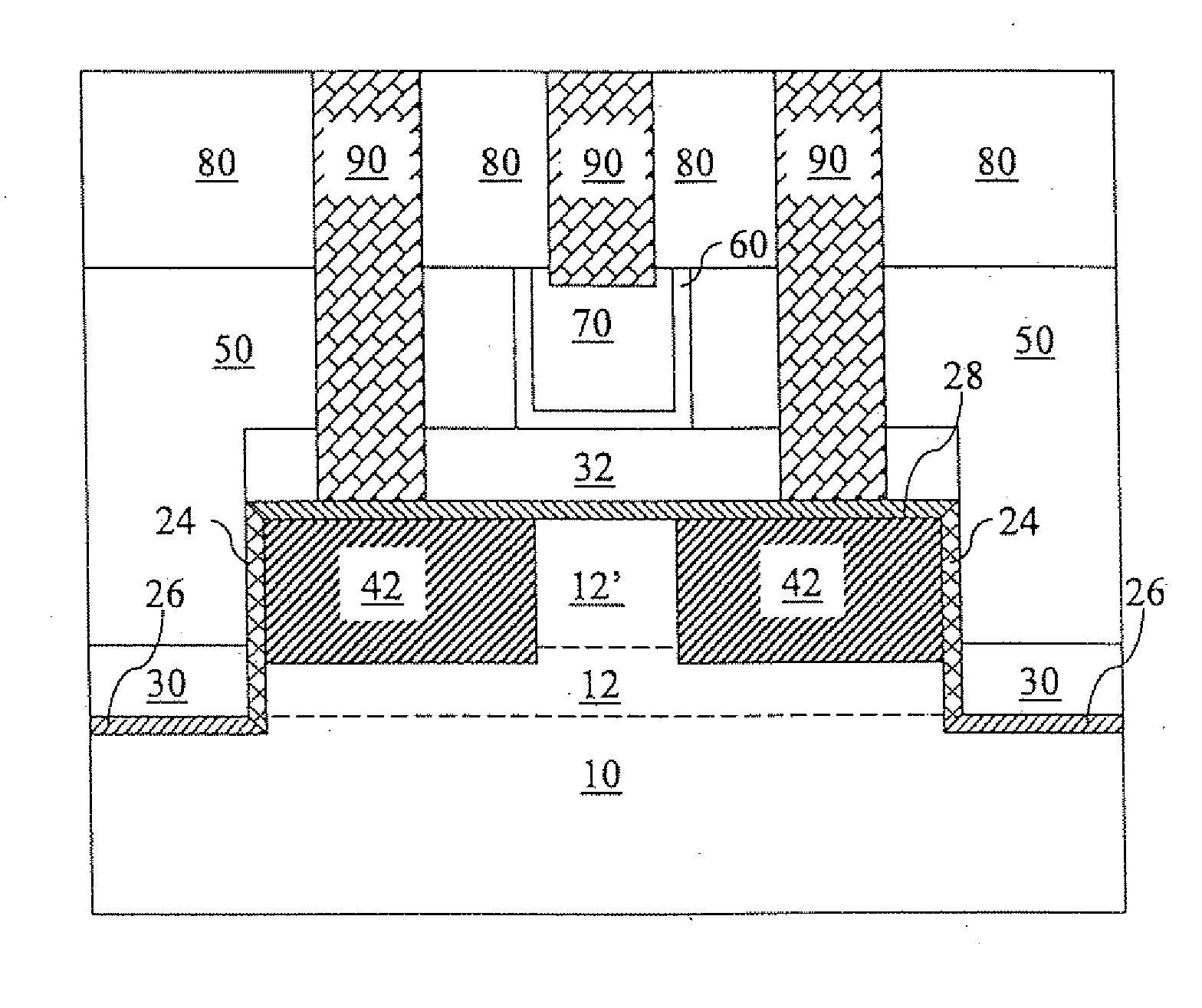

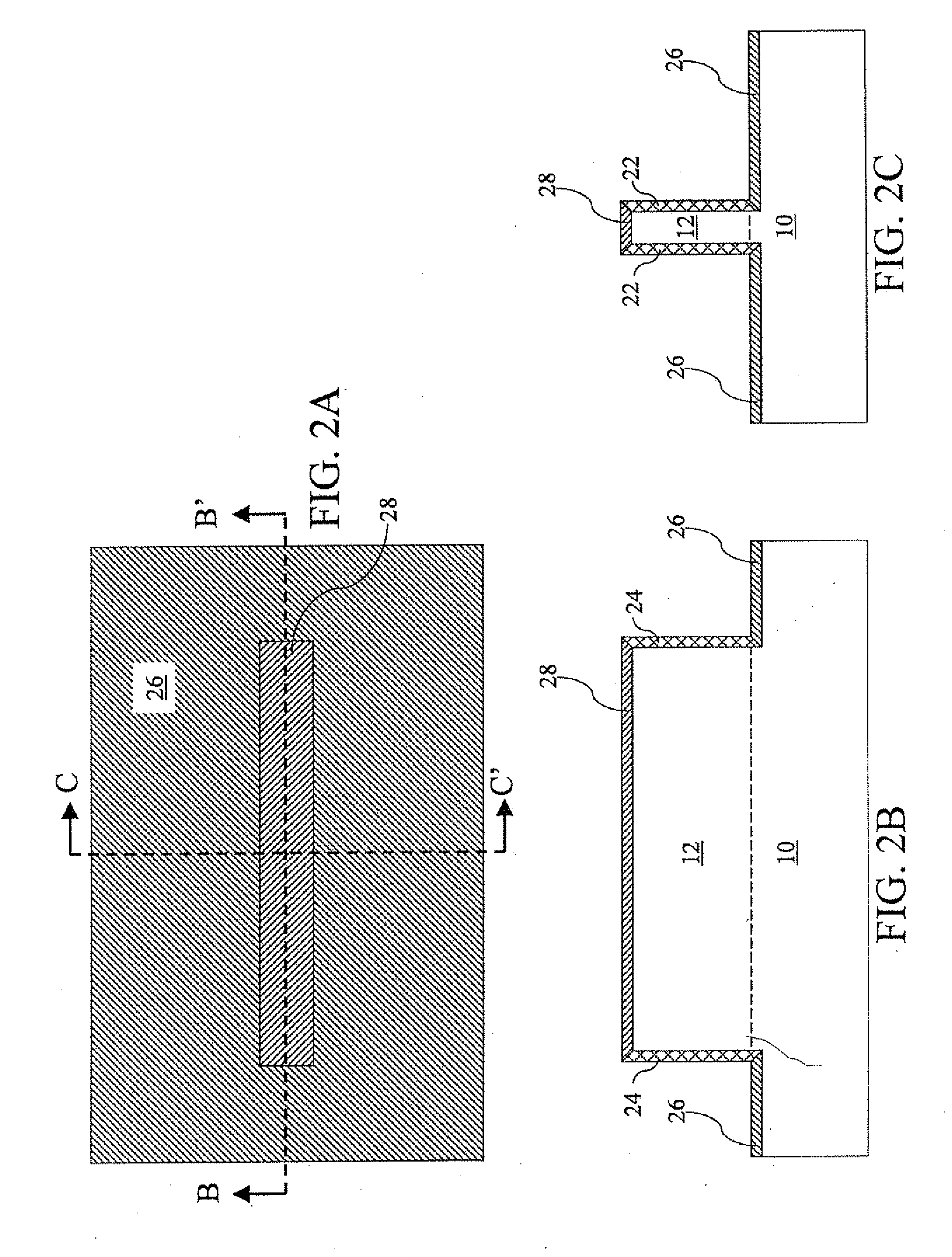

Integrated circuits and fabrication methods are provided. The integrated circuit includes: a varying gate structure disposed over a substrate structure, the varying gate structure including a first gate stack in a first region of the substrate structure, and a second gate stack in a second region of the substrate structure; a first field-effect transistor in the first region, the first field-effect transistor including the first gate stack and having a first threshold voltage; and a second field-effect transistor in the second region, the second field-effect transistor including the second gate stack and having a second threshold voltage, where the first threshold voltage is different from the second threshold voltage. The methods include providing the varying gate structure, the providing including: sizing layer(s) of the varying gate structure with different thickness(es) in different region(s).

Owner:GLOBALFOUNDRIES US INC

CMOS devices with a single work function gate electrode and method of fabrication

InactiveUS20070090416A1Lower threshold voltageEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingCMOSDevice form

Described herein are a device utilizing a gate electrode material with a single work function for both the pMOS and nMOS transistors where the magnitude of the transistor threshold voltages is modified by semiconductor band engineering and article made thereby. Further described herein are methods of fabricating a device formed of complementary (pMOS and nMOS) transistors having semiconductor channel regions which have been band gap engineered to achieve a low threshold voltage.

Owner:TAHOE RES LTD

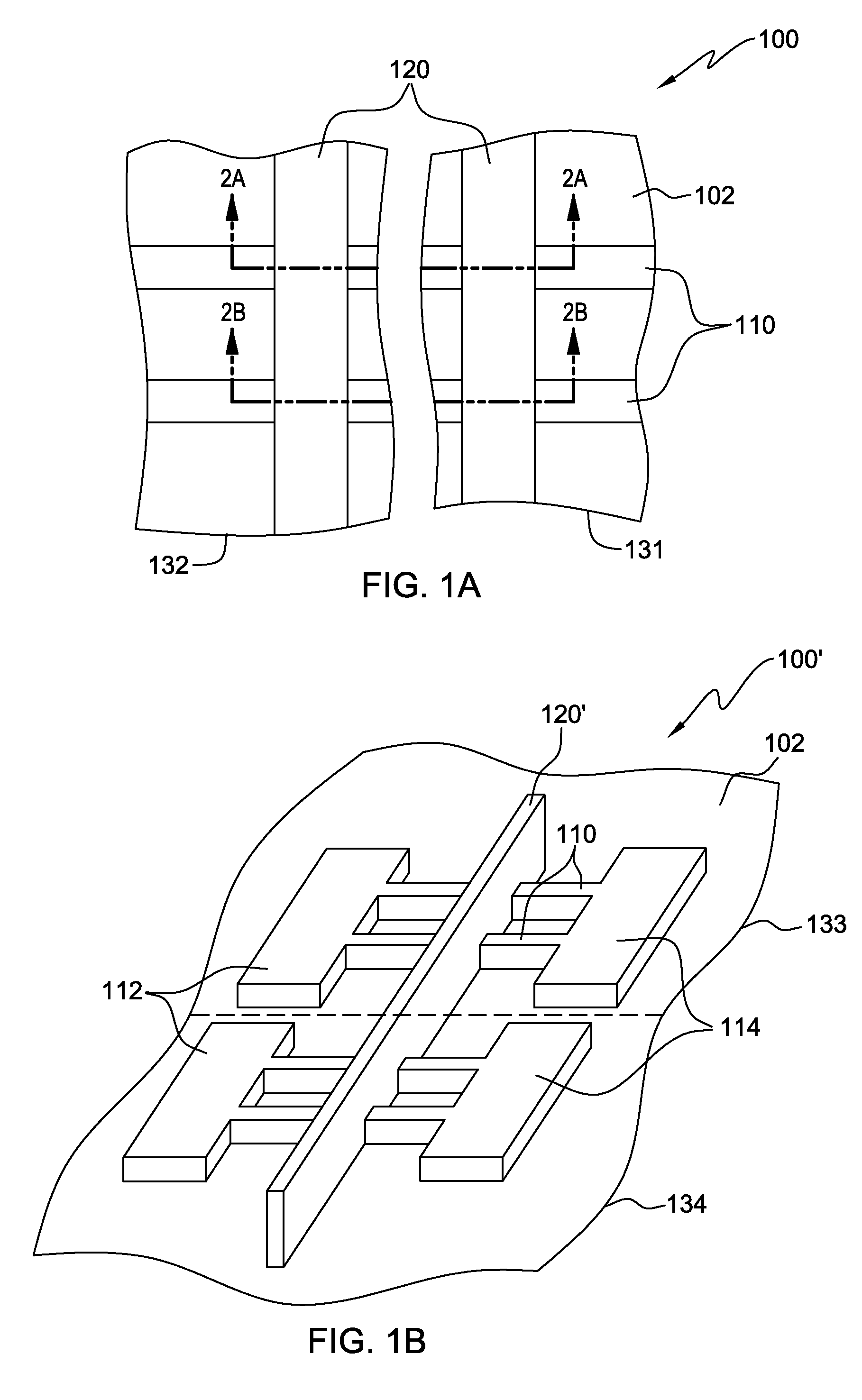

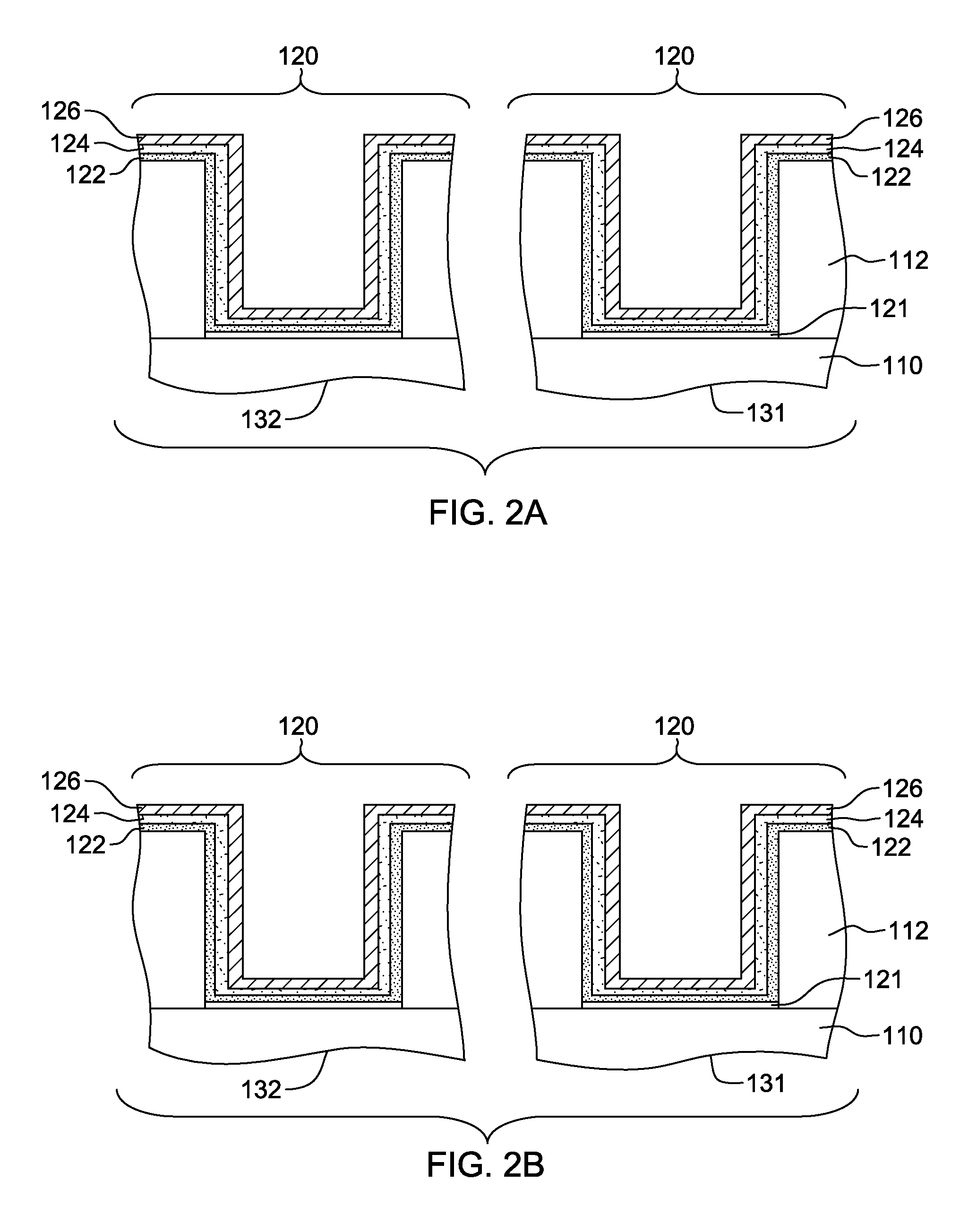

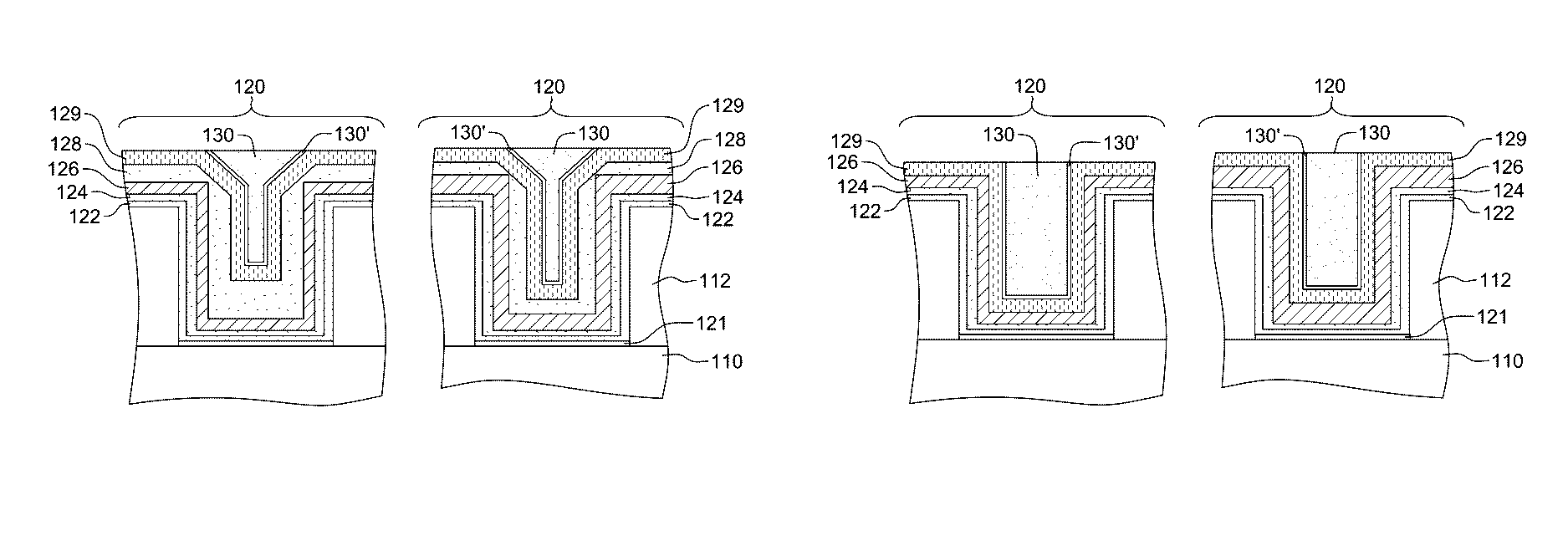

Semiconductor devices with varying threshold voltage and fabrication methods thereof

ActiveUS9748145B1Overcomes shortcomingEnhanced advantageTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceDielectric layer

Semiconductor device fabrication methods are provided which include: providing a structure with at least one region and including a dielectric layer disposed over a substrate; forming a multilayer stack structure including a threshold-voltage adjusting layer over the dielectric layer, the multilayer stack structure including a first threshold-voltage adjusting layer in a first region of the at least one region, and a second threshold-voltage adjusting layer in a second region of the at least one region; and annealing the structure to define a varying threshold voltage of the at least one region, the annealing facilitating diffusion of at least one threshold voltage adjusting species from the first threshold-voltage adjusting layer and the second threshold-voltage adjusting layer into the dielectric layer, where a threshold voltage of the first region is independent of the threshold voltage of the second region.

Owner:GLOBALFOUNDRIES US INC

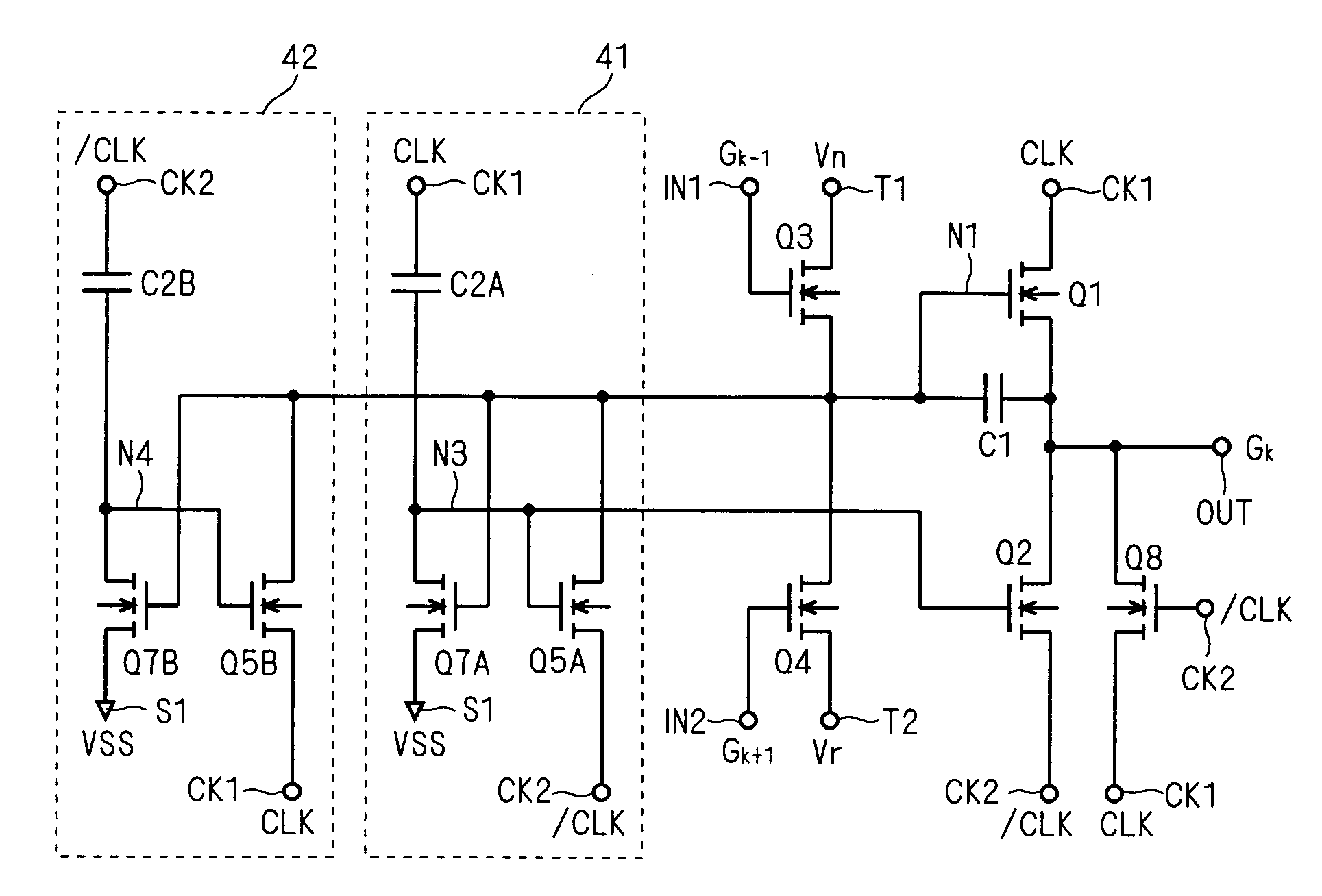

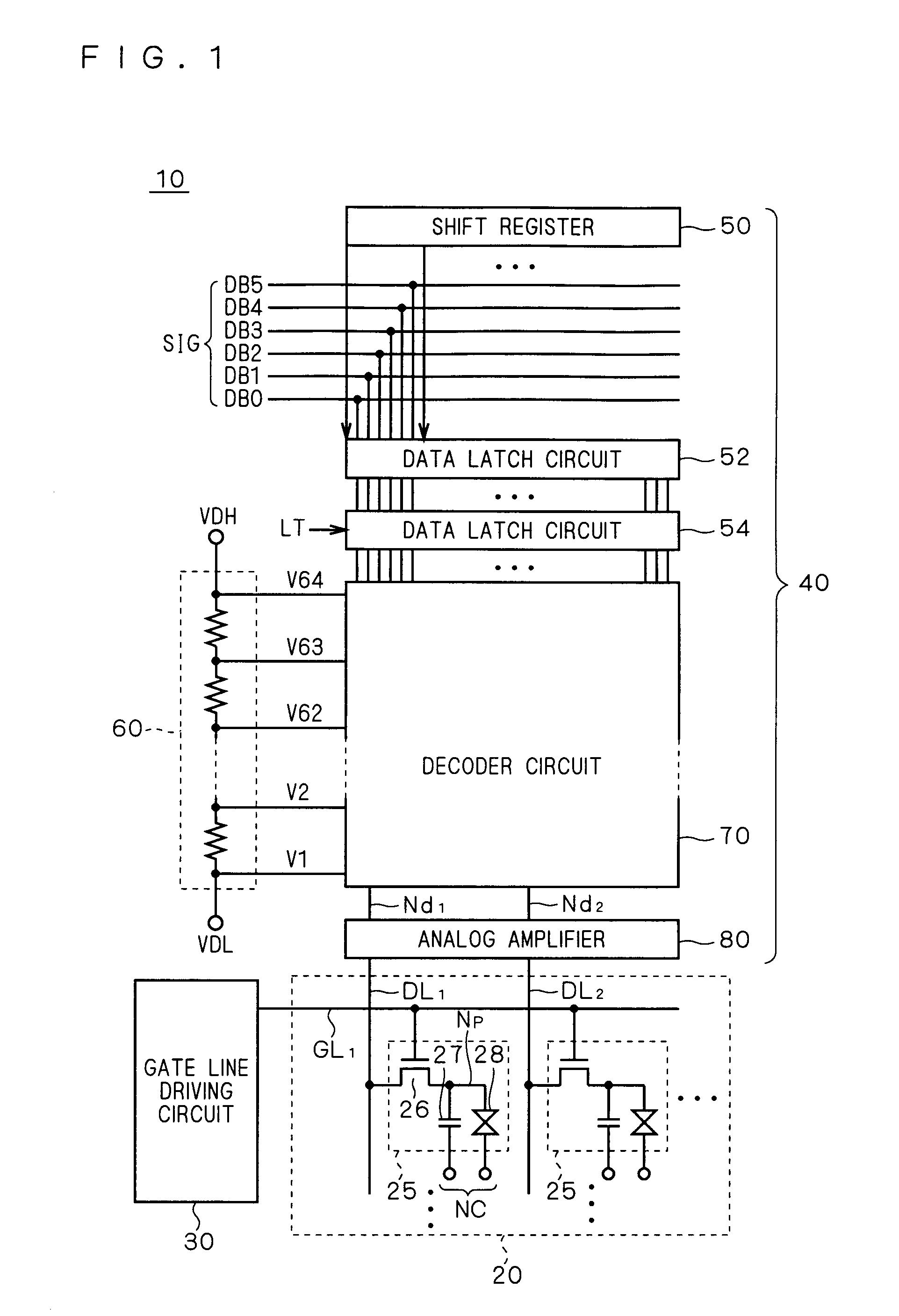

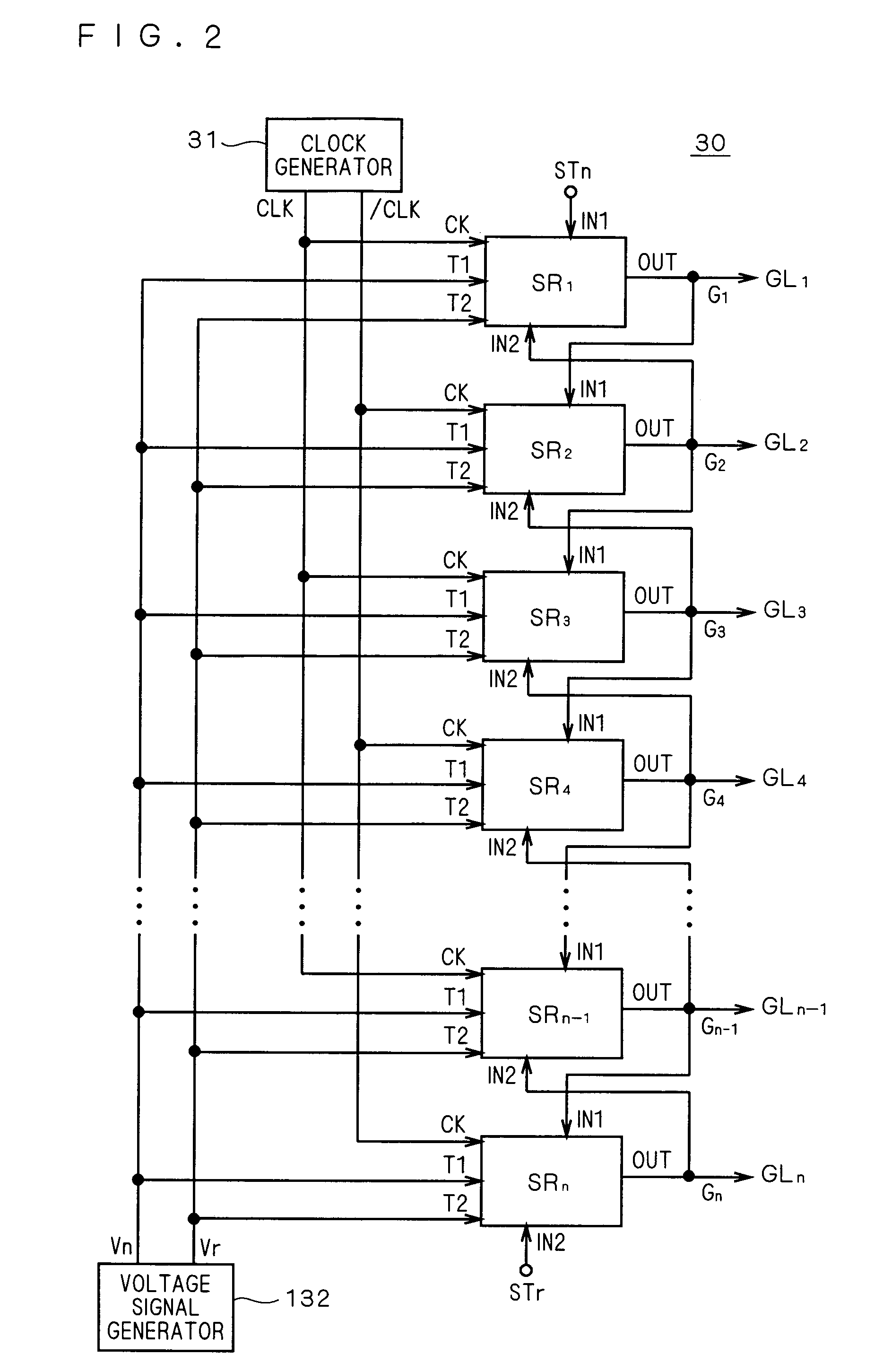

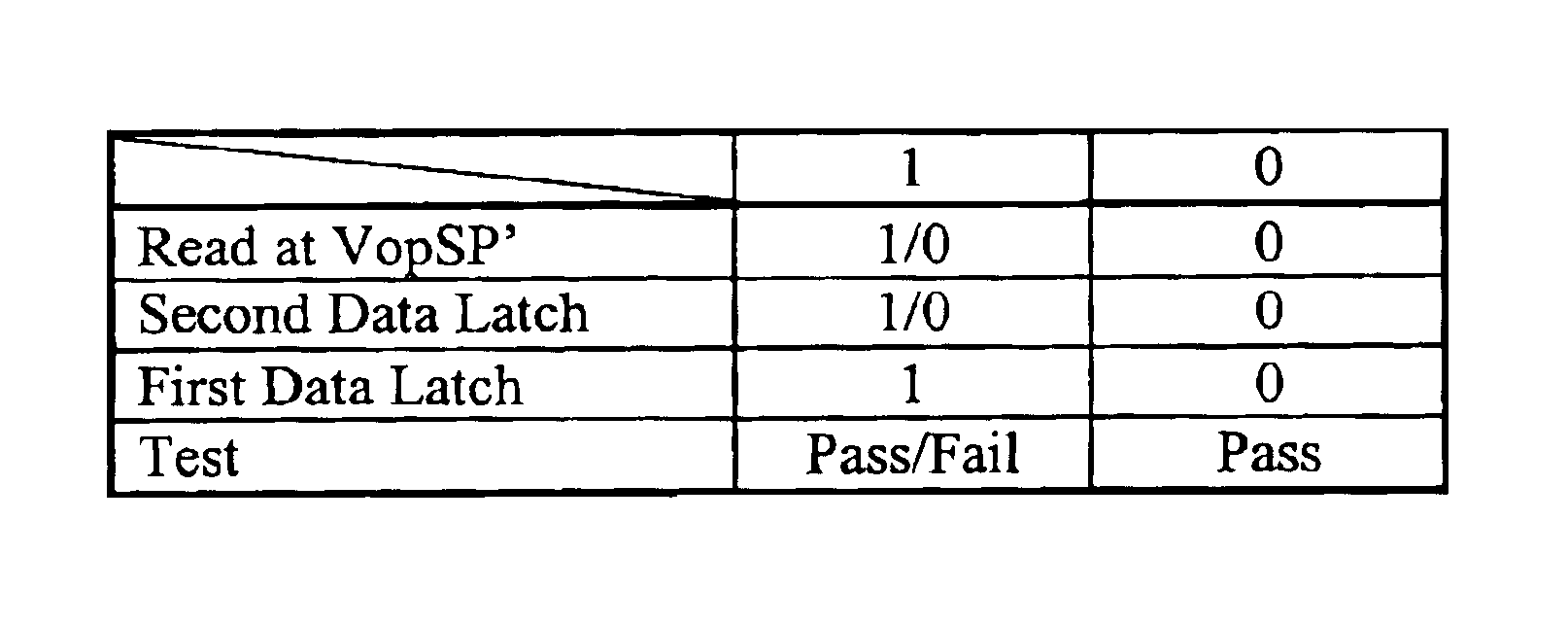

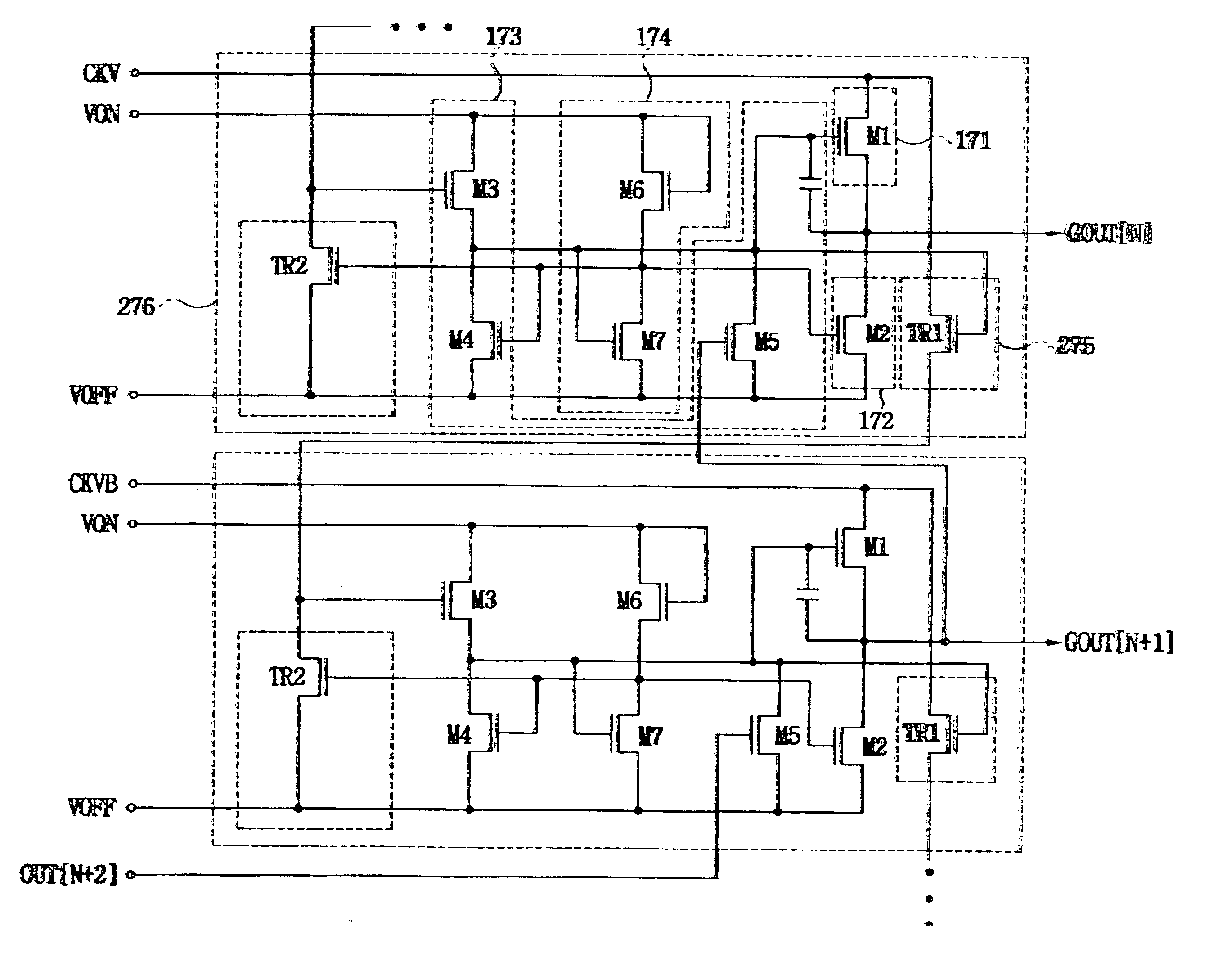

Shift register circuit and image display apparatus containing the same

InactiveUS20080219401A1Avoid failureReduced driving abilityStatic indicating devicesDigital storageShift registerProcessor register

Threshold voltage shifts of transistors which are constituents of a bidirectional shift register are reduced to prevent a malfunction in the shift register. A bidirectional unit shift register includes first and second pull-down circuits (41, 42) connected to the gate of a first transistor (Q1) that supplies a first clock signal (CLK) to an output terminal (OUT). The first pull-down circuit (41) includes a first inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by the first clock signal (CLK), and a second transistor (Q5A) that discharges the gate of the first transistor (Q1) according to the output of the first inverter. The second pull-down circuit (42) includes a second inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by a second clock signal ( / CLK) having a different phase from the first clock signal (CLK), and a third transistor (Q5A) that discharges the gate of the first transistor according to the output of the second inverter.

Owner:TRIVALE TECH LLC

Detecting over programmed memory

ActiveUS6917542B2Lower requirementRead-only memoriesDigital storageComputer architectureThreshold voltage

Owner:SANDISK TECH LLC

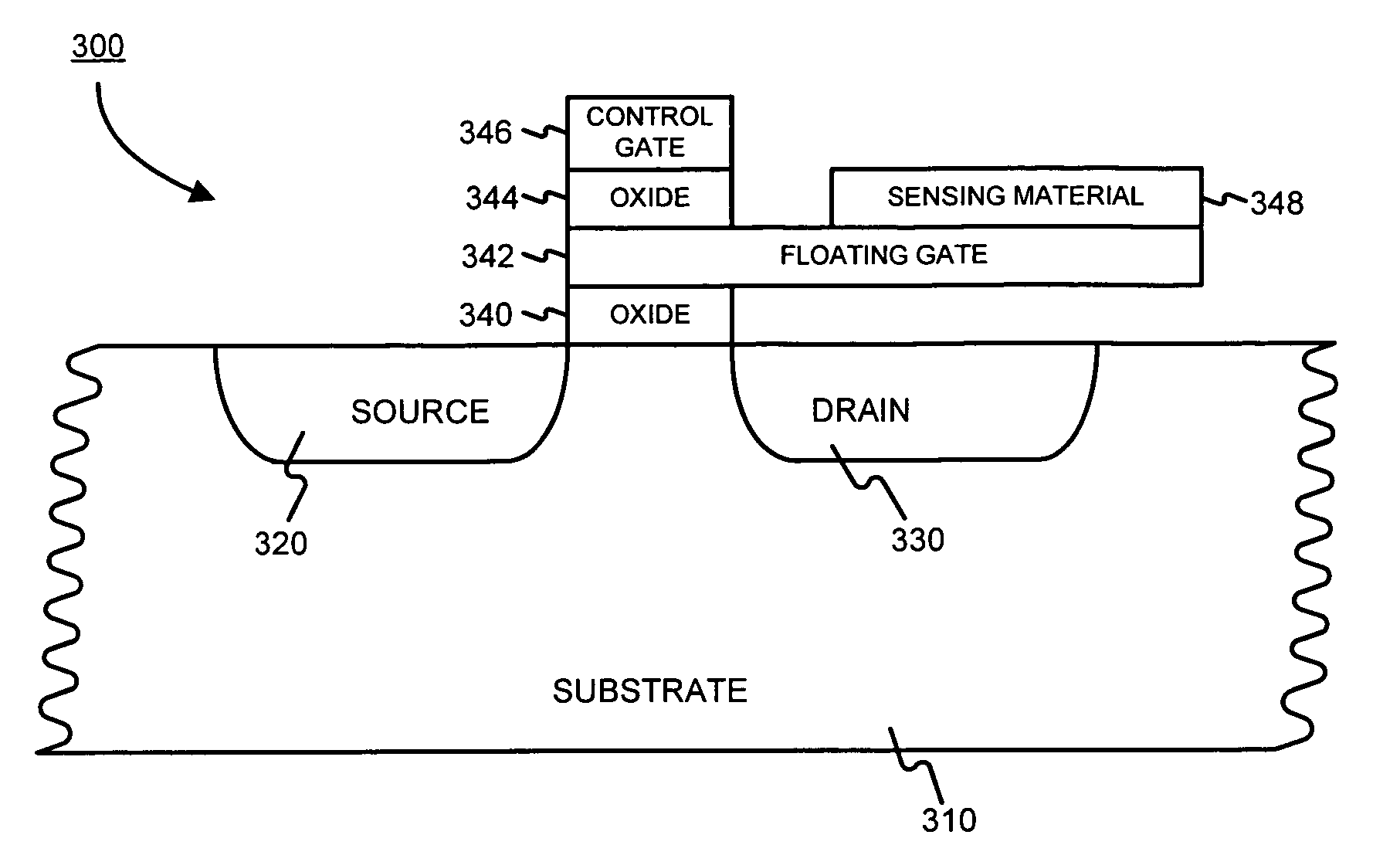

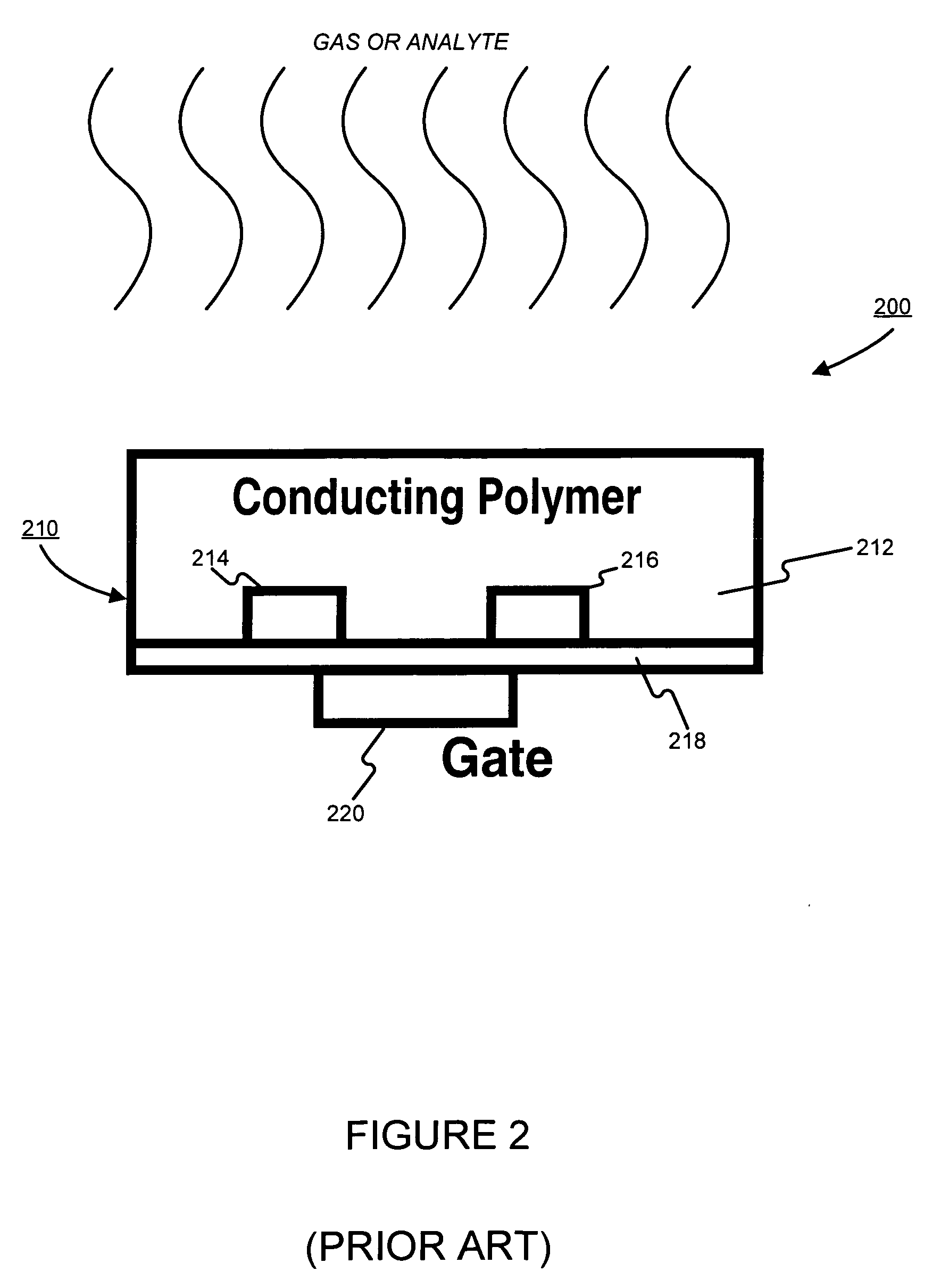

Floating gate field effect transistors for chemical and/or biological sensing

ActiveUS20050230271A1Weather/light/corrosion resistanceVolume/mass flow measurementChemical physicsEngineering

Specific ionic interactions with a sensing material that is electrically coupled with the floating gate of a floating gate-based ion sensitive field effect transistor (FGISFET) may be used to sense a target material. For example, an FGISFET can use (e.g., previously demonstrated) ionic interaction-based sensing techniques with the floating gate of floating gate field effect transistors. The floating gate can serves as a probe and an interface to convert chemical and / or biological signals to electrical signals, which can be measured by monitoring the change in the device's threshold voltage, VT.

Owner:POLYTECHNIC INSTITUTE OF NEW YORK UNIVERSITY

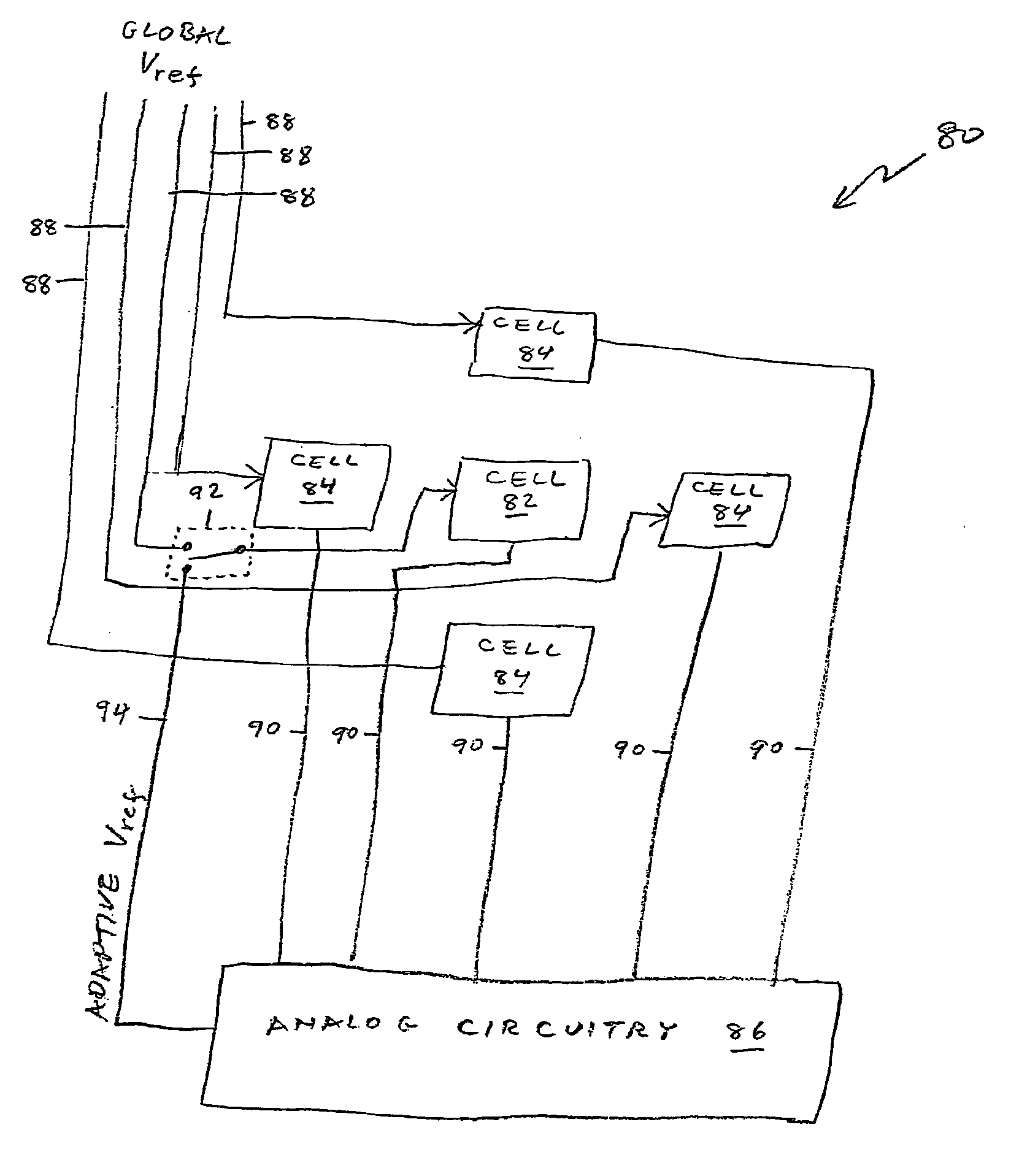

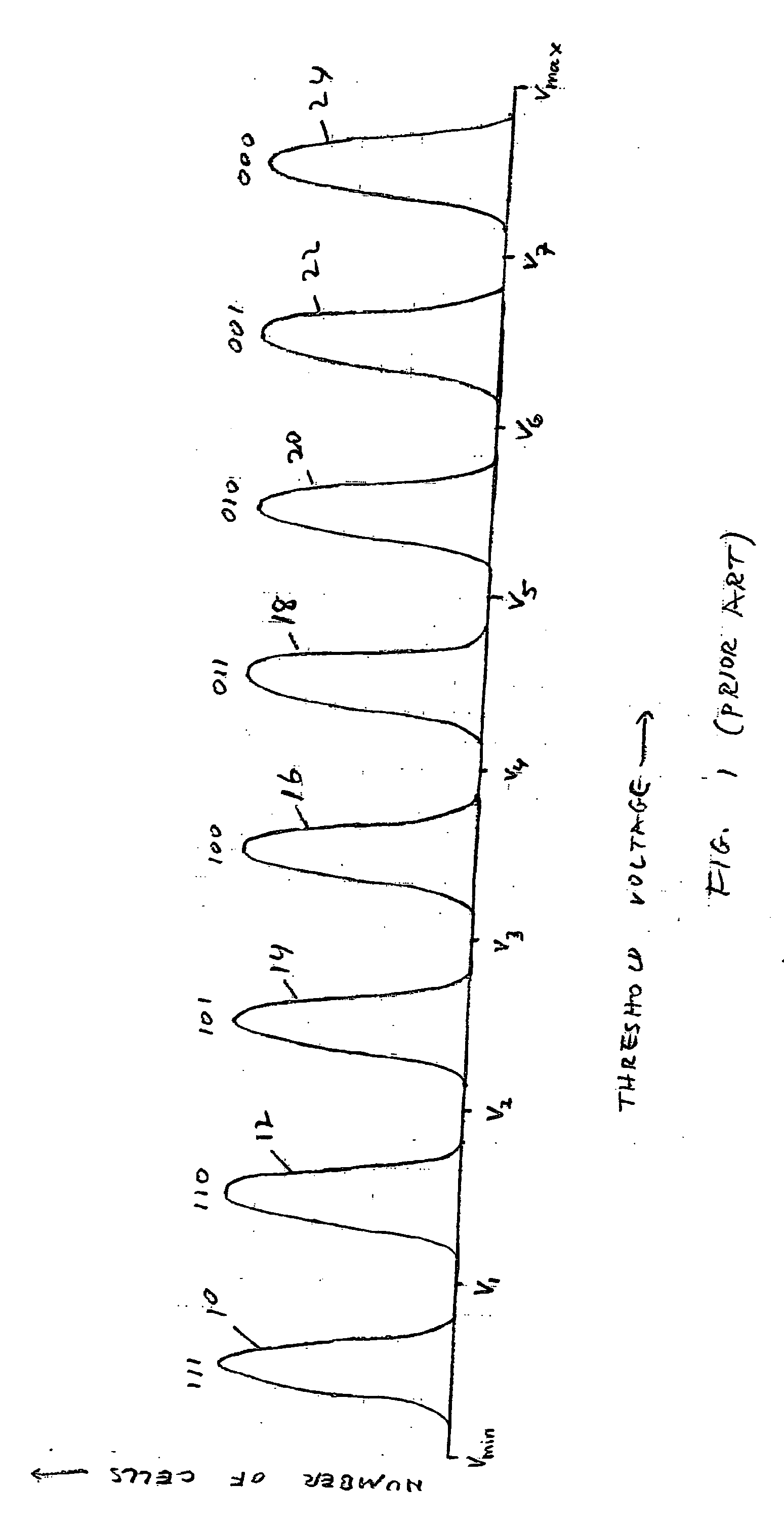

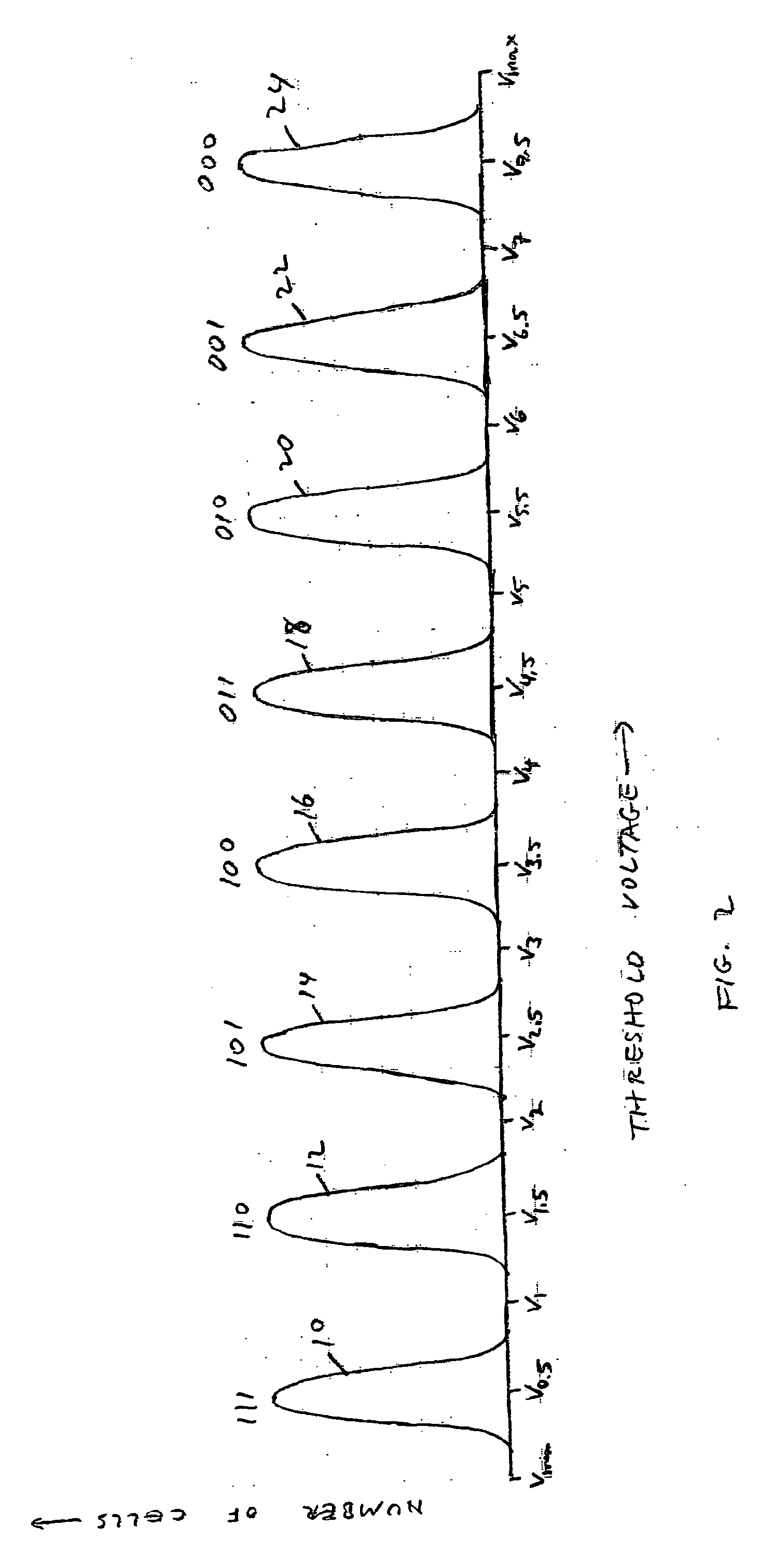

Flash memories with adaptive reference voltages

Cells of a flash memory are read by determining respective adaptive reference voltages for the cells and comparing the cells' threshold voltages to their respective reference voltages. The adaptive reference voltages are determined either from analog measurements of the threshold voltages of the cells' neighbors or from preliminary estimates of the cells' threshold voltages based on comparisons of the cells' threshold voltages with integral or fractional reference voltages common to all the cells. Cells of a flash memory also are read by comparing the cells' threshold voltages to integral reference voltages, comparing the threshold voltages of cells that share a common bit pattern to a fractional reference voltage, and adjusting the reference voltages in accordance with the comparisons.

Owner:WESTERN DIGITAL ISRAEL LTD

Method of driving a shift register, a shift register, a liquid crystal display device having the shift register

InactiveUS6845140B2InhibitionQuality improvementStatic indicating devicesDigital storageShift registerLiquid-crystal display

In a shift register and LCD device having the shift register that may be employed in the liquid crystal display device having a large screen size and a large resolution, the shift register includes stages cascade-connected with each other and each of the stages have a carry buffer for generating a carry signal. The pull-down transistor of each of the stages of the shift register is divided into a first pull-down transistor and a second pull-down transistor. A power voltage Vona larger than the power voltage Von applied to a clock generator is applied to the shift register. A signal delay due to the RC delay of the gate lines may be minimized, the shift register is independent of the variation of the threshold voltage of the TFTs, and image display quality may not be deteriorated.

Owner:SAMSUNG DISPLAY CO LTD

METHOD OF MANUFACTURING ZnO-BASED THIN FILM TRANSISTOR

InactiveUS20080299702A1Reduce carrier concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesInterfacial reactionBottom gate

A ZnO-based thin film transistor (TFT) is provided herein. Also provided is a method for manufacturing the TFT. The ZnO-based TFT is very sensitive to the oxygen concentration present in a channel layer. In order to prevent damage to a channel layer of a bottom gate TFT, and to avoid a deep negative threshold voltage resulting from damage to the channel layer, the method for manufacturing the ZnO-based TFT comprises formation of an etch stop layer or a passivation layer comprising unstable or incompletely bonded oxygen, and annealing the layers to induce an interfacial reaction between the oxide layer and the channel layer and to reduce the carrier concentration.

Owner:SAMSUNG ELECTRONICS CO LTD

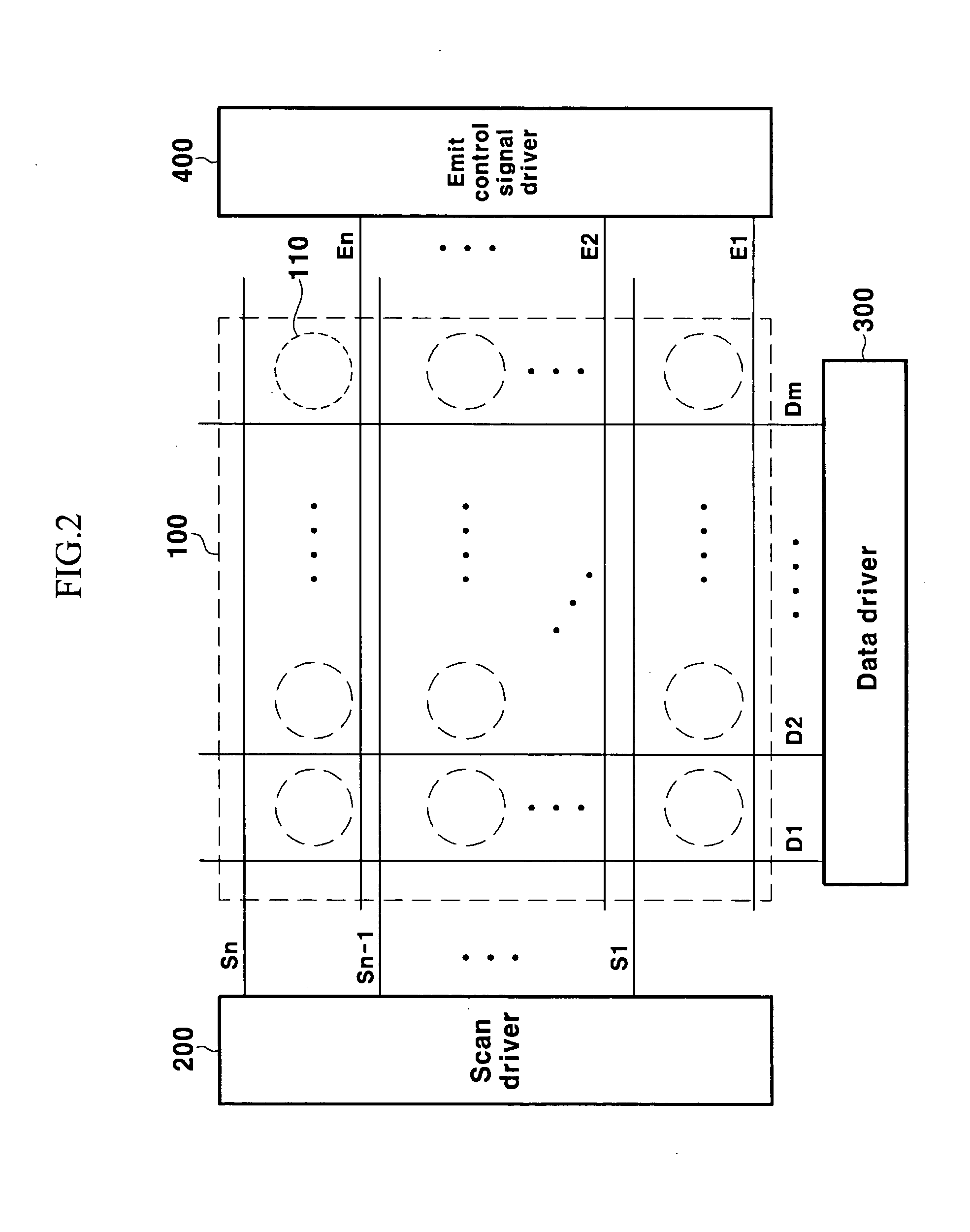

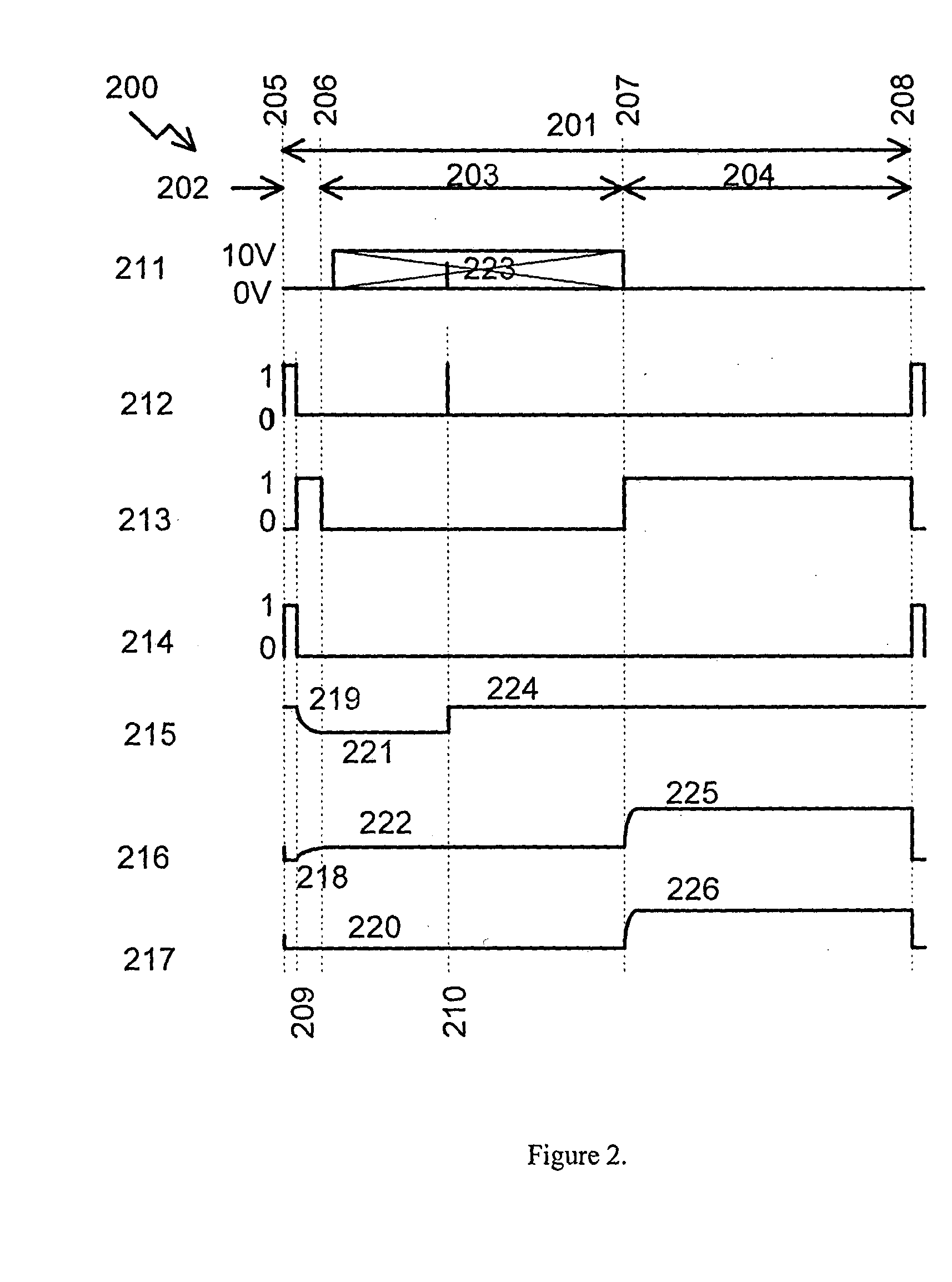

Light emitting display and driving method thereof

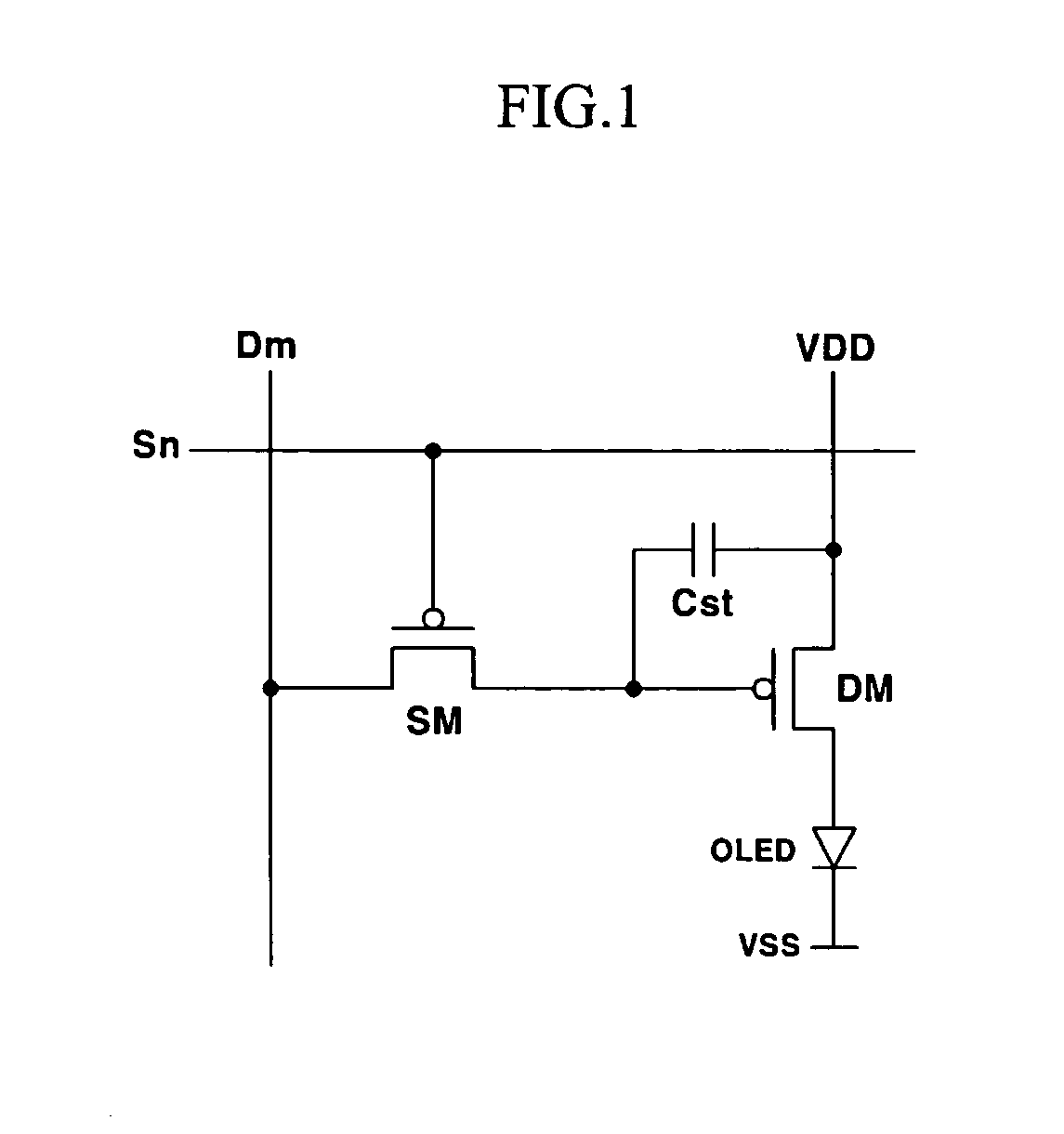

A light emitting display includes pixel circuits capable of compensating for the threshold voltages of their driving transistors. Each pixel circuit includes a driving transistor, a capacitor having one end coupled to a gate electrode of the driving transistor, a first switch coupled between the gate electrode of the driving transistor and a first main electrode, which is turned on in response to a first level of a first control signal for diode-coupling the driving transistor, and a second switch turned on in response to a second level of a second control signal to transmit current flowing out of the first main electrode of the driving transistor to a light emitting element. The second switch is turned on when the first switch is turned on for a first period longer than 0.05 μs and shorter than 2.5 μs. The second switch is turned on when the first switch is turned off.

Owner:SAMSUNG DISPLAY CO LTD

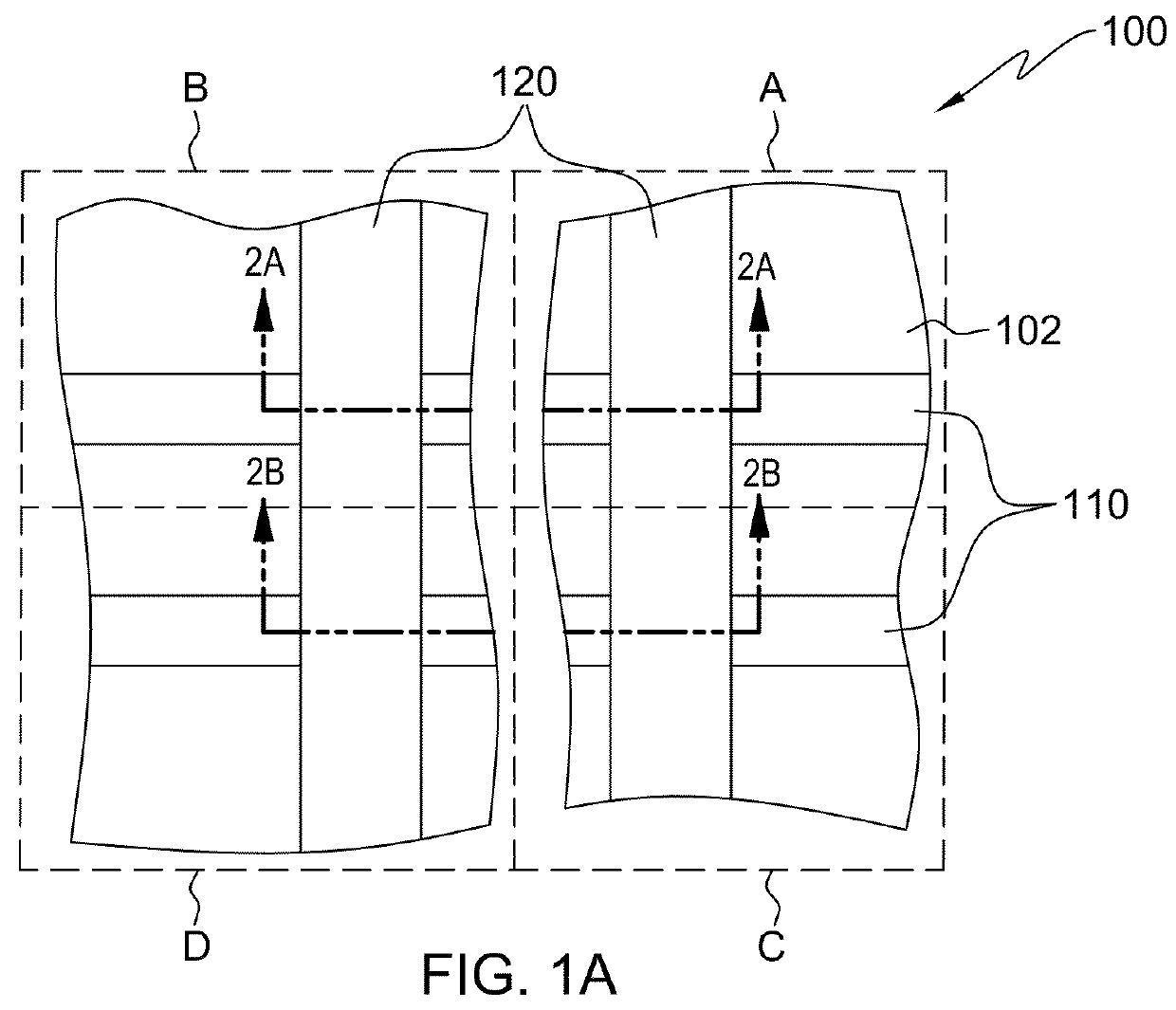

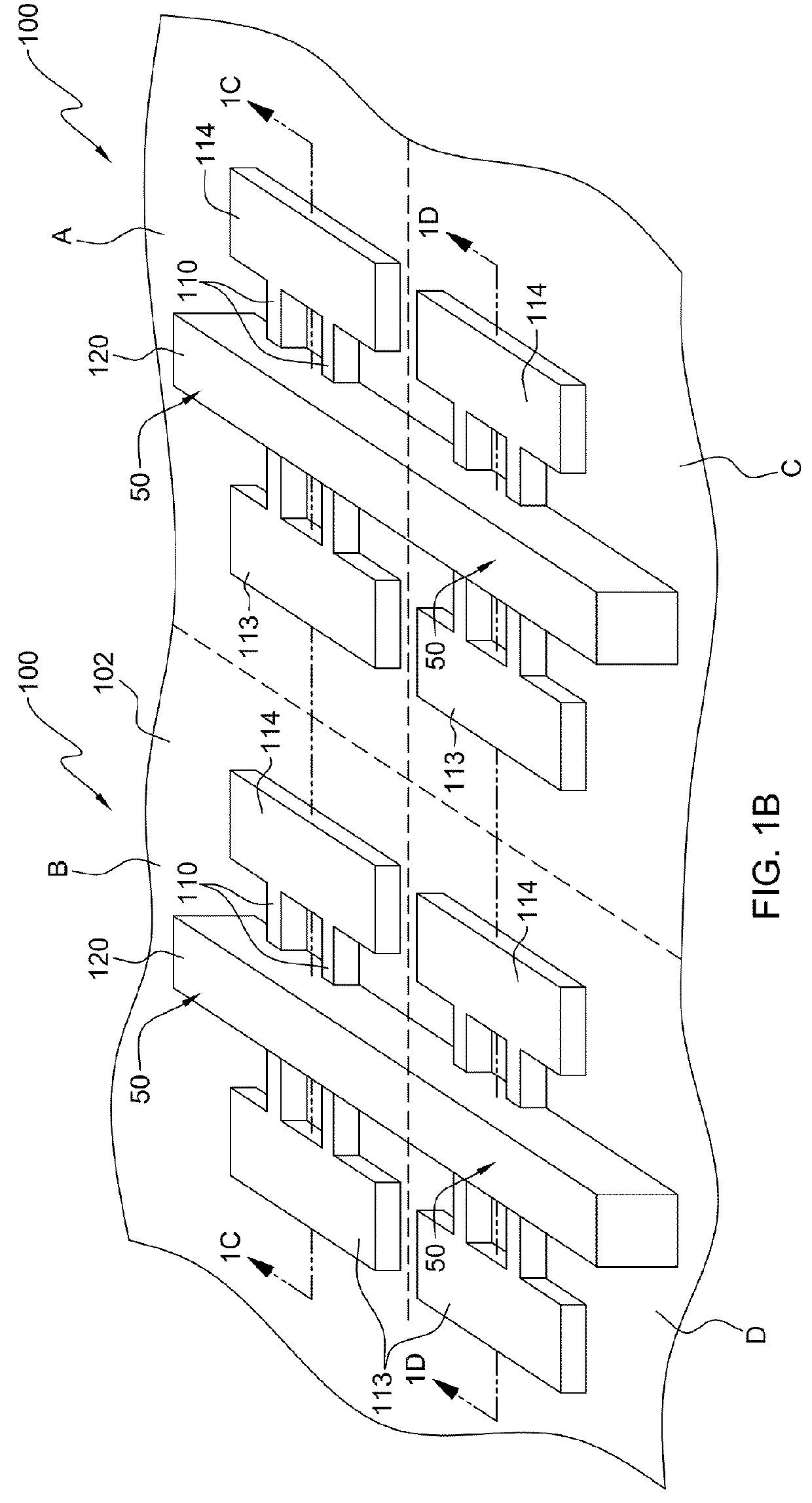

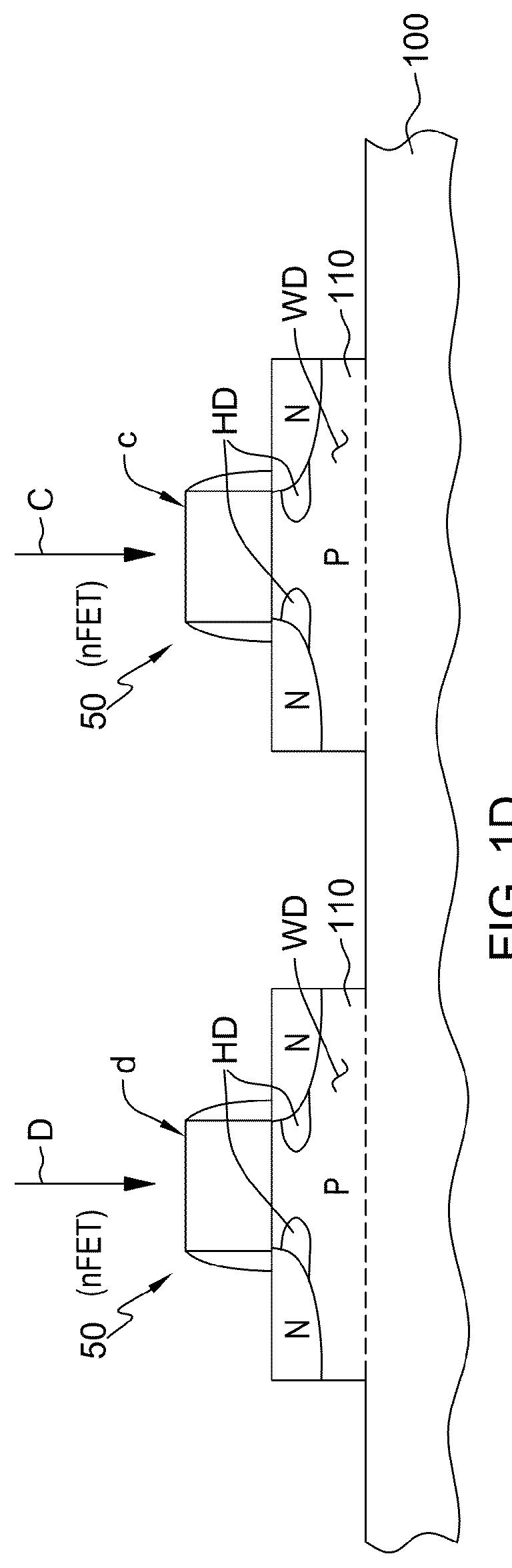

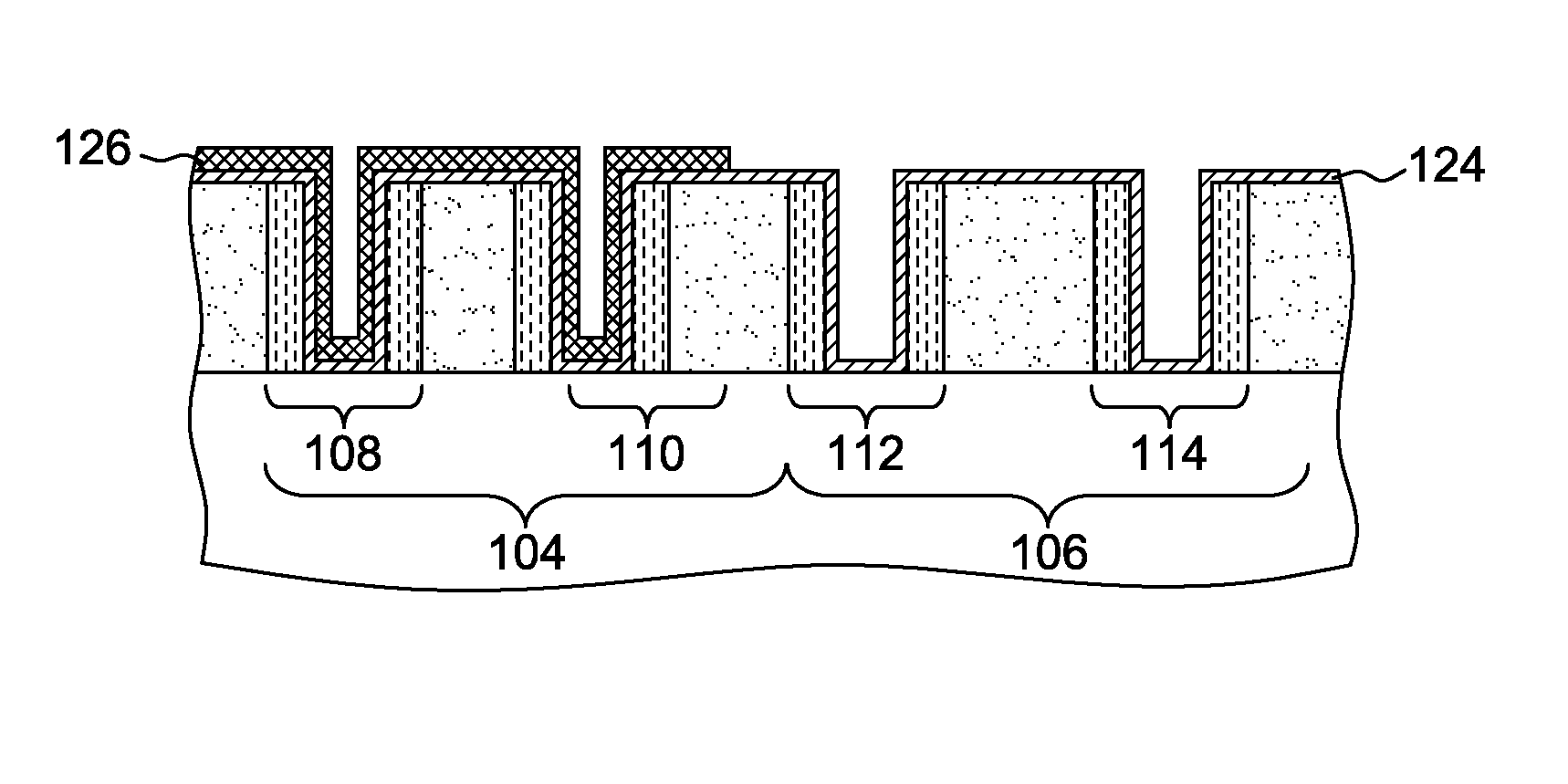

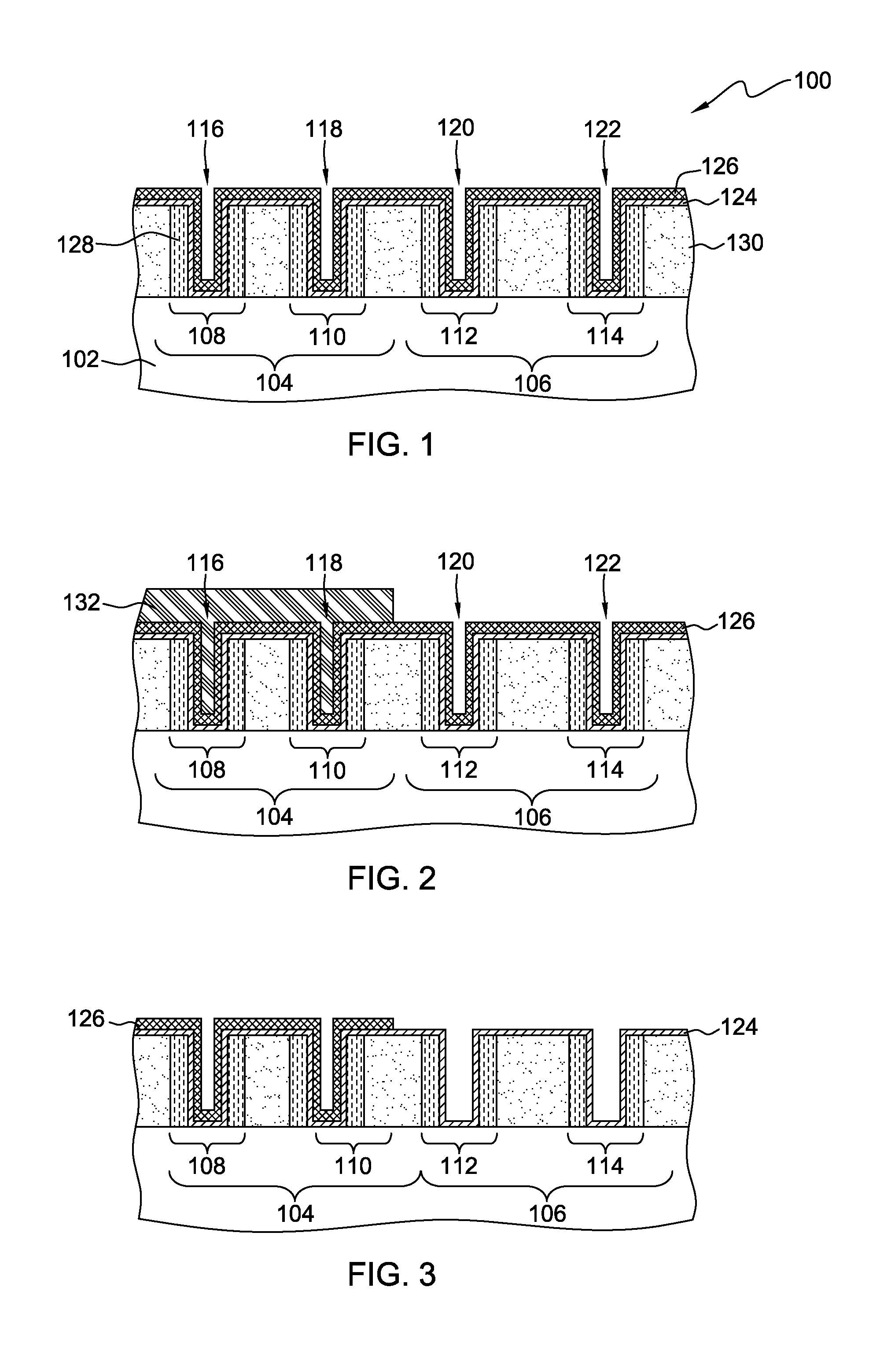

Integrated circuit having multiple threshold voltages

In one aspect there is set forth herein an integrated circuit having a first plurality of field effect transistors and a second plurality of field effect transistor, wherein field effect transistors of the first plurality of field effect transistors each have a first gate stack and wherein field effect transistors of the second plurality of field effect transistors each have a second gate stack, the second gate stack being different from the first gate stack by having a metal layer common to the first gate stack and the second gate stack that includes a first thickness at the first gate stack and a second thickness at the second gate stack.

Owner:GLOBALFOUNDRIES U S INC

Integrated circuits with varying gate structures and fabrication methods

Integrated circuits and fabrication methods are provided. The integrated circuit includes: a varying gate structure disposed over a substrate structure, the varying gate structure including a first gate stack in a first region of the substrate structure, and a second gate stack in a second region of the substrate structure; a first field-effect transistor in the first region, the first field-effect transistor including the first gate stack and having a first threshold voltage; and a second field-effect transistor in the second region, the second field-effect transistor including the second gate stack and having a second threshold voltage, where the first threshold voltage is different from the second threshold voltage. The methods include providing the varying gate structure, the providing including: sizing layer(s) of the varying gate structure with different thickness(es) in different region(s).

Owner:GLOBALFOUNDRIES U S INC

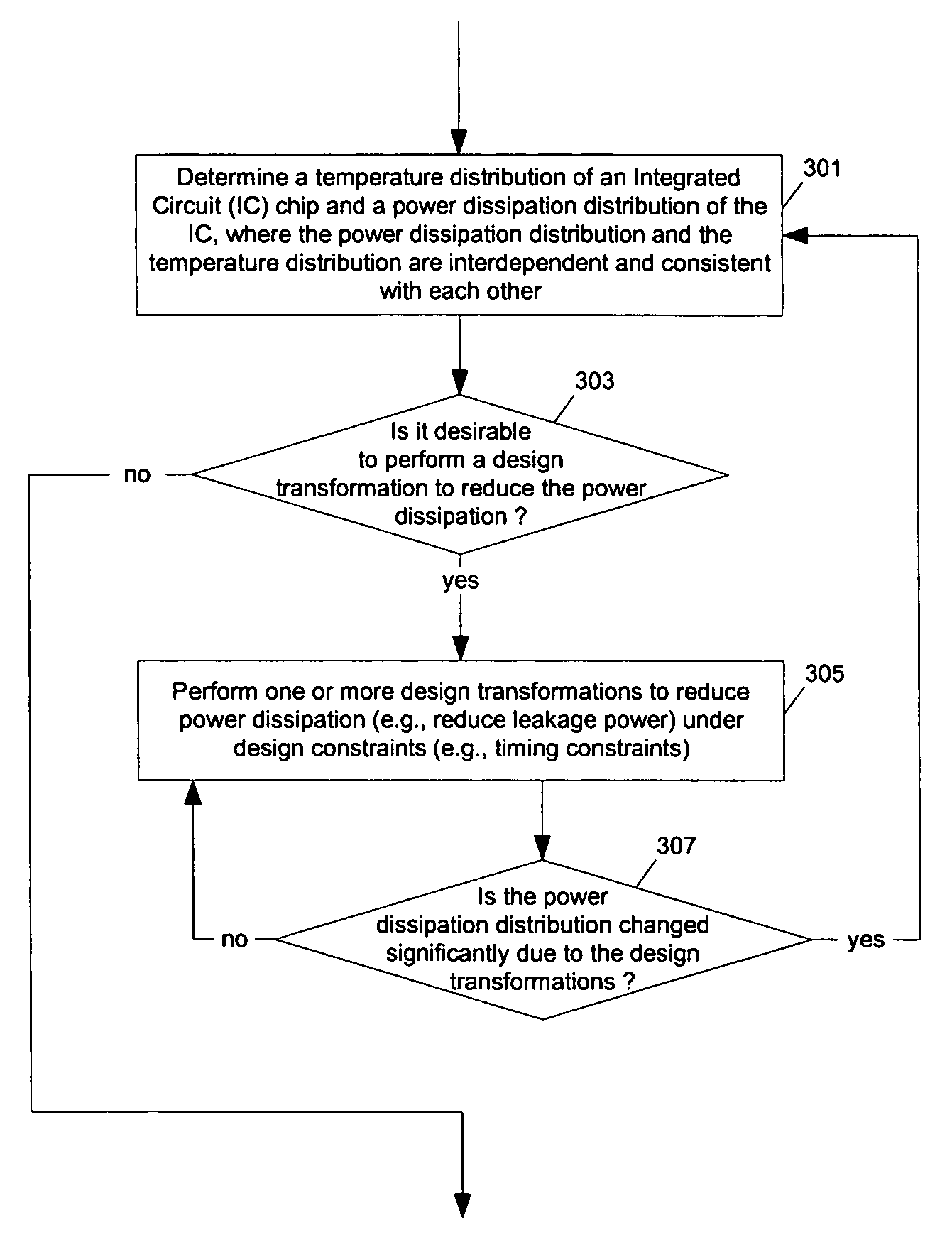

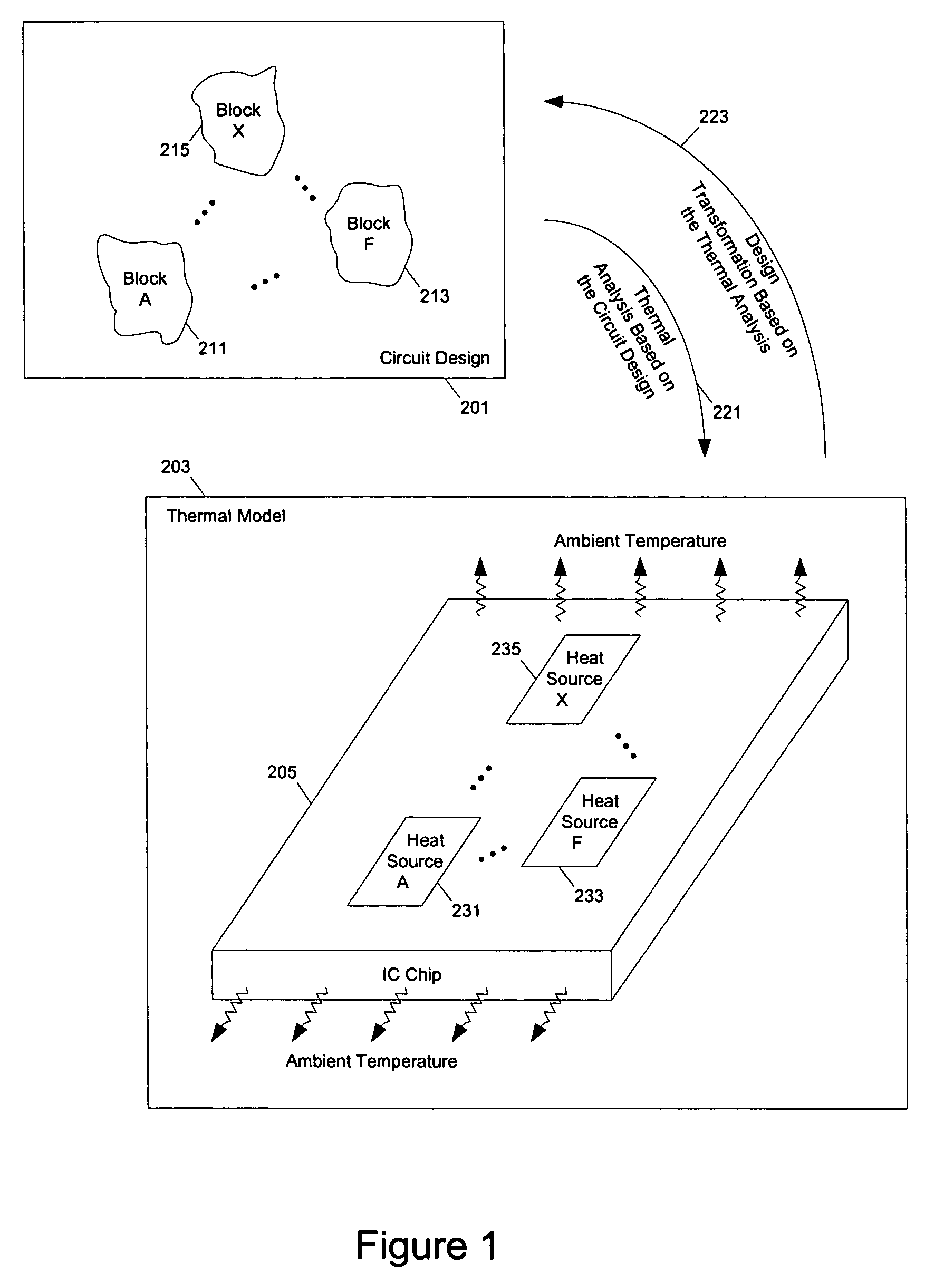

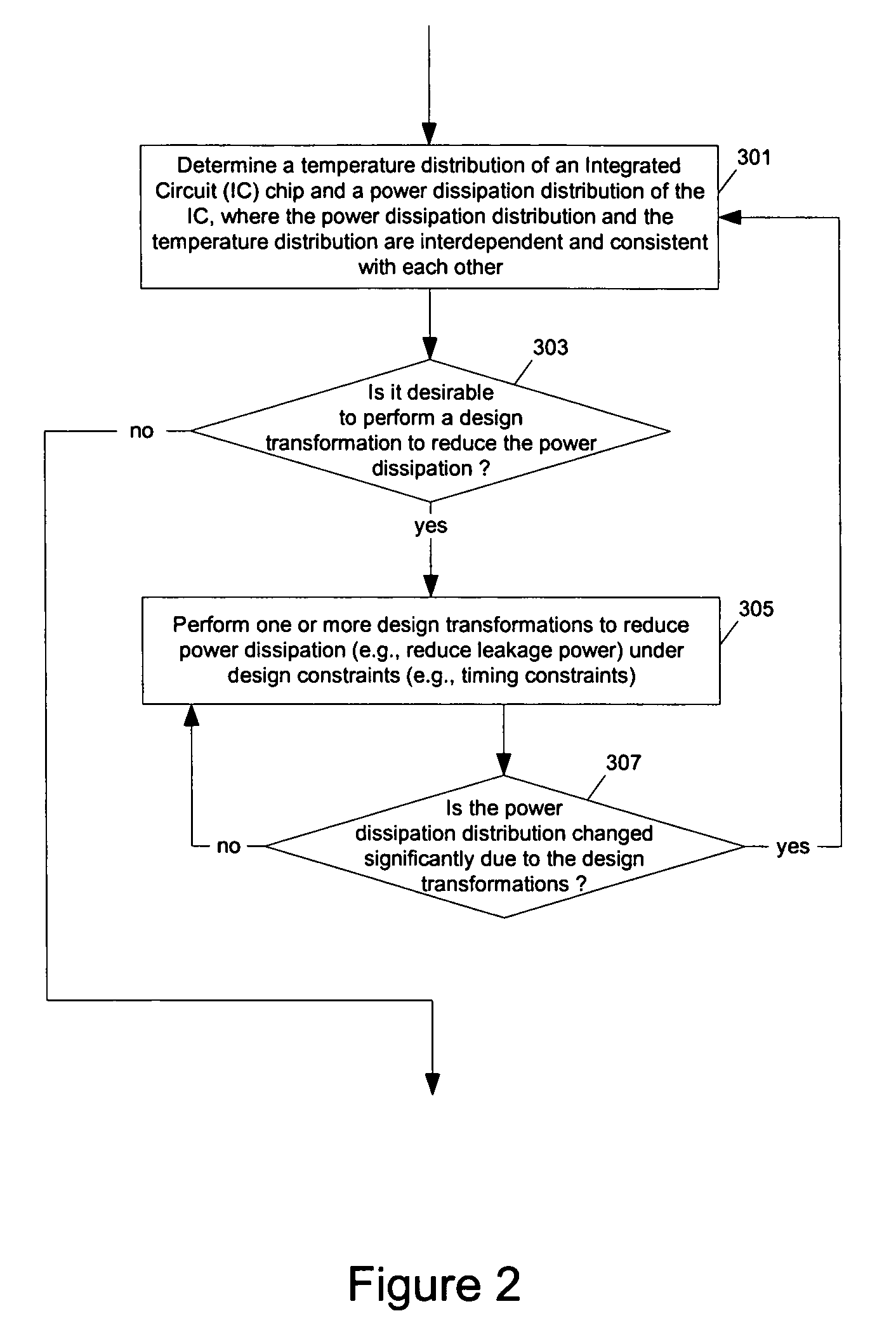

Methods and apparatuses for thermal analysis based circuit design

ActiveUS7366997B1Reduce power consumptionExtension of timeSoftware simulation/interpretation/emulationSpecial data processing applicationsPower usageTransition time

Methods and apparatuses for circuit design to reduce power usage, such as reducing temperature dependent power usage, and / or to improve timing, such as reducing temperature dependent delay or transition time. At least one embodiment of the present invention reduces the power dissipation and improves the timing of an integrated circuit to optimize the design. A thermal analysis is used to determine the temperature dependent power dissipation of a circuit and the temperature distribution of the circuit resulting from dissipating the heat created by the temperature dependent power dissipation. Then, the components of the design are selectively transformed to reduce the power dissipation and to improve timing based on the temperature solution. The transformation may include placement changes and netlist changes, such as the change of transistor threshold voltages for cells or for blocks of the circuit chip.

Owner:SYNOPSYS INC

Common fabrication of different semiconductor devices with different threshold voltages

A multi-device semiconductor structure including a p-type logic device, a p-type memory device, a n-type logic device and a n-type memory device are provided on a bulk silicon substrate. Each of these devices includes a dielectric layer and either a n-type or a p-type work function layer disposed over the dielectric layer. Some of the various device types of the multi-device semiconductor structure are protected, and impurities, such as aluminum and / or nitrogen, are added to the exposed work function layers to achieve one or more other desired work functions with different threshold voltages.

Owner:GLOBALFOUNDRIES INC

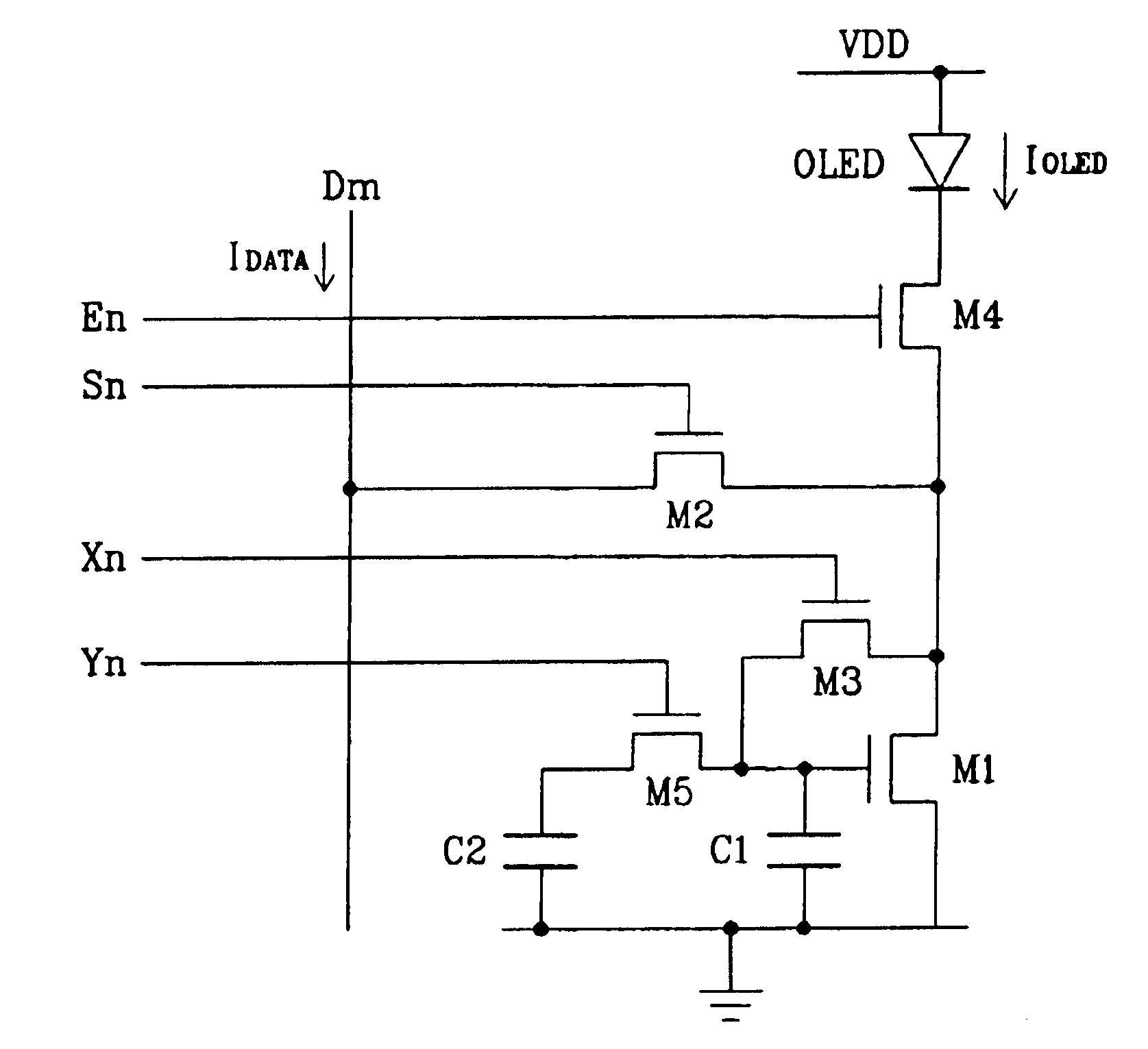

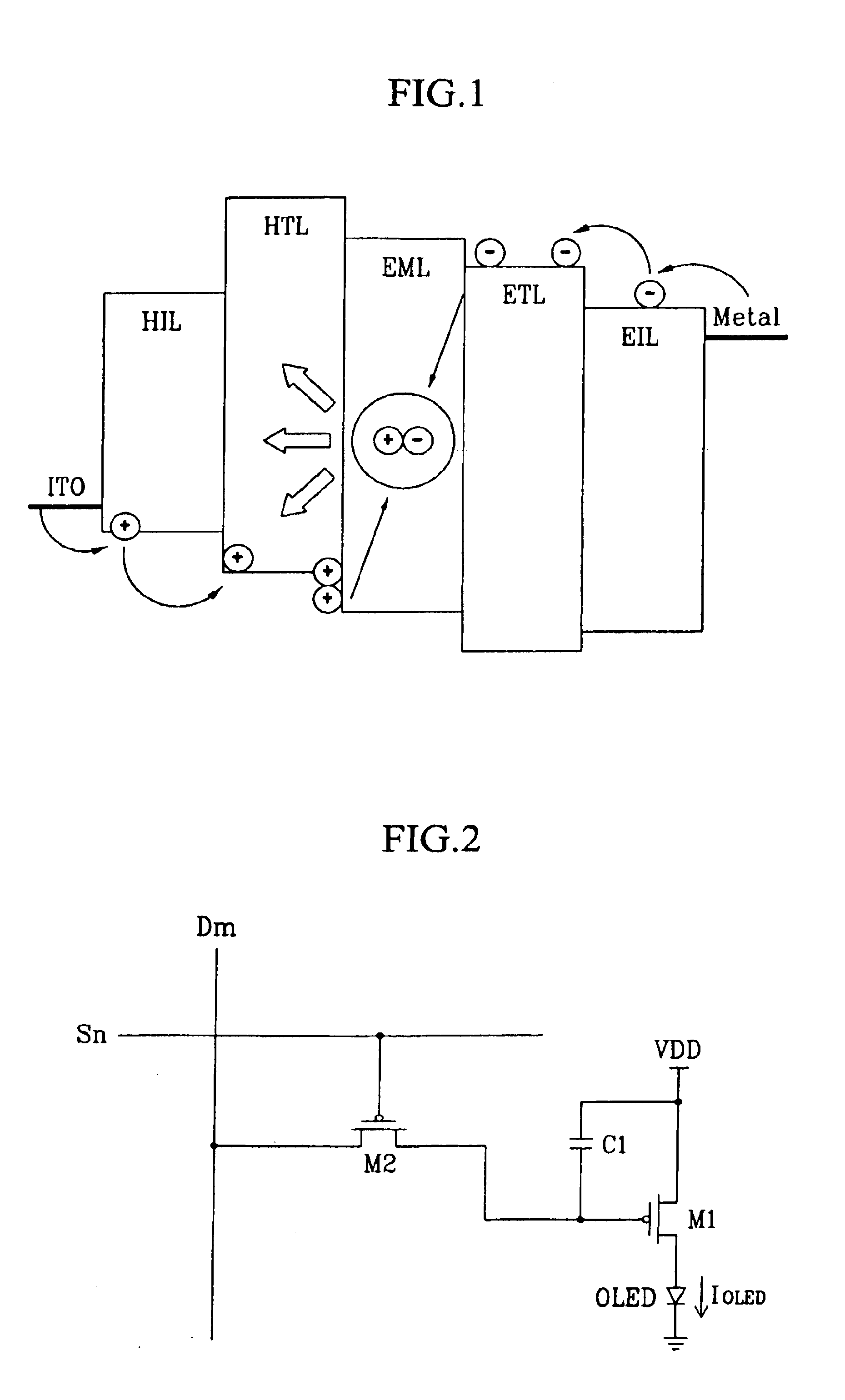

Light emitting display, display panel, and driving method thereof

A light emitting display for compensating for the threshold voltage of transistor or mobility and fully charging a data line. A transistor and first through third switches are formed on a pixel circuit of an organic EL display. The transistor supplies a driving current for emitting an organic EL element (OLED). The first switch diode-connects the transistor. A first storage unit stores a first voltage corresponding to a threshold voltage of the transistor. A second switch transmits a data current in response to a select signal. A second storage unit stores a second voltage corresponding to the data current. A third switch transmits the driving current to the OLED. A third voltage determined by coupling of the first and second storage units is applied to a transistor to supply the driving current to the OLED.

Owner:SAMSUNG DISPLAY CO LTD

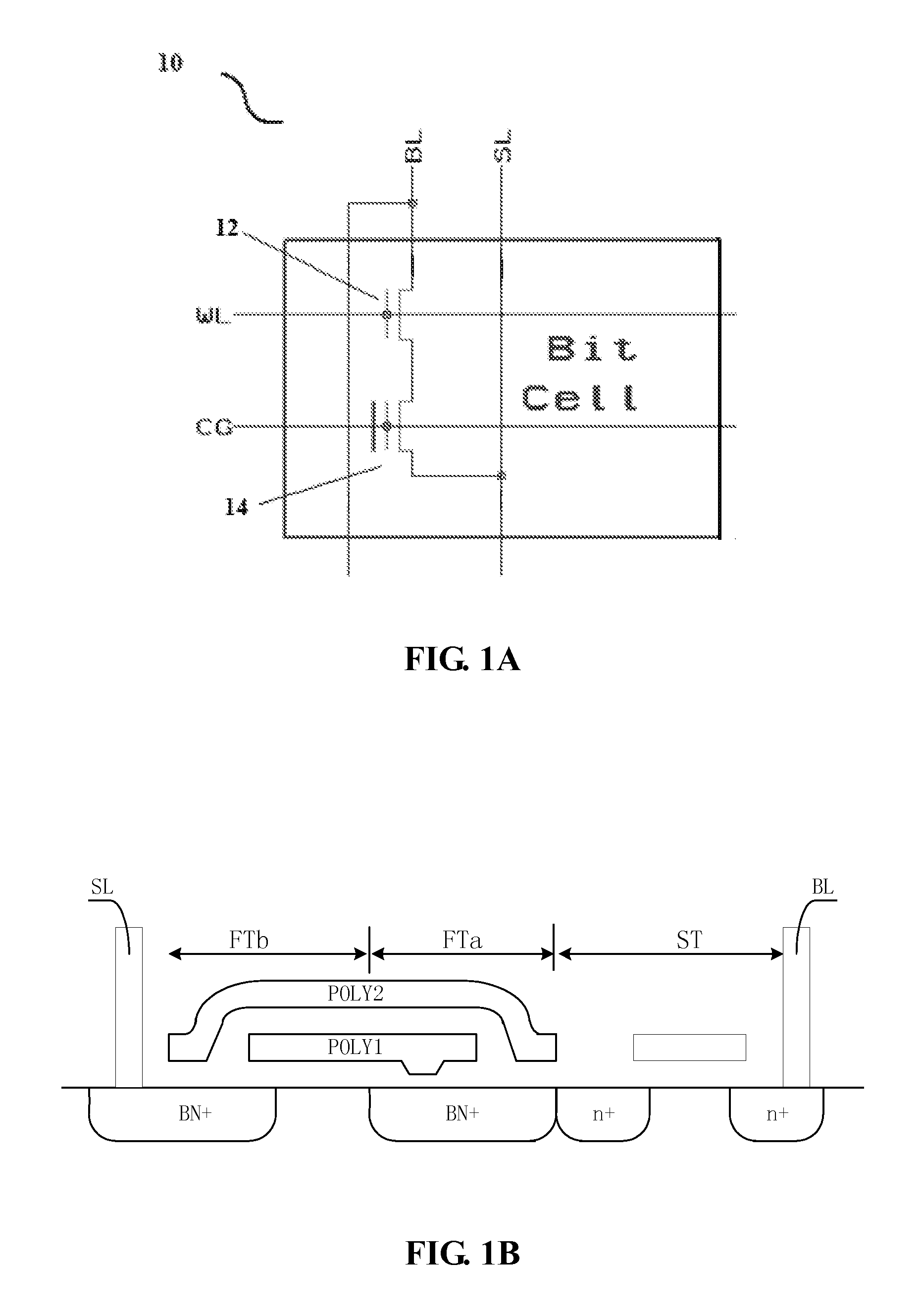

Single-electron floating-gate MOS memory

A Single Electron MOS Memory (SEMM), in which one bit of information is represented by storing only one electron, has been demonstrated at room temperature. The SEMM is a floating gate Metal-Oxide-Semiconductor (MOS) transistor in silicon with a channel width (about 10 nanometers) which is smaller than the Debye screening length of a single electron stored on the floating gate, and a nanoscale polysilicon dot (about 7 nanometers by 7 nanometers by 2 nanometers) as the floating gate which is positioned between the channel and the control gate. An electron stored on the floating gate can screen the entire channel from the potential on the control gate, and lead to: (i) a discrete shift in the threshold voltage; (ii) a staircase relation between the charging voltage and the shift; and (iii) a self-limiting charging process. The structure and fabrication of the SEMM is well adapted to the manufacture of ultra large-scale integrated circuits.

Owner:MINNESOTA RGT UNIV OF A CORP OF MN

Integrated circuit having multiple threshold voltages

In one aspect there is set forth herein an integrated circuit having a first plurality of field effect transistors and a second plurality of field effect transistor, wherein field effect transistors of the first plurality of field effect transistors each have a first gate stack and wherein field effect transistors of the second plurality of field effect transistors each have a second gate stack, the second gate stack being different from the first gate stack by having a metal layer common to the first gate stack and the second gate stack that includes a first thickness at the first gate stack and a second thickness at the second gate stack.

Owner:GLOBALFOUNDRIES US INC

Graphene-based transistor

ActiveUS20090020764A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantGate dielectric

A graphene layer is formed on a surface of a silicon carbide substrate. A dummy gate structure is formed over the fin, in the trench, or on a portion of the planar graphene layer to implant dopants into source and drain regions. The dummy gate structure is thereafter removed to provide an opening over the channel of the transistor. Threshold voltage adjustment implantation may be performed to form a threshold voltage implant region directly beneath the channel, which comprises the graphene layer. A gate dielectric is deposited over a channel portion of the graphene layer. After an optional spacer formation, a gate conductor is formed by deposition and planarization. The resulting graphene-based field effect transistor has a high carrier mobility due to the graphene layer in the channel, low contact resistance to the source and drain region, and optimized threshold voltage and leakage due to the threshold voltage implant region.

Owner:GLOBALFOUNDRIES US INC

Process for making and programming and operating a dual-bit multi-level ballistic flash memory

An fast program, ultra-high density, dual-bit, multi-level flash memory process, which can be applied to a ballistic step split gate side wall transistor, or to a ballistic planar split gate side wall transistor, which enables program operation by low voltage requirement on the floating gate during program is described. Two side wall floating gates are paired with a single word line select gate, and word lines are arranged to be perpendicular both the bit lines and control gate lines. Two adjacent memory cells on the same word line do not require an isolation region. Also, the isolation region between adjacent memory cells sharing the same bitline is defined by the minimum lithography feature, utilizing a self align fill technique. Adjacent memory cells on the same word line share bitline diffusion as well as a third poly control gate. Control gates allow program and read access to the individual floating gate. In addition to the dual-bit nature of the cell, density can be even further improved by multi-level storage. In one embodiment, the dual multi-level structure is applied to the ballistic step split gate side wall transistor. In a second embodiment, the dual multi-level structure is applied to the ballistic planar split gate side wall transistor. Both types of ballistic transistors provide fast, low voltage programming. The control gates are used to override or suppress the various threshold voltages on associated floating gates, in order to program to and read from individual floating gates. The targets for this non-volatile memory array are to provide the capabilities of high speed, low voltage programming (band width) and high density storage.

Owner:HALO LSI DESIGN & DEVICE TECH

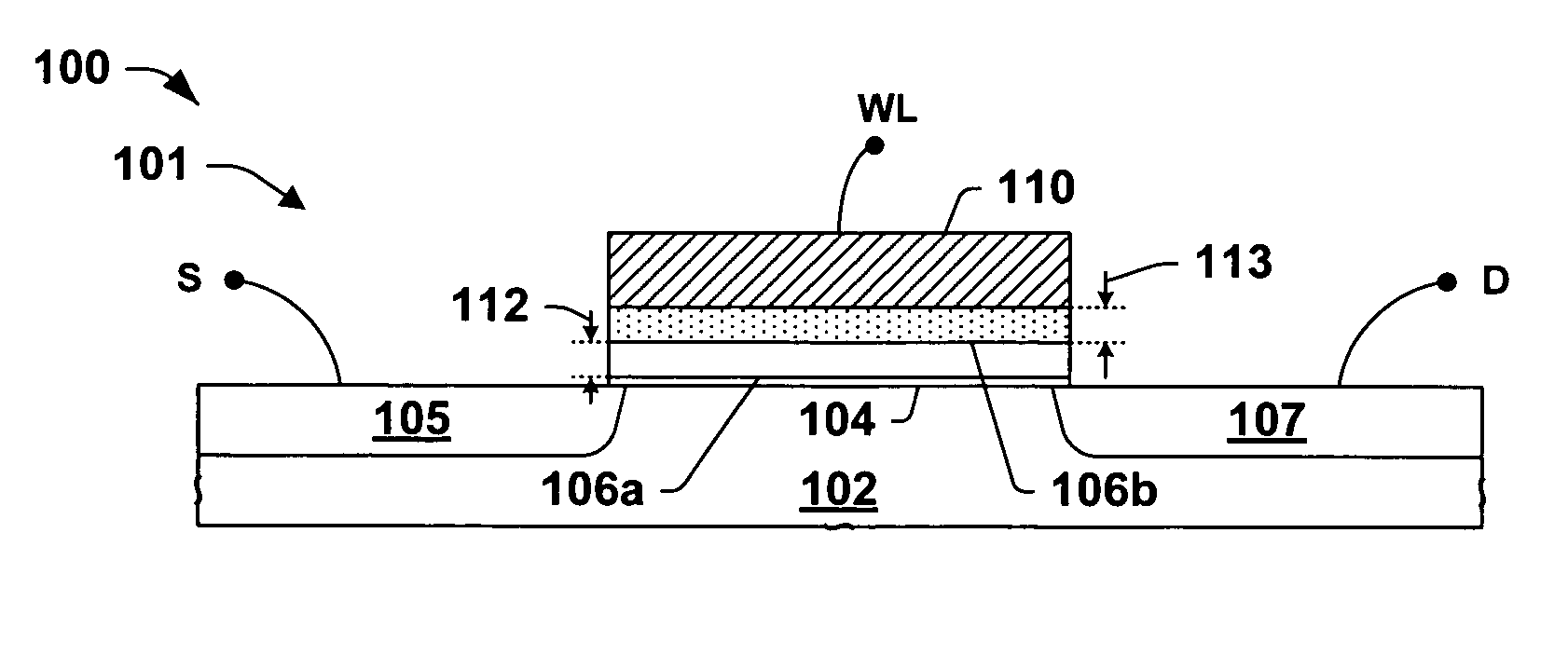

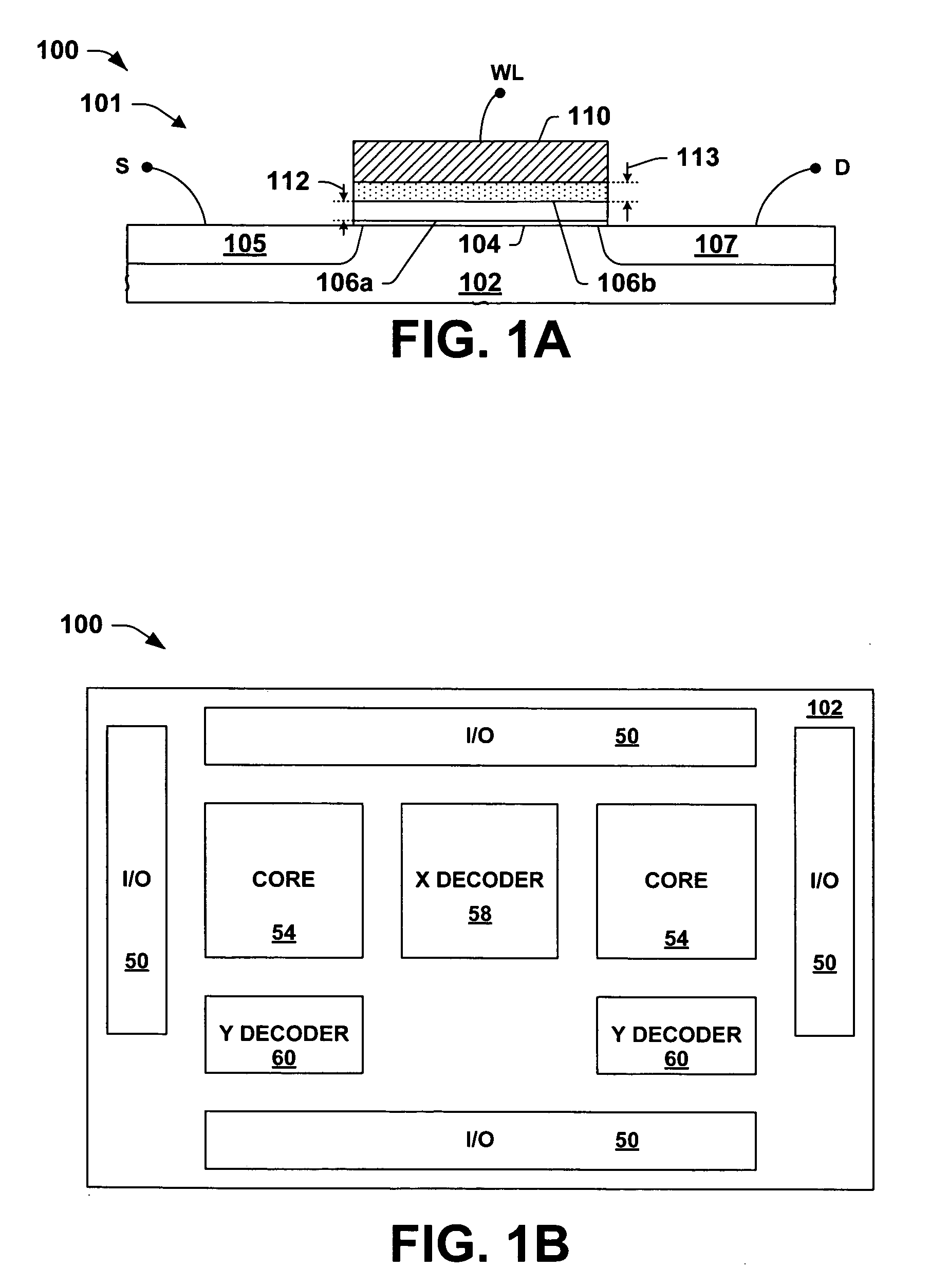

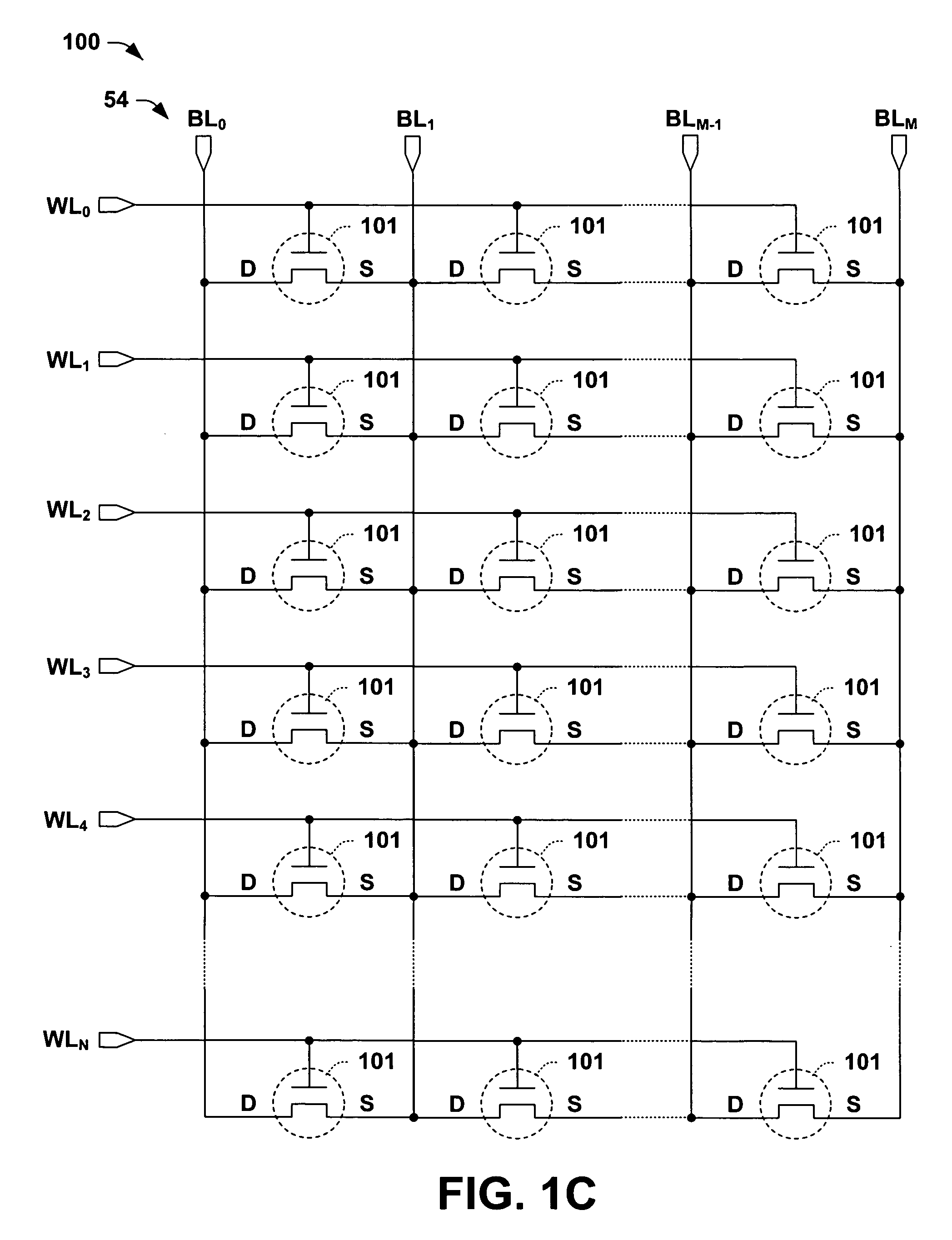

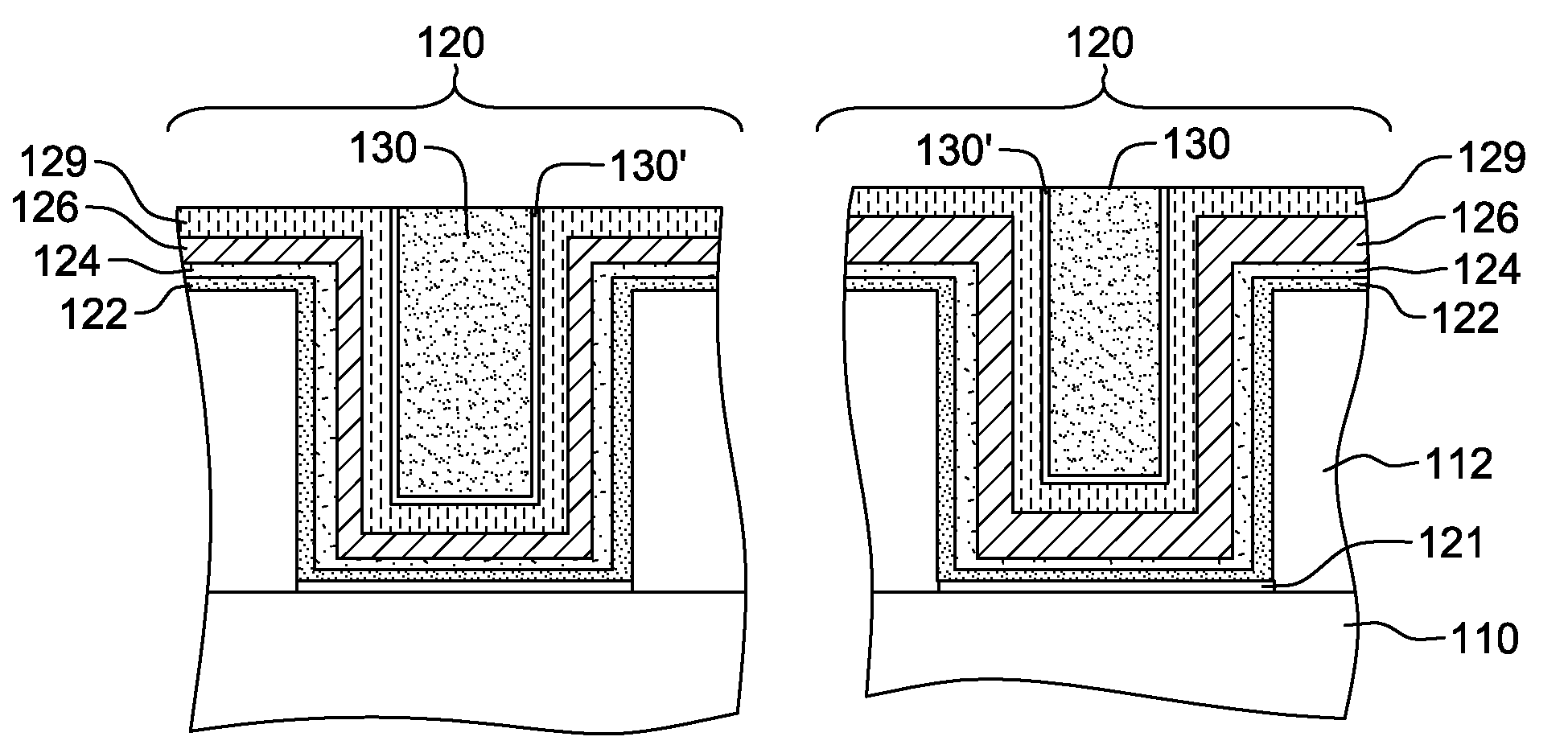

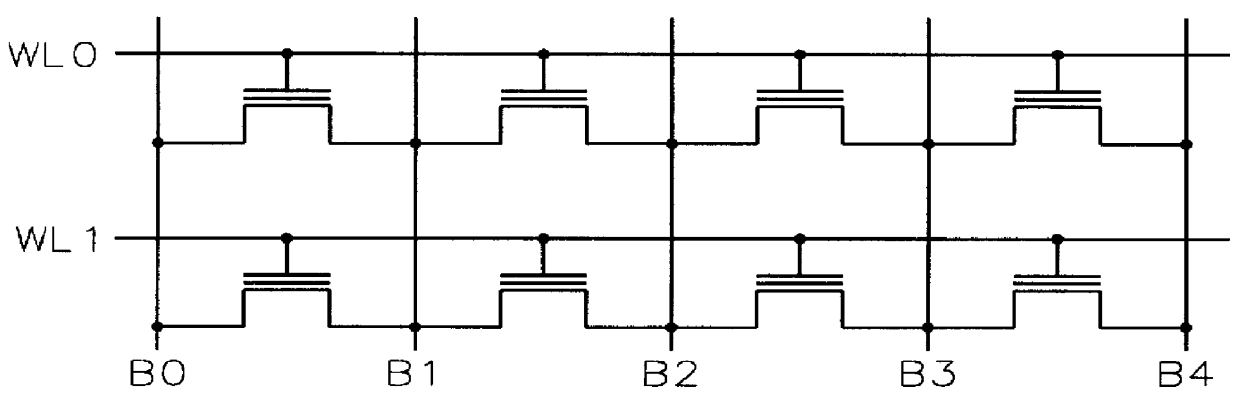

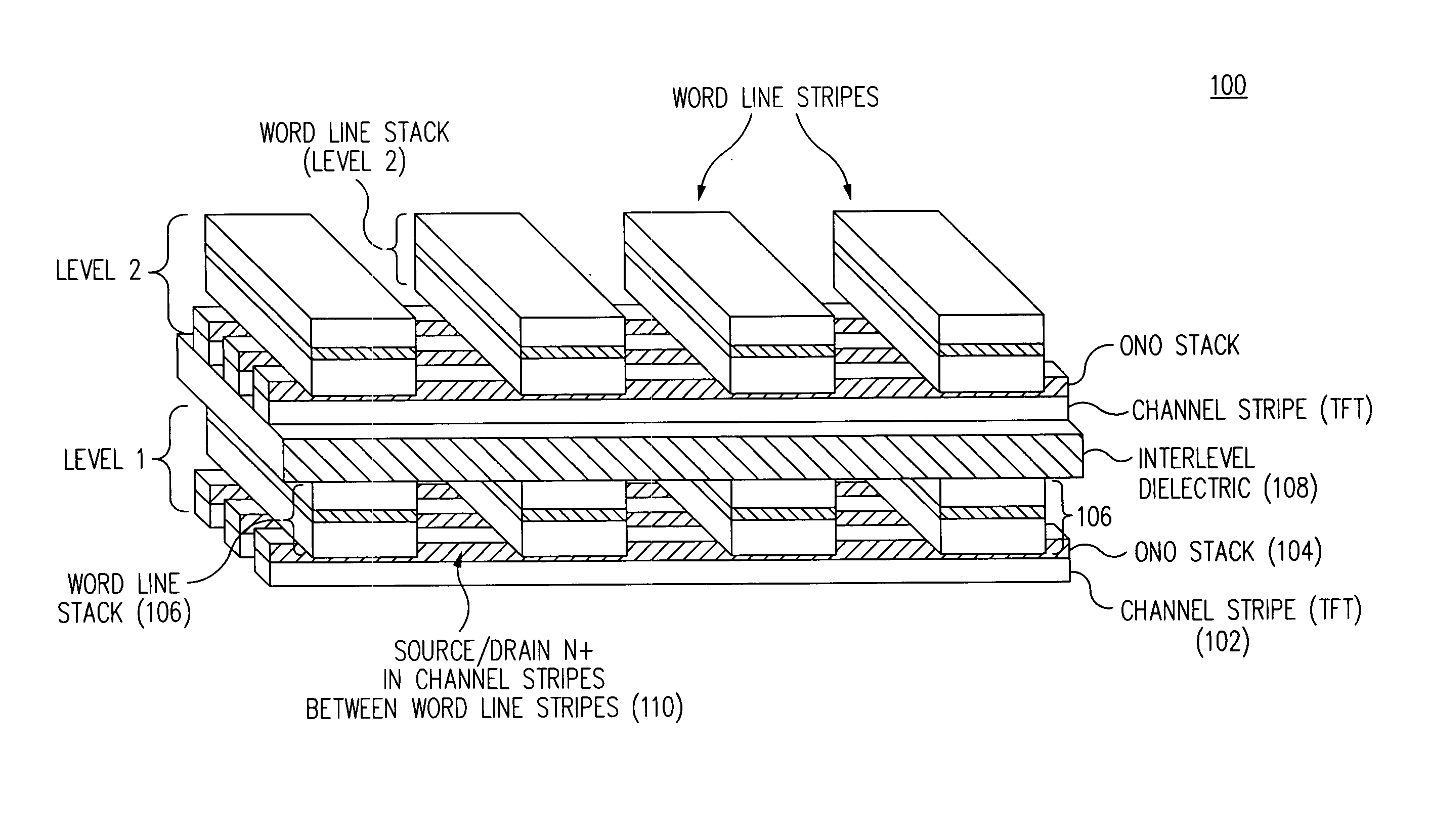

Programmable memory array structure incorporating series-connected transistor strings and methods for fabrication and operation of same

A three-dimensional flash memory array incorporates thin film transistors having a charge storage dielectric arranged in series-connected NAND strings to achieve a 4F<2 >memory cell layout. The memory array may be programmed and erased using only tunneling currents, and no leakage paths are formed through non-selected memory cells. Each NAND string includes two block select devices for respectively coupling one end of the NAND string to a global bit line, and the other end to a shared bias node. Pairs of NAND strings within a block share the same global bit line. The memory cells are preferably depletion mode SONOS devices, as are the block select devices. The memory cells may be programmed to a near depletion threshold voltage, and the block select devices are maintained in a programmed state having a near depletion mode threshold voltage. NAND strings on more than one layer may be connected to global bit lines on a single layer. By interleaving the NAND strings on each memory level and using two shared bias nodes per block, very little additional overhead is required for the switch devices at each end of the NAND strings. The NAND strings on different memory levels are preferably connected together by way of vertical stacked vias, each preferably connecting to more than one memory level. Each memory level may be produced with less than three masks per level.

Owner:SANDISK TECH LLC

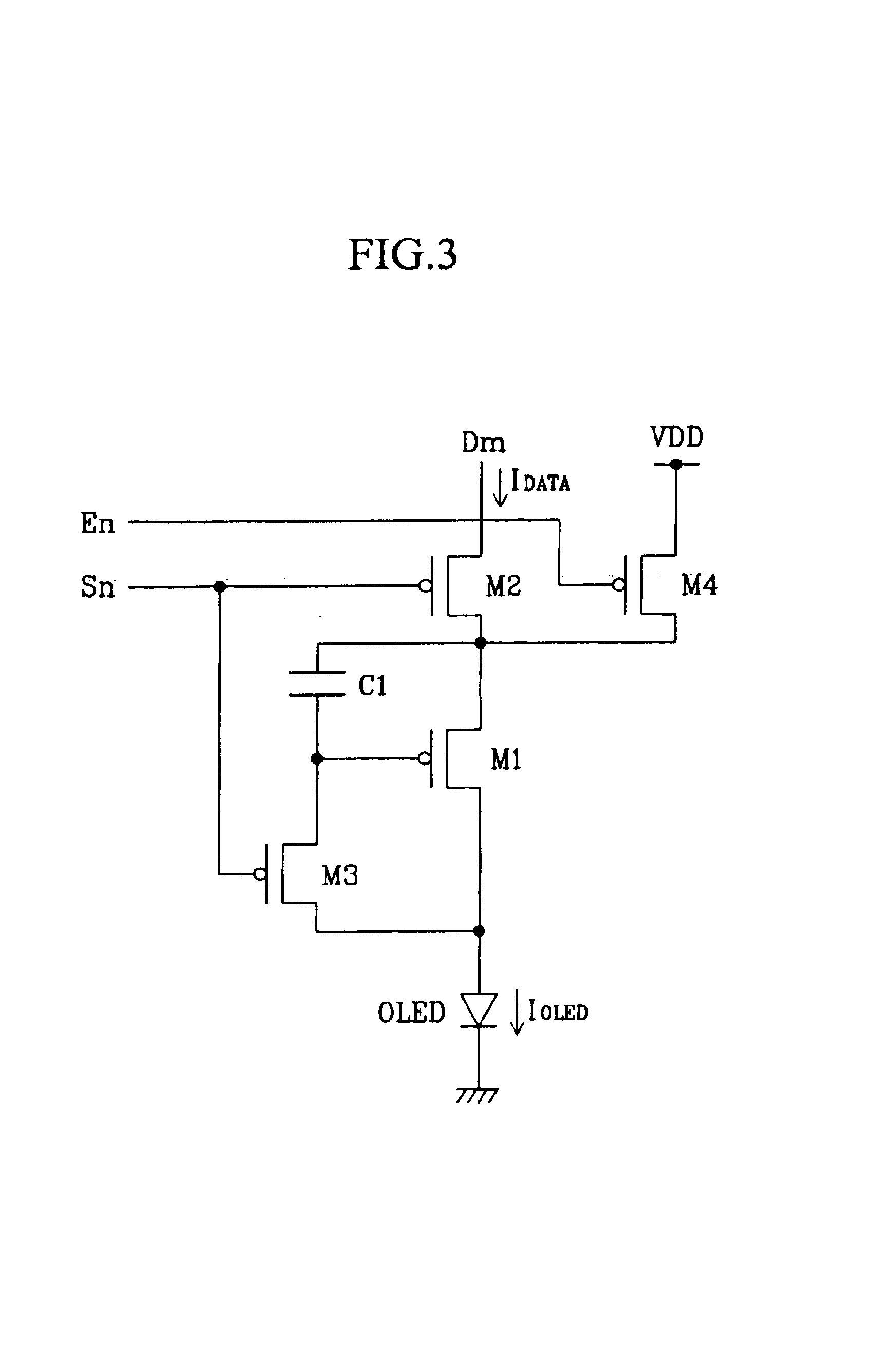

Active-matrix light emitting display and method for obtaining threshold voltage compensation for same

ActiveUS20050067970A1Cathode-ray tube indicatorsInput/output processes for data processingCapacitanceActive matrix

An active matrix display includes a plurality of pixels arranged in an array, a first transistor and a second transistor associated with each pixel, the first and second transistors positioned within the array for controlling current flow through each pixel, a light emitting diode associated with each pixel; and a storage capacitor associated with each pixel, wherein, during a time period for establishment of a threshold voltage on the storage capacitor for the first transistor, a voltage equal to the sum of the threshold voltage and a voltage for compensating for turnoff of the second transistor is established on the storage. capacitor.

Owner:TWITTER INC