Patents

Literature

6737 results about "Band gap" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In solid-state physics, a band gap, also called an energy gap or bandgap, is an energy range in a solid where no electron states can exist. In graphs of the electronic band structure of solids, the band gap generally refers to the energy difference (in electron volts) between the top of the valence band and the bottom of the conduction band in insulators and semiconductors. It is the energy required to promote a valence electron bound to an atom to become a conduction electron, which is free to move within the crystal lattice and serve as a charge carrier to conduct electric current. It is closely related to the HOMO/LUMO gap in chemistry. If the valence band is completely full and the conduction band is completely empty, then electrons cannot move in the solid; however, if some electrons transfer from the valence to the conduction band, then current can flow (see carrier generation and recombination). Therefore, the band gap is a major factor determining the electrical conductivity of a solid. Substances with large band gaps are generally insulators, those with smaller band gaps are semiconductors, while conductors either have very small band gaps or none, because the valence and conduction bands overlap.

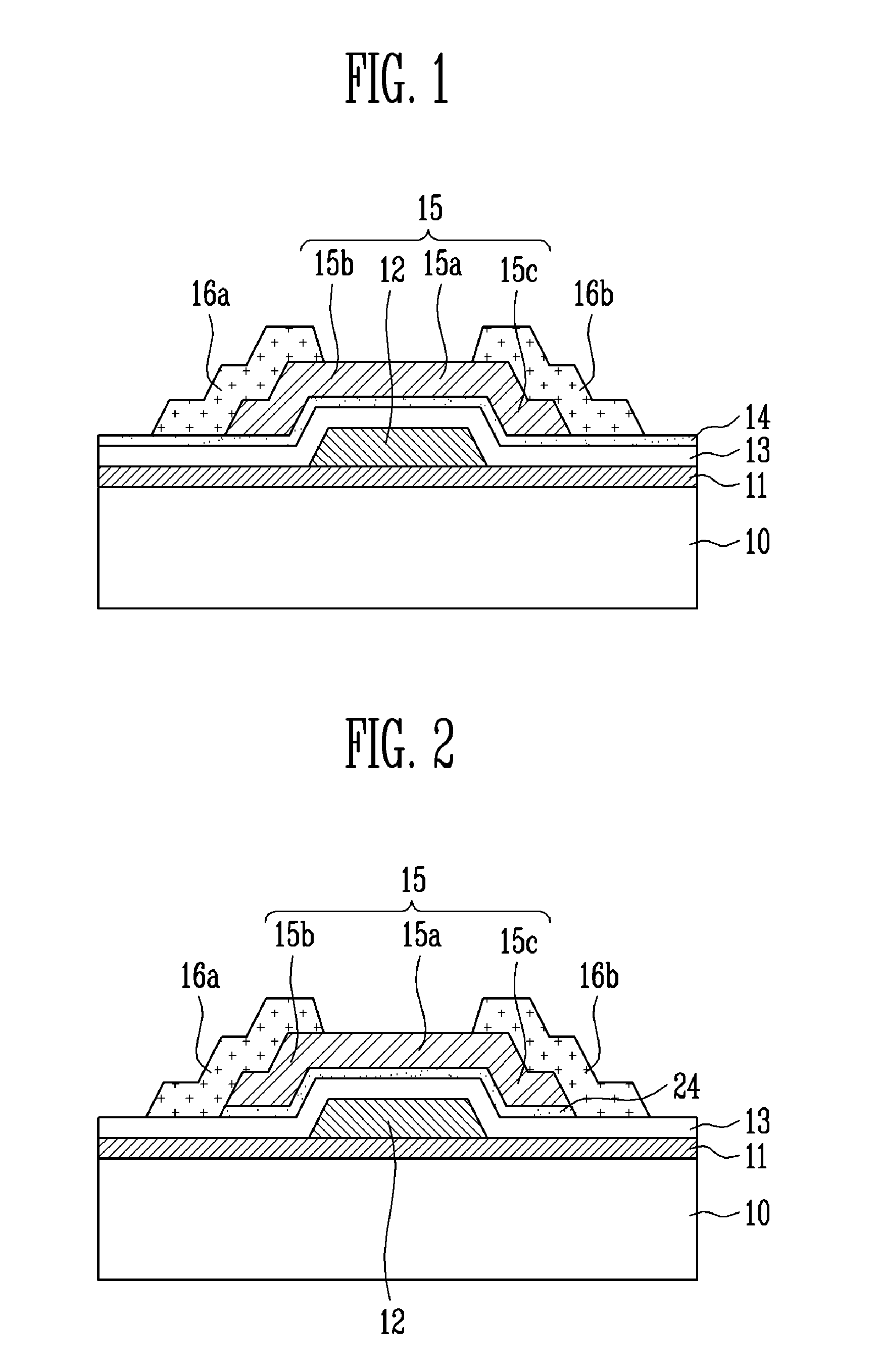

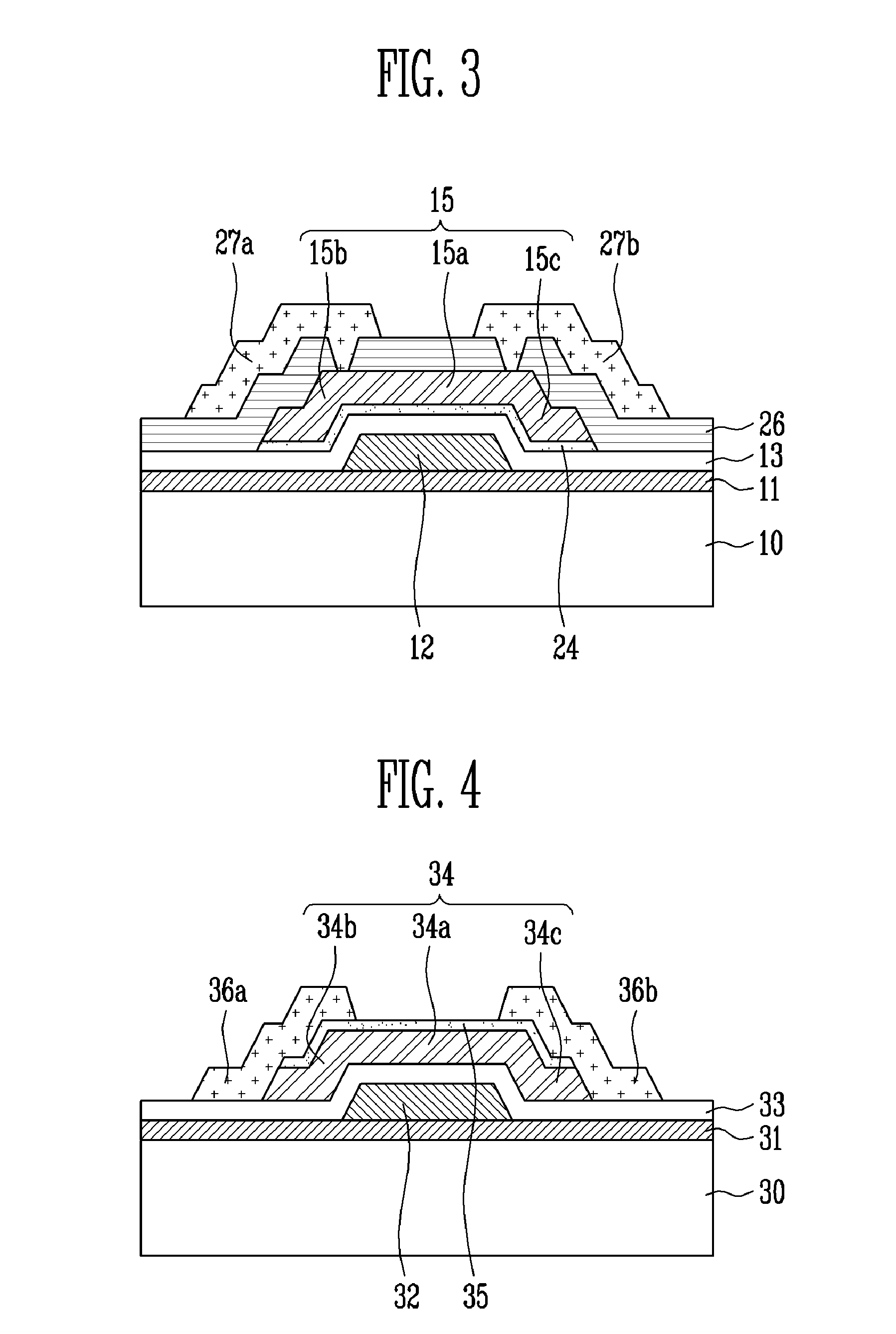

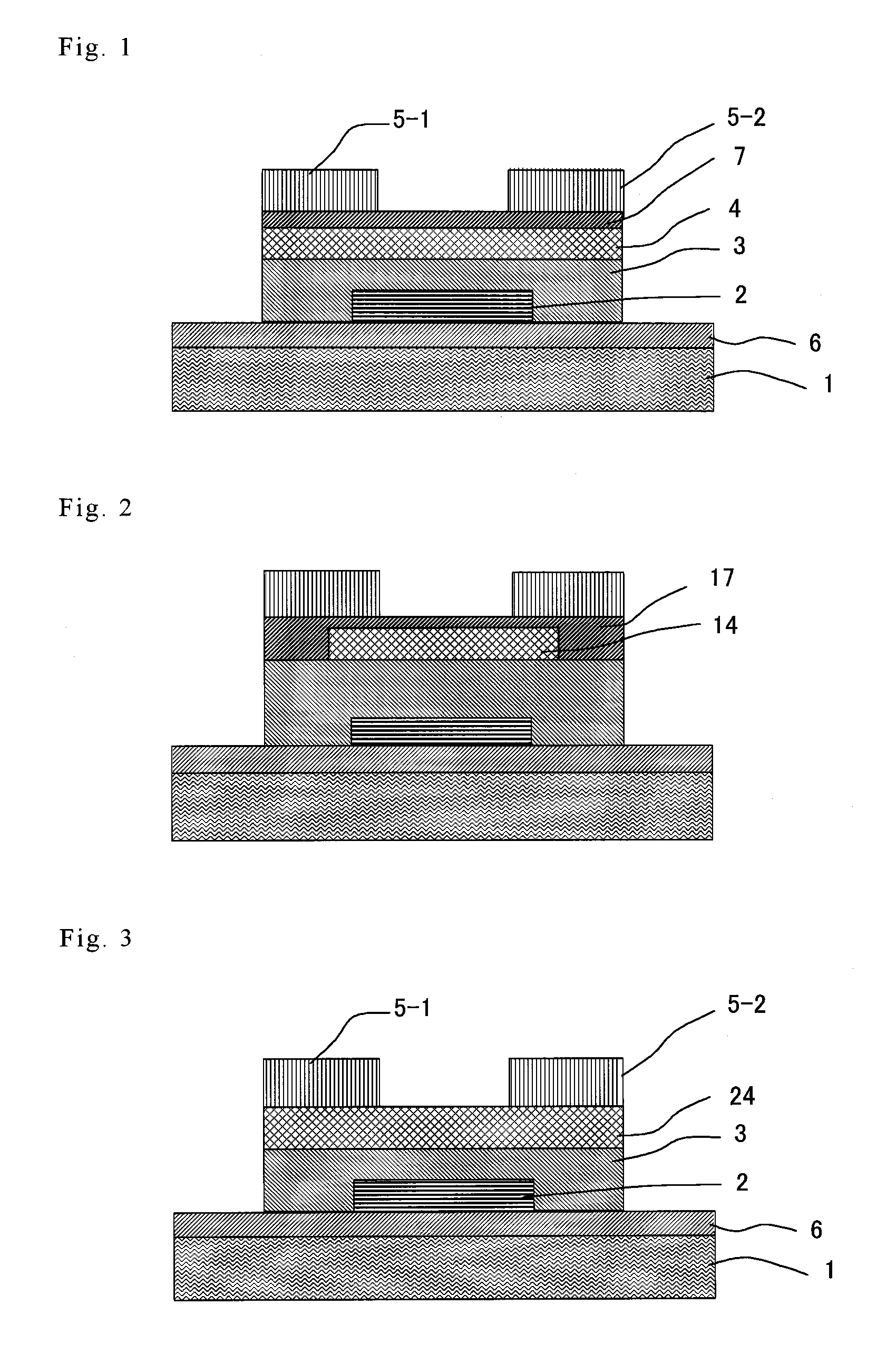

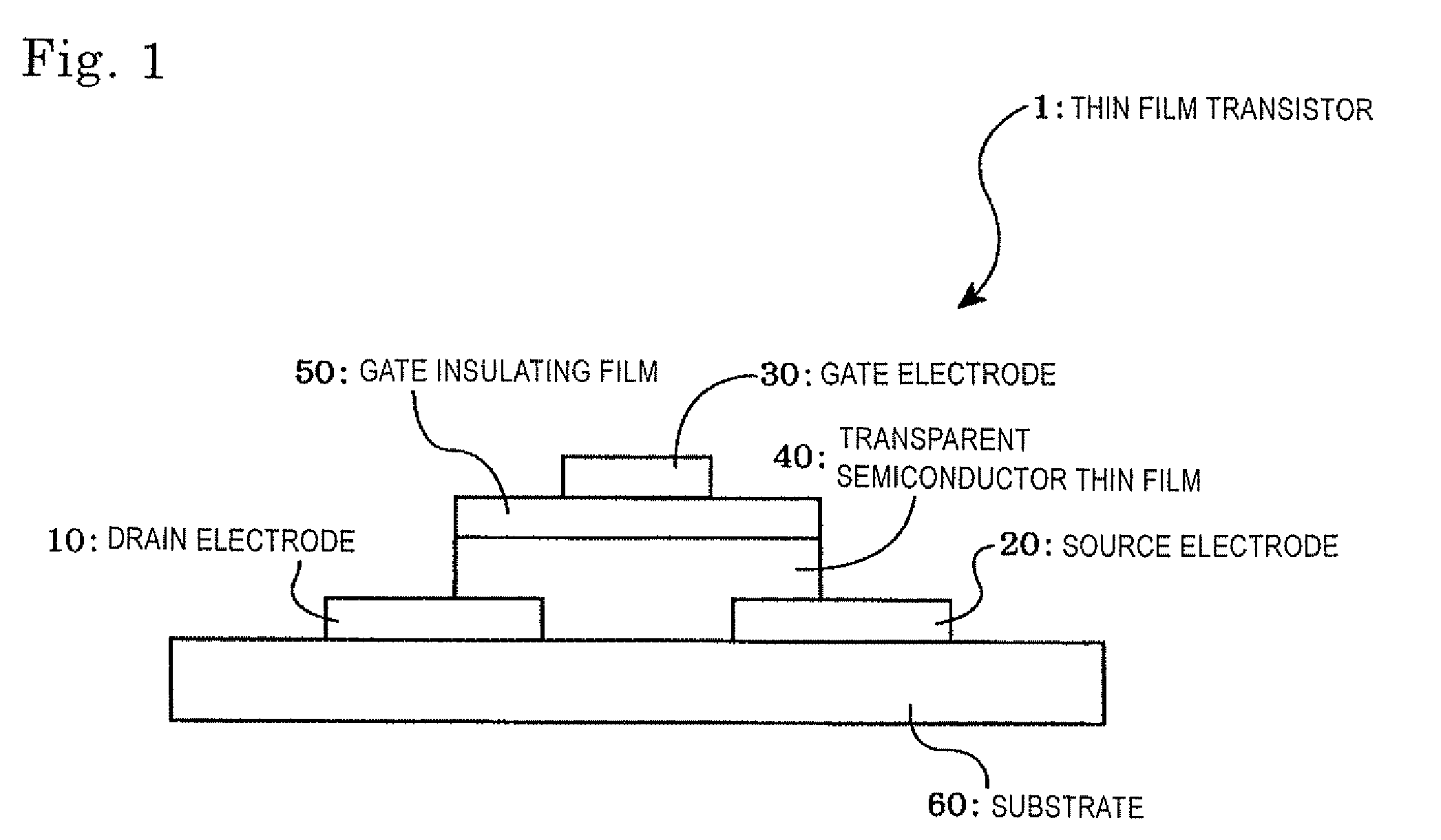

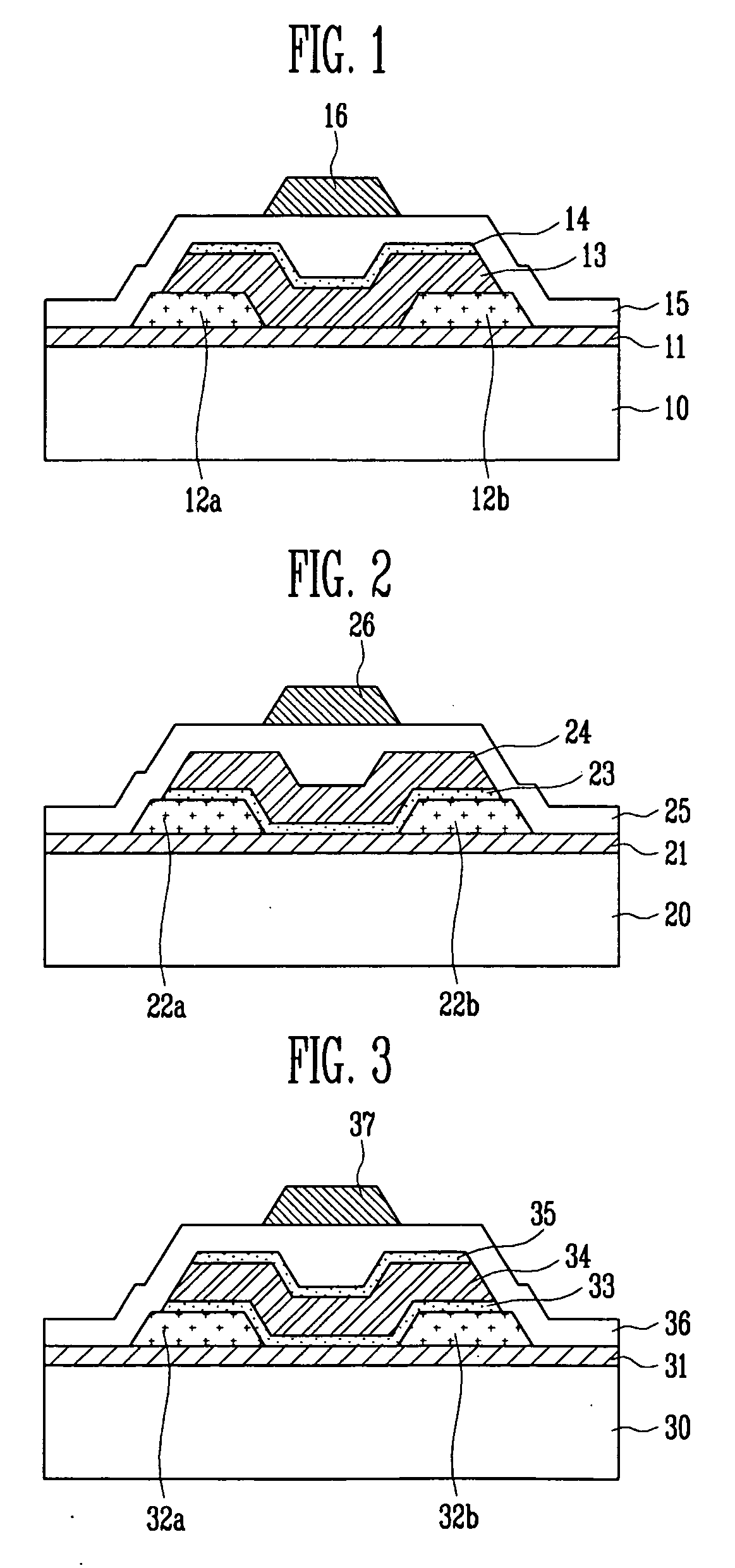

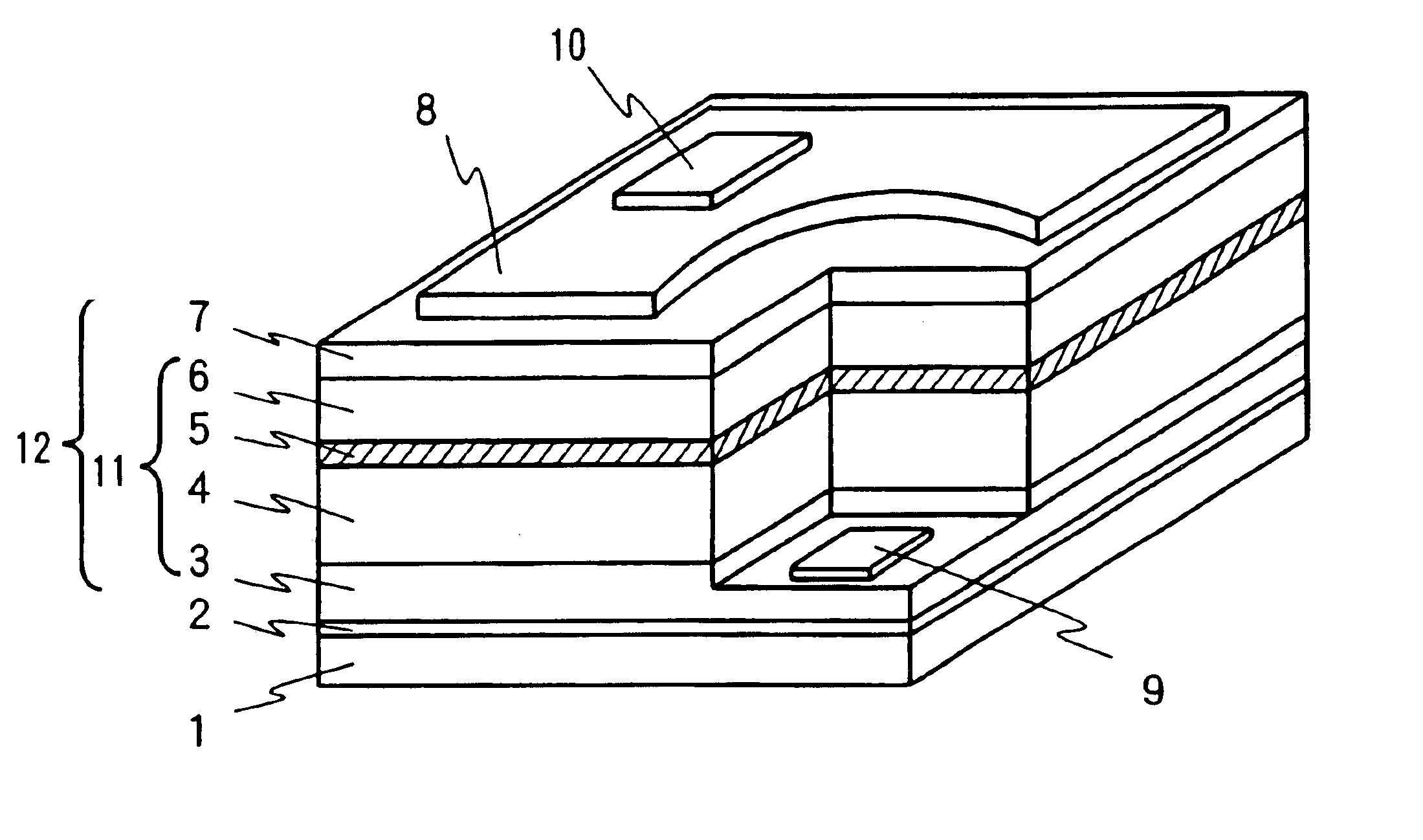

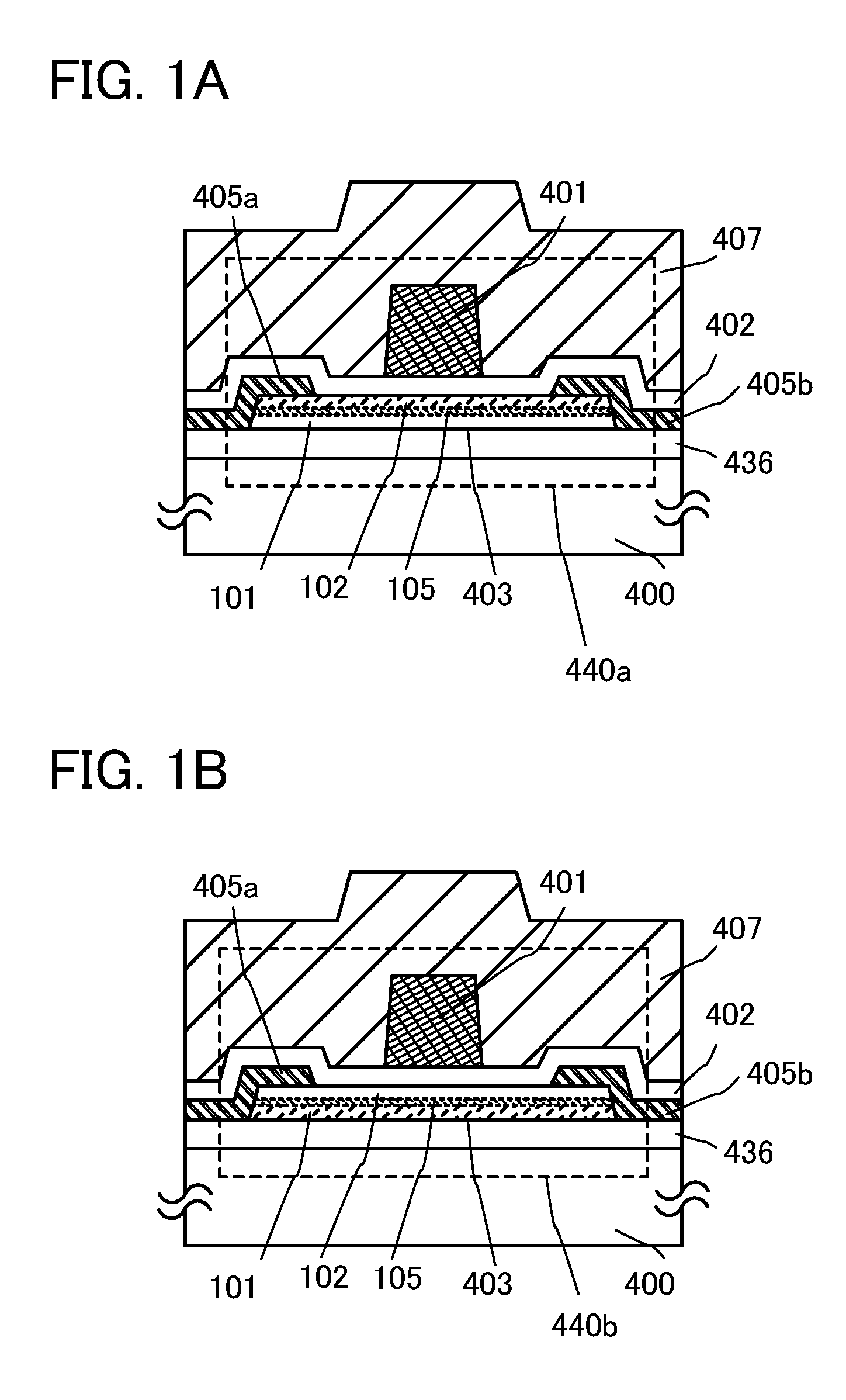

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS8148779B2Improve featuresAvoid chargingSolid-state devicesSemiconductor/solid-state device manufacturingTrappingEngineering

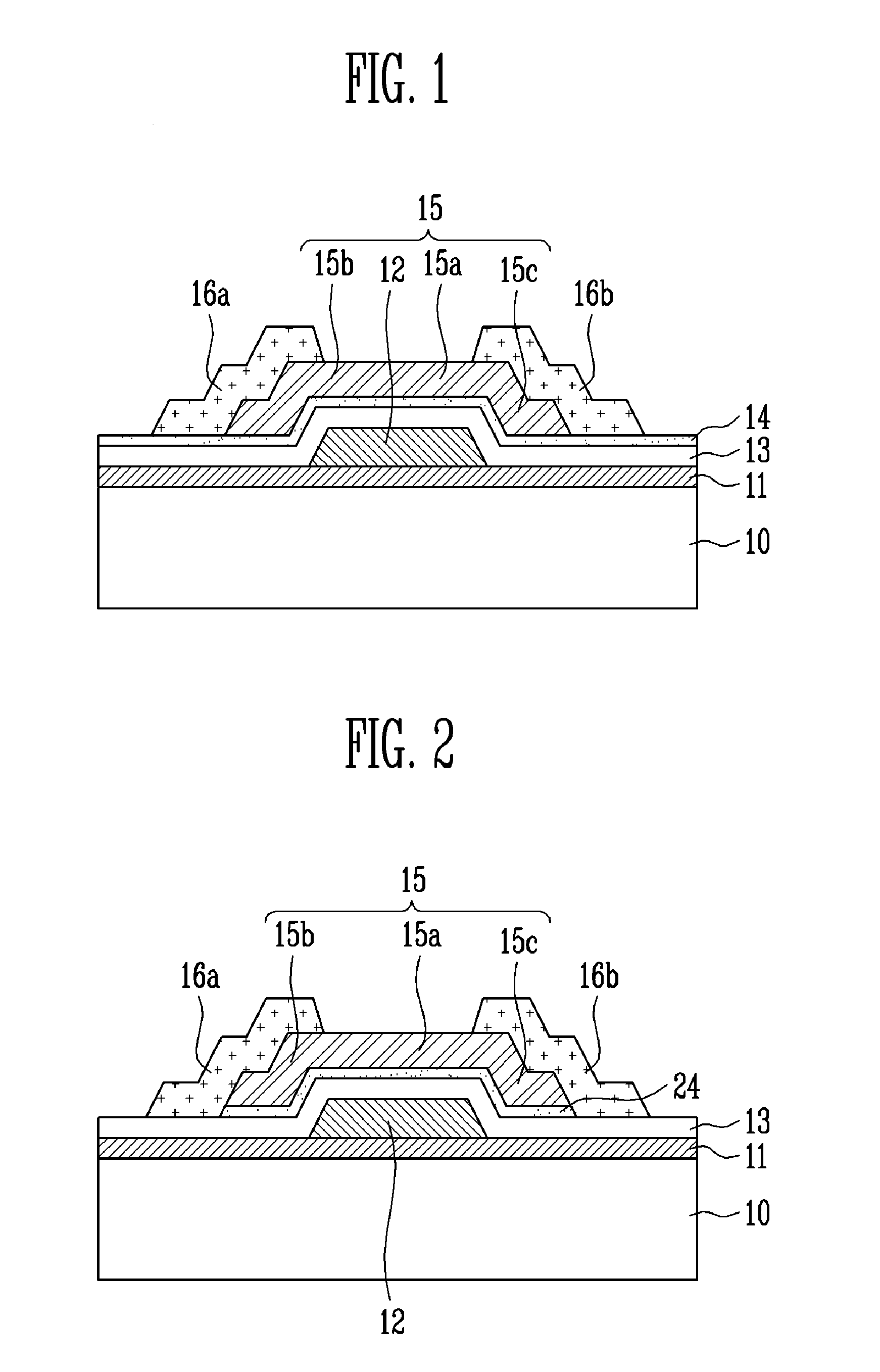

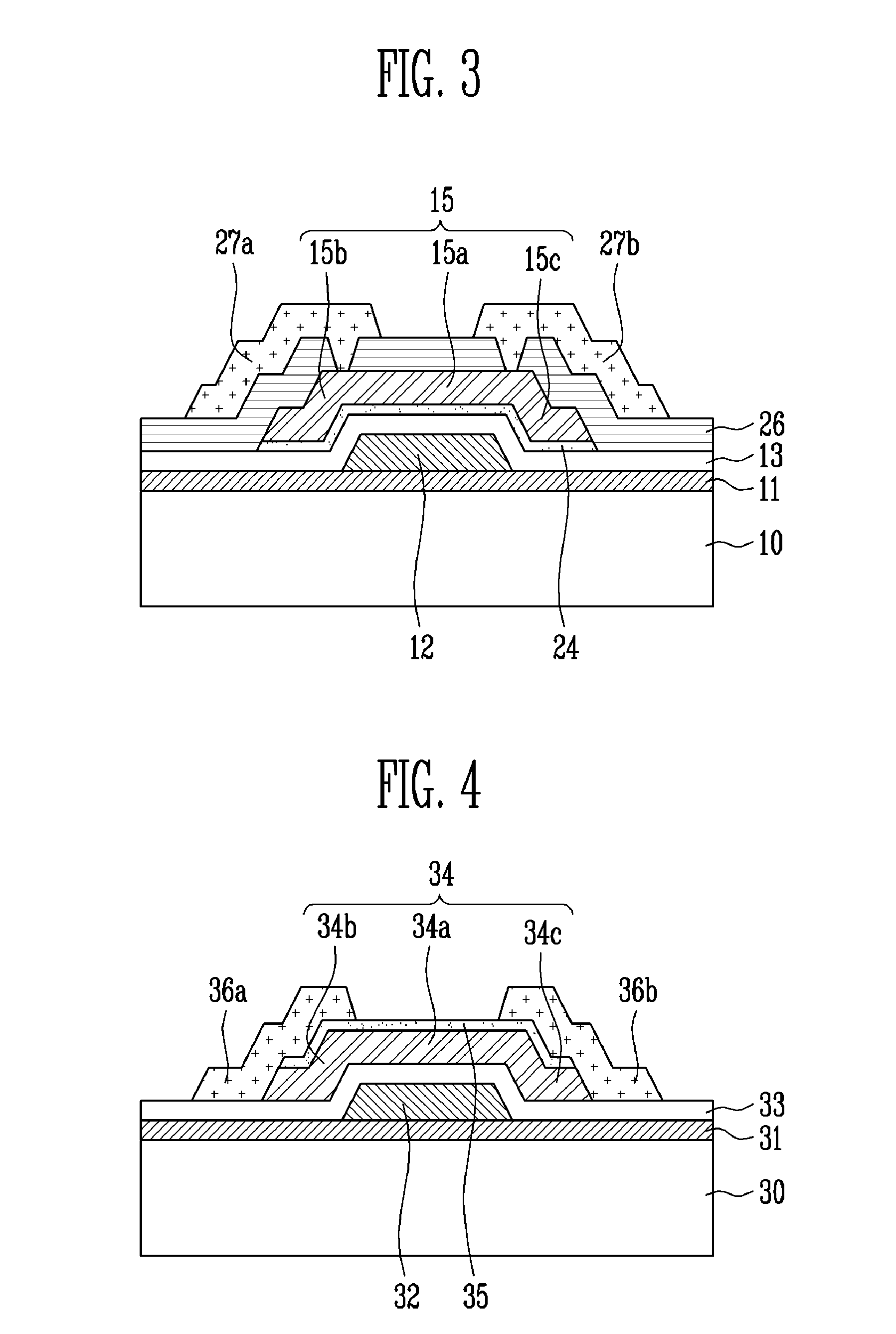

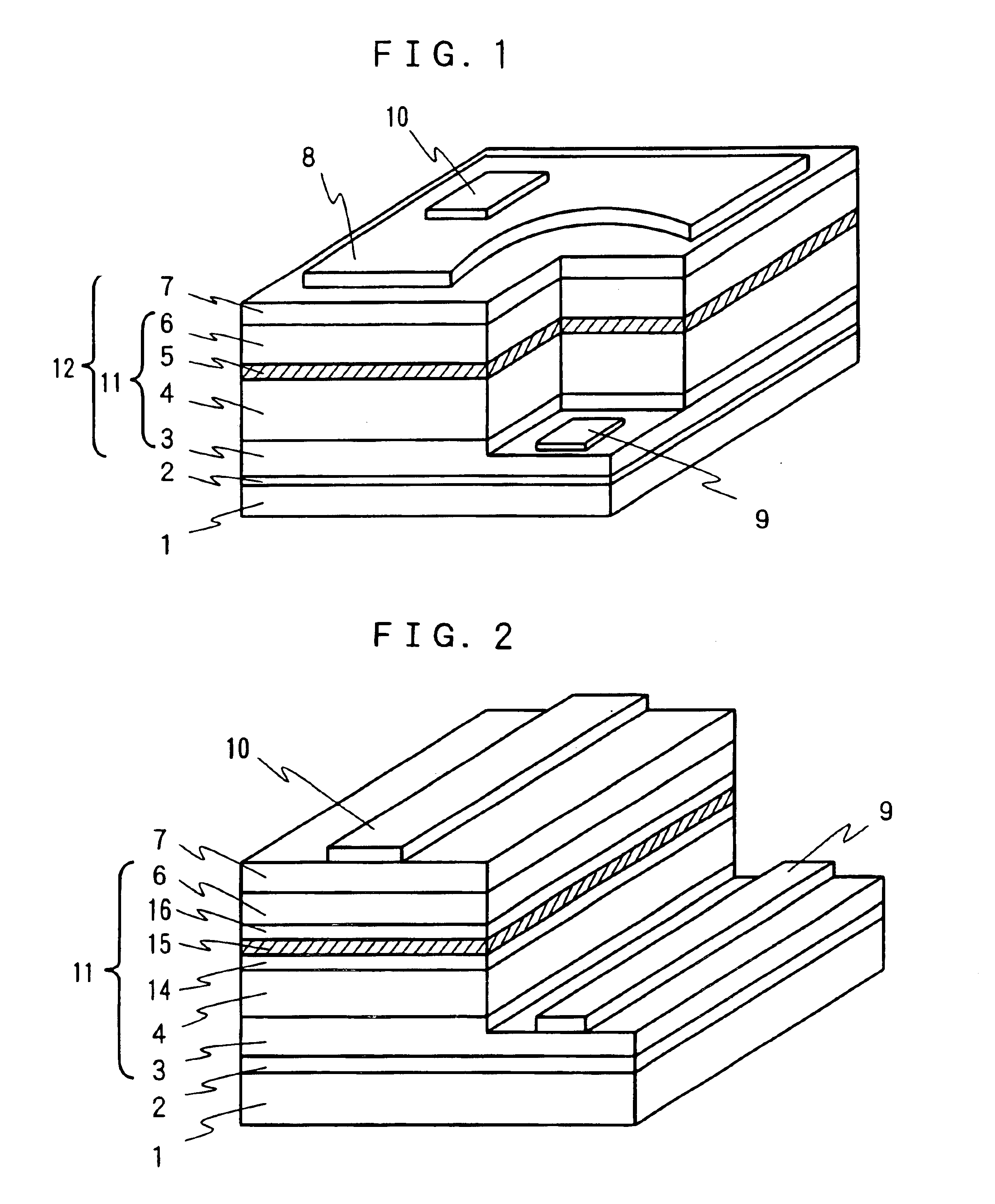

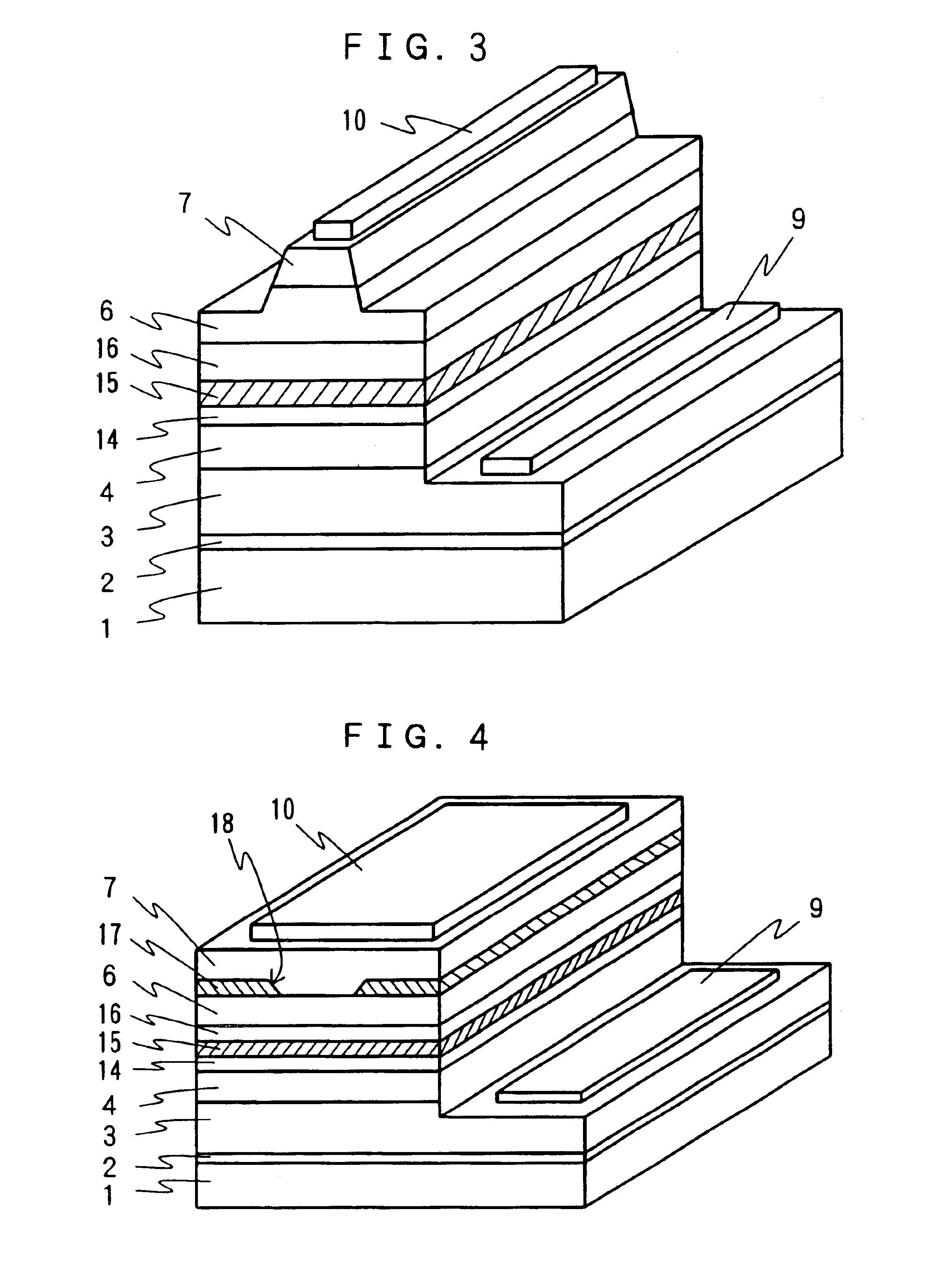

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include a gate electrode formed on a substrate; an active layer made of an oxide semiconductor and insulated from the gate electrode by a gate insulating layer; source and drain electrodes coupled to the active layer; and an interfacial stability layer formed on one or both surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristic as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

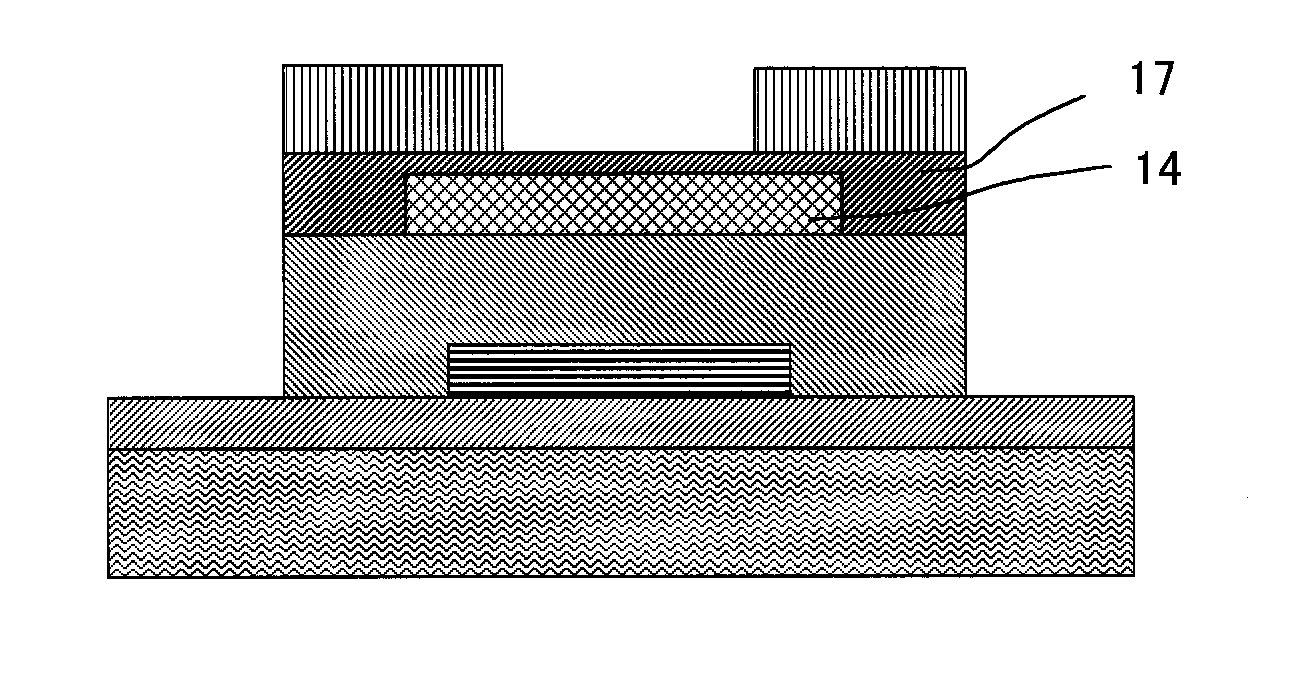

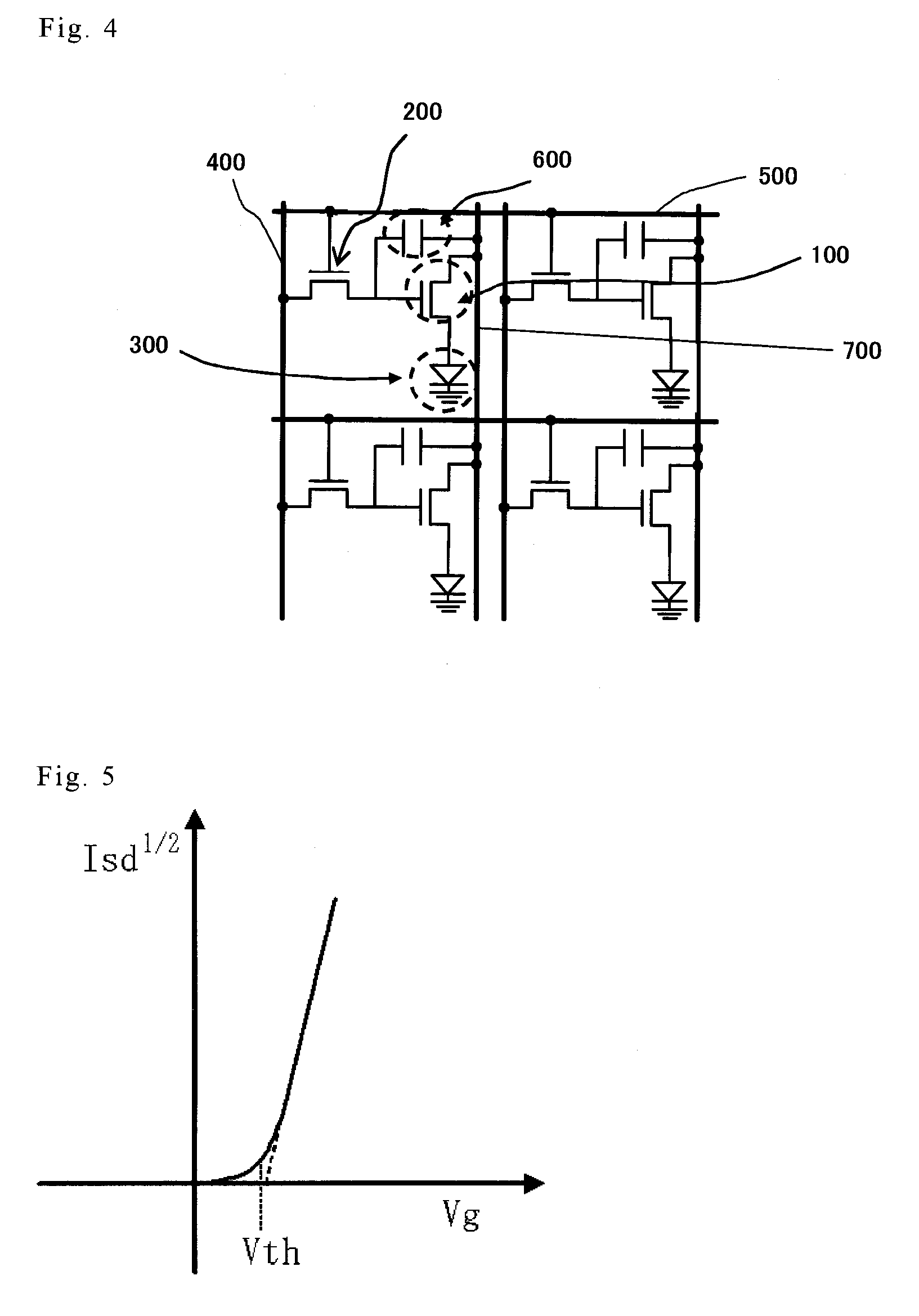

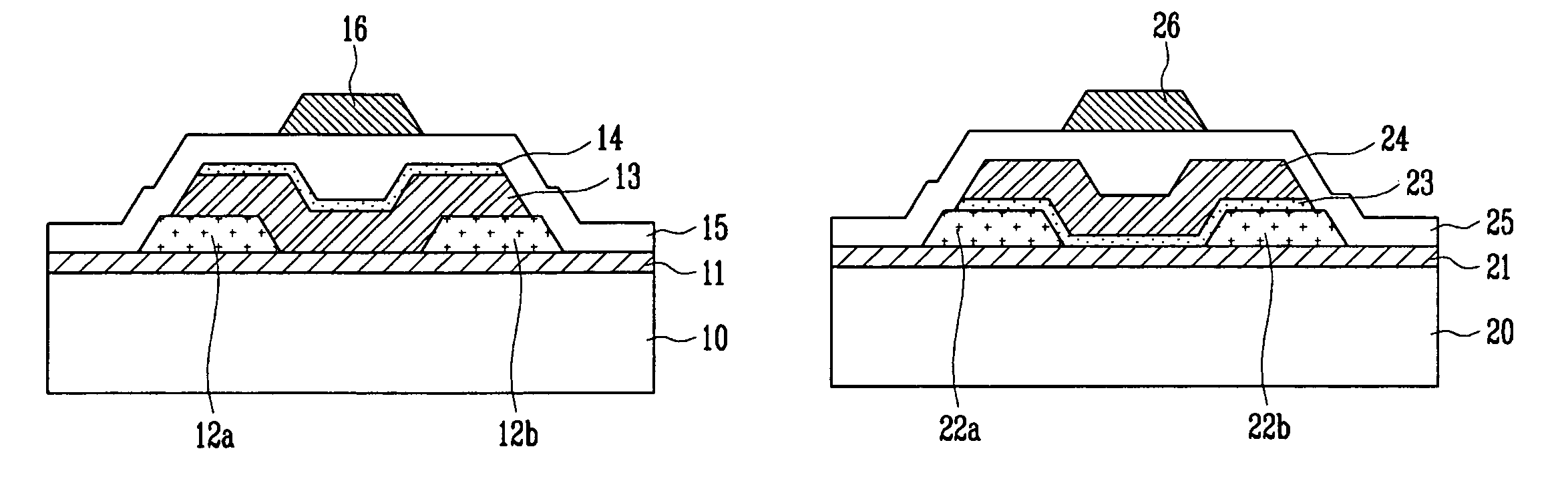

Thin film field effect transistor and display

ActiveUS8188480B2High concentrationElectroluminescent light sourcesSolid-state devicesDisplay deviceField-effect transistor

A TFT is provided which includes, on a substrate, at least a gate electrode, a gate insulating layer, an active layer containing an amorphous oxide semiconductor, a source electrode and a drain electrode, wherein a resistance layer containing an amorphous oxide and having a thickness of more than 3 nm is disposed between the active layer and at least one of the source electrode or the drain electrode, and a band gap of the active layer is smaller than a band gap of the resistance layer. Also, a display using the TFT is provided.

Owner:SAMSUNG DISPLAY CO LTD

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS7994500B2Improve featuresAvoid chargingSemiconductor/solid-state device detailsSolid-state devicesTrappingOxide thin-film transistor

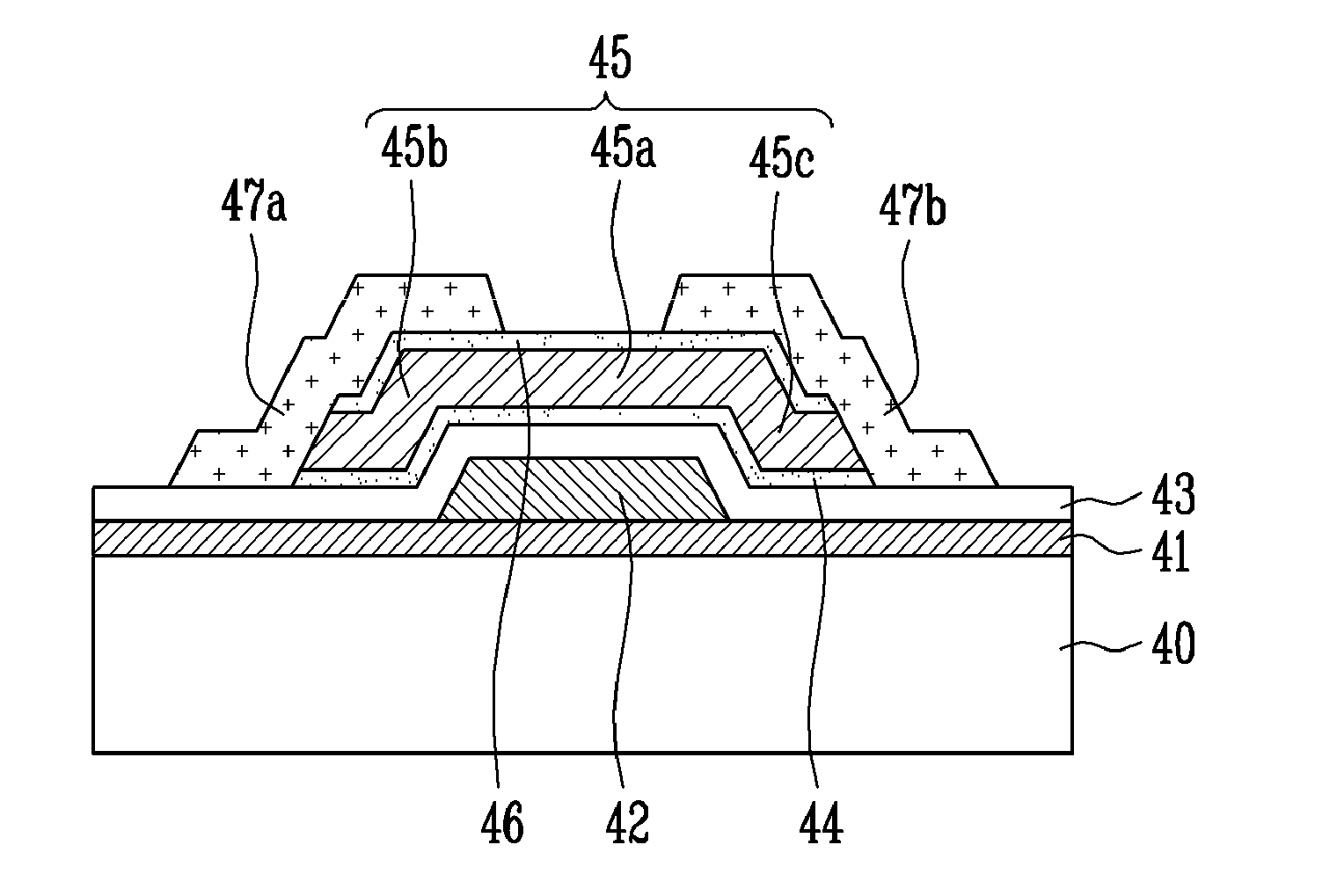

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include source and drain electrodes formed on a substrate; an active layer formed of an oxide semiconductor disposed on the source and drain electrodes; a gate electrode; and an interfacial stability layer formed on at least one of top and bottom surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristics as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

Water-soluble fluorescent nanocrystals

InactiveUS6444143B2High quantum yieldHigh spectral purityMaterial nanotechnologyNanosensorsQuantum yieldOrganic layer

A water soluble semiconductor nanocrystal capable of light emission is provided, including a quantum dot having a selected band gap energy, a layer overcoating the quantum dot, the overcoating layer comprised of a material having a band gap energy greater than that of the quantum dot, and an organic outer layer, the organic layer comprising a compound having a least one linking group for attachment of the compound to the overcoating layer and at least one hydrophilic group space apart from the linking group by a hydrophobic region sufficient to prevent electron charge transfer across the hydrophobic region. The particle size of the nanocrystal core is in the range of about 12.ANG. to about 150.ANG., with a deviation of less than 10% in the core. The coated nanocrystal exhibits photoluminescende having quantum yield of greater than 10% in water.

Owner:MASSACHUSETTS INST OF TECH

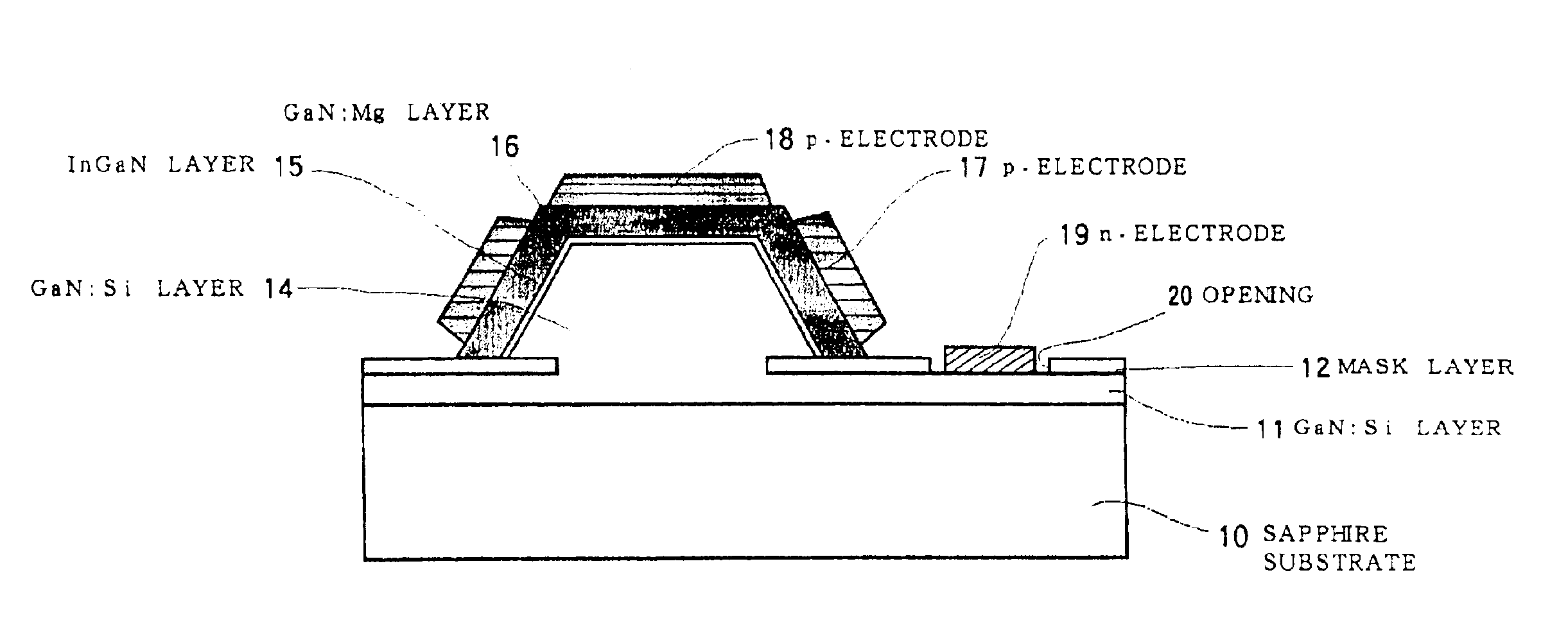

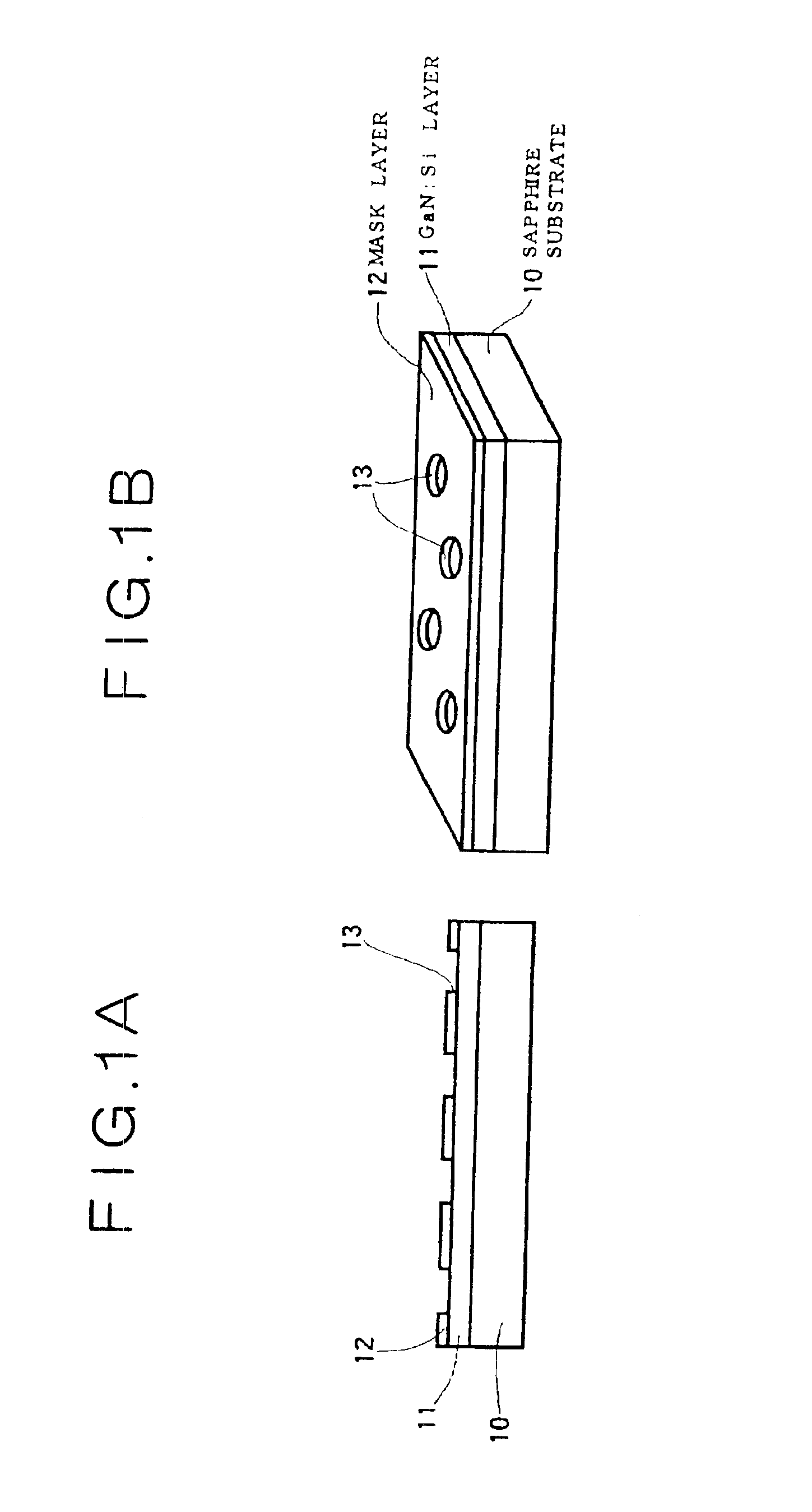

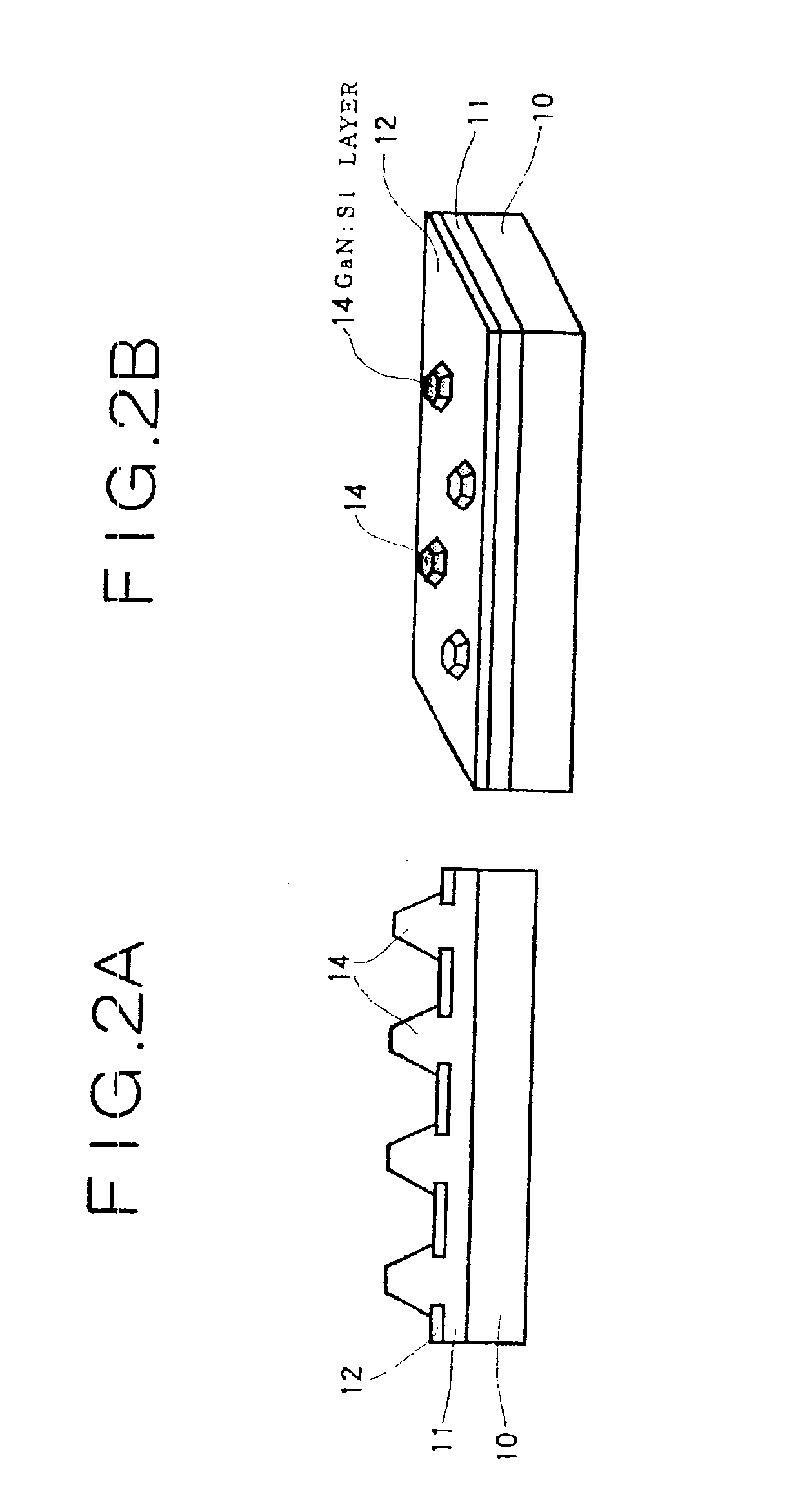

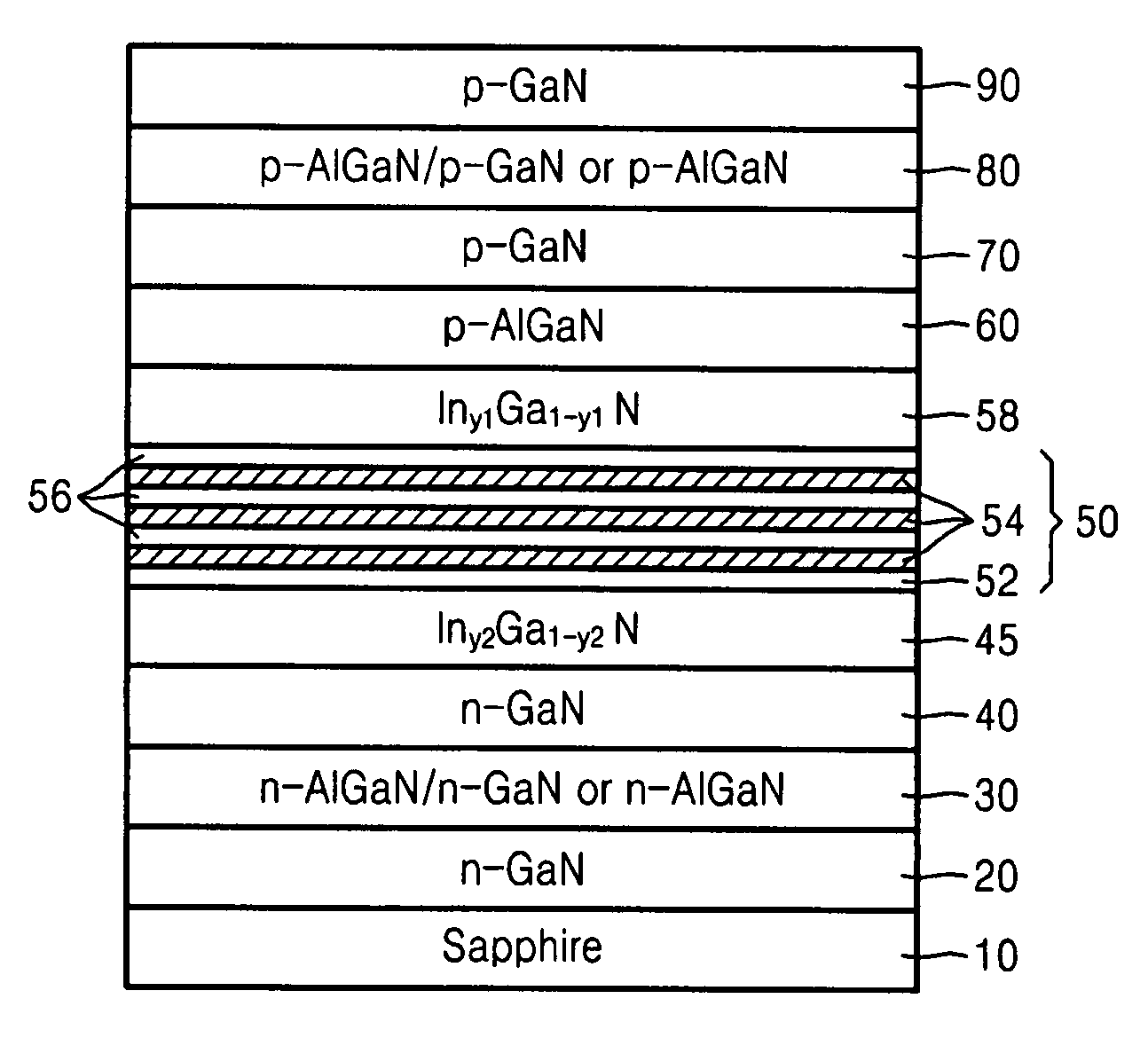

Semiconductor light-emitting device and semiconductor light-emitting device

InactiveUS7087932B2Well formedSolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeCrystallinity

Owner:SAMSUNG ELECTRONICS CO LTD

Nitride based semiconductor device

ActiveUS7084420B2Improve efficiencyEliminate the effects ofNanoopticsSemiconductor lasersDevice materialQuantum well

The present invention provides a nitride based semiconductor device comprising an active layer having a quantum well layer and a quantum barrier layer, wherein the device includes an electron emitting layer formed of at least two repeats of a first nitride semiconductor layer and a second nitride semiconductor layer having different compositions between a n-type nitride semiconductor layer and the active layer, the first nitride semiconductor layer has an energy band gap greater than that of the quantum well layer, smaller than that of the quantum barrier layer, and decreasing closer to the active layer, and the second nitride semiconductor layer has an energy band gap at least higher than that of the adjacent first nitride semiconductor layer(s) and has a thickness capable of tunneling electrons.

Owner:SAMSUNG ELECTRONICS CO LTD

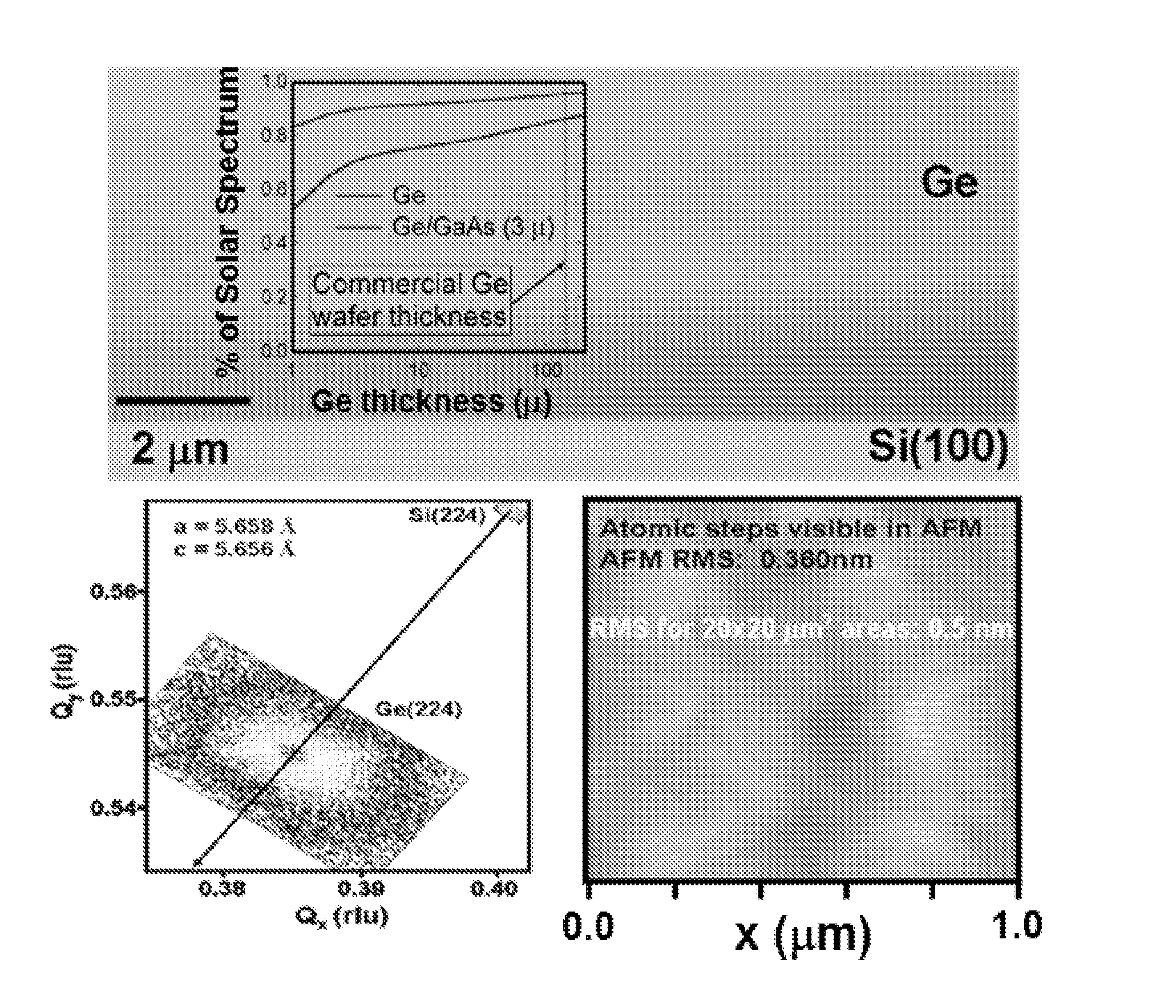

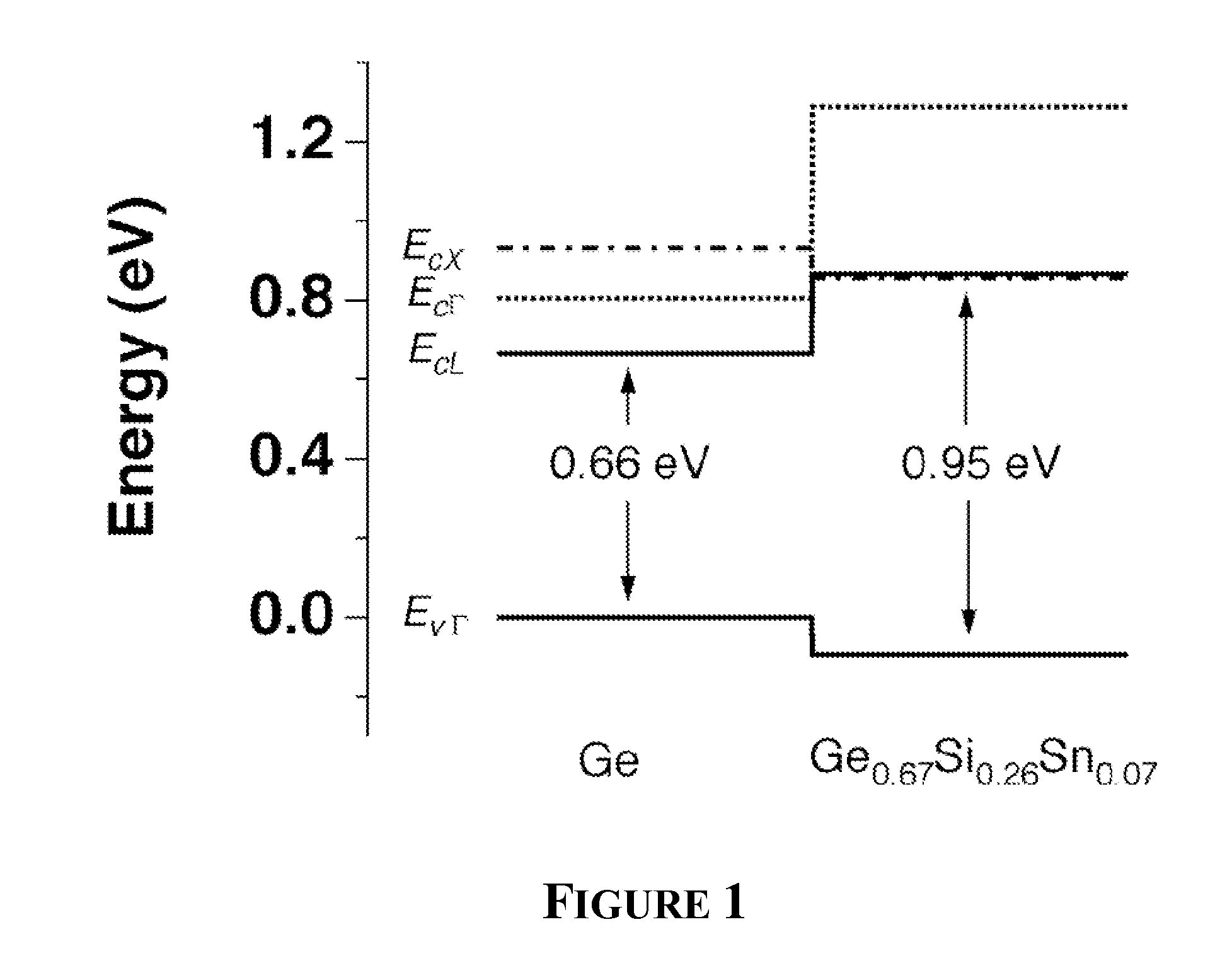

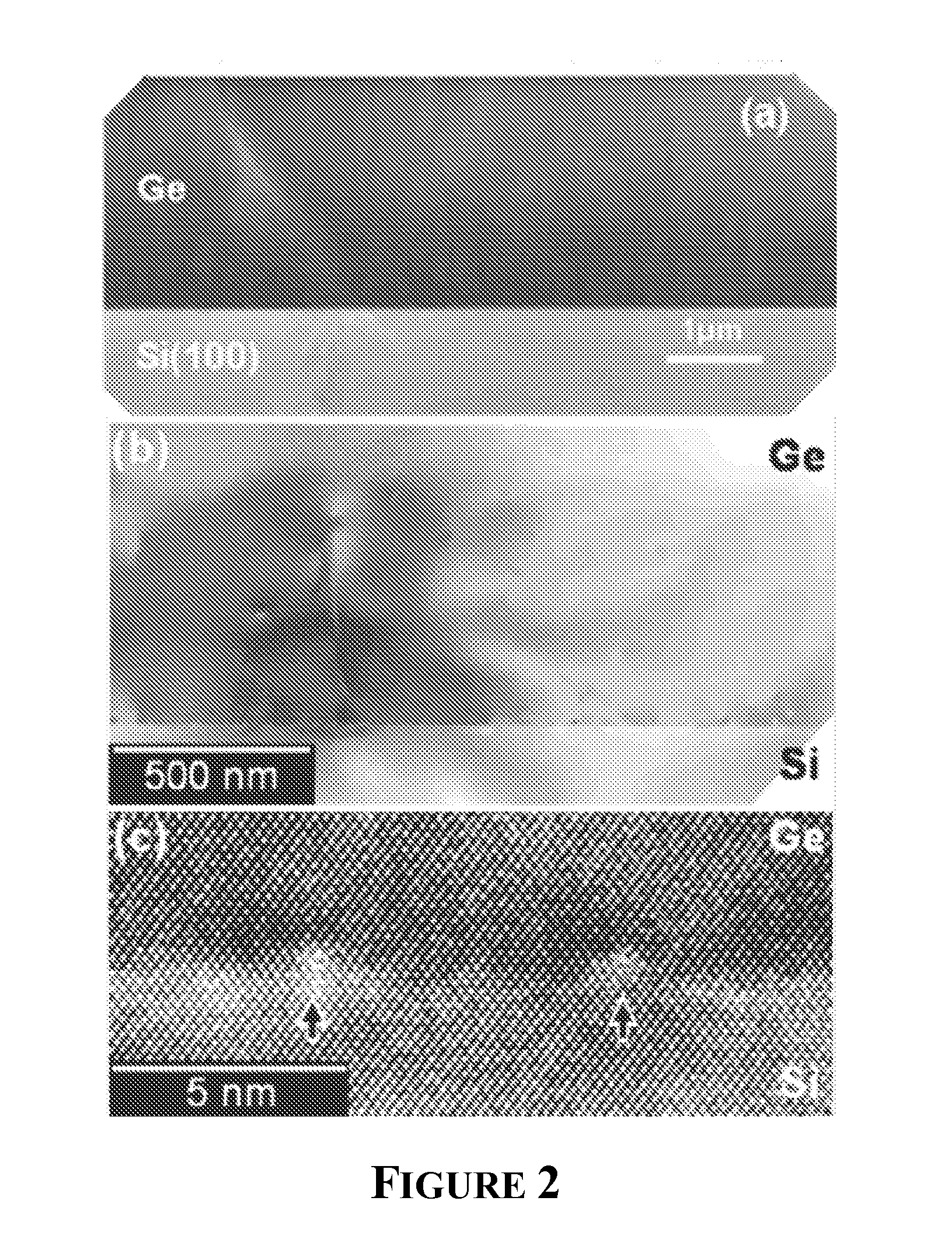

Hybrid Group IV/III-V Semiconductor Structures

InactiveUS20110254052A1Low costImprove efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor structureAlloy

Described herein are semiconductor structures comprising (i) a Si substrate; (ii) a buffer region formed directly over the Si substrate, wherein the buffer region comprises (a) a Ge layer having a threading dislocation density below about 105 cm−2; or (b) a Ge1-xSnx layer formed directly over the Si substrate and a Ge1-x-ySixSny layer formed over the Ge1-xSnx layer; and (iii) a plurality of III-V active blocks formed over the buffer region, wherein the first III-V active block formed over the buffer region is lattice matched or pseudomorphically strained to the buffer region. Further, methods for forming the semiconductor structures are provided and novel Ge1-x-ySixSny, alloys are provided that are lattice matched or pseudomorphically strained to Ge and have tunable band gaps ranging from about 0.80 eV to about 1.4O eV.

Owner:ARIZONA STATE UNIVERSITY

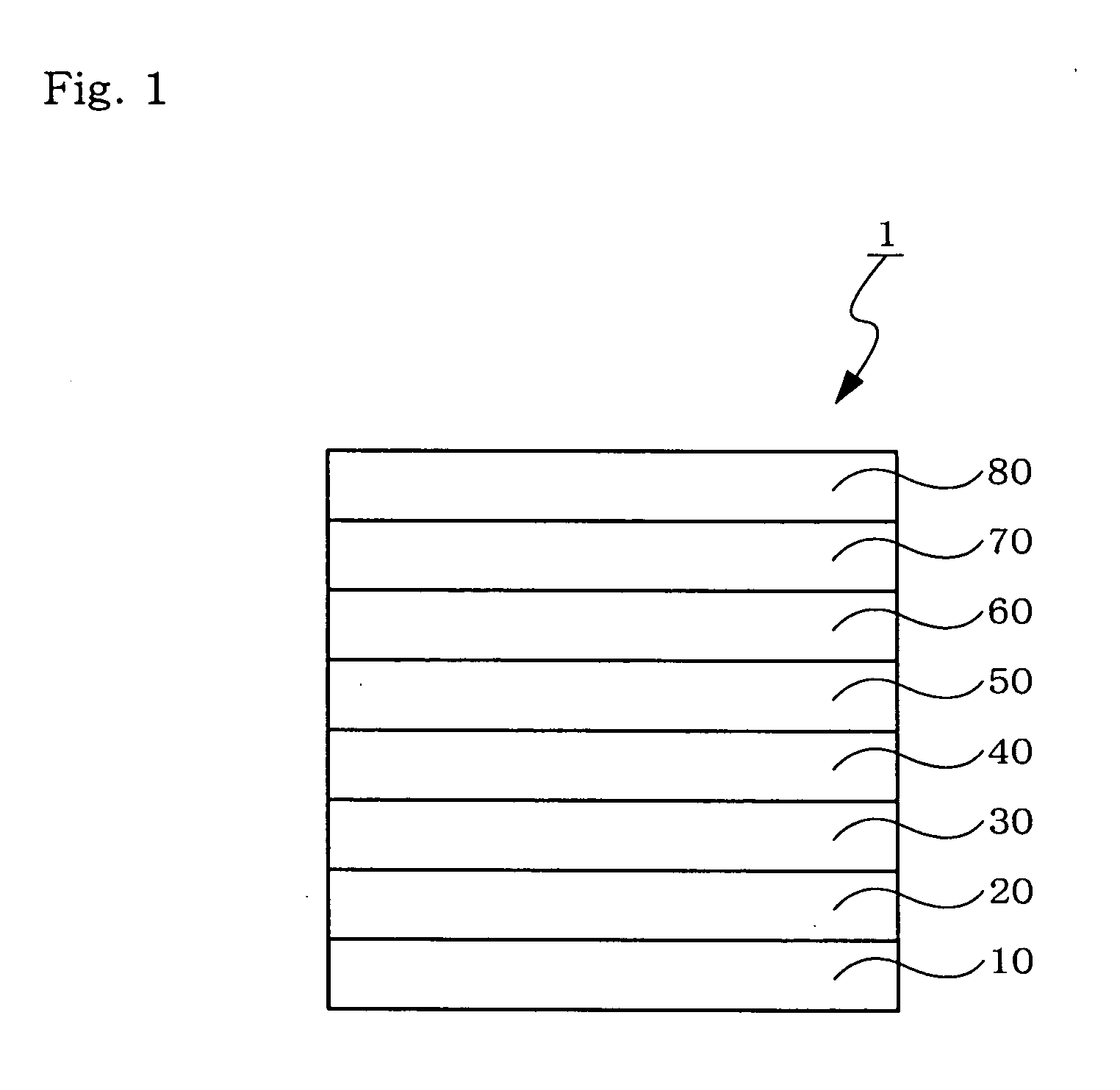

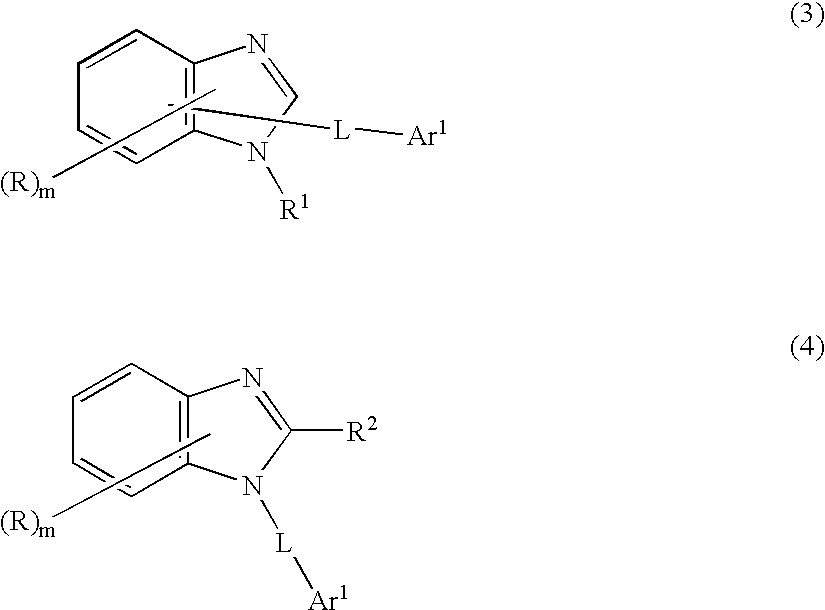

Organic electroluminescent device

InactiveUS20070104977A1Improve efficiencyHigh color purityDischarge tube luminescnet screensLamp detailsDopantAryl

An organic electroluminescent device 1 comprising, an emitting layer (50) and an electron-transporting layer (60) between a cathode (80) and an anode (20), the electron-transporting layer (60) comprising a compound represented by formula (1), the emitting layer (50) comprising a host material which is a compound with an energy gap of 2.8 eV or less represented by formula (2) and a dopant which is an indenoperylene derivative, A-B (1) wherein A is an aromatic hydrocarbon group with three or more carbocycles and B is a substituted or unsubstituted heterocyclic group, X—(Y)n (2) wherein X is a condensed aromatic ring group with three or more carbocycles, Y is a group selected from substituted or unsubstituted aryl, substituted or unsubstituted diarylamino, substituted or unsubstituted arylalkyl and substituted or unsubstituted alkyl groups, and n is an integer of 1 to 6, provided that Ys may be the same or different when n is 2 or more.

Owner:IDEMITSU KOSAN CO LTD

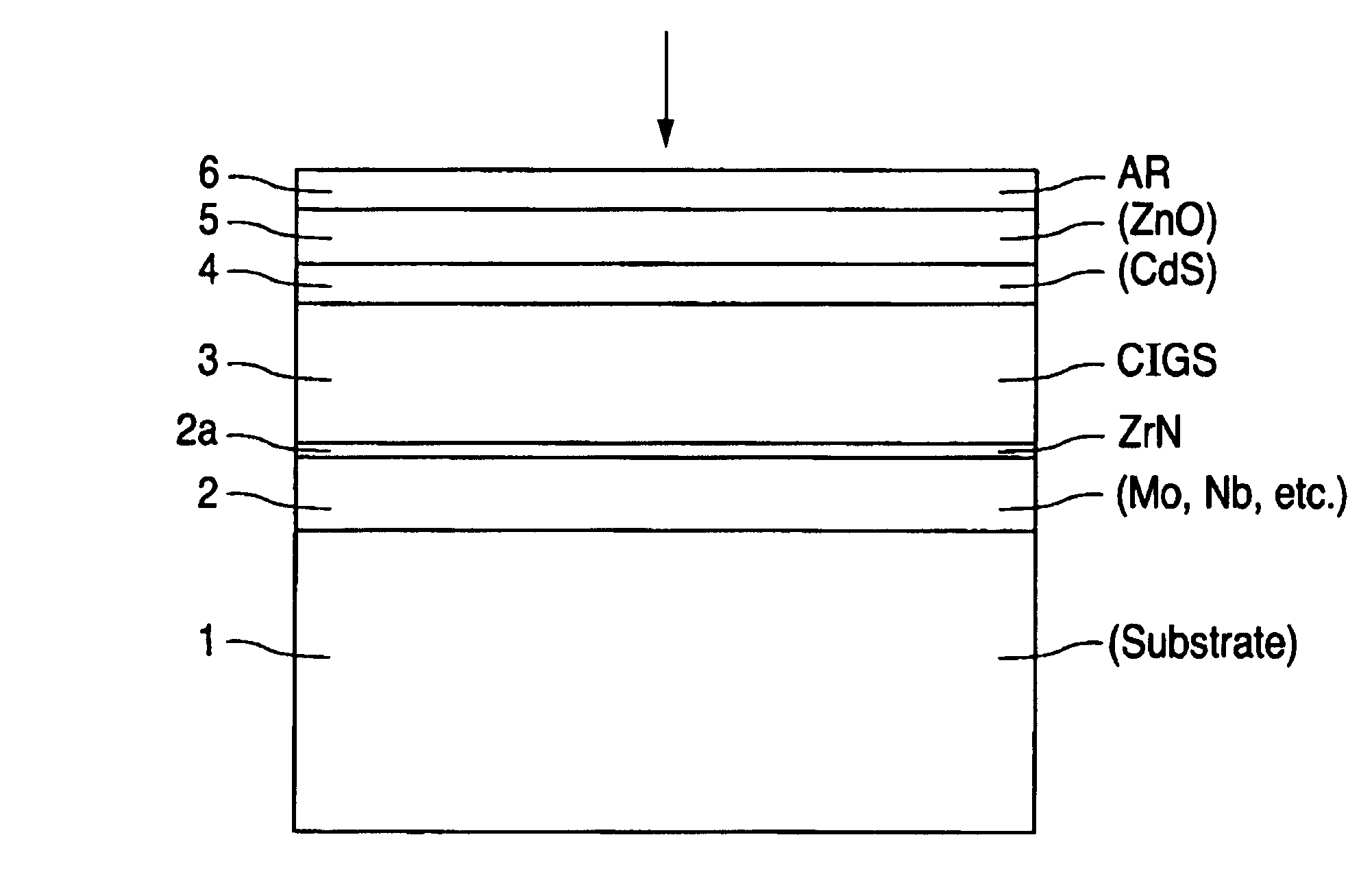

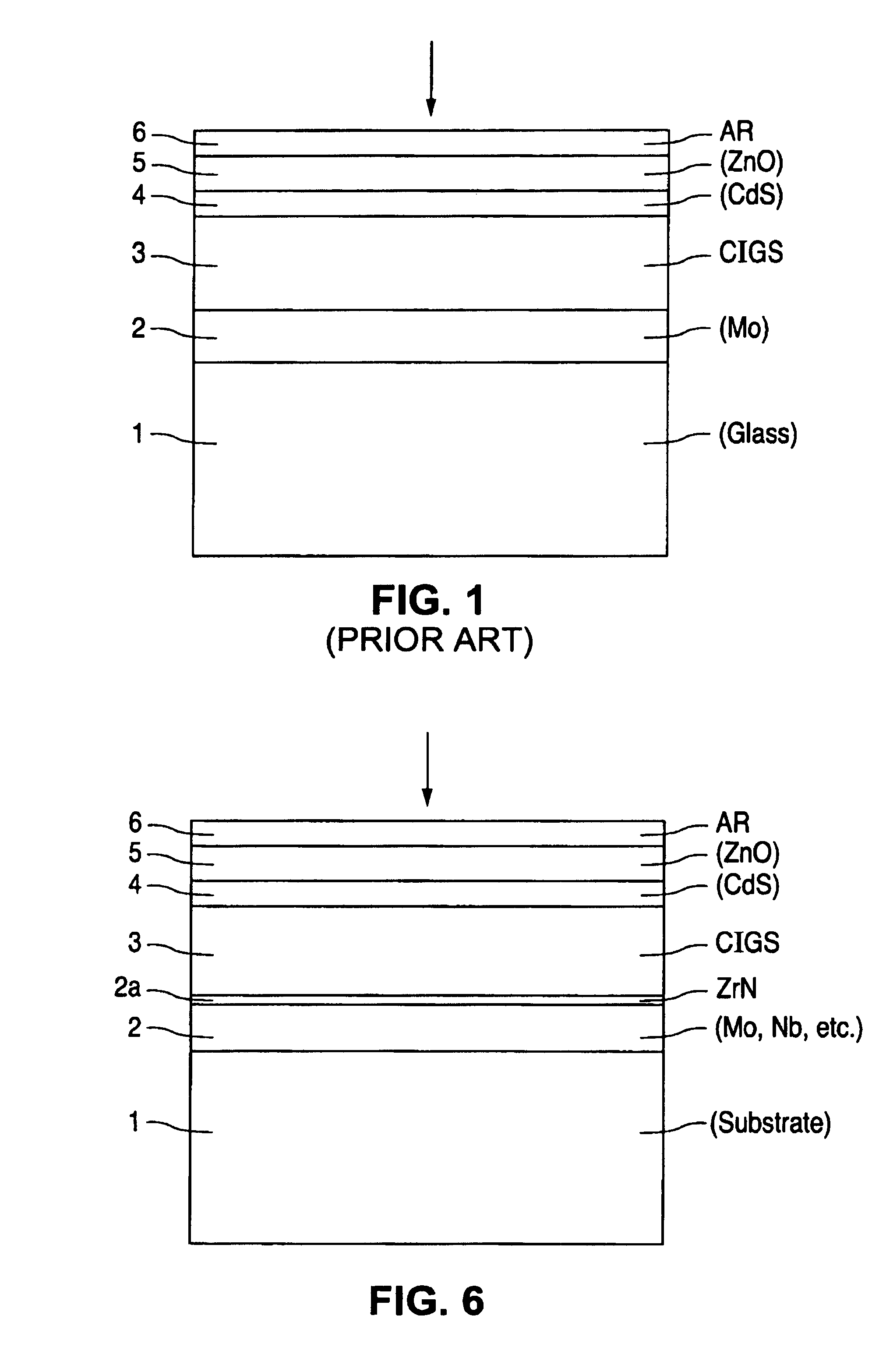

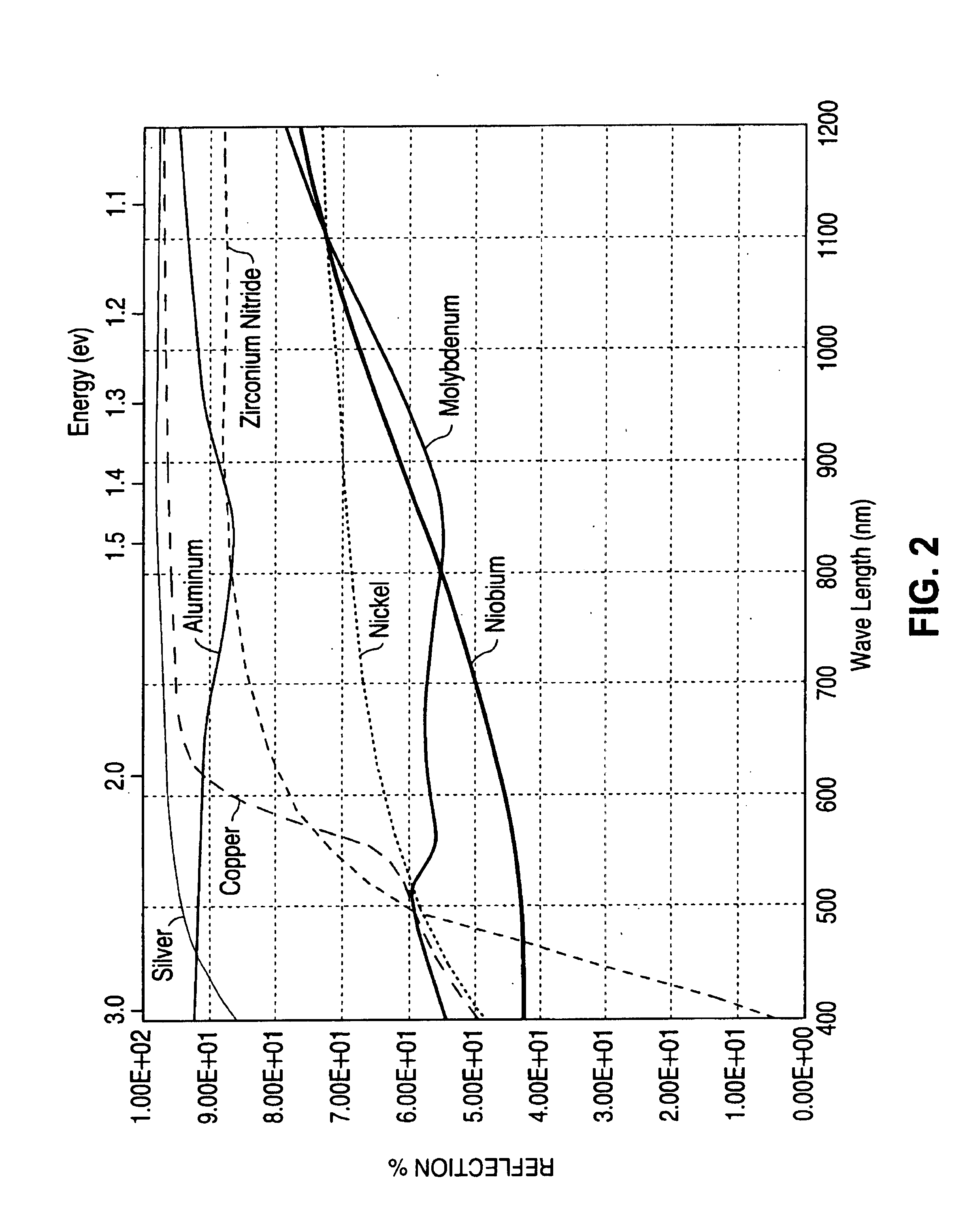

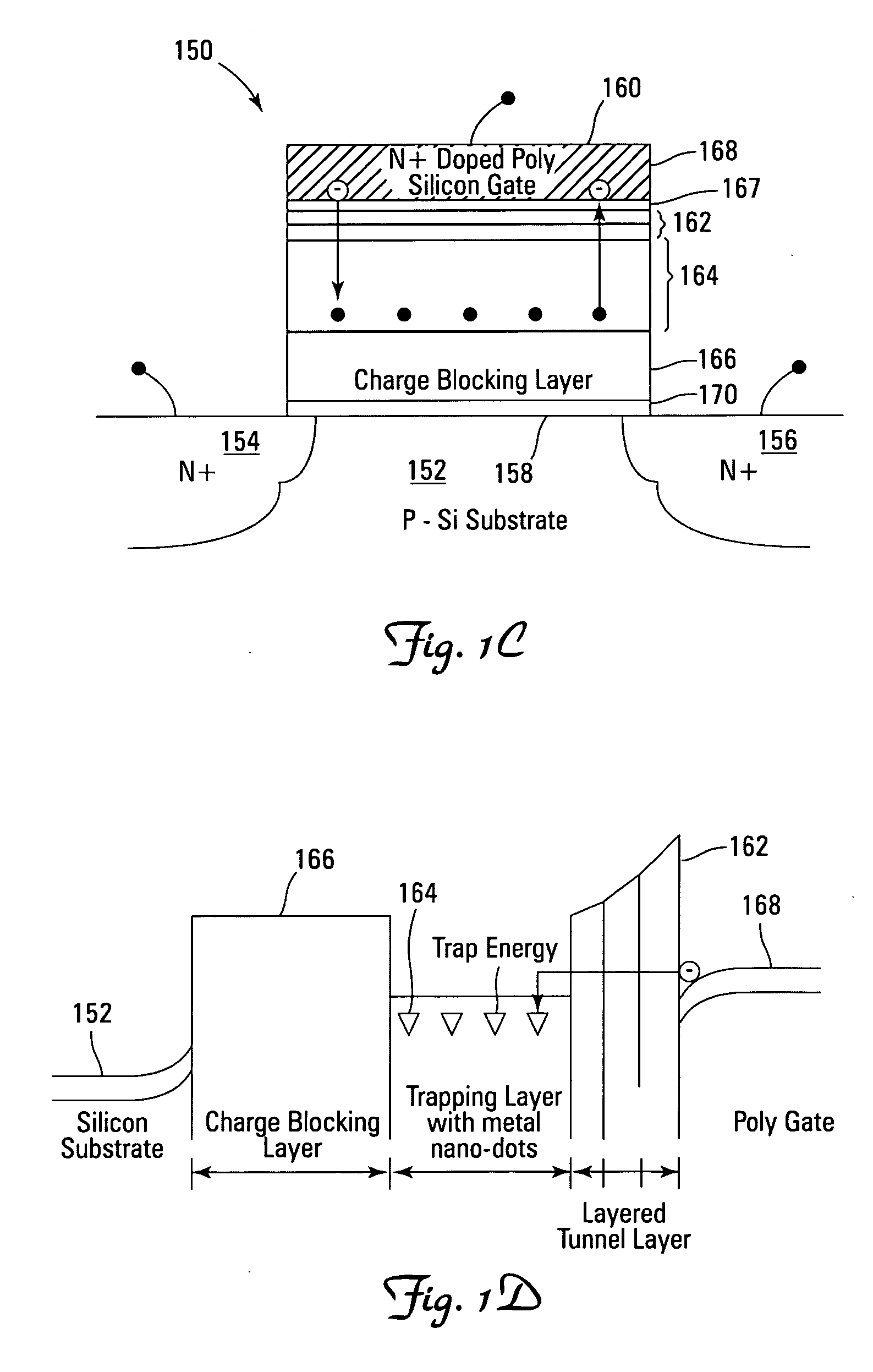

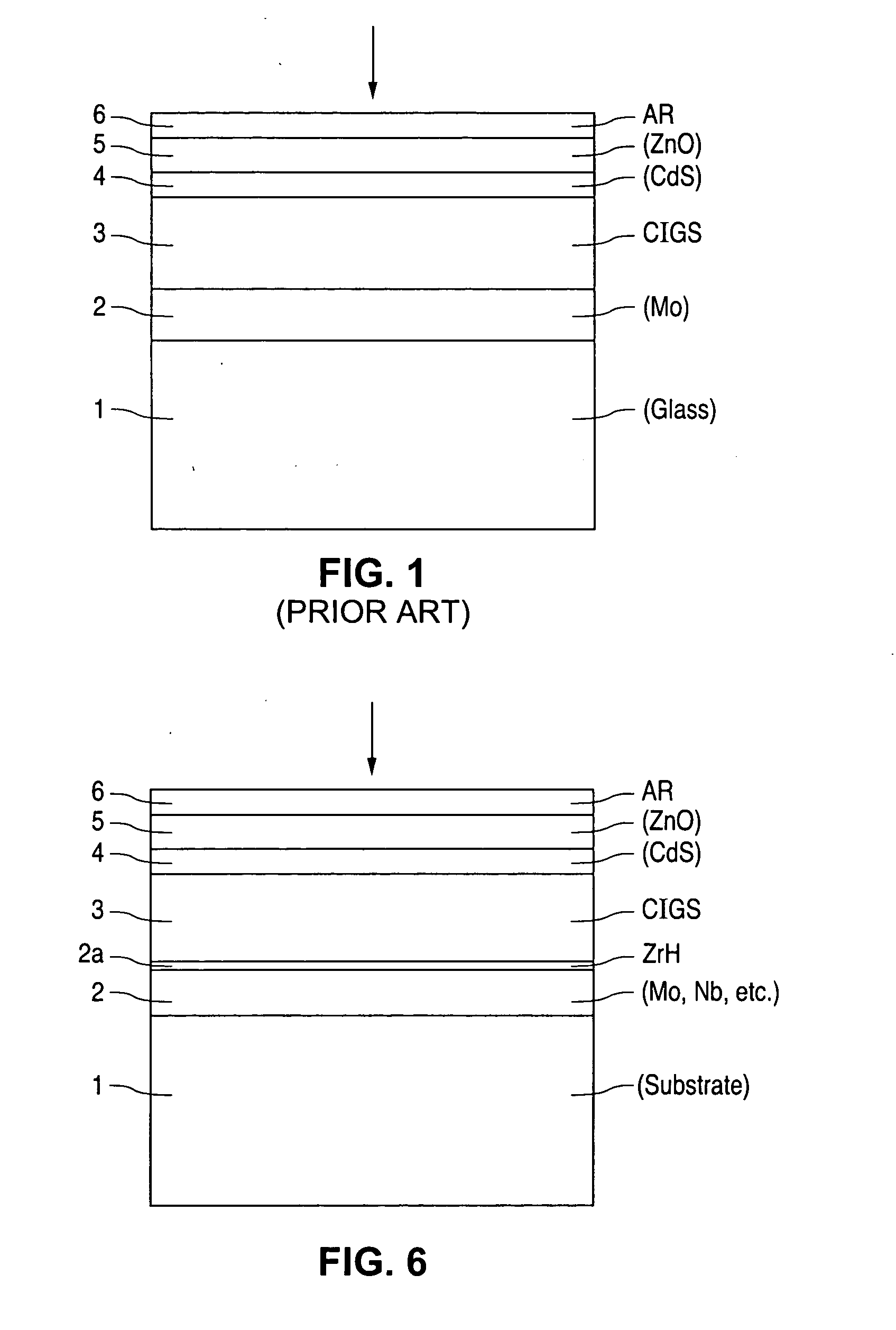

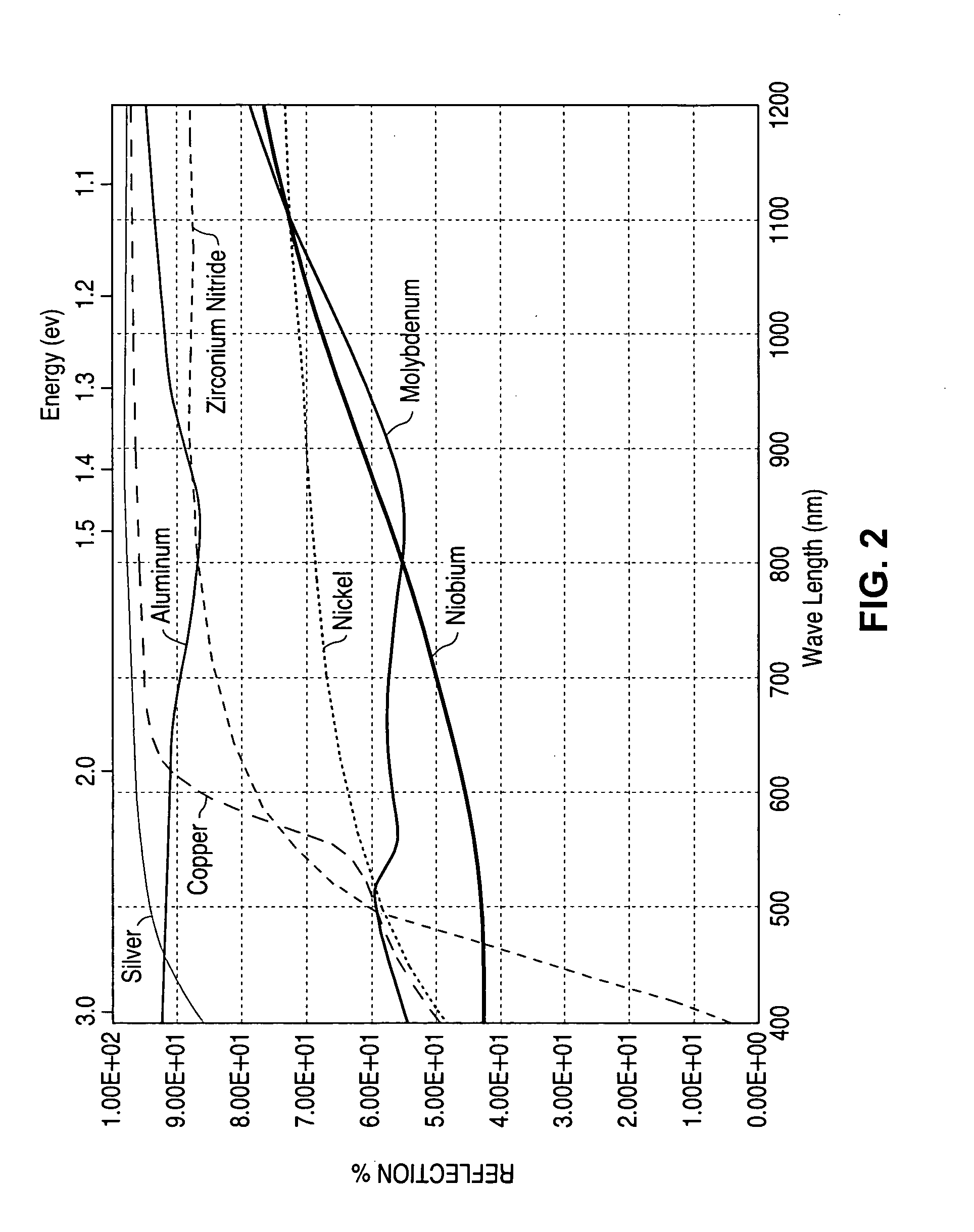

Thin-film solar cells

InactiveUS6974976B2Increase reflectionInhibition formationFinal product manufactureVacuum evaporation coatingIndiumElectrical battery

A method of manufacturing improved thin-film solar cells entirely by sputtering includes a high efficiency back contact / reflecting multi-layer containing at least one barrier layer consisting of a transition metal nitride. A copper indium gallium diselenide (Cu(InXGa1−X)Se2) absorber layer (X ranging from 1 to approximately 0.7) is co-sputtered from specially prepared electrically conductive targets using dual cylindrical rotary magnetron technology. The band gap of the absorber layer can be graded by varying the gallium content, and by replacing the gallium partially or totally with aluminum. Alternately the absorber layer is reactively sputtered from metal alloy targets in the presence of hydrogen selenide gas. RF sputtering is used to deposit a non-cadmium containing window layer of ZnS. The top transparent electrode is reactively sputtered aluminum doped ZnO. A unique modular vacuum roll-to-roll sputtering machine is described. The machine is adapted to incorporate dual cylindrical rotary magnetron technology to manufacture the improved solar cell material in a single pass.

Owner:BEIJING APOLLO DING RONG SOLAR TECH

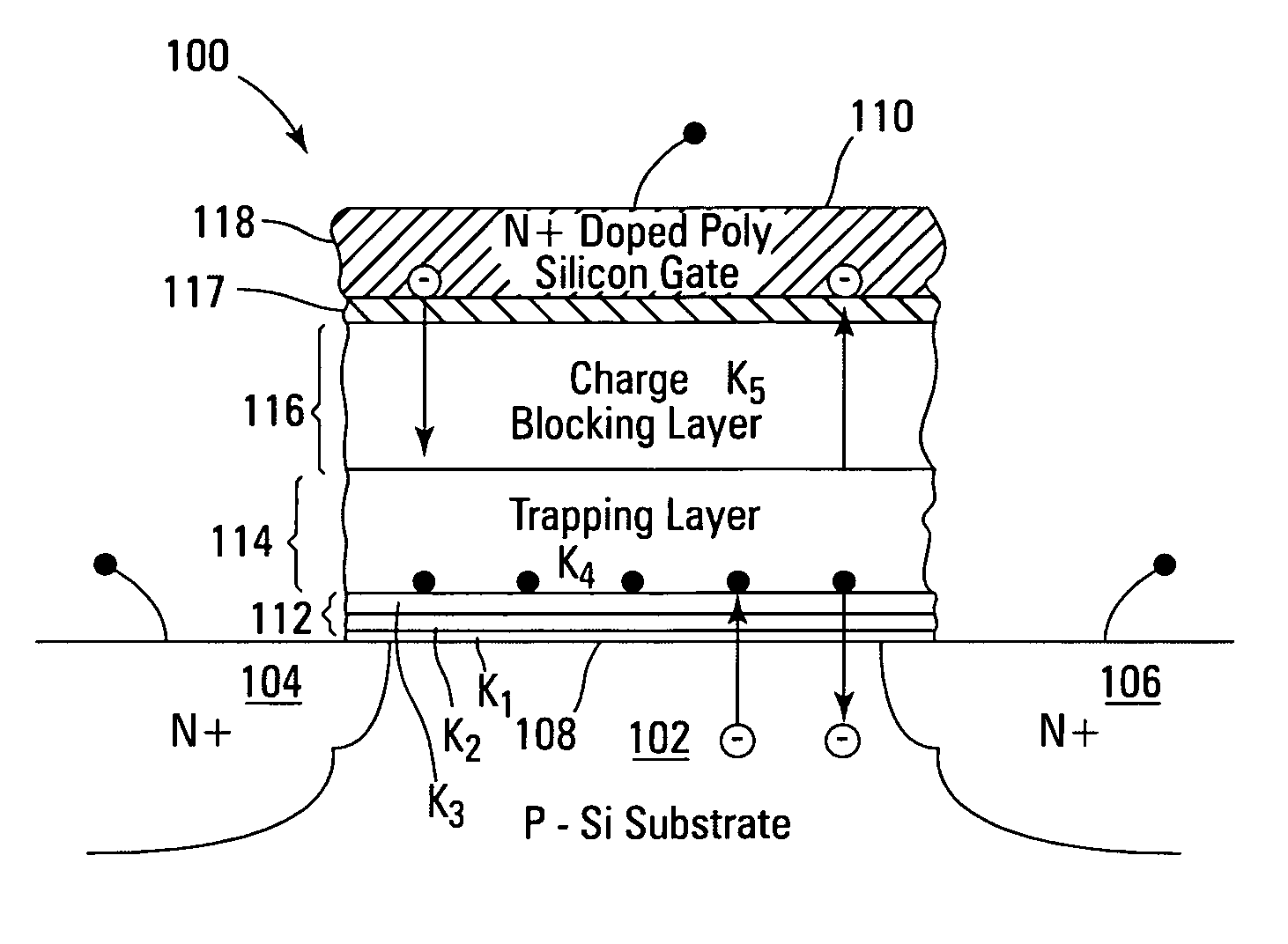

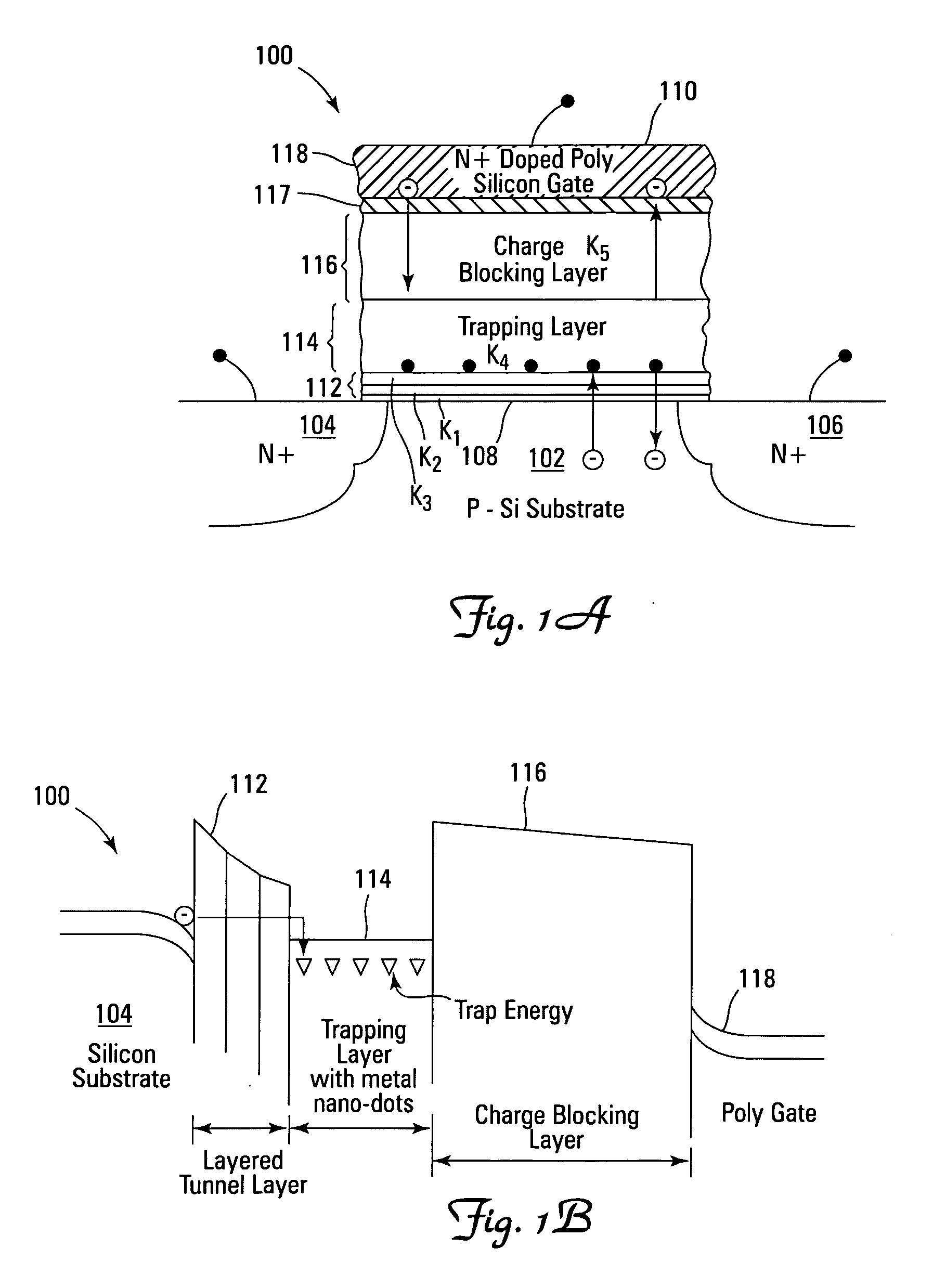

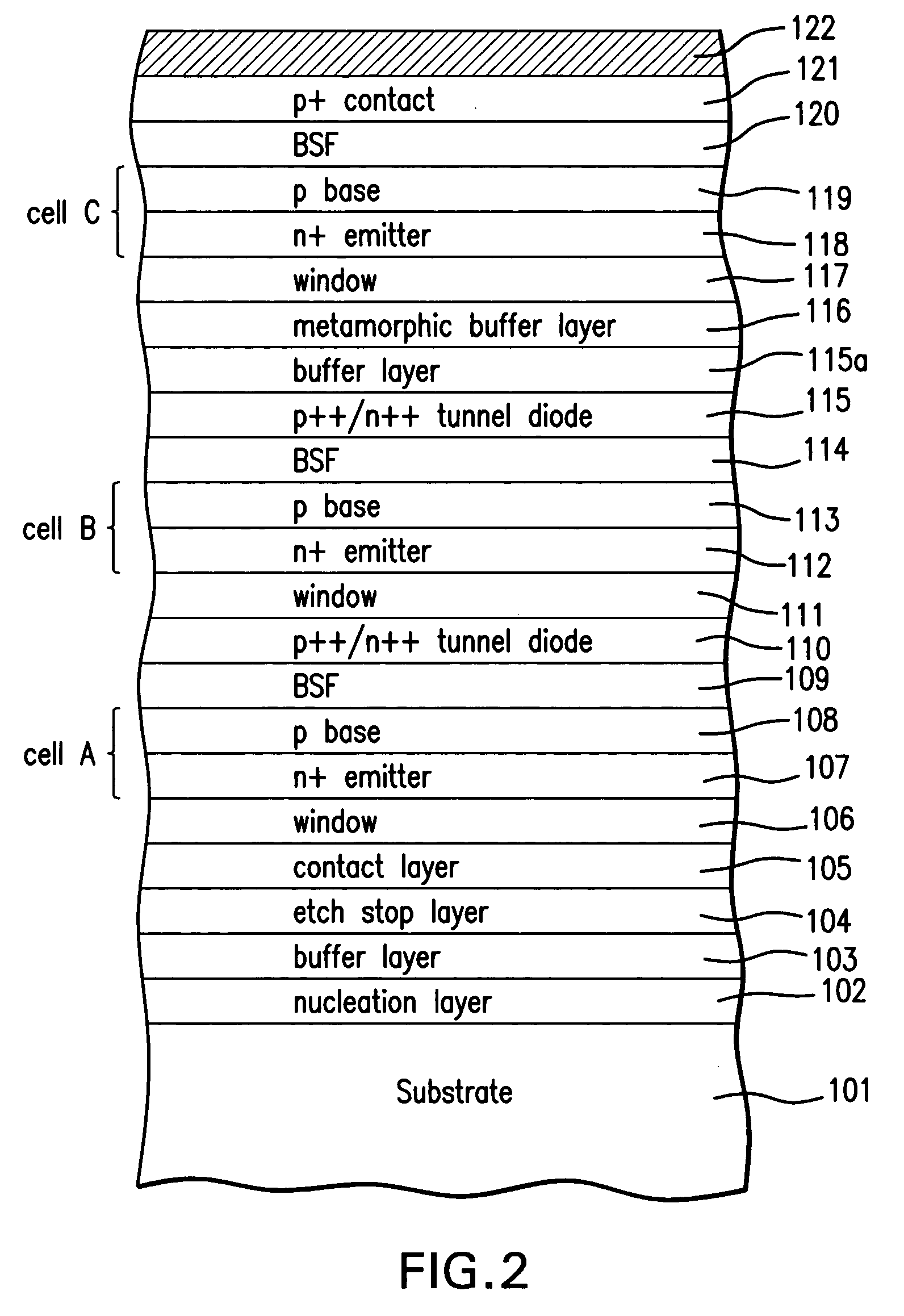

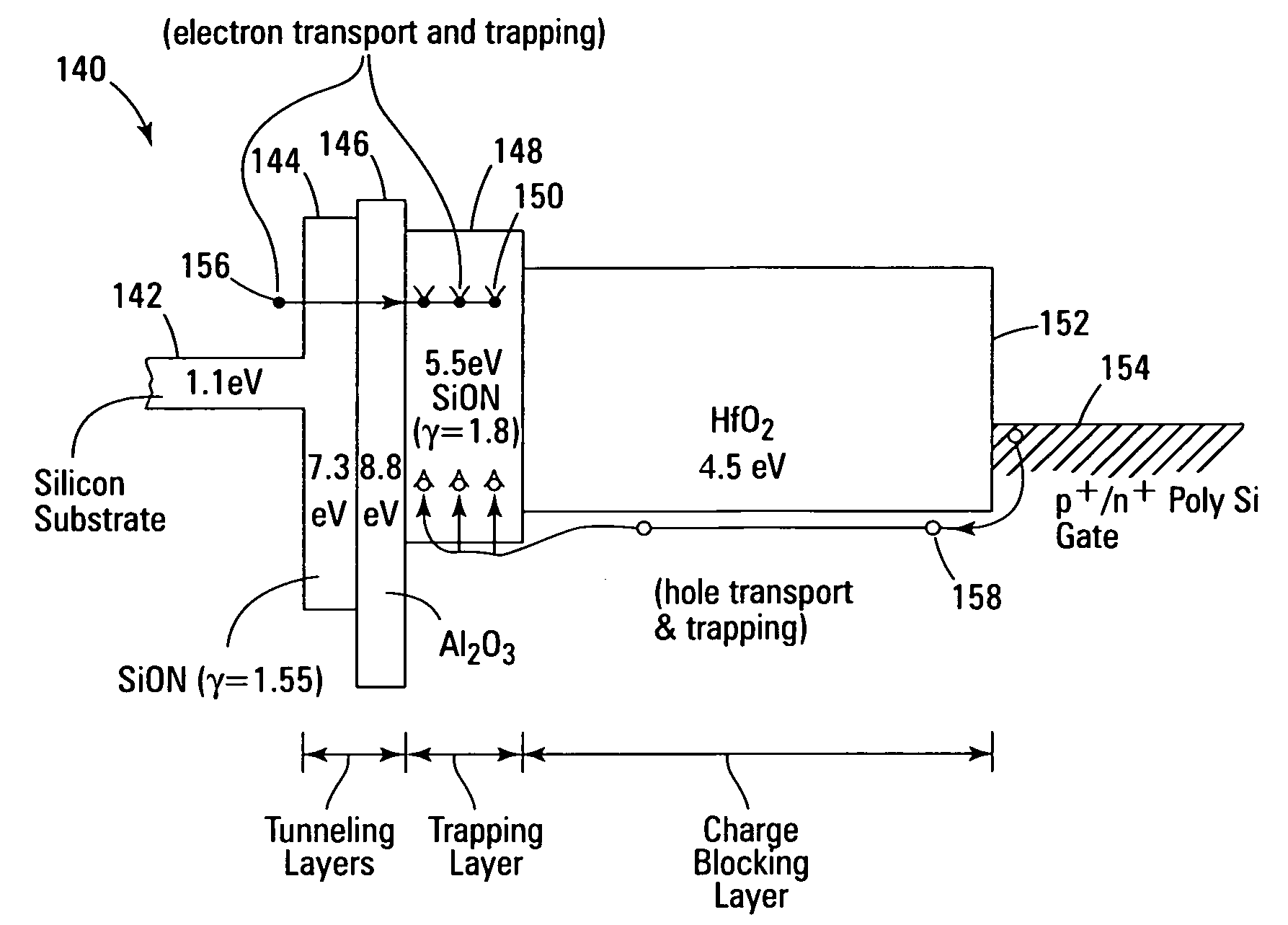

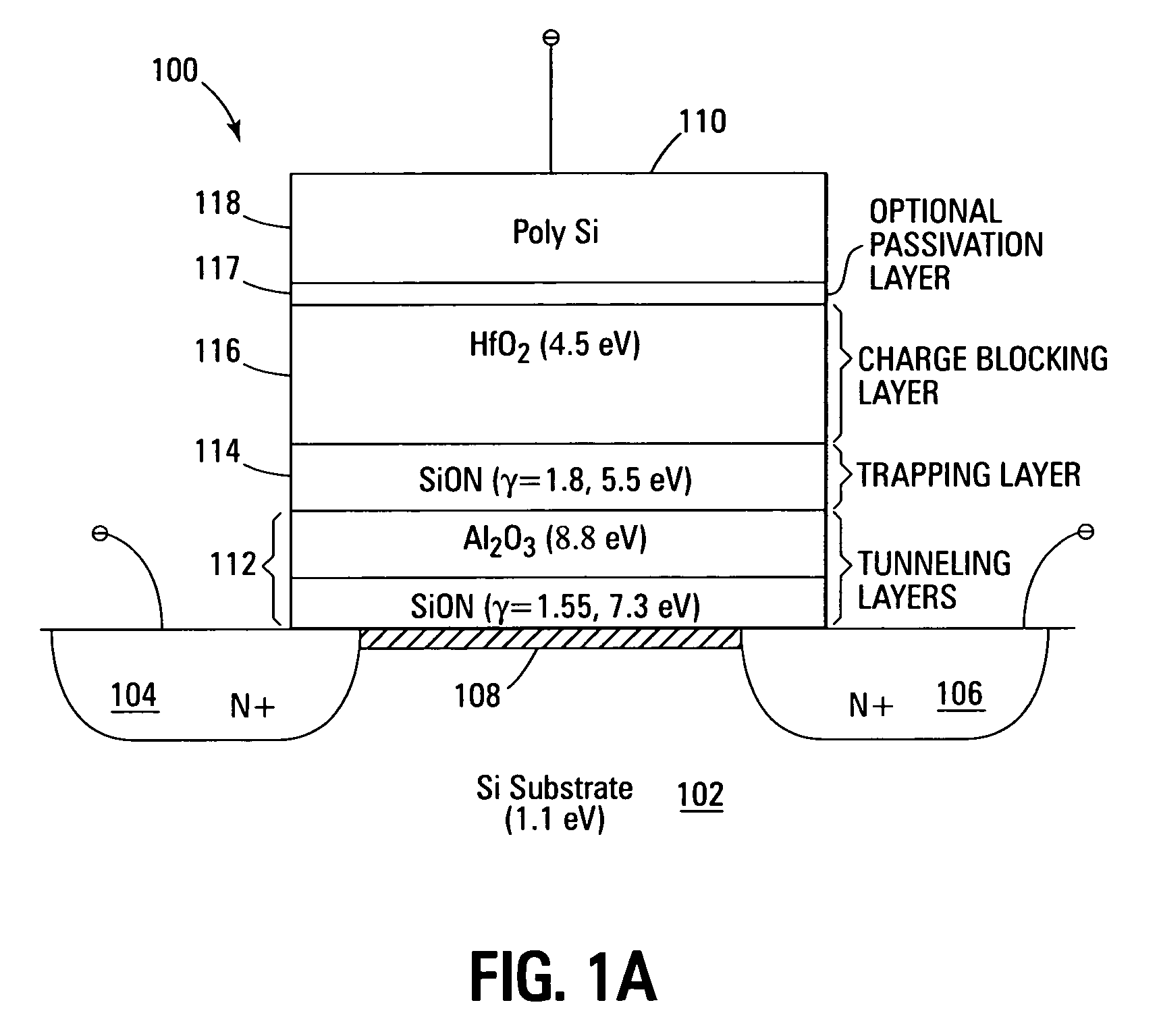

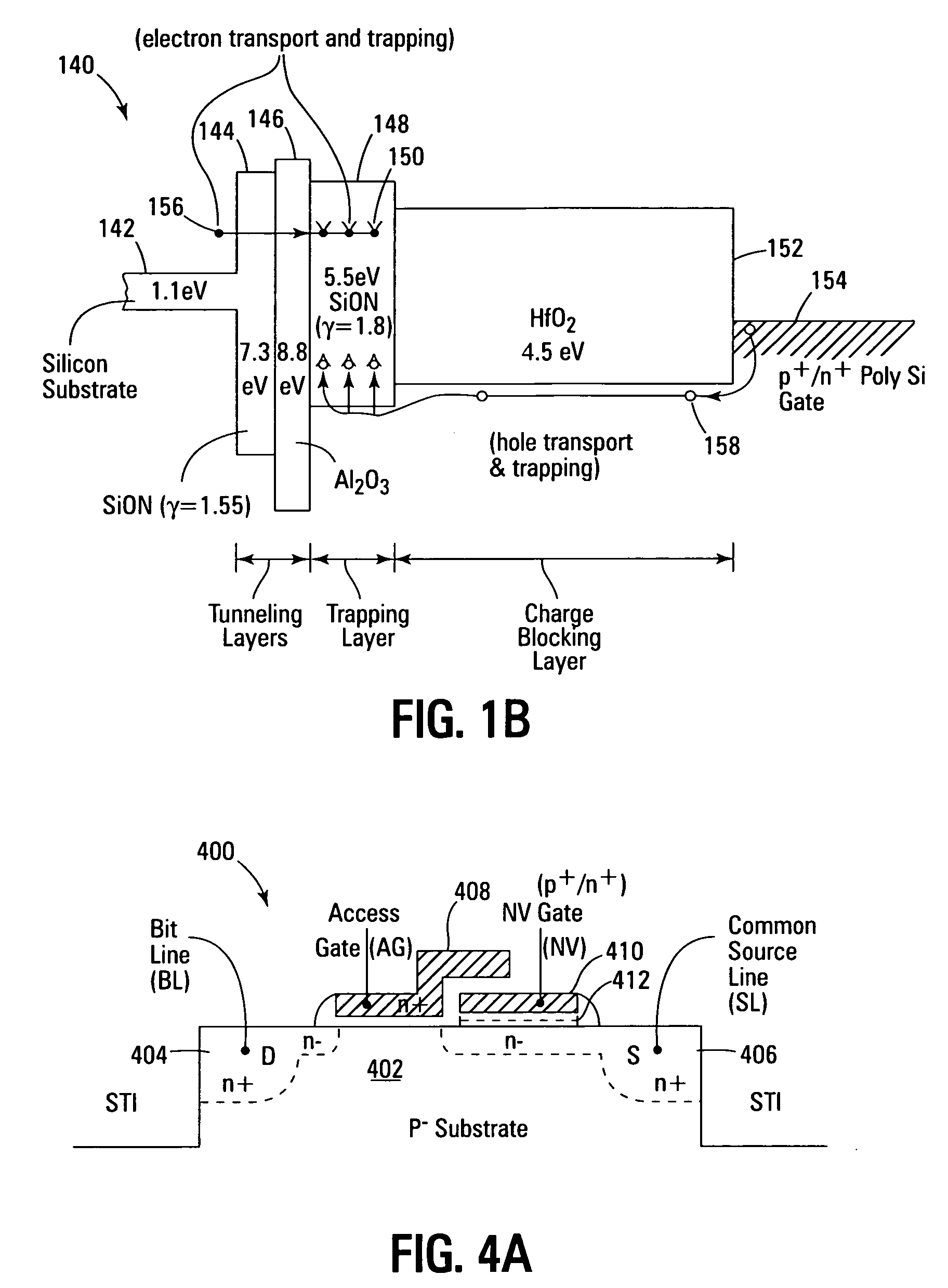

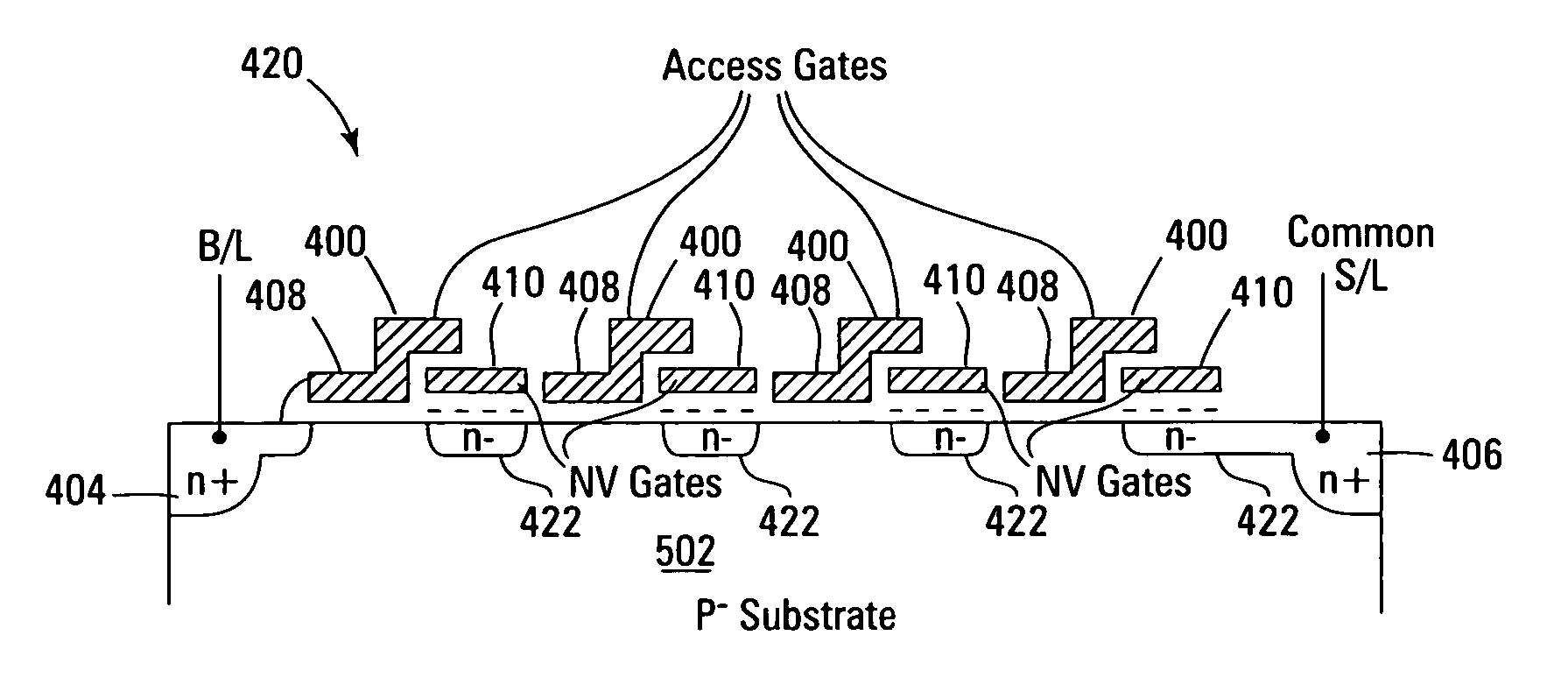

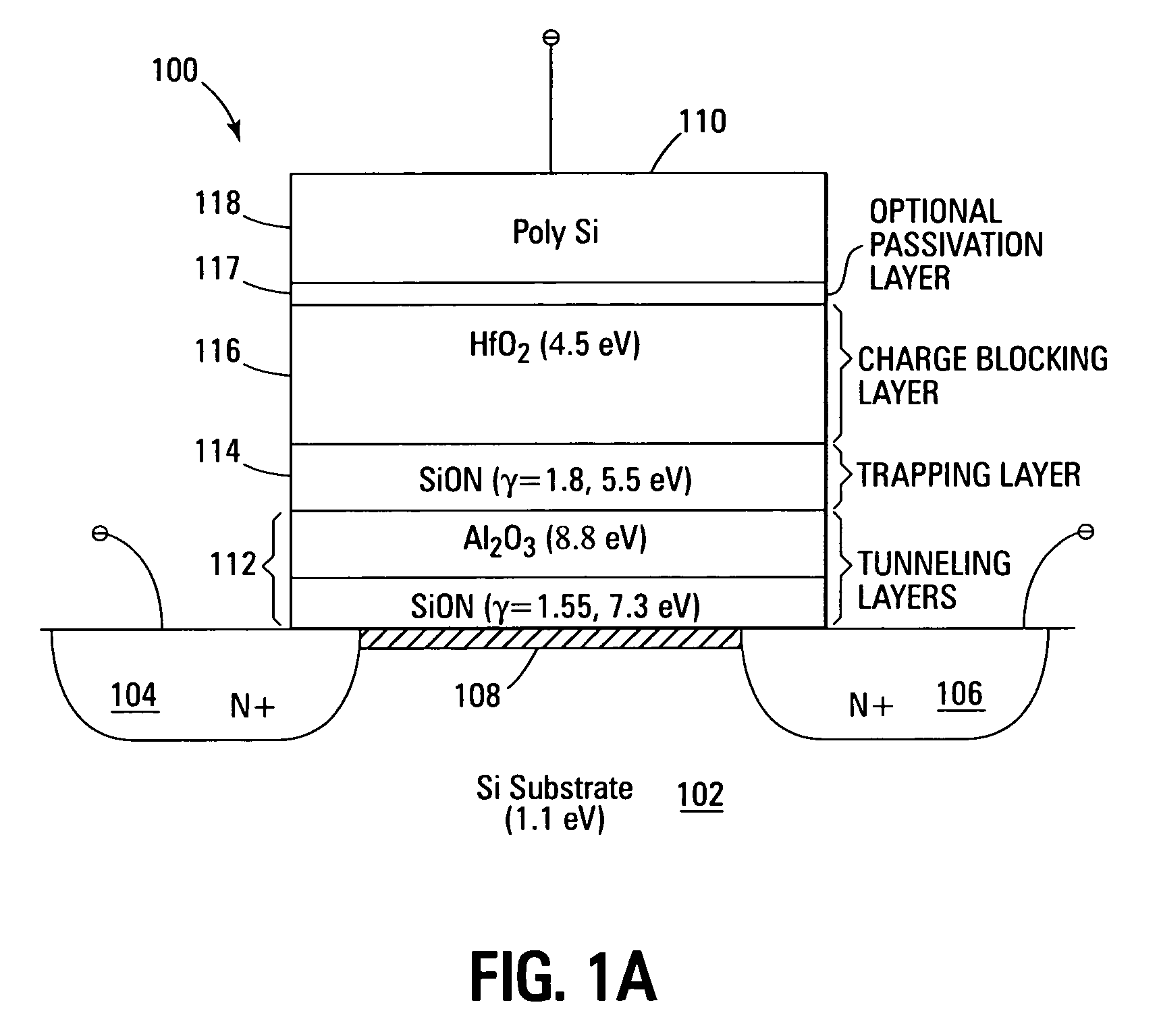

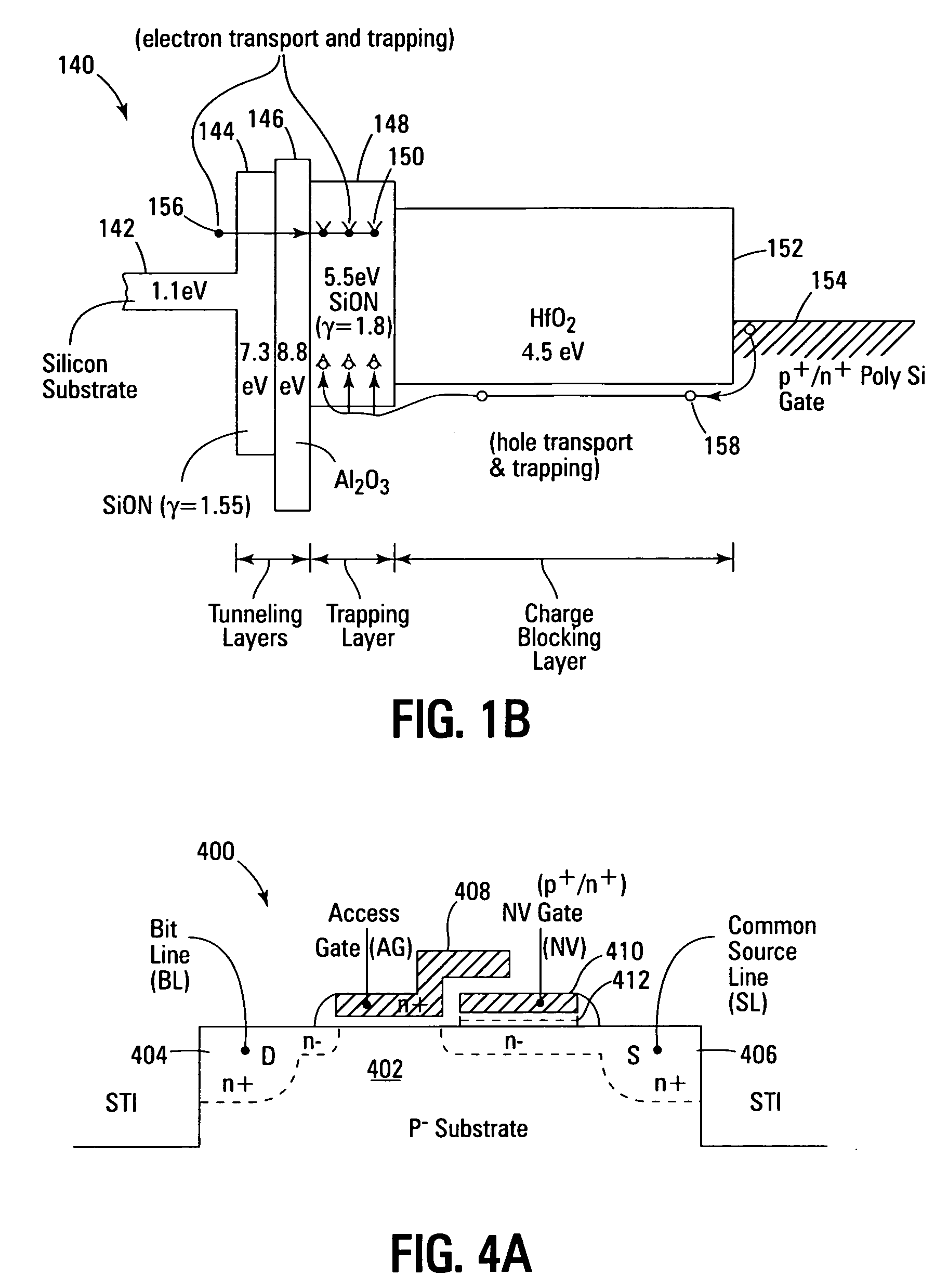

Novel low power non-volatile memory and gate stack

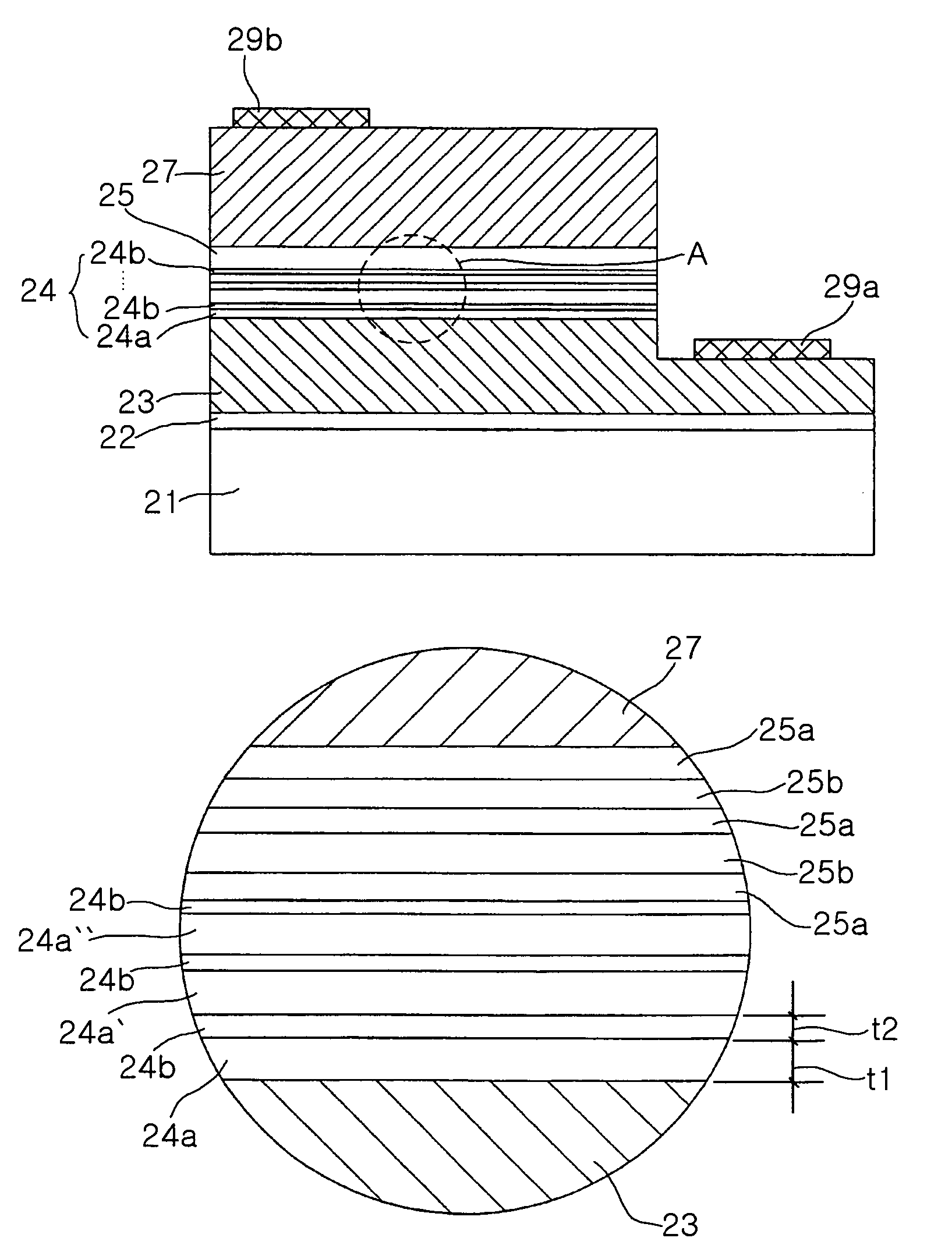

ActiveUS20060261401A1High charge blocking barrierExcellent charge retentionTransistorNanoinformaticsCharge retentionLow voltage

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

Manufacturing apparatus and method for large-scale production of thin-film solar cells

ActiveUS20050109392A1Cheap productionLow costPV power plantsFinal product manufactureIndiumElectrical battery

A method of manufacturing improved thin-film solar cells entirely by sputtering includes a high efficiency back contact / reflecting multi-layer containing at least one barrier layer consisting of a transition metal nitride. A copper indium gallium diselenide (Cu(InXGa1-x)Se2) absorber layer (X ranging from 1 to approximately 0.7) is co-sputtered from specially prepared electrically conductive targets using dual cylindrical rotary magnetron technology. The band gap of the absorber layer can be graded by varying the gallium content, and by replacing the gallium partially or totally with aluminum. Alternately the absorber layer is reactively sputtered from metal alloy targets in the presence of hydrogen selenide gas. RF sputtering is used to deposit a non-cadmium containing window layer of ZnS. The top transparent electrode is reactively sputtered aluminum doped ZnO. A unique modular vacuum roll-to-roll sputtering machine is described. The machine is adapted to incorporate dual cylindrical rotary magnetron technology to manufacture the improved solar cell material in a single pass.

Owner:BEIJING APOLLO DING RONG SOLAR TECH

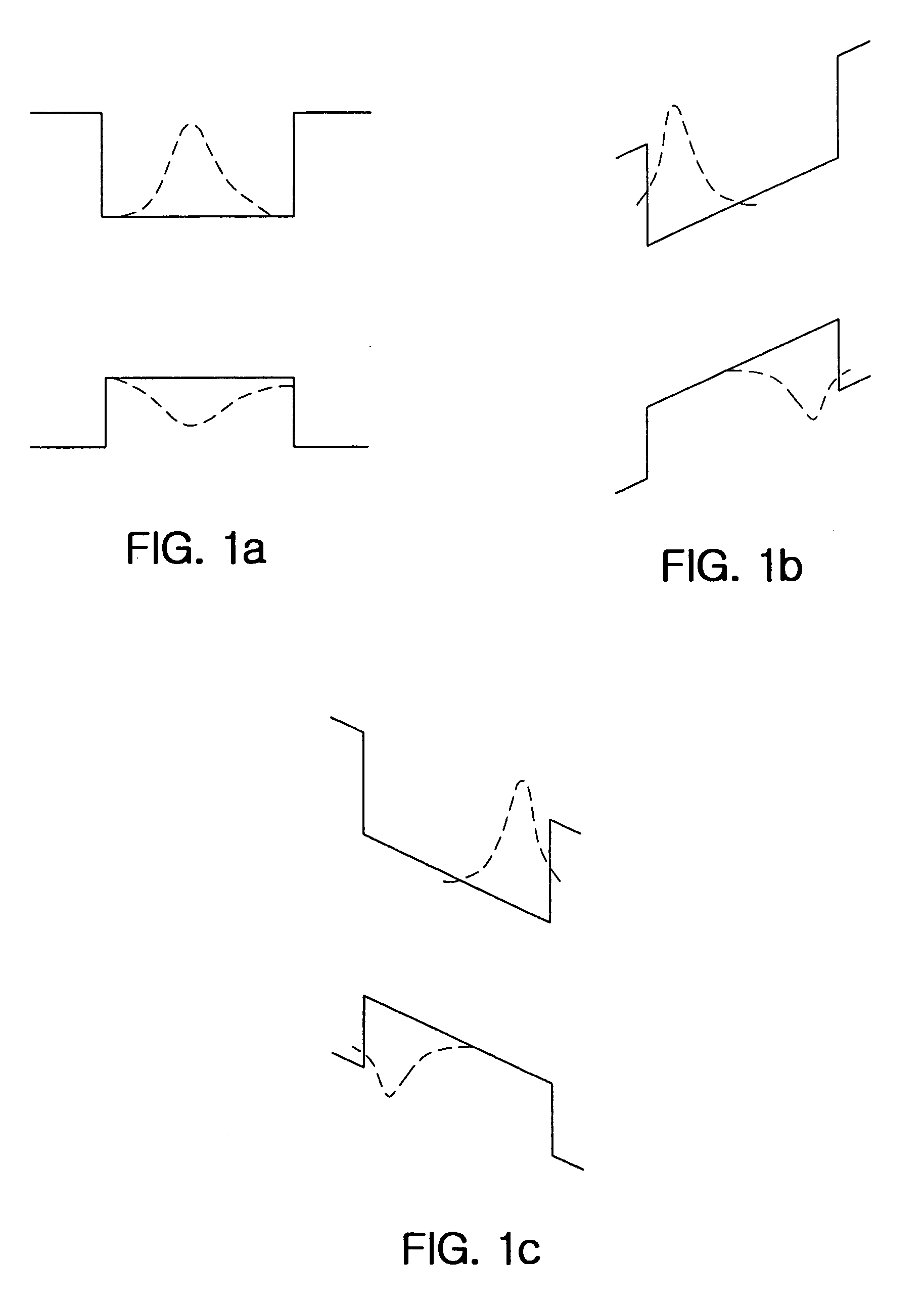

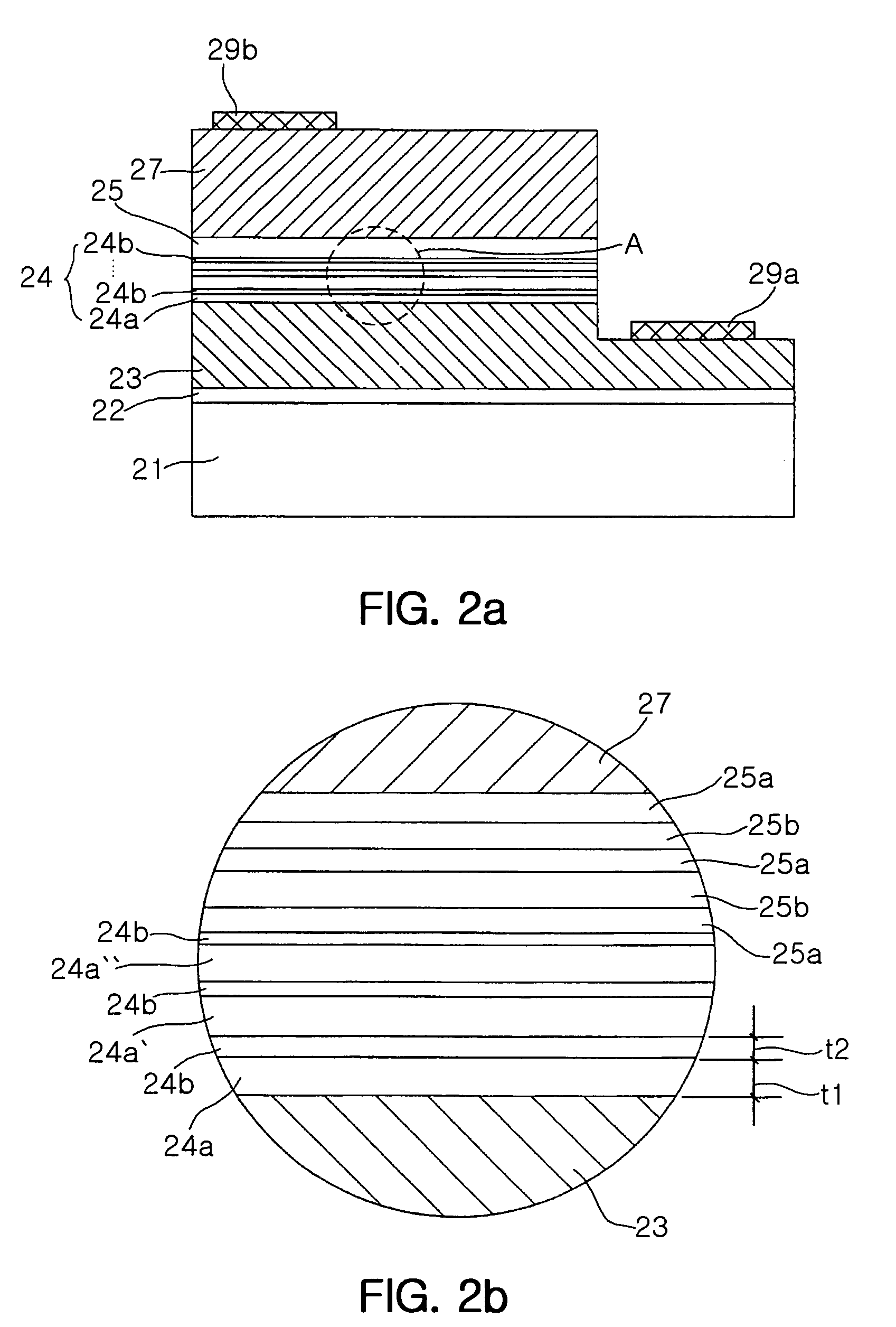

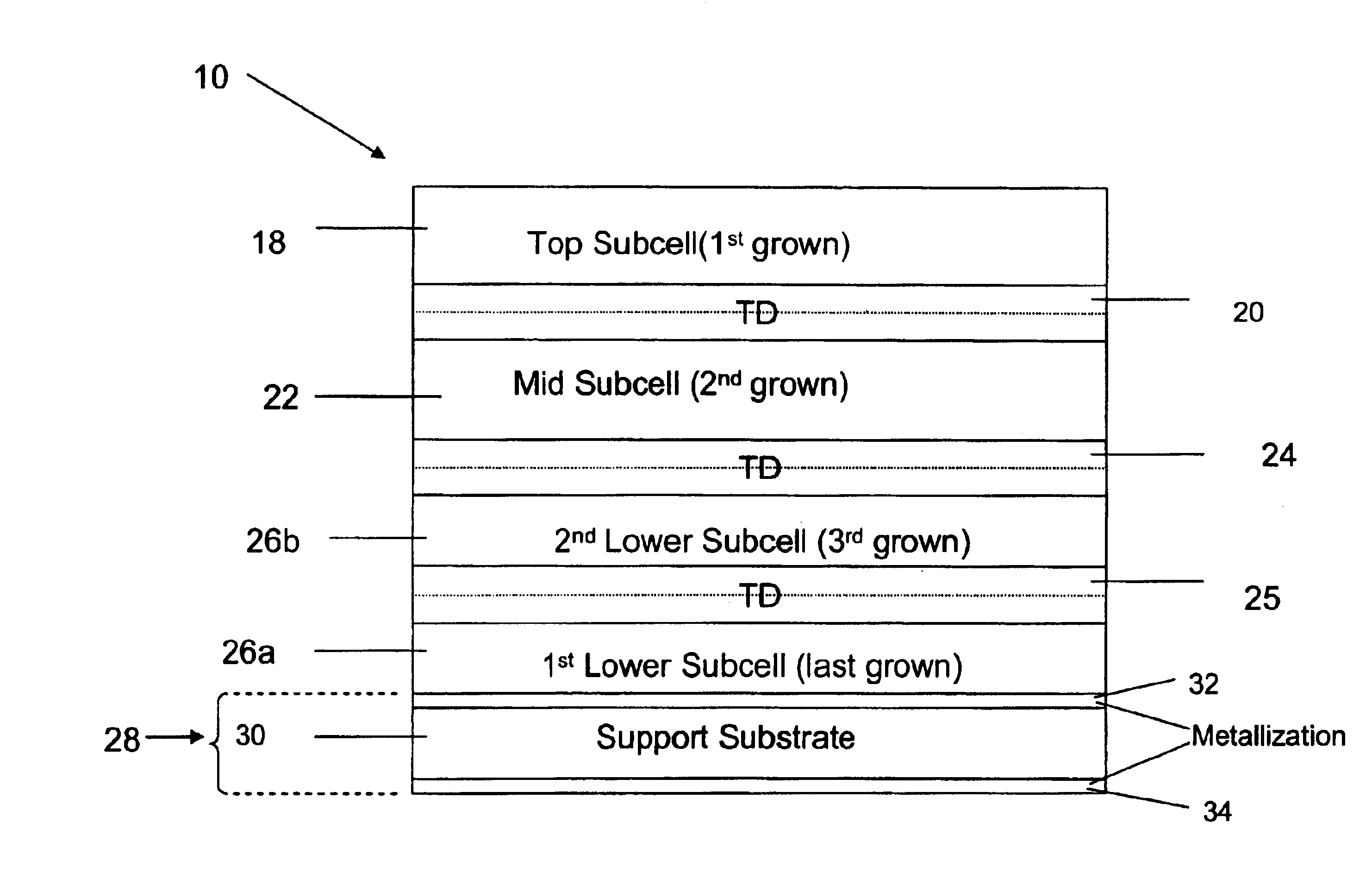

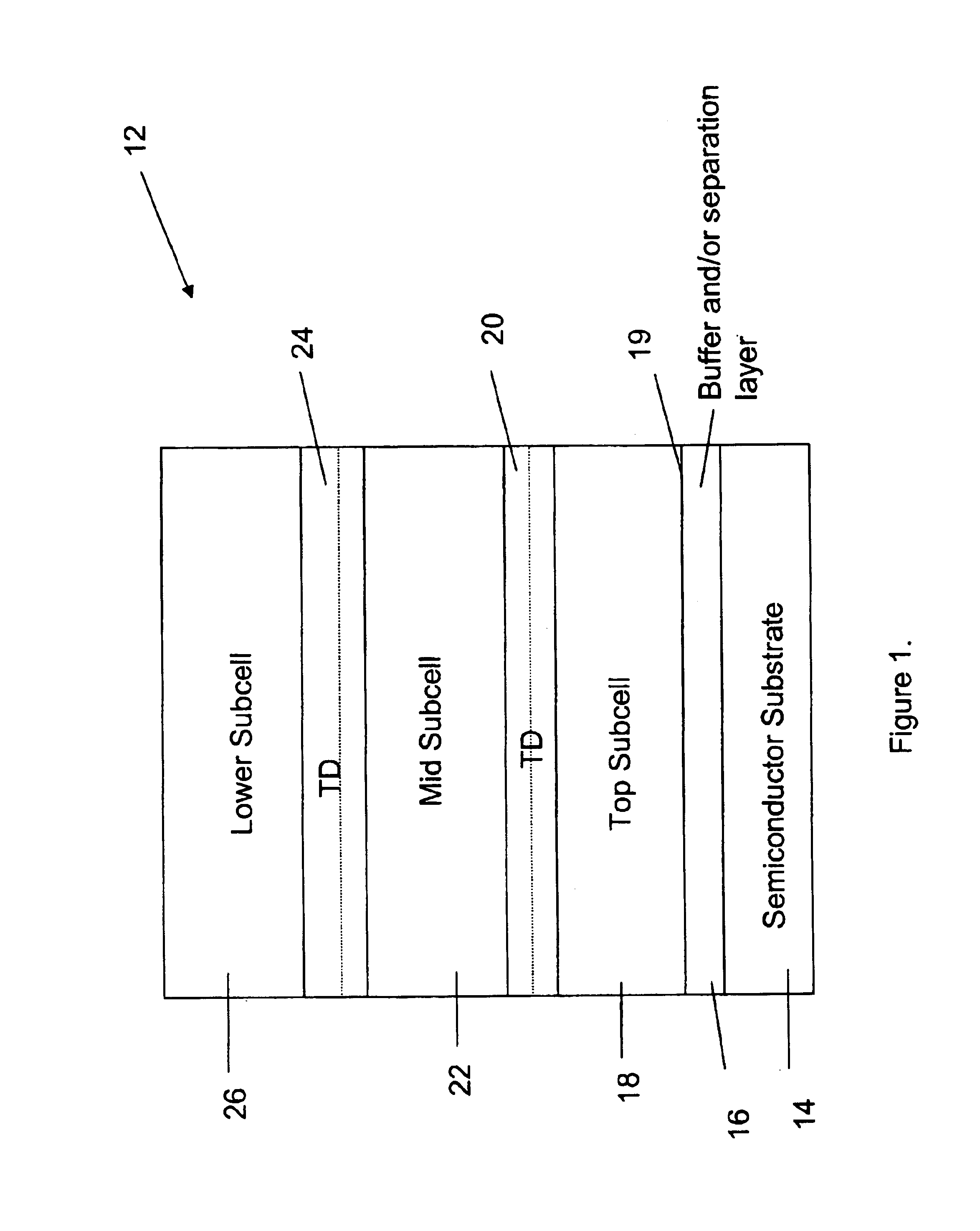

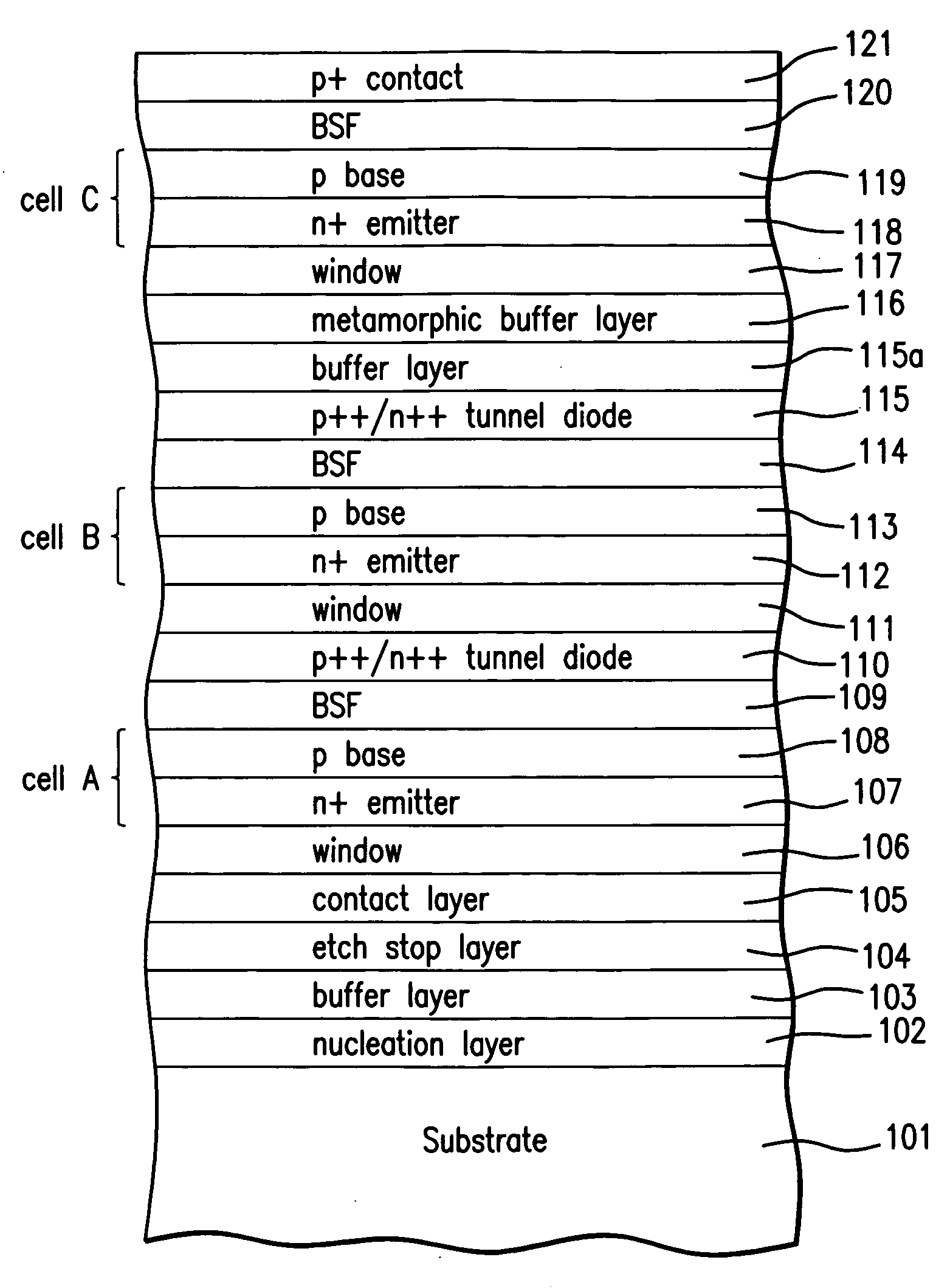

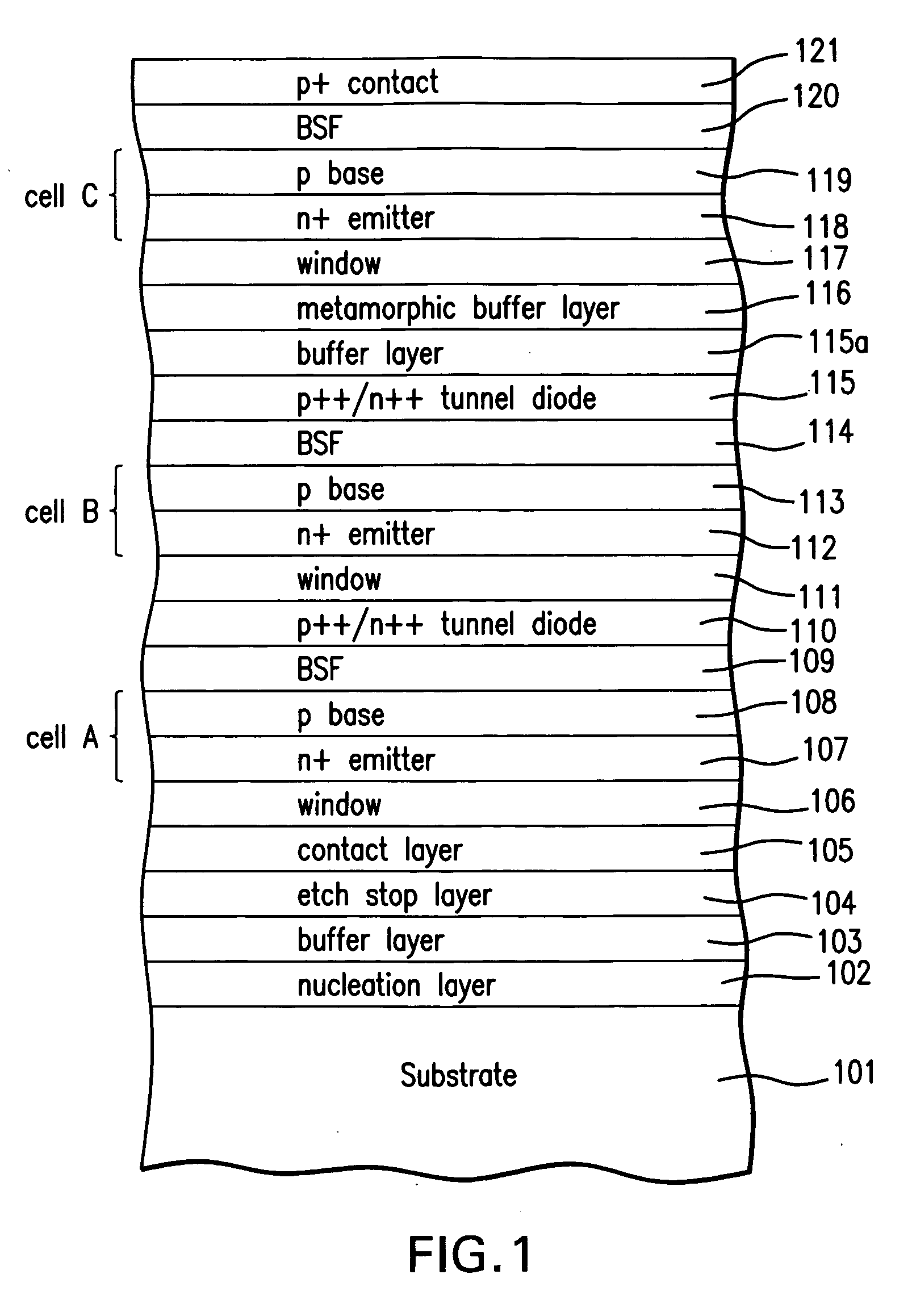

High efficiency, monolithic multijunction solar cells containing lattice-mismatched materials and methods of forming same

ActiveUS6951819B2Improve performanceRelieve pressureSemiconductor/solid-state device manufacturingPhotovoltaic energy generationLattice mismatchSemiconductor

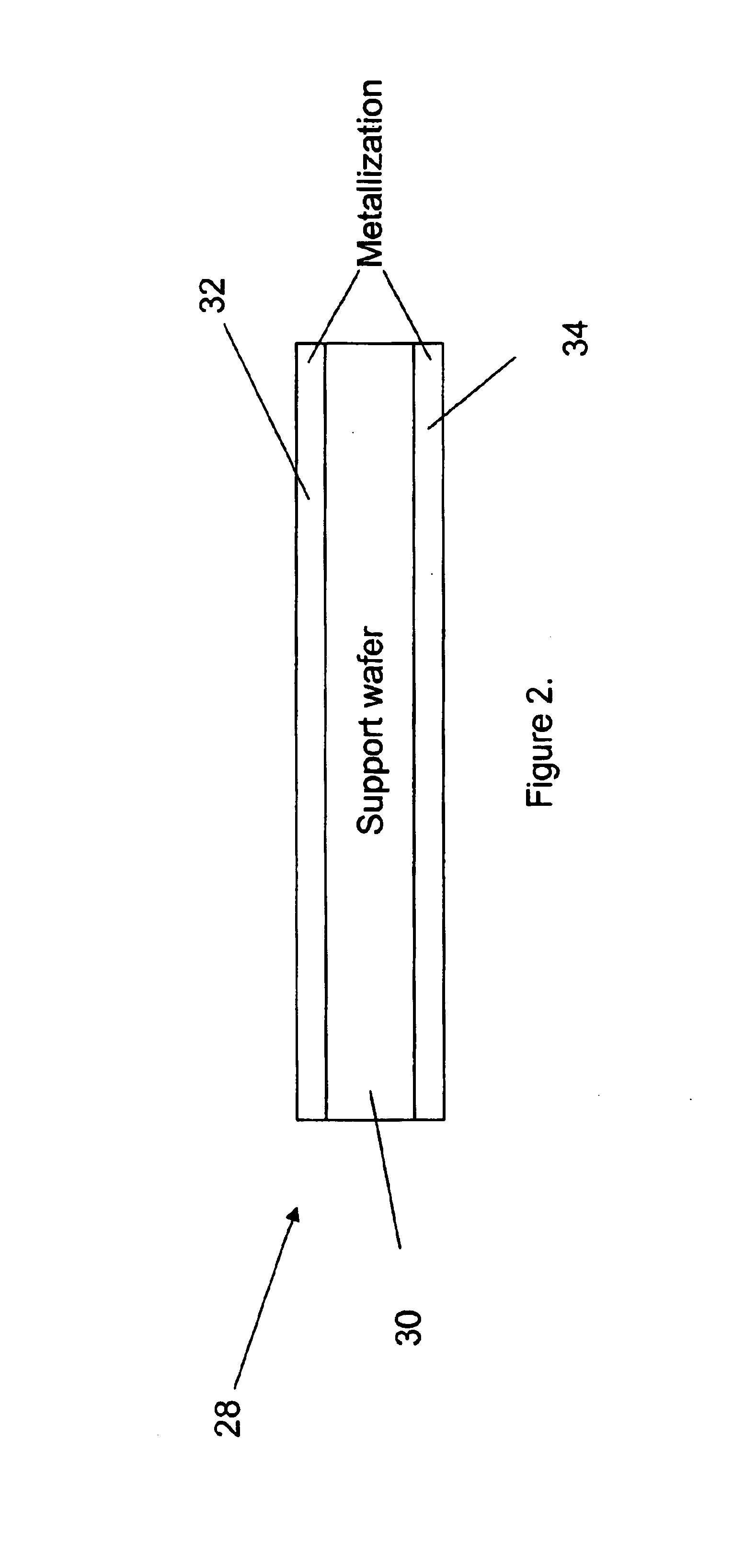

In one embodiment, a method of forming a multijunction solar cell having lattice mismatched layers and lattice-matched layers comprises growing a top subcell having a first band gap over a growth semiconductor substrate. A middle subcell having a second band gap is grown over the top subcell, and a lower subcell having a third band gap is grown over the middle subcell. The lower subcell is substantially lattice-mismatched with respect to the growth semiconductor substrate. The first band gap of the top subcell is larger than the second band gap of the middle subcell. The second band gap of the middle subcell is larger than the third band gap of the lower subcell. A support substrate is formed over the lower subcell, and the growth semiconductor substrate is removed. In various embodiments, the multijunction solar cell may further comprise additional lower subcells. A parting layer may also be provided between the growth substrate and the top subcell in certain embodiments. Embodiments of this reverse process permit the top and middle subcells to have high performance by having atomic lattice spacing closely matched to that of the growth substrate. Lower subcells can be included with appropriate band gap, but with lattice spacing mismatched to the other subcells. The reduced performance caused by strain resulting from mismatch can be mitigated without reducing the performance of the upper subcells.

Owner:OSTENDO TECH INC

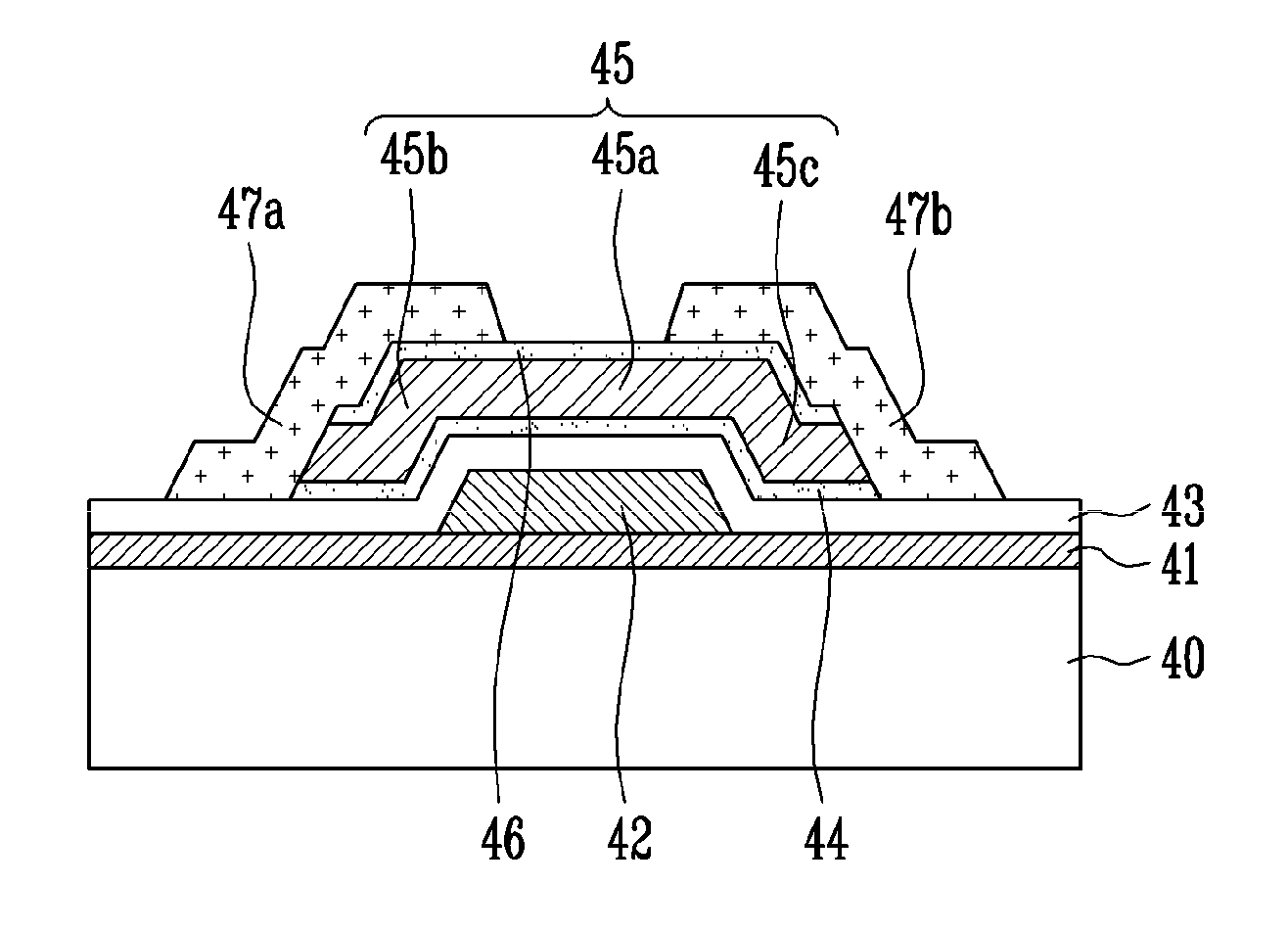

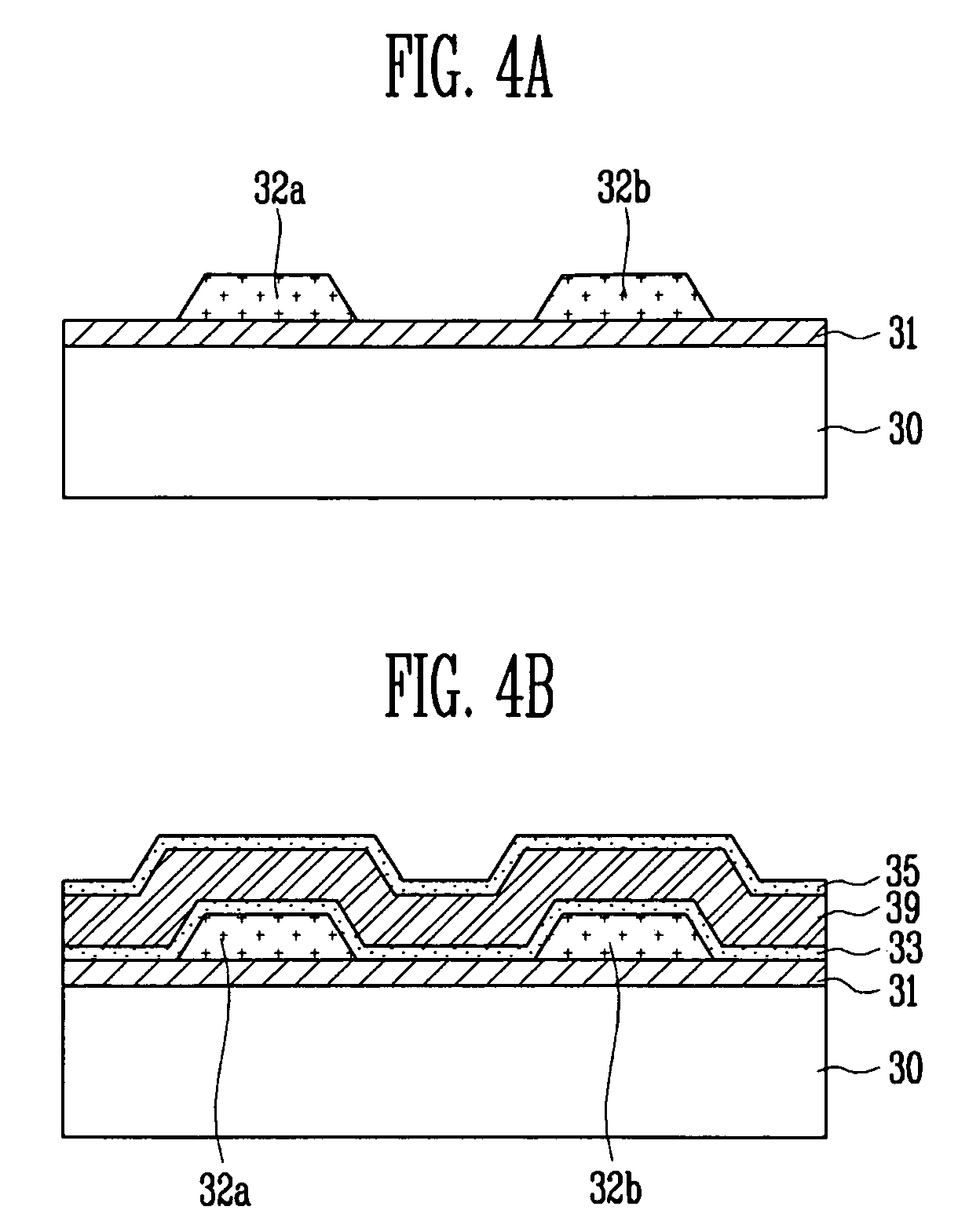

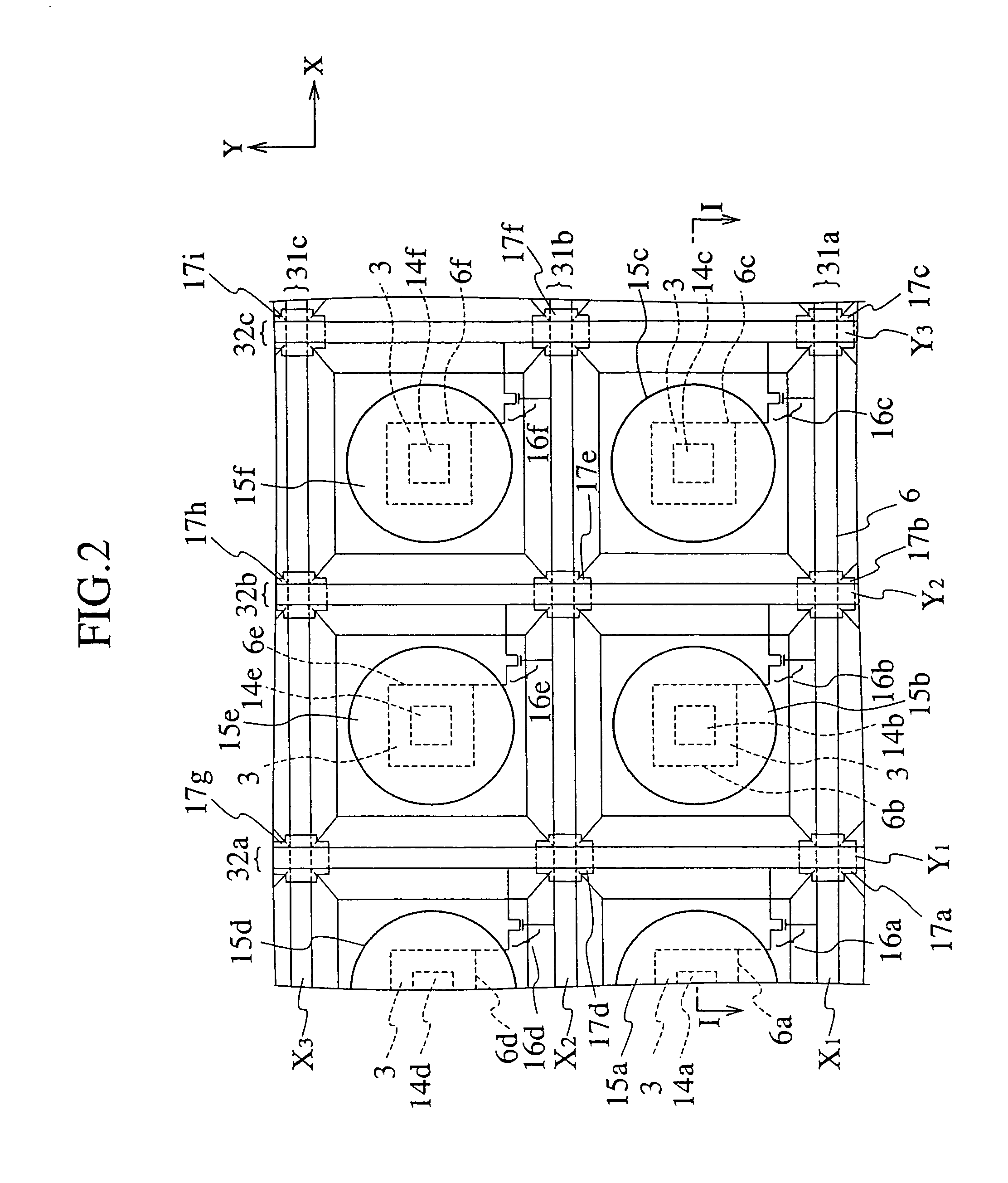

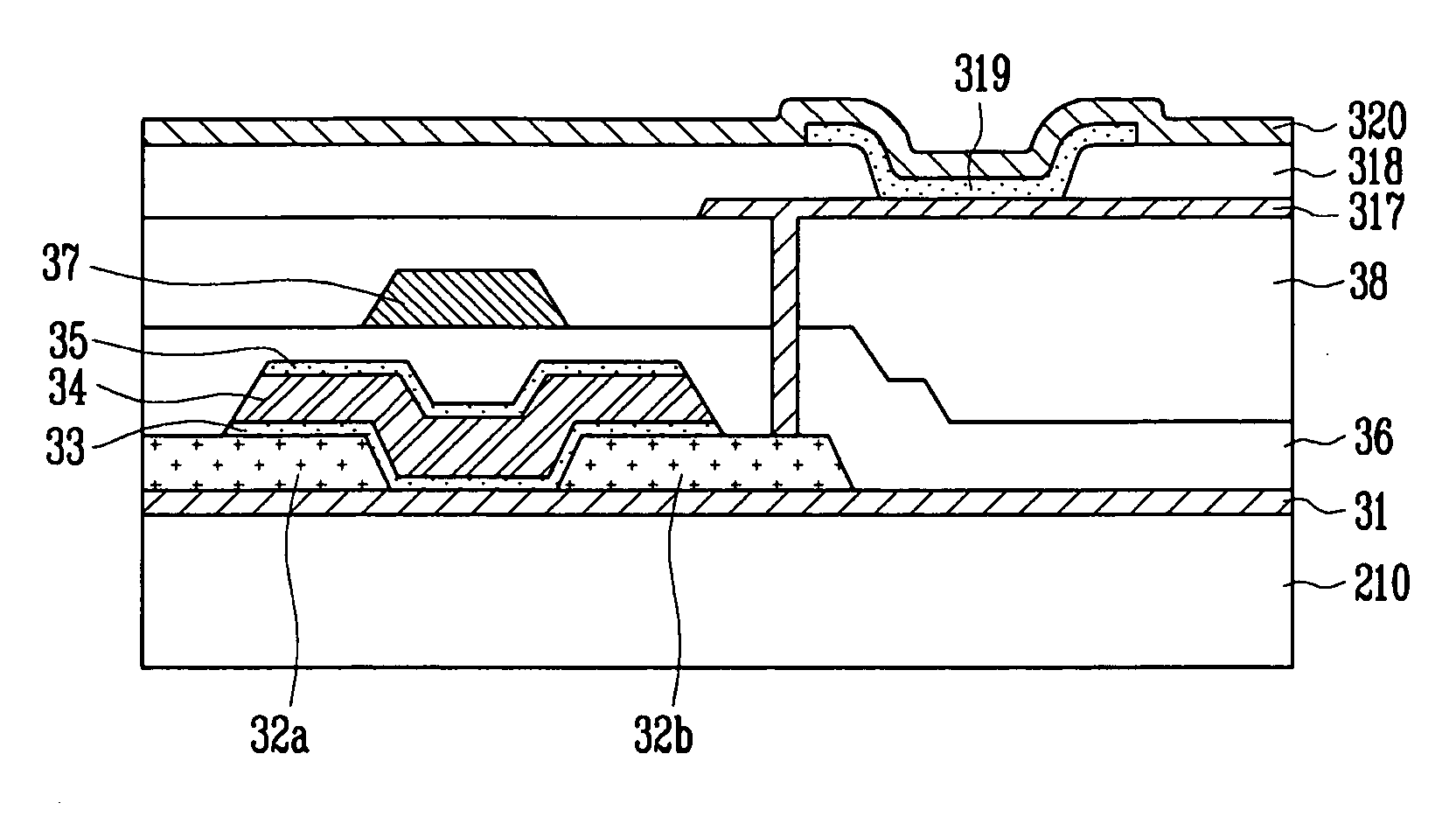

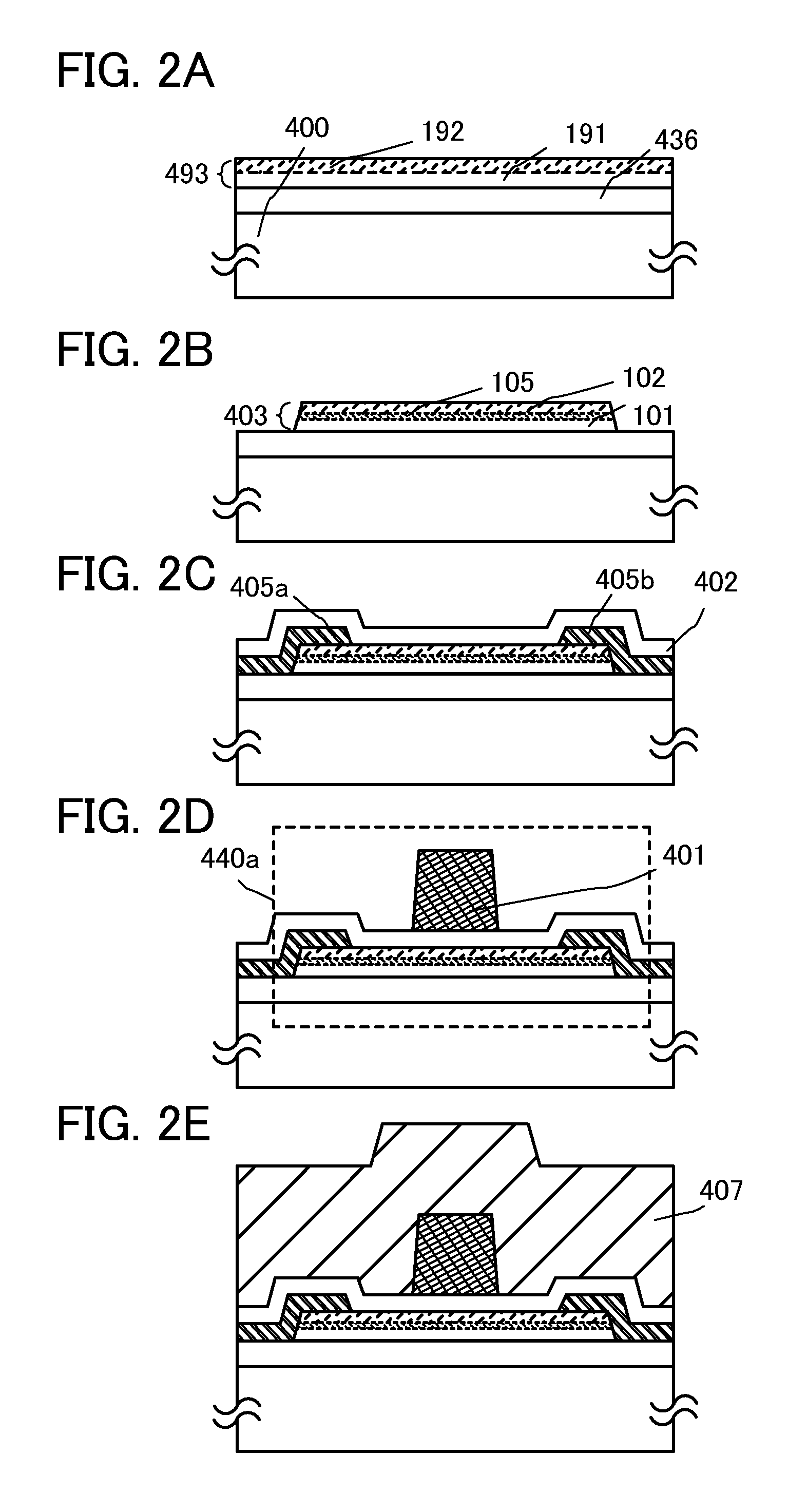

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS20090321731A1Improve featuresAvoid chargingSemiconductor/solid-state device manufacturingNon-linear opticsTrappingEngineering

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include a gate electrode formed on a substrate; an active layer made of an oxide semiconductor and insulated from the gate electrode by a gate insulating layer; source and drain electrodes coupled to the active layer; and an interfacial stability layer formed on one or both surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristic as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

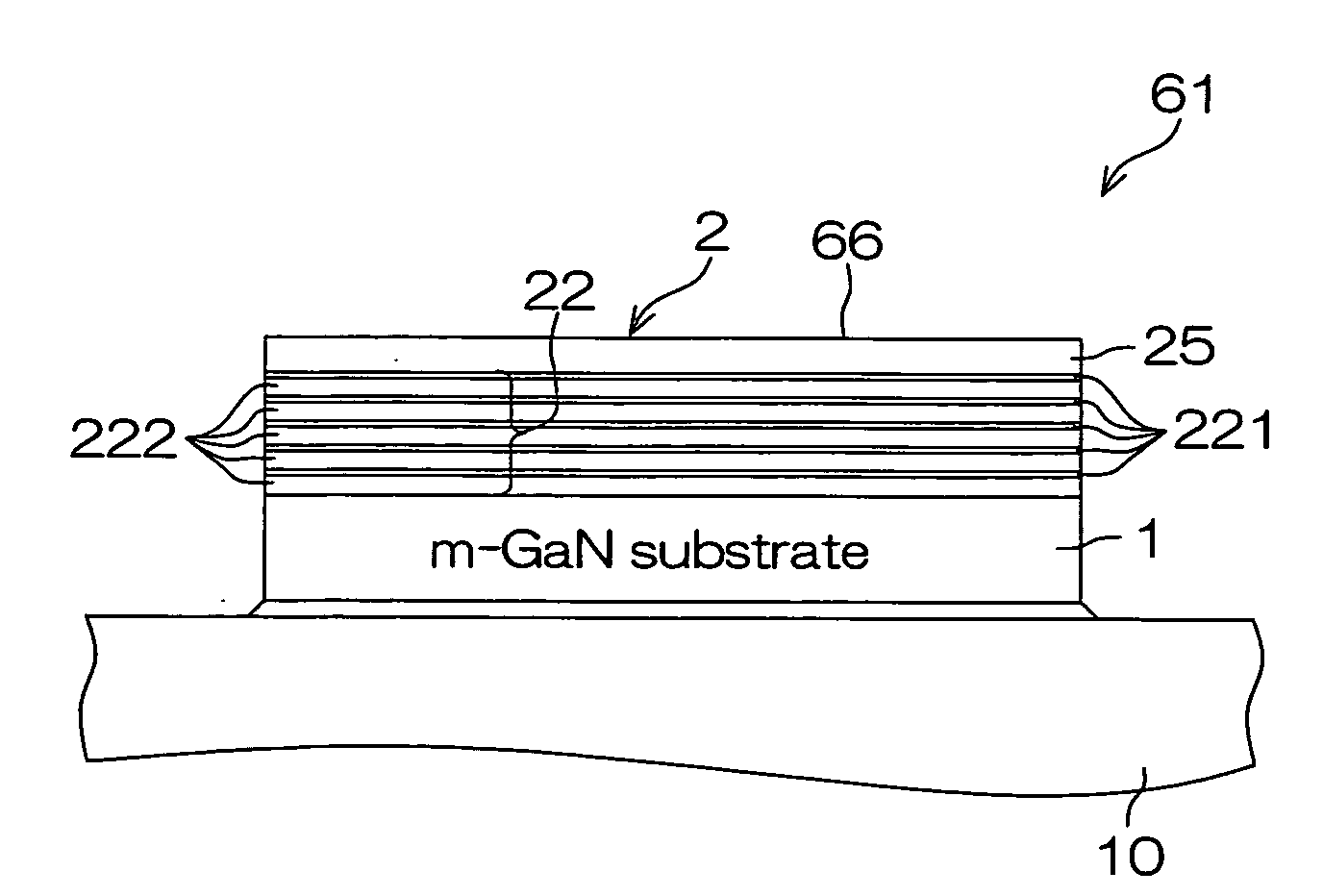

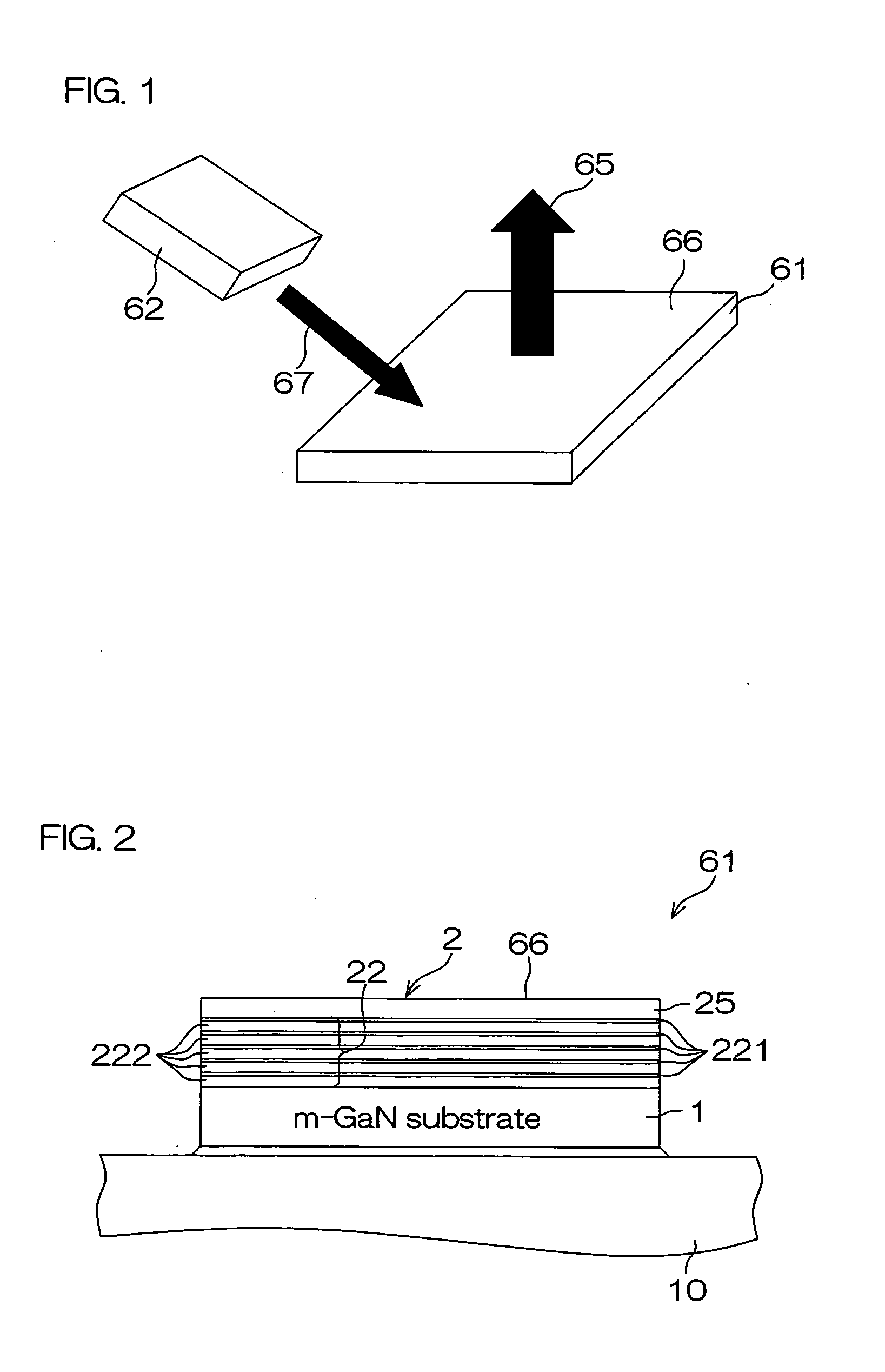

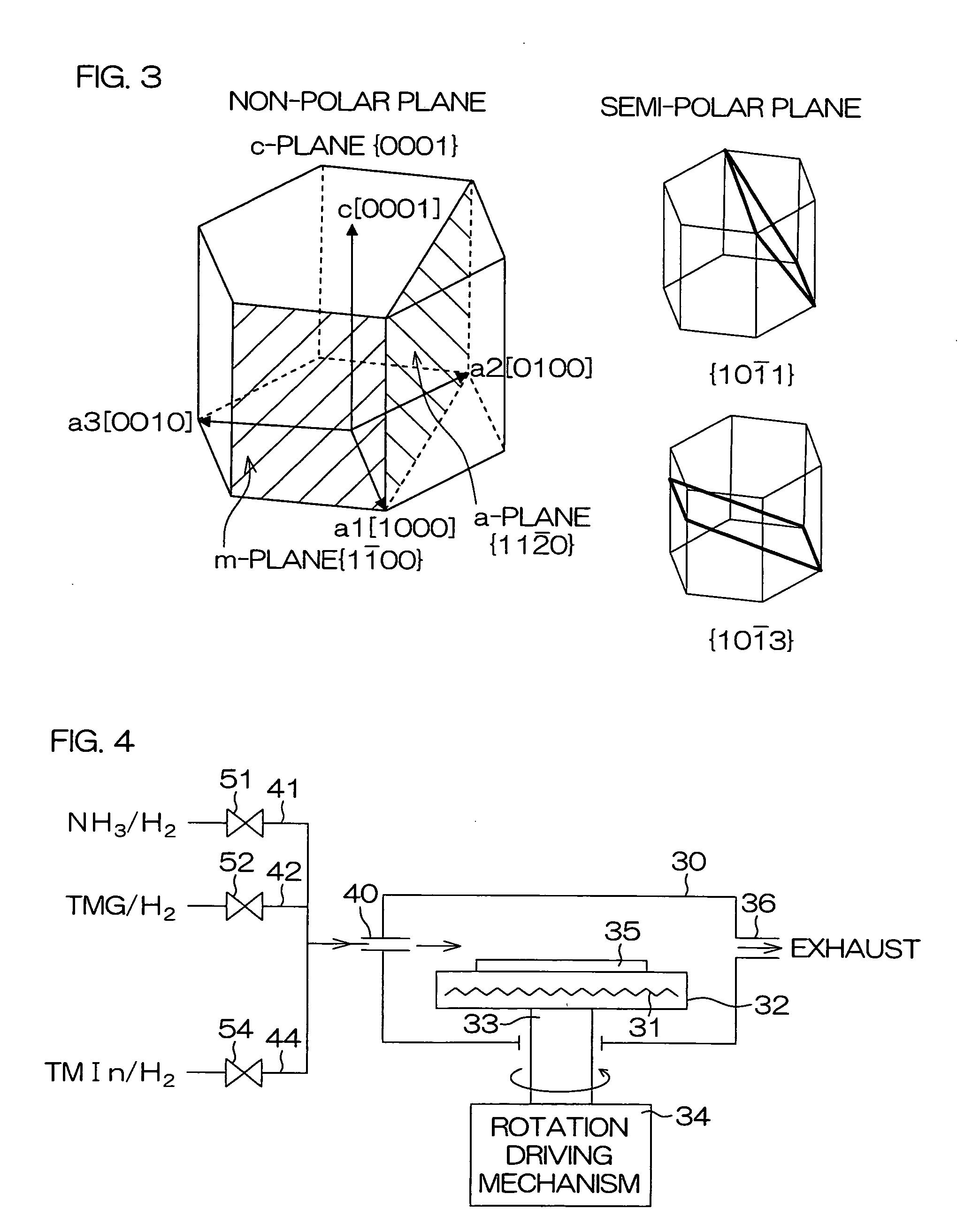

Light emitting device

InactiveUS20080232416A1Improve efficiencyImprove propertiesLaser detailsLaser active region structureLength waveWide band

Owner:ROHM CO LTD

Semiconductor optoelectronic device and method of fabricating the same

ActiveUS20080095492A1Reducing internal lossImprove internal quantum efficiencyNanoopticsSemiconductor lasersQuantum wellOpto electronic

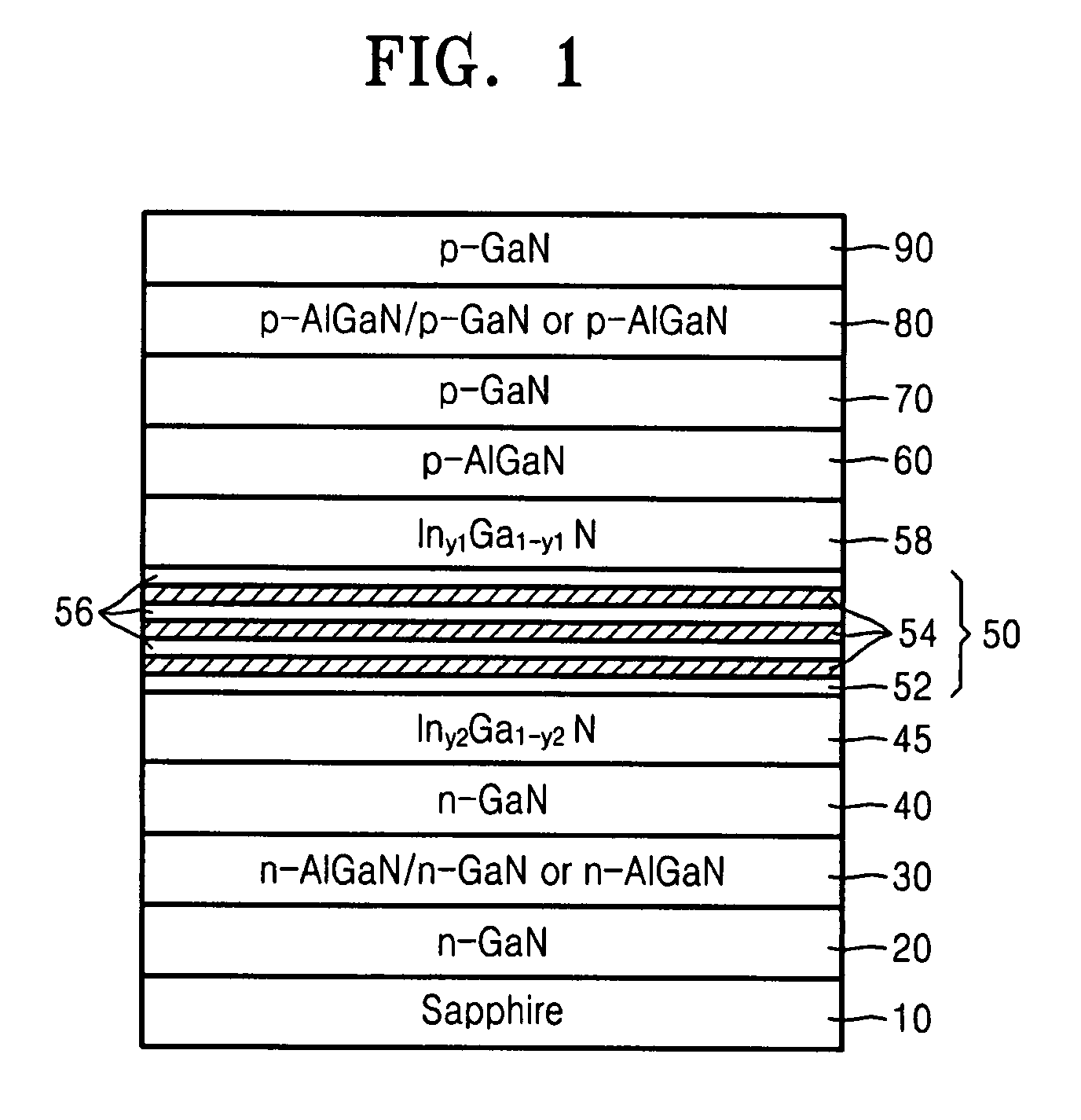

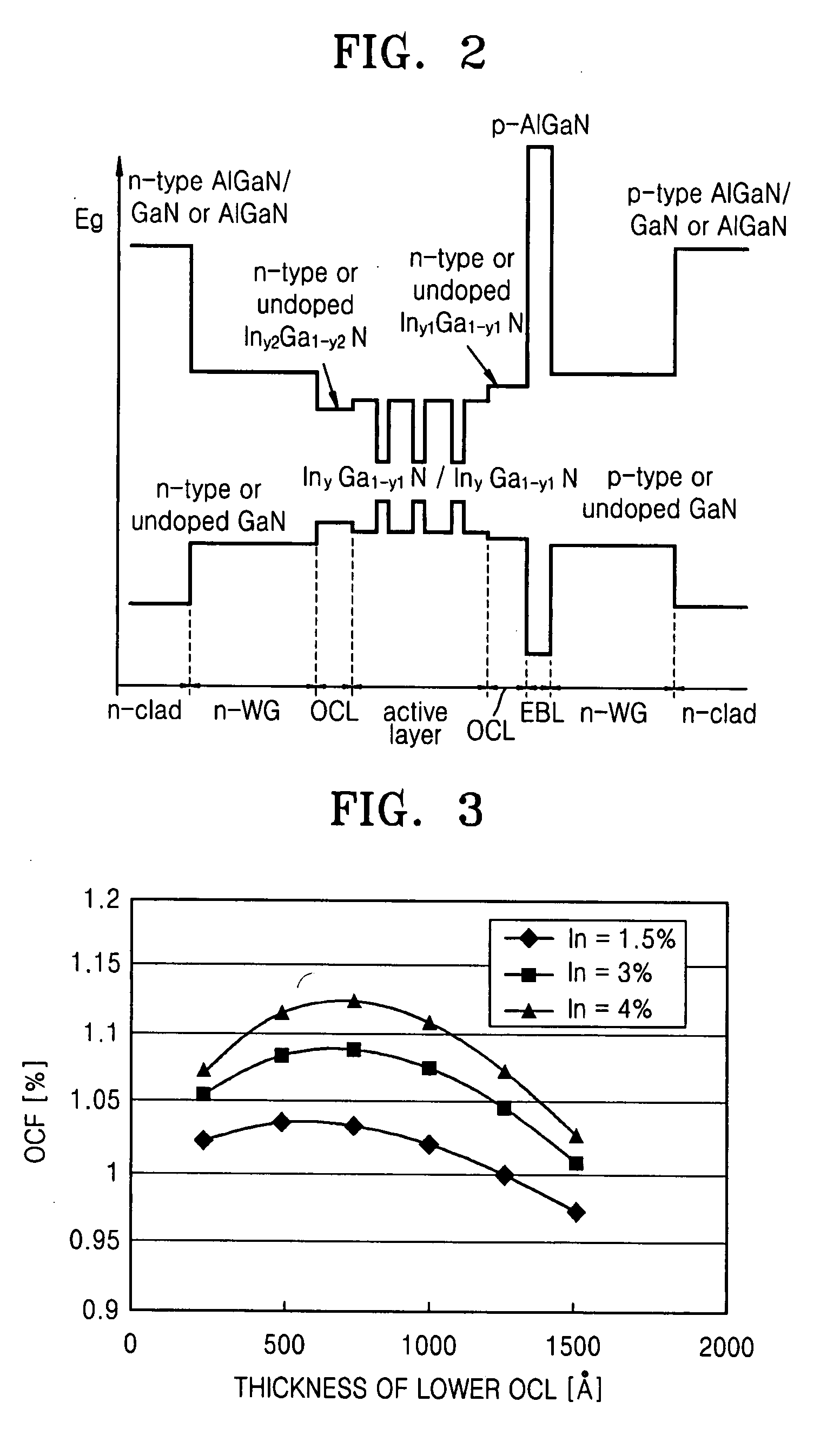

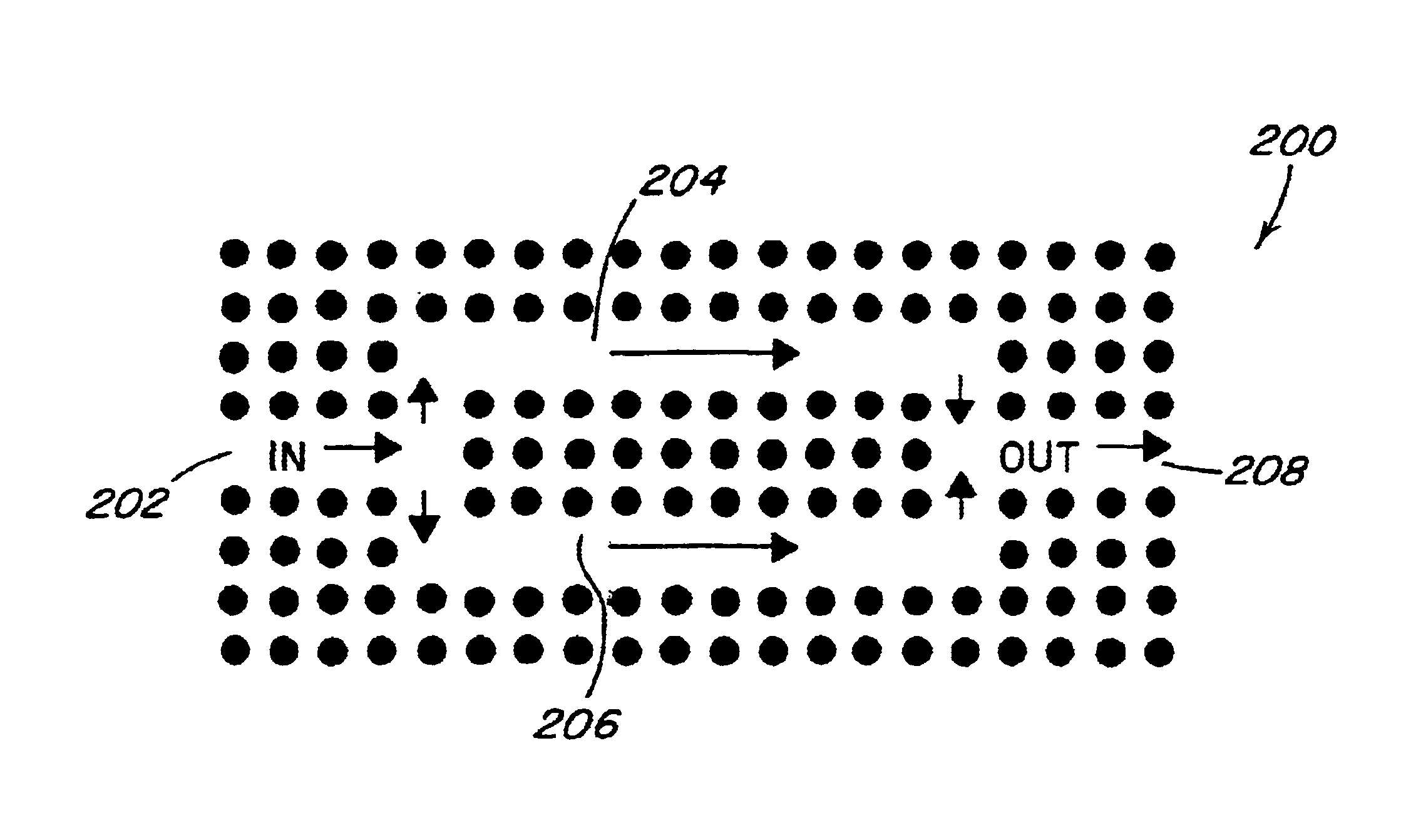

Provided is a semiconductor opto-electronic device that may comprise an active layer including a quantum well and a barrier layer on a substrate, upper and lower waveguide layers on and underneath the active layer, respectively, and upper and lower clad layers on and underneath the upper and lower waveguide layers, respectively. The semiconductor opto-electronic device may further comprise an upper optical confinement layer (OCL) between the active layer and the upper waveguide layer and having an energy gap smaller than the energy gap of the upper waveguide layer and equal to or larger than the energy gap of the barrier layer, and a lower OCL between the active layer and the lower waveguide layer and having an energy gap smaller than the energy gap of the lower waveguide layer and equal to or smaller than the energy gap of the barrier layer. Also provided is a method of fabricating the semiconductor opto-electronic device.

Owner:SAMSUNG ELECTRONICS CO LTD

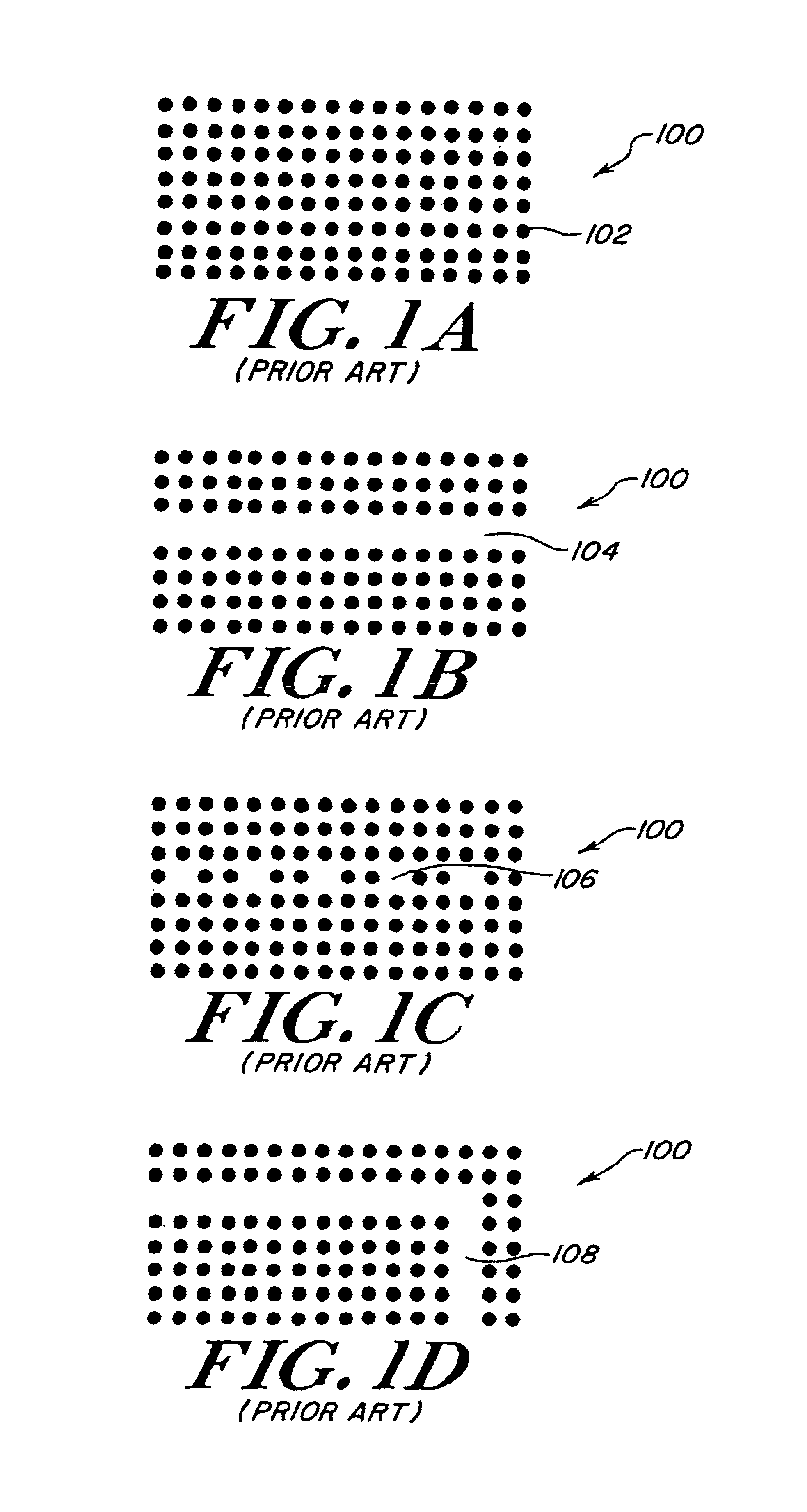

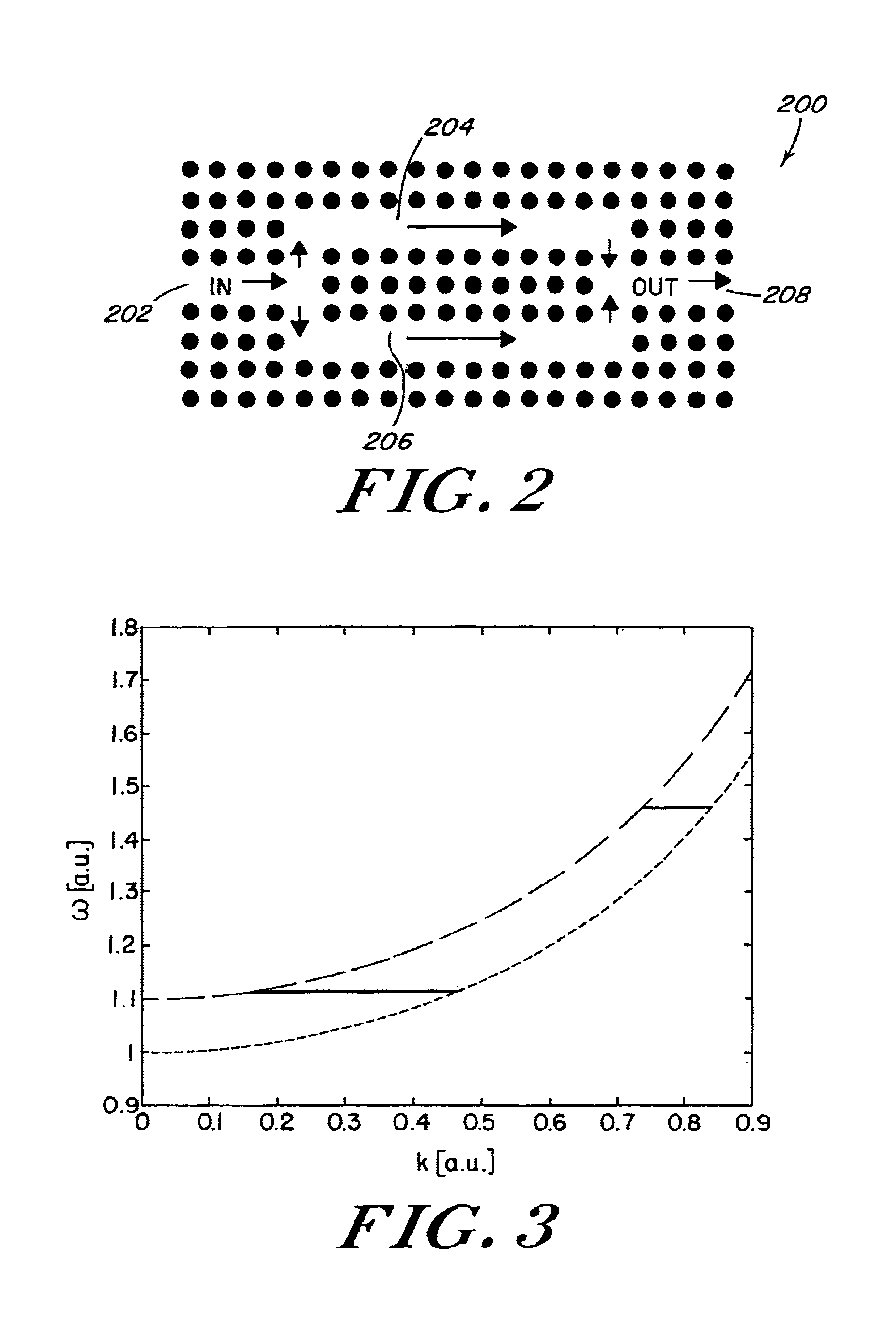

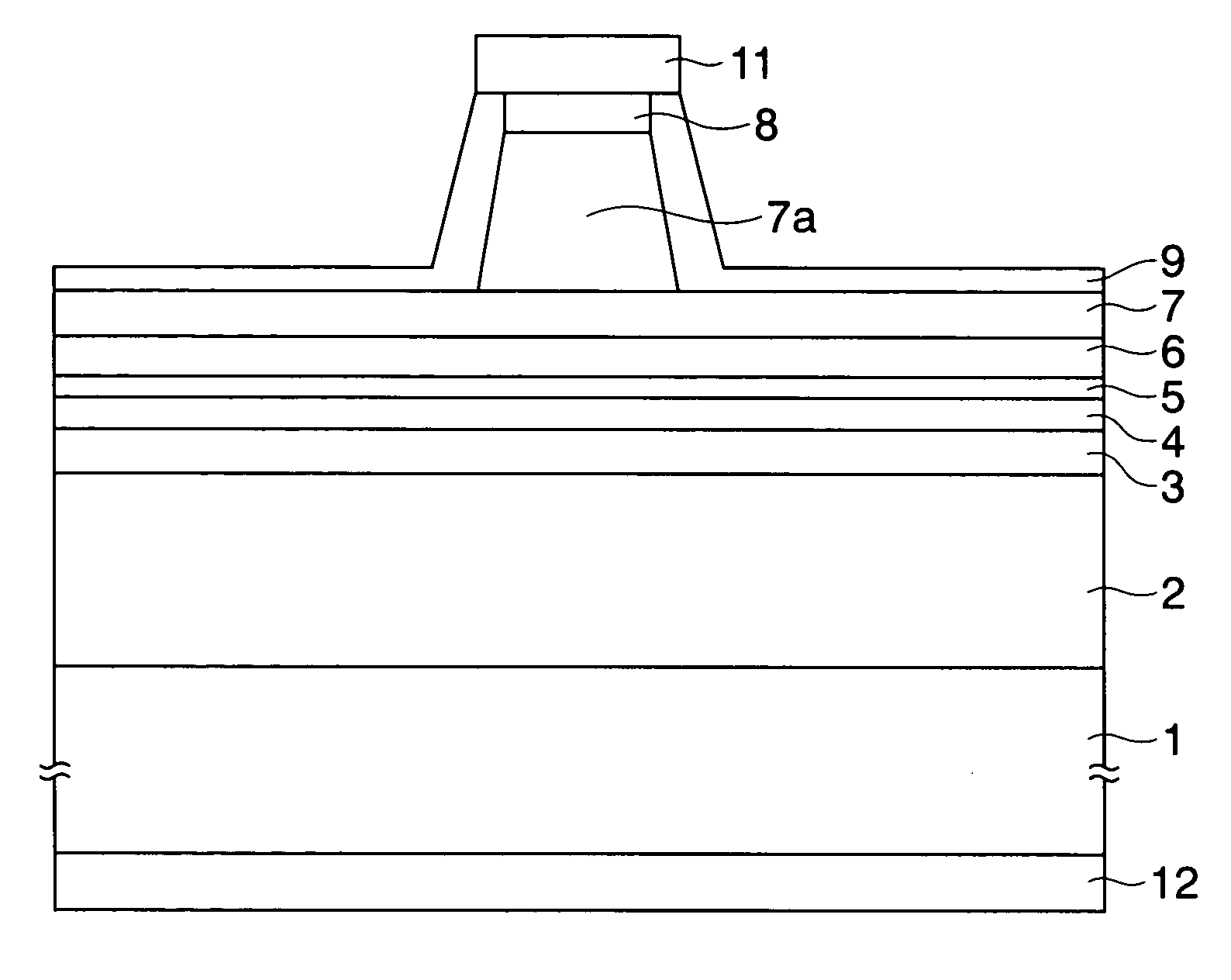

Mach-Zehnder interferometer using photonic band gap crystals

InactiveUS6917431B2Small sizeLarge operating bandwidthLaser detailsLaser optical resonator constructionPhotonic crystalMach–Zehnder interferometer

A photonic crystal optical switch having a periodic dielectric structure including at least one input waveguide. First and second waveguide arms branch from the input waveguide in which the relative optical path lengths of electromagnetic radiation within the arms are controlled by stimuli. At least one output waveguide that combines the electromagnetic radiation propagating within the first and second waveguide arms.

Owner:MASSACHUSETTS INST OF TECH

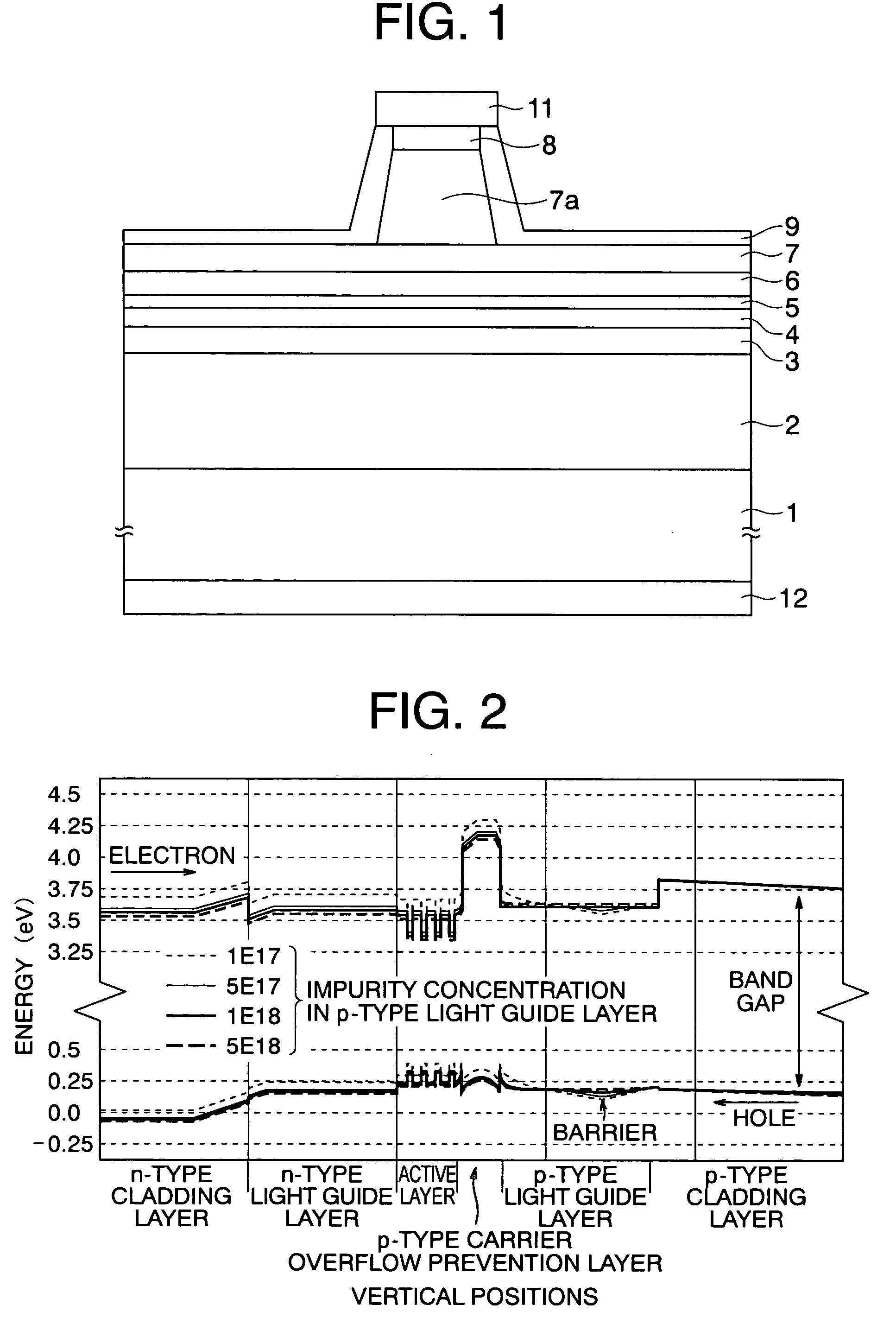

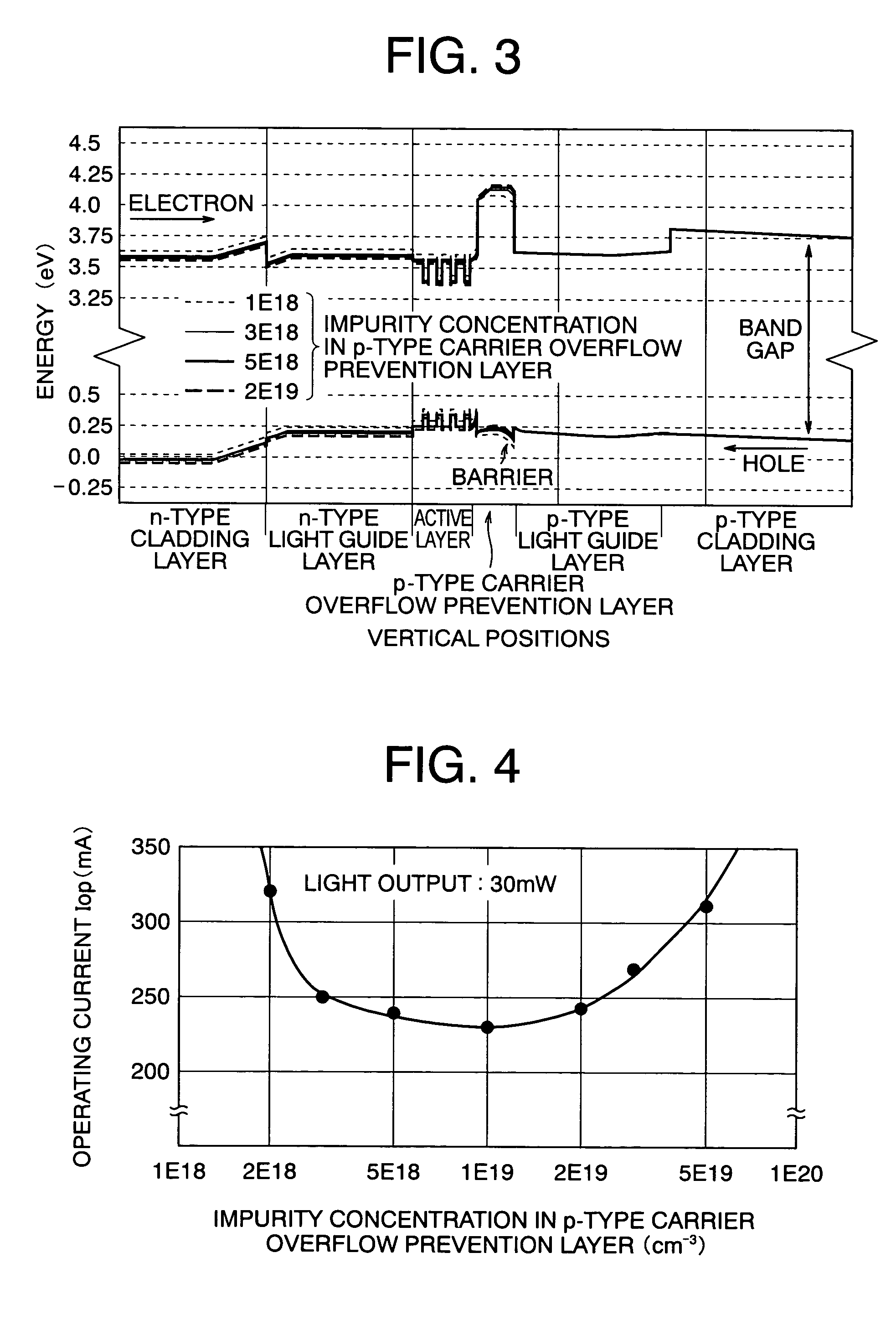

Semiconductor light-emitting element and method of manufacturing the same

Disclosed is a semiconductor light-emitting element, comprising an n-type-cladding layer; a light guide layer positioned on the n-type cladding layer; a multiple quantum well structure active layer positioned on the light guide layer; a p-type carrier overflow prevention layer positioned on the active layer and having an impurity concentration of 5×1018 cm−3 to not more than 3×1019 cm−3; a p-type light guide layer positioned on the p-type carrier overflow prevention layer and-having an impurity concentration of 1×1018 cm−3 or more and less-than that of the p-type carrier overflow prevention layer; and a p-type cladding layer positioned on the p-type light guide layer and having a band gap narrower than the p-type carrier overflow prevention layer, and a method of manufacturing the same.

Owner:KK TOSHIBA

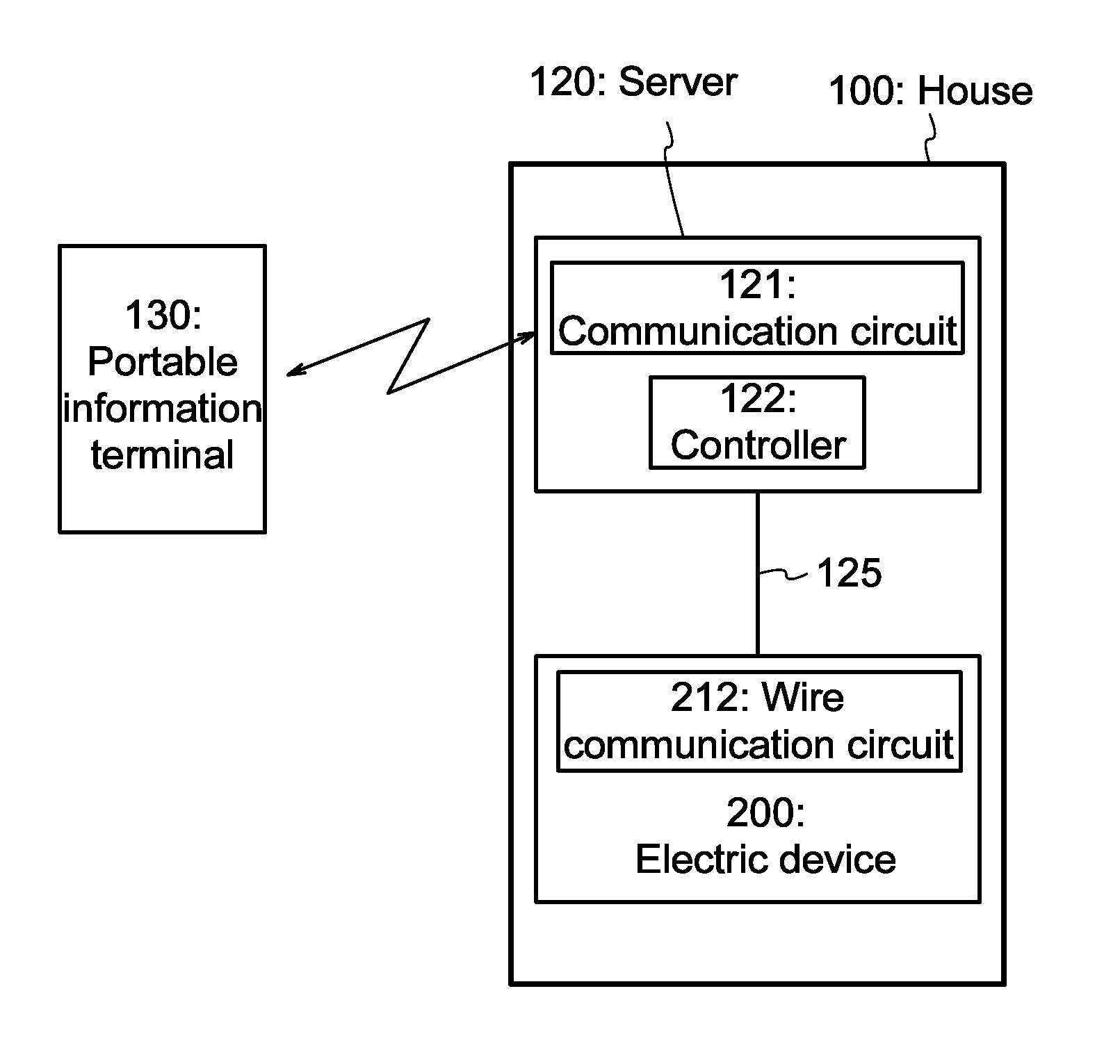

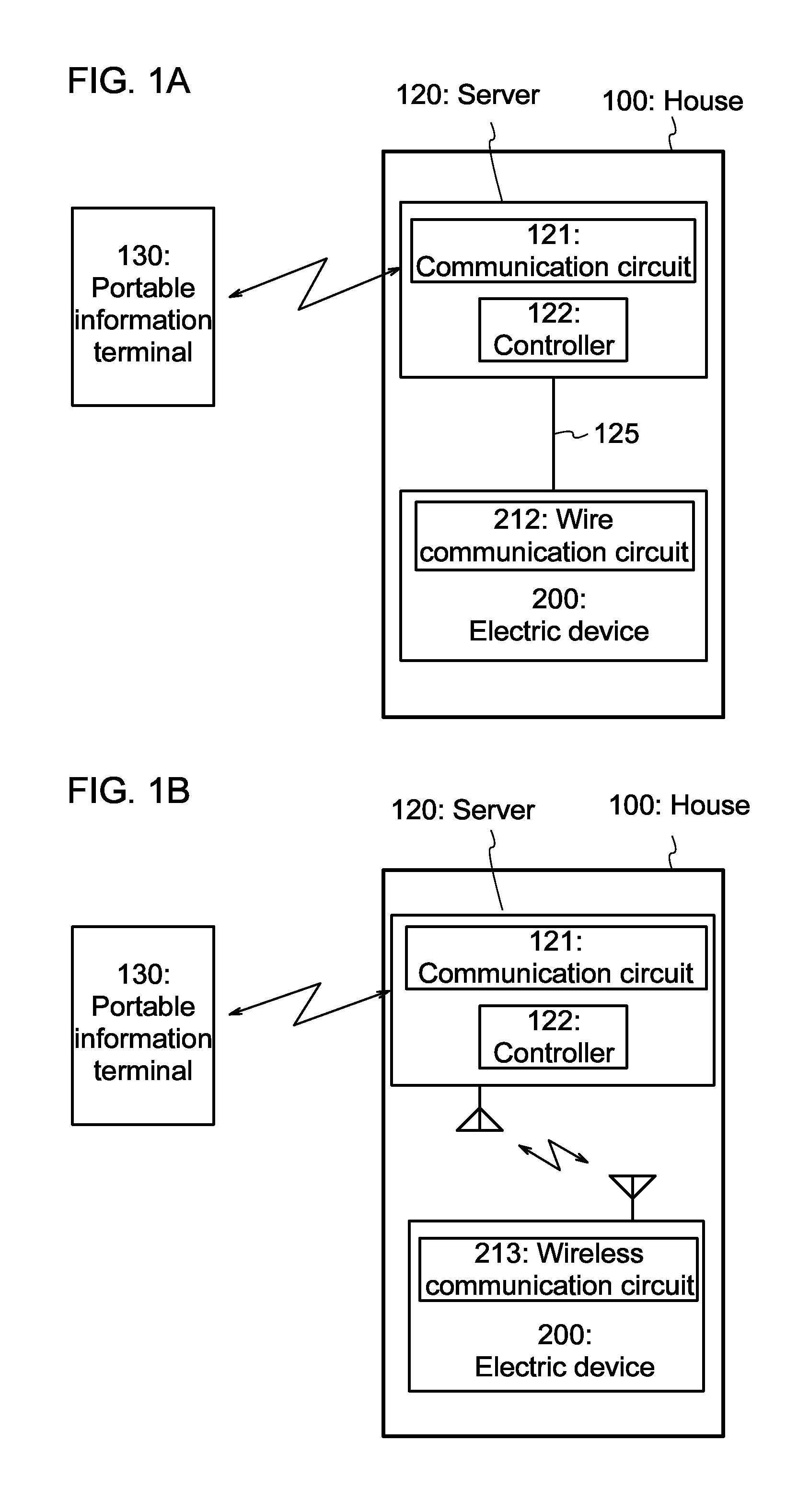

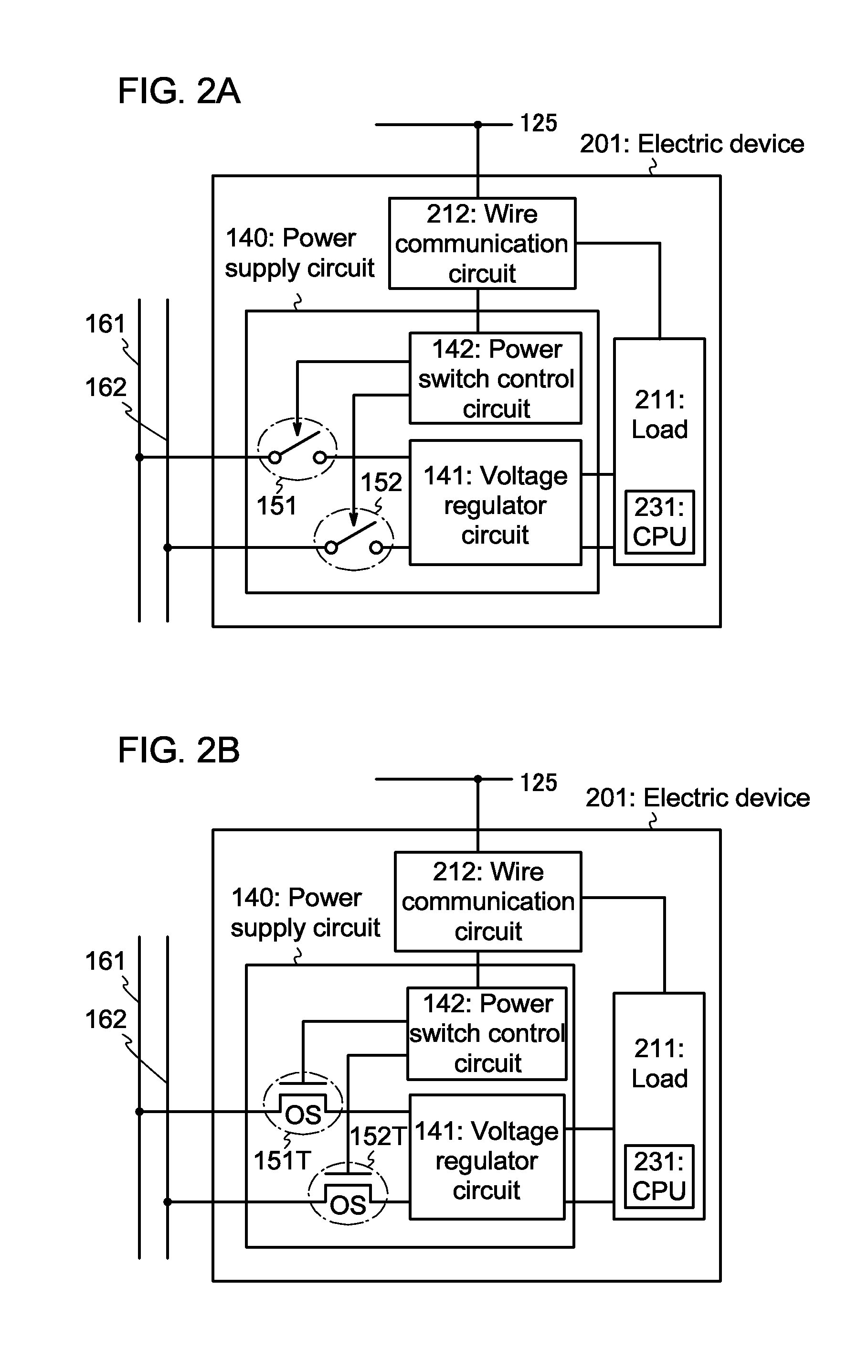

Remote control system

ActiveUS20140009270A1Total current dropReduce power consumptionTransistorElectric signal transmission systemsRemote controlComputer terminal

Provided is a remote control system with which leakage current flowing in a switch can be reduced so that power consumption can be reduced. The remote control system includes a portable information terminal, a server, and an electric device. The on / off of the switch included in the electric device is controlled using information transmitted from the portable information terminal to the server. The switch includes a transistor formed using a semiconductor whose band gap is larger than that of single crystal silicon in a channel formation region.

Owner:SEMICON ENERGY LAB CO LTD

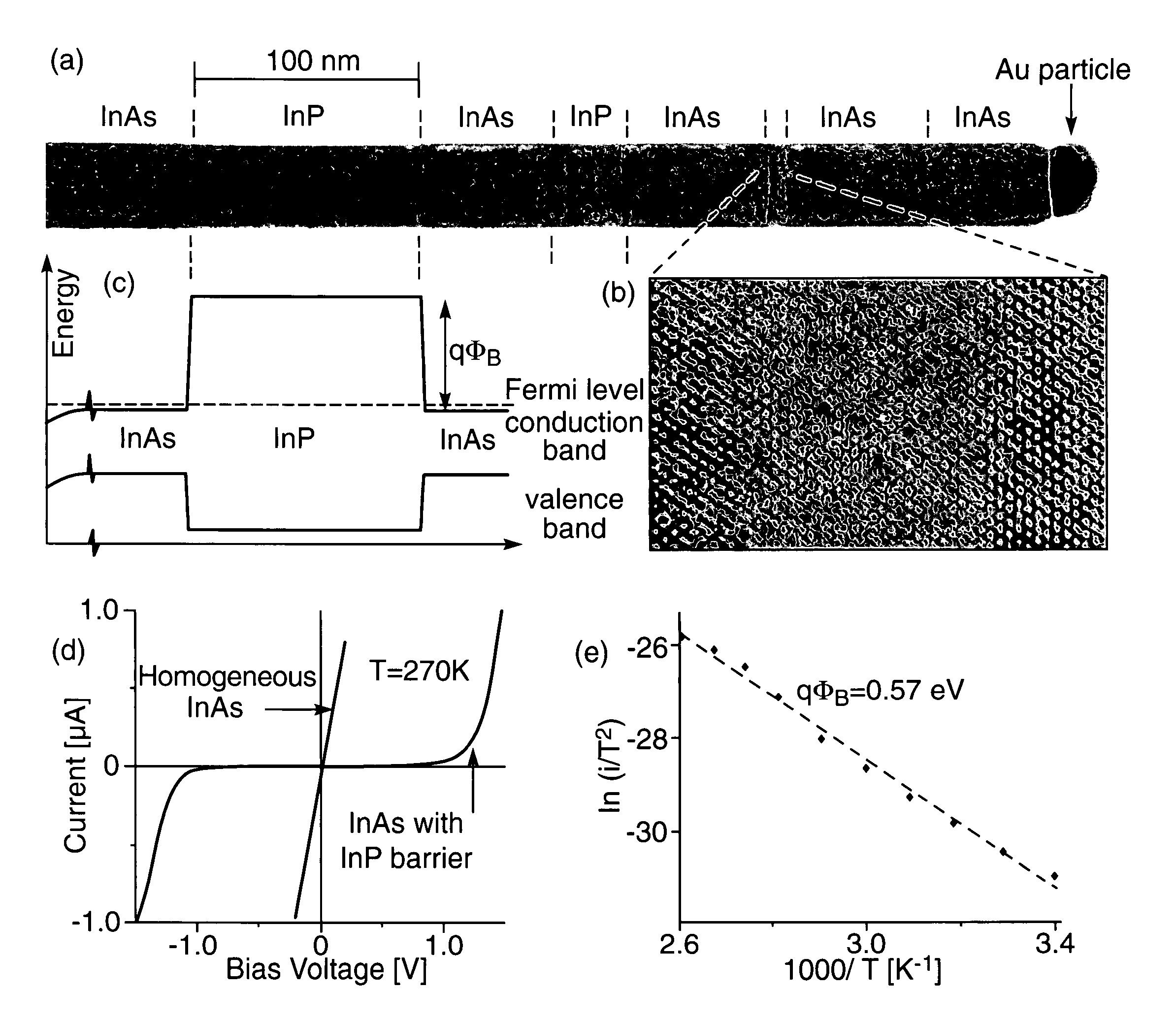

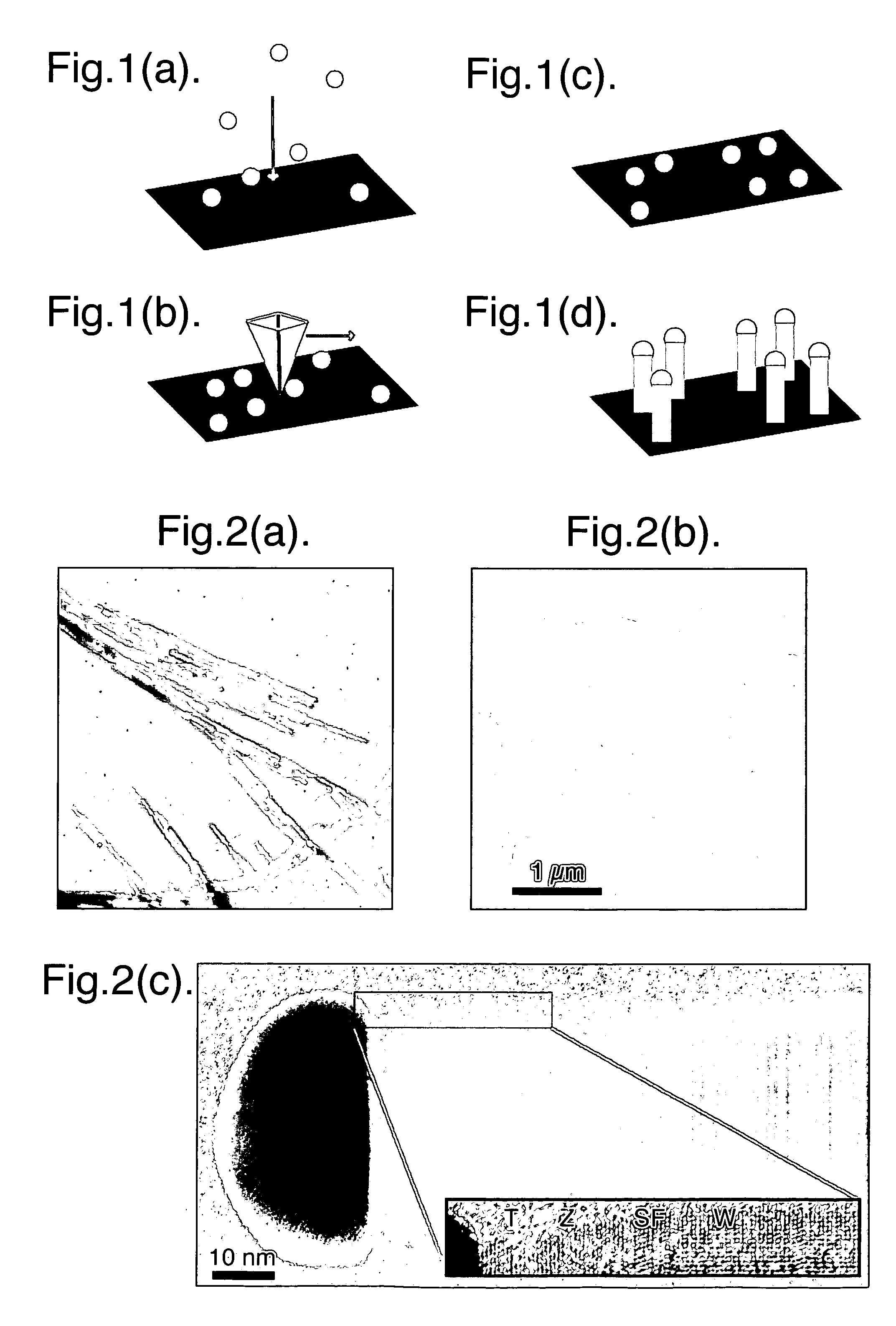

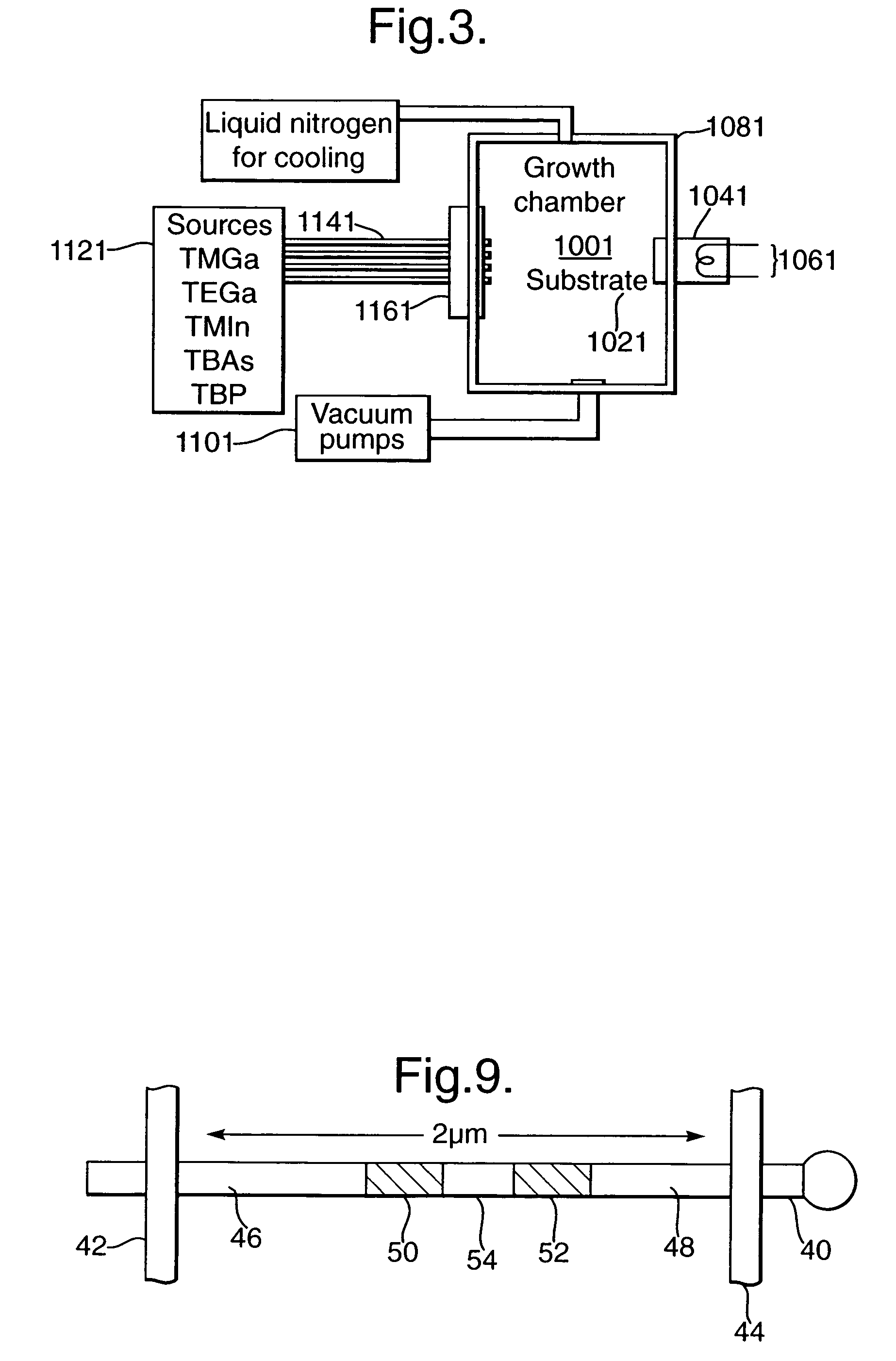

Nanostructures and methods for manufacturing the same

InactiveUS7335908B2Accurate weighingEnhances width controlPolycrystalline material growthIndividual molecule manipulationPhotonicsWhiskers

A resonant tunneling diode, and other one dimensional electronic, photonic structures, and electromechanical MEMS devices, are formed as a heterostructure in a nanowhisker by forming length segments of the whisker with different materials having different band gaps.

Owner:QUNANO

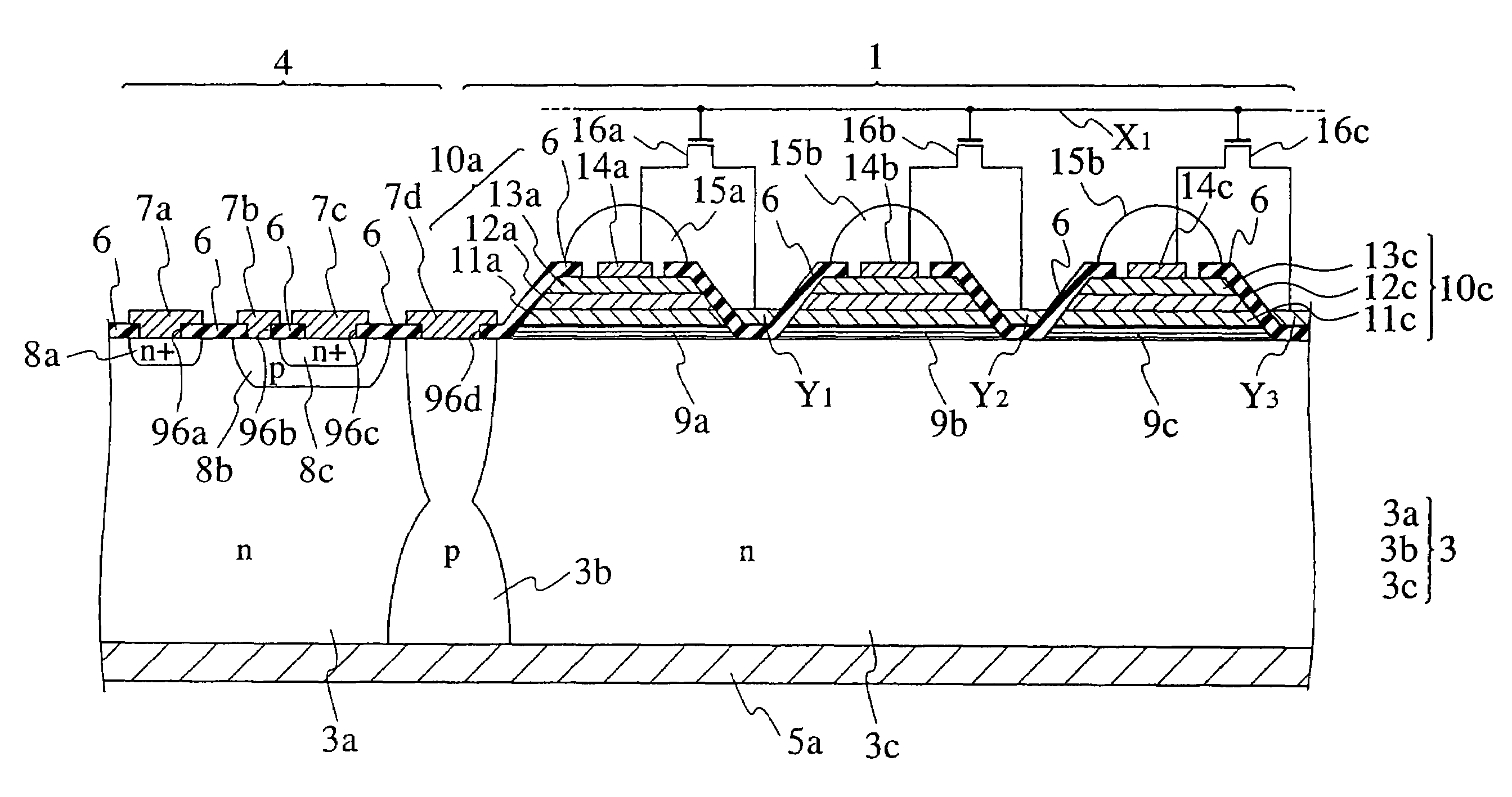

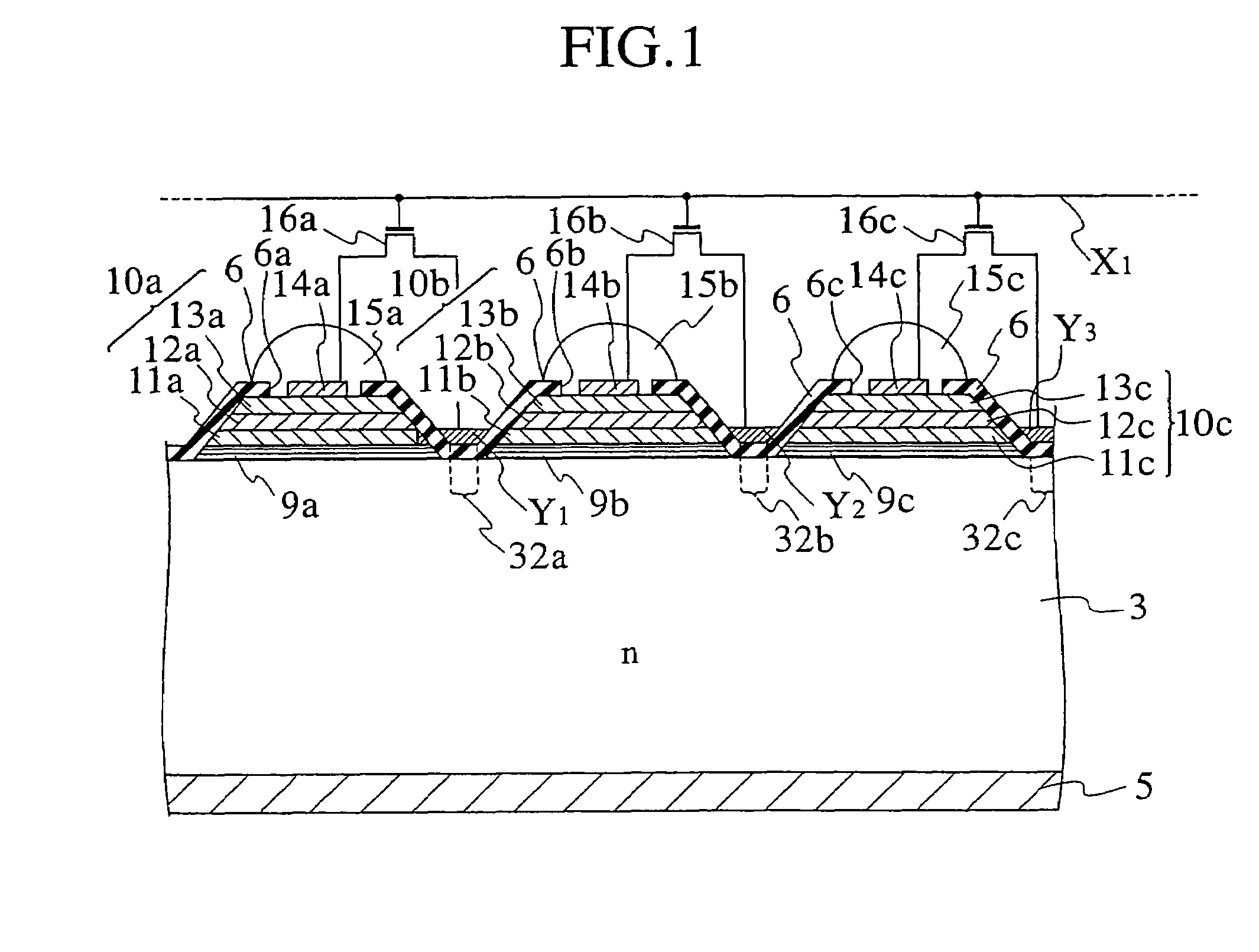

Semiconductor light-emitting device using phosphors for performing wavelength conversion

ActiveUS7323723B2Small lossImprove display speedDischarge tube luminescnet screensLamp detailsSemiconductor materialsPhosphor

A semiconductor light-emitting device includes substrate (3), a plurality of light-emitting-element-layers (10a, 10b, 10c, . . . ) of semiconductor material formed on the substrate (3) so as to be isolated from each other and having a wider band gap than the substrate (3), and phosphors (15a, 15b, 15c, . . . ) converting wavelengths of light from the light-emitting-element-layers (10a, 10b, 10c, . . . ) into other wavelengths.

Owner:SANKEN ELECTRIC CO LTD

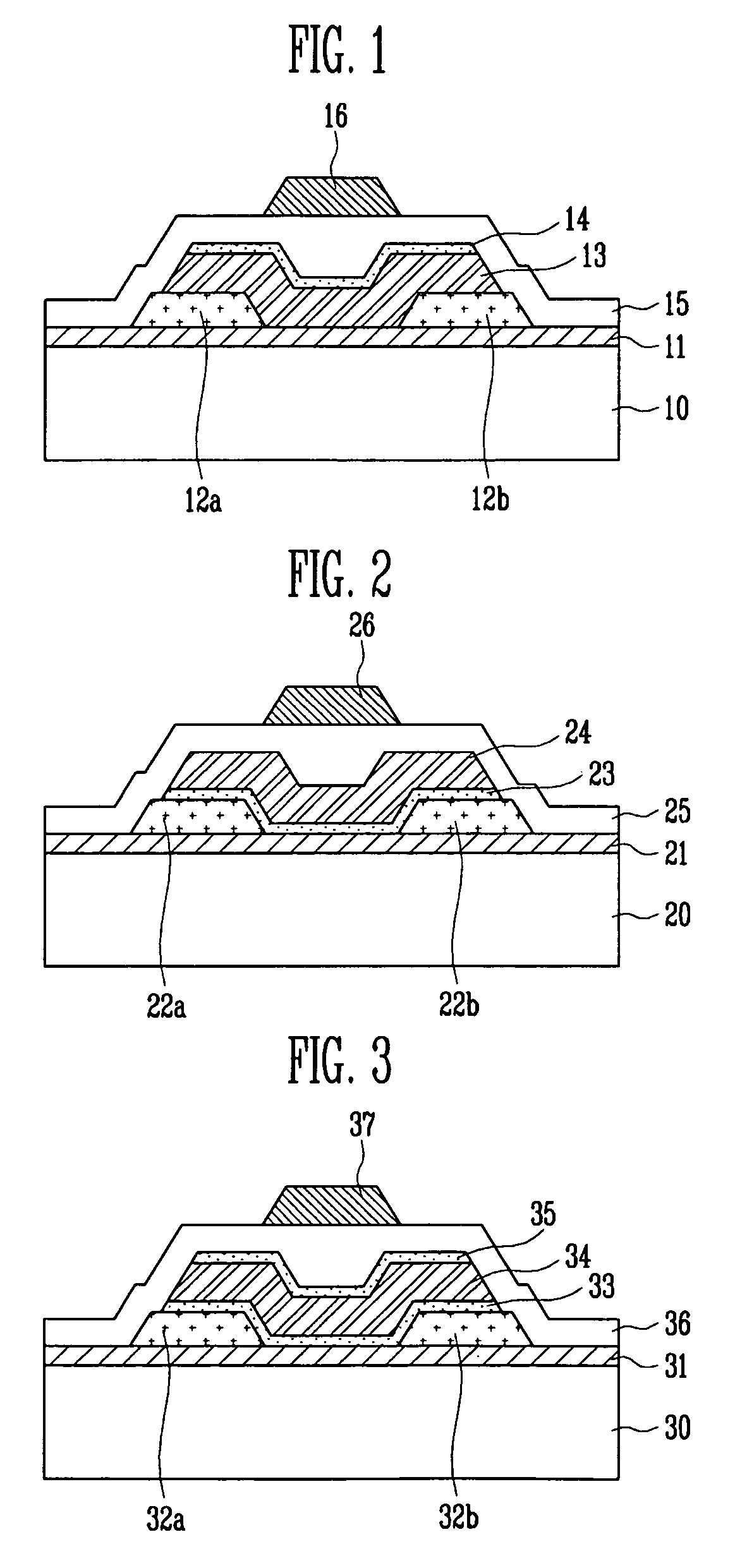

Semiconductor thin film, method for manufacturing the same, thin film transistor, and active-matrix-driven display panel

ActiveUS7998372B2Hardly erroneously operatesSmall currentNanotechConductive materialIndiumActive matrix

Disclosed is a semiconductor thin film which can be formed at a relatively low temperature even on a flexible resin substrate. Since the semiconductor thin film is stable to visible light and has high device characteristics such as transistor characteristics, in the case where the semiconductor thin film is used as a switching device for driving a display, even when overlapped with a pixel part, the luminance of a display panel does not deteriorate. Specifically, a transparent semiconductor thin film 40 is produced by forming an amorphous film containing zinc oxide and indium oxide and then oxidizing the film so that the resulting film has a carrier density of 10+17 cm−3 or less, a Hall mobility of 2 cm2 / V·sec or higher, and an energy band gap of 2.4 EV or more.

Owner:IDEMITSU KOSAN CO LTD

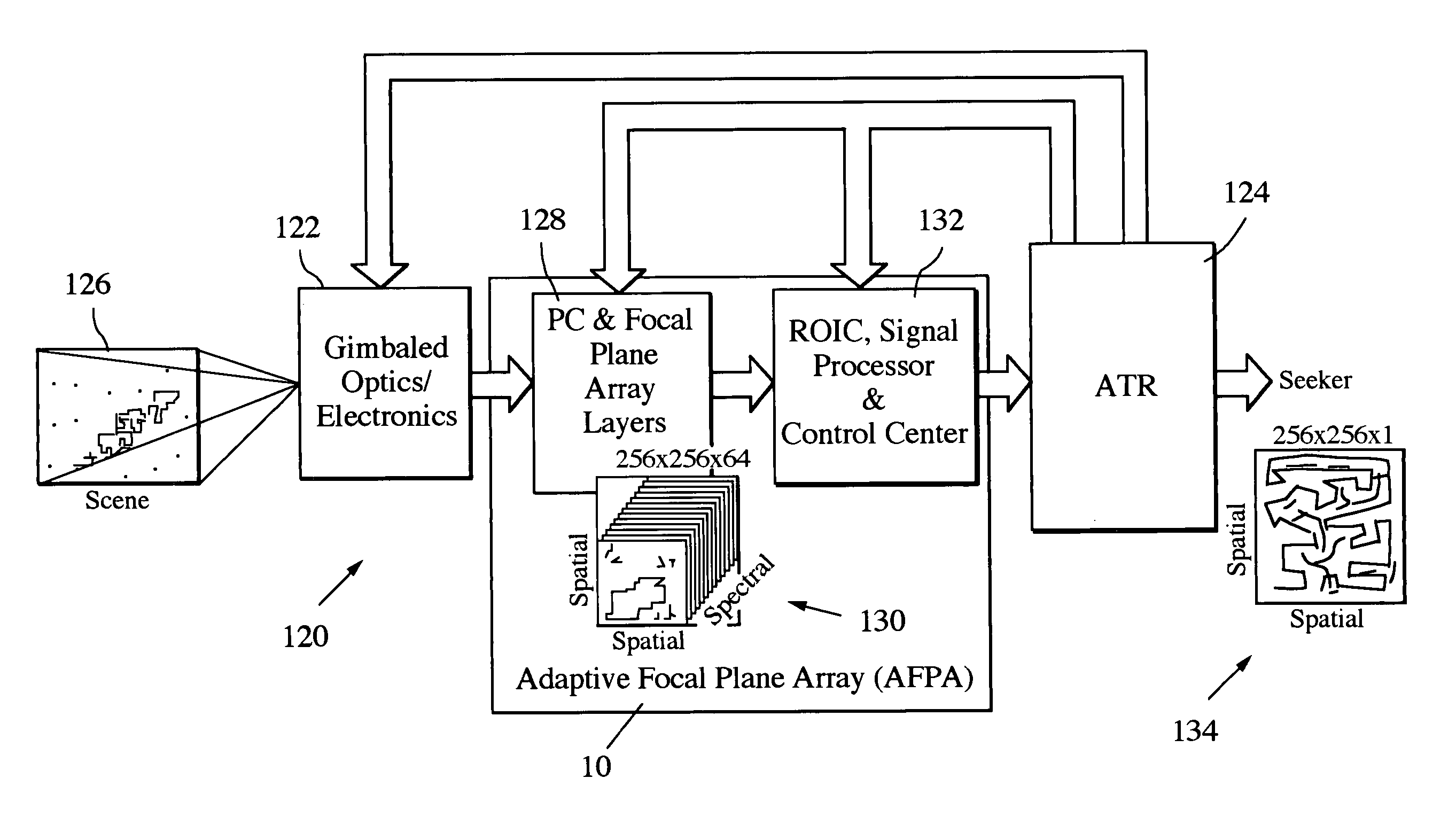

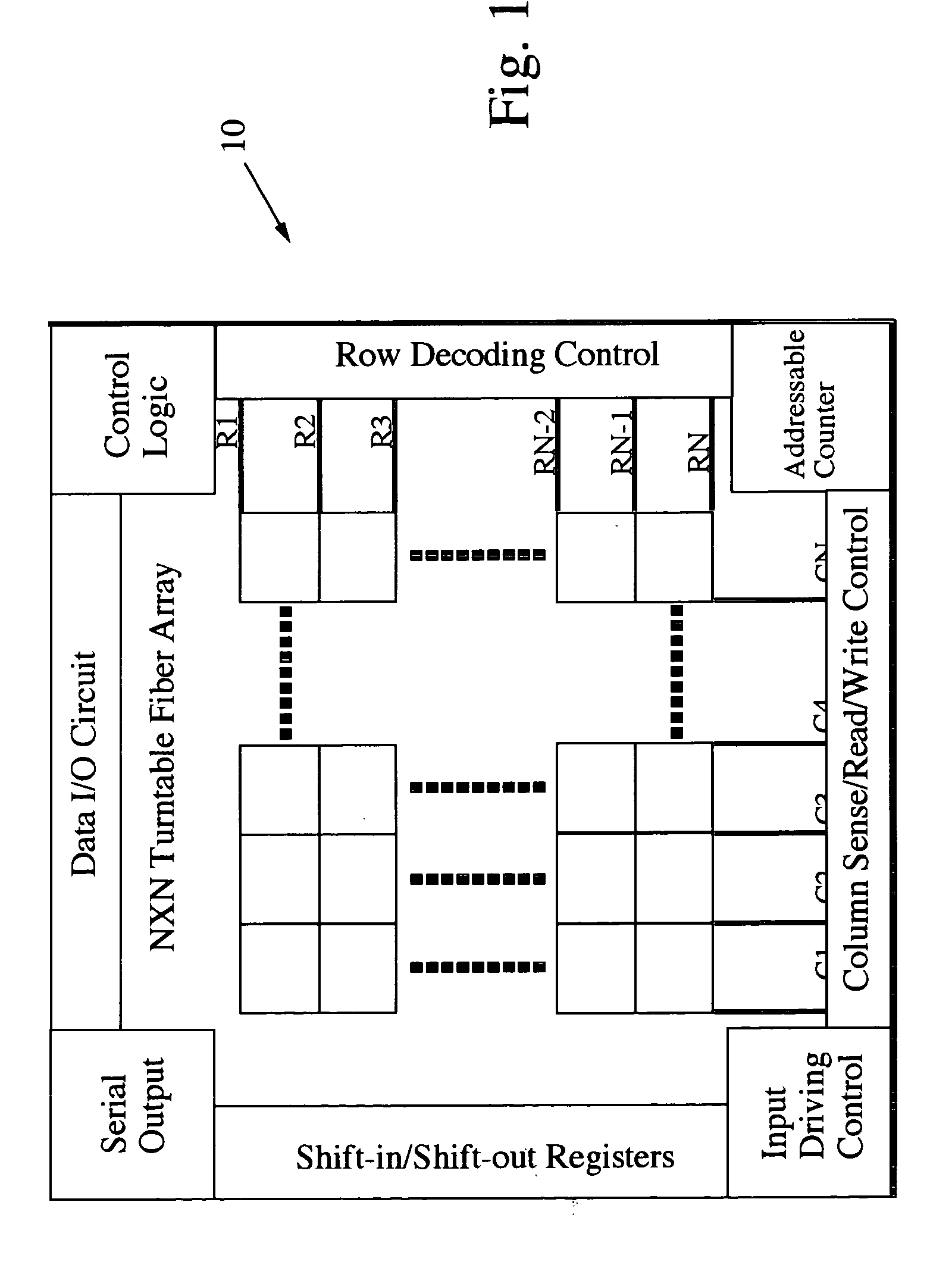

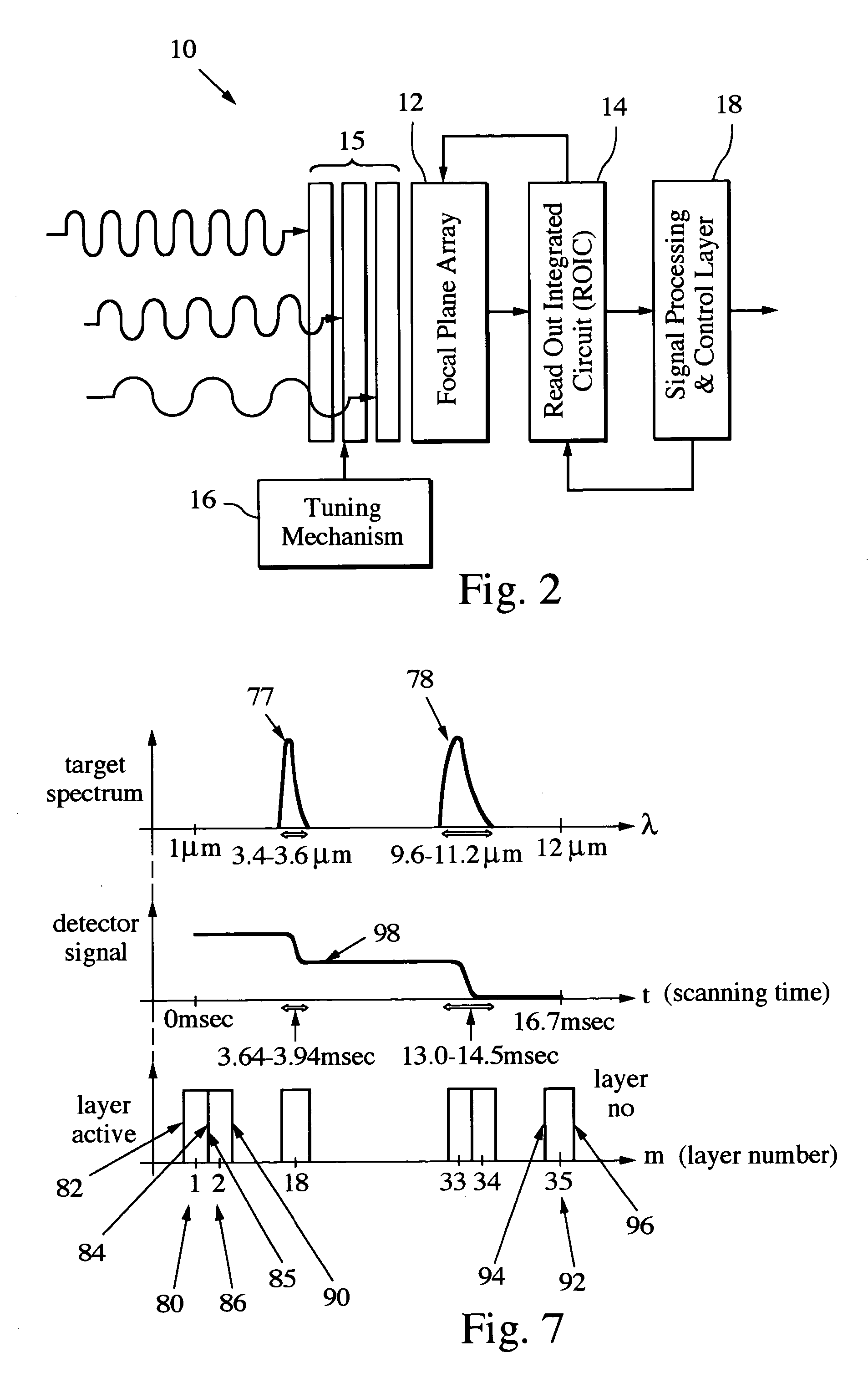

Multispectral imaging chip using photonic crystals

ActiveUS20060054780A1Low data rateHigh resolutionTelevision system detailsTelevision system scanning detailsPhotonic bandgapPhotonics

On-chip multispectral imaging and data management is provided in the form of an Adaptive Focal Plane Array (AFPA) that is capable of spectral tunability at the pixel level. Layers of photonic crystals are registered with pixels of a broadband focal plane array. Spectral tuning is accomplished by switching the photonic crystal layers on / off and / or by changing their material structure to tune their photonic band gaps and provide a passband for incident photons. The photonic crystal layers are preferably segmented to independently address different regions or “cells” of pixels down to a pixel-by-pixel resolution. The AFPA may simultaneously sense different regions of a scene at different spectral wavelengths, spatial resolutions and sensitivities.

Owner:RAYTHEON CO

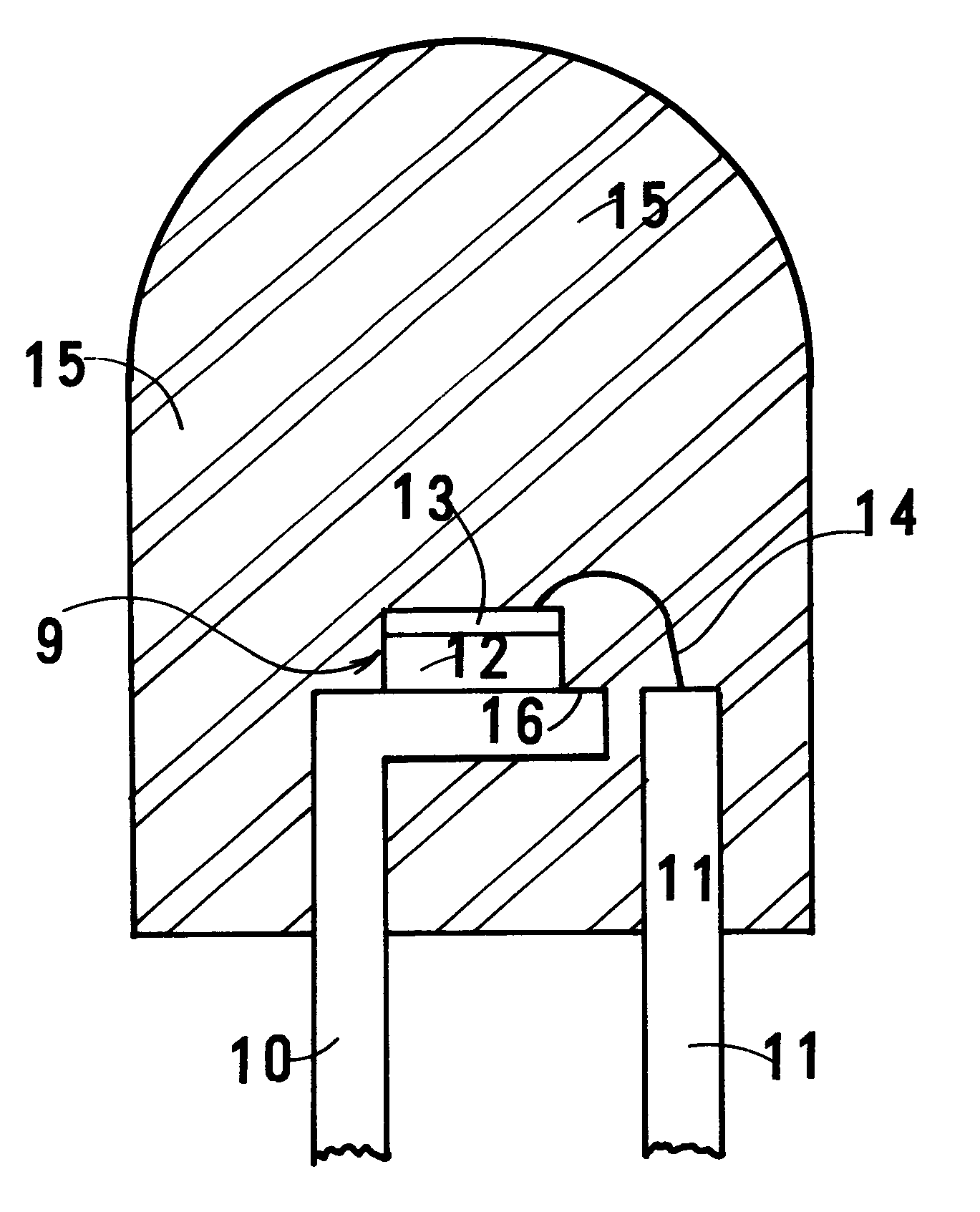

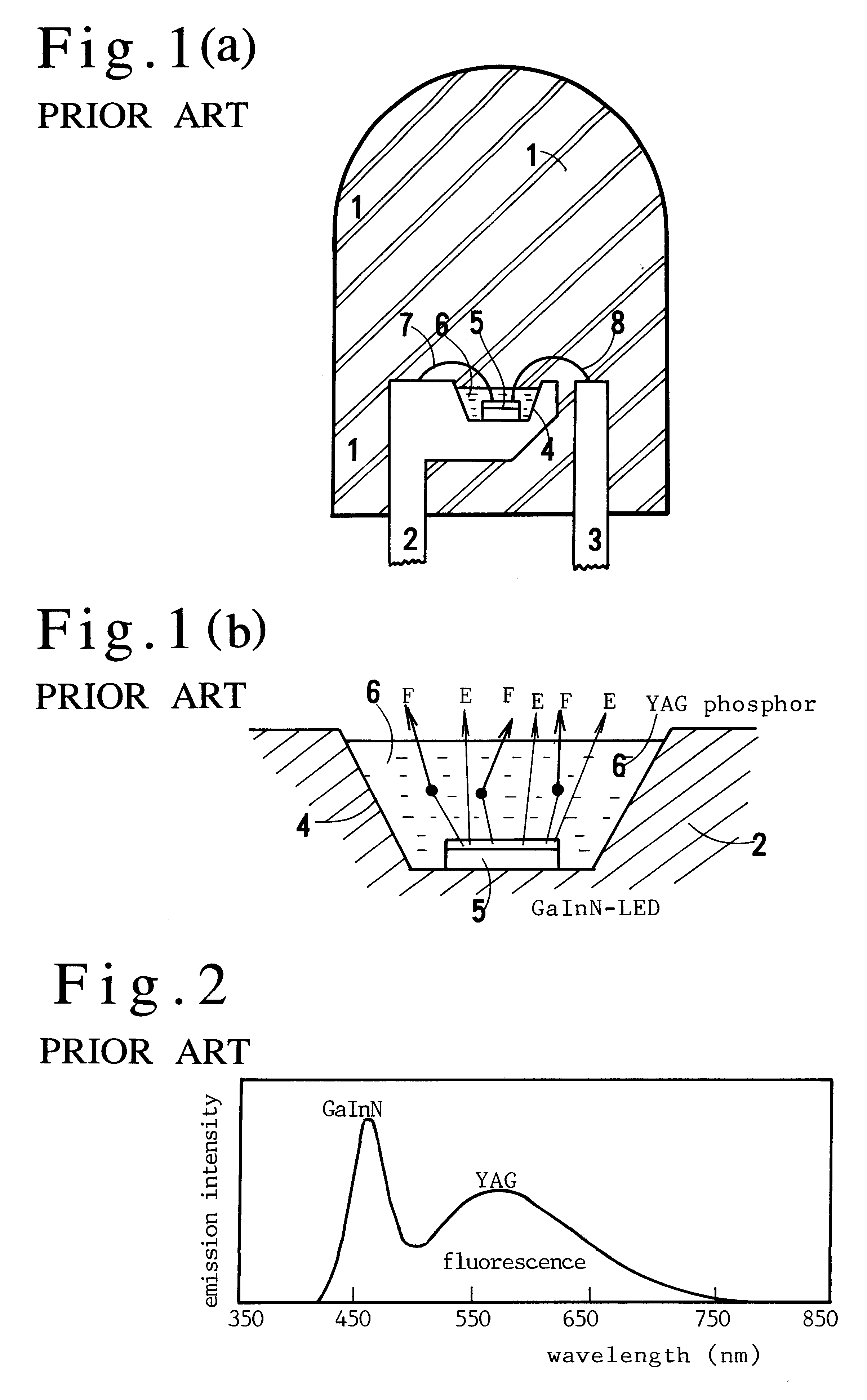

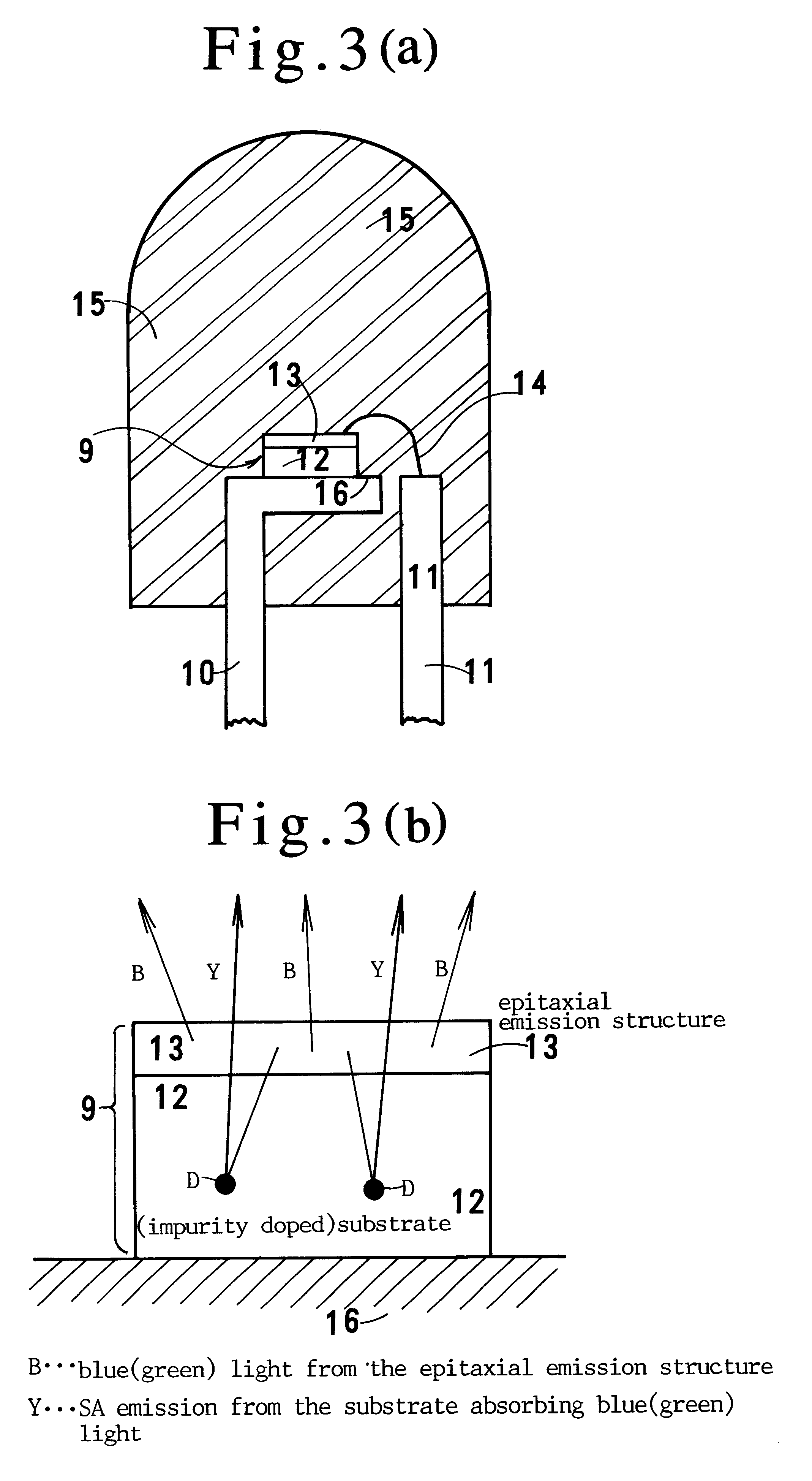

Substrate-fluorescent LED

InactiveUS6509651B1Easy to moveEasy to getTransistorDischarge tube luminescnet screensFluorescenceGreen-light

A substrate-fluorescent LED having a fluorescent-impurity doped substrate and an epitaxial emission structure including an active layer and being made on the substrate. The epitaxial emission structure emits blue or green light corresponding to the band gap of the active layer. The substrate absorbs a part of the blue or green light and makes fluorescence of a longer wavelength. Neutral color light or white light is emitted from the LED. The fluorescent substrate is n-AlGaAs(Si dope), GaP(Zn+O dope), ZnSe(Cu+I, Ag+I, Al+I dope), GaN(O.C.Va(N) dope) or so.

Owner:SUMITOMO ELECTRIC IND LTD

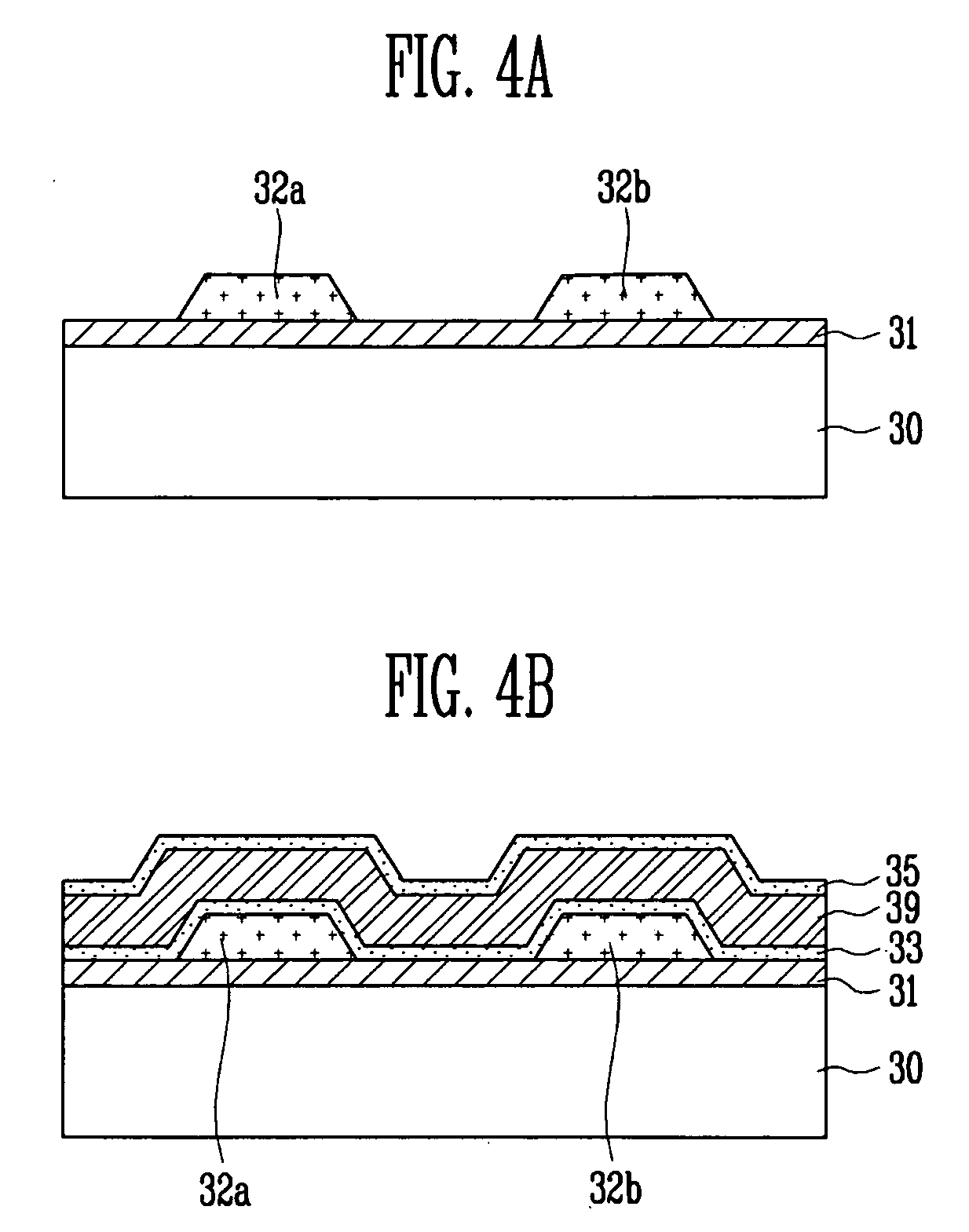

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS20090321732A1Improve featuresAvoid chargingSemiconductor/solid-state device manufacturingNon-linear opticsTrappingEngineering

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include source and drain electrodes formed on a substrate; an active layer formed of an oxide semiconductor disposed on the source and drain electrodes; a gate electrode; and an interfacial stability layer formed on at least one of top and bottom surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristics as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor light-emitting device and method for manufacturing the same

InactiveUS7132691B1High crystallinityHigh light emitting efficiencyLaser detailsLaser active region structureCrystallinityActive layer

It has a structure in which an active layer (5) that emits light by electric current injection is sandwiched between an n-type cladding layer (4) and a p-type cladding layer (6) made of materials having a larger band gap than the active layer (5), wherein the active layer (5) is made, for example, of CdxZn1−xO (0≦x<1). It is further more preferable if the cladding layers (4), (6) are made, for example, of MgyZn1−yO (0≦y<1). This narrows the band gap of the ZnO materials, and an oxide semiconductor capable of being wet-etched, easy to handle with, and excellent in crystallinity can be used as a material for an active layer or a cladding layer of a semiconductor light emitting device such as a blue light emitting diode or a blue laser diode in which an active layer is sandwiched between cladding layers, so that a blue semiconductor light emitting device being excellent in light emission characteristics can be obtained.

Owner:ROHM CO LTD

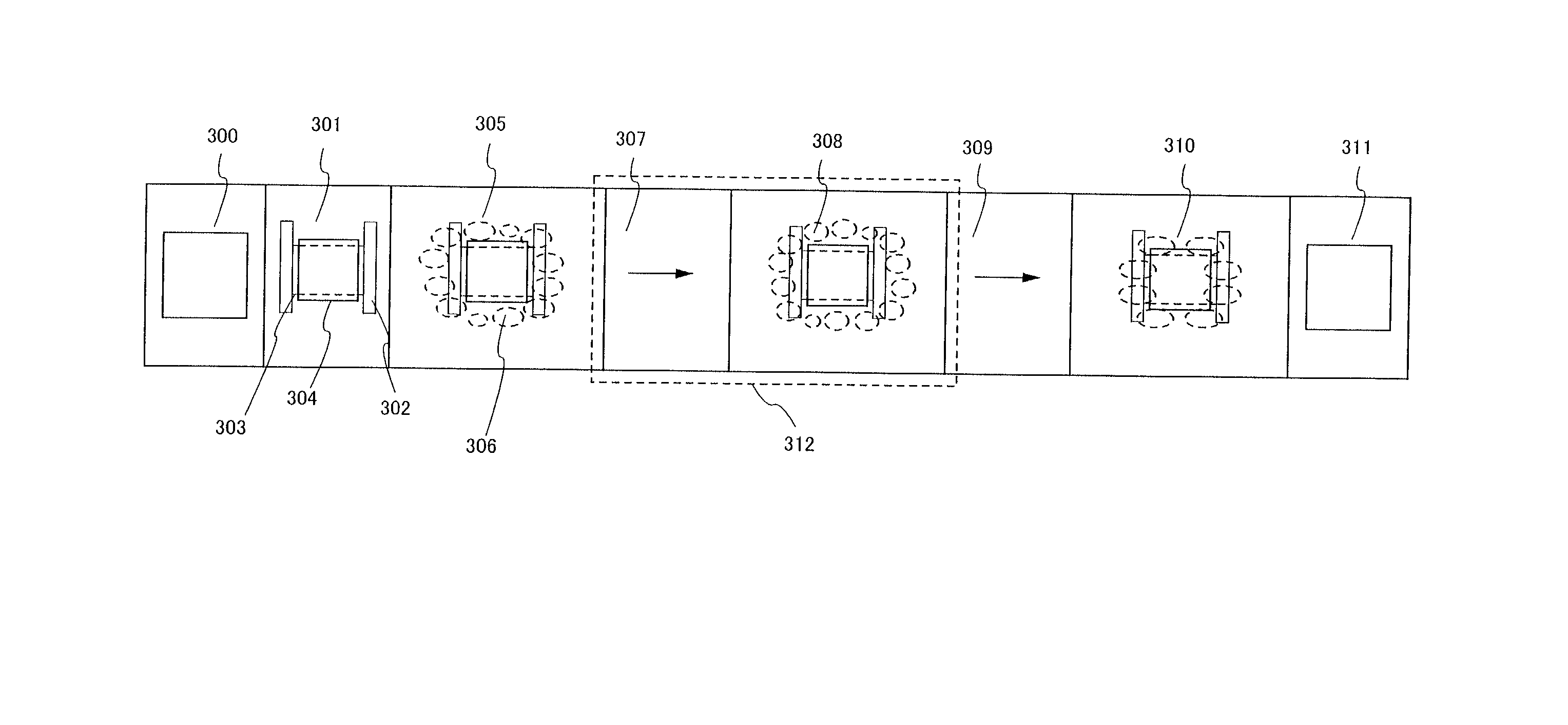

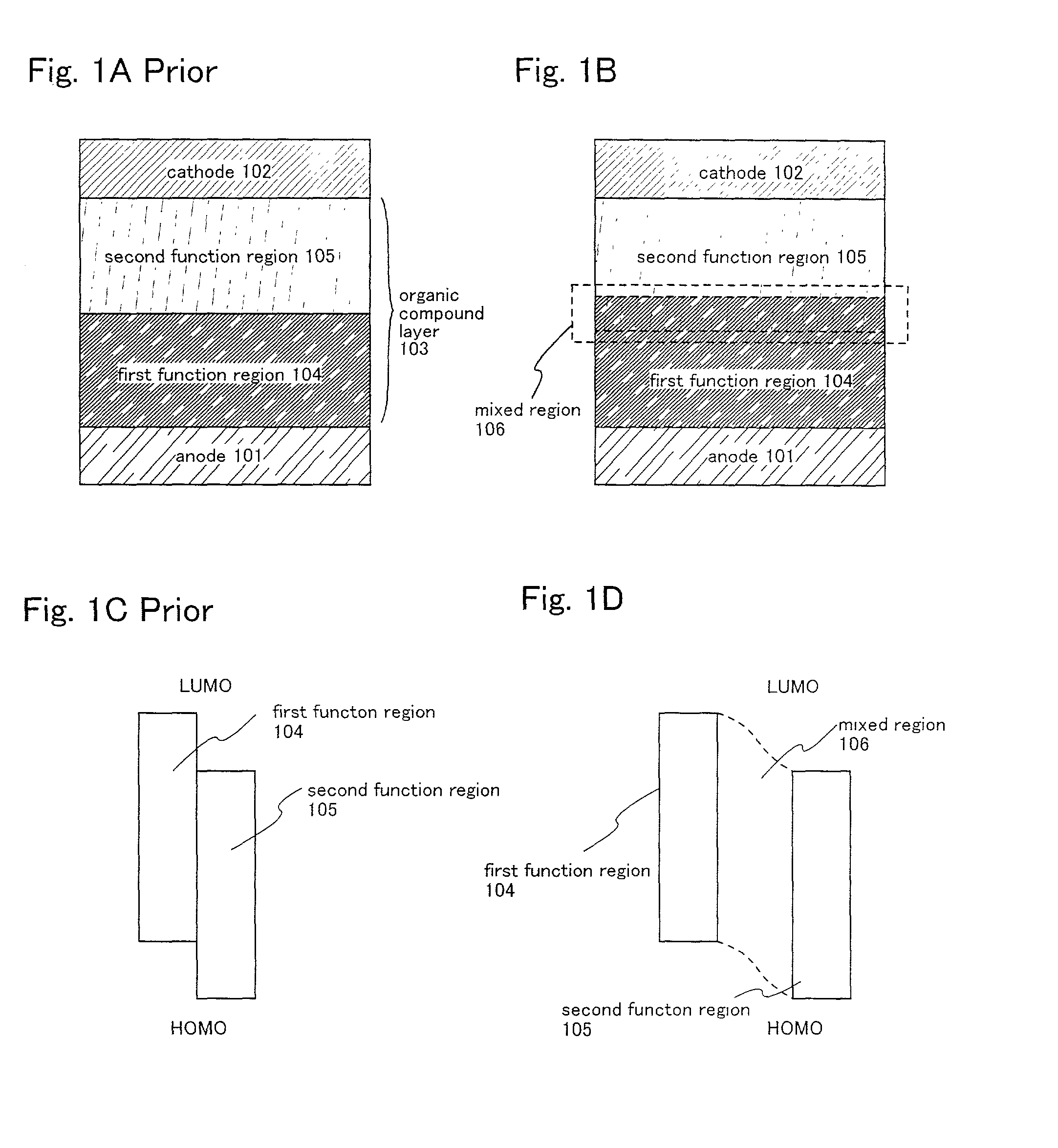

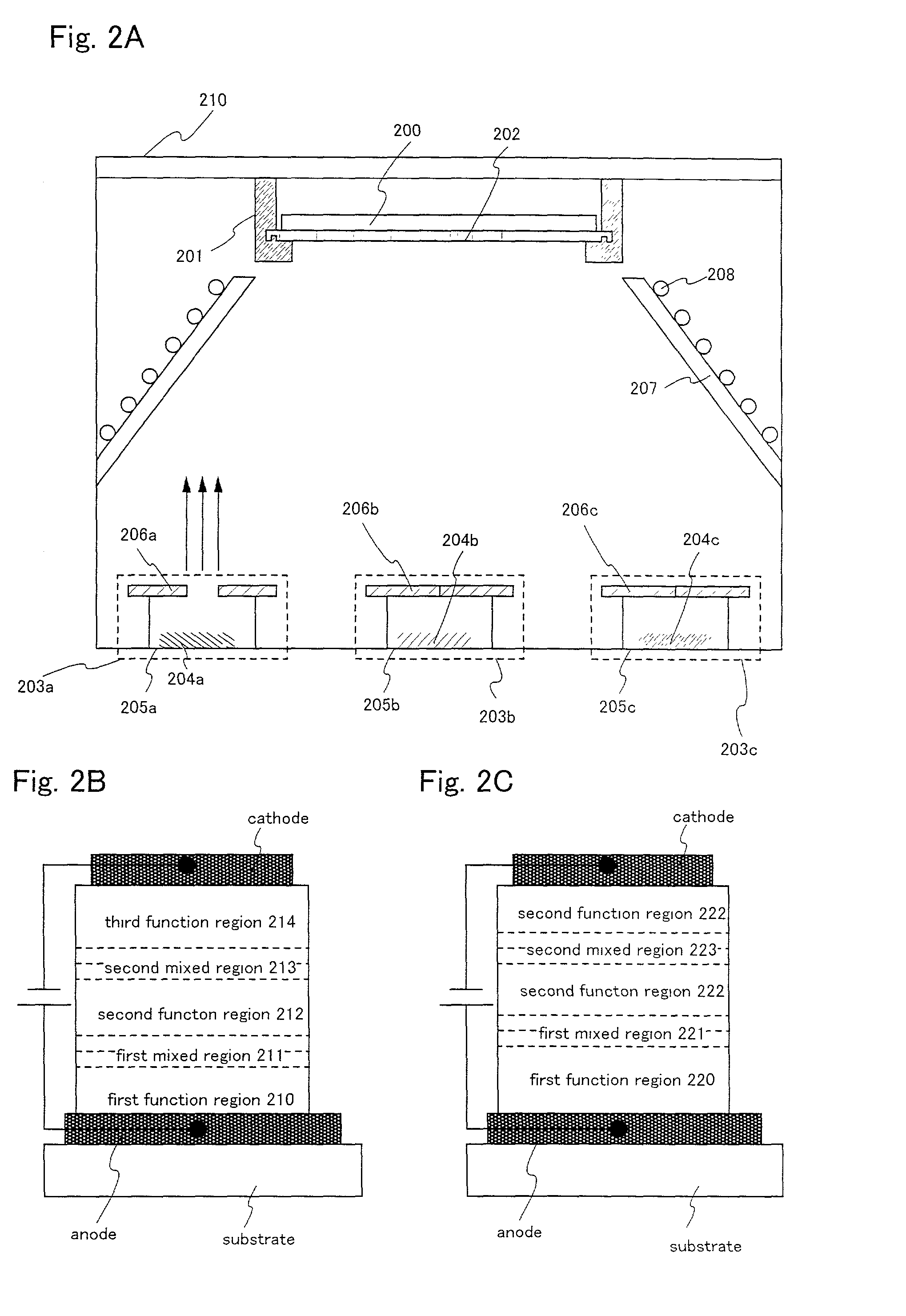

Deposition apparatus and deposition method

A deposition apparatus is provided for manufacturing an organic compound layer having a plurality of function regions. The deposition apparatus includes a plurality of evaporation sources within a deposition chamber, for enabling continuous formation of respective function regions comprised of organic compounds and, further, formation of a mixed region at an interface between adjacent ones of the function regions. With the deposition apparatus having such fabrication chamber, it is possible to prevent impurity contamination between the functions regions and further possible to form an organic compound layer with an energy gap relaxed at the interface.

Owner:SEMICON ENERGY LAB CO LTD

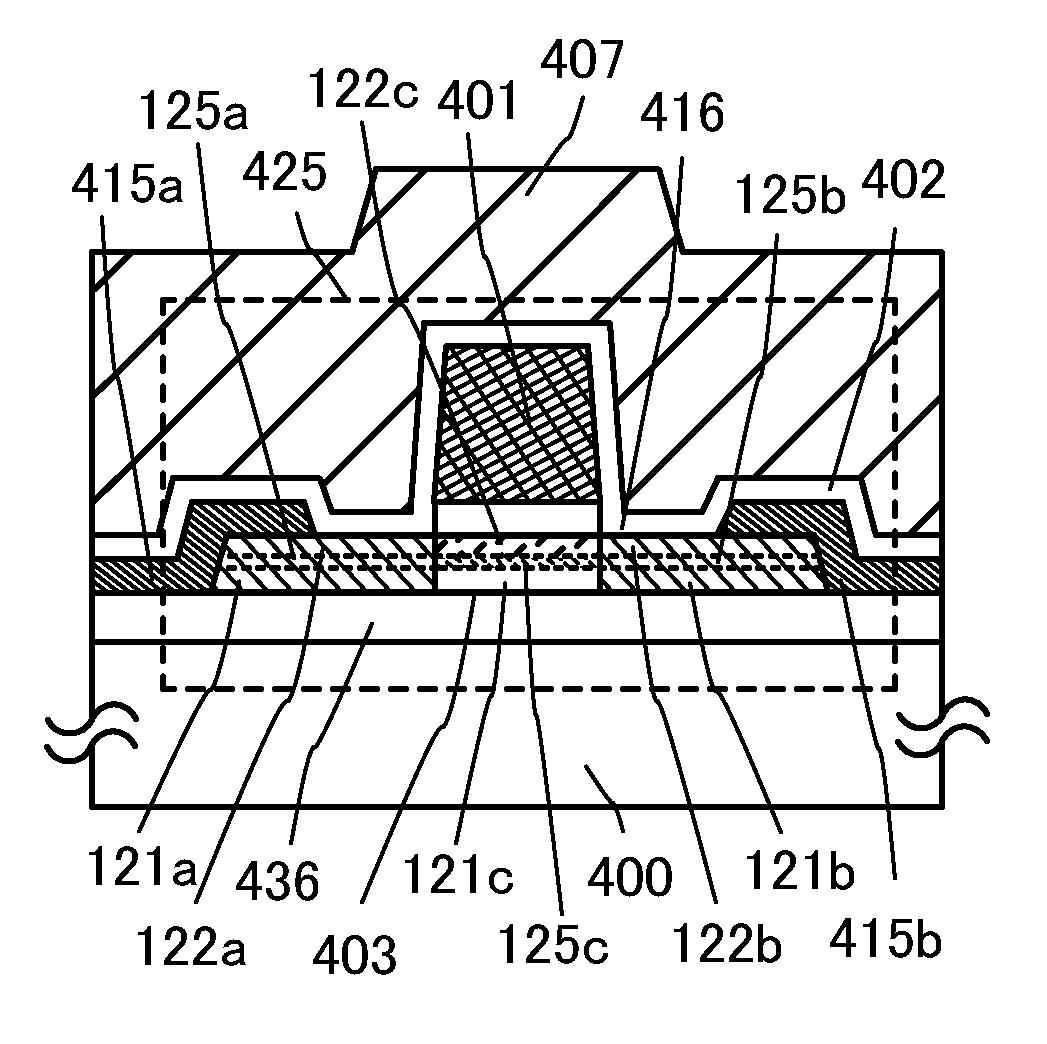

Semiconductor device and method for manufacturing semiconductor device

ActiveUS20130009209A1Improve performanceReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

Owner:SEMICON ENERGY LAB CO LTD

Metamorphic layers in multijunction solar cells

ActiveUS20070277873A1Maximize energy efficiencyFinal product manufacturePhotovoltaic energy generationSemiconductor materialsLattice mismatch

A method of forming a multijunction solar cell comprising an upper subcell, a middle subcell, and a lower subcell comprising providing first substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on said substrate having a first band gap; forming a second solar subcell over said first subcell having a second band gap smaller than said first band gap; and forming a grading interlayer over said second subcell having a third band gap larger than said second band gap forming a third solar subcell having a fourth band gap smaller than said second band gap such that said third subcell is lattice mismatched with respect to said second subcell.

Owner:SOLAERO TECH CORP

Band-engineered multi-gated non-volatile memory device with enhanced attributes

ActiveUS7279740B2Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC

Band-engineered multi-gated non-volatile memory device with enhanced attributes

ActiveUS20060258090A1Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC