Patents

Literature

3125results about How to "Small current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Amorphous Oxide And Thin Film Transistor

InactiveUS20070194379A1High ionicityGeneration of oxygen defects is less frequentTransistorVacuum evaporation coatingCharge carrierElectron

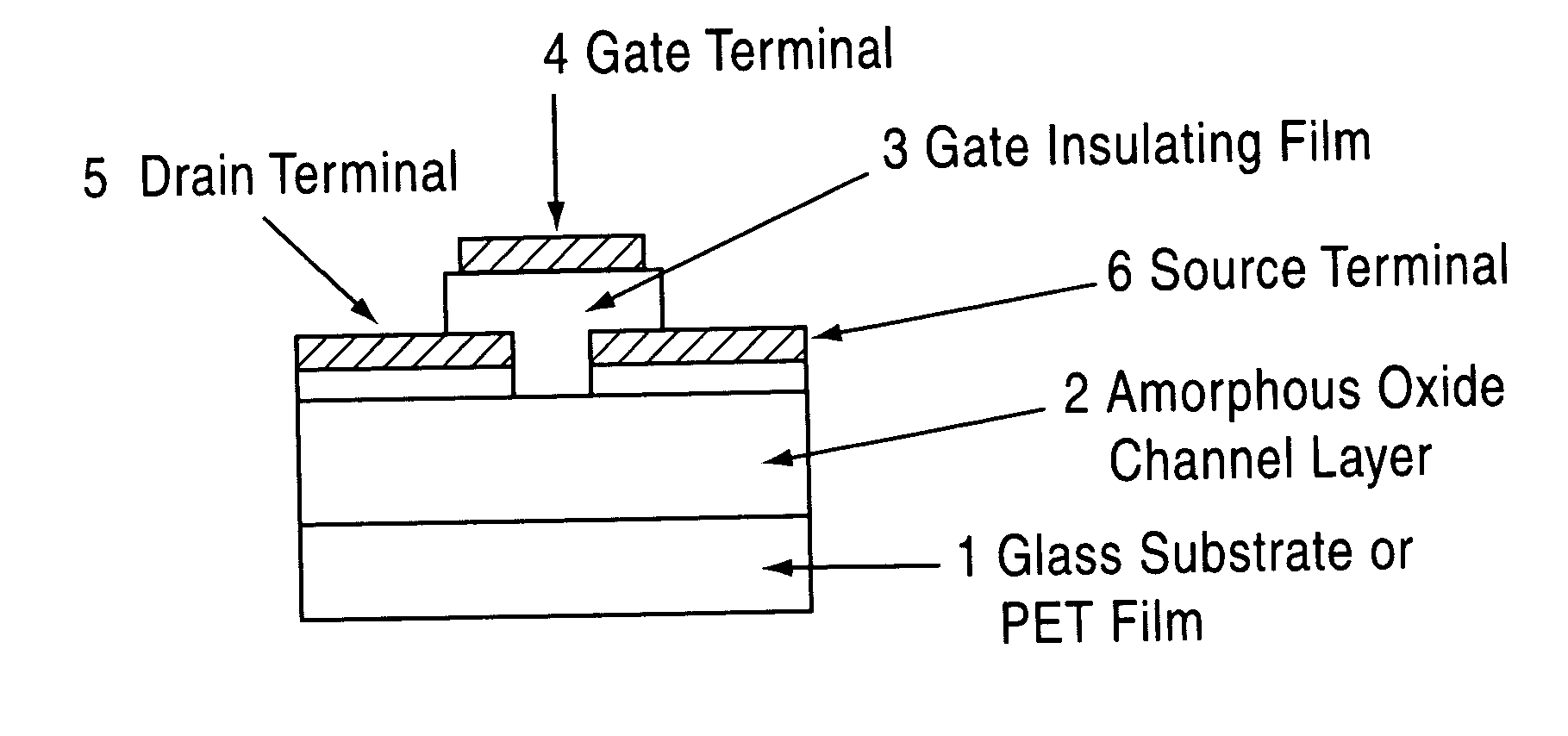

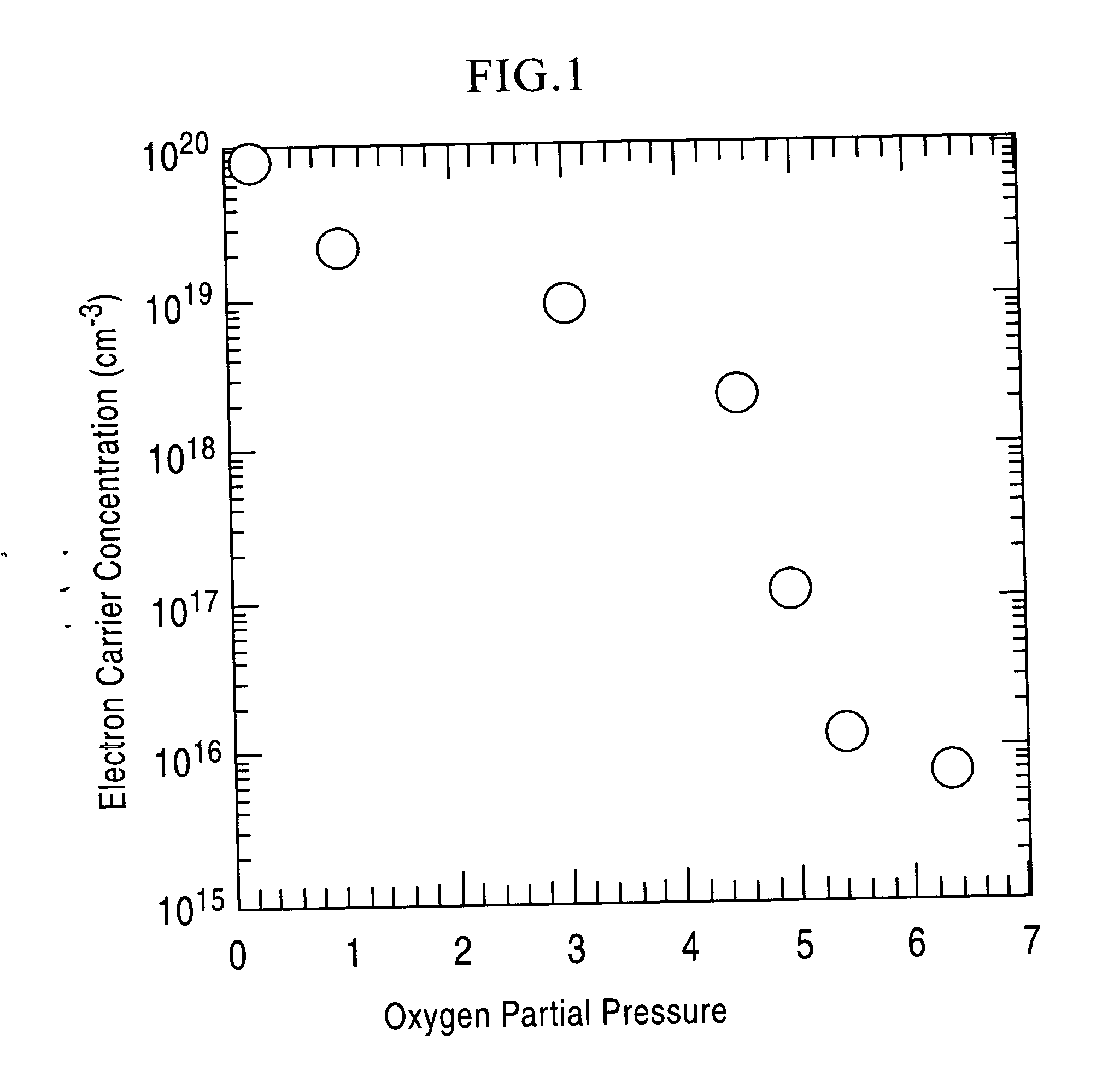

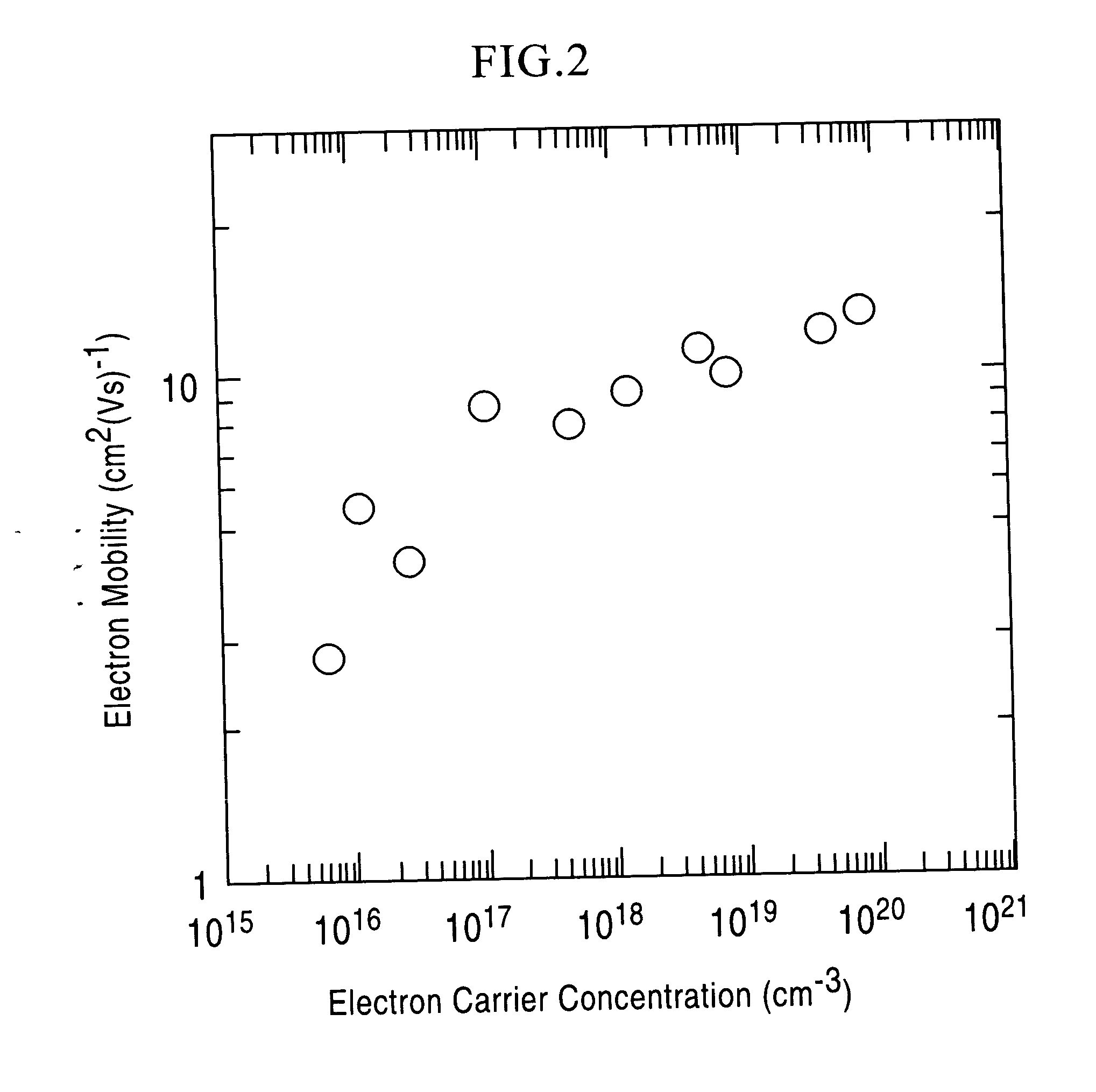

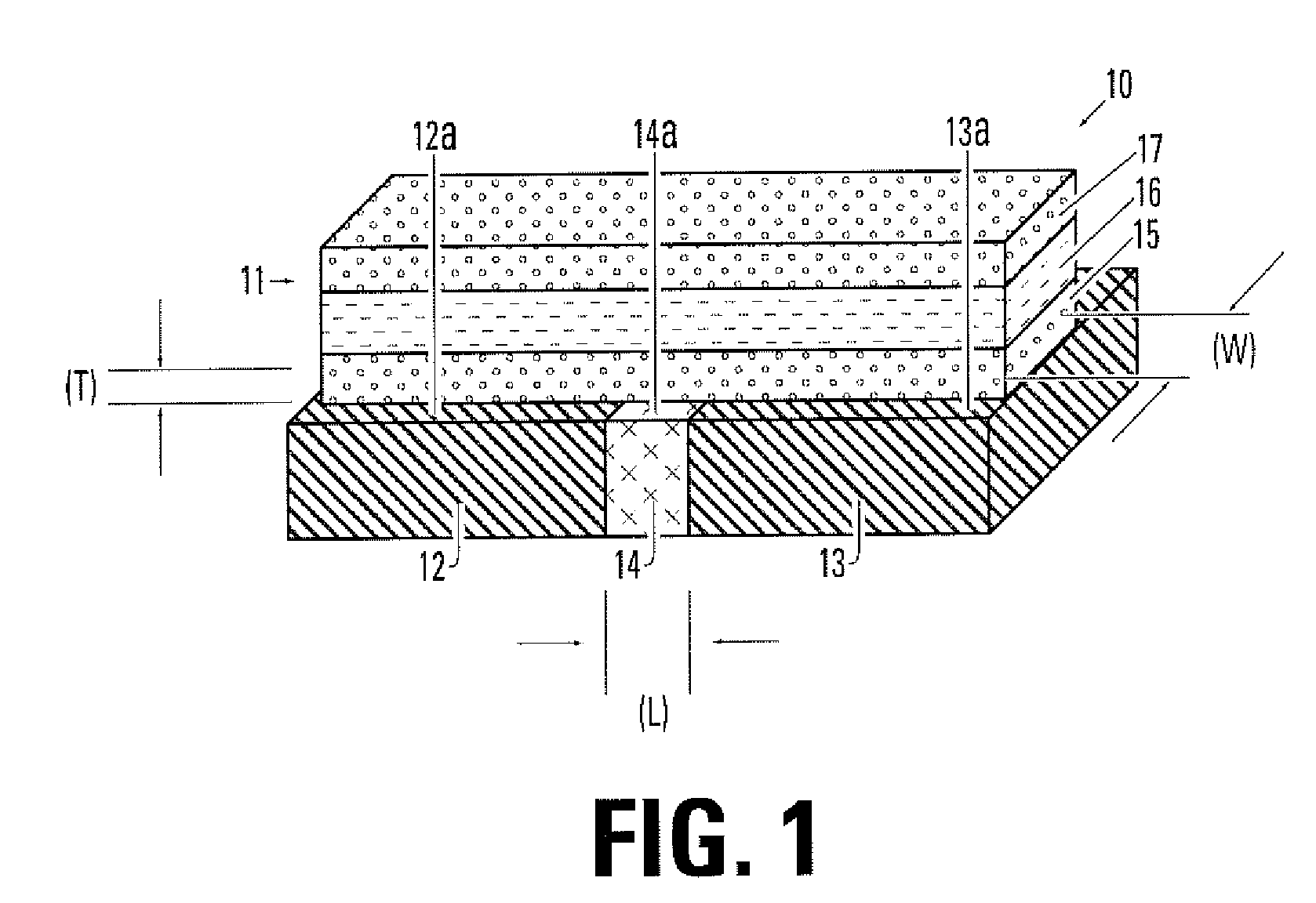

The present invention relates to an amorphous oxide and a thin film transistor using the amorphous oxide. In particular, the present invention provides an amorphous oxide having an electron carrier concentration less than 1018 / cm3, and a thin film transistor using such an amorphous oxide. In a thin film transistor having a source electrode 6, a drain electrode 5, a gate electrode 4, a gate insulating film 3, and a channel layer 2, an amorphous oxide having an electron carrier concentration less than 1018 / cm3 is used in the channel layer 2.

Owner:JAPAN SCI & TECH CORP

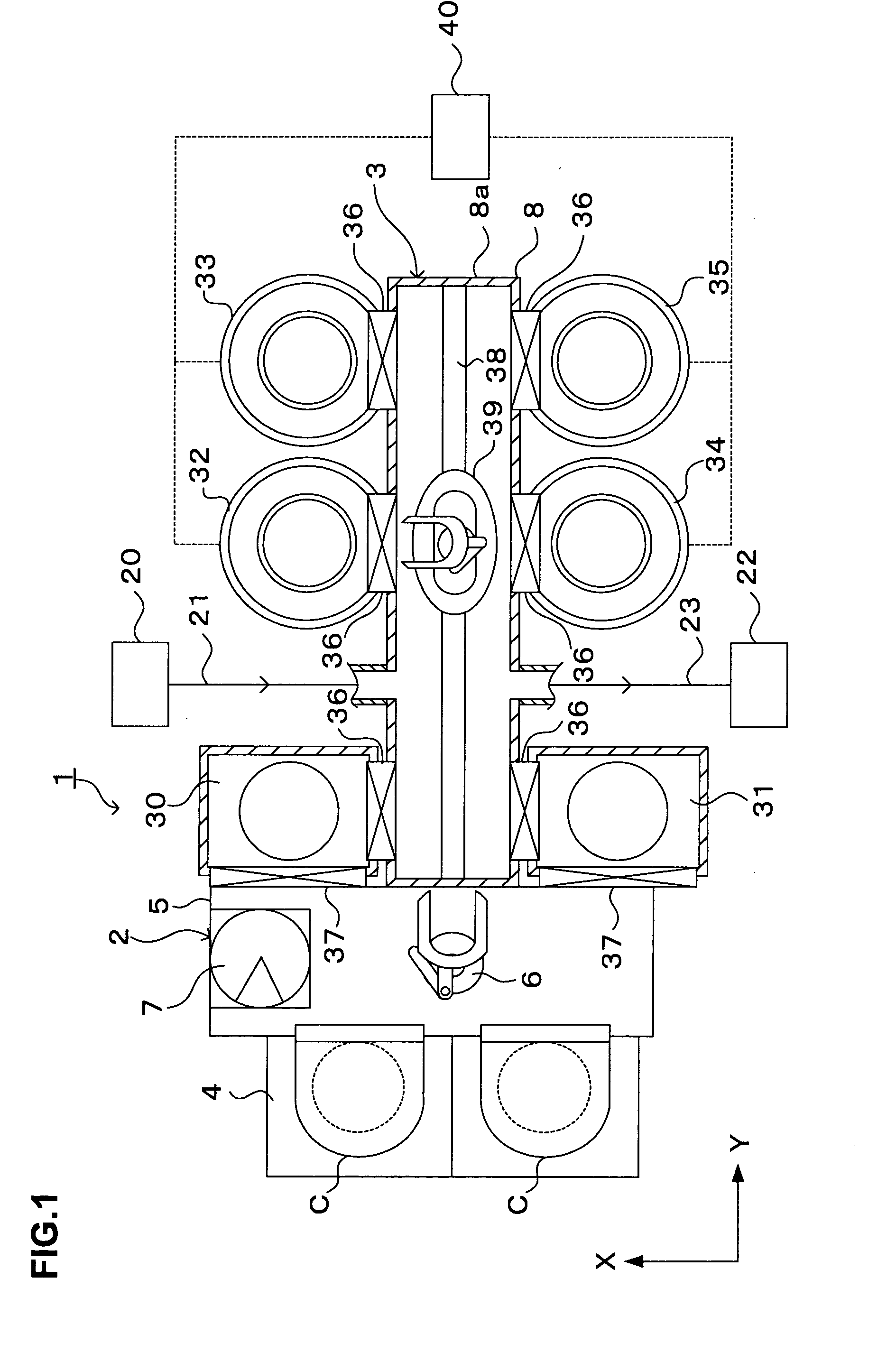

Substrate processing method, computer readable recording medium and substrate processing apparatus

InactiveUS20070062453A1Low dielectric constantImprove heat resistanceElectric discharge tubesSemiconductor/solid-state device detailsMicrowaveEngineering

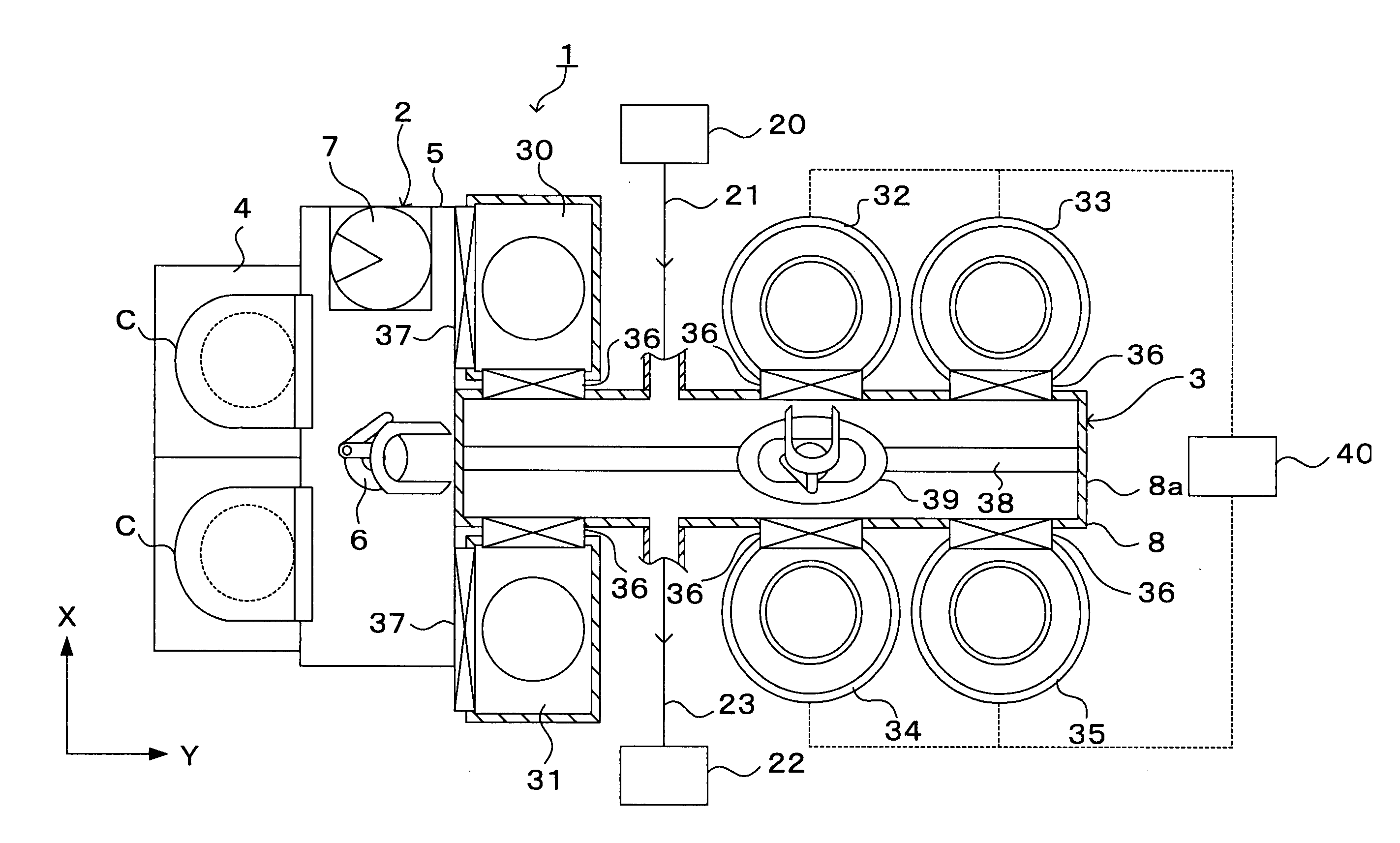

In the present invention, Ar gas for plasma generation is supplied to a plasma generation region and butyne gas having a multiple bond is supplied to a film formation region at a substrate side as source gas, inside of a process vessel in an insulating film forming apparatus. A microwave is supplied inside of the process vessel from a radial line slot antenna under a state in which a bias voltage is not applied to a substrate W. A plasma is thereby generated in the plasma generation region, the butyne gas in the film formation region is activated by the plasma, and an insulating film of amorphous carbon is formed on the substrate.

Owner:TOKYO ELECTRON LTD

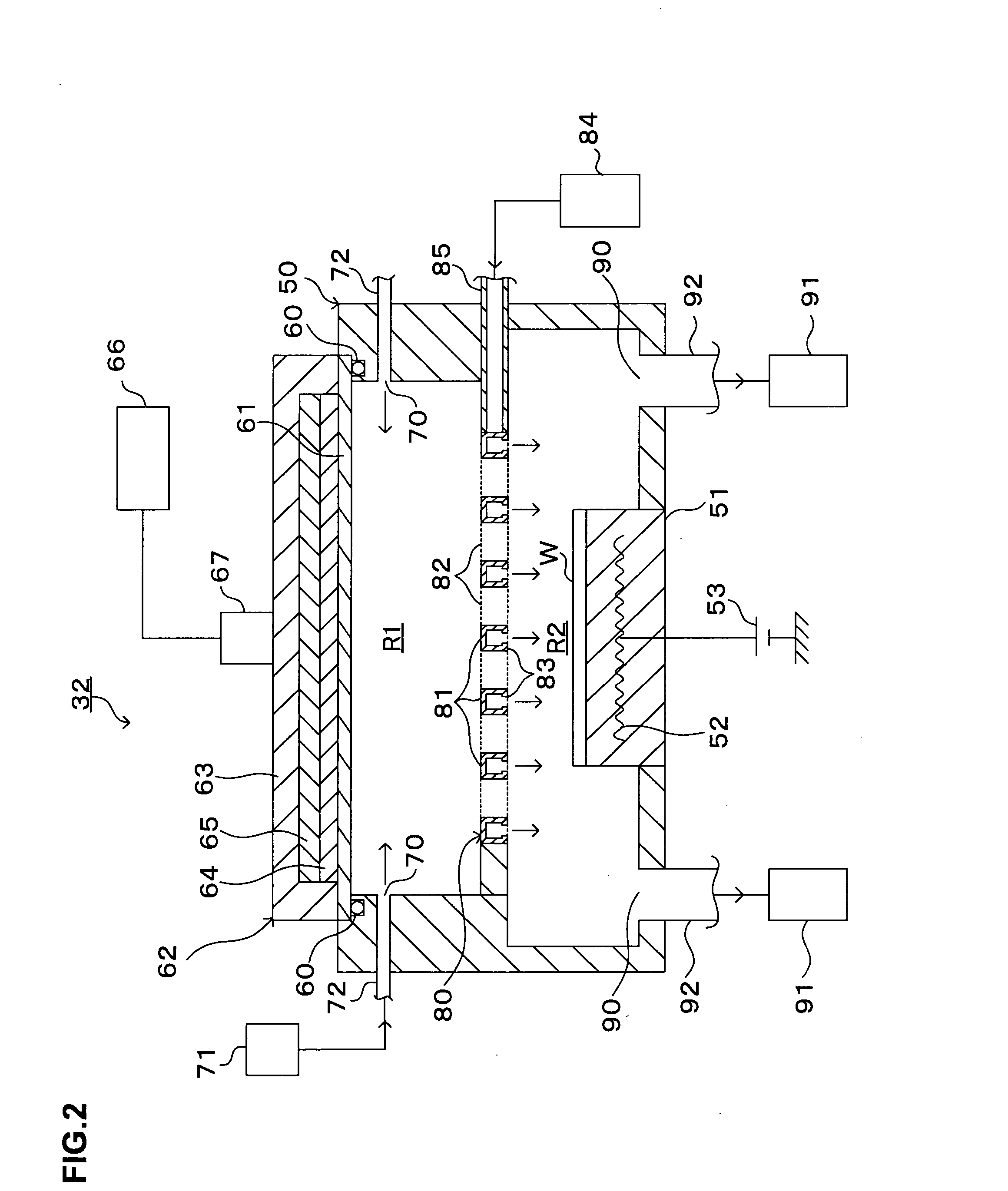

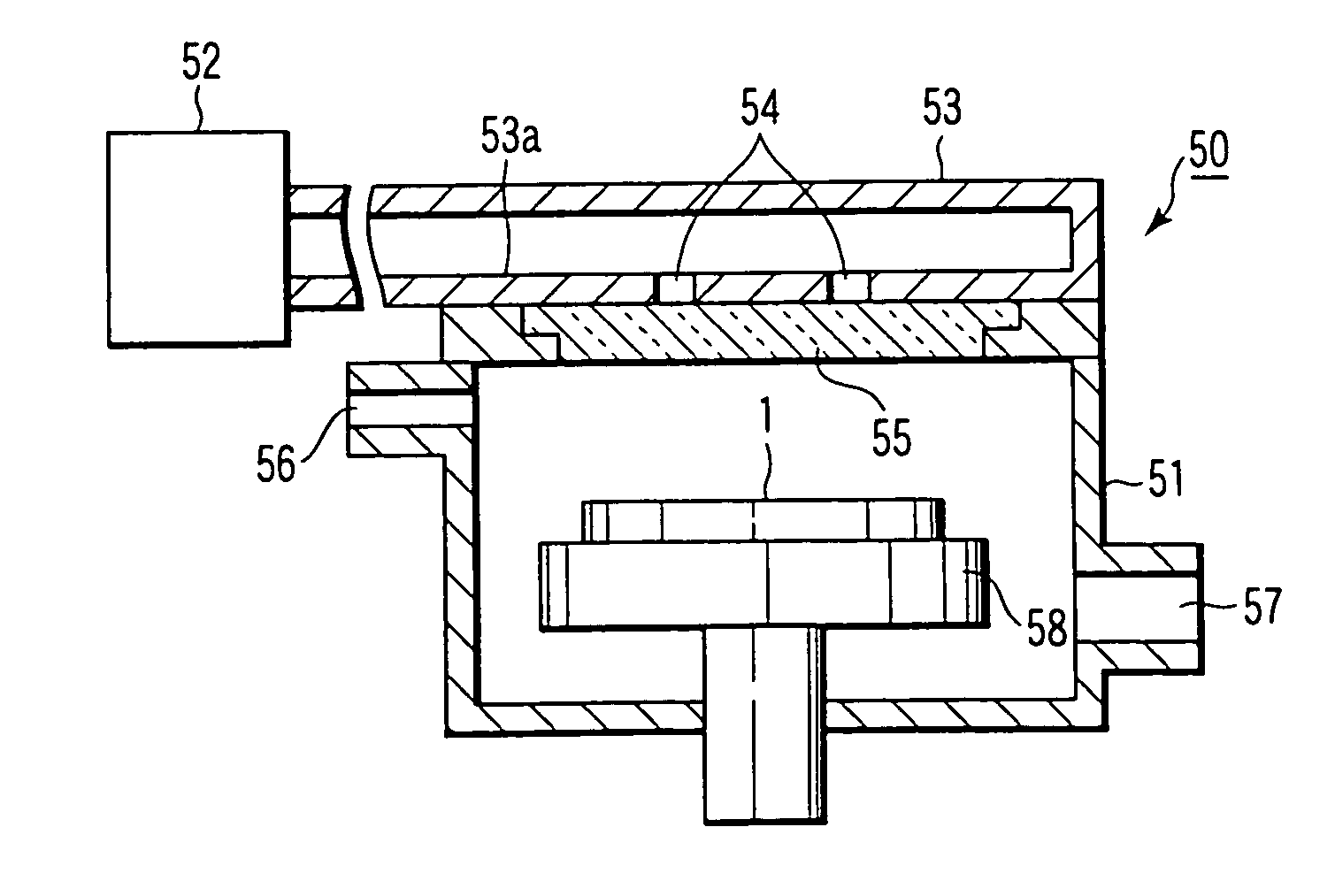

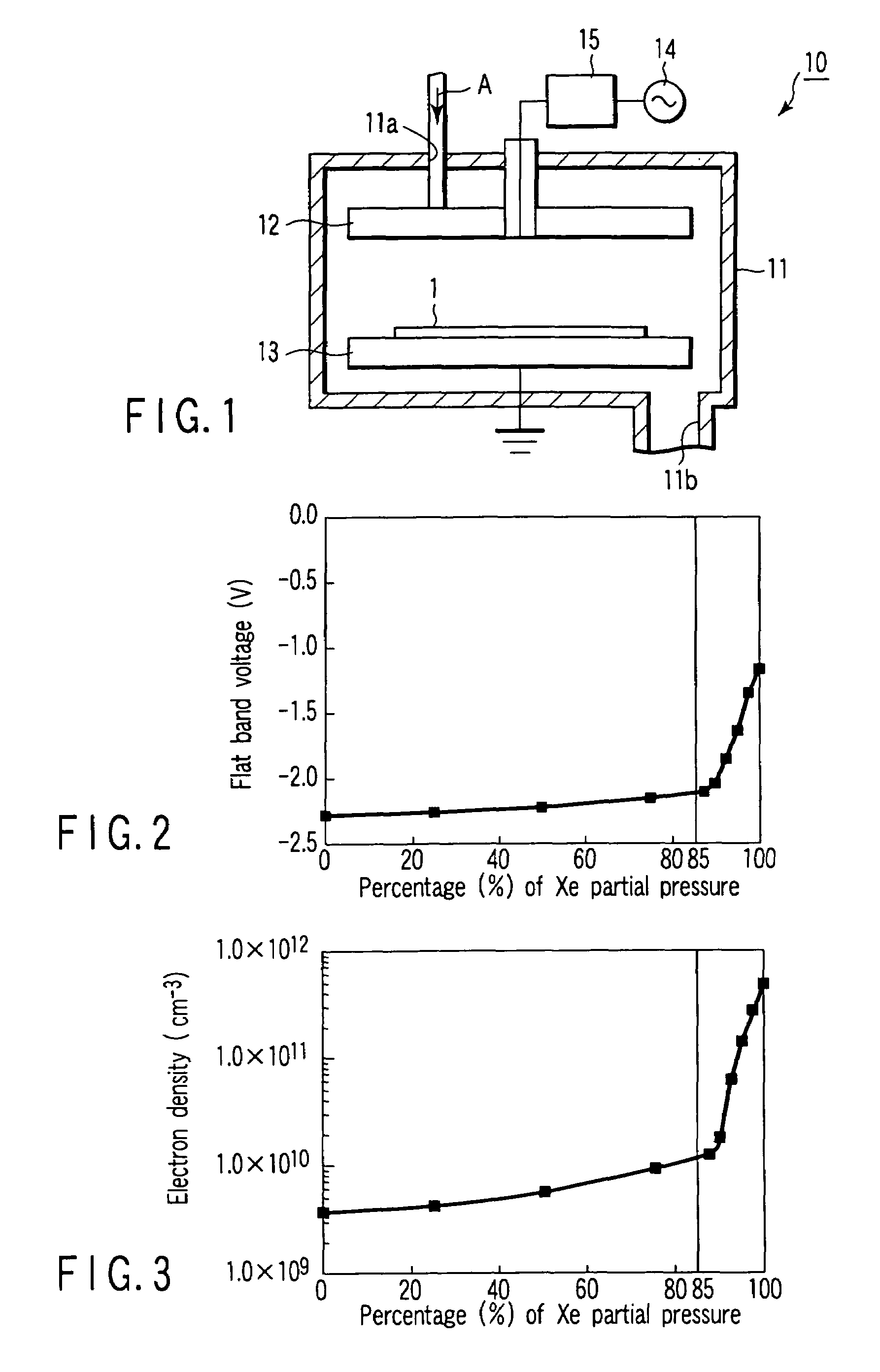

Film-forming method, method of manufacturing semiconductor device, semiconductor device, method of manufacturing display device, and display device

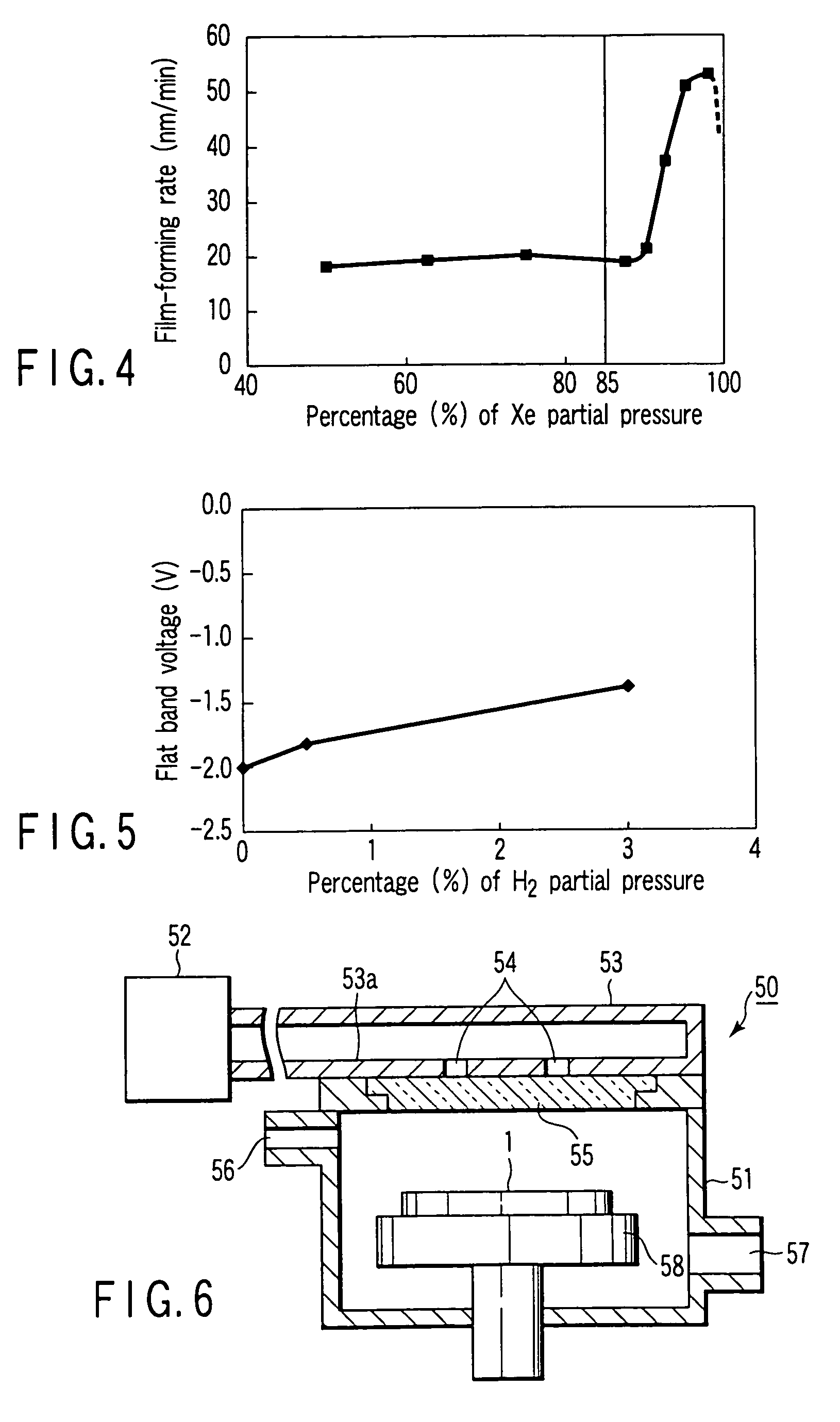

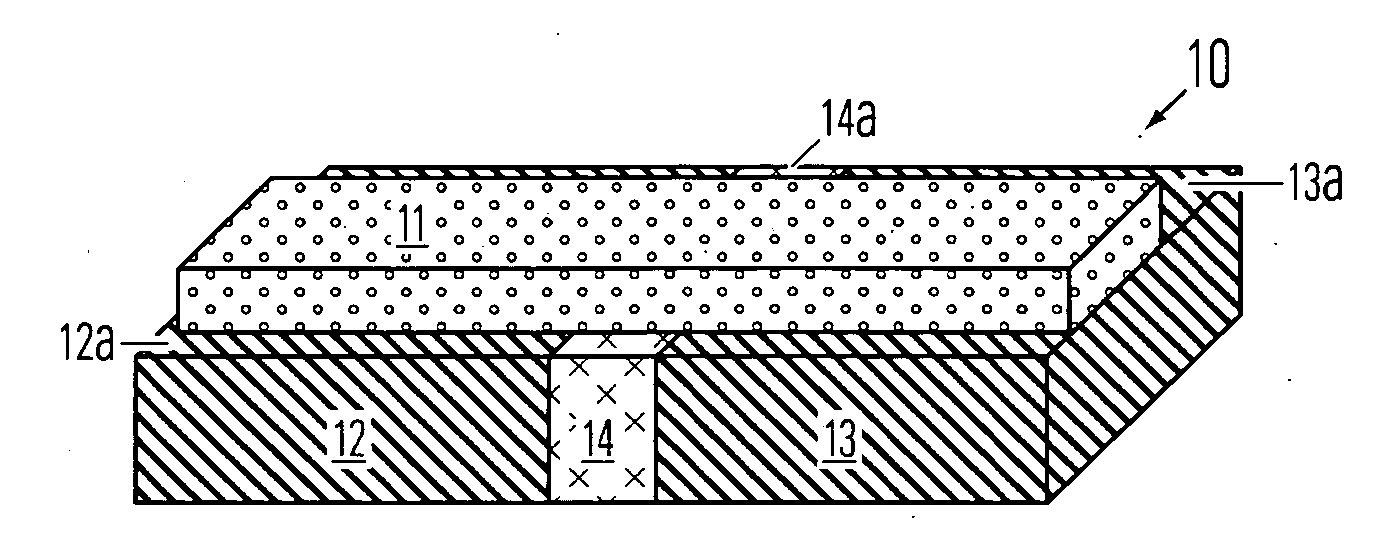

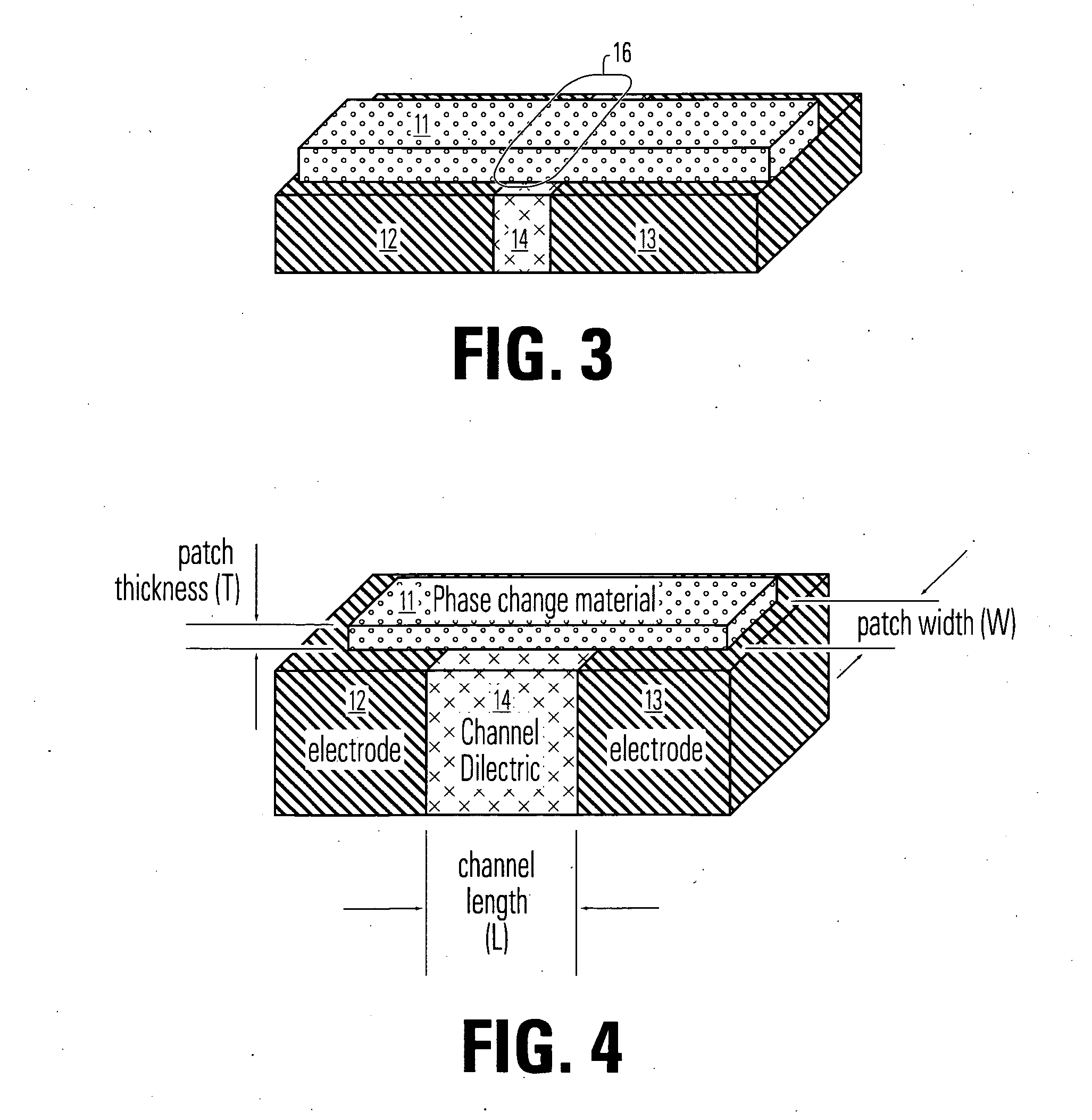

InactiveUS7307028B2Small currentTransistorSemiconductor/solid-state device manufacturingNoble gasDevice material

Disclosed is a film-forming method, comprising supplying into a plasma processing chamber at least three kinds of gases including a silicon compound gas, an oxidizing gas, and a rare gas, the percentage of the partial pressure of the rare gas (Pr) based on the total pressure being not smaller than 85%, i.e., 85%≦Pr<100%, and generating a plasma within the plasma processing chamber so as to form a film of silicon oxide on a substrate to be processed.

Owner:ADVANCED LCD TECH DEVMENT CENT

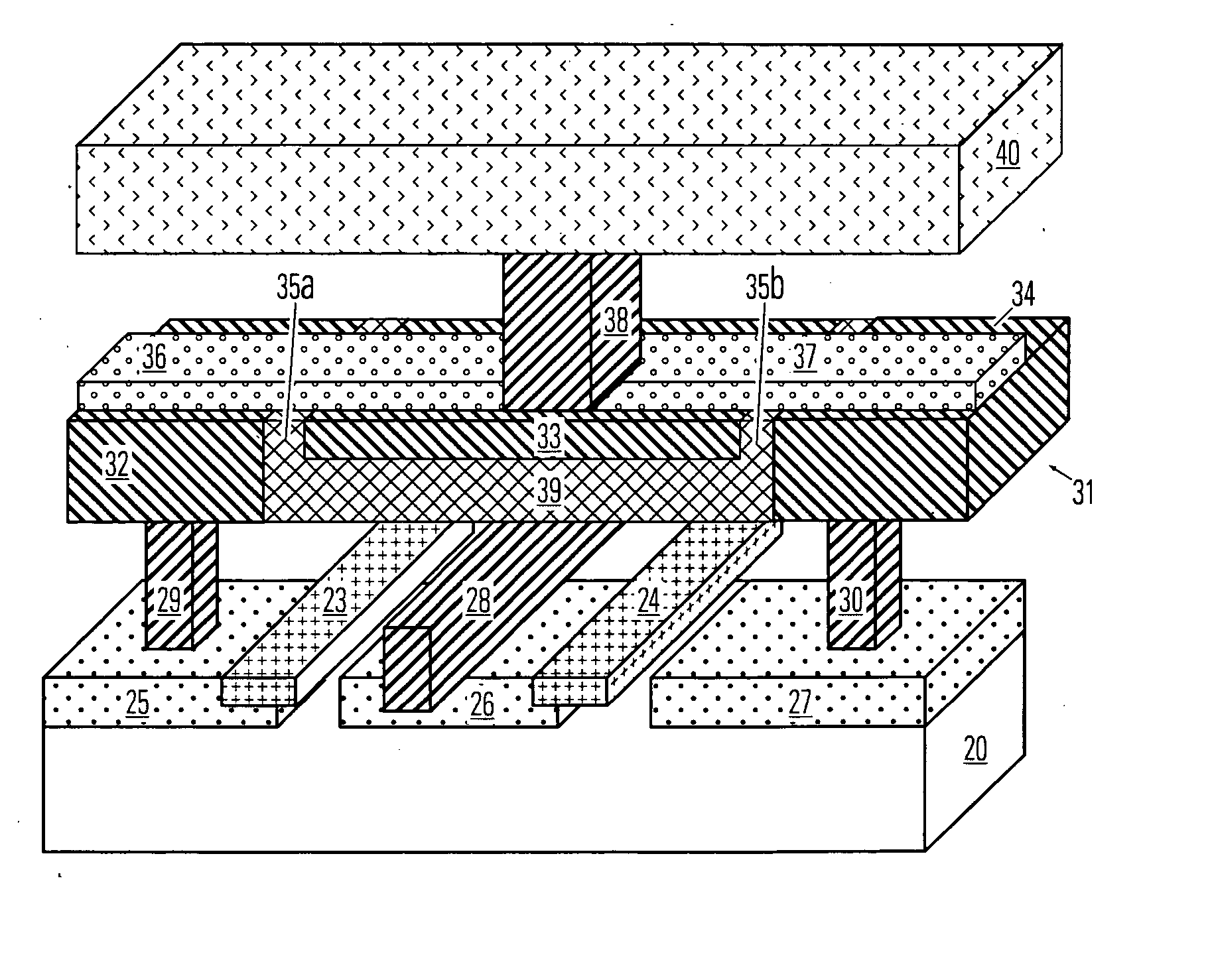

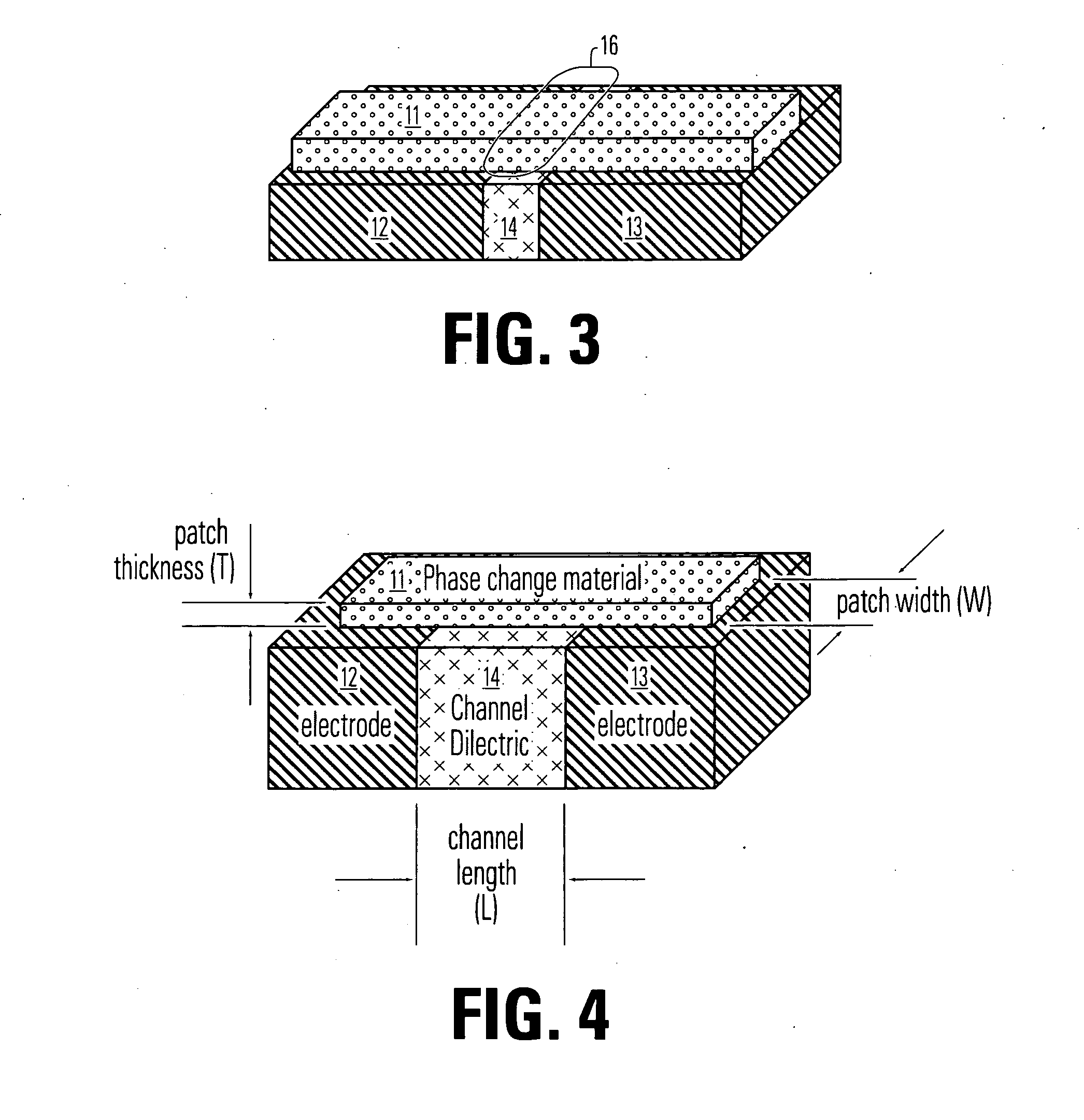

Thin film fuse phase change RAM and manufacturing method

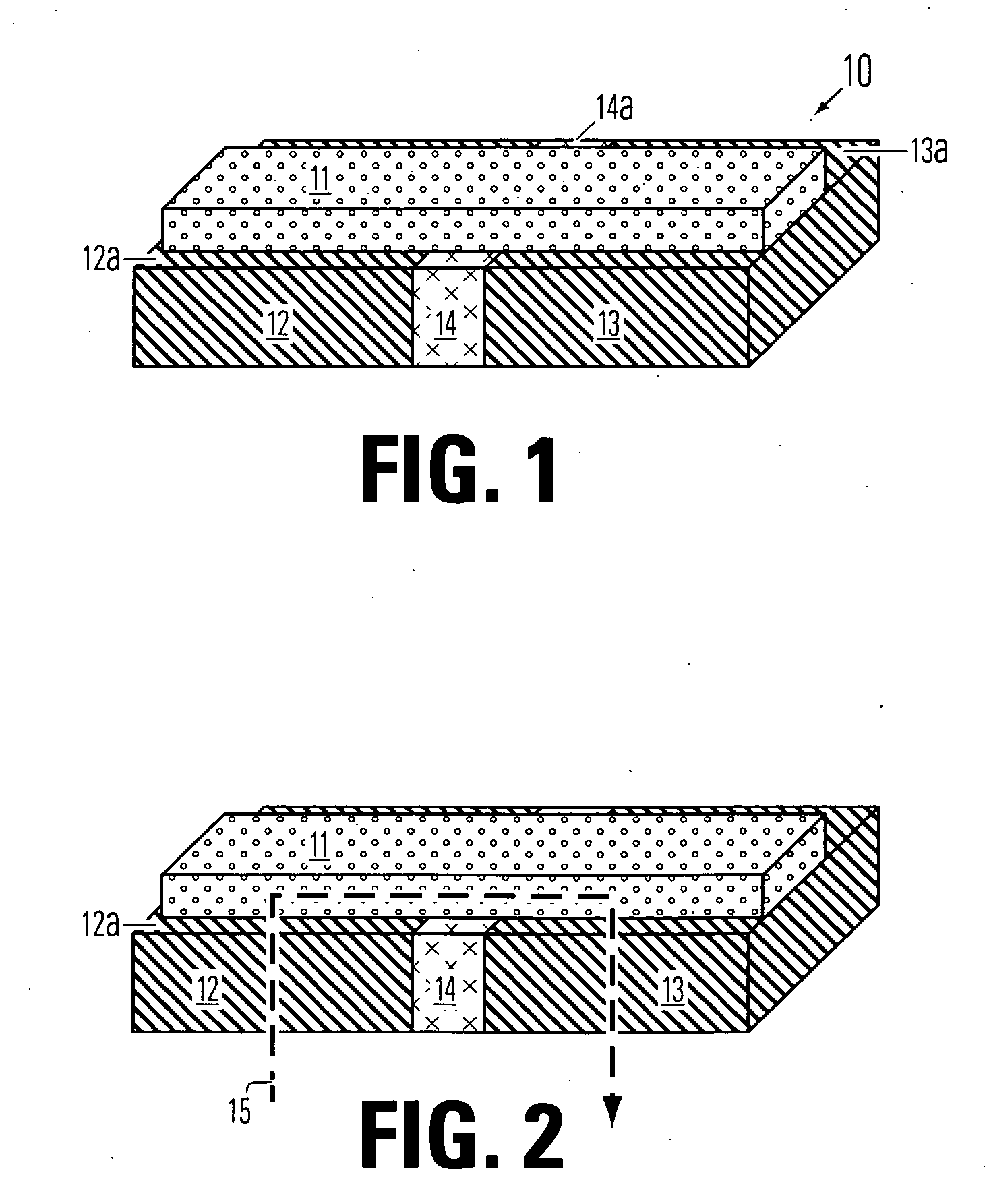

ActiveUS20060284279A1Simple structureReduce power consumptionSolid-state devicesDigital storageEngineeringPhase change

A memory device comprising a first electrode having a top side, a second electrode having a top side and an insulating member between the first electrode and the second electrode. The insulating member has a thickness between the first and second electrodes near the top side of the first electrode and the top side of the second electrode. A bridge of memory material crosses the insulating member, and defines an inter-electrode path between the first and second electrodes across the insulating member. An array of such memory cells is provided. In the array, a plurality of electrode members and insulating members therebetween comprise an electrode layer on an integrated circuit. The bridges of memory material have sub-lithographic dimensions.

Owner:MACRONIX INT CO LTD

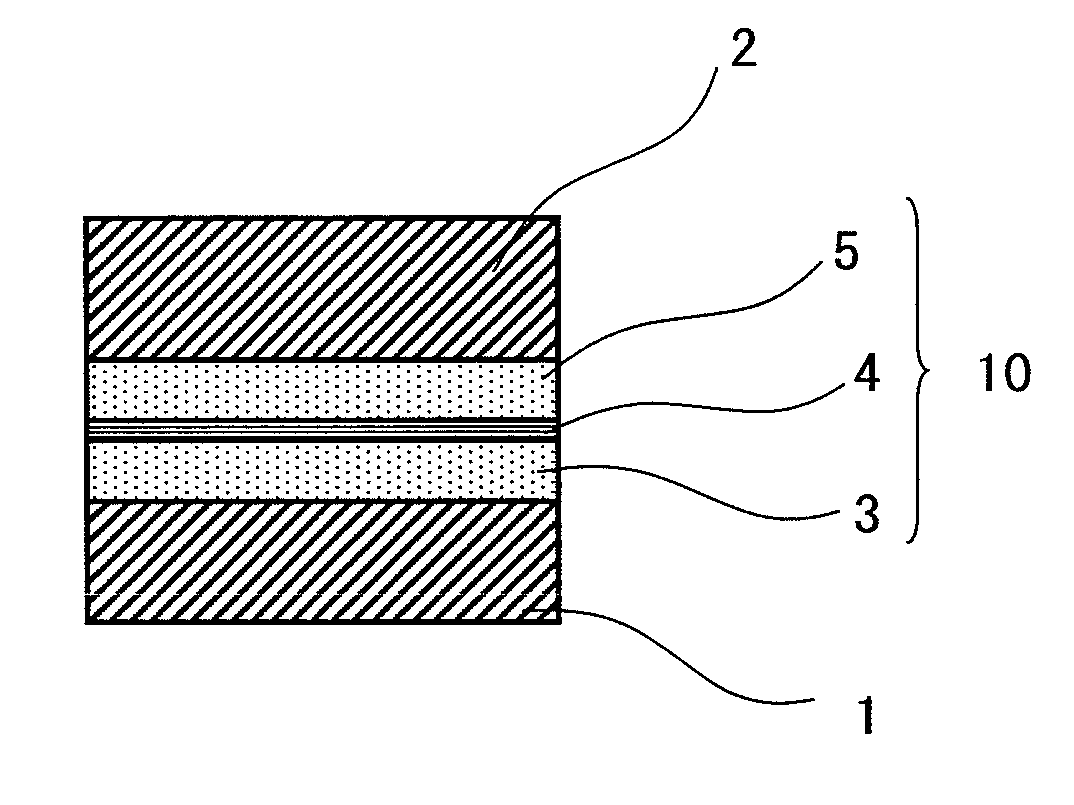

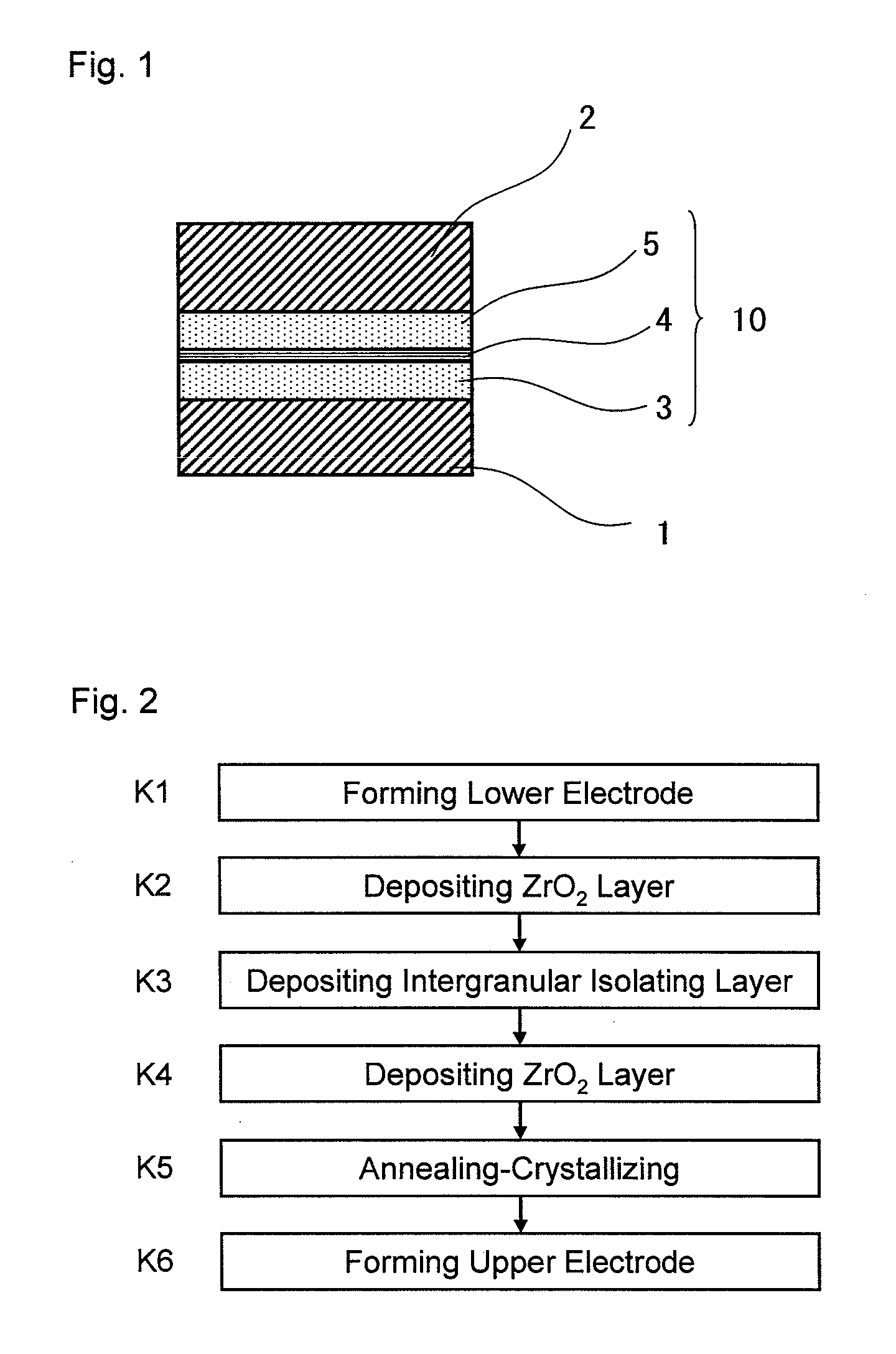

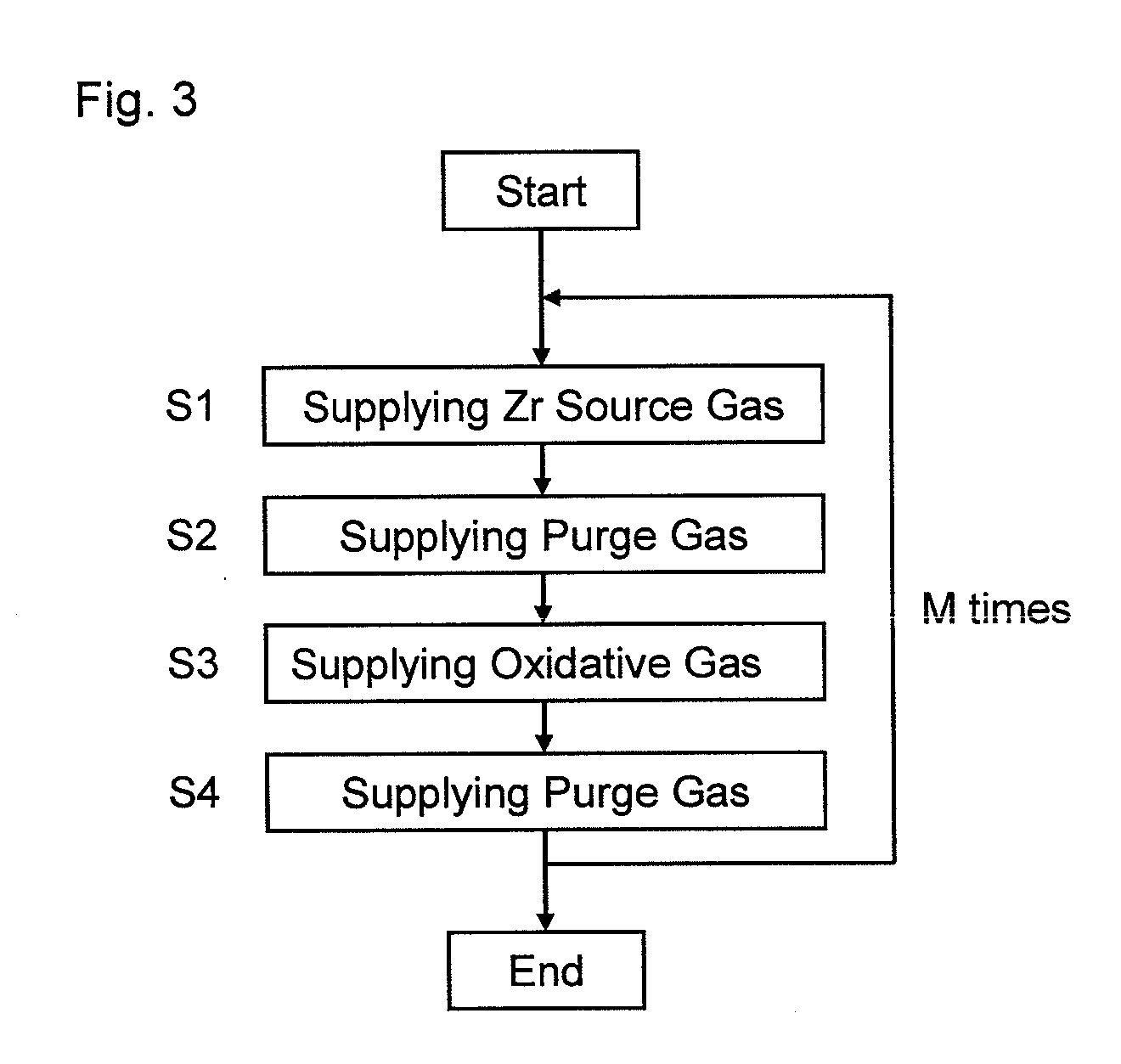

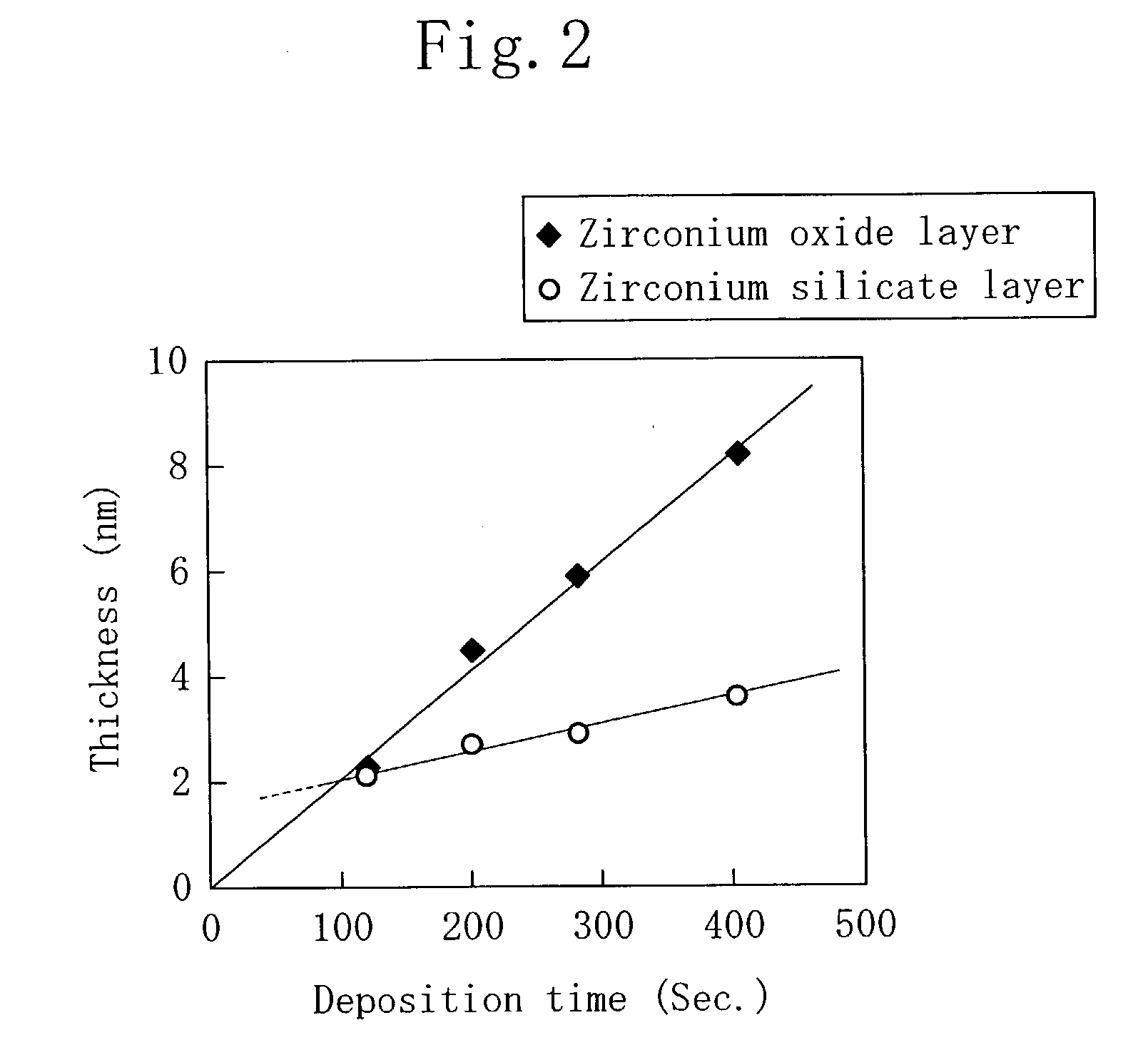

Insulating film, method of manufacturing the same, and semiconductor device

InactiveUS20110048769A1High dielectric constantSmall currentThin/thick film capacitorCeramicsCapacitanceSemiconductor

An exemplary aspect of the invention provides an insulating film which has a high dielectric constant and has small leakage current even when it is sandwiched between electrodes. The insulating film comprises two zirconium oxide layers in crystallized state; and an intergranular isolating layer composed of an amorphous material having a dielectric constant higher than that of zirconium oxide in crystallized state; wherein the intergranular isolating layer is sandwiched between the two zirconium oxide layers. The insulating film is properly used as a capacitive insulating film in a semiconductor device comprising a memory cell including a capacitor element having the capacitive insulating film between an upper electrode and a lower electrode, or as an intergate insulating film in a semiconductor device comprising a nonvolatile memory device having the intergate insulating film between a control gate electrode and a floating gate electrode.

Owner:ELPIDA MEMORY INC

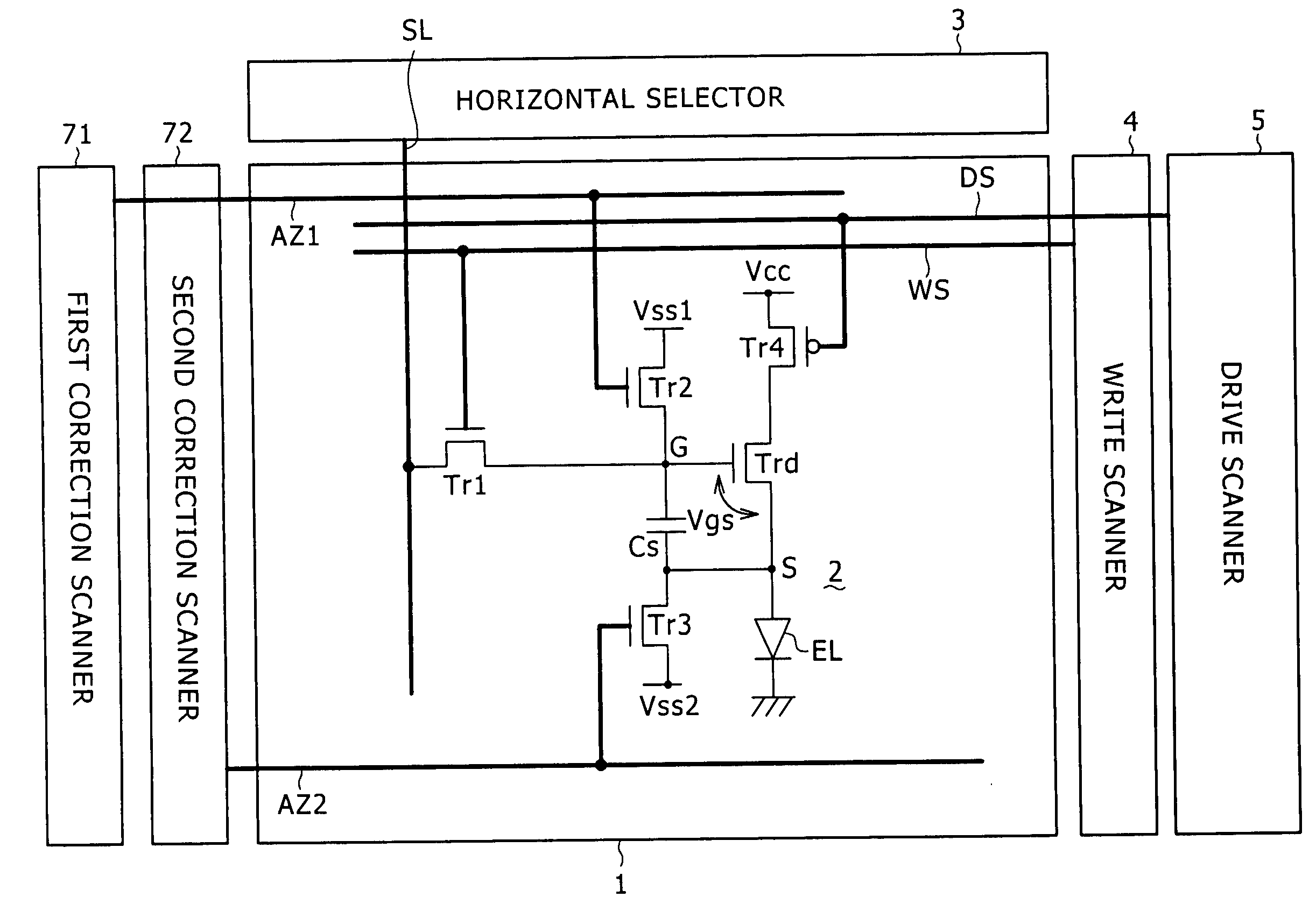

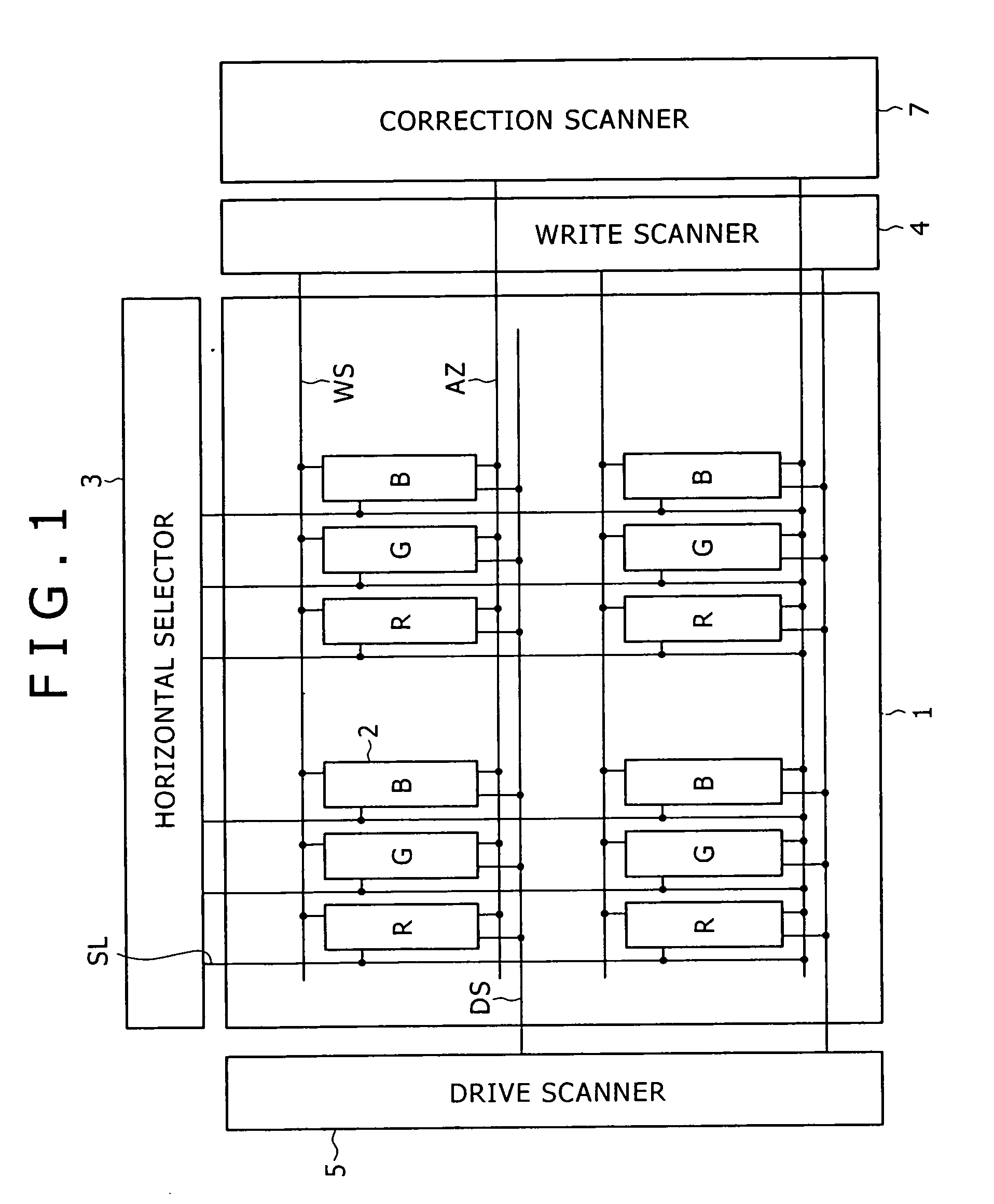

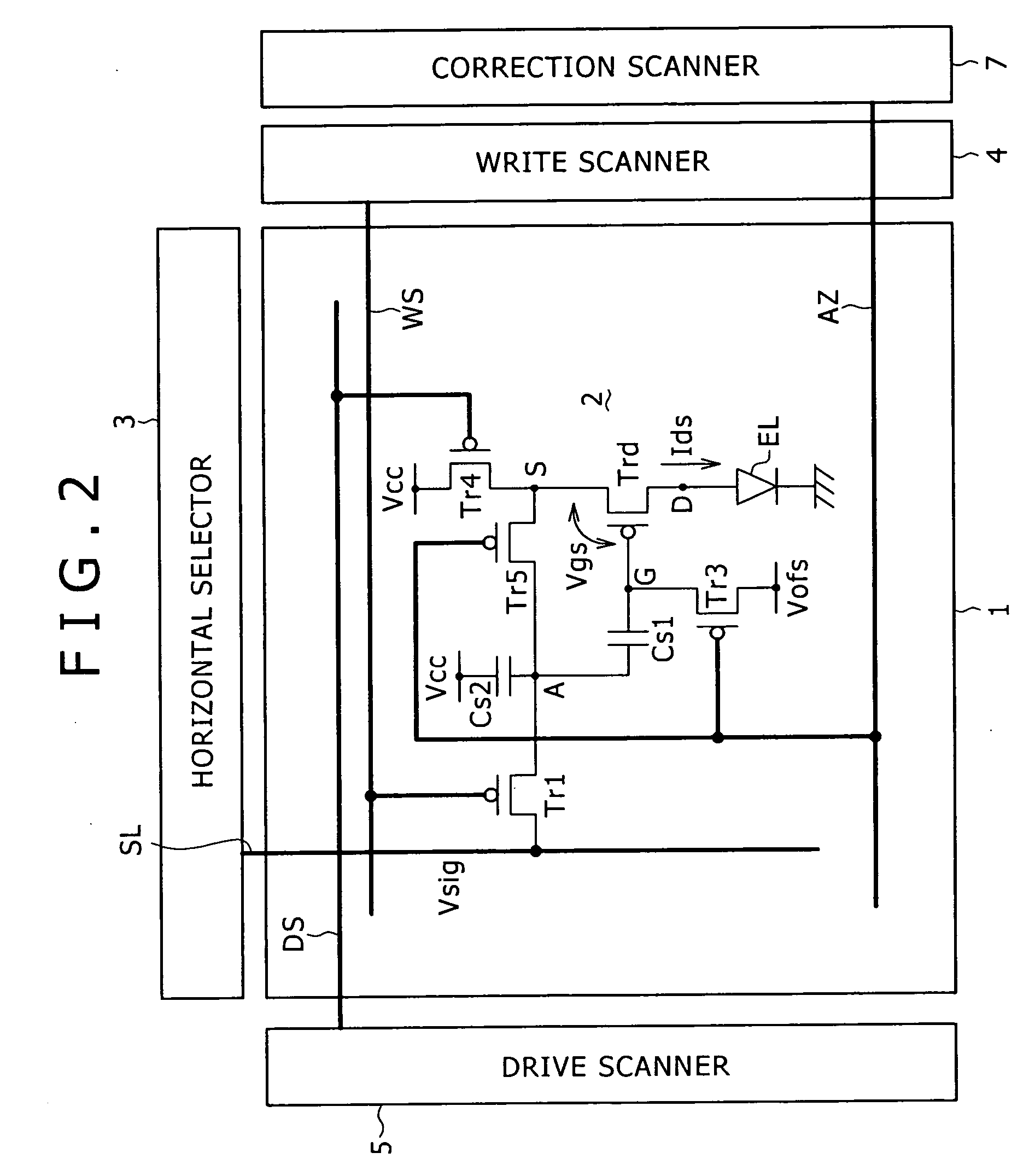

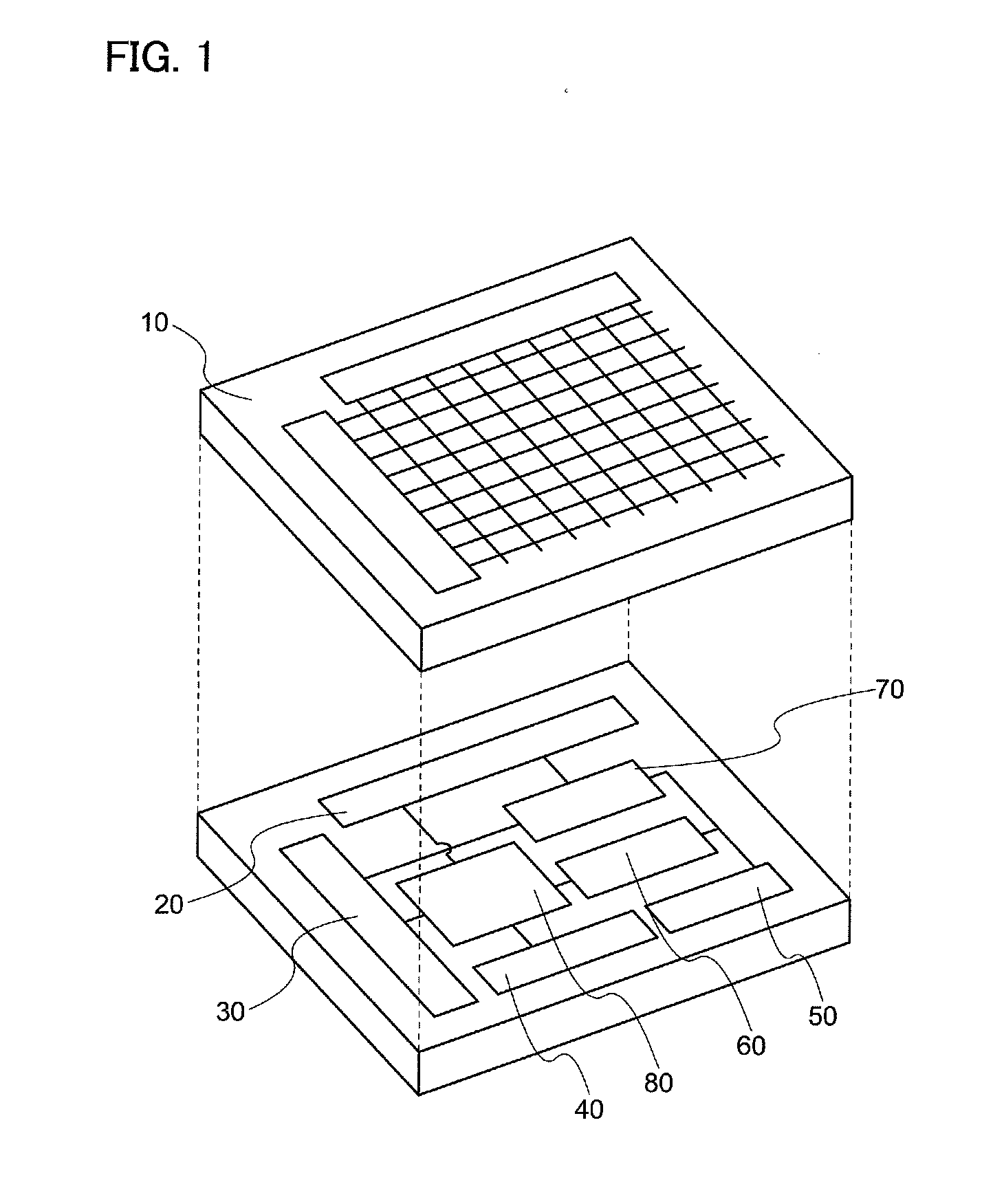

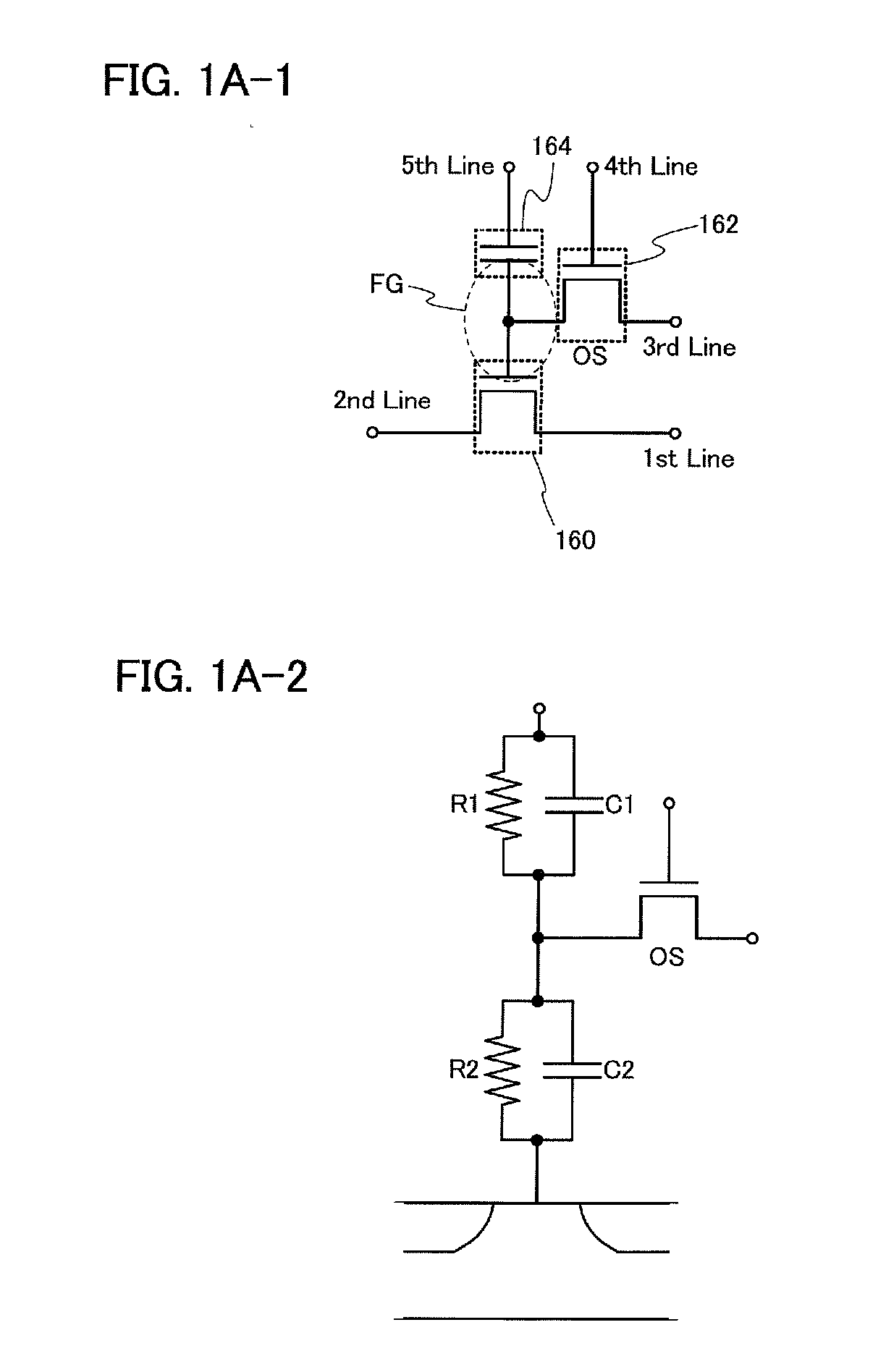

Pixel circuit, display and driving method thereof

InactiveUS20060170628A1Eliminate dependenciesImprove mobilityElectroluminescent light sourcesHeater elementsCapacitanceScan line

The invention provides a pixel circuit that can cancel the influence of the mobility of a drive transistor. A drive transistor supplies to a light-emitting element, an output current dependent upon an input voltage during a certain emission period. The light-emitting element emits light with a luminance dependent upon a video signal in response to the output current supplied from the drive transistor. The pixel circuit includes a correction unit that corrects the input voltage held by a capacitive part before the emission period or at the beginning of the emission period, in order to cancel the dependence of the output current on the carrier mobility. The correction unit operates during part of a sampling period in response to control signals supplied from scan lines. Specifically, the correction unit extracts the output current from the drive transistor while the video signal is sampled, and negatively feeds back the output current to the capacitive part to thereby correct the input voltage.

Owner:SONY CORP

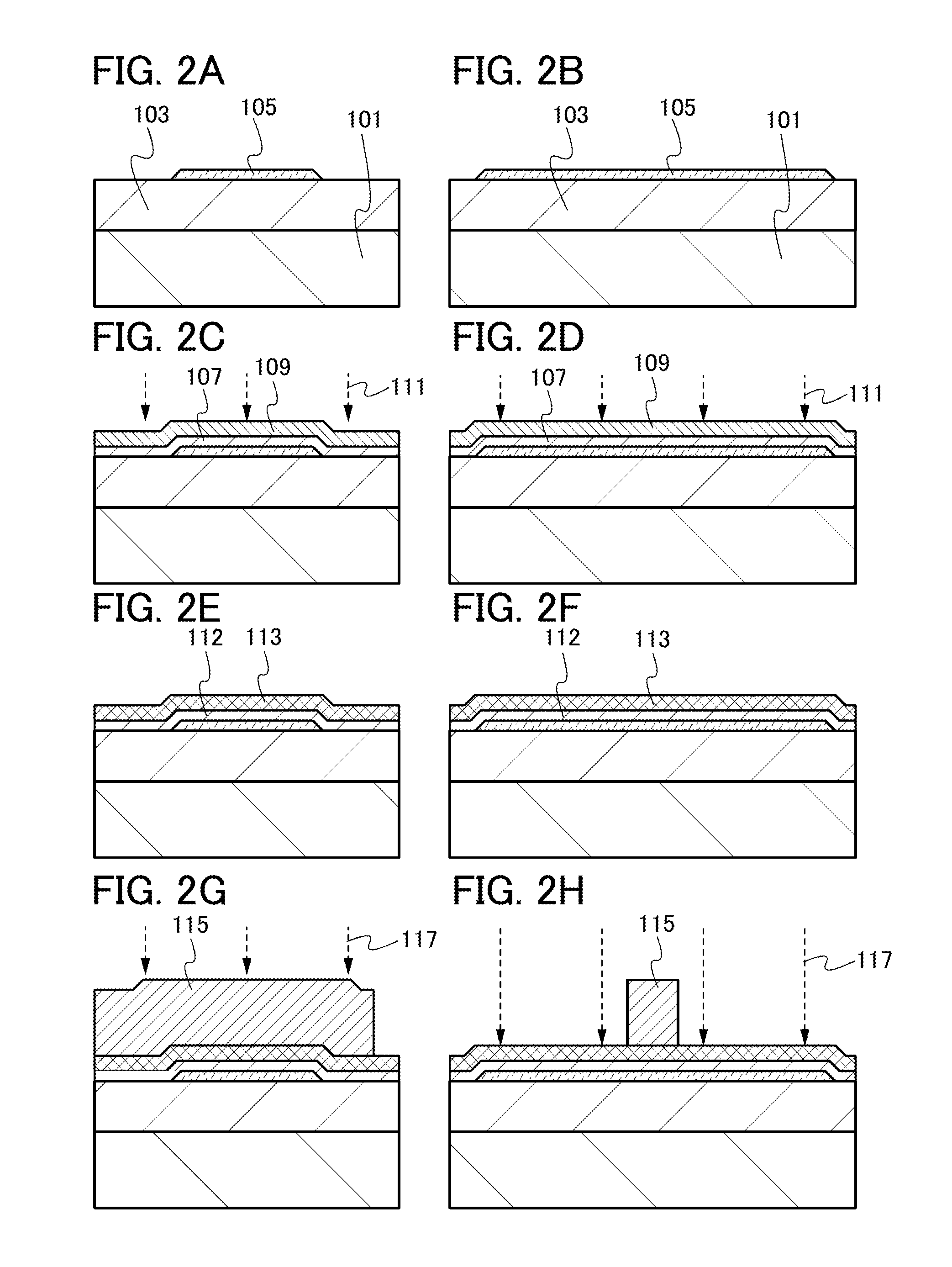

Manufacturing methods for thin film fuse phase change ram

InactiveUS20060286709A1Simple structureReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryOptoelectronics

A method for manufacturing a memory device comprises forming an electrode layer on a substrate which comprises circuitry made using front-end-of-line procedures. The electrode layer includes a first electrode and a second electrode, and an insulating member between the first and second electrodes for each phase change memory cell to be formed. A bridge of memory material is formed on the top surface of the electrode layer across the insulating member for each memory cell to be formed. An access structure over the electrode layer is made by forming a patterned conductive layer over said bridge, and forming a contact between said first electrode and said patterned conductive layer.

Owner:MACRONIX INT CO LTD

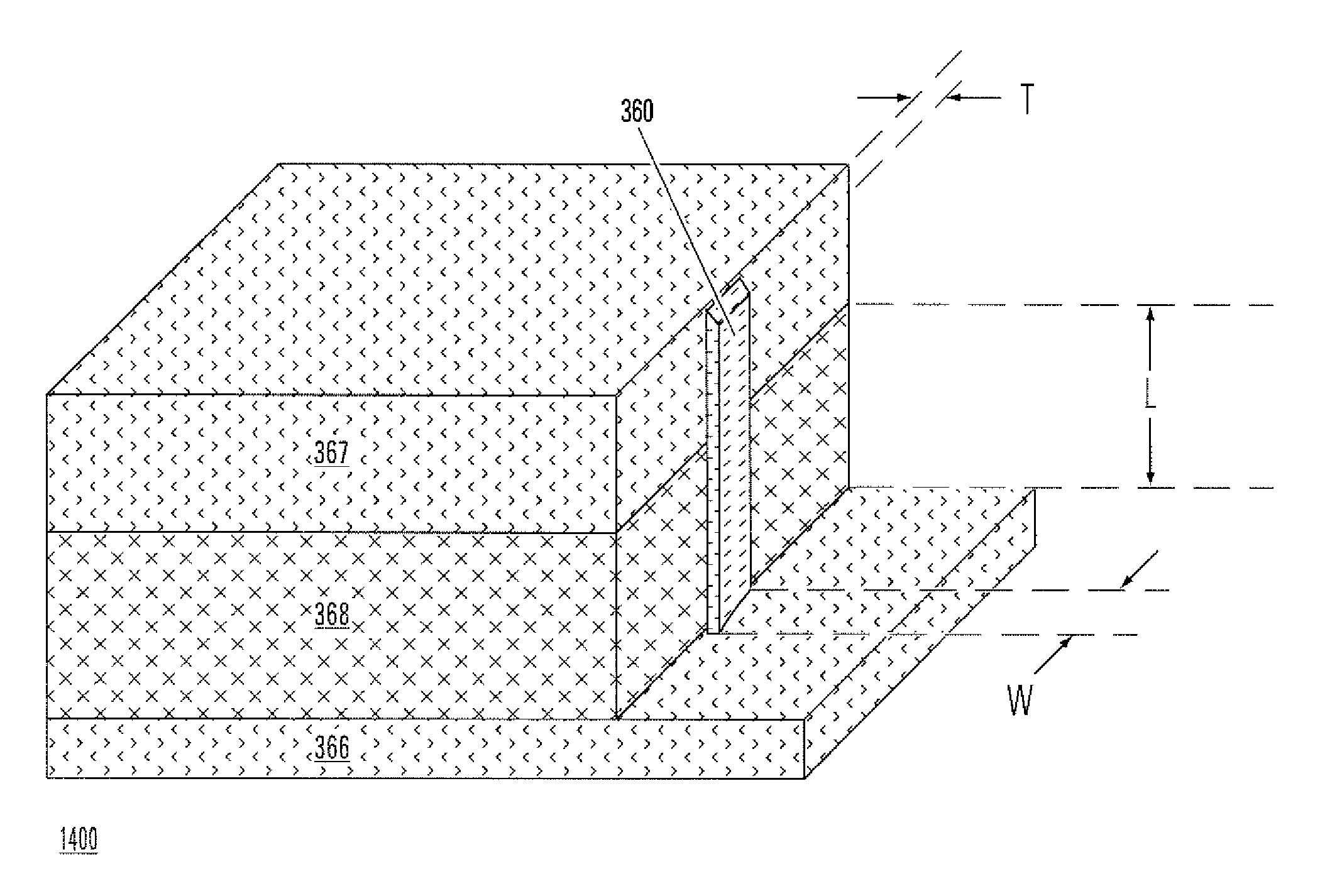

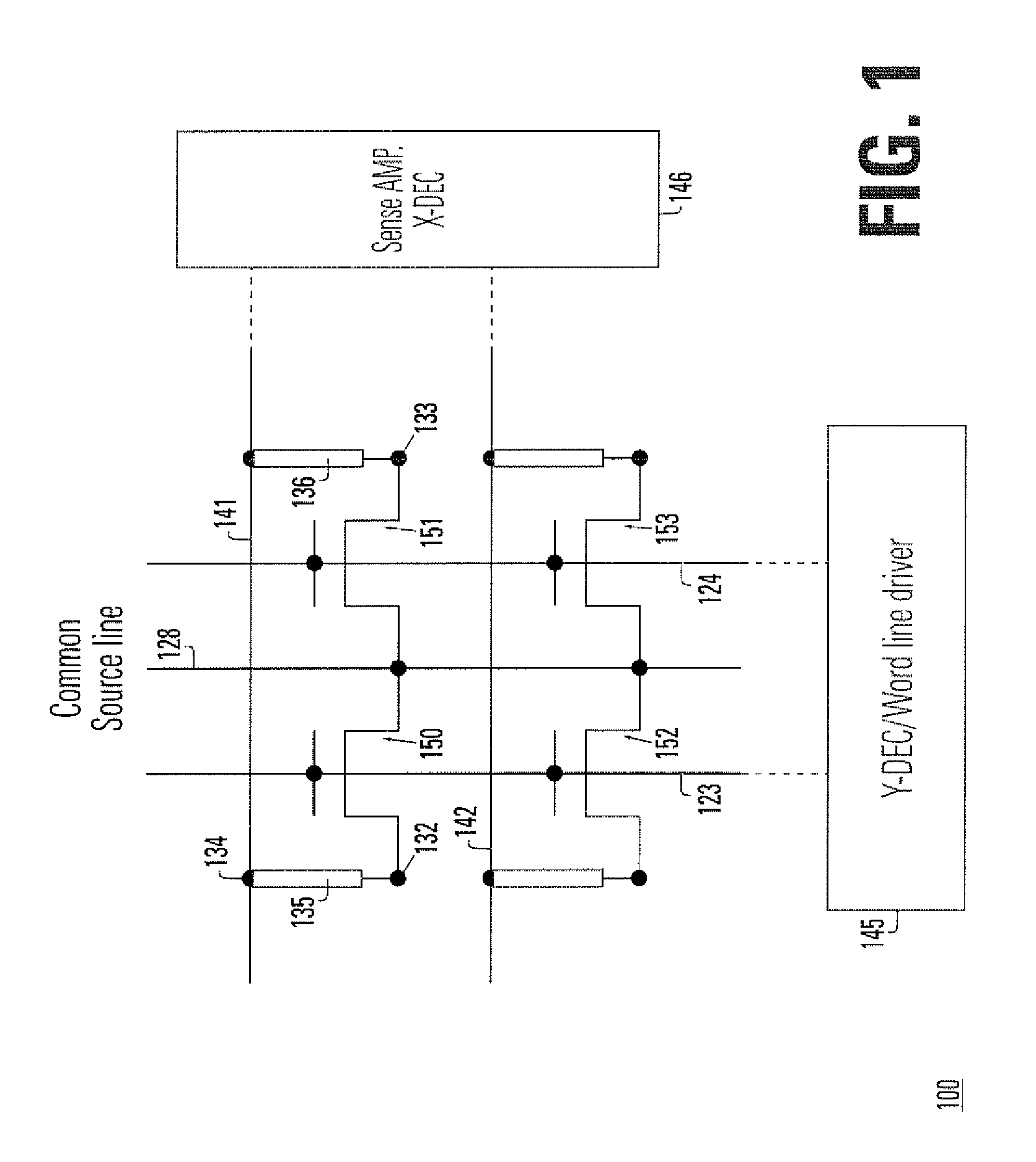

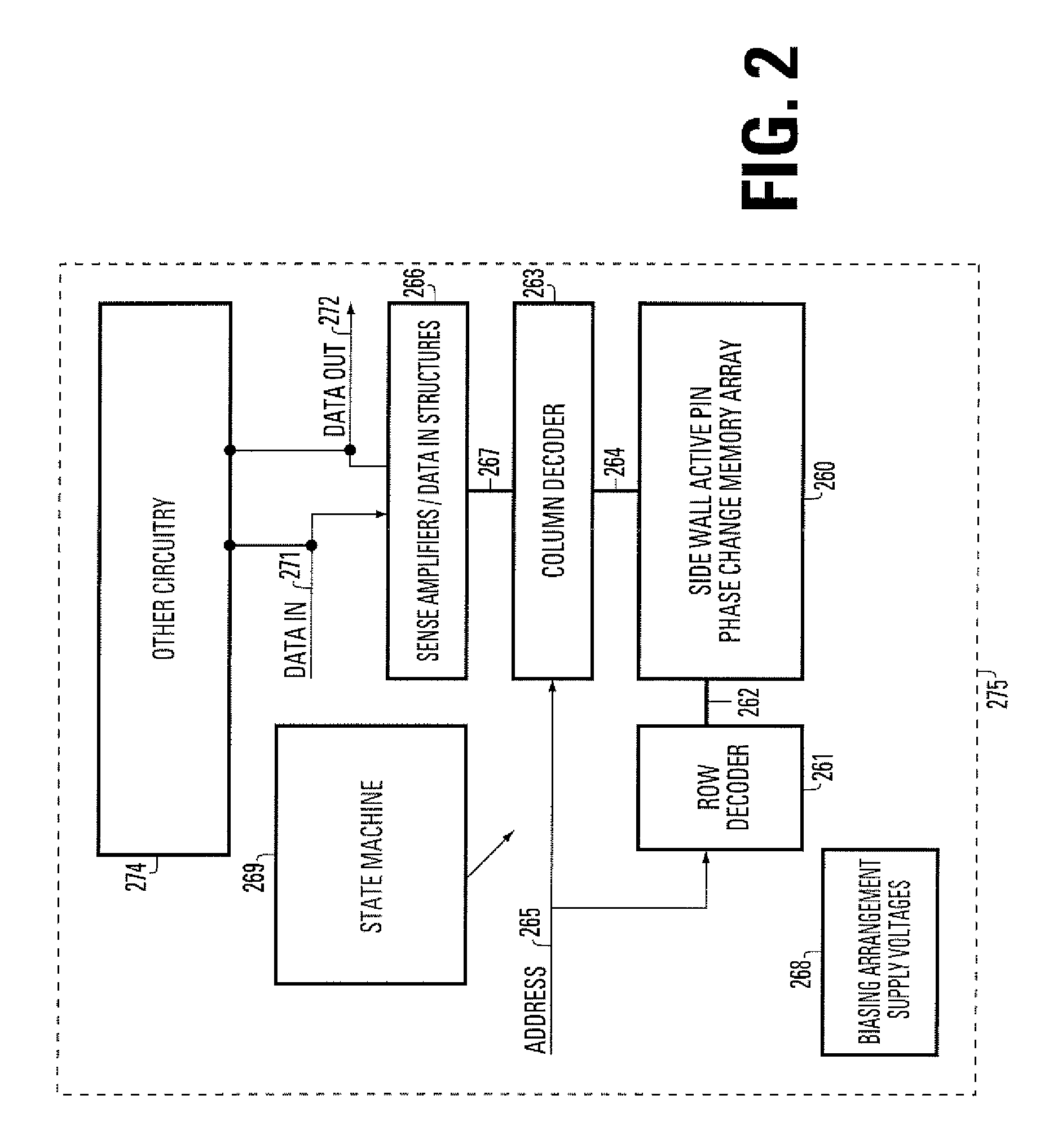

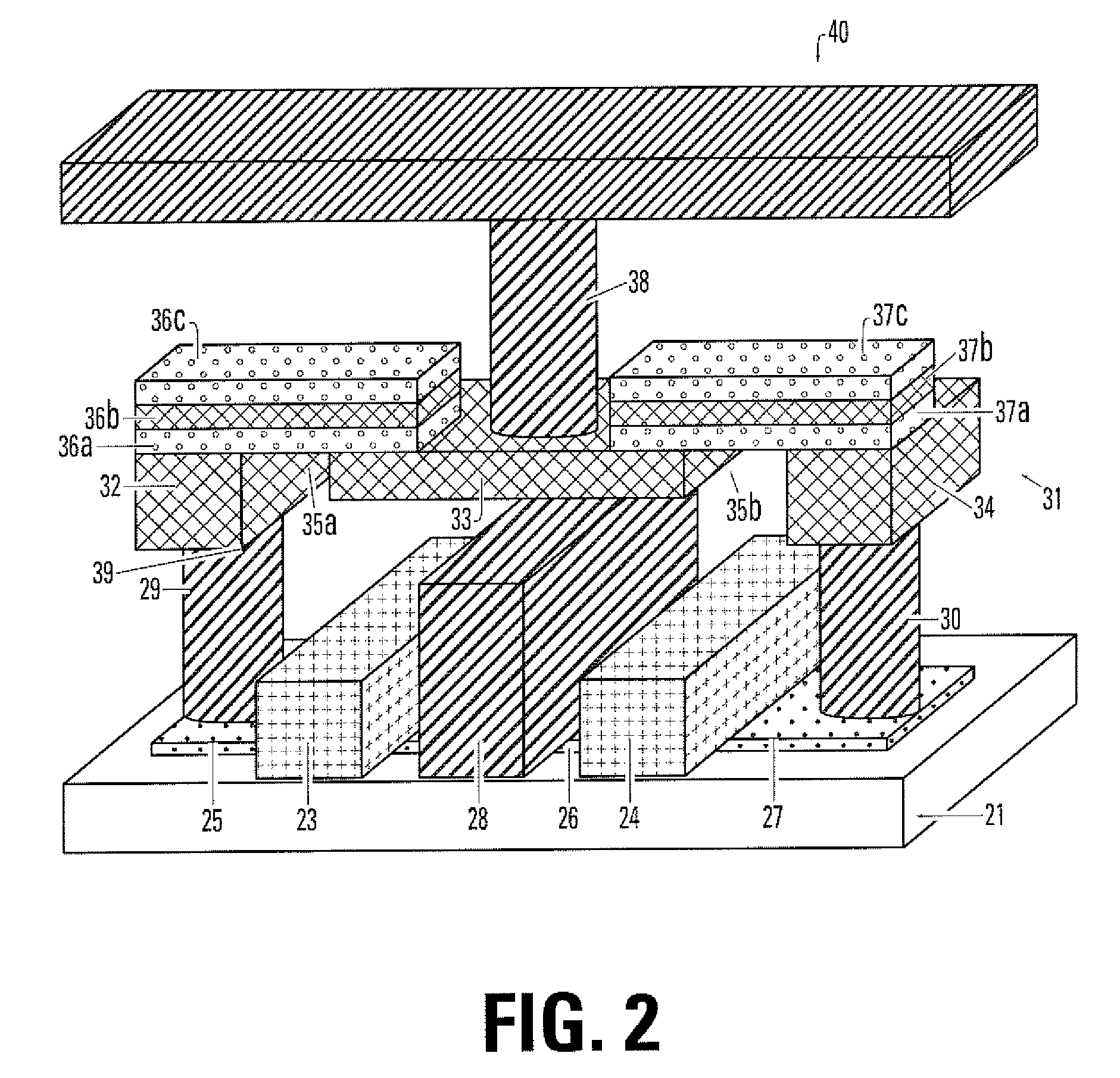

Vertical Side Wall Active Pin Structures in a Phase Change Memory and Manufacturing Methods

ActiveUS20070176261A1Reduce electrical currentLow resistivitySolid-state devicesSemiconductor devicesEngineeringPhase-change material

A programmable resistor memory, such as a phase change memory, with a memory element comprising narrow vertical side wall active pins is described. The side wall active pins comprise a programmable resistive material, such as a phase change material. In a first aspect of the invention, a method of forming a memory cell is described which comprises forming a stack comprising a first electrode having a principal surface with a perimeter, an insulating layer overlying a portion of the principal surface of the first electrode, and a second electrode vertically separated from the first electrode and overlying the insulating layer. Side walls on the insulating layer and on the second electrode are positioned over the principle surface of the first electrode with a lateral offset from the perimeter of the first electrode.

Owner:MACRONIX INT CO LTD

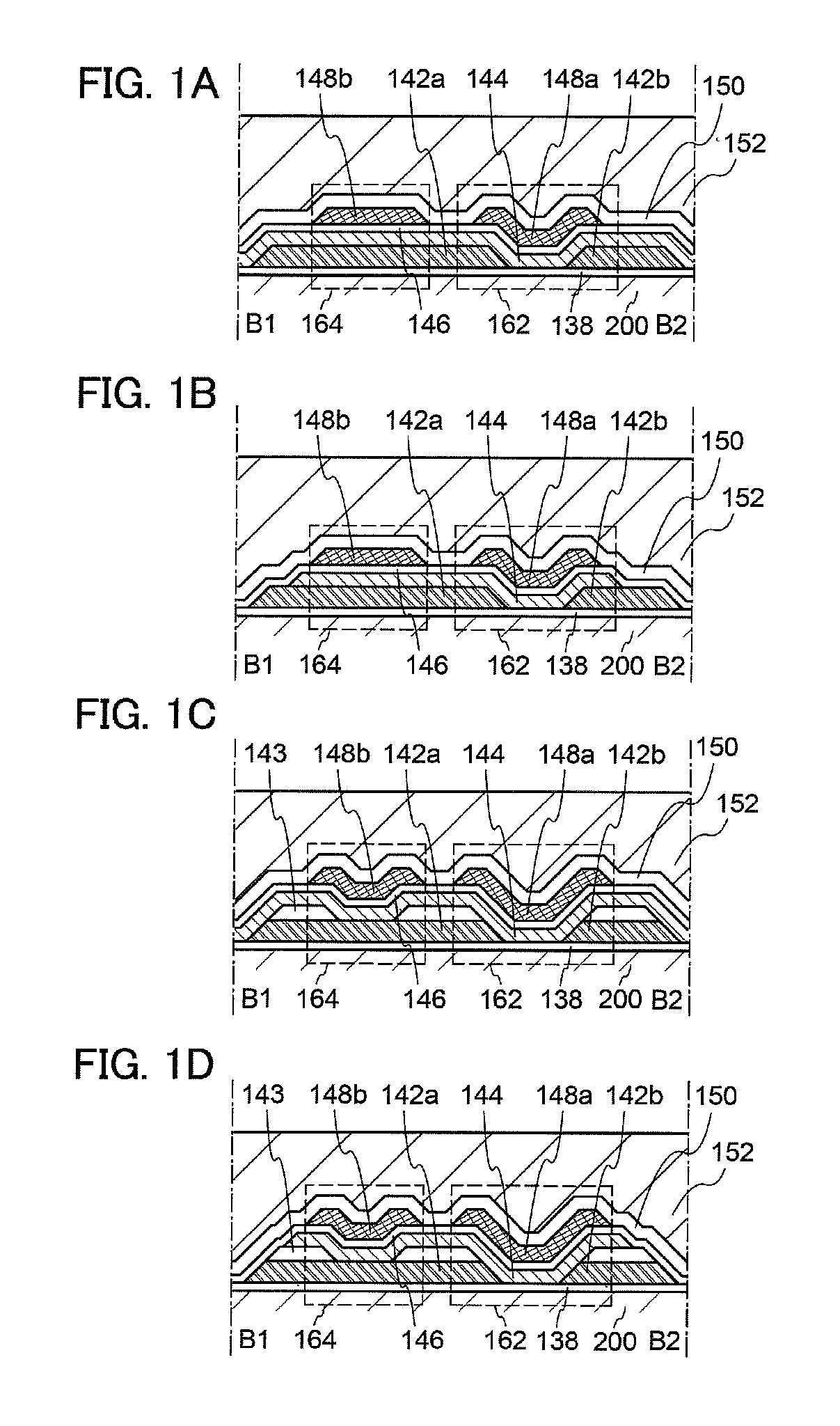

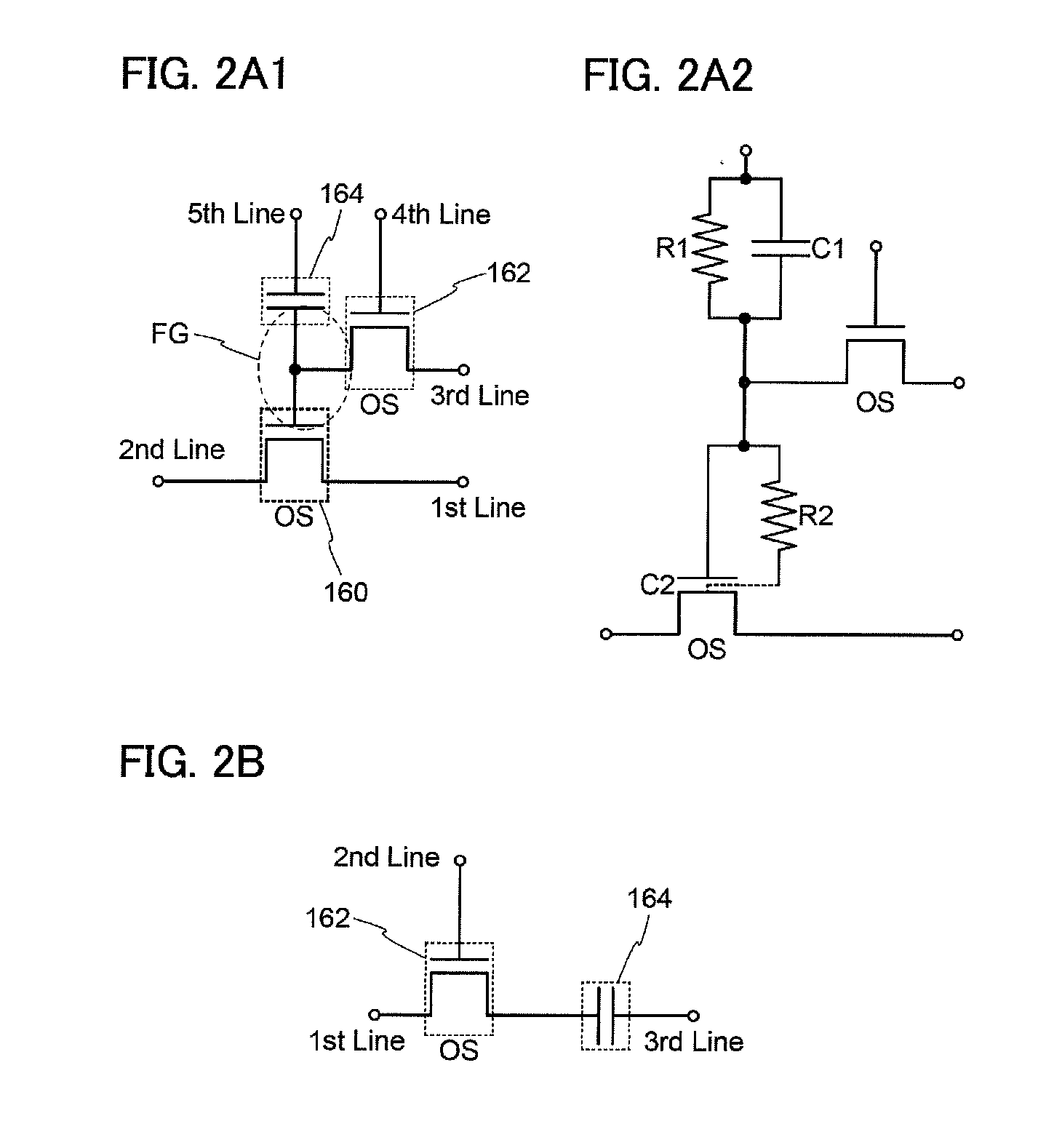

Semiconductor device

ActiveUS20110156027A1Long storageReduce power consumptionTransistorSolid-state devicesSemiconductor materialsEngineering

An object of one embodiment of the present invention is to provide a semiconductor device with a novel structure in which stored data can be stored even when power is not supplied in a data storing time and there is no limitation on the number of times of writing. The semiconductor device includes a first transistor which includes a first channel formation region using a semiconductor material other than an oxide semiconductor, a second transistor which includes a second channel formation region using an oxide semiconductor material, and a capacitor. One of a second source electrode and a second drain electrode of the second transistor is electrically connected to one electrode of the capacitor.

Owner:SEMICON ENERGY LAB CO LTD

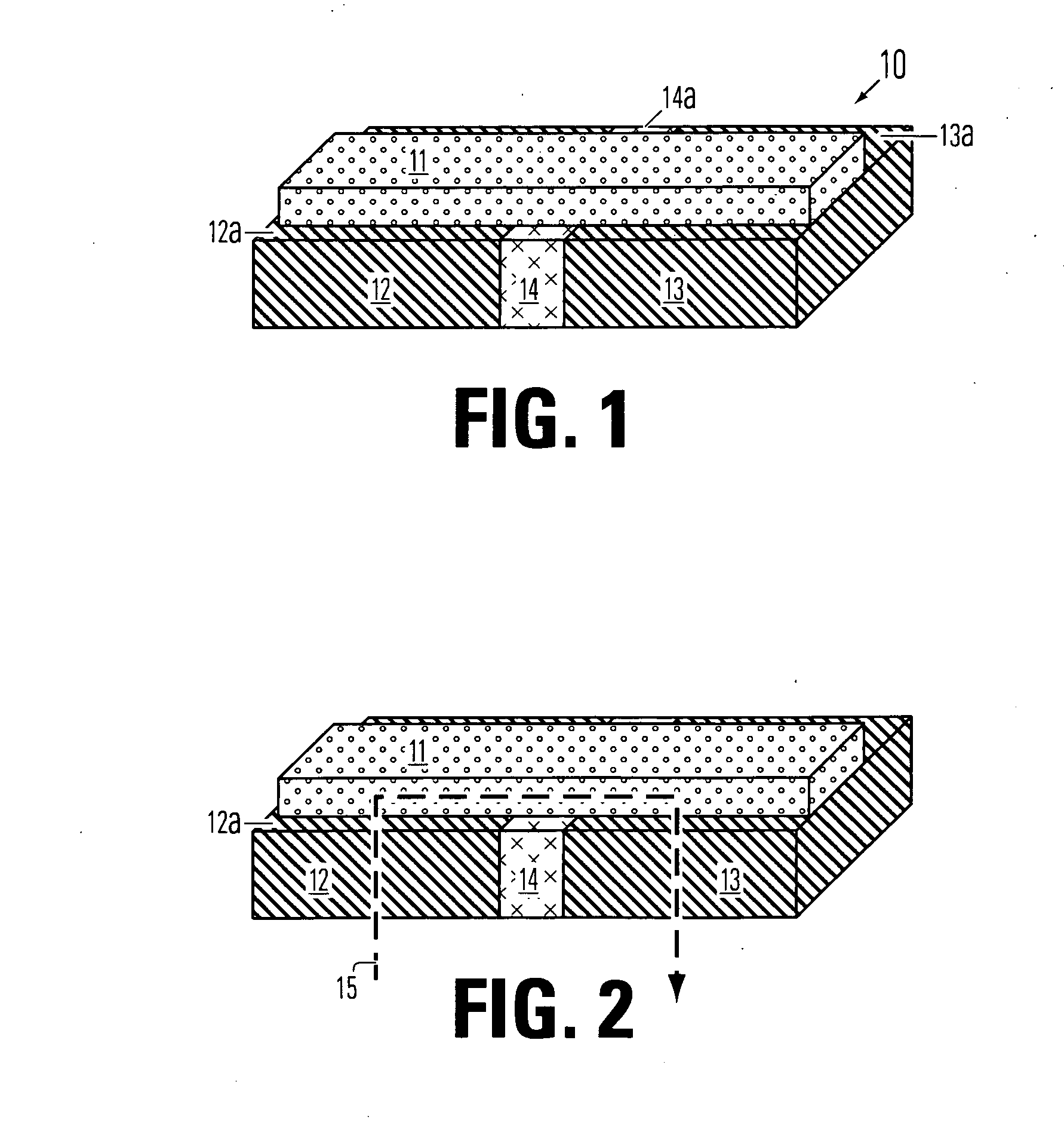

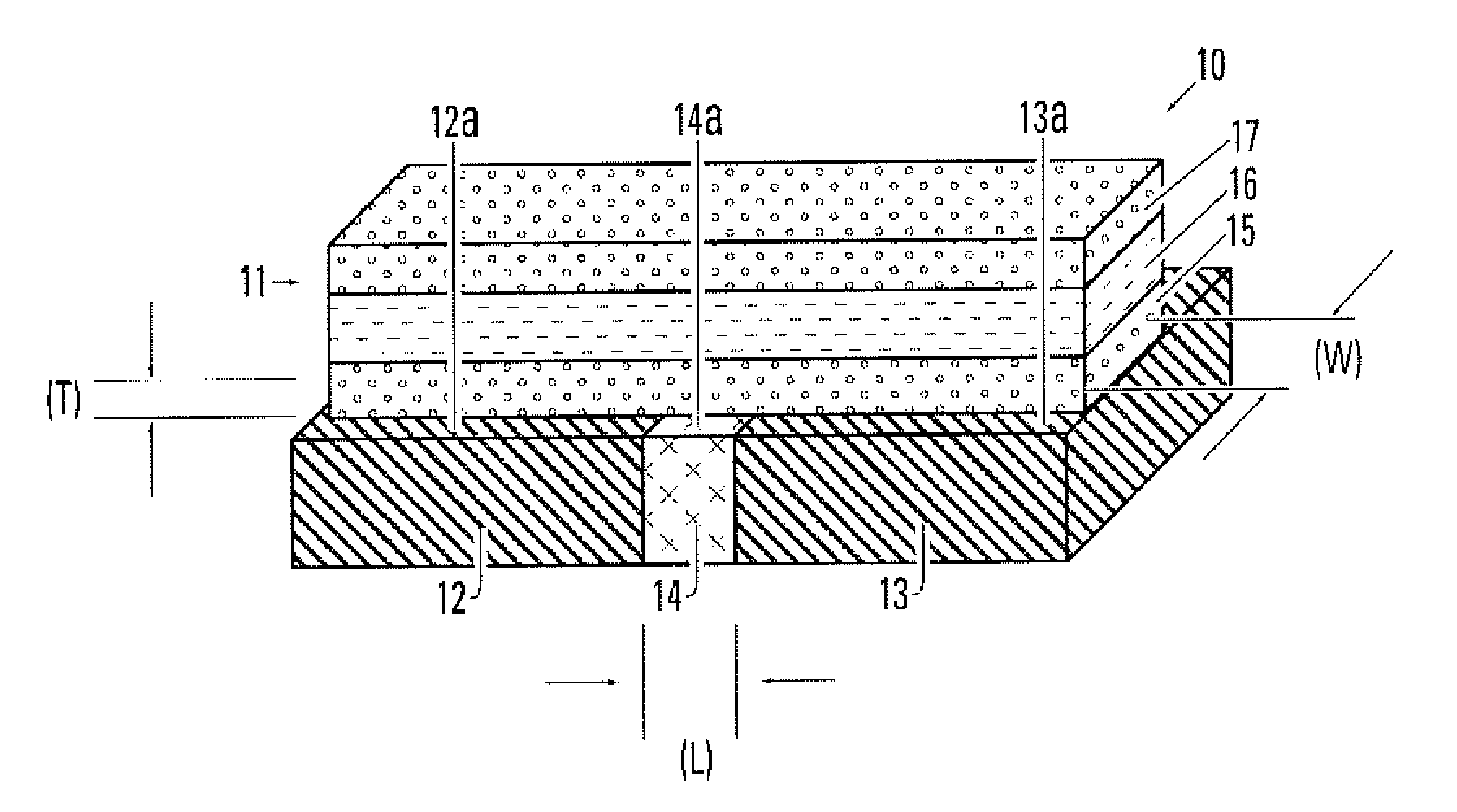

Thin film fuse phase change cell with thermal isolation layer and manufacturing method

ActiveUS20060284214A1Simple structureReduce power consumptionSolid-state devicesDigital storageThermal isolationEngineering

A memory device comprising a first electrode having a top side, a second electrode having a top side and an insulating member between the first electrode and the second electrode. The insulating member has a thickness between the first and second electrodes near the top side of the first electrode and the top side of the second electrode. A bridge of memory material crosses the insulating member, and defines an inter-electrode path between the first and second electrodes across the insulating member. An array of such memory cells is provided. The bridge comprises an active layer of memory material on the first side having at least two solid phases and a blanket of thermal insulating material overlying the memory material having thermal conductivity less than that of an overlying electrically insulating layer.

Owner:MACRONIX INT CO LTD

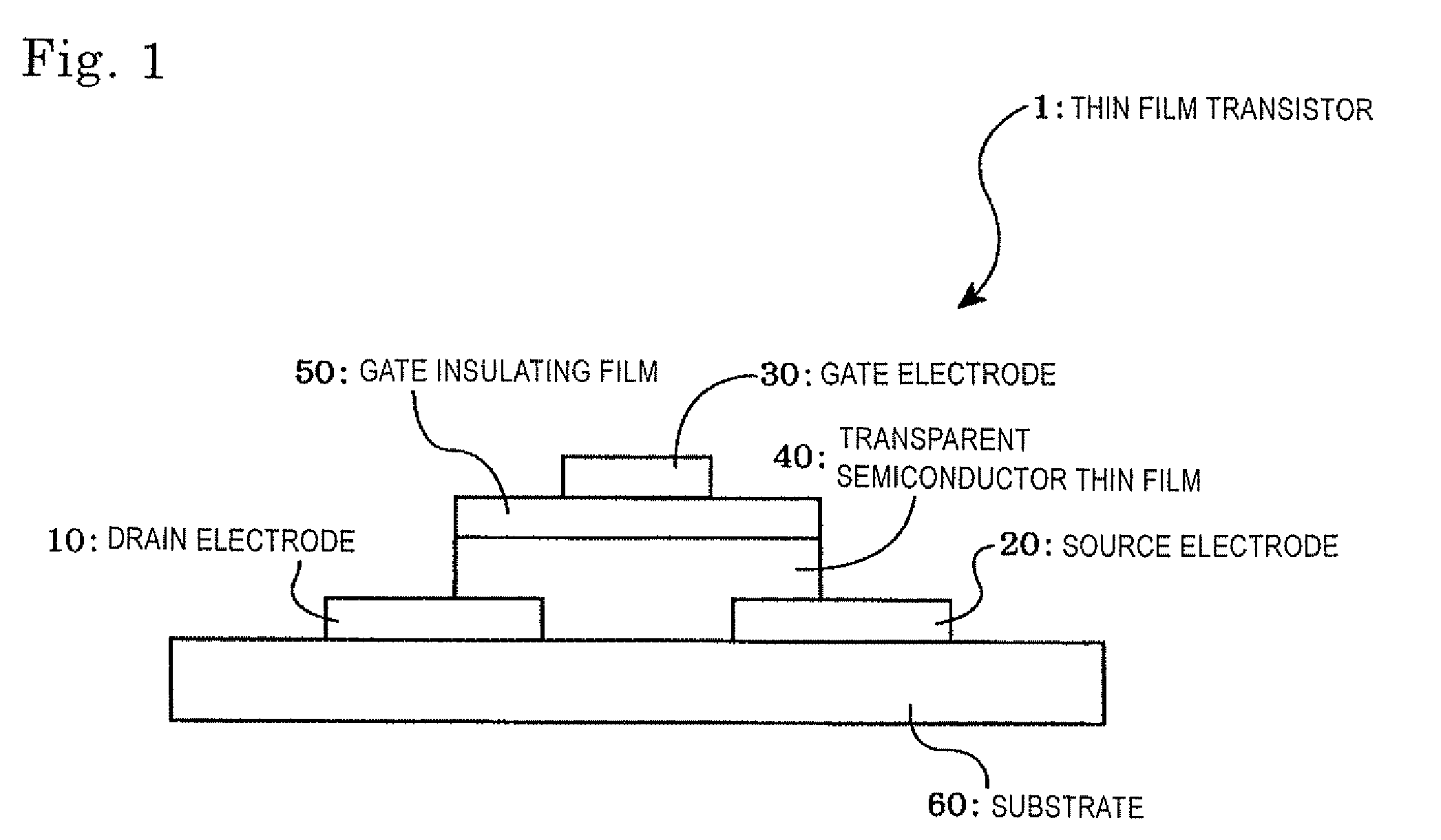

Semiconductor thin film, method for manufacturing the same, thin film transistor, and active-matrix-driven display panel

ActiveUS7998372B2Hardly erroneously operatesSmall currentNanotechConductive materialIndiumActive matrix

Disclosed is a semiconductor thin film which can be formed at a relatively low temperature even on a flexible resin substrate. Since the semiconductor thin film is stable to visible light and has high device characteristics such as transistor characteristics, in the case where the semiconductor thin film is used as a switching device for driving a display, even when overlapped with a pixel part, the luminance of a display panel does not deteriorate. Specifically, a transparent semiconductor thin film 40 is produced by forming an amorphous film containing zinc oxide and indium oxide and then oxidizing the film so that the resulting film has a carrier density of 10+17 cm−3 or less, a Hall mobility of 2 cm2 / V·sec or higher, and an energy band gap of 2.4 EV or more.

Owner:IDEMITSU KOSAN CO LTD

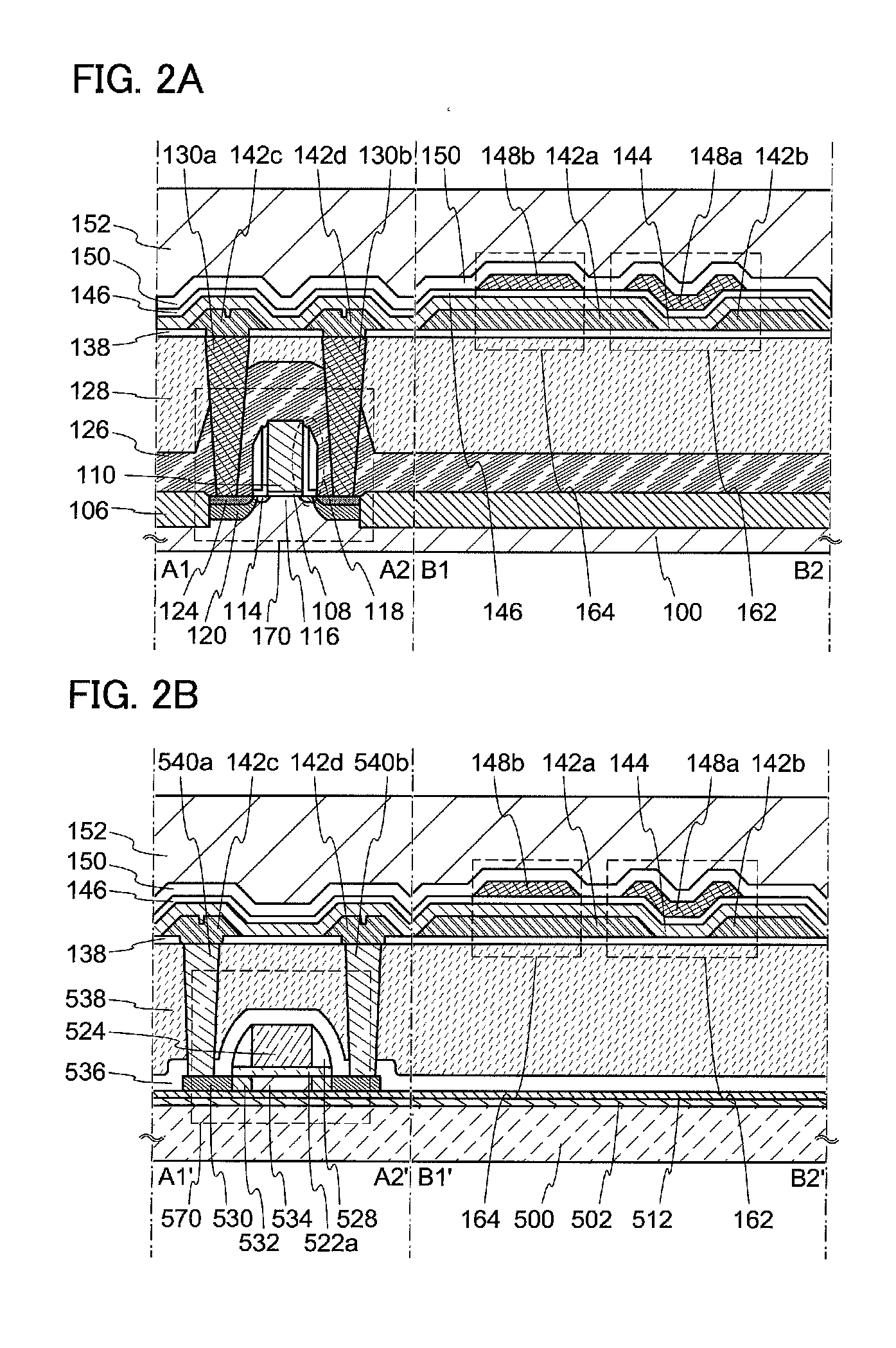

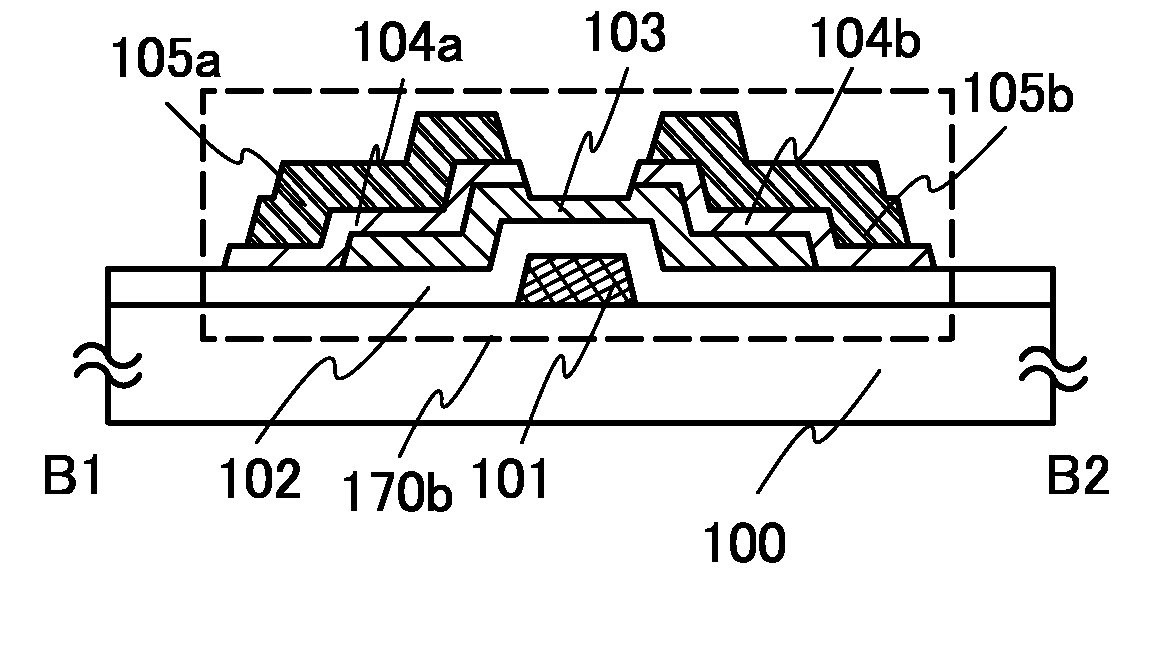

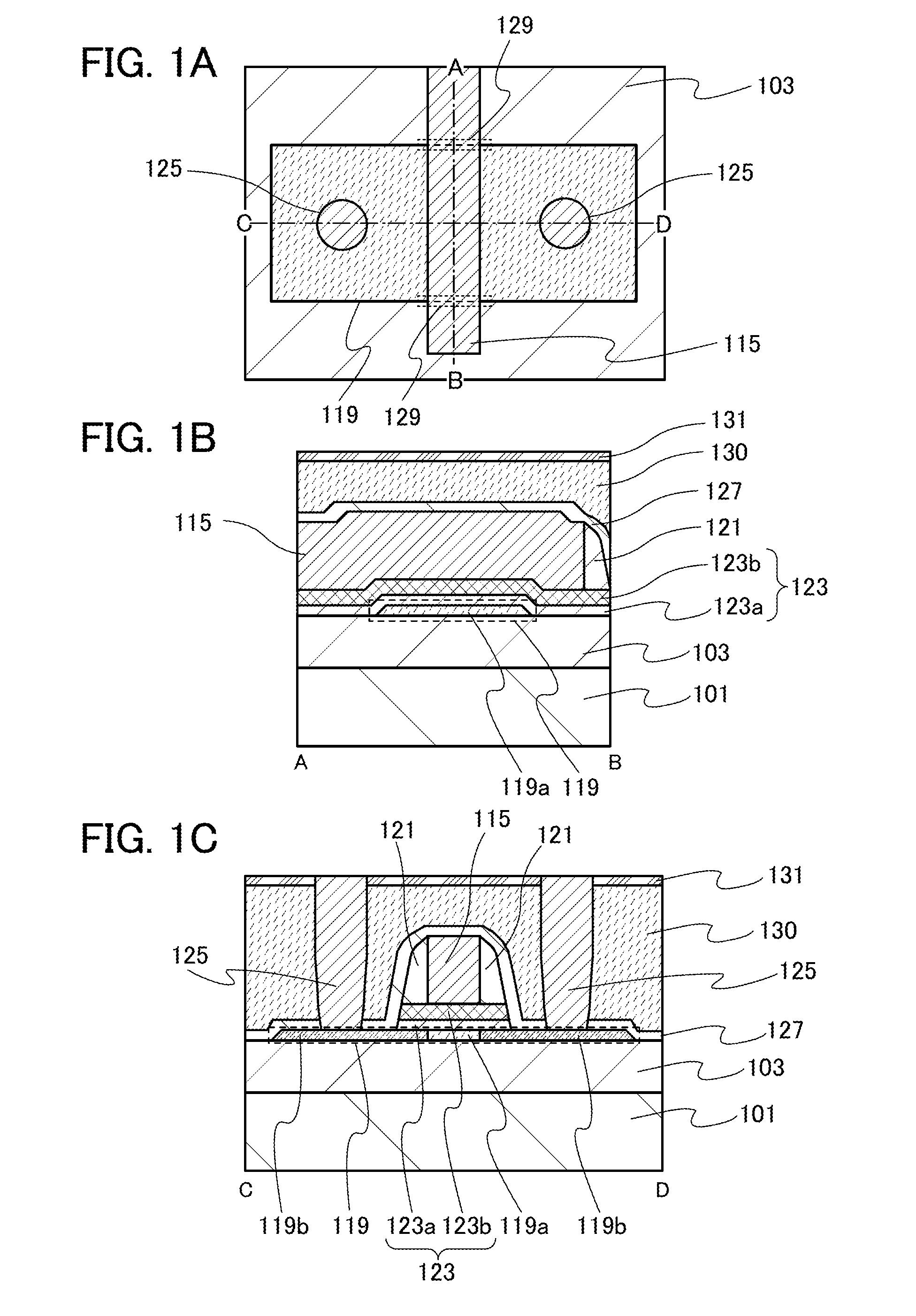

Semiconductor device and method for manufacturing the same

ActiveUS20100025679A1Small currentHigh on-off ratioStatic indicating devicesSolid-state devicesOhmic contactCharge carrier

An embodiment is to include an inverted staggered (bottom gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

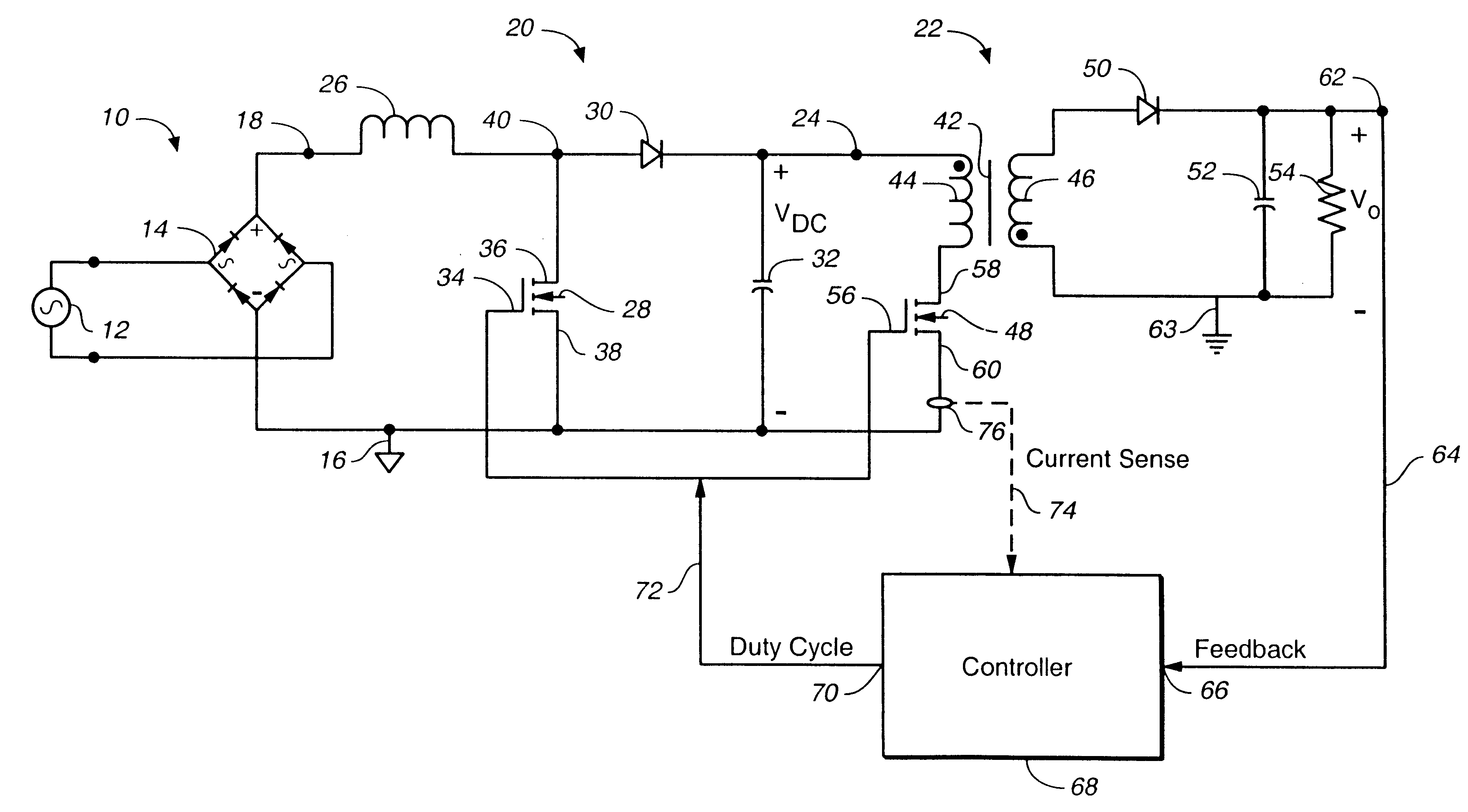

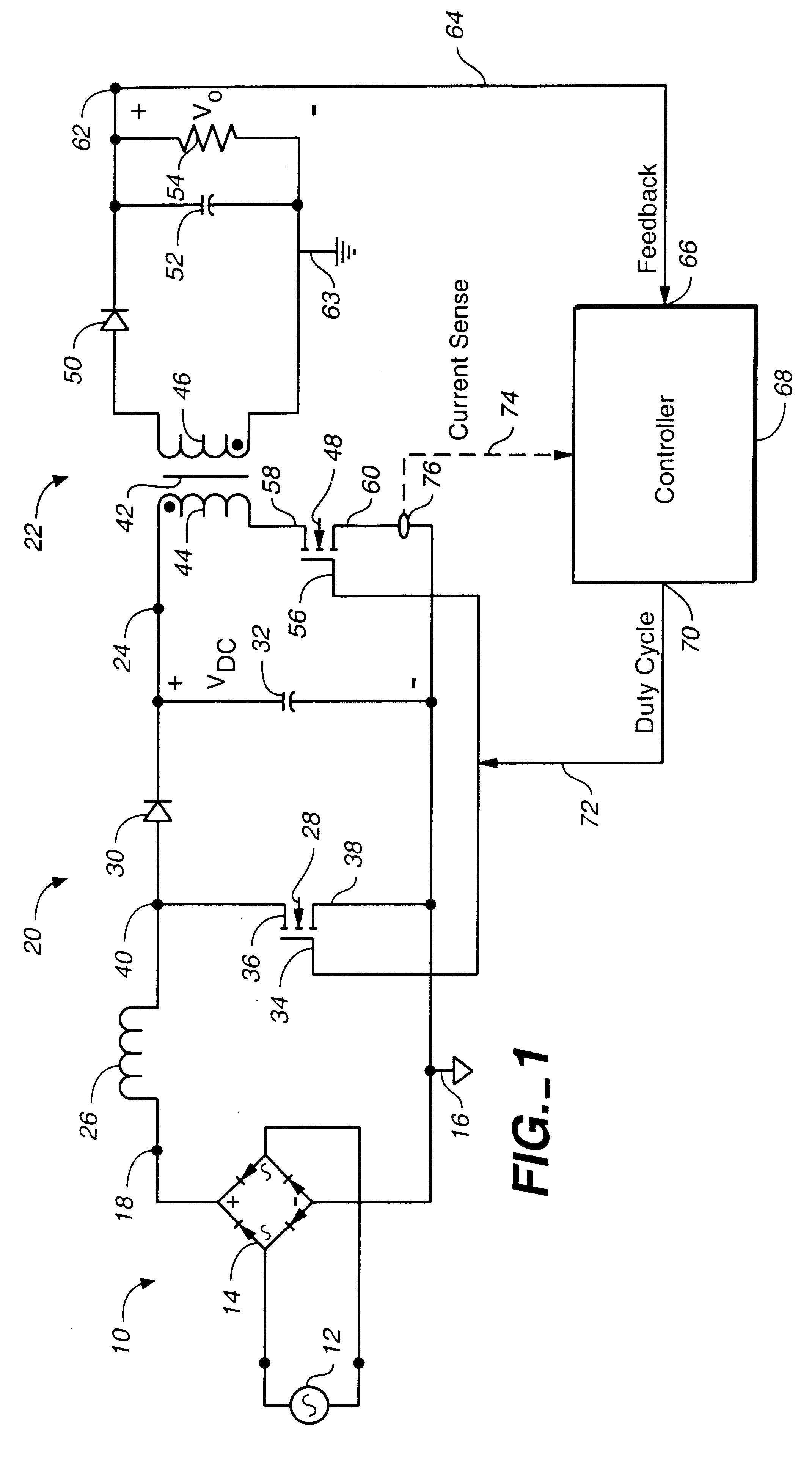

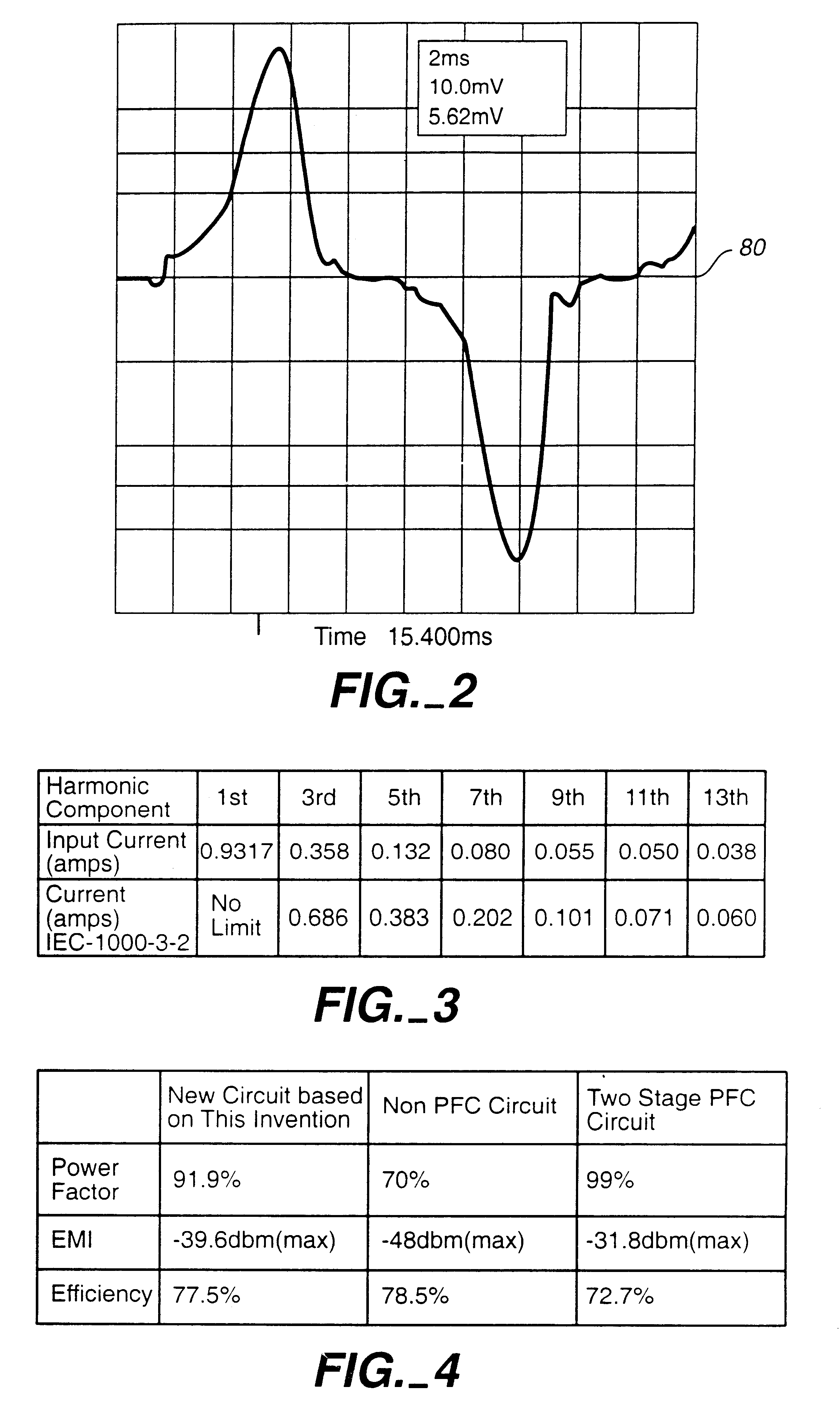

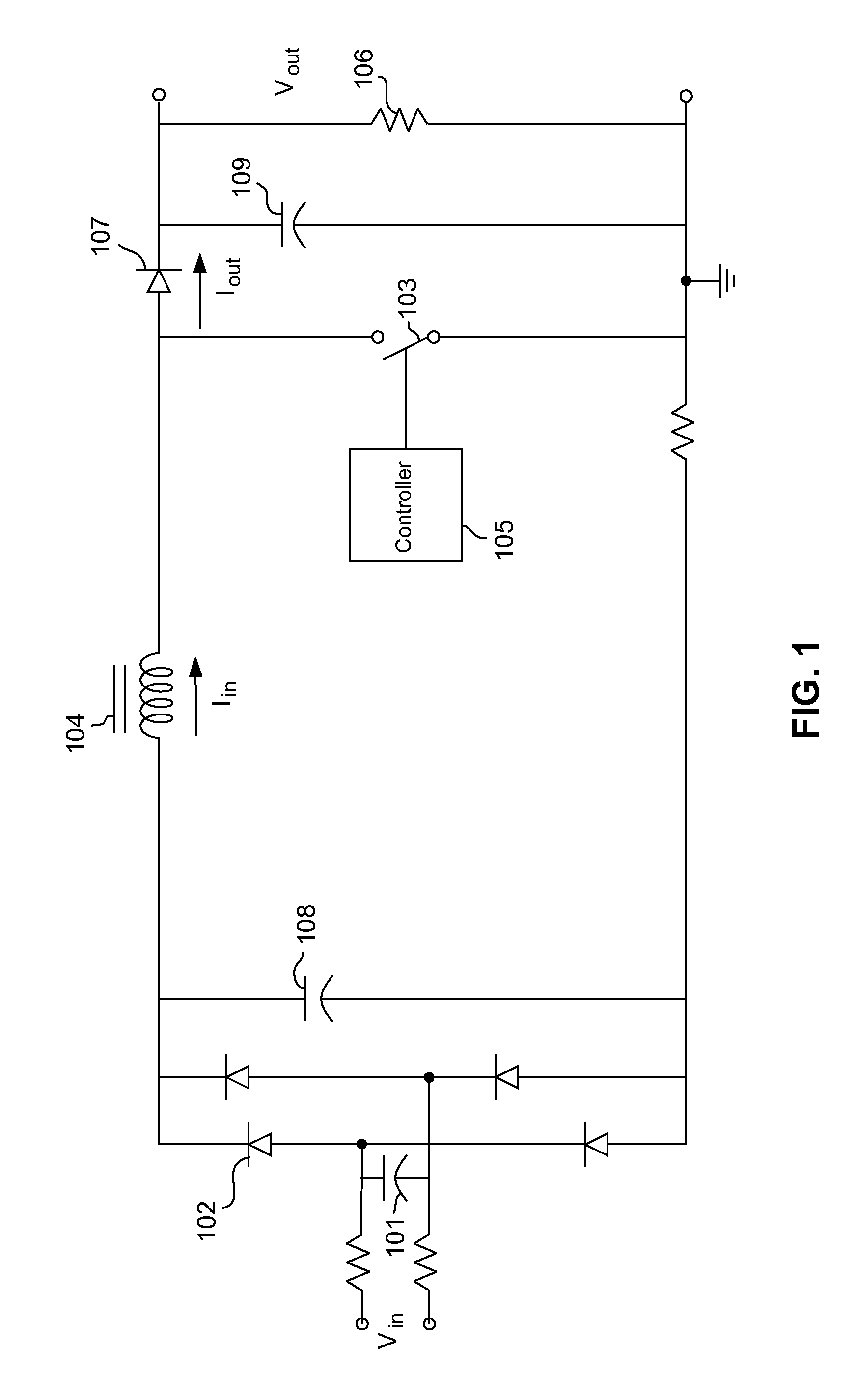

Topology and control method for power factor correction

InactiveUS6344986B1Reduce electromagnetic interferenceReduce output voltageAc-dc conversion without reversalEfficient power electronics conversionTransverterInductor

In a power factor corrected AC-to-DC power supply system, a DC-to-DC power converter is coupled to the output of an AC-to-DC power converter in order to produce a regulated DC output signal from a rectified AC input signal. The AC-to-DC power converter and the DC-to-DC power converter each includes a switch for controlling the operation of their respective power converter. The AC-to-DC converter includes an inductor. The system provides power factor correction for minimizing harmonic distortion by including a controller that receives the regulated DC output voltage as a feedback signal, and in response, produces a series of drive pulses having predetermined constant duty cycle. These pulses are simultaneously fed to each switch, to operate the respective converters alternately between ON and OFF states. When the AC-to-DC converter is driven by a fixed duty cycle of the series of pulses, power factor correction is improved since the current flowing through the inductor is substantially proportional to the waveform of the rectified AC input signal. By preselecting the value of the inductor, the AC-to-DC converter is operable in a discontinuous mode when the instantaneous rectified AC input signal is low and in a continuous mode when the instantaneous rectified AC input signal is high.

Owner:ASTEC INT LTD

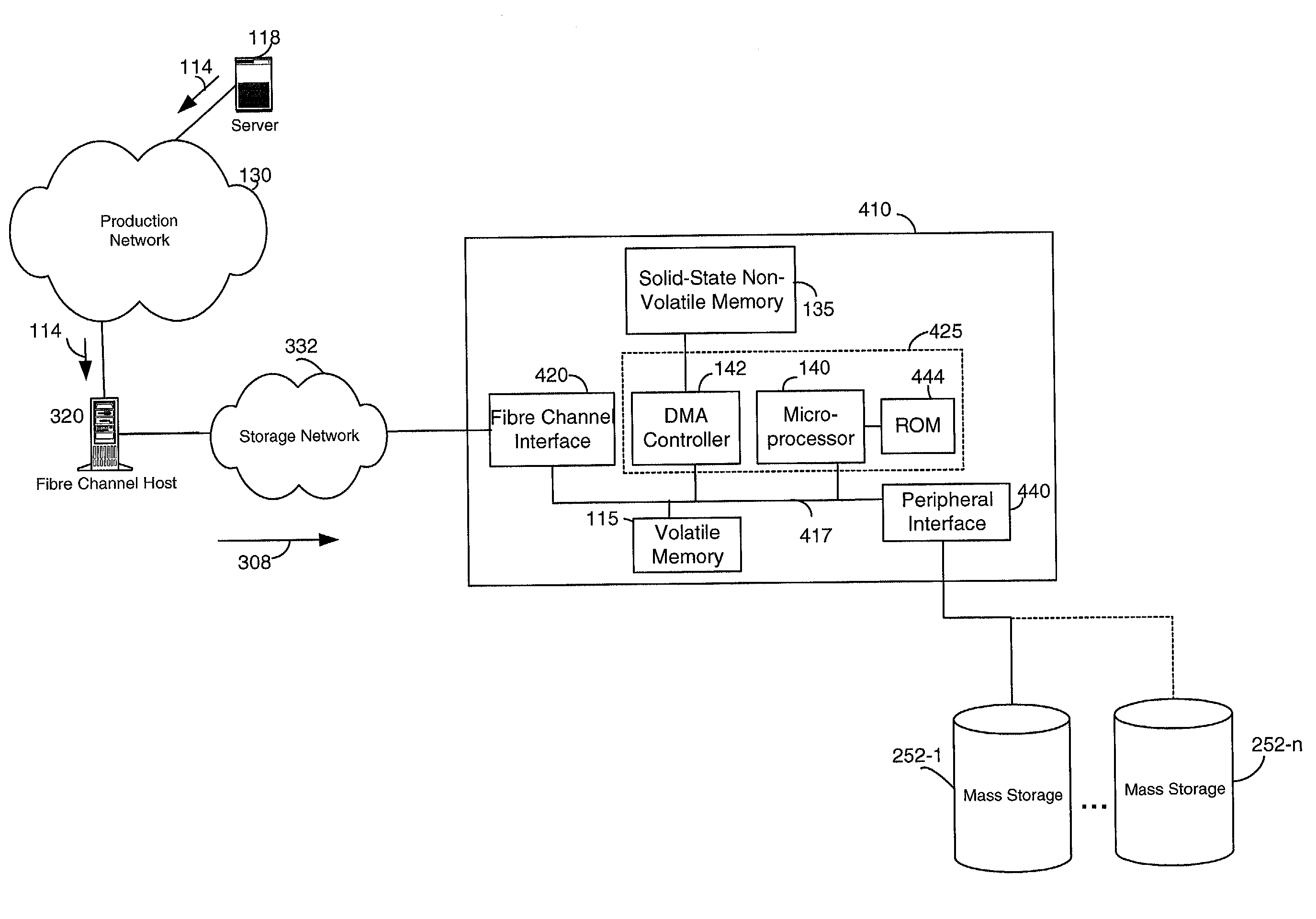

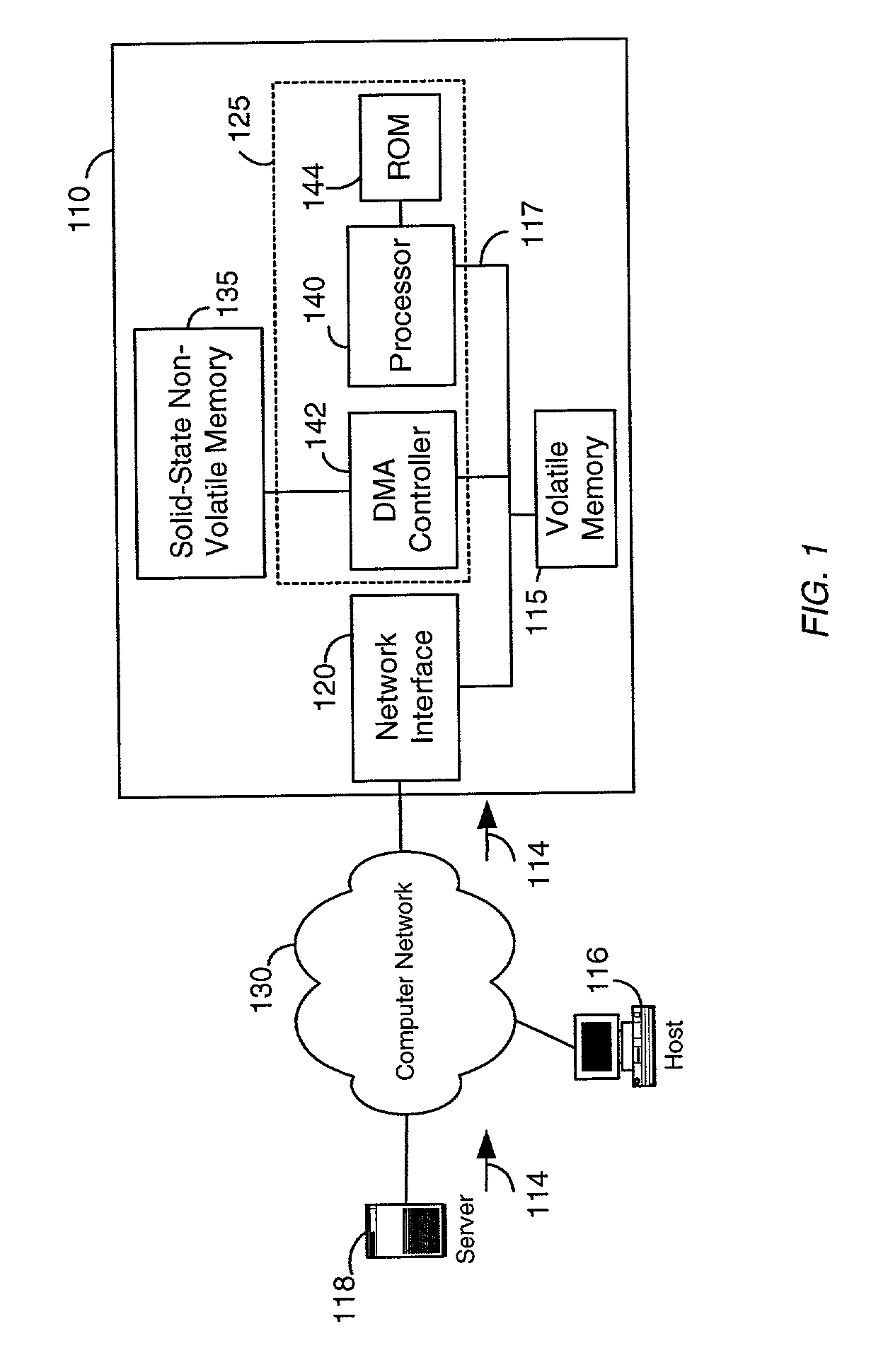

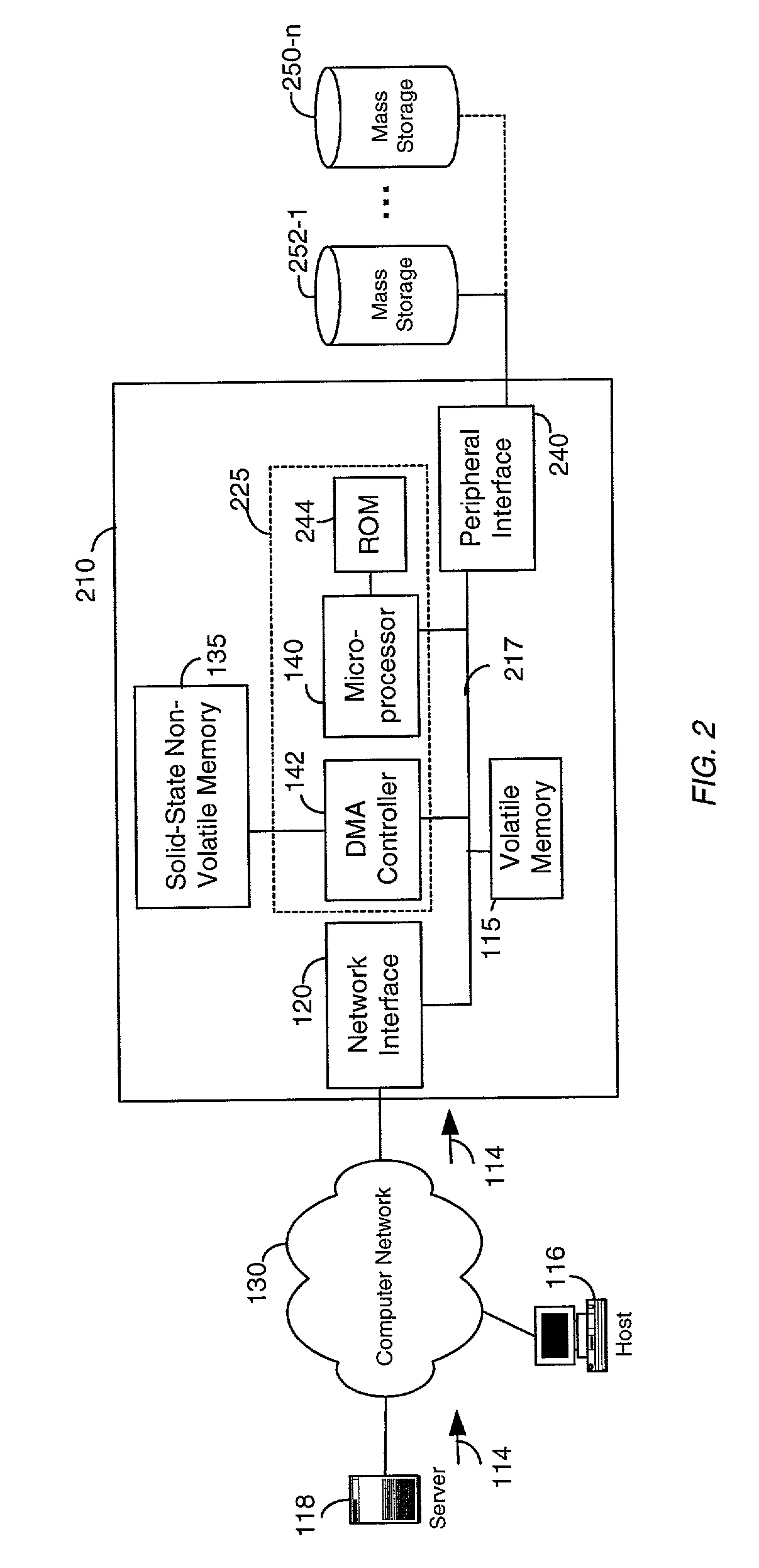

Network storage device having solid-state non-volatile memory

InactiveUS6981070B1Great access timeSmall currentMemory architecture accessing/allocationInput/output to record carriersMass storageRAID

A network storage device. In one embodiment, the network storage device of the present invention uses solid-state non-volatile memory (e.g., flash-memory) as a storage medium, and has at least one interface configured for coupling to a computer network. The network storage device of the present invention is accessible to client(s) and / or server(s) of the computer network, and uses solid-state non-volatile memory to store data received therefrom. The network storage device may also be configured to include a memory for caching data to be written to the solid-state non-volatile memory. In order to provide additional storage, the network storage device may also include a peripheral interface or another network interface for coupling to a mass storage device (e.g., a RAID system), and / or another network interface for coupling to a network of mass storage devices. The network storage device may be a stand-alone unit, or may be implemented as part of a network server, or as part of a mass storage device.

Owner:BITMICRO LLC

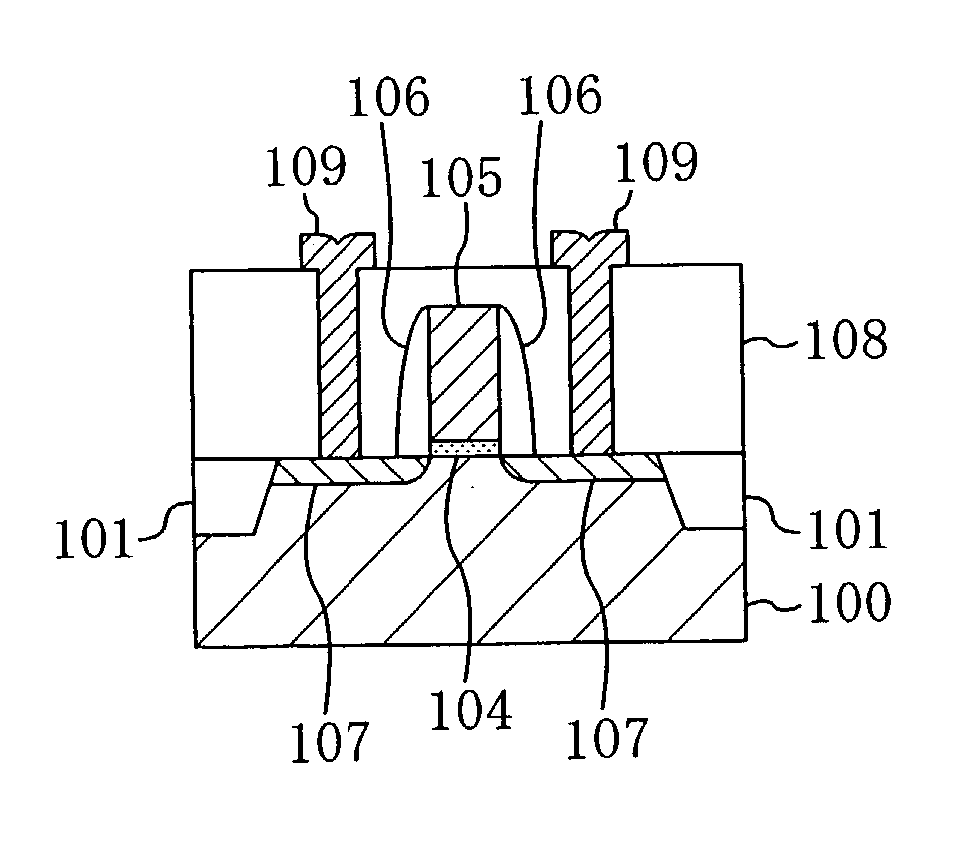

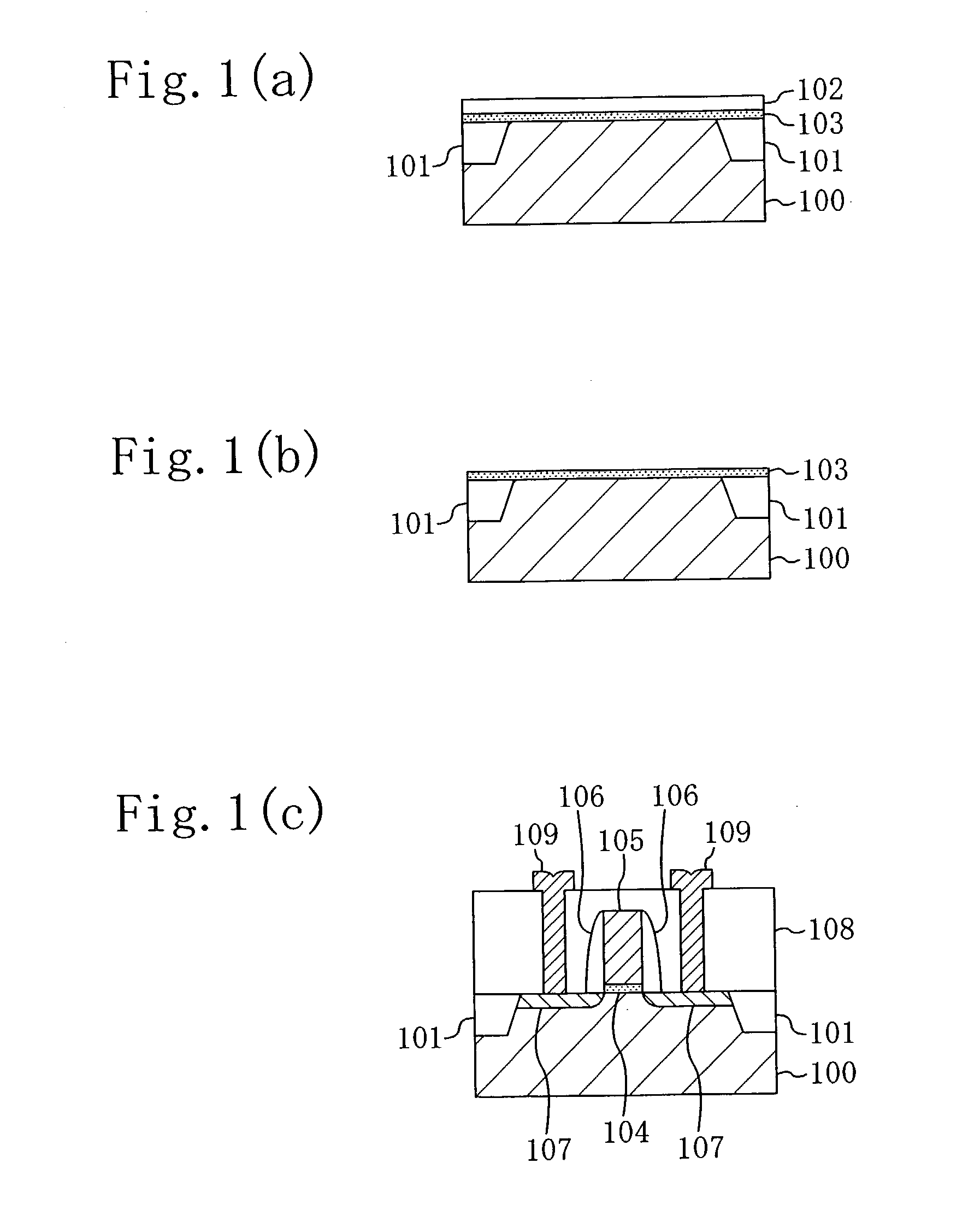

Semiconductor device and method for manufacture thereof

InactiveUS20030173586A1Increase currentSmall currentSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSilicon

Owner:PANNOVA SEMIC

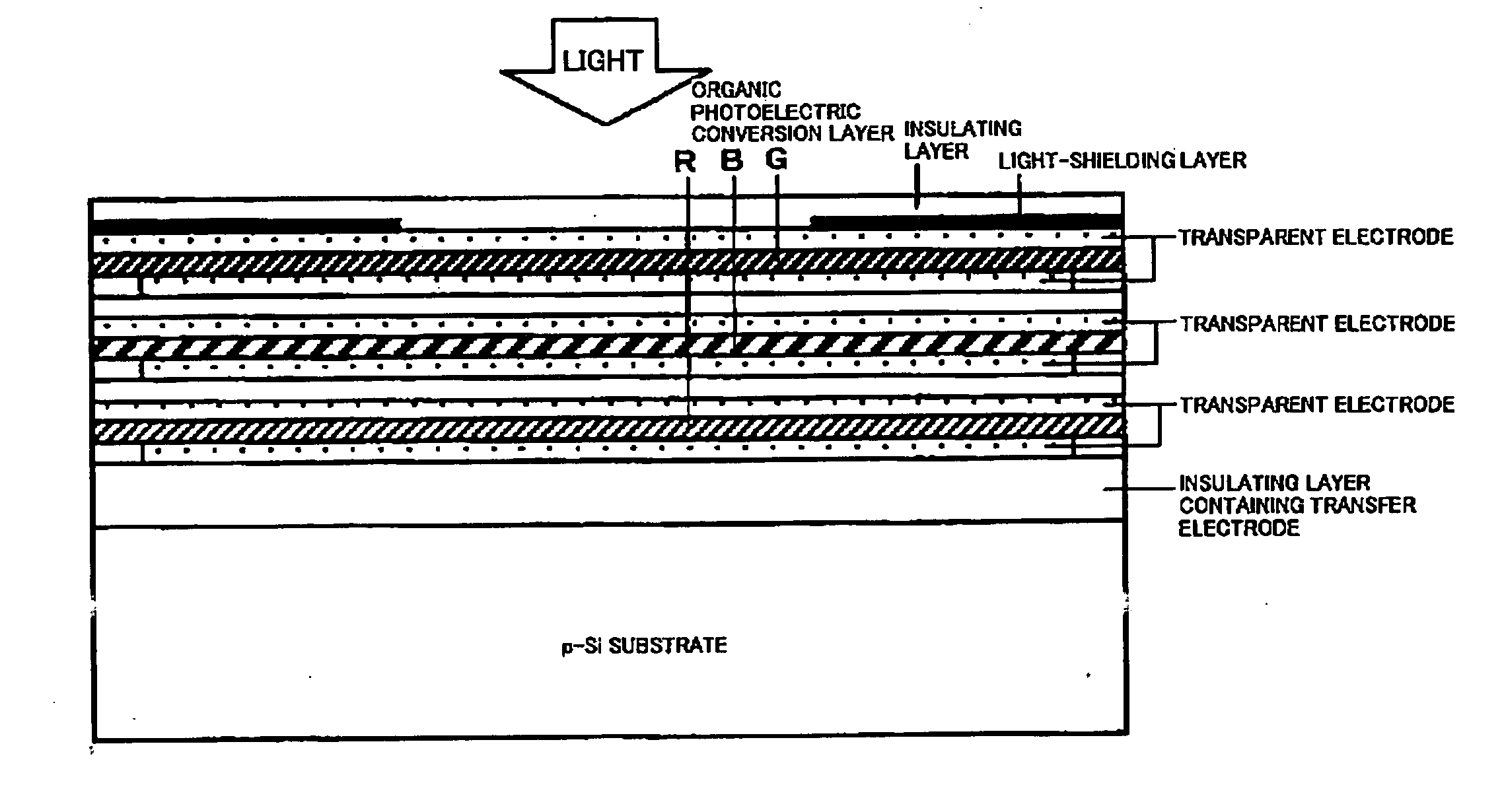

Organic photoelectric conversion device and stack type photoelectric conversion device

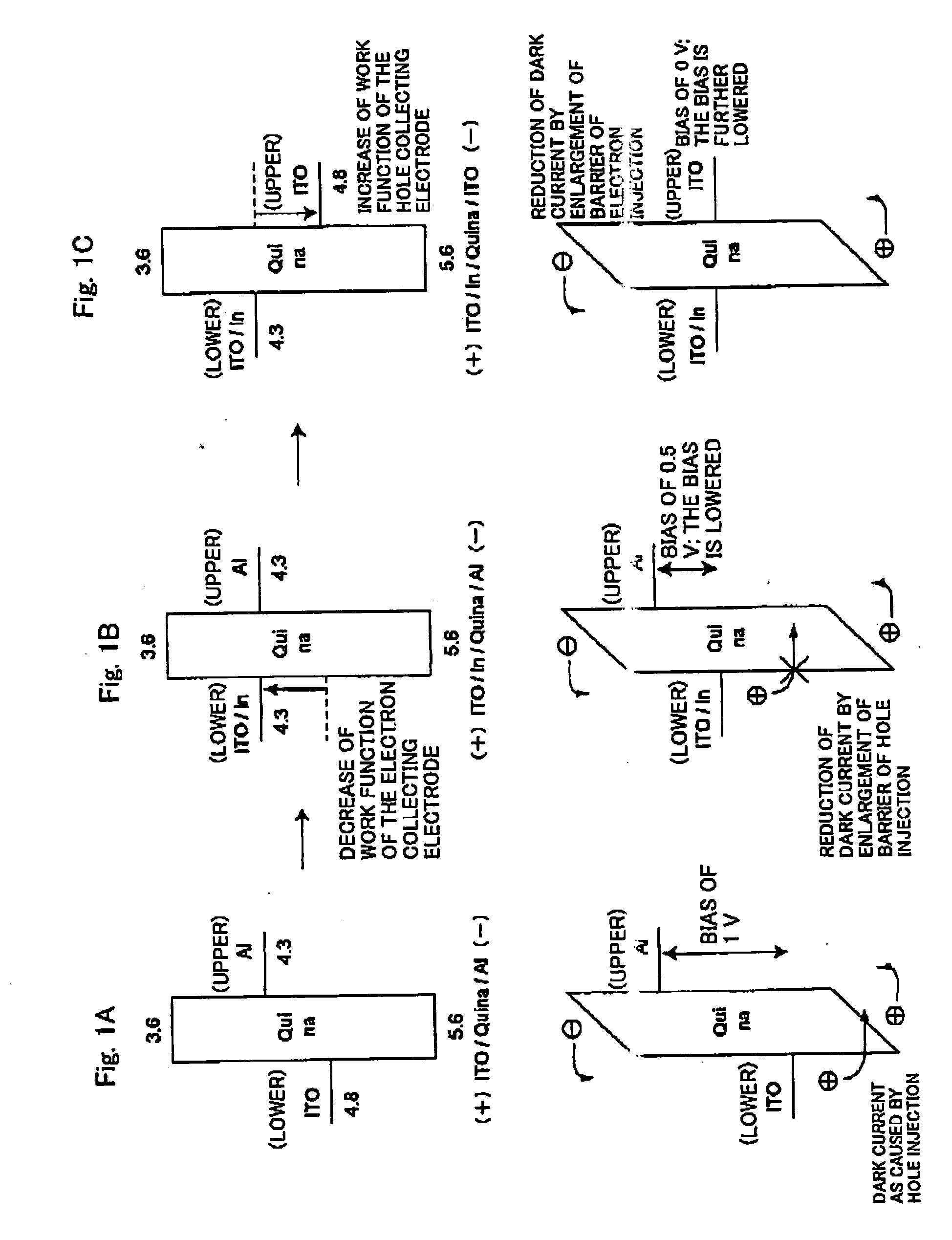

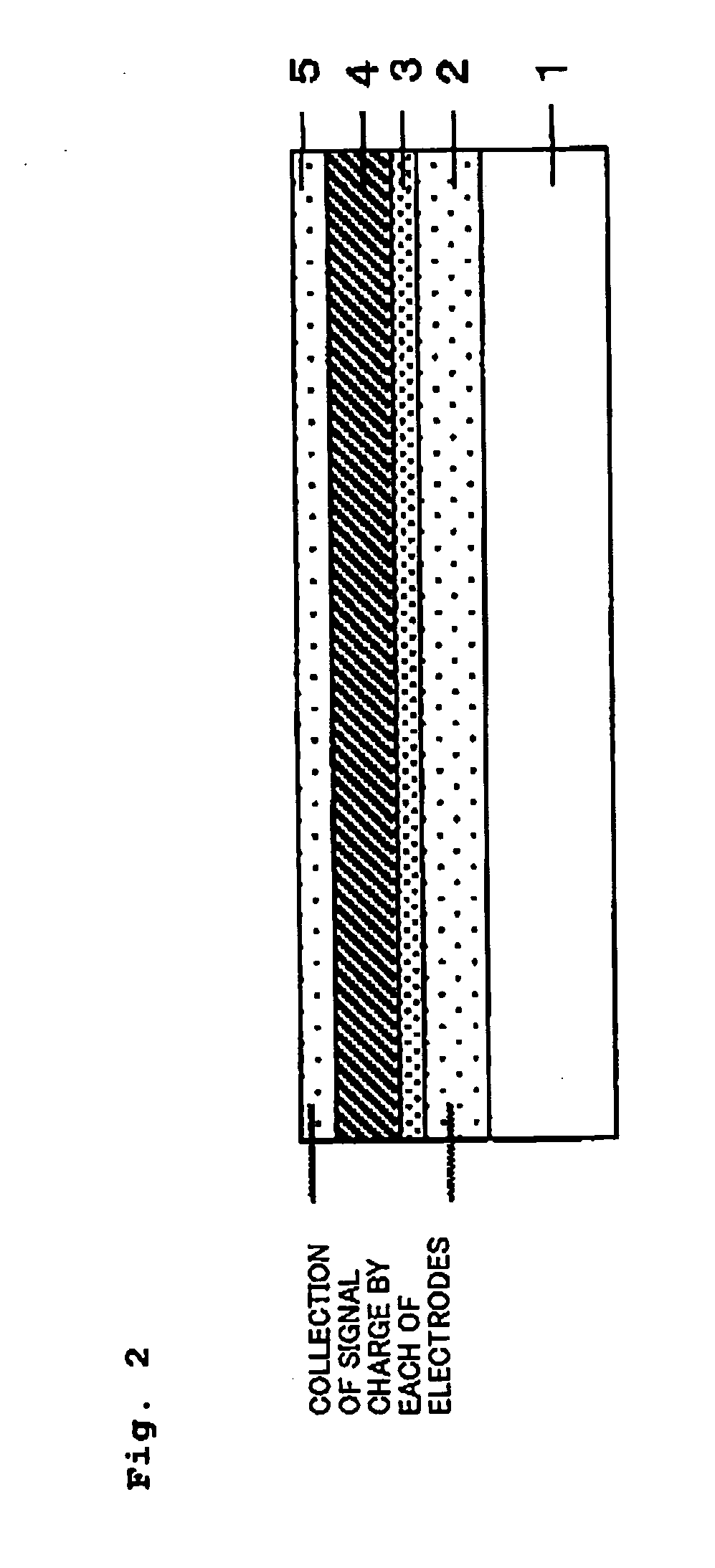

InactiveUS20070120045A1Total current dropReduce noiseSolid-state devicesMaterial analysis by optical meansOrganic layerPhotoelectric conversion

An organic photoelectric conversion device comprising; a lower electrode; an organic layer; and an upper electrode provided in this order, in which at least one of the lower electrode and the upper electrode is a transparent electrode and an electron is collected in a side of one of the lower electrode and the upper electrode and a hole is collected in a side of other of the lower electrode and the upper electrode so as to read out photocurrent, wherein the electrode in the side of collecting an electron is the transparent electrode and has a word function of 4.5 eV or less.

Owner:FUJIFILM CORP +1

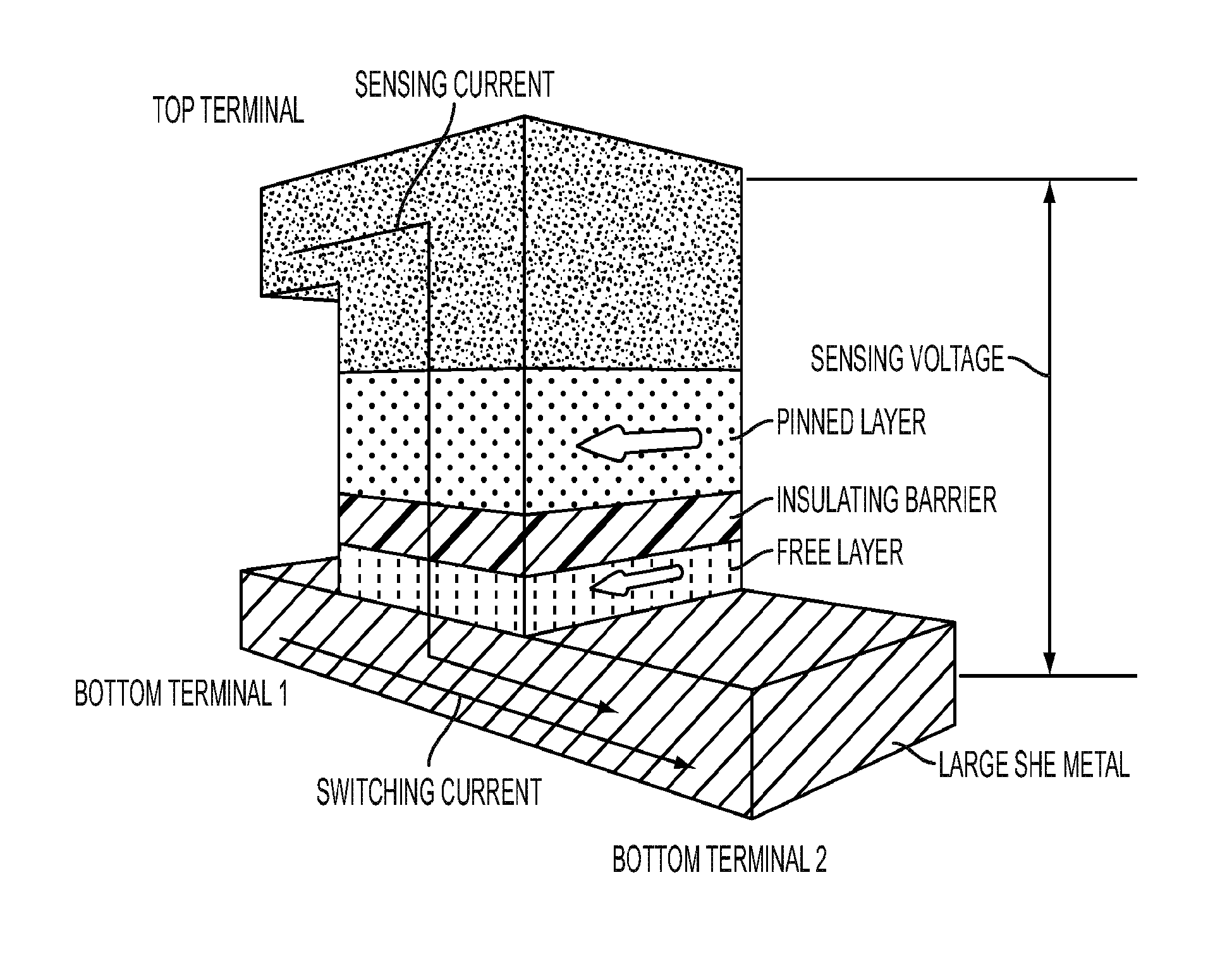

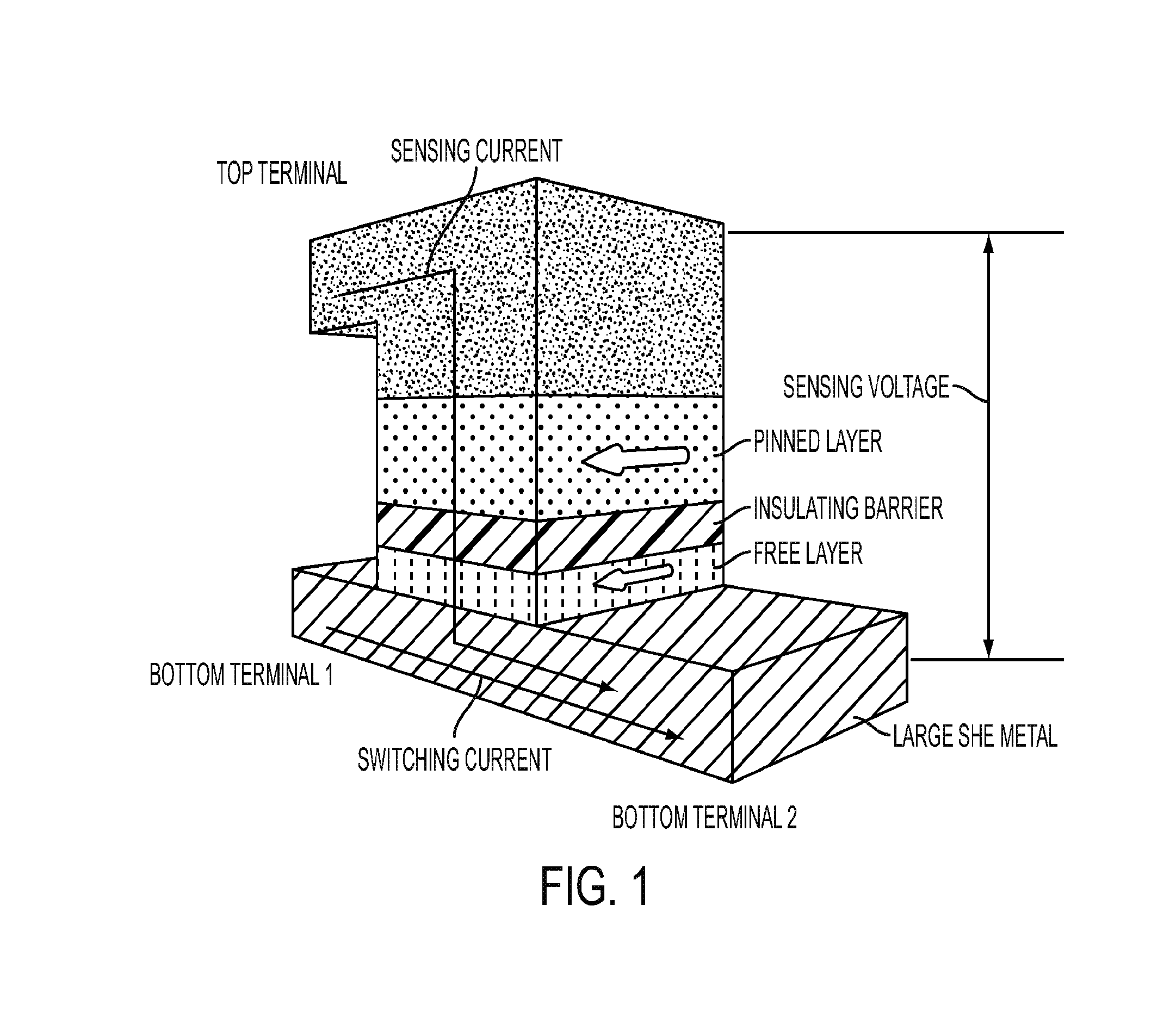

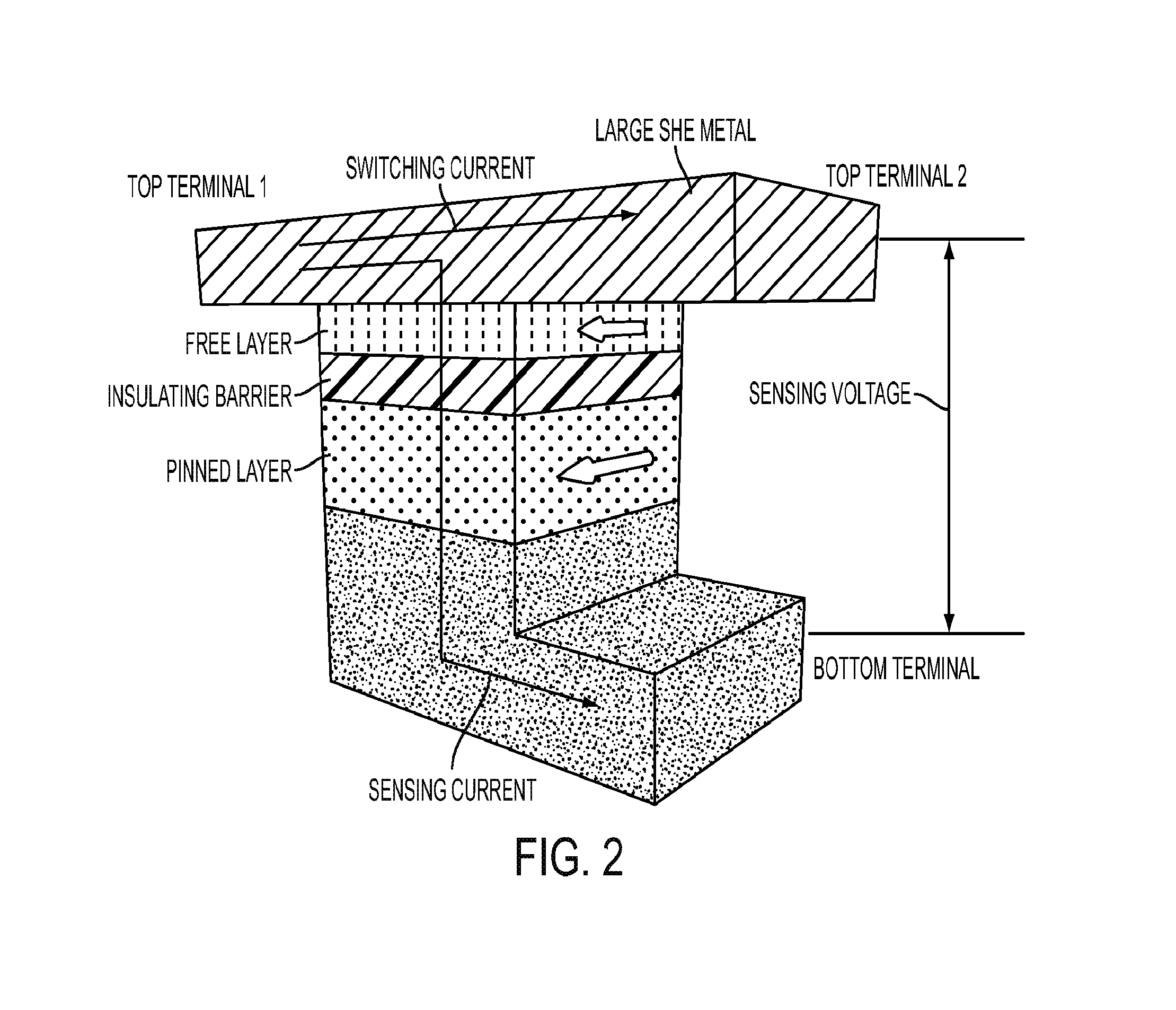

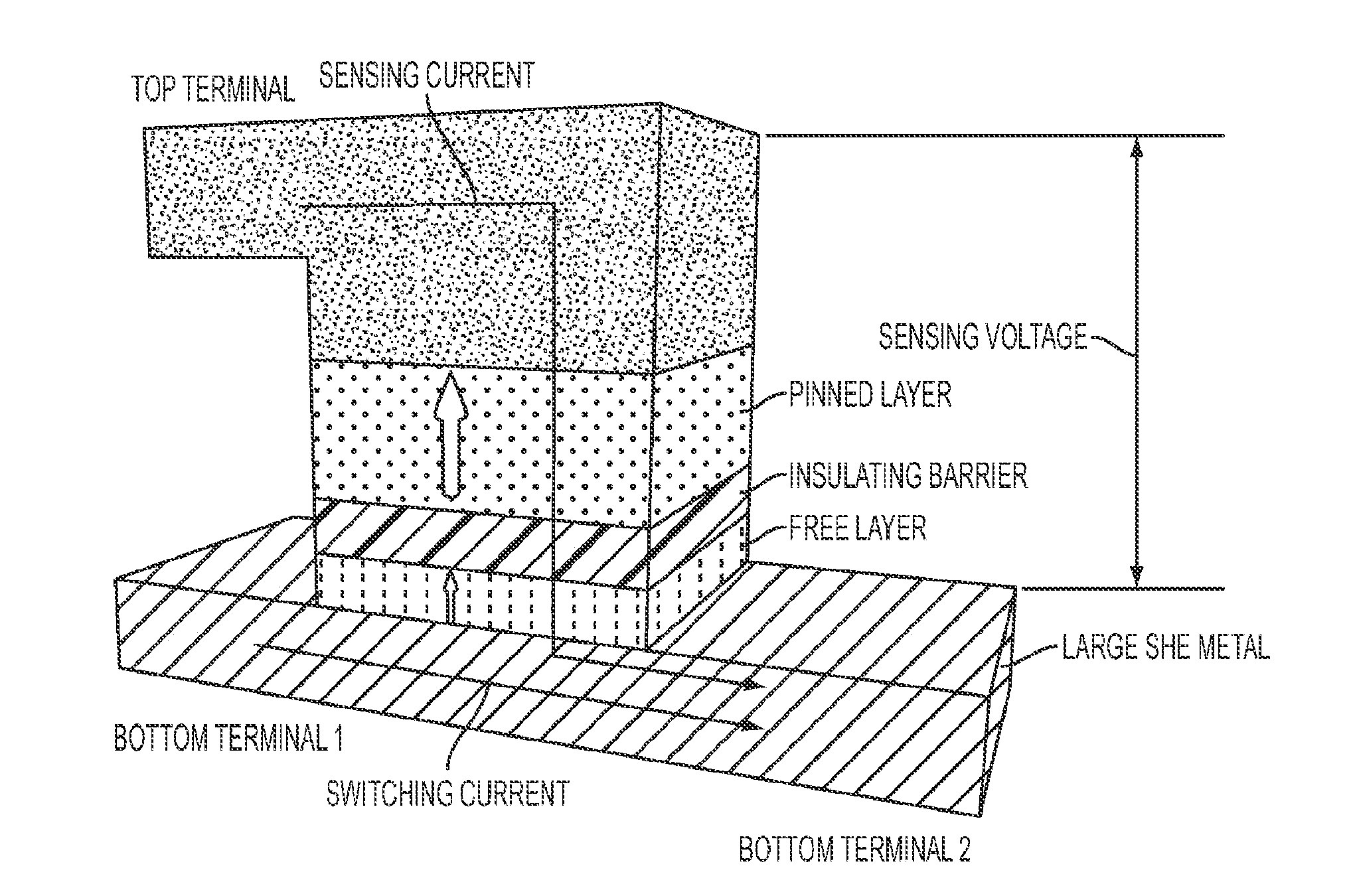

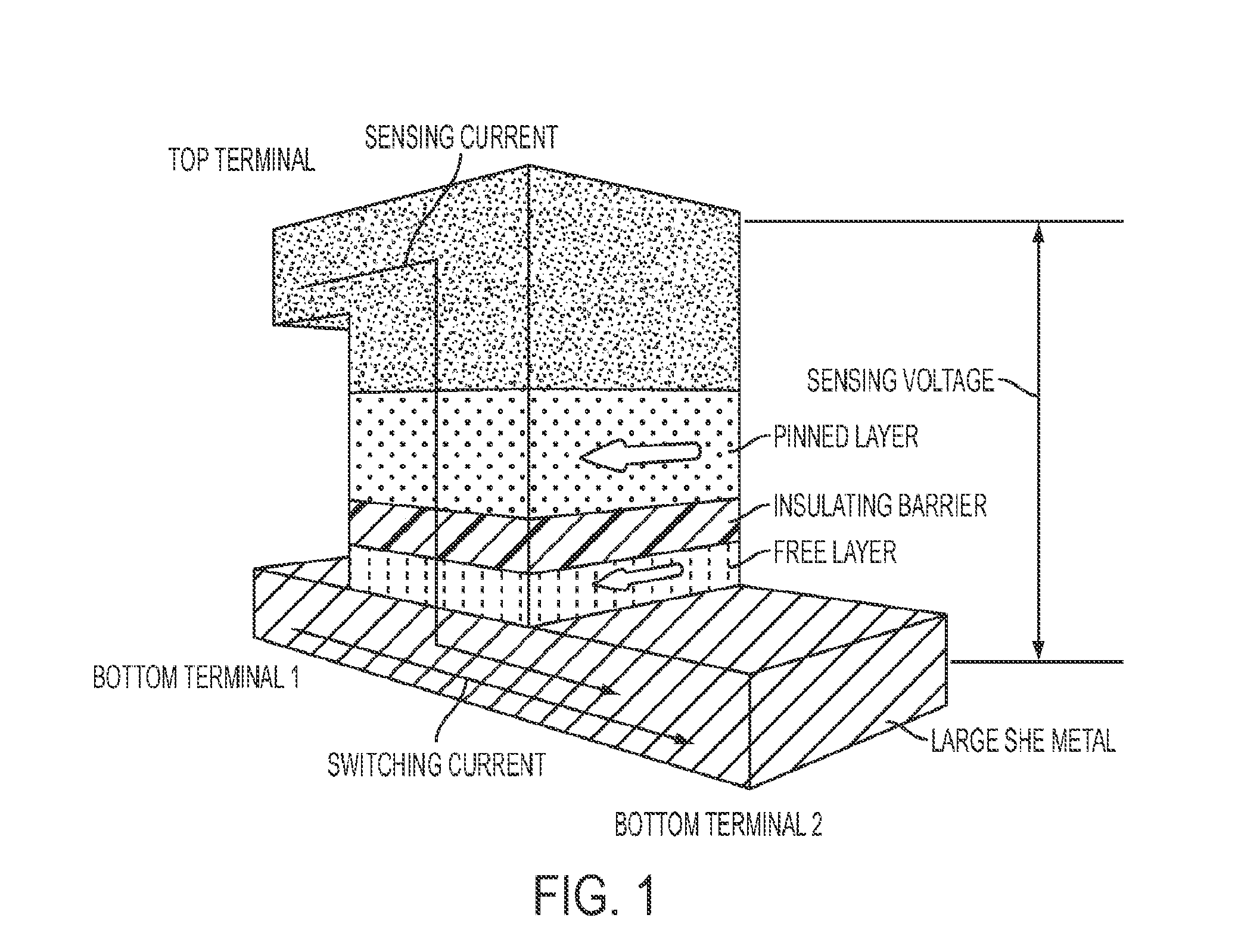

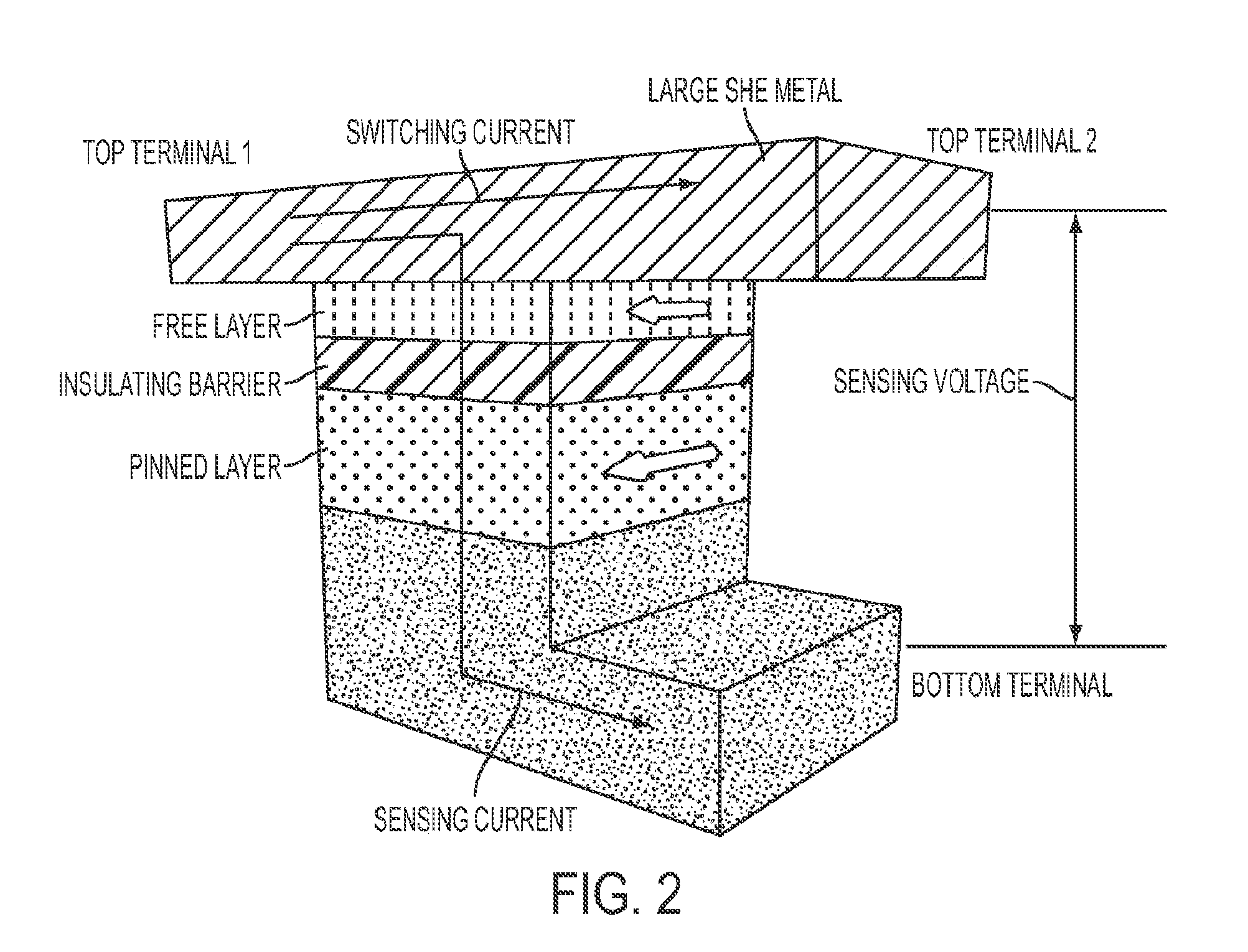

Spin hall effect magnetic apparatus, method and applications

ActiveUS20140169088A1Improve efficiencySmall costSolid-state devicesRead-only memoriesTungstenPower flow

An ST-MRAM structure, a method for fabricating the ST-MRAM structure and a method for operating an ST-MRAM device that results from the ST-MRAM structure each utilize a spin Hall effect base layer that contacts a magnetic free layer and effects a magnetic moment switching within the magnetic free layer as a result of a lateral switching current within the spin Hall effect base layer. This resulting ST-MRAM device uses an independent sense current and sense voltage through a magnetoresistive stack that includes a pinned layer, a non-magnetic spacer layer and the magnetic free layer which contacts the spin Hall effect base layer. Desirable non-magnetic conductor materials for the spin Hall effect base layer include certain types of tantalum materials and tungsten materials that have a spin diffusion length no greater than about five times the thickness of the spin Hall effect base layer and a spin Hall angle at least about 0.05.

Owner:CORNELL UNIVERSITY

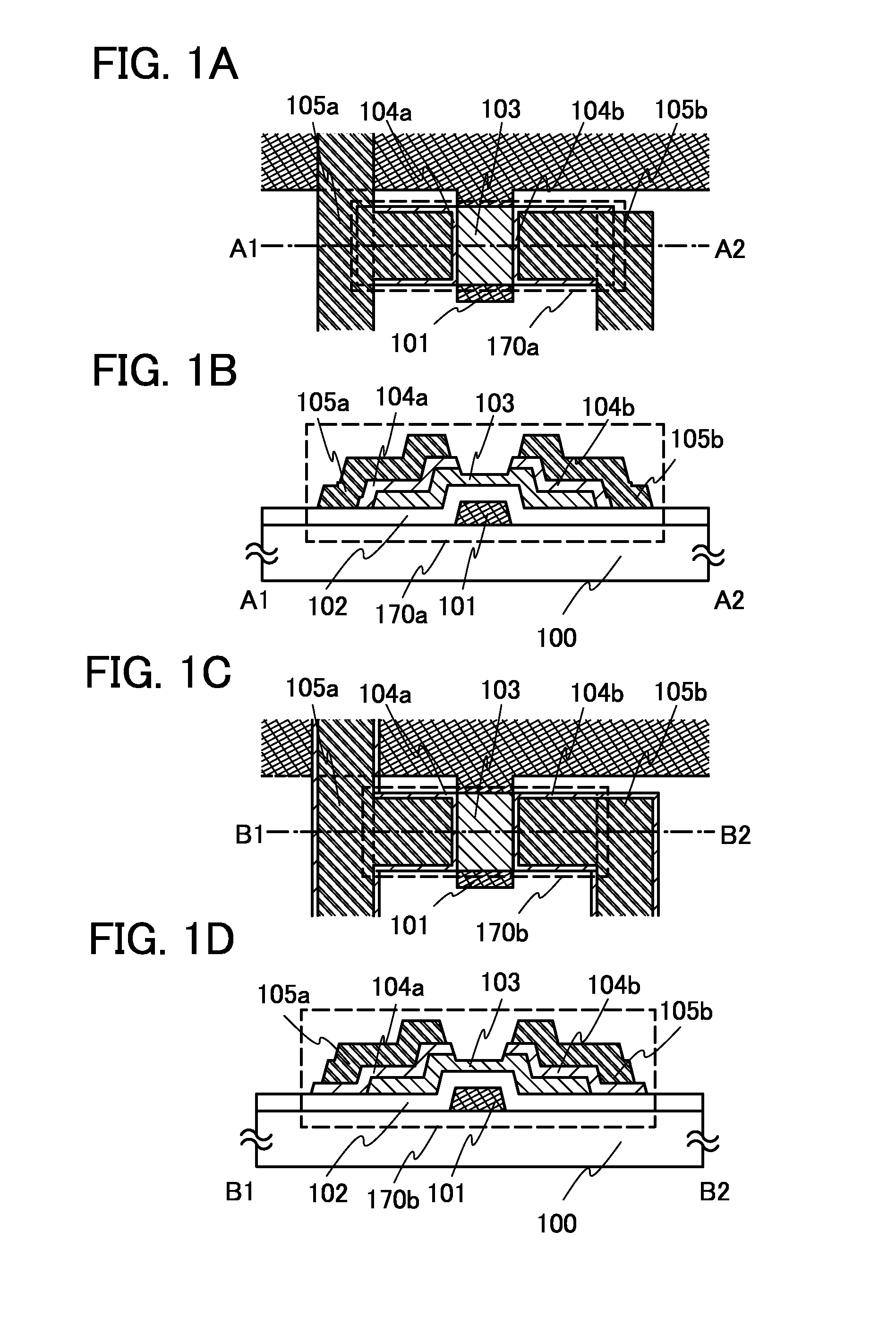

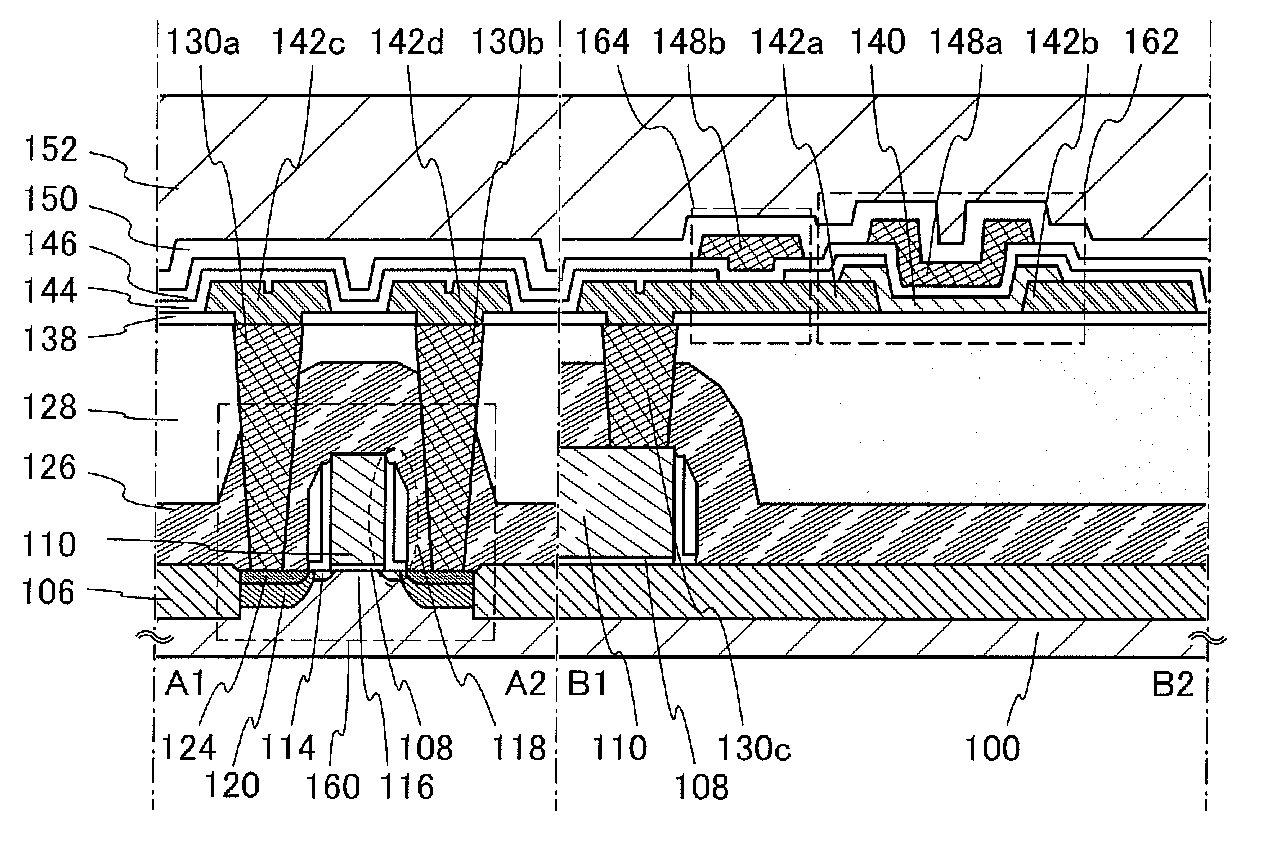

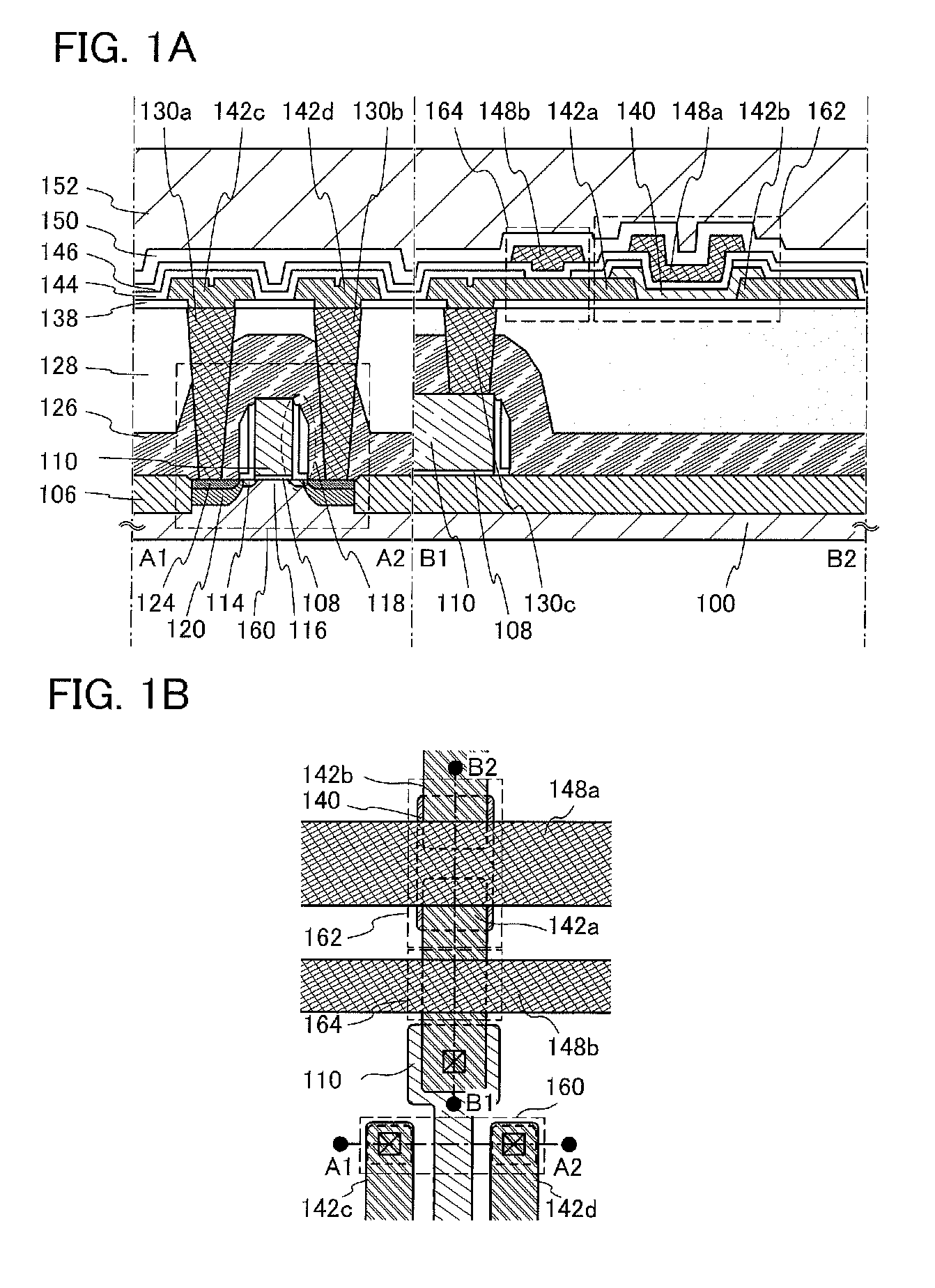

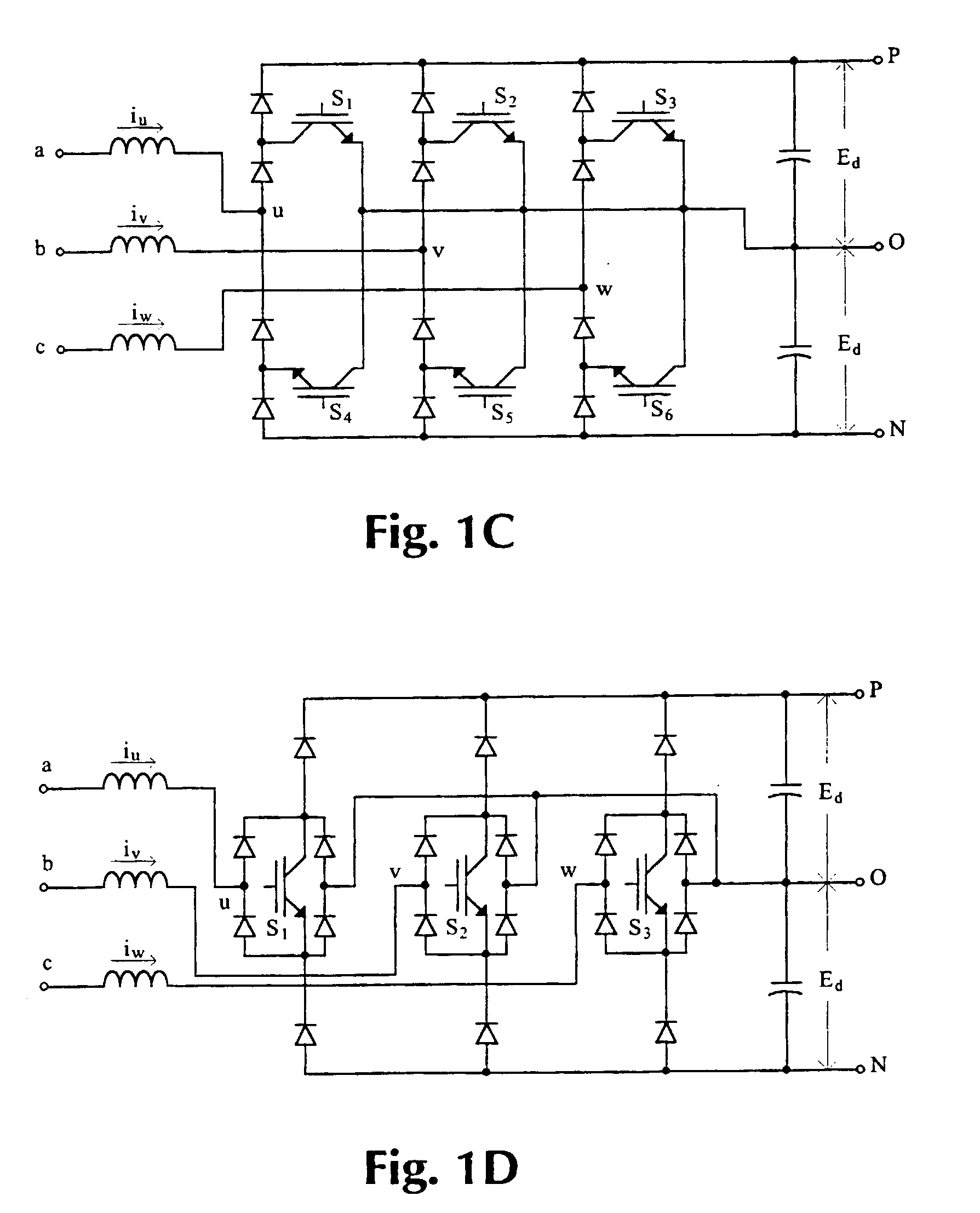

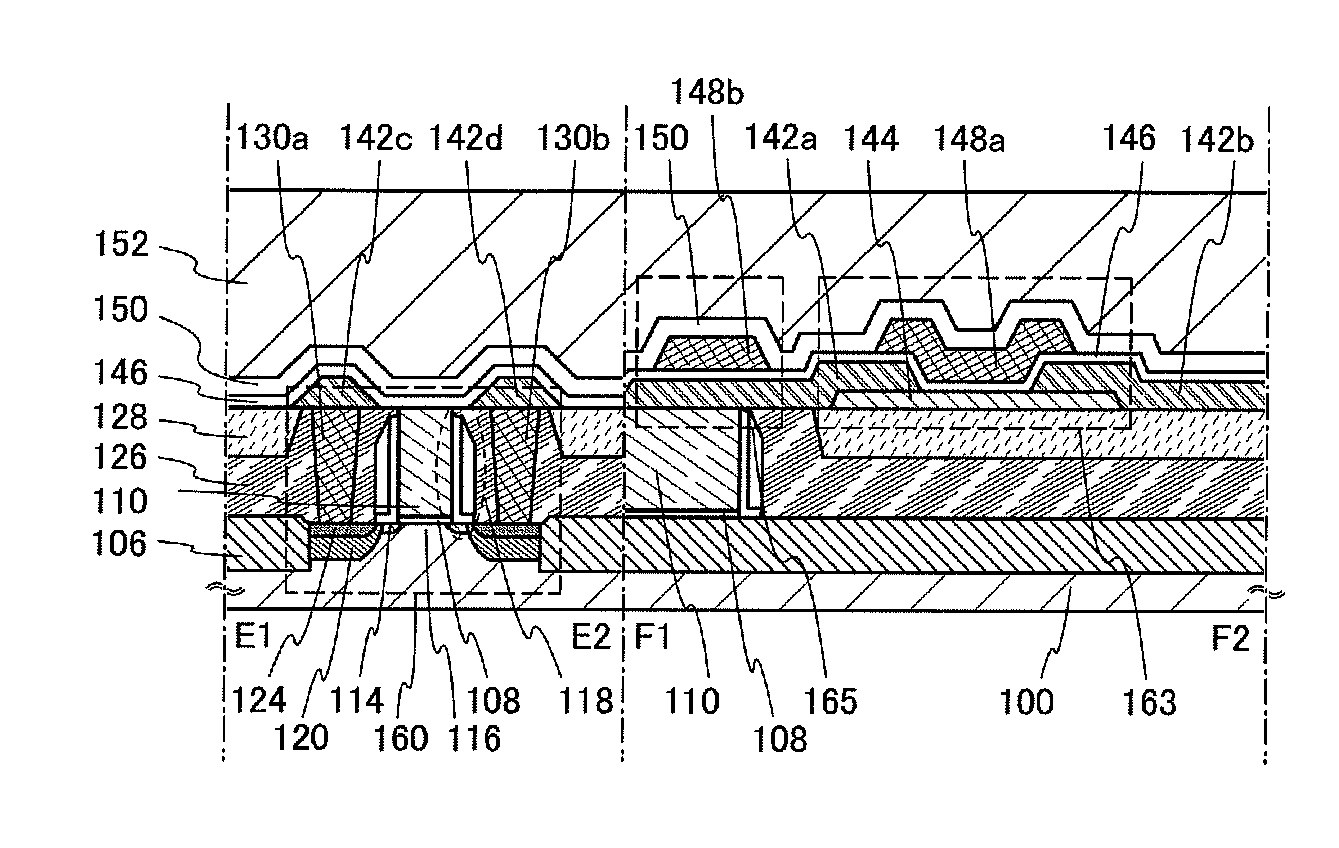

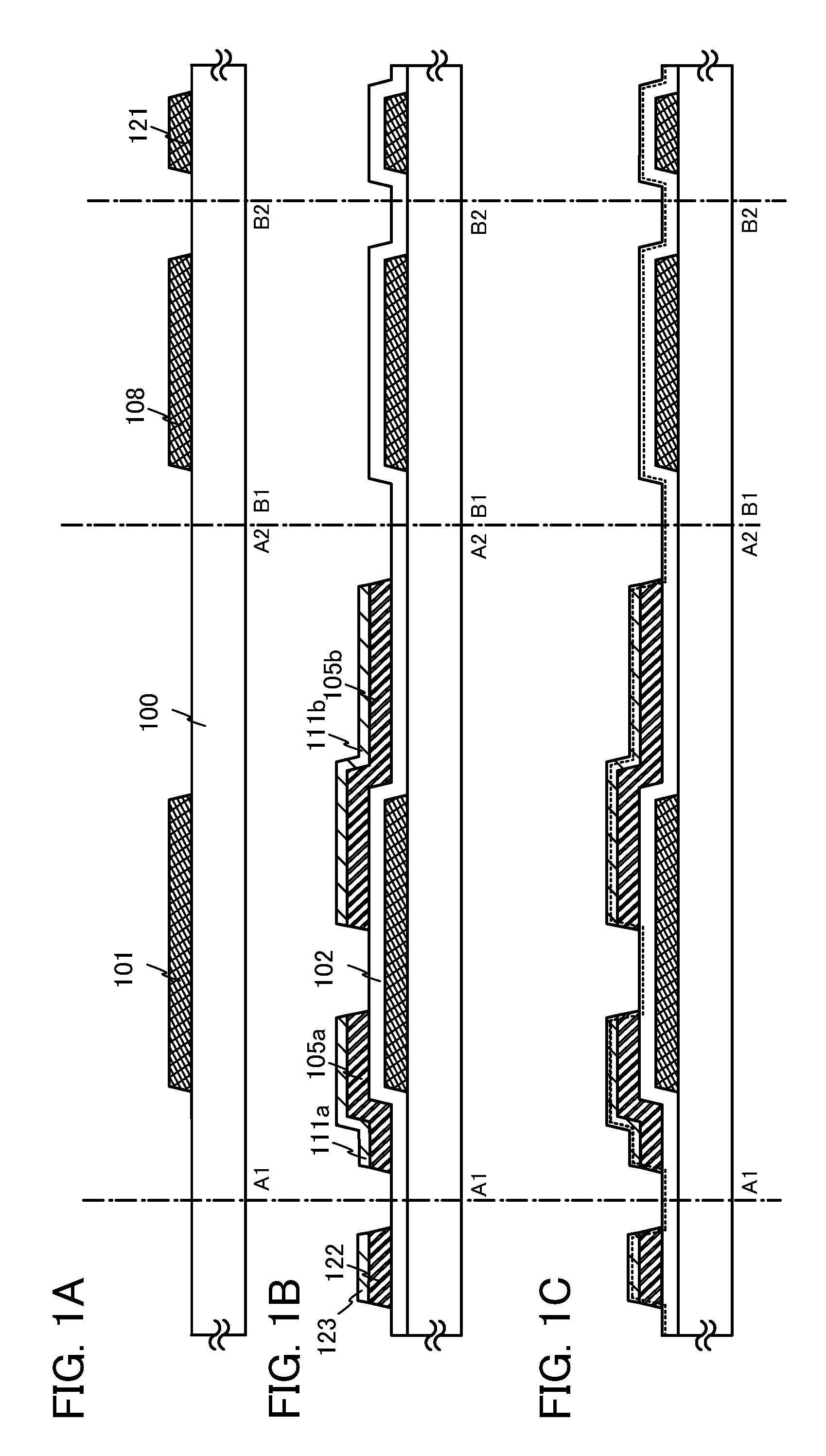

Semiconductor device

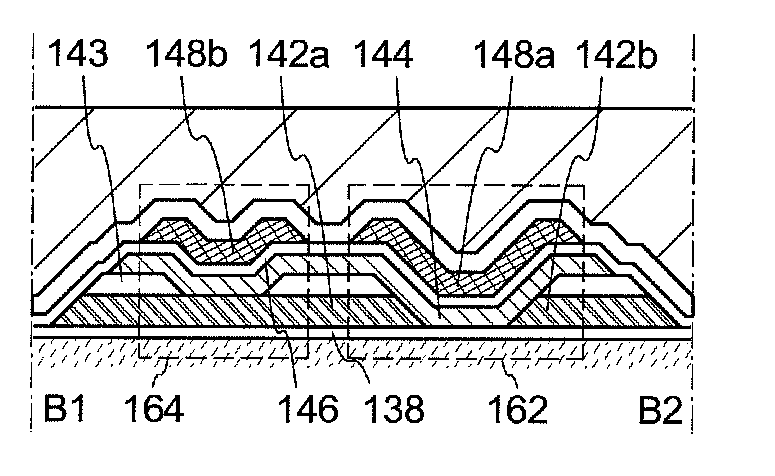

InactiveUS20110147737A1Reduce power consumptionFrequency of refresh can be lowTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

A first transistor including a channel formation region, a first gate insulating layer, a first gate electrode, and a first source electrode and a first drain electrode; a second transistor including an oxide semiconductor layer, a second source electrode and a second drain electrode, a second gate insulating layer, and a second gate electrode; and a capacitor including one of the second source electrode and the second drain electrode, the second gate insulating layer, and an electrode provided to overlap with one of the second source electrode and the second drain electrode over the second gate insulating layer are provided. The first gate electrode and one of the second source electrode and the second drain electrode are electrically connected to each other.

Owner:SEMICON ENERGY LAB CO LTD

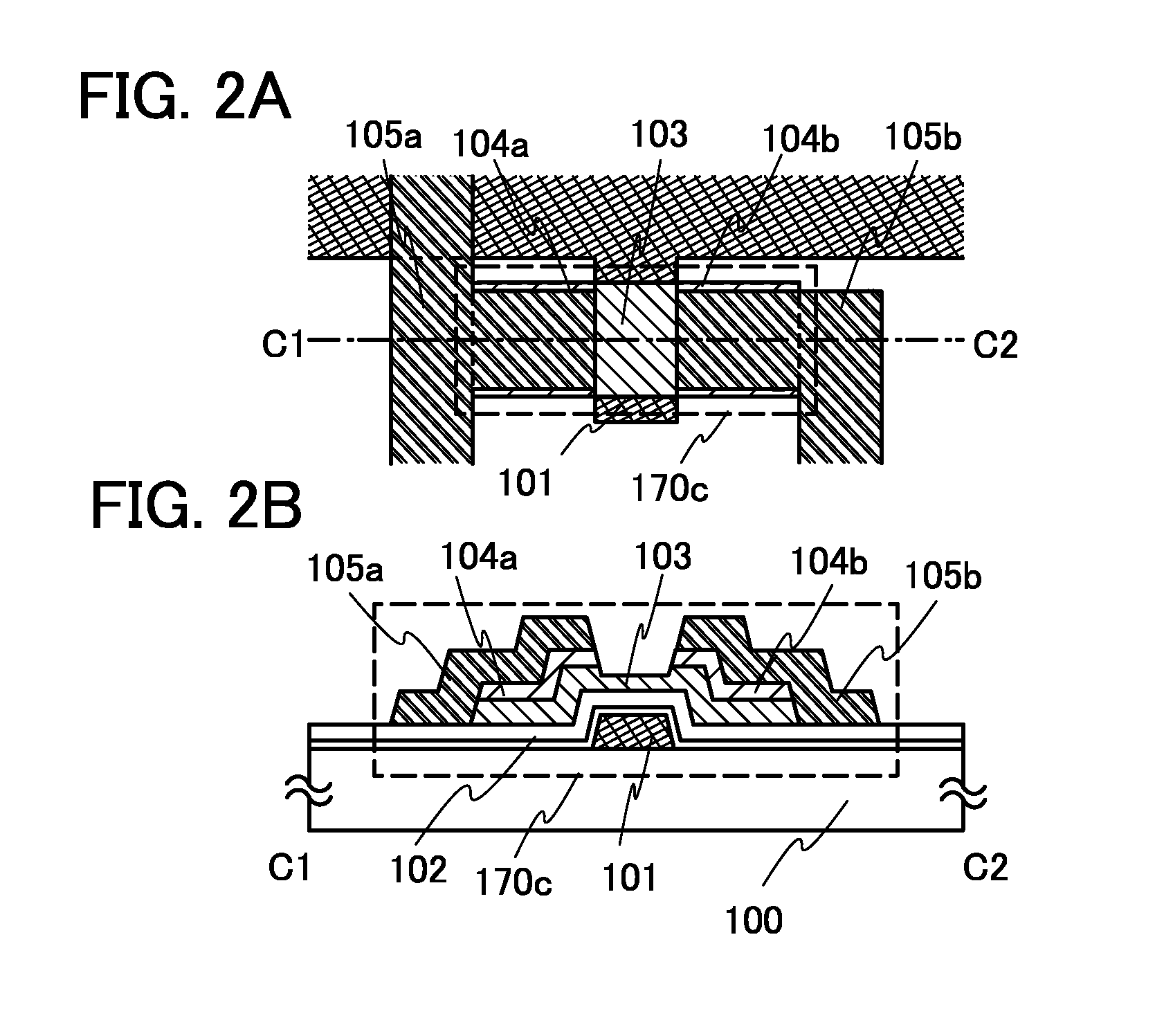

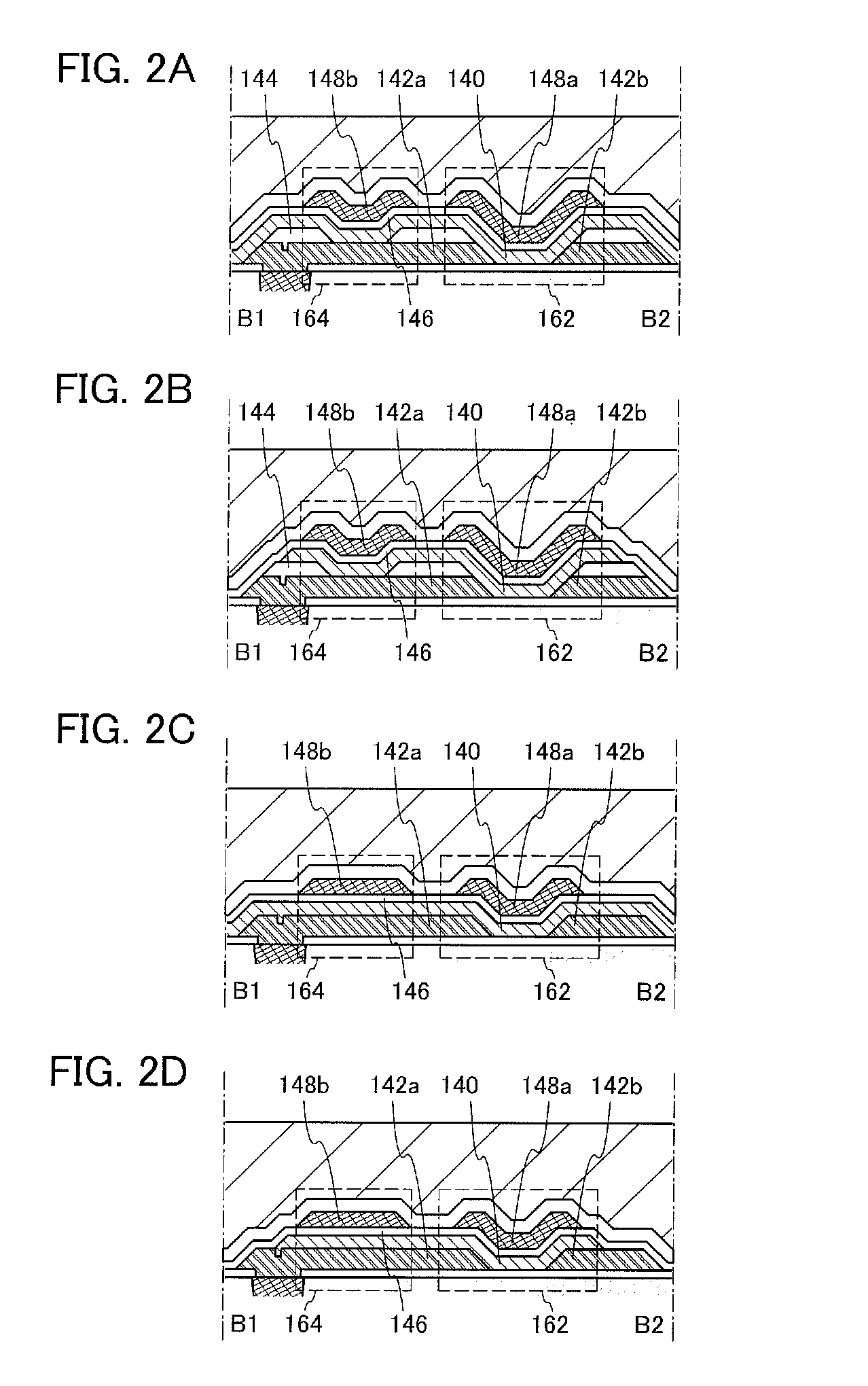

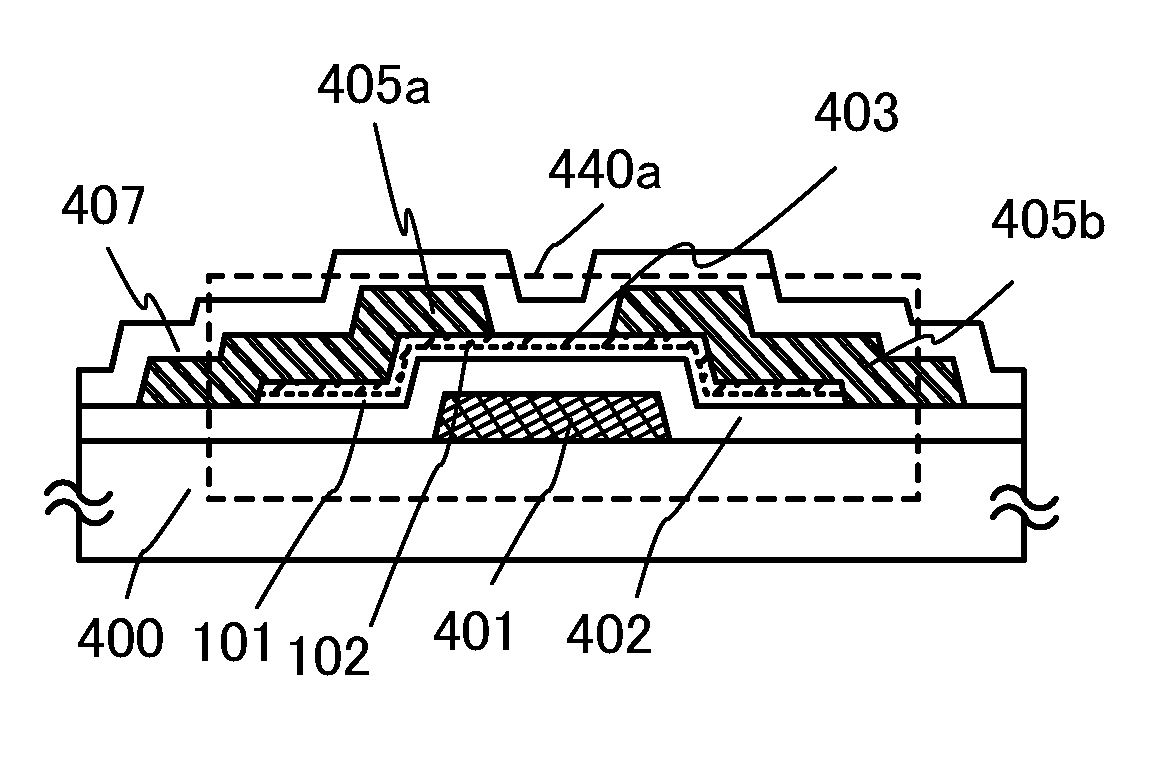

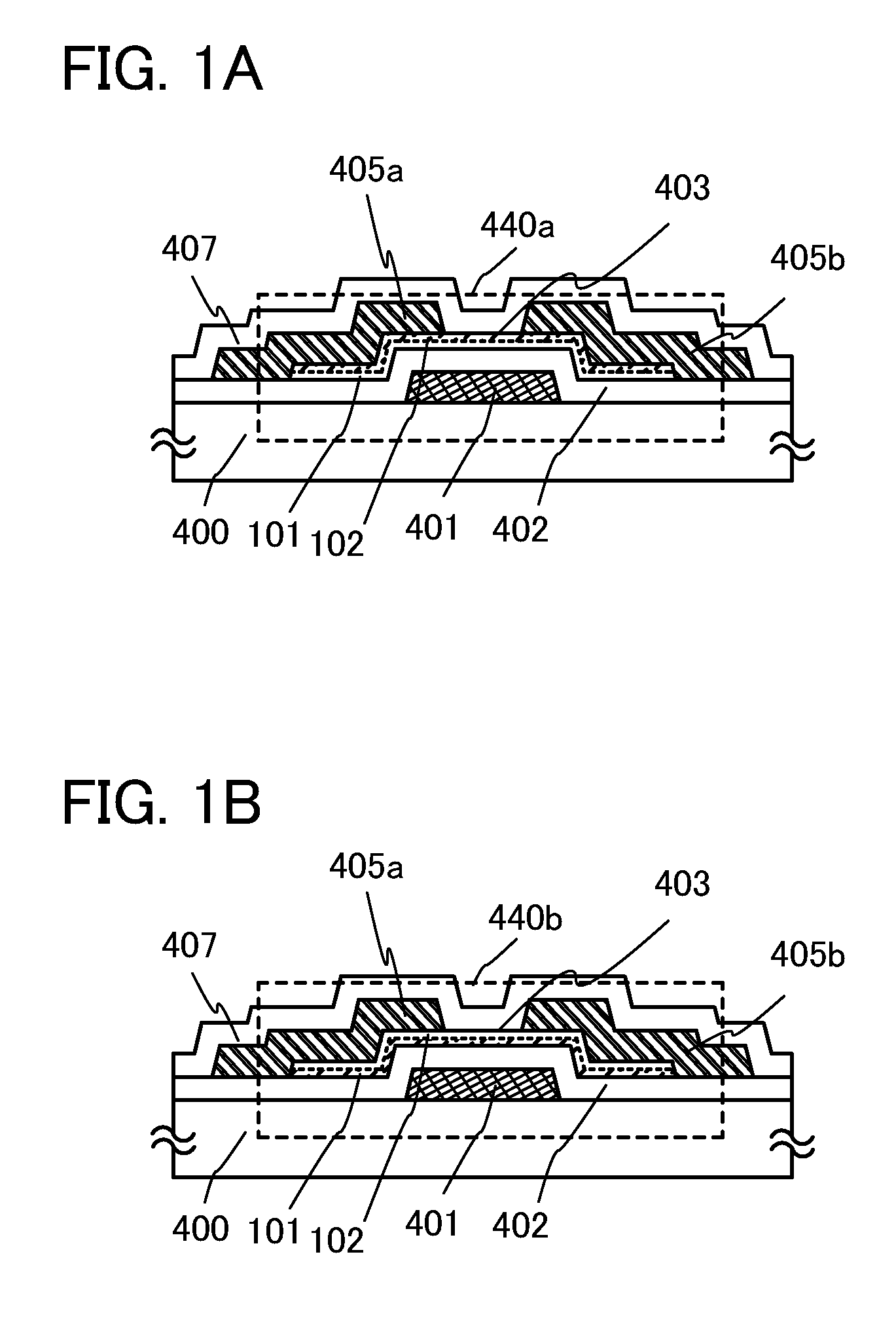

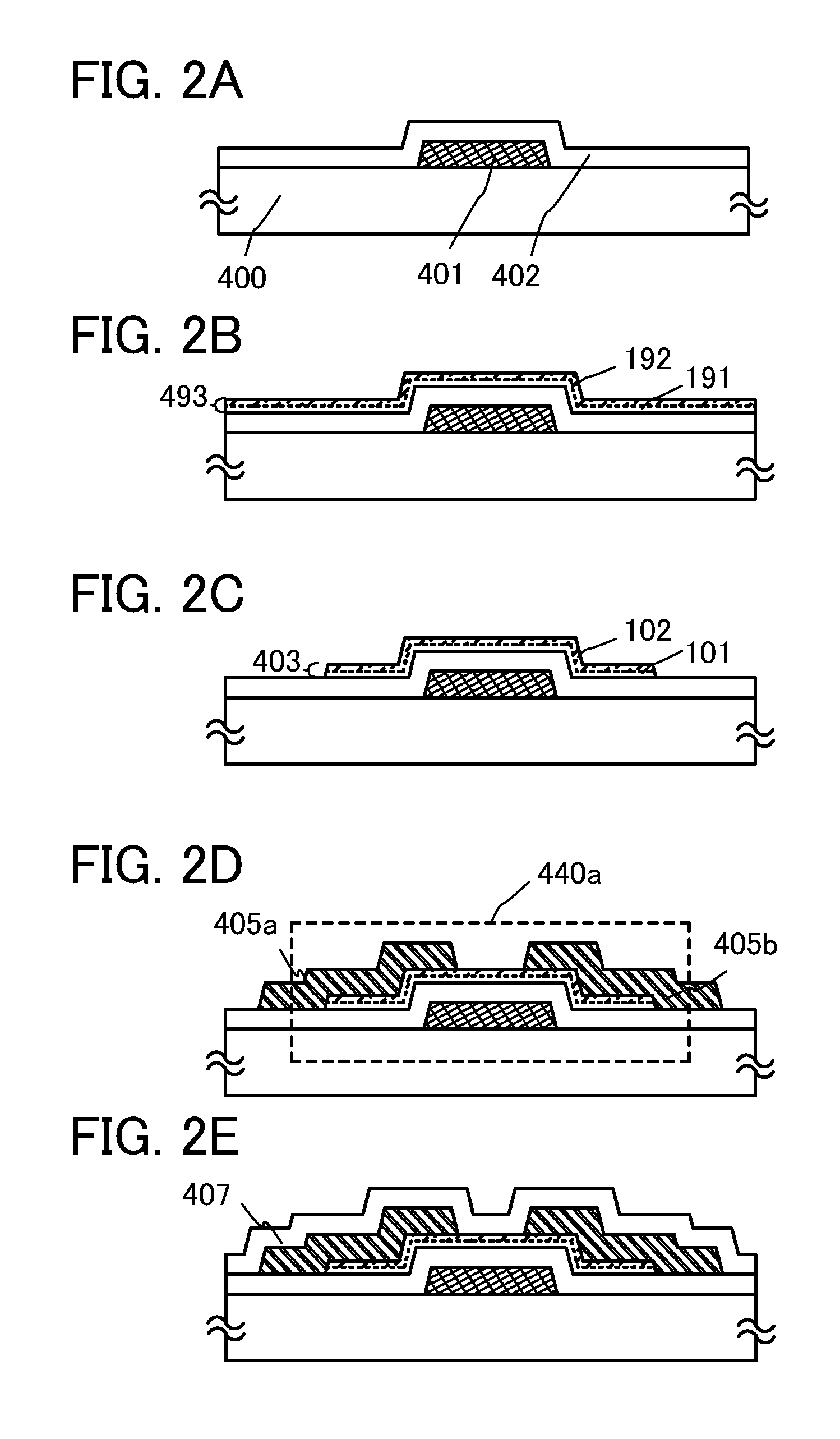

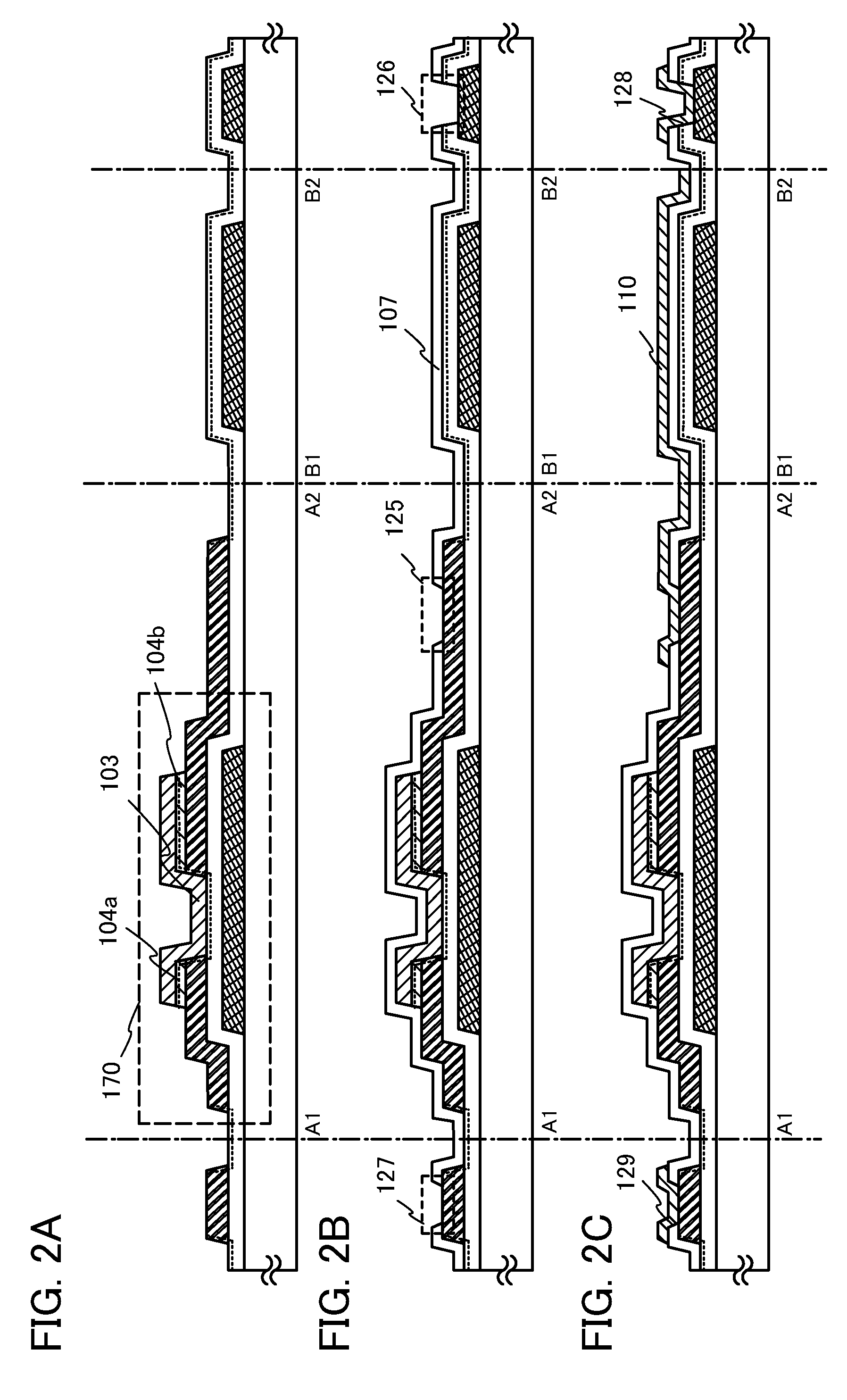

Semiconductor device and manufacturing method thereof

ActiveUS20130009219A1High performanceHigh accuracyTransistorElectroluminescent light sourcesOxide semiconductorBand gap

Provided are a transistor which has electrical characteristics requisite for its purpose and uses an oxide semiconductor layer and a semiconductor device including the transistor. In the bottom-gate transistor in which at least a gate electrode layer, a gate insulating film, and the semiconductor layer are stacked in this order, an oxide semiconductor stacked layer including at least two oxide semiconductor layers whose energy gaps are different from each other is used as the semiconductor layer. Oxygen and / or a dopant may be added to the oxide semiconductor stacked layer.

Owner:SEMICON ENERGY LAB CO LTD

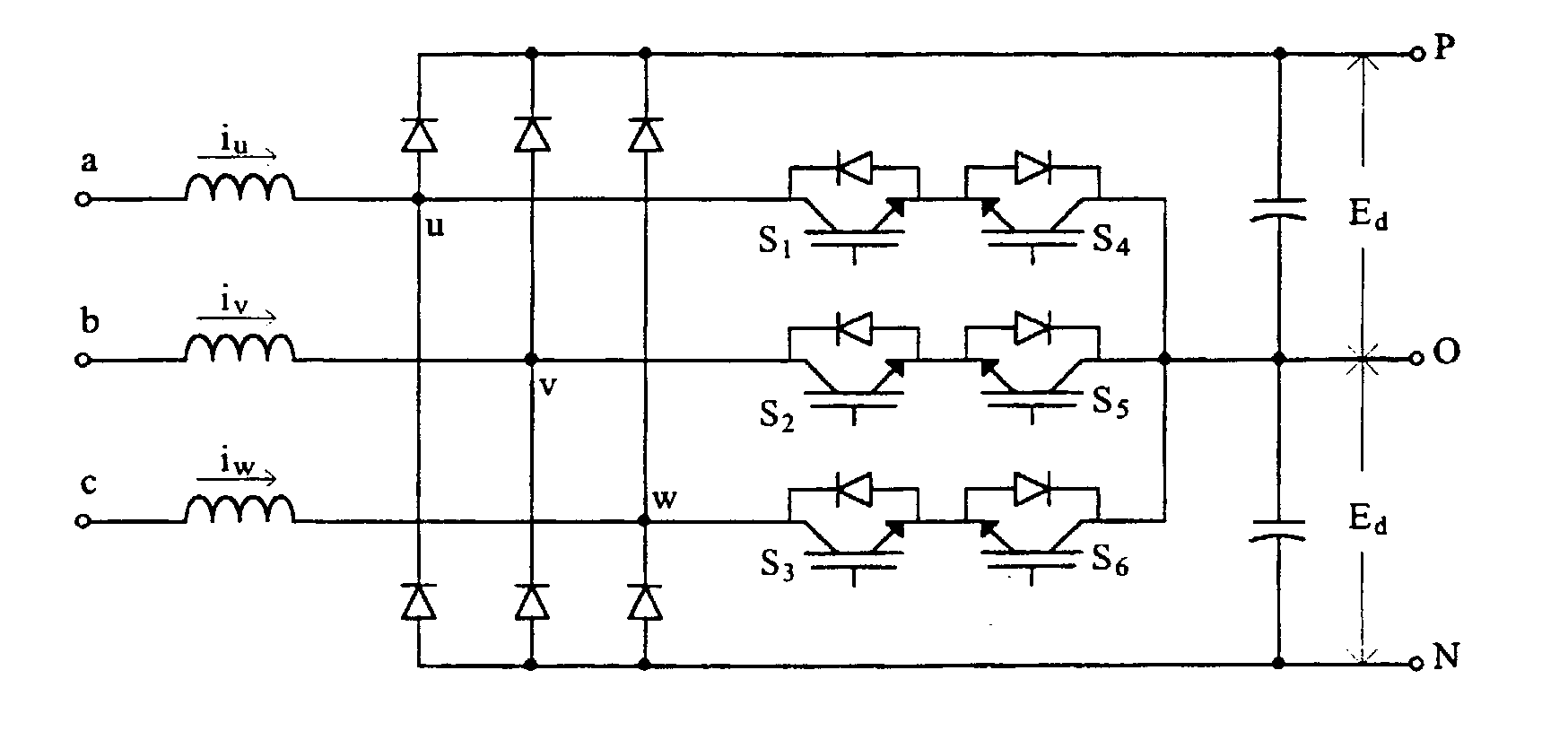

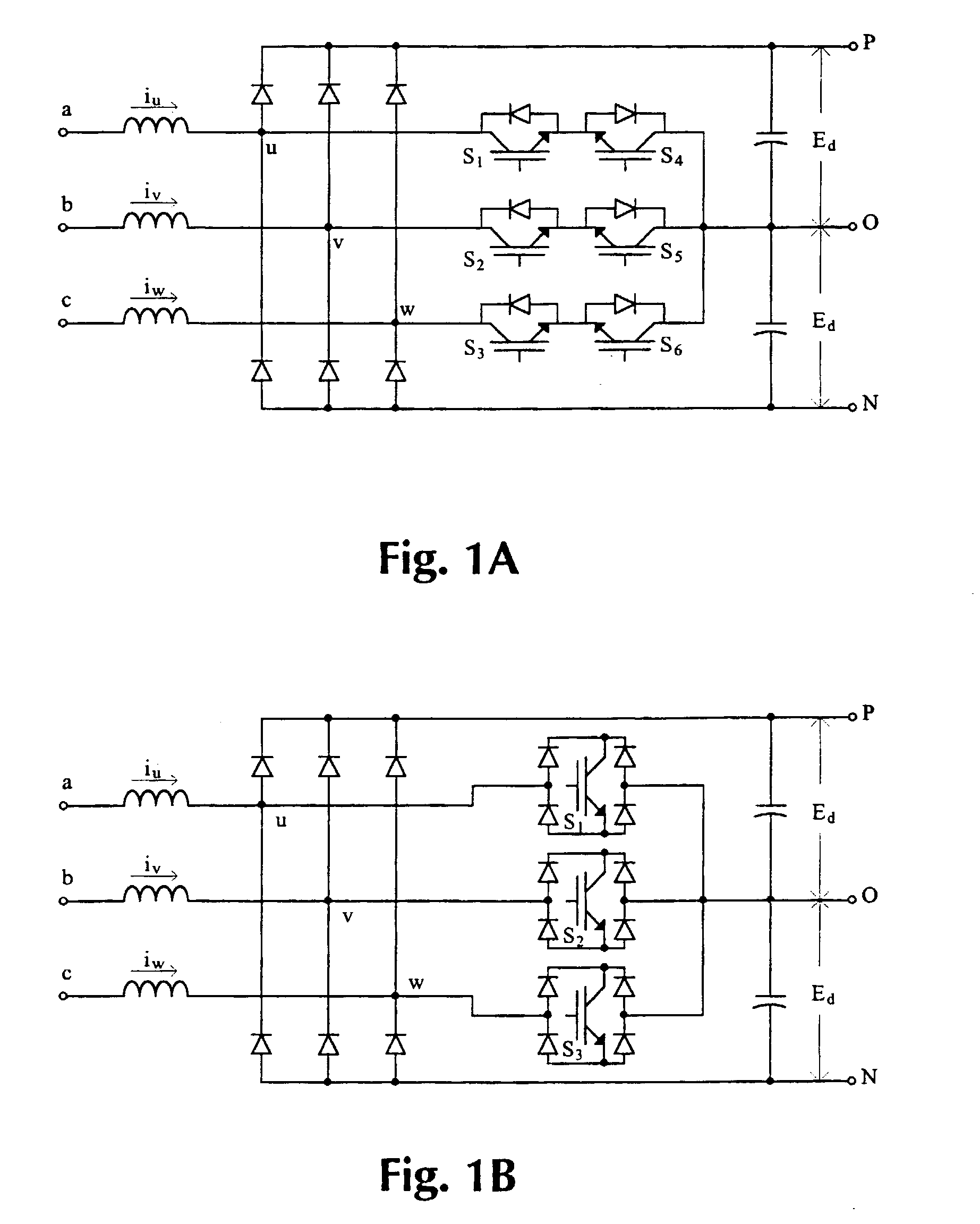

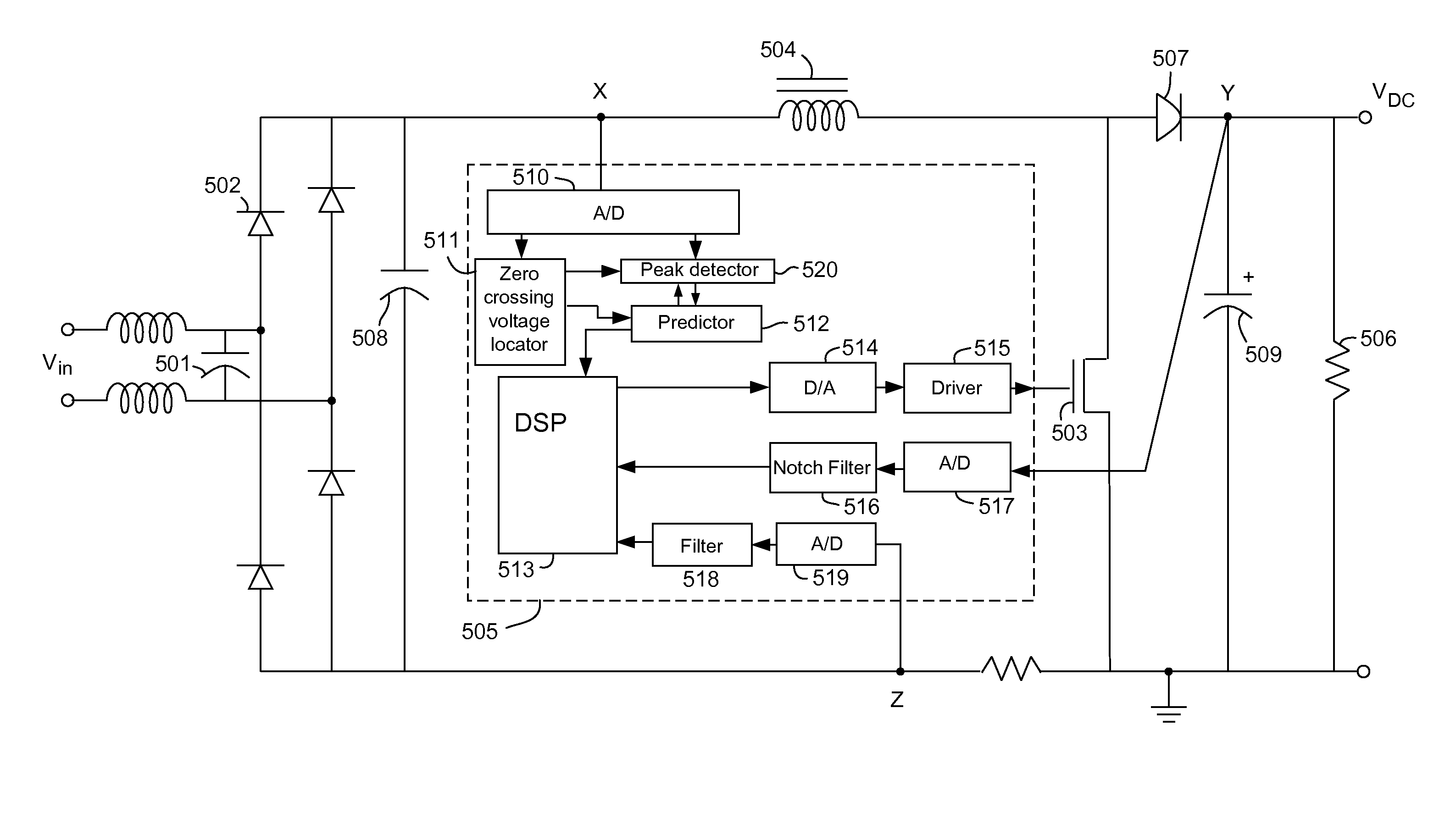

Method and control circuitry for a three-phase three-level boost-type rectifier

InactiveUS20030128563A1Easy to analyzePoor waveform qualityAc-dc conversion without reversalEfficient power electronics conversionThree levelDynamic balance

A synchronized control method for a three-phase three-level boost-type rectifier with reduced input current ripple and balanced output voltages is disclosed. The proposed control allows simplifying the control circuit as much as possible without compromising the rectifier performance. In fact, besides simplicity, the control method featured synchronized command signals to de switching devices, minimized input current ripple, full controllability of the output voltage, dynamic balance of the output center point, constant switching frequency, simplified design of EMC filters, good transient and steady state performance, and low cost. The invention described first the most important configurations that the three-phase three-level boost-type rectifier may assume and studied the converter's operation. The concept involved for output voltage, input current, neutral point balance and control system design was presented.

Owner:VERTIV CORP

Method for manufacturing semiconductor device

InactiveUS20130203214A1Effective diffusionTotal current dropTransistorSolid-state devicesDevice materialPhysical chemistry

To improve productivity of a transistor that includes an oxide semiconductor and has good electrical characteristics. In a top-gate transistor including a gate insulating film and a gate electrode over an oxide semiconductor film, a metal film is formed over the oxide semiconductor film, oxygen is added to the metal film to form a metal oxide film, and the metal oxide film is used as a gate insulating film. After an oxide insulating film is formed over the oxide semiconductor film, a metal film may be formed over the oxide insulating film. Oxygen is added to the metal film to form a metal oxide film and added also to the oxide semiconductor film or the oxide insulating film.

Owner:SEMICON ENERGY LAB CO LTD

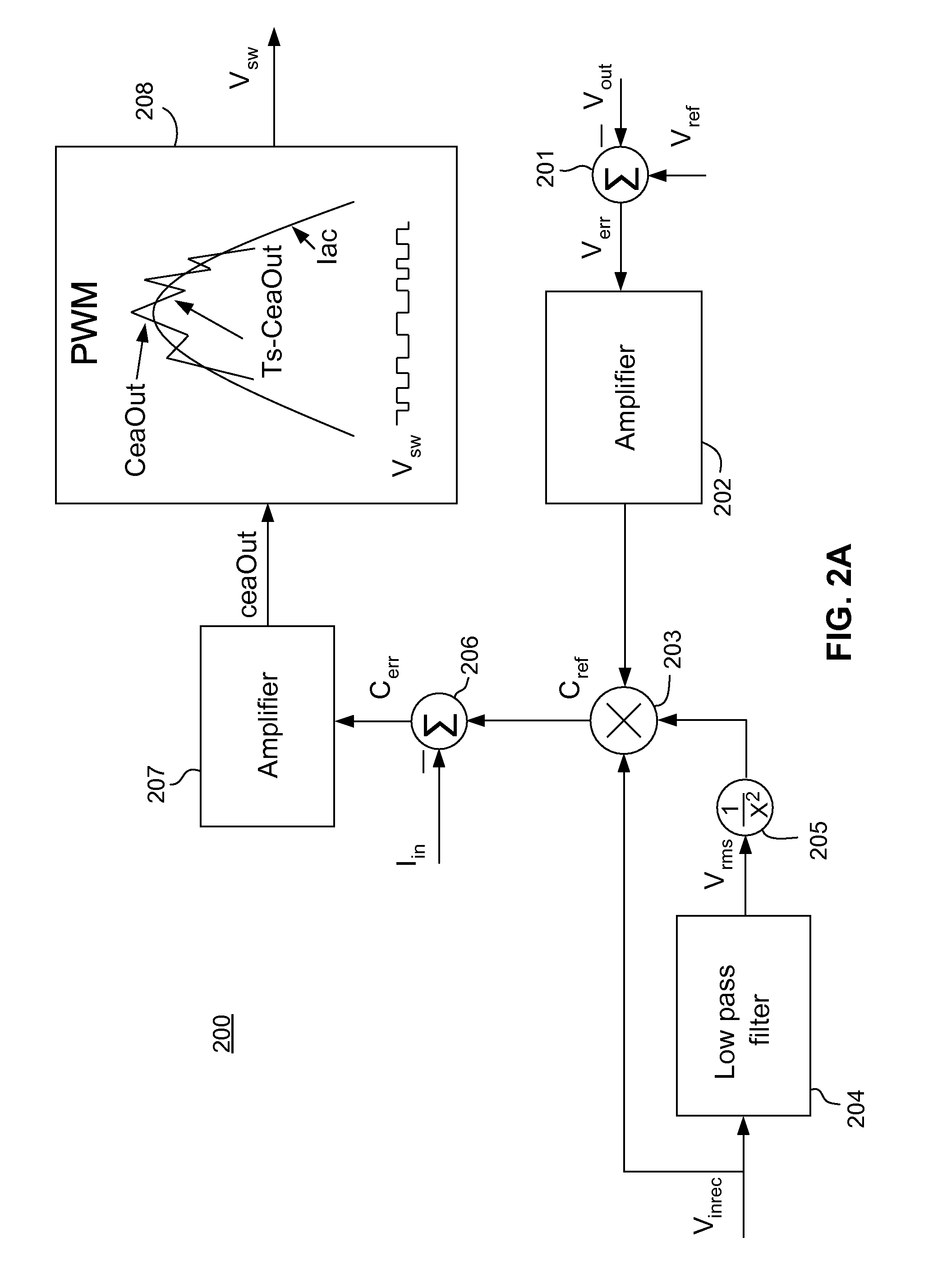

Power factor correction boost converter with continuous, discontinuous, or critical mode selection

ActiveUS7733678B1Small sizeReduce Harmonic DistortionAc-dc conversion without reversalEfficient power electronics conversionConstant powerAverage current

In a method and apparatus for controlling power factor correction in mixed operation modes, a frequency of the input voltage is obtained by detecting the zero crossing points of the input voltage. A peak of the input voltage is obtained by detecting input voltage with 90 degree phase. Thus, the present invention predicts the input voltage by its frequency and peak and the characteristic of the sine wave. A digital signal processor computes the duty and frequency of a boost switch, switching the operation mode of the boost converter among continuous mode, critical mode and discontinuous mode according to input voltage or the load. According to another aspect, the operation is switched to critical mode from the average current mode when a zero current is detected before the charging and recharging cycle of the boost switch is finished. Overcurrent protection may be achieved by controlling current in response to detected voltage to provide a substantially constant power level. The overcurrent protection may be adaptive in nature.

Owner:MARVELL ASIA PTE LTD

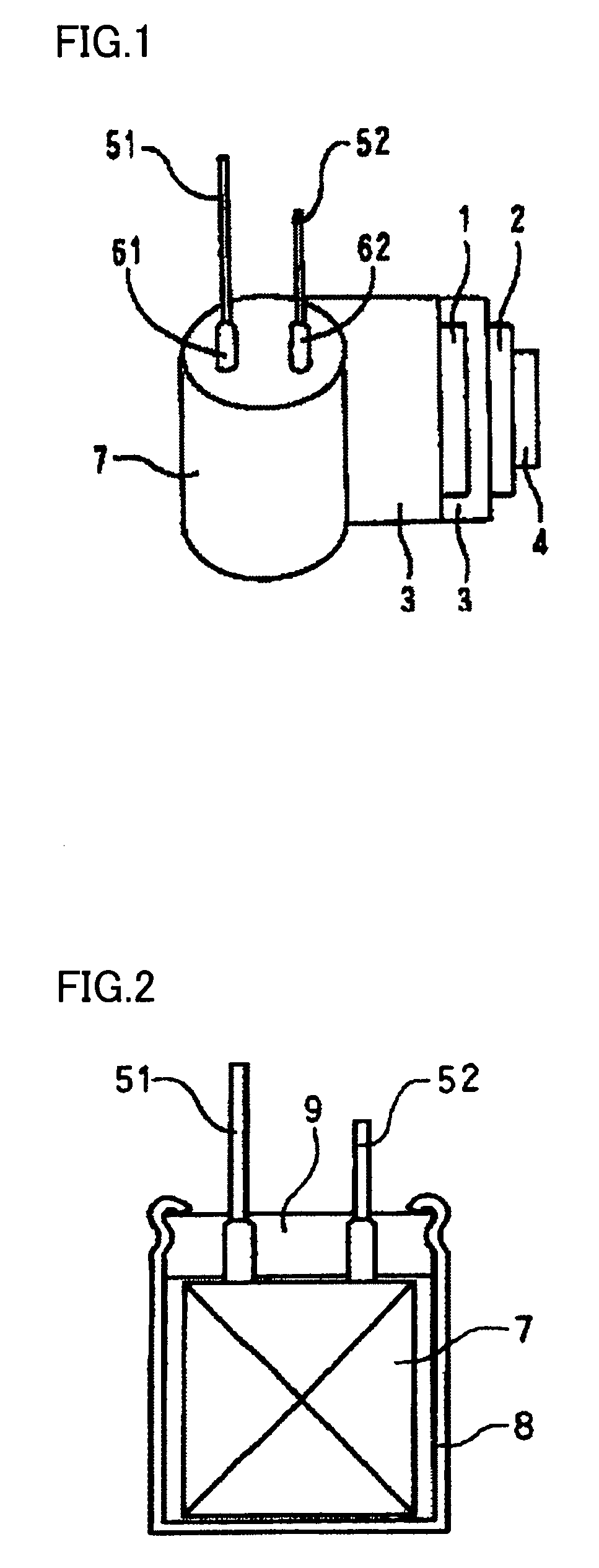

Method of manufacturing electrolytic capacitor and electrolytic capacitor

ActiveUS7497879B2Improve pressure resistanceSmall currentHybrid capacitor electrolytesSolid electrolytic capacitorsDielectricElectrolysis

A method of manufacturing an electrolytic capacitor including the following steps as well as an electrolytic capacitor manufactured by the method are provided. The method includes: a dispersion impregnation step of impregnating, with a dispersion containing electrically conductive solid particles or powder and a solvent, a capacitor element having an anode foil with a dielectric coating film formed thereon and an opposite cathode foil that are wound with a separator interposed therebetween; a dry step of evaporating the solvent after the dispersion impregnation step to form an electrically conductive solid layer on a surface of the dielectric coating film; and an electrolytic solution impregnation step of impregnating a gap in the electrically conductive solid layer with an electrolytic solution. Accordingly, an electrolytic capacitor that can be manufactured more easily that is excellent in voltage proofing property and that has a lower ESR and a lower leakage current is provided.

Owner:SANYO ELECTRIC CO LTD +1

Semiconductor device

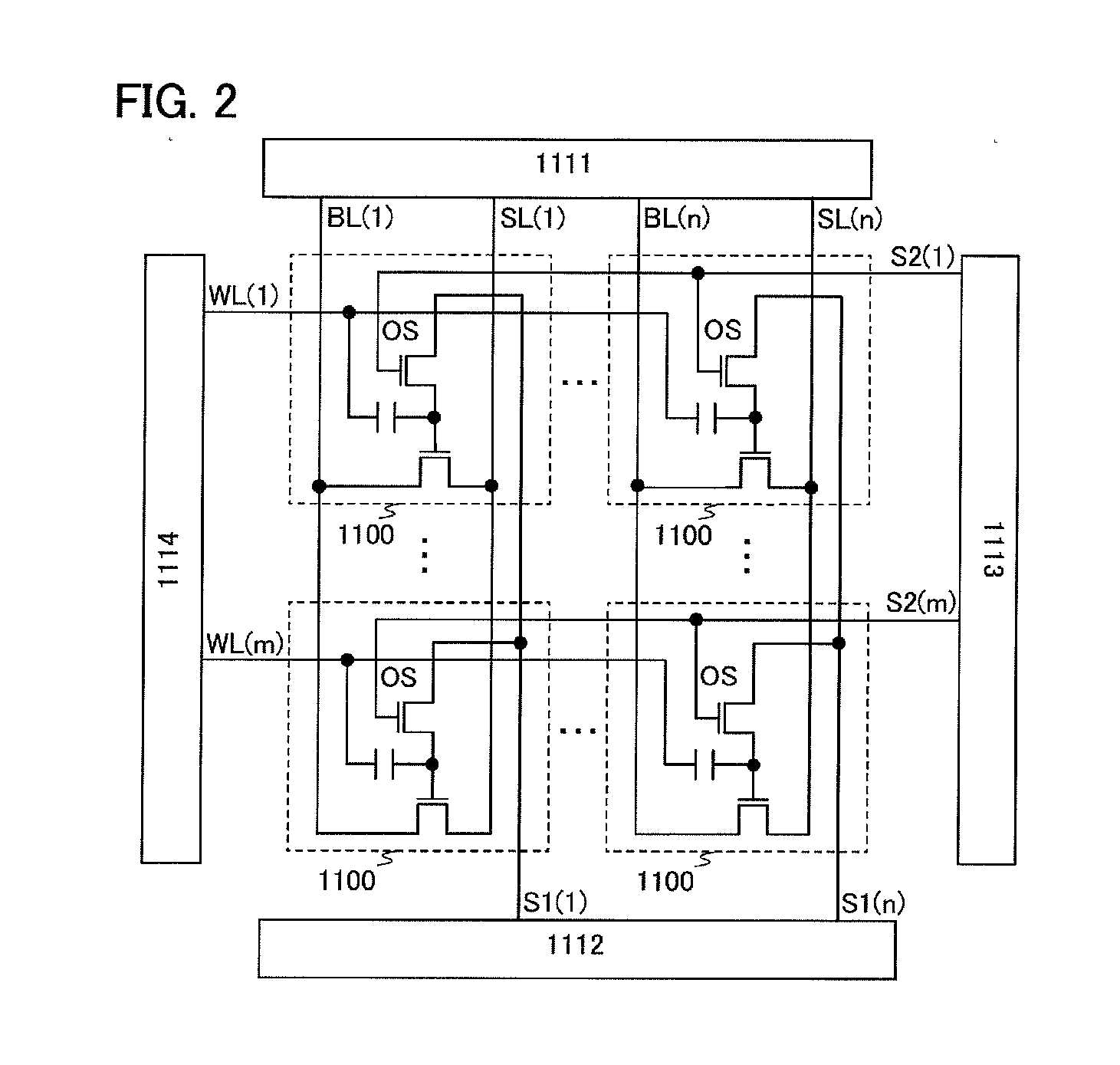

ActiveUS20110157961A1Reduce power consumptionFrequency of refresh can be lowTransistorSolid-state devicesPower semiconductor deviceDriver circuit

The semiconductor device includes a source line, a bit line, a first signal line, a second signal line, a word line, memory cells connected in parallel between the source line and the bit line, a first driver circuit electrically connected to the source line and the bit line, a second driver circuit electrically connected to the first signal line, a third driver circuit electrically connected to the second signal line, and a fourth driver circuit electrically connected to the word line. The memory cell includes a first transistor including a first gate electrode, a first source electrode, and a first drain electrode, a second transistor including a second gate electrode, a second source electrode, and a second drain electrode, and a capacitor. The second transistor includes an oxide semiconductor material.

Owner:SEMICON ENERGY LAB CO LTD

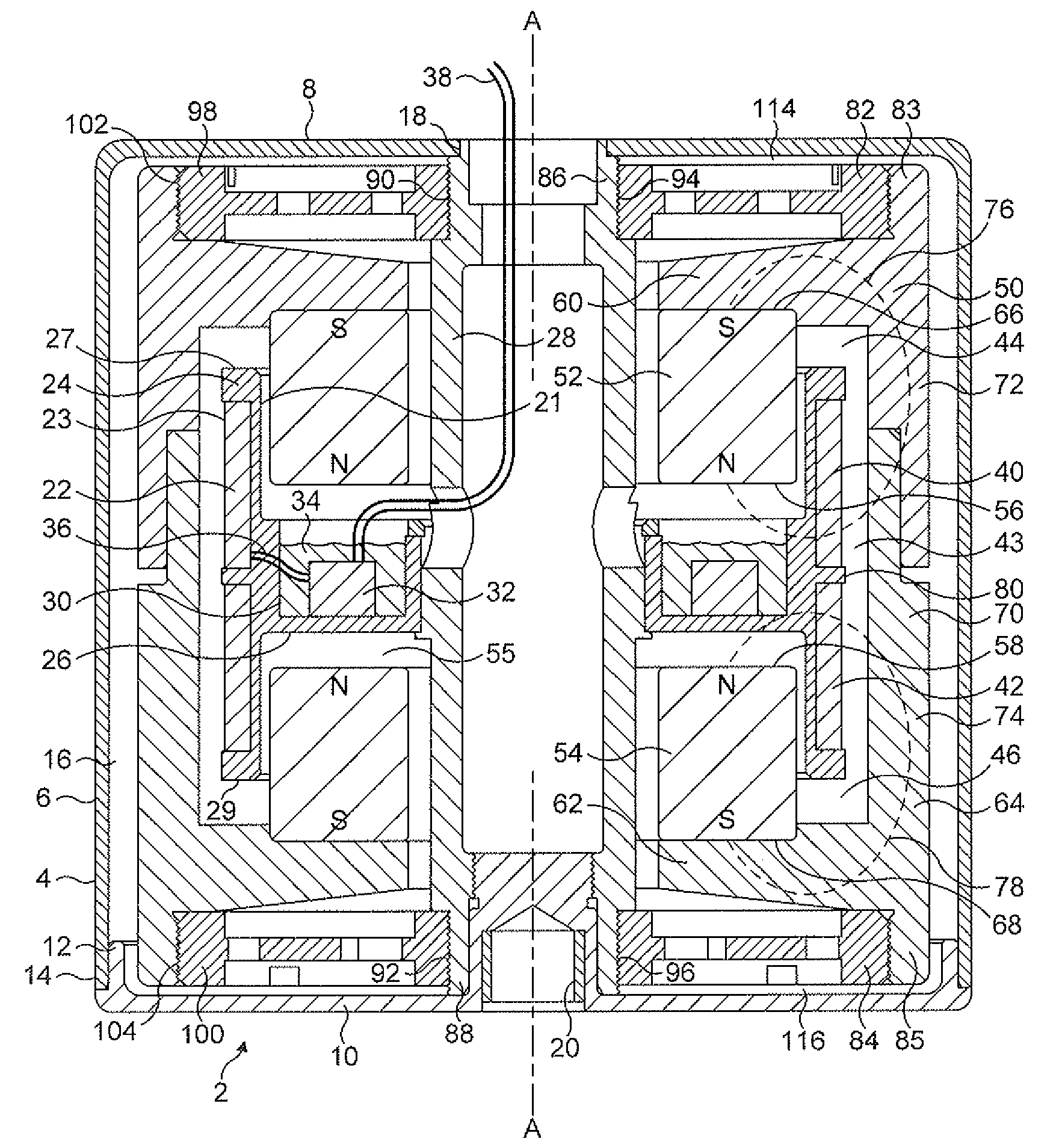

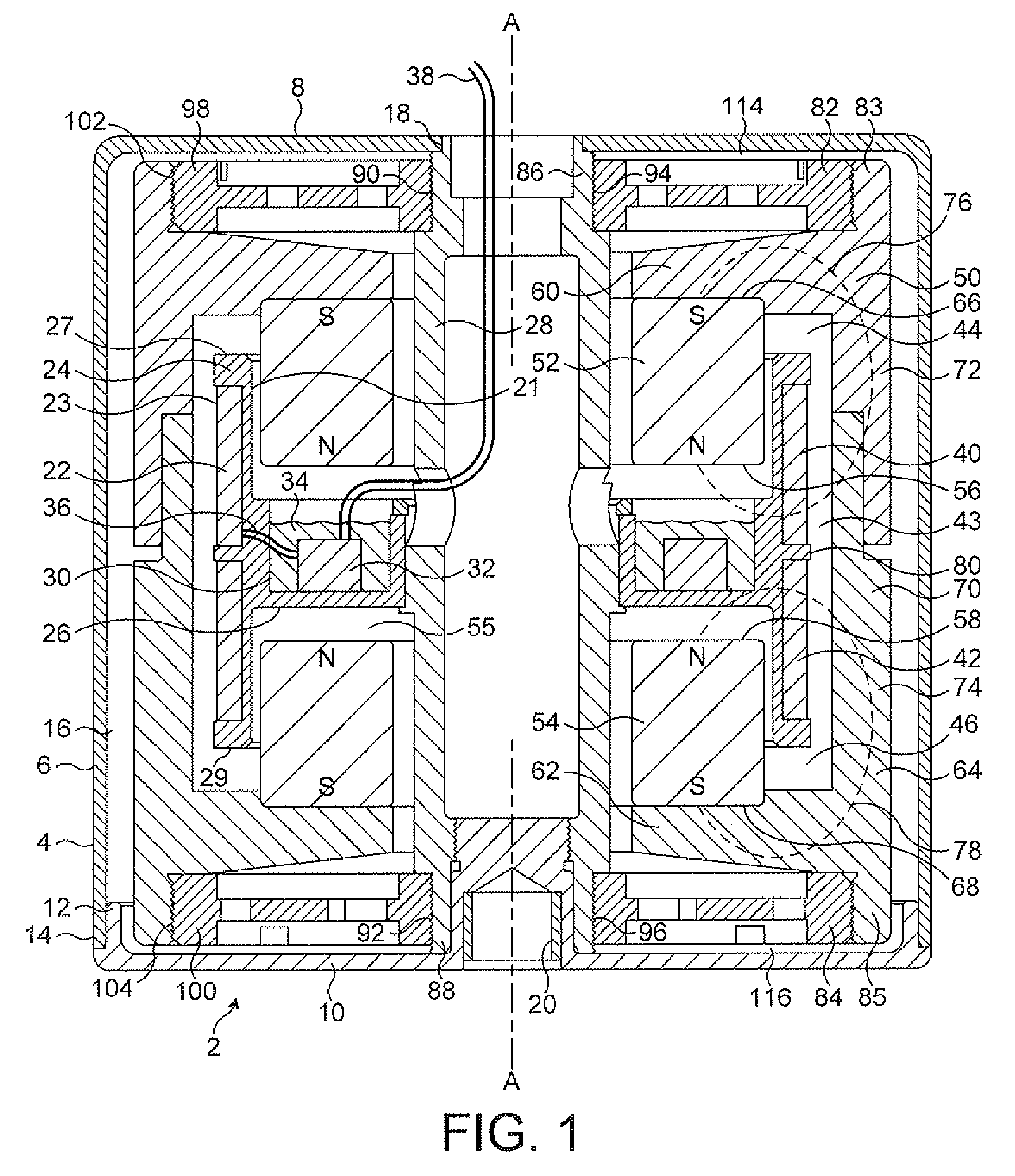

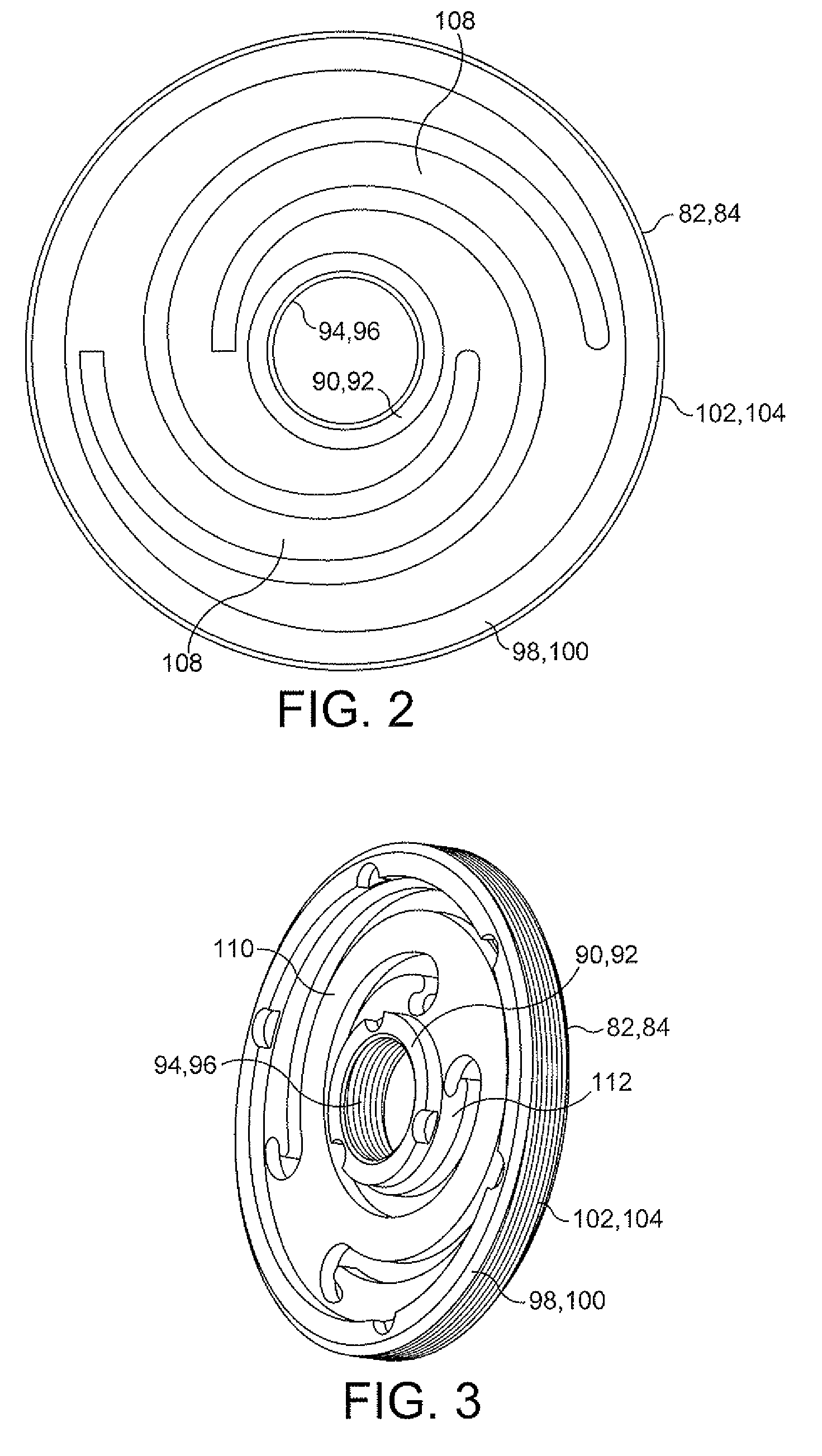

Electromechanical generator for converting mechanical vibrational energy into electrical energy

ActiveUS7586220B2Quality improvementSmall currentReciprocating/oscillating/vibrating magnetic circuit partsMachines/enginesFixed positionVibrational energy

An electromechanical generator for converting mechanical vibrational energy into electrical energy, the electromechanical generator comprising a housing, an electrically conductive coil assembly fixedly mounted in the housing, the coil assembly having radially inner and outer sides, and upper and lower edges, thereof, a mount for the coil assembly extending inwardly of the radially inner side for fixing the coil assembly in a fixed position in the housing, a magnetic core assembly movably mounted in the housing for linear vibrational motion along an axis, and a biasing device mounted between the housing and the magnetic core assembly to bias the magnetic core assembly in opposed directions along the axis towards a central position, wherein the magnetic core assembly encloses the electrically conductive coil assembly on the radially outer side and on the upper and lower edges, and on a part of the radially inner side, the magnetic core assembly having a gap on a radially inner portion thereof through which the mount extends, and the radially inner portion including two opposed magnets spaced along the axis.

Owner:HITACHI RAIL LTD +1

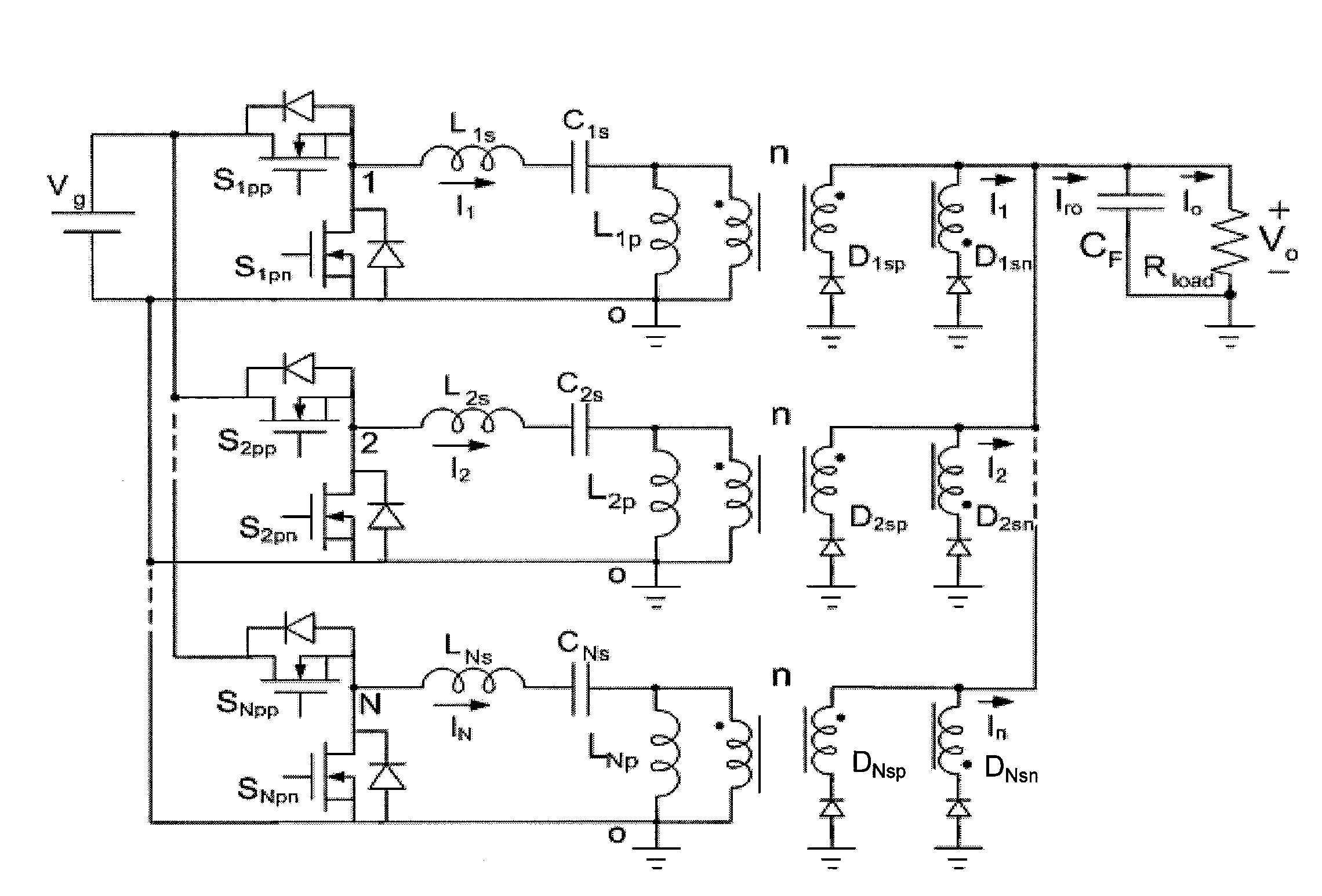

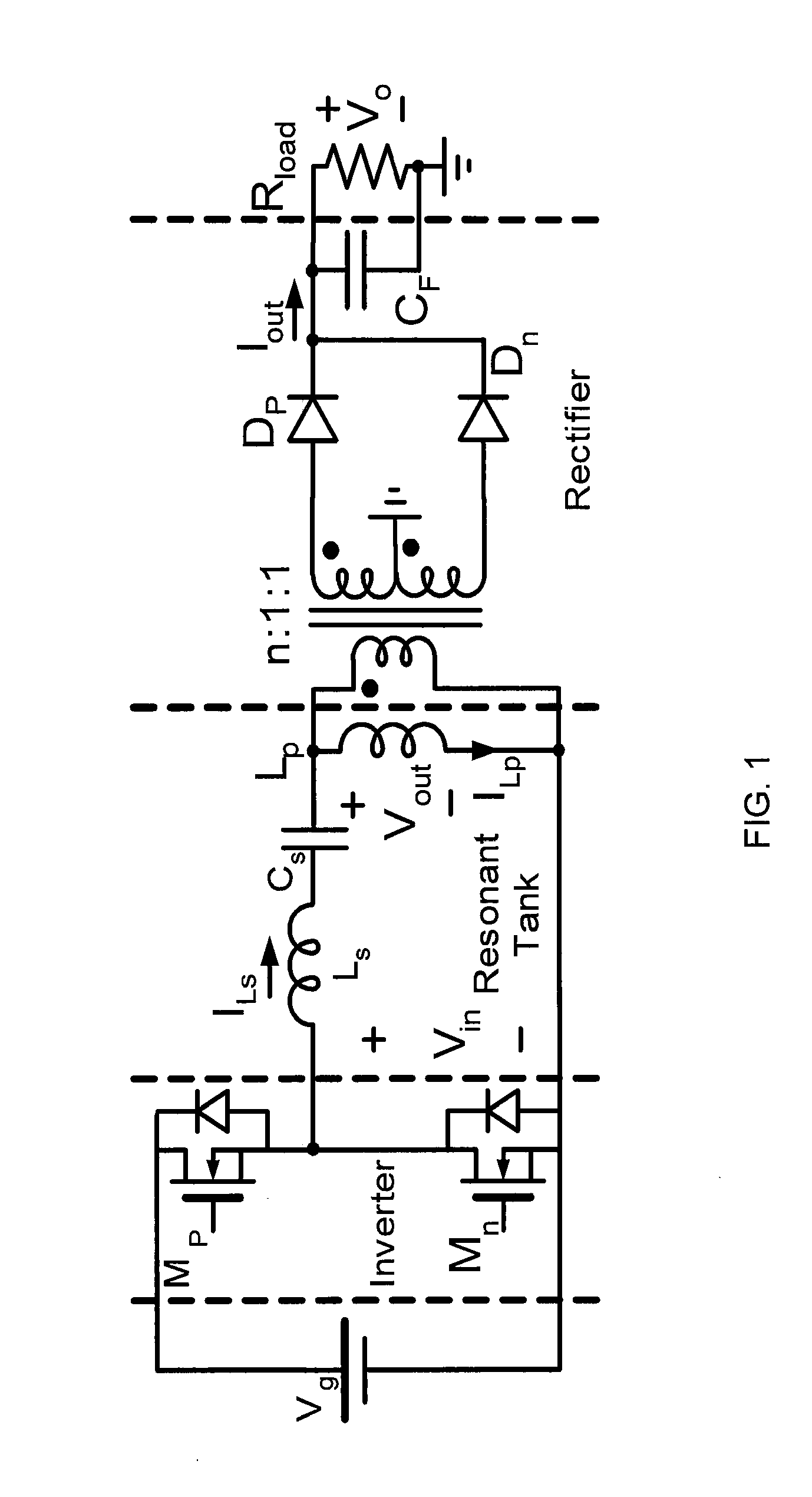

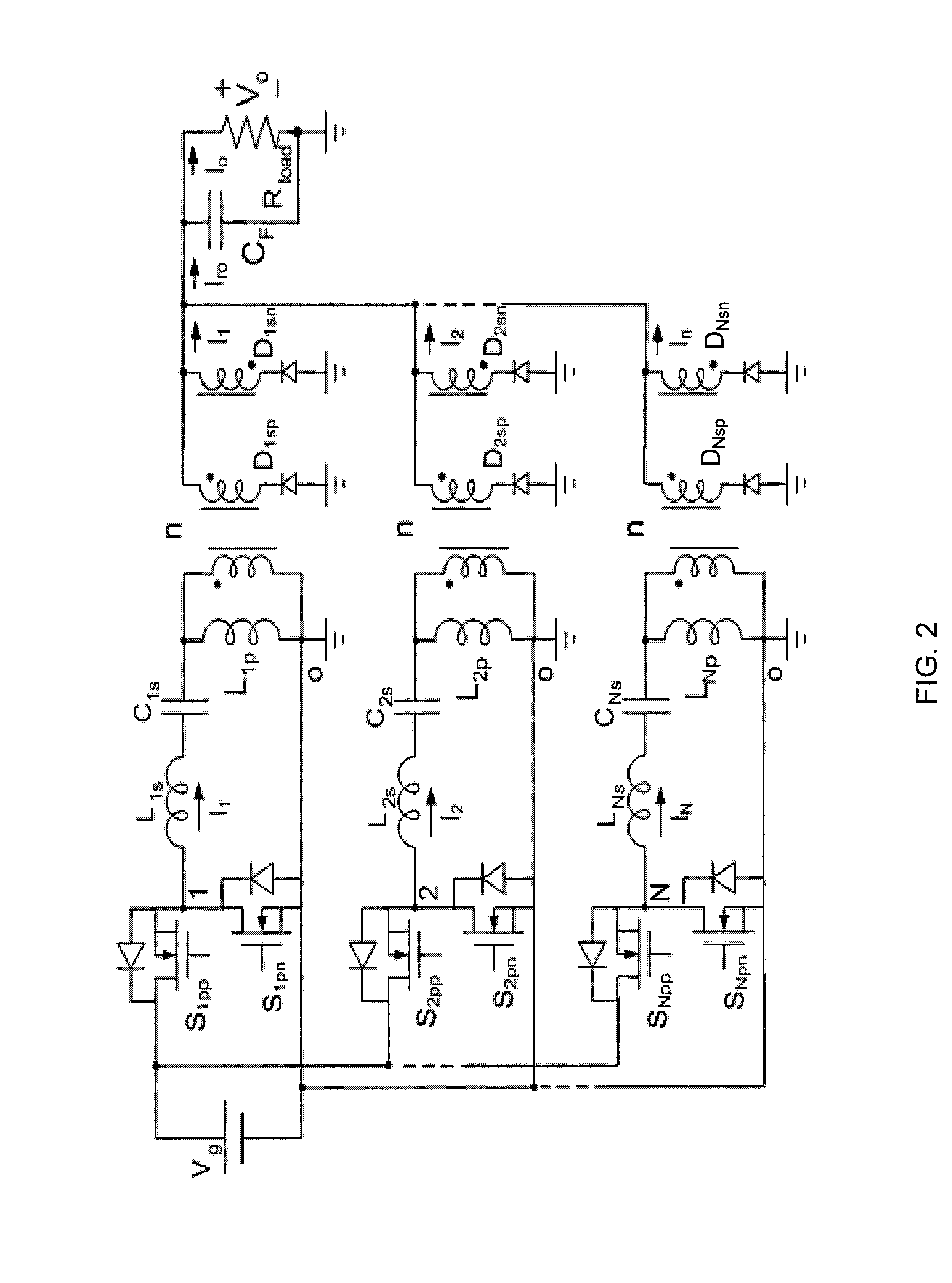

Multiphase resonant converter for dc-dc applications

ActiveUS20080298093A1Small currentImprove efficiencyAc-dc conversion without reversalEfficient power electronics conversionPhase shiftedEngineering

The various embodiments and example provided herein are generally directed to novel multiphase resonant converters. In an embodiment, a multiphase resonant converter comprises N unit resonant converters having inputs and outputs connected in parallel, respectively. Each unit converter comprises an inverter, a LLC series resonant tank, and a rectifier. In a preferred embodiment, the inverters of the N unit converters are driven by N drive signals phase-shifted 2π / N degrees apart. During operation, the current of the multiphase converter is shared among the unit converters, resulting in a smaller current in each unit converter. The smaller current in each unit converter reduces conduction losses, thereby increasing the efficiency of the multiphase converter. In addition, the smaller current in each unit converter reduces the amount of stress placed on individual components of the converter allowing for the use of lower tolerance components. Further, the multiphase converter has automatic current sharing ability.

Owner:RGT UNIV OF CALIFORNIA

Spin hall effect magnetic apparatus, method and applications

ActiveUS20150348606A1Improve efficiencySmall costRead-only memoriesDigital storageElectrical conductorSpin Hall effect

Owner:CORNELL UNIVERSITY

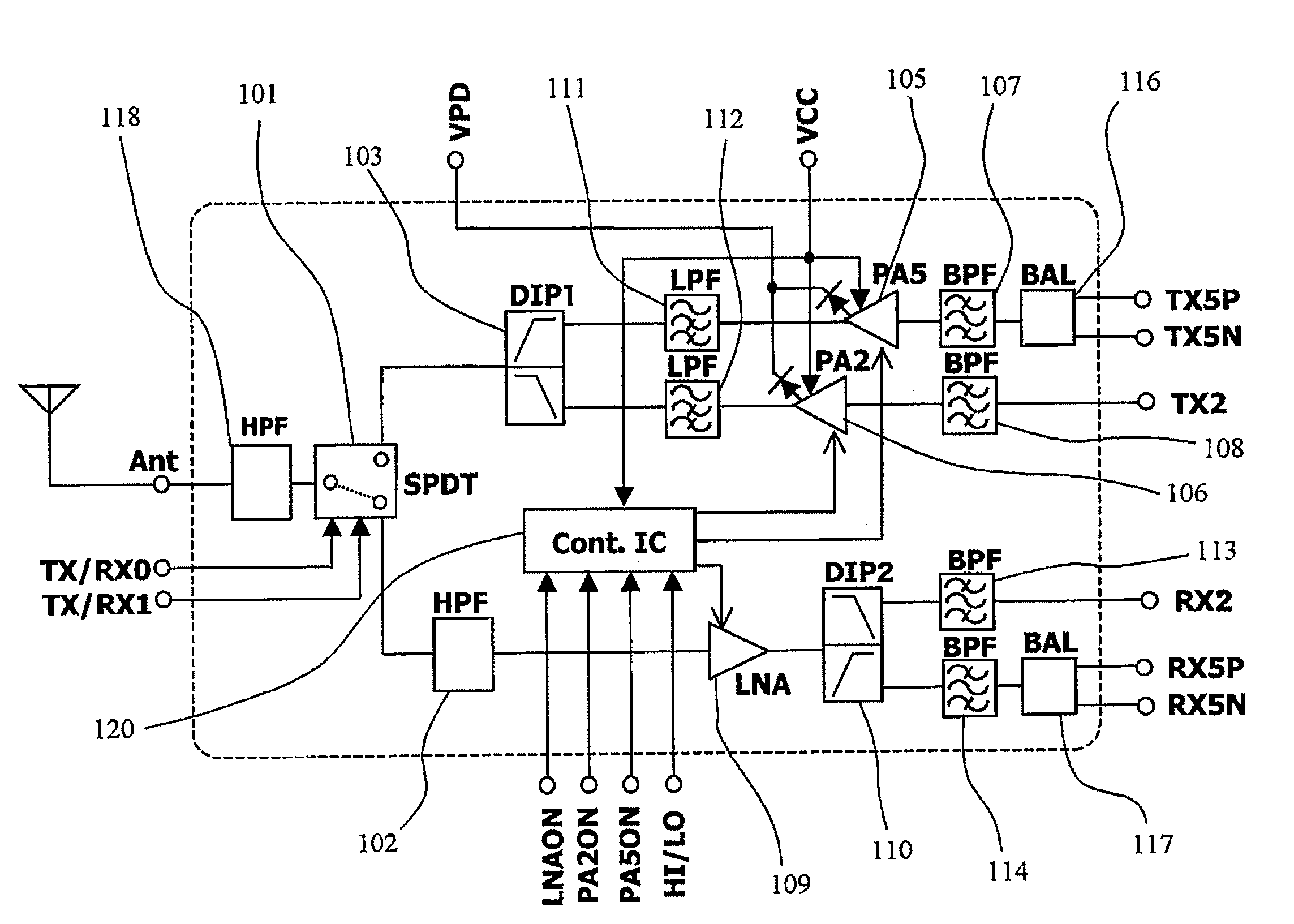

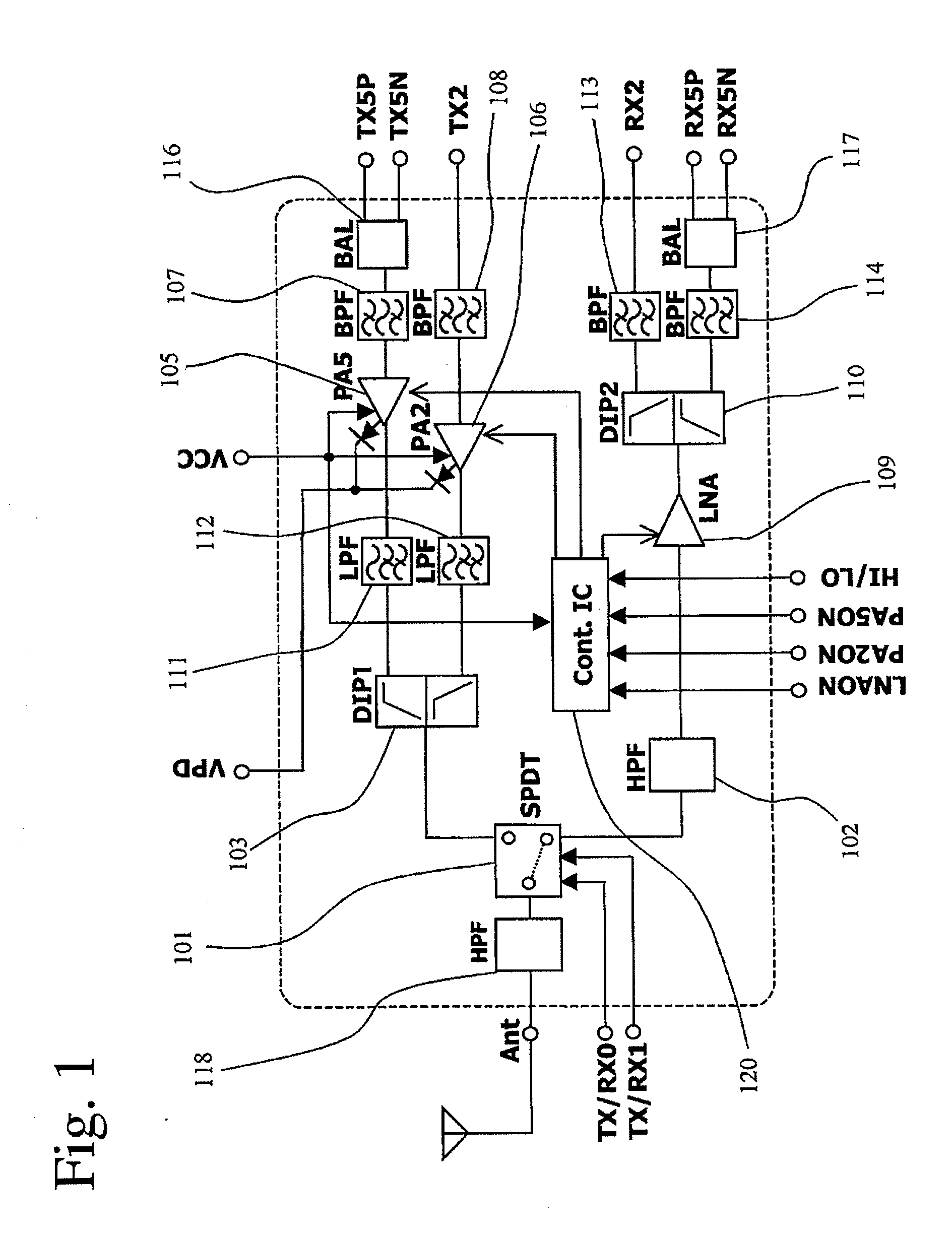

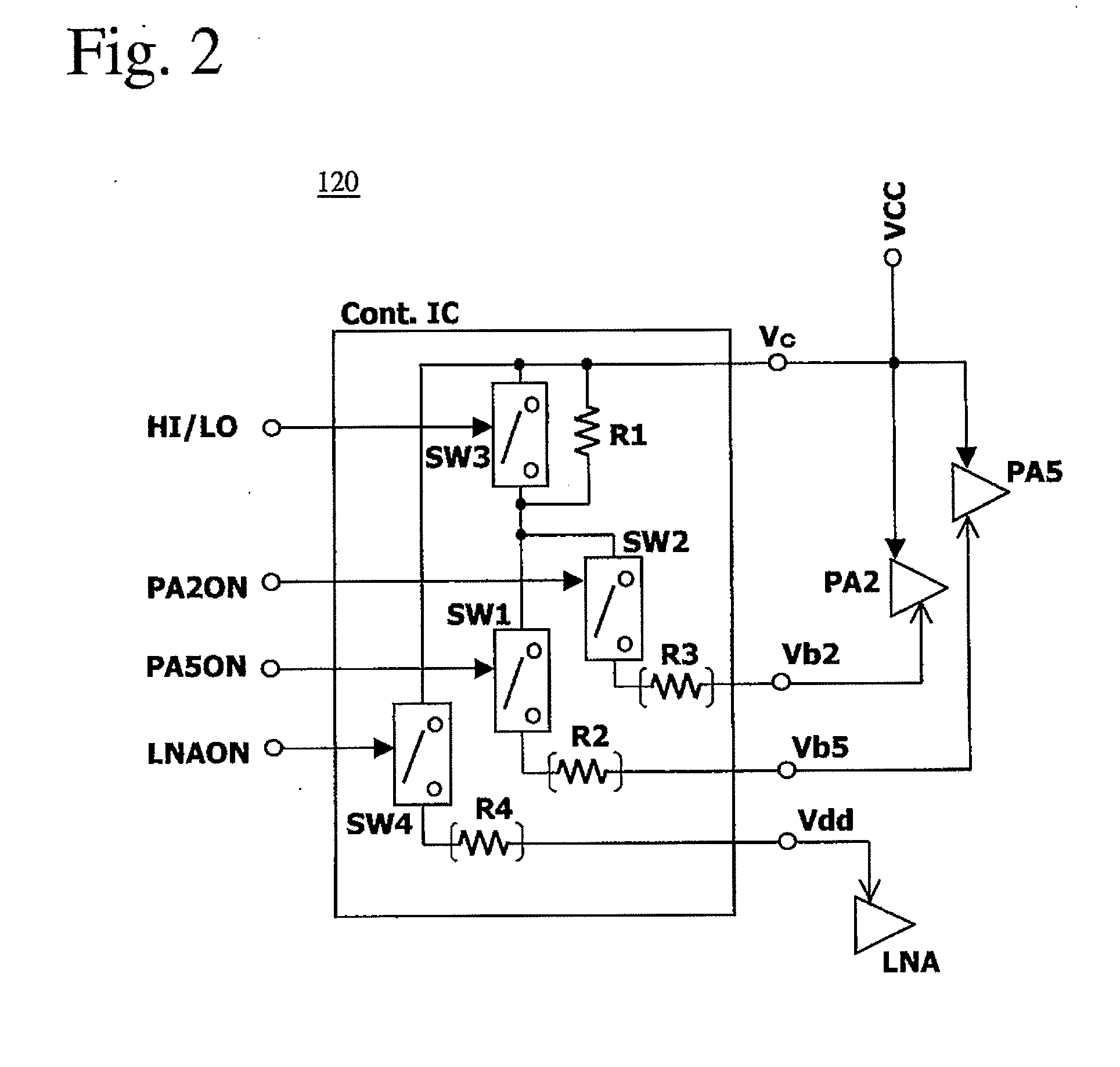

High-frequency circuit, high-frequency device and communications apparatus

ActiveUS20090207764A1Improve receiver sensitivityLow current consumptionSolid-state devicesTransmission path multiple useAudio power amplifierCommunication device

A high-frequency circuit for wireless communications selectively using a first frequency band and a second frequency band lower than the first frequency band, comprising an antenna terminal; first and second transmission terminals to which transmitting signals in the first and second frequency bands are input; first and second receiving terminals from which received signals in the first and second frequency bands are output; a diplexer circuit for branching a first-frequency-band-signal path and a second-frequency-band-signal path; a switch circuit for switching a path for a transmitting signal and a path for a received signal; a low-noise amplifier circuit disposed between the switch circuit and the second receiving terminal for amplifying a received signal in the second frequency band; and first and second filter circuits disposed between the antenna terminal and the low-noise amplifier circuit in this order from the antenna terminal, both filter circuits passing a received signal in the second frequency band but blocking a frequency band lower than the second frequency band, and the band blocked by the first filter circuit being lower than the band blocked by the second filter circuit.

Owner:HITACHI METALS LTD

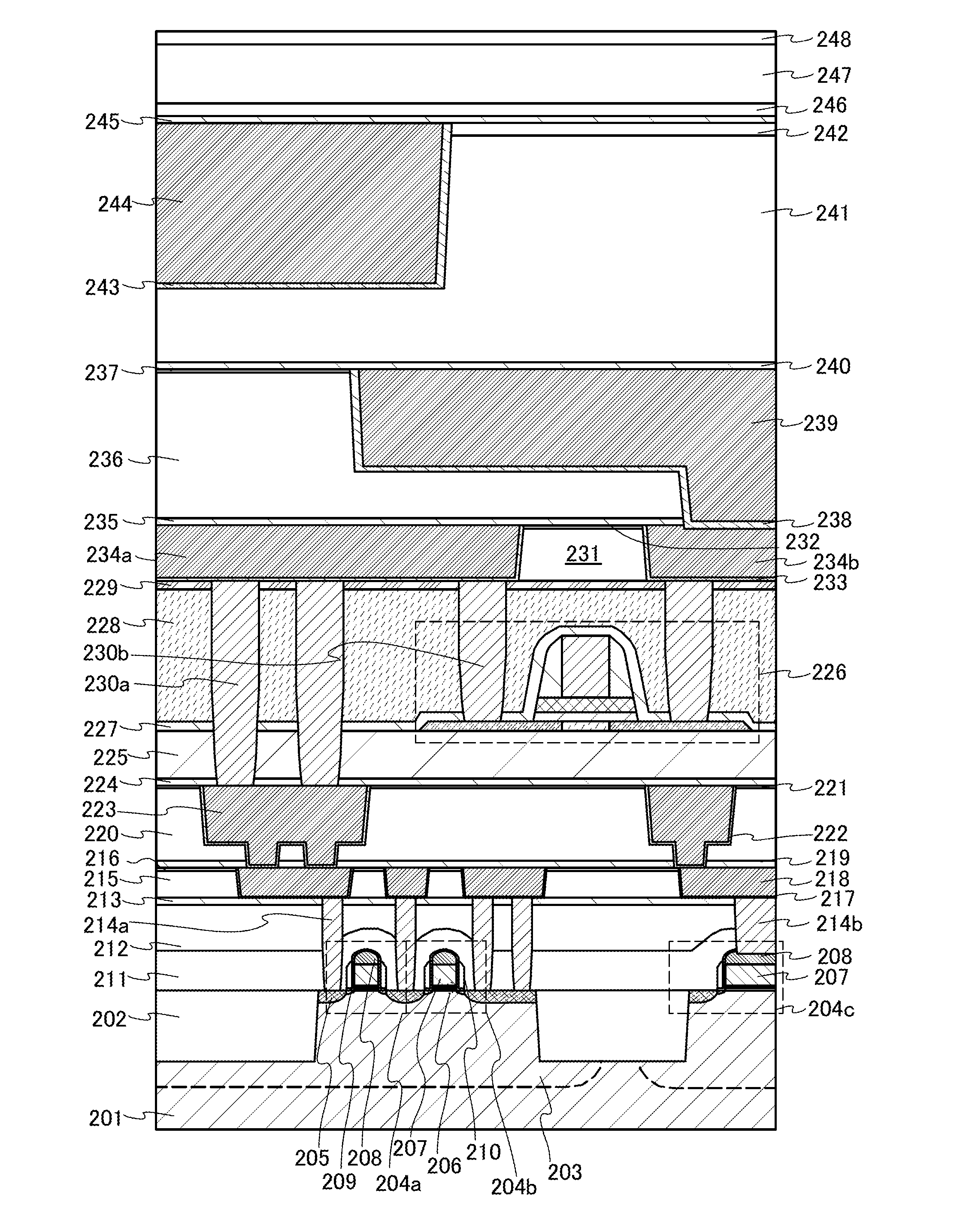

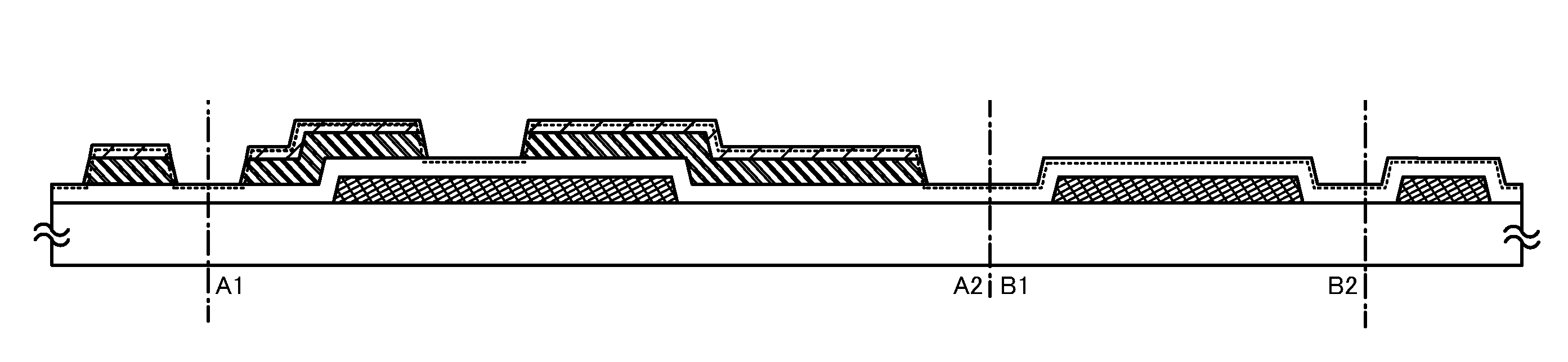

Semiconductor device and method for manufacturing the same

ActiveUS20100065838A1Small currentHigh on-off ratioTransistorSolid-state devicesProduction rateSemiconductor package

An object is to provide a semiconductor device including a thin film transistor with excellent electrical characteristics and high reliability and a method for manufacturing the semiconductor device with high mass productivity. A main point is to form a low-resistance oxide semiconductor layer as a source or drain region after forming a drain or source electrode layer over a gate insulating layer and to form an oxide semiconductor film thereover as a semiconductor layer. It is preferable that an oxygen-excess oxide semiconductor layer be used as a semiconductor layer and an oxygen-deficient oxide semiconductor layer be used as a source region and a drain region.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS20110156117A1Long storageReduce power consumptionTransistorSolid-state devicesEngineeringData storing

An object of the present invention is to provide a semiconductor device having a novel structure in which in a data storing time, stored data can be stored even when power is not supplied, and there is no limitation on the number of writing. A semiconductor device includes a first transistor including a first source electrode and a first drain electrode; a first channel formation region for which an oxide semiconductor material is used and to which the first source electrode and the first drain electrode are electrically connected; a first gate insulating layer over the first channel formation region; and a first gate electrode over the first gate insulating layer. One of the first source electrode and the first drain electrode of the first transistor and one electrode of a capacitor are electrically connected to each other.

Owner:SEMICON ENERGY LAB CO LTD