Patents

Literature

531results about How to "Leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

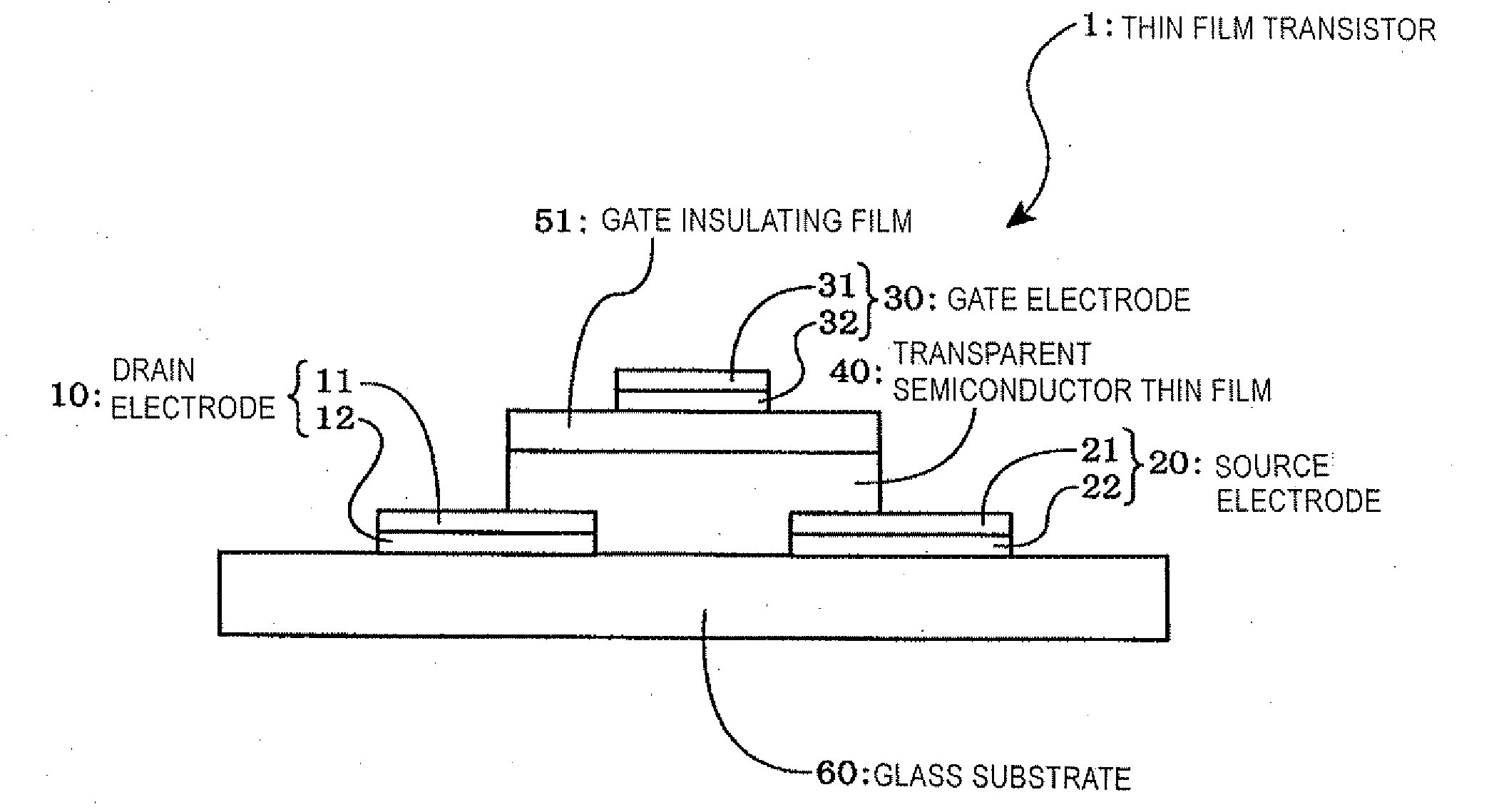

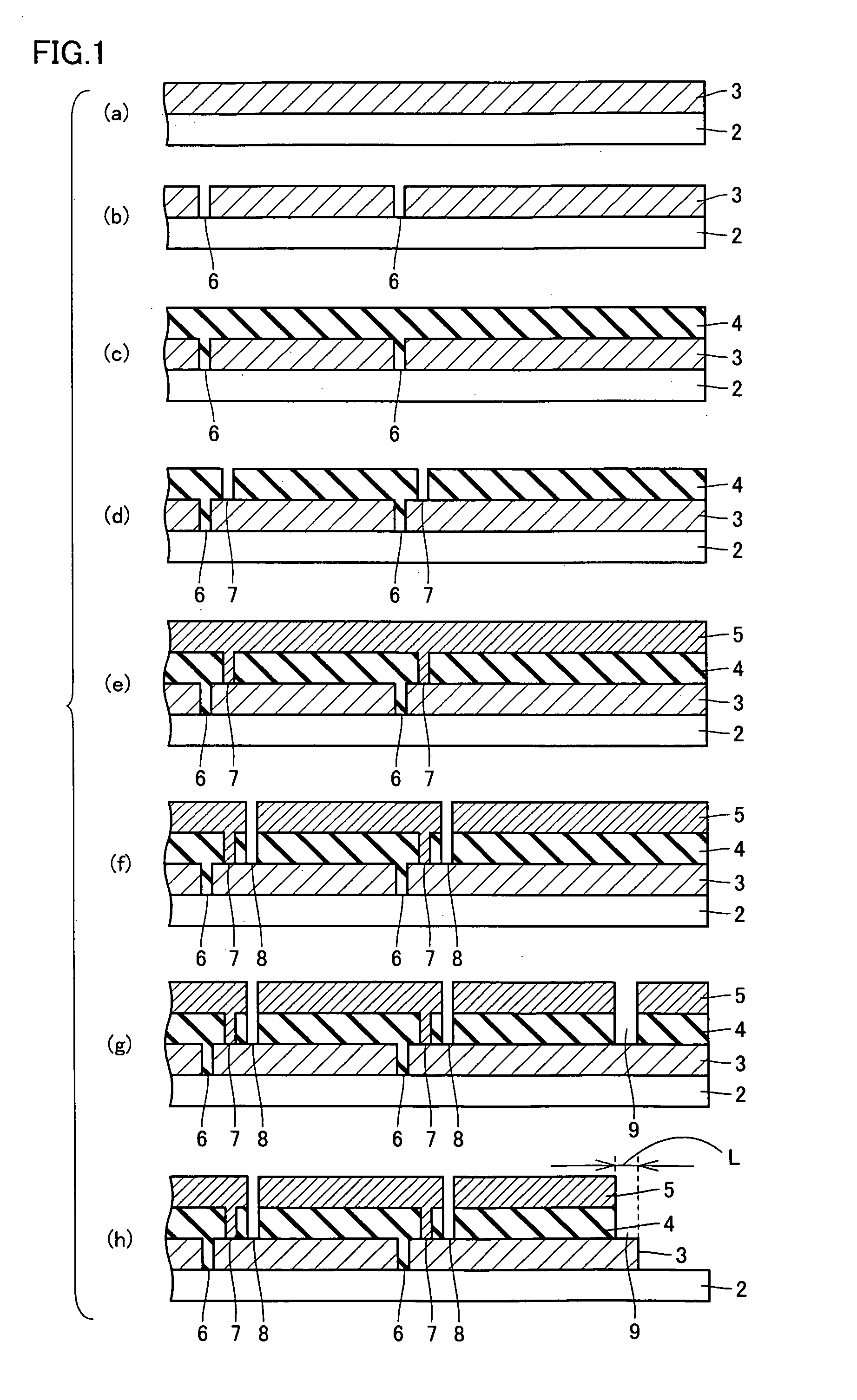

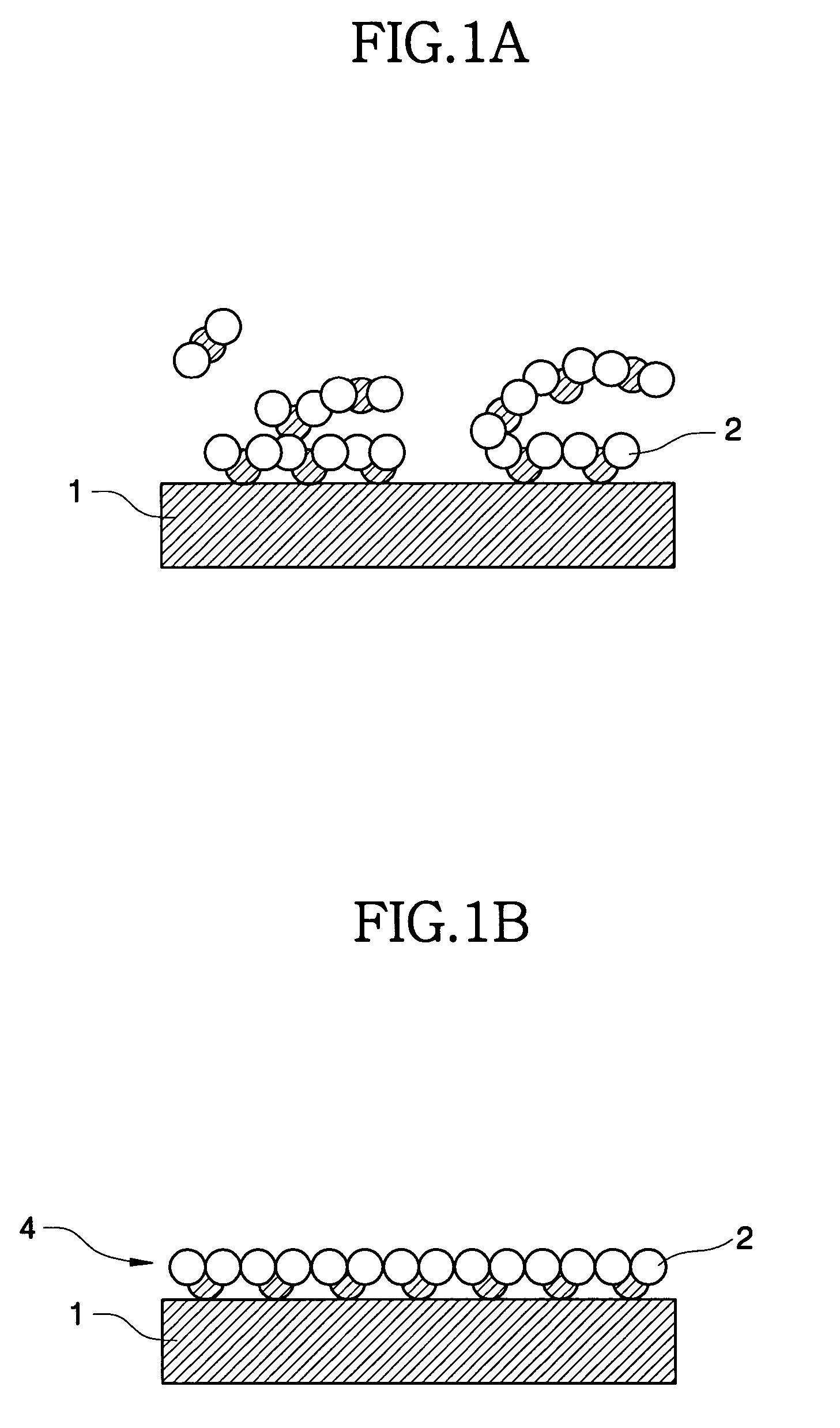

Amorphous Oxide And Thin Film Transistor

InactiveUS20070194379A1High ionicityGeneration of oxygen defects is less frequentTransistorVacuum evaporation coatingCharge carrierElectron

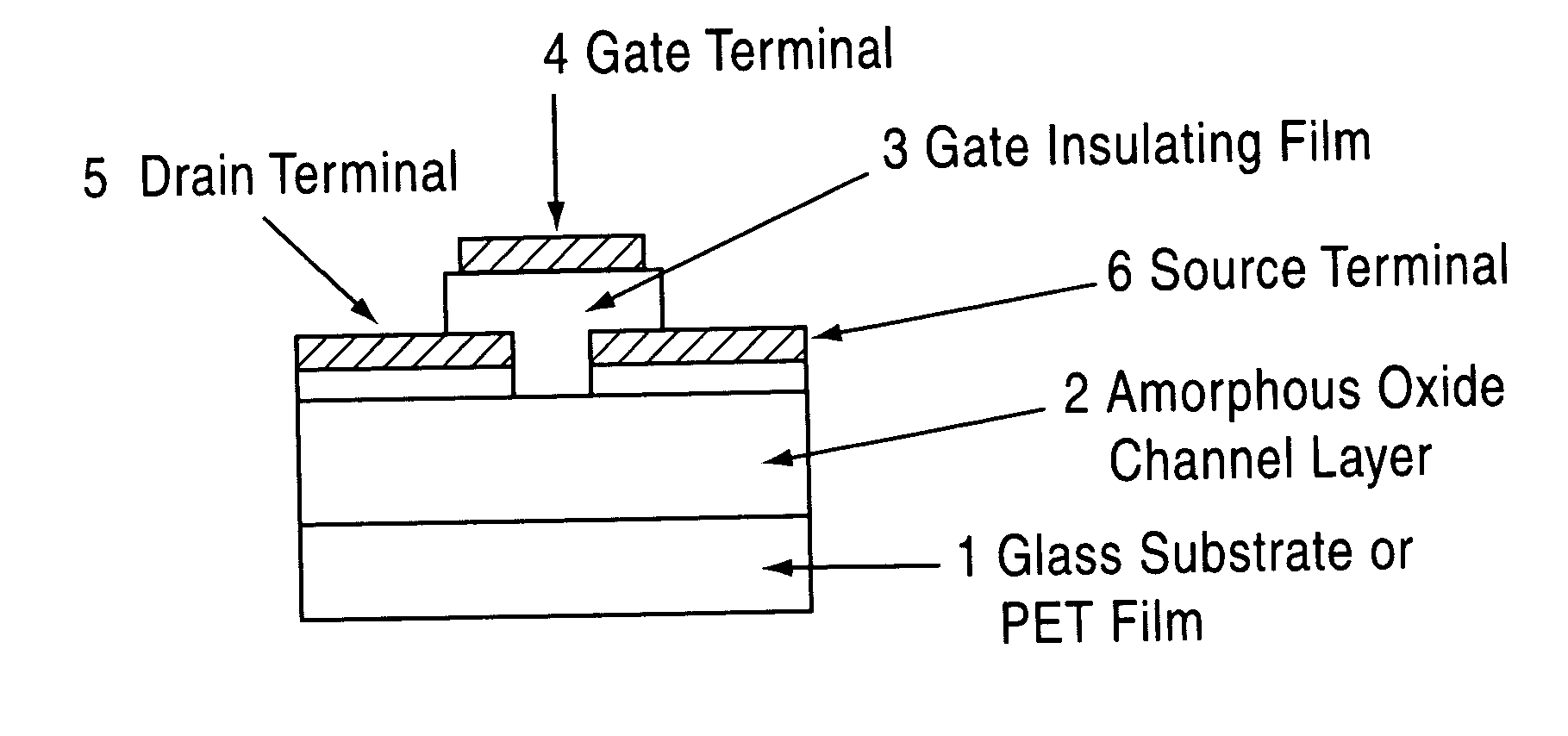

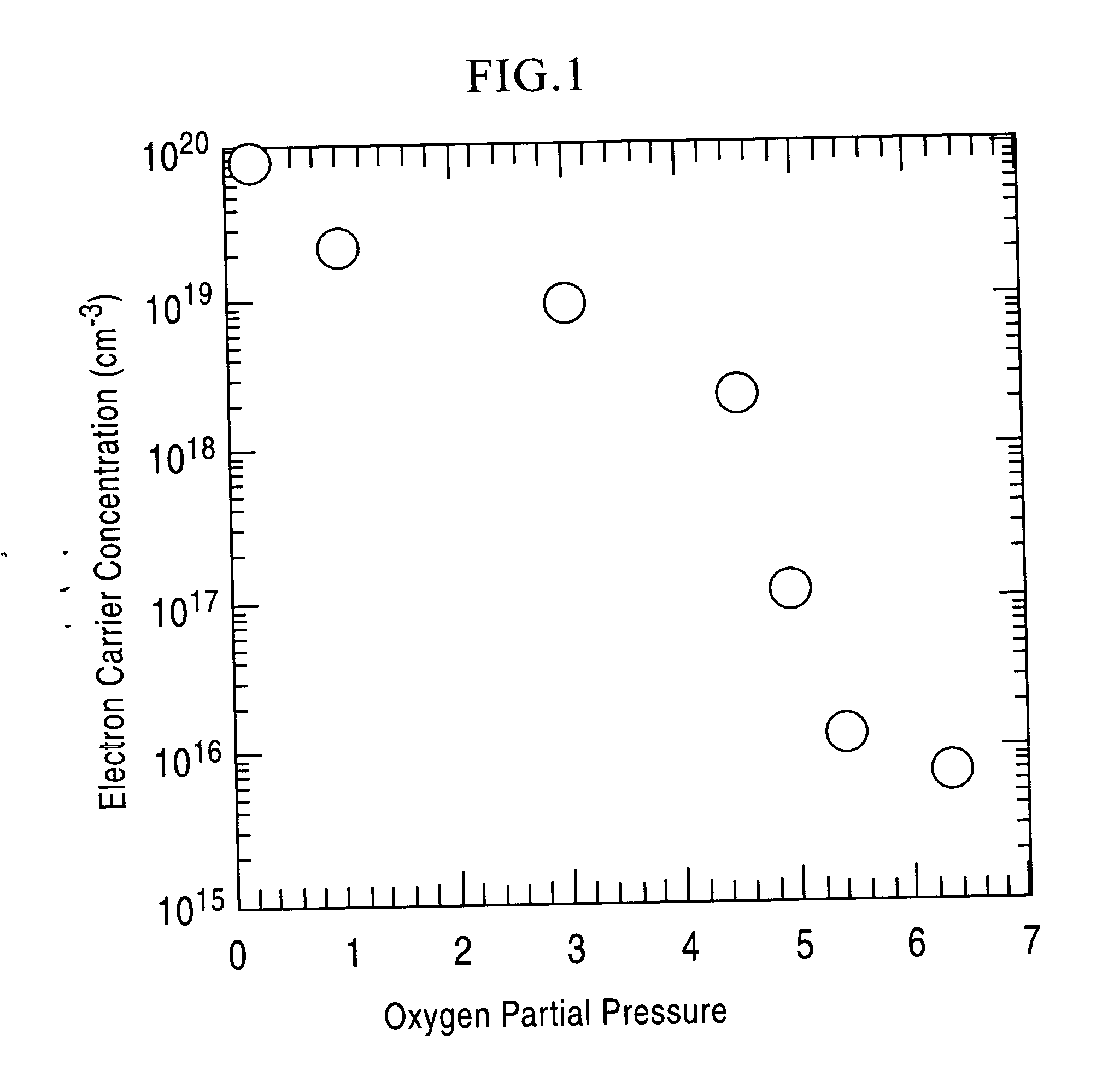

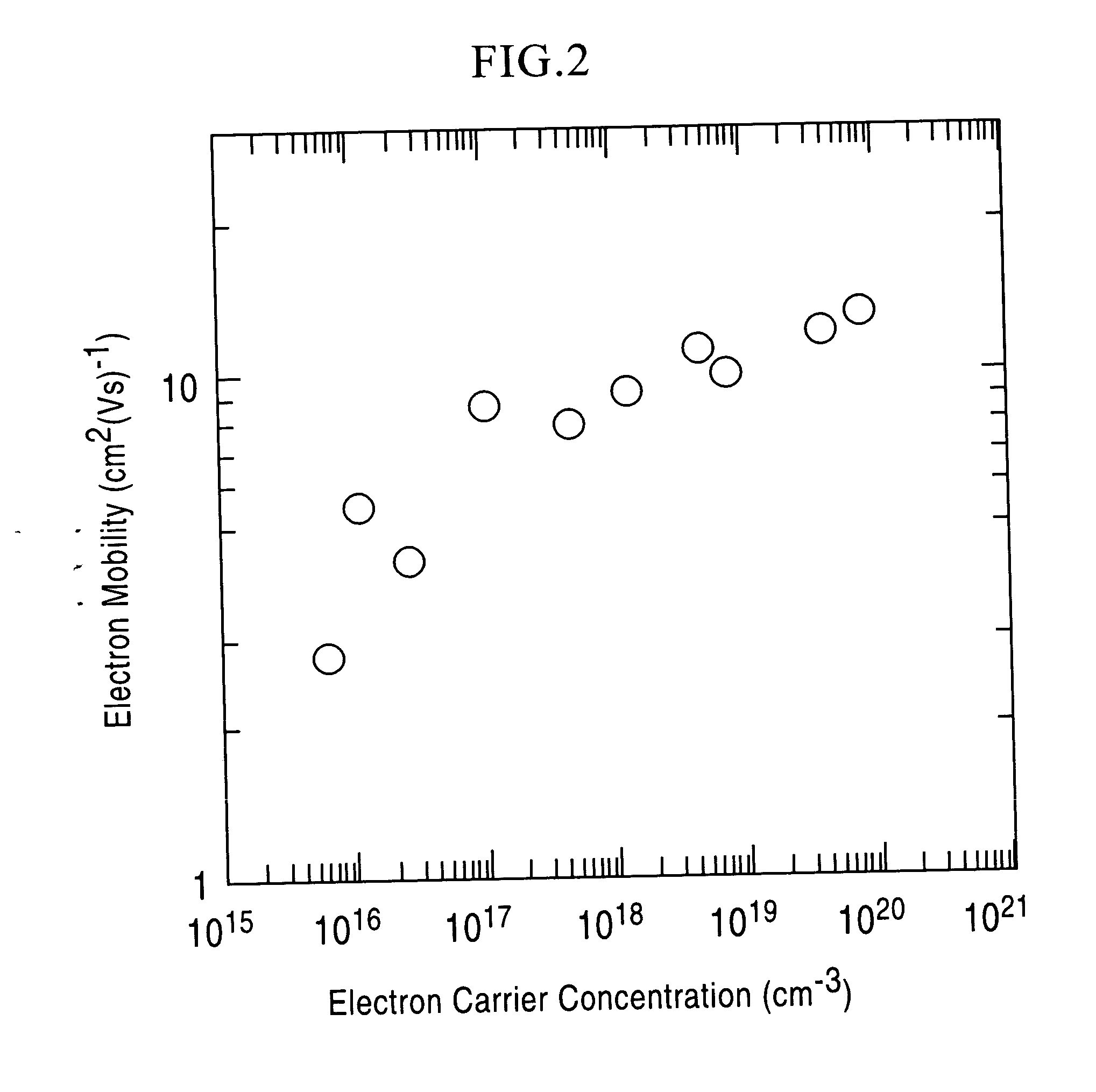

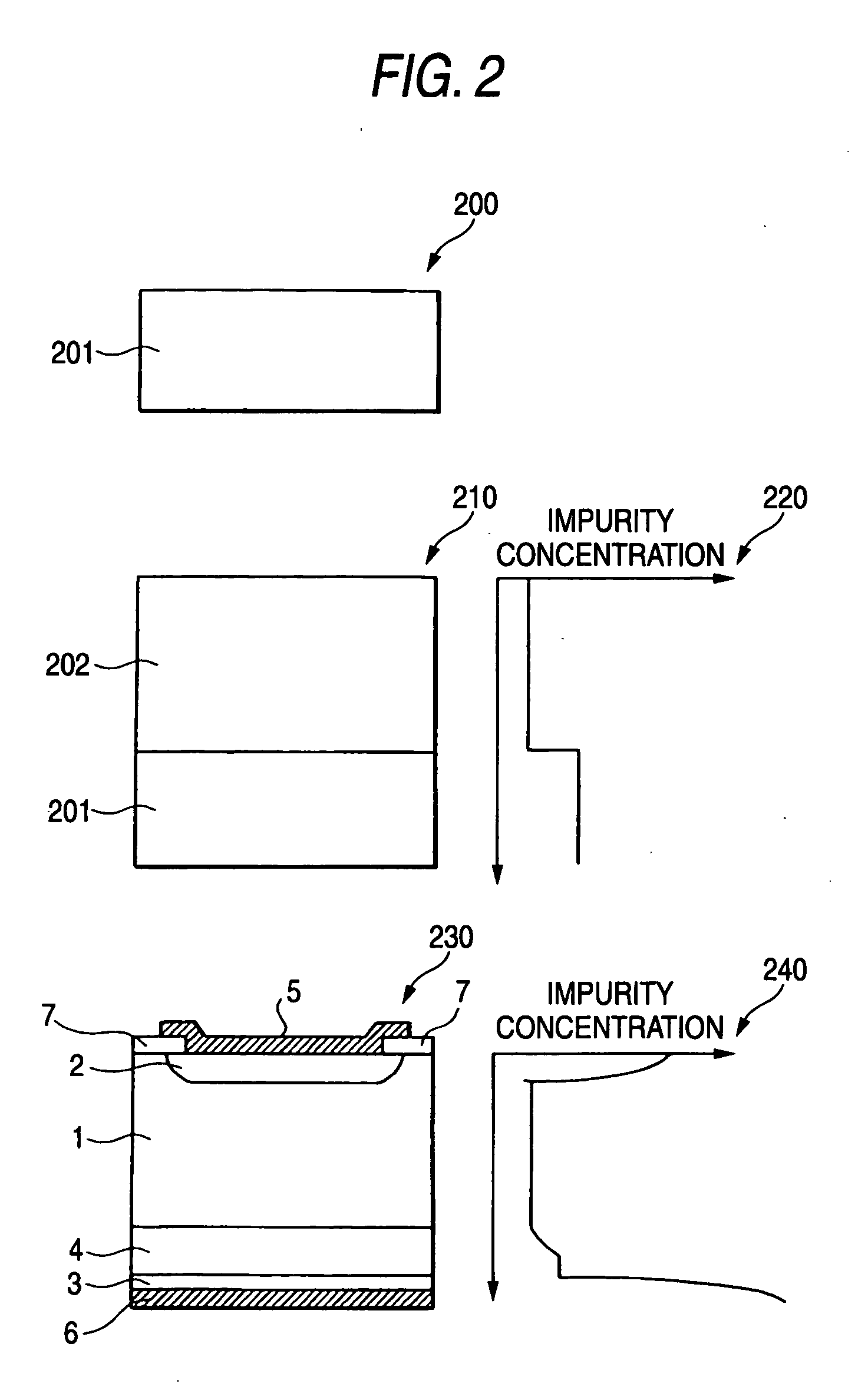

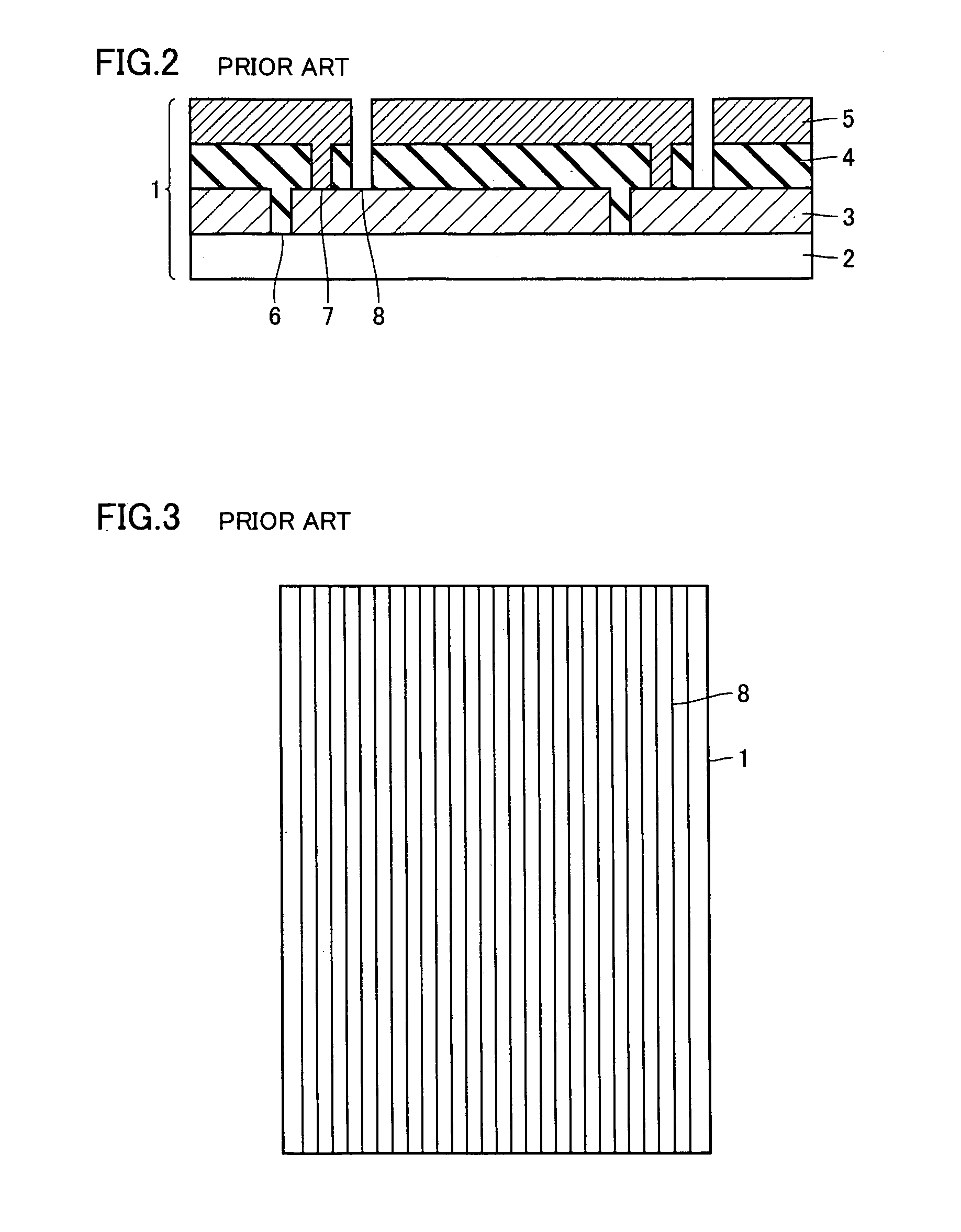

The present invention relates to an amorphous oxide and a thin film transistor using the amorphous oxide. In particular, the present invention provides an amorphous oxide having an electron carrier concentration less than 1018 / cm3, and a thin film transistor using such an amorphous oxide. In a thin film transistor having a source electrode 6, a drain electrode 5, a gate electrode 4, a gate insulating film 3, and a channel layer 2, an amorphous oxide having an electron carrier concentration less than 1018 / cm3 is used in the channel layer 2.

Owner:JAPAN SCI & TECH CORP

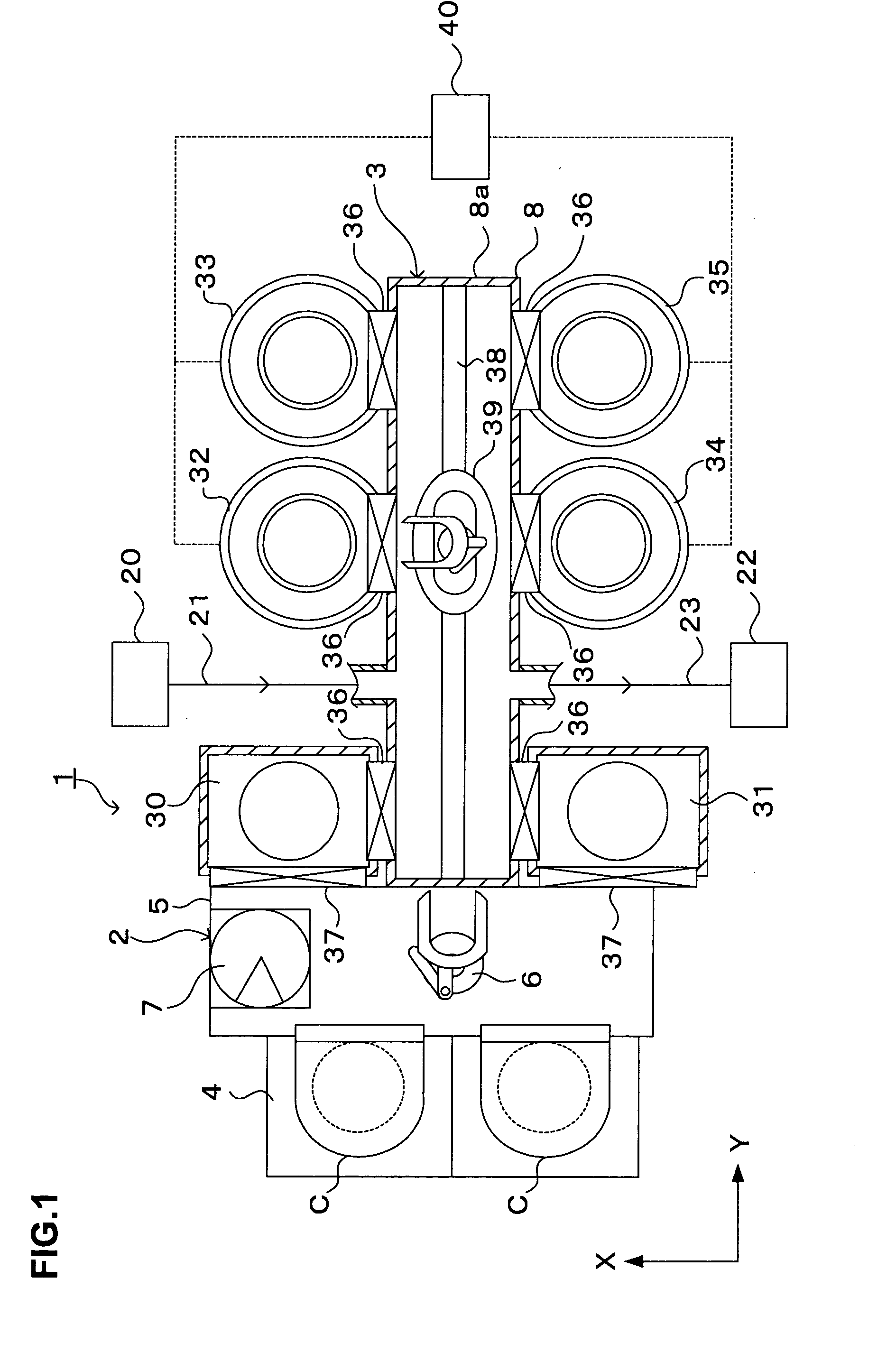

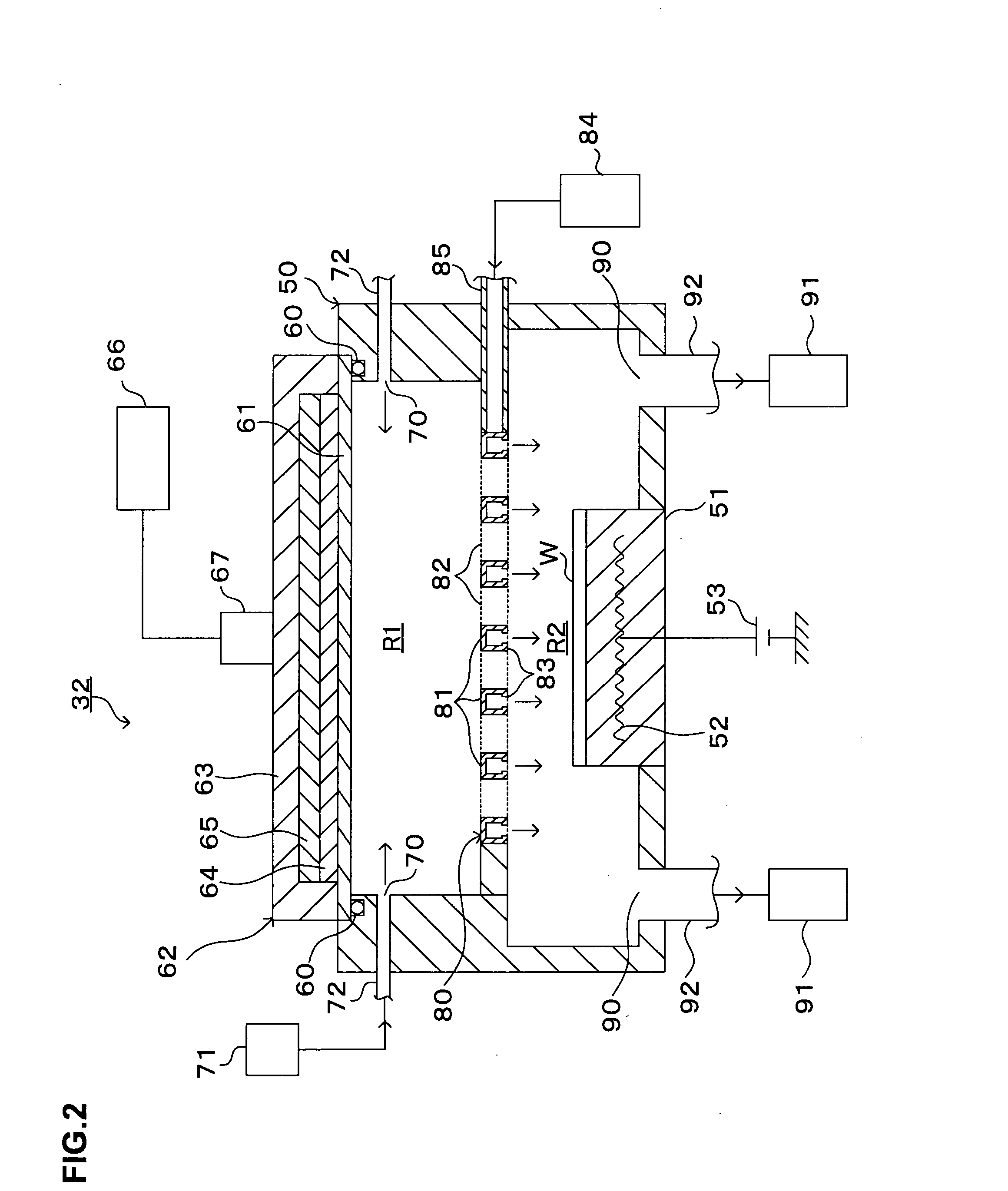

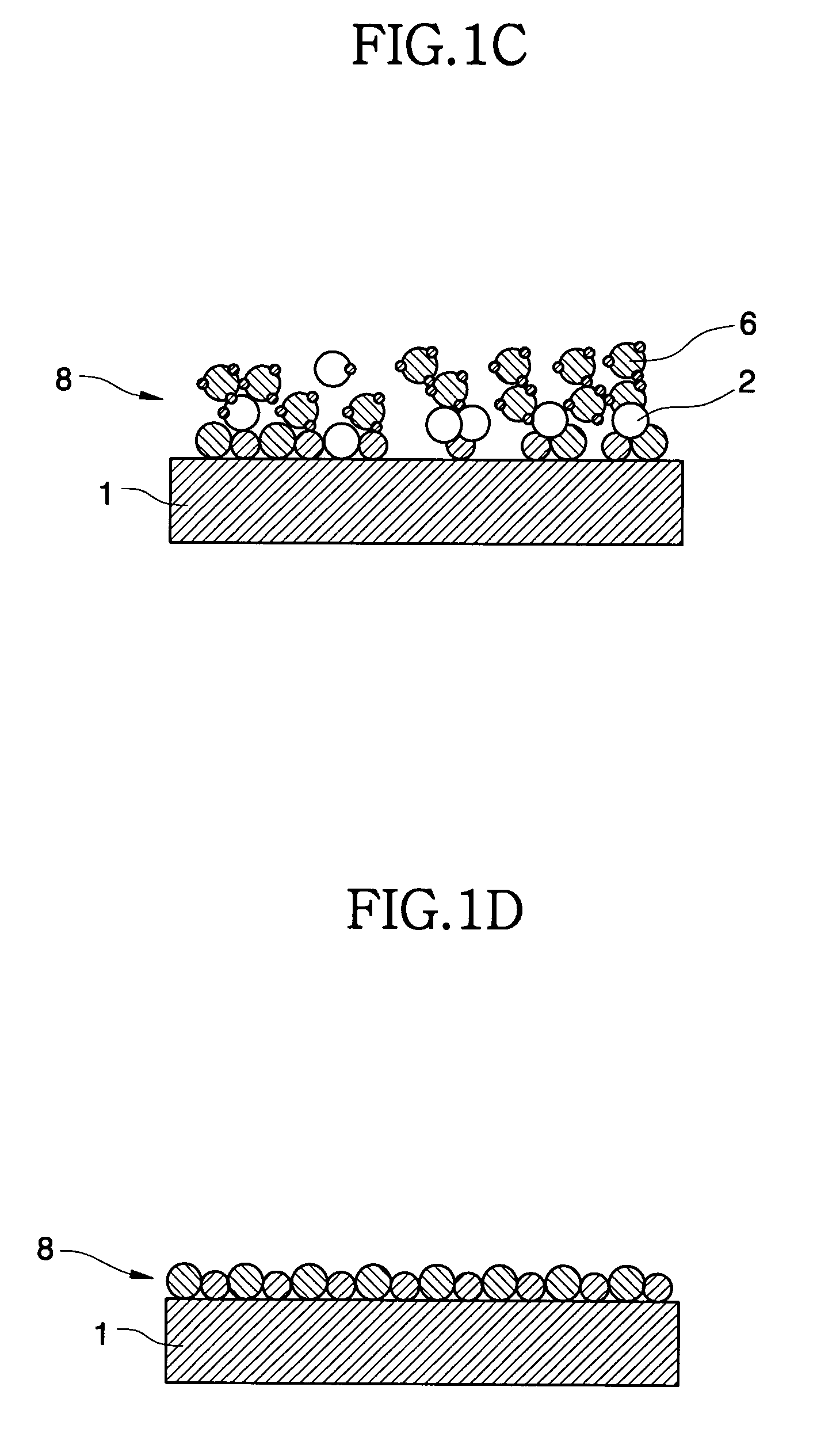

Substrate processing method, computer readable recording medium and substrate processing apparatus

InactiveUS20070062453A1Low dielectric constantImprove heat resistanceElectric discharge tubesSemiconductor/solid-state device detailsMicrowaveEngineering

In the present invention, Ar gas for plasma generation is supplied to a plasma generation region and butyne gas having a multiple bond is supplied to a film formation region at a substrate side as source gas, inside of a process vessel in an insulating film forming apparatus. A microwave is supplied inside of the process vessel from a radial line slot antenna under a state in which a bias voltage is not applied to a substrate W. A plasma is thereby generated in the plasma generation region, the butyne gas in the film formation region is activated by the plasma, and an insulating film of amorphous carbon is formed on the substrate.

Owner:TOKYO ELECTRON LTD

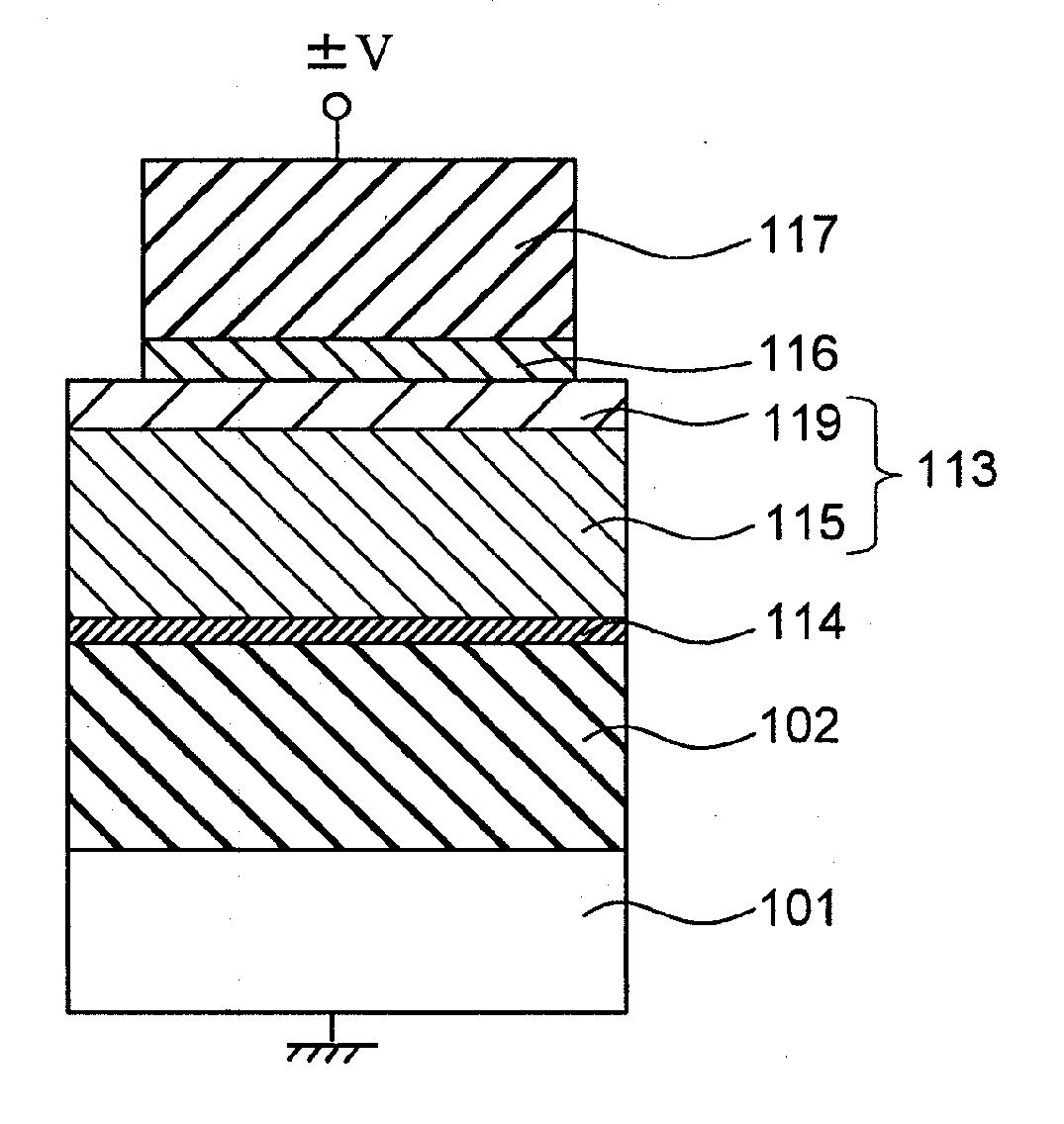

Method for manufacturing semiconductor device

InactiveUS20120064690A1Leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialTitanium nitride

A method for manufacturing a semiconductor device includes at least forming a lower electrode made of titanium nitride on a semiconductor substrate, forming a dielectric film comprising zirconium oxide, in which at least the uppermost layer of the dielectric film is formed by an atomic layer deposition (ALD) method on the lower electrode, forming a first protective film on the dielectric film without exceeding the film forming temperature of the ALD method over 70° C., and forming an upper electrode made of a titanium nitride on the first protective film.

Owner:ELPIDA MEMORY INC

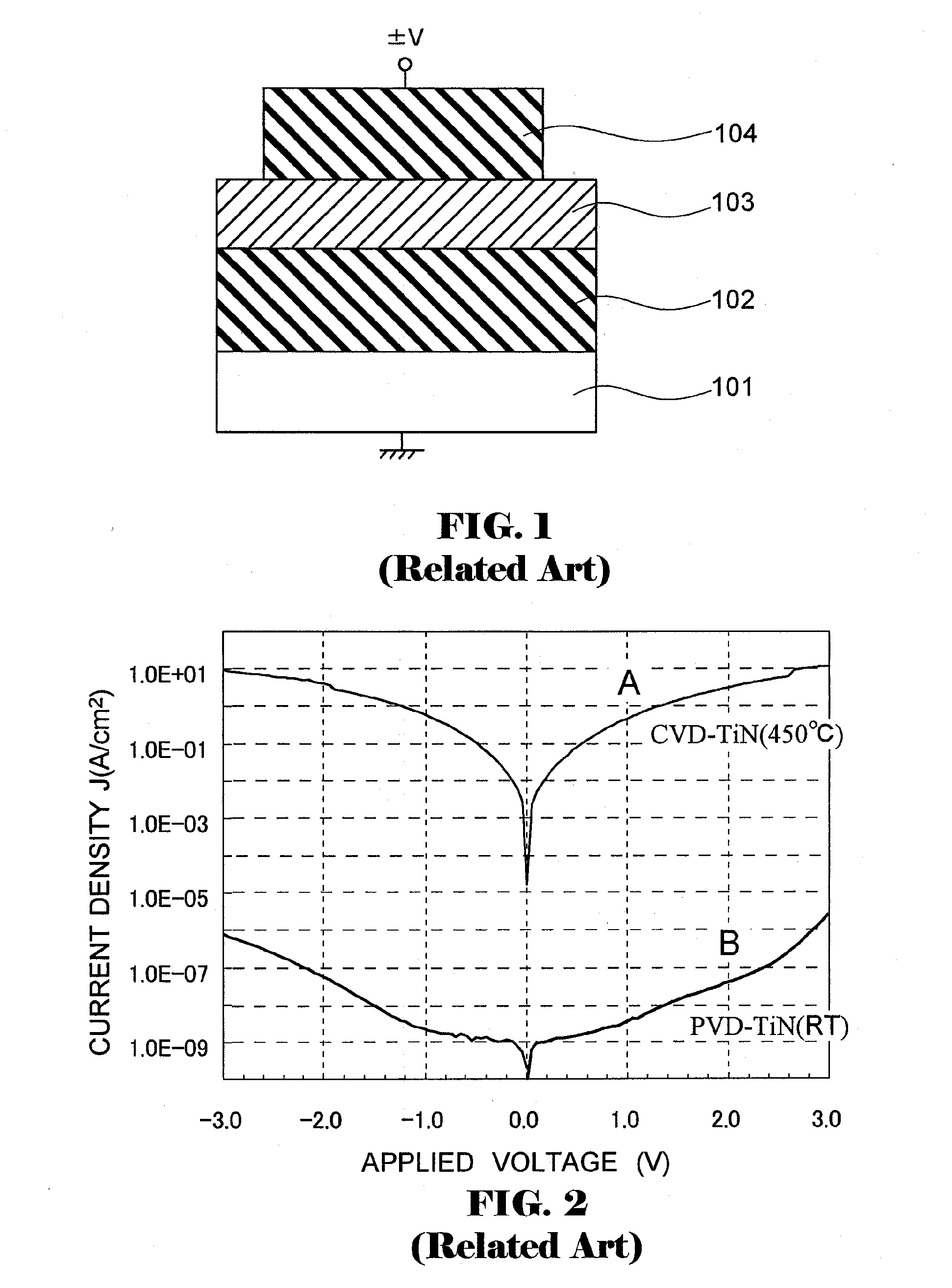

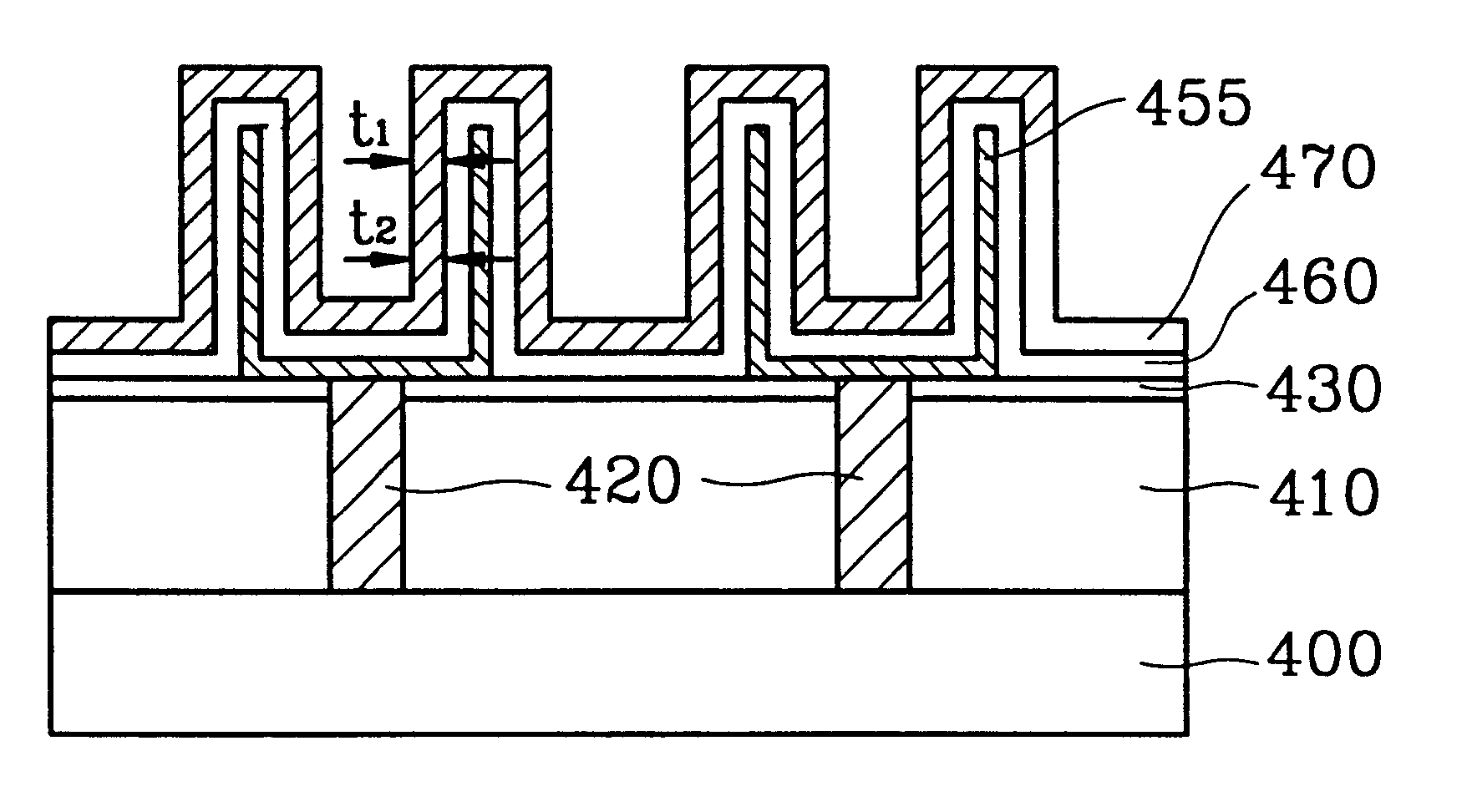

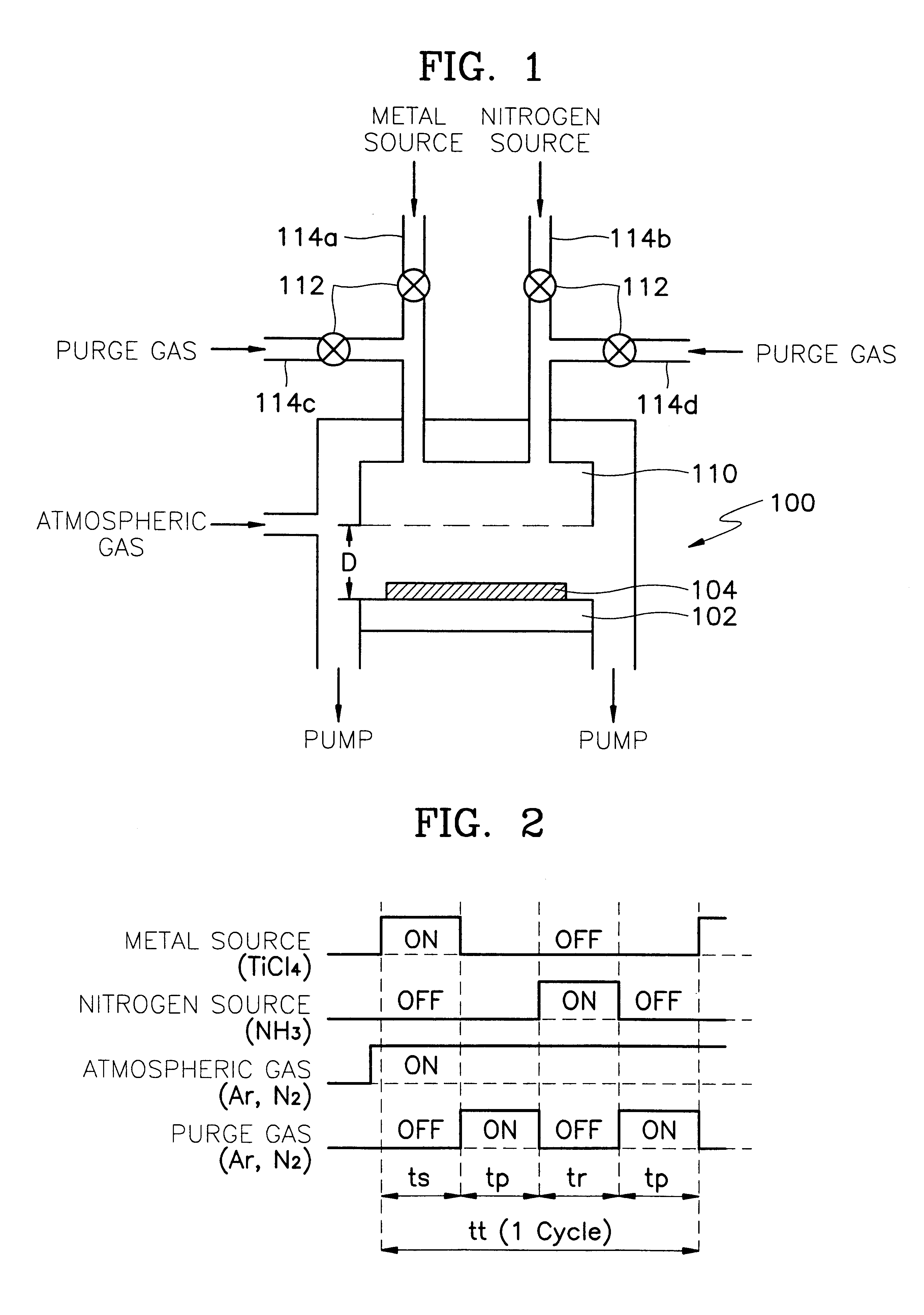

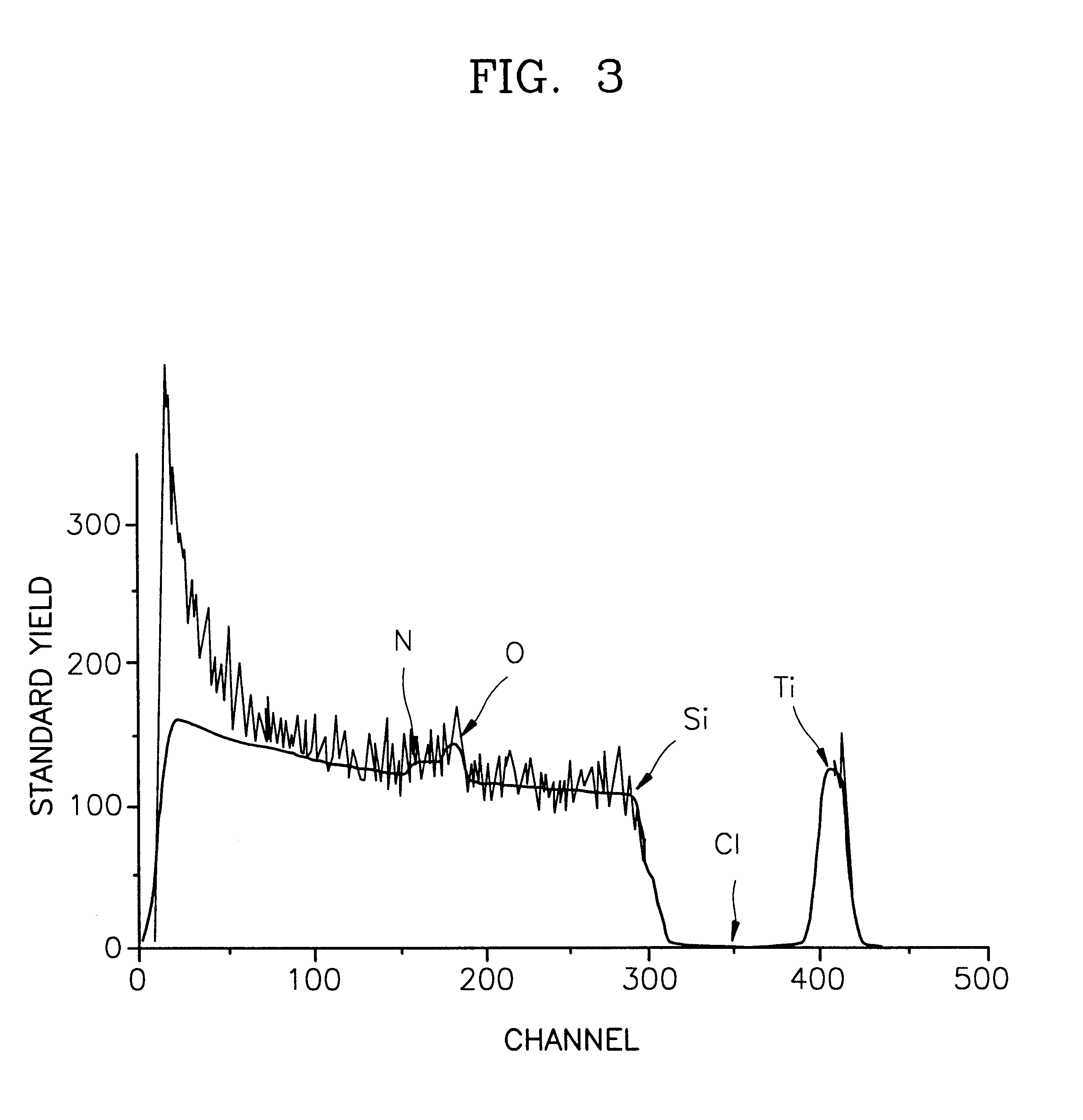

Method of forming metal nitride film by chemical vapor deposition and method of forming metal contact and capacitor of semiconductor device using the same

InactiveUS20010034097A1Good step coverageLow resistivitySemiconductor/solid-state device manufacturingCapacitorsChemical physicsDevice material

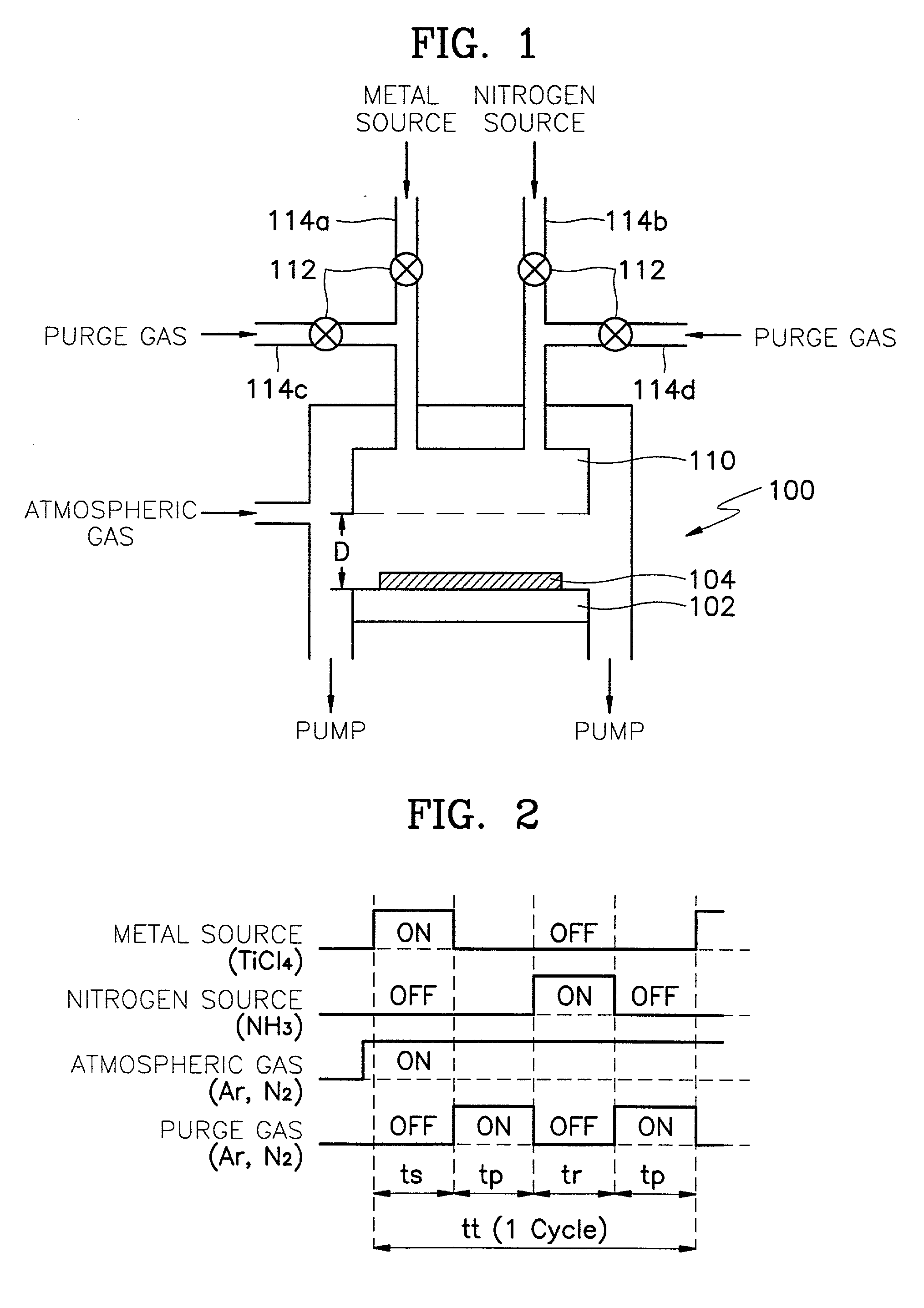

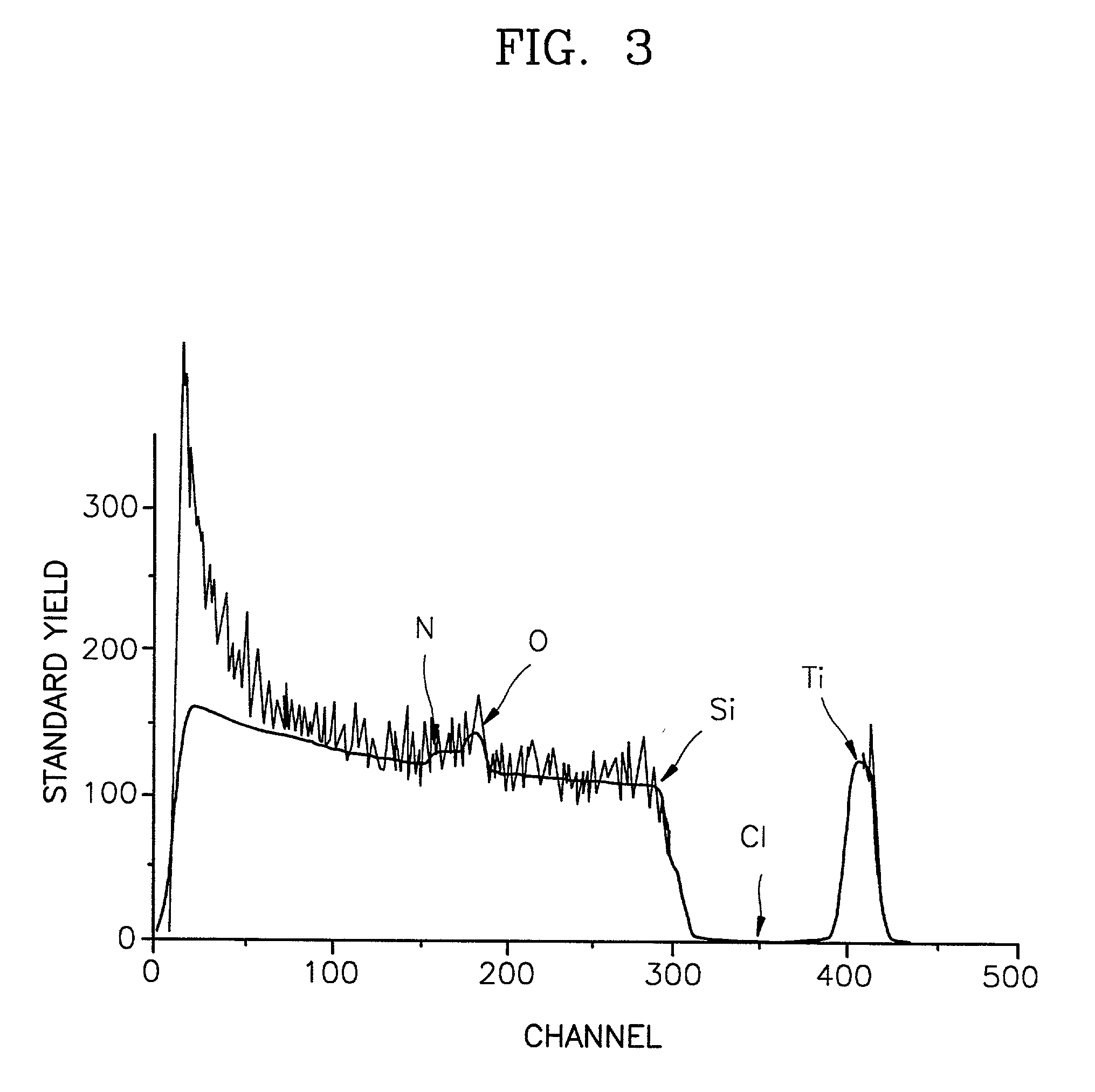

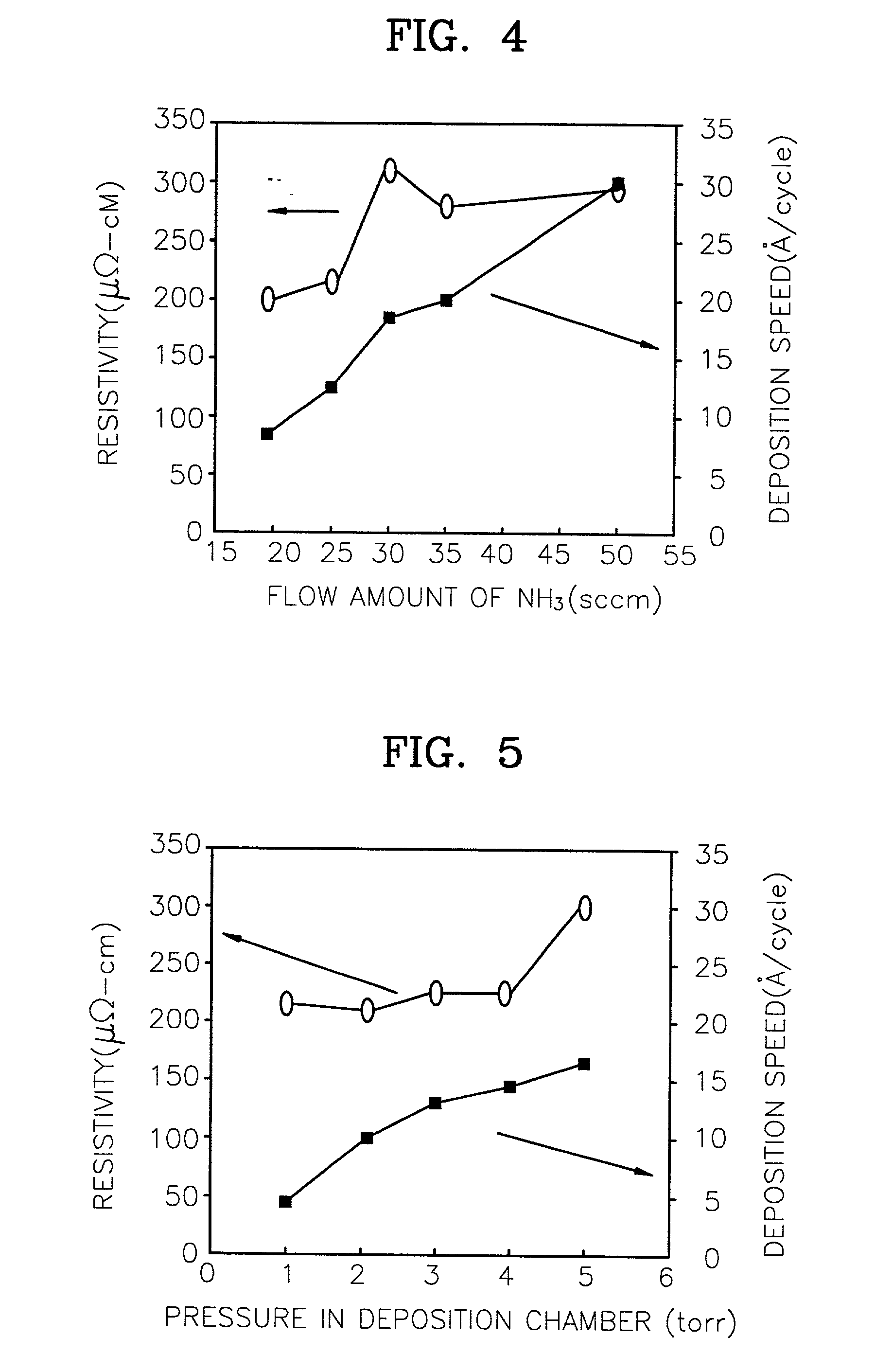

A method of forming a metal nitride film using chemical vapor deposition (CVD), and a method of forming a metal contact and a semiconductor capacitor of a semiconductor device using the same, are provided. The method of forming a metal nitride film using chemical vapor deposition (CVD) in which a metal source and a nitrogen source are used as a precursor, includes the steps of inserting a semiconductor substrate into a deposition chamber, flowing the metal source into the deposition chamber, removing the metal source remaining in the deposition chamber by cutting off the inflow of the metal source and flowing a purge gas into the deposition chamber, cutting off the purge gas and flowing the nitrogen source into the deposition chamber to react with the metal source adsorbed on the semiconductor substrate, and removing the nitrogen source remaining in the deposition chamber by cutting off the inflow of the nitrogen source and flowing the purge gas into the deposition chamber. Accordingly, the metal nitride film having low resistivity and a low content of Cl even with excellent step coverage can be formed at a temperature of 500° C. or lower, and a semiconductor capacitor having excellent leakage current characteristics can be manufactured. Also, a deposition speed, approximately 20 A / cycle, is suitable for mass production.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of forming metal nitride film by chemical vapor deposition and method of forming metal contact and capacitor of semiconductor device using the same

InactiveUS6348376B2Good step coverageLow resistivitySemiconductor/solid-state device manufacturingCapacitorsDevice materialNitrogen source

A method of forming a metal nitride film using chemical vapor deposition (CVD), and a method of forming a metal contact and a semiconductor capacitor of a semiconductor device using the same, are provided. The method of forming a metal nitride film using chemical vapor deposition (CVD) in which a metal source and a nitrogen source are used as a precursor, includes the steps of inserting a semiconductor substrate into a deposition chamber, flowing the metal source into the deposition chamber, removing the metal source remaining in the deposition chamber by cutting off the inflow of the metal source and flowing a purge gas into the deposition chamber, cutting off the purge gas and flowing the nitrogen source into the deposition chamber to react with the metal source adsorbed on the semiconductor substrate, and removing the nitrogen source remaining in the deposition chamber by cutting off the inflow of the nitrogen source and flowing the purge gas into the deposition chamber. Accordingly, the metal nitride film having low resistivity and a low content of Cl even with excellent step coverage can be formed at a temperature of 500° C. or lower, and a semiconductor capacitor having excellent leakage current characteristics can be manufactured. Also, a deposition speed, approximately 20 A / cycle, is suitable for mass production.

Owner:SAMSUNG ELECTRONICS CO LTD

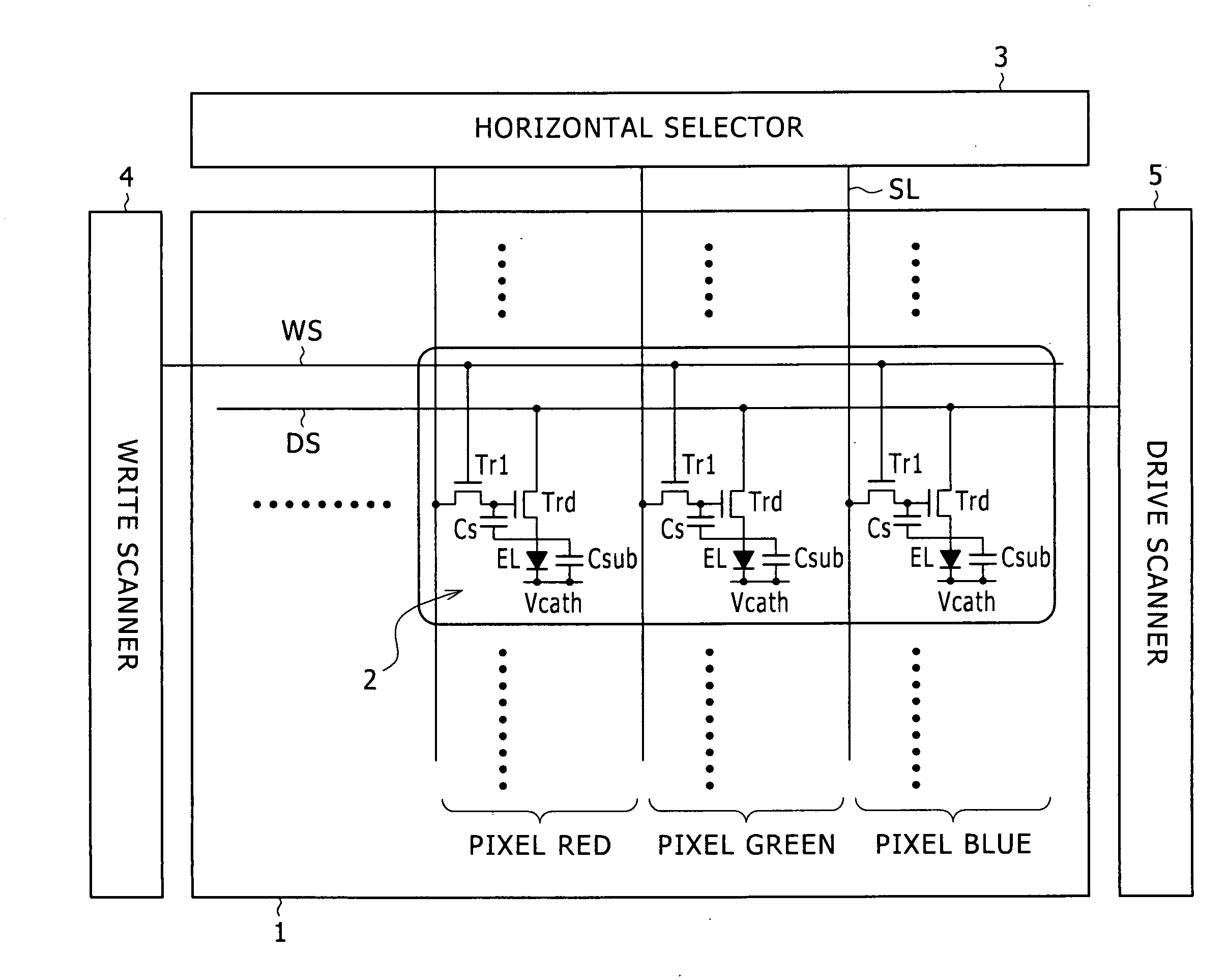

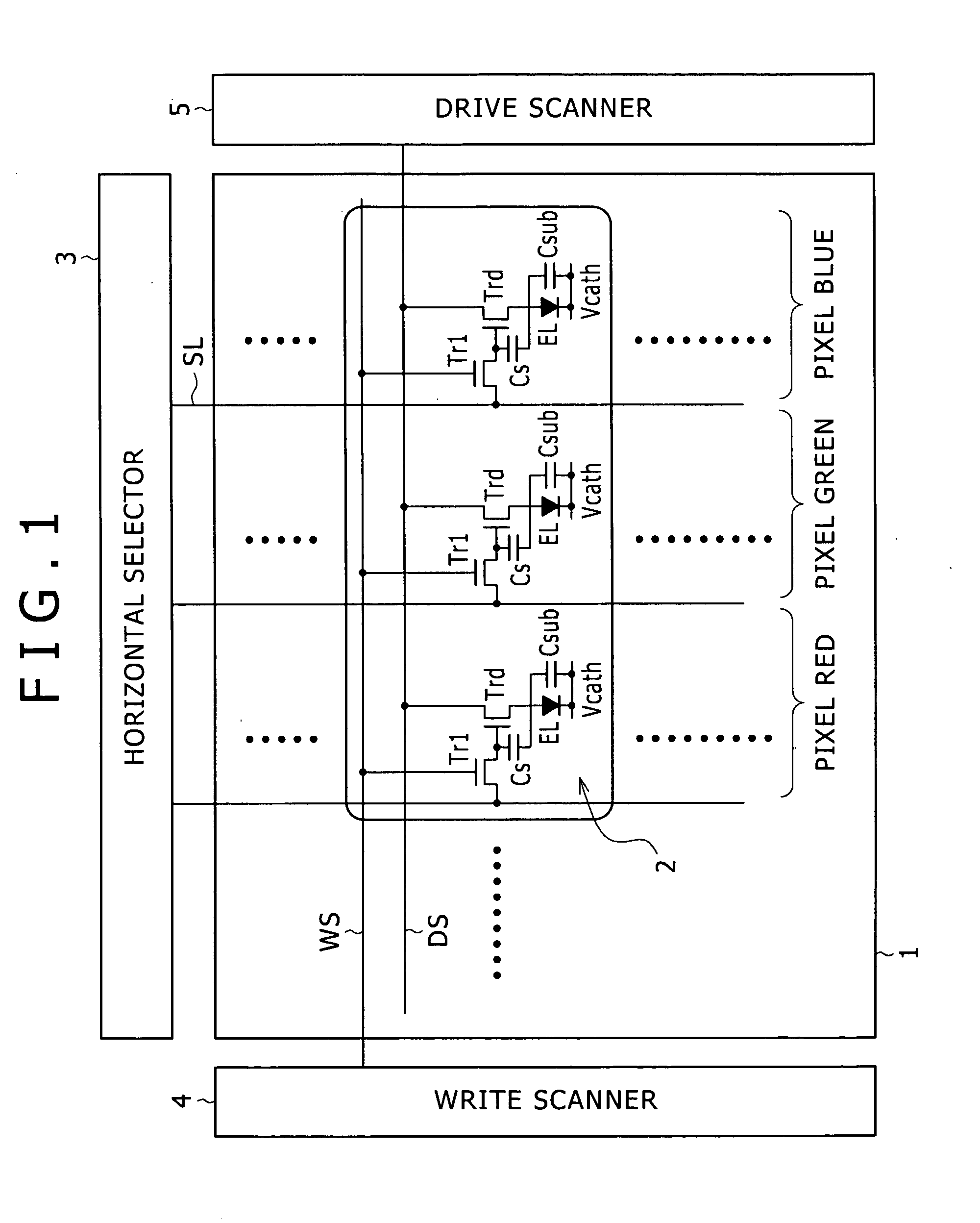

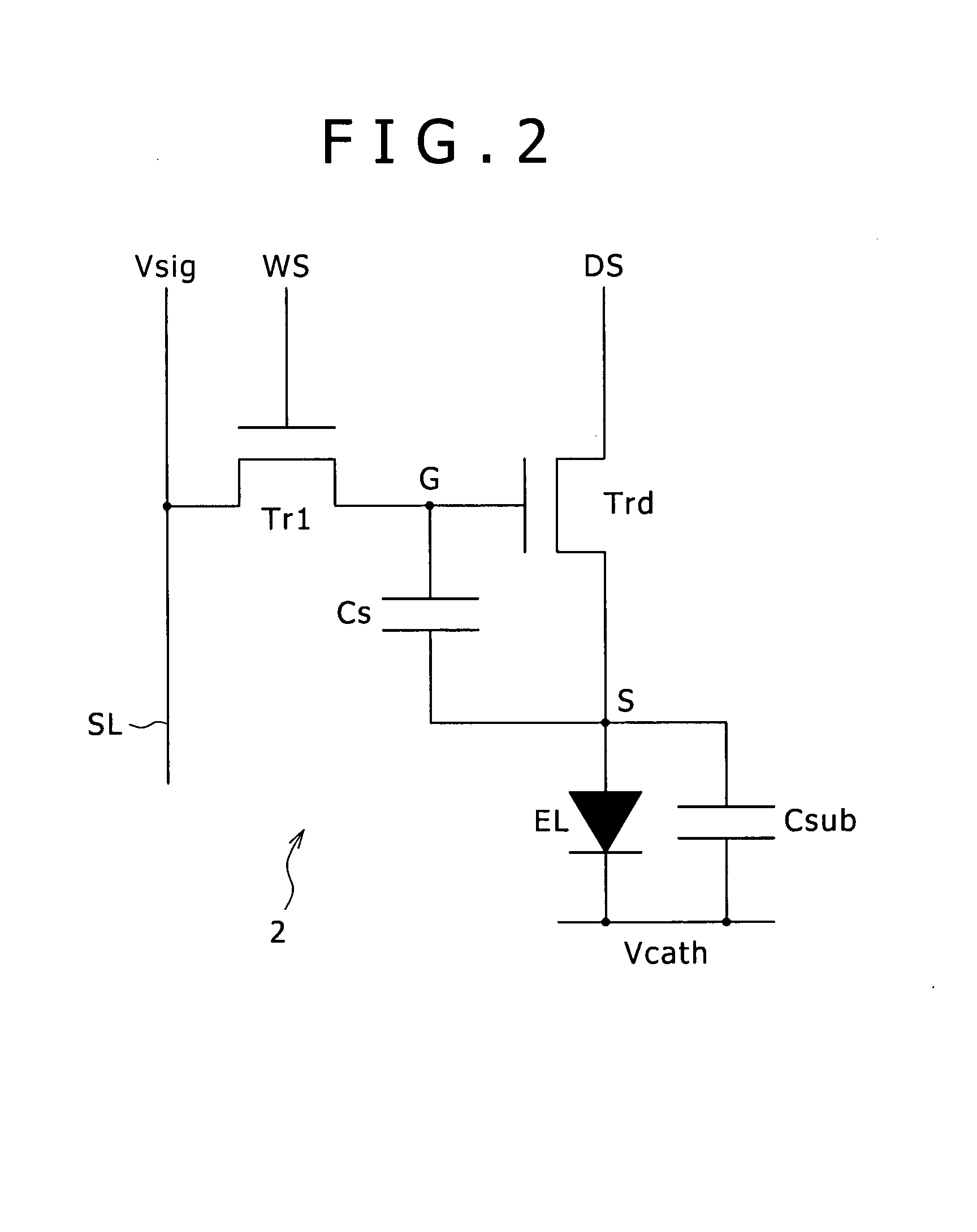

Display apparatus and drive method thereof and electronic device

InactiveUS20080231625A1Small fluctuationQuality improvementElectrical apparatusElectroluminescent light sourcesControl signalScan line

Disclosed herein is a display apparatus including a pixel array section and a drive section. The pixel array section has power supply lines, scan lines arranged in row, signal lines arranged in column, and pixels arranged in matrix at intersections of each of the scan lines and each of the signal lines. The drive transistor is connected at one of a pair of current terminals to the light emitting device and at the other of the pair of current terminals to the power supply line. The drive section supplies a control signal to each scan line and a video signal to each signal line to drive each pixel, executing a threshold voltage correcting operation, a write operation, and a light emitting operation.

Owner:JOLED INC

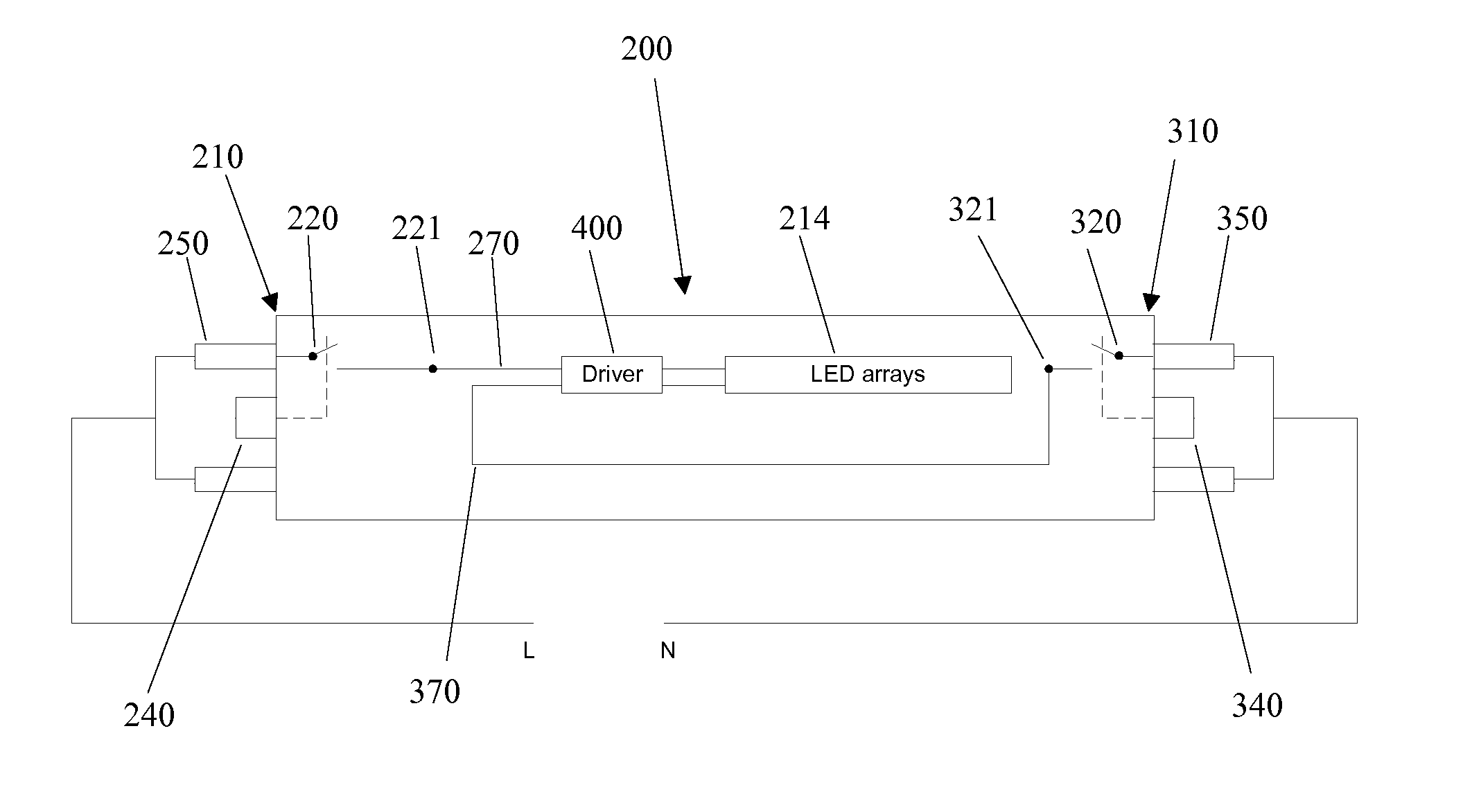

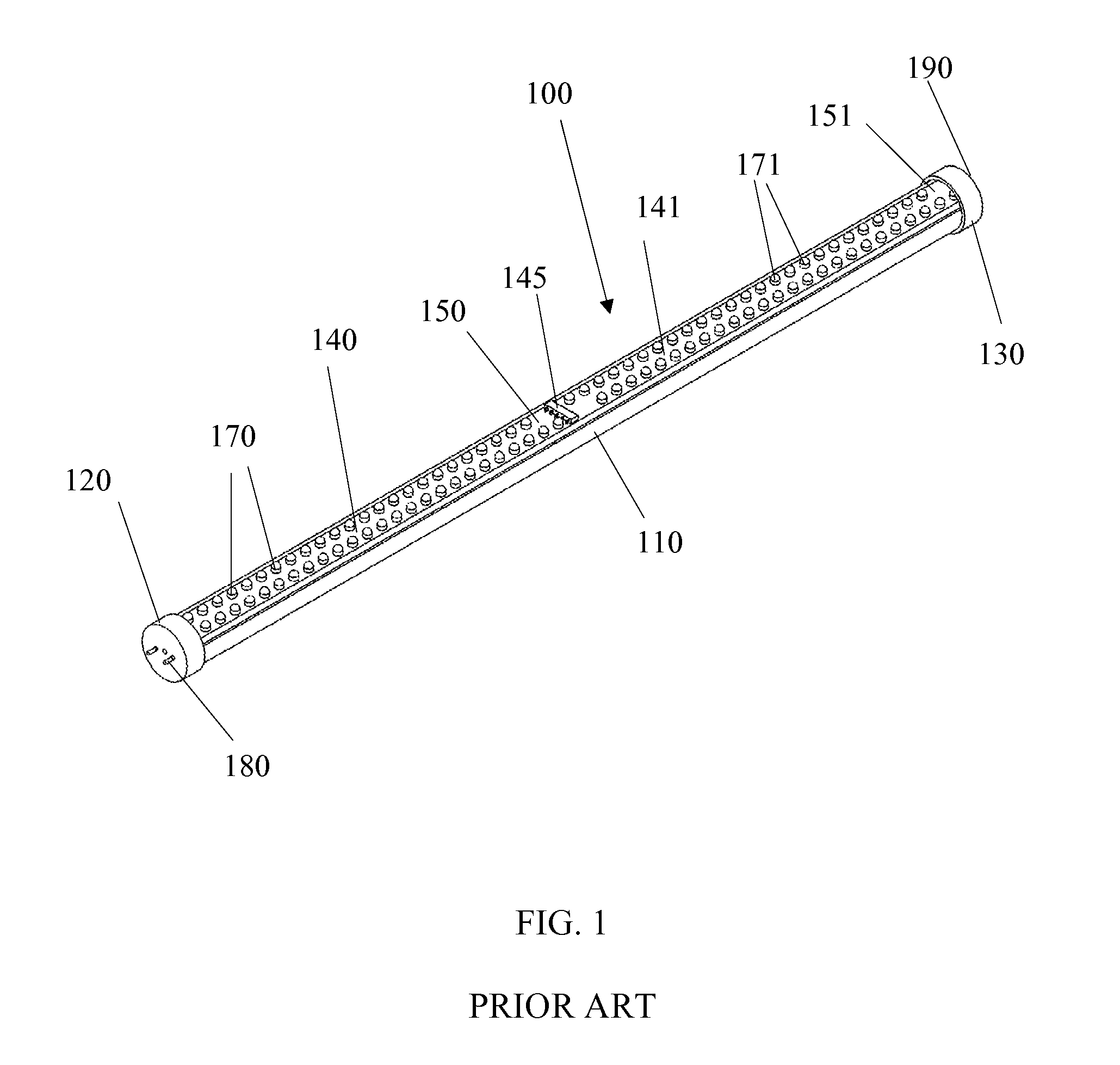

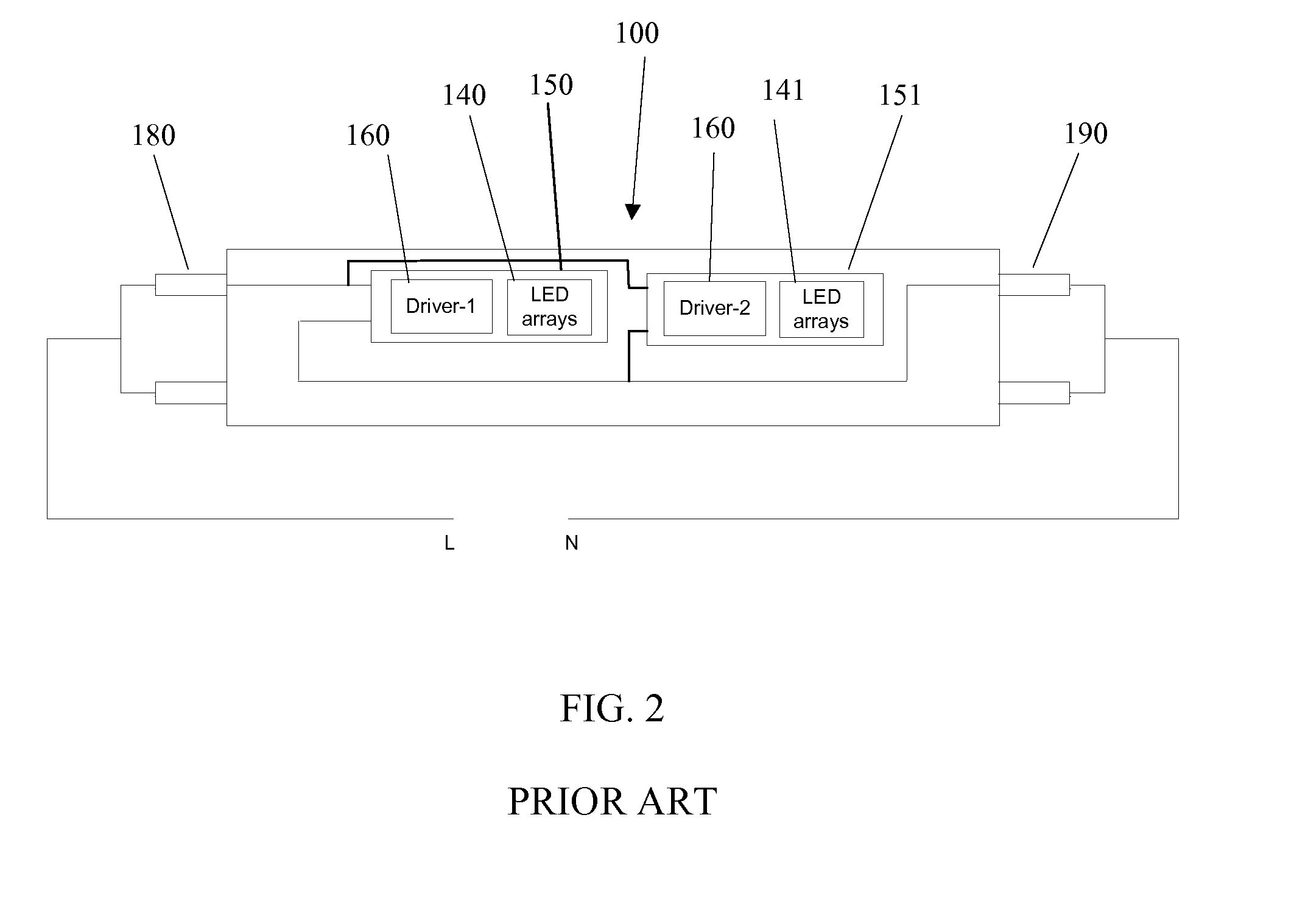

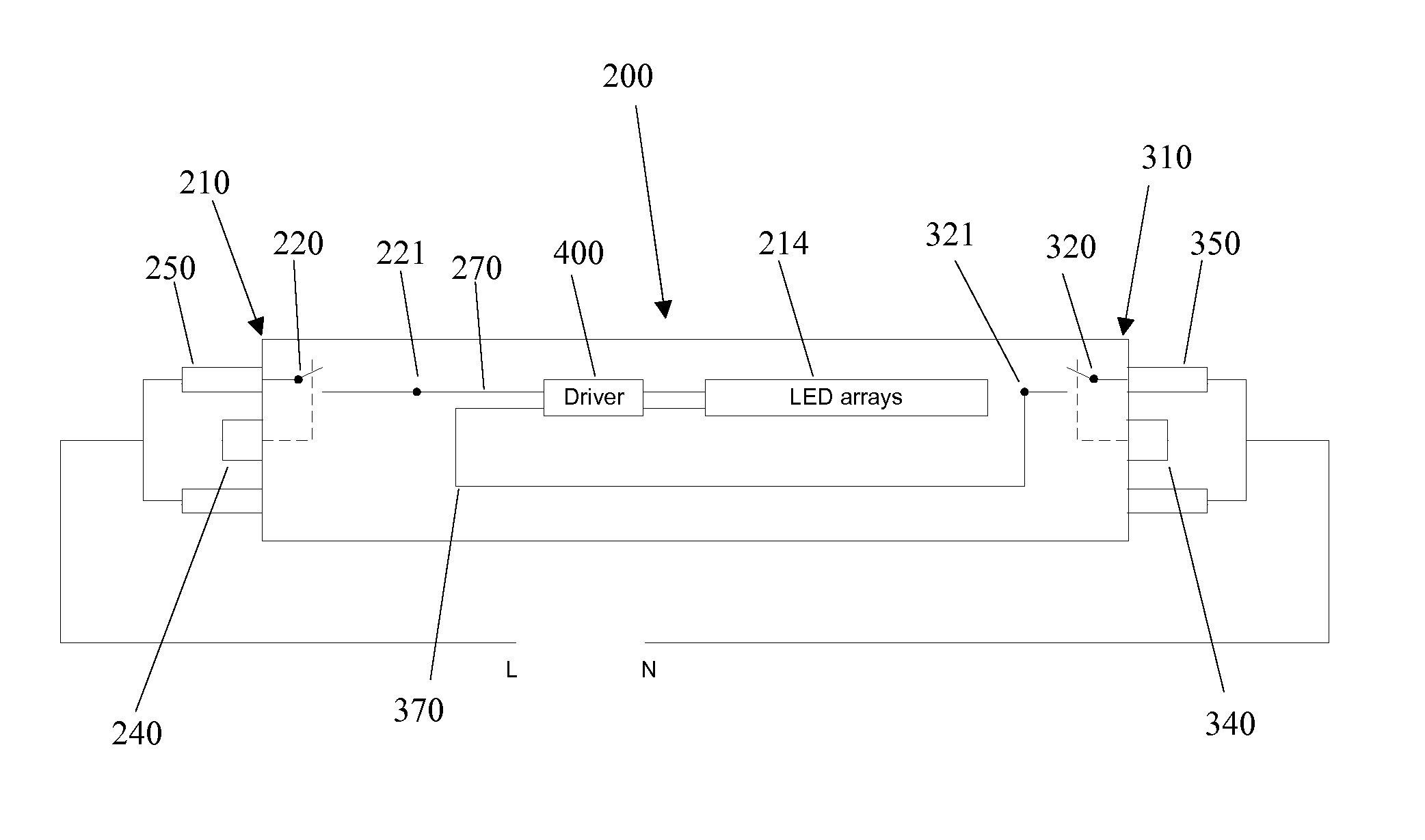

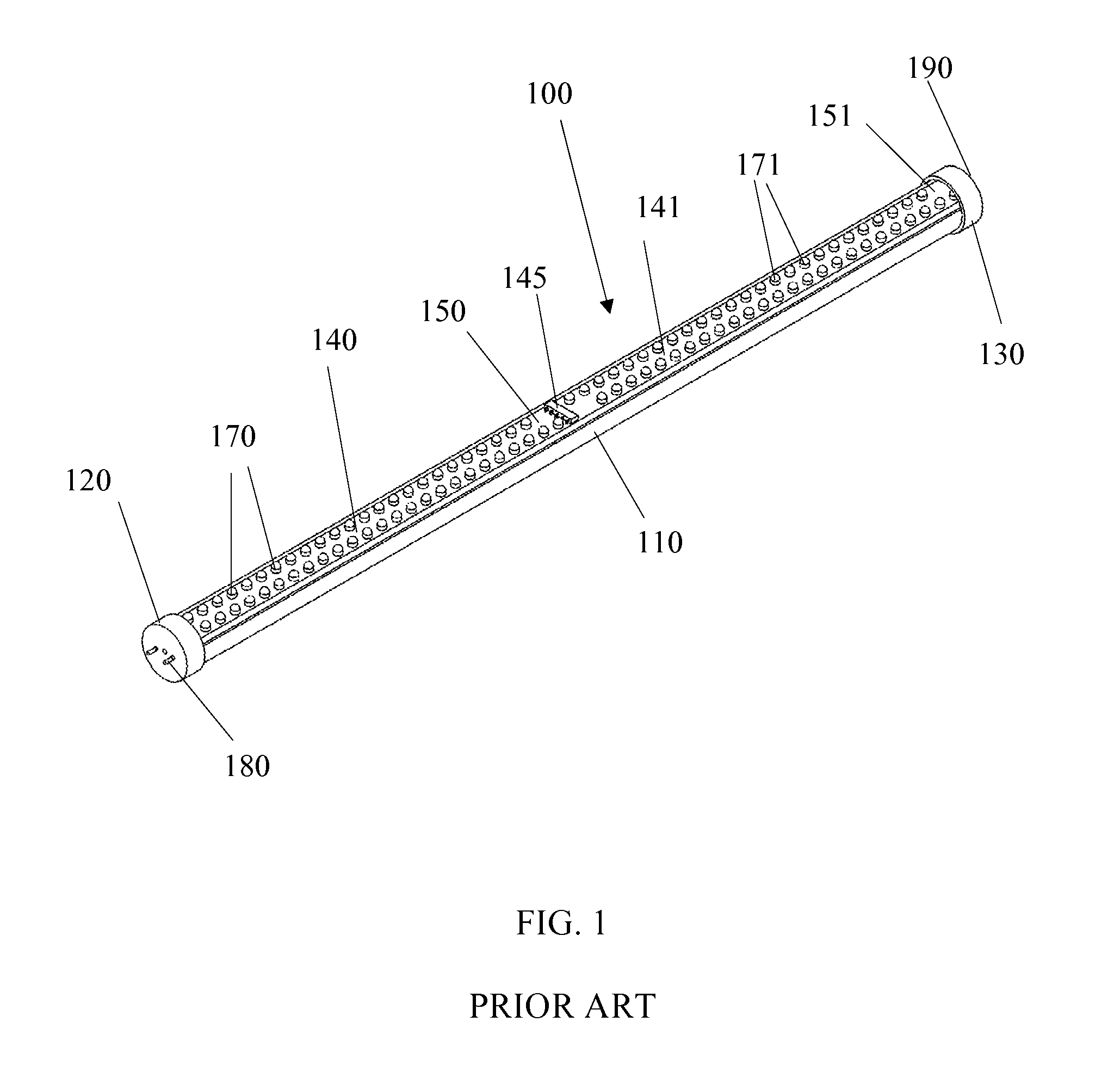

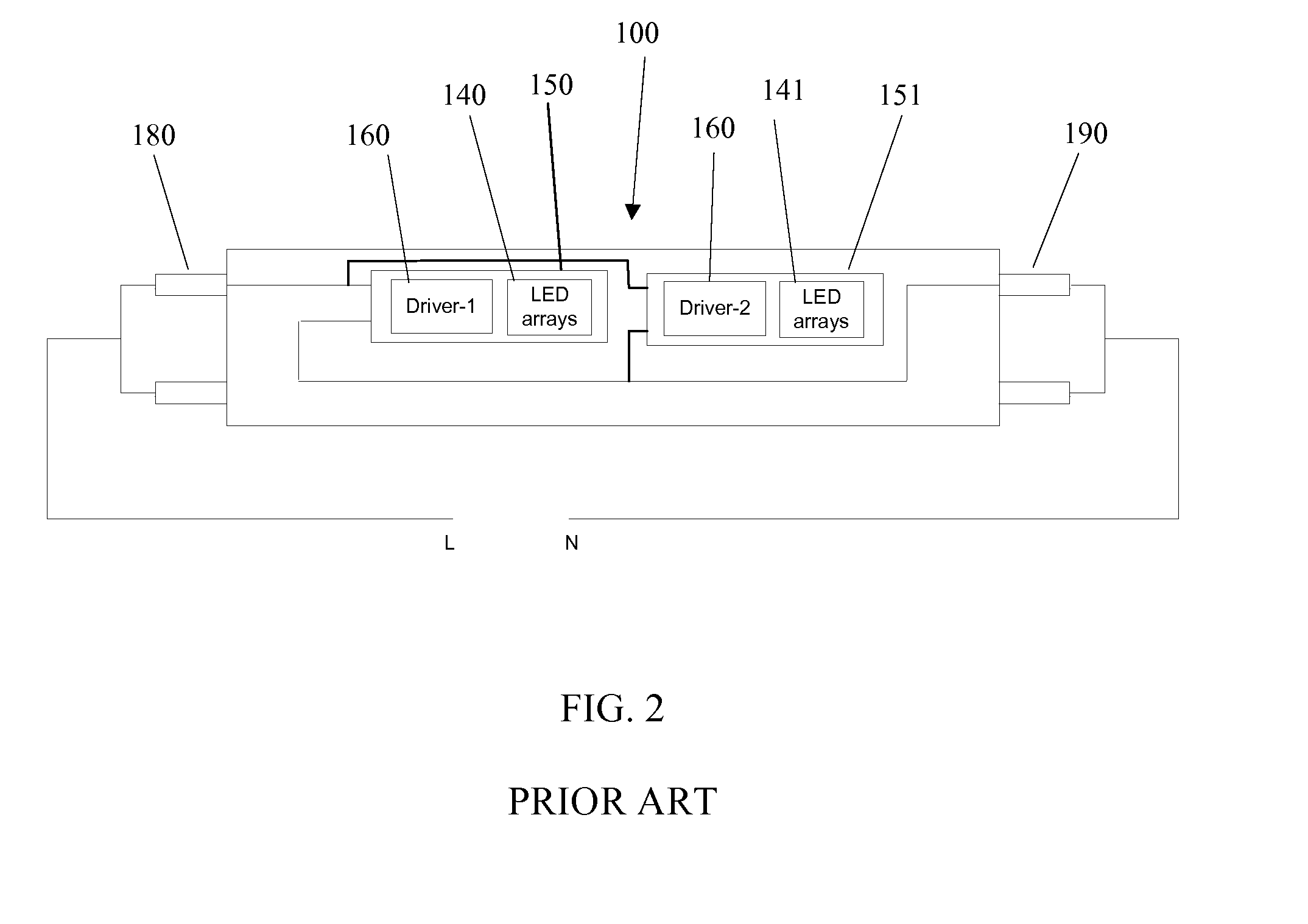

Linear solid-state lighting with shock protection switches

ActiveUS20110149563A1Leakage currentEliminate leakage currentPoint-like light sourceElongate light sourcesSmart lightingEngineering

A linear light-emitting diode (LED)-based solid-state device comprising at least two shock protection switches, at least one each at the two ends of the device, fully protects a person from possible electric shock during re-lamping with LED lamps.

Owner:ALEDDRA INC

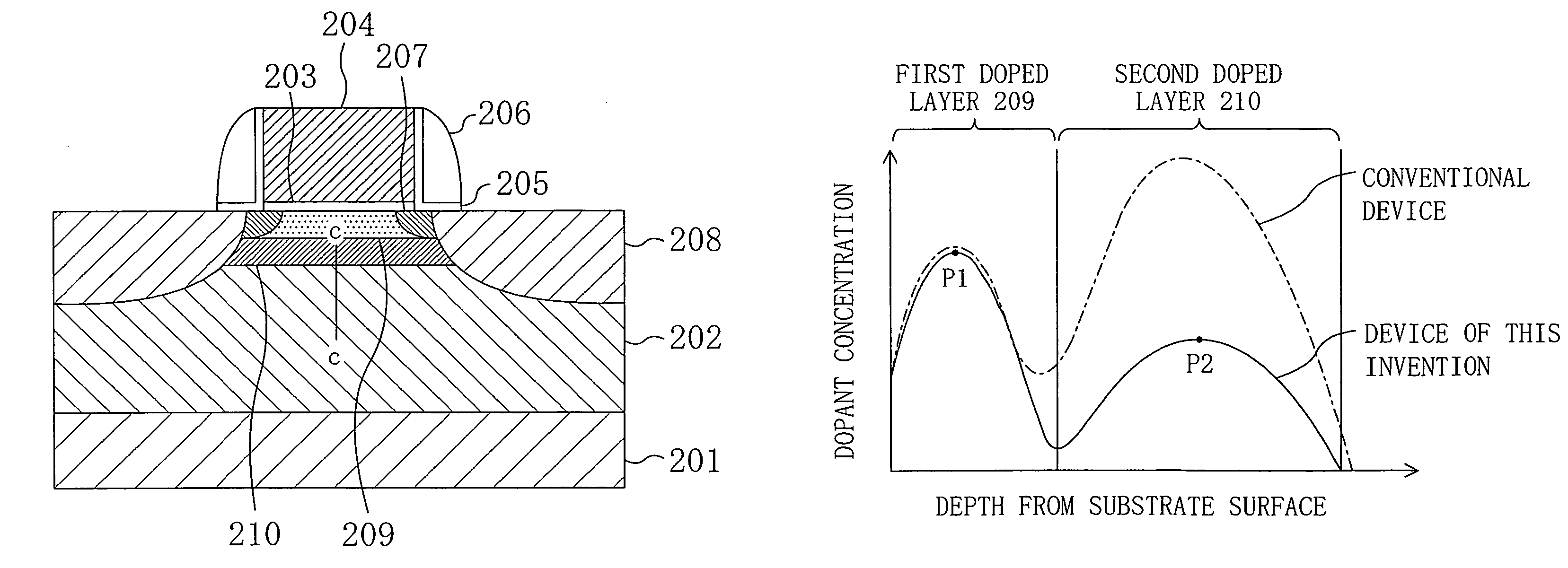

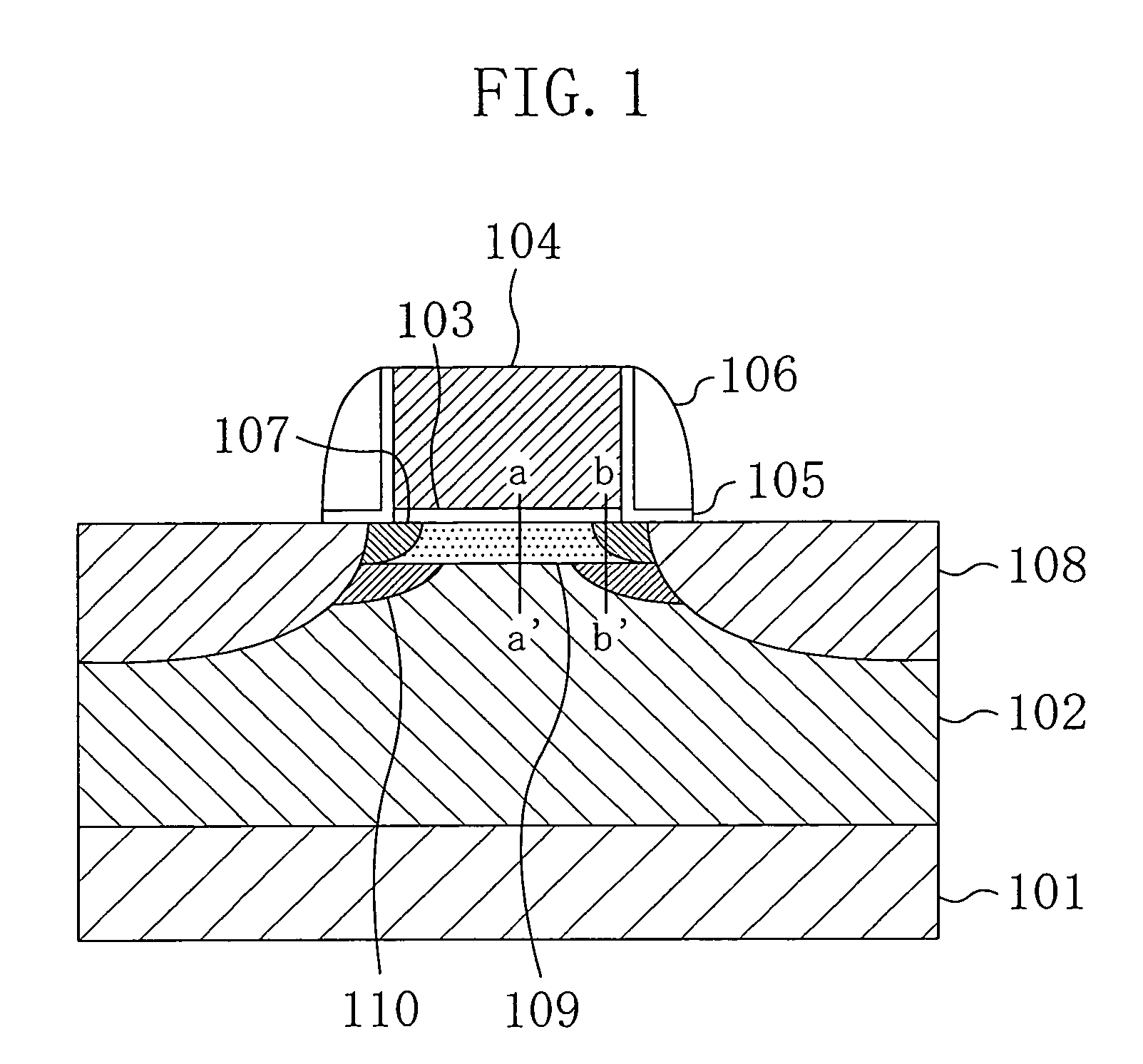

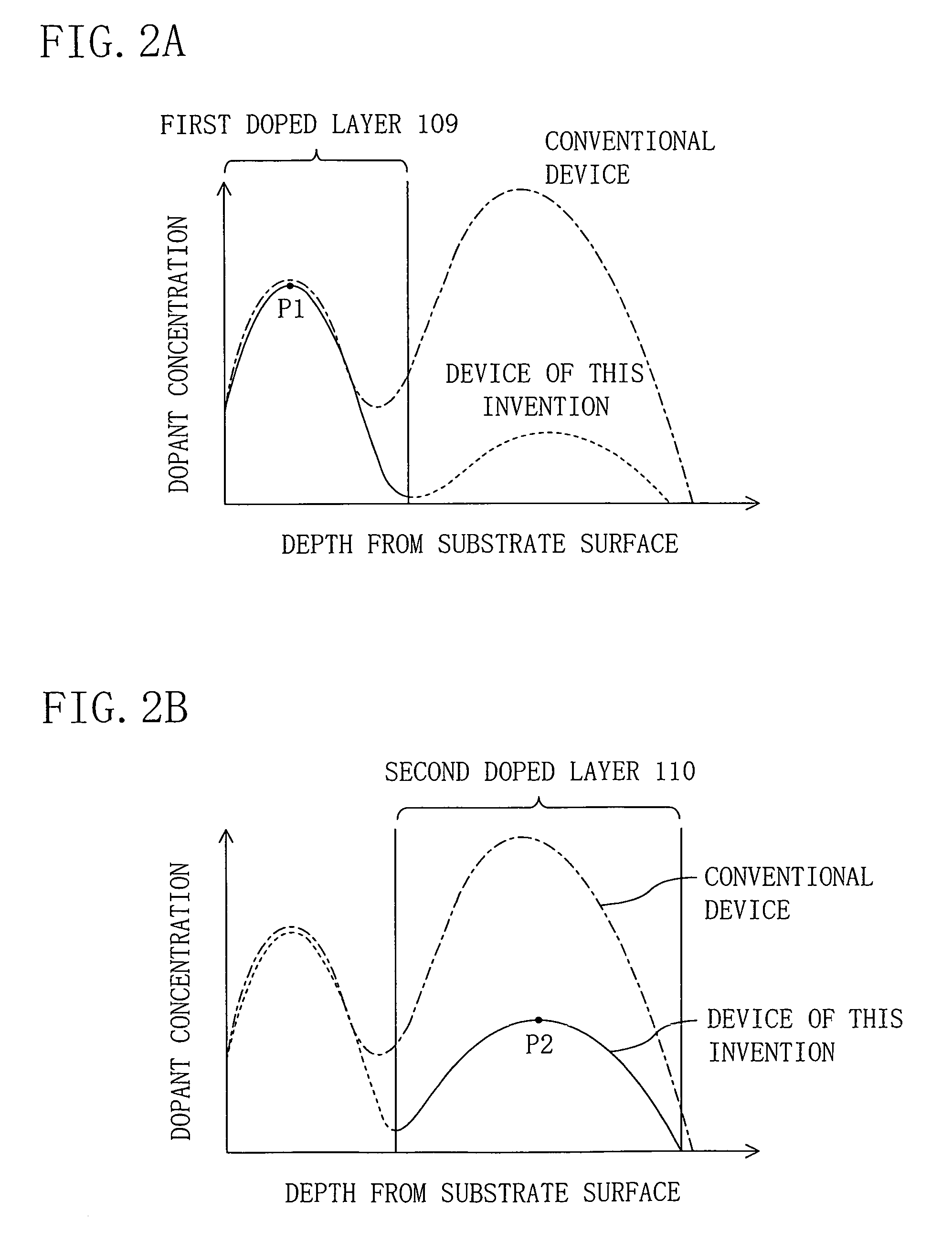

Semiconductor device and method for fabricating the same

ActiveUS7301208B2Increase powerImprove leakage currentTransistorSemiconductor/solid-state device manufacturingDopantPeak value

A first doped layer of a conductivity type opposite to that of source / drain regions is formed in a semiconductor substrate under a gate electrode. A second doped layer of the conductivity type opposite to that of the source / drain regions is formed in the semiconductor substrate below the first doped layer. The first doped layer has a first peak in dopant concentration distribution in the depth direction. The first peak is located at a position shallower than the junction depth of the source / drain regions. The second doped layer has a second peak in dopant concentration distribution in the depth direction. The second peak is located at a position deeper than the first peak and shallower than the junction depth of the source / drain regions. The dopant concentration at the first peak is higher than that at the second peak.

Owner:GK BRIDGE 1

Field-effect semiconductor device, and method of fabrication

ActiveUS20100155720A1Leakage currentLittle and no physical impairmentSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionField effect

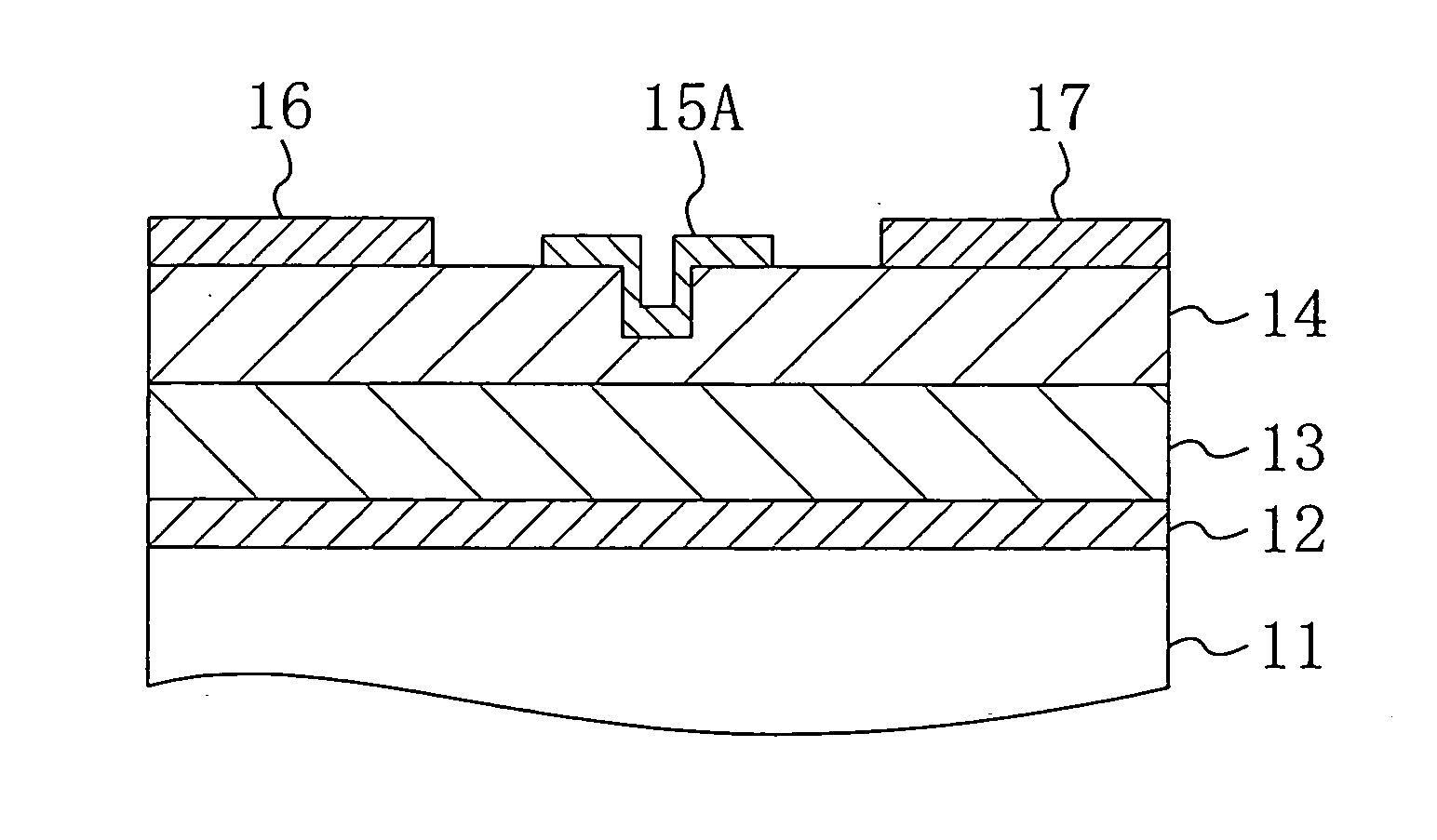

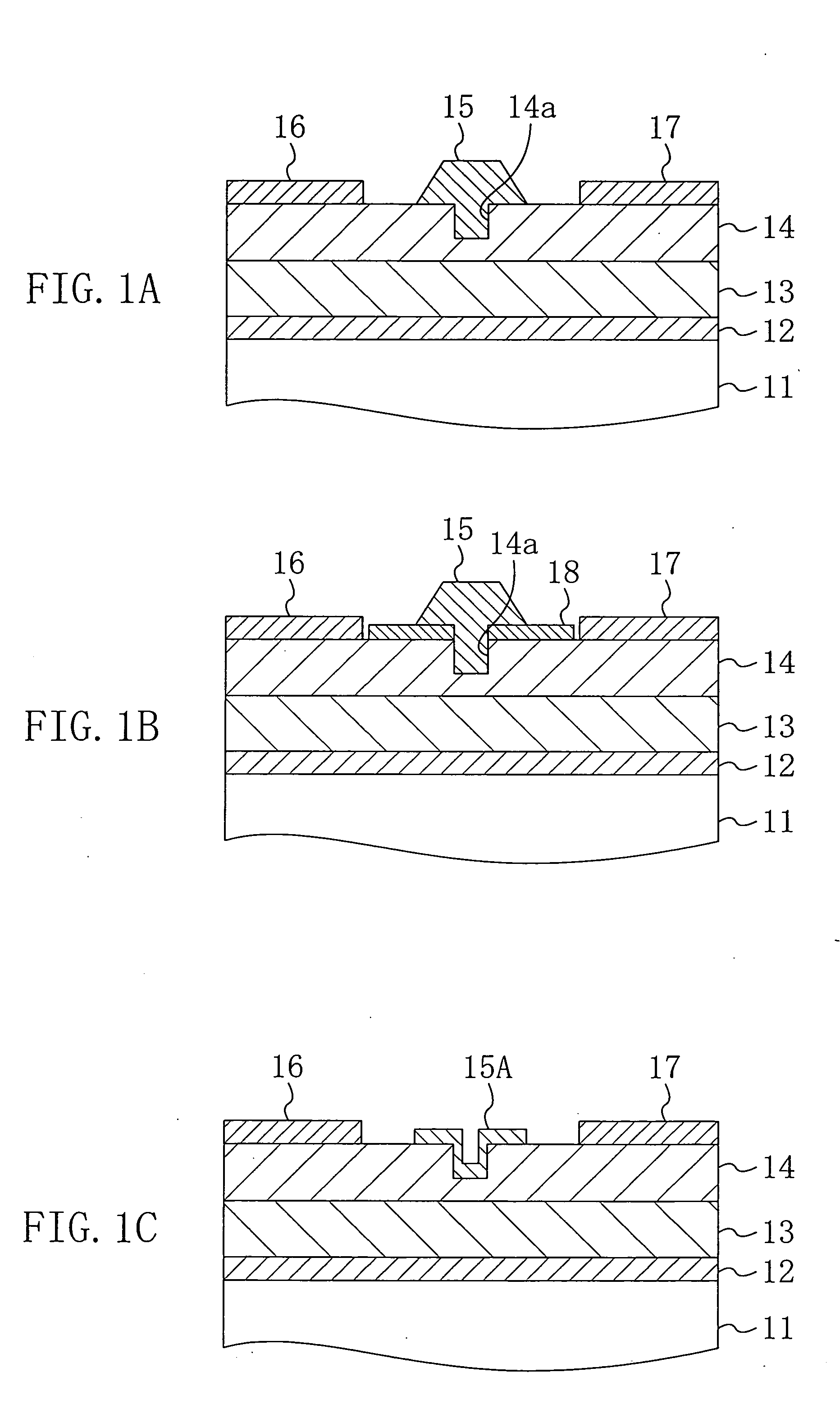

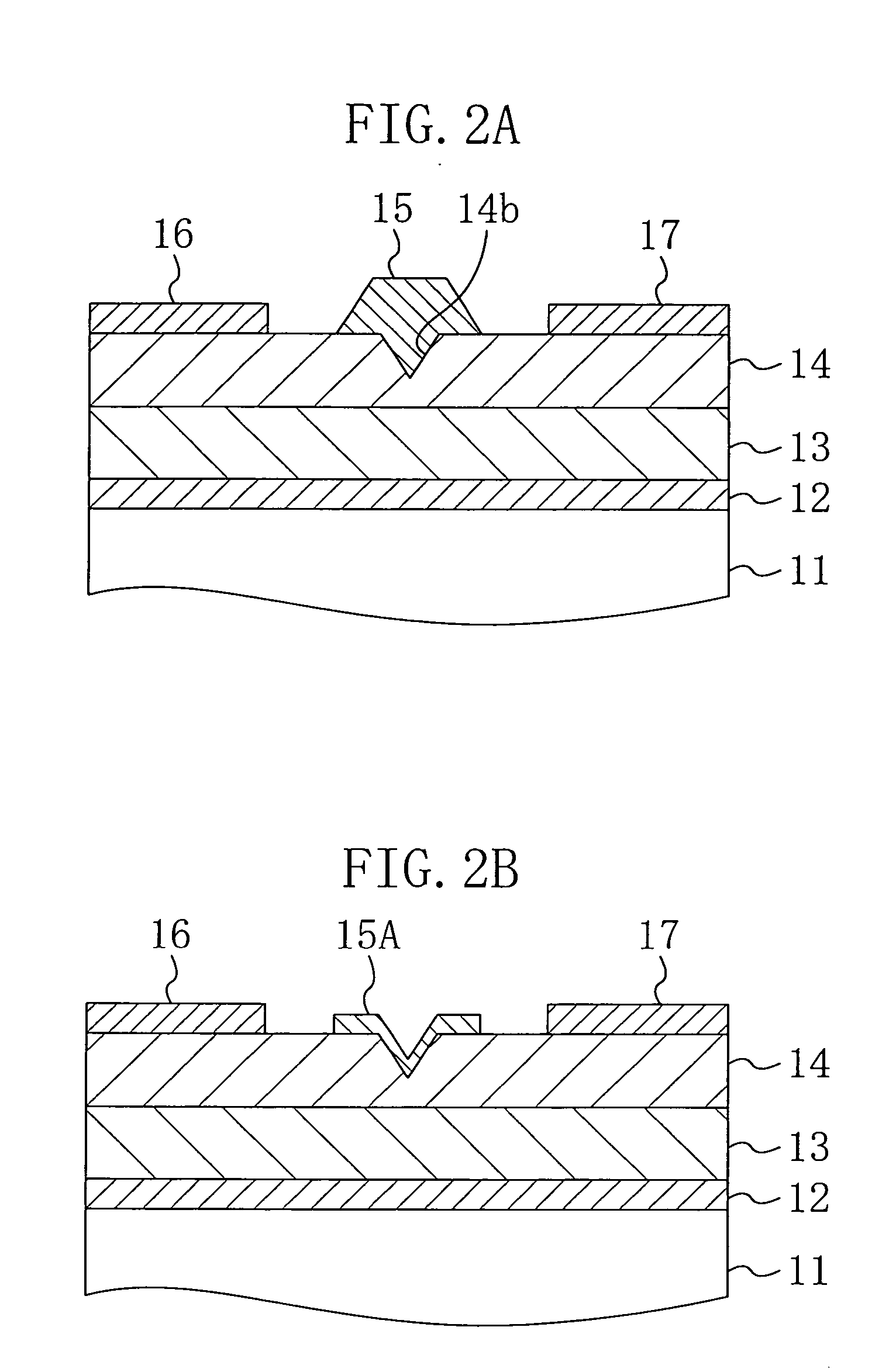

A heterojunction field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on a major surface of the main semiconductor region and electrically coupled to the 2DEG layer. Between these electrodes, a gate electrode is received in a recess in the major surface of the main semiconductor region via a p-type metal oxide semiconductor film and insulating film, whereby a depletion zone is normally created in the 2DEG layer, making the device normally off. The p-type metal oxide semiconductor film of high hole concentration serves for the normally-off performance of the device with low gate leak current, and the insulating film for further reduction of gate leak current.

Owner:SANKEN ELECTRIC CO LTD

Spacer structure in MRAM cell and method of its fabrication

ActiveUS20070120210A1Leakage currentMagnetic-field-controlled resistorsSolid-state devicesBit lineDielectric layer

Methods are presented for fabricating an MTJ element having a precisely controlled spacing between its free layer and a bit line and, in addition, having a protective spacer layer formed abutting the lateral sides of the MTJ element to eliminate leakage currents between MTJ layers and the bit line. Each method forms a dielectric spacer layer on the lateral sides of the MTJ element and, depending on the method, includes an additional layer that protects the spacer layer during etching processes used to form a Cu damascene bit line. At various stages in the process, a dielectric layer is also formed to act as a CMP stop layer so that the capping layer on the MTJ element is not thinned by the CMP process that planarizes the surrounding insulation. Subsequent to planarization, the stop layer is removed by an anisotropic etch of such precision that the MTJ element capping layer is not thinned and serves to maintain an exact spacing between the bit line and the MTJ free layer.

Owner:TAIWAN SEMICON MFG CO LTD

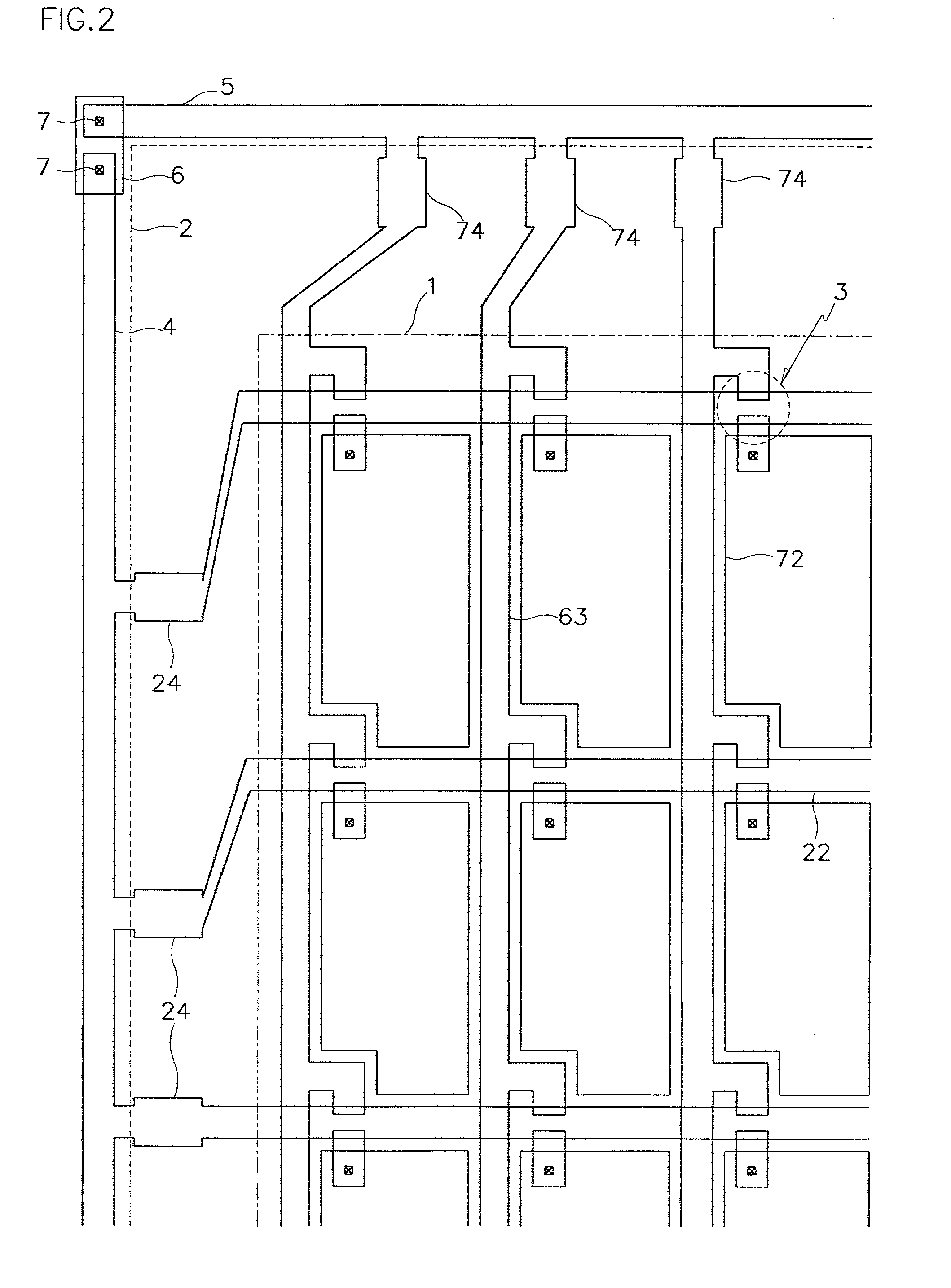

Thin film transistor array panel for a liquid crystal display and methods for manufacturing the same

InactiveUS20020130324A1Reduces contact resistivitySimple manufacturing methodSolid-state devicesSemiconductor/solid-state device manufacturingPhysicsLiquid-crystal display

Owner:SAMSUNG DISPLAY CO LTD

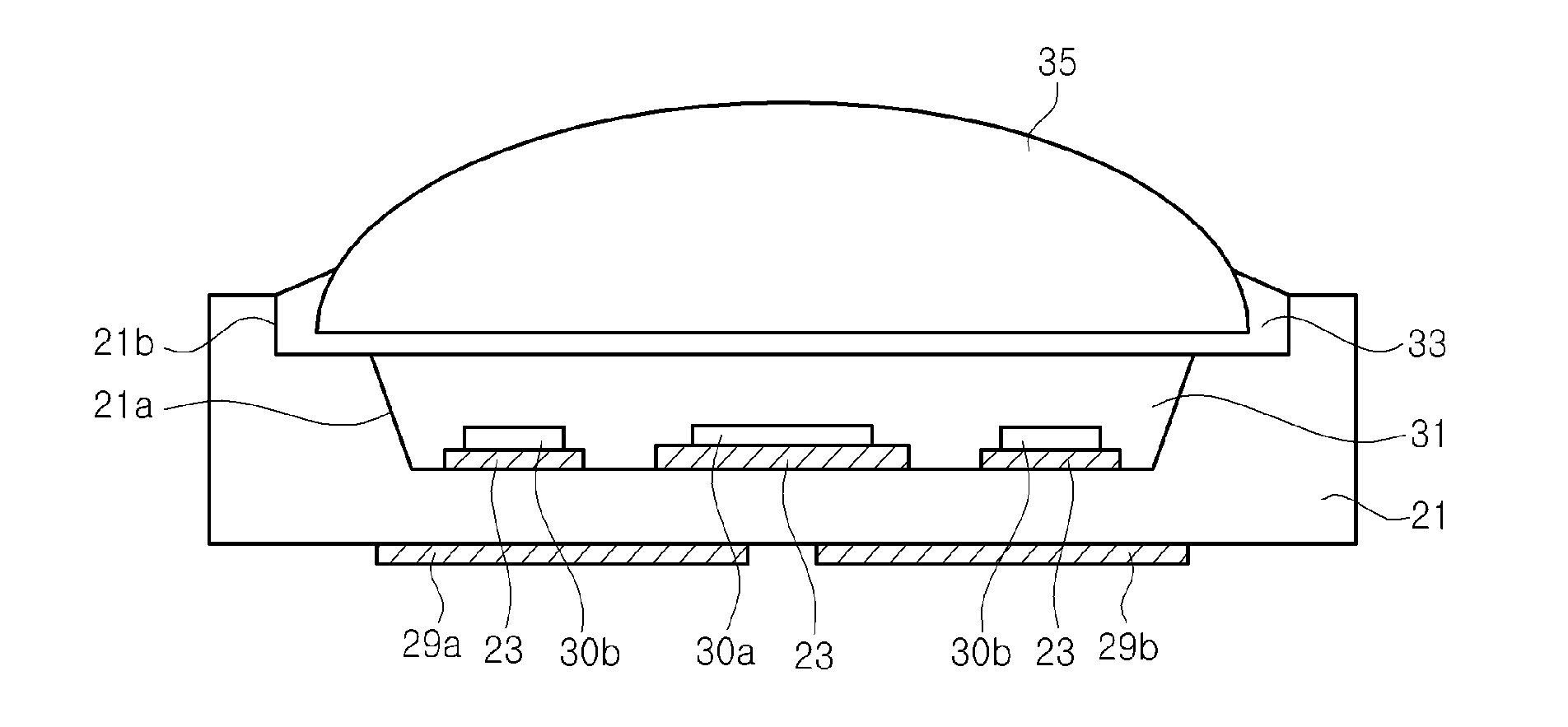

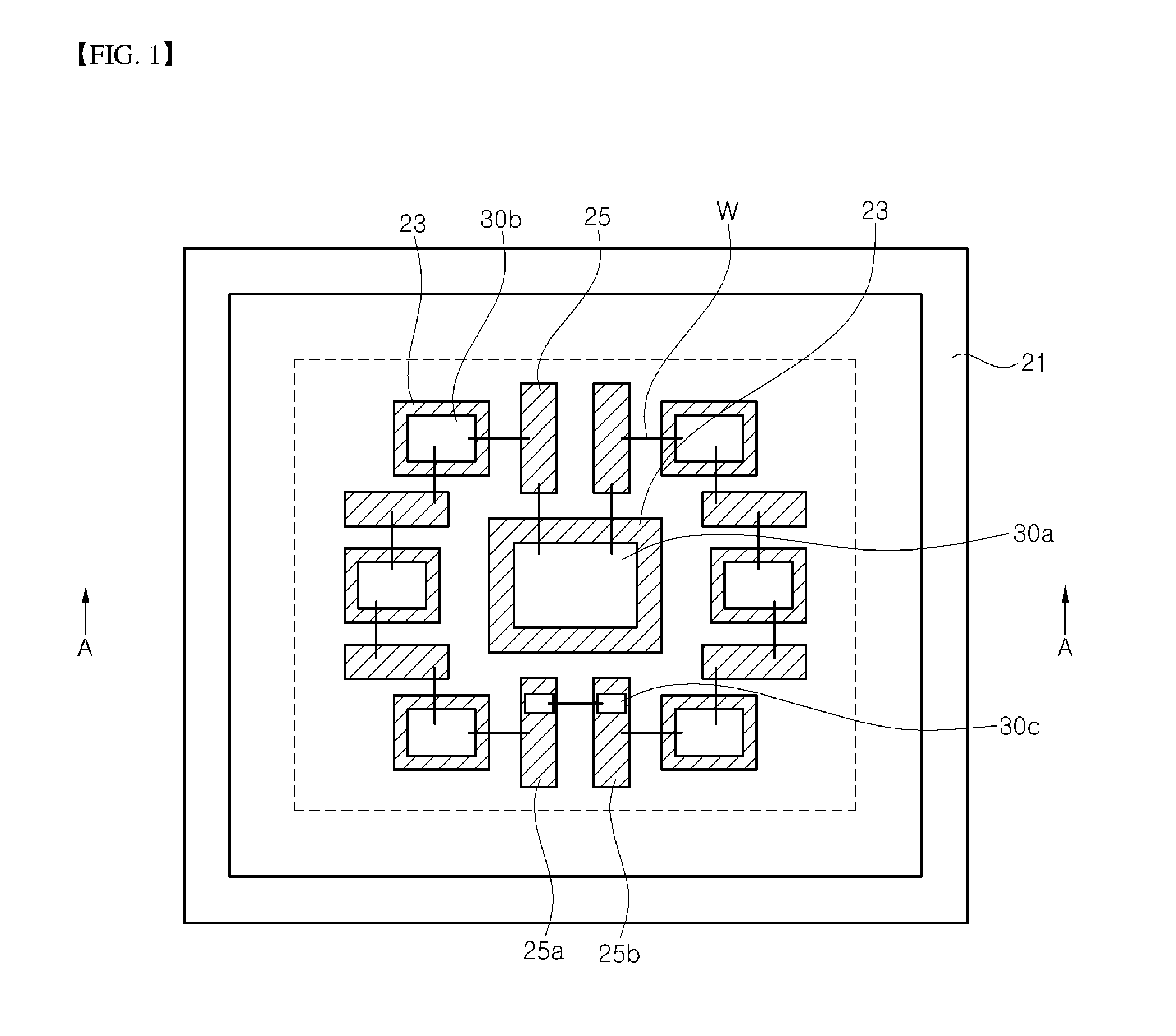

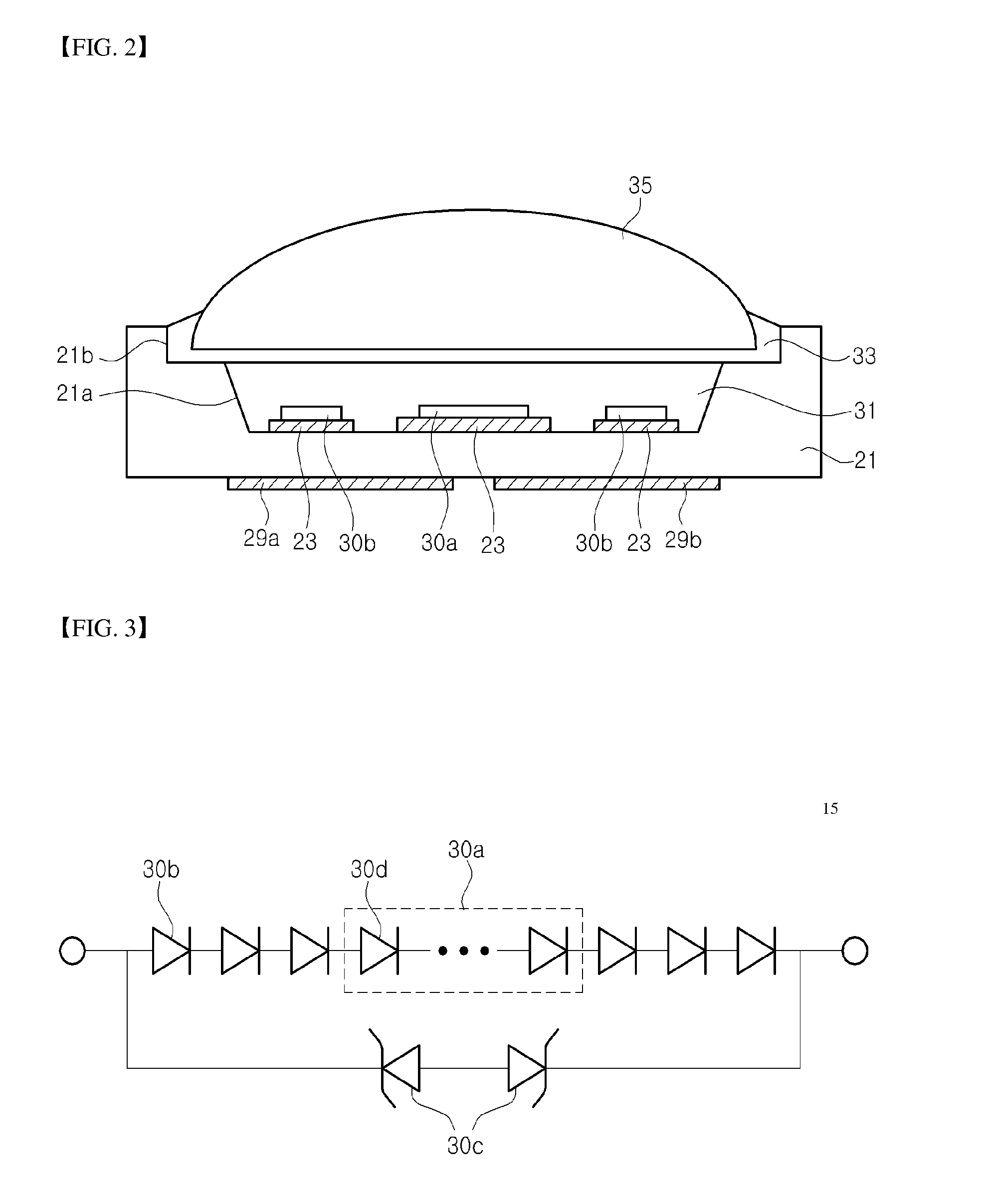

Light emitting diode package

ActiveUS20120056217A1Reduce package sizePrevent leakageSolid-state devicesSemiconductor devicesPhosphorLight-emitting diode

Disclosed herein is a light emitting diode package including a package body having a cavity, a light emitting diode chip having a plurality of light emitting cells connected in series to one another, a phosphor converting a frequency of light emitted from the light emitting diode chip, and a pair of lead electrodes. The light emitting cells are connected in series between the pair of lead electrodes.

Owner:SEOUL SEMICONDUCTOR

Linear solid-state lighting with shock protection switches

ActiveUS8147091B2Leakage currentImprove production efficiencyPoint-like light sourceLighting support devicesSmart lightingEngineering

A linear light-emitting diode (LED)-based solid-state device comprising at least two shock protection switches, at least one each at the two ends of the device, fully protects a person from possible electric shock during re-lamping with LED lamps.

Owner:ALEDDRA INC

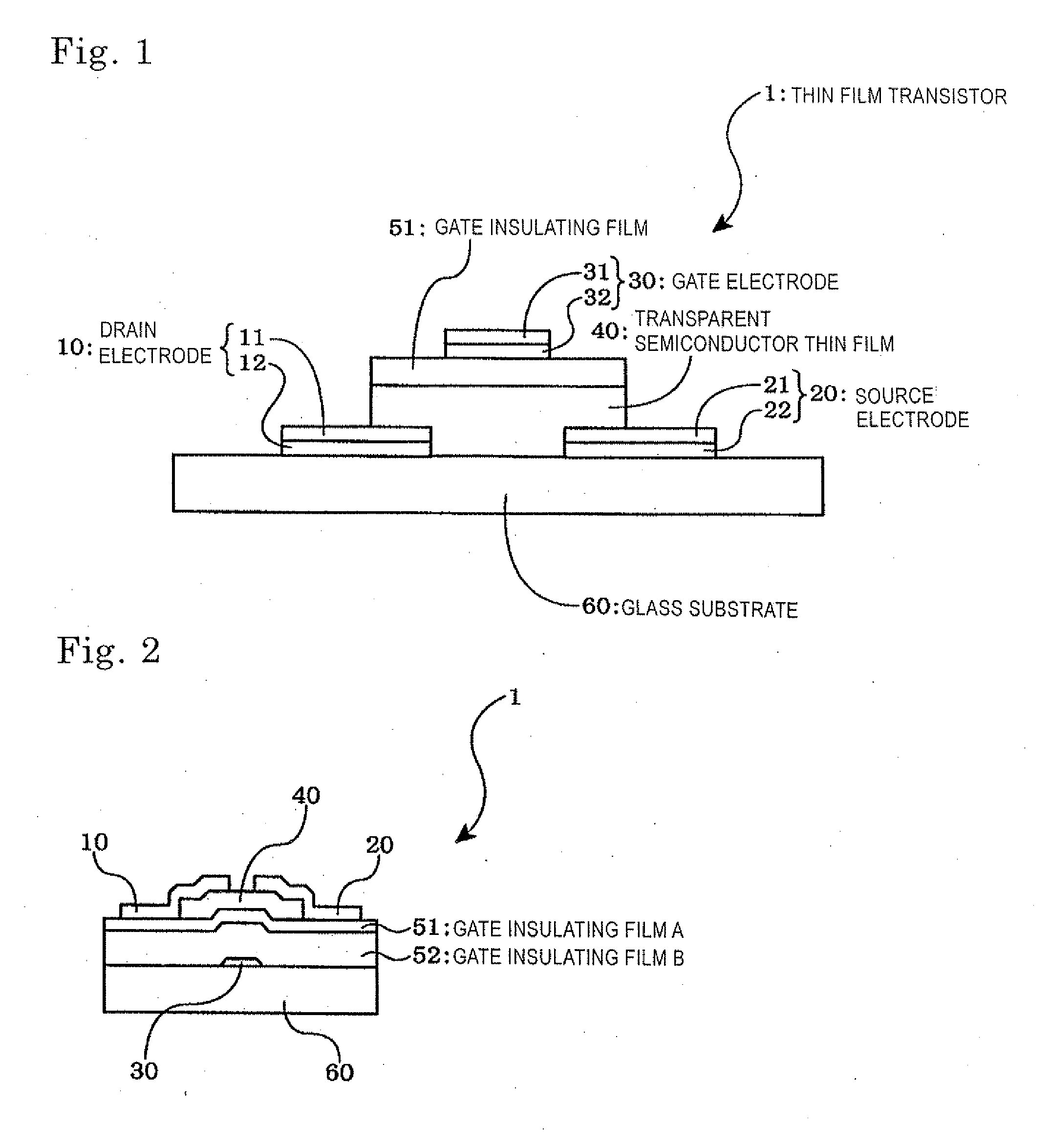

Semiconductor thin film and method for manufacturing same, and thin film transistor

ActiveUS20090267064A1Hardly erroneously operatesSmall currentTransistorTin compoundsCharge carrierZinc

The present invention provides a semiconductor thin film which can be manufactured at a relatively low temperature even on a flexible resin substrate. As a semiconductor thin film having a low carrier concentration, a high Hall mobility and a large energy band gap, an amorphous film containing zinc oxide and tin oxide is formed to obtain a carrier density of 10+17 cm−3 or less, a Hall mobility of 2 cm2 / V·sec or higher, and an energy band gap of 2.4 eV or more. Then, the amorphous film is oxidized to form a transparent semiconductor thin film 40.

Owner:IDEMITSU KOSAN CO LTD

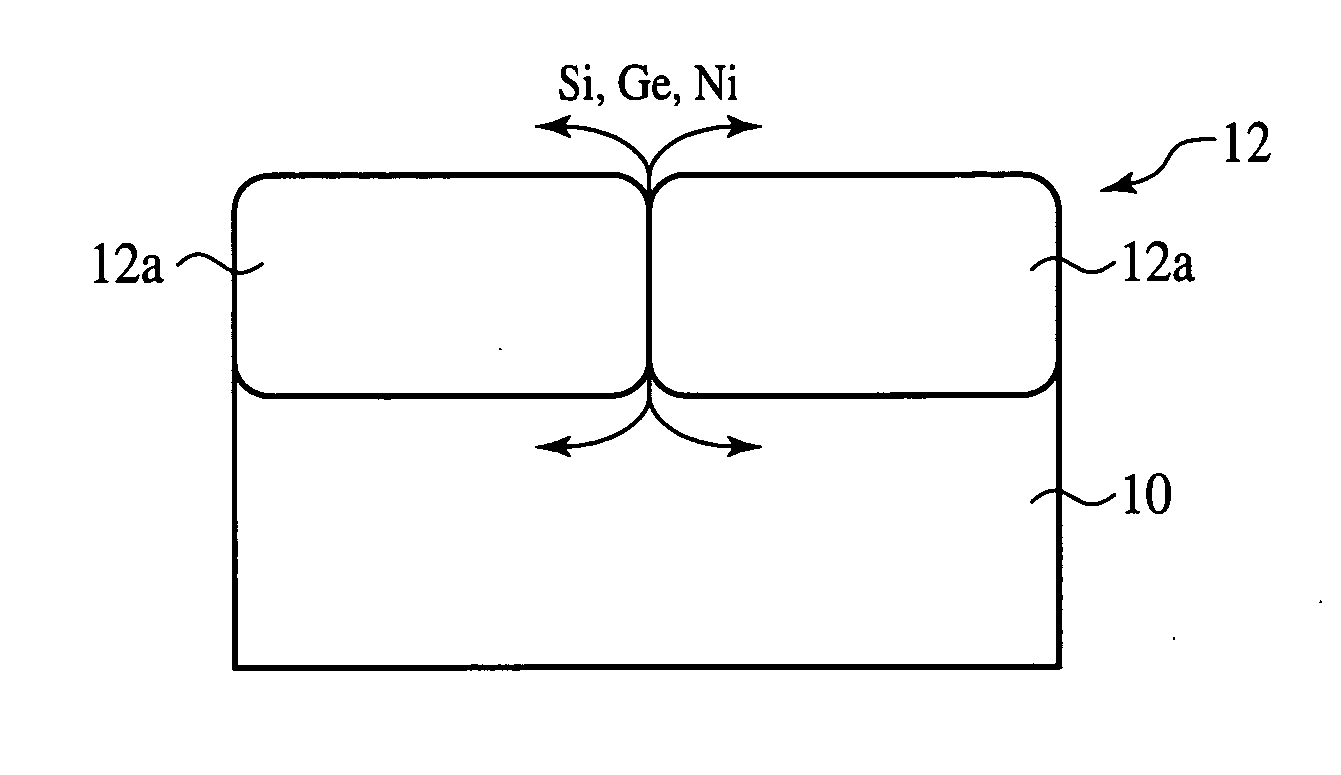

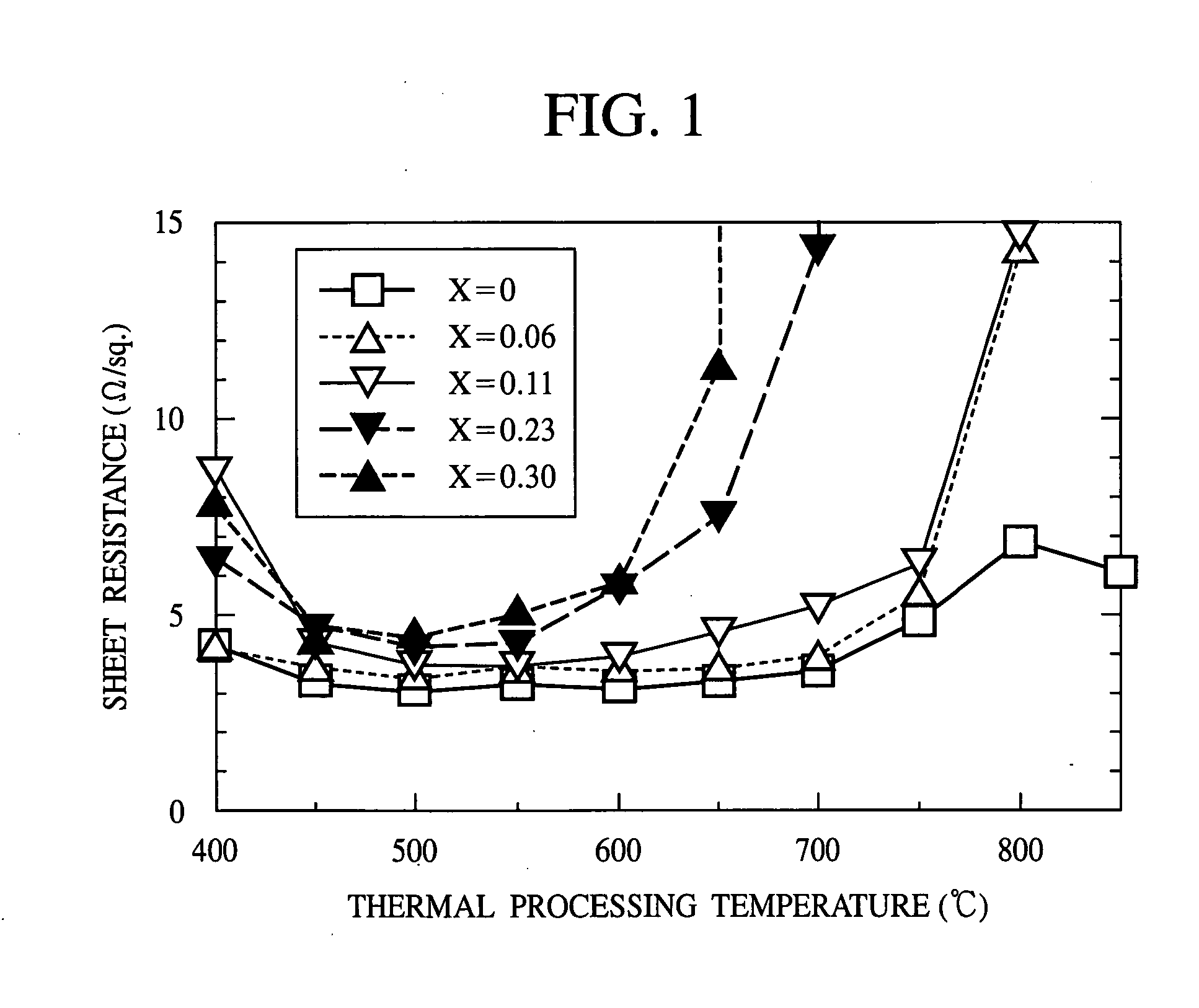

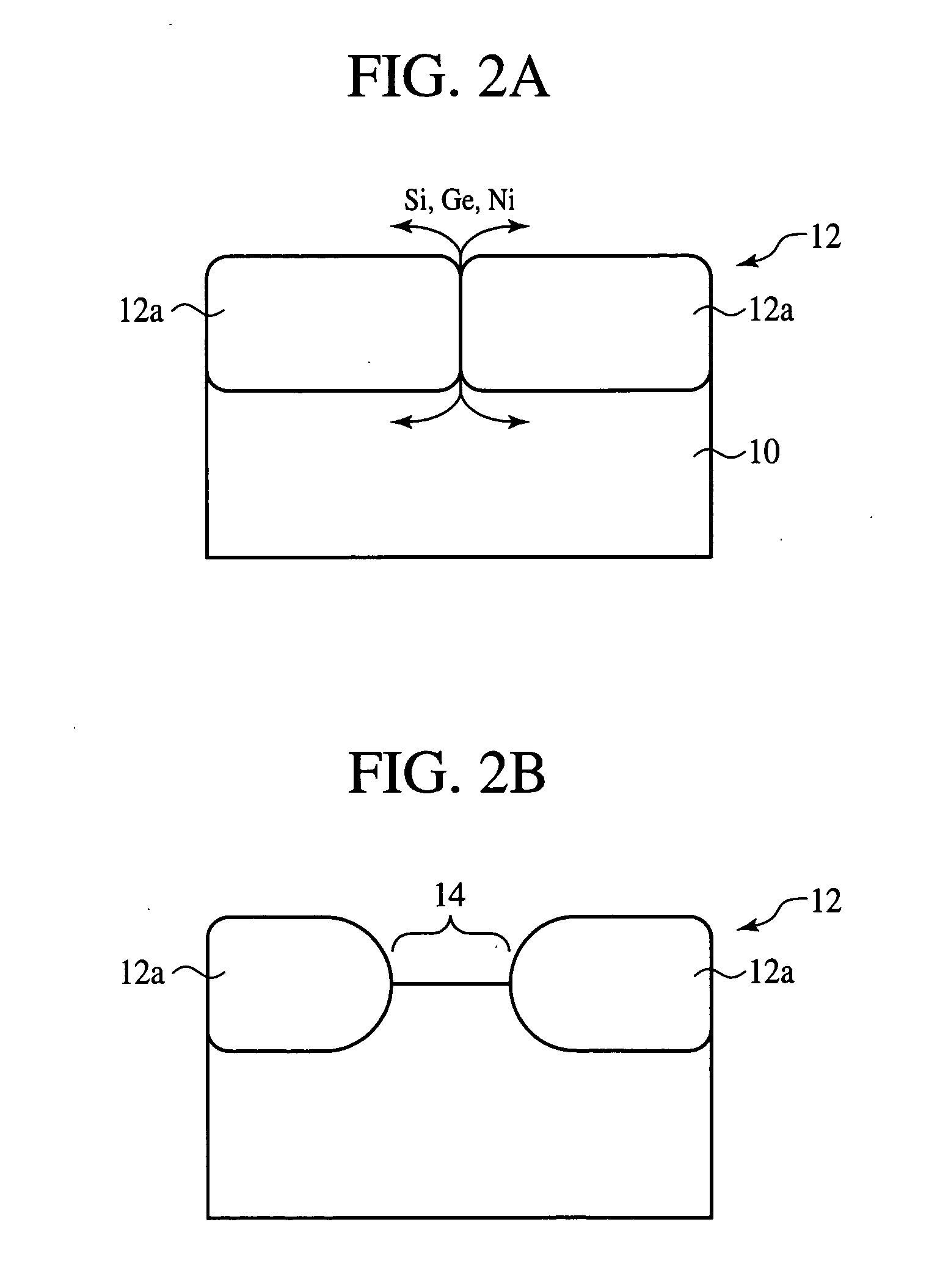

Semiconductor device fabrication method

ActiveUS20060281288A1Improve electrical characteristicsReduce sheet resistanceTransistorSemiconductor/solid-state device manufacturingSemiconductorGrain boundary

The semiconductor device fabrication method comprising the step of forming a gate electrode 54p on a semiconductor substrate 34; the step of forming a source / drain diffused layer 64p in the semiconductor substrate 34 on both sides of the gate electrode 54p; the step of burying a silicon germanium layer 100b in the source / drain diffused layer 64p; the step of forming an amorphous layer at an upper part of the silicon germanium layer 101; the step of forming a nickel film 66 on the amorphous layer 101; and the step of making thermal processing to react the nickel film 66 and the amorphous layer 101 with each other to form a silicide film 102b on the silicon germanium layer 100b. Because of no crystal boundaries in the amorphous layer 101 to react with the nickel film 66, the silicidation homogeneously goes on. Because of no crystal faces in the amorphous layer 101, the Ni(Si1-xGex)2 crystals are prevented from being formed in spikes. Thus, even when the silicon germanium layer 100b is silicided by using a thin nickel film 66, the sheet resistance can be low, and the junction leak current can be suppressed.

Owner:FUJITSU LTD

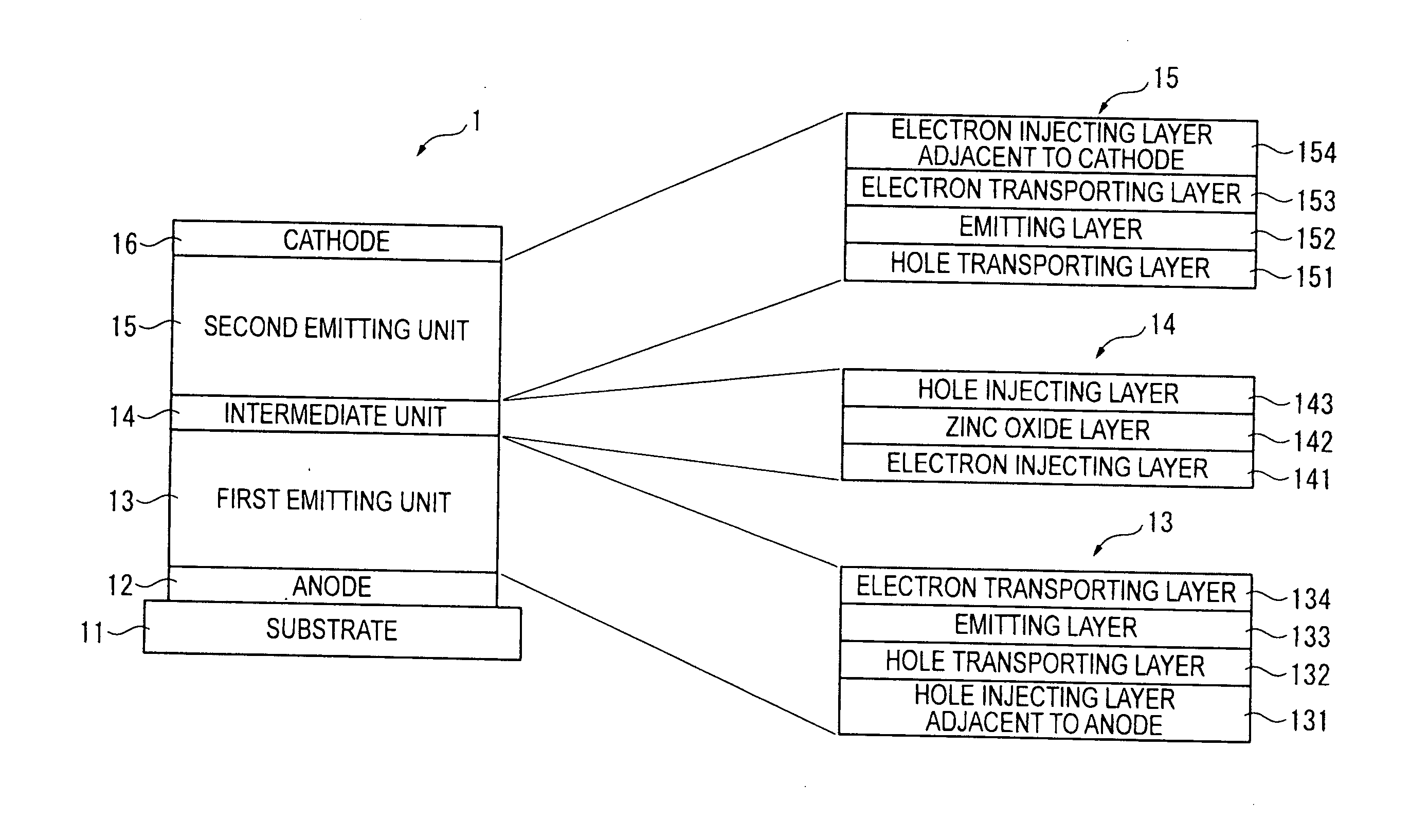

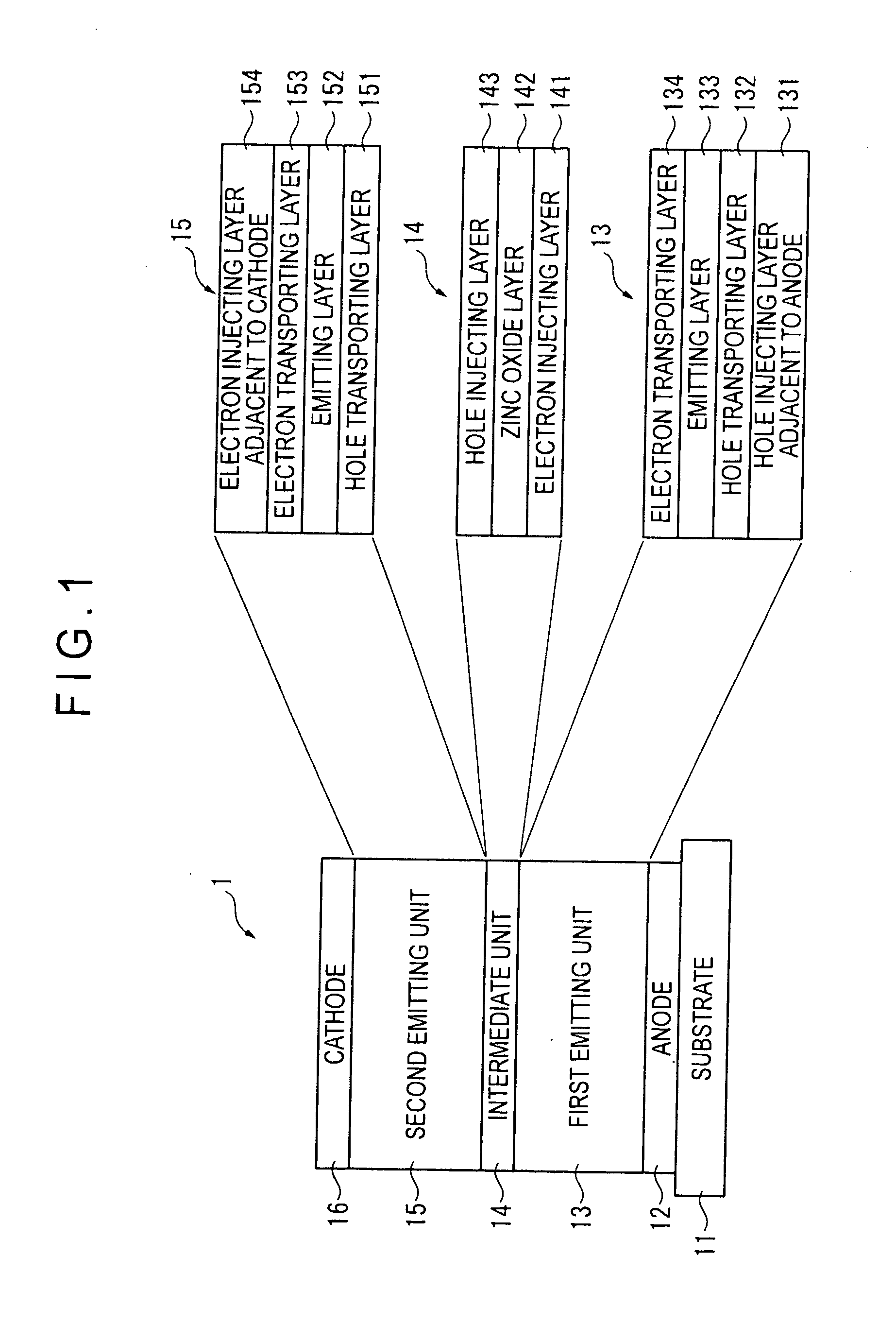

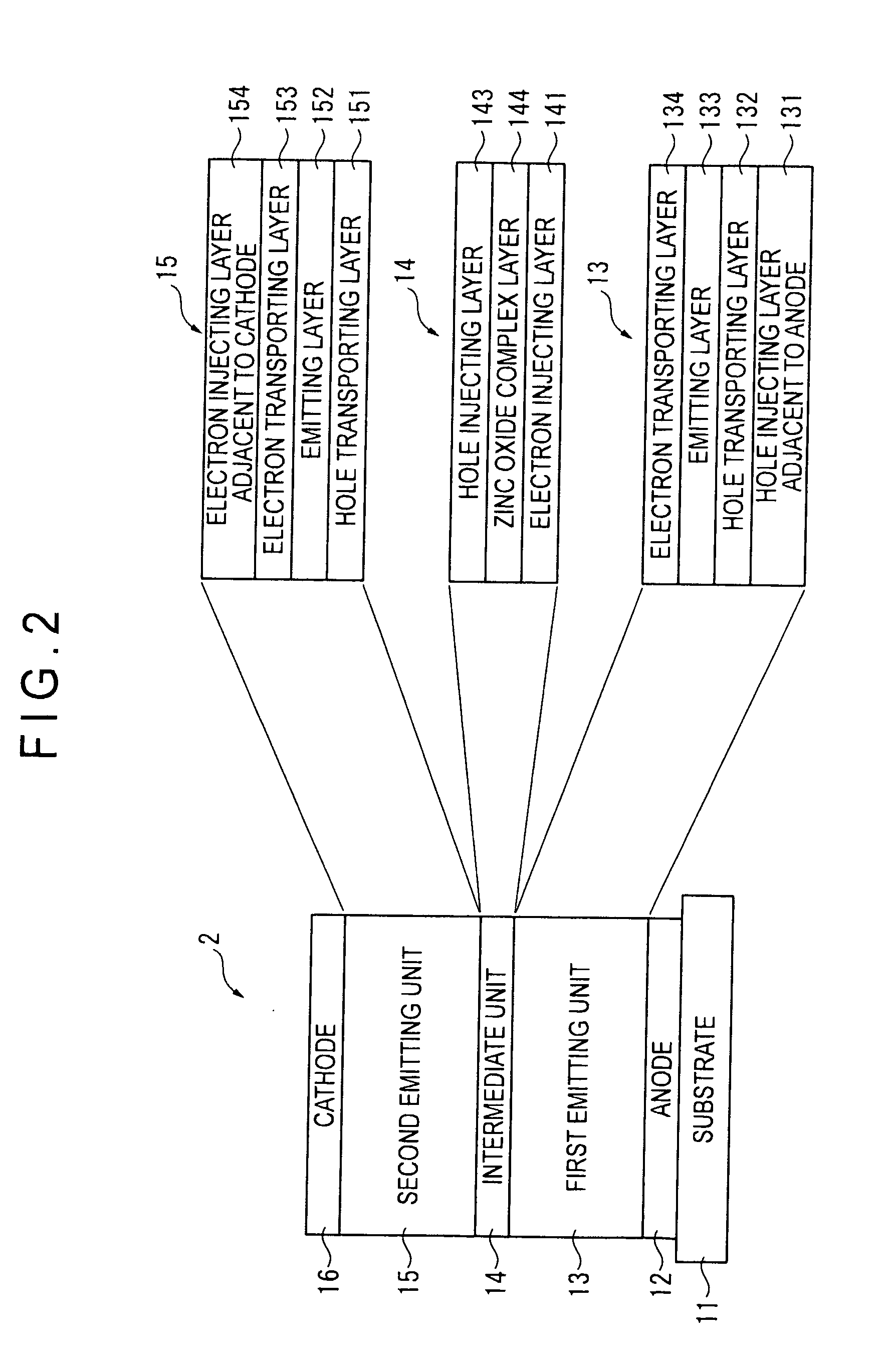

Organic electroluminescence device and method for producing organic electroluminescence device

ActiveUS20120012820A1Reduce reflectivityReduce the differenceSolid-state devicesSemiconductor/solid-state device manufacturingHole injection layerOrganic electroluminescence

An organic electroluminescence device includes: an anode; a cathode opposed to the anode; and a plurality of emitting units including at least a first emitting unit and a second emitting unit. The plurality of emitting units each includes: an emitting layer; and an intermediate unit between the first emitting unit and the second emitting unit. The intermediate unit includes an electron injecting layer, a zinc oxide layer and a hole injecting layer in this sequence from the anode. The electron injecting layer contains an electron donating material and is adjacent to the first emitting unit. The hole injecting layer contains an organic electron accepting material and is adjacent to the second emitting unit.

Owner:IDEMITSU KOSAN CO LTD

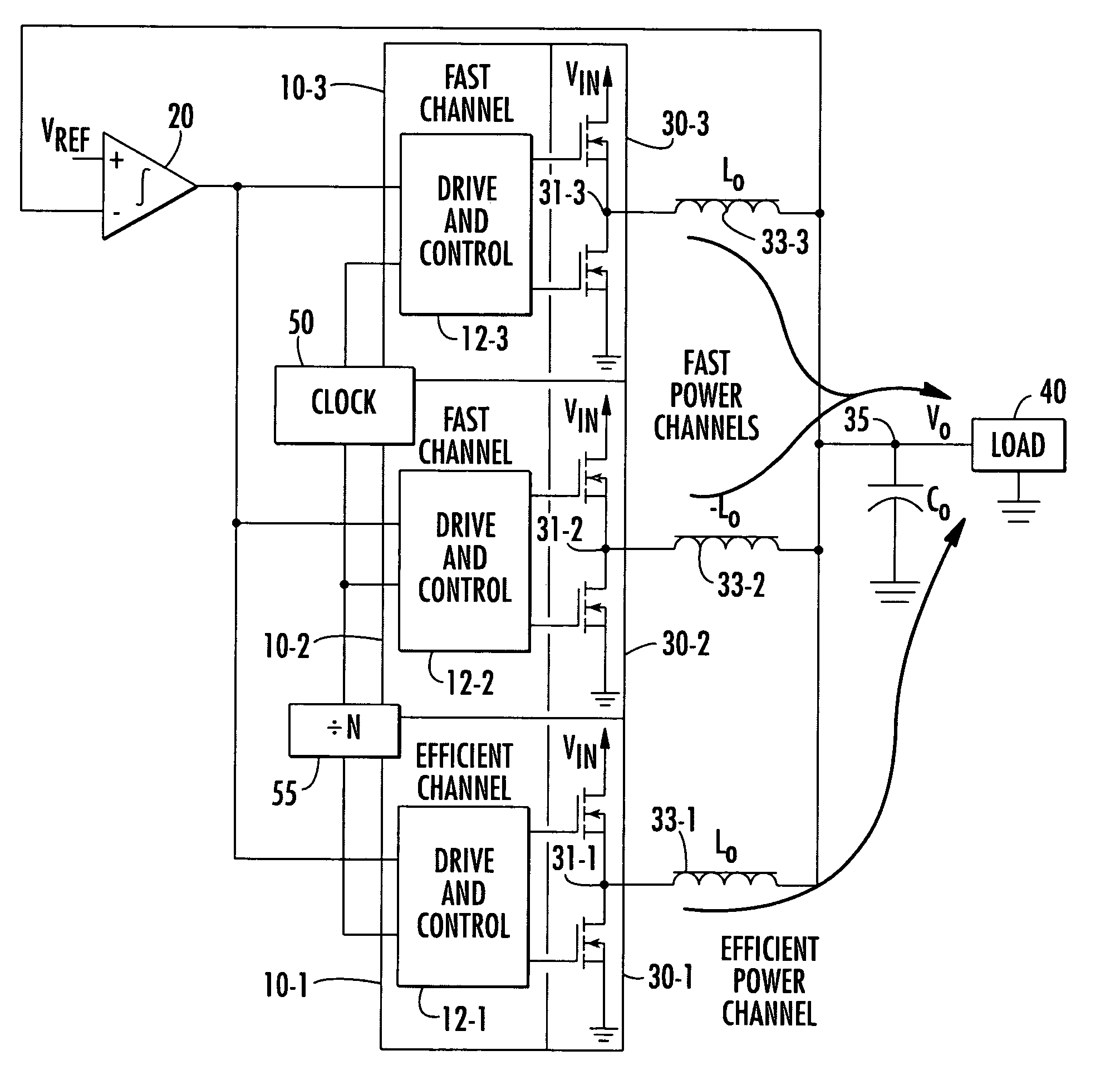

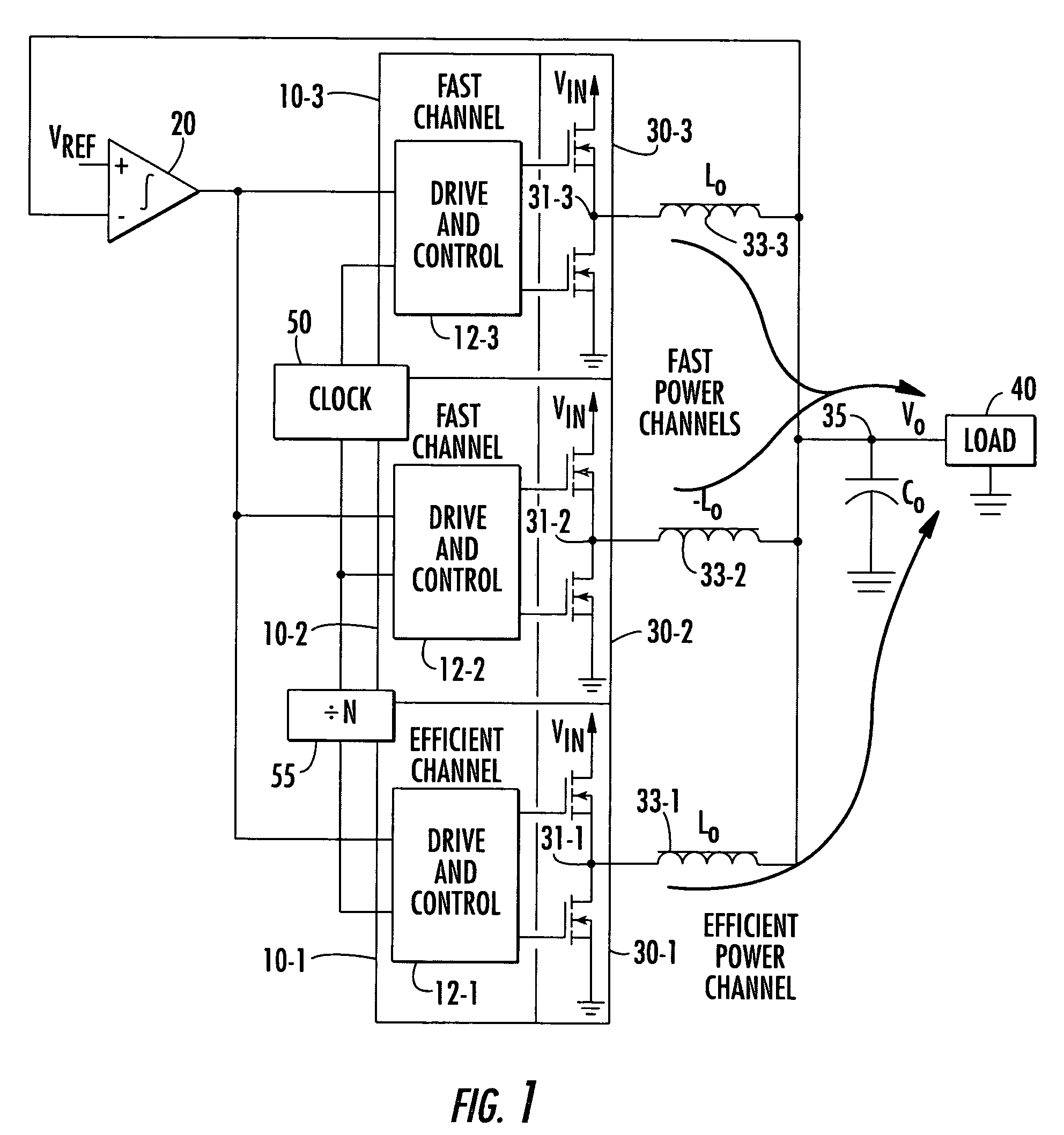

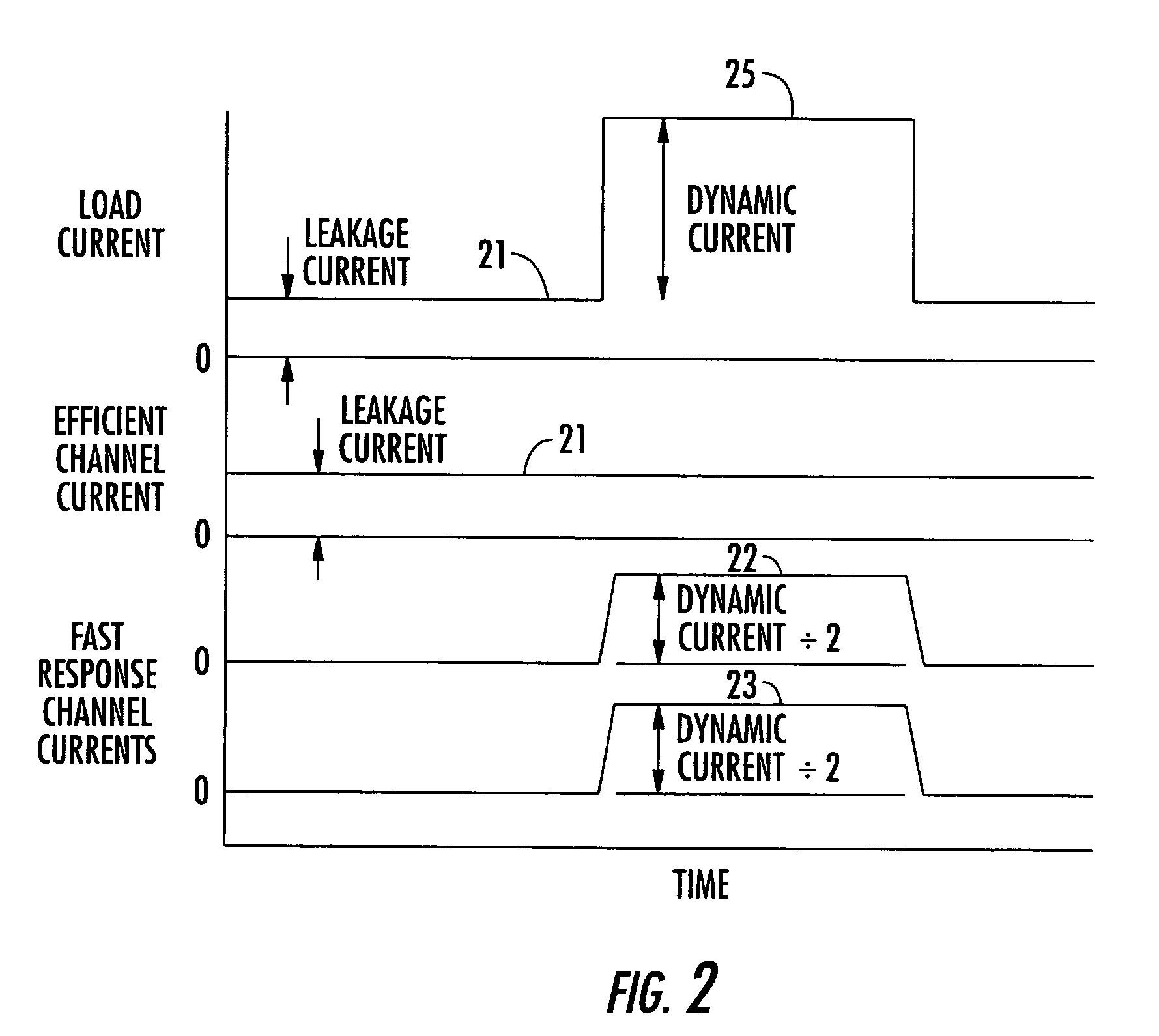

Asymmetrical multiphase DC-to-DC power converter

ActiveUS6995548B2Improve efficiencyLeakage currentEfficient power electronics conversionApparatus without intermediate ac conversionDc dc converterTransverter

A multiphase DC-DC converter architecture, in which respectively different channels have different operational performance parameters. These different parameters are selected so as to enable the converter to achieve an extended range of high efficiency. The converter contains a combination of one or more fast response time-based converter channels, and one or more highly efficient converter channels in respectively different phases thereof and combines the outputs of all the channels. The efficiency of the asymmetric multiphase converter is higher at light loads (up to approximately 12 amps), enabling it to offer longer battery life in applications that spend most of their operating time in the leakage mode, as noted above.

Owner:INTERSIL INC

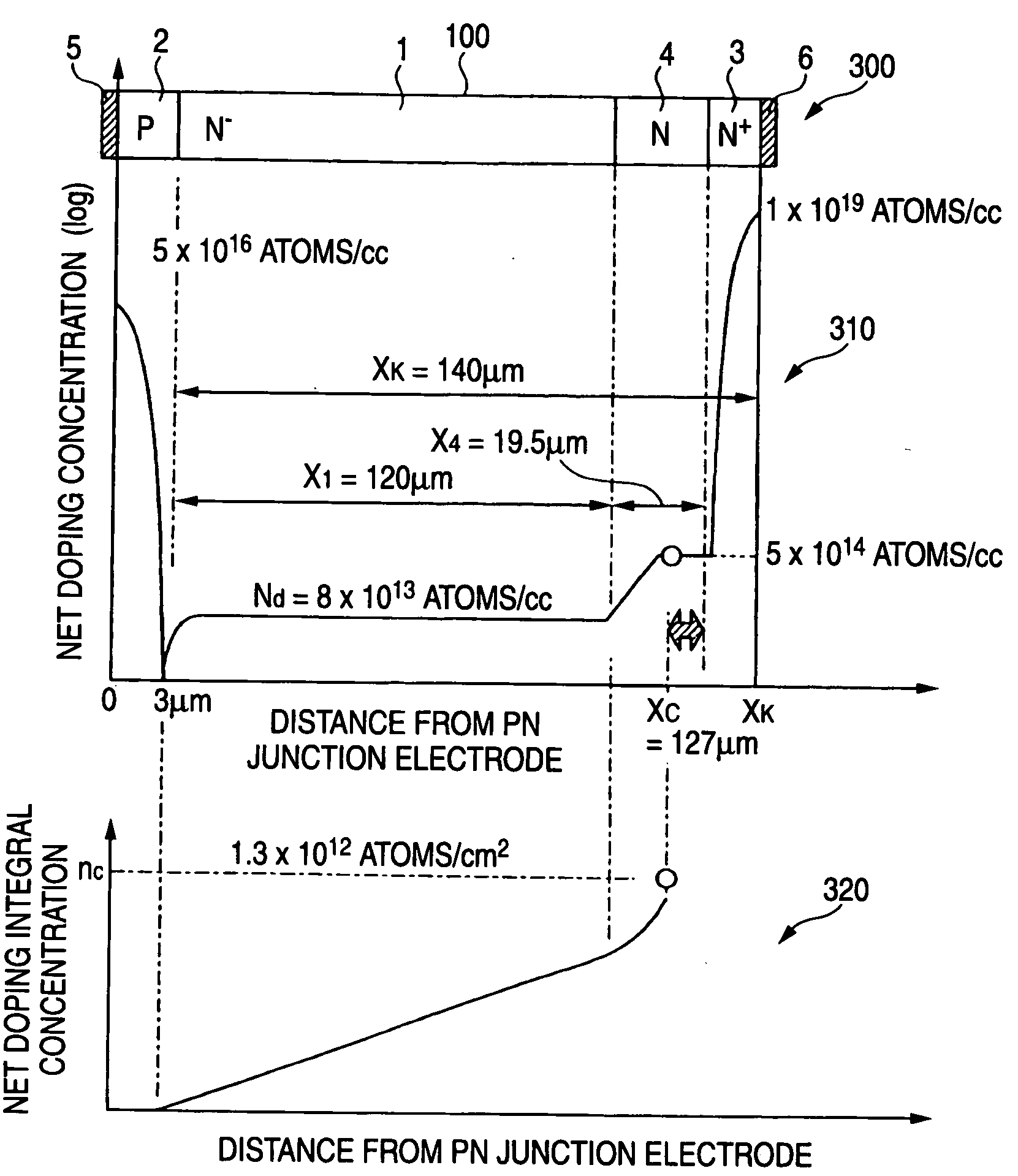

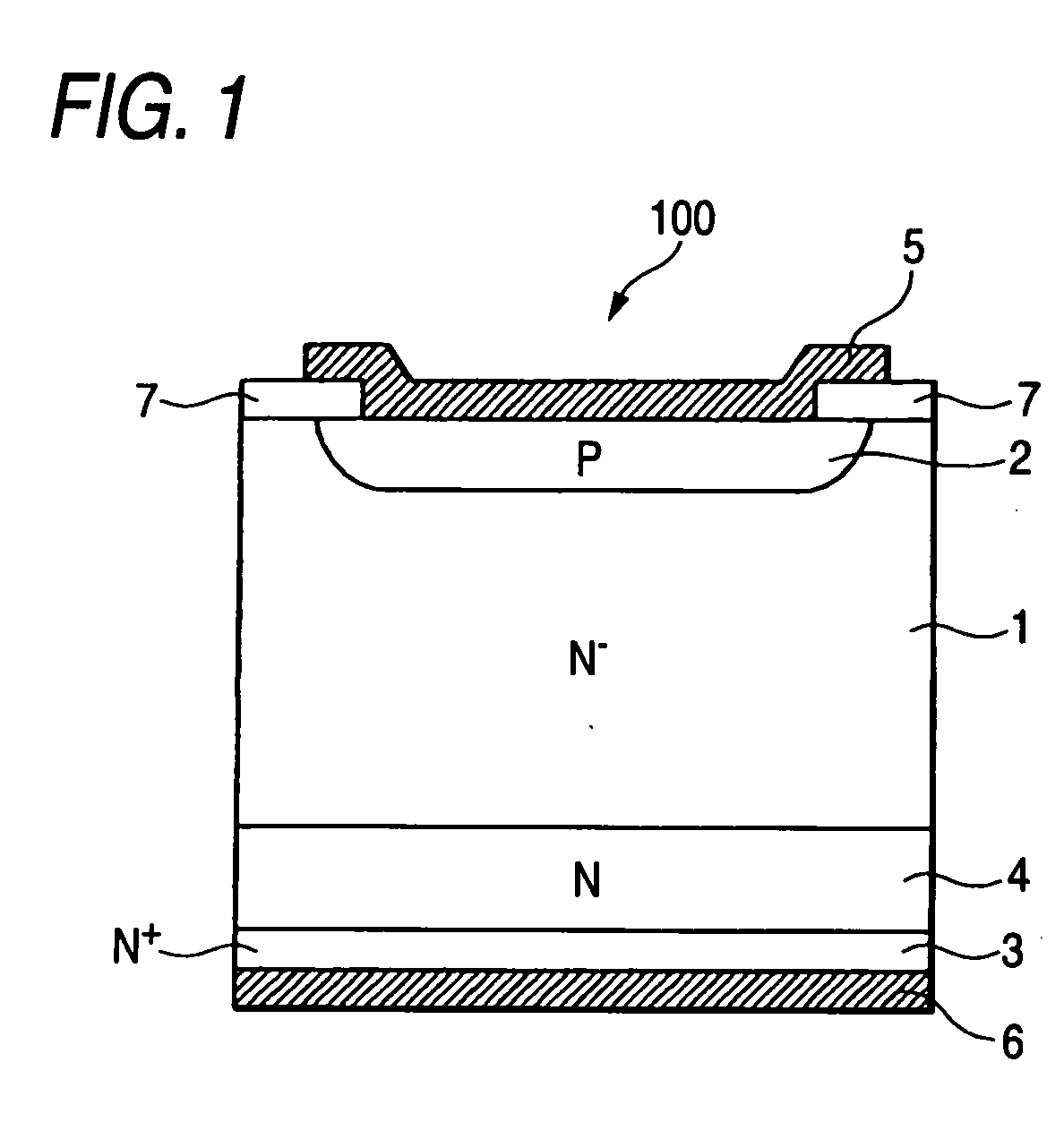

Semiconductor device and method of manufacturing the same

ActiveUS20070108558A1Small reverse leakage currentReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesReverse biasSemiconductor

A semiconductor device formed by decreasing thickness of a substrate by grinding, and performing ion implantation. In a diode in which a P anode layer and an anode electrode are formed at a side of a right face of an N− drift layer, and an N+ cathode layer and a cathode electrode are formed at a side of a back face of the N− drift layer, an N cathode buffer layer is formed thick compared with the N+-type cathode layer between the N−-type drift layer and the N+ cathode layer, the buffer layer being high in concentration compared with the N− drift layer, and low compared with the N+ cathode layer. When a reverse bias voltage is applied, a depletion layer is stopped in the middle of the N cathode buffer layer, and thus prevented from reaching the N+ cathode layer, so that the leakage current is suppressed.

Owner:FUJI ELECTRIC CO LTD

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20050139838A1Adjustable quantityReduce the impactSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialConductive materials

A semiconductor device of the present invention includes: a III-V nitride semiconductor layer including a channel region in which carriers travel; a concave portion provided in an upper portion of the channel region in the III-V nitride semiconductor layer; and a Schottky electrode consisting of a conductive material forming a Schottky junction with the semiconductor layer, and formed on a semiconductor layer, which spreads over the concave portion and peripheral portions of the concave portion, on the III-V nitride semiconductor layer. A dimension of the concave portion in a depth direction is set so that a portion of the Schottky electrode provided in the concave portion can adjust a quantity of the carriers traveling in the channel region.

Owner:PANASONIC CORP

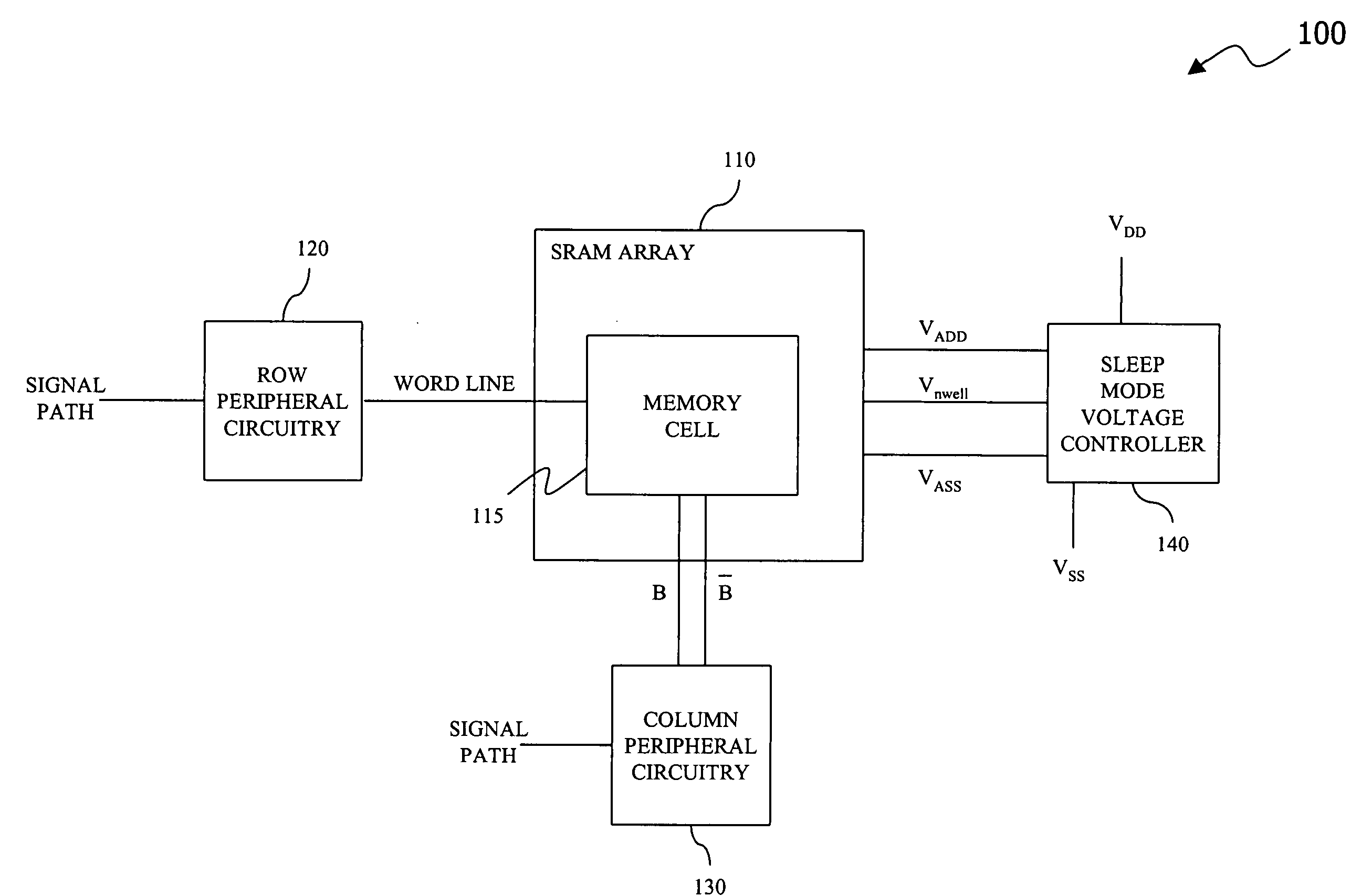

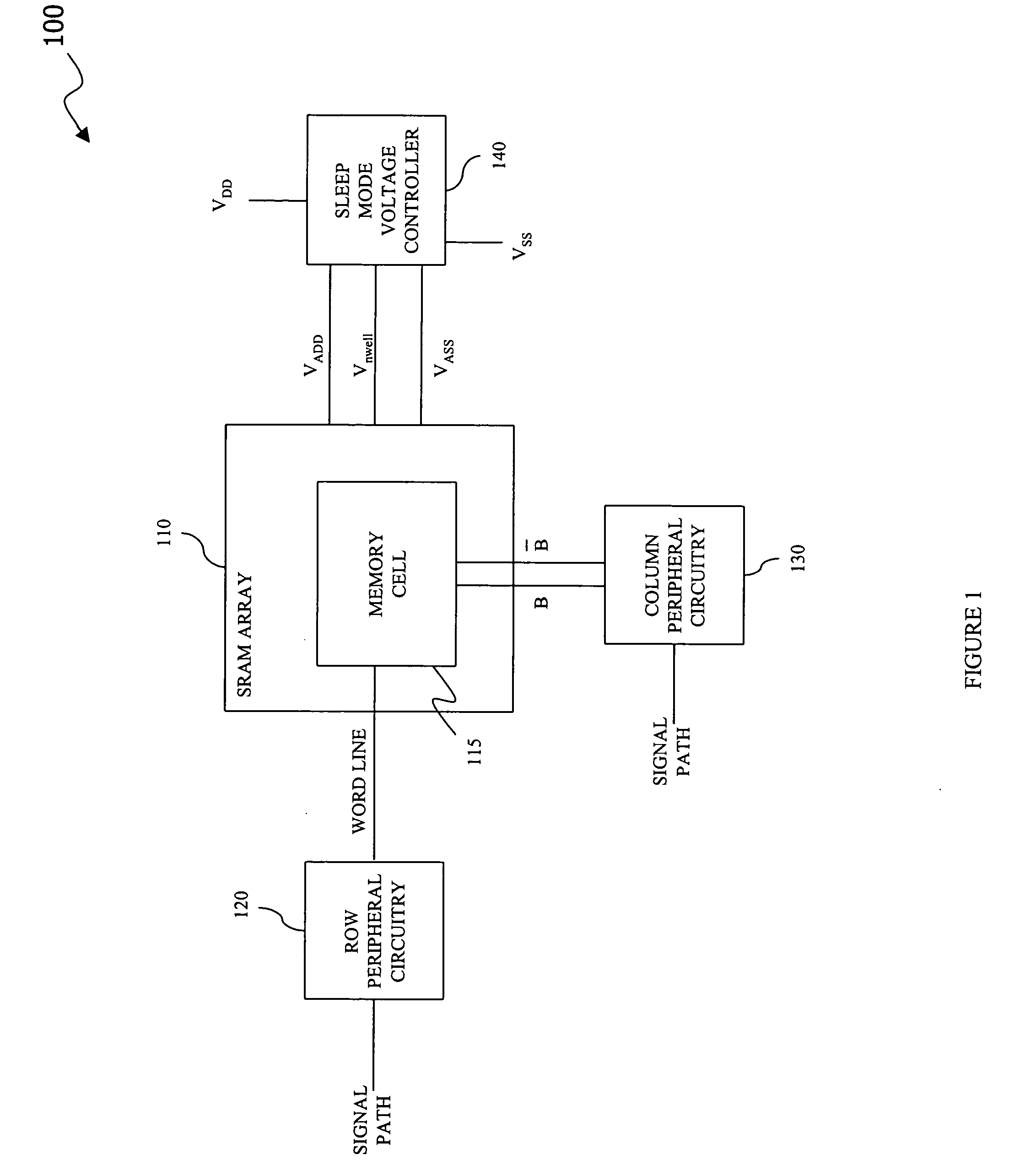

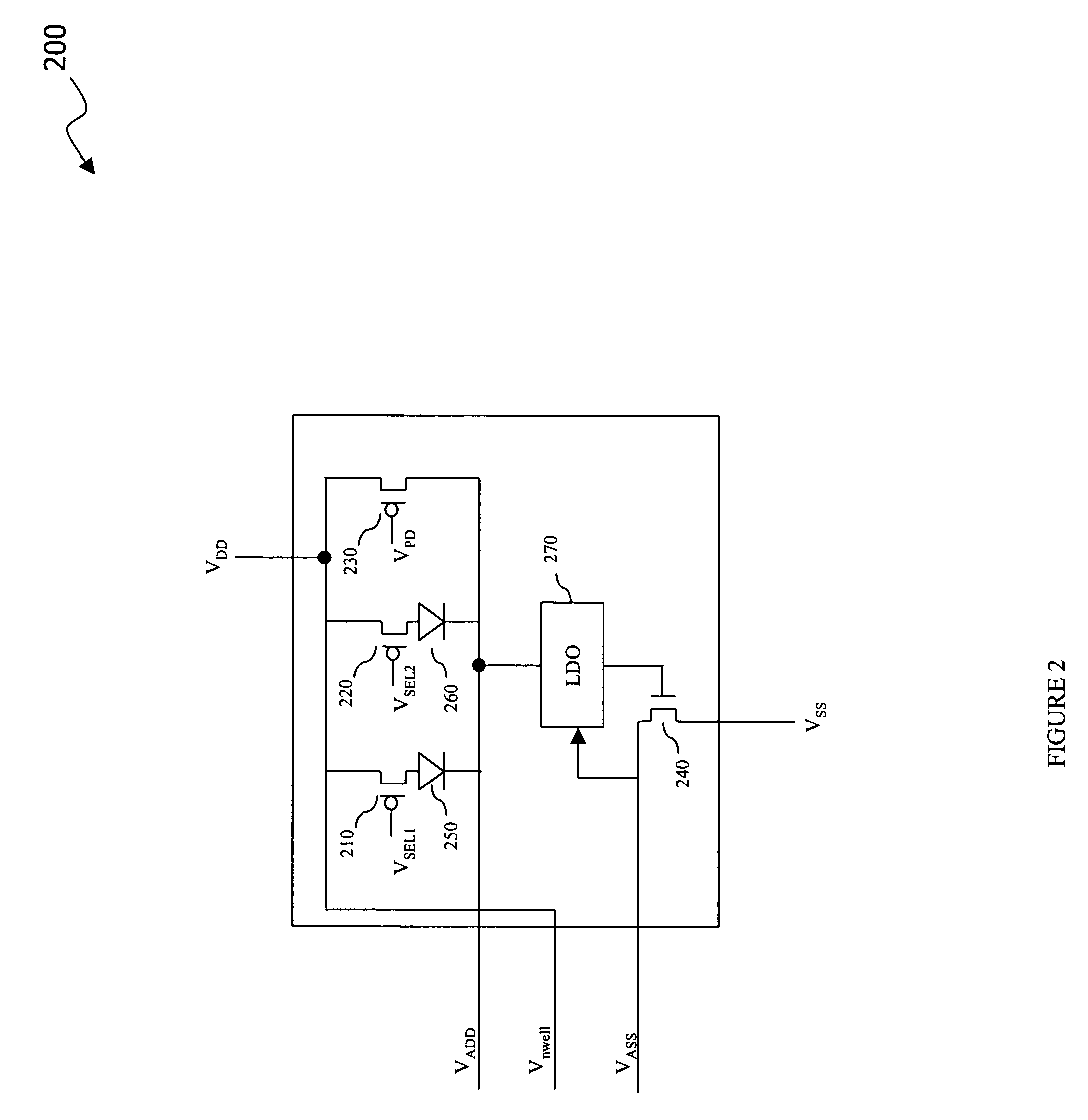

SRAM device and a method of operating the same to reduce leakage current during a sleep mode

ActiveUS20050128789A1Reducing subthreshold current leakageIncreasing diode gate leakageDigital storageBit lineHemt circuits

An SRAM device and a method of operating an SRAM device. In one embodiment, the SRAM device includes (1) an SRAM array coupled to row peripheral circuitry by a word line and coupled to column peripheral circuitry by bit lines and (2) a sleep mode voltage controller configured to provide both an array high supply voltage VADD that is lower than a high operating voltage VDD and an array low supply voltage VASS that is higher than a low operating voltage VSS to the SRAM array during a sleep mode.

Owner:TEXAS INSTR INC

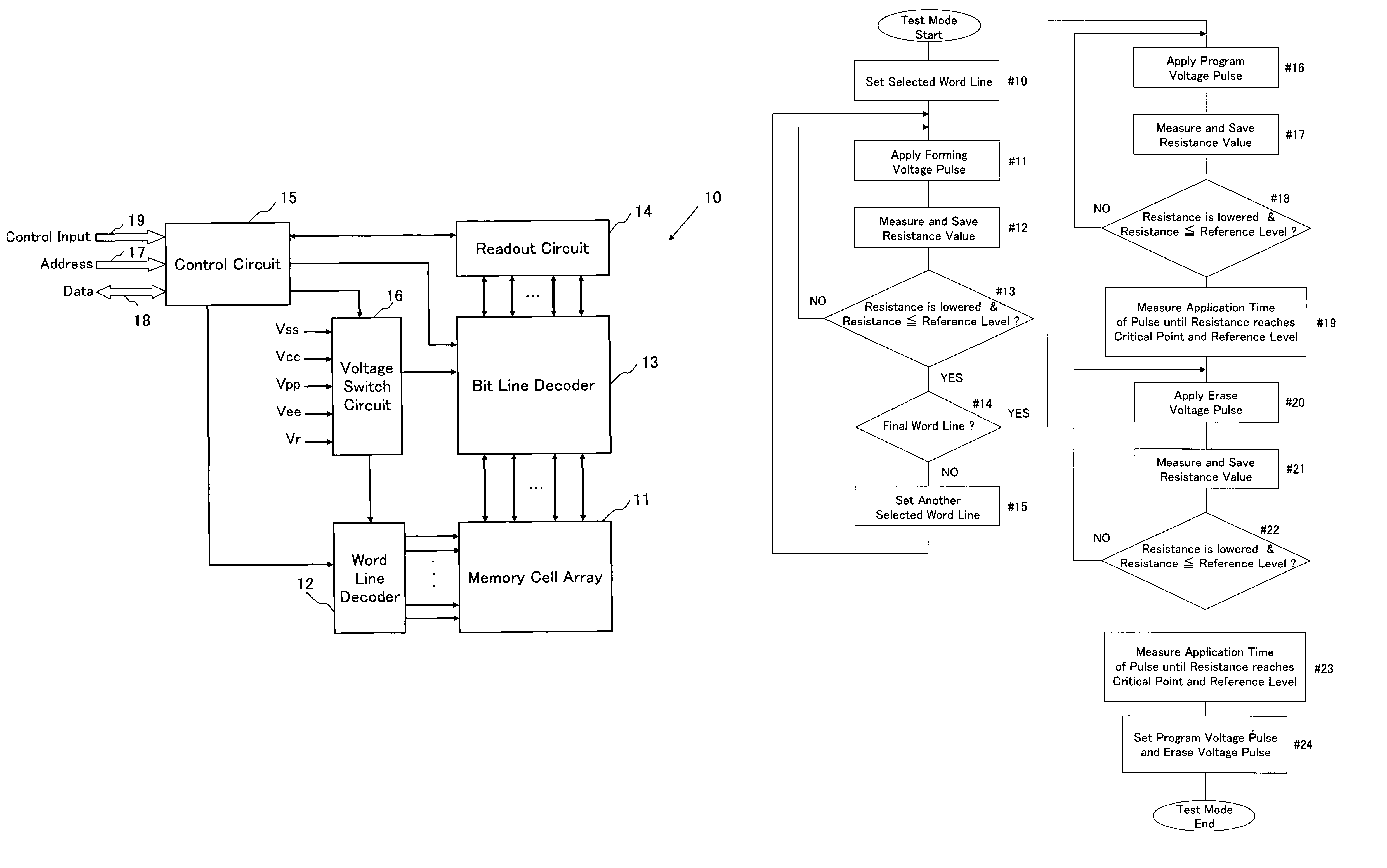

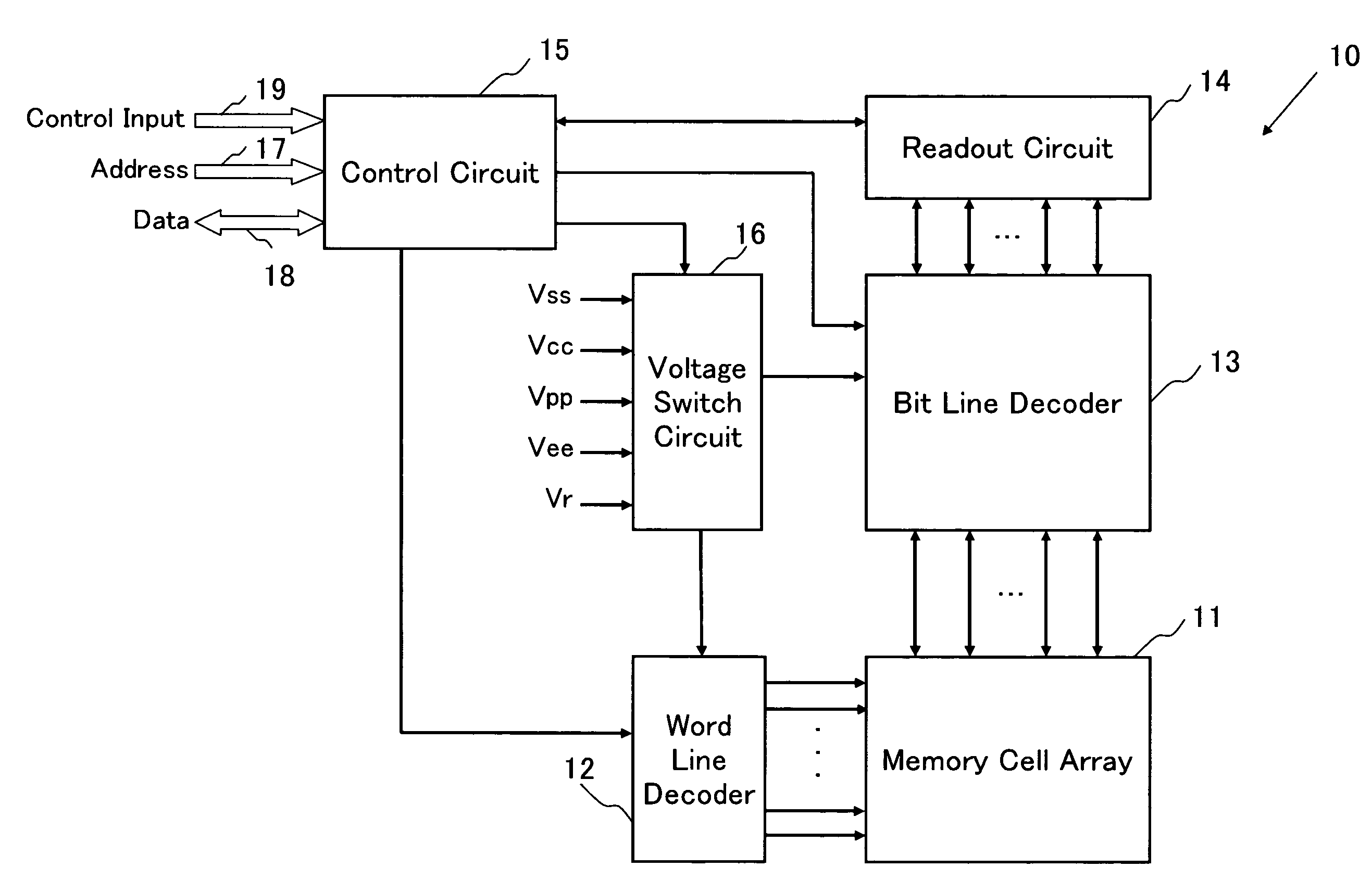

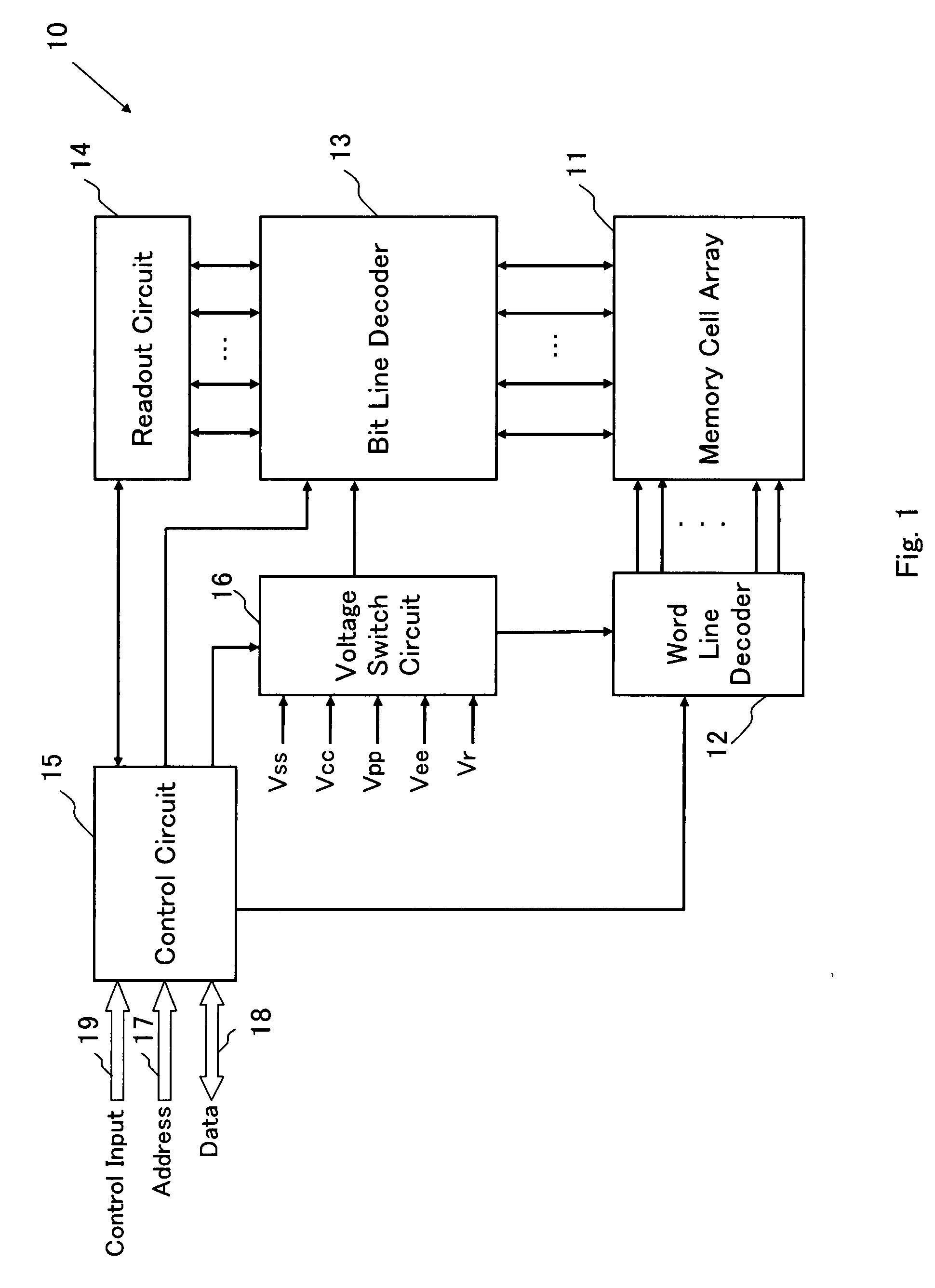

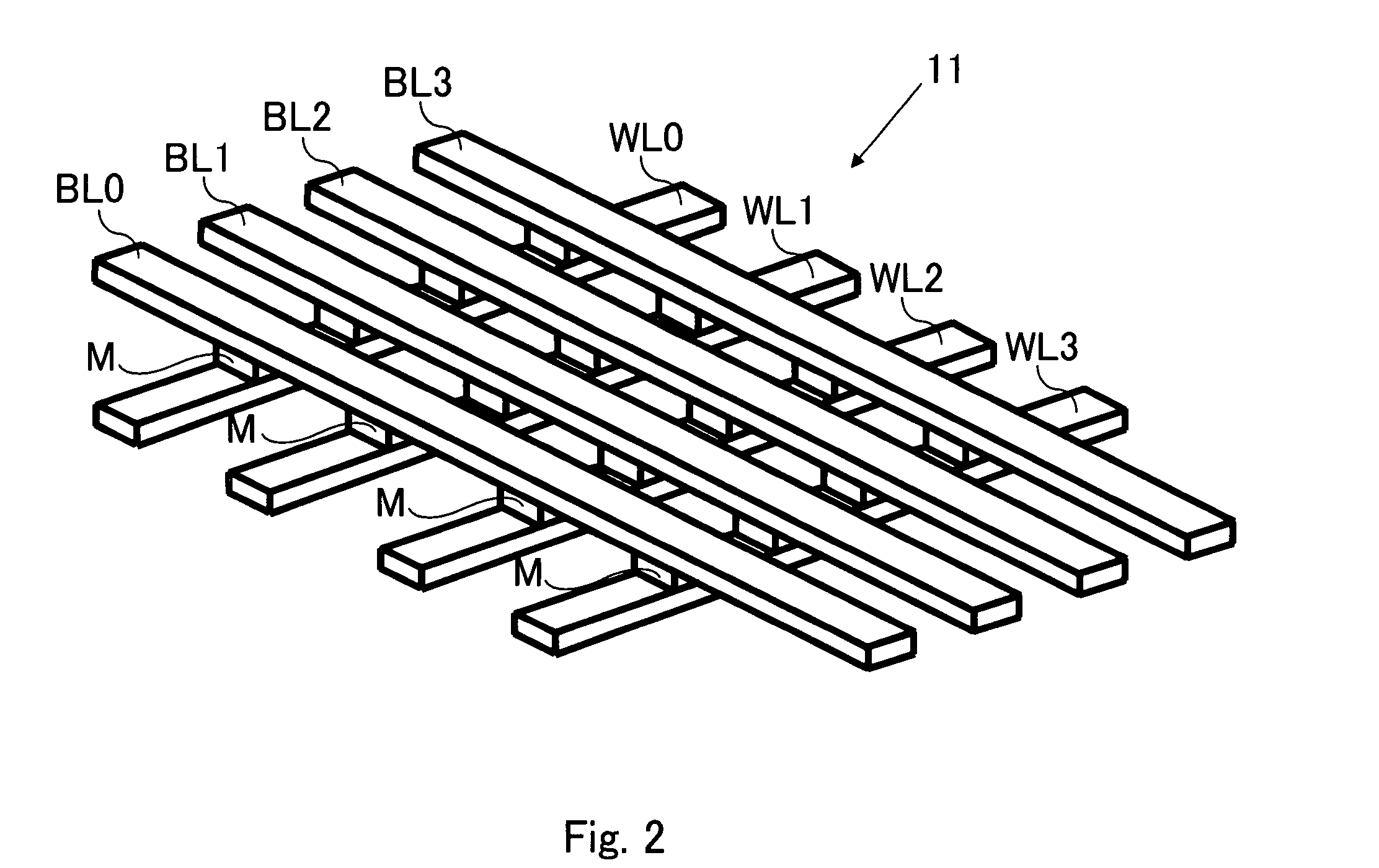

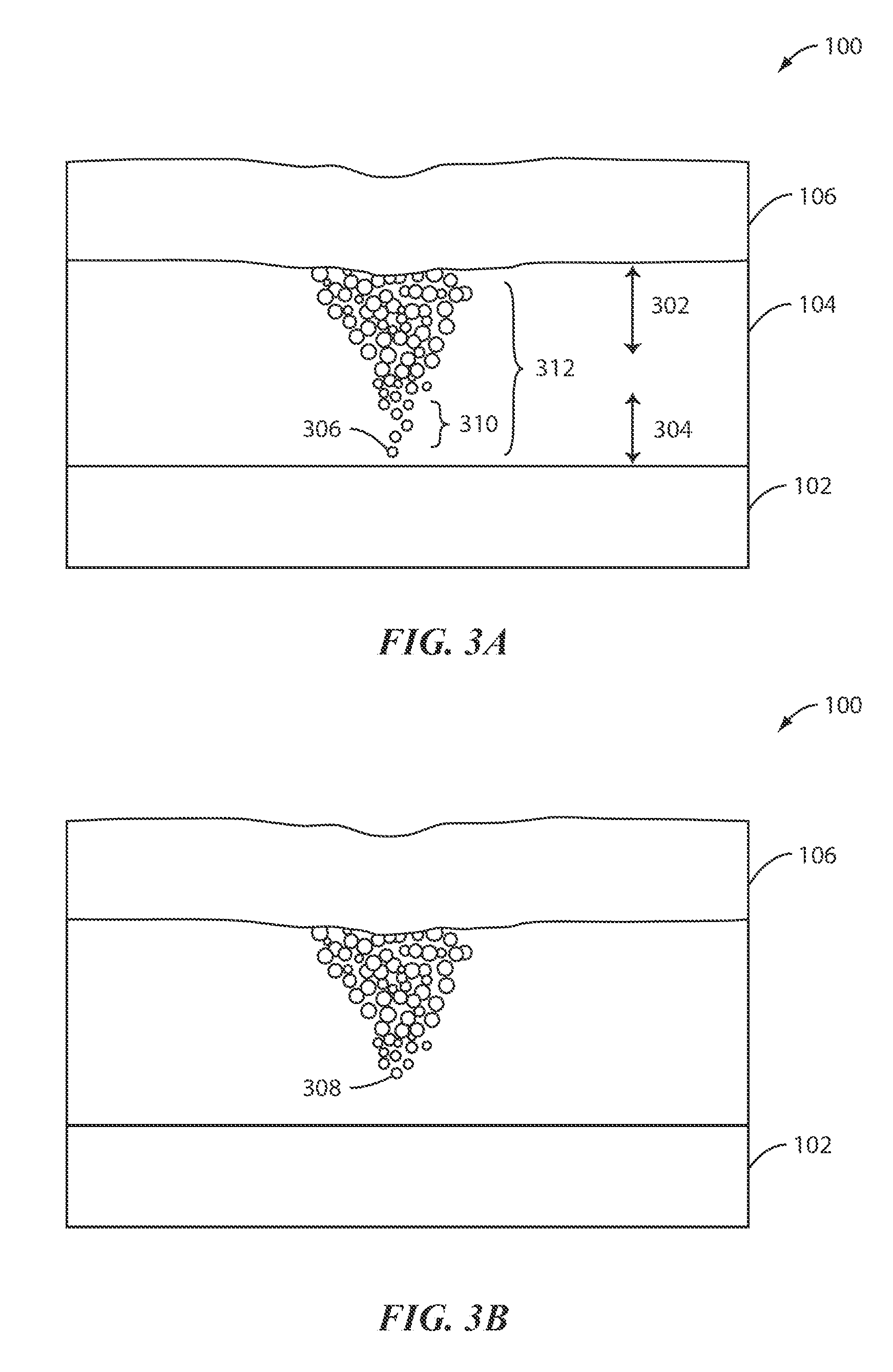

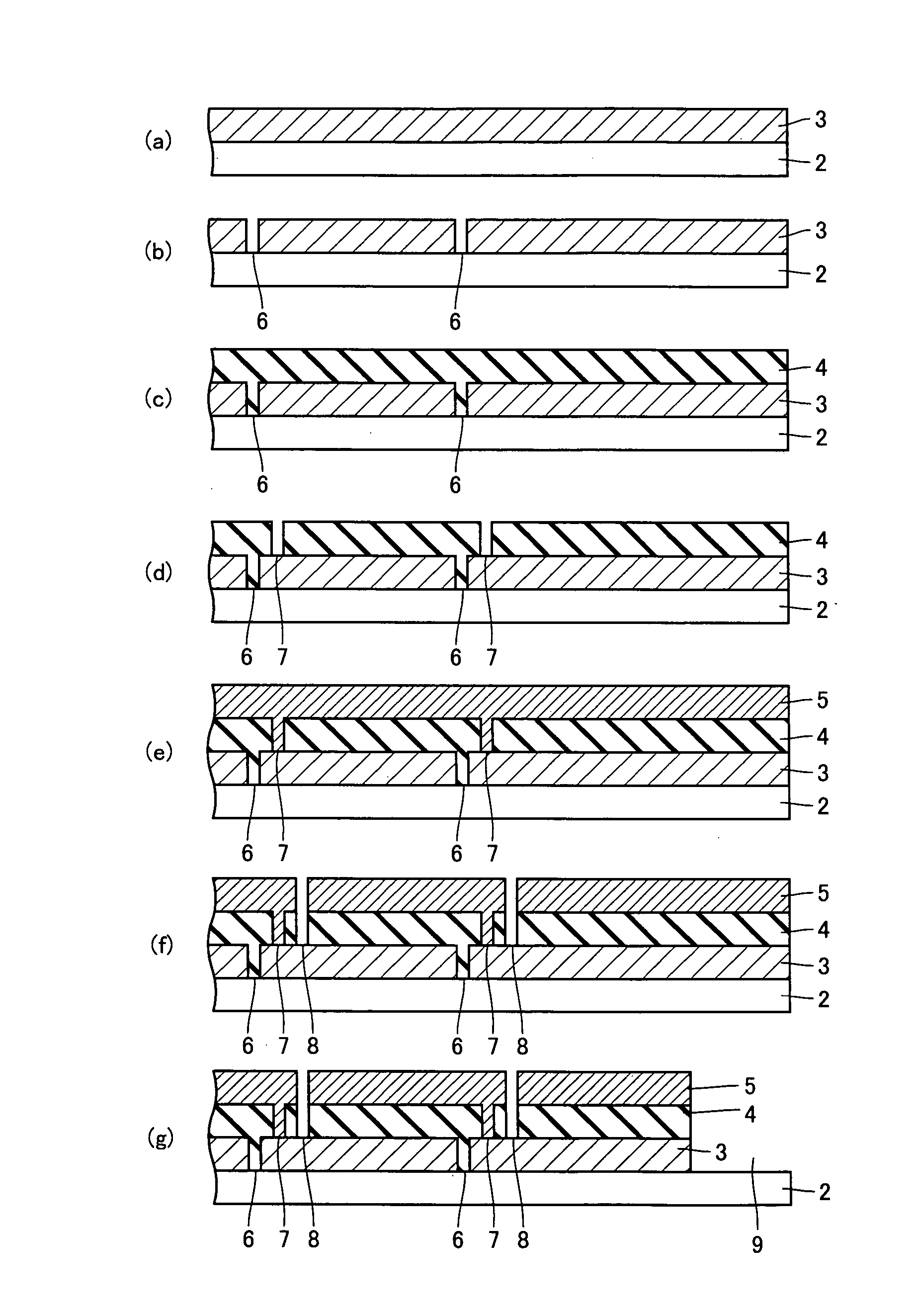

Method of controlling the resistance in a variable resistive element and non-volatile semiconductor memory device

InactiveUS7558099B2Mono-polar switching action stable and consistentStableness of the memory actionsDigital storageVoltage pulseElectrical polarity

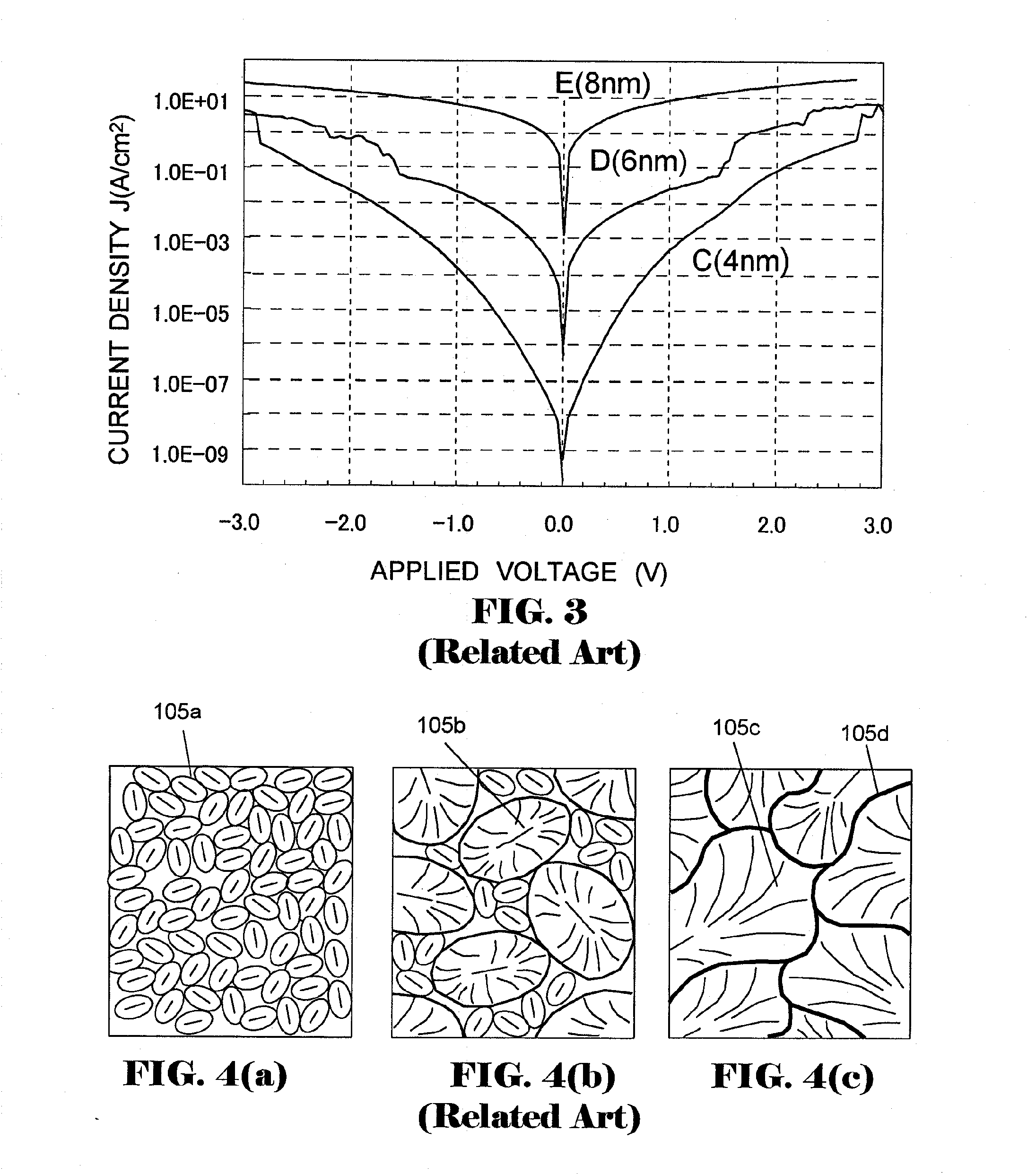

The method of controlling a resistance of a variable resistive element comprises a forming step for shifting the variable resistive element from an initial state after the production to a variable resistance state capable of a stable mono-polar switching action where a variable resistive characteristic of the variable resistive element is turned to a program resistive characteristic by applying a program voltage pulse to the variable resistive element for first pulse application time and to an erase resistive characteristic by applying an erase voltage pulse equal in polarity to the program voltage pulse to the variable resistive element for second pulse application time longer than the first pulse application time, wherein one or more forming voltage pulses equal in polarity to the program voltage pulse is applied to the variable resistive element for third pulse application time longer than the second pulse application time.

Owner:DENSO CORP

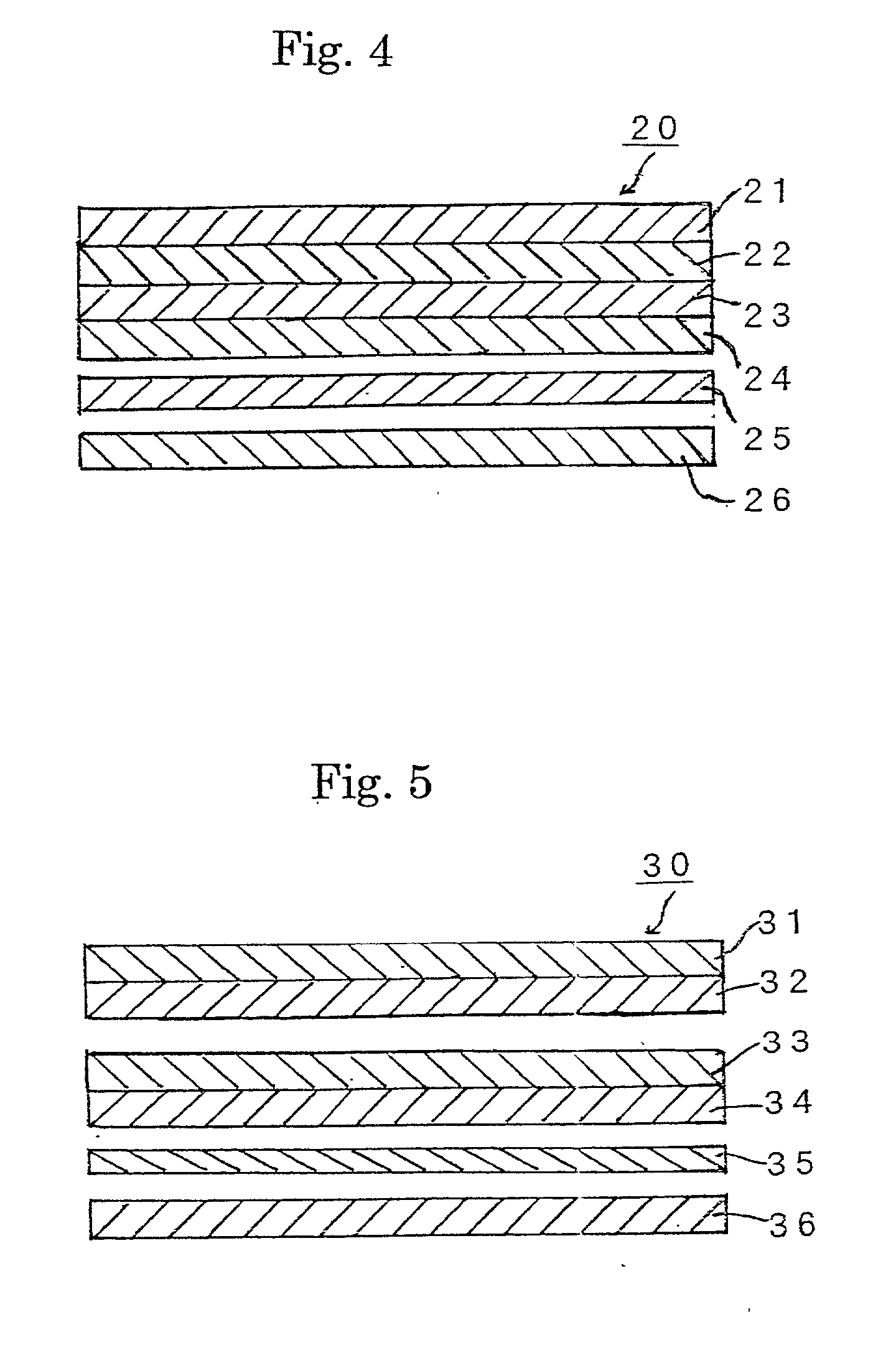

Backside covering material for a solar cell module and its use

InactiveUS20020129848A1Enhanced durability and moisture resistanceGood insulatorFilm/foil adhesivesPV power plantsWeather resistanceEngineering

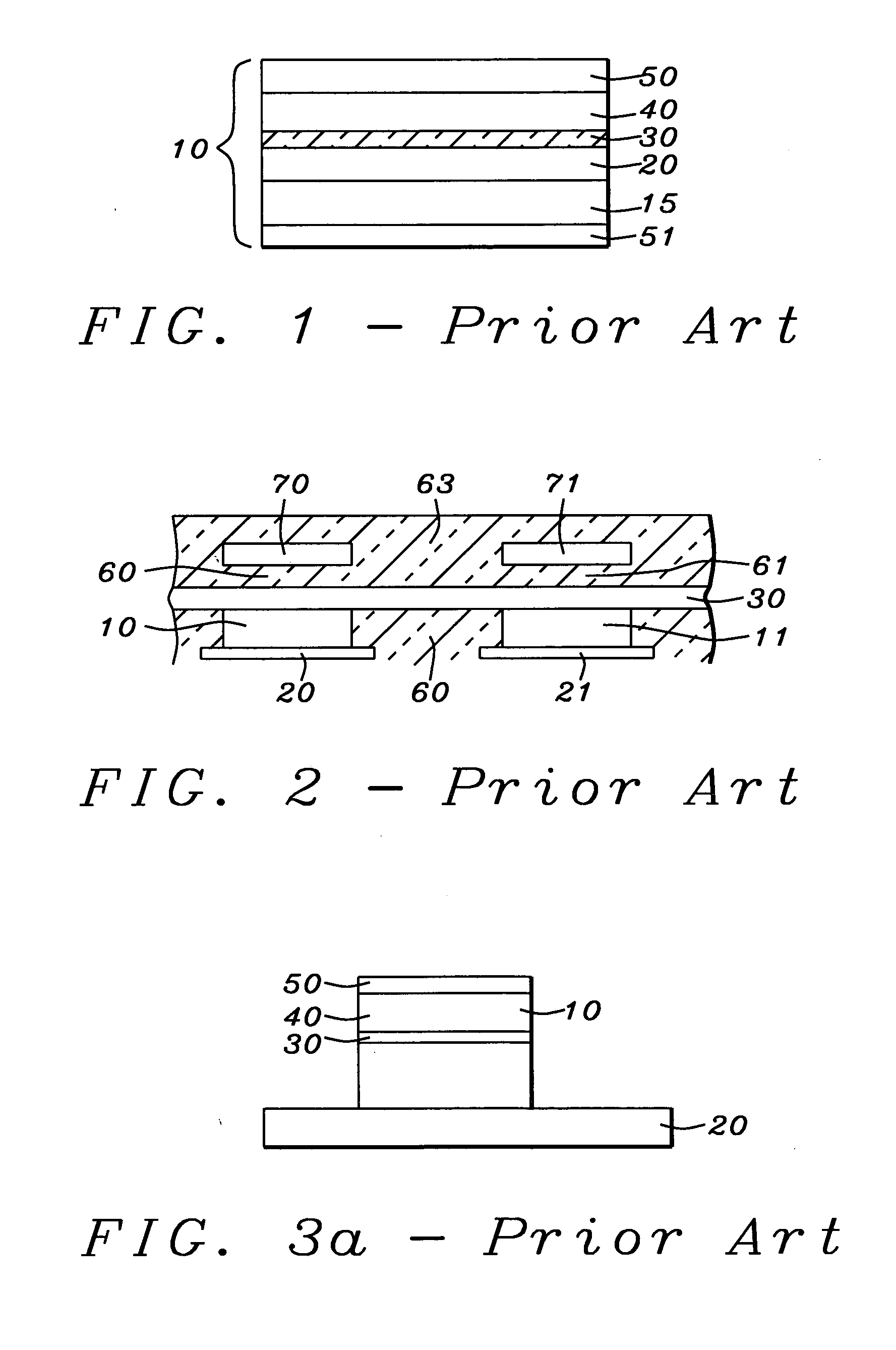

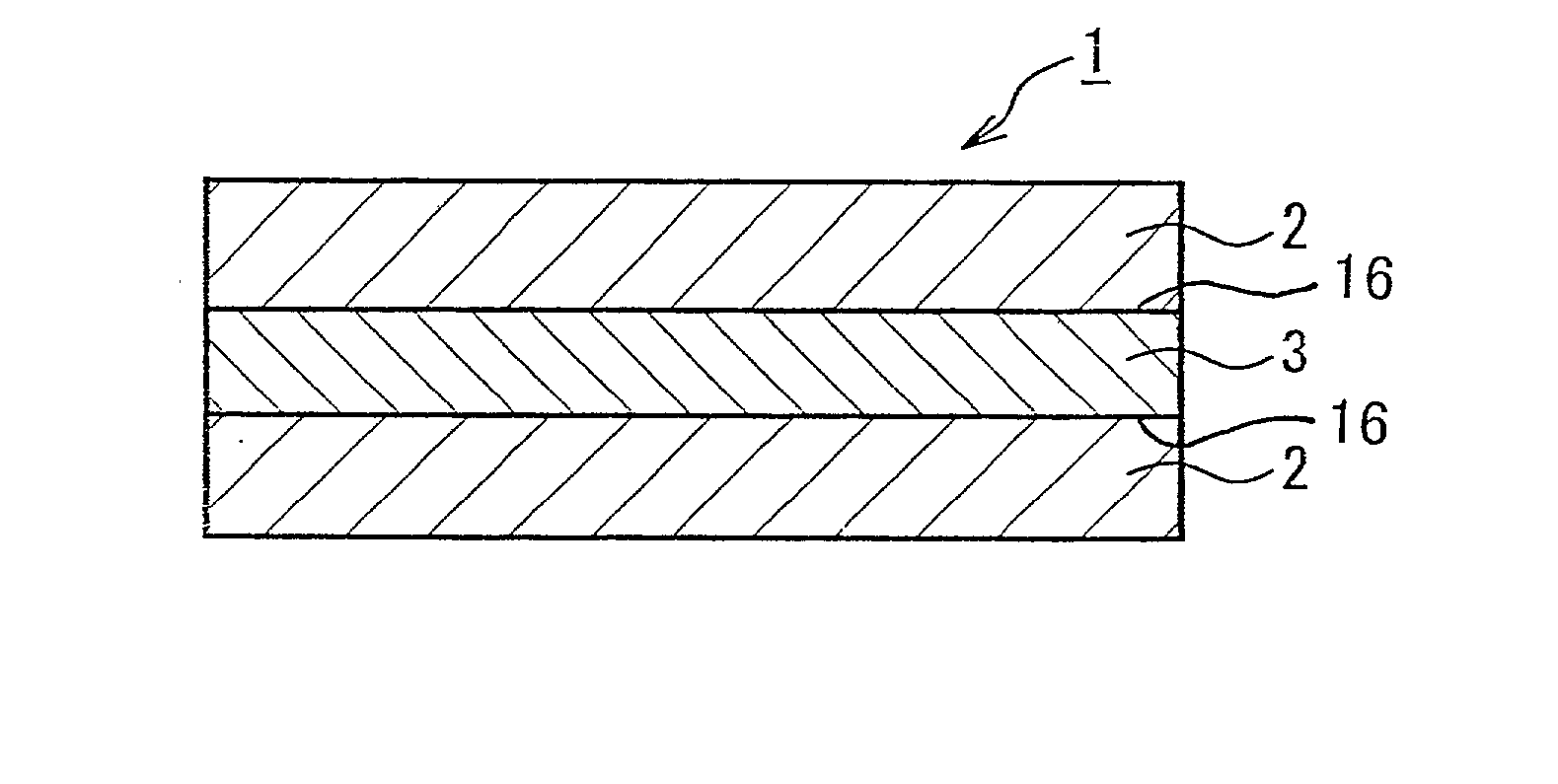

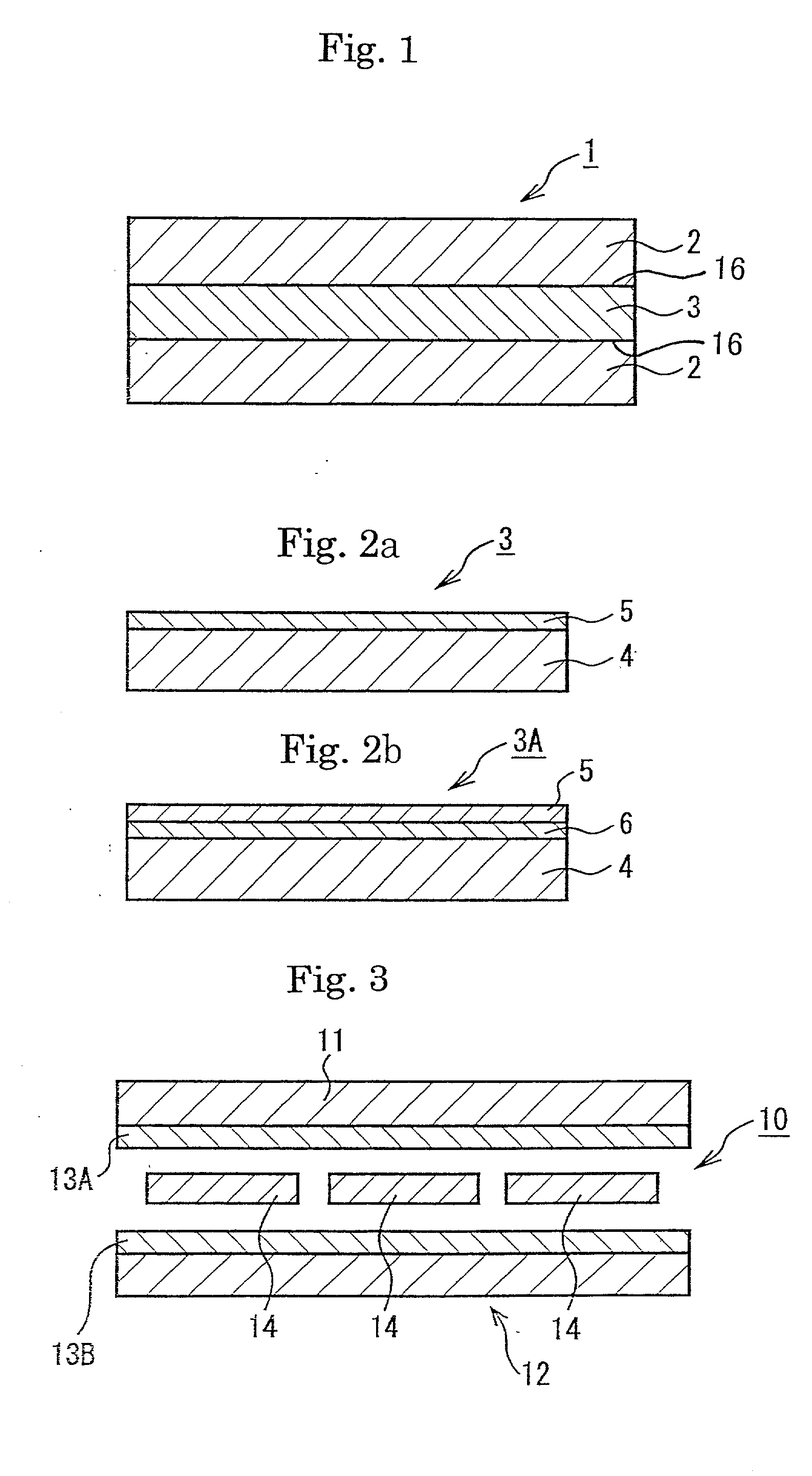

The present invention provides a light and thin backside covering material for a solar cell module which is excellent in moisture resistance and durability and has a good insulator without causing a short circuit with underlying wire nor leak current. Also the invention provides a durable and high performance solar cell module using this backside covering material as a rear surface protection member. The backside covering material for a solar cell module is a three-layer laminated film, wherein a moisture resistant film is sandwiched with two films having heat resistance and weather resistance. A deposited layer 5 of inorganic oxide is formed on a surface of a base film 4 to make the moisture resistant film 3.

Owner:BRIDGESTONE CORP

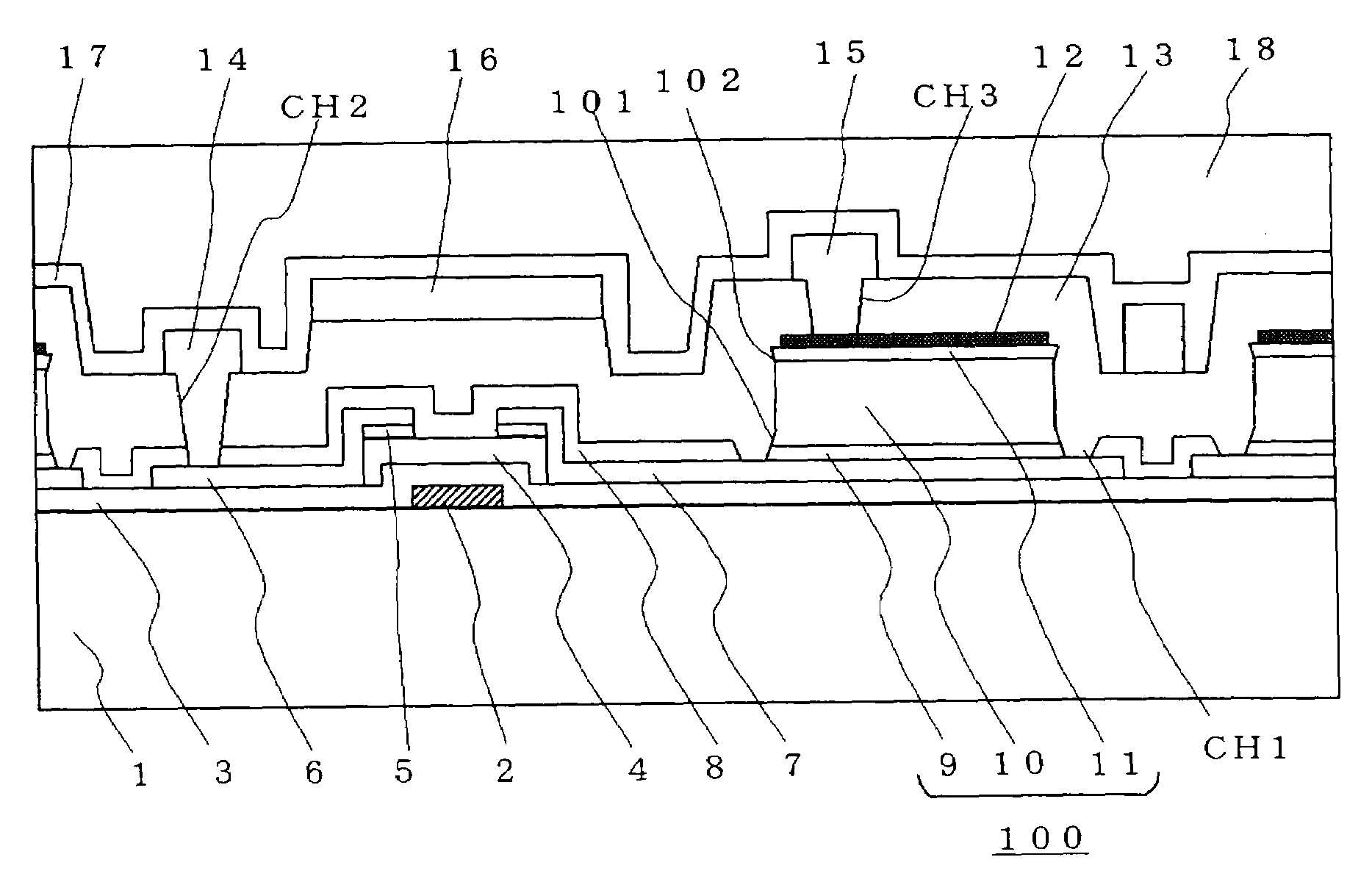

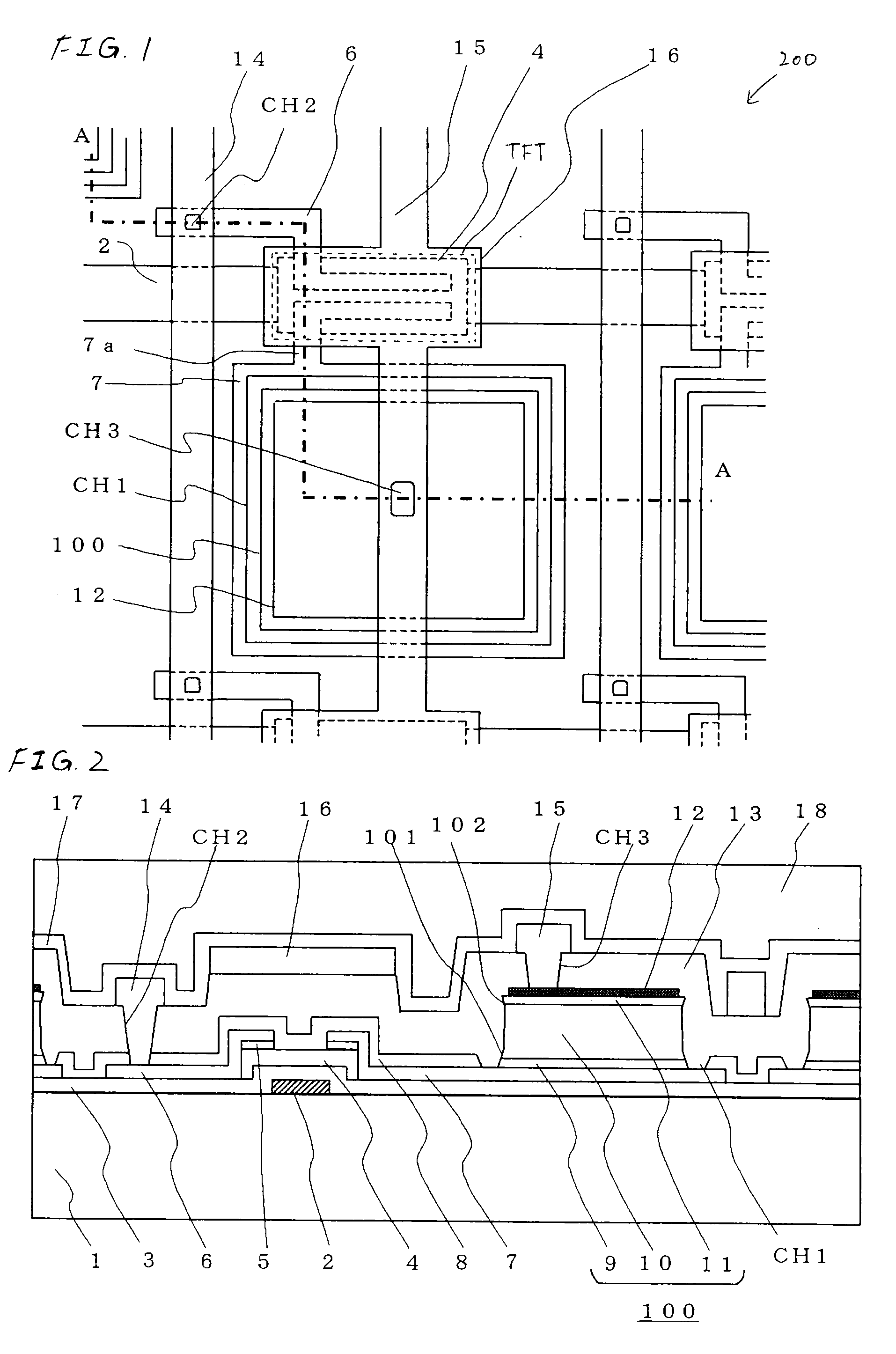

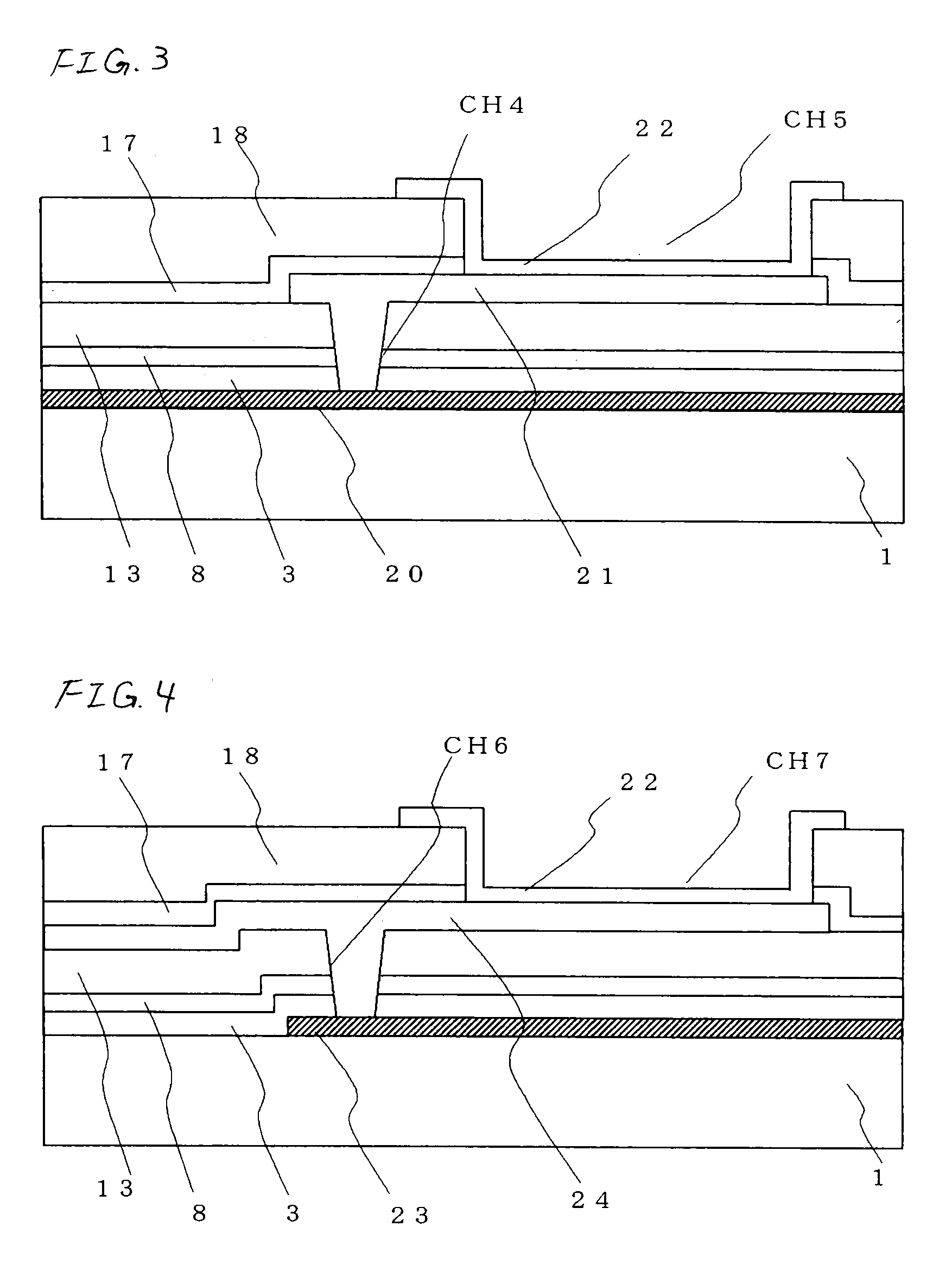

Photosensor

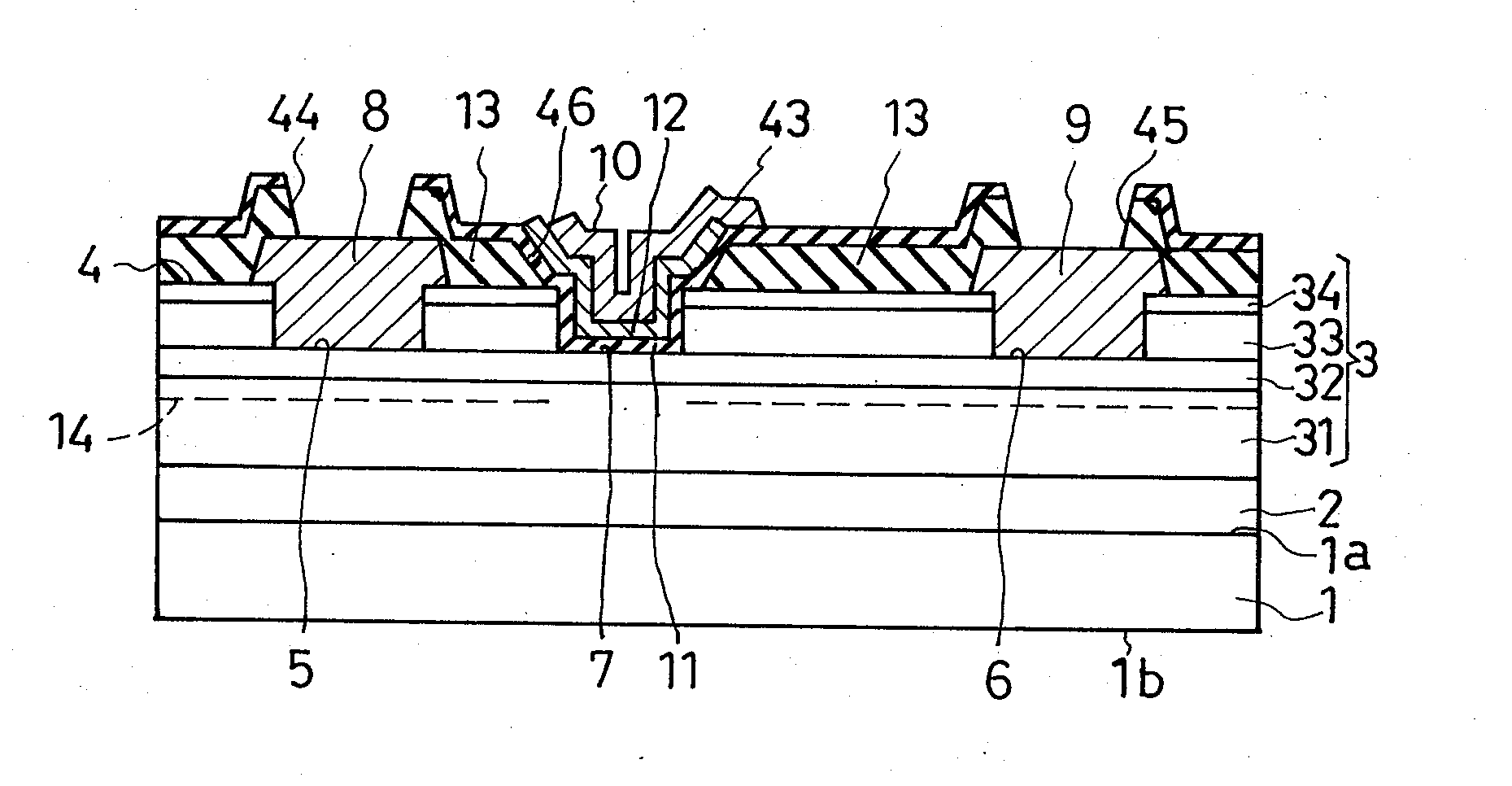

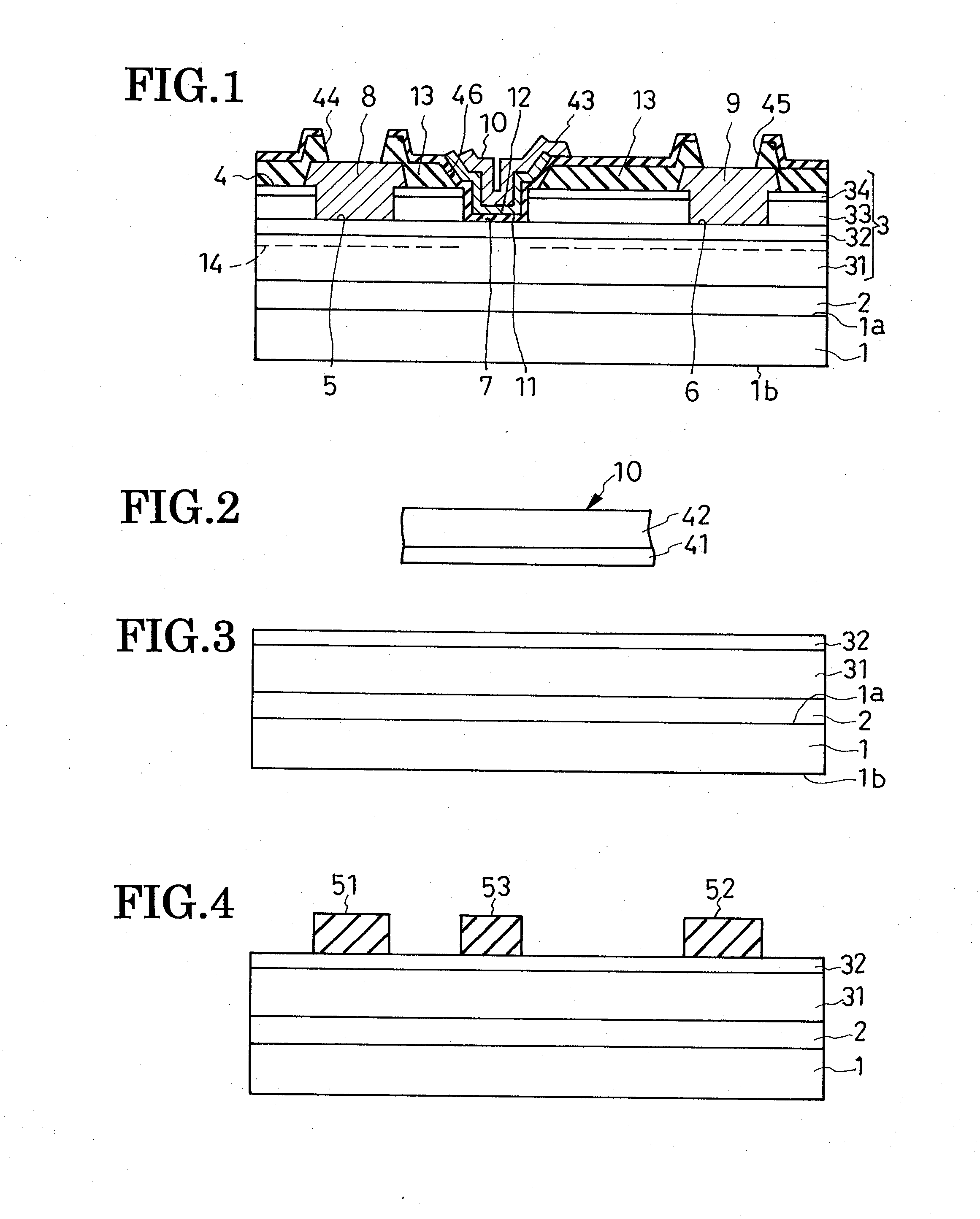

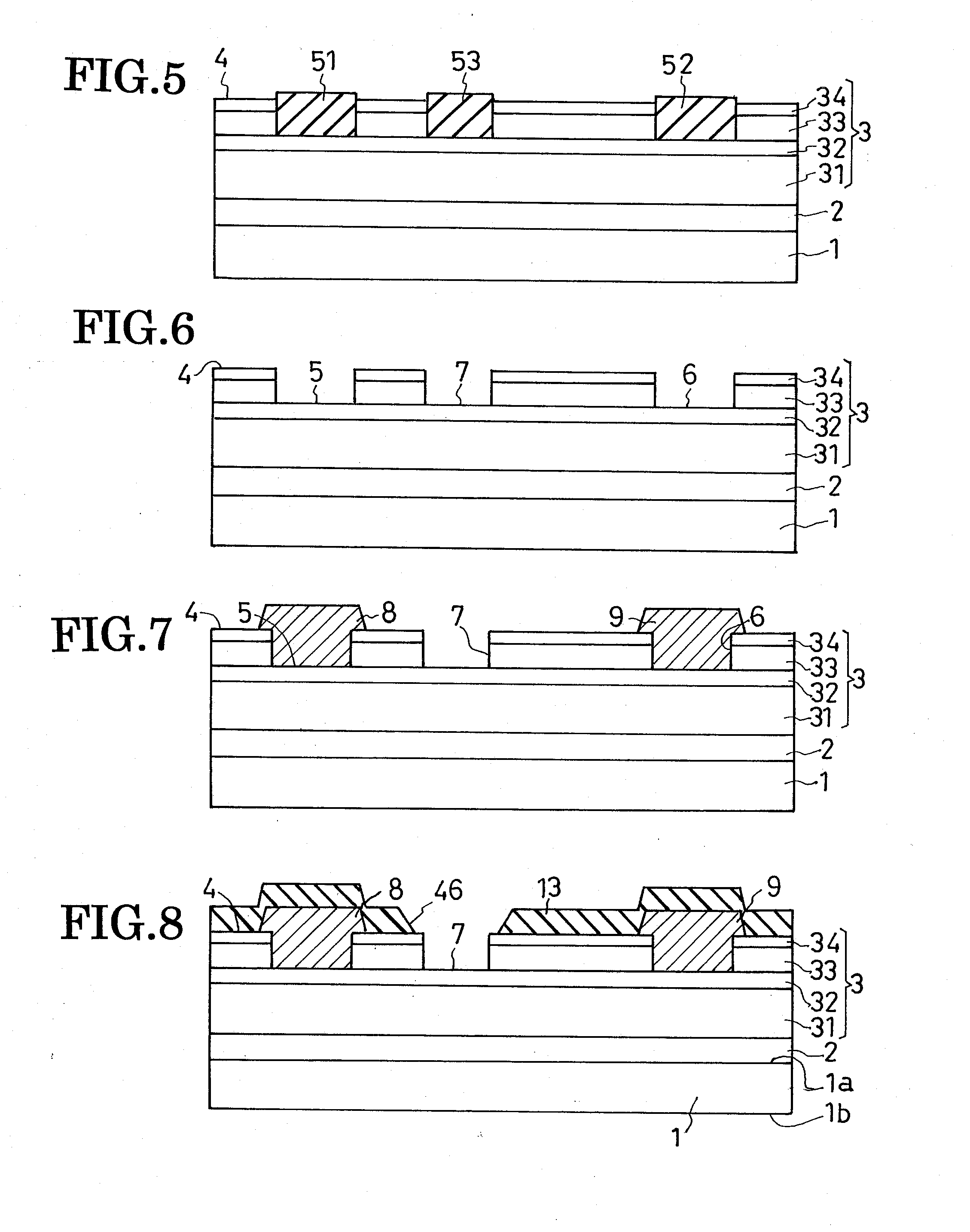

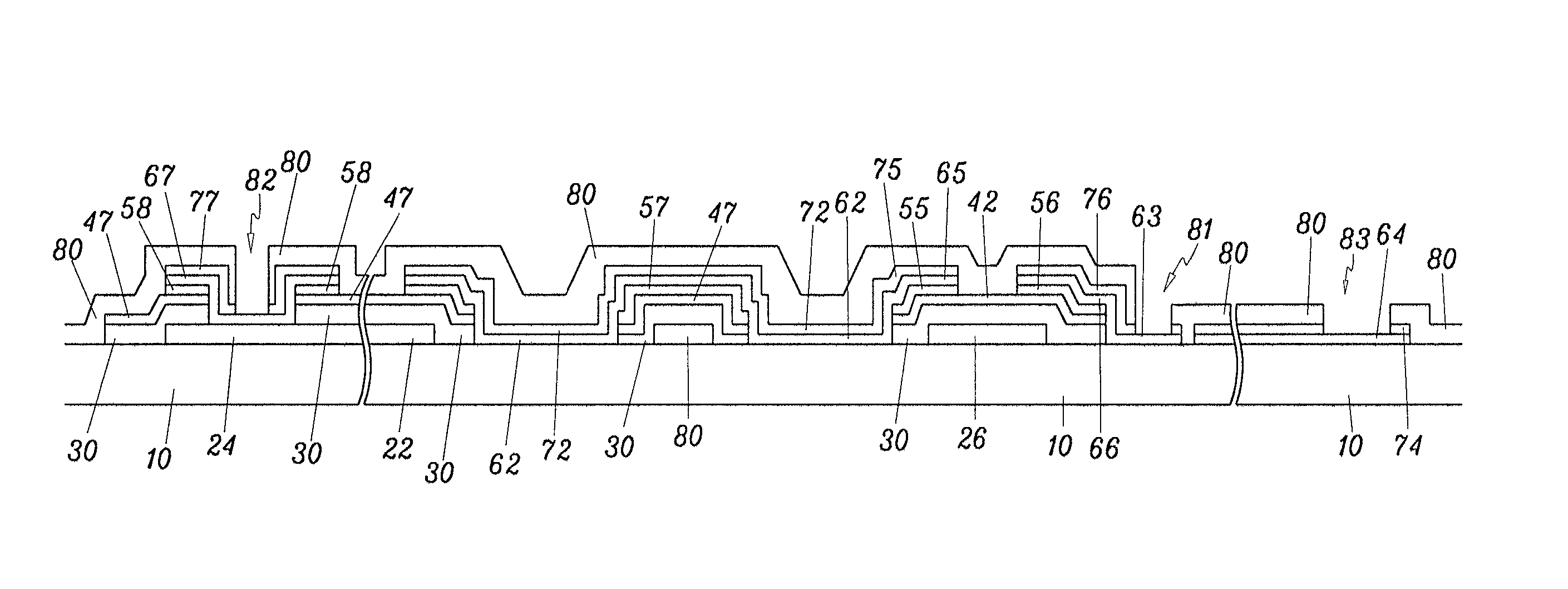

For a photosensor, an array substrate is provided, wherein the edge of a photodiode is enclosed by the opening edge of a contact hole formed on a drain electrode.

Owner:MITSUBISHI ELECTRIC CORP

Method of controlling the resistance in a variable resistive element and non-volatile semiconductor memory device

InactiveUS20070195581A1Mono-polar switching action stable and consistentStableness of the memory actionsDigital storageVoltage pulseElectrical polarity

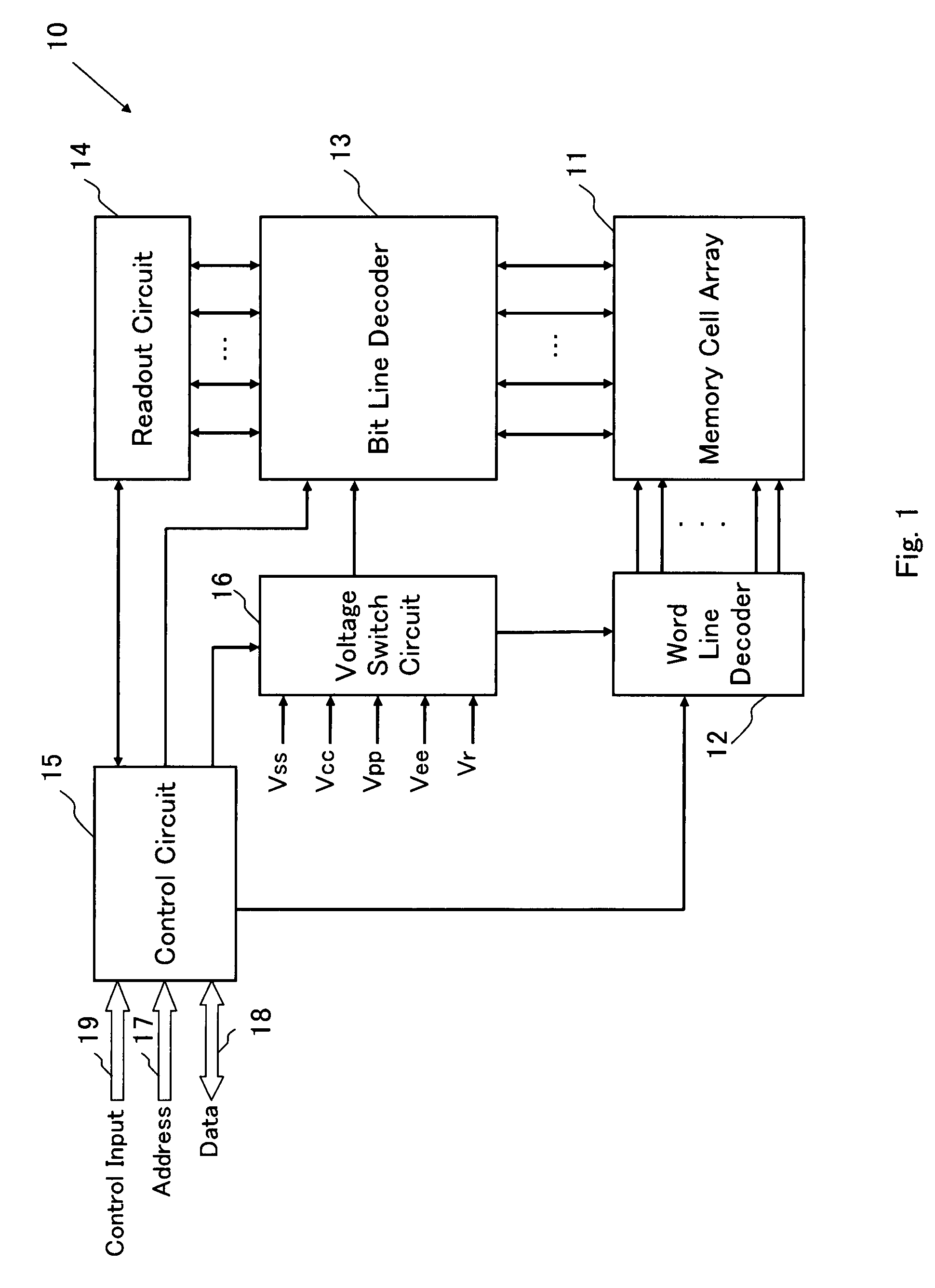

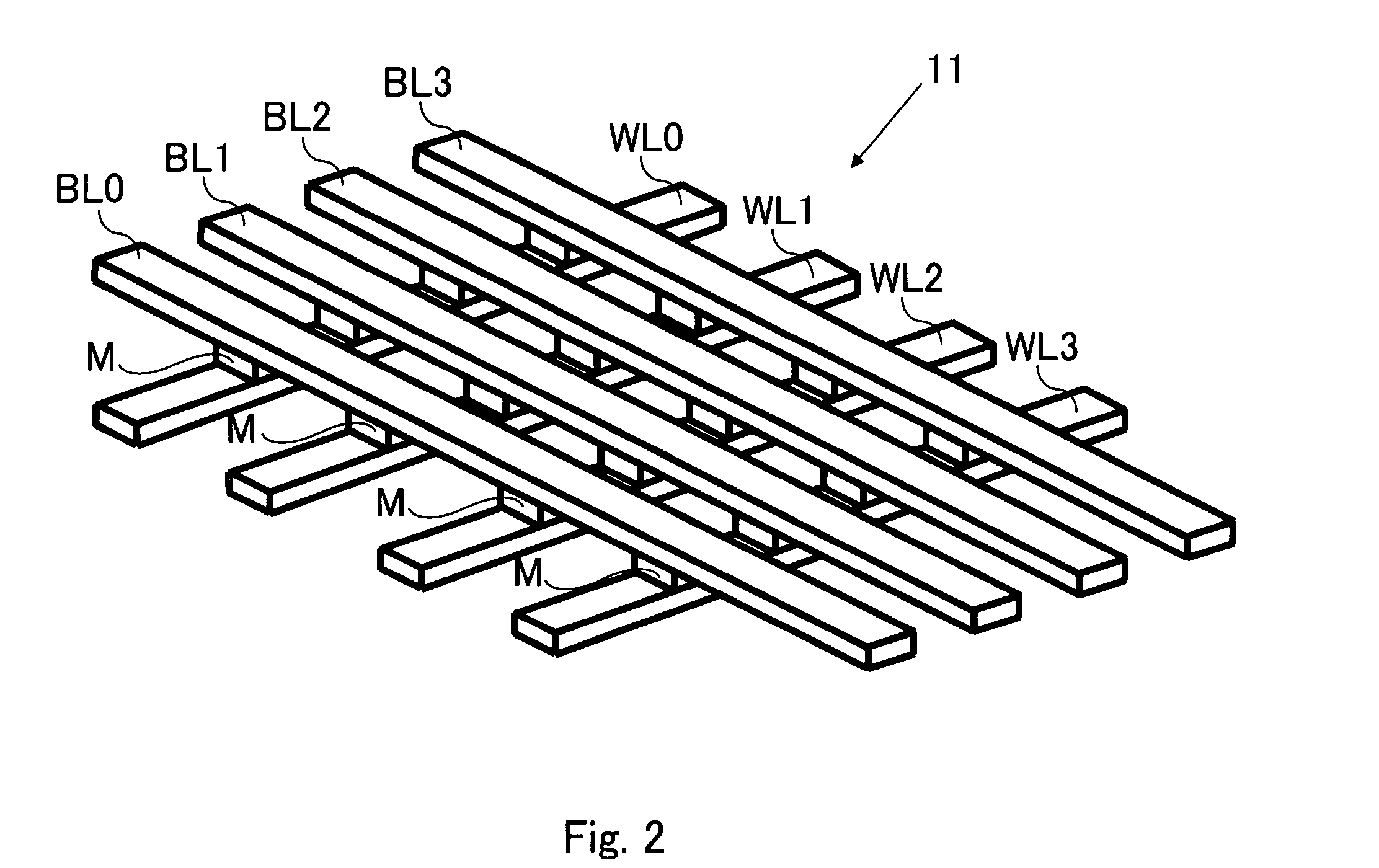

The method of controlling a resistance of a variable resistive element comprises a forming step for shifting the variable resistive element from an initial state after the production to a variable resistance state capable of a stable mono-polar switching action where a variable resistive characteristic of the variable resistive element is turned to a program resistive characteristic by applying a program voltage pulse to the variable resistive element for first pulse application time and to an erase resistive characteristic by applying an erase voltage pulse equal in polarity to the program voltage pulse to the variable resistive element for second pulse application time longer than the first pulse application time, wherein one or more forming voltage pulses equal in polarity to the program voltage pulse is applied to the variable resistive element for third pulse application time longer than the second pulse application time.

Owner:DENSO CORP

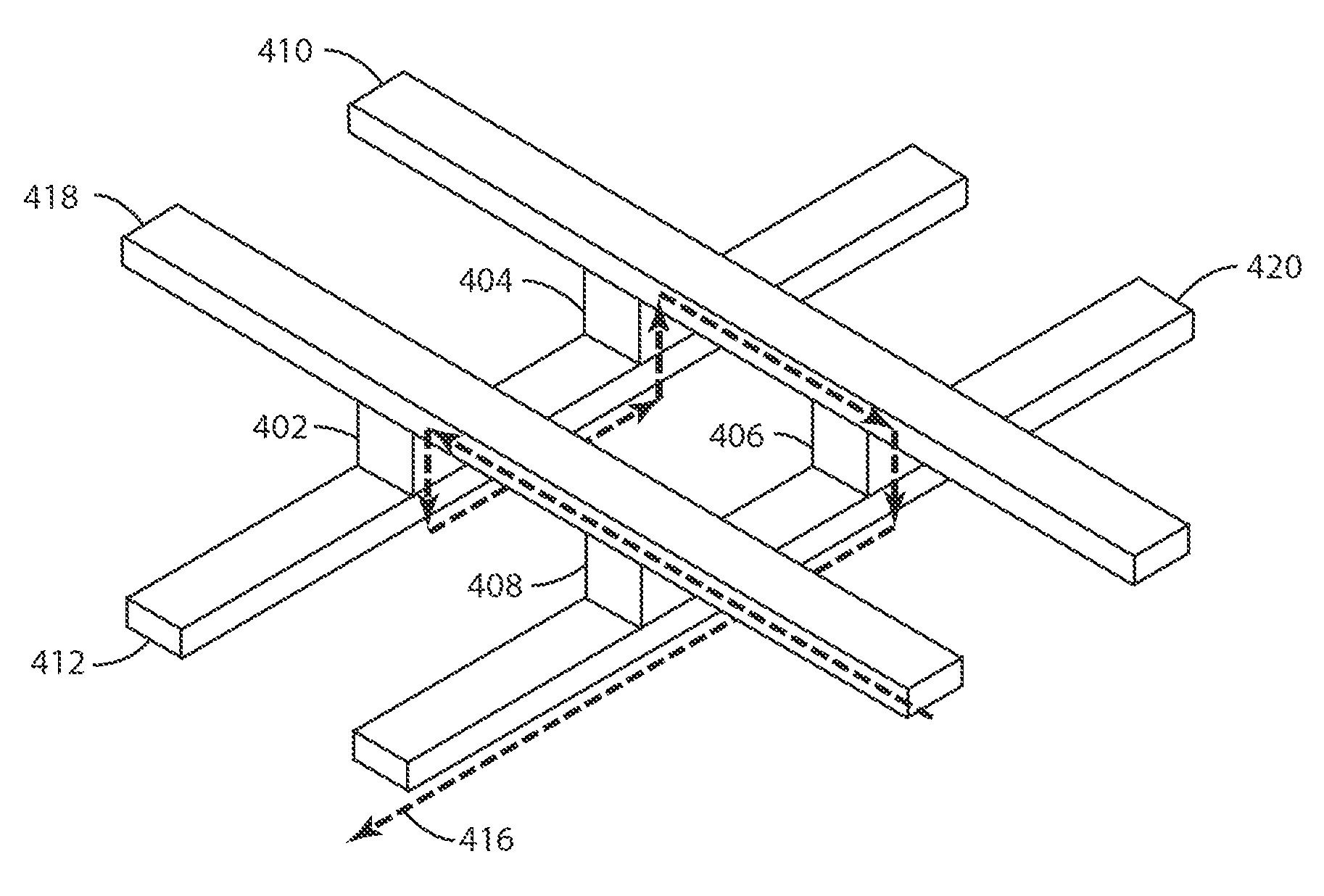

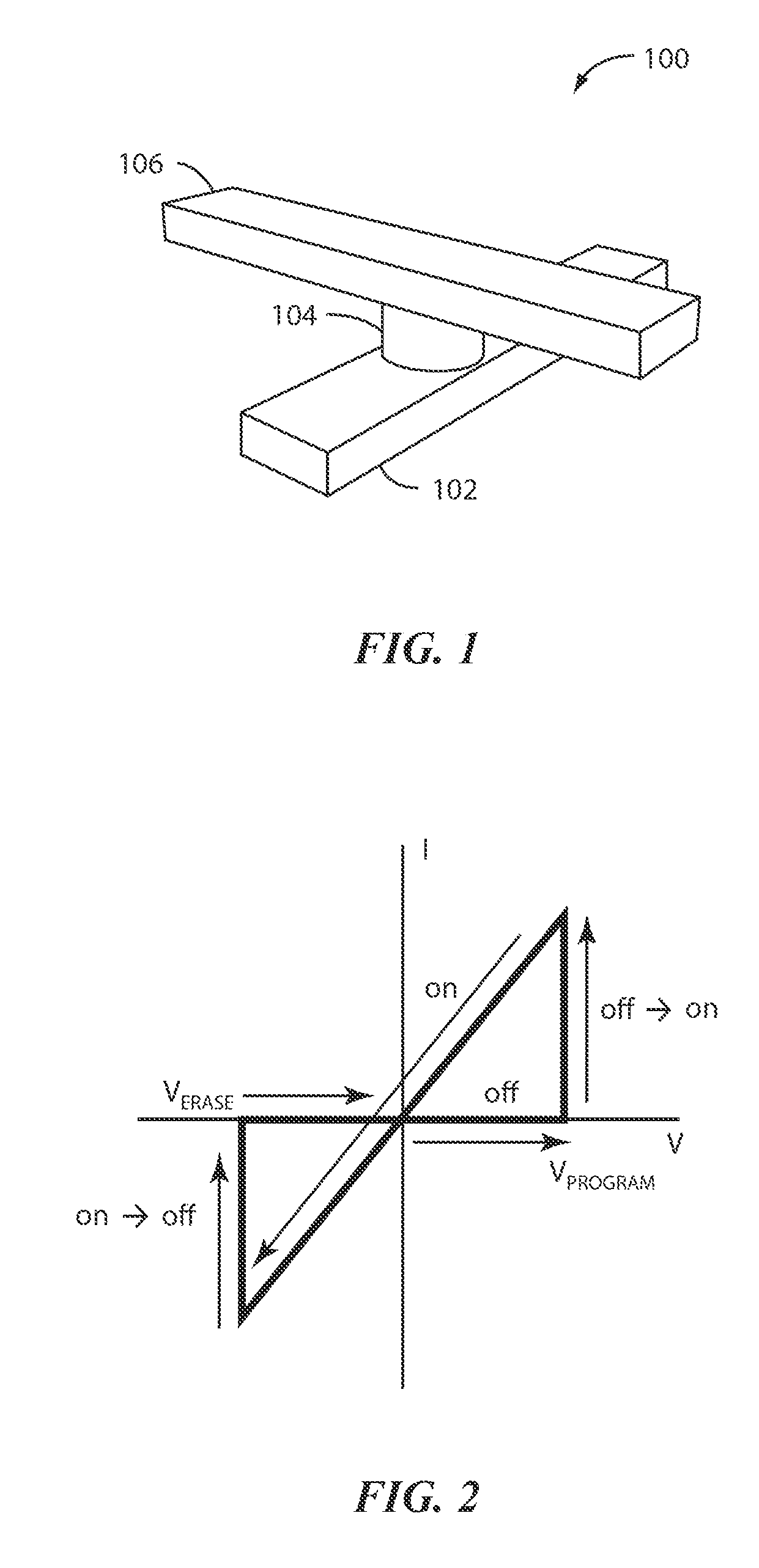

Switching device having a non-linear element

ActiveUS8502185B2High densityFast switching speedTransistorSolid-state devicesLinear elementNonlinear element

A switching device includes a substrate; a first electrode formed over the substrate; a second electrode formed over the first electrode; a switching medium disposed between the first and second electrode; and a nonlinear element disposed between the first and second electrodes and electrically coupled in series to the first electrode and the switching medium. The nonlinear element is configured to change from a first resistance state to a second resistance state on application of a voltage greater than a threshold.

Owner:CROSSBAR INC

Method of fabricating a thin-film solar cell, and thin-film solar cell

InactiveUS20060266409A1Low conversion efficiencyTotal current dropPhotovoltaic energy generationSemiconductor devicesPhotoelectric conversionLaser light

There is provided a method of fabricating a thin-film solar cell including the steps of: irradiating a first laser light from a side of the substrate to remove the semiconductor and back surface electrode layers; and irradiating a second laser light from the side of the substrate to remove the transparent electrode, semiconductor and back surface electrode layers at a region outer than the region irradiated with the first laser light. There is provided a thin-film solar cell including a transparent electrode layer, a photoelectric conversion semiconductor layer and a back surface electrode layer deposited on a transparent insulator substrate in this order, wherein the solar cell has a perimeter with the transparent electrode layer protruding outer than the semiconductor and back surface electrode layers.

Owner:SHARP KK

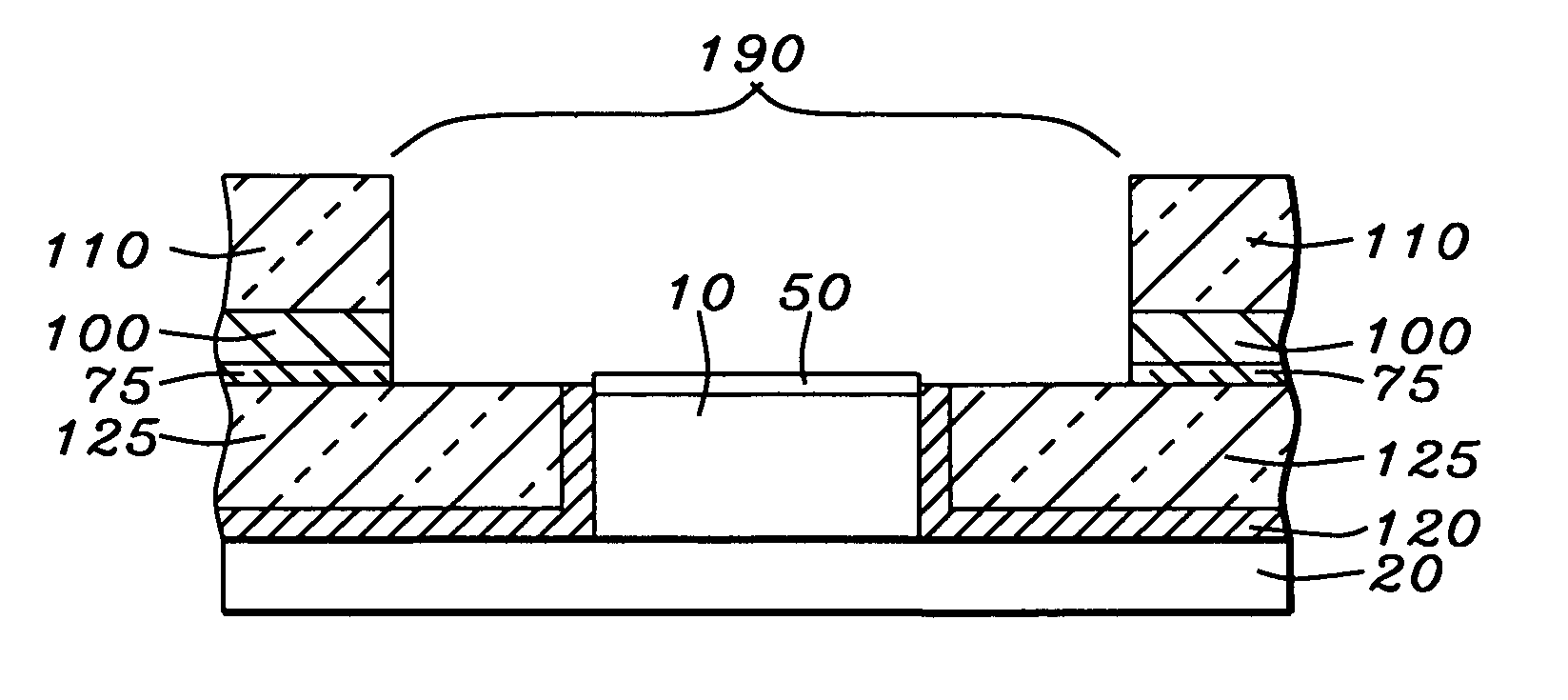

Gan semiconductor device

ActiveUS20060097278A1Reliable suppressionInhibit currentLaser detailsSemiconductor laser structural detailsElectrical conductorDevice material

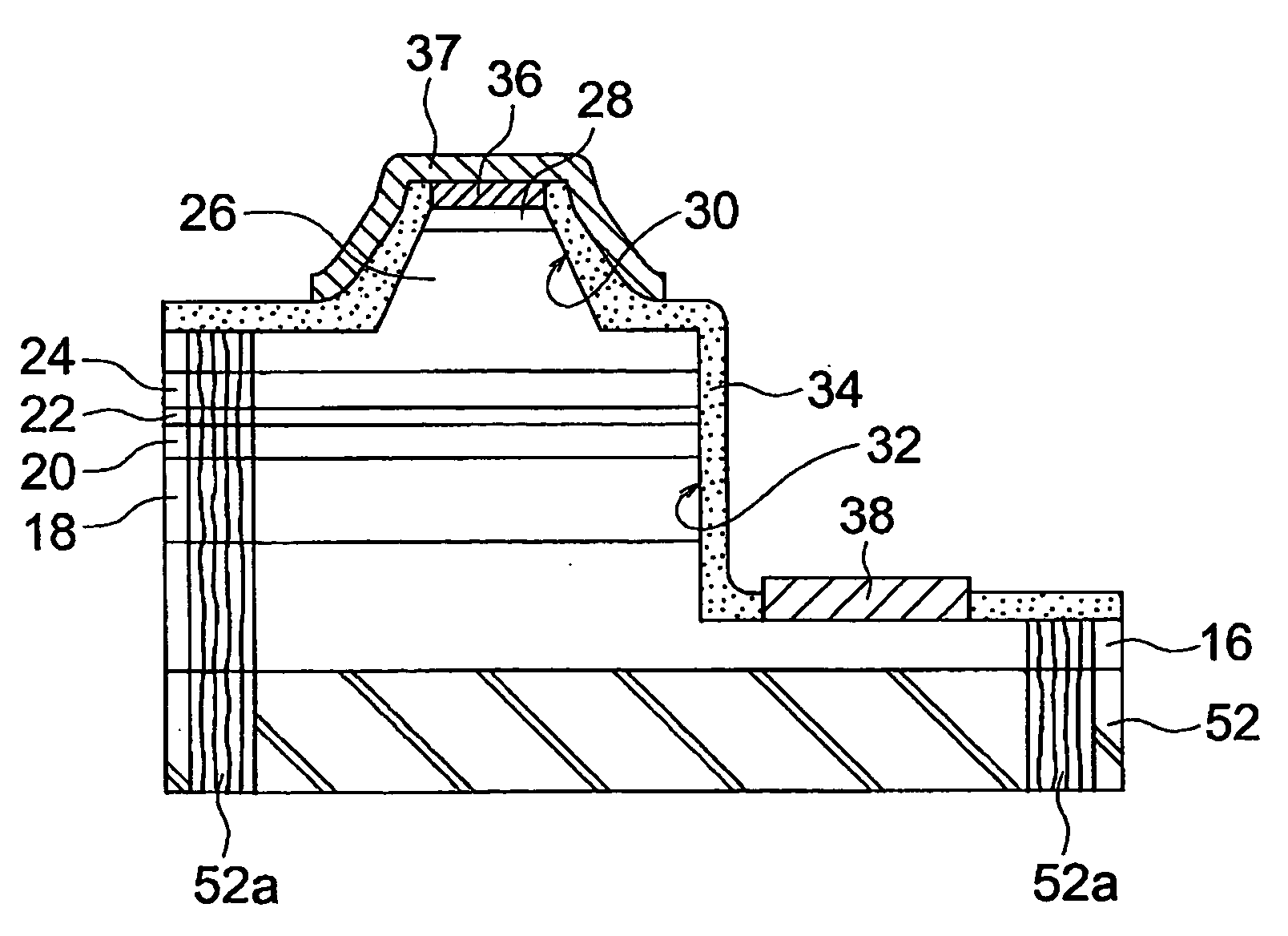

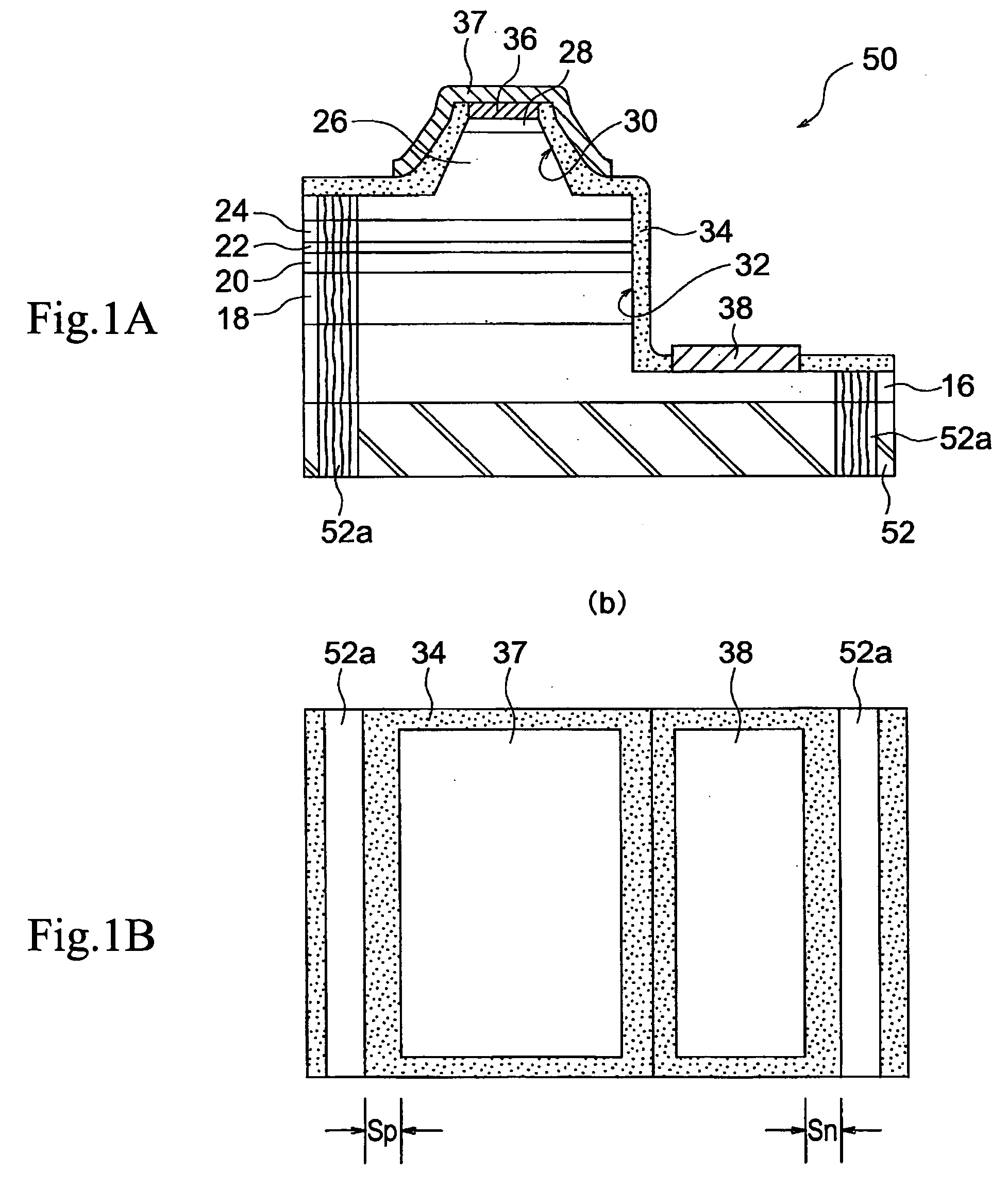

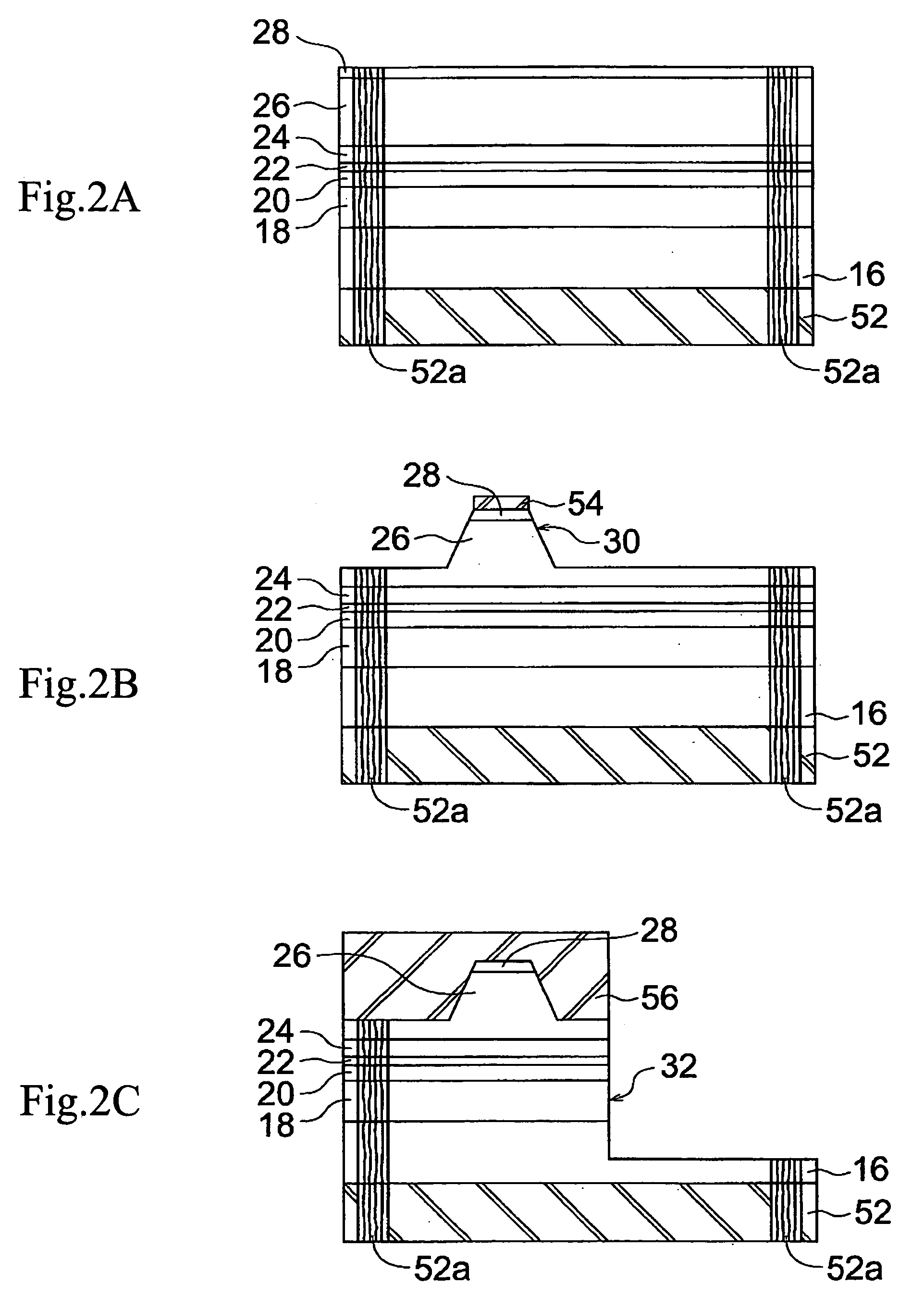

Provided is a GaN-based semiconductor light emitting device formed on a GaN single-crystal substrate and having a configuration capable of reducing a current leak. A GaN-based semiconductor laser device (50) is disclosed as an example of the GaN-based semiconductor light emitting device, and it is a semiconductor laser device having a structure such that a p-side electrode and an n-side electrode are provided on a multilayer structure of GaN-based compound semiconductor layers. The GaN-based semiconductor laser device (50) is similar in configuration to a conventional GaN-based semiconductor laser device formed on a sapphire substrate except that a GaN single-crystal substrate (52) is used in place of the sapphire substrate and that the multilayer structure is directly formed on the GaN single-crystal substrate (52) without providing a GaN-ELO structure layer. The GaN single-crystal substrate (52) has continuous belt-shaped core portions (52a) each having a width of 10 μm. These core portions (52a) are spaced apart from each other by a distance of about 400 μm. A laser stripe (30), a pad metal (37) for the p-side electrode (36), and the n-side electrode (38) are provided on the multilayer structure in a region except the core portions (52a) of the GaN single-crystal substrate (52). The horizontal distance Sp between the pad metal (37) and the core portion (52a) adjacent thereto is 95 μm, and the horizontal distance Sn between the n-side electrode (38) and the core portion (52a) adjacent thereto is also 95 μm.

Owner:SONY CORP

Semiconductor device and method of manufacturing the same

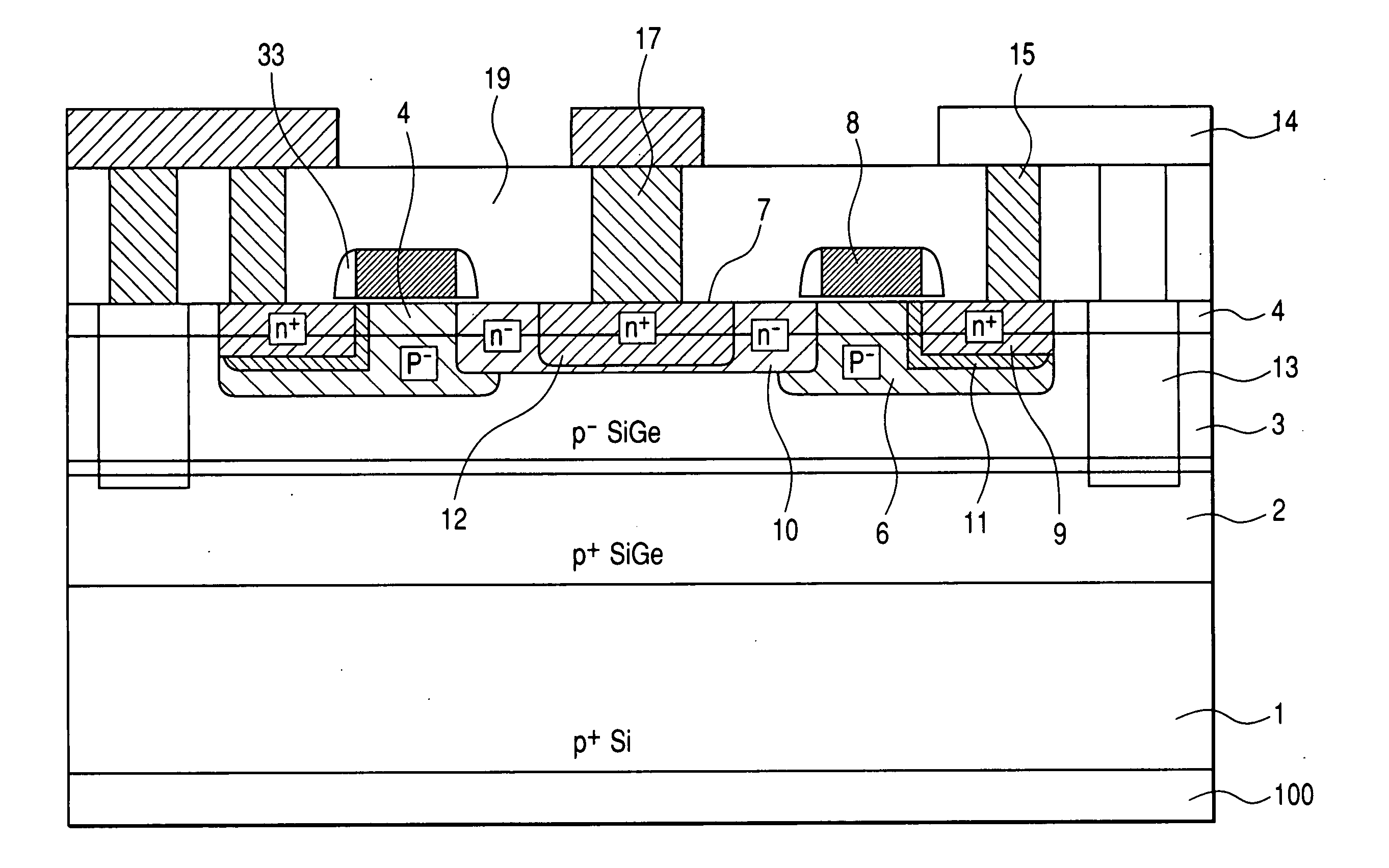

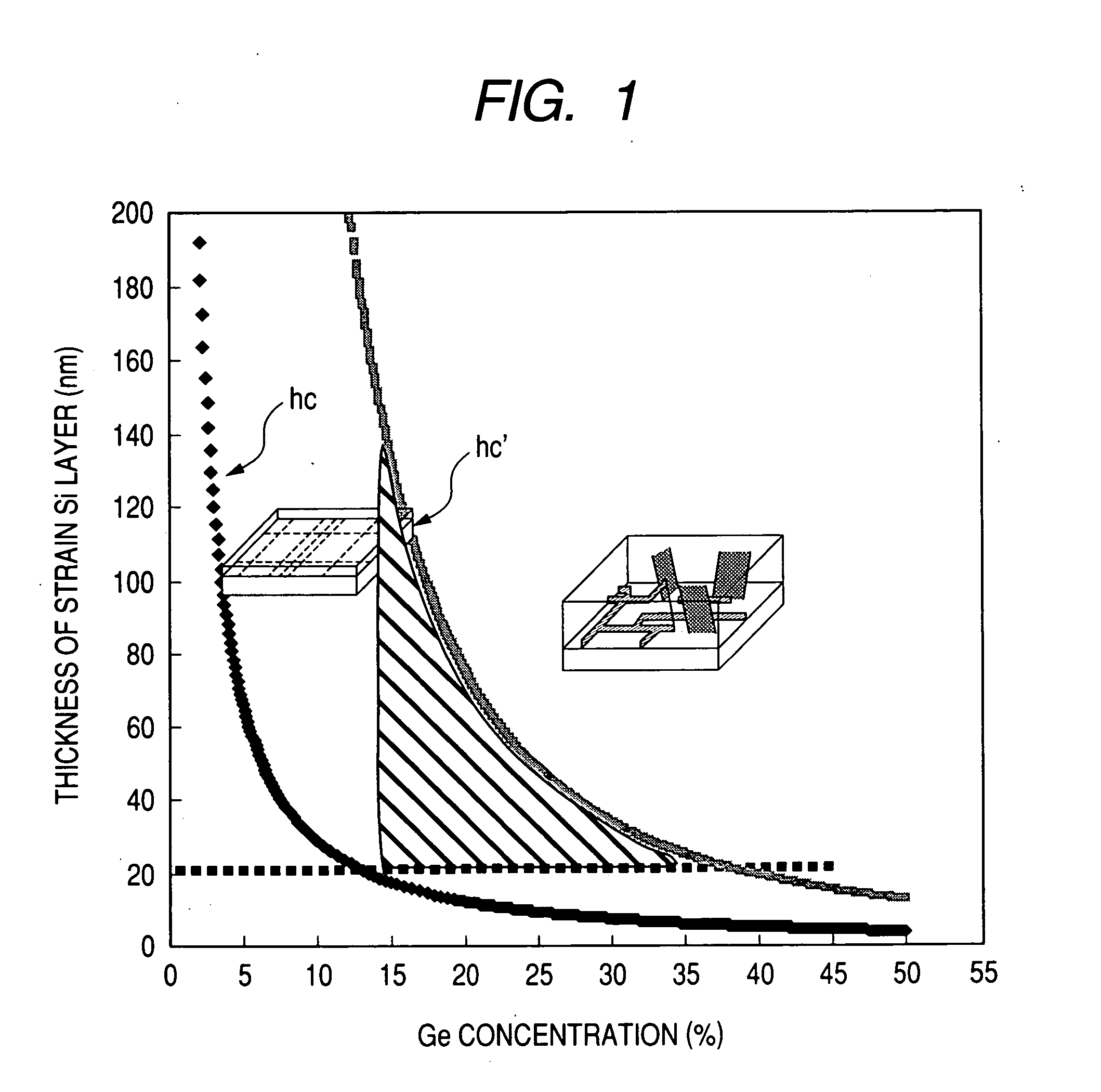

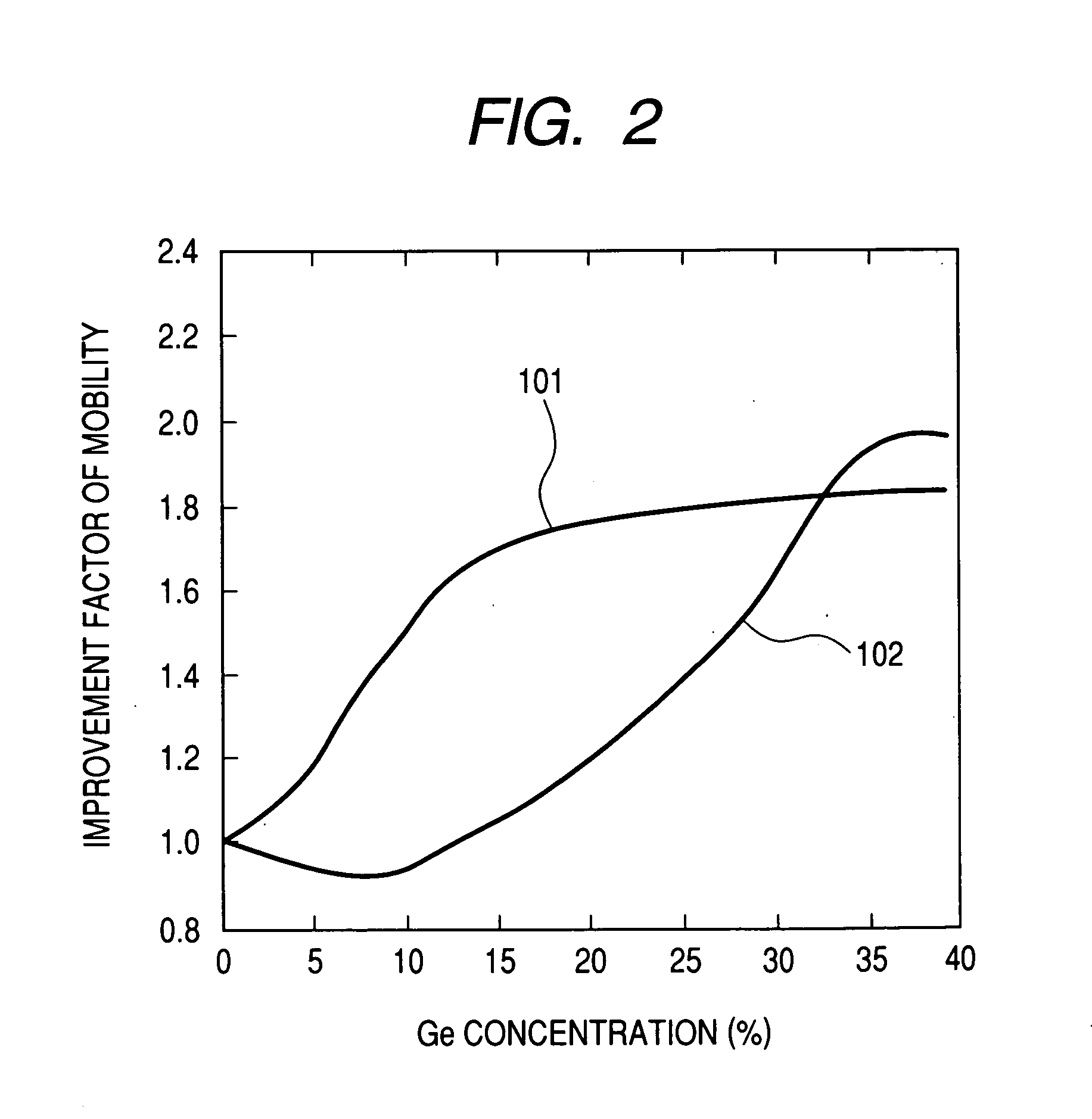

InactiveUS20060081836A1High film thicknessEasy to useSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSHigh frequency power

In a field effect semiconductor device for high frequency power amplification, it is difficult to achieve size reduction and increased efficiency simultaneously while ensuring voltage withstanding. A further improvement in efficiency is attained by using a strained Si channel for LDMOS at an output stage for high frequency power amplification. Further, the efficiency is improved as much as possible while decreasing a leak current, by optimizing the film thickness of the strained Si layer having a channel region, inactivation of defects and a field plate structure.

Owner:RENESAS TECH CORP

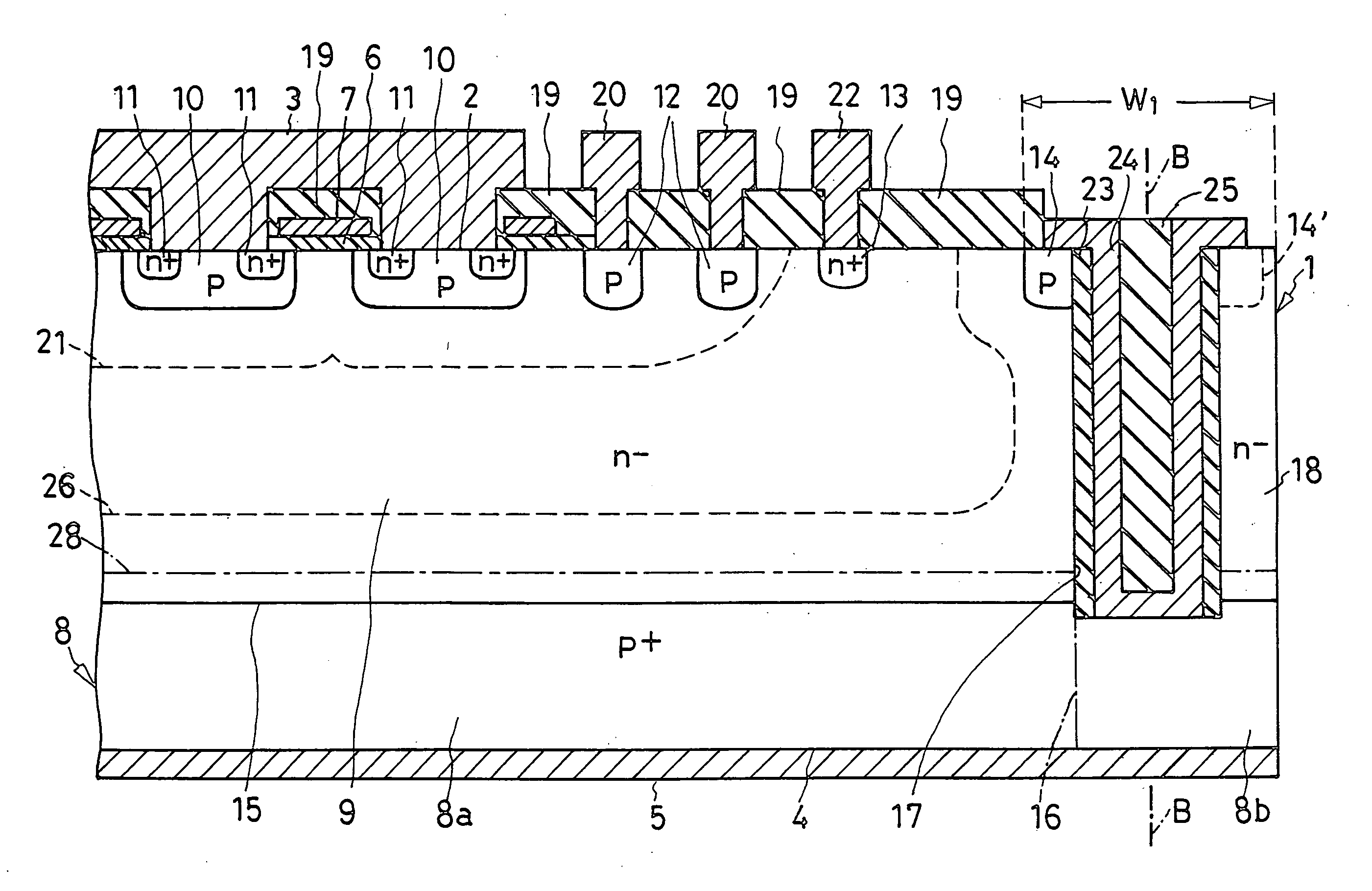

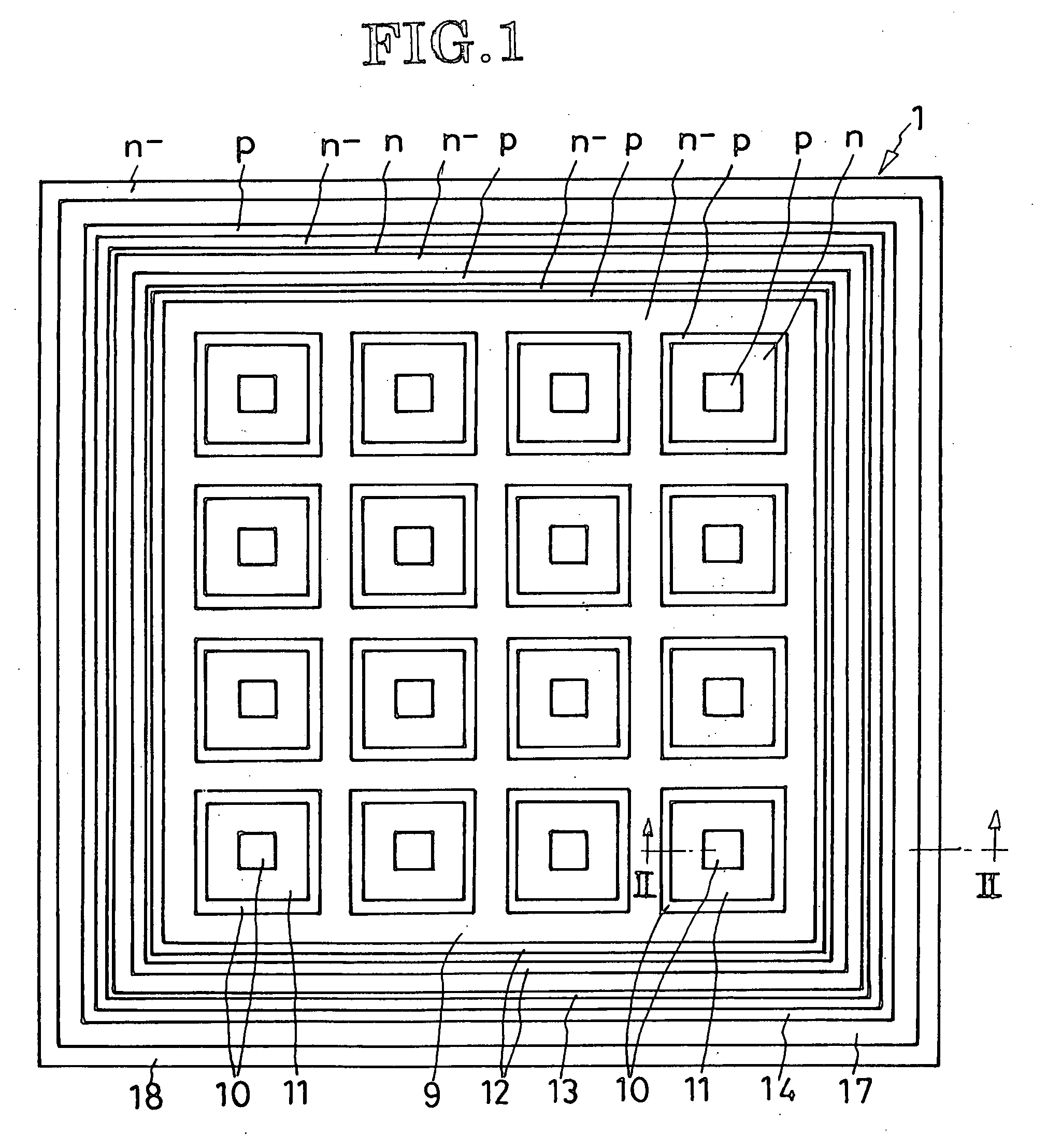

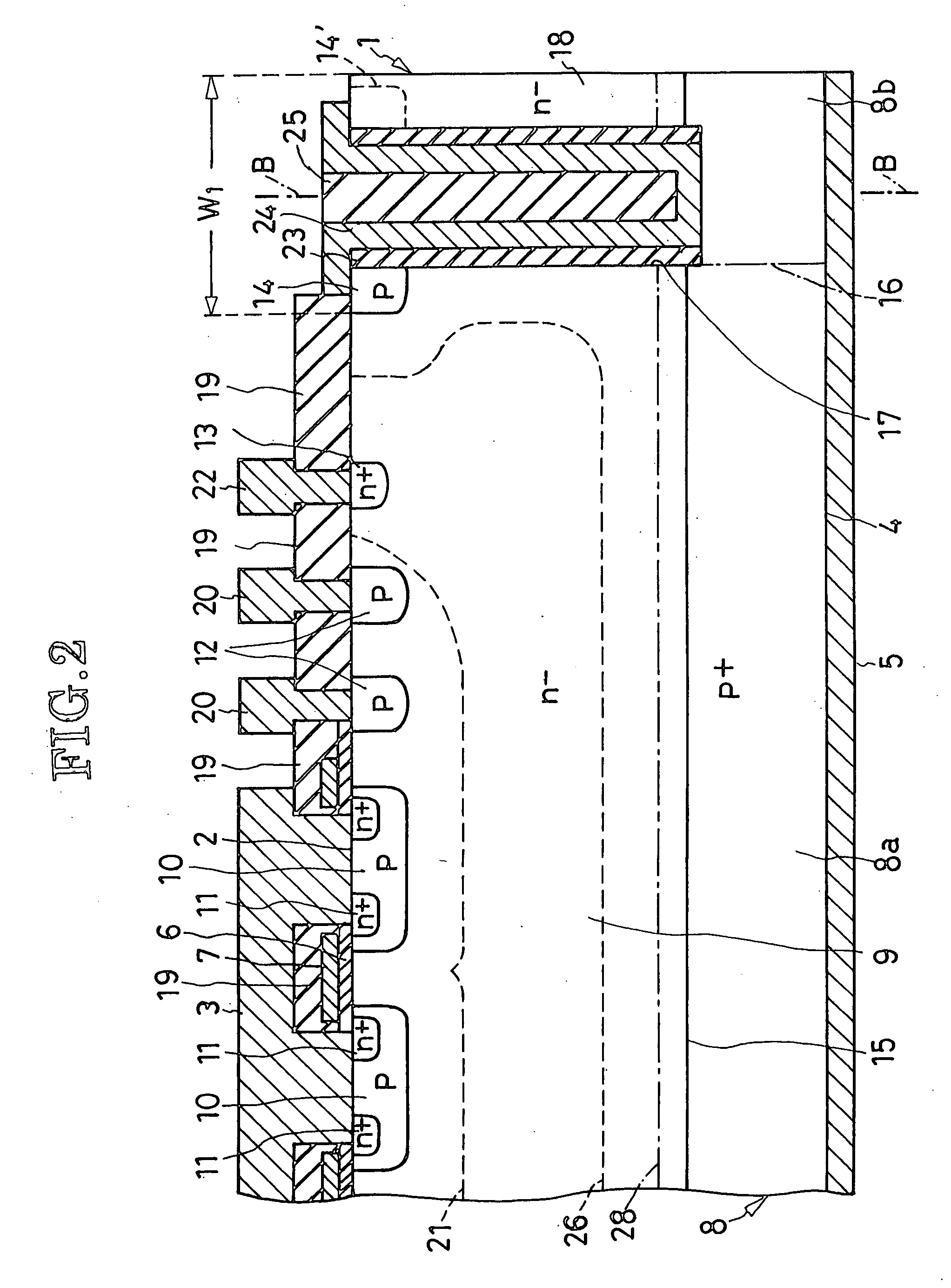

IGBT or like semiconductor device of high voltage-withstanding capability

ActiveUS20060267091A1High voltageLeakage currentTransistorSolid-state devicesInsulated-gate bipolar transistorSemiconductor

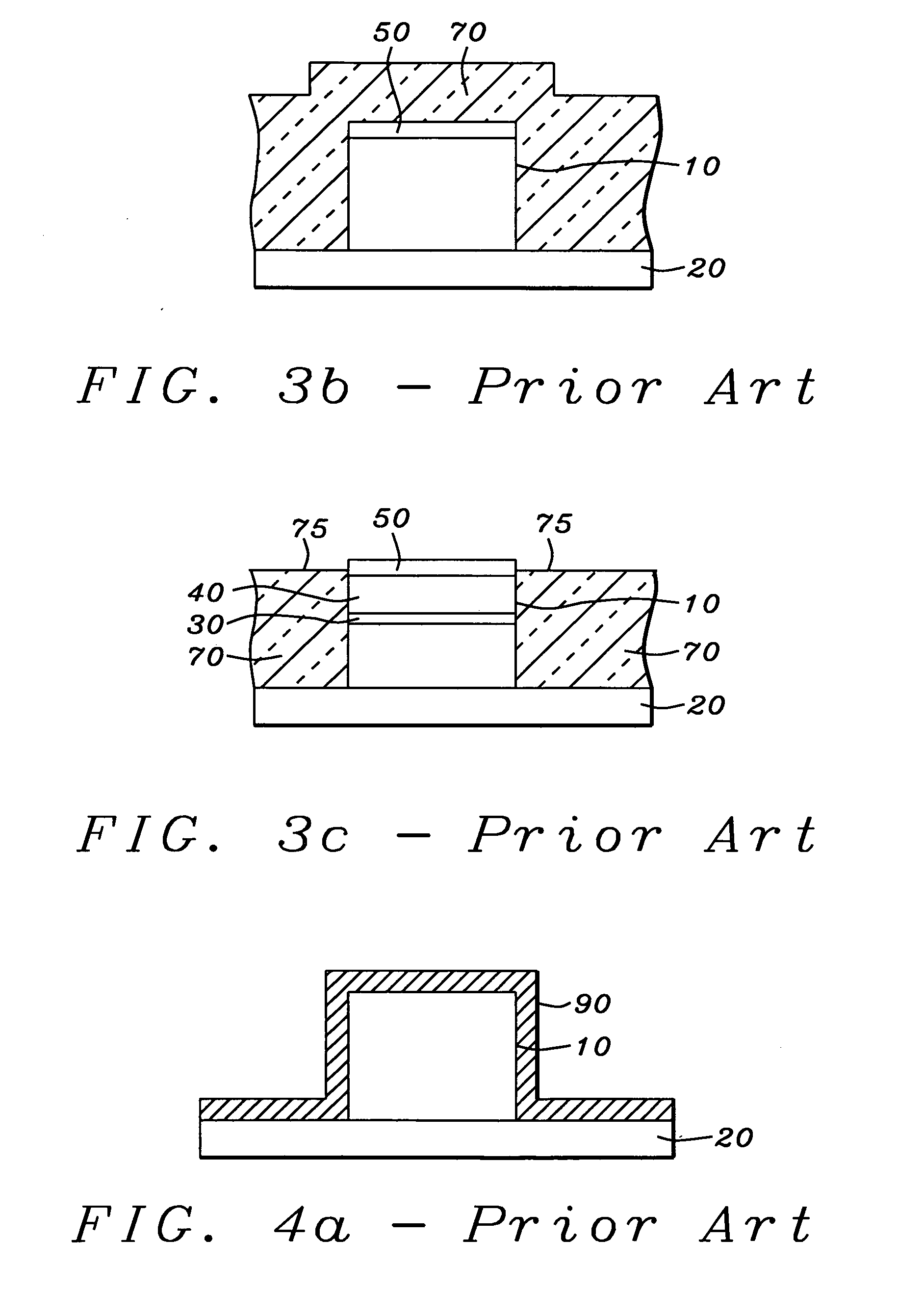

A multiple-cell insulated-gate-bipolar-transistor chip is disclosed which includes a semiconductor substrate having formed therein a p+-type collector region and an n−-type base region, with a pn junction therebetween. An annular trench is etched in the substrate so as to surround the array of IGBT cells. Received in the trench are a dielectric layer which is held against the base region, and an electroconductive layer which is held against the base region via the dielectric layer and which is electrically coupled to the collector region. When the pn junction between the collector and base regions is reverse biased, the electroconductive layer creates at the annular periphery of the base region a depletion layer which is joined to a depletion layer created in the base region by the pn junction, thereby preventing current leakage from the side surfaces of the IGBT chip.

Owner:SANKEN ELECTRIC CO LTD

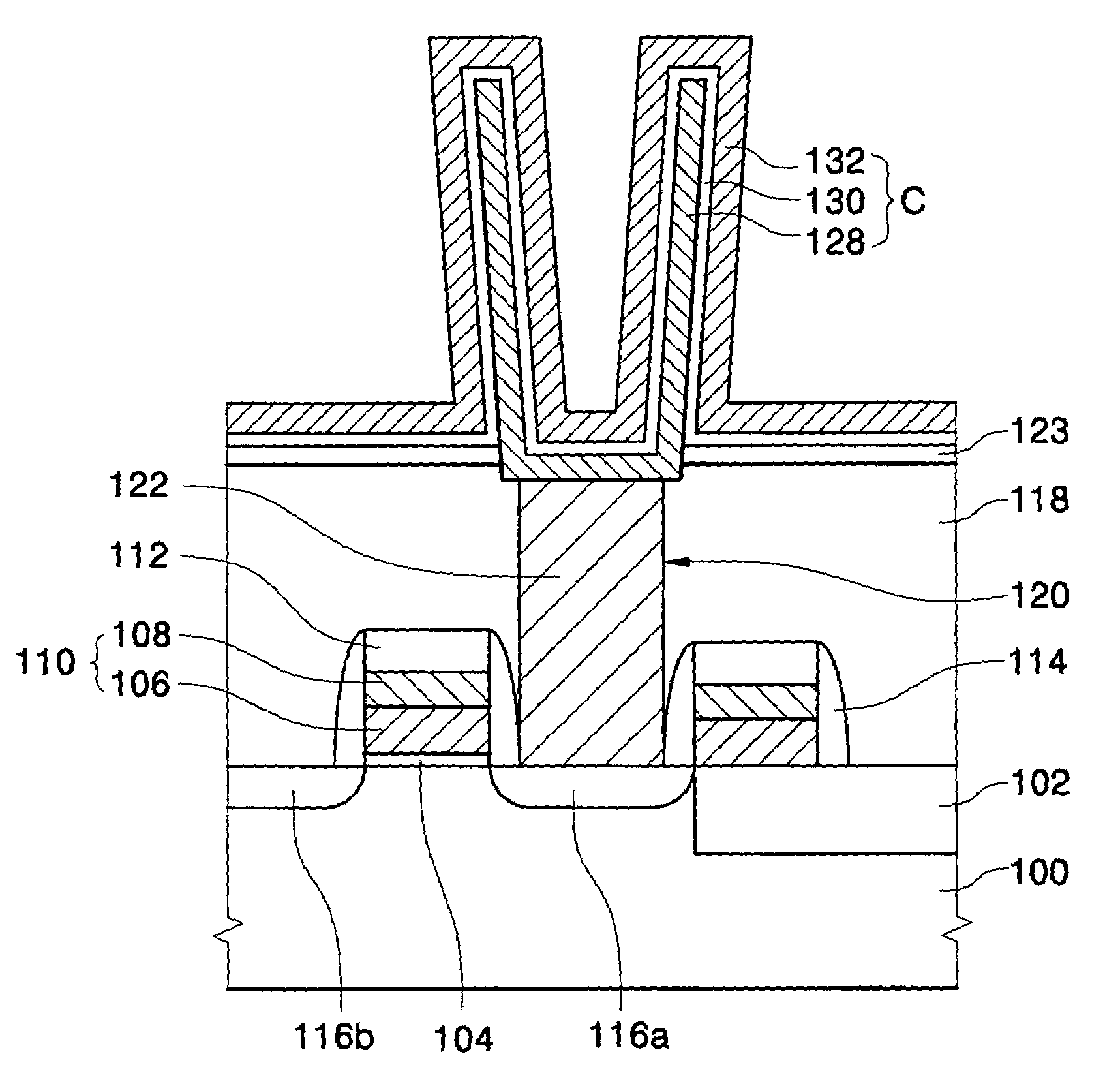

Method of forming material using atomic layer deposition and method of forming capacitor of semiconductor device using the same

InactiveUS7087482B2Good step coverageIncrease currentSemiconductor/solid-state device manufacturingCapacitorsSemiconductorDevice material

Disclosed are methods of forming dielectric materials using atomic layer deposition (ALD) and methods of forming dielectric layers from such materials on a semiconductor device. The ALD process utilizes a first reactant containing at least one alkoxide group that is chemisorbed onto a surface of a substrate and then reacted with an activated oxidant that contains no hydroxyl group to form a dielectric material exhibiting excellent step coverage and improved leakage current characteristics.

Owner:SAMSUNG ELECTRONICS CO LTD