Patents

Literature

877 results about "Application time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

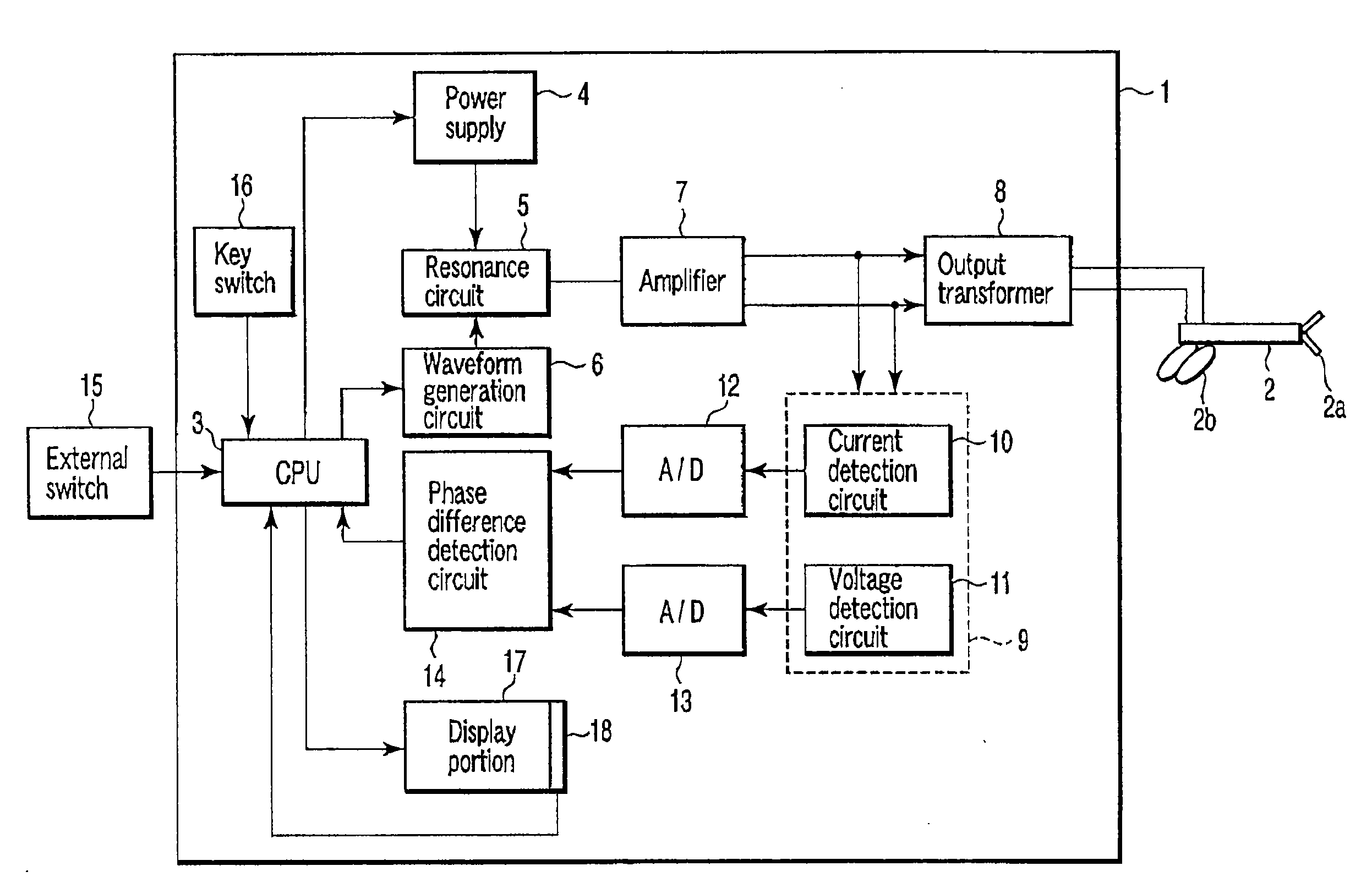

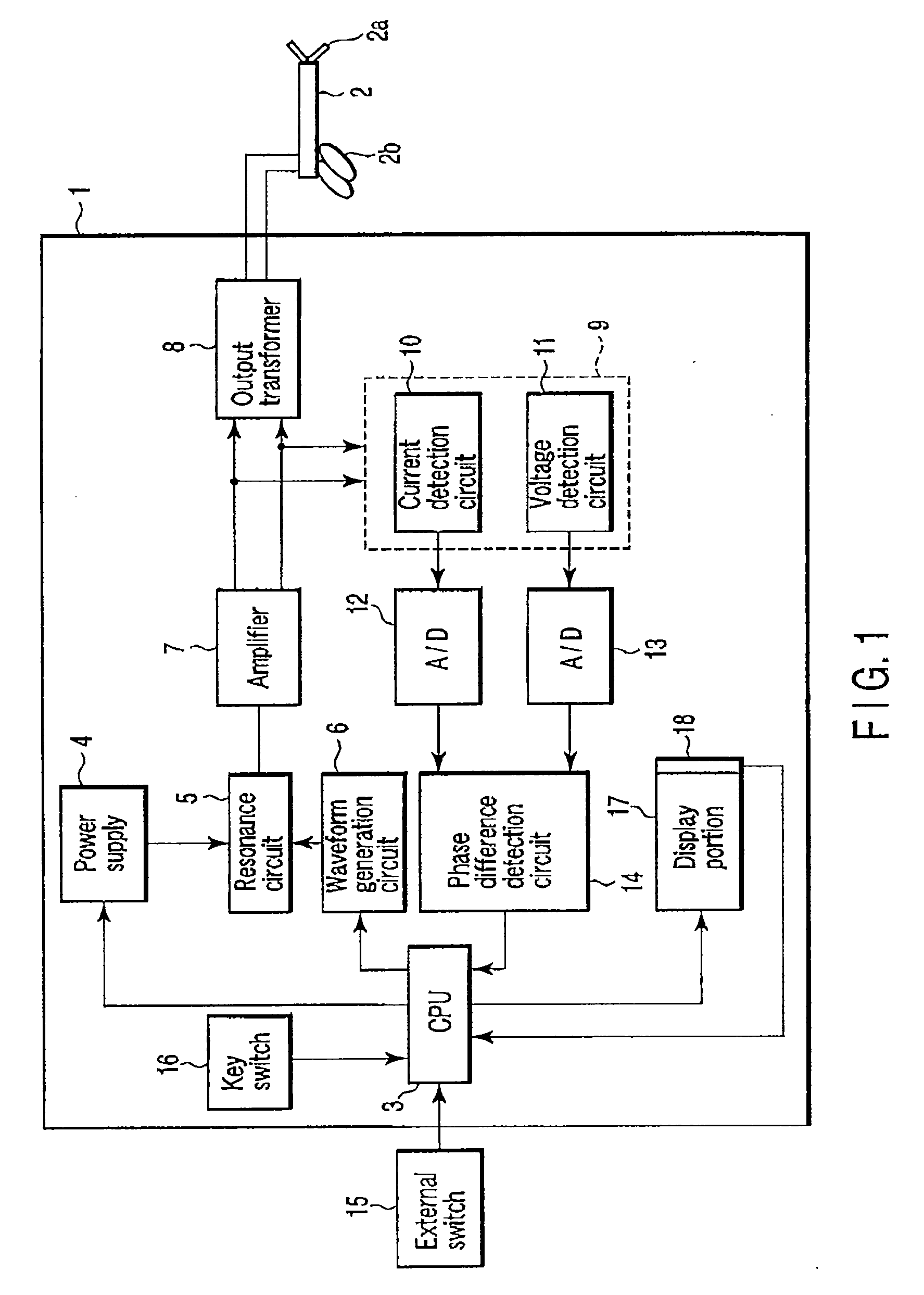

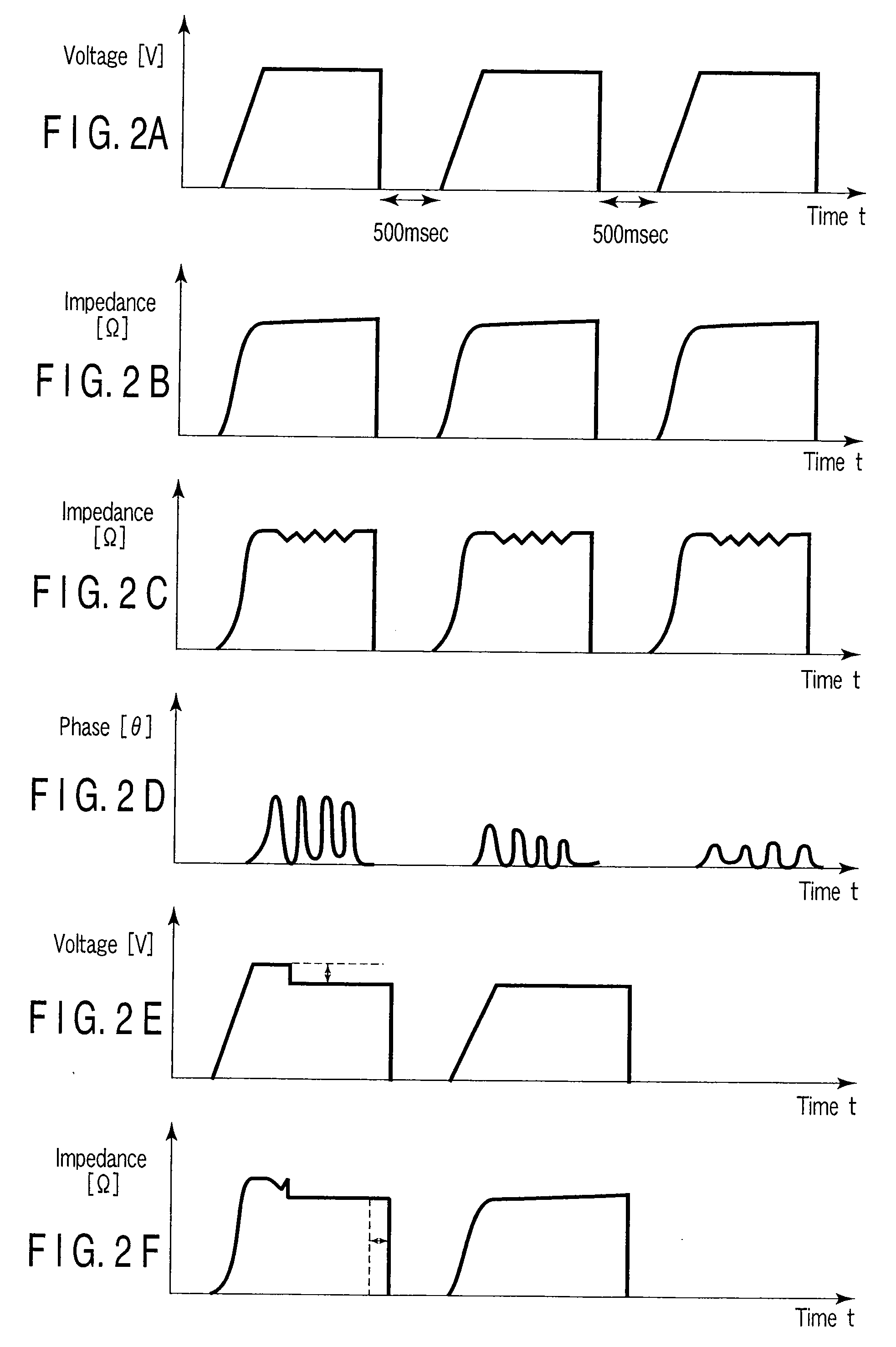

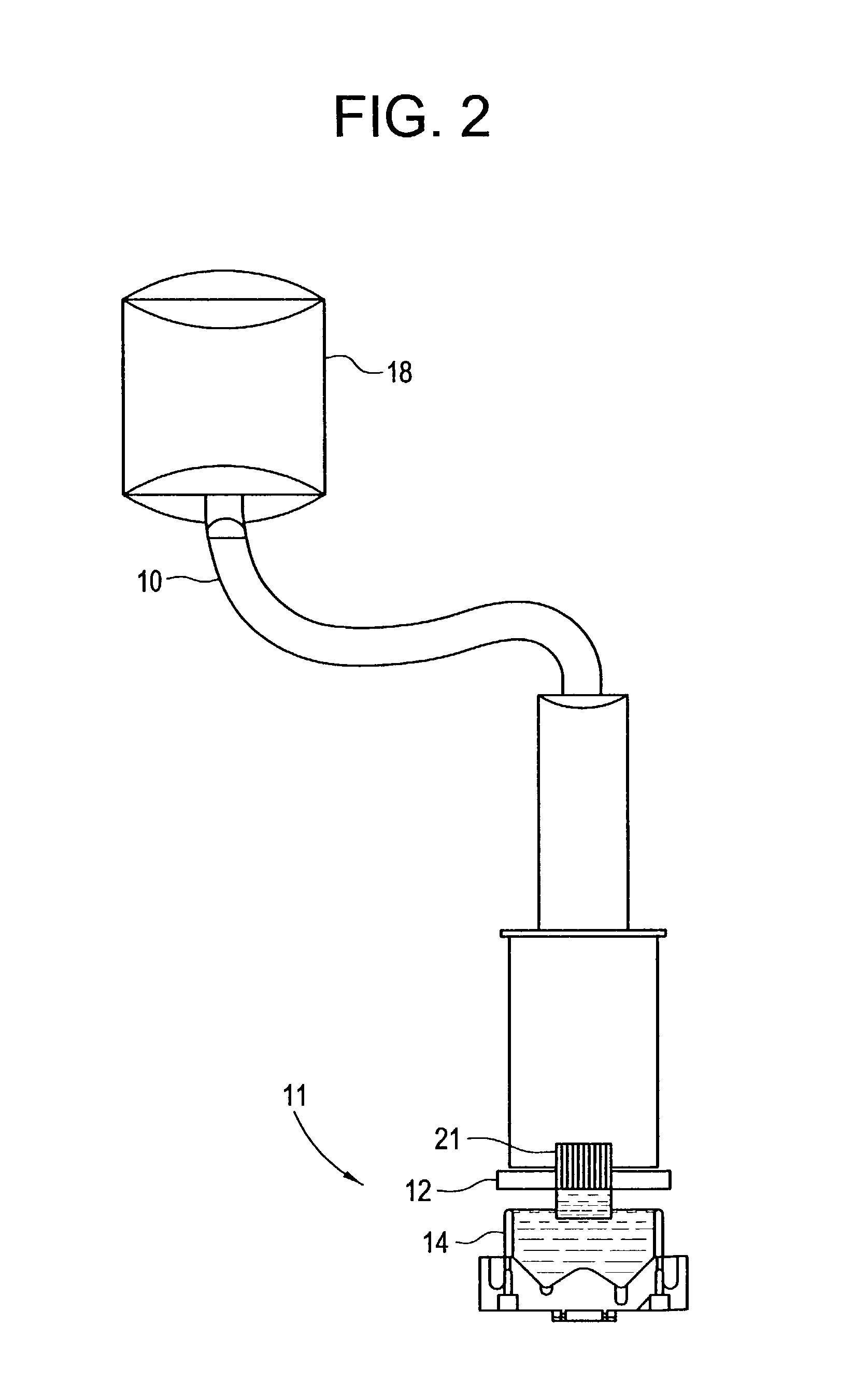

Electric processing system

InactiveUS20080082098A1Quality improvementSimple processSurgical instrument detailsSurgical forcepsElectricityHigh frequency power

There is provided an electric processing system which sequentially monitors a phase difference of intermittently output high-frequency powers in the case of performing feedback control with respect to a high-frequency power applied to bipolar type sealing forceps, reduces the high-frequency power and prolongs an application time at the time of occurrence of abnormal discharge (a spark) at distal ends, thereby terminating the abnormal discharge (extinguishing the spark) to carry out sealing processing.

Owner:OLYMPUS MEDICAL SYST CORP

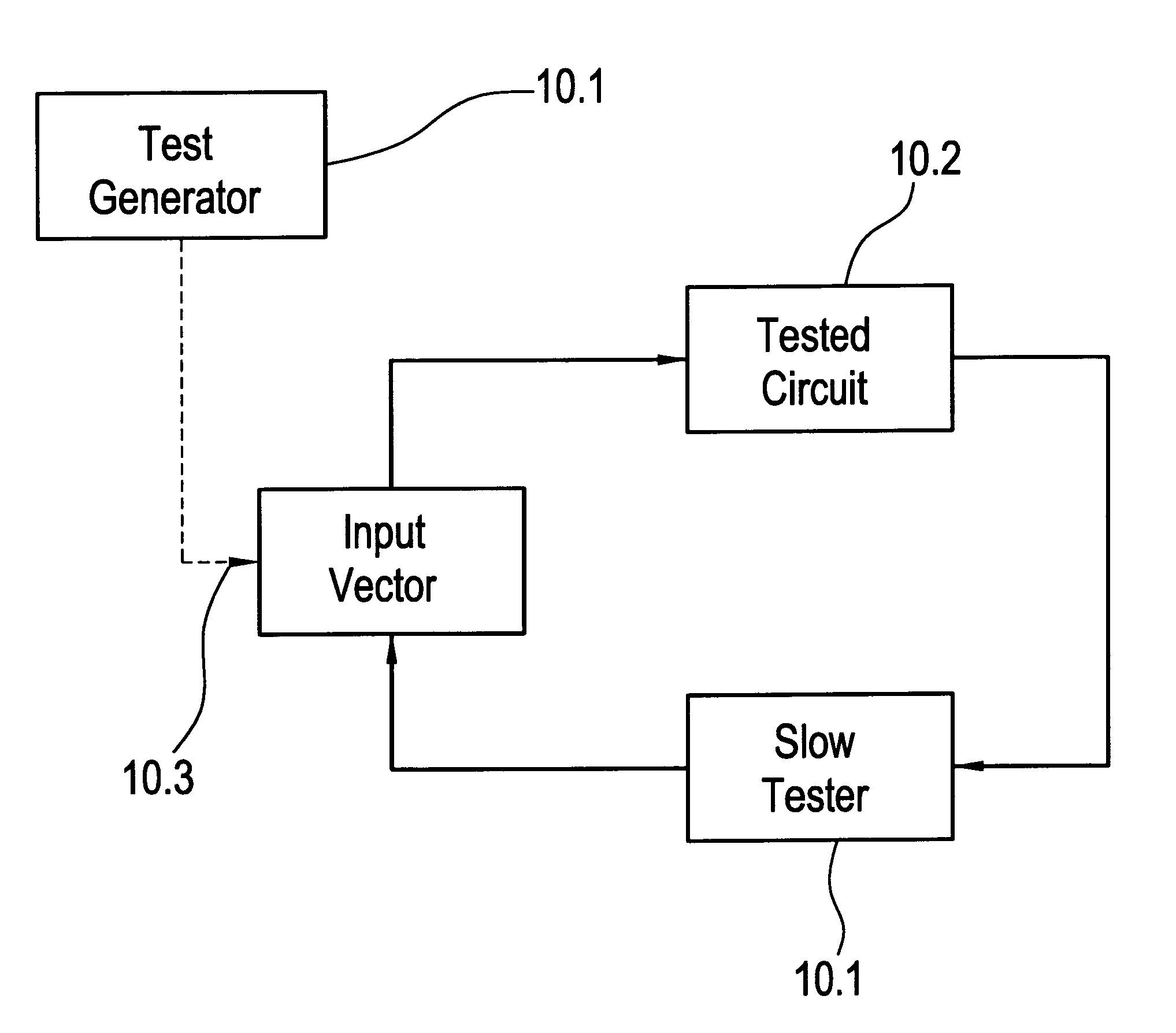

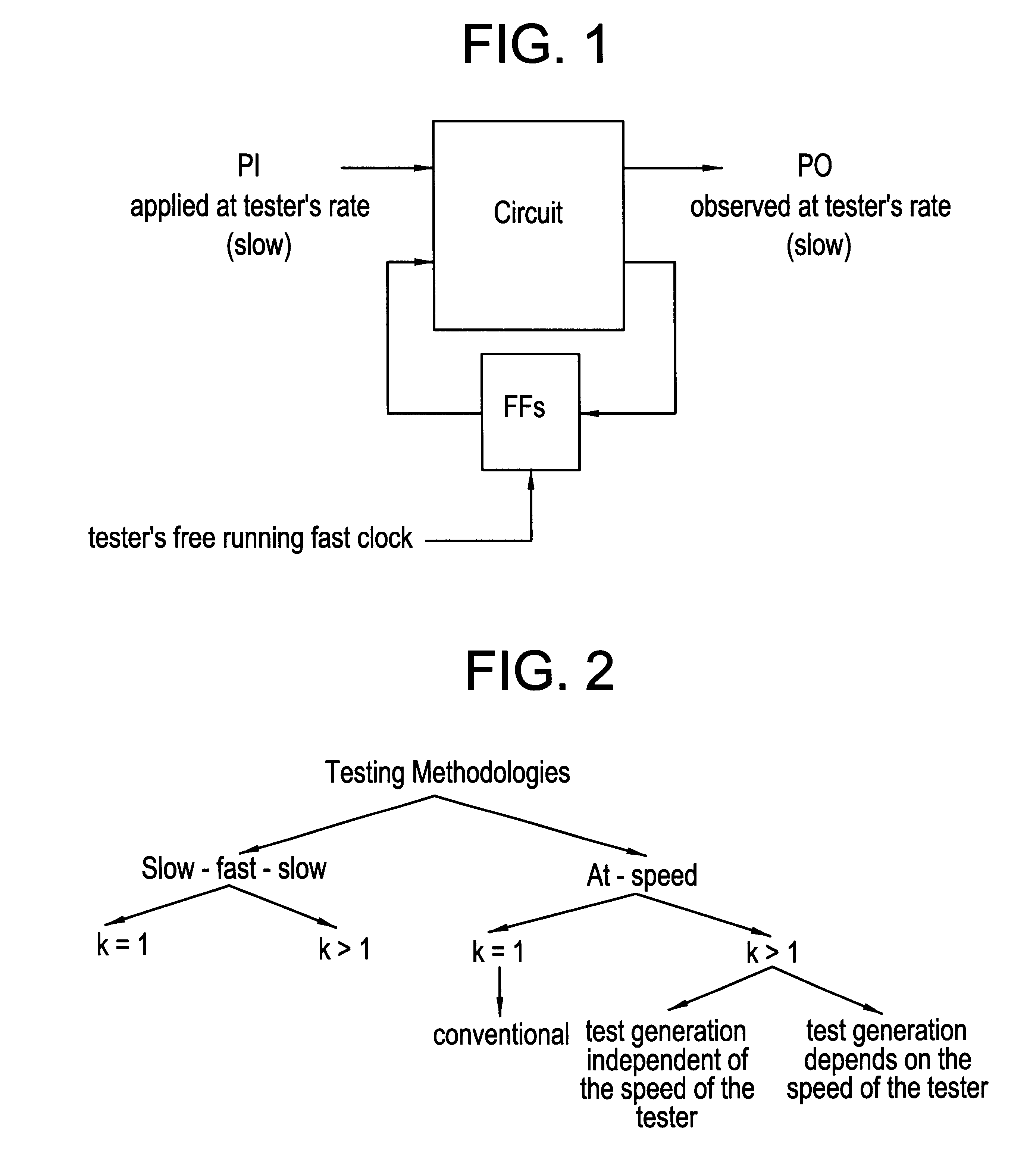

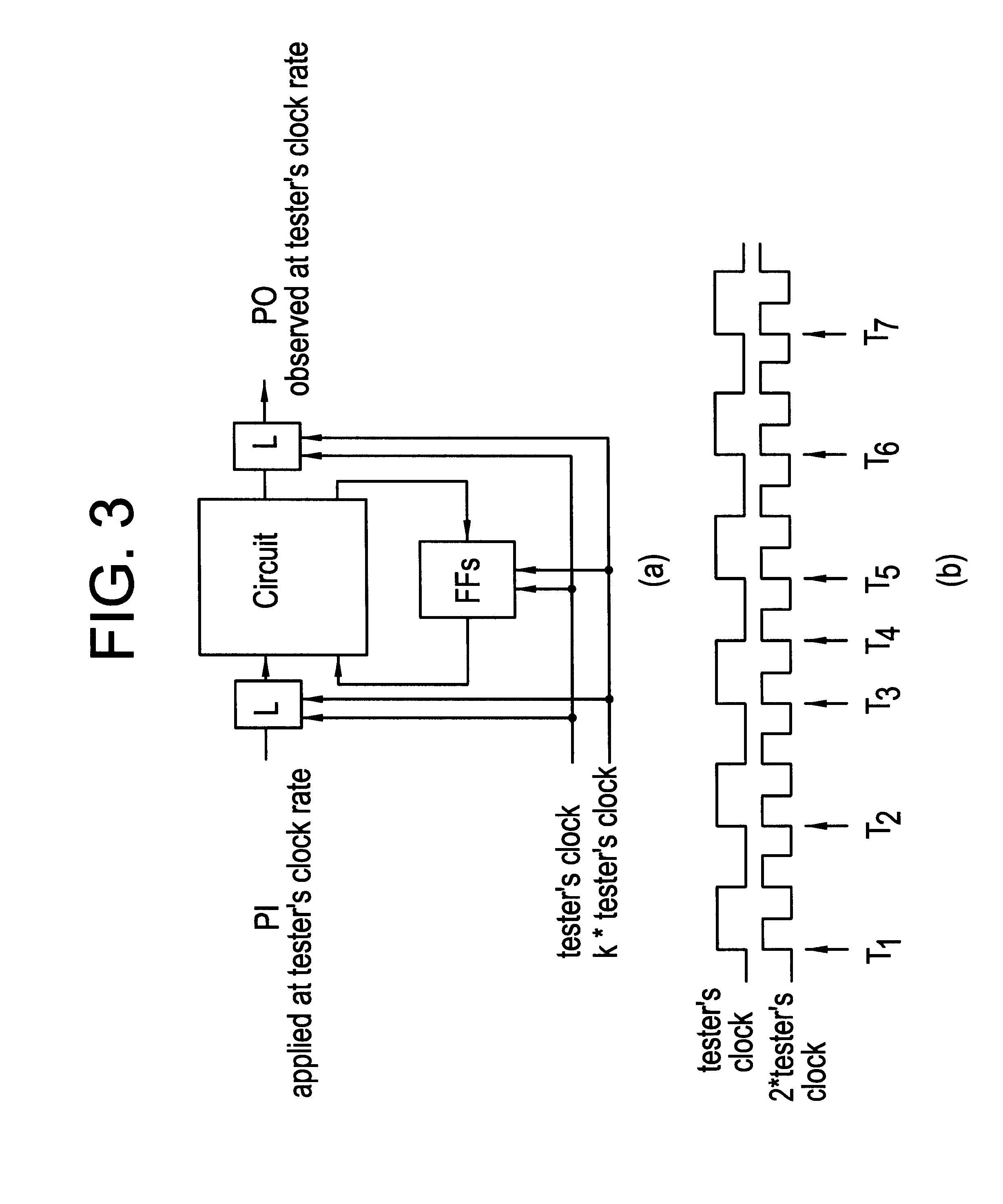

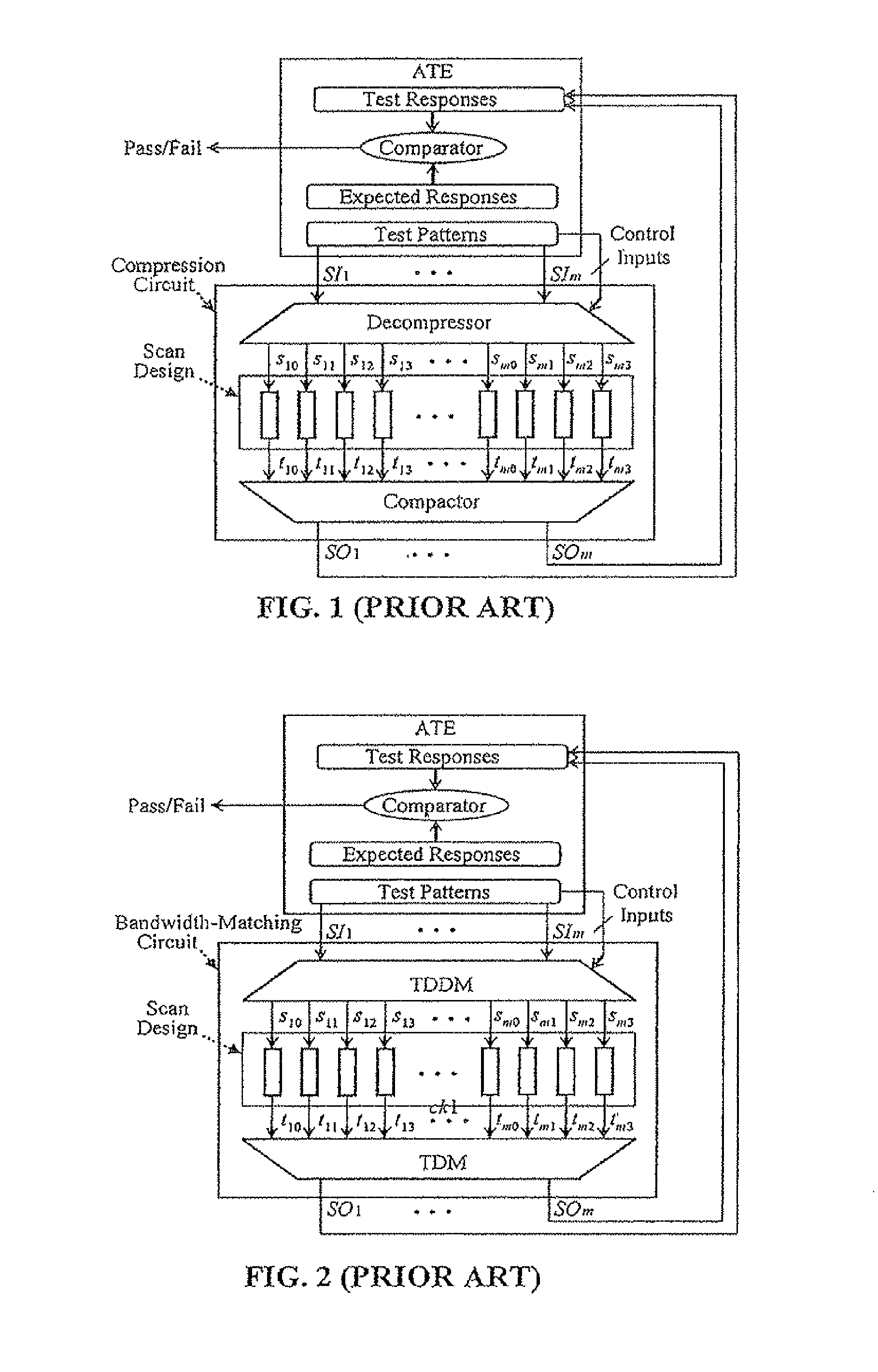

System and method for testing high speed VLSI devices using slower testers

InactiveUS6345373B1Shorten application timeLow fault coverageDigital circuit testingError detection/correctionGeneration processFault coverage

At-speed strategies for testing high speed designs on slower testers. At-speed testing schemes is provided that integrates the tester's speed limitations with the test generation process. Due to constraints placed at the test generation process, these schemes might result in a reduced fault coverage. To increase the fault coverage and reduce the test application time, the slow-fast-slow and at-speed strategies can be combined for testing high speed designs on slower testers. A slow tester that uses test vectors that are generated while taking into account the speed of the tester.

Owner:NEC CORP +1

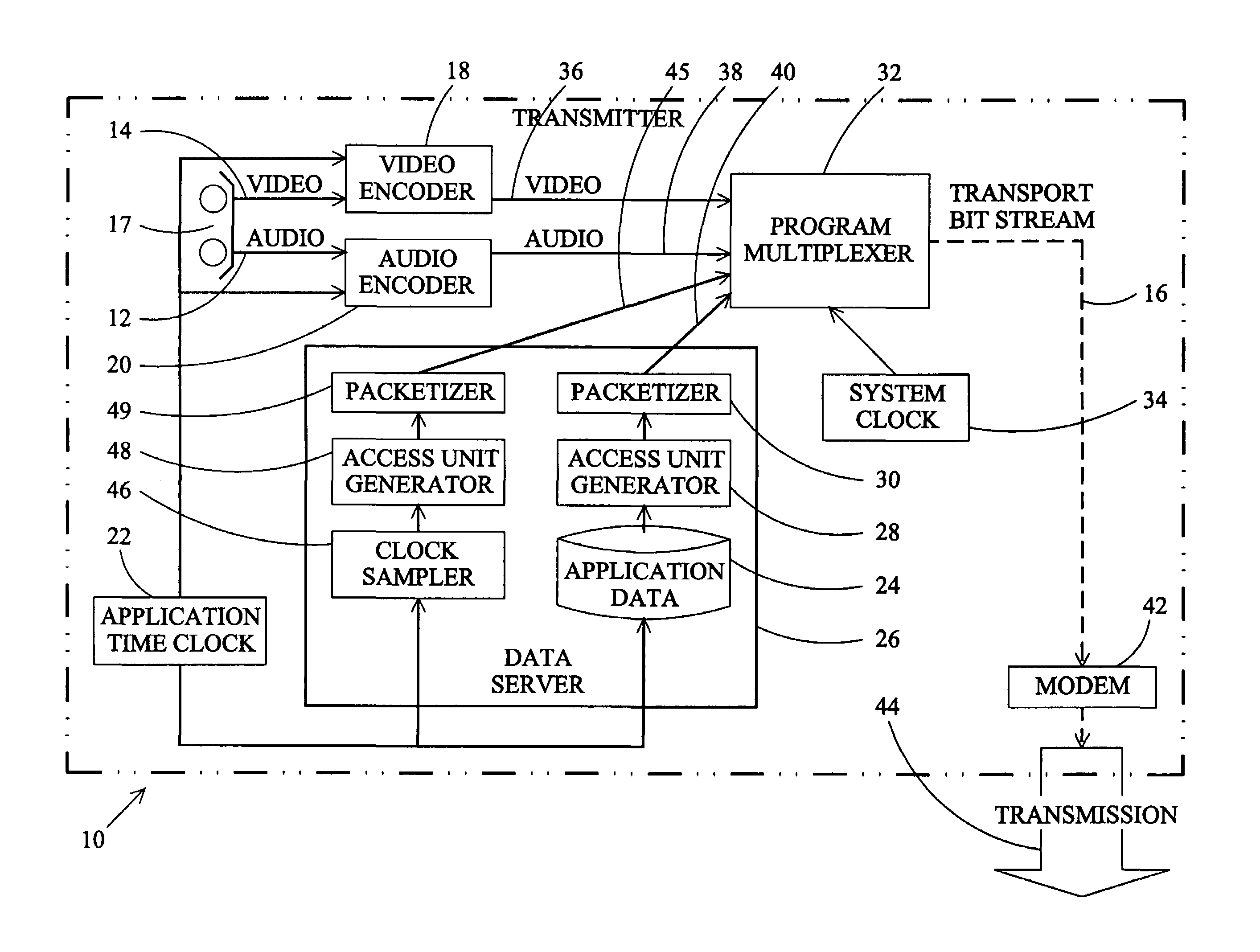

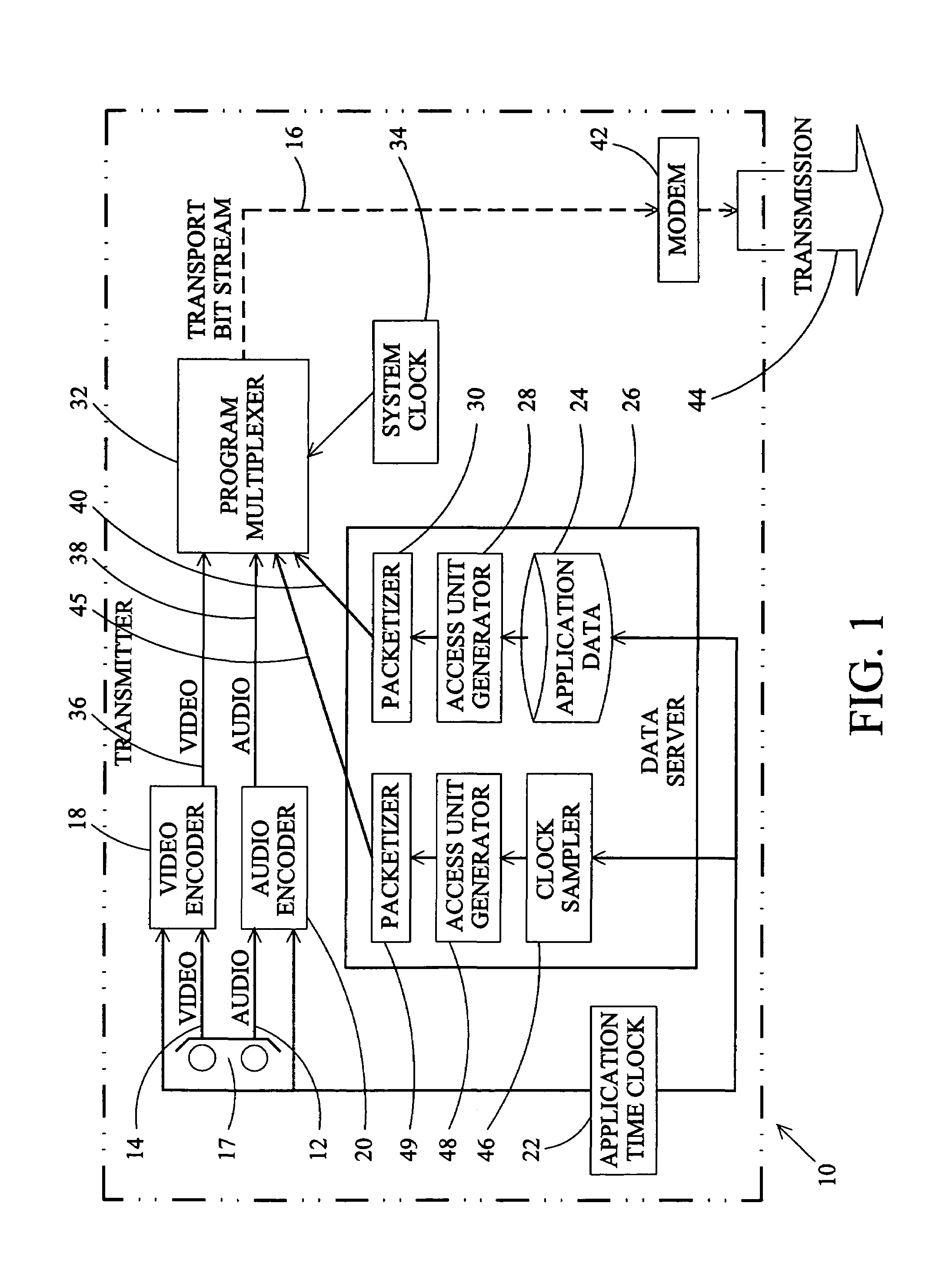

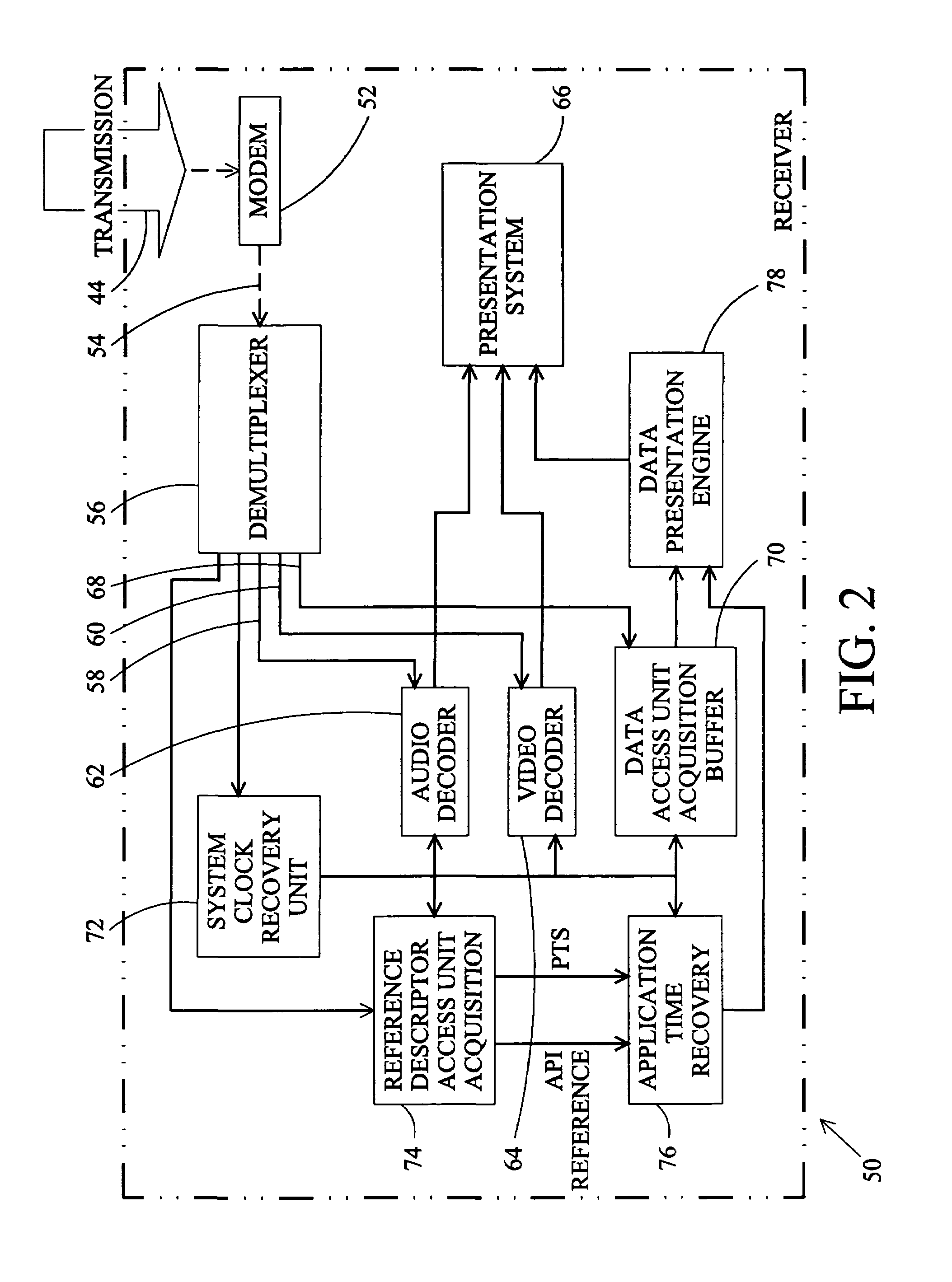

Method of synchronizing events with a digital television audio-visual program

InactiveUS7174560B1Television system detailsPicture reproducers using cathode ray tubesData accessAsynchronous data

A method and apparatus for synchronizing an event produced at a digital television receiver with an instant of a transmitted video, audio, or data element of a digital television program is disclosed. In a digital television system, a system time clock generates a timeline that is used to synchronize the presentation of the video, audio, and data elements of the television program. An application time is used in program production to synchronize instants of the several program elements. To synchronize a receiver generated event with an instant of a transmitted video, audio, or data program element, samples of the application time are transmitted to a receiver in a synchronized data service. A reconstructed application time is generated at the receiver as a function of the current system time, the application time sample, and the presentation time stamp of the data access unit in which the application time sample was transmitted. The presentation time of the program instant is associated with an application time correlating the event and the instant. The correlating application time is transmitted to the receiver as part of a synchronous or asynchronous data service and the event is instigated when the reconstructed application time corresponds to the correlating application time. A clock for generating a reconstructed application time synchronized to the system time is also disclosed.

Owner:SHARP KK

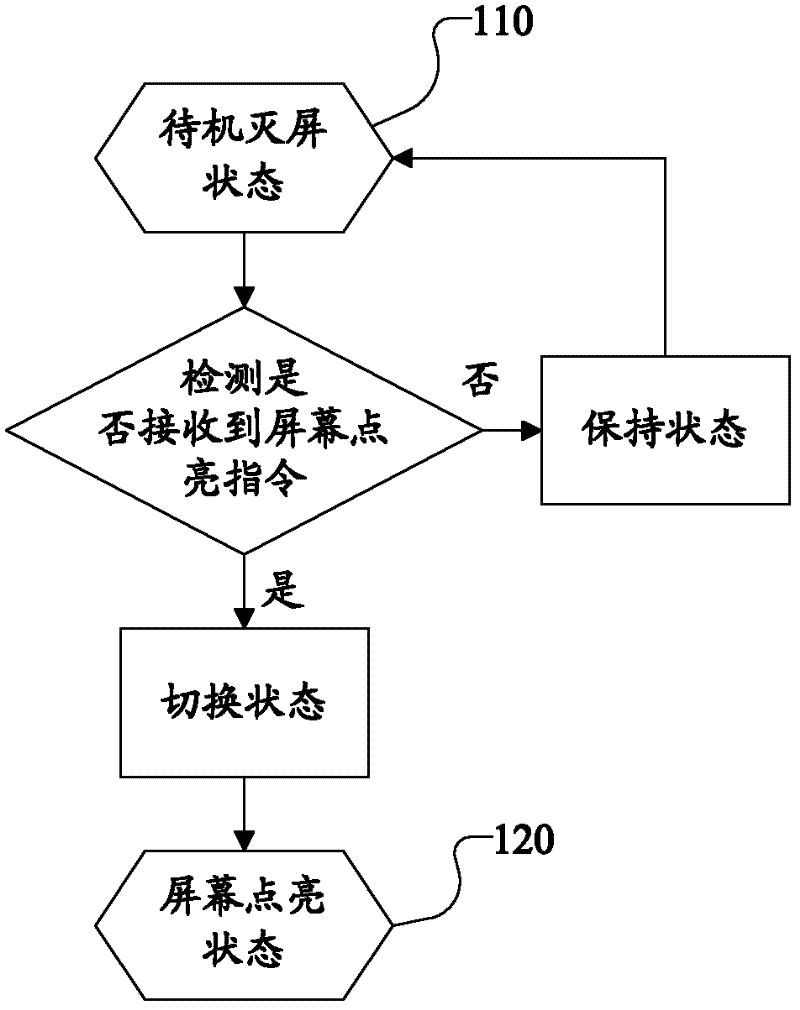

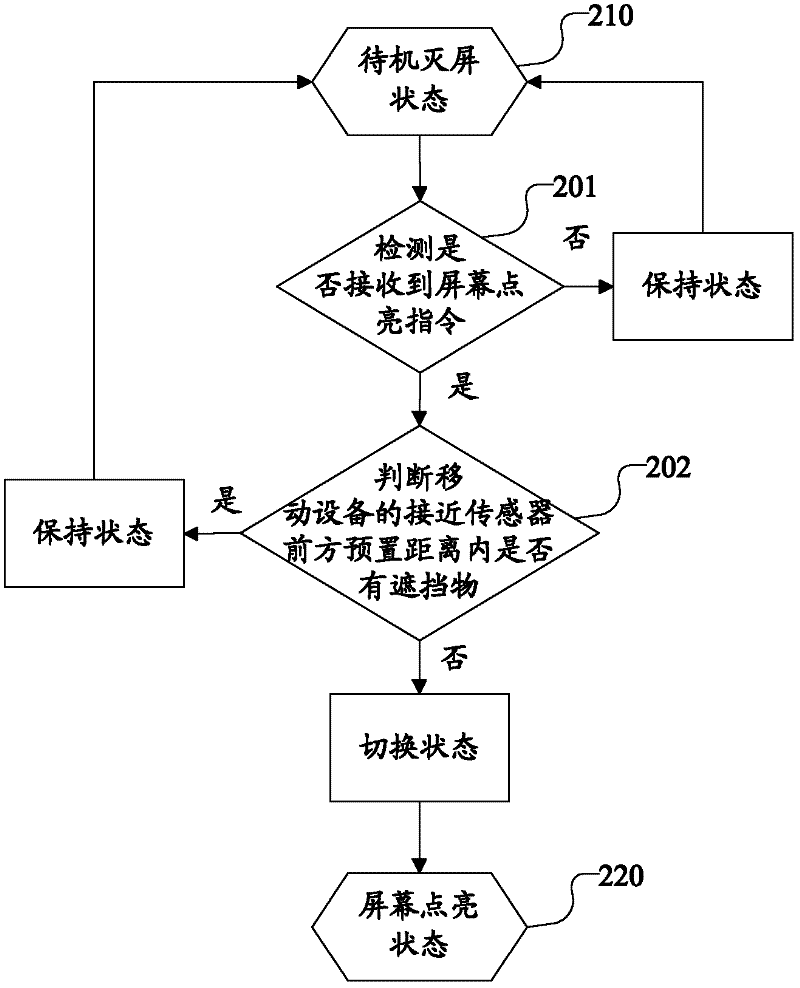

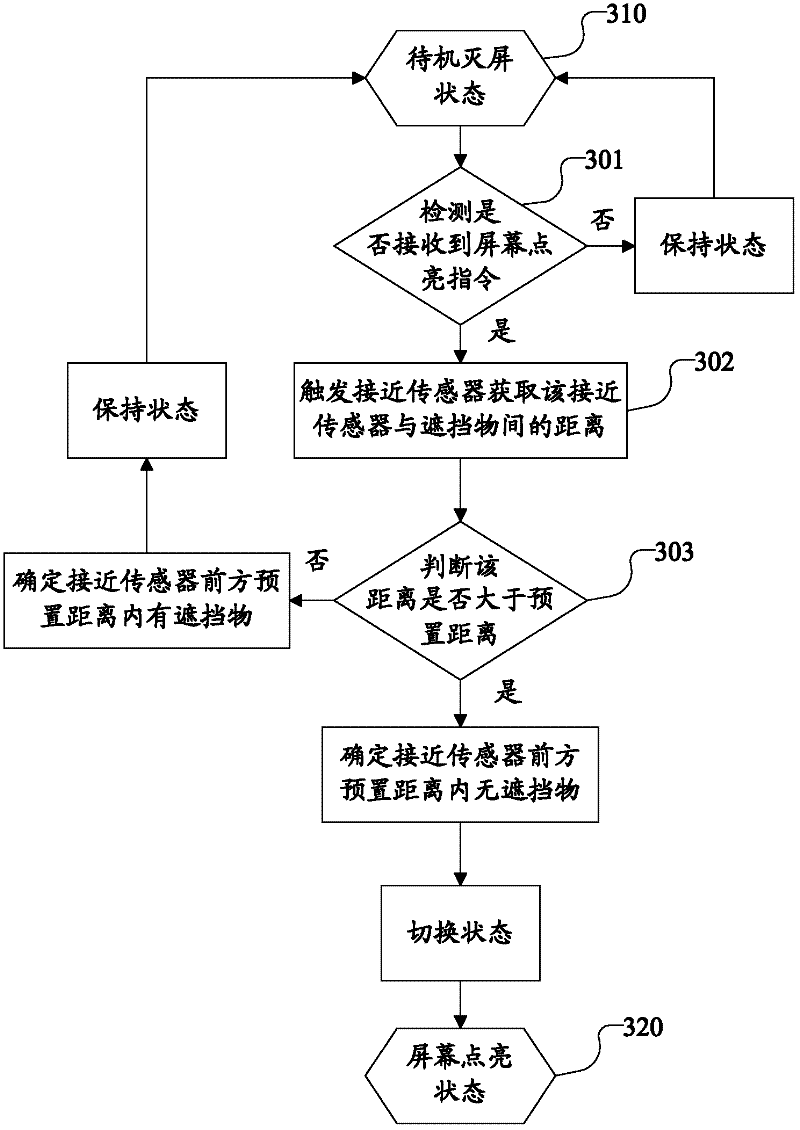

Control method of mobile equipment screen status and associated mobile equipment

InactiveCN102520852ASave battery powerExtended use timePower managementEnergy efficient ICTProximity sensorScreening status

The embodiment of the invention discloses a control method of a mobile equipment screen status and associated mobile equipment, which is used for preventing the mobile equipment from being switched from a standby screen-off status to a screen-on status caused by mistake triggering of screen lightening order transmission. The method comprises the following steps that: when the mobile equipment stays at a standby screen-off status, if a screen lightening order is received, whether a shield exists within a preset distance in front of an approaching sensor of the mobile equipment or not is judged; and if the shield exists within the preset distance in front of the approaching sensor, the mobile equipment maintains the standby screen-off status, and if no shield exists in the preset distance in front of the approaching sensor, the mobile equipment is switched from the standby screen-off status to the screen-on status. Due to the adoption of the control method, the power of the batteries of the mobile equipment can be saved, and the application time of the mobile equipment can be prolonged.

Owner:HUAWEI DEVICE CO LTD

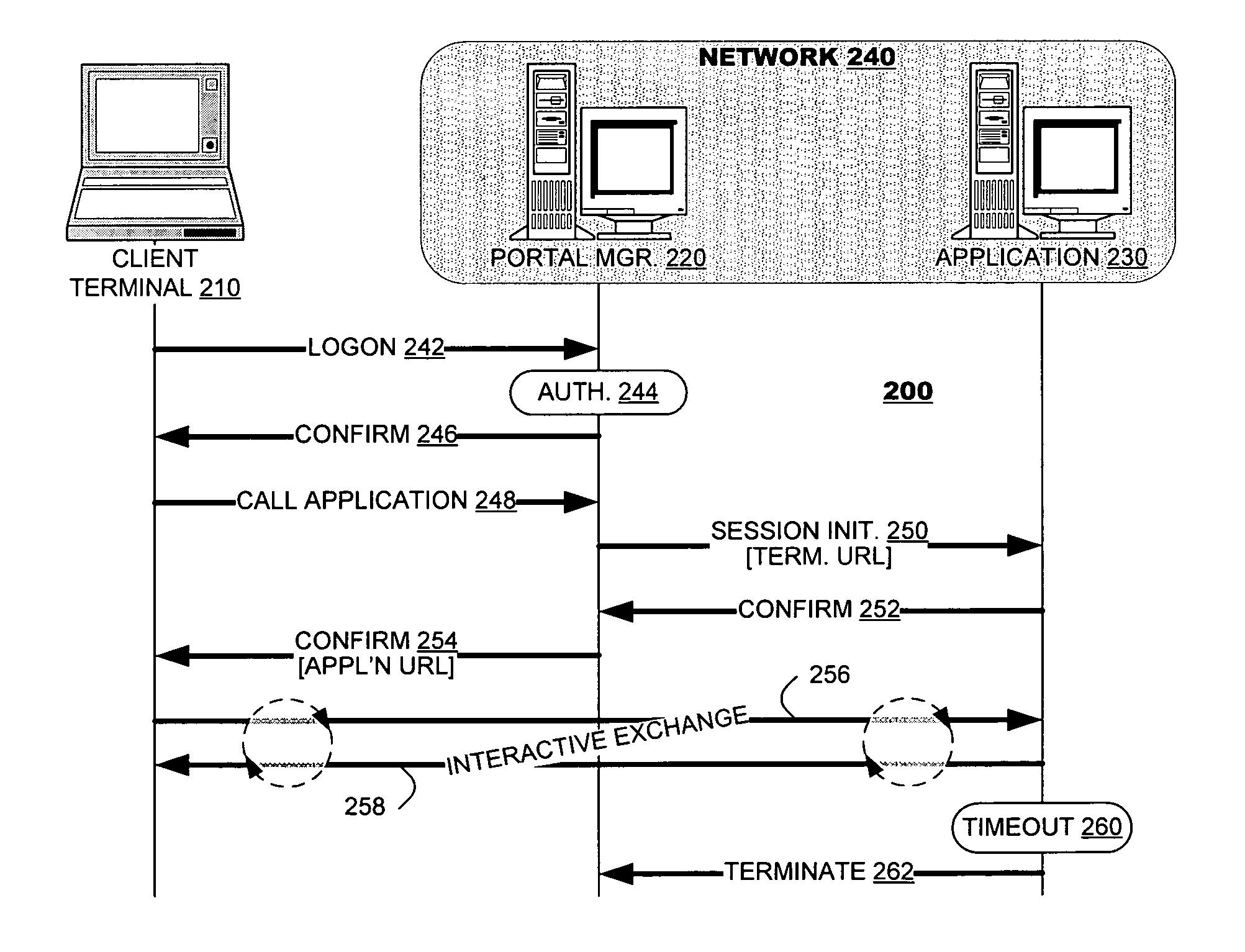

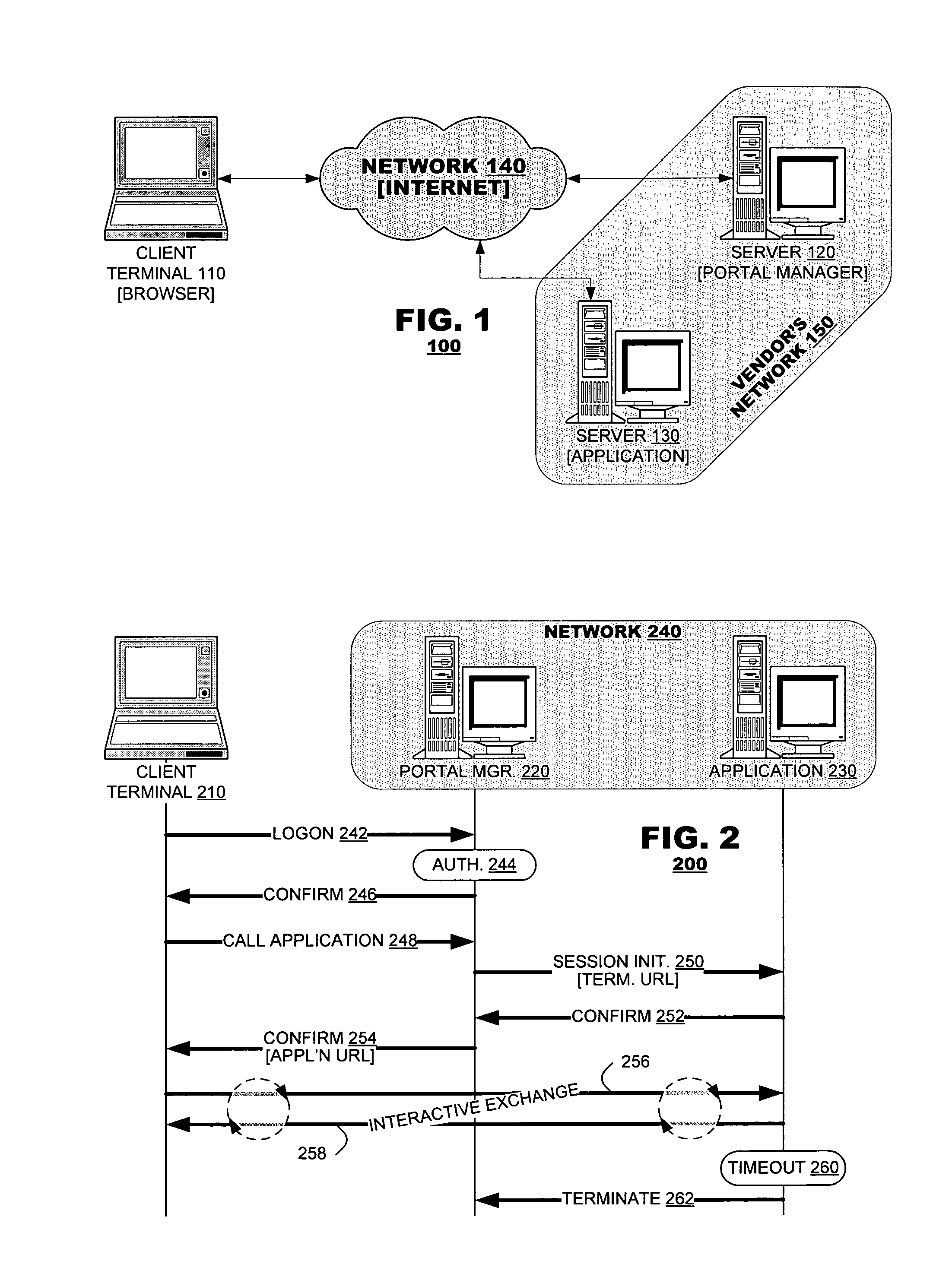

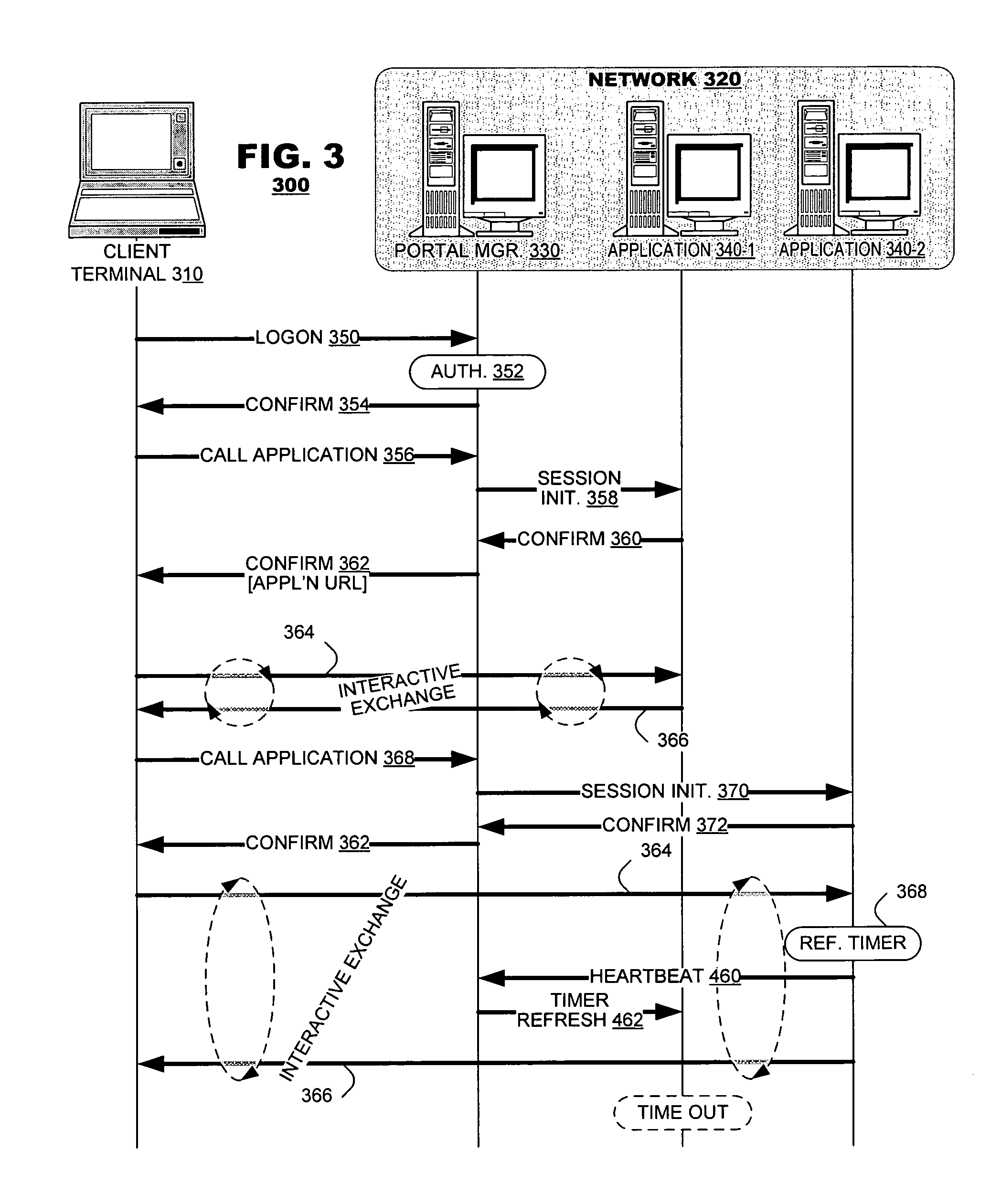

Session manager for web-based applications

ActiveUS20060212589A1Multiple digital computer combinationsTransmissionCommunications managementSession management

A communication manager for web-based applications receives indications of application time outs via a callback mechanism. During session initiation, the communication manager provides a termination address to an application along with a session ID. If the session times out due to inactivity, the application may signal the communication manager that the session ID is invalid by sending a message to the termination address. Alternatively, when a communication manager establishes communication sessions for several applications with a common external terminal, the communication manager may receive messages identifying terminal activity at one of the applications and may signal to the other applications to keep their sessions active.

Owner:SAP AG

Self-hardening material and process for layerwise formation of models

ActiveUS20100291314A1Additive manufacturing apparatusPretreated surfacesParticulatesApplication time

The invention relates to a self-hardening material for layerwise construction of three-dimensional components, whereby the material comprises at least one particulate material and a separately applied bonding agent for bonding the particulate material, and has a setting time which is at least several times as long as the application time of a particulate layer.

Owner:VOXELJET AG

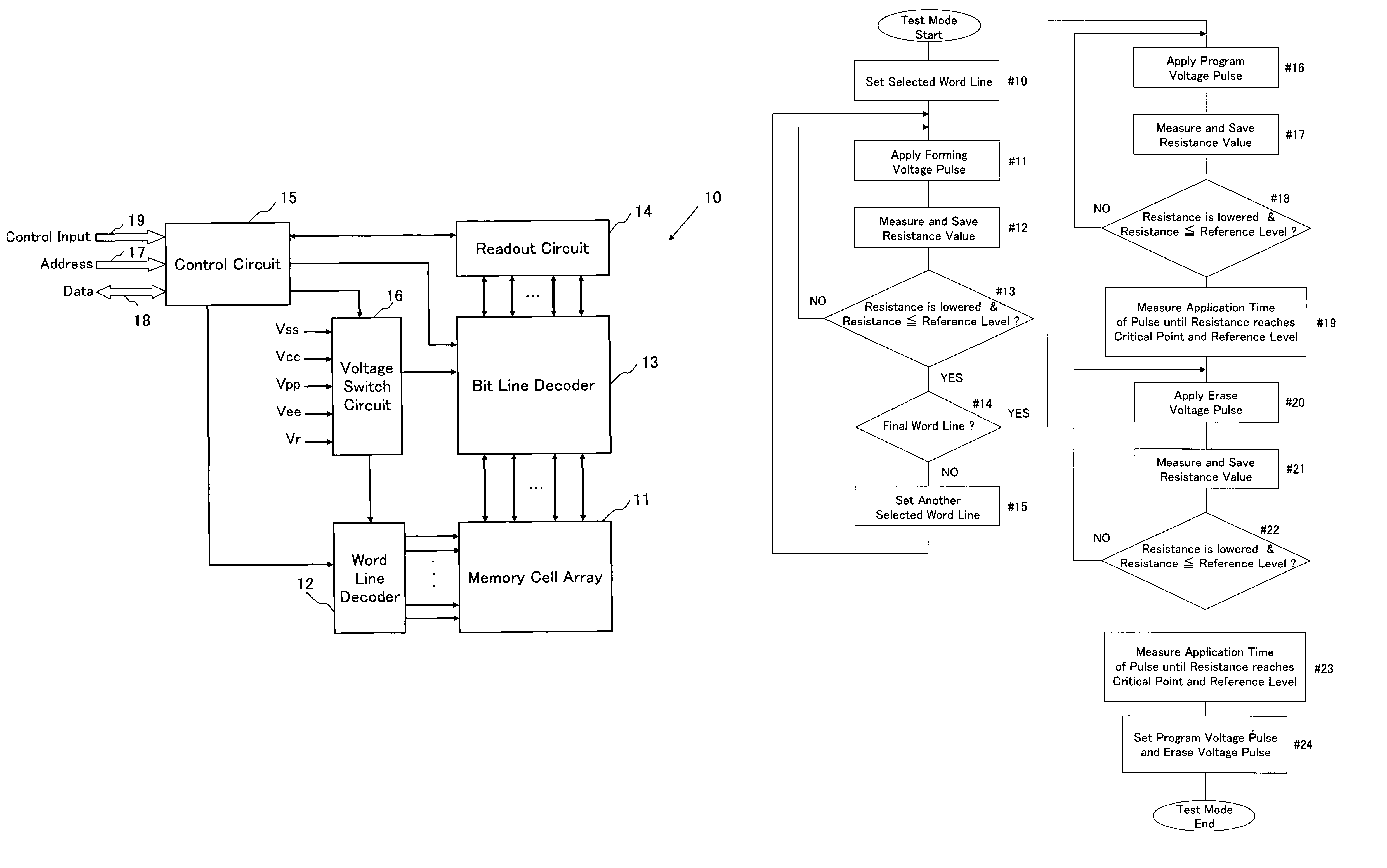

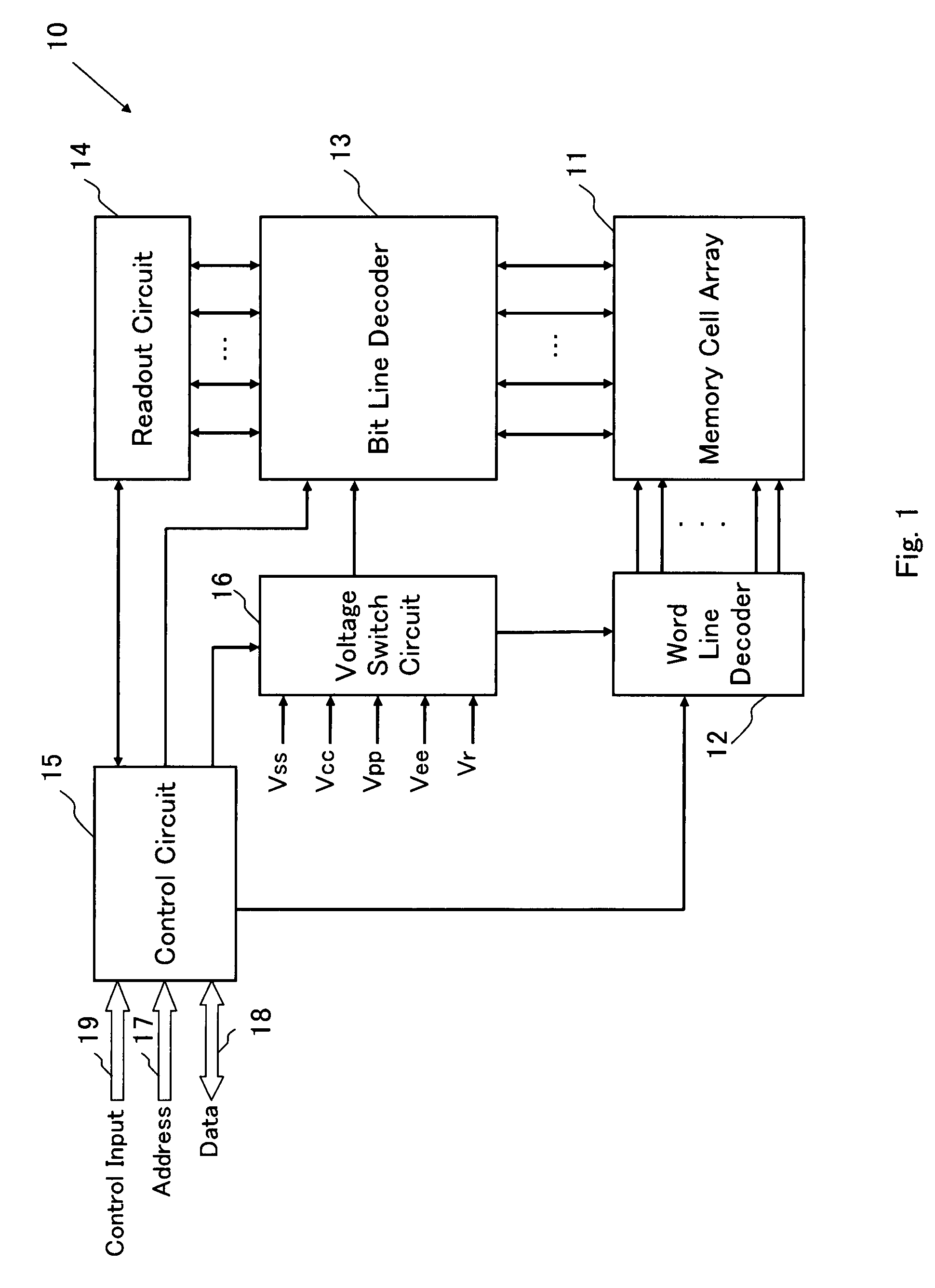

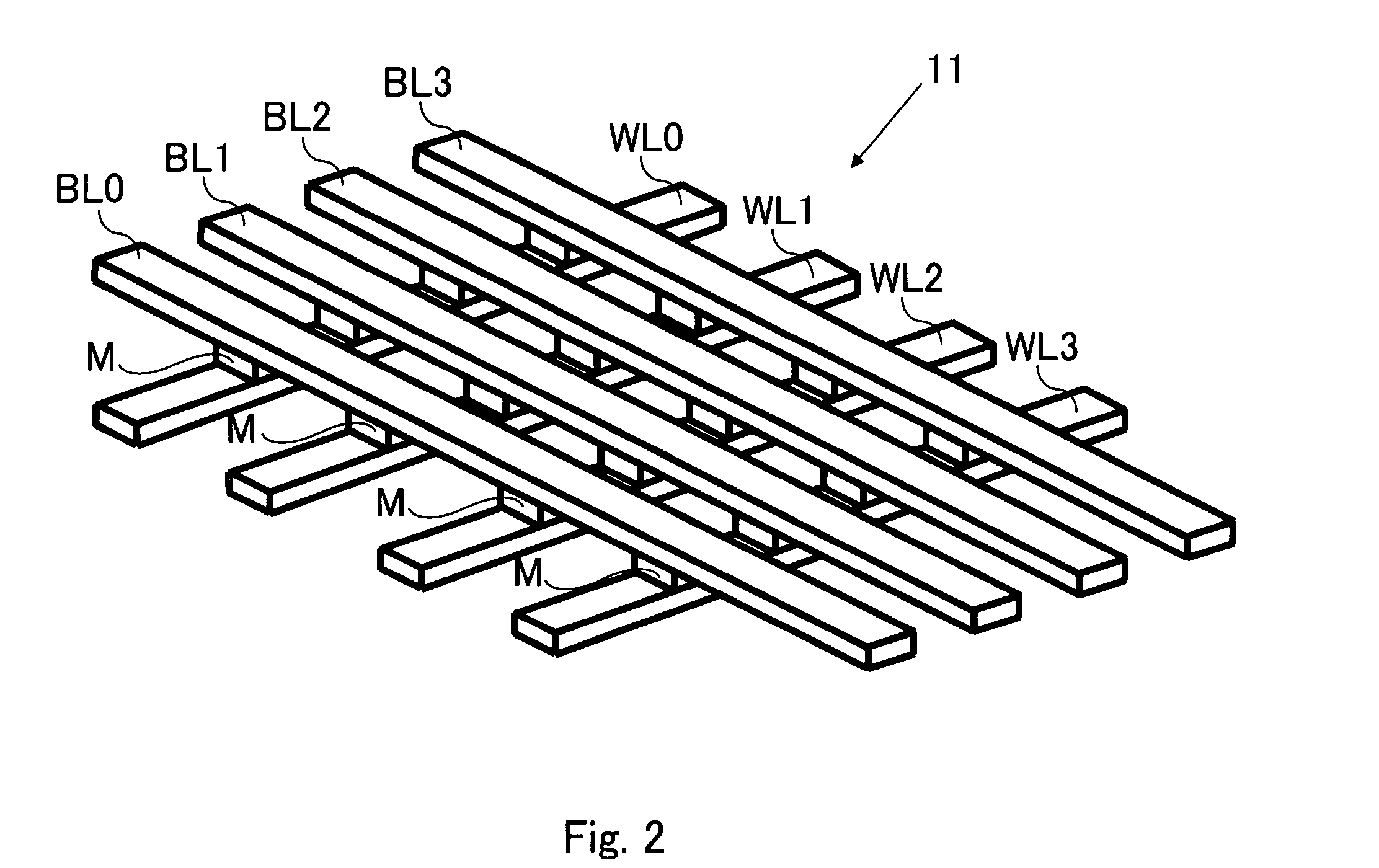

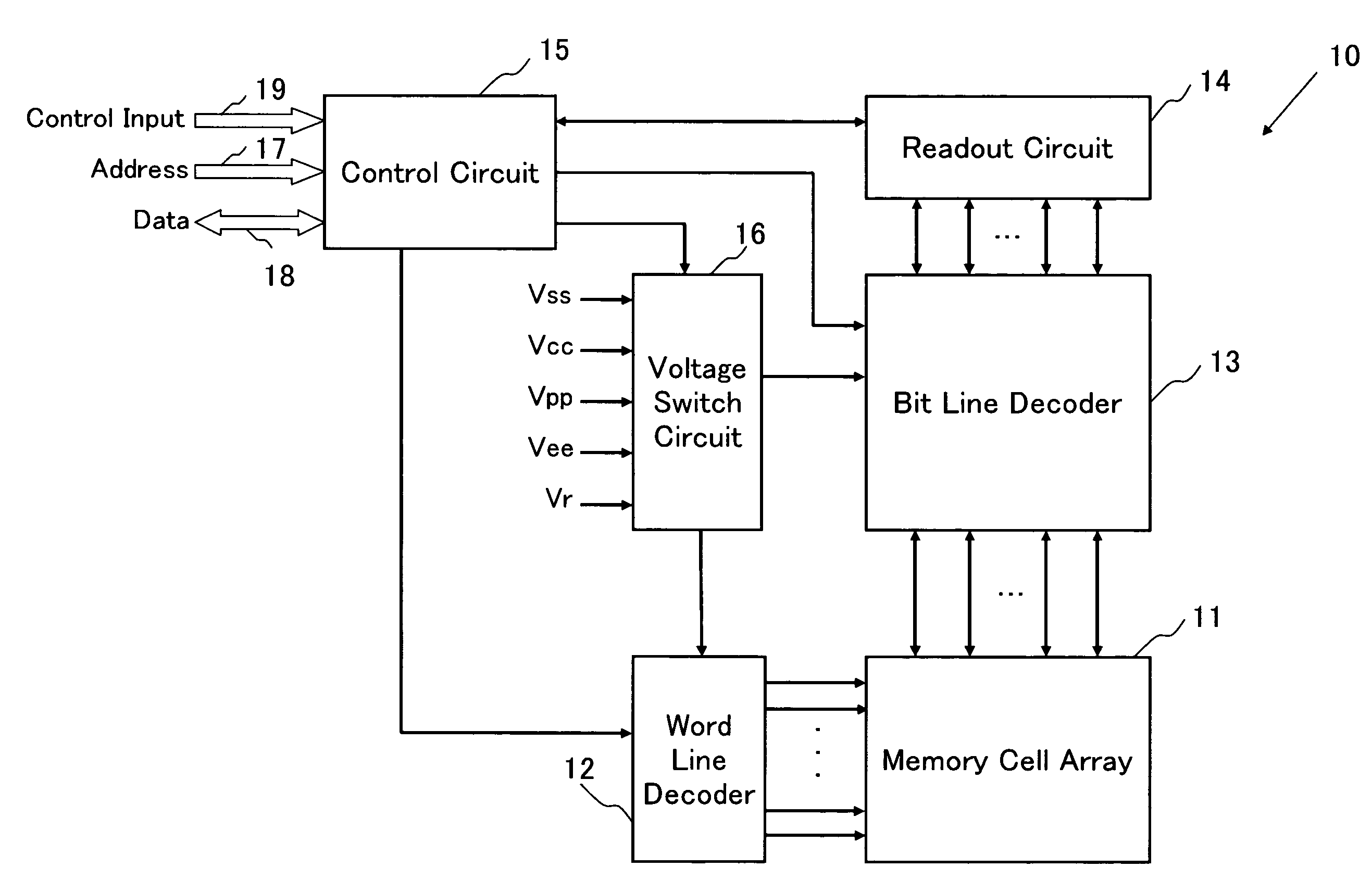

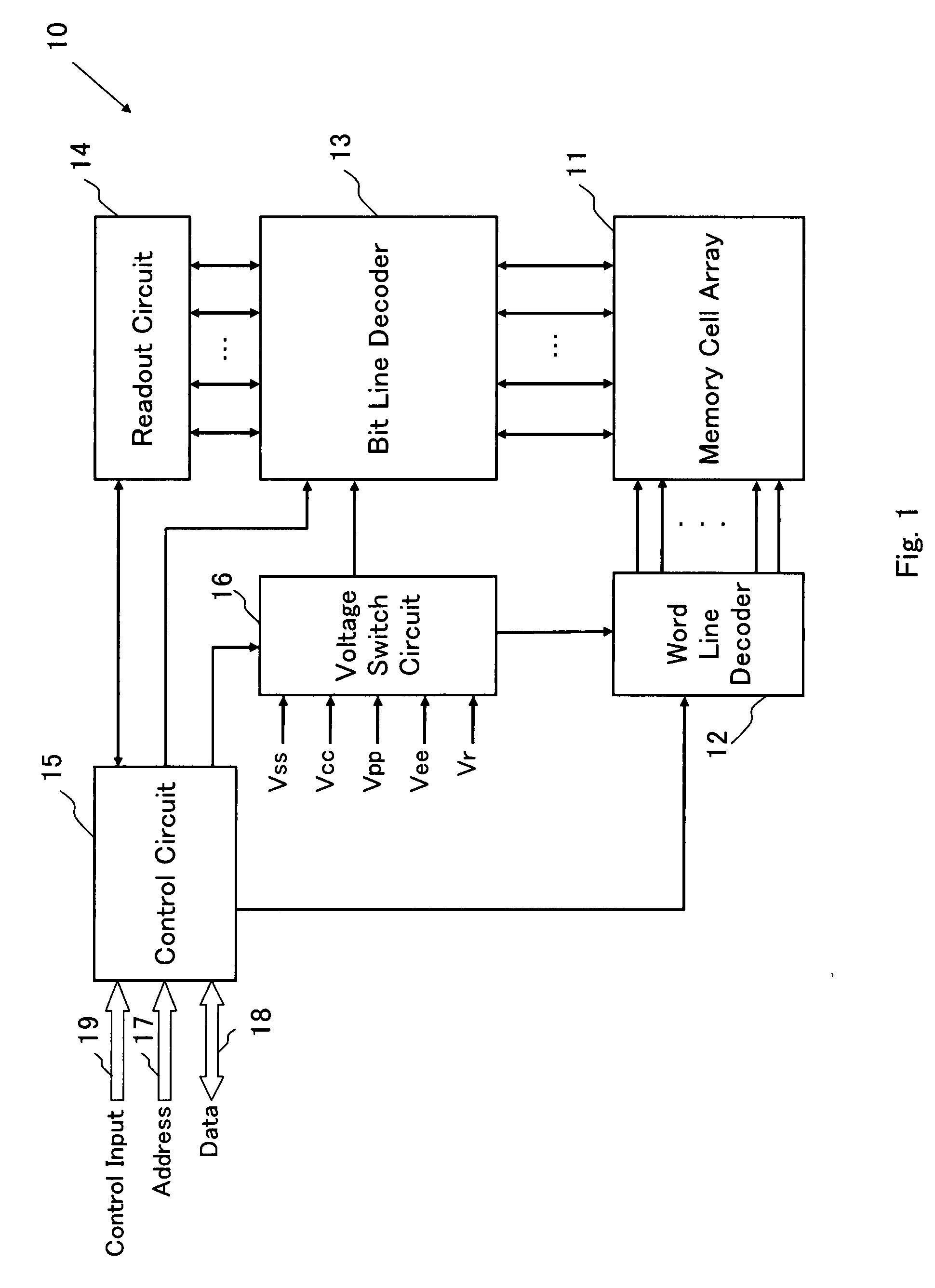

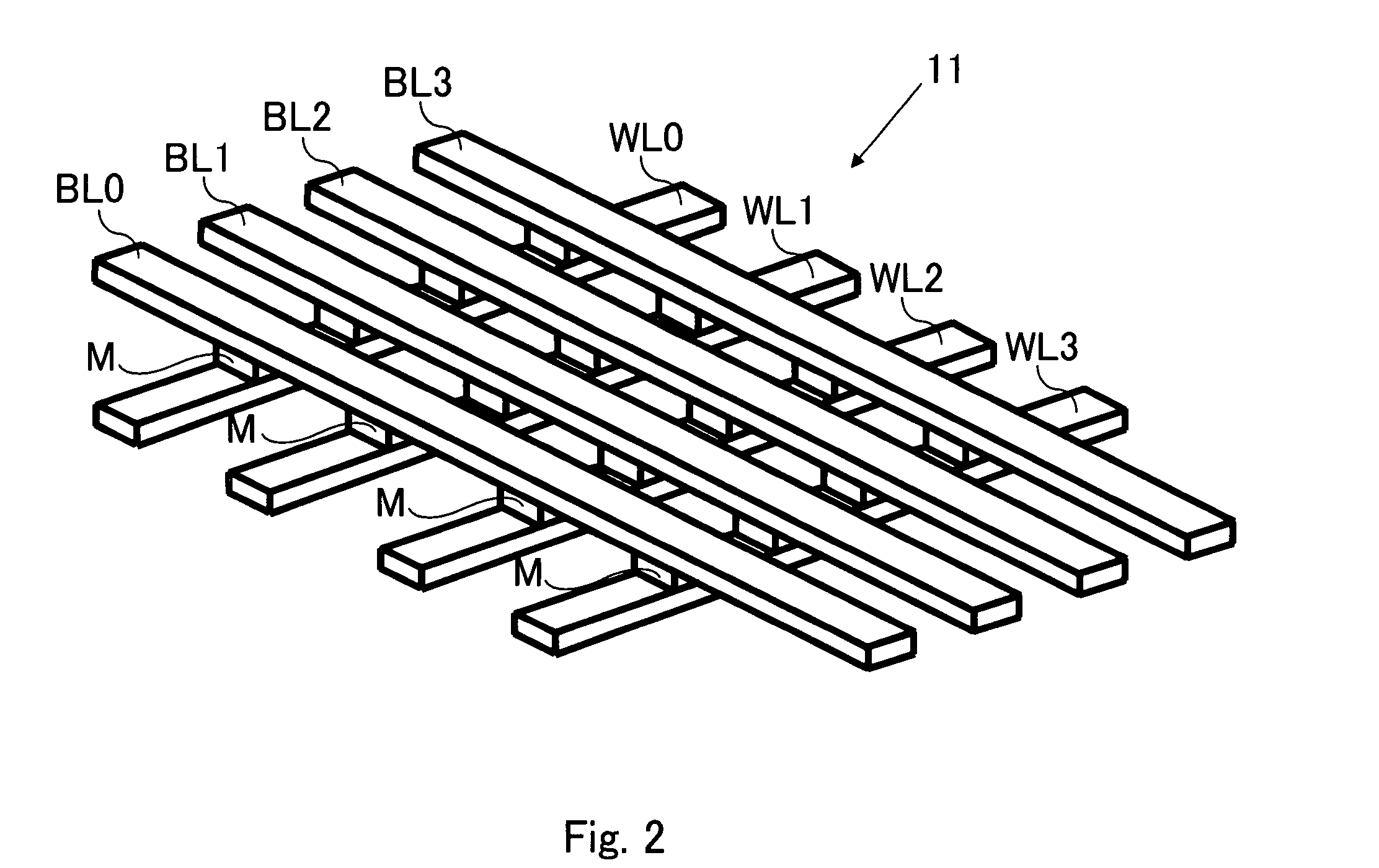

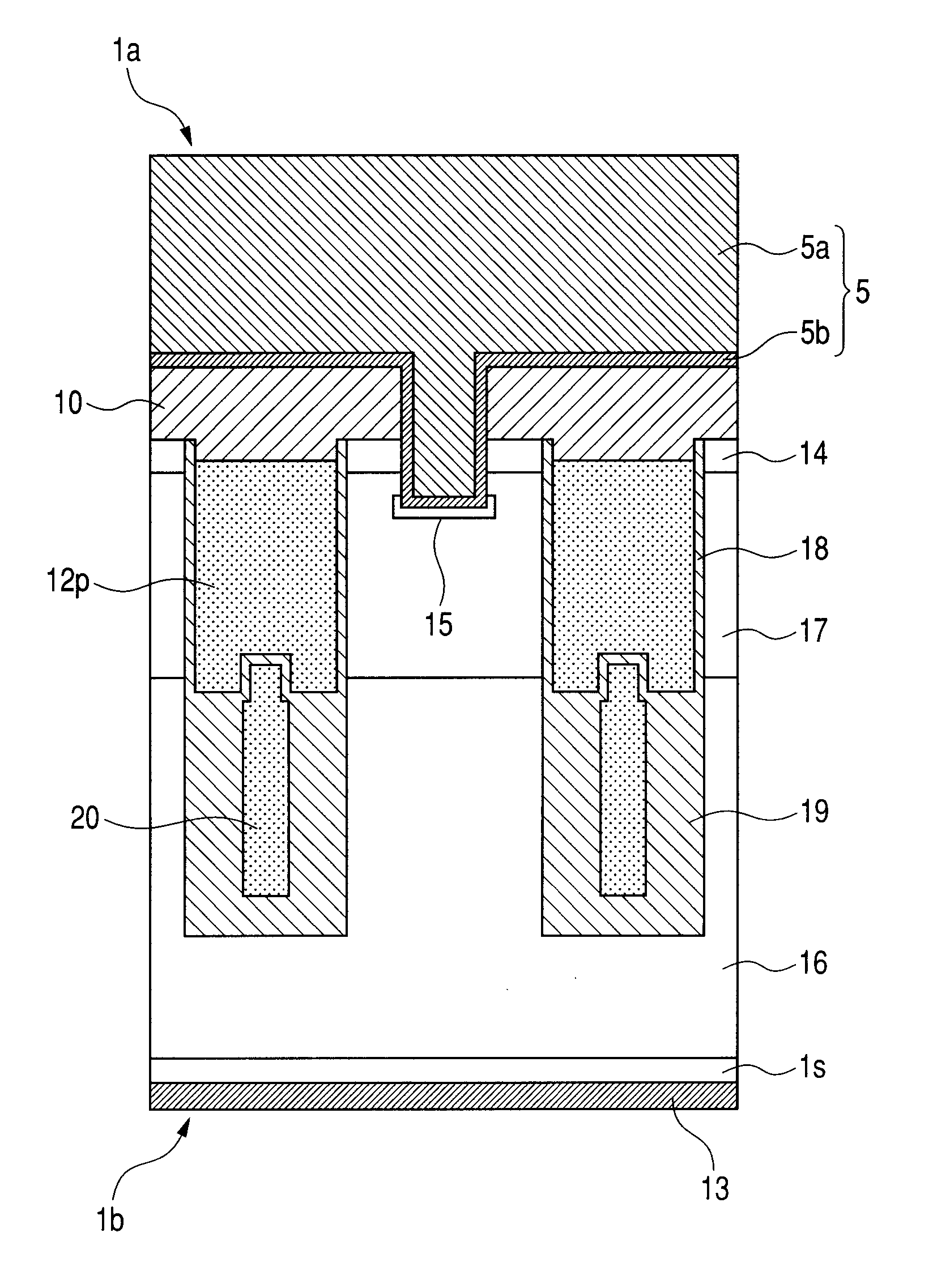

Method of controlling the resistance in a variable resistive element and non-volatile semiconductor memory device

InactiveUS7558099B2Mono-polar switching action stable and consistentStableness of the memory actionsDigital storageVoltage pulseElectrical polarity

The method of controlling a resistance of a variable resistive element comprises a forming step for shifting the variable resistive element from an initial state after the production to a variable resistance state capable of a stable mono-polar switching action where a variable resistive characteristic of the variable resistive element is turned to a program resistive characteristic by applying a program voltage pulse to the variable resistive element for first pulse application time and to an erase resistive characteristic by applying an erase voltage pulse equal in polarity to the program voltage pulse to the variable resistive element for second pulse application time longer than the first pulse application time, wherein one or more forming voltage pulses equal in polarity to the program voltage pulse is applied to the variable resistive element for third pulse application time longer than the second pulse application time.

Owner:DENSO CORP

Method of controlling the resistance in a variable resistive element and non-volatile semiconductor memory device

InactiveUS20070195581A1Mono-polar switching action stable and consistentStableness of the memory actionsDigital storageVoltage pulseElectrical polarity

The method of controlling a resistance of a variable resistive element comprises a forming step for shifting the variable resistive element from an initial state after the production to a variable resistance state capable of a stable mono-polar switching action where a variable resistive characteristic of the variable resistive element is turned to a program resistive characteristic by applying a program voltage pulse to the variable resistive element for first pulse application time and to an erase resistive characteristic by applying an erase voltage pulse equal in polarity to the program voltage pulse to the variable resistive element for second pulse application time longer than the first pulse application time, wherein one or more forming voltage pulses equal in polarity to the program voltage pulse is applied to the variable resistive element for third pulse application time longer than the second pulse application time.

Owner:DENSO CORP

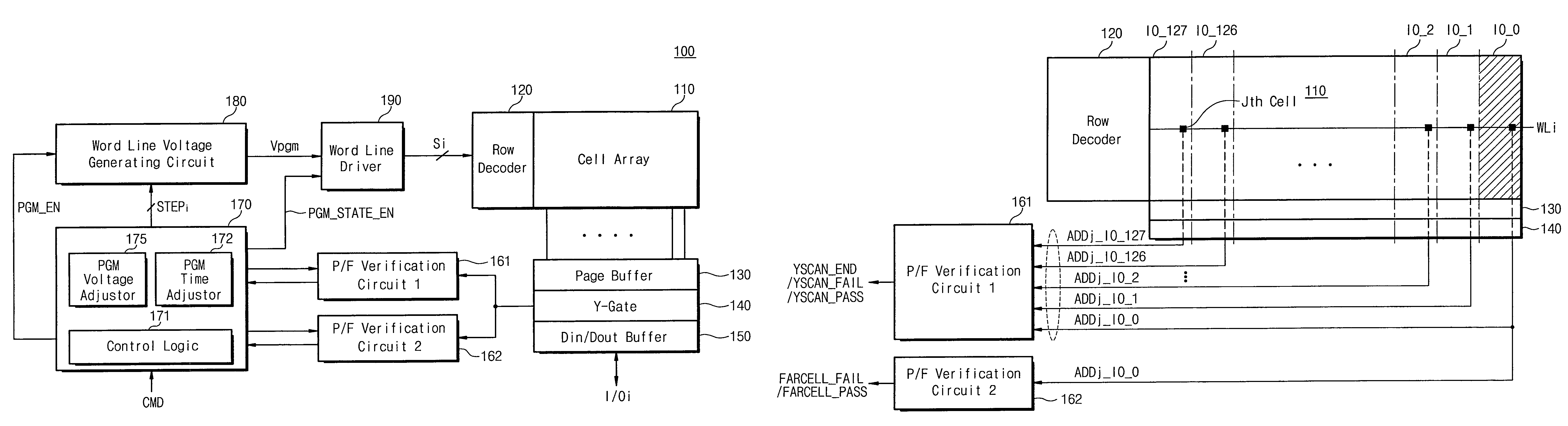

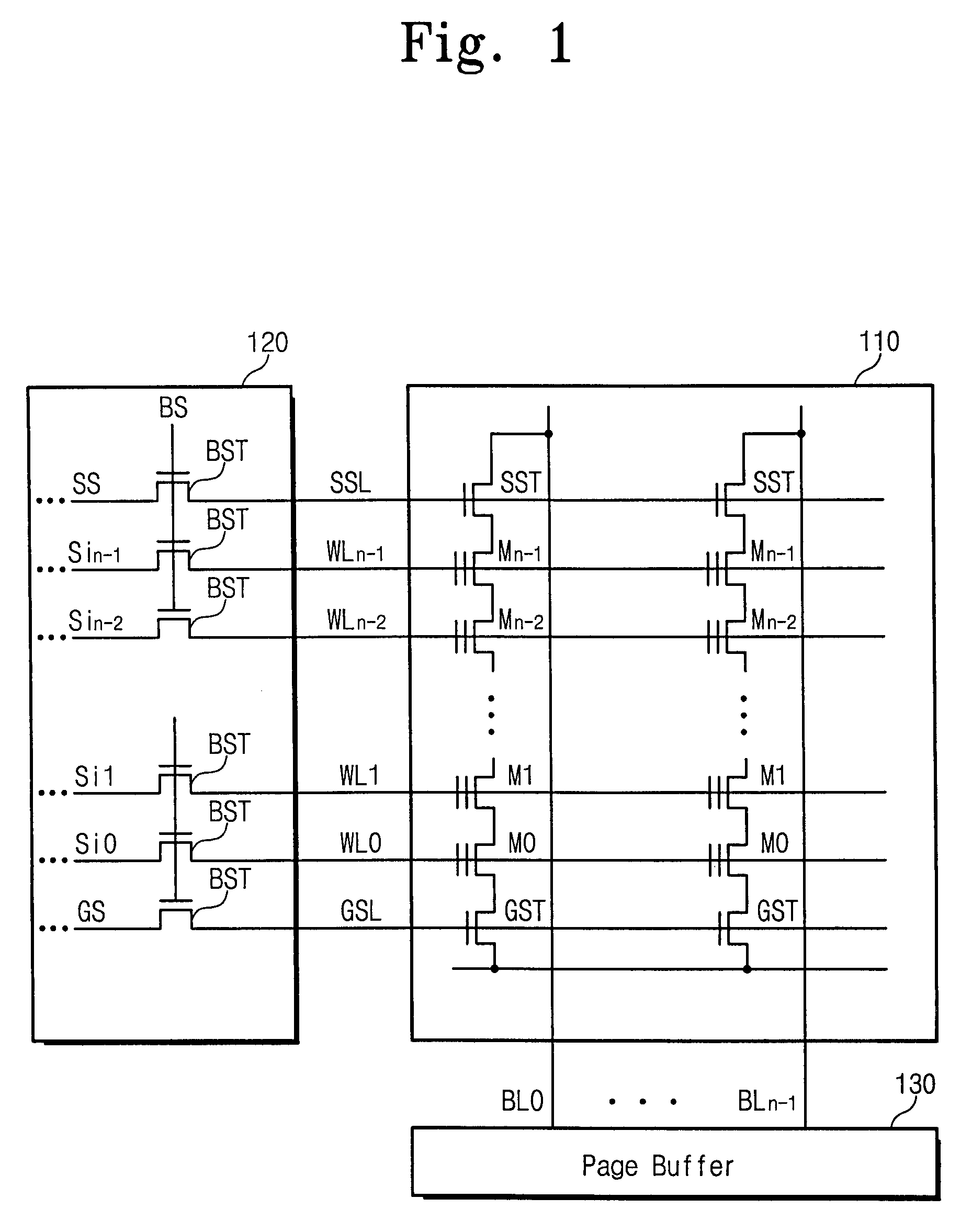

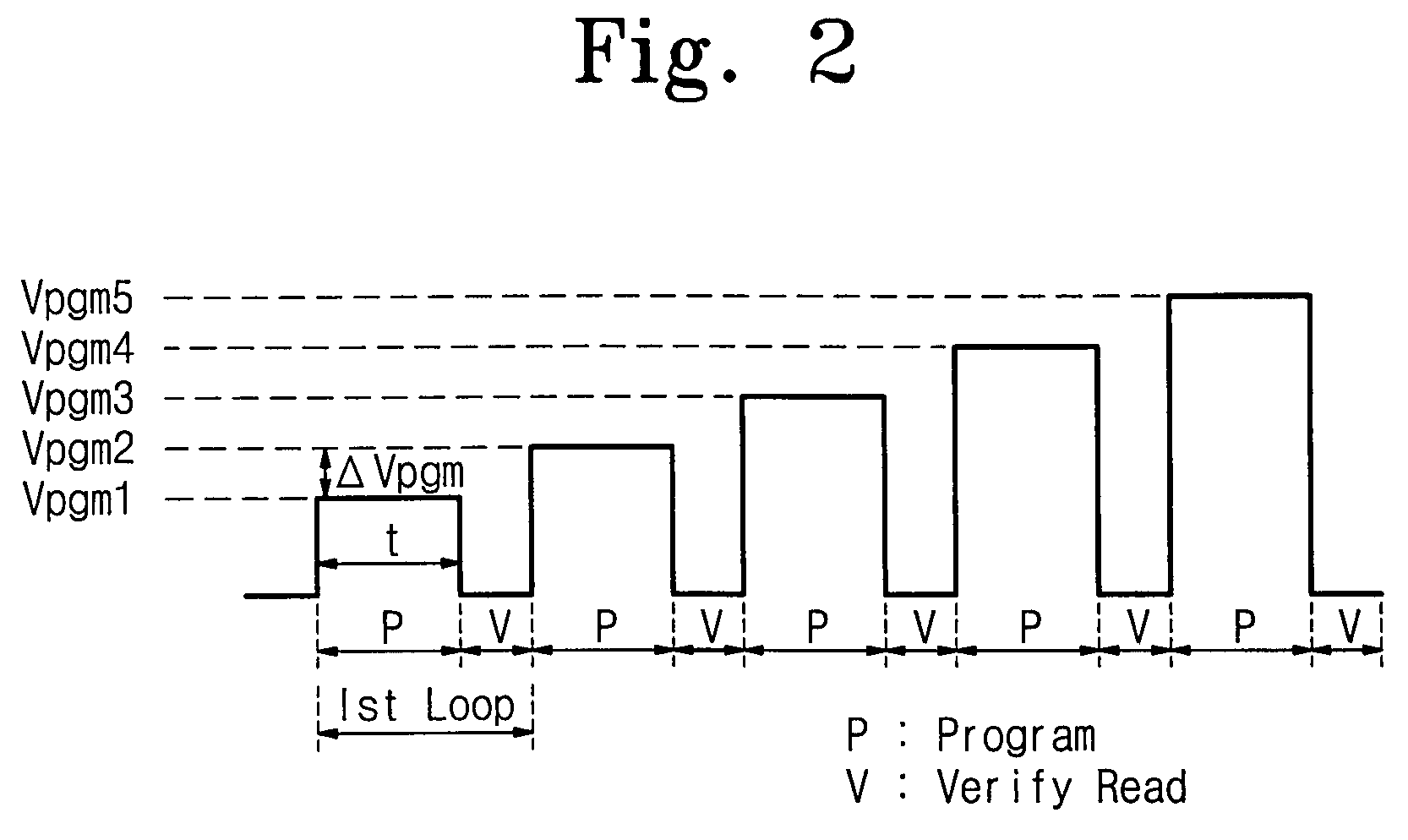

Nonvolatile memory device and related programming method

In a nonvolatile memory device, a first verification result indicates whether a block of memory cells has been successfully programmed and a second verification result indicates whether a far cell in the block has been is successfully programmed. A controller defines the level and application time for the program voltage applied during a next program loop in response to the first and second verification results.

Owner:SAMSUNG ELECTRONICS CO LTD

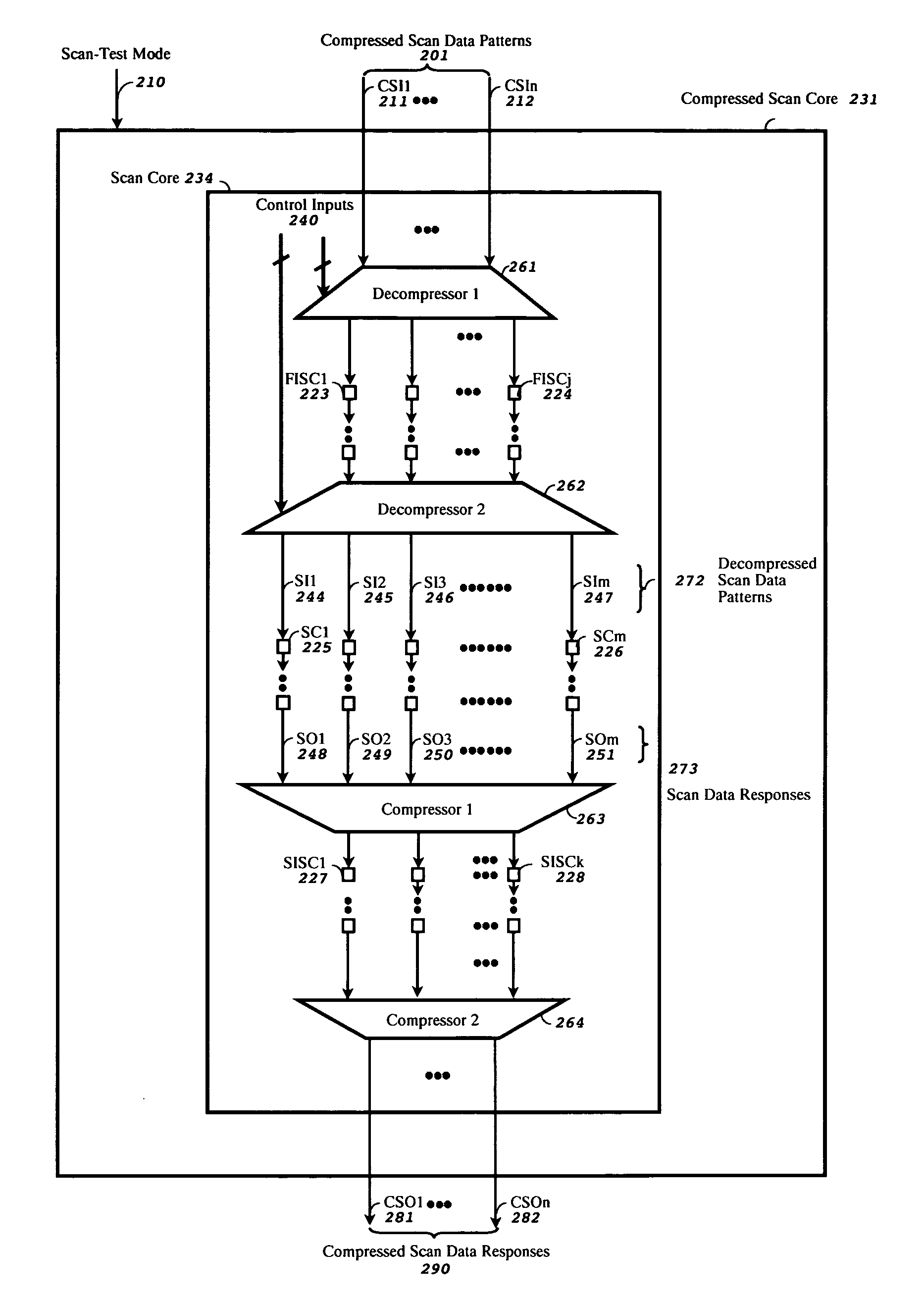

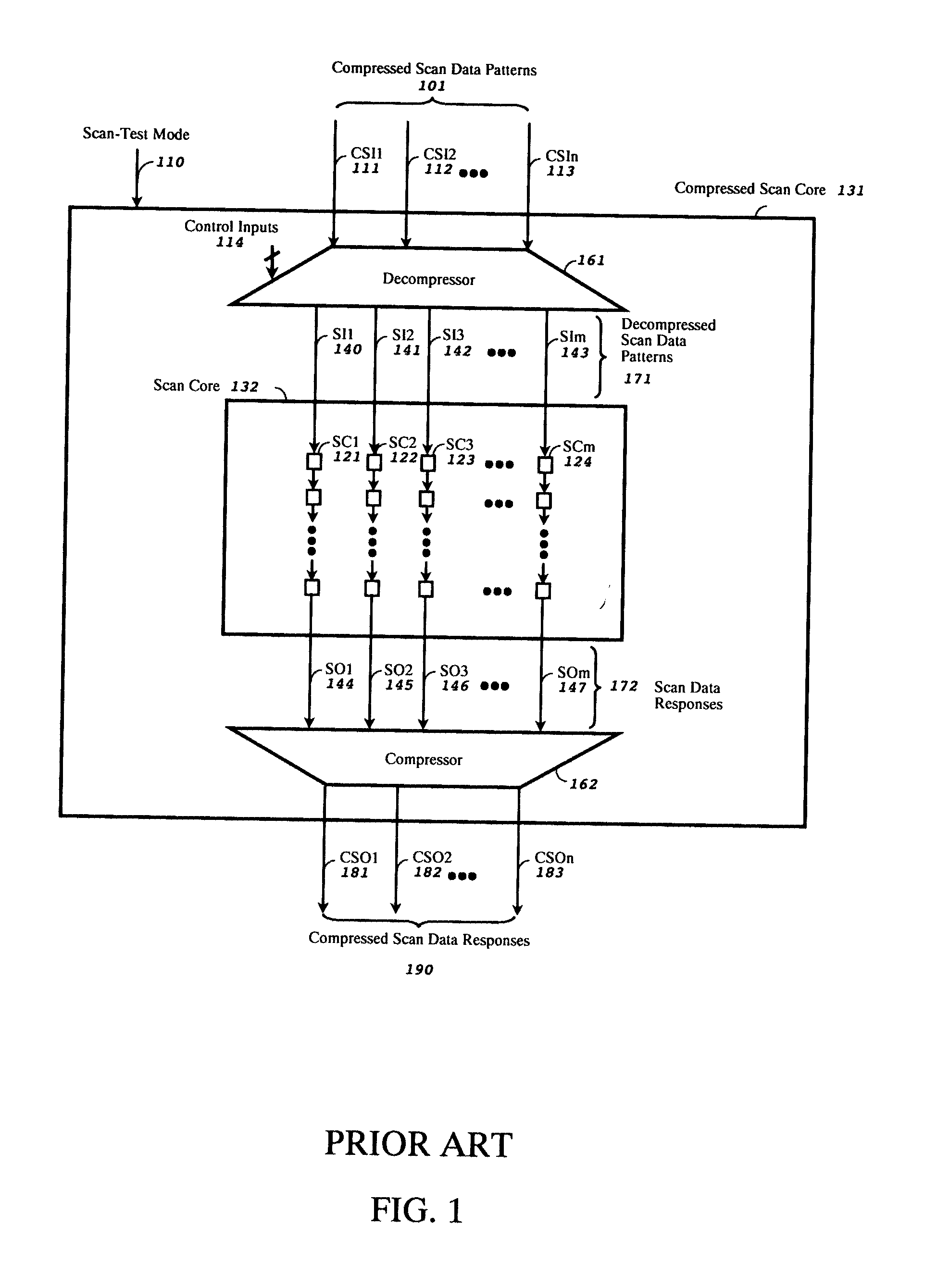

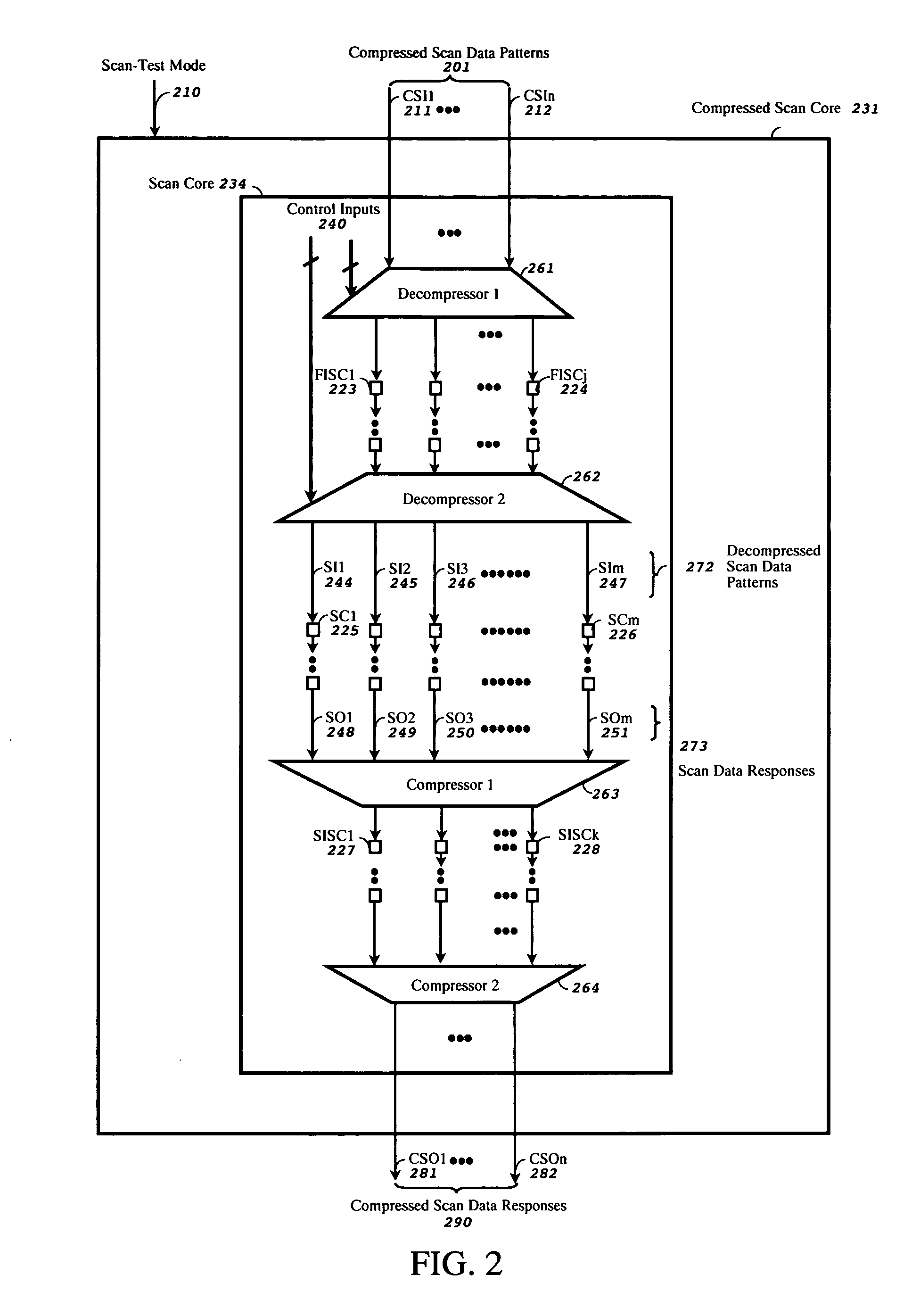

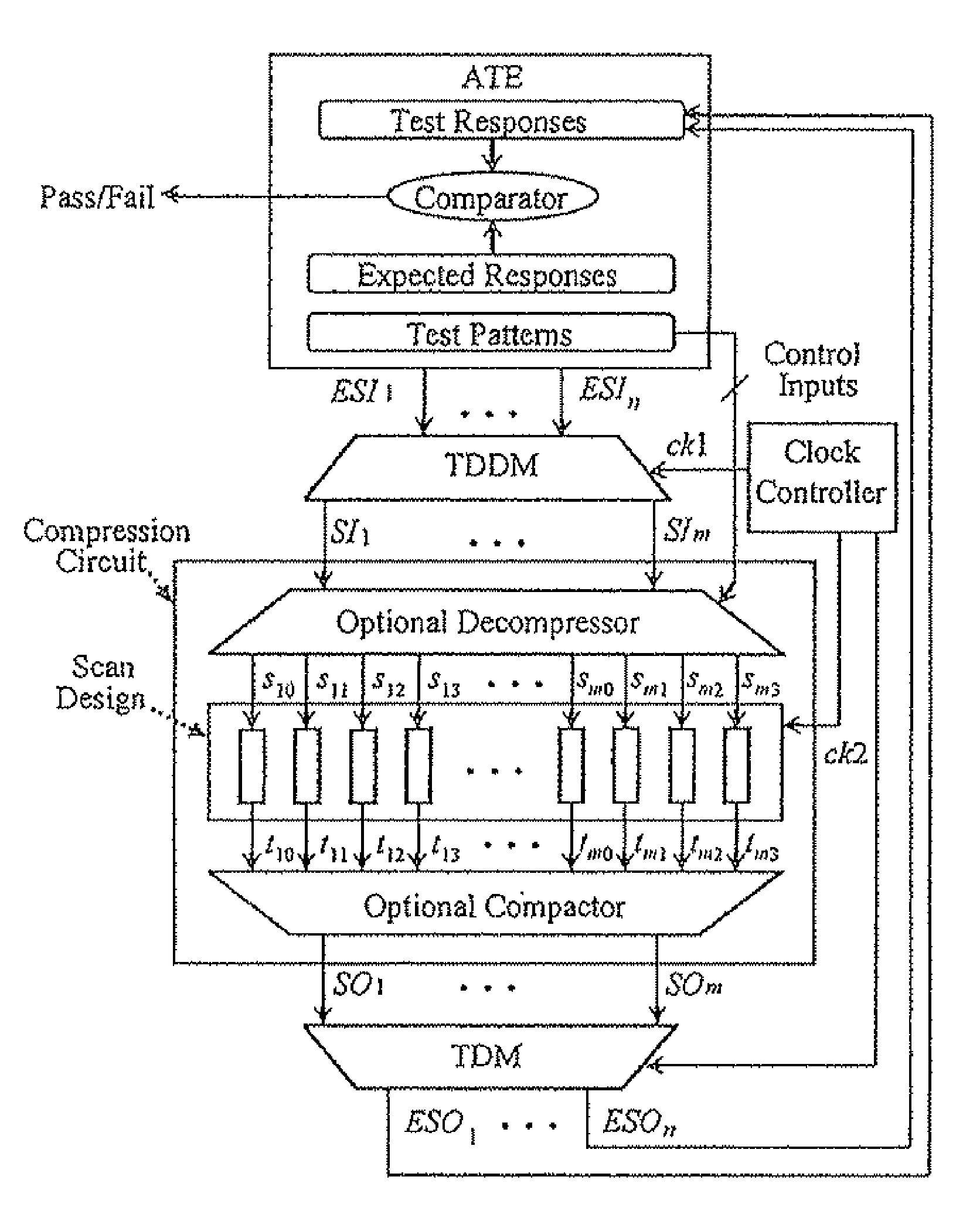

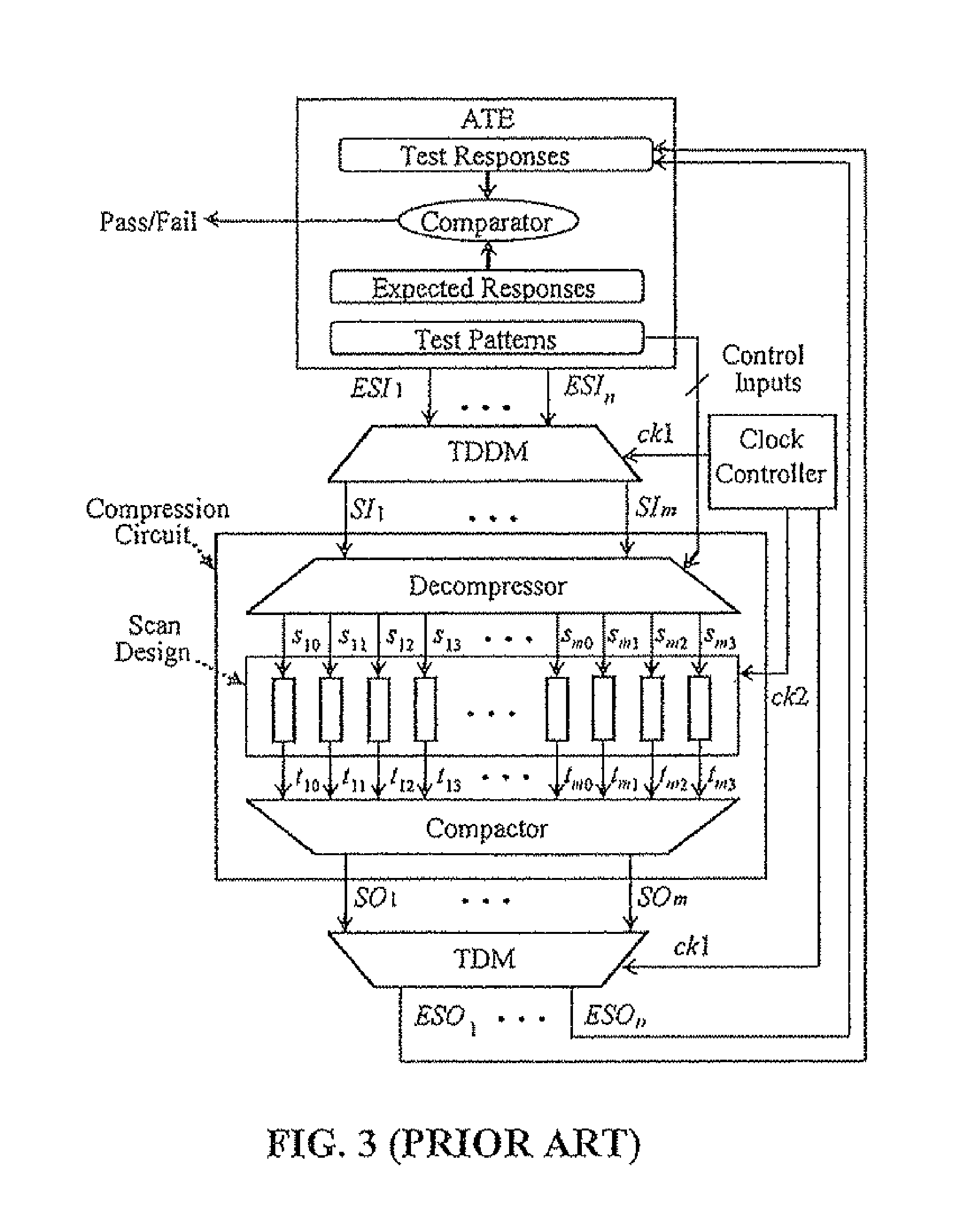

Method and apparatus for multi-level scan compression

InactiveUS20050268194A1Improve balanceElectronic circuit testingError detection/correctionEngineeringApplication time

A multi-level scan compression method and apparatus for reducing test data volume and test application time in a scan-based integrated circuit without reducing the speed of the scan chain operation in scan-test mode or self-test mode. The scan-based integrated circuit contains one or more scan chains, each scan chain comprising one or more scan cells coupled in series. The method and apparatus comprises two or more decompressors embedded between N compressed scan inputs and M scan chains, where N<M, to broadcast compressed scan data patterns driven through the N compressed scan inputs into decompressed scan data patterns stored in the M scan chains. The multi-level scan compression approach allows us to speed up the shift-in / shift-out operation during decompression using two or more decompressors separated by intermediate scan chains. The method and apparatus further comprises two or more compressors separated by intermediate scan chains to speed up the shift-in / shift-out operation during compression.

Owner:SYNTEST TECH

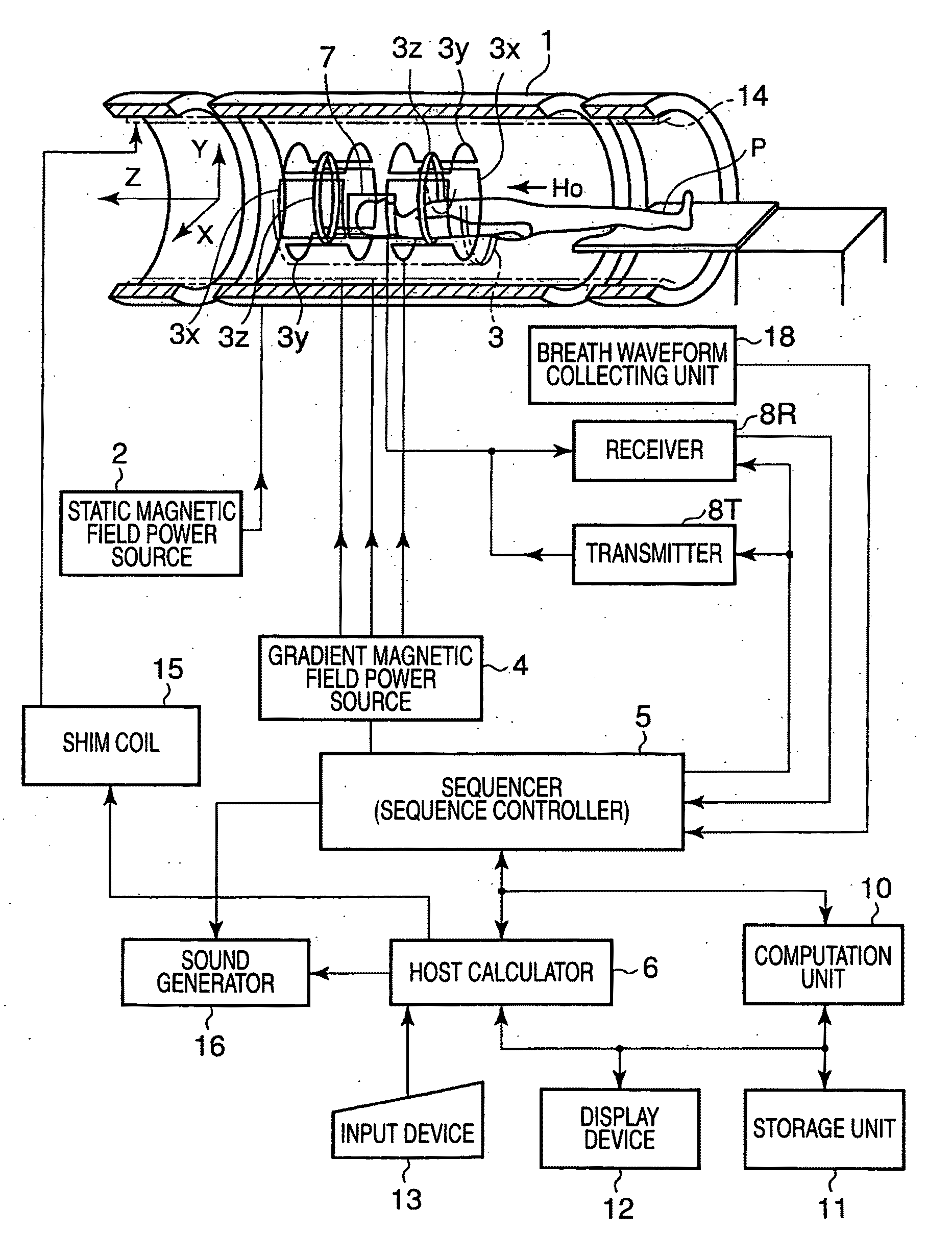

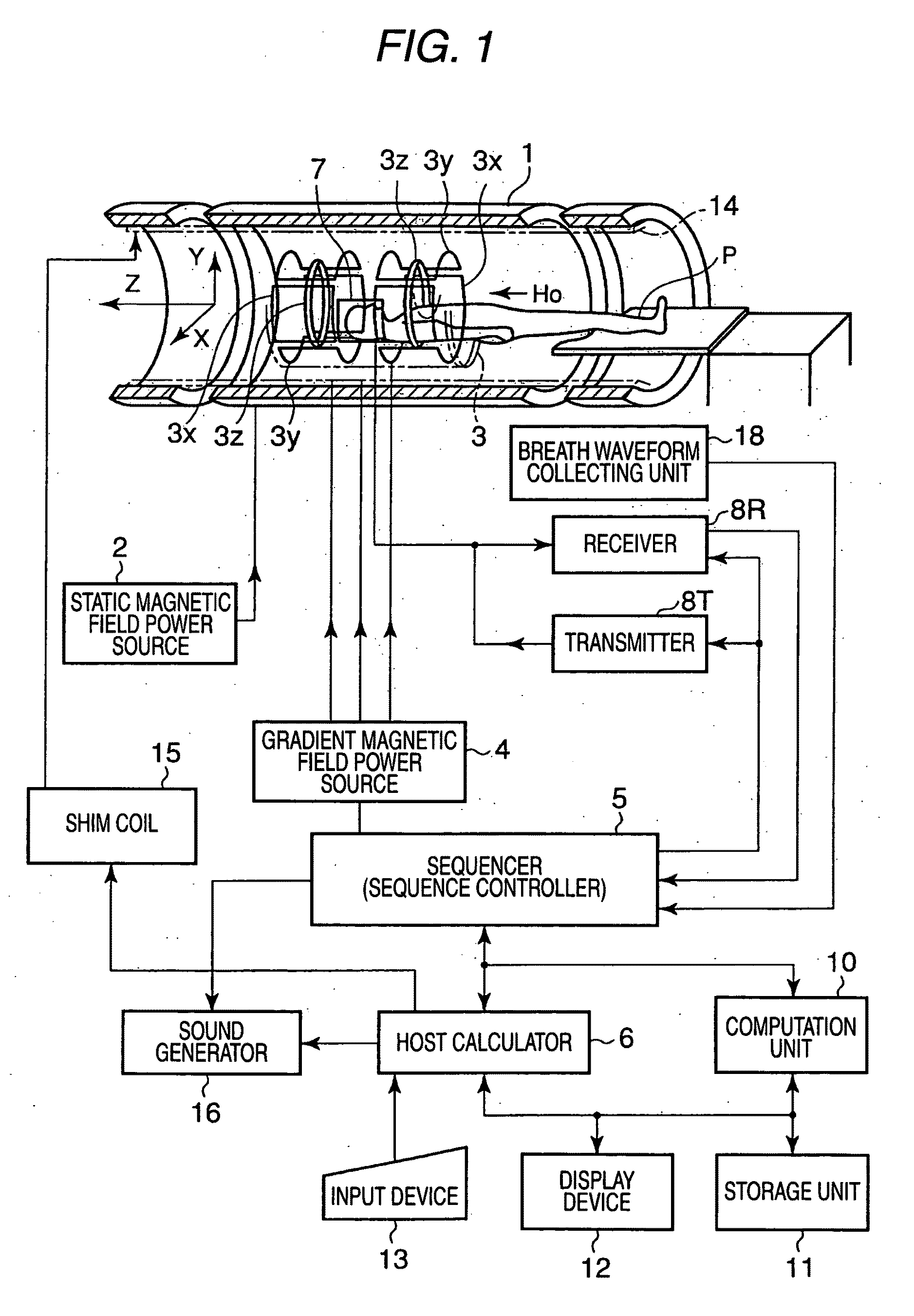

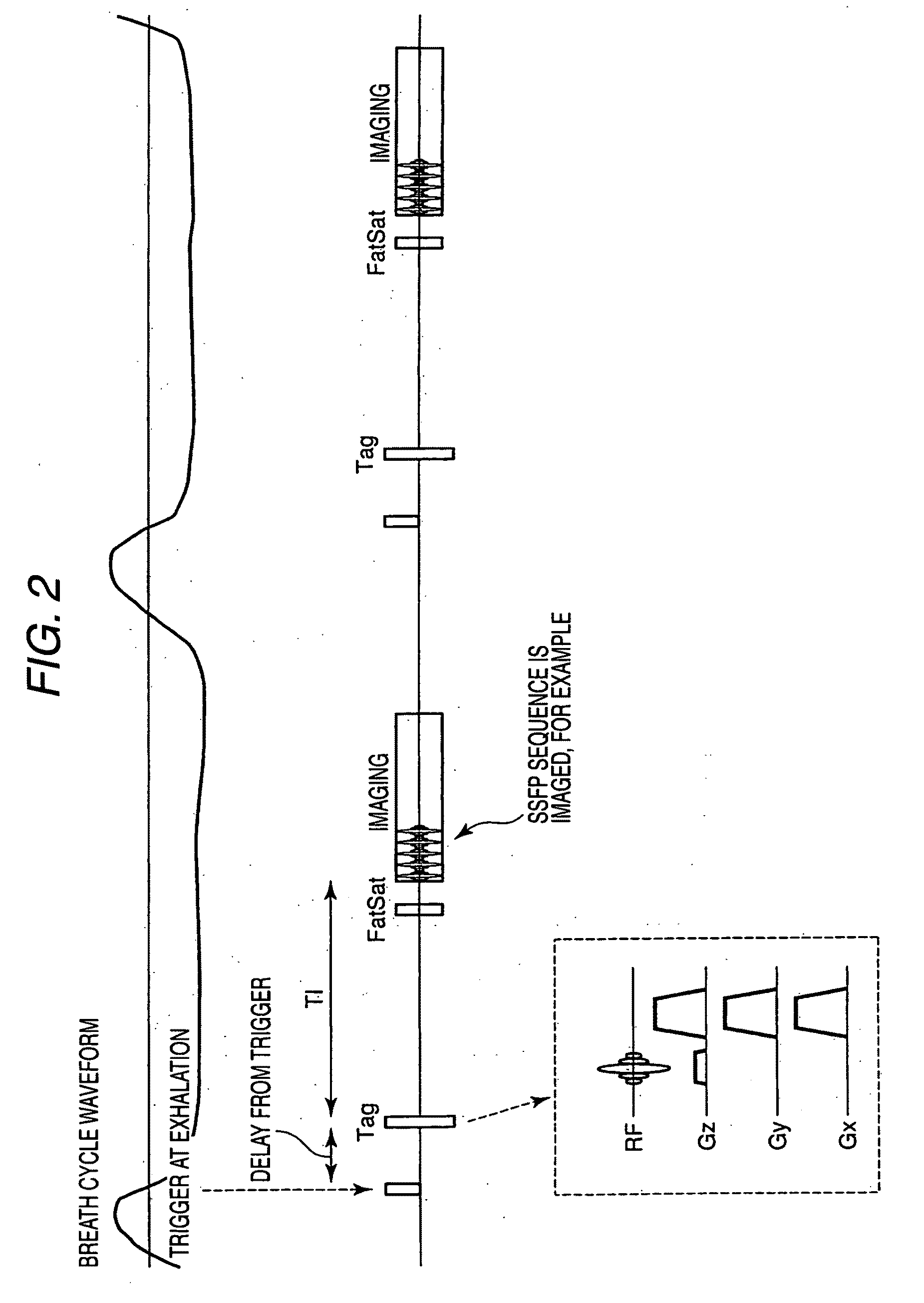

Magnetic resonance imaging apparatus and magnetic resonance imaging method

ActiveUS20090005670A1Diagnostic recording/measuringMeasurements using NMR imaging systemsAscending aortaResonance

An IR pulse is applied to a tag region B that is disposed at the upstream side of the ascending aorta relative to a tag region A at a timing with a second predetermined delay time TD2 (for example, 600 ms) from the application time of an IR pulse to the tag region A to thereby perform tagging. By this tagging, it is possible to suppress the MR signals derived from the substantial portions and the blood within the tag region B. Subsequently, an imaging scan is performed after a predetermined time lapse TIA (for example, 1200 ms) from the application time of the IR pulse to the tag region A or after a predetermined time lapse TIB (for example, 600 ms) from the application time of the IR pulse to the tag region B.

Owner:TOSHIBA MEDICAL SYST CORP

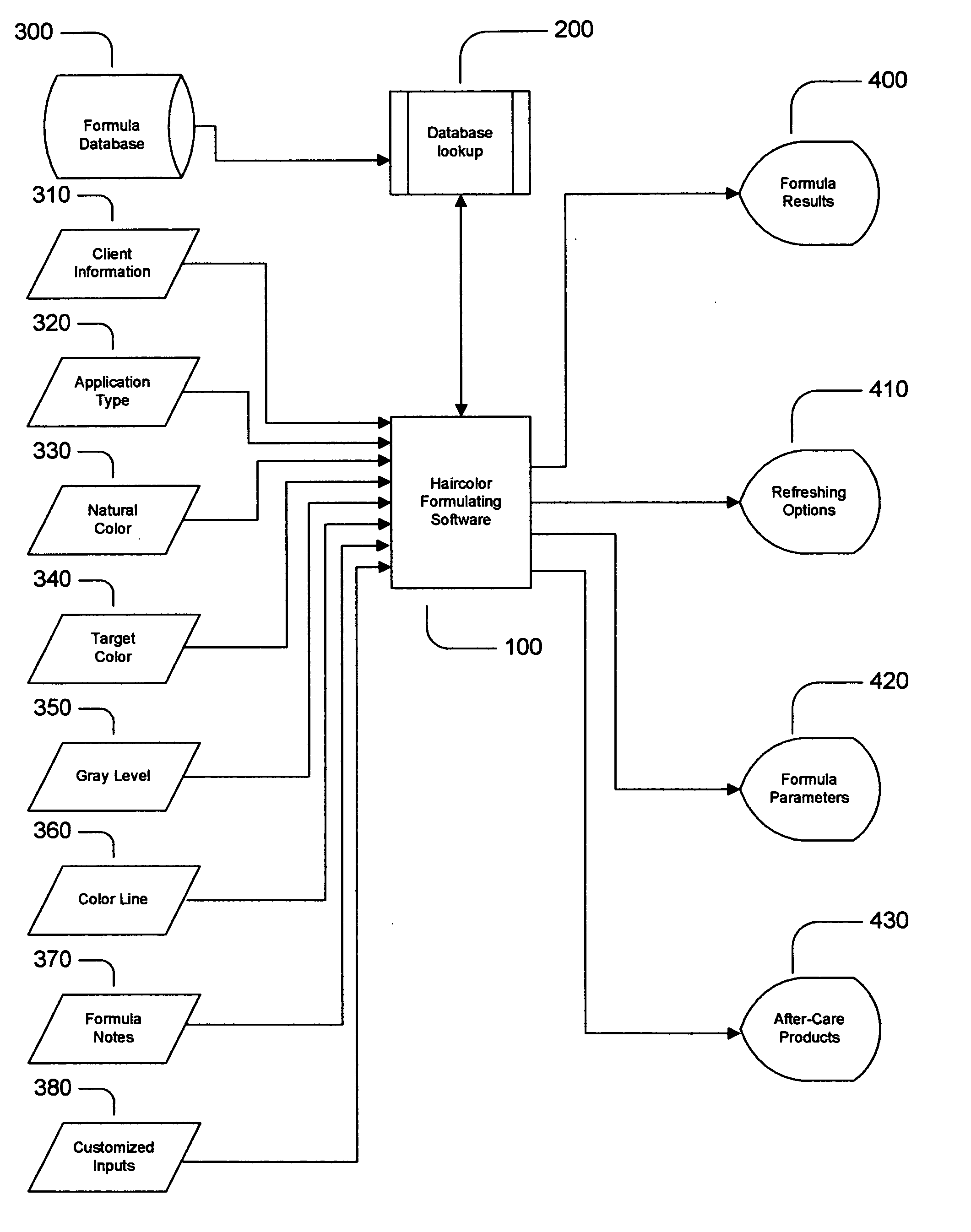

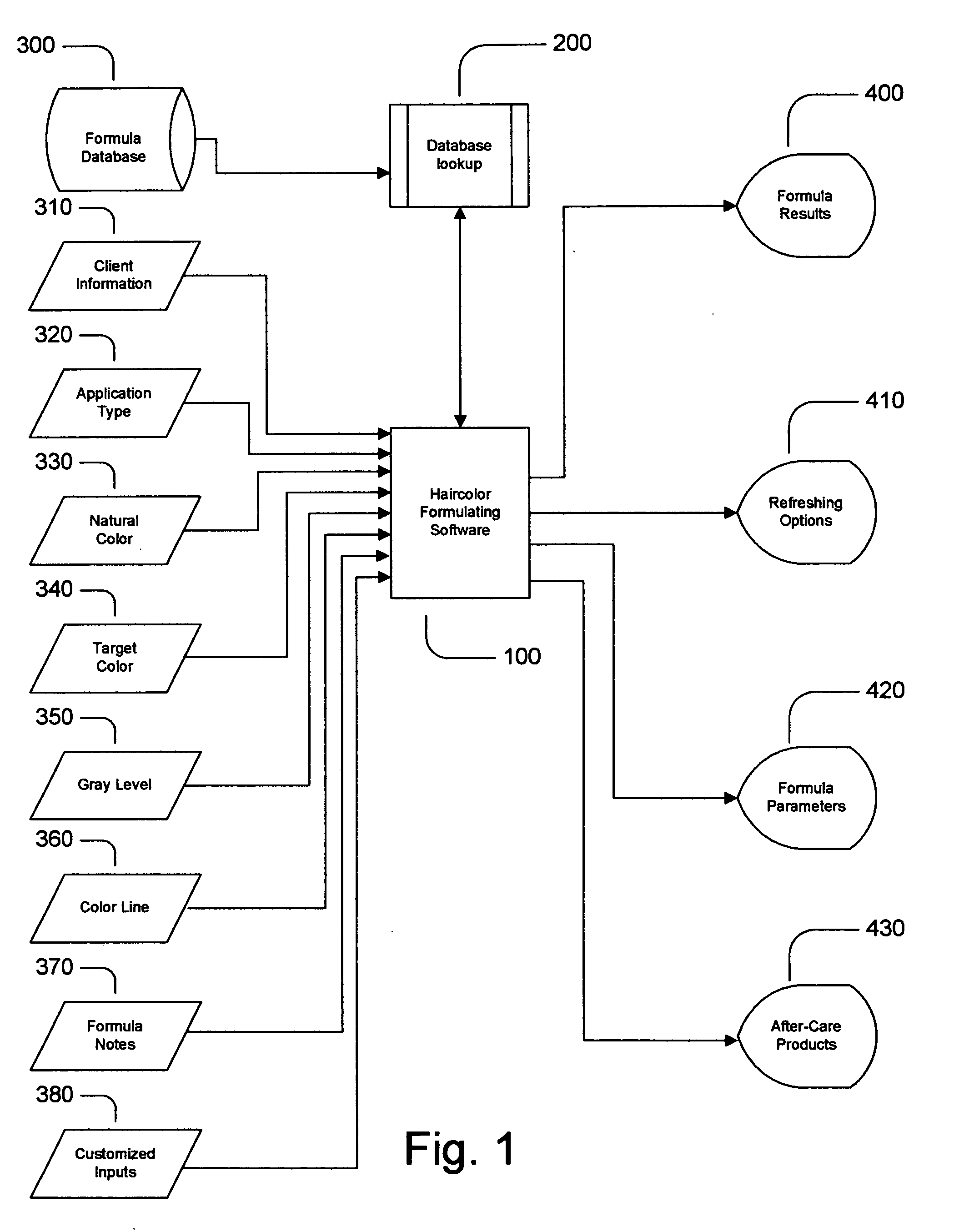

Computer implemented method and system for formulating haircolor

A computer implemented method and system for determining the formula or formulas of haircoloring agents to be used in the process of coloring hair, including the steps of receiving input on the current color, state, and desired color of the hair, and using a database of haircoloring formulas to determine the coloring agents to be used, quantities of such coloring agents, application time of such coloring agents, and refreshing options that can be applied to the hair to treat and correct faded hair ends. The computer in some embodiments is portable, and includes a processor, an electronic storage means in which the haircolor formula database is stored, and software that defines the process by which the correct haircolor formula is determined. The computer software determines the best formula and process steps to be taken to achieve the desired haircolor.

Owner:SALON TECH

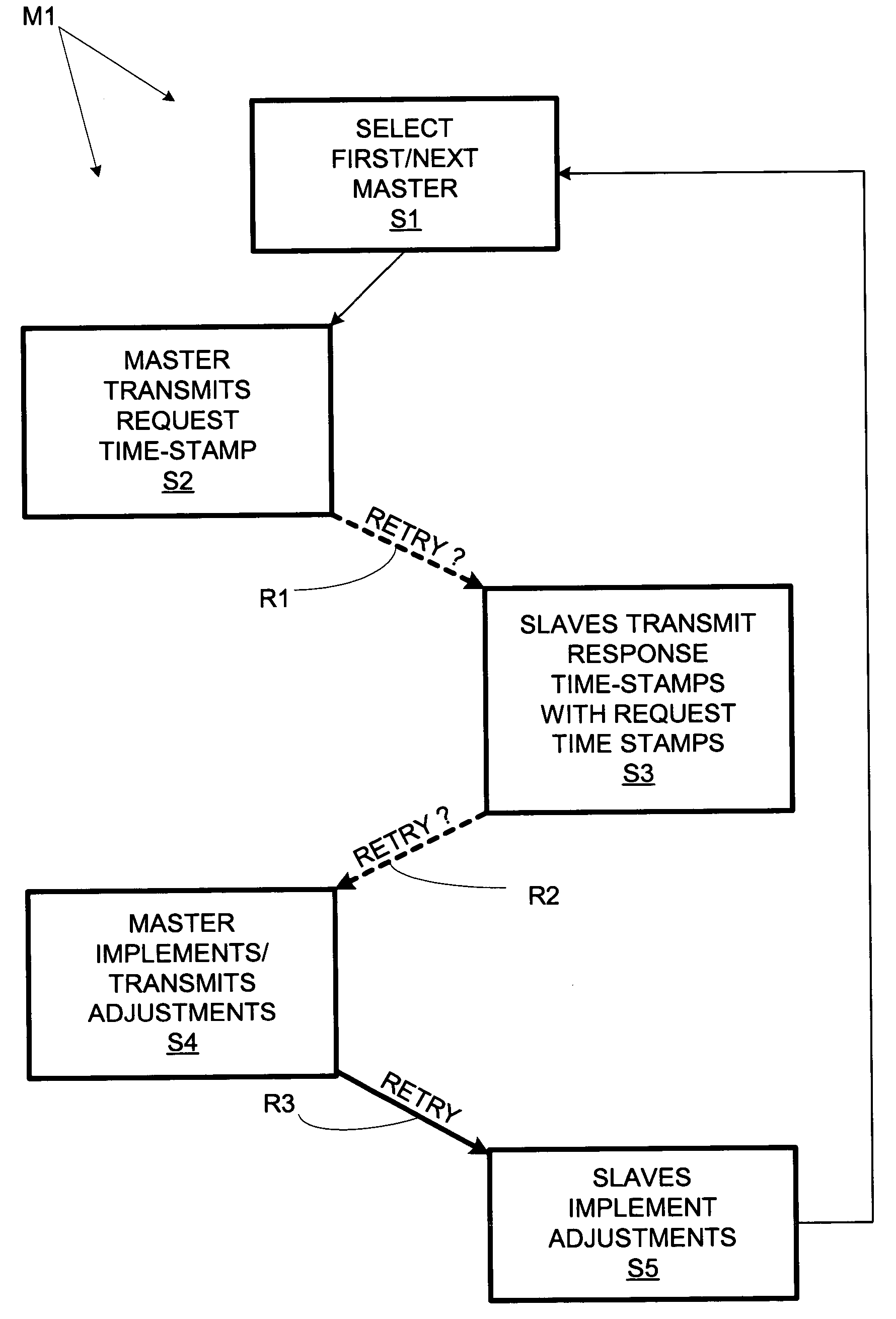

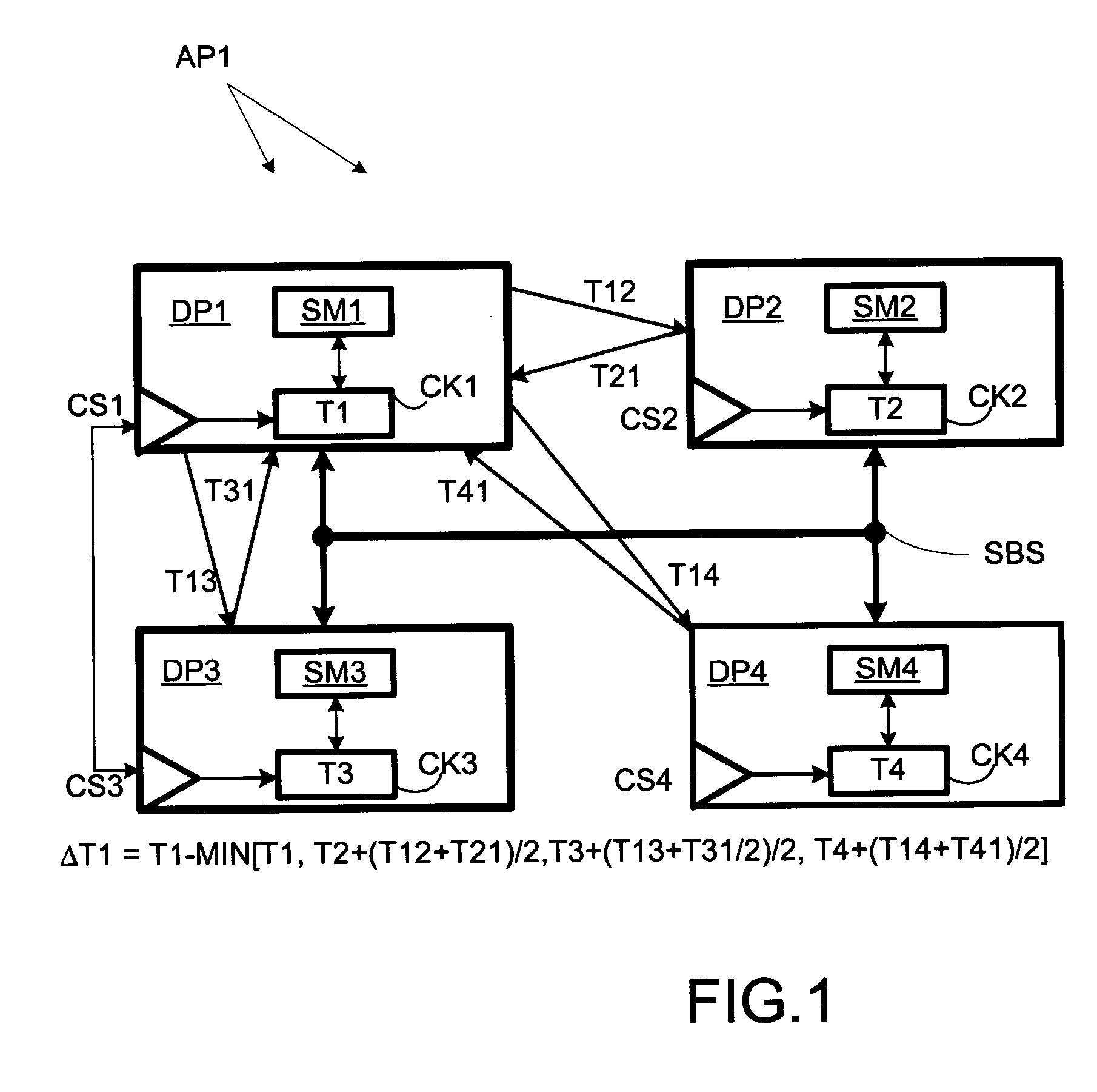

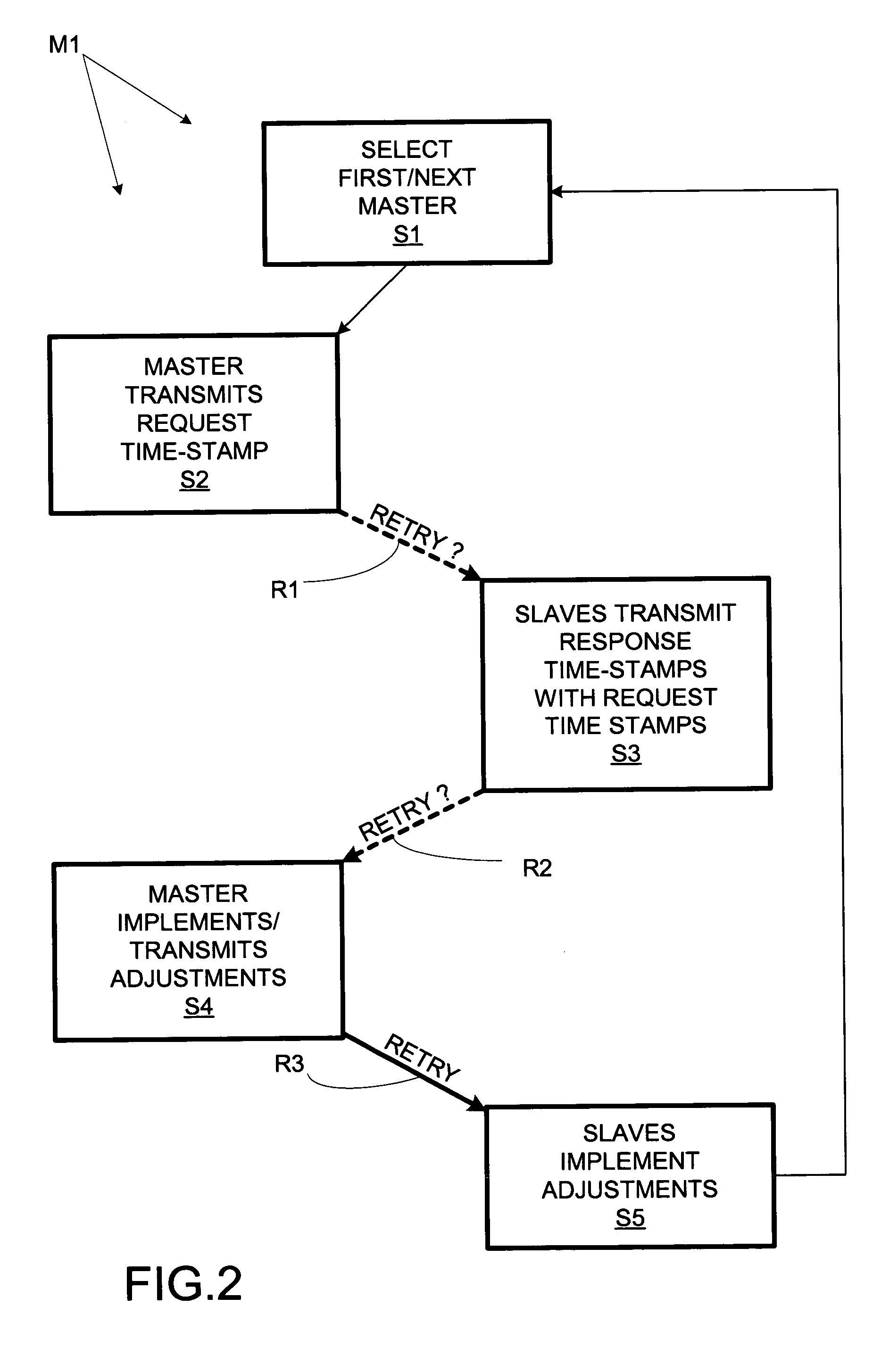

Multiprocessor system with interactive synchronization of local clocks

ActiveUS20050033947A1Little in obtainingError detection/correctionDigital computer detailsPrimary stationSlave clock

A multiprocessor computer system comprises multiple data processors, each with an internal clock for providing time stamps to application software. The processors take turns as synchronization masters. The present master transmits a “request” time stamp (indicating the time of transmission according to the local clock) to the other (“slave”) processors. Each slave processor responds by returning a “response” time stamp (indicating the time of transmission of the response according to the local slave clock) of its own along with the received request time stamp. The master calculates clock adjustment values from the time of receipt of the responses and the included time stamps. This allows asynchronous clocks to be synchronized so that application time stamps can be validly compared across processors.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

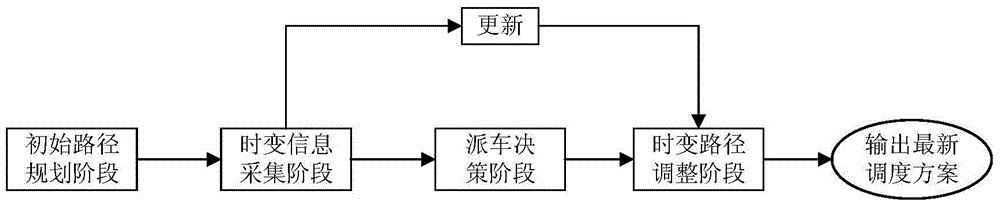

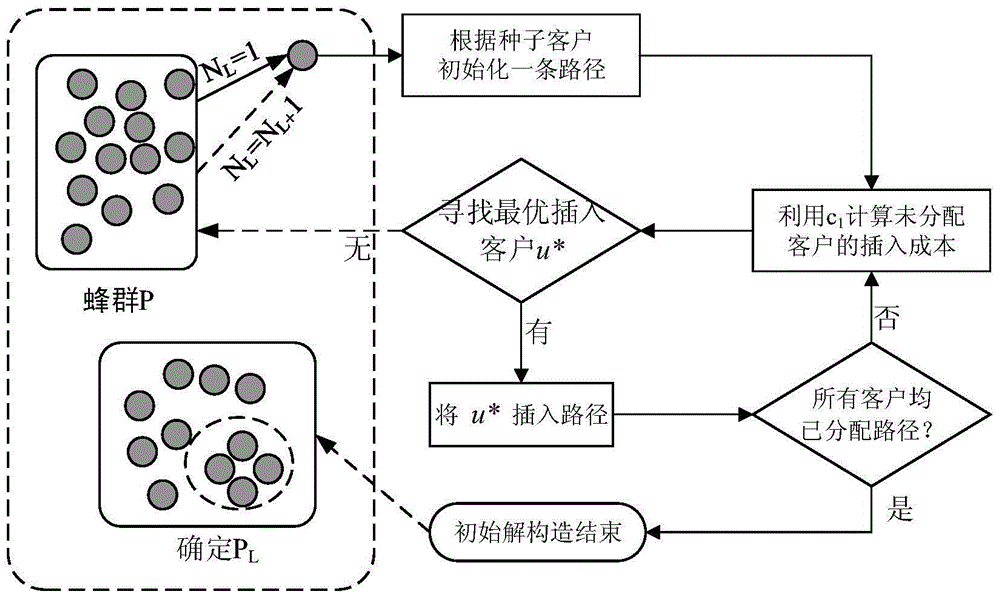

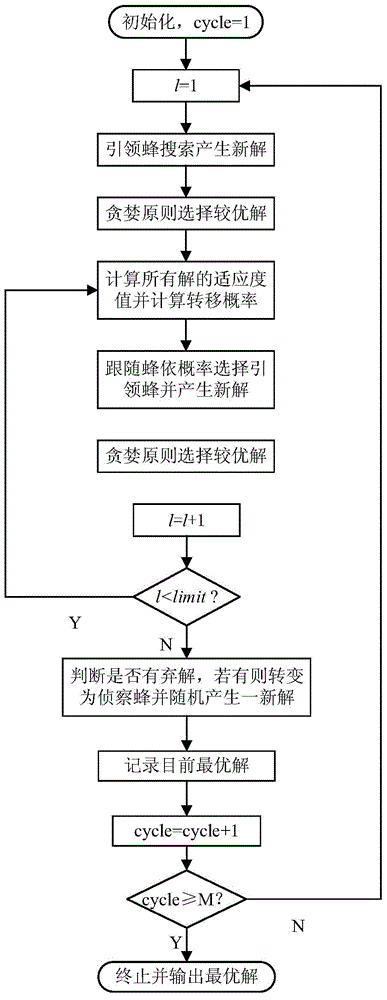

Related logistics transportation optimized dispatching method with time-varying time window

InactiveCN104598994ASolve the real problemFast convergenceForecastingArtificial lifeLogistics managementBees algorithm

The invention relates to a related logistics transportation optimized dispatching method with a time-varying time window. The related logistics transportation optimized dispatching method with the time-varying time window comprises the specific following steps of 1 obtaining demand information of a reservation client through a distribution center; 2 performing initial path planning on the known client through a II insertion method; 3 improving a bee algorithm and optimizing an initial path based on a differential evolution algorithm; 4 collecting time varying information through the distribution center, obtaining new time window information of the client and recording application time of the new time window of the client; judging a key point at the time when the new information comes; 6 inserting the time-varying client to the initial path which is to be solved in the step 3 through the improved II insertion method to achieve optimization of the time-varying path; 7 ending. According to the related logistics transportation optimized dispatching method with the time-varying time window, a final dispatching scheme for related logistics transportation dispatching with the time-varying time window is obtained.

Owner:GUANGDONG YIFU NETWORK TECH

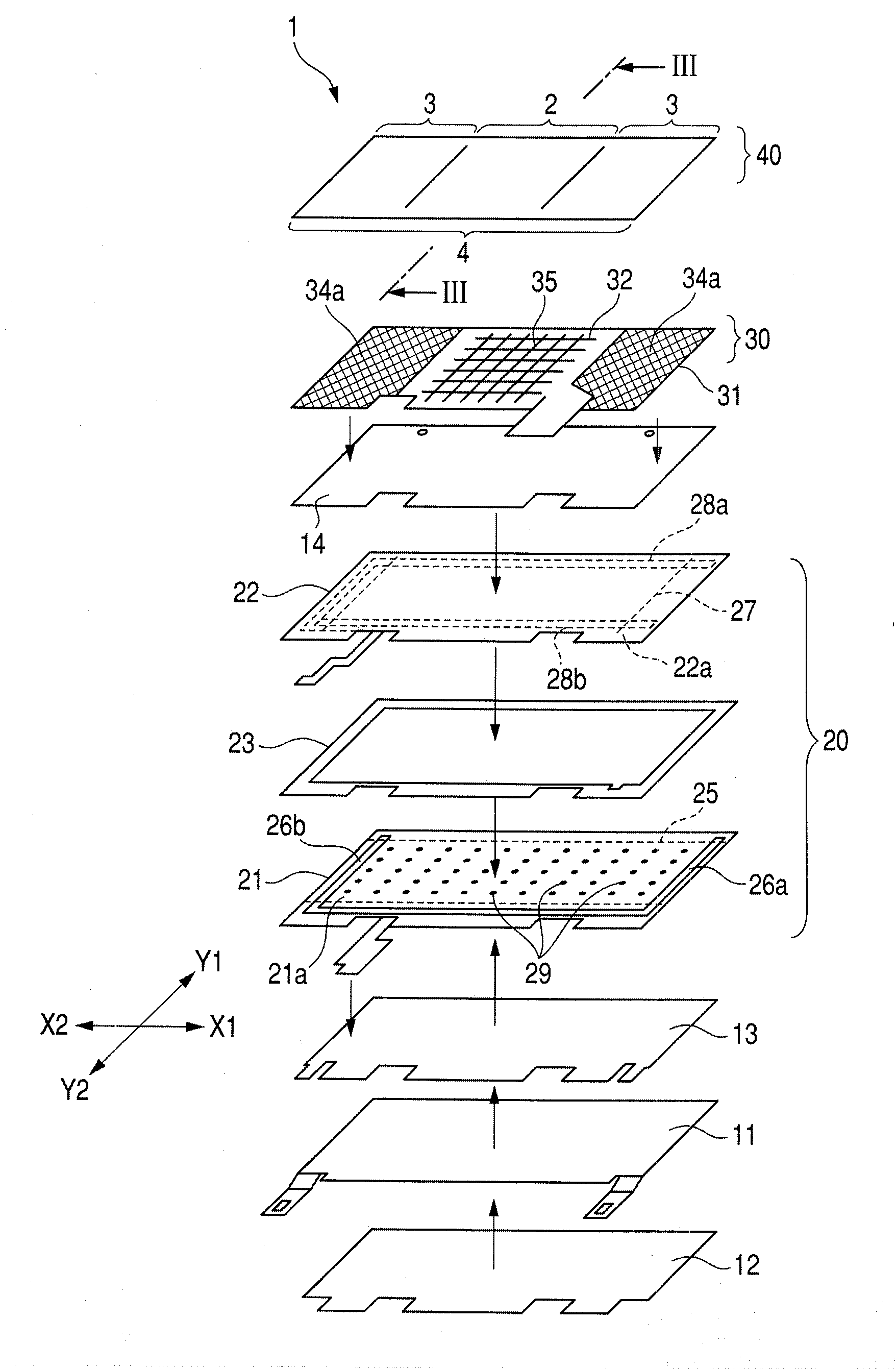

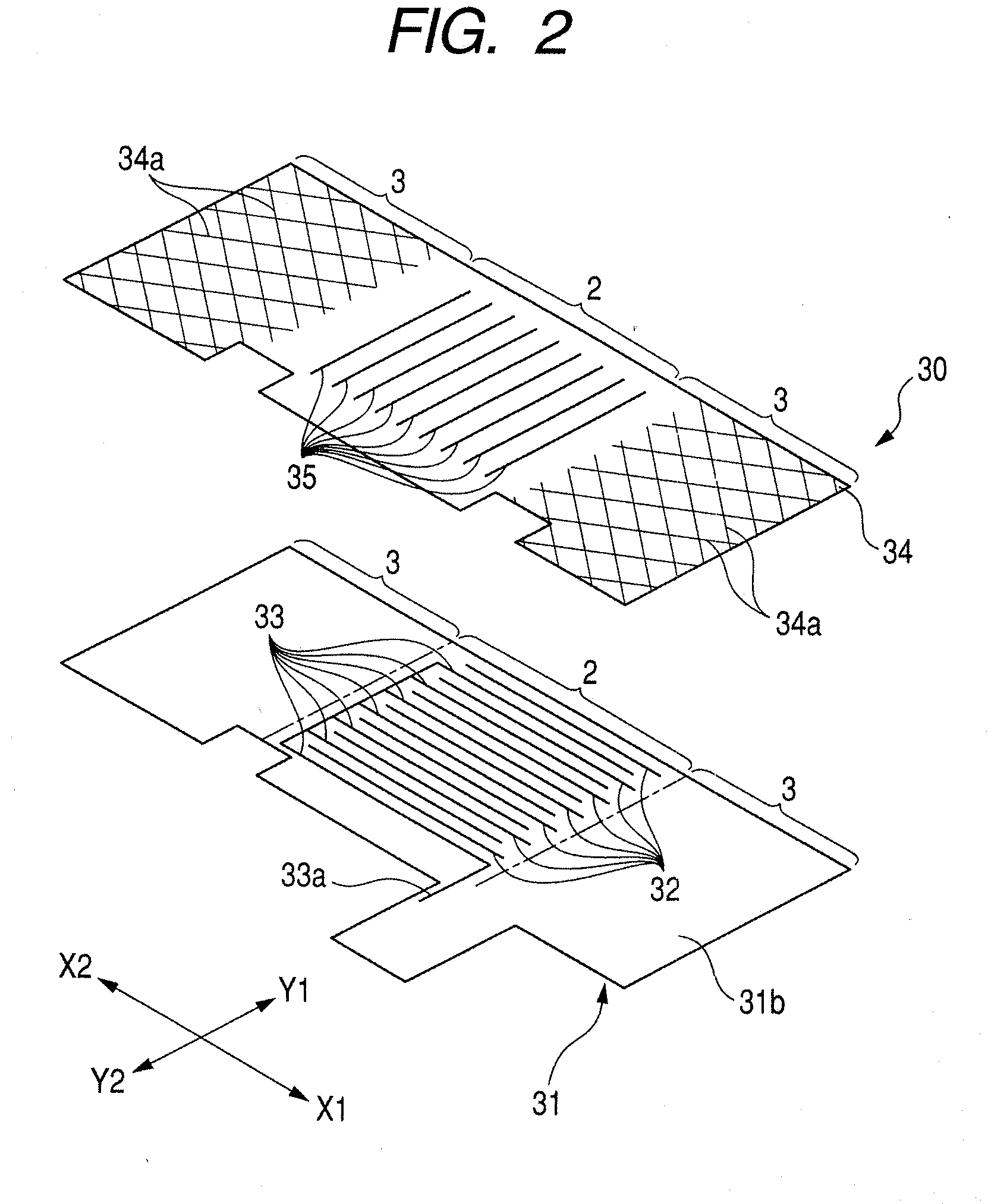

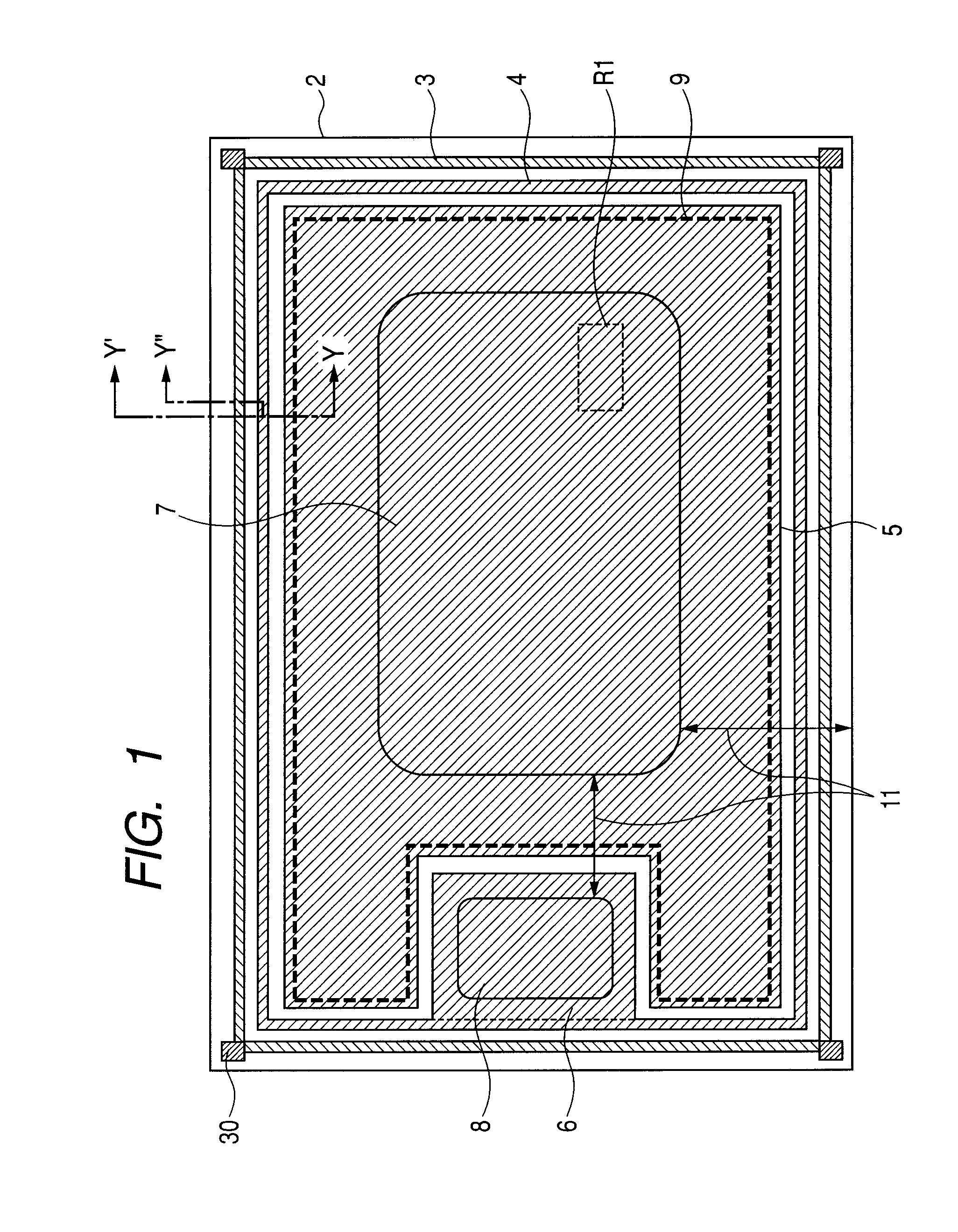

Input device

InactiveUS20090211818A1Reduce the number of layersReduce thicknessTransmission systemsGraph readingManufacturing cost reductionCapacitance

Disclosed is an input device capable of decreasing the number of layers of a detecting portion to reduce manufacturing costs and easily deforming layers provided above a pressure sensitive detecting portion. A capacitance-type detecting portion that detects the contact position of a finger on the basis of a variation in capacitance is provided on a pressure sensitive detecting portion that includes a lower detection layer formed on a lower base sheet and an upper detection layer formed on an upper base sheet. A voltage is applied to the pressure sensitive detecting portion and the capacitance-type detecting portion such that the application times of the voltages do not overlap each other. Therefore, it is possible to prevent interference between the detection operations of the two detecting portions.

Owner:ALPS ALPINE CO LTD

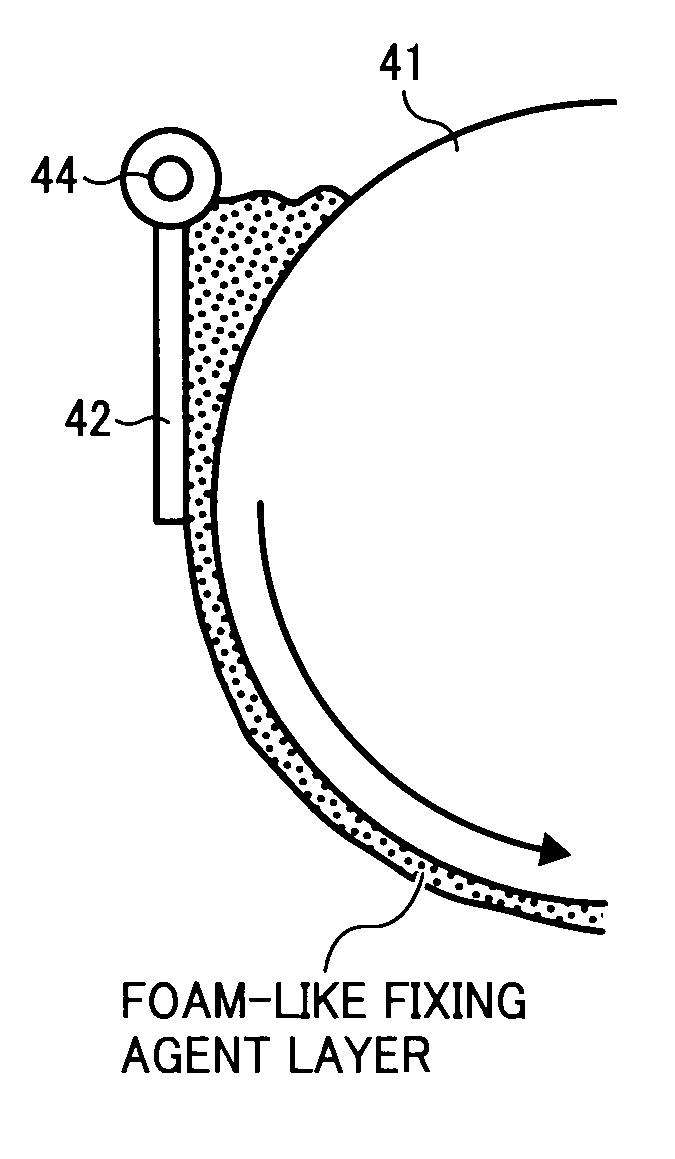

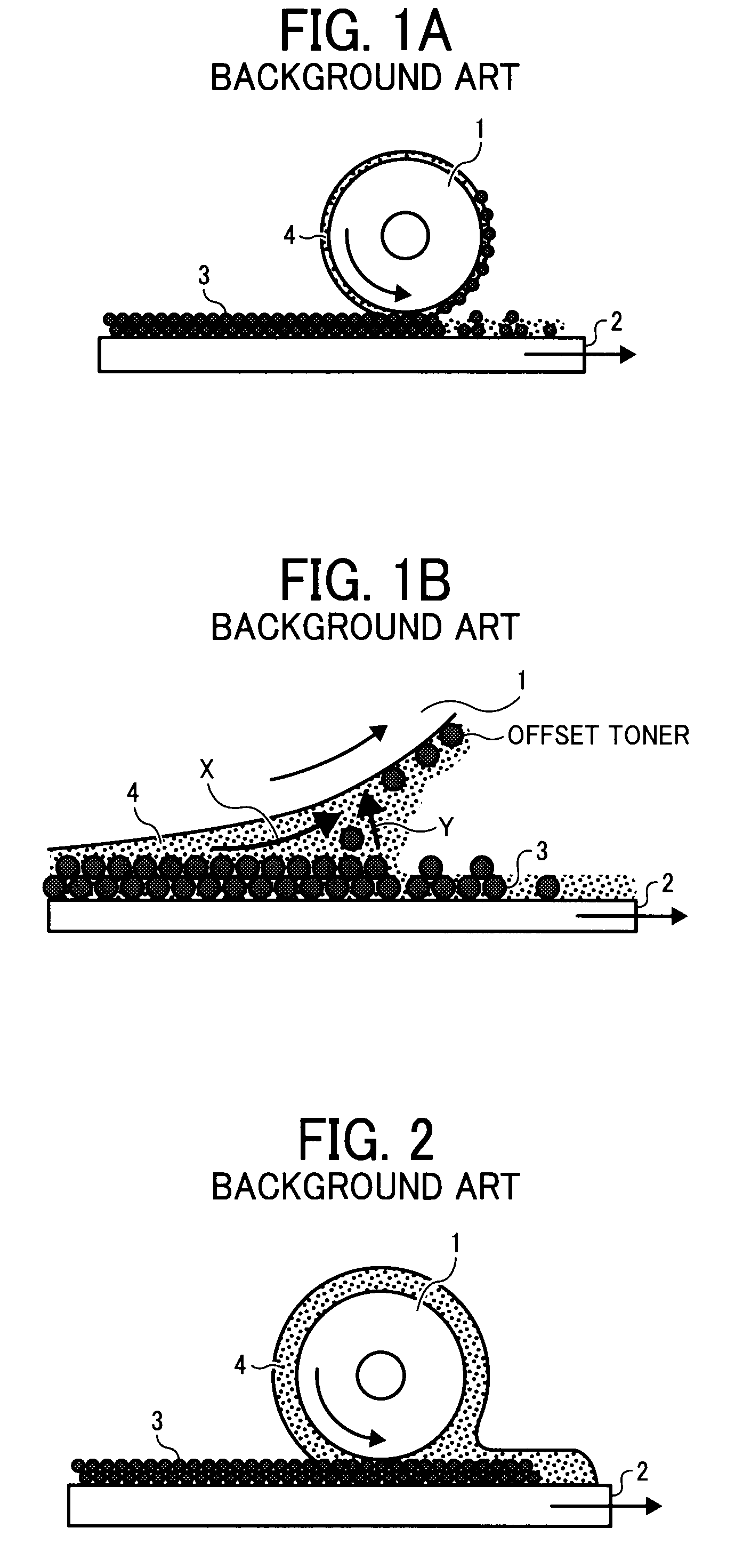

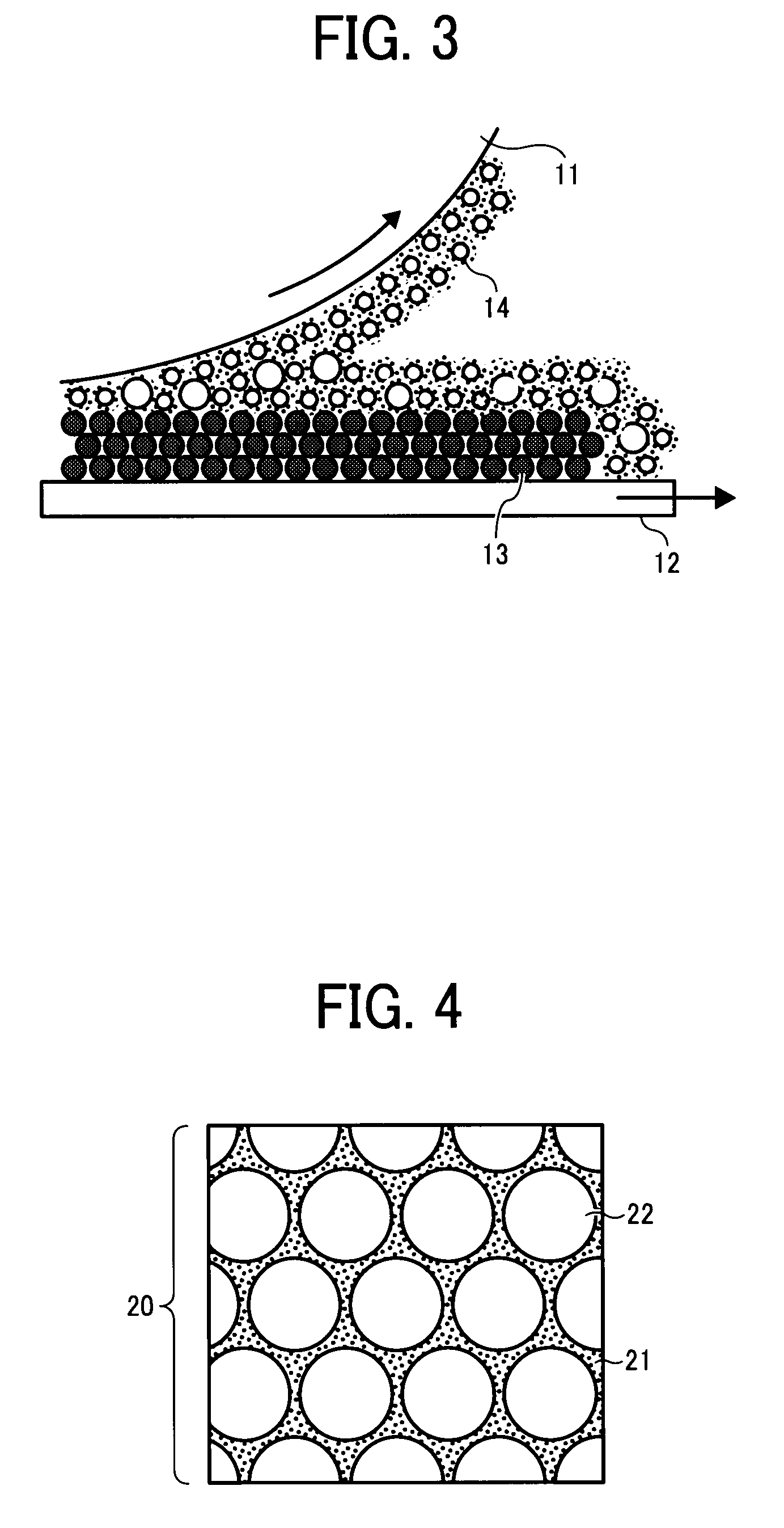

Fixing device, and image forming method and image forming apparatus using the same

InactiveUS20090003903A1Electrographic process apparatusElectrographic processes using charge patternParticulatesImage formation

A fixing device, and an image forming method and an image forming apparatus using the fixing device. The fixing device includes an application unit to apply a foam-like fixing agent including a softener to particulates including a resin on a medium, the softener softening the particulates by at least partially dissolving or swelling the resin and a thickness control unit to control a layer thickness of the foam-like fixing agent such that an application time during which the foam-like fixing agent is applied to the particulates is not shorter than a penetration time required for the foam-like fixing agent to penetrate through a layer of the particulates to the medium.

Owner:RICOH KK

Simplified fertilizer application method of wheat and corn crop rotation anniversary

ActiveCN102017839ALow costInhibition of conversion rateFertilising methodsHorticultureAgricultural scienceHabit

The invention relates to a simplified fertilizer application method of wheat and corn crop rotation anniversary, which is changed into an anniversary fertilizer application method that fertilizer application is carried out twice in a wheat season and fertilizer application is carried out once in a corn season from a traditional habitual fertilizer application method that the fertilizer application is carried out twice or three times in a wheat season and fertilizer application is carried out more than twice in a corn season. Wheat slow release fertilizer and corn slow release fertilizer are applied on crops, which not only can plan and consider the nutrient requirement of the anniversary of two-crop crops and ensure dependable crop and increasing yield of the crops but also can simplify fertilizer application times to a great extend and save labor force.

Owner:INST OF SOIL & FERTILIZER SHANDONG ACAD OF AGRI SCI

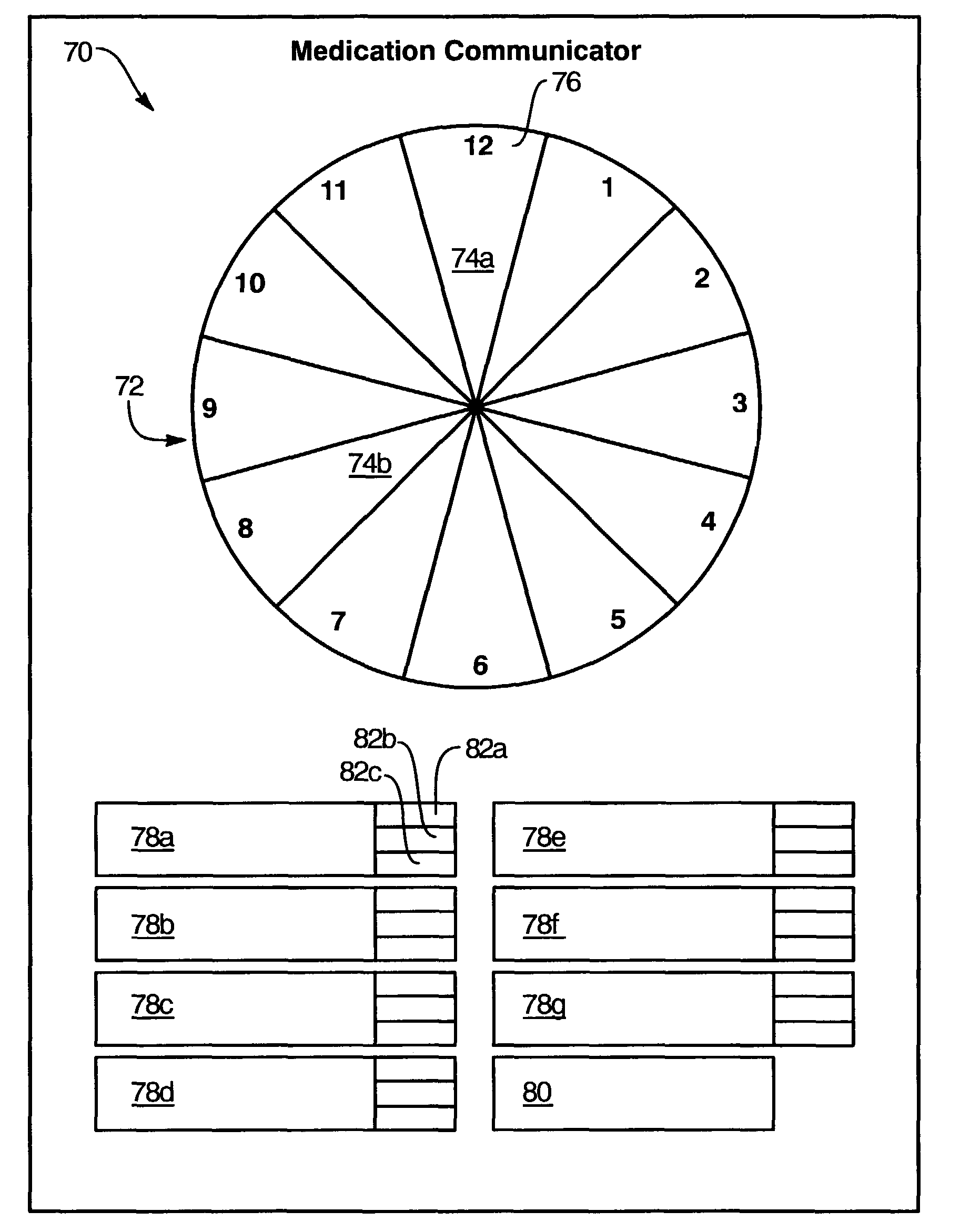

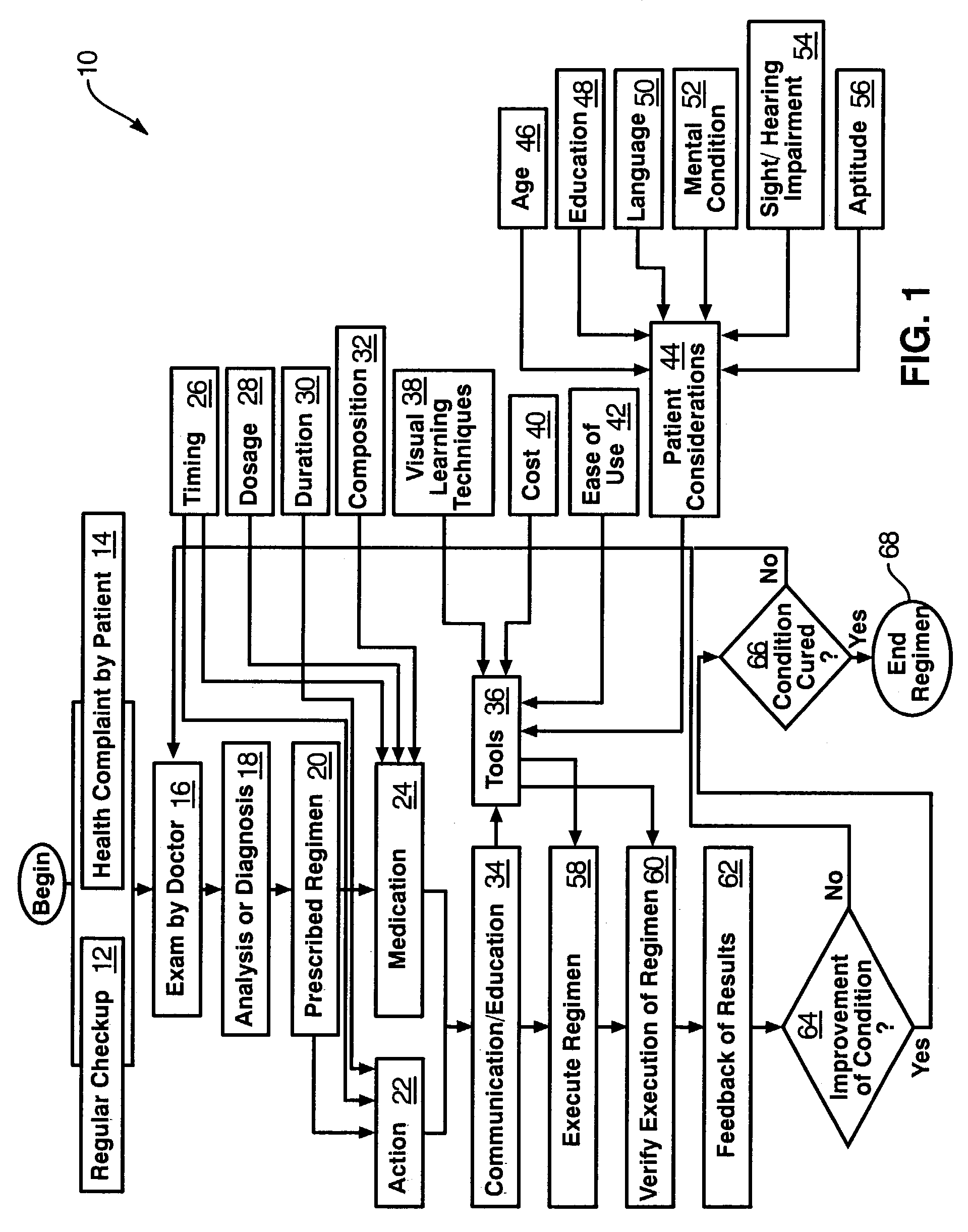

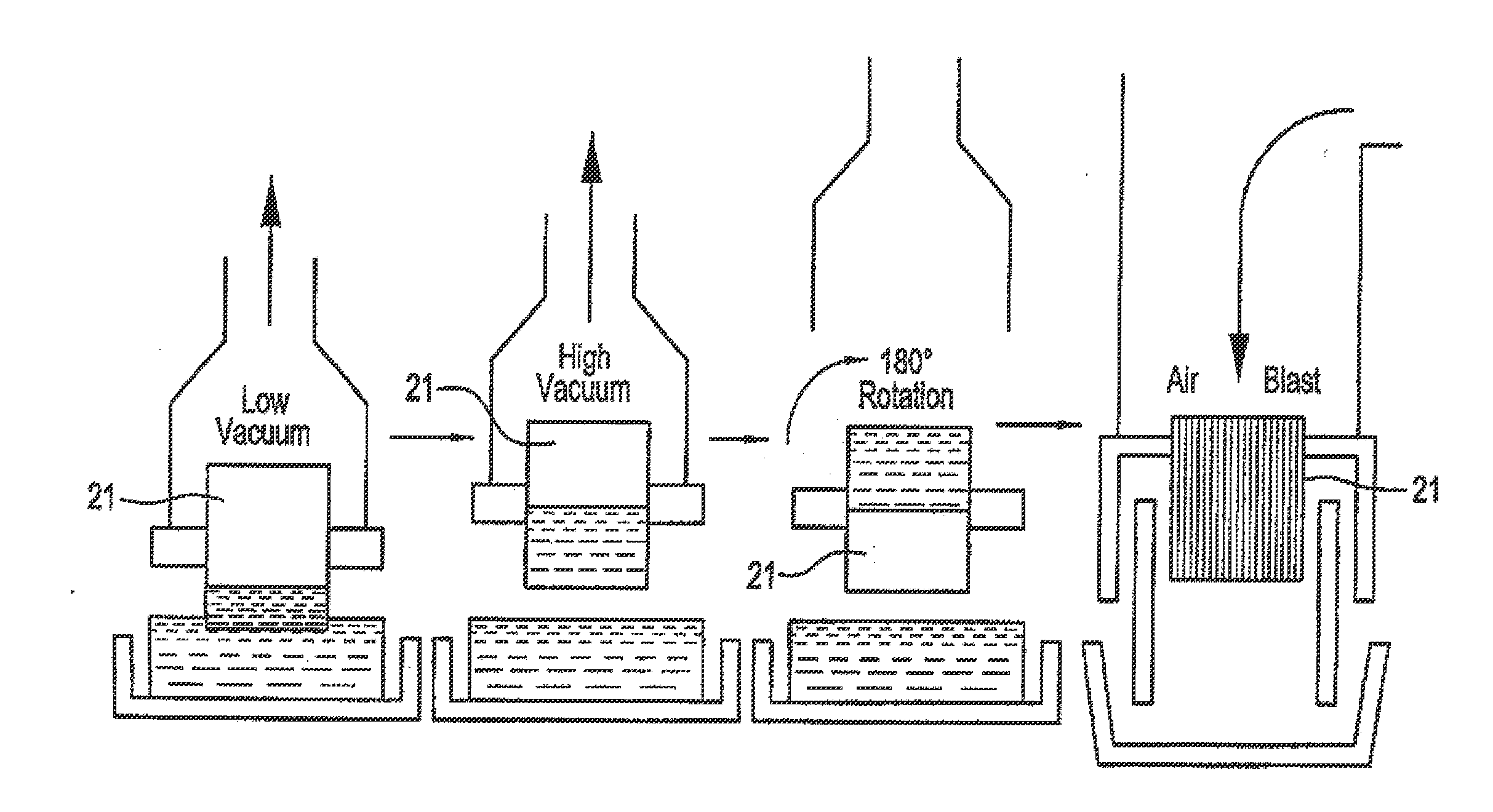

Medication regimen communicator apparatus and method

InactiveUS7773460B2Easy to understandImprove visualizationVisual indicationDrug and medicationsTeaching toolApplication time

A “medication communicator” chart is used as a teaching tool to educate patients and to schedule events corresponding to a prescribed medication regimen. The “medication communicator” chart includes a scheduling graph having the shape of a 12-hour or 24-hour analog clock. The scheduling graph is divided into regions corresponding to each hour of a day for scheduling event information. Fields, on the “medication communicator” chart, are receptive to labels communicating information corresponding to numerous medications in the medication regimen. Timing indicators may be applied to the regions of the scheduling graph to indicate consumption or application times of each of the medications.

Owner:HOLT LINDSAY

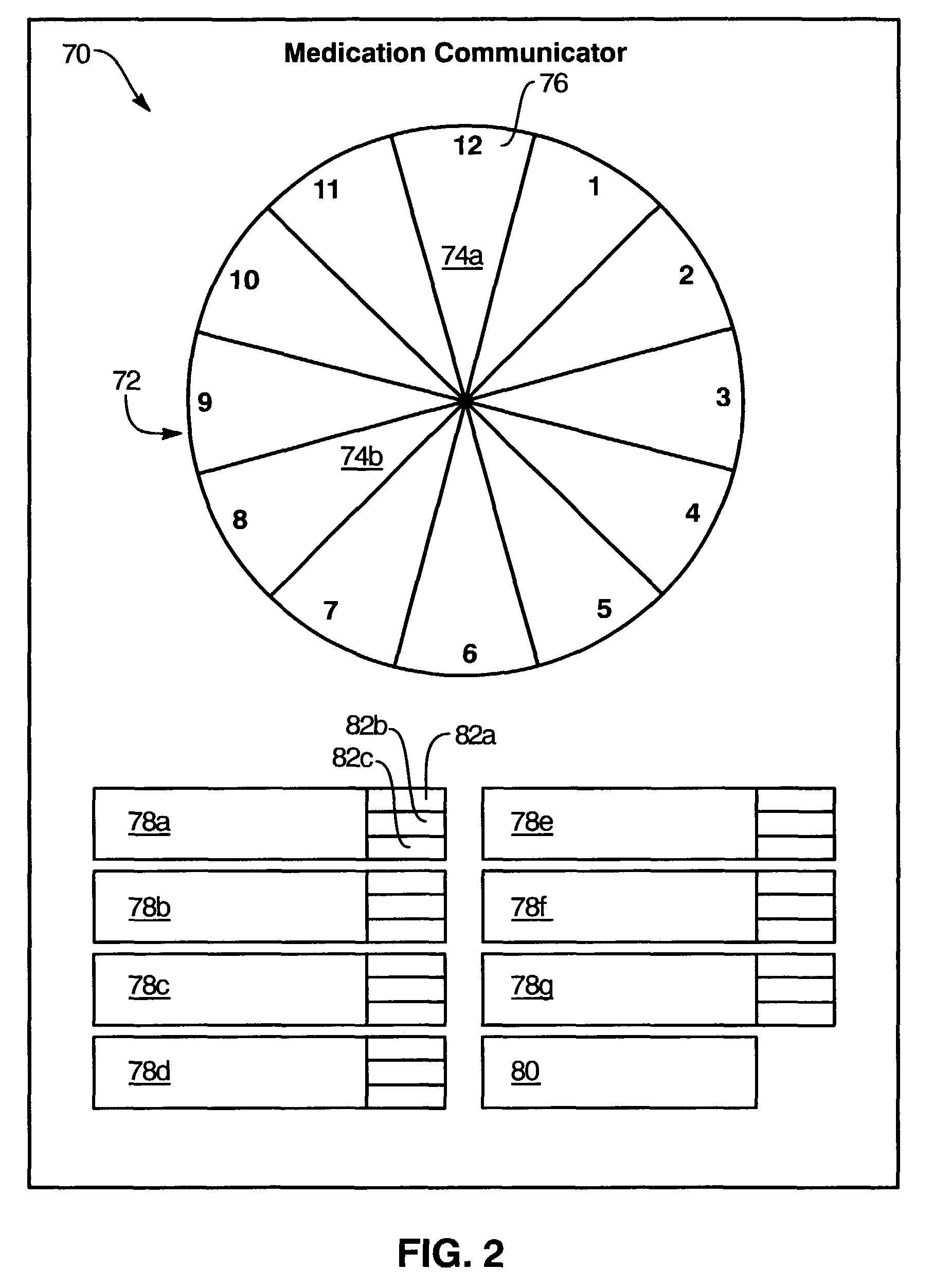

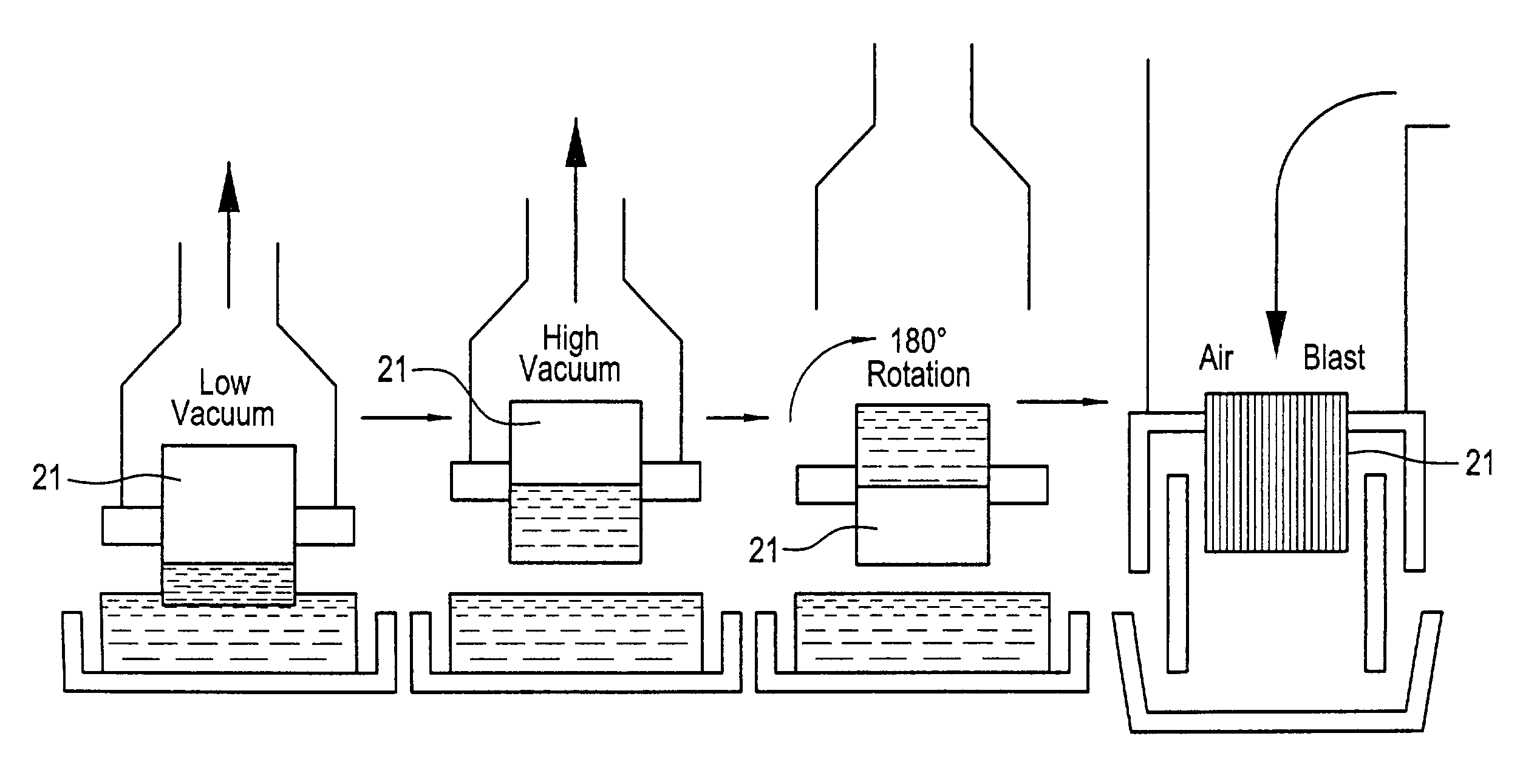

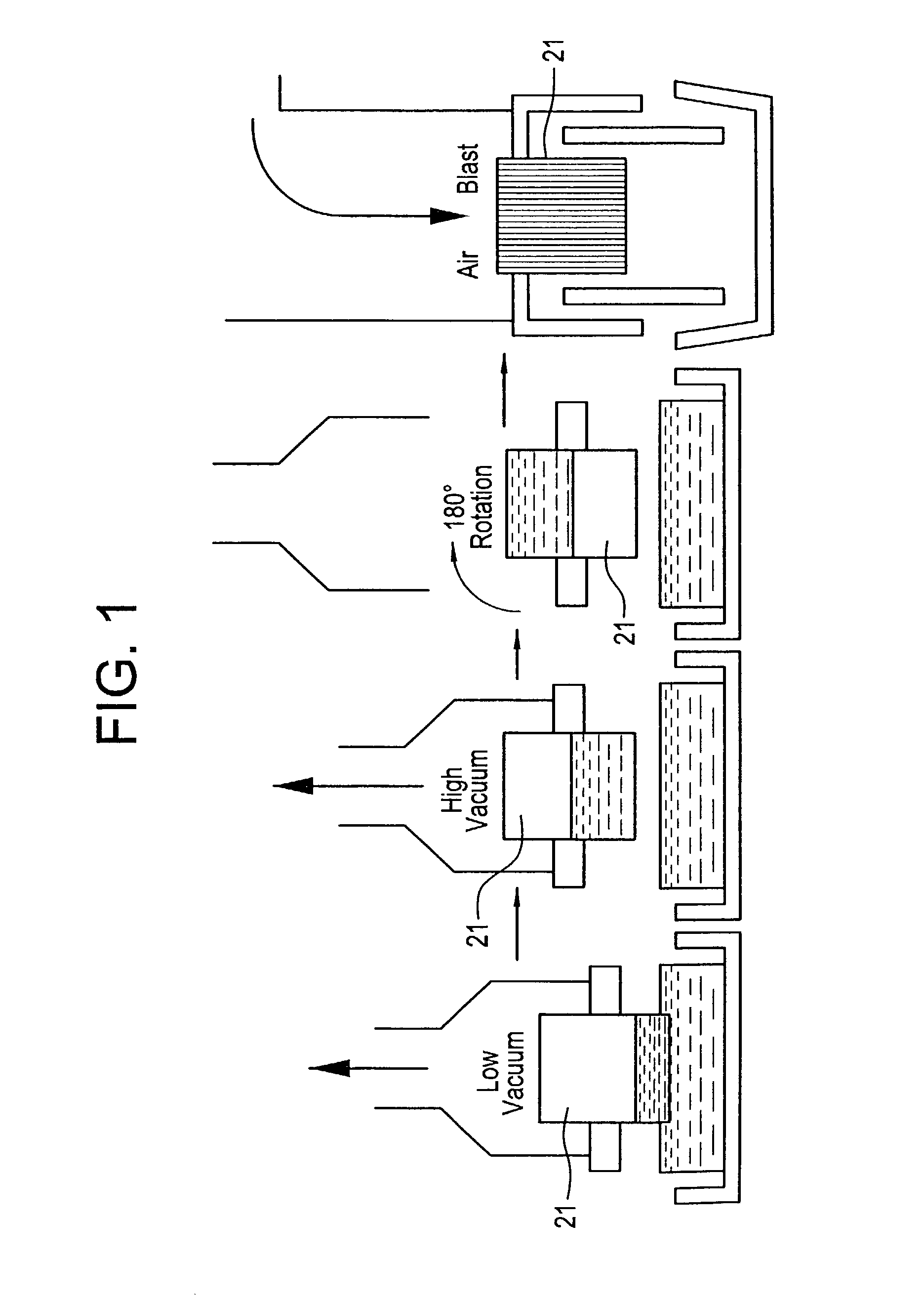

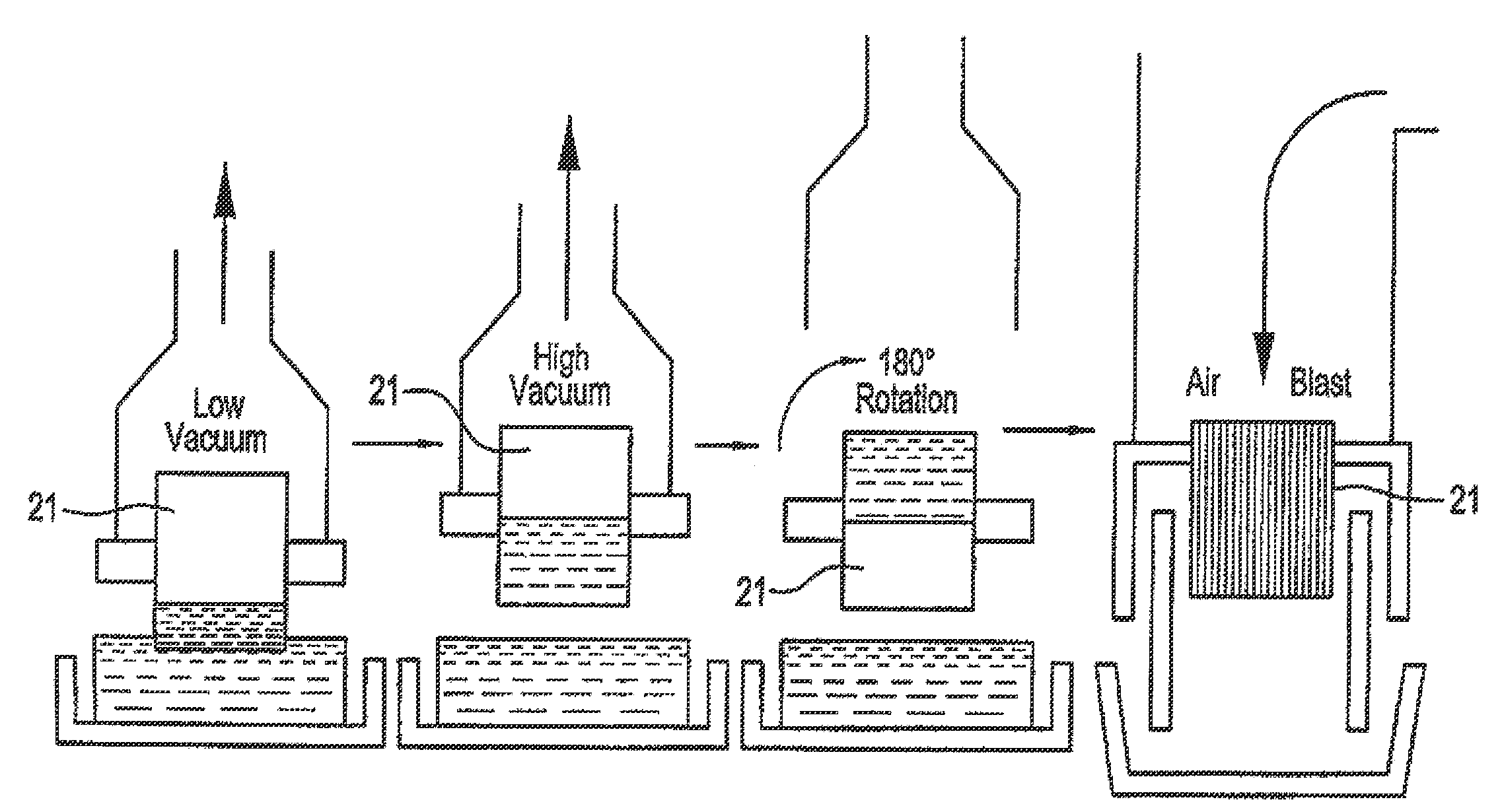

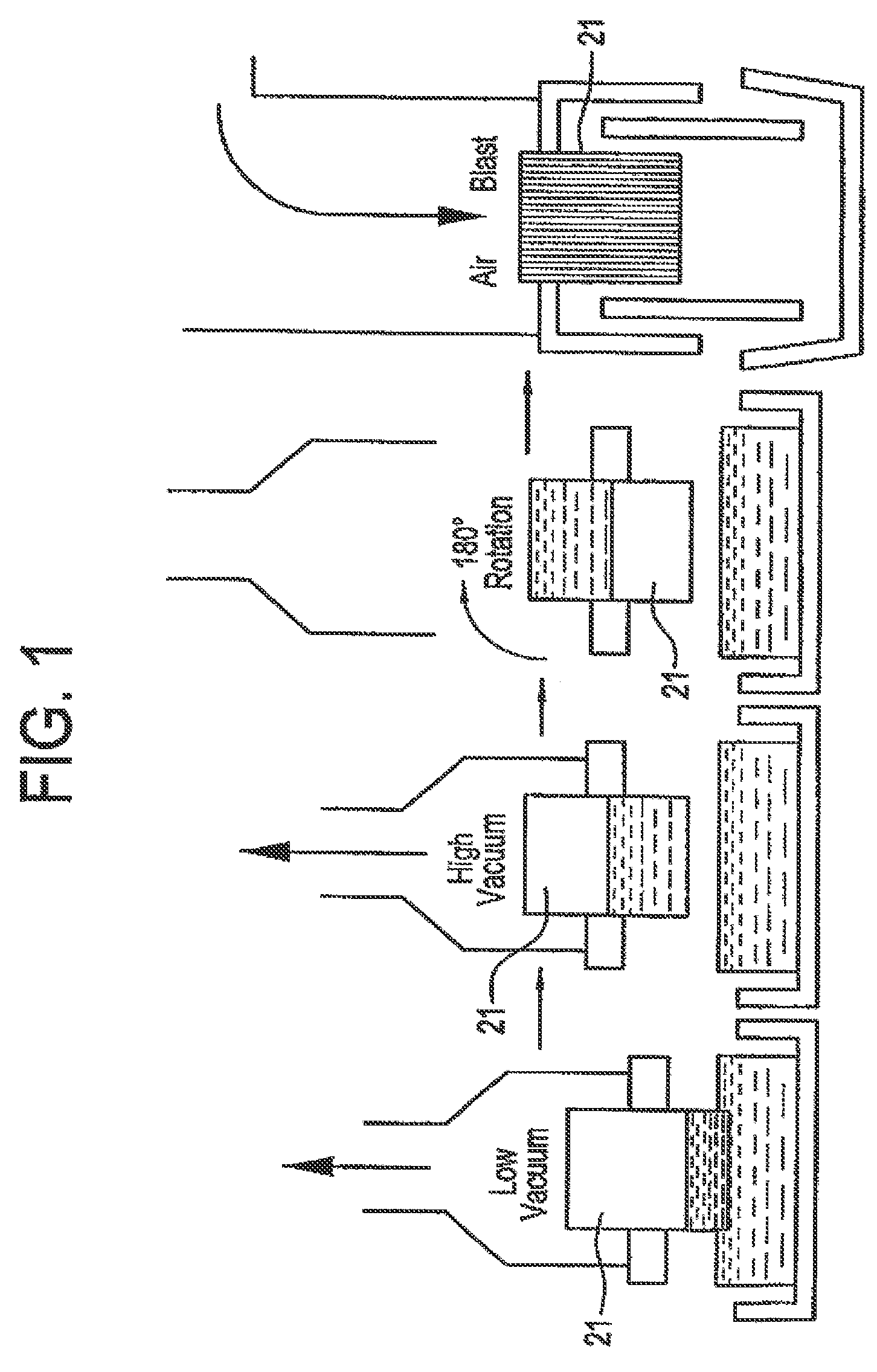

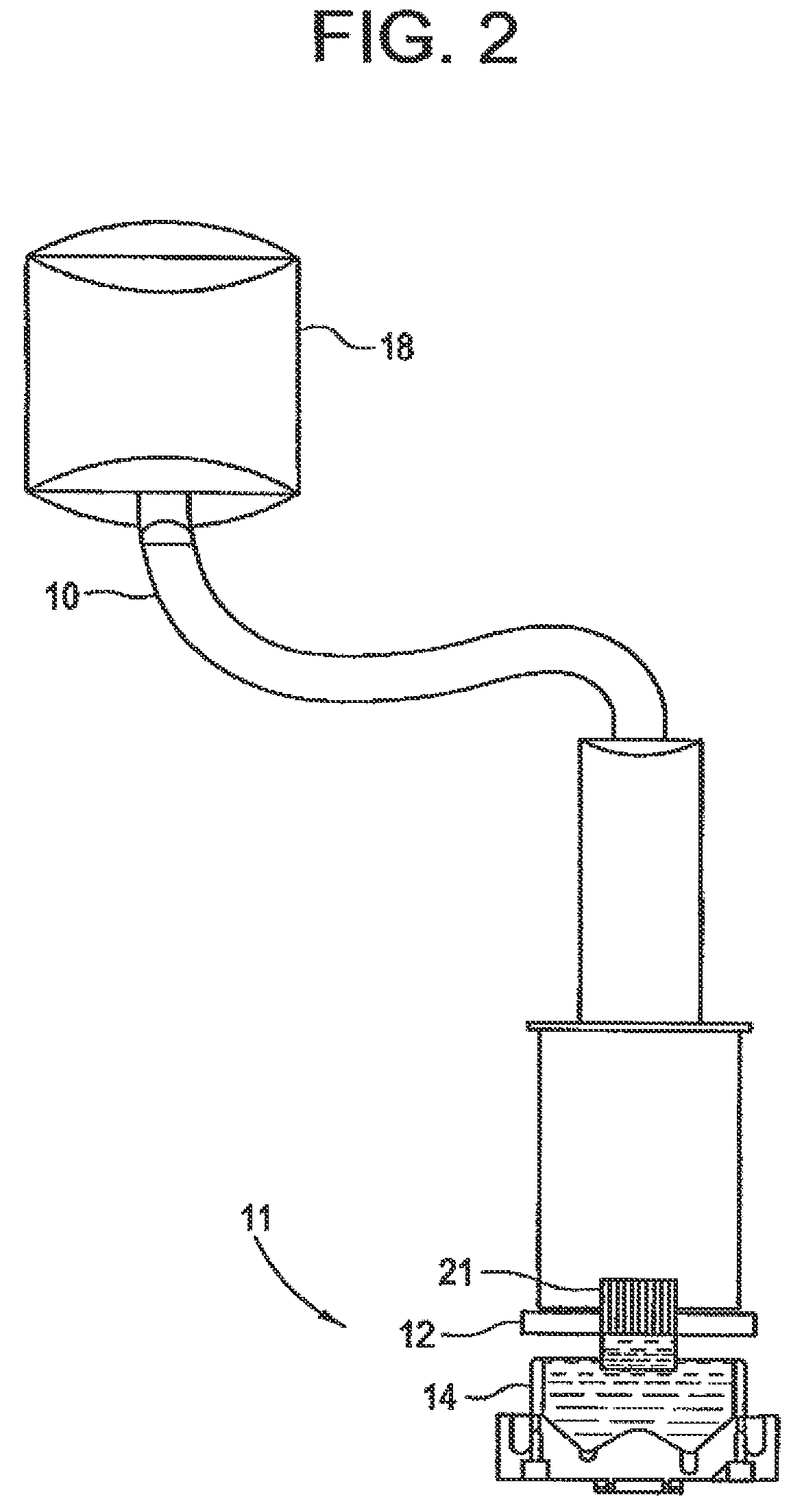

Method for Catalyst Coating of a Substrate

InactiveUS20080145531A1Uniform profileEasy to controlPretreated surfacesCatalyst activation/preparationSlurryApplication time

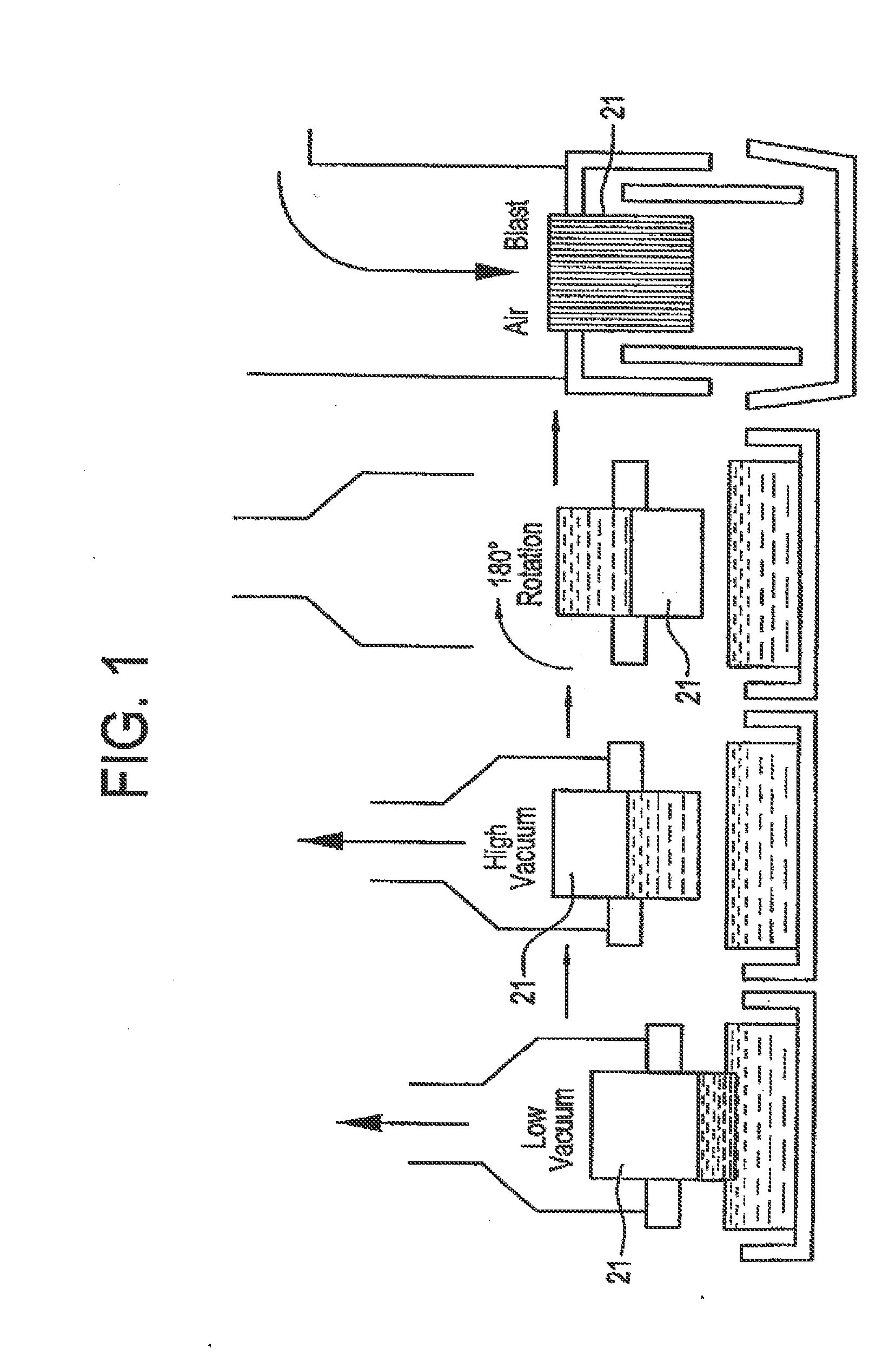

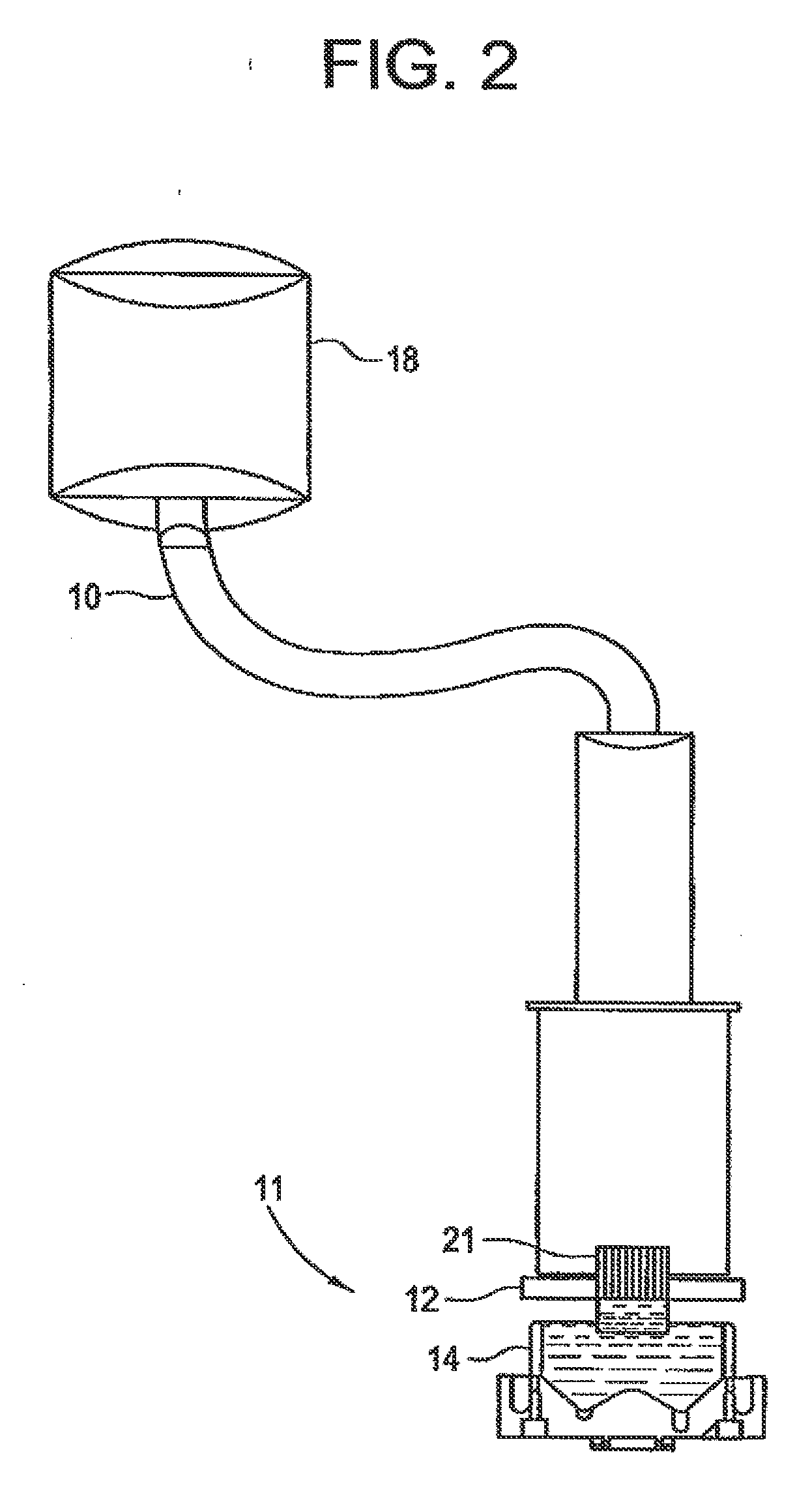

A catalyst composition is applied to an interior of a hollow substrate. The composition is coated on the substrate by immersing the substrate into a vessel containing a bath of coating slurry. A vacuum is then applied to the partially immersed substrate. The intensity of the vacuum and its application time is sufficient to draw the coating slurry upwardly from the bath into each of a plurality of channels located in the interior of the hollow substrate. After removing the substrate from the bath, it is rotated 180°. A blast of pressurized air is applied at an intensity and for a time sufficient to distribute the coating slurry within the channels of the substrate to form a uniform coating profile therein.

Owner:BASF CATALYSTS LLC

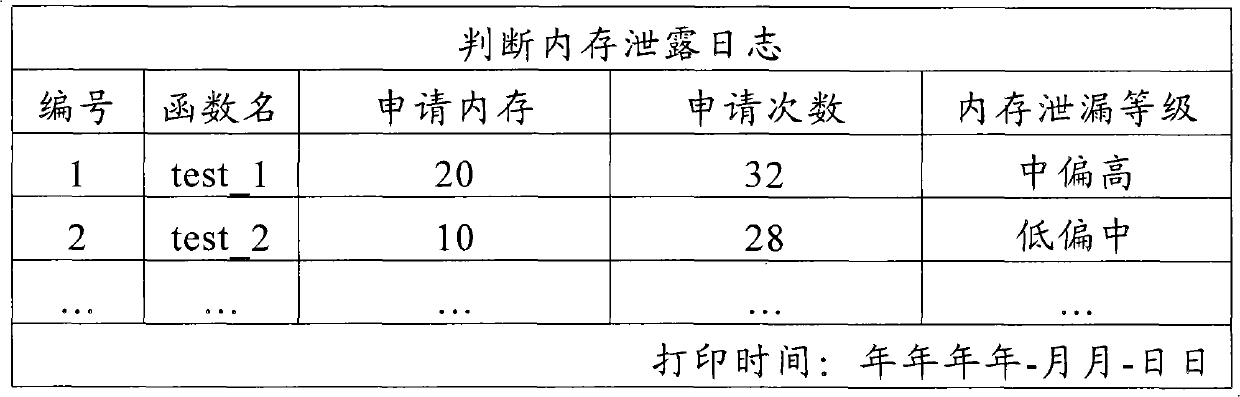

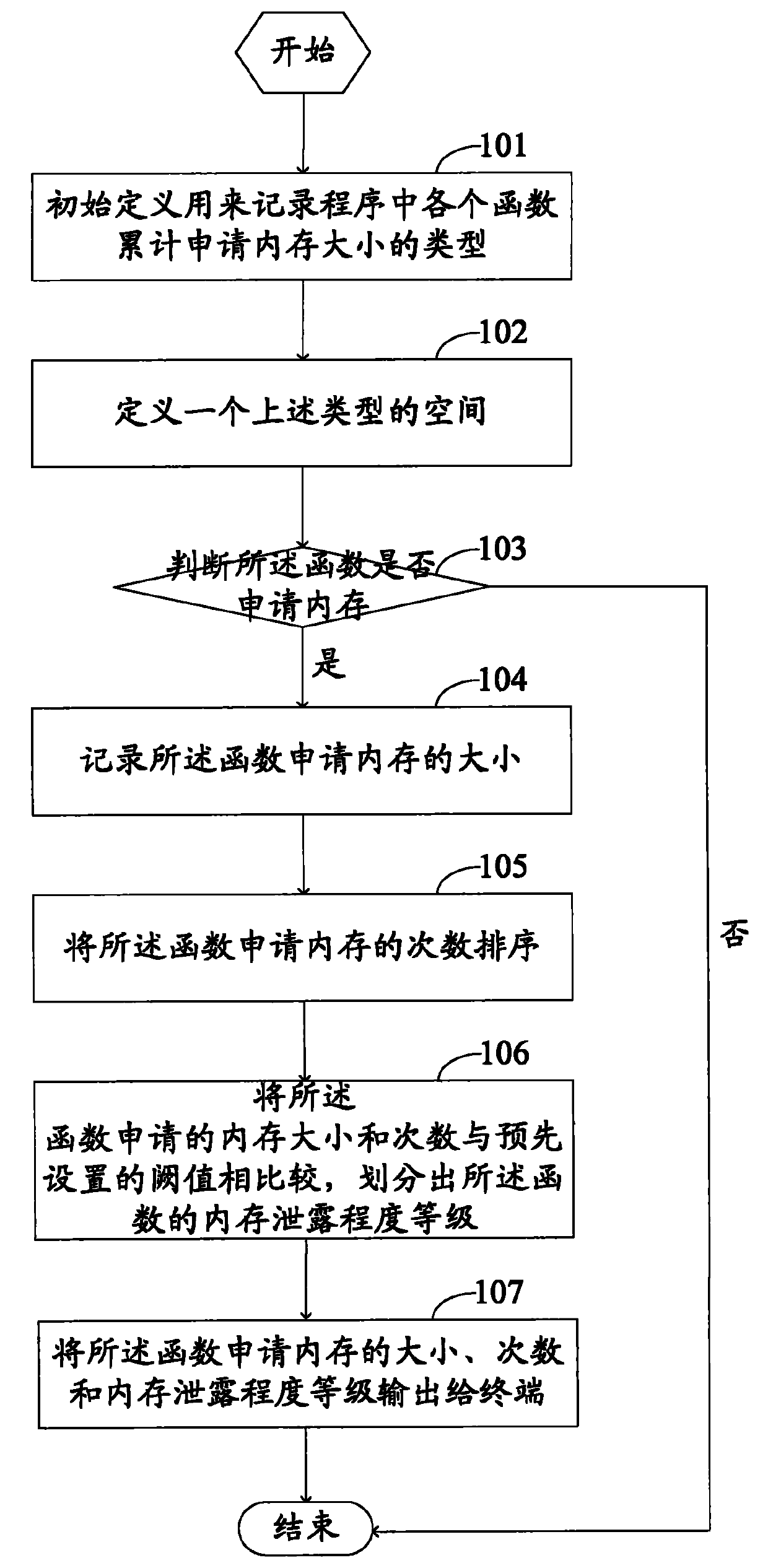

System and method for judging memory leak

The invention provides a method for judging memory leak, comprising the following steps of: when a function application memory is judged aiming at each function in a program, accumulating the memory capacity and the application times of the named function application; when a function release memory is judged, reducing the released memory capacity from the memory capacity of the named function accumulated application and reducing release memory times from accumulated application times; sequencing the memory capacity and the times of the function application in different names in a descending mode by using the memory capacity as priority; ensuring and outputting a level of a memory leak degree according to the memory capacity and the times of the function accumulated application in different names; in addition, the invention provides a system for realizing the method in order to sequence memory distribution and information release according to the memory application times and liberate a programmer from large fussy analytical work.

Owner:BEIJING HAITAI FANGYUAN HIGH TECH

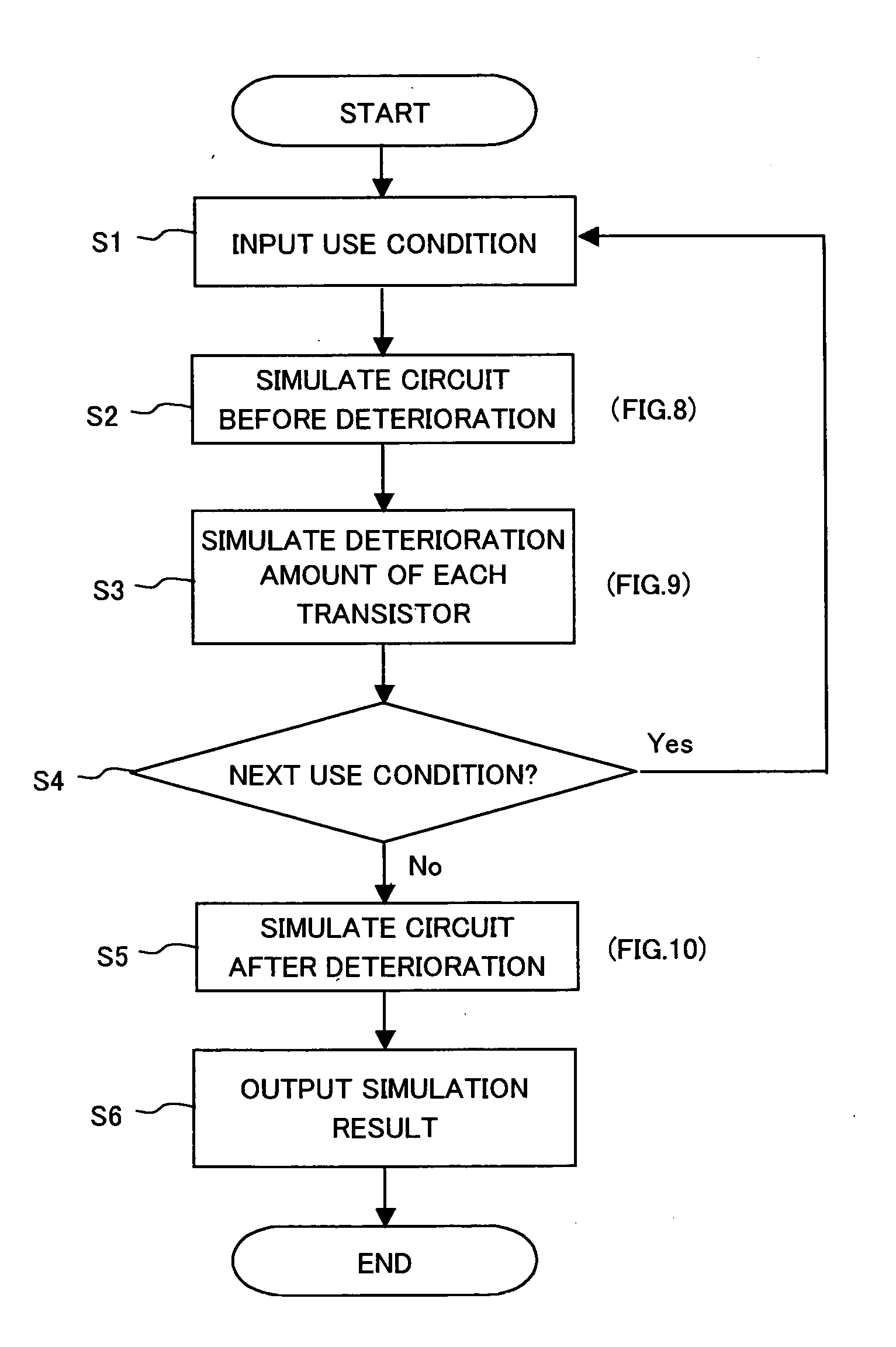

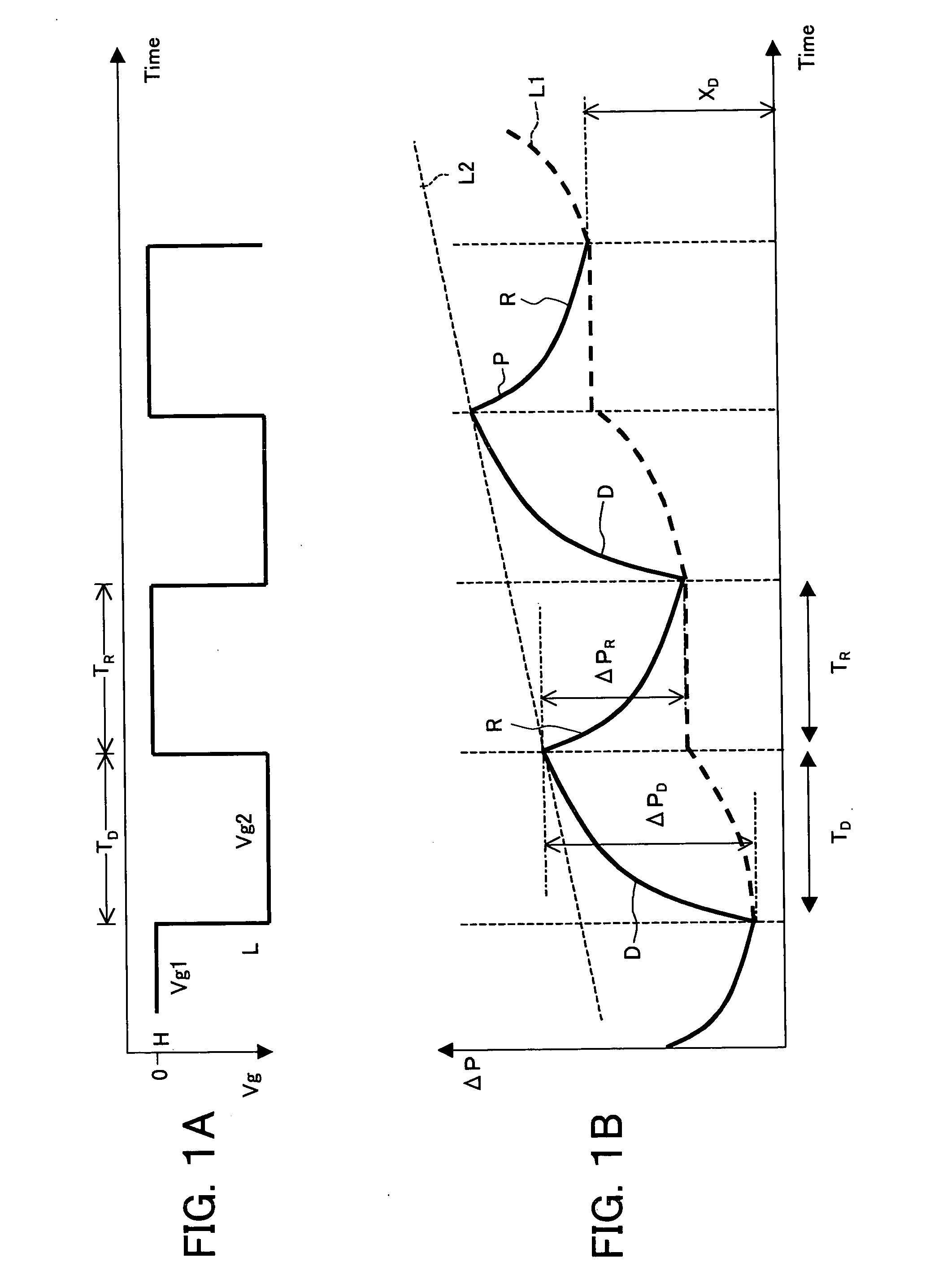

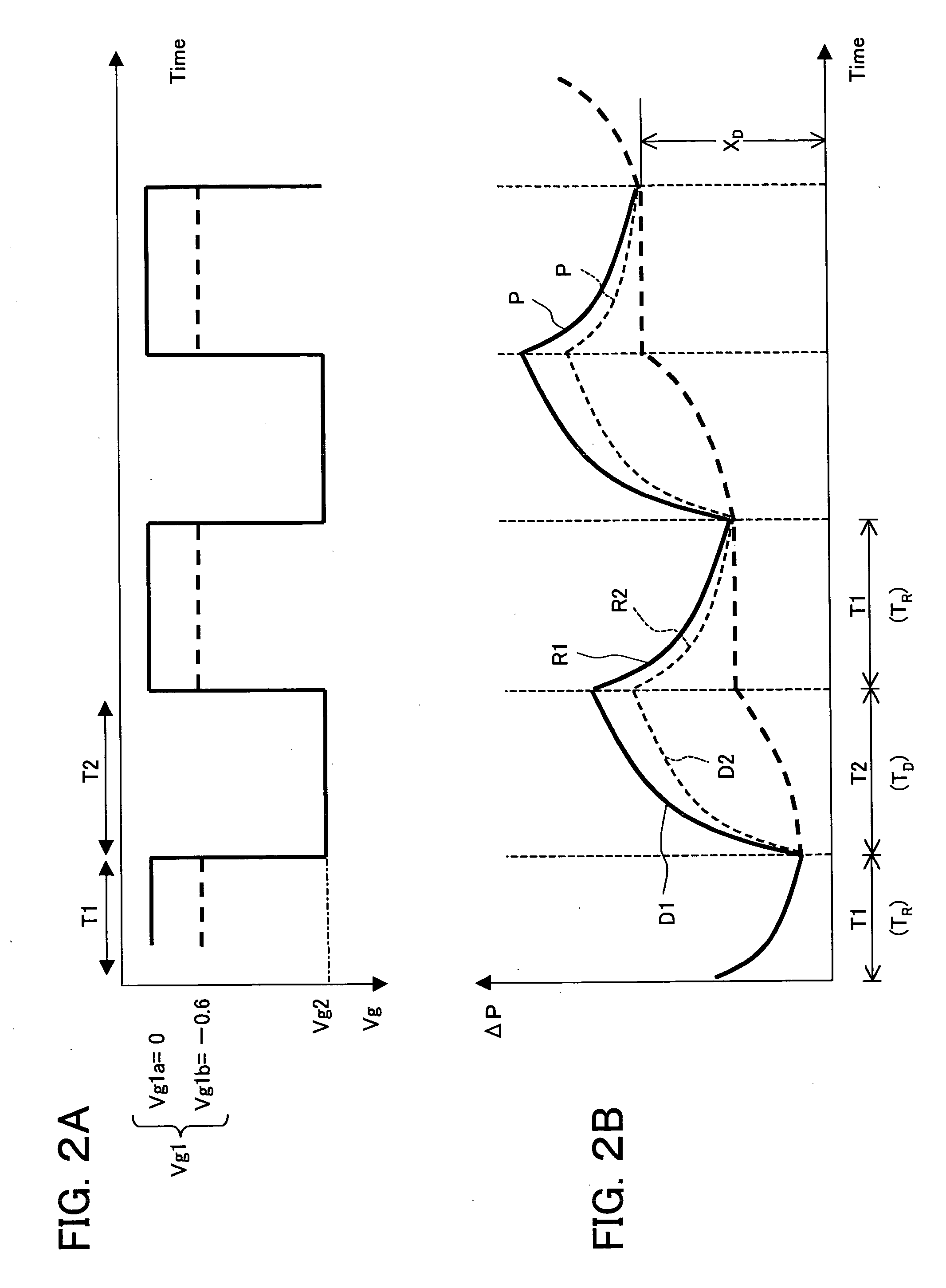

Semiconductor circuit device simulation method and semiconductor circuit device simulator

InactiveUS20050138581A1Accurate estimateSimulation is accurateTransistorAnalogue computers for electric apparatusDevice materialRecovery period

A simulator for accurately simulating a deterioration amount and a recovery amount of transistor characteristics, by which a semiconductor device can be designed with high reliability, and the method are provided. When a gate voltage of a negative level (a negative bias voltage) “Vg” is applied to a gate of the transistor, characteristics of the transistor are deteriorated. When application of the negative level gate voltage “Vg” is terminated (when applying a bias free voltage), the deteriorated transistor characteristics are recovered. In a deterioration period and a recovery period, a logarithm “log(t)” is obtained for an application time “t” of the gate voltage, a deterioration amount ΔPD(t)=CD+BD·log(t) is calculated by using constants CD and BD depending on the negative bias voltage, a recovery amount ΔPR(t)=CR+BR·log(t) is calculated by using constants CR and BR depending on the bias free voltage, and the deterioration amount (ΔPD), the recovery amount (ΔPR) and a basic deterioration amount (XD) are summed up. Preferably, passage of time is divided, and a deterioration amount and a recovery amount are obtained for each time zone by using different deterioration and recovery functions for each time zone.

Owner:SONY CORP

Method and apparatus for testing 3D integrated circuits

InactiveUS8522096B2Reduce testing costsIncrease data rateElectronic circuit testingFault coverageEngineering

A method and apparatus for testing a scan-based 3D integrated circuit (3DIC) using time-division demultiplexing / multiplexing allowing for high-data-rate scan patterns applied at input / output pads converting into low-data-rate scan patterns applied to each embeddded module in the 3DIC. A set of 3D design guidelines is proposed to reduce the number of test times and the number of through-silicon vias (TSVs) required for both pre-bond testing and post-bond testing. The technique allows reuse of scan patterns developed for pre-bond testing of each die (layer) for post-bond testing of the whole 3DIC. It further reduces test application time without concerns for I / O pad count limit and risks for fault coverage loss.

Owner:SYNTEST TECH

Method for applying a catalyst composition to the interior of a hollow substrate

InactiveUS7374792B2Easy to controlControl thicknessPretreated surfacesCatalyst activation/preparationSlurryApplication time

A catalyst composition is applied to an interior of a hollow substrate. The composition is coated on the substrate by immersing the substrate into a vessel containing a bath of coating slurry. A vacuum is then applied to the partially immersed substrate. The intensity of the vacuum and its application time is sufficient to draw the coating slurry upwardly from the bath into each of a plurality of channels located in the interior of the hollow substrate. After removing the substrate from the bath it is rotated 180°. A blast of pressurized air is applied at an intensity and for a time sufficient to distribute the coating slurry within the channels of the substrate to form a uniform coating profile therein.

Owner:BASF CATALYSTS LLC

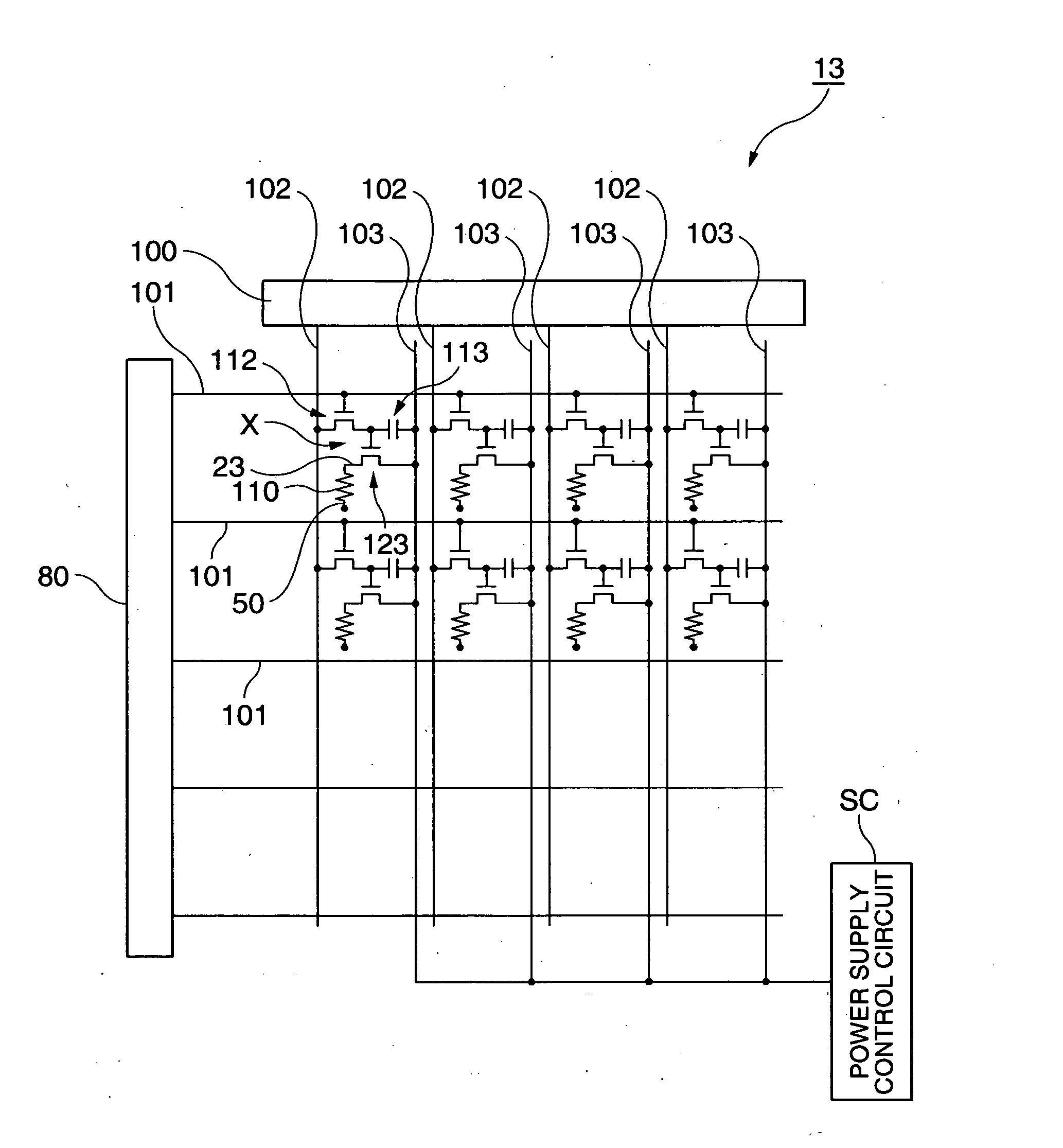

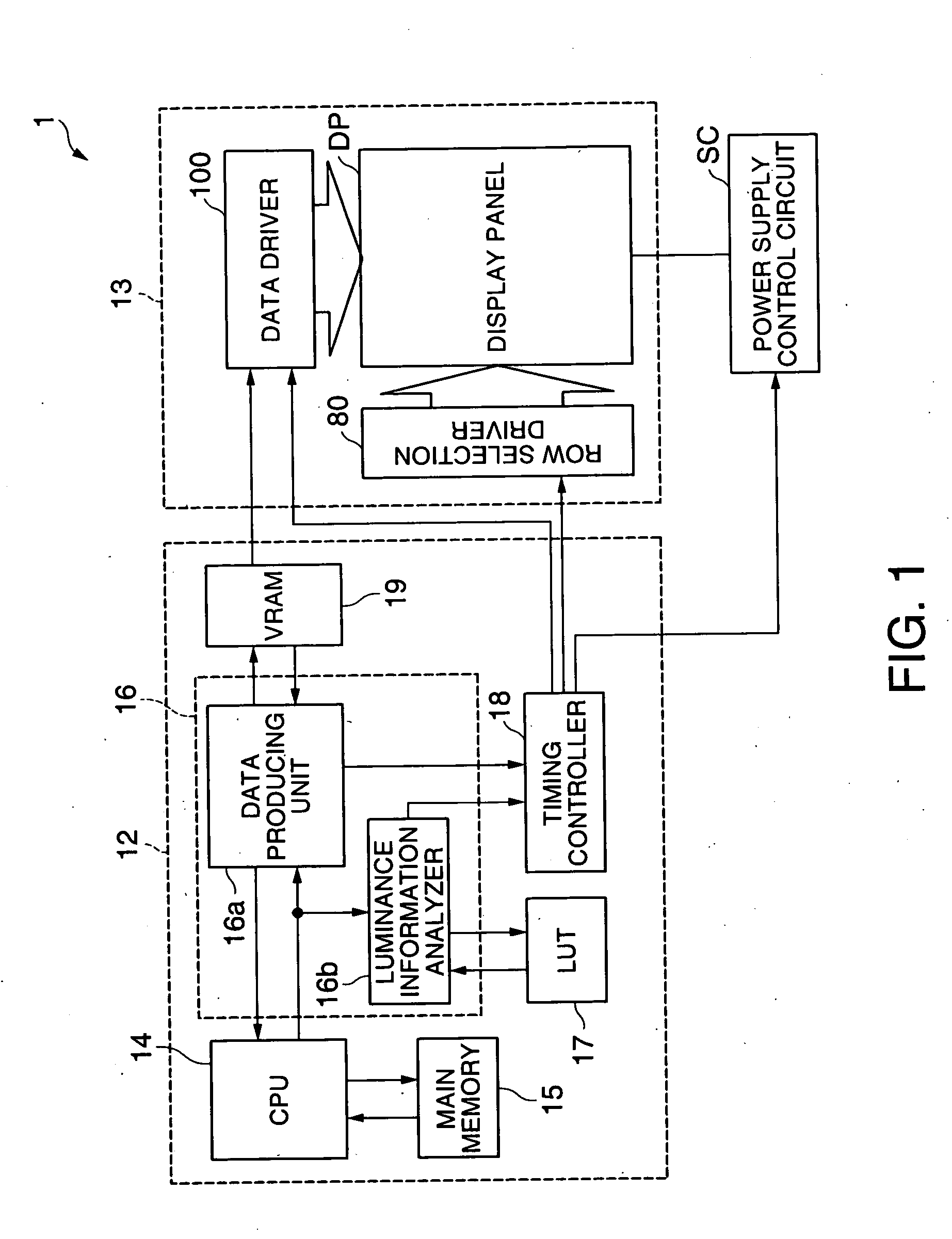

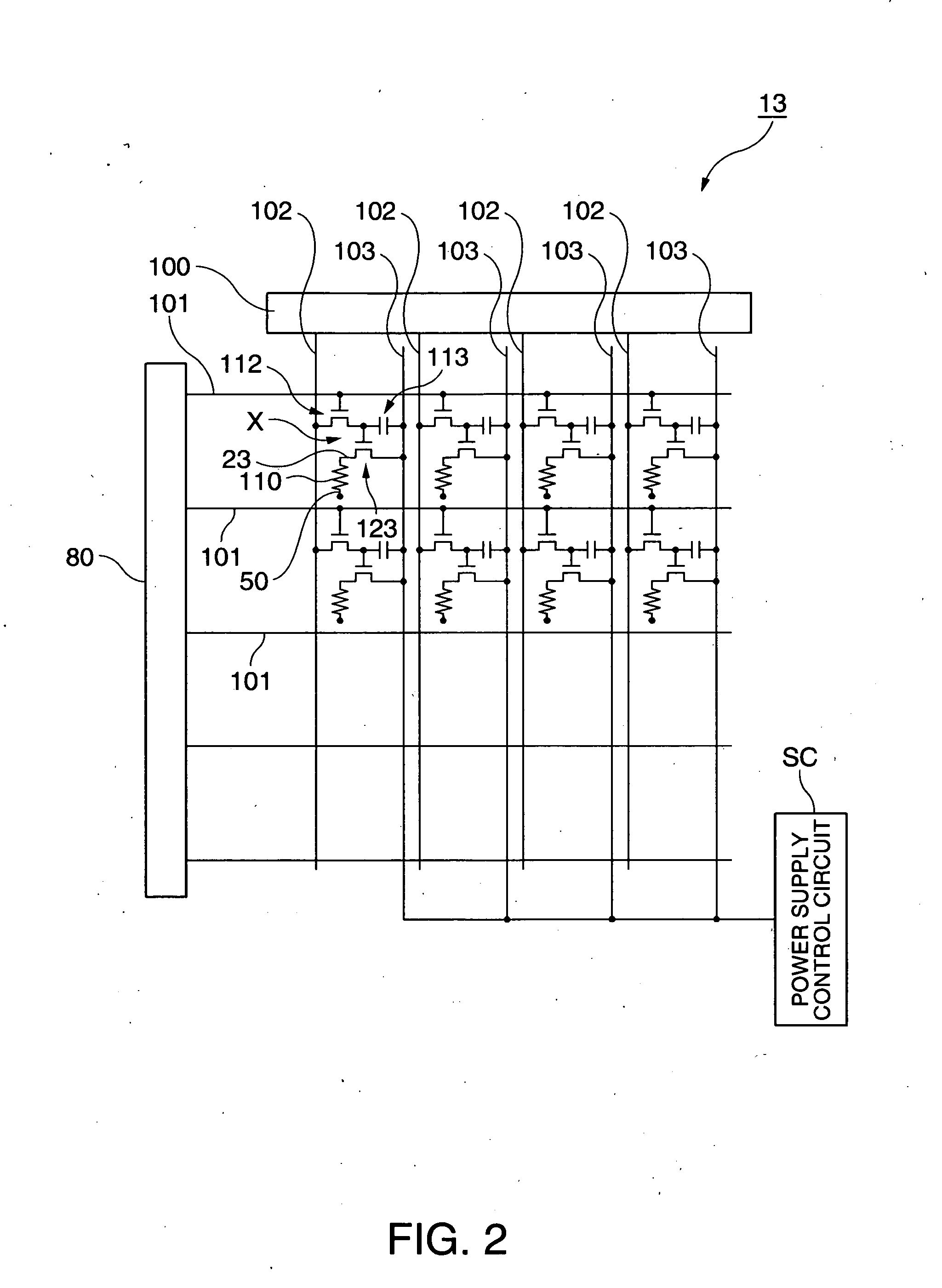

Organic electro-luminescence device, driving method thereof and electronic apparatus

InactiveUS20060208657A1Without shortening its effective emission time periodsStatic indicating devicesElectrical polarityConductive materials

An organic electro-luminescence (EL) device including at least an emission layer between an anode and a cathode that are opposed to each other, including an anode buffer layer that is composed of an electrically conductive material and is provided between the anode and the emission layer, a cathode buffer layer that is composed of an electrically conductive material and is provided between the cathode and the emission layer, and a drive unit that applies a forward bias voltage and a reverse bias voltage that have opposite polarities to the anode and the cathode with setting application time periods of the forward bias voltage and the reverse bias voltage according to a luminance ratio of an image to be displayed.

Owner:SEIKO EPSON CORP

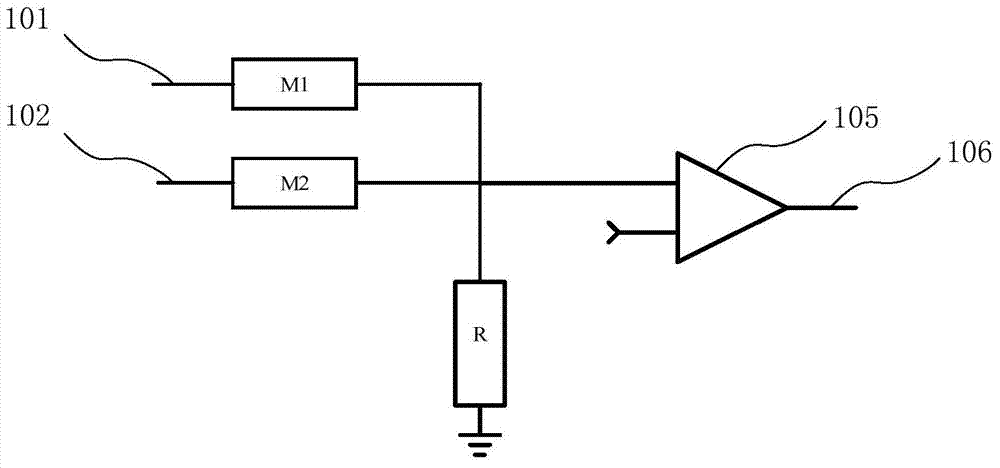

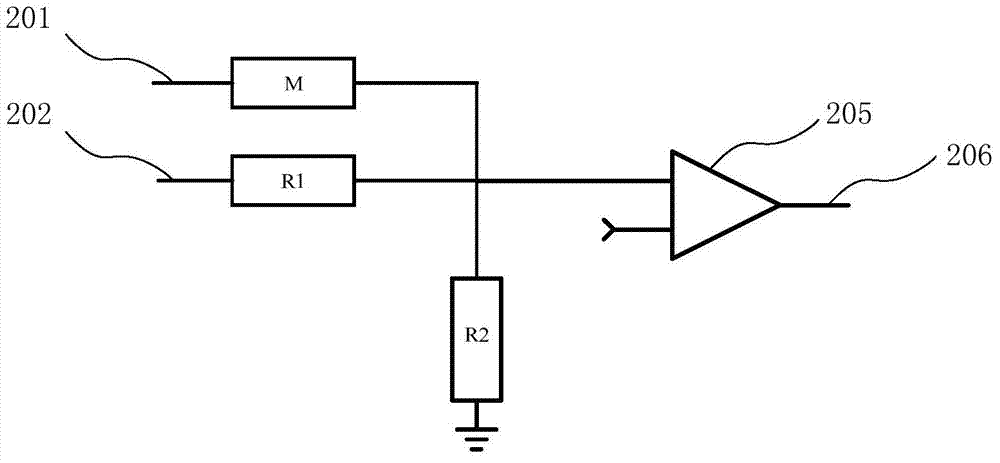

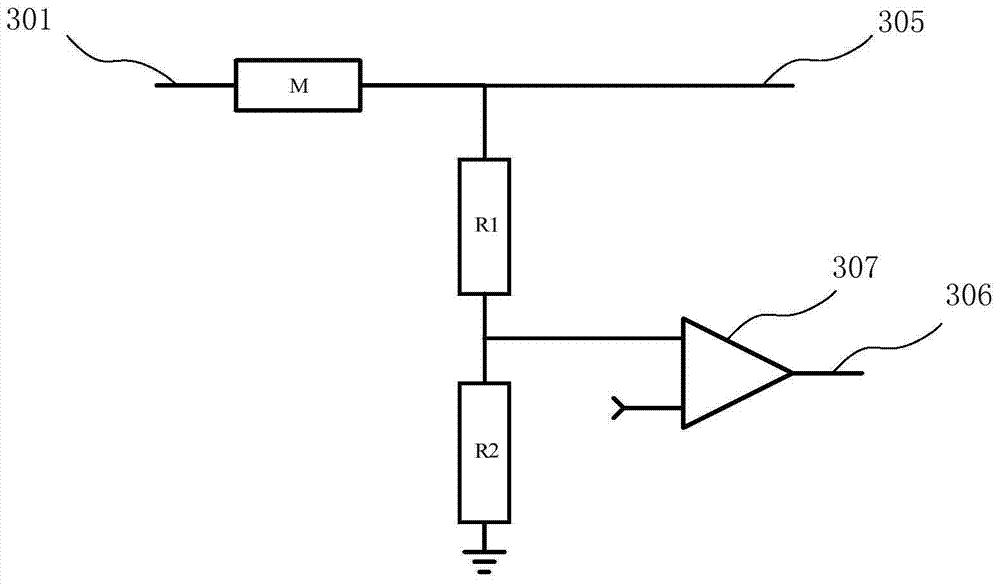

Associative memory circuit based on memory resistor

The invention discloses an associative memory circuit based on a memory resistor. The associative memory circuit based on the memory resistor comprises the memory resistor, a first resistor, a second resistor and a calculation comparator. The first resistor and the memory resistor are connected to a first input end of the calculation comparator in series in sequence. A non-series-connection connecting end of the memory resistor serves as a first input end of the associative memory circuit. A series-connection connecting end of the first resistor and the memory resistor serves as a second input end of the associative memory circuit. One end of the second resistor is connected to the first input end of the calculation comparator and the other end of the second resistor is grounded. A second input end of the calculation comparator is used for being connected with reference voltage. The output end of the calculation comparator is used as the output end of the associative memory circuit. The first input end and the second input end of the associative memory circuit are used for receiving conditioned stimulus signals and receiving unconditioned stimulus signals respectively. The output end of the associative memory circuit is used for outputting response signals. By the adoption of the associative memory circuit based on the memory resistor, the forming process and the forgetting process of biological associative memory can be simulated according to the relation between the application time of the conditioned stimulus signals and the application time of the unconditioned stimulus signals.

Owner:HUAZHONG UNIV OF SCI & TECH

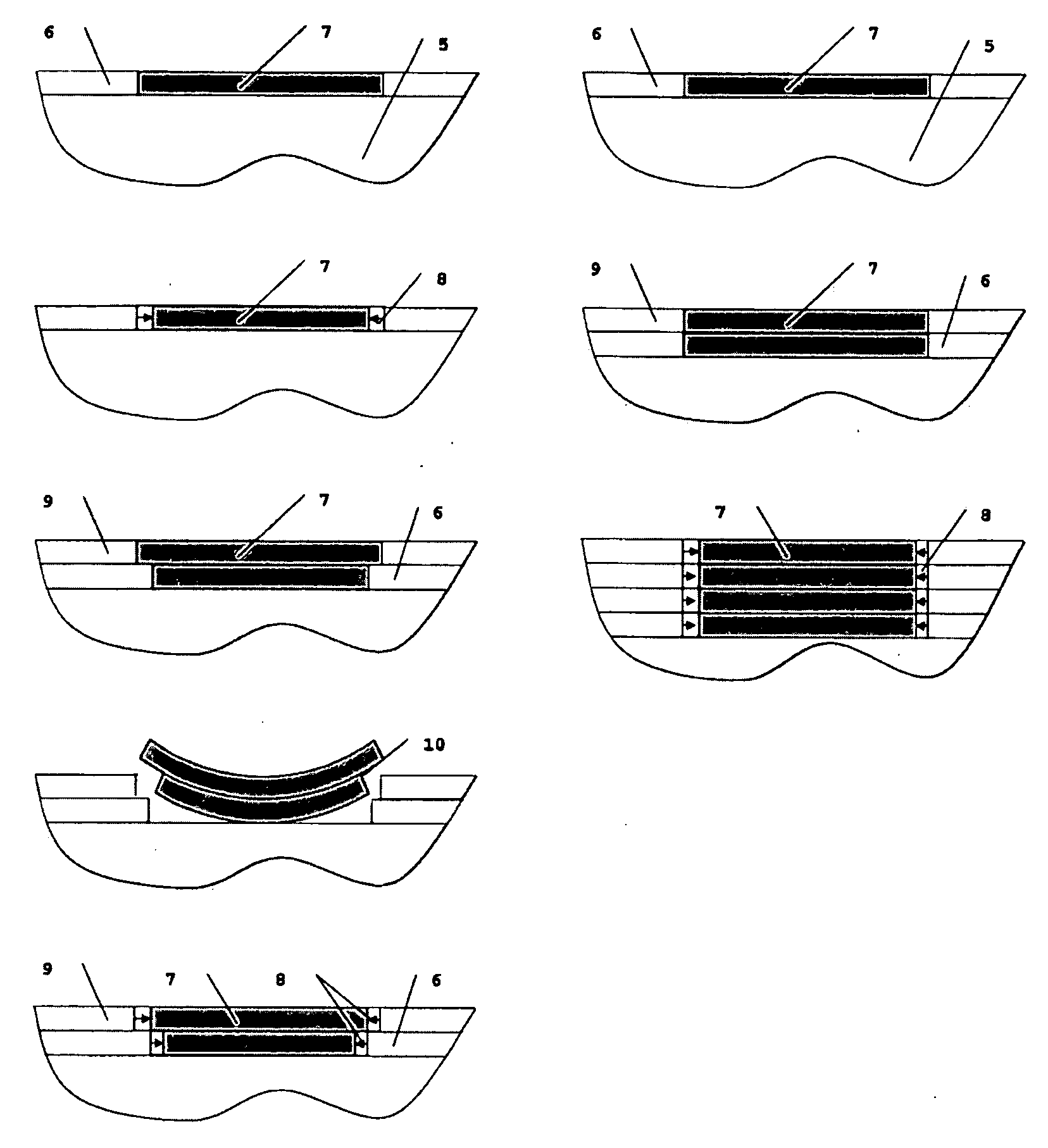

Herd management technology

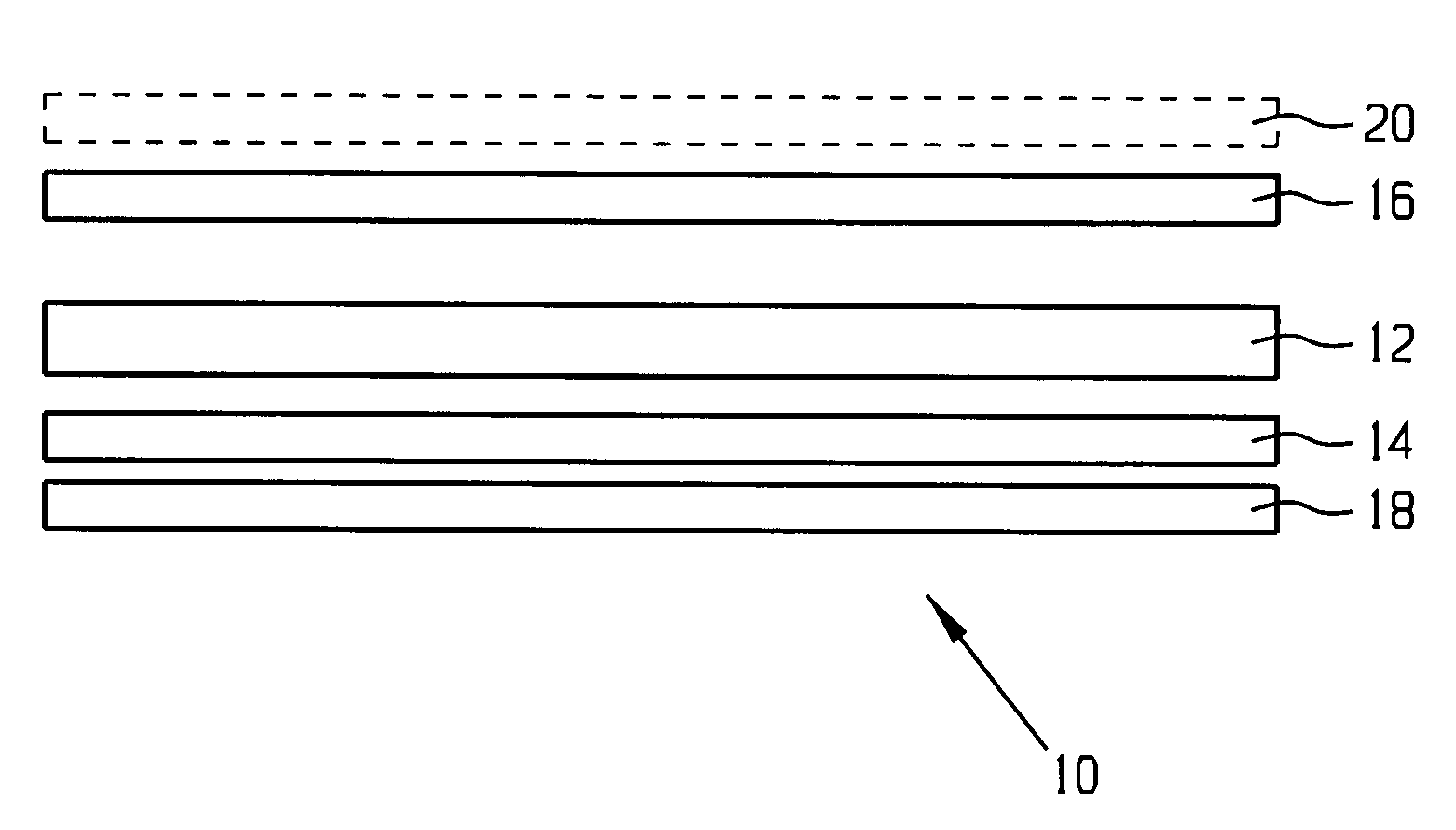

ActiveUS20080110406A1Practical and reliable and accurate and efficientSimple methodAnimal reproductionSurgeryPregnancyEstrus Detection

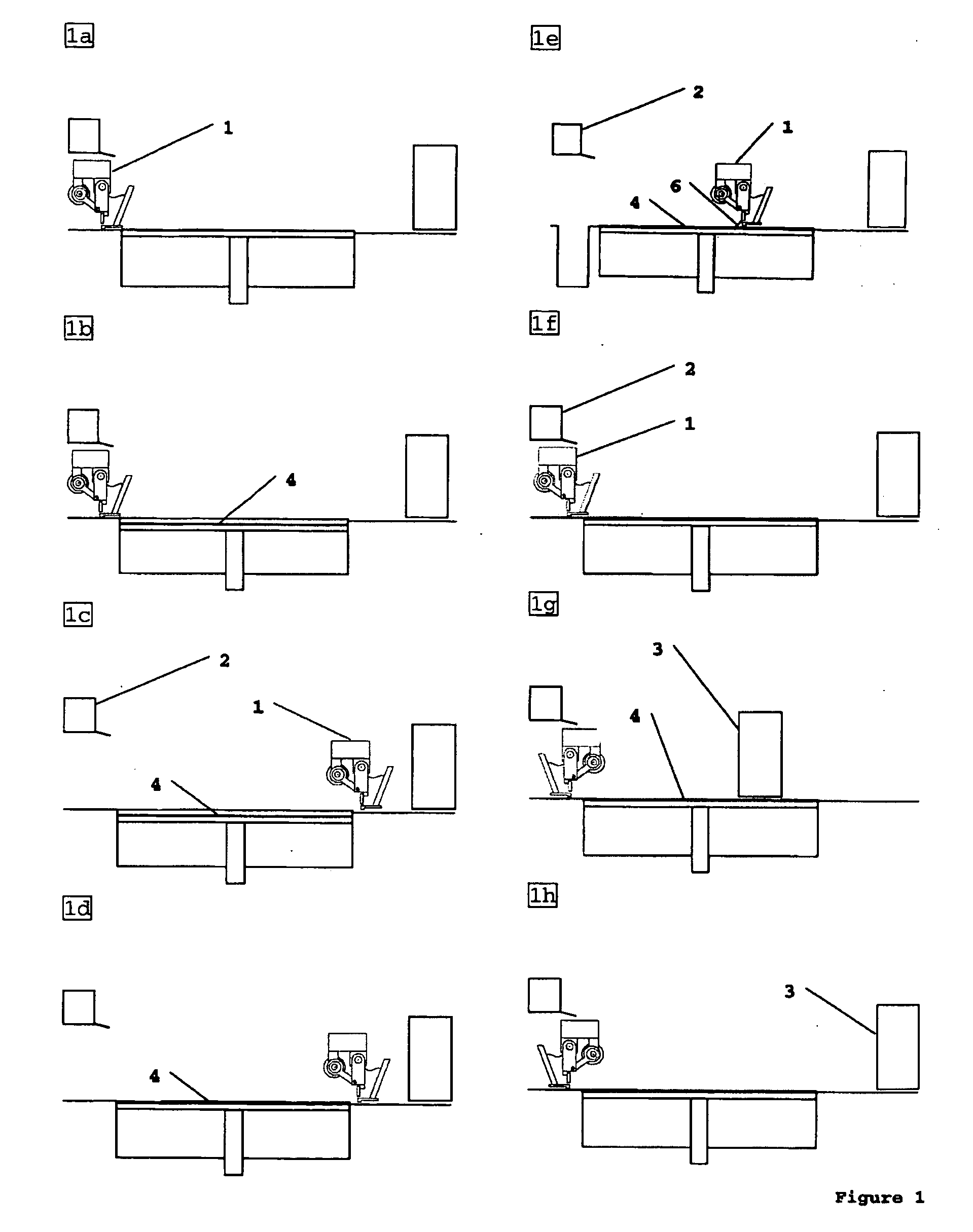

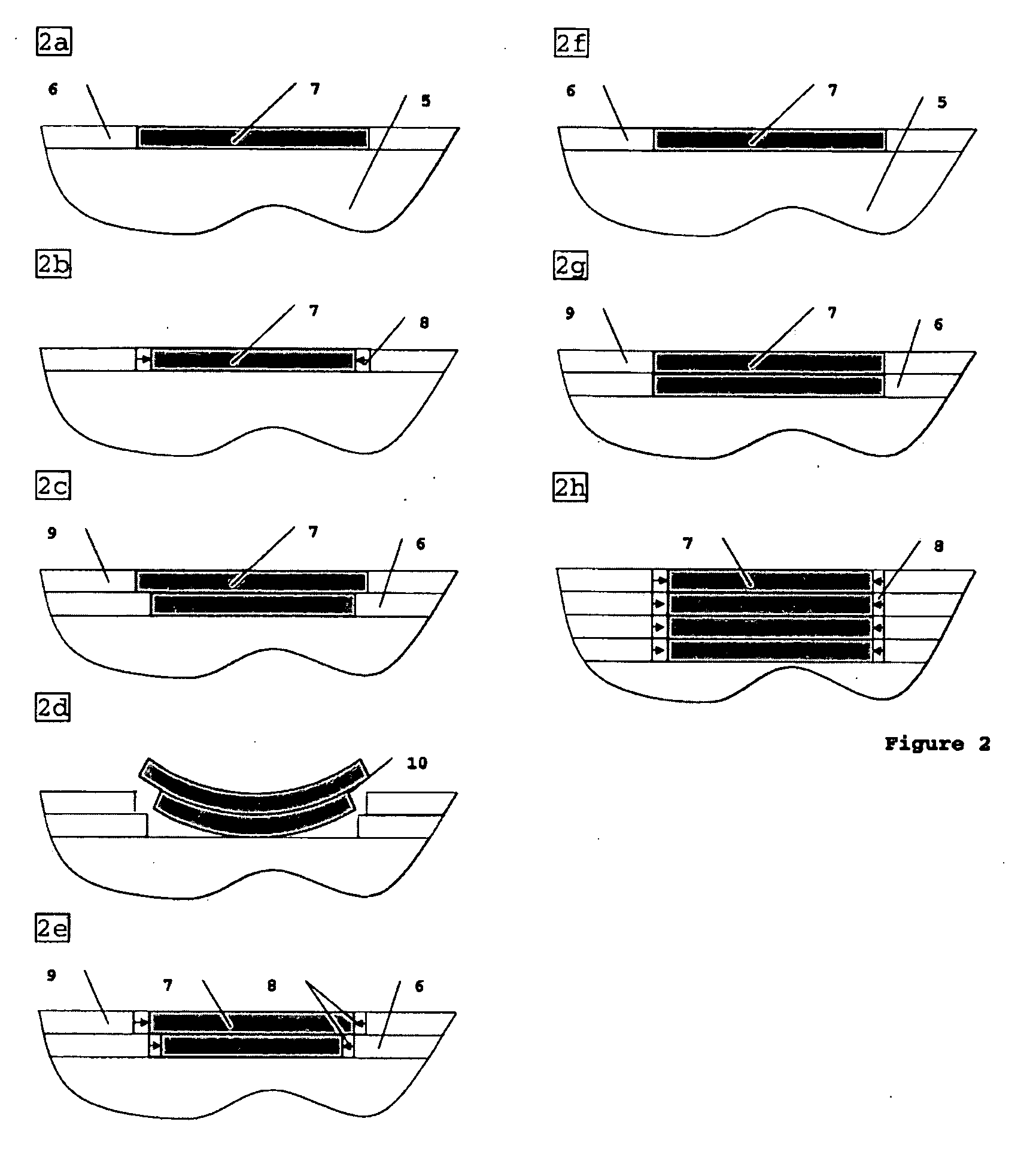

A method of determining breeding status in animals by (a) determining a breeding event (cyclicity, mounting, pregnancy, open) time, (b) providing an estrus or other breeding event detection apparatus, (c) affixing the estrus detection apparatus at a predetermined location on a female animal at a predetermined application time prior to the breeding event time, and (d) monitoring the estrus detection apparatus for activation thereof. An indicator apparatus is provided for use in indicating when an animal is in estrus. The apparatus is configured to be affixed to the rump of an animal to detect and indicate when the animal has been mounted and, thus, when the animal is in estrus. The apparatus is affixed to the animal by an adhesive layer. Layered on the top surface of the adhesive layer is an indicator layer that is in turn covered with a floodcoat layer. The floodcoat layer is adapted for removal upon the mounting of the first animal by a second animal. Removal of the floodcoat layer exposes the indicator layer indicating that the first animal has been mounted, thereby indicating that the first animal is in heat. The floodcoat layer is highly visible and may be seen from a distance.

Owner:ANDERSON MARK

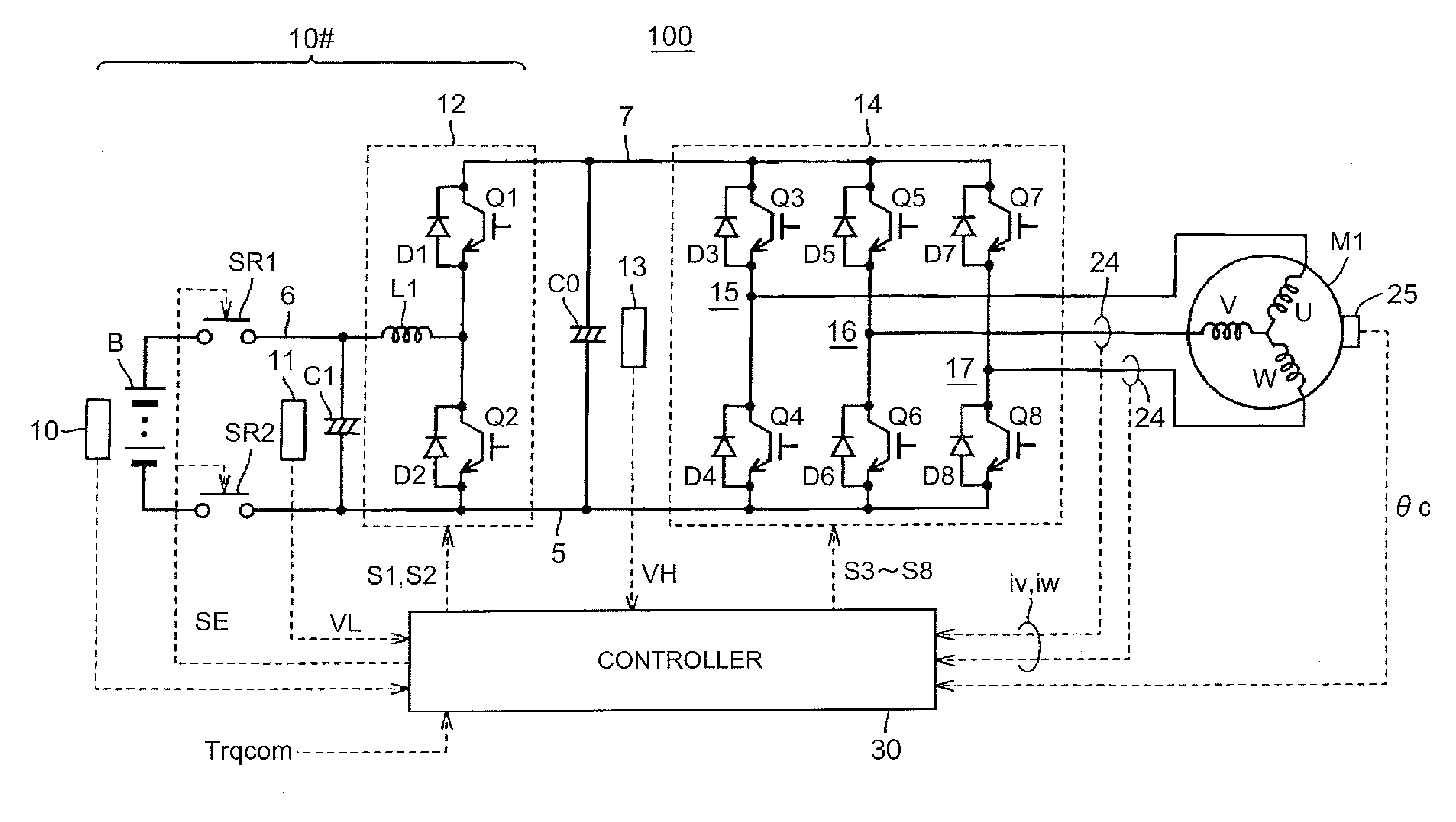

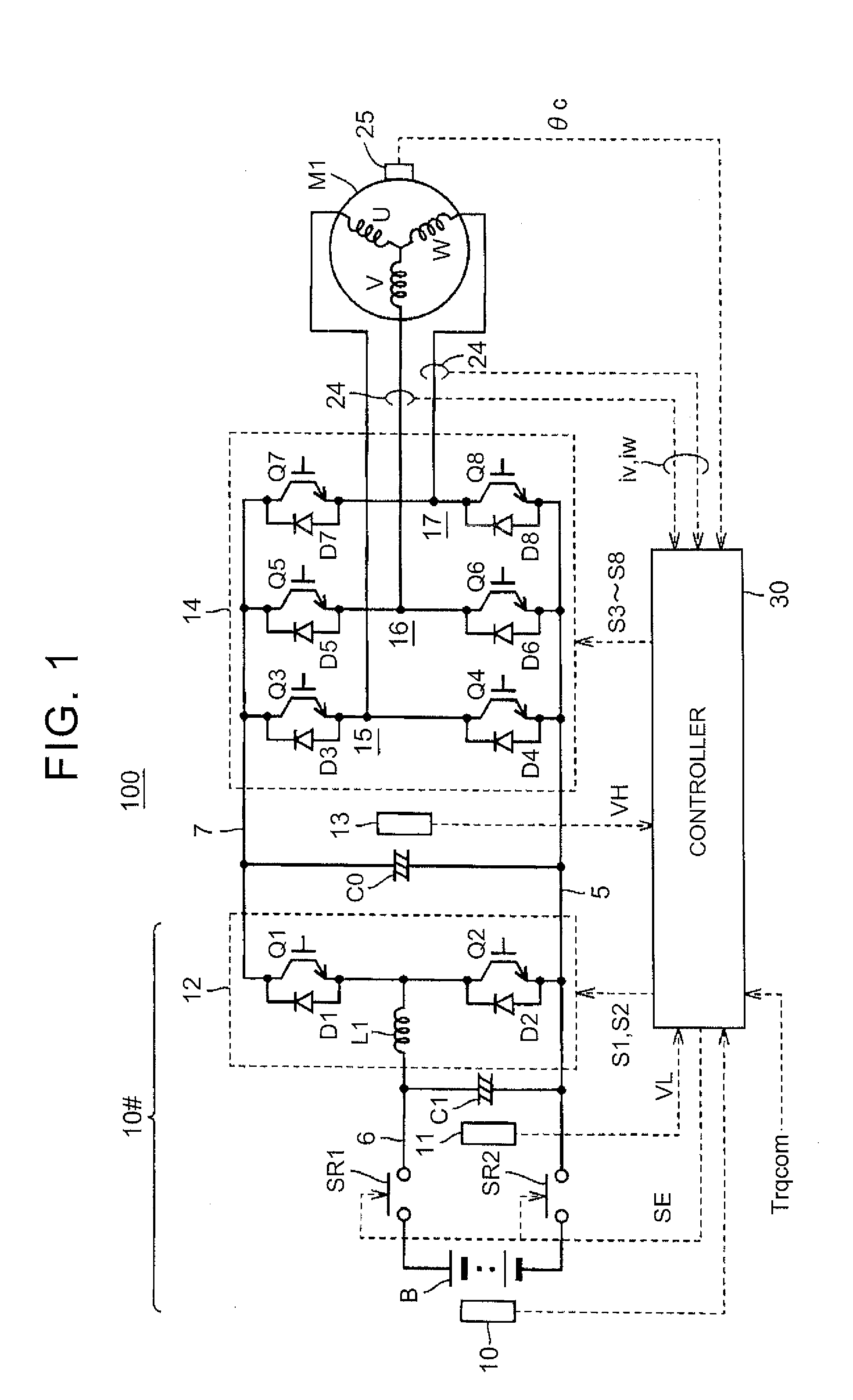

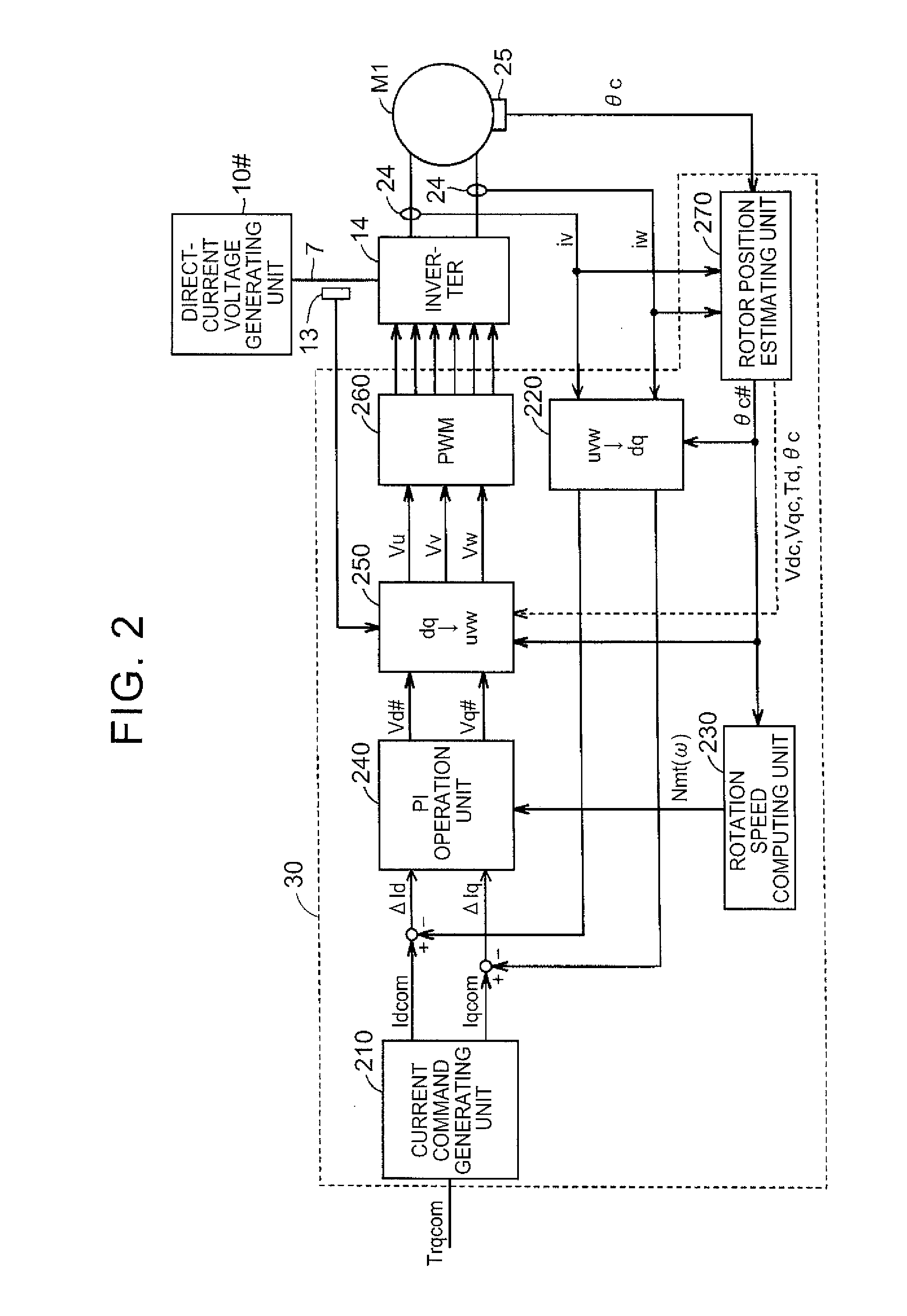

Rotor position estimating device, electric motor control system and rotor position estimating method

InactiveUS20140062353A1Accurate estimatePrecise positioningElectronic commutation motor controlMotor/generator/converter stoppersControl systemEngineering

A rotor position estimating device includes a voltage application unit, a current detecting unit and an estimating unit. The voltage application unit is configured to apply a d-axis voltage to an electric motor including a salient-pole rotor during a stop of the electric motor. The current detecting unit is configured to detect a q-axis current flowing through the electric motor at the time when the d-axis voltage is applied. The estimating unit is configured to estimate a rotor position during a stop of the electric motor on the basis of the q-axis current detected by the current detecting unit. The voltage application unit is configured to set a voltage application time in correspondence with peak timing at which the q-axis current reaches a peak in a transitional response characteristic of the q-axis current at the time when the d-axis voltage is applied.

Owner:TOYOTA JIDOSHA KK

Method for catalyst coating of a substrate

InactiveUS7521087B2Easy to controlControl thicknessPretreated surfacesCatalyst activation/preparationSlurryApplication time

A catalyst composition is applied to an interior of a hollow substrate. The composition is coated on the substrate by immersing the substrate into a vessel containing a bath of coating slurry. A vacuum is then applied to the partially immersed substrate. The intensity of the vacuum and its application time is sufficient to draw the coating slurry upwardly from the bath into each of a plurality of channels located in the interior of the hollow substrate. After removing the substrate from the bath, it is rotated 180°. A blast of pressurized air is applied at an intensity and for a time sufficient to distribute the coating slurry within the channels of the substrate to form a uniform coating profile therein.

Owner:BASF CATALYSTS LLC

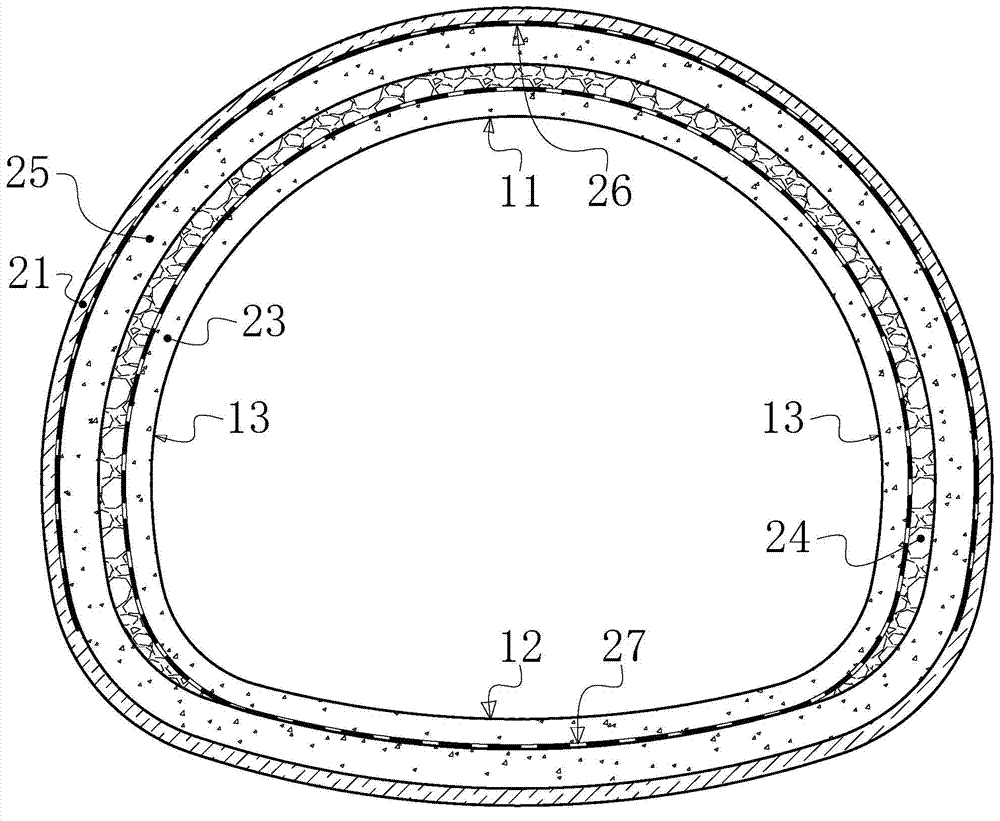

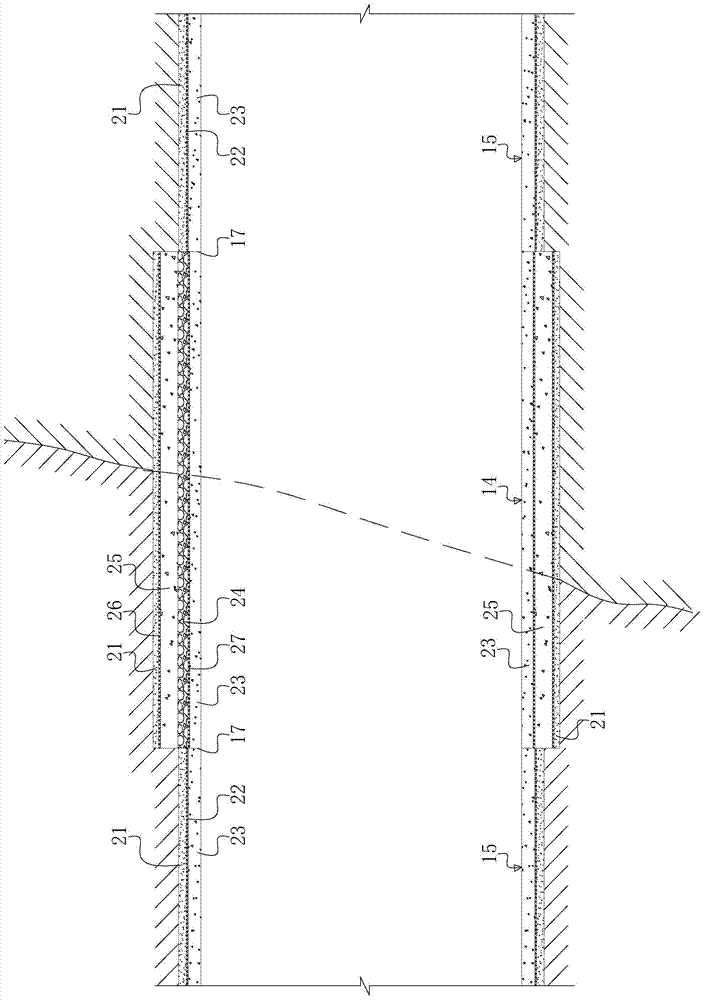

Tunnel supporting structure across active fault

ActiveCN103485796AOvercoming the problem of timing of applicationConstruction safetyUnderground chambersTunnel liningActive faultFoam concrete

The invention relates to a tunnel supporting structure, and in particular to a tunnel supporting structure across an active fault. The tunnel supporting structure comprises a fault across section and common supporting sections connected with the two ends of the tunnel supporting structure, wherein the common supporting sections adopt combined lining structures; the fault across section is orderly provided with a secondary lining, a foam concrete layer, a primary lining, a first waterproof layer and a preliminary support from inside to outside along the radial direction of the tunnel; the primary support, the first waterproof layer and the primary lining form the combined lining structure. The tunnel supporting structure is capable of overcoming the problem of application time selection, and is safe and convenient to construct. The primary lining is capable of partially bearing stress generated by the fault due to creep; in the meantime, the foam concrete is capable of providing a displacement space and absorbing energy; finally, the secondary lining is used for forming safety stock of the structure and ensuring that the clearance is not affected by fault movement; the tunnel supporting structure is high in safety storage, and has excellent shock resistance and excellent ability of resisting damage caused by fault creep and fault movement.

Owner:SICHUAN DEPT OF TRANSPORTATION HIGHWAY PLANNING PROSPECTING & DESIGN RES INST

P-channel power mosfet

InactiveUS20110215399A1Reduce the degree of deteriorationImprove reliabilitySemiconductor devicesTest measurementEngineering

In characteristic test measurements of double-gate-in-trench p-channel power MOSFETs each having a p+ polysilicon gate electrode and a p+ field plate electrode in a trench, which were fabricated according to common design techniques, it has been found that, under conditions where a negative gate bias is applied continuously at high temperature with respect to the substrate, an absolute value of threshold voltage tends to increase steeply after the lapse of a certain period of stress application time. To solve this problem, the present invention provides a p-channel power MOSFET having an n-type polysilicon linear field plate electrode and an n-type polysilicon linear gate electrode in each trench part thereof.

Owner:RENESAS ELECTRONICS CORP