Patents

Literature

8960 results about "MOSFET" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The metal–oxide–semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), also known as the metal–oxide–silicon transistor (MOS transistor, or MOS), is a type of field-effect transistor that is fabricated by the controlled oxidation of a semiconductor, typically silicon. It has a covered gate, whose voltage determines the conductivity of the device. This ability to change conductivity with the amount of applied voltage can be used for amplifying or switching electronic signals. The MOSFET was invented by Egyptian engineer Mohamed M. Atalla and Korean engineer Dawon Kahng at Bell Labs in November 1959. It is the basic building block of modern electronics, and the most widely manufactured device in history, with an estimated total of 13 sextillion (1.3 × 10²²) MOSFETs manufactured between 1960 and 2018.

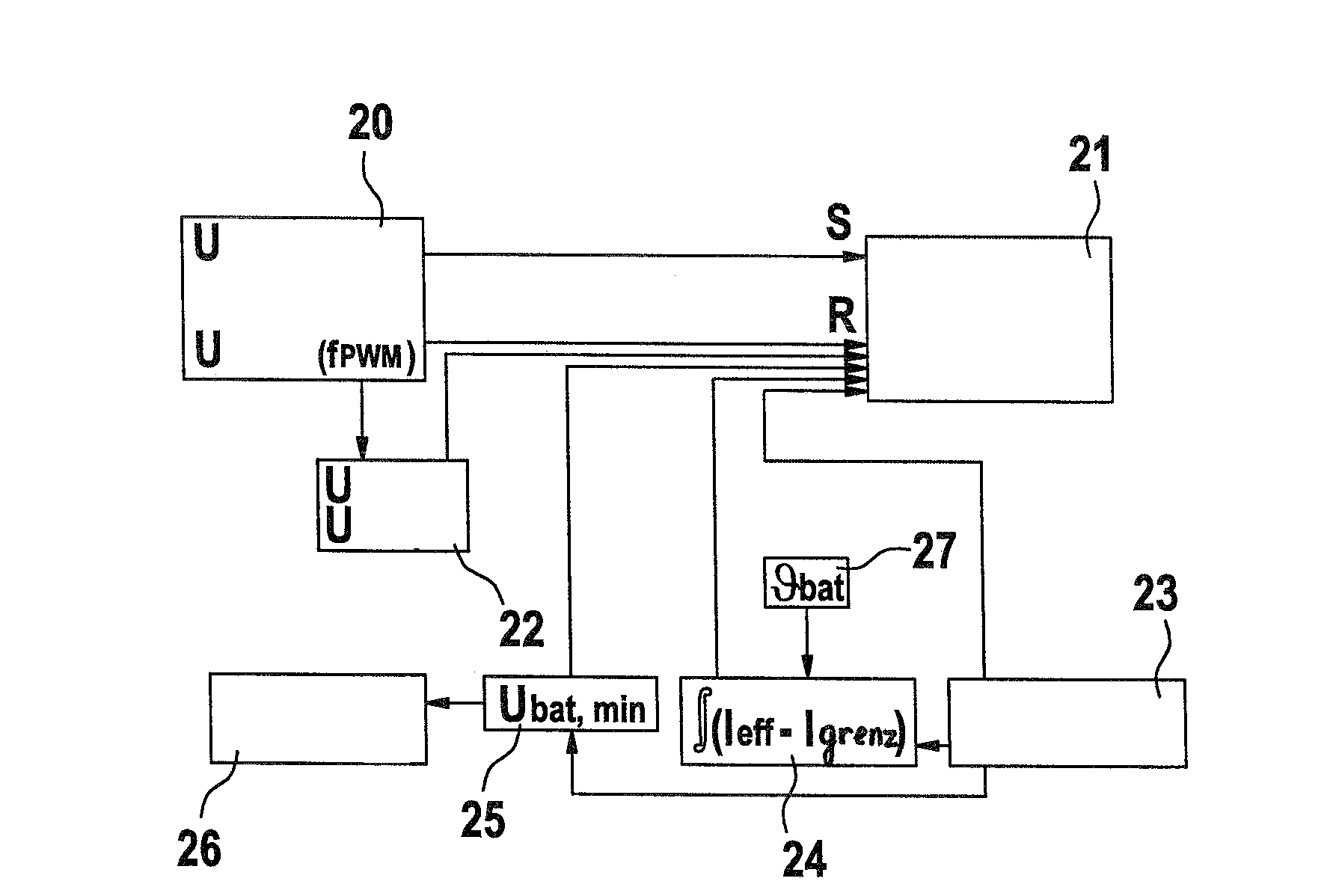

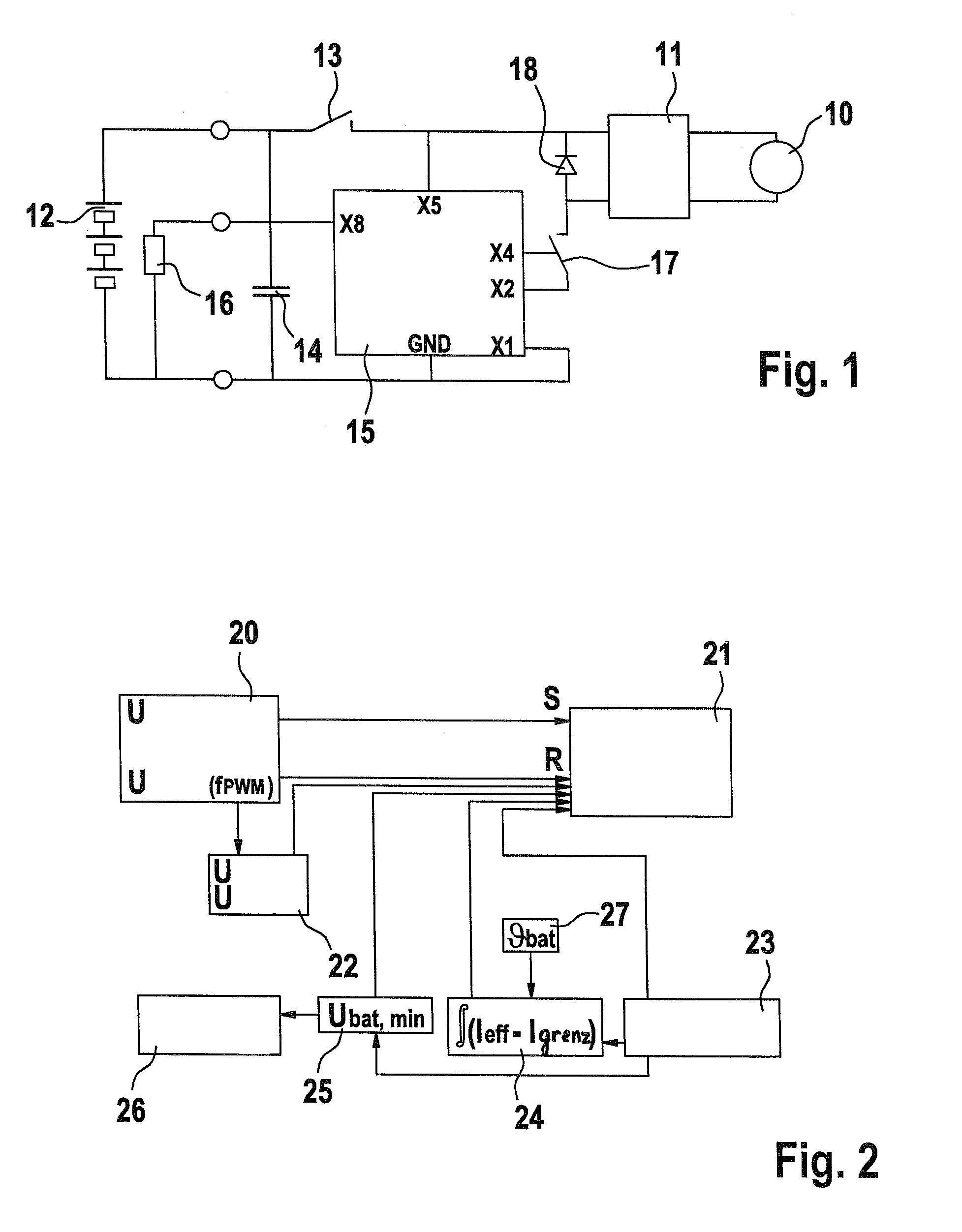

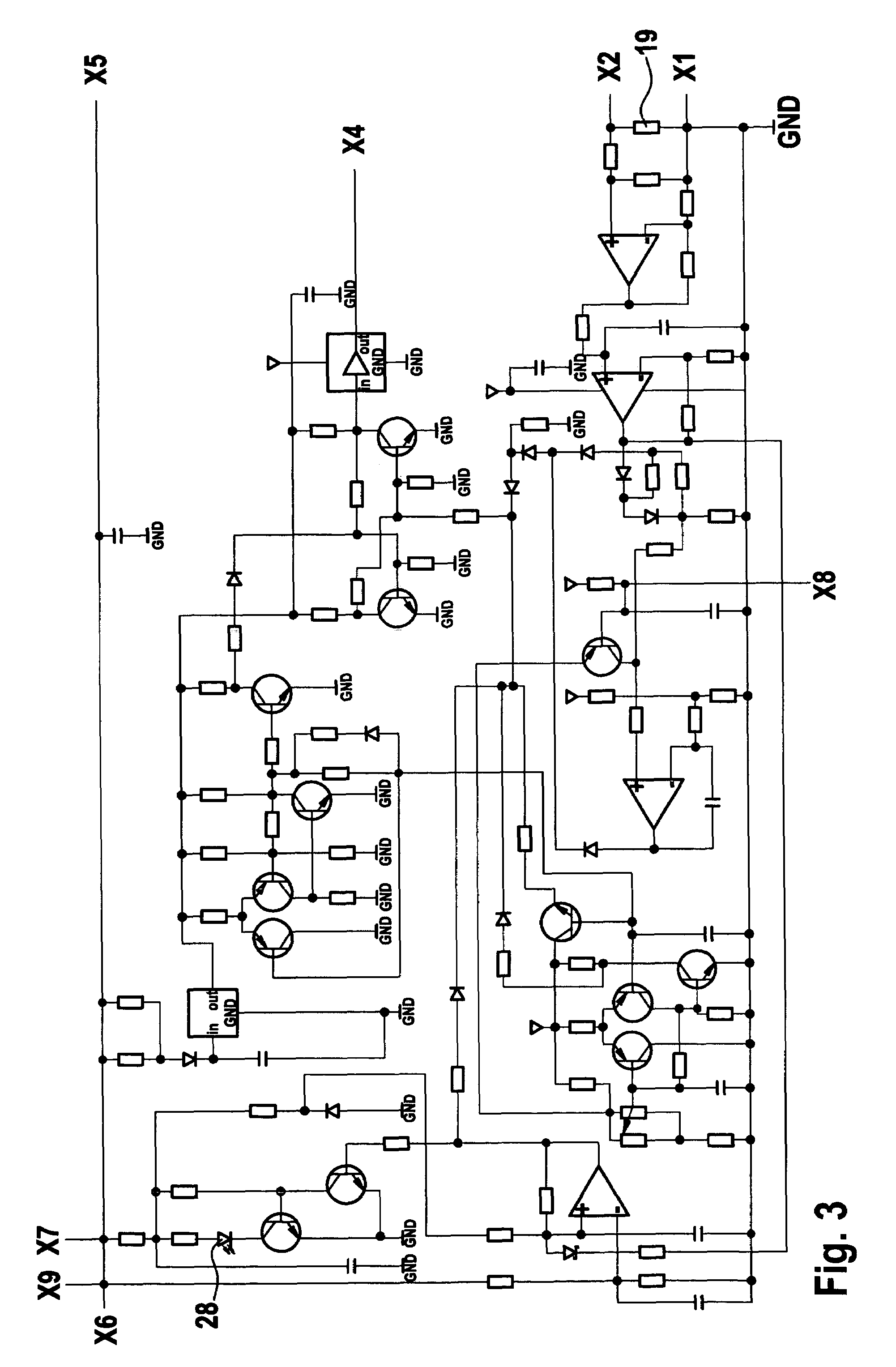

Method for operating a power tool

ActiveUS7336048B2Maintain good propertiesReduce widthTemperatue controlEmergency protective arrangements for automatic disconnectionMOSFETElectricity

In a method for operating a power tool with an energy accumulator, in particular a rechargeable energy accumulator, which supplies power to an electric drive motor, a clock frequency is generated by an electronic unit, with which a gate of a MOSFET—which supplies operating voltage to the drive motor—is switched on with each cycle, and a switching-off of the MOSFET is carried out within one cycle using different signals, as a function of operating parameters.

Owner:ROBERT BOSCH GMBH

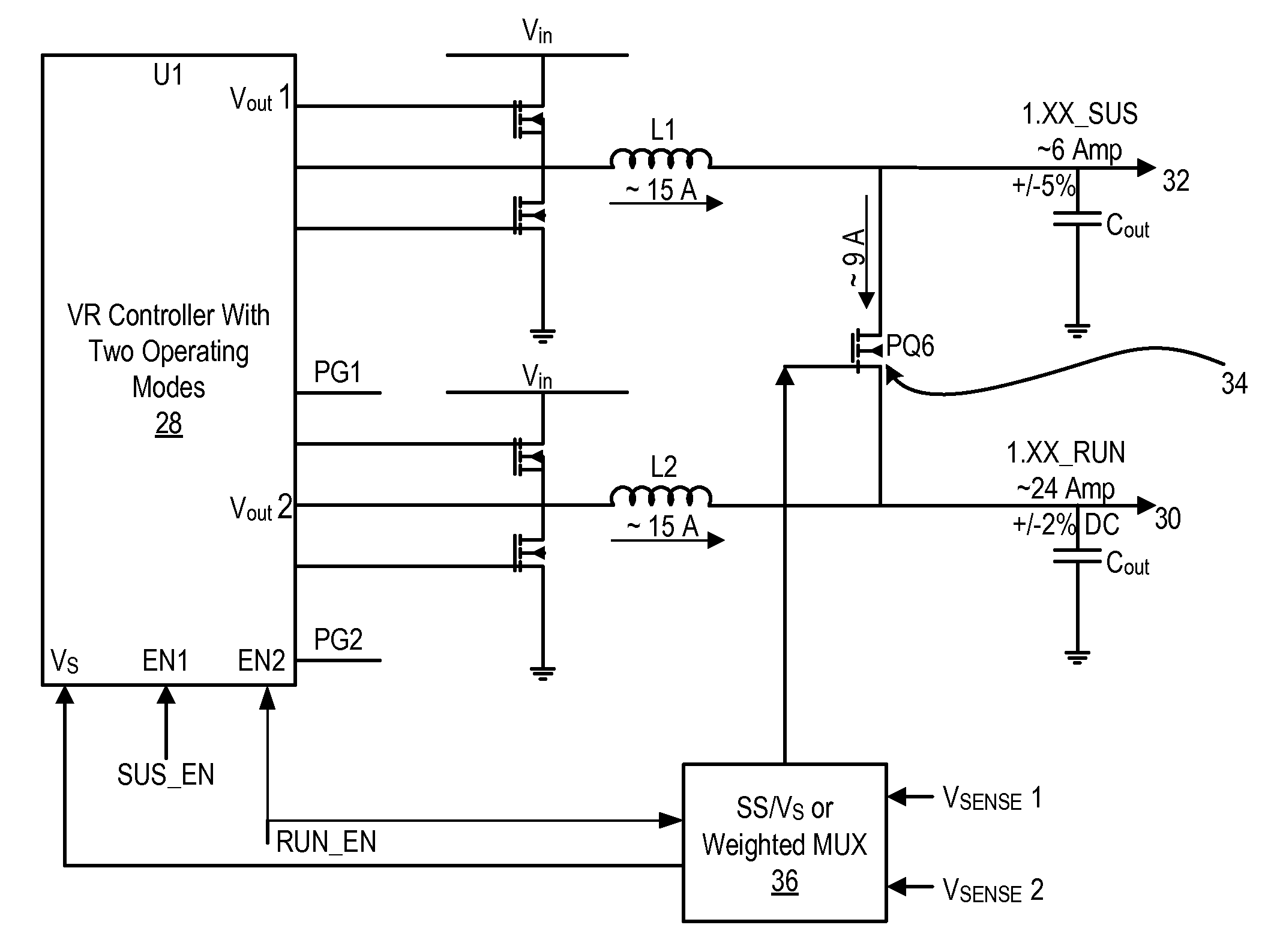

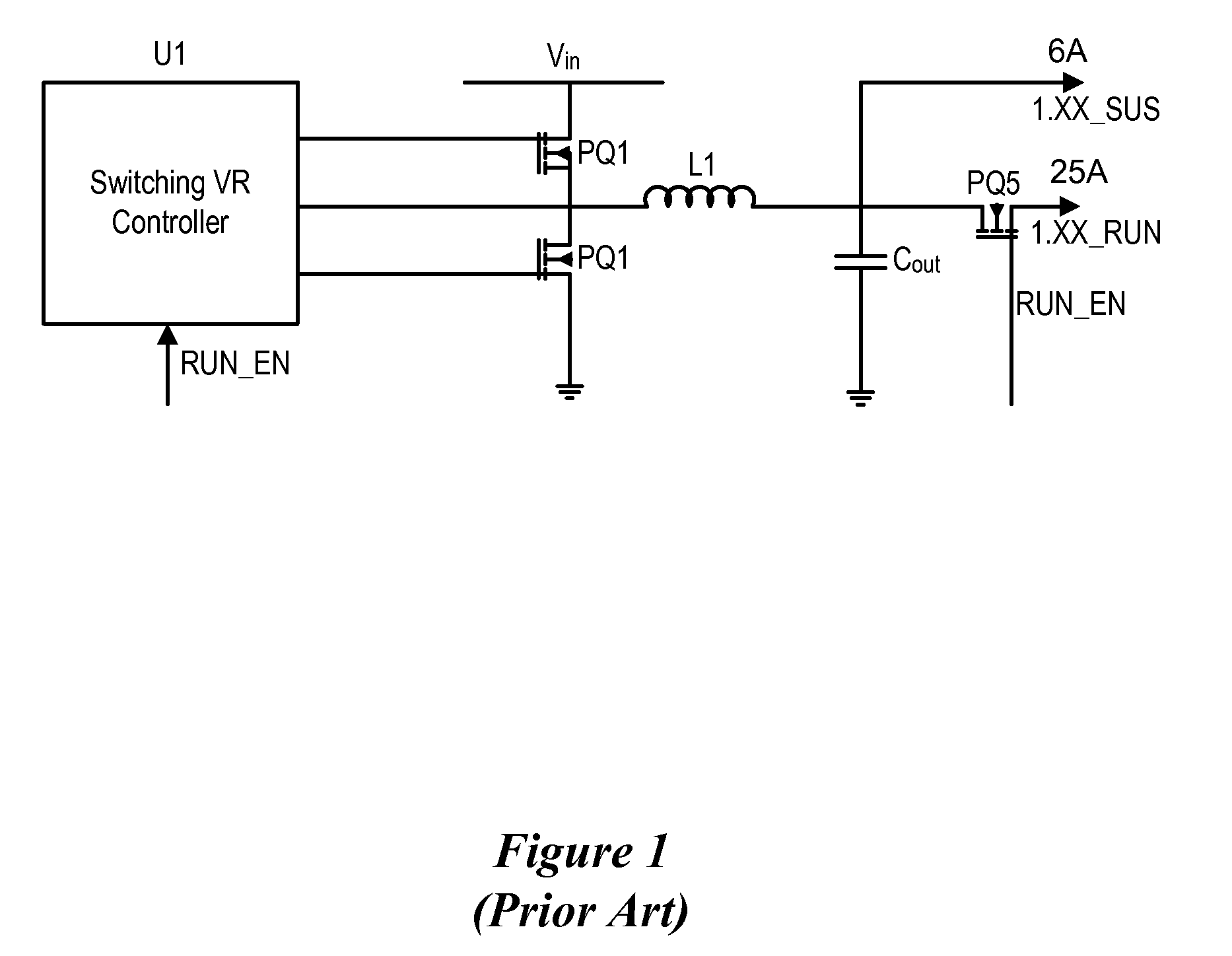

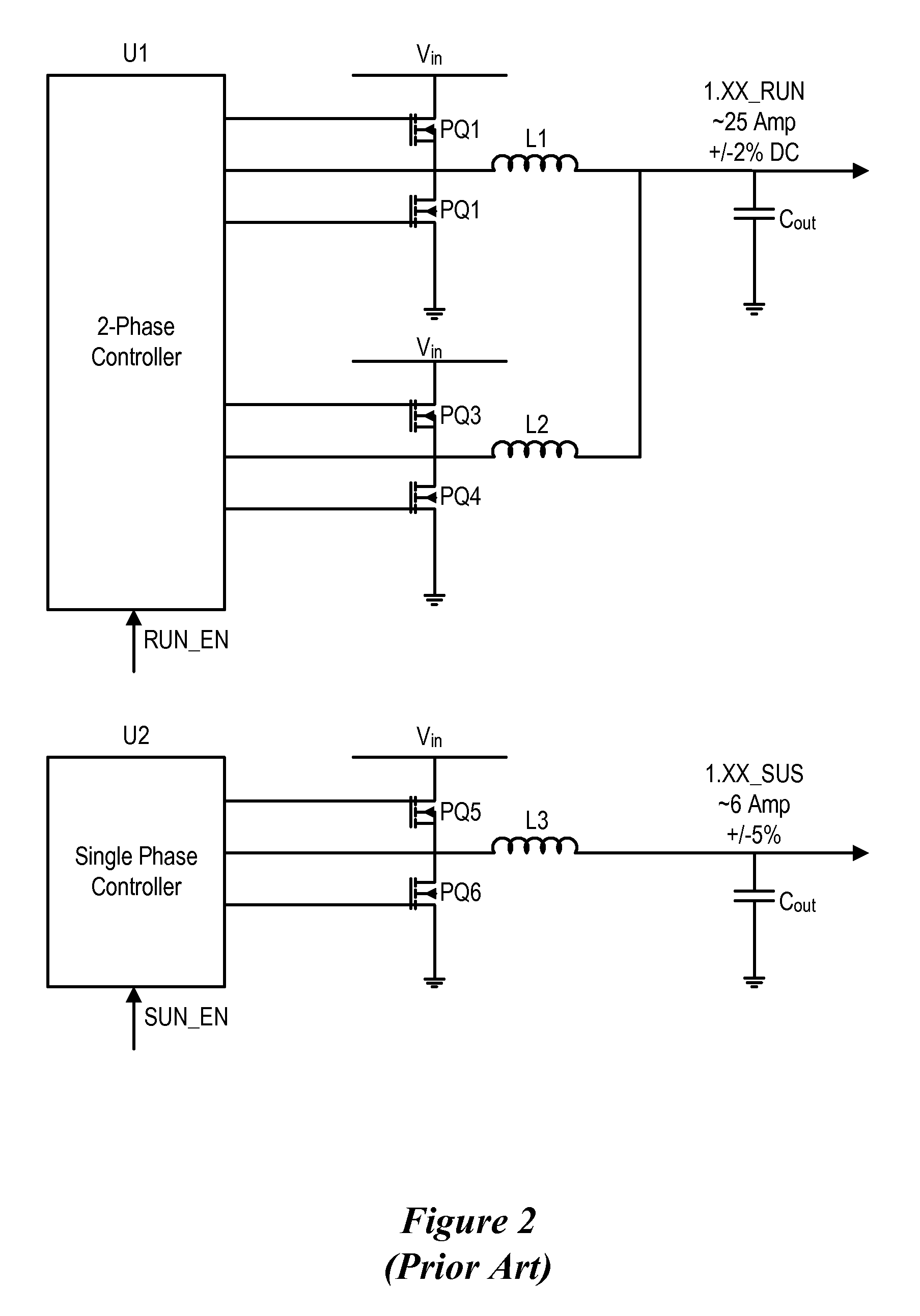

System and method for powering an information handling system in multiple power states

ActiveUS8063619B2Reduce disadvantagesReduce problemsElectric signal transmission systemsDc network circuit arrangementsMOSFETVoltage regulation

Power is supplied to an information handling system chipset with a single voltage regulator having dual phases. A first phase of the voltage regulator provides power to a low power state power rail in an independent mode to support a low power state, such as a suspend or hibernate state. A second phase of the voltage regulator provides power to a run power state power rail in combination with the first phase by activation of a switch, such as a MOSFET load switch, that connects the low power state power rail and the run power state power rail. Voltage sensed from both power rails is applied to control voltage output so that the run power state power rail is maintained within more precise constraints than the low power state power rail.

Owner:DELL PROD LP

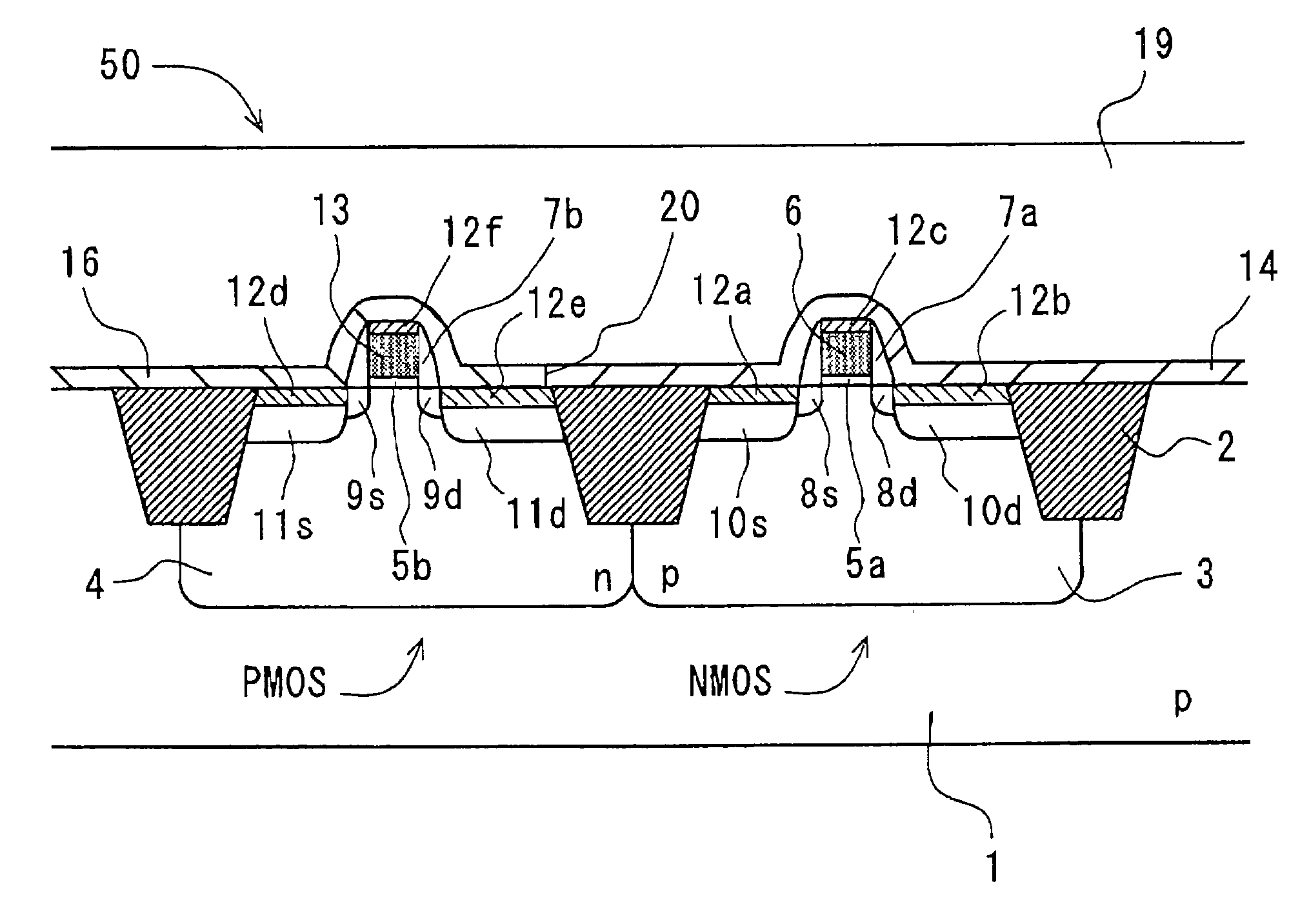

Semiconductor device and method of fabricating the same

InactiveUS20030040158A1TransistorSemiconductor/solid-state device manufacturingMOSFETElectron mobility

A semiconductor device improves the electron mobility in the n-channel MOSFET and reduces the bend or warp of the semiconductor substrate or wafer. The fist nitride layer having a tensile stress is formed on the substrate to cover the n-channel MOSFET. The tensile stress of the first nitride layer serves to relax a compressive stress existing in the channel region. The second nitride layer having an actual compressive stress is formed on the substrate to cover the p-channel MOSFET. The first and second nitride layers serve to decrease bend or warp of the substrate. Preferably, the first nitride layer is a nitride layer of Si formed by a LPCVD process, and the second nitride layer is a nitride layer of Si formed by a PECVD process.

Owner:NEC ELECTRONICS CORP

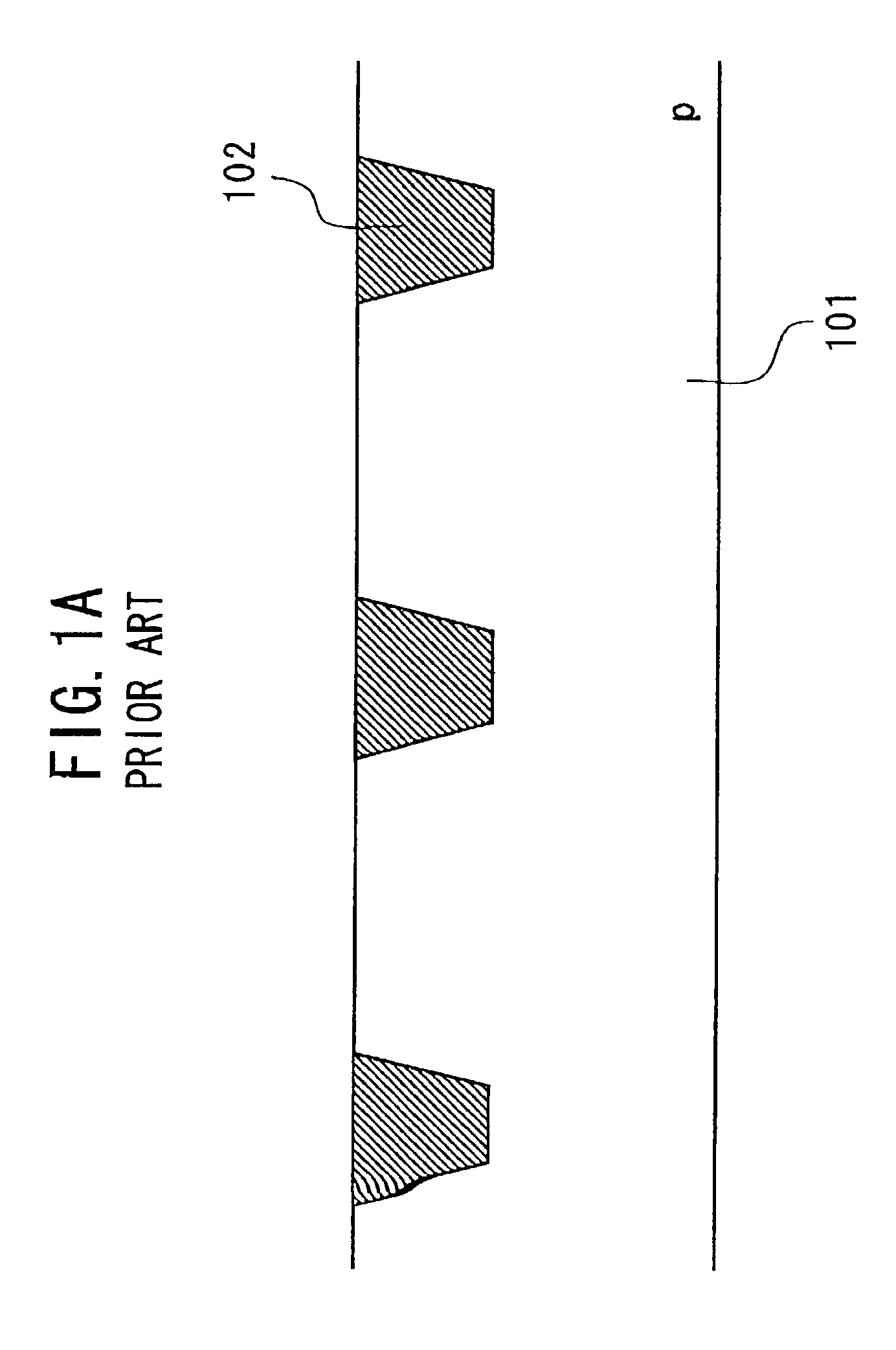

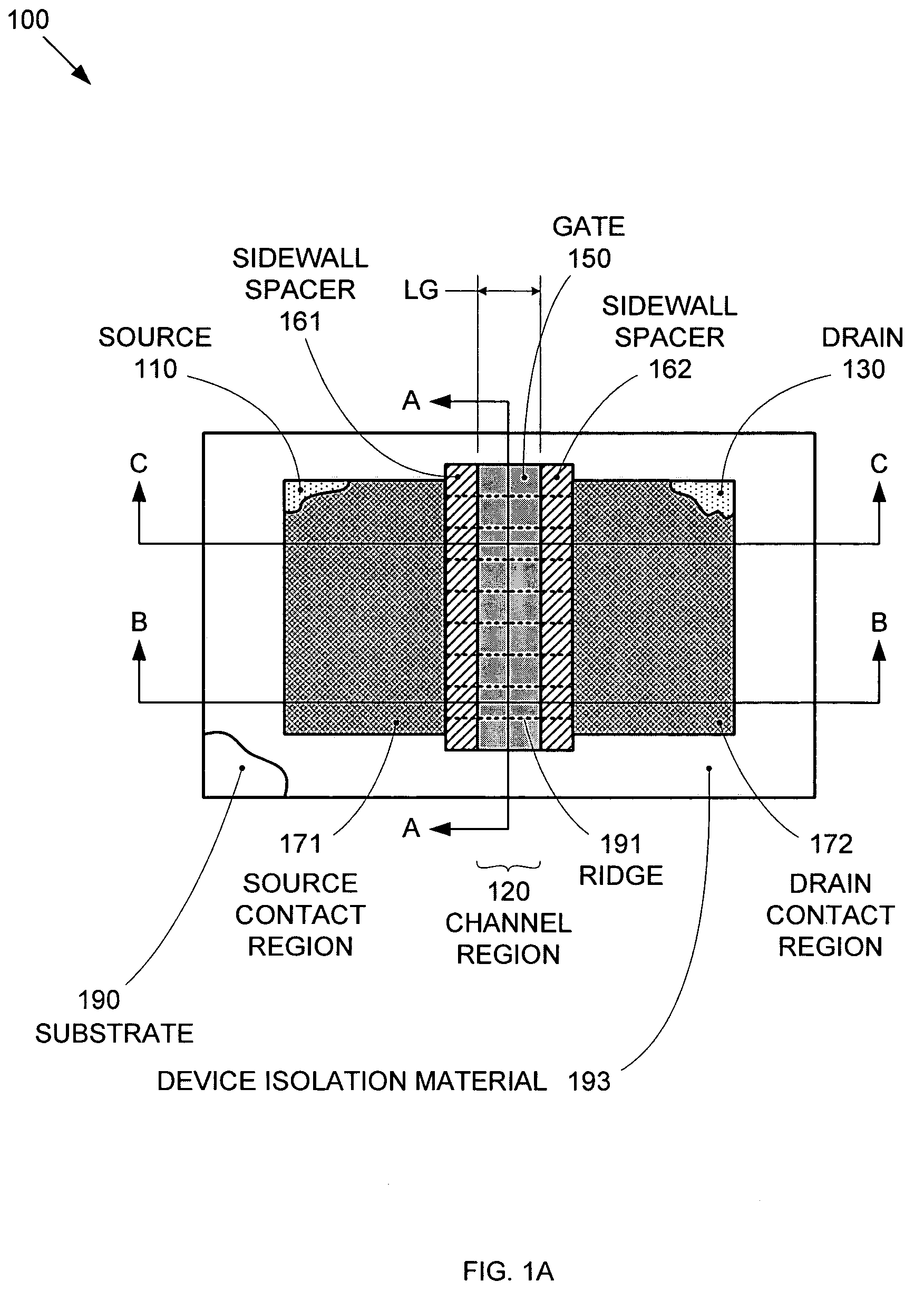

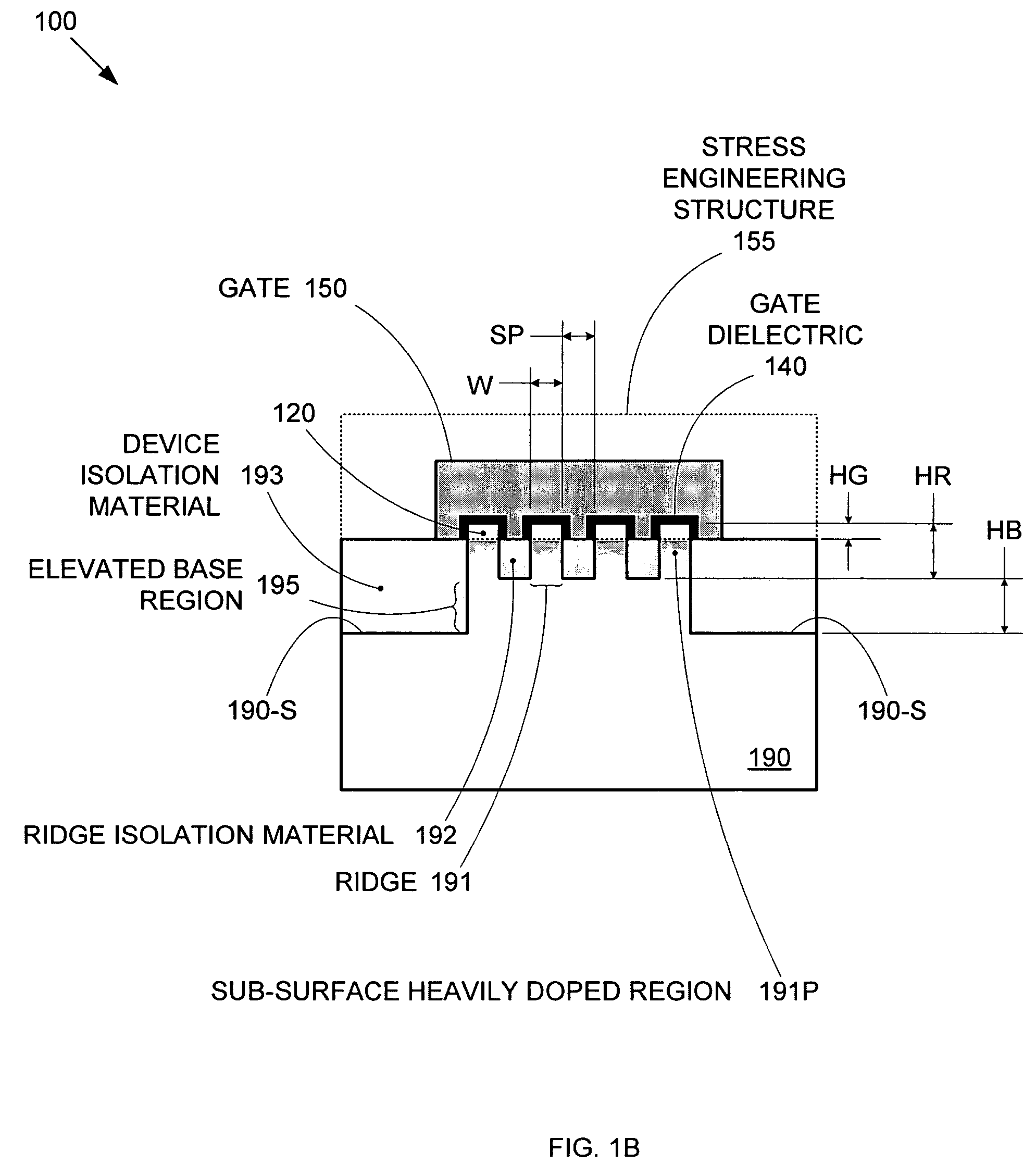

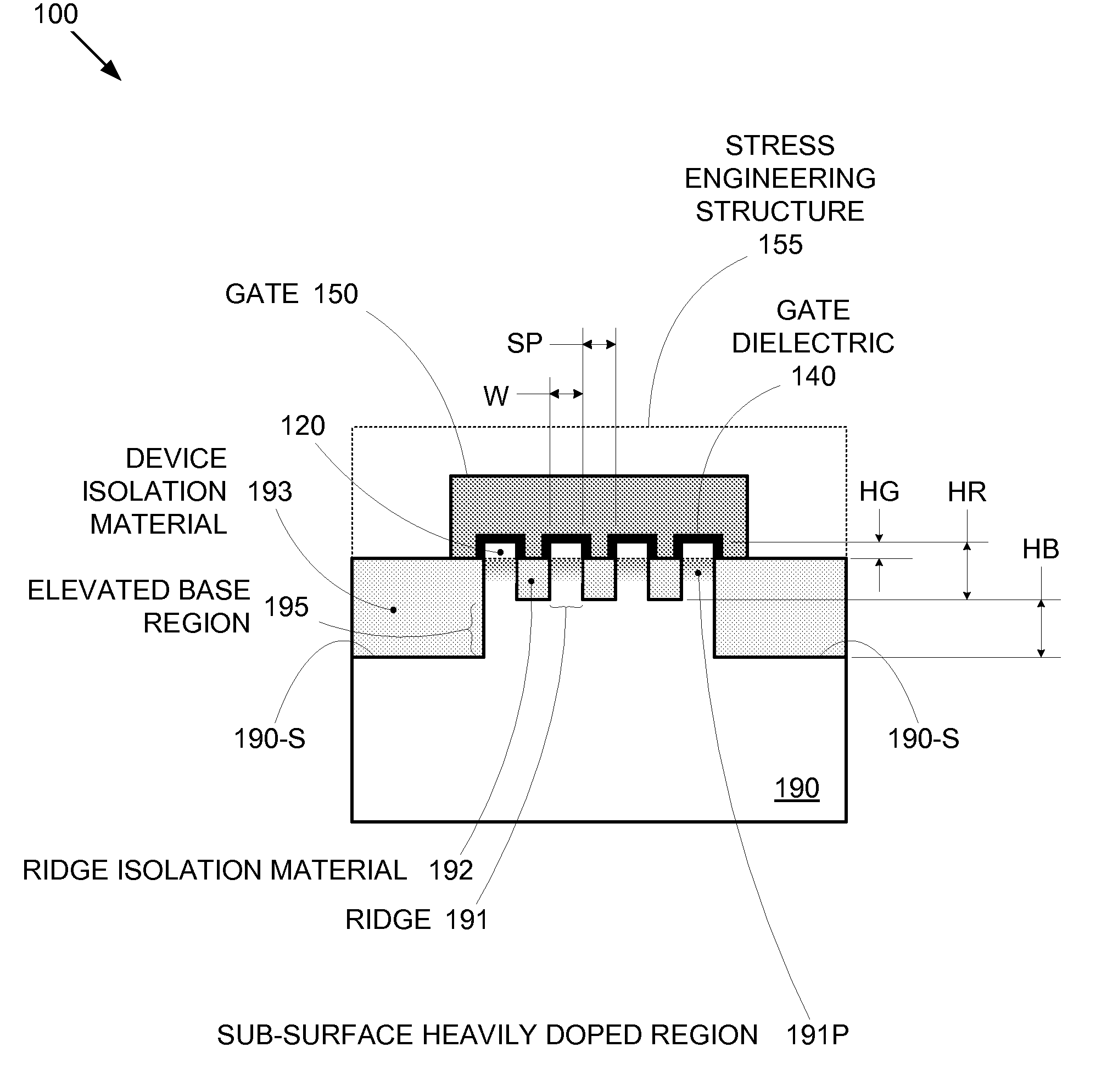

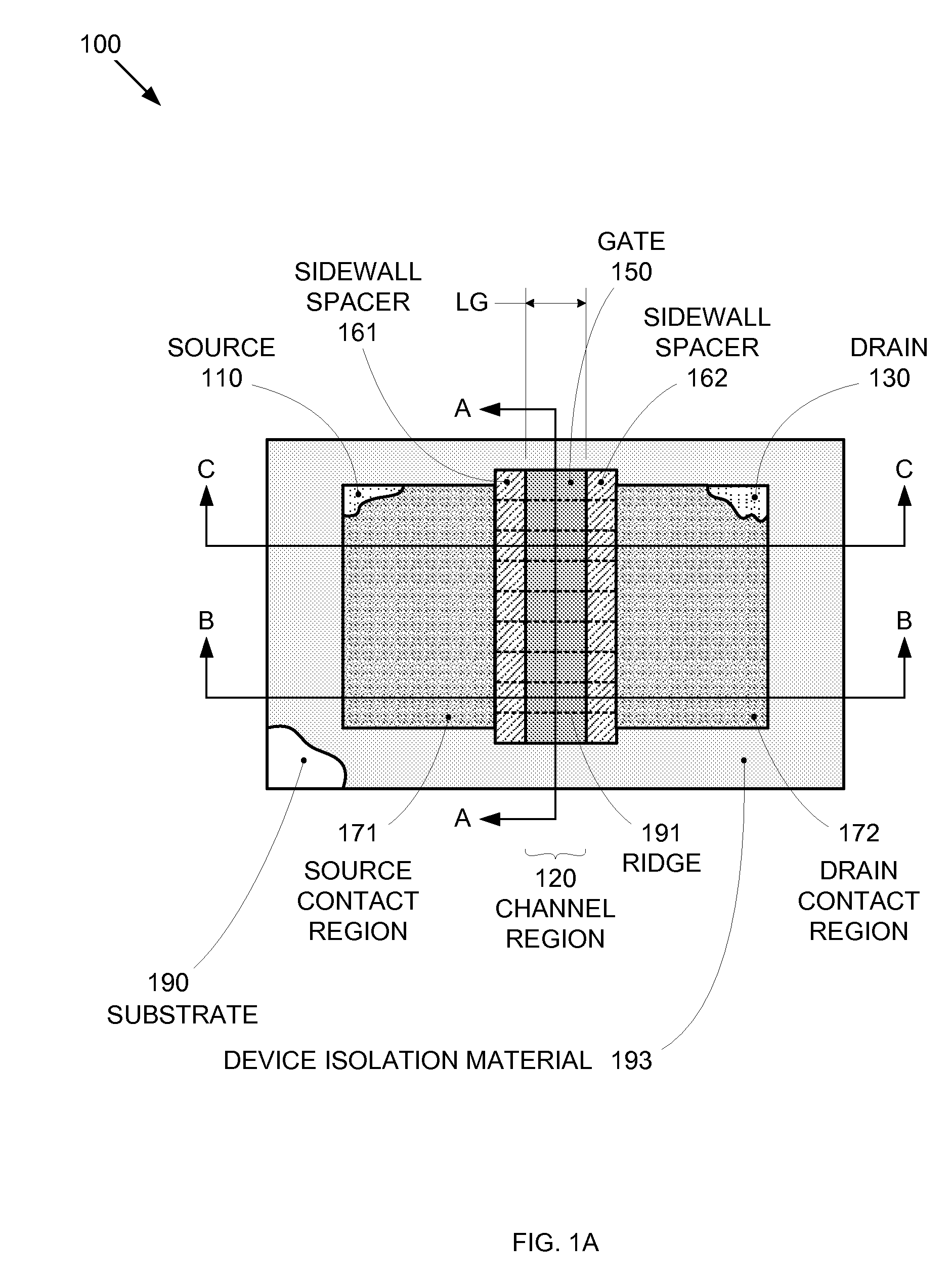

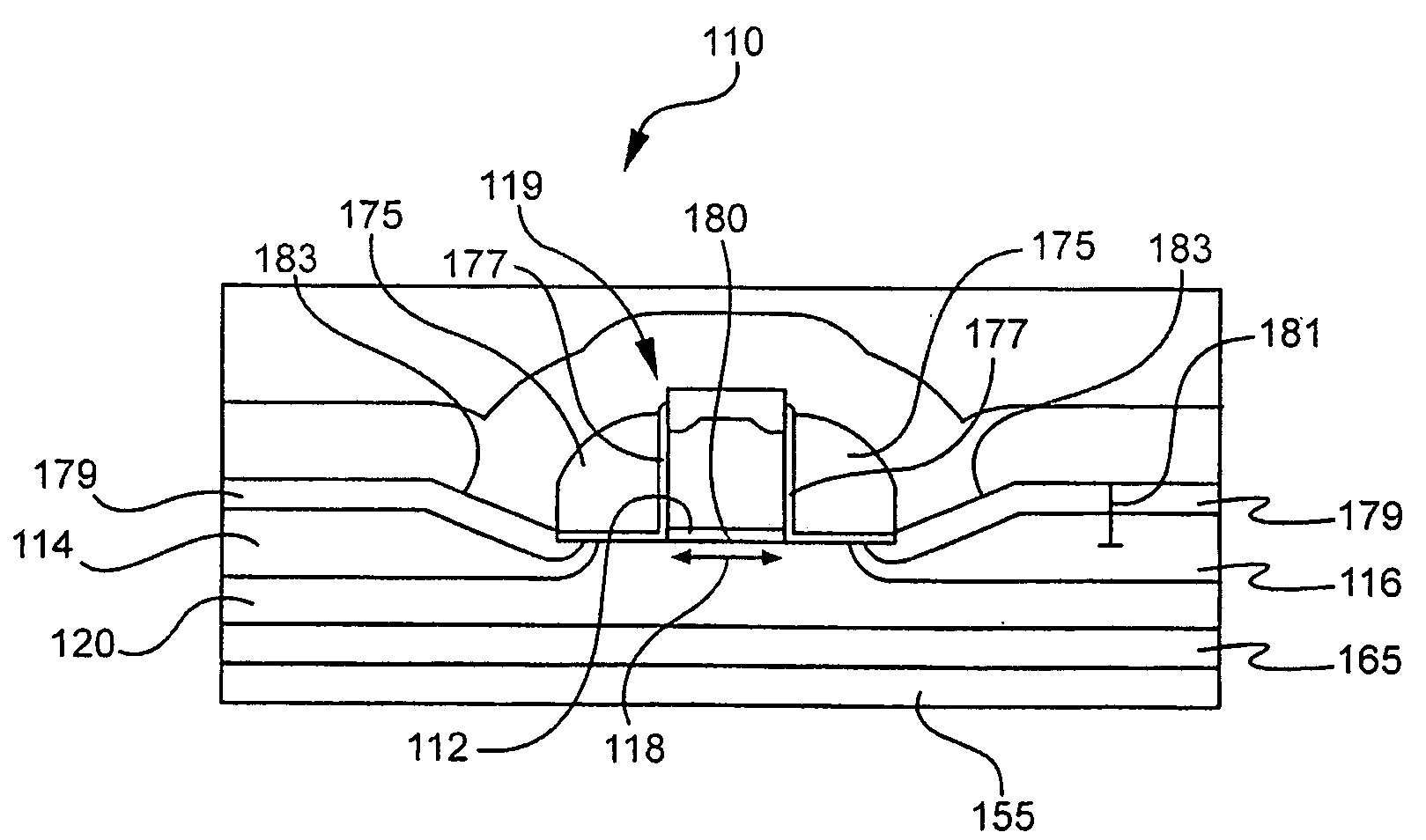

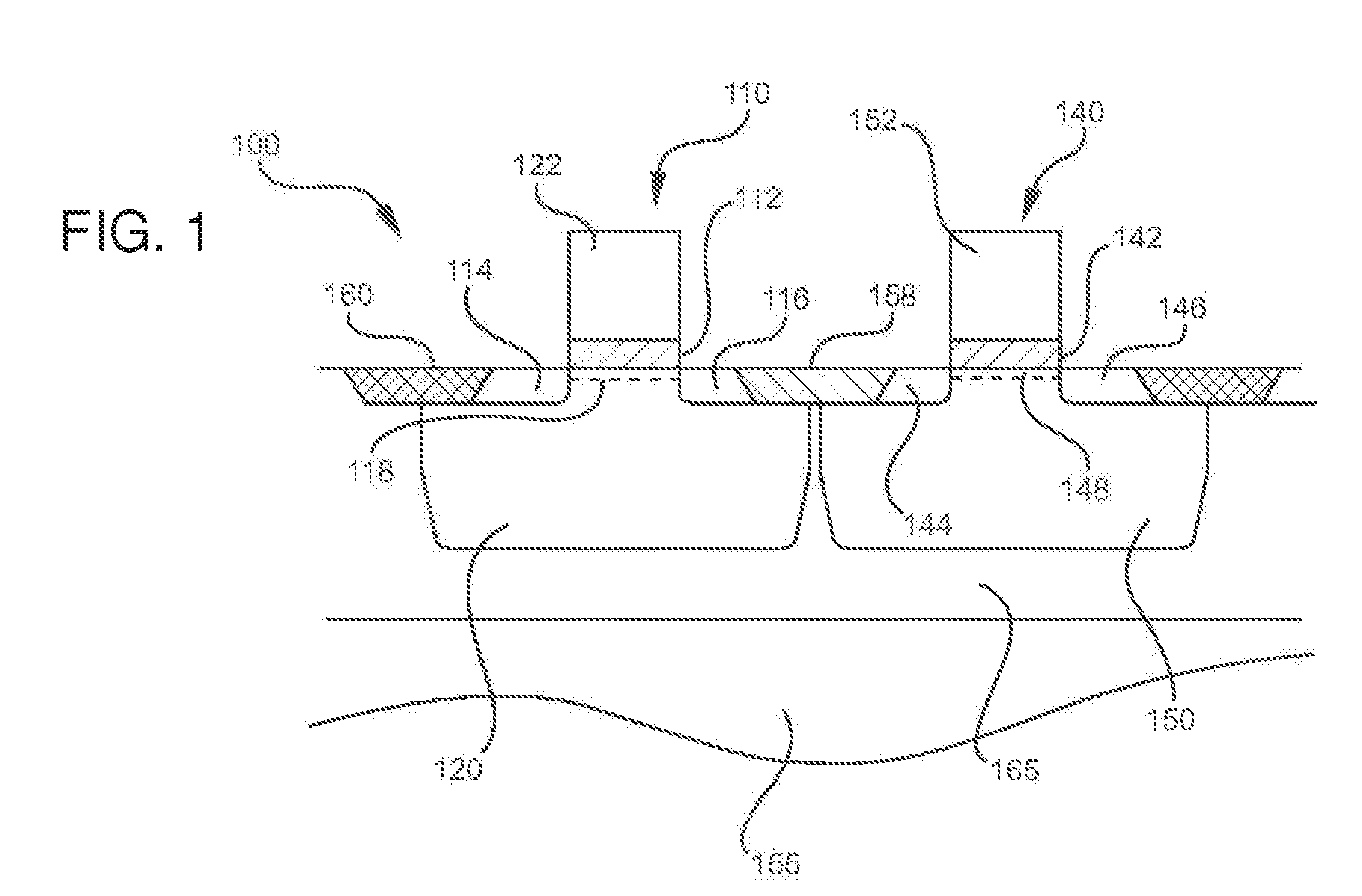

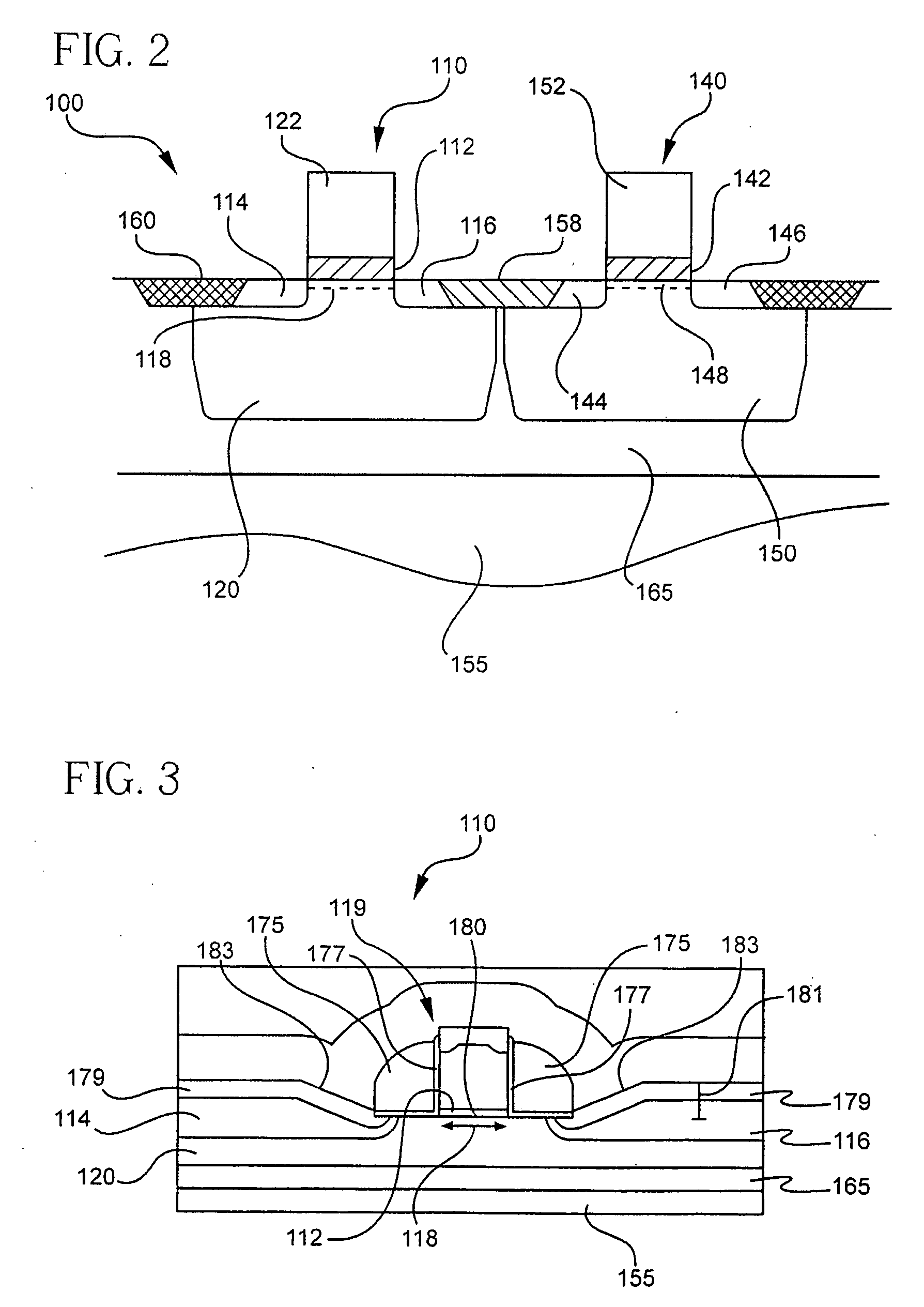

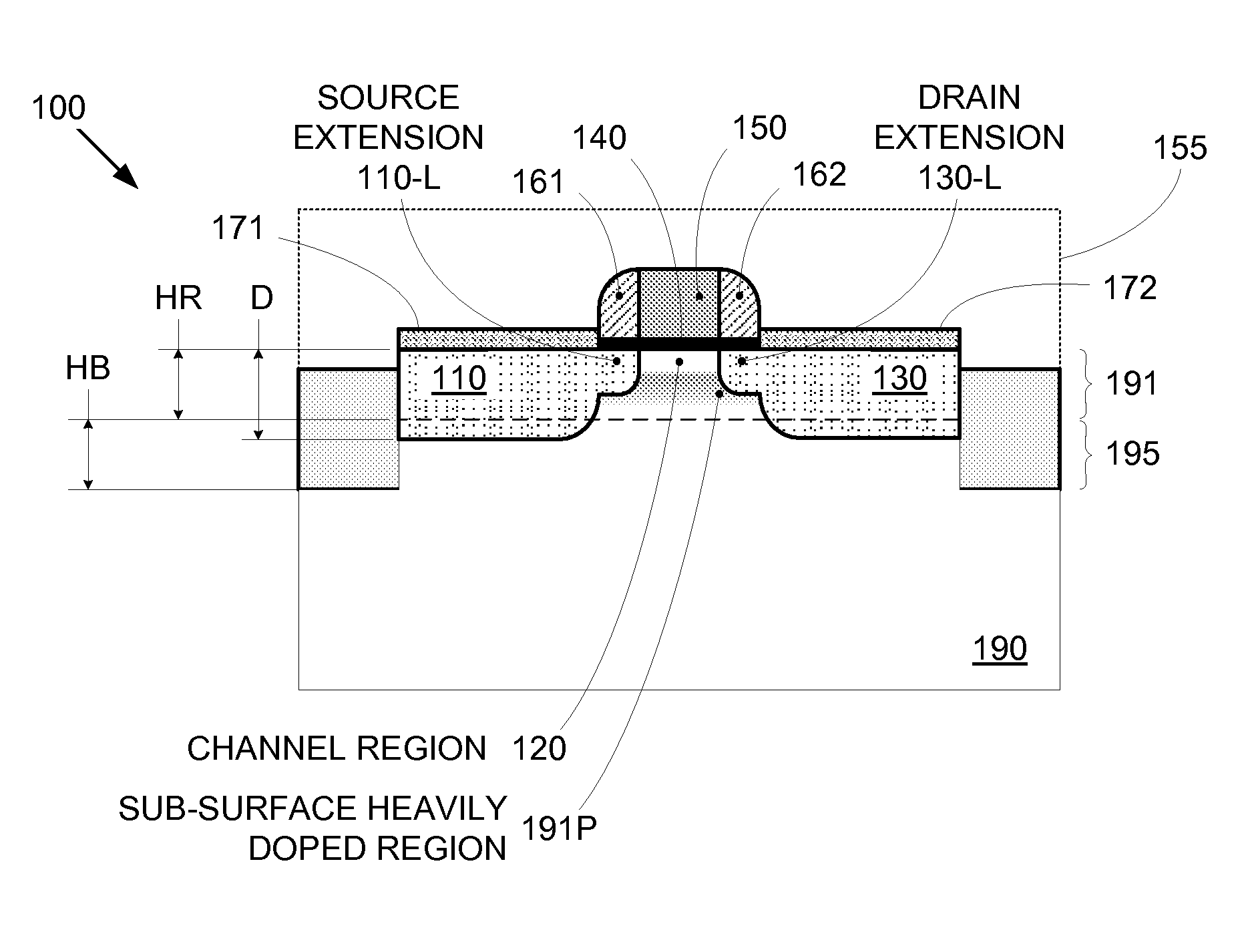

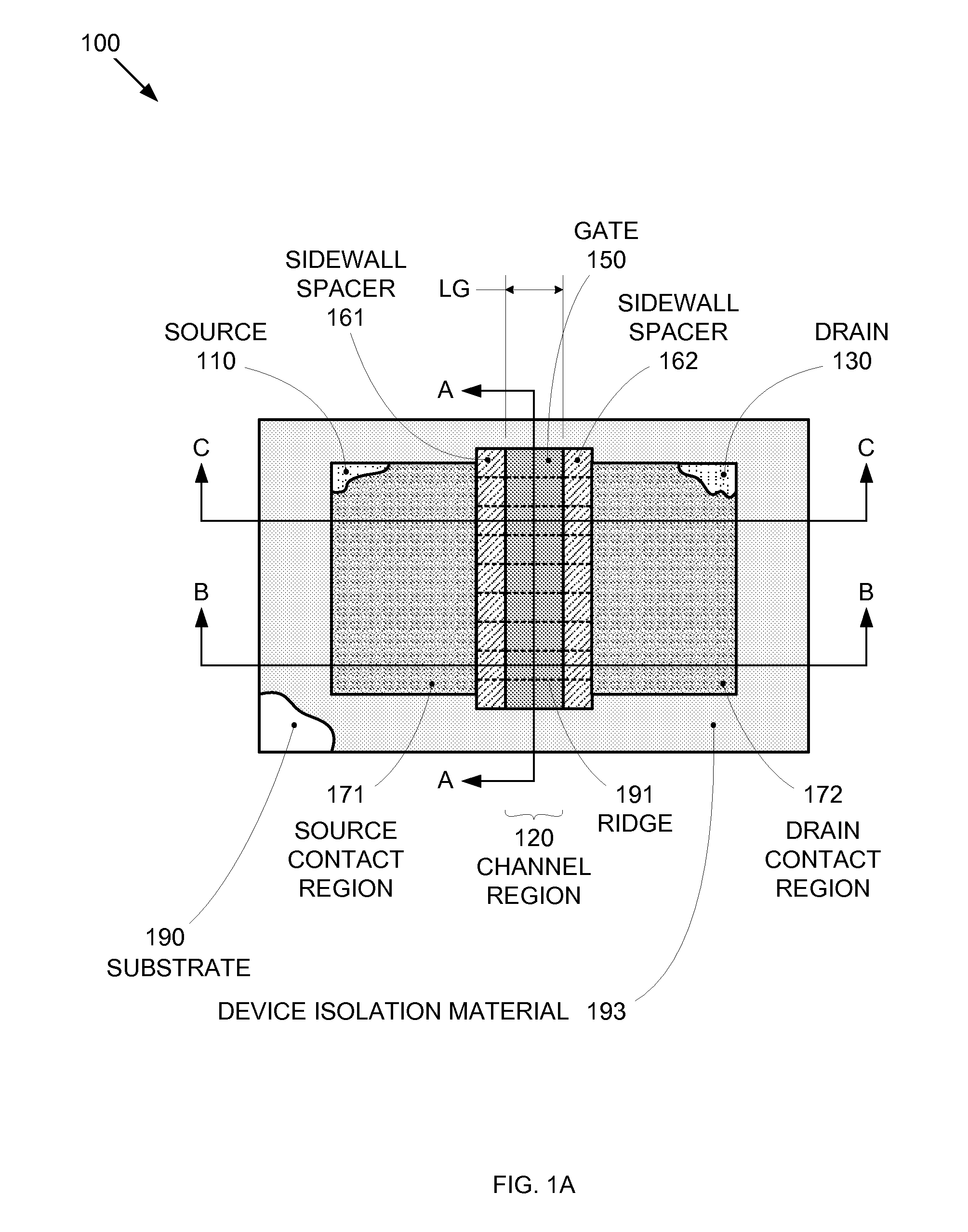

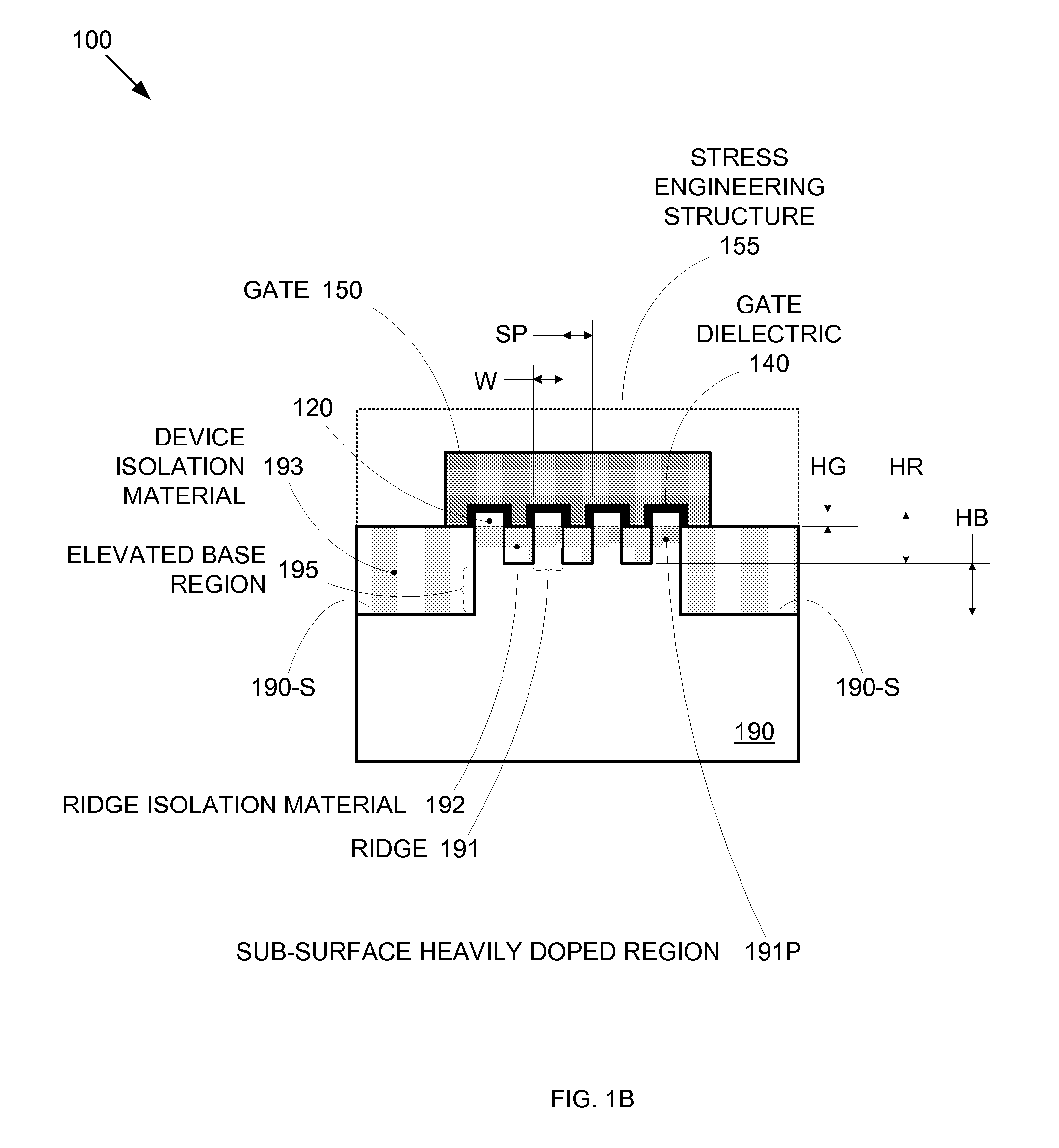

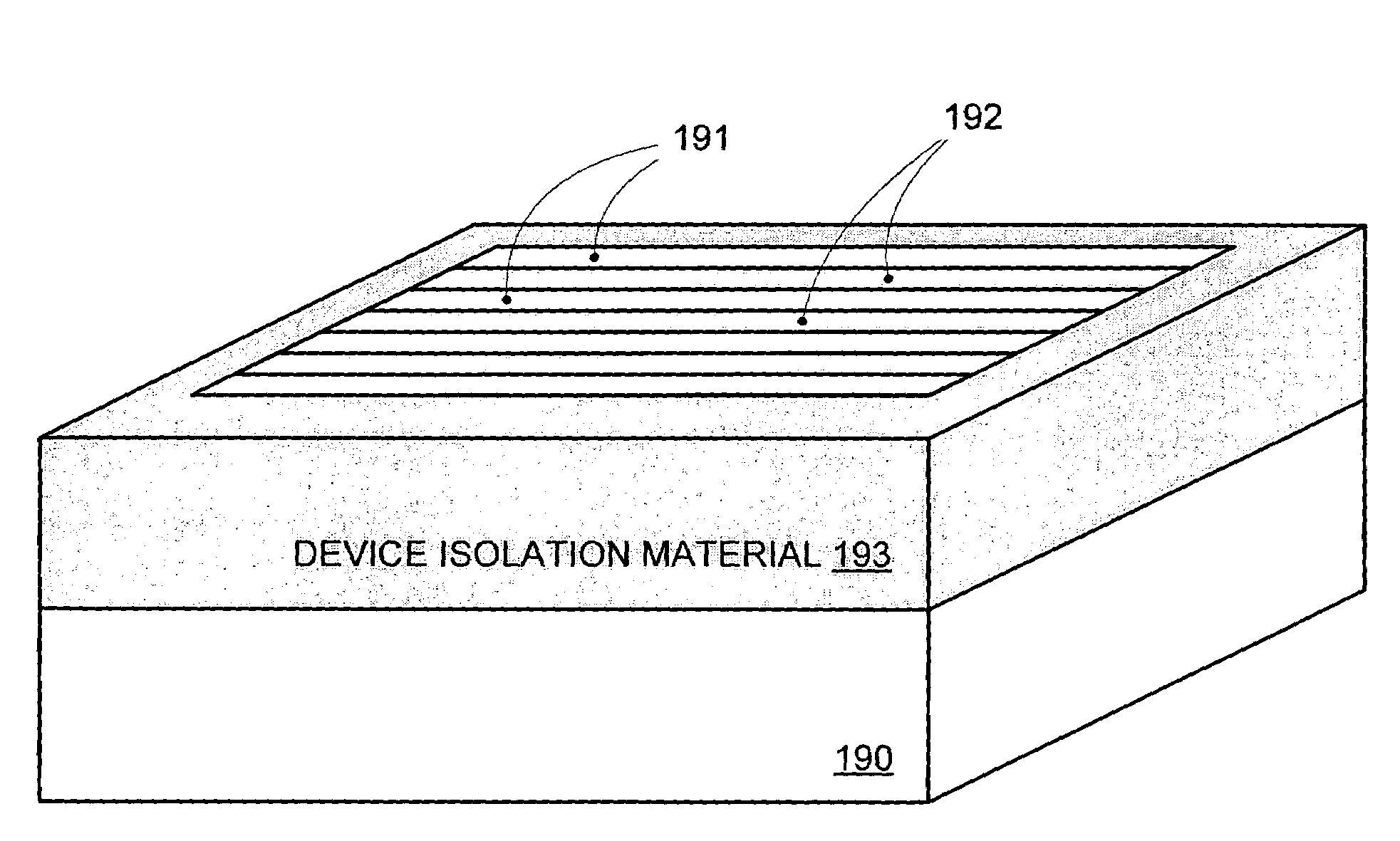

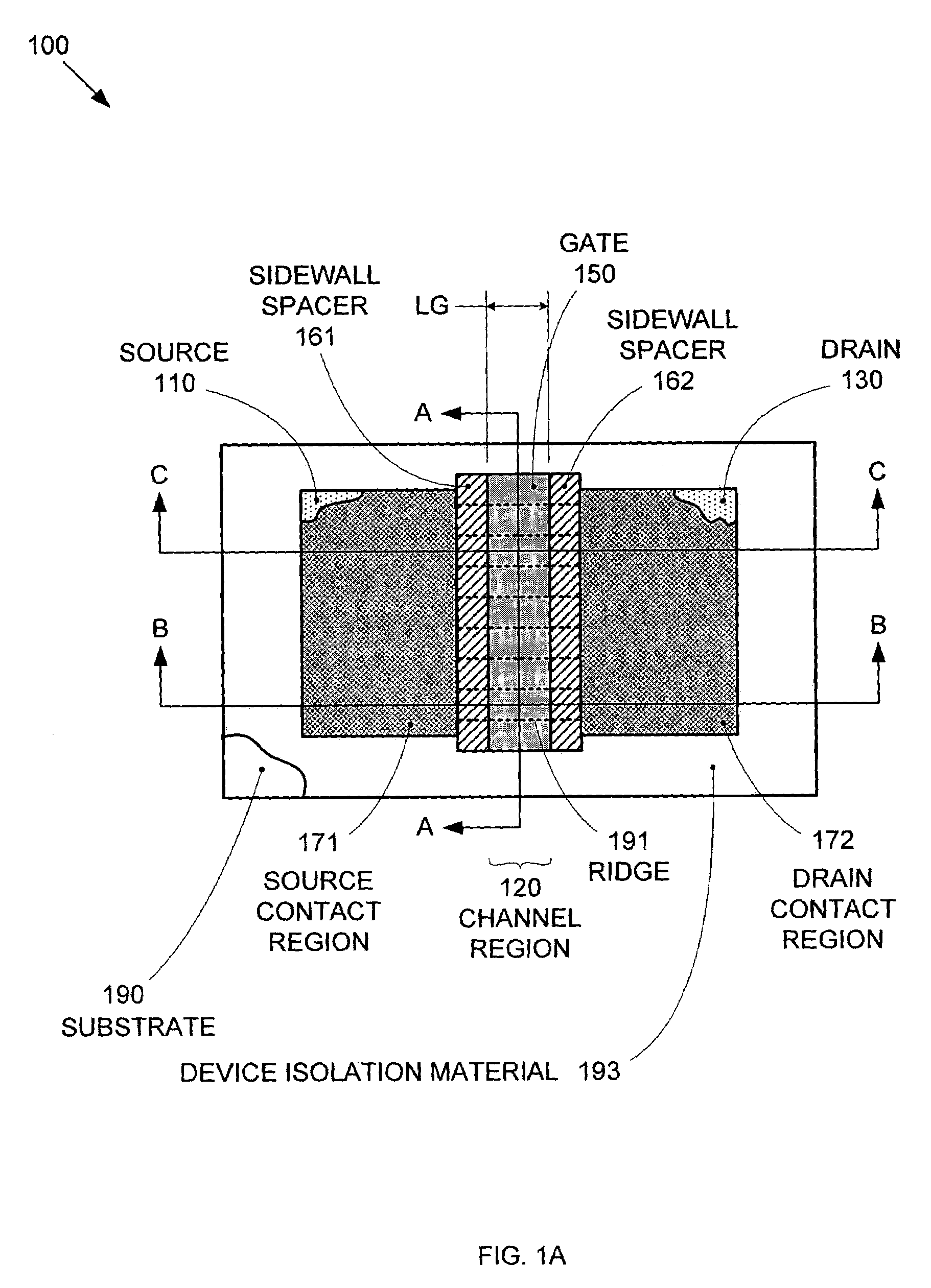

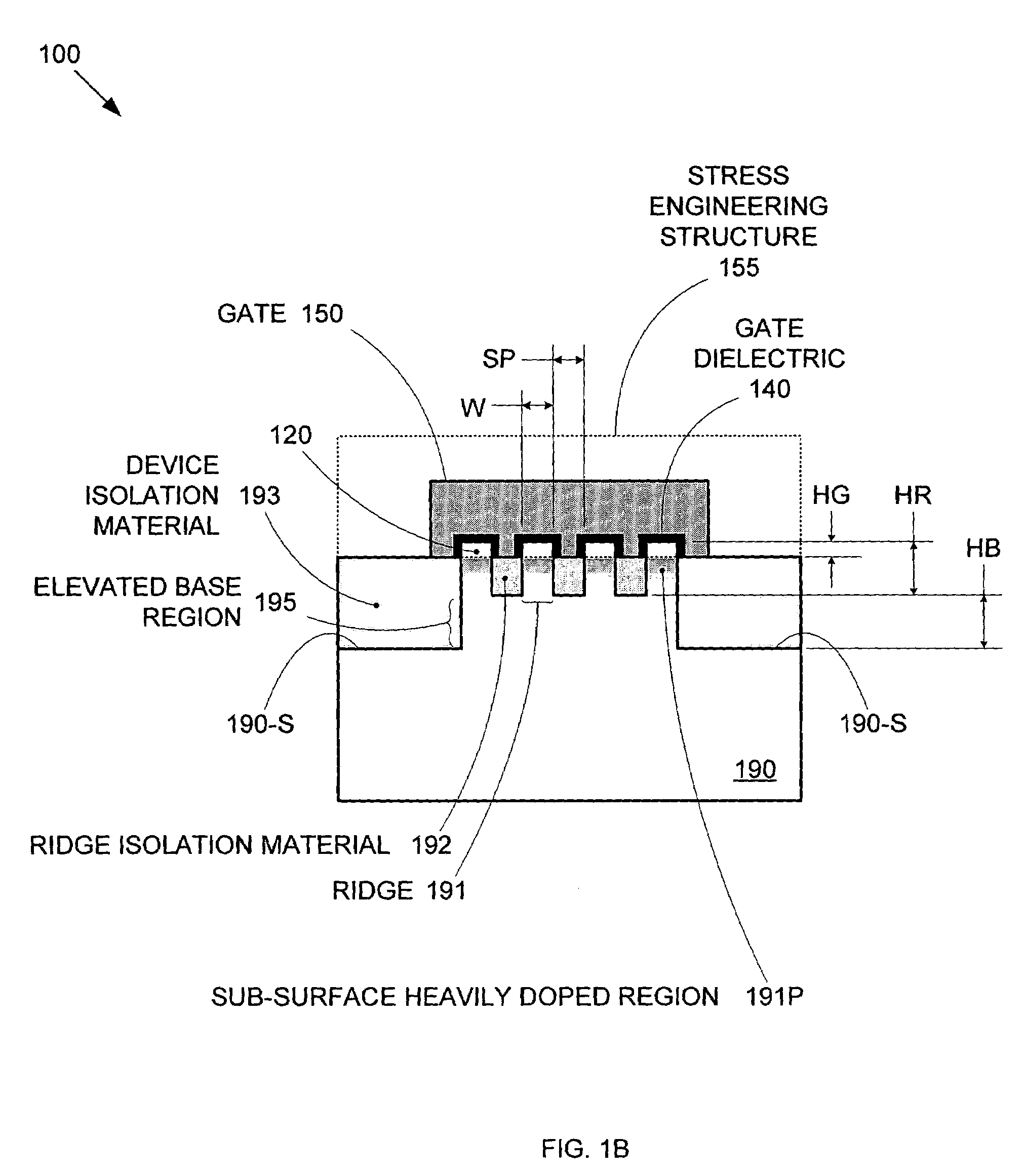

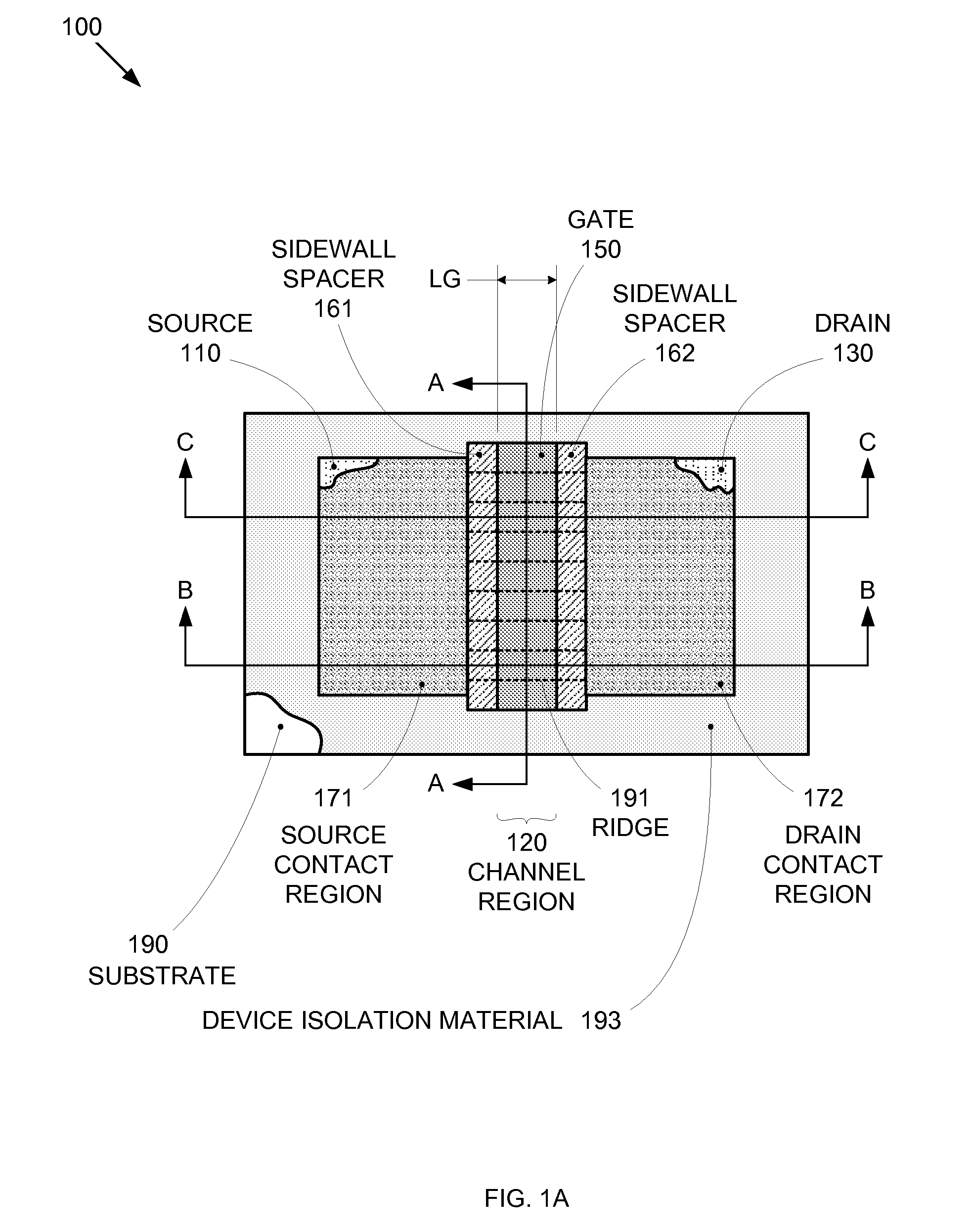

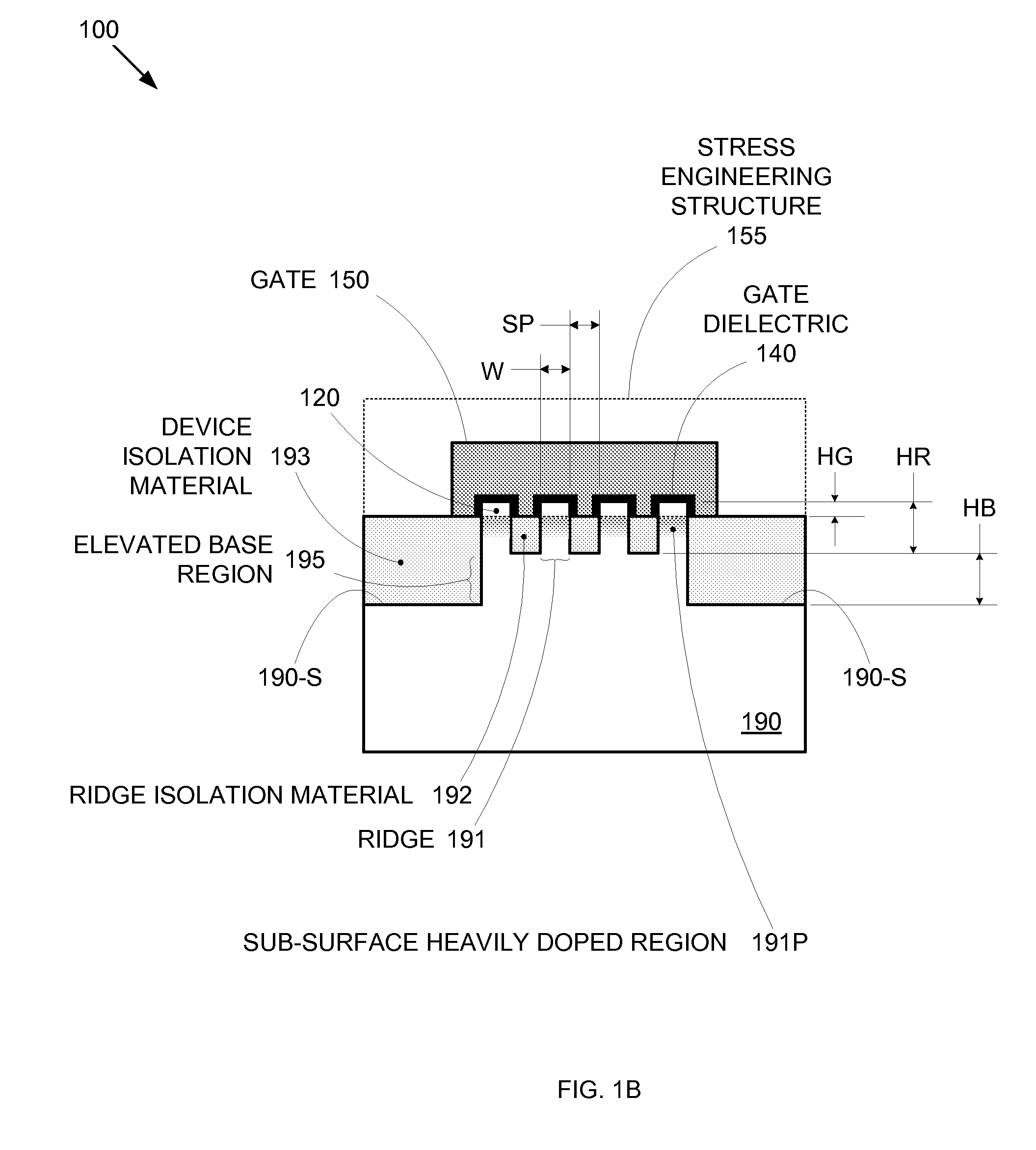

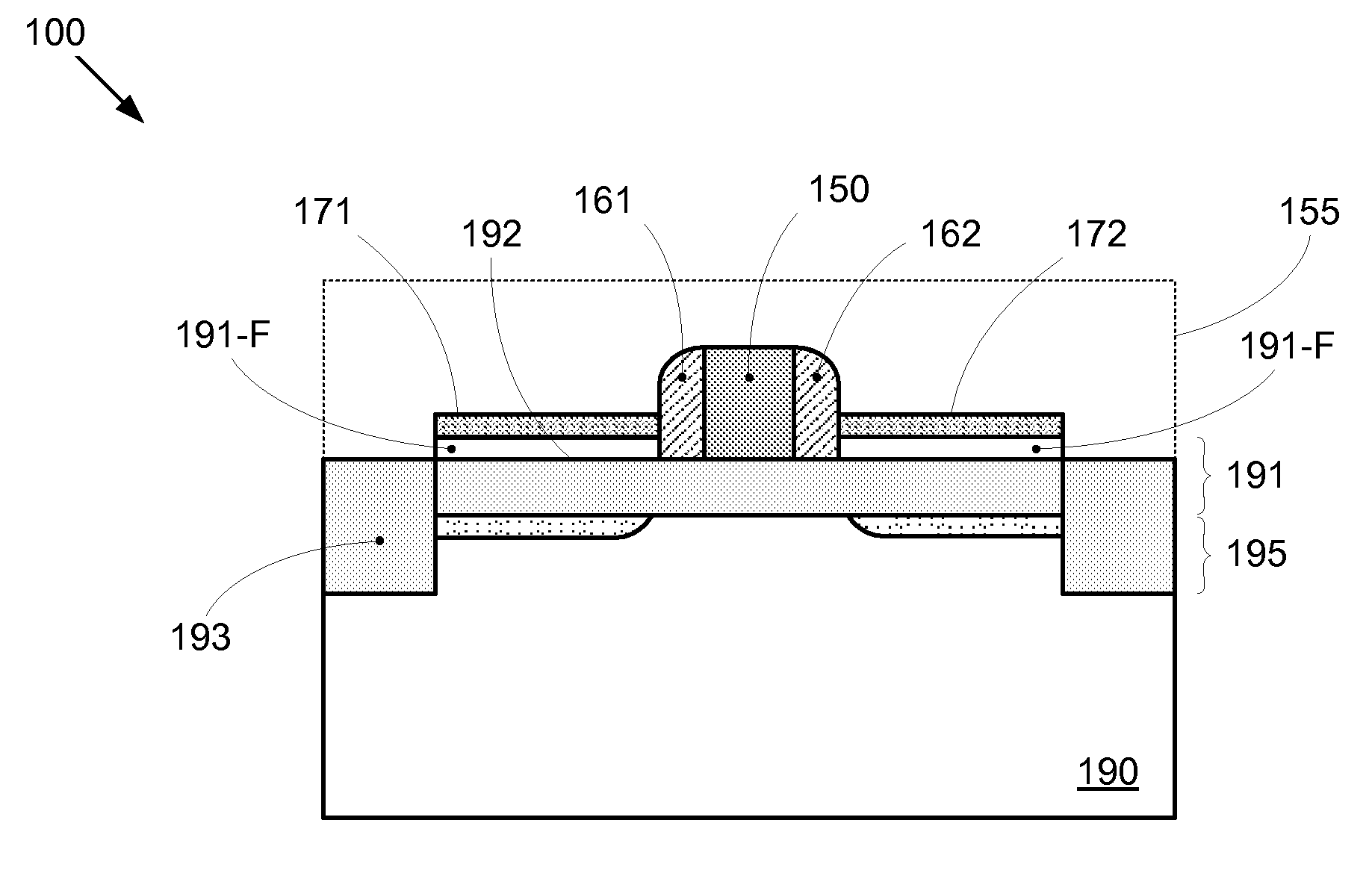

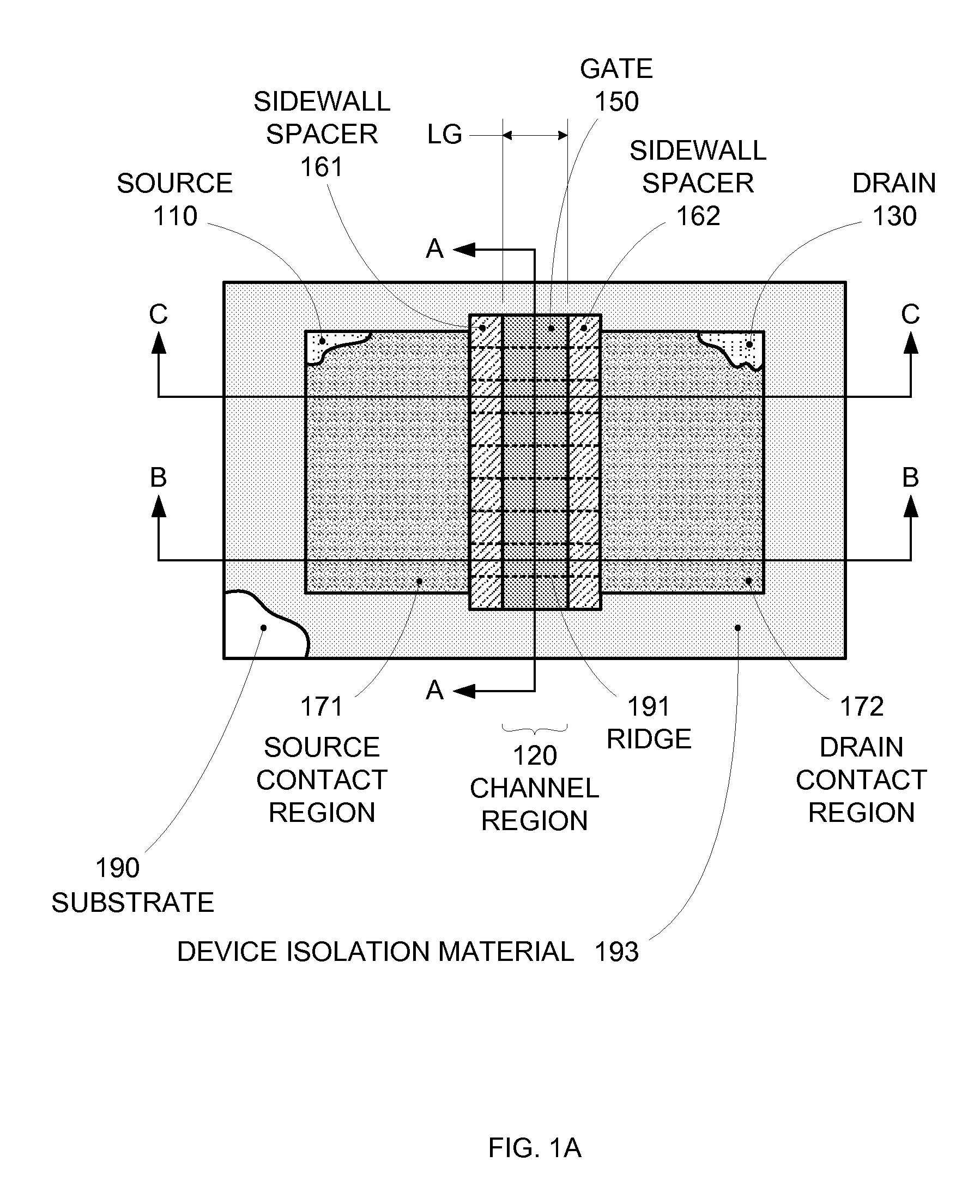

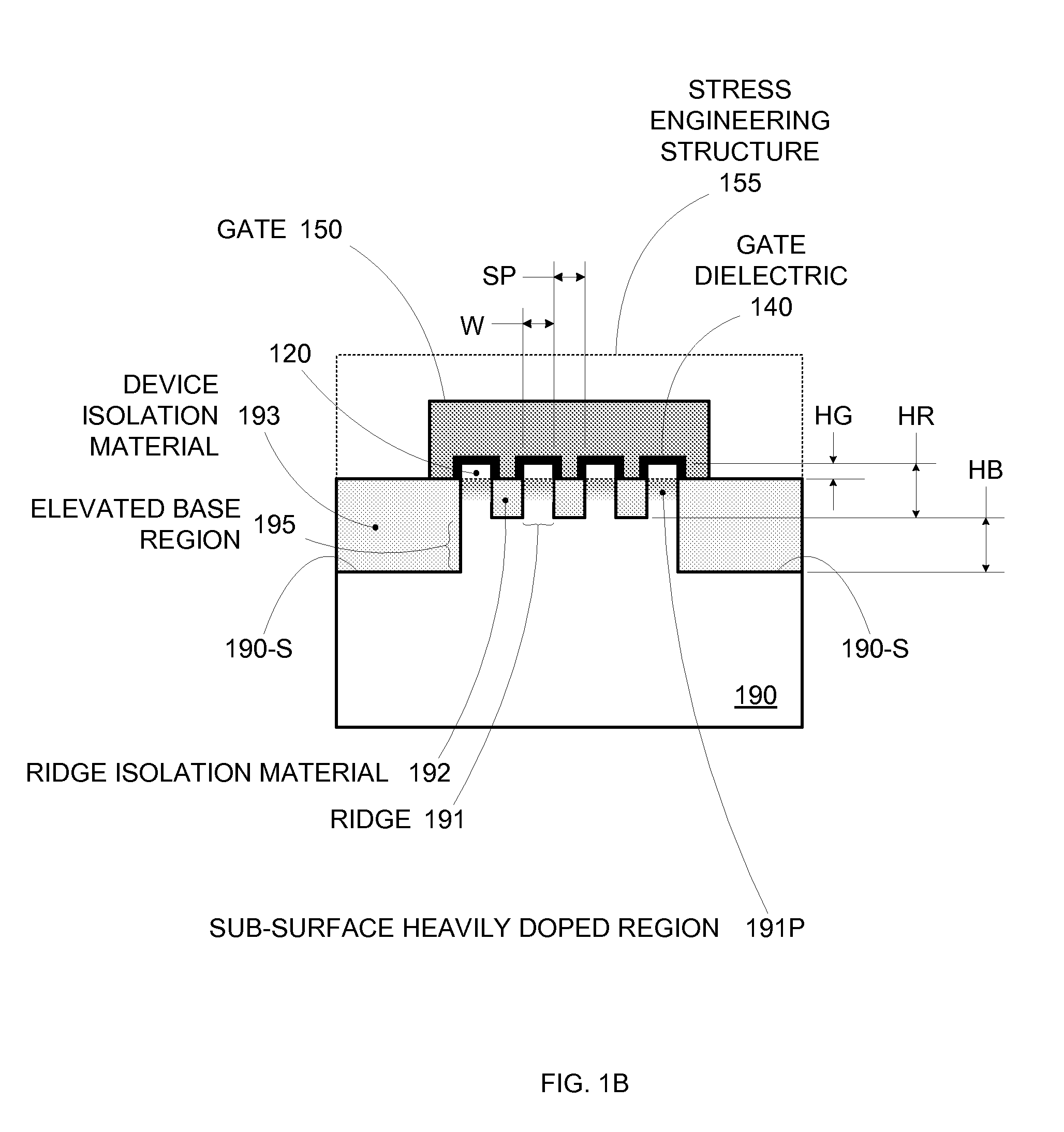

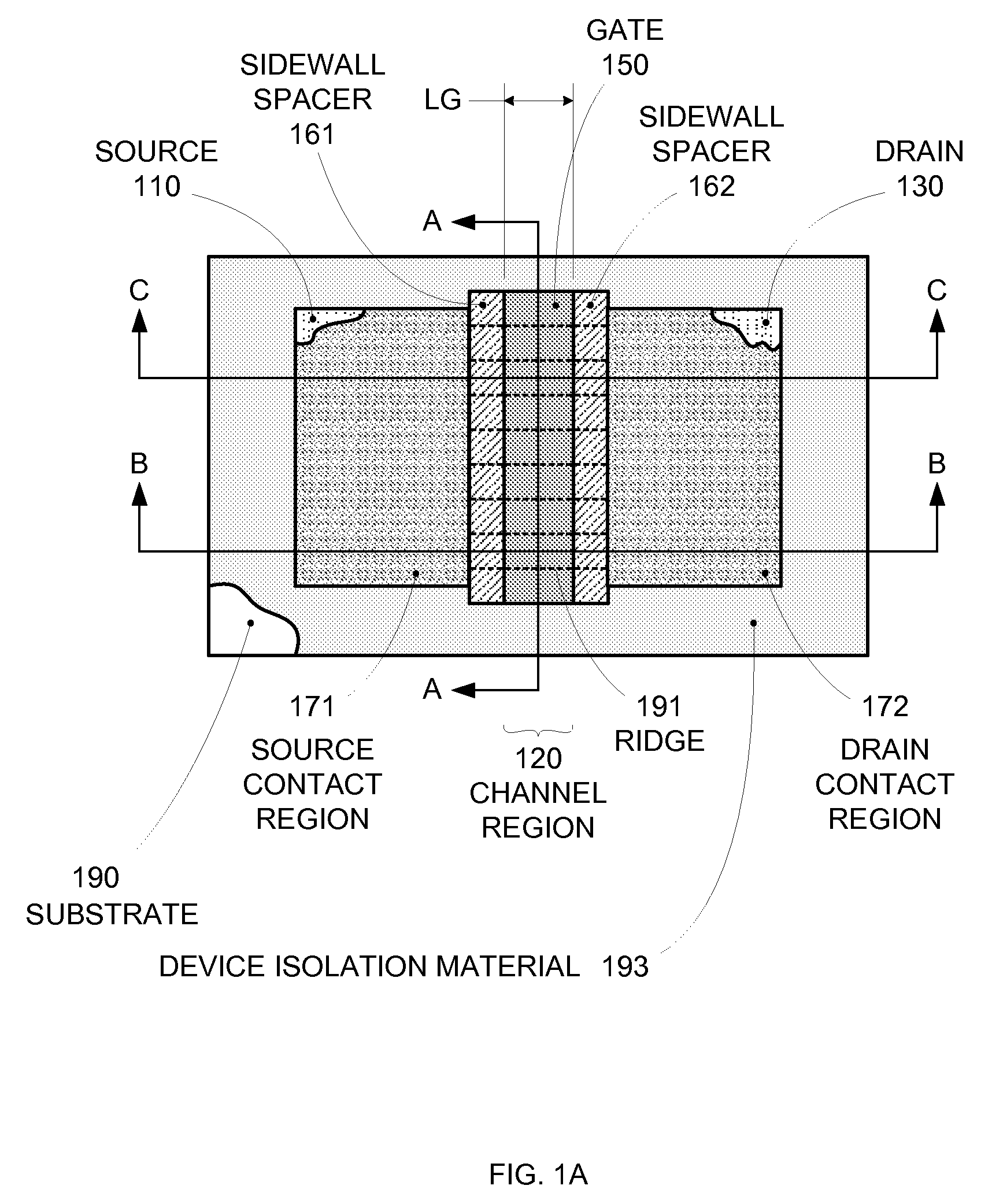

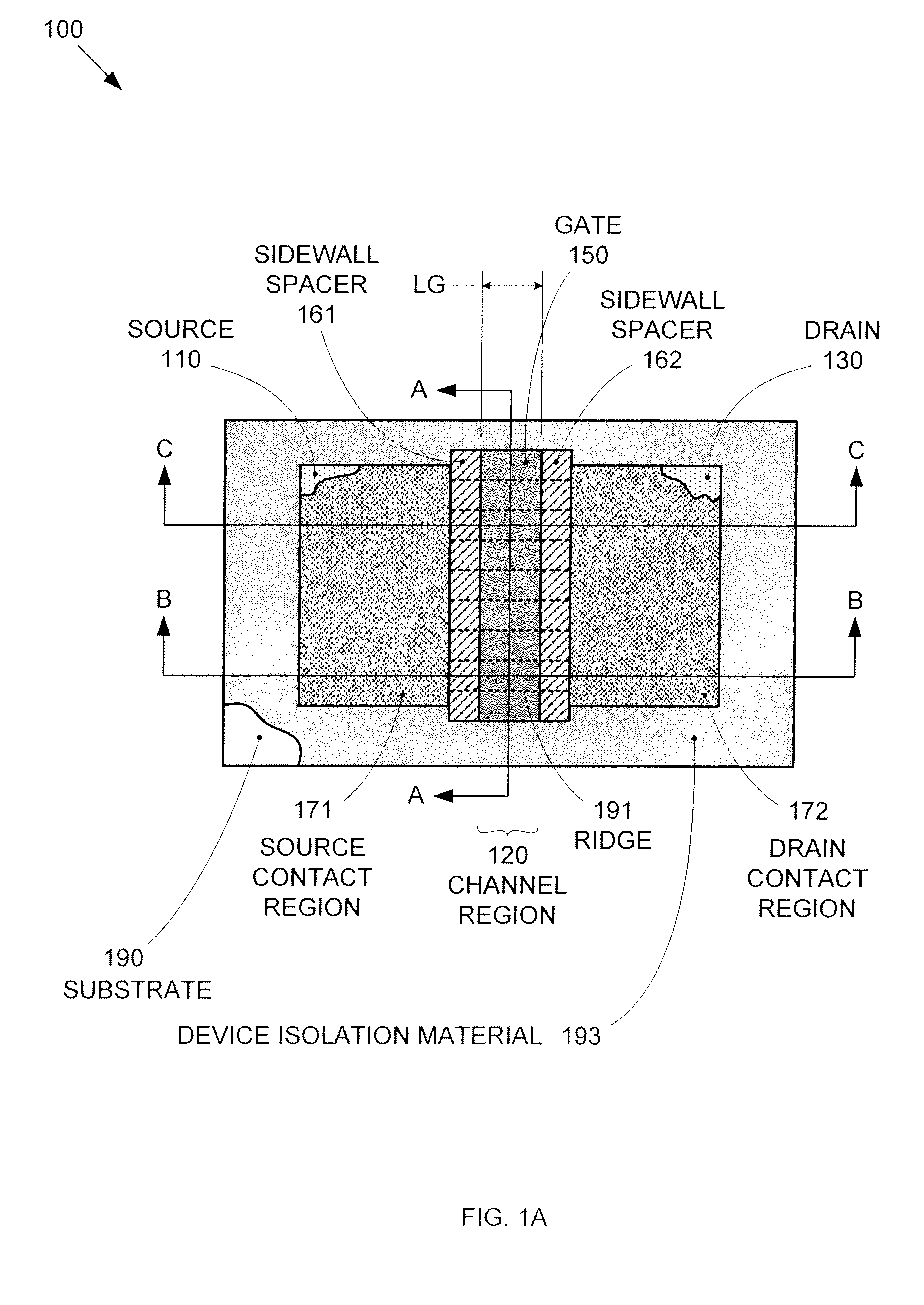

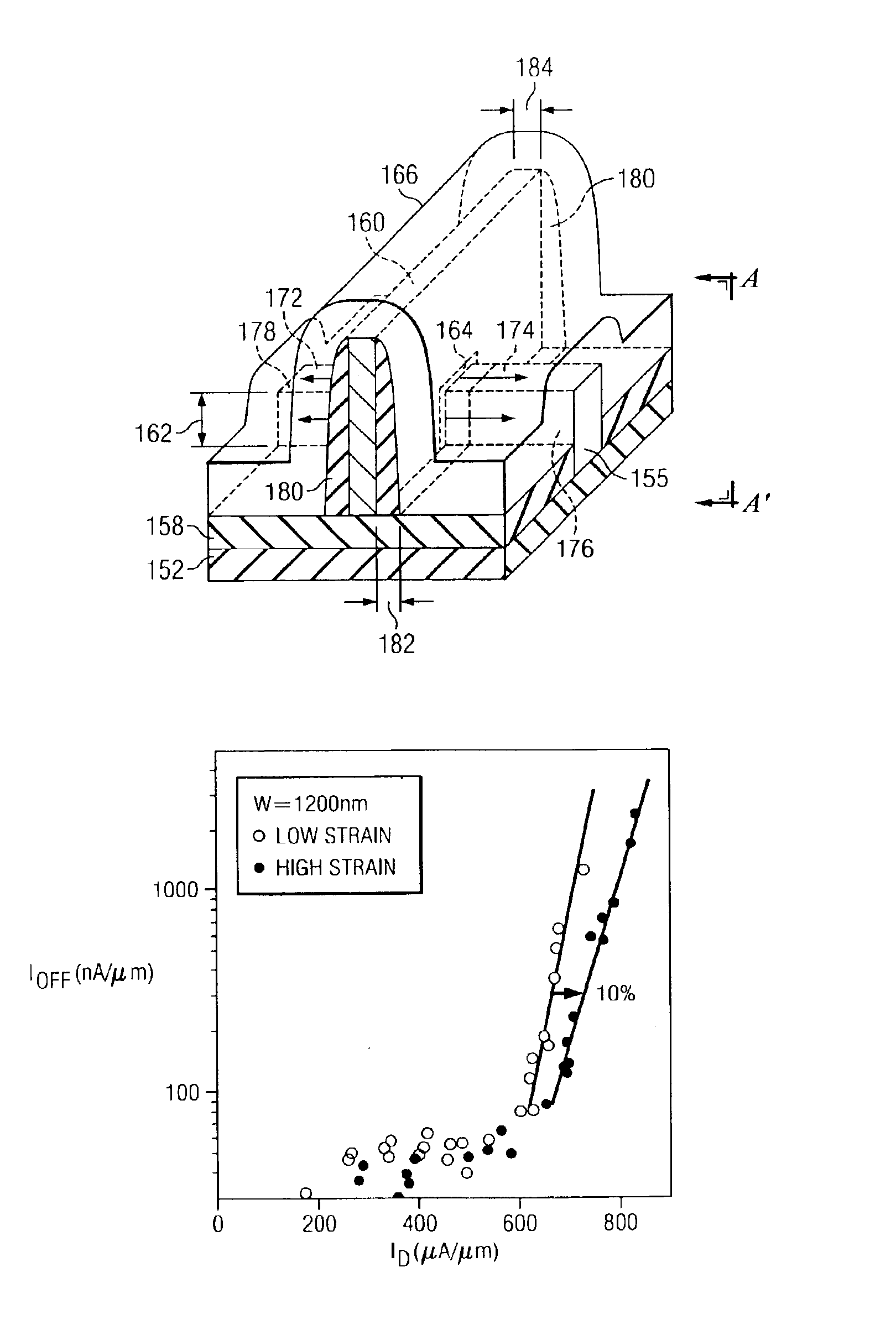

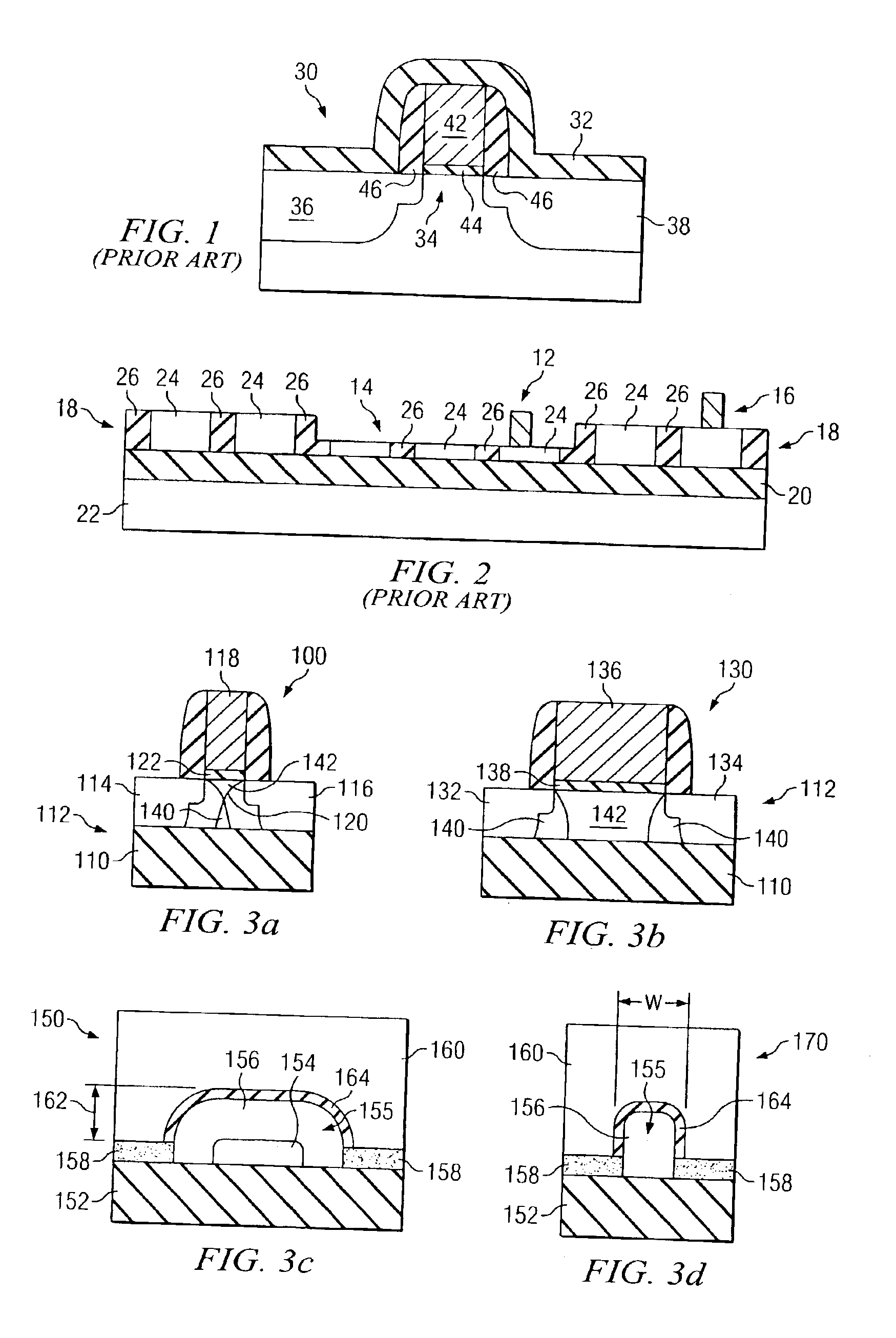

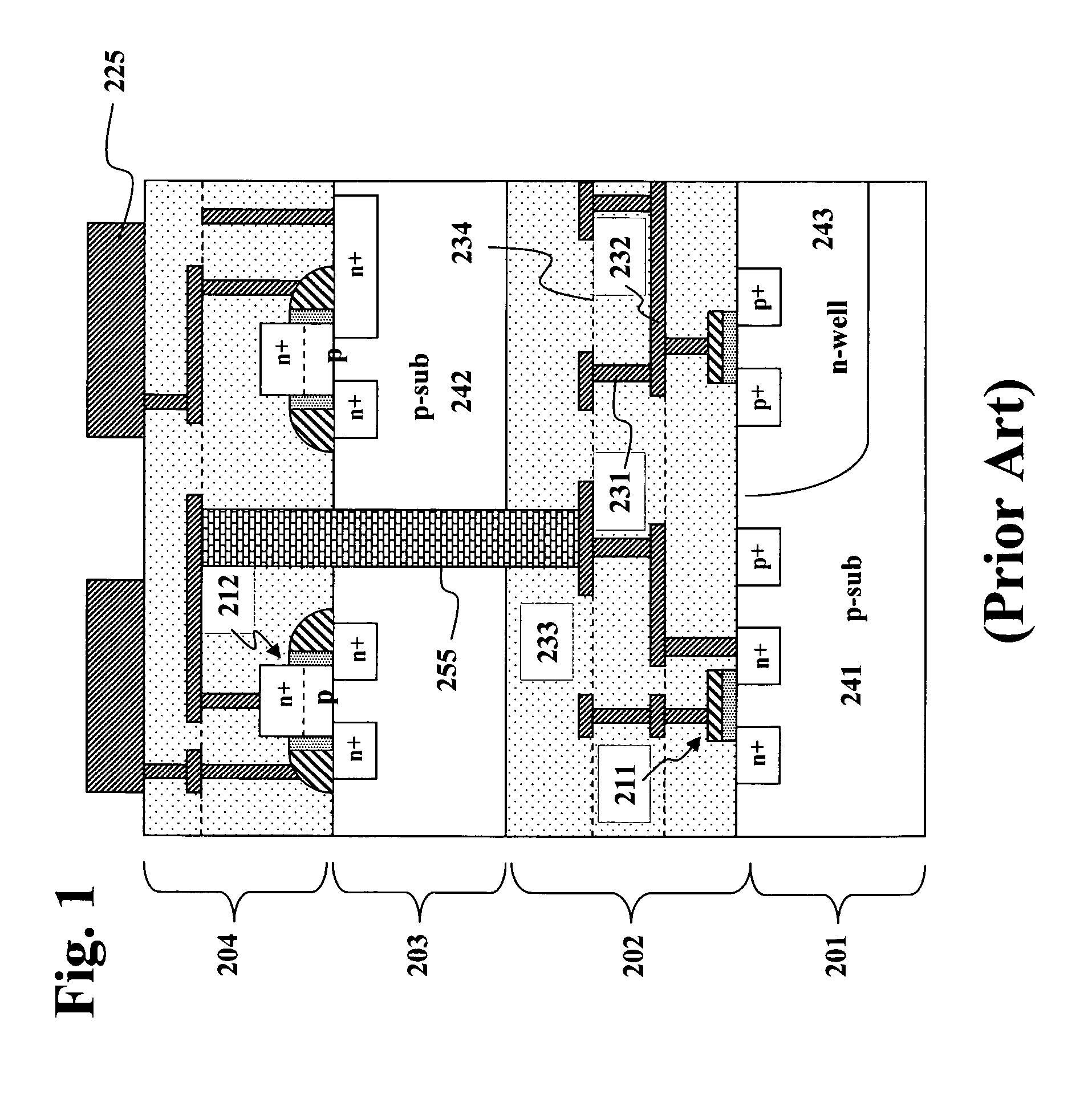

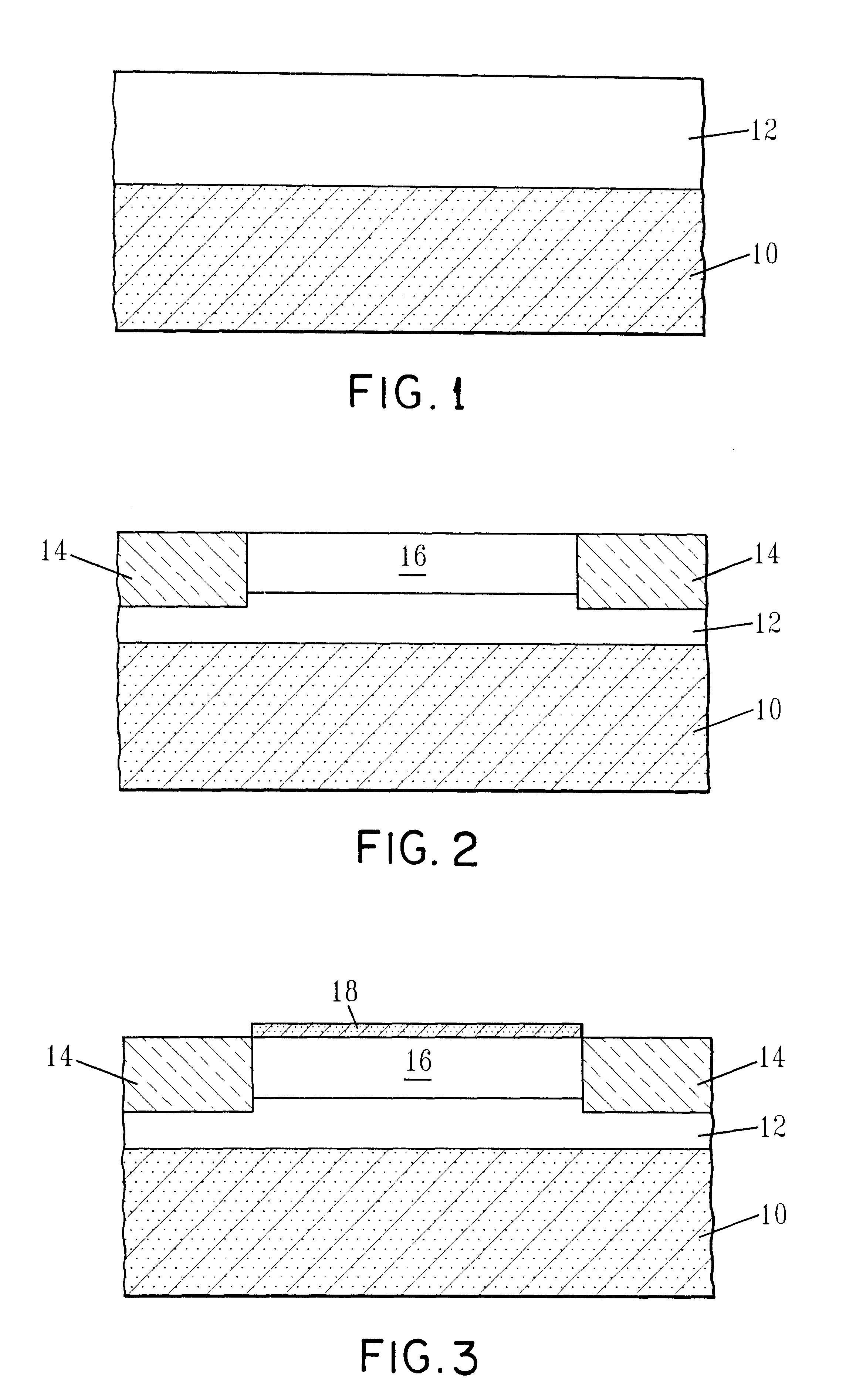

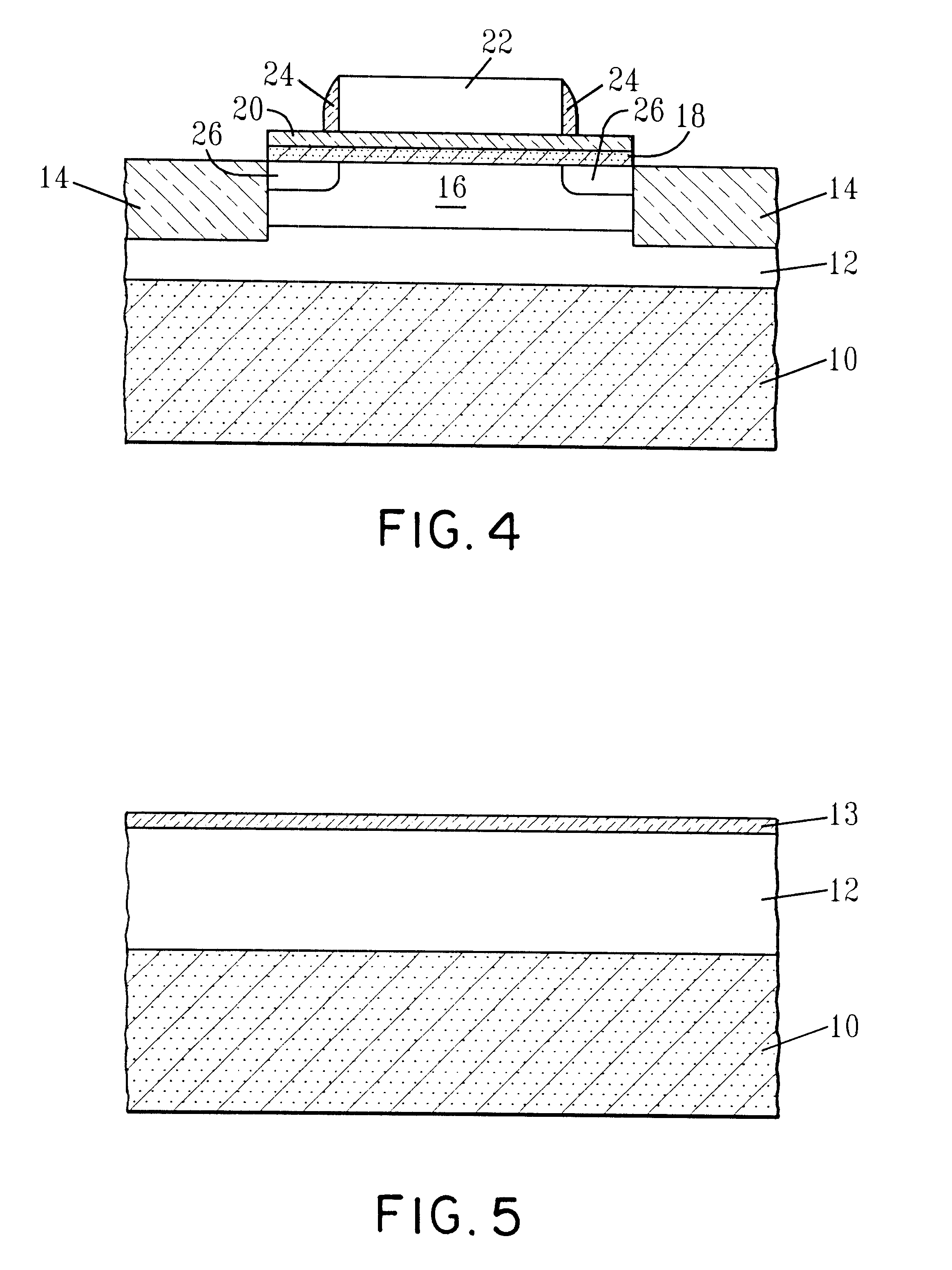

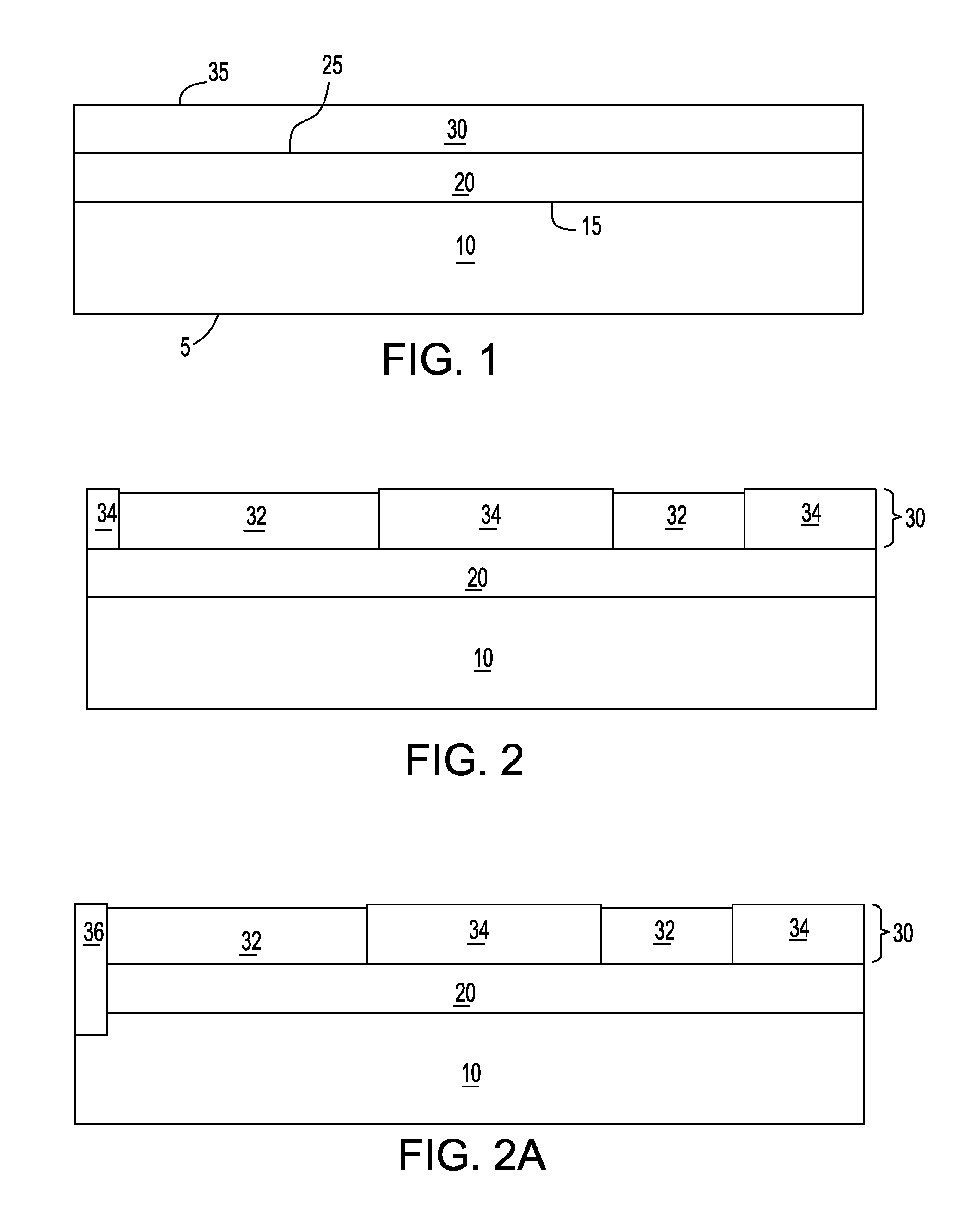

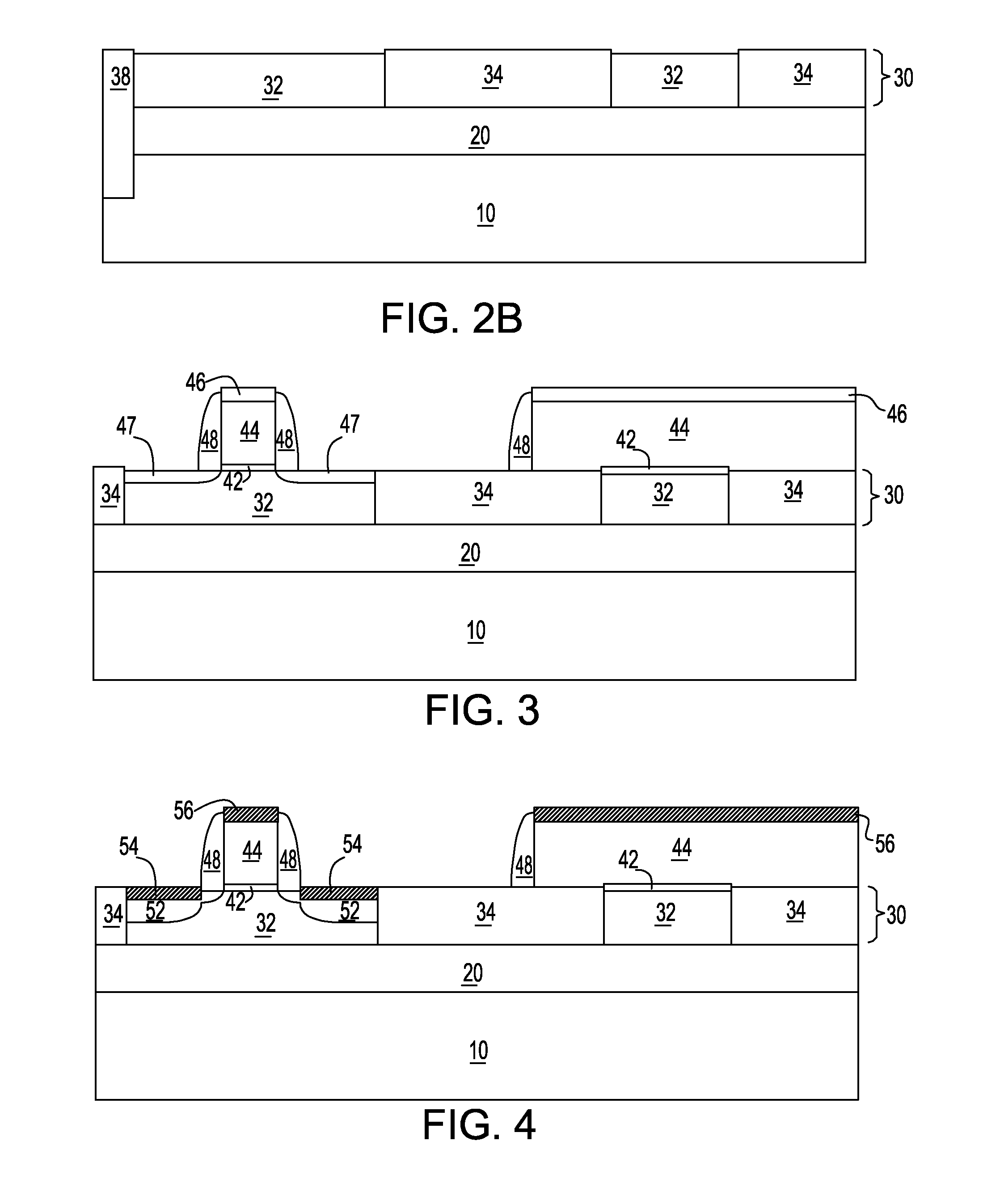

Segmented channel MOS transistor

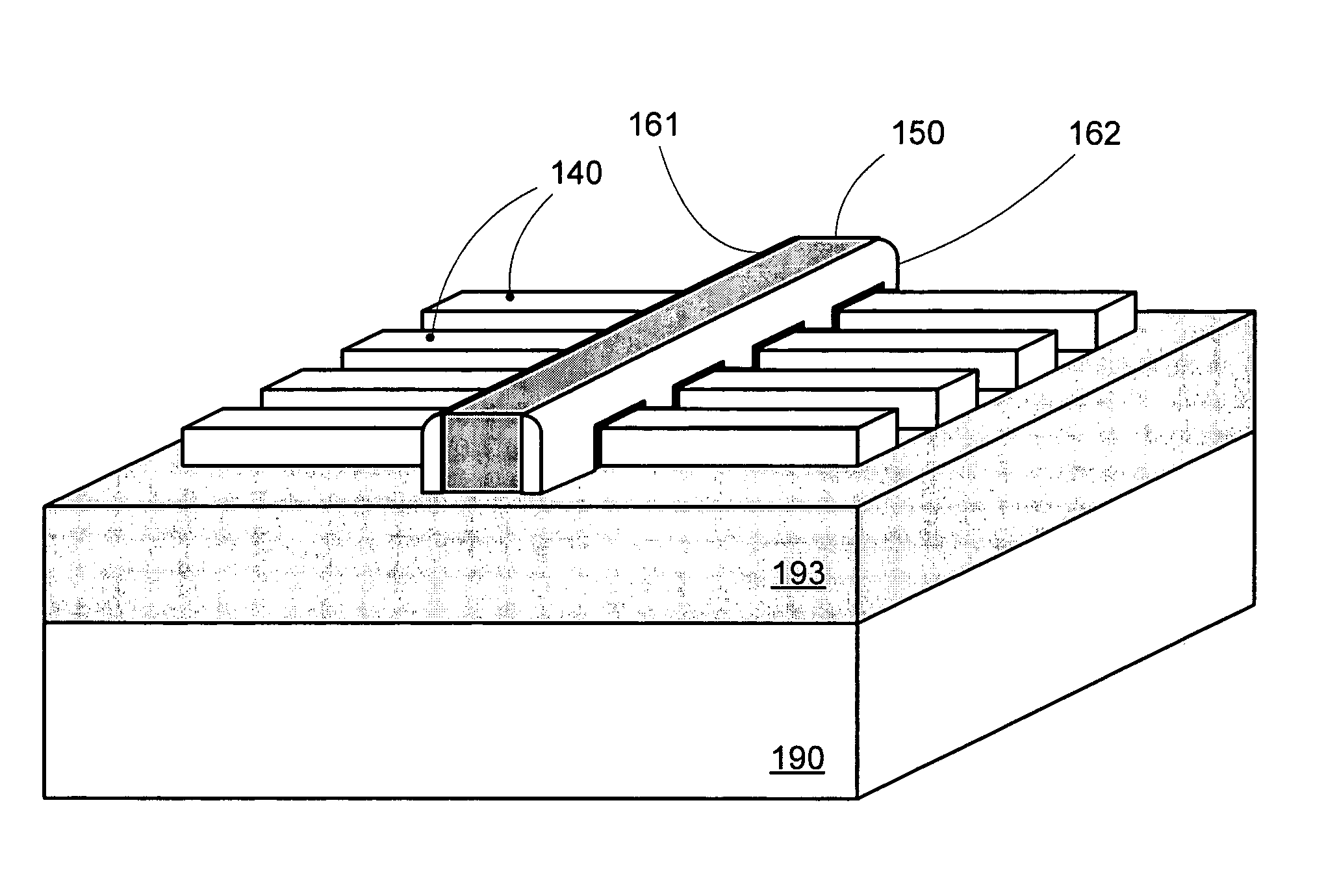

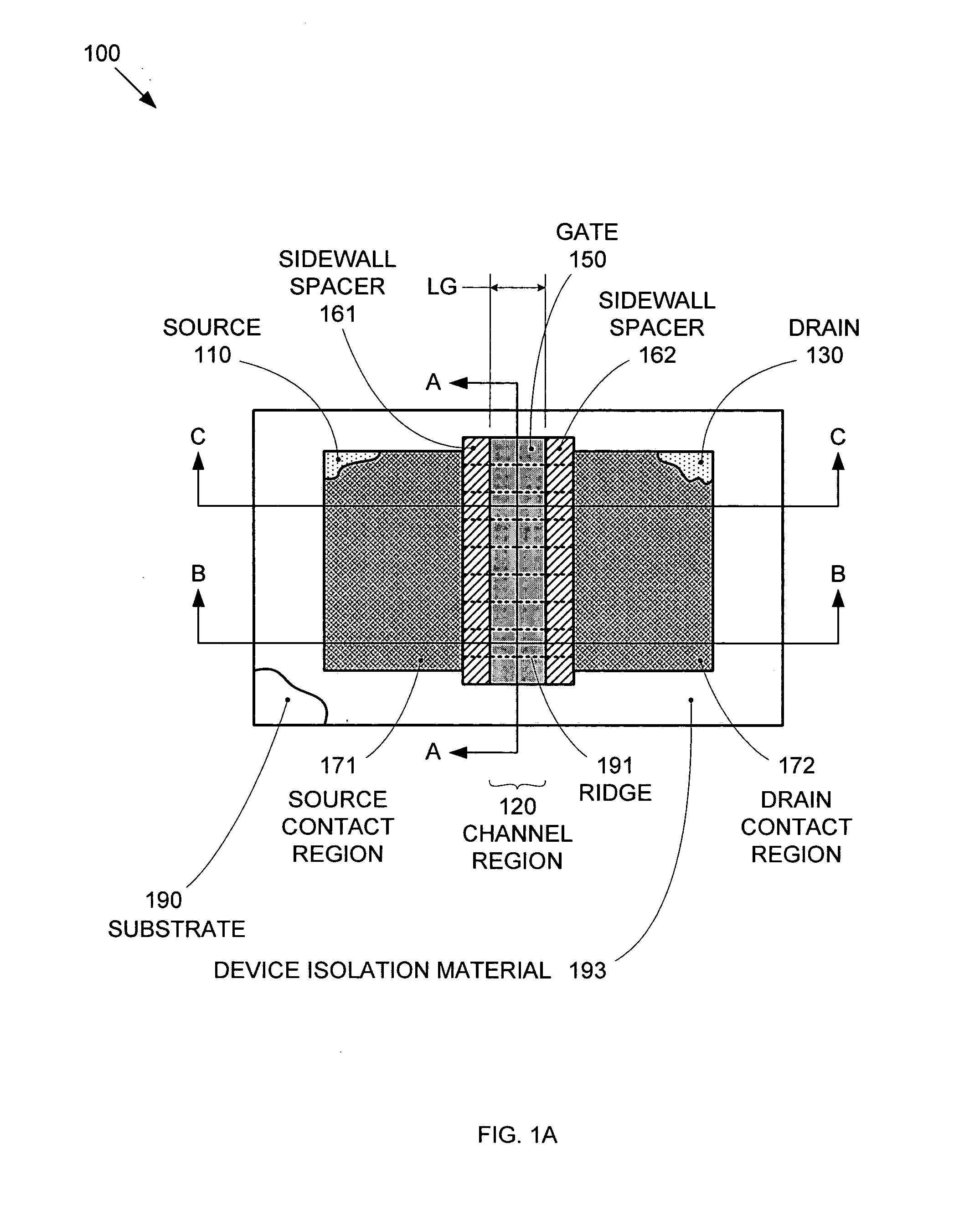

ActiveUS7247887B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETLithographic artist

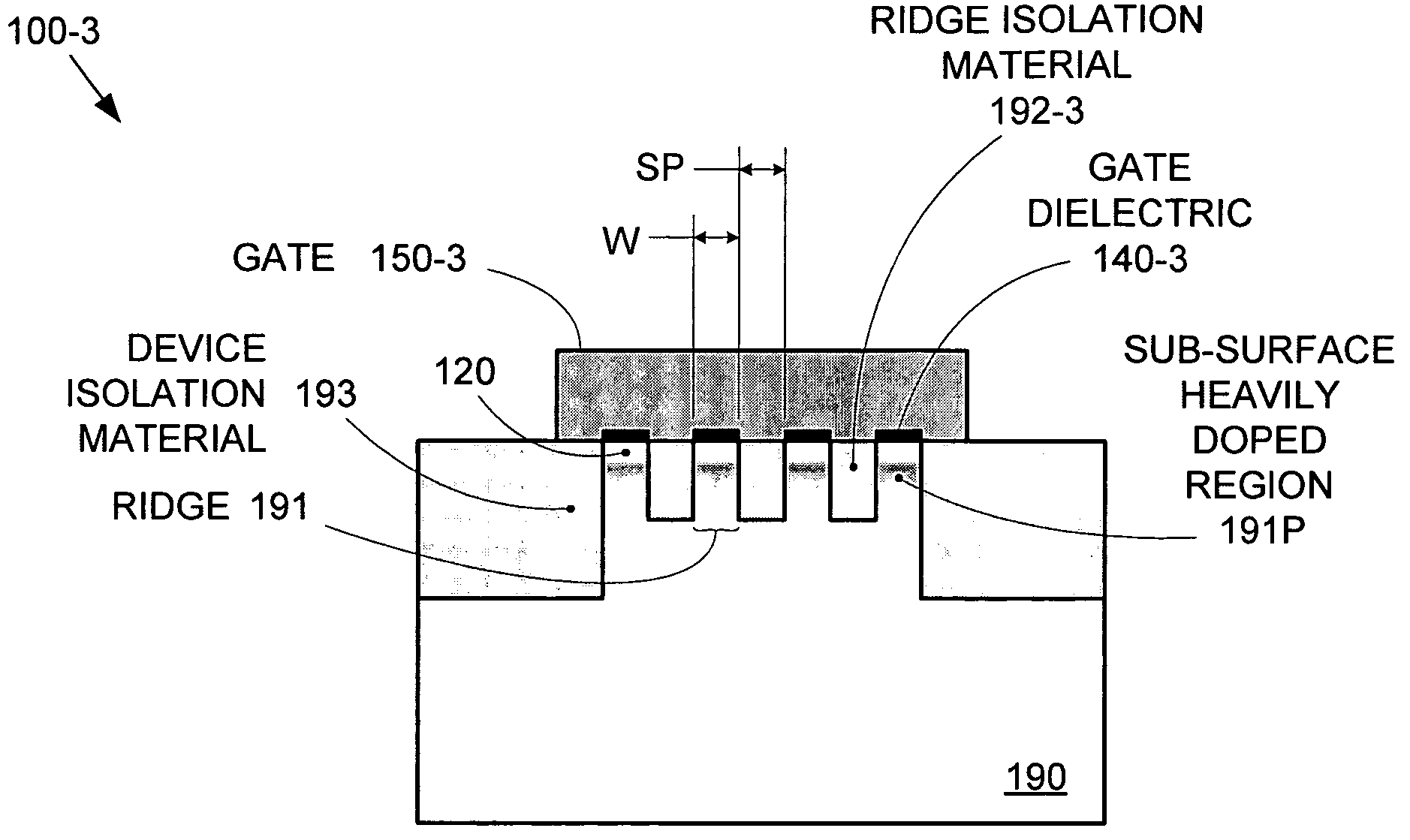

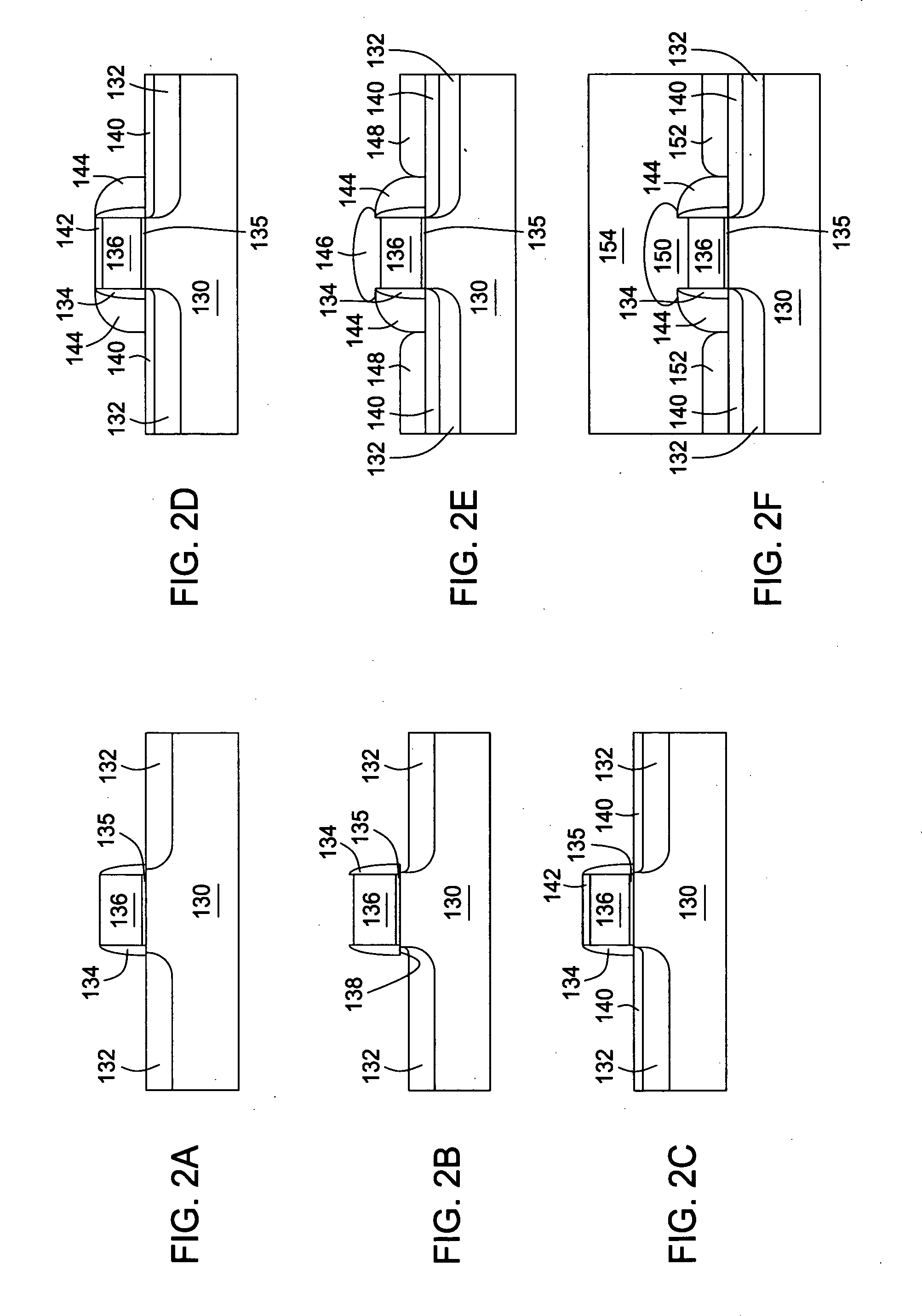

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

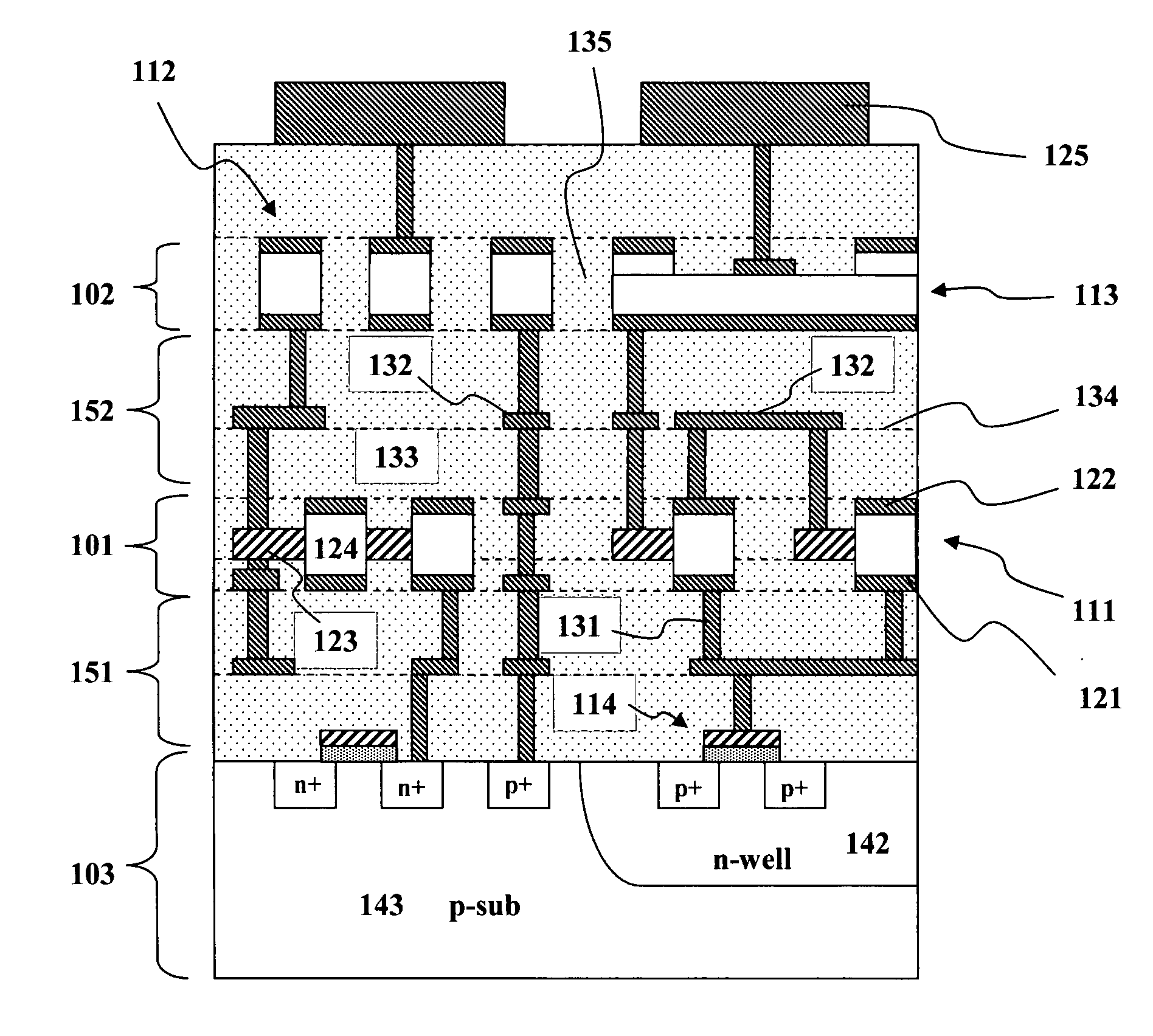

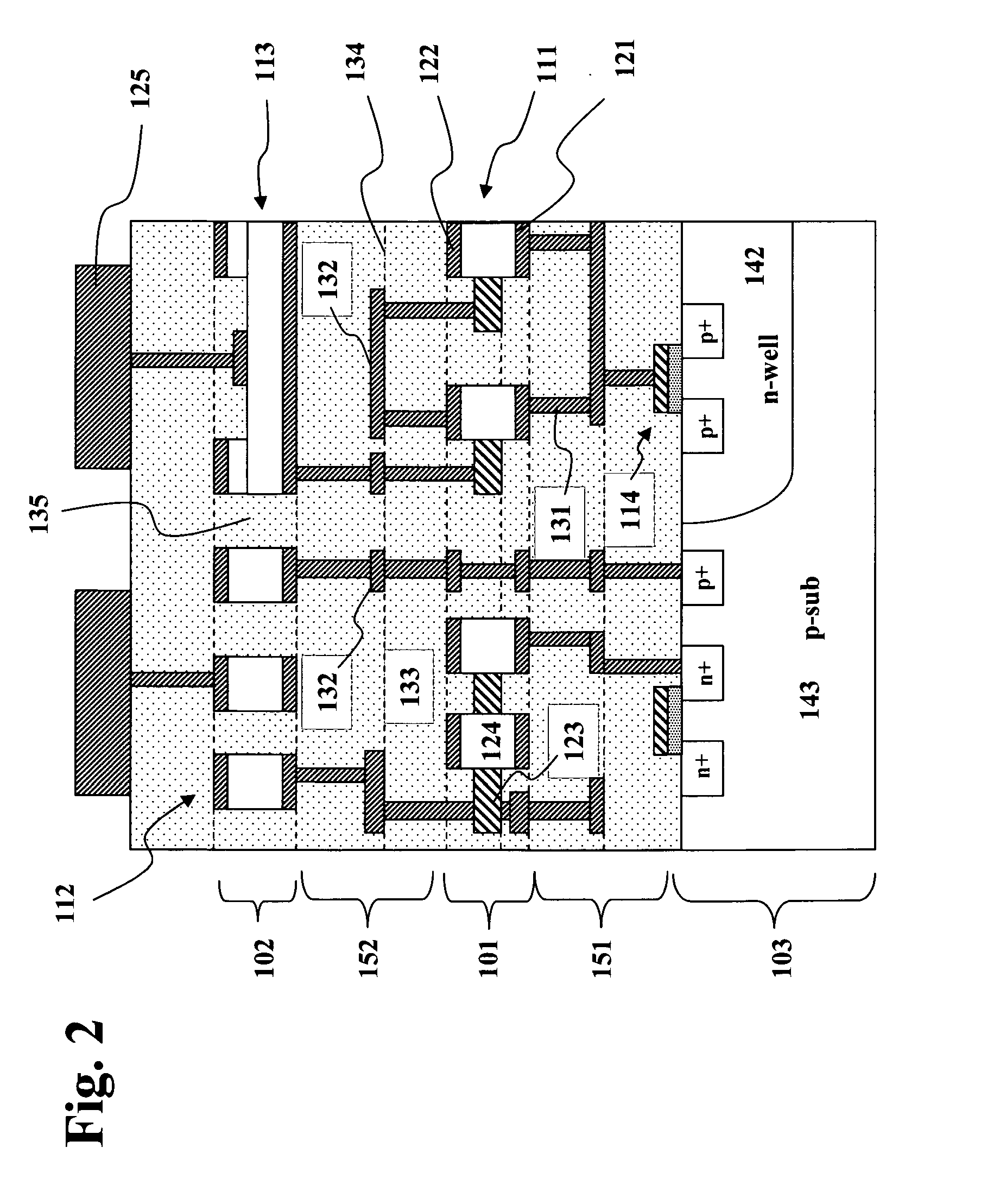

Integrated circuit on corrugated substrate

ActiveUS7190050B2Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

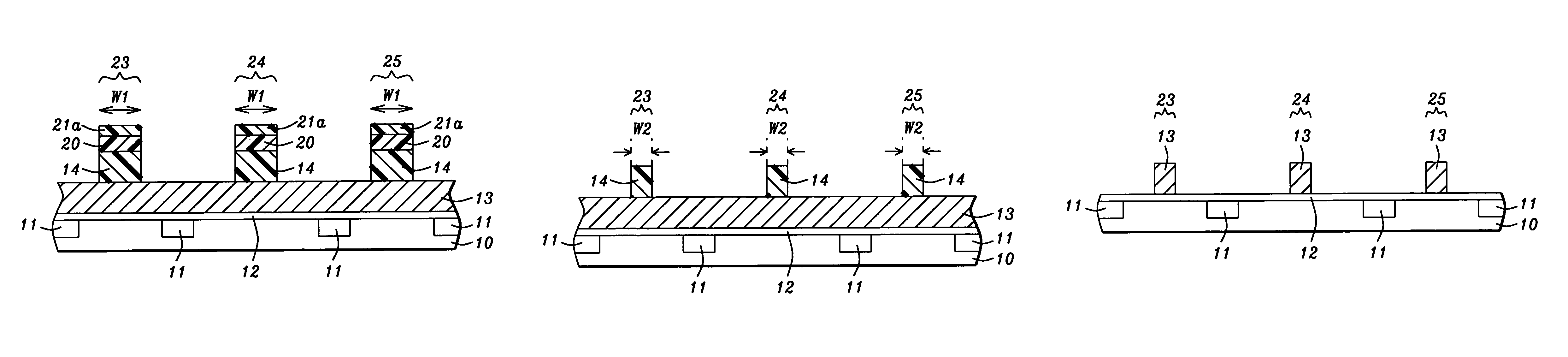

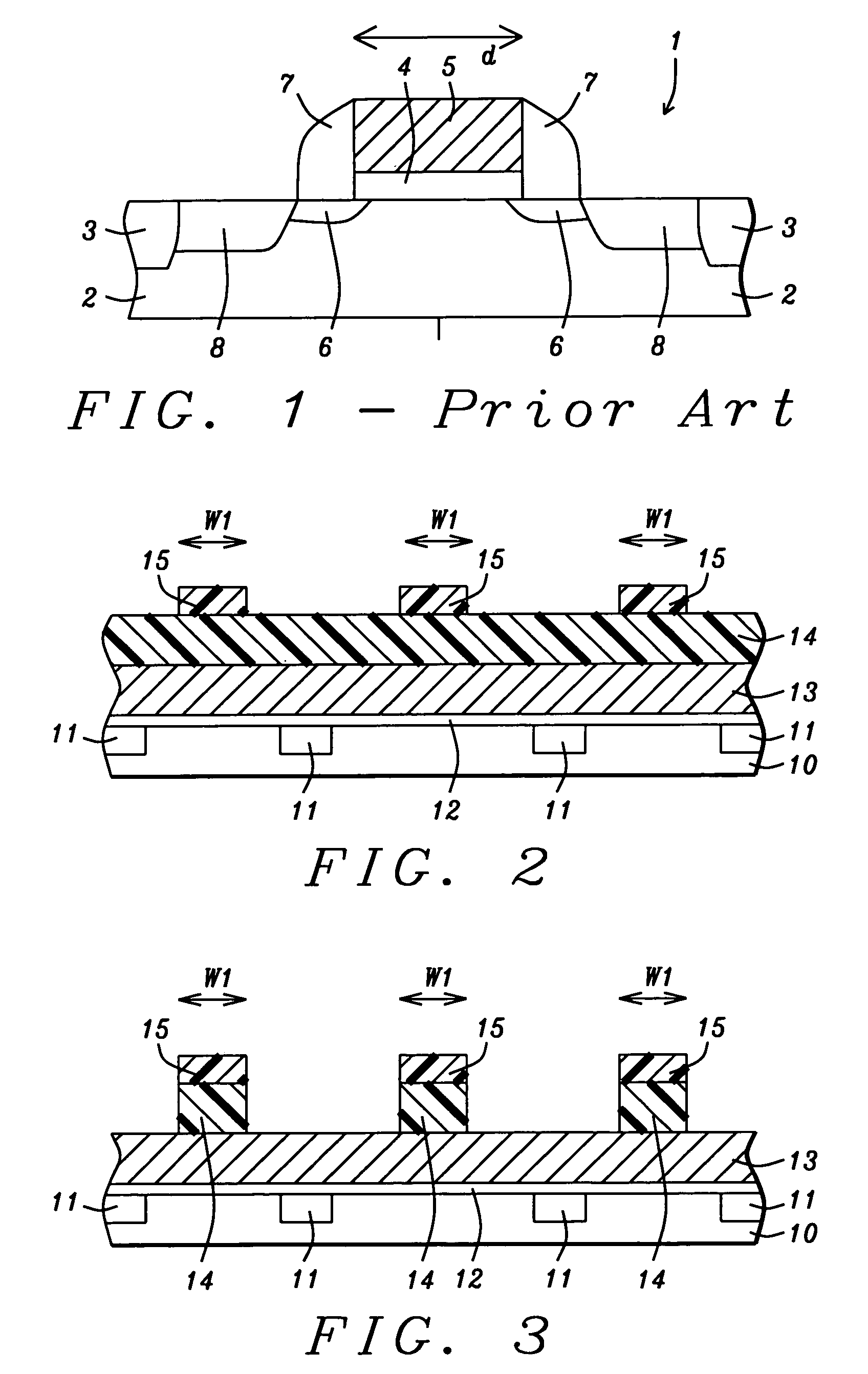

Method of trimming technology

ActiveUS7354847B2Easy to controlAvoid insufficient thicknessSolid-state devicesSemiconductor/solid-state device manufacturingResistMOSFET

A process for trimming a photoresist layer during the fabrication of a gate electrode in a MOSFET is described. A bilayer stack with a top photoresist layer on a thicker organic underlayer is patternwise exposed with 193 nm or 157 nm radiation to form a feature having a width w1 in the top layer. A pattern transfer through the underlayer is performed with an anisotropic etch based on H2 / N2 and SO2 chemistry. The feature formed in the bilayer stack is trimmed by 10 nm or more to a width w2 by a HBr / O2 / Cl2 plasma etch. The pattern transfer through an underlying gate layer is performed with a third etch based on HBr / O2 / Cl2 chemistry. The underlayer is stripped by an O2 ashing with no damage to the gate electrode. Excellent profile control of the gate electrode is achieved and a larger (w1−w2) is possible than in prior art methods.

Owner:TAIWAN SEMICON MFG CO LTD

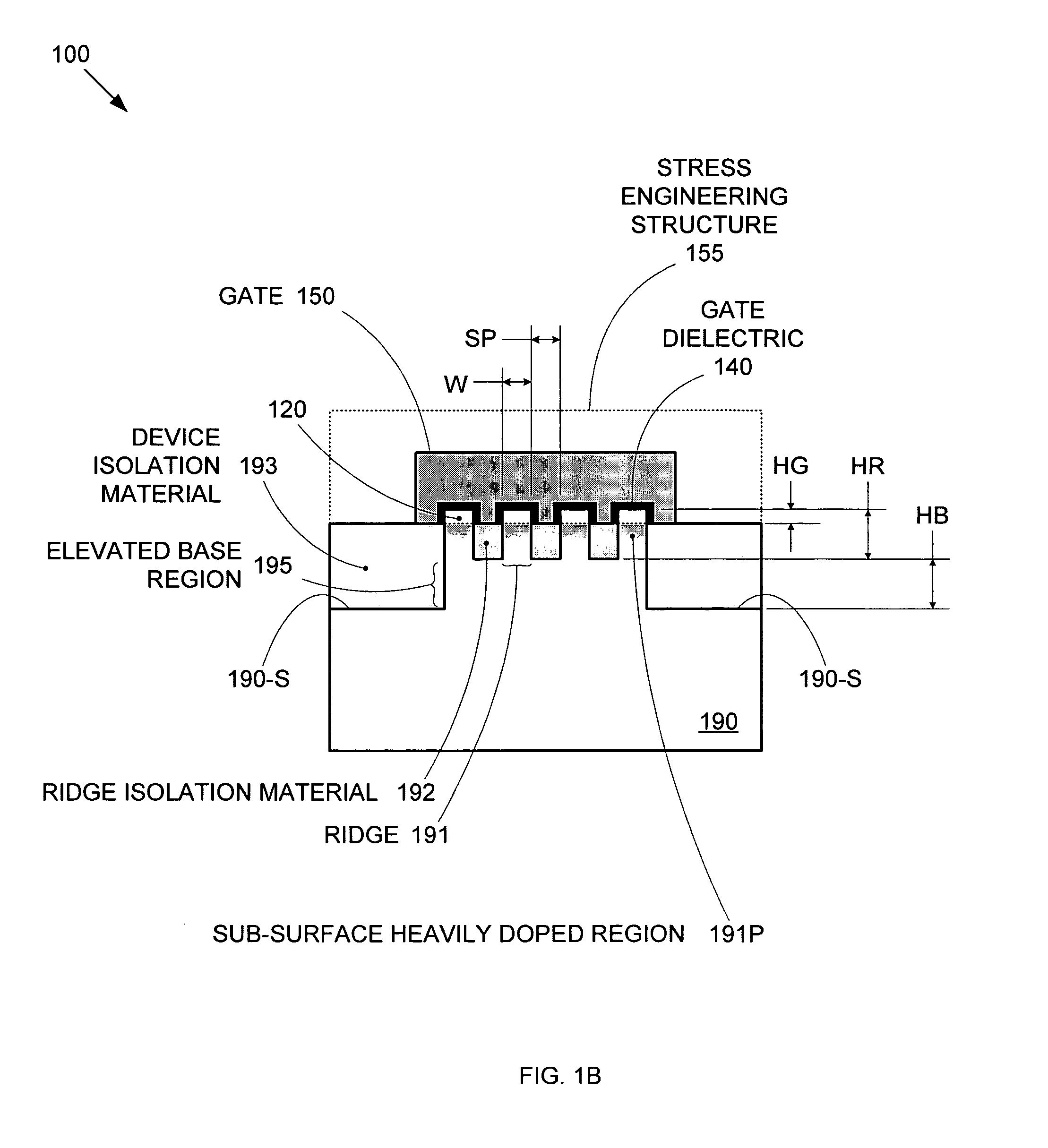

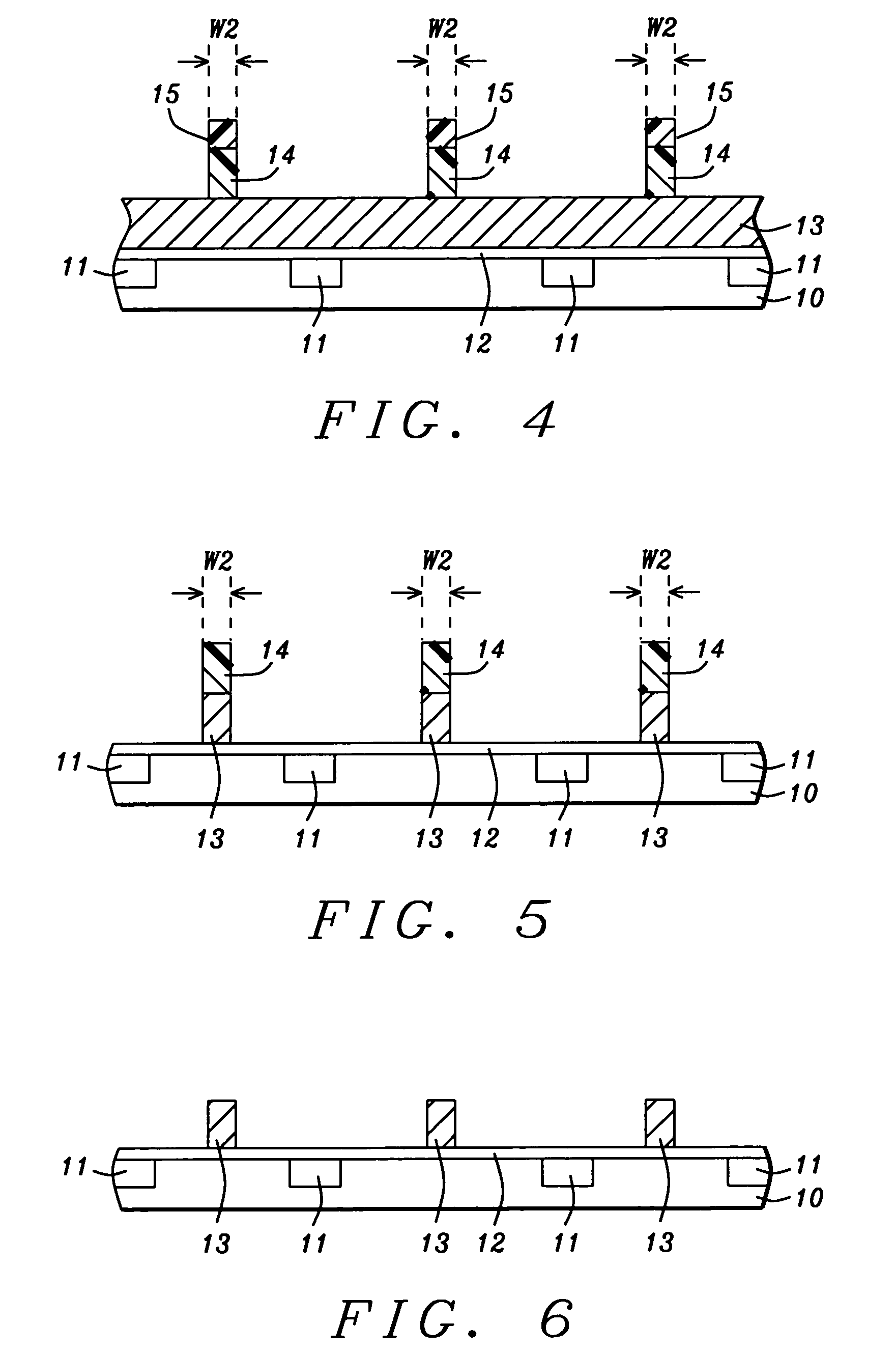

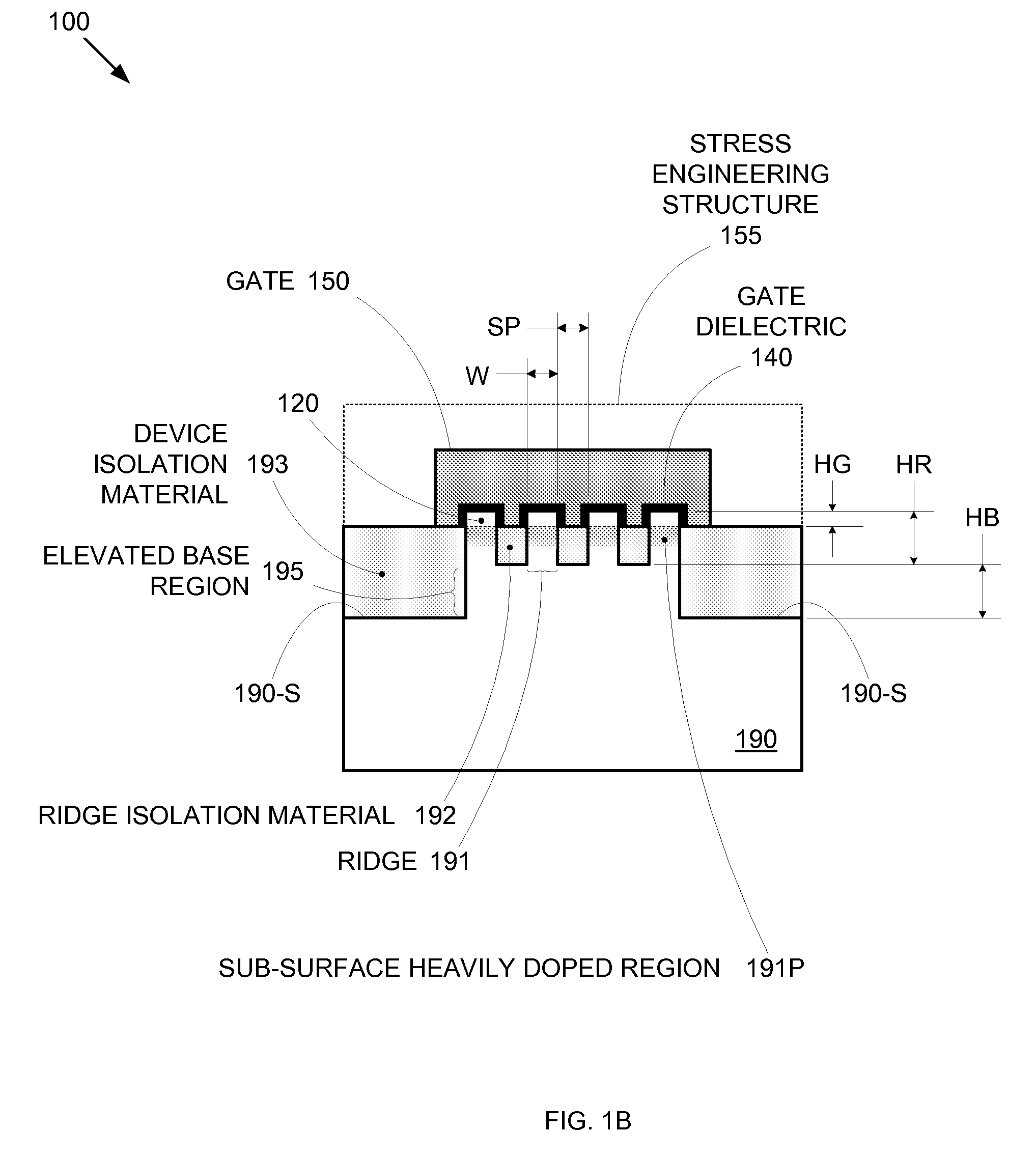

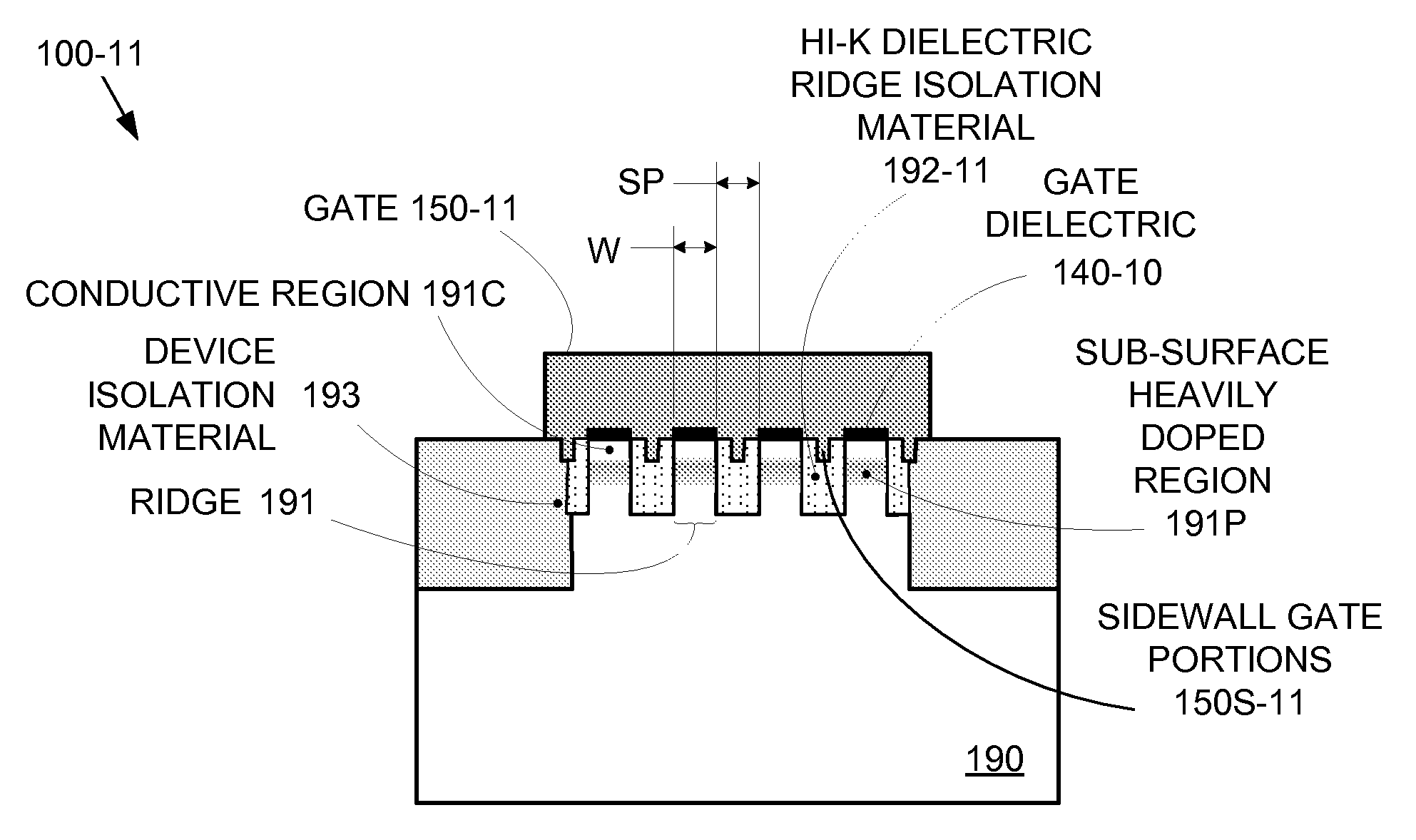

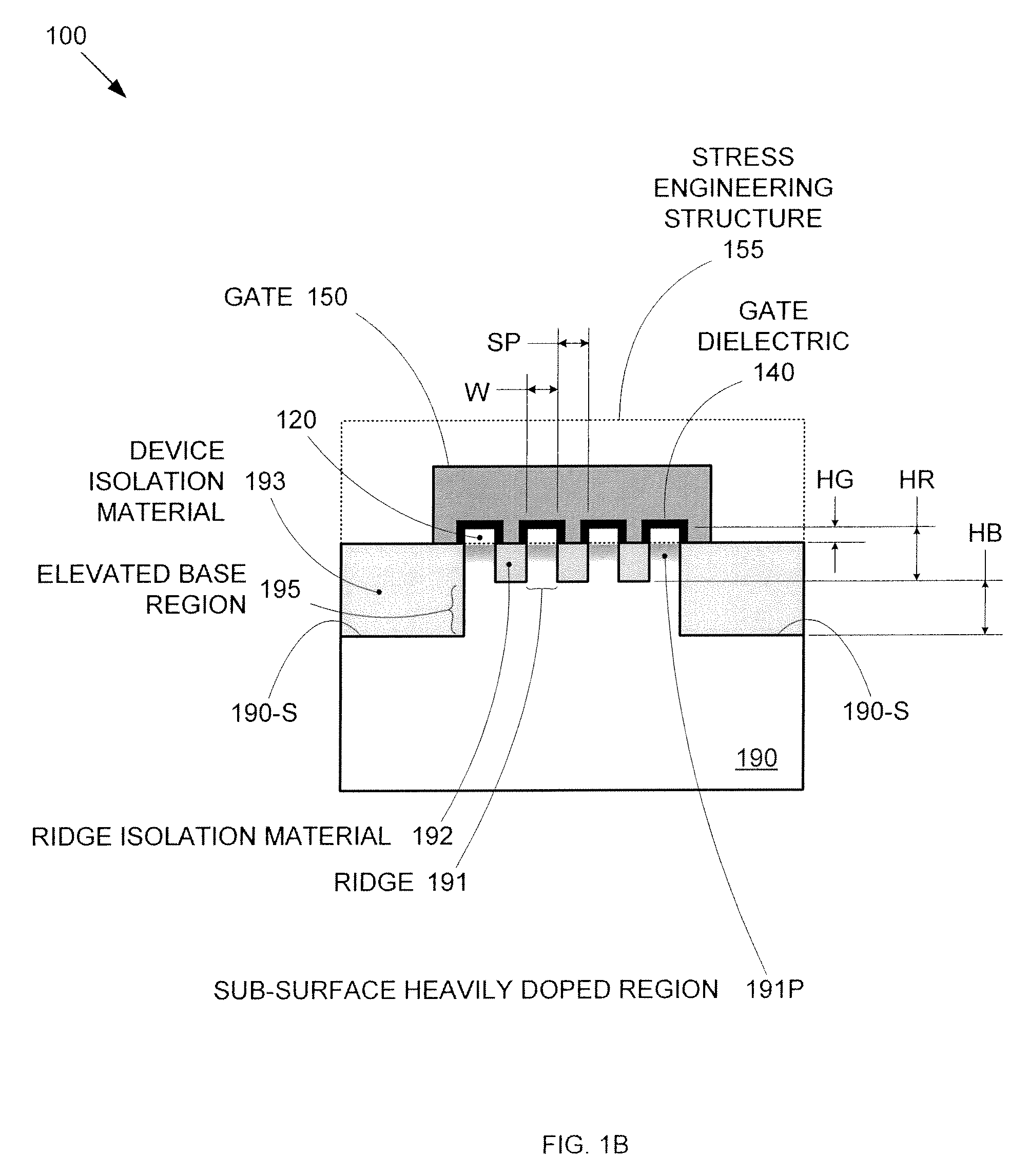

Enhanced Segmented Channel MOS Transistor with Multi Layer Regions

ActiveUS20070120156A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Phosphorus Containing Si Epitaxial Layers in N-Type Source/Drain Junctions

ActiveUS20080182075A1Keep the pressureLayered productsSemiconductor/solid-state device manufacturingMOSFETHigh concentration

Methods for formation of epitaxial layers containing n-doped silicon are disclosed. Specific embodiments pertain to the formation and treatment of epitaxial layers in semiconductor devices, for example, Metal Oxide Semiconductor Field Effect Transistor (MOSFET) devices. In specific embodiments, the formation of the n-doped epitaxial layer involves exposing a substrate in a process chamber to deposition gases including a silicon source, a carbon source and an n-dopant source. An epitaxial layer may have considerable tensile stress which may be created in a significant amount by a high concentration of n-dopant. A layer having n-dopant may also have substitutional carbon. Phosphorus as an n-dopant with a high concentration is provided. A substrate having an epitaxial layer with a high level of n-dopant is also disclosed.

Owner:APPLIED MATERIALS INC

Sequential Selective Epitaxial Growth

ActiveUS20070122954A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETCMOS

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. A multi step epitaxial process can be used to extend the ridges with different dopant types, high mobility semiconductor, and or advanced multi-layer strutures. For CMOS integrated circuits a capping layer is formed over the a first region. Epitaxial layers are formed in a second region. Then the capping layer is removed from the first region and a capping layer is formed over the second region. Epitaxial layers can than be formed in the first region.

Owner:SYNOPSYS INC

Method of IC production using corrugated substrate

ActiveUS7265008B2Improve performance consistencyImprove performanceLaser detailsSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

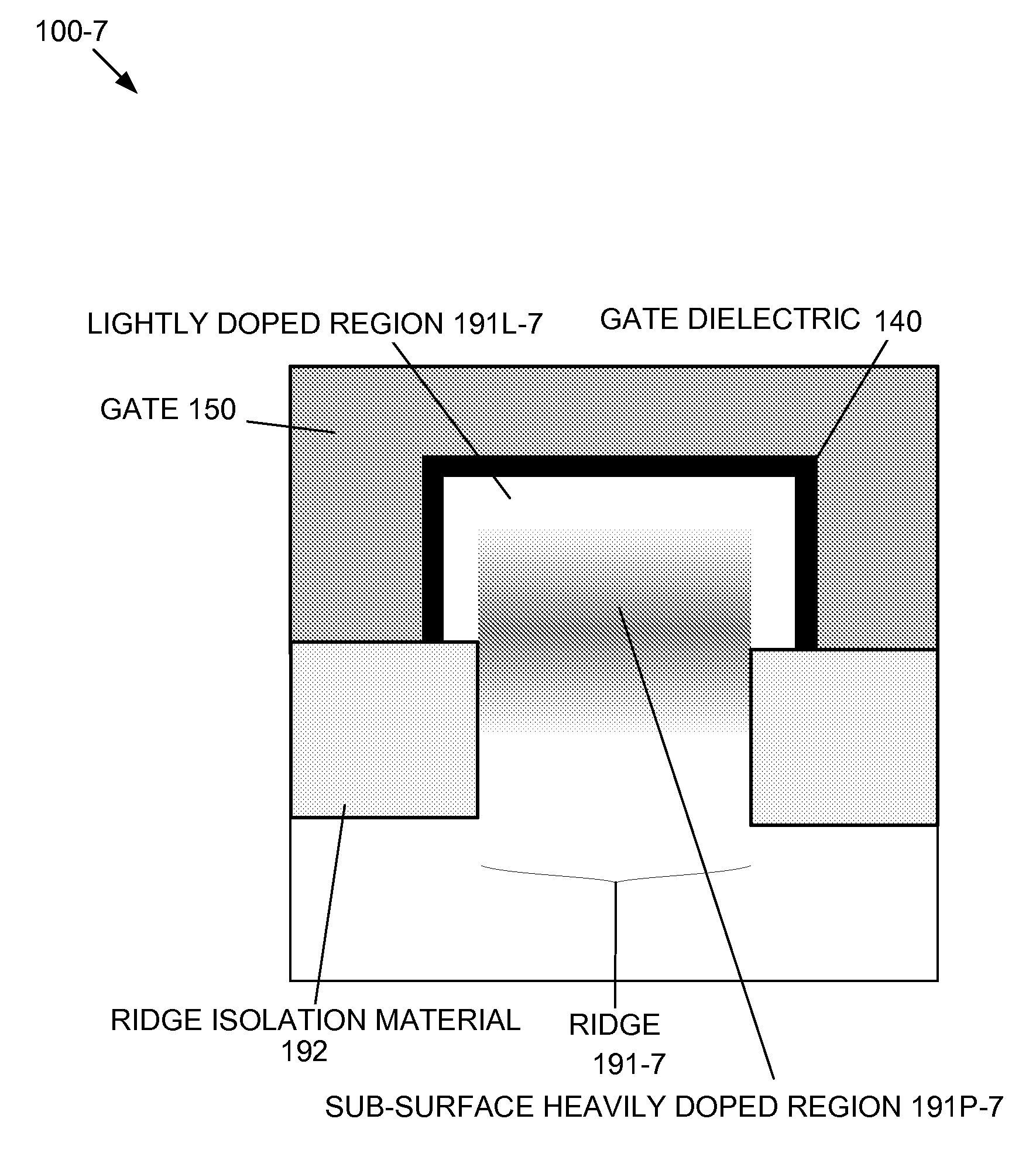

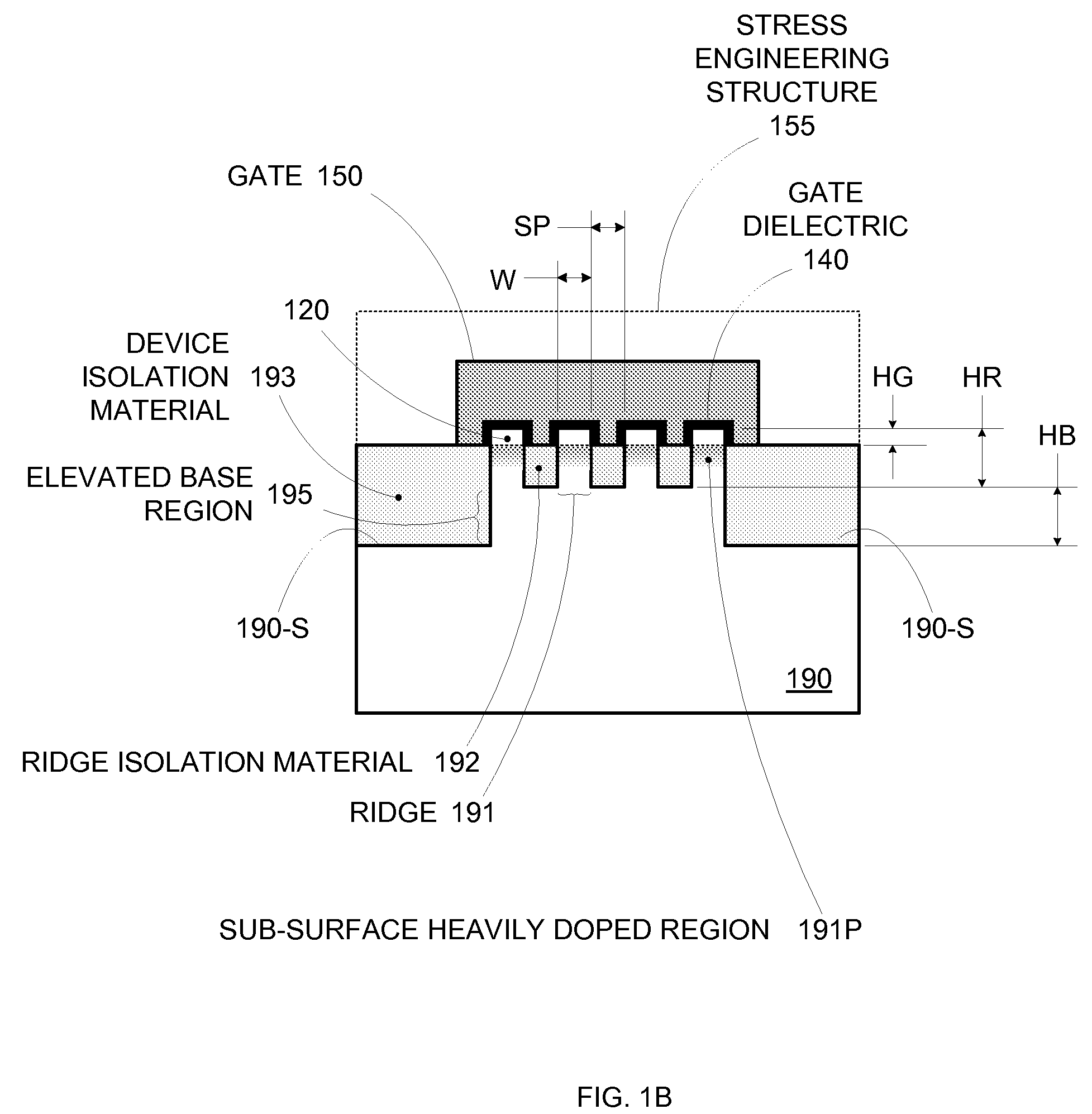

Enhanced segmented channel MOS transistor with narrowed base regions

ActiveUS7508031B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably produced. Ridges on the corrugated substrate can be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials, high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced Segmented Channel MOS Transistor with High-Permittivity Dielectric Isolation Material

ActiveUS20070122953A1Increase costImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with high-permittivity dielectric isolation material

ActiveUS7605449B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Integrated Circuit On Corrugated Substrate

ActiveUS20070132053A1Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETSemiconductor materials

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

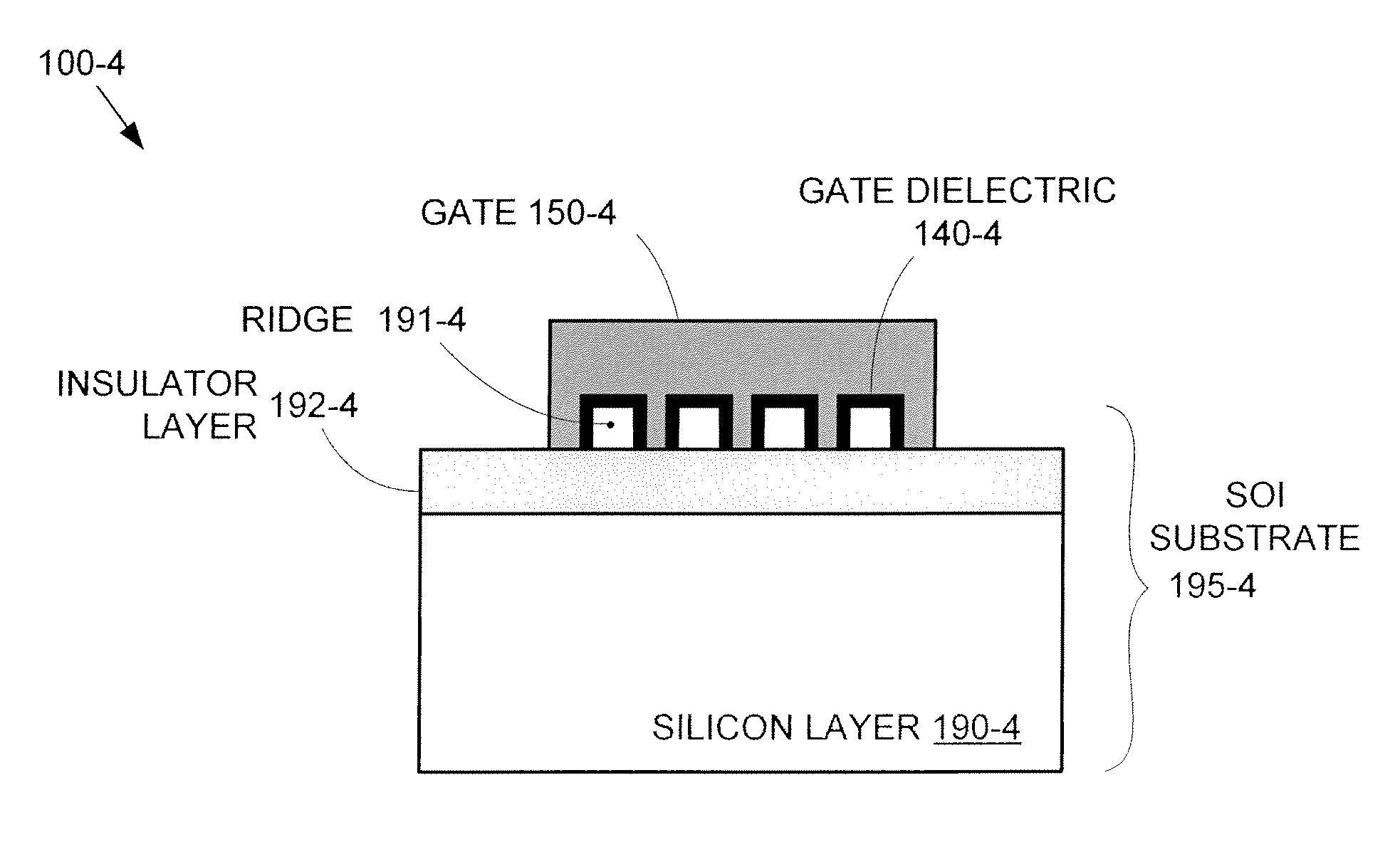

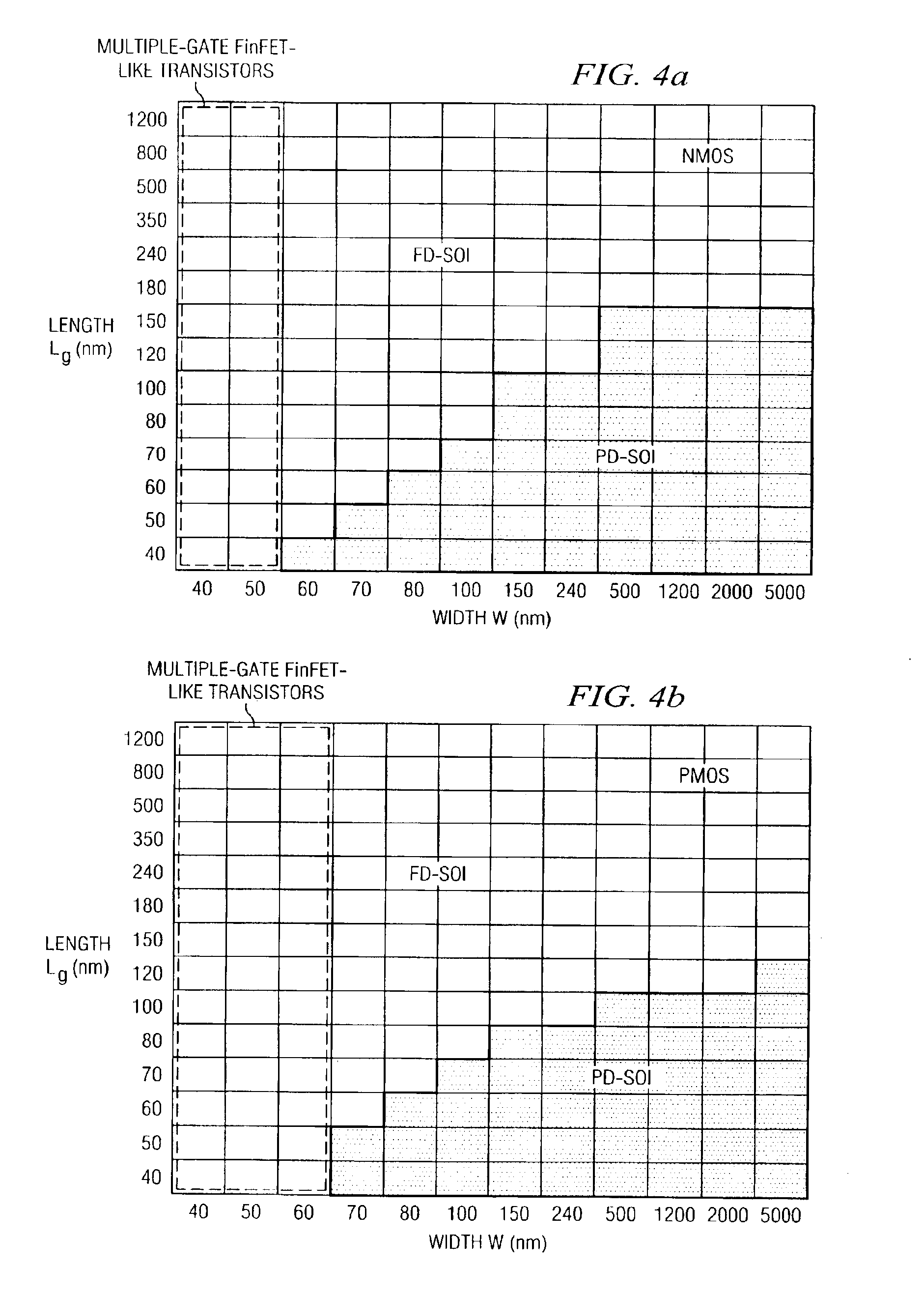

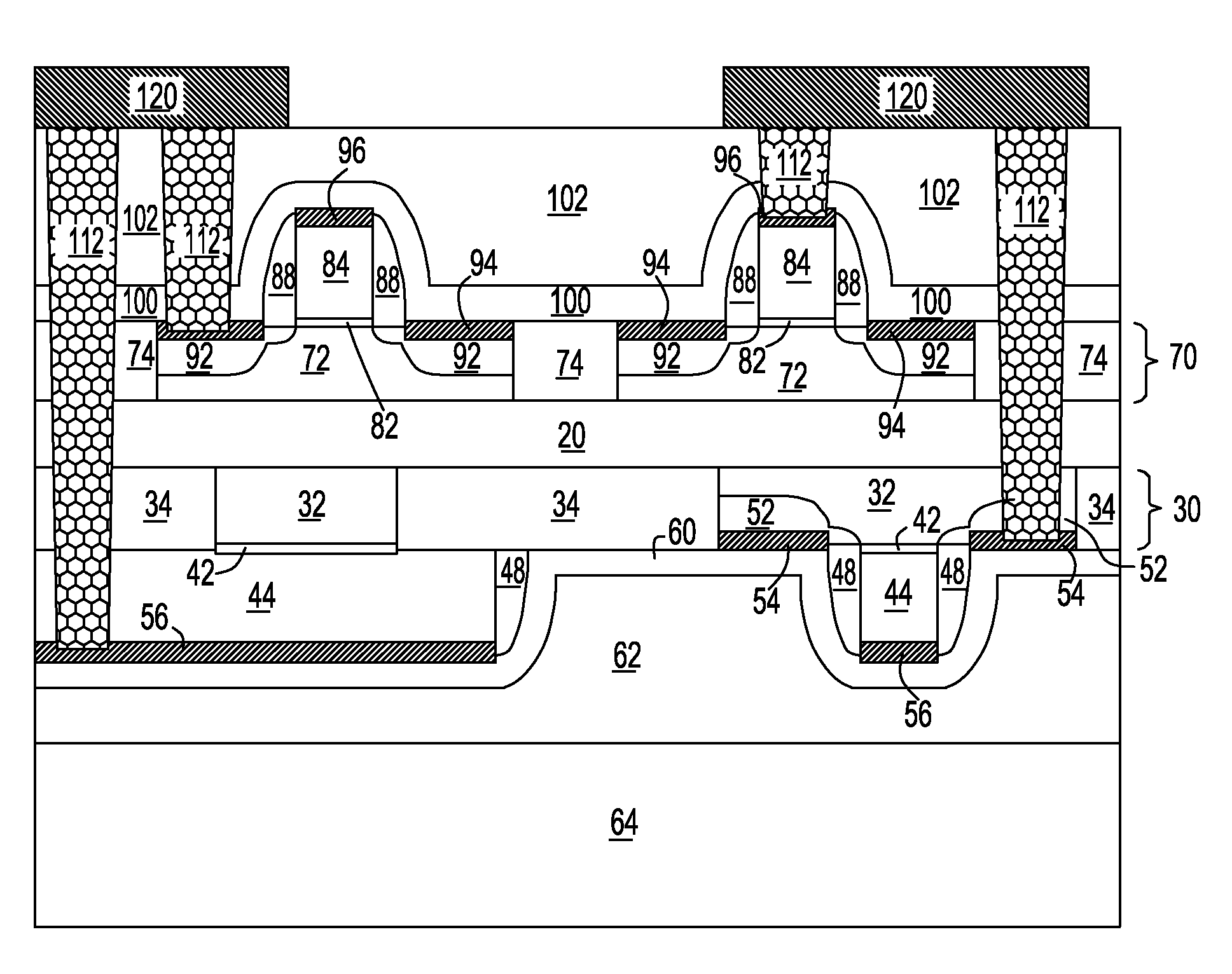

Semiconductor-on-insulator chip incorporating strained-channel partially-depleted, fully-depleted, and multiple-gate transistors

InactiveUS6867433B2Good effectSuppression of floating body effectTransistorSolid-state devicesMOSFETSemiconductor chip

In accordance with a preferred embodiment of the present invention, a silicon-on-insulator (SOI) chip includes a silicon layer of a predetermined thickness overlying an insulator layer. A multiple-gate fully-depleted SOI MOSFET including a strained channel region is formed on a first portion of the silicon layer. A planar SOI MOSFET including a strained channel region formed on another portion of the silicon layer. For example, the planar SOI MOSFET can be a planar fully-depleted SOI (FD-SOI) MOSFET or the planar SOI MOSFET can be a planar partially-depleted SOI (PD-SOI) MOSFET.

Owner:TAIWAN SEMICON MFG CO LTD

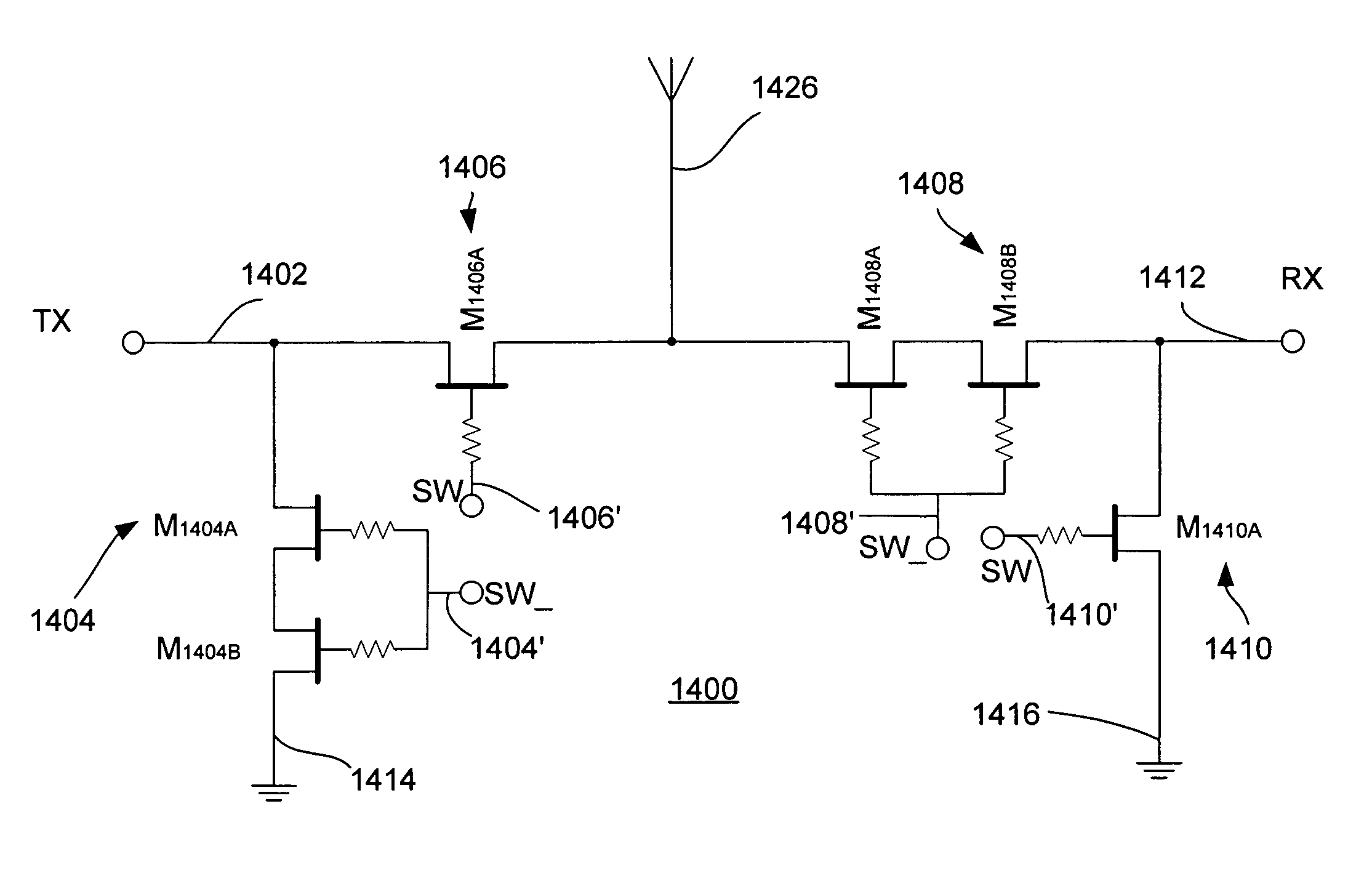

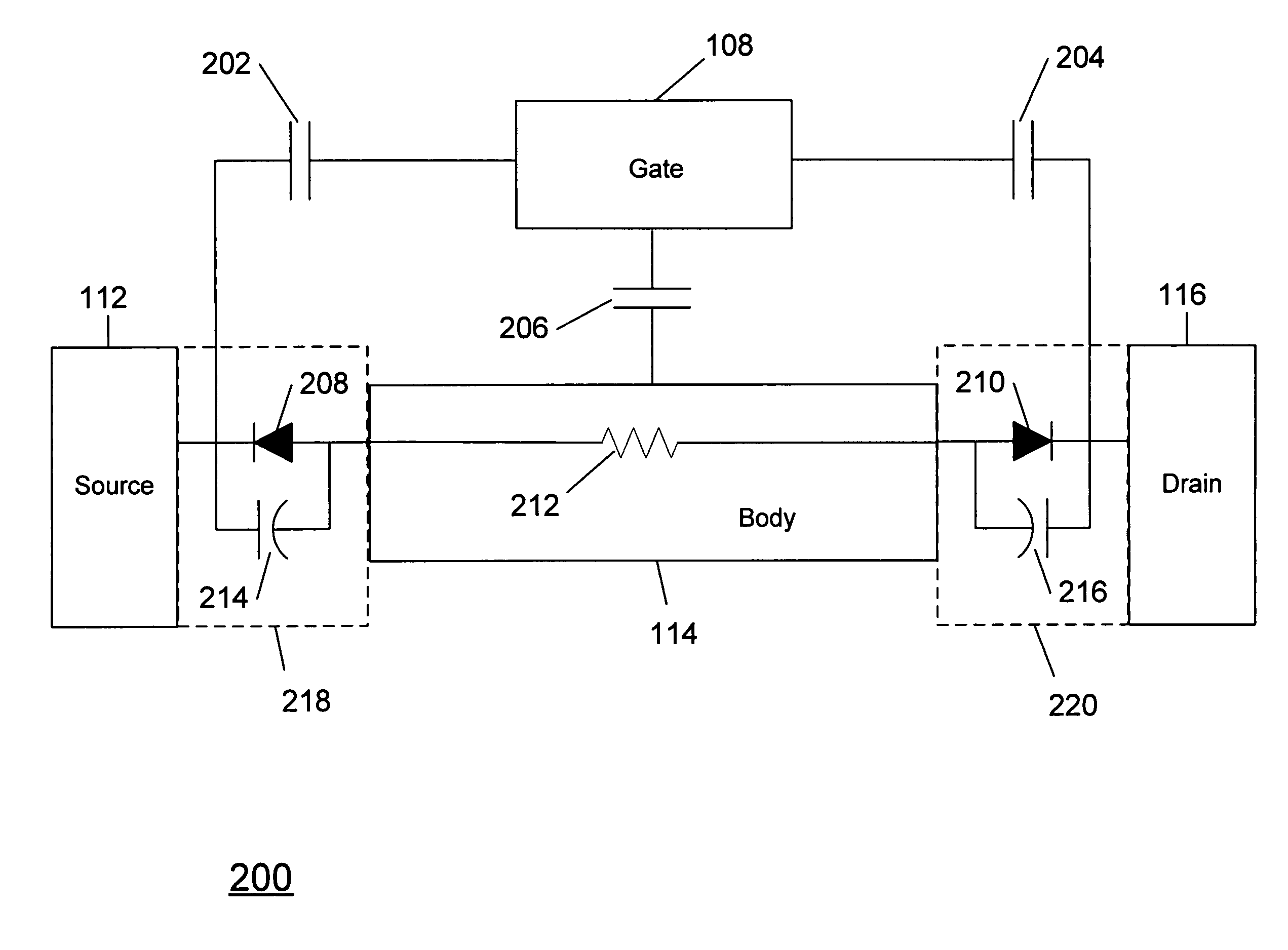

Symmetrically and asymmetrically stacked transistor group RF switch

A silicon-on-insulator (SOI) RF switch adapted for improved power handling capability using a reduced number of transistors is described. In one embodiment, an RF switch includes pairs of switching and shunting stacked transistor groupings to selectively couple RF signals between a plurality of input / output nodes and a common RF node. The switching and shunting stacked transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. In one embodiment, the transistor groupings are “symmetrically” stacked in the RF switch (i.e., the transistor groupings all comprise an identical number of transistors). In another embodiment, the transistor groupings are “asymmetrically” stacked in the RF switch (i.e., at least one transistor grouping comprises a number of transistors that is unequal to the number of transistors comprising at least one other transistor grouping). The stacked configuration of the transistor groupings enable the RF switch to withstand RF signals of varying and increased power levels. The asymmetrically stacked transistor grouping RF switch facilitates area-efficient implementation of the RF switch in an integrated circuit. Maximum input and output signal power levels can be withstood using a reduced number of stacked transistors.

Owner:PSEMI CORP

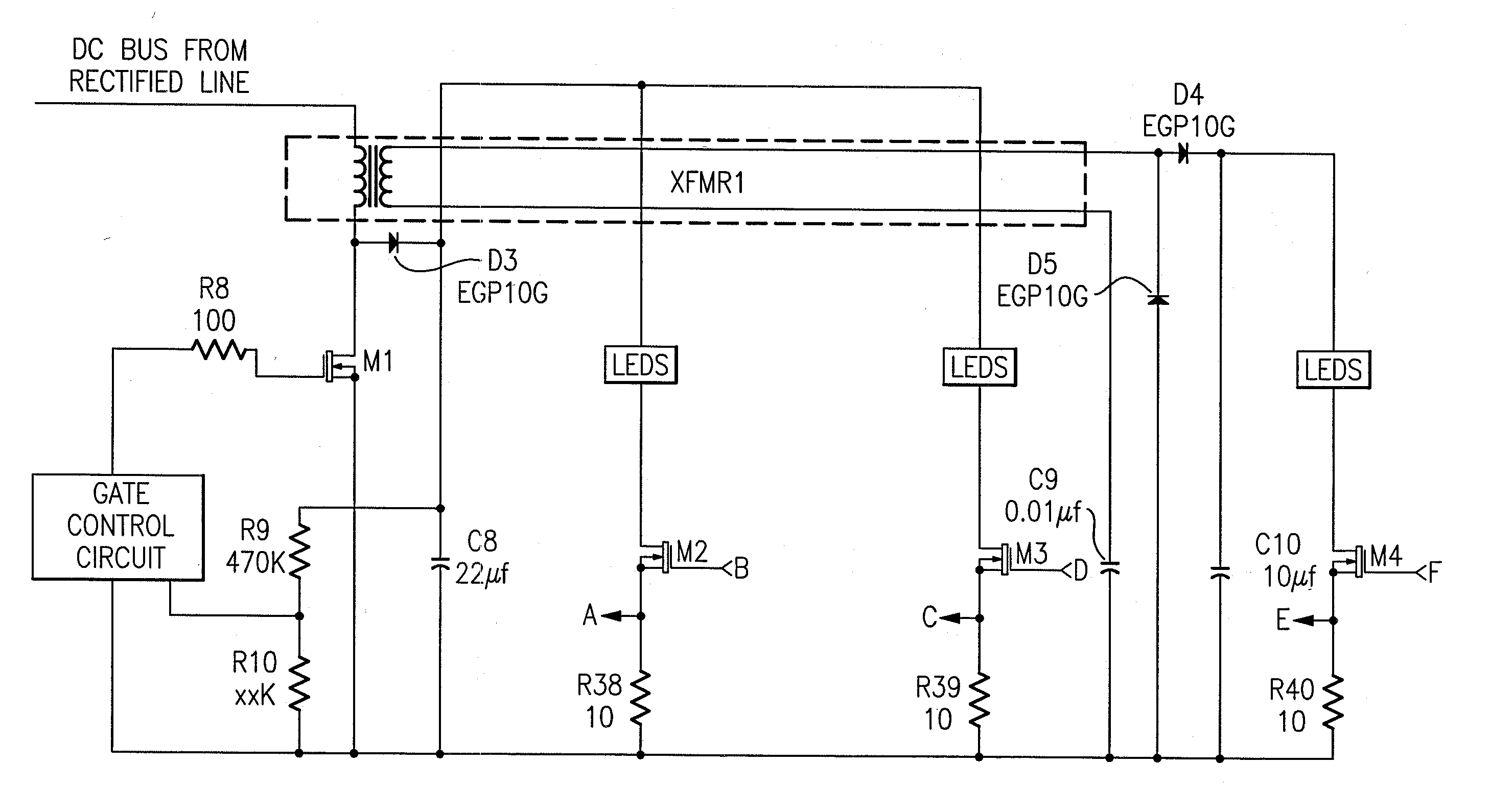

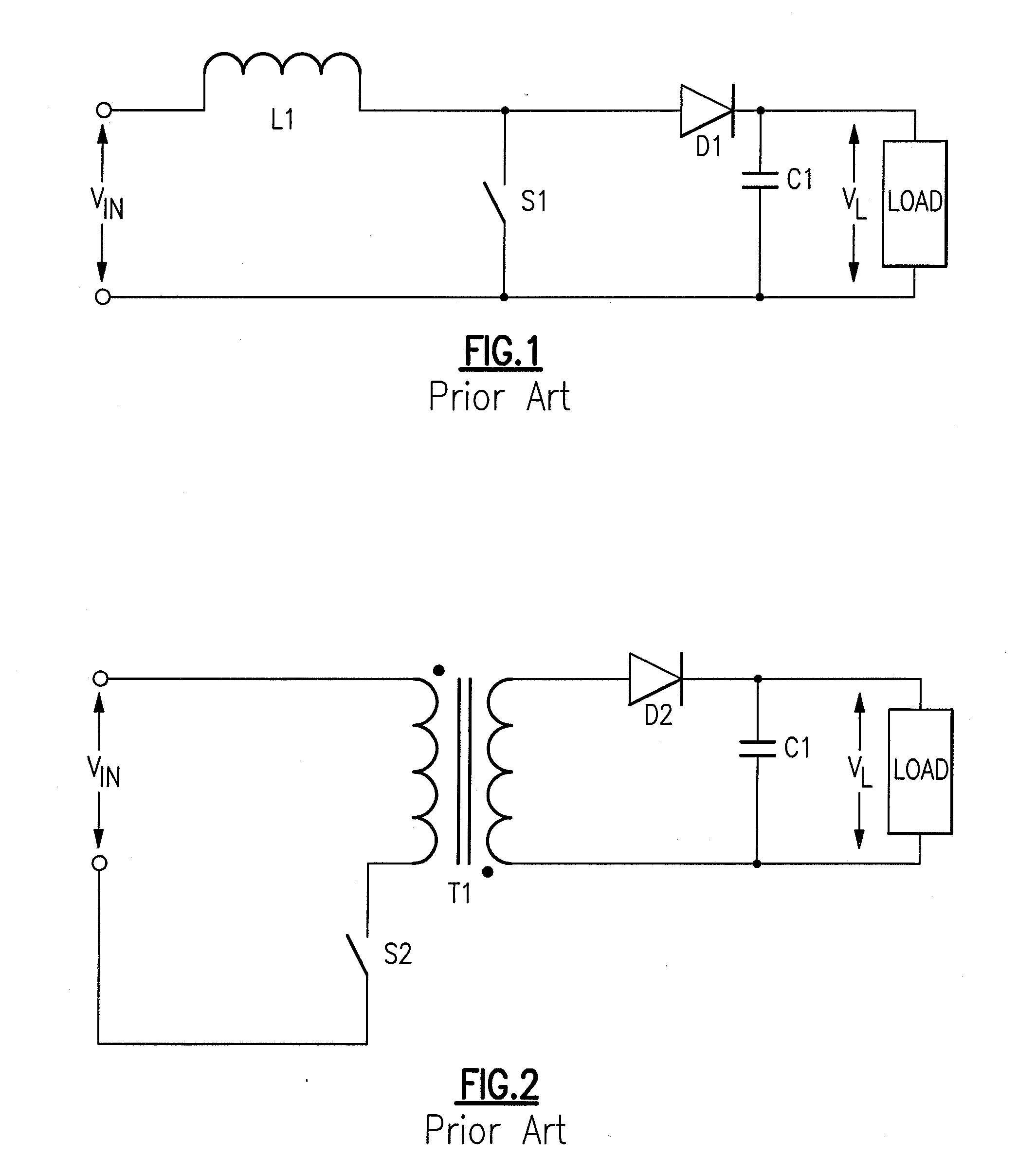

Circuitry for supplying electrical power to loads

ActiveUS20080088248A1Consumes spaceIncrease lossDc network circuit arrangementsDc-dc conversionMOSFETTransformer

A power supply, comprising a boost converter which provides voltage to a first load, and a flyback converter which provides voltage to a second load and which utilizes an inductive element of the boost converter as a primary winding of a transformer of the flyback converter. Also, a power supply comprising a MOSFET which is disposed between solid state elements and a second reference potential and which controls current flowing through the solid state elements. Also, a circuit comprising a transformer, a first circuit portion comprising the primary winding of the transformer and a second circuit portion comprising the secondary winding of the transformer. Also, a power supply comprising means for using a common transformer for providing a boost converter and a flyback converter. Also, a power supply comprising a transformer, means for providing a boost converter utilizing the transformer, and means for providing a flyback converter utilizing the transformer.

Owner:IDEAL IND LIGHTING LLC

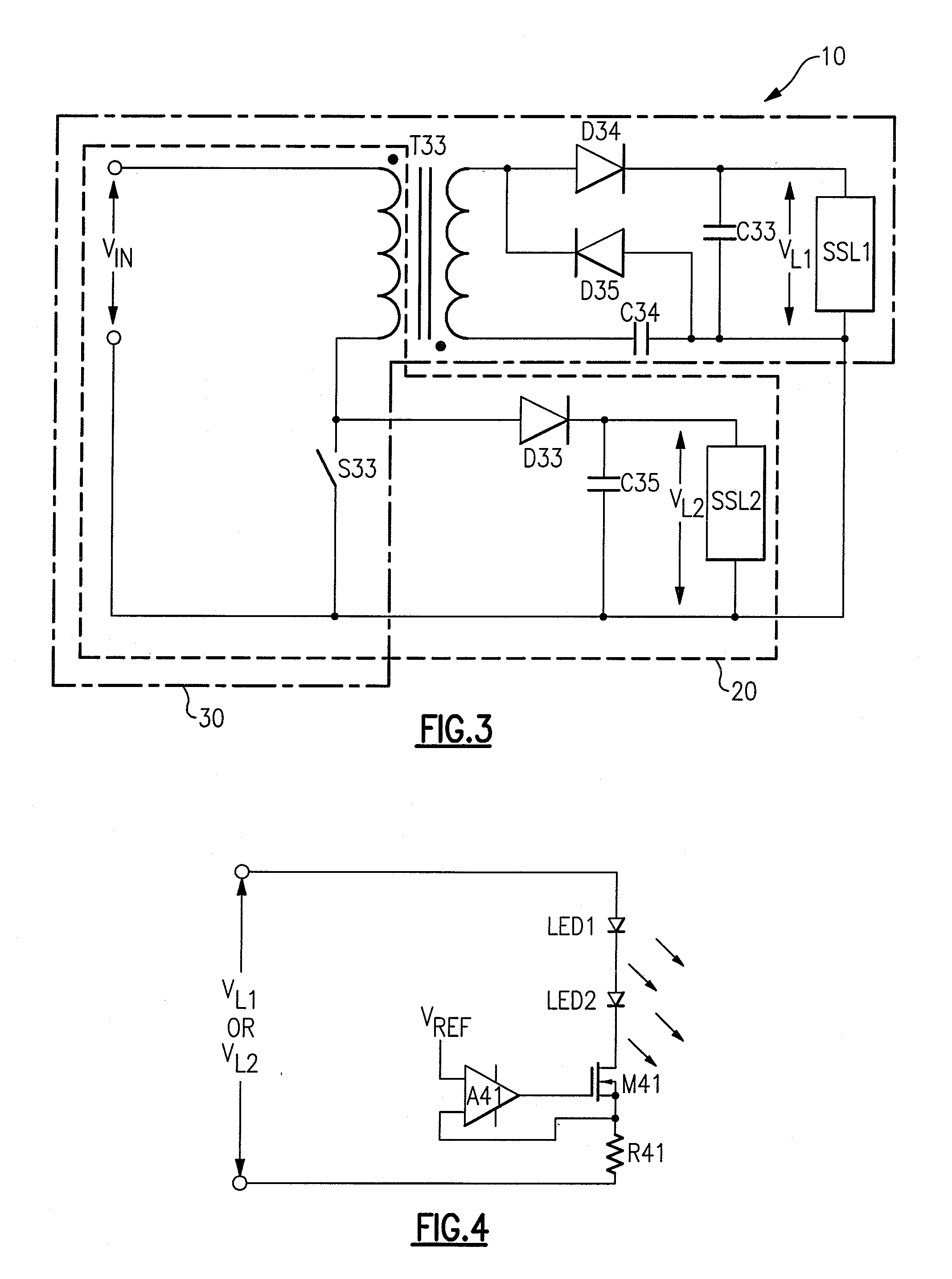

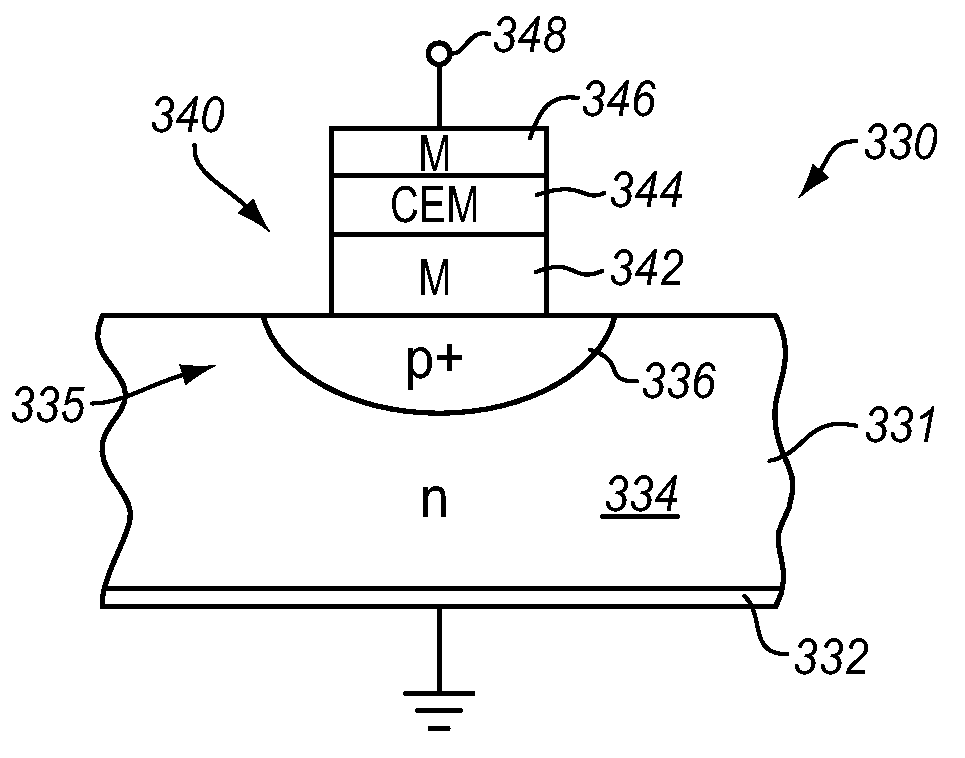

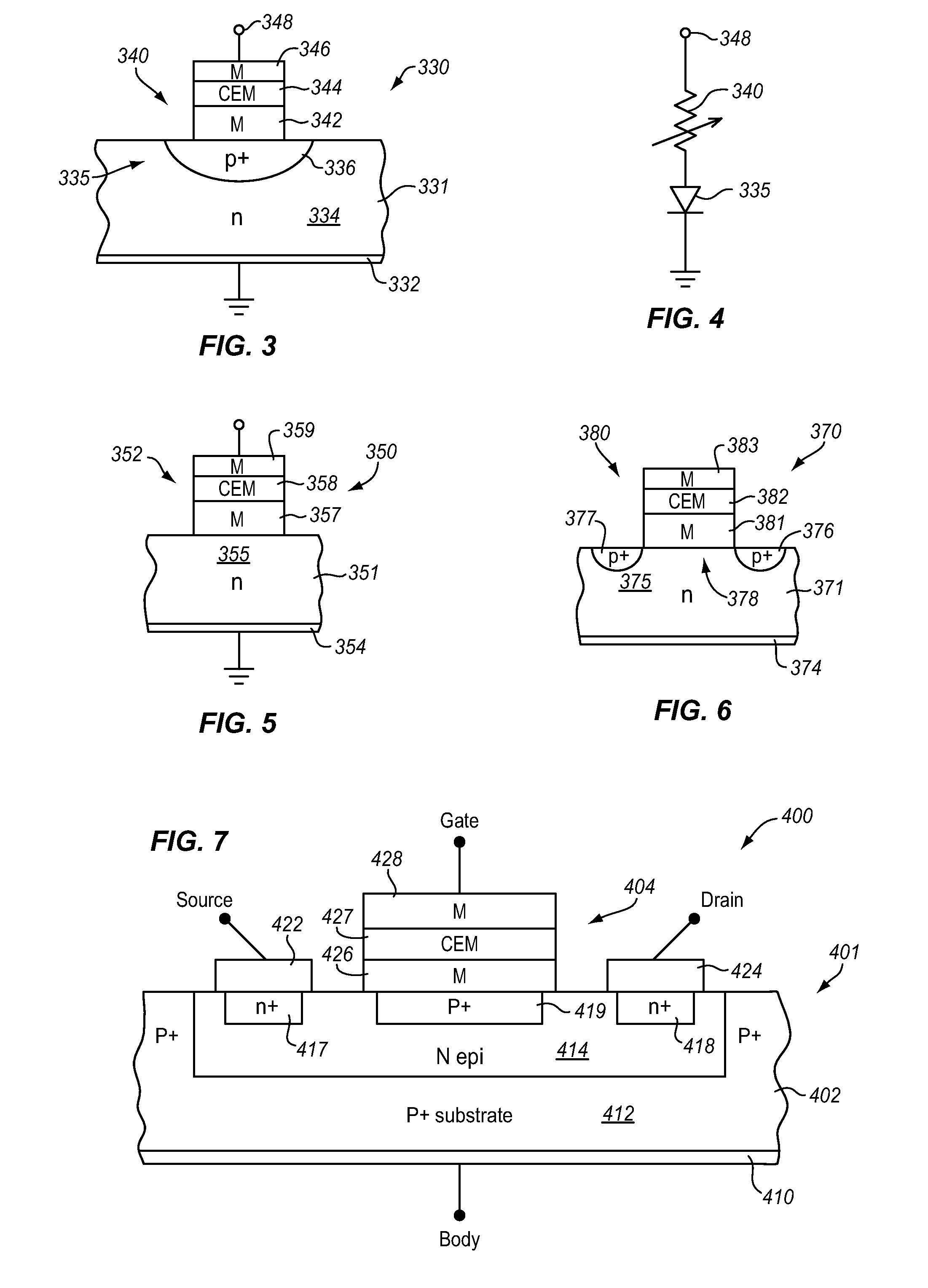

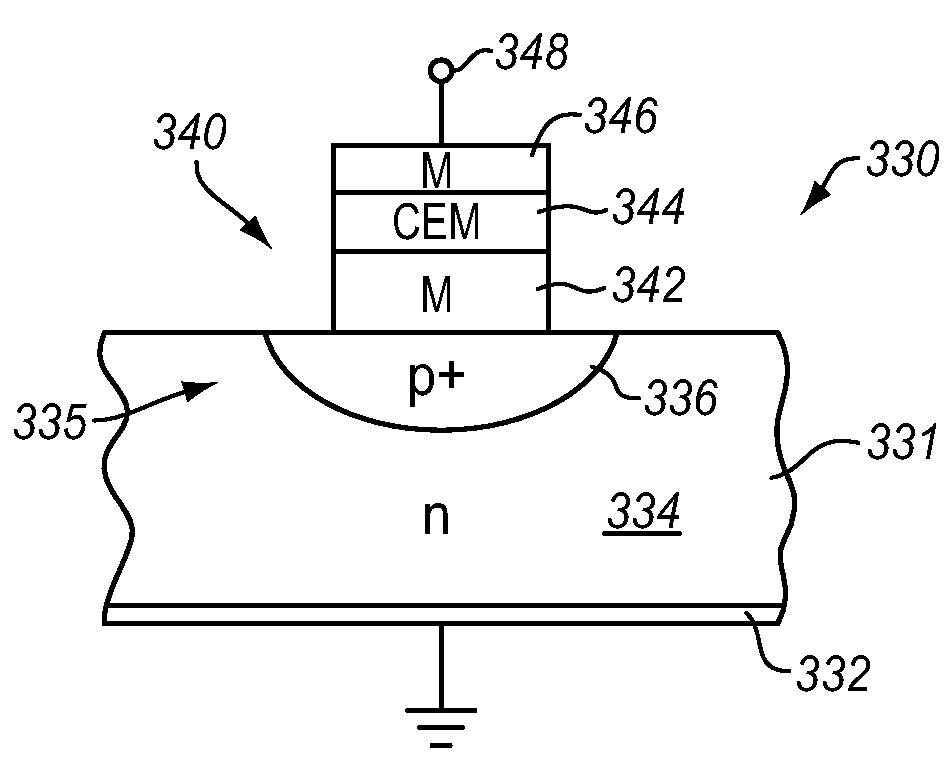

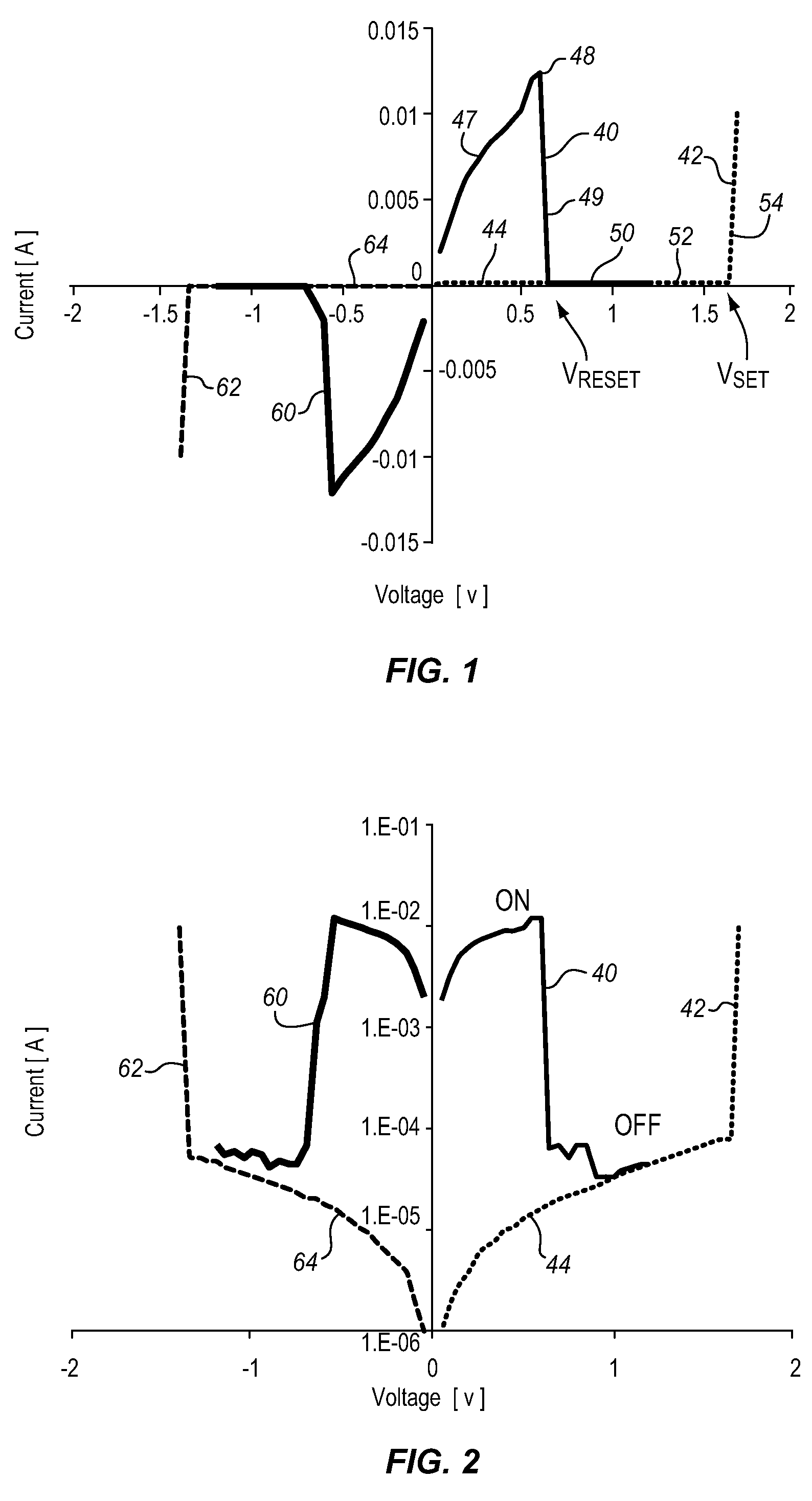

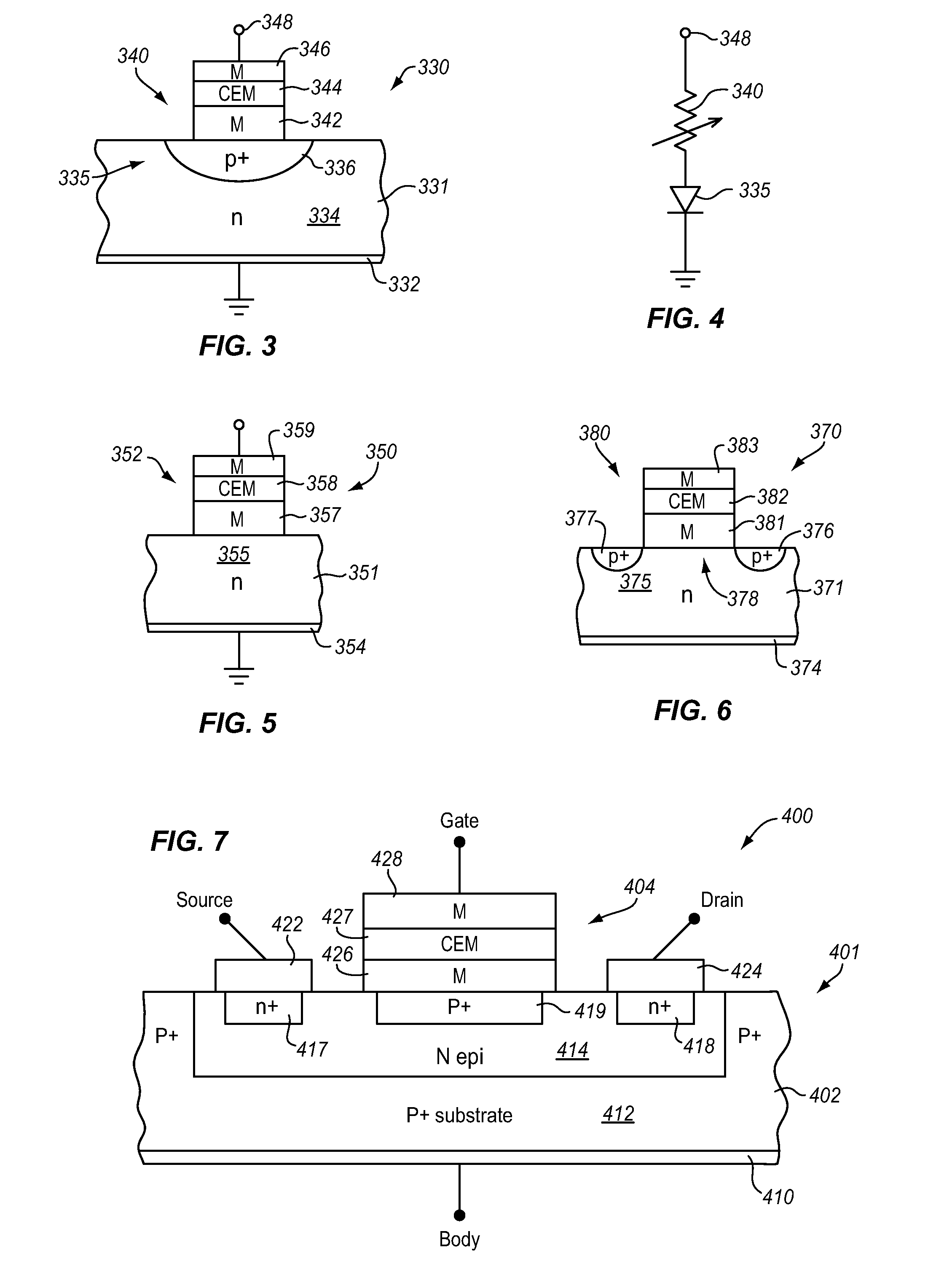

Non-volatile resistance switching memories and methods of making same

An integrated circuit memory cell including: a semiconductor having a first active area, a second active area, and a channel between the active areas; and a layer of a variable resistance material (VRM) directly above the channel. In one embodiment, there is a first conductive layer between the VRM and the channel and a second conductive layer directly above the VRM layer. The VRM preferably is a correlated electron material (CEM). The memory cell comprises a FET, such as a JFET or a MESFET. In another embodiment, there is a layer of an insulating material between the VRM and the channel. In this case, the memory cell may include a MOSFET structure.

Owner:SYMETRIX MEMORY

Method to fabricate a strained Si CMOS structure using selective epitaxial deposition of Si after device isolation formation

InactiveUS6429061B1Thickness minimizationTransistorSemiconductor/solid-state device manufacturingCMOSMOSFET

A strained Si CMOS structure is formed by steps which include forming a relaxed SiGe layer on a surface of a substrate; forming isolation regions and well implant regions in said relaxed SiGe layer; and forming a strained Si layer on said relaxed SiGe layer. These processing steps may be used in conjunction with conventional gate processing steps in forming a strained MOSFET structure.

Owner:SAMSUNG ELECTRONICS CO LTD

Two-sided semiconductor-on-insulator structures and methods of manufacturing the same

ActiveUS20080179678A1Semiconductor/solid-state device detailsSolid-state devicesMOSFETElectrical conductor

Both sides of a semiconductor-on-insulator substrate are utilized to form MOSFET structures. After forming first type devices on a first semiconductor layer, a handle wafer is bonded to the top of a first middle-of-line dielectric layer. A lower portion of a carrier substrate is then removed to expose a second semiconductor layer and to form second type devices thereupon. Conductive vias may be formed through the buried insulator layer to electrically connect the first type devices and the second type devices. Use of block masks is minimized since each side of the buried insulator has only one type of devices. Two levels of devices are present in the structure and boundary areas between different types of devices are reduced or eliminated, thereby increasing packing density of devices. The same alignment marks may be used to align the wafer either front side up or back side up.

Owner:TAIWAN SEMICON MFG CO LTD

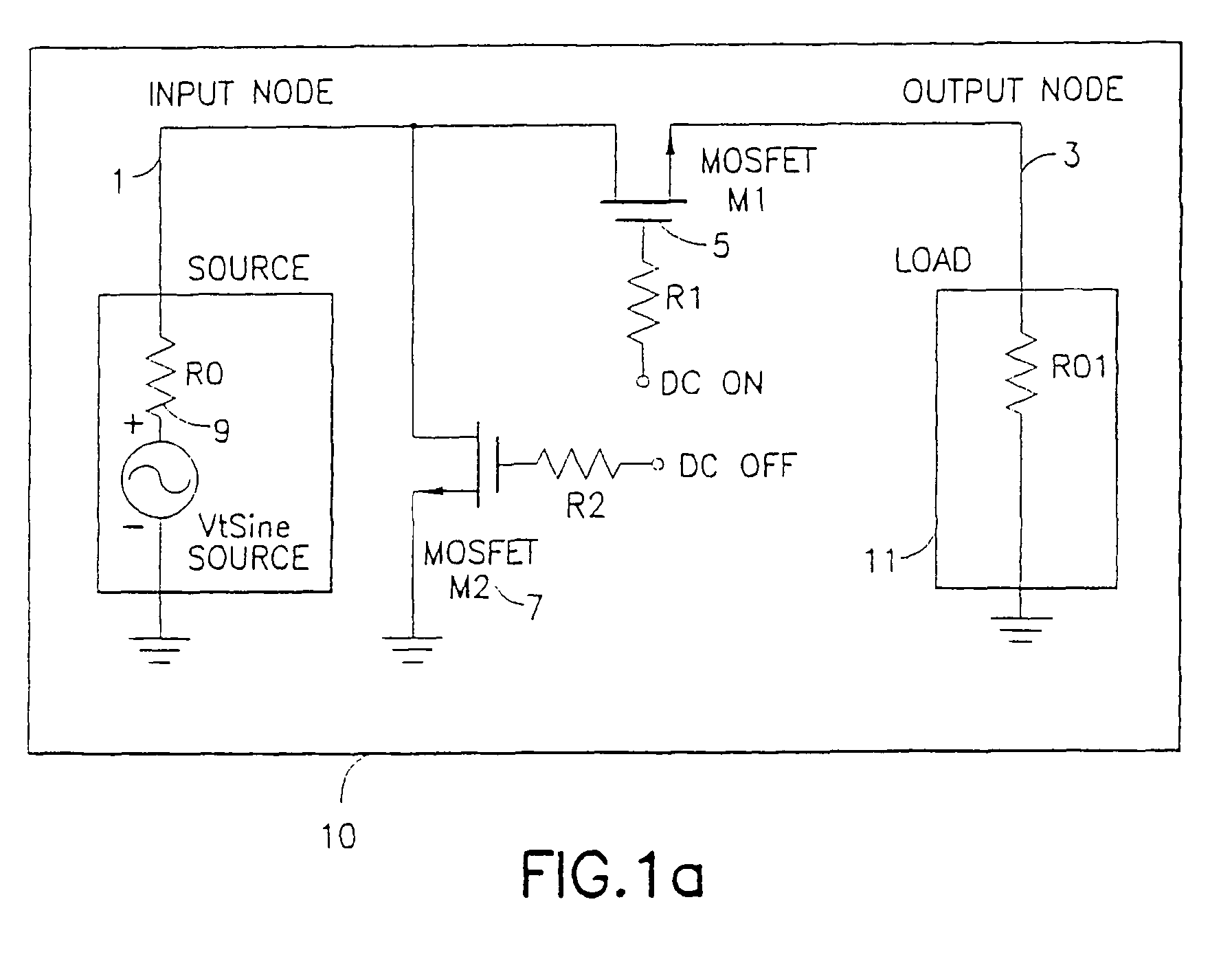

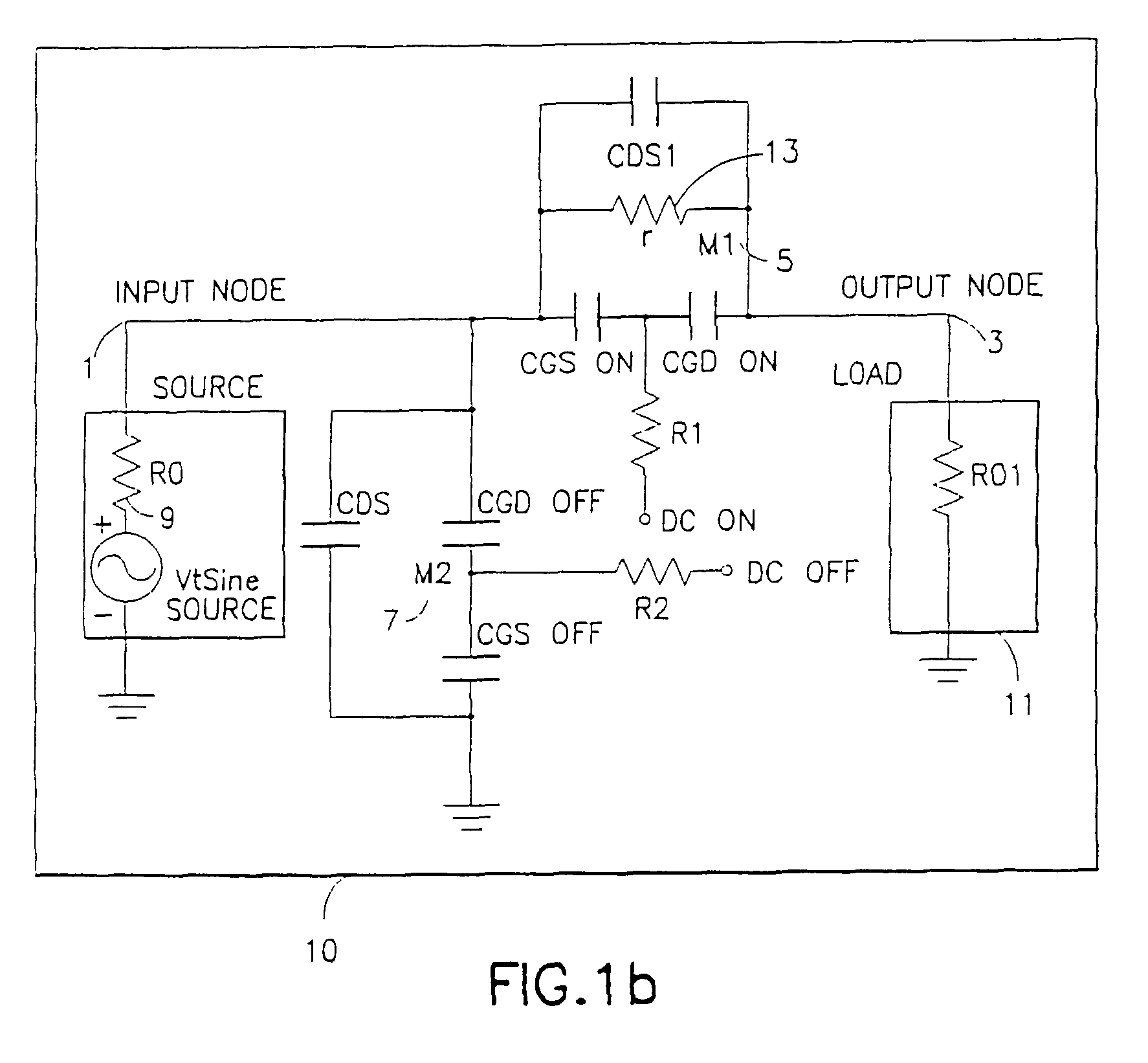

Method and apparatus for use in improving linearity of MOSFET's using an accumulated charge sink

ActiveUS7910993B2Improving nonlinear responseImprove harmonicsSolid-state devicesElectronic switchingCapacitanceMOSFET

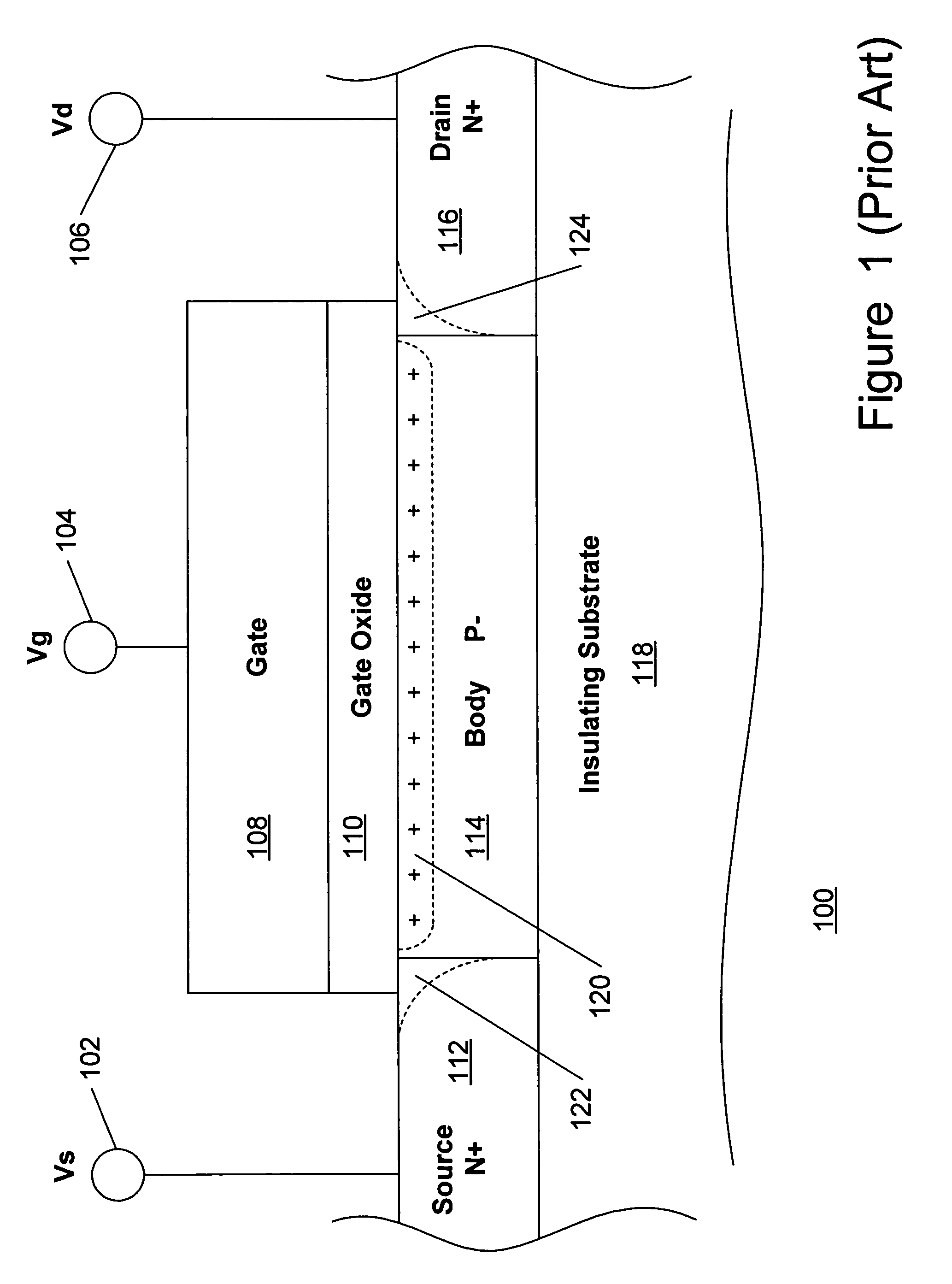

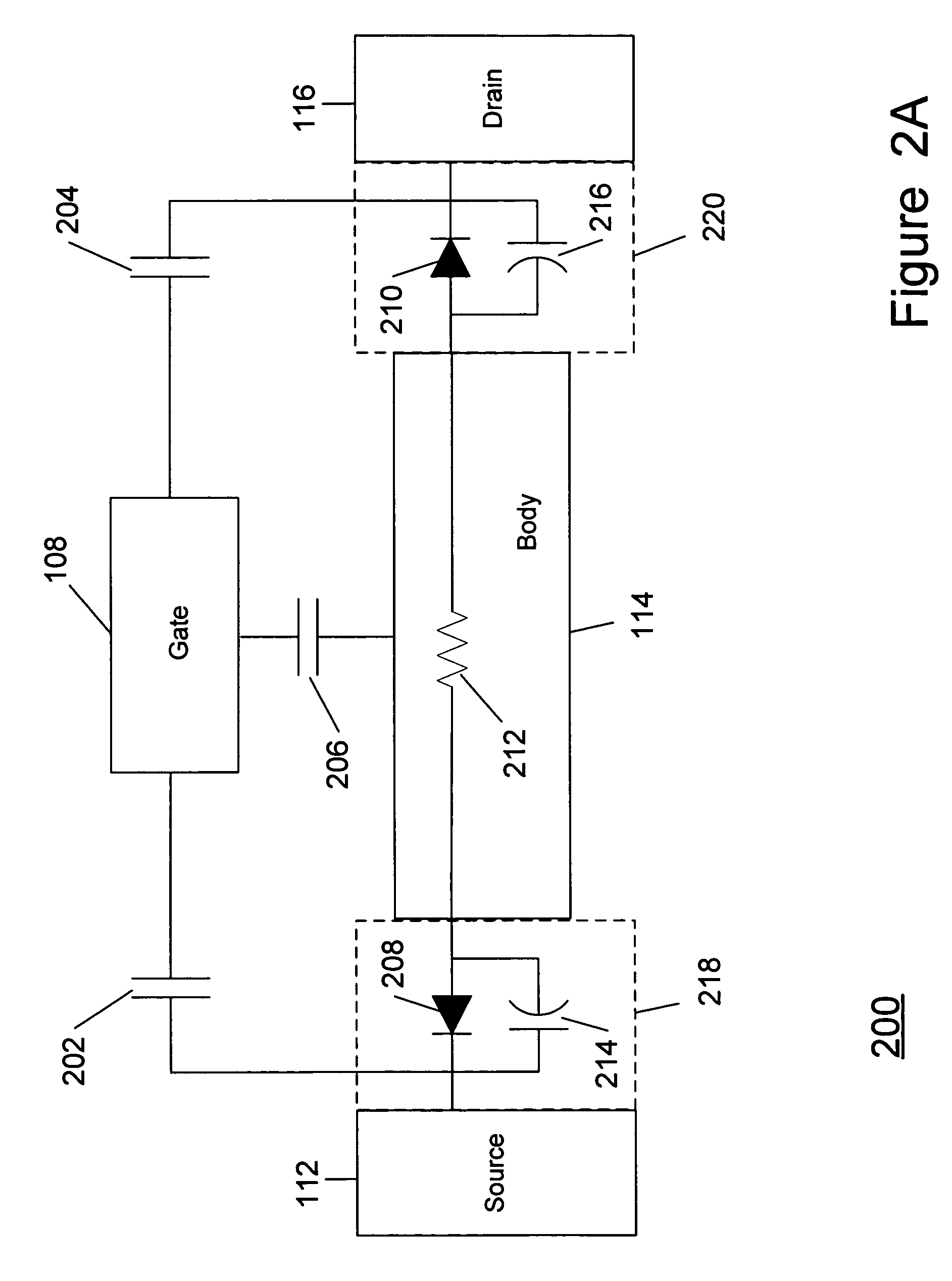

A method and apparatus for use in improving the linearity characteristics of MOSFET devices using an accumulated charge sink (ACS) are disclosed. The method and apparatus are adapted to remove, reduce, or otherwise control accumulated charge in SOI MOSFETs, thereby yielding improvements in FET performance characteristics. In one exemplary embodiment, a circuit having at least one SOI MOSFET is configured to operate in an accumulated charge regime. An accumulated charge sink, operatively coupled to the body of the SOI MOSFET, eliminates, removes or otherwise controls accumulated charge when the FET is operated in the accumulated charge regime, thereby reducing the nonlinearity of the parasitic off-state source-to-drain capacitance of the SOI MOSFET. In RF switch circuits implemented with the improved SOI MOSFET devices, harmonic and intermodulation distortion is reduced by removing or otherwise controlling the accumulated charge when the SOI MOSFET operates in an accumulated charge regime.

Owner:PSEMI CORP

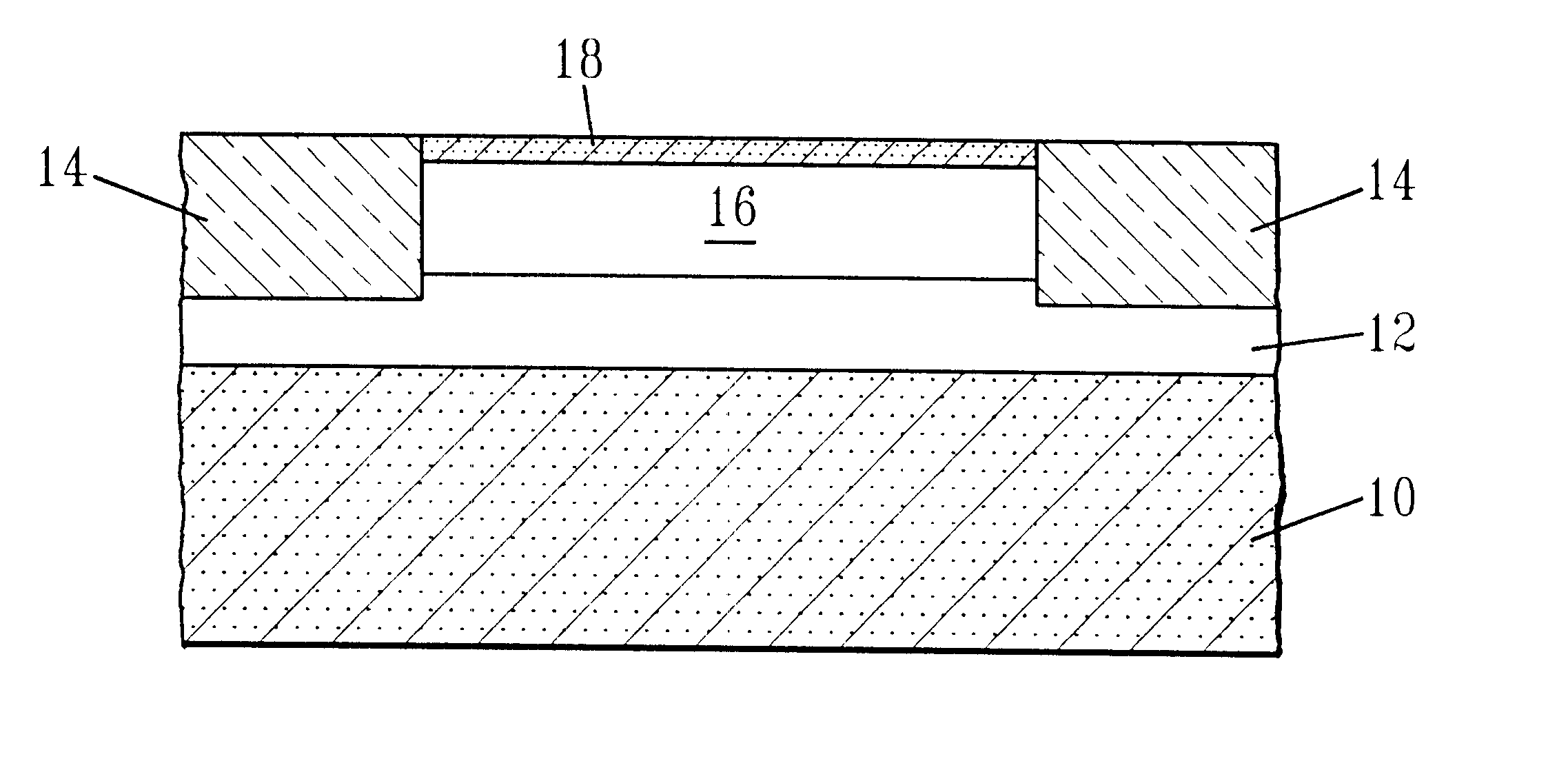

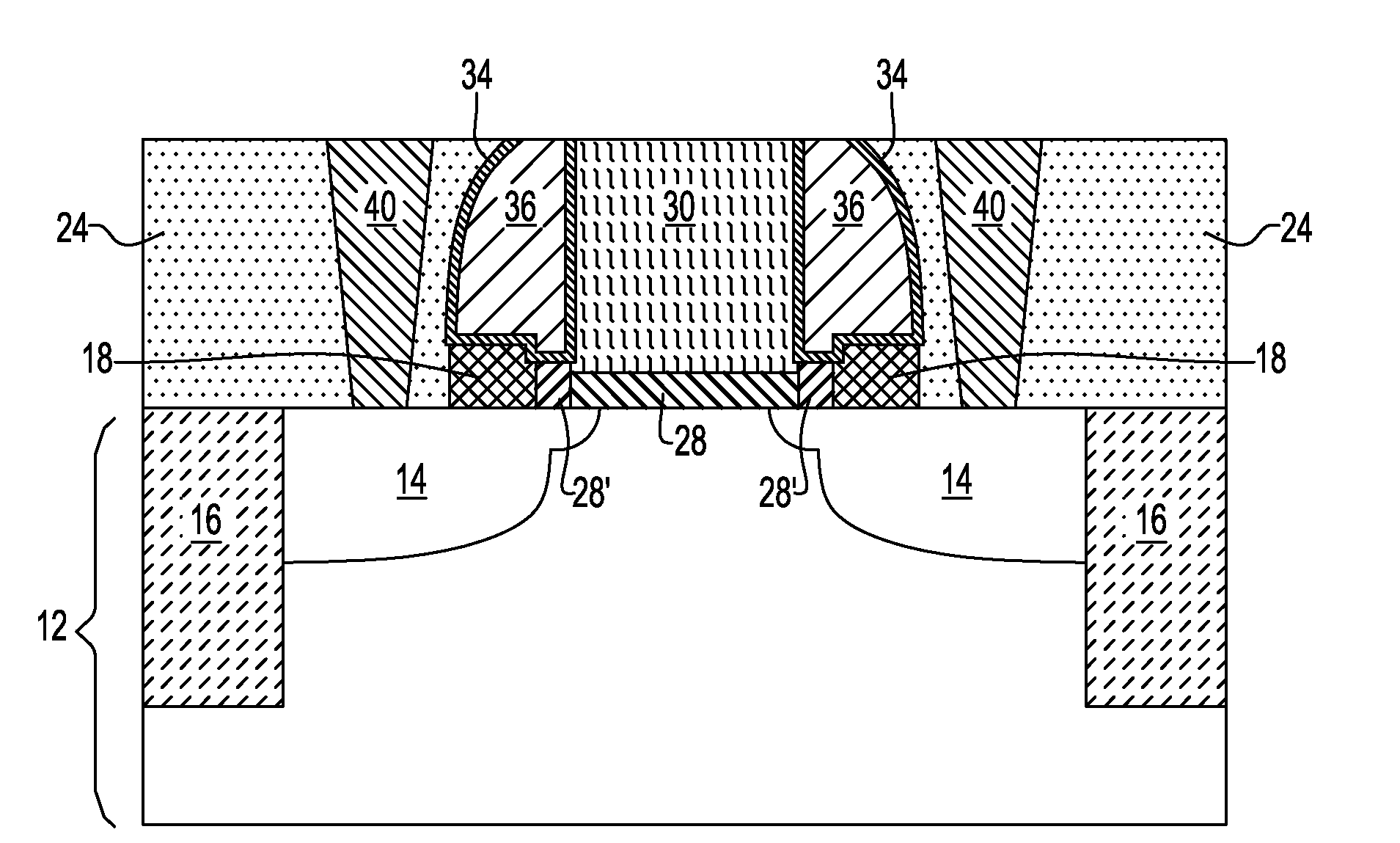

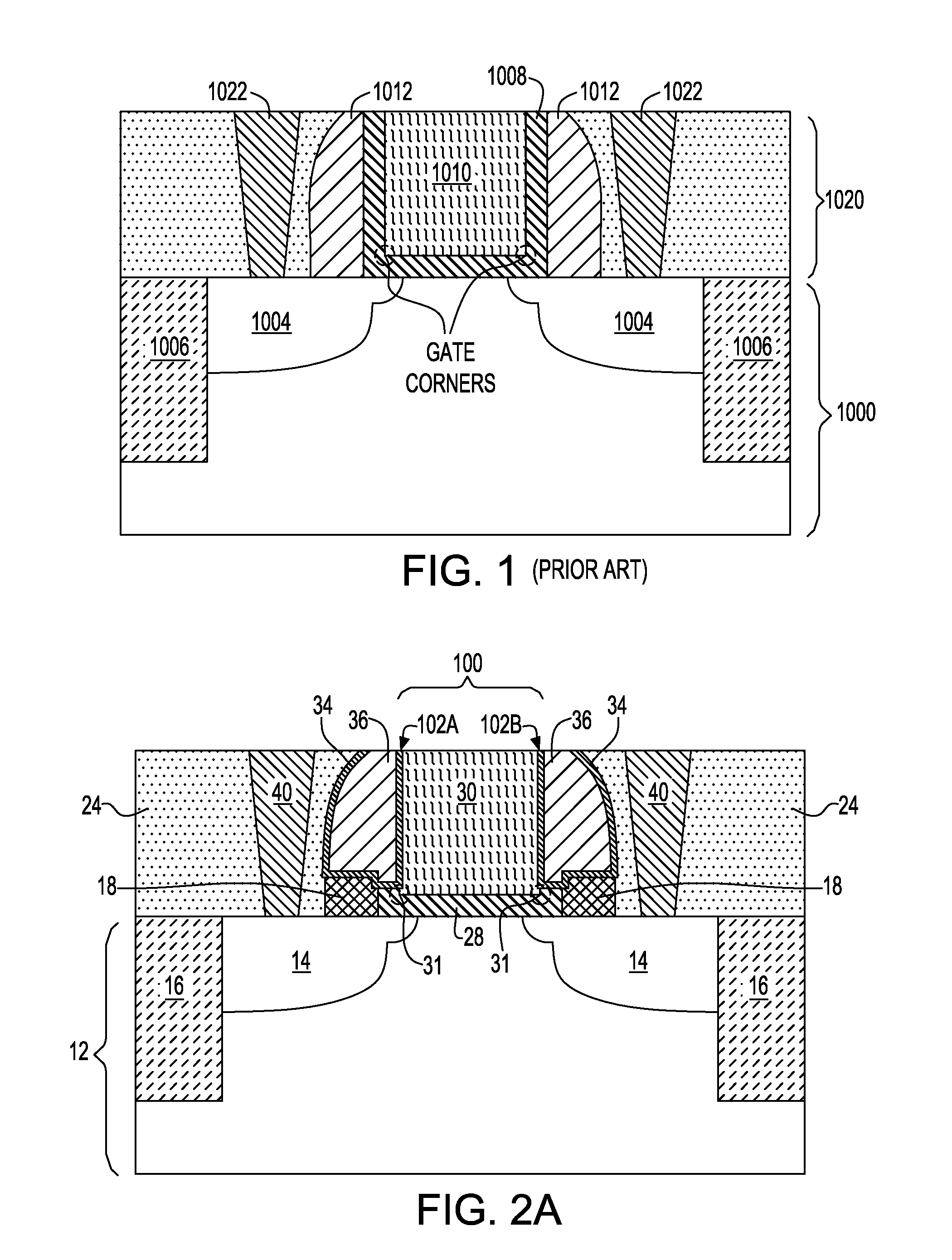

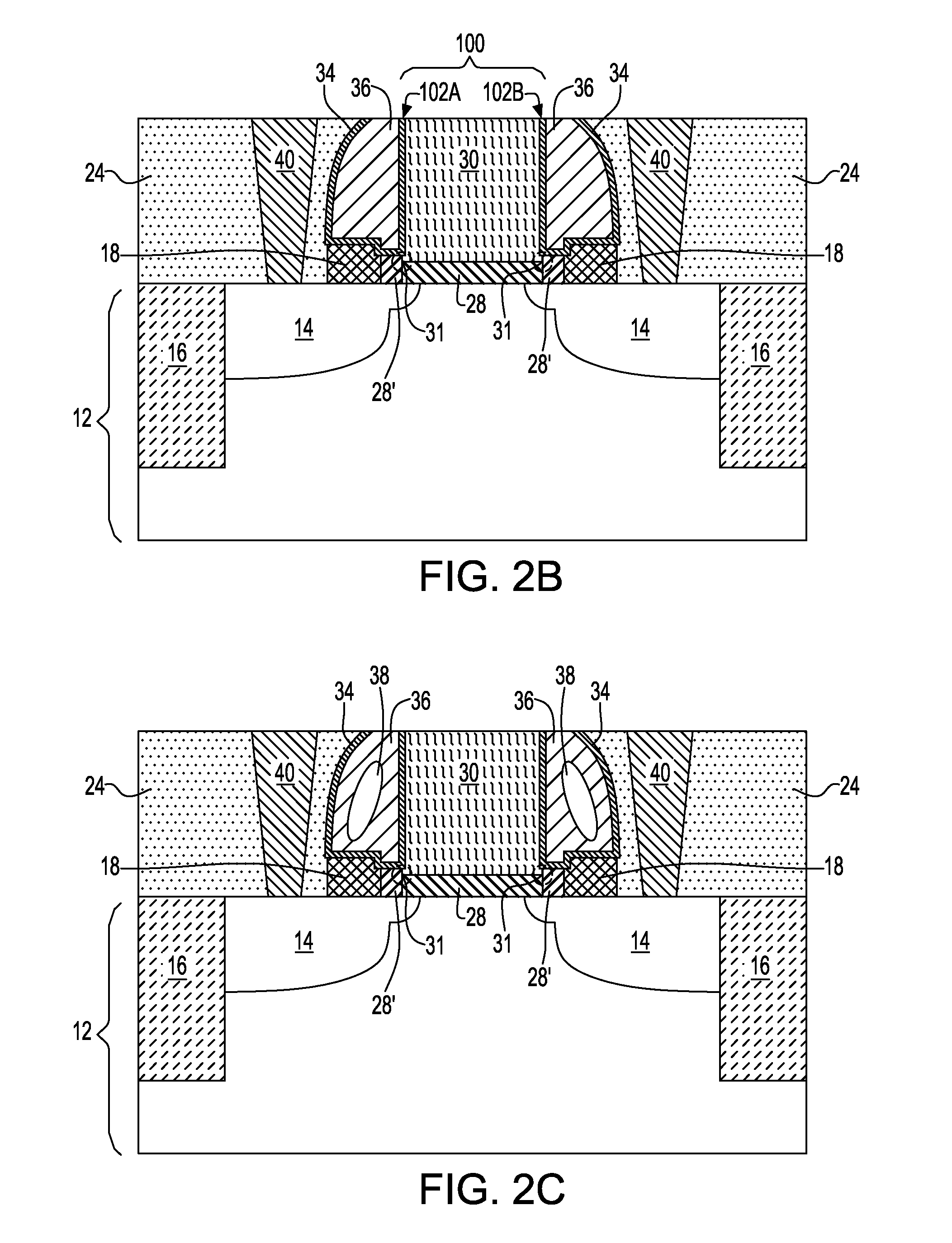

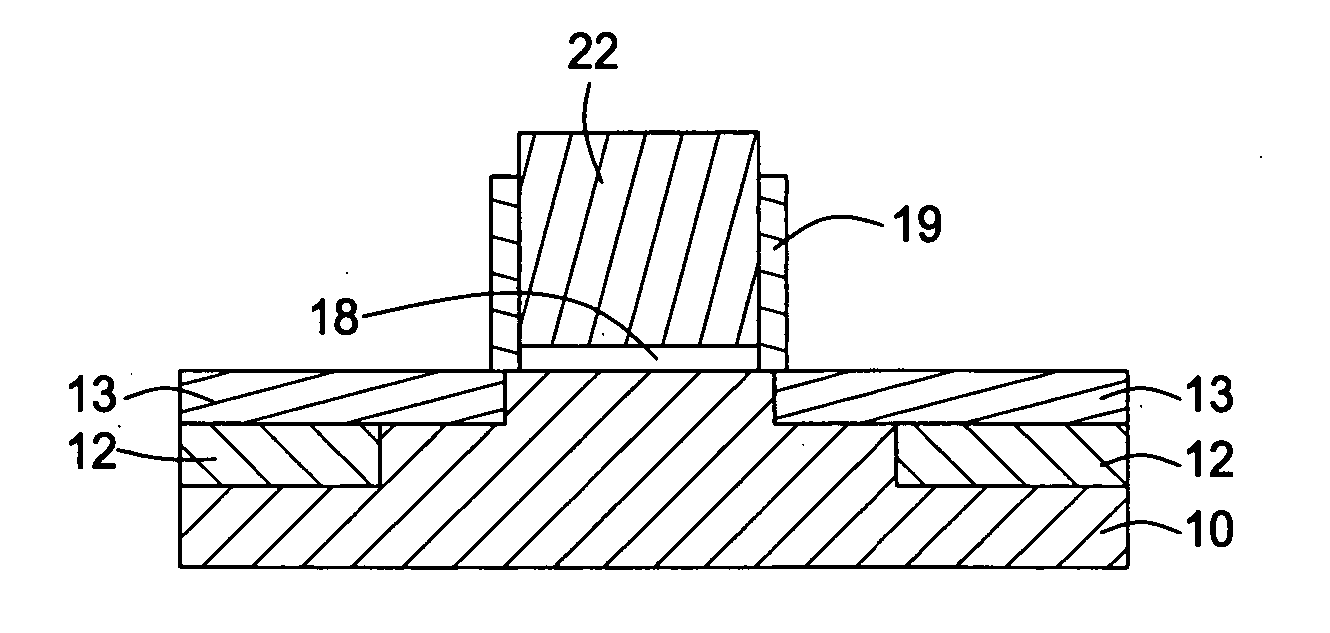

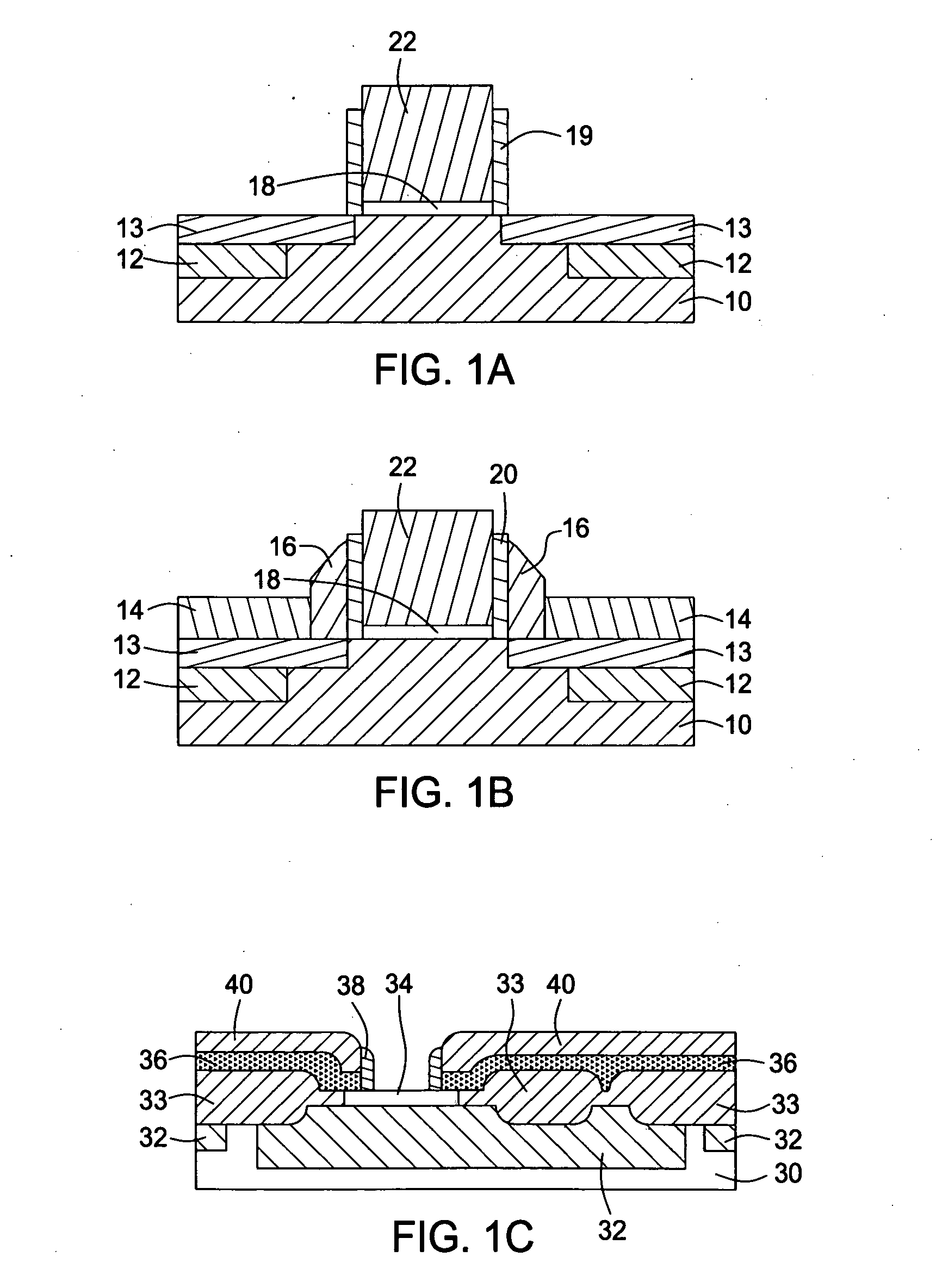

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

InactiveUS20090001480A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETElectrical conductor

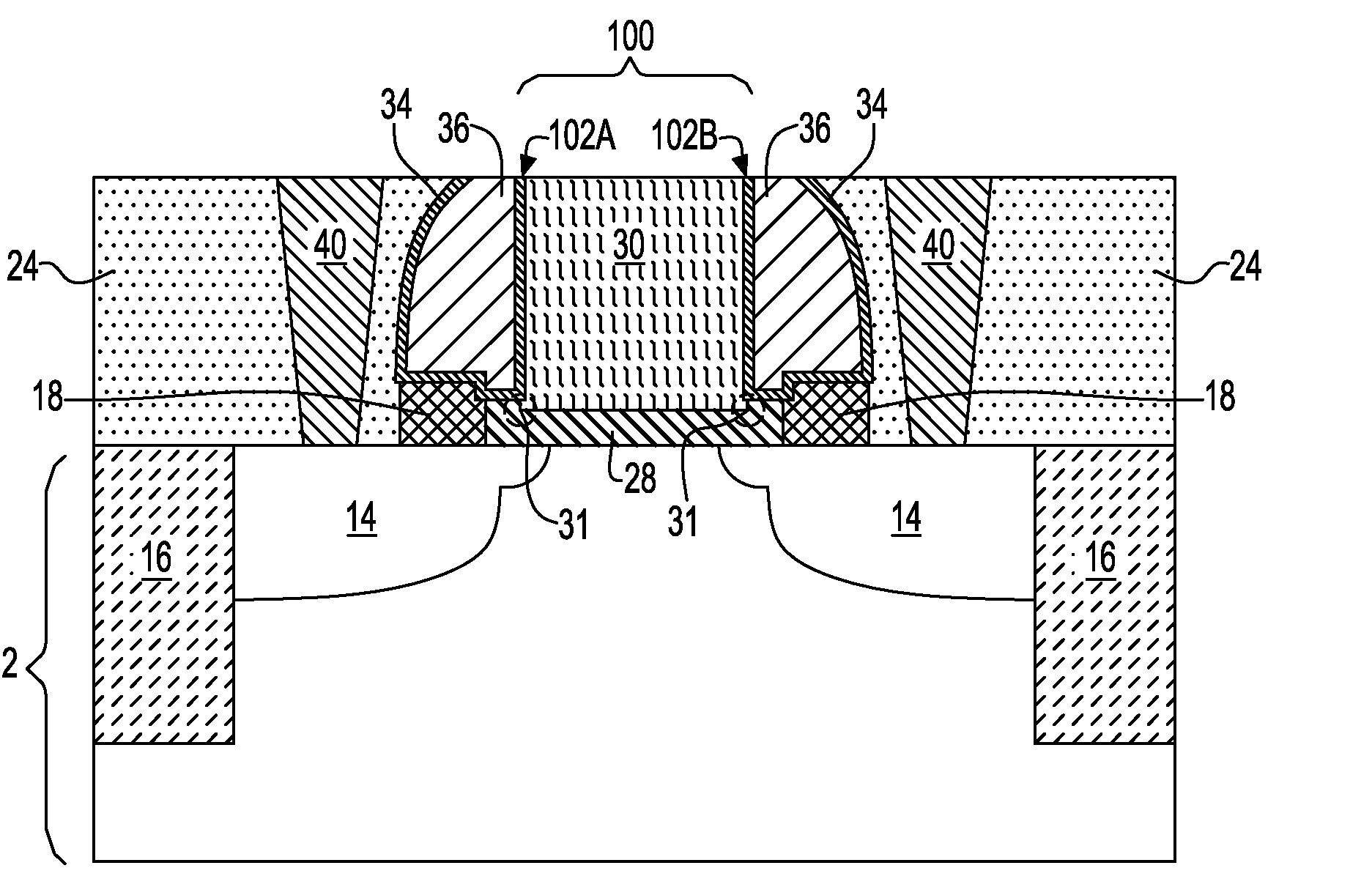

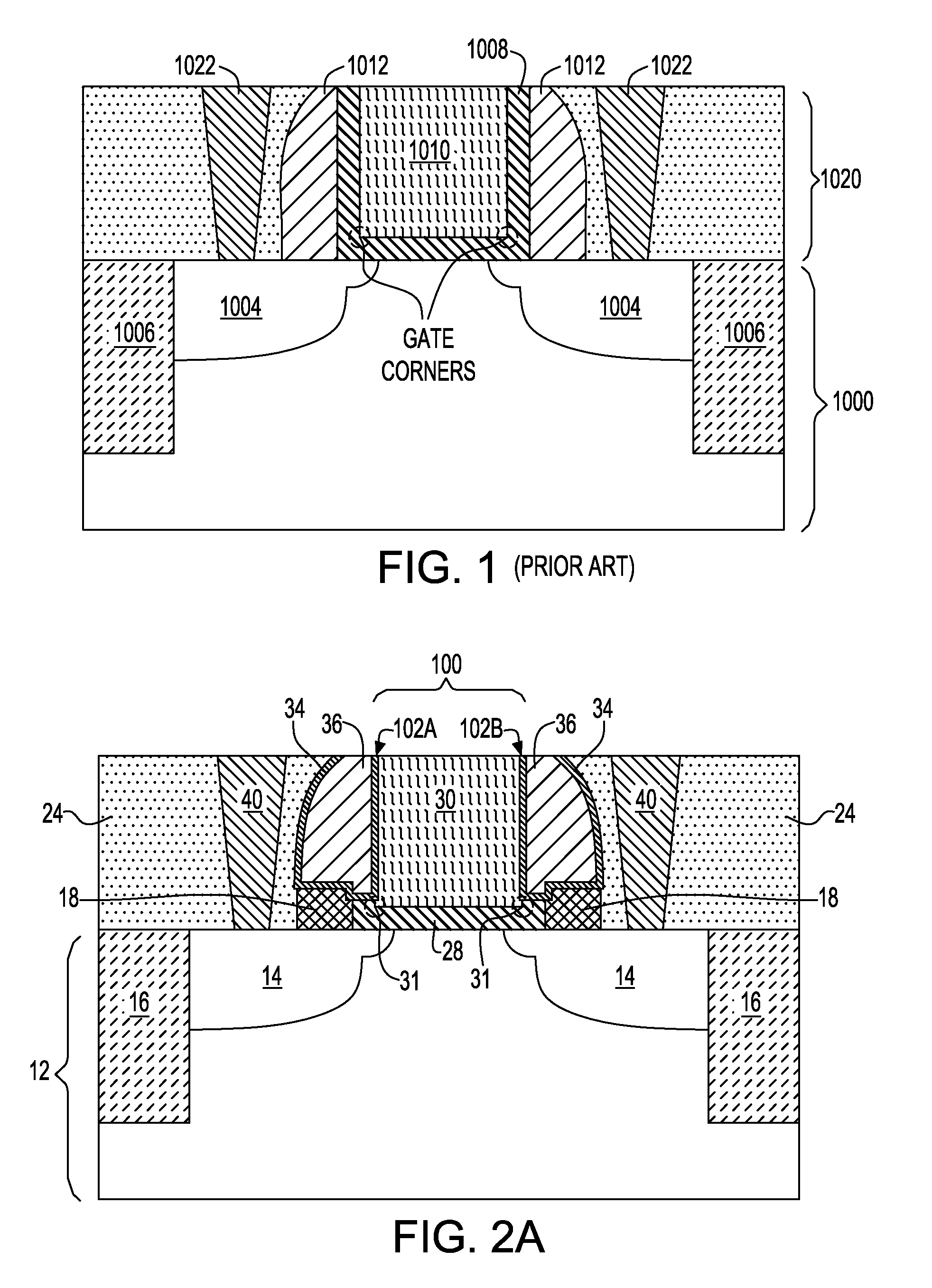

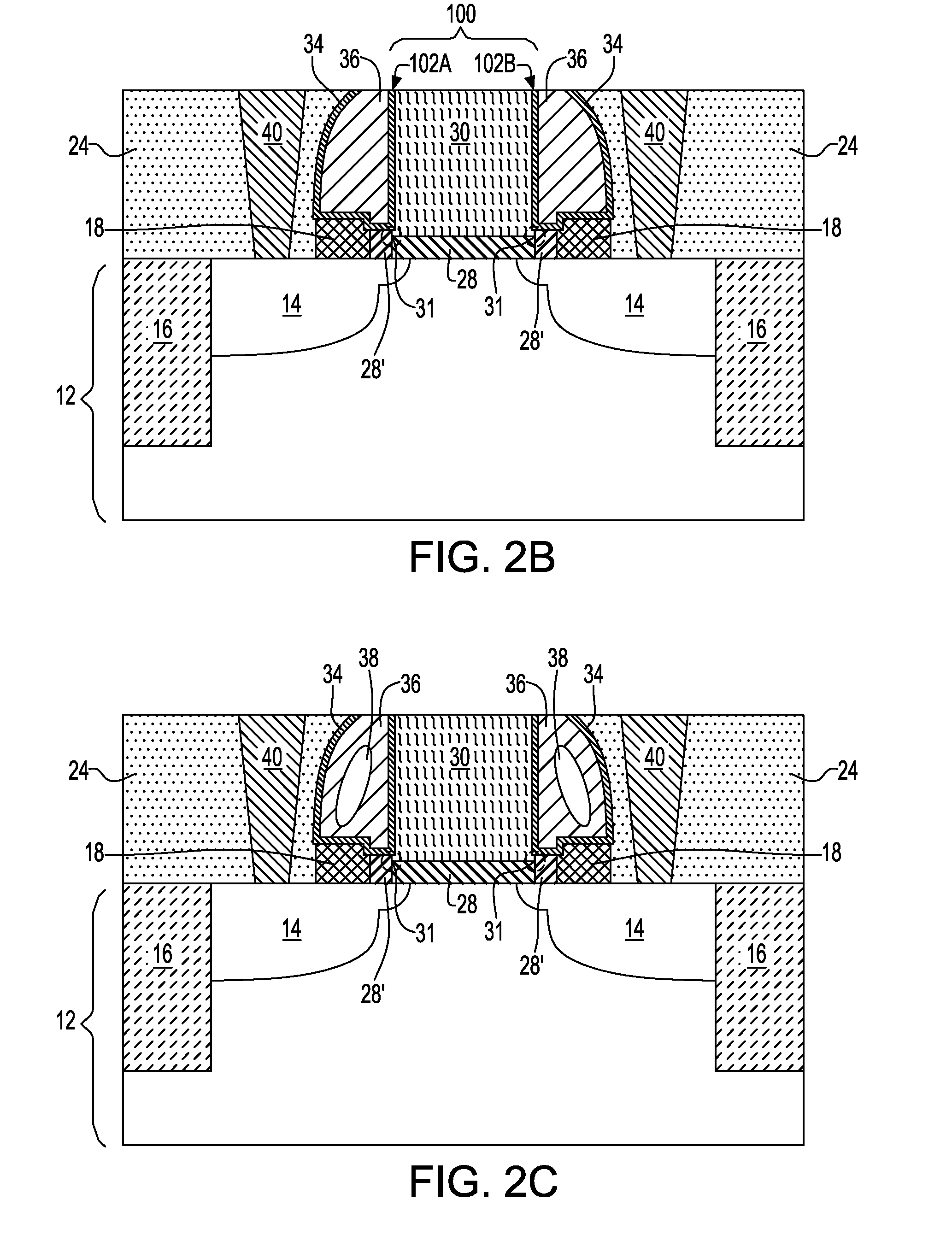

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

Non-volatile resistance switching memories and methods of making same

An integrated circuit memory cell including: a semiconductor having a first active area, a second active area, and a channel between the active areas; and a layer of a variable resistance material (VRM) directly above the channel. In one embodiment, there is a first conductive layer between the VRM and the channel and a second conductive layer directly above the VRM layer. The VRM preferably is a correlated electron material (CEM). The memory cell comprises a FET, such as a JFET or a MESFET. In another embodiment, there is a layer of an insulating material between the VRM and the channel. In this case, the memory cell may include a MOSFET structure.

Owner:SYMETRIX MEMORY

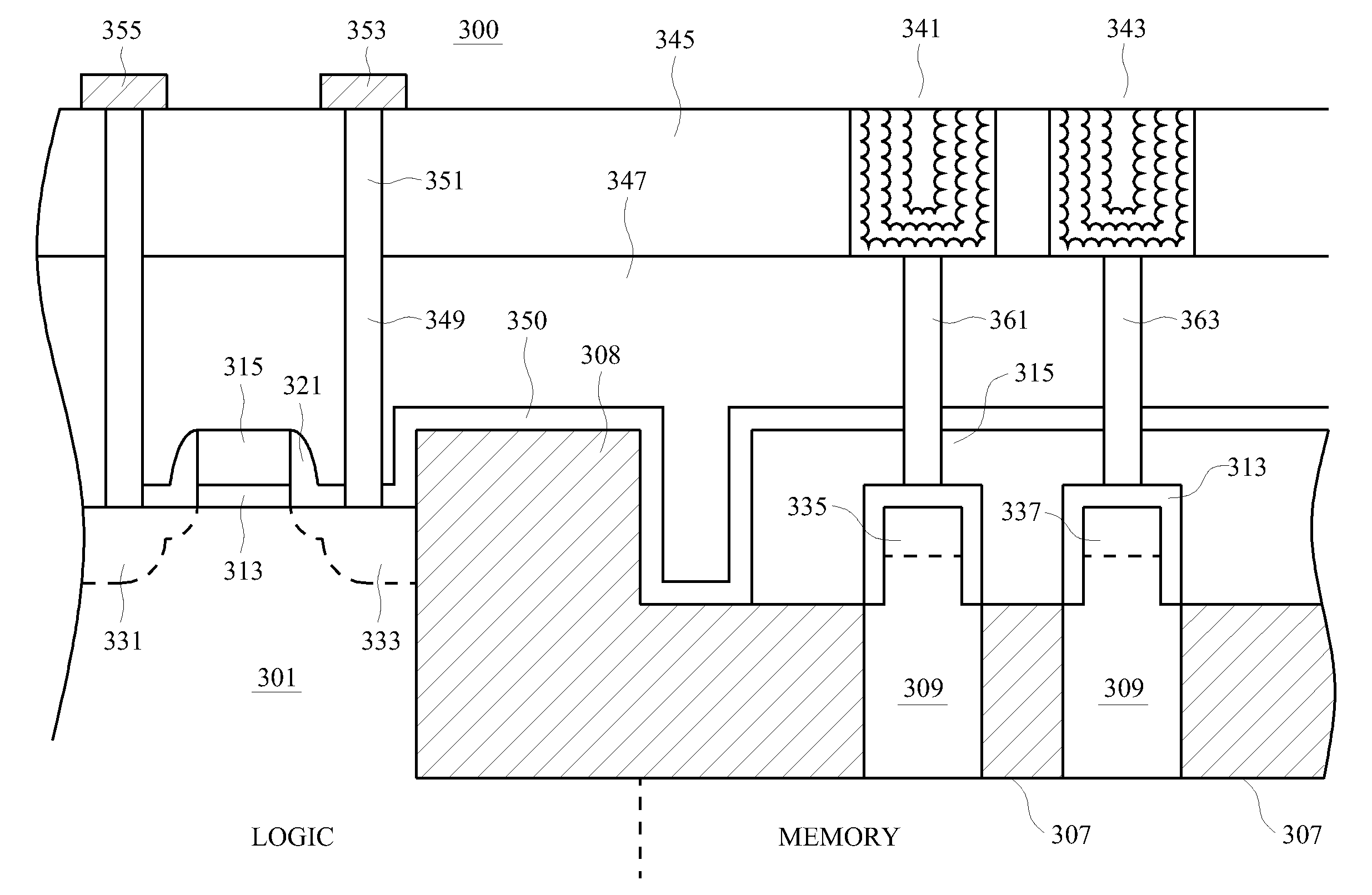

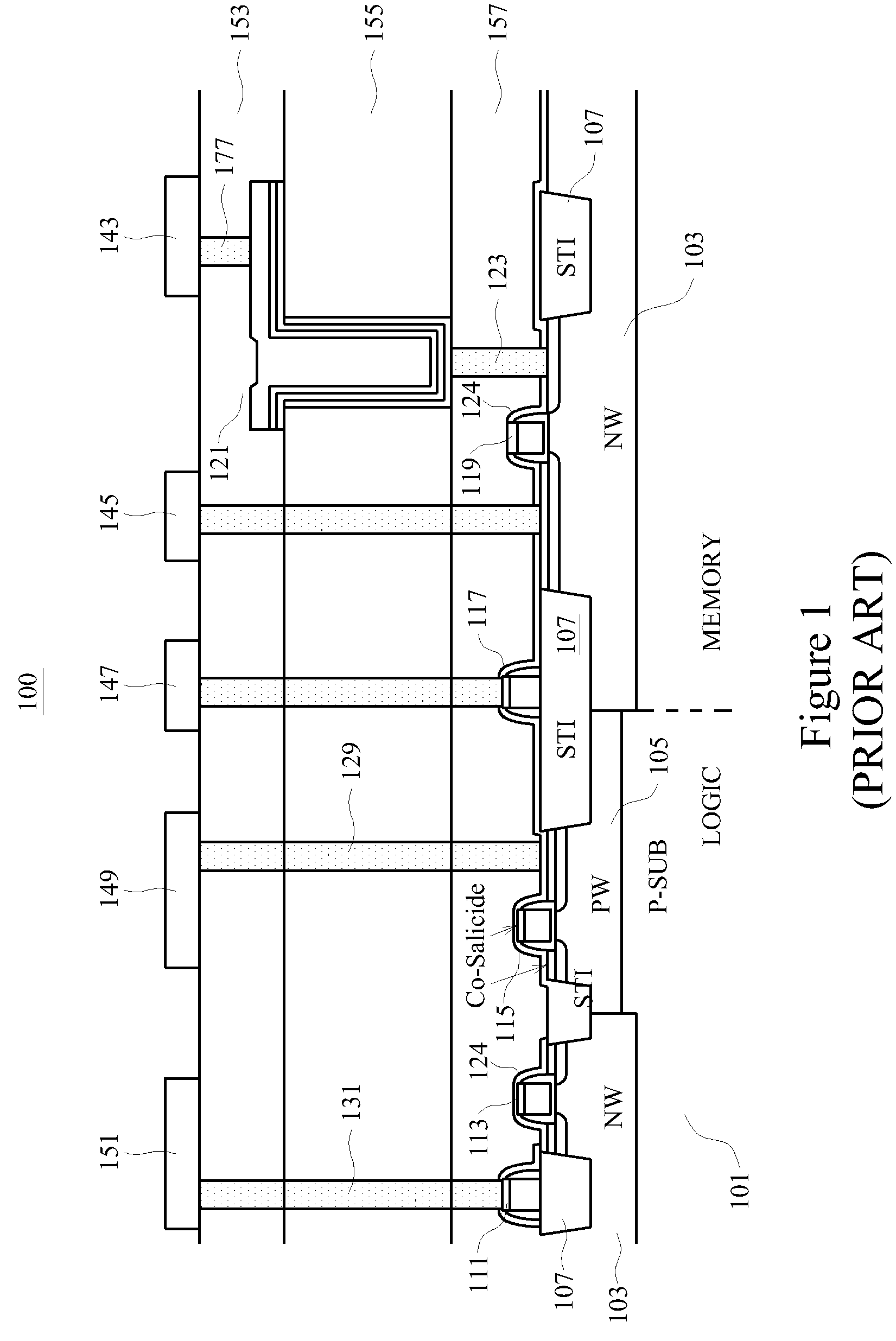

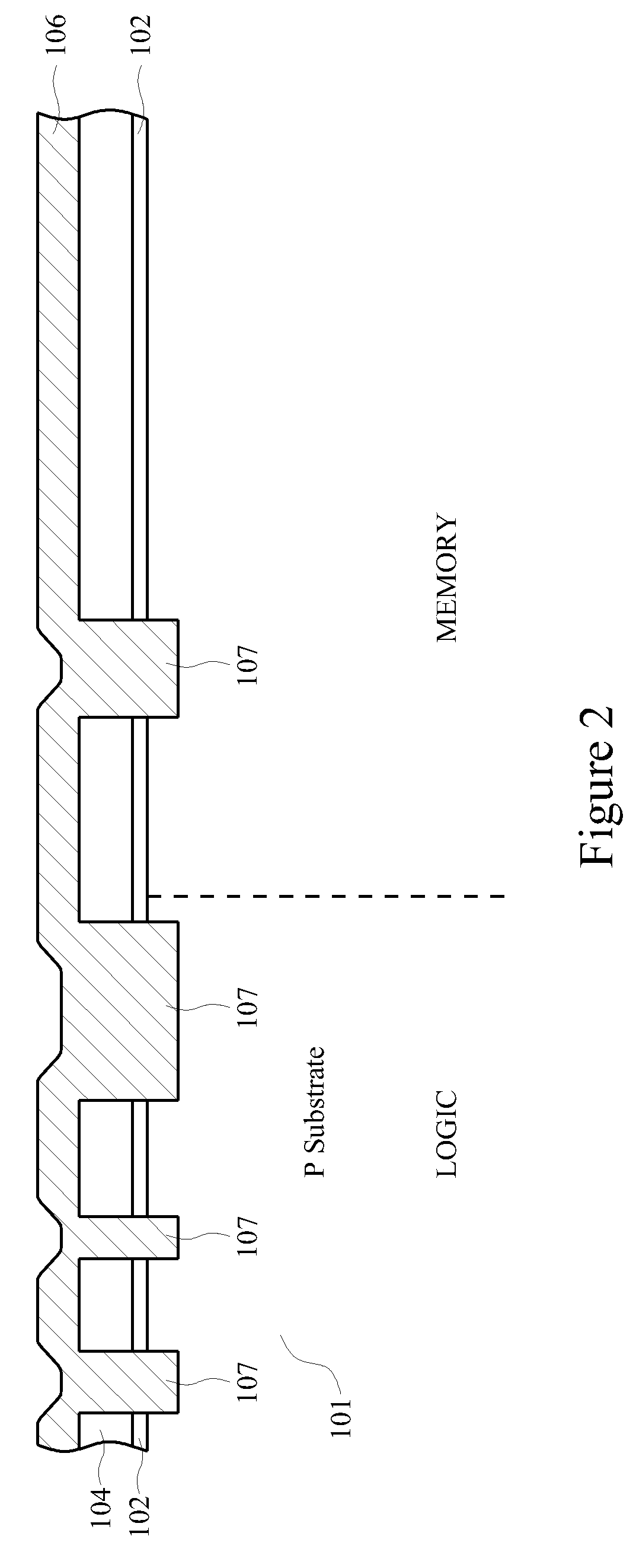

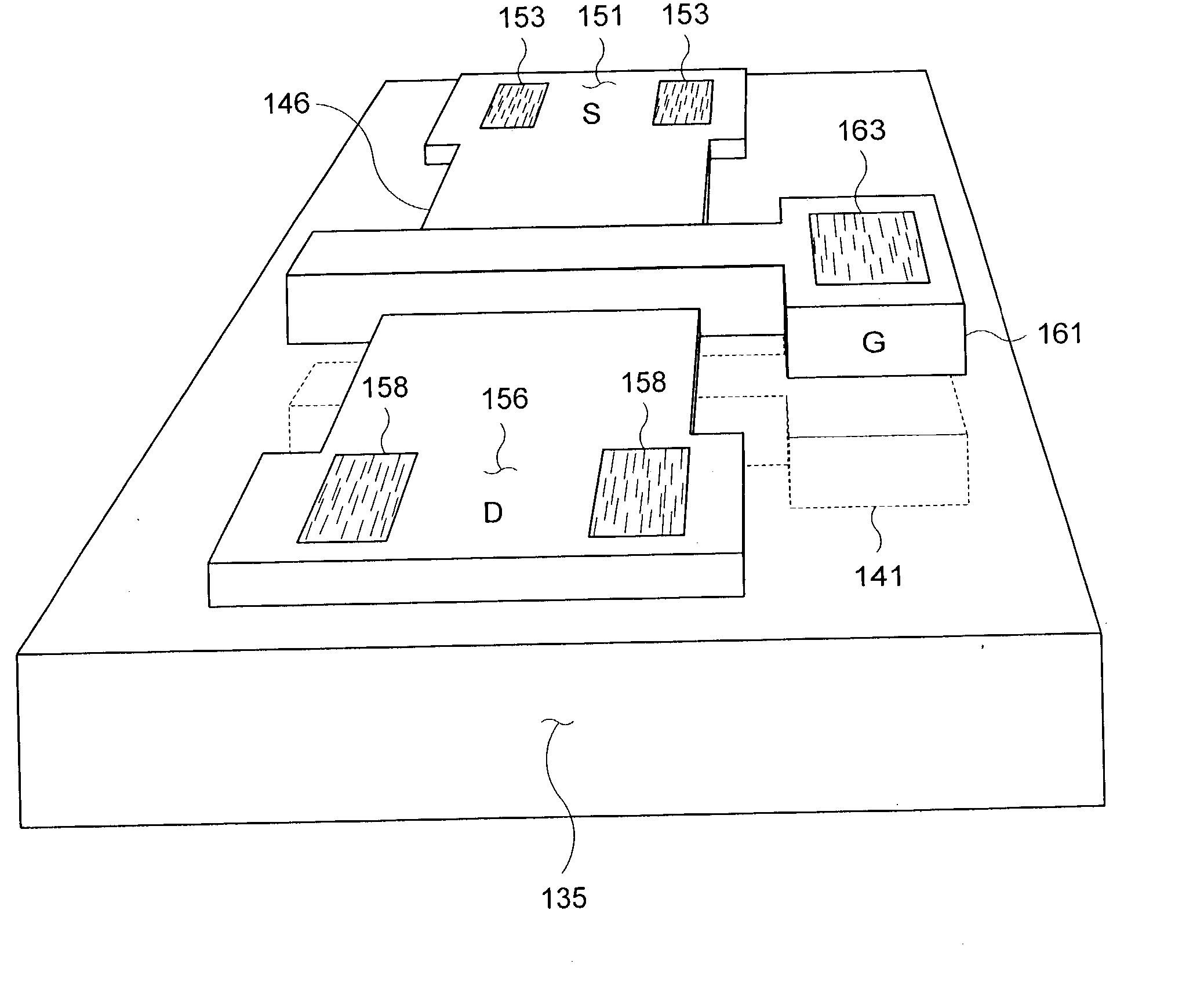

Method and structure for a 1T-RAM bit cell and macro

InactiveUS7425740B2Increase capacitanceTransistorSolid-state devicesMetal-insulator-metalCapacitance

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

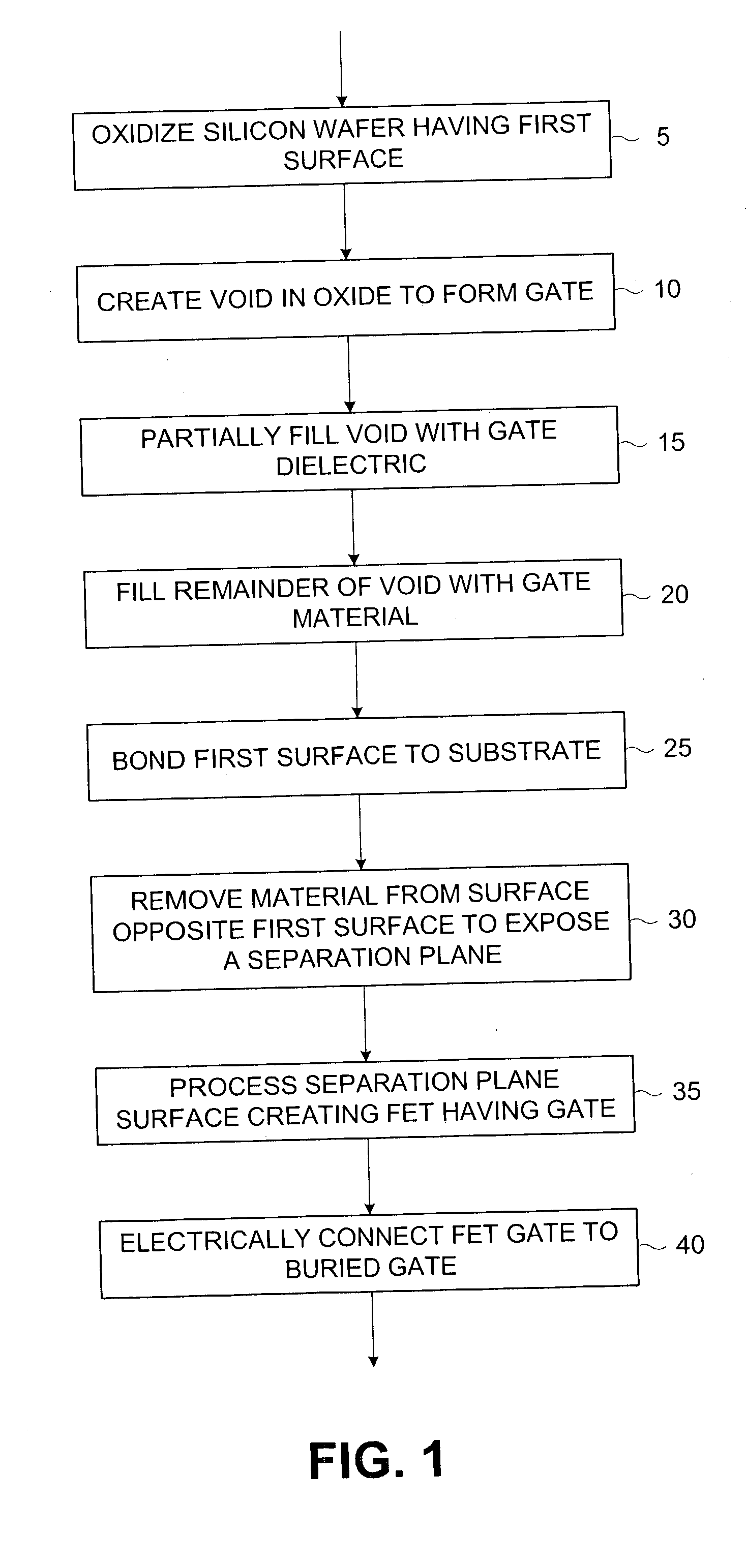

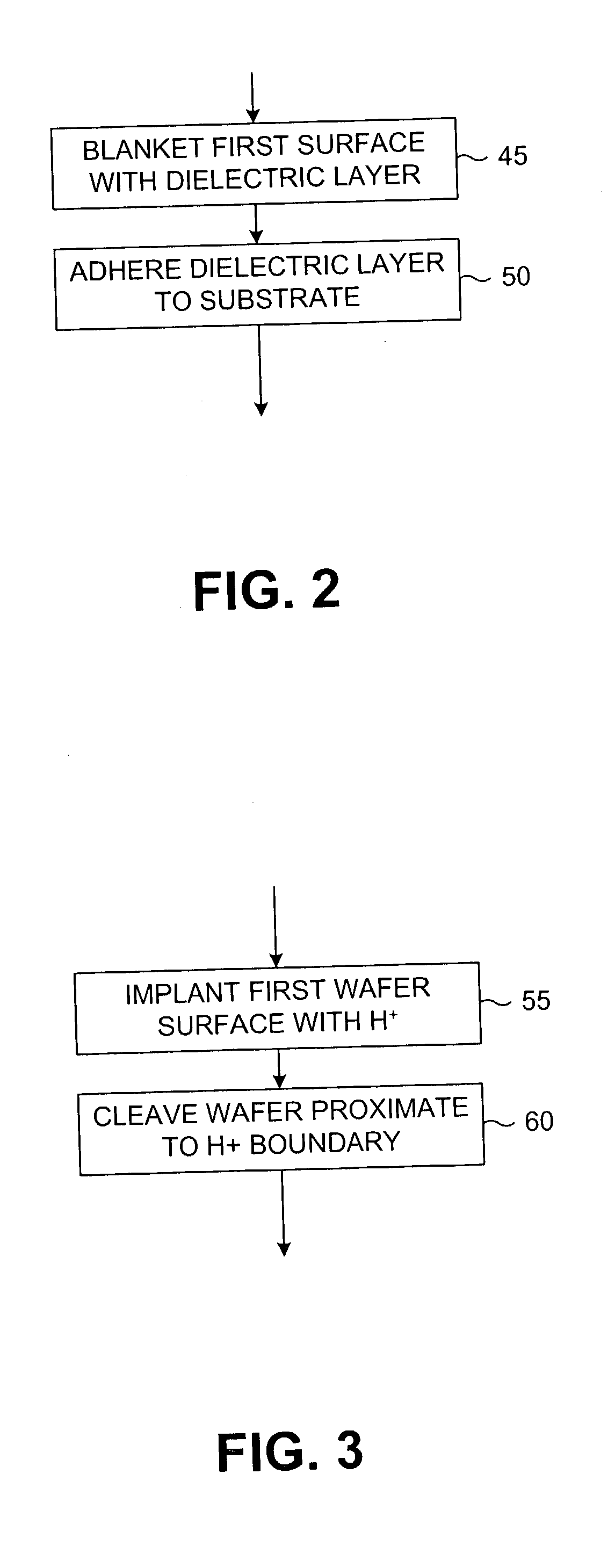

All-around MOSFET gate and methods of manufacture thereof

InactiveUS20050003592A1Prolonging durationTransistorSemiconductor/solid-state device manufacturingMOSFETEngineering

Metal oxide field effect transistor having a channel and a gate that surrounds the channel on four sides. Method of manufacture of the transistor includes processing the back of a silicon wafer to form a buried gate that is electrically connected to the gate of a conventional field effect transistor to form an all-around structure.

Owner:MINDSPEED TECH INC

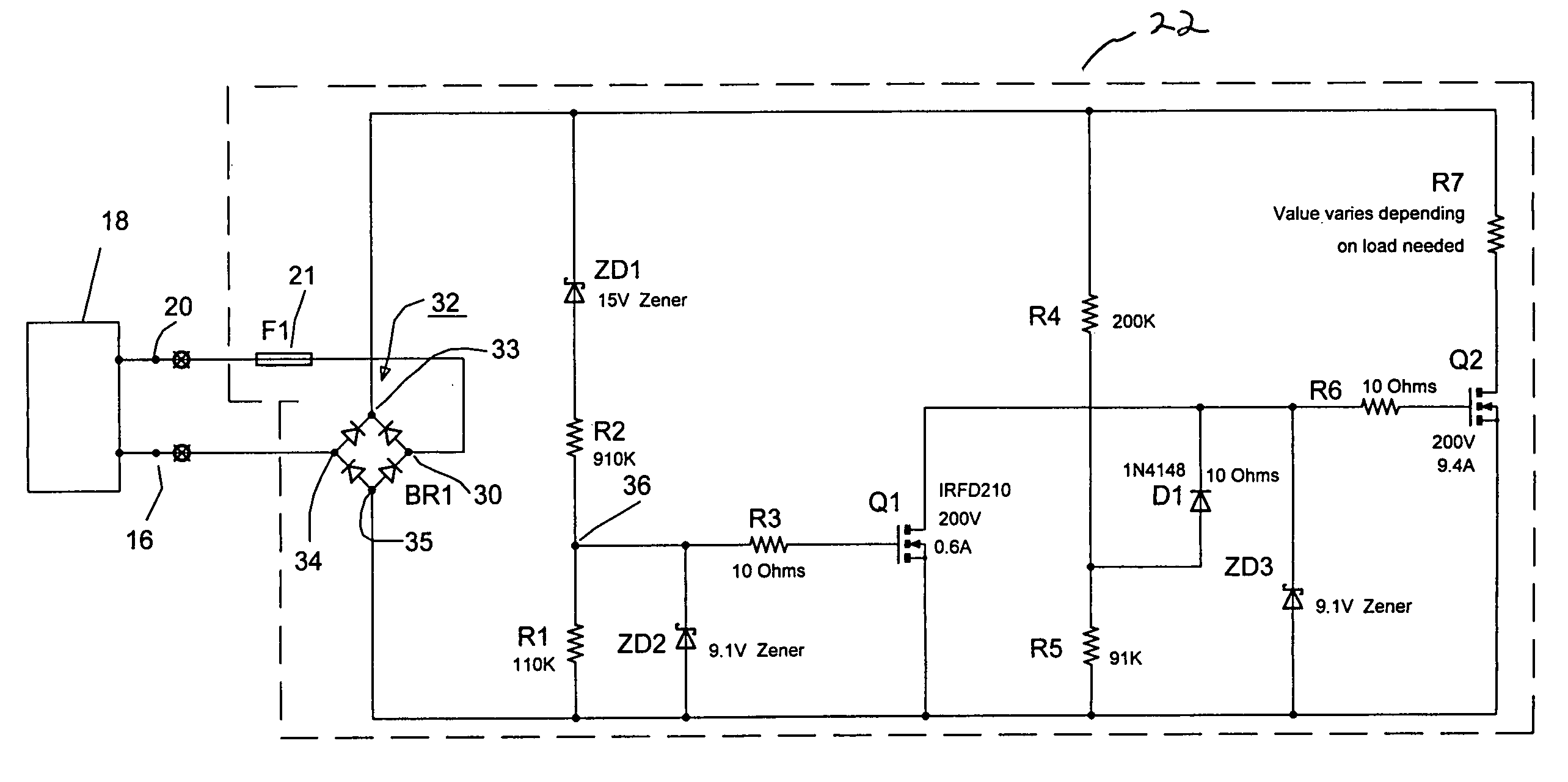

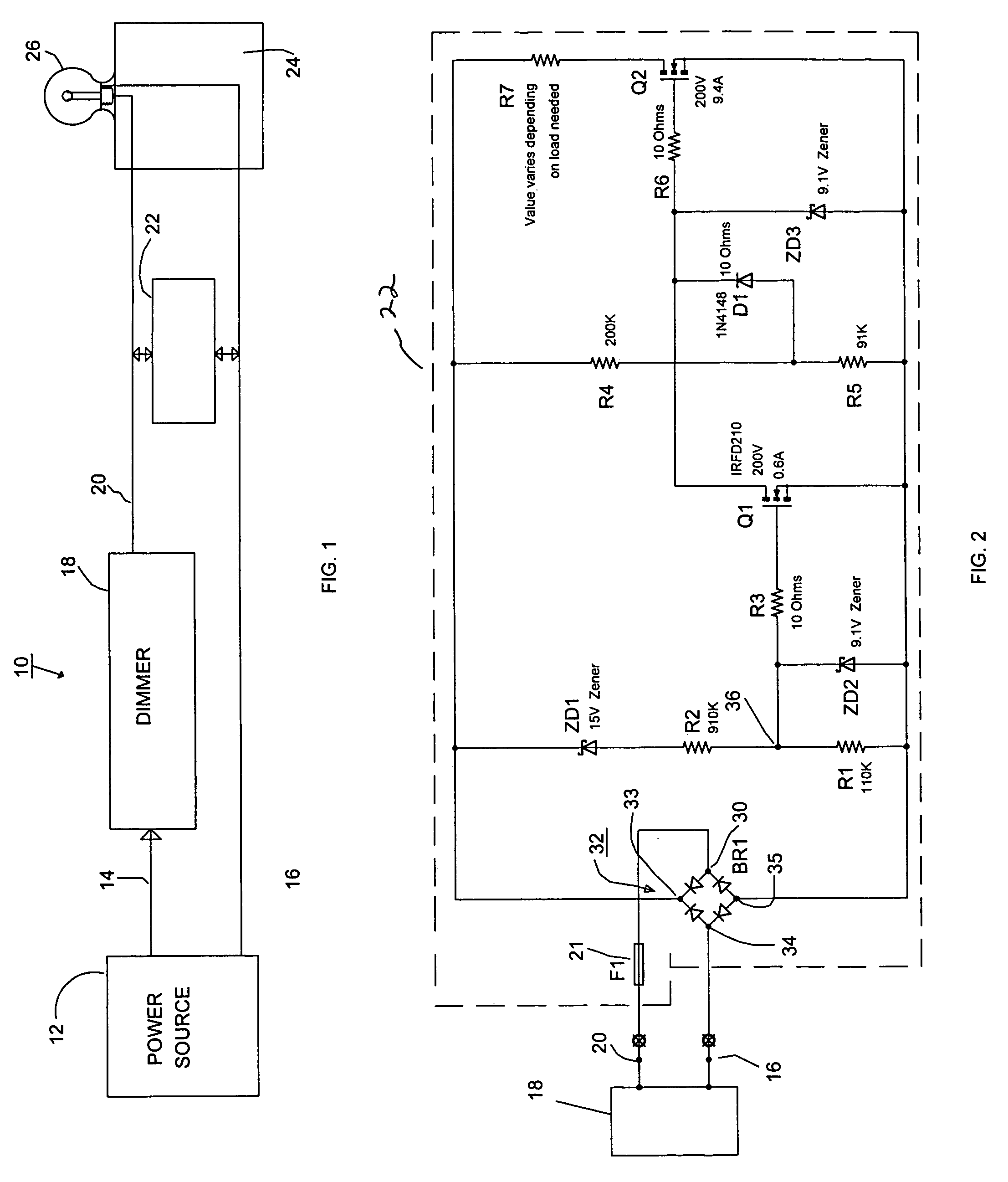

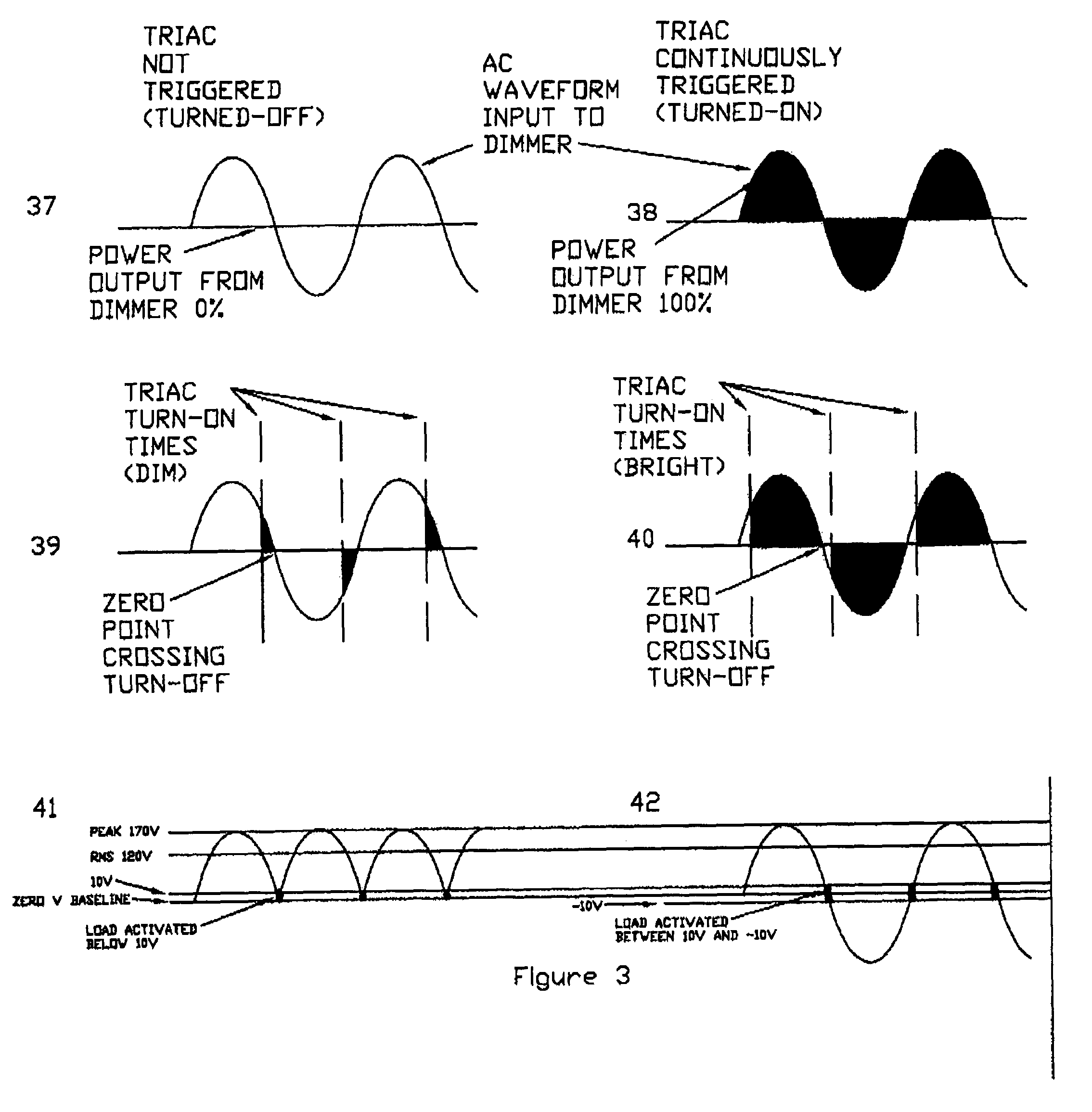

Dimmer circuit for LED

InactiveUS7102902B1Low heat generationReduce heatAc-dc conversion without reversalConversion with intermediate conversion to dcMOSFETZener diode

The AC output from a source is rectified and applied to a resistor / Zener diode circuit connection which determines the magnitude of the rectified voltage applied via a circuit to a first MOSFET device. The inverted output of the first MOSFET device is applied to the gate electrode of a second MOSFET device in a manner such that the second MOSFET device is ON even when the AC output passes through zero. The output of the second MOSFET device is connected to a resistor which determines the magnitude of the load applied to the dimmer.

Owner:LEDTRONICS

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

ActiveUS20090321853A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

Methods to fabricate MOSFET devices using selective deposition process

ActiveUS20050079692A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMOSFETSelective deposition

In one embodiment, a method for fabricating a silicon-based device on a substrate surface is provided which includes depositing a first silicon-containing layer by exposing the substrate surface to a first process gas comprising Cl2SiH2, a germanium source, a first etchant and a carrier gas and depositing a second silicon-containing layer by exposing the first silicon-containing layer to a second process gas comprising SiH4 and a second etchant. In another embodiment, a method for depositing a silicon-containing material on a substrate surface is provided which includes depositing a first silicon-containing layer on the substrate surface with a first germanium concentration of about 15 at % or more. The method further provides depositing on the first silicon-containing layer a second silicon-containing layer wherein a second germanium concentration of about 15 at % or less, exposing the substrate surface to air to form a native oxide layer, removing the native oxide layer to expose the second silicon-containing layer, and depositing a third silicon-containing layer on the second silicon-containing layer. In another embodiment, a method for depositing a silicon-containing material on a substrate surface is provided which includes depositing epitaxially a first silicon-containing layer on the substrate surface with a first lattice strain, and depositing epitaxially on the first silicon-containing layer a second silicon-containing layer with a second lattice strain greater than the first lattice strain.

Owner:APPLIED MATERIALS INC

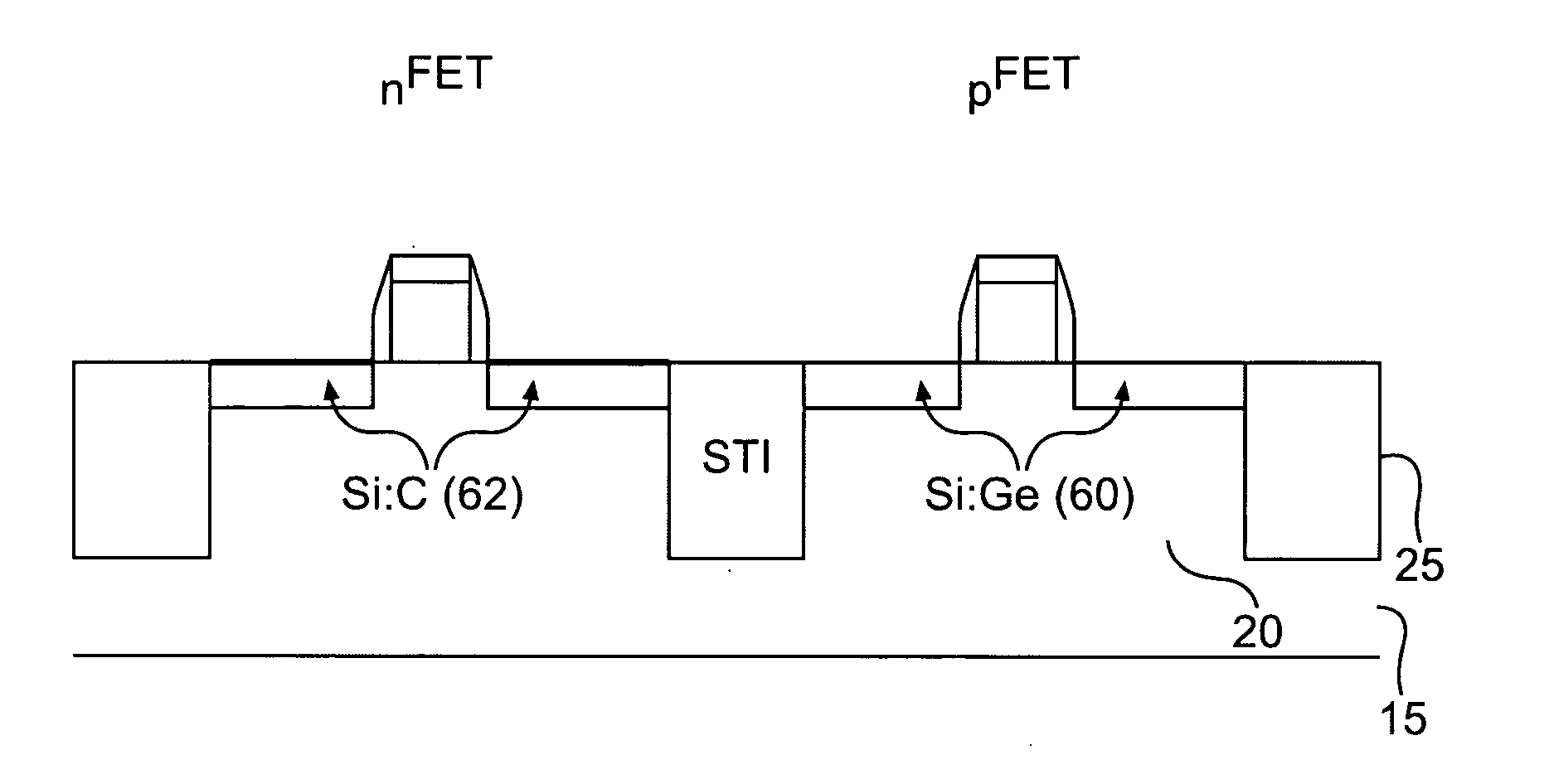

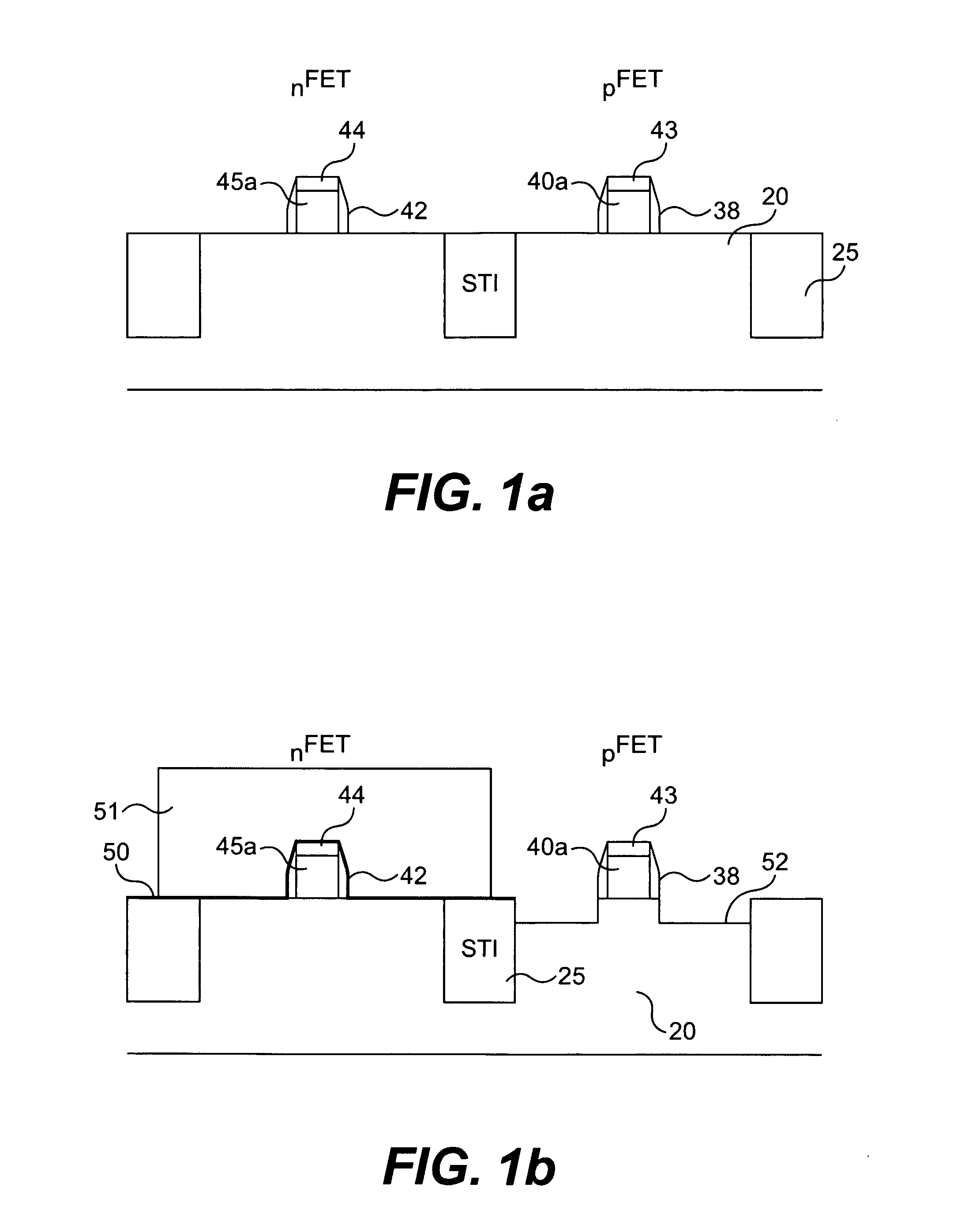

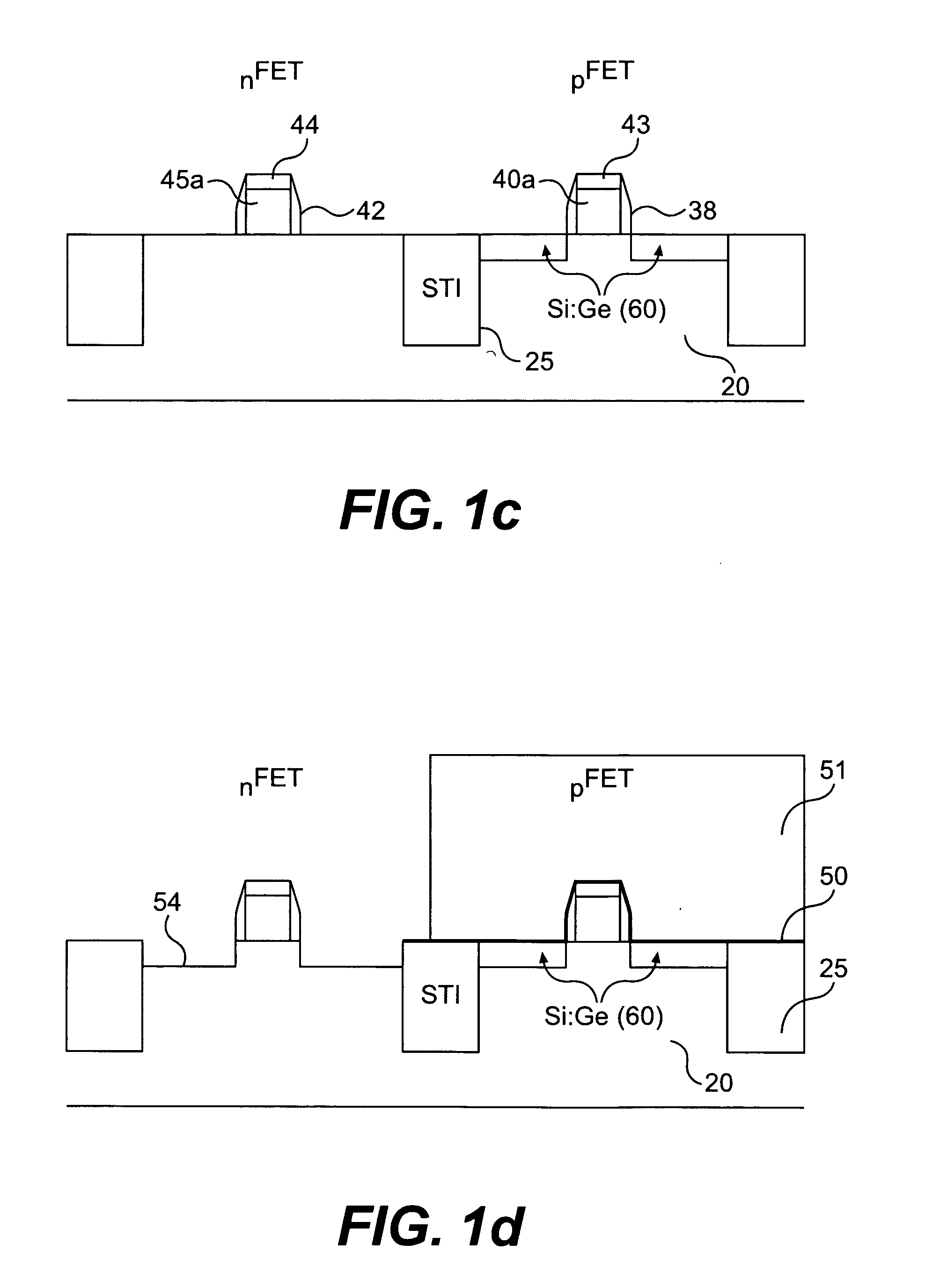

High performance stress-enhanced MOSFETs using Si:C and SiGe epitaxial source/drain and method of manufacture

A semiconductor device and method of manufacturing a semiconductor device. The semiconductor device includes channels for a pFET and an nFET. A SiGe layer is selectively grown in the source and drain regions of the pFET channel and a Si:C layer is selectively grown in source and drain regions of the nFET channel. The SiGe and Si:C layer match a lattice network of the underlying Si layer to create a stress component. In one implementation, this causes a compressive component in the pFET channel and a tensile component in the nFET channel.

Owner:AURIGA INNOVATIONS INC