Patents

Literature

152results about How to "Improve area efficiency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

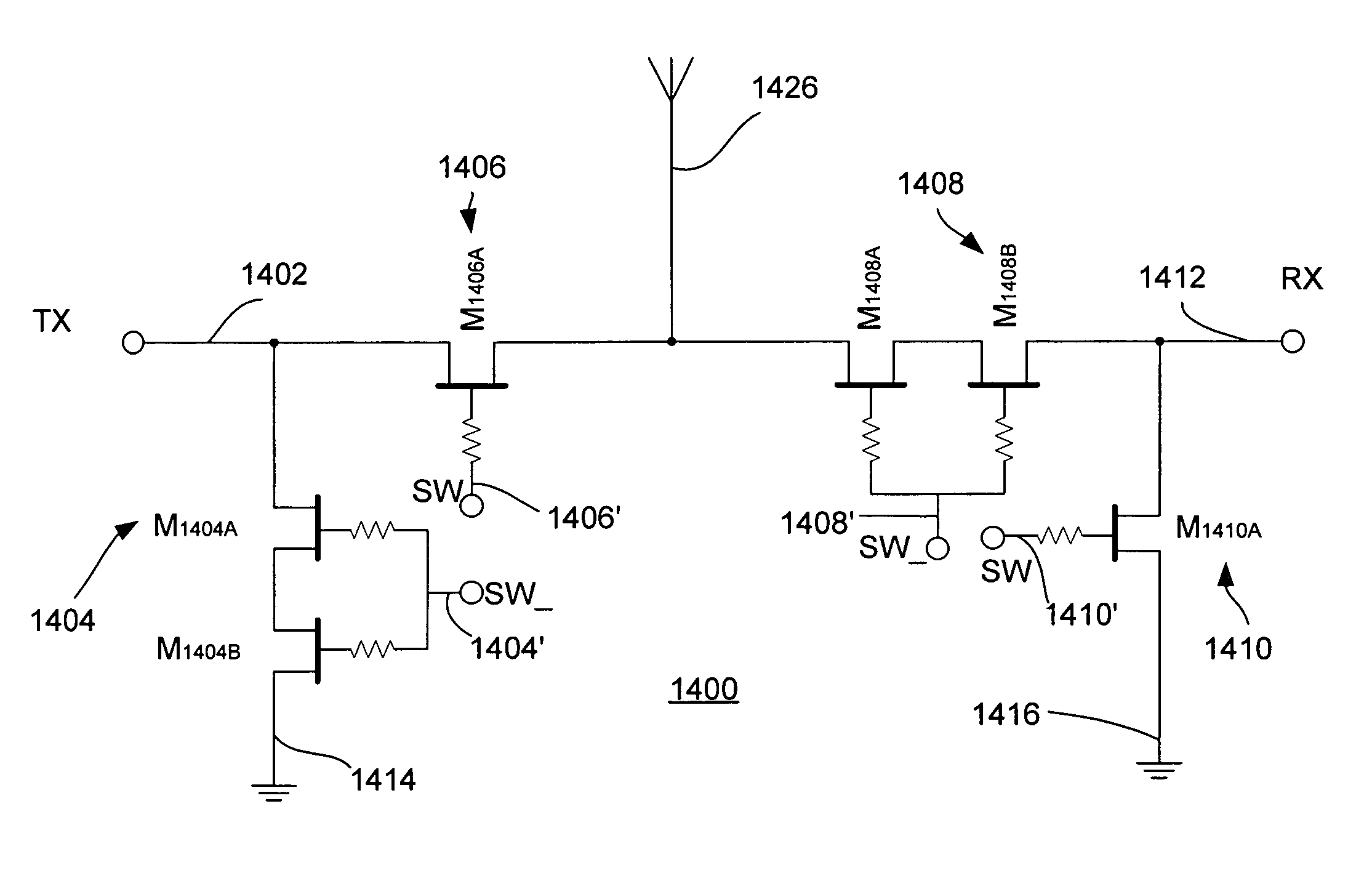

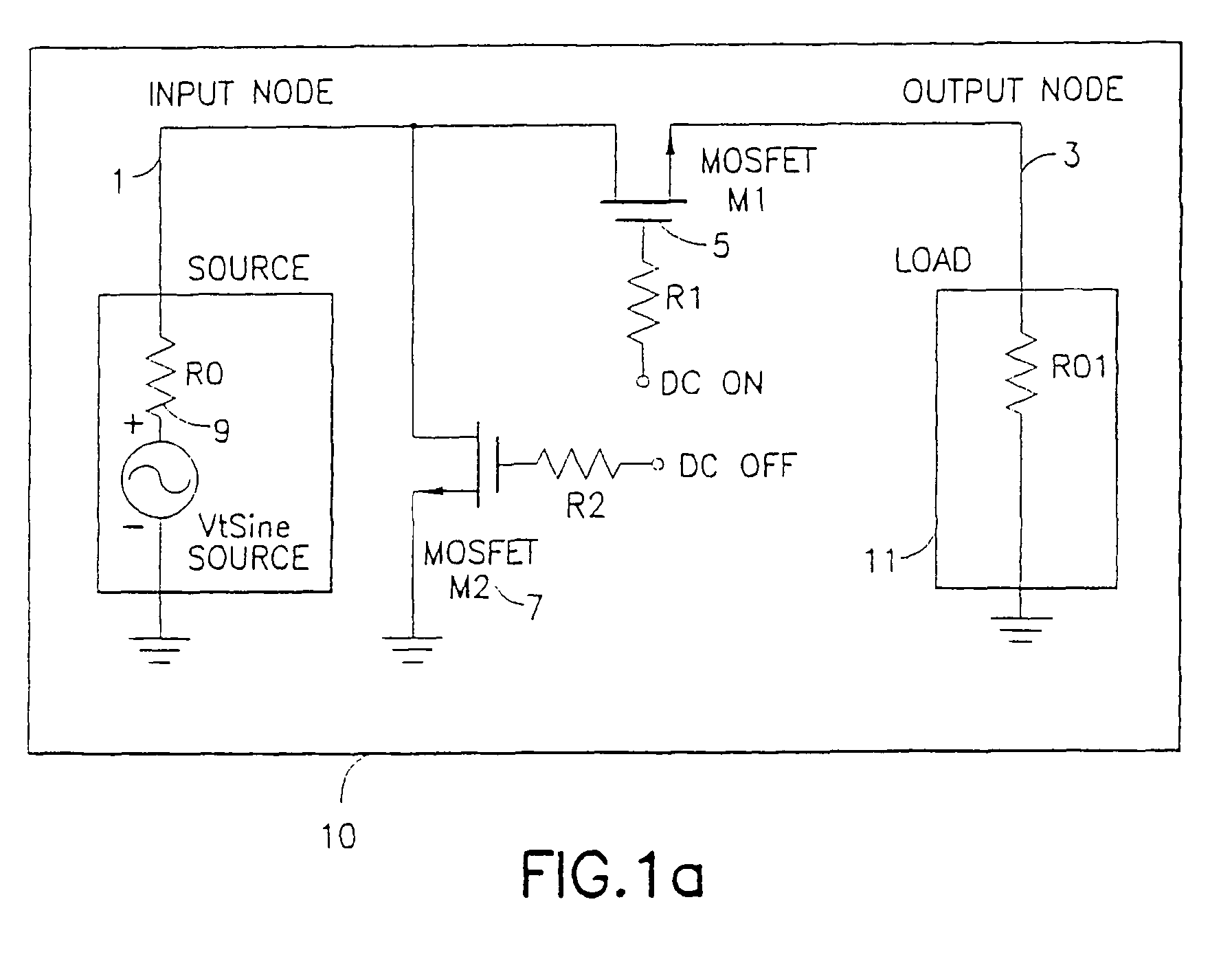

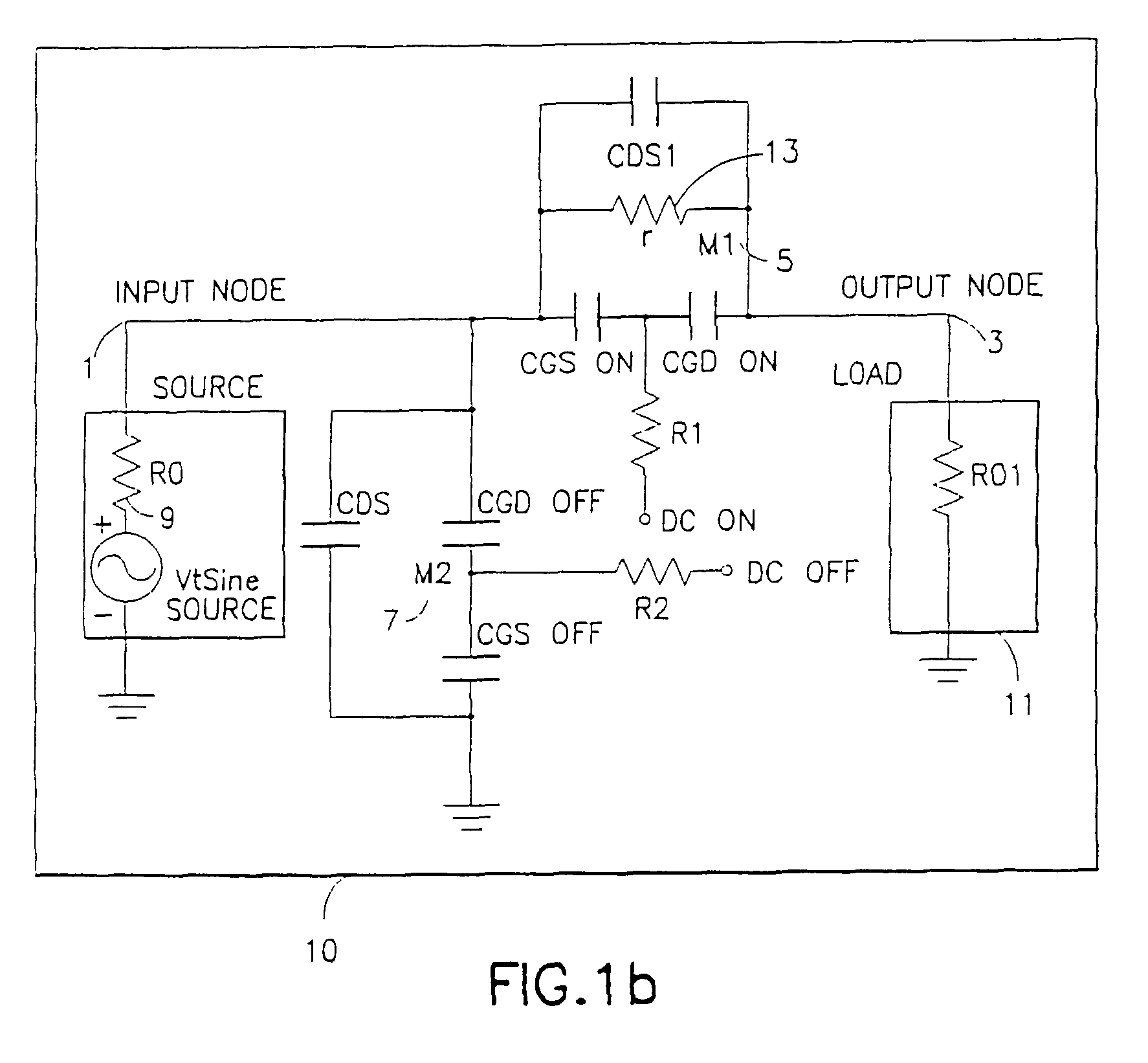

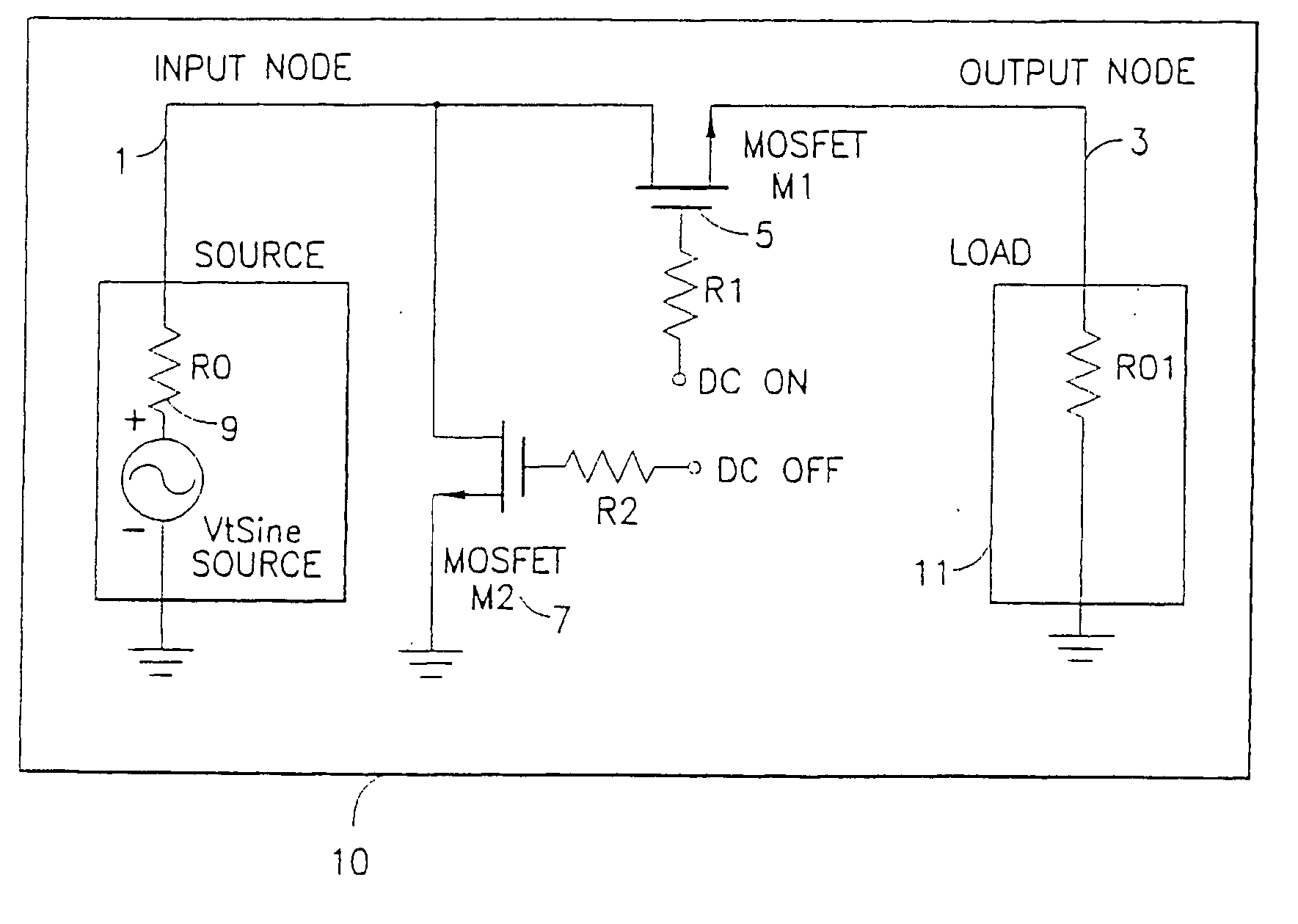

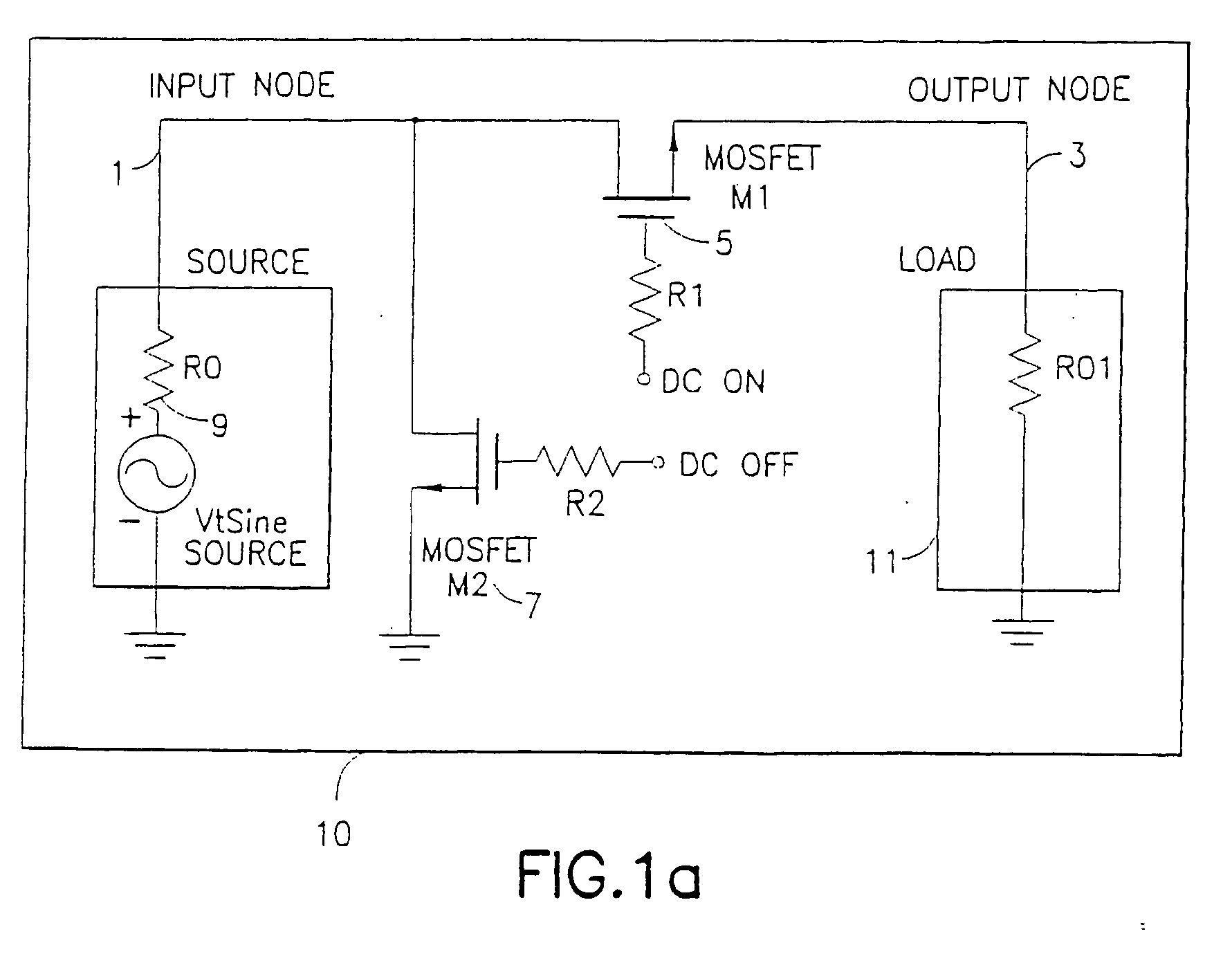

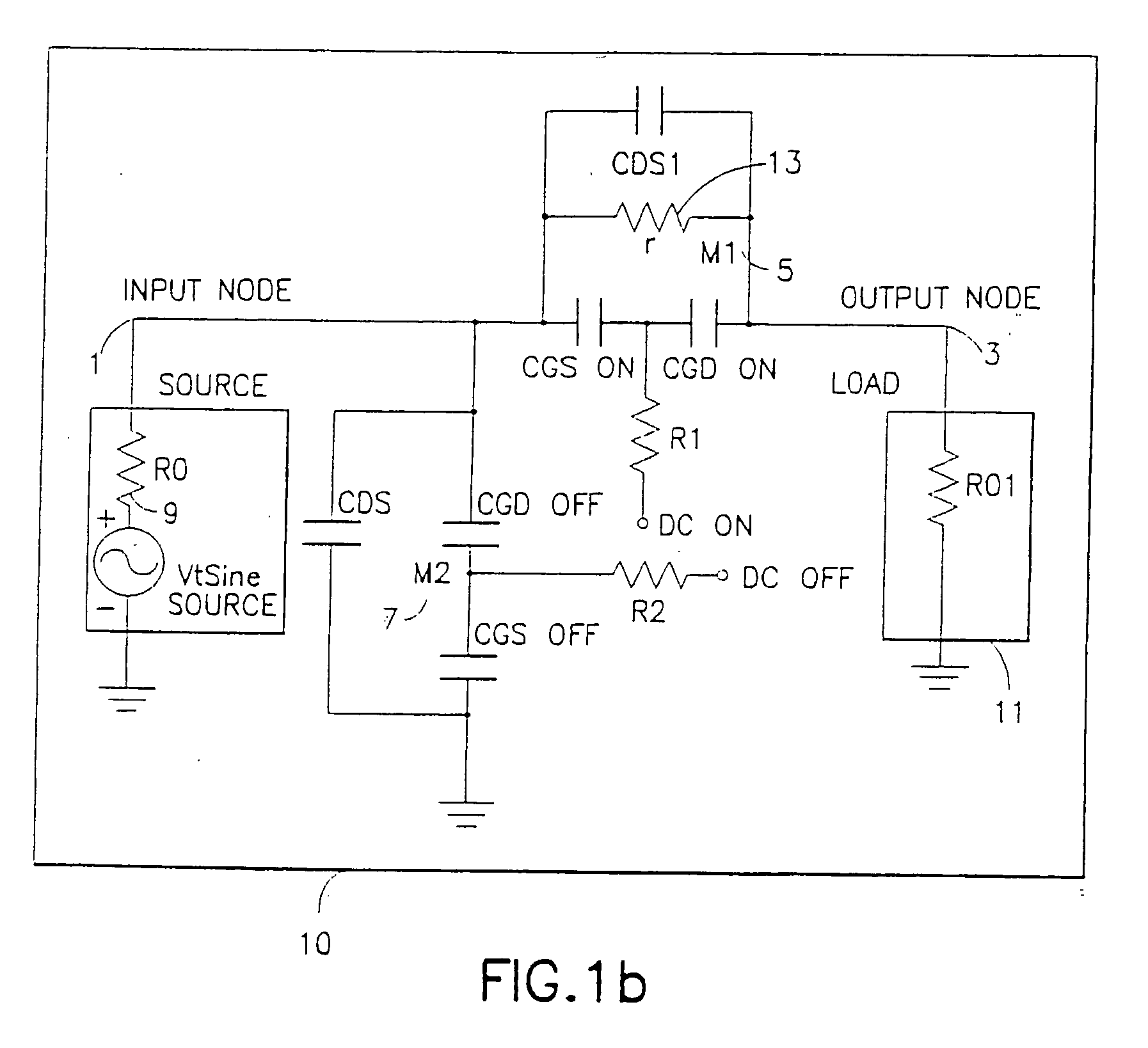

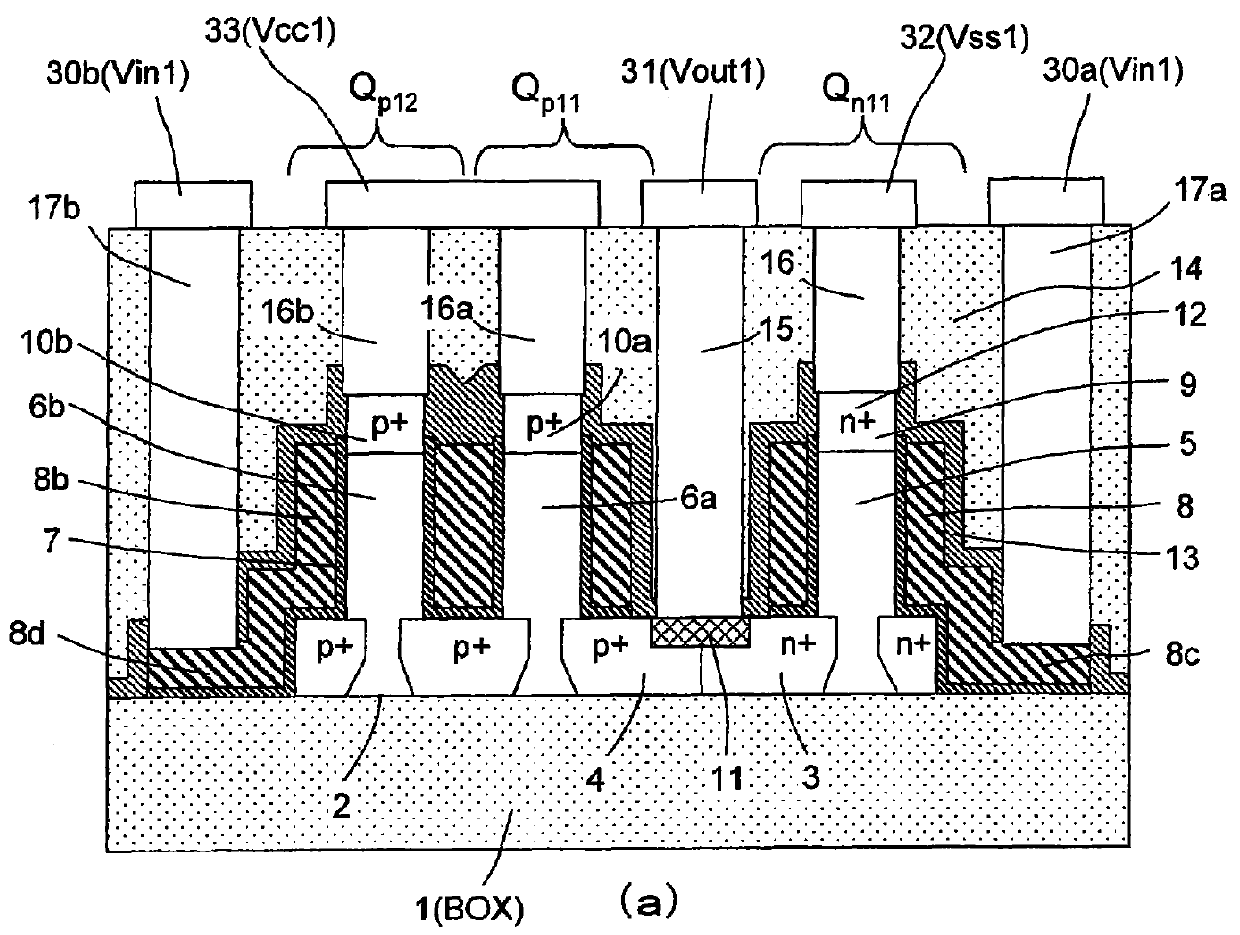

Symmetrically and asymmetrically stacked transistor group RF switch

A silicon-on-insulator (SOI) RF switch adapted for improved power handling capability using a reduced number of transistors is described. In one embodiment, an RF switch includes pairs of switching and shunting stacked transistor groupings to selectively couple RF signals between a plurality of input / output nodes and a common RF node. The switching and shunting stacked transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. In one embodiment, the transistor groupings are “symmetrically” stacked in the RF switch (i.e., the transistor groupings all comprise an identical number of transistors). In another embodiment, the transistor groupings are “asymmetrically” stacked in the RF switch (i.e., at least one transistor grouping comprises a number of transistors that is unequal to the number of transistors comprising at least one other transistor grouping). The stacked configuration of the transistor groupings enable the RF switch to withstand RF signals of varying and increased power levels. The asymmetrically stacked transistor grouping RF switch facilitates area-efficient implementation of the RF switch in an integrated circuit. Maximum input and output signal power levels can be withstood using a reduced number of stacked transistors.

Owner:PSEMI CORP

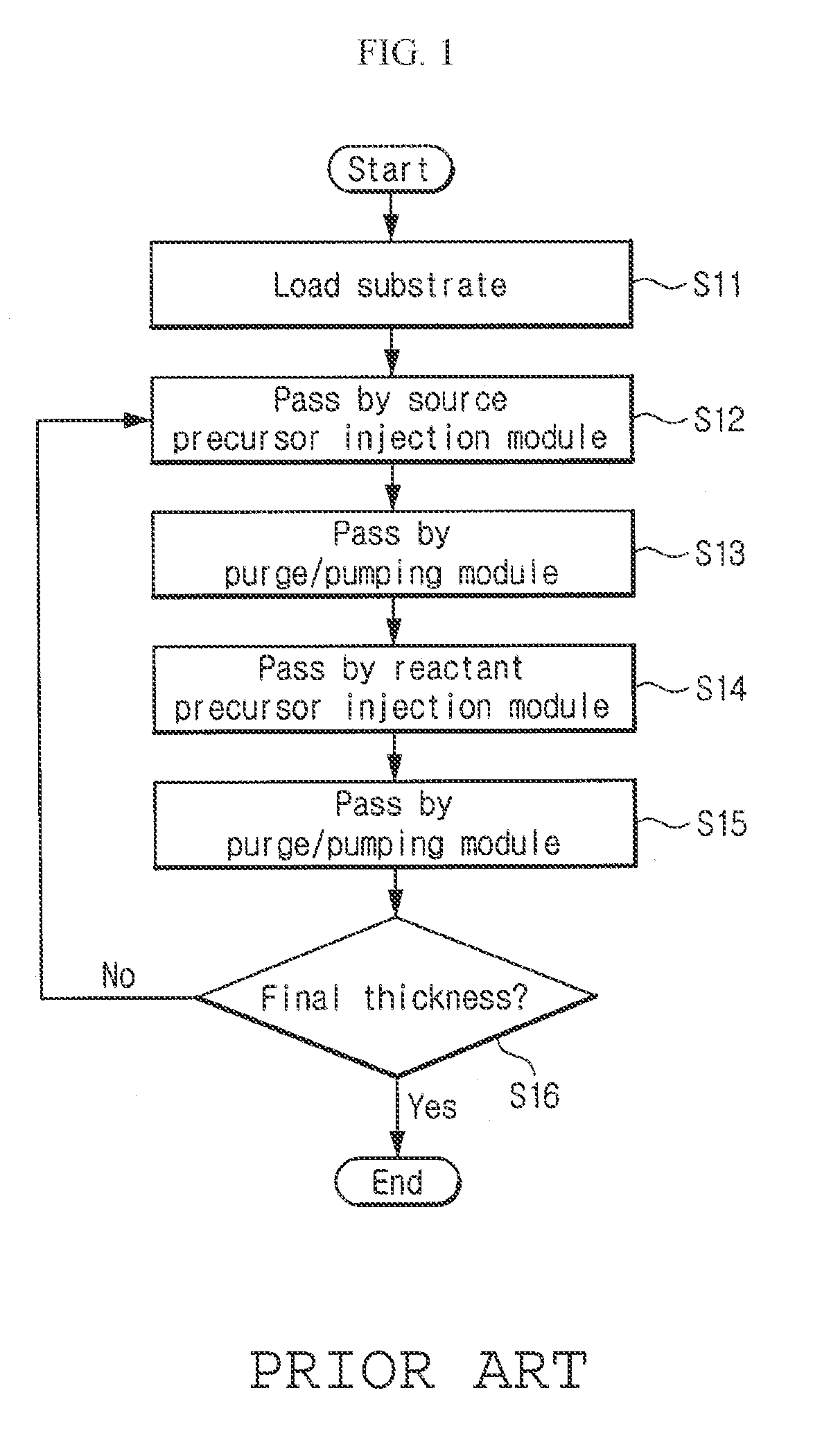

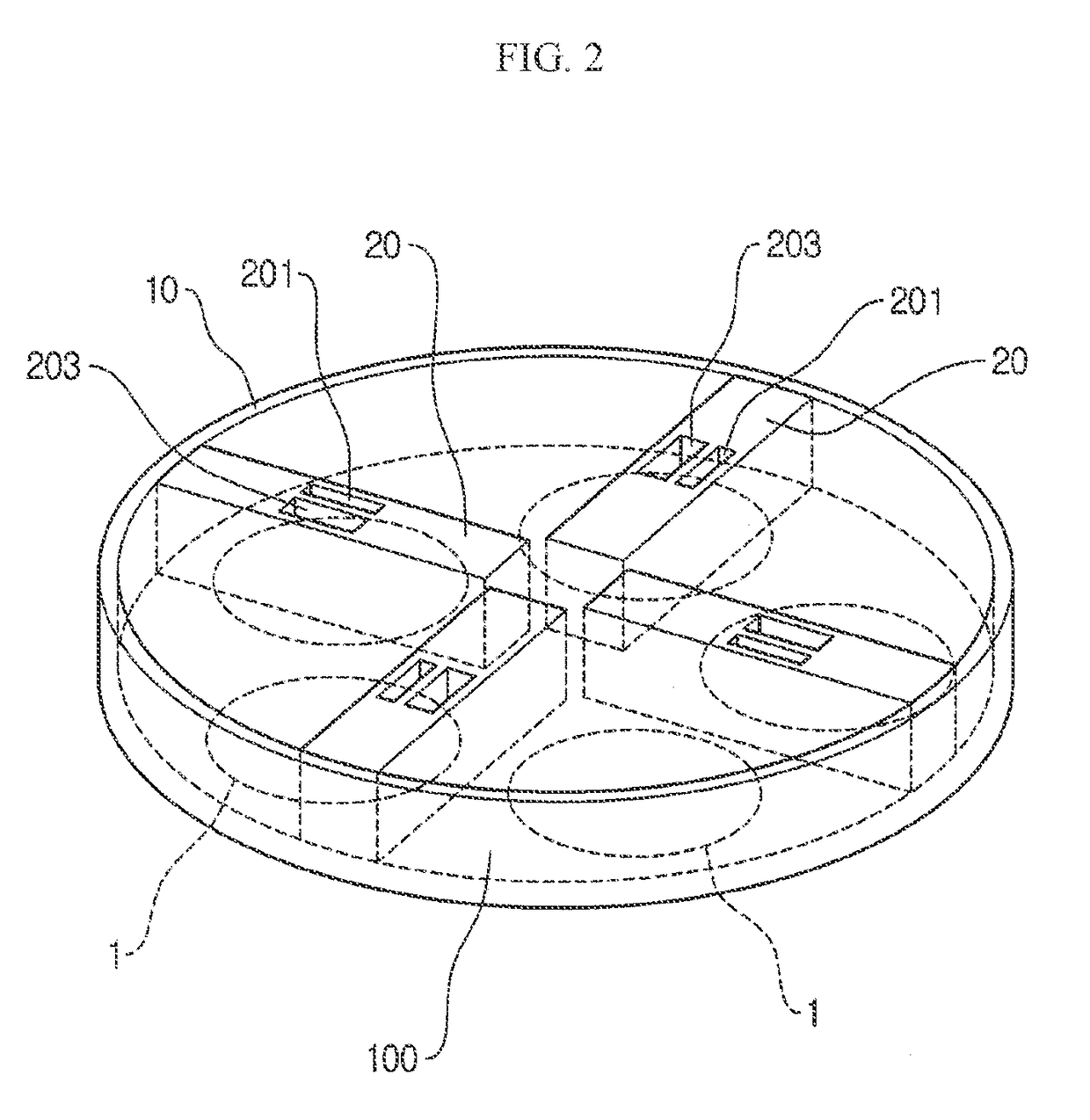

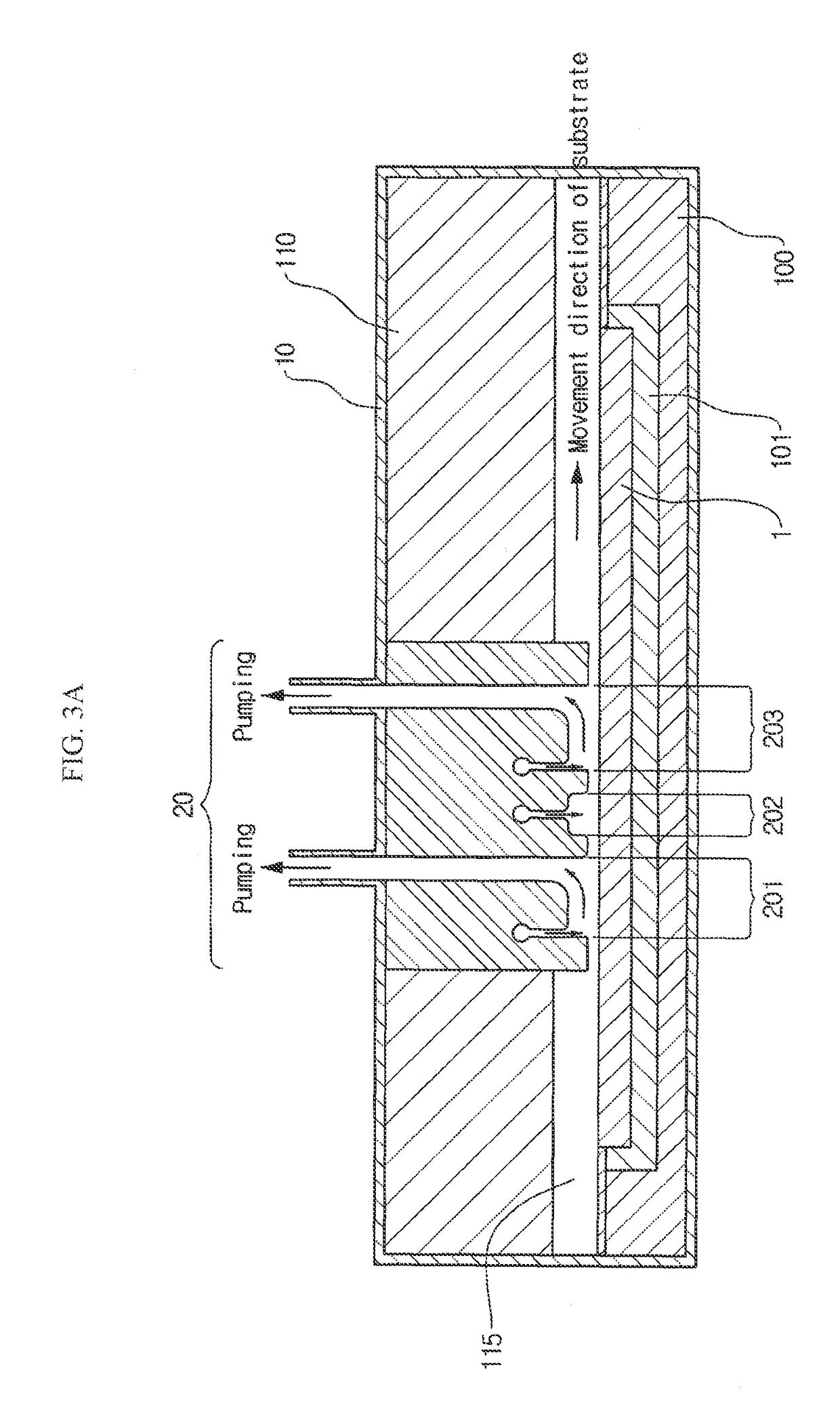

Vapor deposition reactor for forming thin film

InactiveUS8470718B2Improve area efficiencyArea minimizationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringRelative motion

A vapor deposition reactor includes a chamber filled with a first material, and at least one reaction module in the chamber. The reaction module may be configured to make a substrate pass the reaction module through a relative motion between the substrate and the reaction module. The reaction module may include an injection unit for injecting a second material to the substrate. A method for forming thin film includes positioning a substrate in a chamber, filling a first material in the chamber, moving the substrate relative to a reaction module in the chamber, and injecting a second material to the substrate while the substrate passes the reaction module.

Owner:VEECO ALD

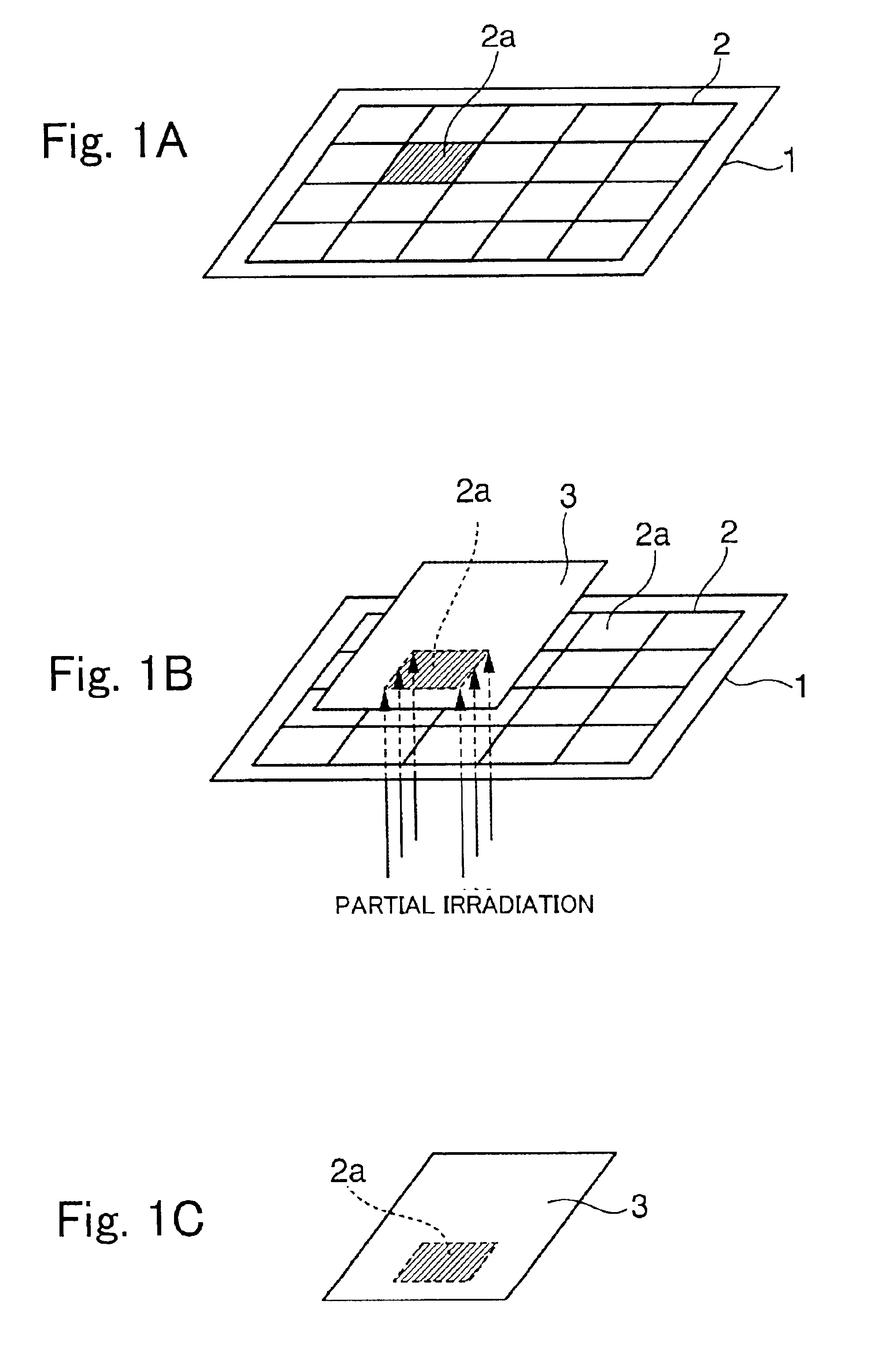

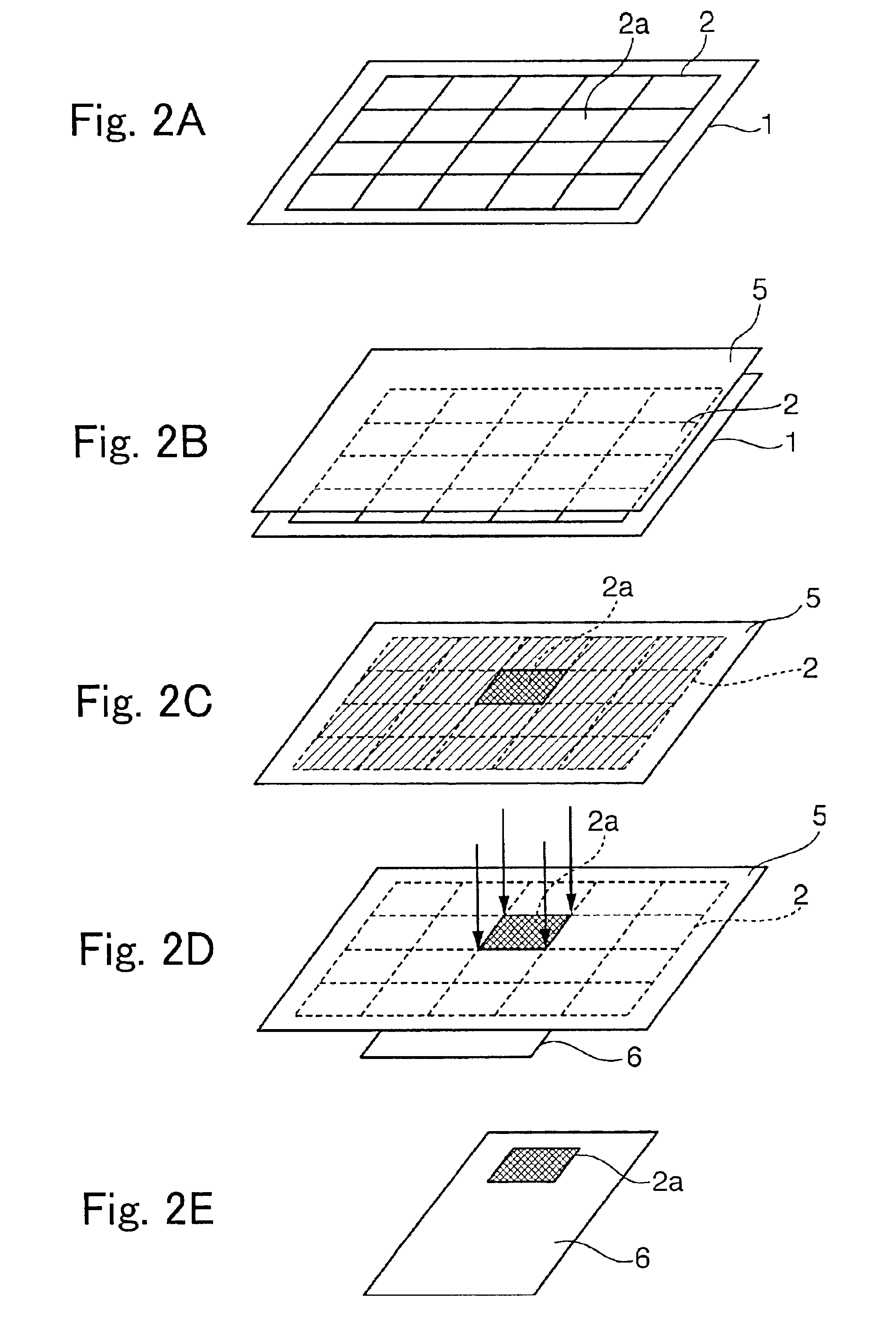

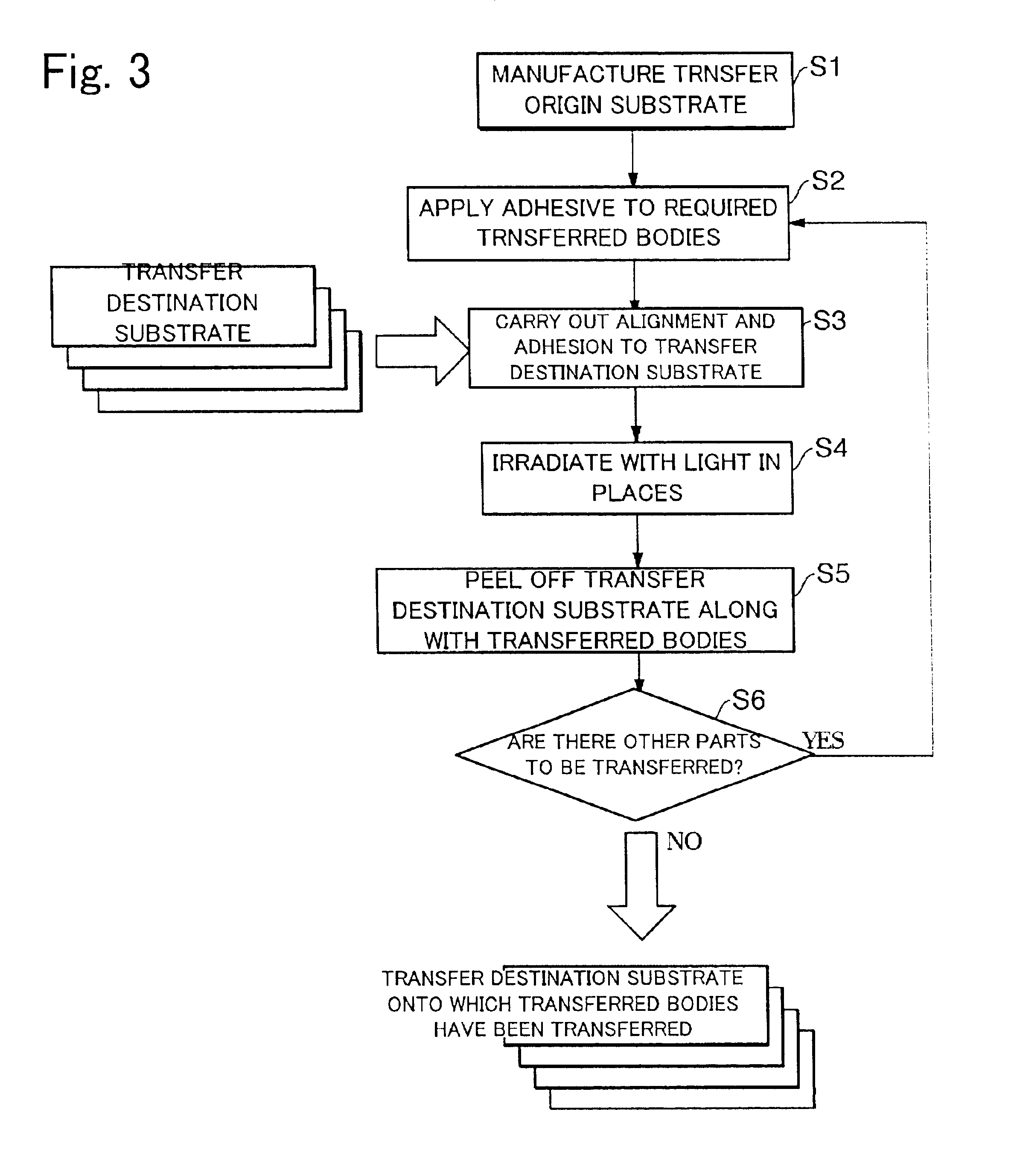

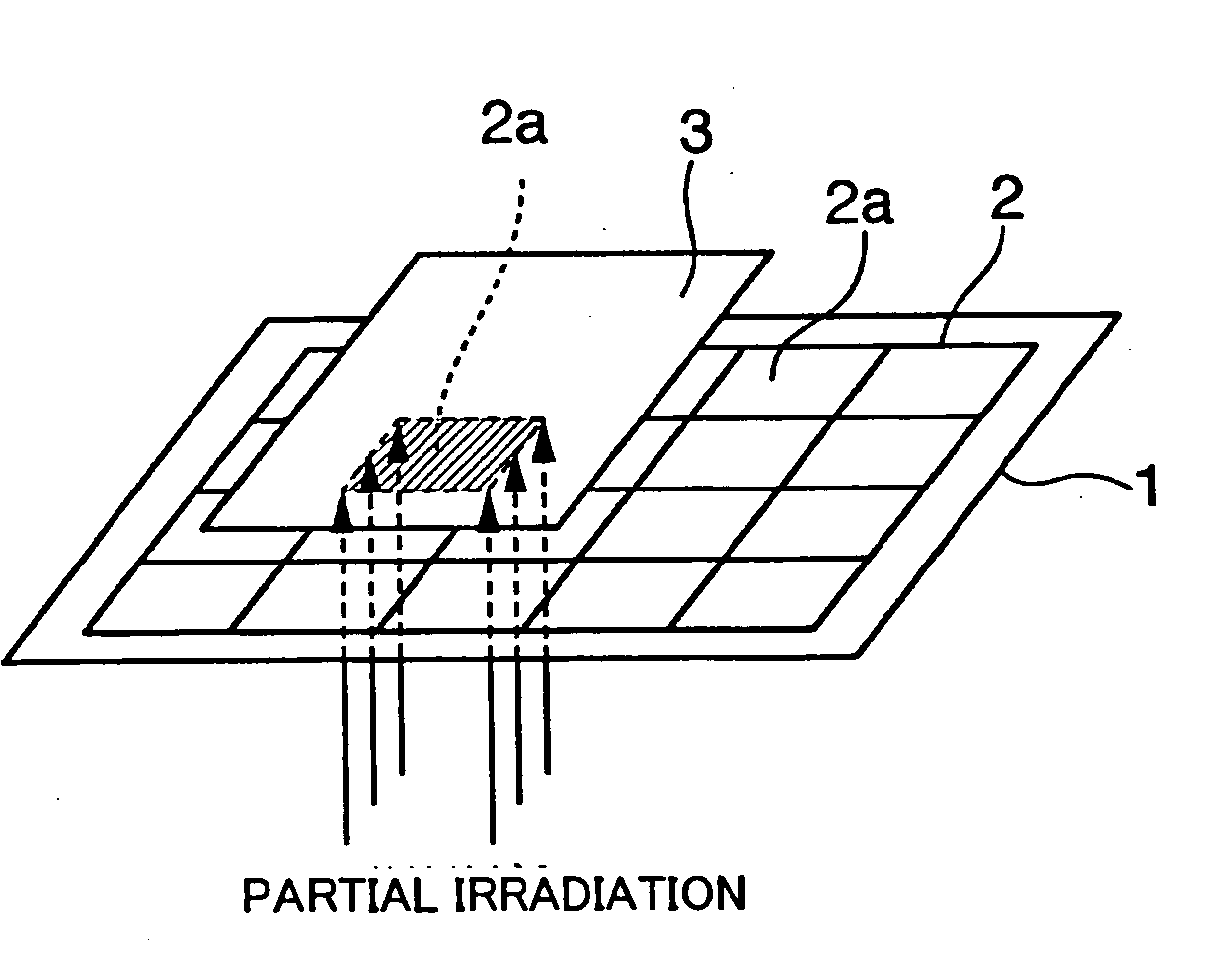

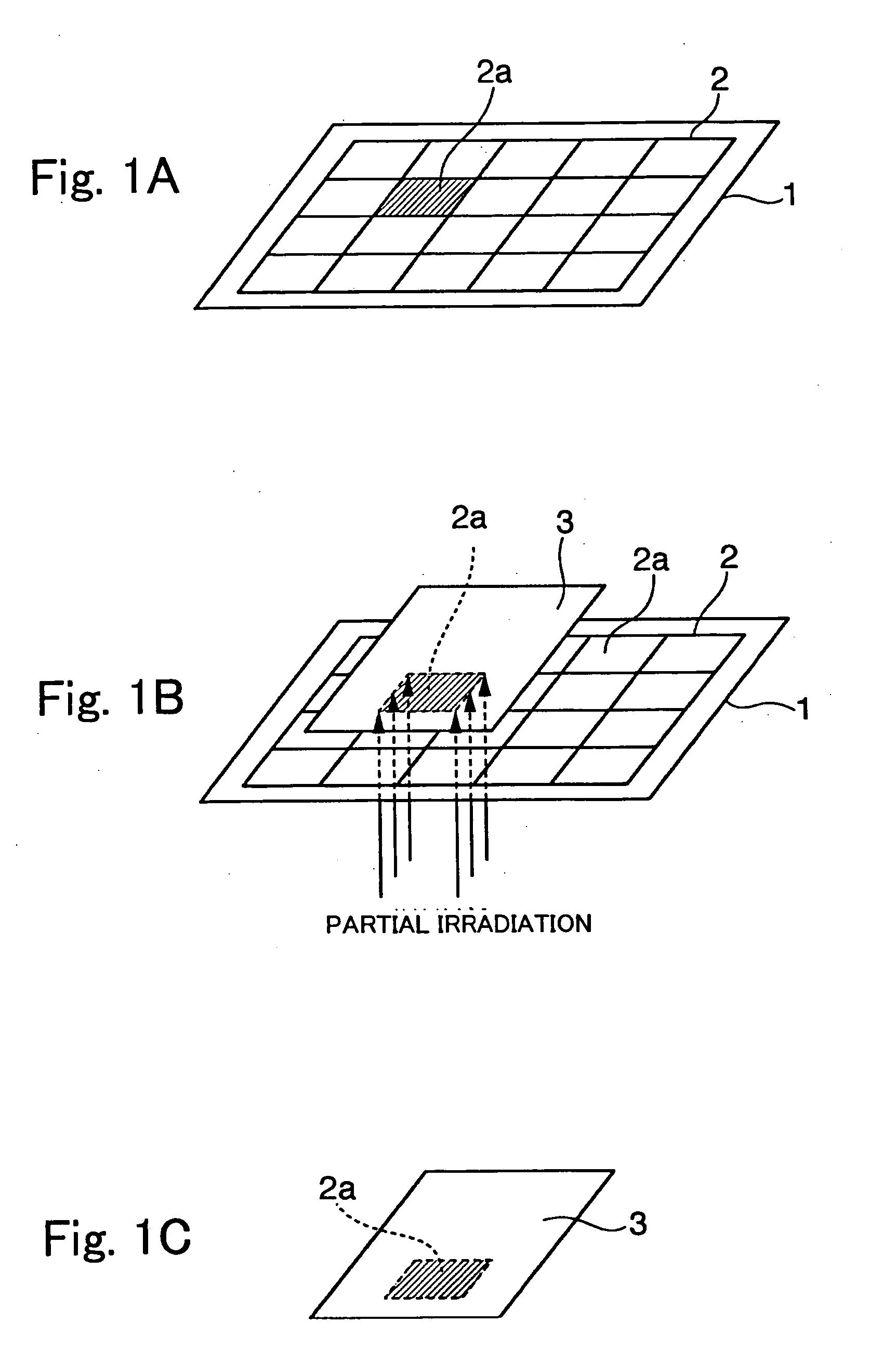

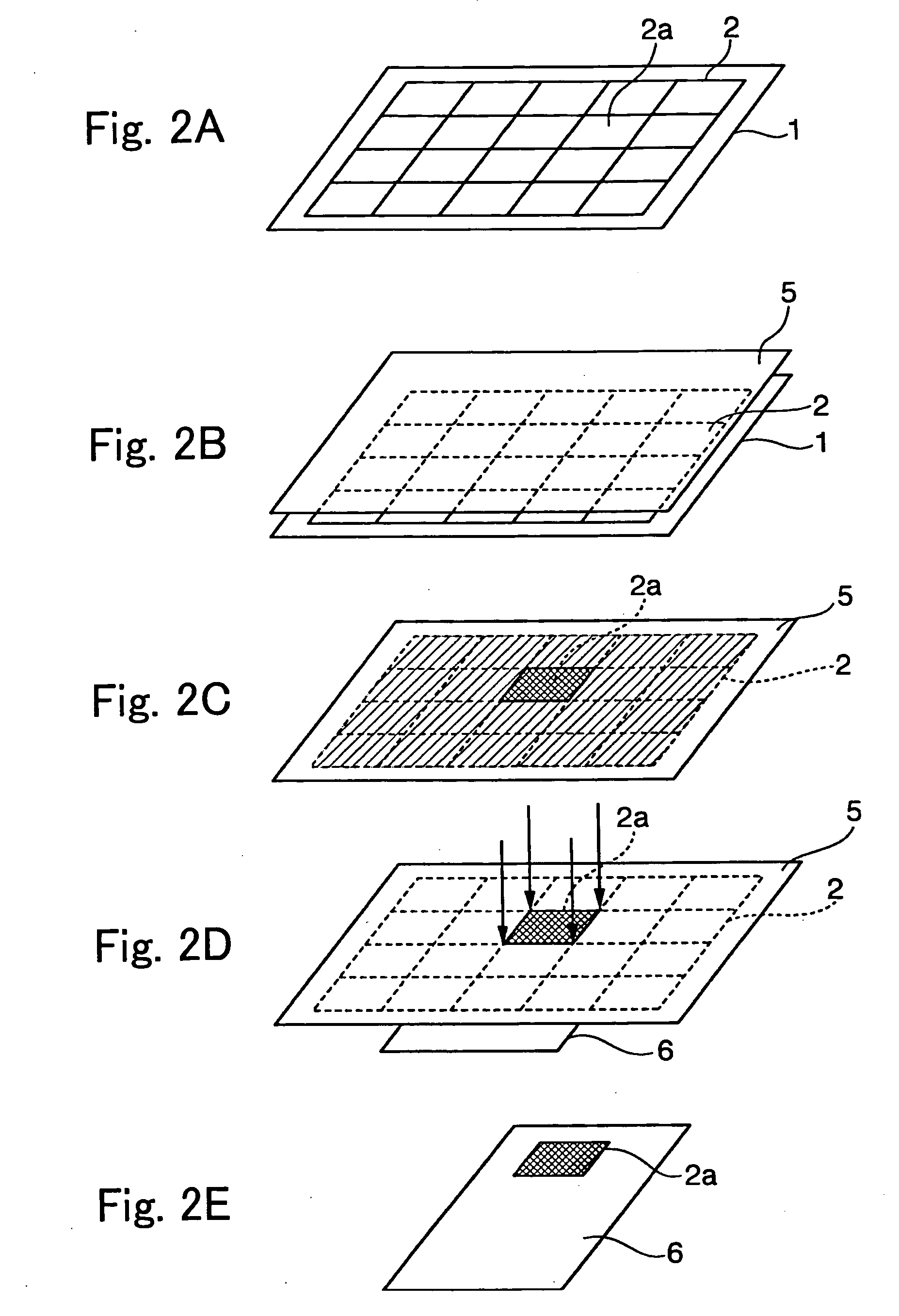

Transfer method, method of manufacturing thin film devices, method of manufacturing integrated circuits, circuit board and manufacturing method thereof, electro-optical apparatus and manufacturing method thereof, IC card, and electronic appliance

InactiveUS6887650B2Reduce material usageImprove area efficiencyMaterial nanotechnologyElectric discharge heatingIntegrated circuitElectronic equipment

Owner:SAMSUNG ELECTRONICS CO LTD

Symmetrically and asymmetrically stacked transistor grouping RF switch

InactiveUS20060194567A1Reduce areaImprove area efficiencyTransistorDc-dc conversionMOSFETEngineering

A silicon-on-insulator (SOI) RF switch adapted for improved power handling capability using a reduced number of transistors is described. In one embodiment, an RF switch includes pairs of switching and shunting stacked transistor groupings to selectively couple RF signals between a plurality of input / output nodes and a common RF node. The switching and shunting stacked transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. In one embodiment, the transistor groupings are “symmetrically” stacked in the RF switch (i.e., the transistor groupings all comprise an identical number of transistors). In another embodiment, the transistor groupings are “asymmetrically” stacked in the RF switch (i.e., at least one transistor grouping comprises a number of transistors that is unequal to the number of transistors comprising at least one other transistor grouping). The stacked configuration of the transistor groupings enable the RF switch to withstand RF signals of varying and increased power levels. The asymmetrically stacked transistor grouping RF switch facilitates area-efficient implementation of the RF switch in an integrated circuit. Maximum input and output signal power levels can be withstood using a reduced number of stacked transistors.

Owner:PSEMI CORP

Transfer method, method of manufacturing thin film devices, method of maufacturing integrated circuits, circuit board and manufacturing method thereof, electro-optical apparatus and manufacturing method thereof, IC card, and electronic appliance

InactiveUS20050106839A1Reduce material usageImprove area efficiencyMaterial nanotechnologySemiconductor/solid-state device detailsEngineeringIntegrated circuit

Owner:SEIKO EPSON CORP

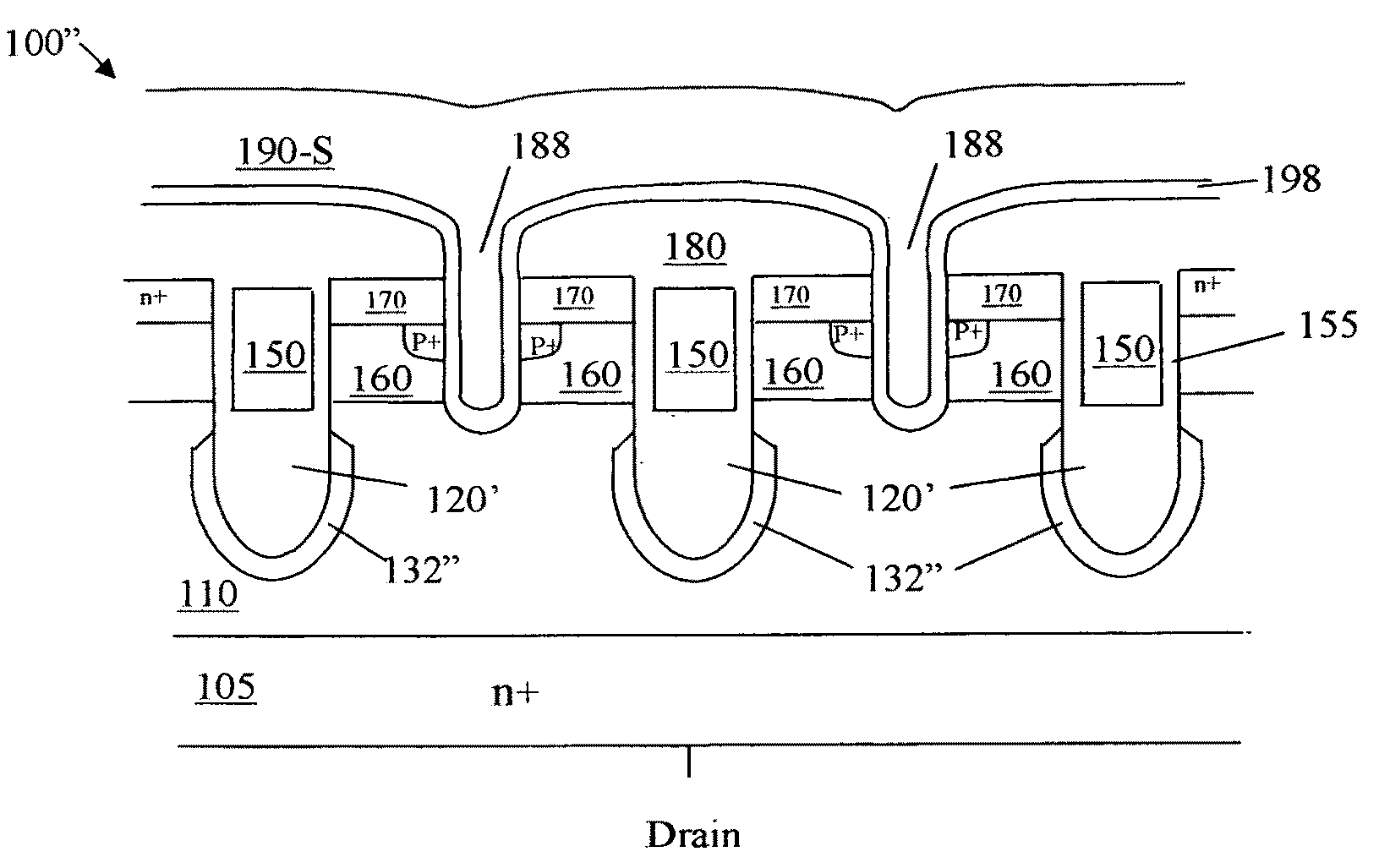

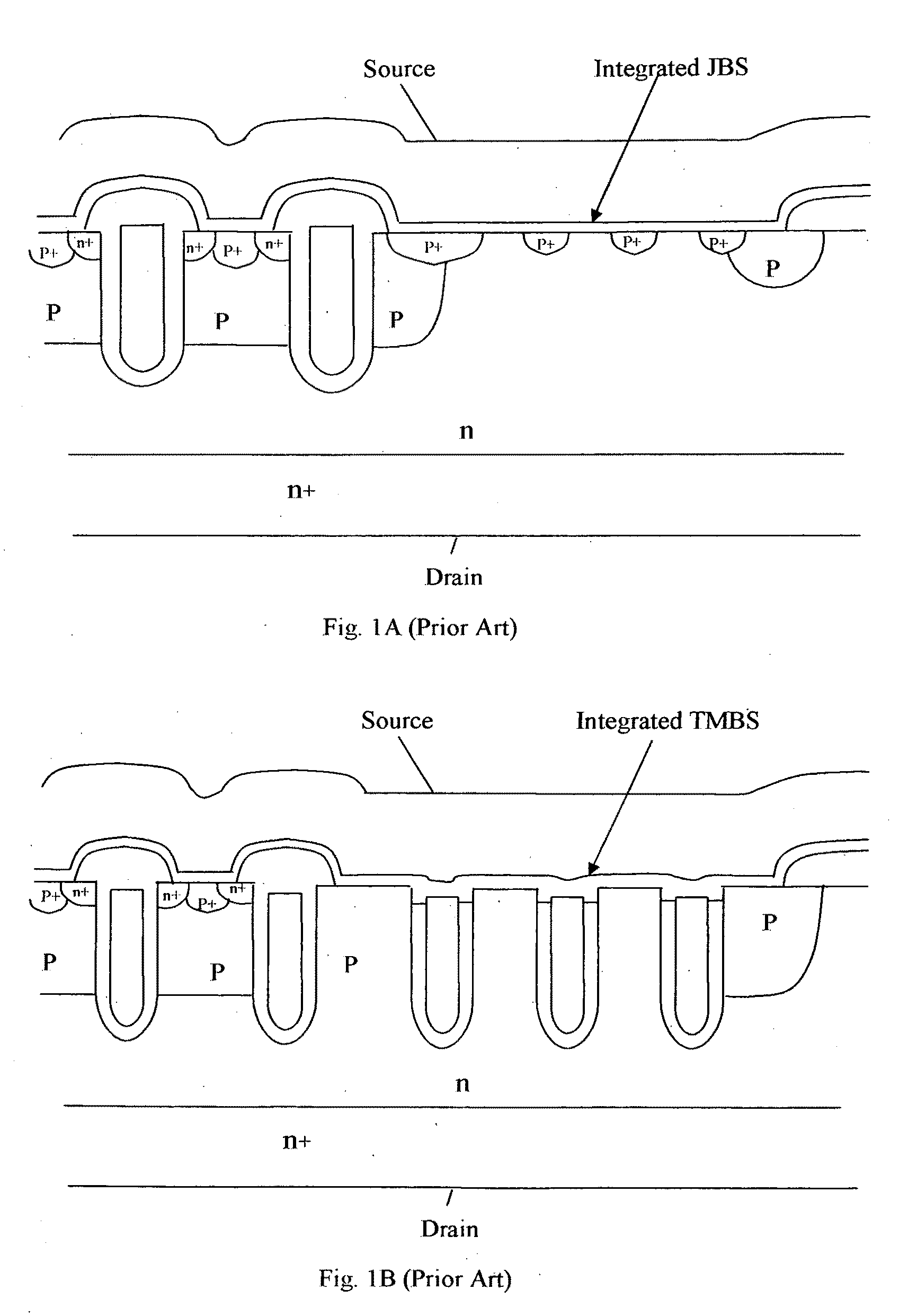

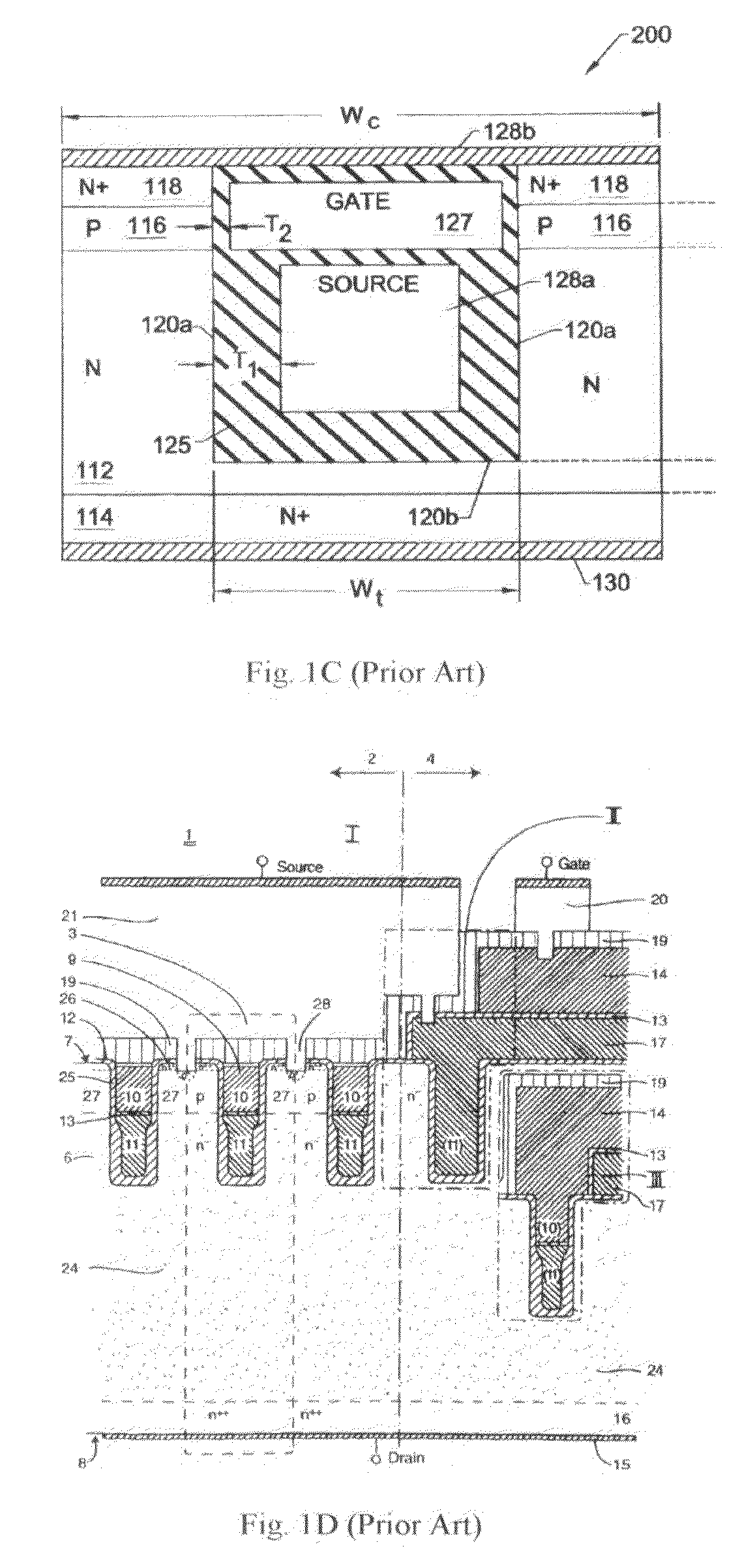

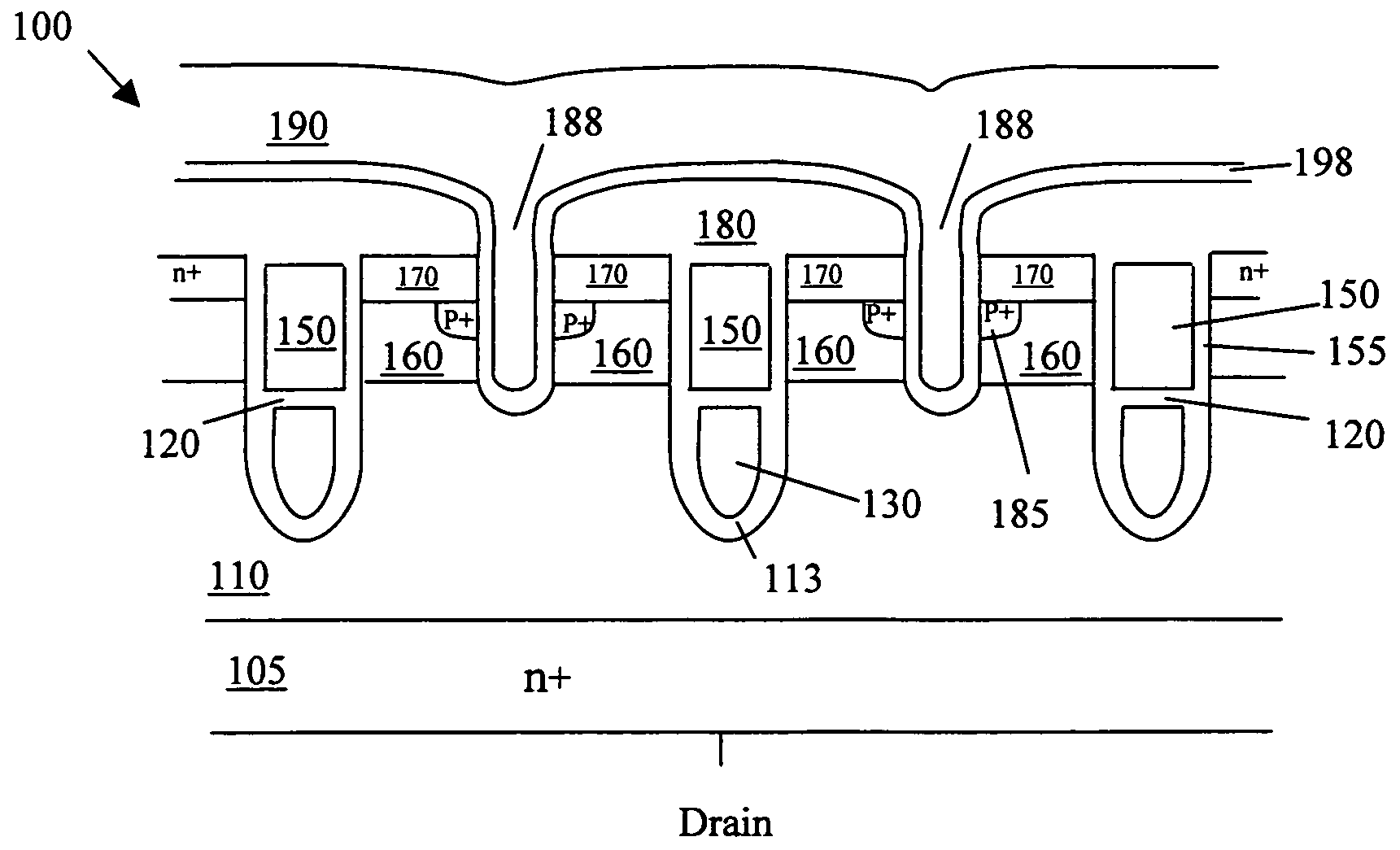

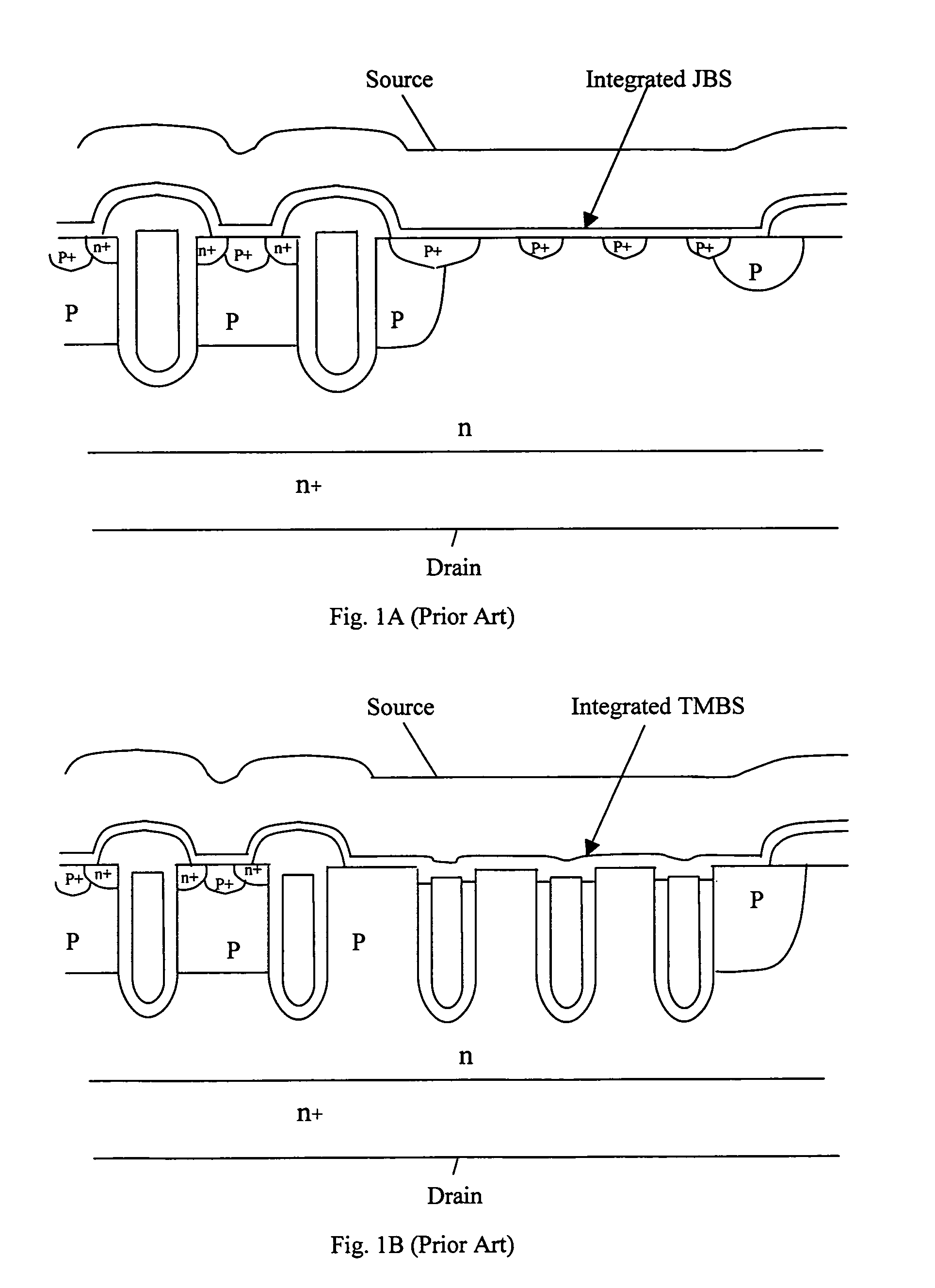

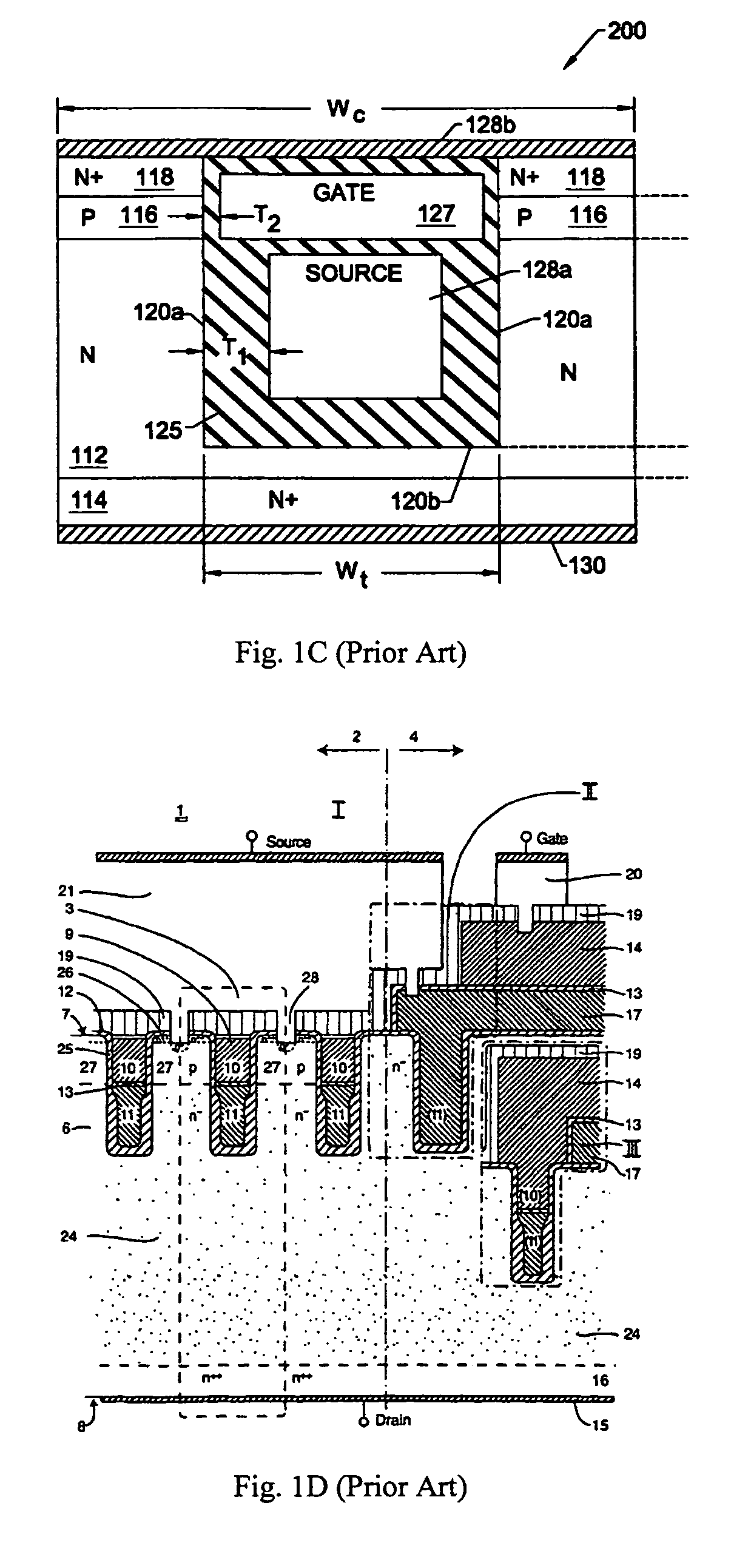

Shielded gate trench (SGT) MOSFET cells implemented with a schottky source contact

ActiveUS20090072301A1Improve switching performanceImprove area efficiencySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETInsulation layer

This invention discloses a semiconductor power device that includes a plurality of power transistor cells surrounded by a trench opened in a semiconductor substrate. At least one active cell further includes a trenched source contact opened between the trenches wherein the trenched source contact opened through a source region into a body region for electrically connecting the source region to a source metal disposed on top of an insulation layer wherein a trench bottom surface of the trenched source contact further covered with a conductive material to function as an integrated Schottky barrier diode in said active cell. A shielding structure is disposed at the bottom and insulated from the trenched gate to provide shielding effect for both the trenched gate and the Schottky diode.

Owner:ALPHA & OMEGA SEMICON LTD

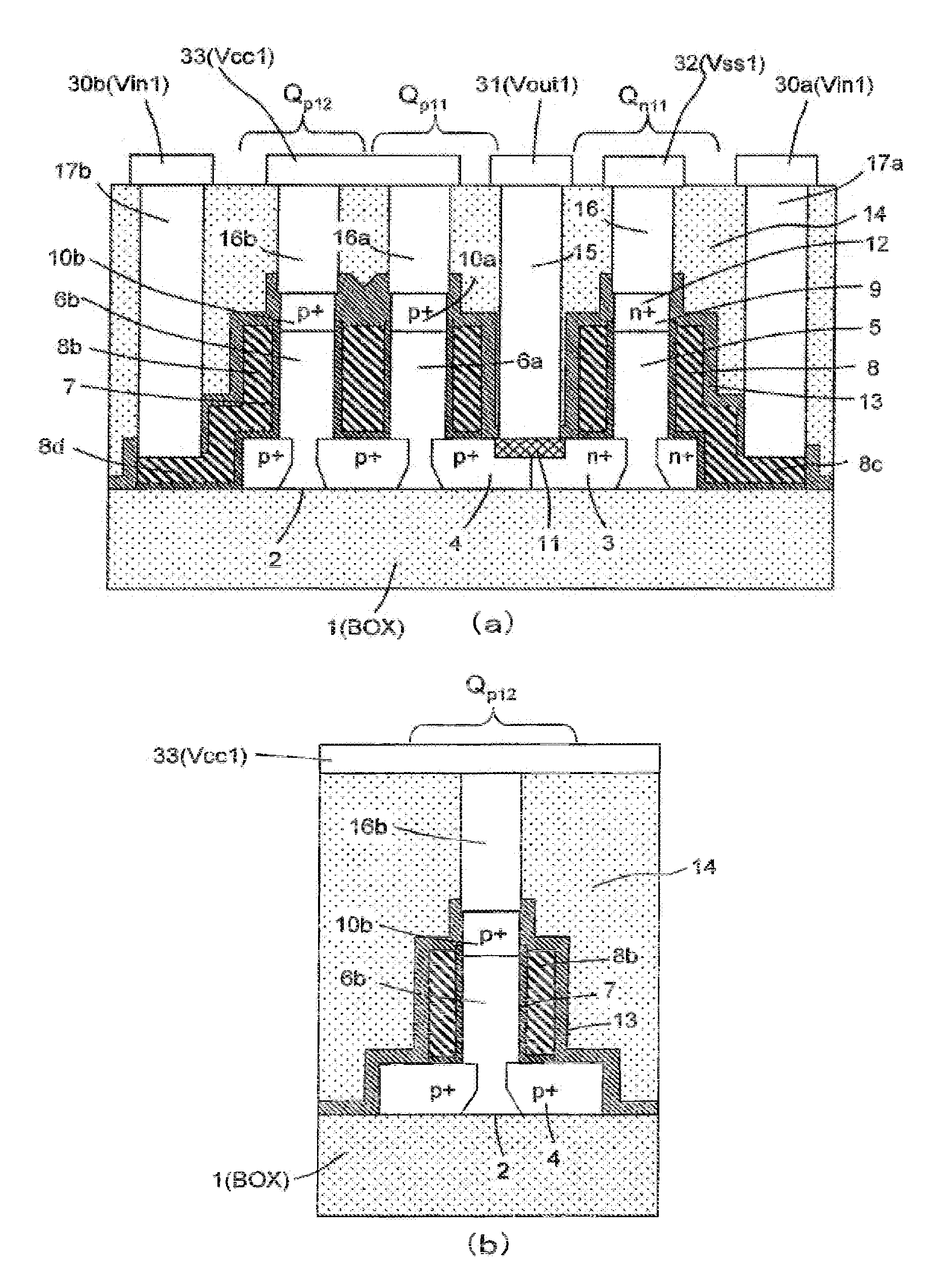

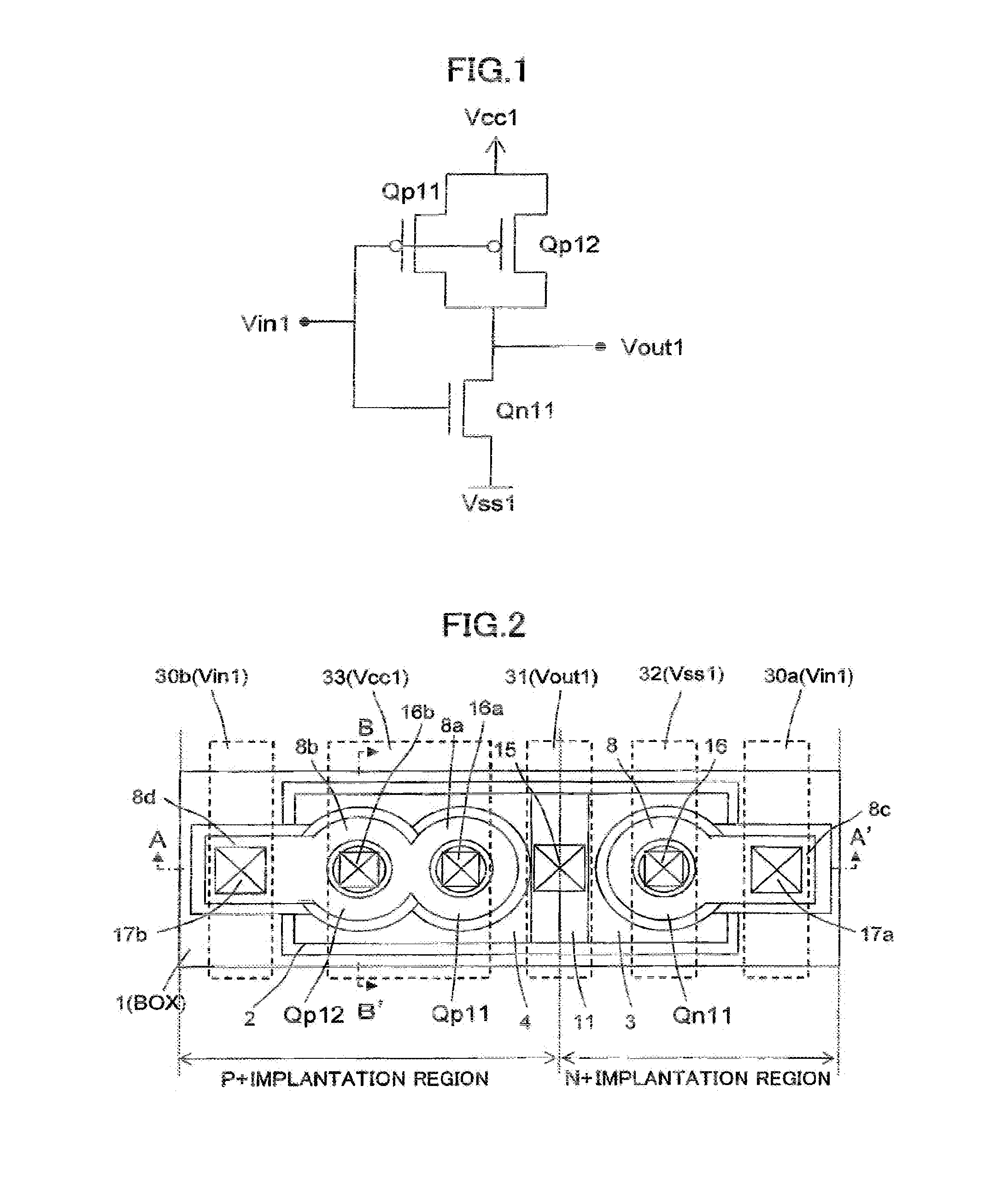

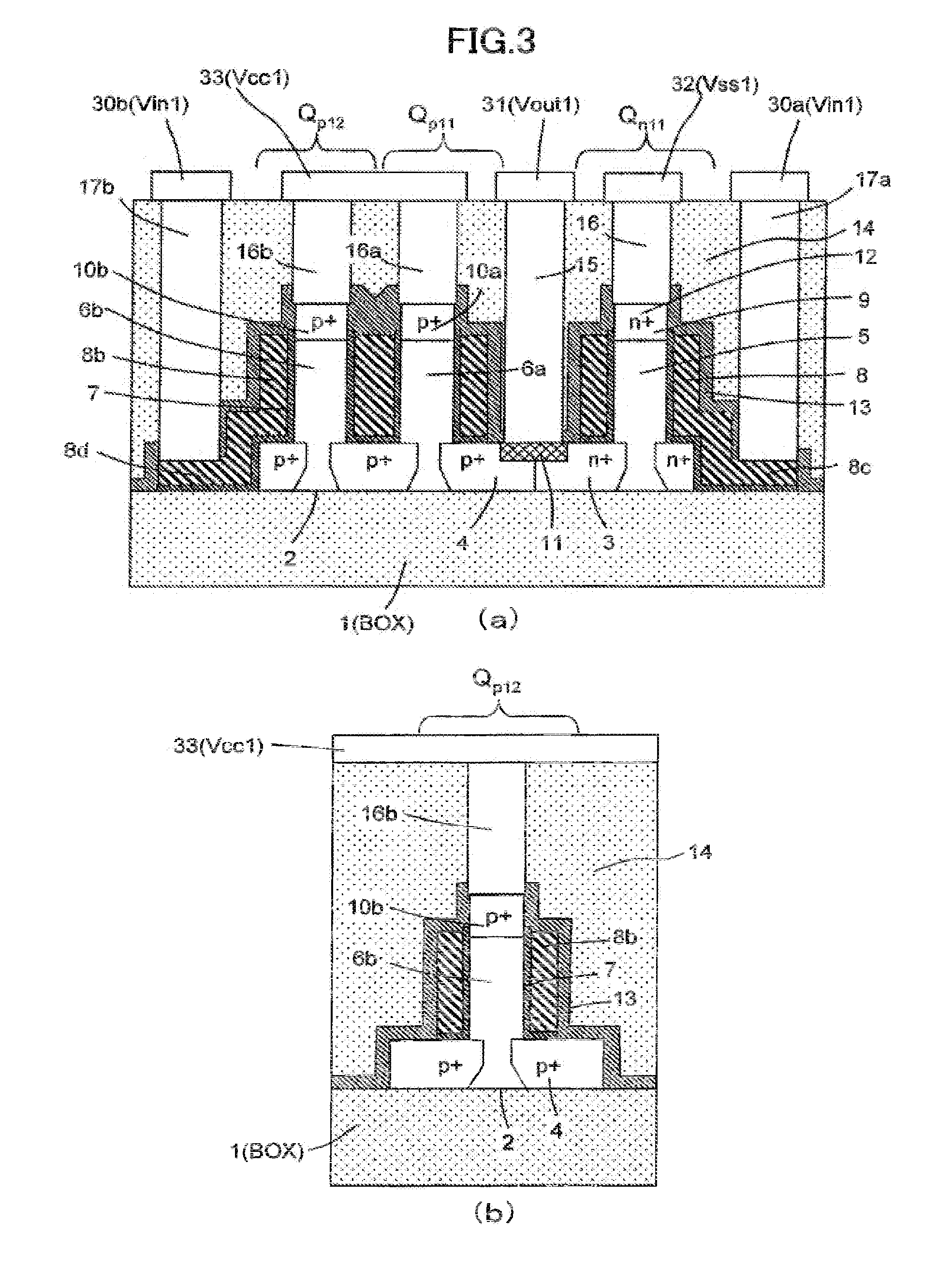

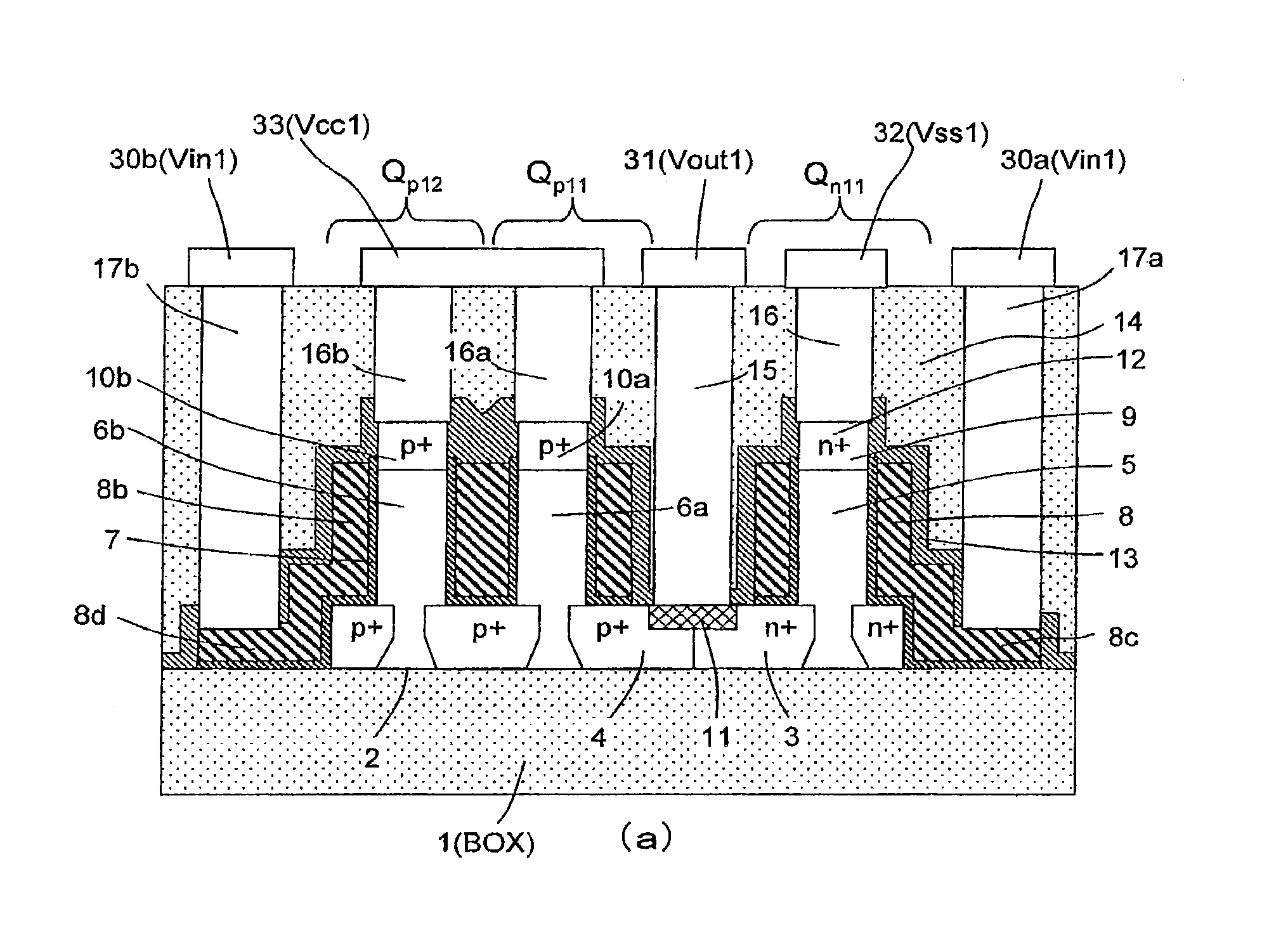

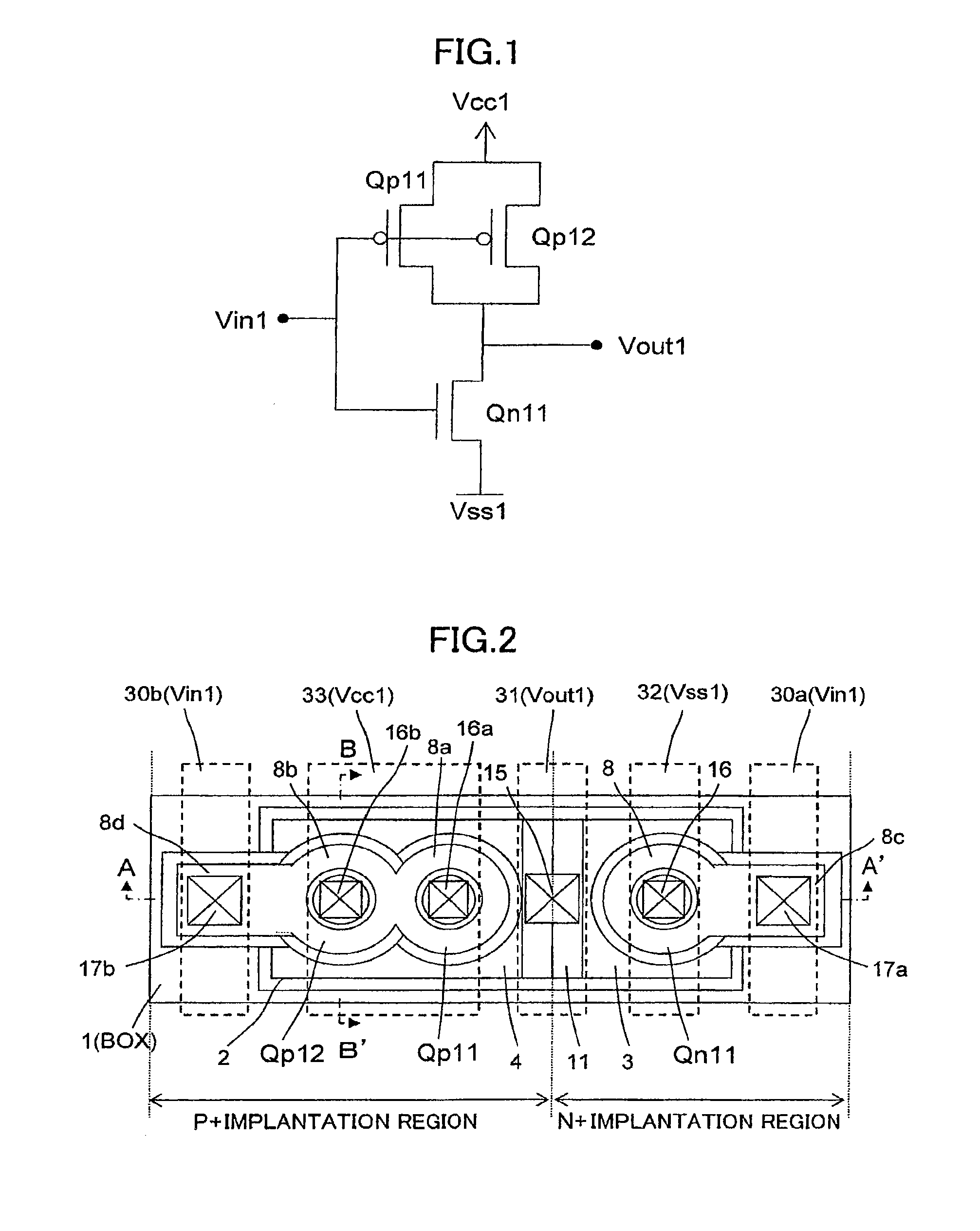

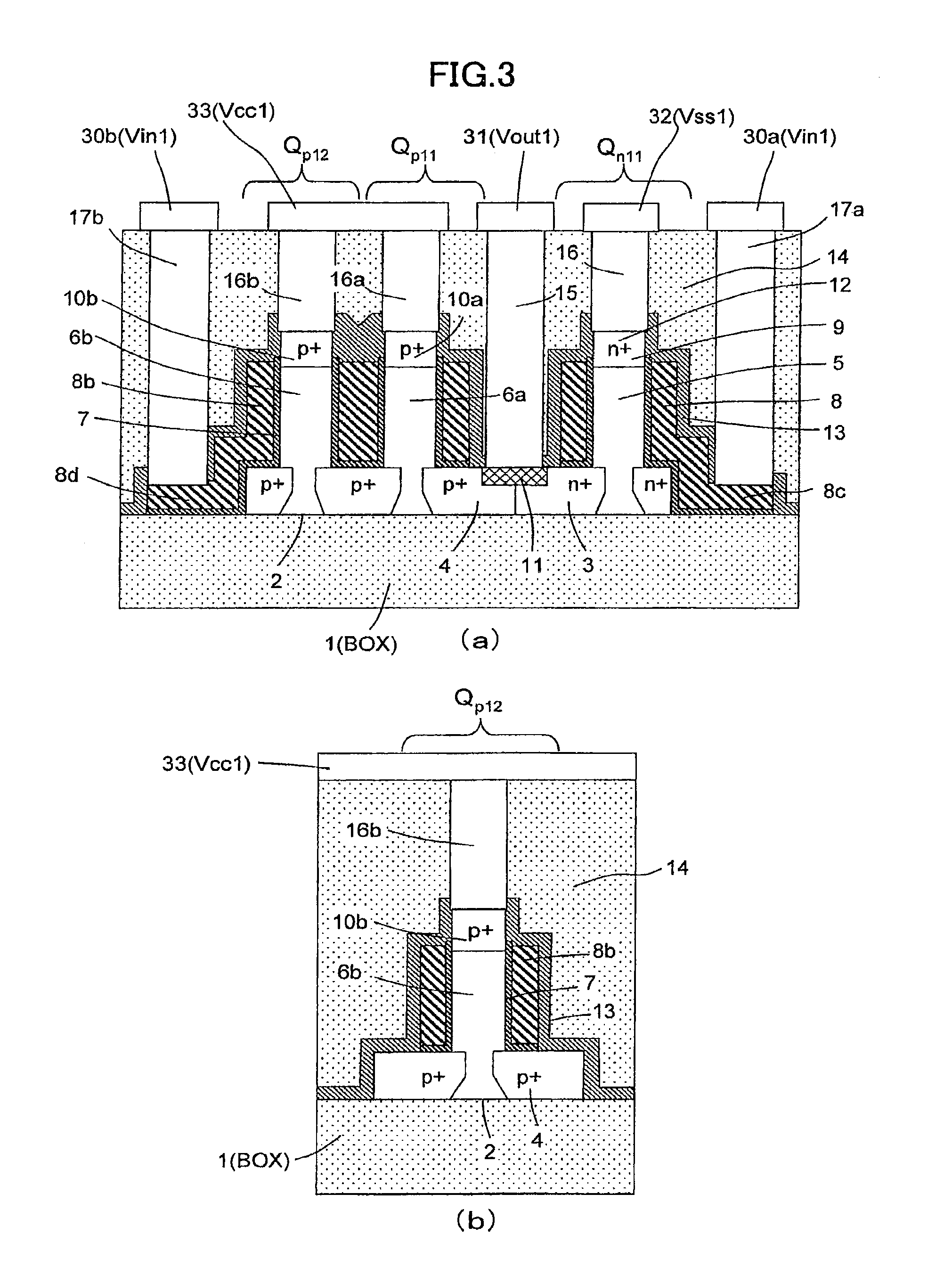

Semiconductor device and production method therefor

ActiveUS8188537B2Easy to integrateImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingCondensed matter physicsSemiconductor

It is intended to provide a semiconductor device including a MOS transistor, comprising: a semiconductor pillar; one of a drain region and a source region formed in contact with a lower part of the semiconductor pillar; a first gate formed around a sidewall of the semiconductor pillar through a first dielectric film therebetween; and an epitaxial semiconductor layer formed on a top surface of the semiconductor pillar, wherein the other of the source region and the drain region is formed so as to be at least partially in the epitaxial semiconductor layer, and wherein: the other of the source region and the drain region has a top surface having an area greater than that of the top surface of the semiconductor pillar.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

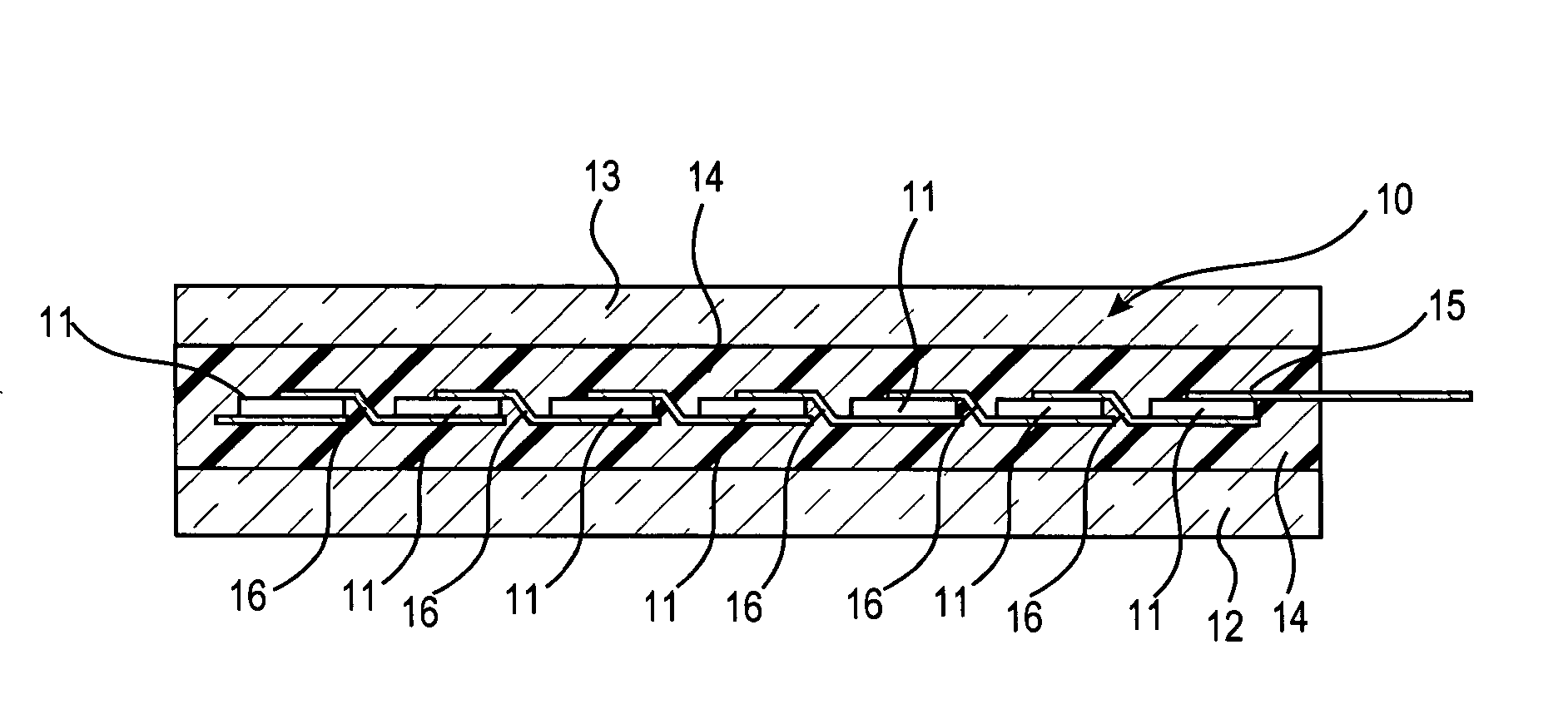

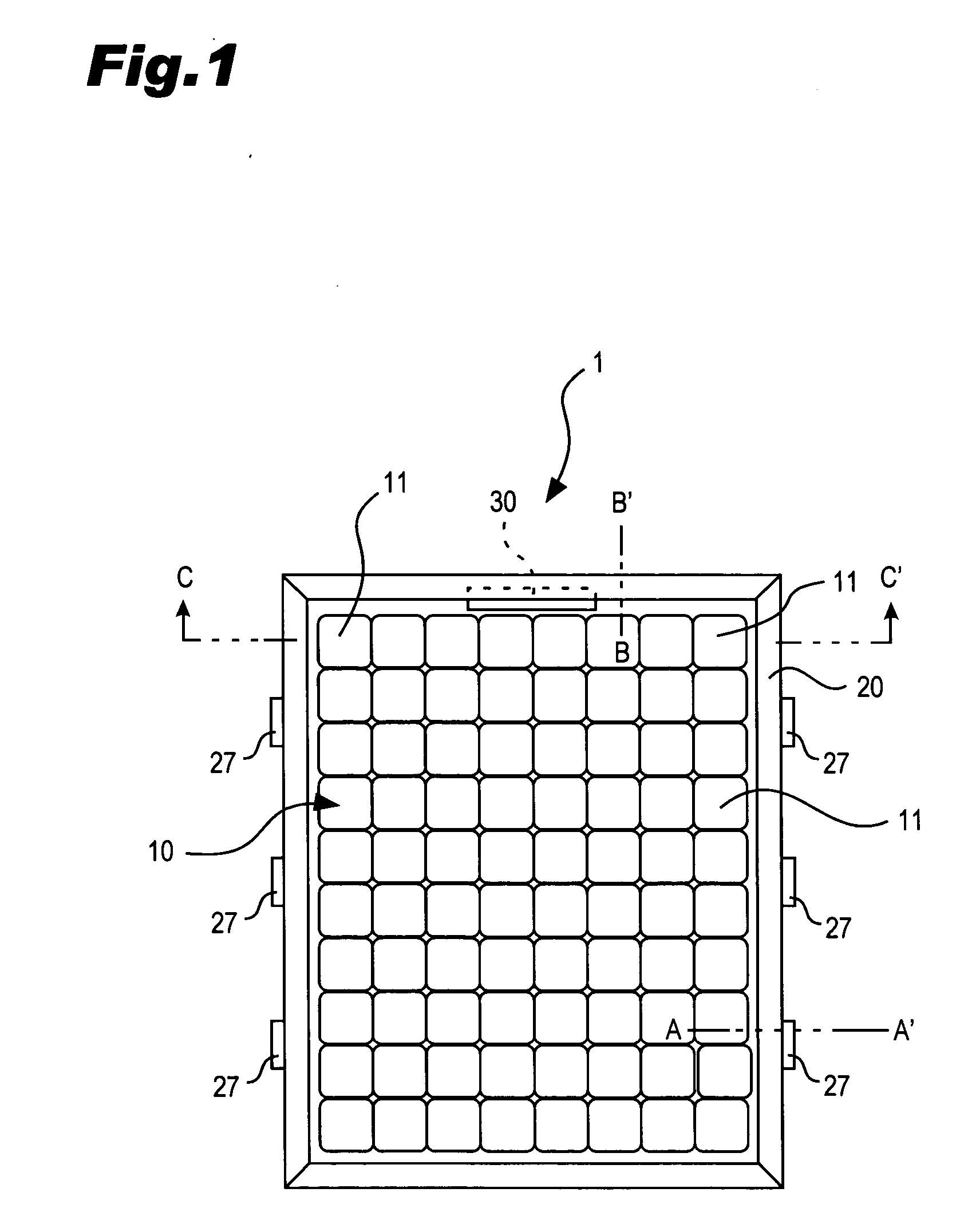

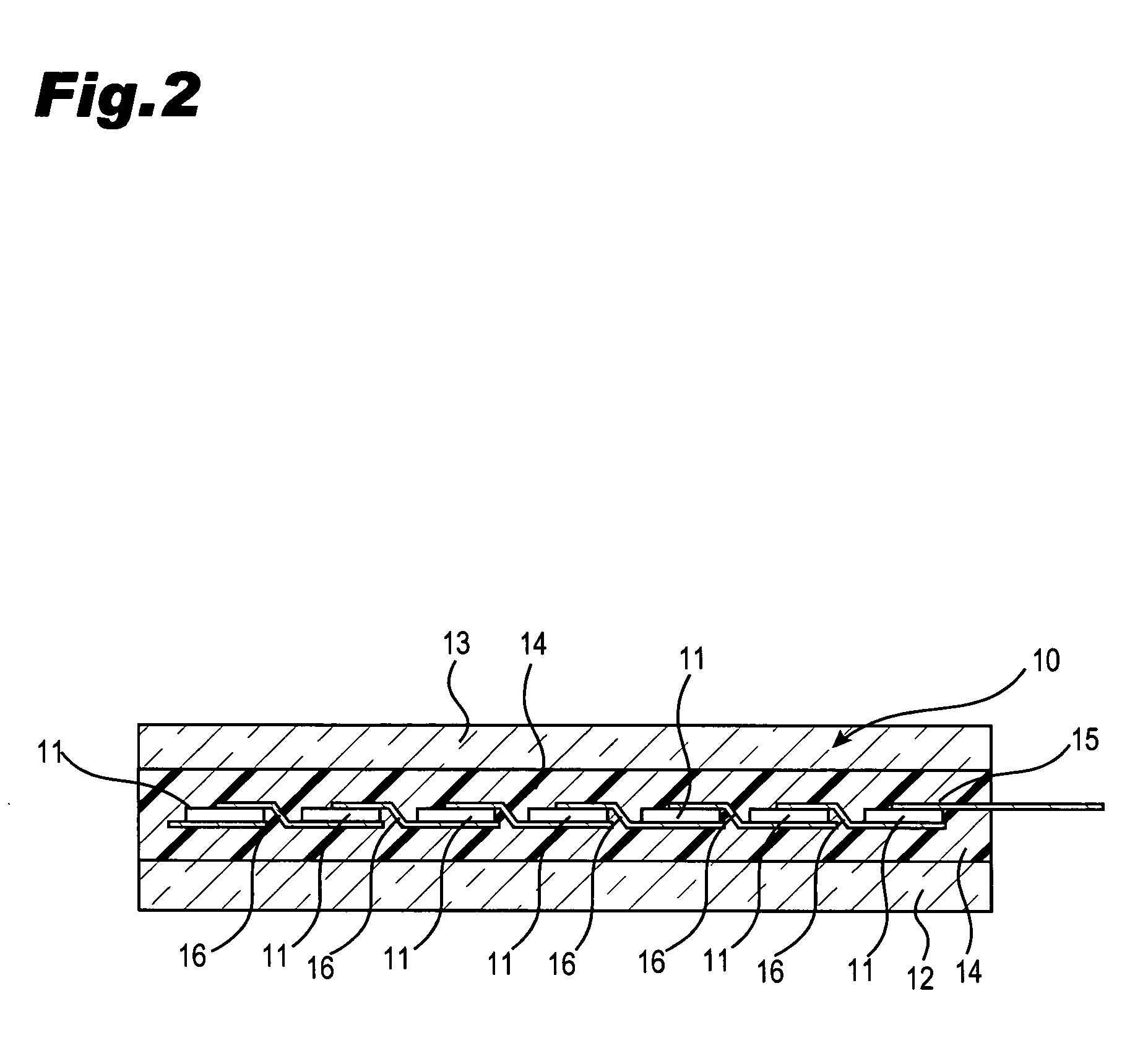

Photovoltaic module

ActiveUS20060219291A1Reduces dimensionImprove area efficiencyPhotovoltaic supportsPV power plantsSolar cellPhotovoltaics

The present invention provides a photovoltaic module which prevents enlargement of the dimensions of a photovoltaic submodule by reducing ineffective parts which do not contribute to power generation. The photovoltaic module comprises a photovoltaic submodule including a plurality of solar cells interposed between two light-transmitting substrates through the intermediary of an encapsulant, and a connecting lead extending from an edge between the two light-transmitting substrates for outputting generated electric current, a terminal box 30 attached near to the edge of the photovoltaic submodule housing a connecting part between the connecting lead and a cable for outputting generated electric current to the outside, and an outer frame set around the outer circumference of the photovoltaic submodule. An opening 28 through which the connecting lead and the terminal box are inserted is provided to the outer frame at a position which receives at least the terminal box.

Owner:SANYO ELECTRIC CO LTD

Shielded gate trench (SGT) MOSFET cells implemented with a schottky source contact

ActiveUS7453119B2Improve switching performanceImprove area efficiencyTime-division multiplexDiodeMOSFETInsulation layer

Owner:ALPHA & OMEGA SEMICON LTD

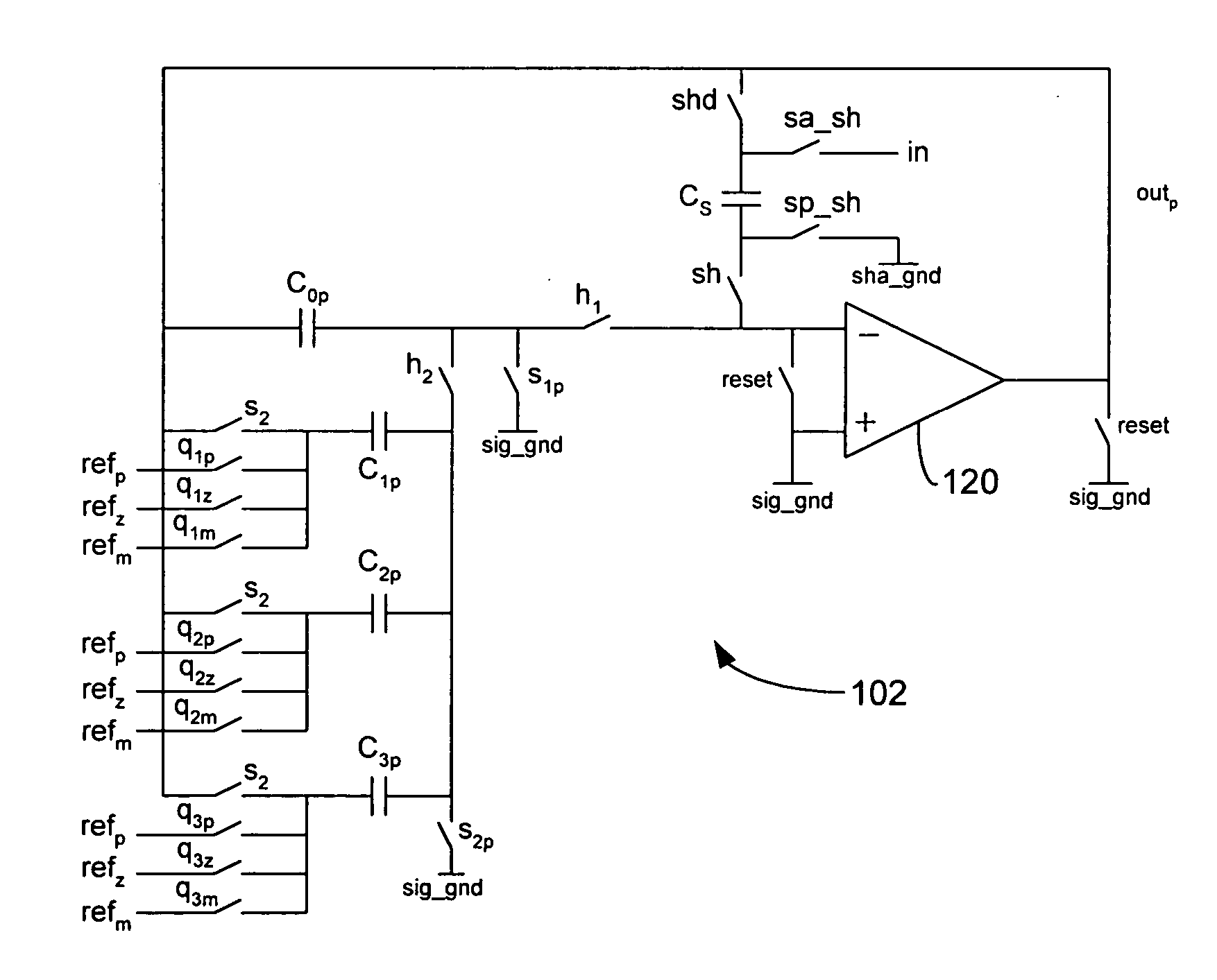

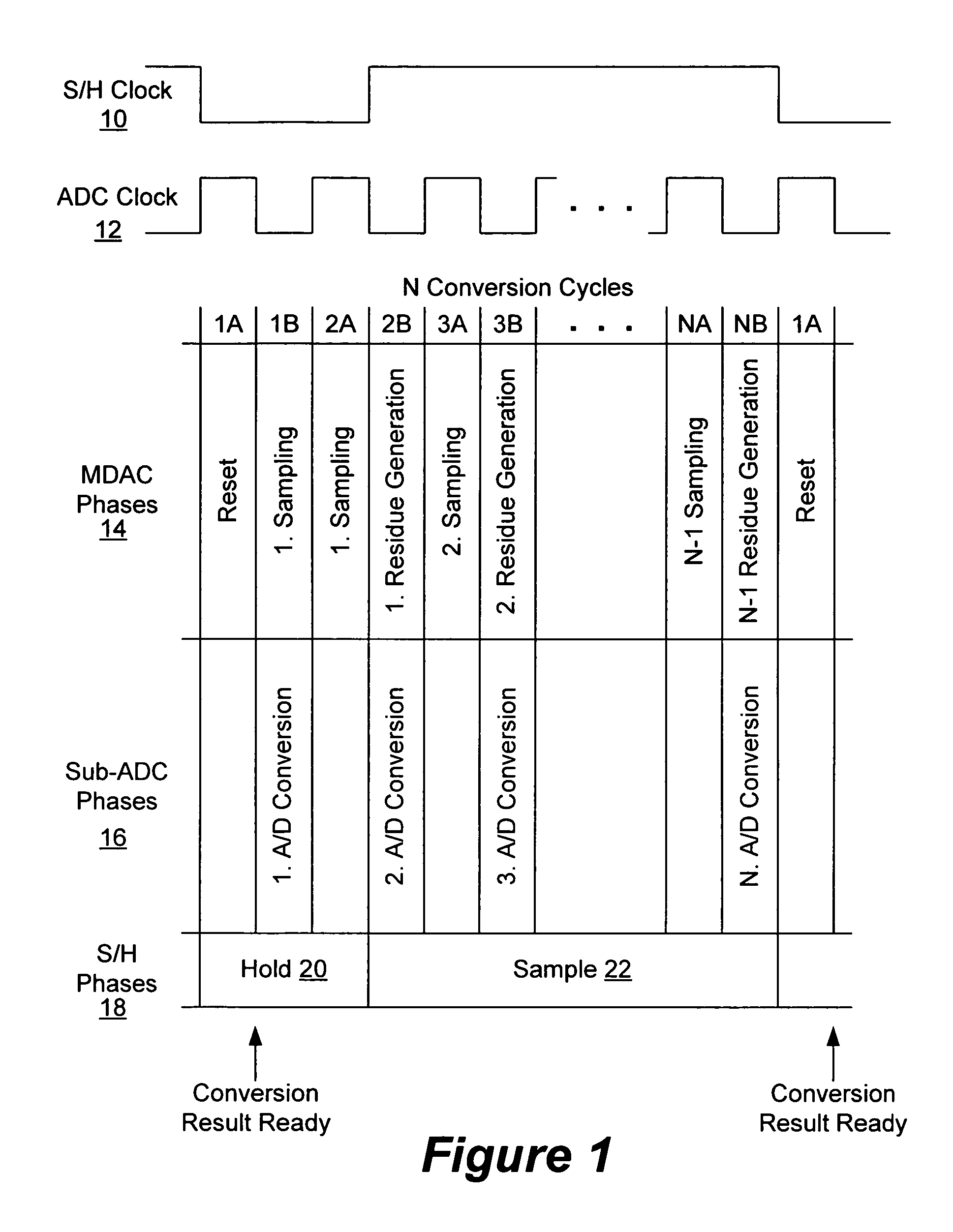

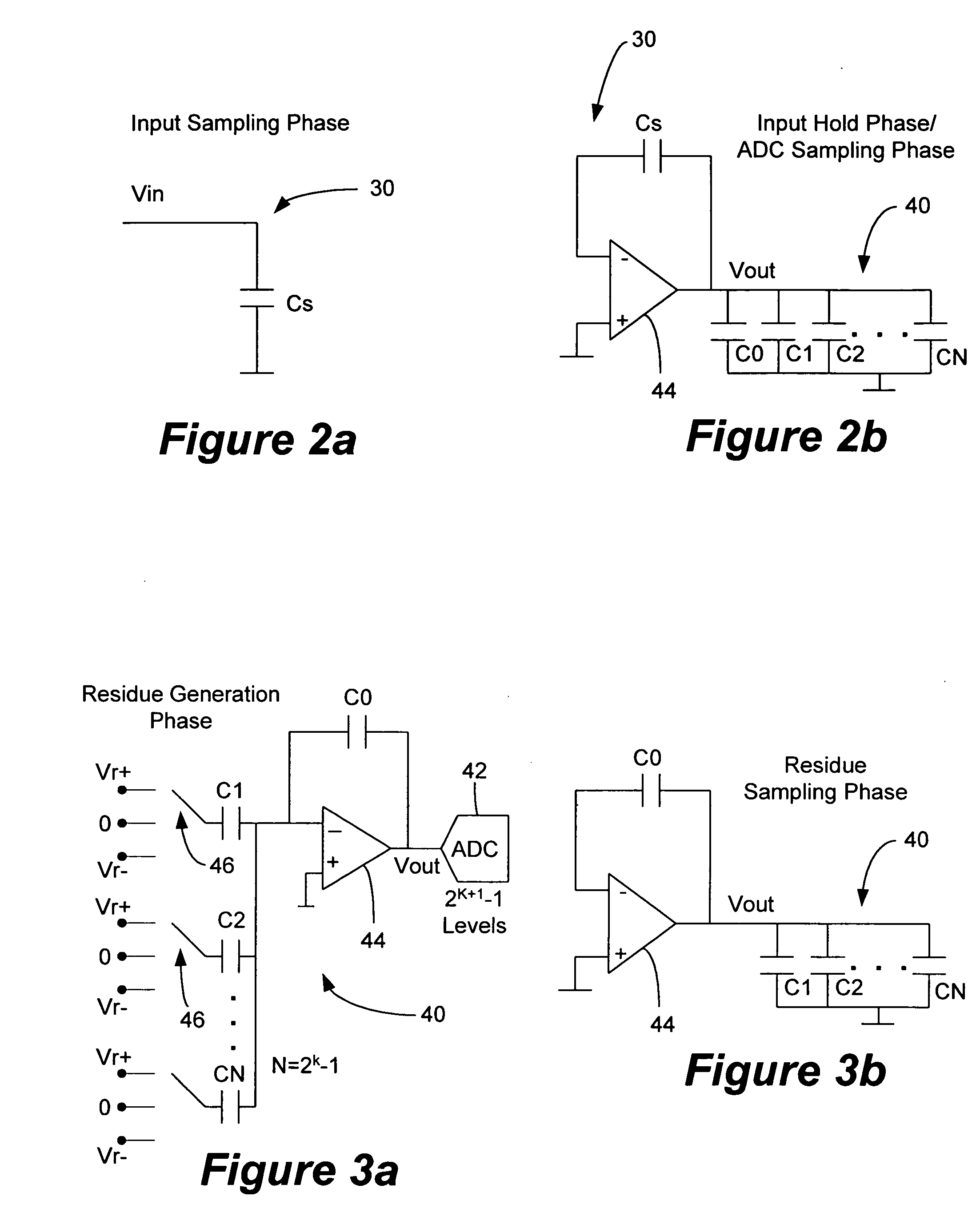

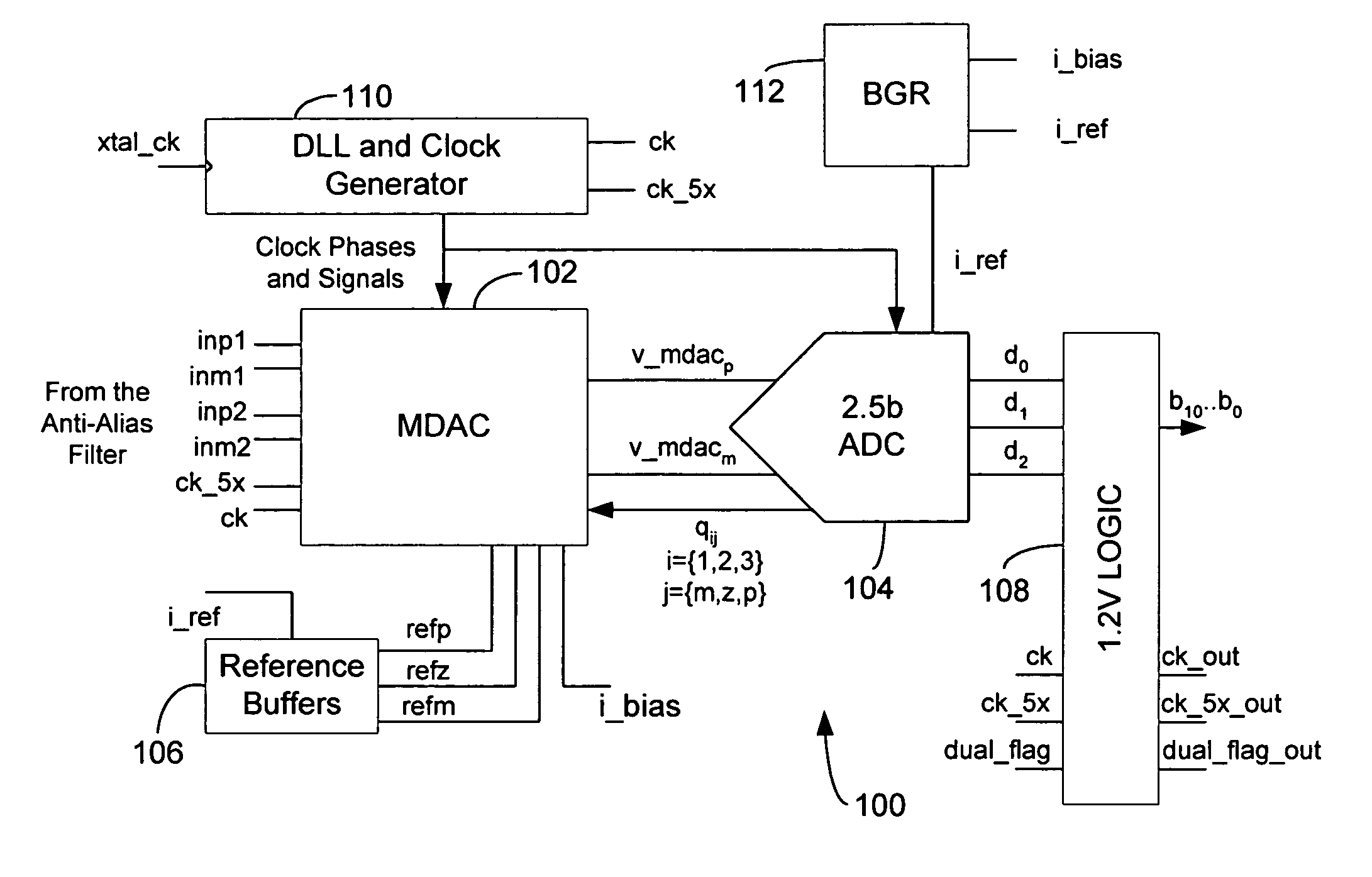

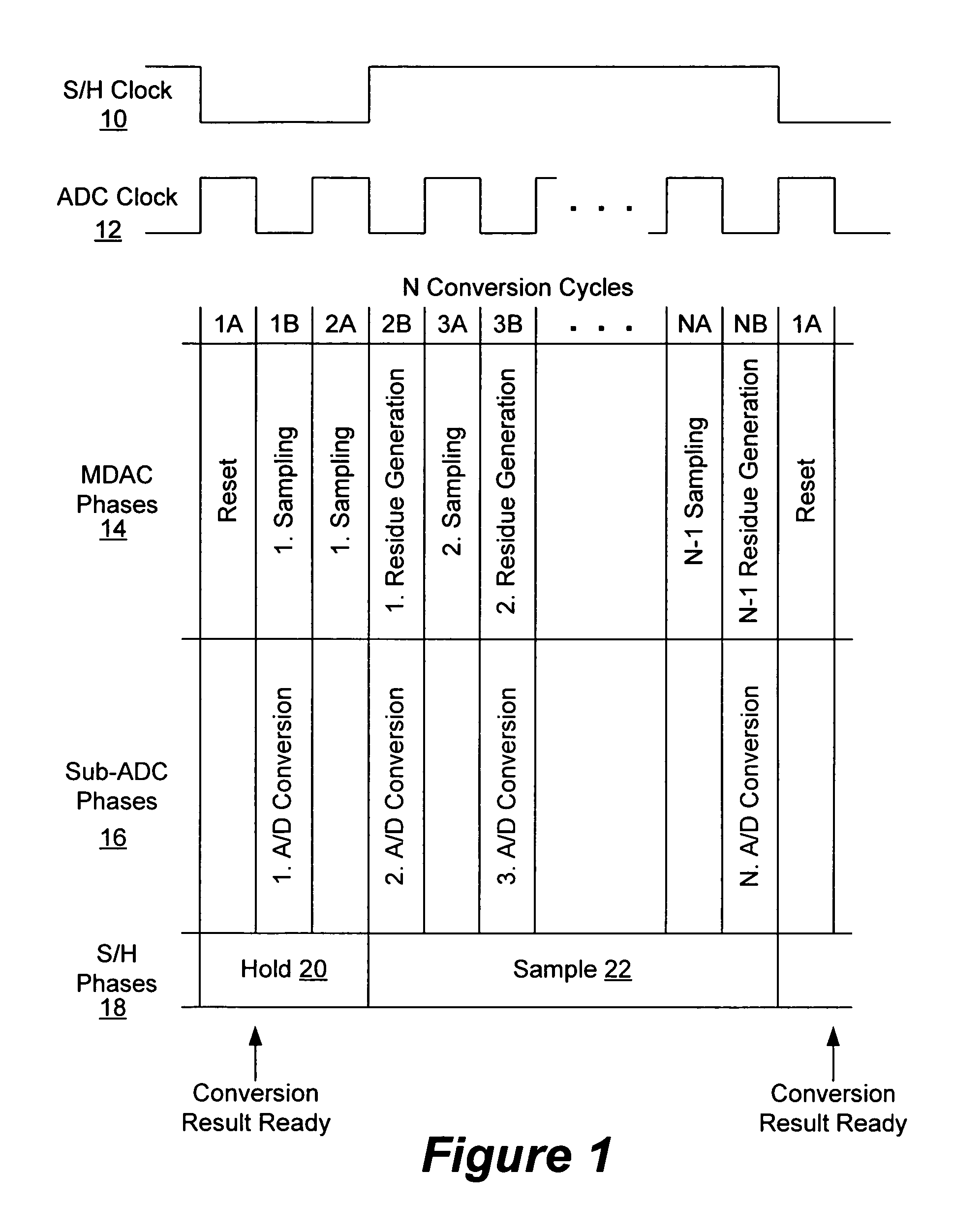

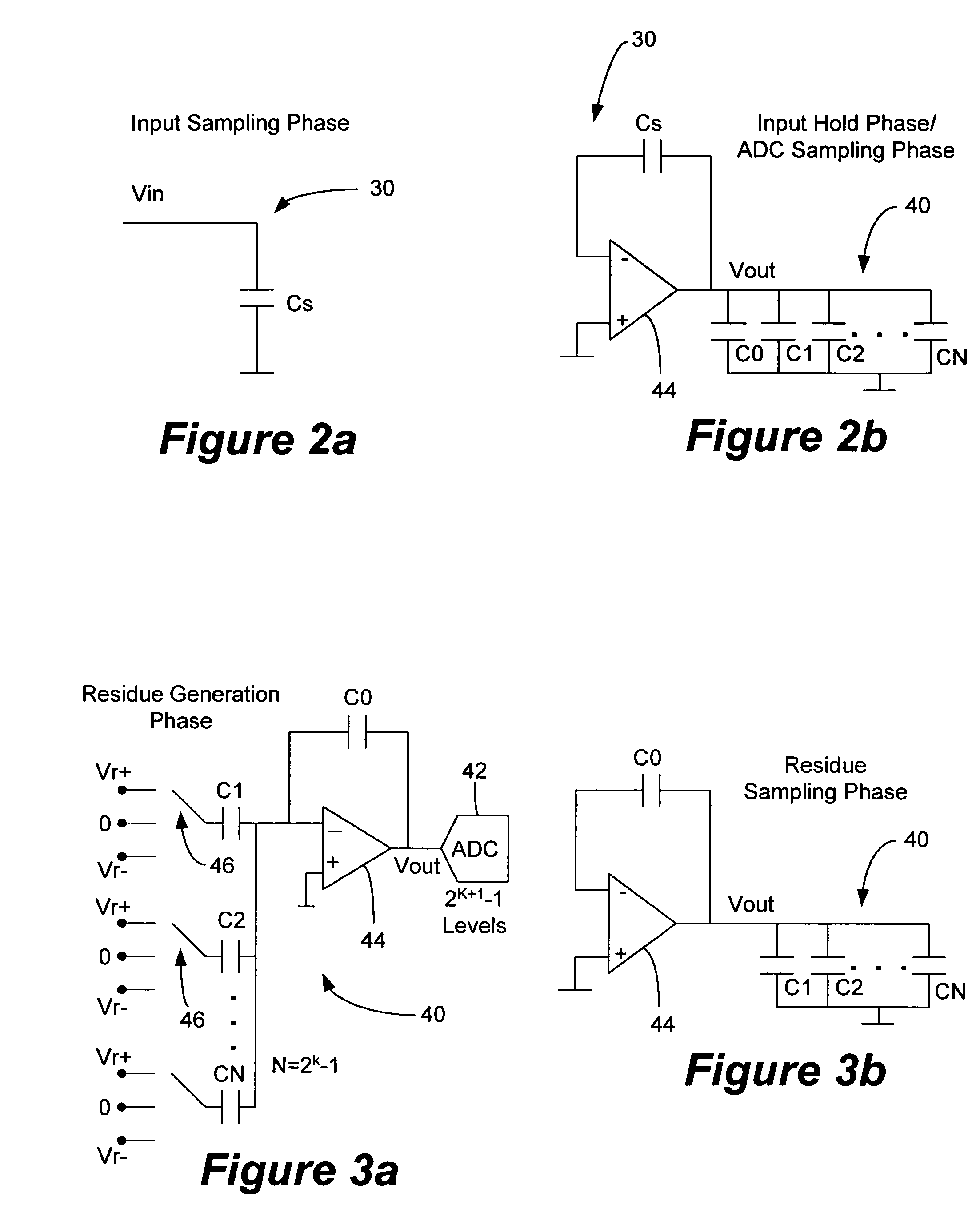

Architecture for an algorithmic analog-to-digital converter

ActiveUS20050140537A1Improve area efficiencyHighly suitableElectric signal transmission systemsPulse automatic controlAudio power amplifierControl signal

An algorithmic analog-to-digital converter (ADC) includes a sample-and-hold circuit and an ADC processing unit operating in parallel and sharing a single operational amplifier. The ADC processing unit includes an MDAC with a switched capacitor topology and a sub-ADC. The ADC processing unit is clocked by an internal clock that is N times faster than the sample-and-hold clock. Each cycle is further sub-divided into two phases. During one phase the capacitors are coupled to a residue or sampled voltage provided by the MDAC, and during another phase the capacitor are coupled to a reference voltage determined by the switch control signals generated by the sub-ADC. A set of data bits is generated by the ADC processing unit during each ADC clock cycle. The N sets of data bits are added to generate the digital output stream.

Owner:SYNAPTICS INC

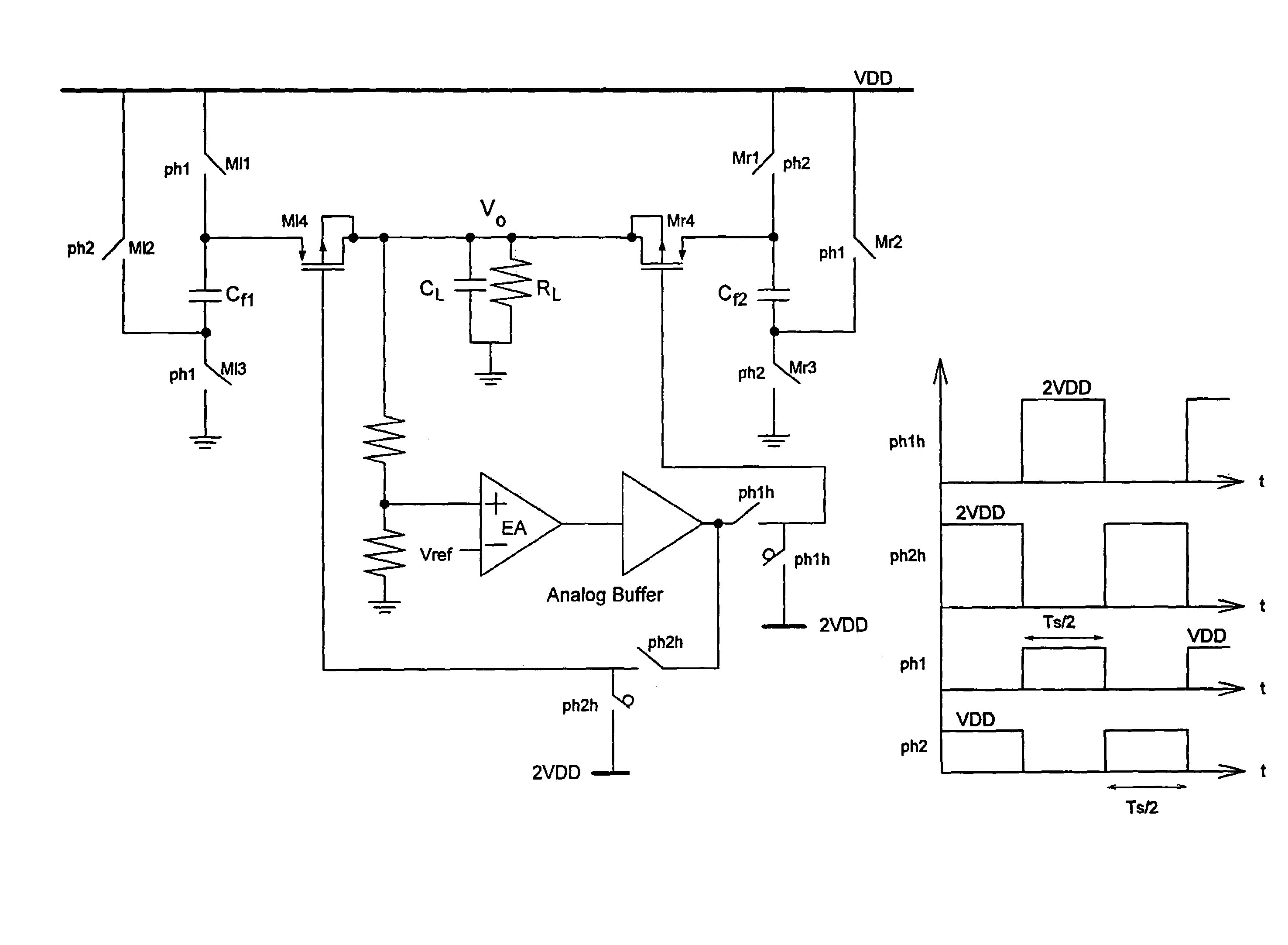

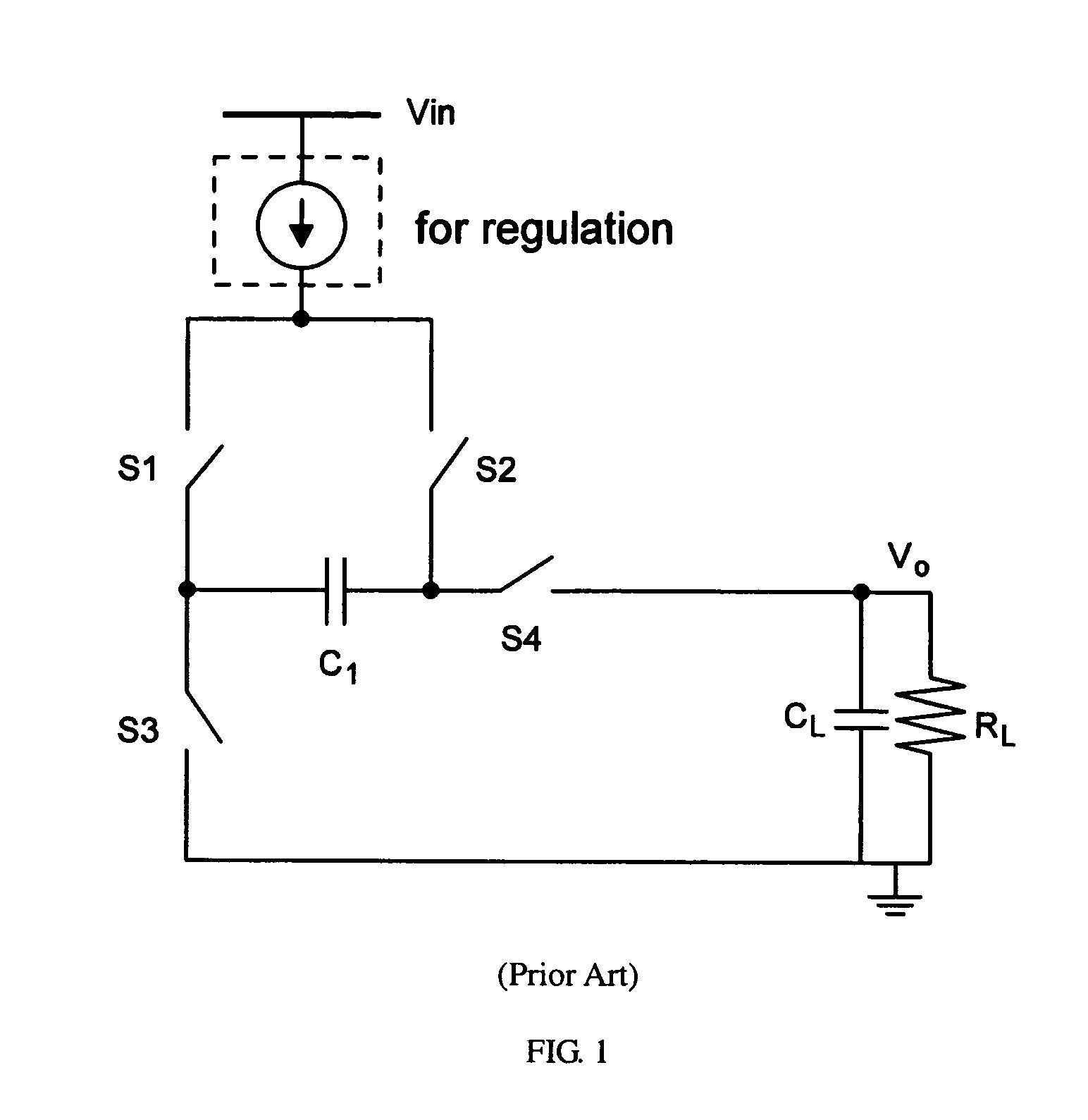

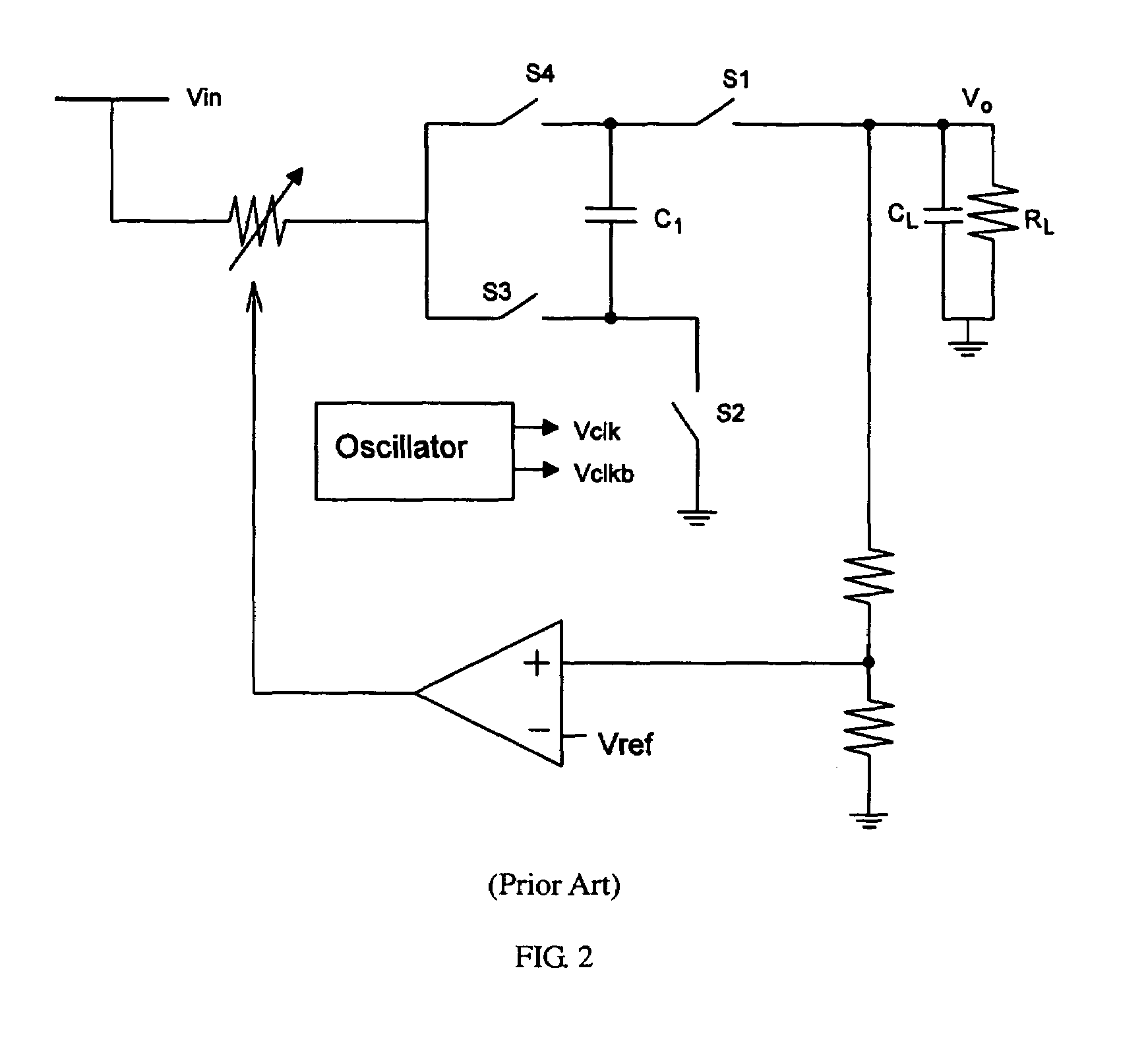

Switched-capacitor regulators

ActiveUS7375992B2Improve area efficiencyIncreases magnitudeAc-dc conversionApparatus without intermediate ac conversionCapacitancePole splitting

A switched-capacitor regulator is provided for regulating the output voltage of a voltage supply. The switched-capacitor regulator includes a supply input terminal capable of receiving a supply voltage, two or more flying capacitors, a regulation switch located between each flying capacitor and the supply input terminal, and a voltage control circuit. The activity of the regulation switches is controlled by the voltage control circuit. In one embodiment of the invention, the voltage control circuit includes a feedback resistance area having one or more feedback resistors located between the output of the flying capacitors and a ground terminal, a first gain stage connected to the feedback resistance area, and two or more second switchable gain stages, which are each connected to a regulation switch and the first gain stage. The switched-capacitor regulator operates in pseudo-continuous regulator mode using three-stage switchable operational amplifiers with time-multiplexed pole-splitting compensation.

Owner:THE HONG KONG UNIV OF SCI & TECH

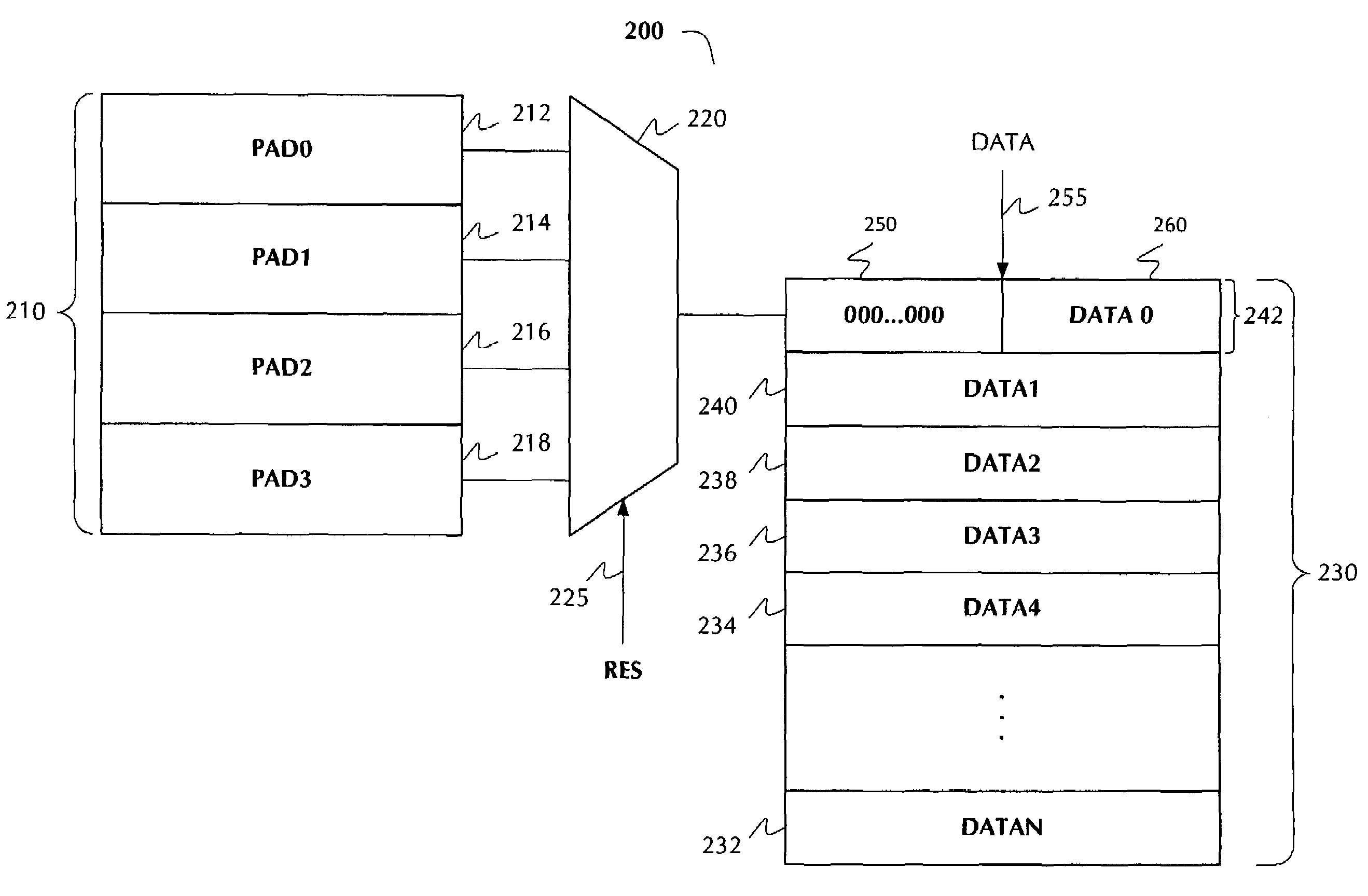

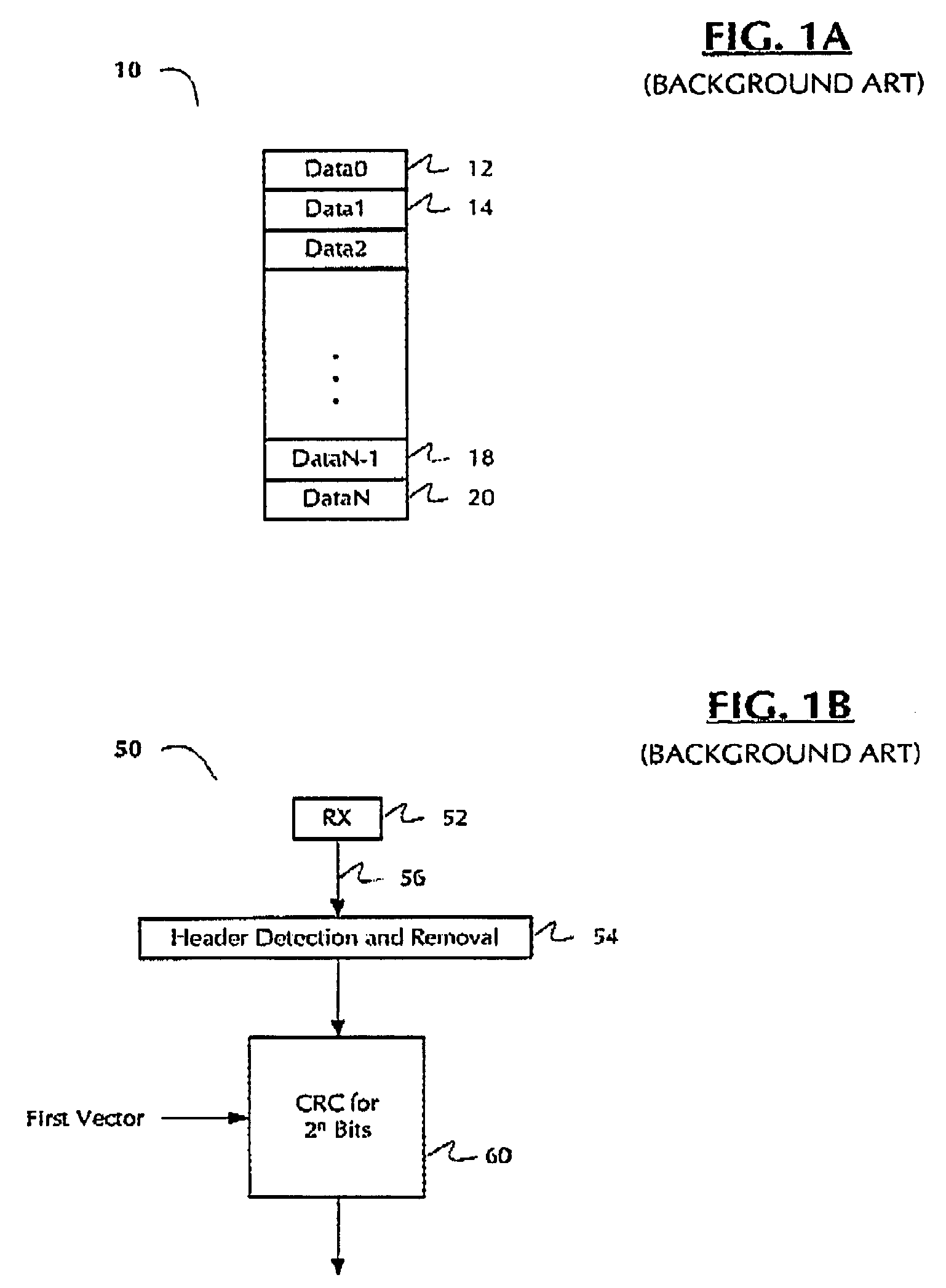

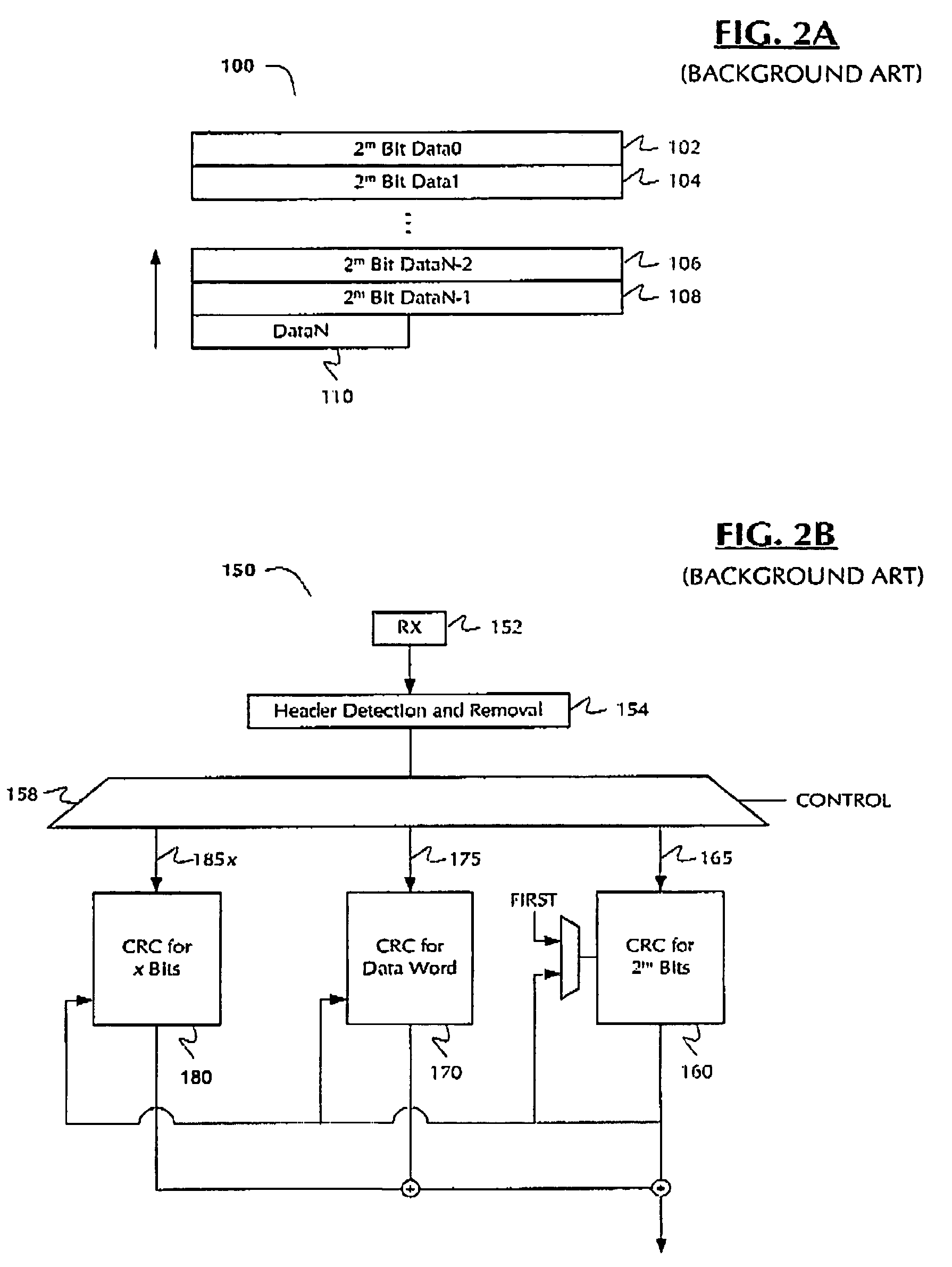

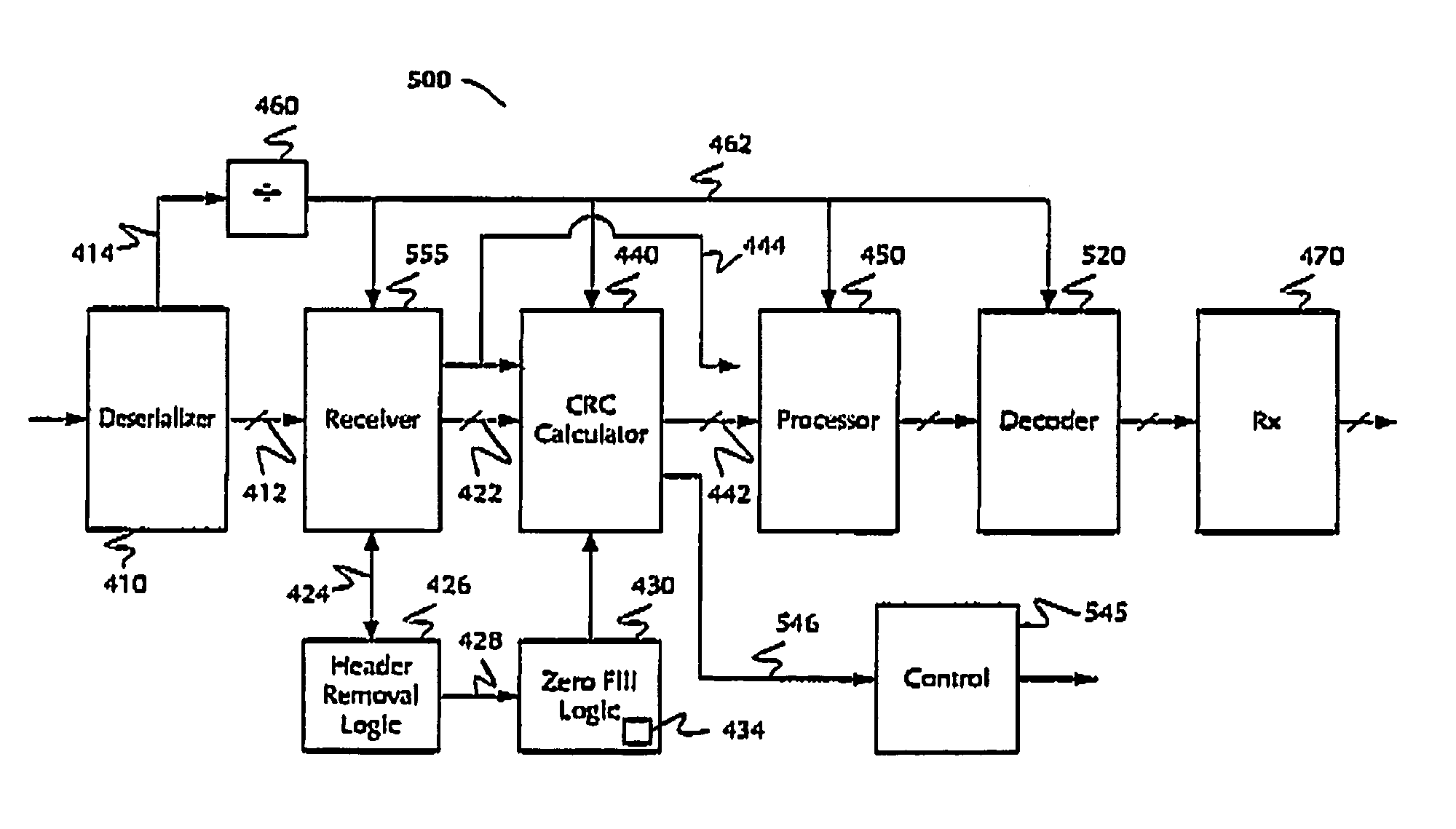

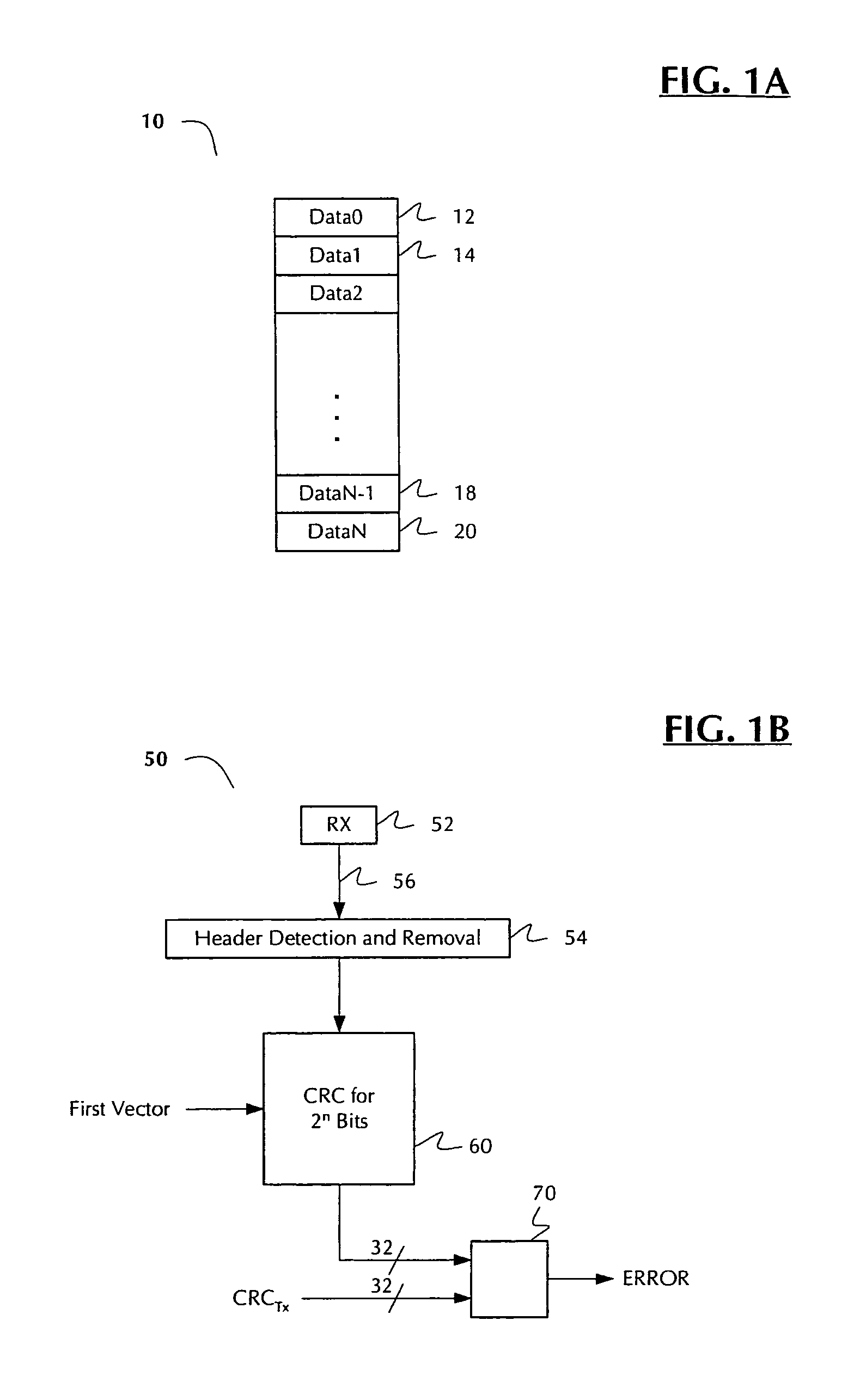

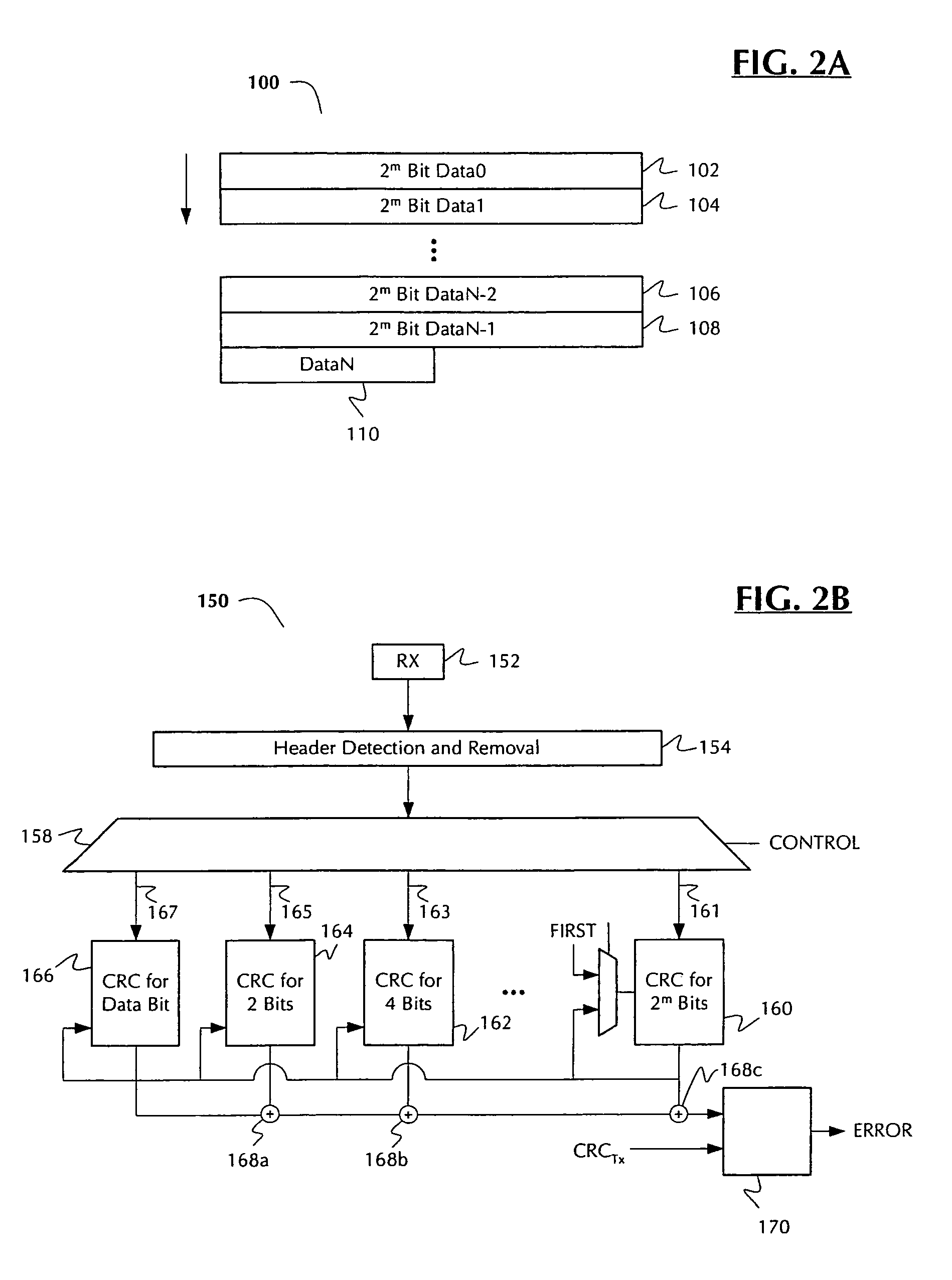

Methods, architectures, circuits, software and systems for CRC determination

ActiveUS7360142B1Increase computing speedImprove operationCode conversionError detection onlyDigital dataError checking

Methods, circuits, architectures, and systems for error detection in transmitted data. The method generally includes the steps of (i) partitioning the unit of digital data into one or more full data lines and a remainder, wherein each of the full data lines comprises a predetermined number of data blocks, each of the data blocks has a first fixed length, the predetermined number is an integer of at least 2, and the remainder has a length less than the predetermined number times the first fixed length; (ii) if the remainder contains at least one data bit, adding to the remainder a padding vector having a length sufficient to generate a padded data line having the predetermined number of data blocks; and (iii) performing error checking calculations on the full data lines and the padded data line. The present invention reduces the chip area and power consumption, while improving system performance.

Owner:MARVELL ISRAEL MISL

Semiconductor device and production method therefor

ActiveUS20120196415A1Easy to integrateImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering physics

A method of producing a semiconductor device including a MOS transistor, includes the steps of forming, on a top surface of at least one of semiconductor pillars, an epitaxial layer having a top surface larger in area than the top surface of the at least one of the semiconductor pillars and forming a source region or a drain region so as to be at least partially in the epitaxial layer.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

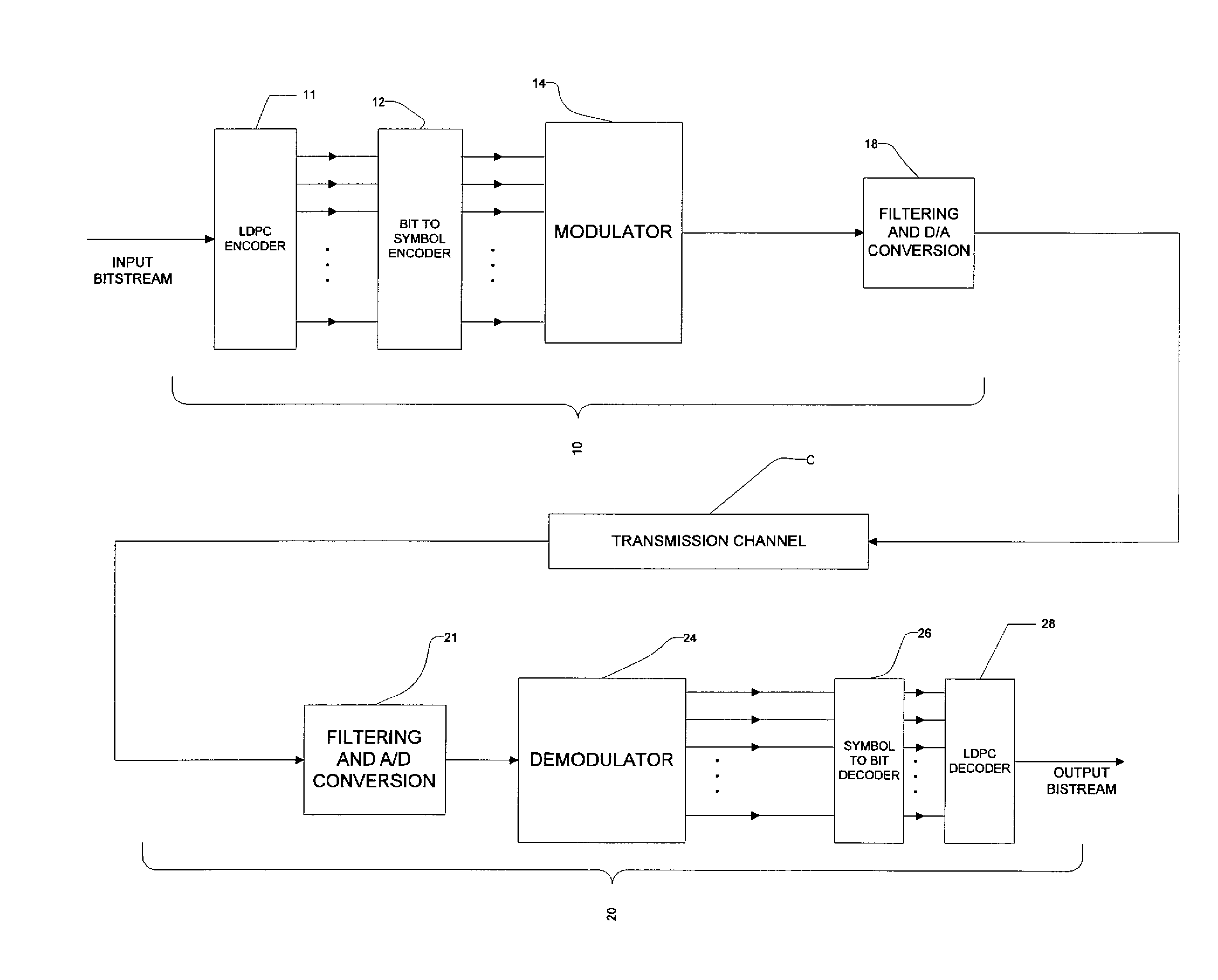

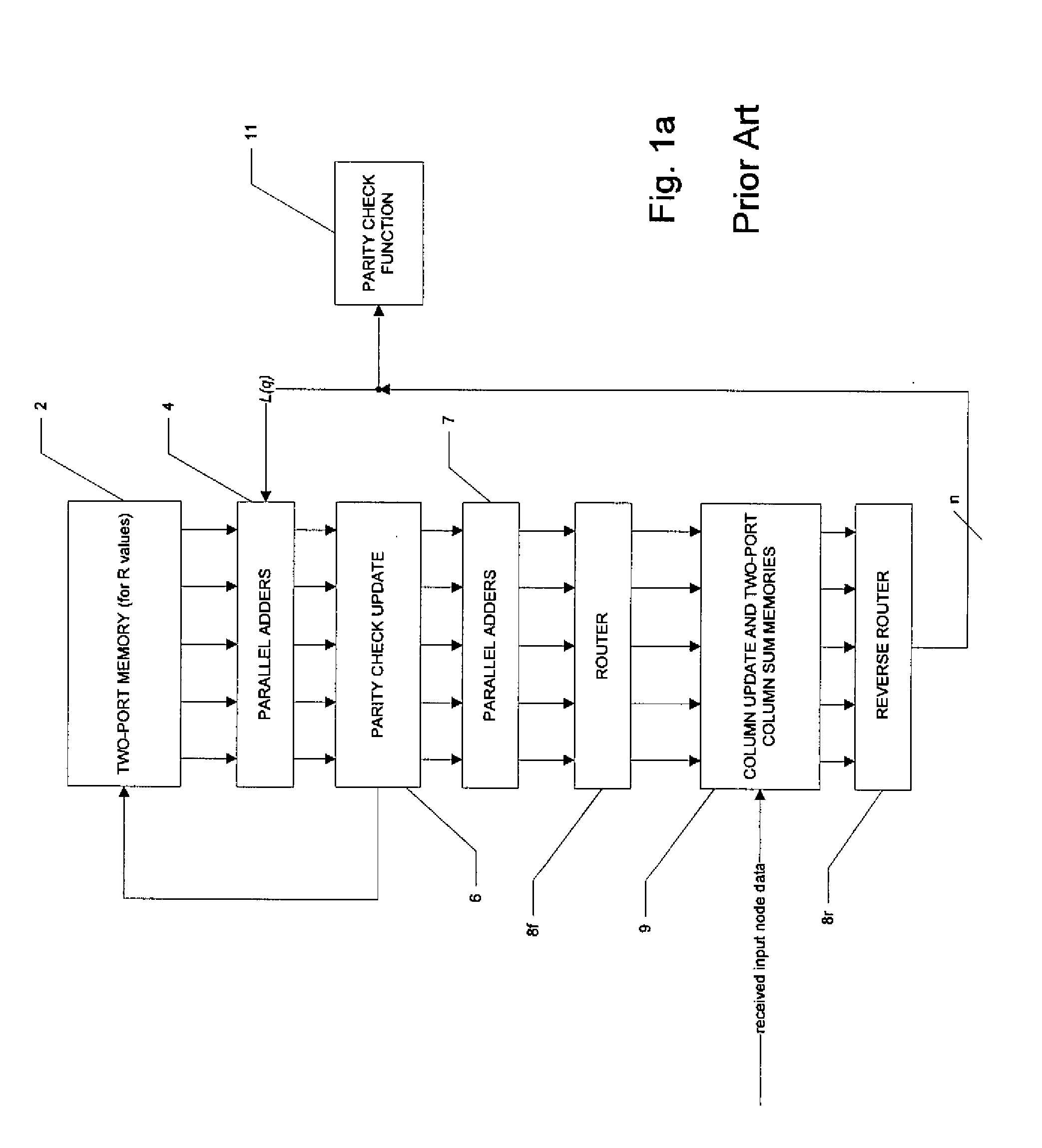

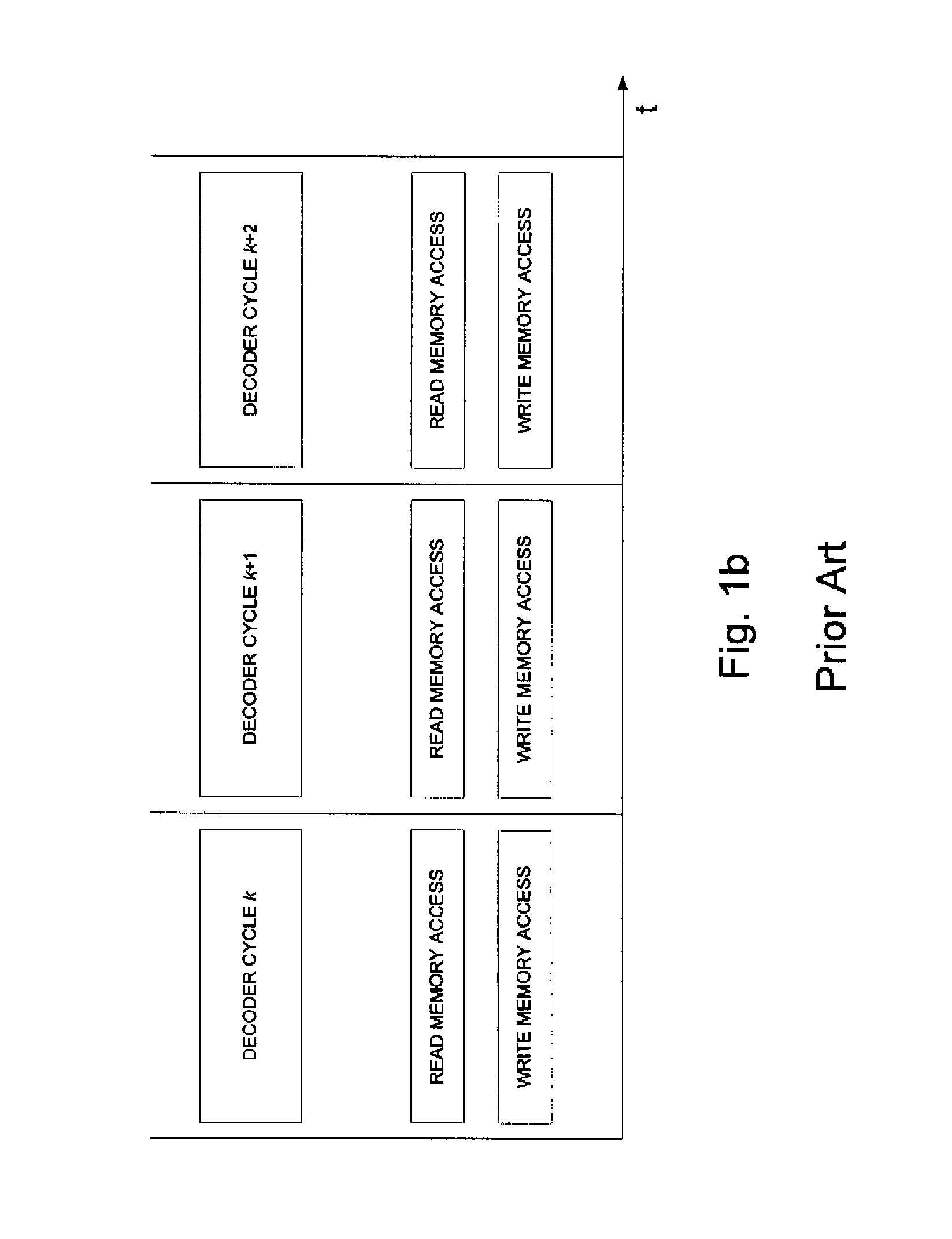

Memory Access in Low-Density Parity Check Decoders

InactiveUS20090282316A1Adversely impacting performanceImprove area efficiencyError correction/detection using multiple parity bitsCode conversionComputer architectureParity-check matrix

Low Density Parity Check (LDPC) decoder circuitry in which memory resources are realized as single-port memory. The decoder circuitry includes a single port memory for storing log-likelihood ratio (LLR) estimates of input node data states for individual rows of a parity check matrix. The decoder circuitry also includes multiple instances of single-port column sum memories, which store updated LLR estimates for each input node. In each case, the memory resources include logic circuitry that executes at least one write cycle and one read cycle to the memory within each decoder cycle. Because the decoder cycle time is much longer than the necessary memory cycle time, particularly in LDPC decoding, data can be written to and read from single-port memory resources in ample time for the decoding operation.

Owner:TEXAS INSTR INC

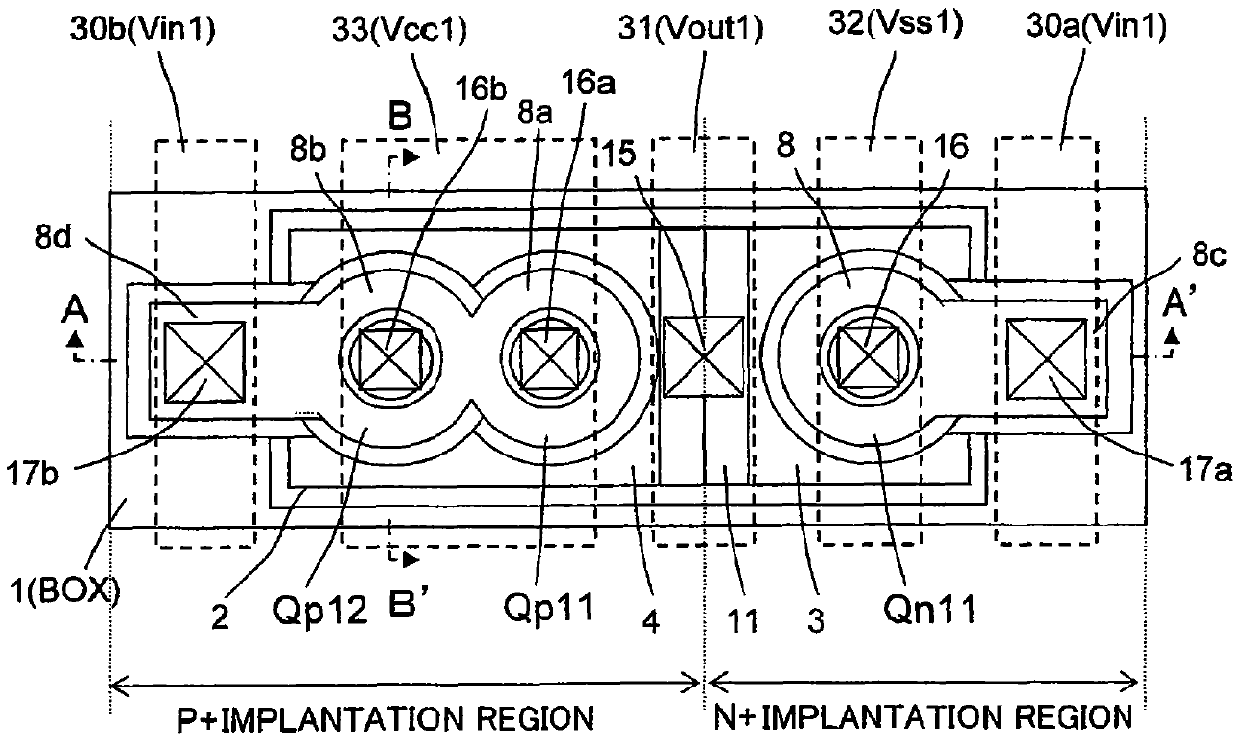

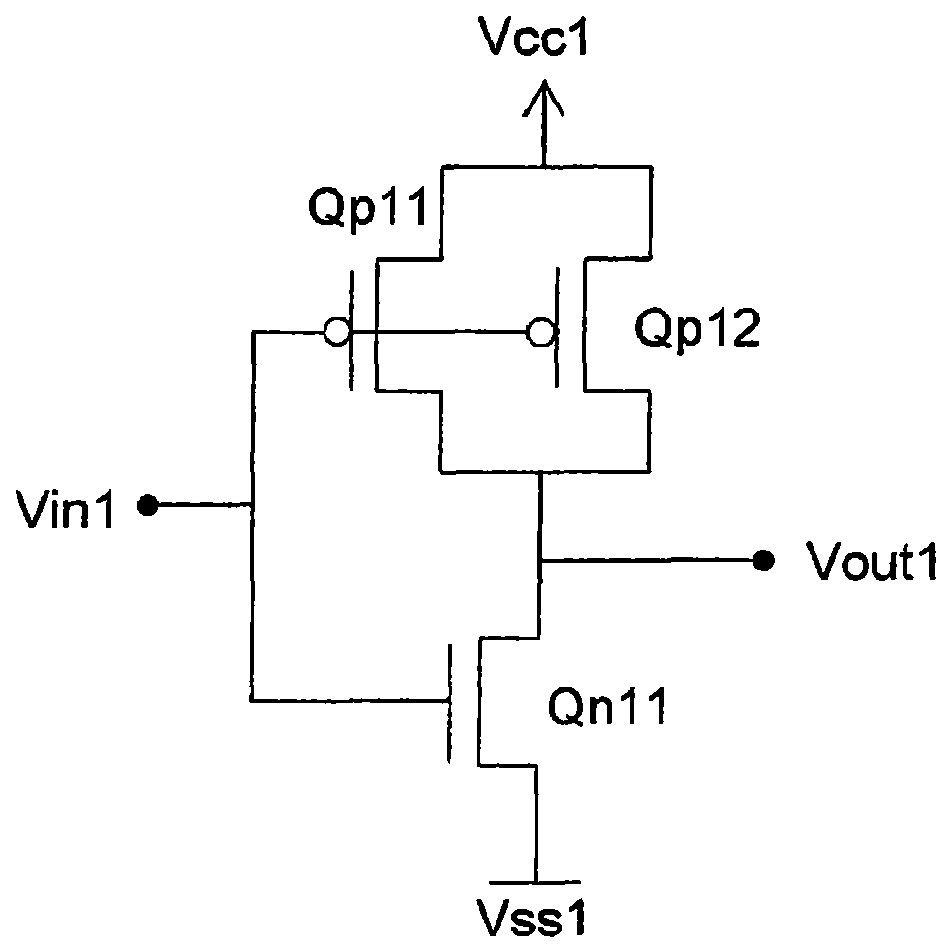

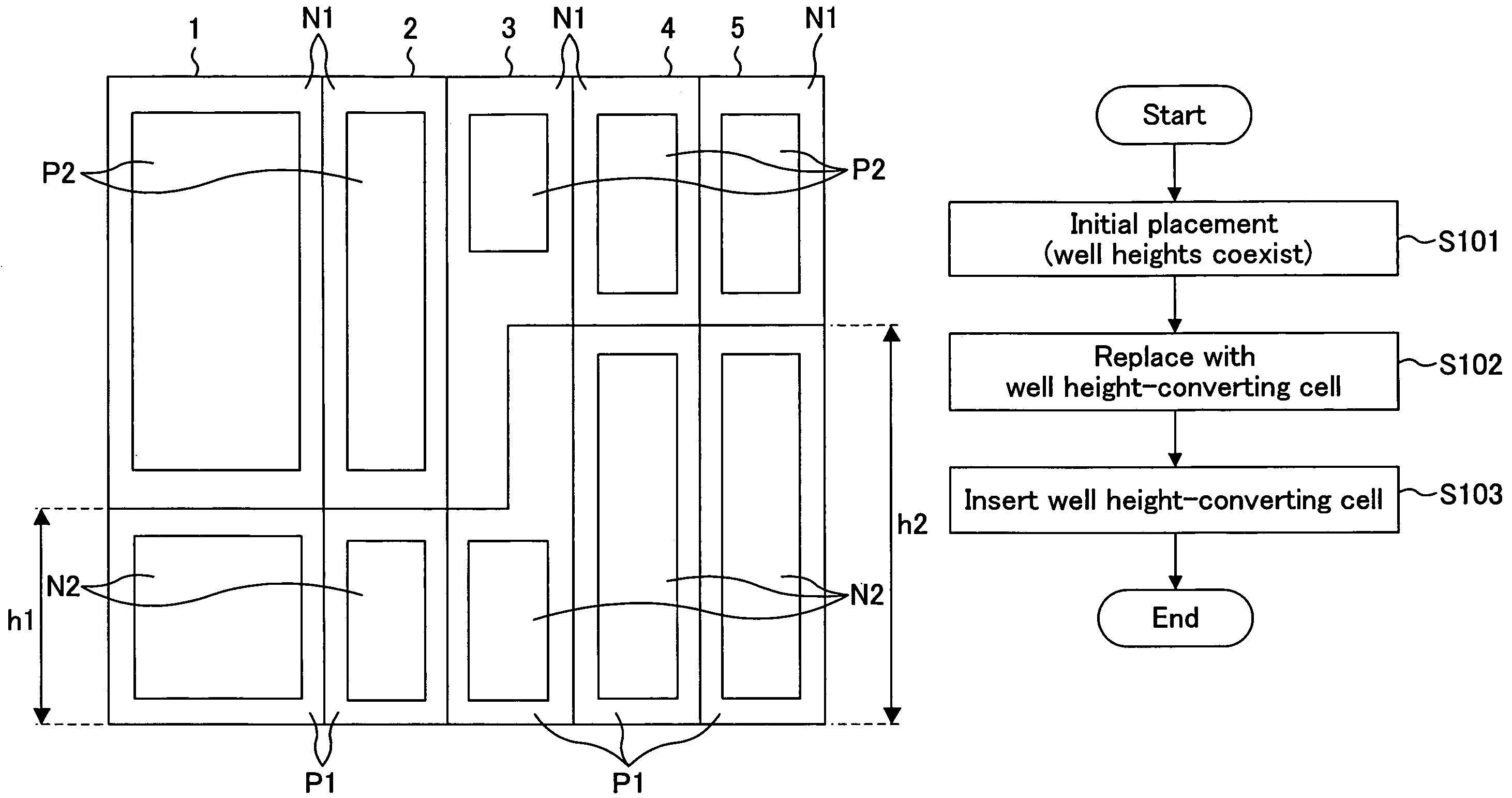

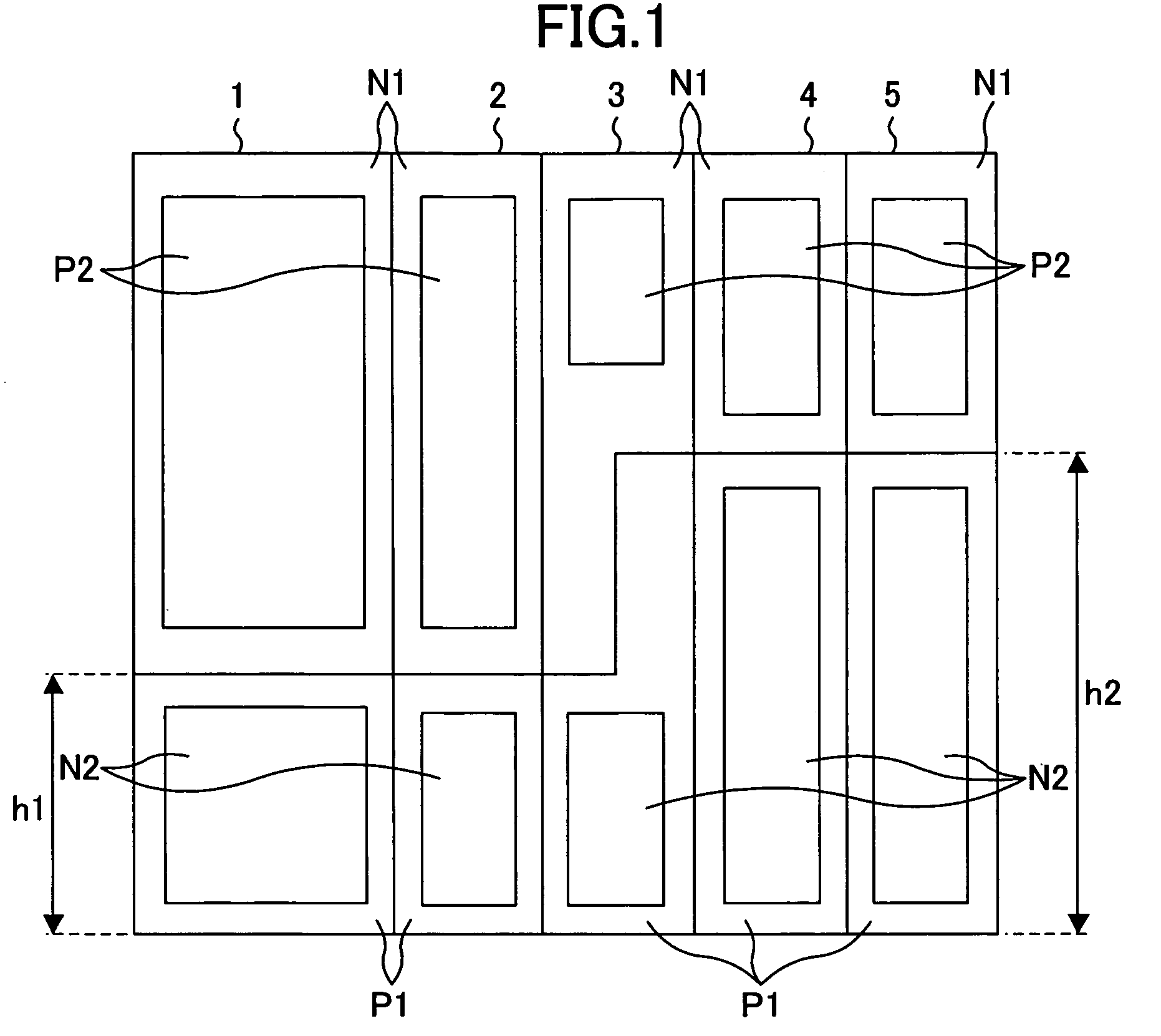

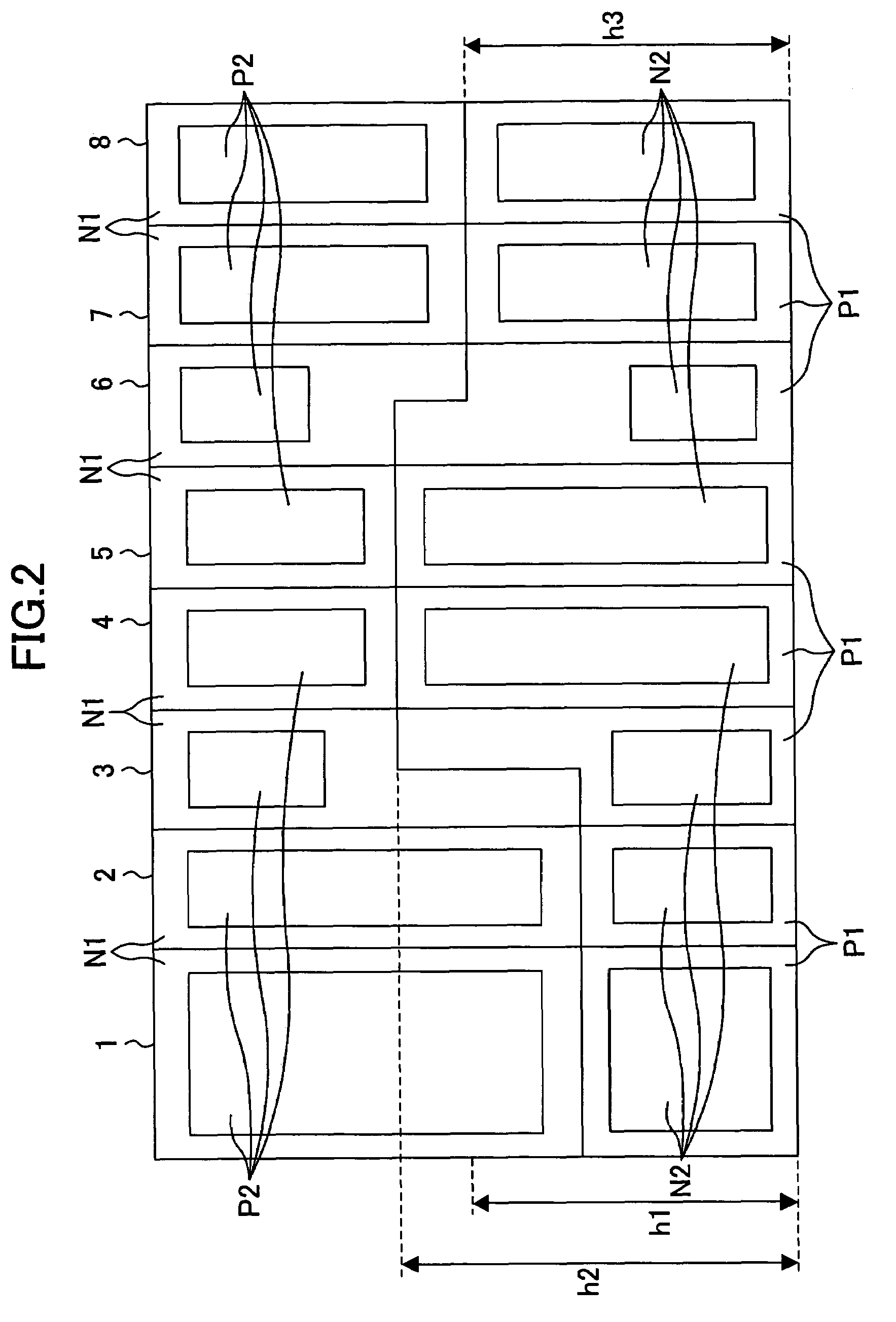

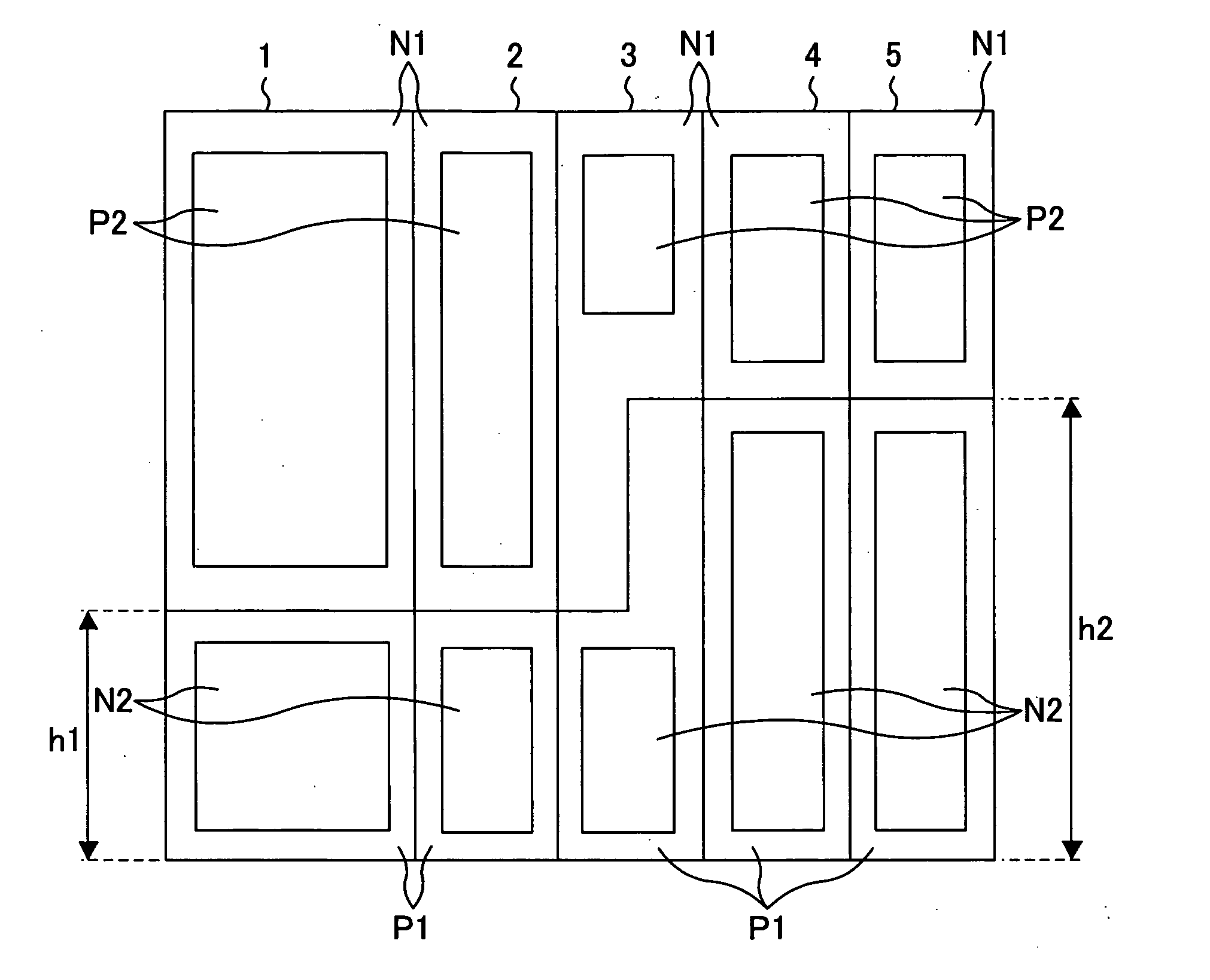

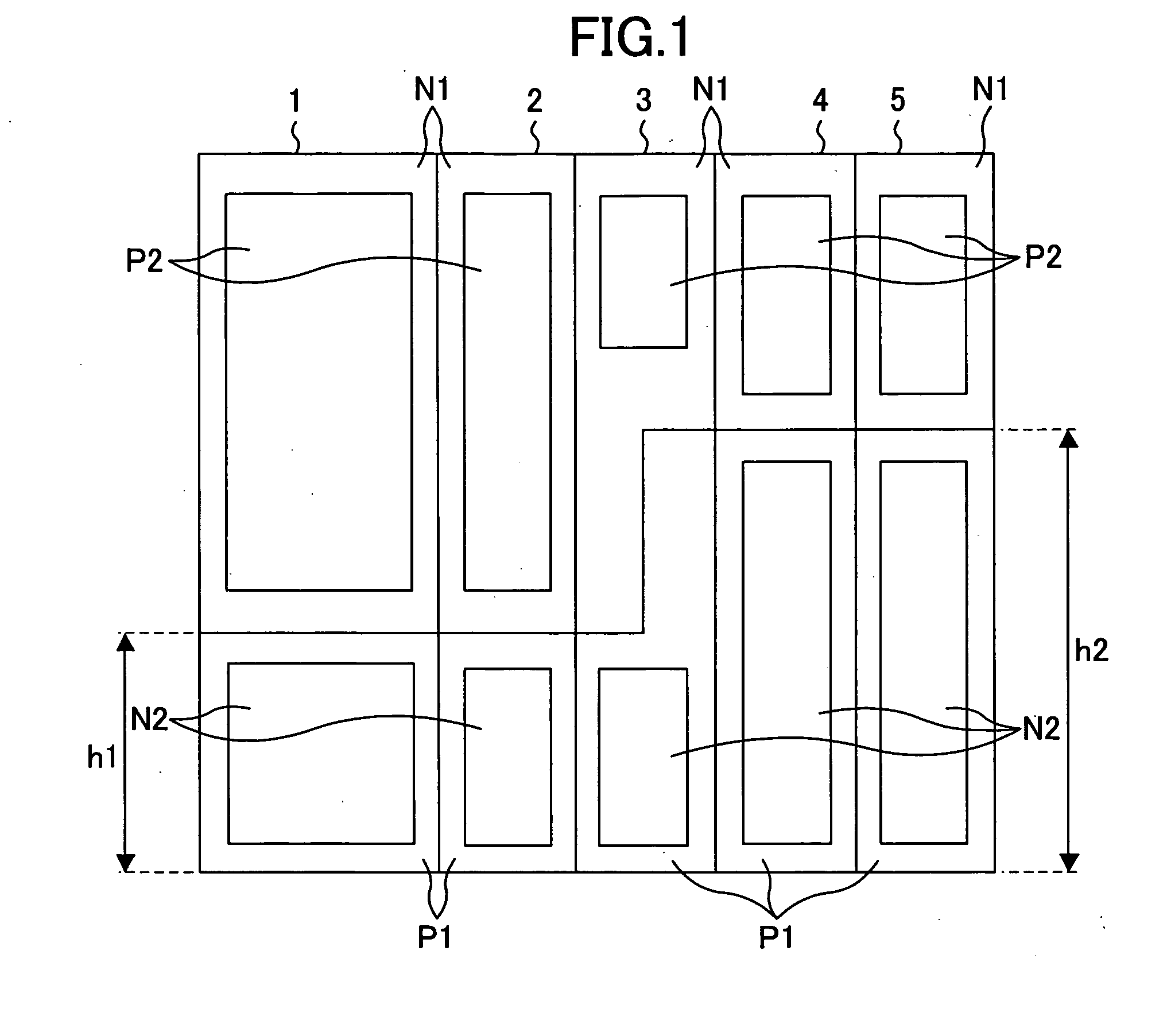

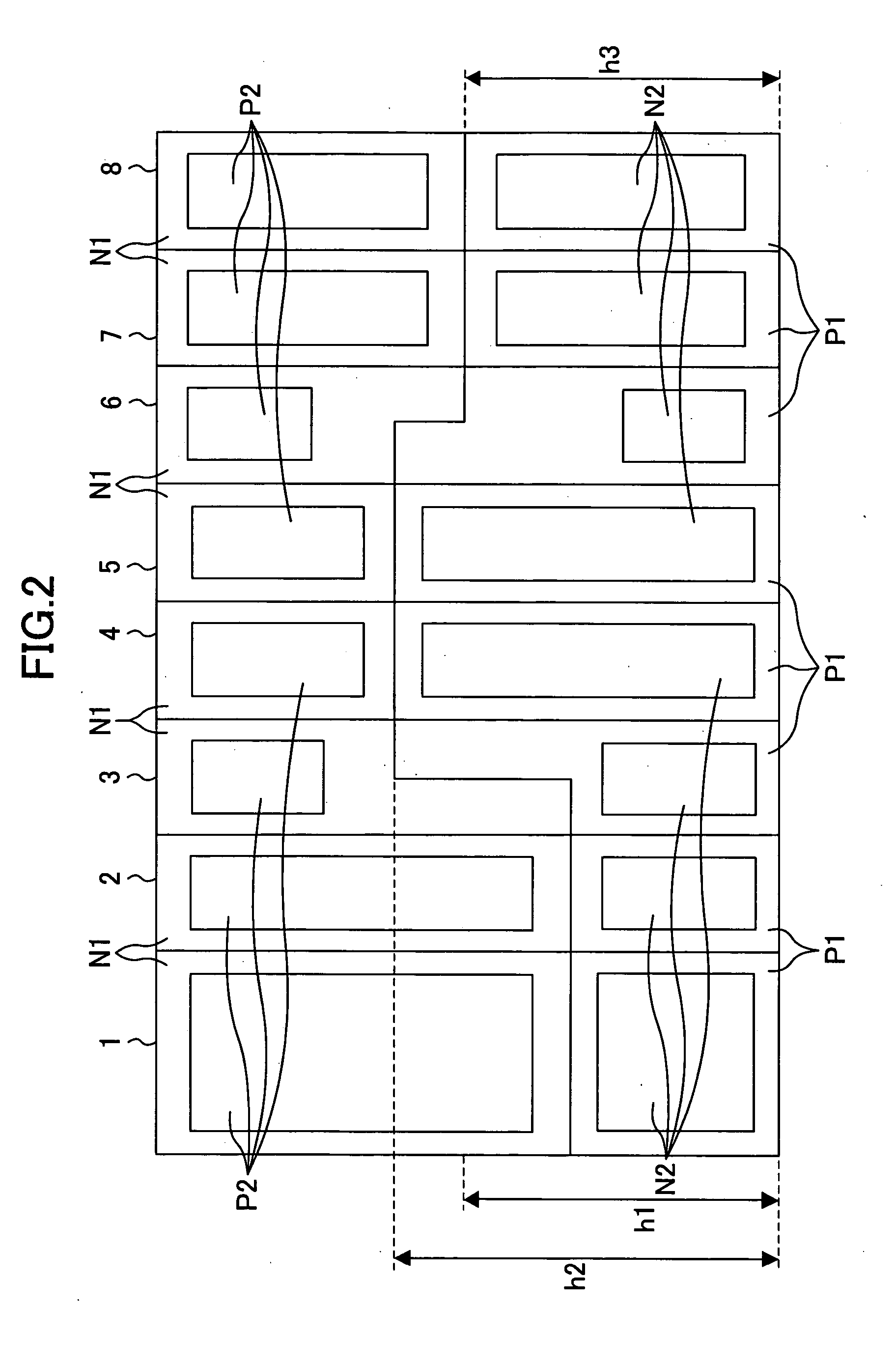

Standard cell, standard cell library, semiconductor device, and placing method of the same

InactiveUS7302660B2Satisfactory level of area efficiencySolve the lack of heightSolid-state devicesSemiconductor/solid-state device manufacturingBorder lineEngineering

Of a plurality of standard cells in which an N-well region and a P-well region are vertically formed, some standard cells have a border line between the N-well region and the P-well region which is set to be a low height (first height), and other standard cells have a border line between the N-well region and the P-well region which is set to be a high height (second height), depending on the size of a transistor formed in the standard cell. Although these standard cells have different border lines, a standard cell for linking the border lines is provided. In such a standard cell, an empty space is created by forming a small-size transistor therein, and the empty space is utilized so that, for example, a left end of the border line is set to have the first height and a right end of the border line is set to have the second height, whereby the border line is converted so as to link the heights therein.

Owner:SOCIONEXT INC

Architecture for an algorithmic analog-to-digital converter

ActiveUS7068202B2Improve area efficiencyHighly suitableElectric signal transmission systemsPulse automatic controlDigital down converterAudio power amplifier

An algorithmic analog-to-digital converter (ADC) includes a sample-and-hold circuit and an ADC processing unit operating in parallel and sharing a single operational amplifier. The ADC processing unit includes an MDAC with a switched capacitor topology and a sub-ADC. The ADC processing unit is clocked by an internal clock that is N times faster than the sample-and-hold clock. Each cycle is further sub-divided into two phases. During one phase the capacitors are coupled to a residue or sampled voltage provided by the MDAC, and during another phase the capacitor are coupled to a reference voltage determined by the switch control signals generated by the sub-ADC. A set of data bits is generated by the ADC processing unit during each ADC clock cycle. The N sets of data bits are added to generate the digital output stream.

Owner:SYNAPTICS INC

Methods, circuits, architectures, software and systems for determining a data transmission error and/or checking or confirming such error determinations

InactiveUS7434150B1Increase profitReduce power consumptionCode conversionError detection onlyError checkingPresent method

Methods, circuits, architectures, and systems for error detection in transmitted data. The method generally includes the steps of (a) performing an error checking calculation on the transmitted data and appended error checking code; (b) determining the calculated error checking code state; and (c) if it has a predetermined state, indicating that there is no error in the transmitted data. The circuitry generally comprises (1) an error checking code calculation circuit configured to calculate error checking code on the transmitted data and the appended error checking code; (2) a vector selector configured to select one of a plurality of error checking vectors; and (3) a logic circuit configured to determine the calculated error checking code state and, if it has a predetermined state, indicate that there is no error in the transmitted data. The software generally includes a set of instructions configured to implement or carry out the present method. The architectures and / or systems generally include those that embody one or more of the inventive concepts disclosed herein. In the present invention, an error checking calculation is performed on error checking code transmitted with the data. If the transmitted data and error checking code are error-free, the error checking calculation gives a result having a known and / or predetermined state. This technique enables one to confirm or determine that the data transmission was error-free without use of or need for a wide, complicated comparator, thereby reducing the chip area dedicated to error detection, increasing the utilization efficiency of the circuitry on the chip, and reducing power consumption.

Owner:MARVELL ISRAEL MISL

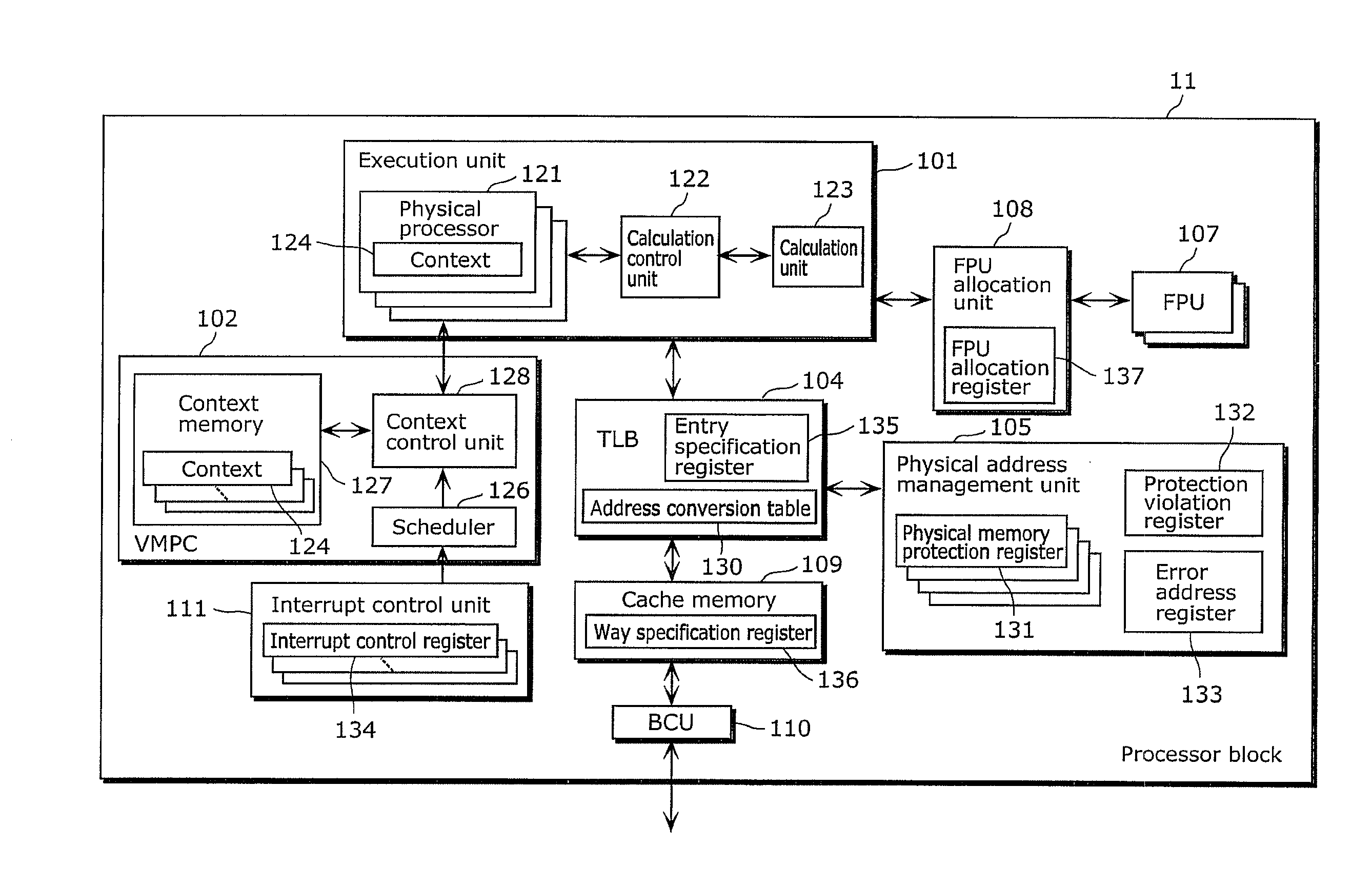

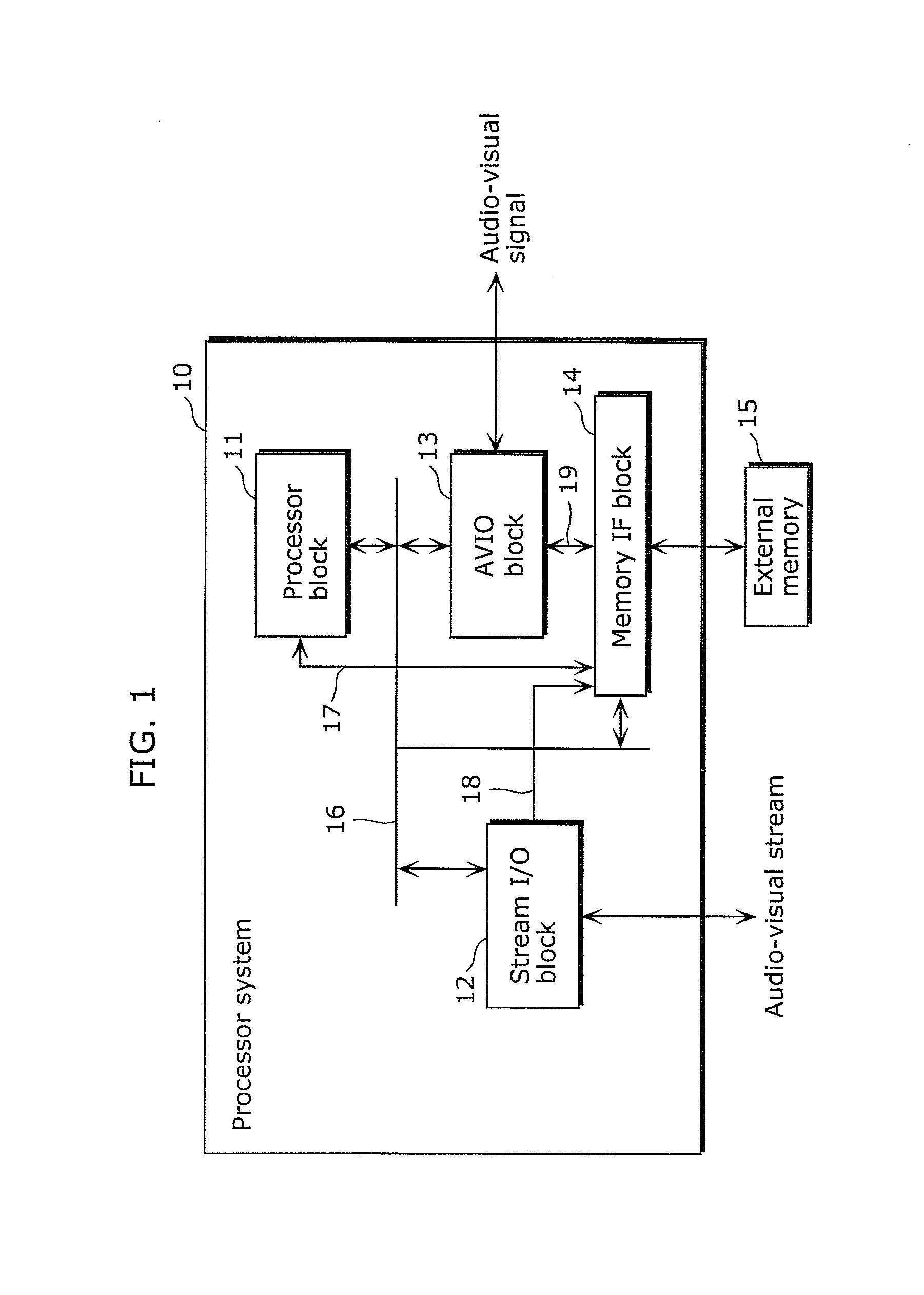

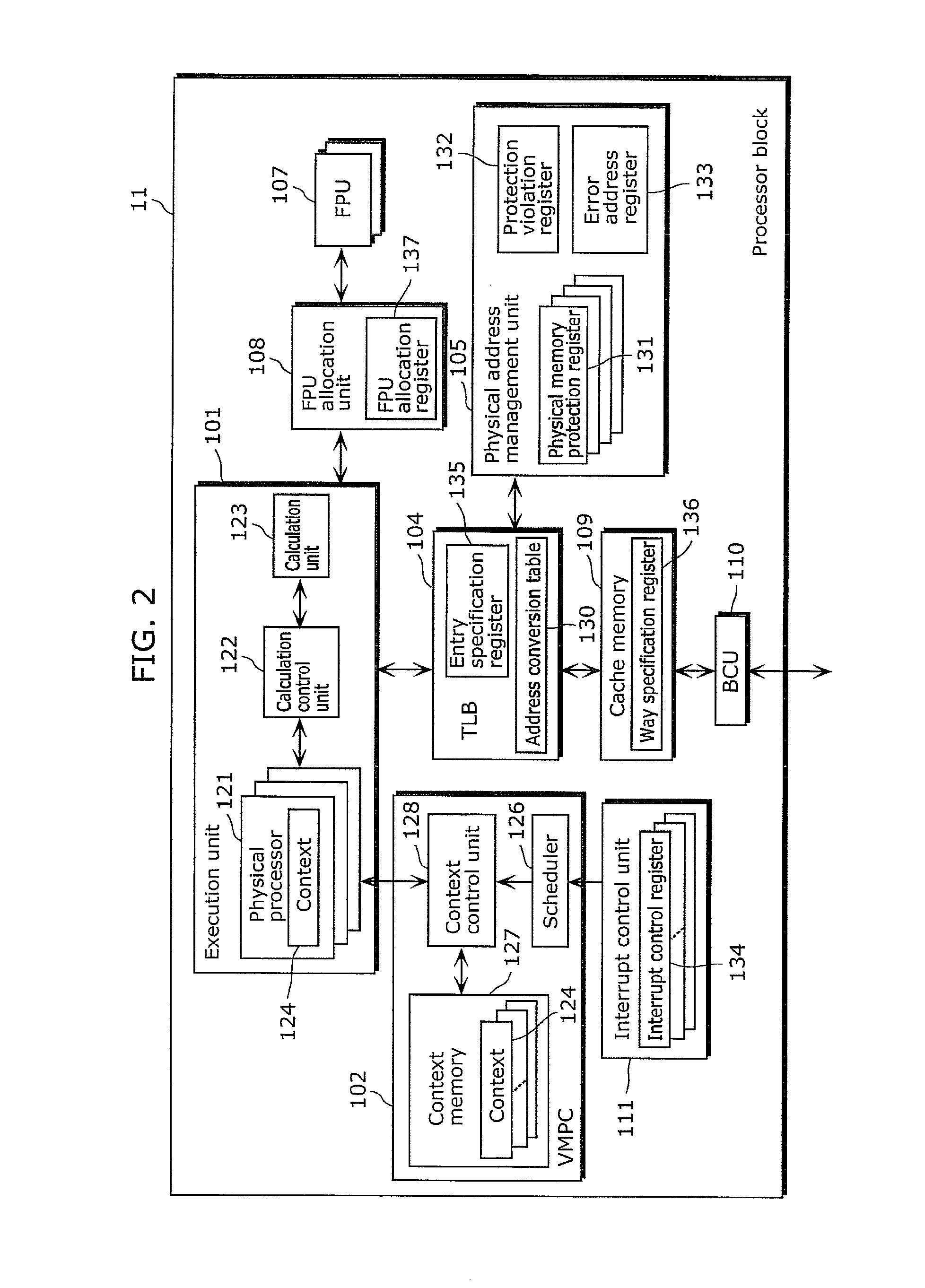

Multithread processor and digital television system

InactiveUS20120008674A1Complicate designDecrease in robustnessProgram synchronisationPicture reproducers using cathode ray tubesLogical addressVirtual space

A multithread processor including: an execution unit including a physical processor; and a translation lookaside buffer (TLB) which converts, to a physical address, a logical address output from the execution unit, and logical processors are implemented on the physical processor, a first logical processor that is a part of the logical processors constitutes a first subsystem having a first virtual space, a second logical processor that is a part of the logical processors and different from the first logical processor constitutes a second subsystem having a second virtual space, each of the first and the second subsystems has processes to be assigned to the logical processors, and the logical address includes: a first TLB access virtual identifier for identifying one of the first and the second subsystems; and a process identifier for identifying a corresponding one of the processes in each of the first and the second subsystems.

Owner:PANASONIC CORP

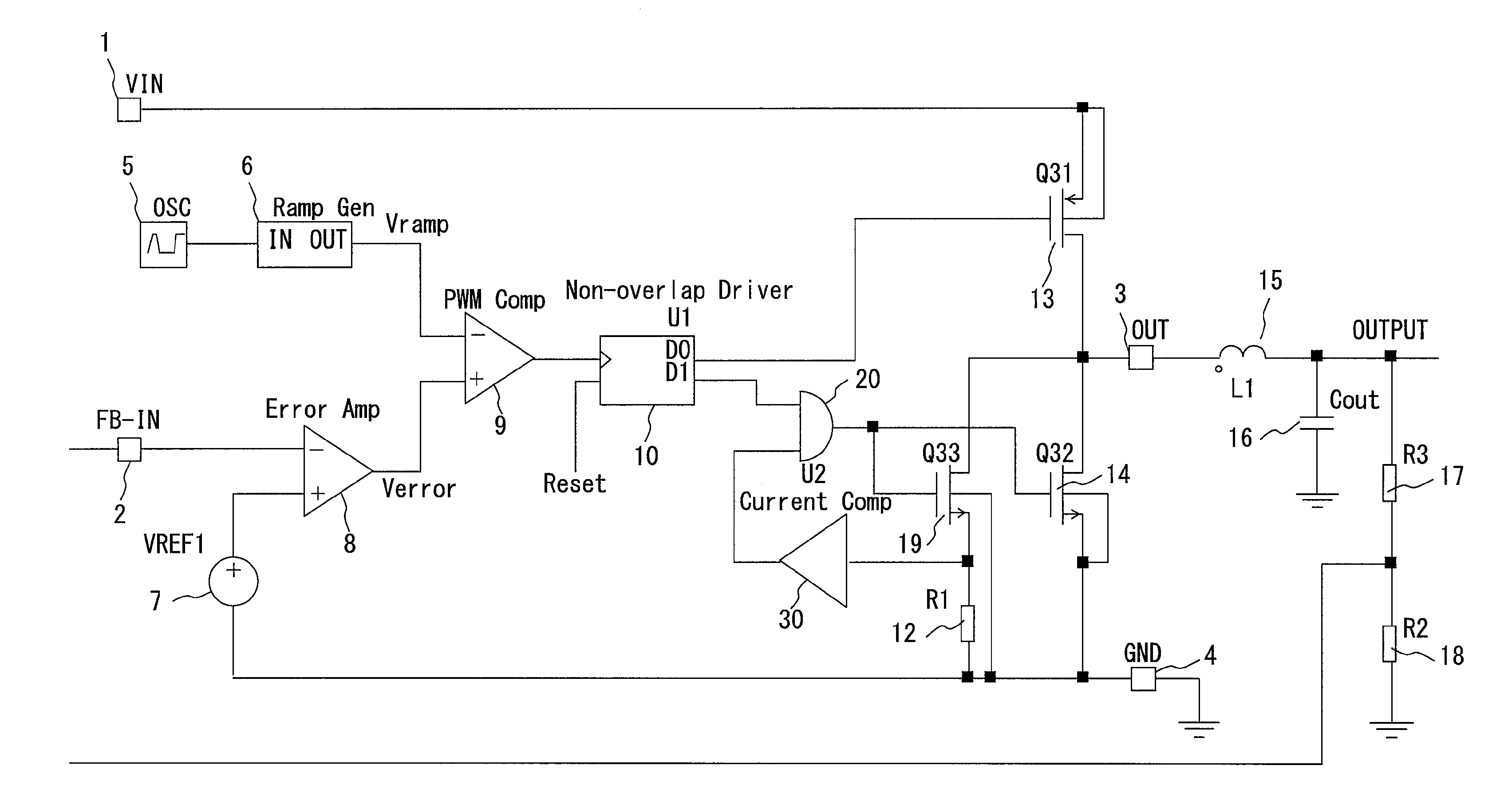

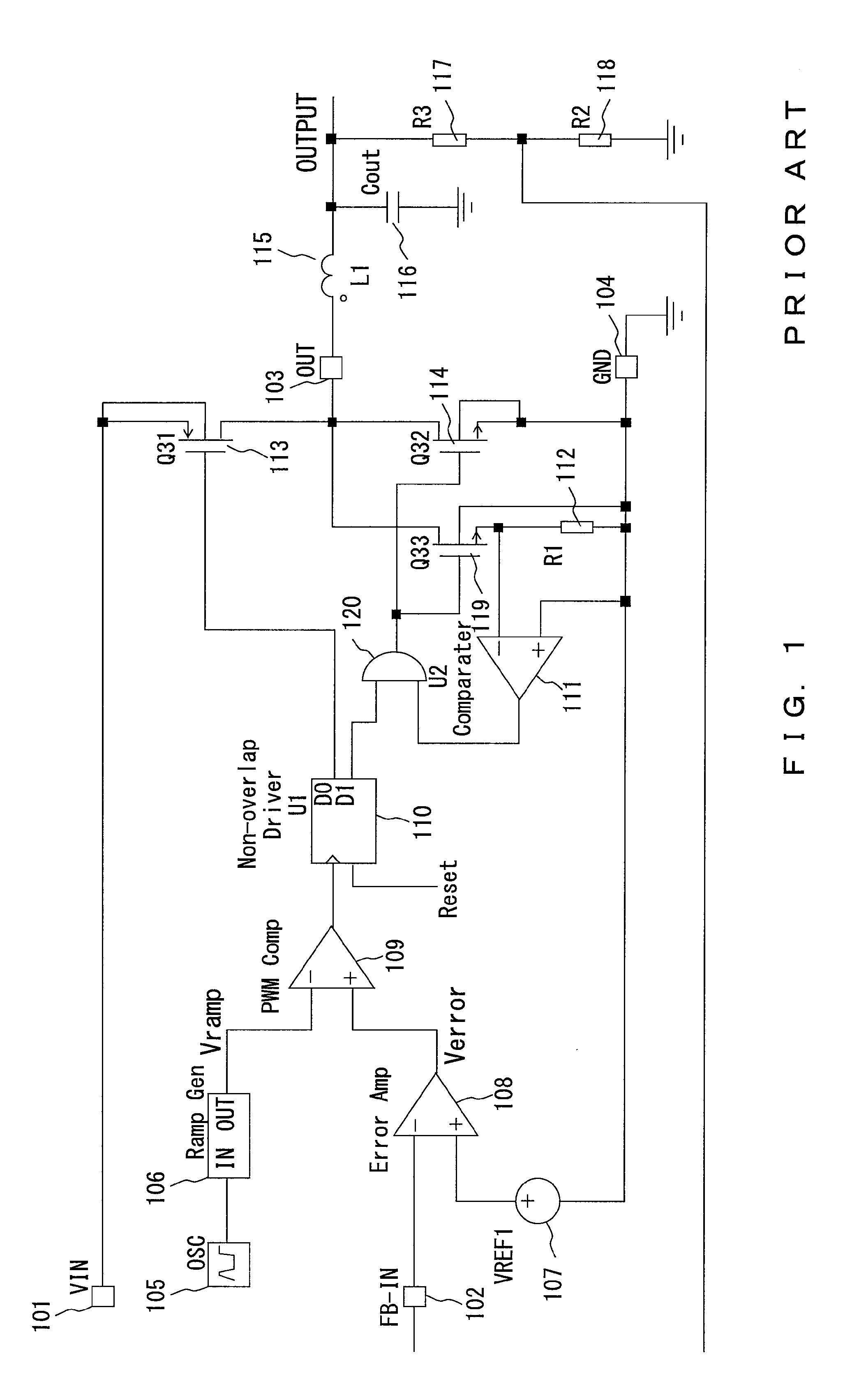

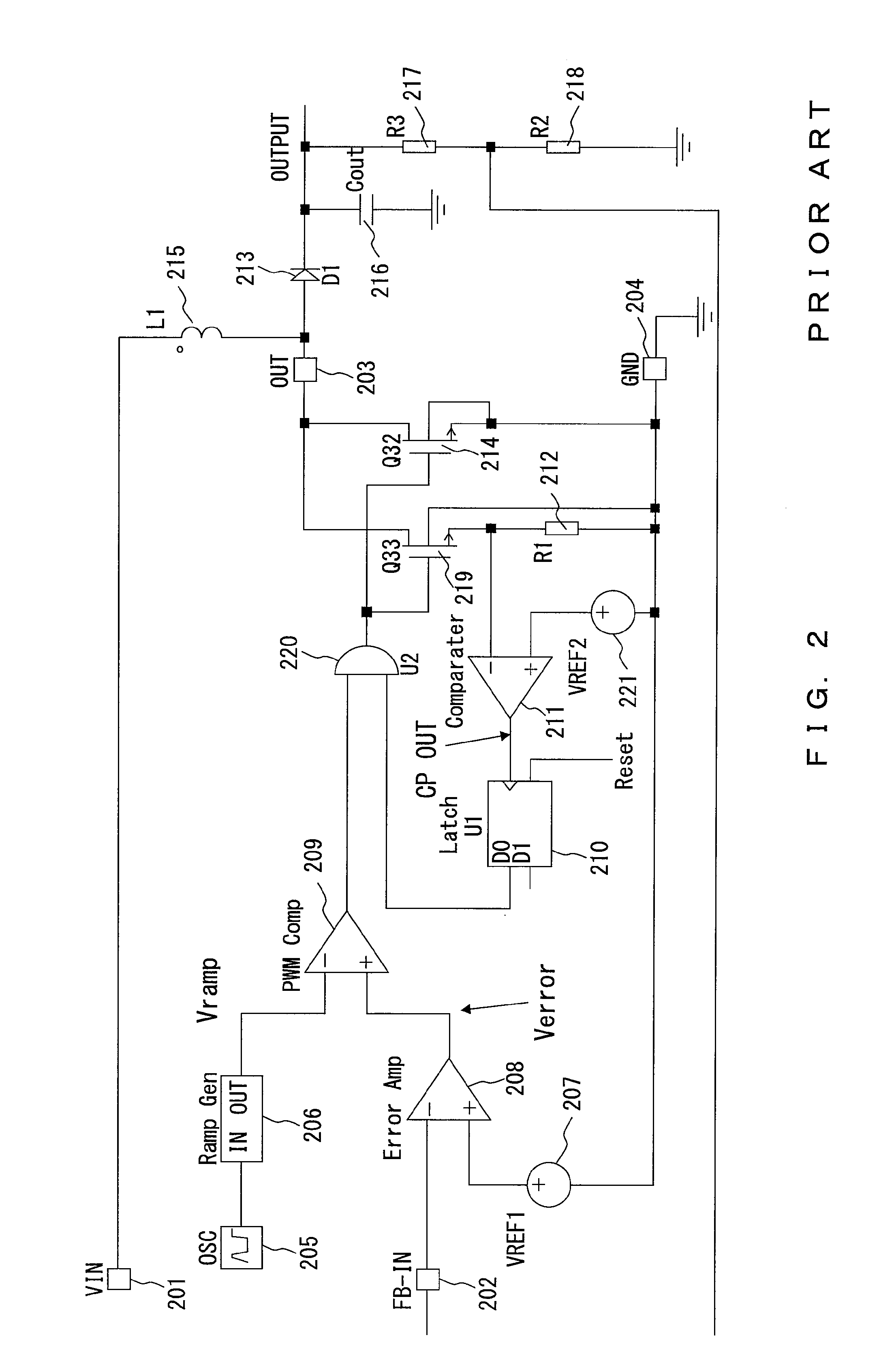

Abnormal current preventive circuit of dc-dc converter

InactiveUS20100067152A1Short delayLess influenceMultiple input and output pulse circuitsEfficient power electronics conversionDc dc converterEngineering

The voltage of a detection resistor connected to the drain of a low-side switching device is normally a negative voltage, but a positive voltage appears when a countercurrent occurs in an abnormal state. A current comparator monitors the voltage of the detection resistor, transmits high output to an AND circuit whole the voltage of the detection resistor is a negative voltage to maintain the output voltage of the current comparator in a low state when an output signal of a driver can be transmitted to the low-side switching device, and allows the output voltage of the current comparator in a low state when the voltage of the detection resistor becomes a positive voltage, thereby forcibly turning off the low-side switching device.

Owner:FUJI ELECTRIC CO LTD

Standard cell, standard cell library, semiconductor device, and placing method of the same

InactiveUS20060138464A1Increase in area can be suppressedReduce numberSolid-state devicesSemiconductor/solid-state device manufacturingStandard cellEngineering

Of a plurality of standard cells in which an N-well region and a P-well region are vertically formed, some standard cells have a border line between the N-well region and the P-well region which is set to be a low height (first height), and other standard cells have a border line between the N-well region and the P-well region which is set to be a high height (second height), depending on the size of a transistor formed in the standard cell. Although these standard cells have different border lines, a standard cell for linking the border lines is provided. In such a standard cell, an empty space is created by forming a small-size transistor therein, and the empty space is utilized so that, for example, a left end of the border line is set to have the first height and a right end of the border line is set to have the second height, whereby the border line is converted so as to link the heights therein.

Owner:SOCIONEXT INC

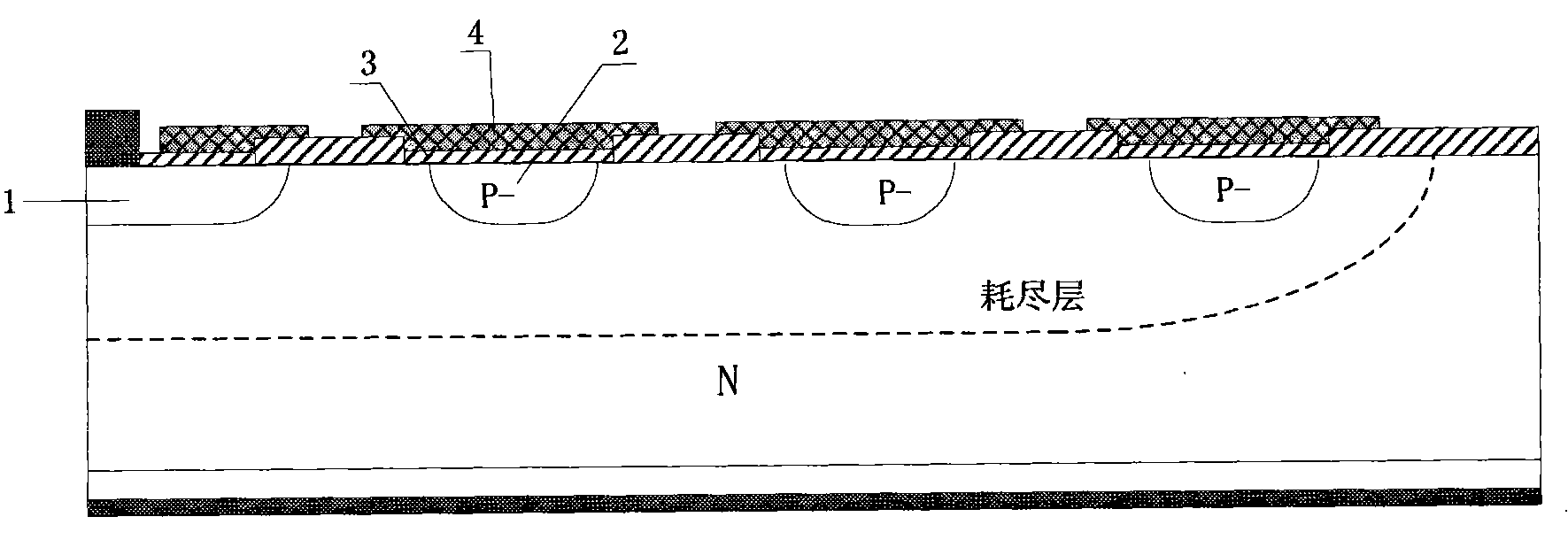

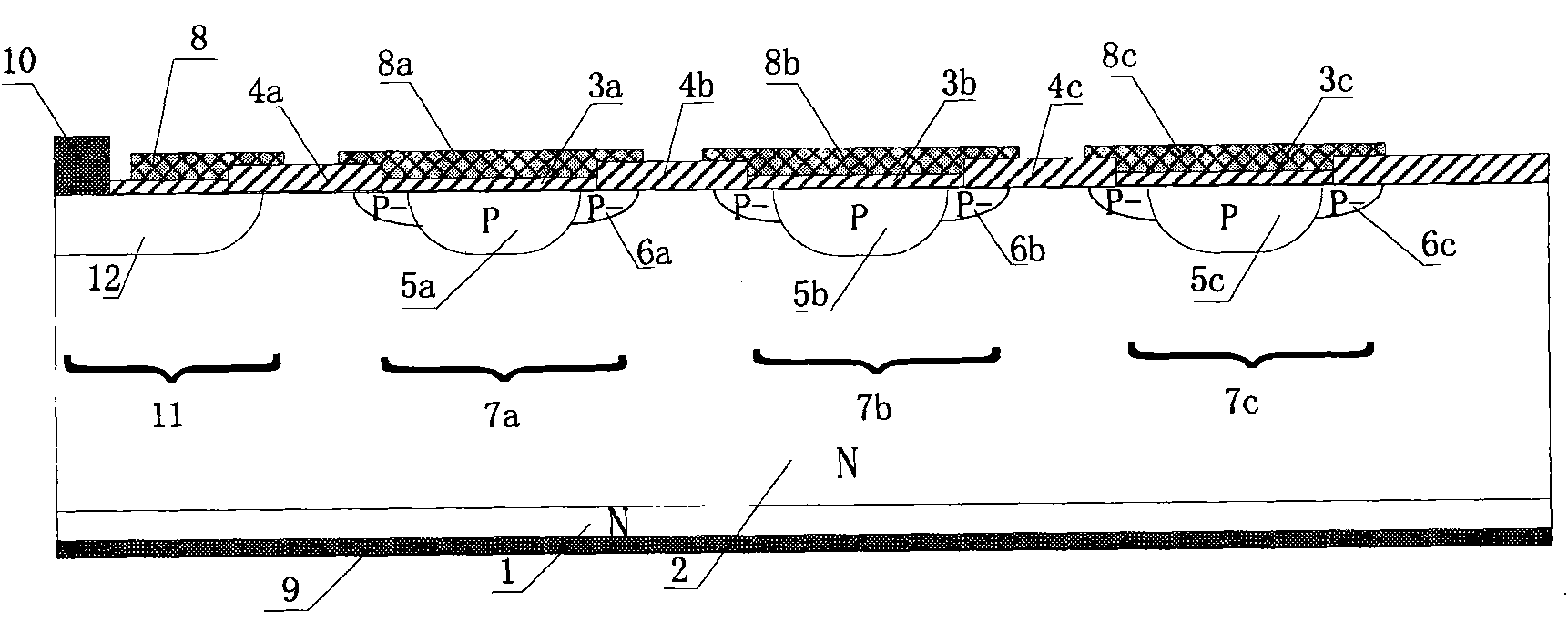

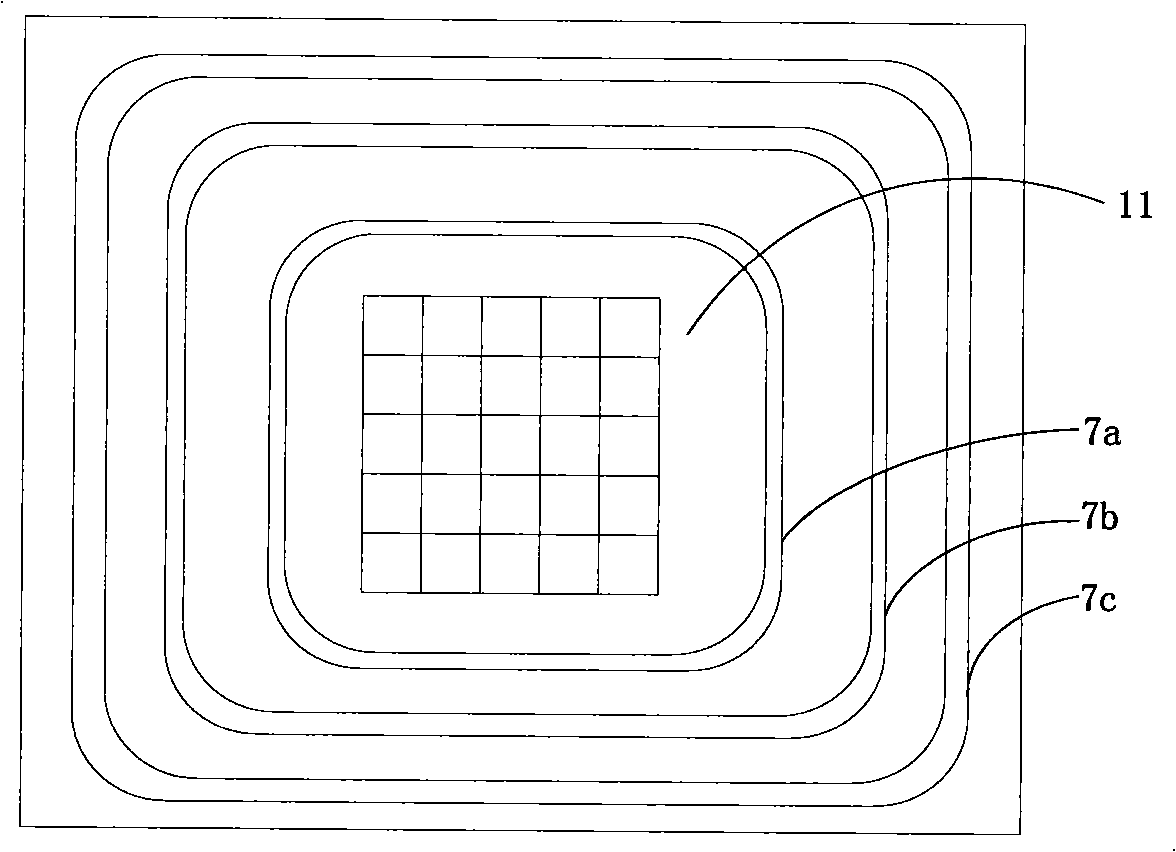

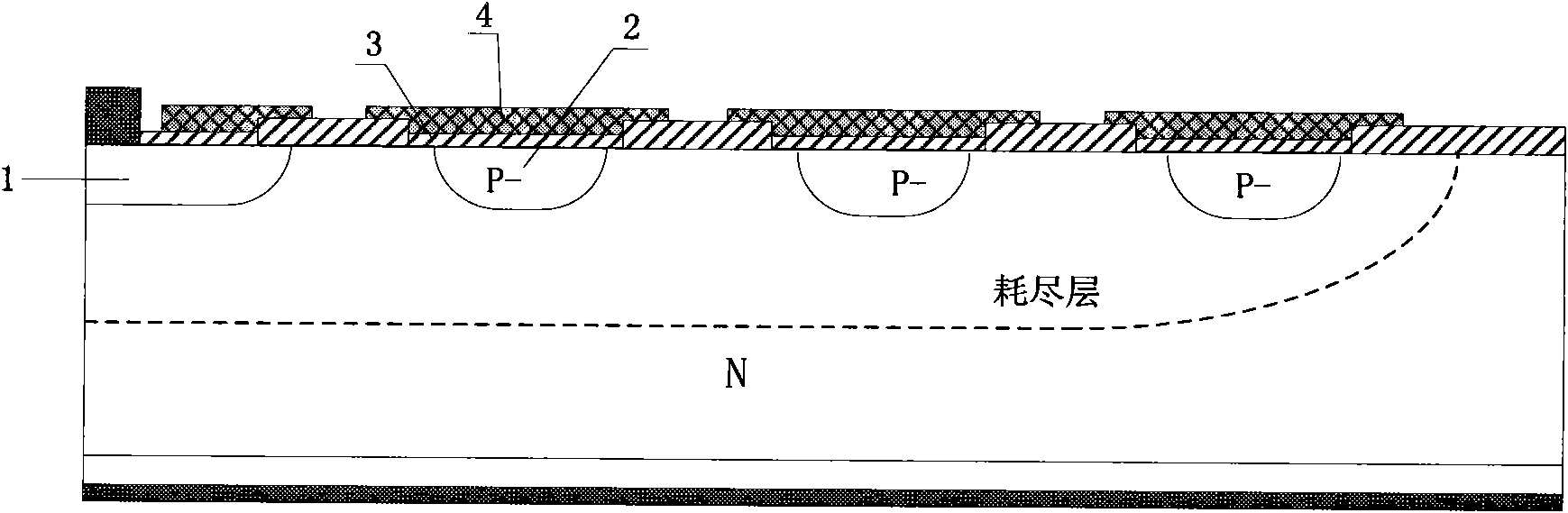

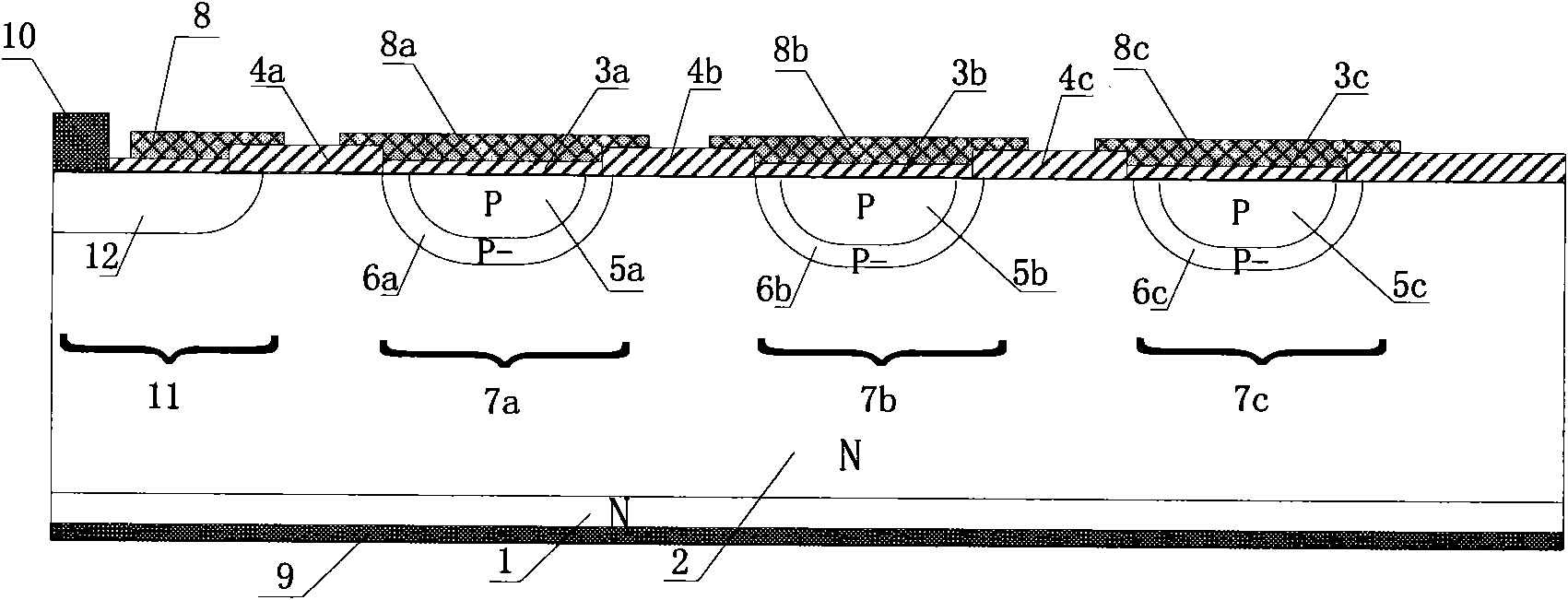

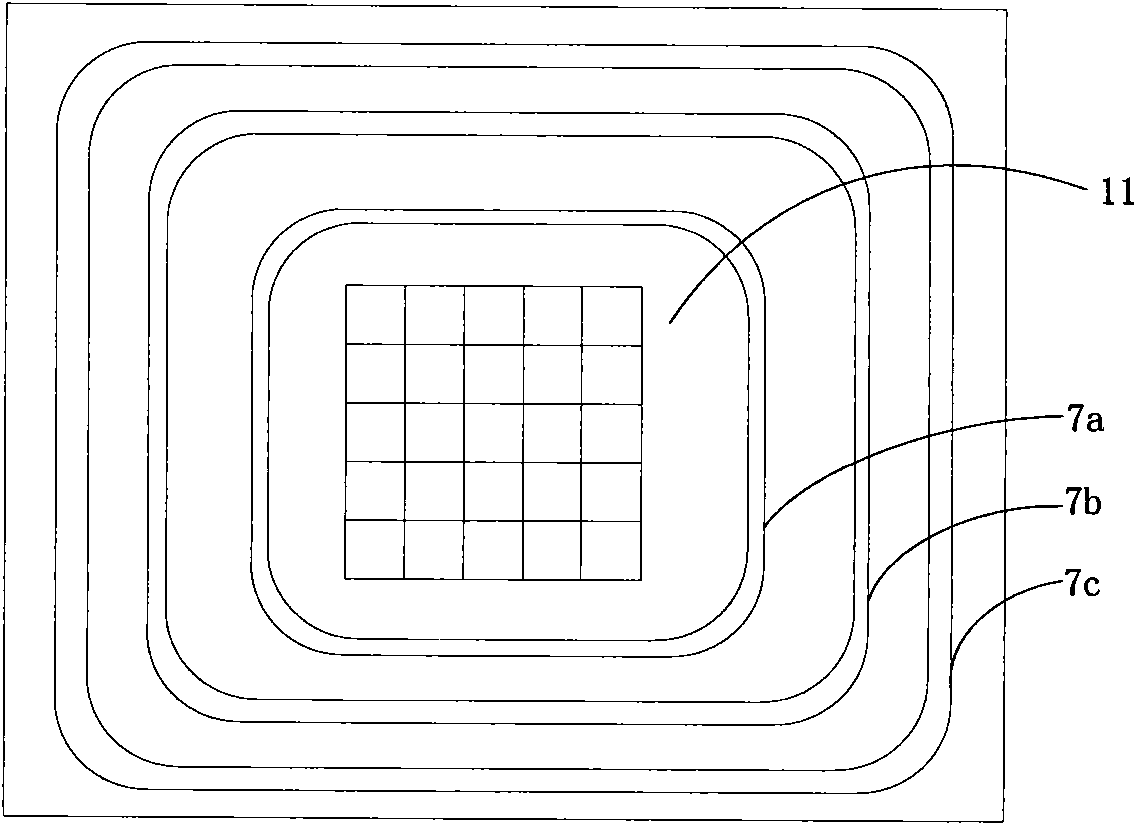

Edge terminal structure of high-voltage power semiconductor device

InactiveCN101969068AReduce electric field strengthReduce concentrationSolid-state devicesSemiconductor devicesPower semiconductor deviceElectrical field strength

The invention discloses an edge terminal structure of a high-voltage power semiconductor device. The edge terminal structure comprises a plurality of field limiting rings which wind the power semiconductor device and have a conduction type opposite to that of a substrate; one or two side of each field limiting ring is provided with a doped region which has a conduction type the same as that of the field limiting ring and the doping concentration smaller than that of the field limiting ring; the field limiting rings are coated with field plates; and the field limiting rings and the field plates are separated by silicon dioxide layers. The material of the field plate can be selected from copper, aluminum, polysilicon, oxygen-doped polysilicon and the like. The doped regions with lower concentration are added around the conventional field limiting rings, so the intensity of electric field lines of an edge cellular can be effectively reduced, the electric field strength borne by the edge cellular is reduced, the breakdown voltage is improved, the area efficiency of the edge terminal structure is effectively improved, the chip area is saved, and the chip cost is reduced.

Owner:ZHEJIANG UNIV +1

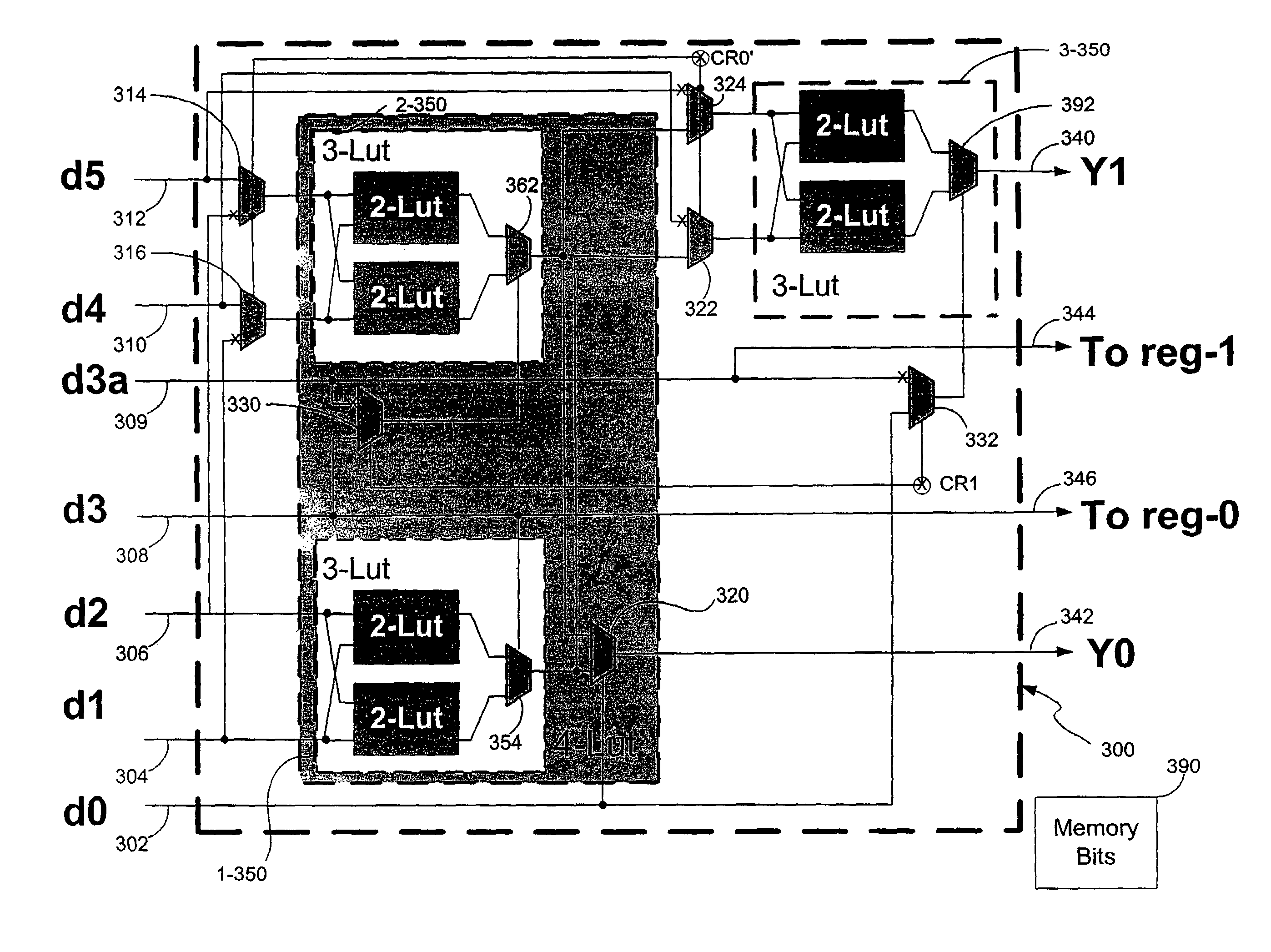

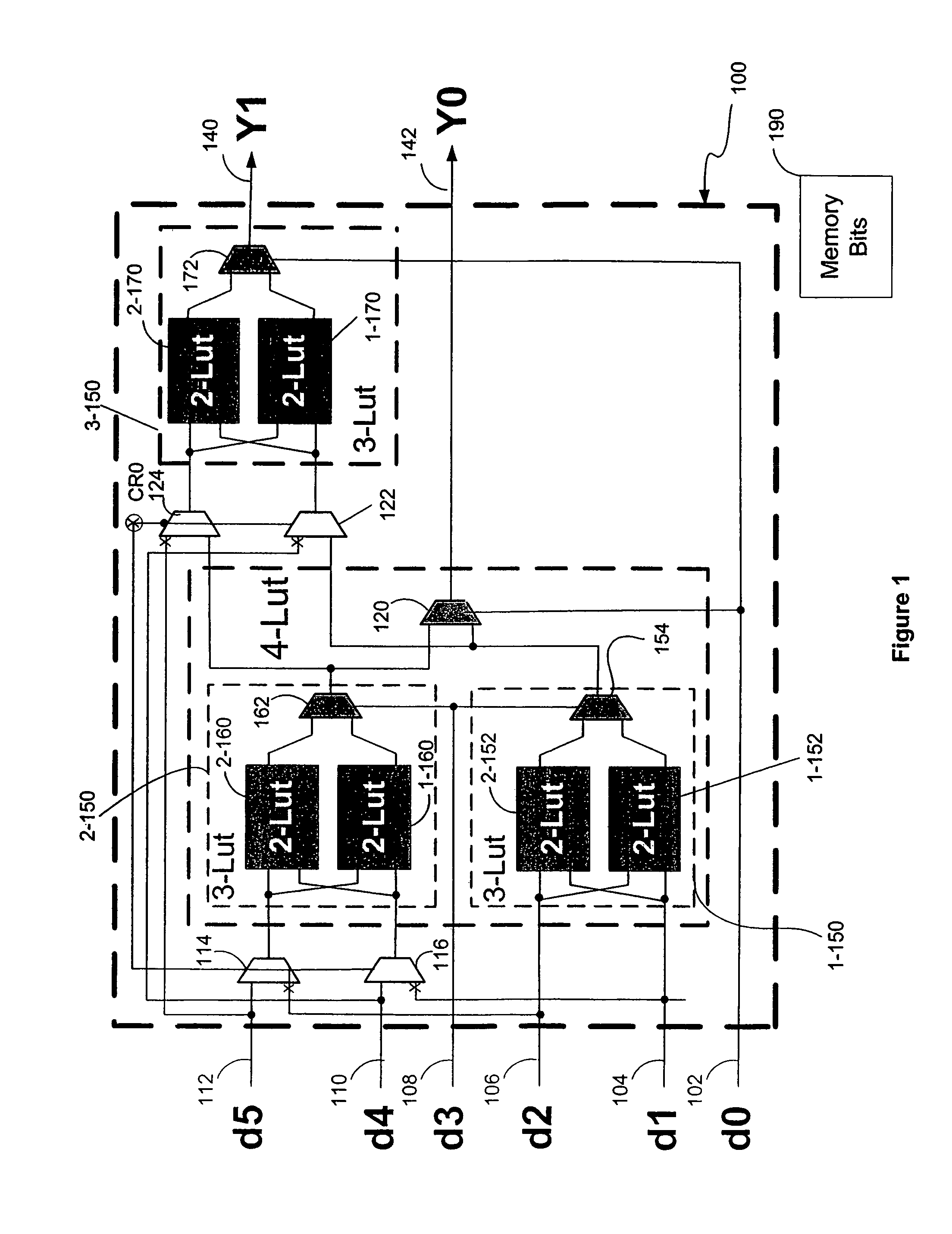

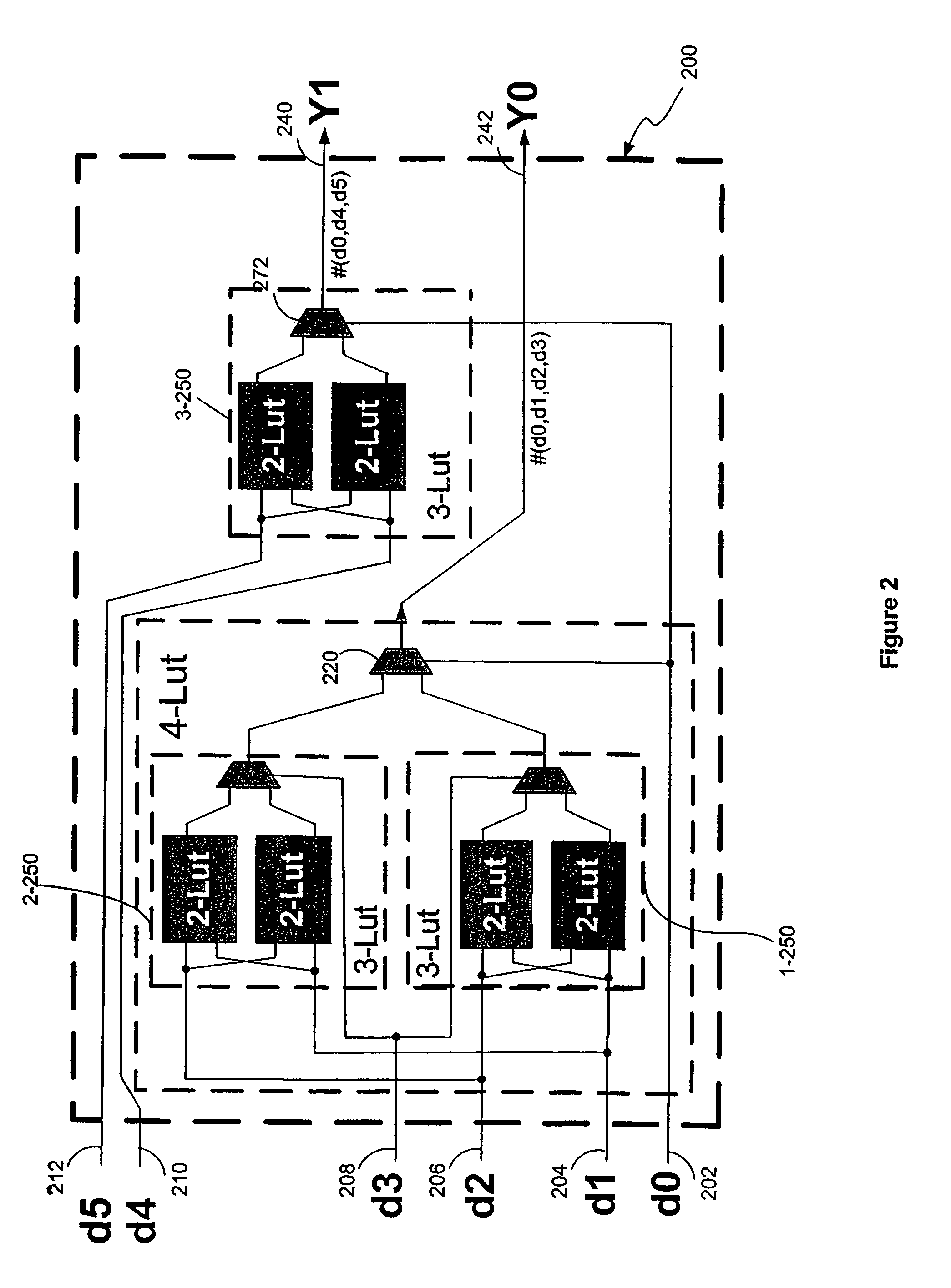

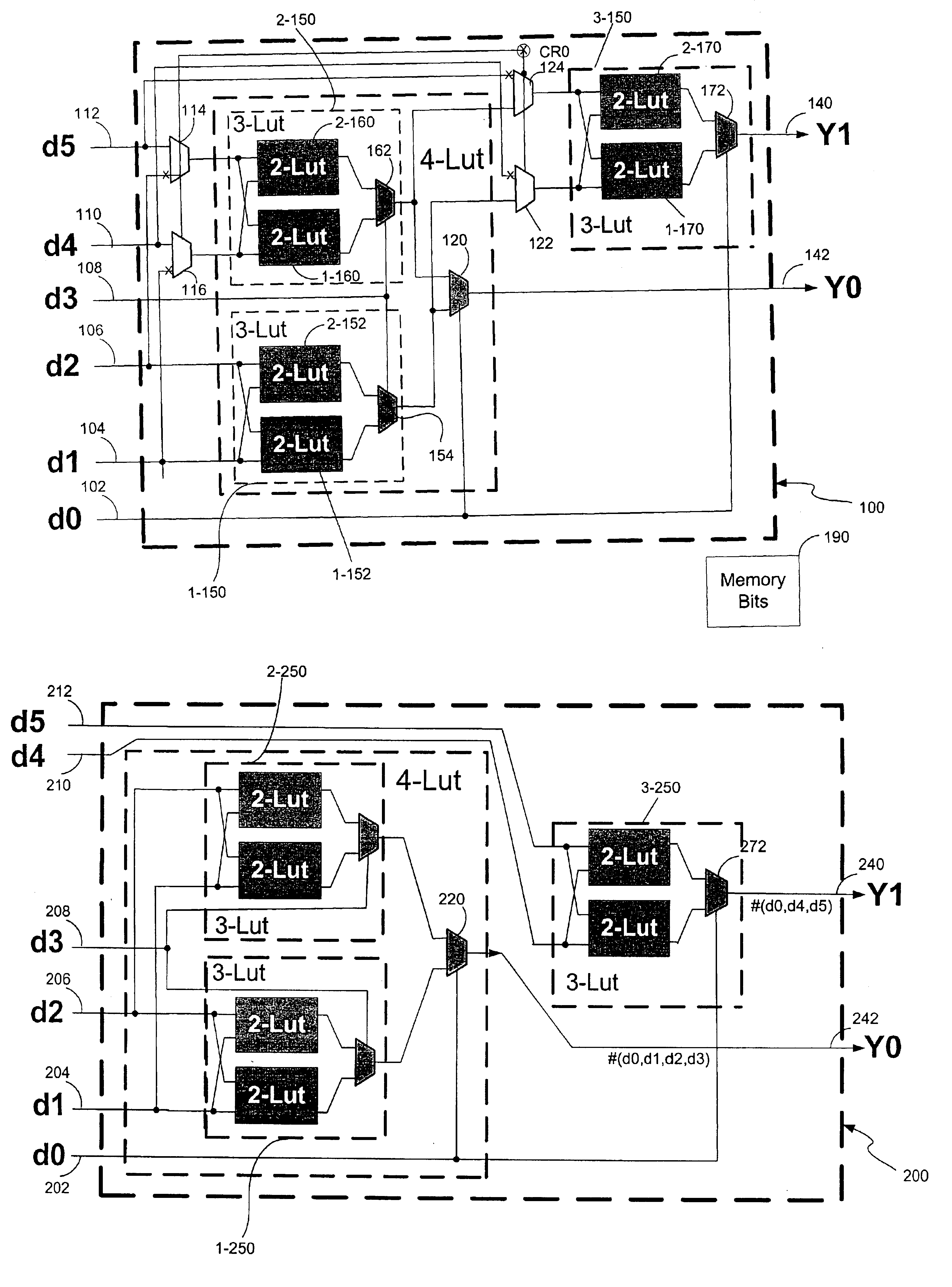

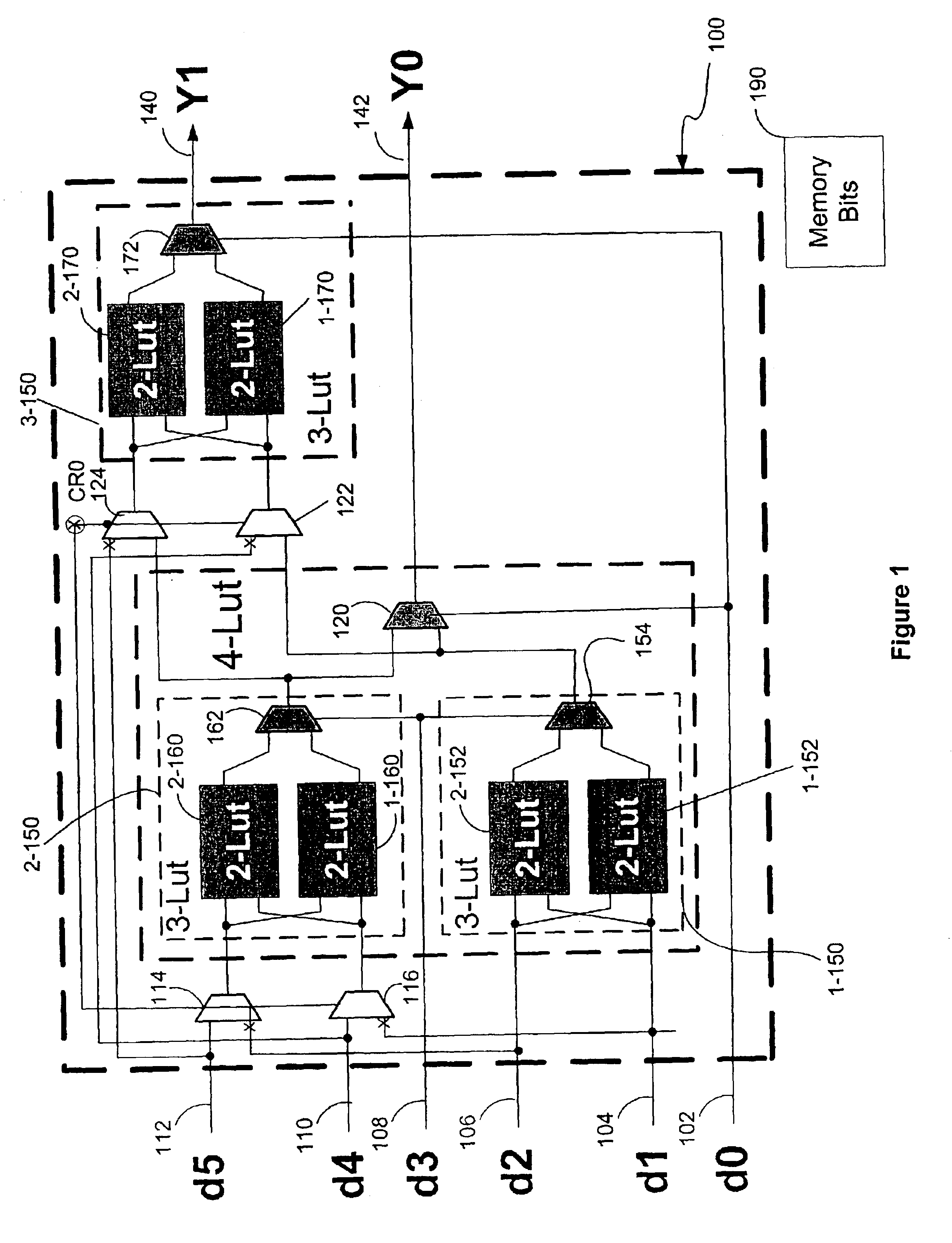

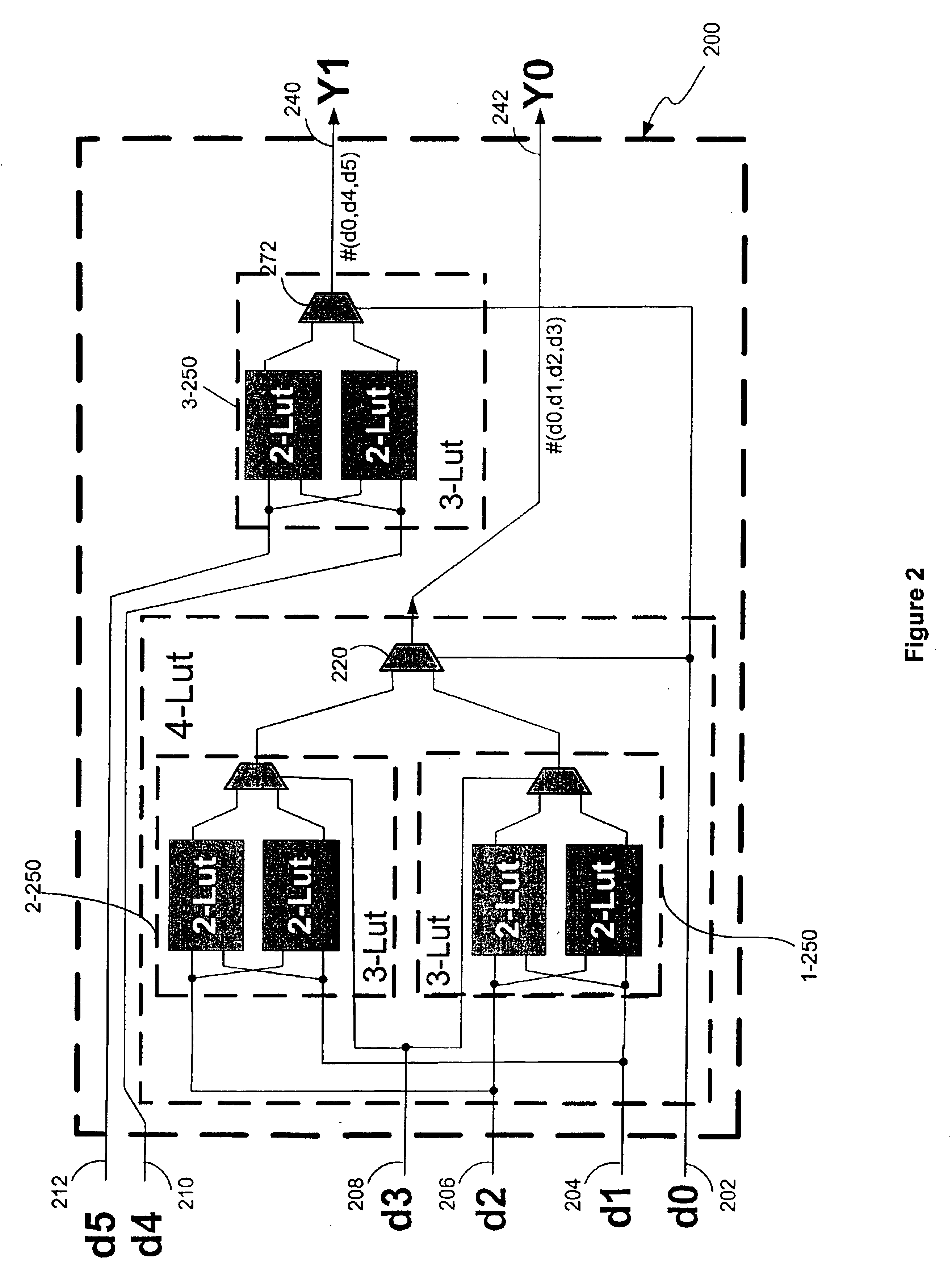

Fracturable incomplete look up table area efficient logic elements

InactiveUS7030650B1Reduce areaIncrease percentageSolid-state devicesLogic circuits using elementary logic circuit componentsTheoretical computer scienceSilicon

Disclosed is a configurable logic circuit that includes at least 6 inputs and at least two outputs. The configurable logic element can carry out only a subset of all 6-input logic functions and, thus, requires a substantially smaller silicon area than a 6-LUT that can perform all 6-input logic functions. Also, the configurable logic circuit can be configured such that a first subset of the inputs drive one of the outputs and a second subset of the inputs drive another output.

Owner:ALTERA CORP

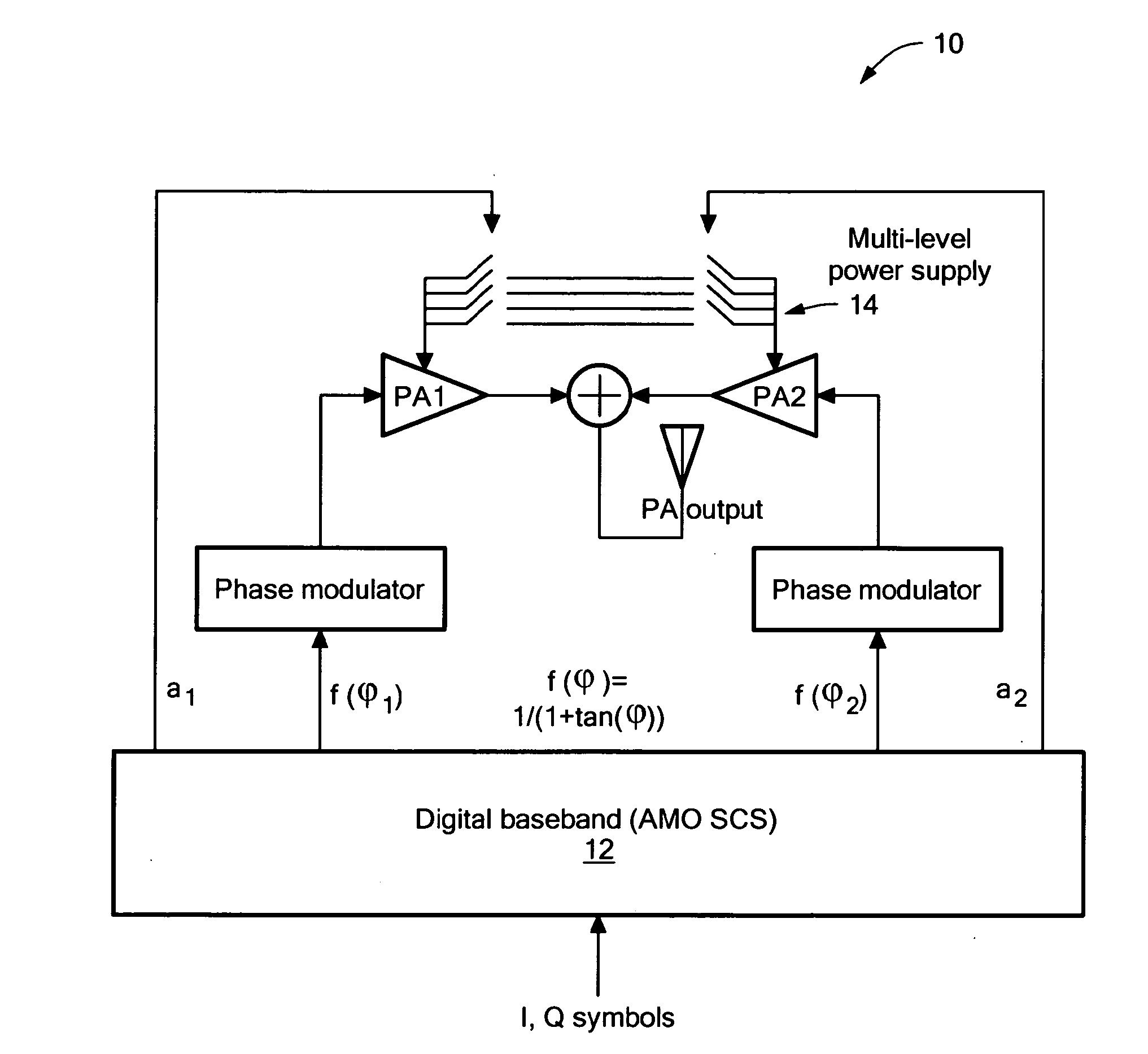

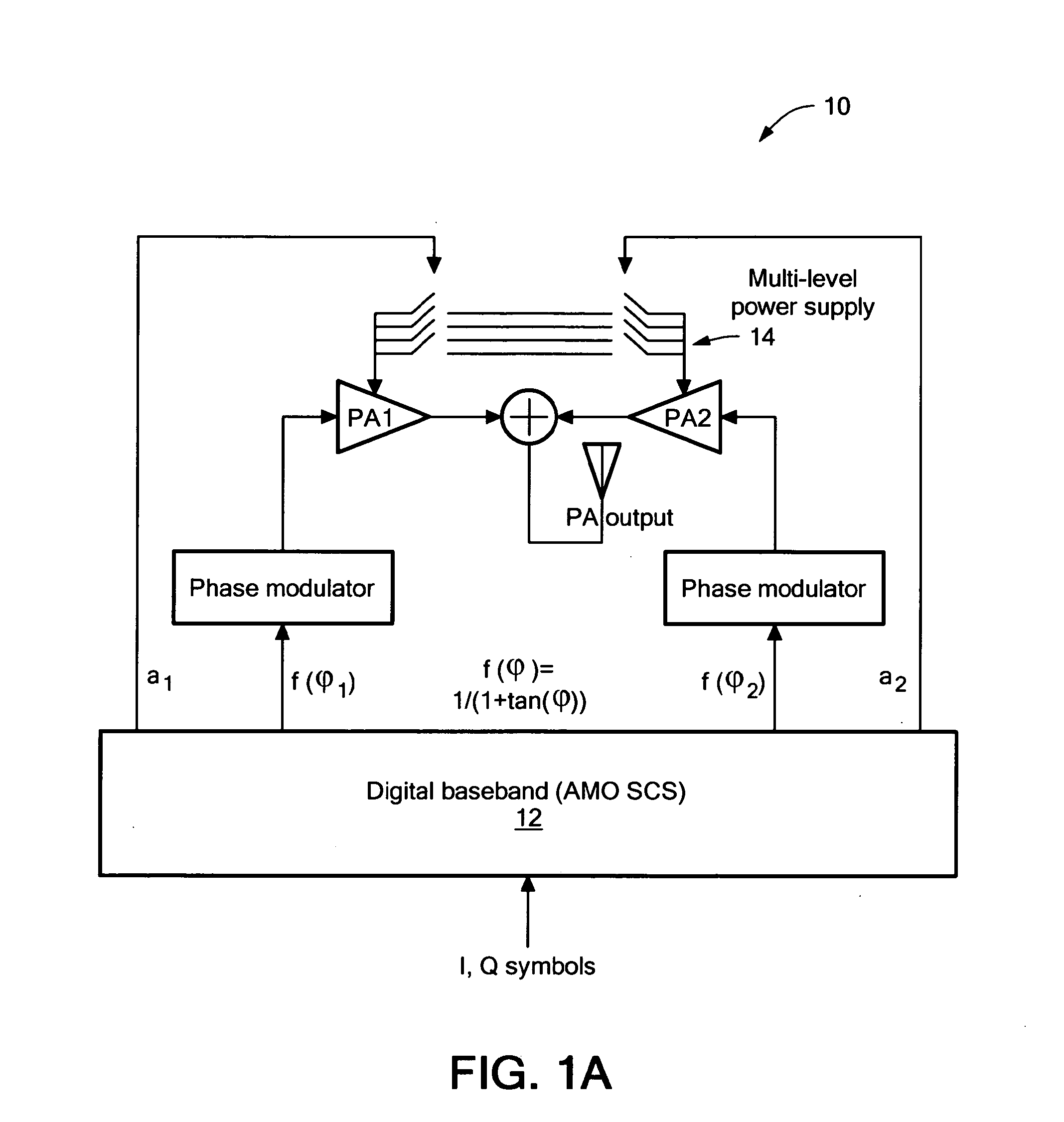

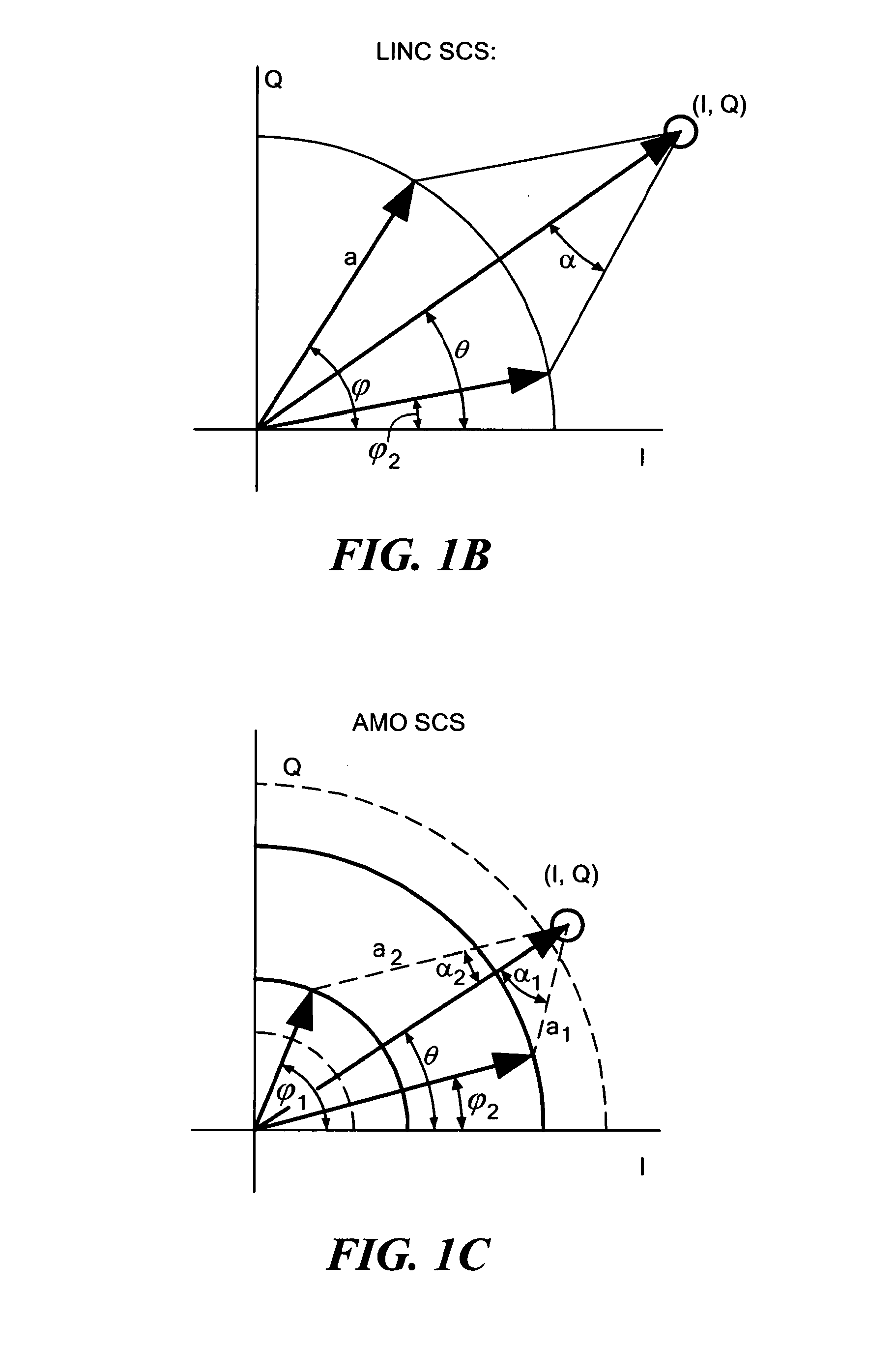

Hardware-Efficient Signal-Component Separator For Outphasing Power Amplifiers

ActiveUS20150124907A1Reduce (orCost in computerAmplitude demodulation by homodyne/synchrodyne circuitsHigh frequency amplifiersNon symmetricOperand

Described herein is a fixed-point piece-wise linear (FP PWL) approximation technique for computations of nonlinear functions. The technique results in circuit designs having relatively few and simple arithmetic operations, short arithmetic operands and small-sized look-up tables and the circuits resultant there from can be efficiently pipelined to run at multi-GSamples / s throughputs. In one exemplary embodiment, the FP PWL approximation technique was used in the design of an energy-efficient high-throughput and high-precision signal component separator (SCS) for use with in an asymmetric-multilevel-outphasing (AMO) power amplifier. The FP PWL approximation technique is appropriate for use in any application requiring high-throughput, area and power constrained hardware implementations of nonlinear functions.

Owner:MASSACHUSETTS INST OF TECH

Fracturable incomplete look up table for area efficient logic elements

InactiveUS6888373B2Reduce areaIncrease percentageSolid-state devicesLogic circuits using elementary logic circuit componentsTheoretical computer scienceSilicon

Disclosed is a configurable logic circuit that includes at least 6 inputs and at least two outputs. The configurable logic element can carry out only a subset of all 6-input logic functions and, thus, requires a substantially smaller silicon area than a 6-LUT that can perform all 6-input logic functions. Also, the configurable logic circuit can be configured such that a first subset of the inputs drive one of the outputs and a second subset of the inputs drive another output.

Owner:ALTERA CORP

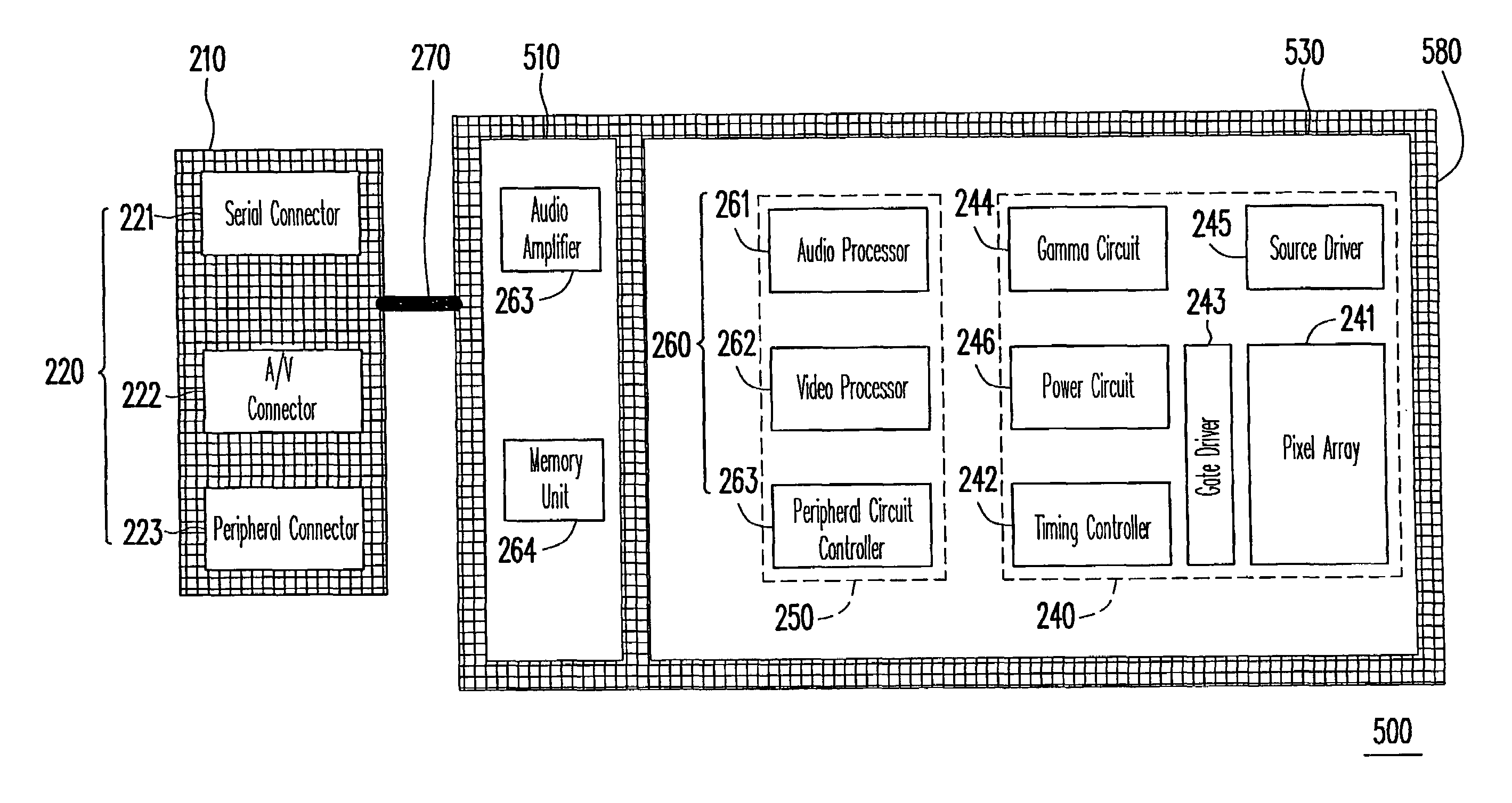

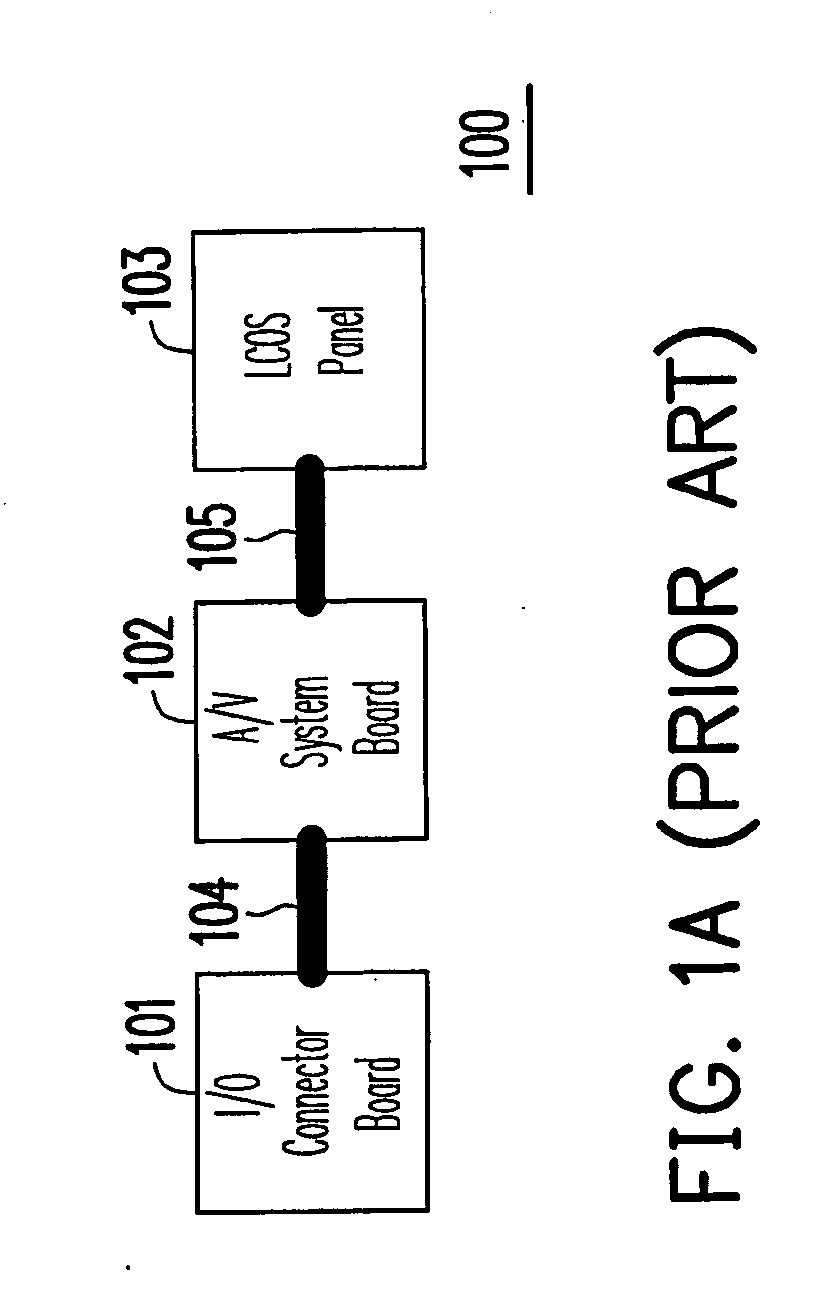

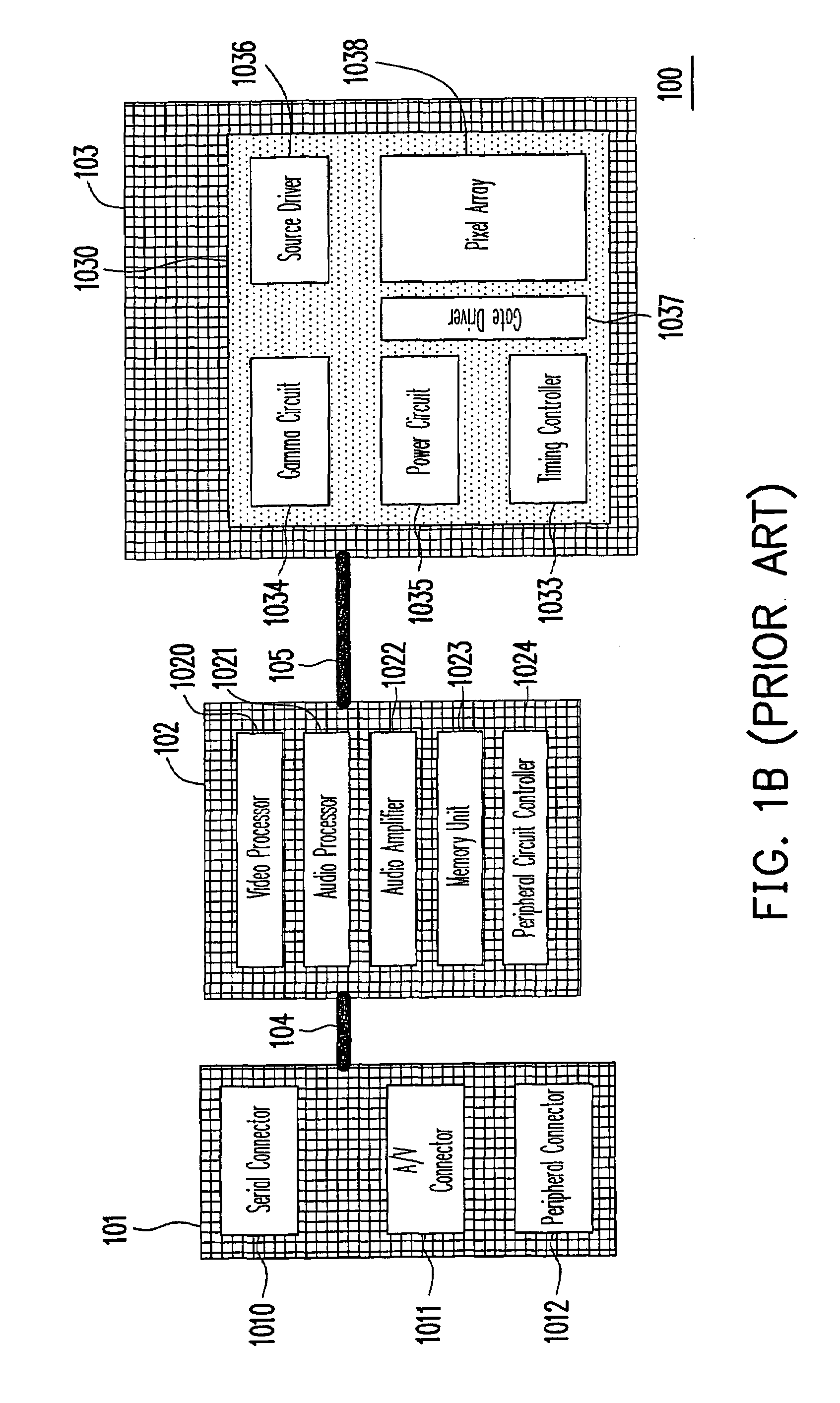

Liquiid crystal on silicon (LCOS) display and package thereof

InactiveUS20080266469A1Improve area efficiencyIncreasing system integrationStatic indicating devicesNon-linear opticsSilicon chipElectric cables

The present invention provides a LCOS display. The display comprises a first PCB, an interface module, a first silicon chip, and a flat cable. The interface module is disposed on the first PCB and used to receive an audio and video signal. The first silicon chip comprises a display area, a processing area, and a metal layer. The display area comprises a pixel array in a LCOS panel formed on the first silicon chip. The processing area comprises a processing unit formed on the first silicon chip. The metal layer is formed on the first silicon chip for electrically connecting the display area with the processing area. The flat cable is used to electrically connect the interface module with the processing unit.

Owner:HIMAX TECH LTD

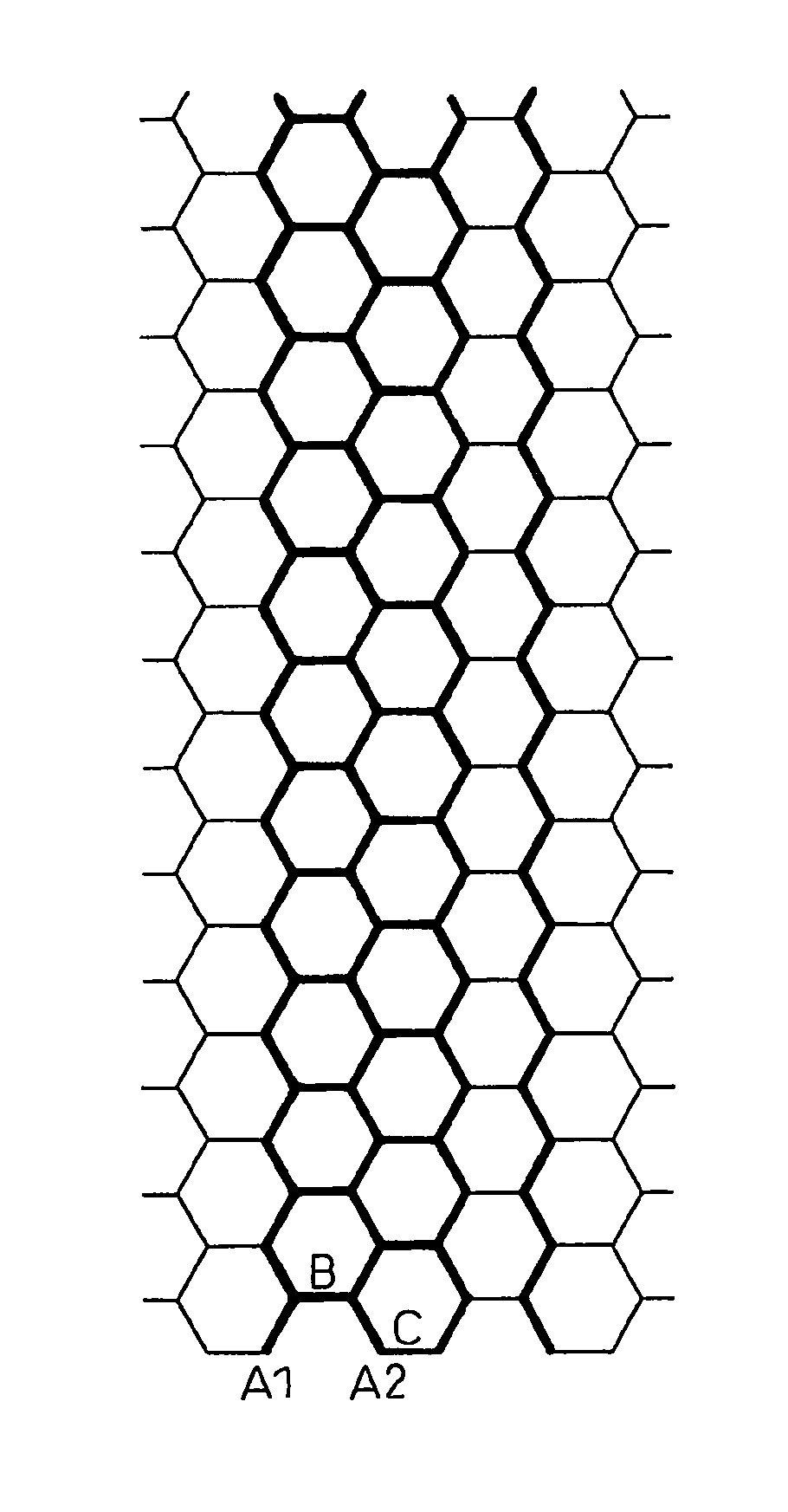

Production method for semiconductor device

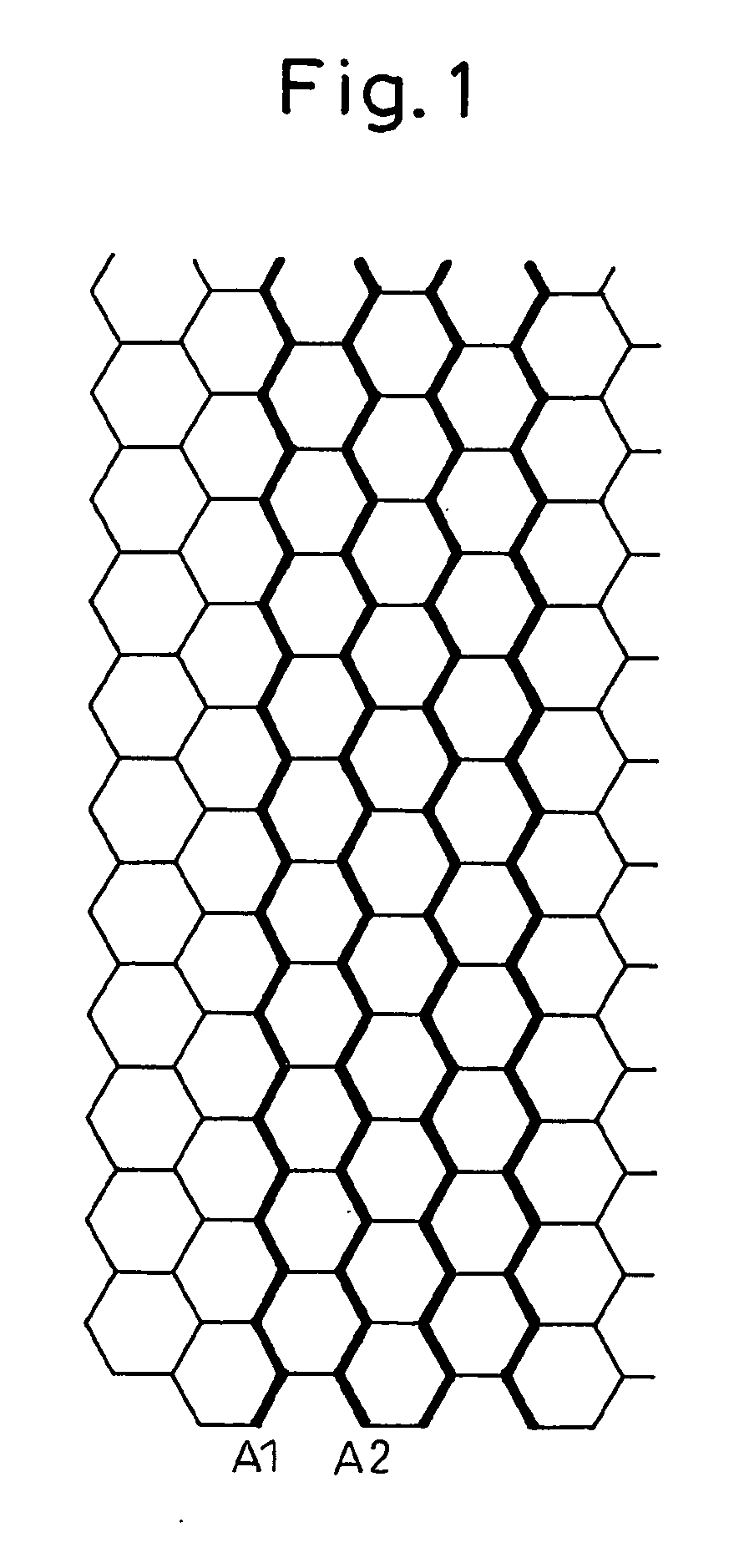

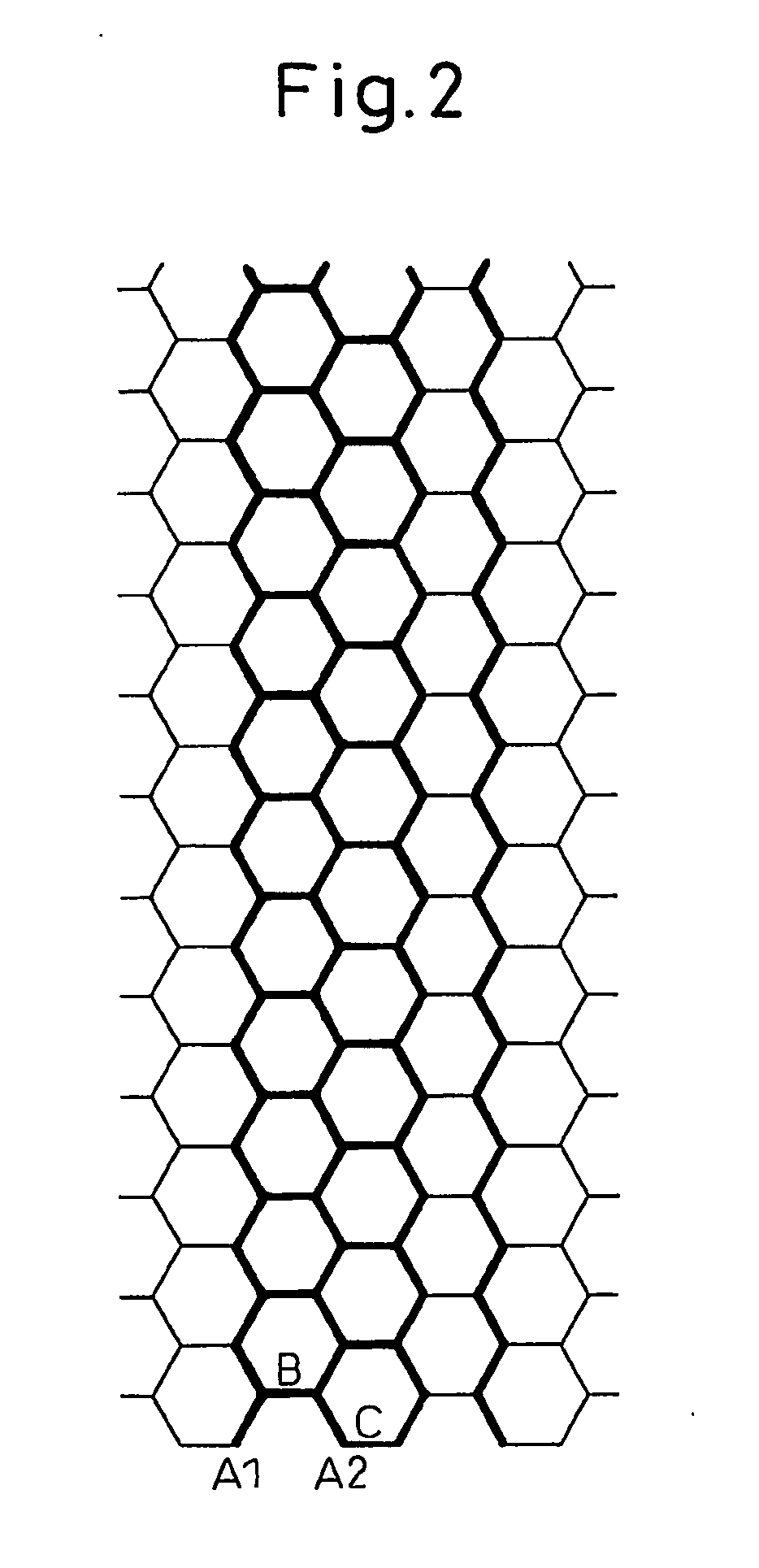

ActiveUS20070148803A1Low costLight extraction efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialLaser beams

An object of the present invention is to provide a method of producing a Group III nitride semiconductor device having a chip form which is pentagonal or more highly polygonal maintaining good area efficiency and at a low cost. The inventive method of producing a Group III nitride semiconductor device having a chip shape which is a pentagonal or more highly polygonal shape comprises a first step of epitaxially growing a Group III nitride semiconductor on a substrate to form a semiconductor wafer; a second step of irradiating said semiconductor wafer with a laser beam to form separation grooves; a third step of grinding and / or polishing the main surface side differently from the epitaxially grown main surface of the substrate; and a fourth step of division into individual chips by applying stress to said separation grooves.

Owner:TOYODA GOSEI CO LTD

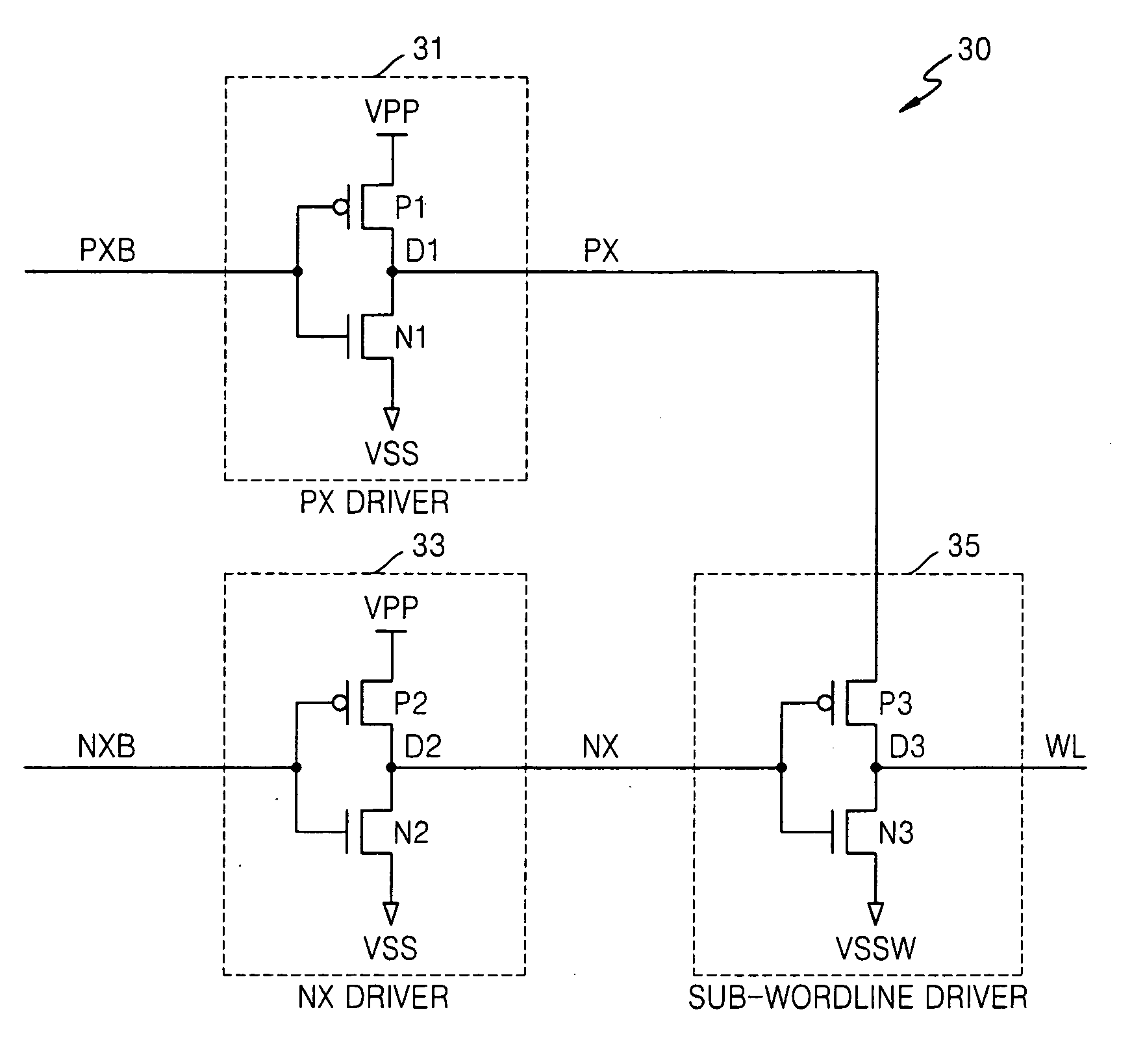

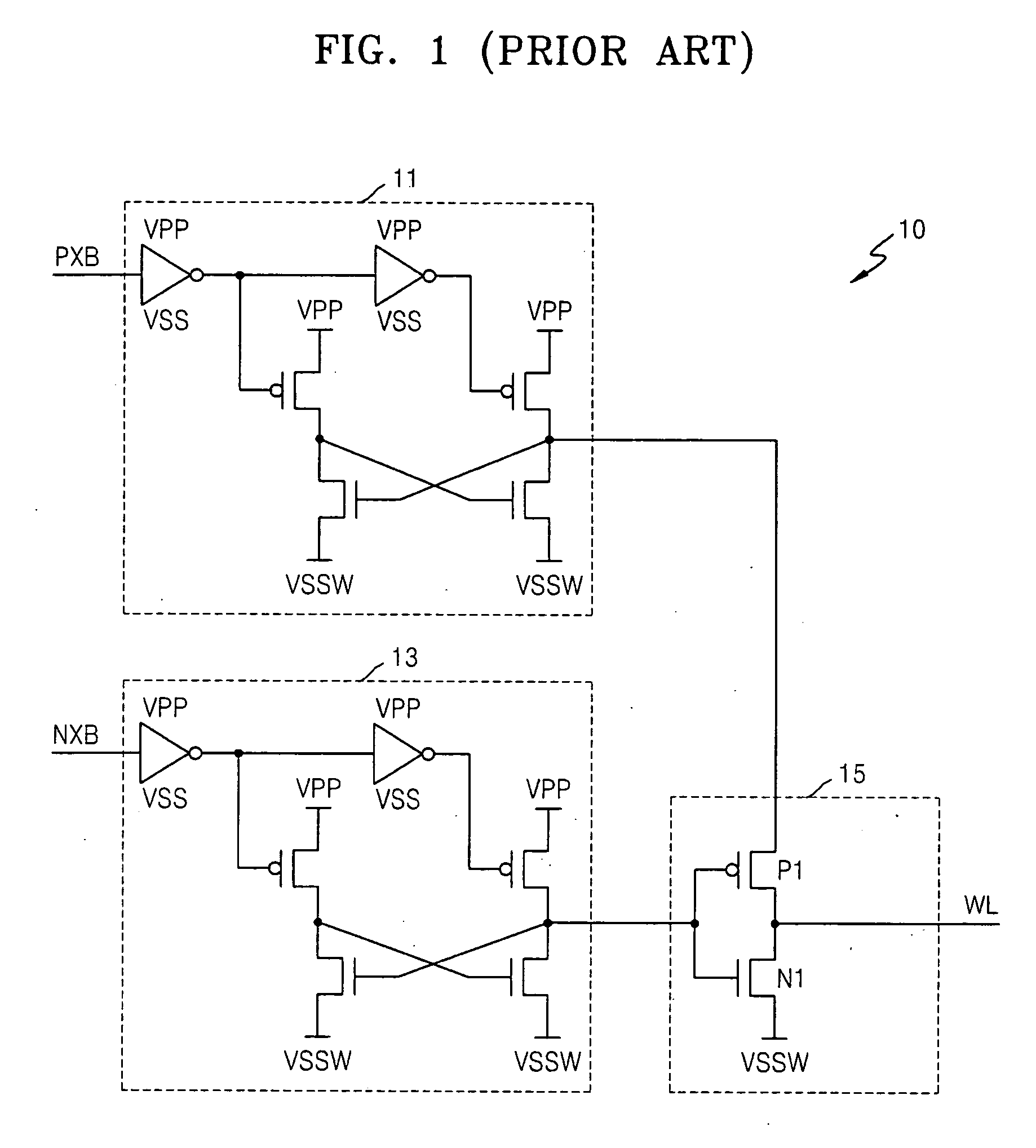

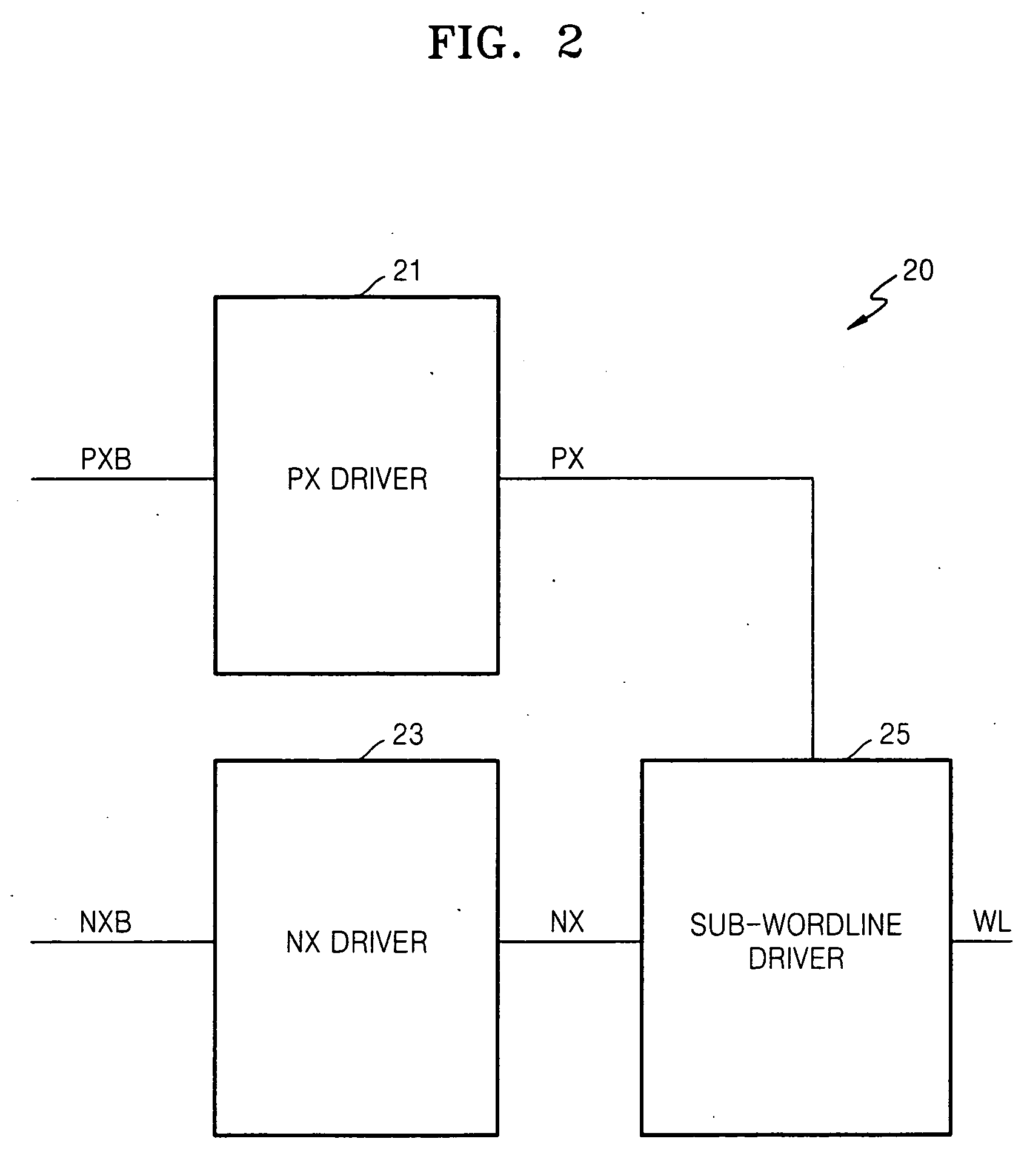

Wordline driver

InactiveUS20070008807A1Improve area efficiencyReduce current consumptionDigital storageLow voltageEngineering

The present invention describes systems and method for driving wordlines of memory devices. Some embodiments include a selection signal driver to generate a selection signal responsive to a first wordline signal, a main wordline driver to generate a main wordline signal responsive to a second wordline signal, the selection signal corresponding to one of the power supply voltage and the ground voltage and the main wordline signal corresponding to the other one of the power supply voltage and the ground voltage, and a sub-wordline driver to generate a sub-wordline signal responsive to the main wordline signal, the sub-wordline signal having a voltage level corresponding to the selection signal or a low voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and production method therefor

ActiveUS20120270374A1Easy to integrateImprove performanceTransistorSolid-state devicesDevice materialEngineering

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

Edge terminal structure of high-voltage power semiconductor device

InactiveCN101969069AReduce areaLow costSolid-state devicesSemiconductor devicesPower semiconductor deviceOxygen

The invention discloses an edge terminal structure of a high-voltage power semiconductor device. The edge terminal structure comprises a plurality of field limiting rings which surround the power semiconductor device and have the conduction type opposite to that of a substrate, wherein doping regions which have the same conduction type as the field limiting rings and lower doping density than the field limiting rings are arranged around the field limiting rings; the field limiting rings are wrapped by the doping regions and coated by field plates; and the field limiting rings are separated from the field plates by using silicon dioxide layers. The field plates can be made of copper, aluminum, polycrystalline silicon, oxygen-doped polycrystalline silicon and the like. Because the doping regions with lower density are arranged around the conventional field limiting rings, the density of edge cell electric field lines can be effectively reduced, the electric field strength born by an edge cell is reduced, the breakdown voltage is increased, the area efficiency of the edge terminal structure is effectively improved, the chip area is saved and the chip cost is reduced.

Owner:ZHEJIANG UNIV +1

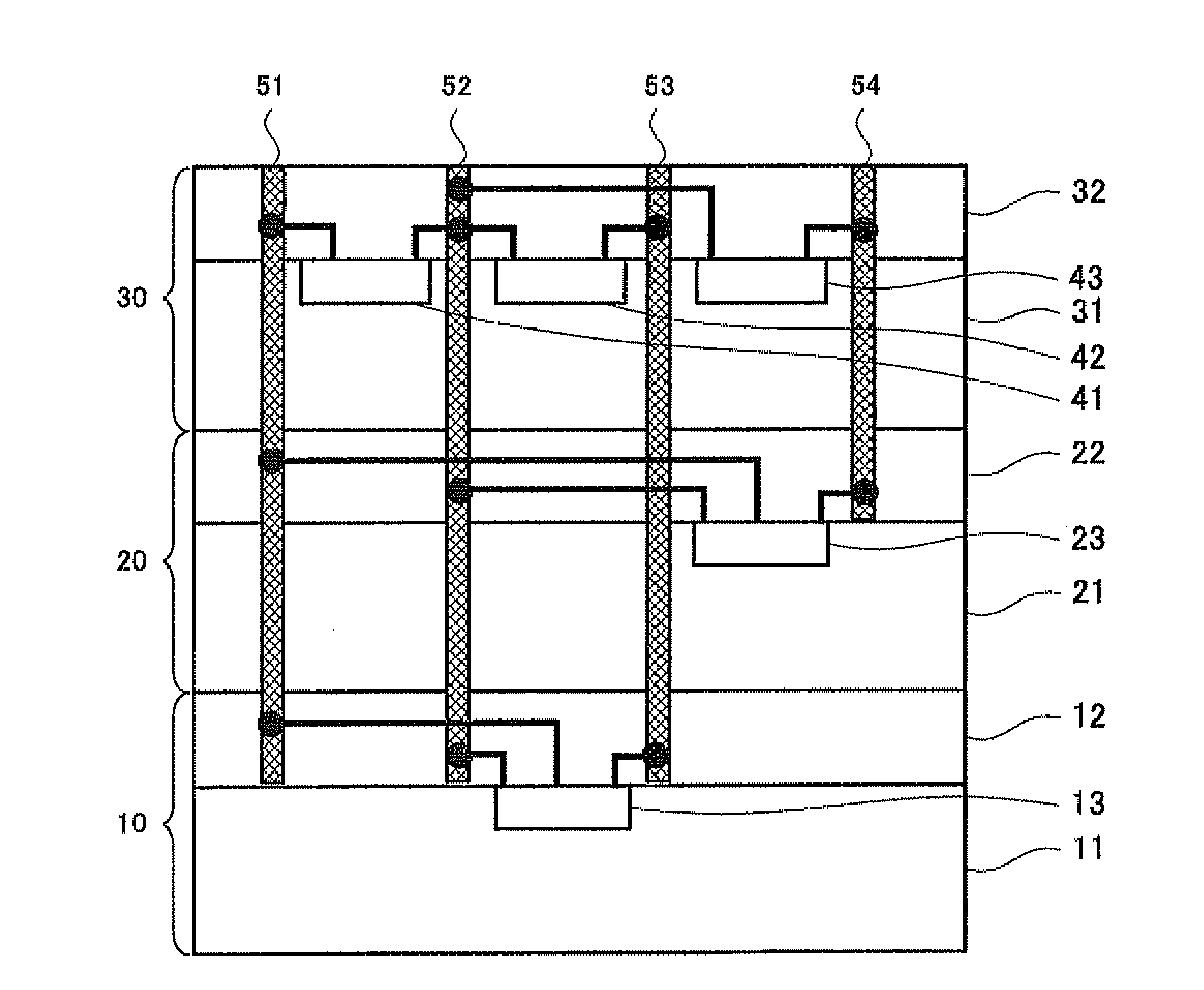

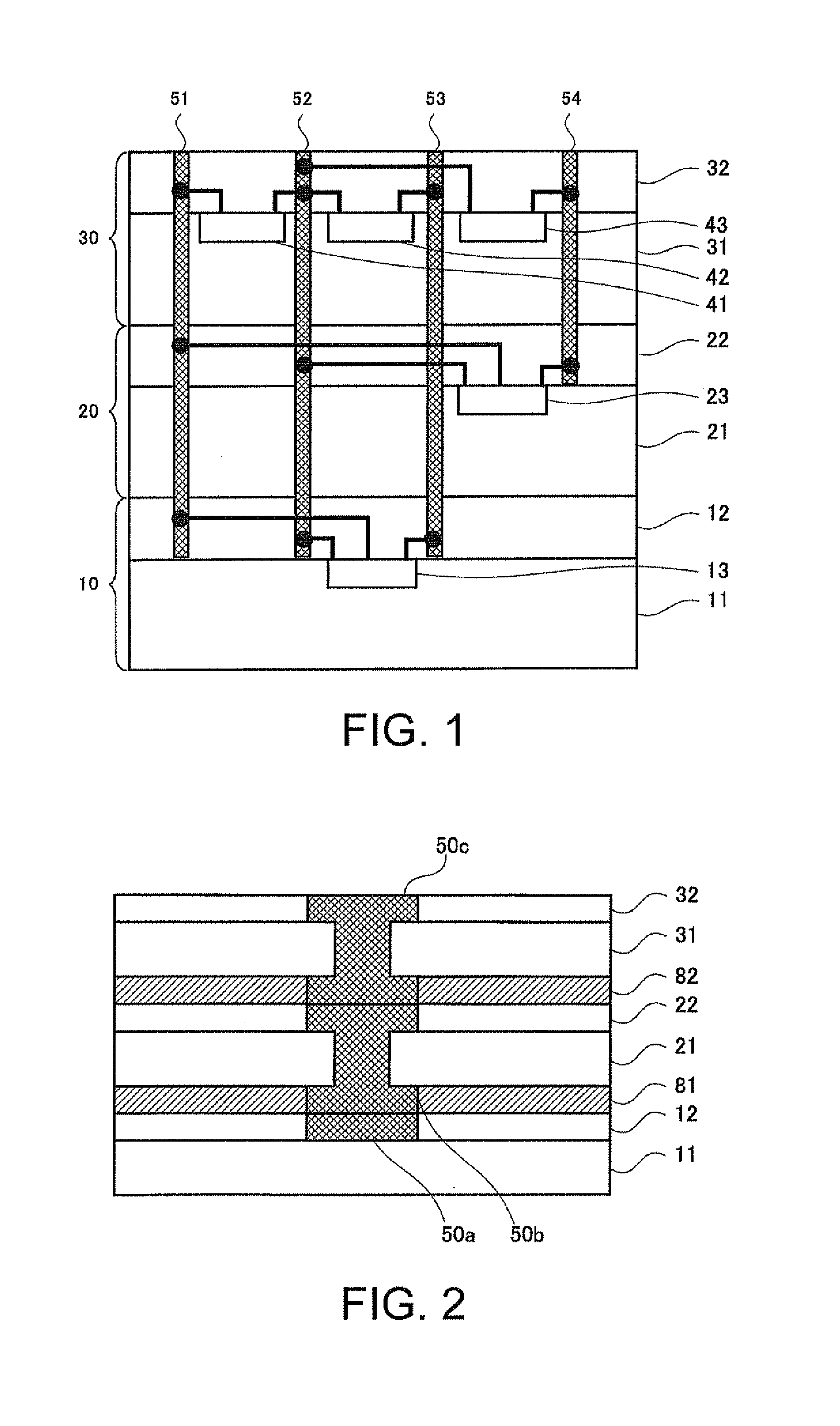

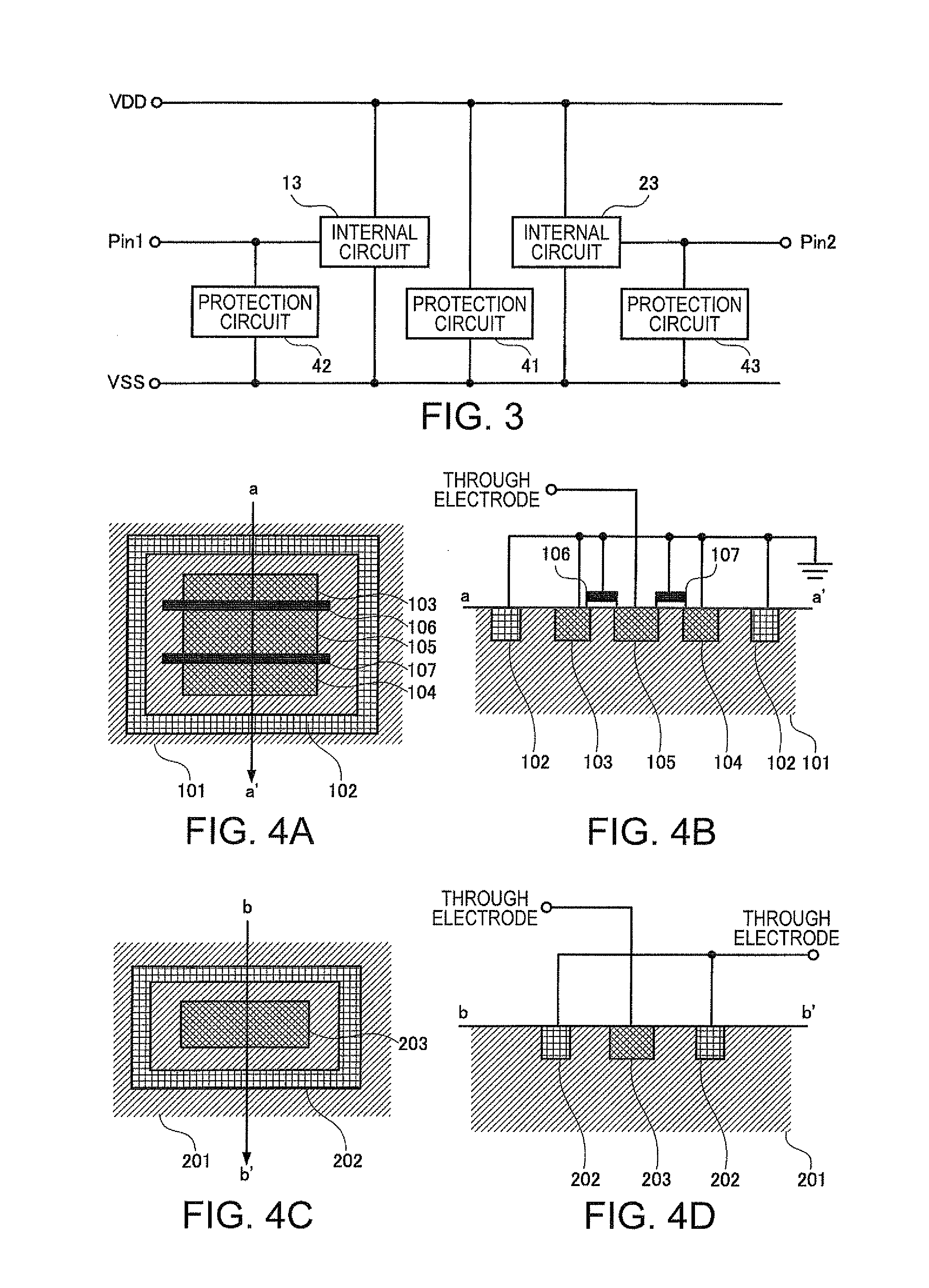

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20100133701A1Improve area efficiencyConvenient ArrangementSemiconductor/solid-state device detailsSolid-state devicesSemiconductorElectrostatic discharge protection

A semiconductor device includes: a plurality of external terminals; a plurality of semiconductor substrates that are layered; a through electrode penetrating through at least one of the semiconductor substrates and electrically connected with any of the external terminals; and a plurality of electrostatic discharge protection circuits provided on any one of the semiconductor substrates. In the device, the through electrode is electrically connected with the plurality of electrostatic discharge protection circuits.

Owner:SEIKO EPSON CORP