Edge terminal structure of high-voltage power semiconductor device

A technology for power semiconductors and edge terminals, applied in semiconductor devices, electric solid state devices, electrical components, etc., can solve the problems of increasing chip cost, increasing chip area, etc., reducing chip cost, reducing electric field strength, and reducing breakdown voltage. improved effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

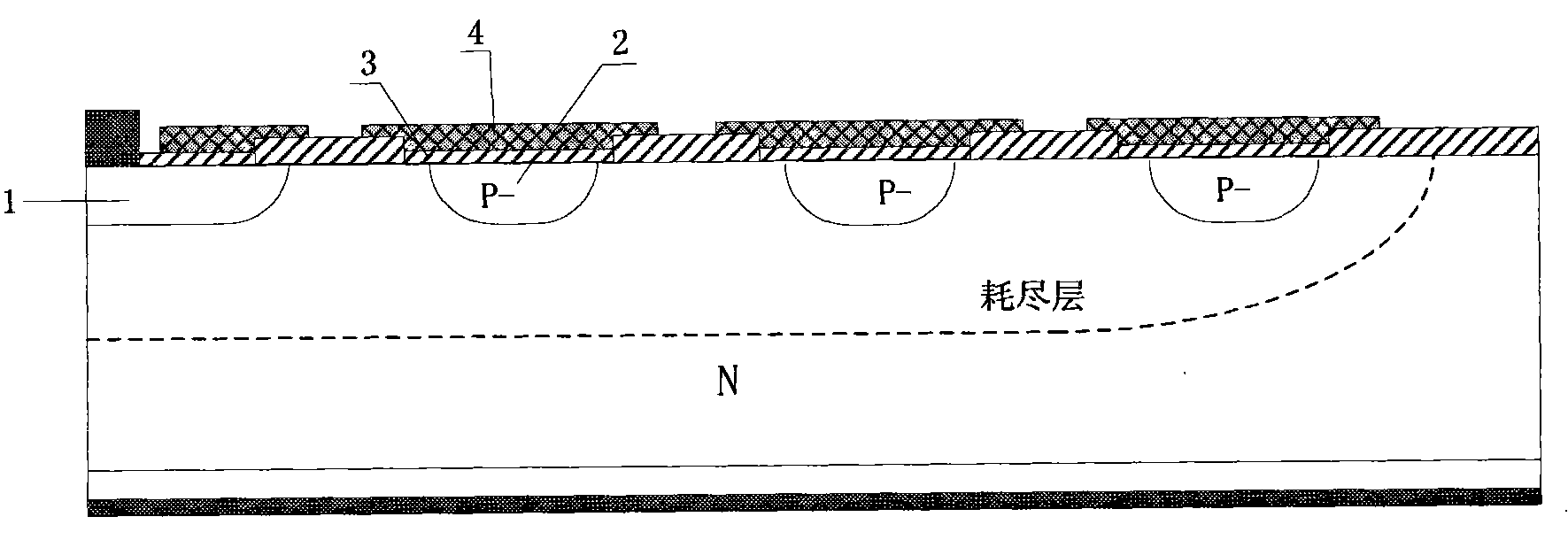

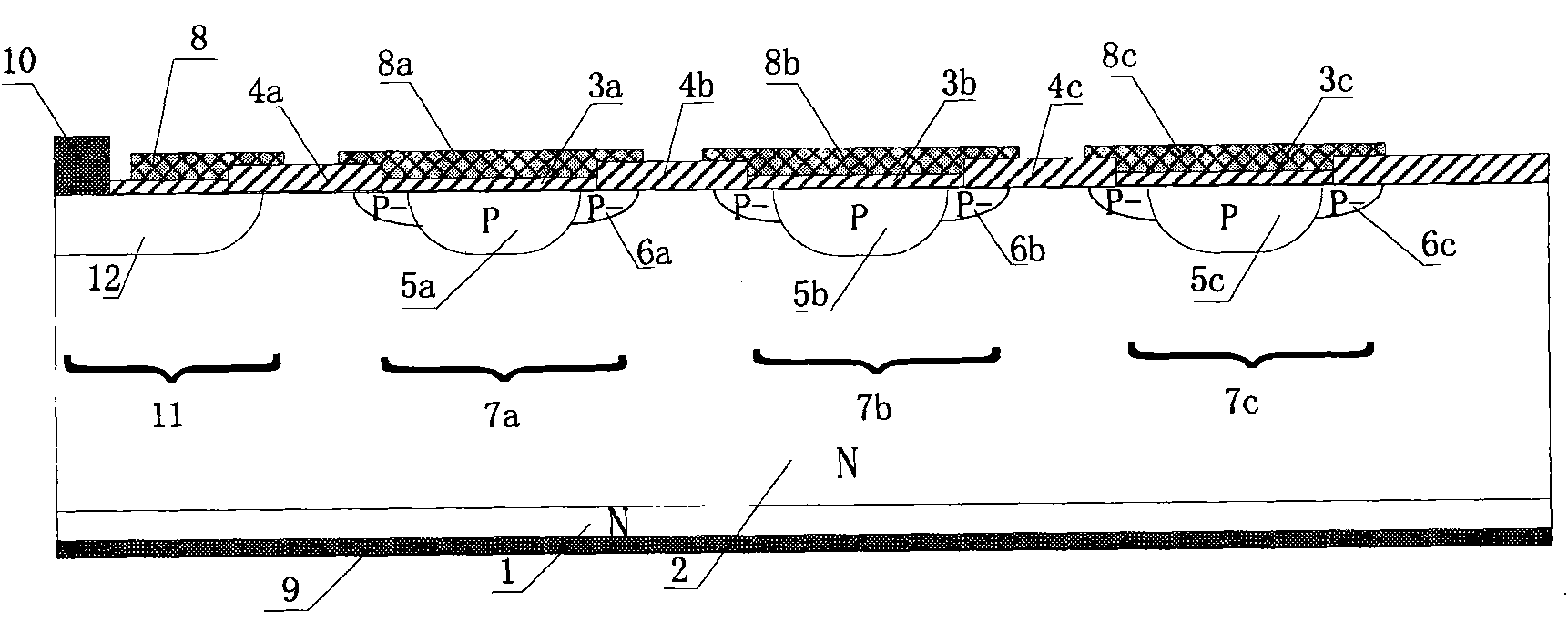

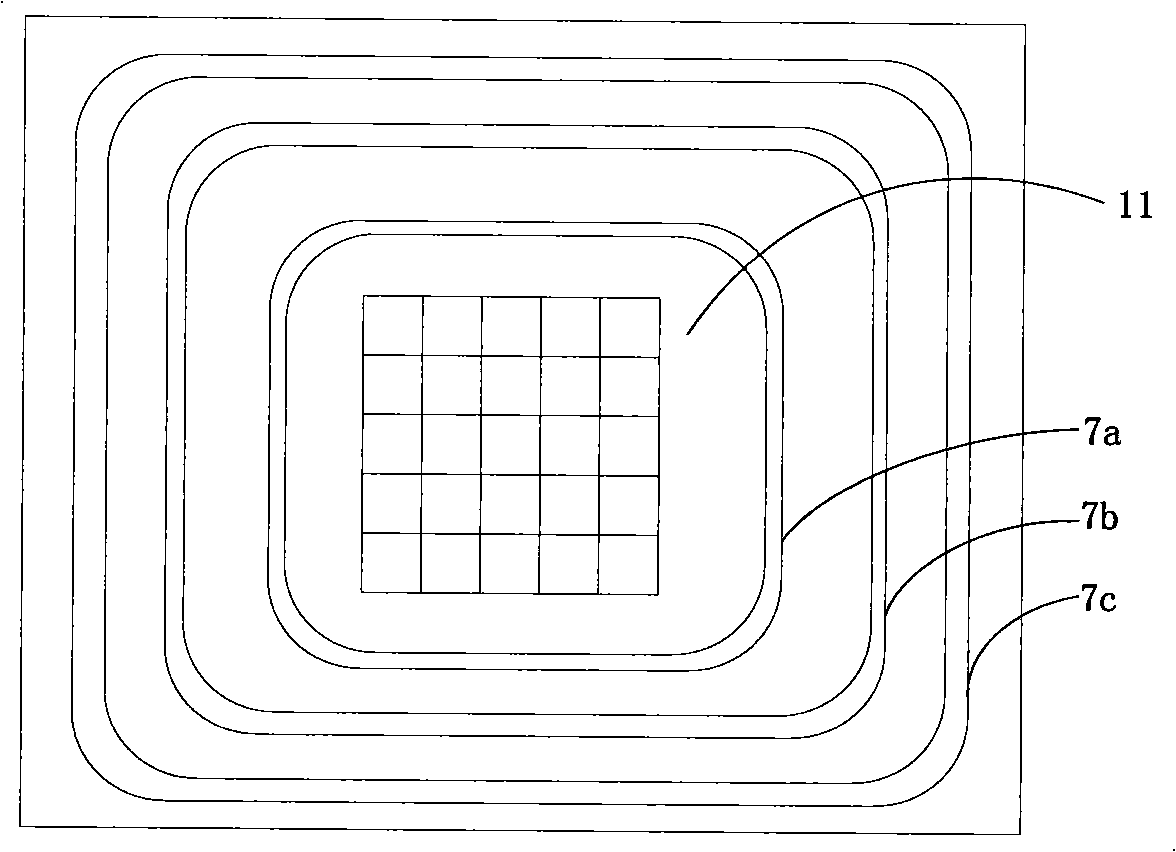

[0019] figure 2 A kind of embodiment of the present invention is provided, as shown in the figure, in arsenic ion (As) concentration is 5*10 22 cm -3 An epitaxial layer 2 of the same conductivity type is epitaxially grown on an N-type silicon substrate 1 (thickness 20 μm). The epitaxial layer 2 has a resistivity of 5Ω*cm and a thickness of 17 μm. A high-voltage power device 12 is provided on the upper surface of the epitaxial layer 2. The device can be VDMOS, LDMOS, BJT, etc. The device is composed of several cells connected in parallel. In the figure, only the edge area of the edge cells is shown as its schematic diagram . An electrode 10 and a field plate 8 are provided on the device 12, which are active regions 11 for realizing core functions of the chip. In addition, an electrode 9 is also provided on the bottom of the substrate 1 as an external electrode of the test chip.

[0020] A P-type doped region 5a is provided on the outside of the device 12 relative to the ...

Embodiment 2

[0025] Such as Figure 4 As shown, the structure of this embodiment is similar to that of Embodiment 1, and instead of adding doped regions on both sides of the traditional field confinement ring, a doped region with a lower concentration is only added on the outside of the field confinement ring relative to the active region 11 , the junction depth of the doped region is 1-1.5 μm, and the field limiting ring 7a is 6 μm away from the active region. Adding an extra doped region only on one side of the field limiting ring can shorten the distance between the field limiting rings, from 8 to 10 μm in Example 1 to 6.5 to 7 μm, which reduces the chip area and reduces the cost. Compared with embodiment 1, this embodiment does not affect the effect of improving the breakdown voltage of edge cells. Figure 6 This example is given with figure 1 The comparison diagram of the electric field distribution of the traditional field confining ring is shown, in which, the left picture is fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More