Patents

Literature

360results about How to "Increase the on-current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

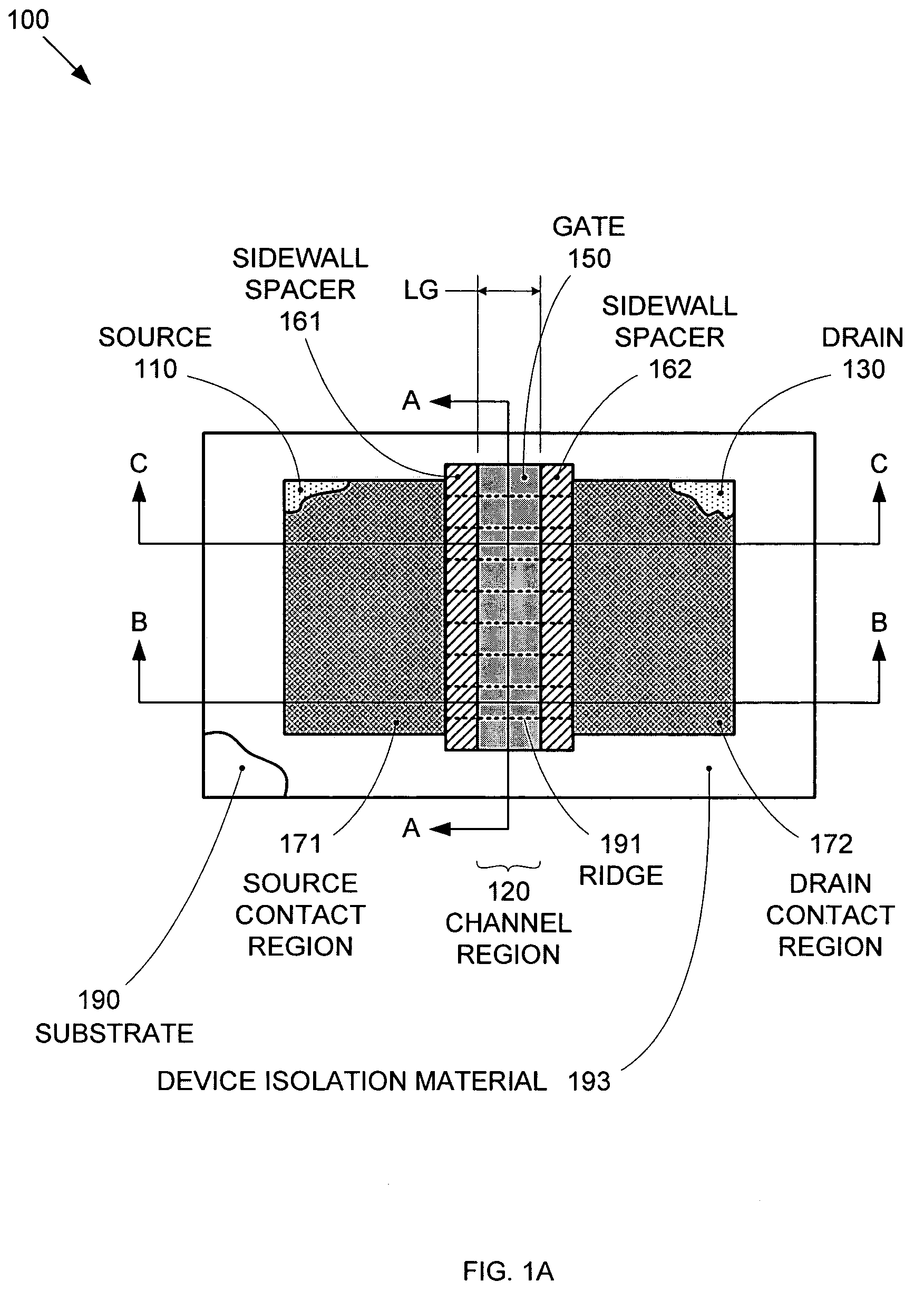

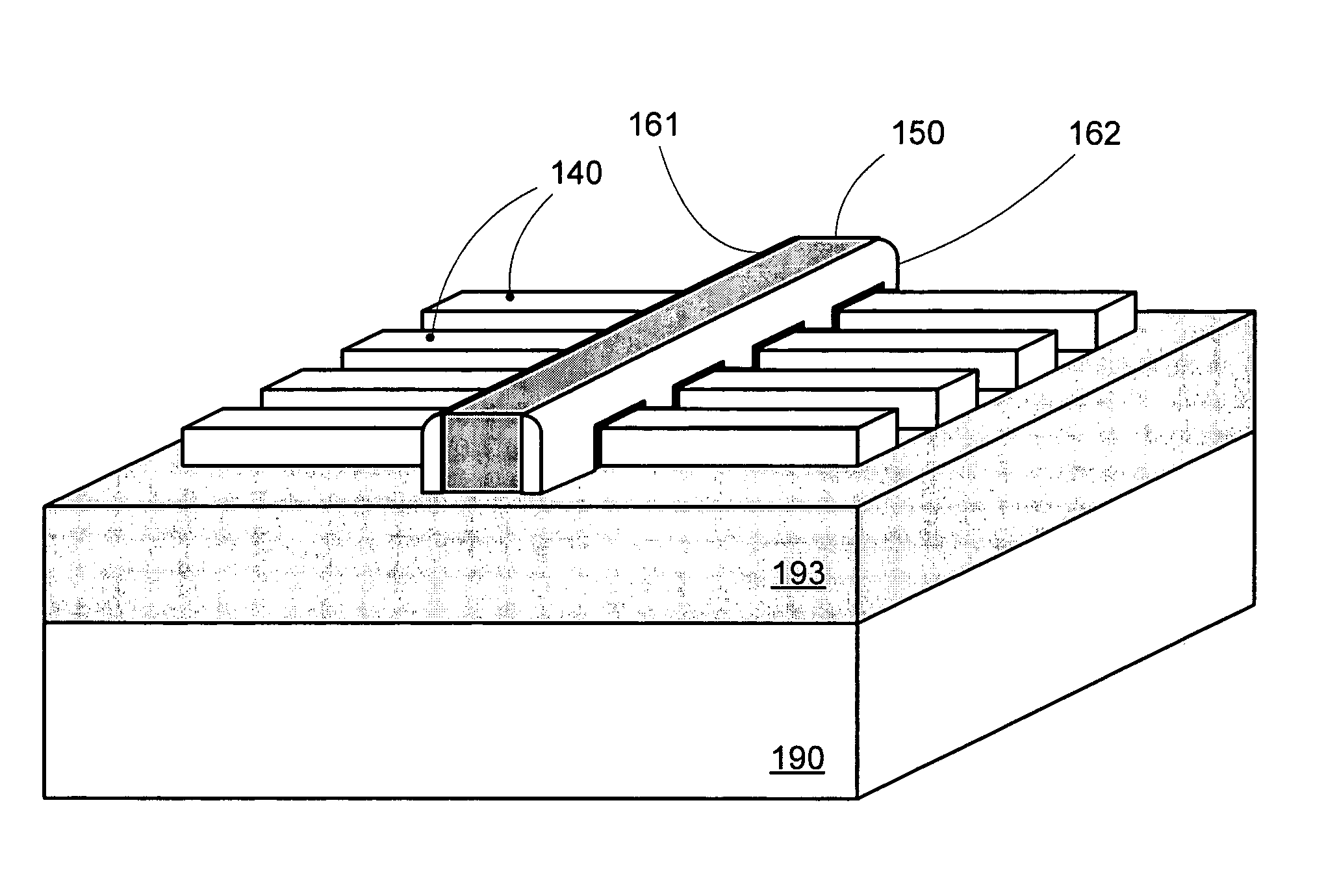

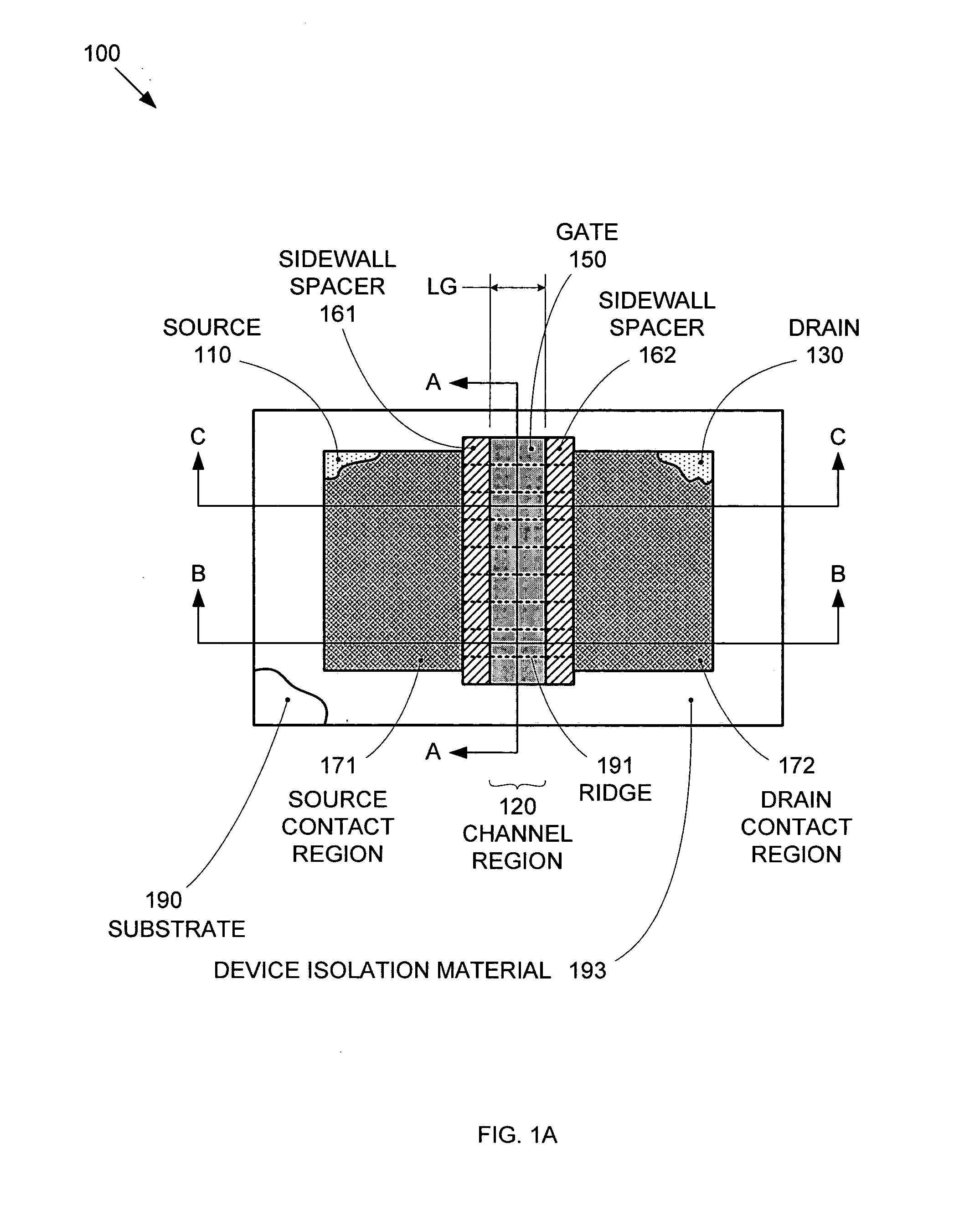

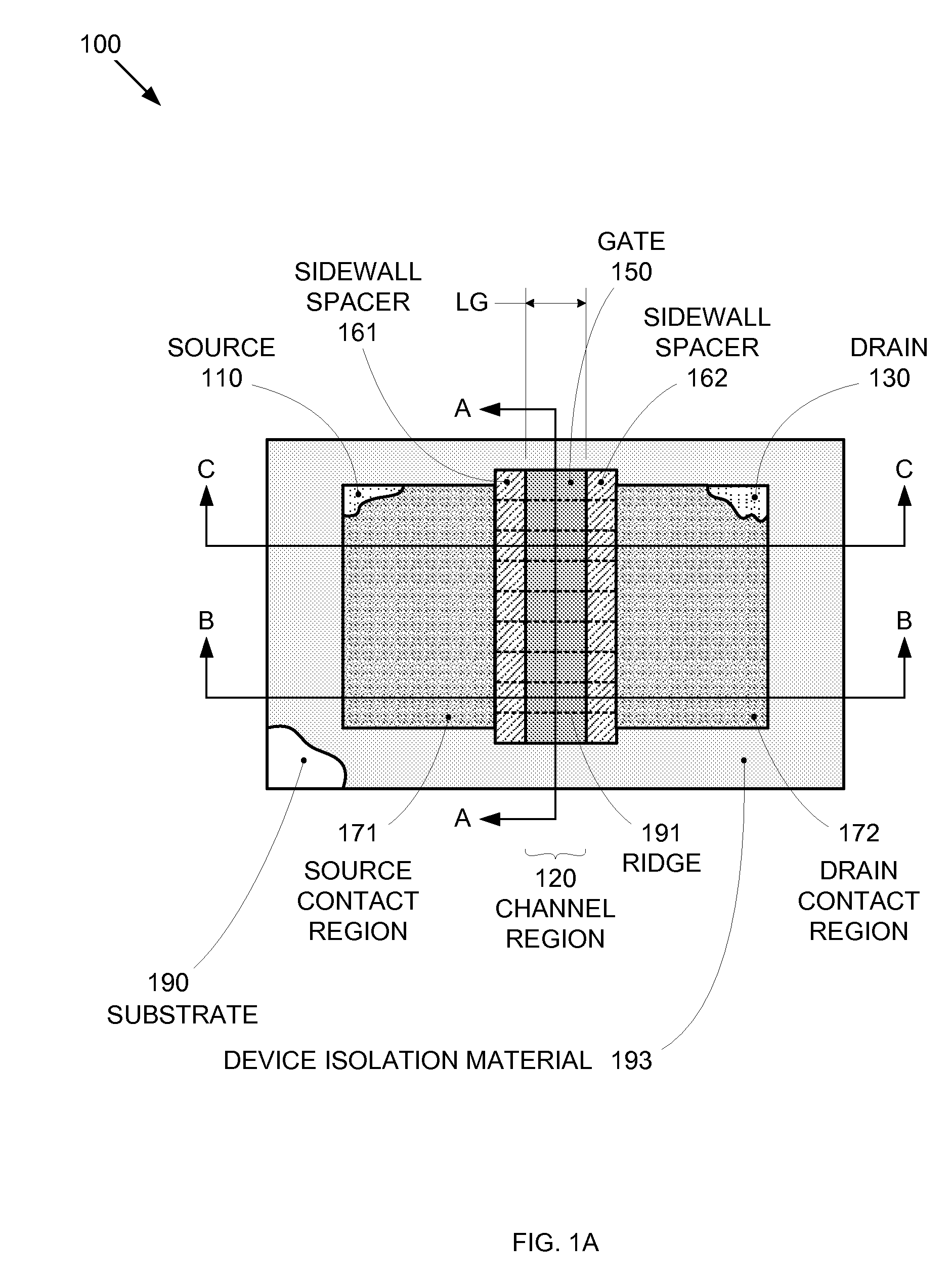

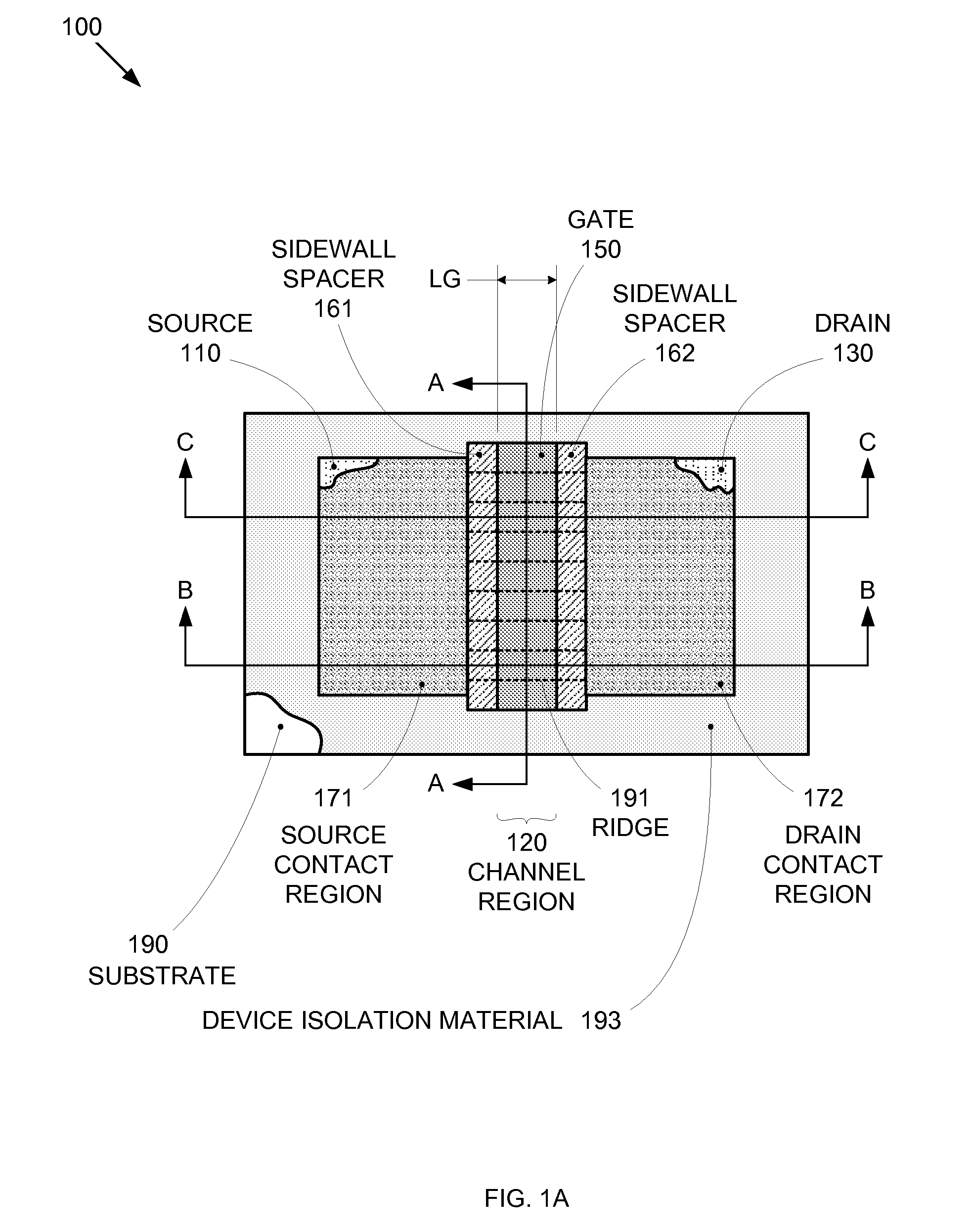

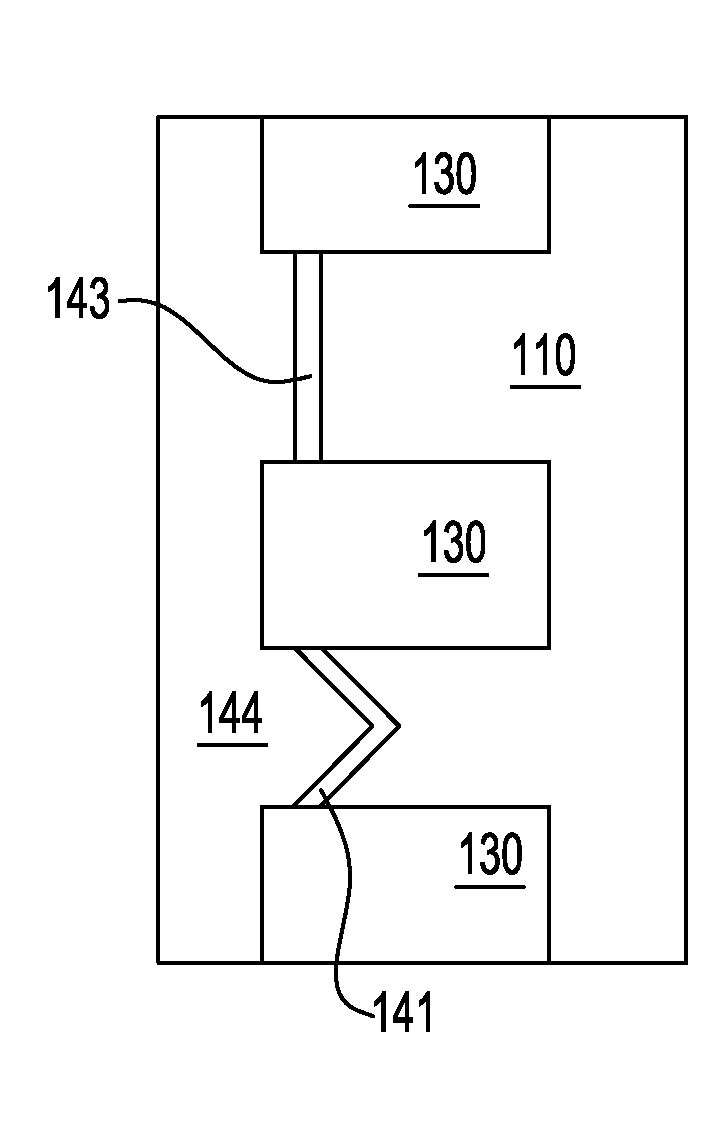

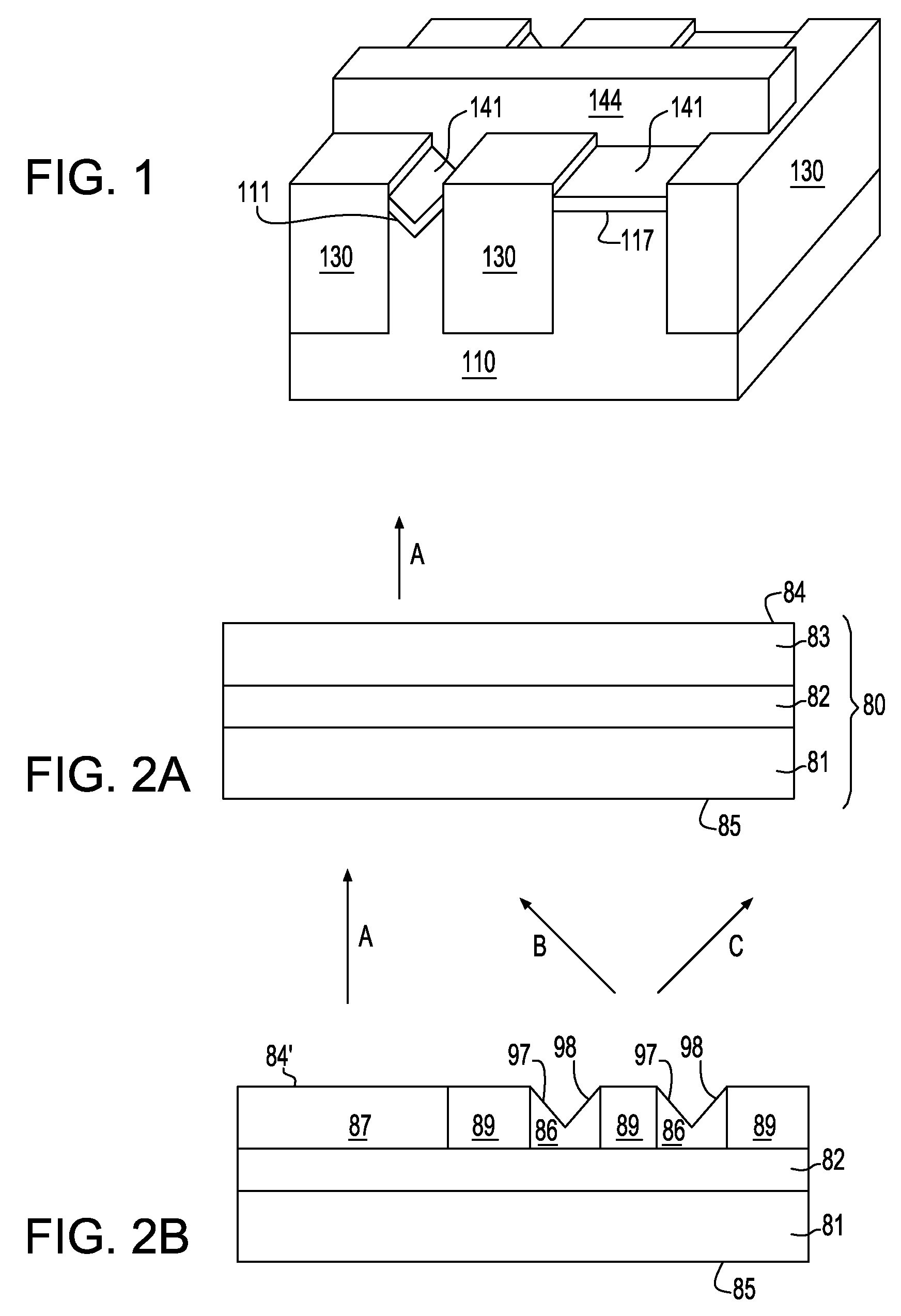

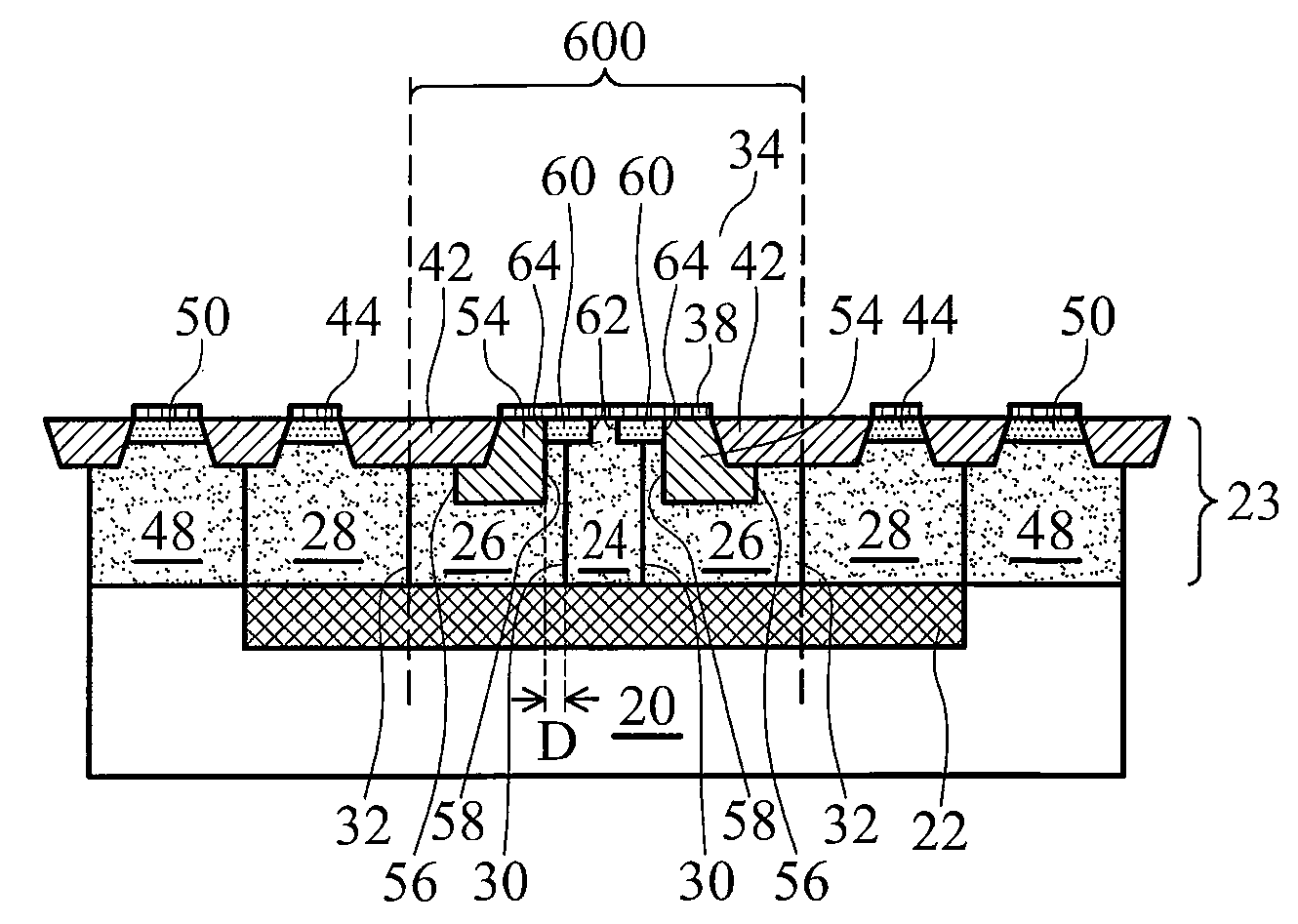

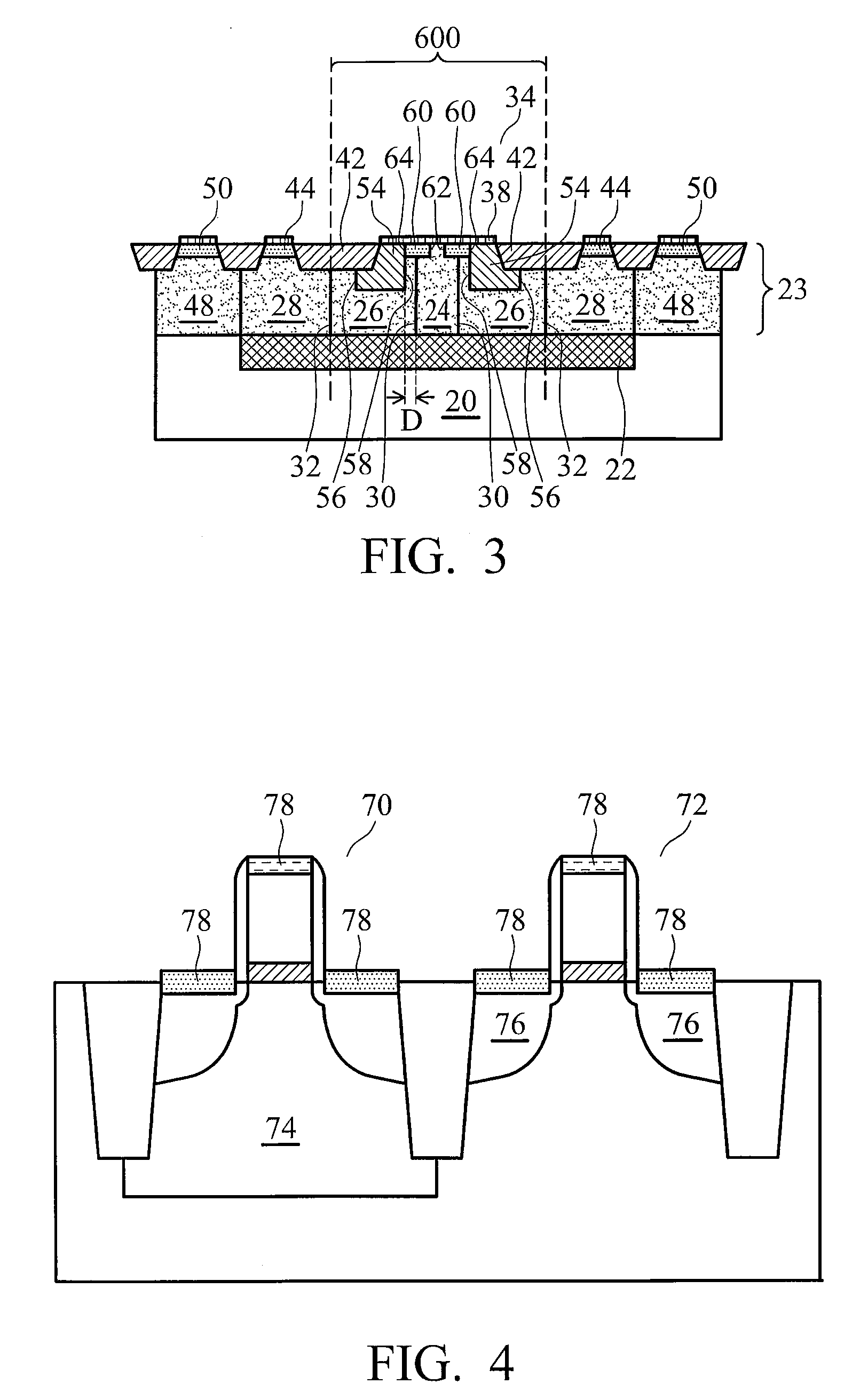

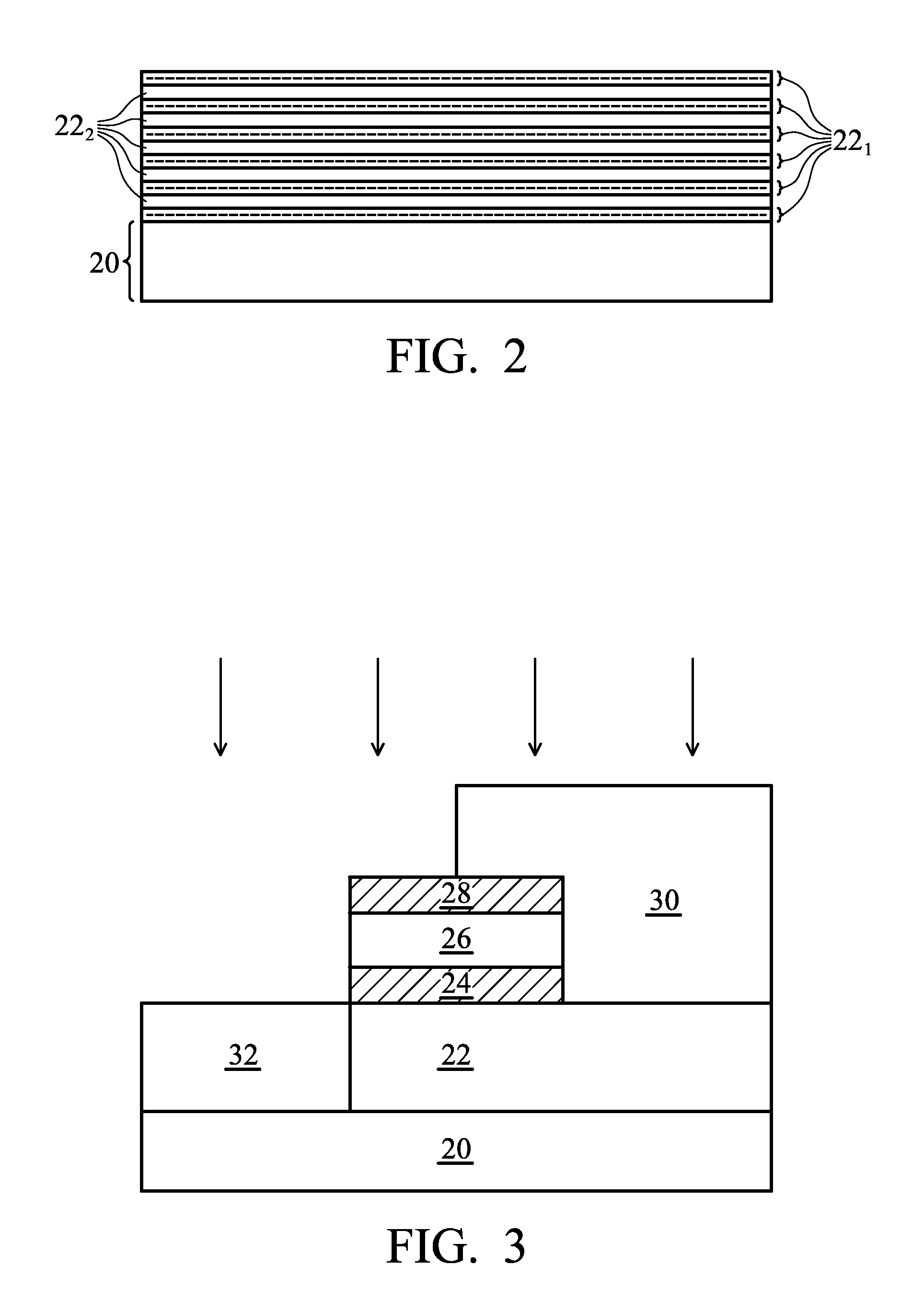

Segmented channel MOS transistor

ActiveUS7247887B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETLithographic artist

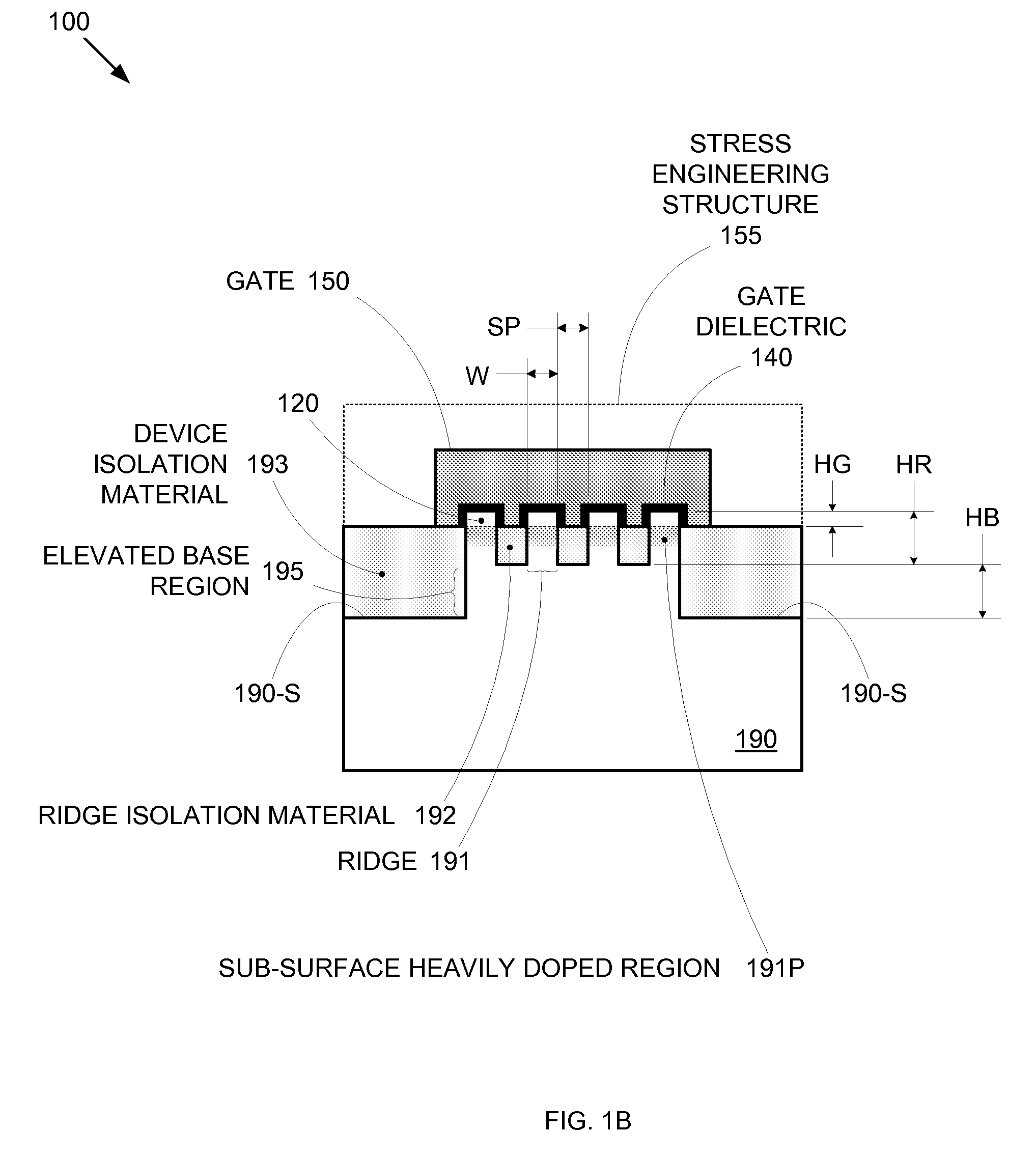

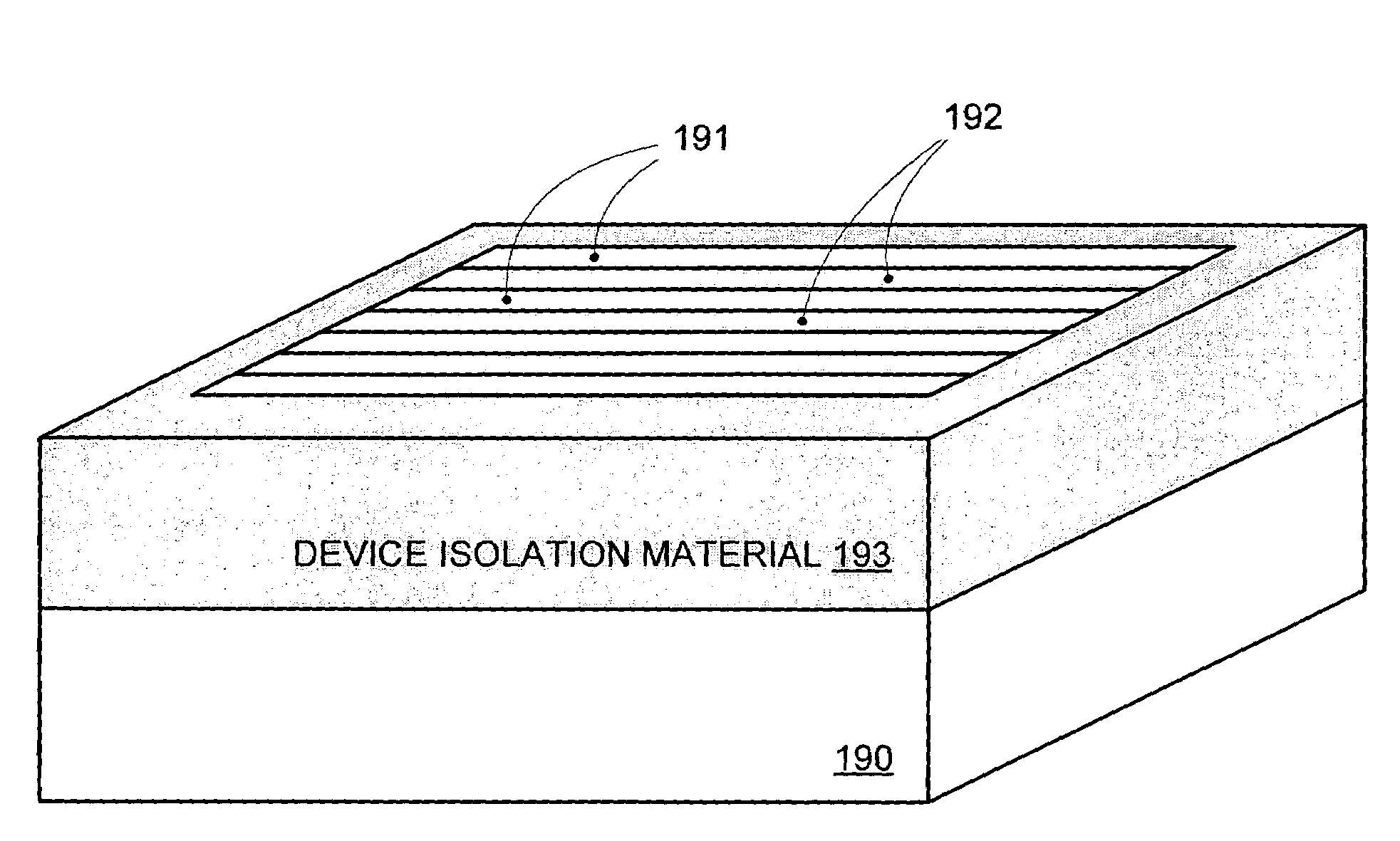

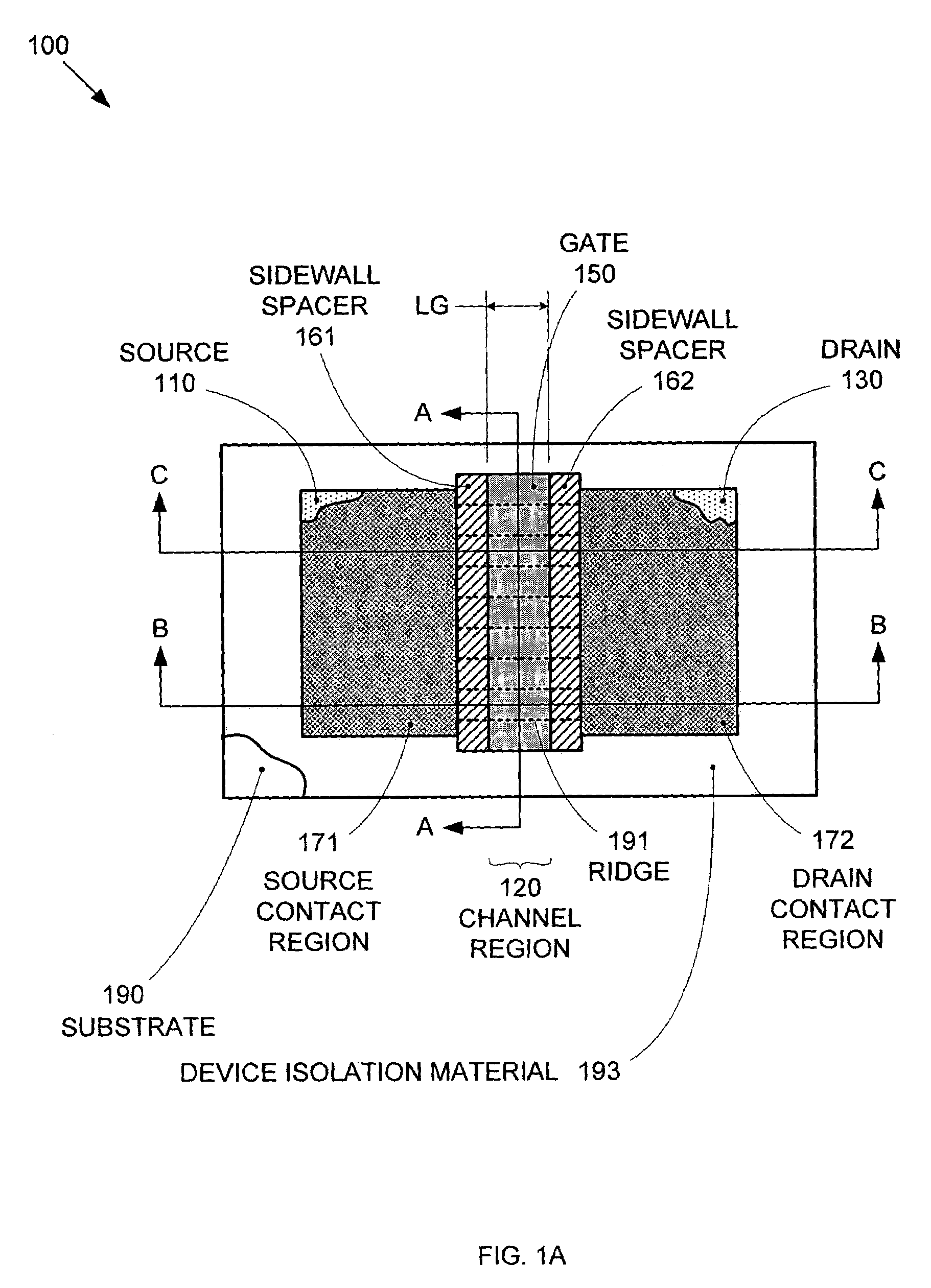

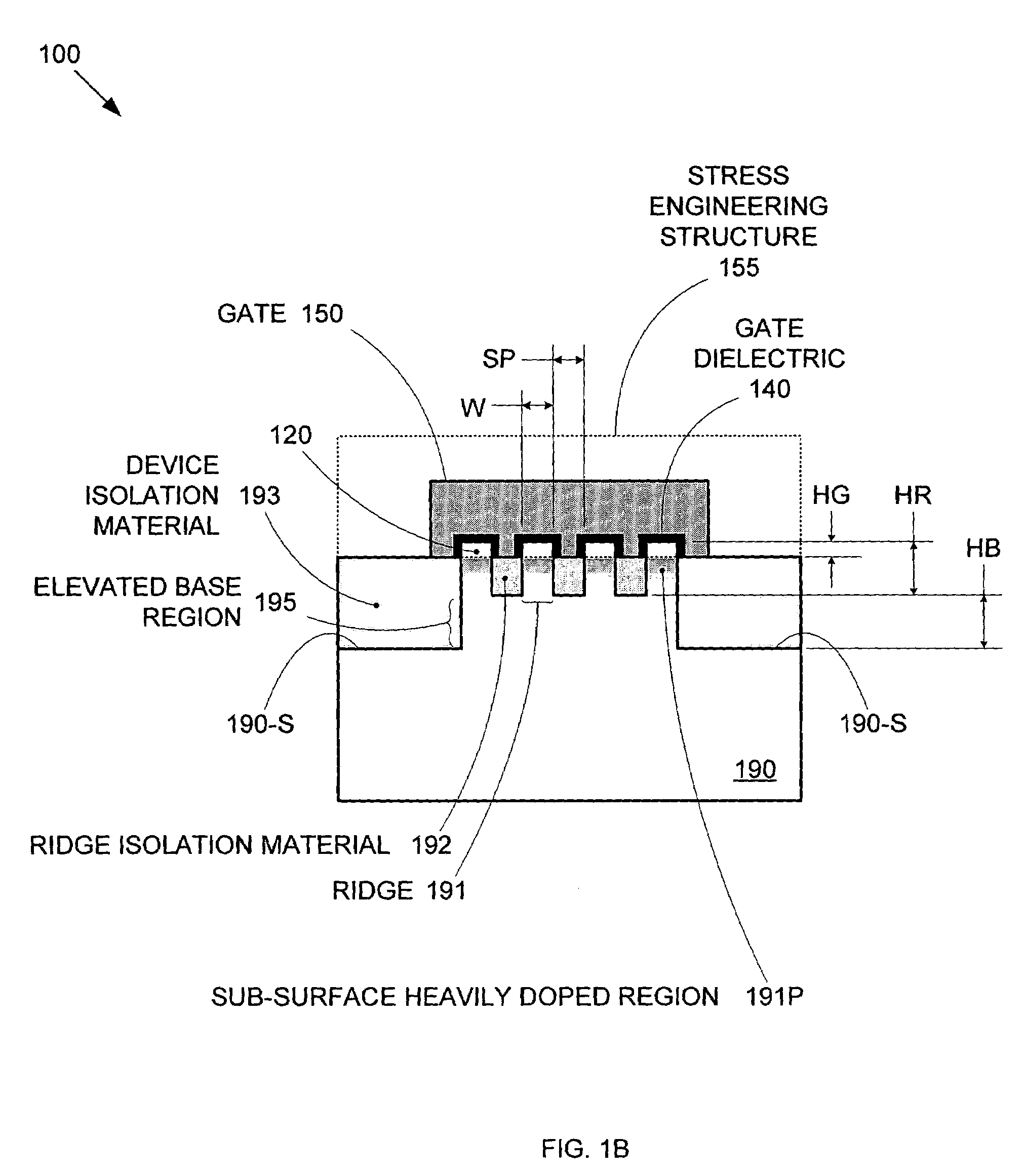

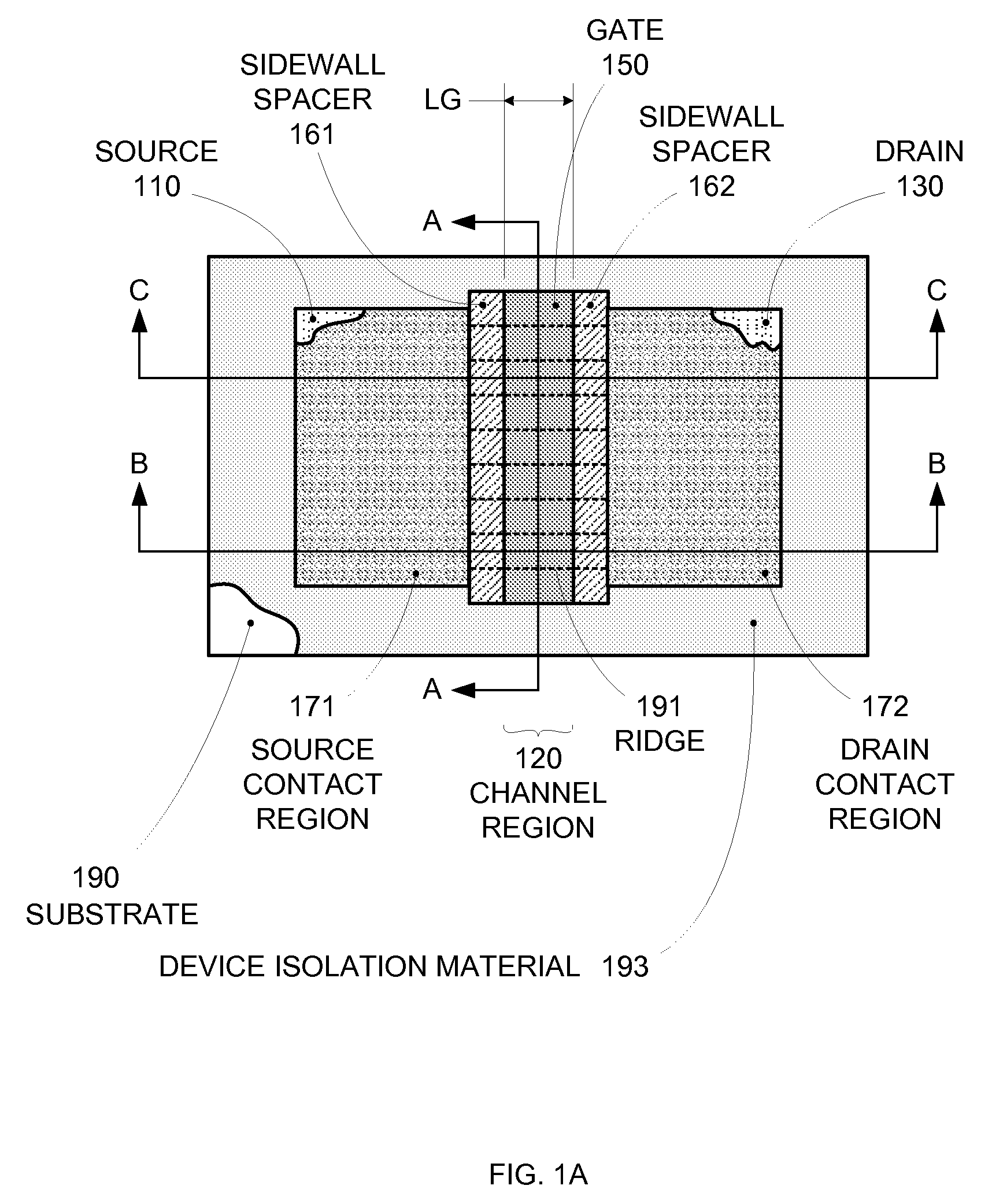

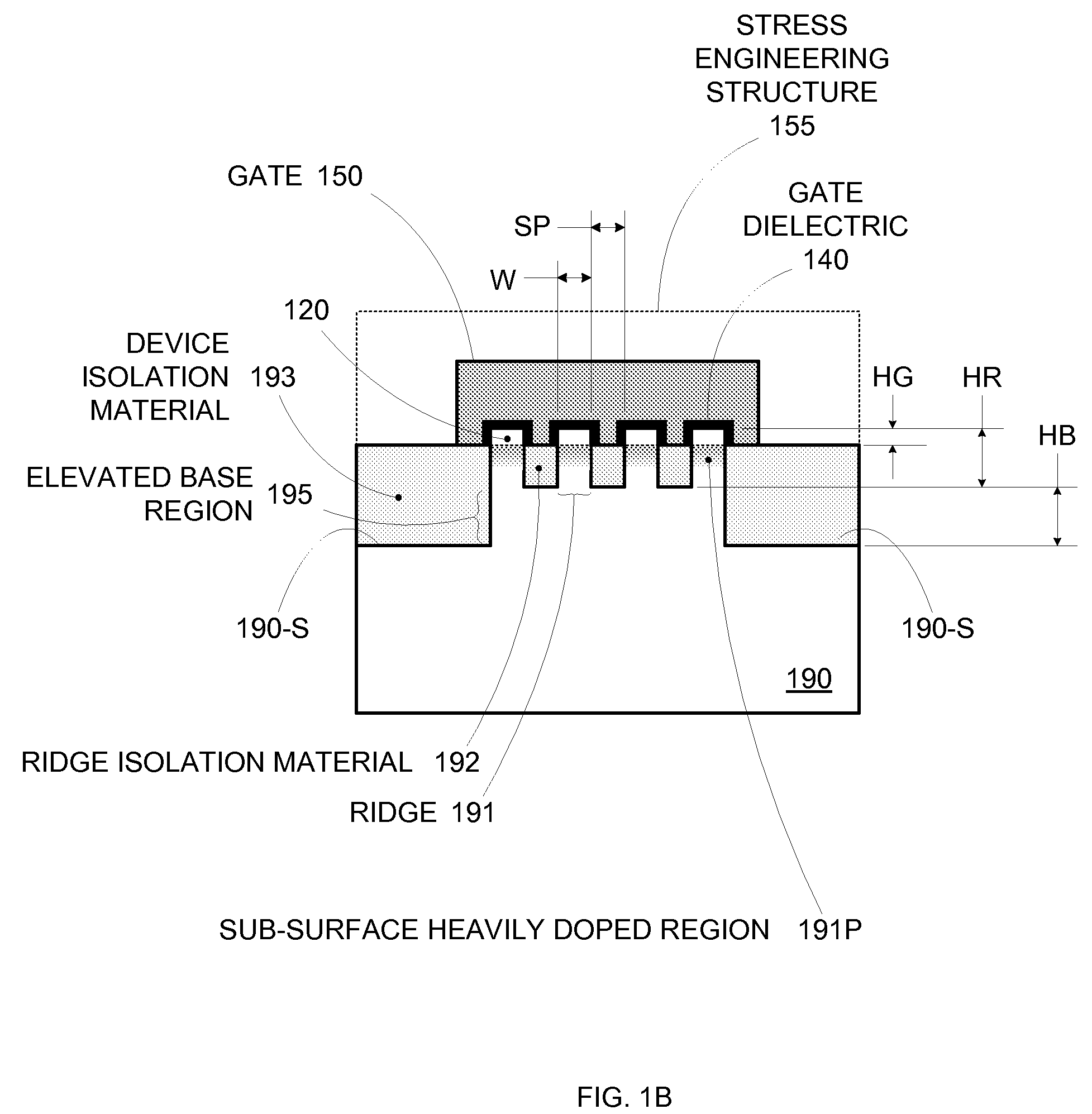

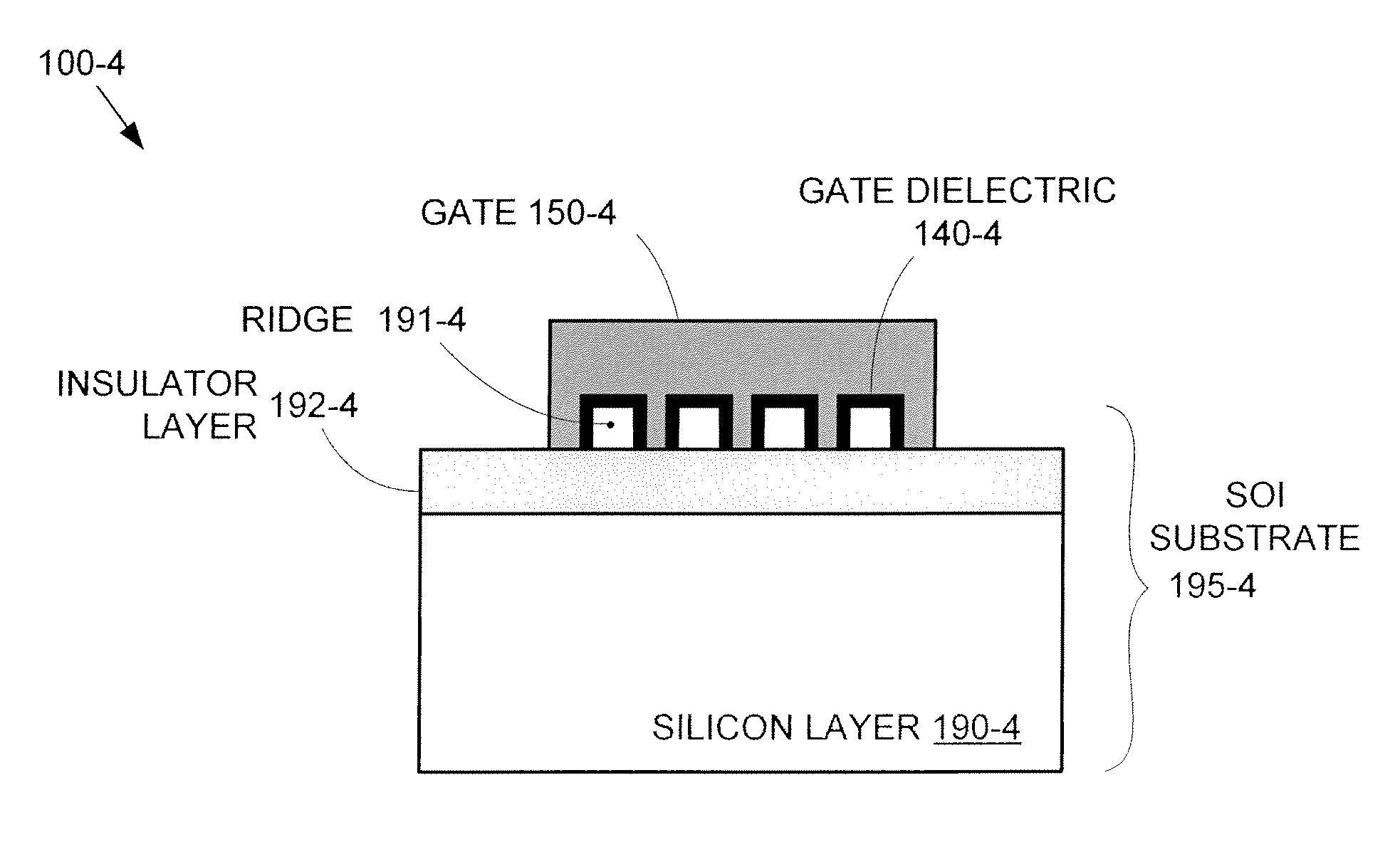

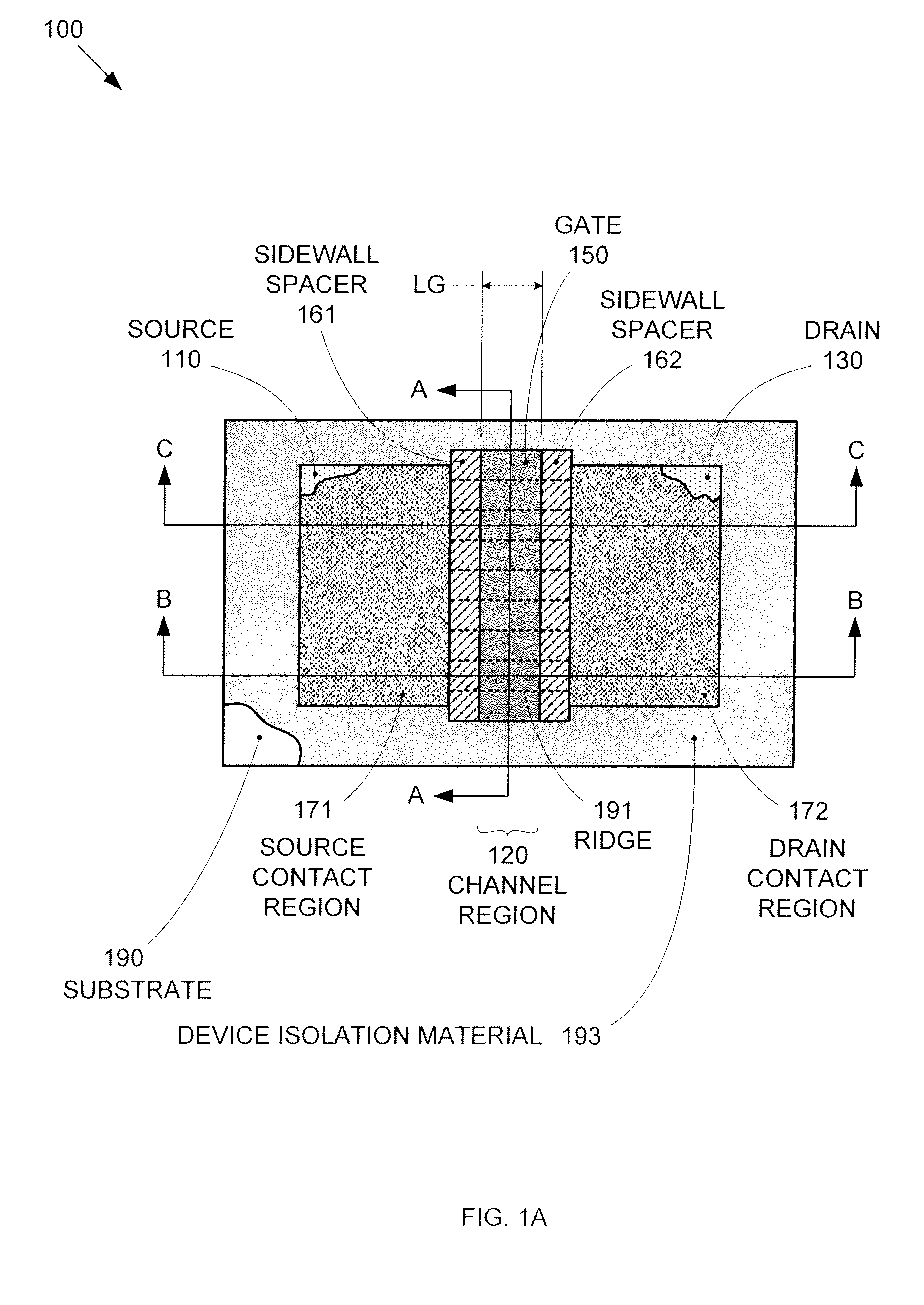

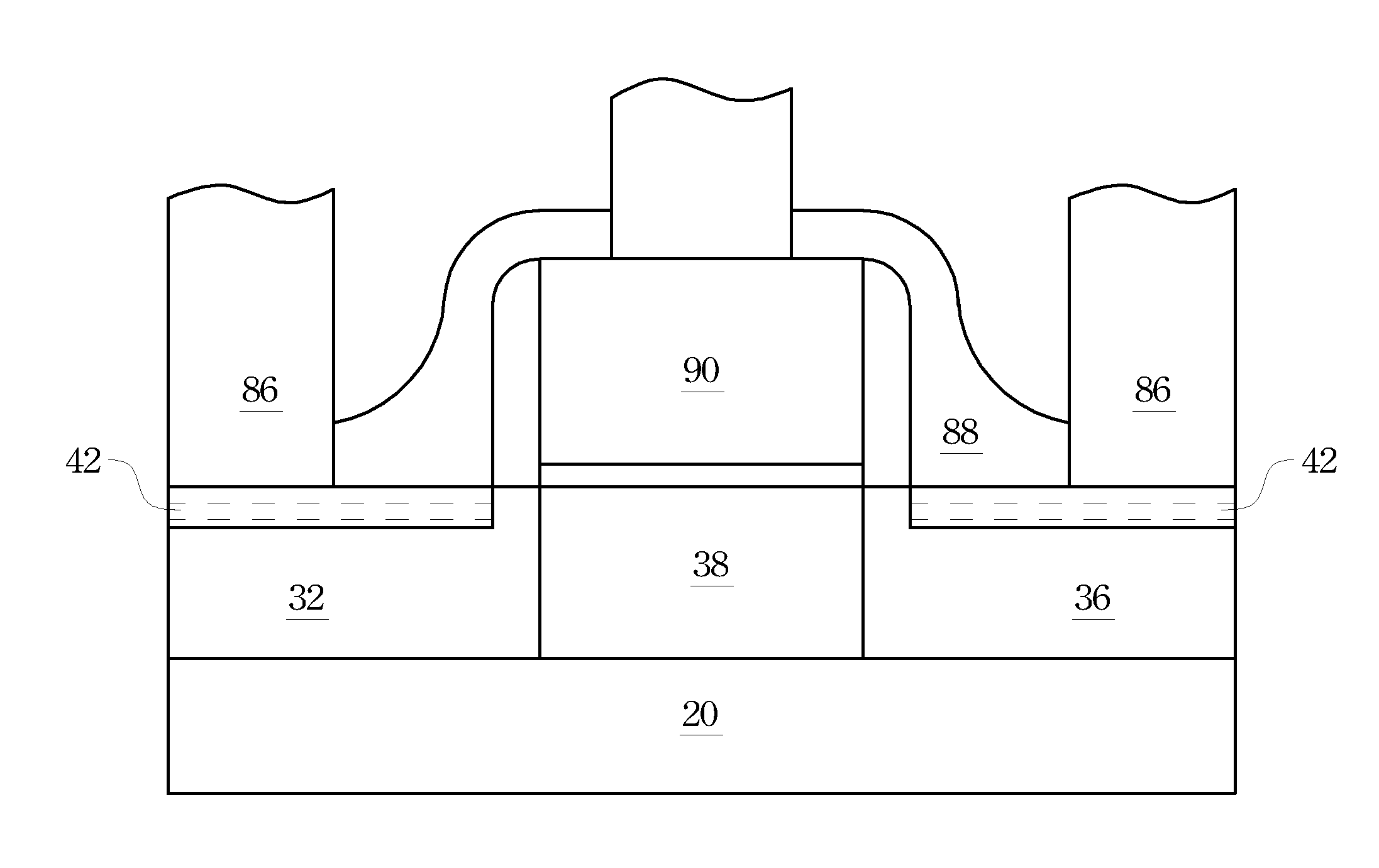

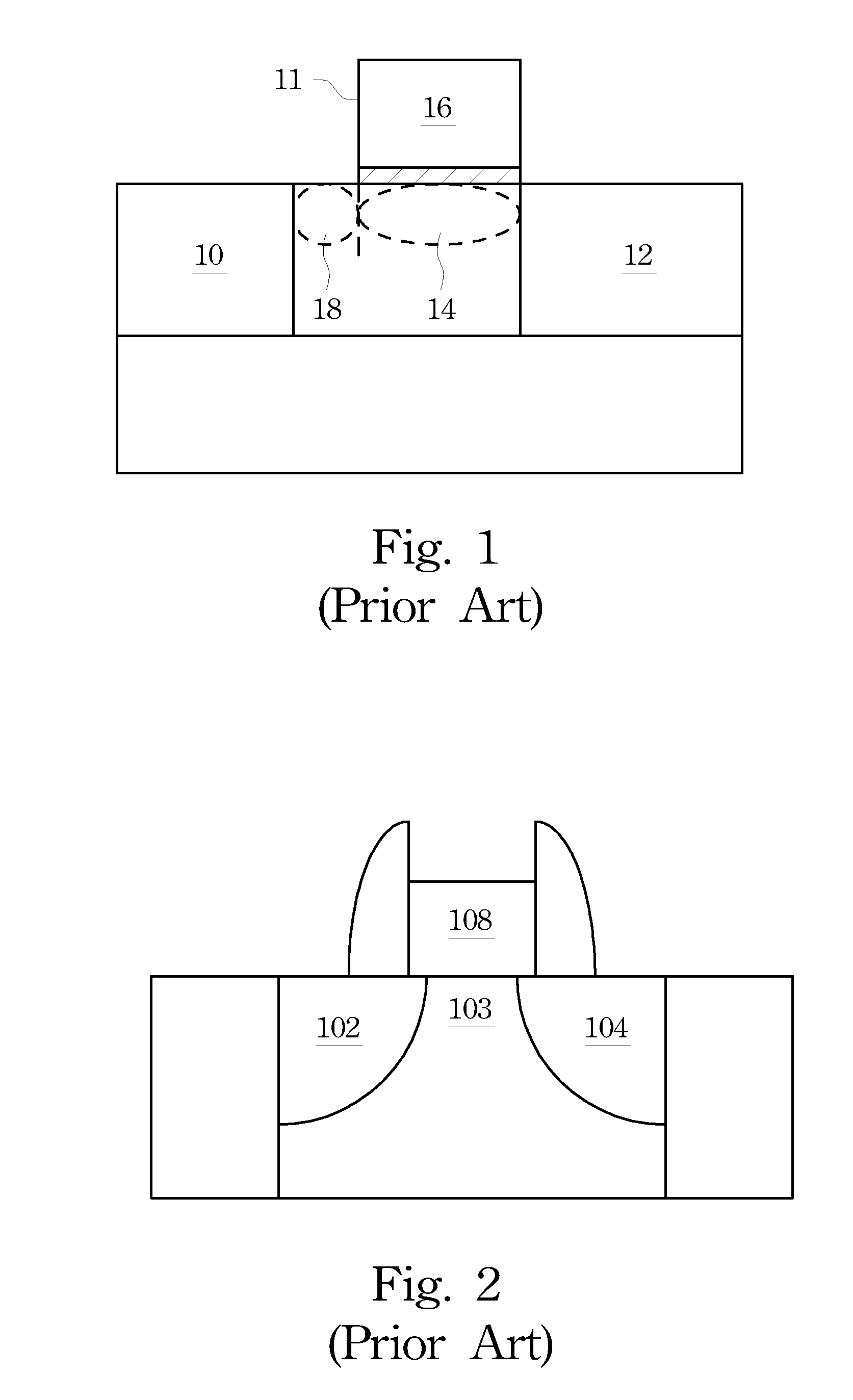

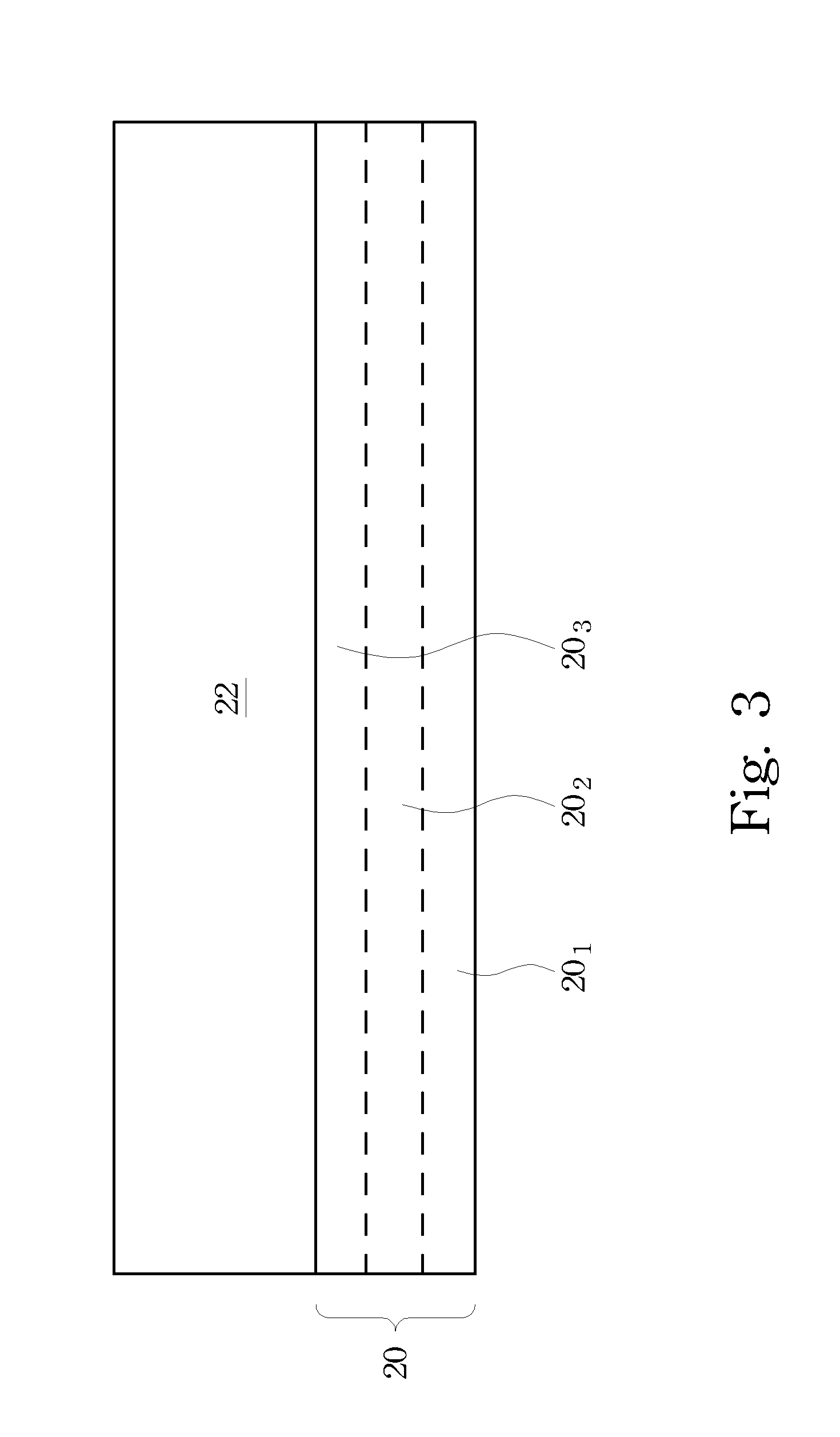

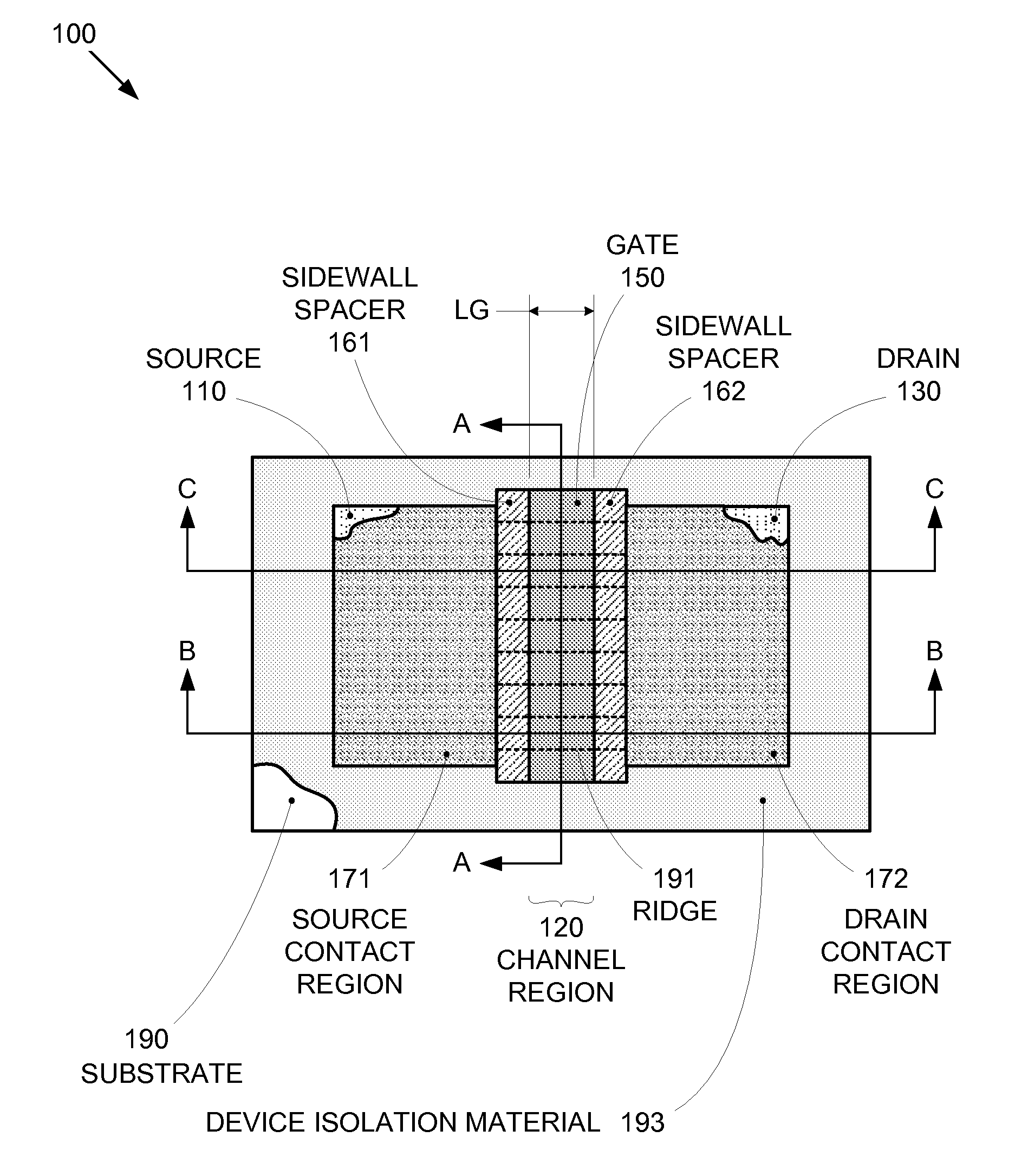

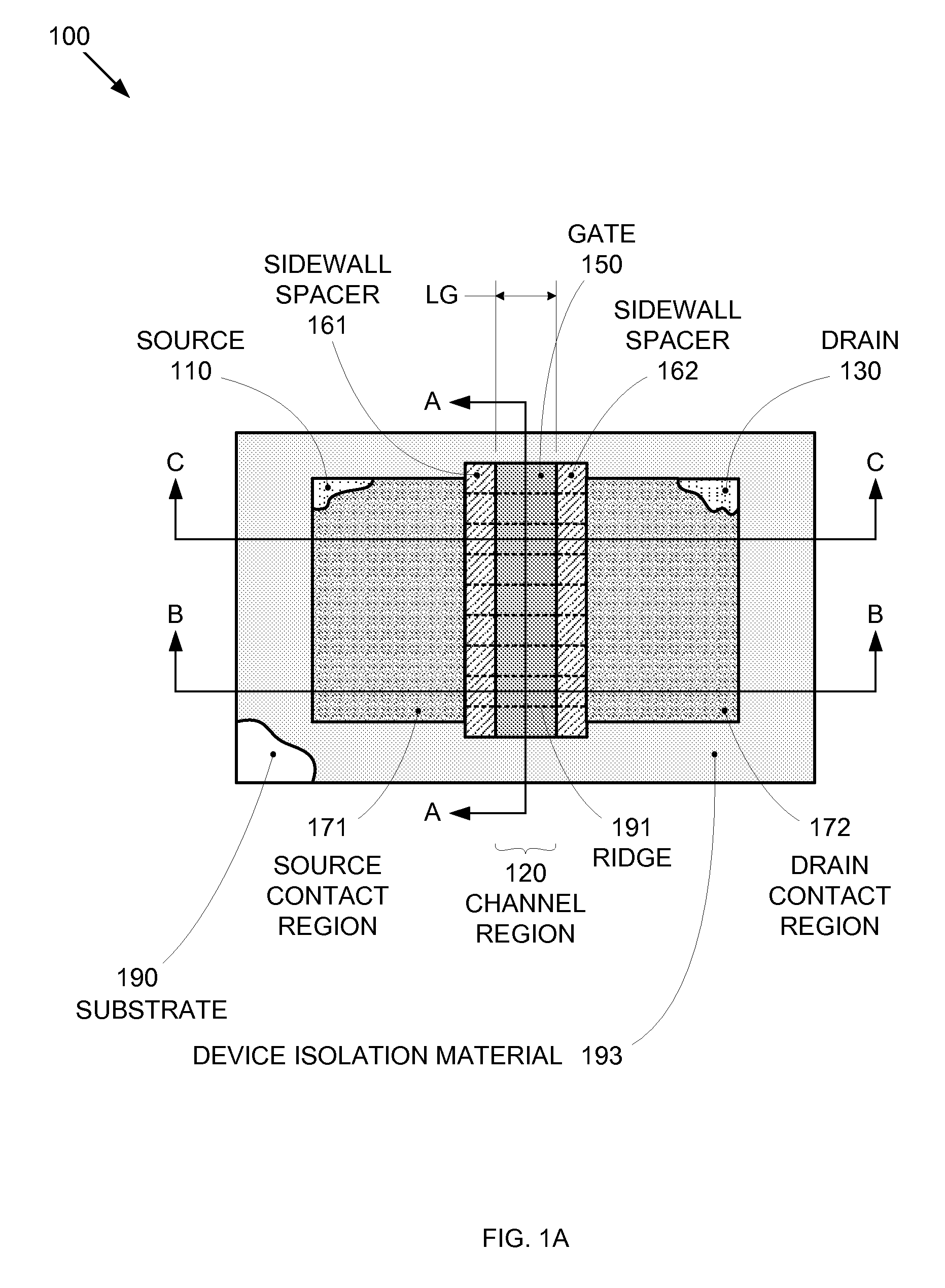

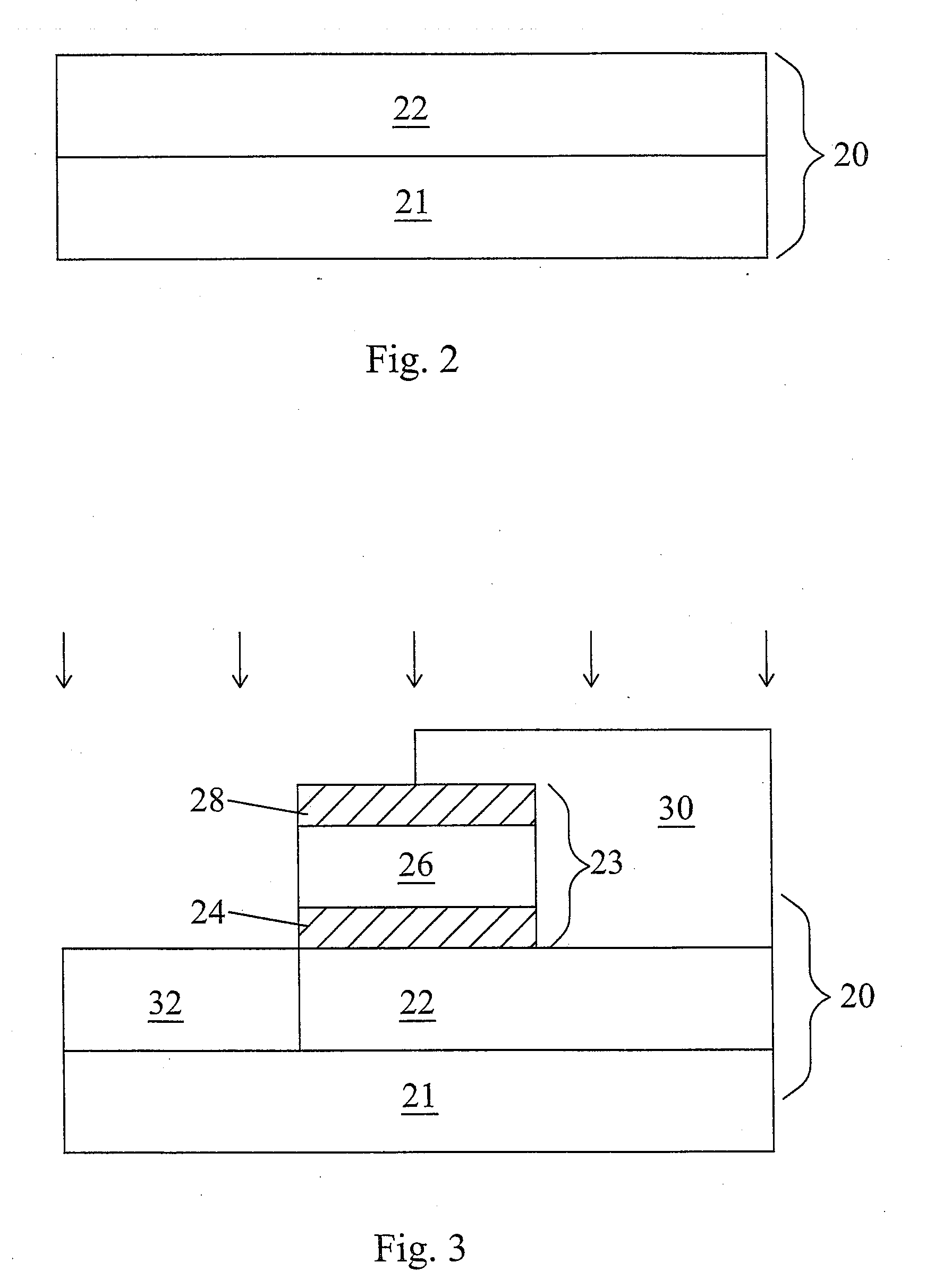

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

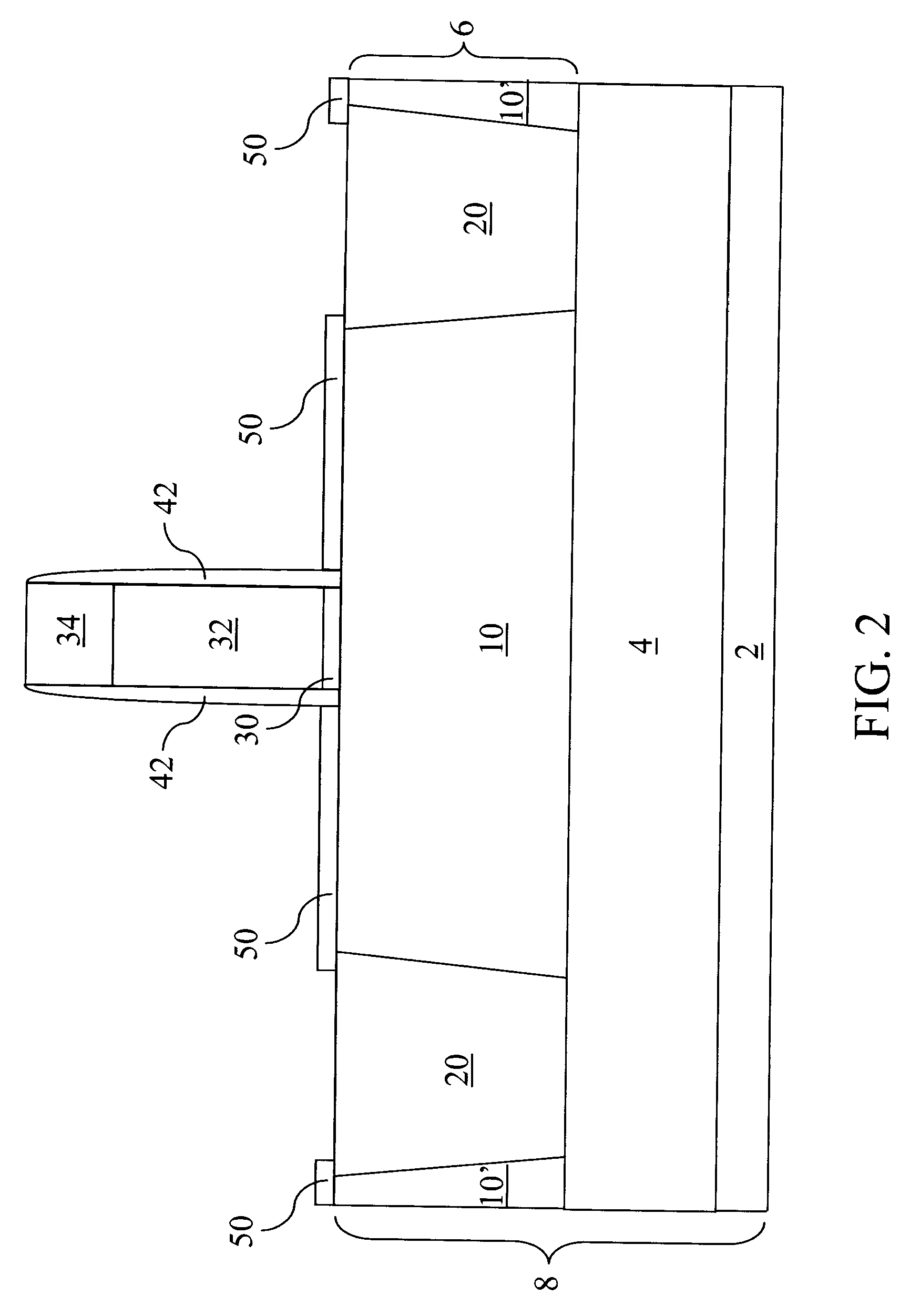

Integrated circuit on corrugated substrate

ActiveUS7190050B2Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

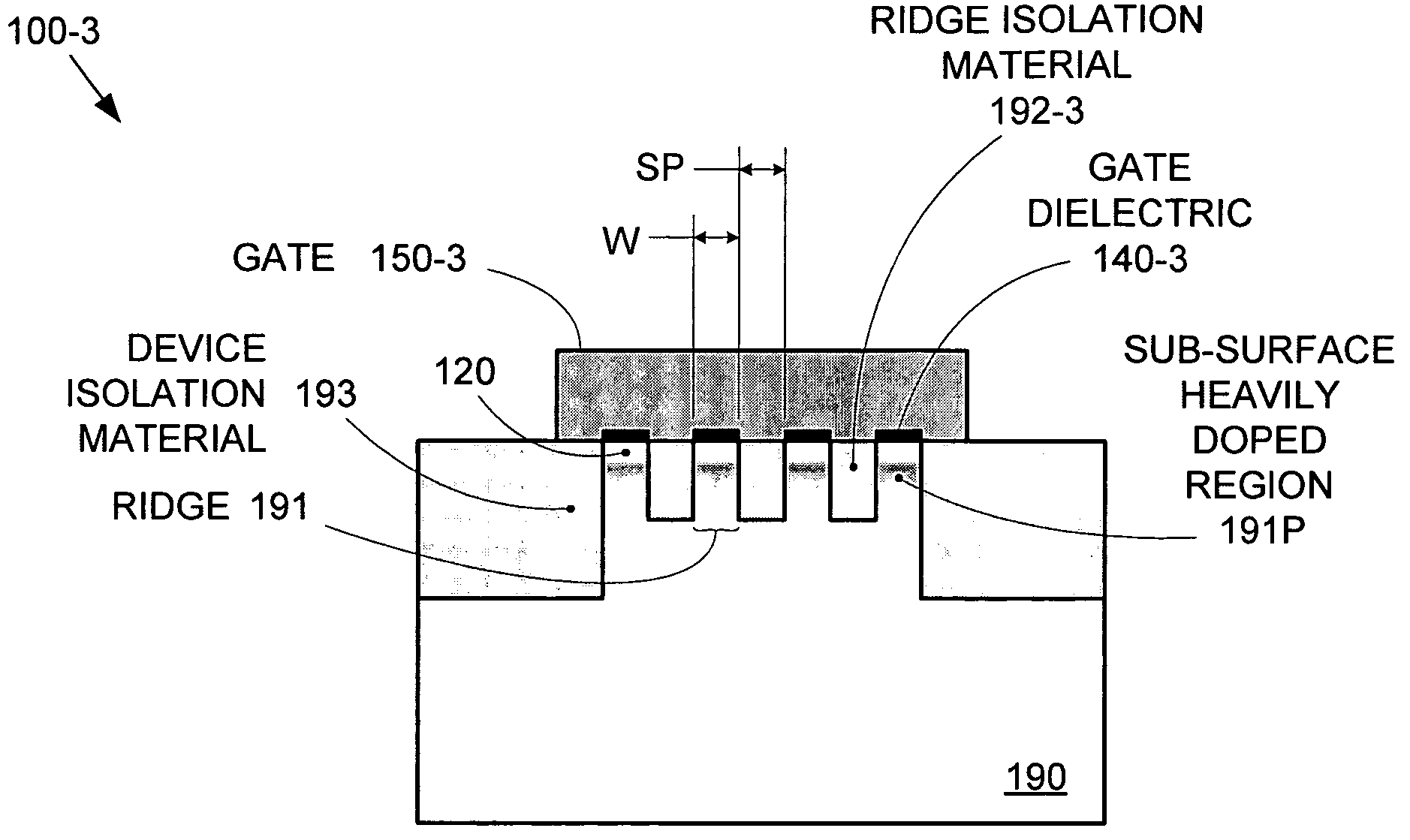

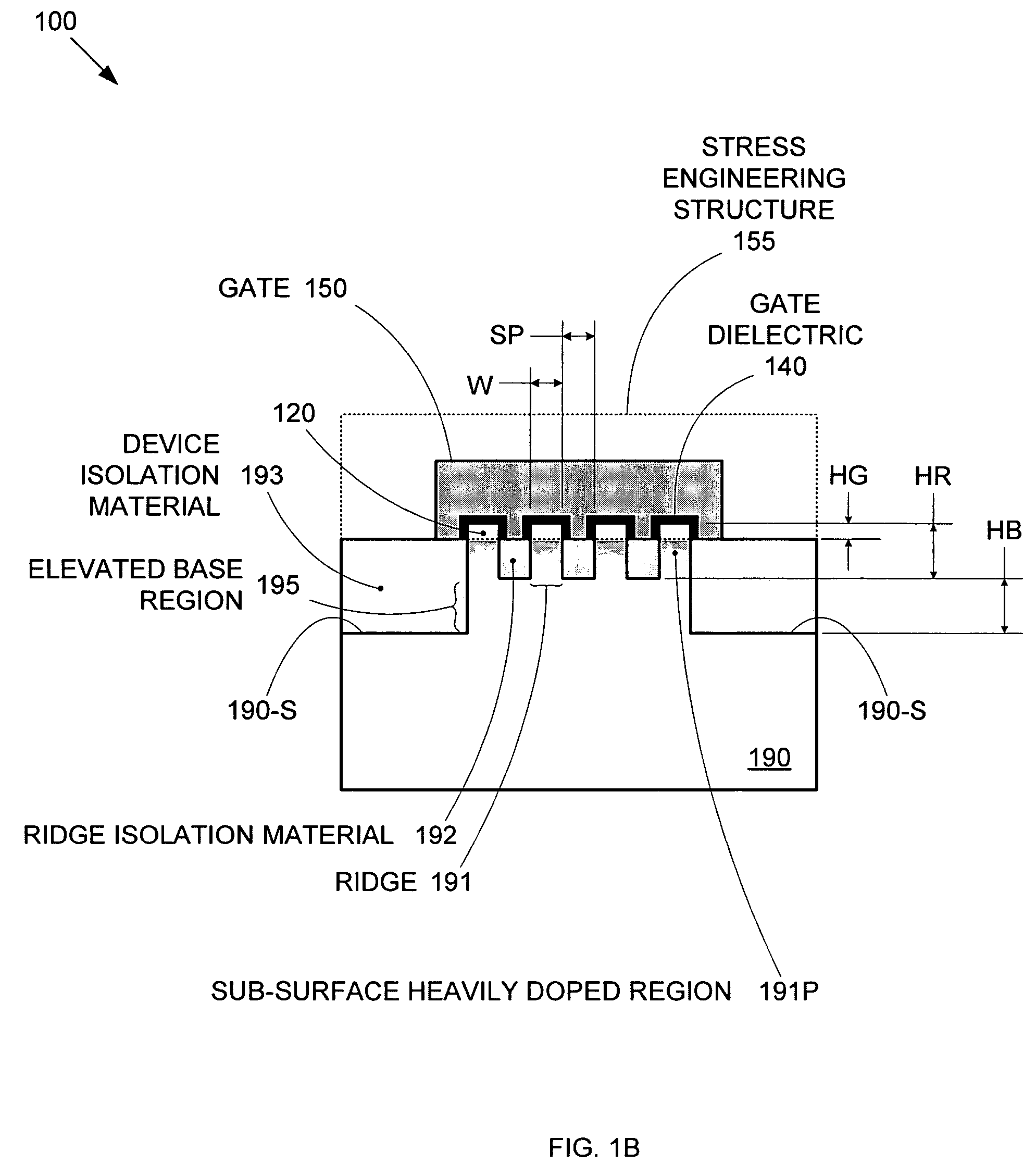

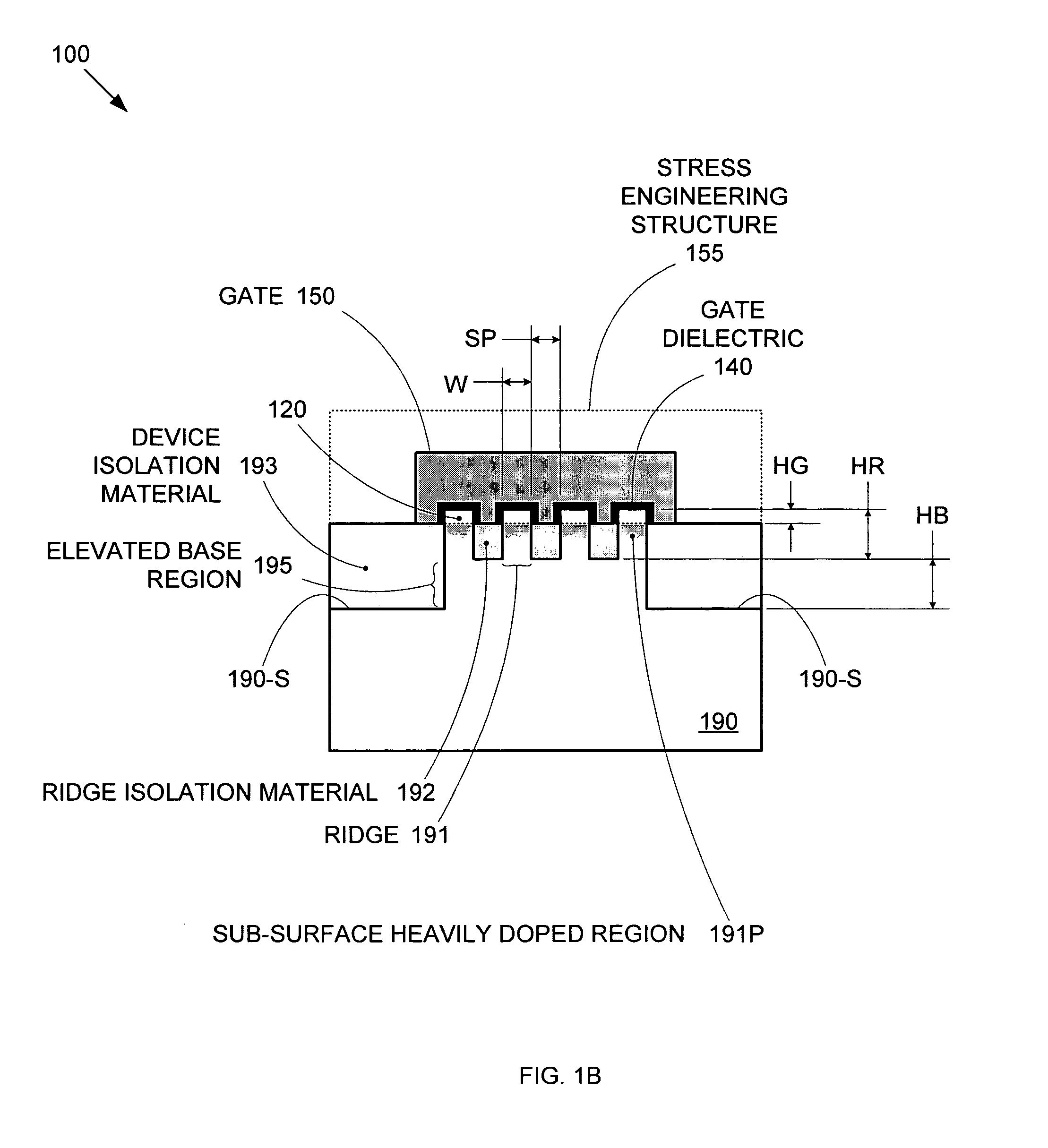

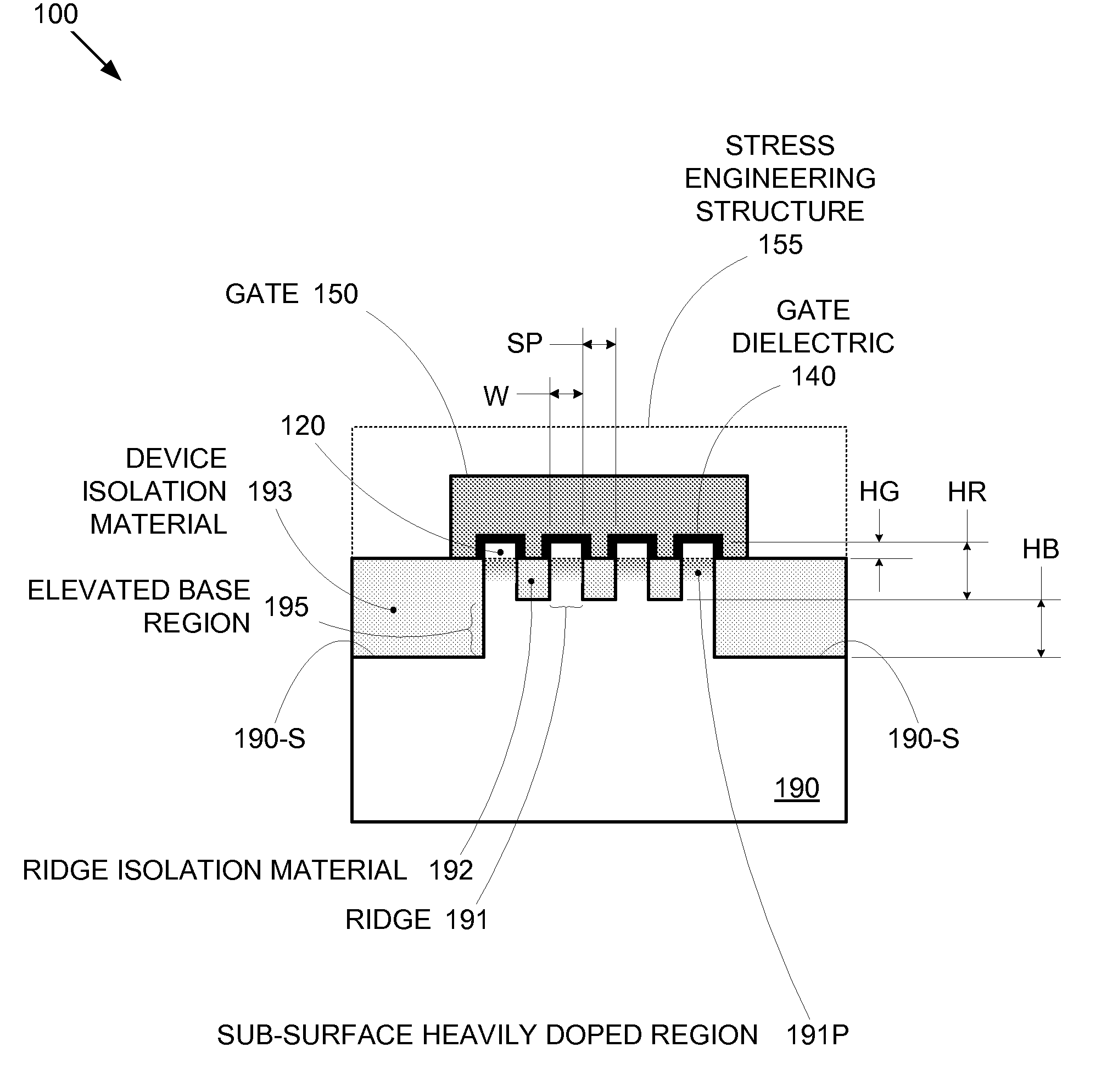

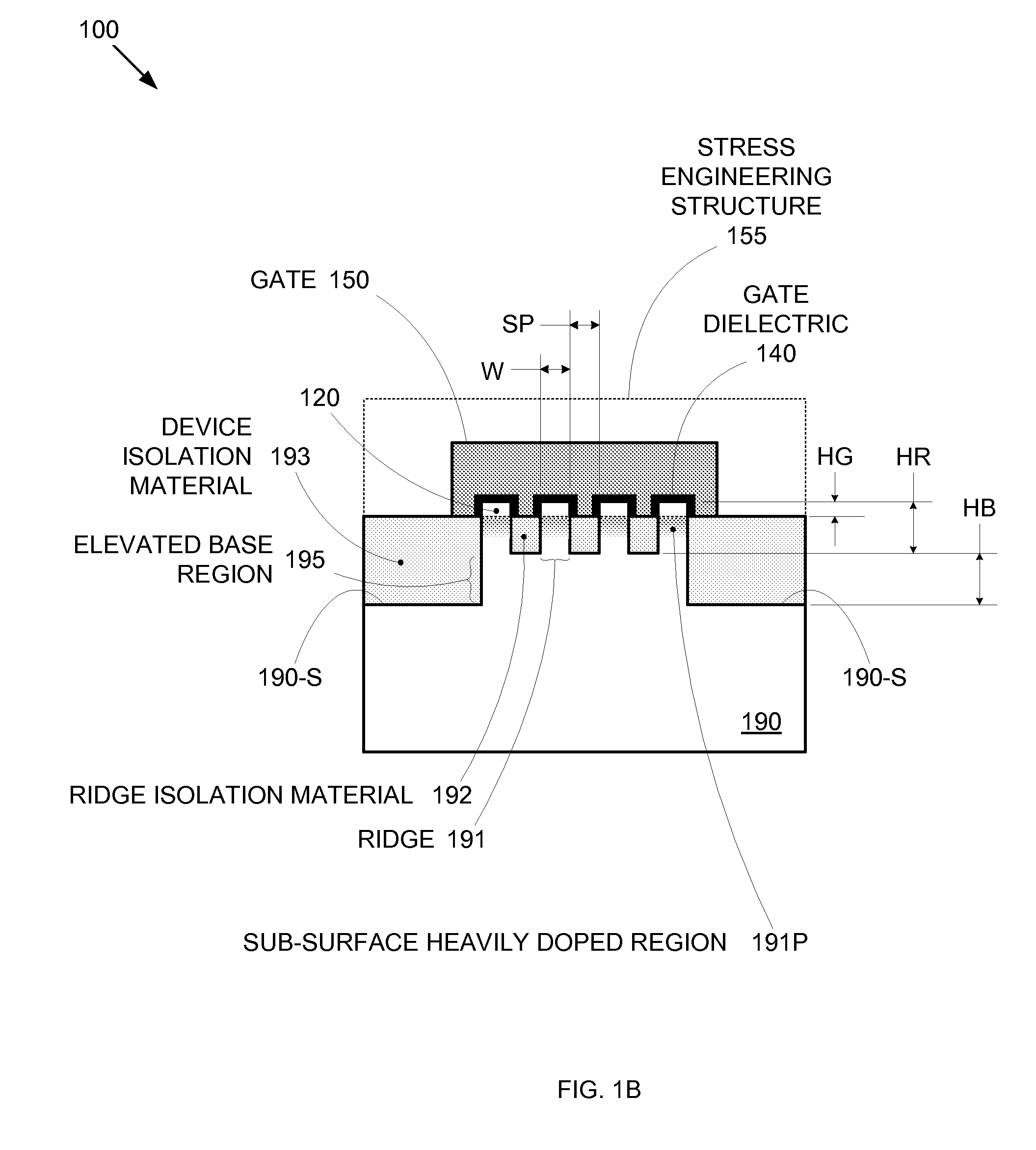

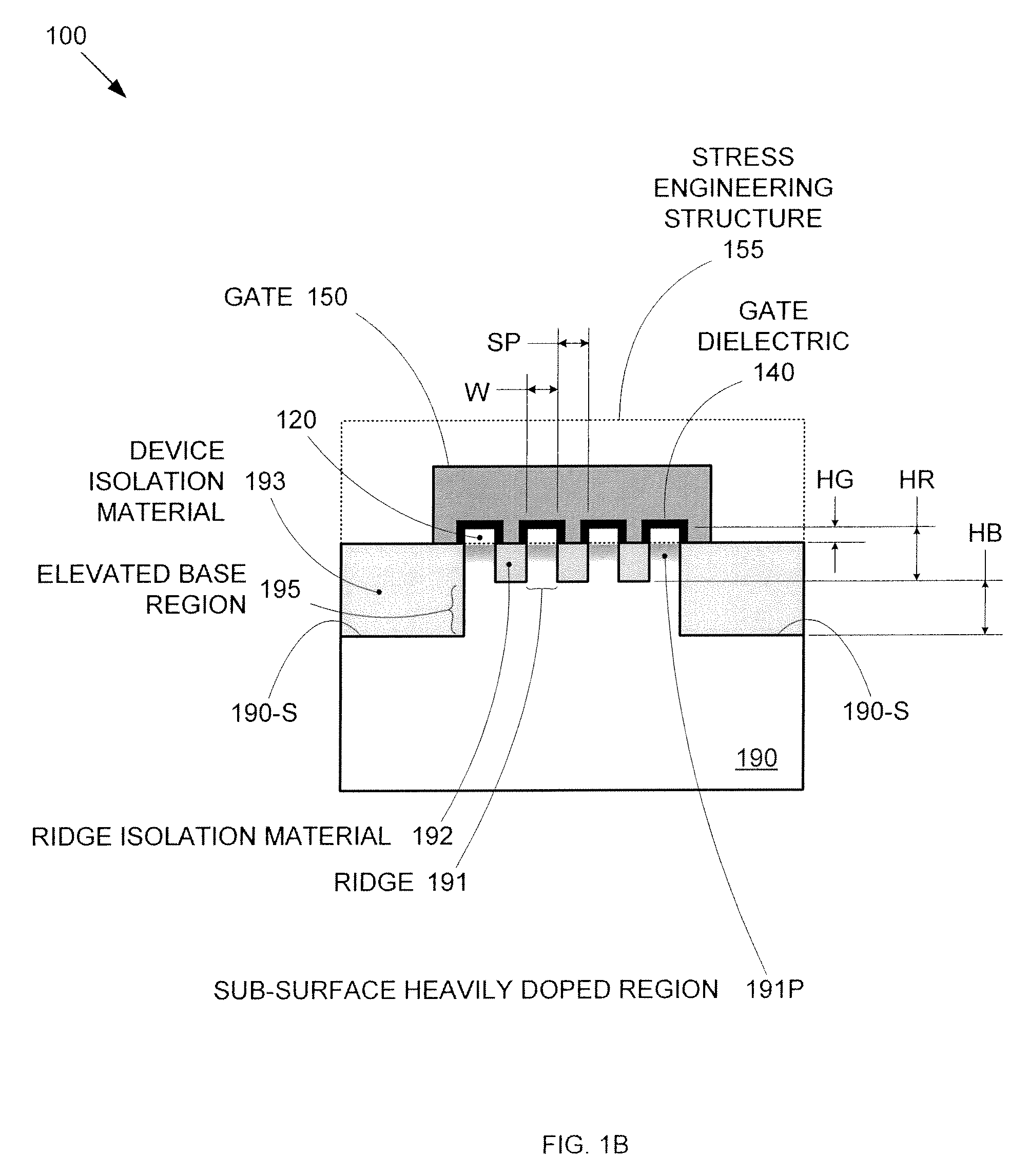

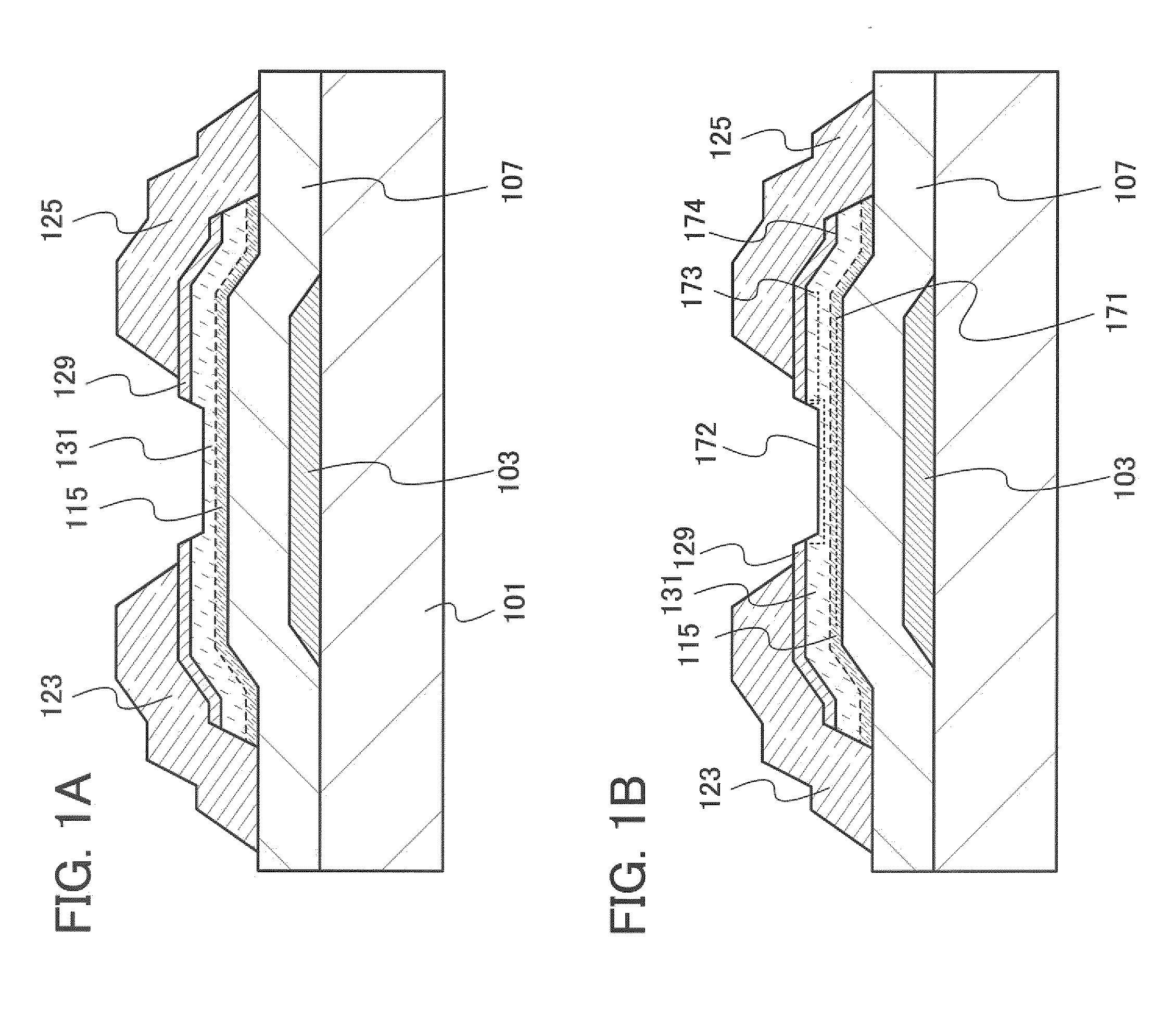

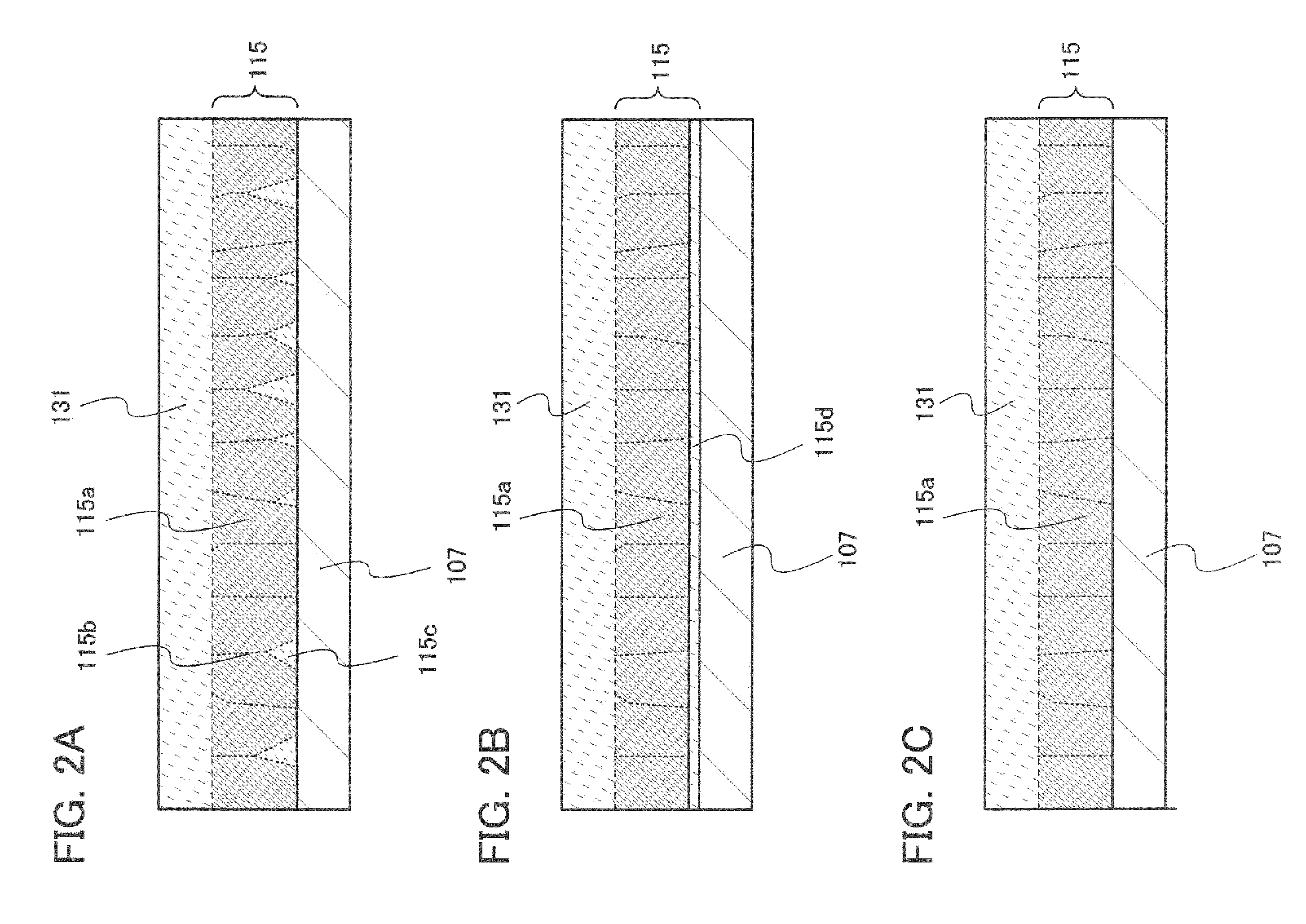

Enhanced Segmented Channel MOS Transistor with Multi Layer Regions

ActiveUS20070120156A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

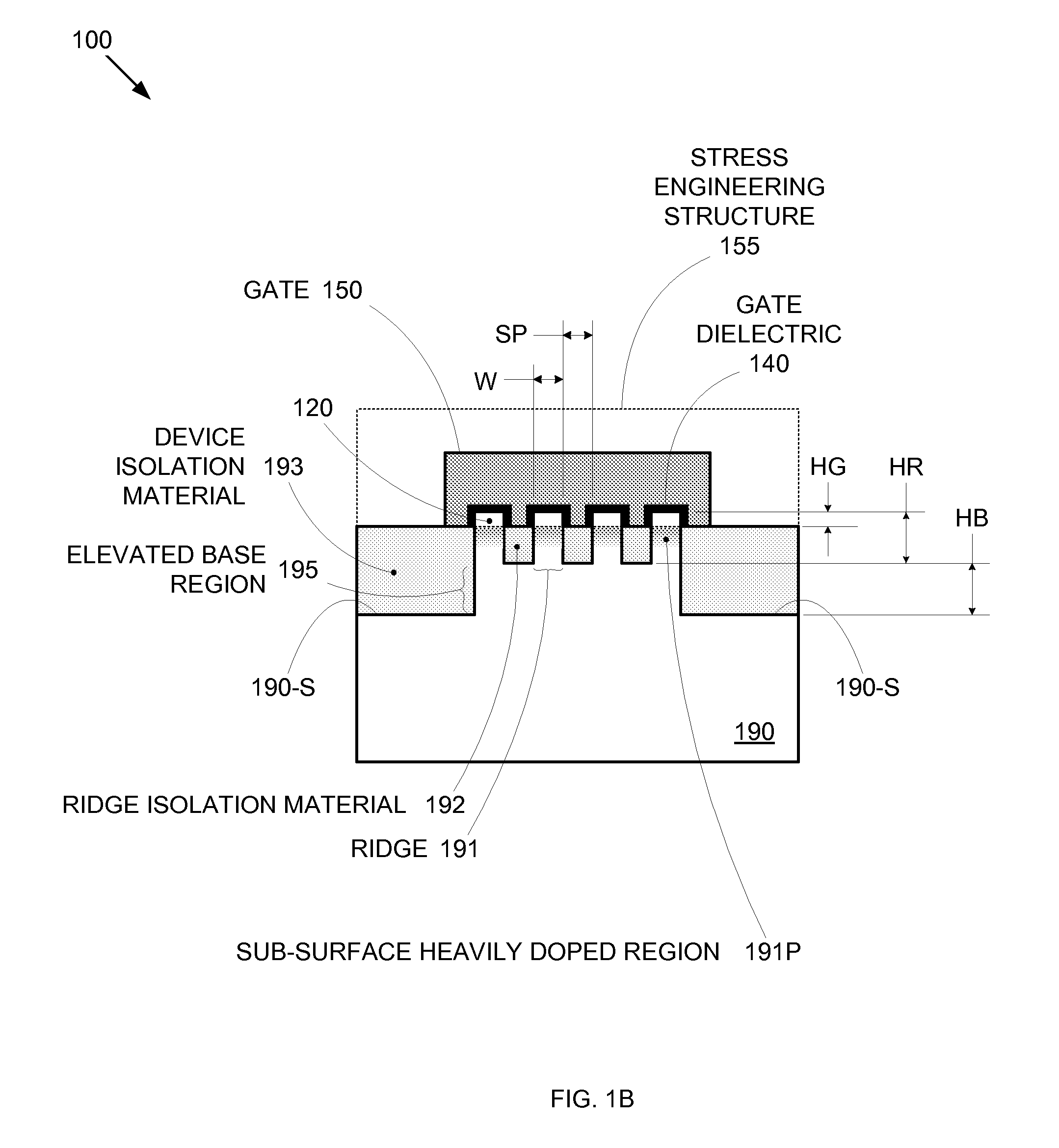

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Method of IC production using corrugated substrate

ActiveUS7265008B2Improve performance consistencyImprove performanceLaser detailsSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

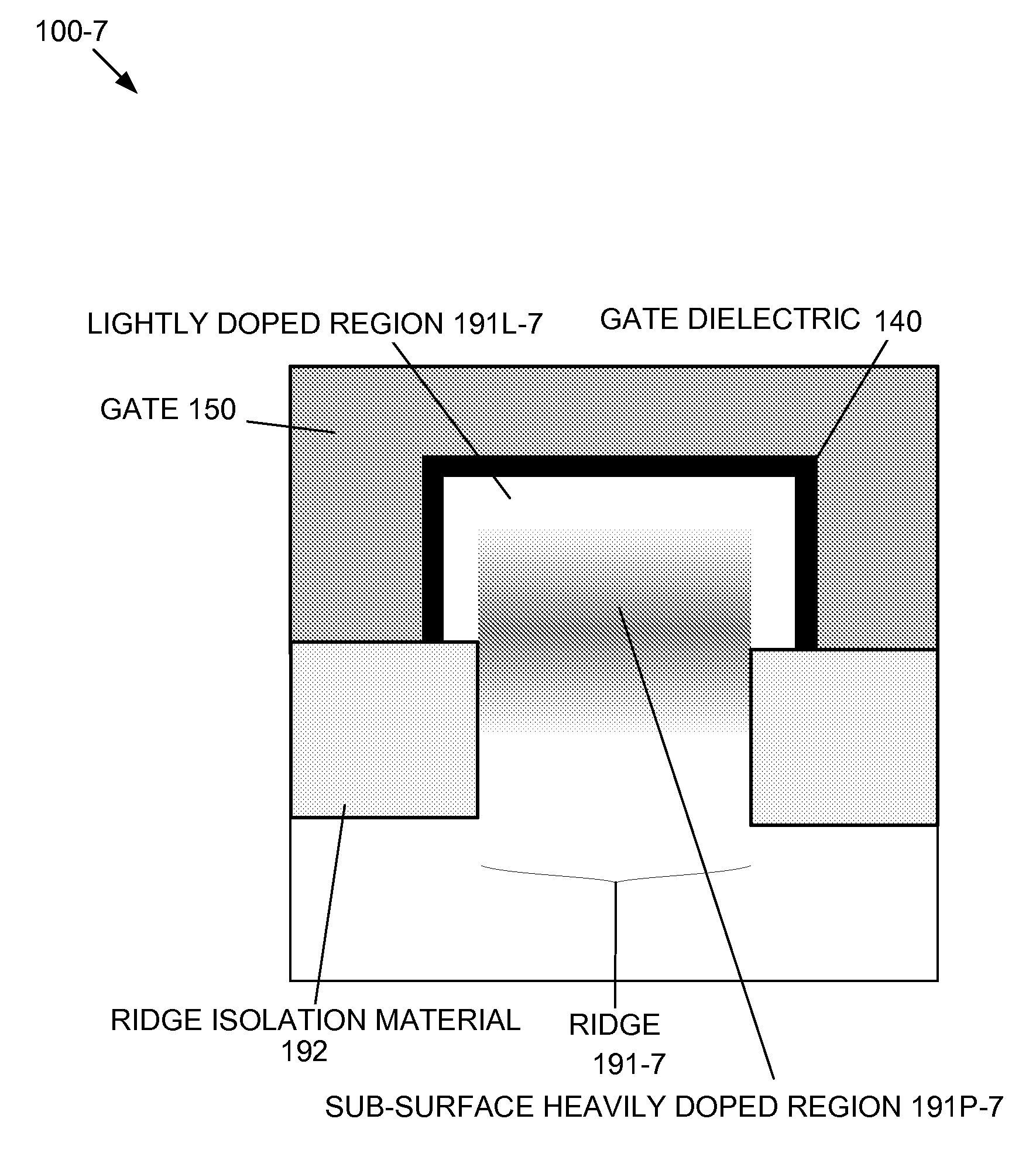

Enhanced segmented channel MOS transistor with narrowed base regions

ActiveUS7508031B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably produced. Ridges on the corrugated substrate can be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials, high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

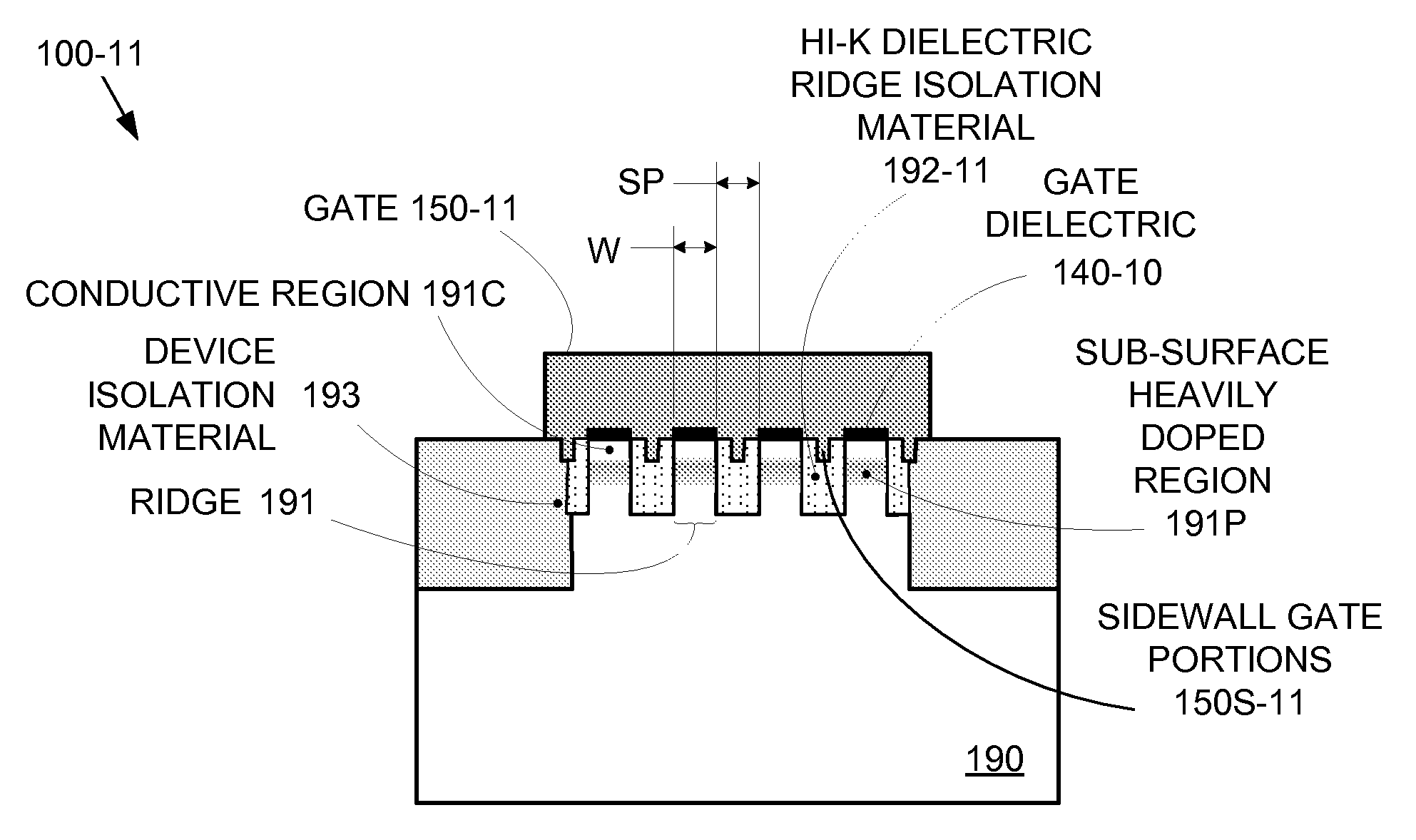

Enhanced segmented channel MOS transistor with high-permittivity dielectric isolation material

ActiveUS7605449B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Integrated Circuit On Corrugated Substrate

ActiveUS20070132053A1Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETSemiconductor materials

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

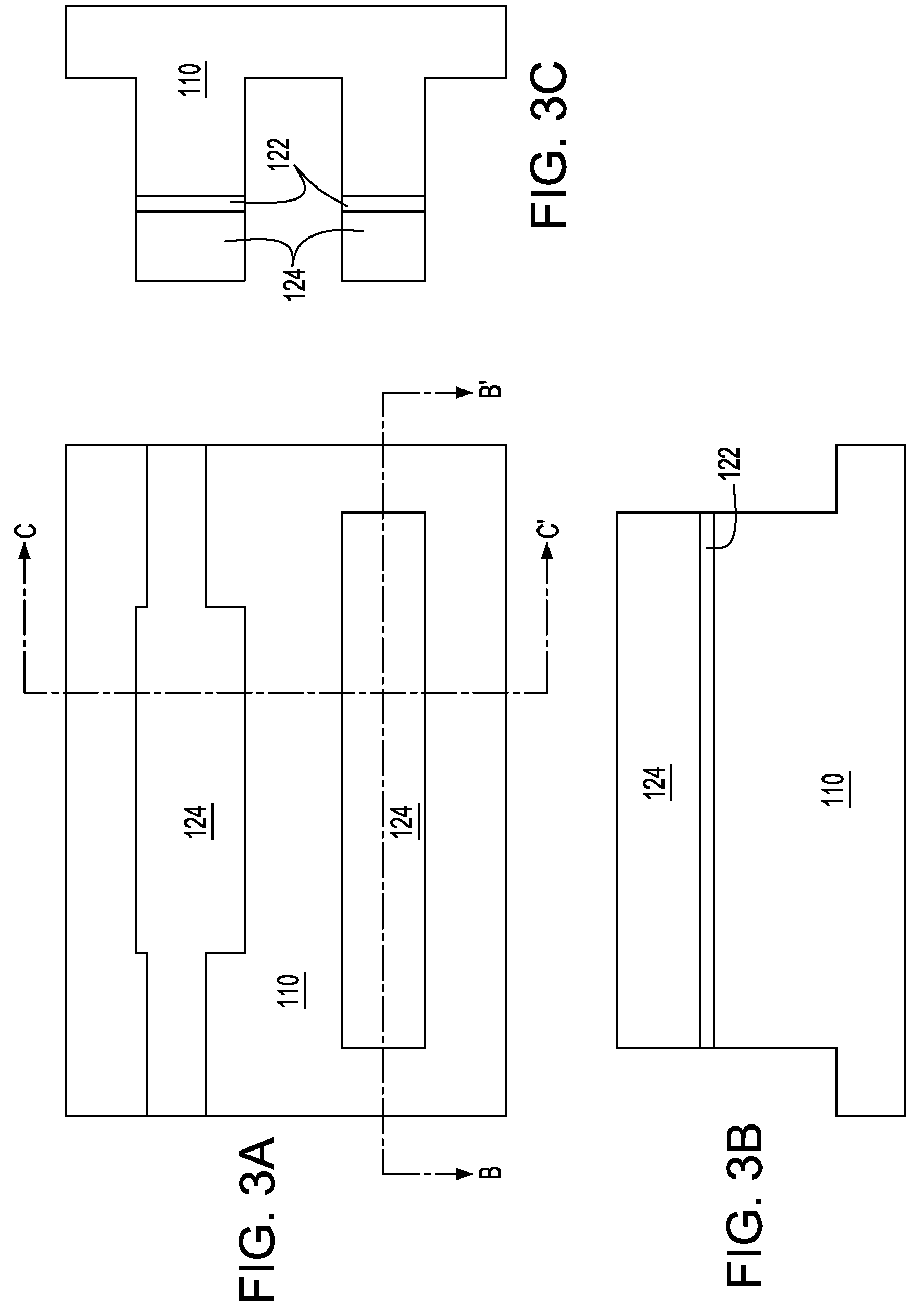

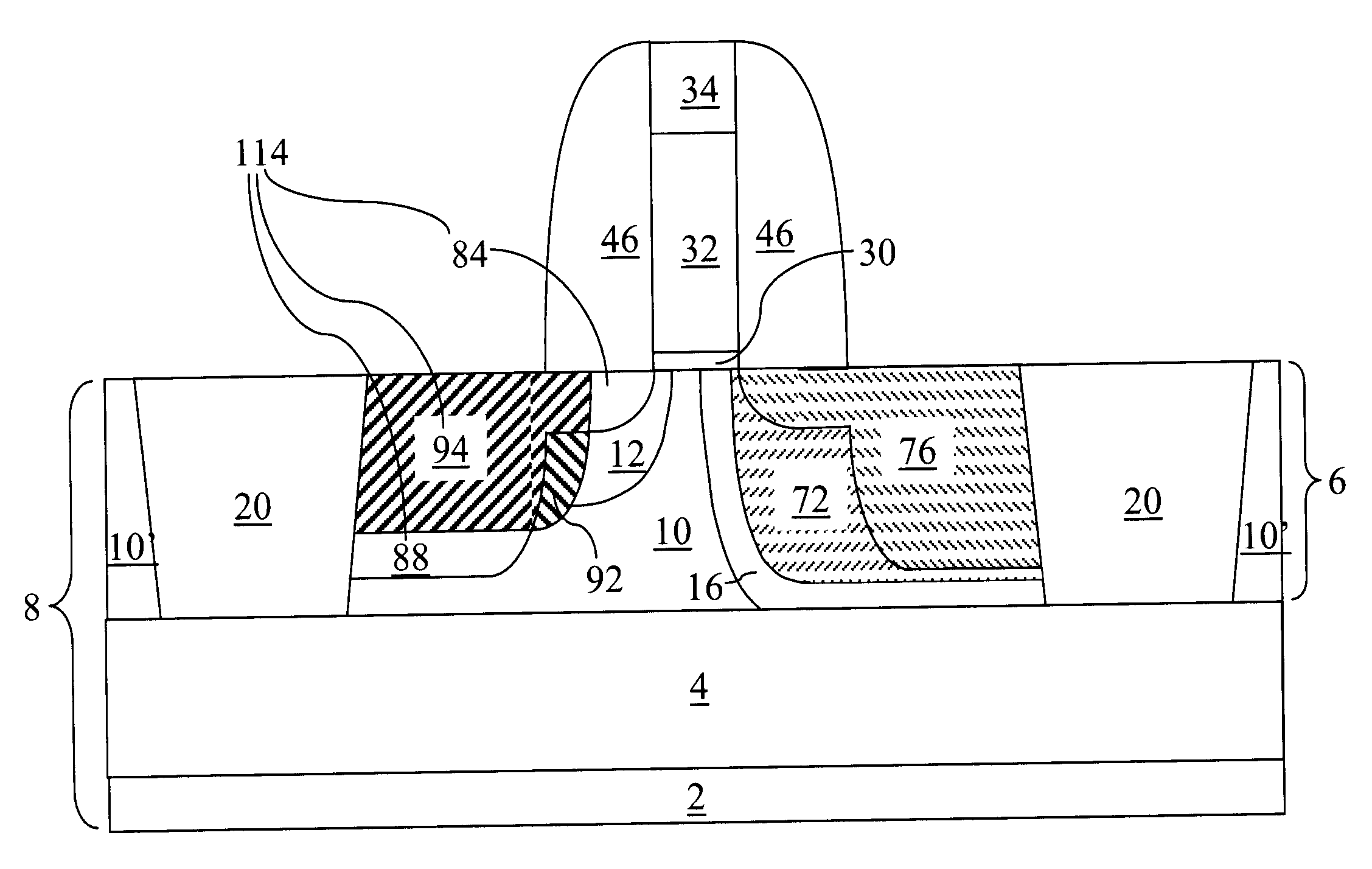

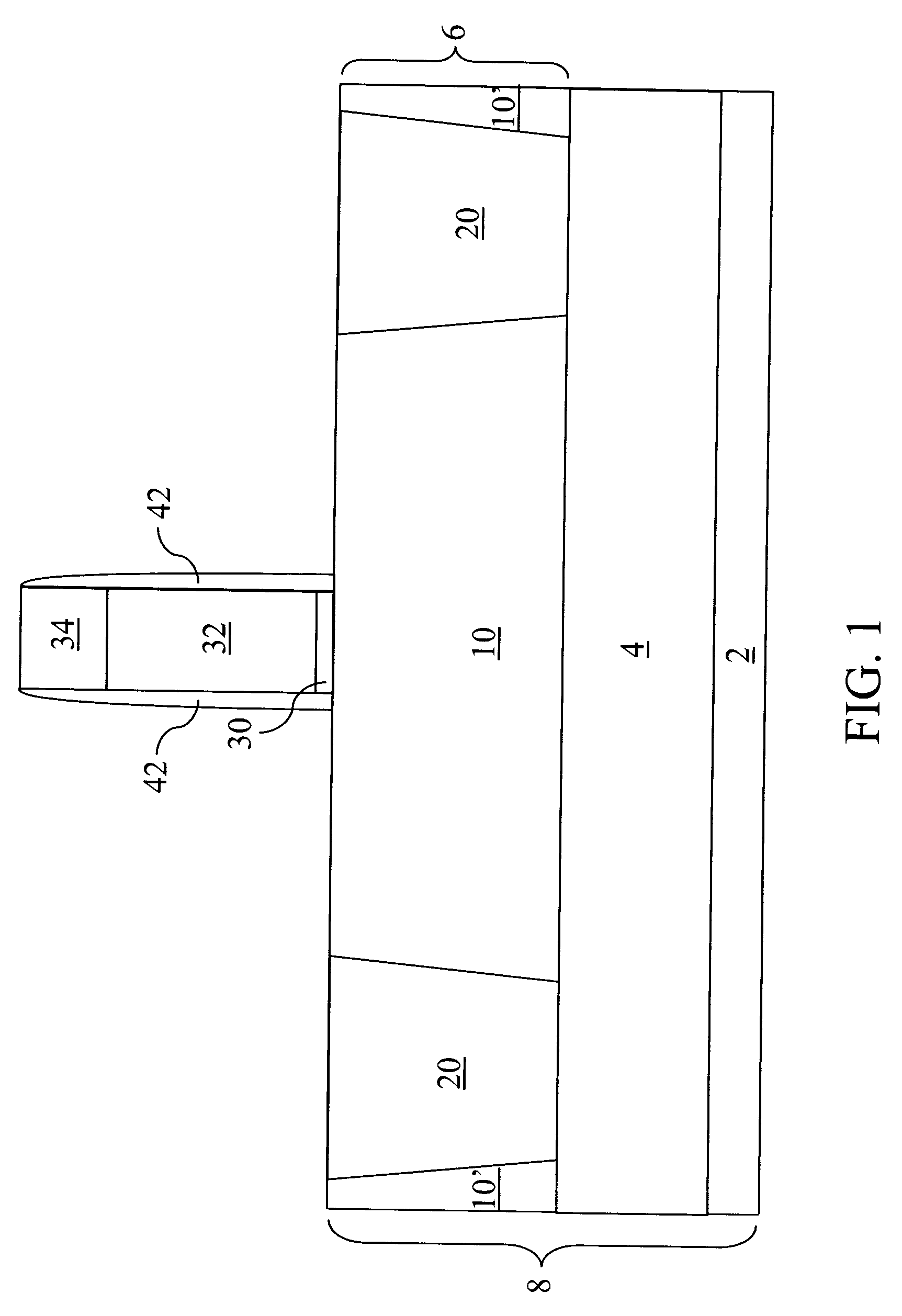

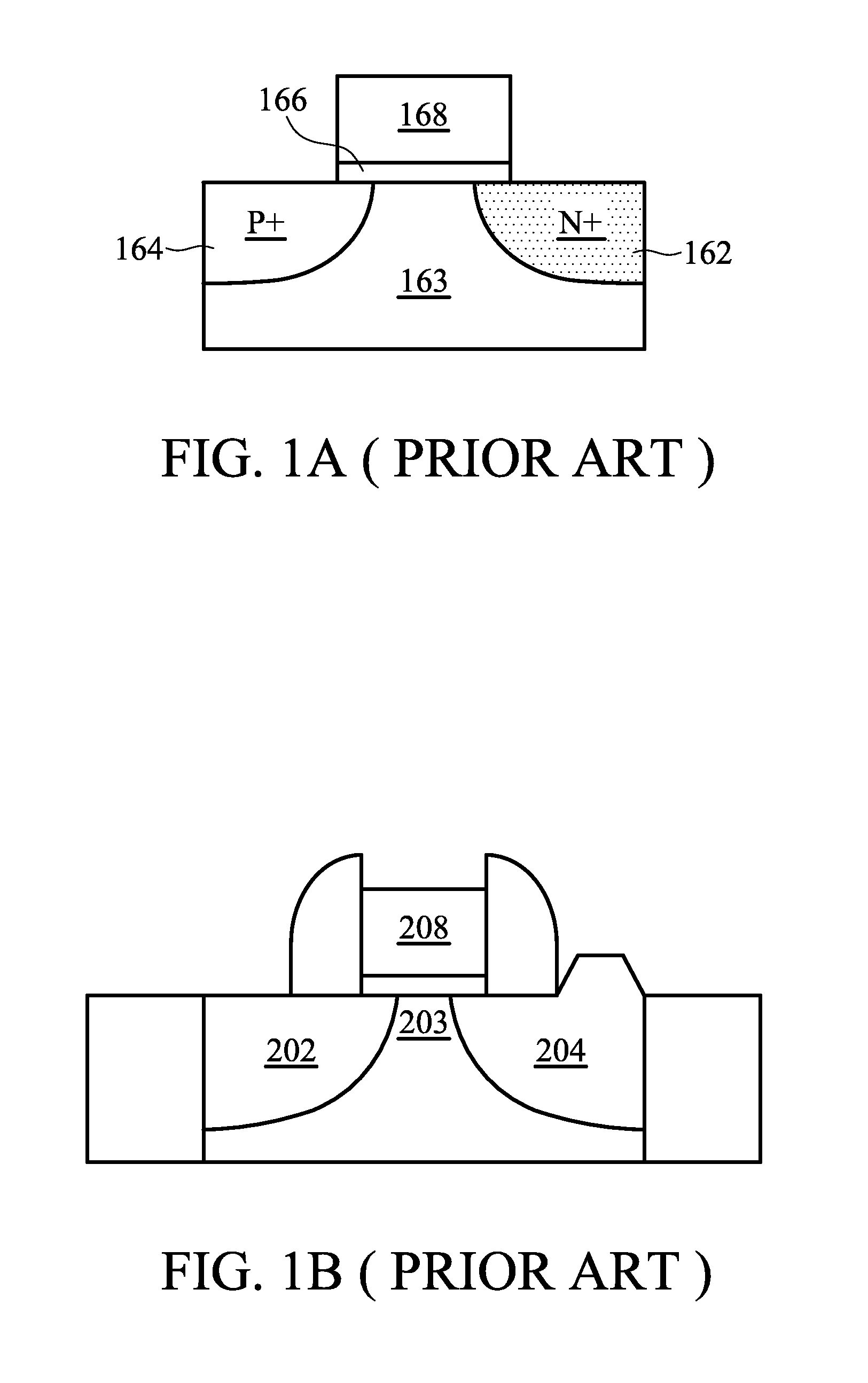

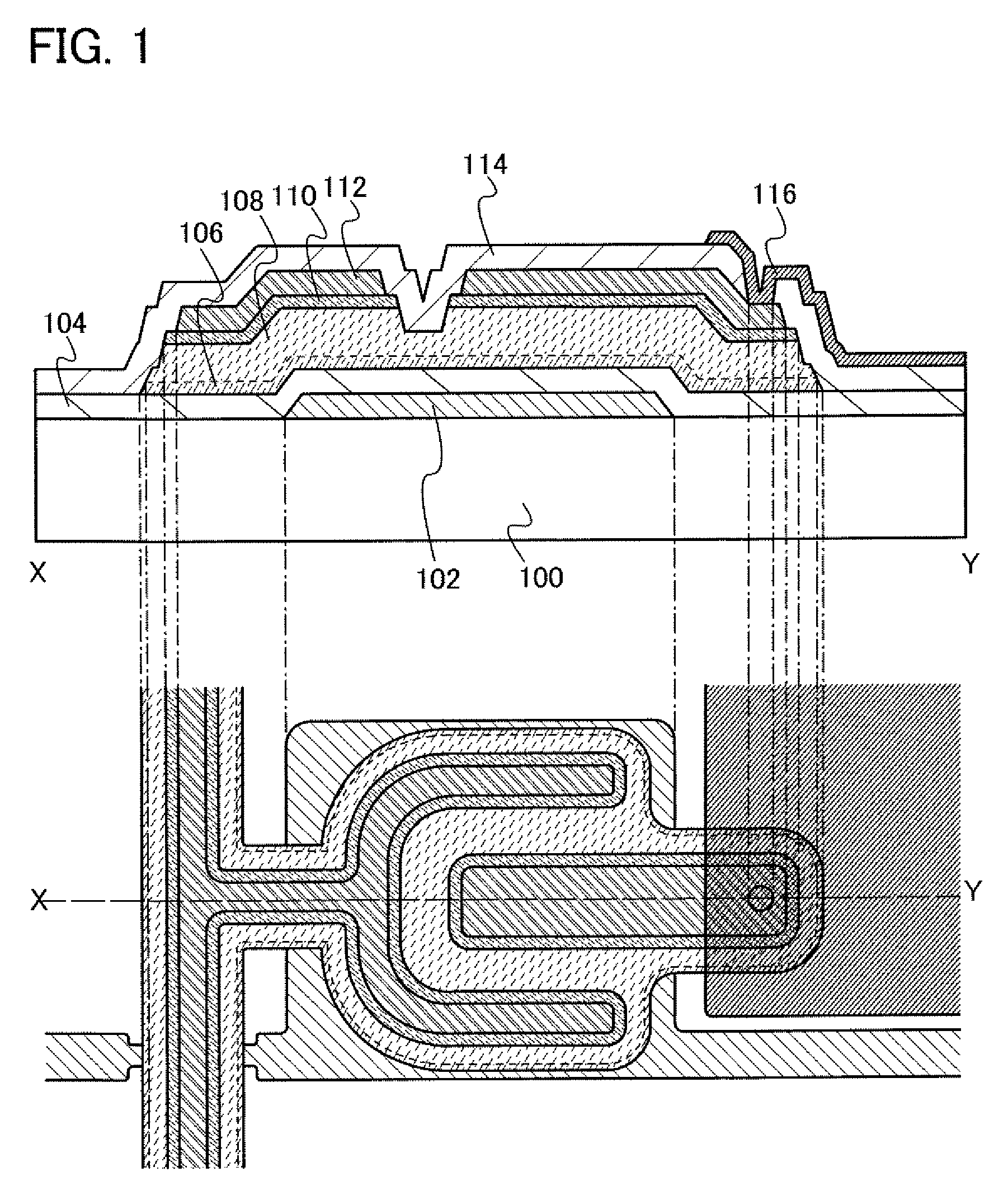

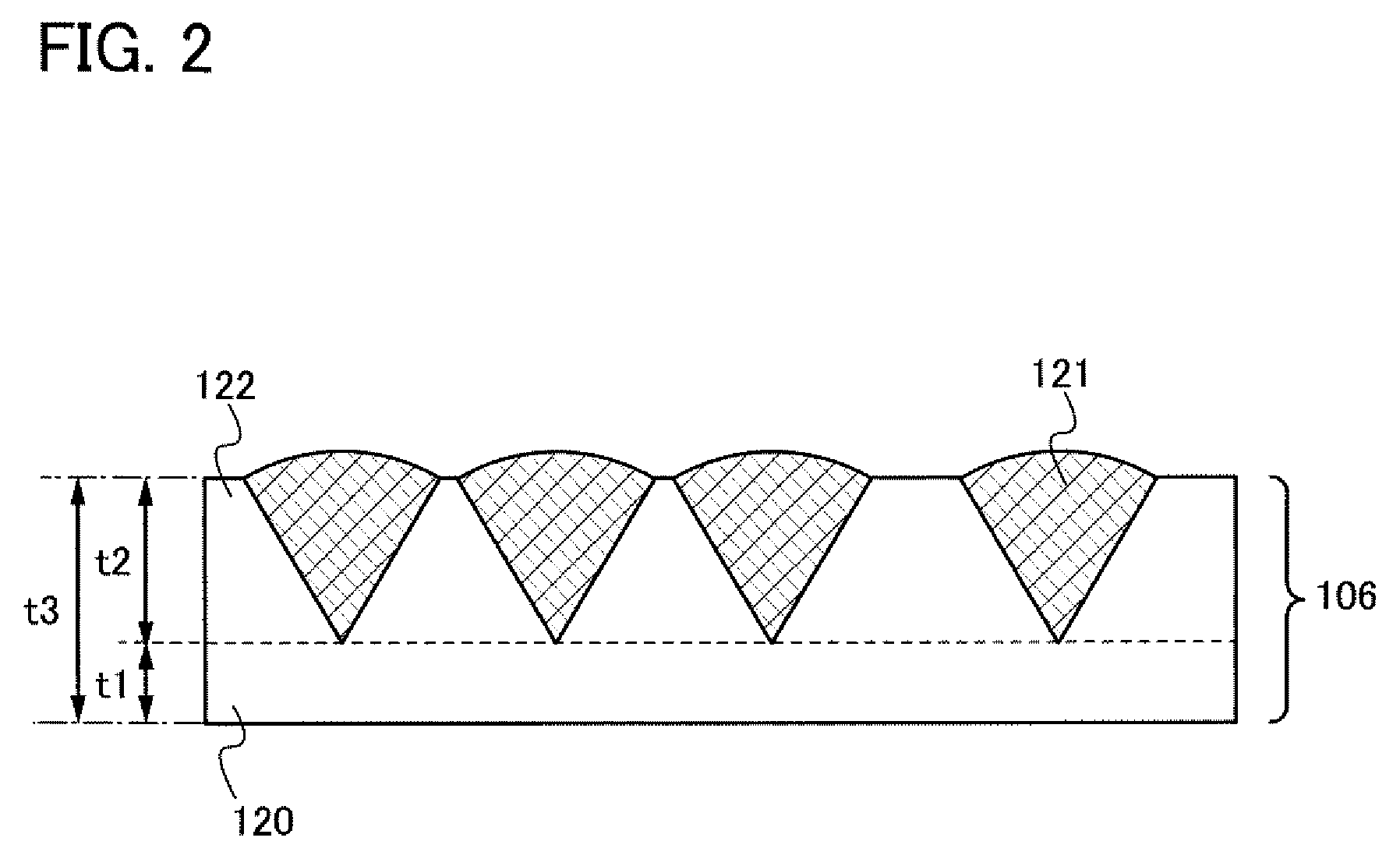

Enhanced mobility CMOS transistors with a v-shaped channel with self-alignment to shallow trench isolation

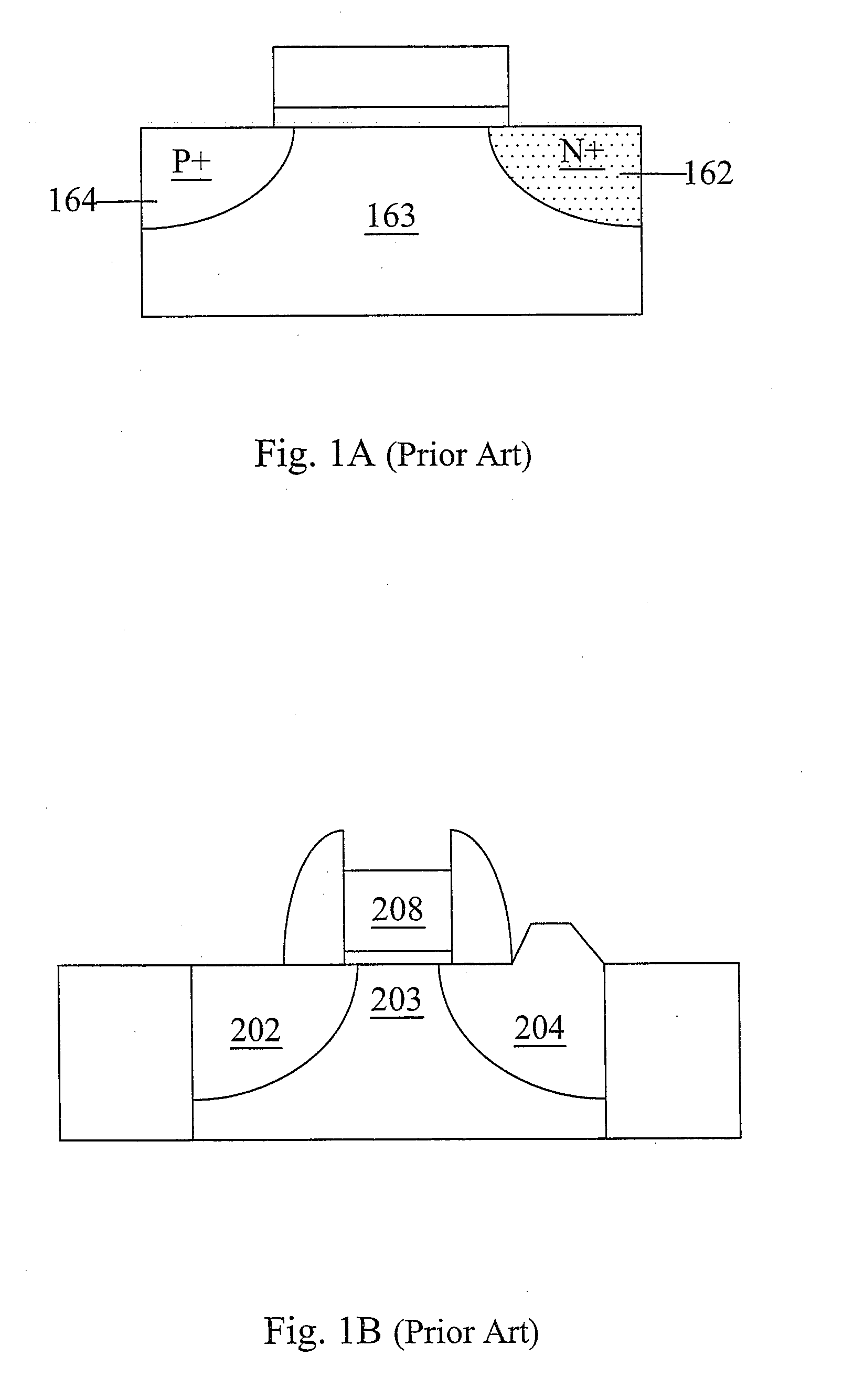

InactiveUS20080173906A1Improve performanceIncrease the on-currentTransistorSolid-state devicesCMOSCharge carrier mobility

The present invention provides structures and methods for a transistor formed on a V-shaped groove. The V-shaped groove contains two crystallographic facets joined by a ridge. The facets have different crystallographic orientations than what a semiconductor substrate normally provides such as the substrate orientation or orientations orthogonal to the substrate orientation. Unlike the prior art, the V-shaped groove is formed self-aligned to the shallow trench isolation, eliminating the need to precisely align the V-shaped grooves with lithographic means. The electrical properties of the new facets, specifically, the enhanced carrier mobility, are utilized to enhance the performance of transistors. In a transistor with a channel on the facets that are joined to form a V-shaped profile, the current flows in the direction of the ridge joining the facets avoiding any inflection in the direction of the current.

Owner:GLOBALFOUNDRIES INC

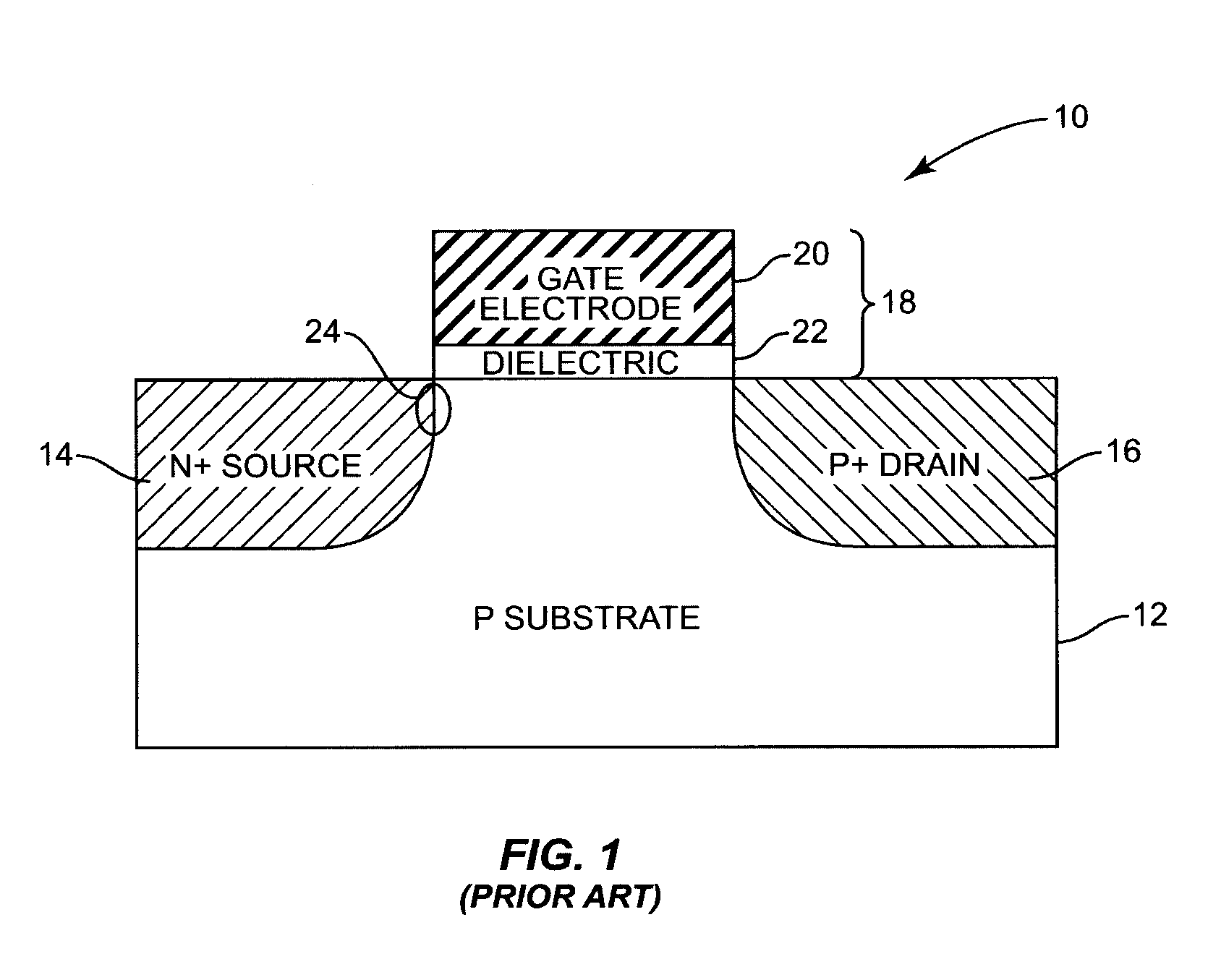

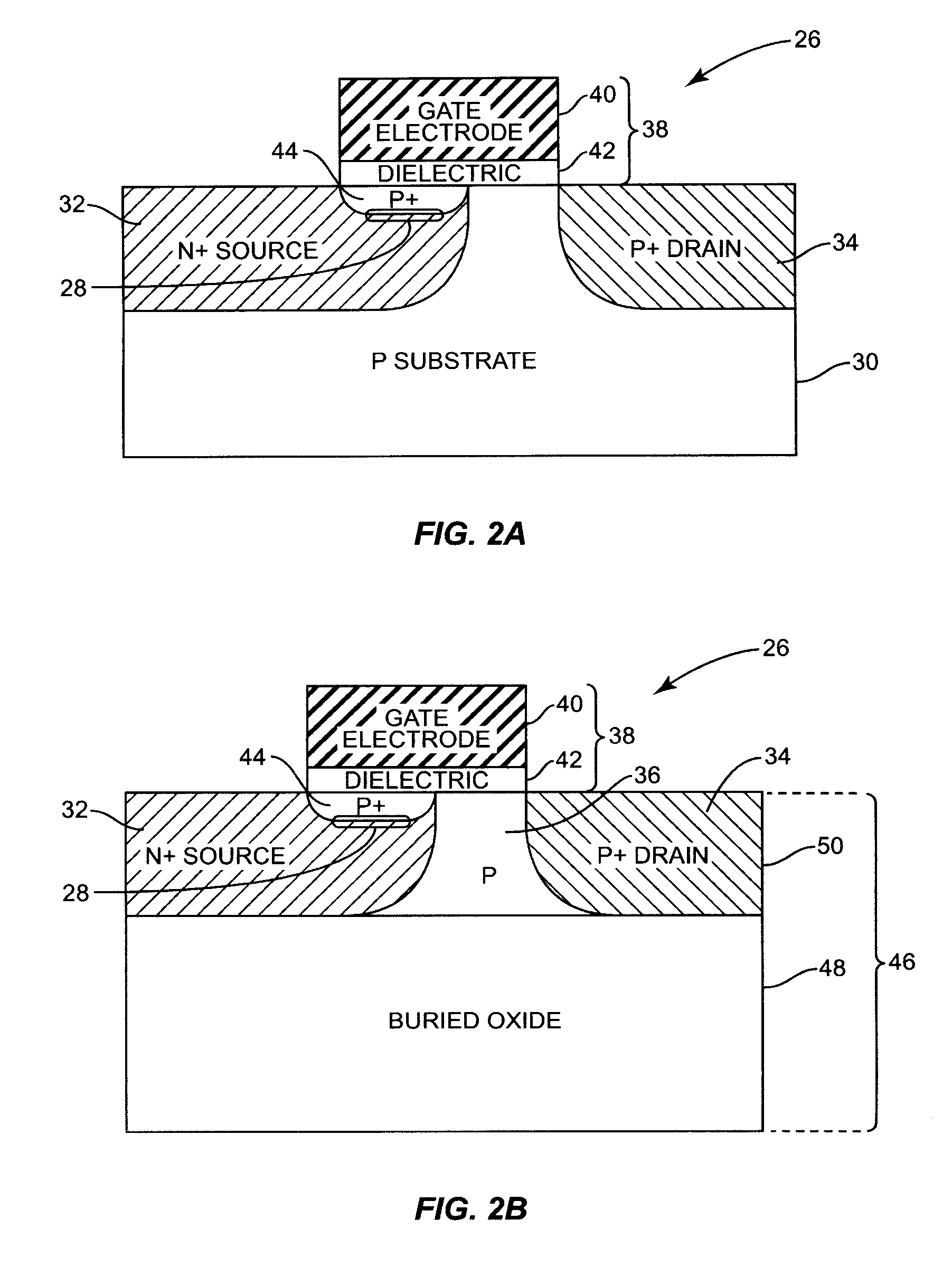

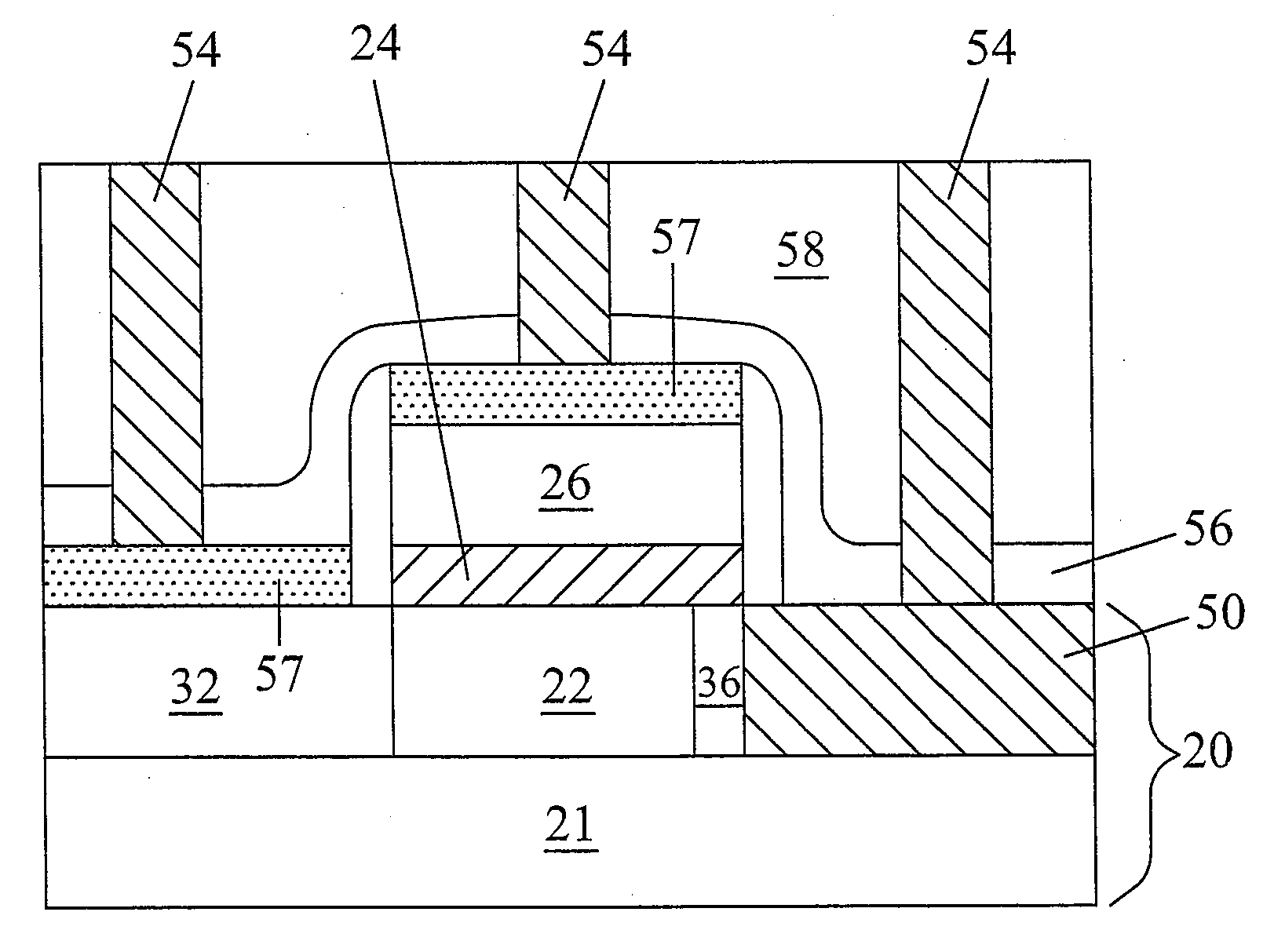

Tunnel Field-Effect Transistor with Narrow Band-Gap Channel and Strong Gate Coupling

InactiveUS20090026553A1Reduce leakage currentImproved sub-threshold swingSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor materials

A semiconductor device and the methods of forming the same are provided. The semiconductor device includes a low energy band-gap layer comprising a semiconductor material; a gate dielectric on the low energy band-gap layer; a gate electrode over the gate dielectric; a first source / drain region adjacent the gate dielectric, wherein the first source / drain region is of a first conductivity type; and a second source / drain region adjacent the gate dielectric. The second source / drain region is of a second conductivity type opposite the first conductivity type. The low energy band-gap layer is located between the first and the second source / drain regions.

Owner:TAIWAN SEMICON MFG CO LTD

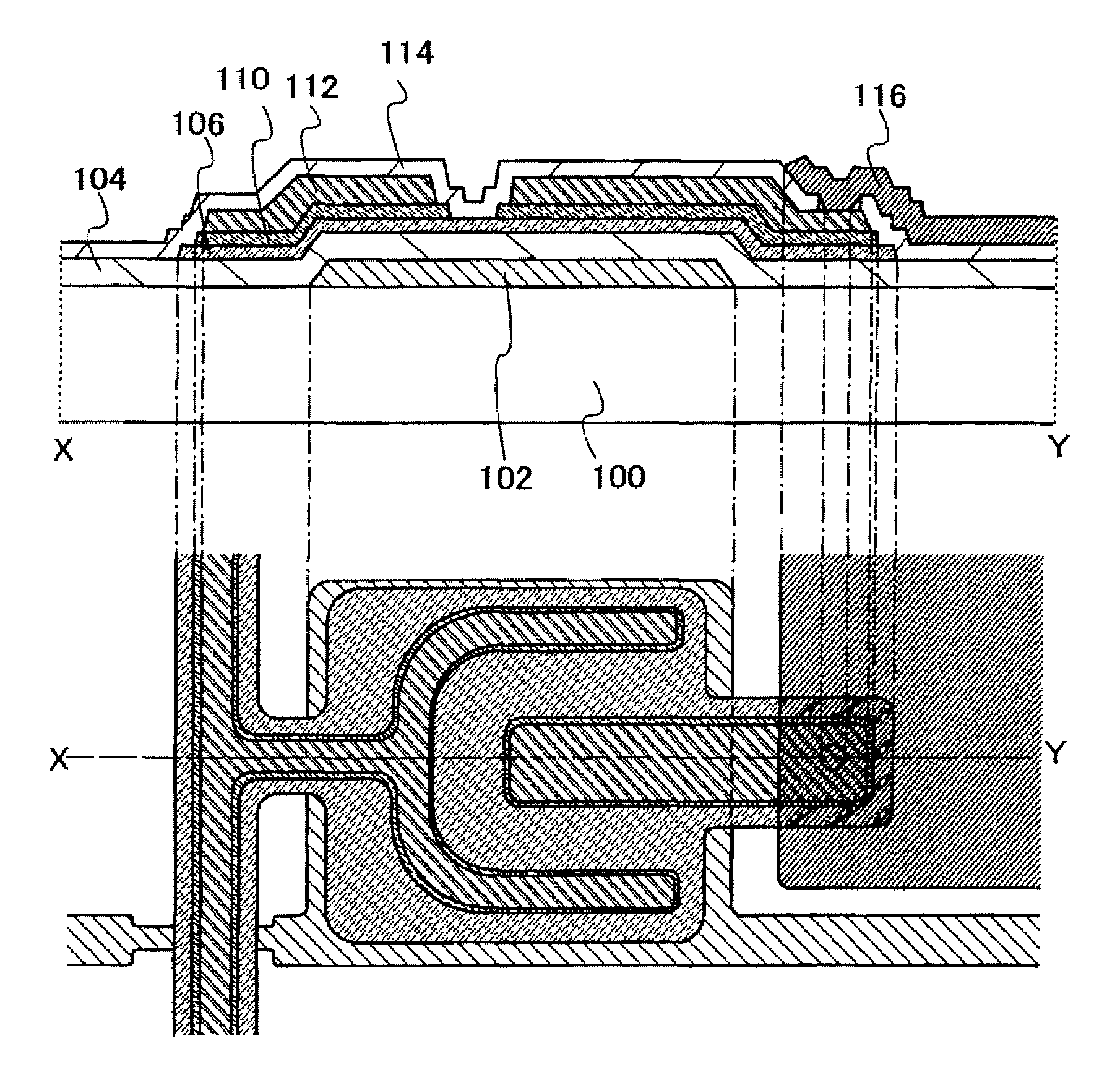

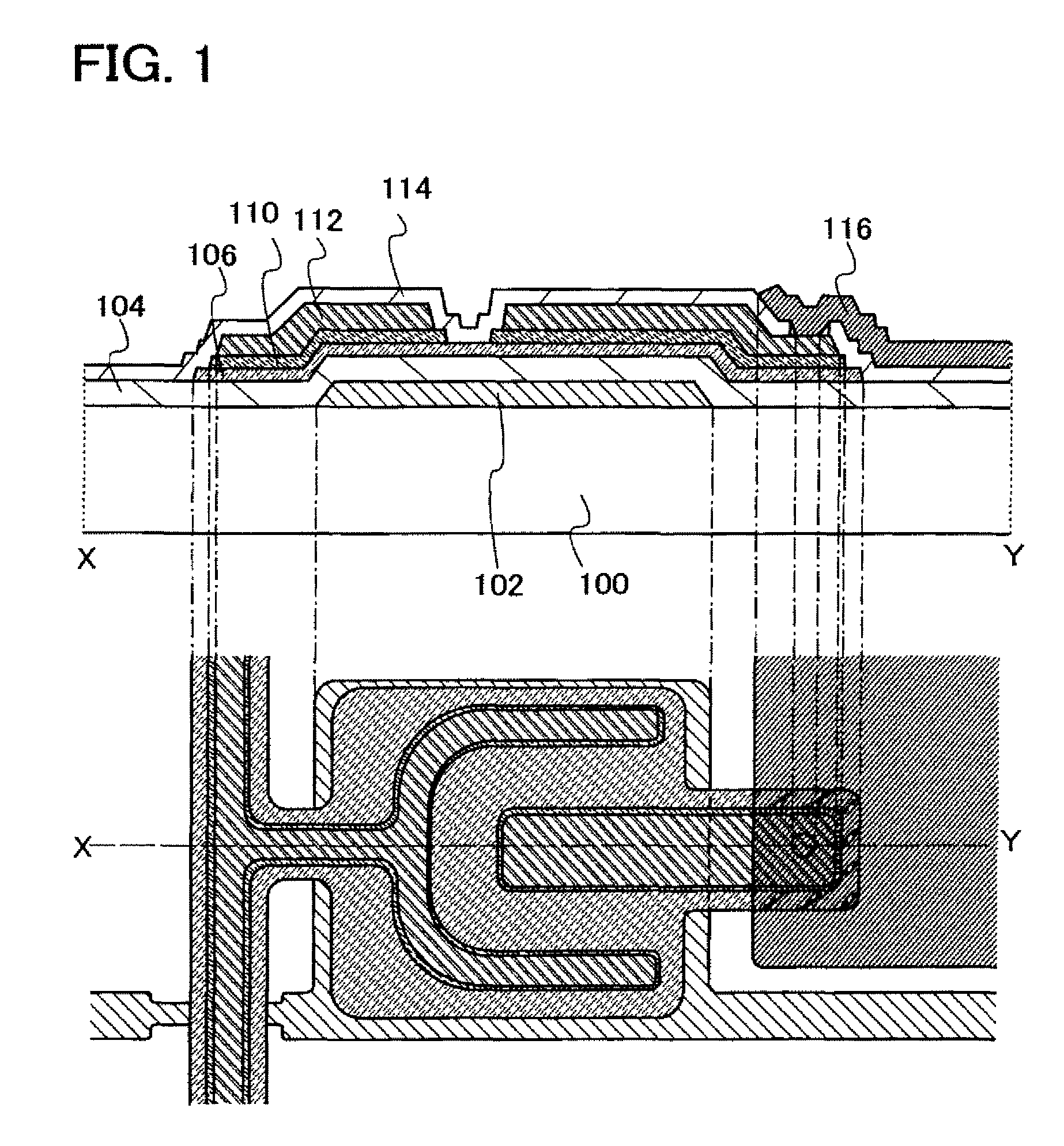

Thin film transistor

InactiveUS20090321737A1Increase the on-currentOff-current can be reducedSolid-state devicesSemiconductor devicesNitrogenSemiconductor

A thin film transistor includes, as a buffer layer, a semiconductor layer which contains nitrogen and includes crystal regions in an amorphous structure between a gate insulating layer and source and drain regions, at least on the source and drain regions side. As compared to a thin film transistor in which an amorphous semiconductor is included in a channel formation region, on-current of a thin film transistor can be increased. In addition, as compared to a thin film transistor in which a microcrystalline semiconductor is included in a channel formation region, off-current of a thin film transistor can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

Field effect transistor containing a wide band gap semiconductor material in a drain

InactiveUS20090121258A1Suppress impact ionizationLarge band gapTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsGate dielectric

A field effect transistor comprising a silicon containing body is provided. After formation of a gate dielectric, gate electrode, and a first gate spacer, a drain side trench is formed and filled with a wide band gap semiconductor material. Optionally, a source side trench may be formed and filled with a silicon germanium alloy to enhance an on-current of the field effect transistor. Halo implantation and source and drain ion implantation are performed to form various doped regions. Since the wide band gap semiconductor material as a wider band gap than that of silicon, impact ionization is reduced due to the use of the wide band gap semiconductor material in the drain, and consequently, a breakdown voltage of the field effect transistor is increased compared to transistors employing silicon in the drain region.

Owner:GLOBALFOUNDRIES INC

Tunneling transistor suitable for low voltage operation

InactiveUS8384122B1Increase the on-currentOn-current of the tunneling transistor is substantially improvedNanotechnologySuperconductor devicesLow voltageEngineering

Several embodiments of a tunneling transistor are disclosed. In one embodiment, a tunneling transistor includes a semiconductor substrate, a source region formed in the semiconductor substrate, a drain region formed in the semiconductor substrate, a gate stack including a metallic gate electrode and a gate dielectric, and a tunneling junction that is substantially parallel to an interface between the metallic gate electrode and the gate dielectric. As a result of the tunneling junction that is substantially parallel with the interface between the metallic gate electrode and the gate dielectric, an on-current of the tunneling transistor is substantially improved as compared to that of a conventional tunneling transistor. In another embodiment, a tunneling transistor includes a heterostructure that reduces a turn-on voltage of the tunneling transistor.

Owner:RGT UNIV OF CALIFORNIA

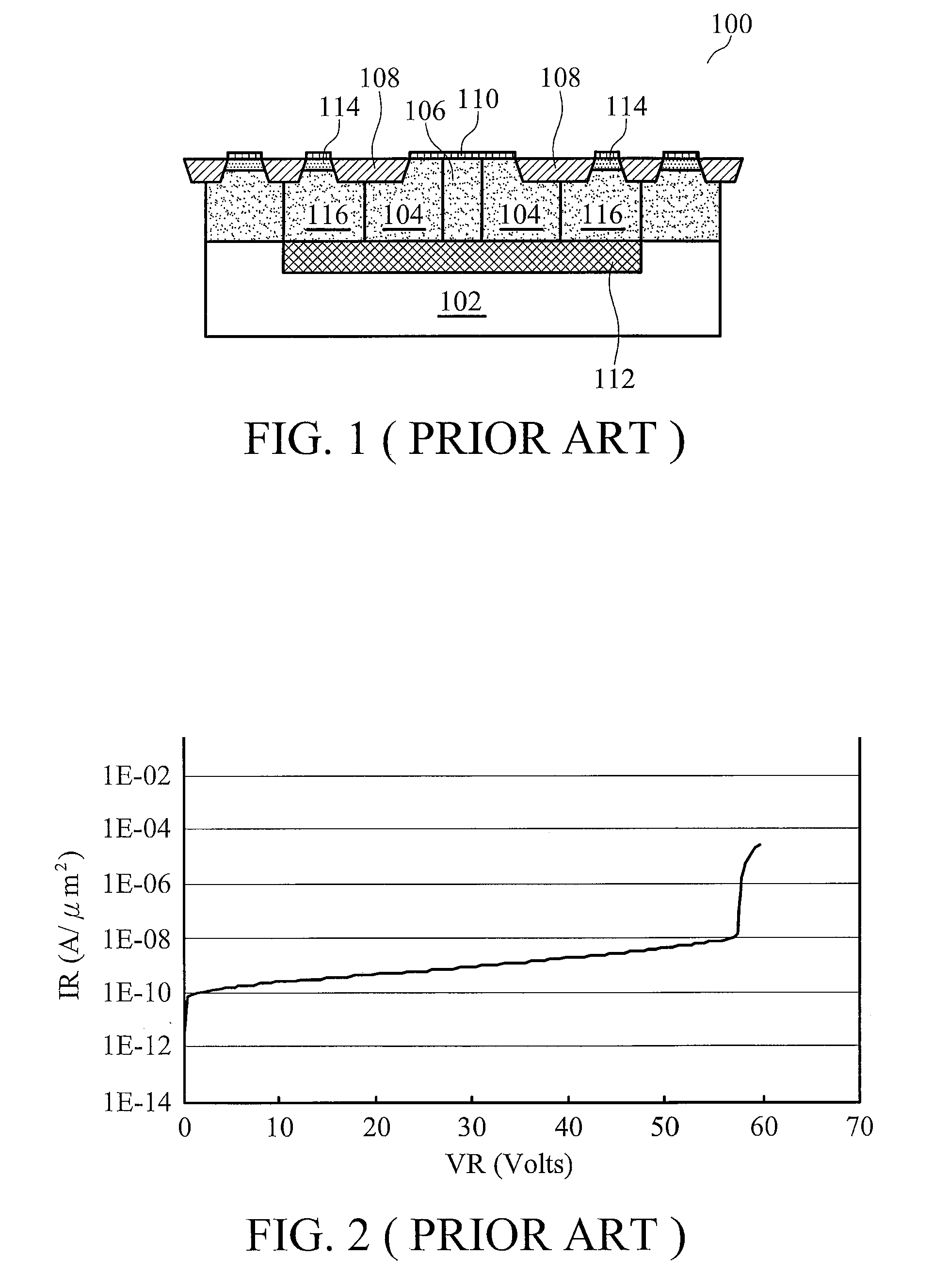

Schottky Diodes Having Low-Voltage and High-Concentration Rings

ActiveUS20090294865A1Improve breakdown voltageReduce leakage currentTransistorSolid-state devicesHigh concentrationSchottky barrier

An integrated circuit structure includes a semiconductor substrate; a first well region of a first conductivity type over the semiconductor substrate; a second well region of a second conductivity type opposite the first conductivity type encircling the first well region; and a metal-containing layer over and adjoining the first well region and extending over at least an inner portion of the second well region. The metal-containing layer and the first well region form a Schottky barrier. The integrated circuit structure further includes an isolation region encircling the metal-containing layer; and a third well region of the second conductivity type encircling at least a central portion of the first well region. The third well region has a higher impurity concentration than the second well region, and includes a top surface adjoining the metal-containing layer, and a bottom surface higher than bottom surfaces of the first and the second well regions.

Owner:TAIWAN SEMICON MFG CO LTD

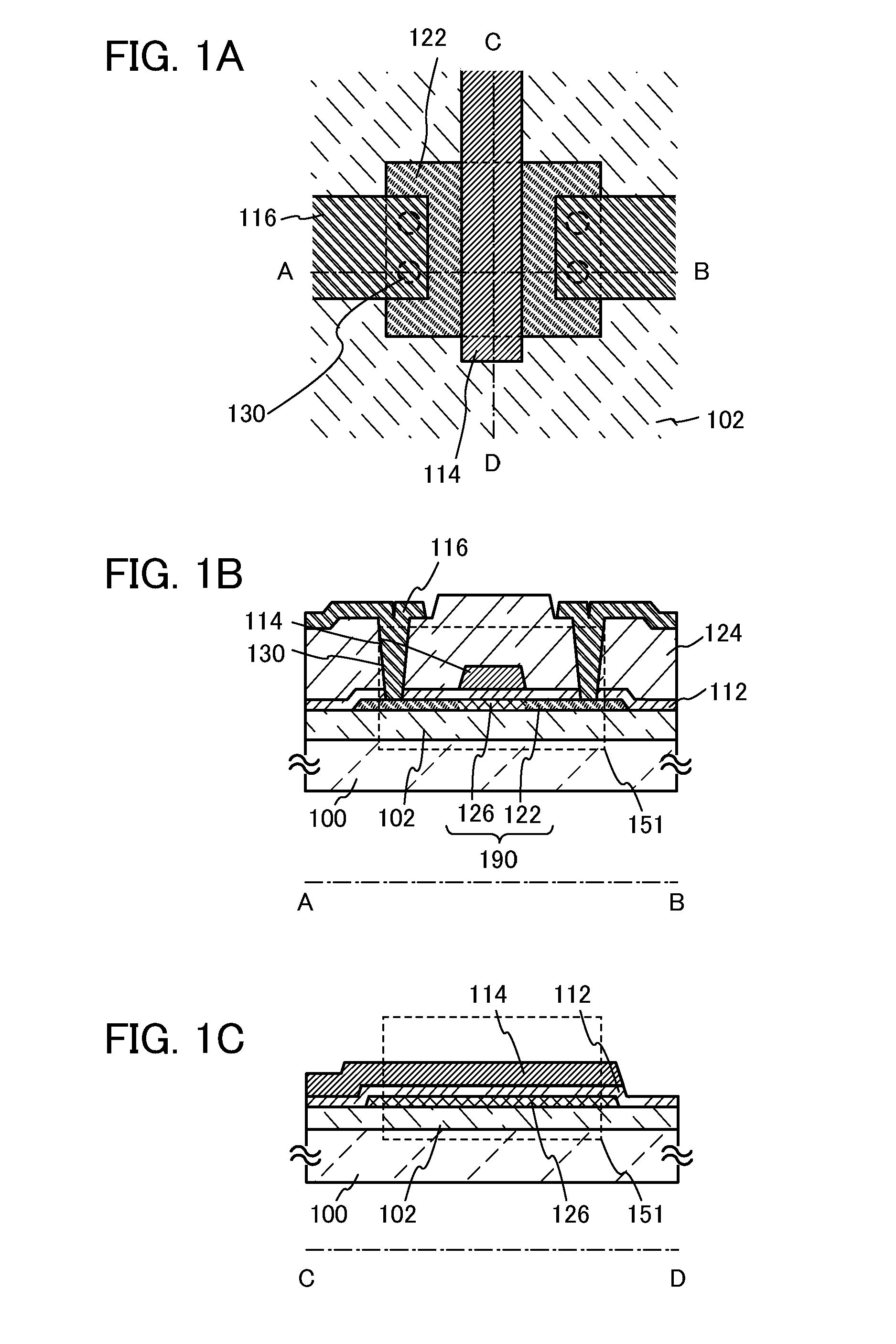

Semiconductor device and method for manufacturing the same

ActiveUS20120161122A1Band gapReduce effective channel lengthSemiconductor/solid-state device manufacturingDigital storagePower semiconductor deviceNitrogen

A miniaturized semiconductor device including a transistor in which a channel formation region is formed using an oxide semiconductor film and variation in electric characteristics due to a short-channel effect is suppressed is provided. In addition, a semiconductor device whose on-state current is improved is provided. A semiconductor device is provided with an oxide semiconductor film including a pair of second oxide semiconductor regions which are amorphous regions and a first oxide semiconductor region located between the pair of second oxide semiconductor regions, a gate insulating film, and a gate electrode provided over the first oxide semiconductor region with the gate insulating film interposed therebetween. One or more kinds of elements selected from Group 15 elements such as nitrogen, phosphorus, and arsenic are added to the second oxide semiconductor regions.

Owner:SEMICON ENERGY LAB CO LTD

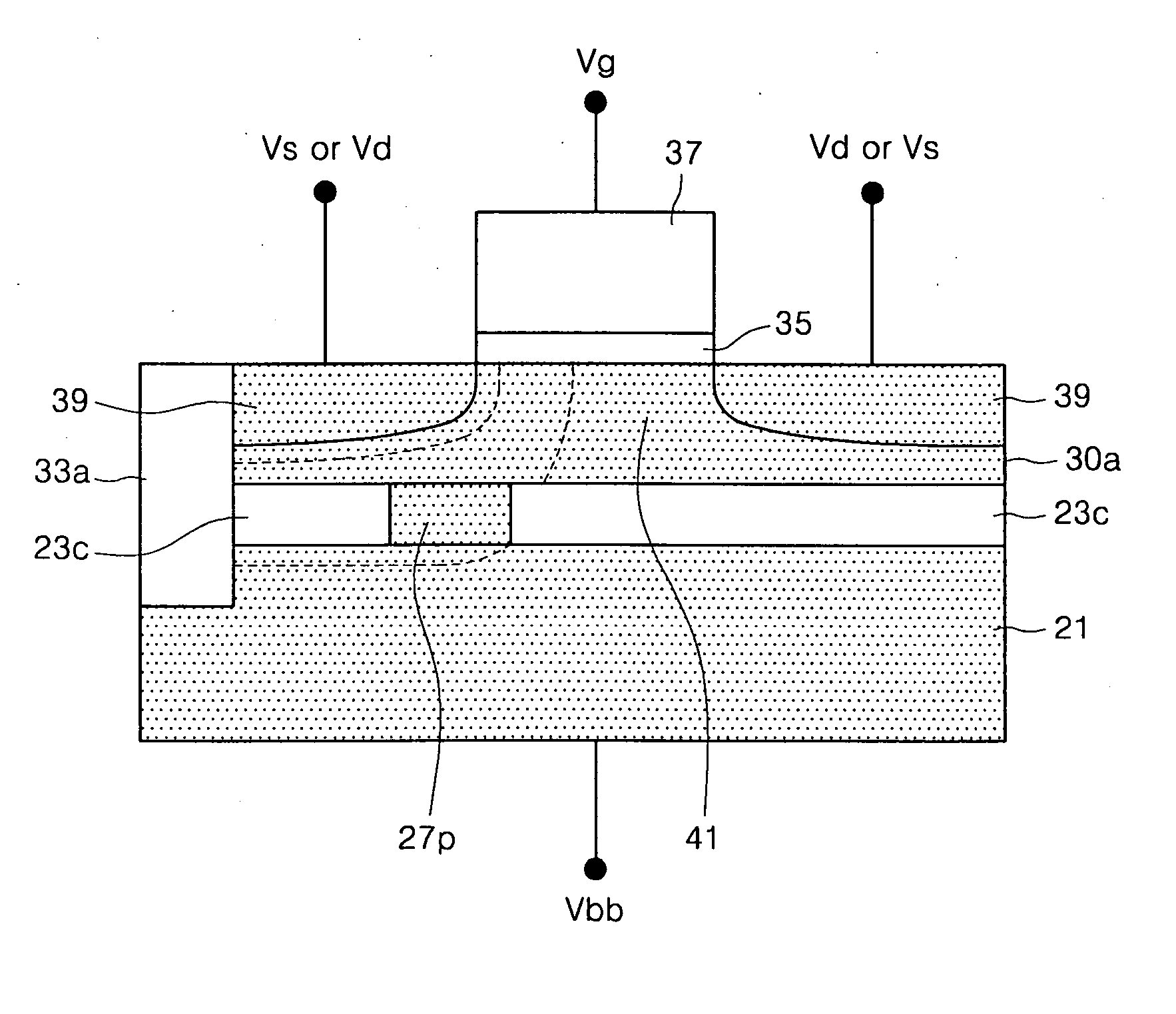

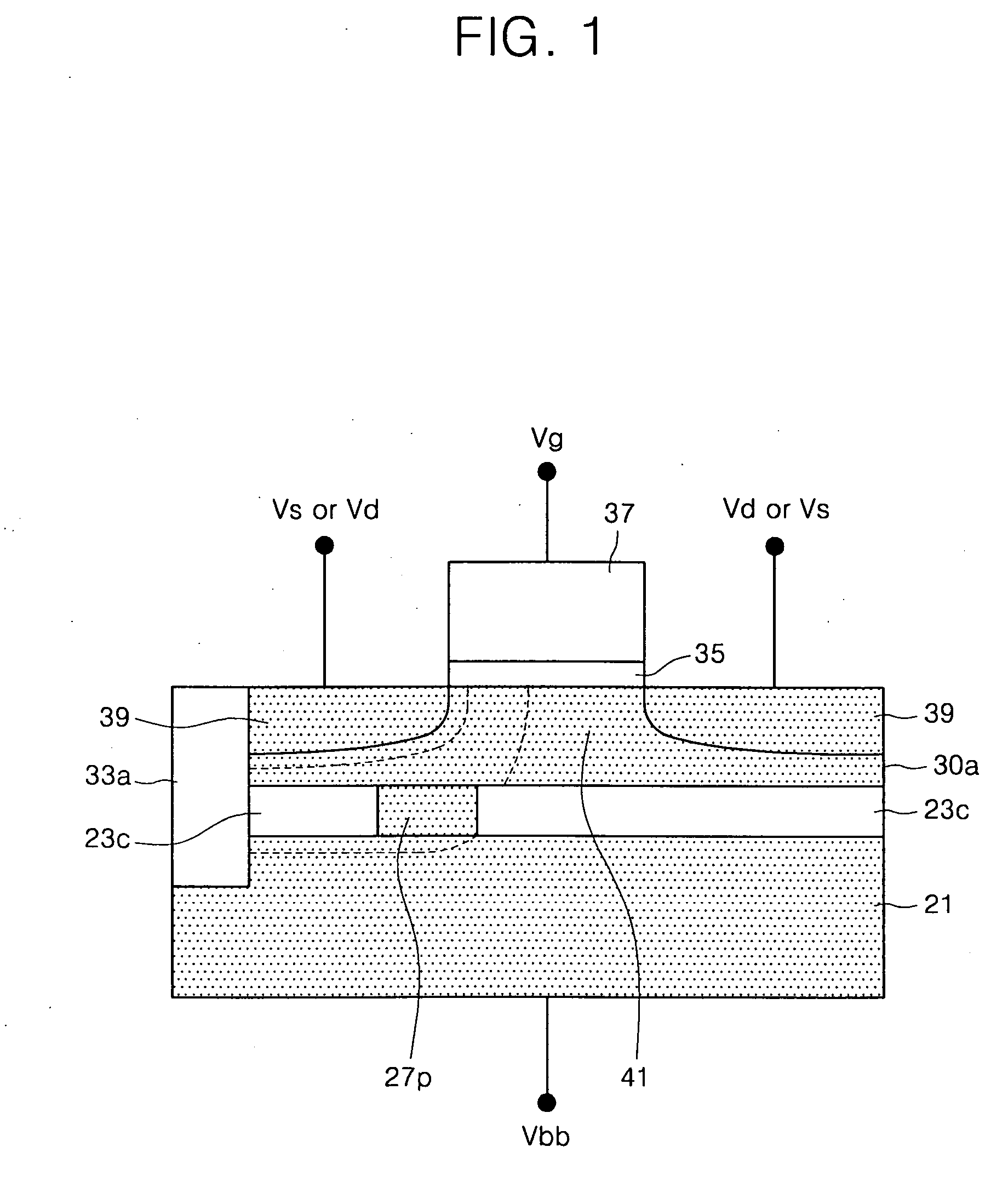

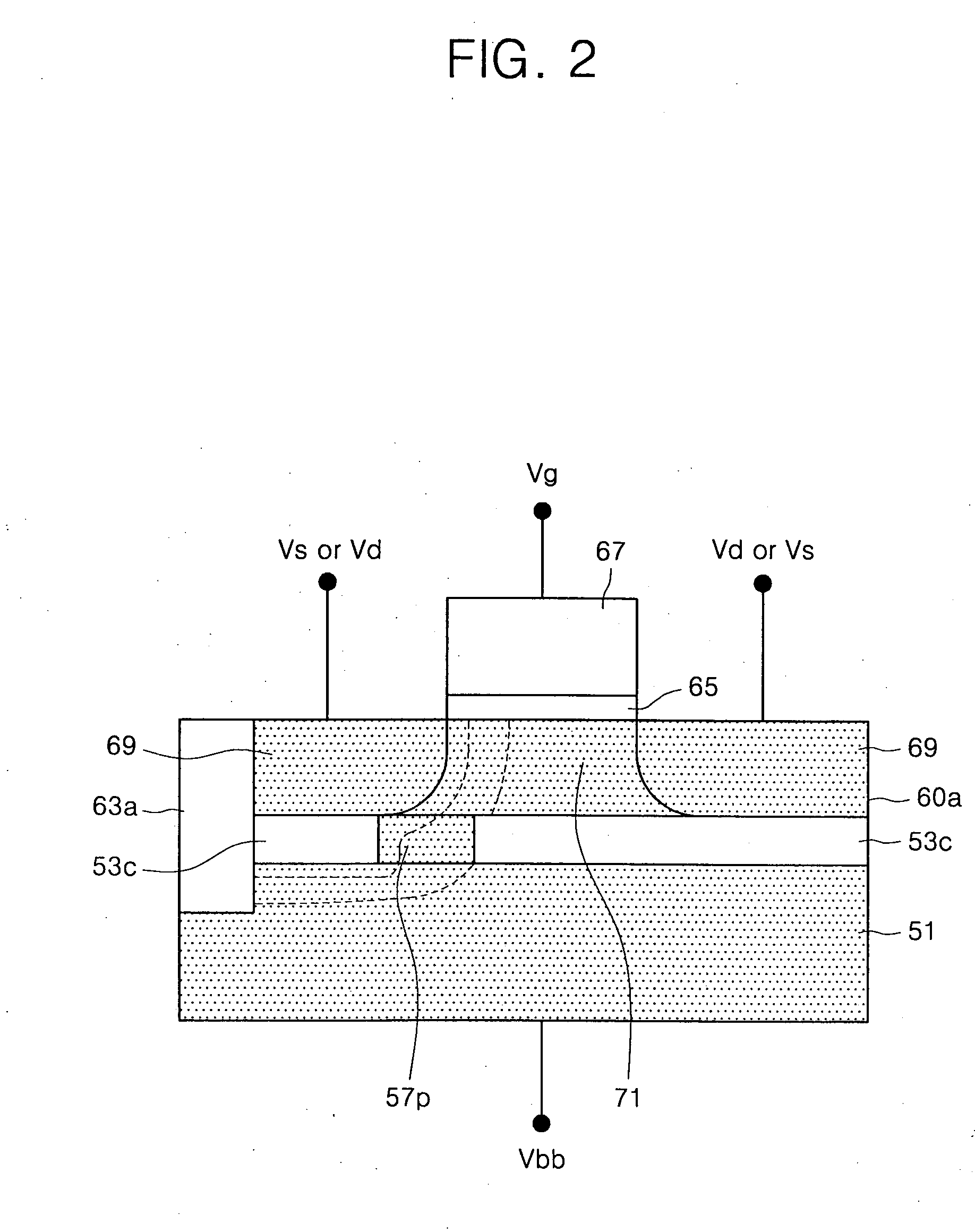

Semiconductor device having two different operation modes employing an asymmetrical buried insulating layer and method for fabricating the same

ActiveUS20050133789A1Increase the on-currentOff-current can be reducedTransistorSolid-state devicesNon symmetricDevice material

According to some embodiments, a semiconductor device includes a lower semiconductor substrate, an upper silicon pattern, and a MOS transistor. The MOS transistor includes a body region formed within the upper silicon pattern and source / drain regions separated by the body region. A buried insulating layer is interposed between the lower semiconductor substrate and the upper silicon pattern. A through plug penetrates the buried insulating layer and electrically connects the body region with the lower semiconductor substrate, the through plug positioned closer to one of the source / drain regions than the other source / drain region. At least some portion of the upper surface of the through plug is positioned outside a depletion layer when a source voltage is applied to the one of the source / drain regions, and the upper surface of the through plug is positioned inside the depletion layer when a drain voltage is applied to the one region.

Owner:SAMSUNG ELECTRONICS CO LTD

Tunnel field-effect transistors with superlattice channels

InactiveUS7834345B2Increase the on-currentReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor

A semiconductor device includes a channel region; a gate dielectric over the channel region; a gate electrode over the gate dielectric; and a first source / drain region adjacent the gate dielectric. The first source / drain region is of a first conductivity type. At least one of the channel region and the first source / drain region includes a superlattice structure. The semiconductor device further includes a second source / drain region on an opposite side of the channel region than the first source / drain region. The second source / drain region is of a second conductivity type opposite the first conductivity type. At most, one of the first source / drain region and the second source / drain region comprises an additional superlattice structure.

Owner:TAIWAN SEMICON MFG CO LTD

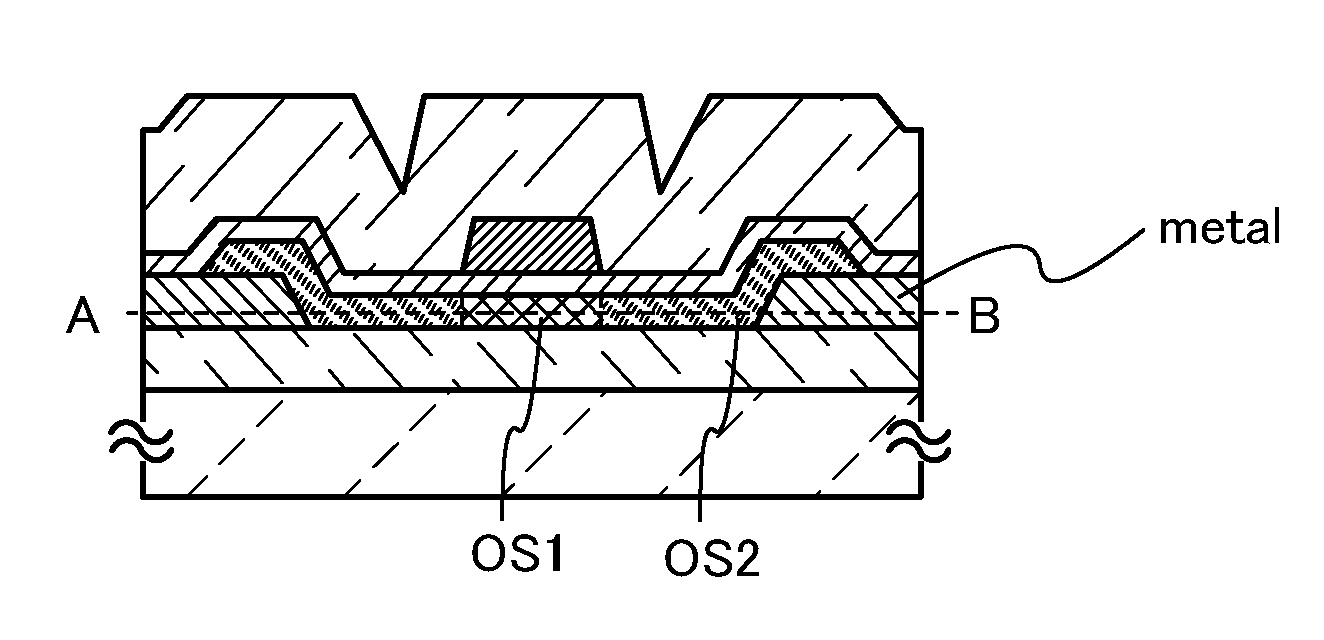

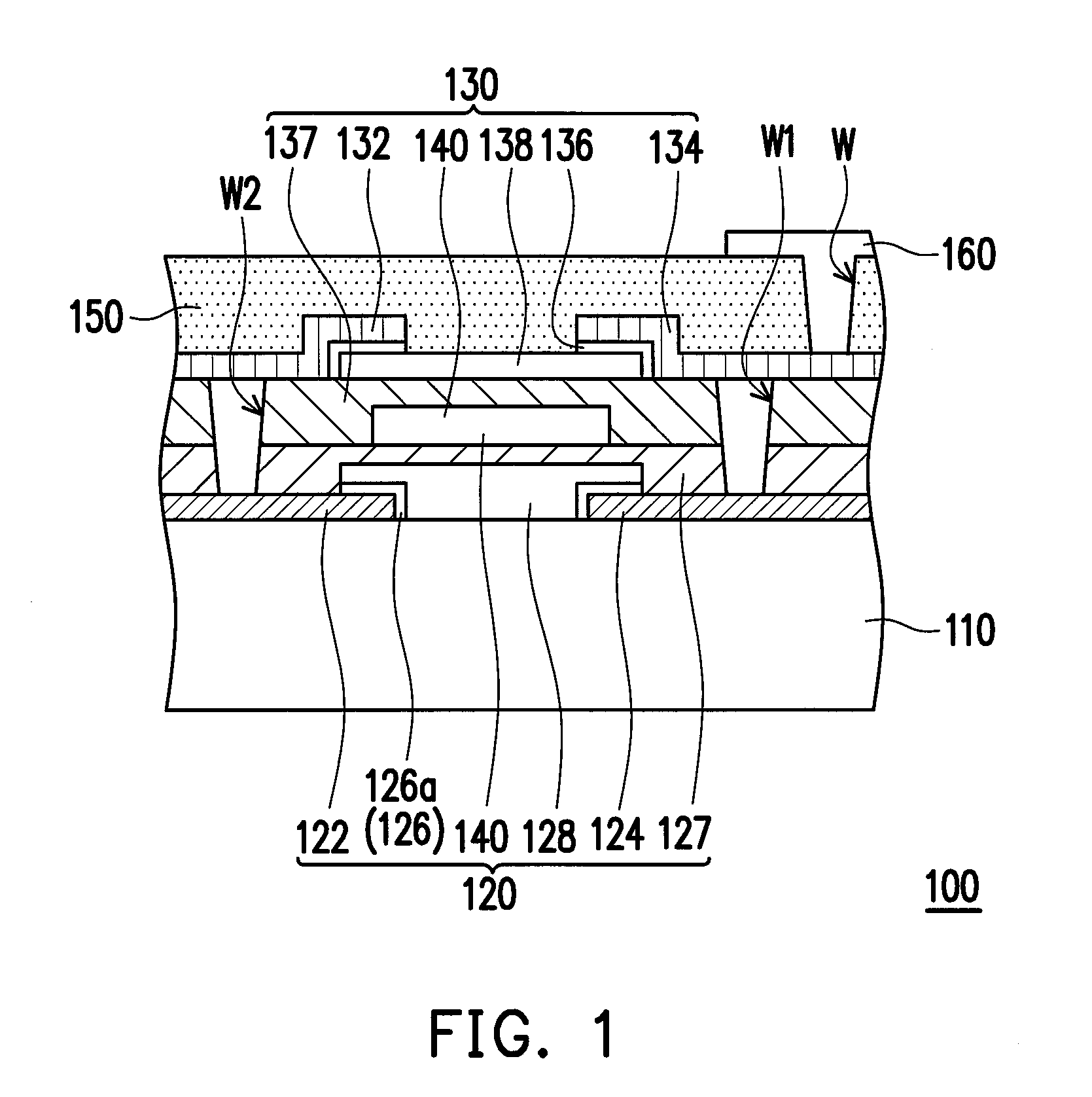

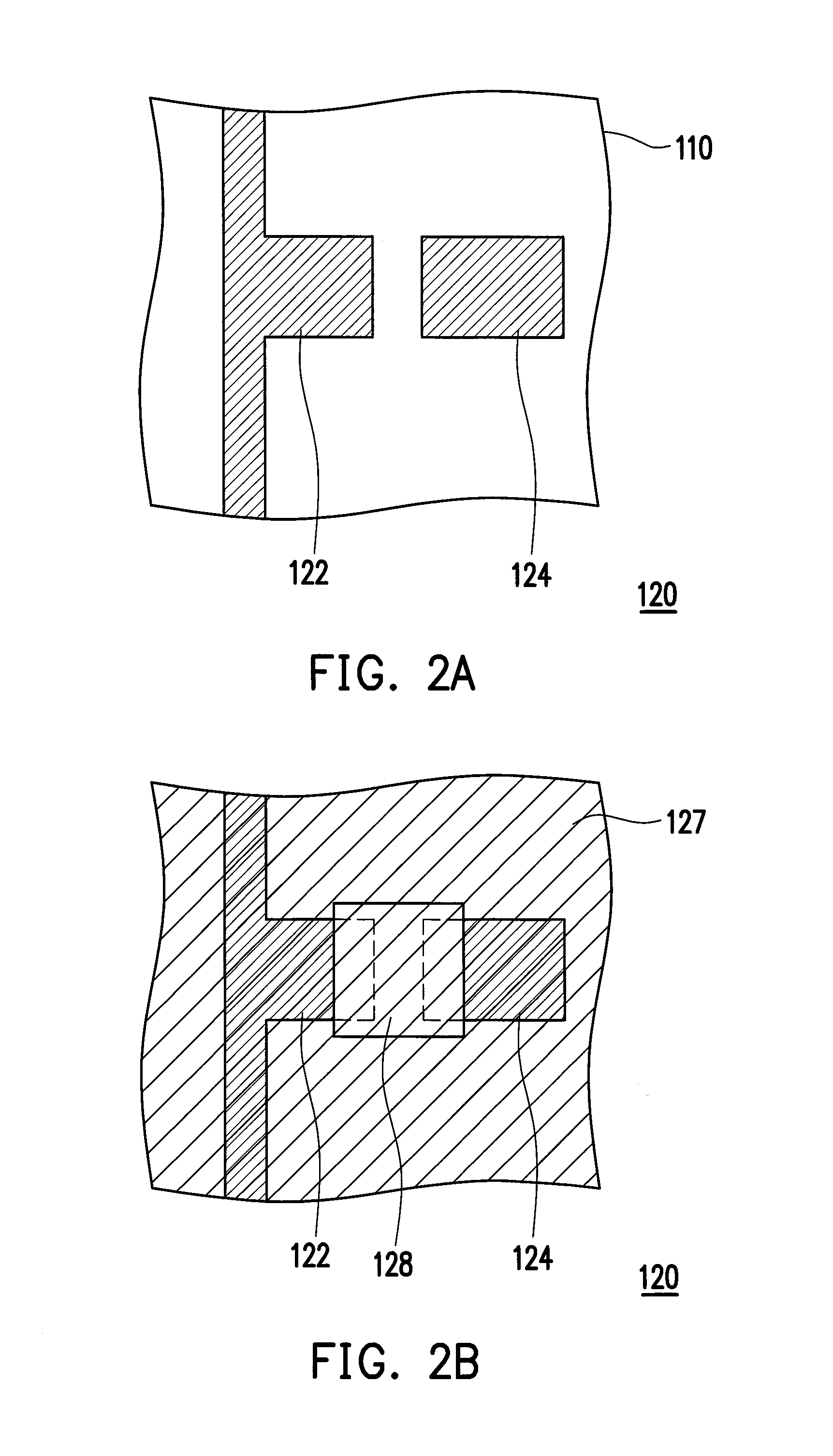

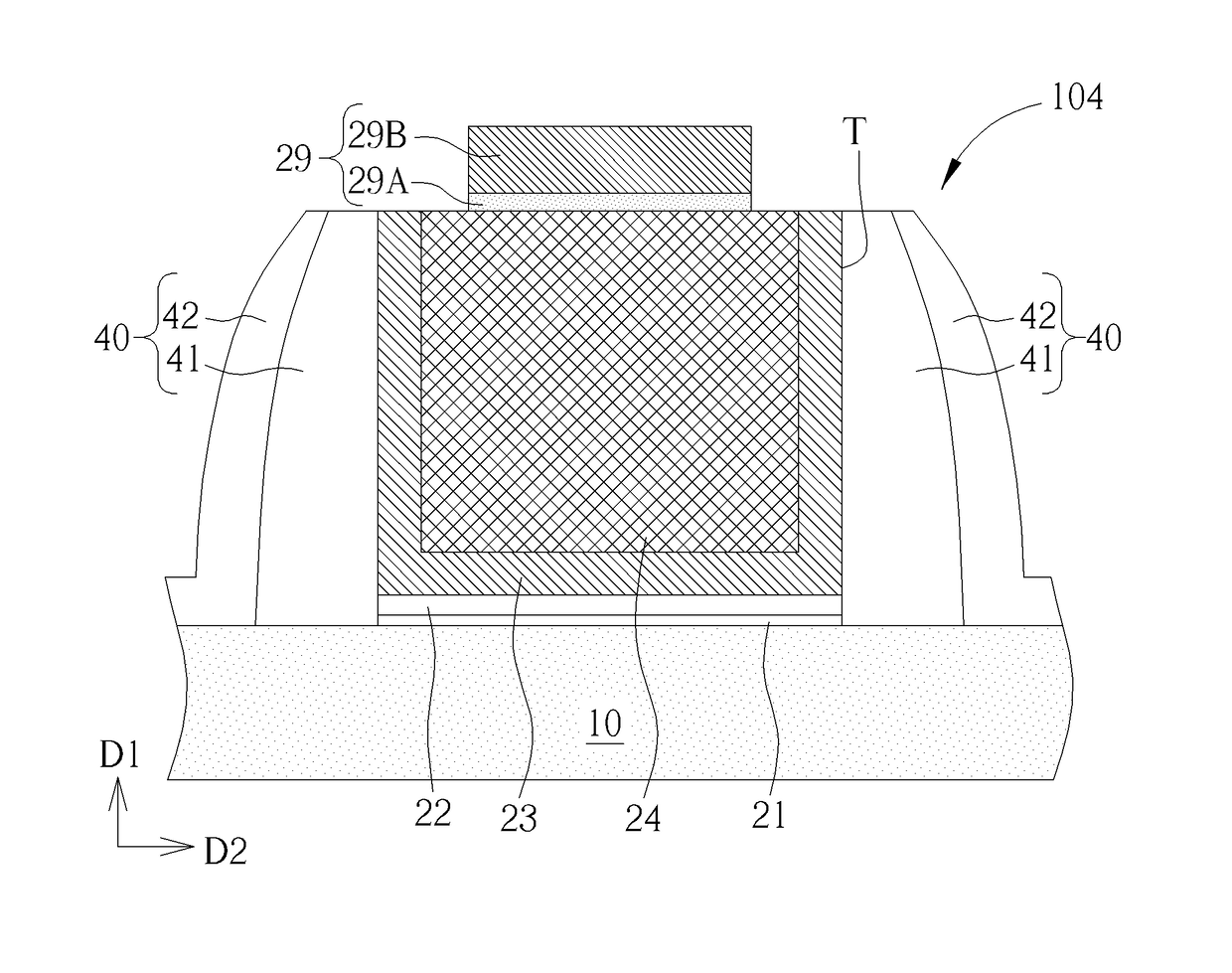

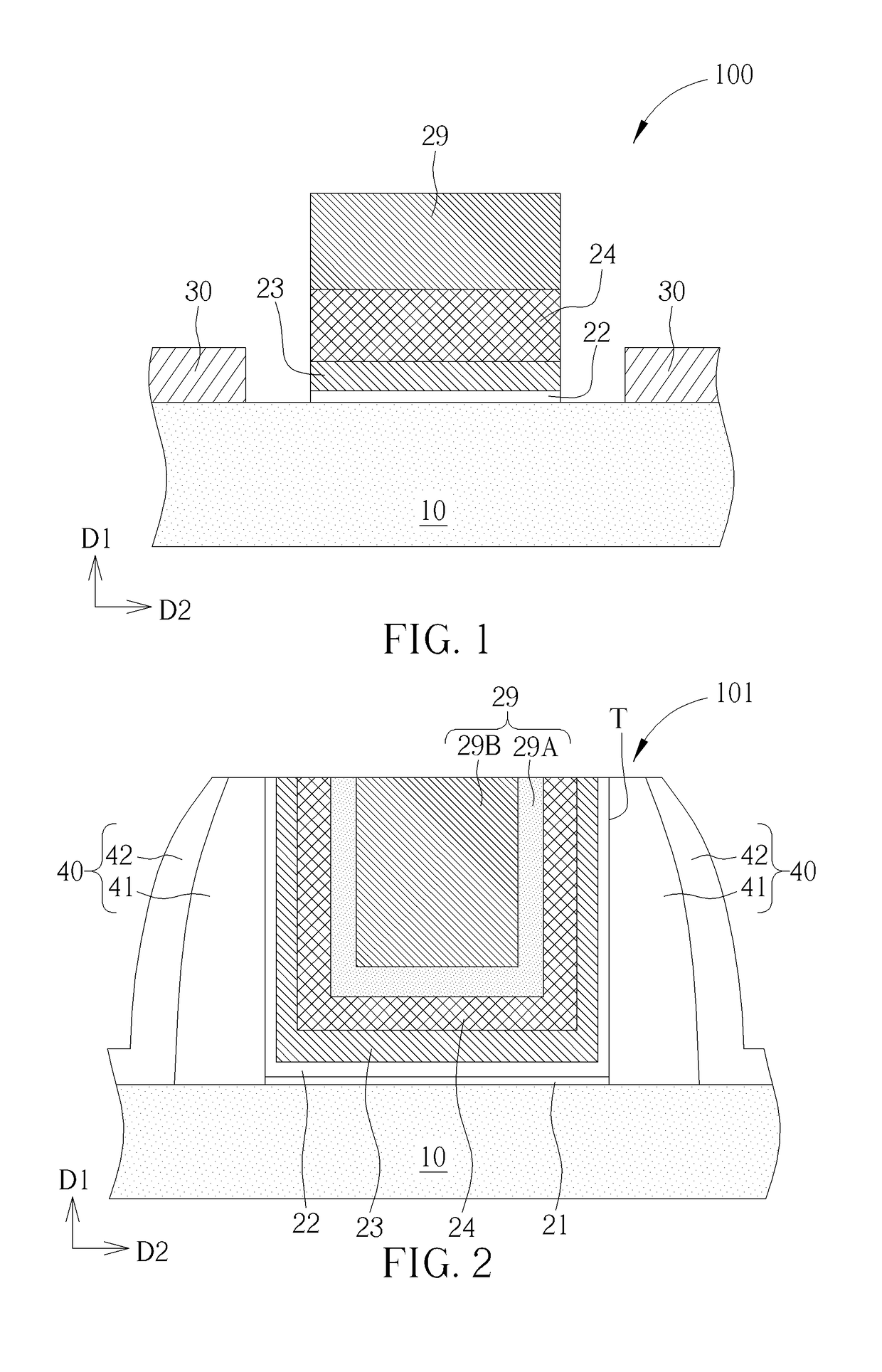

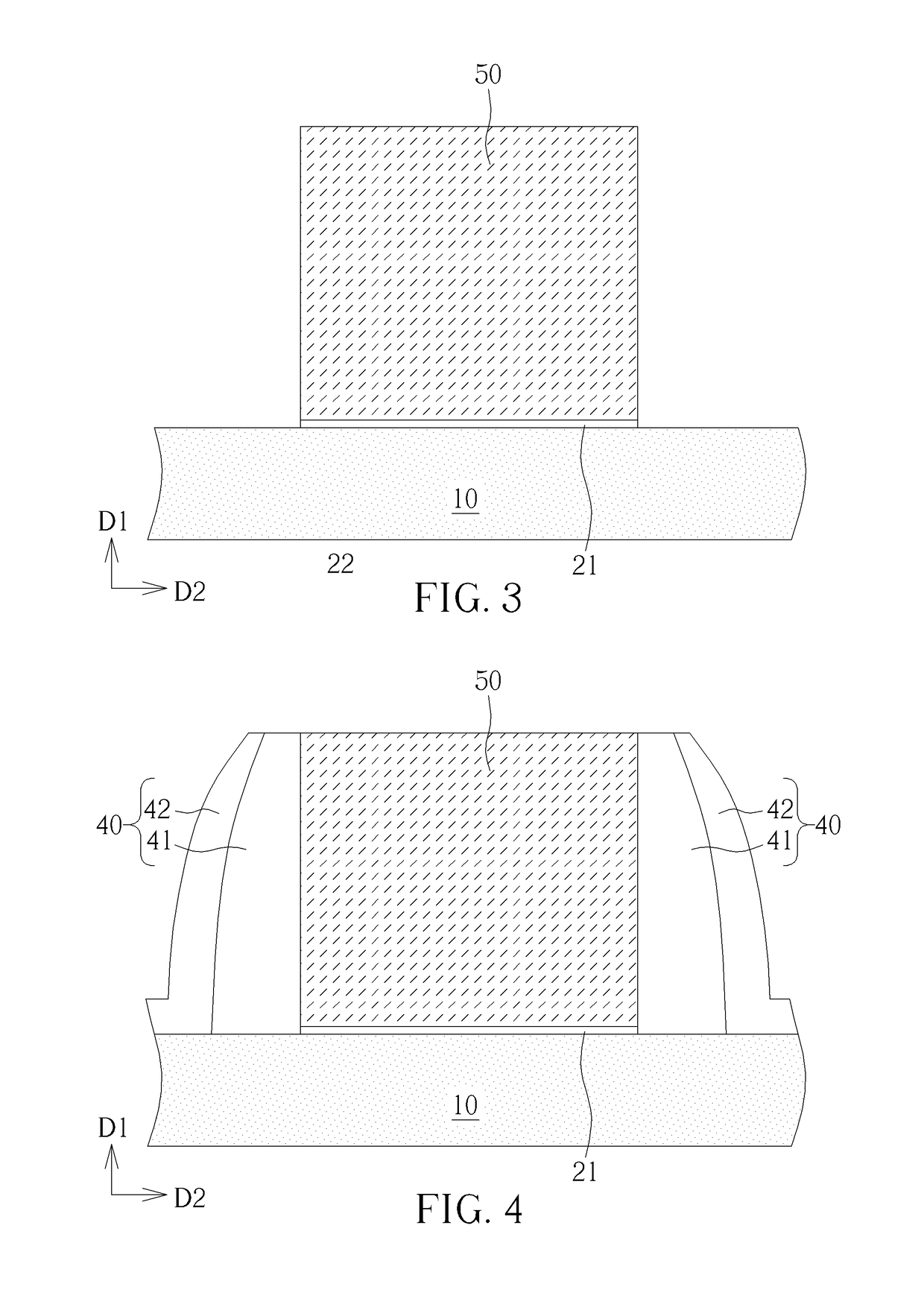

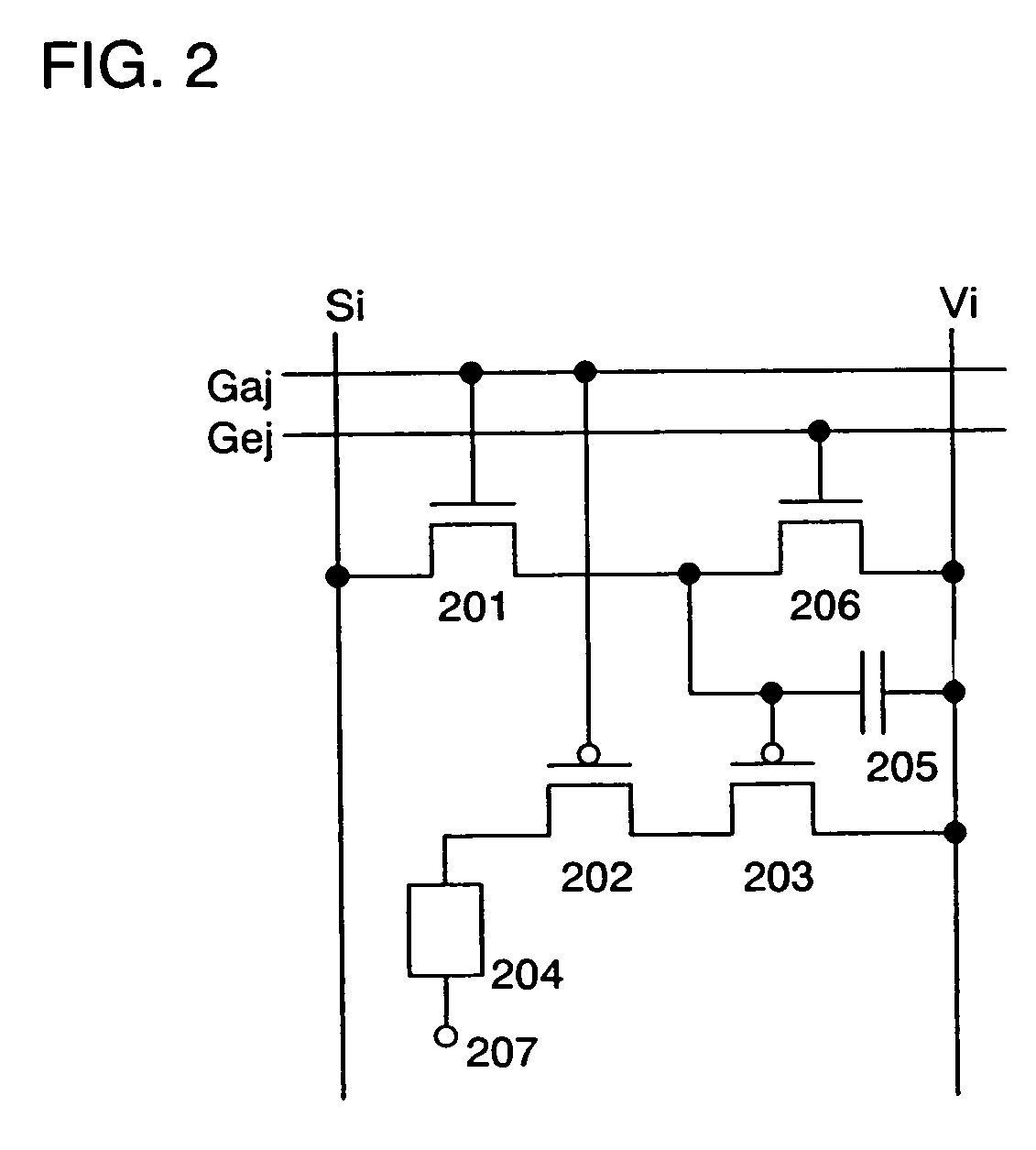

Active device and active device array substrate

InactiveUS20130240886A1Increase the on-currentEffectively improve ON-currentSolid-state devicesSemiconductor devicesEngineeringCommon gate

An active device and an active device array substrate are provided, wherein the active device array substrate includes a substrate and a plurality of active devices being located on the substrate, and at least one of the active devices includes a first thin film transistor and a second thin film transistor. The first thin film transistor is located on the substrate and has a first channel layer. The second thin film transistor stacks on the first thin film transistor, wherein the second thin film transistor has a second channel layer. The first thin film transistor and the second thin film transistor share a common gate electrode and the common gate electrode is located between the first channel layer and the second channel layer.

Owner:DONGGUAN MASSTOP LIQUID CRYSTAL DISPLAY +1

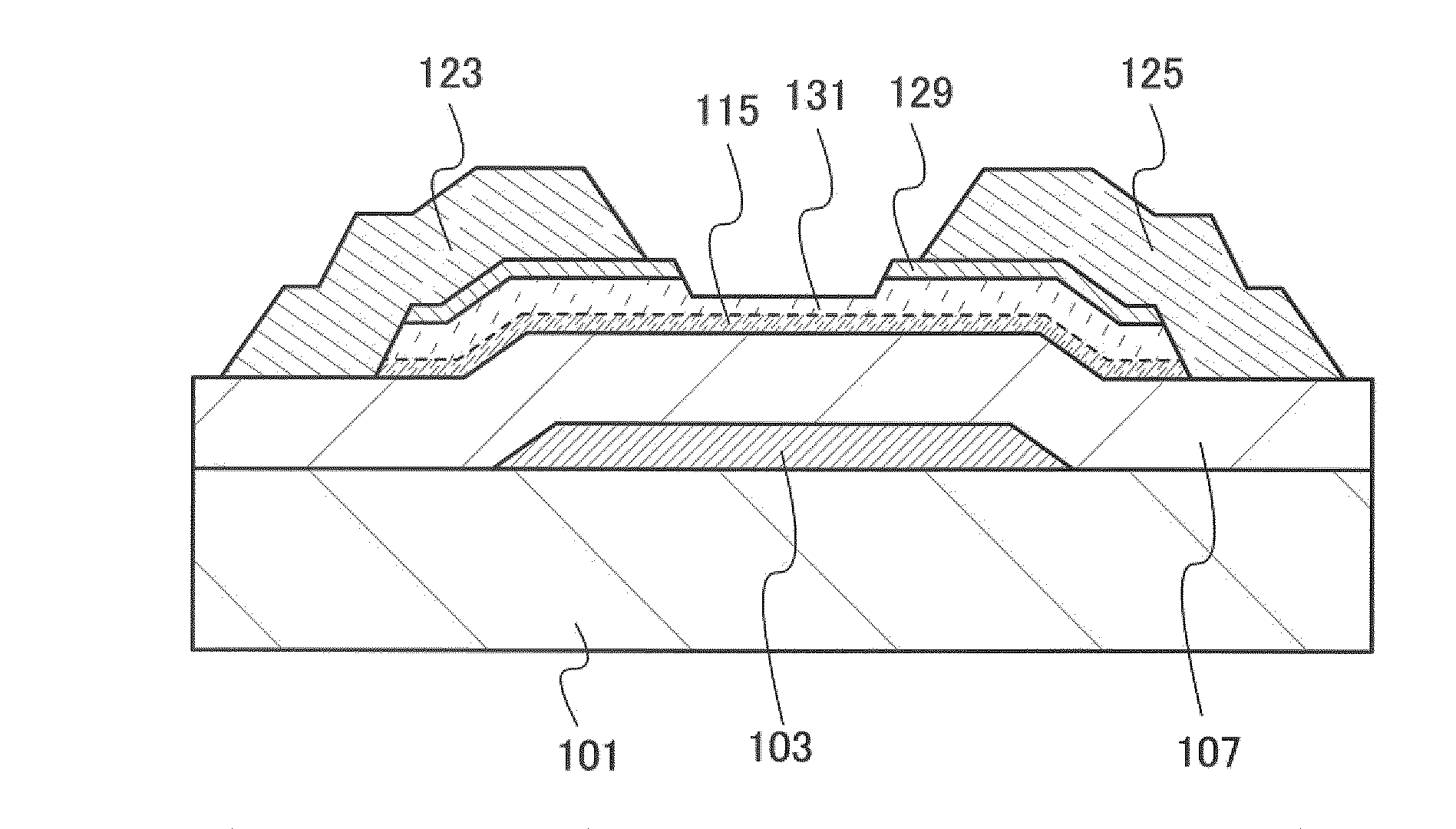

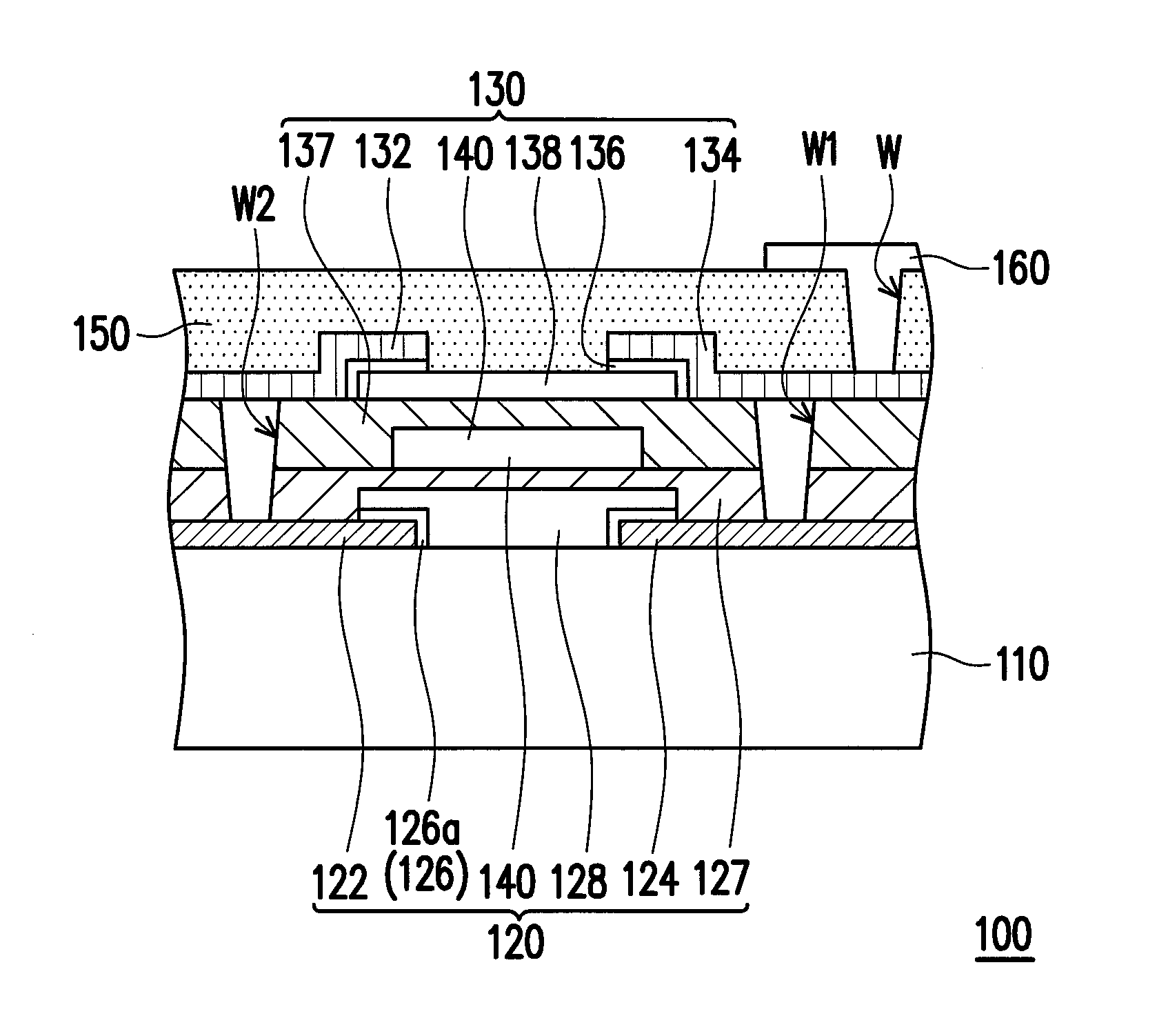

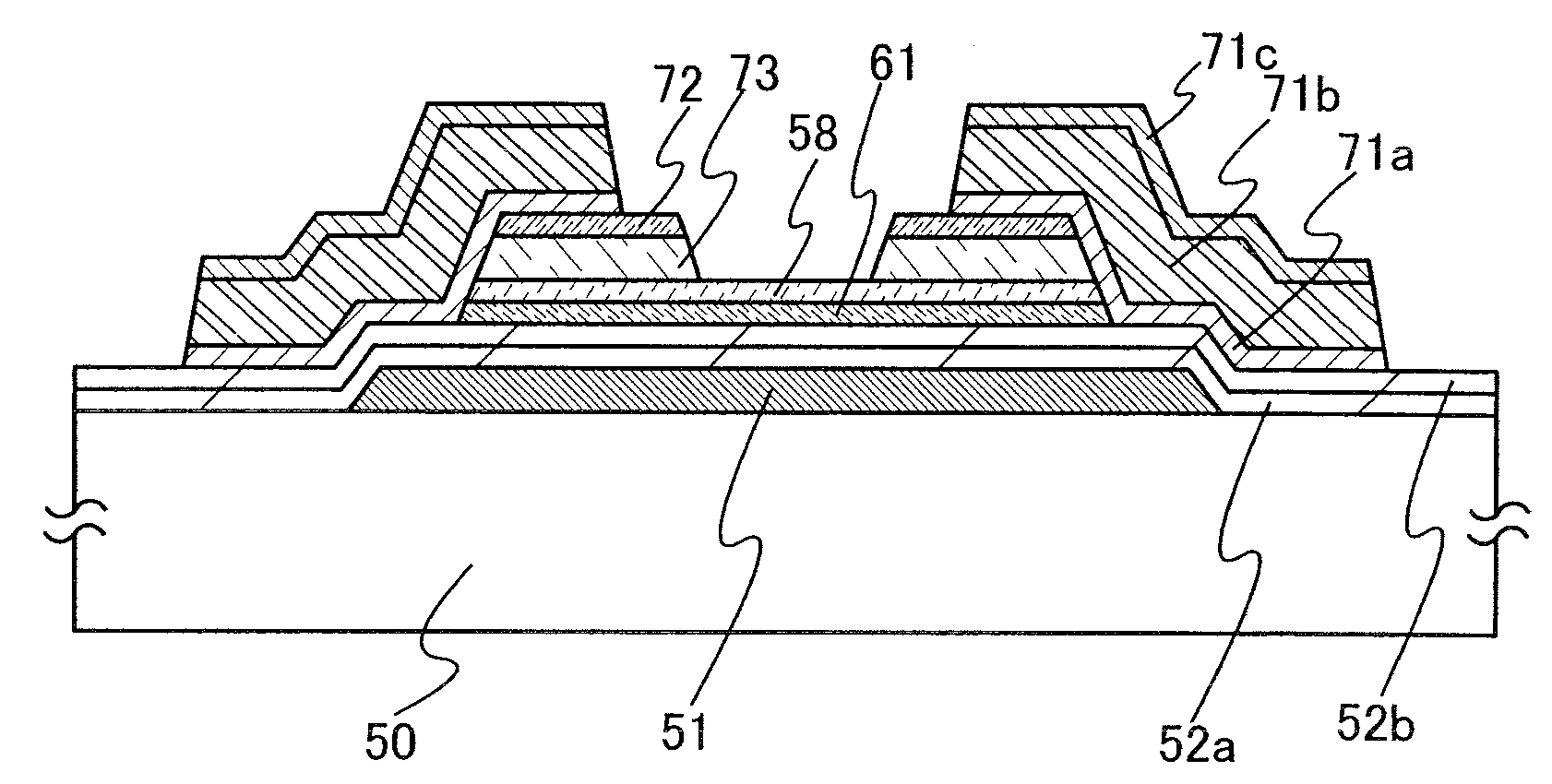

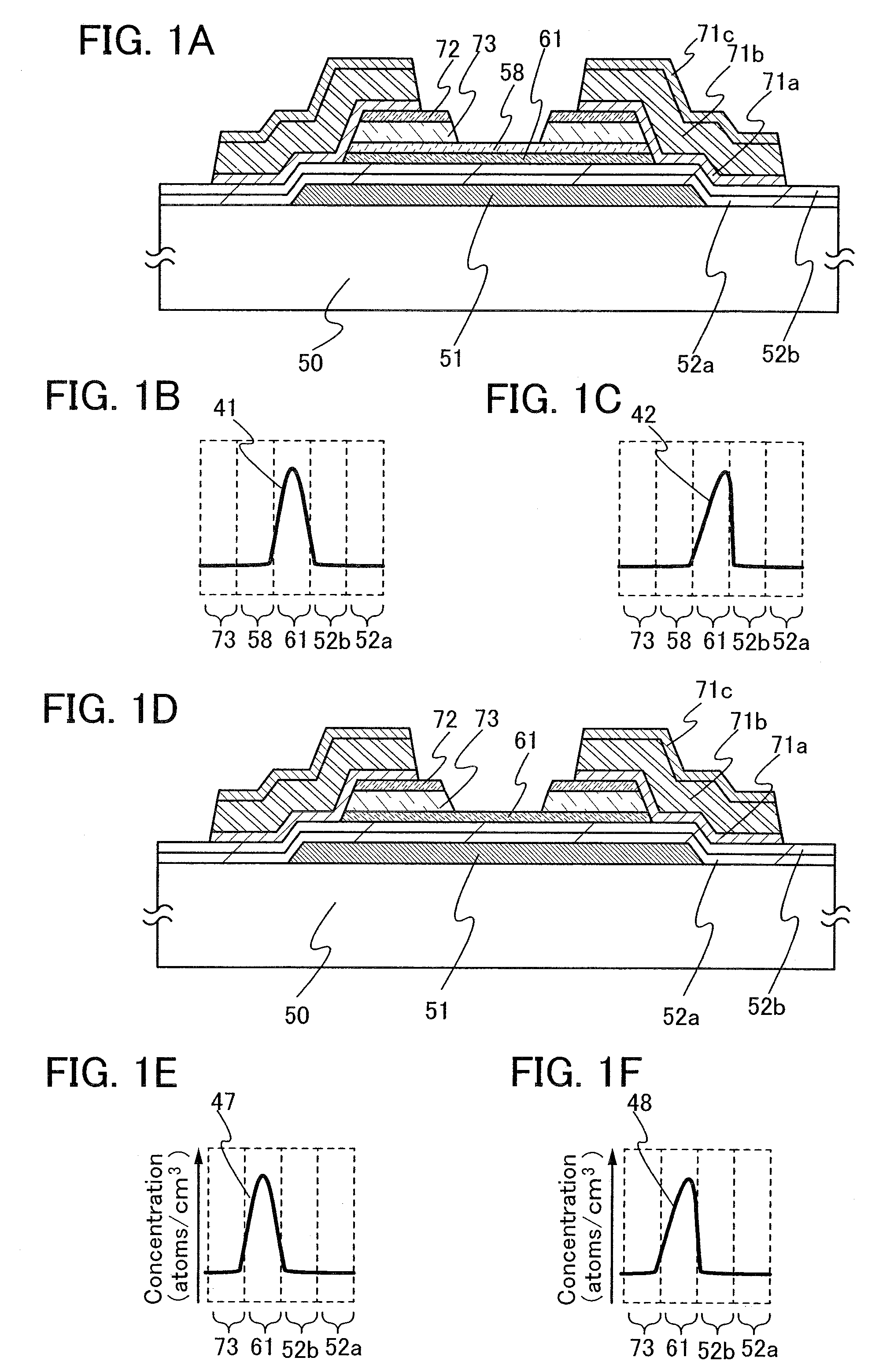

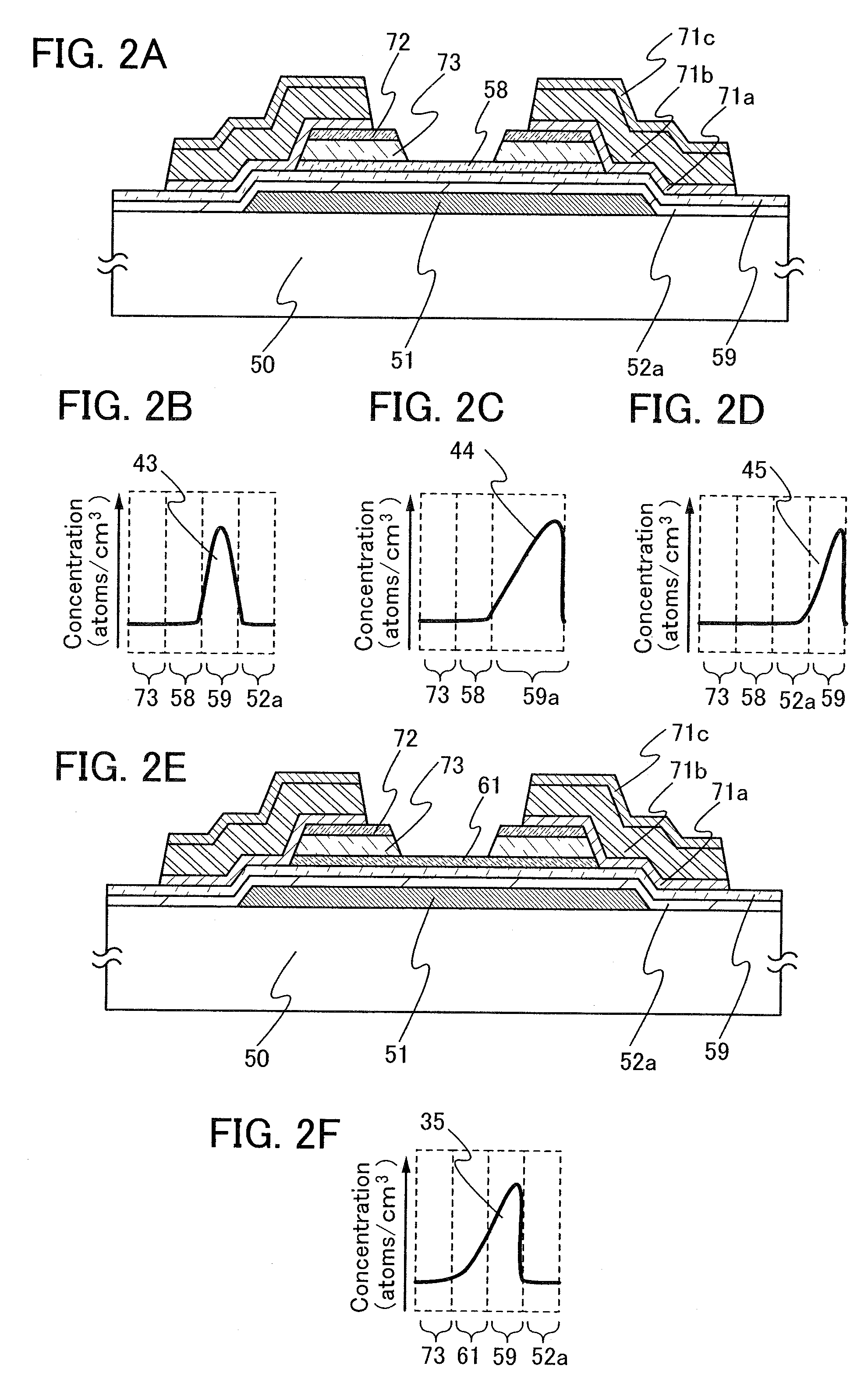

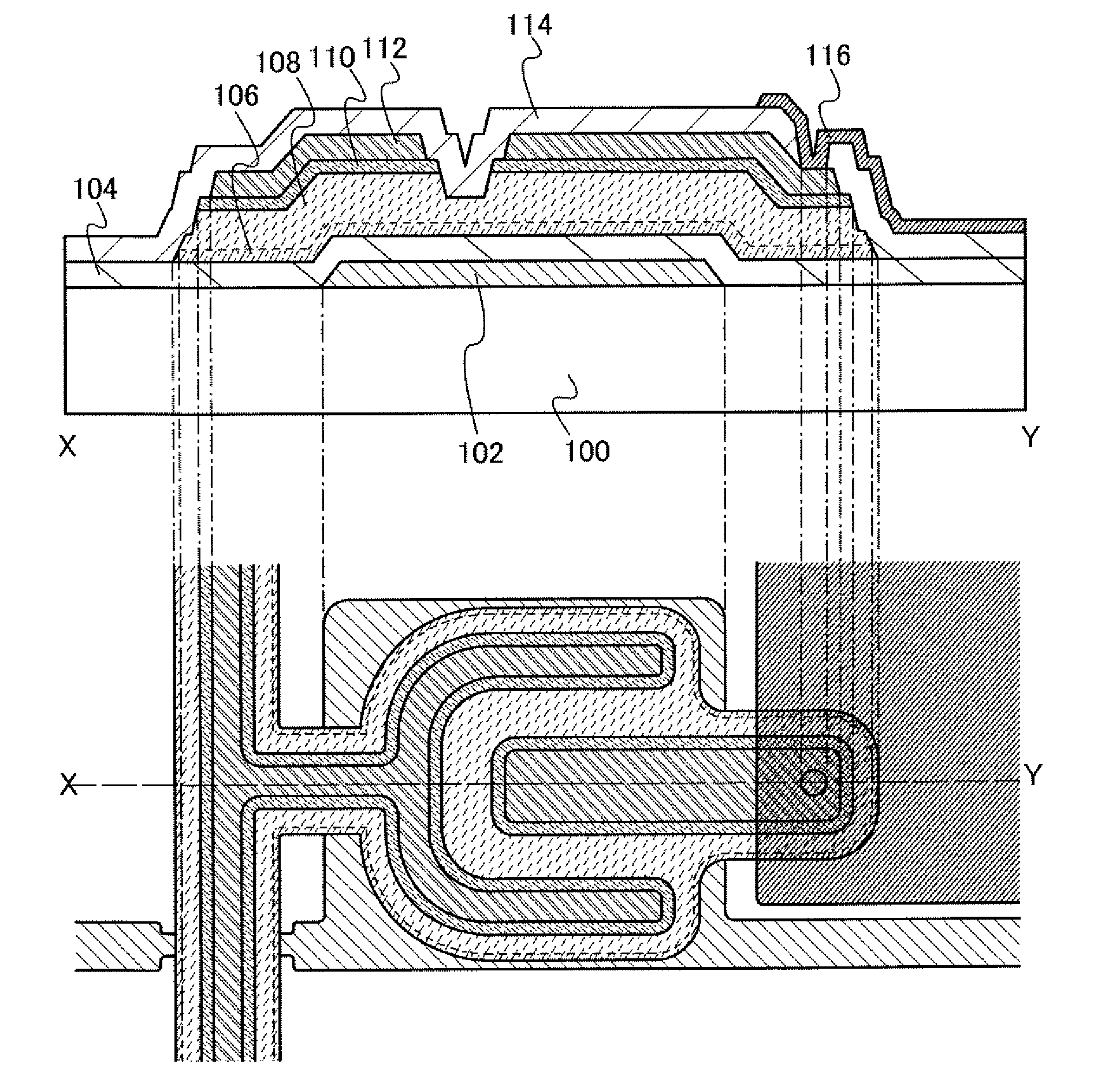

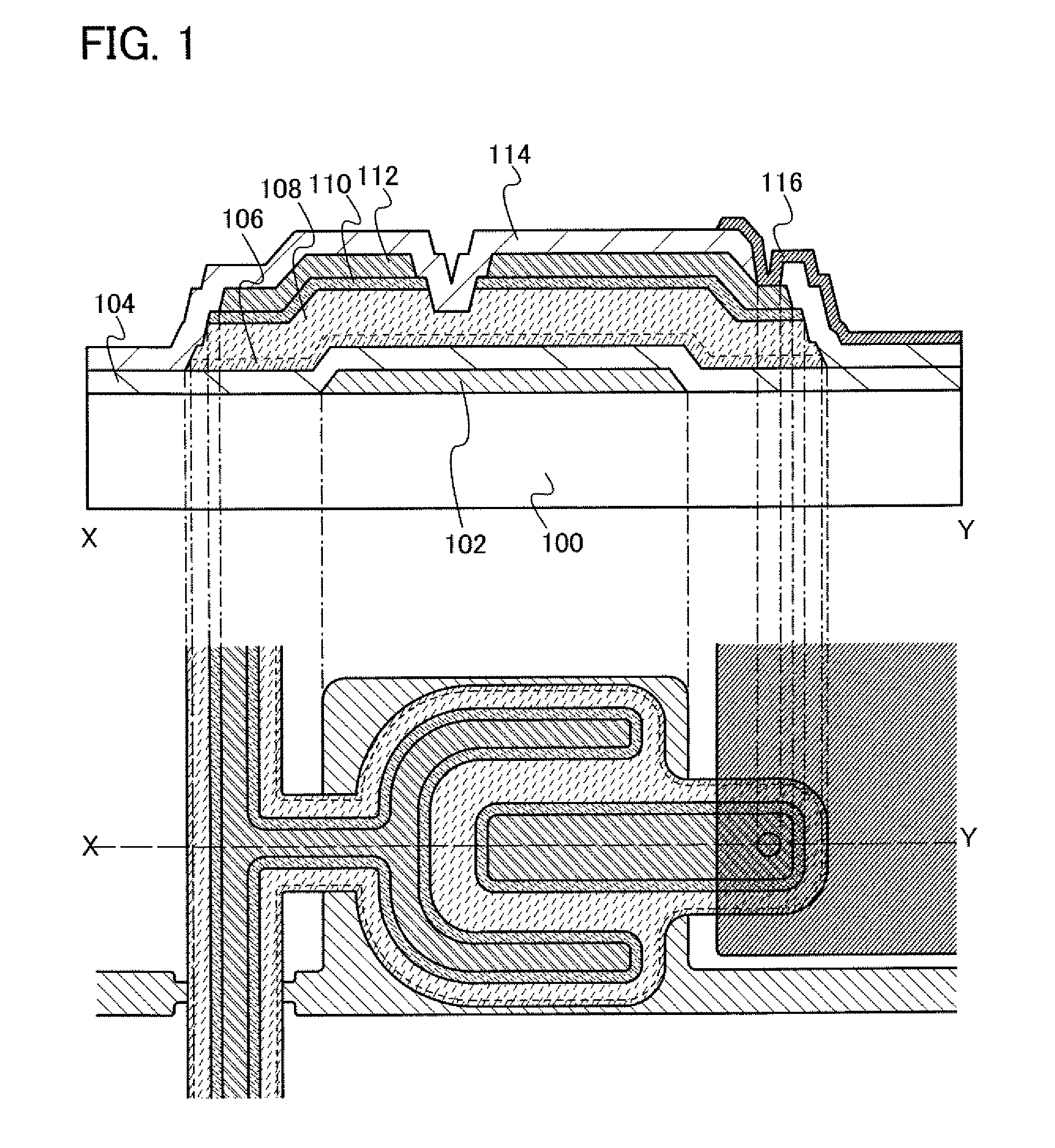

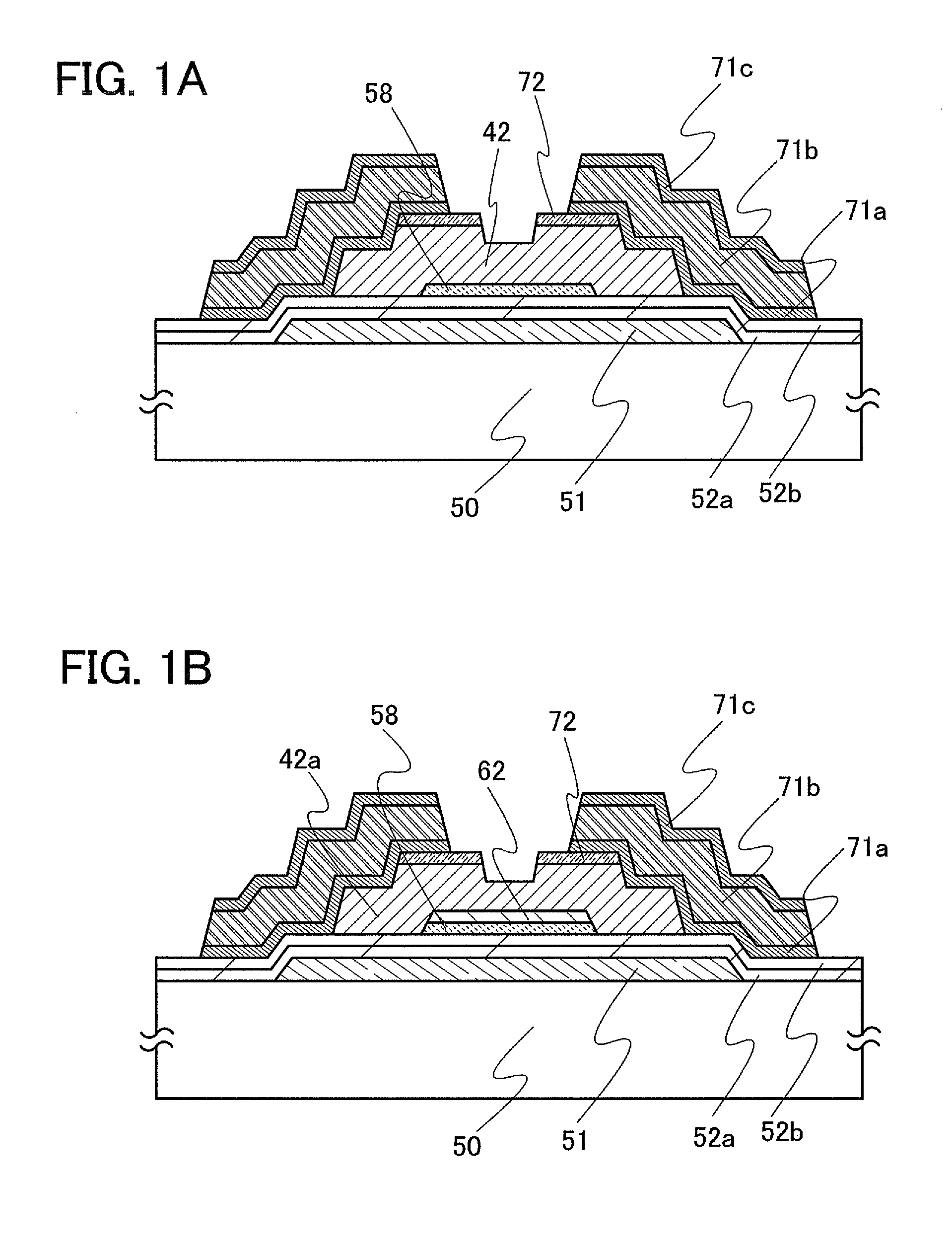

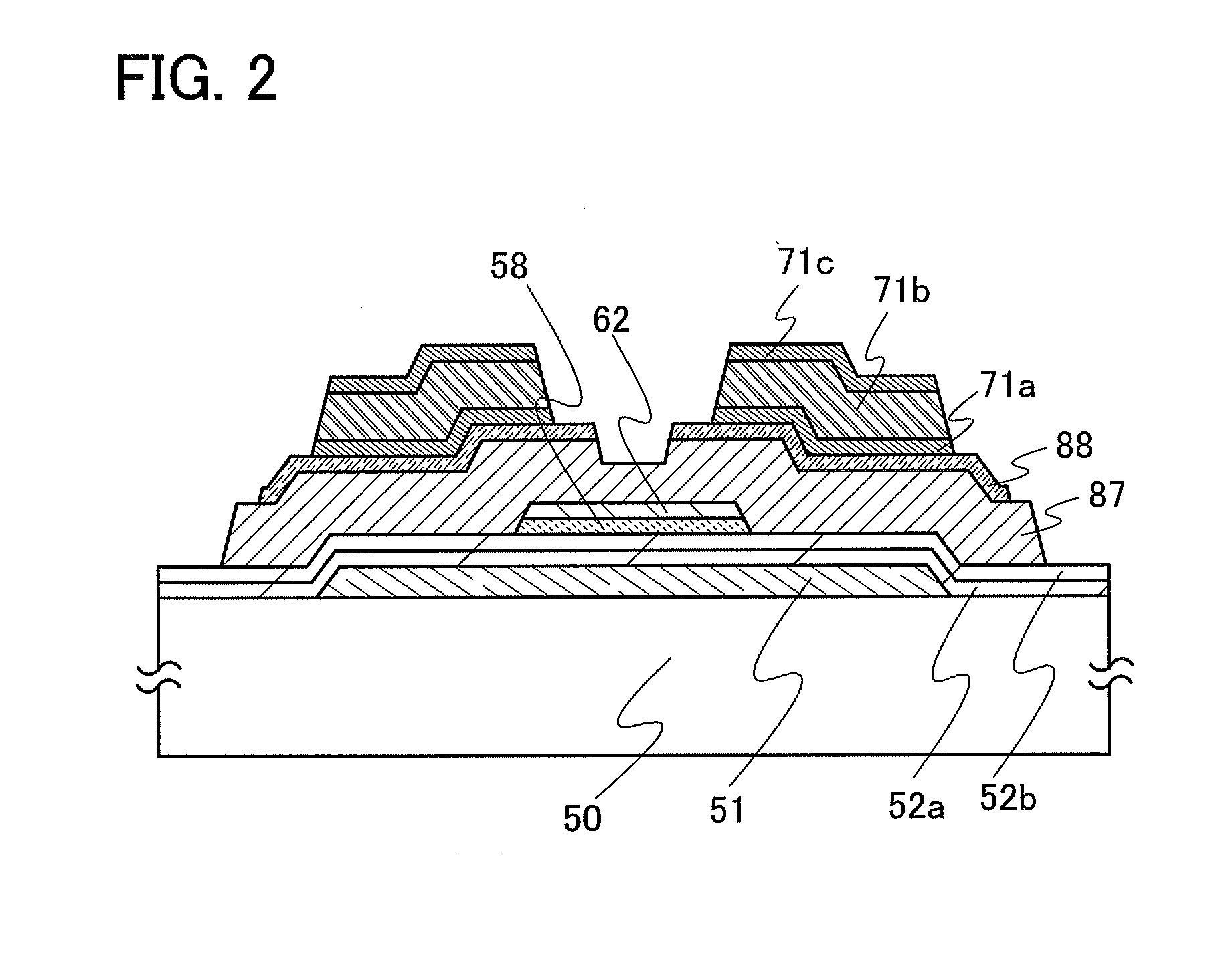

Thin film transistor, display device having thin film transistor, and method for manufacturing the same

InactiveUS20090090915A1High crystallinityExcellent electric characteristicCapacitorsSemiconductor devicesSemiconductorDisplay device

A thin film transistor with excellent electric characteristics, a display device having the thin film transistor, and methods for manufacturing the thin film transistor and the display device are proposed. The thin film transistor includes a gate insulating film formed over a gate electrode, a microcrystalline semiconductor film formed over the gate insulating film, a pair of buffer layers formed over the microcrystalline semiconductor film, a pair of semiconductor films to which an impurity element imparting one conductivity type is added and which are formed over the pair of buffer layers, and wirings formed over the pair of semiconductor films to which the impurity element imparting one conductivity type is added. A part of the gate insulating film or the entire gate insulating film, and / or a part of the microcrystalline semiconductor or the entire microcrystalline semiconductor includes the impurity element which serves as a donor.

Owner:SEMICON ENERGY LAB CO LTD

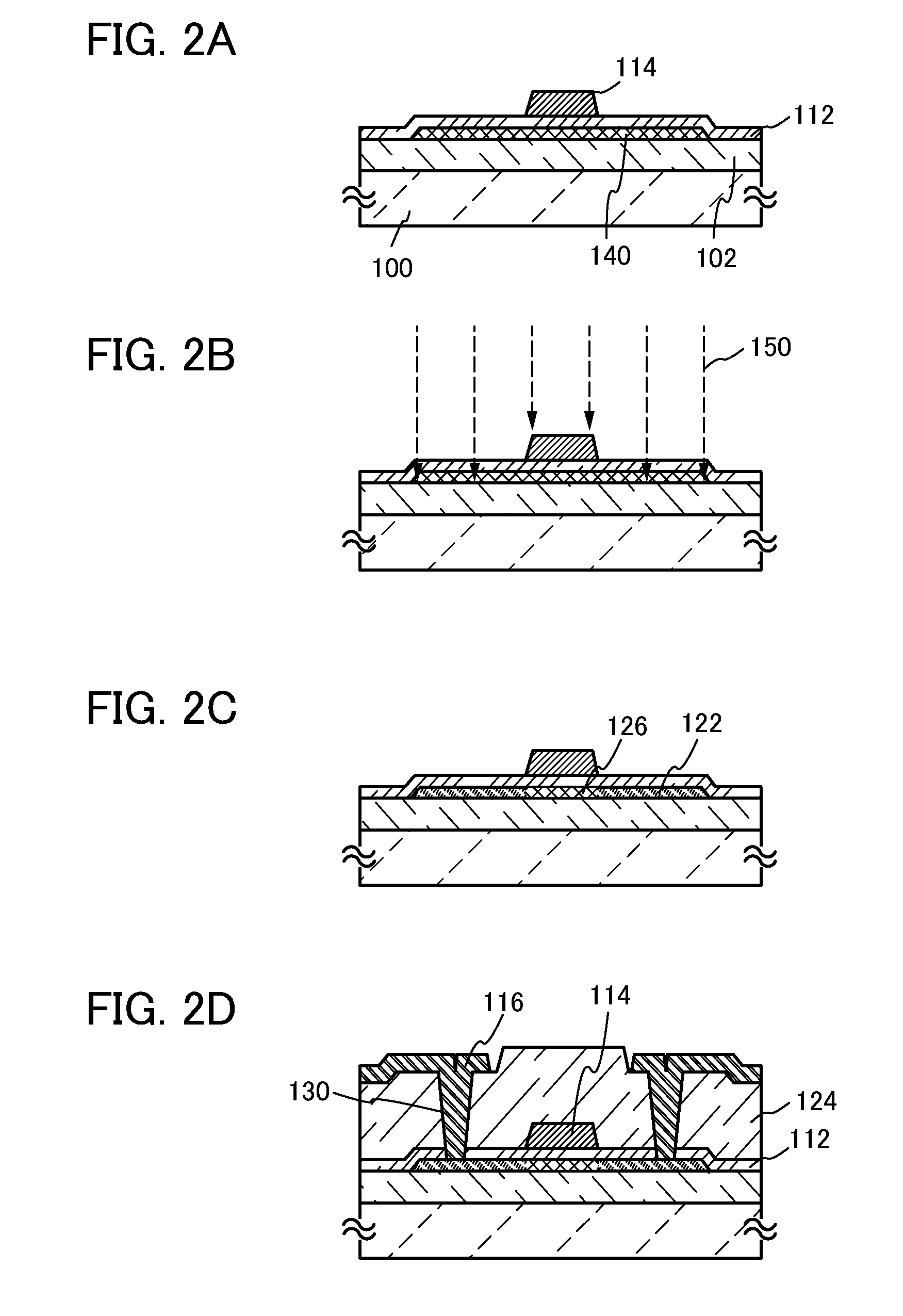

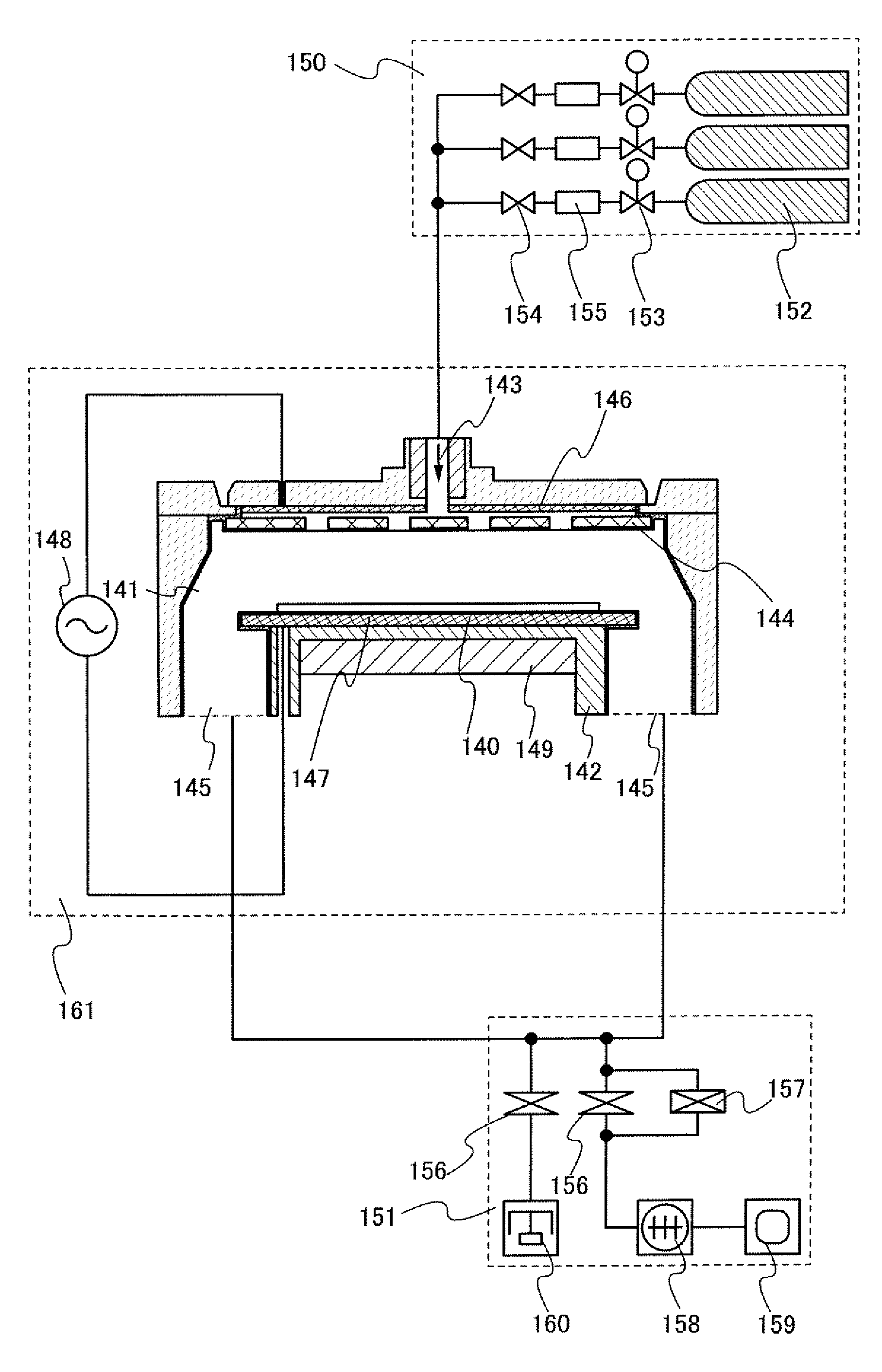

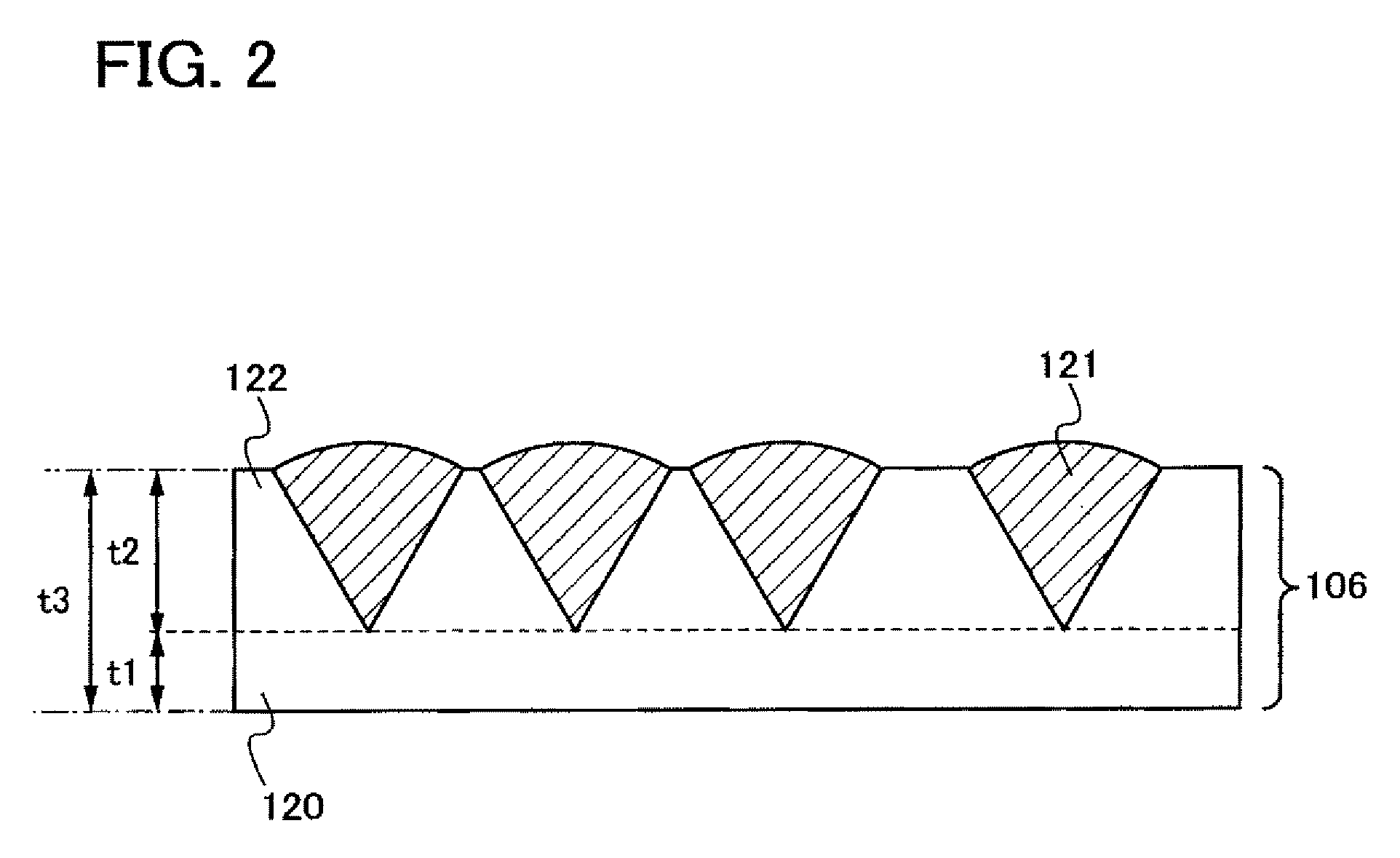

Method for manufacturing thin film transistor having microcrystalline semiconductor film

InactiveUS8138032B2Improve featuresIncrease the on-currentSolid-state devicesSemiconductor/solid-state device manufacturingImpuritySemiconductor

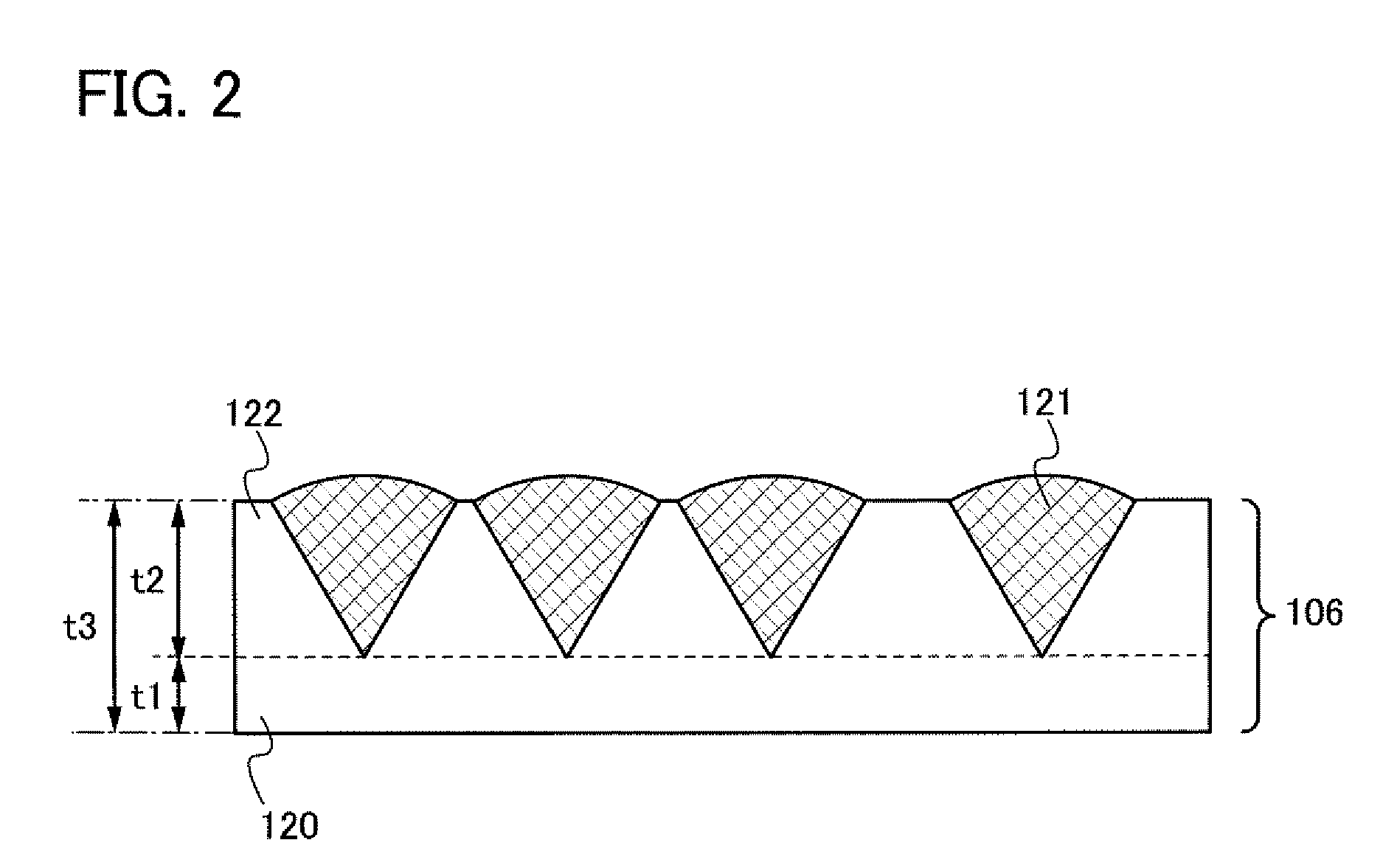

A thin film transistor includes, over a substrate having an insulating surface, a gate insulating layer covering a gate electrode; a semiconductor layer which includes a plurality of crystalline regions in an amorphous structure and which forms a channel formation region, in contact with the gate insulating layer; a semiconductor layer including an impurity element imparting one conductivity type, which forms source and drain regions; and a buffer layer including an amorphous semiconductor between the semiconductor layer and the semiconductor layer including an impurity element imparting one conductivity type. The crystalline regions have an inverted conical or inverted pyramidal crystal particle which grows approximately radially in a direction in which the semiconductor layer is deposited, from a position away from an interface between the gate insulating layer and the semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Thin film transistor and method for manufacturing the same

InactiveUS8119468B2High purityImprove featuresTransistorSolid-state devicesAmorphous siliconCrystalline particle

Disclosed is a thin film transistor which includes, over a substrate having an insulating surface, a gate insulating layer covering a gate electrode; a semiconductor layer which functions as a channel formation region; and a semiconductor layer including an impurity element imparting one conductivity type. The semiconductor layer exists in a state that a plurality of crystalline particles is dispersed in an amorphous silicon and that the crystalline particles have an inverted conical or inverted pyramidal shape. The crystalline particles grow approximately radially in a direction in which the semiconductor layer is deposited. Vertexes of the inverted conical or inverted pyramidal crystal particles are located apart from an interface between the gate insulating layer and the semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Oxide semiconductor transistor and manufacturing method thereof

ActiveUS9722093B1Negative capacitance effectIncrease the on-currentTransistorSolid-state devicesInsulation layerEngineering

An oxide semiconductor transistor includes an oxide semiconductor channel layer, a metal gate, a gate insulation layer, an internal electrode, and a ferroelectric material layer. The metal gate is disposed on the oxide semiconductor channel layer. The gate insulation layer is disposed between the metal gate and the oxide semiconductor channel layer. The internal electrode is disposed between the gate insulation layer and the metal gate. The ferroelectric material layer is disposed between the internal electrode and the metal gate. The ferroelectric material layer in the oxide semiconductor transistor of the present invention is used to enhance the electrical characteristics of the oxide semiconductor transistor.

Owner:UNITED MICROELECTRONICS CORP

Thin film transistor and method for manufacturing the same

InactiveUS20100096631A1Increase currentTotal current dropTransistorSolid-state devicesSemiconductorImpurity

A thin film transistor includes, over a substrate having an insulating surface, a gate insulating layer covering a gate electrode; a semiconductor layer which includes a plurality of crystalline regions in an amorphous structure and which forms a channel formation region, in contact with the gate insulating layer; a semiconductor layer including an impurity element imparting one conductivity type, which forms source and drain regions; and a buffer layer including an amorphous semiconductor between the semiconductor layer and the semiconductor layer including an impurity element imparting one conductivity type. The crystalline regions have an inverted conical or inverted pyramidal crystal particle which grows approximately radially in a direction in which the semiconductor layer is deposited, from a position away from an interface between the gate insulating layer and the semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

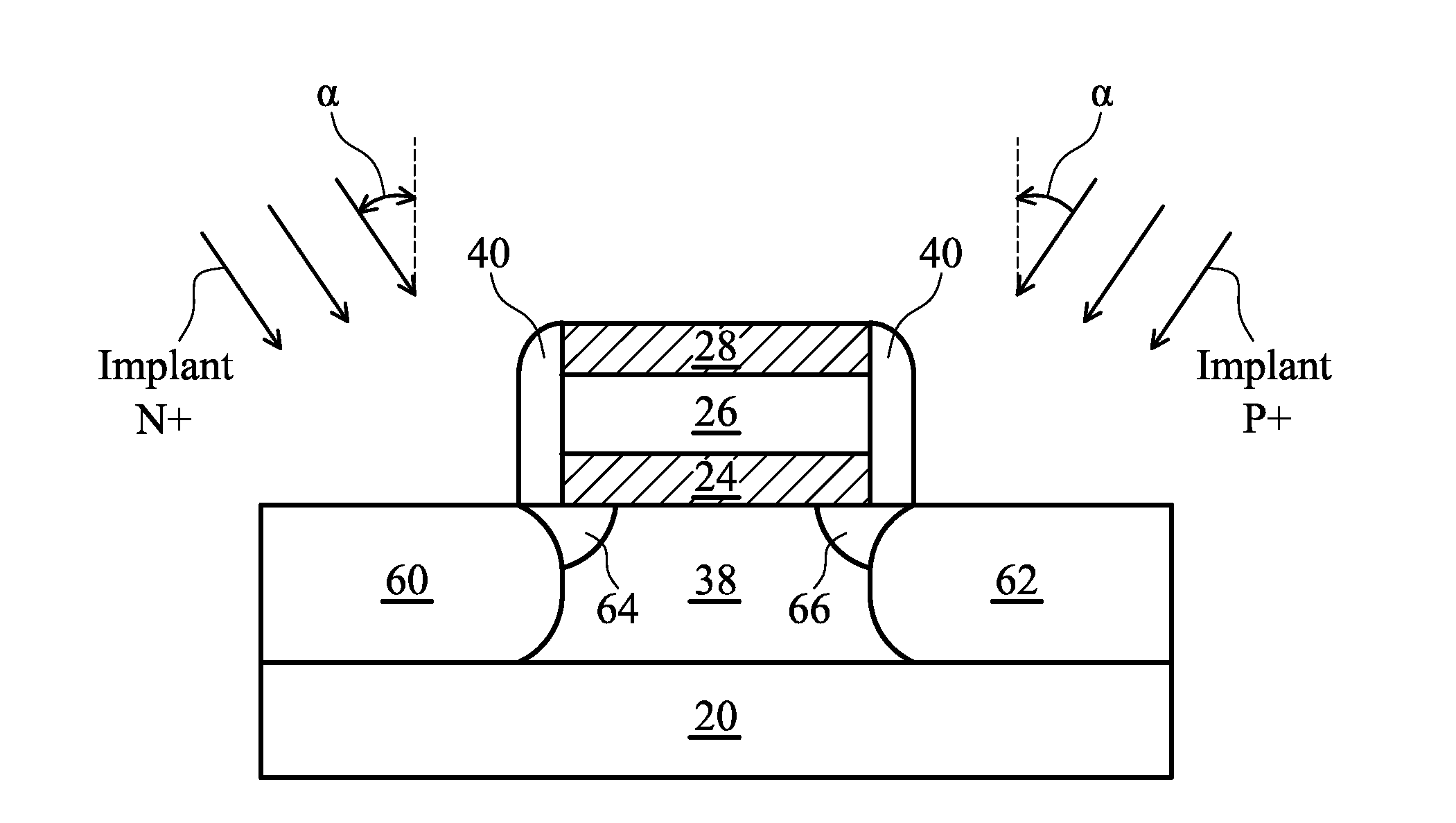

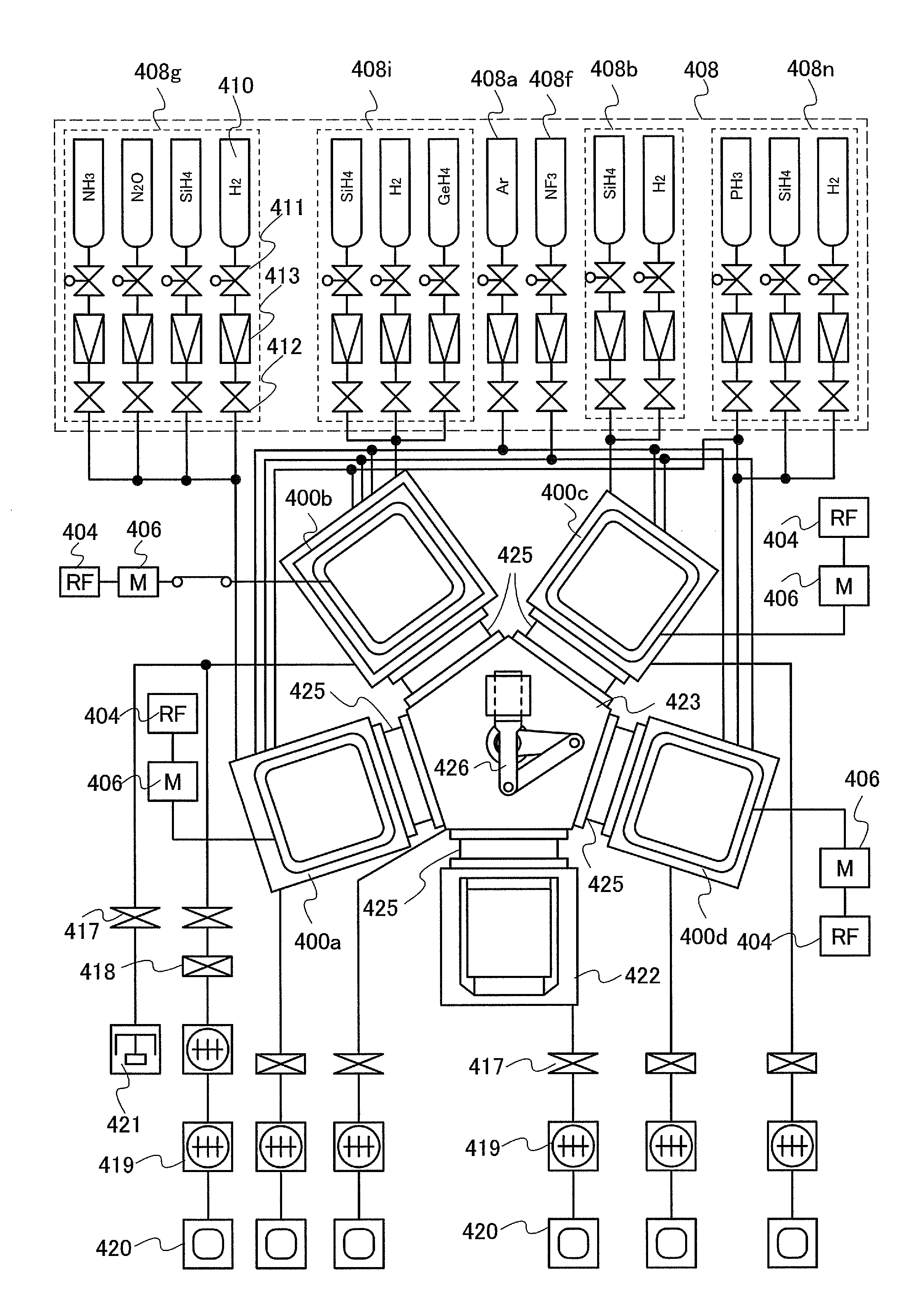

Sequential selective epitaxial growth

ActiveUS7807523B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETCMOS

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. A multi step epitaxial process can be used to extend the ridges with different dopant types, high mobility semiconductor, and or advanced multi-layer strutures. For CMOS integrated circuits a capping layer is formed over the a first region. Epitaxial layers are formed in a second region. Then the capping layer is removed from the first region and a capping layer is formed over the second region. Epitaxial layers can than be formed in the first region.

Owner:SYNOPSYS INC

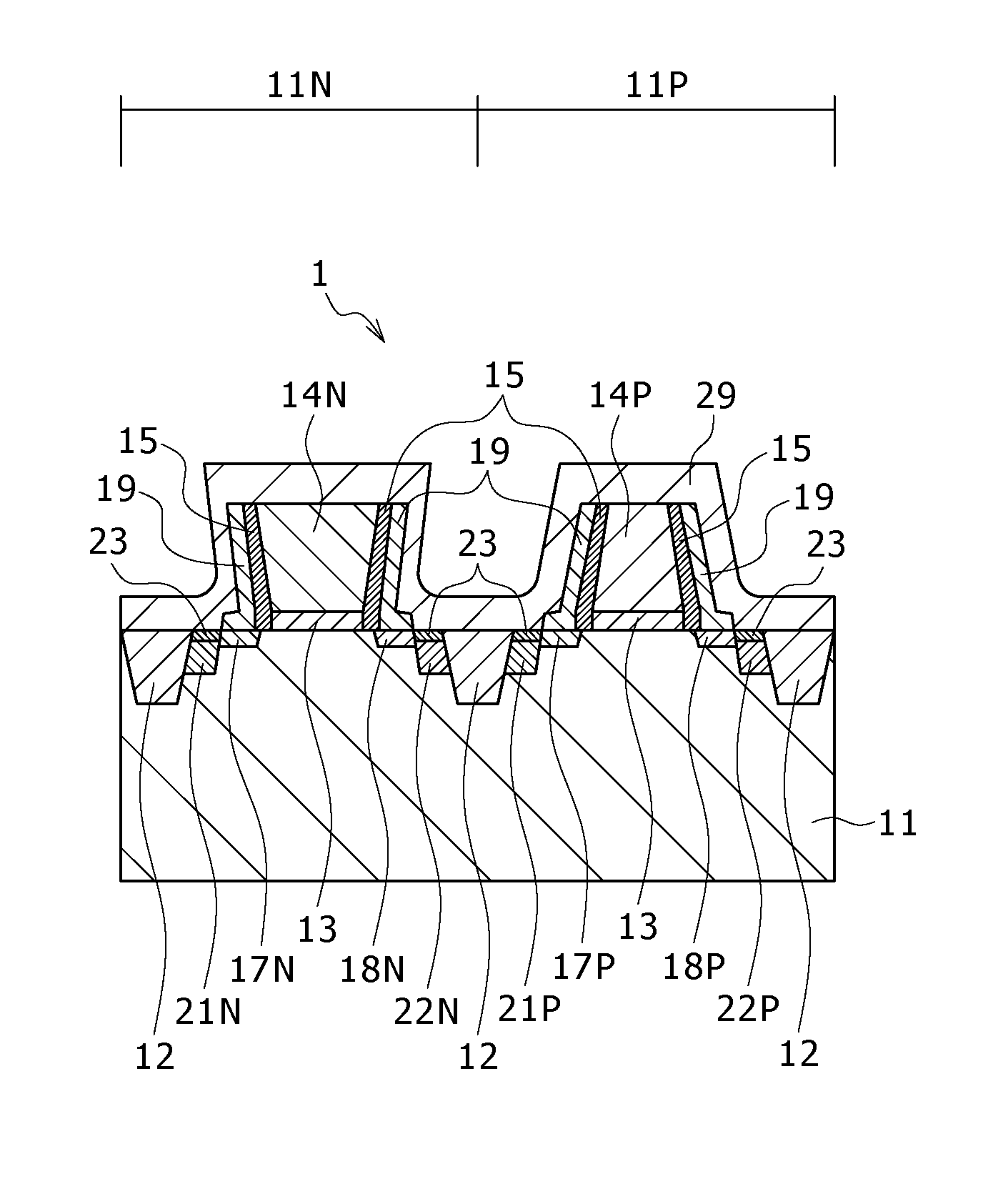

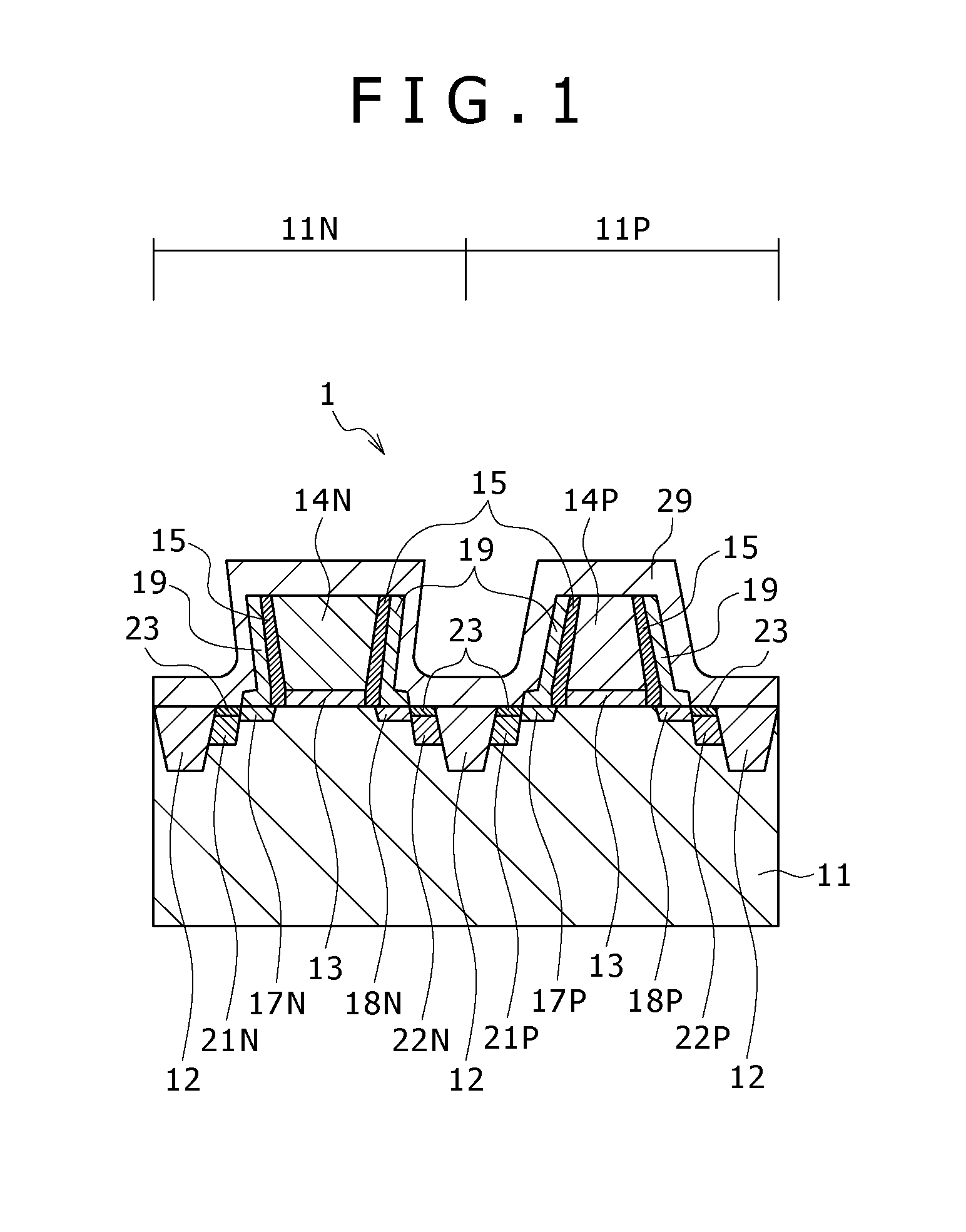

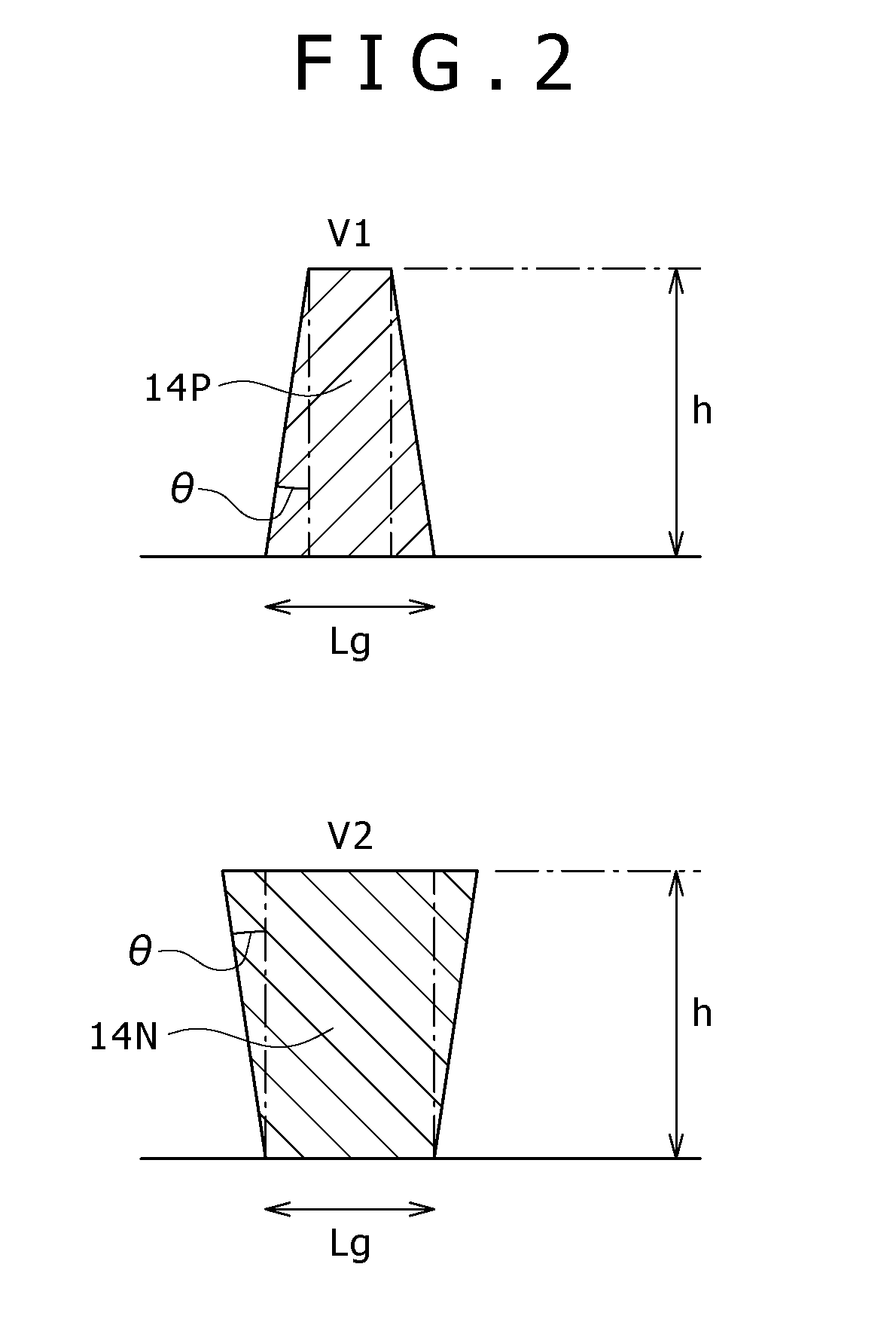

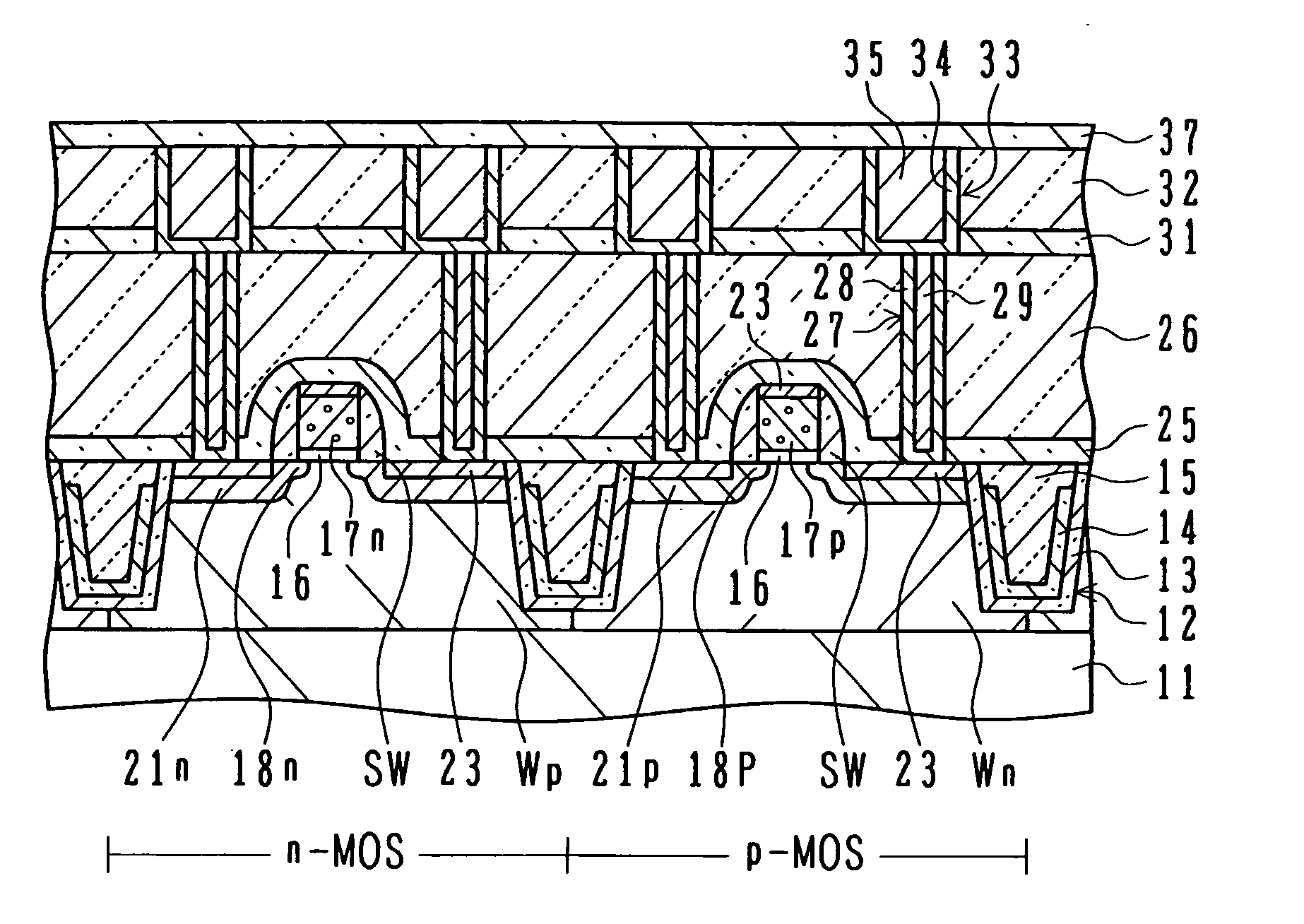

Semiconductor device and method of manufacturing the same

ActiveUS20090057771A1Small volumeStress exert on be increaseTransistorSolid-state devicesSemiconductorDevice material

Disclosed herein is a semiconductor device including a semiconductor substrate provided with an N-type FET and P-type FET, with a gate electrode of the N-type FET and a gate electrode of the P-type FET having undergone full-silicidation, wherein the gate electrode of the P-type FET has such a sectional shape in the gate length direction that the gate length decreases as one goes upwards from a surface of the semiconductor substrate, and the gate electrode of the N-type FET has such a sectional shape in the gate length direction that the gate length increases as one goes upwards from the surface of the semiconductor substrate.

Owner:SONY CORP

Tunnel Field-Effect Transistor with Metal Source

InactiveUS20100123203A1Increase the on-currentReduced source-drain leakage currentDiodePhysicsSemiconductor

A semiconductor device includes a channel region; a gate dielectric over the channel region; and a gate electrode over the gate dielectric. A first source / drain region is adjacent the gate dielectric, wherein the first source / drain region is a semiconductor region and of a first conductivity type. A second source / drain region is on an opposite side of the channel region than the first source / drain region, wherein the second source / drain region is a metal region. A pocket region of a second conductivity type opposite the first conductivity type is horizontally between the channel region and the second source / drain region.

Owner:TAIWAN SEMICON MFG CO LTD

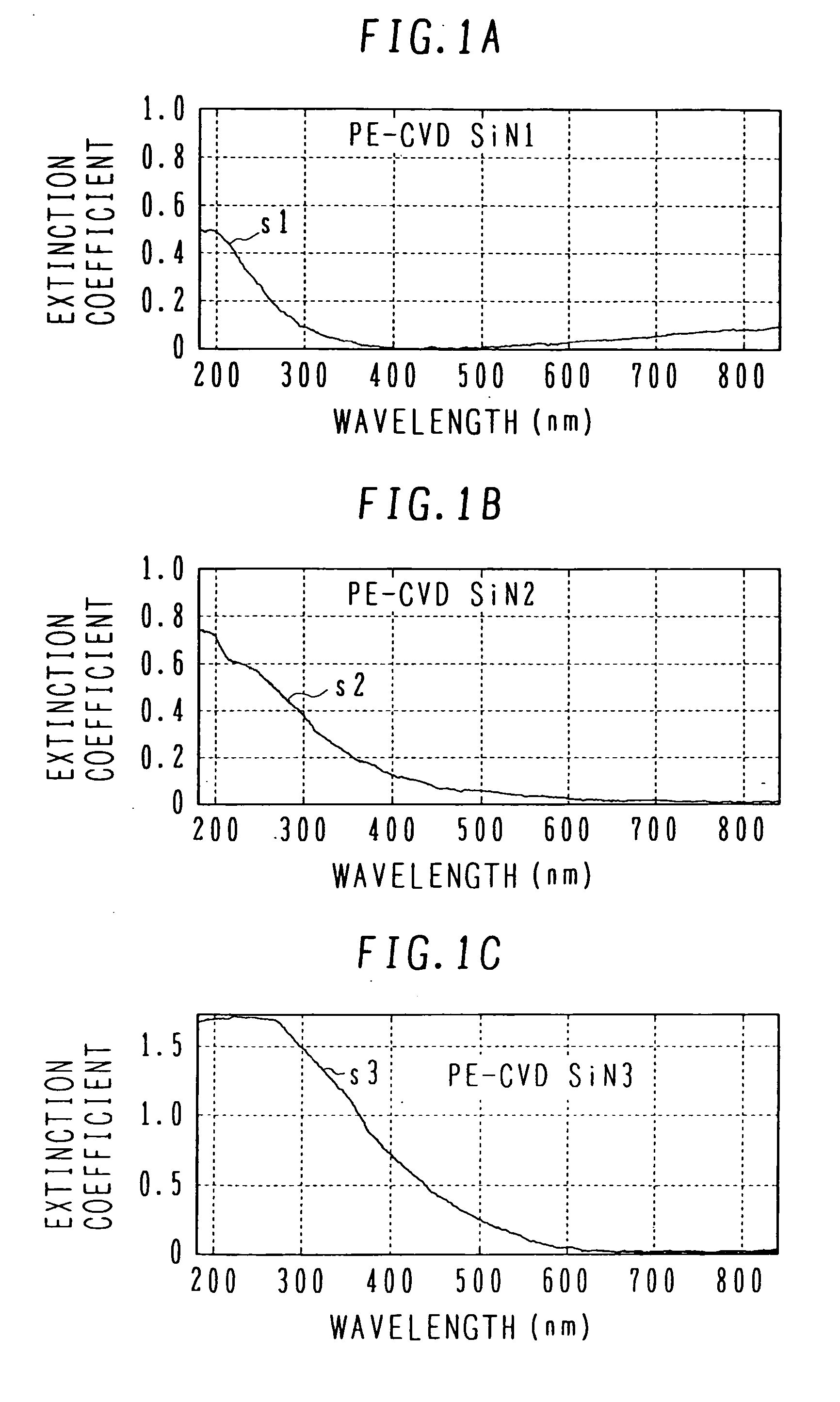

Semiconductor device having STI with nitride liner

ActiveUS20060001104A1Reduce leak currentImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSilicon nitrideP channel

A semiconductor device has: a silicon substrate; trench formed downward from the surface of the silicon substrate, the trench defining active regions on the surface of the silicon substrate; a first liner layer of a silicon nitride film covering an inner wall of the trench; a second liner layer of a silicon nitride layer formed on the first liner layer; an element isolation region of an insulator formed on the second liner layer; a p-channel MOS transistor formed in and on one of the active regions; a contact etch stopper layer of a silicon nitride layer not having a ultraviolet shielding ability, formed above the silicon substrate, and covering the p-channel MOS transistor; and a light shielding film of a silicon nitride layer having the ultraviolet shielding ability and formed above the contact etch stopper layer.

Owner:FUJITSU SEMICON LTD

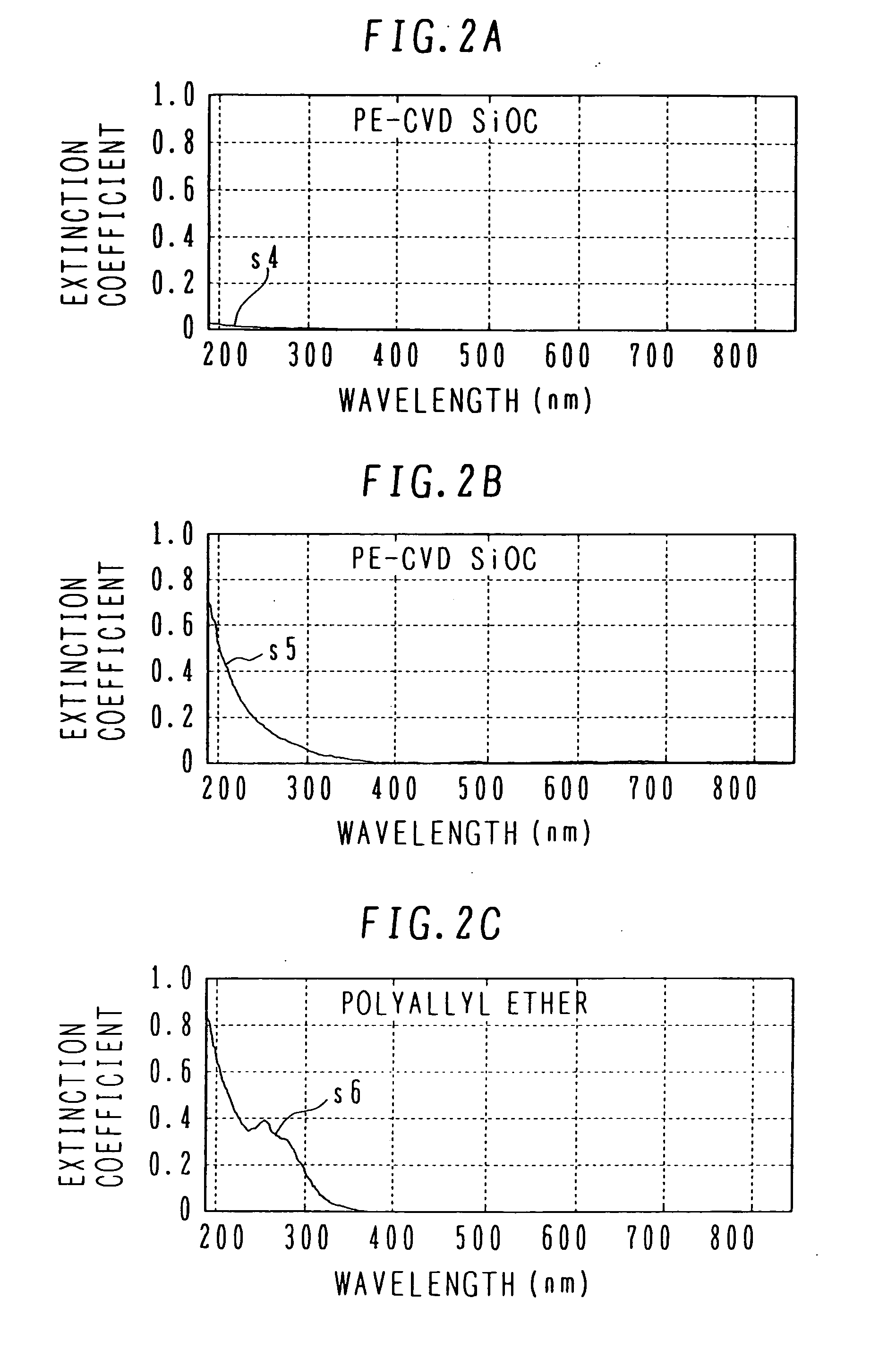

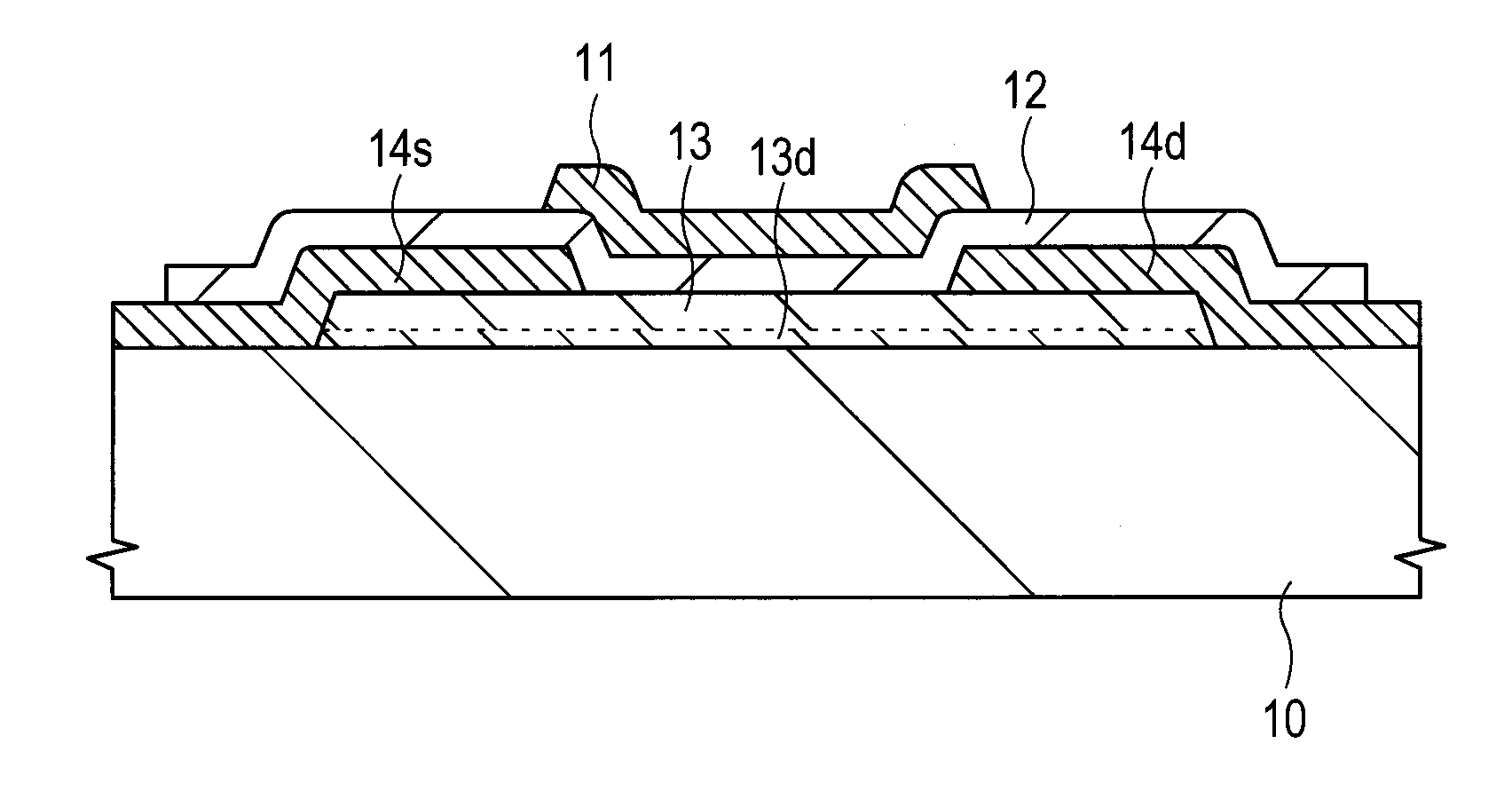

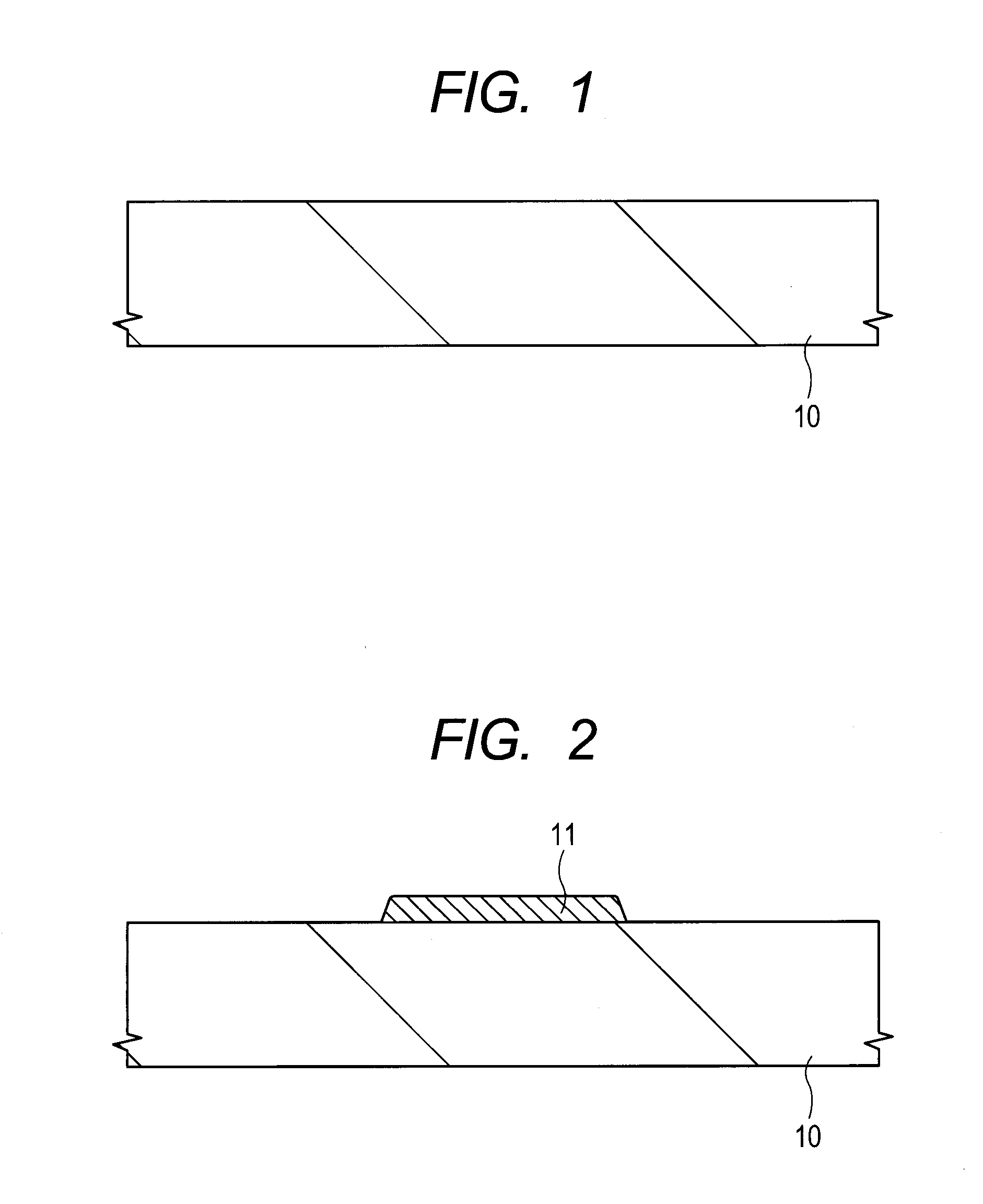

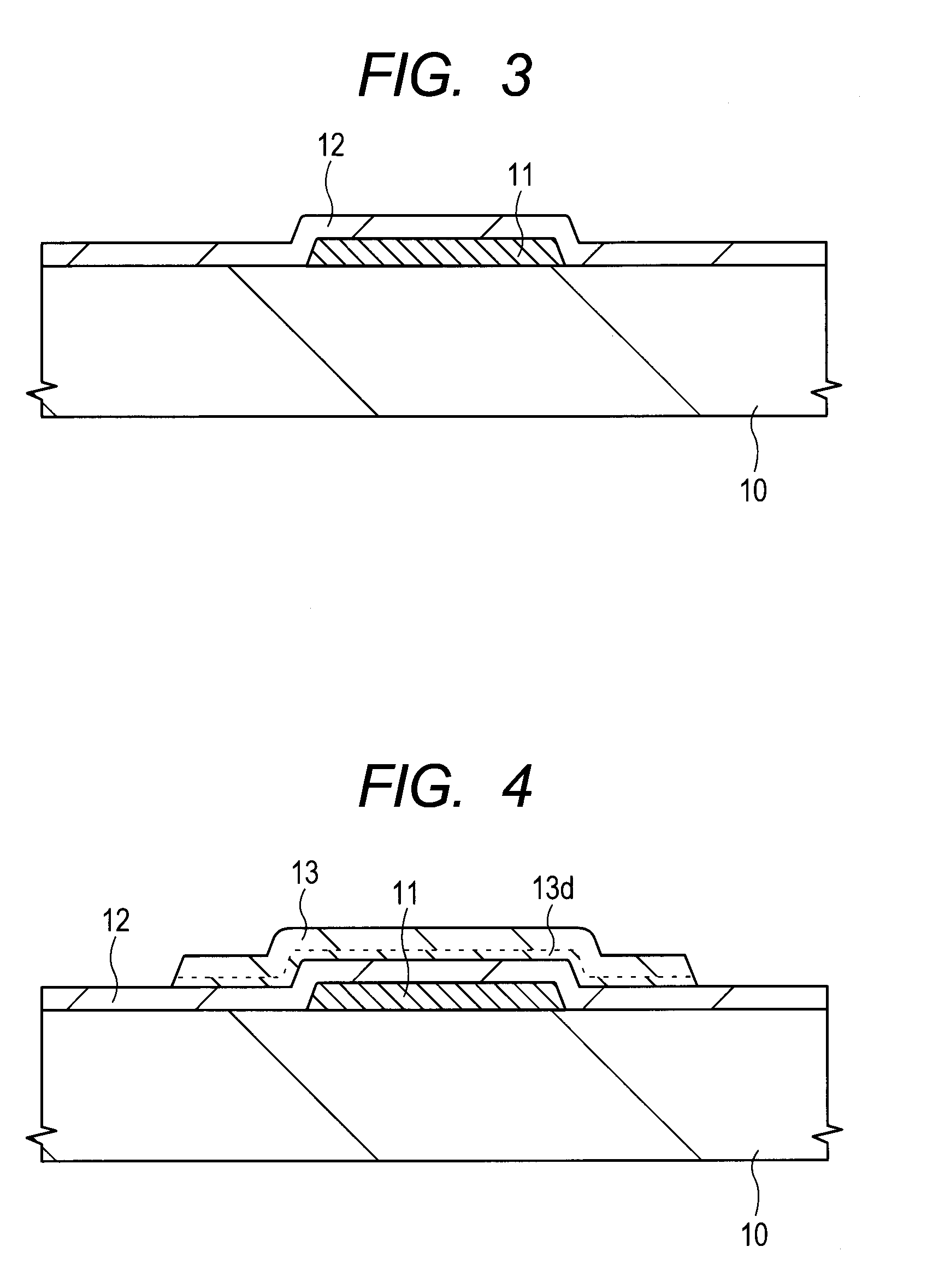

Semiconductor Device, RFID Tag Using the Same and Display Device

InactiveUS20130099229A1Increase the on-currentImprove mobilityTransistorHigh concentrationSub threshold

Disclosed is an oxide semiconductor layer (13) which forms a channel for a thin-film transistor and which includes at least In and oxygen and one or more types of elements from among Zn, Cd, Al, Ga, Si, Sn, Ce, and Ge. A high concentration region (13d) is disposed on one section of the oxide semiconductor layer (13), whereby said region has a maximum In concentration 30 at %; or higher than other regions on the oxide semiconductor layer (13). The film thickness of the oxide semiconductor layer (13) is 100 nm max., and the film thickness of the high concentration region (13d) is 20 nm max. or, preferably, 6 nm max. This enables a thin-film transistor with a sub-threshold slope of 100 mV / decade max., a high on-current, and a high field effect mobility to be achieved.

Owner:HITACHI LTD

Semiconductor device

InactiveUS20090140250A1Improve image qualityLow resistivityTransistorSolid-state devicesImaging qualityDisplay device

An object is to reduce off-current of a thin film transistor. Another object is to improve electric characteristics of a thin film transistor. Further, it is still another object to improve image quality of a display device using the thin film transistor. An aspect of the present invention is a thin film transistor including a semiconductor film formed over a gate electrode and in an inner region of the gate electrode which does not reach an end portion of the gate electrode, with a gate insulating film interposed therebetween, a film covering at least a side surface of the semiconductor film, and a pair of wirings over the film covering the side surface of the semiconductor film; in which an impurity element serving as a donor is added to the semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

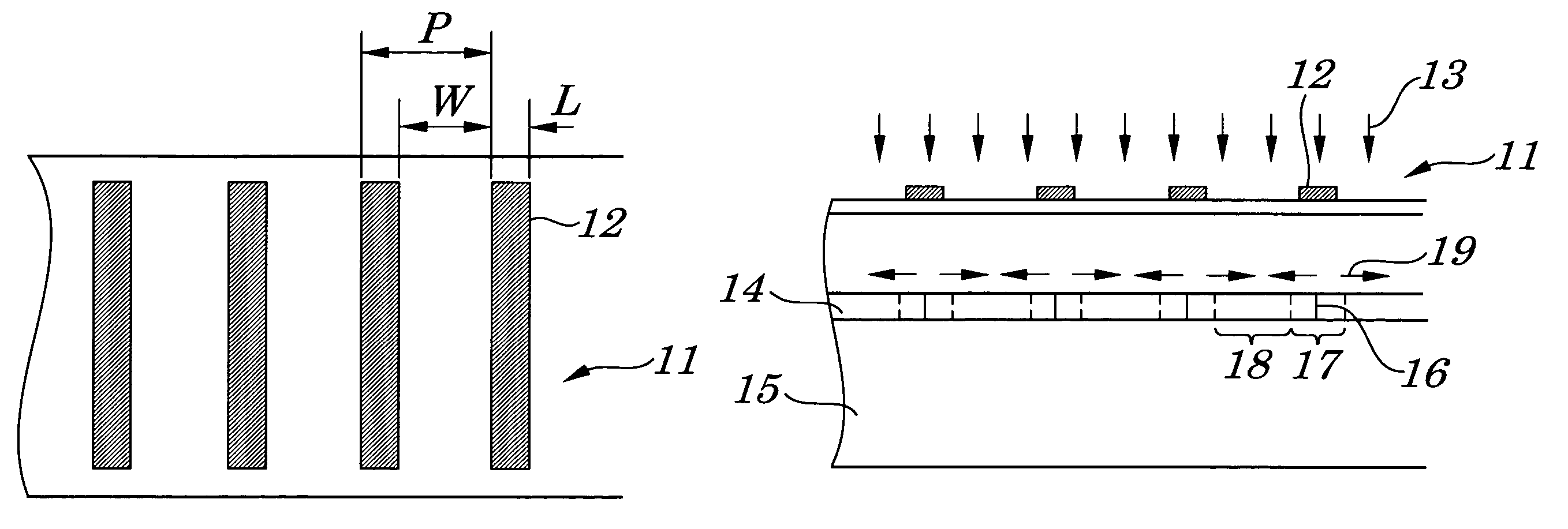

Semiconductor thin film, thin film transistor, method for manufacturing same, and manufacturing equipment of semiconductor thin film

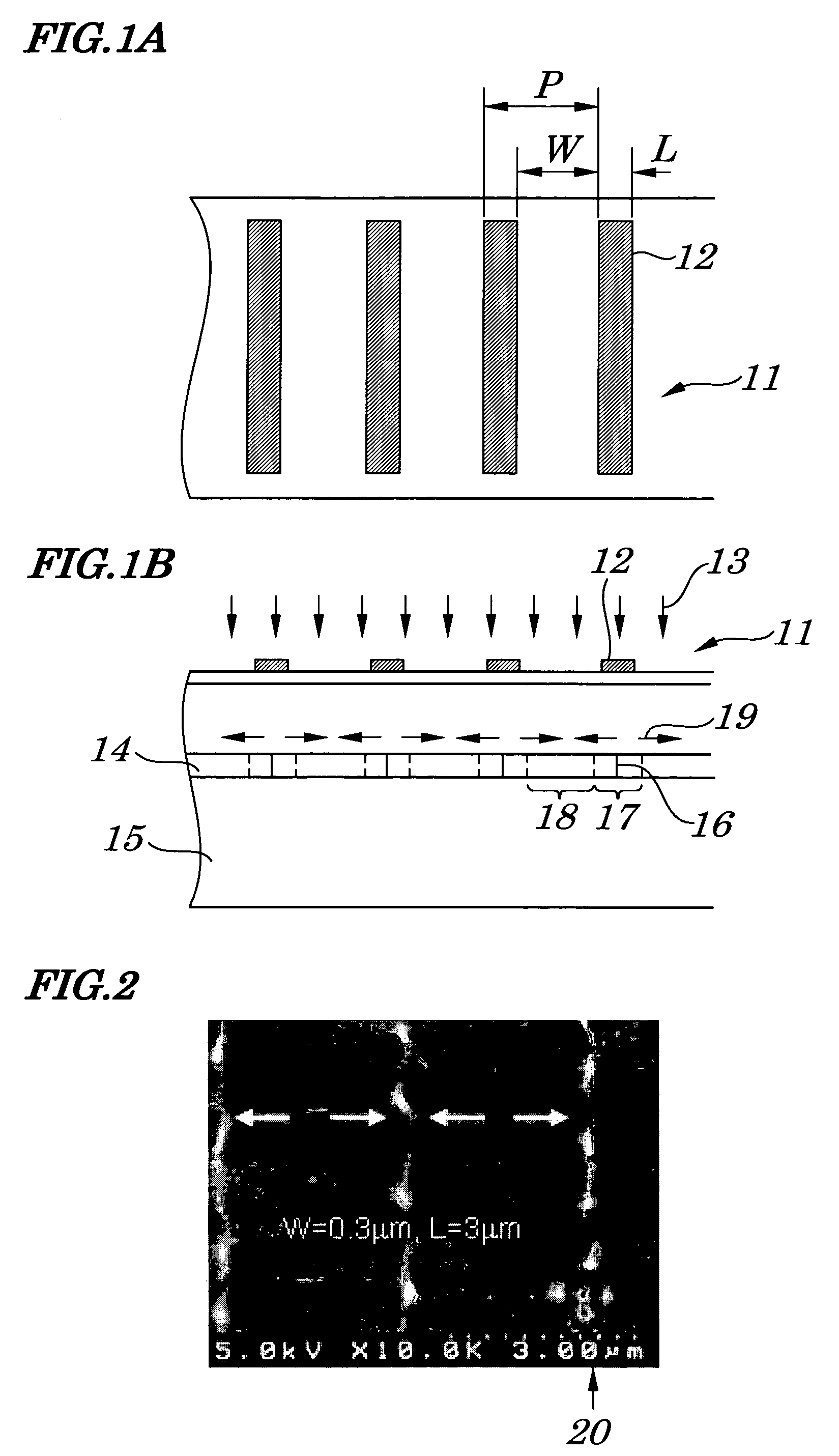

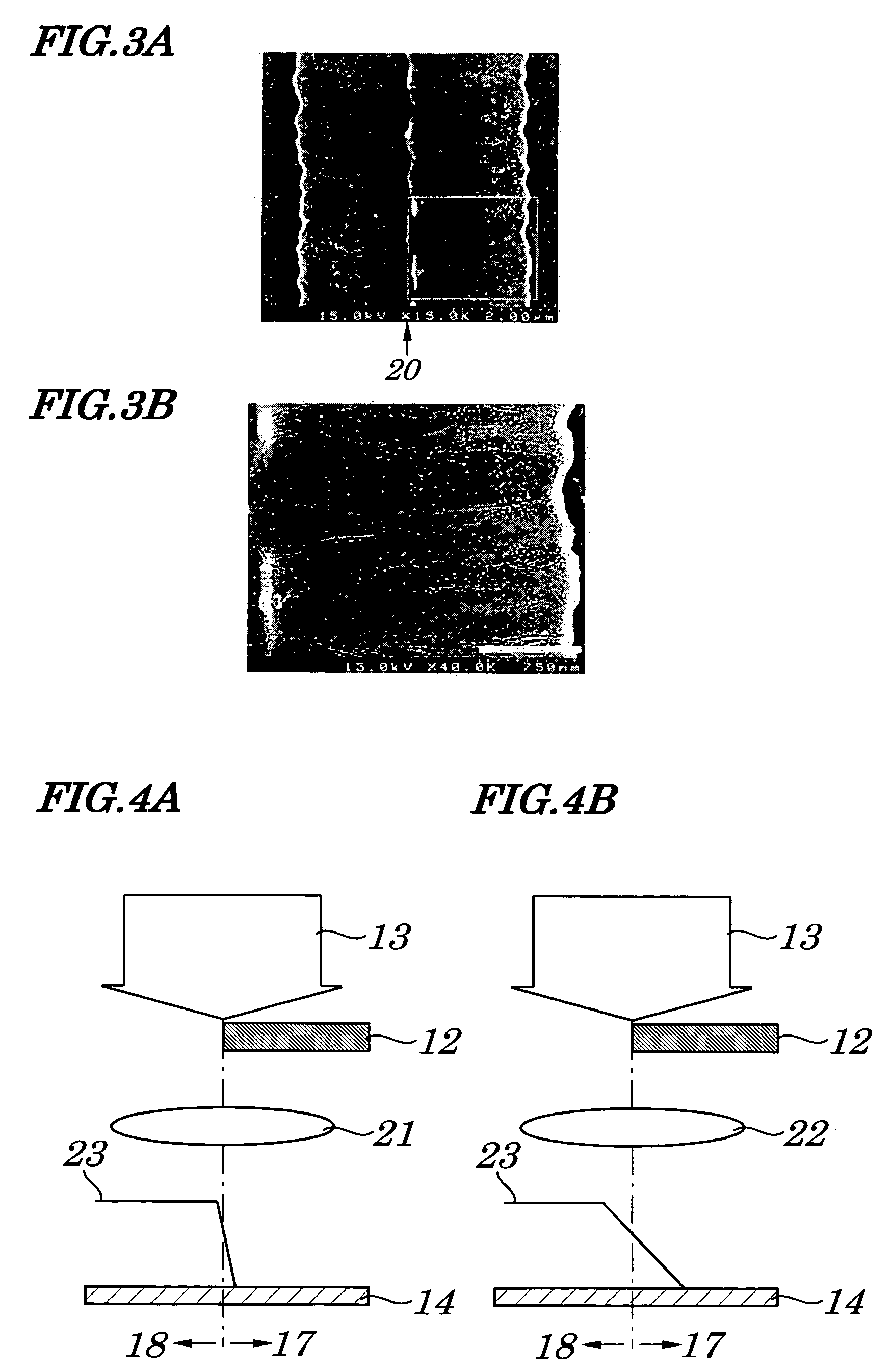

ActiveUS7049184B2Small sizeNo longer be formedTransistorSemiconductor/solid-state device manufacturingImage resolutionLight beam

A method for manufacturing a semiconductor thin film is provided which can form its crystal grains having a uniform direction of crystal growth and being large in size and a manufacturing equipment using the above method, and a method for manufacturing a thin film transistor. In the above method, by applying an energy beam partially intercepted by a light-shielding element, melt and re-crystallization occur with a light-shielded region as a starting point. The irradiation of the beam gives energy to the light-shielded region of the silicon thin film so that melt and re-crystallization occur with the light-shielded region as the starting point and so that a local temperature gradient in the light-shielded region is made to be 1200° C. / μm or more. In the manufacturing method, a resolution of an optical system used to apply the energy beam is preferably 4 μm or less.

Owner:VISTA PEAK VENTURES LLC

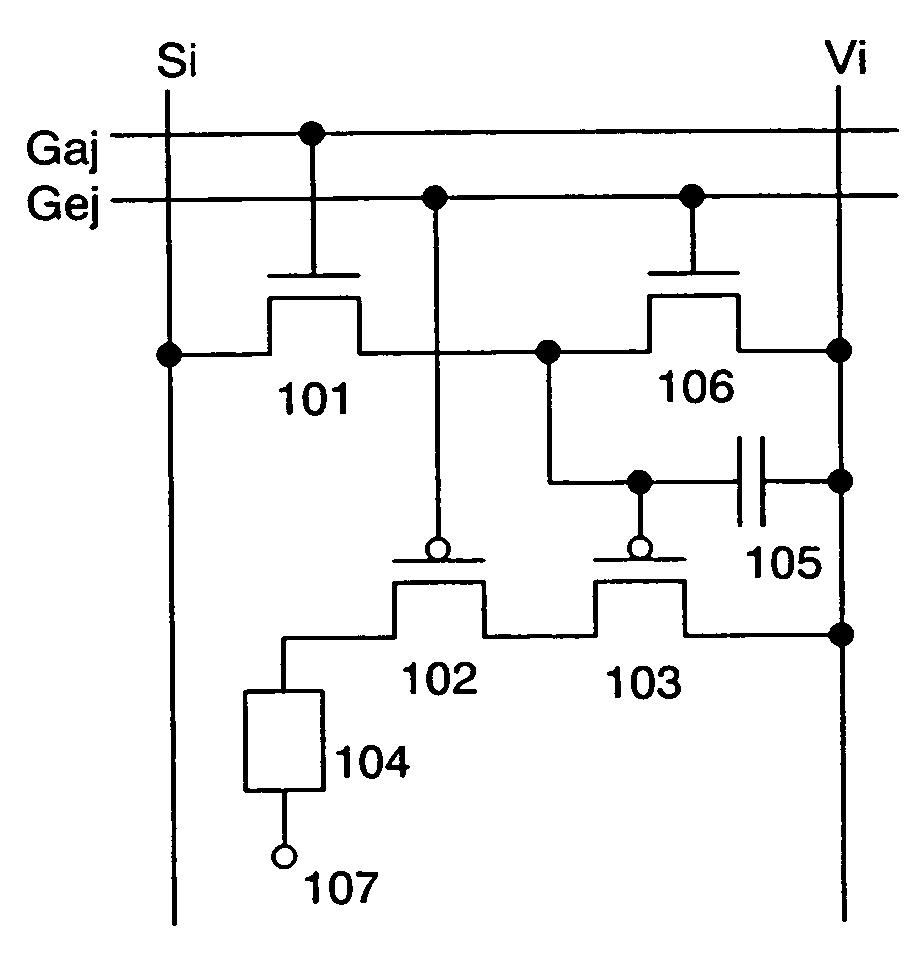

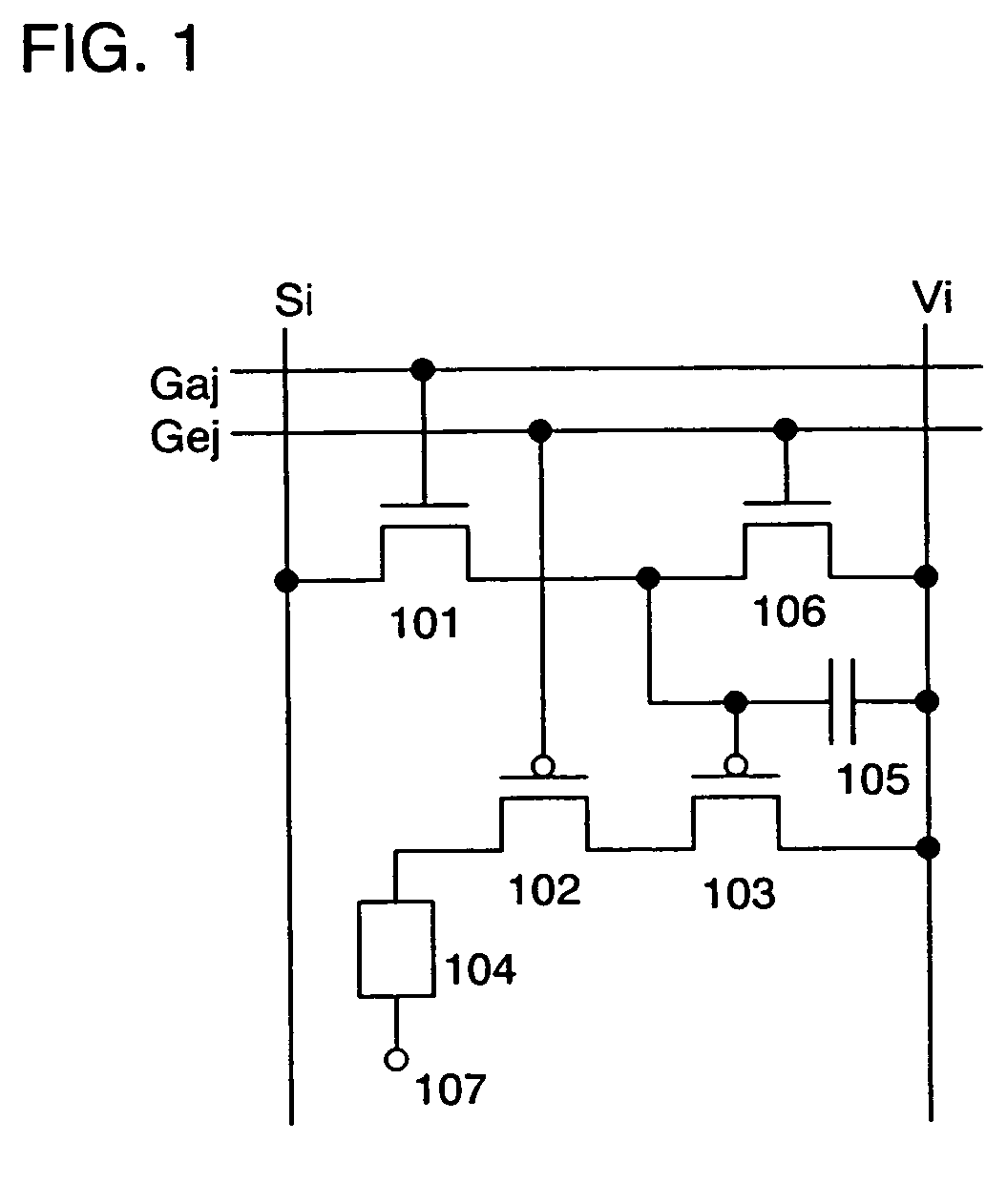

Element substrate and light emitting device

ActiveUS7358942B2Increase storage capacityReduce variationStatic indicating devicesElectric circuit arrangementsLinear regionScan line

A light emitting device and an element substrate which are capable of suppressing variations in luminance intensity of a light emitting element among pixels due to characteristic variations of a driving transistor without suppressing off-current of a switching transistor low and increasing storage capacity of a capacitor. A gate potential of a driving transistor is connected to a first scan line or a second scan line, and the driving transistor operates in a saturation region. A current controlling transistor which operates in a linear region is connected in series to the driving transistor. A video signal which transmits a light emission or non-emission of a pixel is input to the gate of the current controlling transistor through a switching transistor.

Owner:SEMICON ENERGY LAB CO LTD