Patents

Literature

19560results about "Diode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

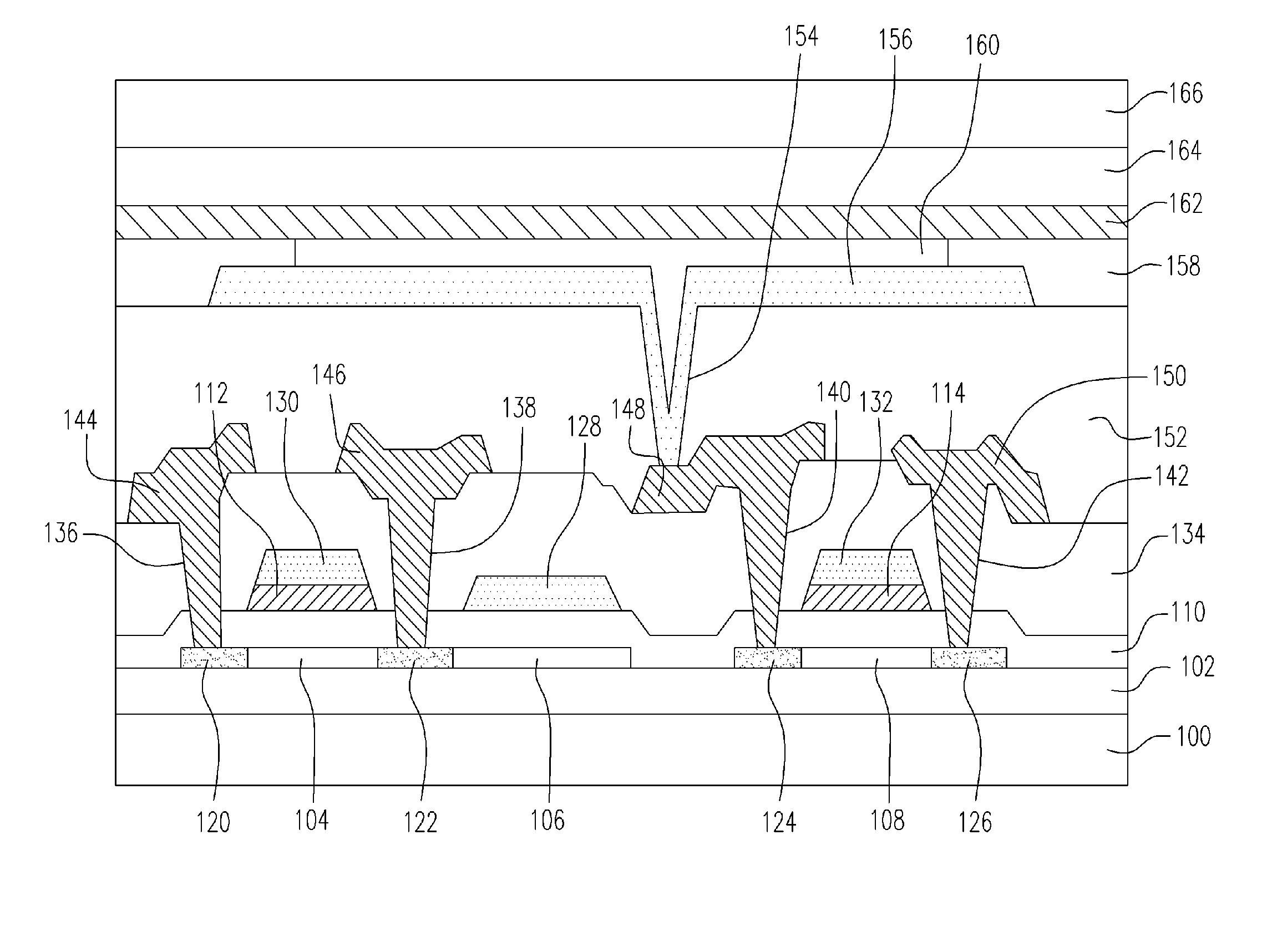

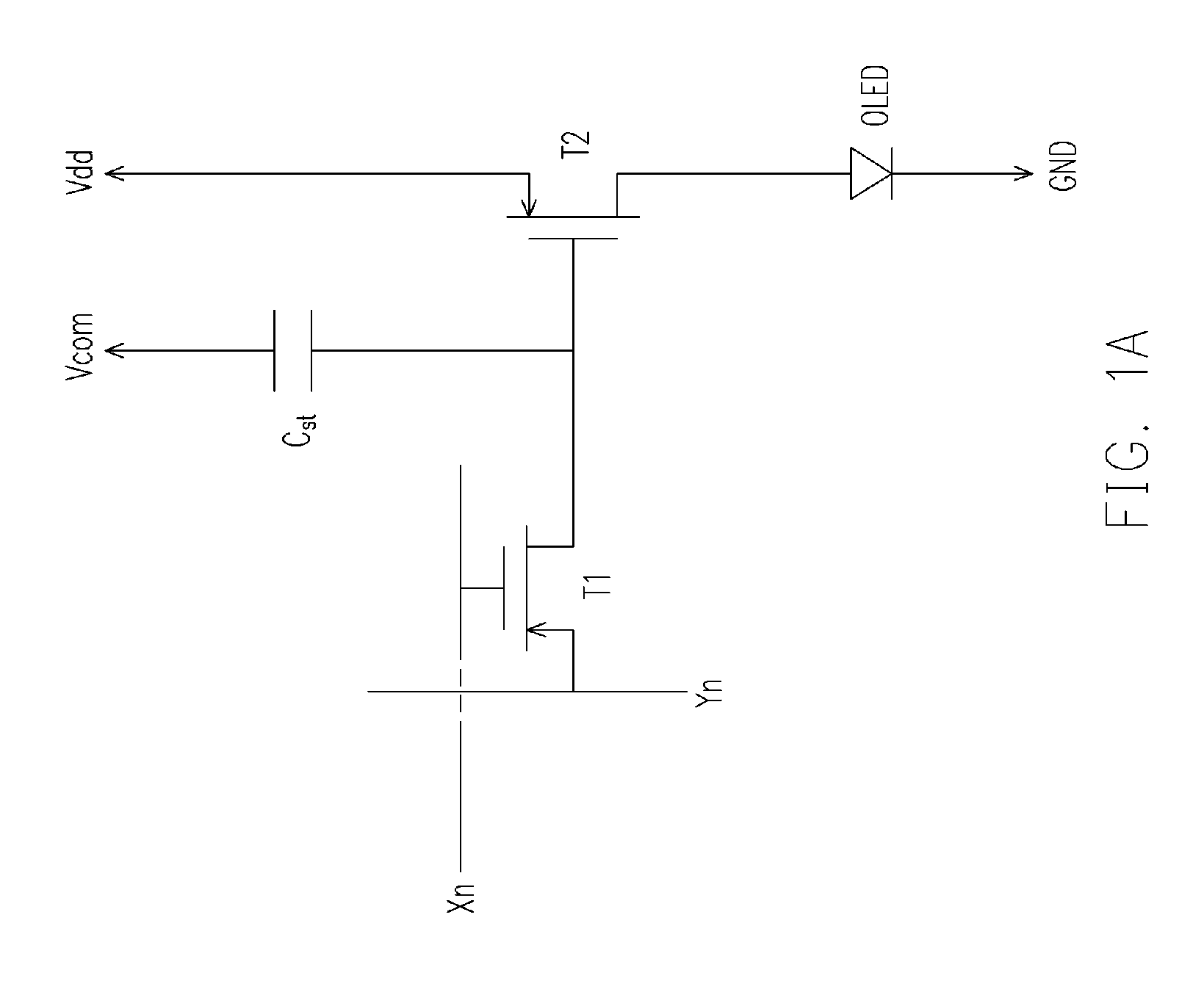

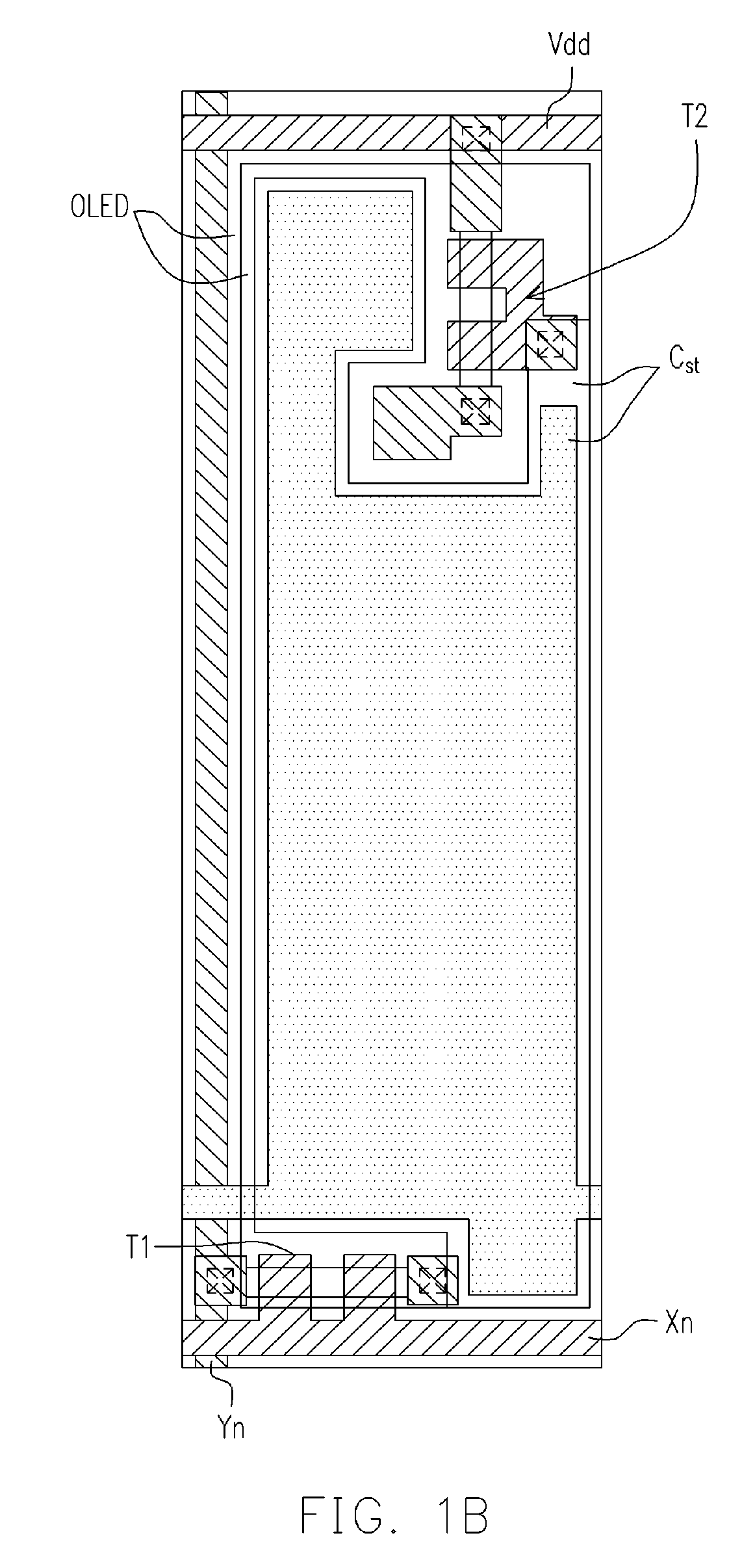

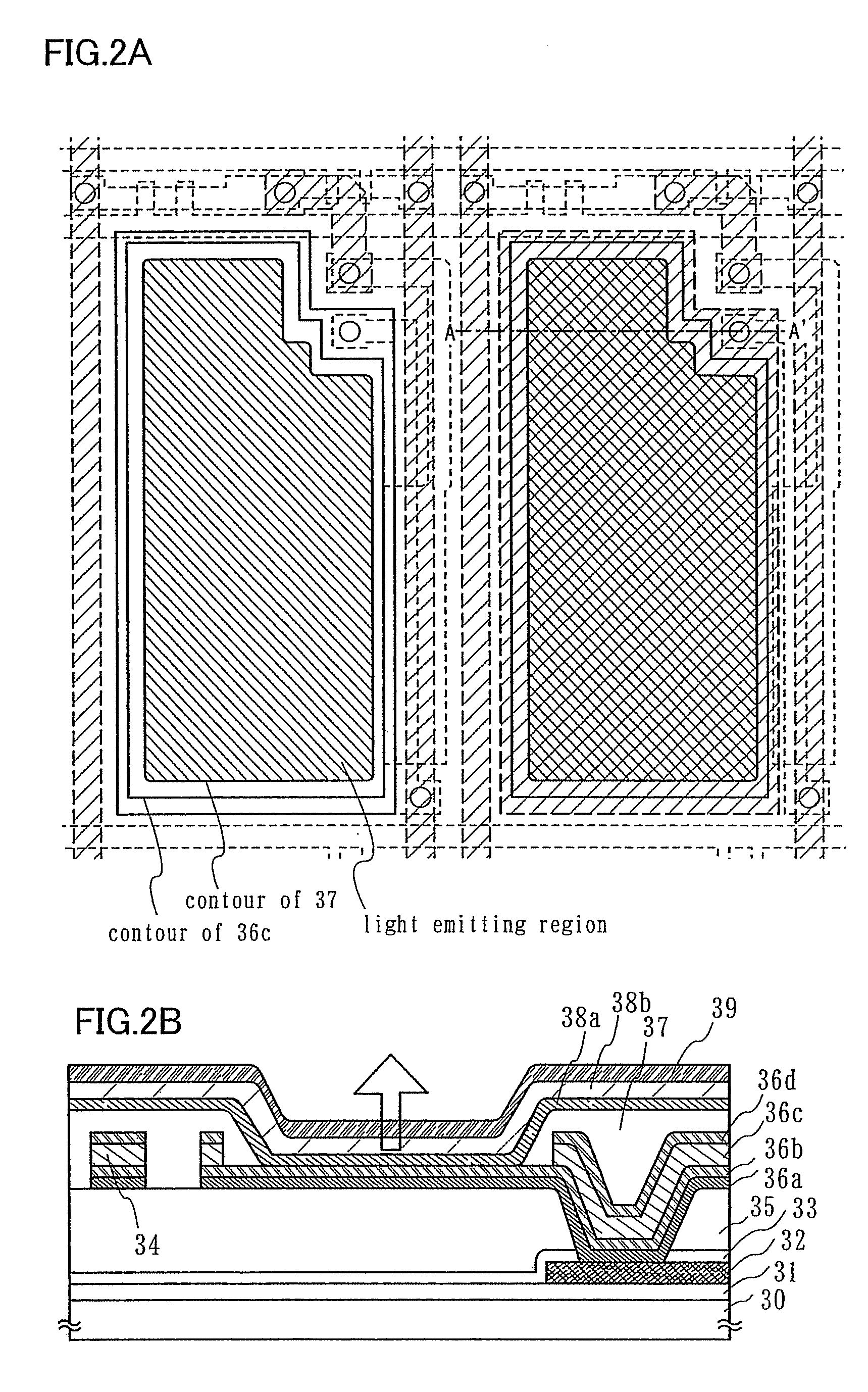

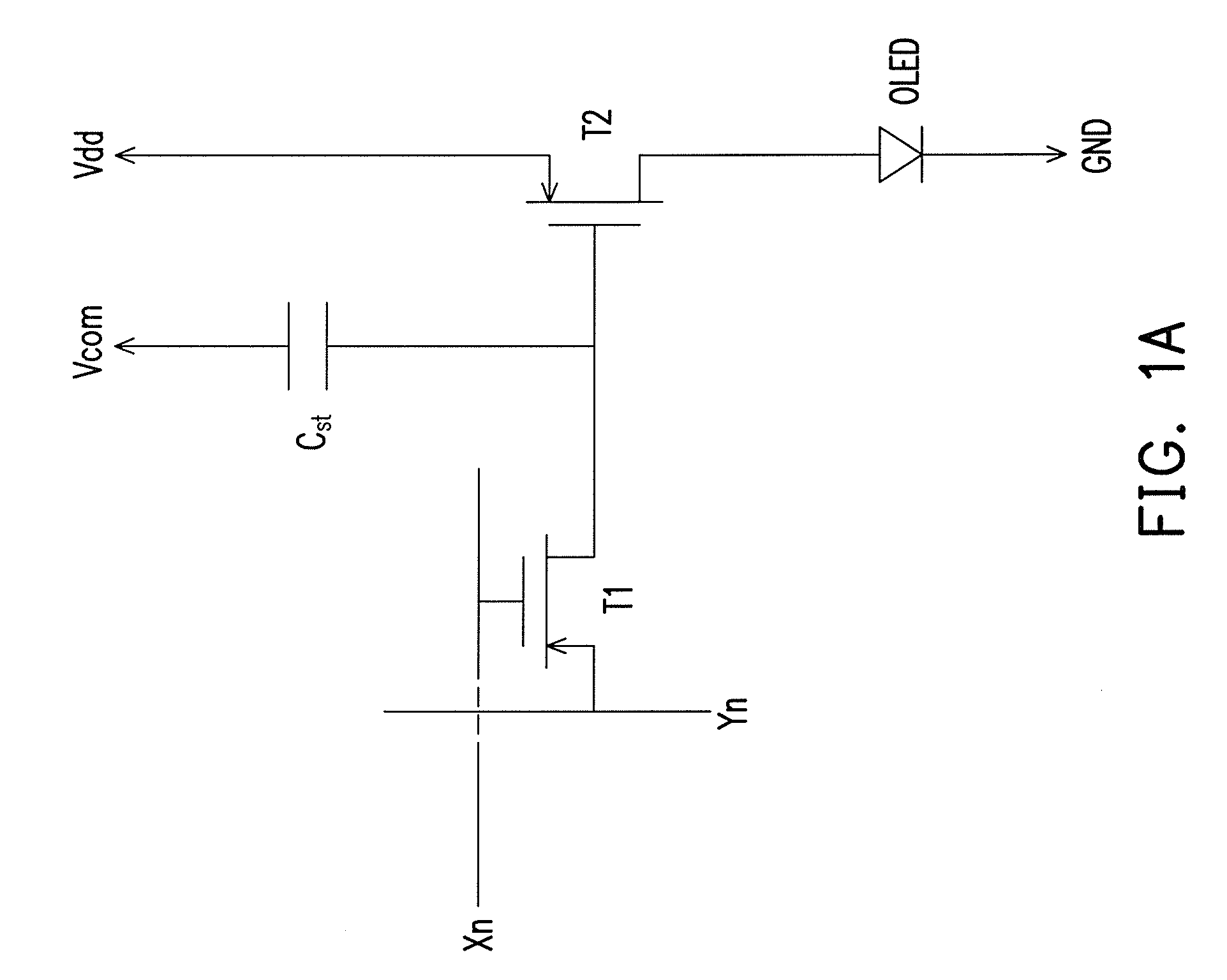

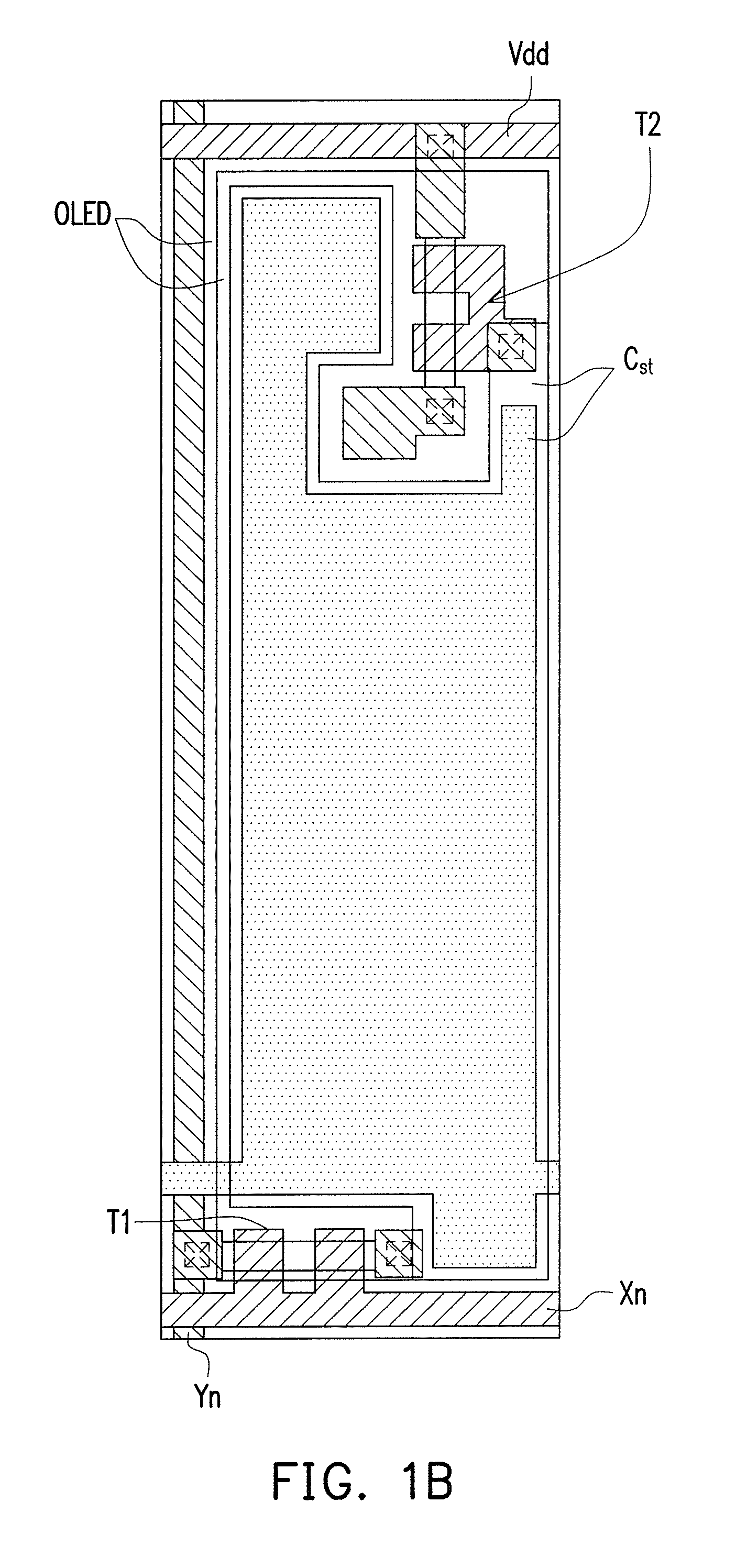

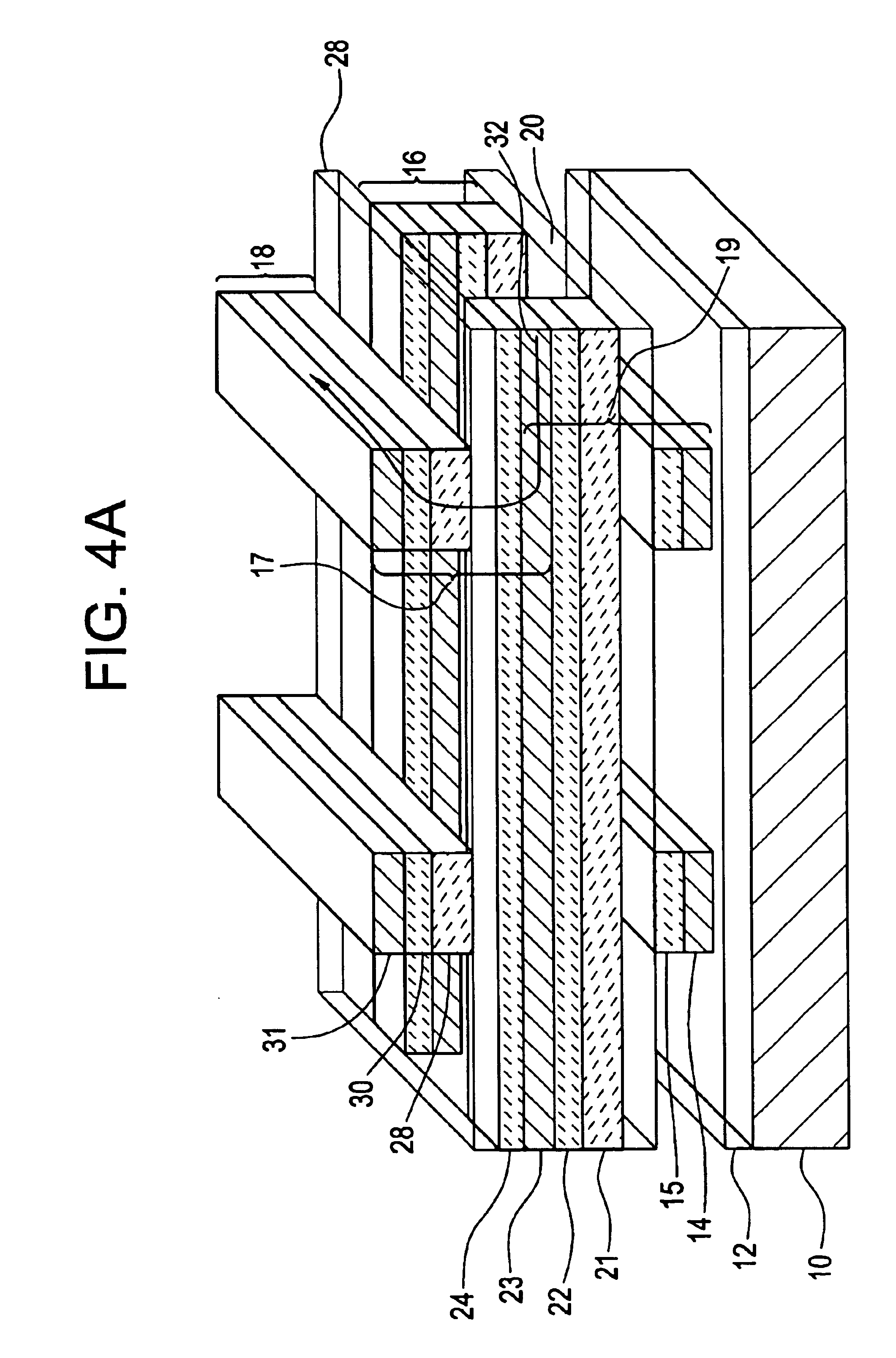

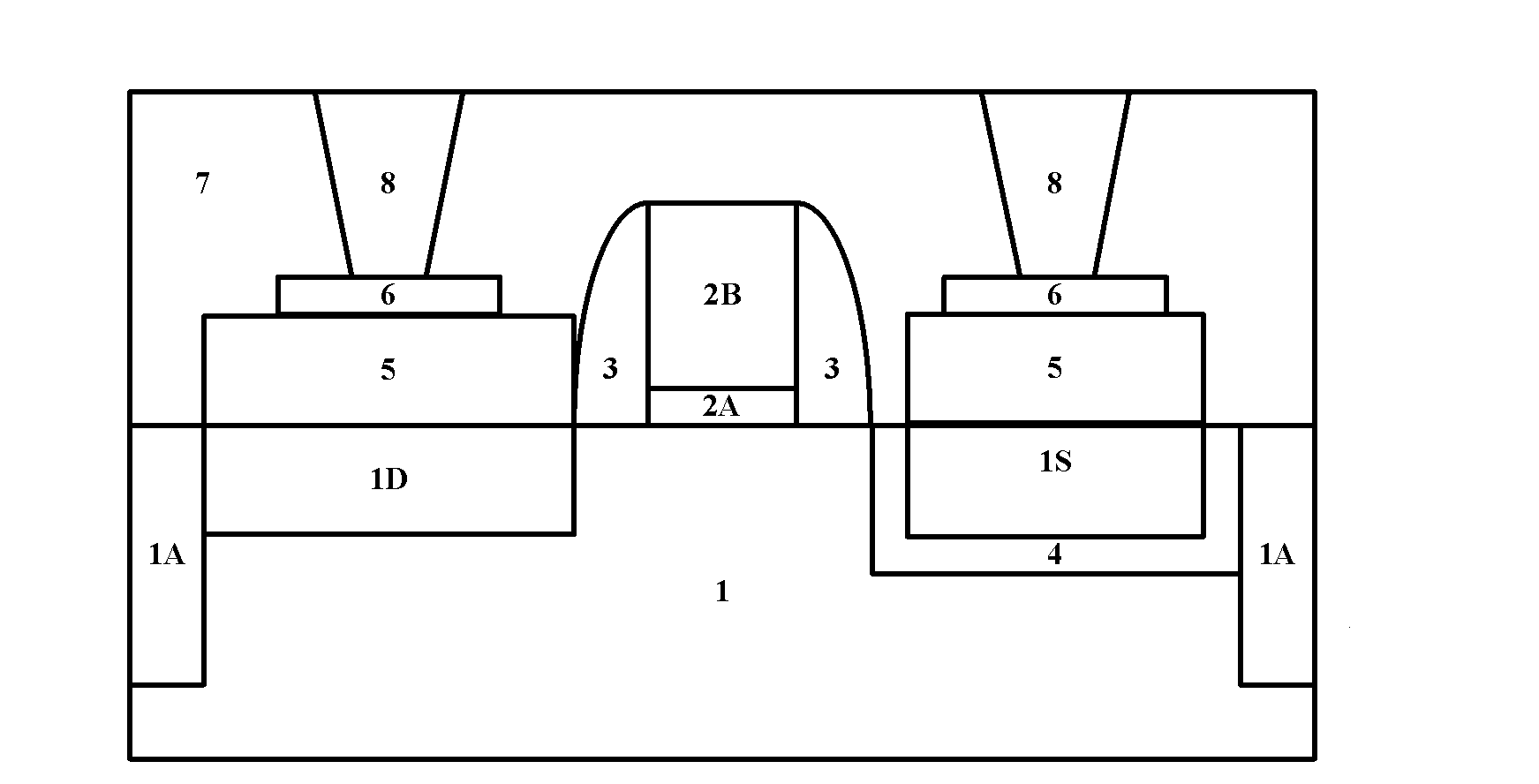

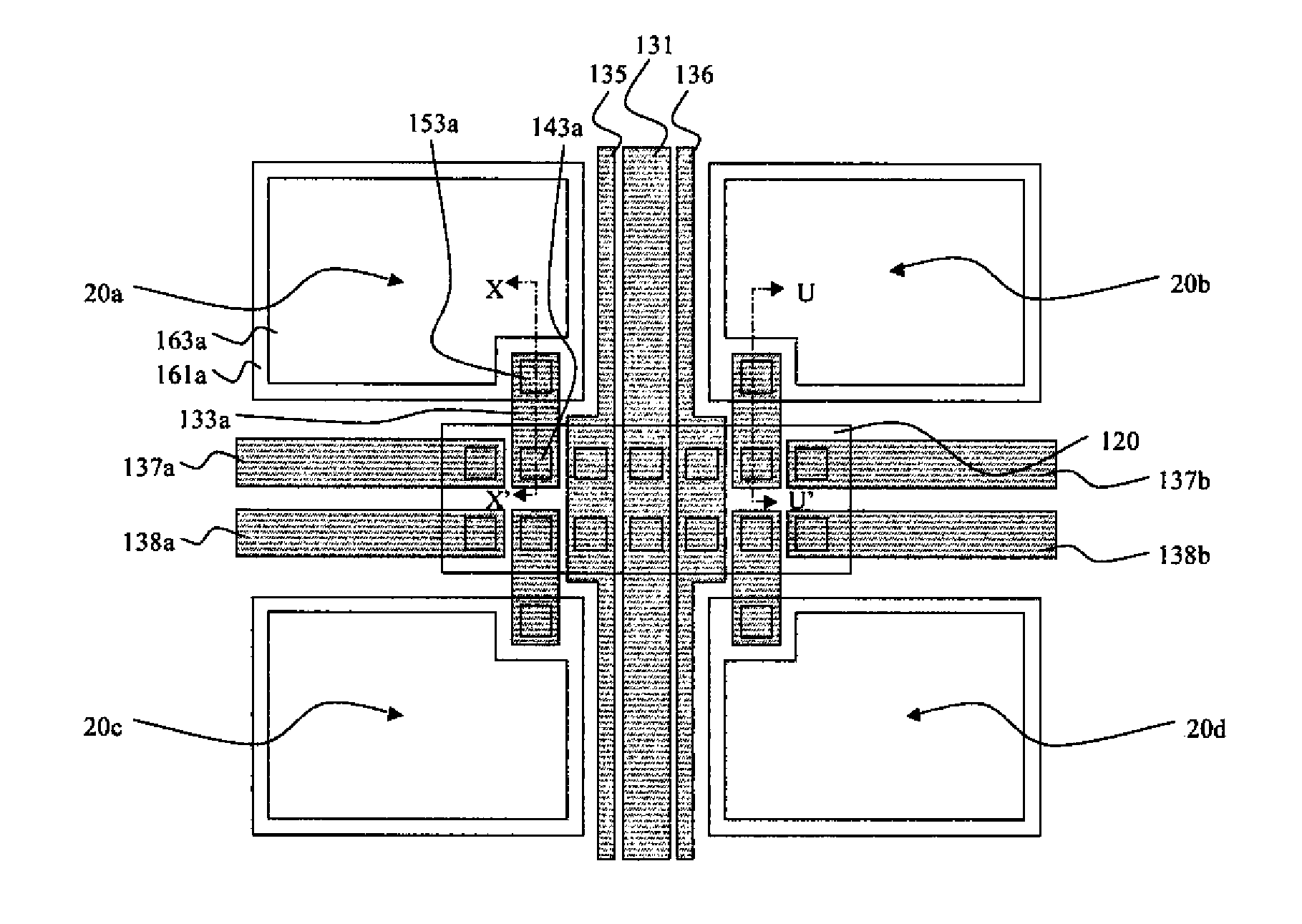

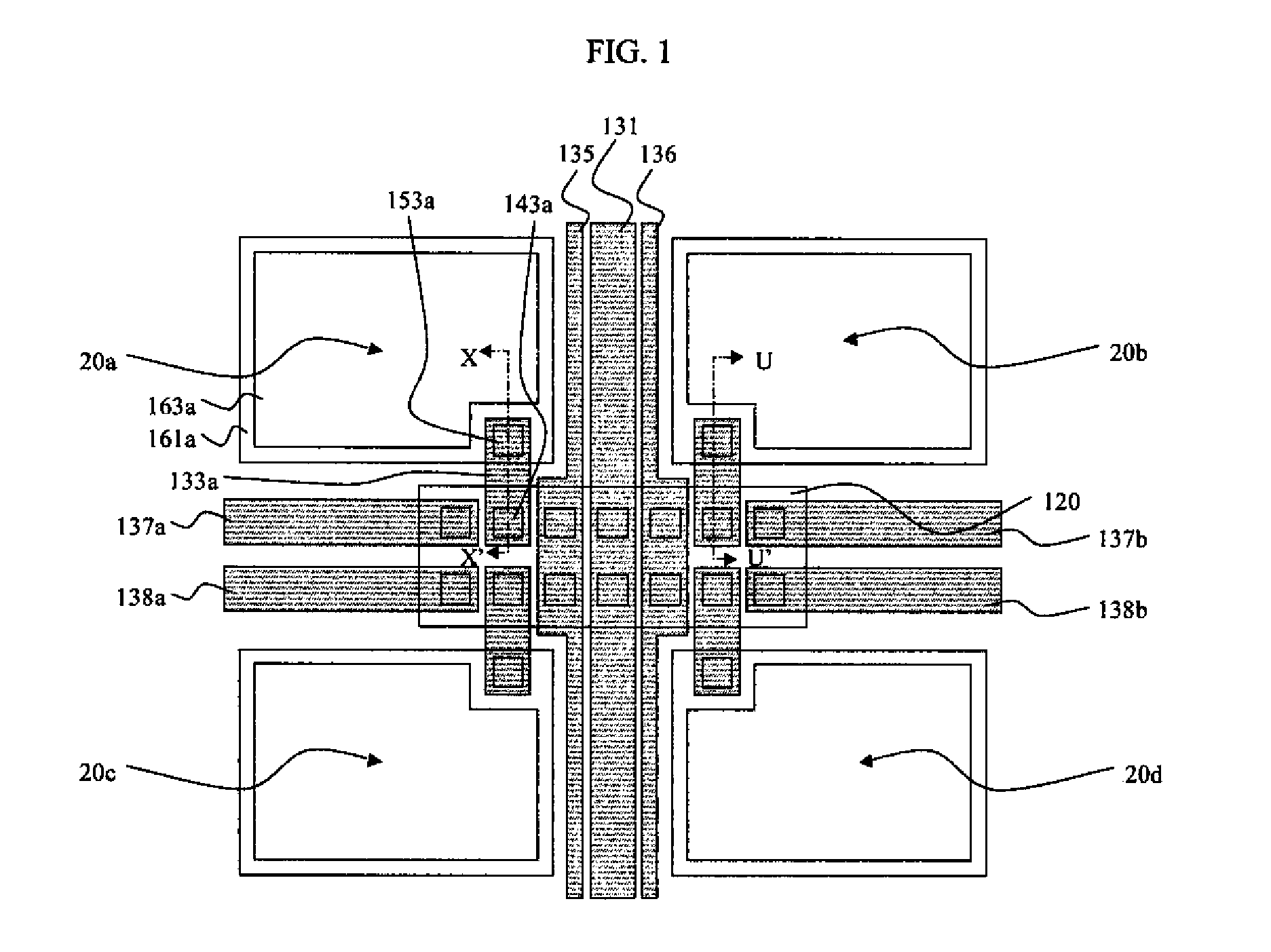

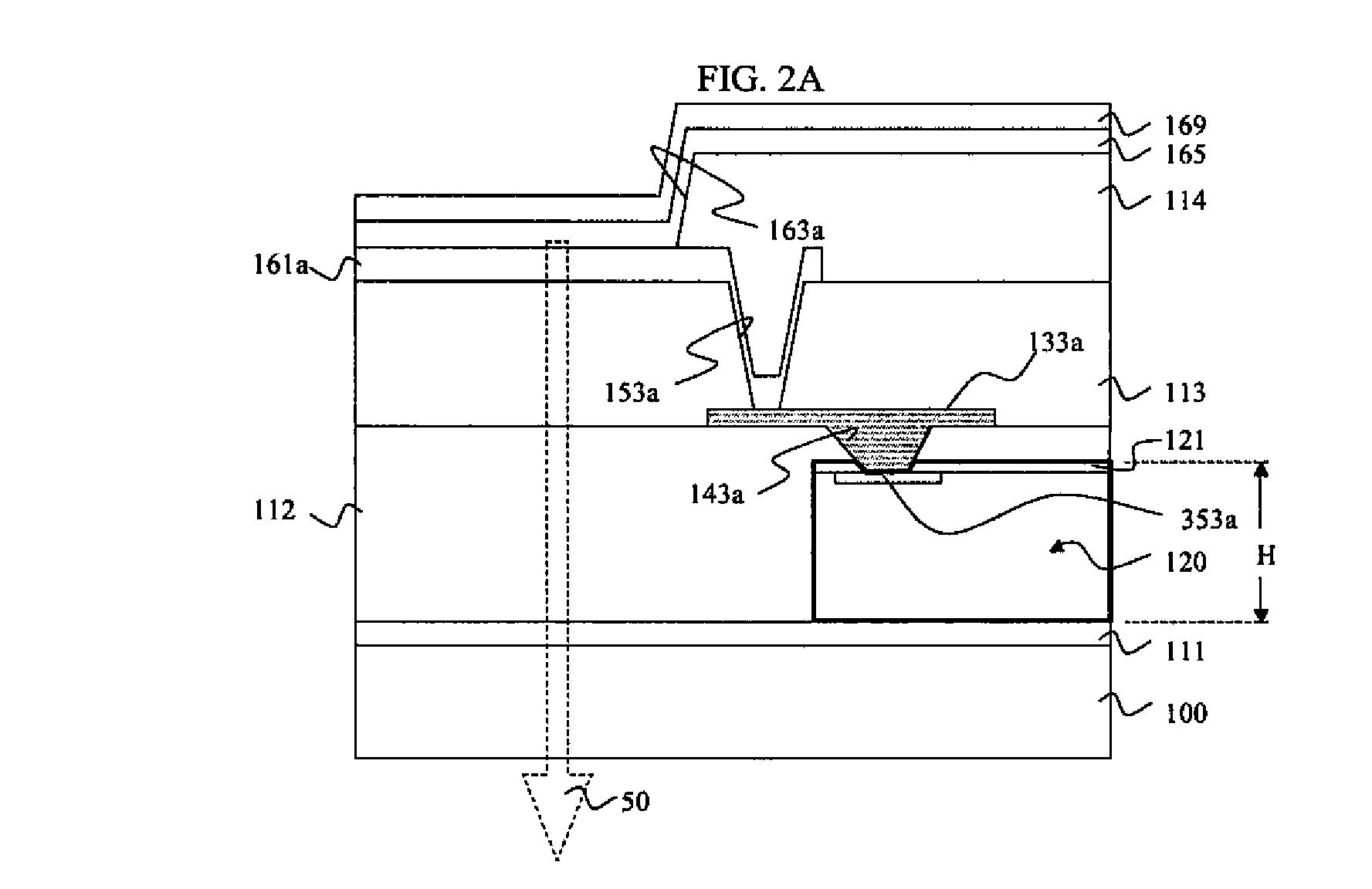

Pixel structure of active matrix organic light-emitting diode and method for fabricating the same

InactiveUS20070152217A1Improve pixel aperture ratioIncrease the aperture ratioSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceScan line

A pixel structure of an active matrix organic light-emitting diode (AMOLED) includes an organic light-emitting diode (OLED), a data line, at least one scan line, at least one switch thin film transistor (TFT), at least one driving TFT and at least one storage capacitor with two transparent electrodes. Since both the electrodes of the transparent storage capacitor are formed by transparent material, the aperture ratio of the pixel and the area of the capacitor largely increase and can reach 50%˜95% of a pixel area. Thus, the display quality of an AMOLED panel can be improved.

Owner:IND TECH RES INST

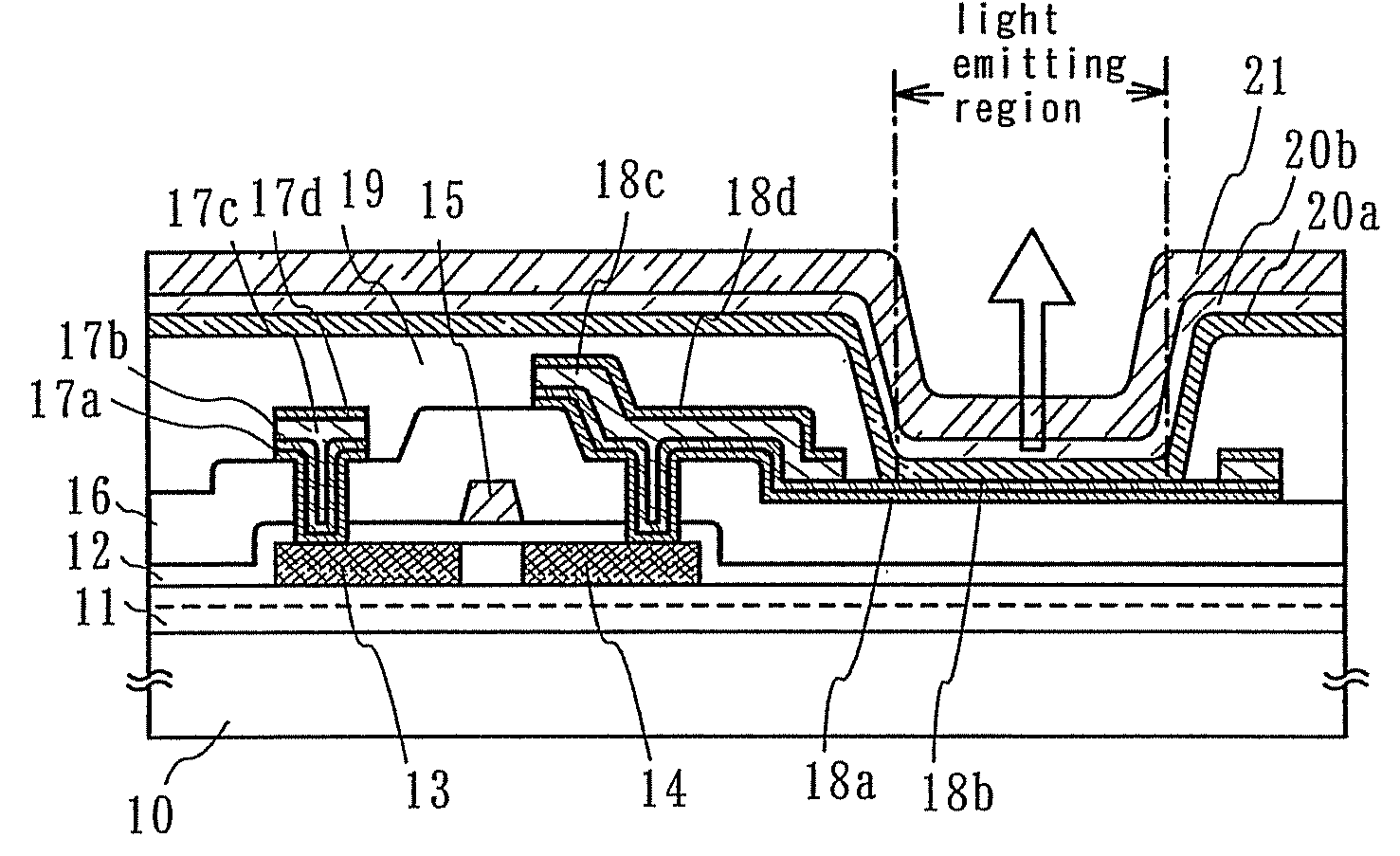

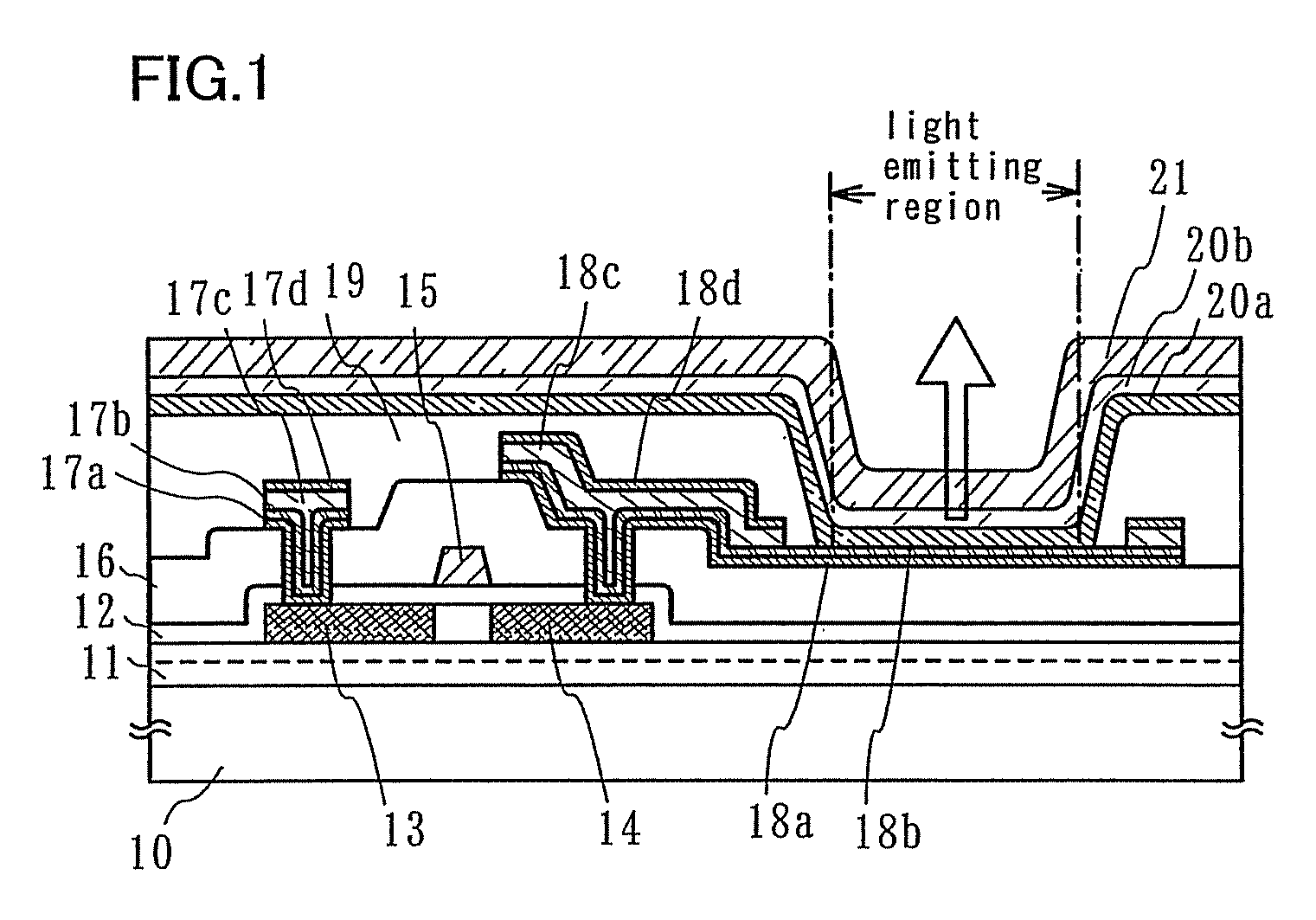

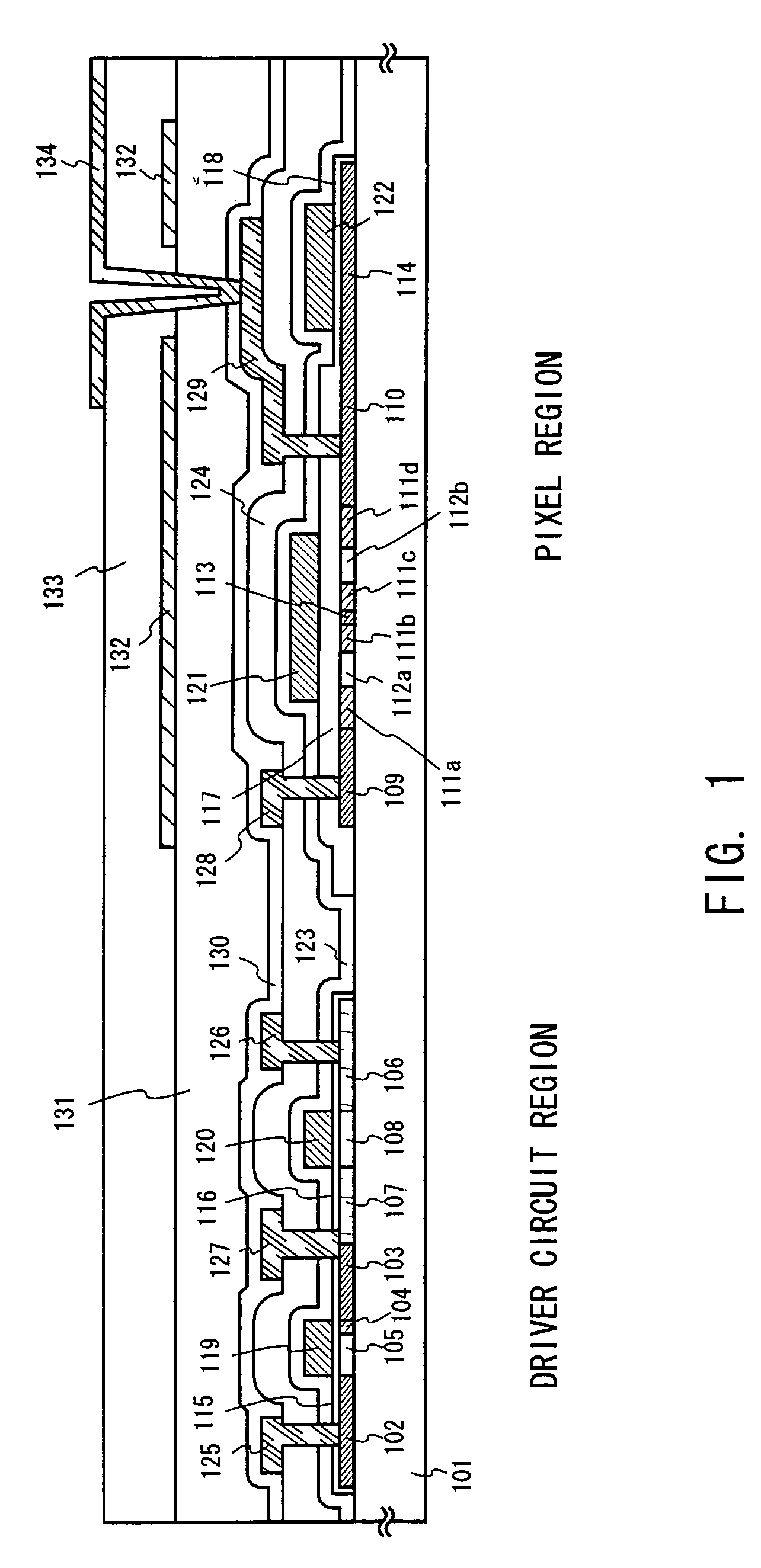

Semiconductor Device and Method for Manufacturing the Same

ActiveUS20090134399A1Good step coverageThin thicknessDischarge tube luminescnet screensElectroluminescent light sourcesActive matrixMetal electrodes

A manufacturing method of an active matrix light emitting device in which the active matrix light emitting device can be manufactured in a shorter time with high yield at low cost compared with conventional ones will be provided. It is a feature of the present invention that a layered structure is employed for a metal electrode which is formed in contact with or is electrically connected to a semiconductor layer of each TFT arranged in a pixel area of an active matrix light emitting device. Further, the metal electrode is partially etched and used as a first electrode of a light emitting element. A buffer layer, a layer containing an organic compound, and a second electrode layer are stacked over the first electrode.

Owner:SEMICON ENERGY LAB CO LTD

Method for fabricating pixel structure of active matrix organic light-emitting diode

ActiveUS20090068773A1Improve pixel aperture ratioIncrease the aperture ratioSolid-state devicesSemiconductor/solid-state device manufacturingActive matrixScan line

Owner:IND TECH RES INST

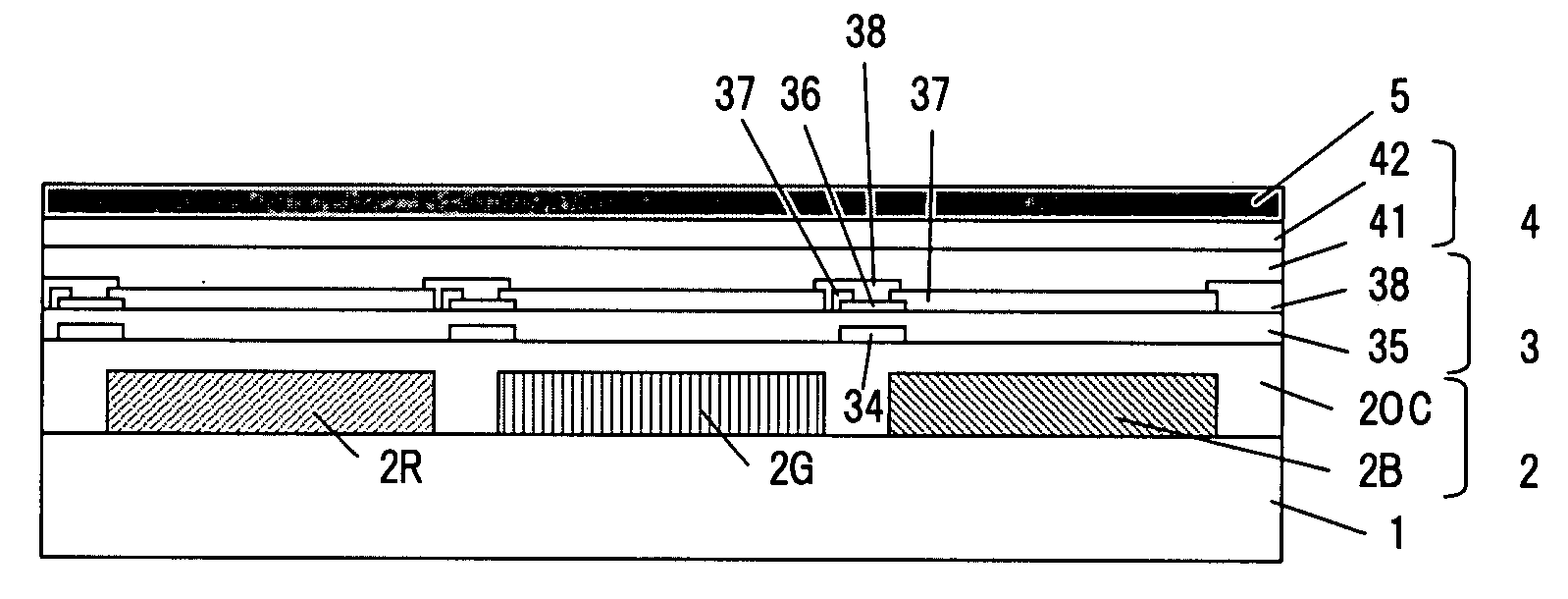

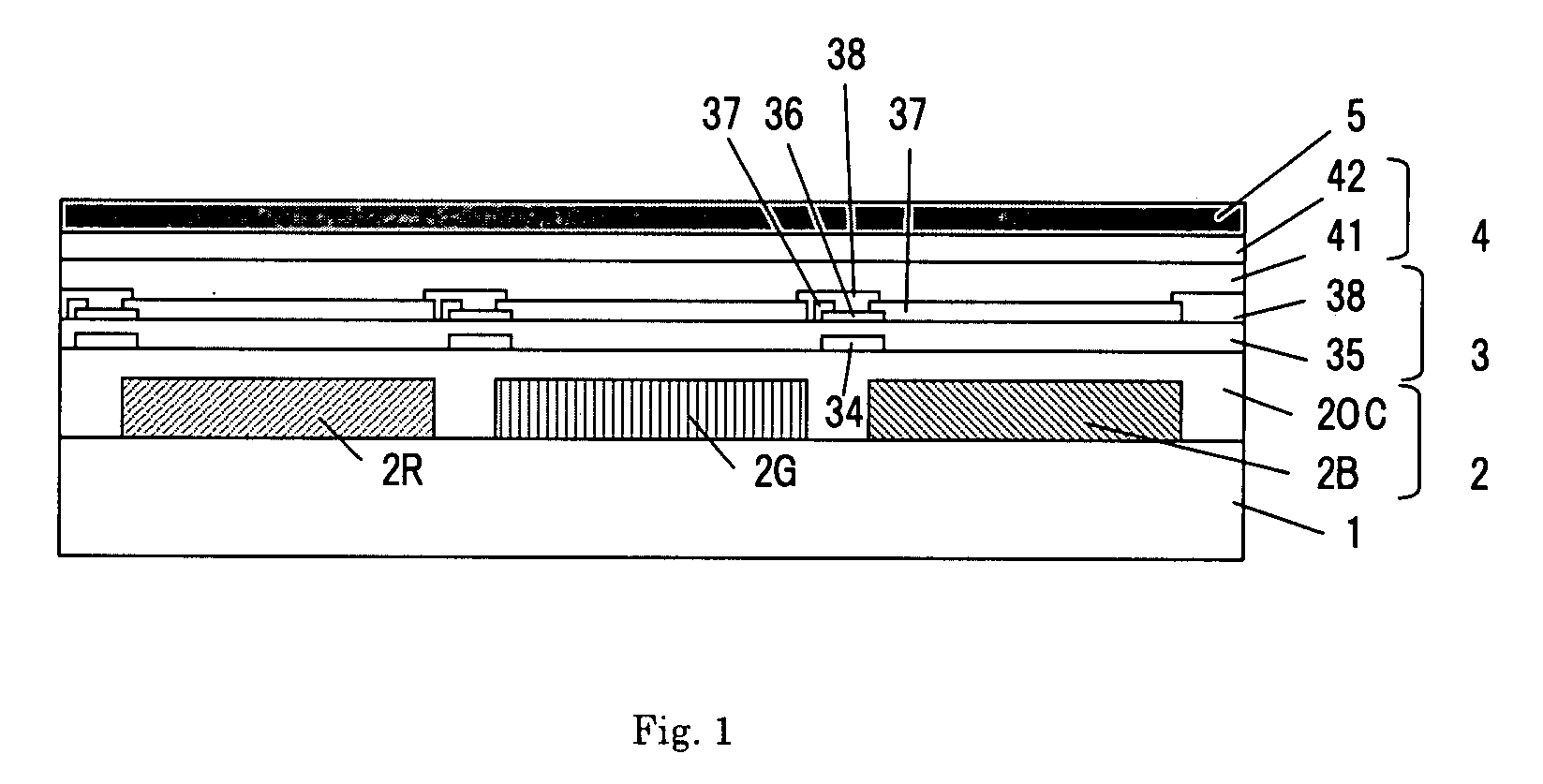

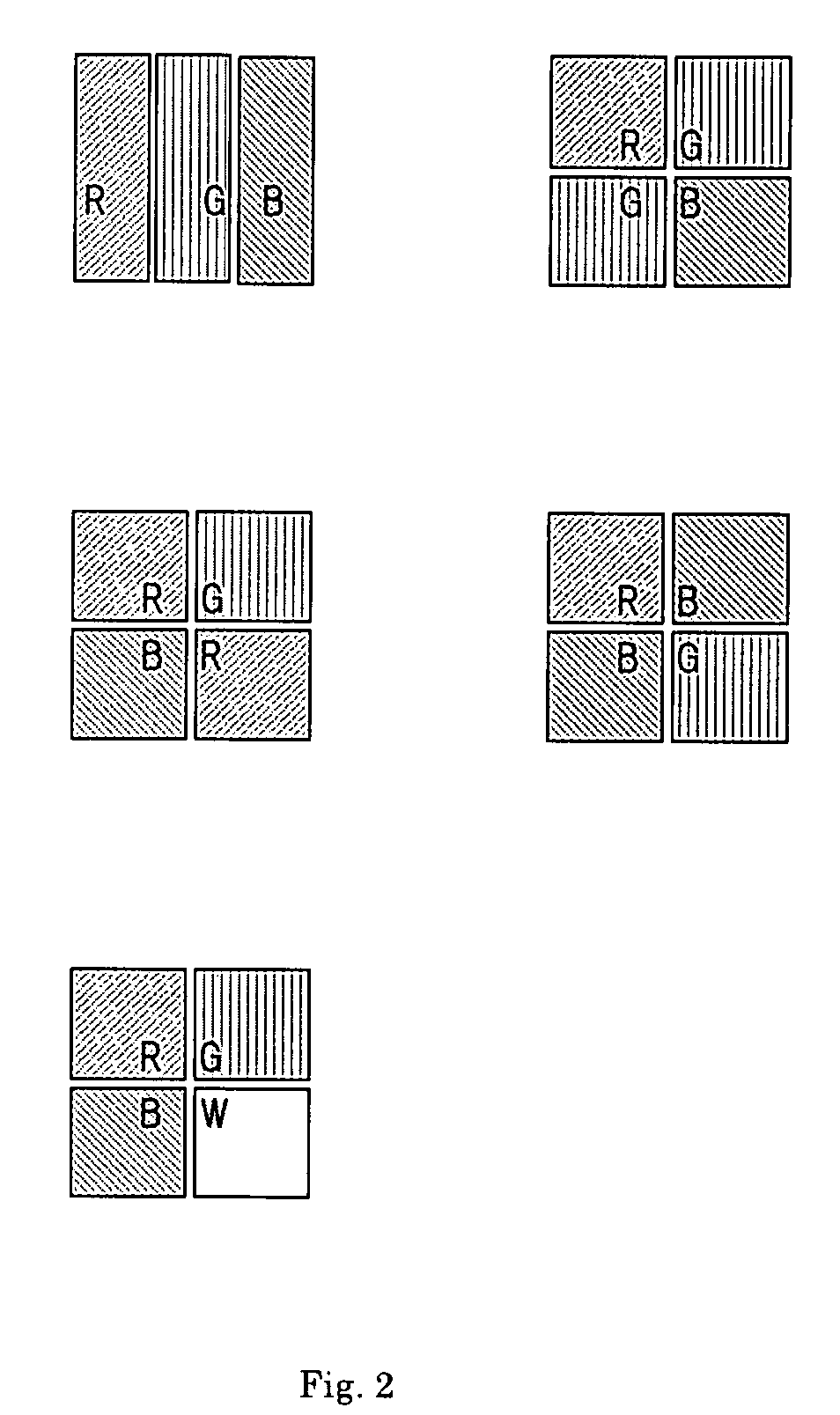

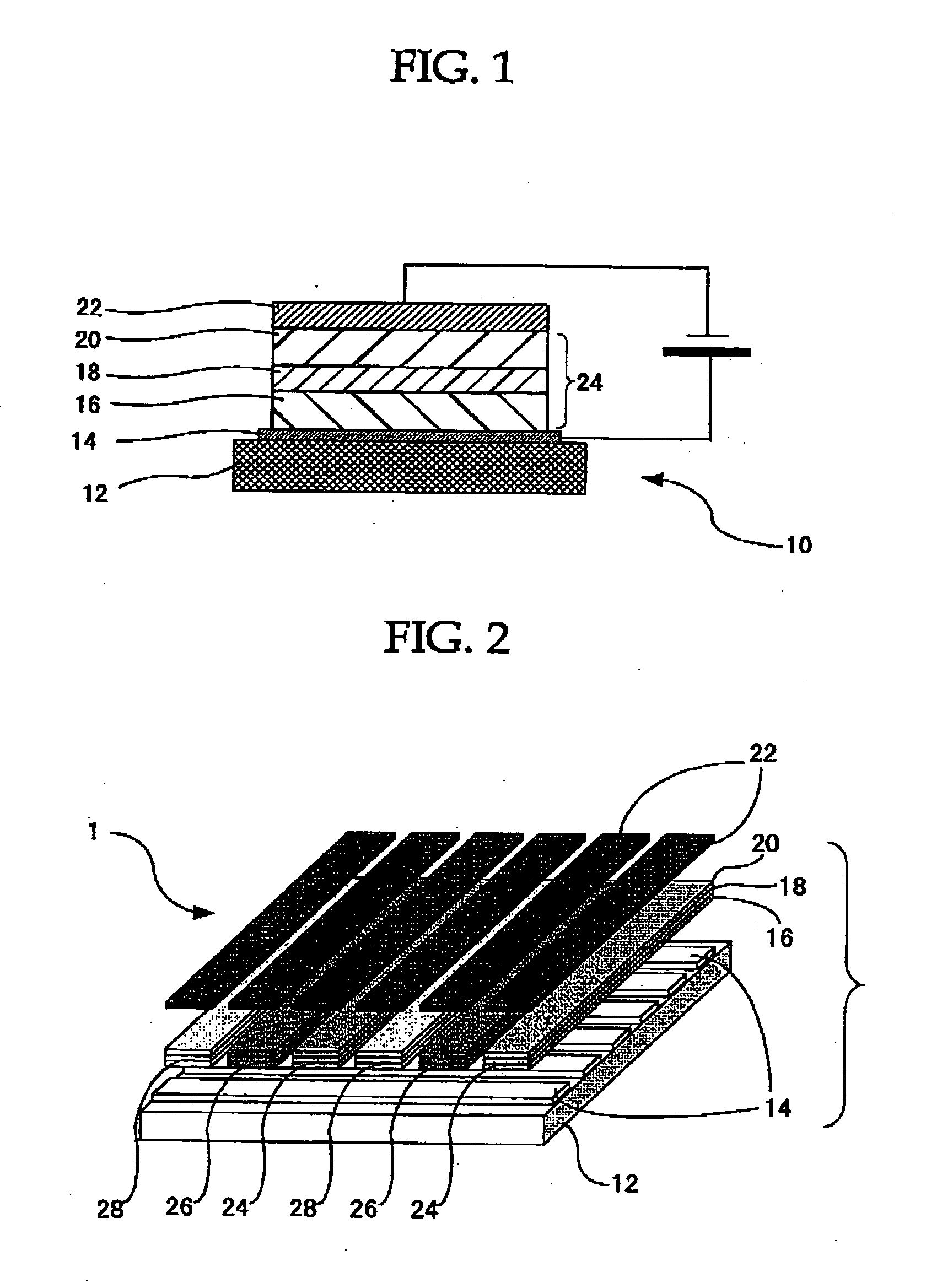

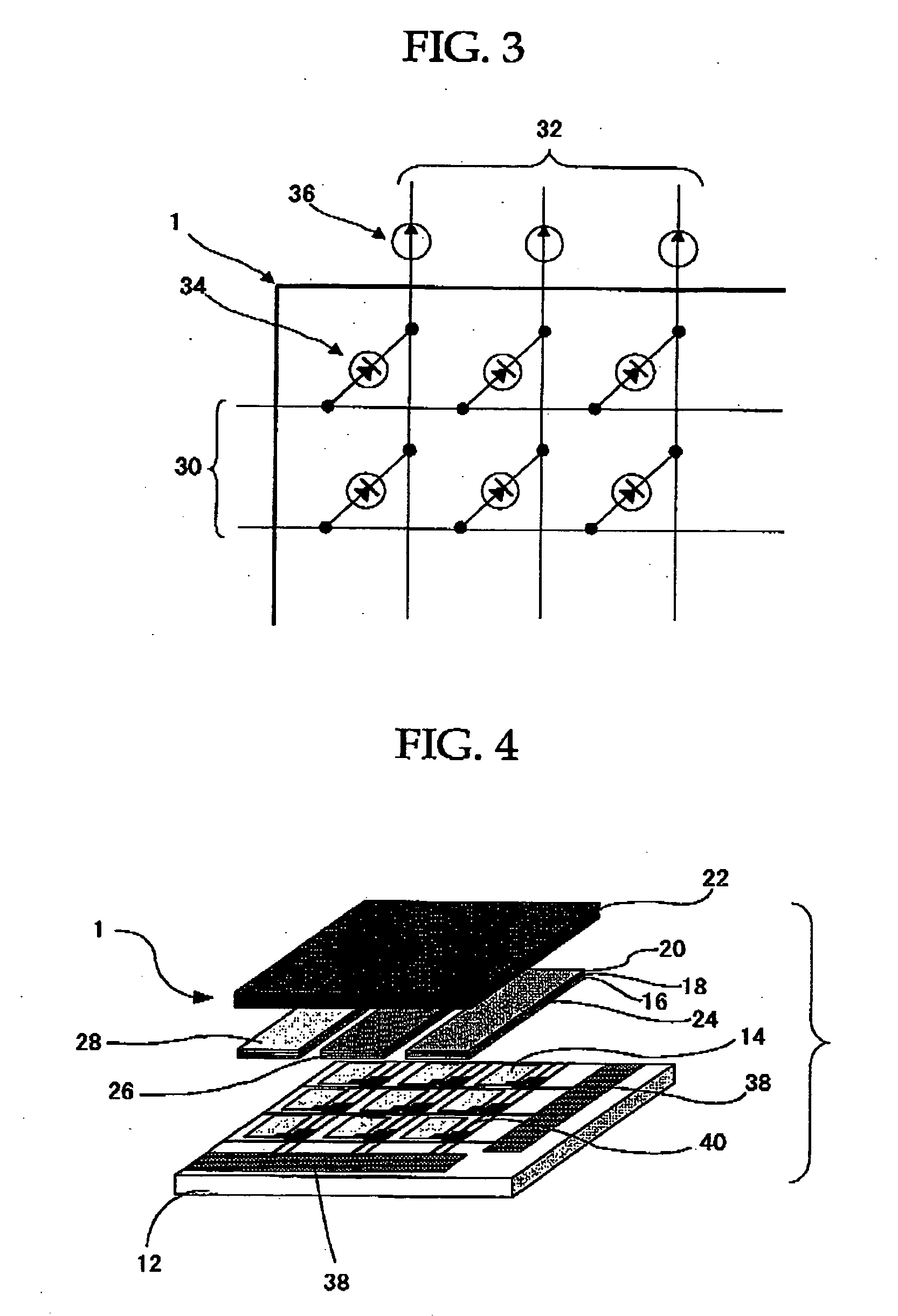

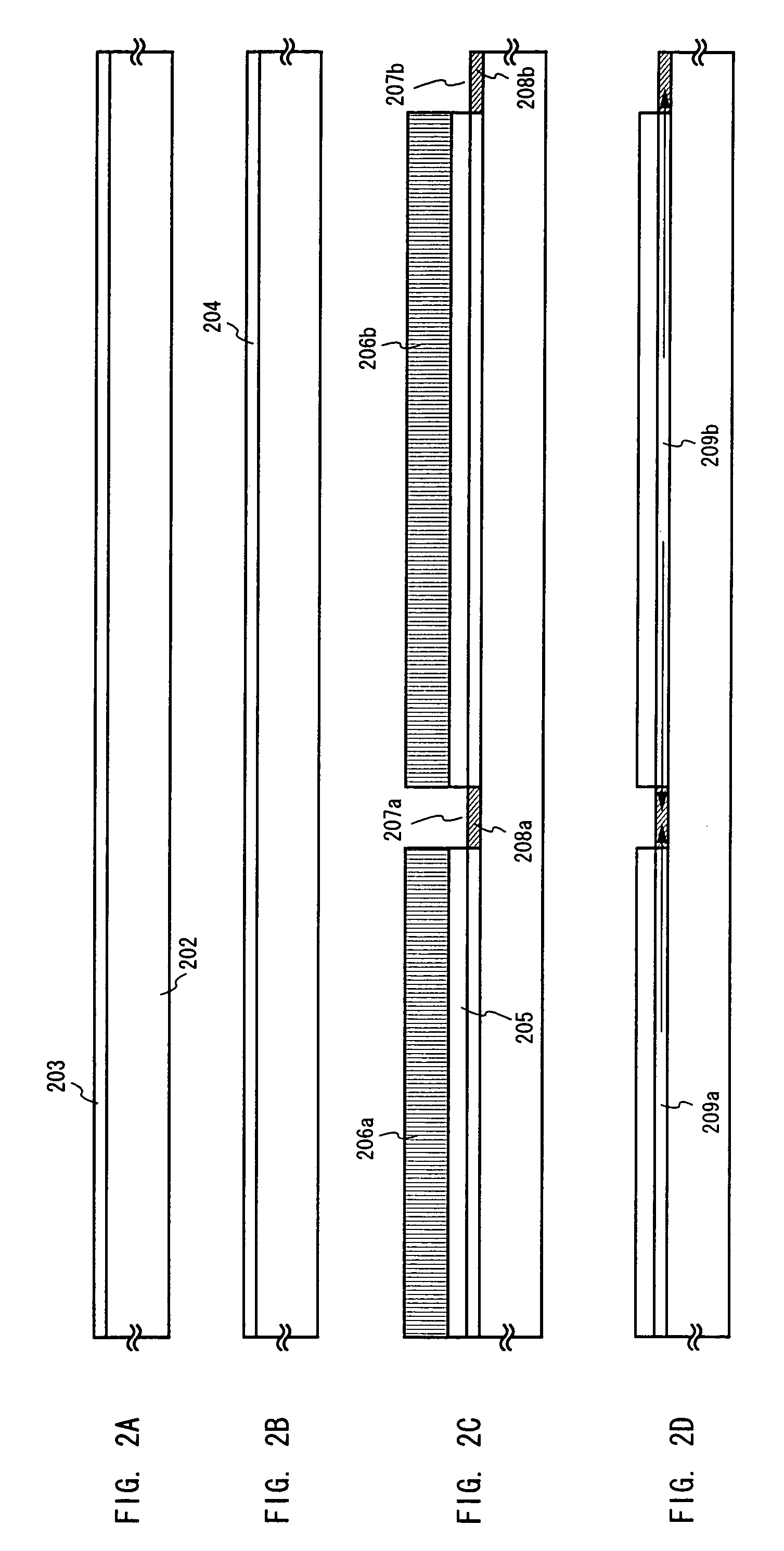

Color el display and method for producing the same

ActiveUS20080129195A1Quality improvementHigh color purityDischarge tube luminescnet screensLamp detailsDisplay deviceEngineering

One embodiment of the present invention is a color EL display characterized in that at least color filters, a thin film transistor circuit, an organic EL layer, and a common electrode are laminated in this order on a transparent substrate. Another embodiment of the invention is a method for producing a color EL display comprising the steps of forming color filters or a transparent substrate; forming a thin film transistor circuit; forming an organic EL layer; and forming a common electrode, wherein process temperatures of the steps of forming the thin film transistor circuit and subsequent steps are 200° C. or less.

Owner:TOPPAN PRINTING CO LTD

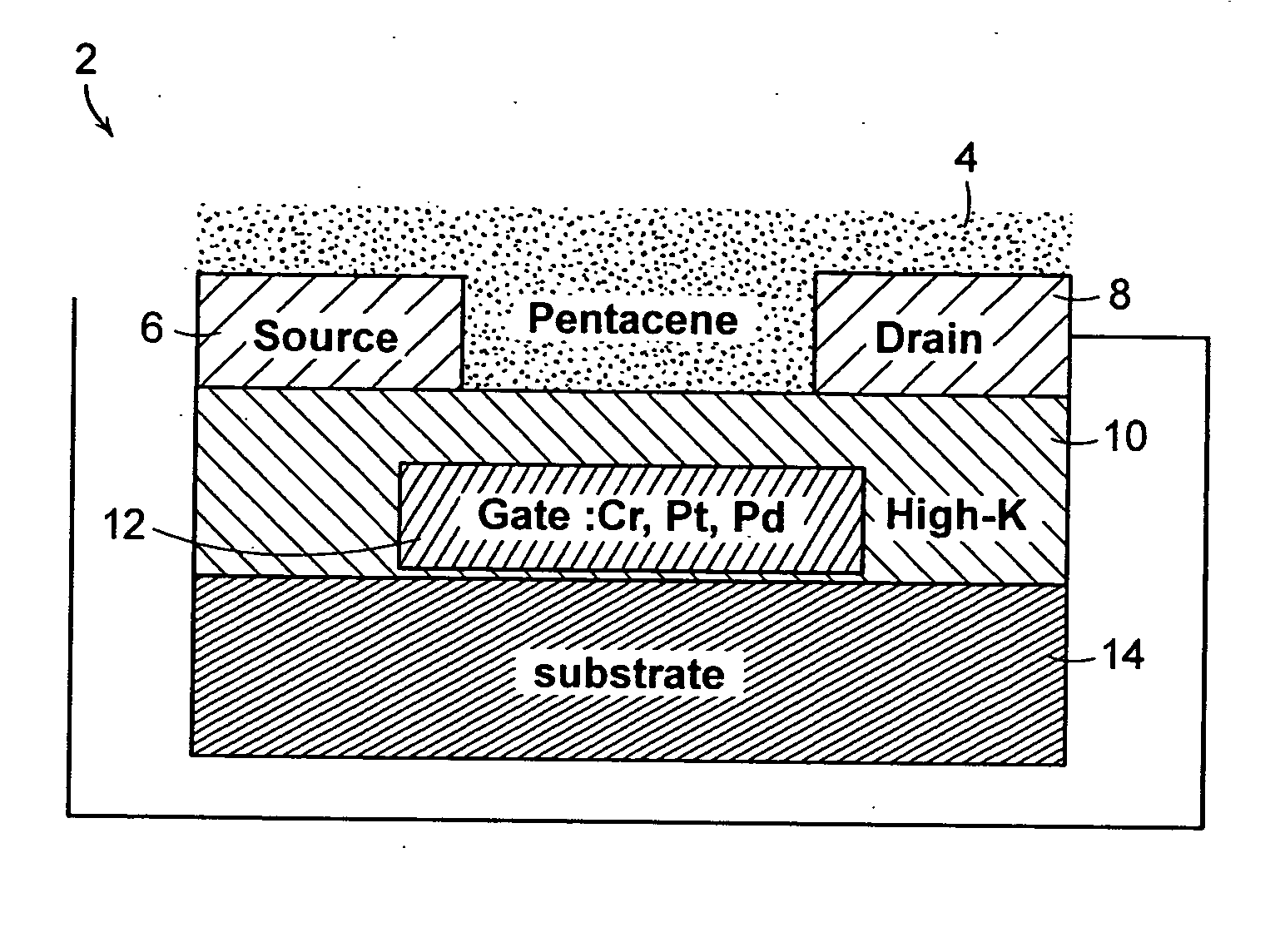

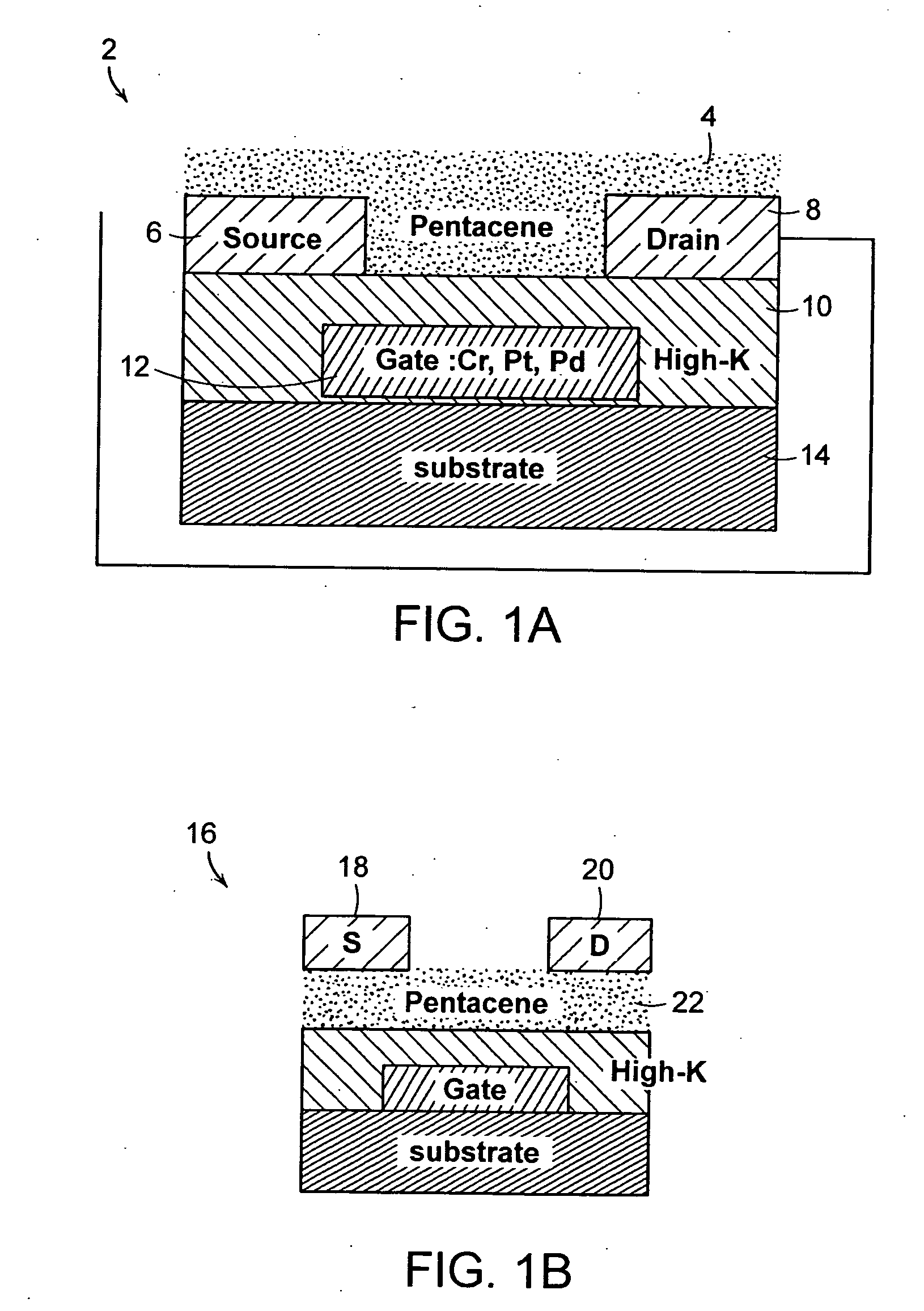

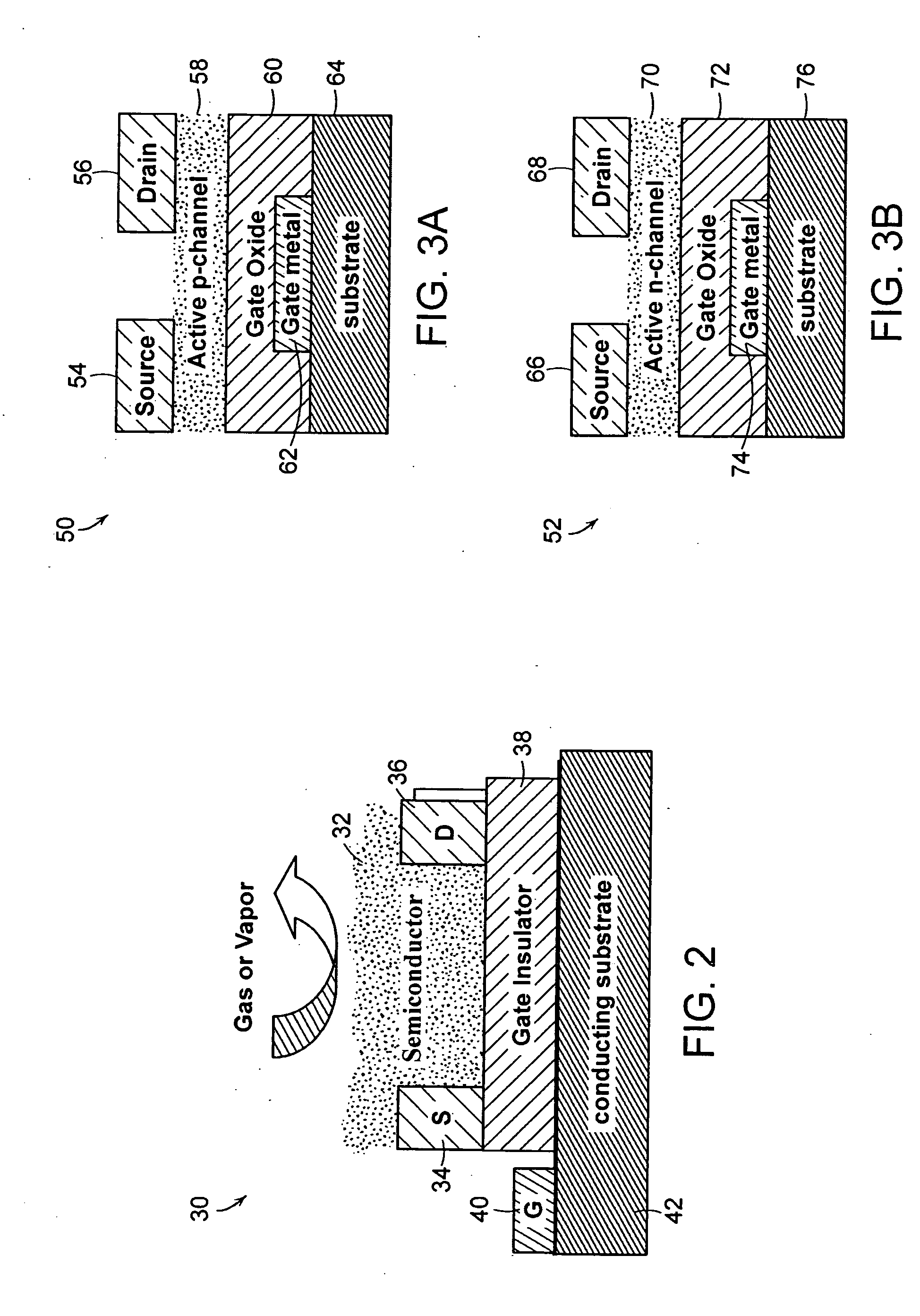

Low voltage flexible organic/transparent transistor for selective gas sensing, photodetecting and CMOS device applications

A thin film transistor (TFT) includes a source electrode, a drain electrode, and a gate electrode. A gate insulator is coupled to the source electrode, drain electrode, and gate electrode. The gate insulator includes room temperature deposited high-K materials so as to allow said thin film transistor to operate at low operating voltage.

Owner:MASSACHUSETTS INST OF TECH

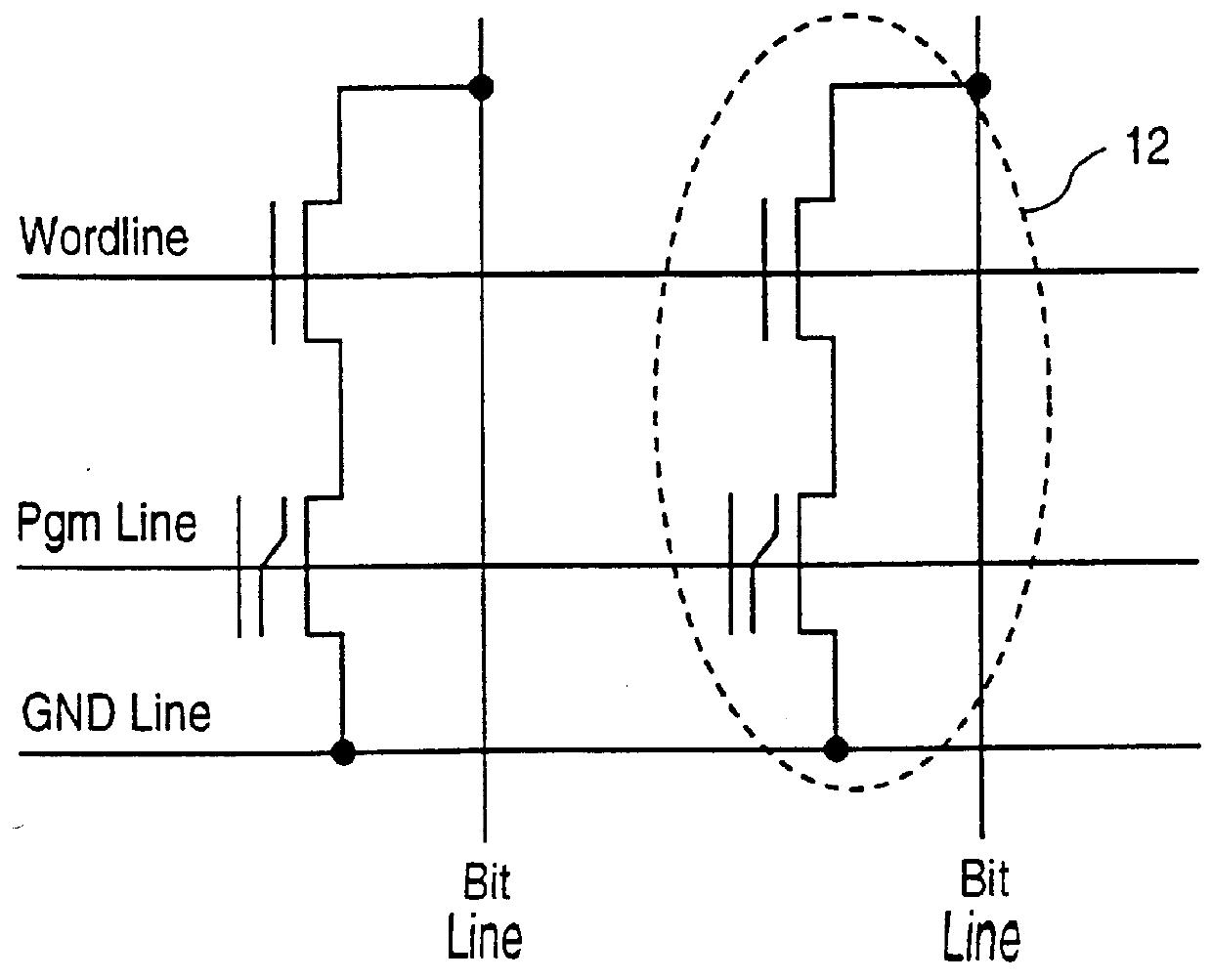

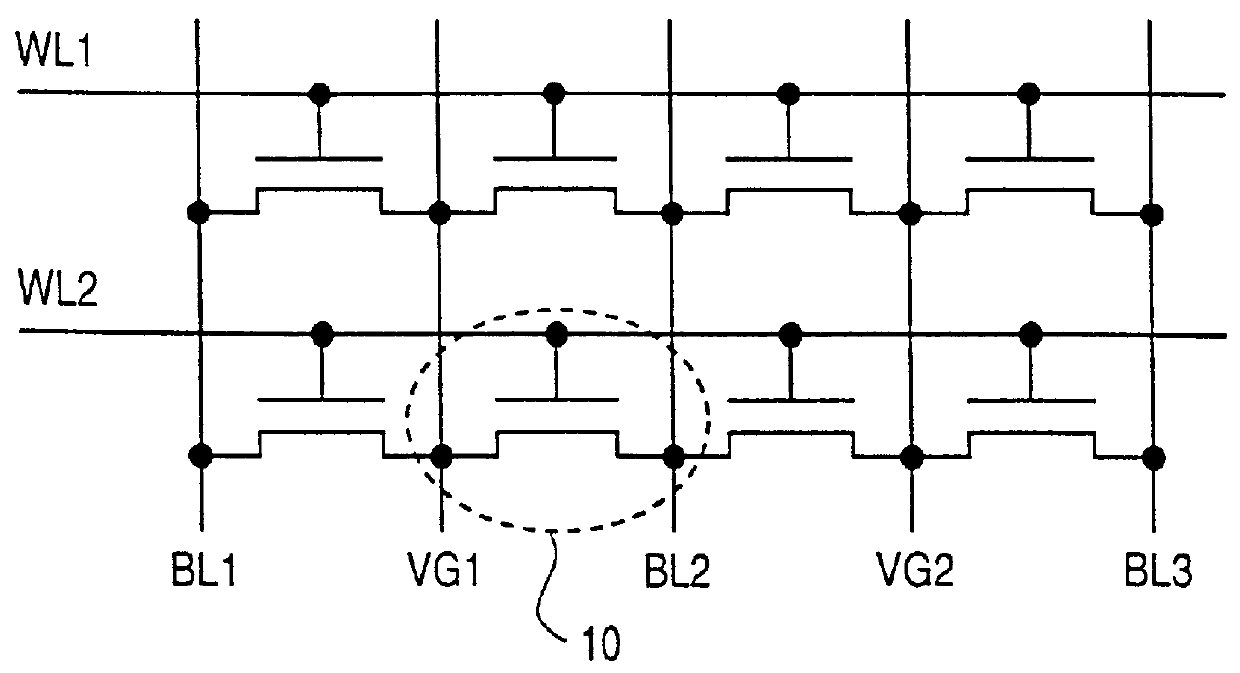

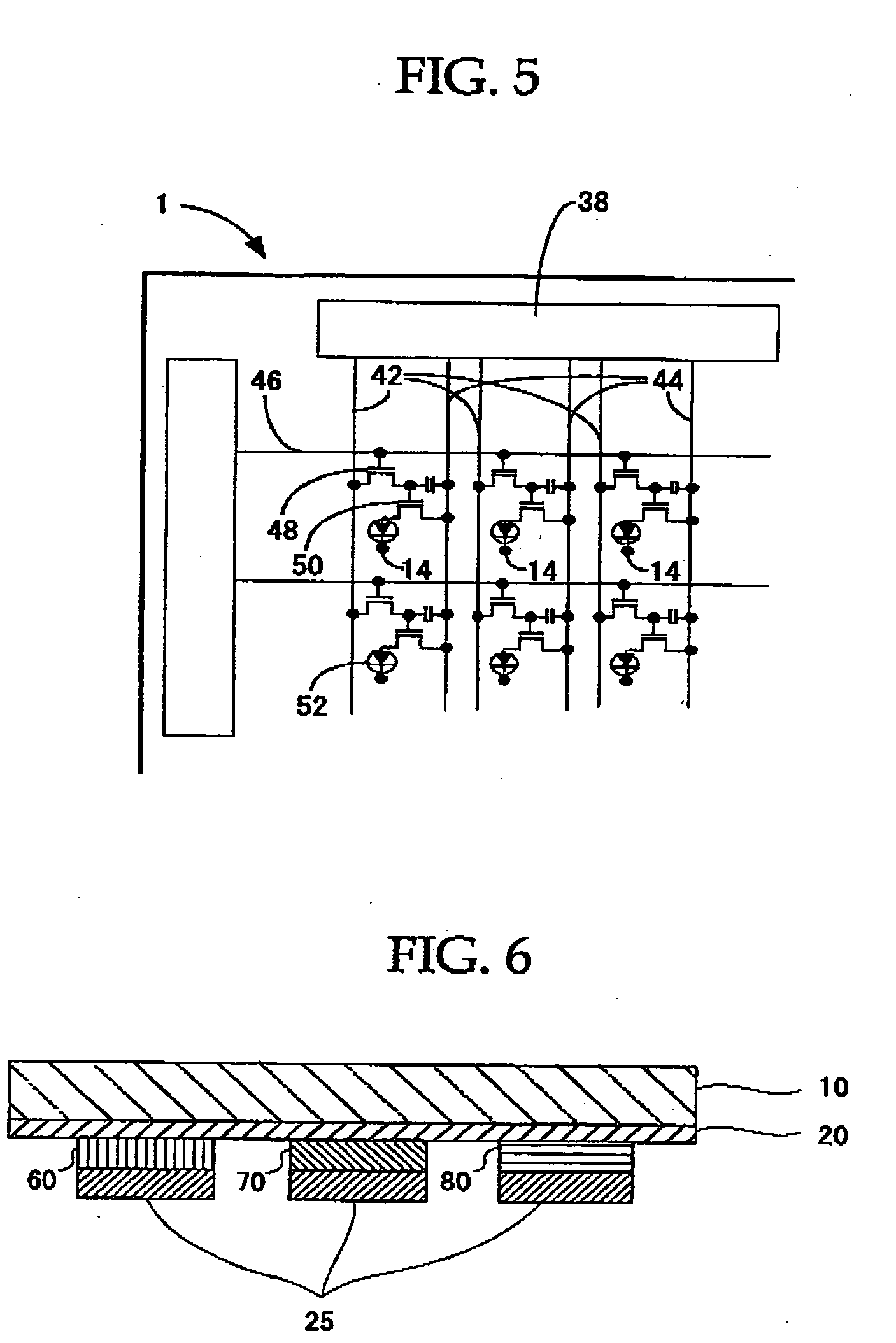

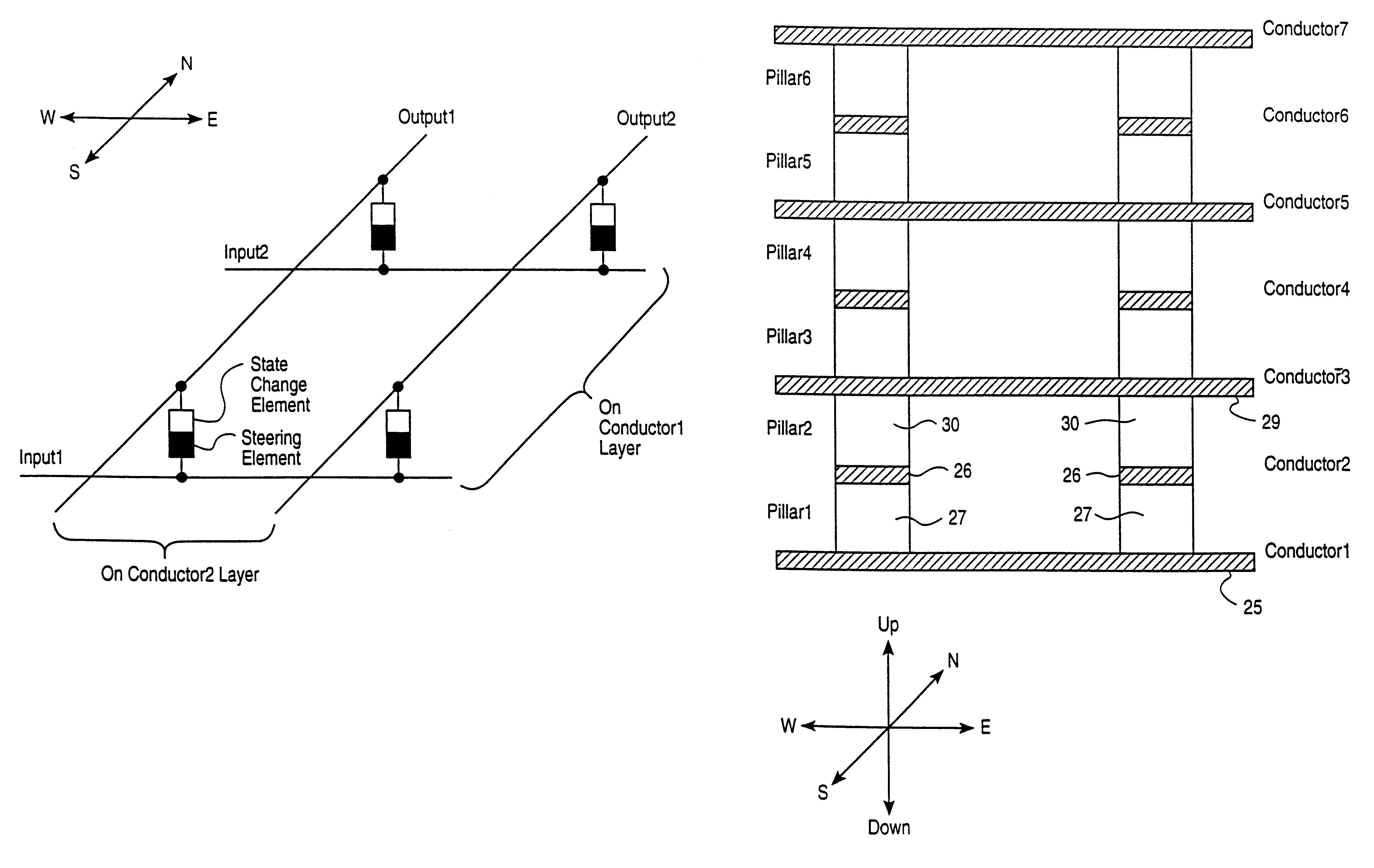

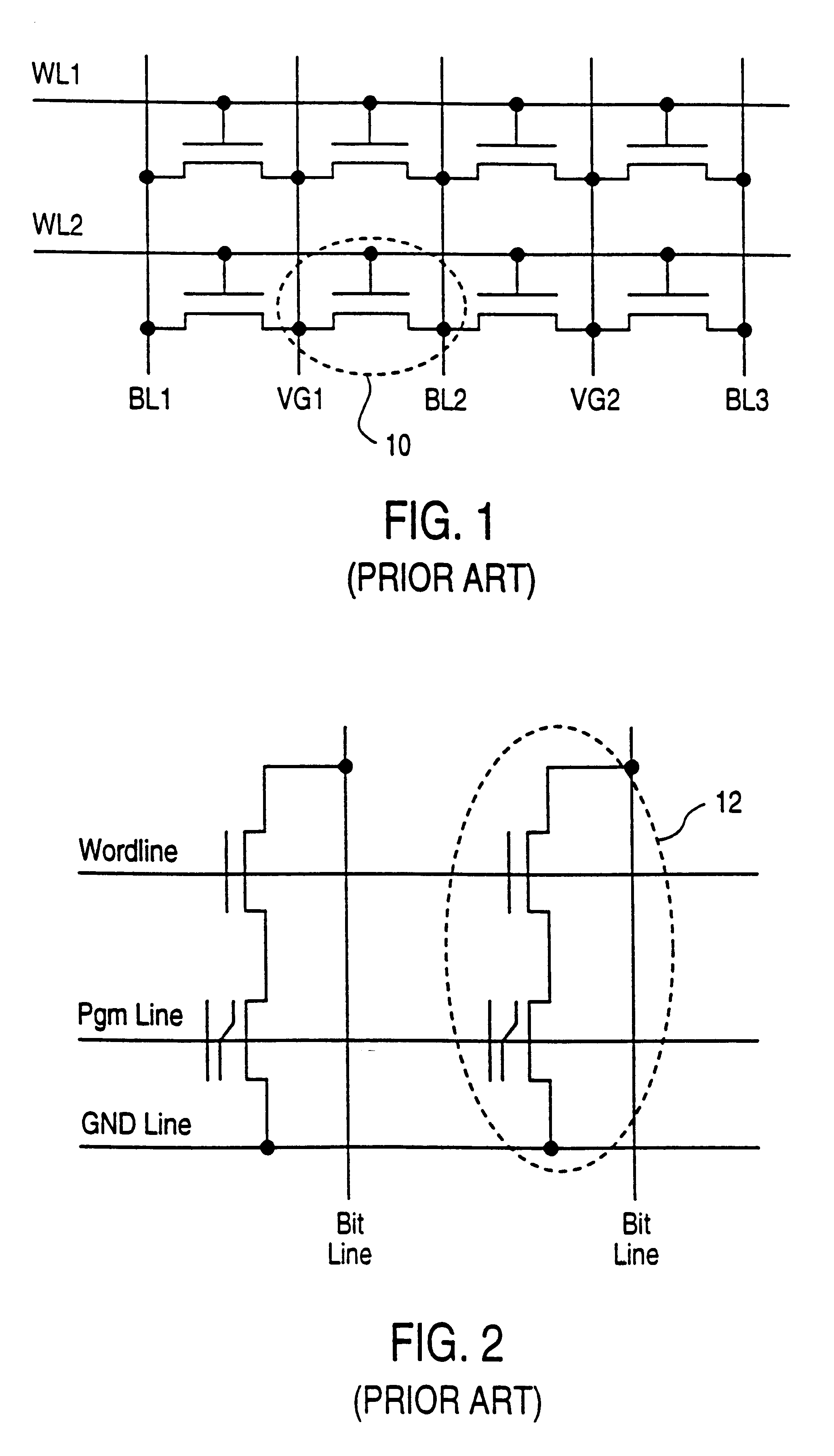

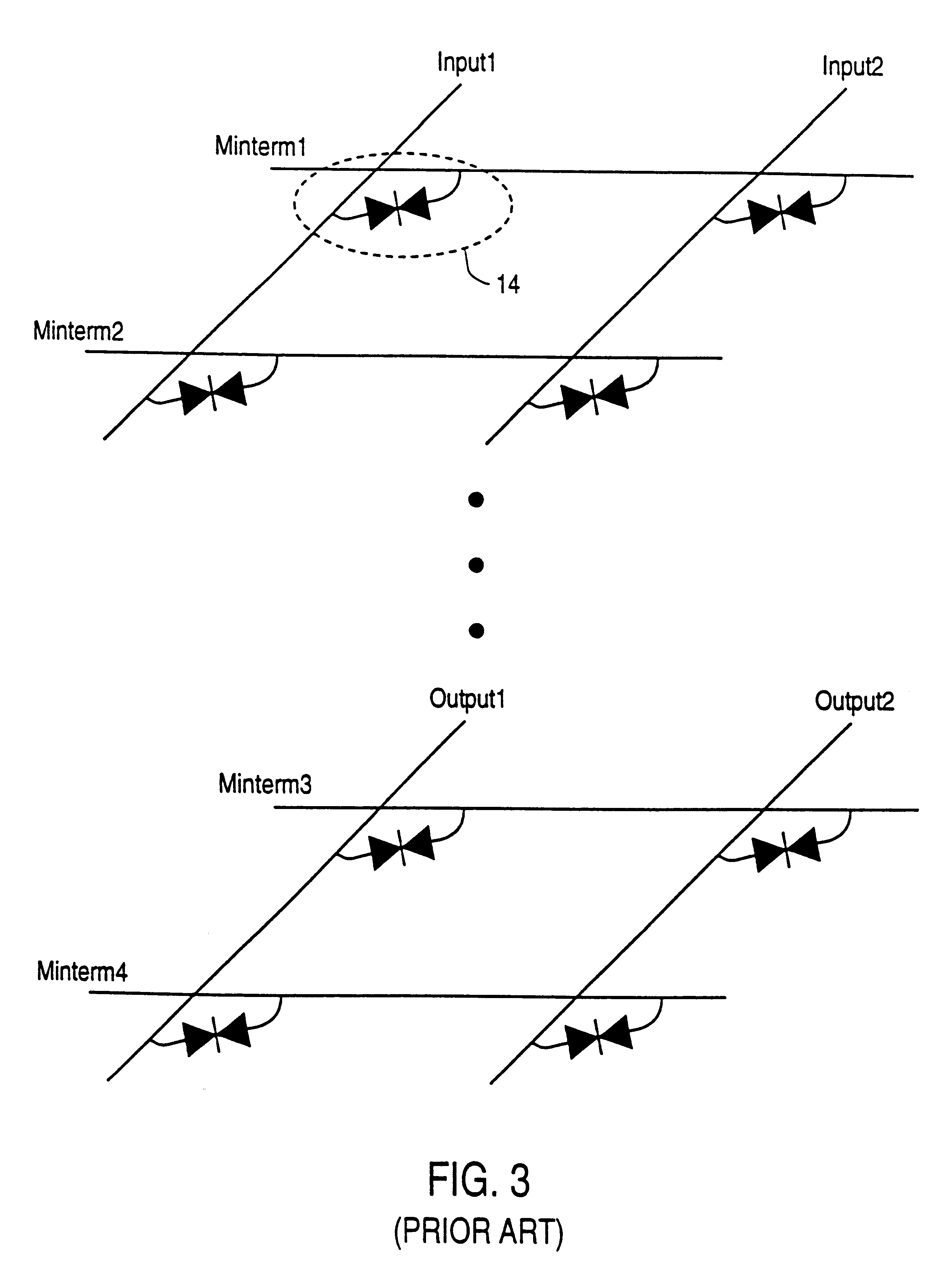

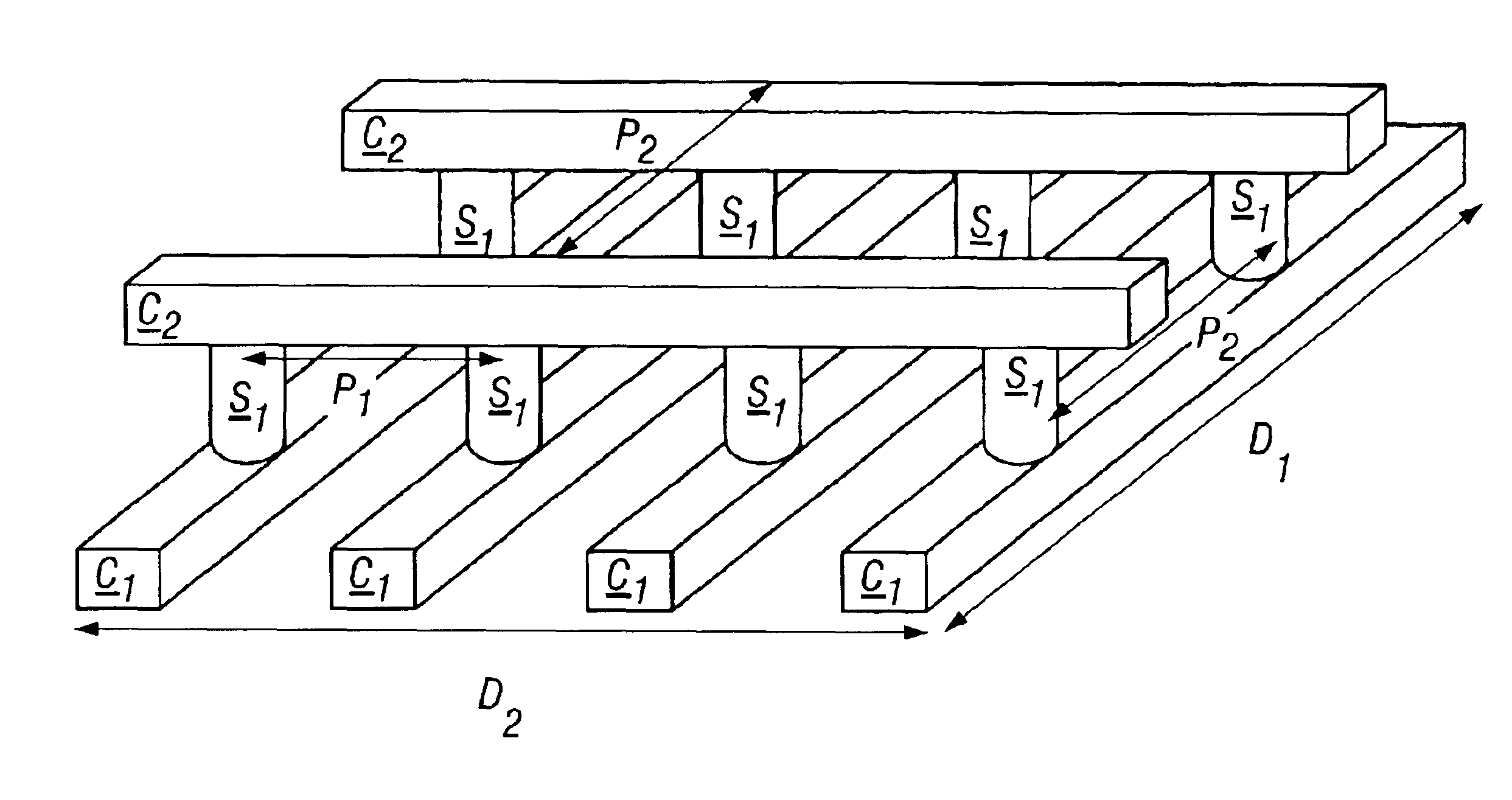

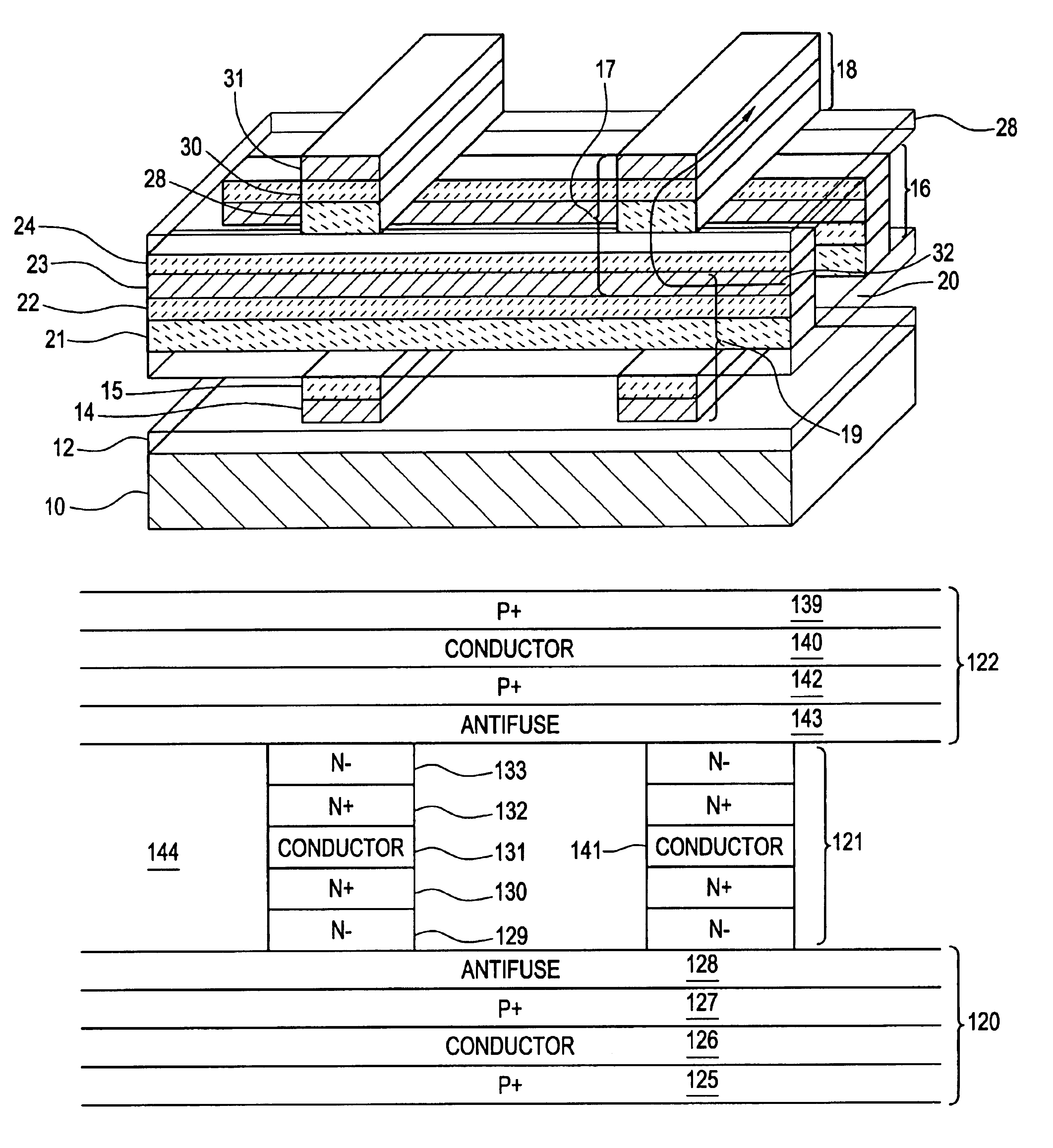

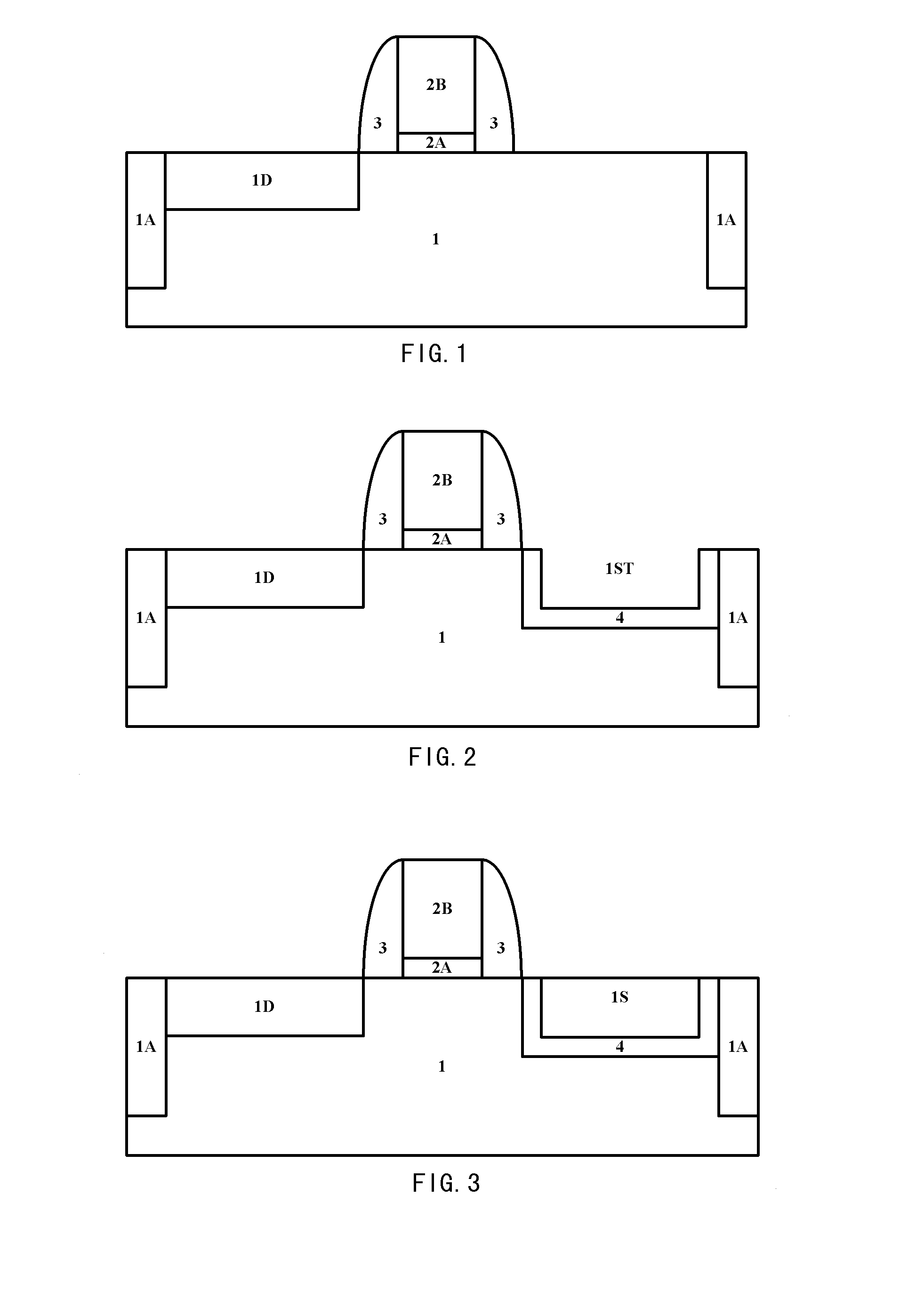

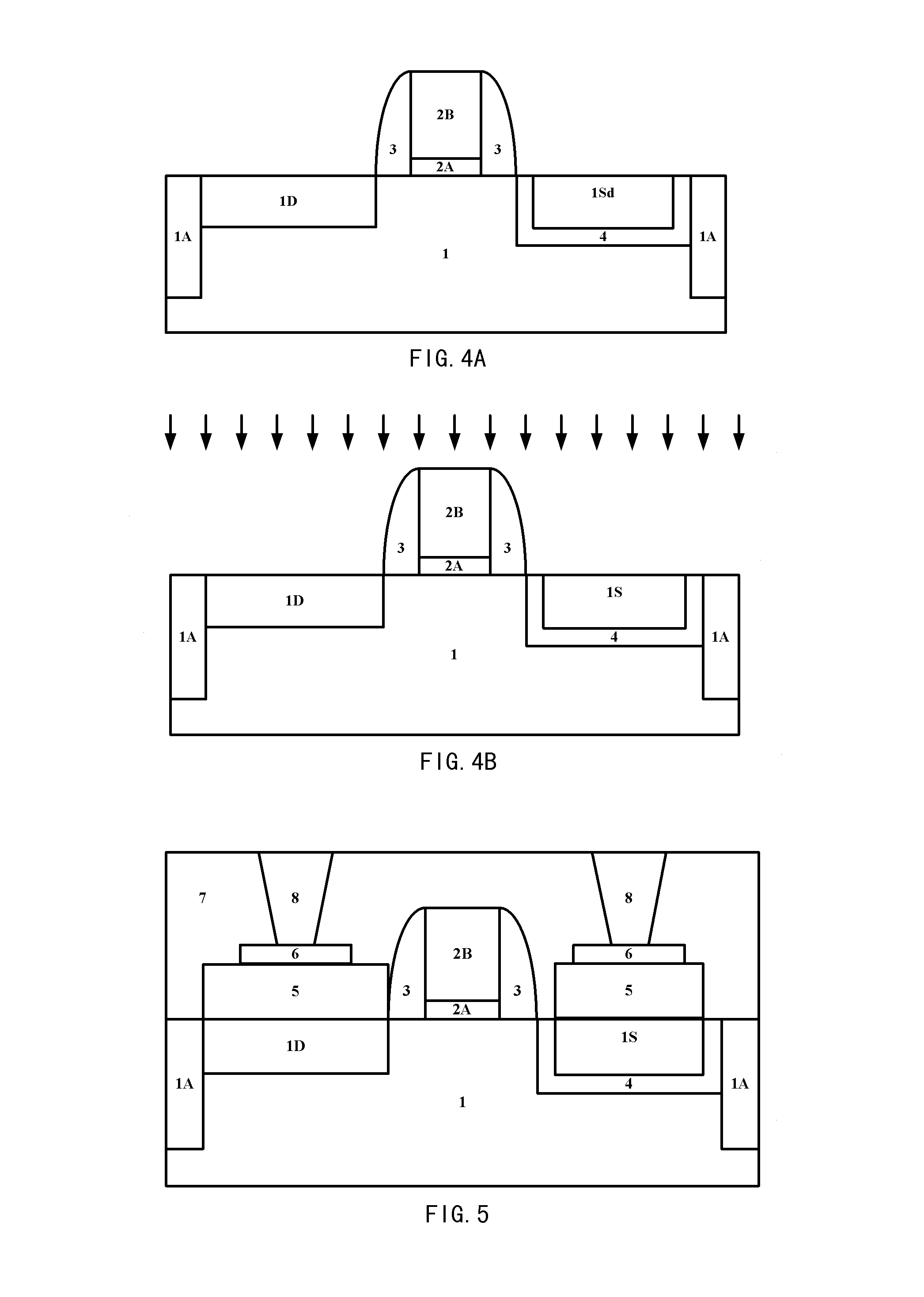

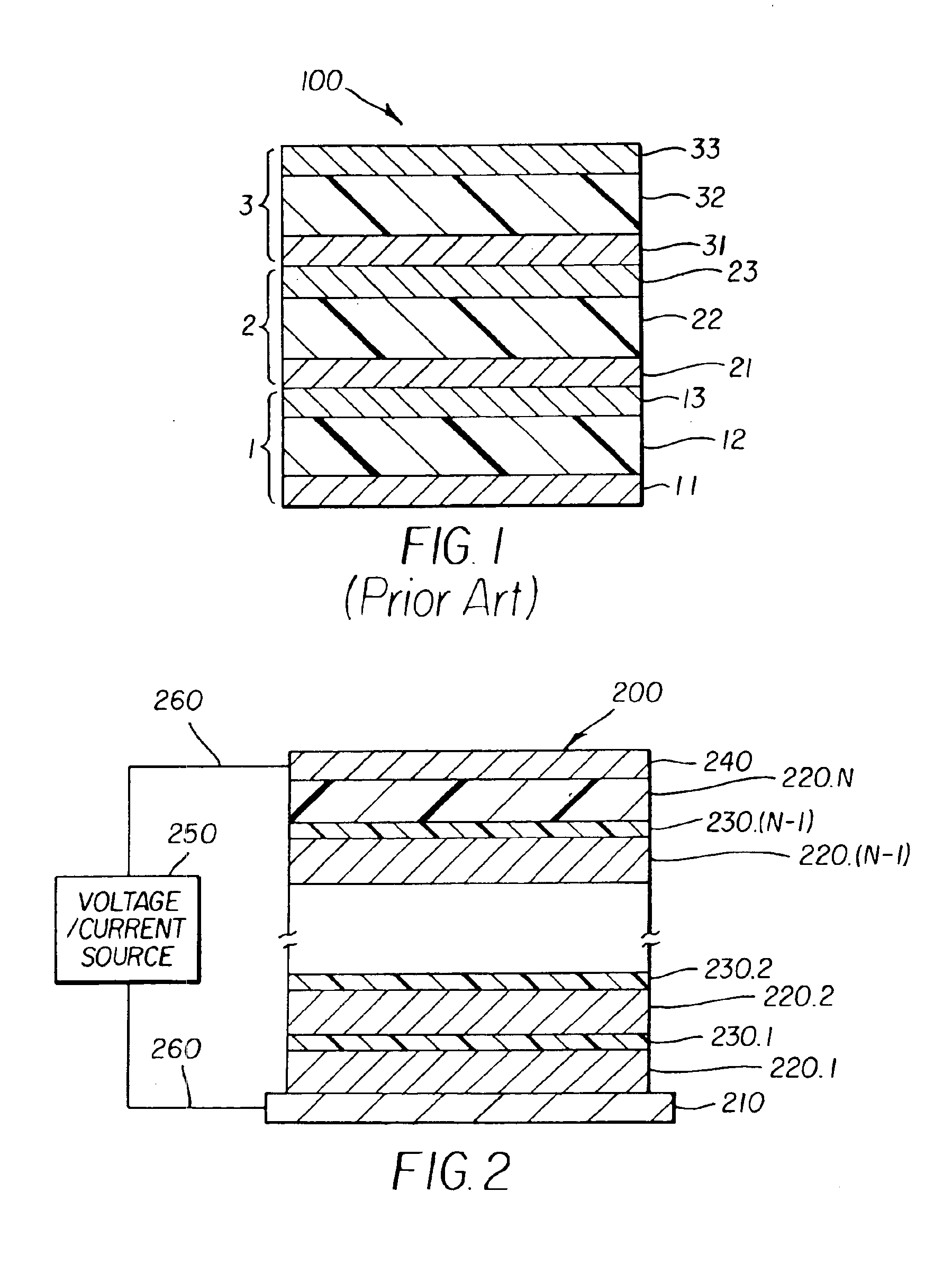

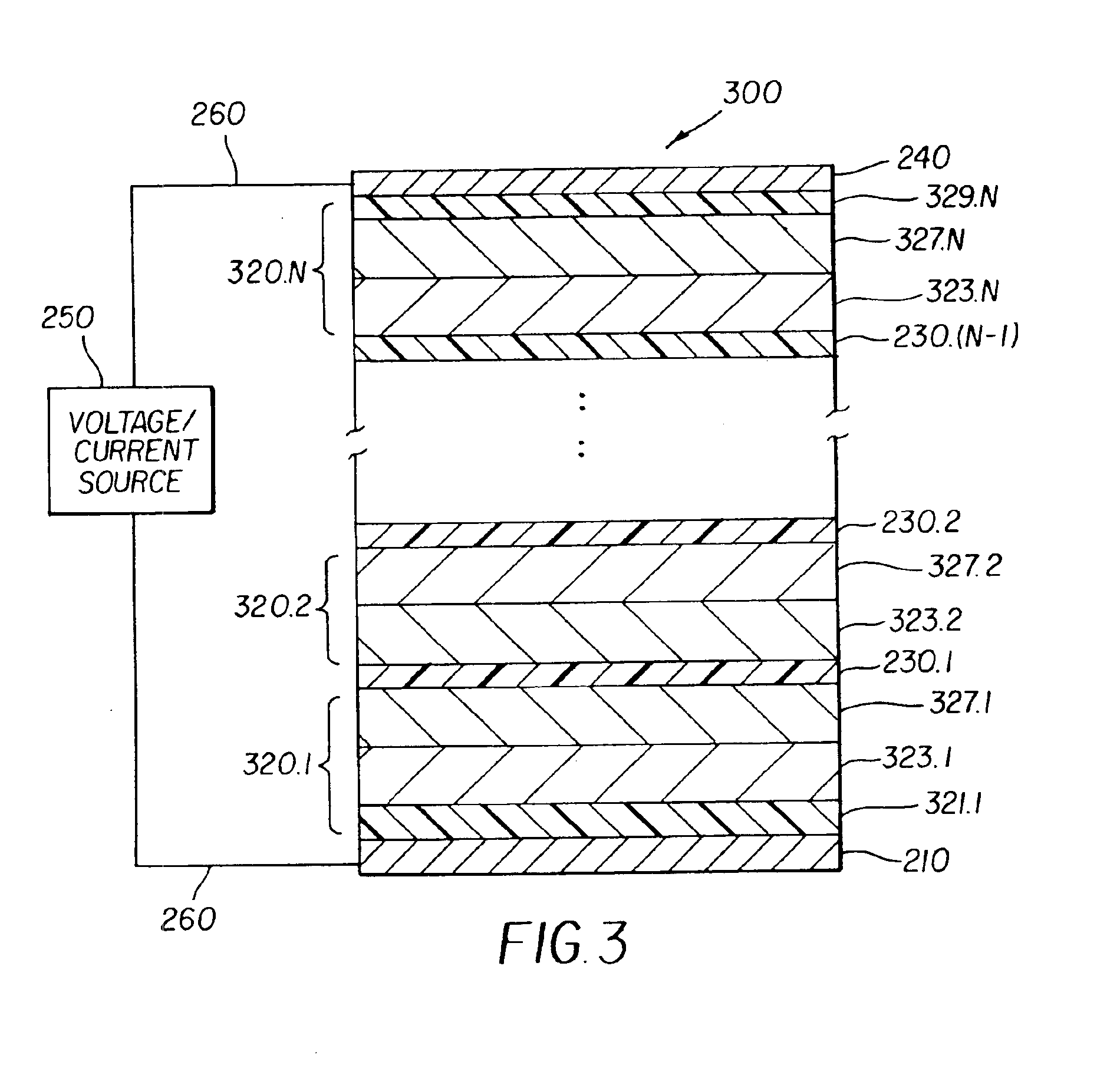

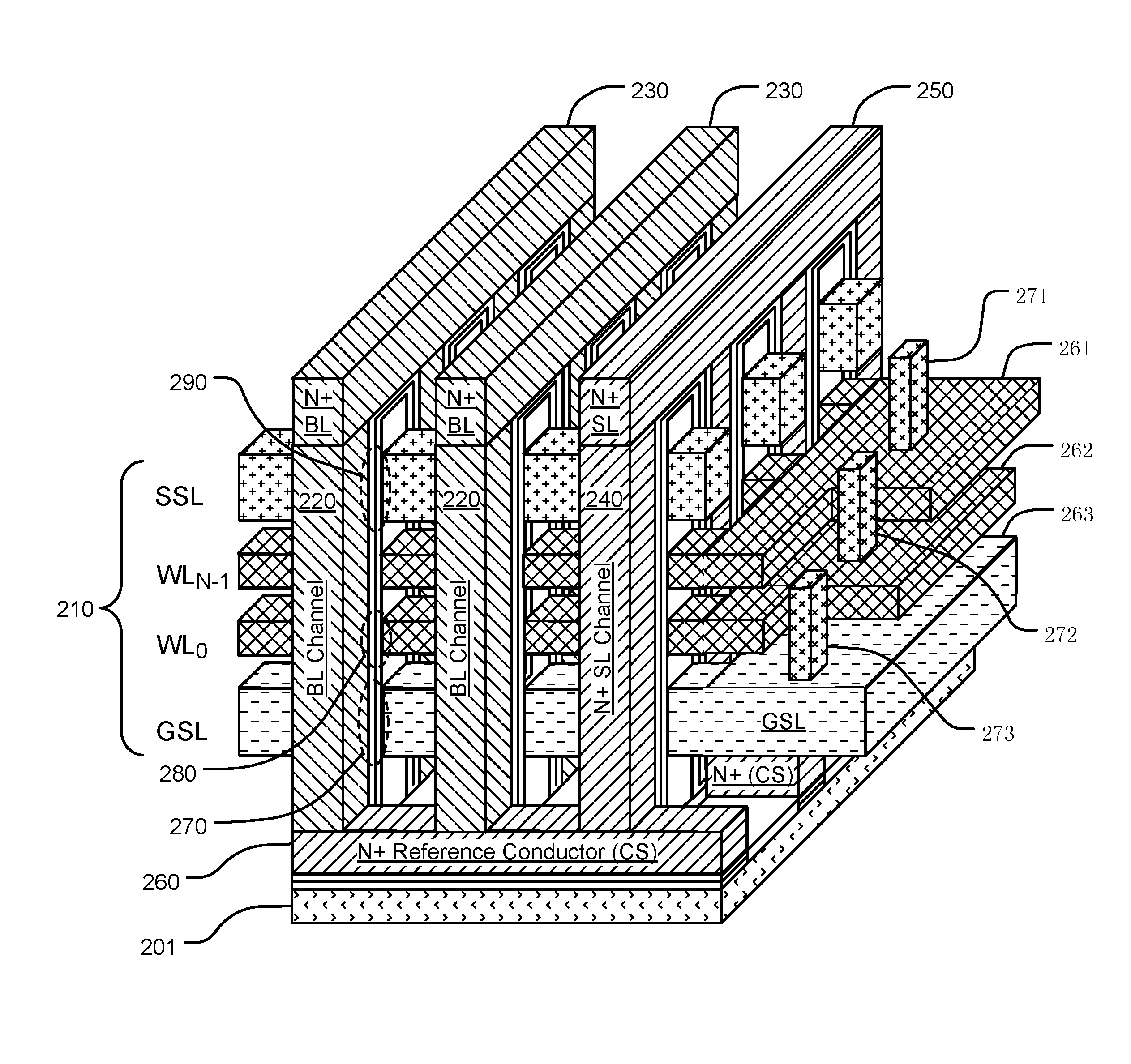

Vertically stacked field programmable nonvolatile memory and method of fabrication

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:RHOMBUS

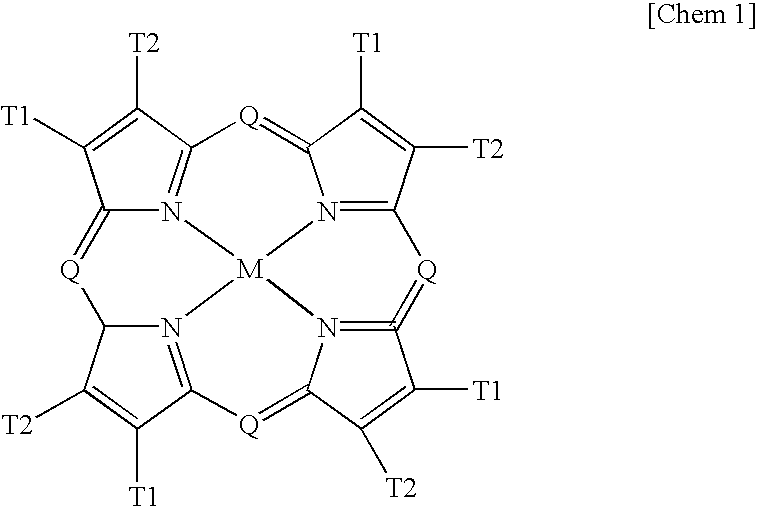

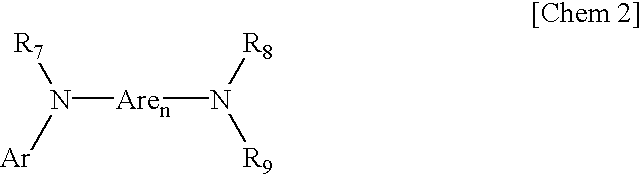

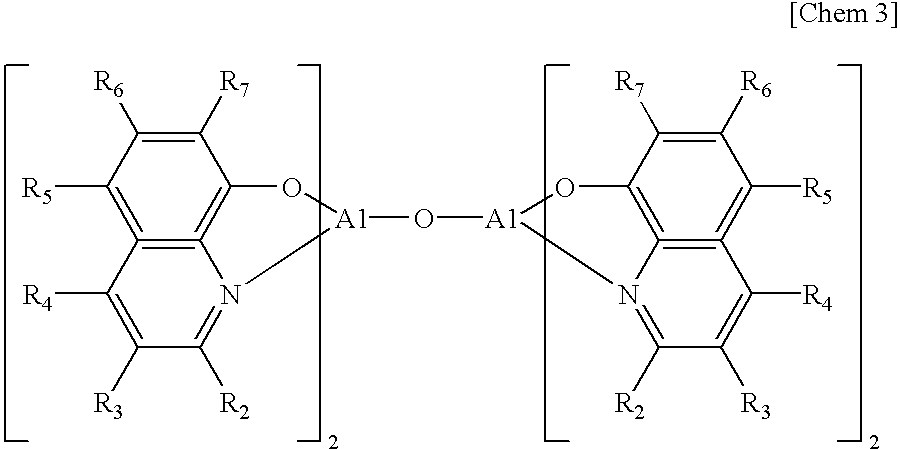

Organometallic complex, organic EL element and organic EL display

InactiveUS20050244673A1Improve efficiencyExcellent lifetimeGroup 8/9/10/18 element organic compoundsSolid-state devicesRheniumNitrogen

An organic EL element includes an organometallic complex including a rhenium atom; one ligand which has a coordinated nitrogen atom and a coordinated oxygen atom, each coordinated with the rhenium atom, and has at least one π conjugation part; and the other ligand coordinated with the rhenium atom in such a way that the ligand saturates the coordination number of the rhenium atom and the charge of the whole organometallic complex is neutral.

Owner:FUJIFILM HLDG CORP +1

Vertically stacked field programmable nonvolatile memory and method of fabrication

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

Memory cell incorporating a chalcogenide element and method of making same

Owner:ROUND ROCK RES LLC

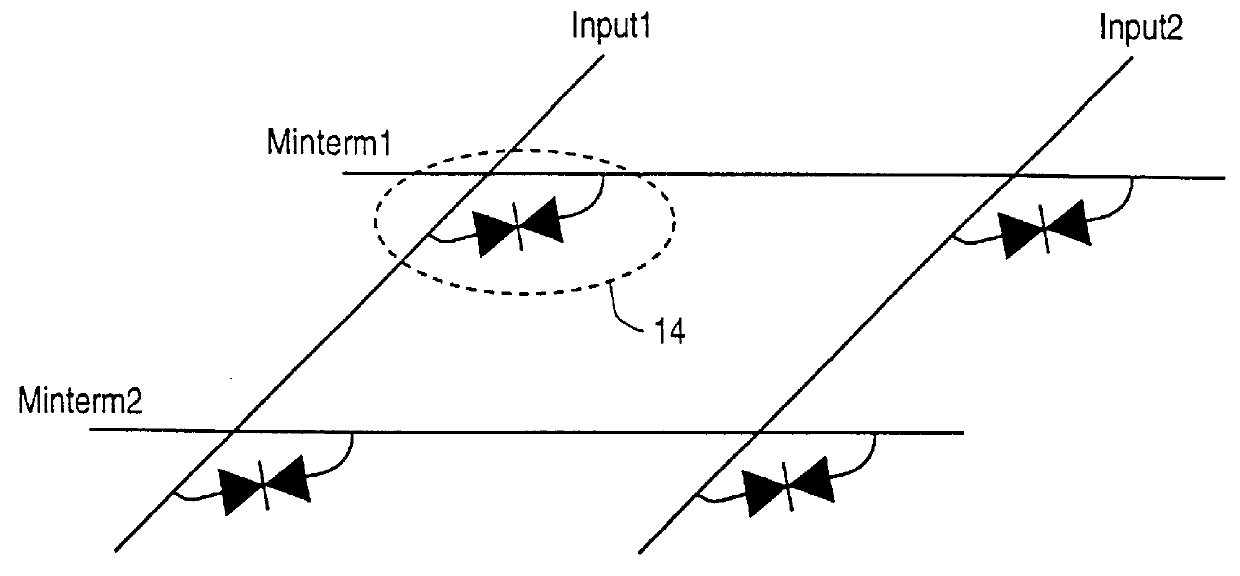

High-density three-dimensional memory cell

InactiveUS6952030B2High densityReduce the overall heightTransistorSemiconductor/solid-state device detailsElectrical conductorHigh density

A three dimensional monolithic memory comprising a memory cell allowing for increased density is disclosed. In the memory cell of the present invention, a bottom conductor preferably comprising tungsten is formed. Above the bottom conductor a semiconductor element preferably comprises two diode portions and an antifuse. Above the semiconductor element are additional conductors and semiconductor elements in multiple stones of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

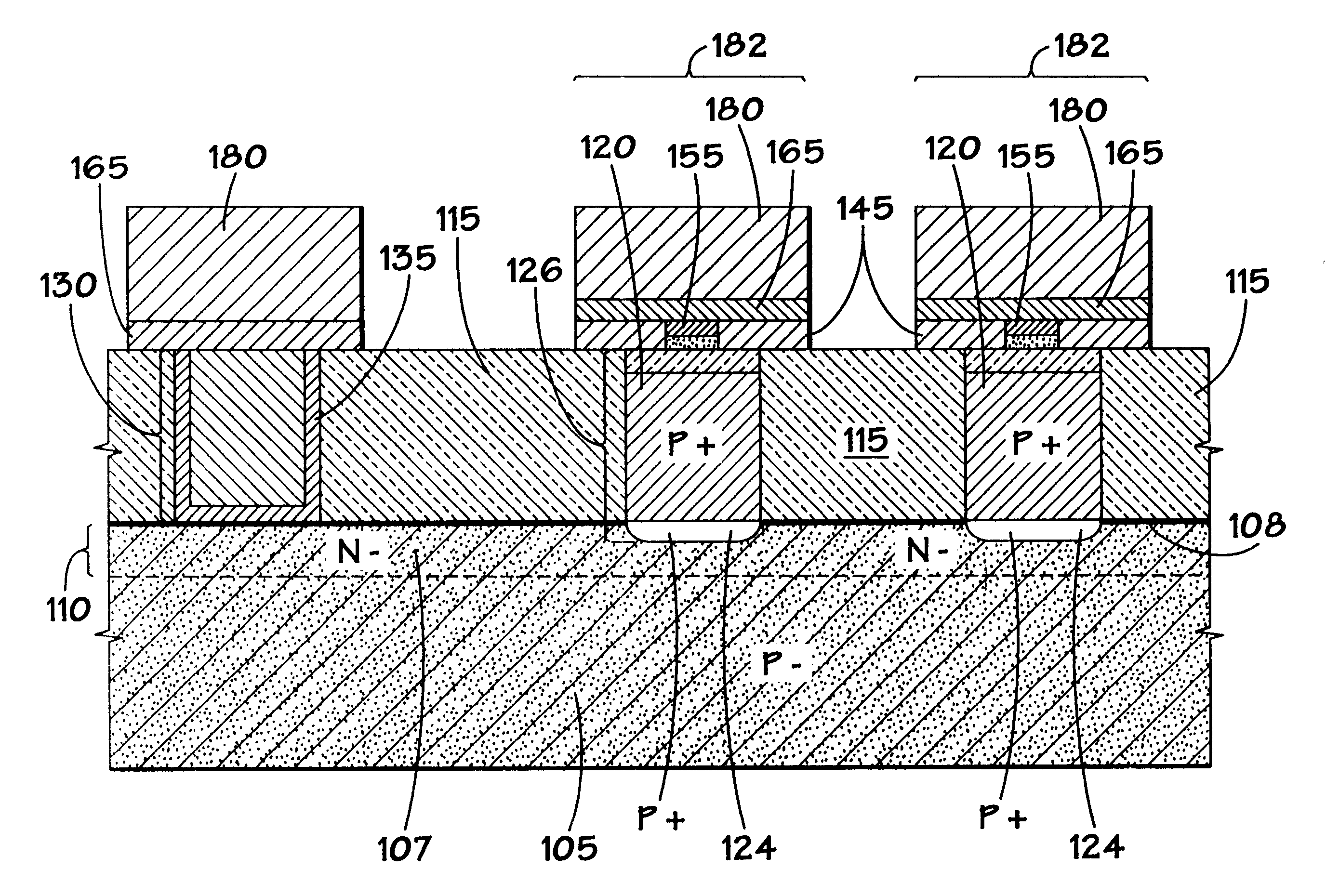

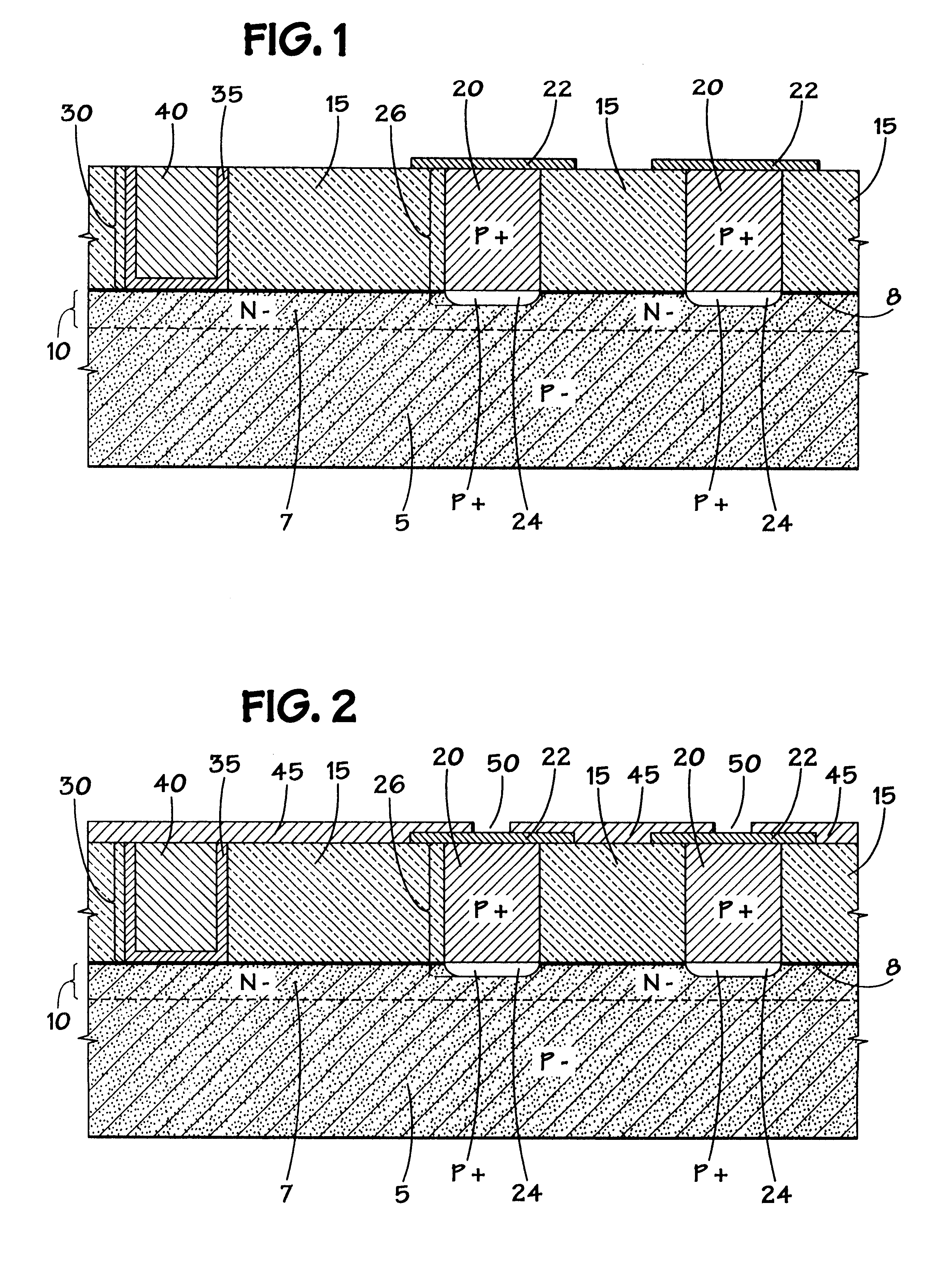

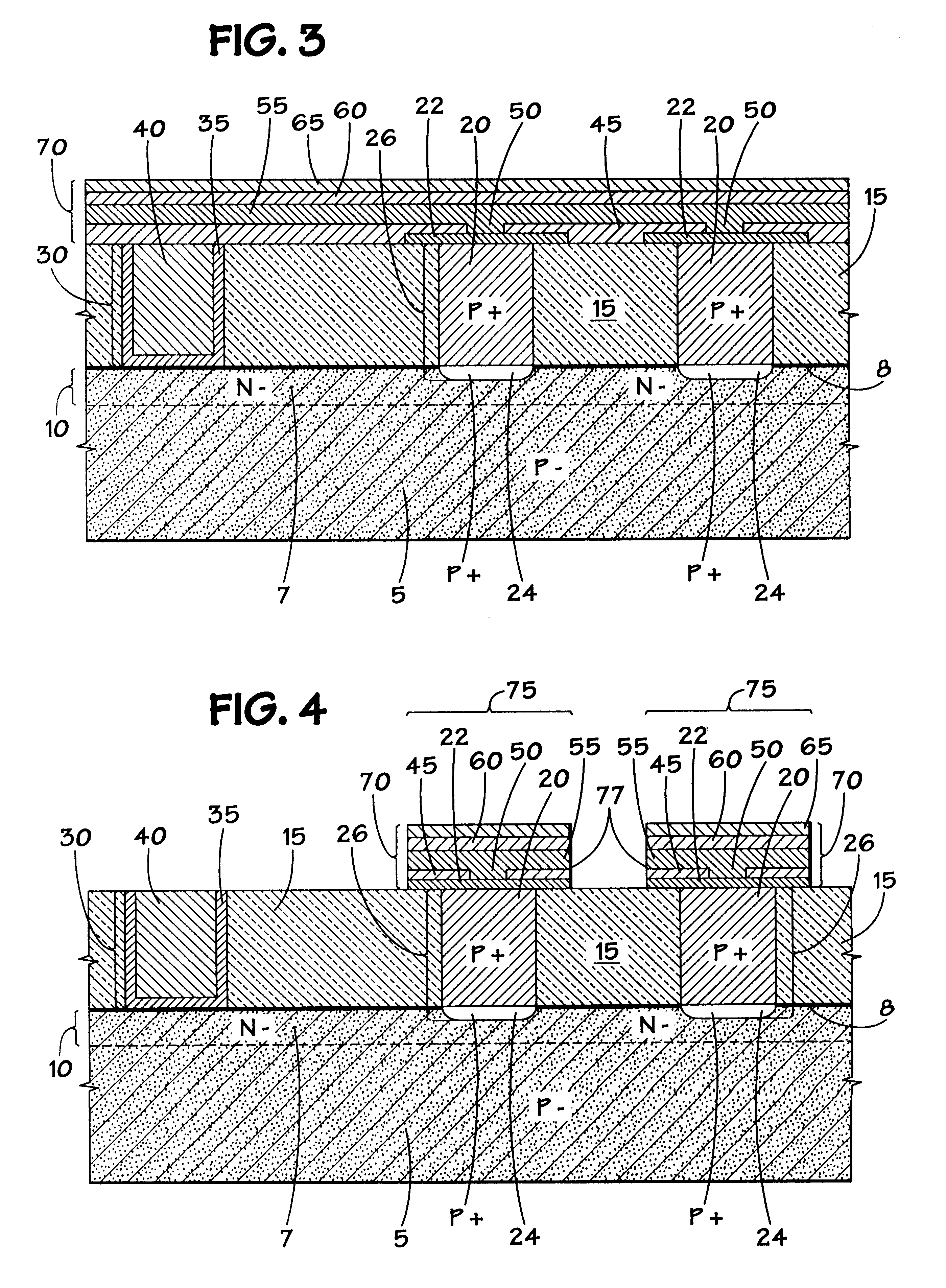

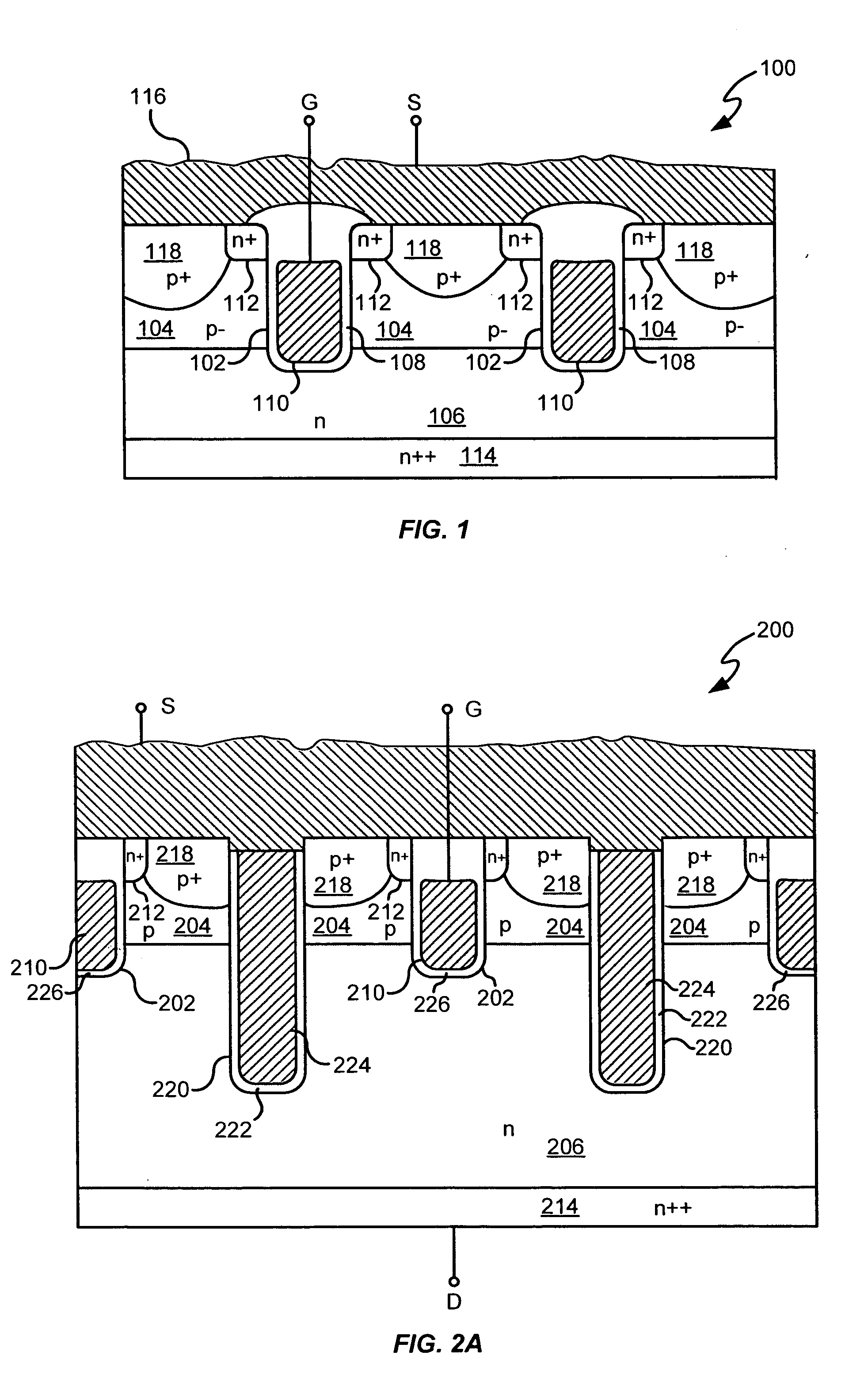

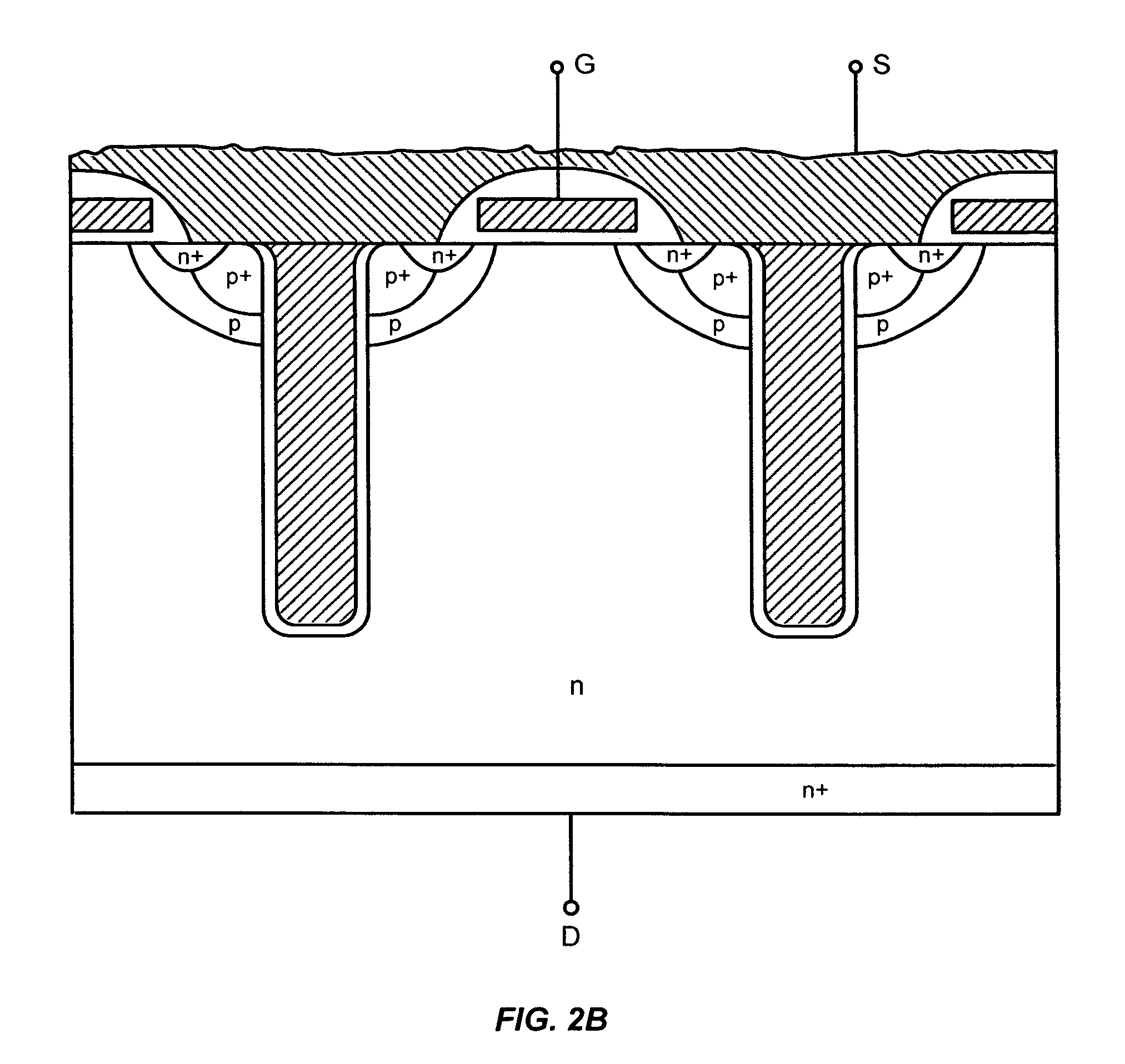

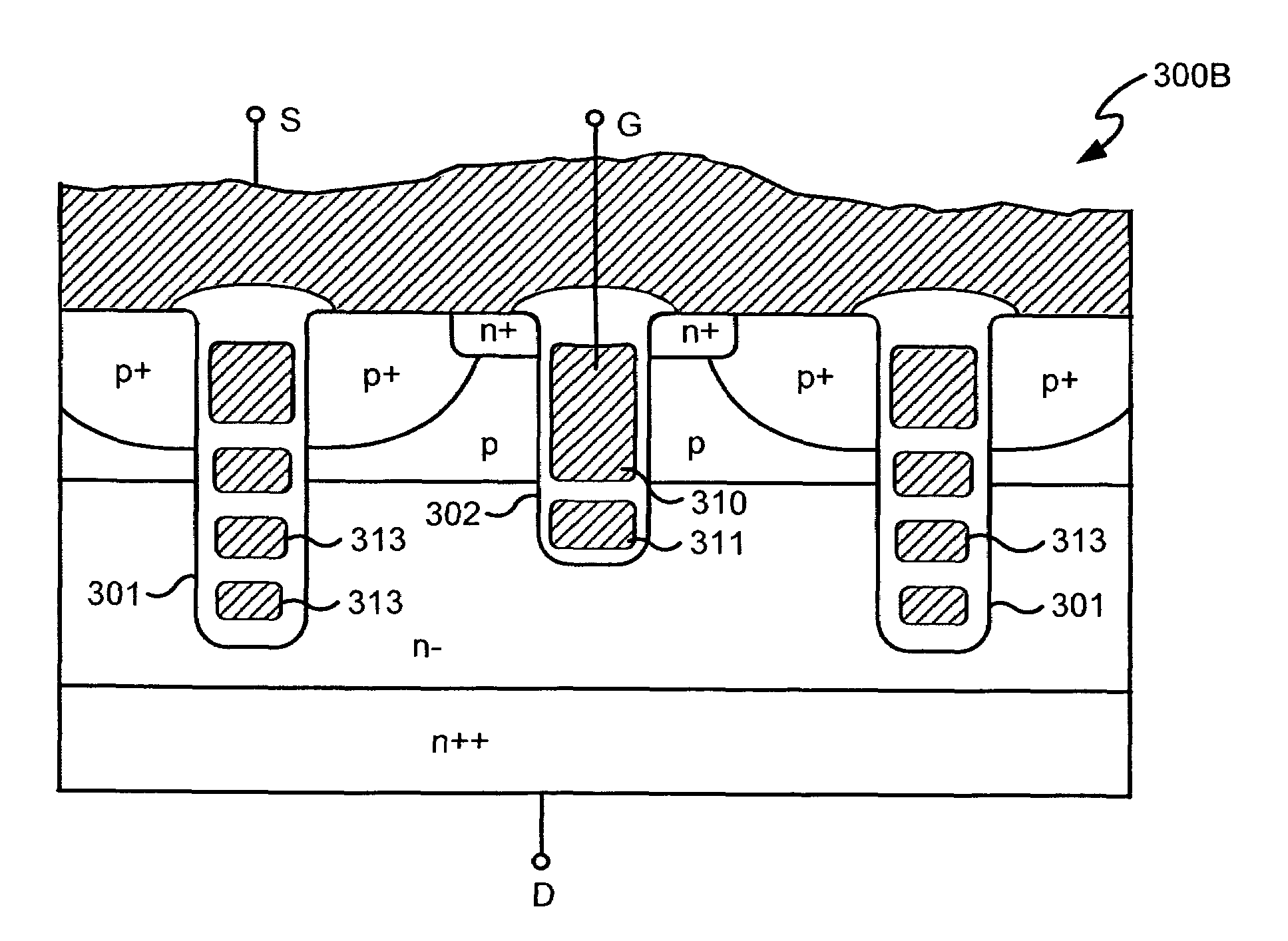

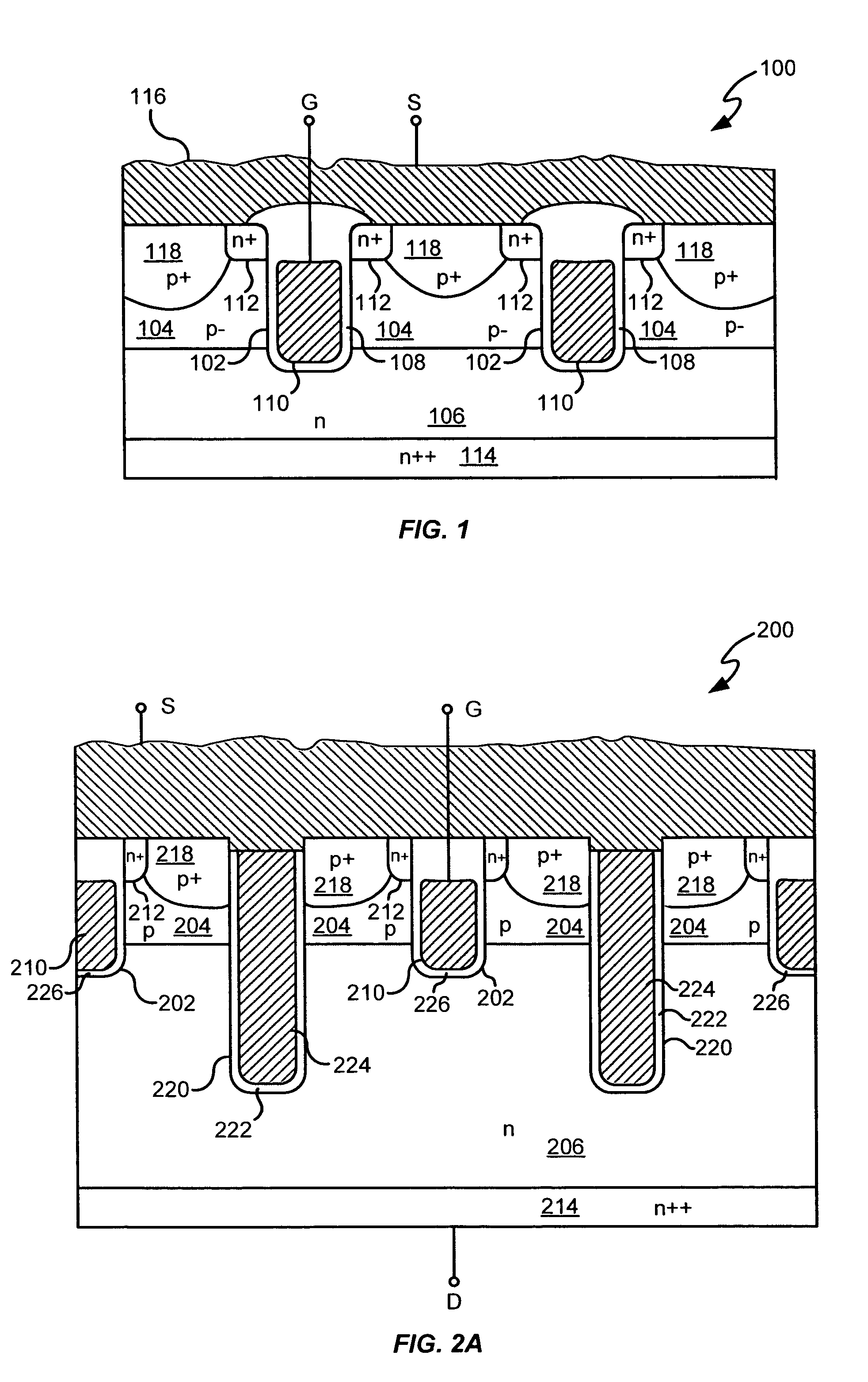

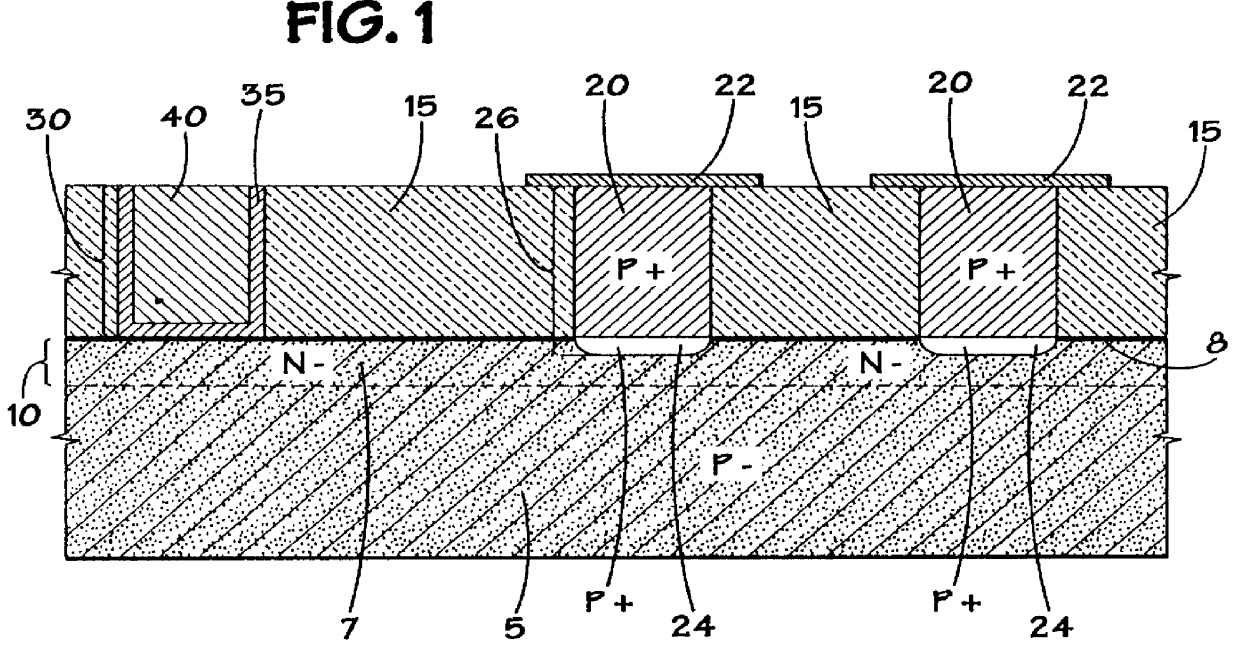

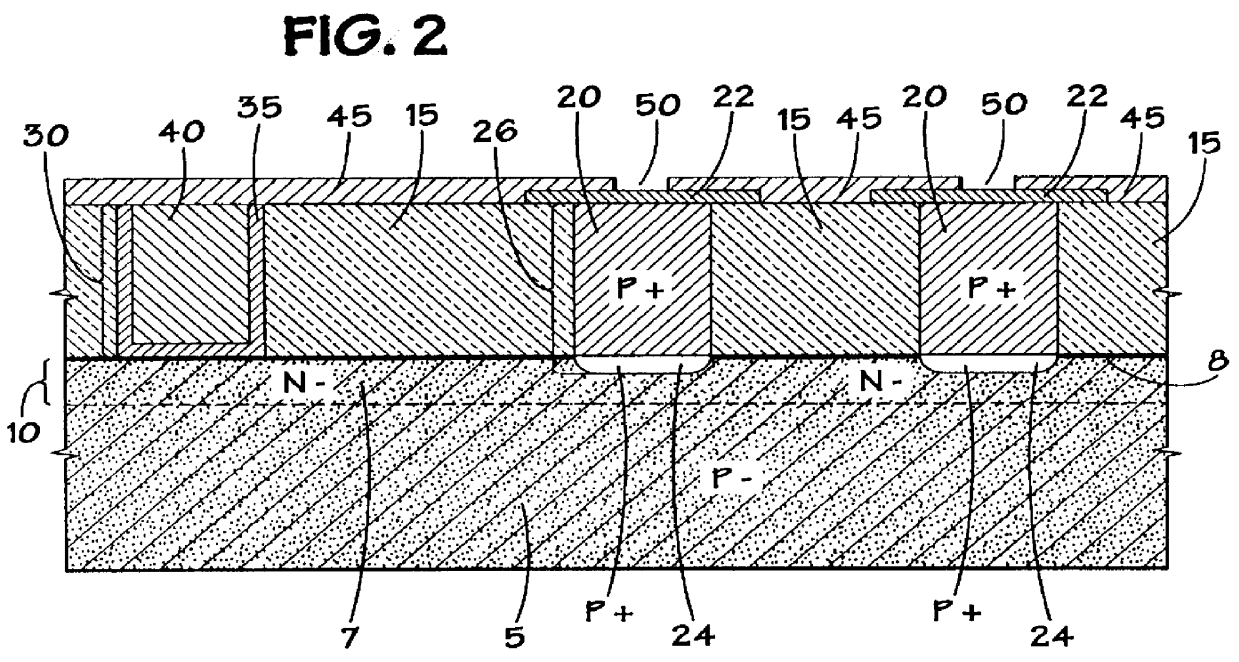

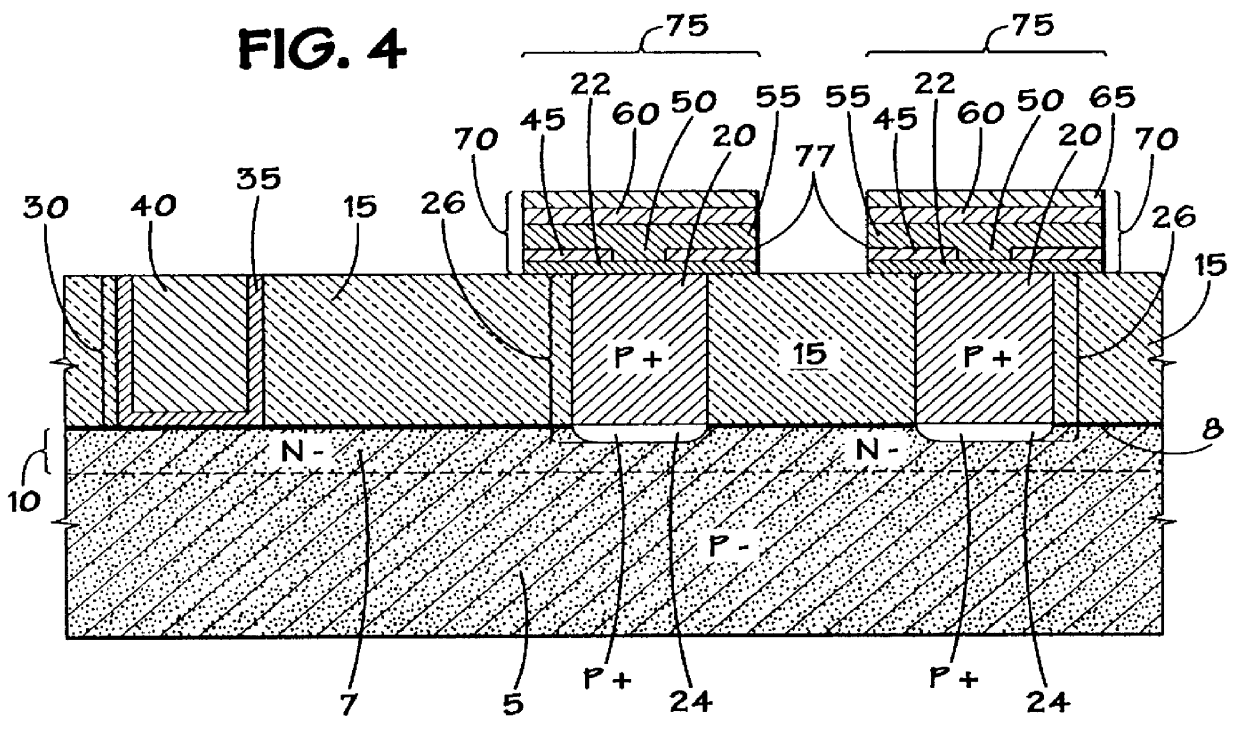

Power semiconductor devices and methods of manufacture

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

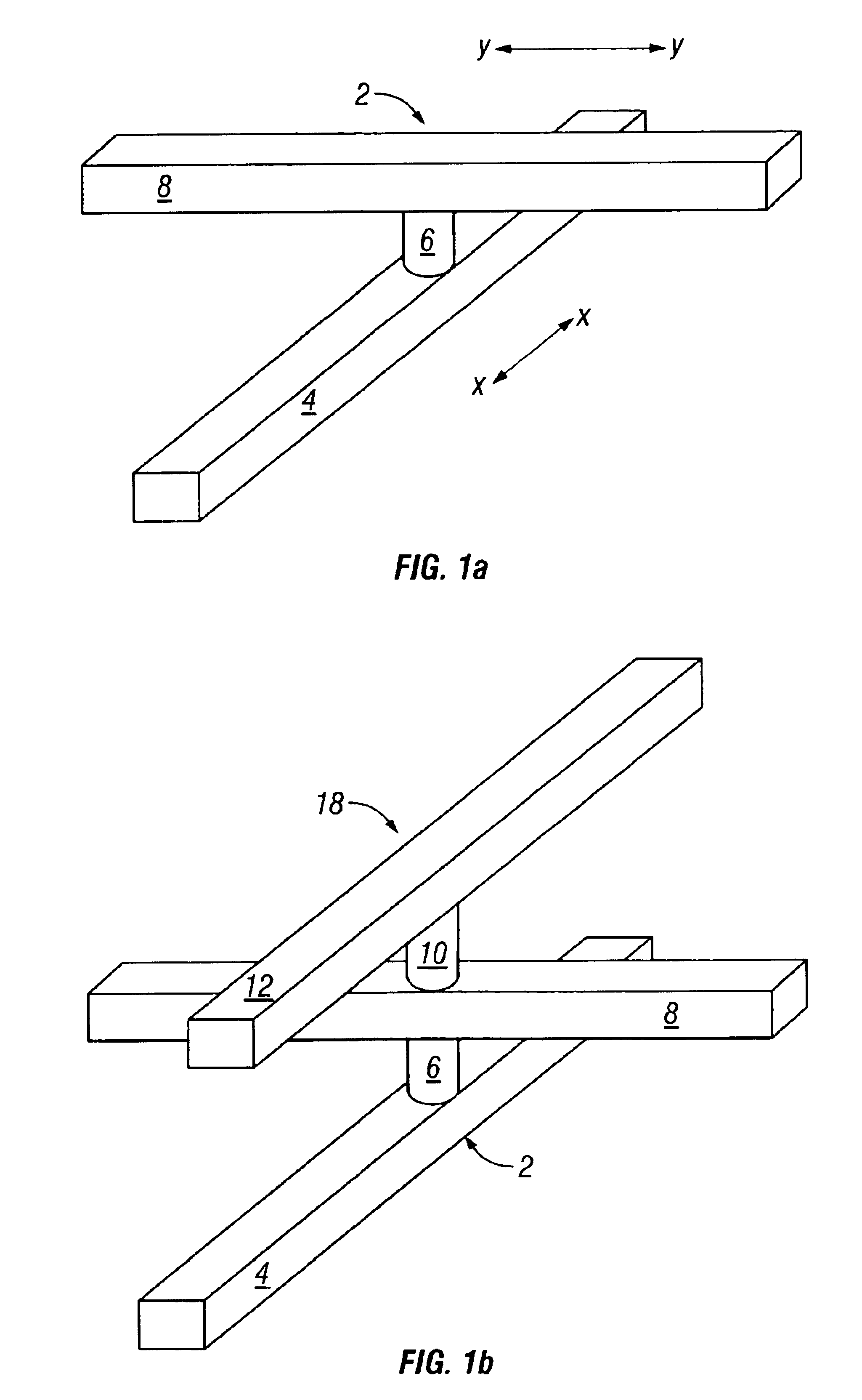

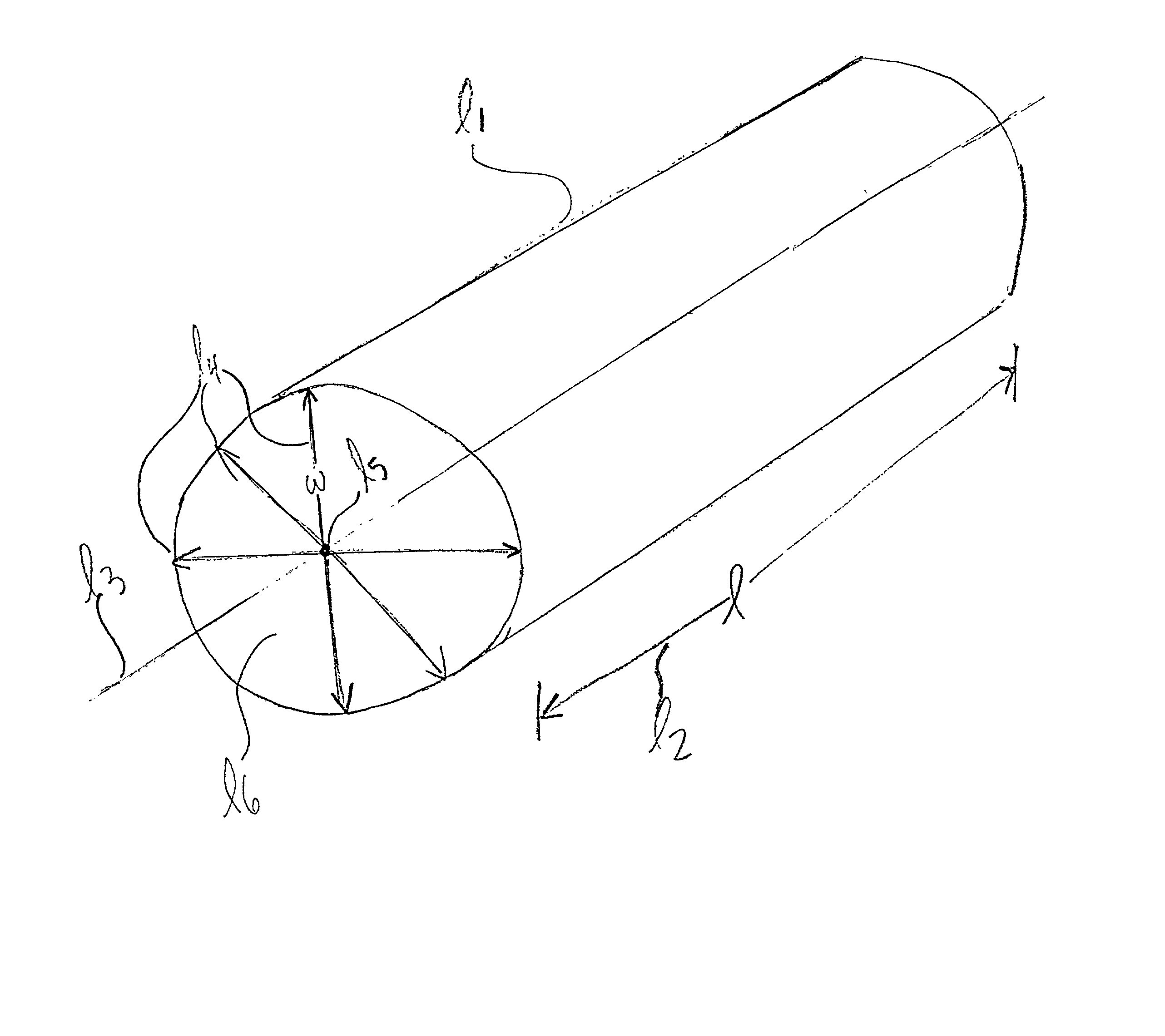

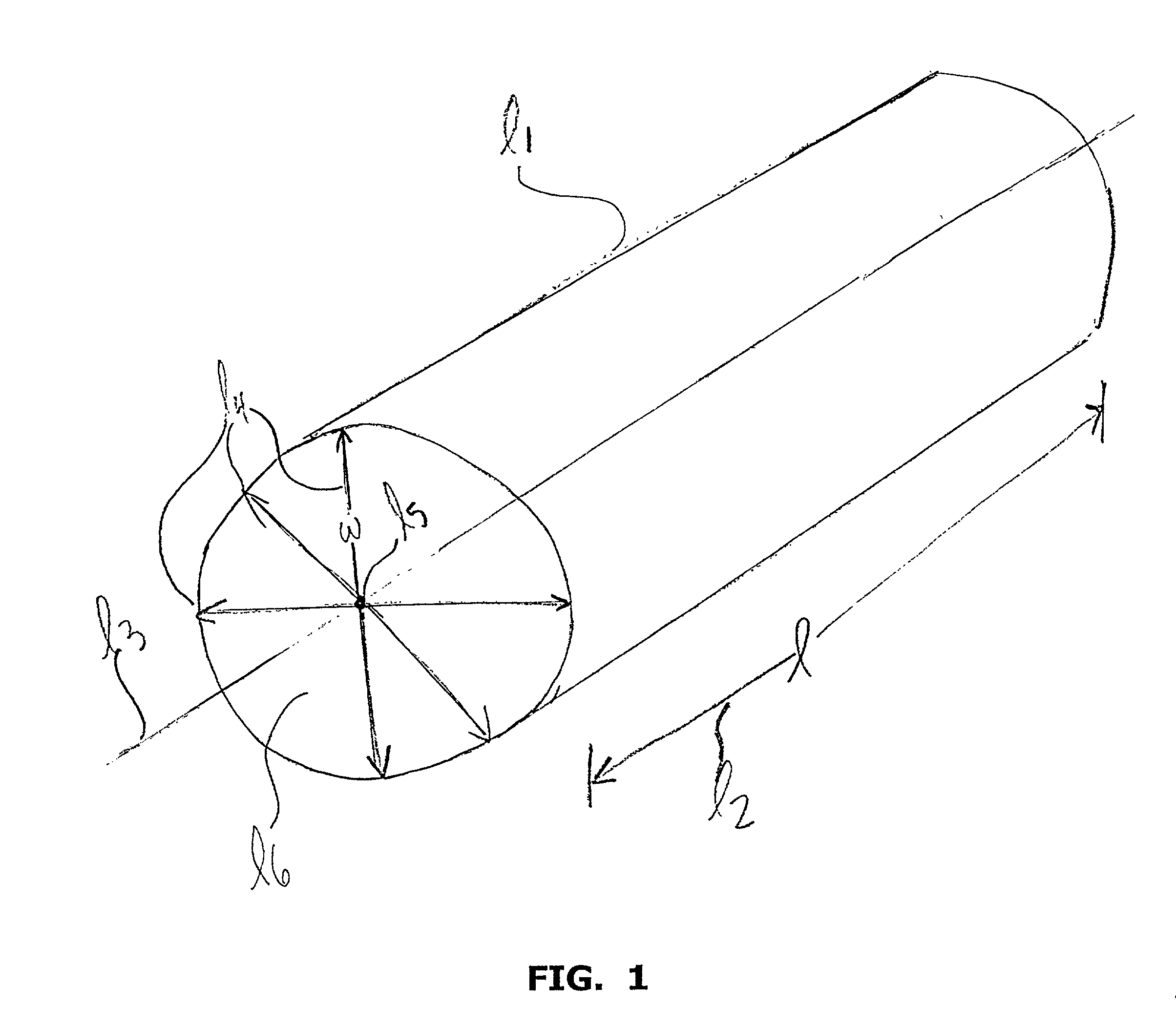

Doped elongated semiconductors, growing such semiconductors, devices including such semiconductors and fabricating such devices

A bulk-doped semiconductor that is at least one of the following: a single crystal, an elongated and bulk-doped semiconductor that, at any point along its longitudinal axis, has a largest cross-sectional dimension less than 500 nanometers, and a free-standing and bulk-doped semiconductor with at least one portion having a smallest width of less than 500 nanometers. Such a semiconductor may comprise an interior core comprising a first semiconductor; and an exterior shell comprising a different material than the first semiconductor. Such a semiconductor may be elongated and my have, at any point along a longitudinal section of such a semiconductor, a ratio of the length of the section to a longest width is greater than 4:1, or greater than 10:1, or greater than 100:1, or even greater than 1000:1. At least one portion of such a semiconductor may a smallest width of less than 200 nanometers, or less than 150 nanometers, or less than 100 nanometers, or less than 80 nanometers, or less than 70 nanometers, or less than 60 nanometers, or less than 40 nanometers, or less than 20 nanometers, or less than 10 nanometers, or even less than 5 nanometers. Such a semiconductor may be a single crystal and may be free-standing. Such a semiconductor may be either lightly n-doped, heavily n-doped, lightly p-doped or heavily p-doped. Such a semiconductor may be doped during growth. Such a semiconductor may be part of a device, which may include any of a variety of devices and combinations thereof, and, and a variety of assembling techniques may be used to fabricate devices from such a semiconductor. Two or more of such a semiconductors, including an array of such semiconductors, may be combined to form devices, for example, to form a crossed p-n junction of a device. Such devices at certain sizes may exhibit quantum confinement and other quantum phenomena, and the wavelength of light emitted from one or more of such semiconductors may be controlled by selecting a width of such semiconductors. Such semiconductors and device made therefrom may be used for a variety of applications.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

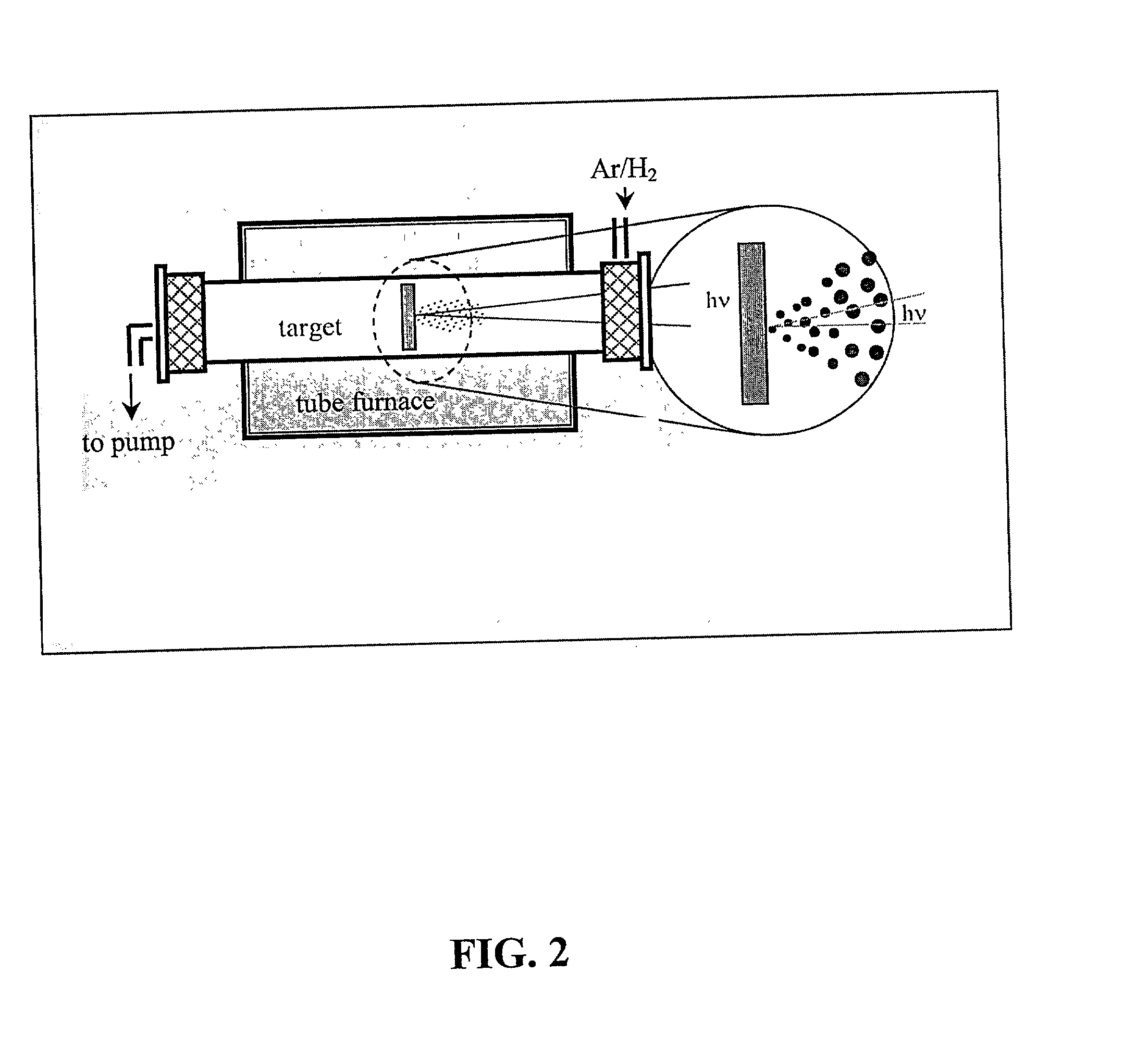

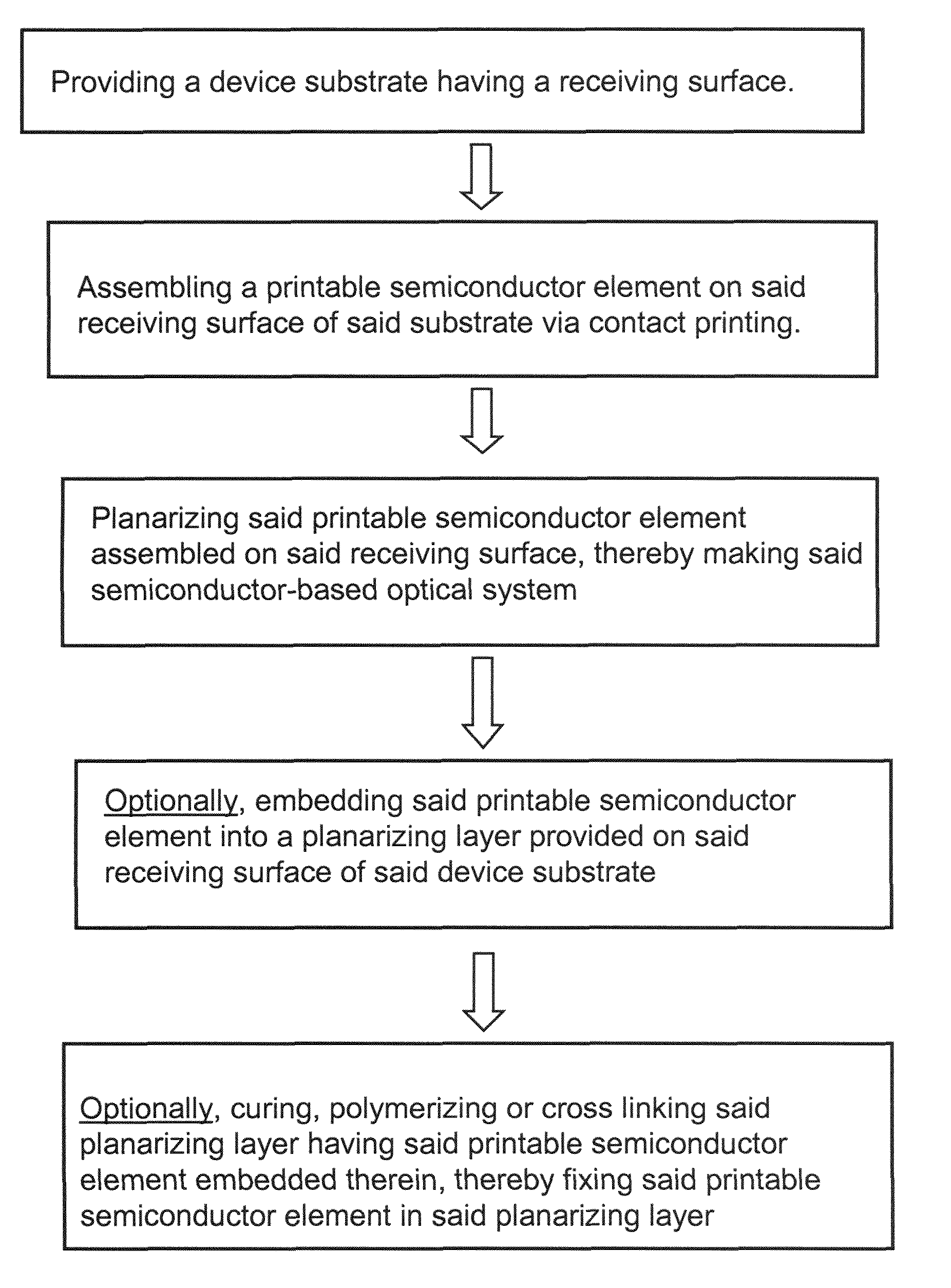

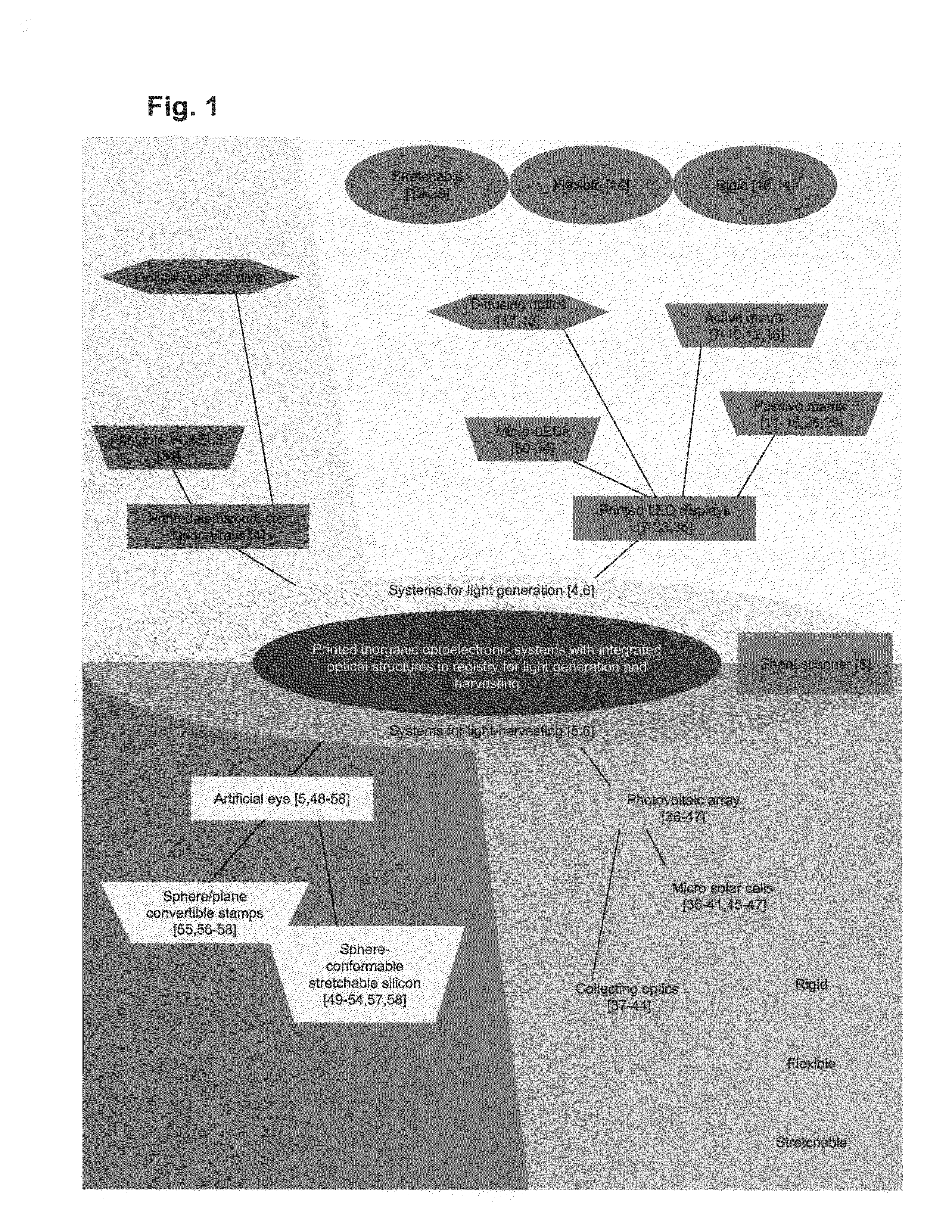

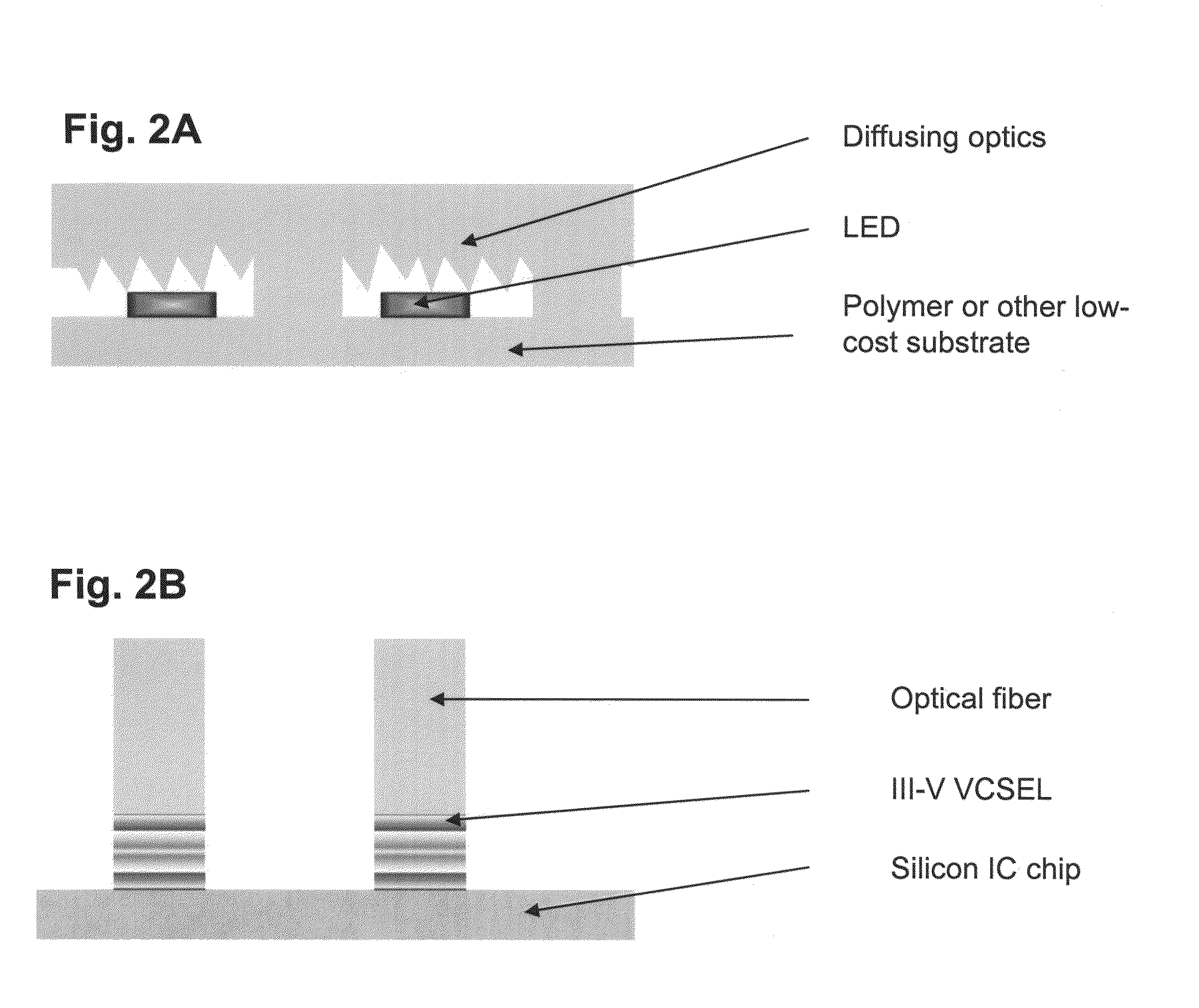

Optical systems fabricated by printing-based assembly

ActiveUS7972875B2Low costImprove performanceFinal product manufactureNanoinformaticsLight sensingSingle crystal

Provided are optical devices and systems fabricated, at least in part, via printing-based assembly and integration of device components. In specific embodiments the present invention provides light emitting systems, light collecting systems, light sensing systems and photovoltaic systems comprising printable semiconductor elements, including large area, high performance macroelectronic devices. Optical systems of the present invention comprise semiconductor elements assembled, organized and / or integrated with other device components via printing techniques that exhibit performance characteristics and functionality comparable to single crystalline semiconductor based devices fabricated using conventional high temperature processing methods. Optical systems of the present invention have device geometries and configurations, such as form factors, component densities, and component positions, accessed by printing that provide a range of useful device functionalities. Optical systems of the present invention include devices and device arrays exhibiting a range of useful physical and mechanical properties including flexibility, shapeability, conformability and stretchablity.

Owner:X DISPLAY CO TECH LTD +1

Nonvolatile memory on SOI and compound semiconductor substrates and method of fabrication

A nonvolatile memory array is provided. The array includes an array of nonvolatile memory devices, at least one driver circuit, and a substrate. The at least one driver circuit is not located in a bulk monocrystalline silicon substrate. The at least one driver circuit may be located in a silicon on insulator substrate or in a compound semiconductor substrate.

Owner:SANDISK TECH LLC

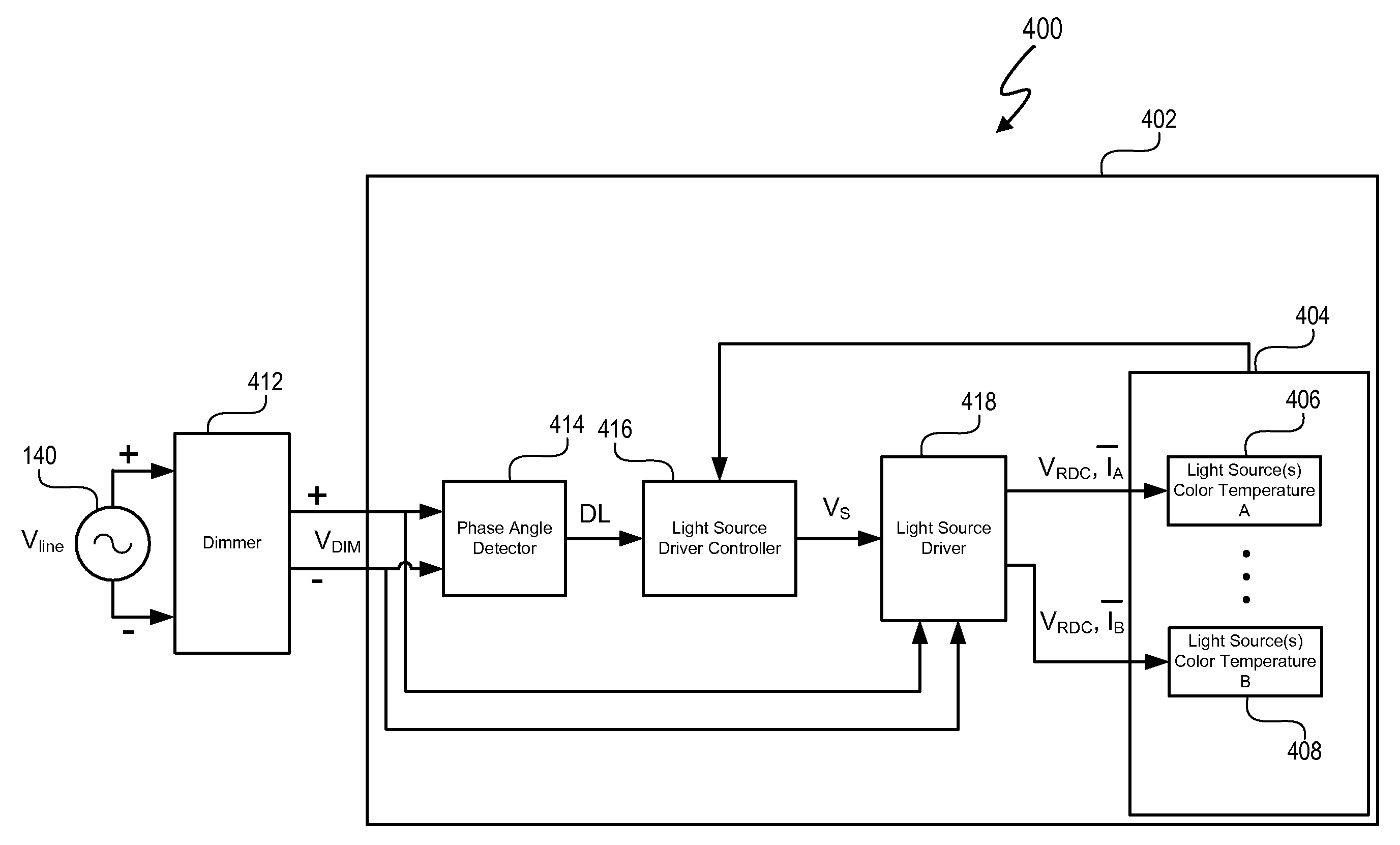

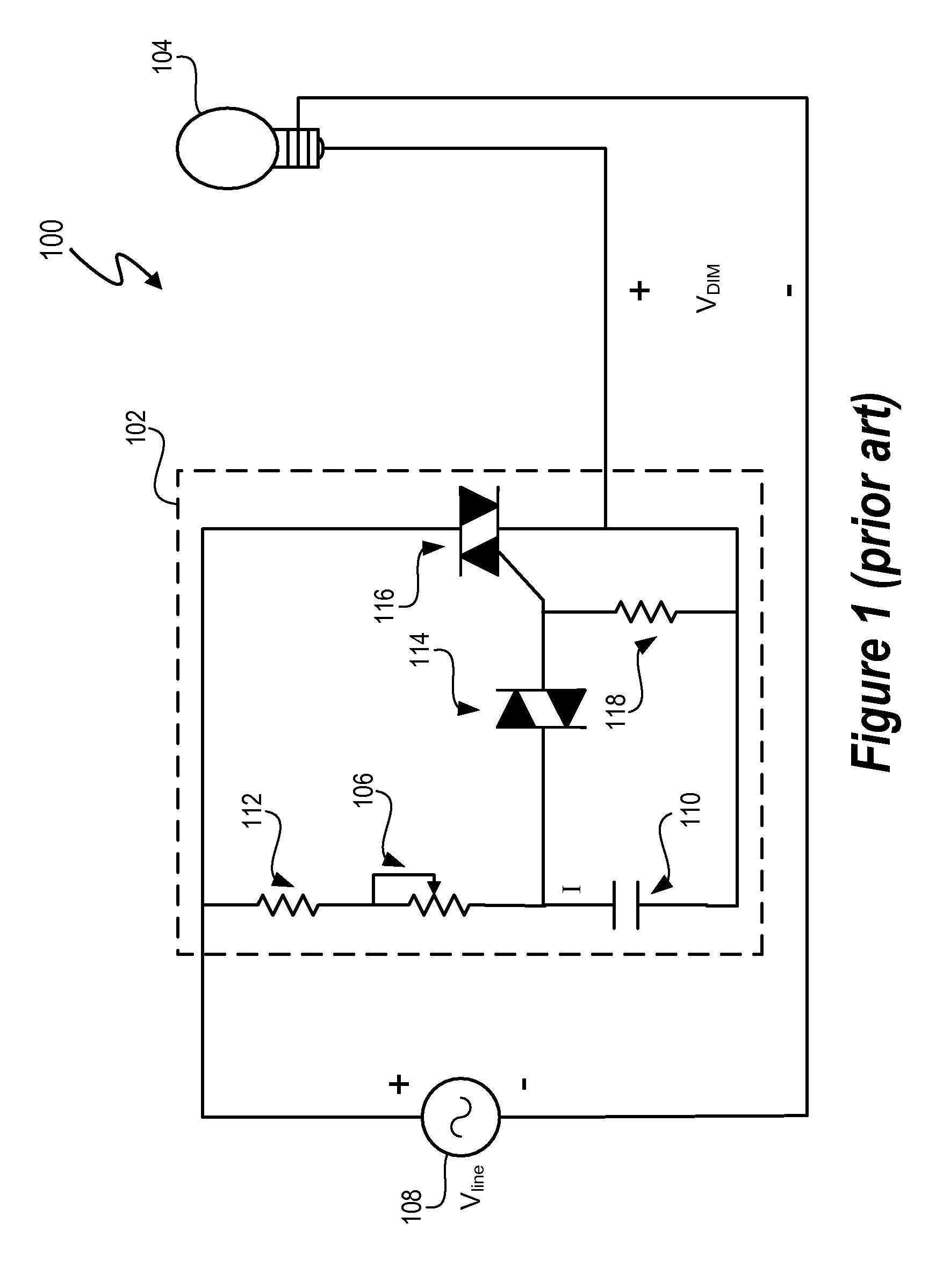

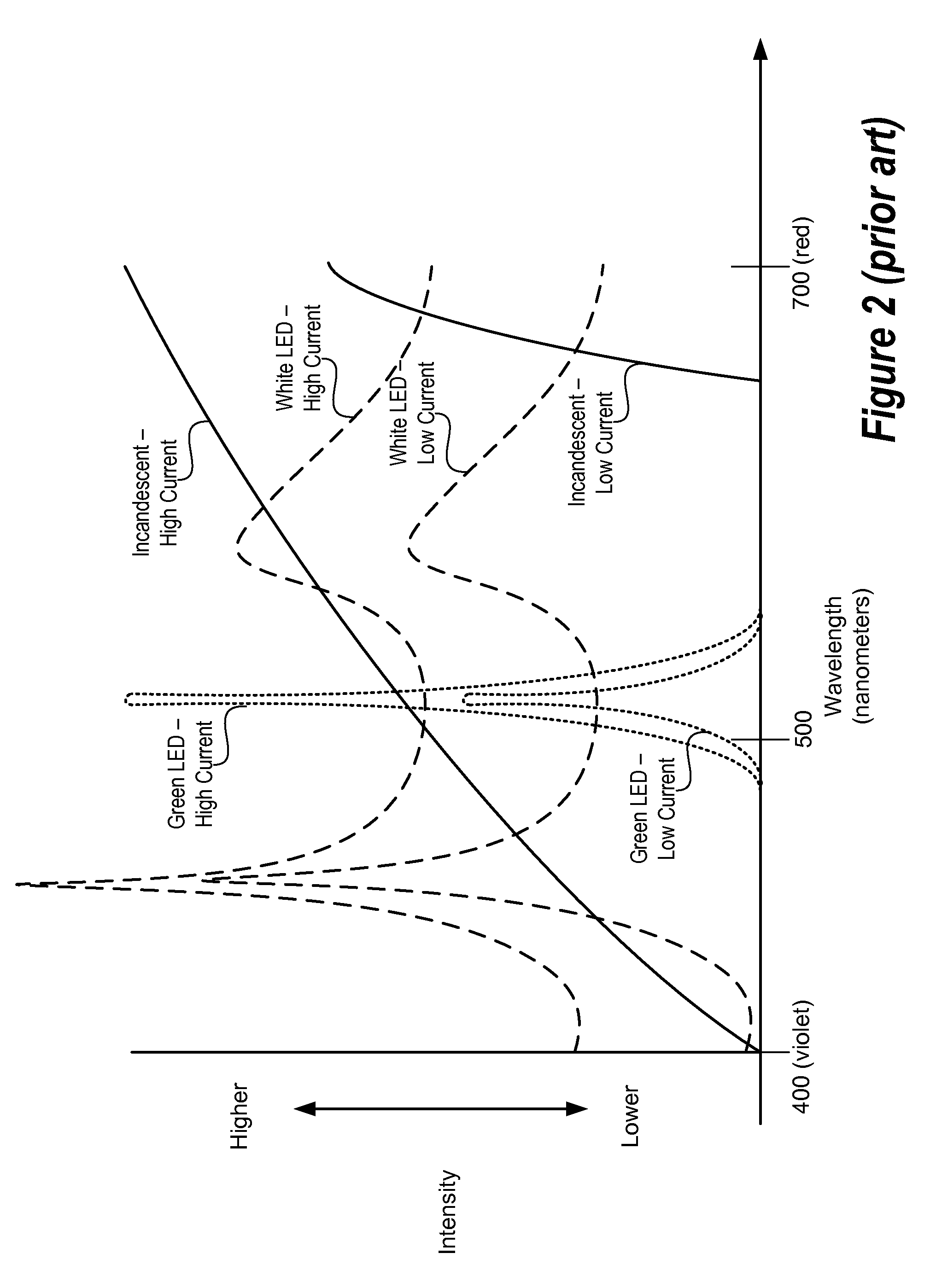

Color variations in a dimmable lighting device with stable color temperature light sources

ActiveUS7288902B1Electroluminescent light sourcesPower supply linesDriving currentGas-discharge lamp

A method and system allow a lighting device having light sources with multiple color temperatures to vary a color temperature of the lighting device in response to changing dimming levels. The light sources are non-incandescent light sources, such as light emitting diodes and / or gas-discharge lights. A dimmer circuit provides a dimming signal that indicates a selected dimming level. The lighting device includes a light source driver and a light source driver controller that cooperate to vary drive currents to the light sources in response to the selected dimming level. By varying the drive currents in different relative amounts, the color temperature of the lighting device changes in response to dimming level changes. In at least one embodiment, changes in the color temperature of the lighting device in response to the dimming level changes simulates the color temperature changes of an incandescent light source.

Owner:SIGNIFY HLDG BV

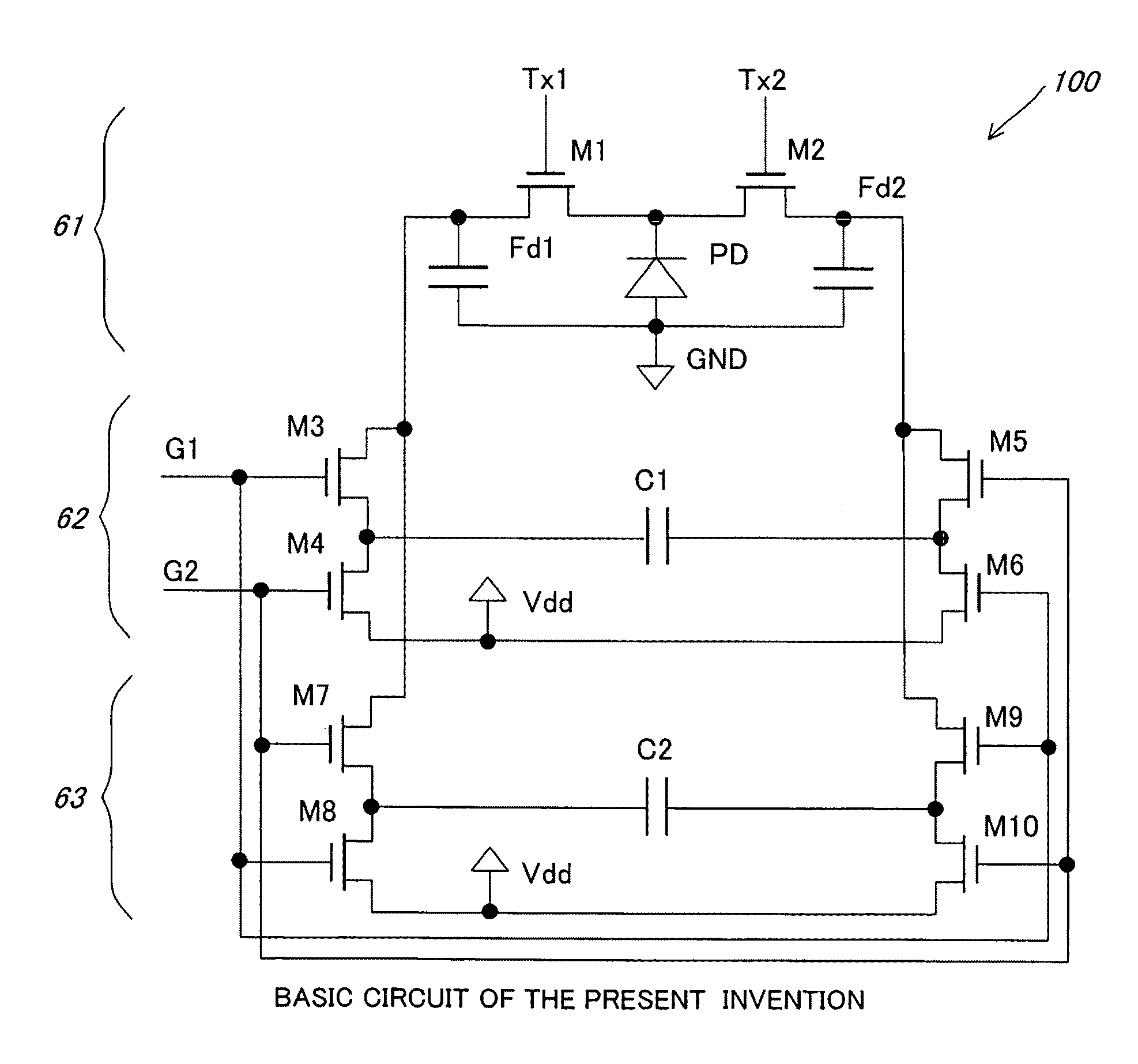

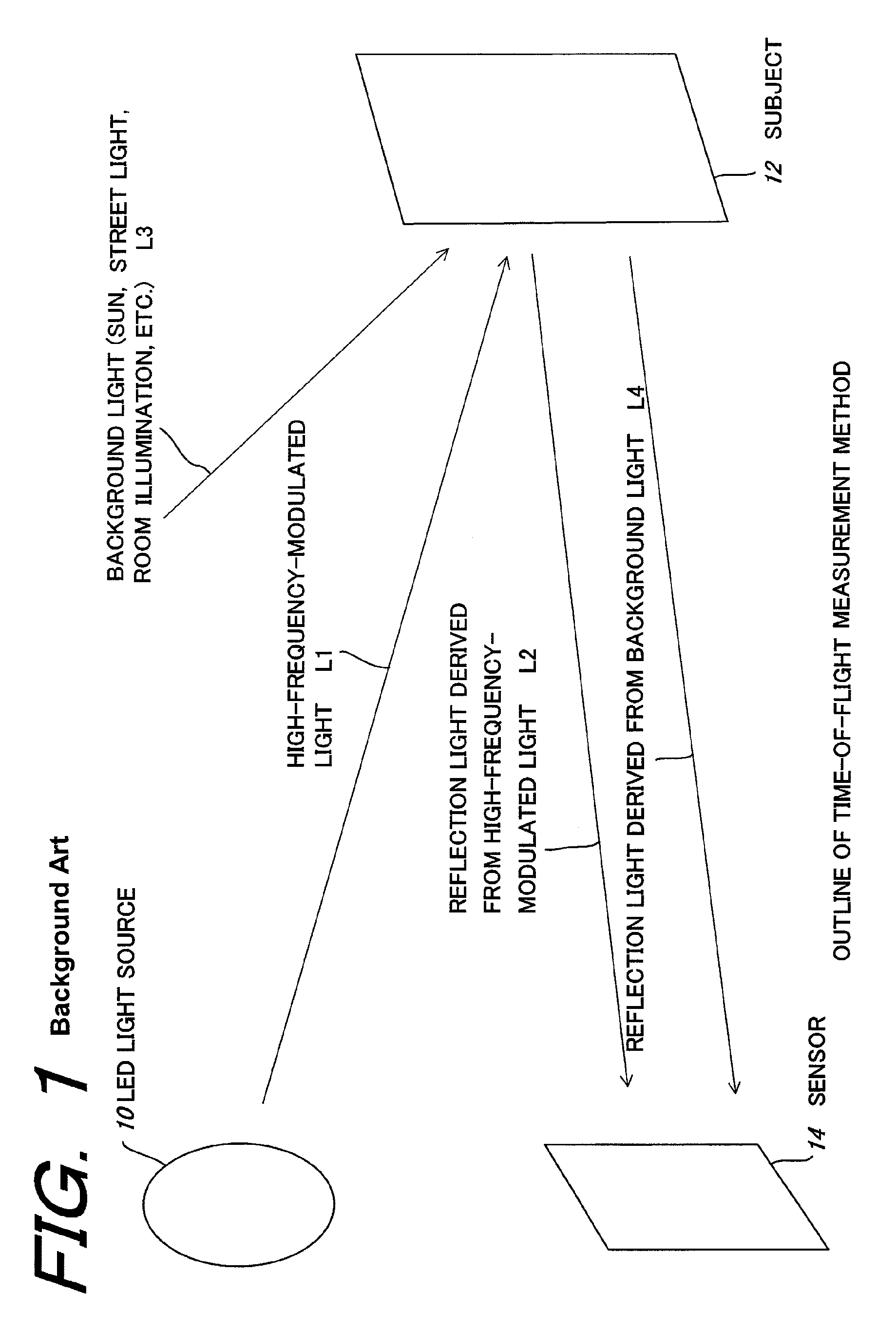

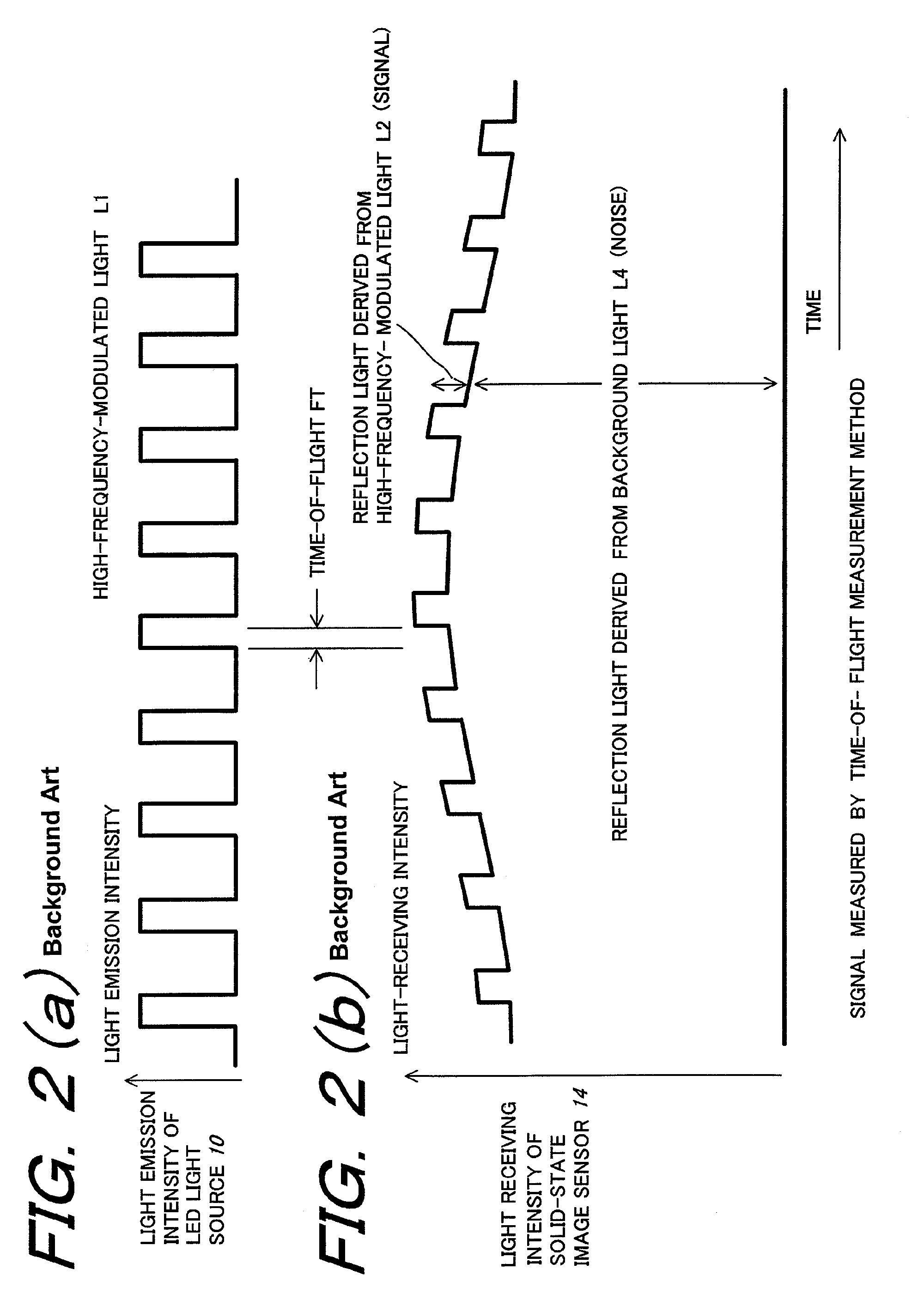

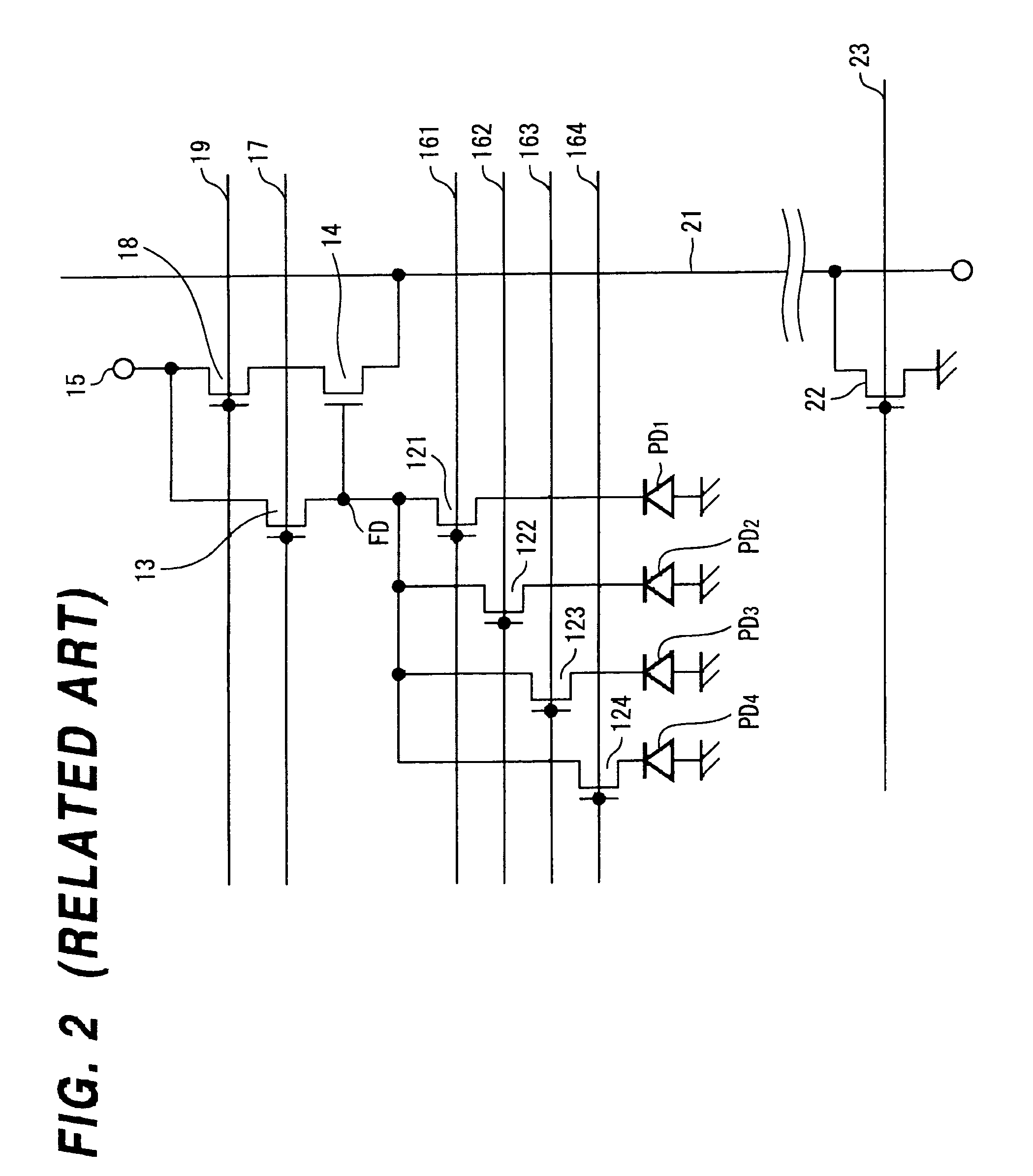

Solid-state image sensor

ActiveUS7683954B2Efficient extractionCancel noiseTelevision system detailsOptical rangefindersLow noiseCapacitor

A solid-state image sensor of a charge sorting method used in a time-of-flight measurement method, in which noise derived from background light, which is caused by the reflection light from the subject derived from background light is eliminated, reflection light from the subject derived from a predetermined light source, which is previously set in the solid-state image sensor, is effectively extracted as a signal component to achieve high sensitivity and low noise, which is a solid-state image sensor that is equipped with a plurality of charge-storage sections, discriminates photoelectrons generated by incoming light on the incoming timing and sort to the above-described plurality of charge-storage sections, and measures the timing of the incoming light, in which the sensor has: a plurality of capacitors that capable of conducting to the plurality of charge-storage sections; and a control section that controls a conducted state between the above-described plurality of charge-storage sections and the above-described plurality of capacitors, in which by selectively conducting the above-described plurality of charge-storage sections and the above-described plurality of capacitors by the control of the above-described control section, the difference component of charge stored in the above-described plurality of charge-storage sections is extracted.

Owner:STANLEY ELECTRIC CO LTD

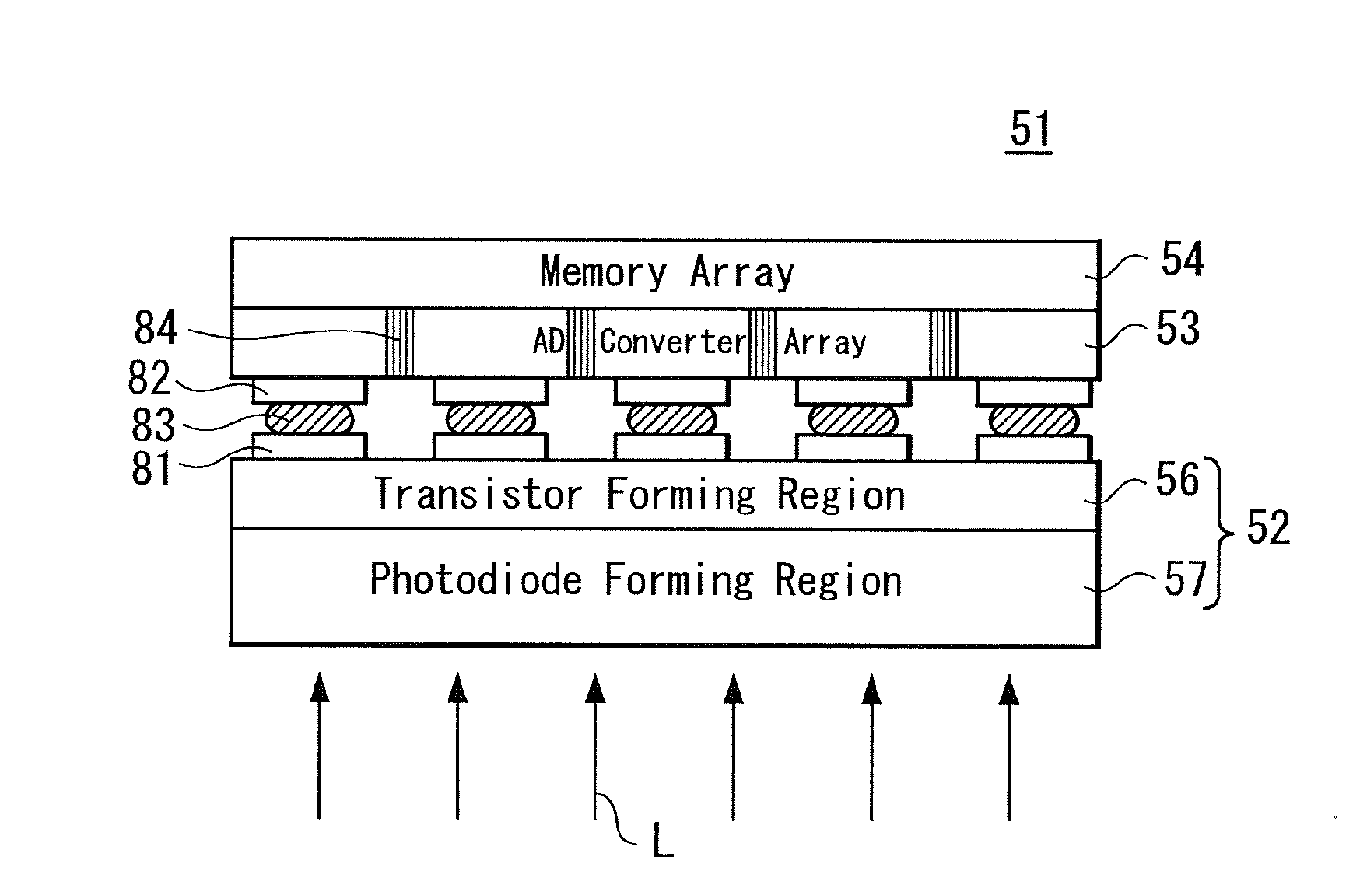

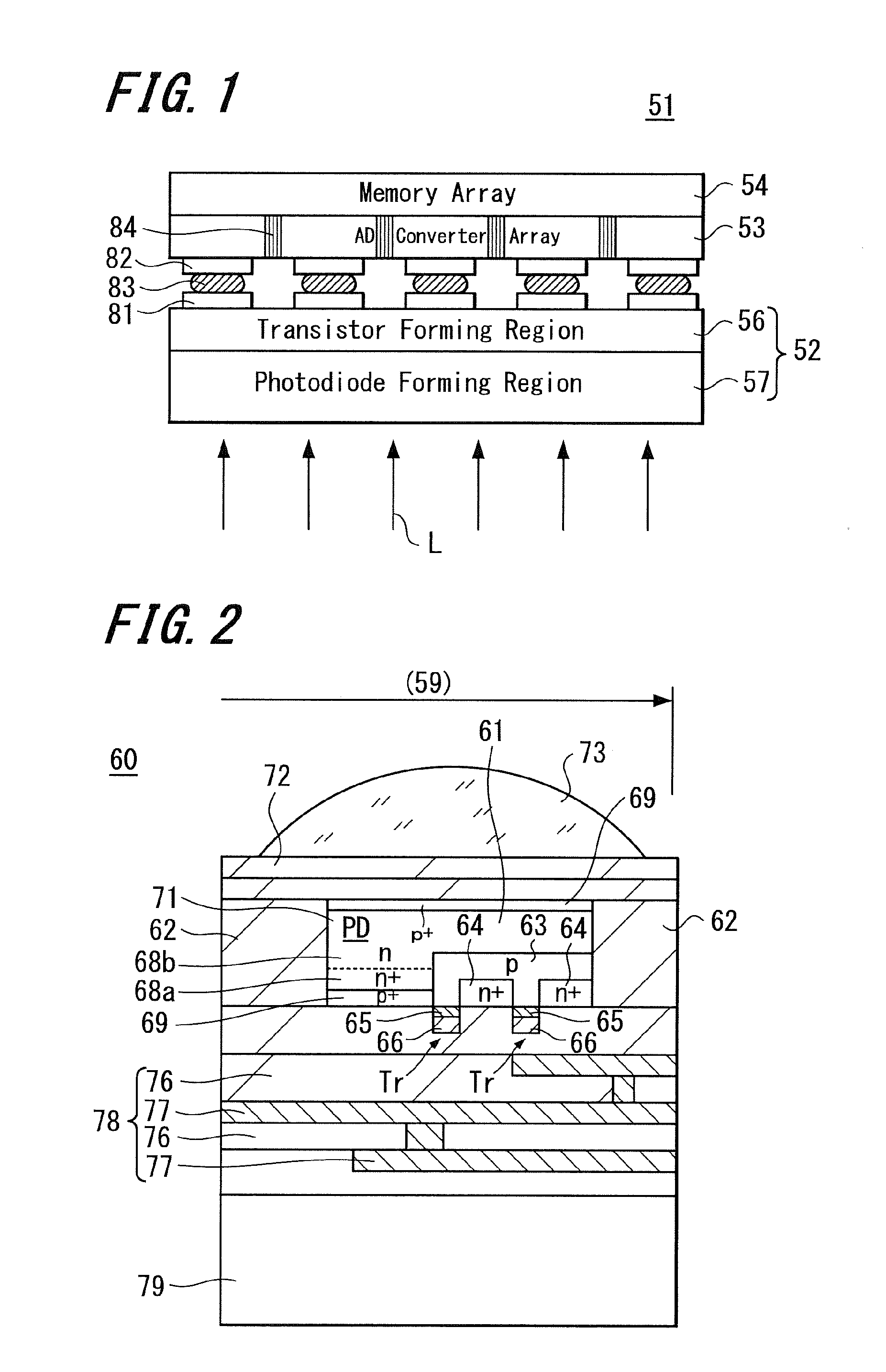

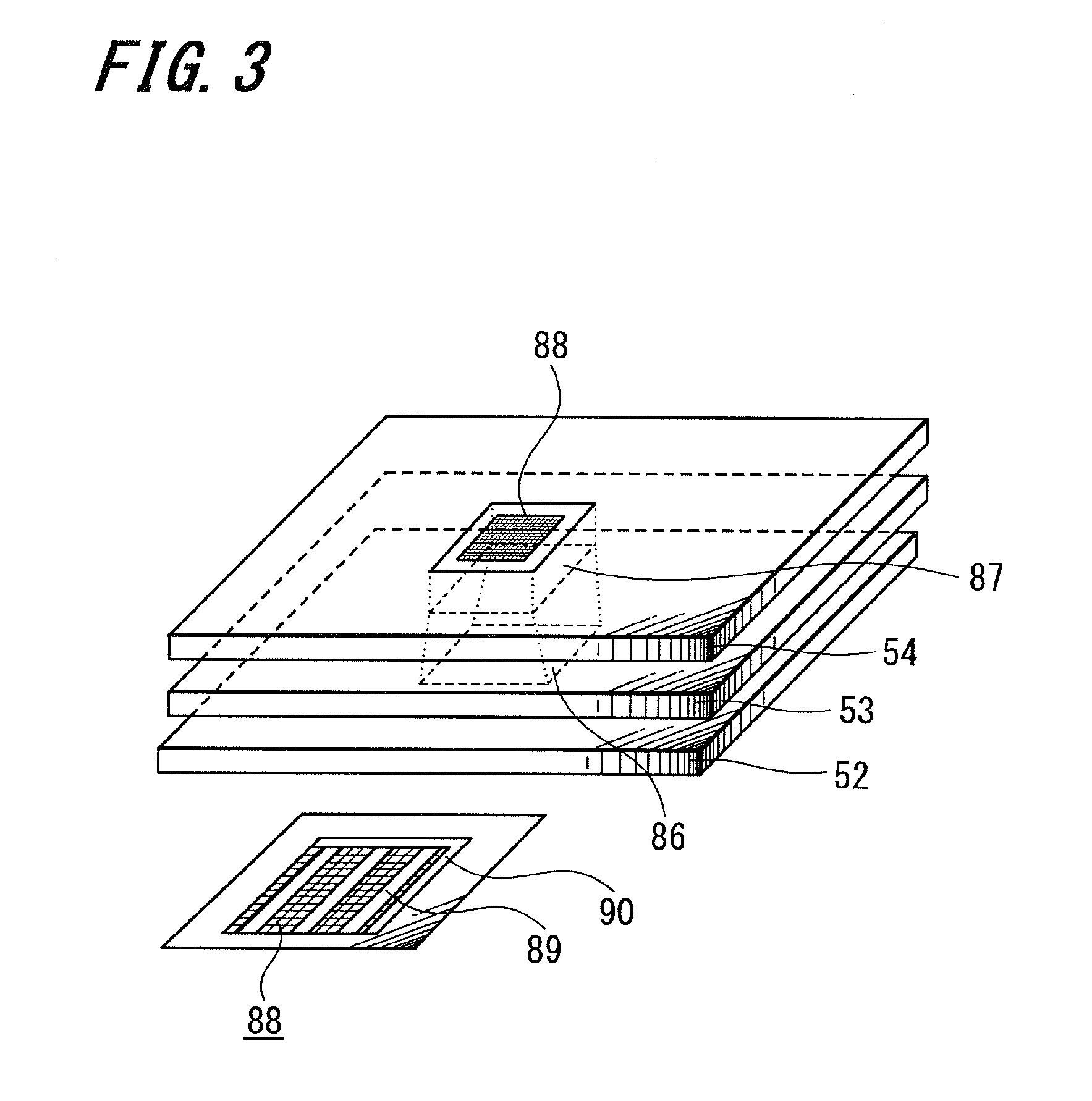

Semiconductor image sensor module and method of manufacturing the same

ActiveUS20100276572A1Increase the aperture ratioIncrease profitTransistorTelevision system detailsCMOSSemiconductor chip

A CMOS type semiconductor image sensor module wherein a pixel aperture ratio is improved, chip use efficiency is improved and furthermore, simultaneous shutter operation by all the pixels is made possible, and a method for manufacturing such semiconductor image sensor module are provided. The semiconductor image sensor module is provided by stacking a first semiconductor chip, which has an image sensor wherein a plurality of pixels composed of a photoelectric conversion element and a transistor are arranged, and a second semiconductor chip, which has an A / D converter array. Preferably, the semiconductor image sensor module is provided by stacking a third semiconductor chip having a memory element array. Furthermore, the semiconductor image sensor module is provided by stacking the first semiconductor chip having the image sensor and a fourth semiconductor chip having an analog nonvolatile memory array.

Owner:SONY CORP

Power semiconductor devices and methods of manufacture

ActiveUS7345342B2Simple structureEasy to packEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

Electro-optical device and electronic device

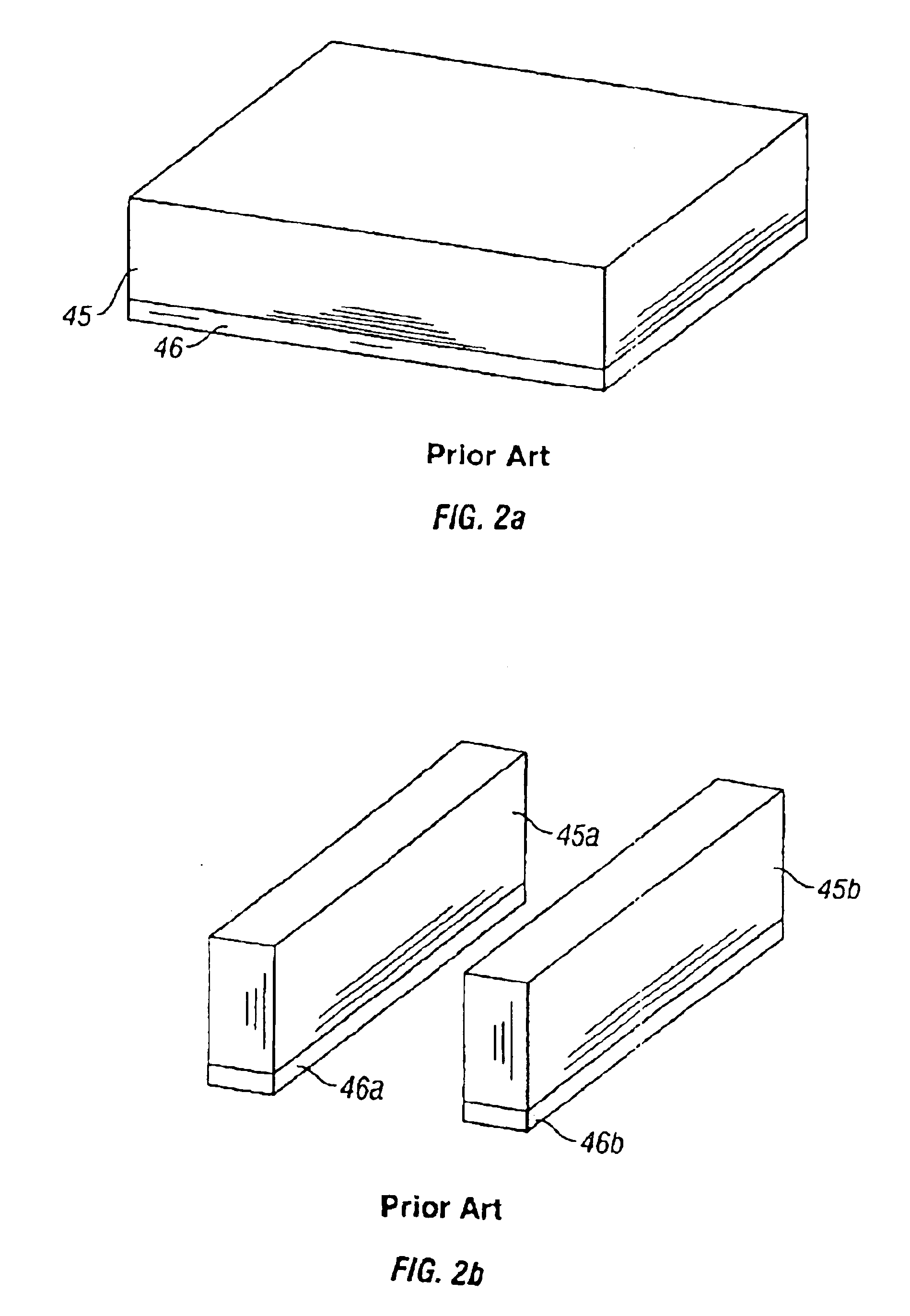

InactiveUS6689492B1Reduce heatReduce releaseDischarge tube luminescnet screensSemiconductor/solid-state device detailsDisplay deviceEngineering

An object of the present invention is to provide an EL display device, which has a high operating performance and reliability. A third passivation film 45 is disposed under an EL element 203 which comprises a pixel electrode (anode) 46, and EL layer 47 and a cathode 48, to make a structure in which heat generated by the EL element 203 is radiated. Further, the third passivation film 45 prevents alkali metals within the EL element 203 from diffusing into the TFTs side, and prevents moisture and oxygen of the TFTs side from penetrating into the EL element 203. More preferably, heat radiating effect is given to a fourth passivation film 50 to make the EL element 203 to be enclosed by heat radiating layers.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS20140048765A1Increase currentReduce power consumptionSemiconductor/solid-state device manufacturingDiodeAlloyGate stack

The present invention discloses a semiconductor device, comprising: a substrate, a gate stack structure on the substrate, source and drain regions in the substrate on both sides of the gate stack structure, and a channel region between the source and drain regions in the substrate, characterized in that the source region in the source and drain regions comprises GeSn alloy, and a tunnel dielectric layer is optionally comprised between the GeSn alloy of the source region and the channel region. In accordance with the semiconductor device and method for manufacturing the same of the present invention, GeSn alloy having a narrow band gap is formed by implanting precursors and performing a laser rapid annealing, the on-state current of TFET is effectively enhanced, accordingly it has an important application prospect in a high performance low power consumption application.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

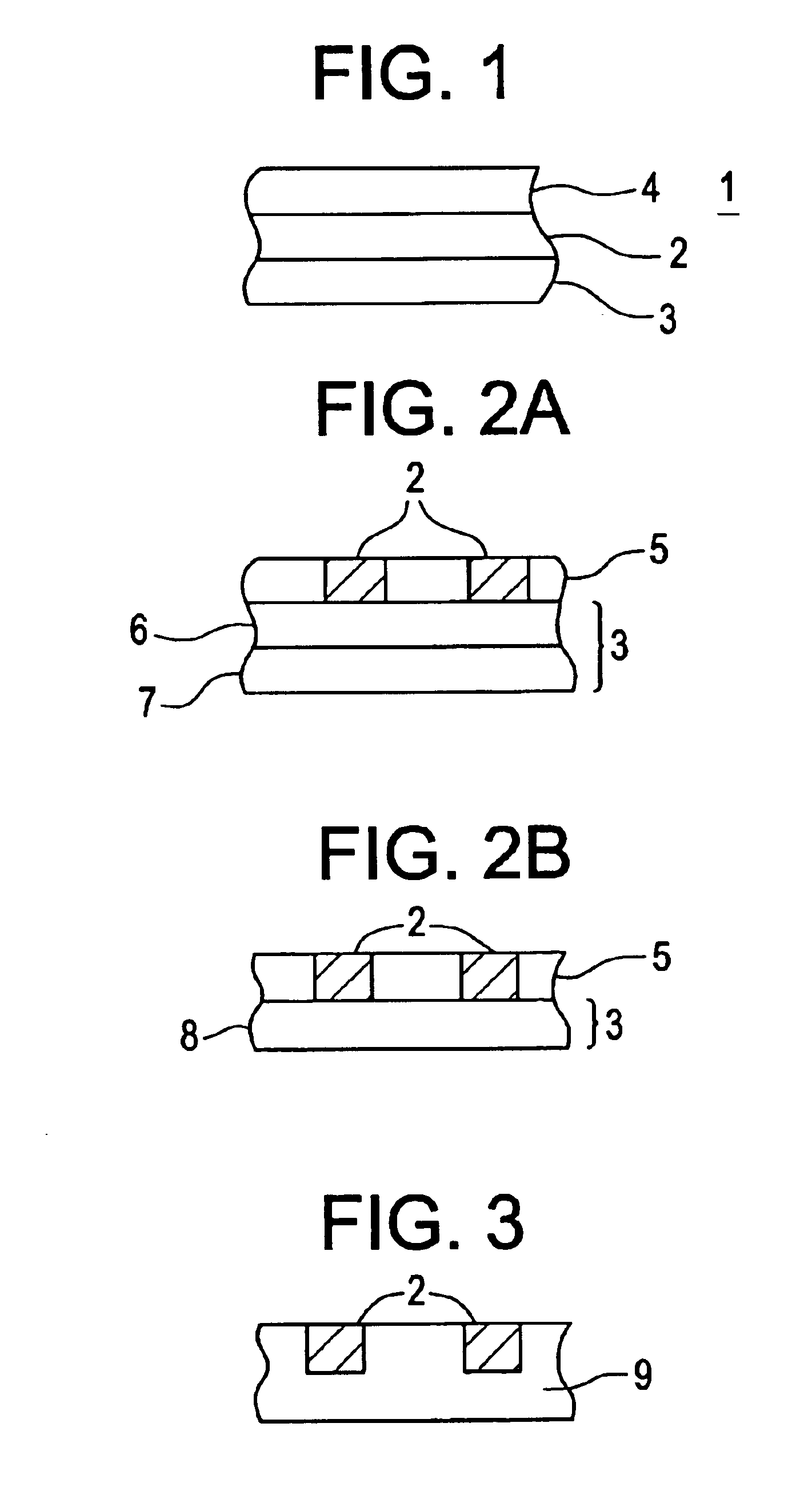

Memory cell incorporating a chalcogenide element

A memory cell incorporating a chalcogenide element and a method of making same is disclosed. In the method, a doped silicon substrate is provided with two or more polysilicon plugs to form an array of diode memory cells. A layer of silicon nitride is disposed over the plugs. Using a poly-spacer process, small pores are formed in the silicon nitride to expose a portion of the polysilicon plugs. A chalcogenide material is disposed in the pores by depositing a layer of chalcogenide material on the silicon nitride layer and planarizing the chalcogenide layer to the silicon nitride layer using CMP. A layer of TiN is next deposited over the plugs, followed by a metallization layer. The TiN and metallization layers are then masked and etched to define memory cell areas.

Owner:ROUND ROCK RES LLC

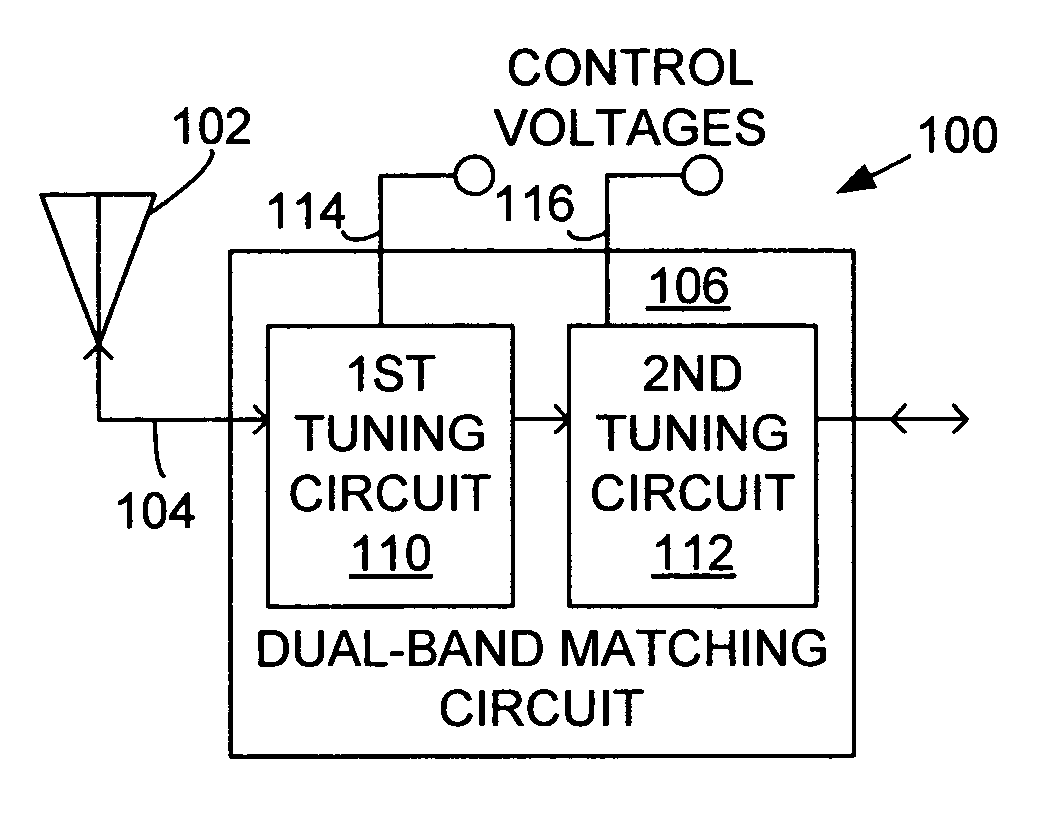

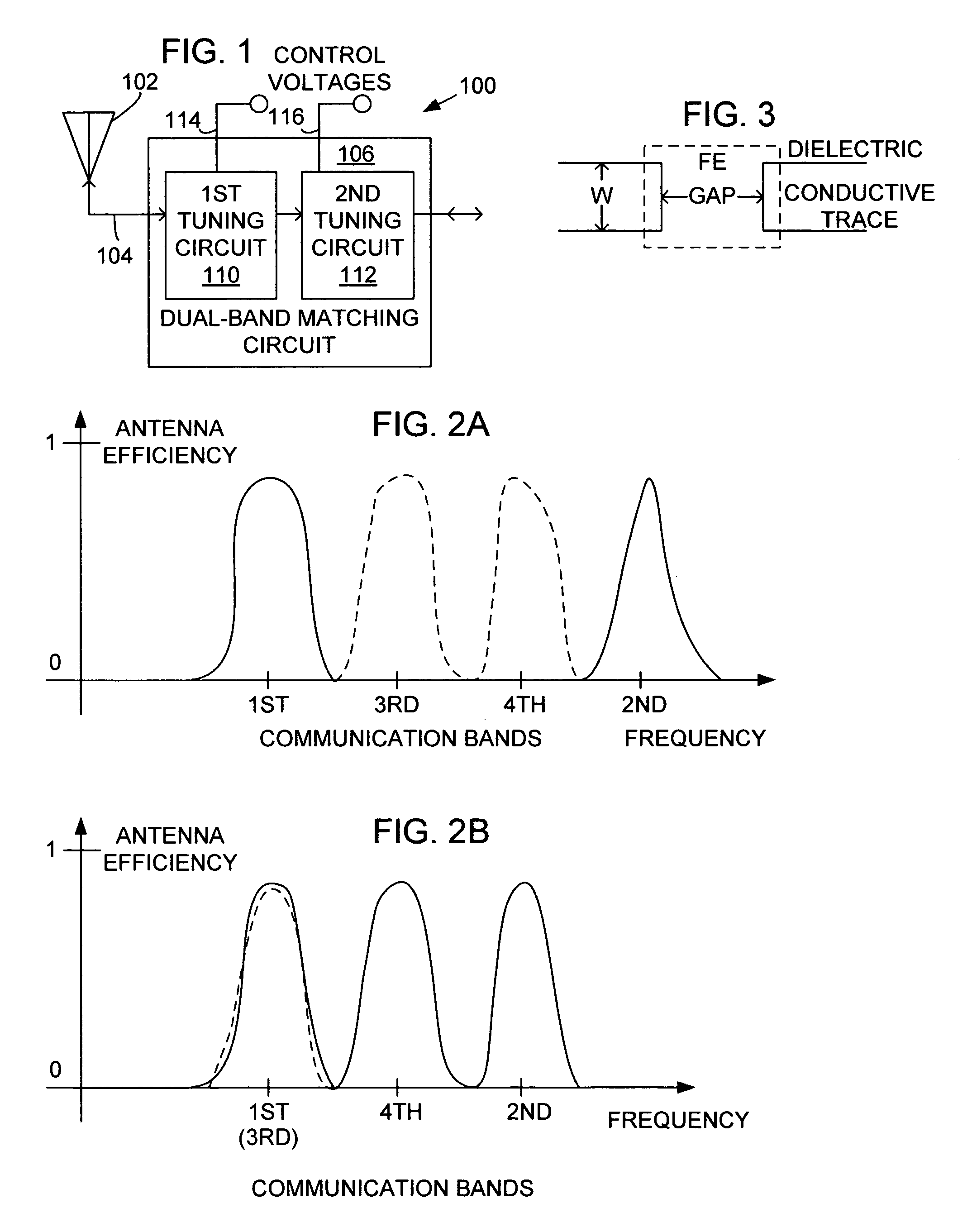

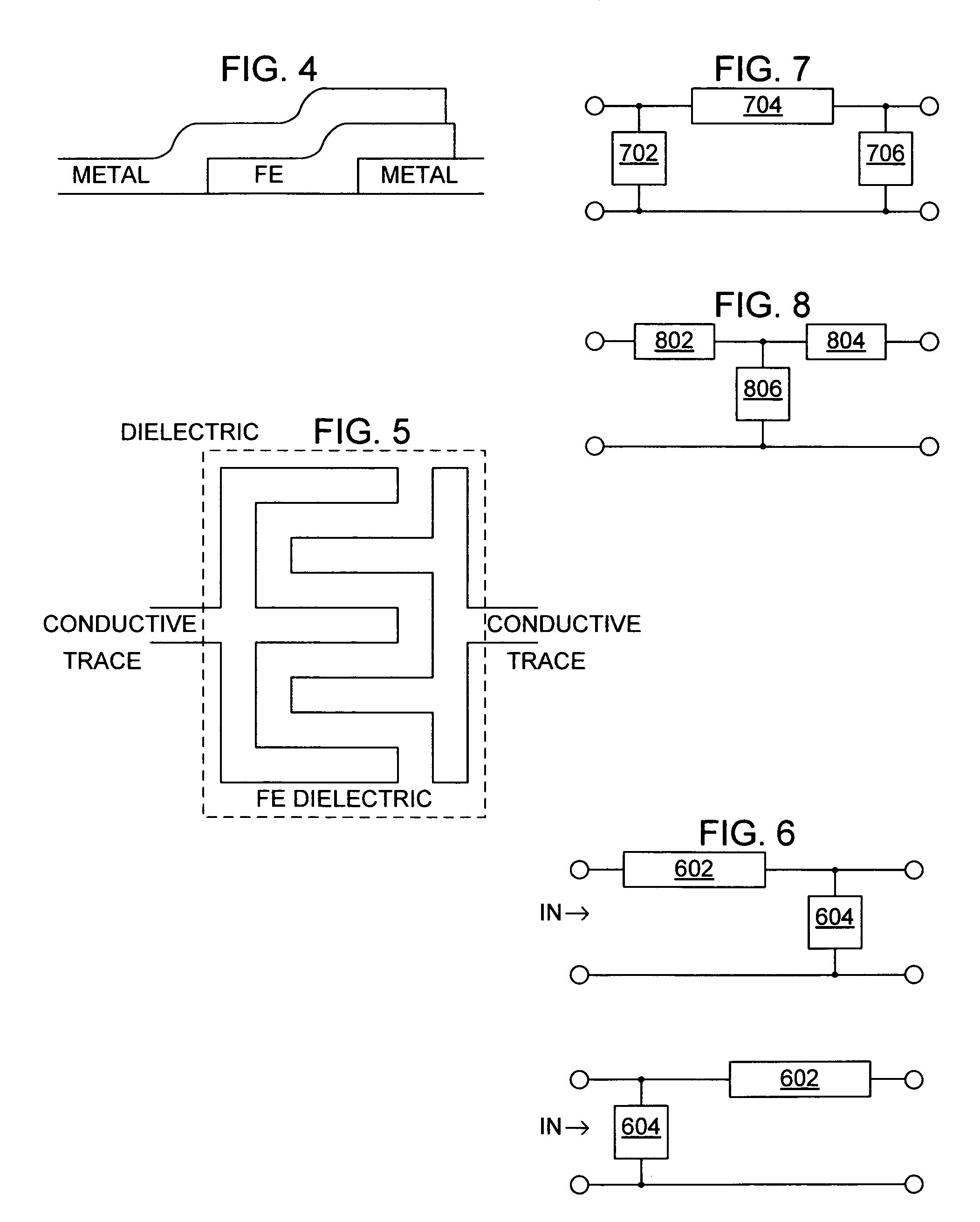

System and method for dual-band antenna matching

A dual-band antenna matching system and a method for dual-band impedance matching are provided. The method comprises: accepting a frequency-dependent impedance from an antenna; and, selectively supplying a conjugate impedance match for the antenna at either a first and a second communication band, or a third and a fourth communication band. More specifically, the method comprises: tuning a first tuning circuit to a first frequency; and, simultaneously tuning a second tuning circuit to a second frequency. In response, a conjugate match is supplied to the antenna in the first communication band in response to the first frequency. Simultaneously, the antenna is matched in the second communication band in response to the second frequency. When the first tuning circuit is tuned to a third frequency, and the second tuning circuit is tuned to a fourth frequency, then conjugate matches are supplied for the third and fourth communication bands, responsive to the third and fourth frequencies, respectively.

Owner:KYOCERA CORP

Electroluminescence display device having a desiccant

InactiveUS6833668B1Increase the aperture ratioReliable sealing structureDischarge tube luminescnet screensElectroluminescent light sourcesDesiccantDisplay device

Powder desiccant is mixed into a seal which adheres a first substrate to a second substrate, thereby sealing a display region. Almost no moisture permeates through the outer surfaces of the substrates sandwiching the display region, while moisture permeating through the seal is adsorbed by the desiccant. An emissive layer is thereby prevented from deterioration due to moisture. By covering the display region with a resin sealing layer composed of resin having desiccant mixed therein, the display region can reliably be protected from moisture. By forming a groove in the substrate and placing a desiccant therein, moisture can be further reliably adsorbed.

Owner:SANYO ELECTRIC CO LTD

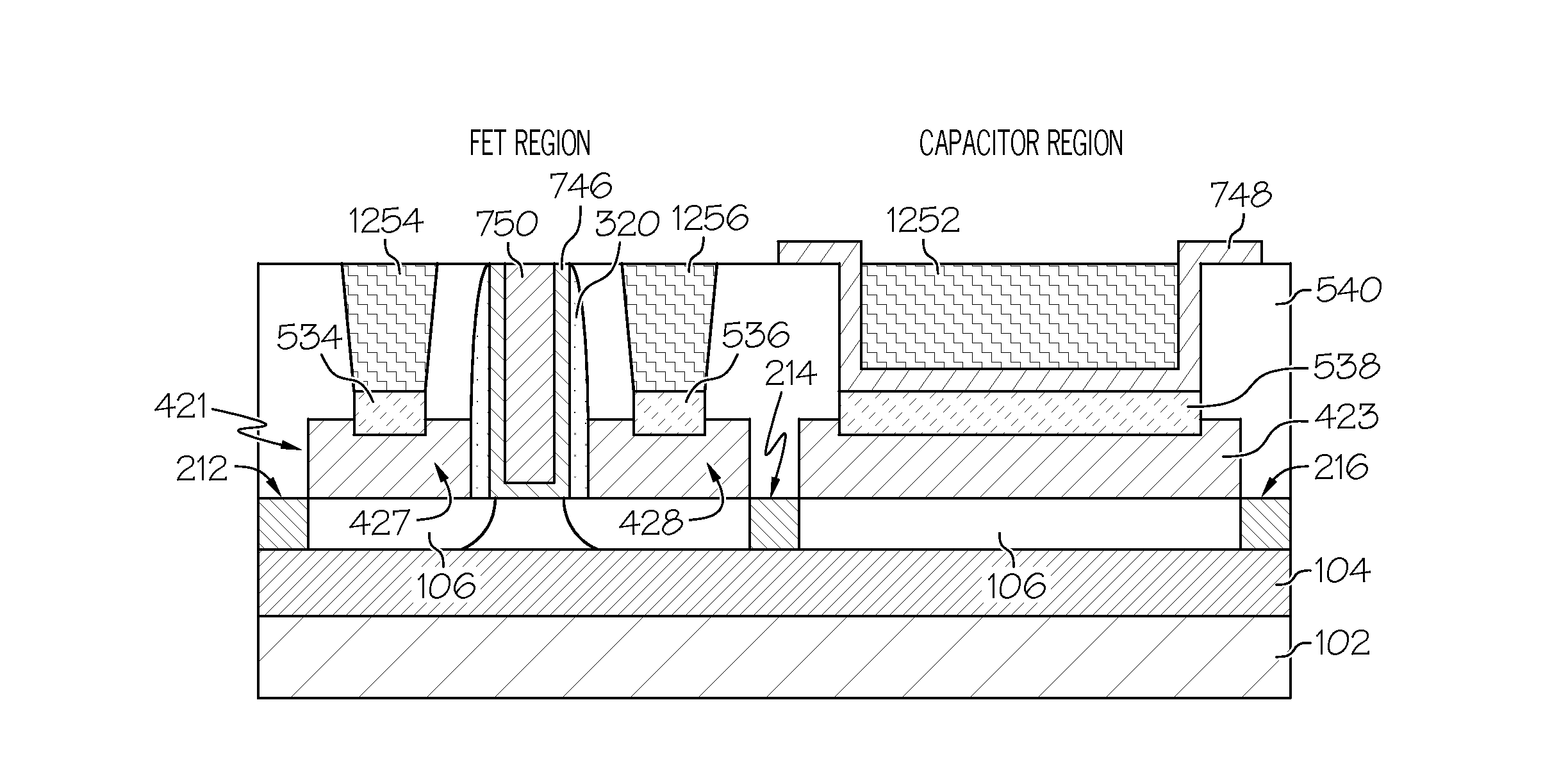

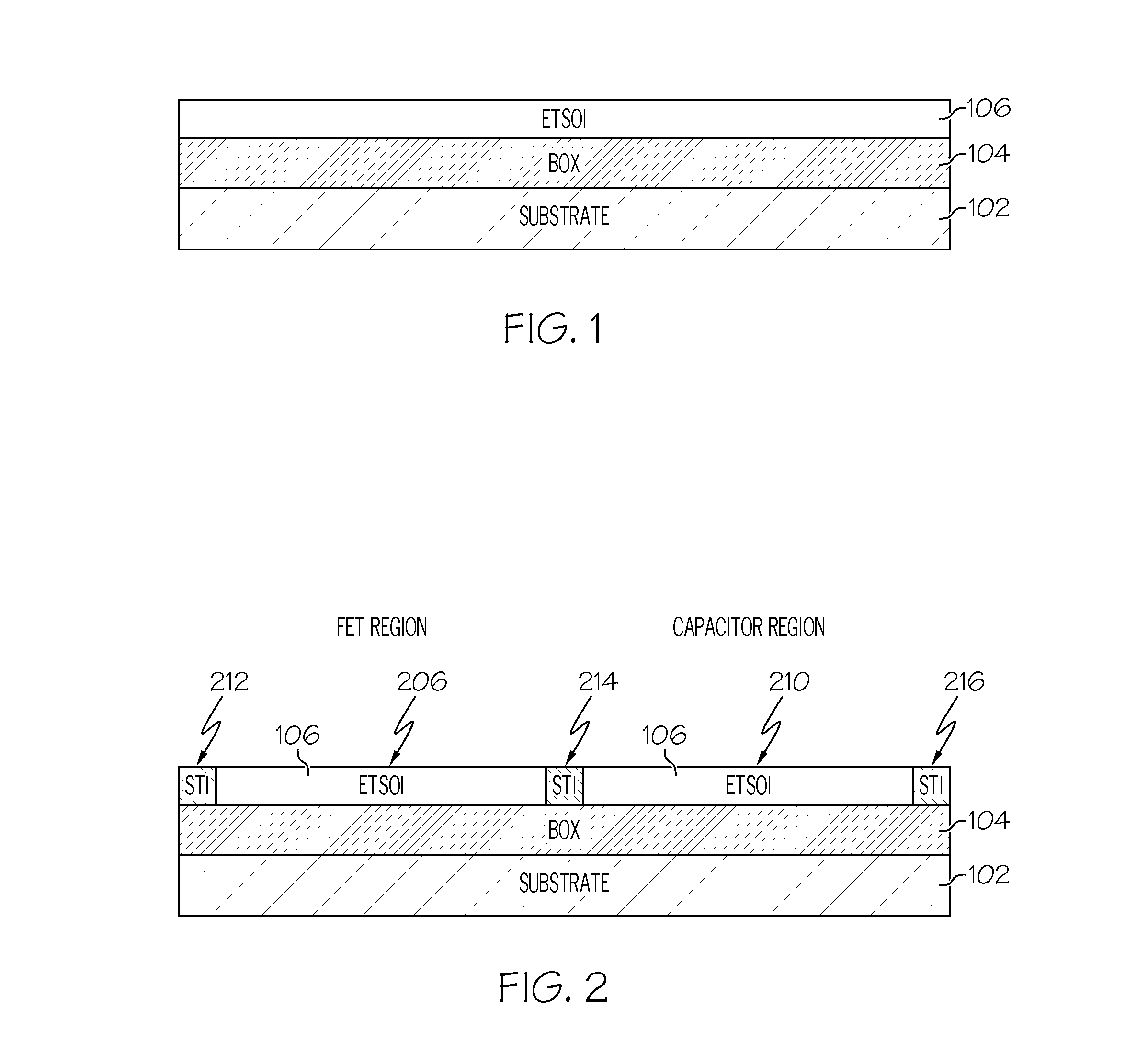

Integrated circuit with a thin body field effect transistor and capacitor

An integrated circuit includes a transistor and a capacitor. The transistor includes a first semiconductor layer and a gate stack located on the first semiconductor layer. The gate stack includes a metal layer and a first high-k dielectric layer. A gate spacer is located on sidewalls of the gate stack. The first high-k dielectric layer is located between the first semiconductor layer and the metal layer and between the gate spacer and sidewalls of the metal layer. A first silicide region is located on a first source / drain region. A second silicide region is located on a second source / drain region. The capacitor includes a first terminal that comprises a third silicide region located on a portion of the second semiconductor. A second high-k dielectric layer is located on the silicide region. A second terminal comprises a metal layer that is located on the second high-k dielectric layer.

Owner:GLOBALFOUNDRIES US INC

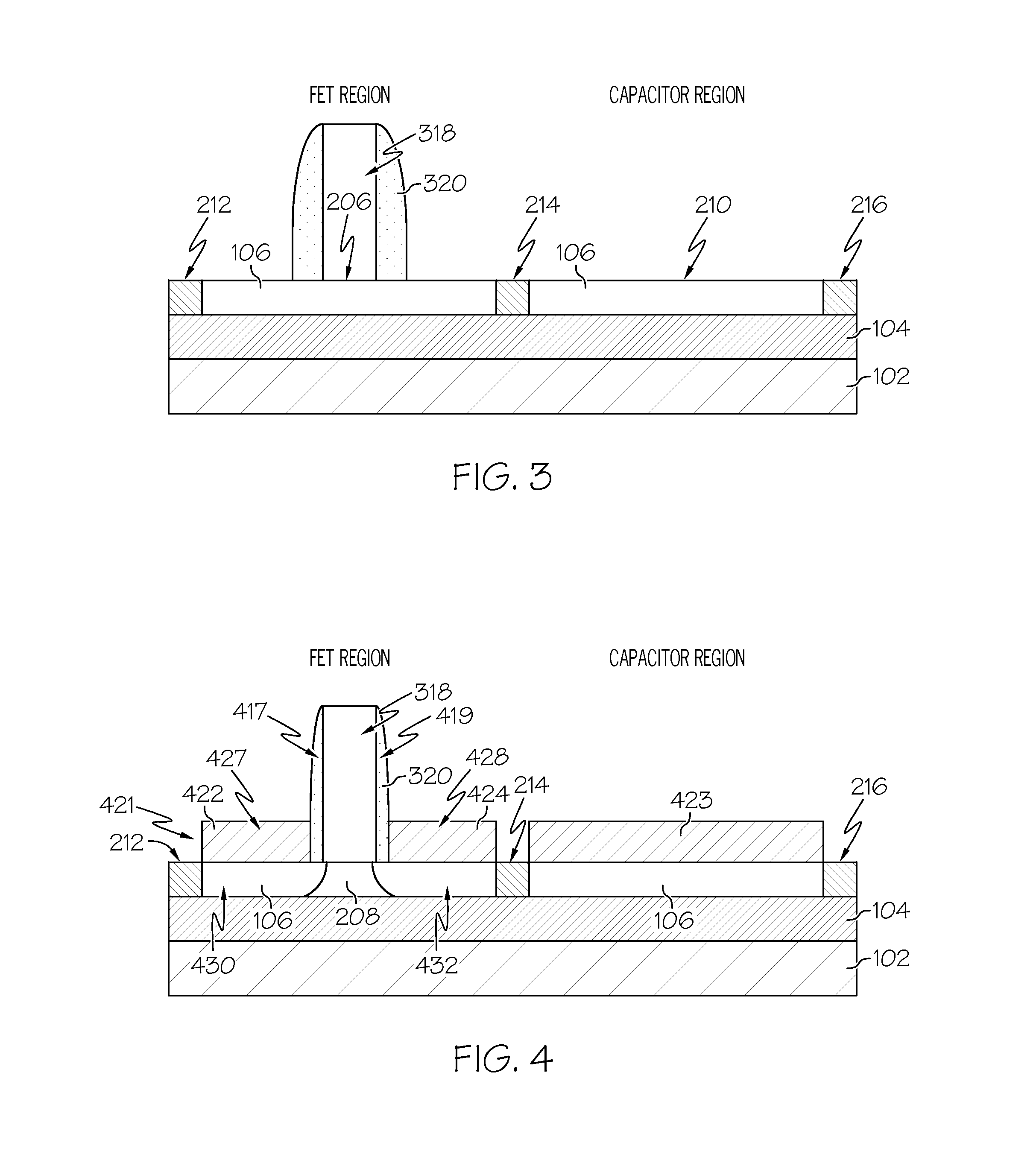

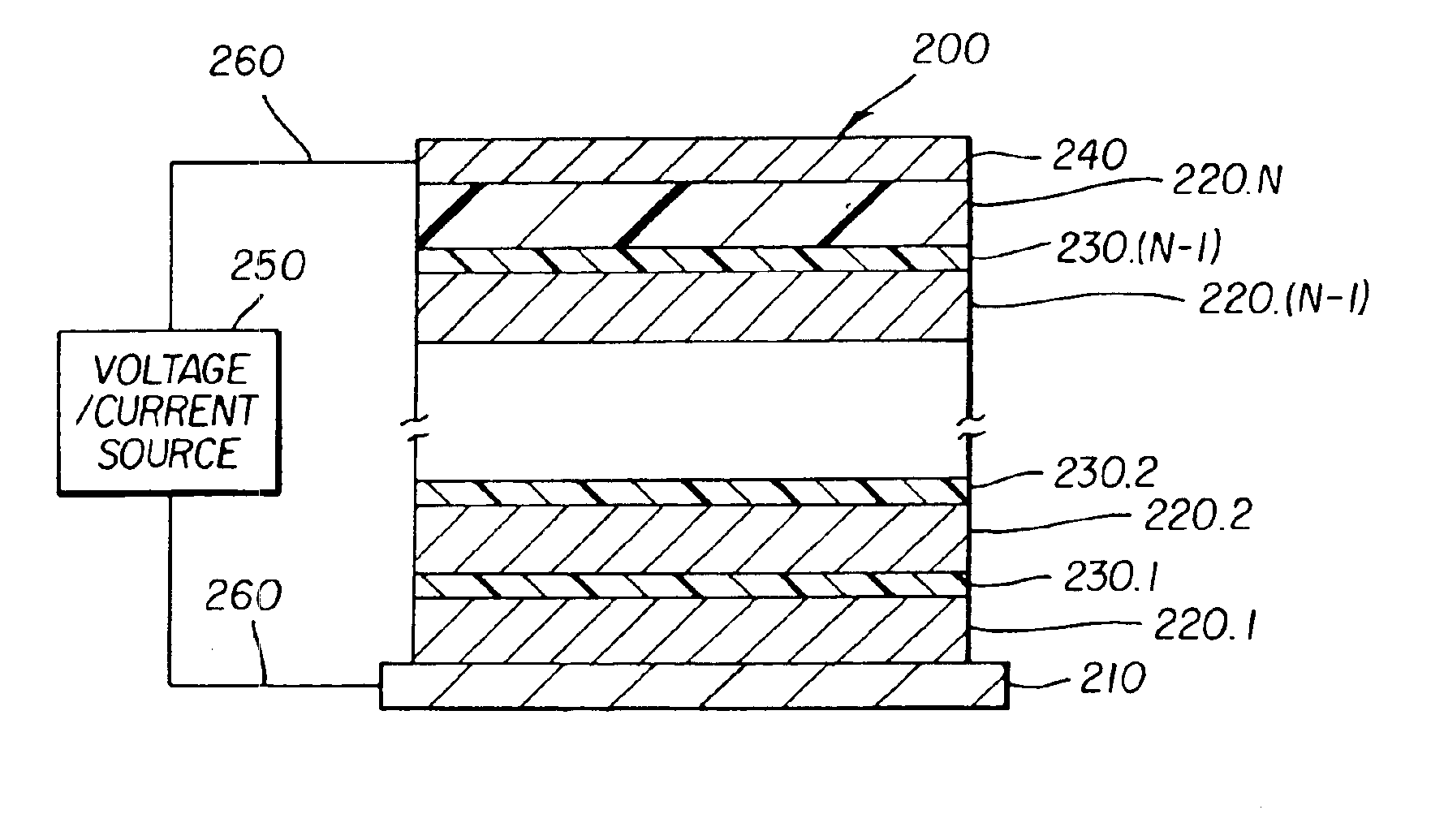

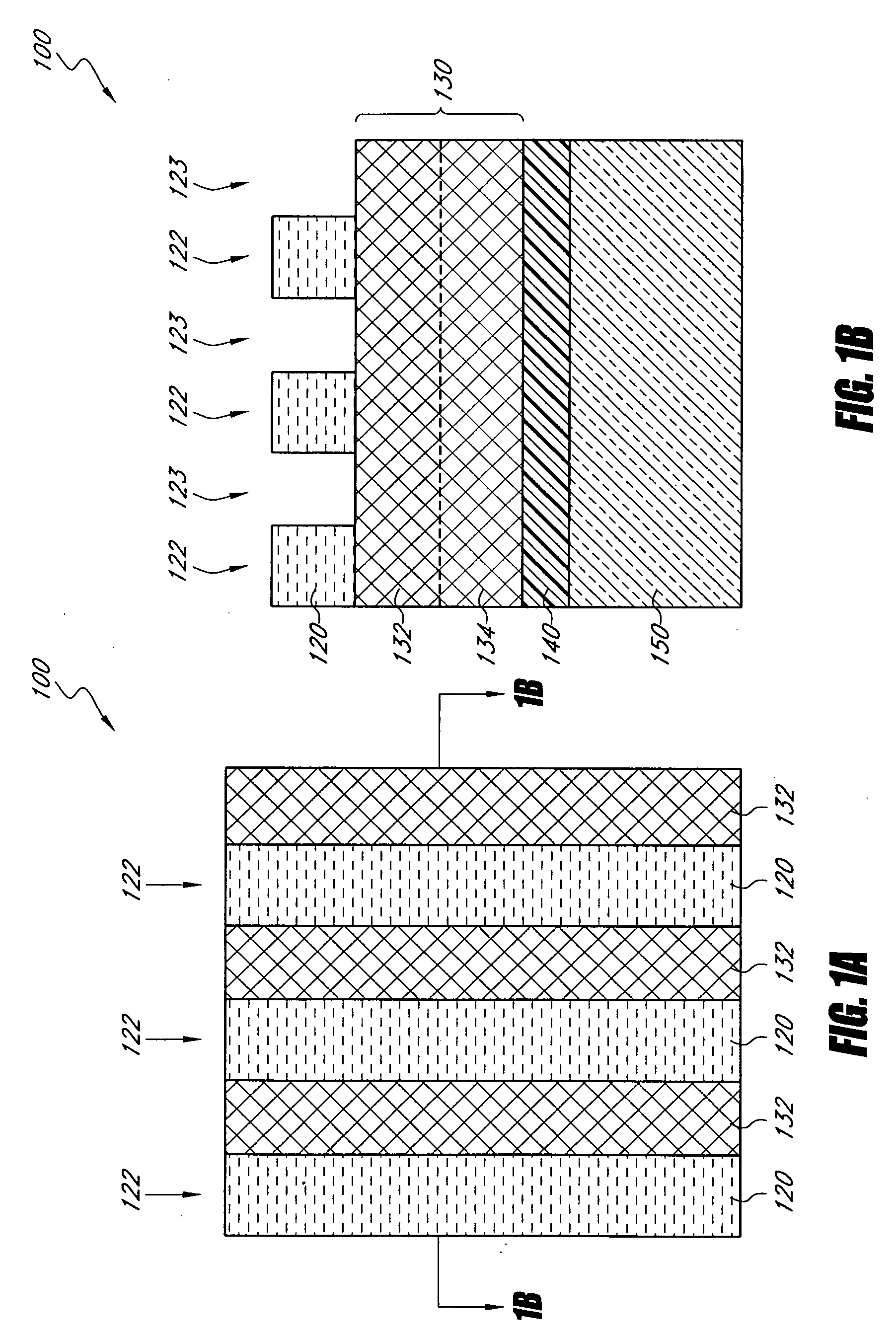

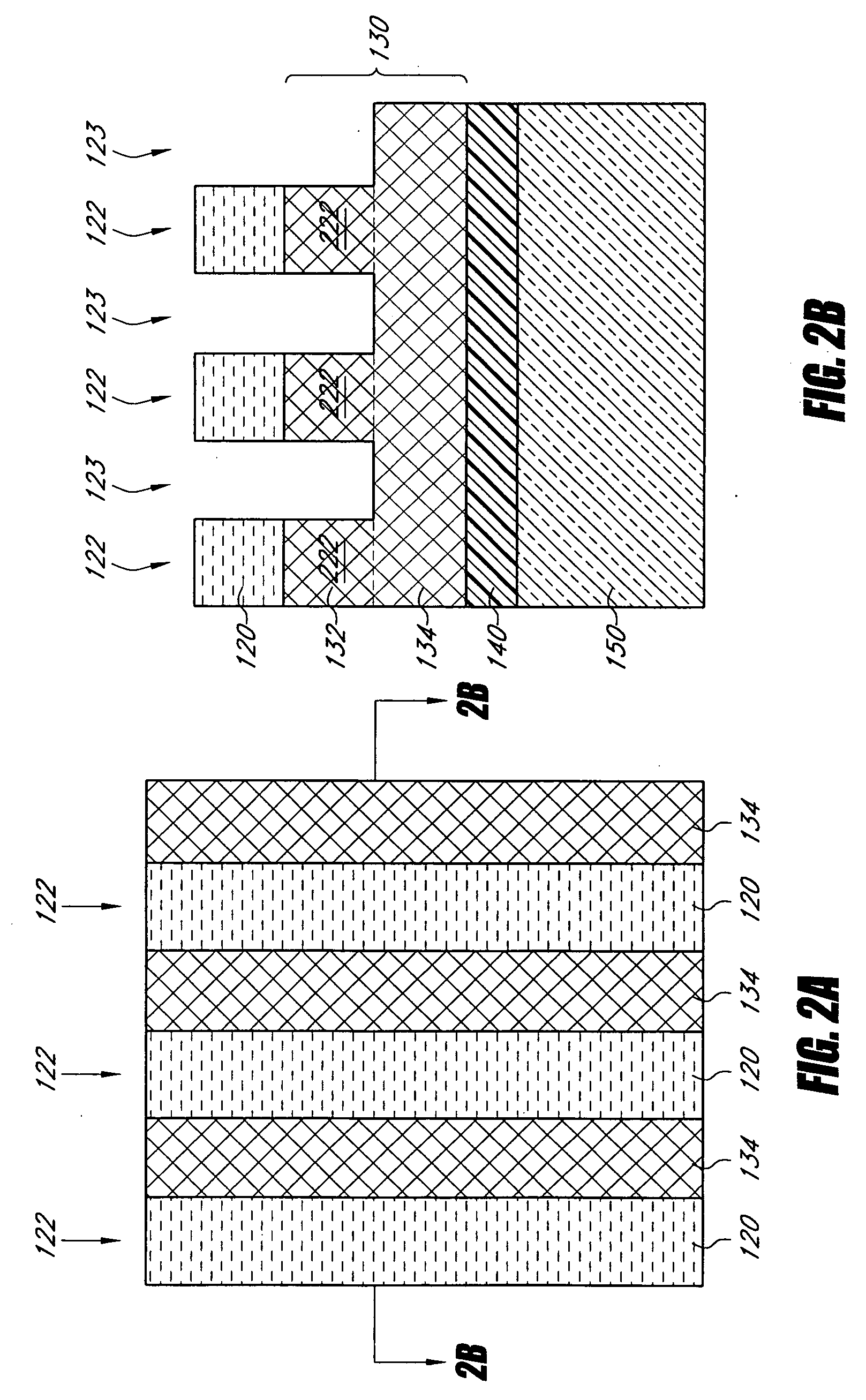

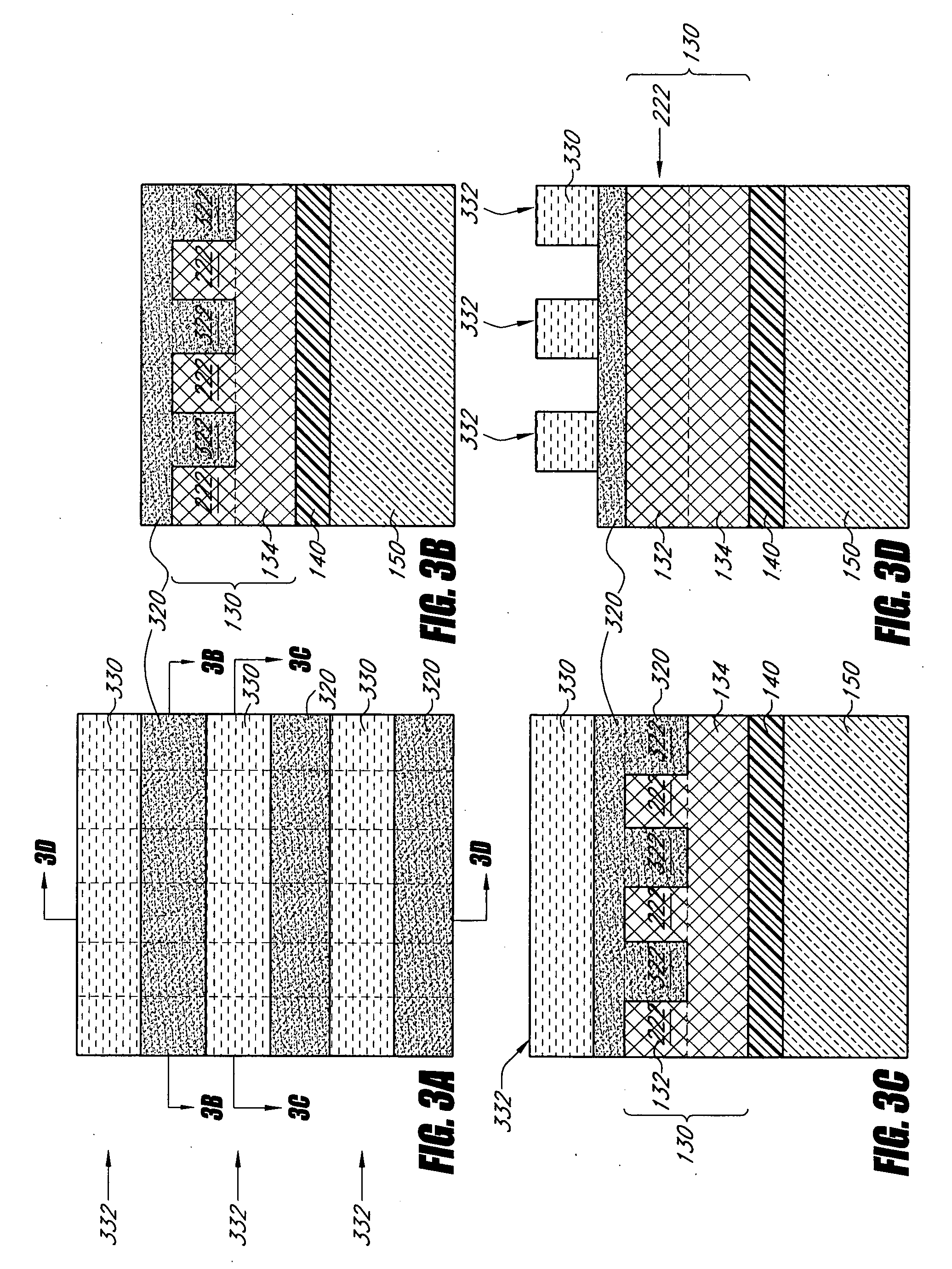

Providing an organic electroluminescent device having stacked electroluminescent units

InactiveUS6872472B2Lowering optical lossesImprove luminous efficiencySolid-state devicesSemiconductor/solid-state device manufacturingOrganic layerElectron transporting layer

A stacked organic electroluminescent device and a method of making such device is disclosed. The device comprises an anode, a cathode, at least two organic electroluminescent units disposed between the anode and the cathode, and a doped organic connector disposed between each adjacent organic electroluminescent unit wherein the organic electroluminescent unit comprises at least one organic hole-transporting layer and one organic electron-transporting layer. The doped organic connector comprises at least one n-type doped organic layer or one p-type doped organic layer, or combinations of layers thereof.

Owner:EASTMAN KODAK CO

Methods for forming arrays of small, closely spaced features

Methods of forming arrays of small, densely spaced holes or pillars for use in integrated circuits are disclosed. Various pattern transfer and etching steps can be used, in combination with pitch-reduction techniques, to create densely-packed features. Conventional photolithography steps can be used in combination with pitch-reduction techniques to form superimposed patterns of crossing elongate features with pillars at the intersections. Spacers are simultaneously applied to sidewalls of both sets of crossing lines to produce a pitch-doubled grid pattern. The pillars facilitate rows of spacers bridging columns of spacers.

Owner:MICRON TECH INC

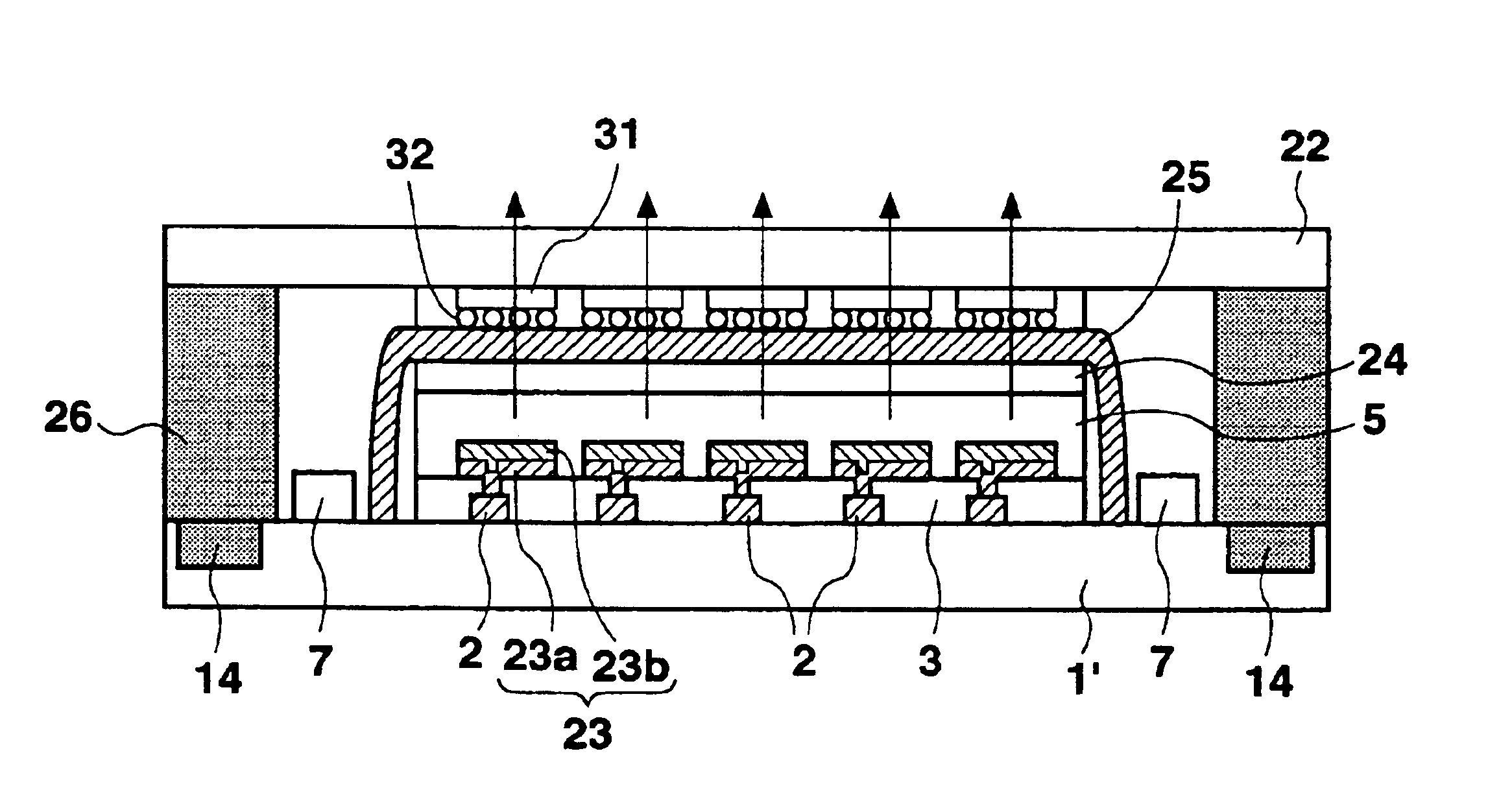

OLED device with embedded chip driving

ActiveUS7999454B2Small sizeReduce thicknessDischarge tube luminescnet screensElectroluminescent light sourcesHemt circuitsElectric current flow

An electroluminescent device having a plurality of current driven pixels arranged in rows and columns, such that when current is provided to a pixel it produces light, including each pixel having first and second electrodes and current responsive electroluminescent media disposed between the first and second electrodes; at least one chiplet having a thickness less than 20 micrometers; including transistor drive circuitry for controlling the operation of at least four pixels, the chiplet being mounted on a substrate and having connection pads; a planarization layer disposed over at least a portion of the chiplet; a first conductive layer over the planarization layer and connected to at least one of the connection pads; and a structure for providing electrical signals through the first conductive layer and at least one of the connection pads of the chiplet so that the transistor drive circuitry of the chiplet controls current to the four pixels.

Owner:X DISPLAY CO TECH LTD +1

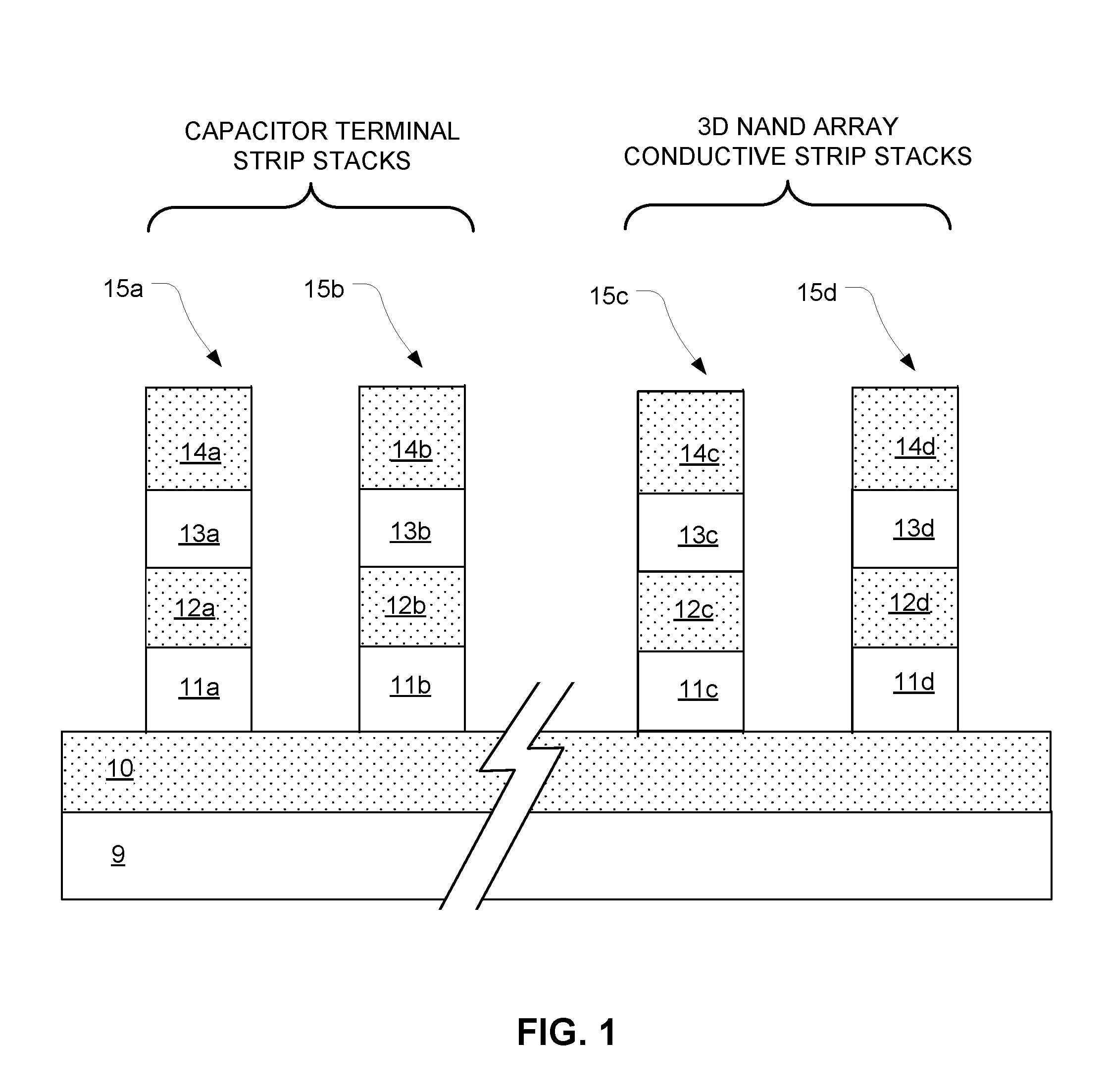

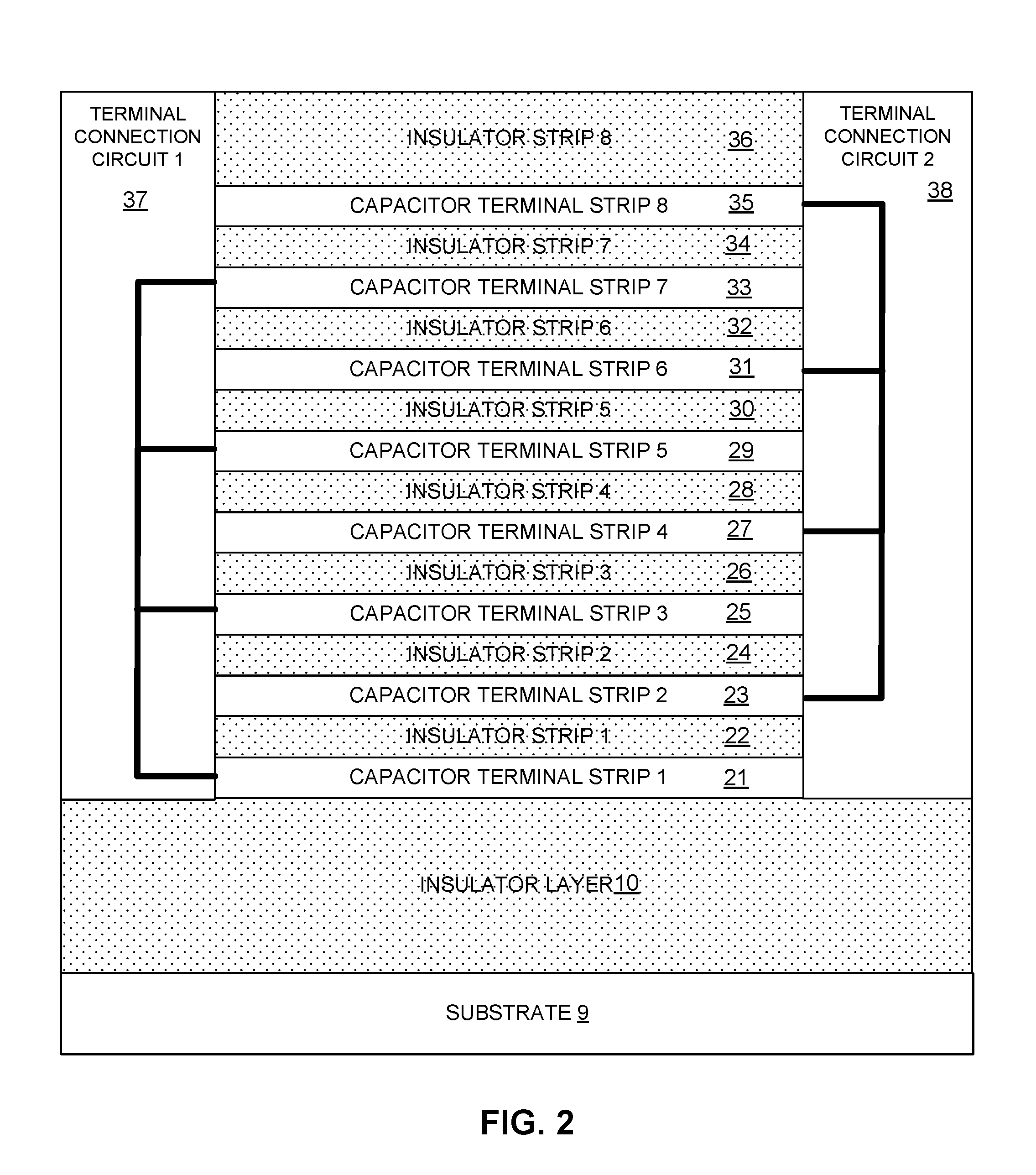

Capacitor With 3D NAND Memory

An integrated circuit includes a 3D NAND memory array with a stack of conductive strips and a capacitor with a stack of capacitor terminal strips. Multiple conductive strips in the stack of conductive strips, and multiple capacitor terminal strips of the stack of capacitor terminal strips, share a same plurality of plane positions relative to the substrate. Different plane positions in the same plurality of plane positions characterize different capacitor terminal strips in the stack of capacitor terminal strips and different conductive strips in the stack of conductive strips, and a same plane position characterizing both a conductive strip in the stack of conductive strips and a capacitor terminal strip in the stack of capacitor terminal strips indicates that the conductive strip and the capacitor terminal strip have a same vertical position relative to each other.

Owner:MACRONIX INT CO LTD

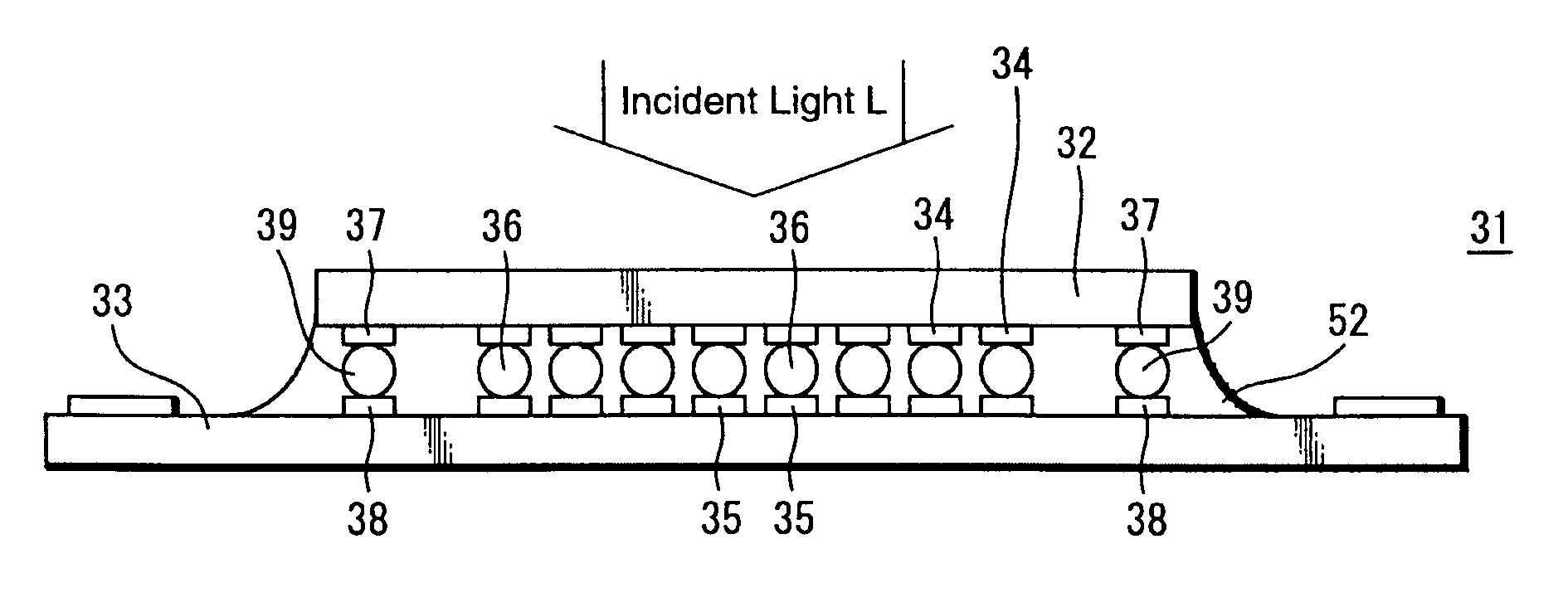

Semiconductor module, MOS type solid-state image pickup device, camera and manufacturing method of camera

ActiveUS20060023109A1Reduce voltageHigh yield manufacturingTransistorTelevision system detailsImaging processingImaging quality

A back-illuminated type MOS (metal-oxide semiconductor) solid-state image pickup device 32 in which micro pads 34, 37 are formed on the wiring layer side and a signal processing chip 33 having micro pads 35, 38 formed on the wiring layer at the positions corresponding to the micro pads 34, 37 of the MOS solid-state image pickup device 32 are connected by micro bumps 36, 39. In a semiconductor module including the MOS type solid-state image pickup device, at the same time an image processing speed can be increased, simultaneity within the picture can be realized and image quality can be improved, a manufacturing process can be facilitated, and a yield can be improved. Also, it becomes possible to decrease a power consumption required when all pixels or a large number of pixels is driven at the same time.

Owner:SONY CORP

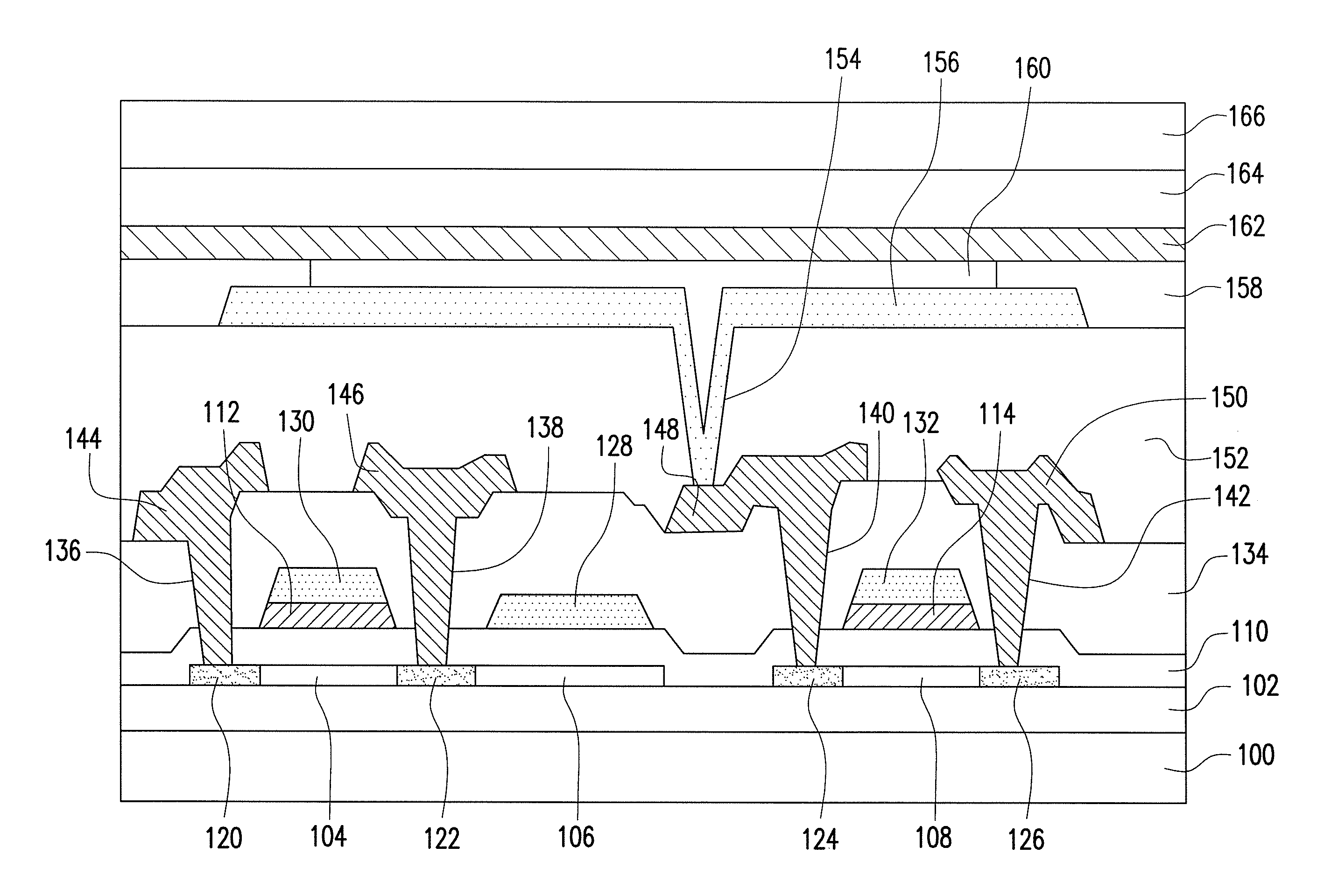

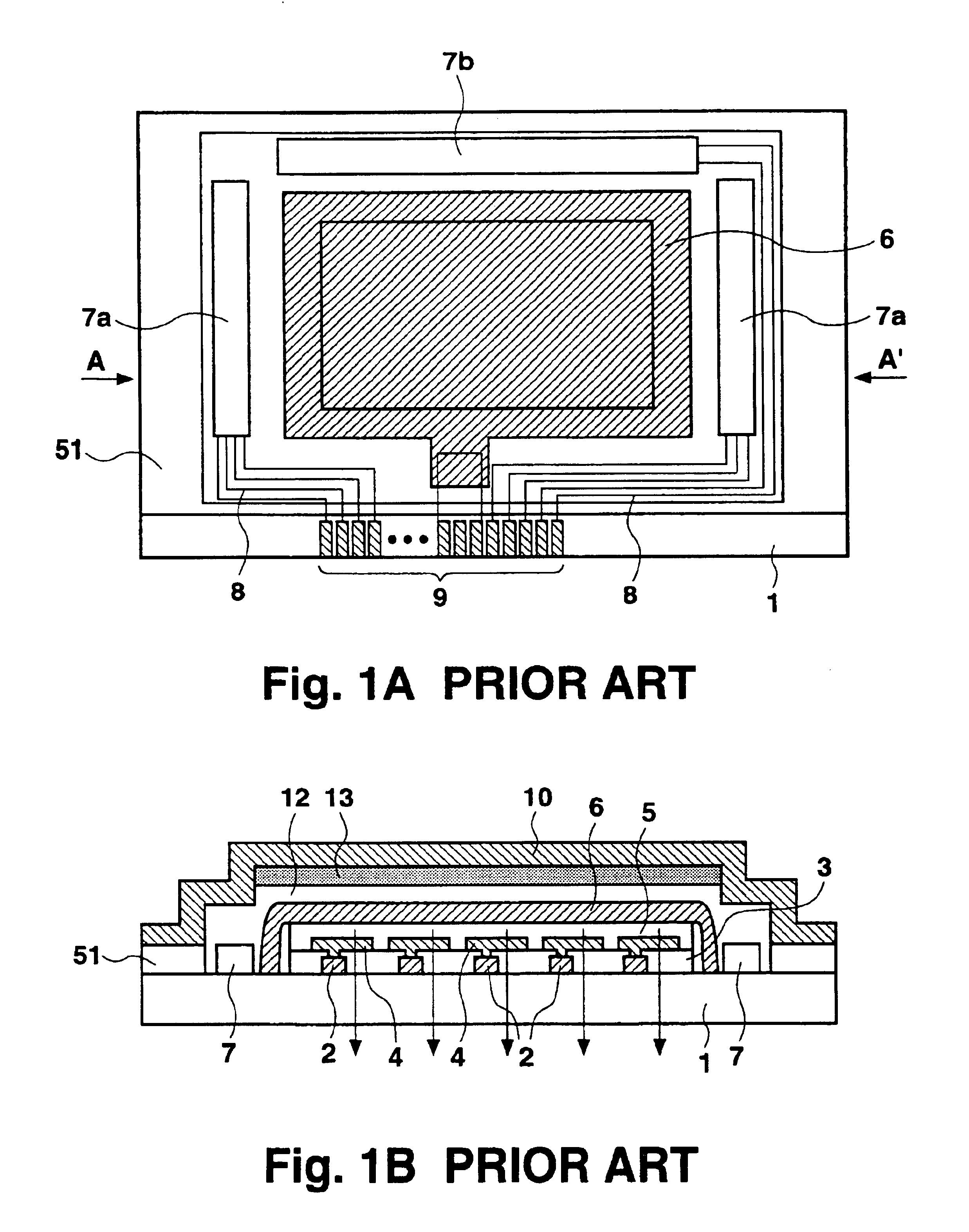

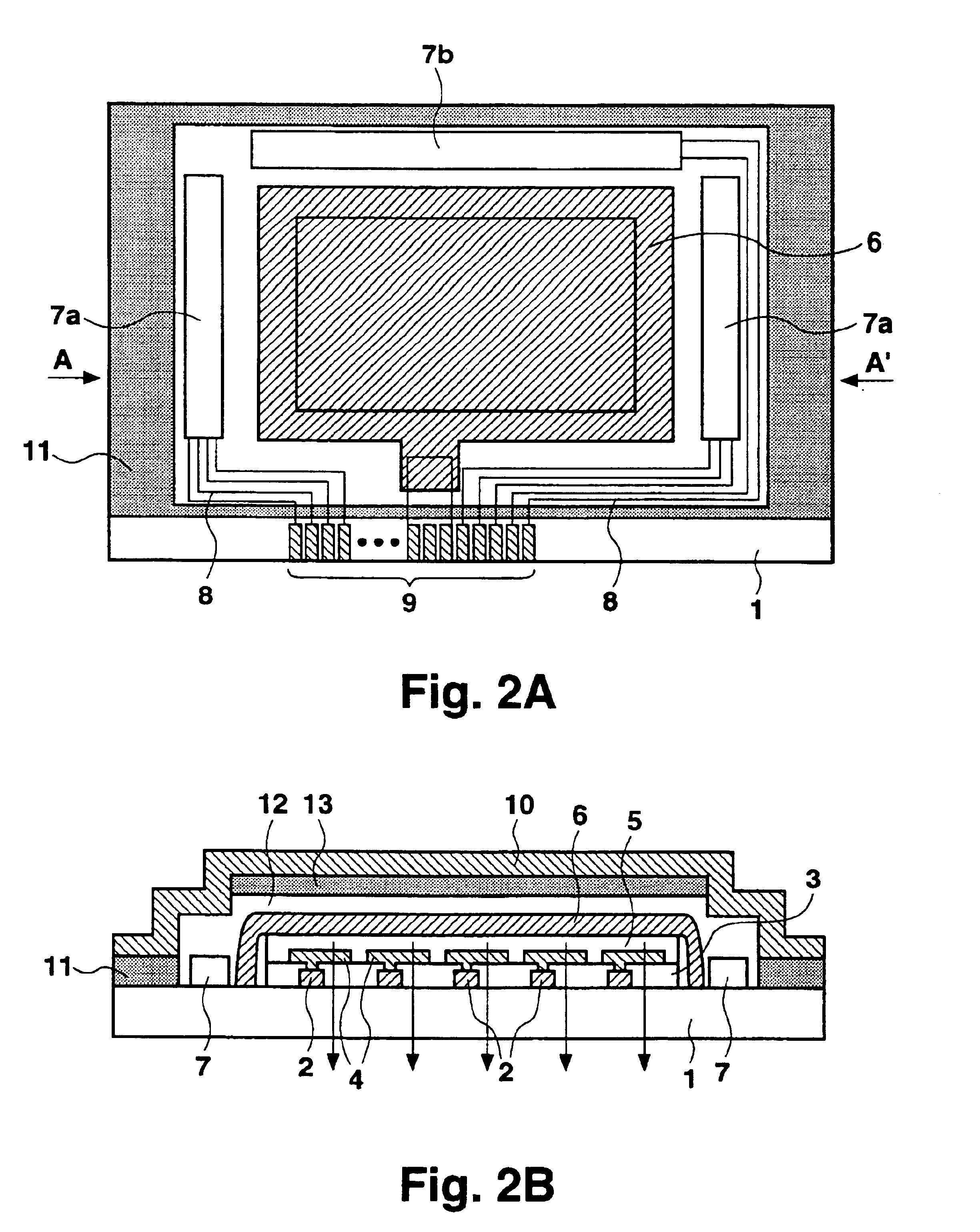

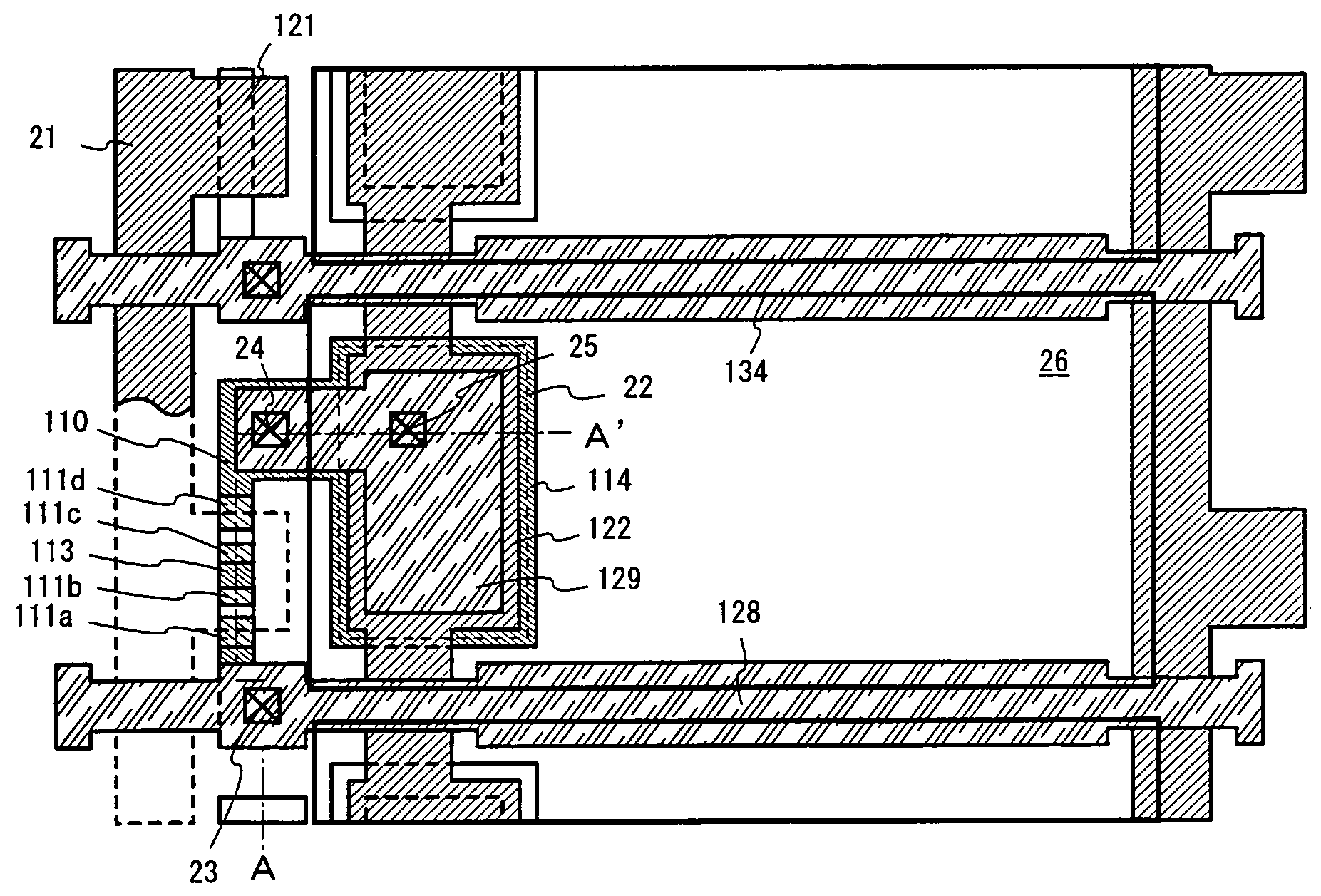

Electrooptical device and a method of manufacturing the same

InactiveUS7122835B1Enlarge regionIncrease opening ratioSolid-state devicesDiodeDriver circuitSemiconductor

To provide a semiconductor device of high reliability by arranging TFTs that have appropriate structures in accordance with circuit functions. In a semiconductor device having a driver circuit portion and a pixel portion on the same insulator, gate insulating films of a driver TFT are designed to be thinner than a gate insulating film of a pixel TFT. In the pixel TFT, channel forming regions are formed under a gate electrode, and a separation region is formed between the channel forming regions. At this point, LDD regions have a region that overlaps with the gate electrode and a region that does not.

Owner:SEMICON ENERGY LAB CO LTD