Patents

Literature

129472results about "Photovoltaic energy generation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

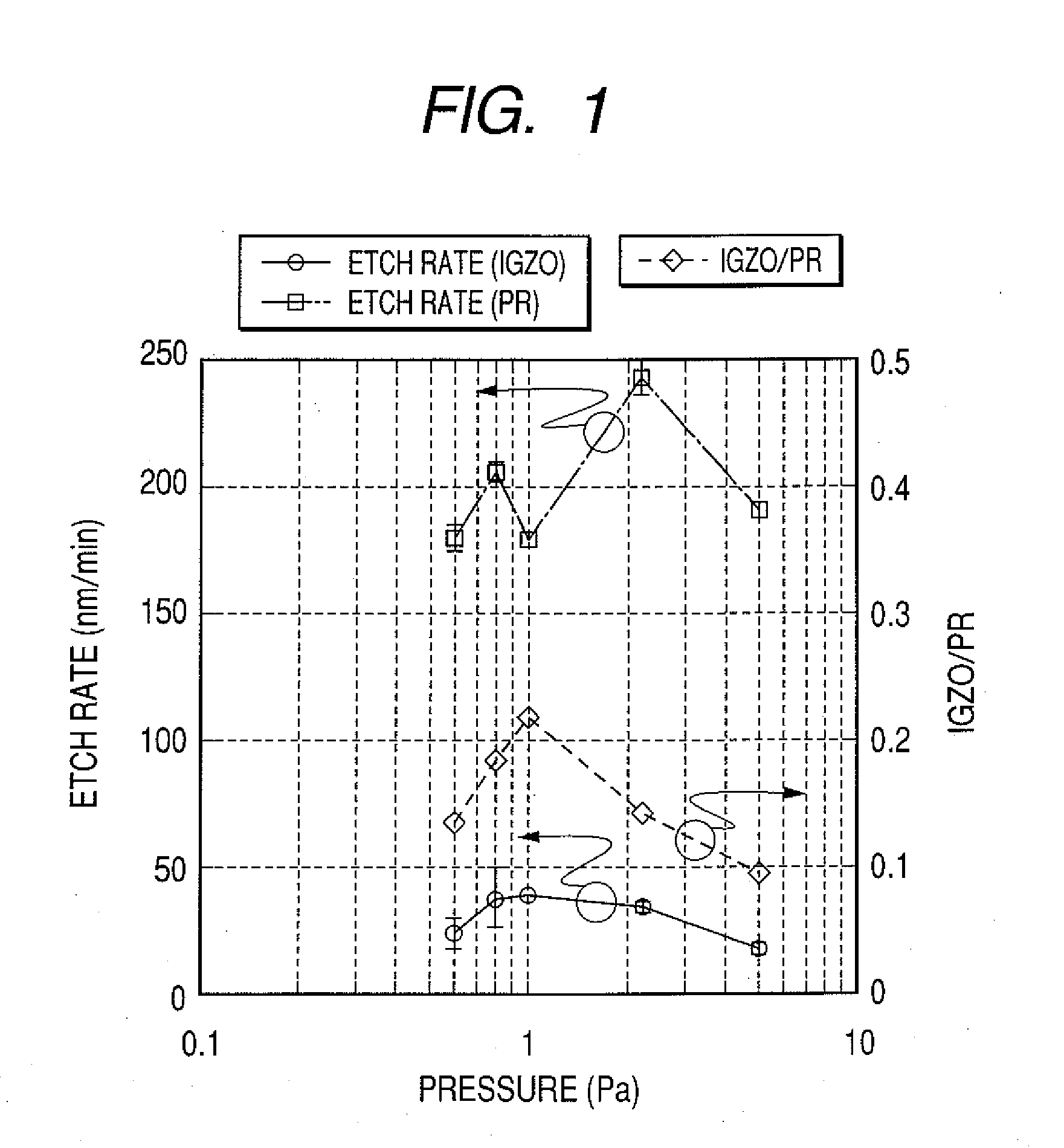

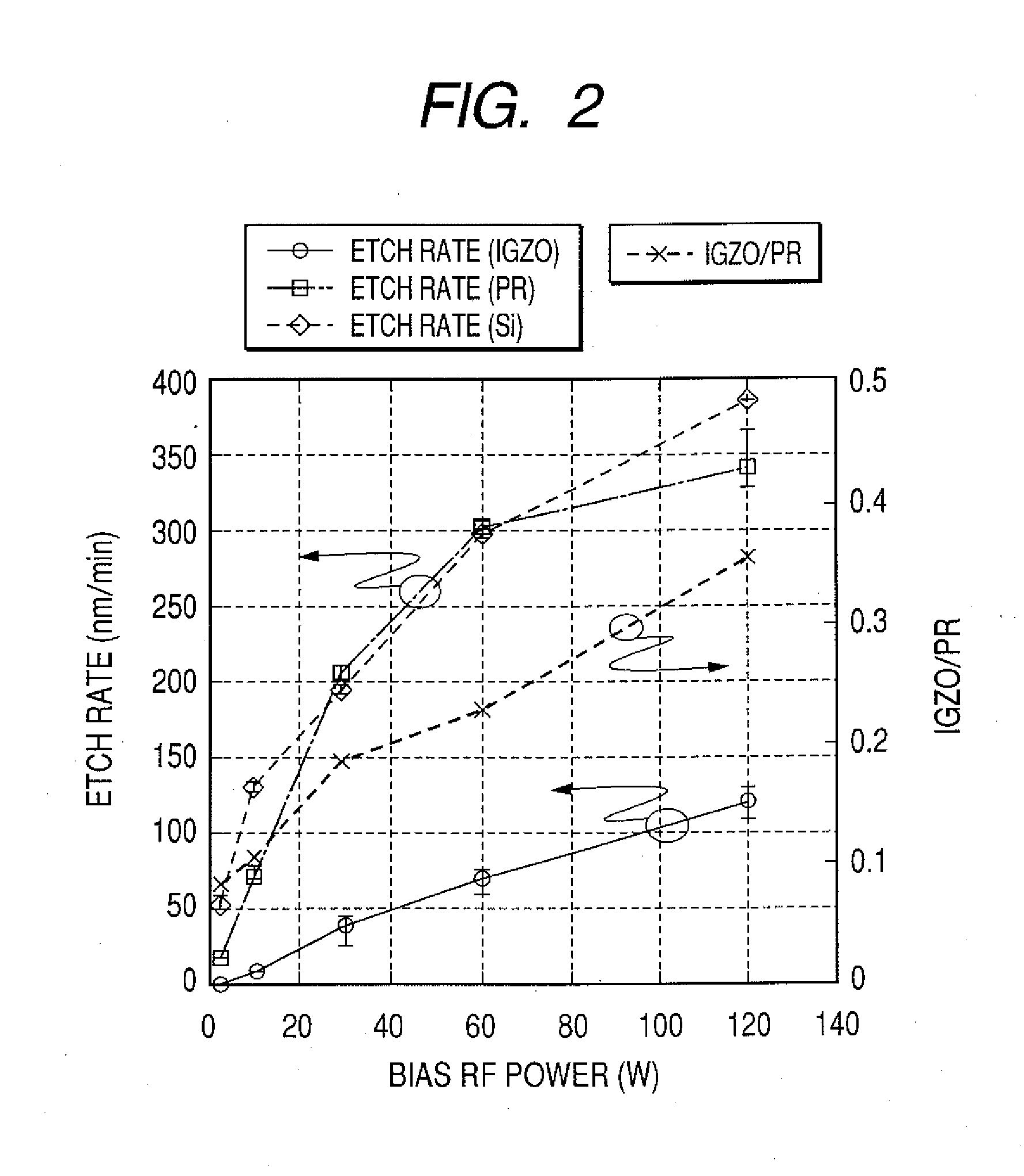

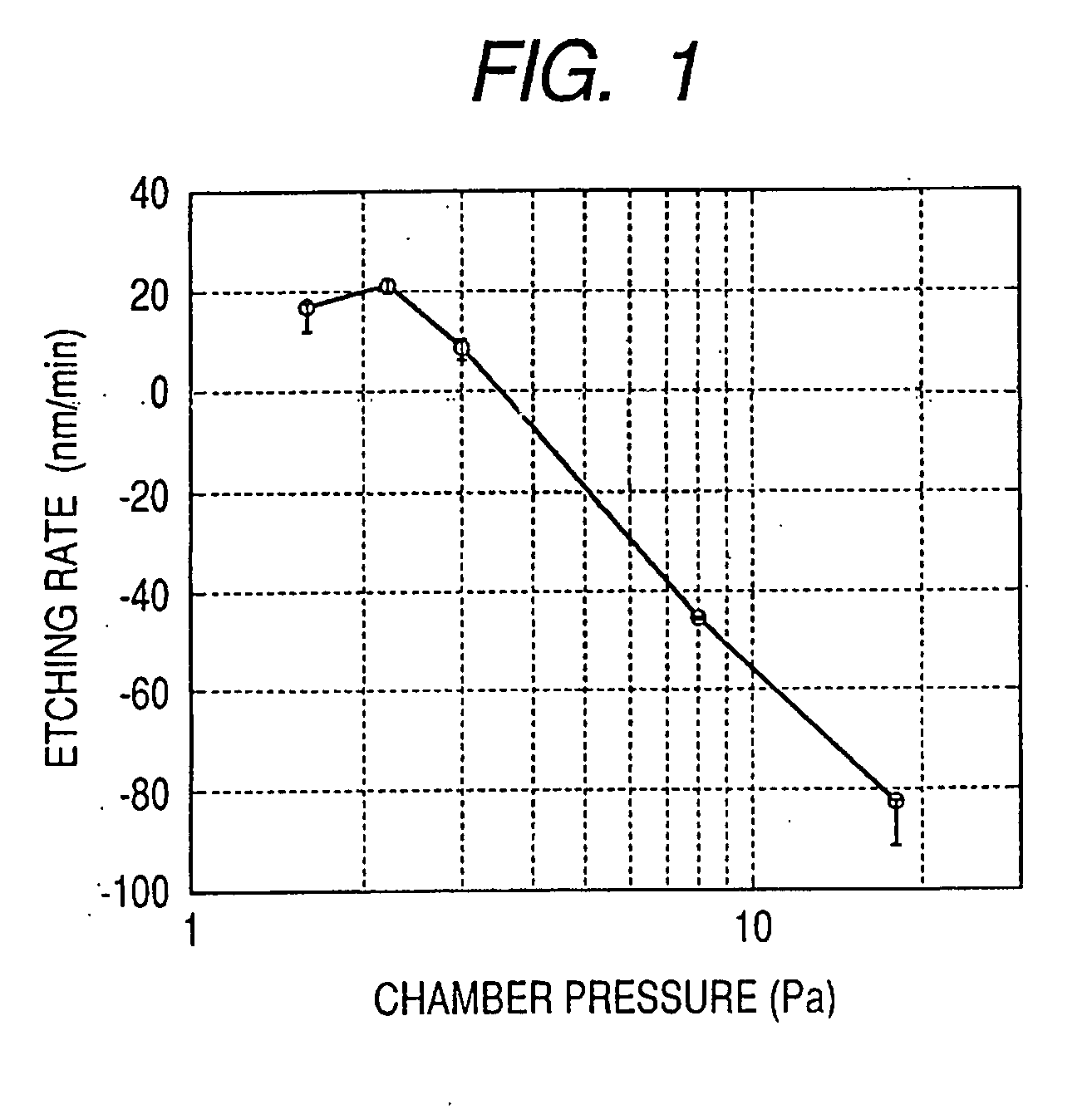

Method of dry etching oxide semiconductor film

InactiveUS20080038929A1Improve processing accuracyIncrease etch rateDecorative surface effectsSemiconductor/solid-state device manufacturingSemiconductorDry etching

Provided is a dry etching method for an oxide semiconductor film containing at least In, Ga, and Zn, which includes etching an oxide semiconductor film in a gas atmosphere containing a halogen-based gas.

Owner:CANON KK

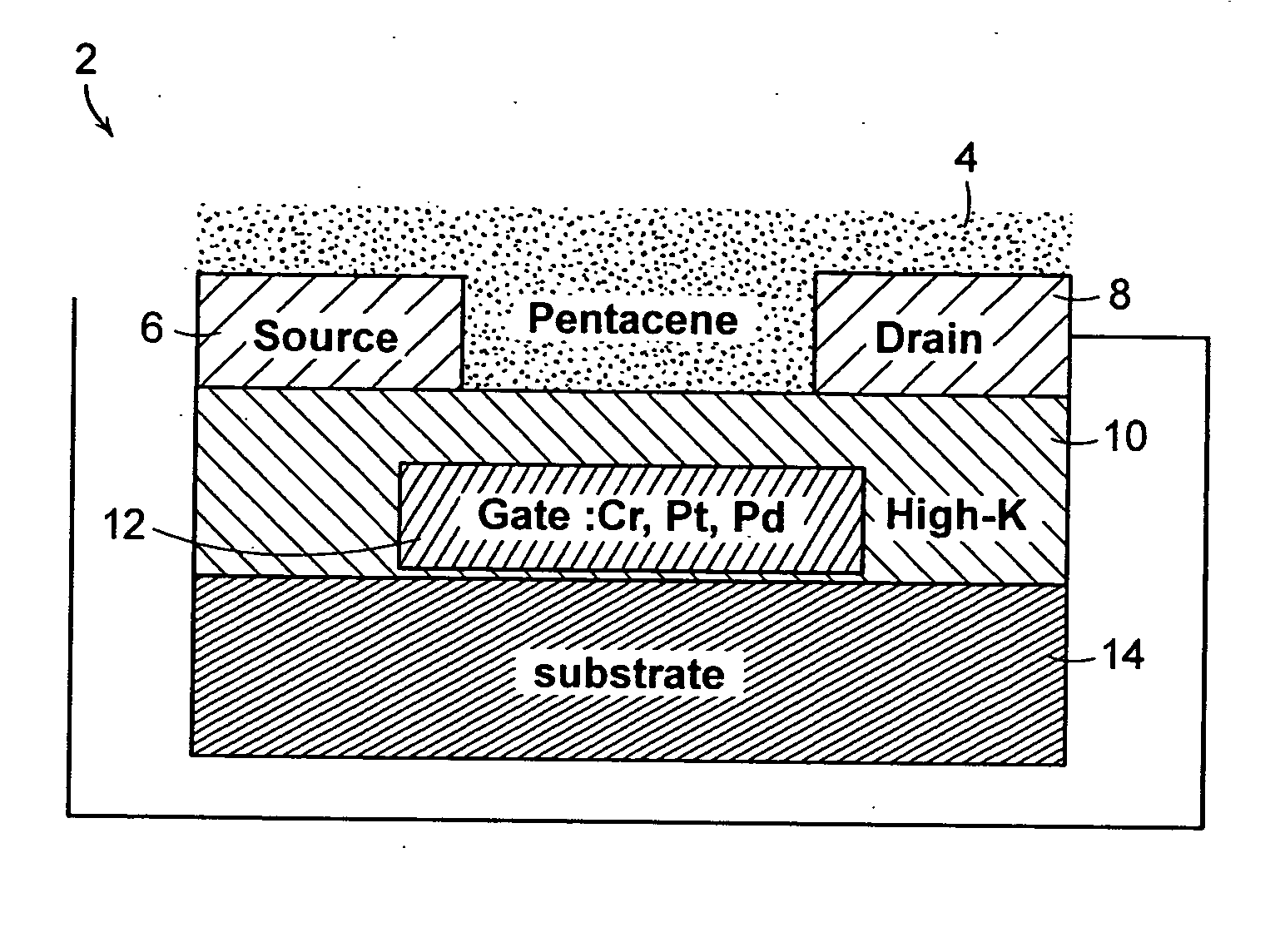

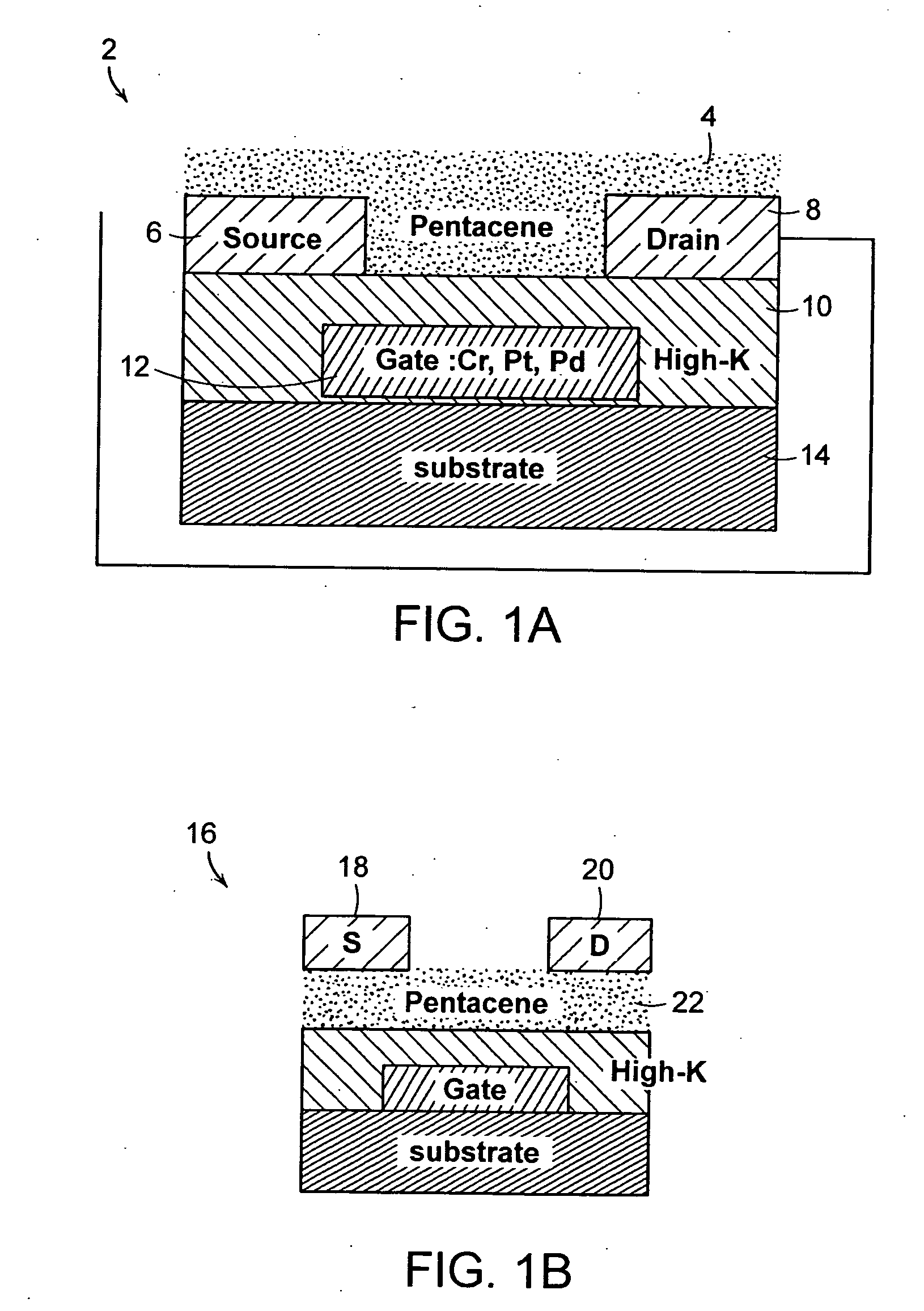

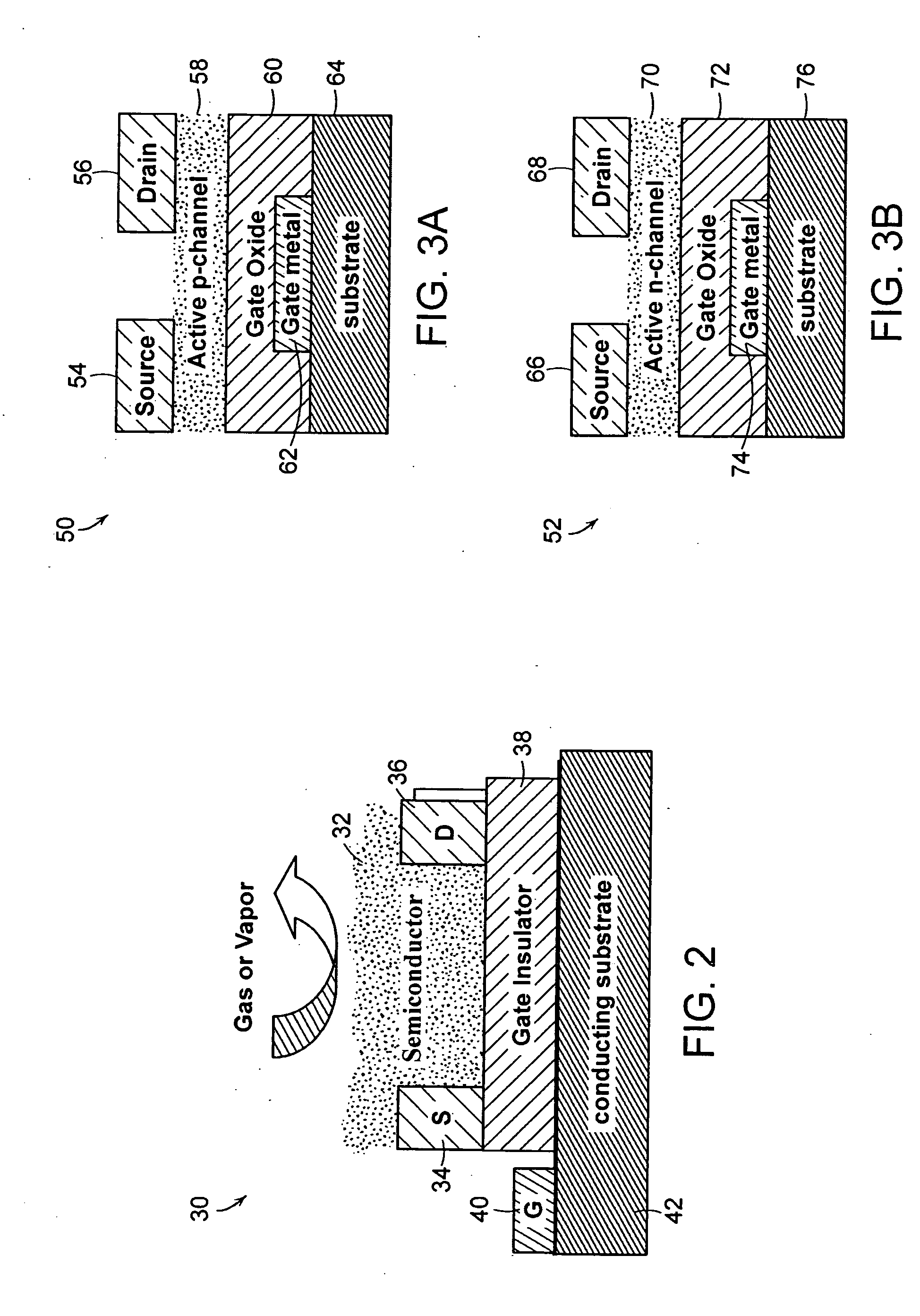

Low voltage flexible organic/transparent transistor for selective gas sensing, photodetecting and CMOS device applications

A thin film transistor (TFT) includes a source electrode, a drain electrode, and a gate electrode. A gate insulator is coupled to the source electrode, drain electrode, and gate electrode. The gate insulator includes room temperature deposited high-K materials so as to allow said thin film transistor to operate at low operating voltage.

Owner:MASSACHUSETTS INST OF TECH

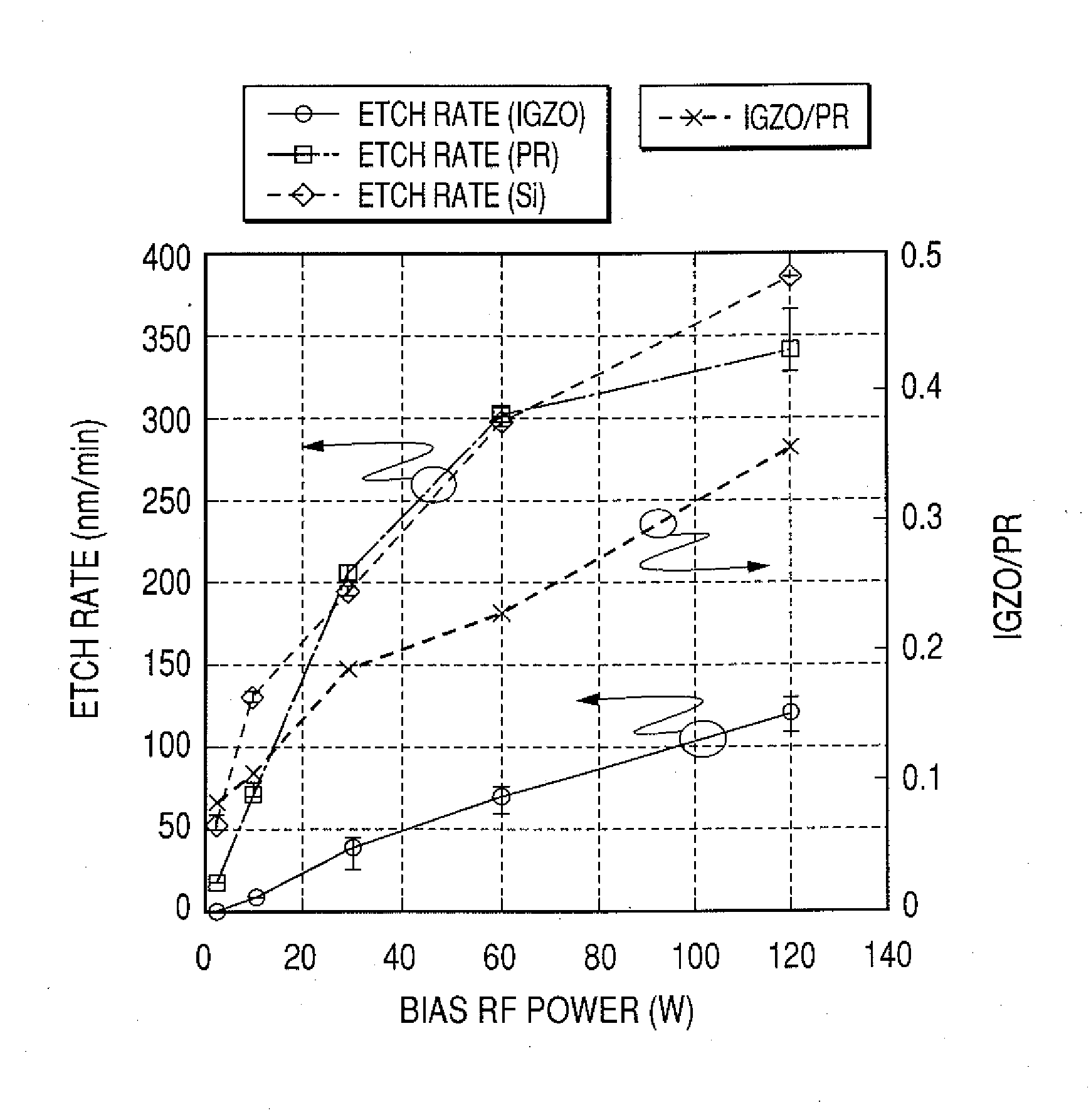

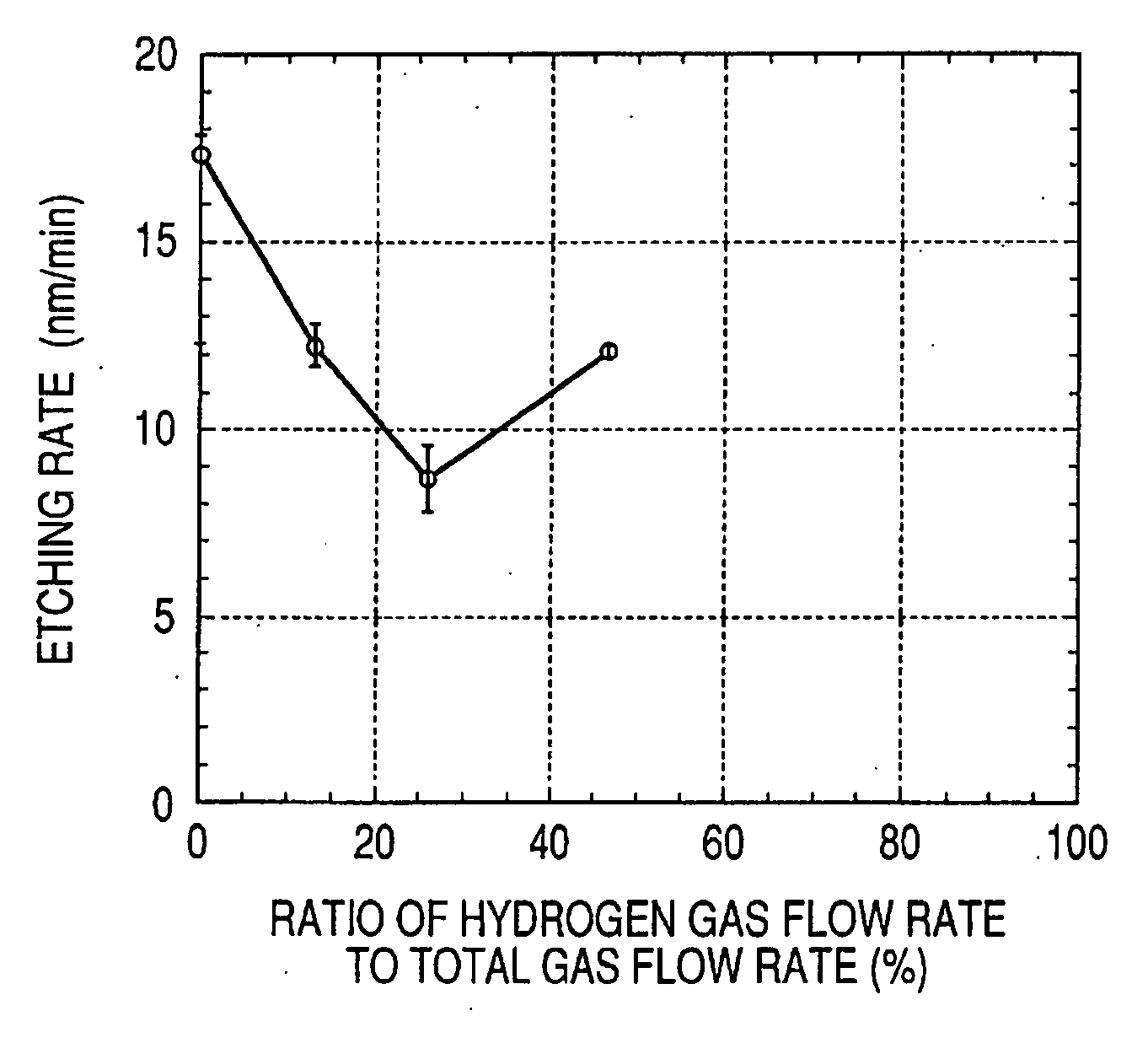

Dry etching method for oxide semiconductor film

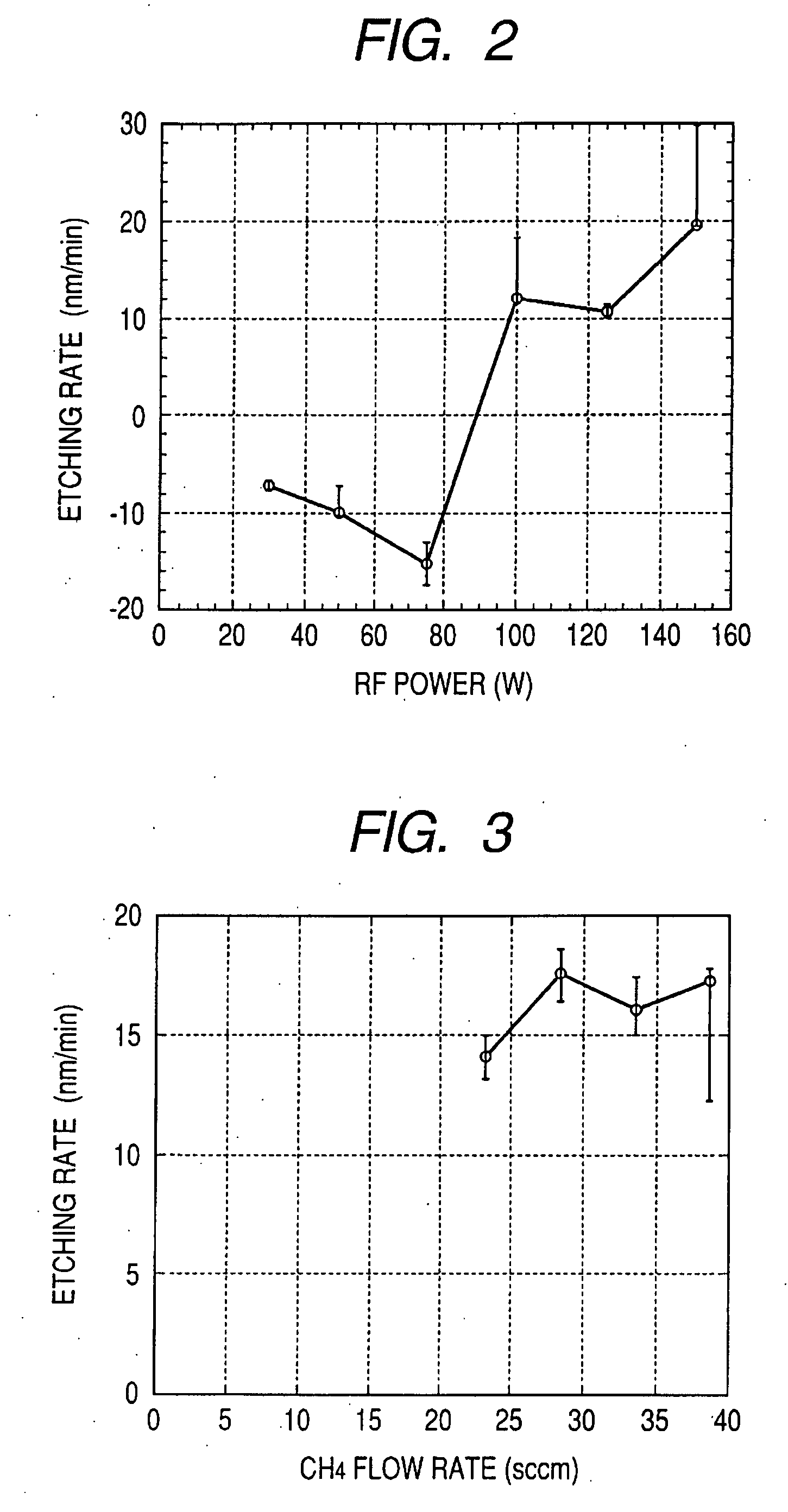

InactiveUS20070287296A1Improve processing accuracyIncrease etch rateDecorative surface effectsSemiconductor/solid-state device manufacturingDry etchingSemiconductor

Provided is a dry etching method for an oxide semiconductor film made of In—Ga—Zn—O, in which an etching gas containing a hydrocarbon is used in a dry etching process for the oxide semiconductor film made of In—Ga—Zn—O formed on a substrate.

Owner:CANON KK

Vertical-type non-volatile memory devices

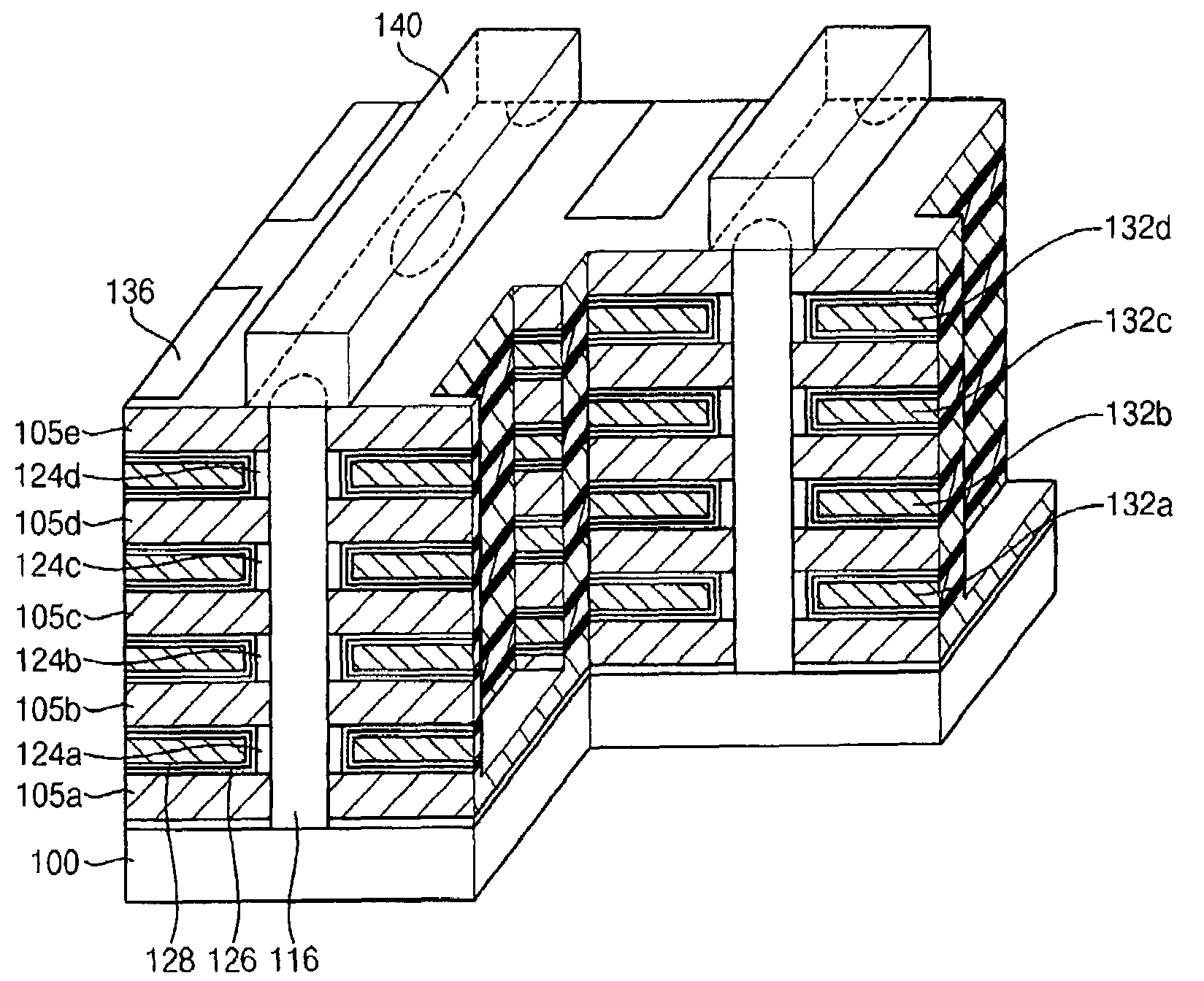

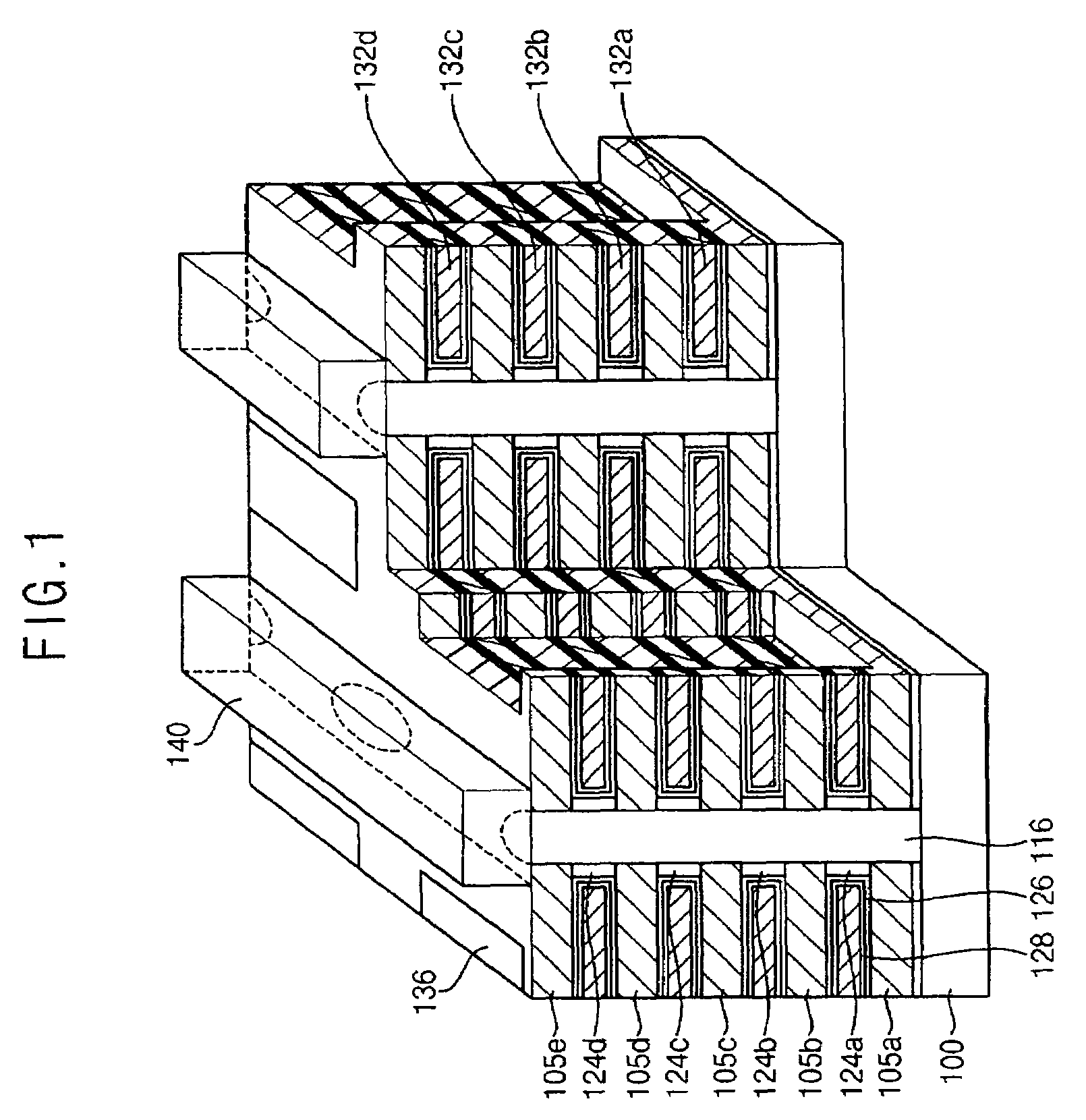

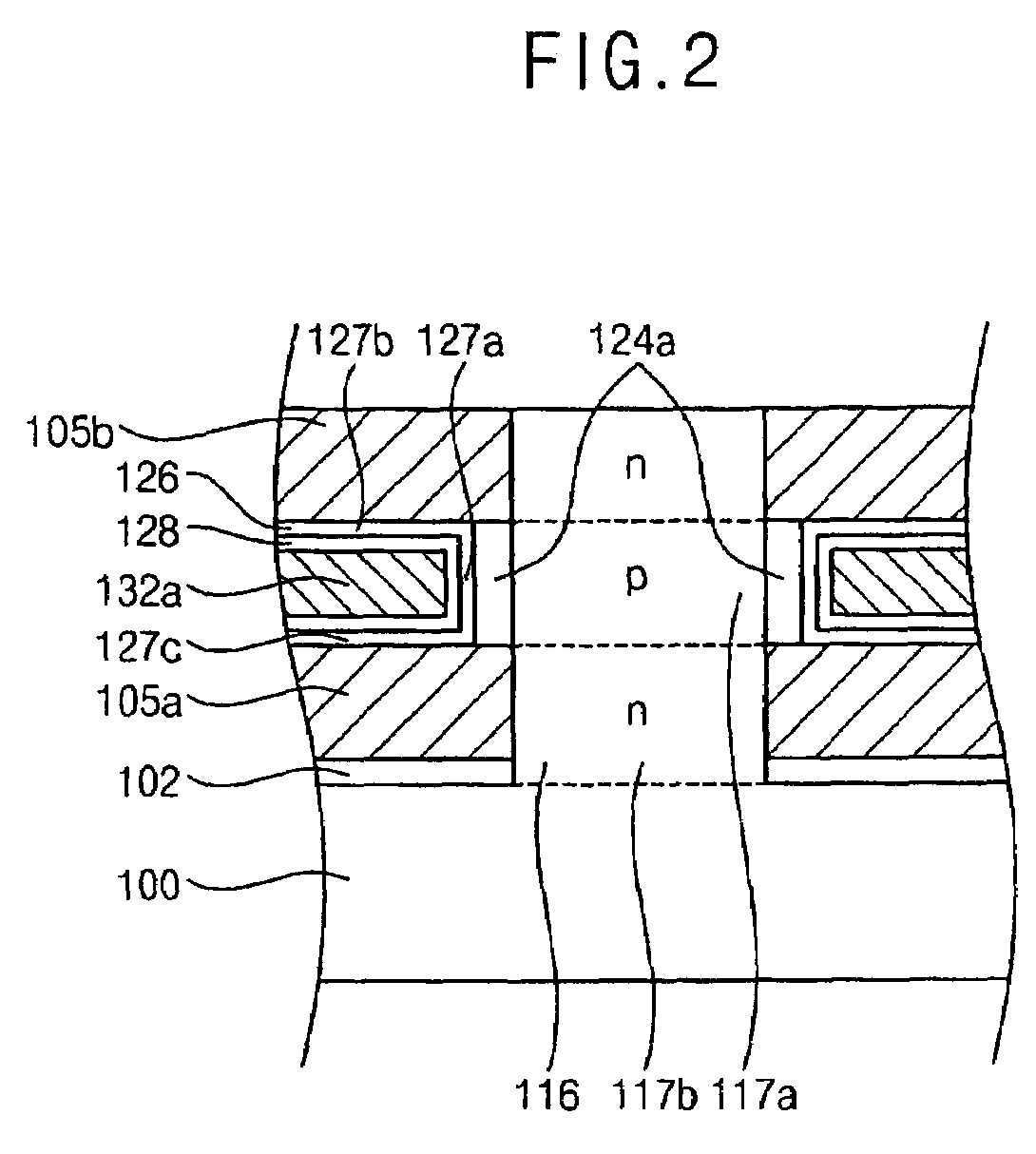

ActiveUS7679133B2Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

In a semiconductor device, and a method of manufacturing thereof, the device includes a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

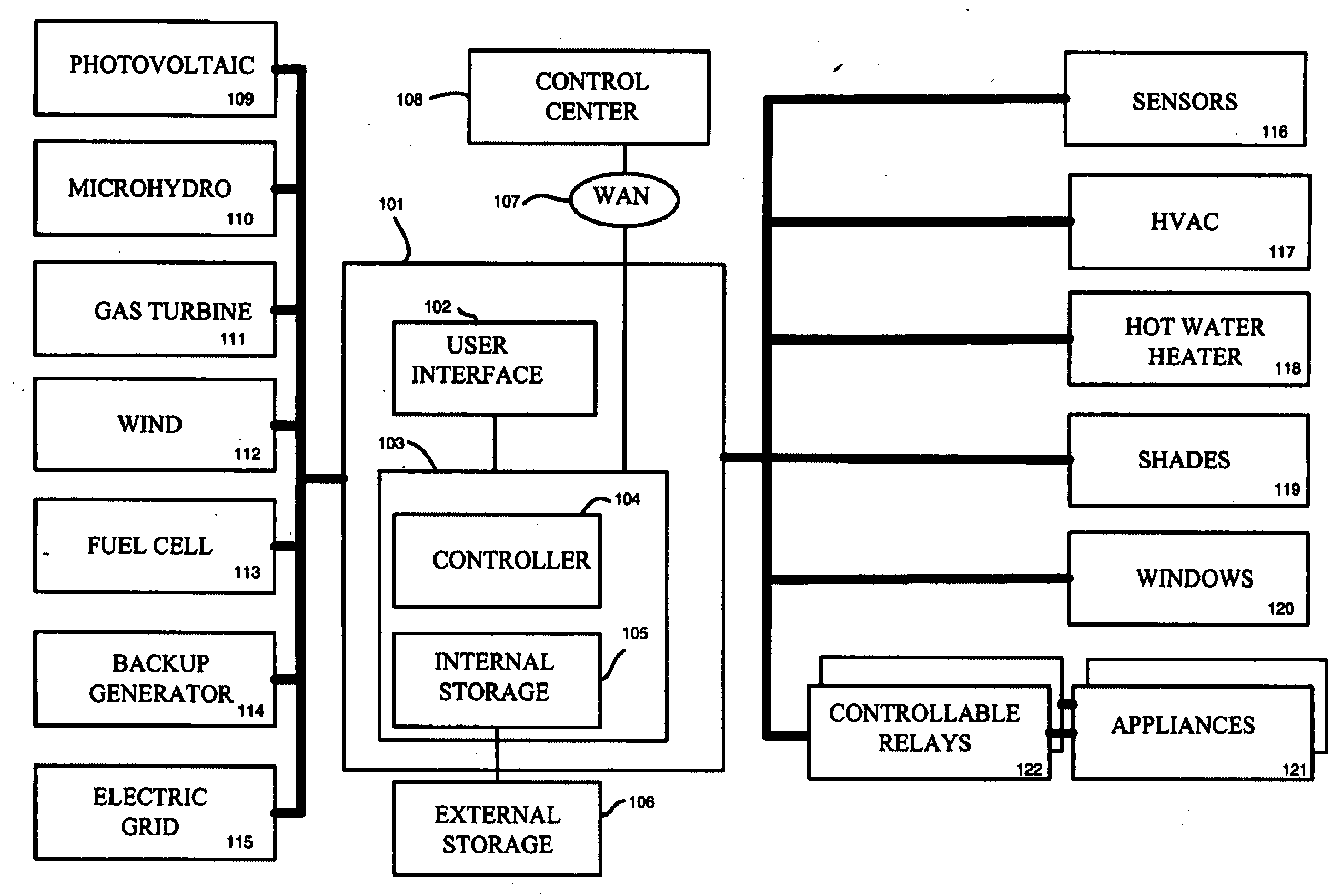

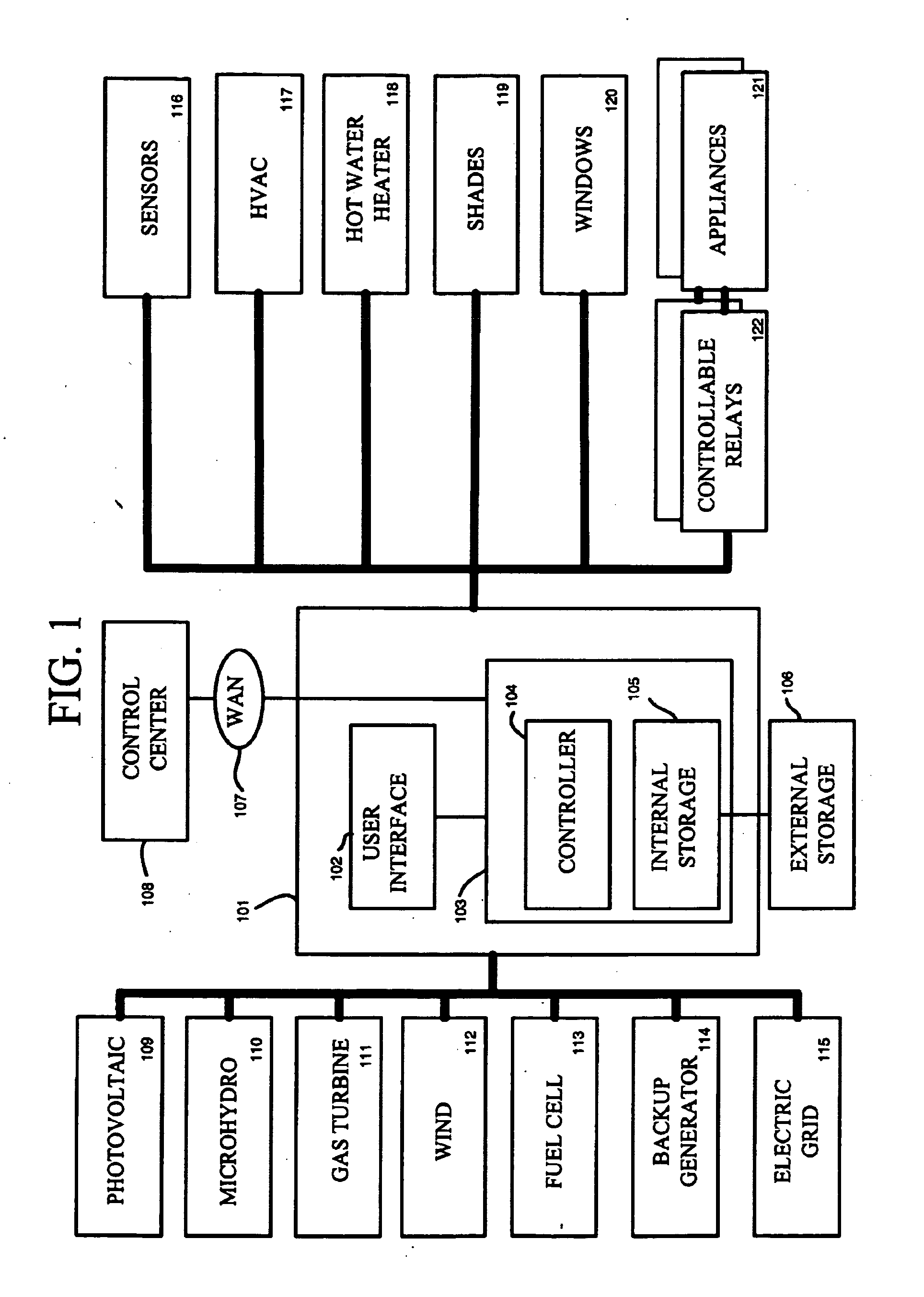

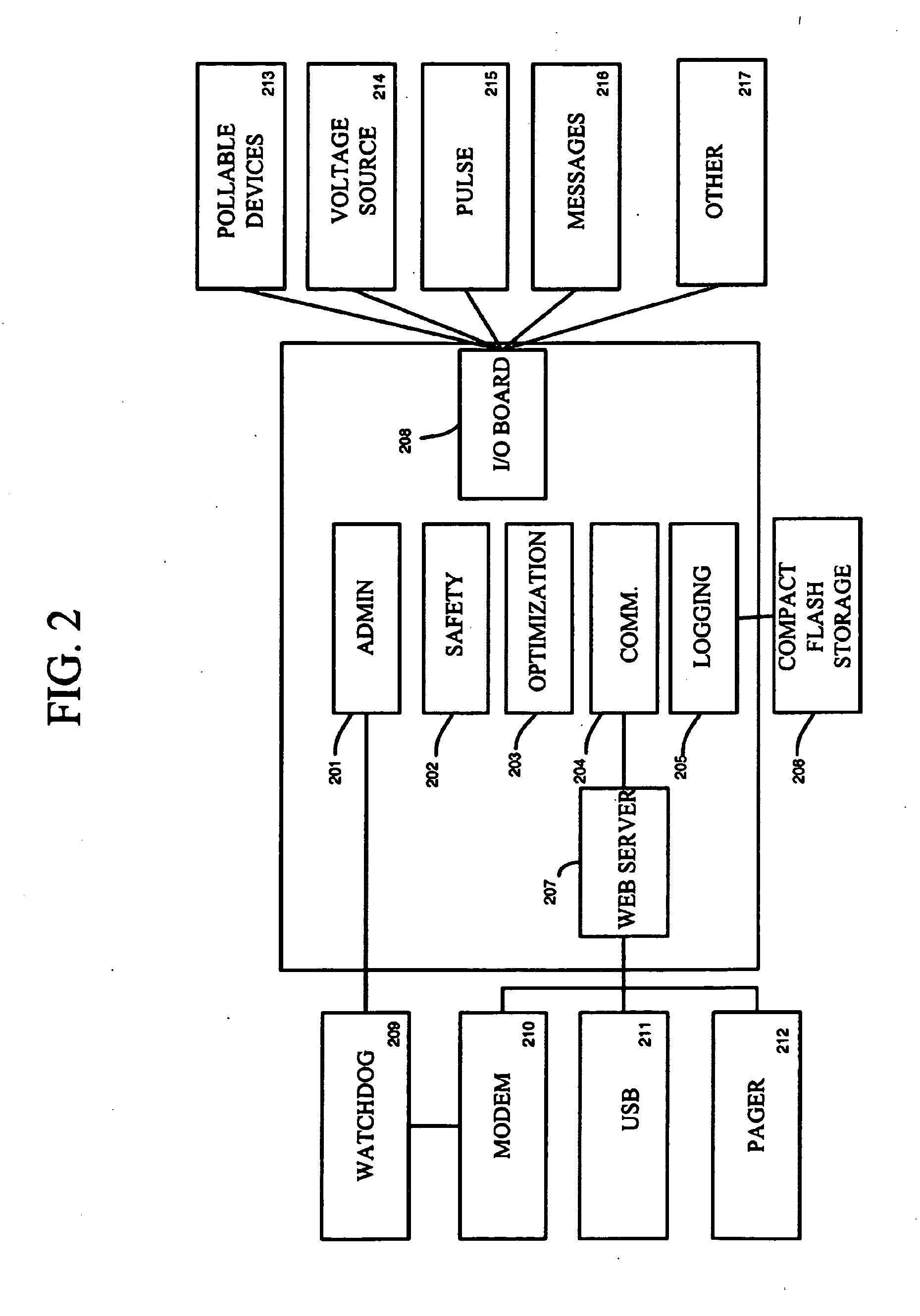

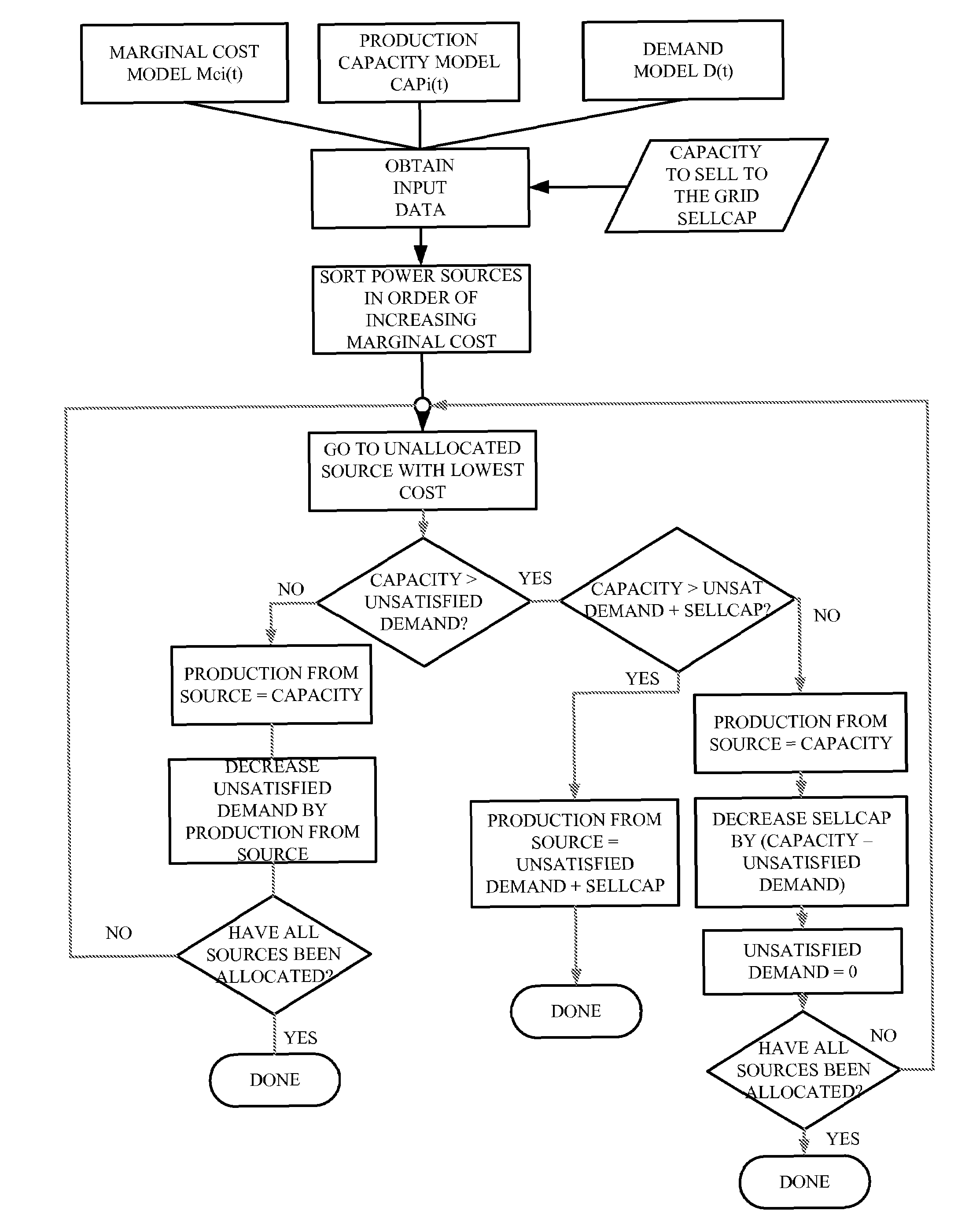

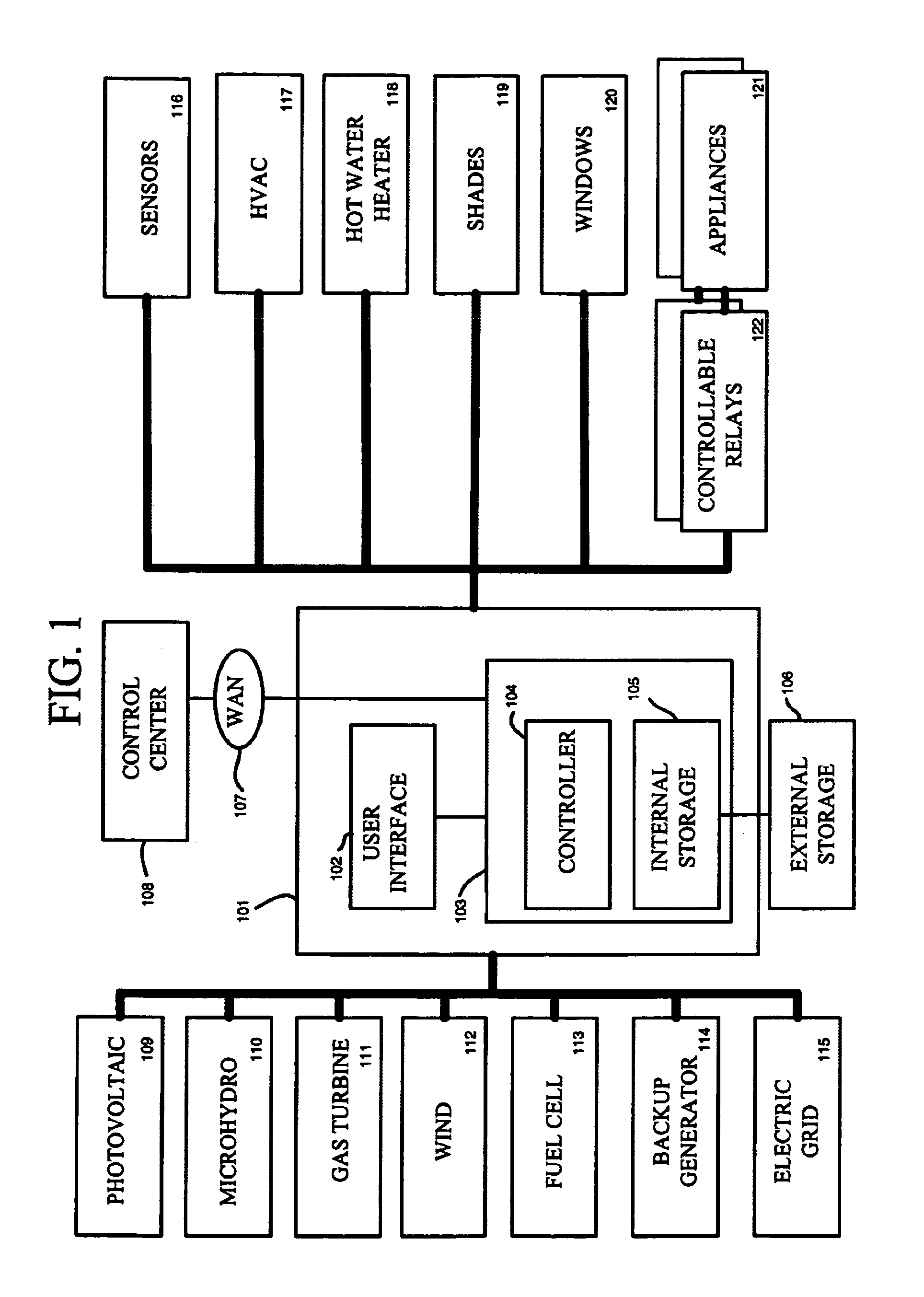

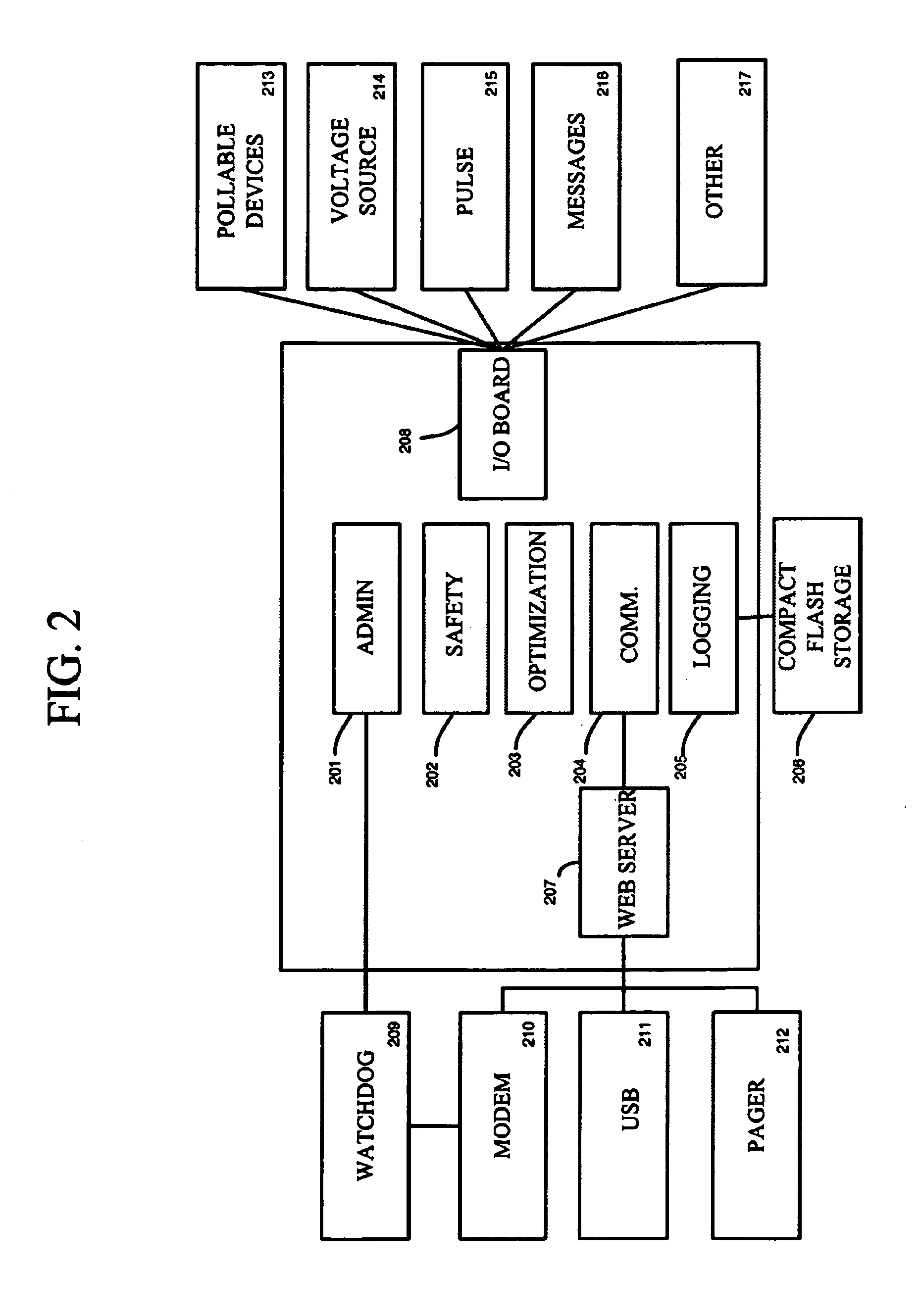

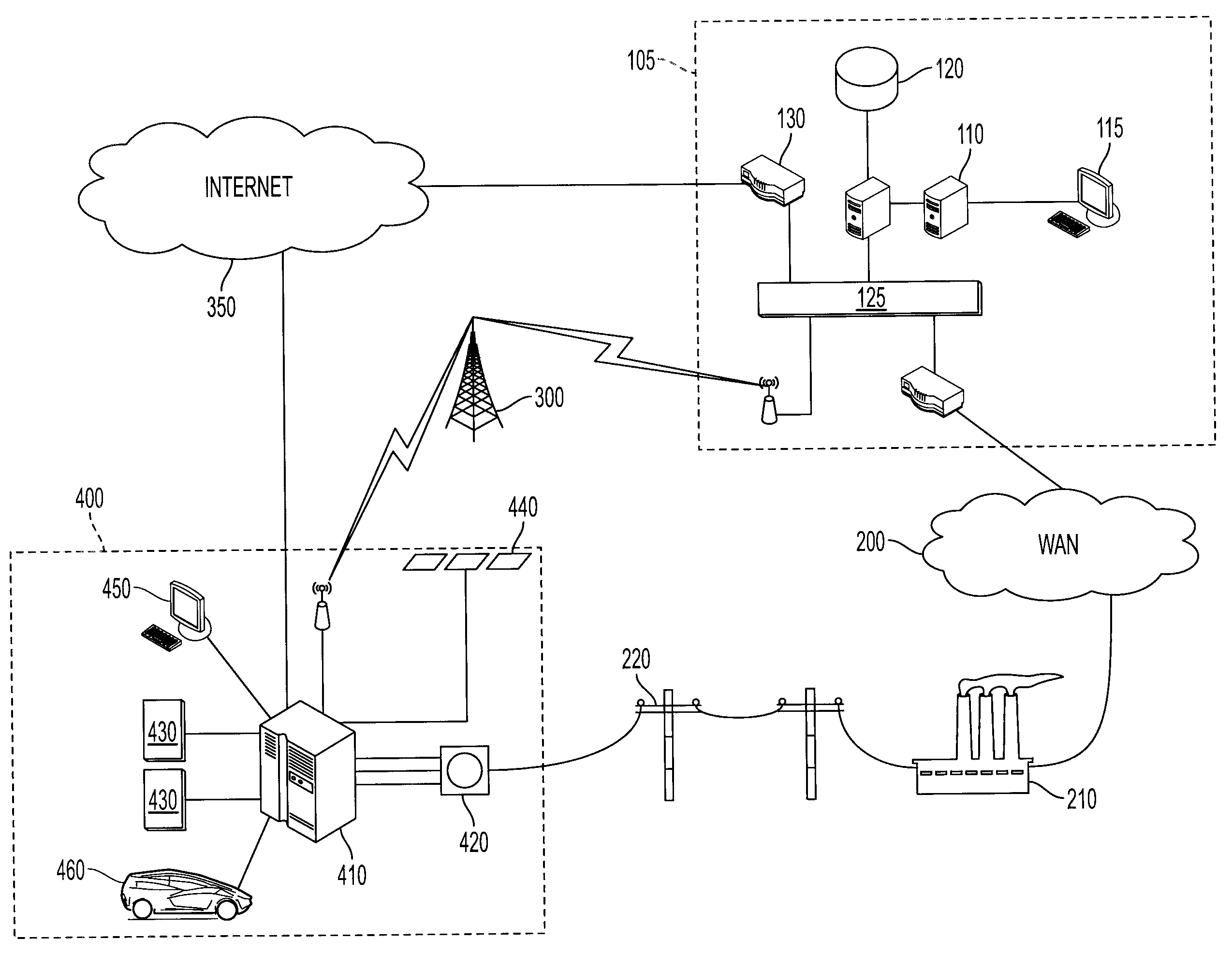

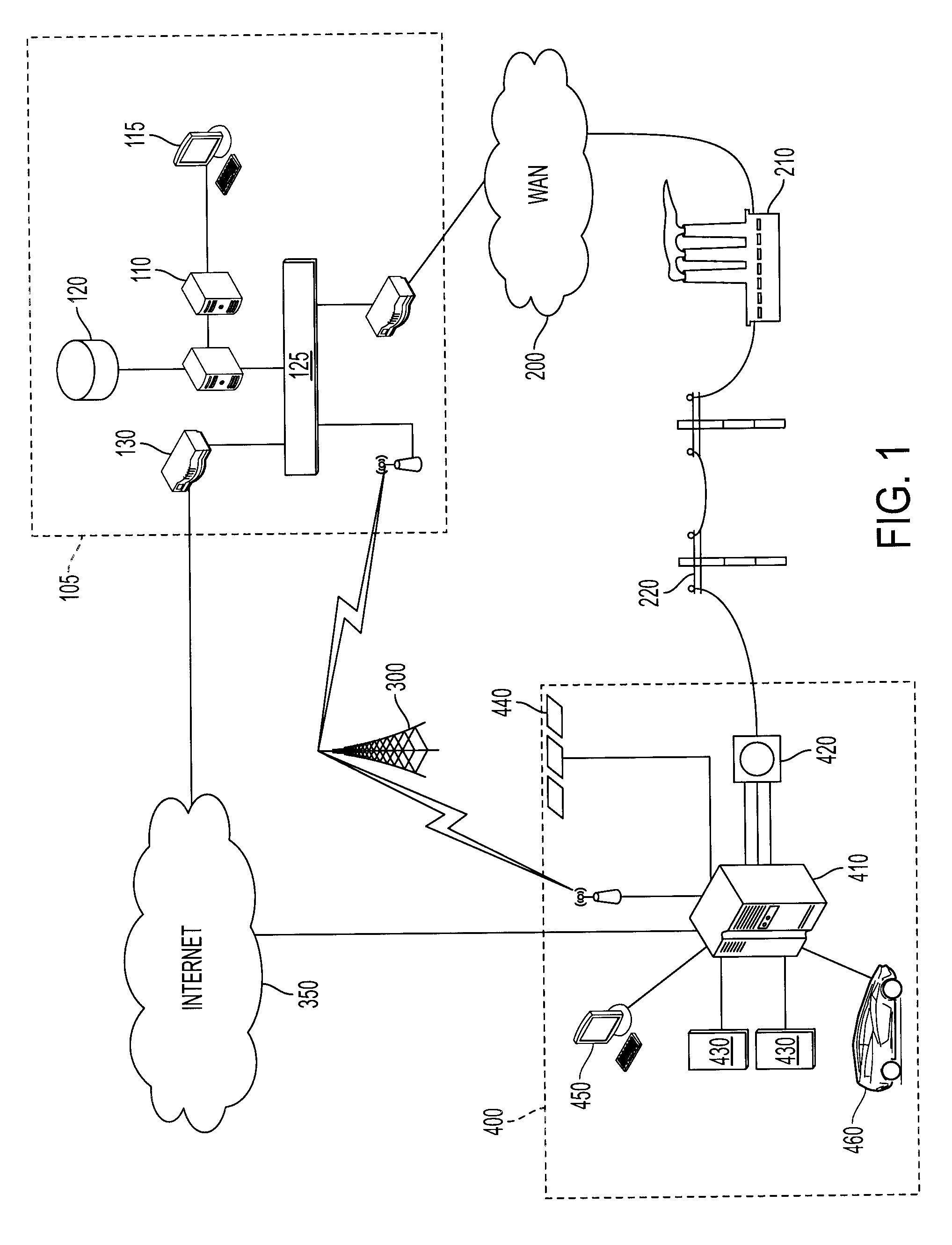

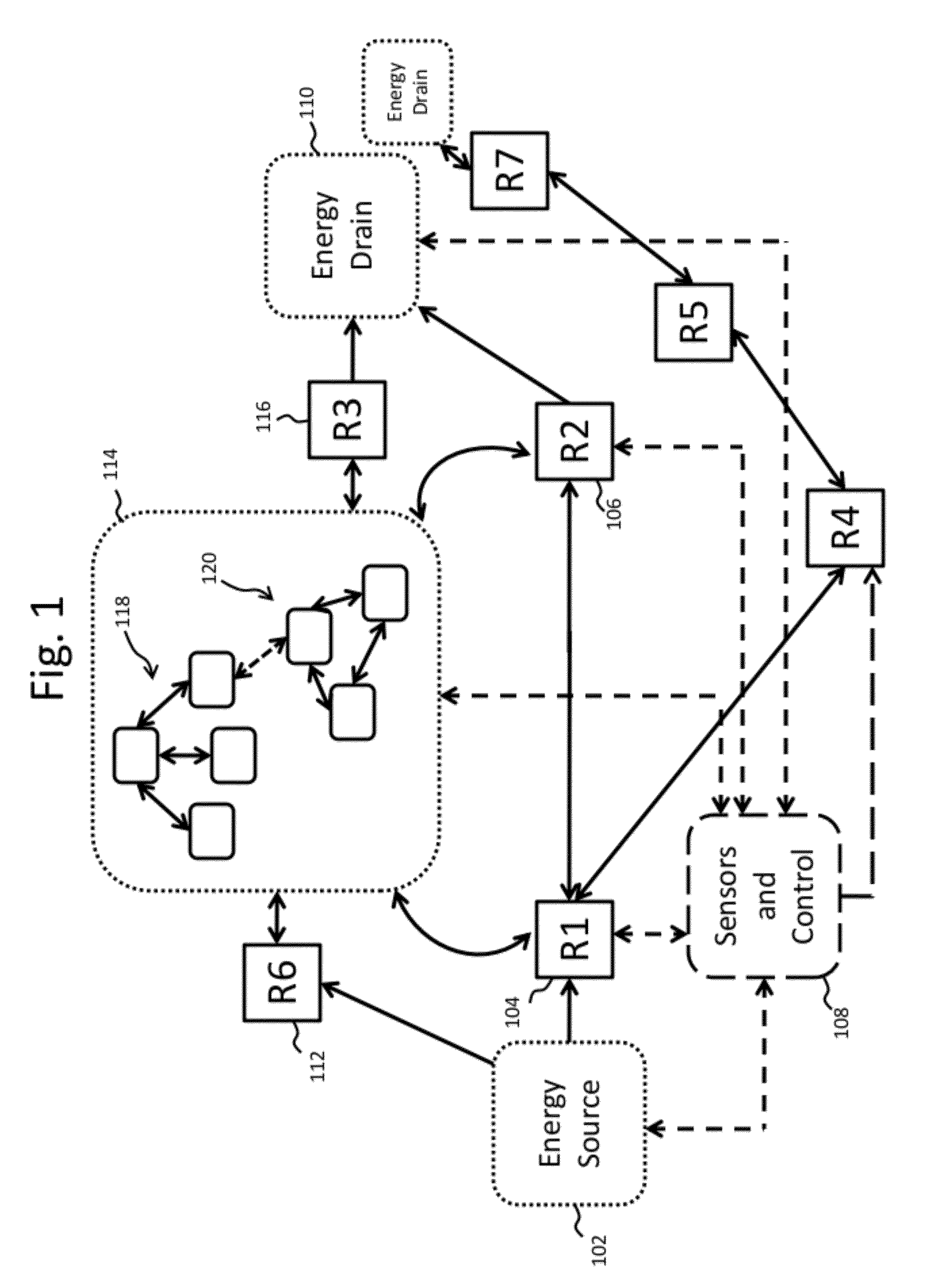

Optimized energy management system

Methods and systems are provided for optimizing the control of energy supply and demand. An energy control unit includes one or more algorithms for scheduling the control of energy consumption devices on the basis of variables relating to forecast energy supply and demand. Devices for which energy consumption can be scheduled or deferred are activated during periods of cheapest energy usage. Battery storage and alternative energy sources (e.g., photovoltaic cells) are activated to sell energy to the power grid during periods that are determined to correspond to favorable cost conditions.

Owner:GRIDPOINT

Optimized energy management system

Methods and systems are provided for optimizing the control of energy supply and demand. An energy control unit includes one or more algorithms for scheduling the control of energy consumption devices on the basis of variables relating to forecast energy supply and demand. Devices for which energy consumption can be scheduled or deferred are activated during periods of cheapest energy usage. Battery storage and alternative energy sources (e.g., photovoltaic cells) are activated to sell energy to the power grid during periods that are determined to correspond to favorable cost conditions.

Owner:GRIDPOINT

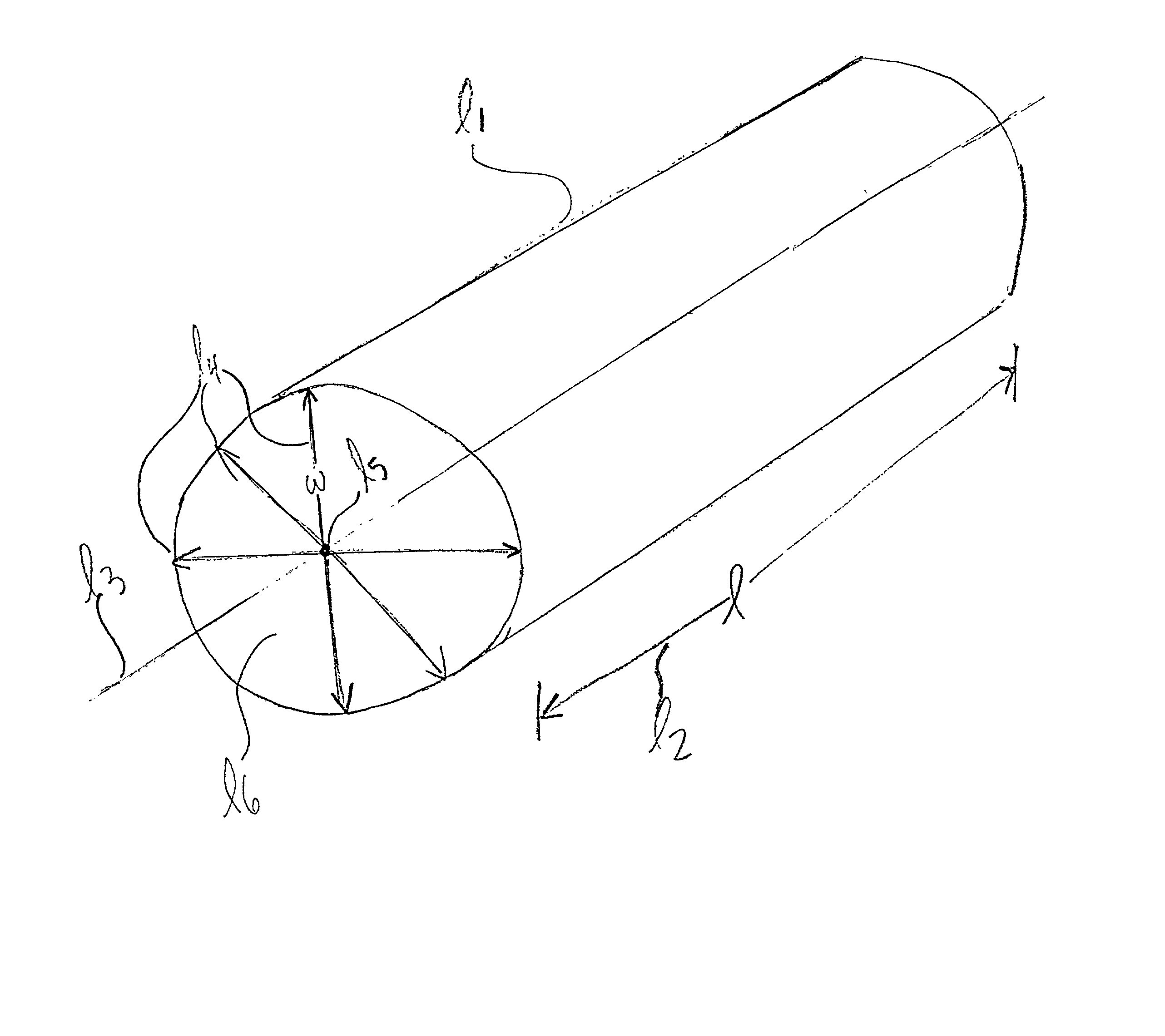

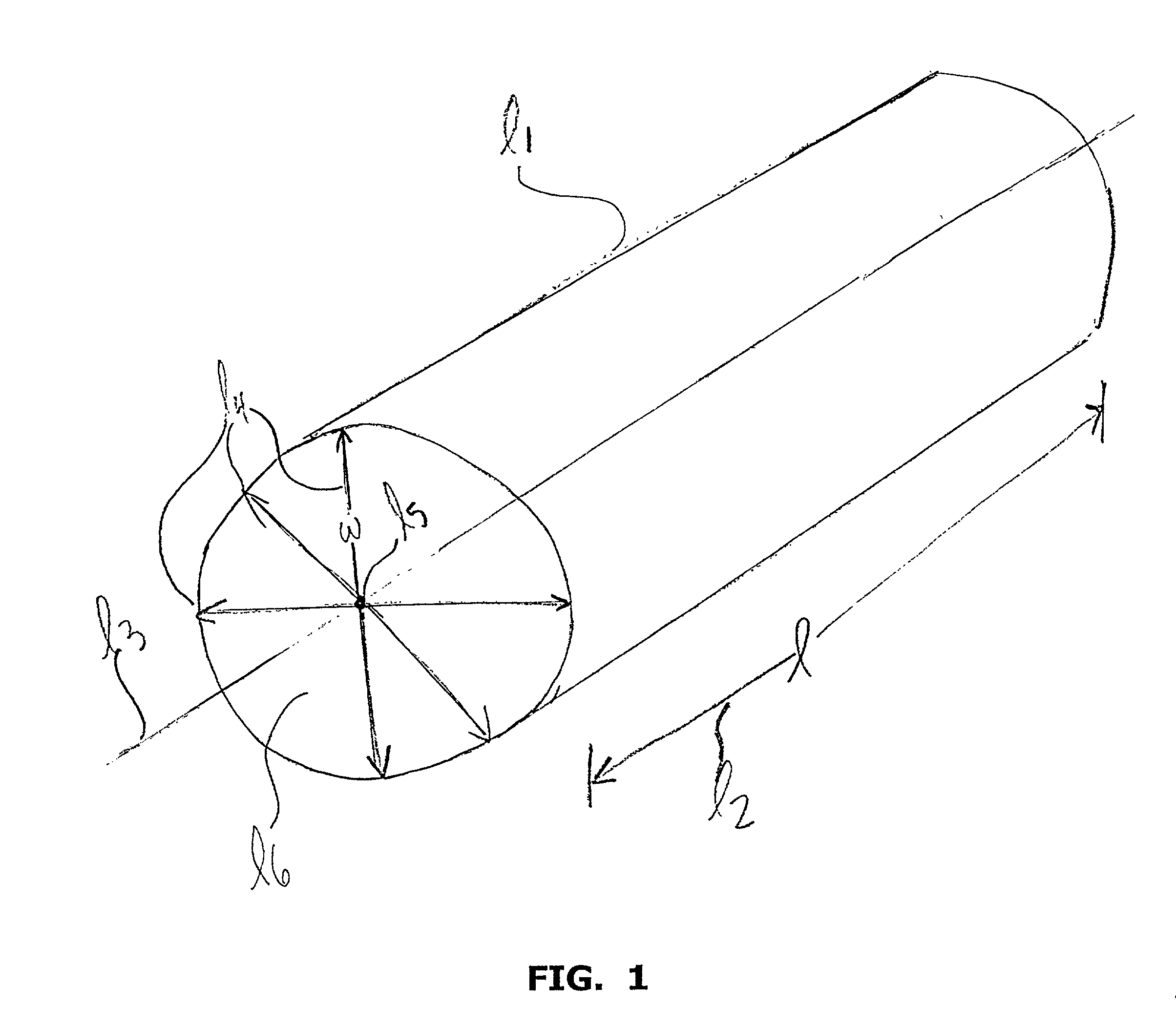

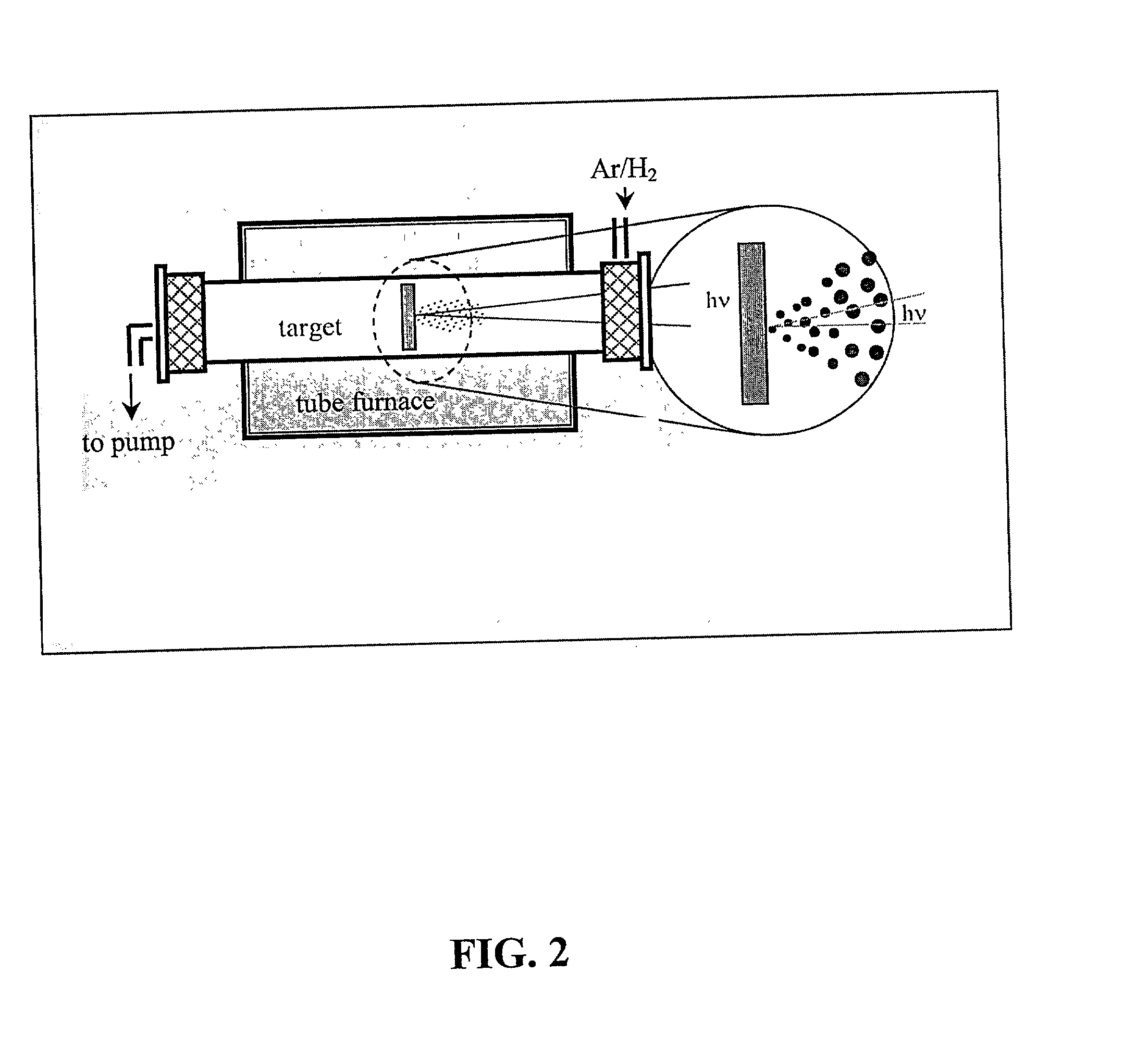

Doped elongated semiconductors, growing such semiconductors, devices including such semiconductors and fabricating such devices

A bulk-doped semiconductor that is at least one of the following: a single crystal, an elongated and bulk-doped semiconductor that, at any point along its longitudinal axis, has a largest cross-sectional dimension less than 500 nanometers, and a free-standing and bulk-doped semiconductor with at least one portion having a smallest width of less than 500 nanometers. Such a semiconductor may comprise an interior core comprising a first semiconductor; and an exterior shell comprising a different material than the first semiconductor. Such a semiconductor may be elongated and my have, at any point along a longitudinal section of such a semiconductor, a ratio of the length of the section to a longest width is greater than 4:1, or greater than 10:1, or greater than 100:1, or even greater than 1000:1. At least one portion of such a semiconductor may a smallest width of less than 200 nanometers, or less than 150 nanometers, or less than 100 nanometers, or less than 80 nanometers, or less than 70 nanometers, or less than 60 nanometers, or less than 40 nanometers, or less than 20 nanometers, or less than 10 nanometers, or even less than 5 nanometers. Such a semiconductor may be a single crystal and may be free-standing. Such a semiconductor may be either lightly n-doped, heavily n-doped, lightly p-doped or heavily p-doped. Such a semiconductor may be doped during growth. Such a semiconductor may be part of a device, which may include any of a variety of devices and combinations thereof, and, and a variety of assembling techniques may be used to fabricate devices from such a semiconductor. Two or more of such a semiconductors, including an array of such semiconductors, may be combined to form devices, for example, to form a crossed p-n junction of a device. Such devices at certain sizes may exhibit quantum confinement and other quantum phenomena, and the wavelength of light emitted from one or more of such semiconductors may be controlled by selecting a width of such semiconductors. Such semiconductors and device made therefrom may be used for a variety of applications.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

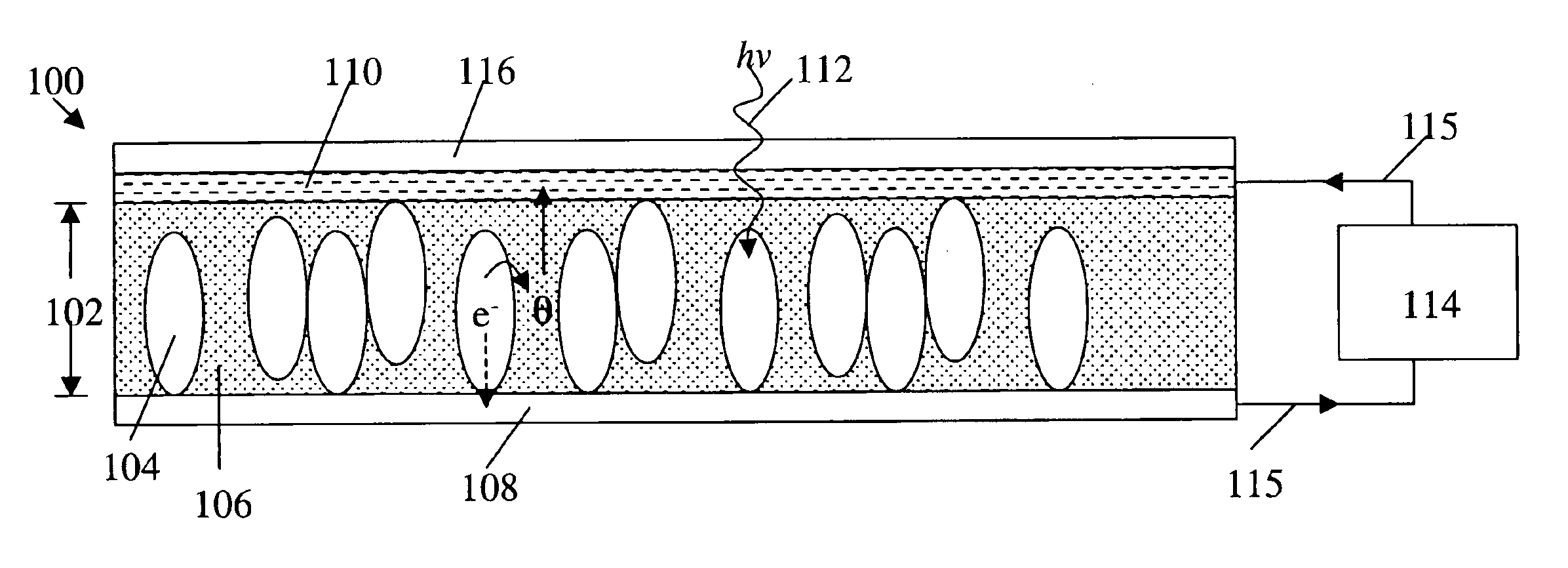

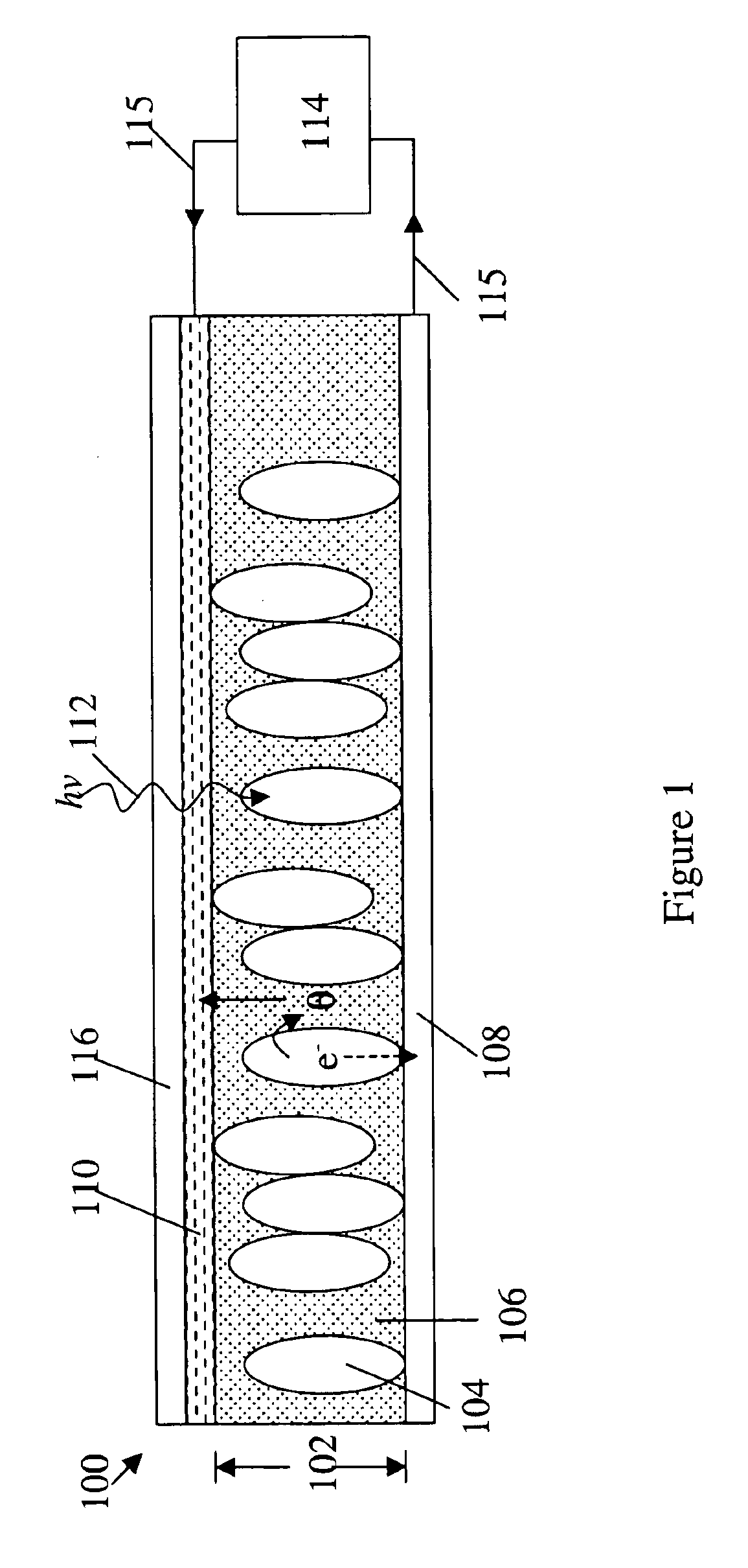

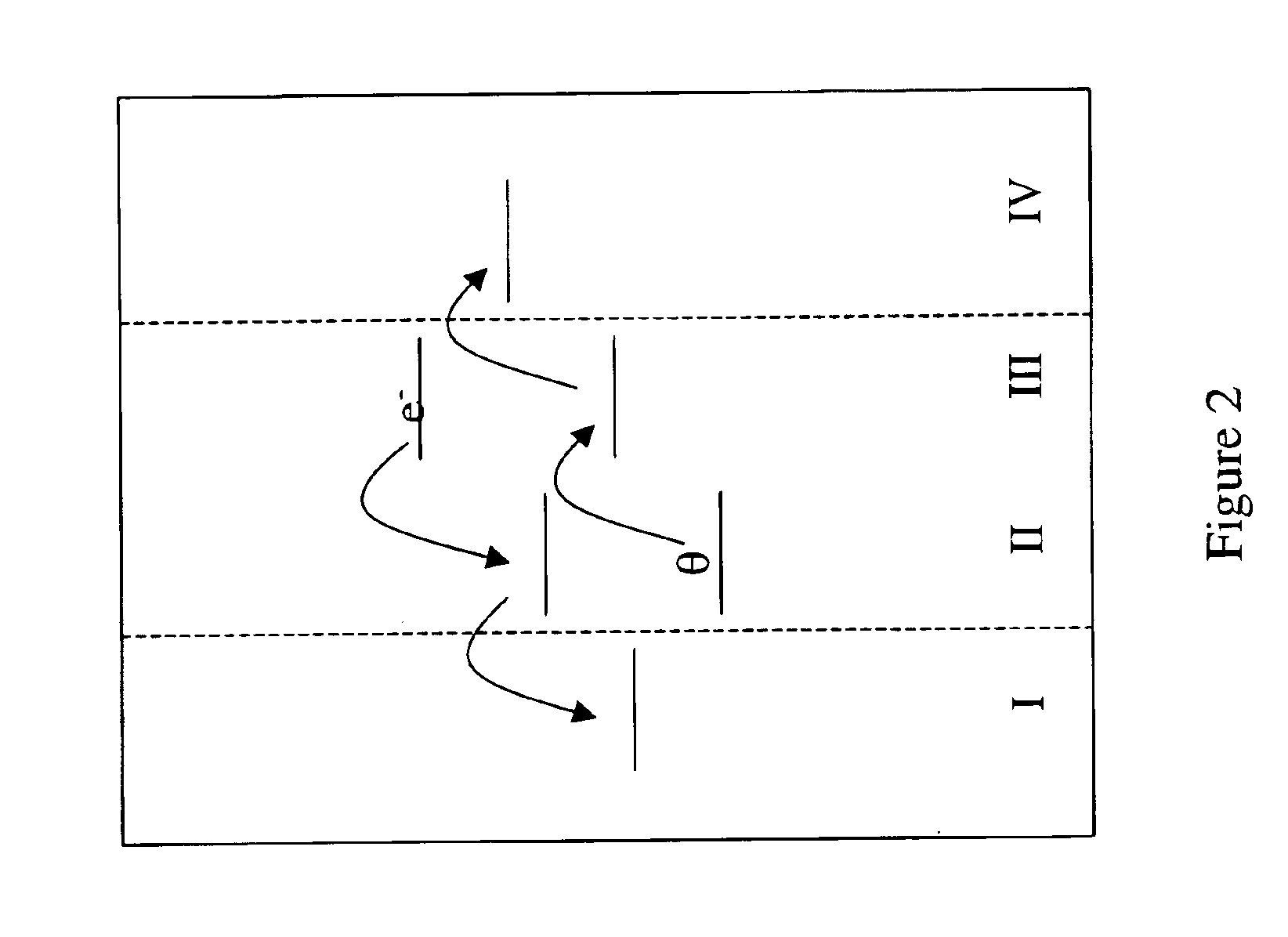

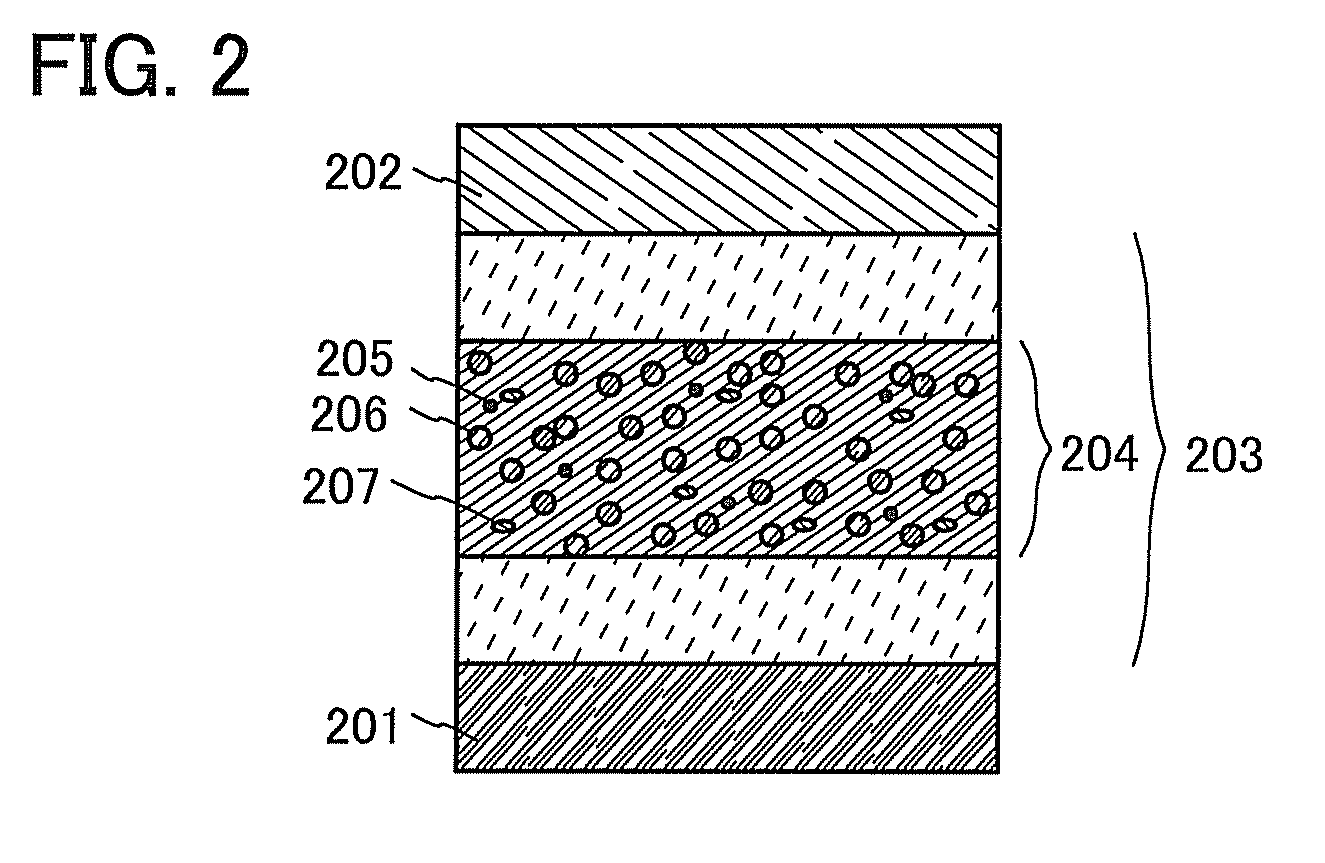

Nanostructure and nanocomposite based compositions and photovoltaic devices

InactiveUS6878871B2Improve equipment efficiencyMaterial nanotechnologyFinal product manufactureSemiconductor nanocrystalsNanostructure

Nanocomposite photovoltaic devices are provided that generally include semiconductor nanocrystals as at least a portion of a photoactive layer. Photovoltaic devices and other layered devices that comprise core-shell nanostructures and / or two populations of nanostructures, where the nanostructures are not necessarily part of a nanocomposite, are also features of the invention. Varied architectures for such devices are also provided including flexible and rigid architectures, planar and non-planar architectures and the like, as are systems incorporating such devices, and methods and systems for fabricating such devices. Compositions comprising two populations of nanostructures of different materials are also a feature of the invention.

Owner:NANOSYS INC

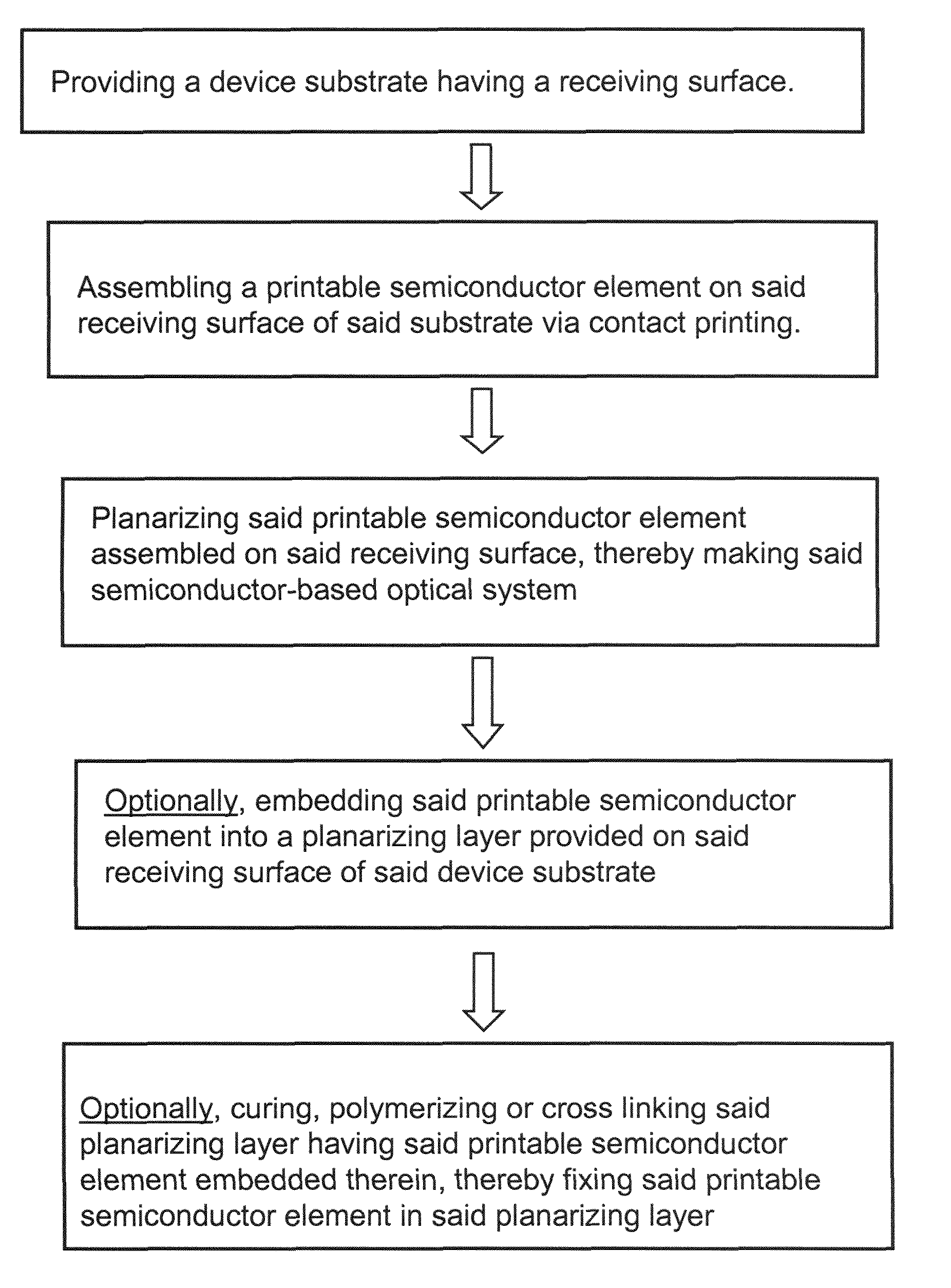

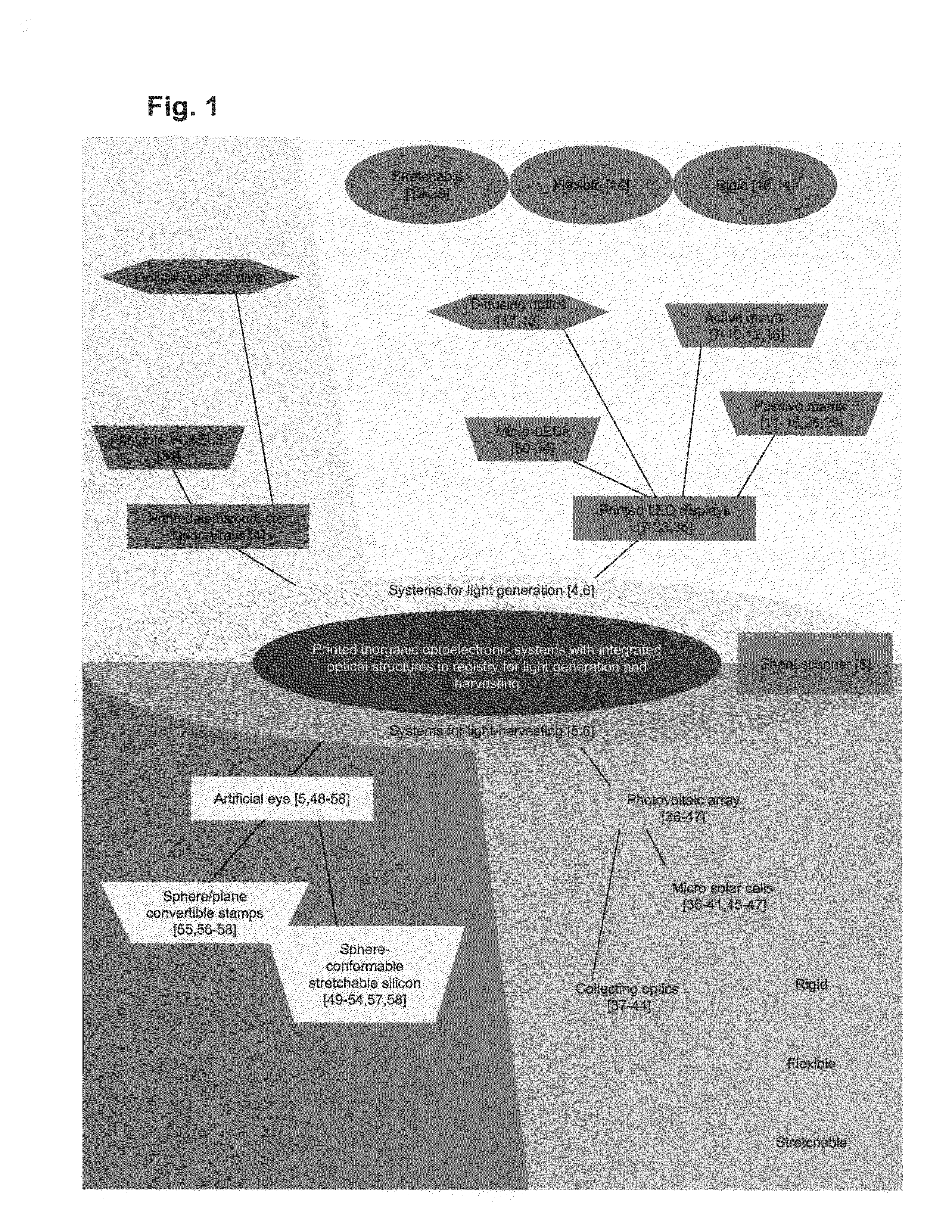

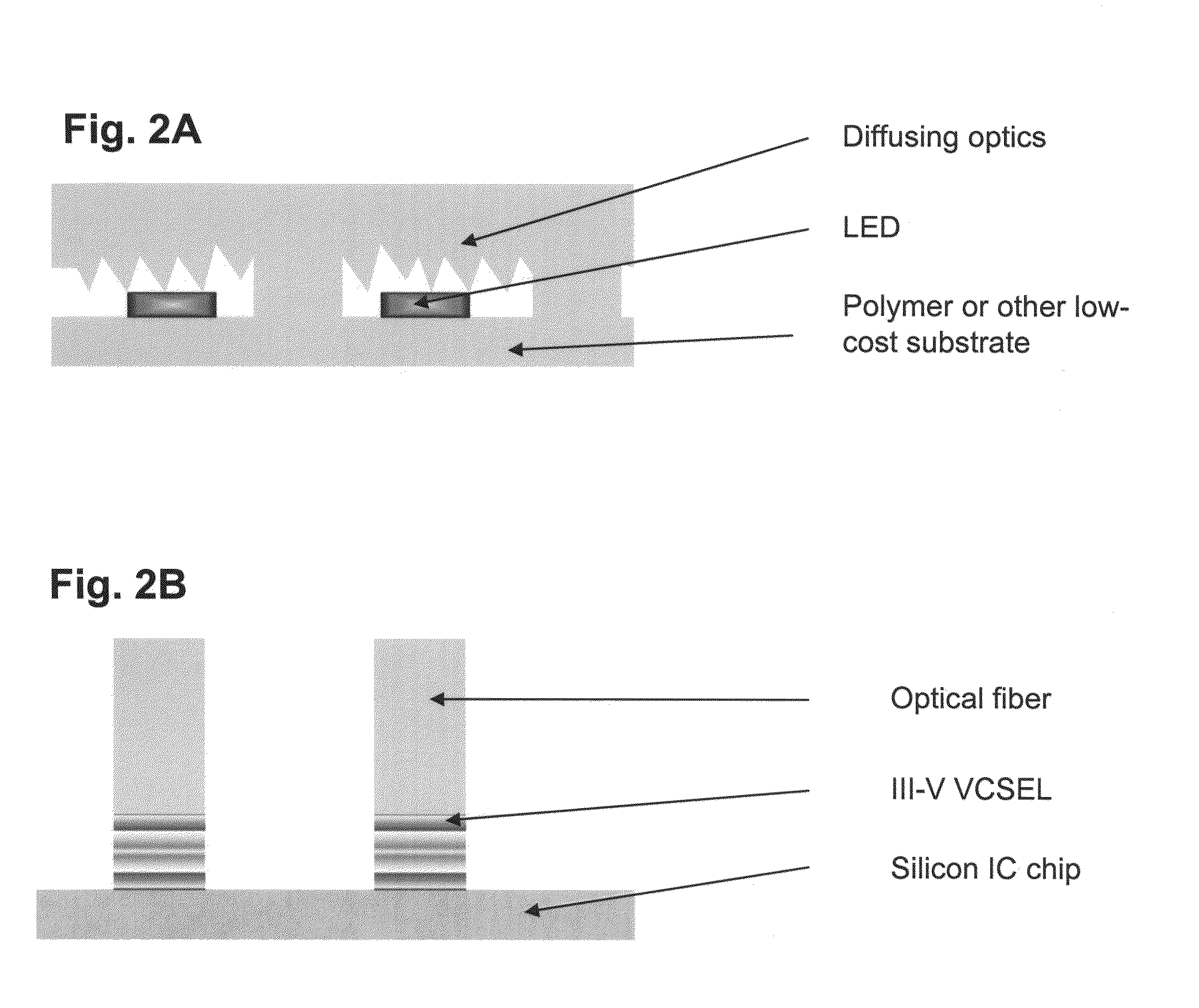

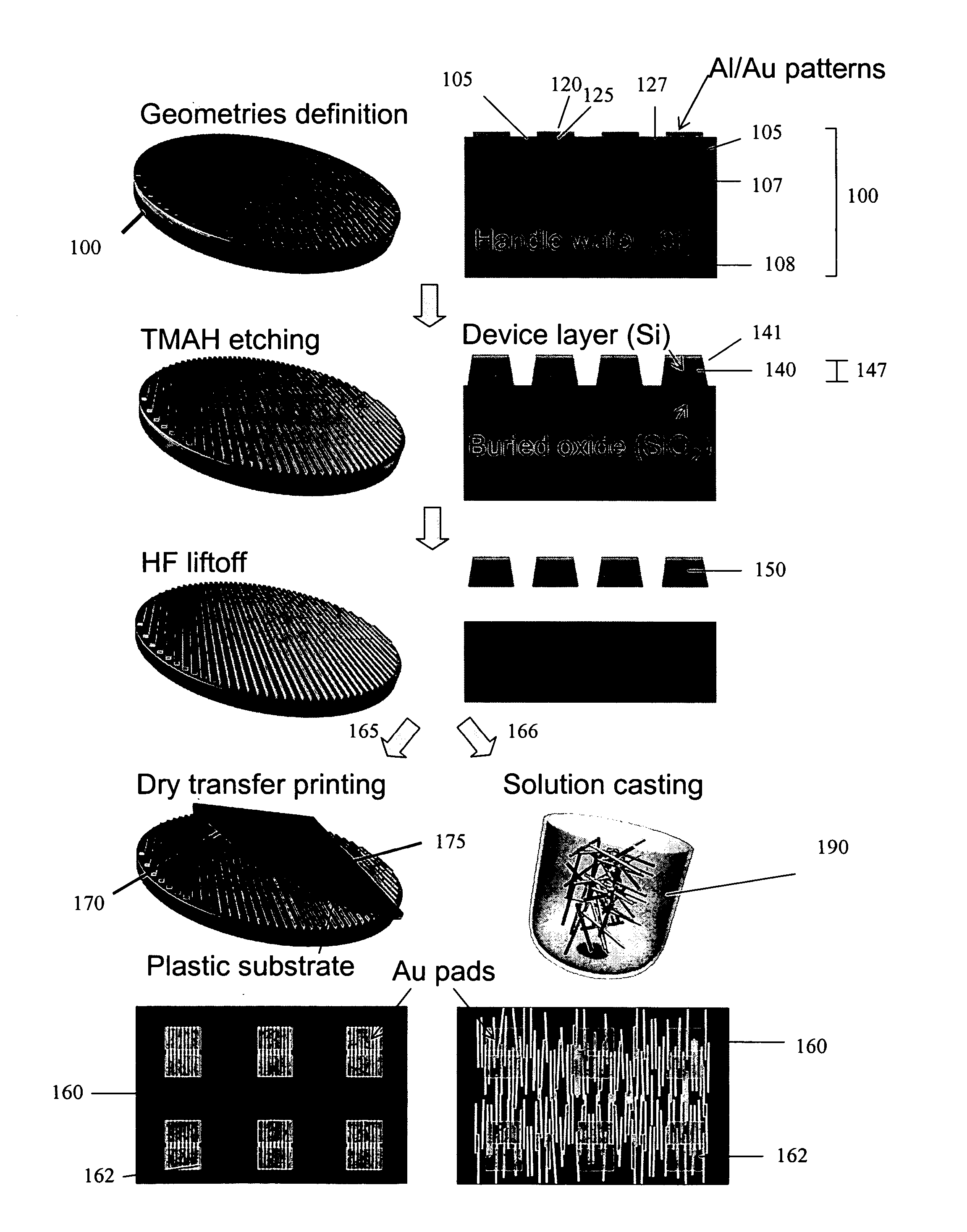

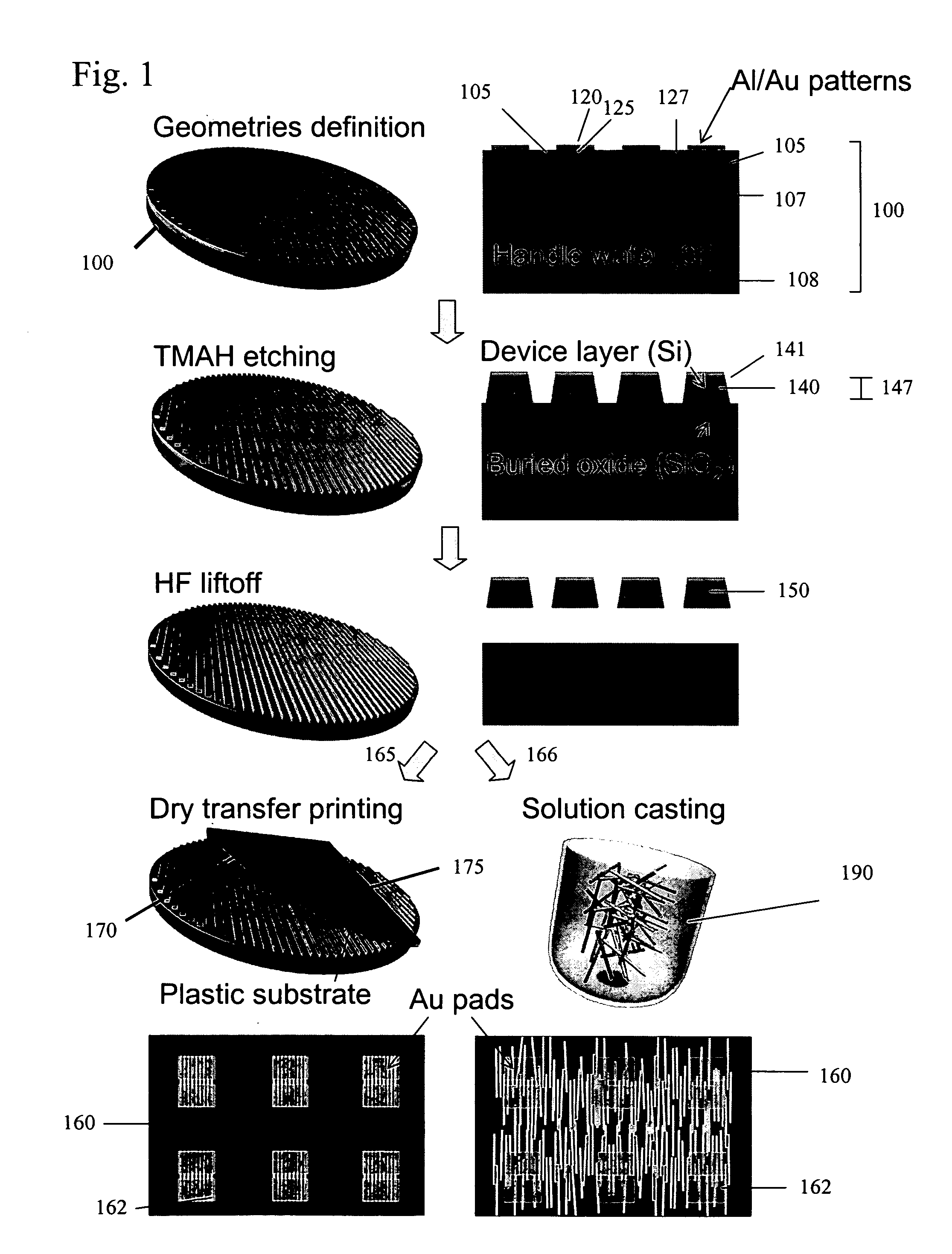

Optical systems fabricated by printing-based assembly

ActiveUS7972875B2Low costImprove performanceFinal product manufactureNanoinformaticsLight sensingSingle crystal

Provided are optical devices and systems fabricated, at least in part, via printing-based assembly and integration of device components. In specific embodiments the present invention provides light emitting systems, light collecting systems, light sensing systems and photovoltaic systems comprising printable semiconductor elements, including large area, high performance macroelectronic devices. Optical systems of the present invention comprise semiconductor elements assembled, organized and / or integrated with other device components via printing techniques that exhibit performance characteristics and functionality comparable to single crystalline semiconductor based devices fabricated using conventional high temperature processing methods. Optical systems of the present invention have device geometries and configurations, such as form factors, component densities, and component positions, accessed by printing that provide a range of useful device functionalities. Optical systems of the present invention include devices and device arrays exhibiting a range of useful physical and mechanical properties including flexibility, shapeability, conformability and stretchablity.

Owner:X DISPLAY CO TECH LTD +1

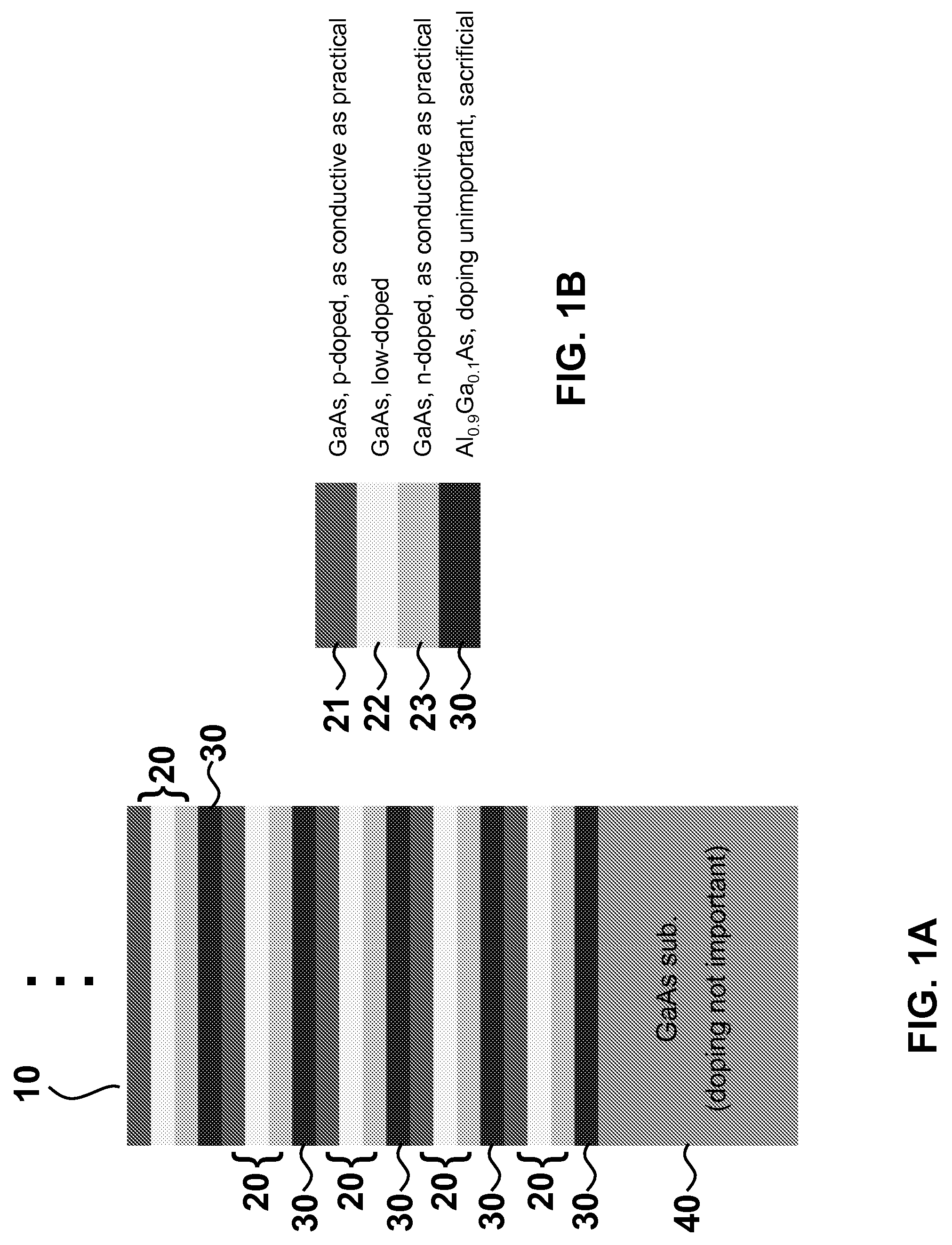

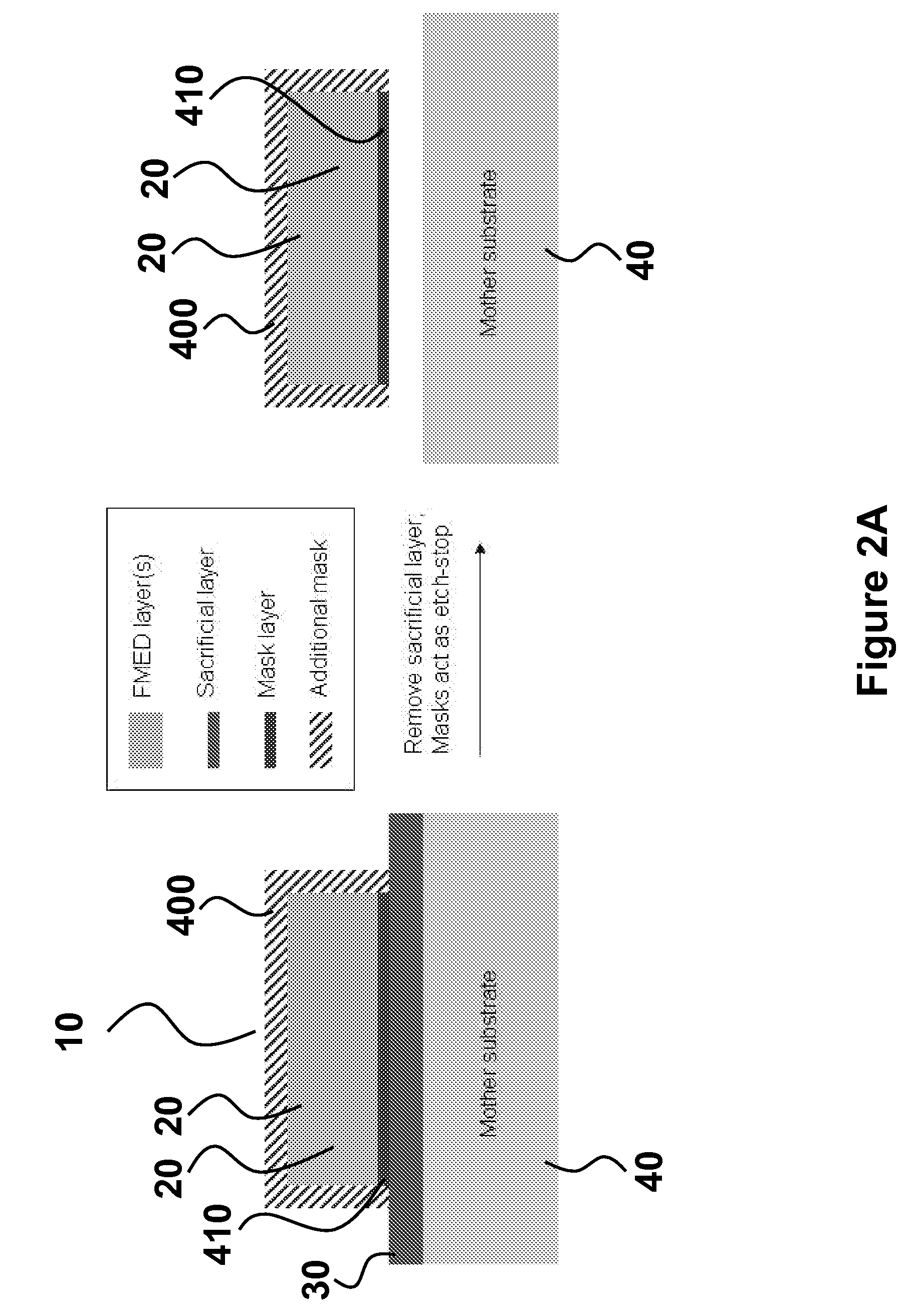

Method of fabricating epitaxial structures

ActiveUS8455290B2Reduce in quantitySimple and direct removalFinal product manufactureSemiconductor/solid-state device manufacturingOptoelectronicsPhysics

Owner:JPMORGAN CHASE BANK NA +1

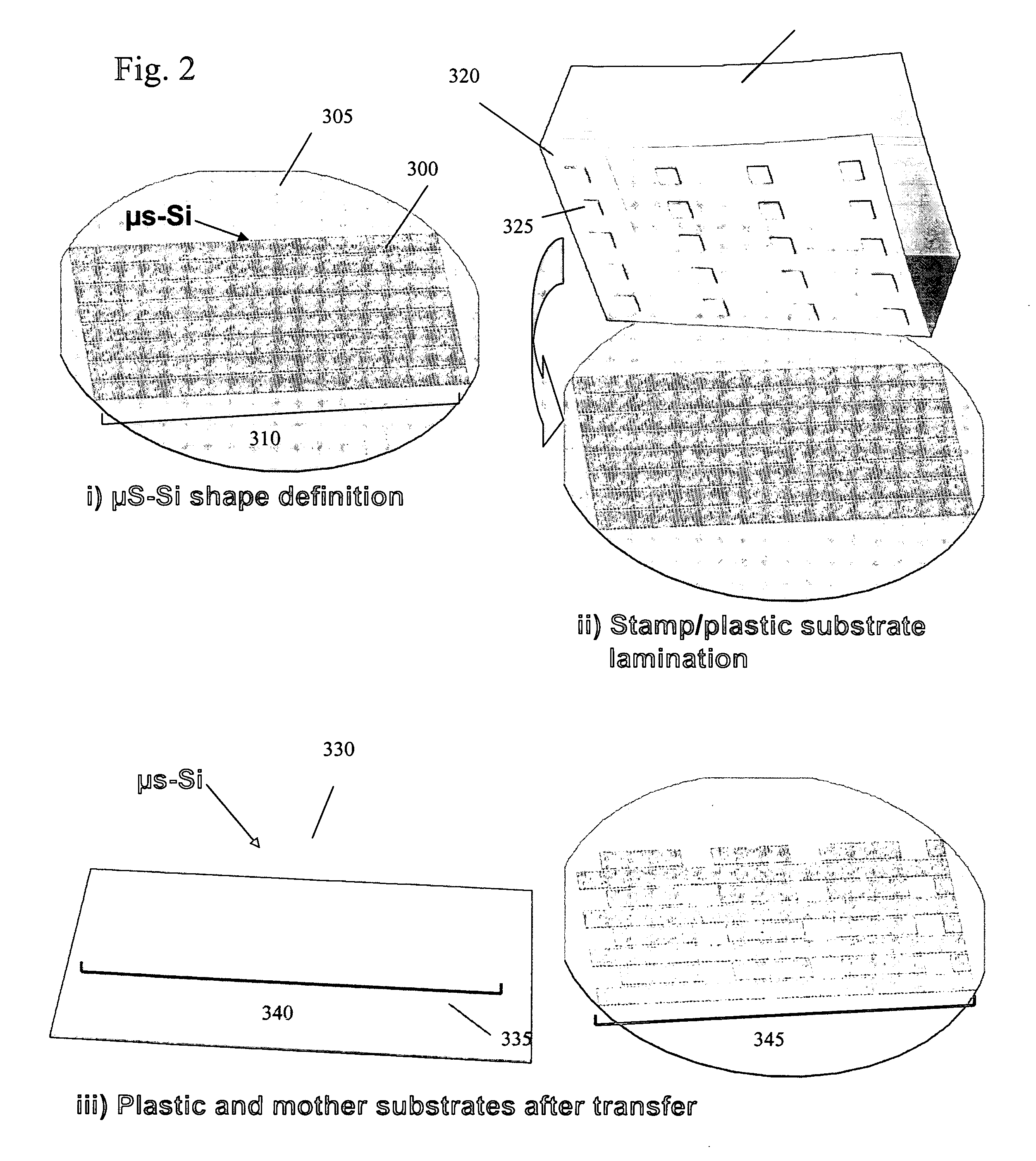

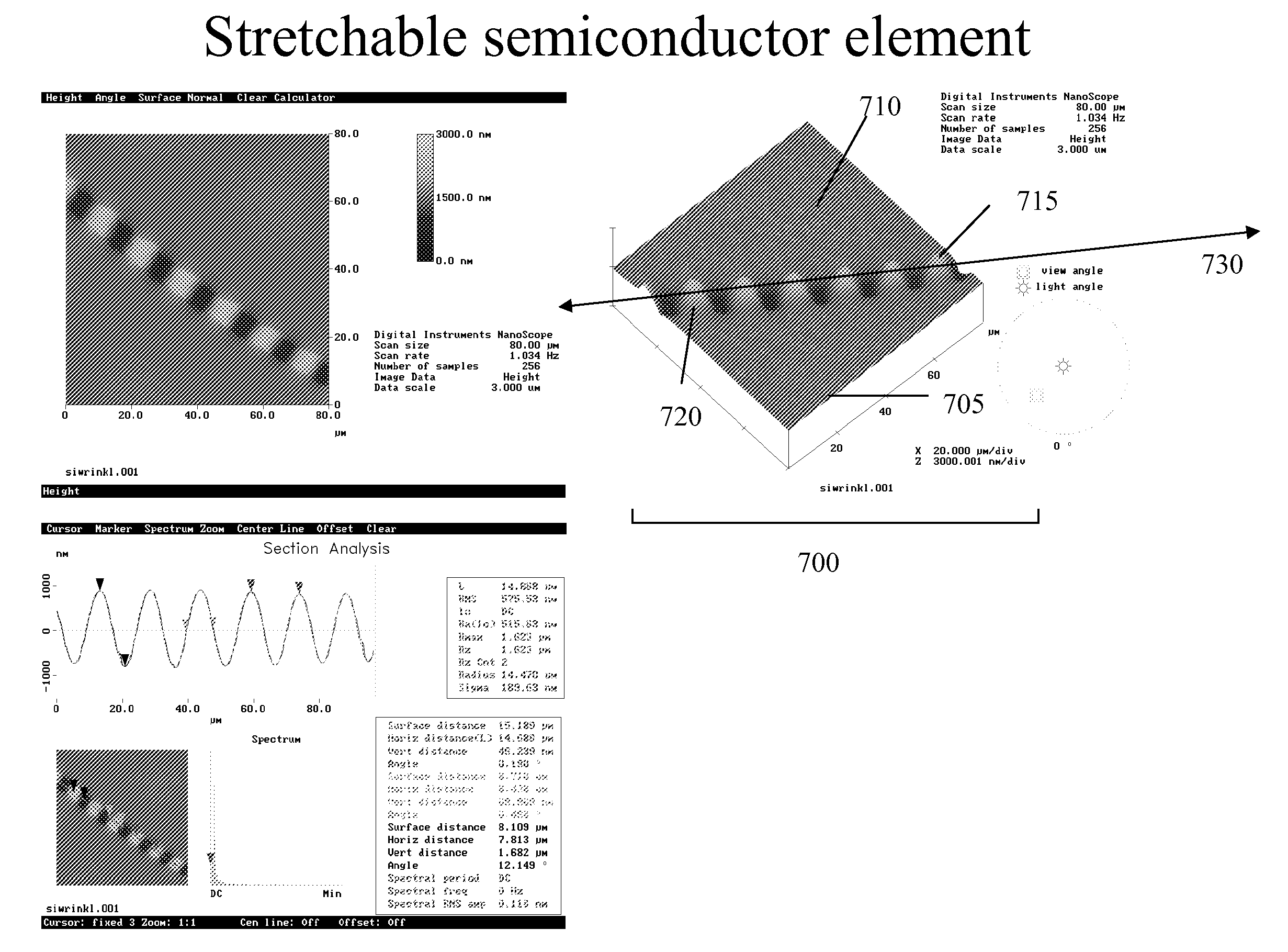

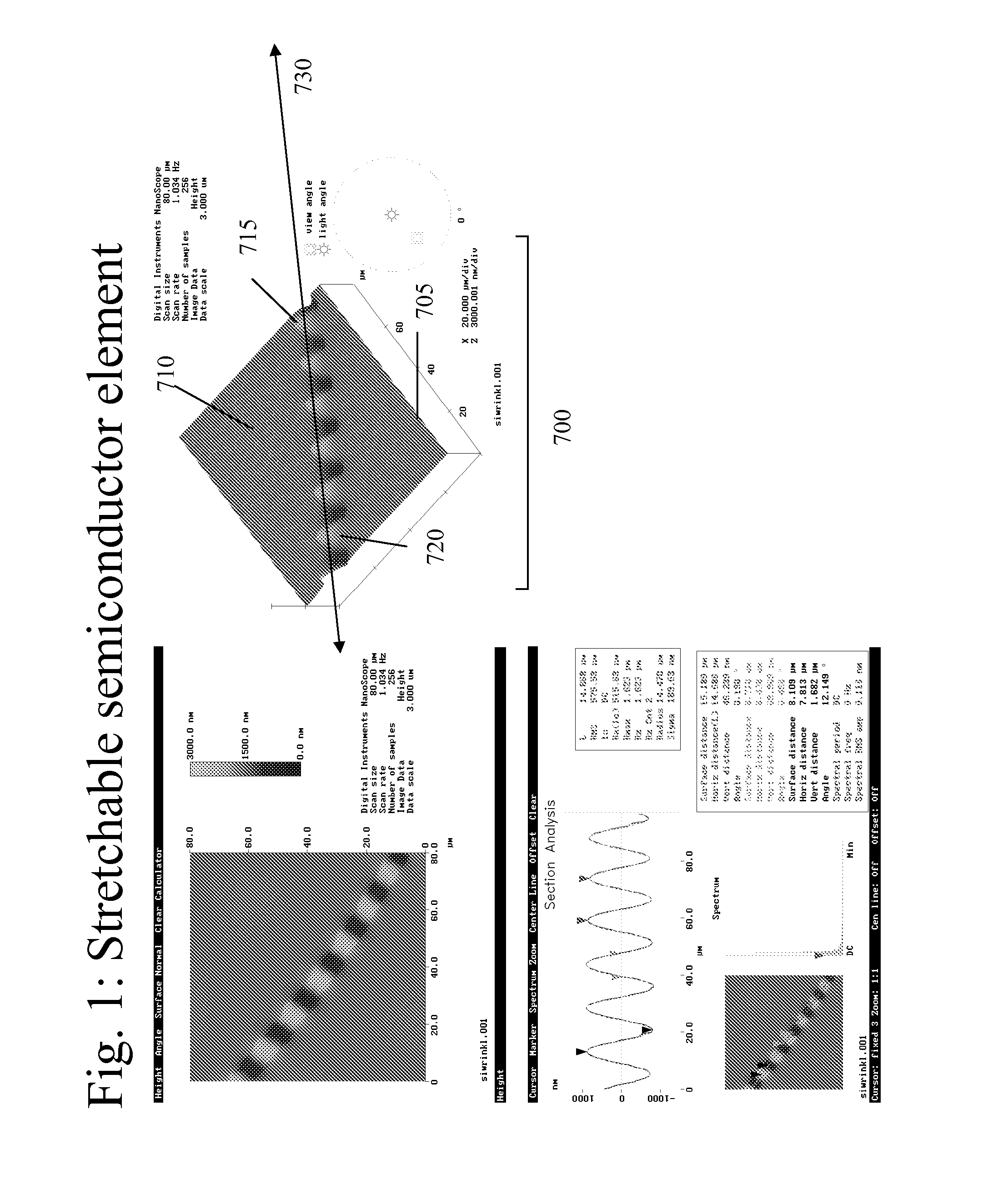

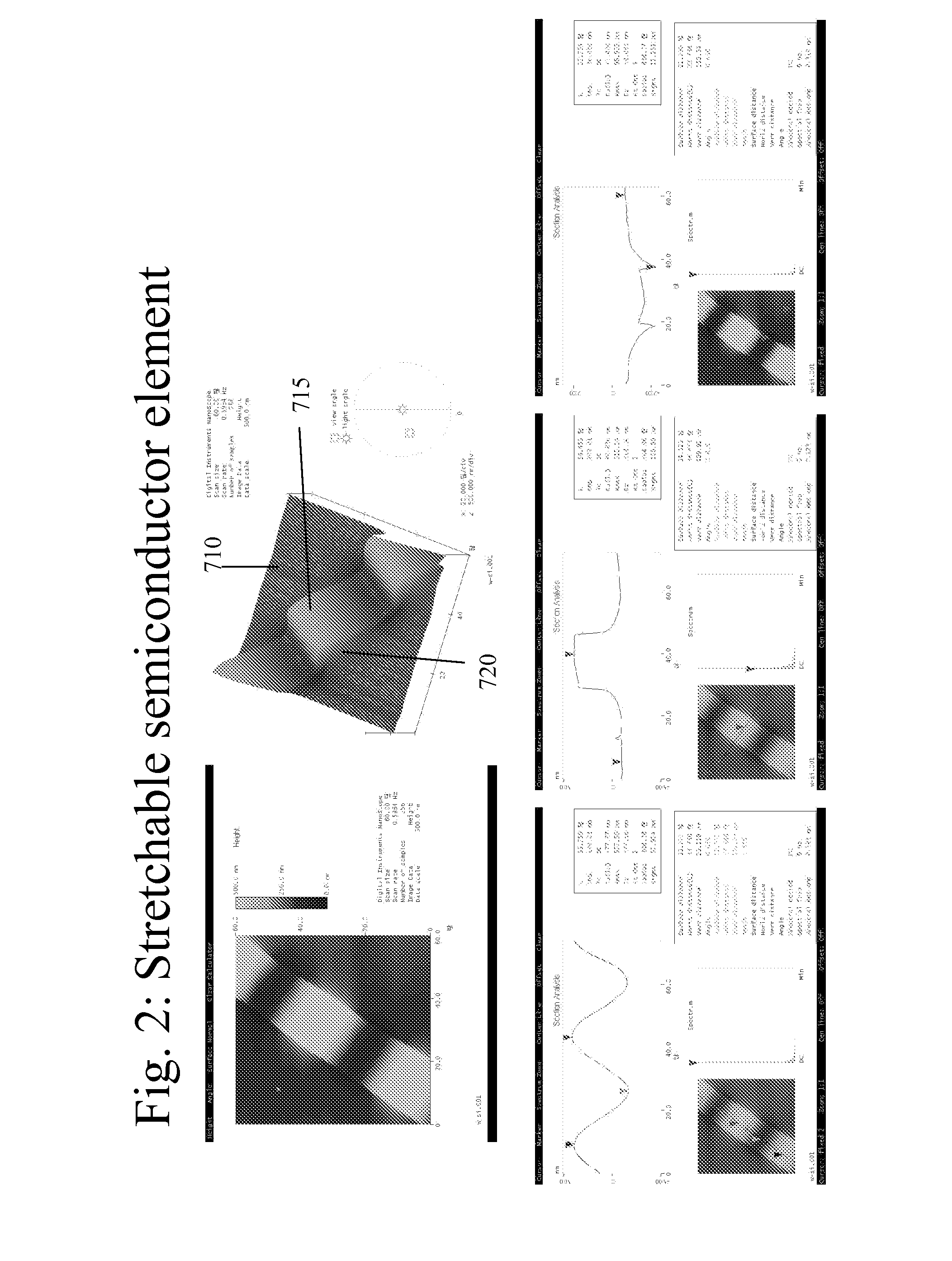

Stretchable semiconductor elements and stretchable electrical circuits

ActiveUS20060038182A1Complete release is preventedLow costTransistorDecorative surface effectsStretchable electronicsSemiconductor structure

The invention provides methods and devices for fabricating printable semiconductor elements and assembling printable semiconductor elements onto substrate surfaces. Methods, devices and device components of the present invention are capable of generating a wide range of flexible electronic and optoelectronic devices and arrays of devices on substrates comprising polymeric materials. The present invention also provides stretchable semiconductor structures and stretchable electronic devices capable of good performance in stretched configurations.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

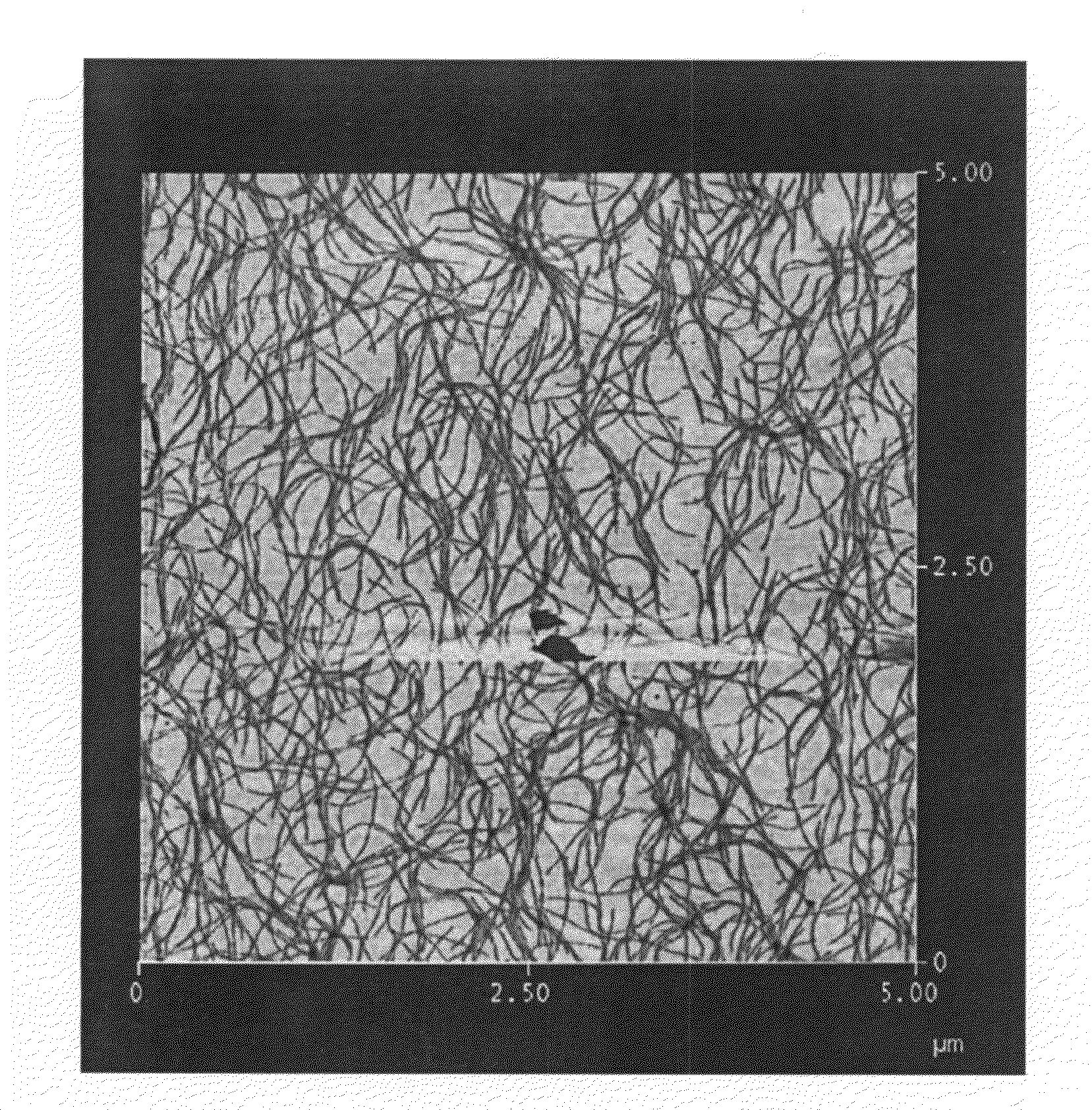

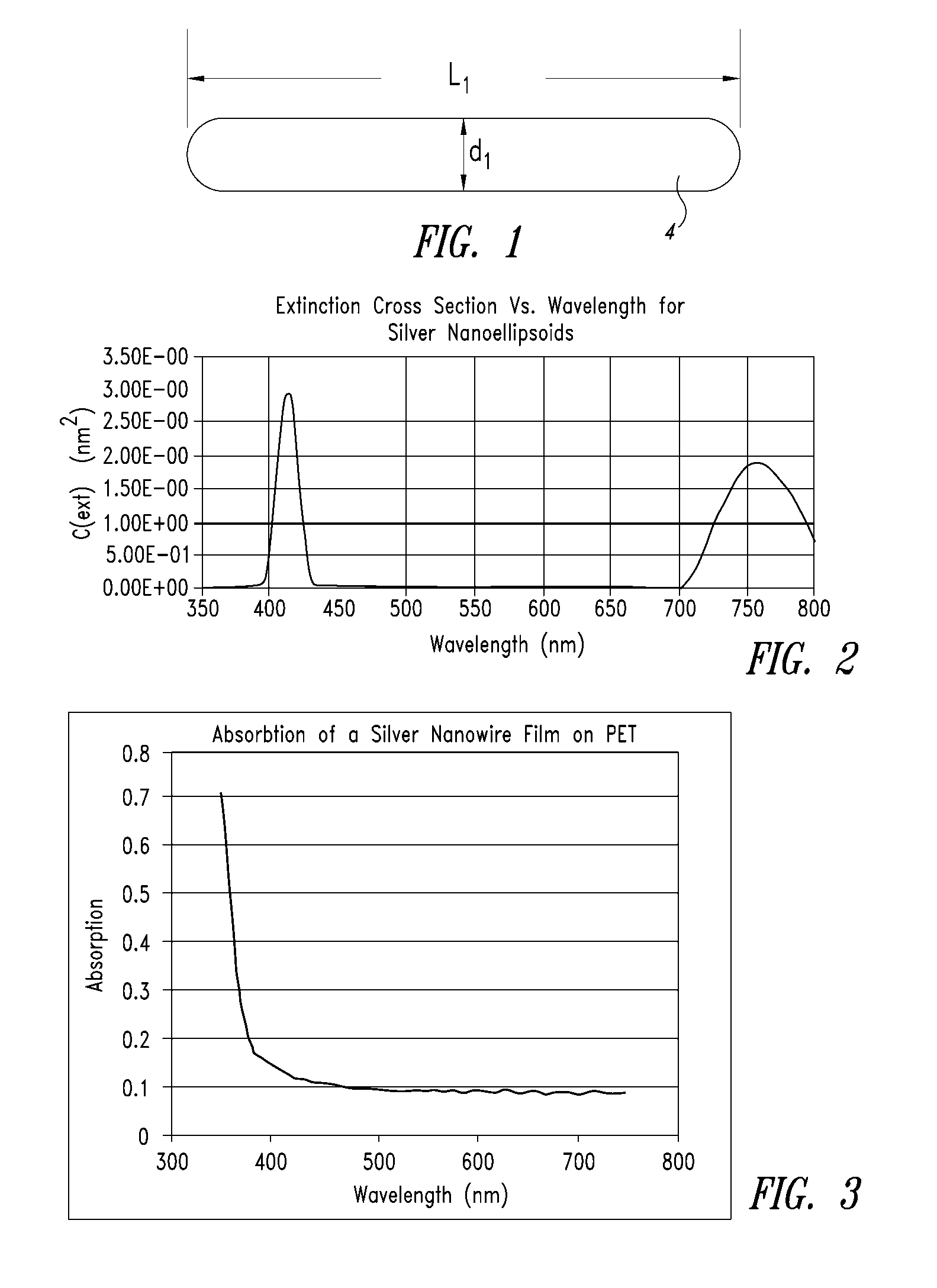

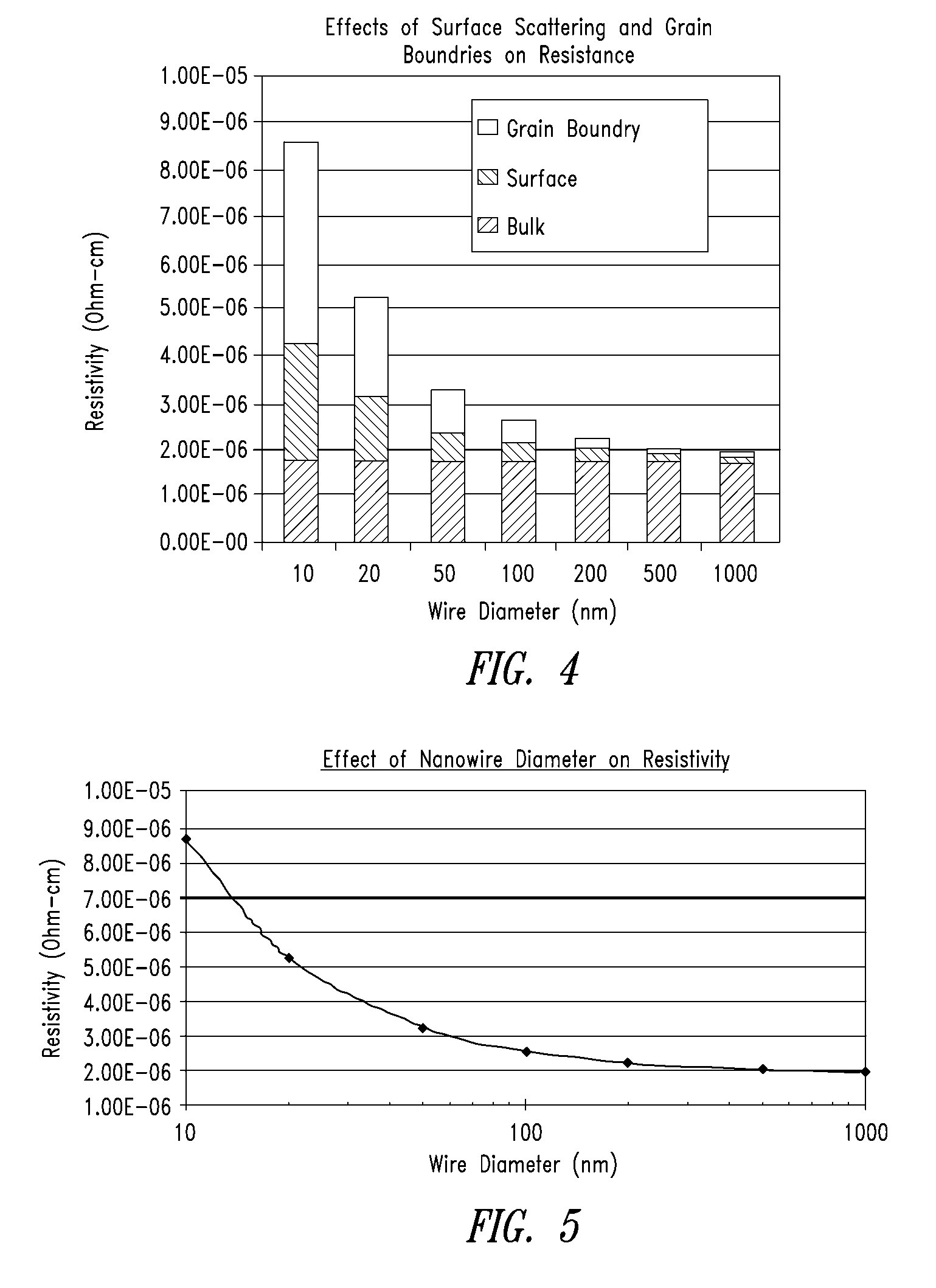

Nanowire-based transparent conductors and applications thereof

A transparent conductor including a conductive layer coated on a substrate is described. More specifically, the conductive layer comprises a network of nanowires that may be embedded in a matrix. The conductive layer is optically clear, patternable and is suitable as a transparent electrode in visual display devices such as touch screens, liquid crystal displays, plasma display panels and the like.

Owner:CHAMP GREAT INTL

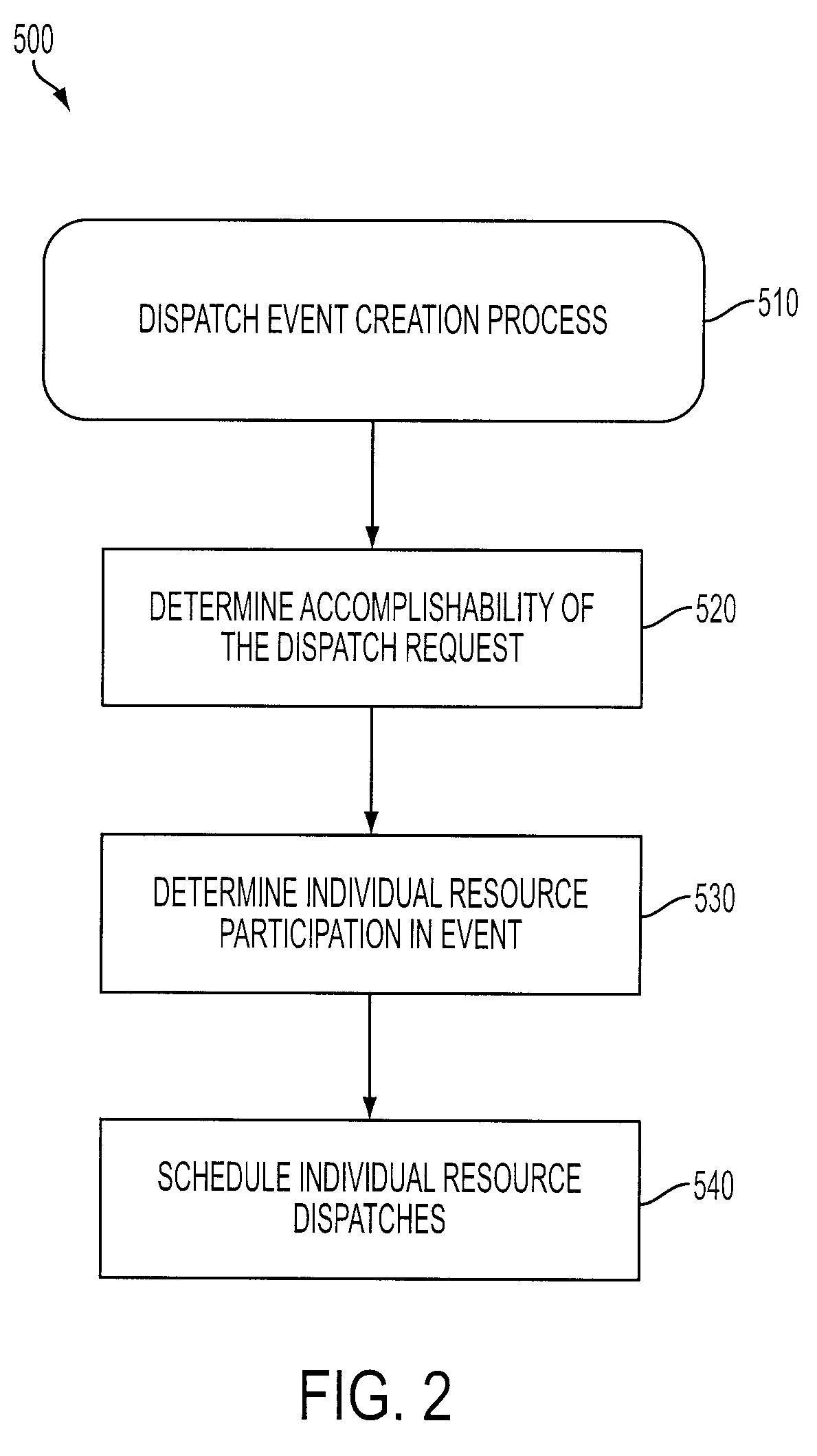

Method and system for scheduling the discharge of distributed power storage devices and for levelizing dispatch participation

Disclosed is a computerized method for dispatching energy from distributed resources in a discharge event so that the energy stored in individual devices is levelized, or so that an operator request is met. Evaluation of event parameters may be deferred. The method may be utilized to dispatch energy from plug-in electric vehicles. Systems and methods to account for electricity dispatched to or from electric vehicles are disclosed. Systems and methods for incentivizing consumers to participate in a dispatch event or curtail energy use are disclosed.

Owner:GRIDPOINT

Stretchable form of single crystal silicon for high performance electronics on rubber substrates

ActiveUS7521292B2Large elongationSignificant flexingTransistorCircuit bendability/stretchabilityEngineeringFlexible electronics

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

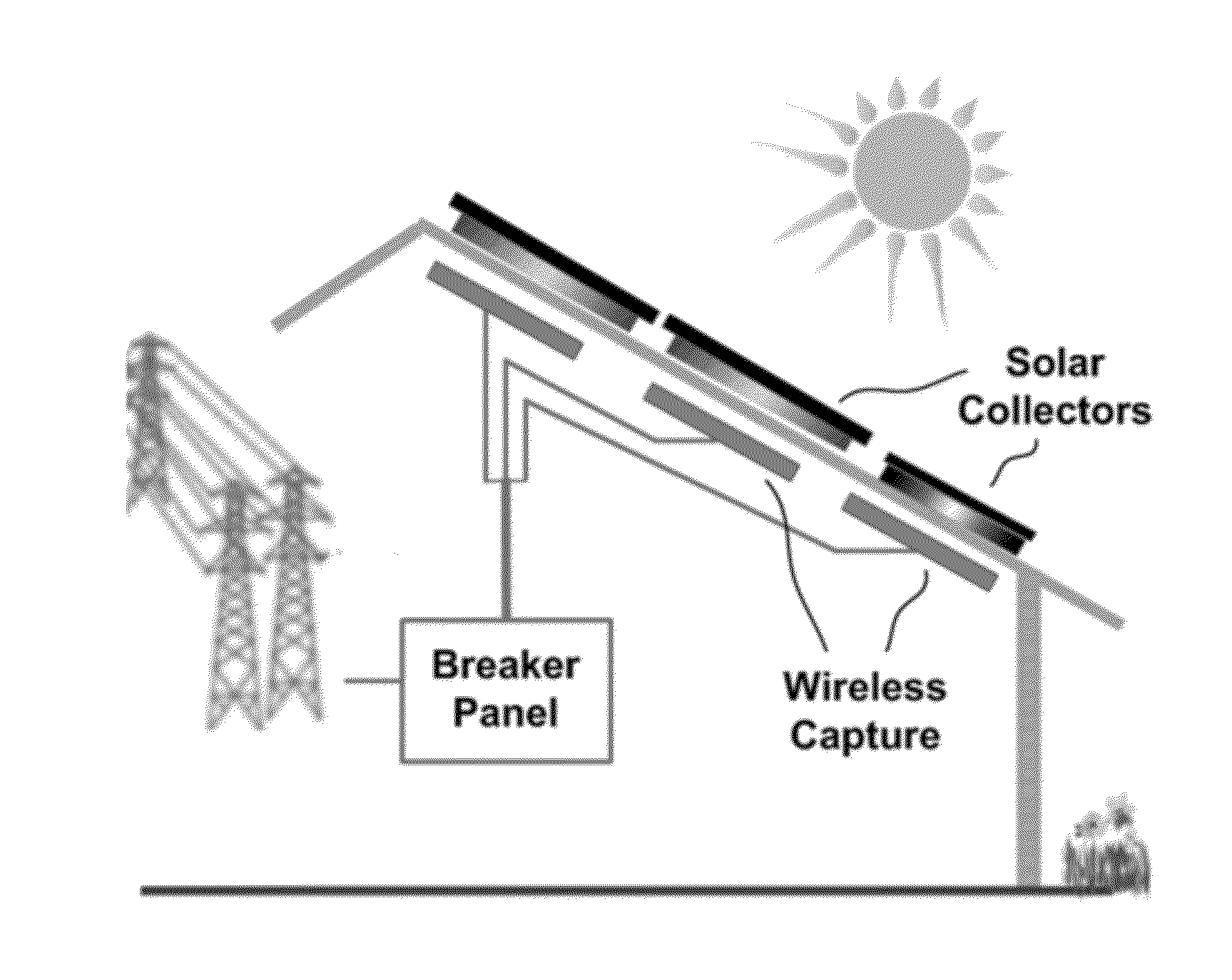

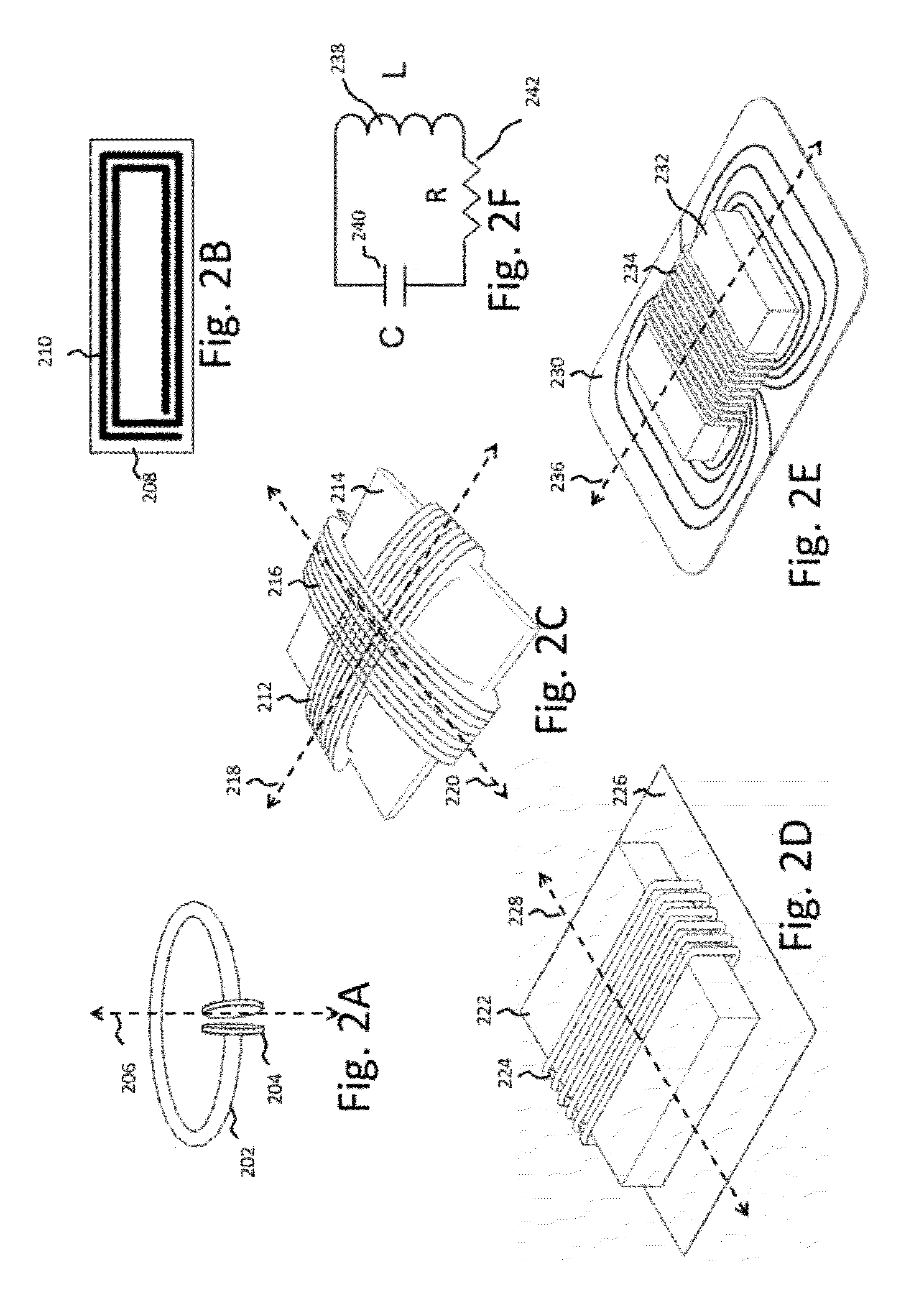

Wireless energy transfer for photovoltaic panels

ActiveUS20120098350A1Reduce cost and complexityMitigate factor drivingMultiple-port networksNear-field transmissionElectric power transmissionEnergy transfer

Described herein are improved configurations for a wireless power transfer involving photovoltaic panels. Described are methods and designs that use electric energy from a photovoltaic module to energize at least one wireless energy source to produce an oscillating magnetic field for wireless energy transfer. The source may be configured and tuned to present an impedance to a photovoltaic module wherein said impedance enables substantial extraction of energy from said photovoltaic module.

Owner:WITRICITY CORP

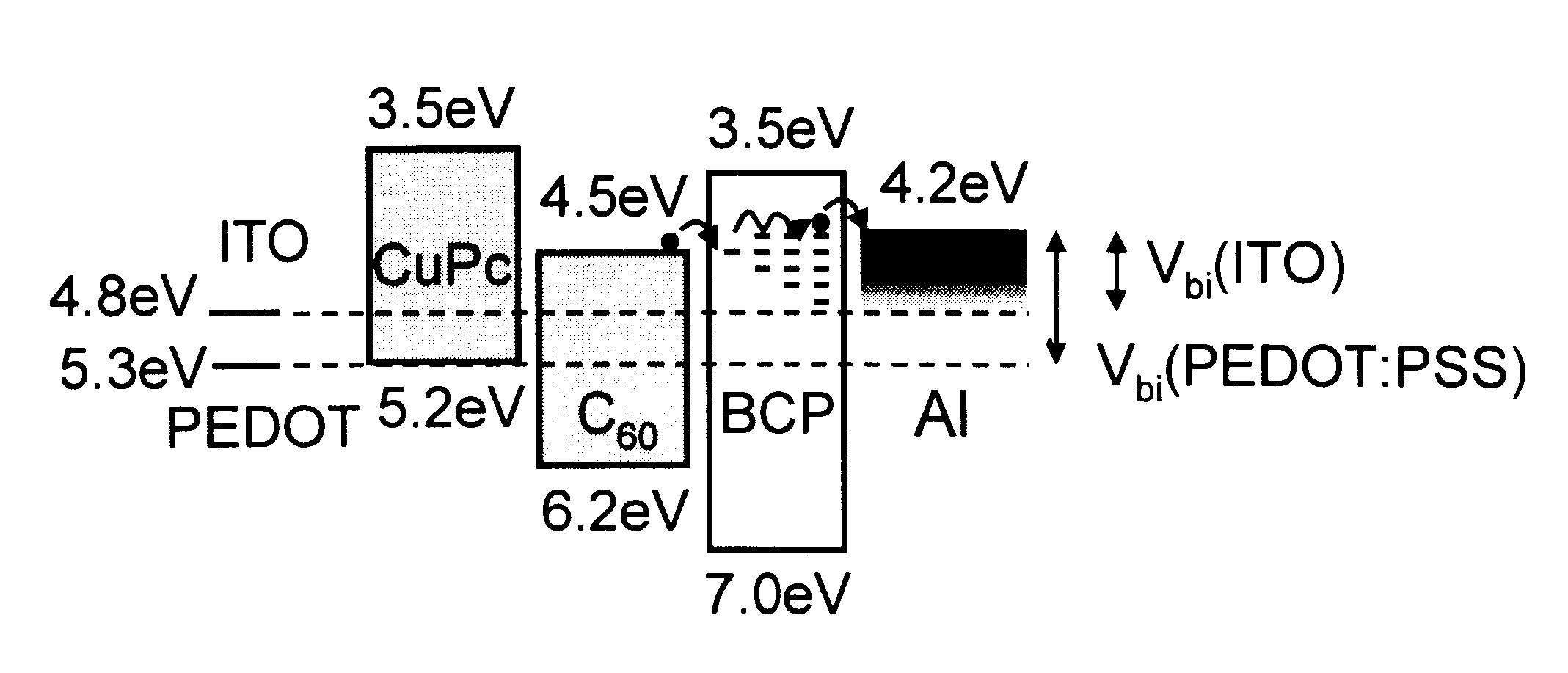

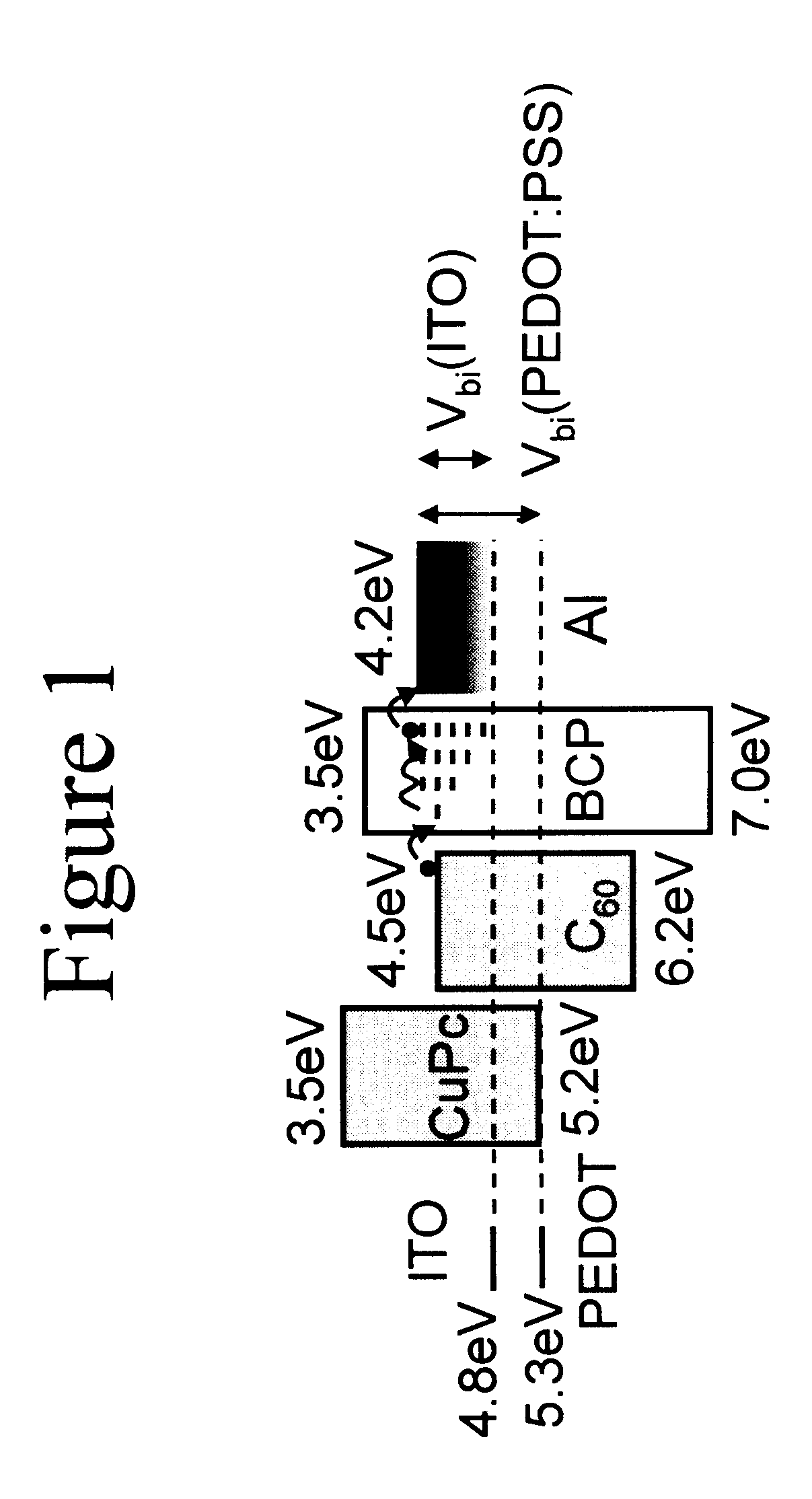

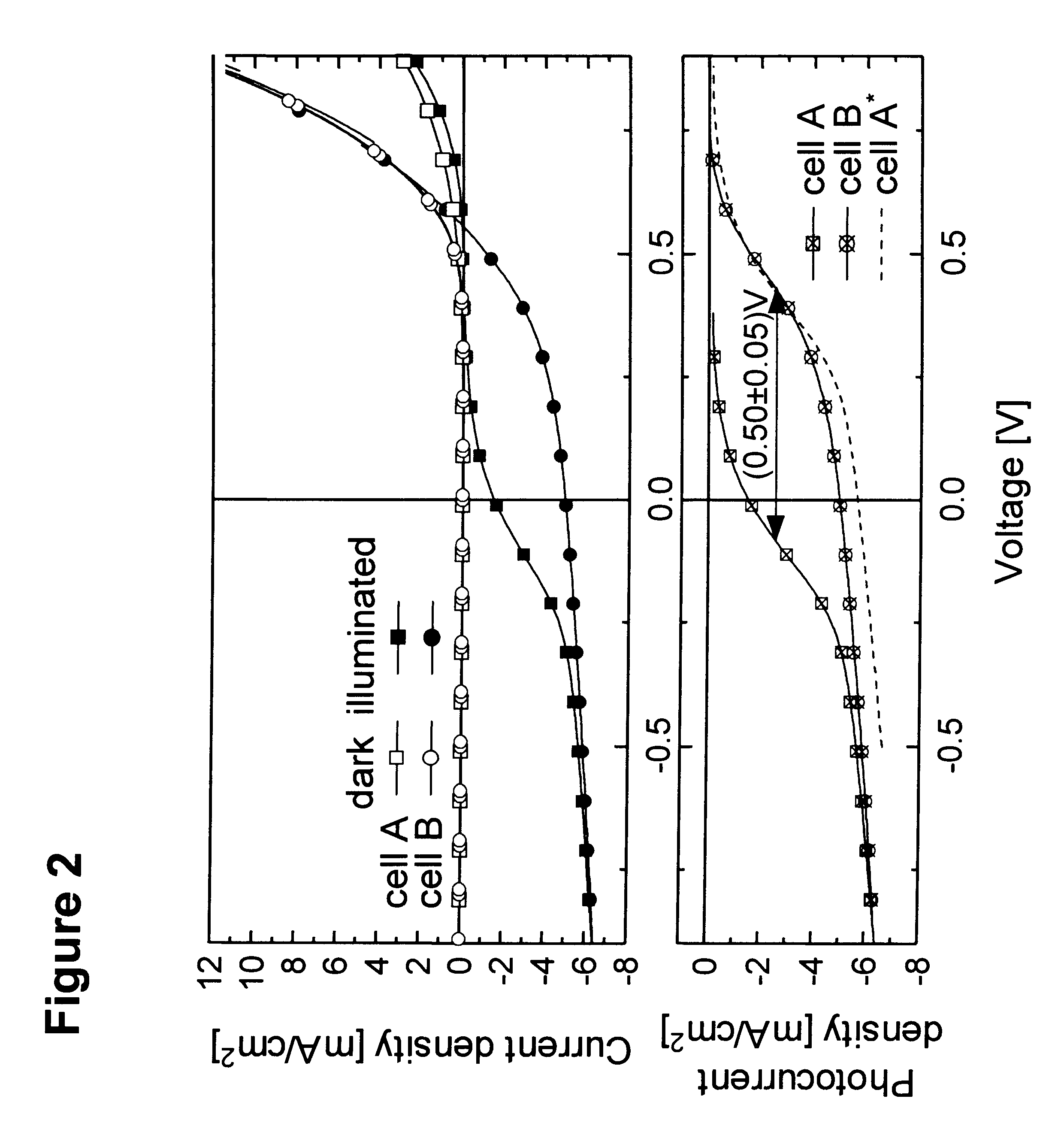

Solar cells using fullerenes

InactiveUS6580027B2Improve efficiencyIncrease the electric field strengthPV power plantsNanoinformaticsSolar cellFullerene

Organic photosensitive optoelectronic devices are disclosed. The devises comprise photoconductive organic thin films in a heterostructure, which include an exciton blocking layer to enhance device efficiency. The use of fullerenes in the electron conducting layer has lead to devices with high efficiency. Single heterostructure, stacked and wave-guide type embodiments are disclosed. Devices having multilayer structures and an exciton blocking layer are also disclosed. Guidelines for selection of exciton blocking layers are provided.

Owner:THE TRUSTEES FOR PRINCETON UNIV

Flexible high-temperature ultrabarrier

InactiveUS7018713B2Final product manufactureSynthetic resin layered productsPolyethylene terephthalateOrganic light emitting device

A flexible barrier assembly having a flexible visible light-transmissive substrate having a Tg greater than or equal to that of heat-stabilized polyethylene terephthalate (“HSPET”) overcoated with a first polymer layer having a Tg greater than or equal to that of HSPET and further overcoated with at least two visible light-transmissive inorganic barrier layers separated by at least one second polymer layer having a Tg greater than or equal to that of HSPET can be used to mount, cover, encapsulate or form moisture- and oxygen-sensitive articles such as organic light emitting devices and light valves.

Owner:3M INNOVATIVE PROPERTIES CO

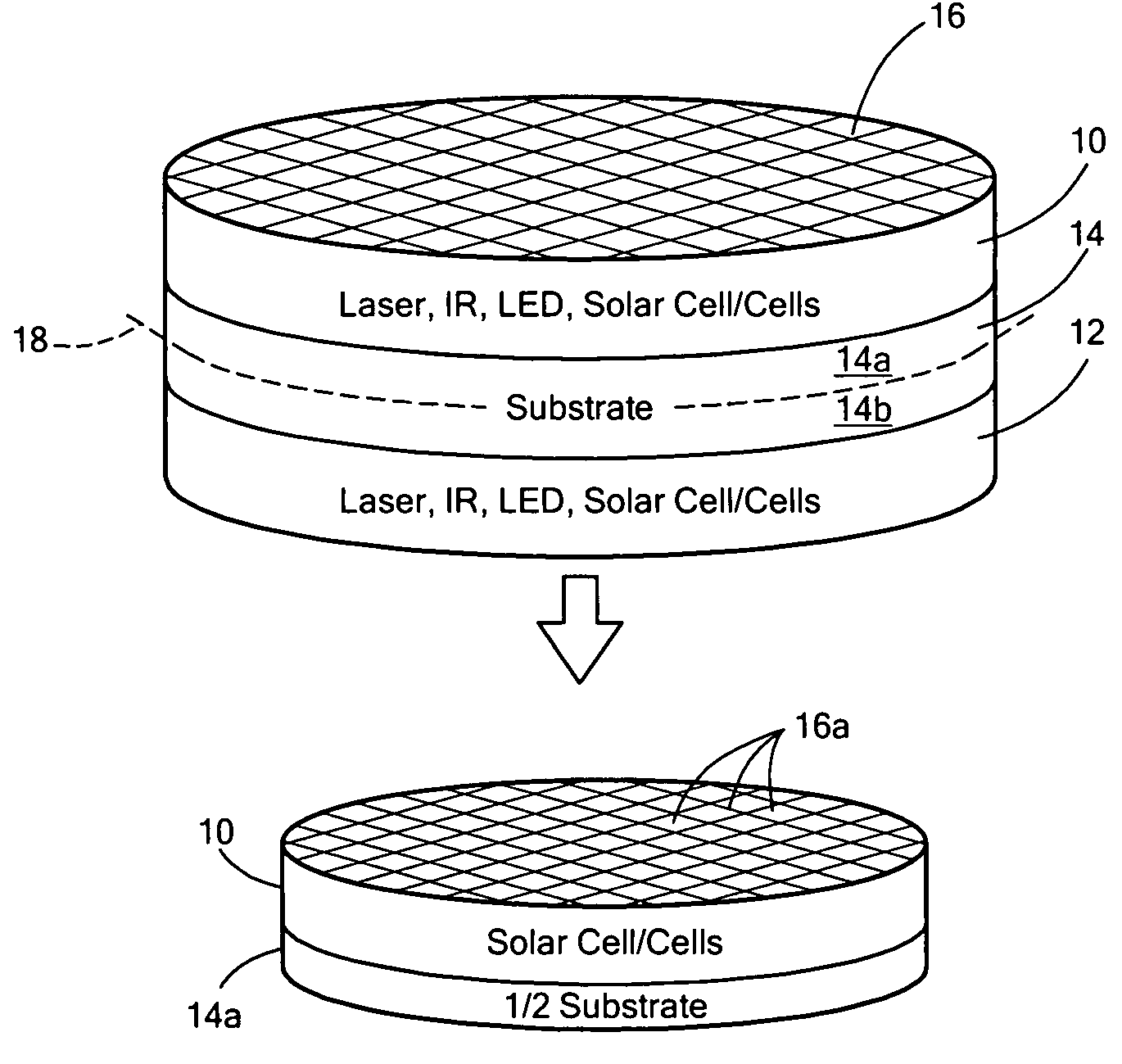

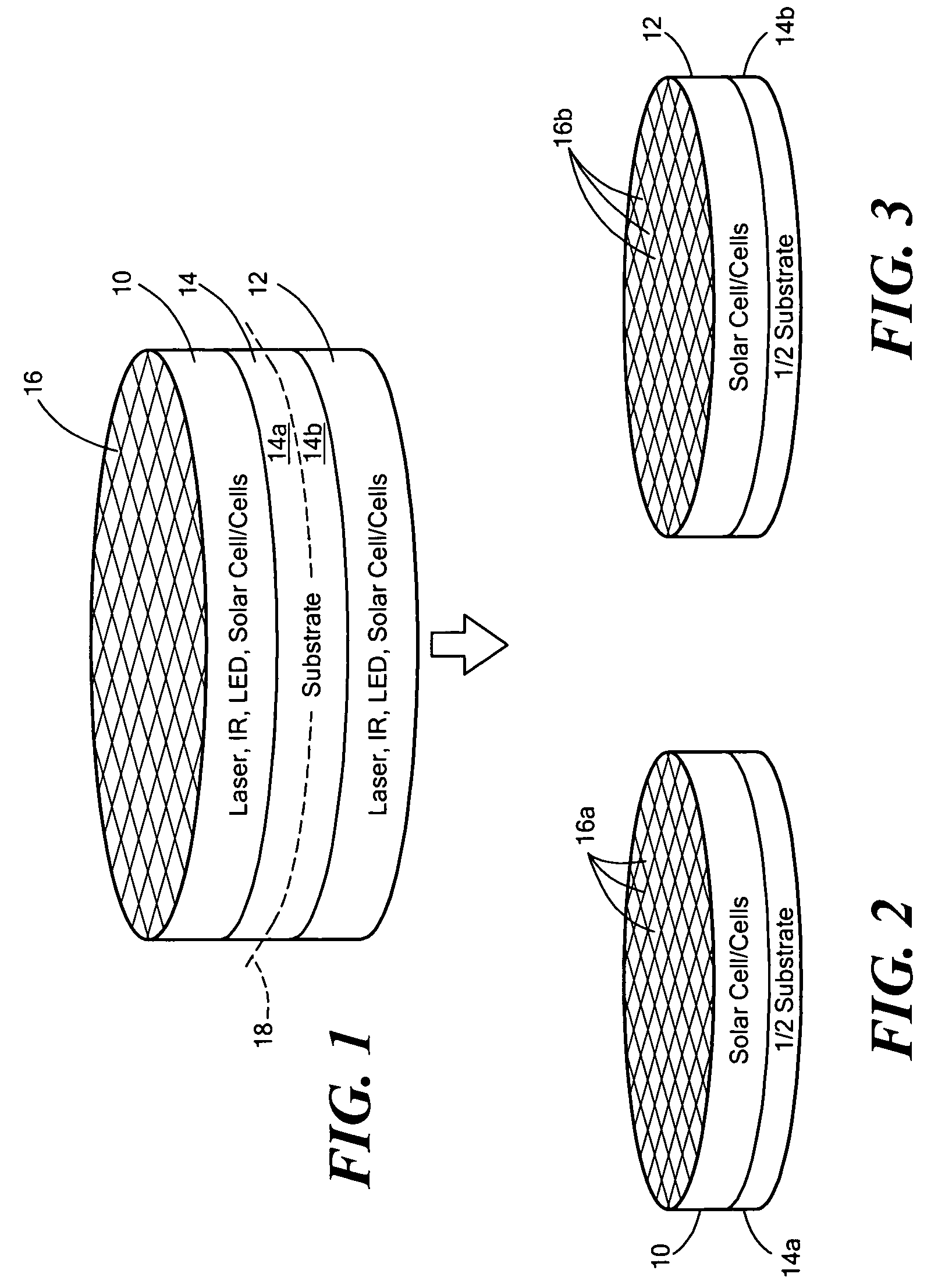

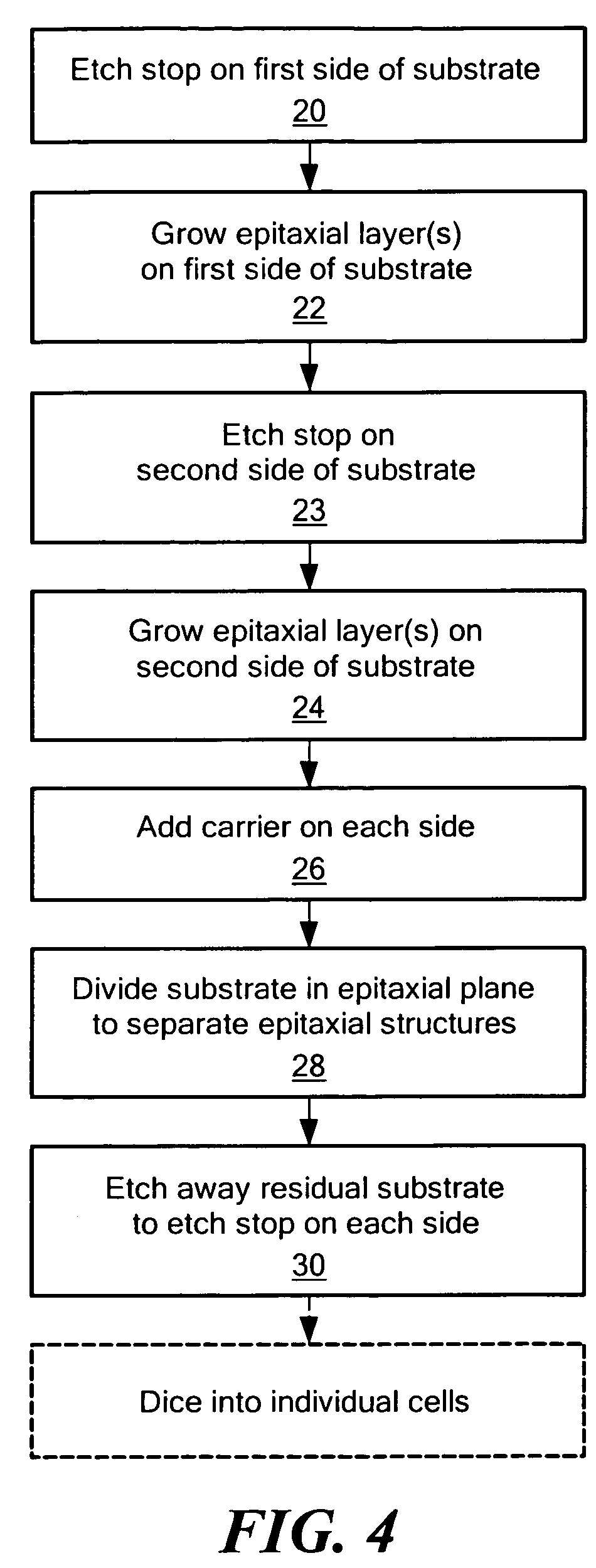

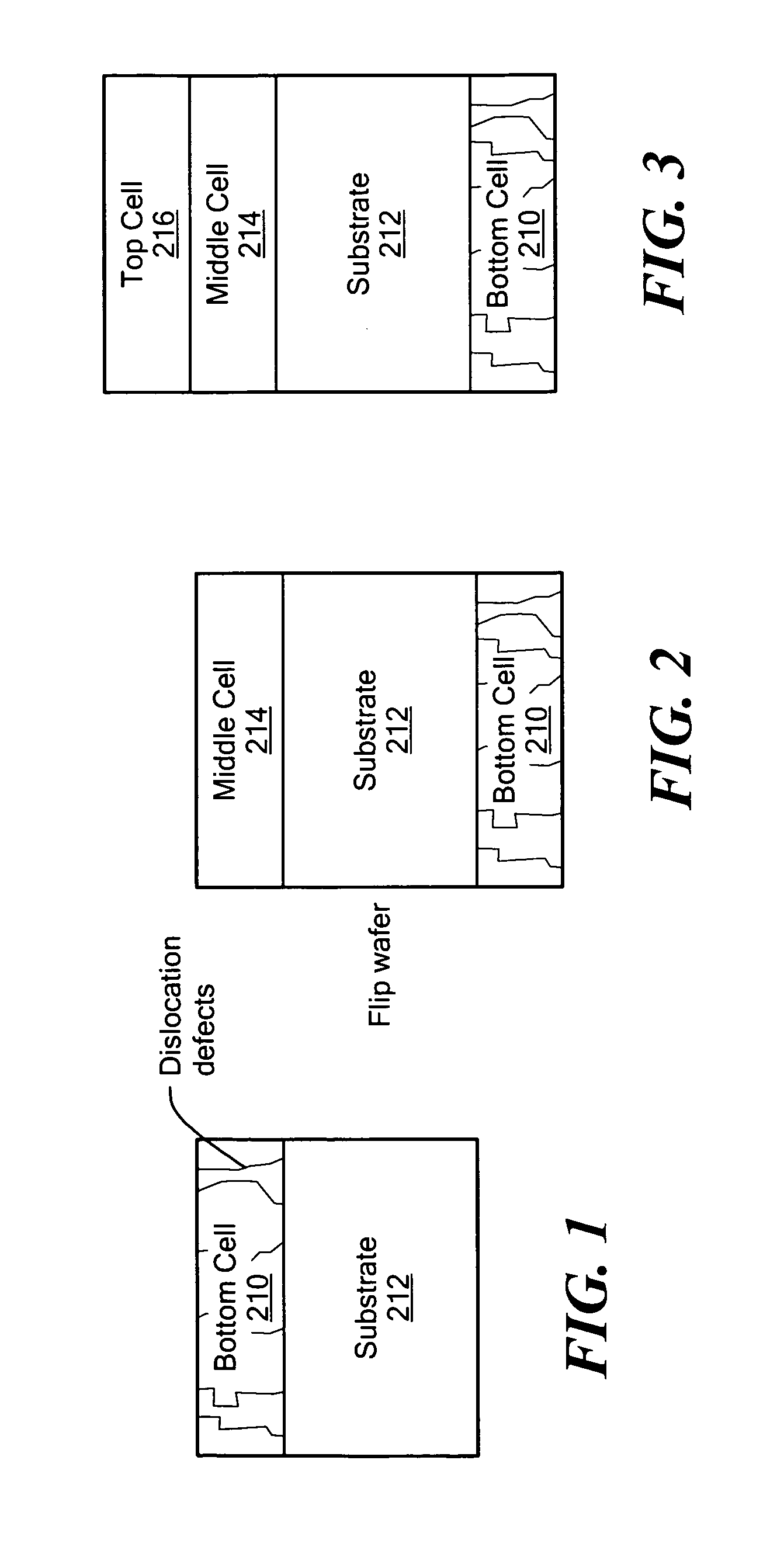

Method of fabricating bifacial tandem solar cells

ActiveUS8852994B2Easy and simpler and reliableSemiconductor/solid-state device manufacturingPhotovoltaic energy generationTandem solar cellOptoelectronics

A method of fabricating on a semiconductor substrate bifacial tandem solar cells with semiconductor subcells having a lower bandgap than the substrate bandgap on one side of the substrate and with subcells having a higher bandgap than the substrate on the other including, first, growing a lower bandgap subcell on one substrate side that uses only the same periodic table group V material in the dislocation-reducing grading layers and bottom subcells as is present in the substrate and after the initial growth is complete and then flipping the substrate and growing the higher bandgap subcells on the opposite substrate side which can be of different group V material.

Owner:MASIMO SEMICON +1

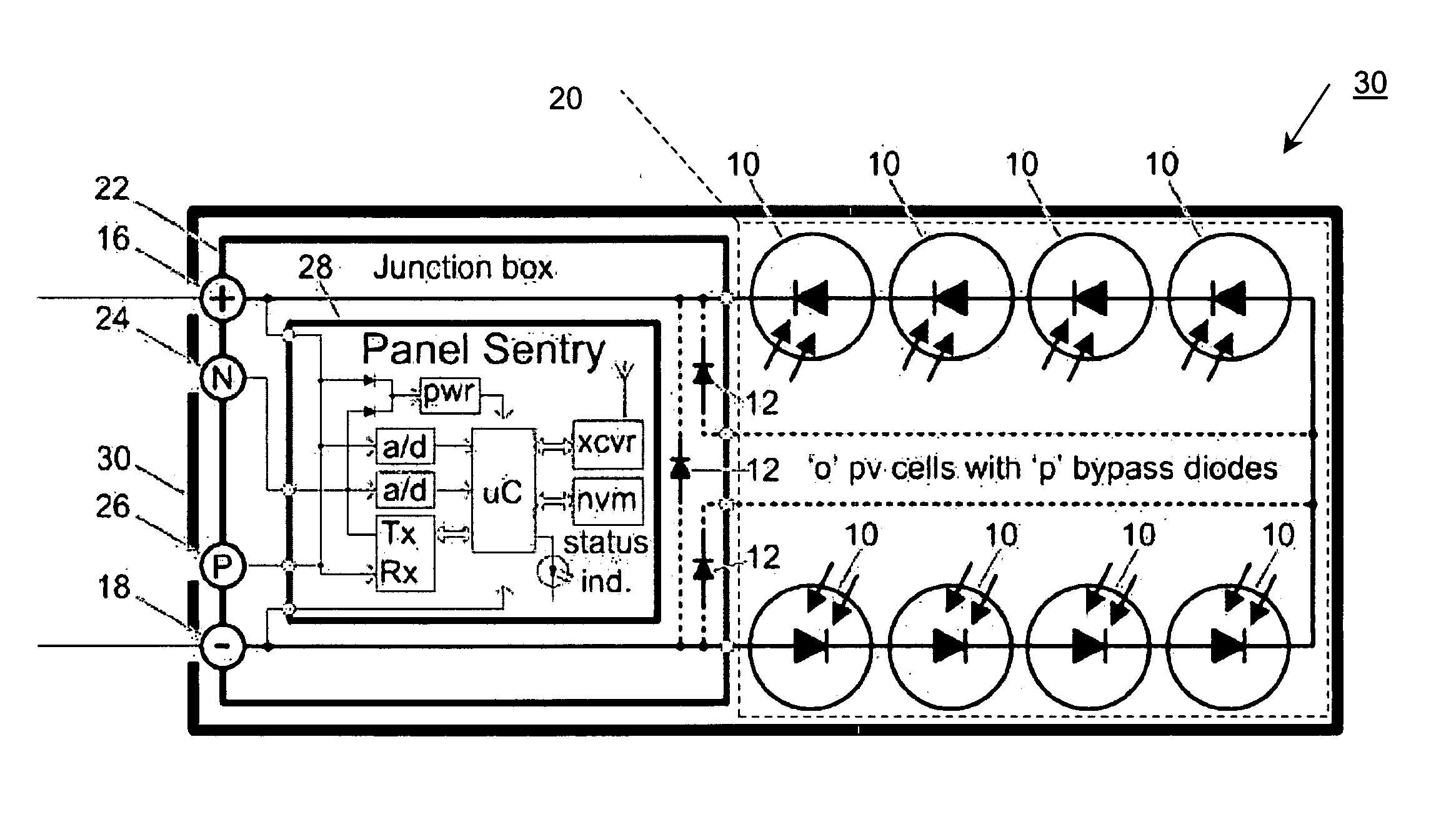

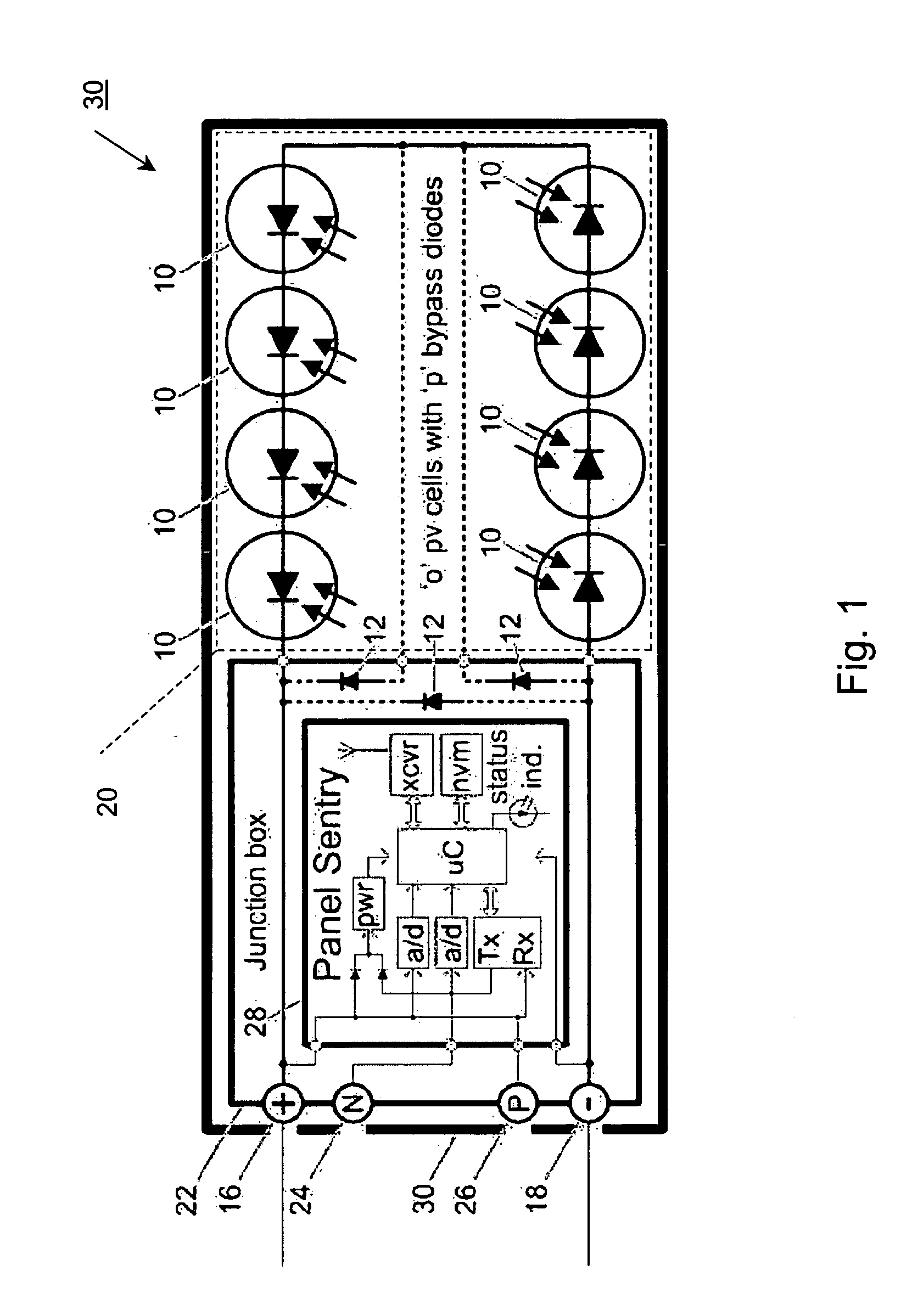

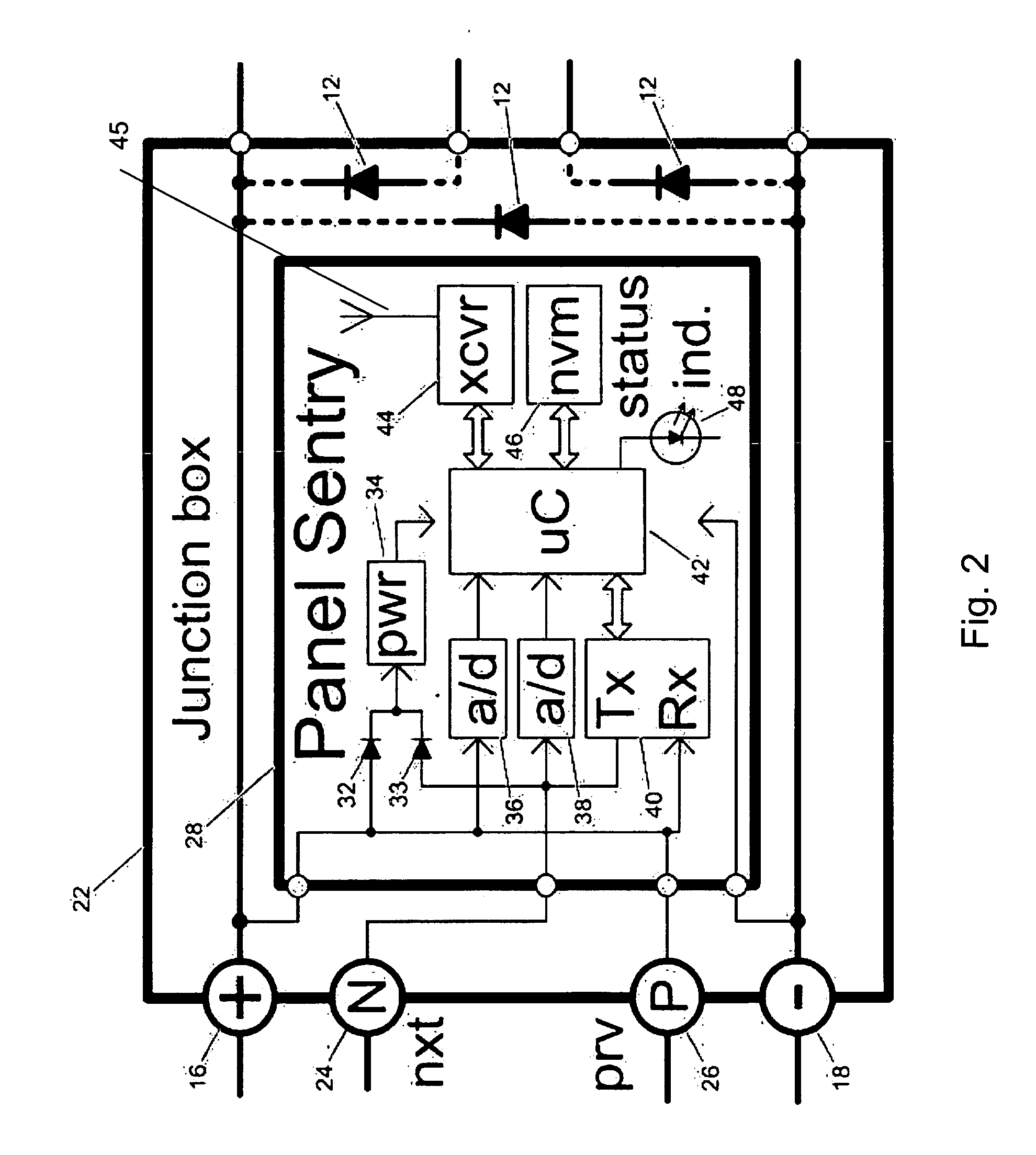

System and method for monitoring photovoltaic power generation systems

InactiveUS20060162772A1Batteries circuit arrangementsPhotovoltaic monitoringDiagnostic dataEngineering

A system and method for monitoring photovoltaic power generation systems or arrays, both on a local (site) level and from a central location. The system includes panel and string combiner sentries or intelligent devices, in bidirectional communication with a master device on the site to facilitate installation and troubleshooting of faults in the array, including performance monitoring and diagnostic data collection.

Owner:SOLAR SENTRY

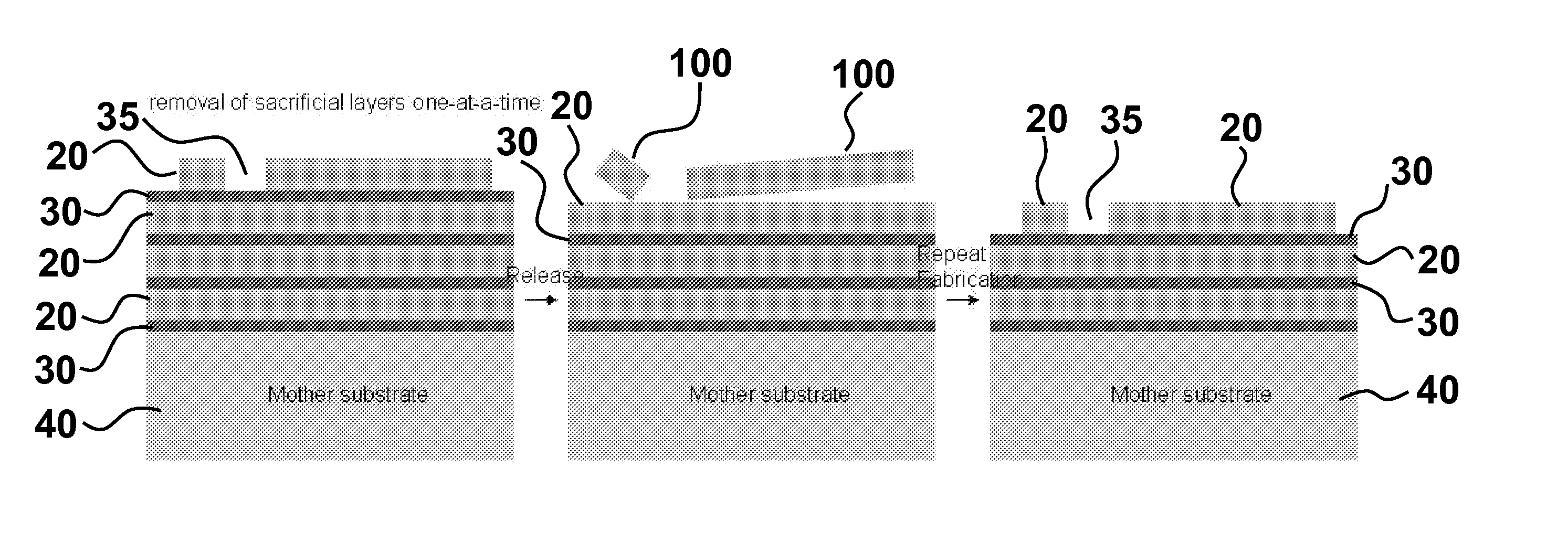

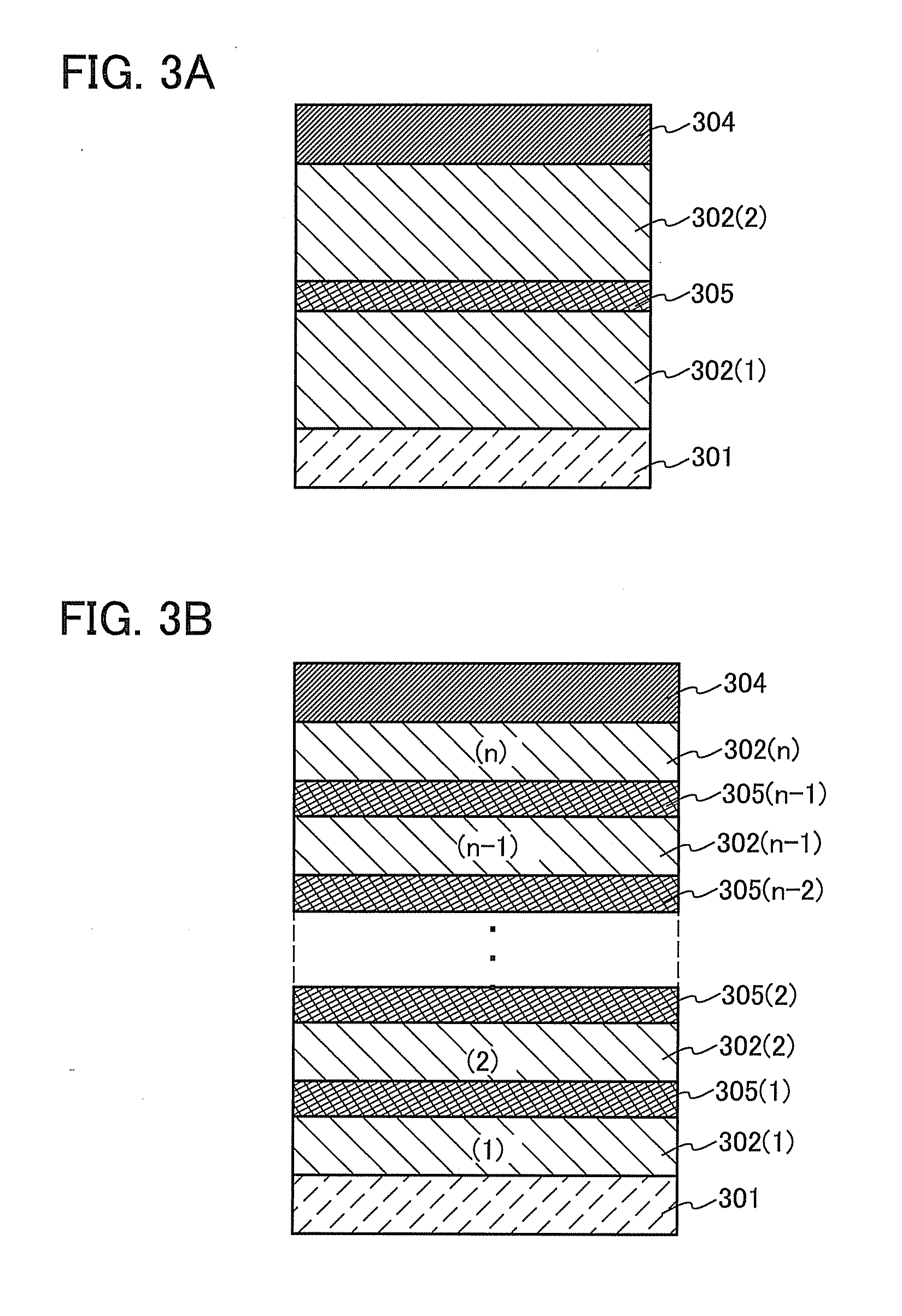

Release strategies for making transferable semiconductor structures, devices and device components

ActiveUS20080108171A1Low cost structureLow costFinal product manufactureNanoinformaticsSemiconductor structureDevice Subassembly

Provided are methods for making a device or device component by providing a multilayer structure having a plurality of functional layers and a plurality of release layers and releasing the functional layers from the multilayer structure by separating one or more of the release layers to generate a plurality of transferable structures. The transferable structures are printed onto a device substrate or device component supported by a device substrate. The methods and systems provide means for making high-quality and low-cost photovoltaic devices, transferable semiconductor structures, (opto-)electronic devices and device components.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Organometallic Complex, Light-Emitting Element, Light-Emitting Device, Electronic Device, and Lighting Device

ActiveUS20130165653A1Improve emission efficiencyHigh color purityGroup 5/15 element organic compoundsGroup 3/13 element organic compoundsNitrogenKetone

As a novel substance having a novel skeleton, an organometallic complex with high emission efficiency which achieves improved color purity by a reduction of half width of an emission spectrum is provided. One embodiment of the present invention is an organometallic complex in which a β-diketone and a six-membered heteroaromatic ring including two or more nitrogen atoms inclusive of a nitrogen atom that is a coordinating atom are ligands. In General Formula (G1), X represents a substituted or unsubstituted six-membered heteroaromatic ring including two or more nitrogen atoms inclusive of a nitrogen atom that is a coordinating atom. Further, R1 to R4 each represent a substituted or unsubstituted alkyl group having 1 to 6 carbon atoms.

Owner:SEMICON ENERGY LAB CO LTD

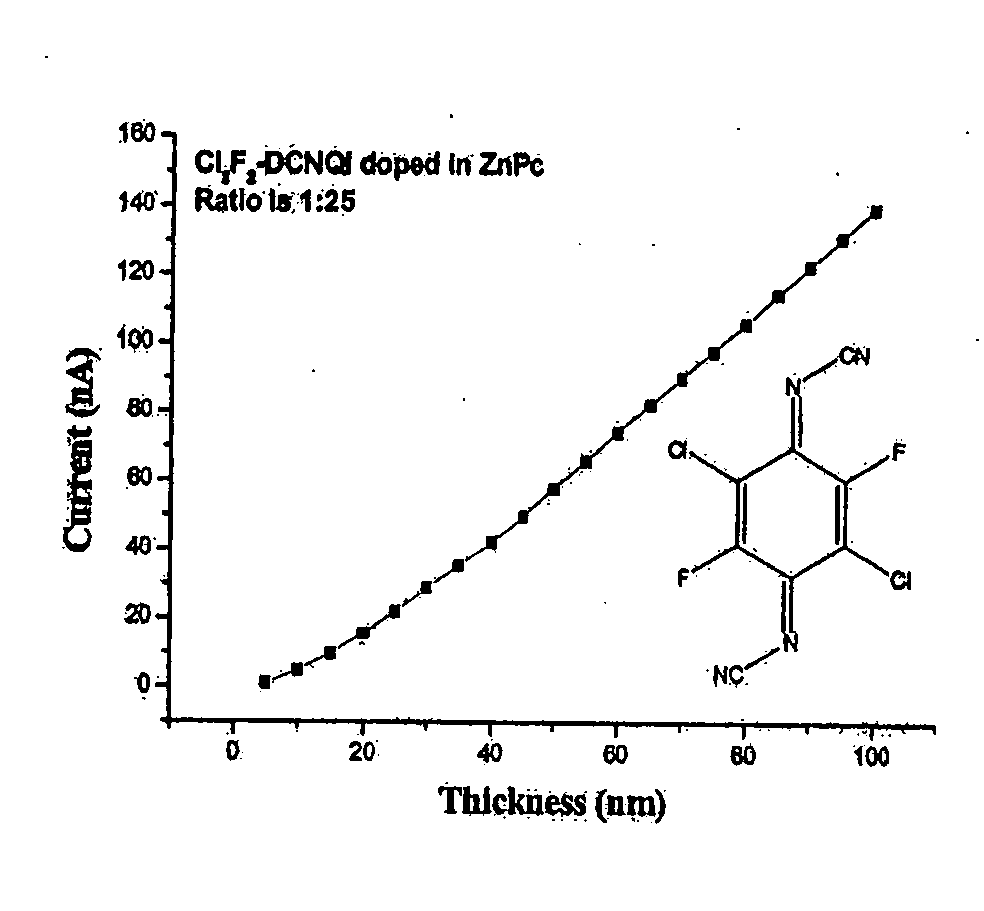

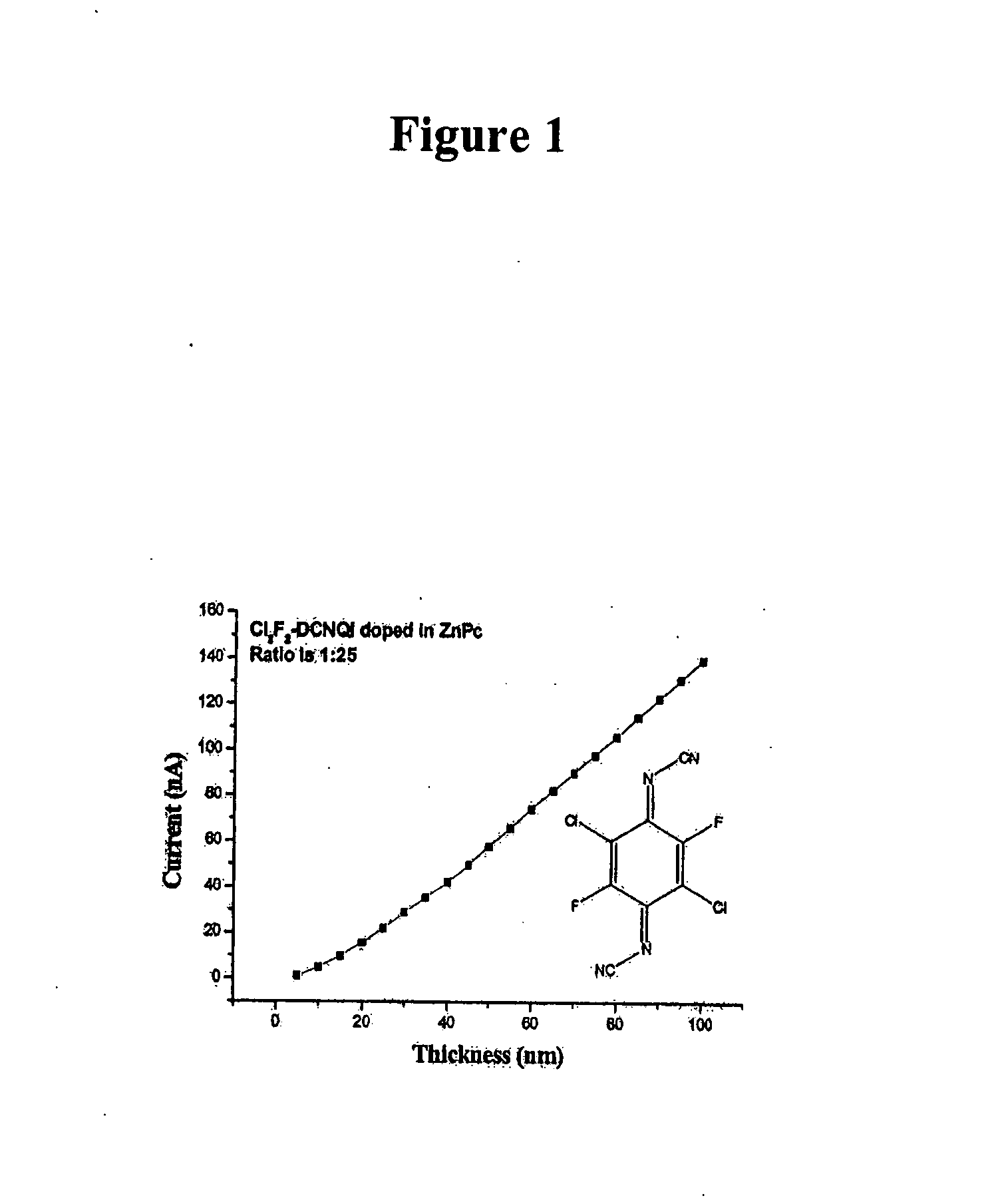

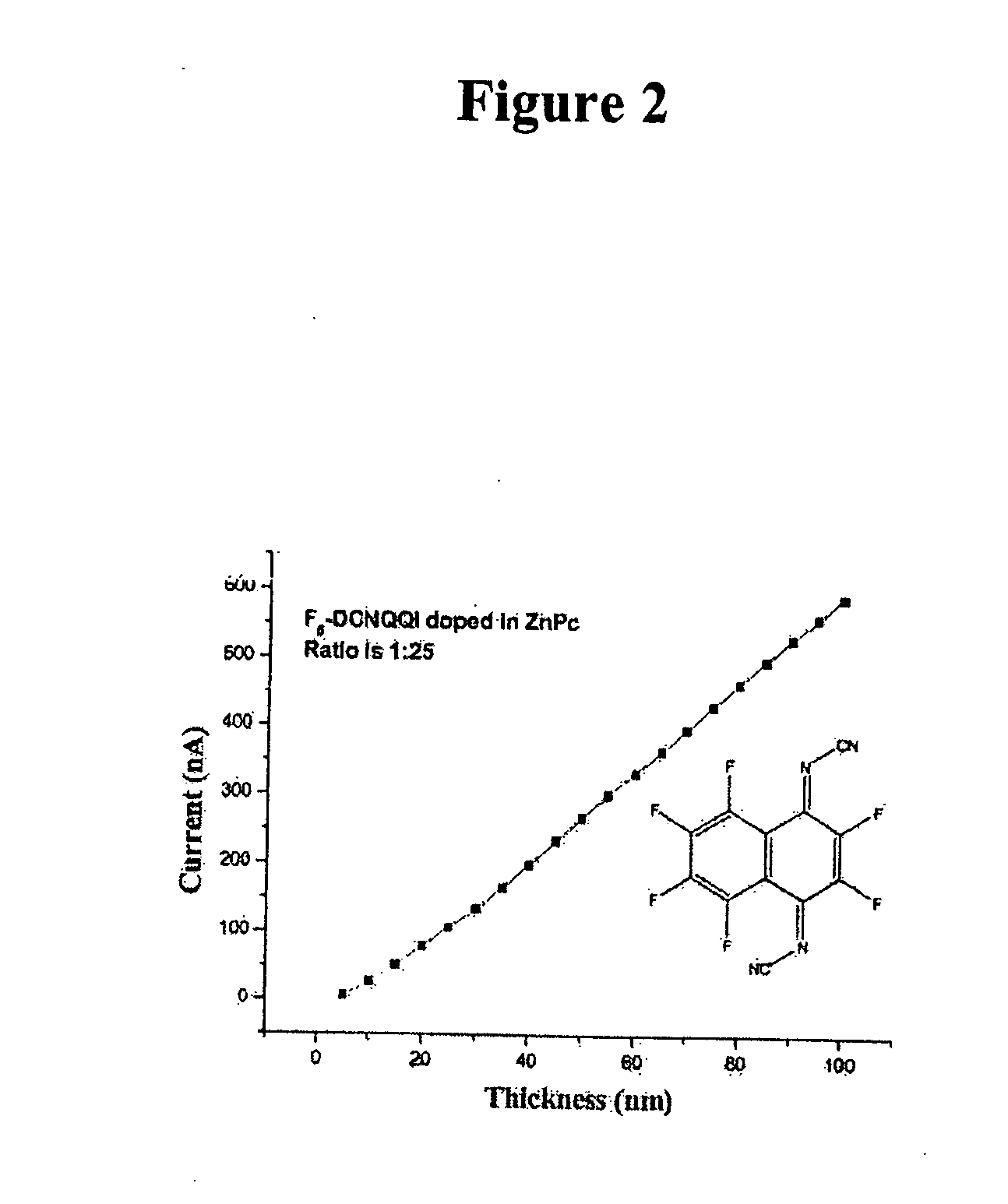

Method of doping organic semiconductors with quinone derivatives and 1, 3, 2 - dioxaborine derivatives

The invention relates to the use of an organic mesomeric compound as organic dopant for doping an organic semiconducting matrix material for varying the electrical properties thereof. In order to be able to handle organic semiconductors more easily in the production process and to be able to produce electronic components with doped organic semiconductors more reproducibly, a quinone or quinone derivative or a 1,3,2-dioxaborine or a 1,3,2-dioxaborine derivative may be used as a mesomeric compound, which under like evaporation conditions has a lower volatility than tetrafluorotetracyanoquinonedimethane (F4TCNQ).

Owner:KUEHL OLAF +4

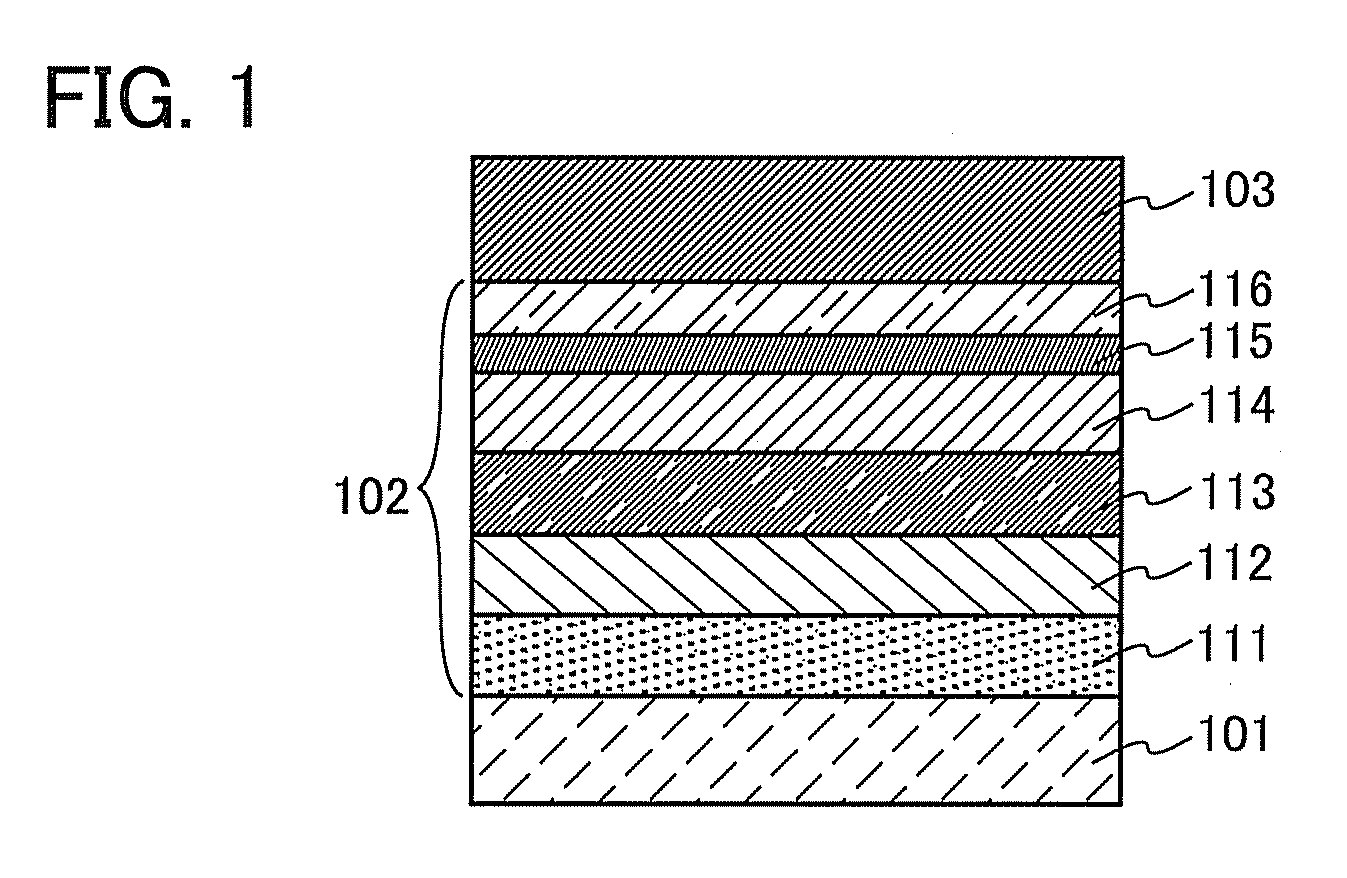

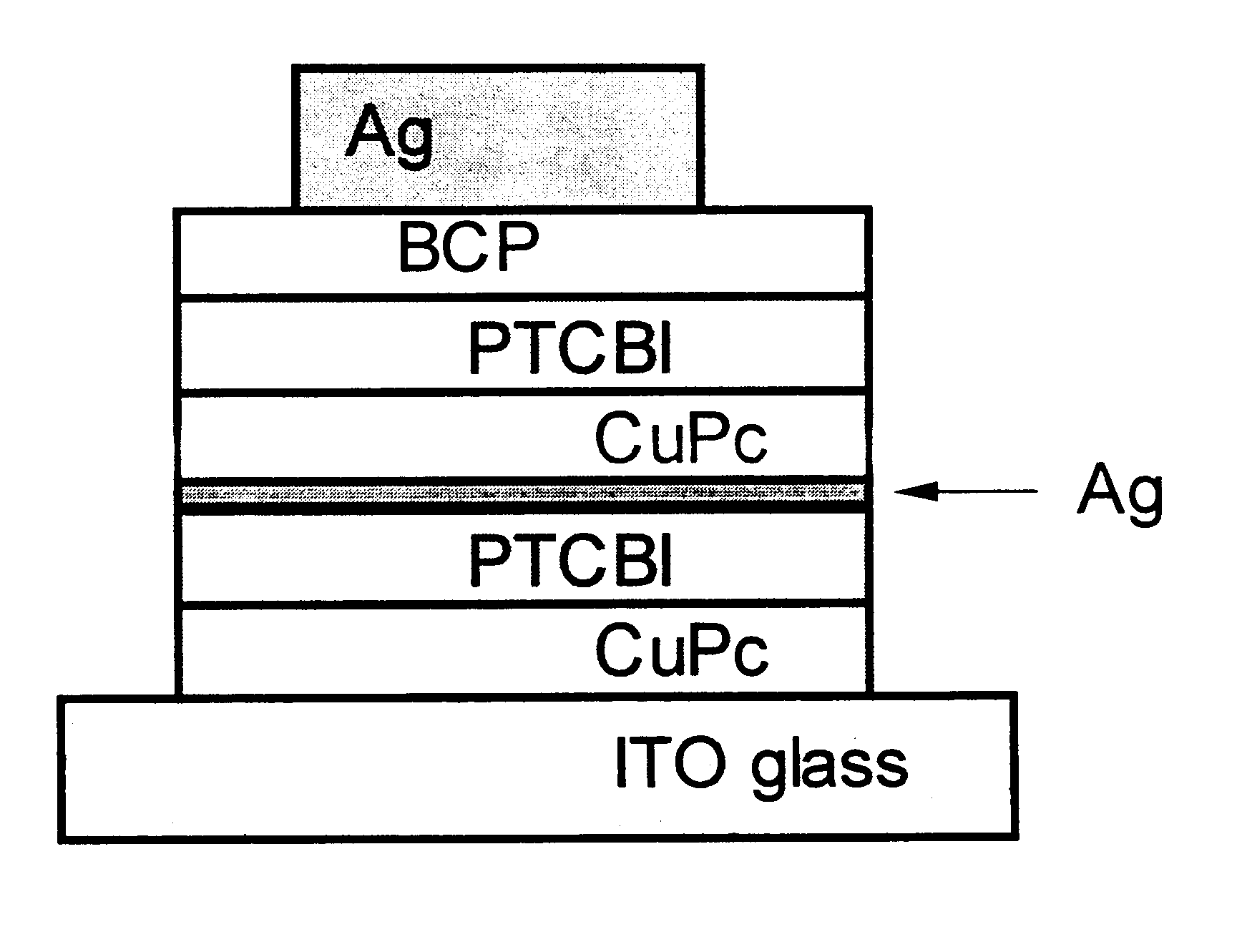

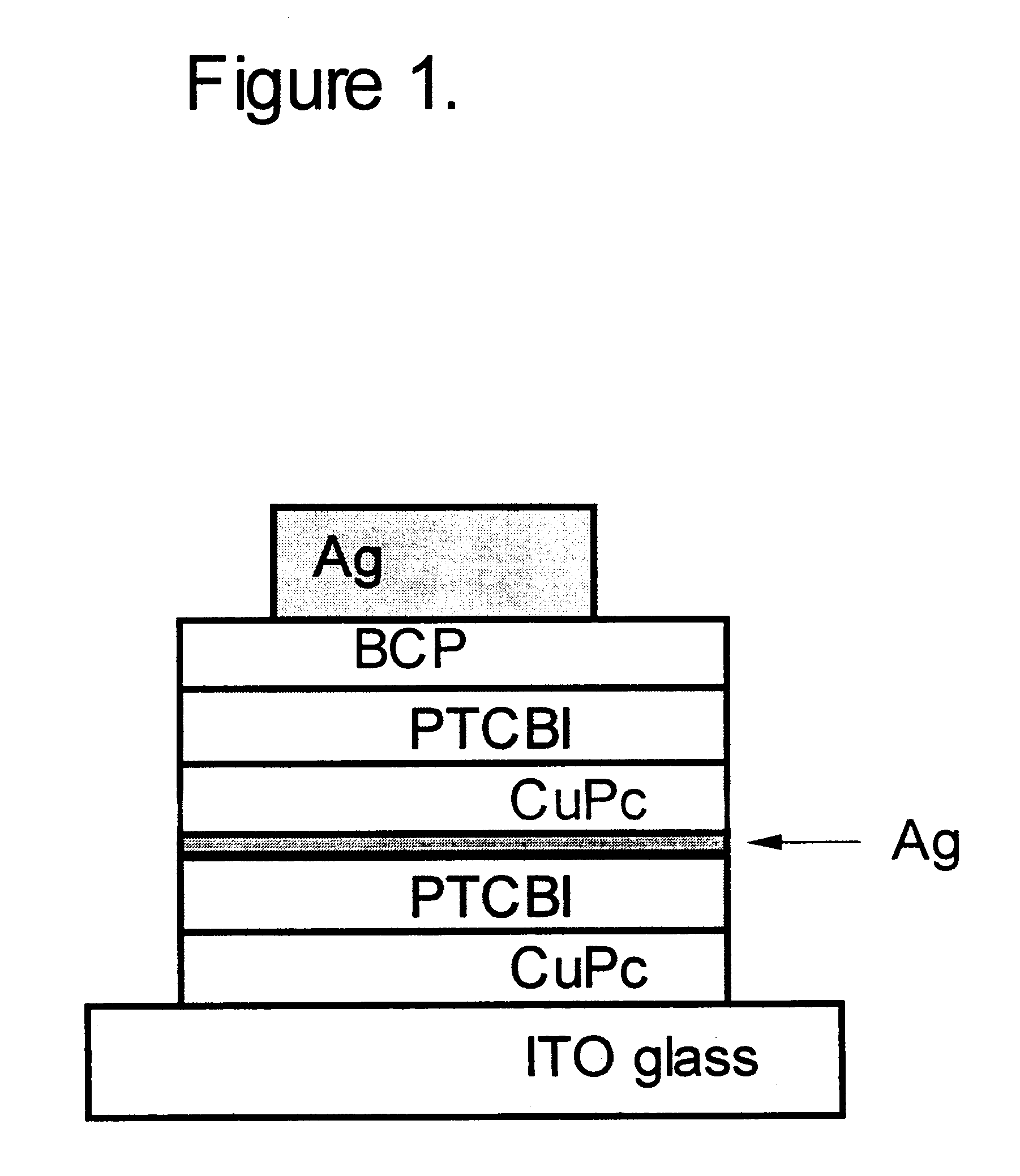

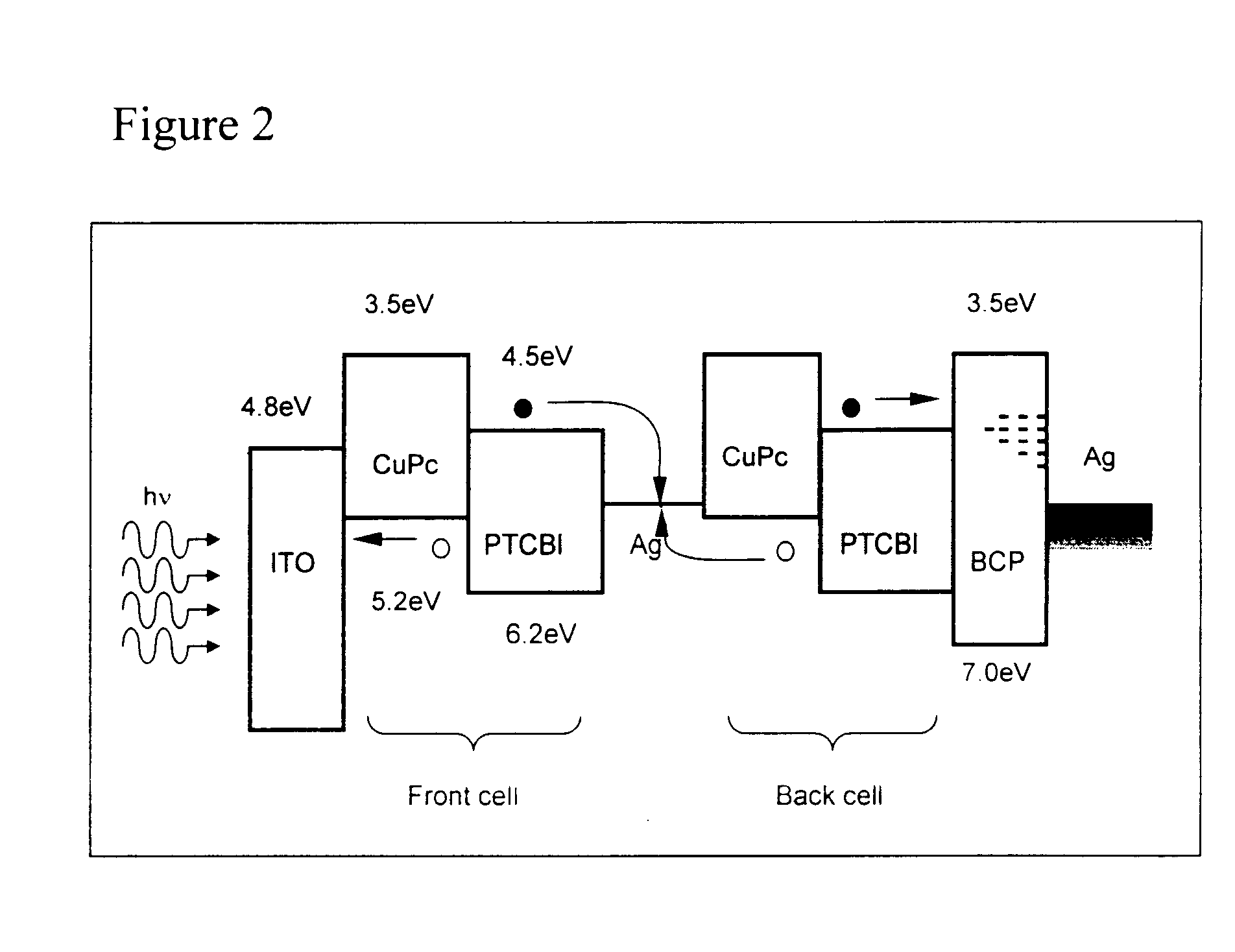

Organic photovoltaic devices

InactiveUS6657378B2Improve efficiencyImprove equipment efficiencyDischarge tube luminescnet screensLamp detailsOrganic solar cellElectron blocking layer

The present invention generally relates to organic photosensitive optoelectronic devices. More specifically, it is directed to organic photovoltaic devices, e.g., organic solar cells. Further, it is directed to an optimized organic solar cell comprising multiple stacked subcells in series. High power conversion efficiency are achieved by fabrication of a photovoltaic cell comprising multiple stacked subcells with thickness optimization and employing an electron blocking layer.

Owner:THE TRUSTEES FOR PRINCETON UNIV

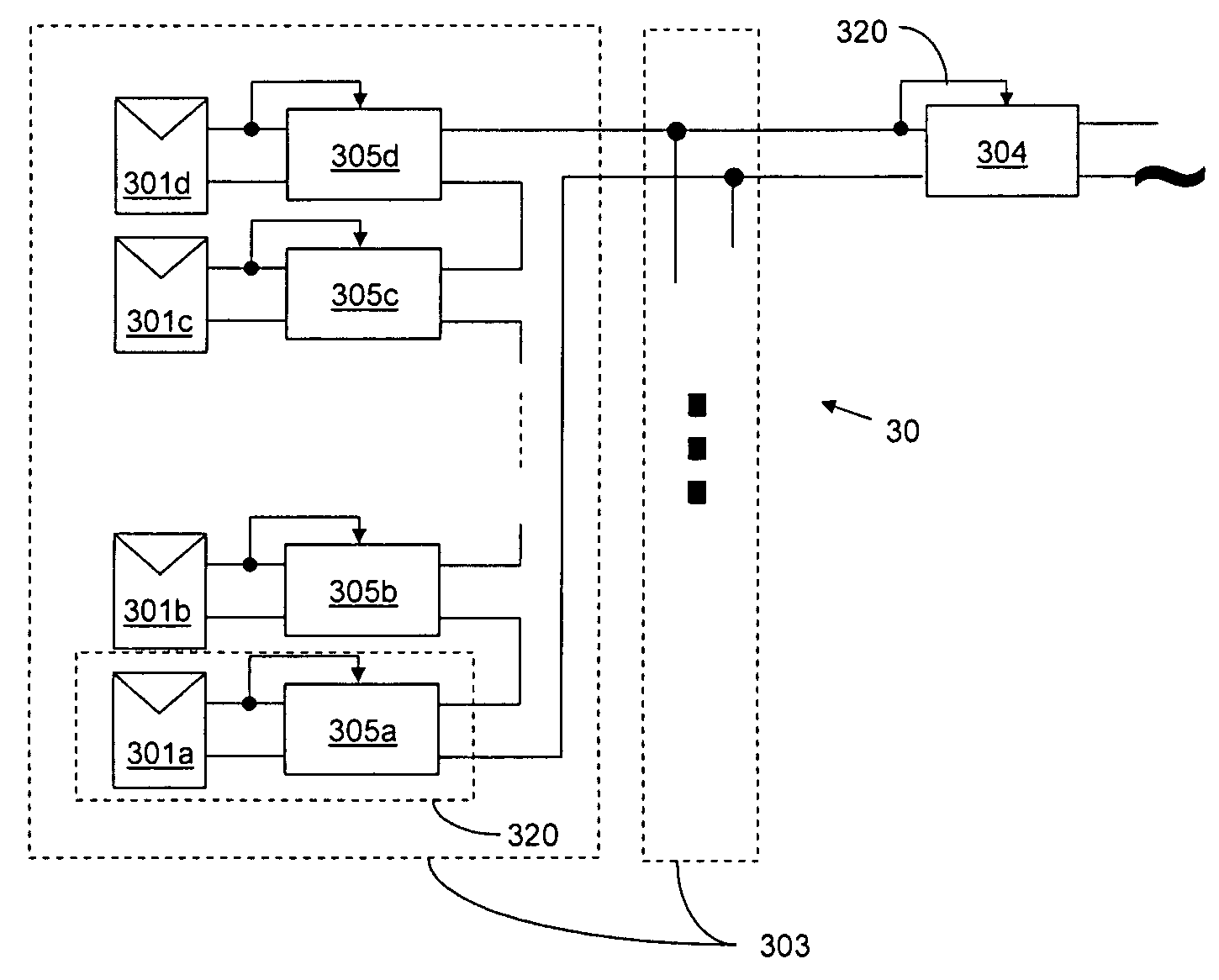

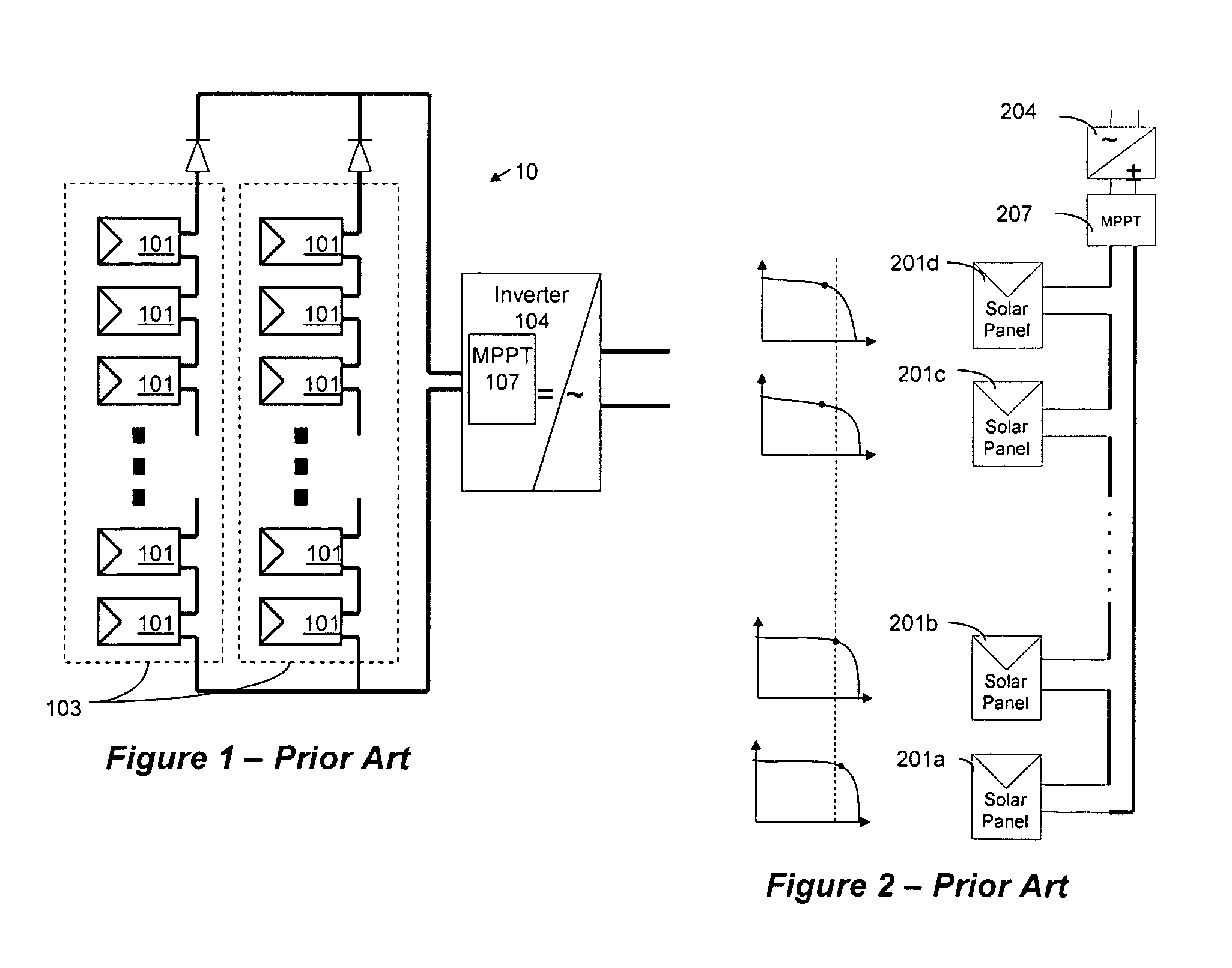

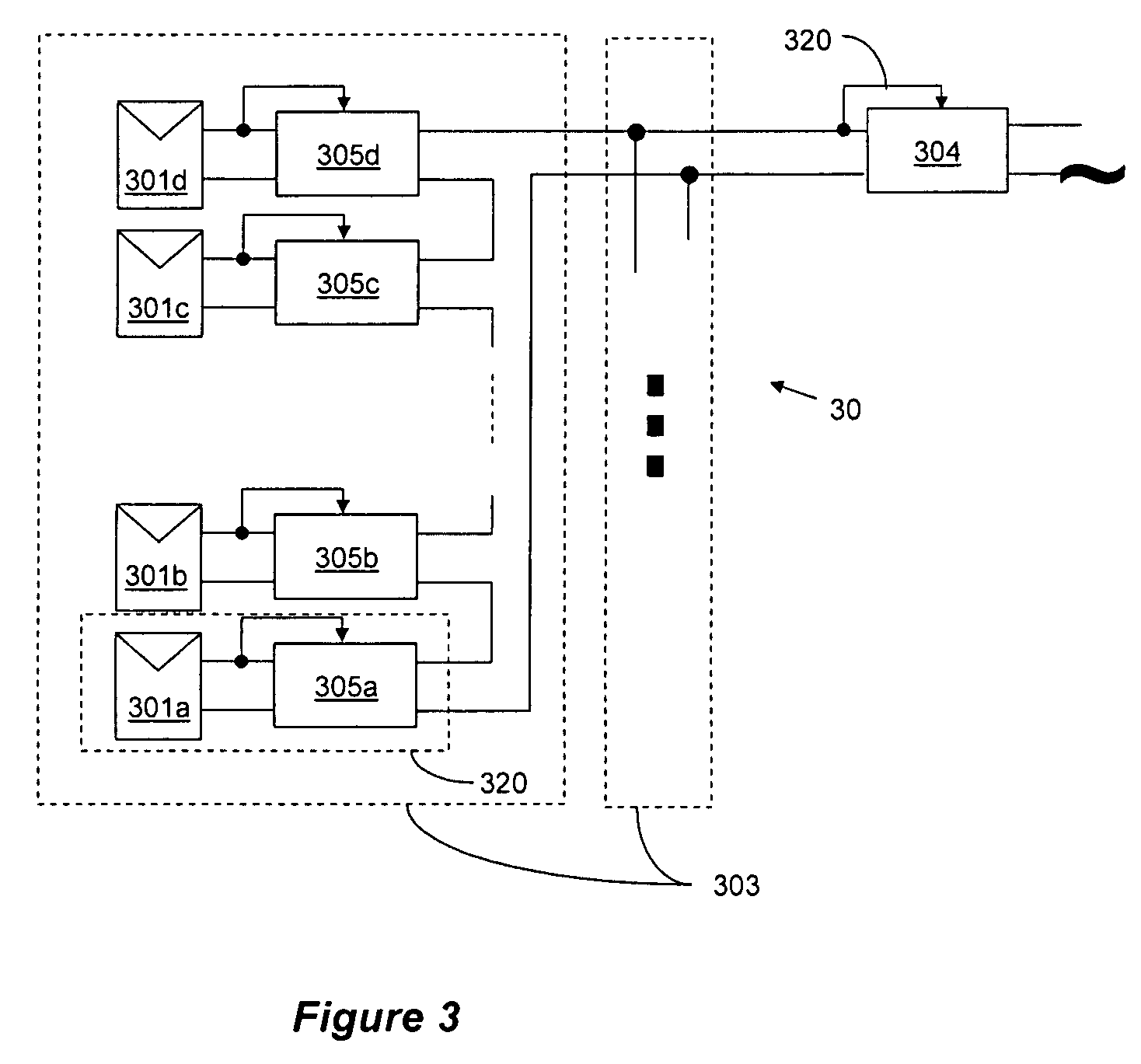

Method for distributed power harvesting using DC power sources

ActiveUS20080150366A1Improve reliabilitySafe operating voltageDc network circuit arrangementsPower network operation systems integrationTransverterVoltage variation

A system and method for combining power from DC power sources. Each power source is coupled to a converter. Each converter converts input power to output power by monitoring and maintaining the input power at a maximum power point. Substantially all input power is converted to the output power, and the controlling is performed by allowing output voltage of the converter to vary. The converters are coupled in series. An inverter is connected in parallel with the series connection of the converters and inverts a DC input to the inverter from the converters into an AC output. The inverter maintains the voltage at the inverter input at a desirable voltage by varying the amount of the series current drawn from the converters. The series current and the output power of the converters, determine the output voltage at each converter.

Owner:SOLAREDGE TECH LTD

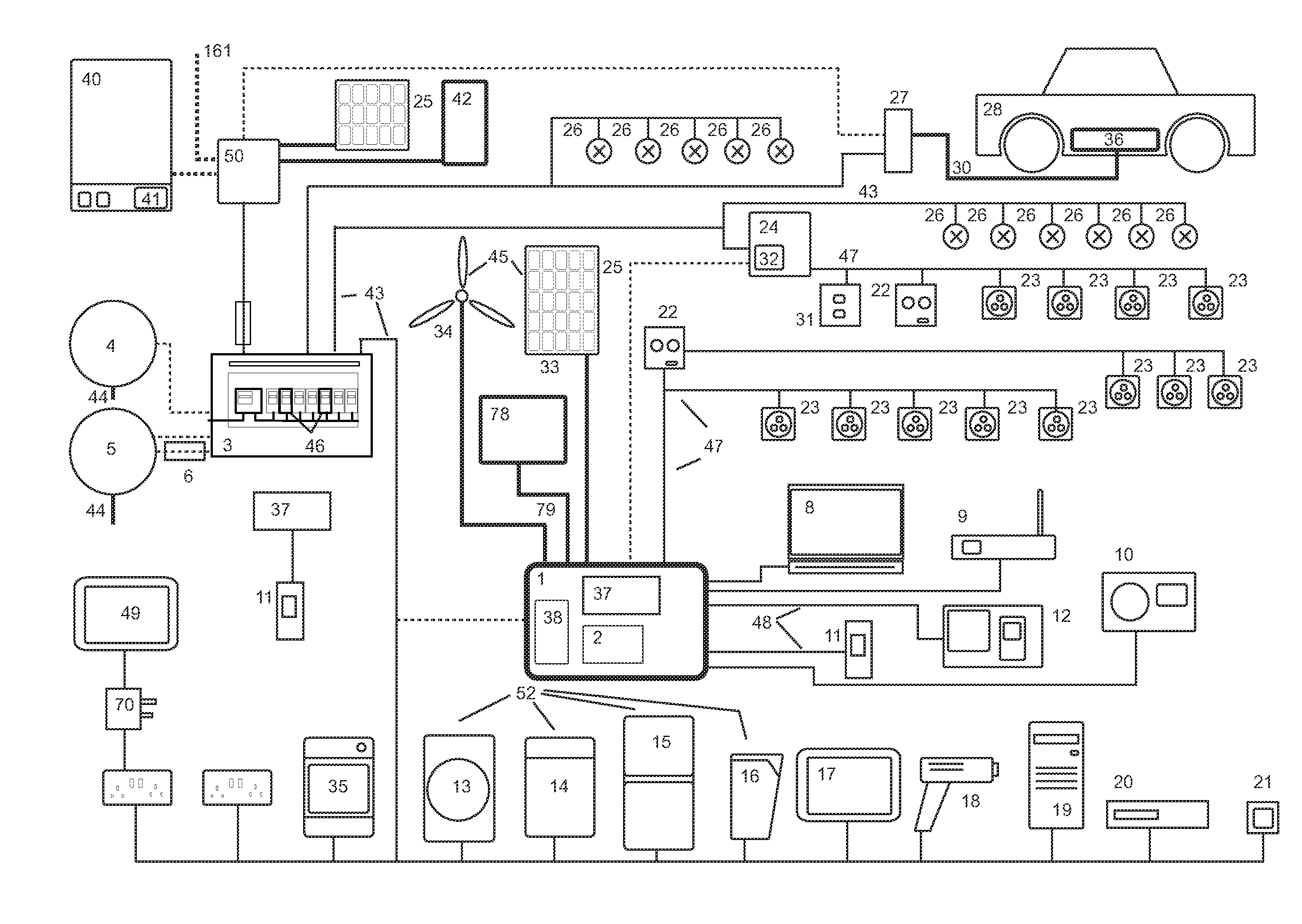

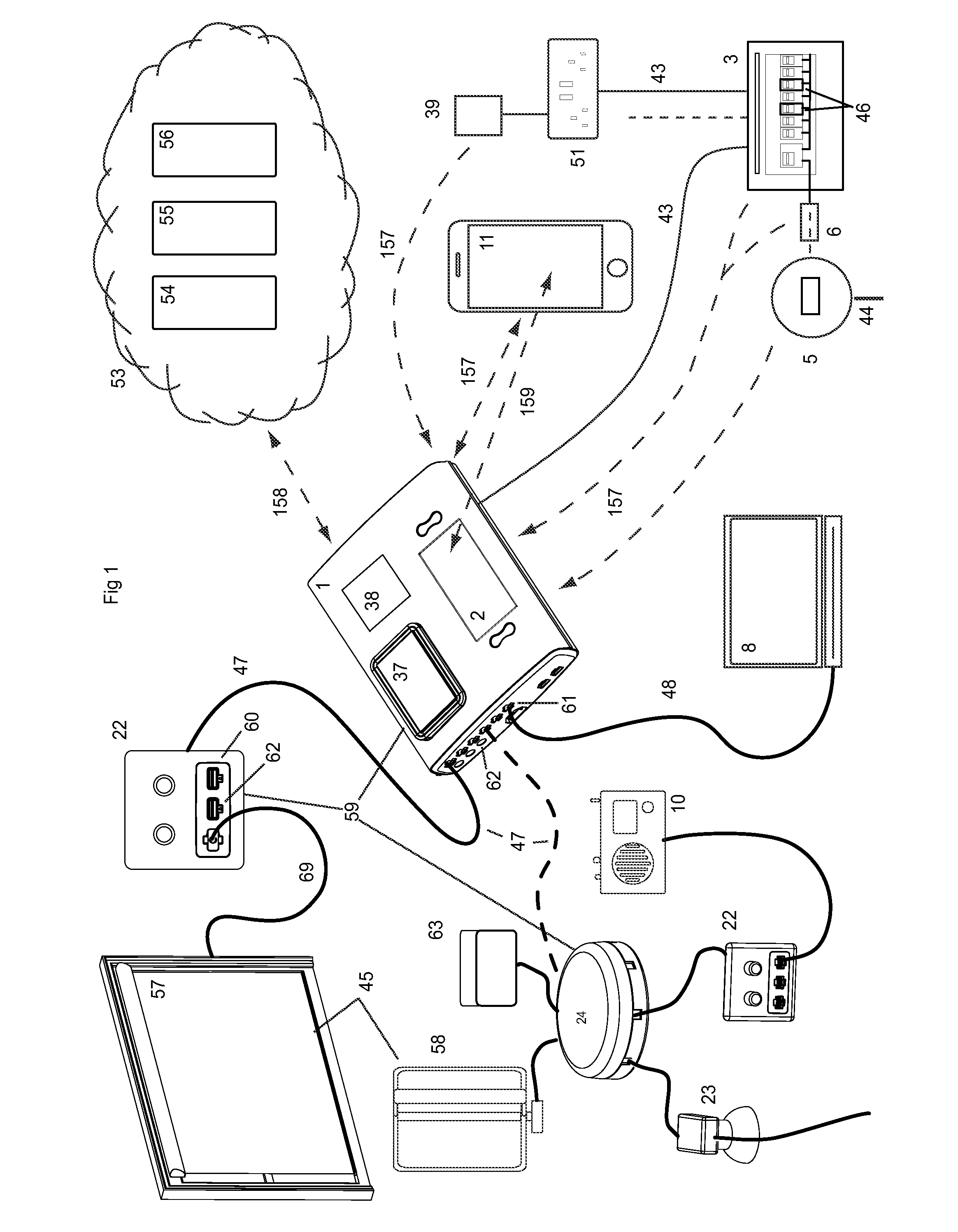

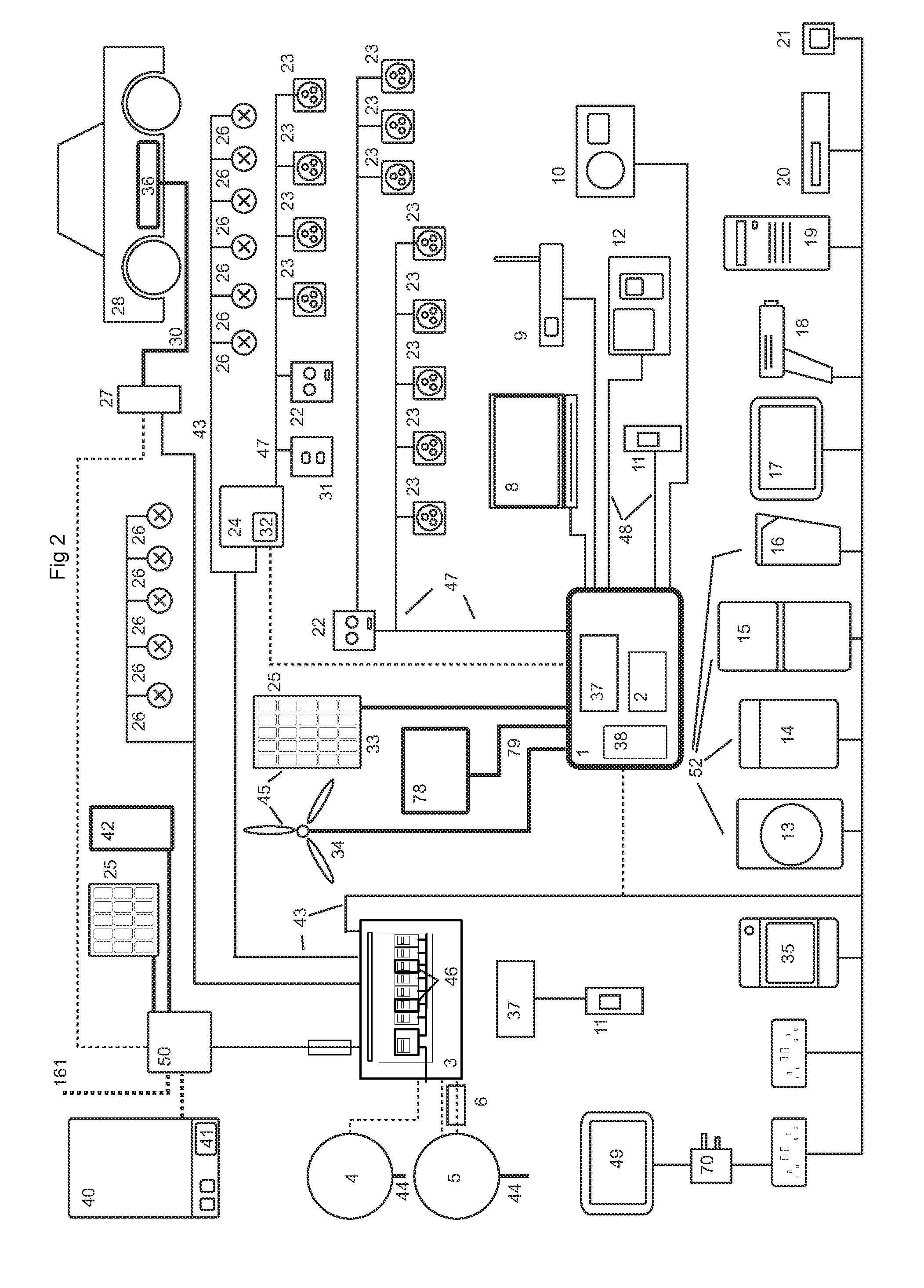

Systems, devices and methods for electricity provision, usage monitoring, analysis, and enabling improvements in efficiency

ActiveUS20100076615A1Facilitating in changing their energy usage behaviourEasy to installPhotovoltaic monitoringLevel controlLight equipmentRenewable technologies

The invention relates generally to systems, devices and methods for the efficient use of utilities, more particularly to the distribution and provision of electricity supply at appropriate voltages, monitoring and usage by end devices, and to facilitating consumers in changing their energy usage behaviour, and to adopt and easily install appropriate sustainable, energy efficient or renewable technologies. Said end devices typically including traditional electric, electronic and lighting appliances requiring AC or DC power provision or low voltage DC power via AC / DC converters.

Owner:MOIXA ENERGY HLDG

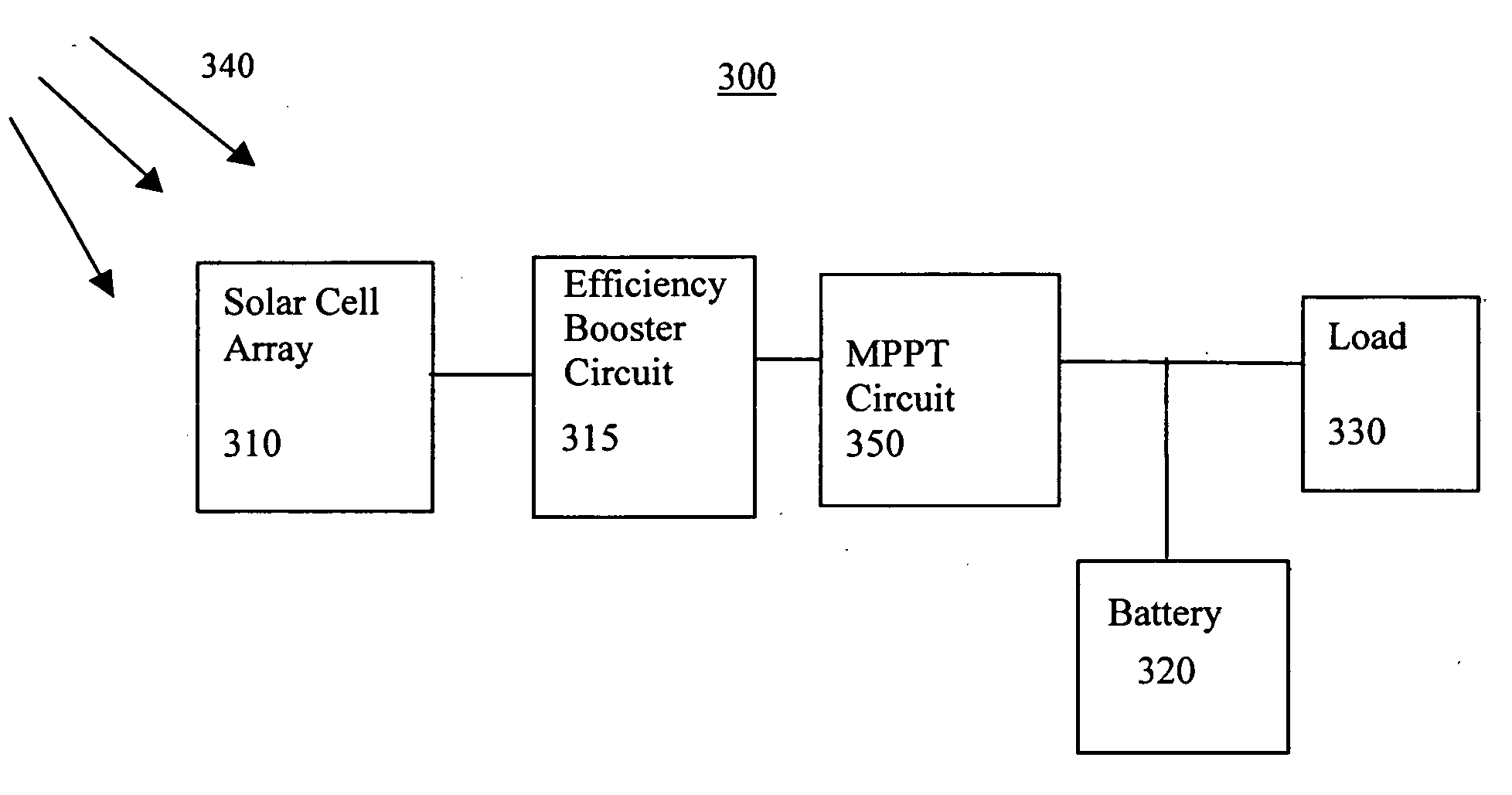

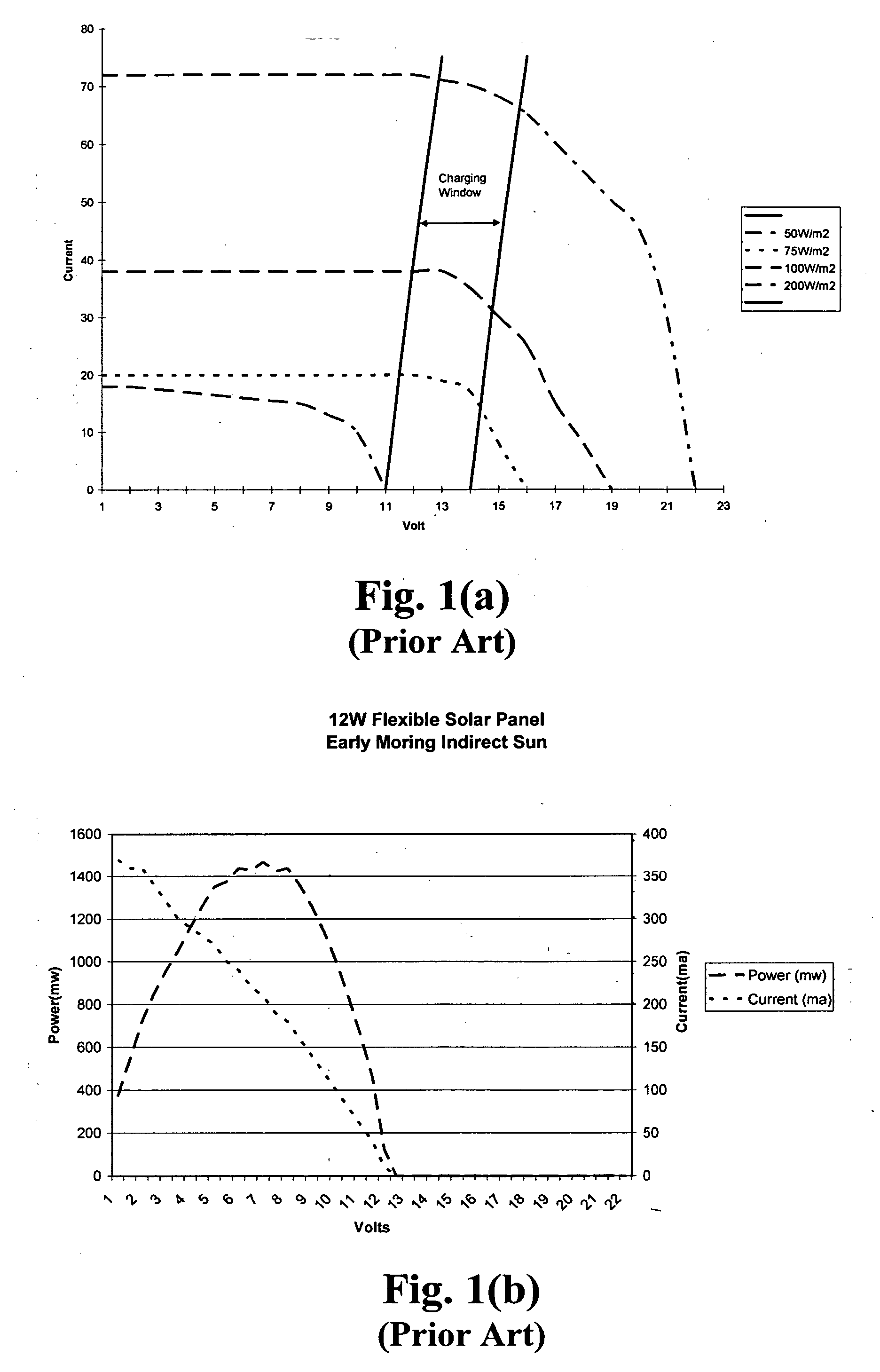

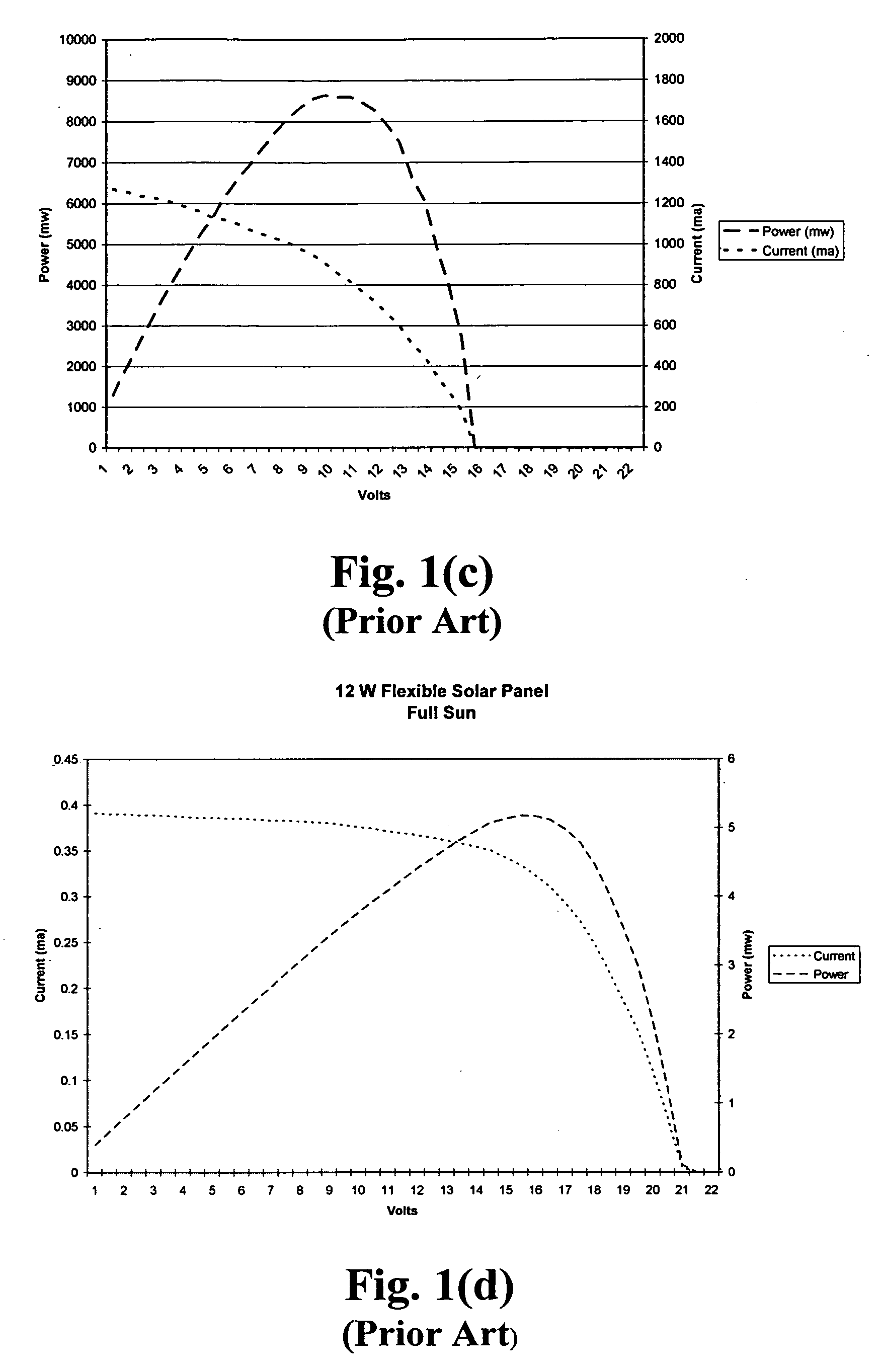

Efficiency booster circuit and technique for maximizing power point tracking

InactiveUS20060174939A1Reduce voltageConsiderable amount of energyBatteries circuit arrangementsPV power plantsSolar cellPoint tracking

The present invention provides an efficiency booster circuit and accompanying switch mode power conversion technique to efficiently capture the power generated from a solar cell array that would normally have been lost, for example, under reduced incident solar radiation. In an embodiment of the invention, the efficiency booster circuit generates an output current from the solar cell power source using a switch mode power converter. A control loop is closed around the input voltage to the converter circuit and not around the output voltage. The output voltage is allowed to float, being clamped by the loading conditions. If the outputs from multiple units are tied together, the currents will sum. If the output(s) are connected to a battery, the battery's potential will clamp the voltage during charge. This technique allows all solar cells in an array that are producing power and connected in parallel to work at their peak efficiency.

Owner:ISG TECH

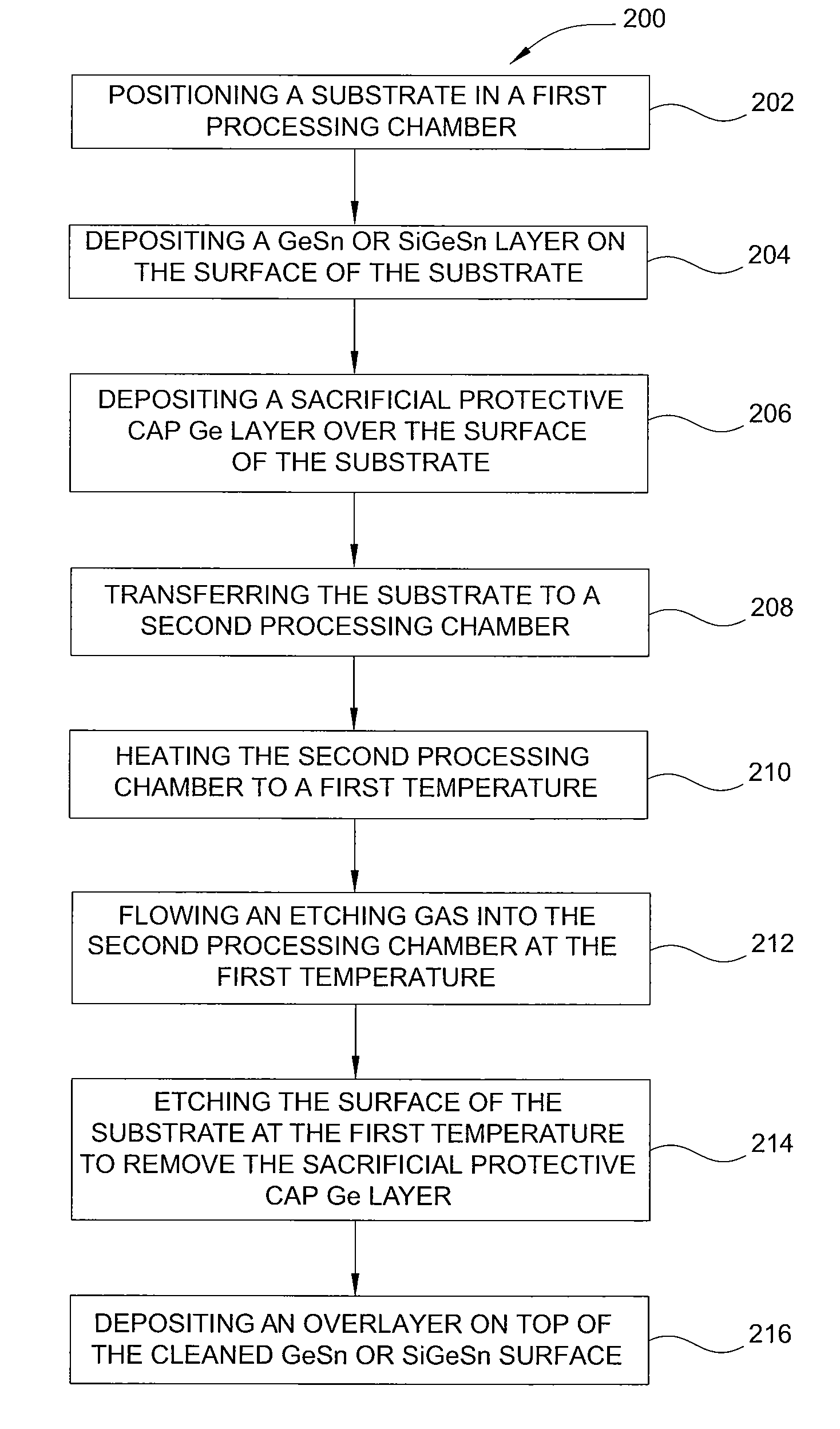

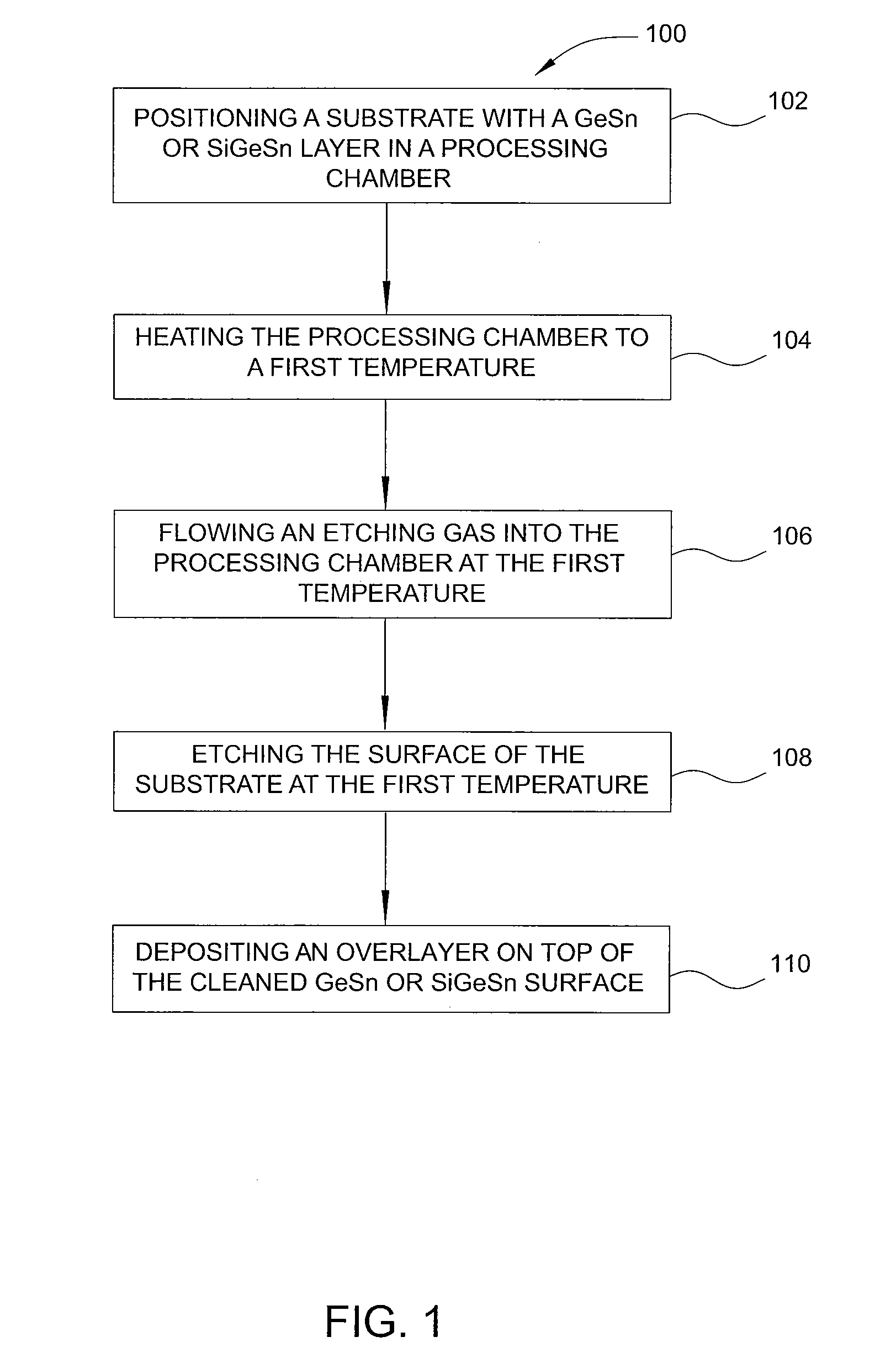

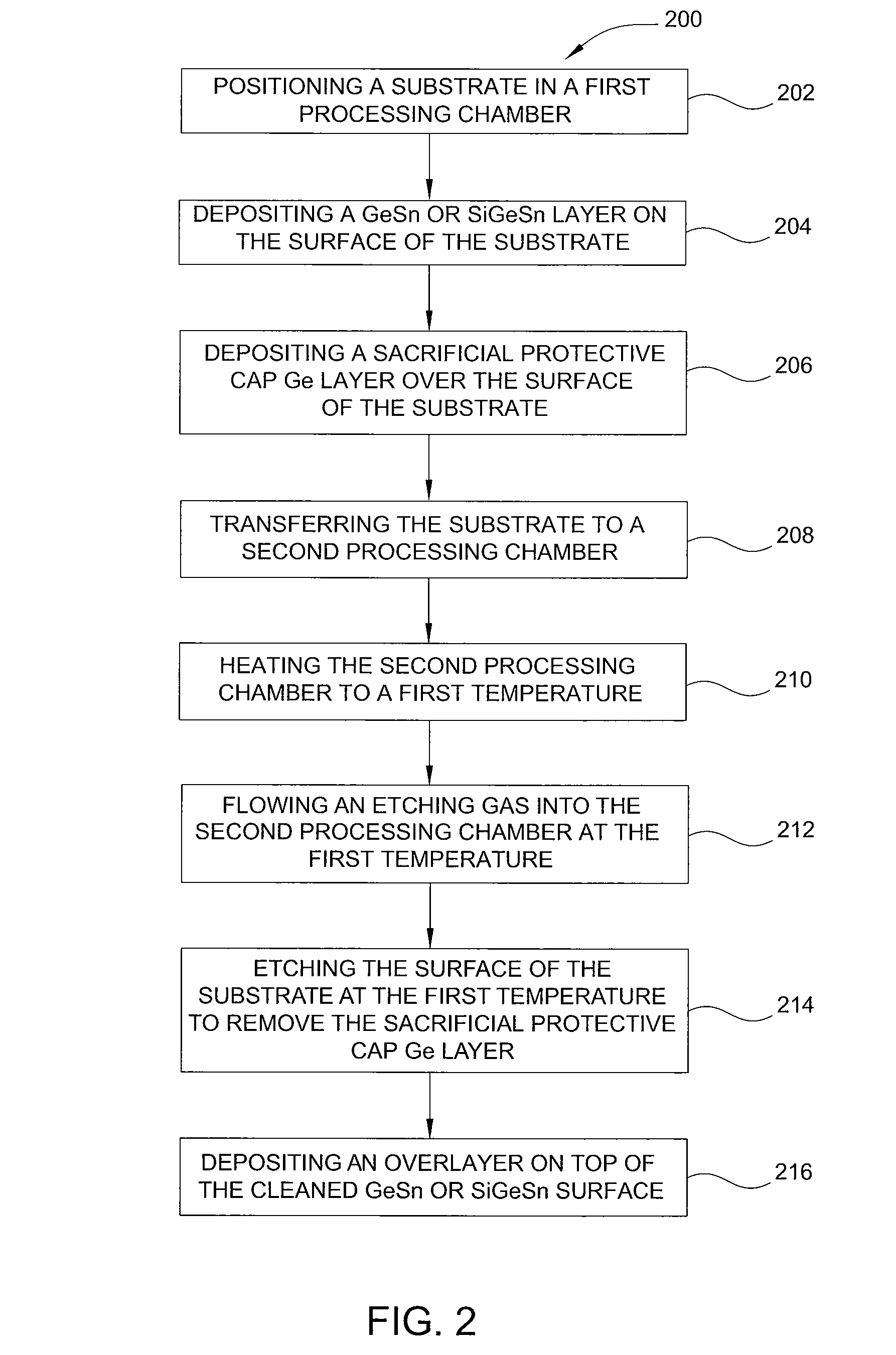

Method of epitaxial germanium tin alloy surface preparation

ActiveUS20130288480A1Increase temperatureStop the flowSemiconductor/solid-state device manufacturingPhotovoltaic energy generationEtchingRapid thermal annealing

Methods of preparing a clean surface of germanium tin or silicon germanium tin layers for subsequent deposition are provided. An overlayer of Ge, doped Ge, another GeSn or SiGeSn layer, a doped GeSn or SiGeSn layer, an insulator, or a metal can be deposited on a prepared GeSn or SiGeSn layer by positioning a substrate with an exposed germanium tin or silicon germanium tin layer in a processing chamber, heating the processing chamber and flowing a halide gas into the processing chamber to etch the surface of the substrate using either thermal or plasma assisted etching followed by depositing an overlayer on the substantially oxide free and contaminant free surface. Methods can also include the placement and etching of a sacrificial layer, a thermal clean using rapid thermal annealing, or a process in a plasma of nitrogen trifluoride and ammonia gas.

Owner:APPLIED MATERIALS INC

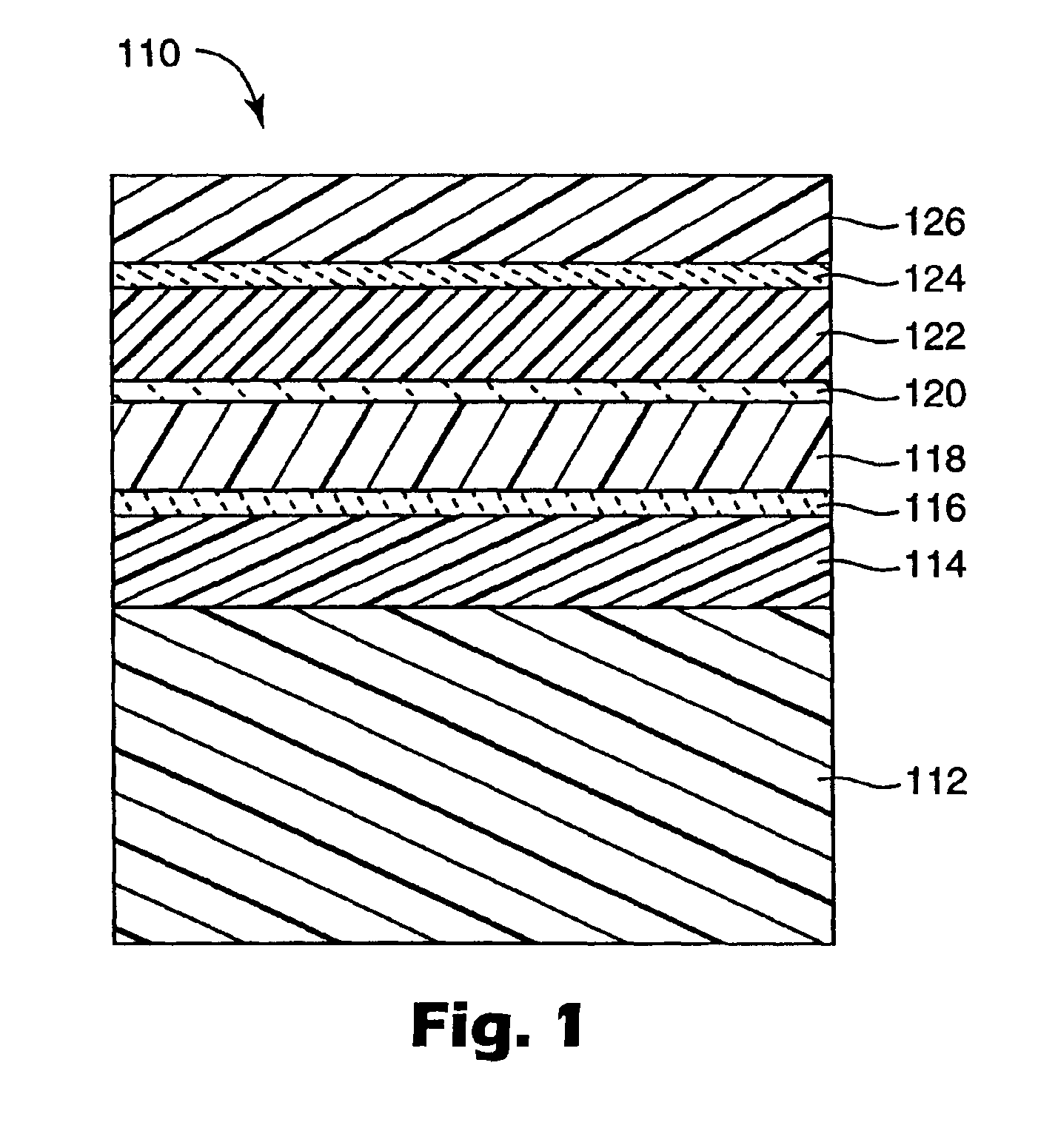

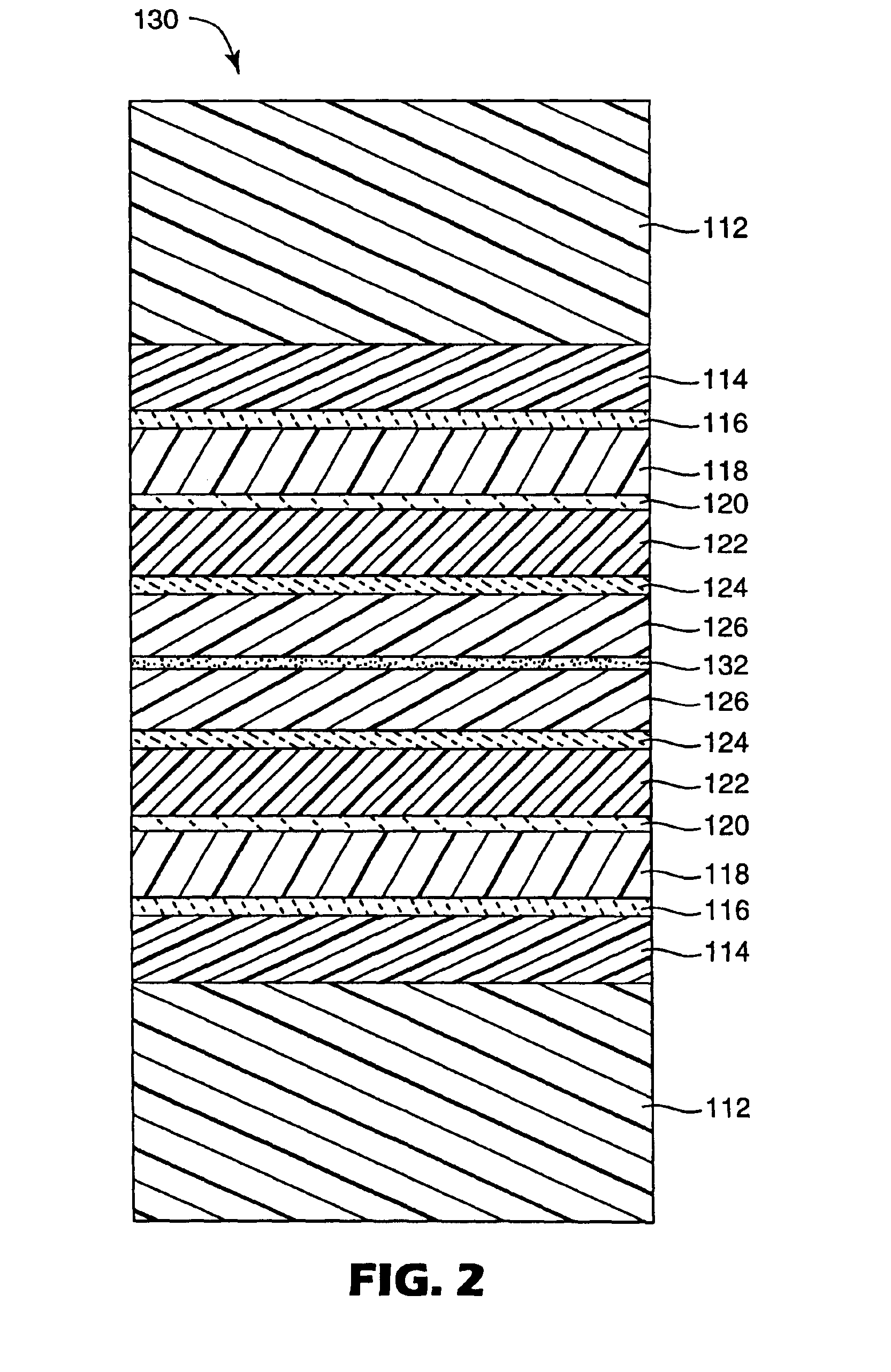

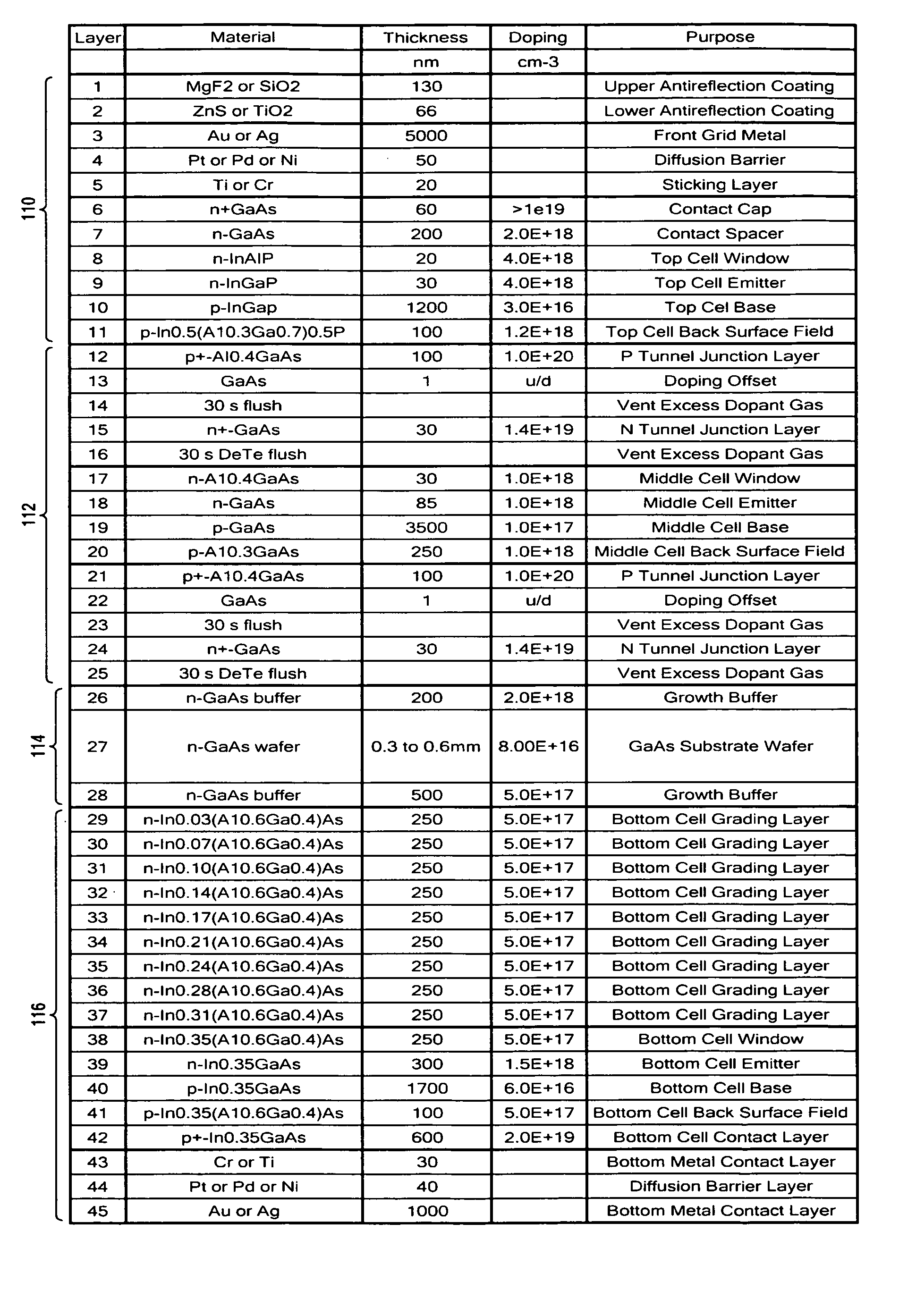

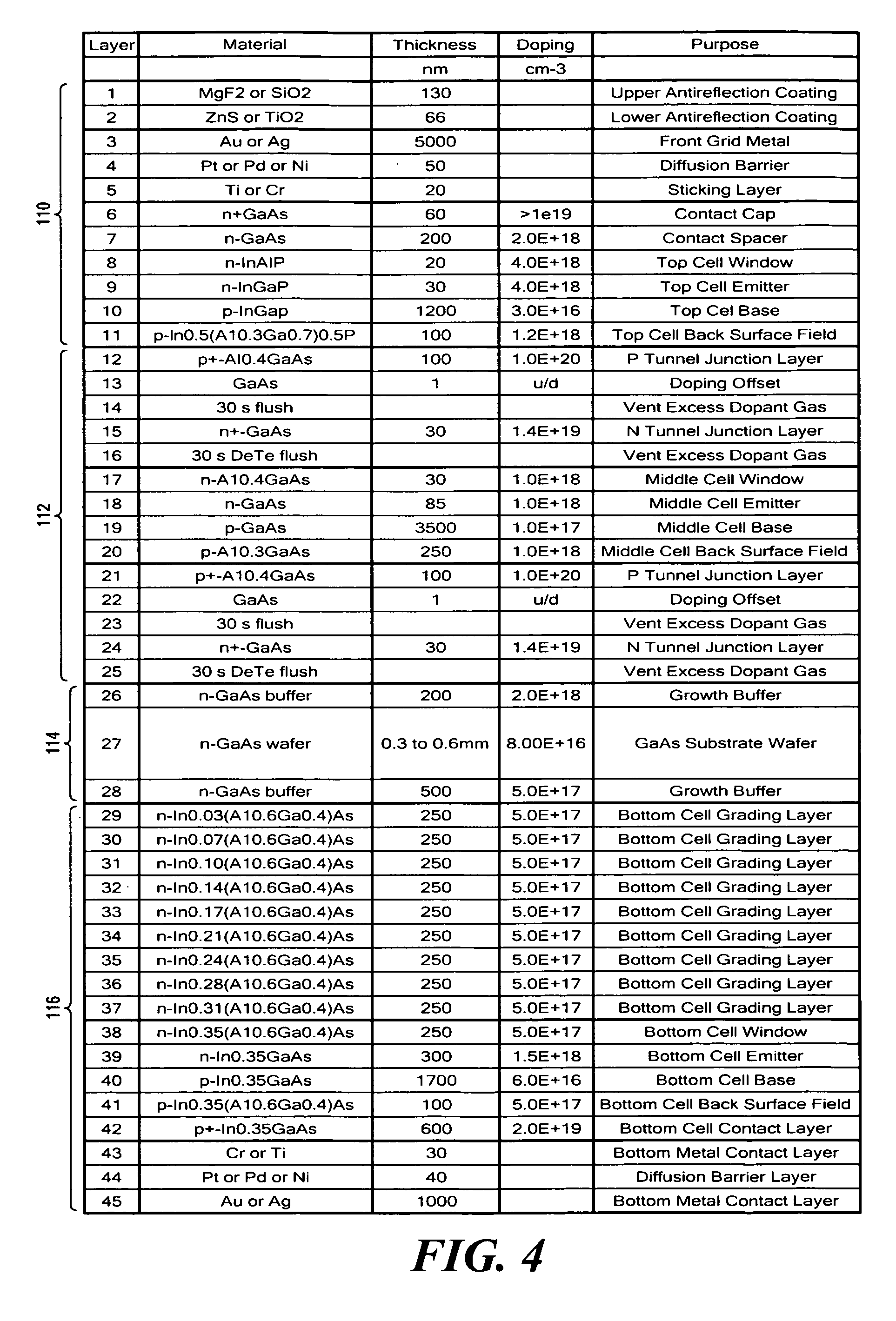

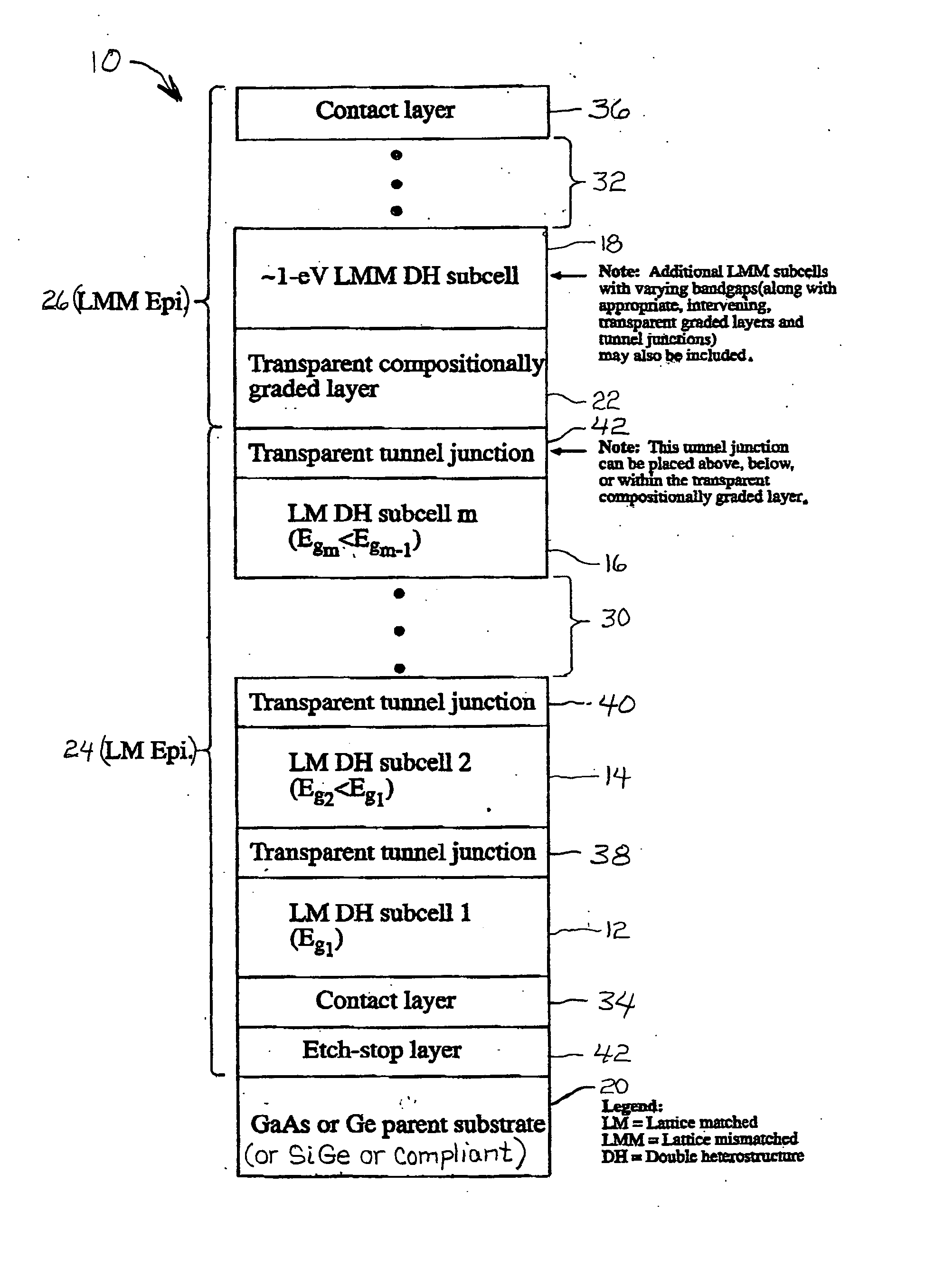

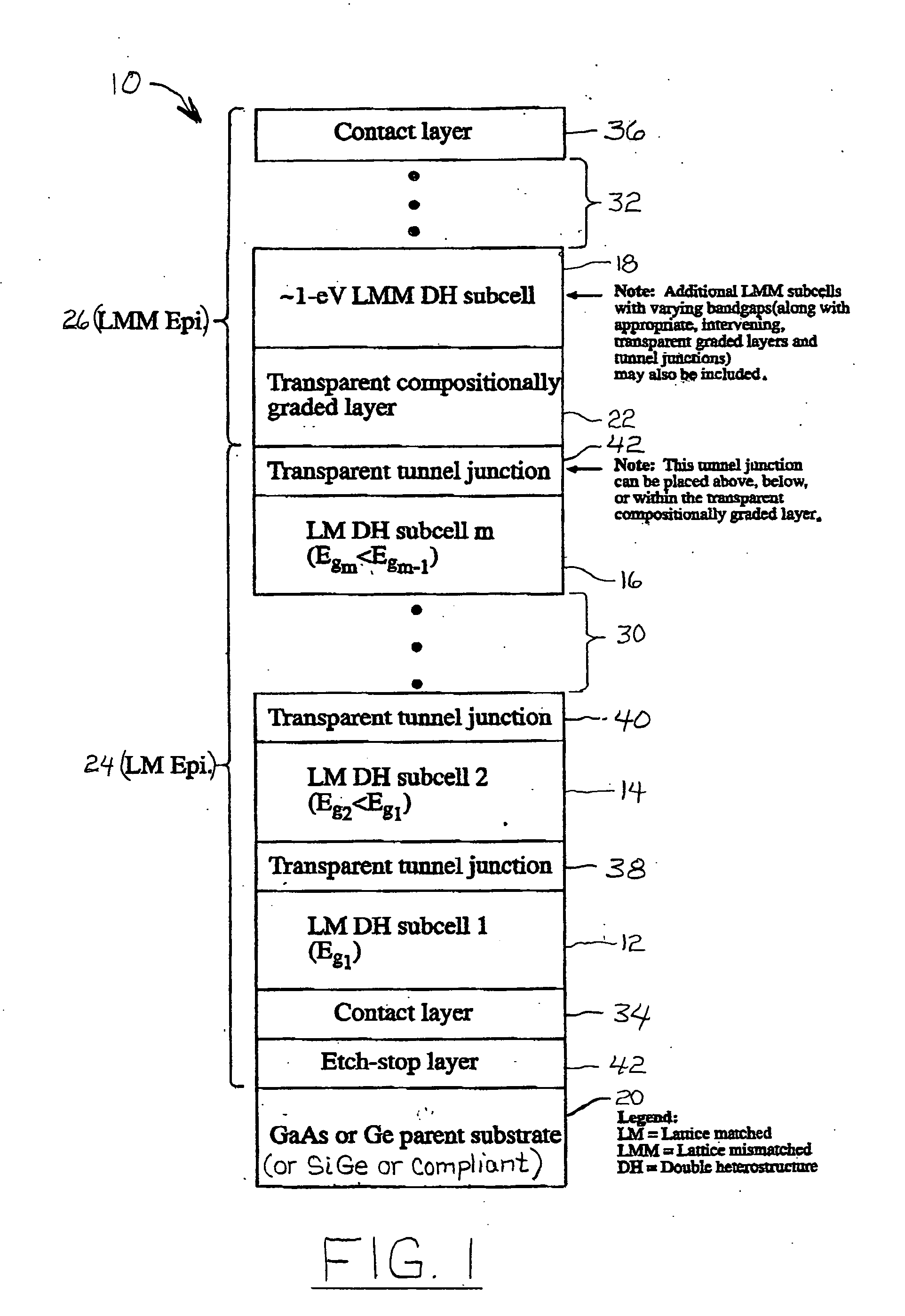

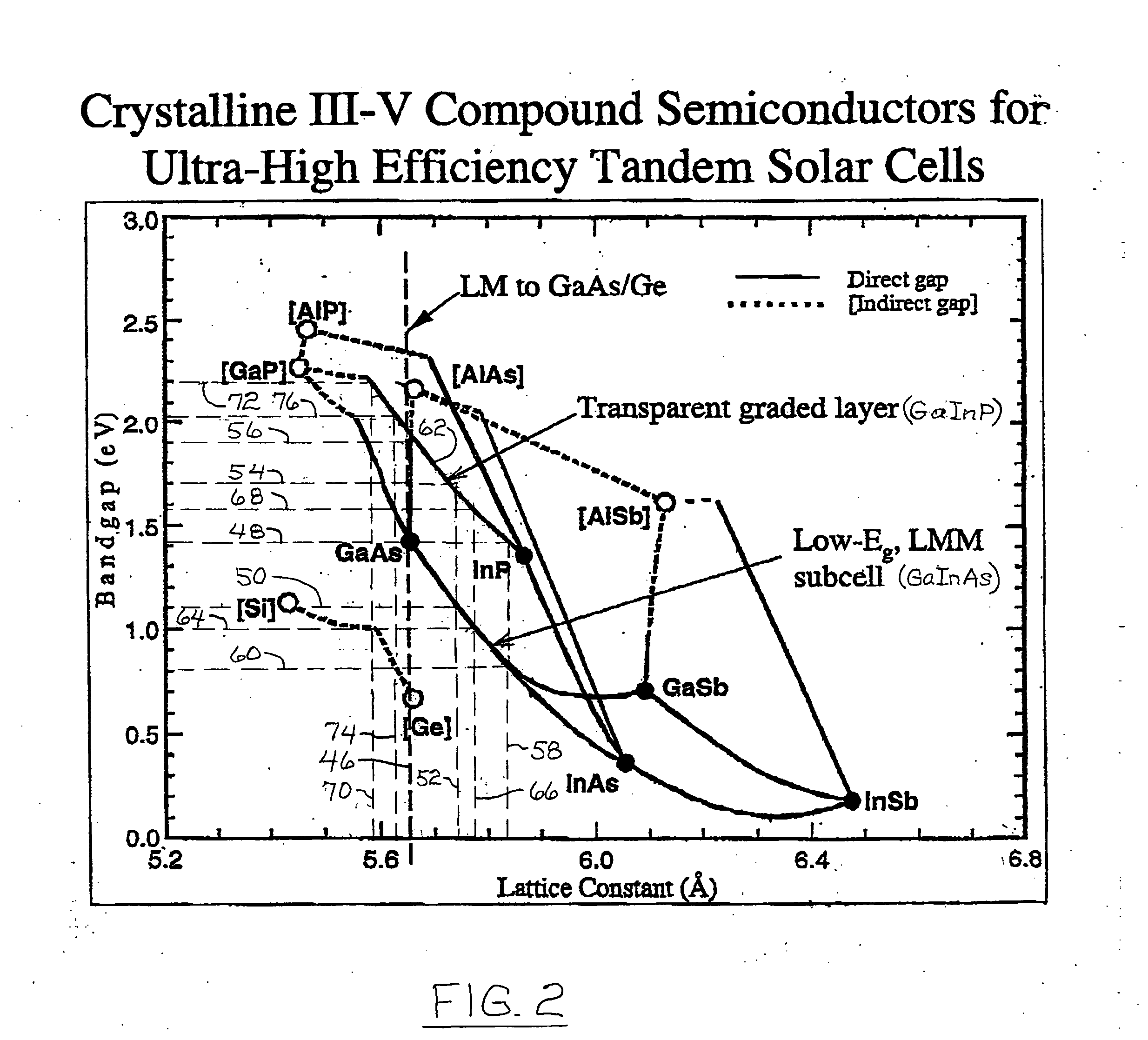

High-efficiency, monolithic, multi-bandgap, tandem photovoltaic energy converters

ActiveUS20060144435A1Improved thermal managementIncrease flexibilityPV power plantsSemiconductor/solid-state device manufacturingHigh energyLattice mismatch

A monolithic, multi-bandgap, tandem solar photovoltaic converter has at least one, and preferably at least two, subcells grown lattice-matched on a substrate with a bandgap in medium to high energy portions of the solar spectrum and at least one subcell grown lattice-mismatched to the substrate with a bandgap in the low energy portion of the solar spectrum, for example, about 1 eV.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

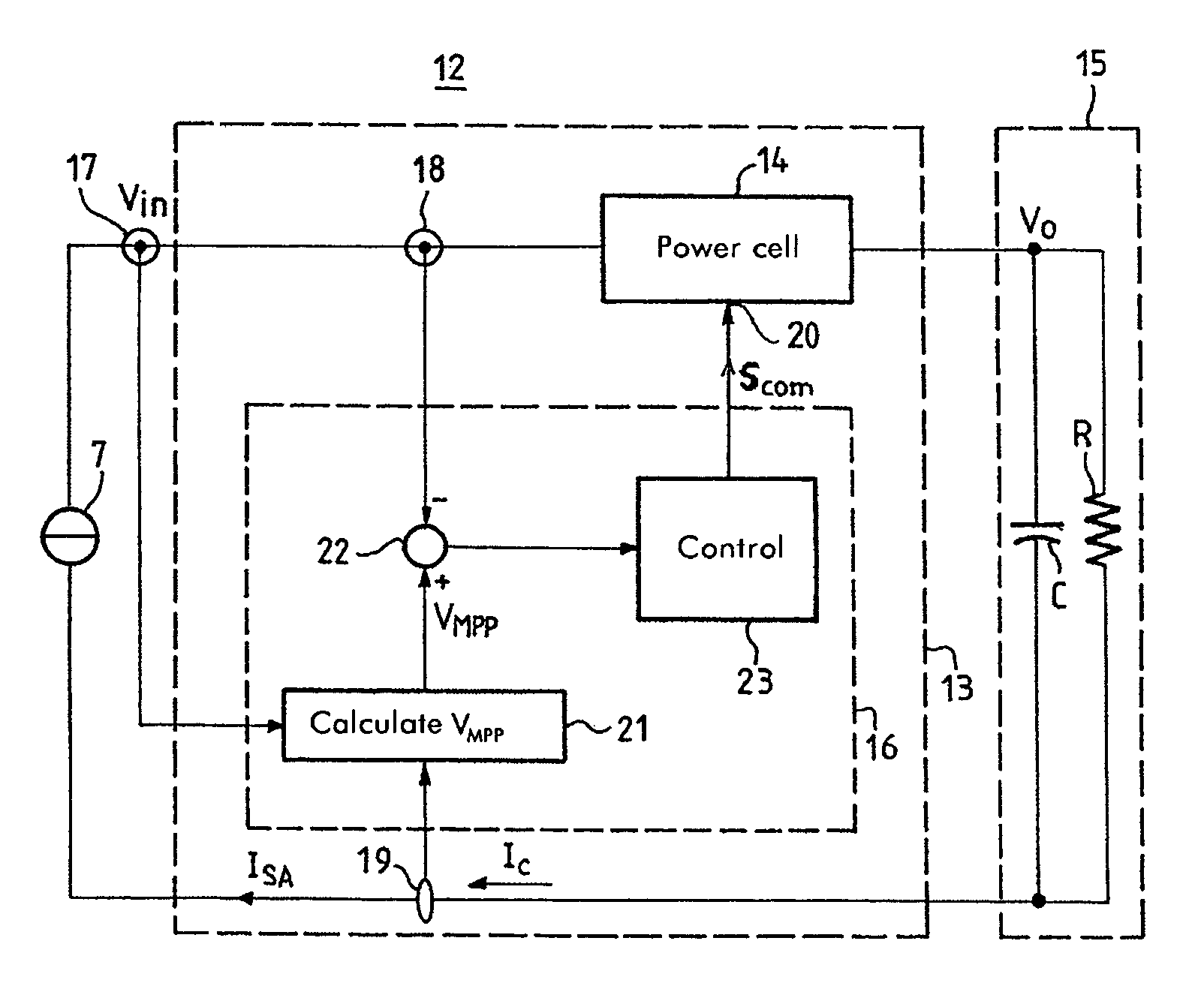

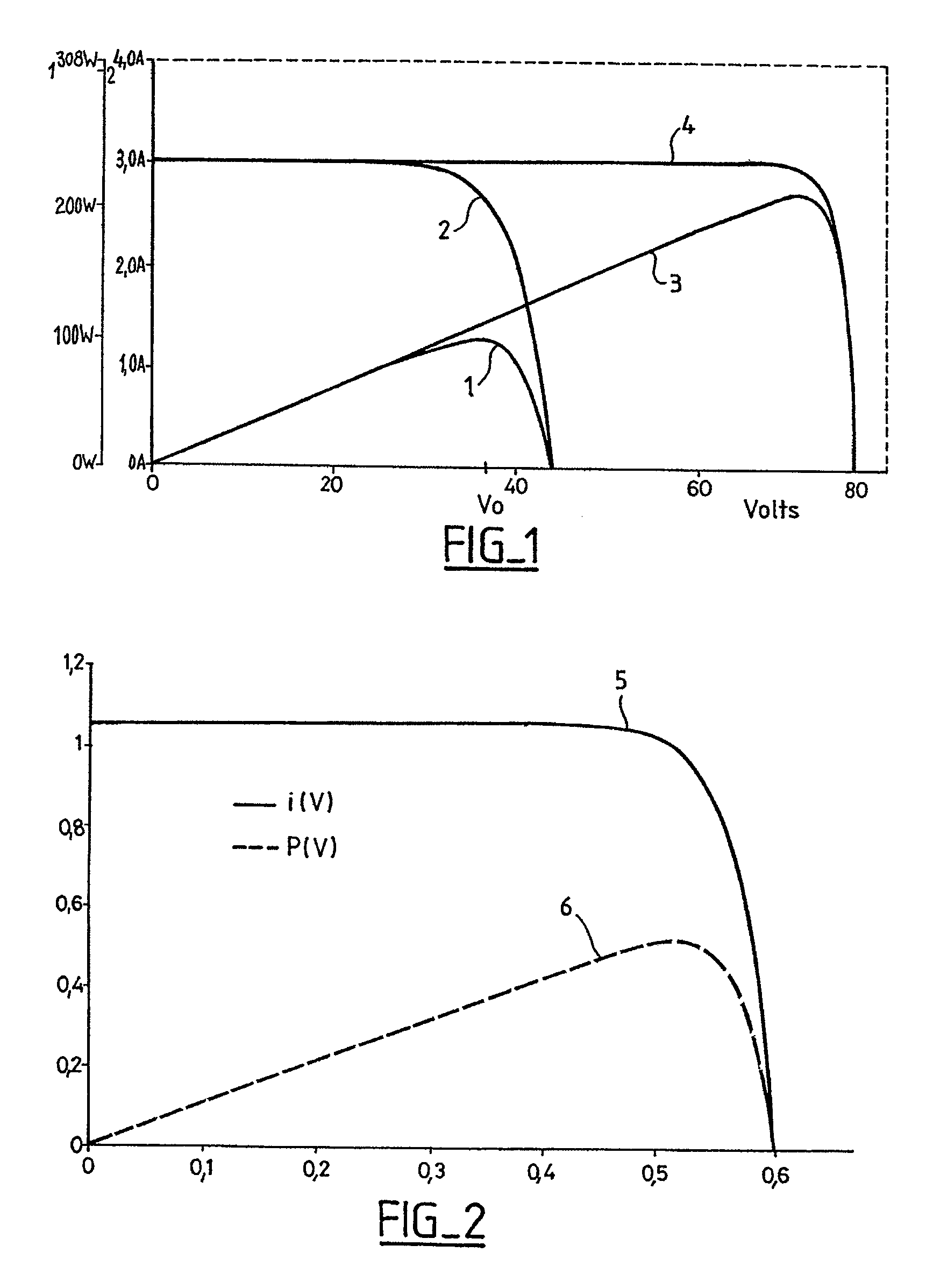

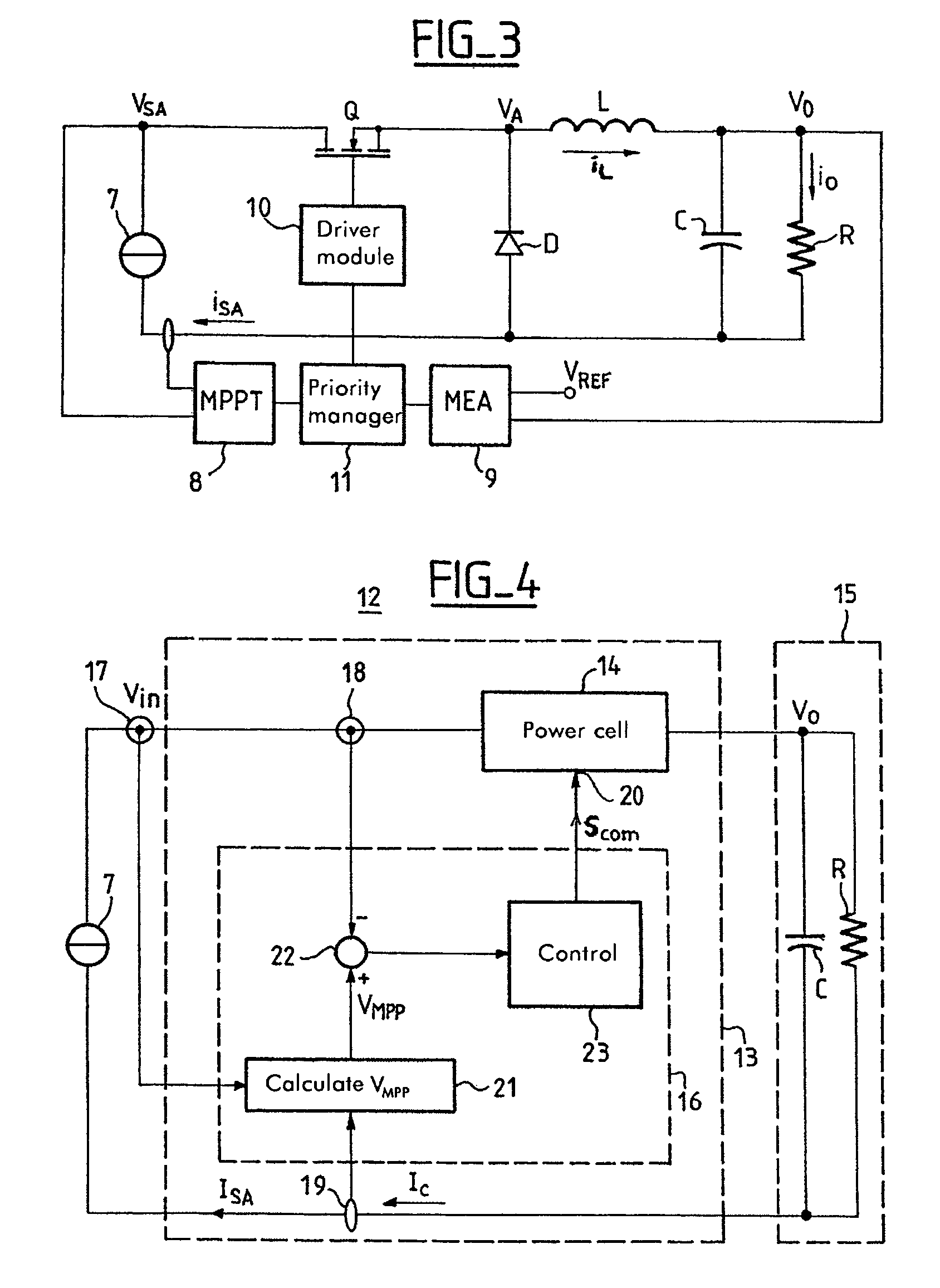

Conditioning circuit for a power supply at the maximum power point, a solar generator, and a conditioning method

InactiveUS6984970B2Batteries circuit arrangementsConversion with intermediate conversion to dcOperating pointSolar generator

The invention relates to a conditioning circuit that measures operating points of a power supply to deduce therefrom the current-voltage characteristic thereof and to determine directly the voltage corresponding to its maximum power point, without using any kind of tracking algorithm that causes the operating point of the power unit to oscillate about the maximum power point. The maximum power point voltage VMPP is supplied to a controller which regulates a power cell by slaving it to the input voltage until the output voltage of the supply is equal to the maximum power point voltage VMPP. The invention also relates to a solar generator and an associated conditioning method. One particular application is to high-power satellites.

Owner:ALCATEL LUCENT SAS

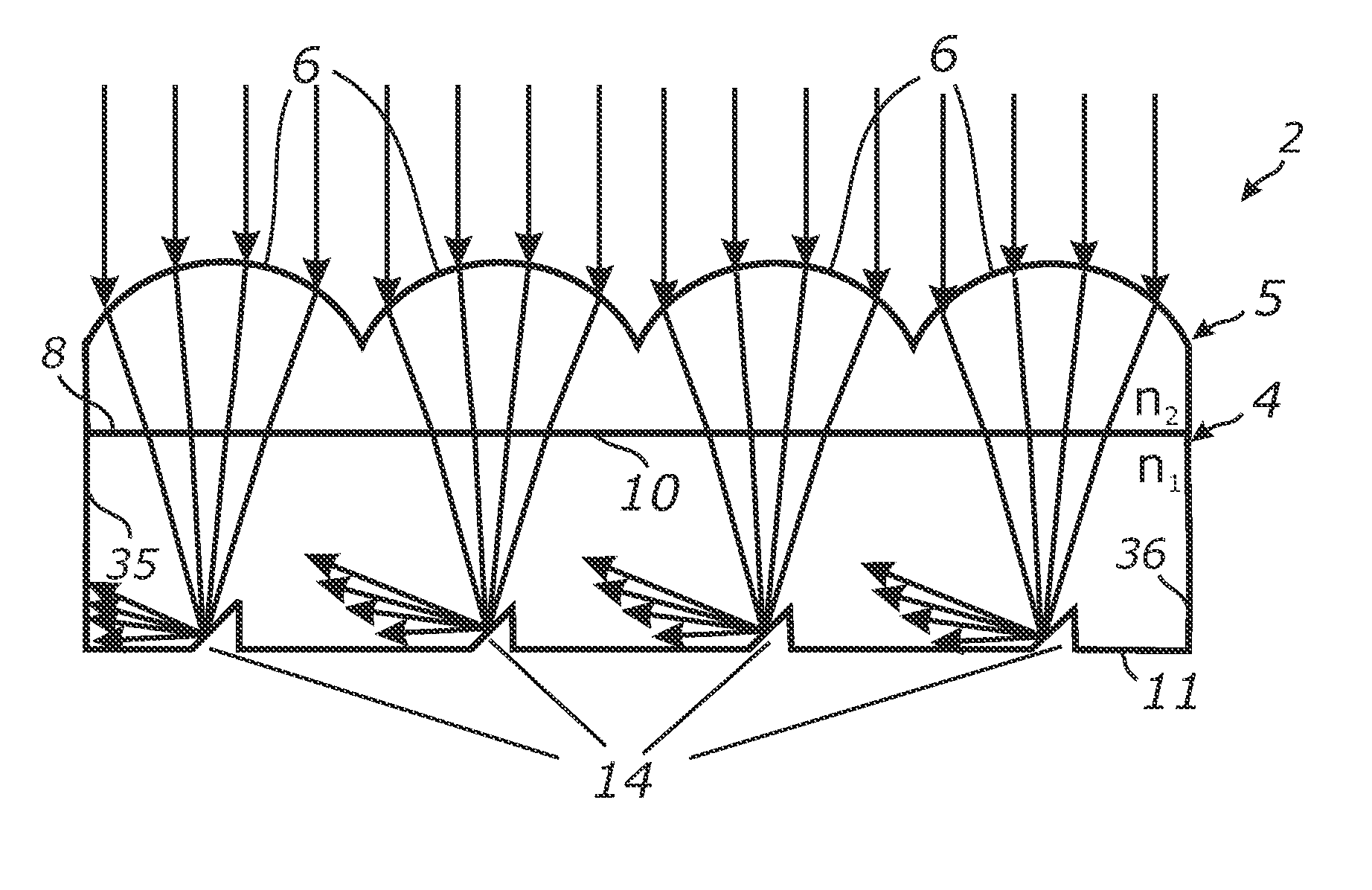

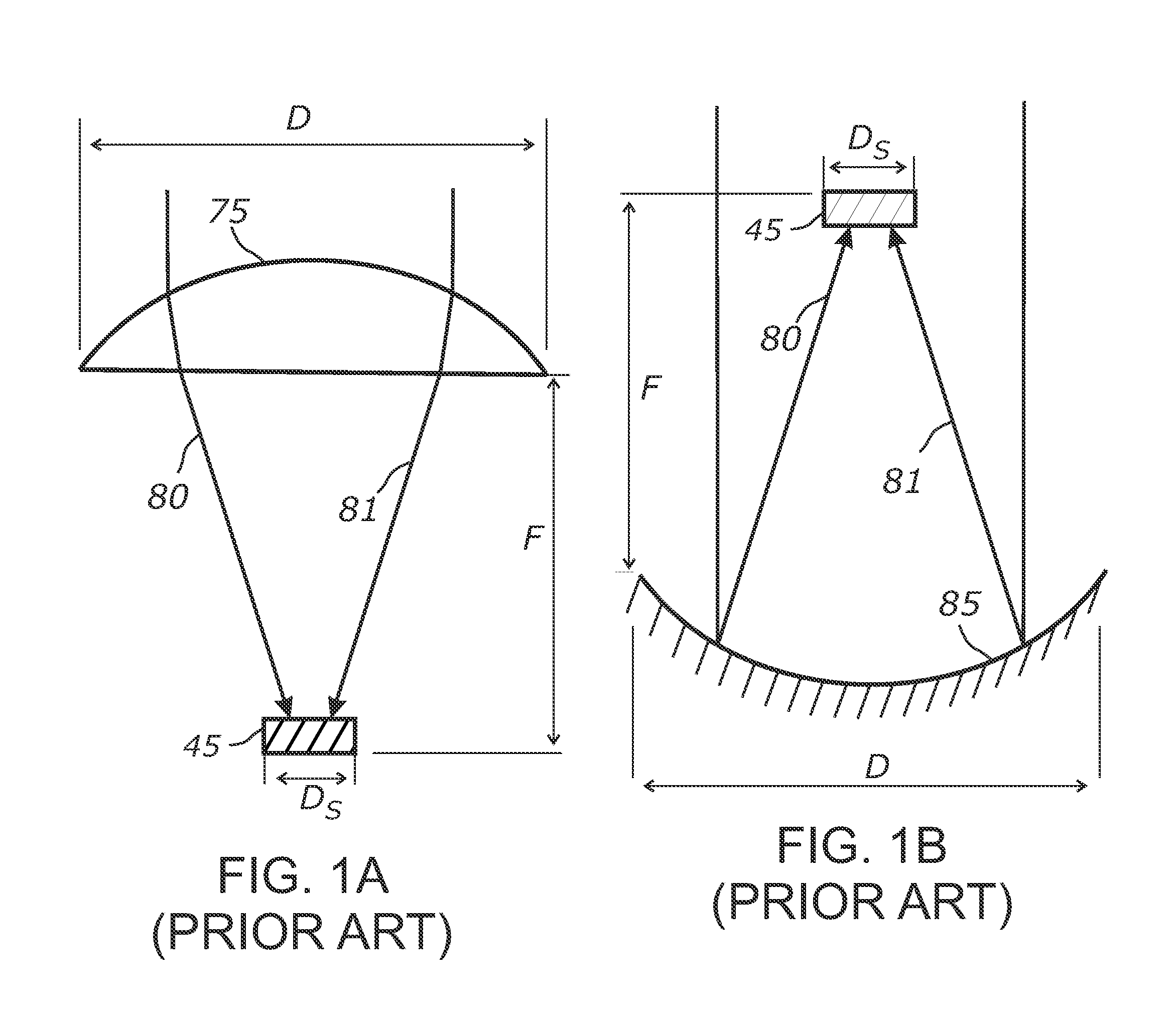

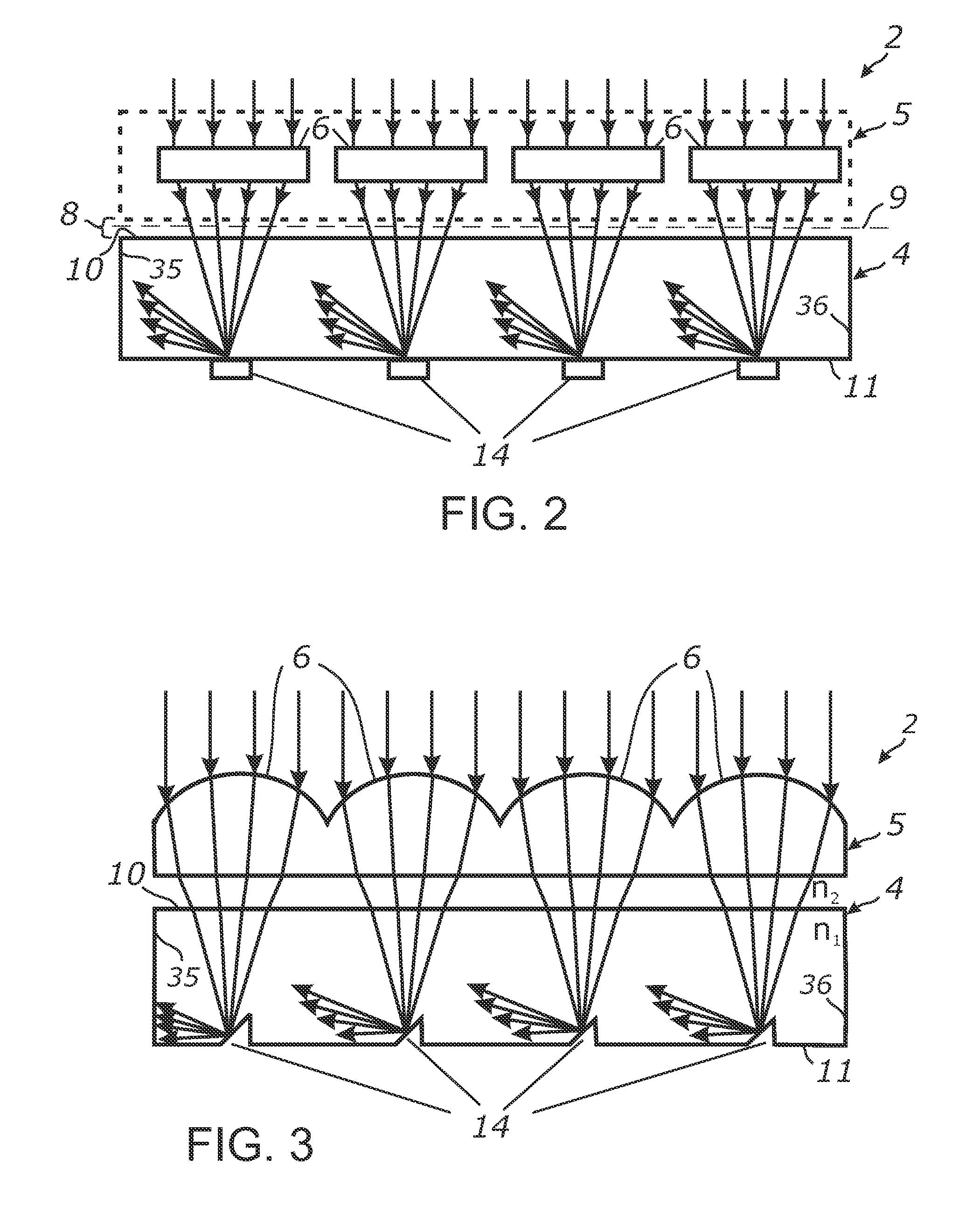

Light collection and illumination systems employing planar waveguide

ActiveUS20100278480A1Easy to transportEasy to harvestProjectorsCoupling light guidesTotal internal reflectionLighting system

An apparatus for distributing light from a waveguide through a collimating array, or collecting light over a given area into a waveguide. Light received within a waveguide is propagated transmissively and retained by total internal reflection, except in response to impinging upon deflector elements which sufficiently redirect the light to escape the waveguide into a collimator array that aligns and distributes the light. In a light collector, a collection array collects and collimates the received light and directs it at the surface of a waveguide, within which deflectors properly positioned in relation to each collector of the collector array, deflect the angle of the light so that it propagates through the waveguide in response to total internal reflection. The apparatus can be fabricated into an efficient and compact form.

Owner:S V V TECH INNOVATIONS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com