Patents

Literature

709 results about "Rapid thermal annealing" patented technology

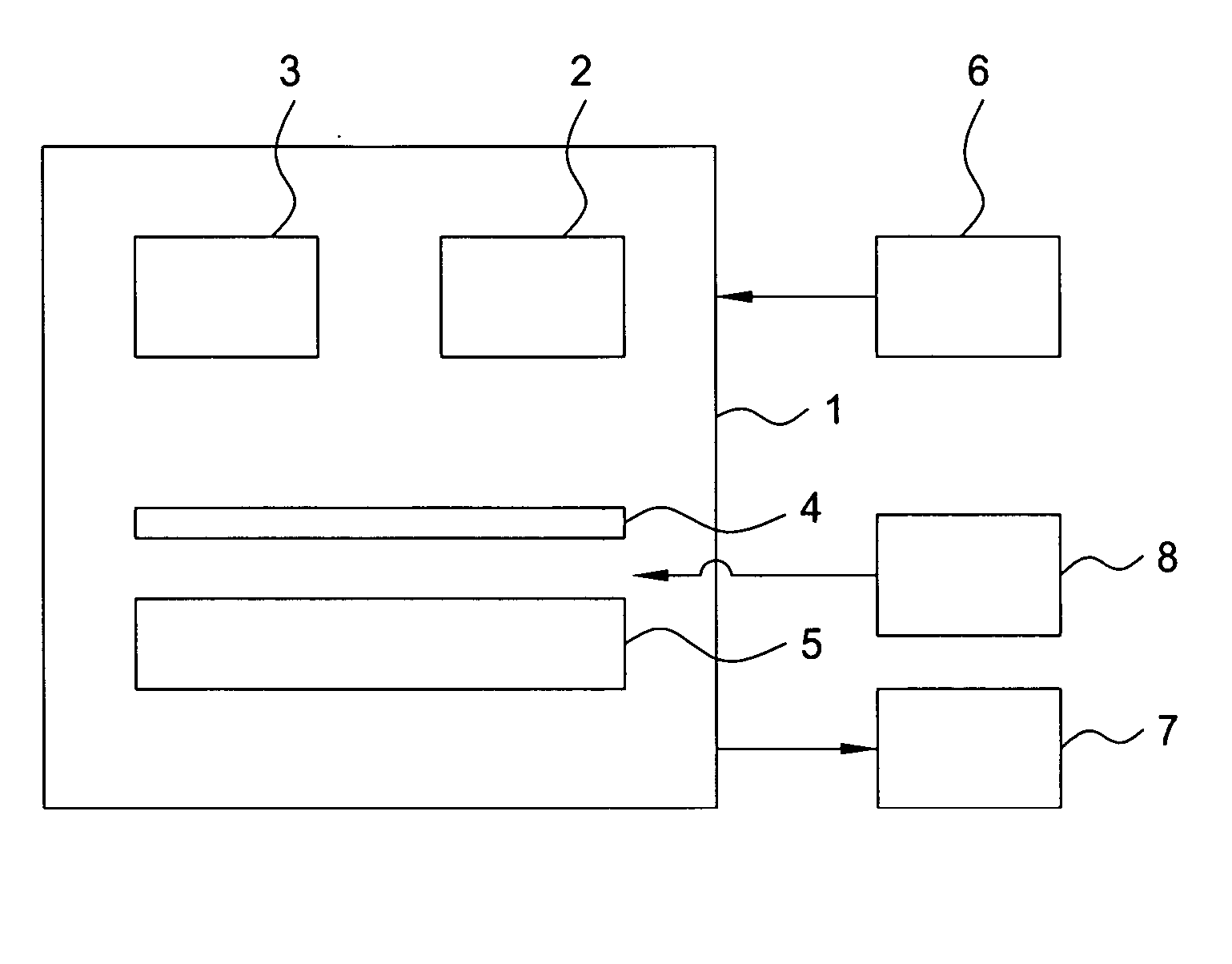

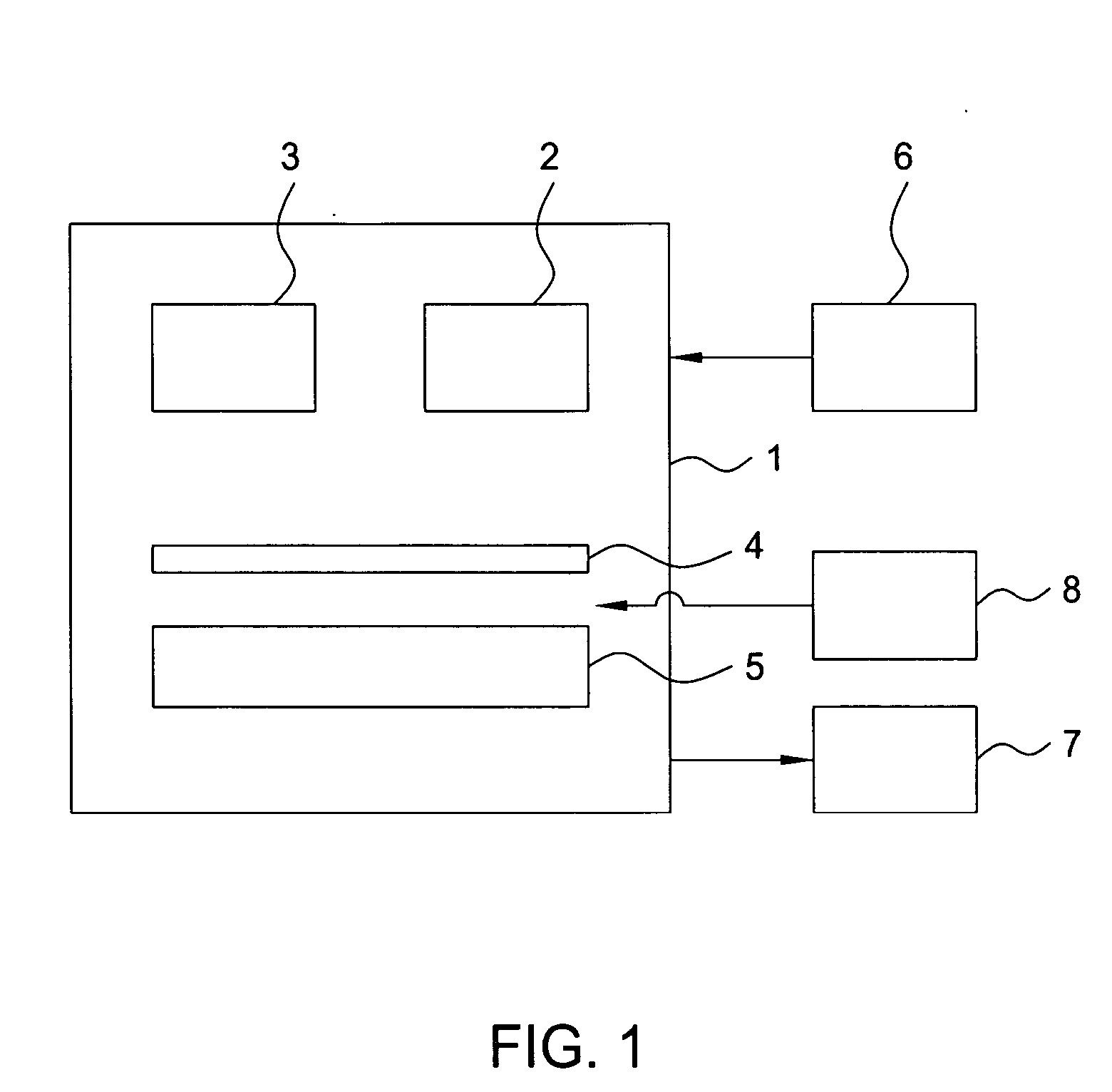

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In the semiconductor industry, rapid thermal annealing (RTA) is a semiconductor process step used for the activation of dopants and the interfacial reaction of metal contacts. In principle, the operation involves rapid heating of a wafer from ambient to approximately 1000–1500 K.

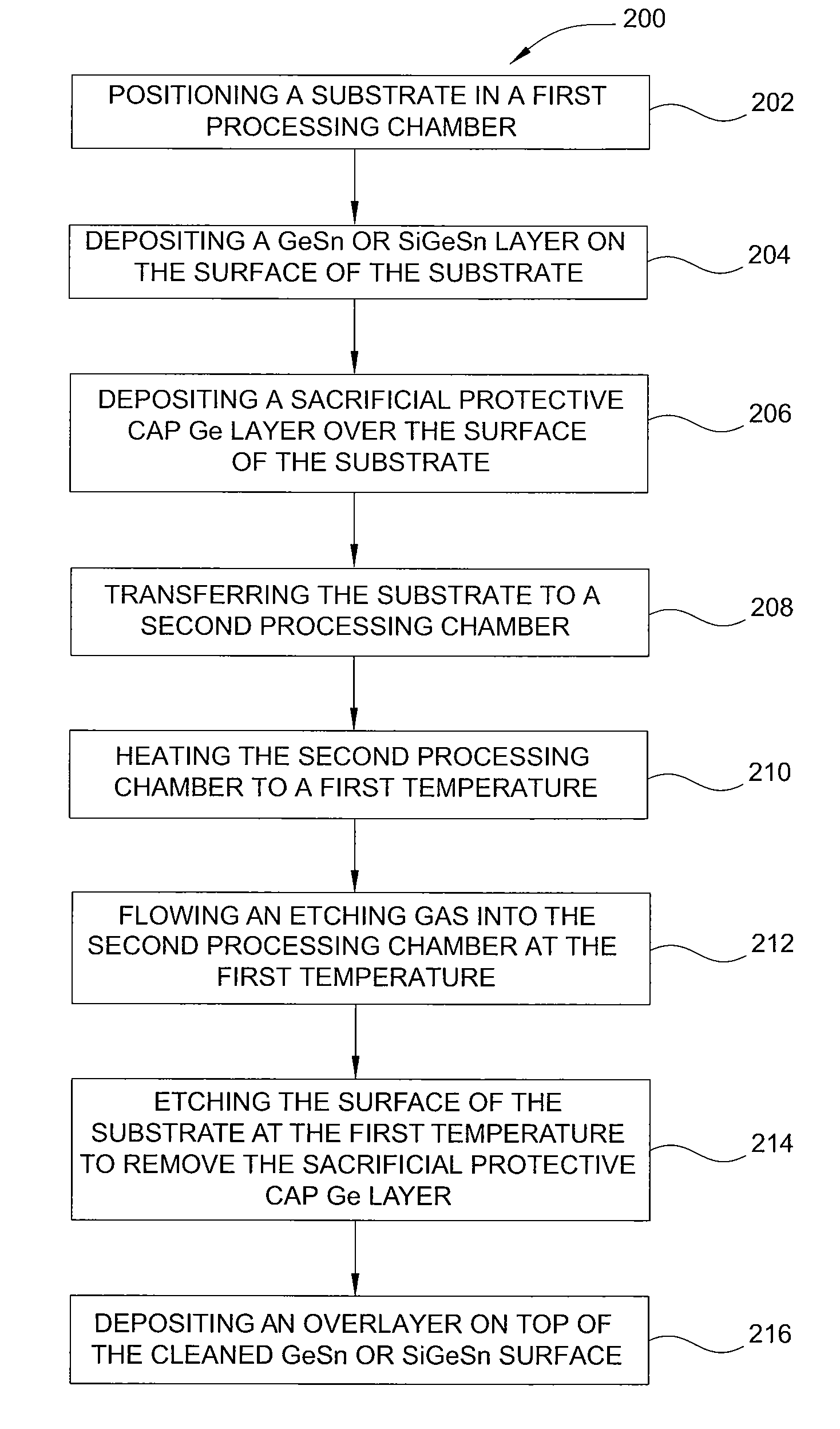

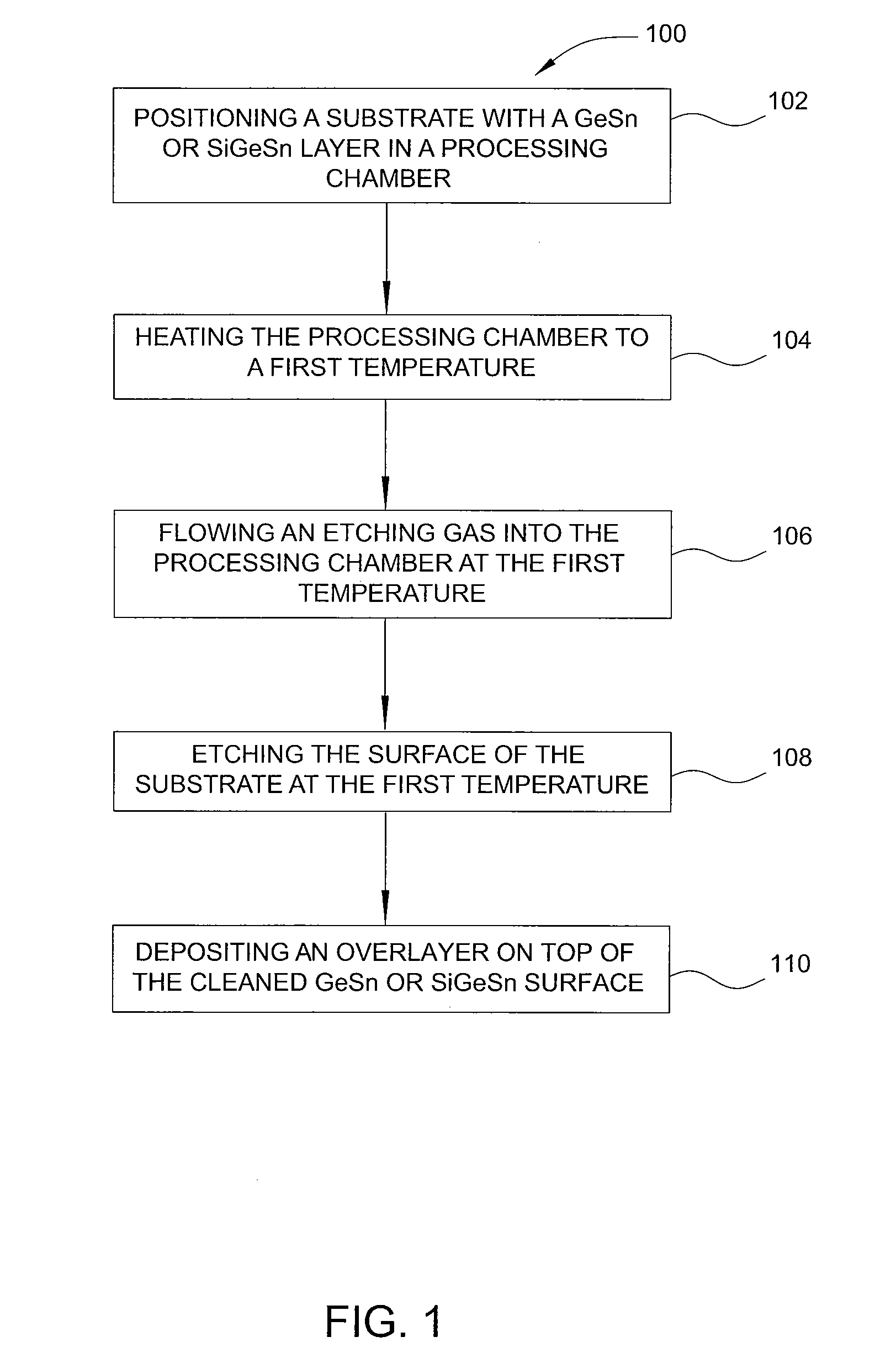

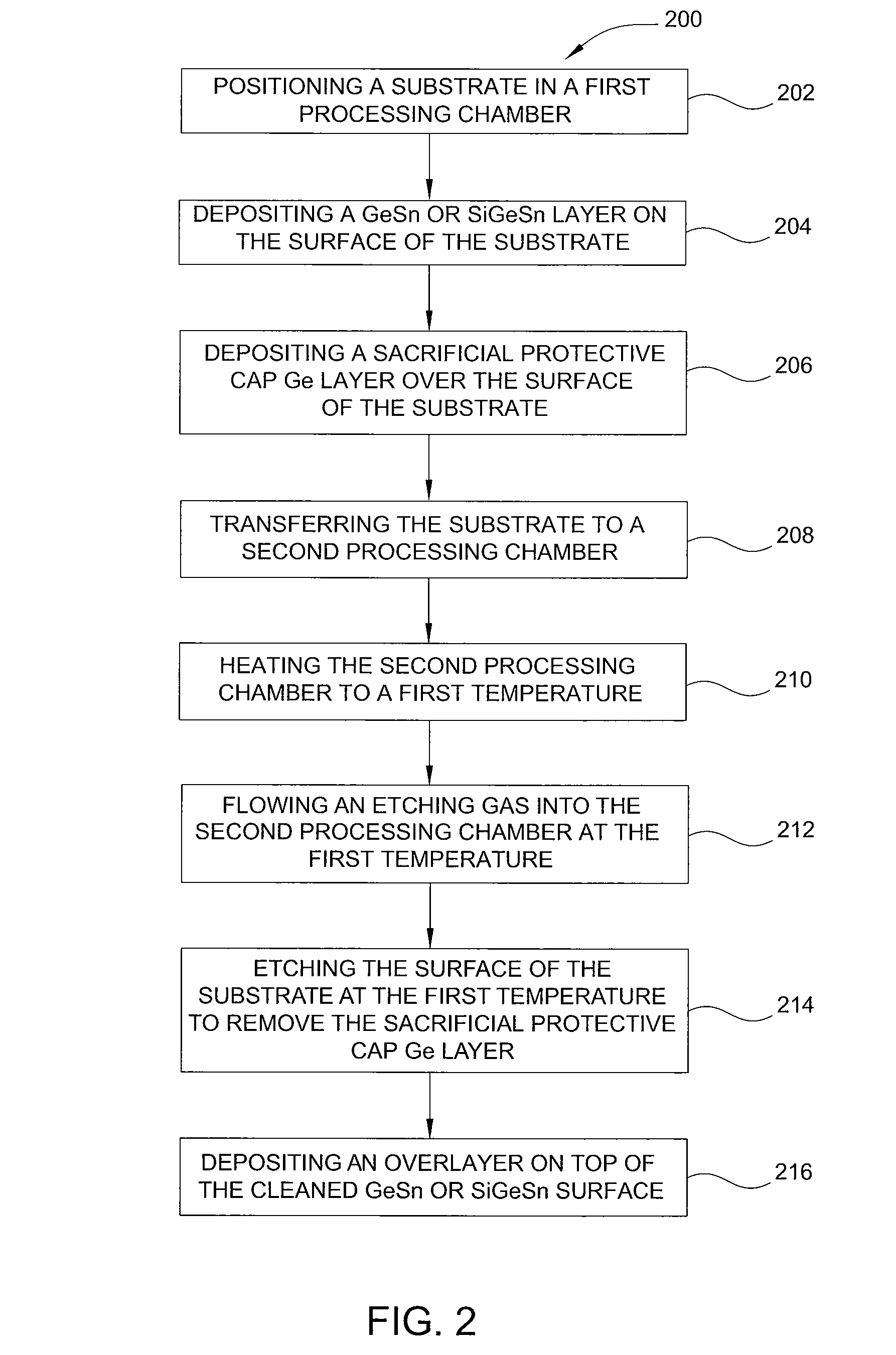

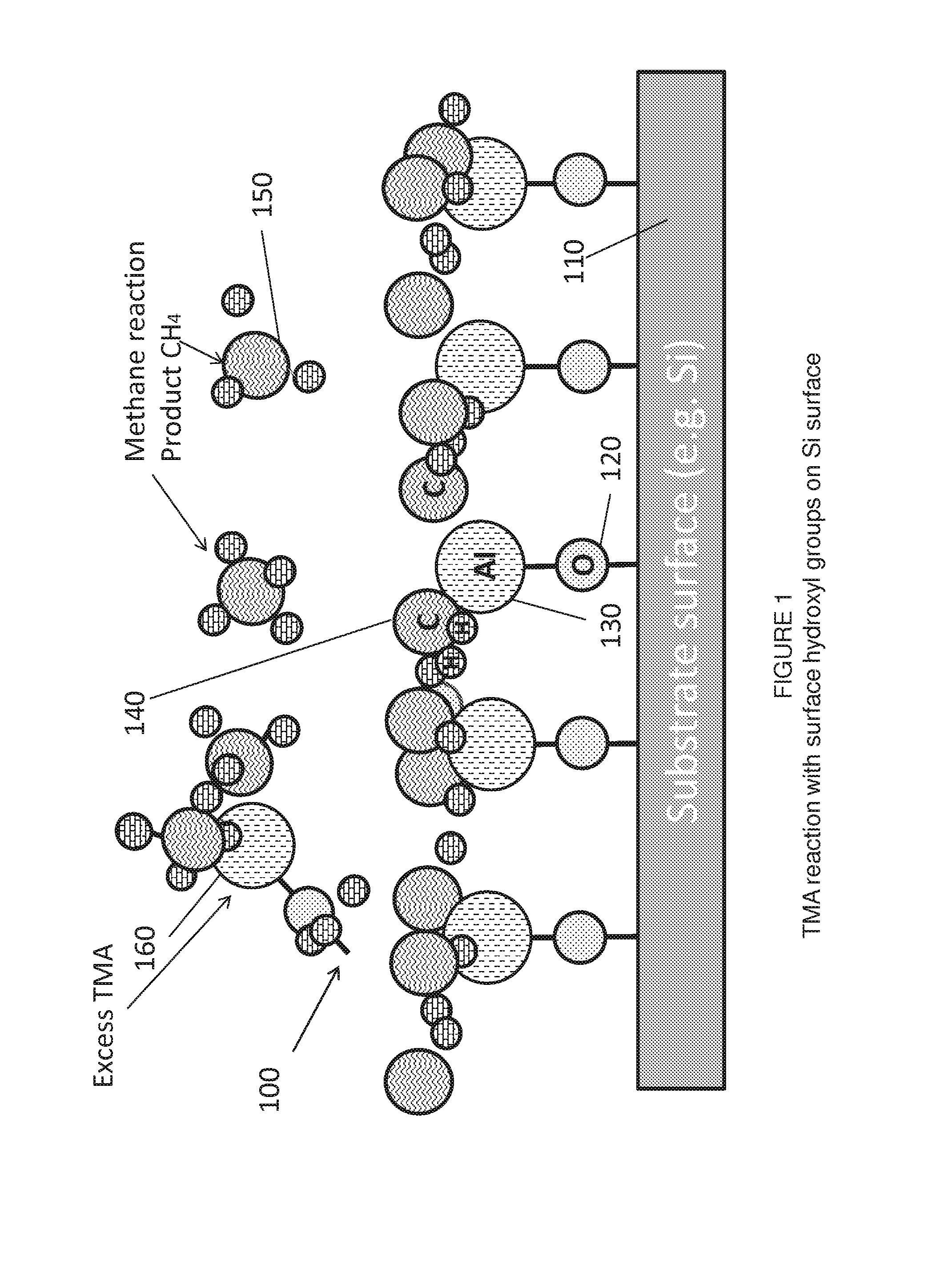

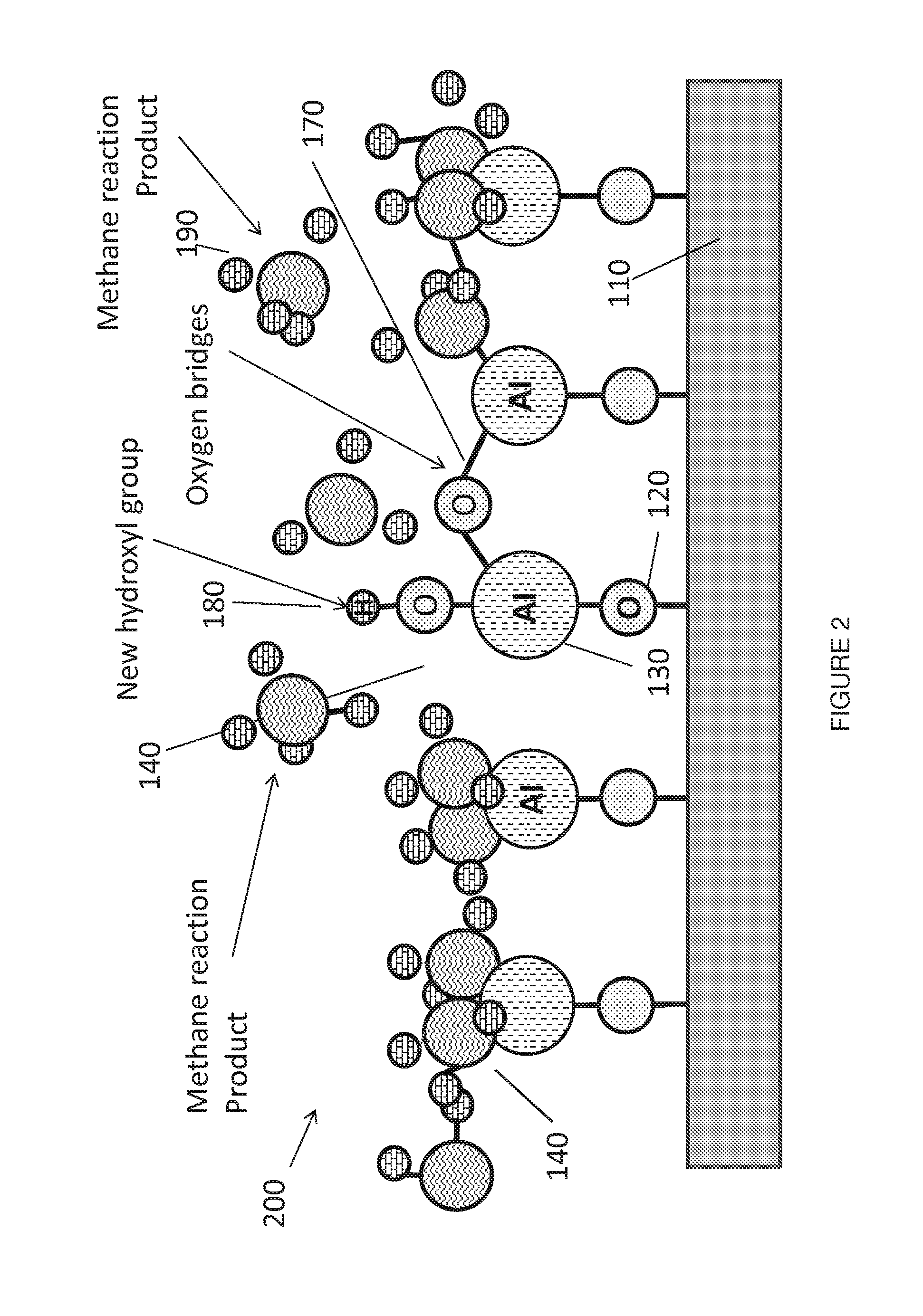

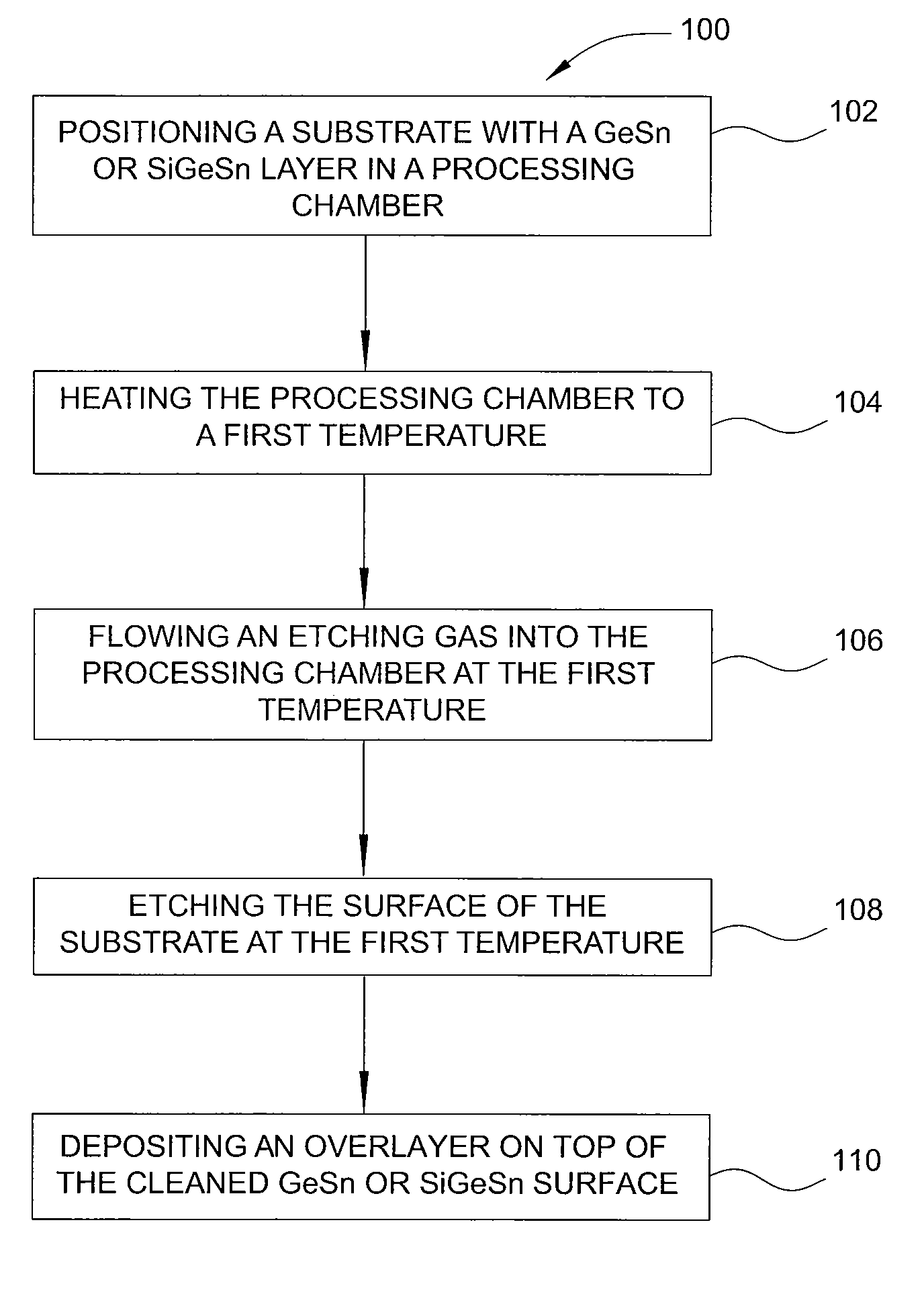

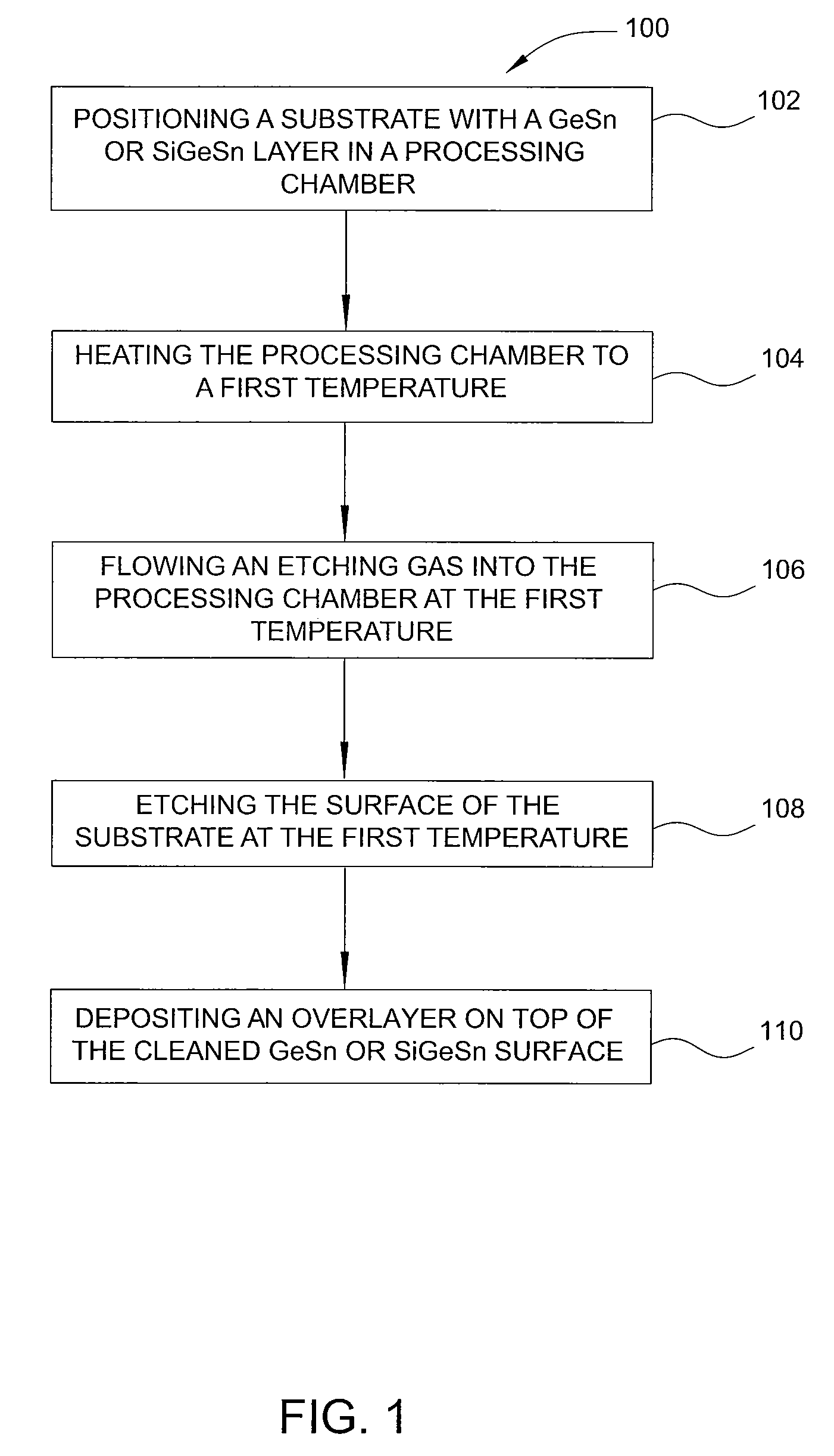

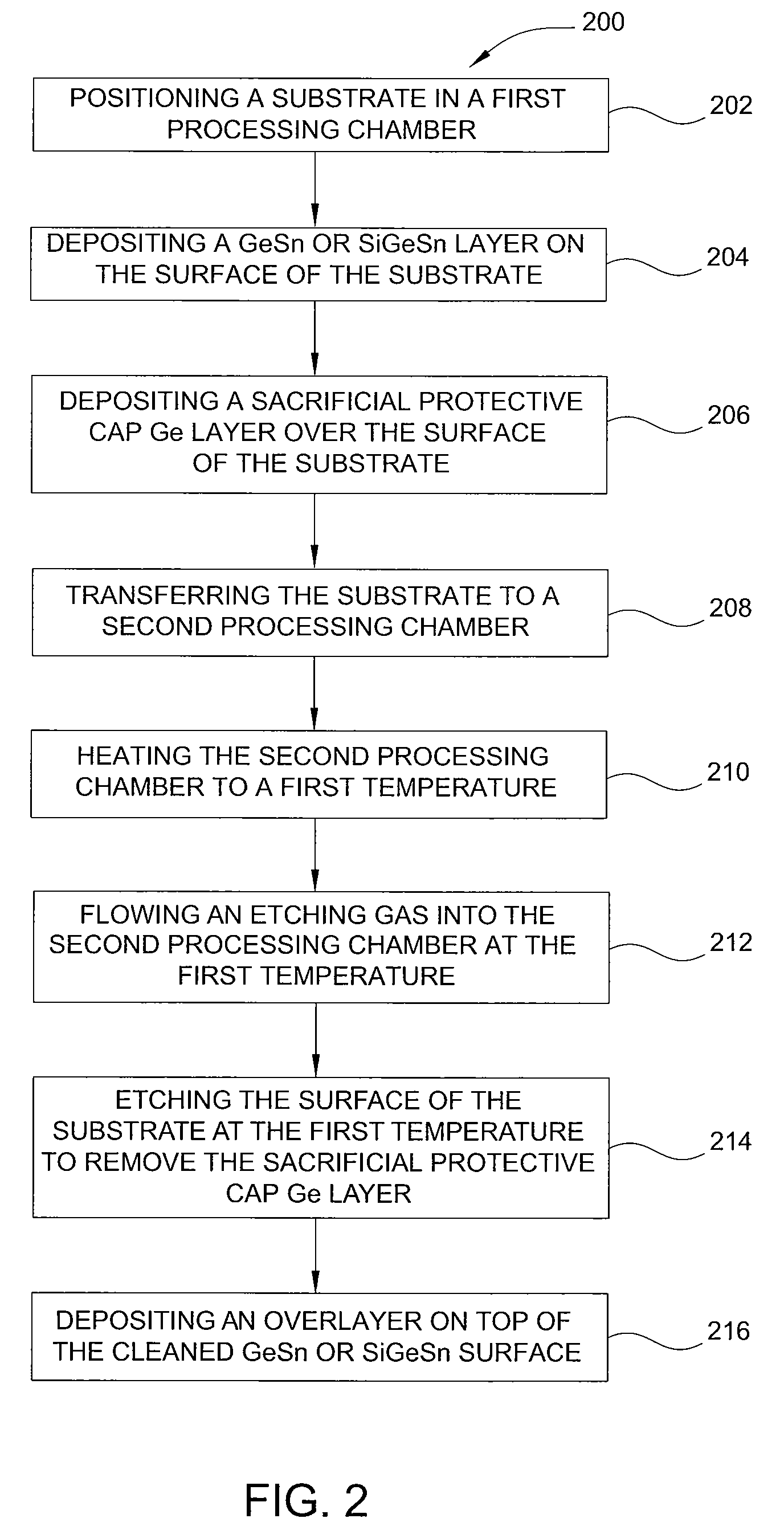

Method of epitaxial germanium tin alloy surface preparation

ActiveUS20130288480A1Increase temperatureStop the flowSemiconductor/solid-state device manufacturingPhotovoltaic energy generationEtchingRapid thermal annealing

Methods of preparing a clean surface of germanium tin or silicon germanium tin layers for subsequent deposition are provided. An overlayer of Ge, doped Ge, another GeSn or SiGeSn layer, a doped GeSn or SiGeSn layer, an insulator, or a metal can be deposited on a prepared GeSn or SiGeSn layer by positioning a substrate with an exposed germanium tin or silicon germanium tin layer in a processing chamber, heating the processing chamber and flowing a halide gas into the processing chamber to etch the surface of the substrate using either thermal or plasma assisted etching followed by depositing an overlayer on the substantially oxide free and contaminant free surface. Methods can also include the placement and etching of a sacrificial layer, a thermal clean using rapid thermal annealing, or a process in a plasma of nitrogen trifluoride and ammonia gas.

Owner:APPLIED MATERIALS INC

Formation of heteroepitaxial layers with rapid thermal processing to remove lattice dislocations

InactiveUS20160155629A1Semiconductor/solid-state device manufacturingWelding/soldering/cutting articlesReaction temperatureGallium nitride

Method and devices are disclosed for device manufacture of gallium nitride devices by growing a gallium nitride layer on a silicon substrate using Atomic Layer Deposition (ALD) followed by rapid thermal annealing. Gallium nitride is grown directly on silicon or on a barrier layer of aluminum nitride grown on the silicon substrate. One or both layers are thermally processed by rapid thermal annealing. Preferably the ALD process use a reaction temperature below 550° C. and preferable below 350° C. The rapid thermal annealing step raises the temperature of the coating surface to a temperature ranging from 550 to 1500° C. for less than 12 msec.

Owner:VEECO INSTR

Method of epitaxial germanium tin alloy surface preparation

Methods of preparing a clean surface of germanium tin or silicon germanium tin layers for subsequent deposition are provided. An overlayer of Ge, doped Ge, another GeSn or SiGeSn layer, a doped GeSn or SiGeSn layer, an insulator, or a metal can be deposited on a prepared GeSn or SiGeSn layer by positioning a substrate with an exposed germanium tin or silicon germanium tin layer in a processing chamber, heating the processing chamber and flowing a halide gas into the processing chamber to etch the surface of the substrate using either thermal or plasma assisted etching followed by depositing an overlayer on the substantially oxide free and contaminant free surface. Methods can also include the placement and etching of a sacrificial layer, a thermal clean using rapid thermal annealing, or a process in a plasma of nitrogen trifluoride and ammonia gas.

Owner:APPLIED MATERIALS INC

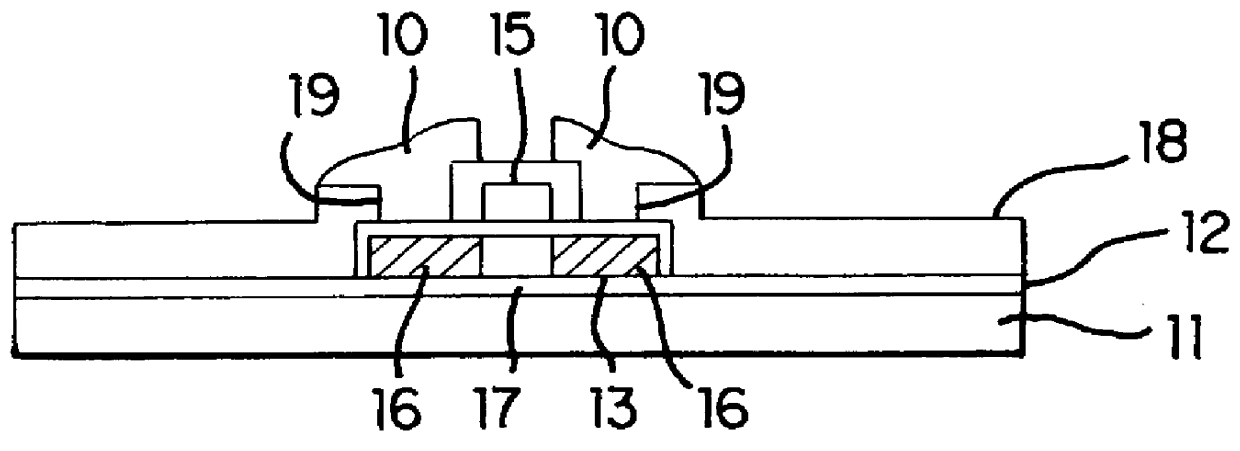

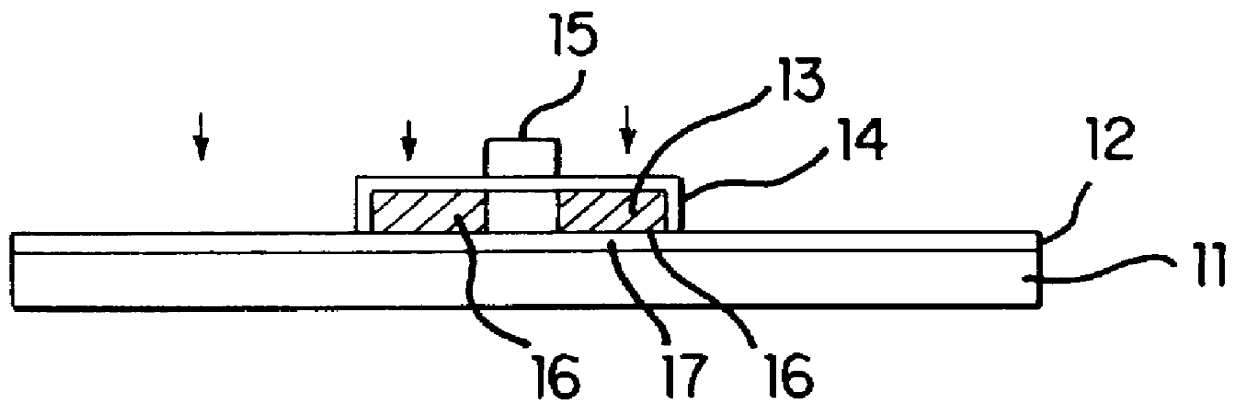

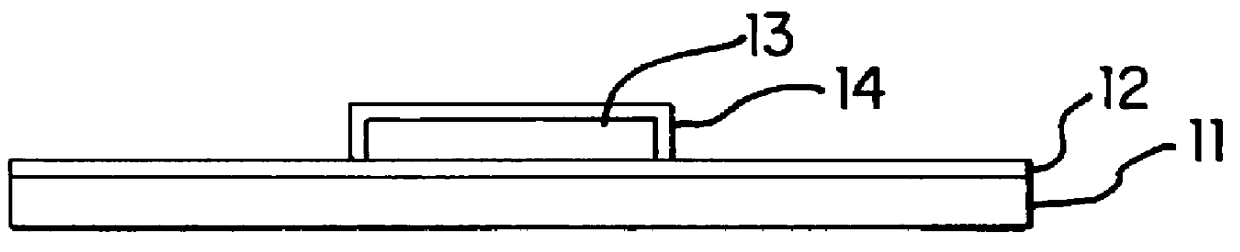

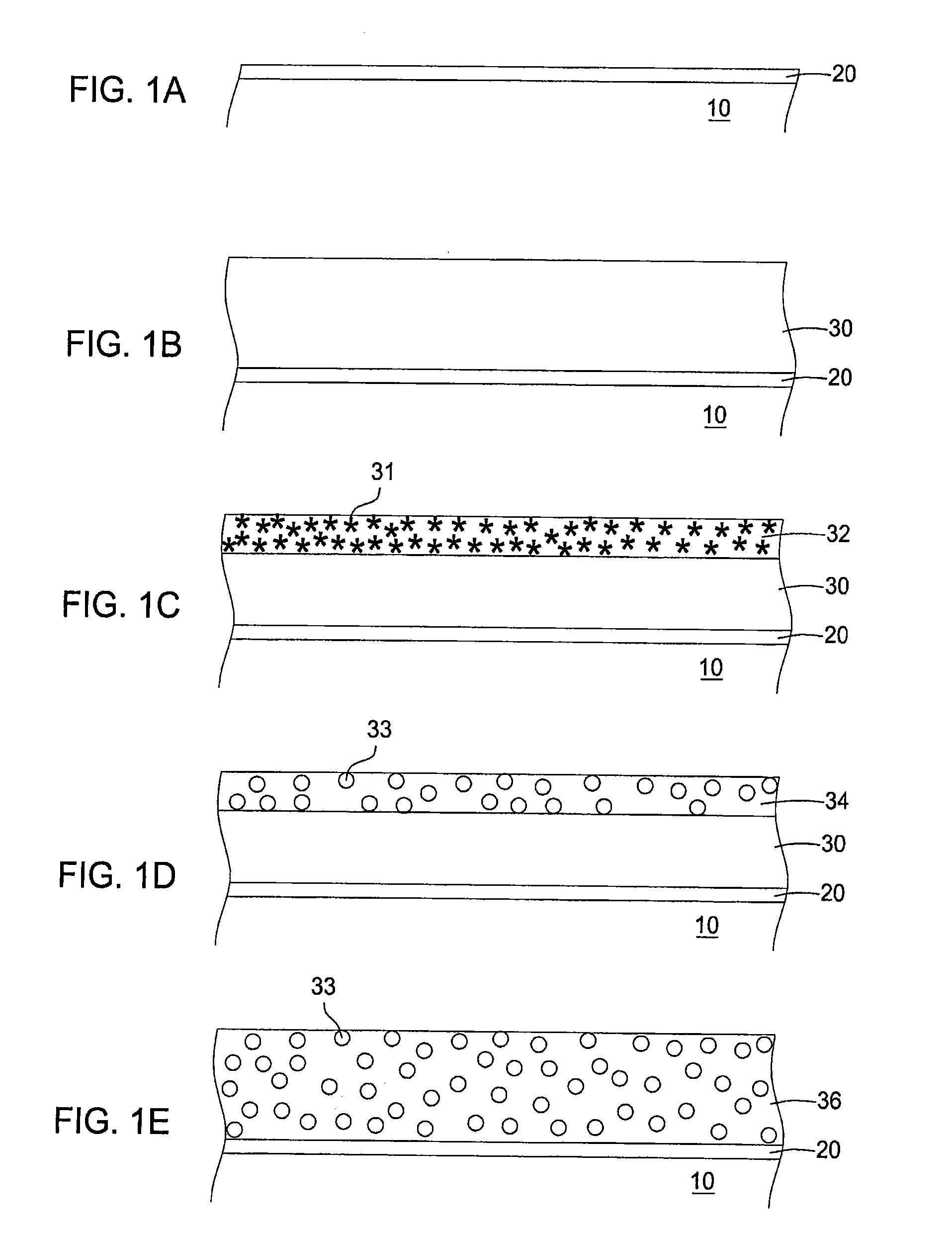

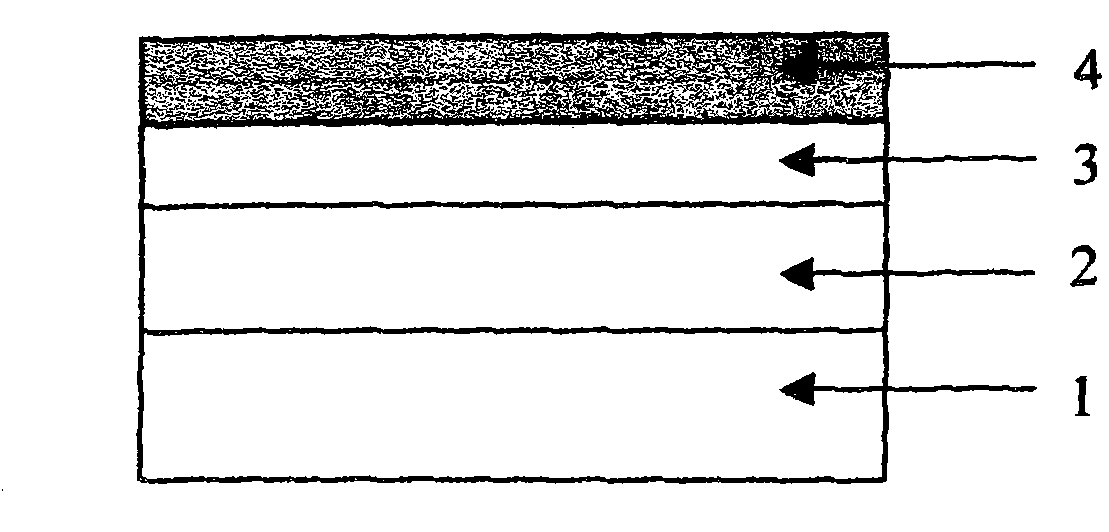

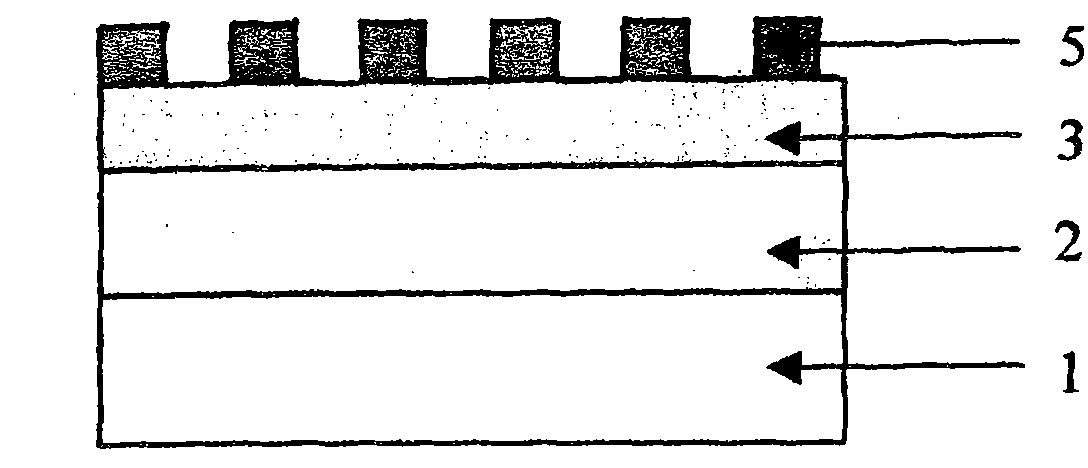

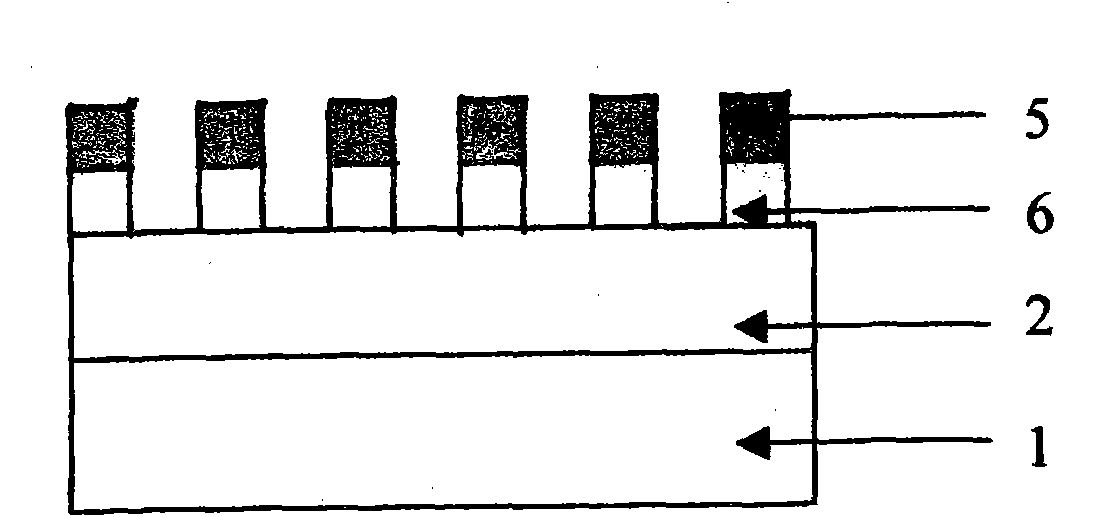

Method for forming crystalline semiconductor layers, a method for fabricating thin film transistors, and method for fabricating solar cells and active matrix liquid crystal devices

InactiveUS6066516AGreat fabricationImprove mobilityTransistorFinal product manufactureActive matrixSolar cell

PCT No. PCT / JP96 / 01775 Sec. 371 Date Jan. 31, 1997 Sec. 102(e) Date Jan. 31, 1997 PCT Filed Jun. 26, 1996 PCT Pub. No. WO97 / 01863 PCT Pub. Date Jan. 16, 1997A crystalline semiconductor layer can be formed by forming a semiconductor film on an inexpensive conventional substrate. Next, perform a first annealing process in which nearly the entire surface of the semiconductor film is exposed to laser irradiation or other forms of irradiation, and then perform a second annealing process consisting of rapid thermal annealing. This enables the formation of a high quality crystalline semiconductor film with high throughput but without subjecting the substrate to undue thermal stress. When this invention is applied to thin film transistors, good transistors having high performance are easily fabricated. When this invention is applied to solar cells, energy conversion efficiency is increased.

Owner:SEIKO EPSON CORP

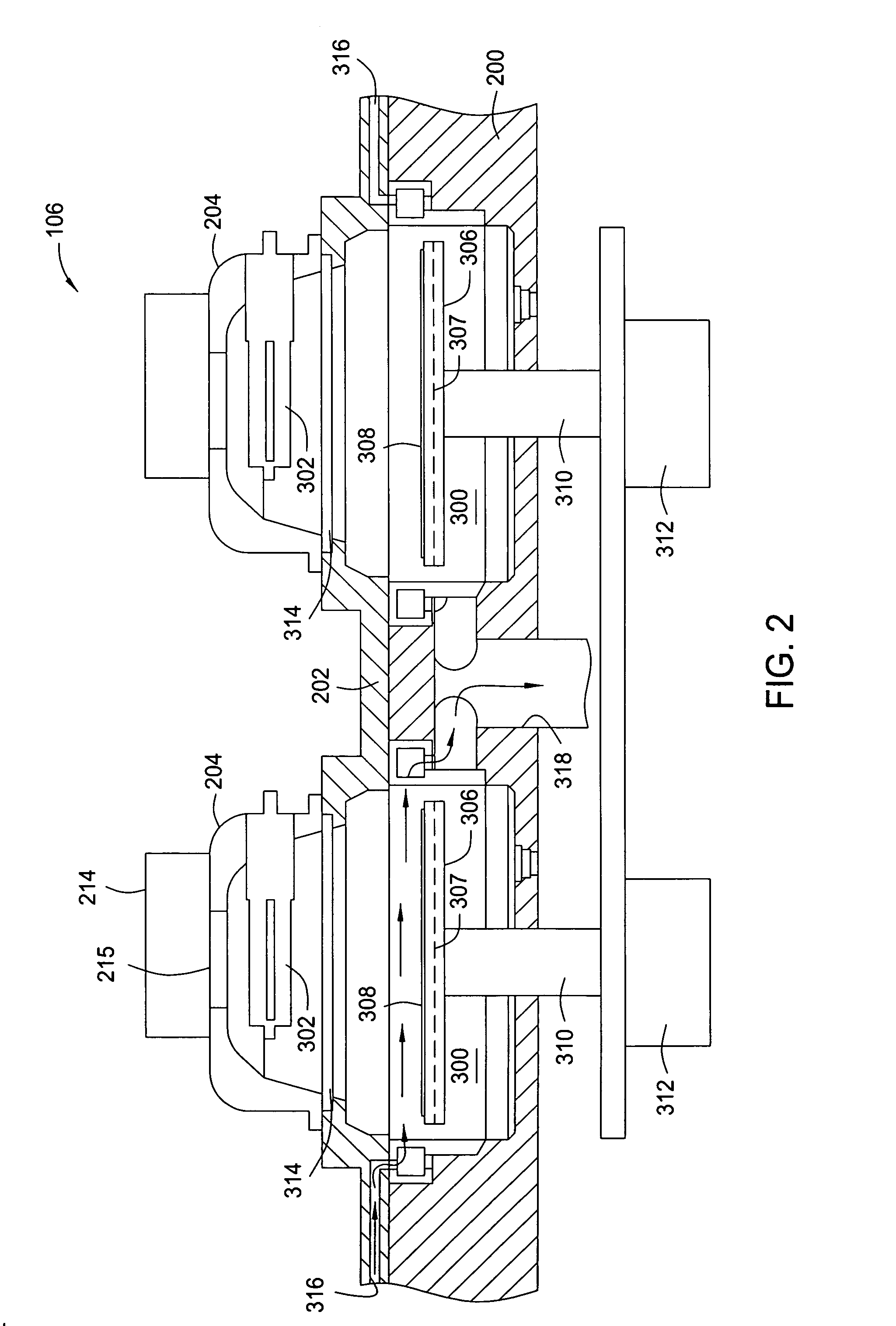

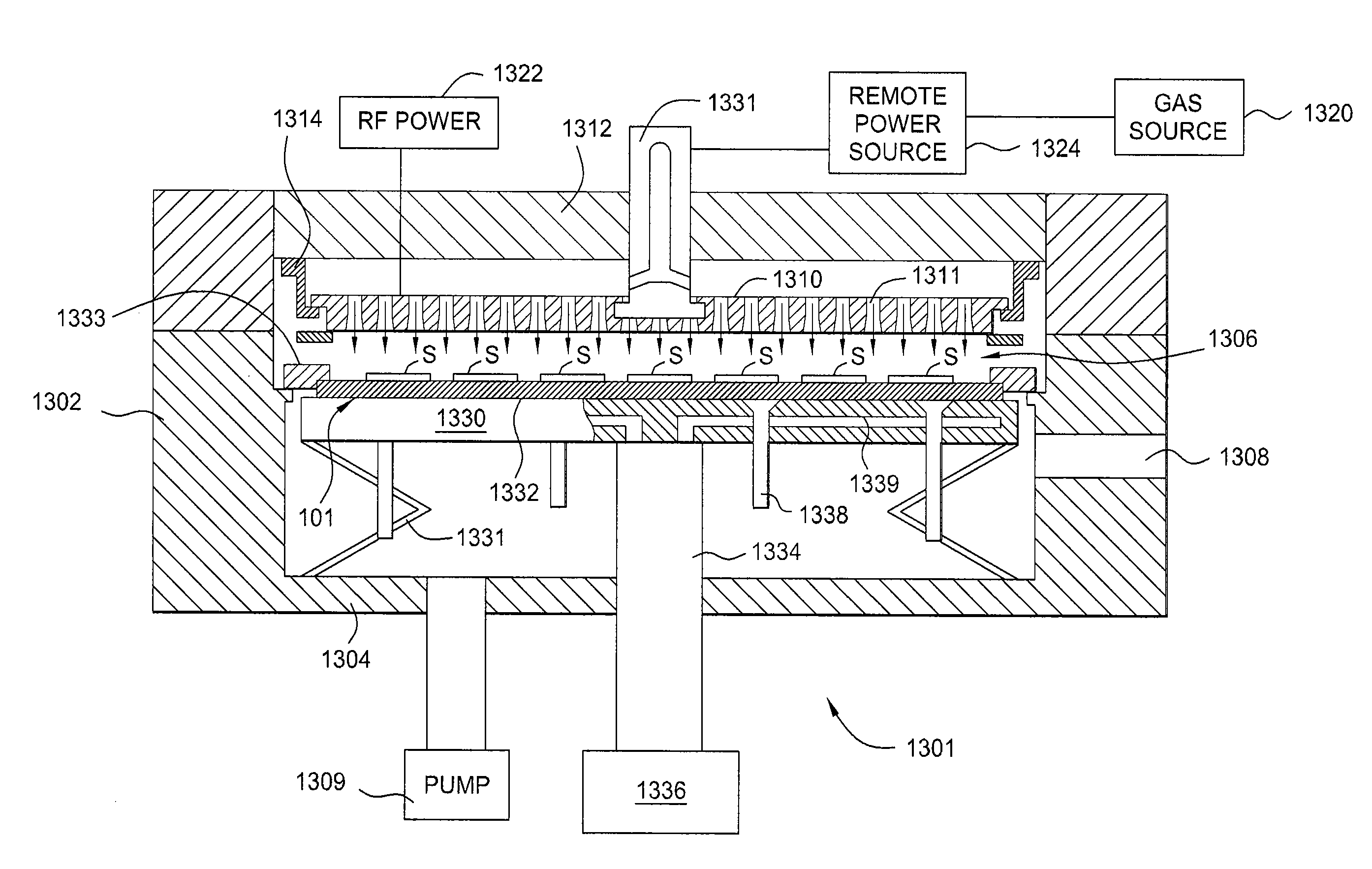

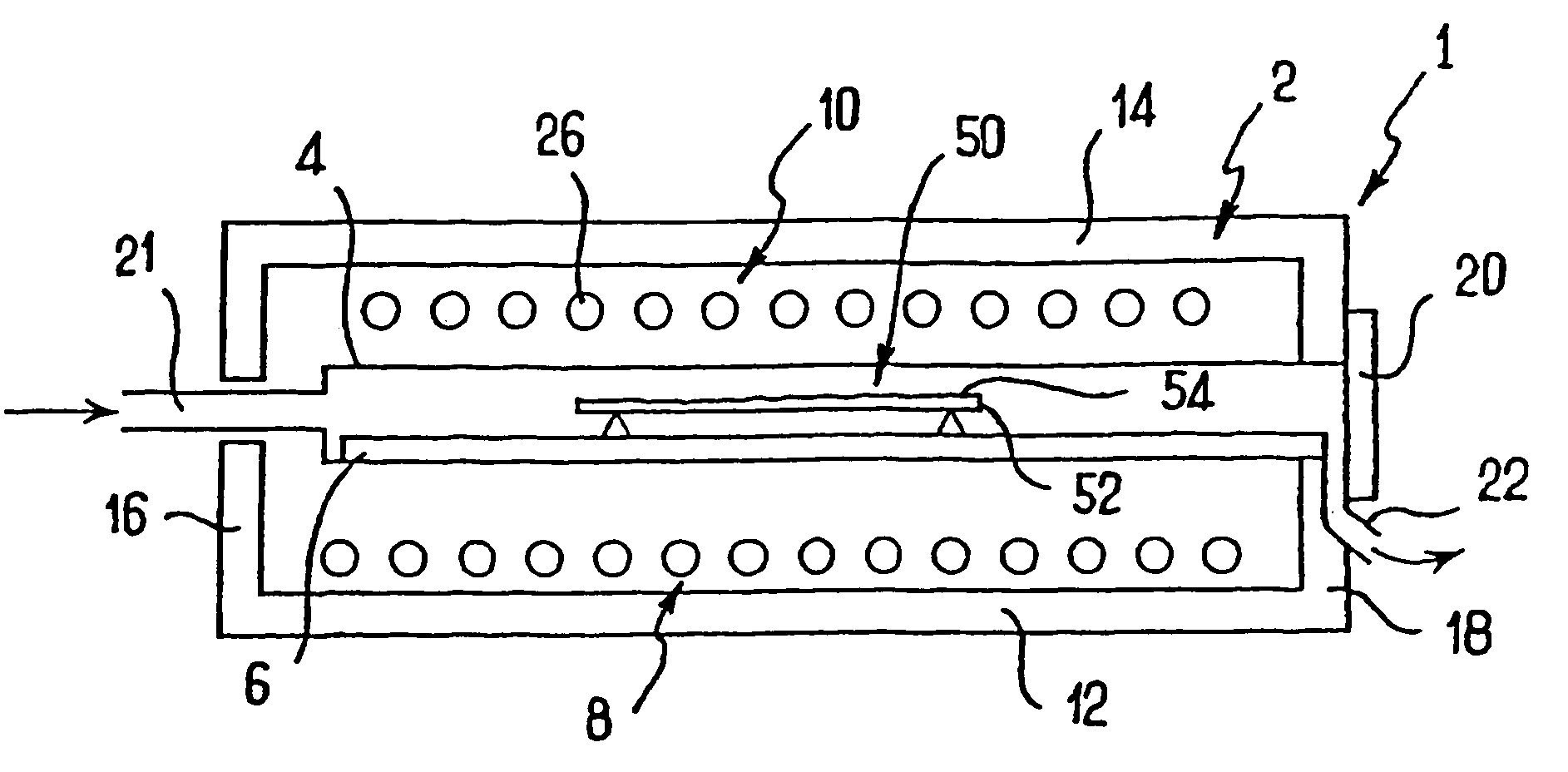

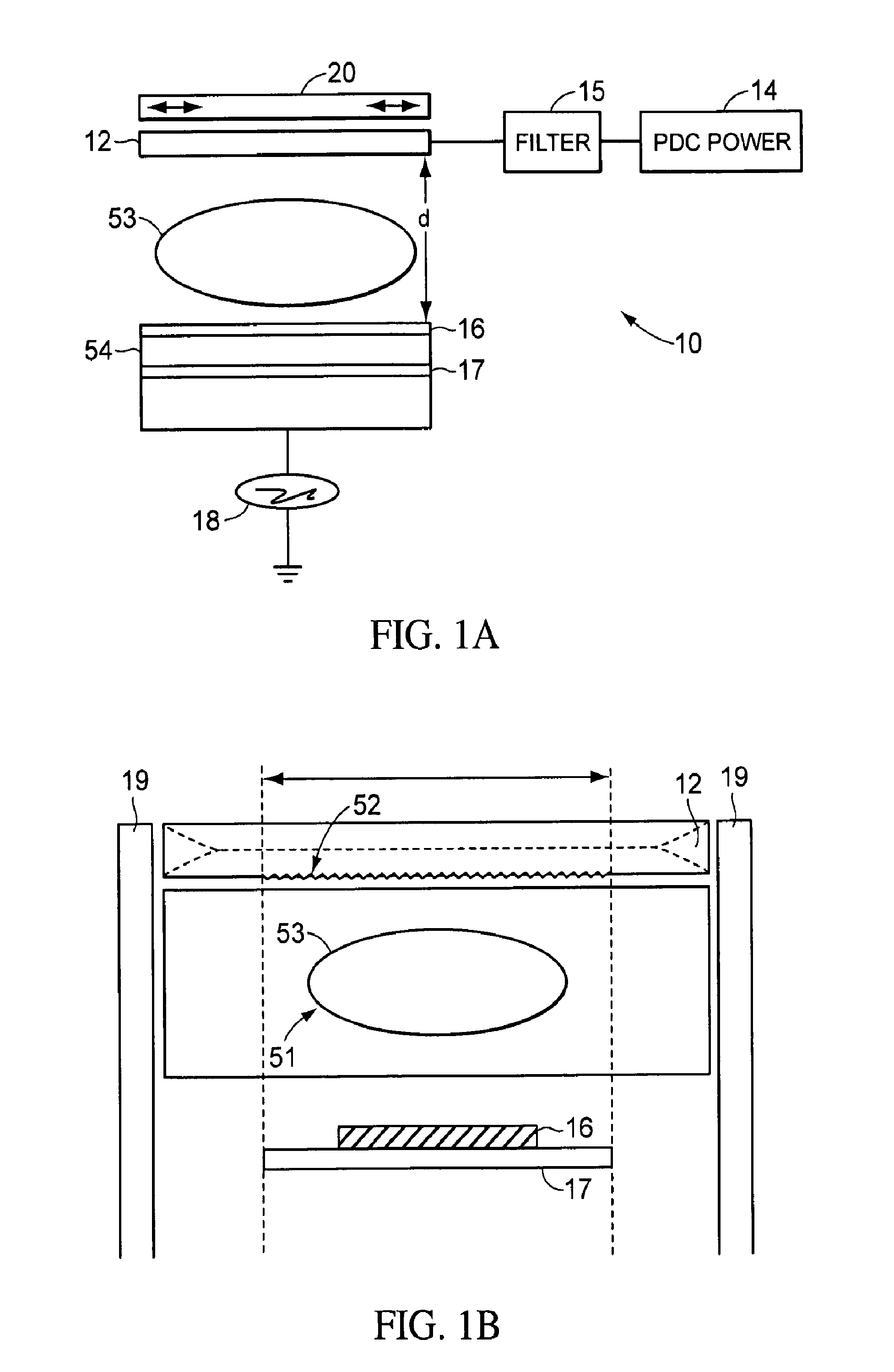

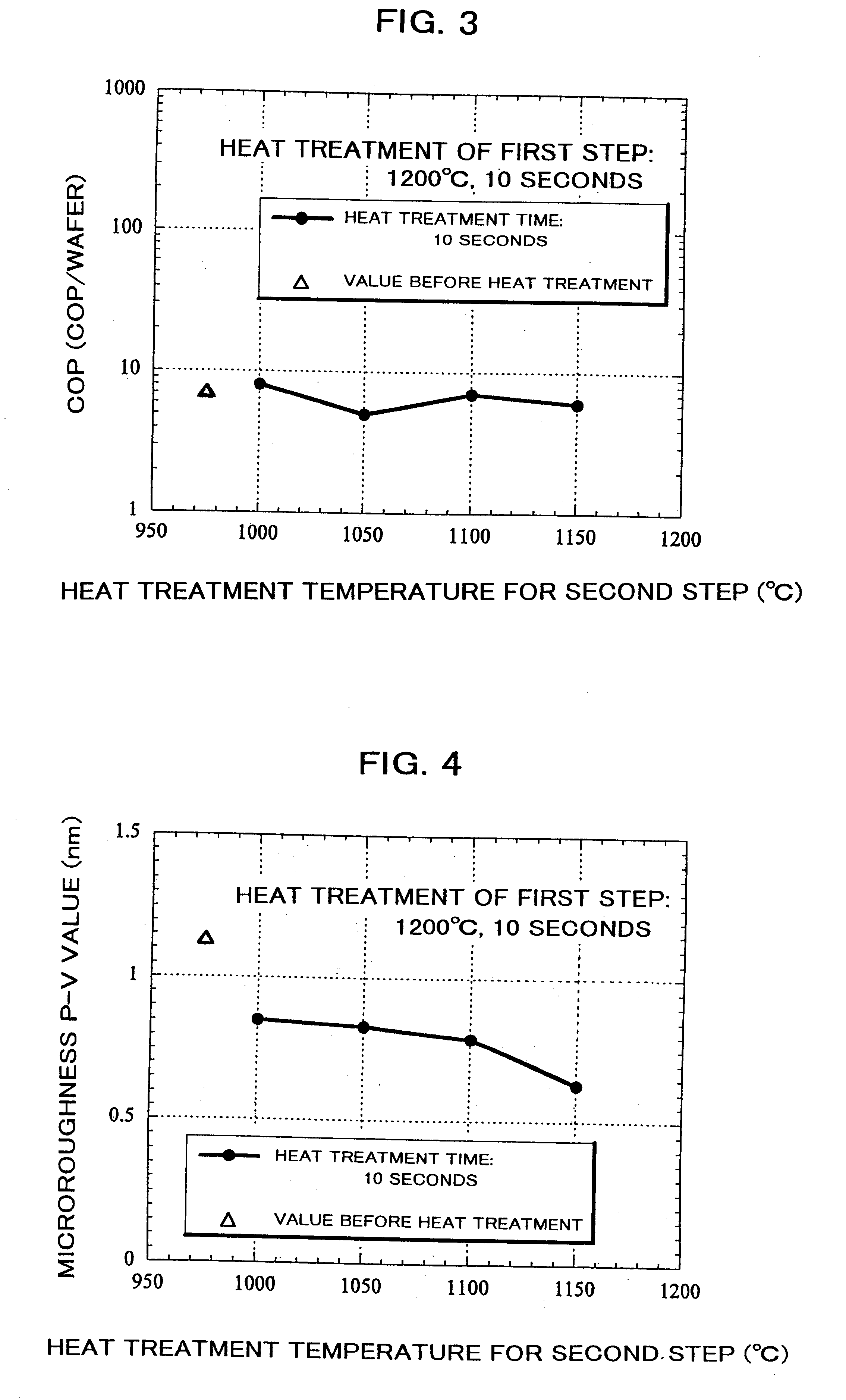

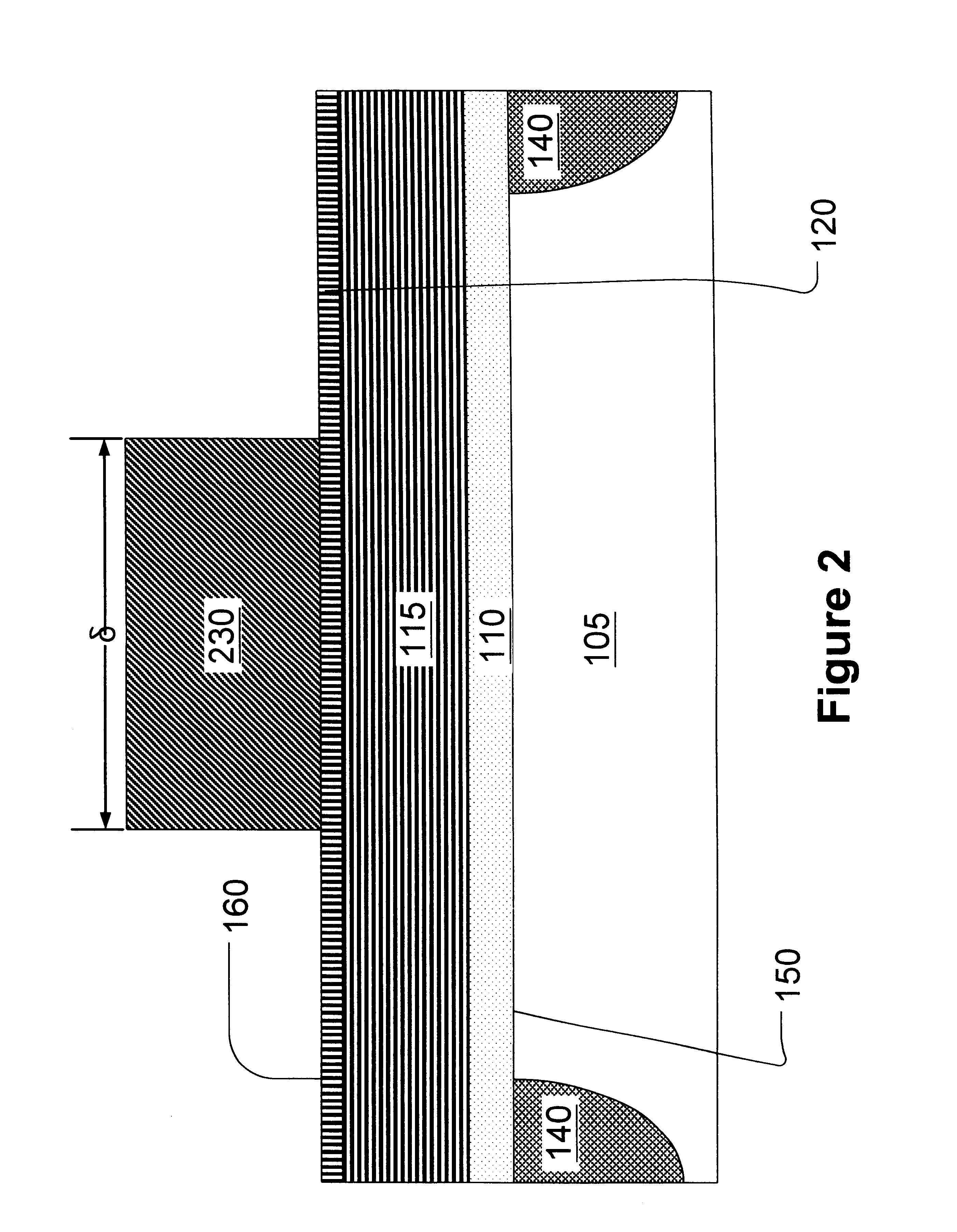

Processing multilayer semiconductors with multiple heat sources

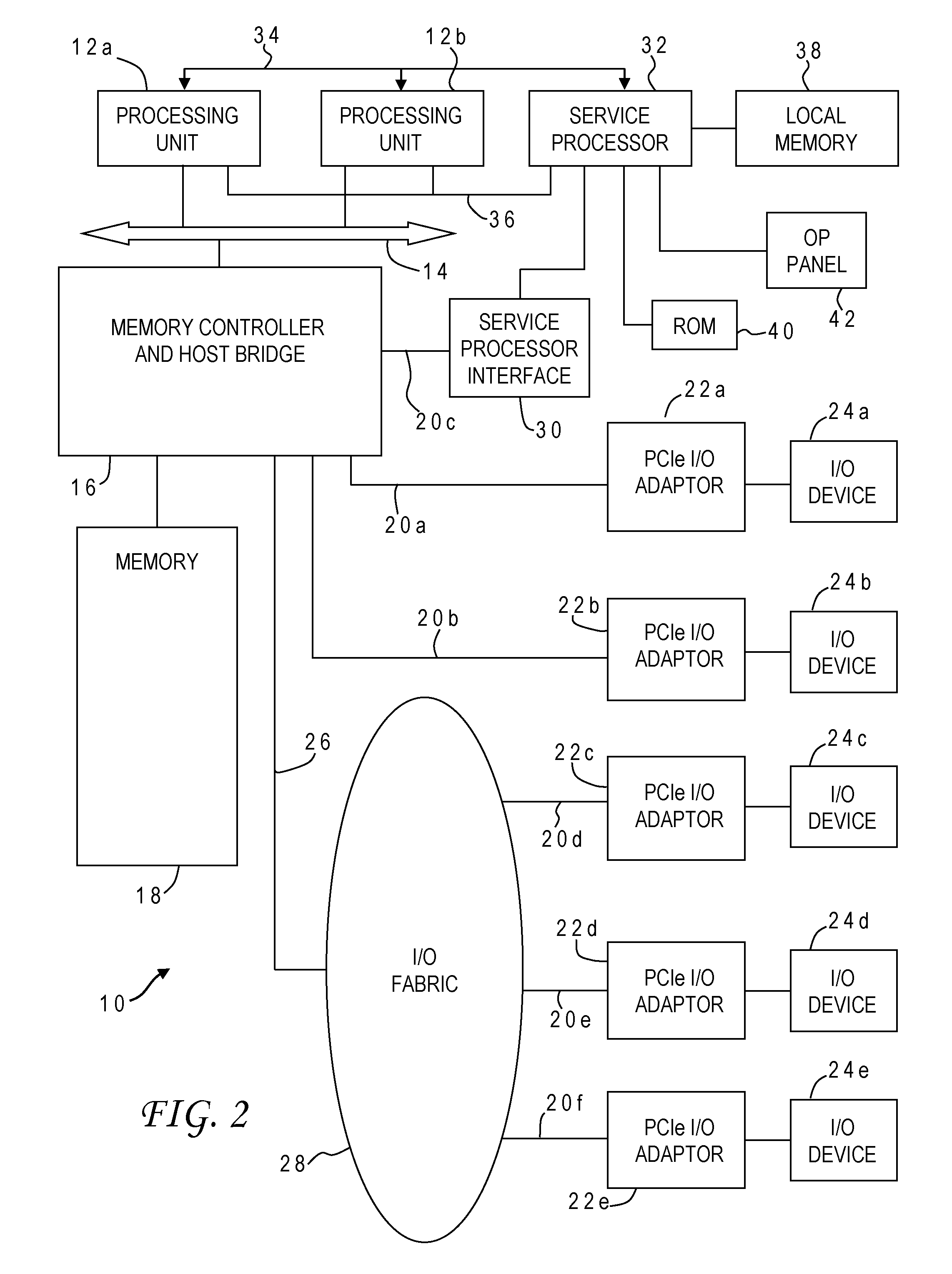

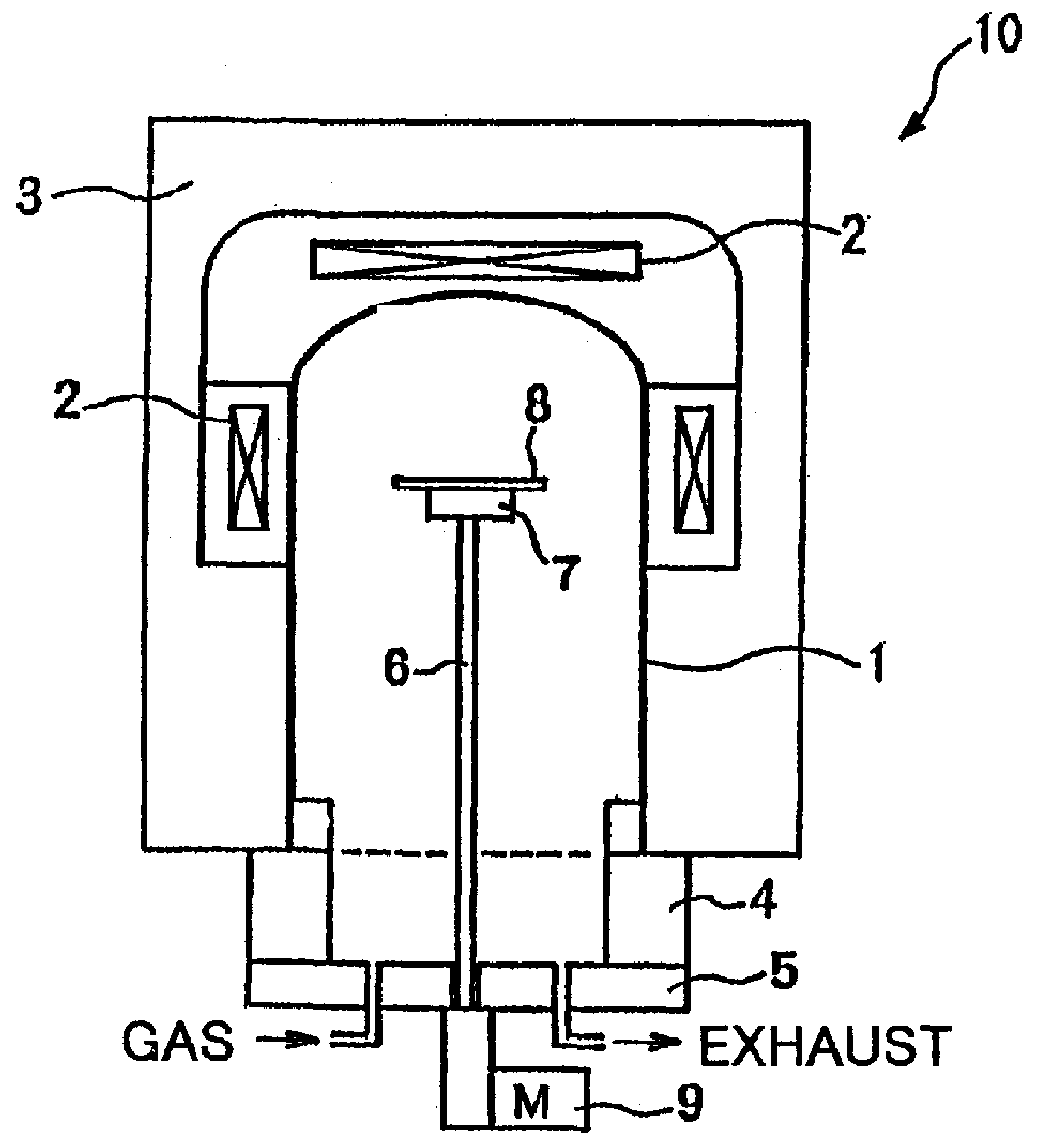

ActiveUS20060018639A1Muffle furnacesSemiconductor/solid-state device manufacturingDistribution systemEngineering

A method and apparatus for rapid thermal annealing comprising a plurality of lamps affixed to a lid of the chamber that provide at least one wavelength of light, a laser source extending into the chamber, a substrate support positioned within a base of the chamber, an edge ring affixed to the substrate support, and a gas distribution assembly in communication with the lid and the base of the chamber. A method and apparatus for rapid thermal annealing comprising a plurality of lamps comprising regional control of the lamps and a cooling gas distribution system affixed to a lid of the chamber, a heated substrate support with magnetic levitation extending through a base of the chamber, an edge ring affixed to the substrate support, and a gas distribution assembly in communication with the lid and the base of the chamber.

Owner:APPLIED MATERIALS INC

Method to control mechanical stress of copper interconnect line using post-plating copper anneal

A method is provided, the method comprising forming a first dielectric layer above a first structure layer, forming a first opening in the first dielectric layer, and forming a first copper structure above the first dielectric layer and in the first opening. The method also comprises annealing the first copper structure using one of a furnace anneal process performed at a temperature ranging from approximately 100-400° C. for a time ranging from approximately 10-90 minutes and a rapid thermal anneal (RTA) process performed at a temperature ranging from approximately 100-400° C. for a time ranging from approximately 10-180 seconds.

Owner:GLOBALFOUNDRIES INC

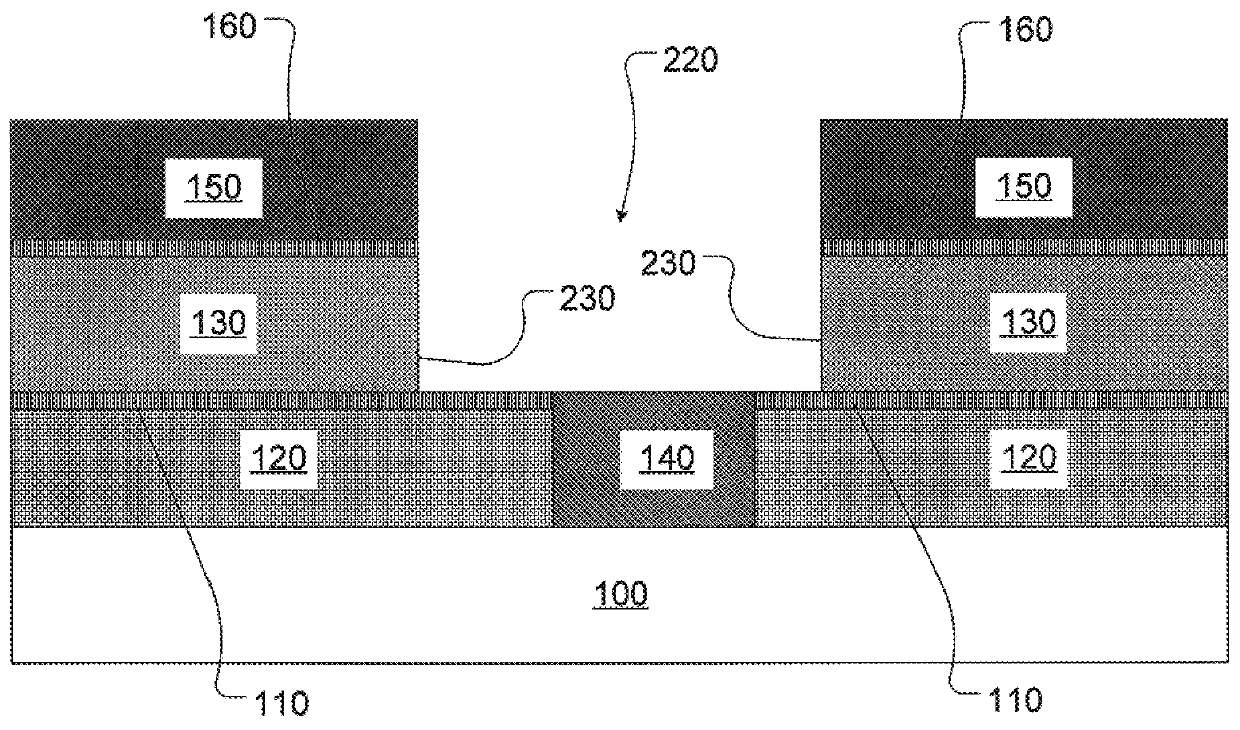

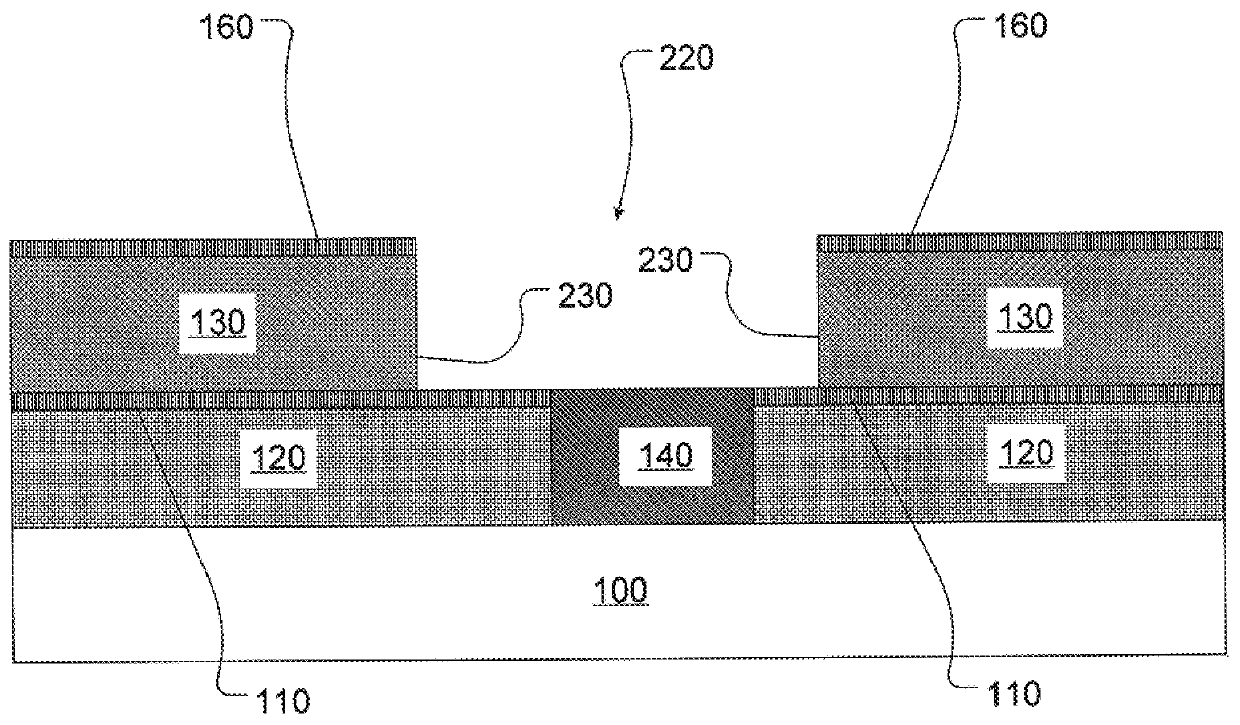

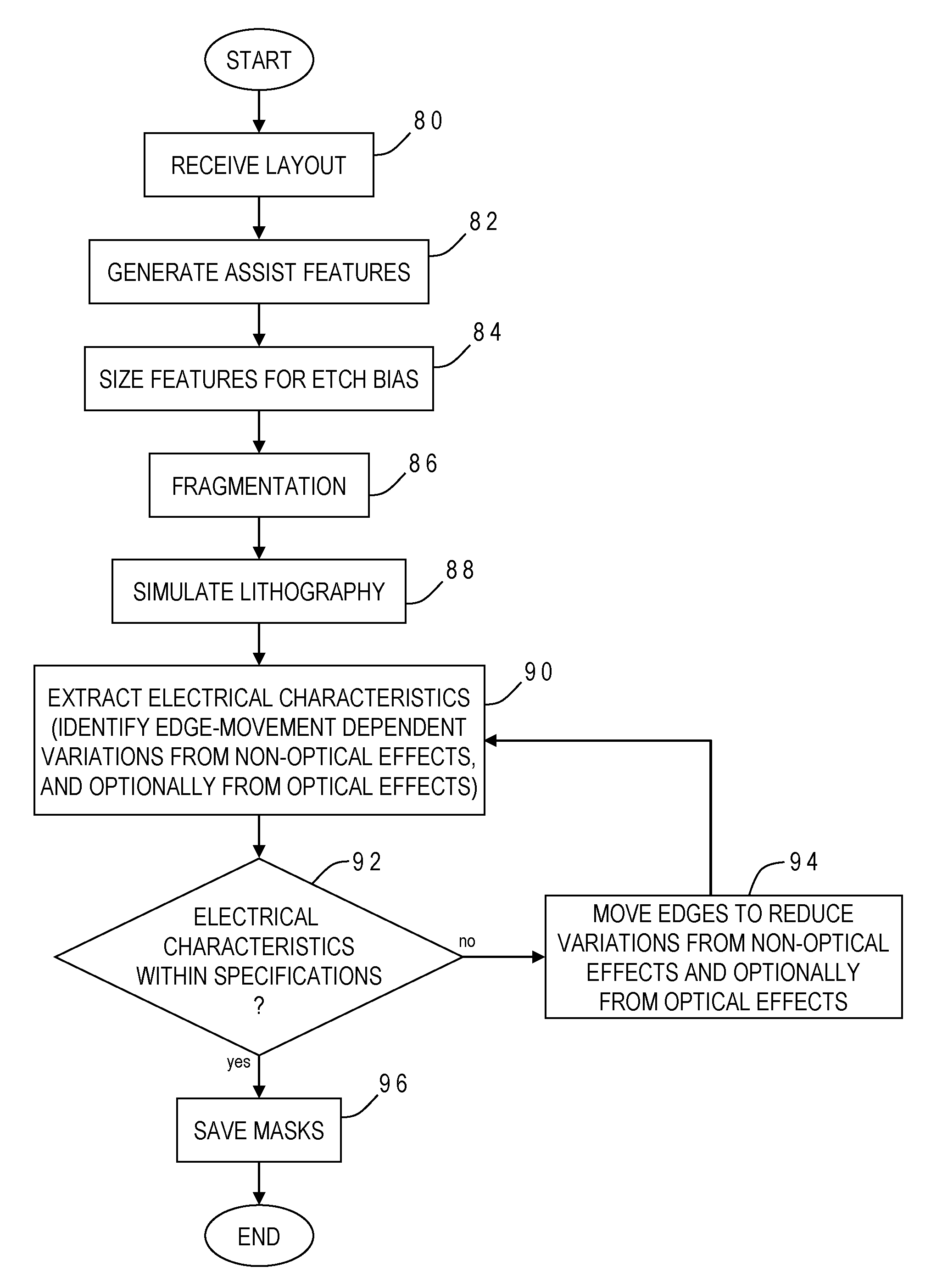

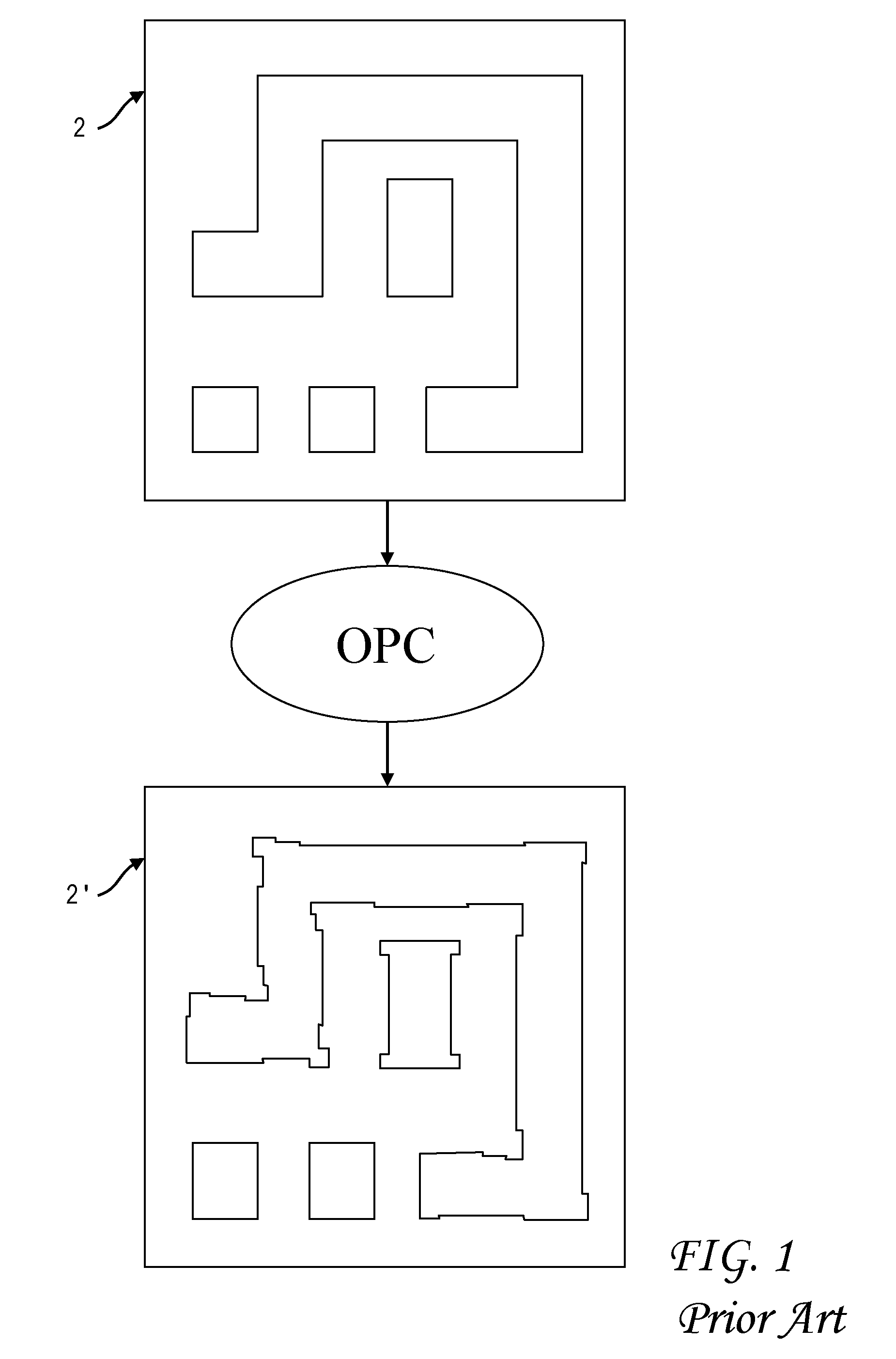

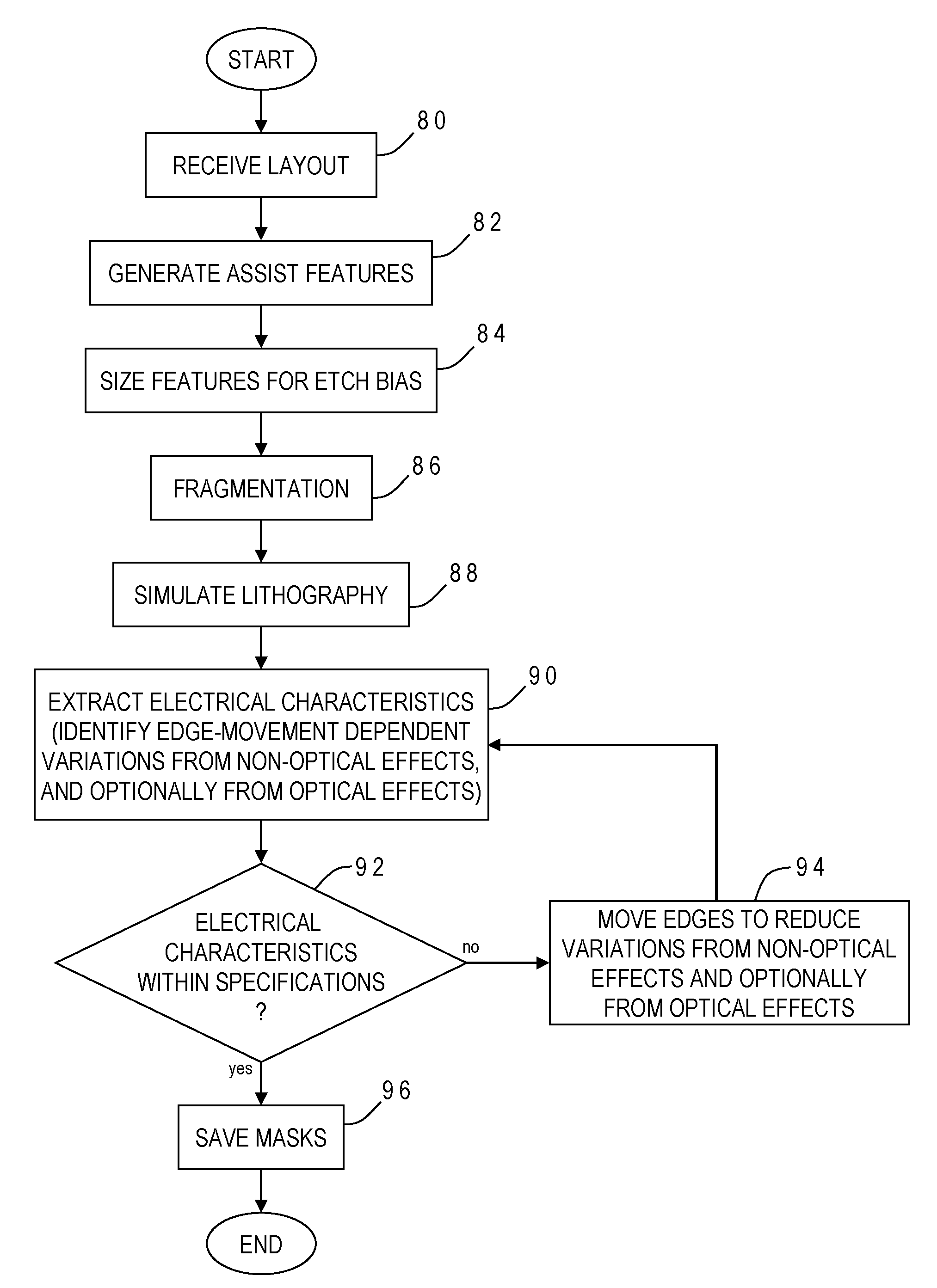

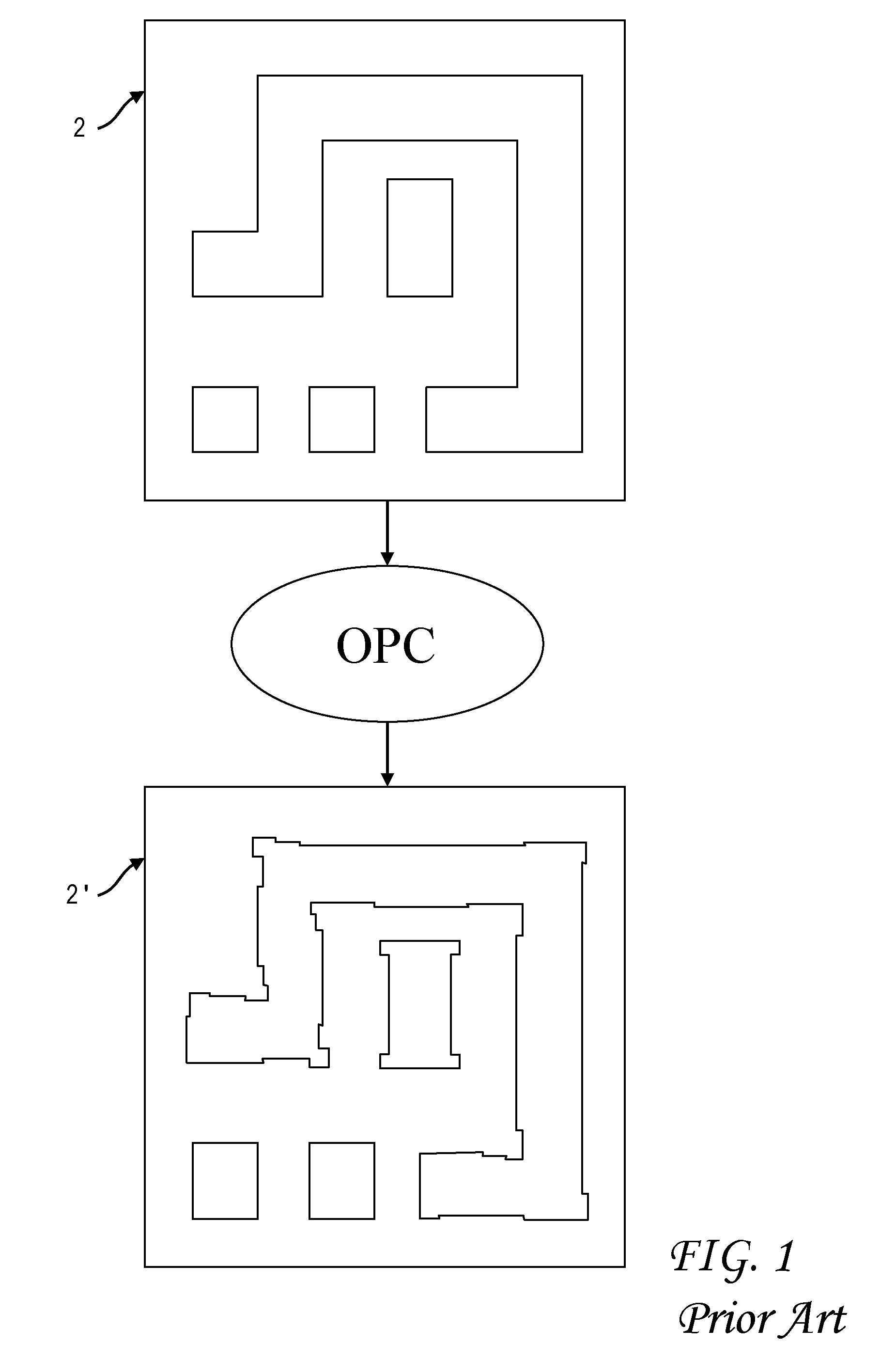

Electrically-driven optical proximity correction to compensate for non-optical effects

ActiveUS8103983B2Improve performancePhotomechanical apparatusOriginals for photomechanical treatmentCapacitanceEngineering

A contour of a mask design for an integrated circuit is modified to compensate for systematic variations arising from non-optical effects such as stress, well proximity, rapid thermal anneal, or spacer thickness. Electrical characteristics of a simulated integrated circuit chip fabricated using the mask design are extracted and compared to design specifications, and one or more edges of the contour are adjusted to reduce the systematic variation until the electrical characteristic is within specification. The particular electrical characteristic preferably depends on which layer is to be fabricated from the mask: on-current for a polysilicon; resistance for contact; resistance and capacitance for metal; current for active; and resistance for vias. For systematic threshold voltage variation, the contour is adjusted to match a gate length which corresponds to an on-current value according to pre-calculated curves for contour current and gate length at a nominal threshold voltage of the chip.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

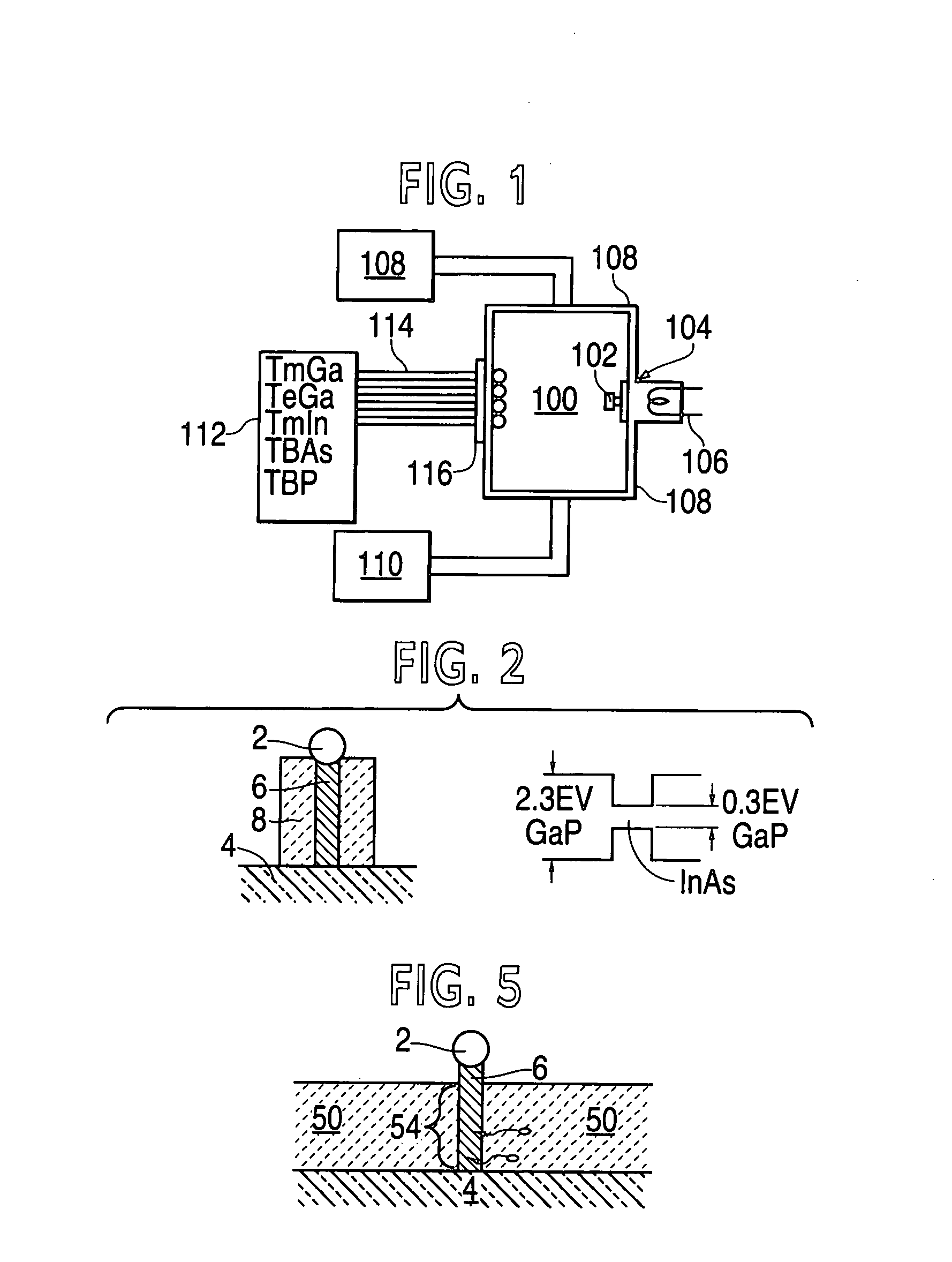

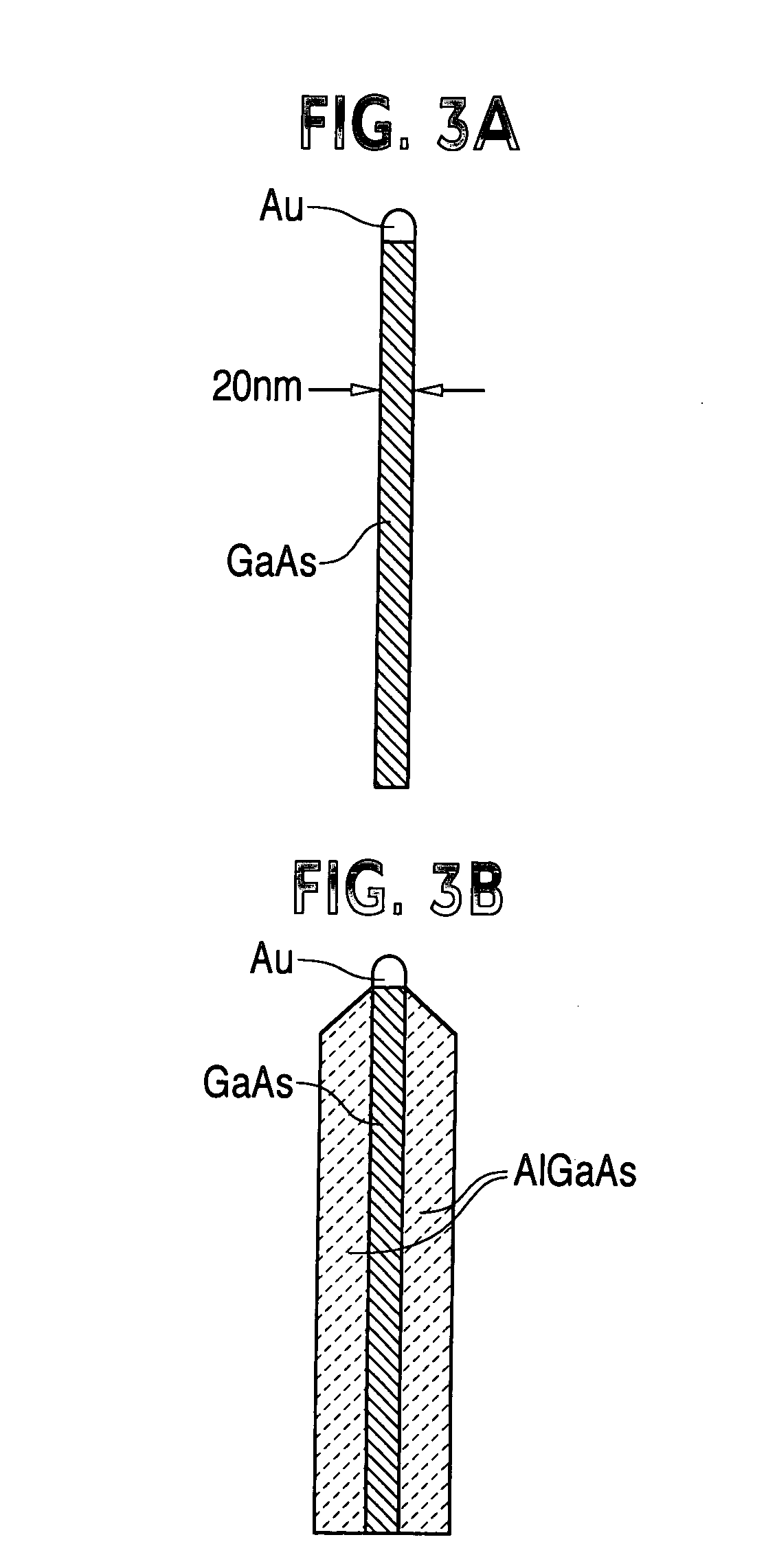

Nanowhiskers with PN junctions, doped nanowhiskers, and methods for preparing them

InactiveUS20050006673A1Good electrical conductivityPermitted diffusionPolycrystalline material growthNanoinformaticsHeterojunctionP–n junction

Nano-engineered structures are disclosed, incorporating nanowhiskers of high mobility conductivity and incorporating pn junctions. In one embodiment, a nanowhisker of a first semiconducting material has a first band gap, and an enclosure comprising at least one second material with a second band gap encloses said nanoelement along at least part of its length, the second material being doped to provide opposite conductivity type charge carriers in respective first and second regions along the length of the of the nanowhisker, whereby to create in the nanowhisker by transfer of charge carriers into the nanowhisker, corresponding first and second regions of opposite conductivity type charge carriers with a region depleted of free carriers therebetween. The doping of the enclosure material may be degenerate so as to create within the nanowhisker adjacent segments having very heavy modulation doping of opposite conductivity type analogous to the heavily doped regions of an Esaki diode. In another embodiment, a nanowhisker is surrounded by polymer material containing dopant material. A step of rapid thermal annealing causes the dopant material to diffuse into the nanowhisker. In a further embodiment, a nanowhisker has a heterojunction between two different intrinsic materials, and Fermi level pinning creates a pn junction at the interface without doping.

Owner:QUNANO

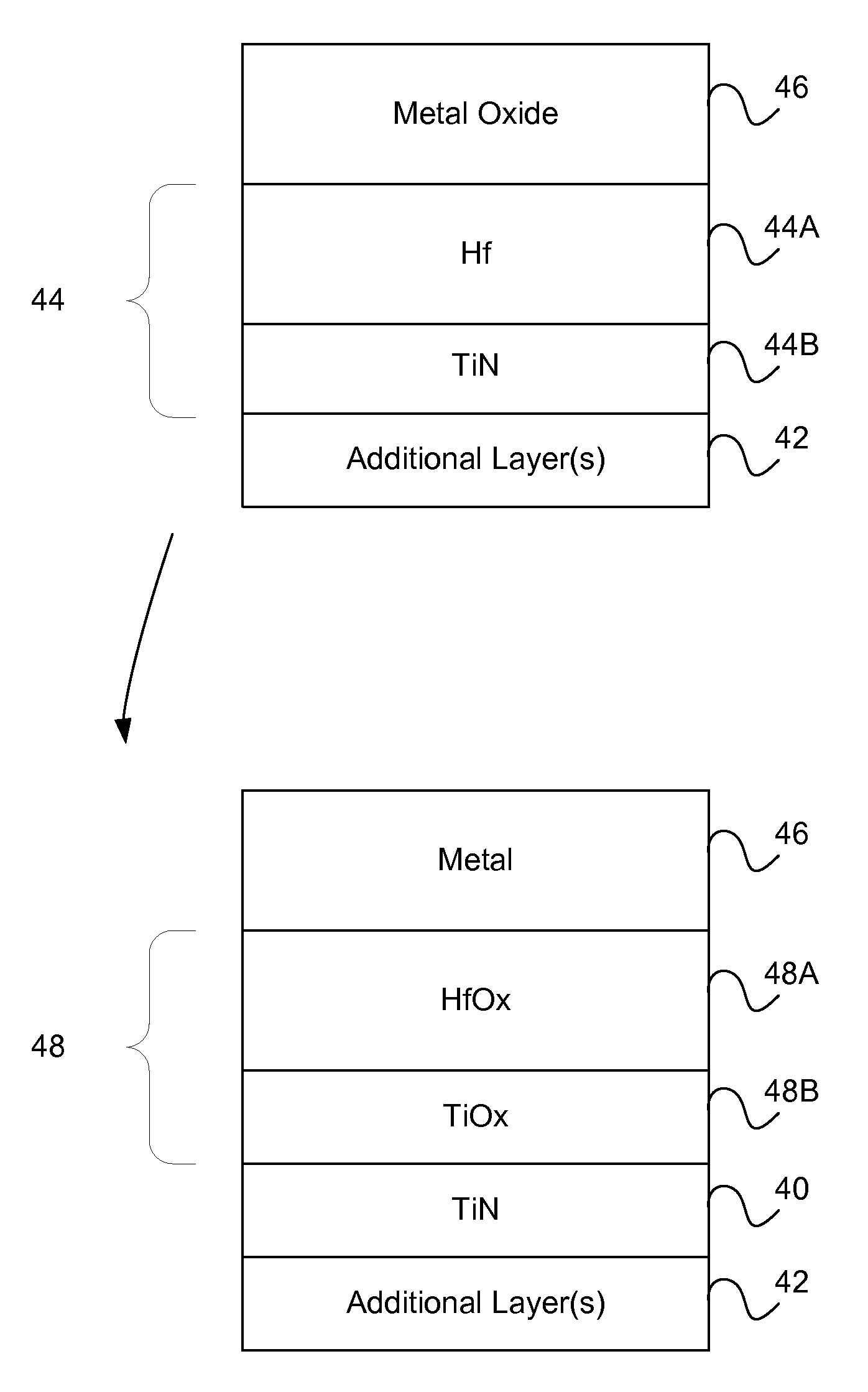

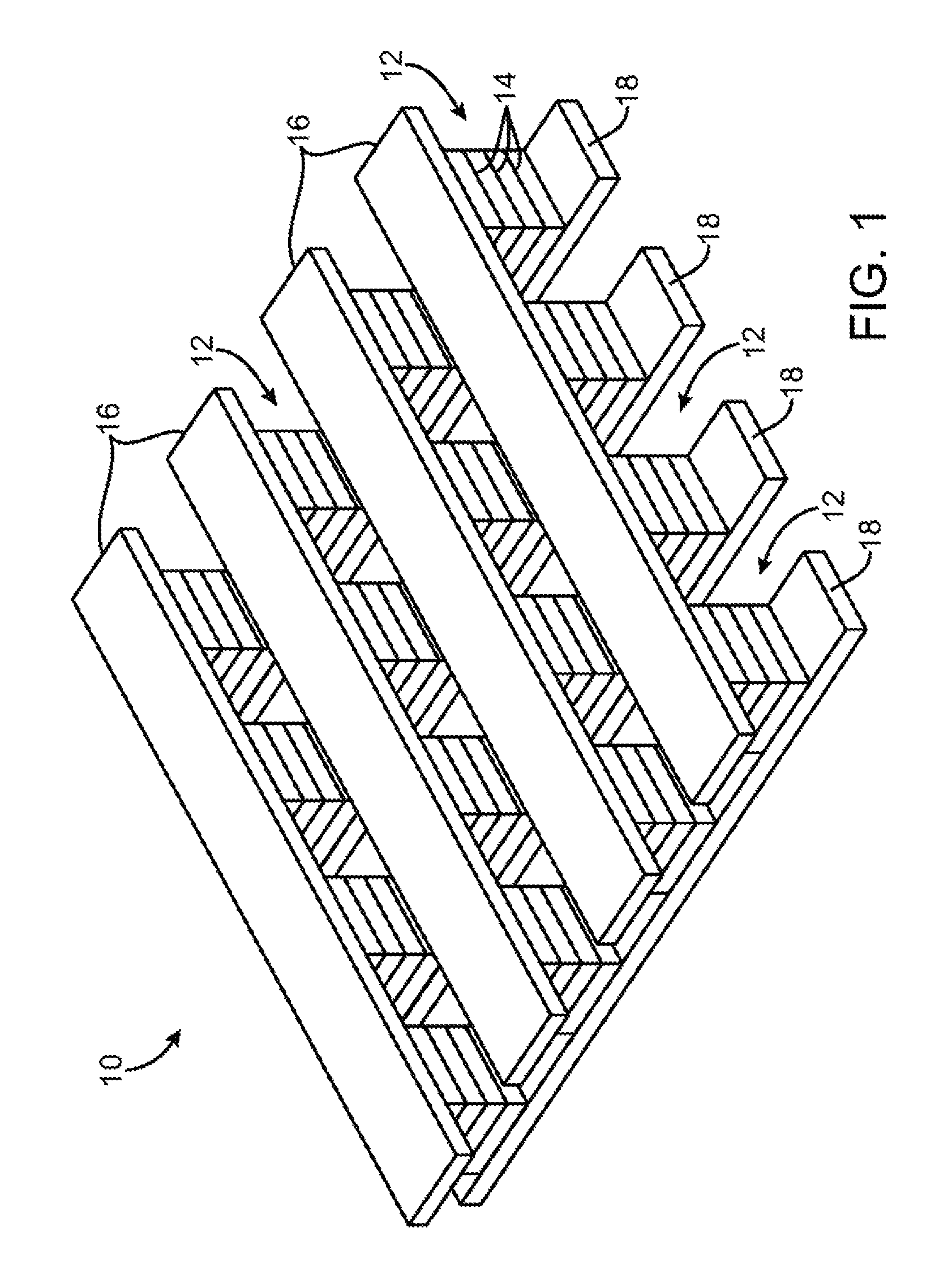

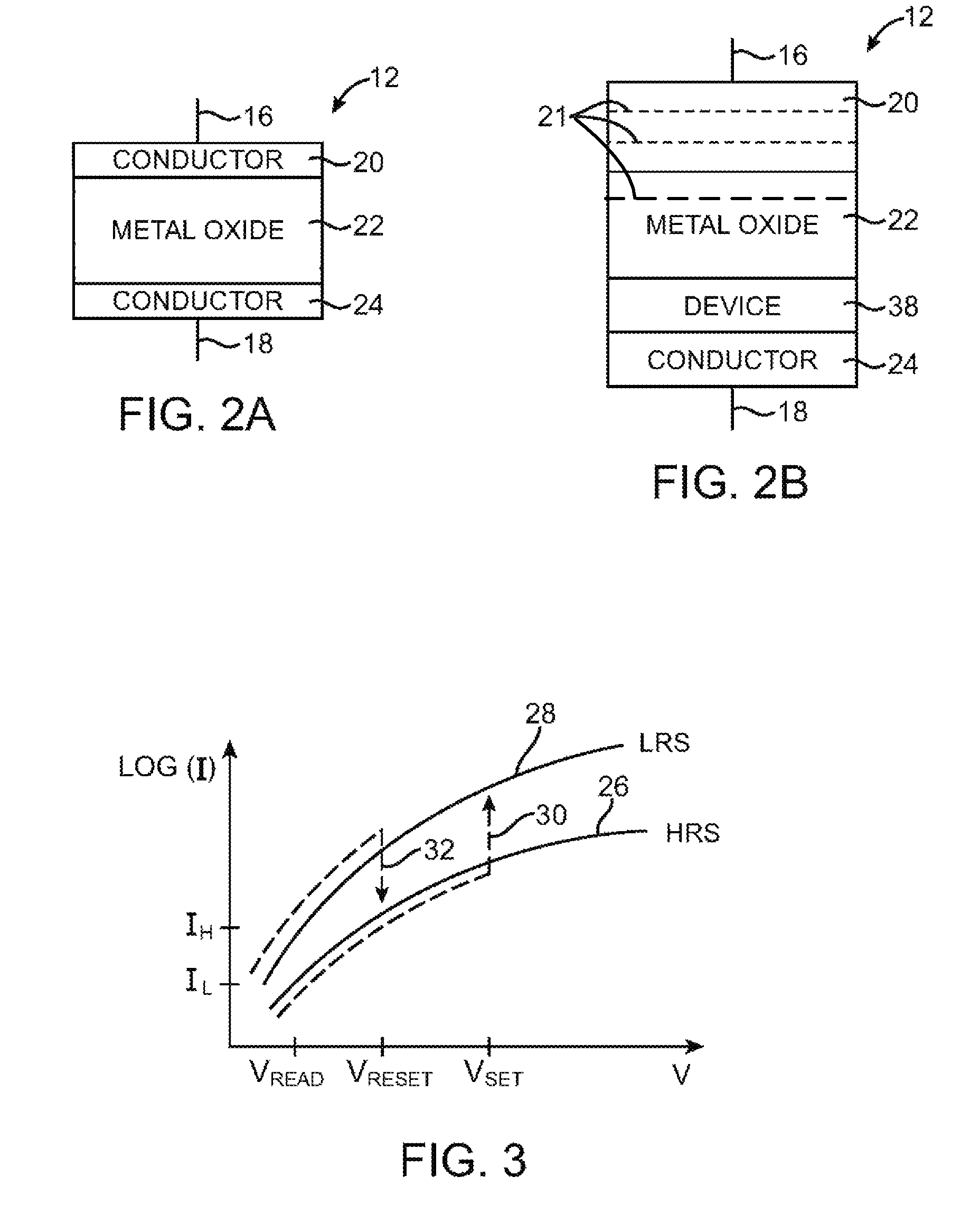

Methods for forming resistive switching memory elements by heating deposited layers

ActiveUS8143092B2Reduce process complexitySolid-state devicesSemiconductor/solid-state device manufacturingOxygenRapid thermal annealing

Resistive switching nonvolatile memory elements are provided. A metal-containing layer and an oxide layer for a memory element can be heated using rapid thermal annealing techniques. During heating, the oxide layer may decompose and react with the metal-containing layer. Oxygen from the decomposing oxide layer may form a metal oxide with metal from the metal-containing layer. The resulting metal oxide may exhibit resistive switching for the resistive switching memory elements.

Owner:INTERMOLECULAR

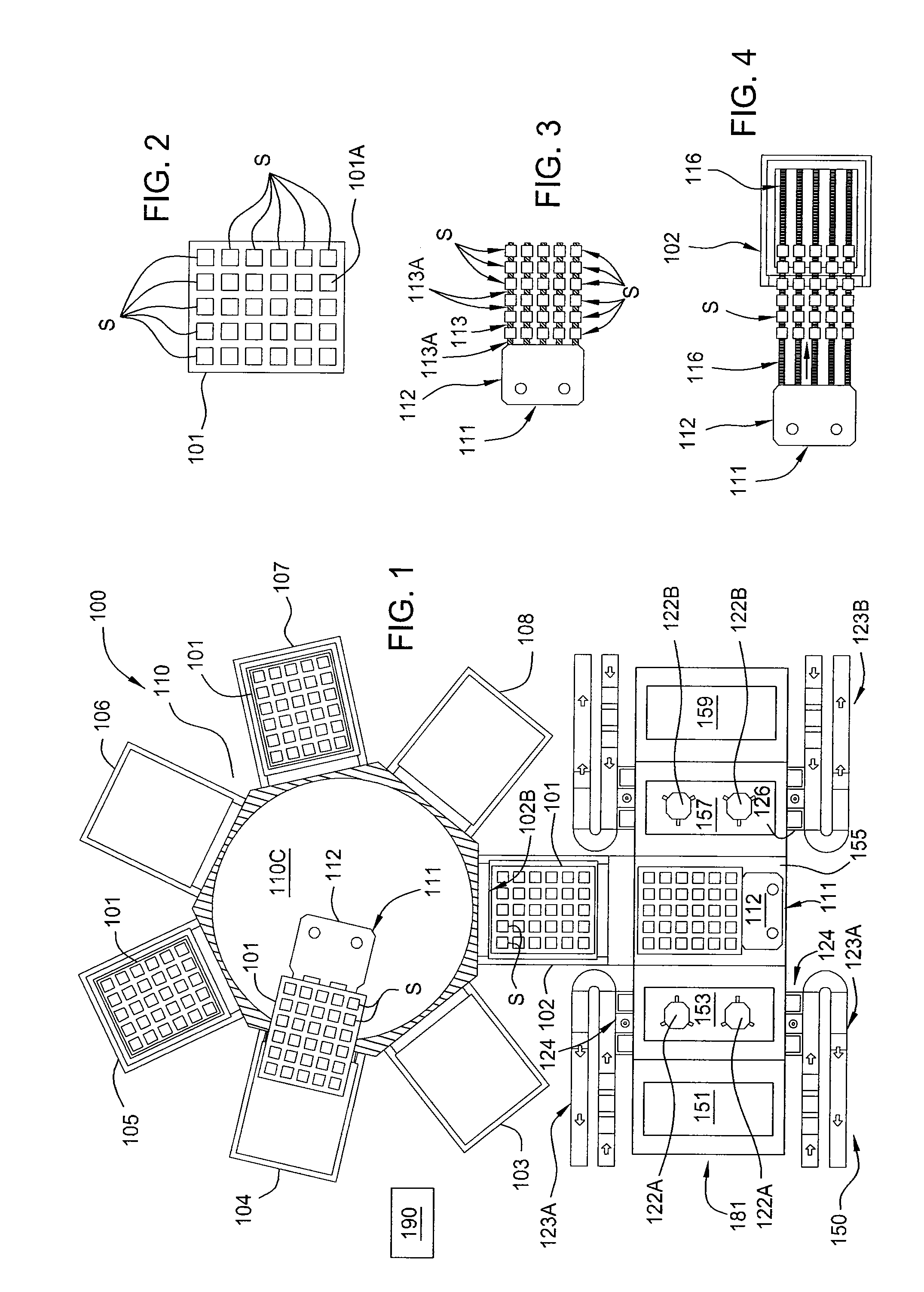

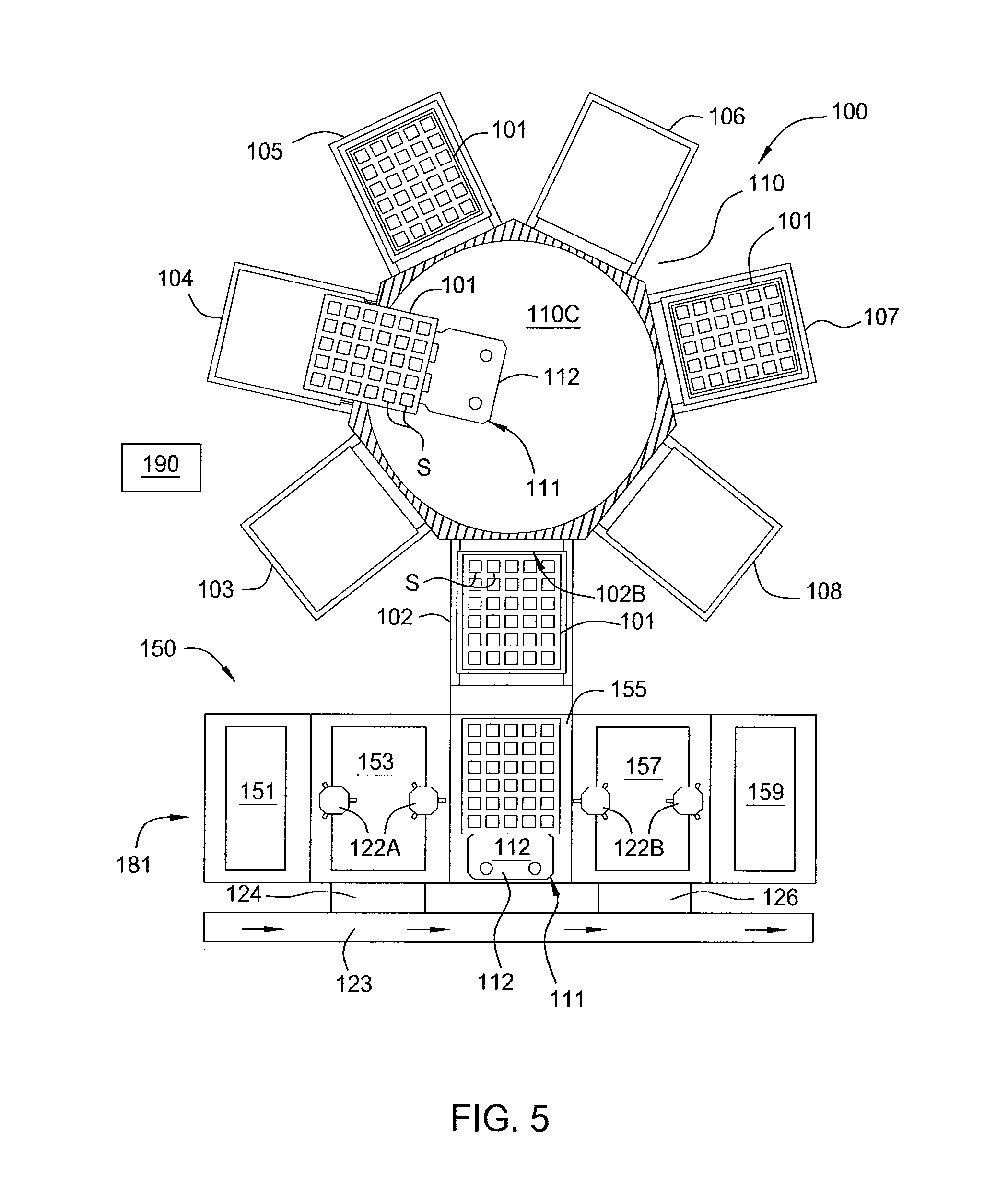

Advanced platform for processing crystalline silicon solar cells

InactiveUS20100087028A1Final product manufactureSemiconductor/solid-state device manufacturingGas phaseEngineering

The present invention generally provides a batch substrate processing system, or cluster tool, for in-situ processing of a film stack used to form regions of a solar cell device. In one configuration, the film stack formed on each of the substrates in the batch contains one or more silicon-containing layers and one or more metal layers that are deposited and further processed within the various chambers contained in the substrate processing system. The processing chambers may be, for example, physical vapor deposition (PVD) or sputtering chambers, plasma enhanced chemical vapor deposition (PECVD) chambers, low pressure chemical vapor deposition (LPCVD) chambers, hot wire chemical vapor deposition (HWCVD) chambers, plasma nitridation (DPN) chambers, ion implant / doping chambers, atomic layer deposition (ALD) chambers, plasma etching chambers, annealing chambers, rapid thermal oxidation (RTO) chambers, rapid thermal annealing (RTA) chambers, substrate reorientation chambers, laser annealing chambers, and / or plasma cleaning stations. In one embodiment, a batch of solar cell substrates is simultaneously transferred in a vacuum or inert environment to prevent contamination from affecting the solar cell formation process.

Owner:APPLIED MATERIALS INC

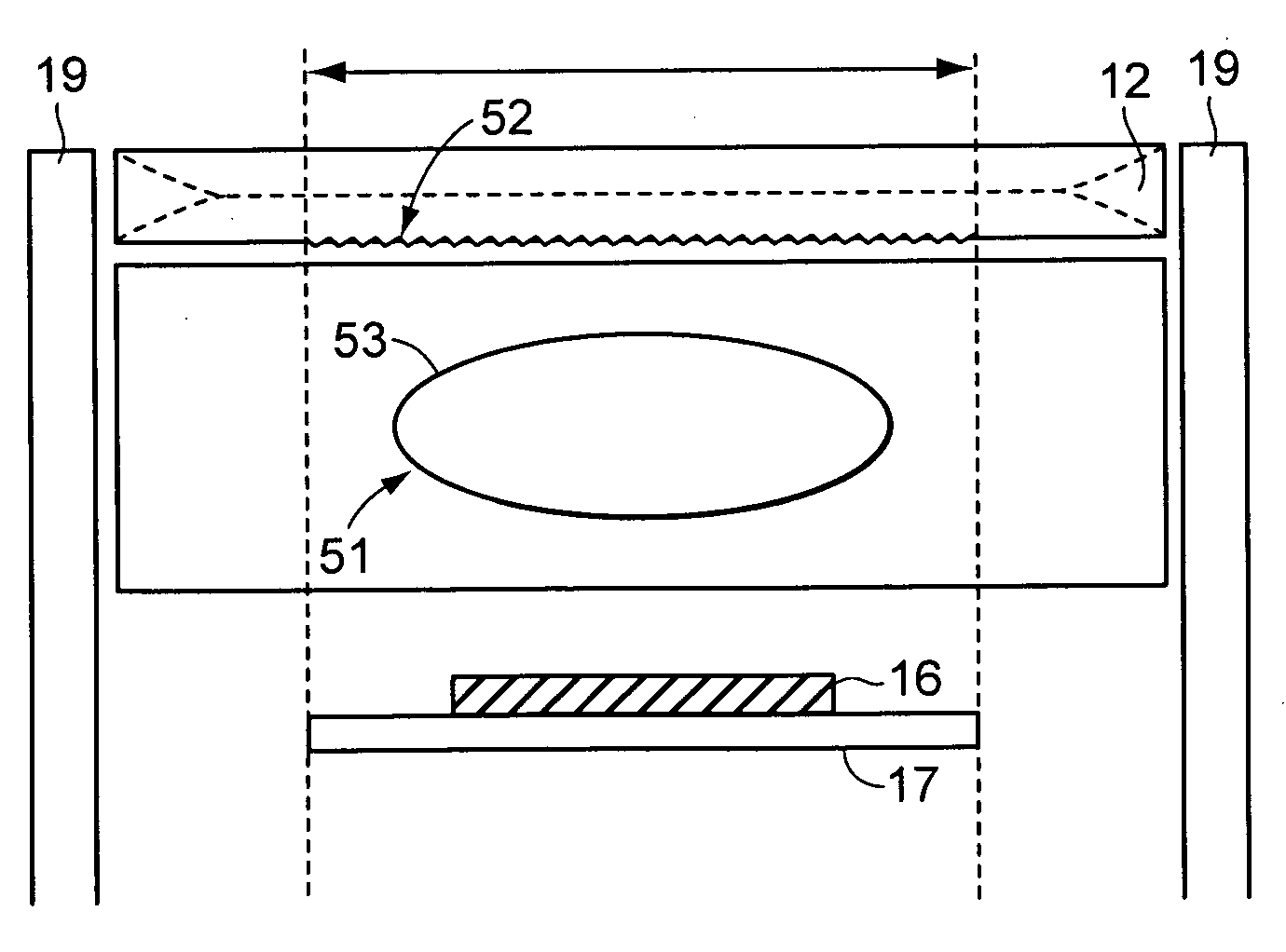

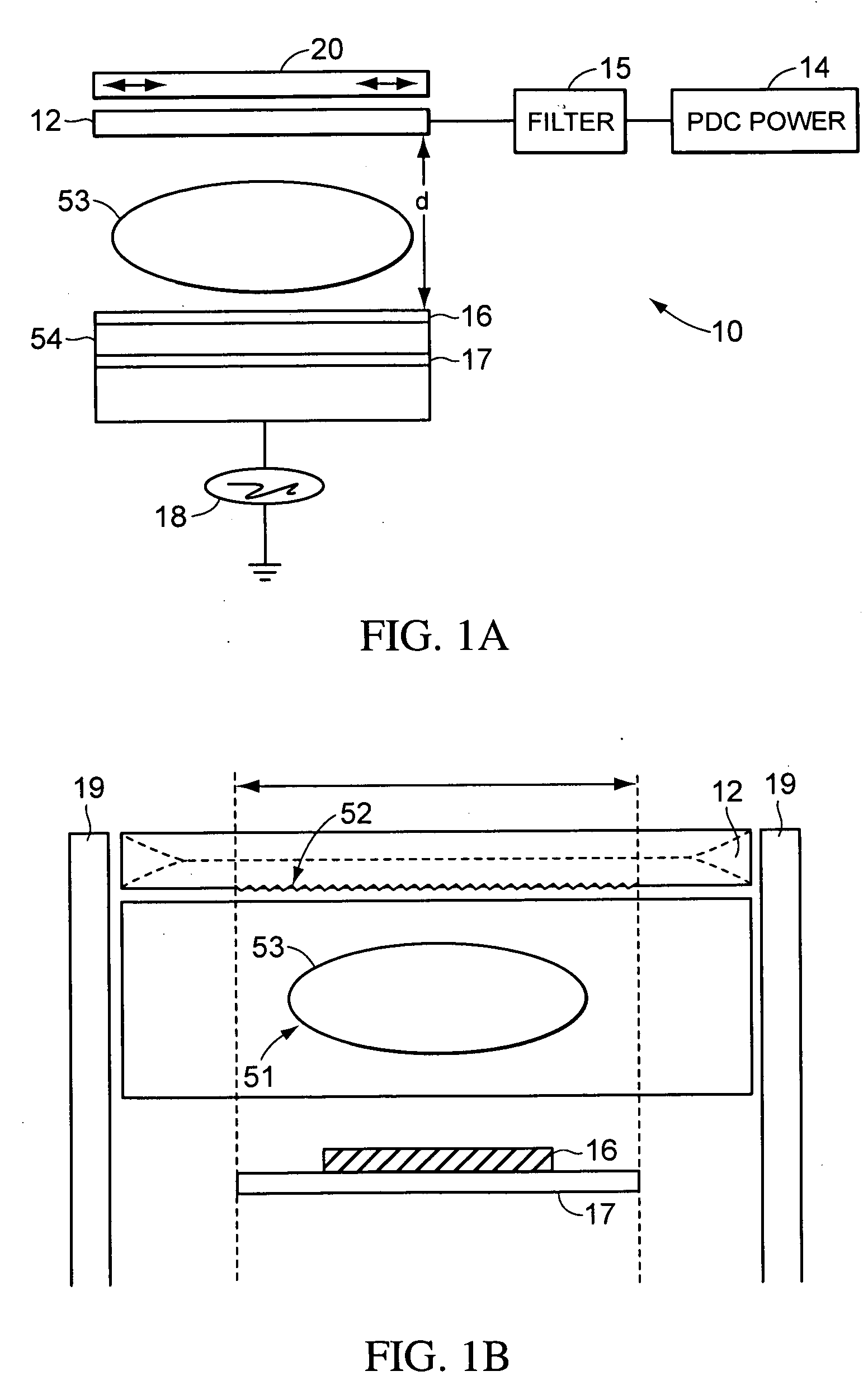

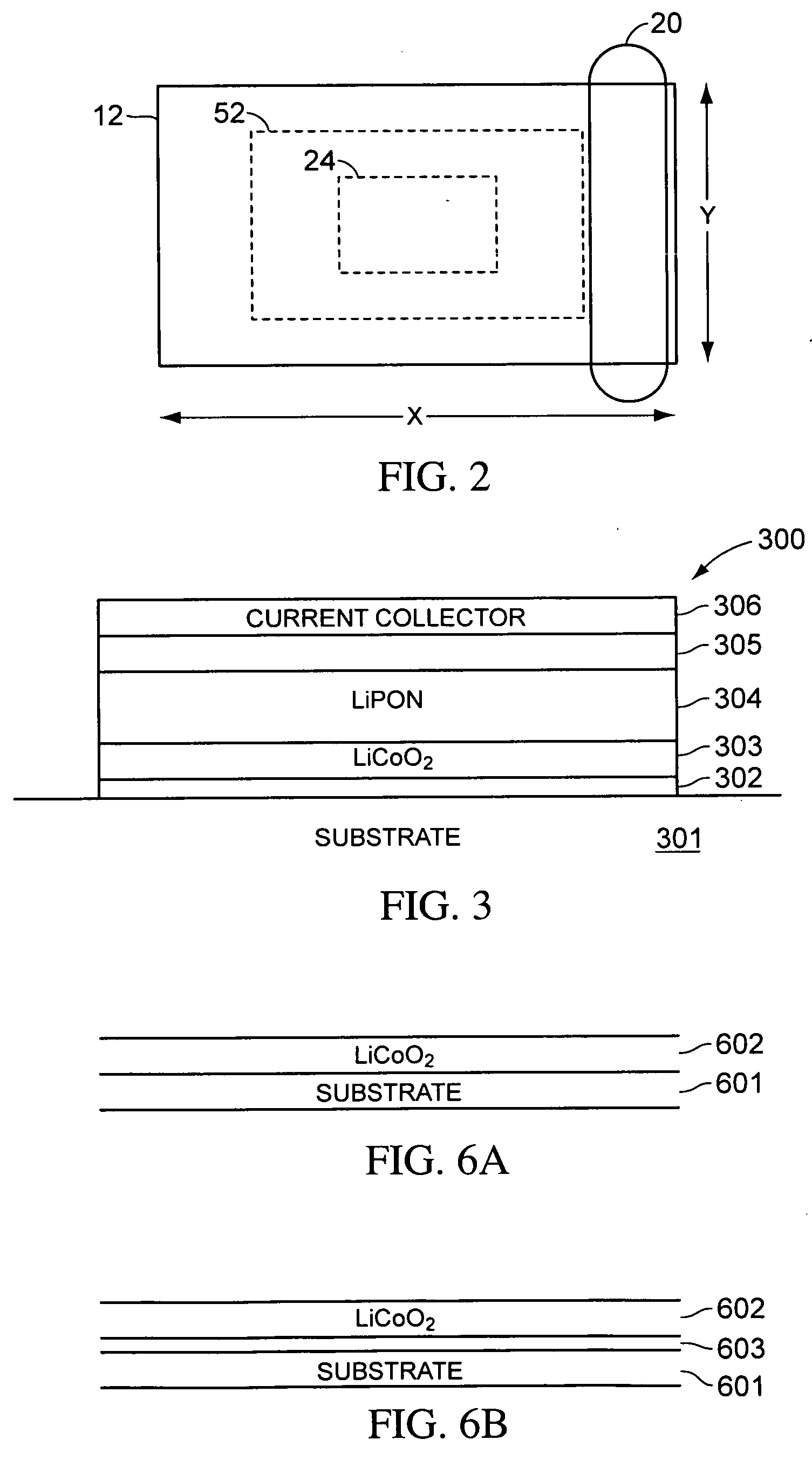

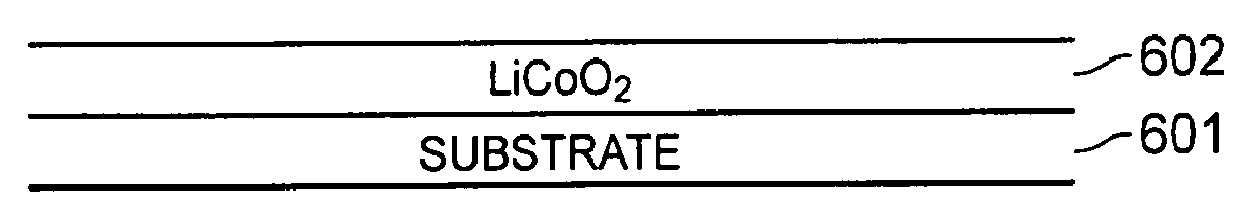

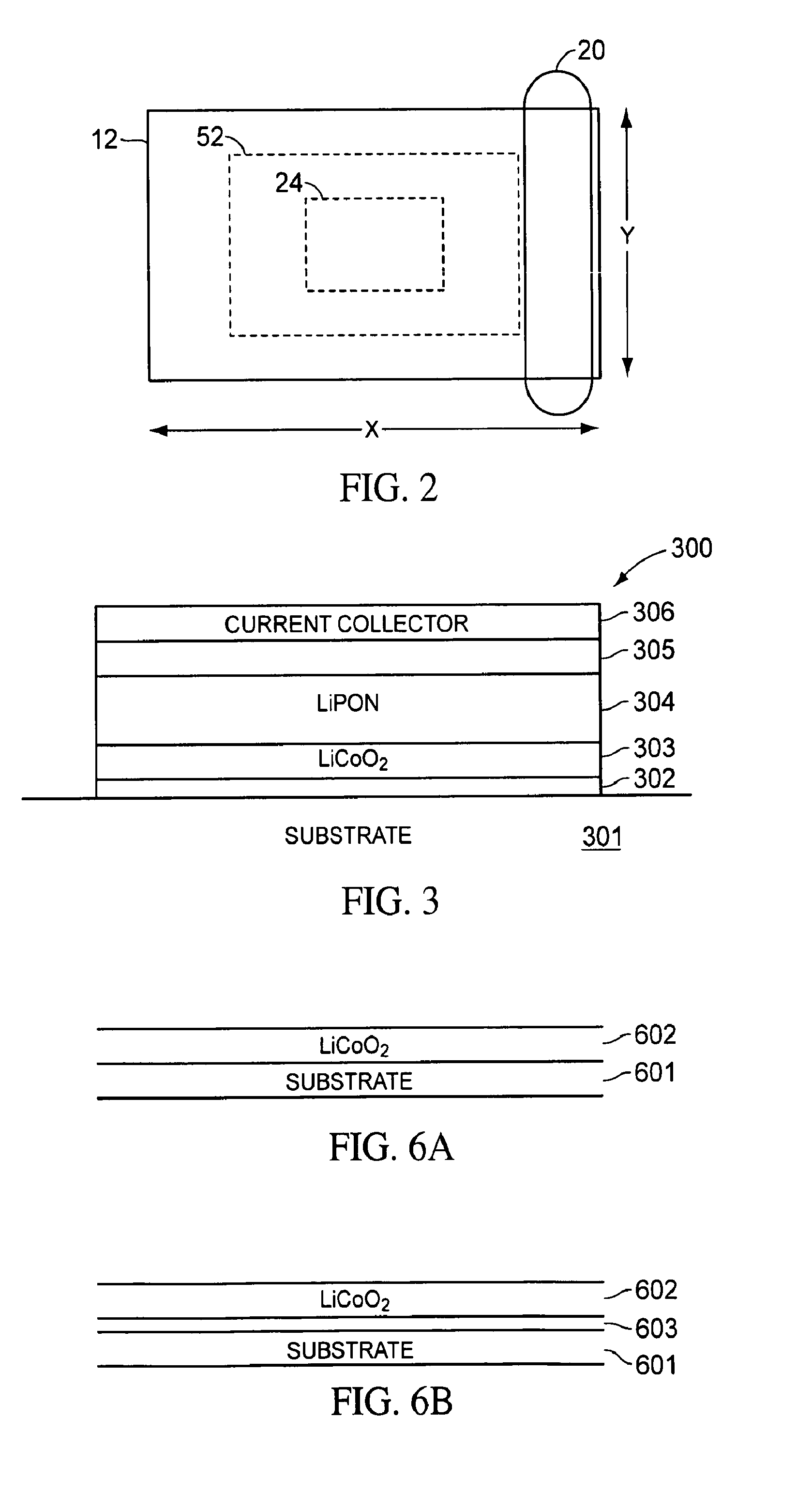

Deposition of LiCoO2

ActiveUS20060134522A1Increase deposition rateIncrease chanceElectrode thermal treatmentFinal product manufactureHigh rateEngineering

In accordance with the present invention, deposition of LiCoO2 layers in a pulsed-dc physical vapor deposition process is presented. Such a deposition can provide a low-temperature, high deposition rate deposition of a crystalline layer of LiCoO2 with a desired <101> or <003> orientation. Some embodiments of the deposition addresses the need for high rate deposition of LiCoO2 films, which can be utilized as the cathode layer in a solid state rechargeable Li battery. Embodiments of the process according to the present invention can eliminate the high temperature (>700° C.) anneal step that is conventionally needed to crystallize the LiCoO2 layer. Some embodiments of the process can improve a battery utilizing the LiCoO2 layer by utilizing a rapid thermal anneal process with short ramp rates.

Owner:DEMARAY

Compositions and methods for selective removal of metal or metal alloy after metal silicide formation

InactiveUS20090212021A1Efficient removalDecorative surface effectsSemiconductor/solid-state device manufacturingEtchingMetal silicide

An aqueous metal etching composition useful for removal of metals such as nickel, cobalt, titanium, tungsten, and alloys thereof, after formation of metal silicides via rapid thermal annealing during complementary metal-oxide-semiconductor (CMOS) transistor fabrication. The aqueous metal etching composition is also useful for selective removal of metal silicides and / or metal nitrides for wafer re-work. In one formulation, the aqueous metal etching composition contains oxalic acid, and a chloride-containing compound, and in other formulations, the composition contains an oxidizer, such as hydrogen peroxide, and a fluoride source, e.g., borofluoric acid. The composition in another specific formulation contains borofluoric acid and boric acid for effective etching of nickel, cobalt, titanium, tungsten, metal alloys, metal silicides and metal nitrides, without attacking the dielectric and the substrate.

Owner:ADVANCED TECH MATERIALS INC

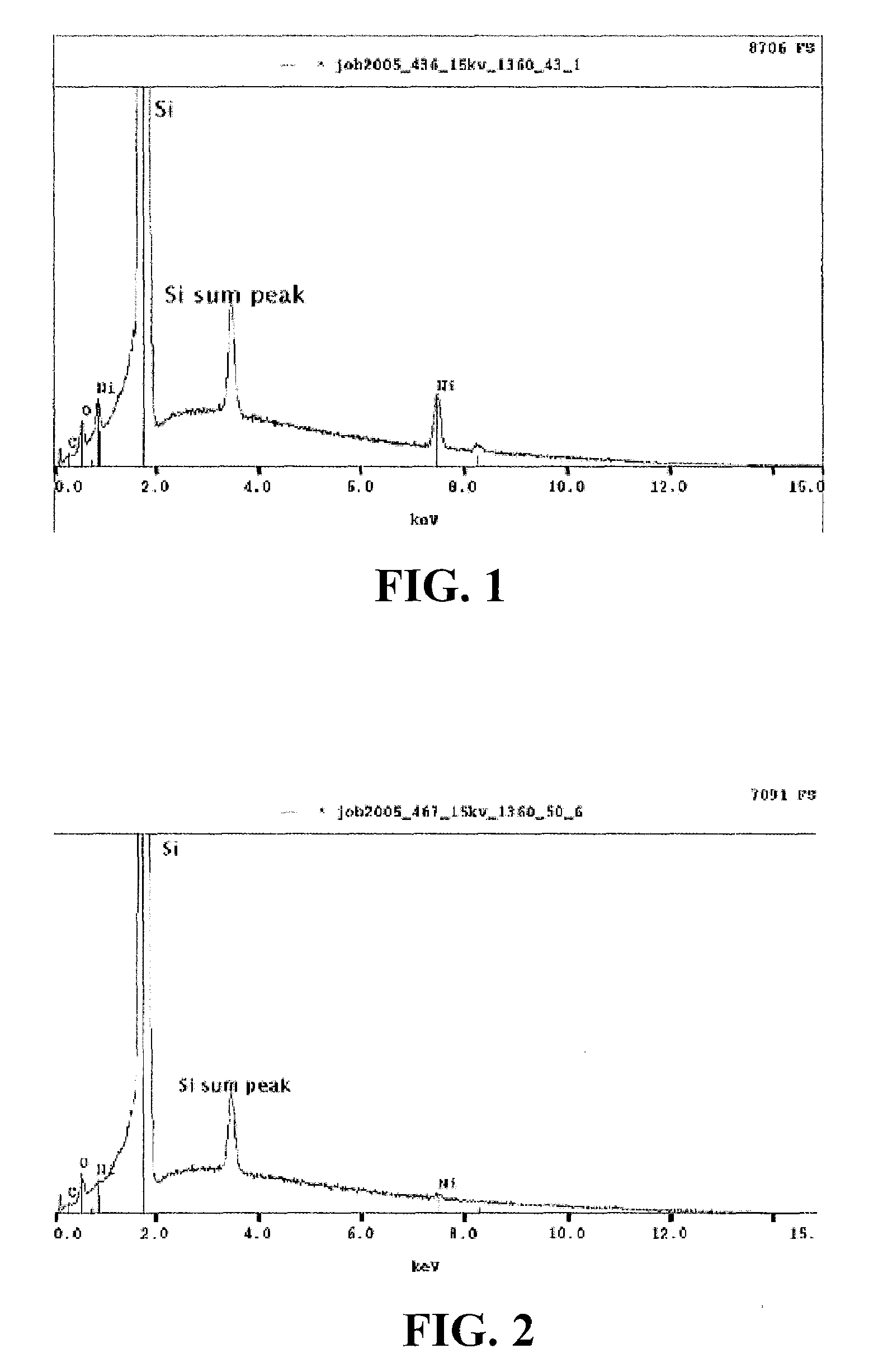

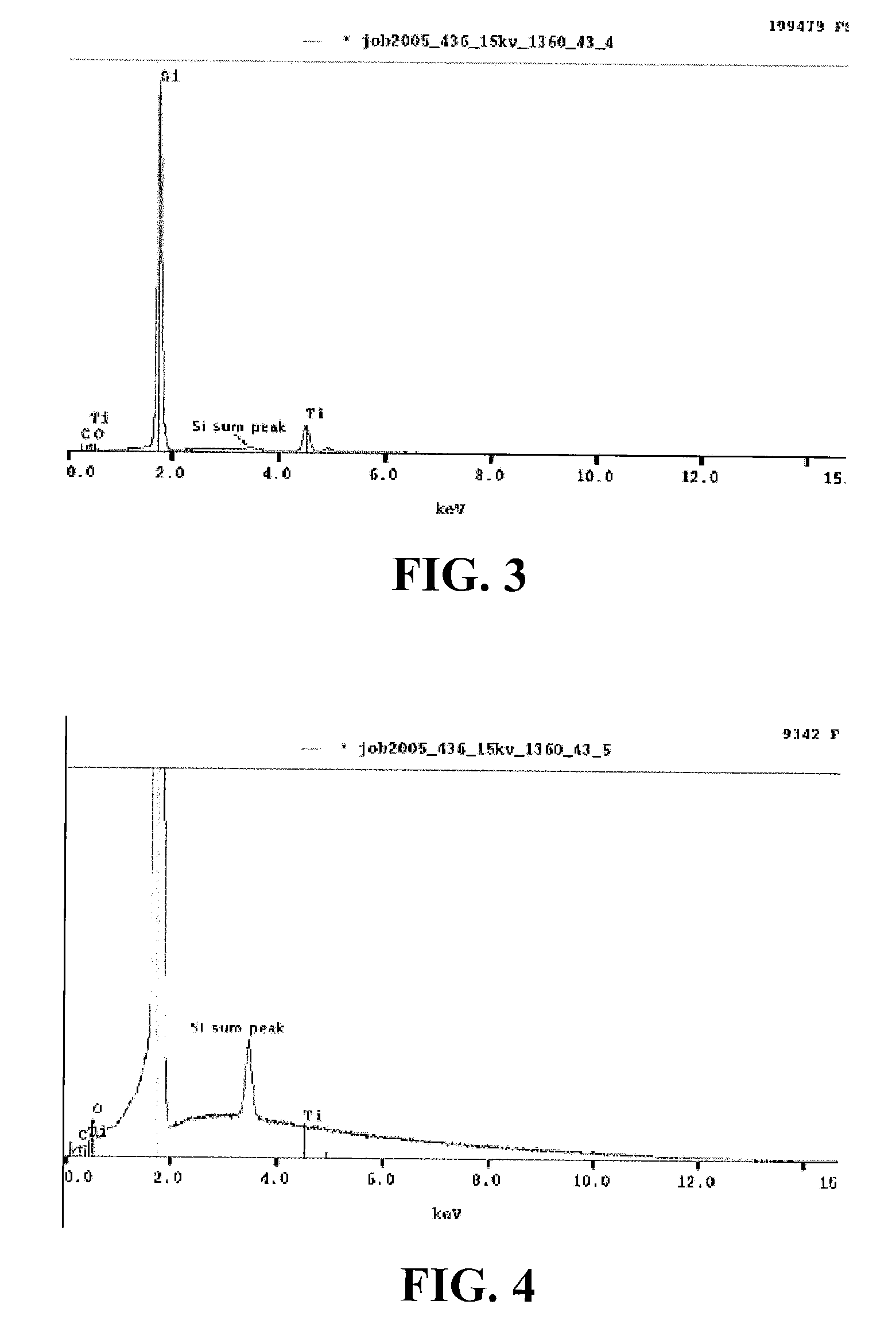

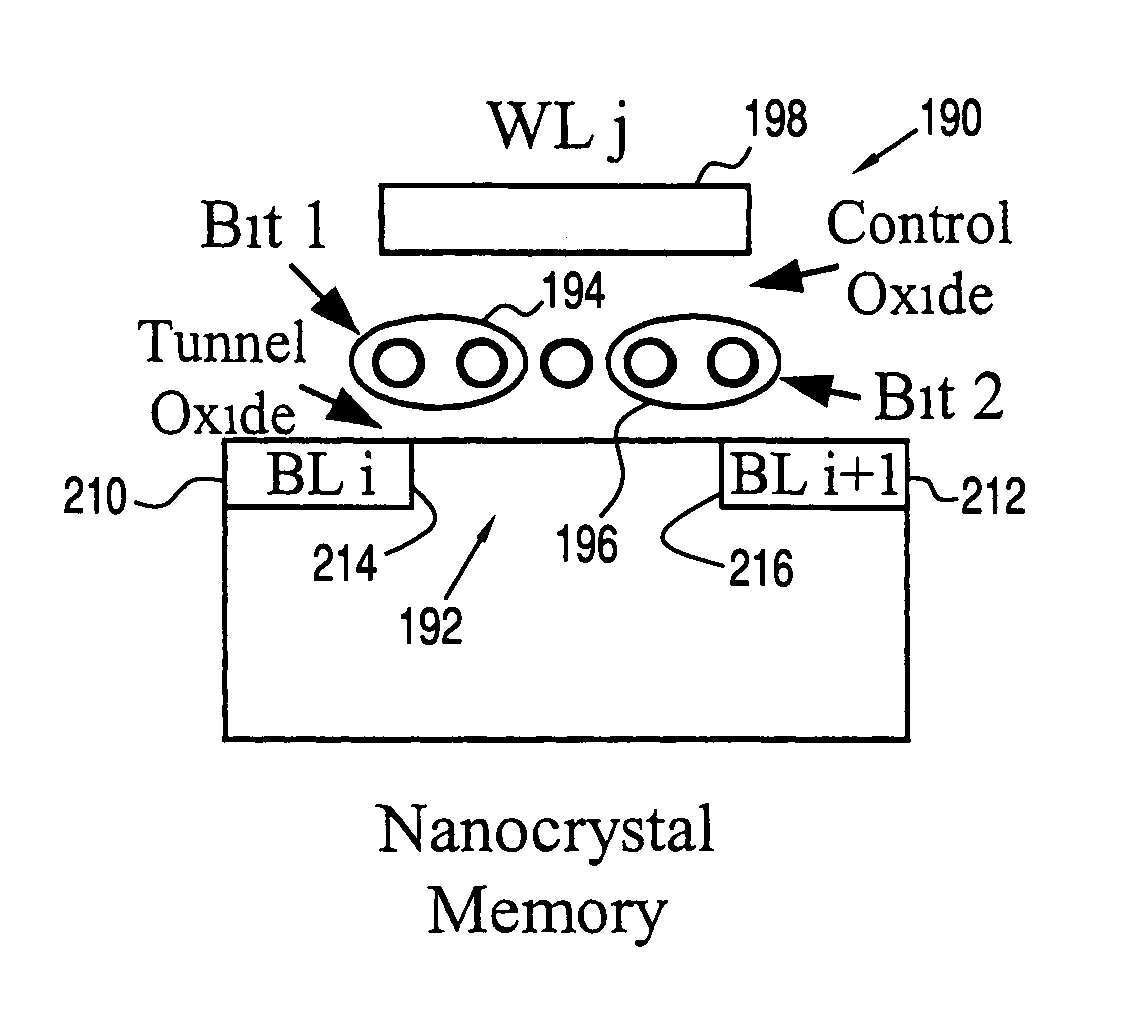

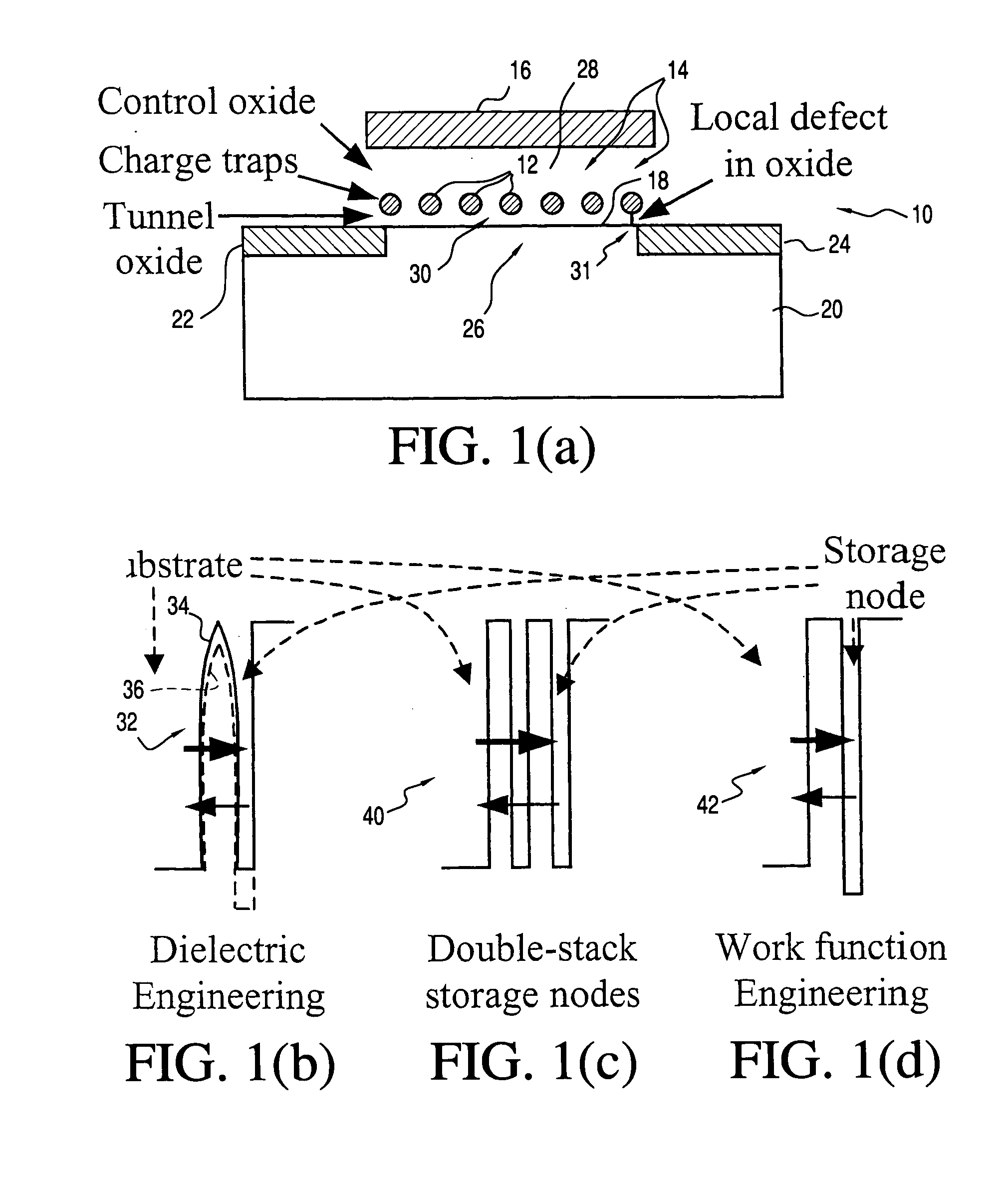

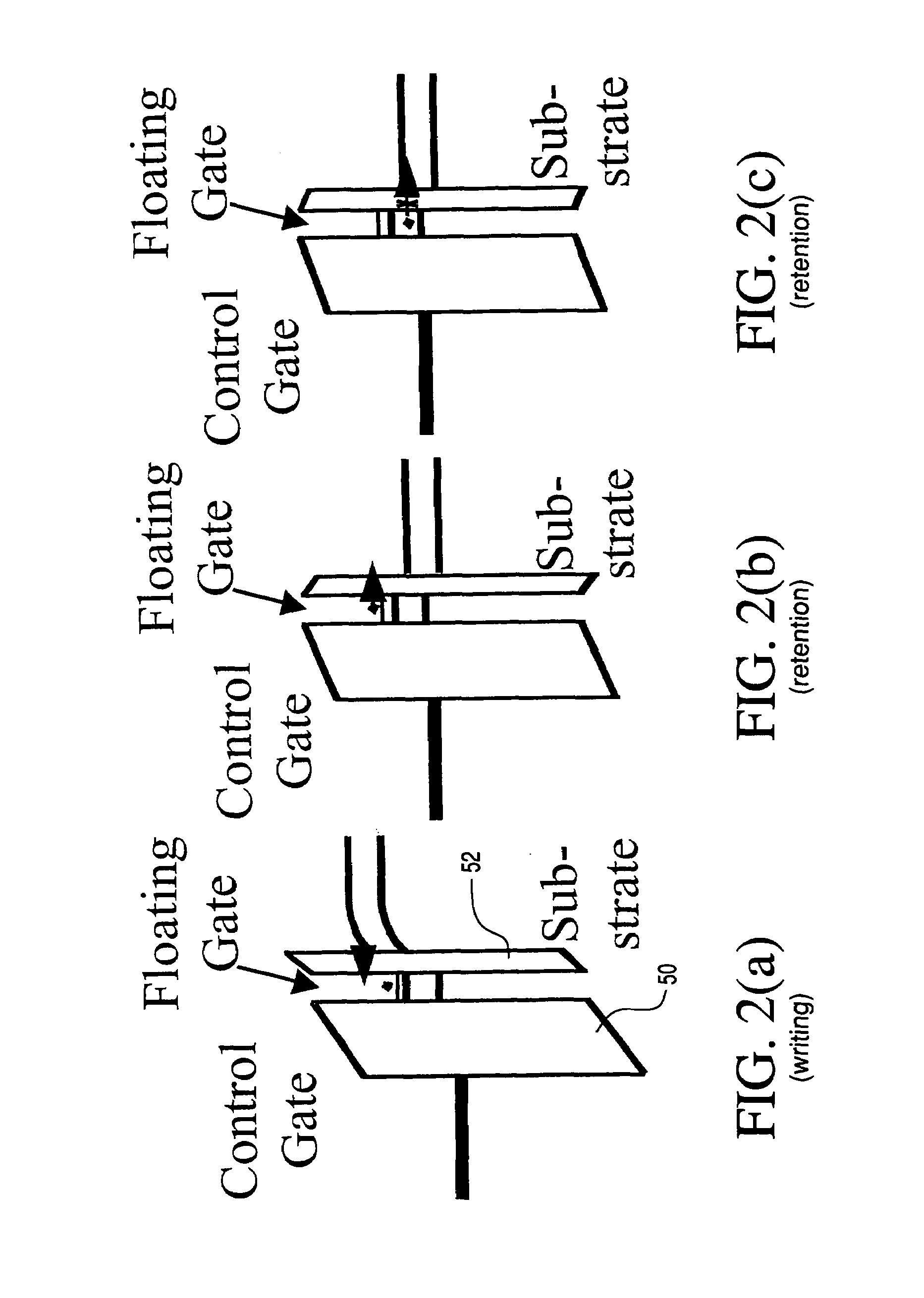

Multibit metal nanocrystal memories and fabrication

ActiveUS7259984B2Improve performanceImprove charge retentionNanoinformaticsRead-only memoriesRetention timeSemiconductor nanocrystals

Metal nanocrystal memories are fabricated to include higher density states, stronger coupling with the channel, and better size scalability, than has been available with semiconductor nanocrystal devices. A self-assembled nanocrystal formation process by rapid thermal annealing of ultra thin metal film deposited on top of gate oxide is integrated with NMOSFET to fabricate such devices. Devices with Au, Ag, and Pt nanocrystals working in the F-N tunneling regime, with hot-carrier injection as the programming mechanism, demonstrate retention times up to 106s, and provide 2-bit-per-cell storage capability.

Owner:CORNELL RES FOUNDATION INC

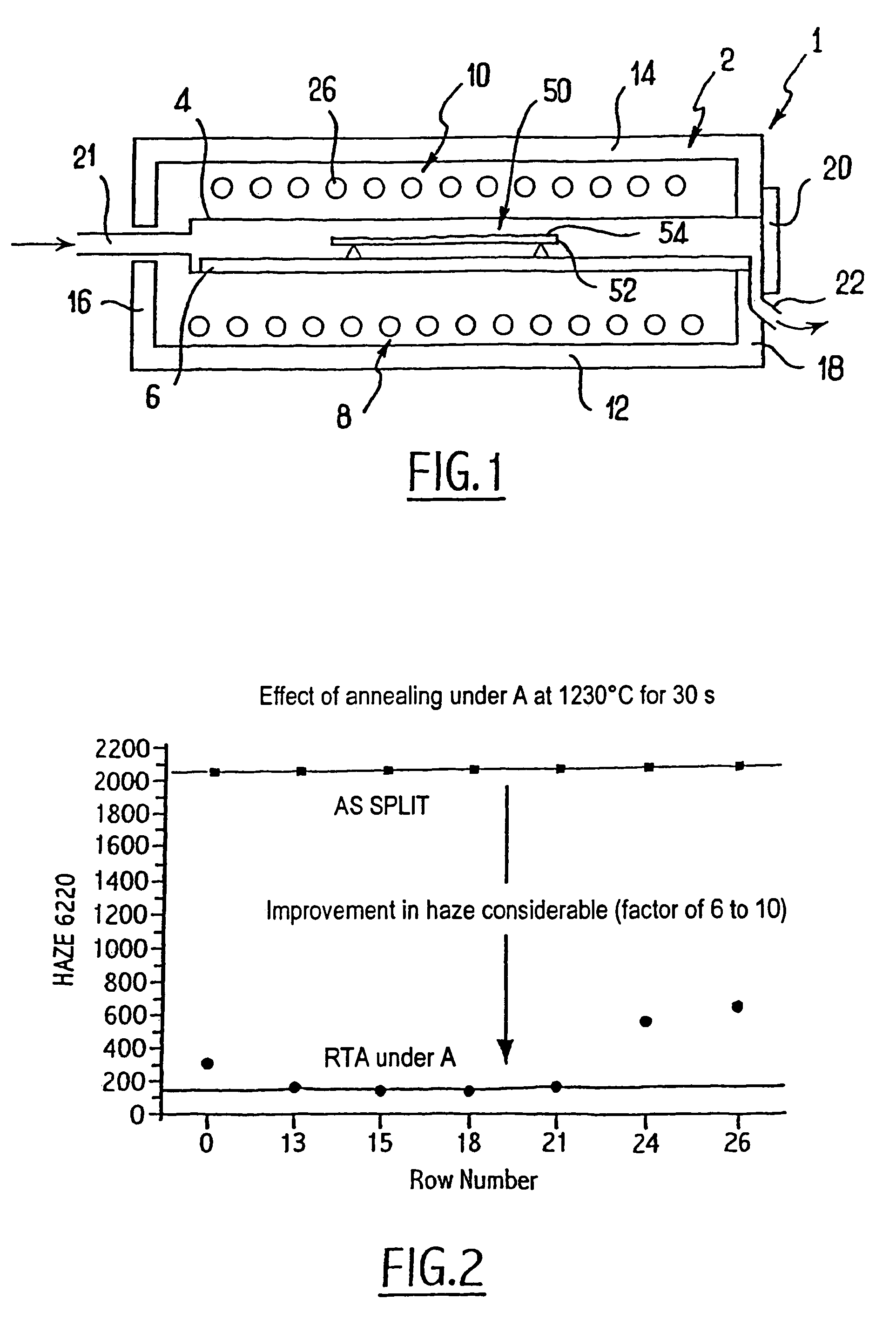

Method for reducing free surface roughness of a semiconductor wafer

InactiveUS6962858B2Reduce roughnessSolid-state devicesSemiconductor/solid-state device manufacturingWaferingSemiconductor materials

The invention provides a method of reducing the roughness of the free surface of a wafer of semiconductor material by applying a rapid thermal annealing process under a pure argon atmosphere for a time sufficient to uniformly heat and smooth the free surface of the wafer.

Owner:SOITEC SA

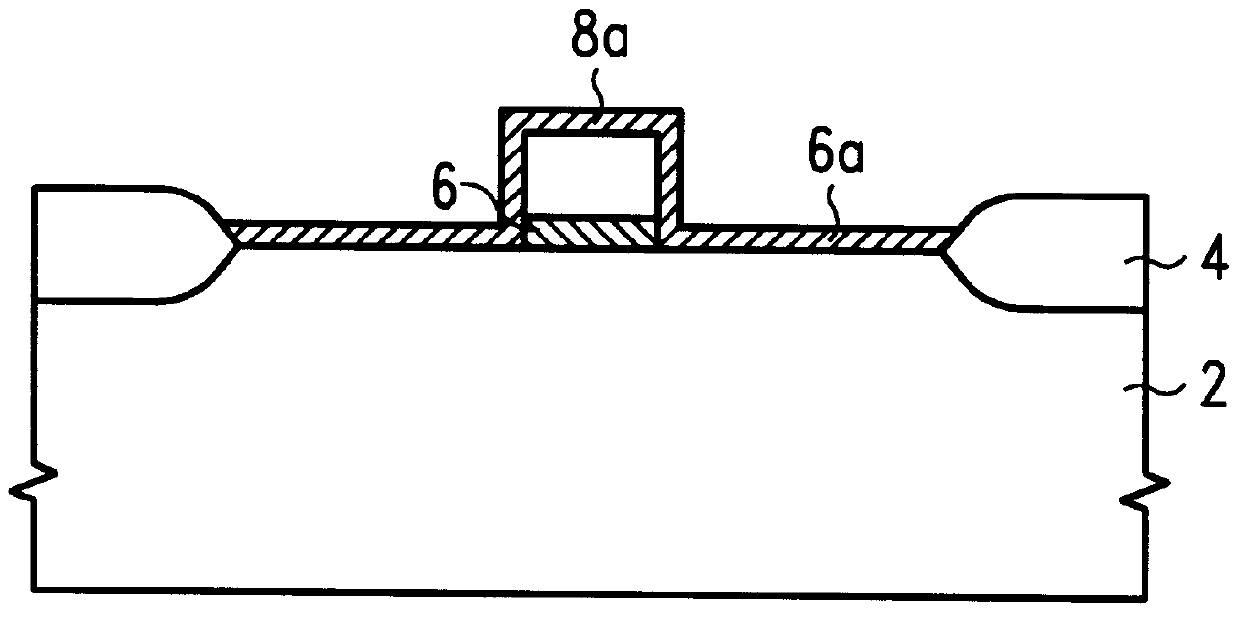

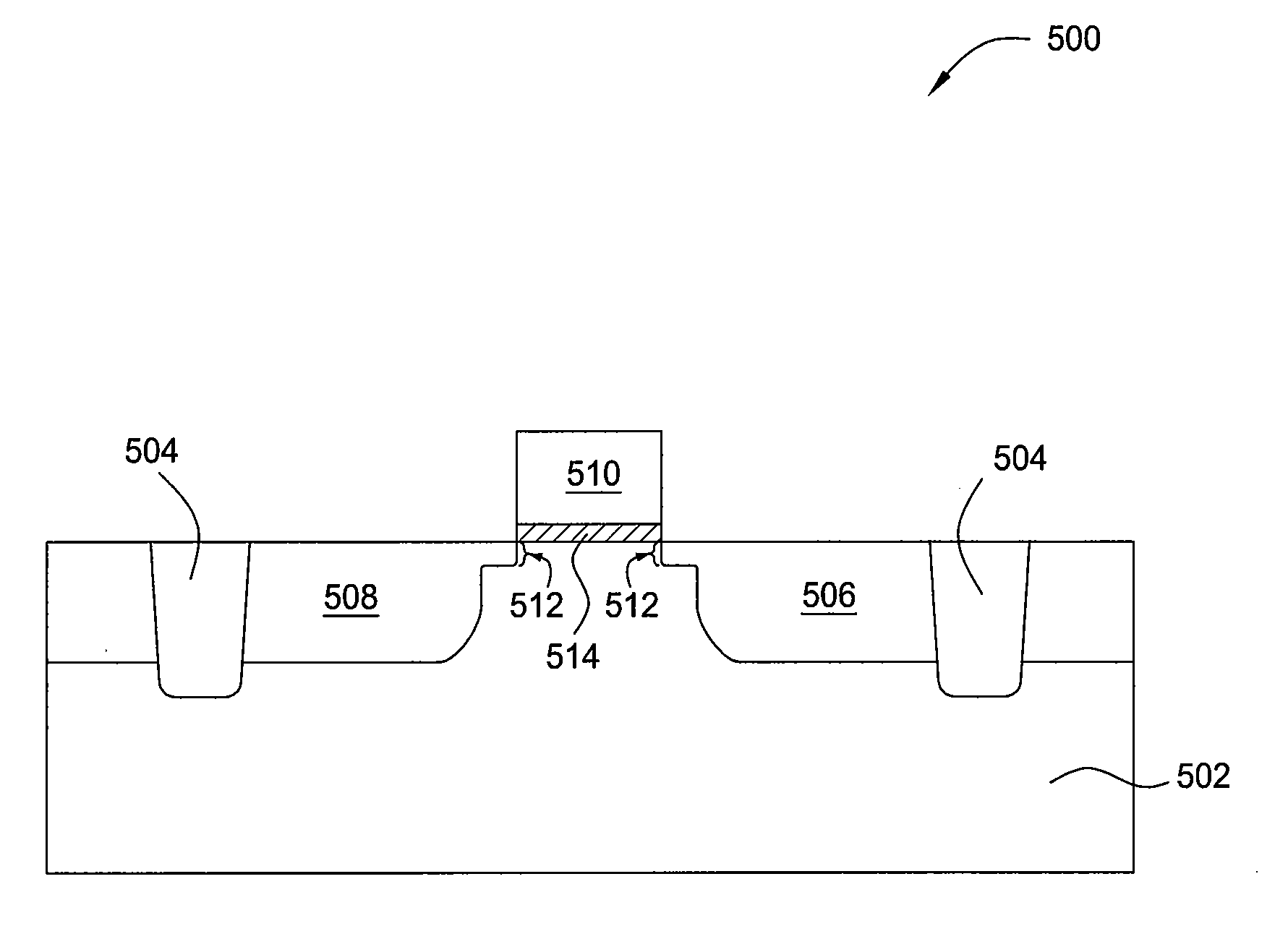

Method of forming a self-aligned silicide MOSFET with an extended ultra-shallow S/D junction

The method of the present invention is a method of including forming a gate oxide layer on the substrate. A polysilicon layer is formed on the gate oxide layer. Then, a photographic and etching steps are used to form a gate structure. An oxidation is performed on the substrate and the gate structure to form an first oxide layer on the substrate and on the surface of the polysilicon gate. A silicon nitride layer is deposited on the first oxide layer. A side-wall spacers is formed on the side walls of the gate structure, a first portion of the first oxide layer remaining between the gate structure and the side-wall spacers, and a second portion of the first oxide layer remaining under the side-wall spacers. Next, a first ion implantation performed into the substrate to form first doped ions regions to serves as source and drain region of the transistor. Then, the side-wall spacers is removed, therefore remained the second portion of the first oxide layer covered by the side-wall spacers. Subsequently, a second ion implantation performed through the second portion of the first oxide layer to form second doped ion regions to serve as an extended source and drain region of the transistor. A rapid thermal annealing performed to form an extended source and drain junction and aligned to the region of the side-wall spacers being disposed.

Owner:TAIWAN SEMICON MFG CO LTD +2

Deposition of LiCoO2

ActiveUS7959769B2Increase deposition rateElectrochemical processing of electrodesElectrode thermal treatmentHigh rateEngineering

In accordance with the present invention, deposition of LiCoO2 layers in a pulsed-dc physical vapor deposition process is presented. Such a deposition can provide a low-temperature, high deposition rate deposition of a crystalline layer of LiCoO2 with a desired (101) or (003) orientation. Some embodiments of the deposition addresses the need for high rate deposition of LiCoO2 films, which can be utilized as the cathode layer in a solid state rechargeable Li battery. Embodiments of the process according to the present invention can eliminate the high temperature (>700° C.) anneal step that is conventionally needed to crystallize the LiCoO2 layer. Some embodiments of the process can improve a battery utilizing the LiCoO2 layer by utilizing a rapid thermal anneal process with short ramp rates.

Owner:SAPURAST RES

Electrically-driven optical proximity correction to compensate for non-optical effects

ActiveUS20100122231A1Simple methodImprove performancePhotomechanical apparatusOriginals for photomechanical treatmentCapacitanceEngineering

A contour of a mask design for an integrated circuit is modified to compensate for systematic variations arising from non-optical effects such as stress, well proximity, rapid thermal anneal, or spacer thickness. Electrical characteristics of a simulated integrated circuit chip fabricated using the mask design are extracted and compared to design specifications, and one or more edges of the contour are adjusted to reduce the systematic variation until the electrical characteristic is within specification. The particular electrical characteristic preferably depends on which layer is to be fabricated from the mask: on-current for a polysilicon; resistance for contact; resistance and capacitance for metal; current for active; and resistance for vias. For systematic threshold voltage variation, the contour is adjusted to match a gate length which corresponds to an on-current value according to pre-calculated curves for contour current and gate length at a nominal threshold voltage of the chip.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

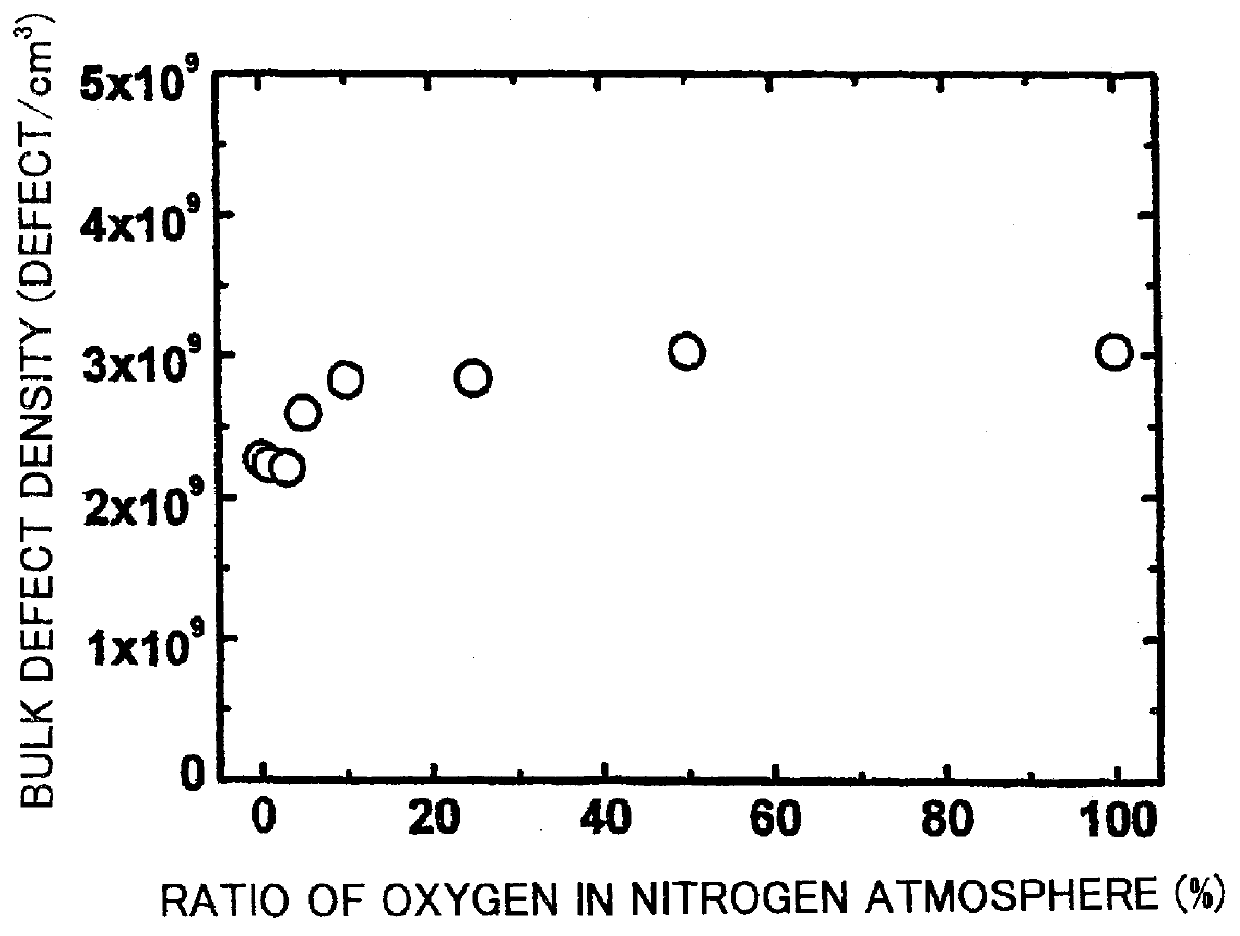

Method for heat treatment of silicon wafer and silicon wafer

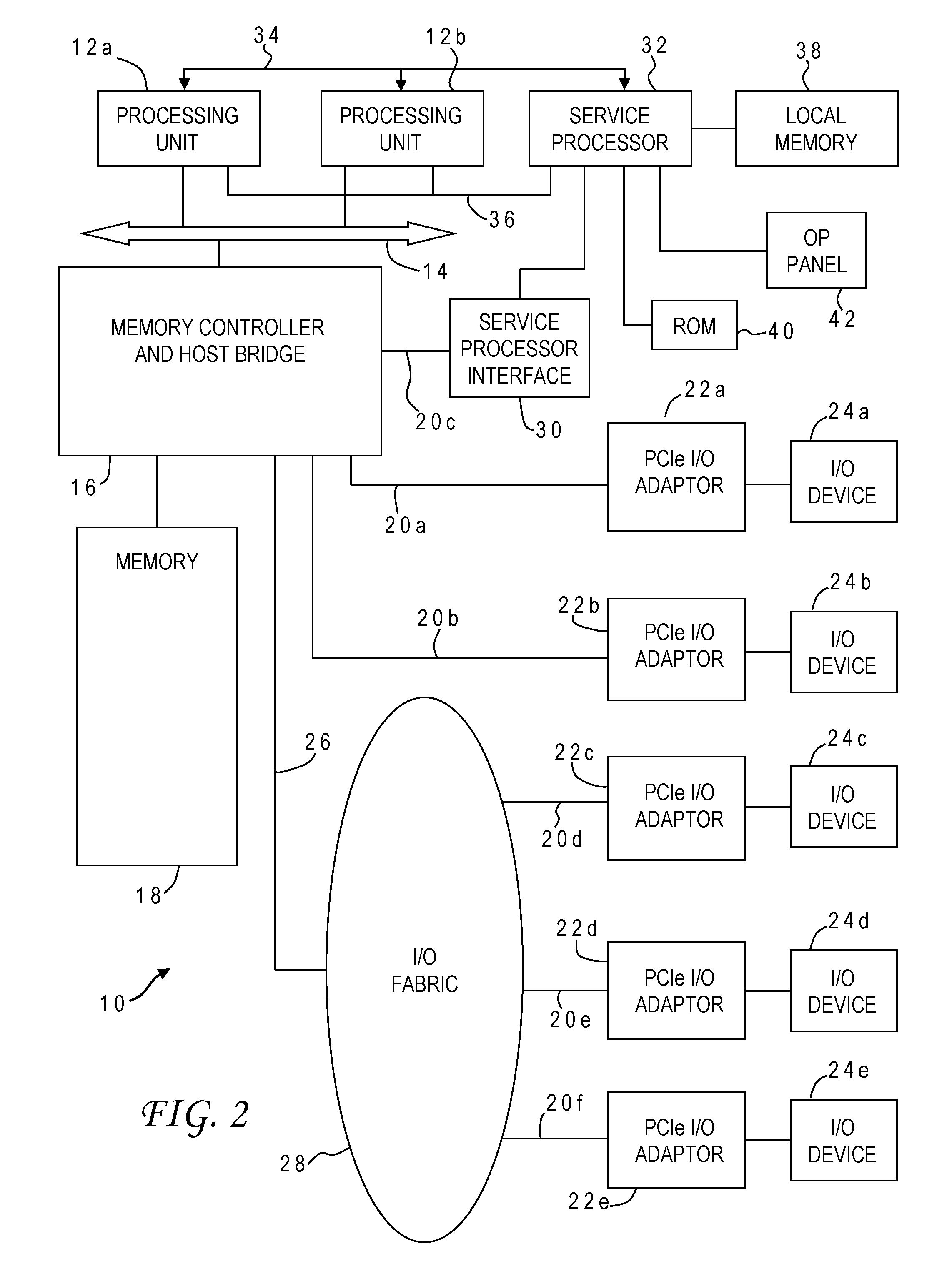

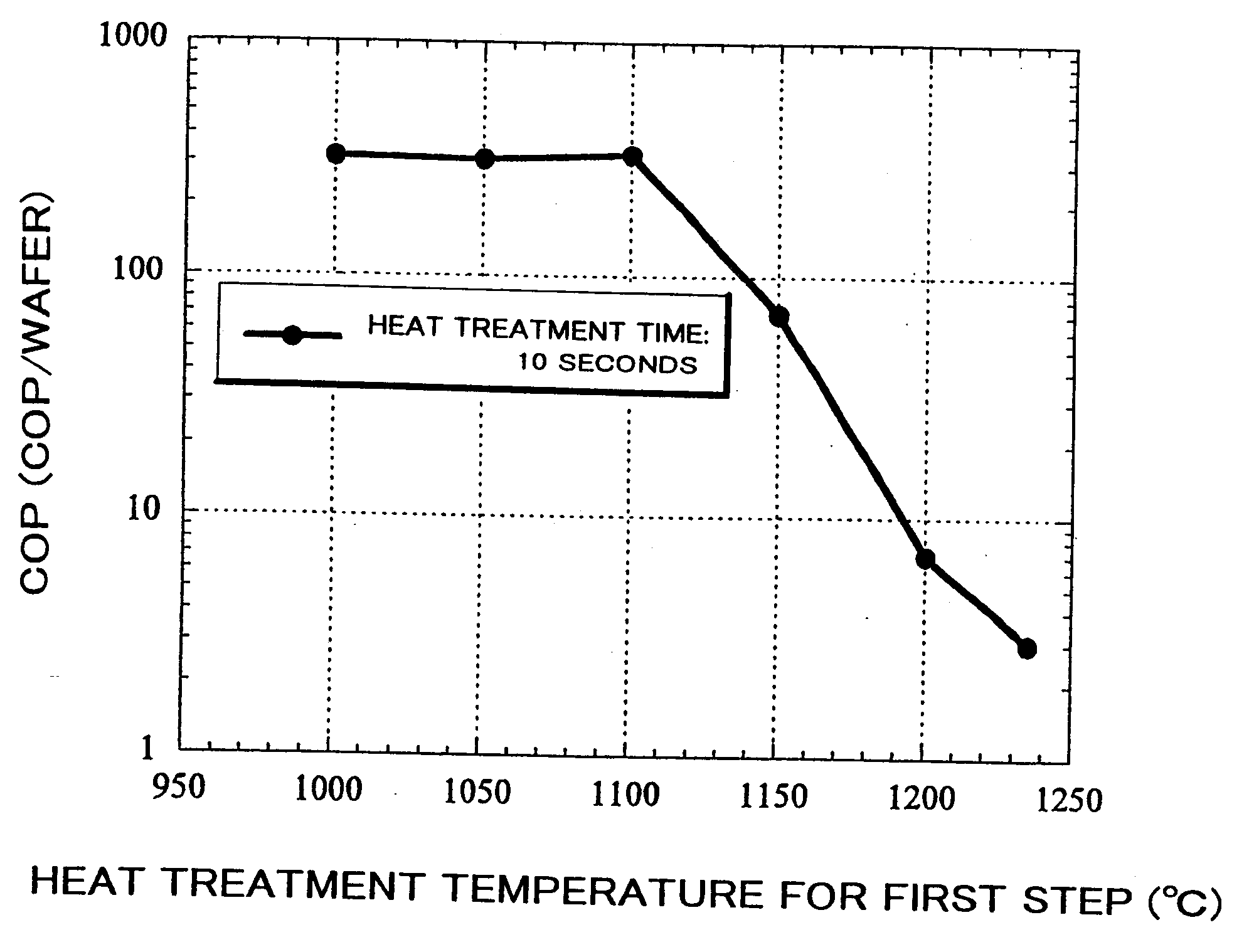

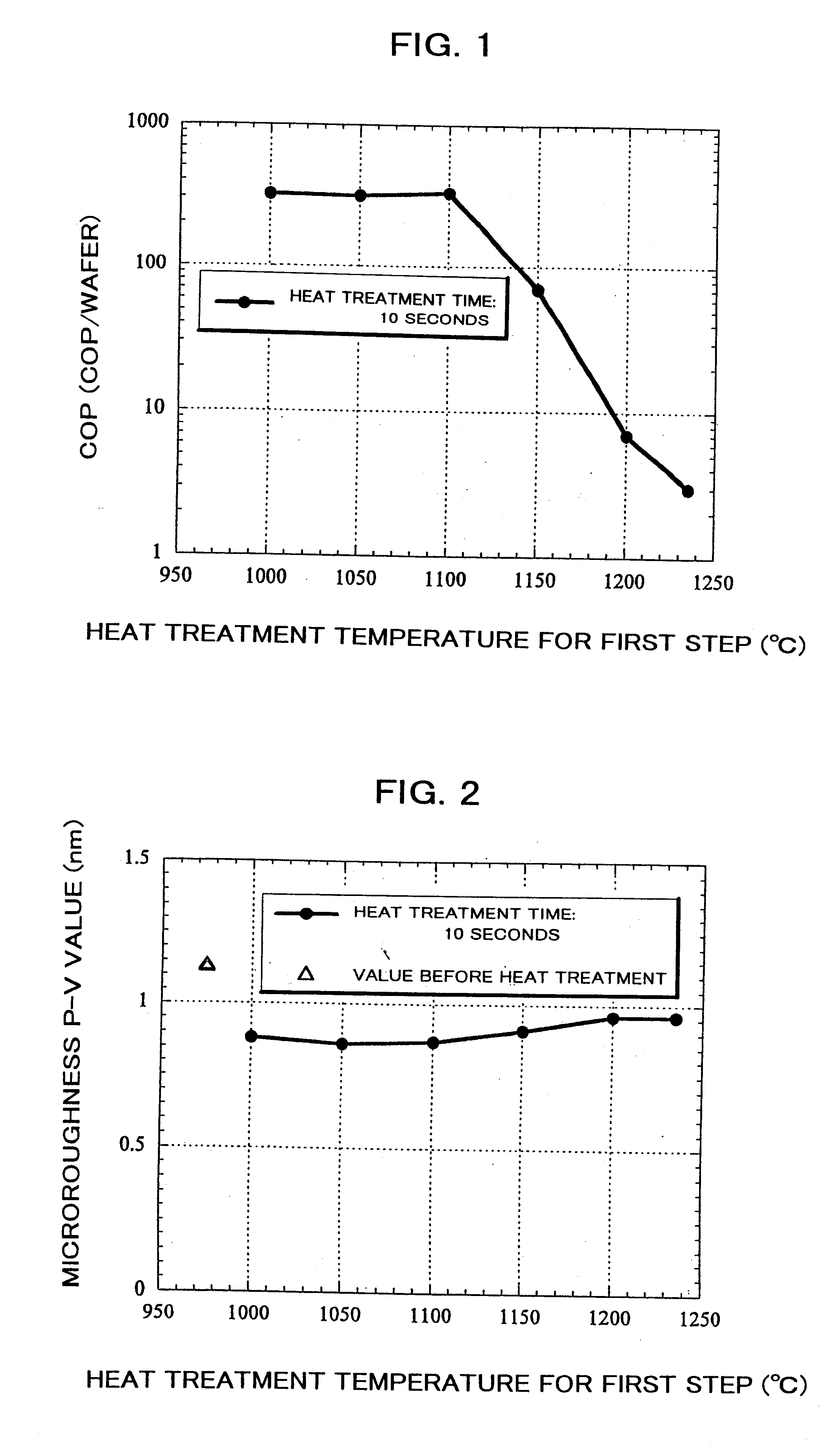

InactiveUS6245311B1Microroughness and haze can be decreasedFew defectSiliconSemiconductor/solid-state device manufacturingElectricityWafering

There is disclosed a method for heat treatment of a silicon wafer performed in a reducing atmosphere containing hydrogen by utilizing a rapid thermal annealer, wherein the heat treatment comprises a plurality of steps each of which is performed with a differently defined heat treatment condition. In this method, the heat treatment comprising a plurality of steps may be continuously performed without taking out the wafer from an RTA apparatus. The method of the present invention can, in particular, reduce COP density of the silicon wafer surface, reduce its microroughness and haze, and thus improve electric characteristics such as oxide dielectric breakdown voltage and mobility of carriers.

Owner:SHIN-ETSU HANDOTAI CO LTD

Poly pre-doping anneals for improved gate profiles

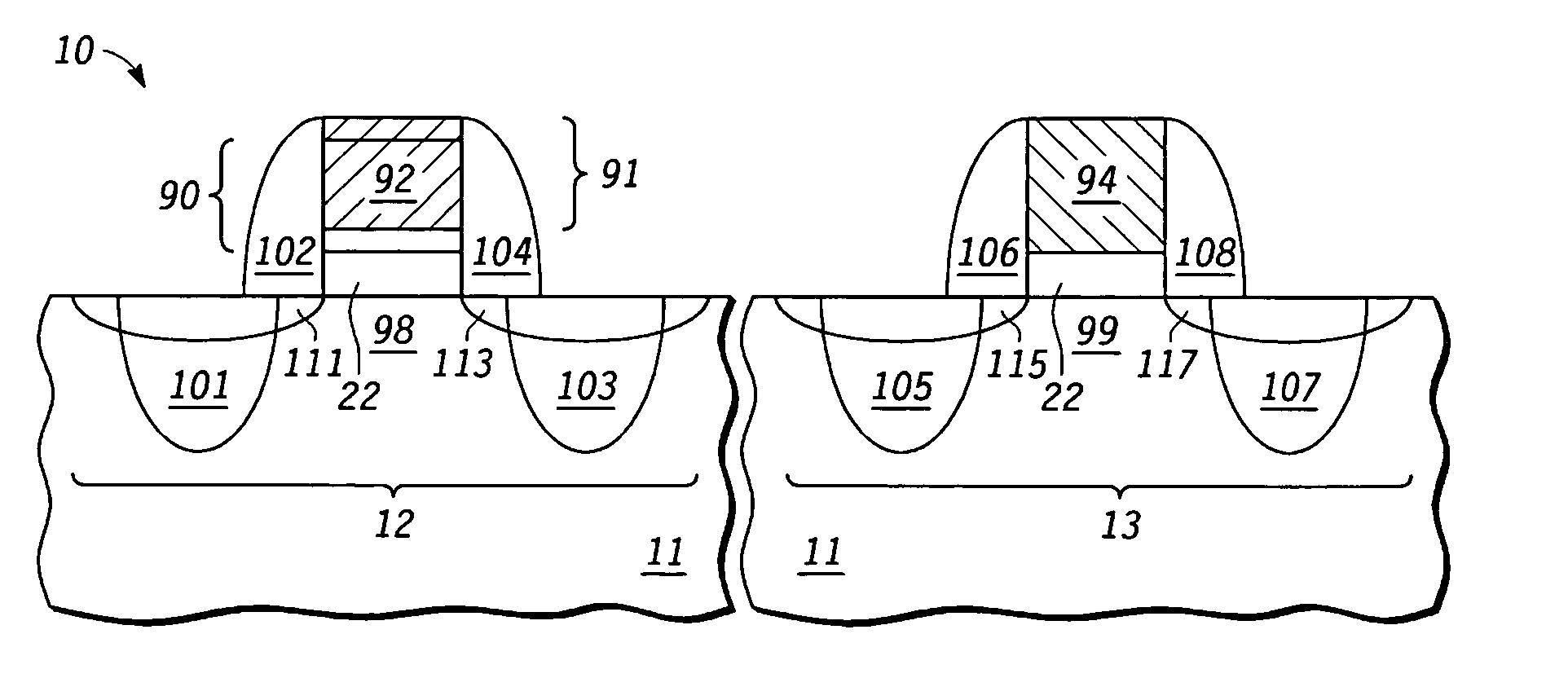

A semiconductor process and apparatus uses a predetermined sequence of patterning and etching steps to etch a gate stack (32) formed over a substrate (11), thereby forming an etched gate (92, 94) having a vertical sidewall profile by implanting the gate stack (32) with a nitrogen (42) and a dopant (52) and then heating the polysilicon gate stack (32) at a selected temperature using rapid thermal annealing (62) to anneal the nitrogen and dopant so that subsequent etching of the polysilicon gate stack (32) creates an etched gate (92, 94) having more idealized vertical gate sidewall profiles.

Owner:FREESCALE SEMICON INC

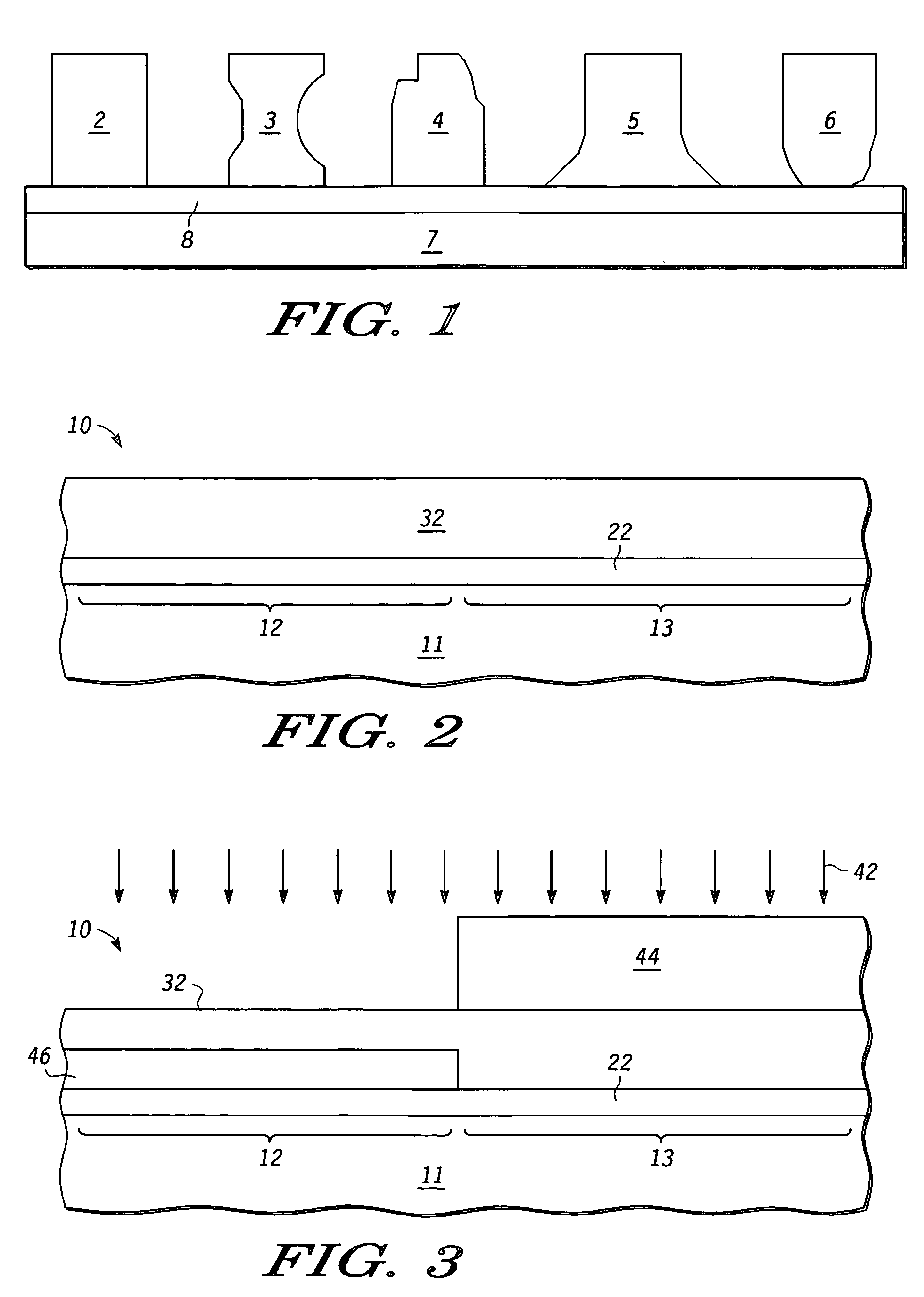

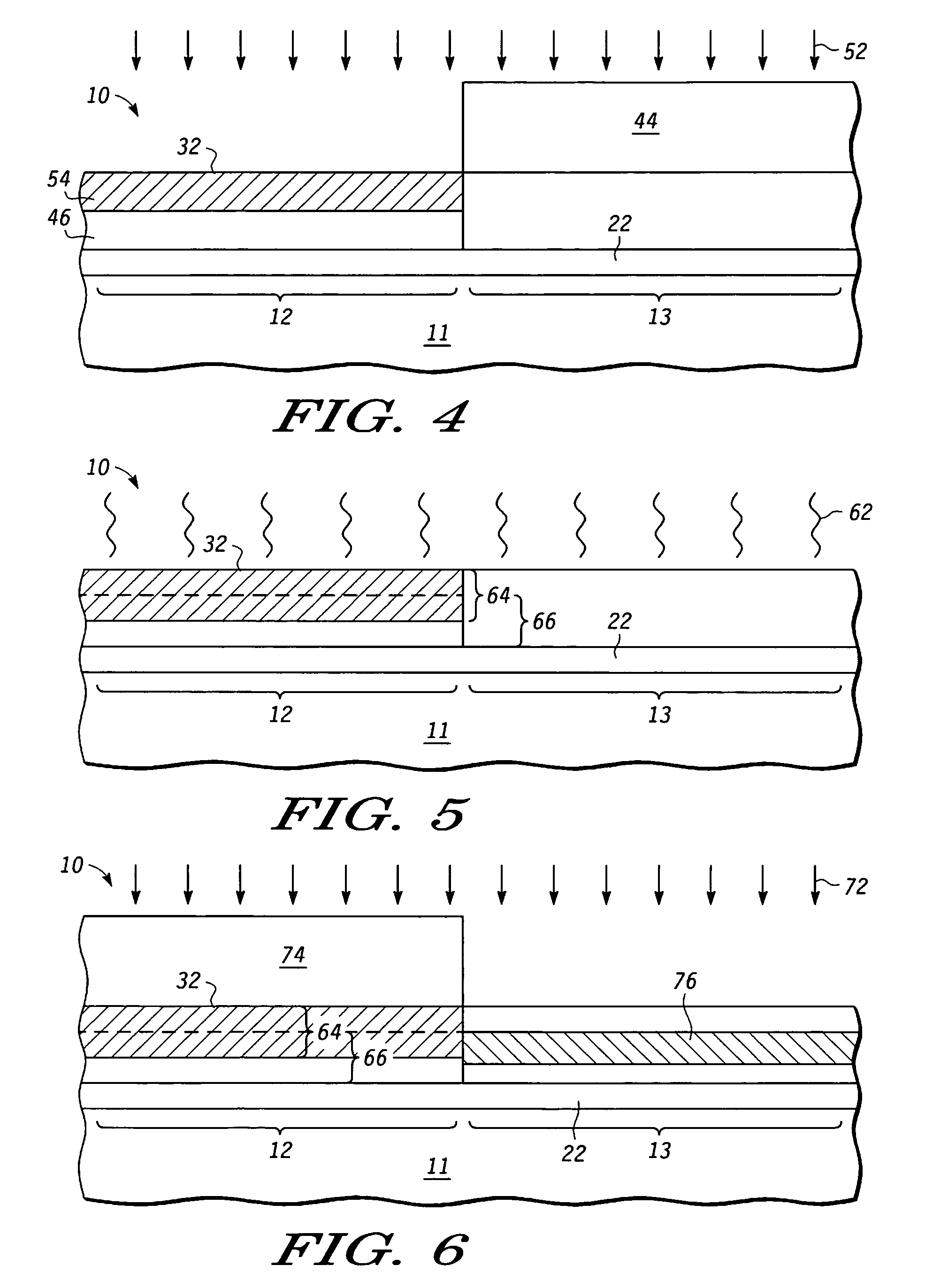

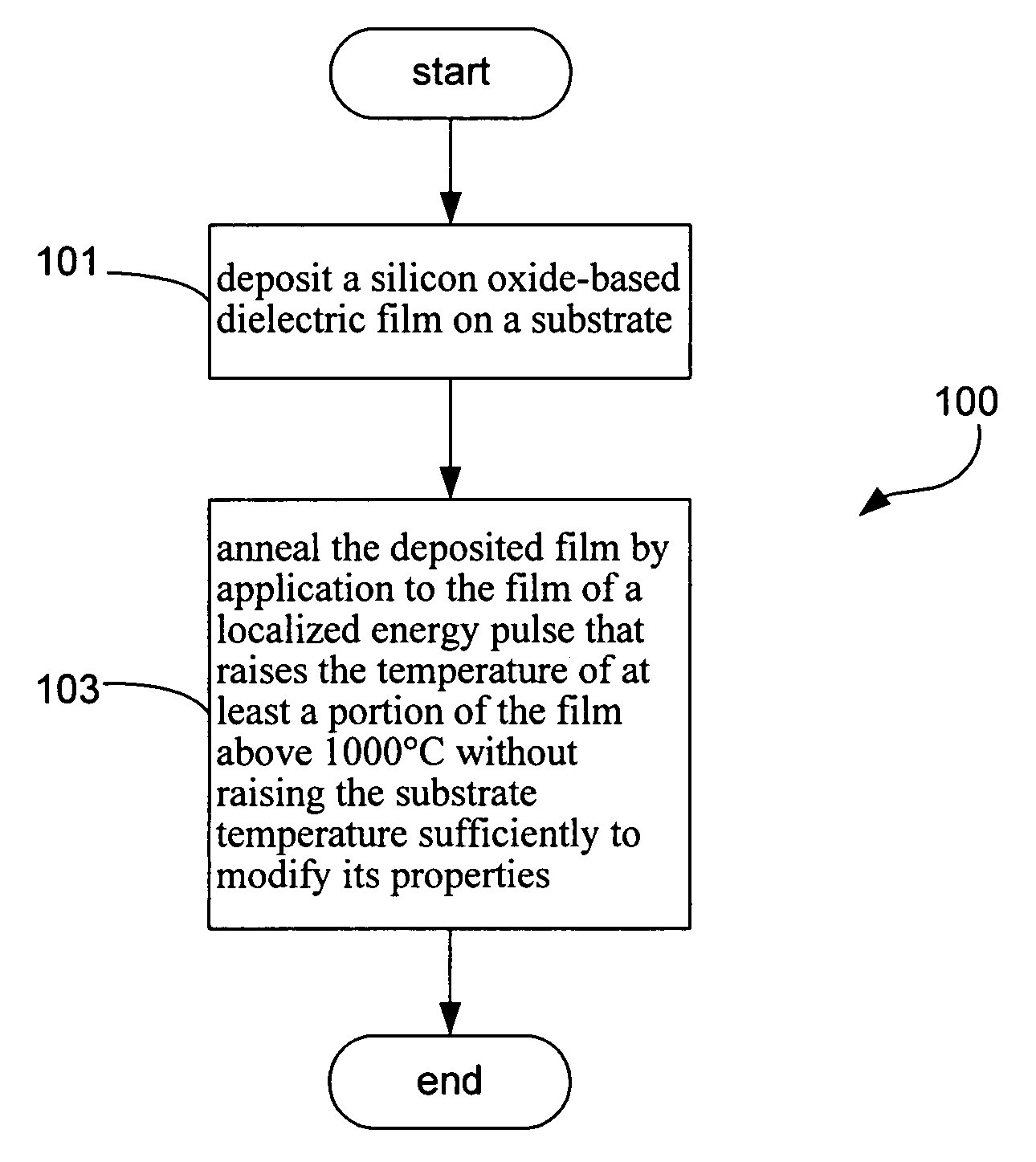

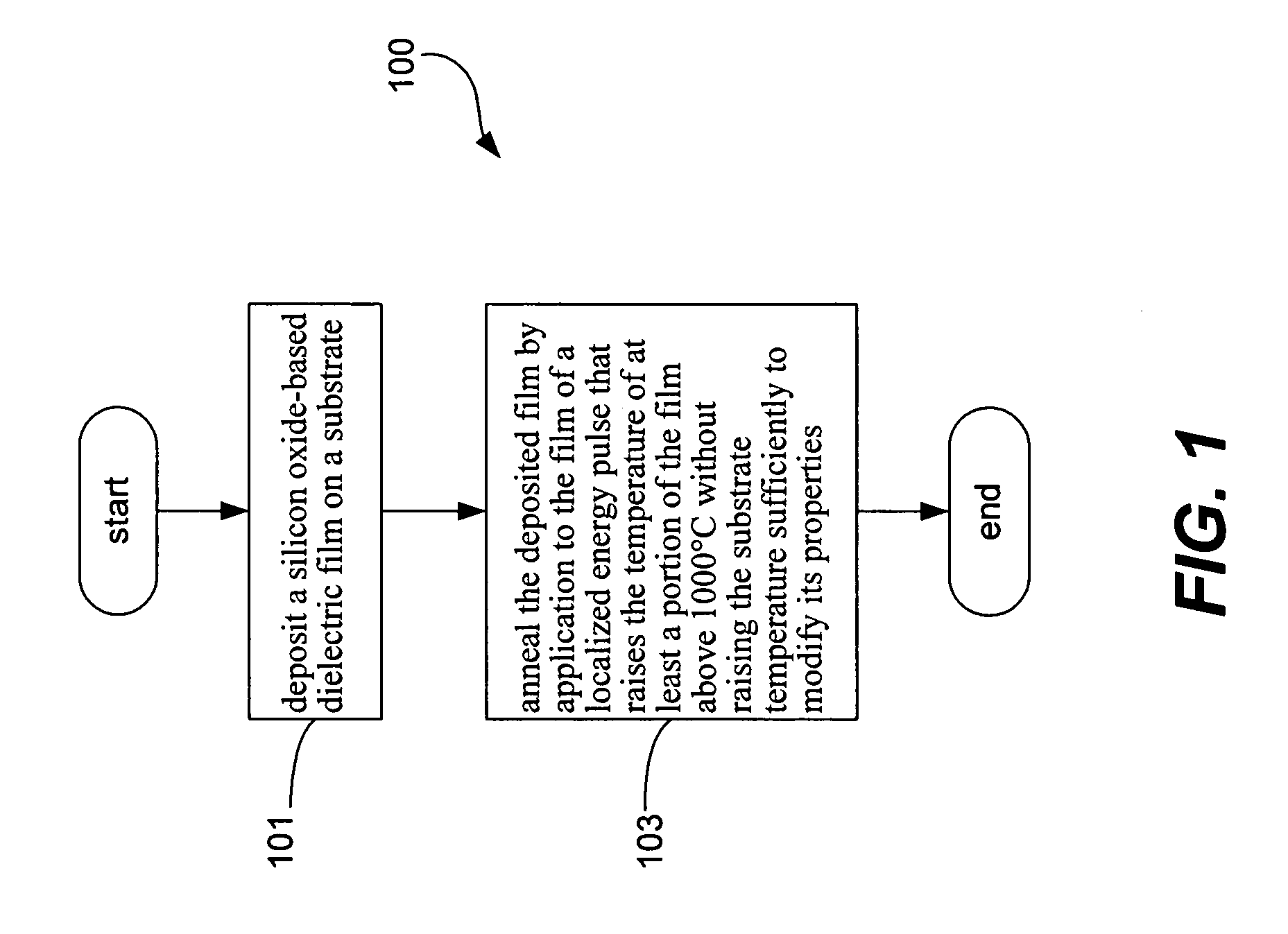

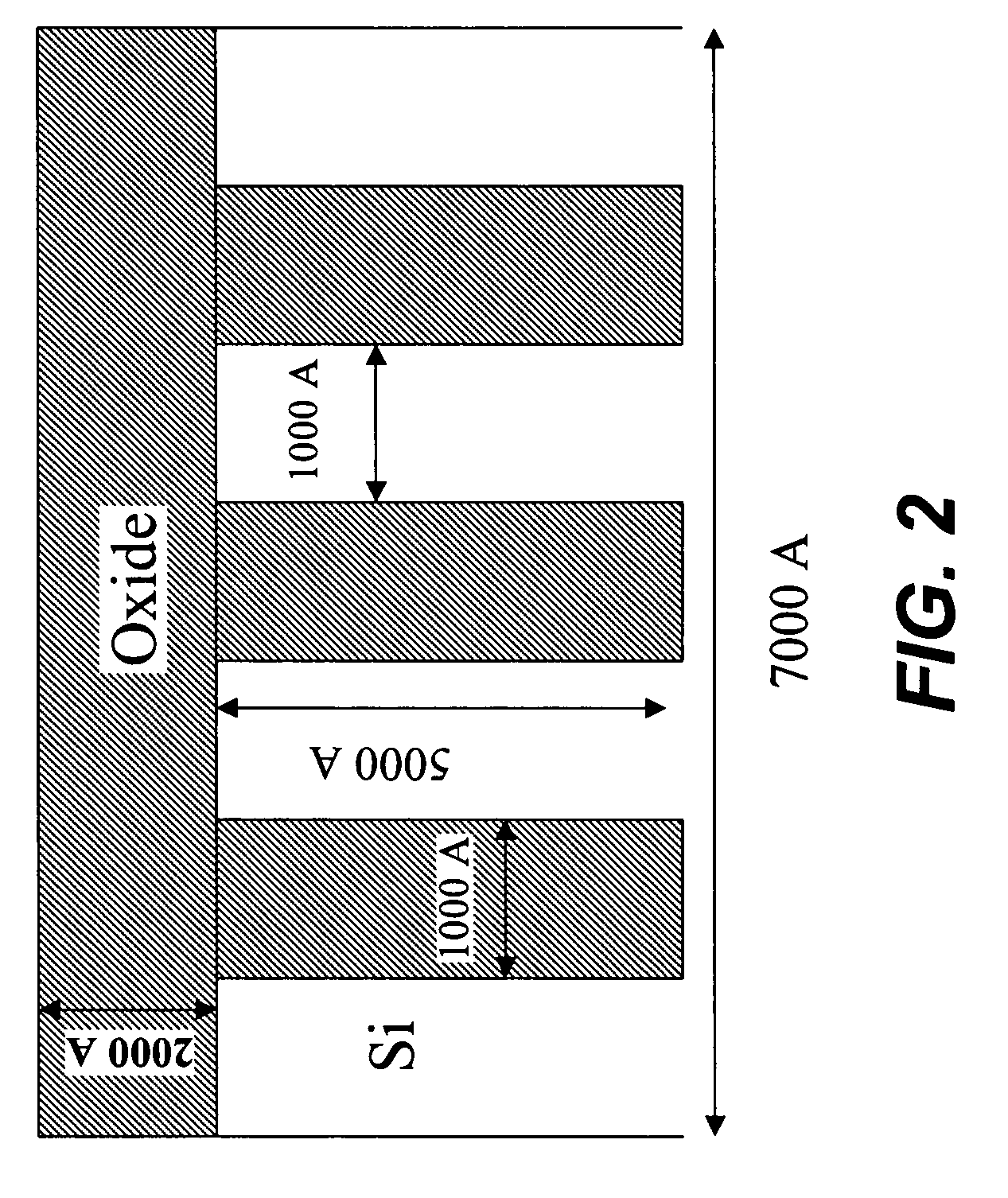

Localized energy pulse rapid thermal anneal dielectric film densification method

A densified dielectric film is formed on a substrate by a process that involves annealing a film deposited on the substrate by application of a localized energy pulse, such as a laser pulse, for example one of about 10 to 100 ns in duration from an excimer laser, that raises the temperature of the film above 1000° C. without raising the substrate temperature sufficiently to modify its properties (e.g., the substrate temperature remains below 550° C. or preferably in many applications below 400° C.). The dielectric deposition may be by any suitable process, for example CVD, SOG (spin-on glass), ALD, or catalyzed PDL. The resulting film is densified without detrimentally impacting underlying substrate layers. The invention enables dielectric gap fill and film densification at low temperature to the 45 nm technology node and beyond, while maintaining oxide film properties.

Owner:NOVELLUS SYSTEMS

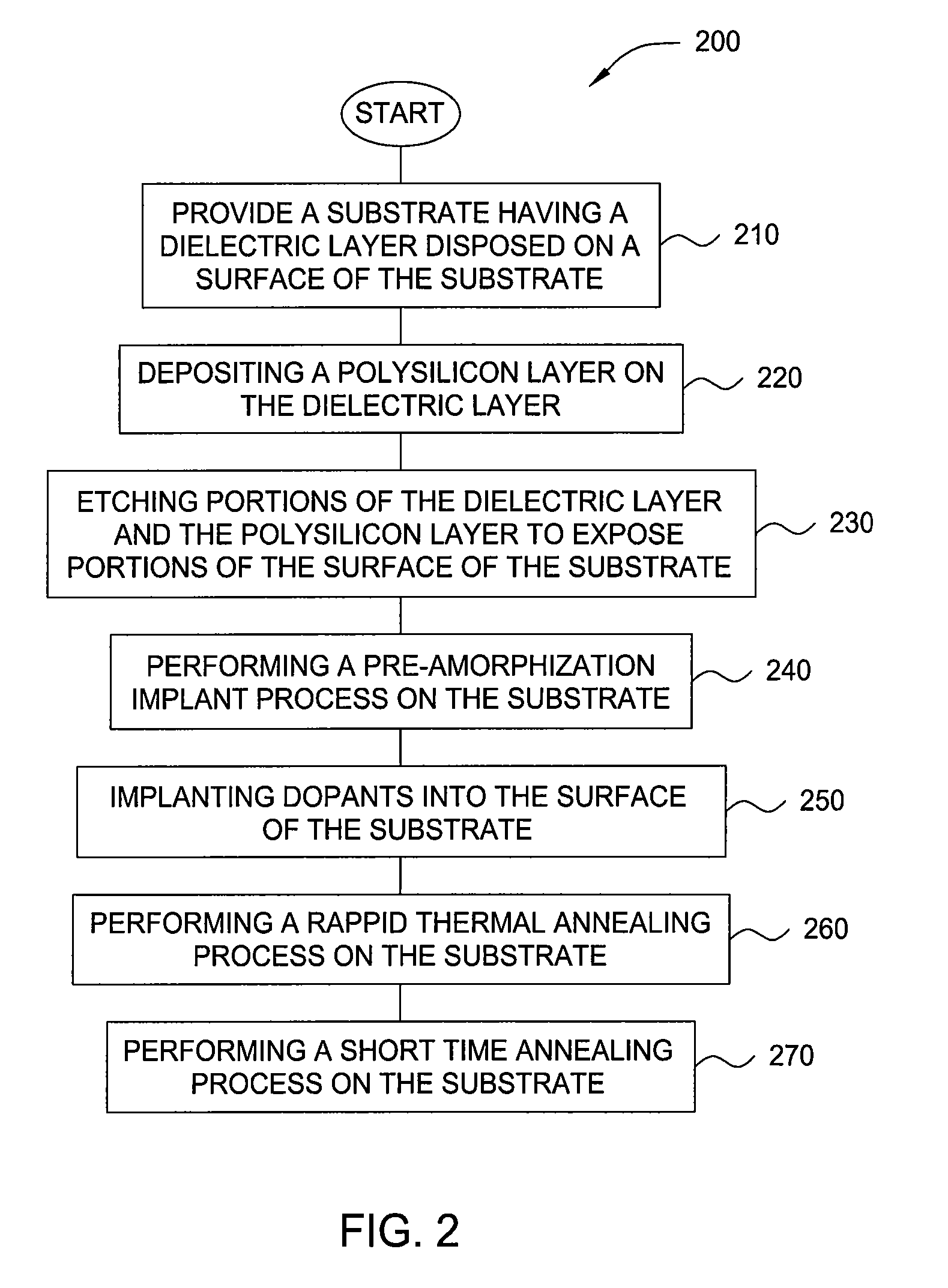

Use of carbon co-implantation with millisecond anneal to produce ultra-shallow junctions

InactiveUS20080023732A1Short timeShort time thermal annealTransistorSemiconductor/solid-state device manufacturingDopantRapid thermal annealing

Embodiments of the present invention include methods for forming an ultra-shallow junction in a substrate. In one embodiment, the method includes providing a silicon substrate, co-implanting the silicon substrate with carbon and a dopant to form a doped silicon substrate, and exposing the silicon substrate to a short time thermal anneal. In certain embodiments, the silicon substrate is exposed to a rapid thermal anneal after co-implanting the silicon substrate but prior to exposing the silicon substrate to a short time thermal anneal. In certain embodiments, the pre-amorphization implant is performed on the silicon substrate prior to implanting the silicon substrate with carbon and a dopant. In certain embodiments, the silicon substrate is a monocrystalline silicon substrate.

Owner:APPLIED MATERIALS INC

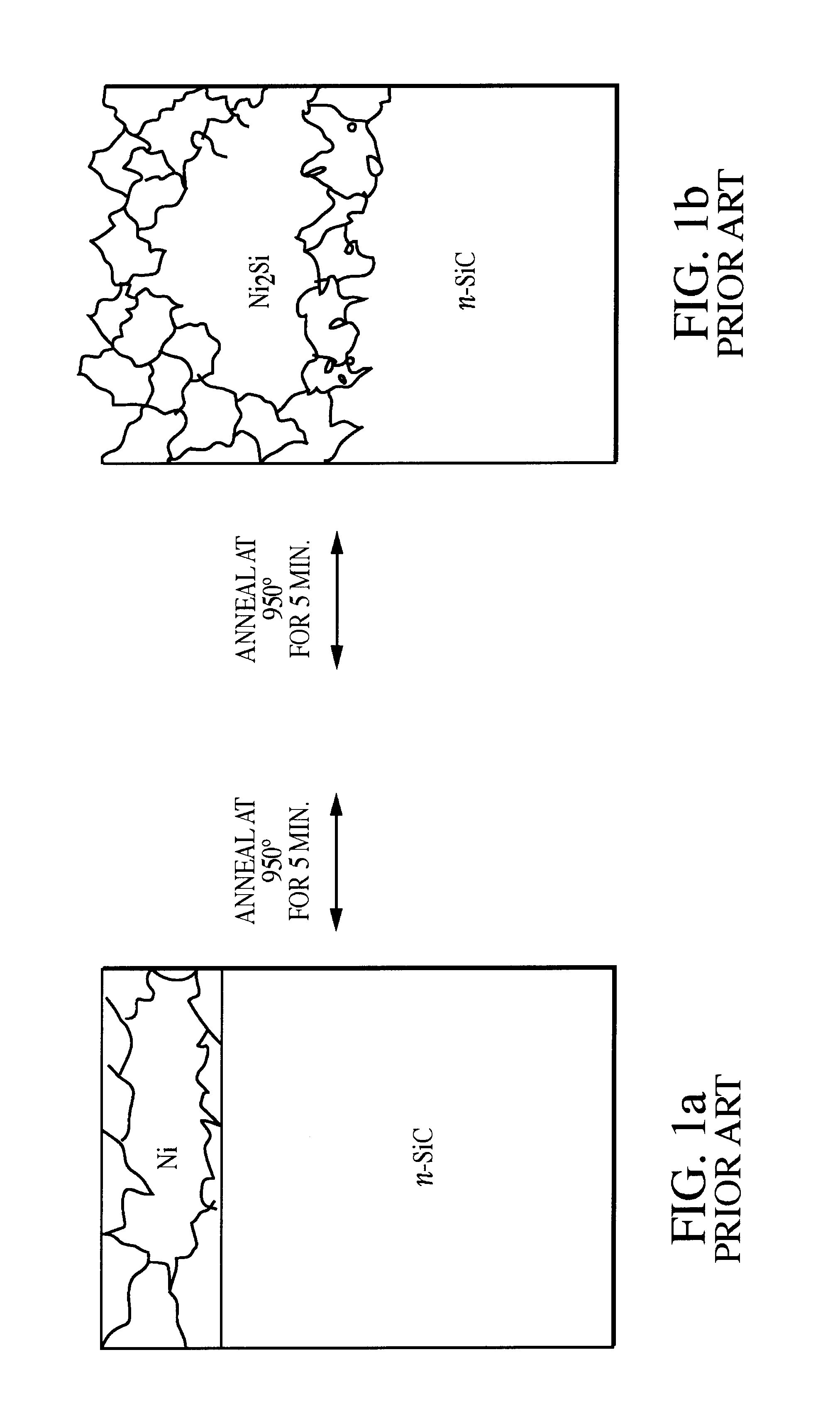

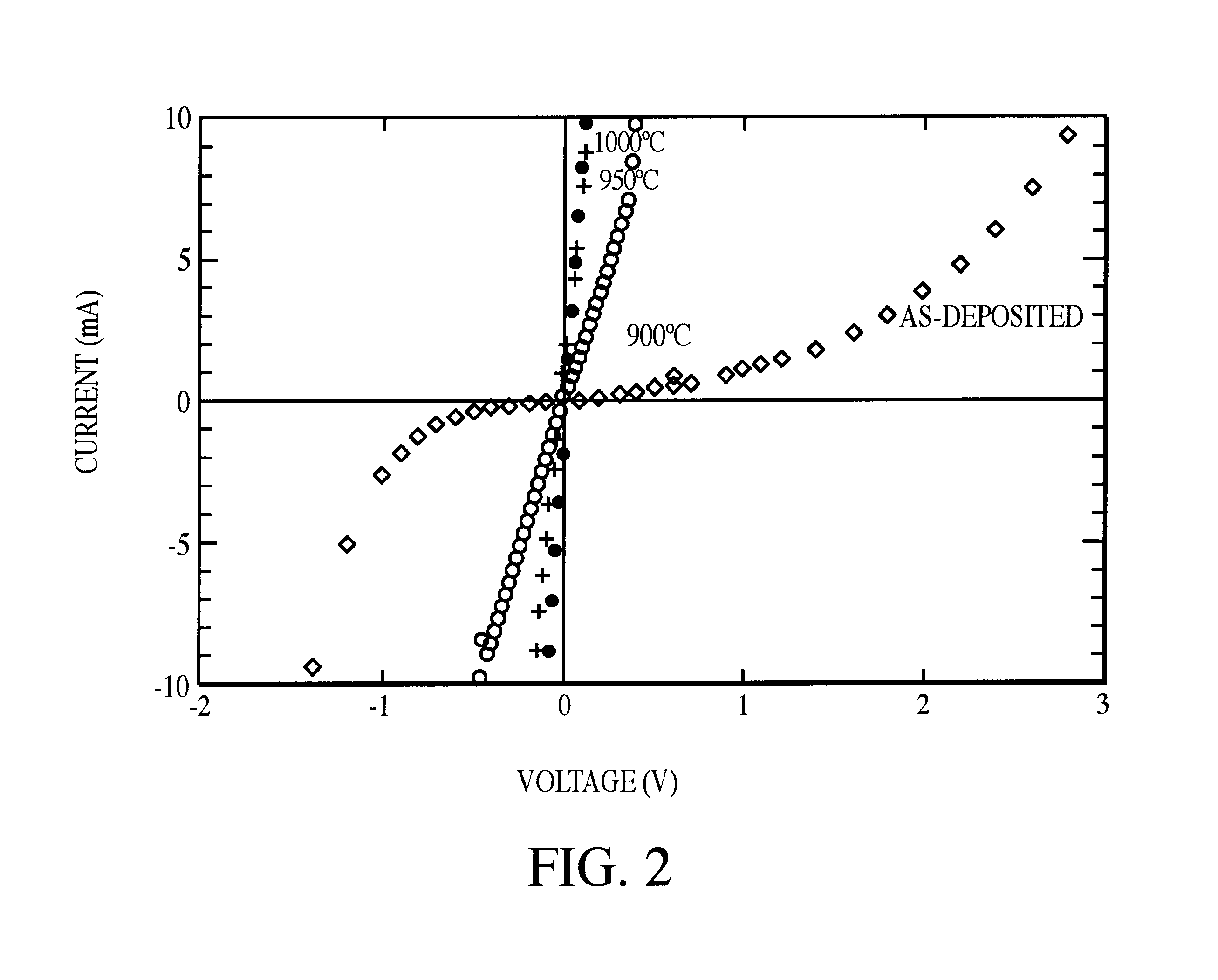

Formulation and fabrication of an improved Ni based composite Ohmic contact to n-SiC for high temperature and high power device applications

InactiveUS6759683B1Semiconductor/solid-state device detailsSolid-state devicesMetallurgyElectrical instability

A composite Pt / Ti / WSi / Ni Ohmic contact has been fabricated by a physical deposition process which uses electron beam evaporation and dc-sputter deposition. The Ni based composite Ohmic contact on n-SiC is rapid thermally annealed (RTA) at 950° C. to 1000° C. for 30s to provide excellent current-voltage characteristics, an abrupt, void free contact-SiC interface, retention of the as-deposited contact layer width, smooth surface morphology and an absence of residual carbon within the contact layer and / or at the Ohmic contact-SiC interface. The annealed produced Ni2Si interfacial phase is responsible for the superior electrical integrity of the Ohmic contact to n-SiC. The effects of contact delamination due to stress associated with interfacial voiding has been eliminated. Wire bonding failure, non-uniform current flow and SiC polytype alteration due to extreme surface roughness have also been abolished. The Ohmic contact also avoids electrical instability associated with carbon inclusions within the contact metallization and / or at the contact-SiC interface, that occur under prolonged high temperature and power device operations. Overall, this contact is reliable for high temperature and high power operations and the stresses inclusive of use under those conditions.

Owner:UNITED STATES OF AMERICA THE AS REPRESENTED BY THE SEC OF THE ARMY

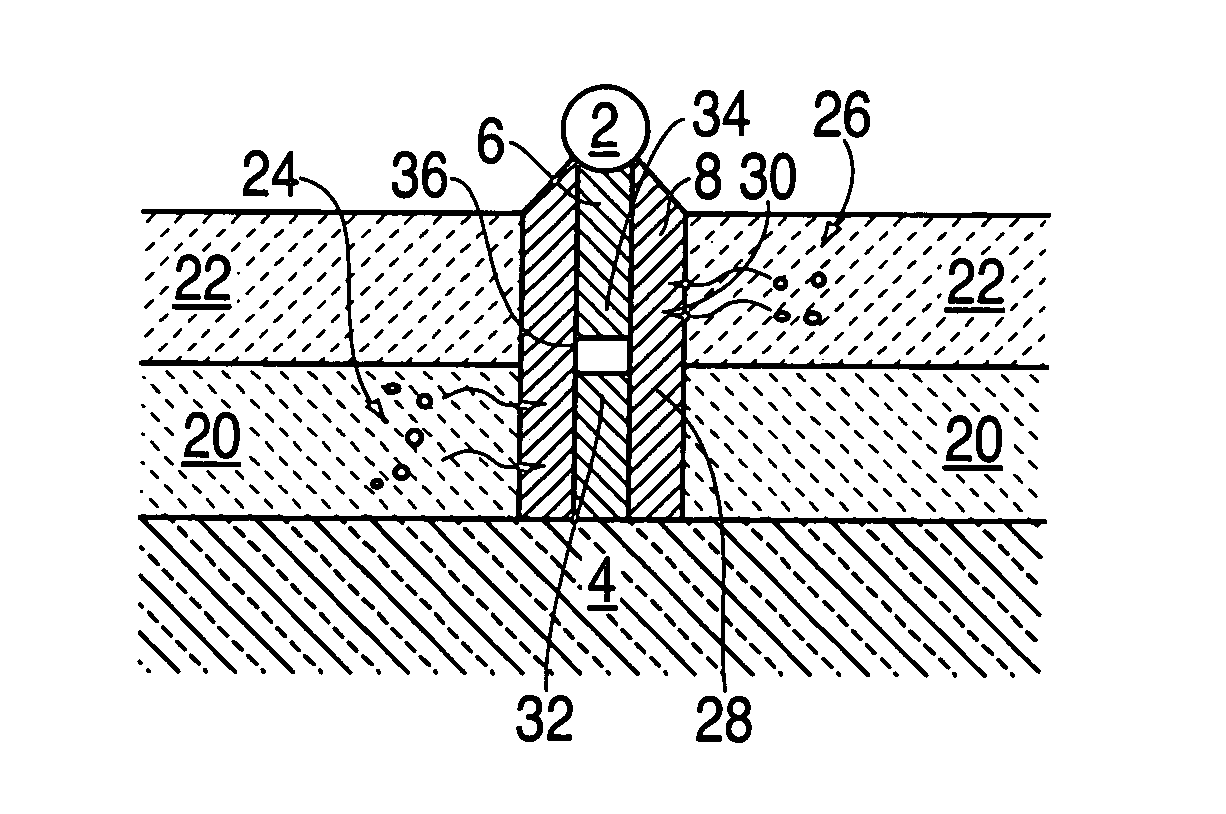

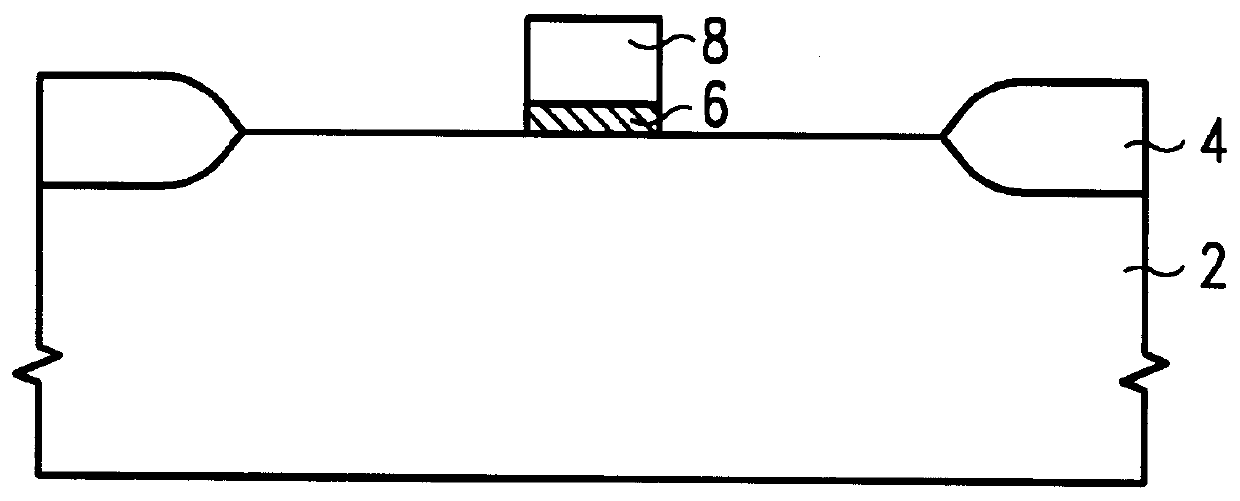

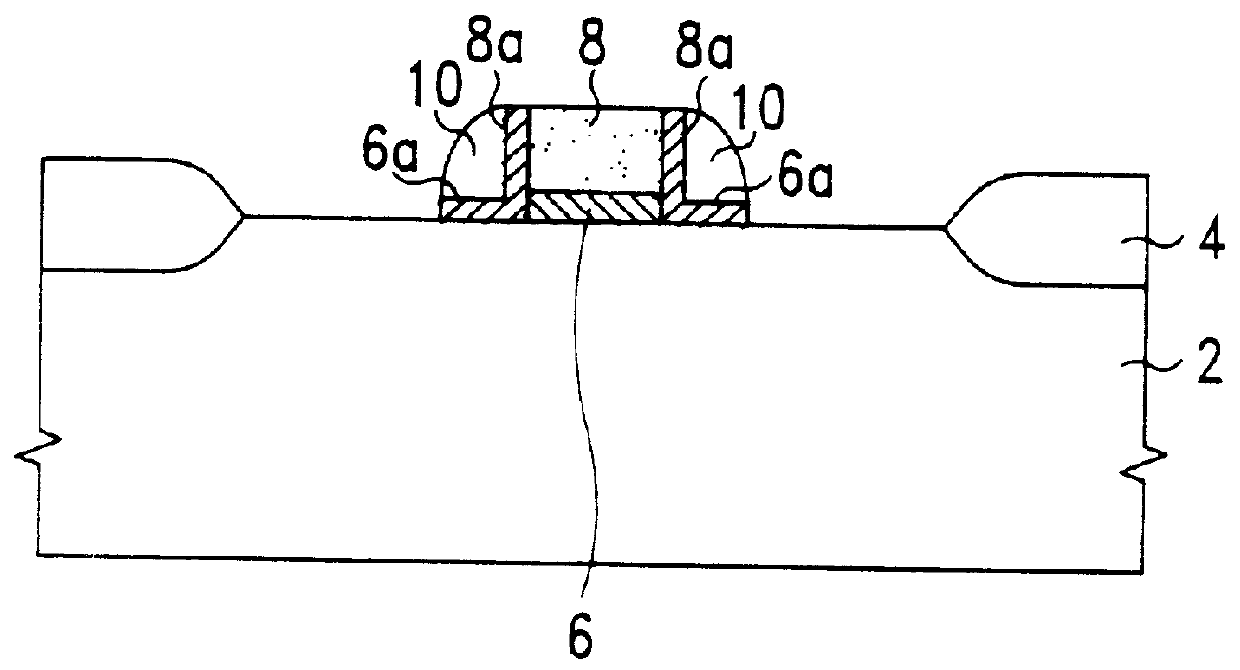

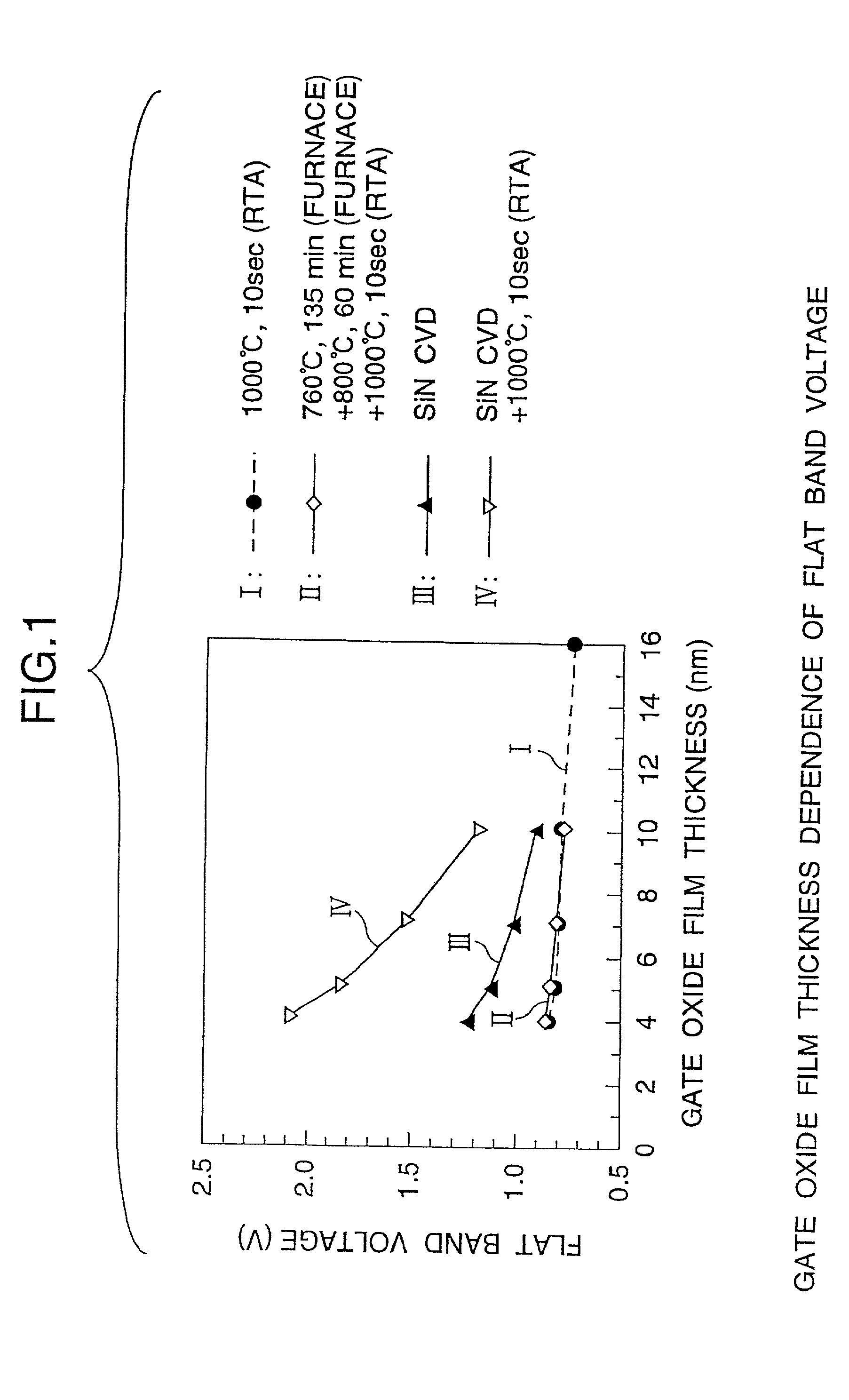

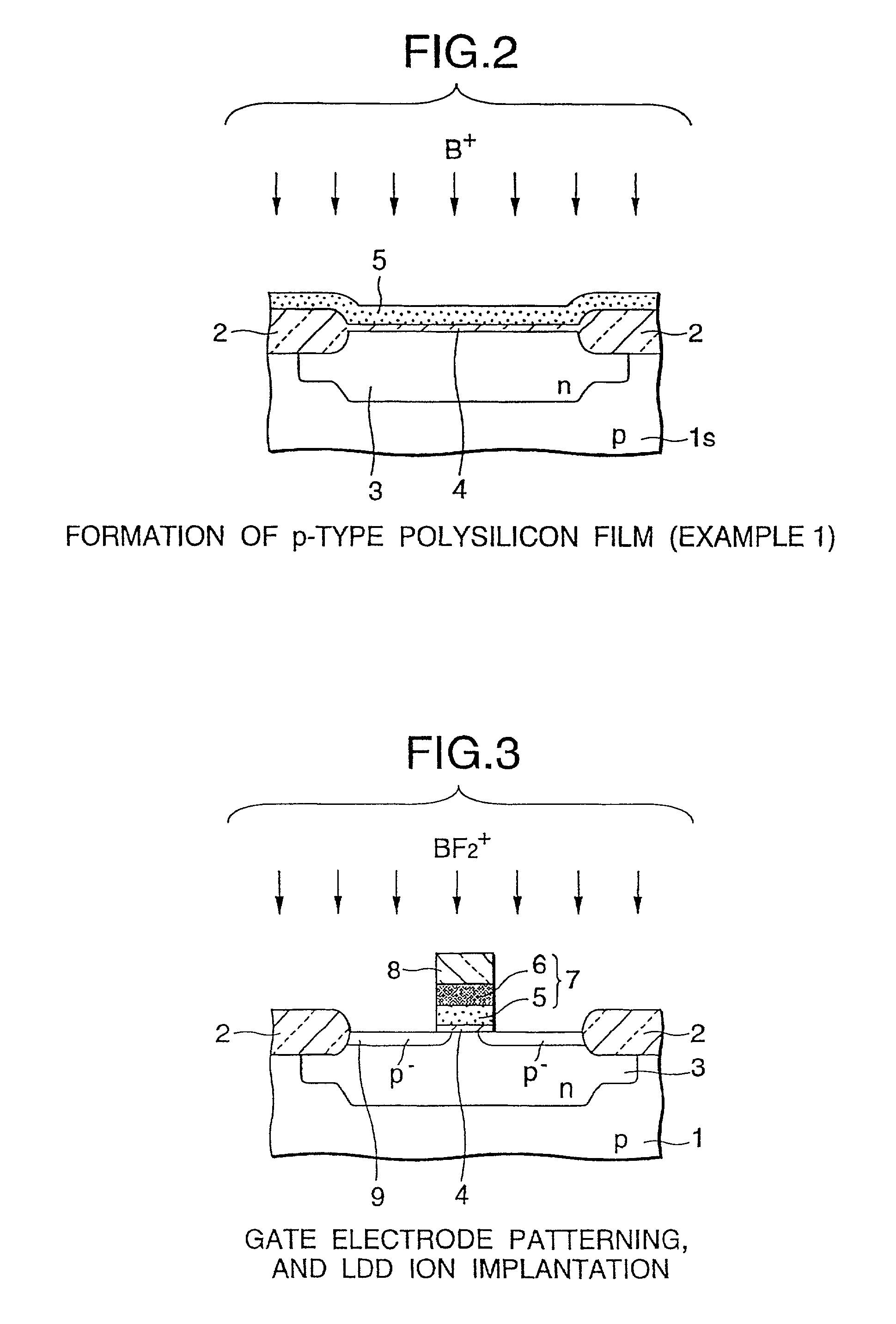

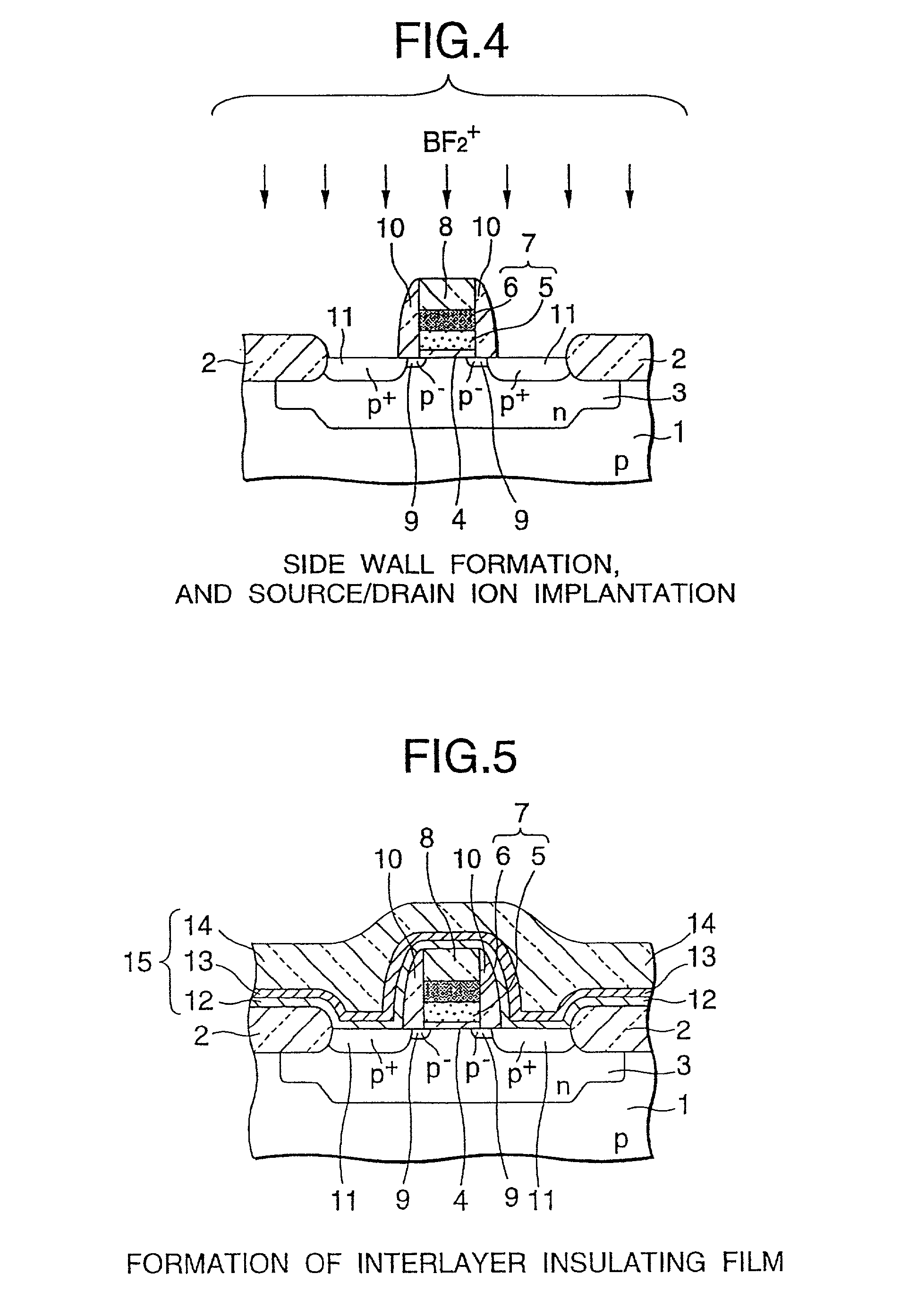

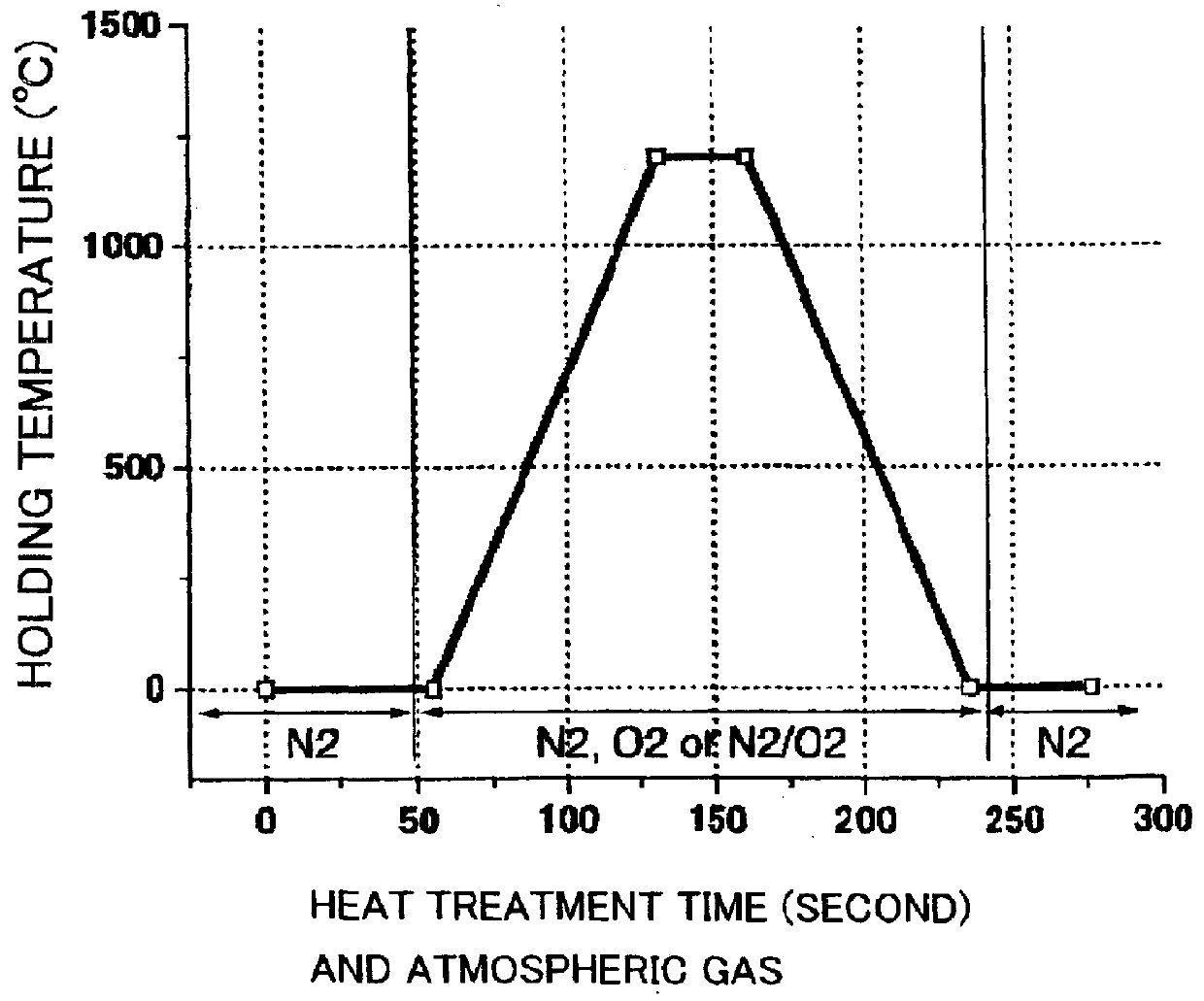

Method for fabricating mos transistors

InactiveUS20010012653A1Inhibited DiffusionTransistorSemiconductor/solid-state device manufacturingHydrogenPunching

In PMOS having a gate electrode 7 of a p-type polysilicon film 5 along with a silicon nitride film 13, boron diffusion from the p-type polysilicon film 5 and boron punching through the gate oxide film 4 are prevented, thereby stabilizing the properties of the PMOS. Hydrogen existing in the silicon nitride film 13 accelerates boron diffusion from the film 5. To prevent it, all subsequent steps after the step of forming the silicon nitride film 13 are effected within a temperature range within which the boron diffusion is not accelerated by hydrogen. Forming the silicon oxide film 14 through reduced pressure CVD is effected in a furnace at a temperature lower than 850.degree. C. Annealing for dopant activation in the compensation region 17 to be formed on the substrate in the bottom of the contact hole 16 is effected in a manner of RTA (rapid thermal annealing) at a temperature lower than 1000.degree. C.

Owner:SONY CORP

Method for heat treatment of silicon substrate, substrate treated by the method, and epitaxial wafer utilizing the substrate

InactiveUS6143071AImprove productivityEasy to processPolycrystalline material growthAfter-treatment detailsNitrogenNitrogen gas

Owner:SHIN-ETSU HANDOTAI CO LTD

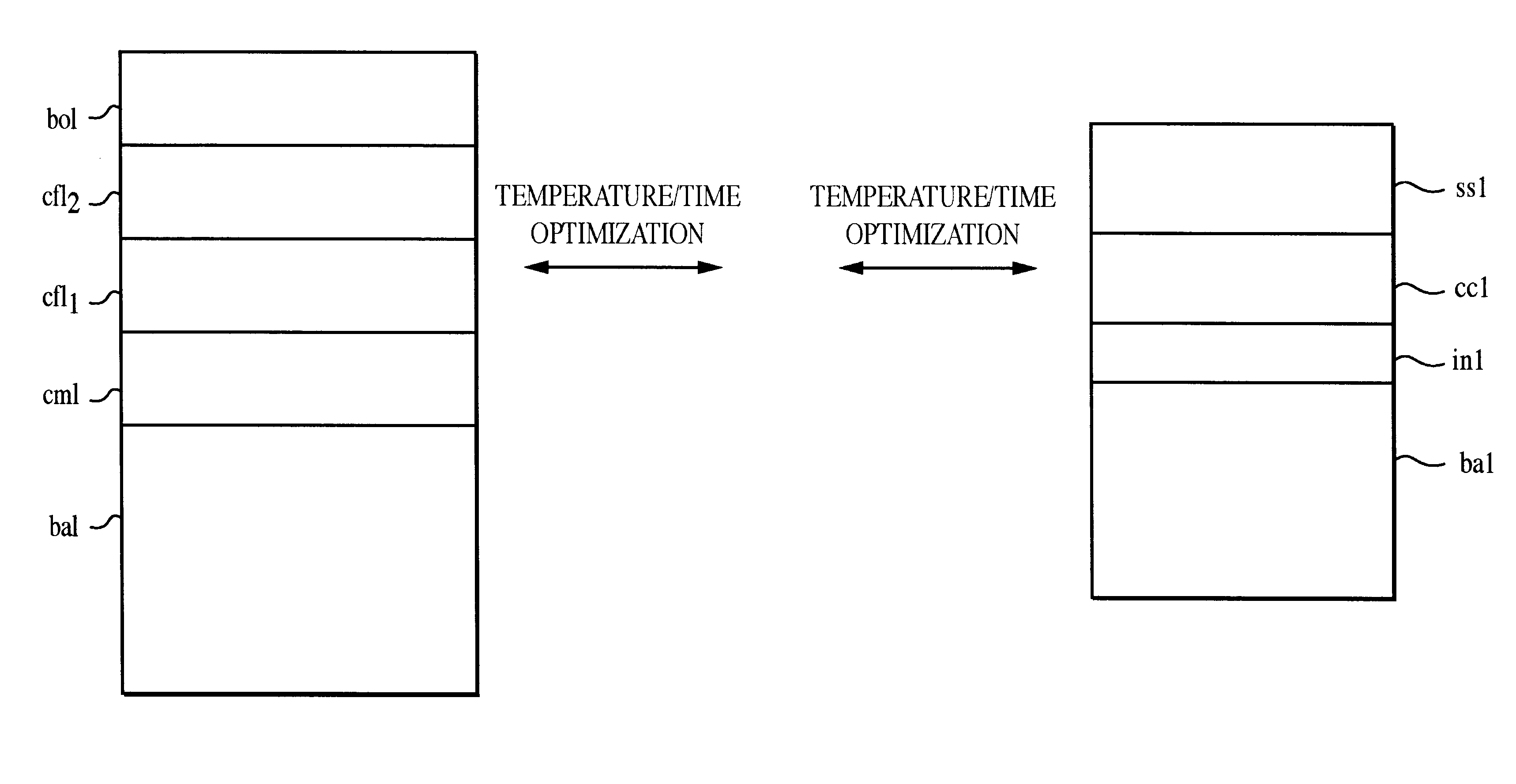

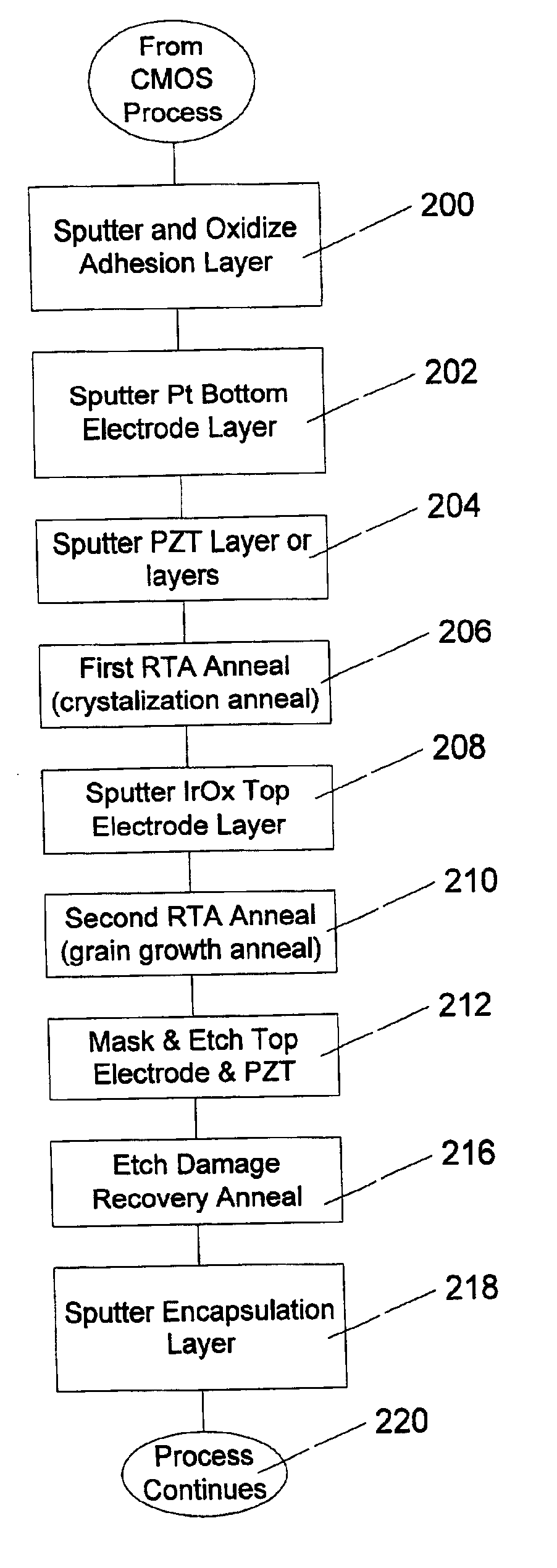

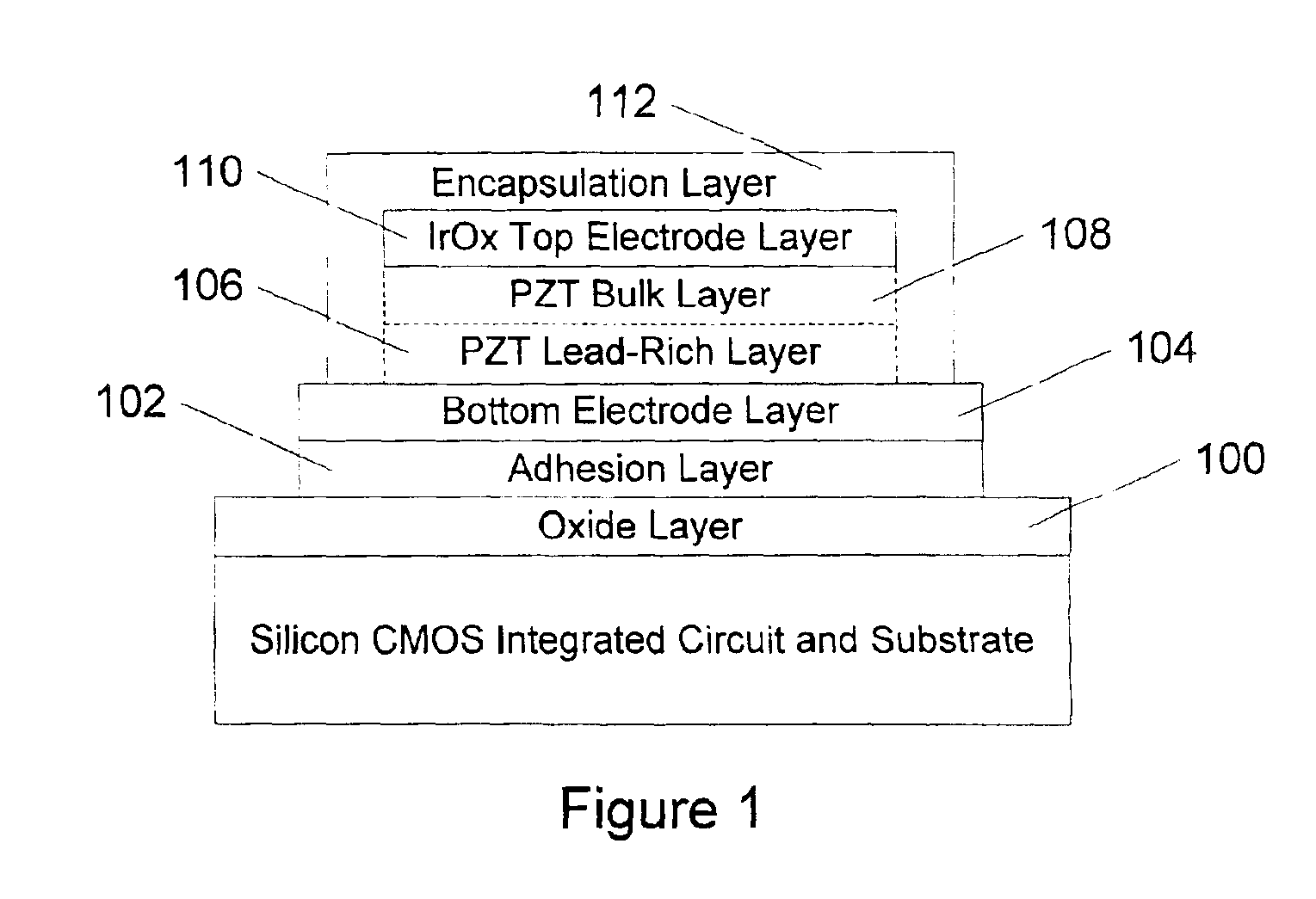

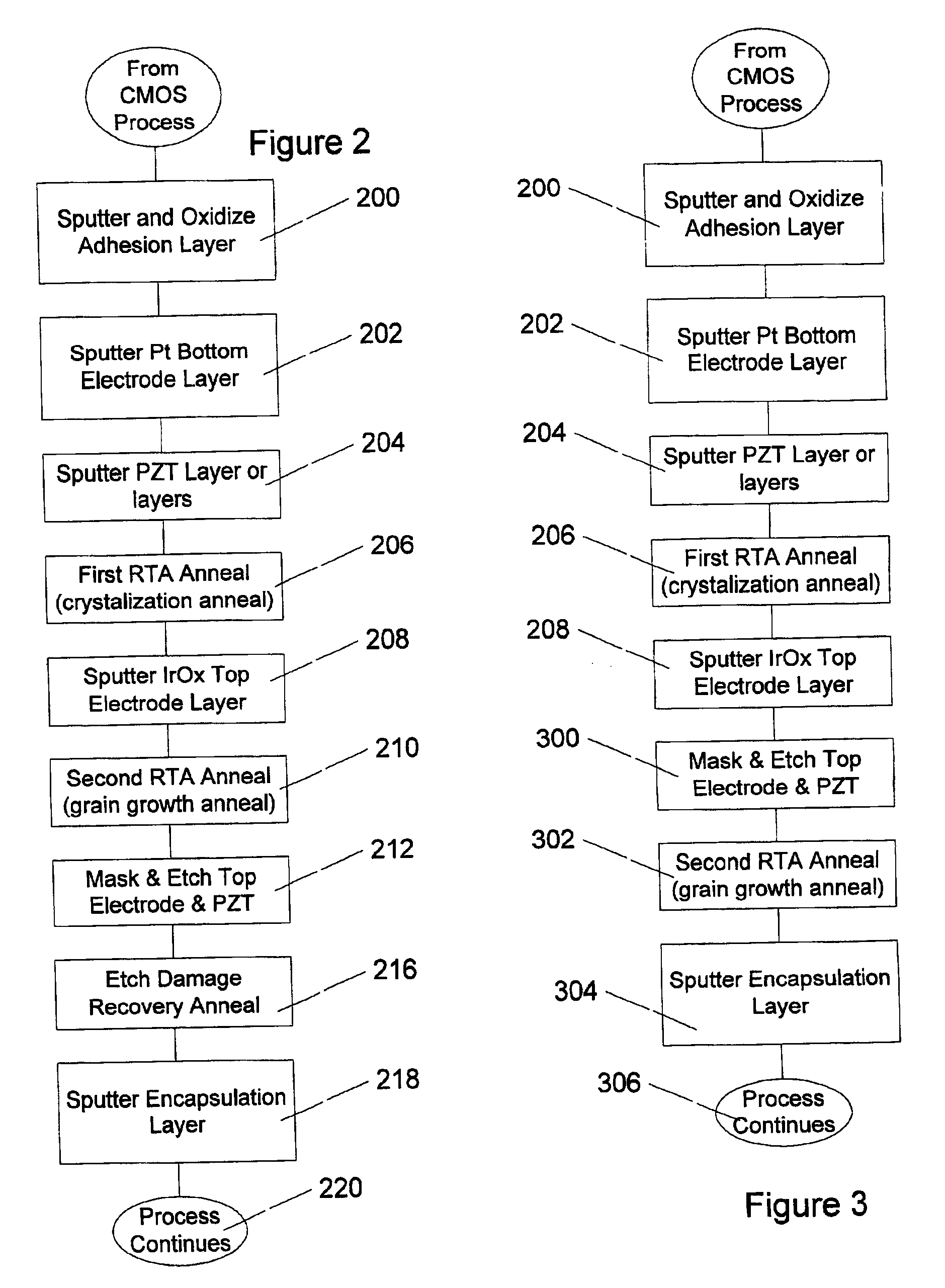

Process for producing high quality PZT films for ferroelectric memory integrated circuits

InactiveUS6887716B2Quality improvementEncourages productionTransistorSolid-state devicesDielectricRapid thermal annealing

A method for fabrication of ferroelectric capacitor elements of an integrated circuit includes steps of deposition of an electrically conductive bottom electrode layer, preferably made of a noble metal. The bottom electrode is covered with a layer of ferroelectric dielectric material. The ferroelectric dielectric is annealed with a first anneal prior to depositing a second electrode layer comprising a noble metal oxide. Deposition of the electrically conductive top electrode layer is followed by annealing the layer of ferroelectric dielectric material and the top electrode layer with a second anneal. The first and the second anneal are performed by rapid thermal annealing.

Owner:FUJITSU SEMICON LTD

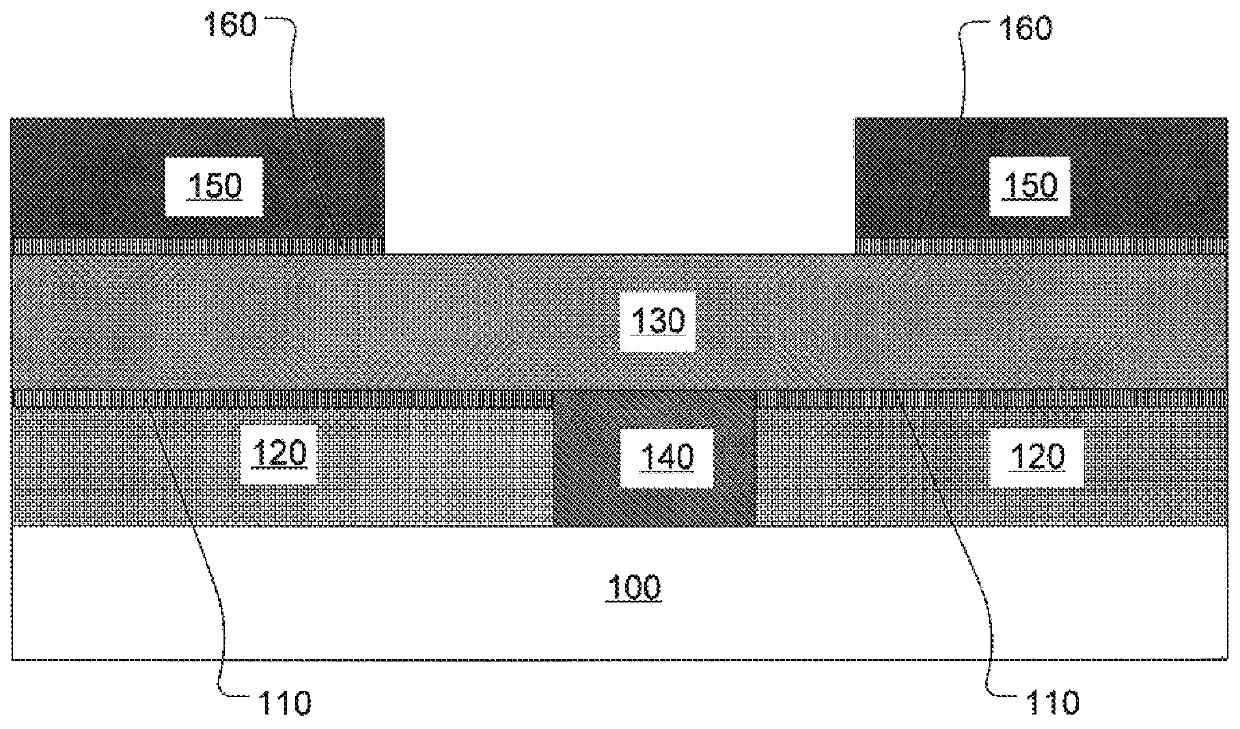

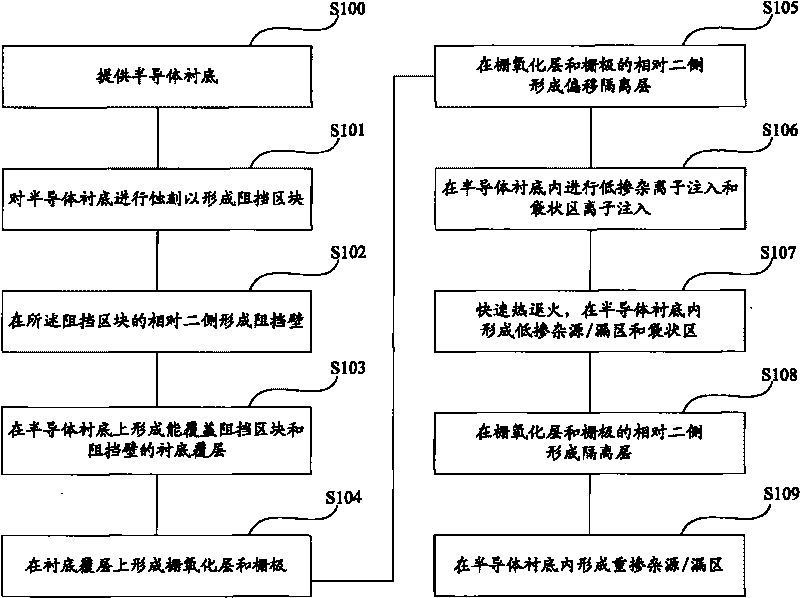

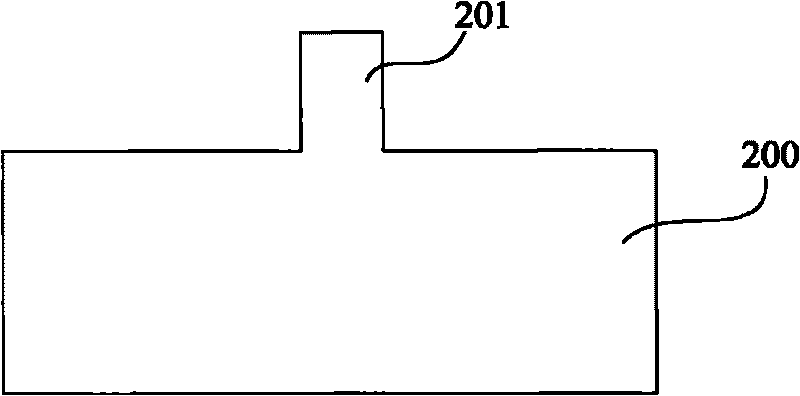

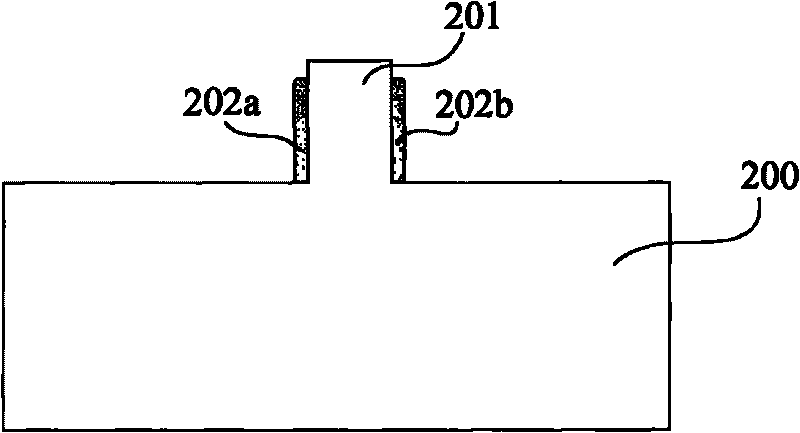

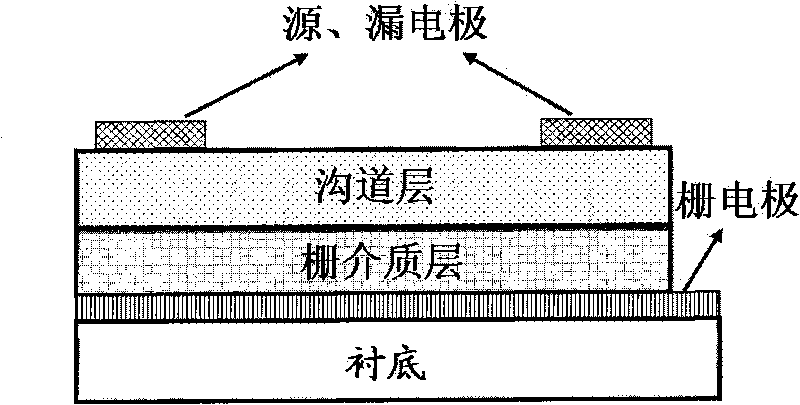

Semiconductor device and manufacture method thereof

InactiveCN101740393AInterpenetration barrierImprove short channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceRapid thermal annealing

The invention relates to a semiconductor device and a manufacture method thereof, wherein the manufacture method comprises the following steps of: providing a semiconductor underlay; etching the semiconductor underlay so as to form a barrier region block; forming barrier walls at both sides of the barrier region block; forming an underlay coating on the semiconductor underlay, wherein the barrier walls and the surface of the underlay coating have fall; forming a gate oxide and a grid electrode on the underlay coating and the semiconductor underlay; carrying out low-doping ion implantation in the semiconductor underlay; carrying out rapid thermal annealing to form a low-doping source / drain region in the semiconductor underlay; forming isolation layers at opposite sides of the gate oxide and the grid electrode; and forming a heavy-doping source / drain region in the semiconductor underlay. The invention has technical scheme that the barrier walls are formed in the semiconductor underlay, thereby effectively separating the interpenetration between the source region and the drain region, obviously improving the short channel effect of the semiconductor device, avoiding the generation of a punch-through effect between the source region and the drain region and improving the electrical behaviour of the semiconductor device. Meanwhile, a bigger process regulating space is provided for the reduction of junction capacitance and the enlargement of process window in the ultra shallow junction process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

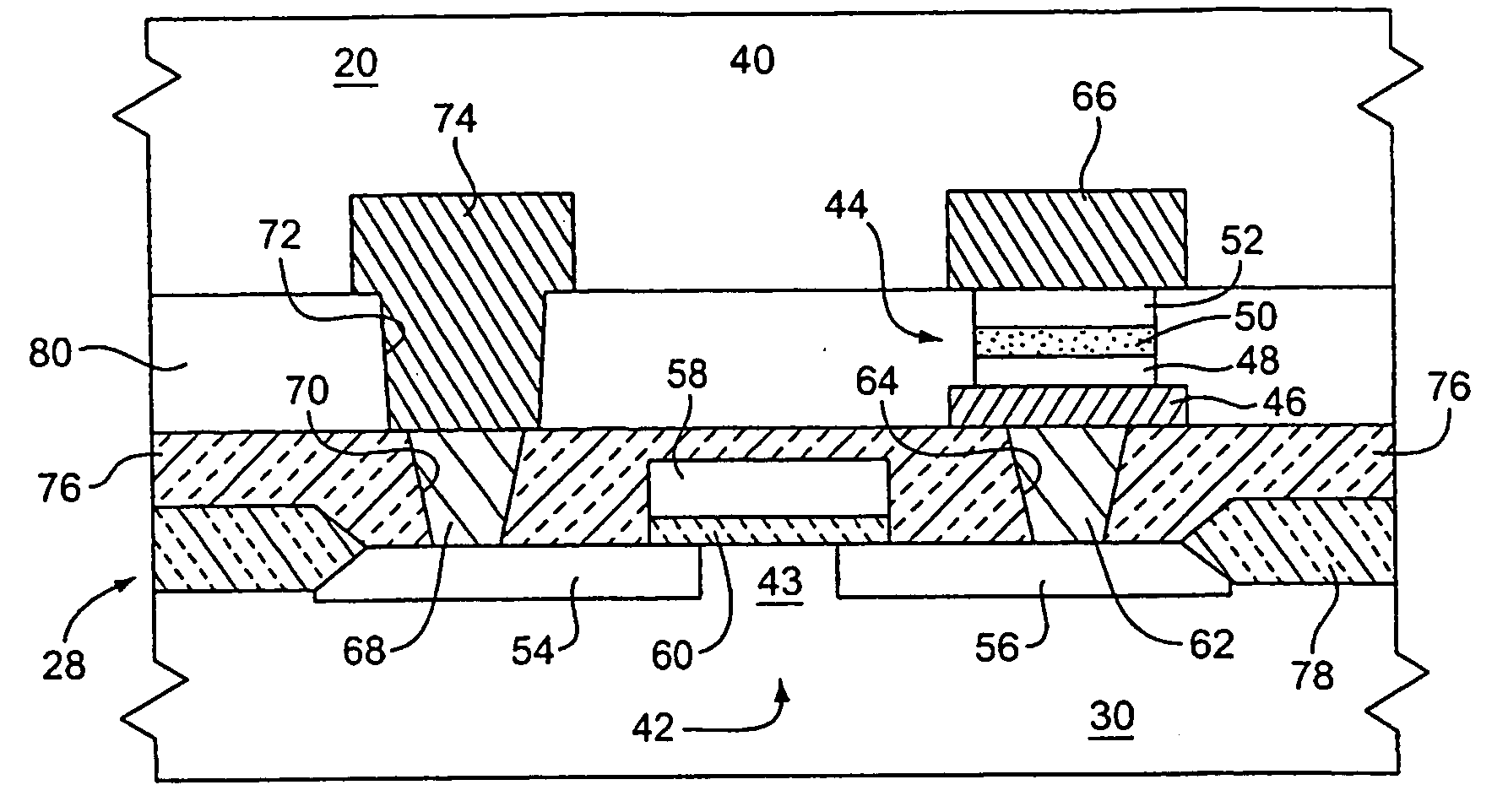

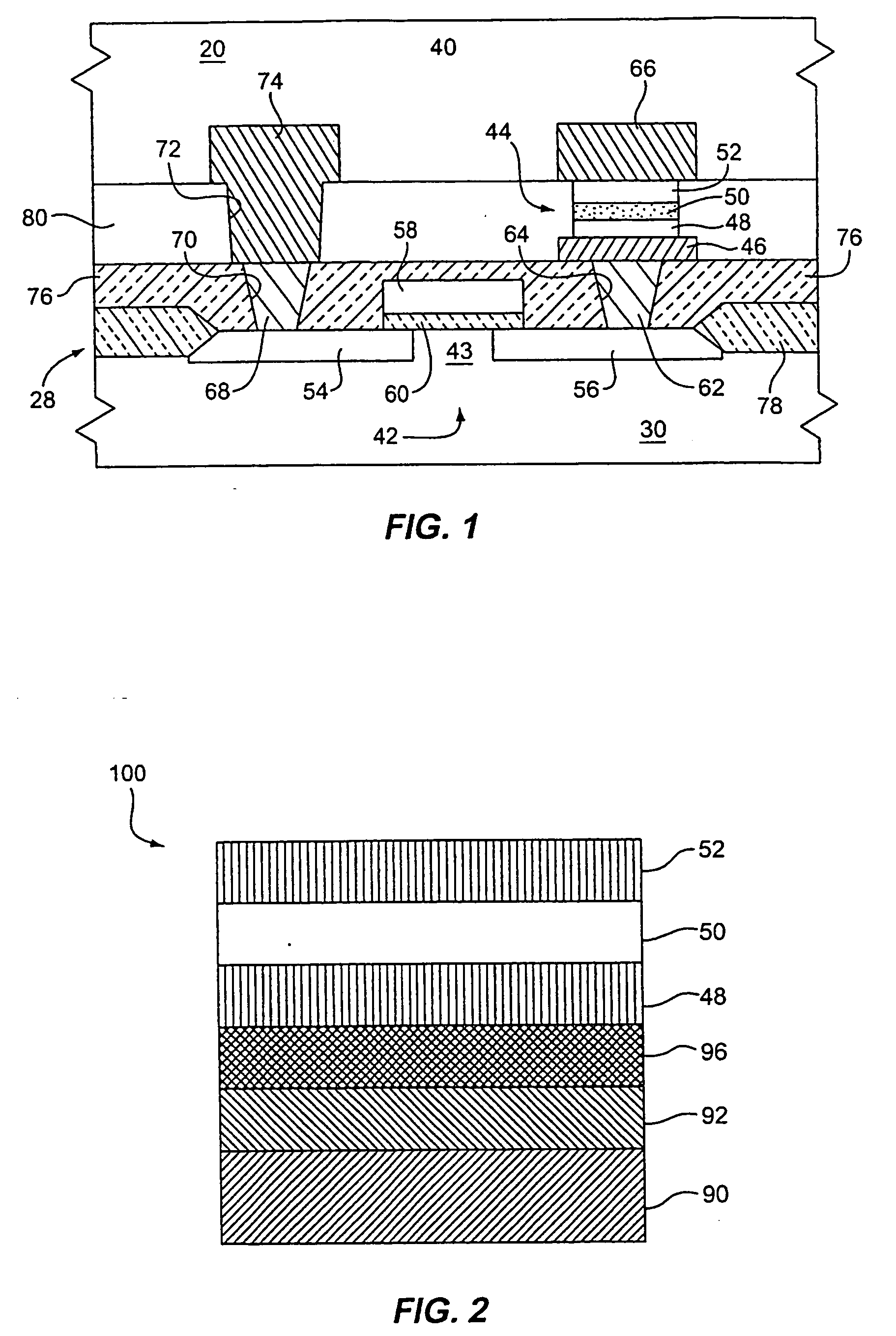

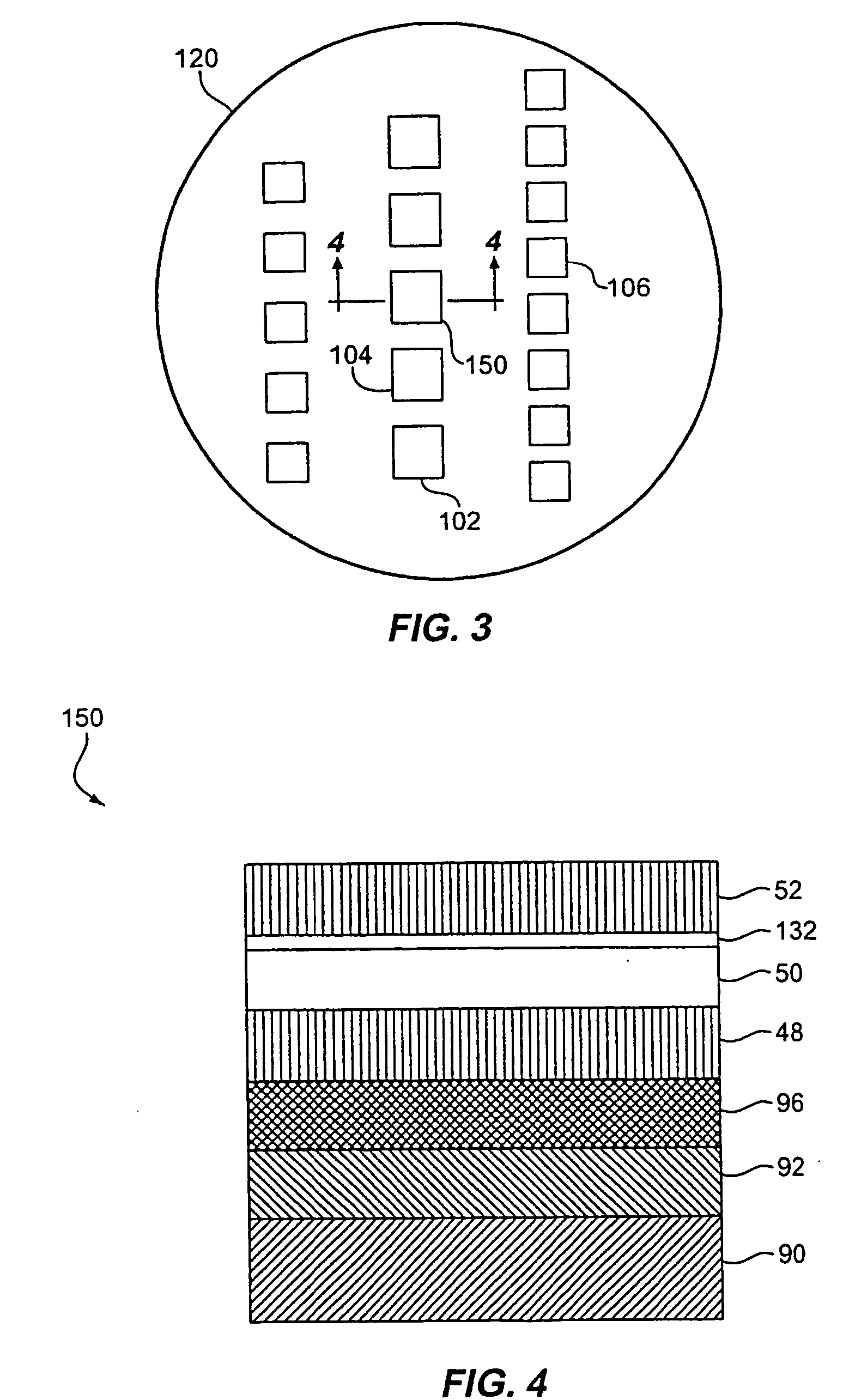

Method of making layered superlattice material with improved microstructure

InactiveUS20040048455A1Solid-state devicesSemiconductor/solid-state device manufacturingCooking & bakingStrontium

In the manufacture of an integrated circuit, a first electrode (48) is formed on a substrate (28). In a first embodiment, a strontium bismuth tantalate layer (50) and a second electrode (52) are formed on top of the first electrode (48). Prior to the final crystallization anneal, the first electrode (48), the strontium bismuth tantalate layer (50) and the second electrode (52) are patterned. The final crystallization anneal is then performed on the substrate (28). In a second embodiment, a second layer (132) of strontium bismuth tantalate is deposited on top of the strontium bismuth tantalate layer (50) prior to the forming of the second electrode (52) on top of the first and second layers (50), (132). In a third embodiment, a carefully controlled UV baking process is performed on the strontium bismuth tantalate layer (50). In a fourth embodiment, an additional rapid thermal annealing process is performed on a substrate subsequent to the patterning process and prior to the final crystallization annealing process.

Owner:SYMETRIX +1

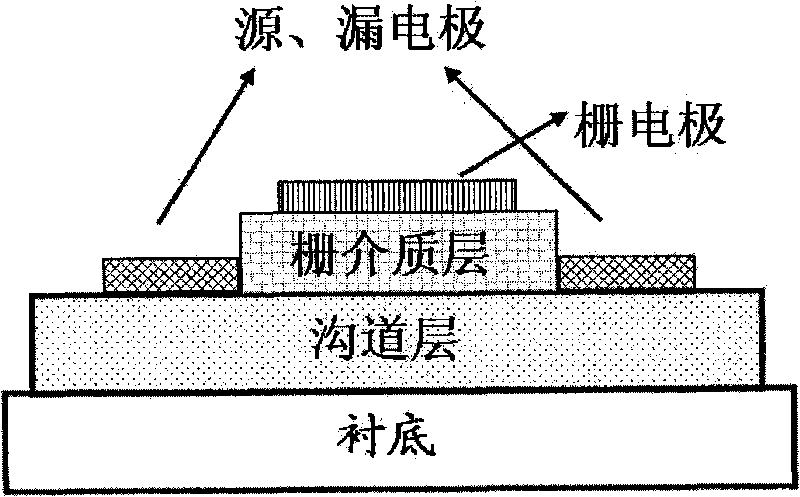

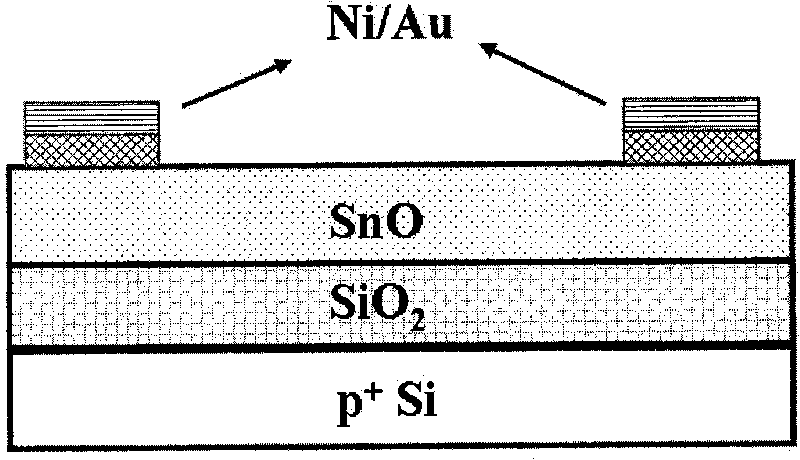

Preparing method of p-type stannous oxide ditch film transistors

InactiveCN101764065AEasy to operateUniform film formationVacuum evaporation coatingSemiconductor/solid-state device manufacturingSTANNOUS OXIDEEvaporation

The present invention discloses a preparing method of p-type stannous oxide ditch film transistors, and p-type conducting stannous oxide ditch layers are prepared by using electron beam evaporation technology and rapid thermal annealing technology. The preparing method is simple and controllable, and can realize low-temperature preparation. The p-type stannous oxide ditch film transistors have high field effect mobility, can be used for organic light-emitting diodes and development of oxide based compensating and logic circuits with low loss and the like, and have wide application prospects in the technical field of displays.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

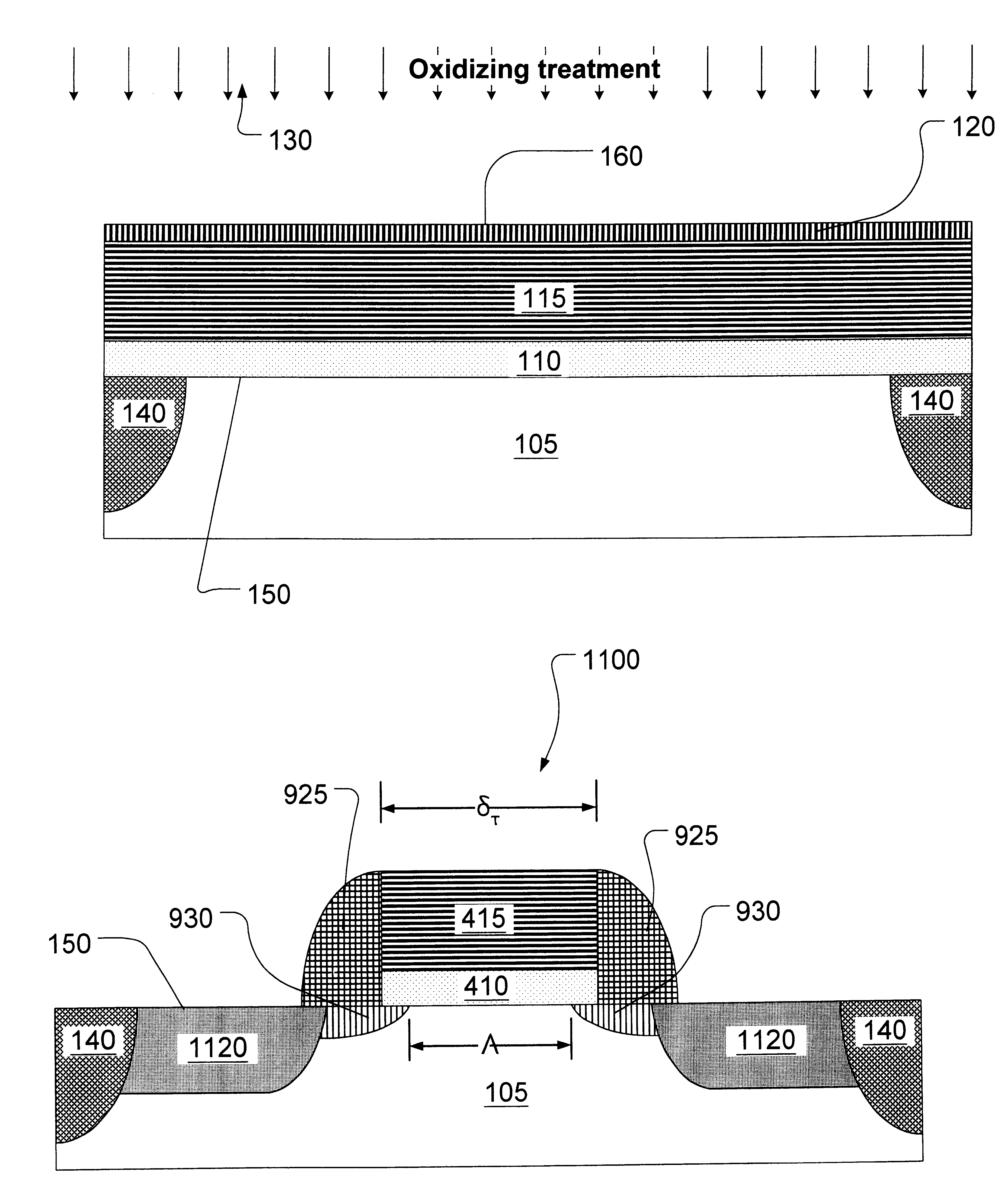

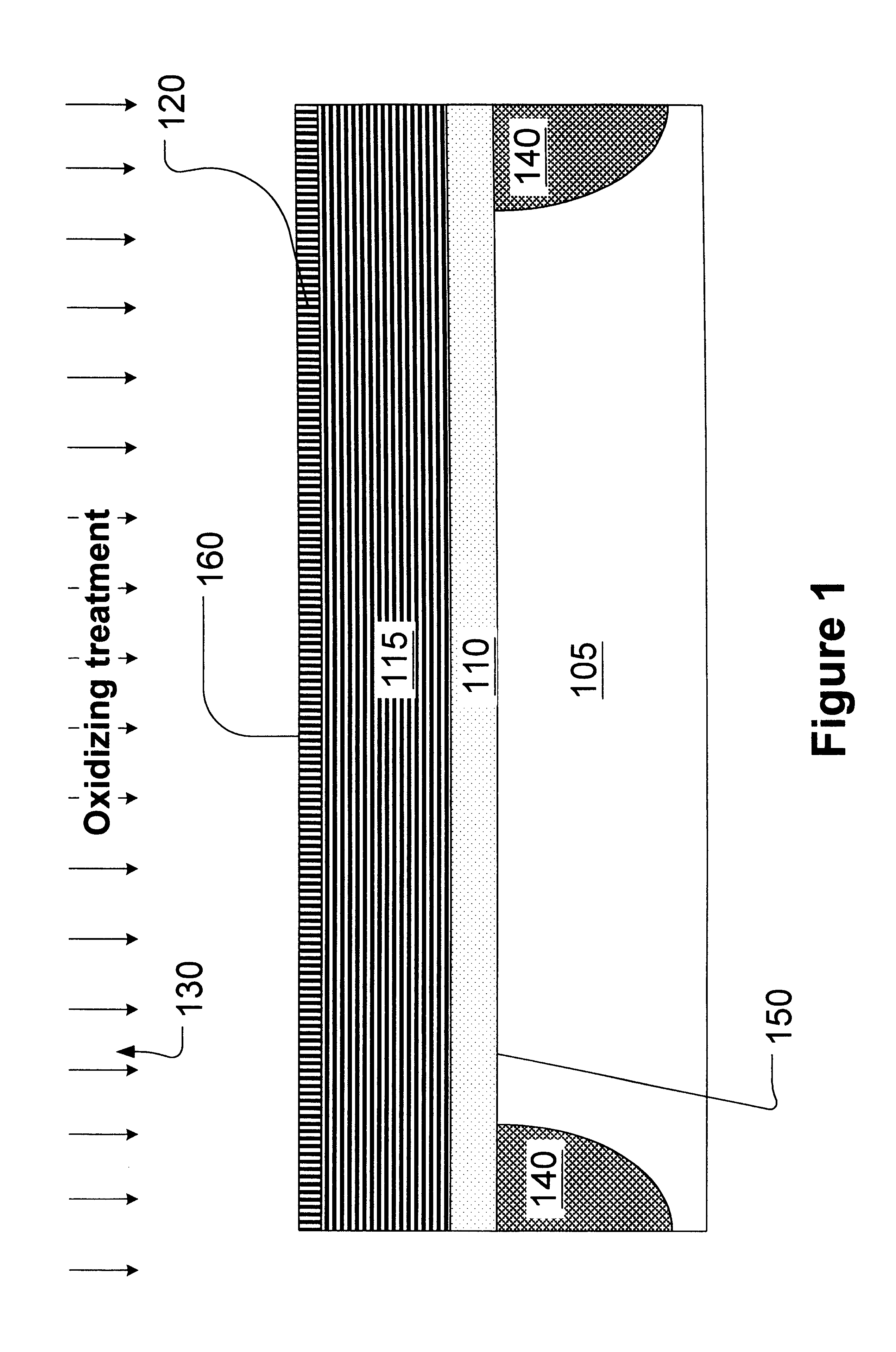

Passivating inorganic bottom anti-reflective coating (BARC) using rapid thermal anneal (RTA) with oxidizing gas

InactiveUS6794279B1Semiconductor/solid-state device manufacturingPhotosensitive materials for photomechanical apparatusAnti-reflective coatingElectrical conductor

A method is provided, the method including forming a gate dielectric layer above a substrate layer and forming a gate conductor layer above the gate dielectric layer. The method also includes forming an inorganic bottom anti-reflective coating layer above the gate conductor layer and treating the inorganic bottom anti-reflective coating layer with an oxidizing treatment during a rapid thermal anneal process.

Owner:GLOBALFOUNDRIES INC

Method for growing group III nitride nanometer material

InactiveCN101898751ALower quality requirementsSimple manufacturing methodNanostructure manufactureNitrogen-metal/silicon/boron binary compoundsNanopillarRapid thermal annealing

The invention relates to a method for growing a group III nitride nanometer material, which comprises the following steps of: (1) epitaxially growing a GaN template, a SiO2 layer and a Ni metal film on a substrate in sequence; (2) enabling the Ni metal film to form self-organized nanometer Ni particles by using a two-step rapid thermal annealing method; (3) and etching the SiO2 layer by a dry method by using the self-organized nanometer Ni particles as a mask to form a SiO2 nanometer column; (4) etching the GaN template by the dry method by using the self-organized nanometer Ni particles and the SiO2 nanometer column formed by etching as masks to form GaN nanometer column array; (5) removing the SiO2 nanometer column and the nanometer Ni particles by using a BOE solution to obtain the GaN nanometer column array; and (6) growing the InN or InGaN group III nitride semiconductor material on the GaN nanometer column array, the side wall thereof and the bottom of the nanometer column array.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com