Patents

Literature

5049 results about "Delamination" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Delamination is a mode of failure where a material fractures into layers. A variety of materials including laminate composites and concrete can fail by delamination. Processing can create layers in materials such as steel formed by rolling and plastics and metals from 3D printing which can fail from layer separation. Also, surface coatings such as paints and films can delaminate from the coated substrate.

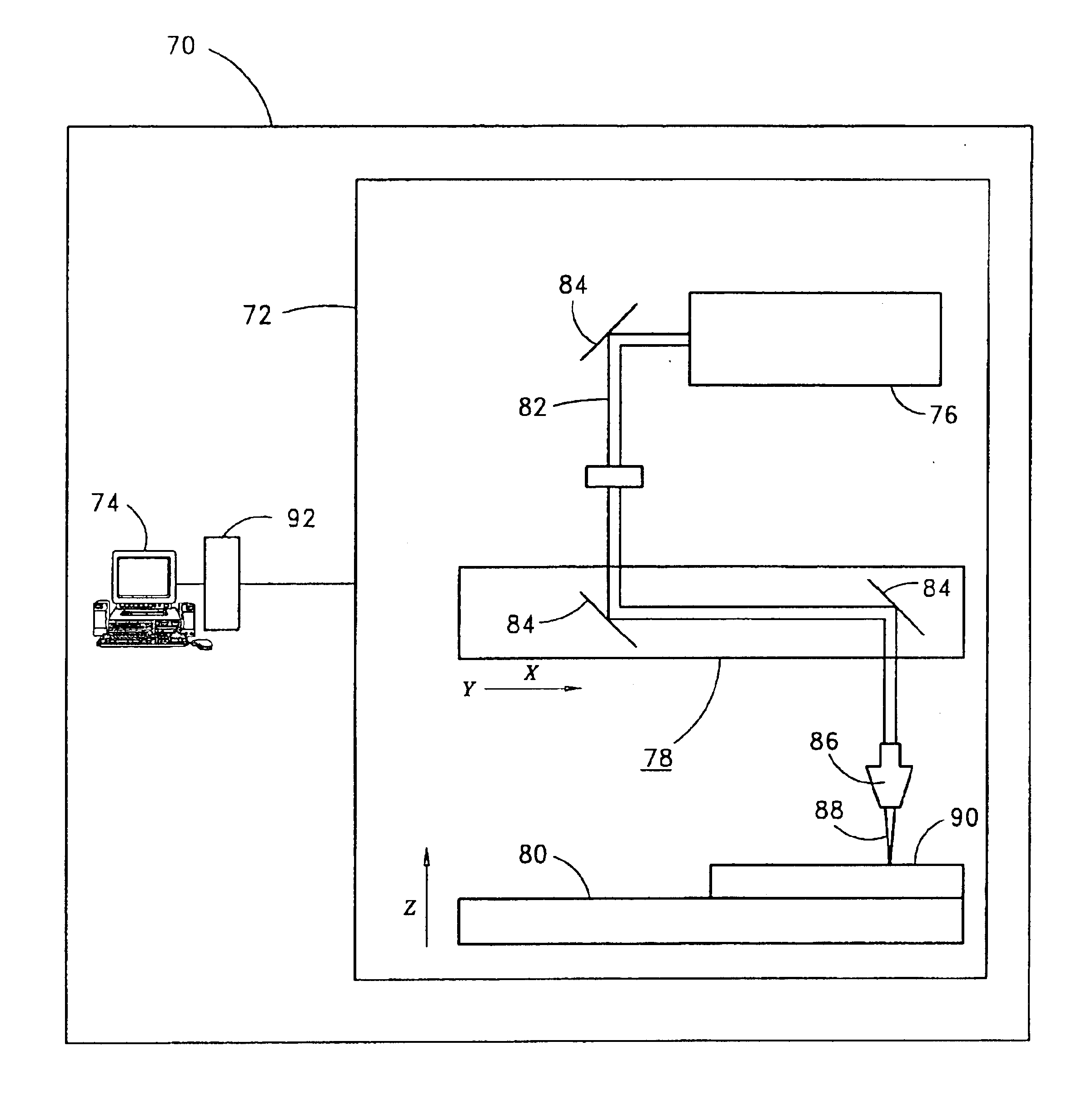

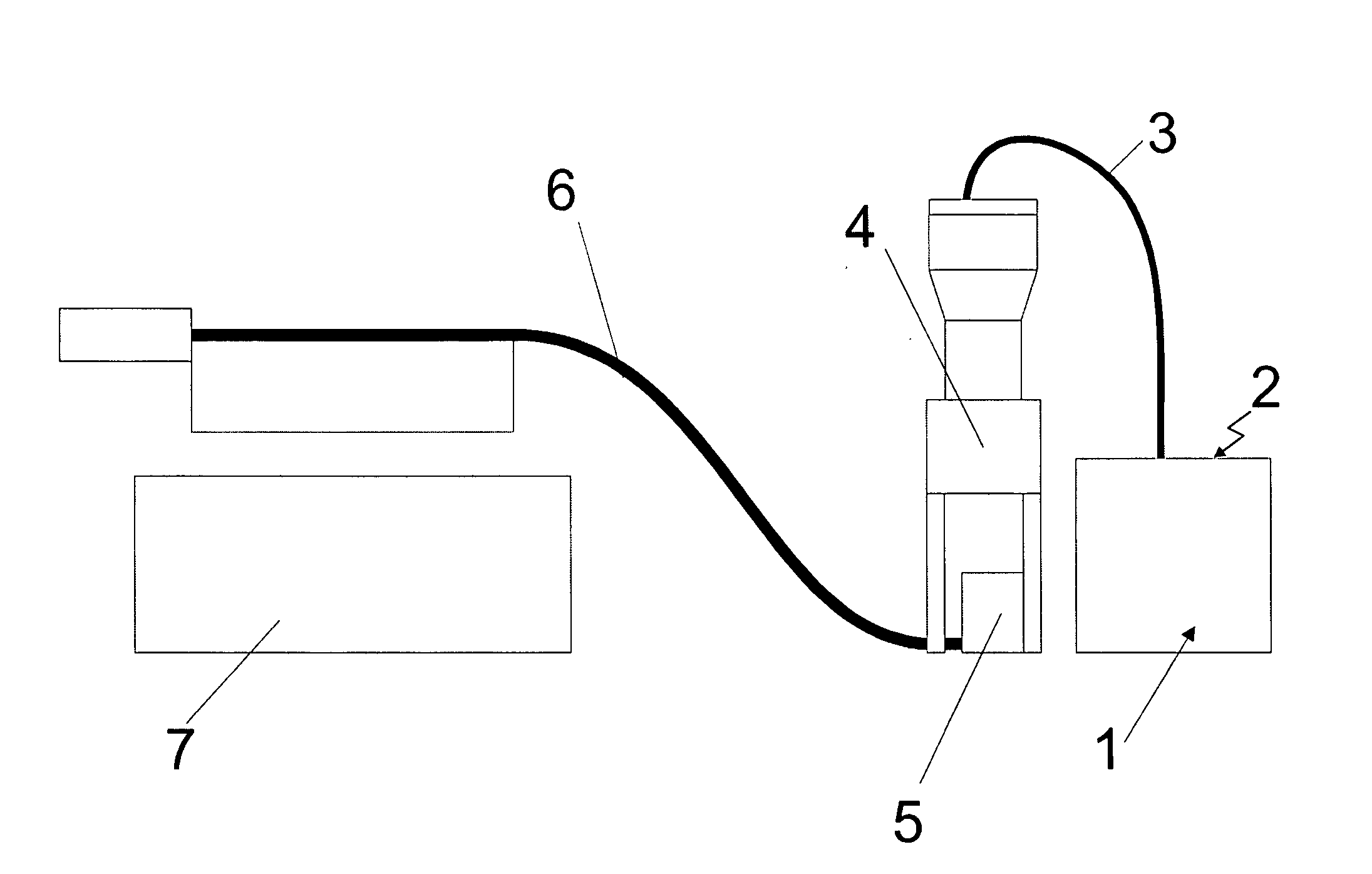

Method of cutting material for use in implantable medical device

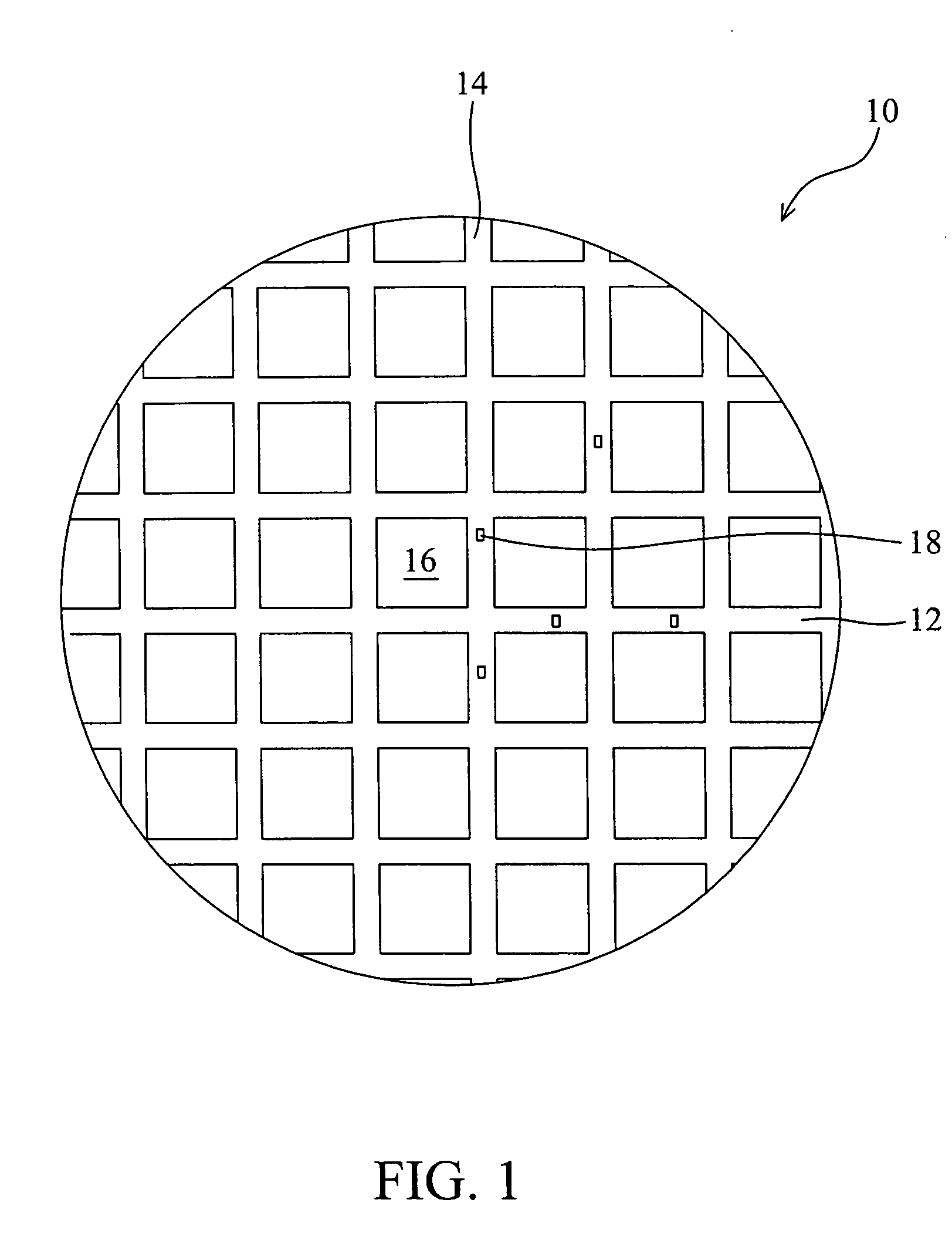

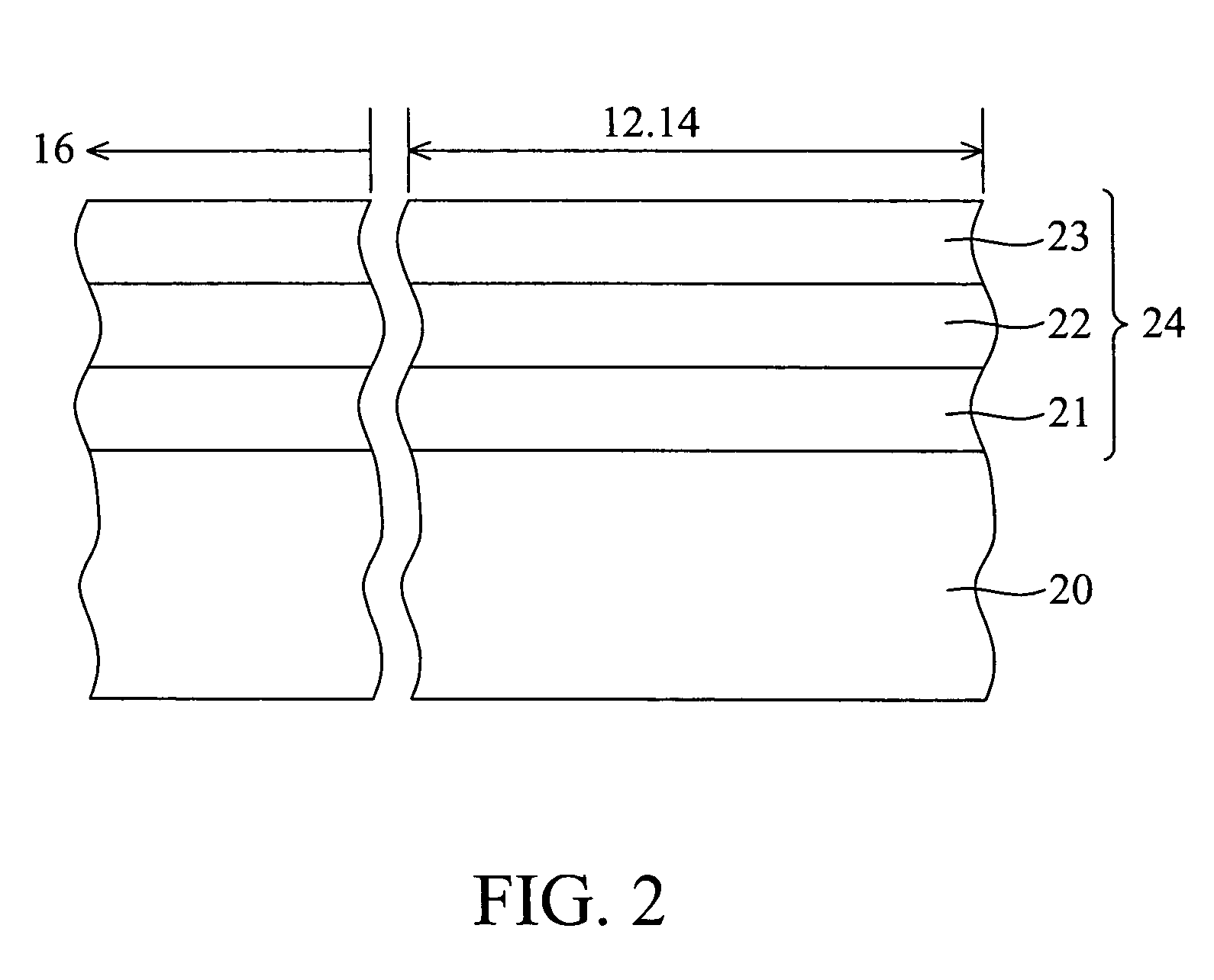

A method of cutting material for use in an implantable medical device employs a plotted laser cutting system. The laser cutting system is computer controlled and includes a laser combined with a motion system. The laser precisely cuts segments out of source material according to a predetermined pattern as designated by the computer. The segments are used in constructing implantable medical devices. The cutting energy of the laser is selected so that the cut edges of the segments are melted to discourage delamination or fraying, but communication of thermal energy into the segment beyond the edge is minimized to avoid damaging the segment adjacent the edge.

Owner:3F THERAPEUTICS

Method of cutting material for use in implantable medical device

A method of cutting material for use in an implantable medical device employs a plotted laser cutting system. The laser cutting system is computer controlled and includes a laser combined with a motion system. The laser precisely cuts segments out of source material according to a predetermined pattern as designated by the computer. The segments are used in constructing implantable medical devices. The cutting energy of the laser is selected so that the cut edges of the segments are melted to discourage delamination or fraying, but communication of thermal energy into the segment beyond the edge is minimized to avoid damaging the segment adjacent the edge.

Owner:3F THERAPEUTICS

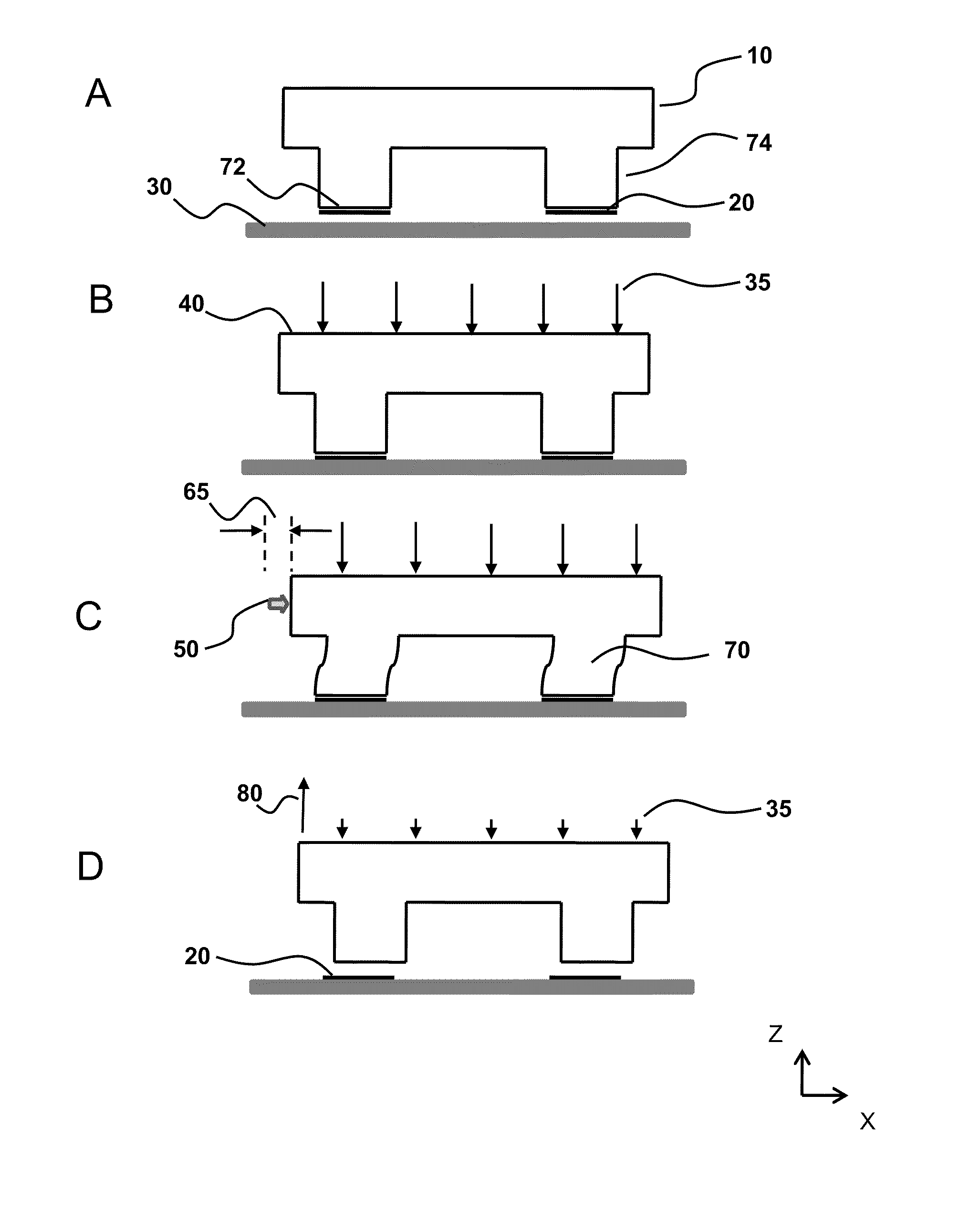

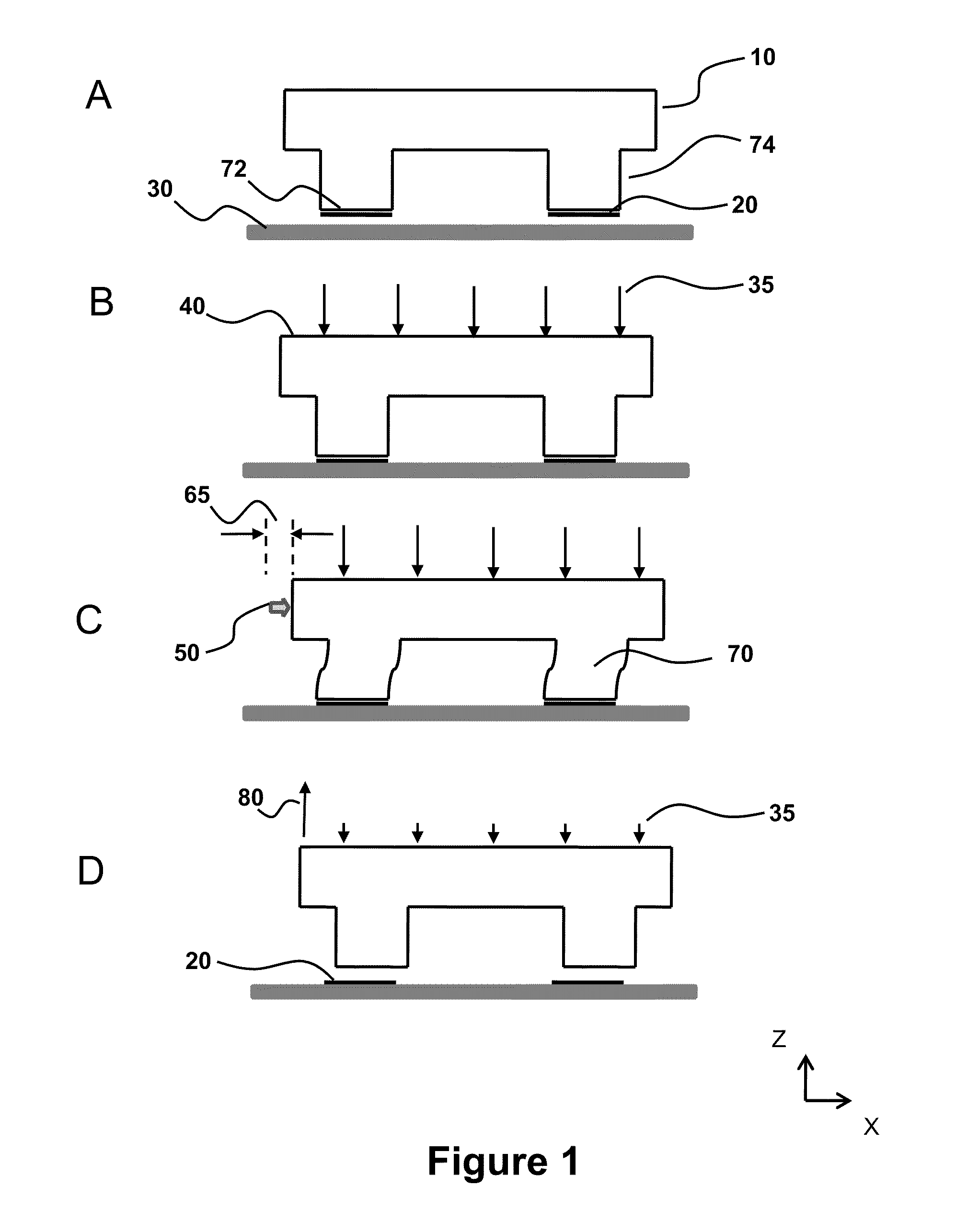

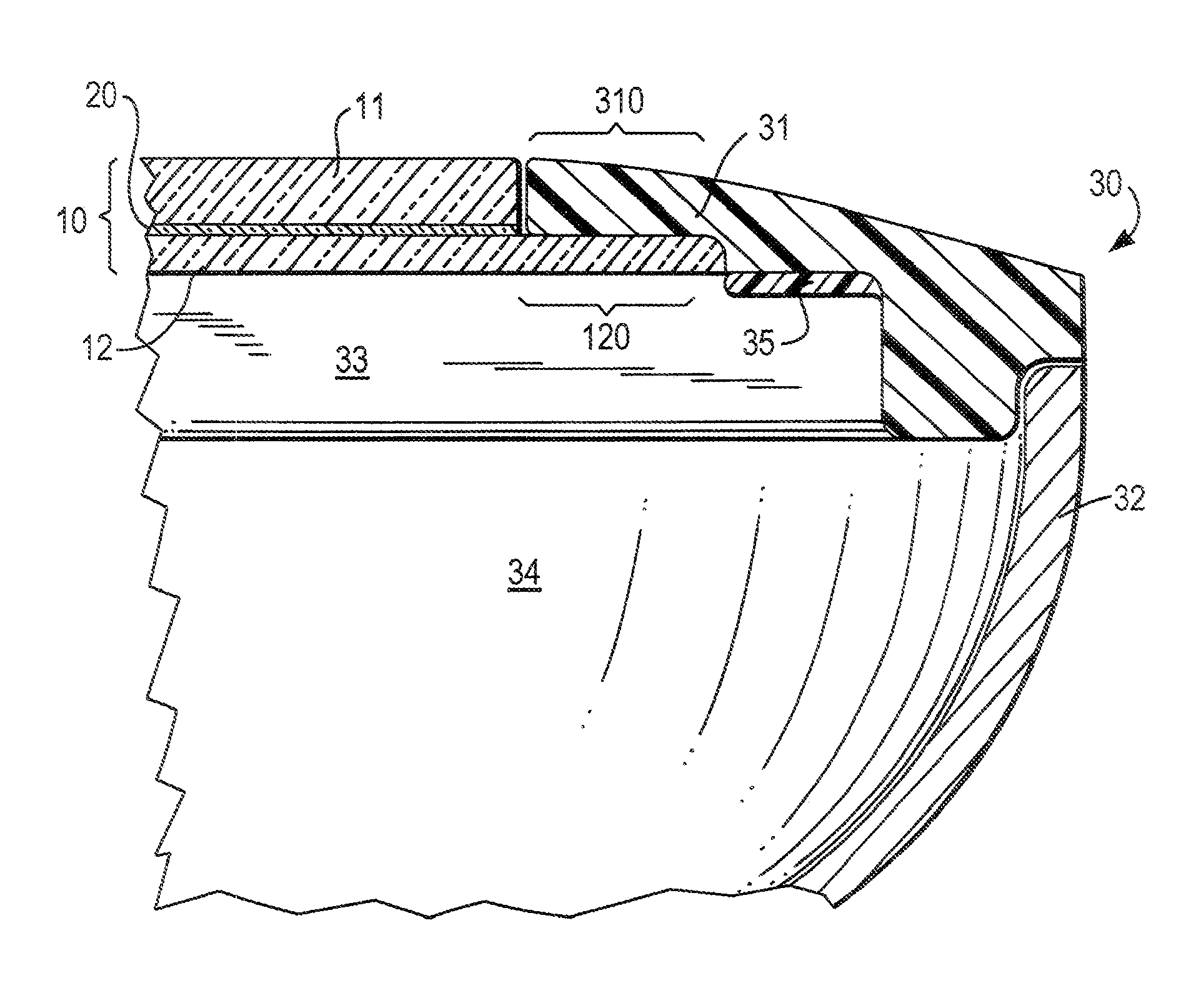

Printing semiconductor elements by shear-assisted elastomeric stamp transfer

ActiveUS8506867B2Sacrificing printing yield and accuracyIncrease chanceConfectionerySolid-state devicesEngineeringVertical displacement

Provided are methods and devices for transfer printing of semiconductor elements to a receiving surface. In an aspect, the printing is by conformal contact between an elastomeric stamp inked with the semiconductor elements and a receiving surface, and during stamp removal, a shear offset is applied between the stamp and the receiving surface. The shear-offset printing process achieves high printing transfer yields with good placement accuracy. Process parameter selection during transfer printing, including time varying stamp-backing pressure application and vertical displacement, yields substantially constant delamination rates with attendant transfer printing improvement.

Owner:X DISPLAY CO TECH LTD

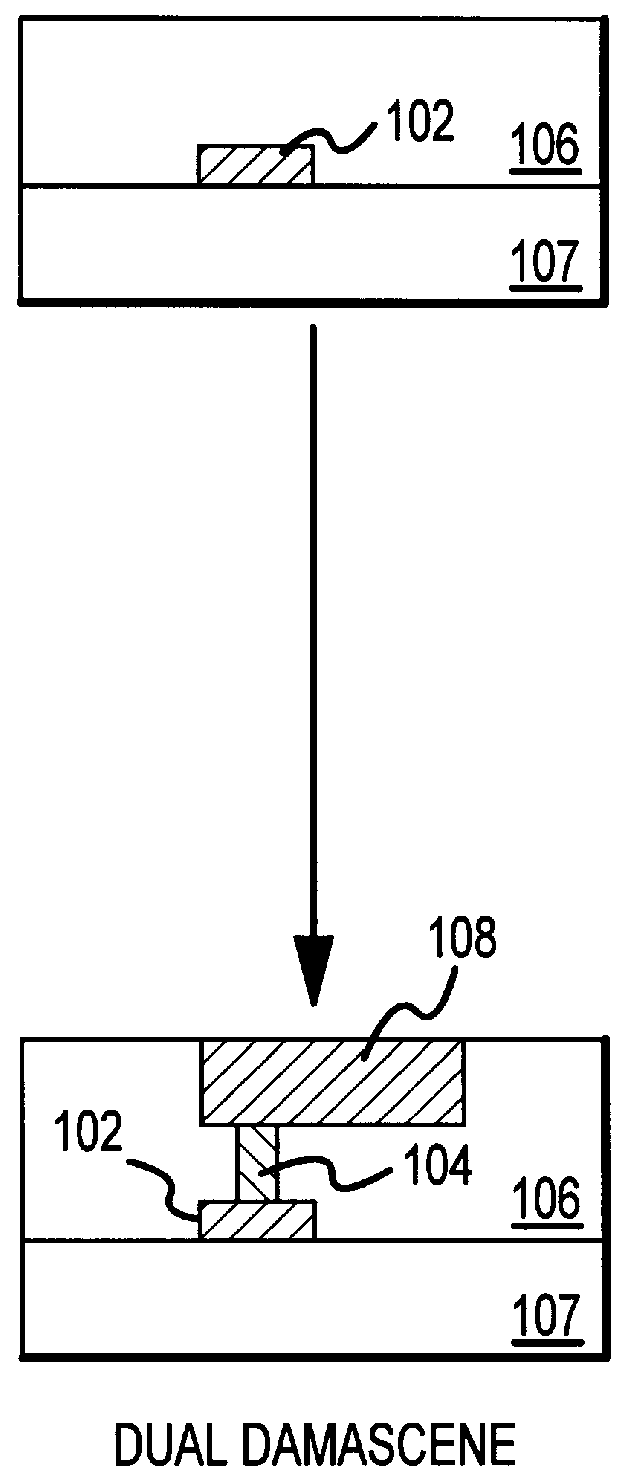

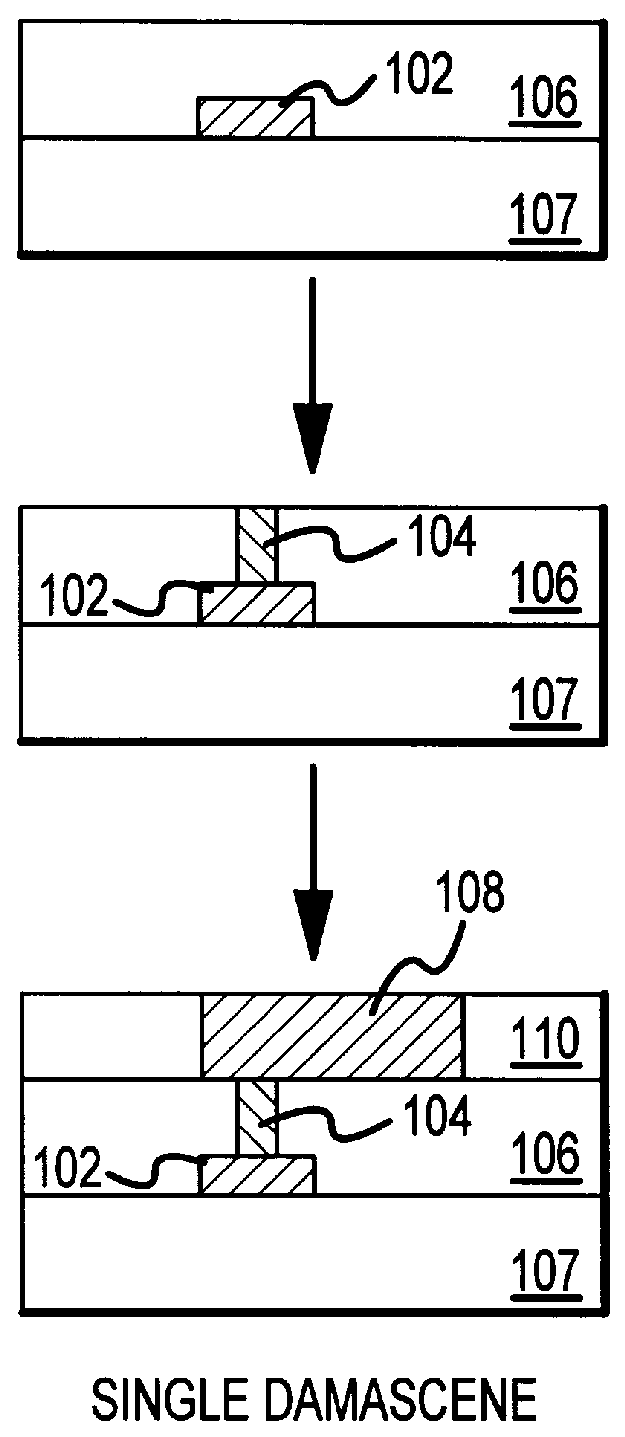

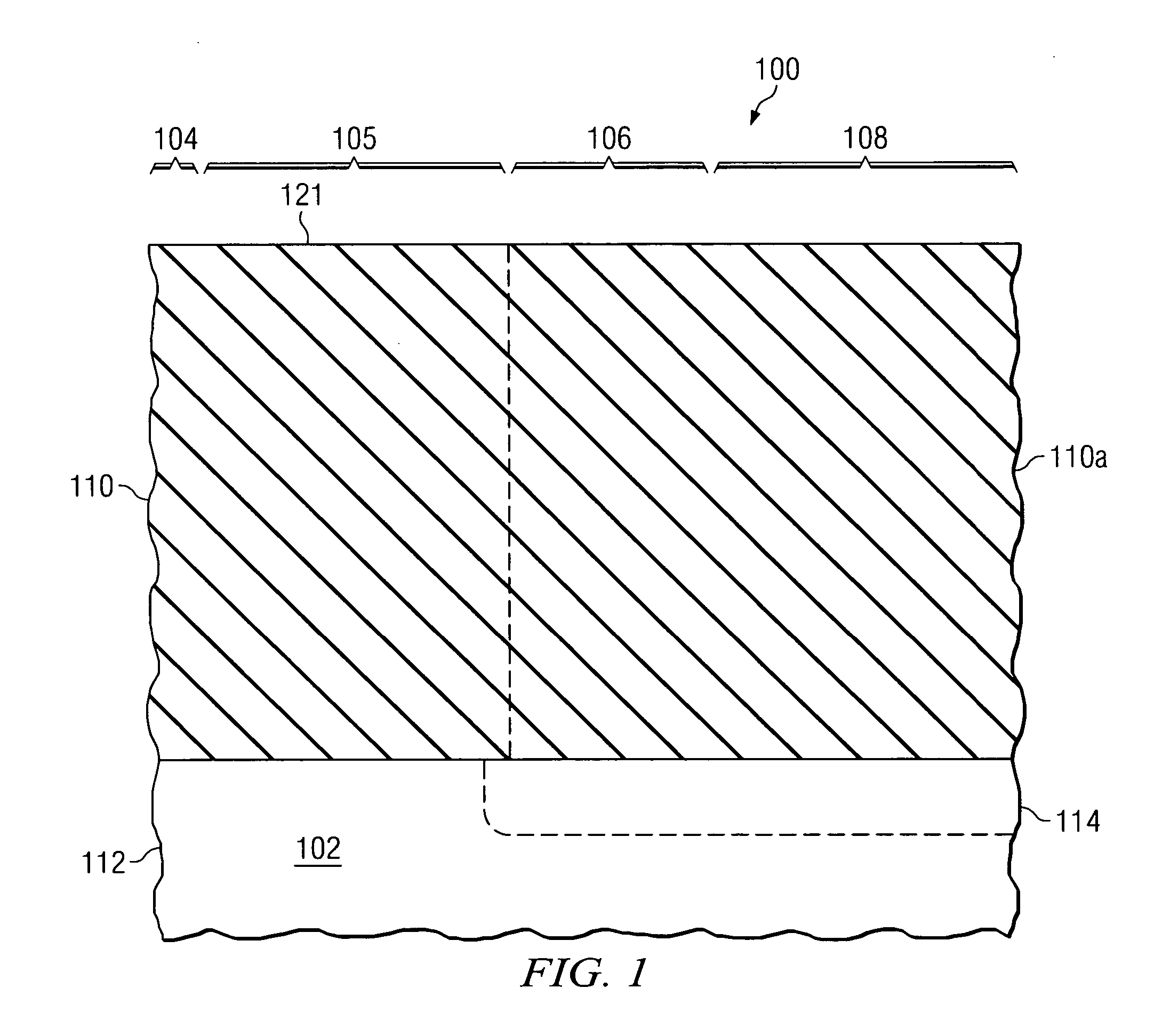

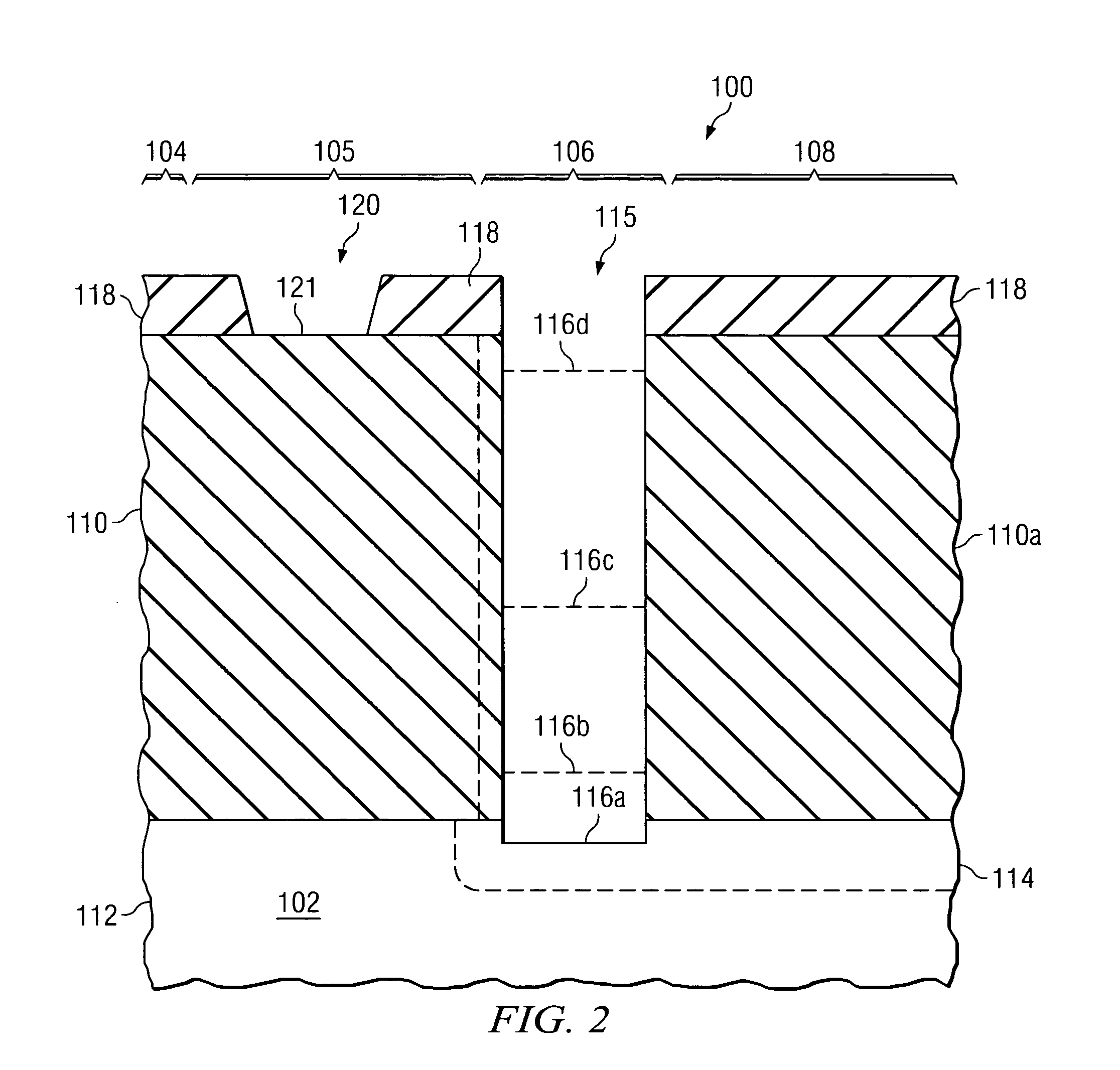

Methods for forming high-performing dual-damascene interconnect structures

Dual damascene methods and structures are provided for IC interconnects which use a dual-damascene process incorporating a low-k dielectric material, high conductivity metal, and an improved hard mask scheme. A pair of hard masks are employed: a silicon dioxide layer and a silicon nitride layer, wherein the silicon dioxide layer acts to protect the silicon nitride layer during dual damascene etch processing, but is subsequently sacrificed during CMP, allowing the silicon nitride layer to act as a the CMP hard mask. In this way, delamination of the low-k material is prevented, and any copper-contaminated silicon dioxide material is removed.

Owner:NEWPORT FAB

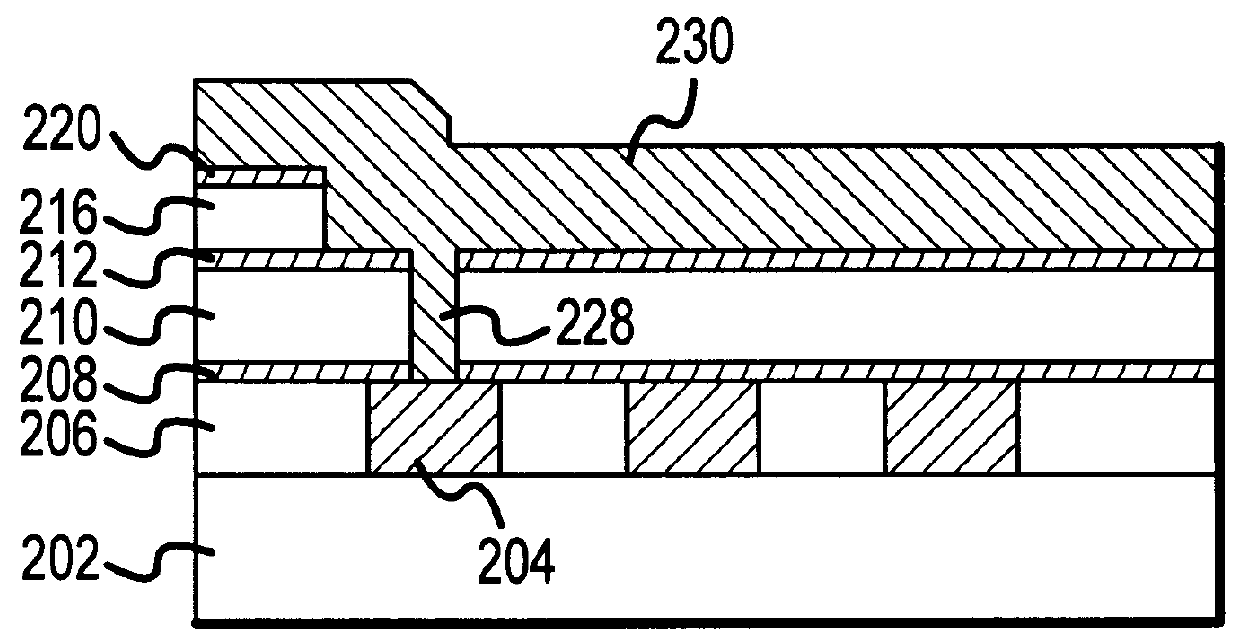

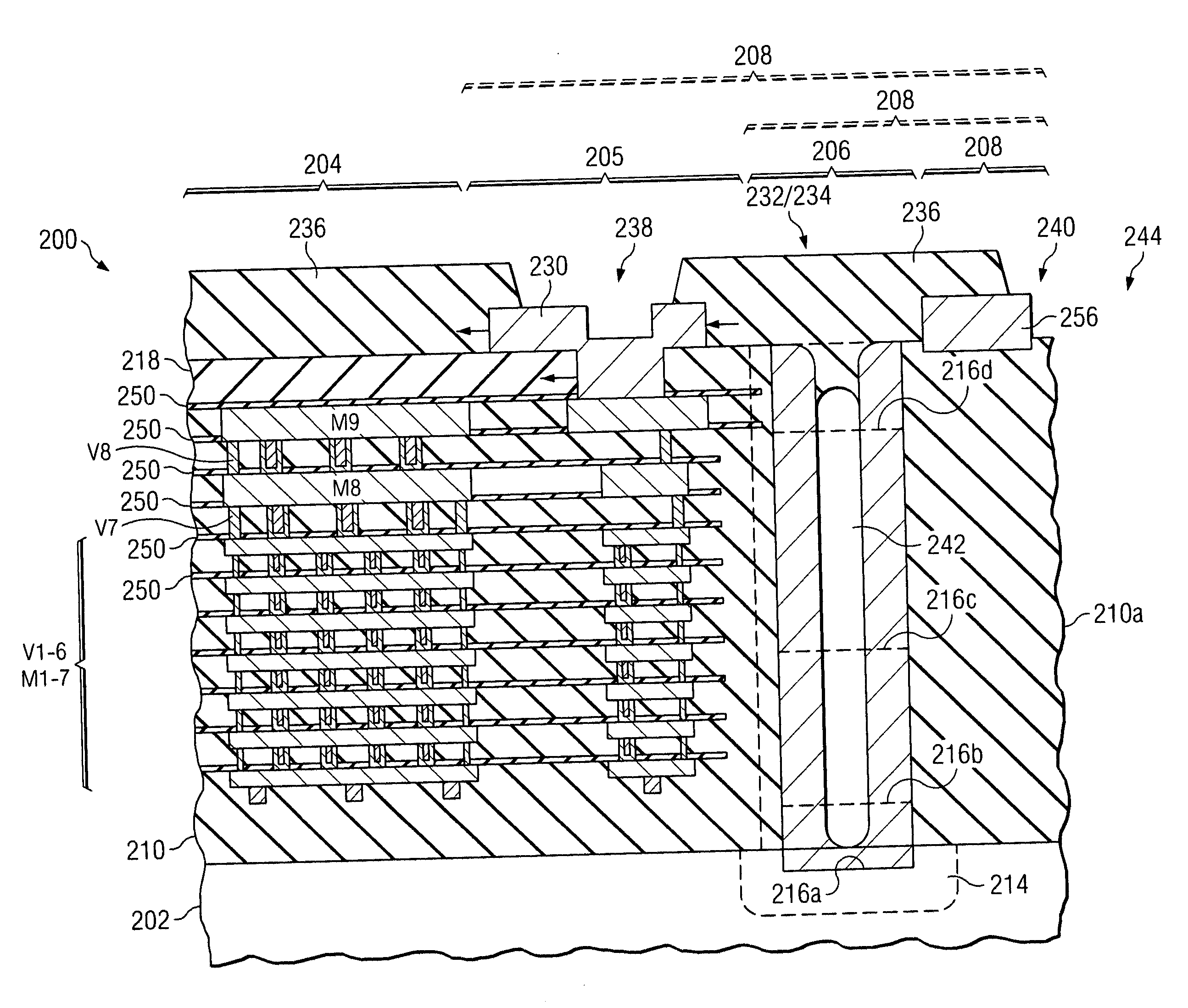

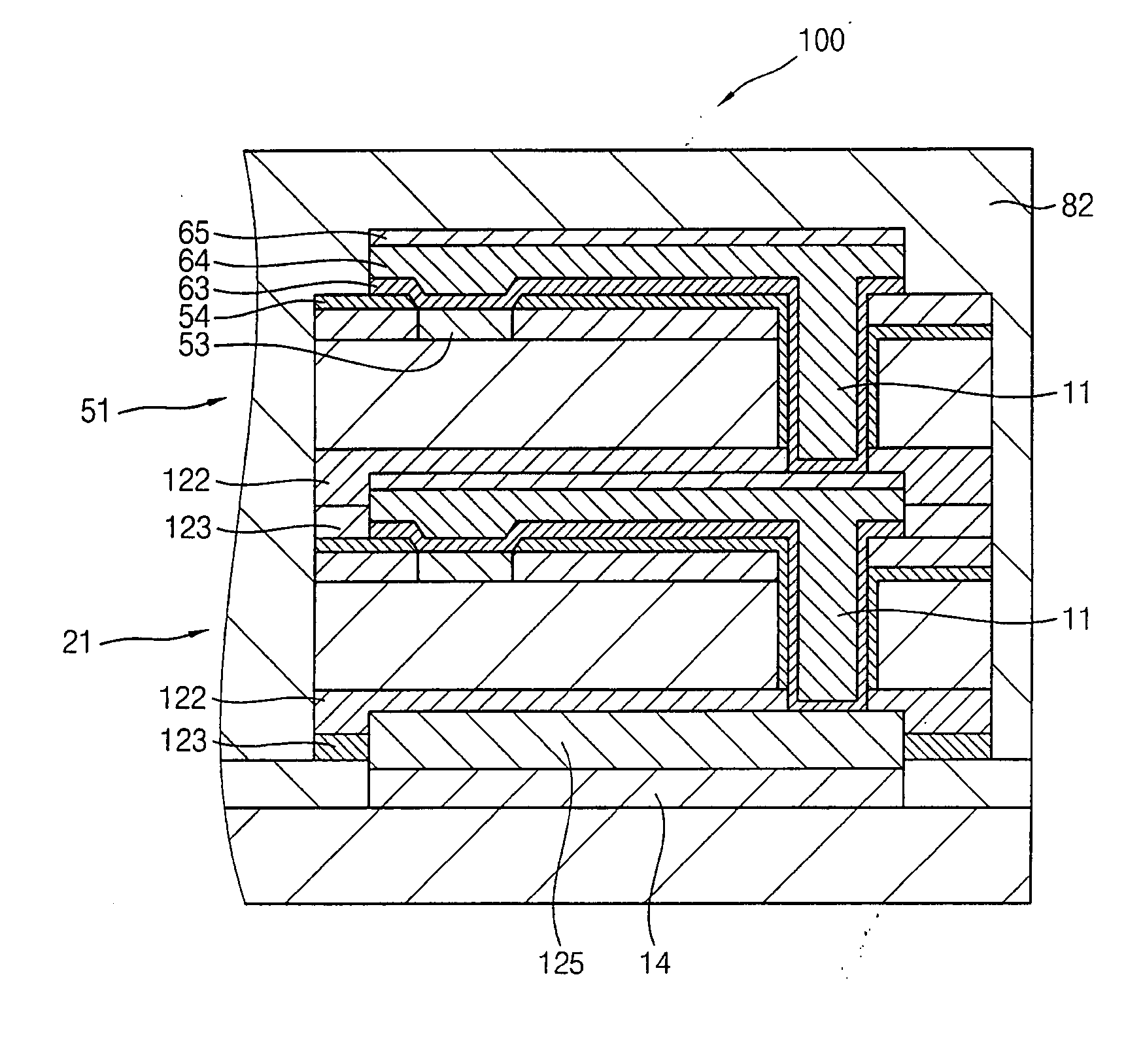

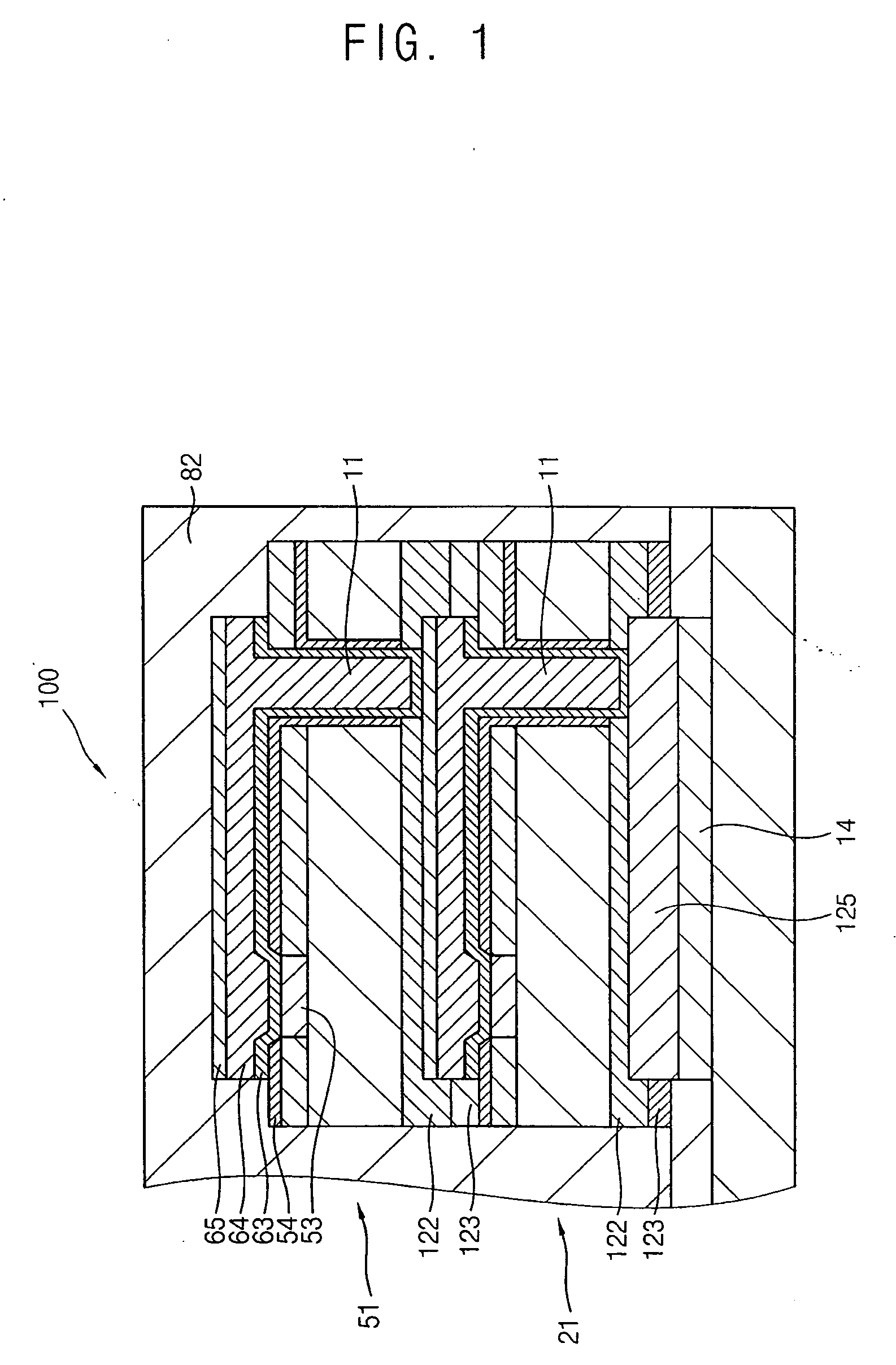

Apparatus and method for manufacturing a semiconductor wafer with reduced delamination and peeling

InactiveUS20060261490A1Avoid layeringAvoid crackingSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor structureLow-k dielectric

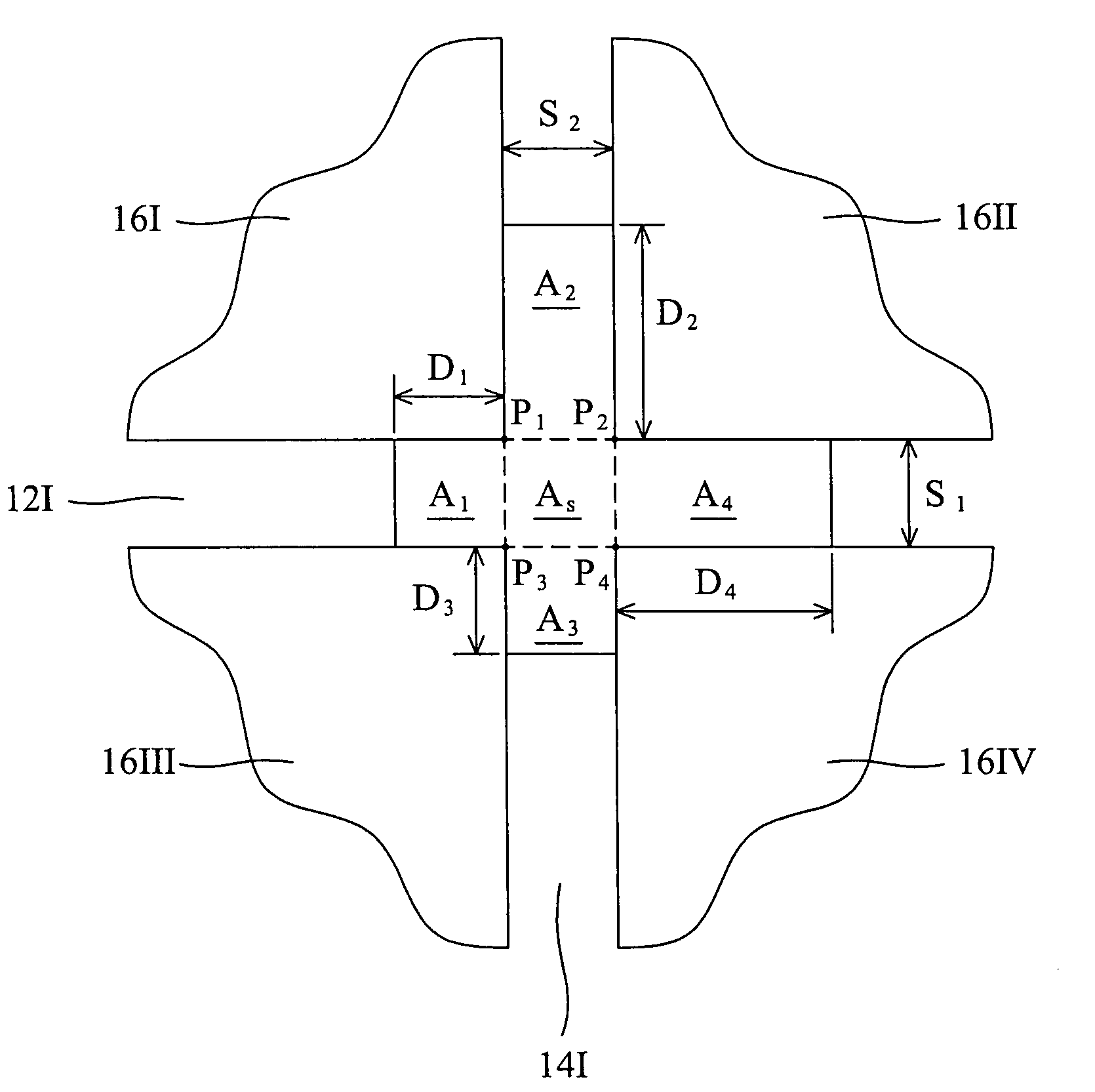

A multi-layered semiconductor structure with free areas limiting the placement of test keys. First and second scribe lines intersect to define one corner point of a die. The first and second scribe lines are part of the multilayered structure and at least one layer of the multi-layer structure is a low-k dielectric layer. Free area A1 is defined on the first scribe line and is defined by the equation A1=D1×S1, where D1 is the distance from the corner point of the die toward the main area of the die, and S1 is the width of the first scribe line. Free area AS is defined at the intersection of the first scribe line and the second scribe line adjacent the die and is defined by the equation AS=S1×S2, where S2 is the width of the second scribe line.

Owner:TAIWAN SEMICON MFG CO LTD

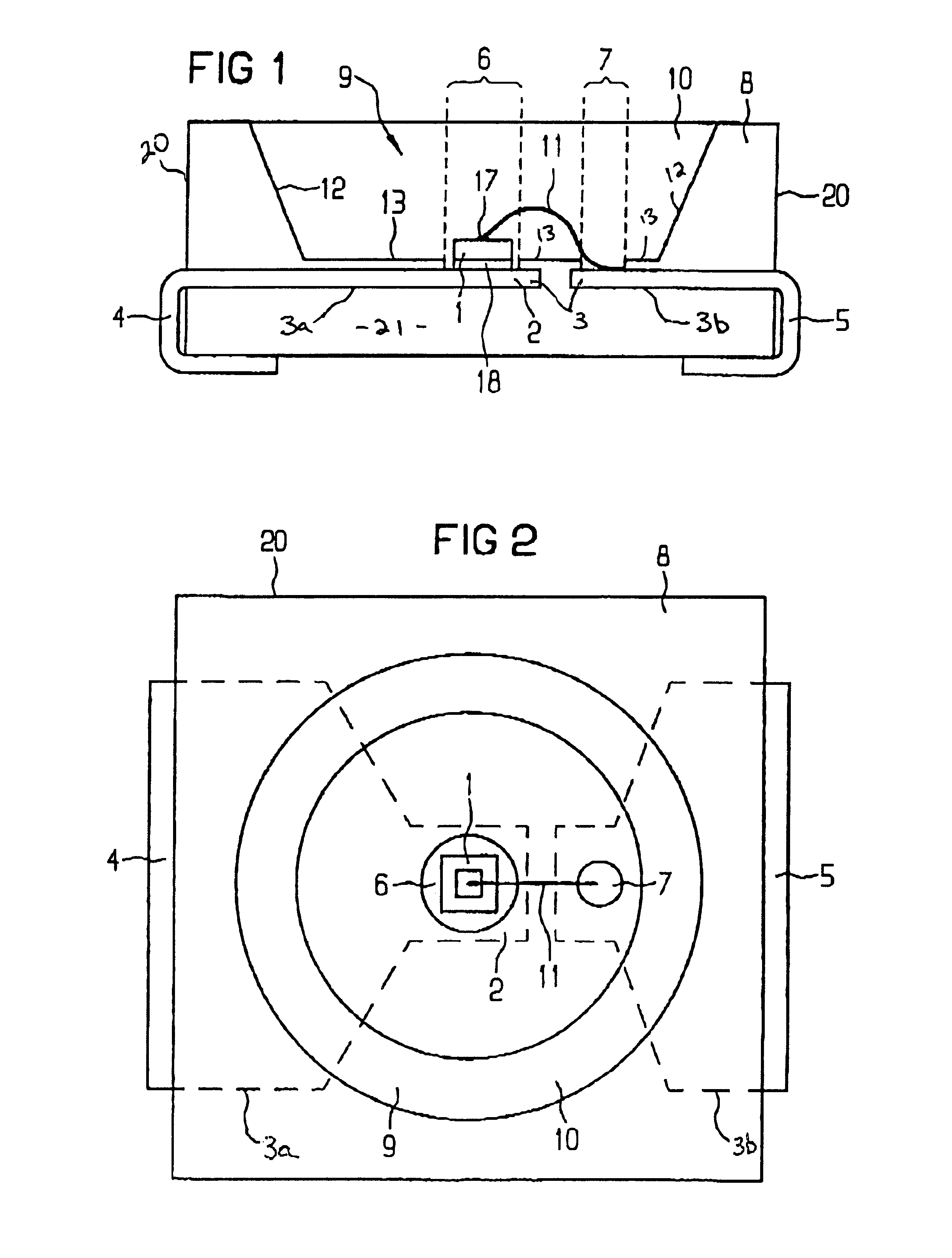

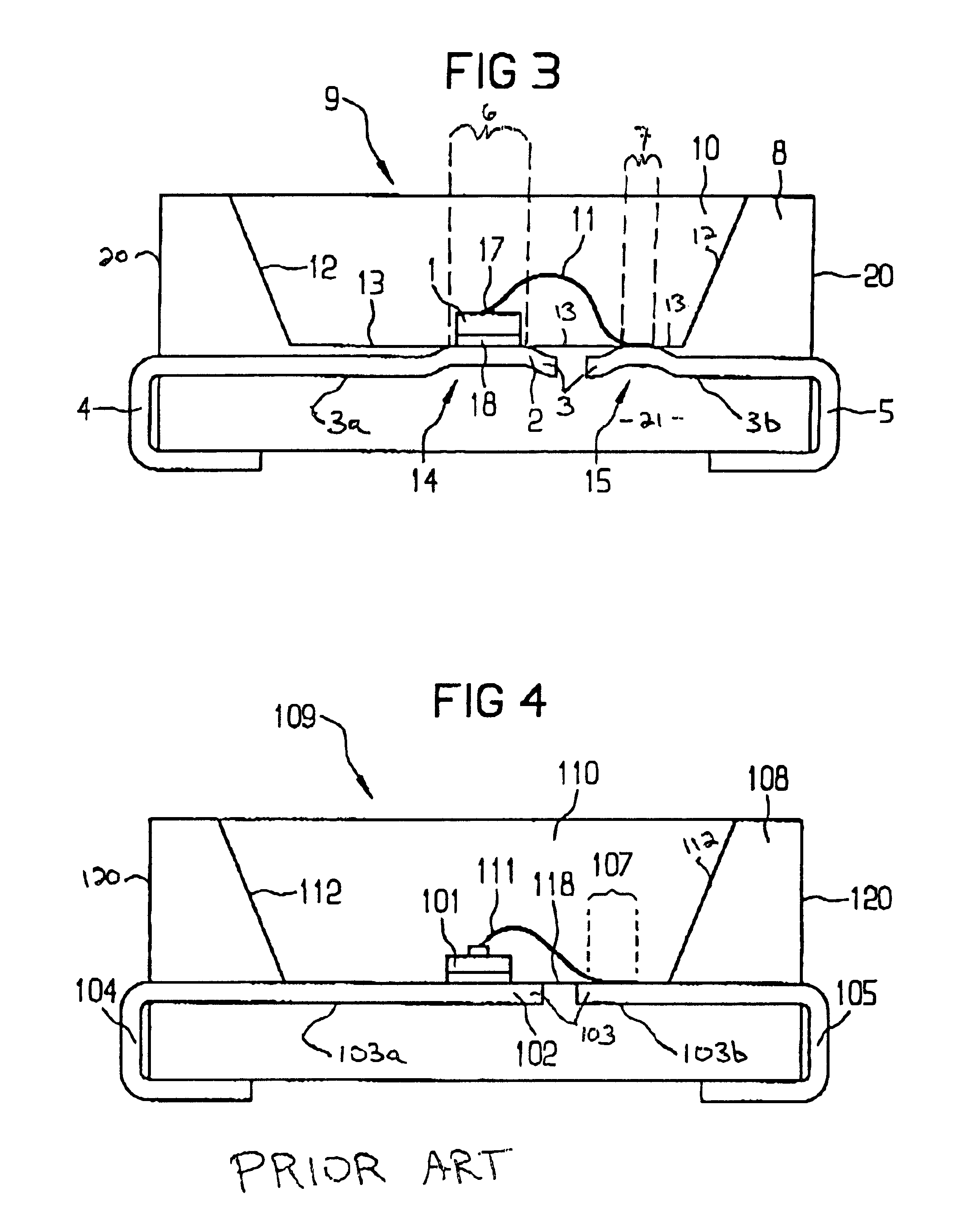

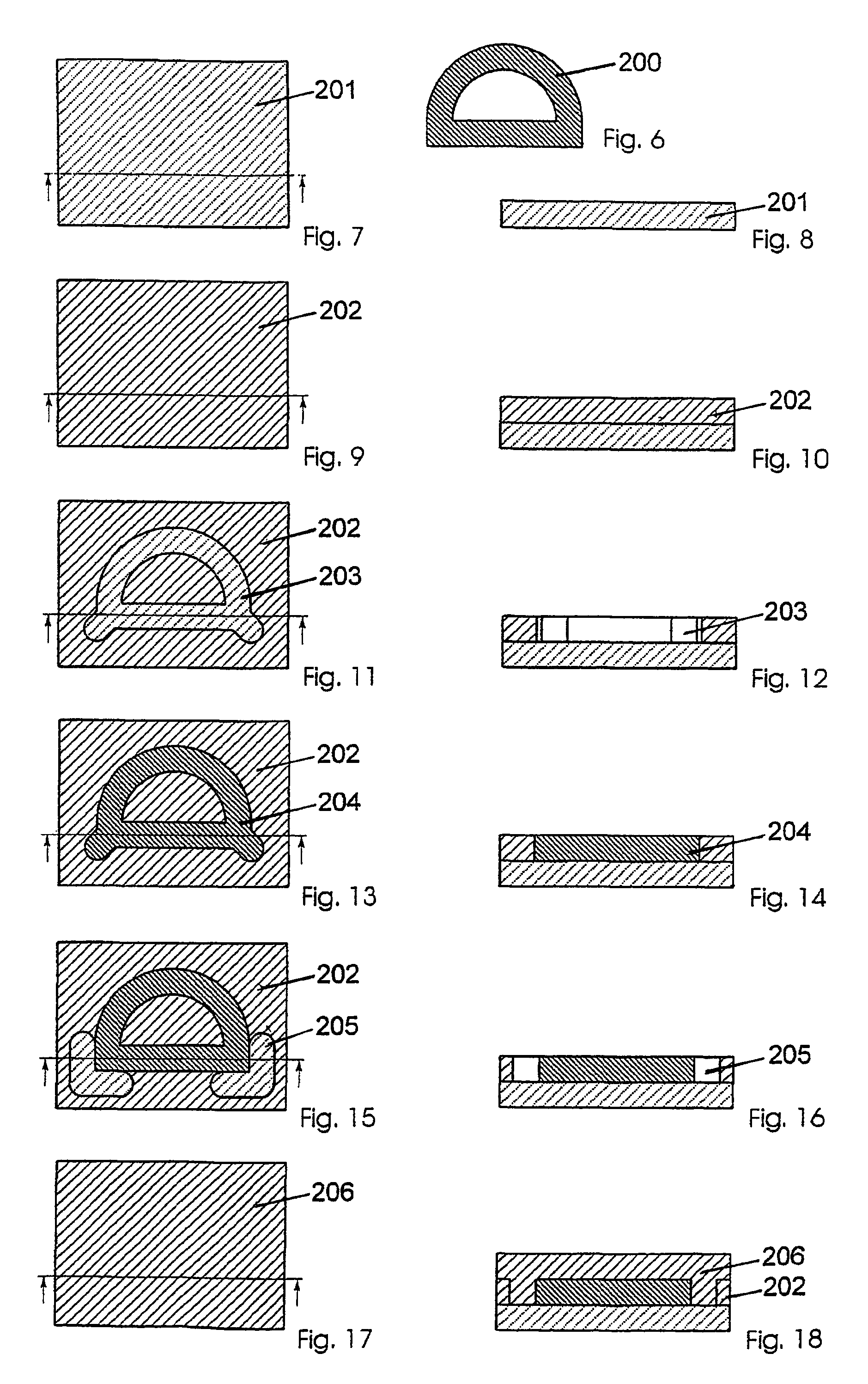

Diode housing

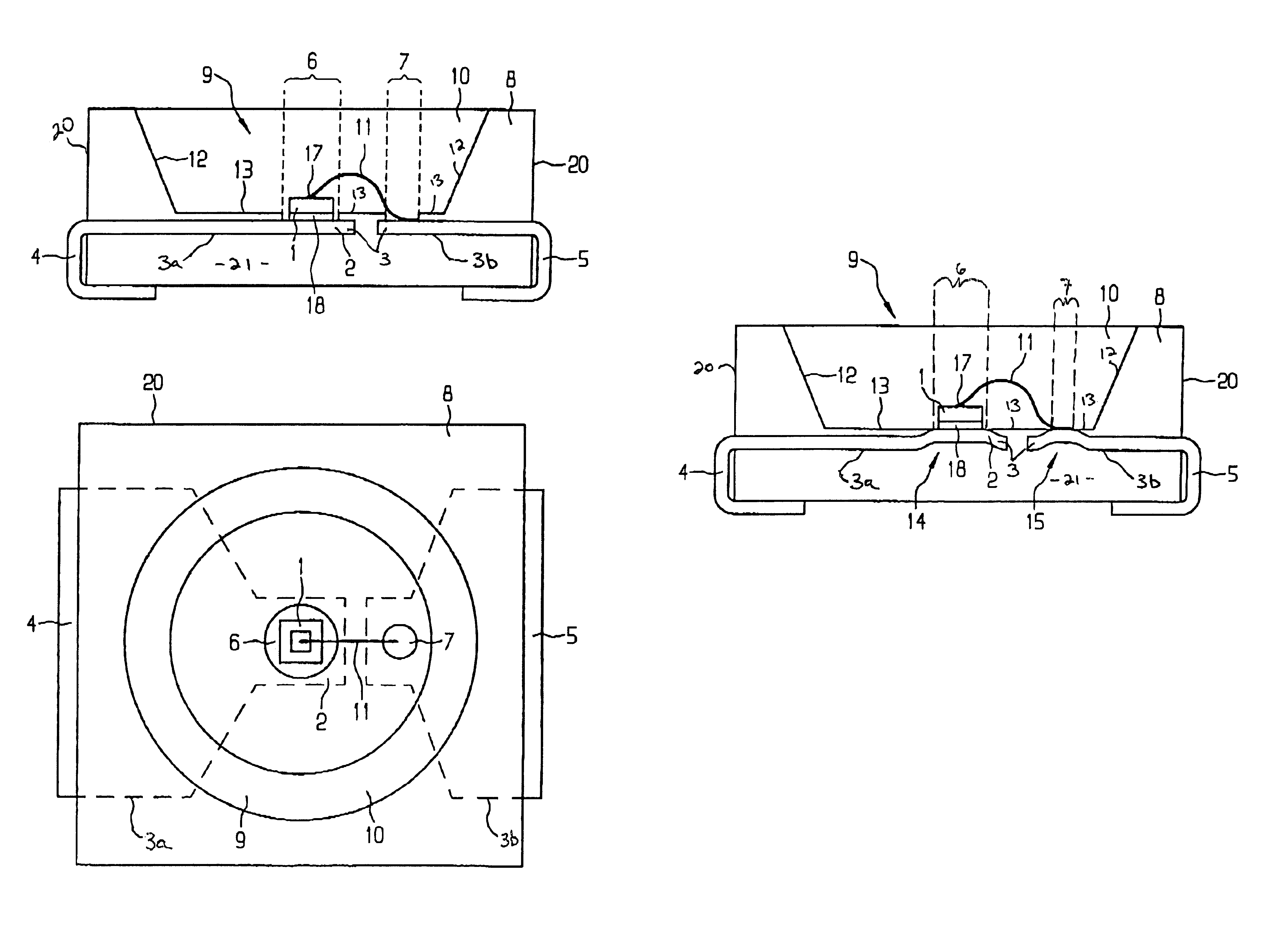

InactiveUS6624491B2Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

A housing accommodating a semiconductor chip is set out. The housing and chip may be used for sending and / or receiving radiation. Popular applications of the housing may be in light emitting diodes. The housing includes a conductor strip that is punched into two electrically isolated portions. The housing further includes a cavity extending inwards from the top of the housing. The conductor portions include respective areas that are exposed at the bottom of the cavity. The semiconductor chip is bonded to one of the exposed areas and a wire bonds the chip to the second exposed area. The conductor portions also terminate in exposed electrodes, which allow for electrical connection of the chip with external devices. A window is formed in the cavity and the walls of the housing that form the cavity may be made of a reflective material. The electrodes remain unexposed to the window but for any residual areas about the chip and bonding wire within the first and second exposed areas. By minimizing the area of the conductor exposed to the window, delamination brought about by the different thermal expansions of the window and conductor are minimized and / or eliminated. Likewise, with a reflective housing covering the base of the cavity that accommodates the window, internal radiation reflection is increased over that which was achieved with an exposed conductor.

Owner:OSRAM GMBH

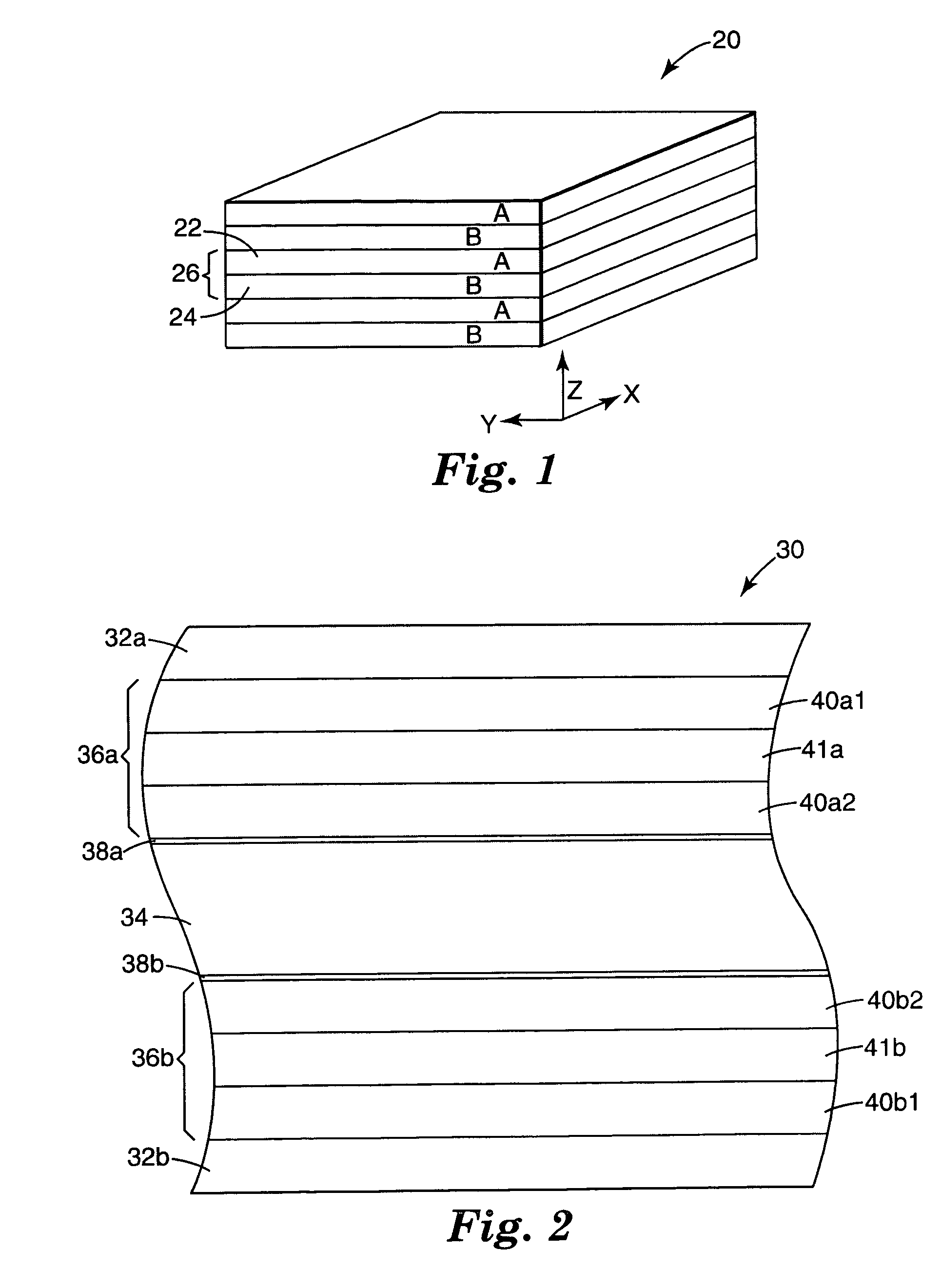

Cards and laminates incorporating multilayer optical films

New constructions of multilayer optical films, laminates thereof, and cards incorporating same are disclosed. In a card, the multilayer optical film can be sandwiched between relatively thick polymer layers using adhesive layers that are at least 0.5 mils thick but that may collectively account for no more than 3 mils of thickness. The cards can if desired be highly transmissive in the visible yet highly opaque in portions of the infrared. The resulting cards can have reduced angel hair formation during card stamping, increased resistance to delamination, and reduced haze.

Owner:3M INNOVATIVE PROPERTIES CO

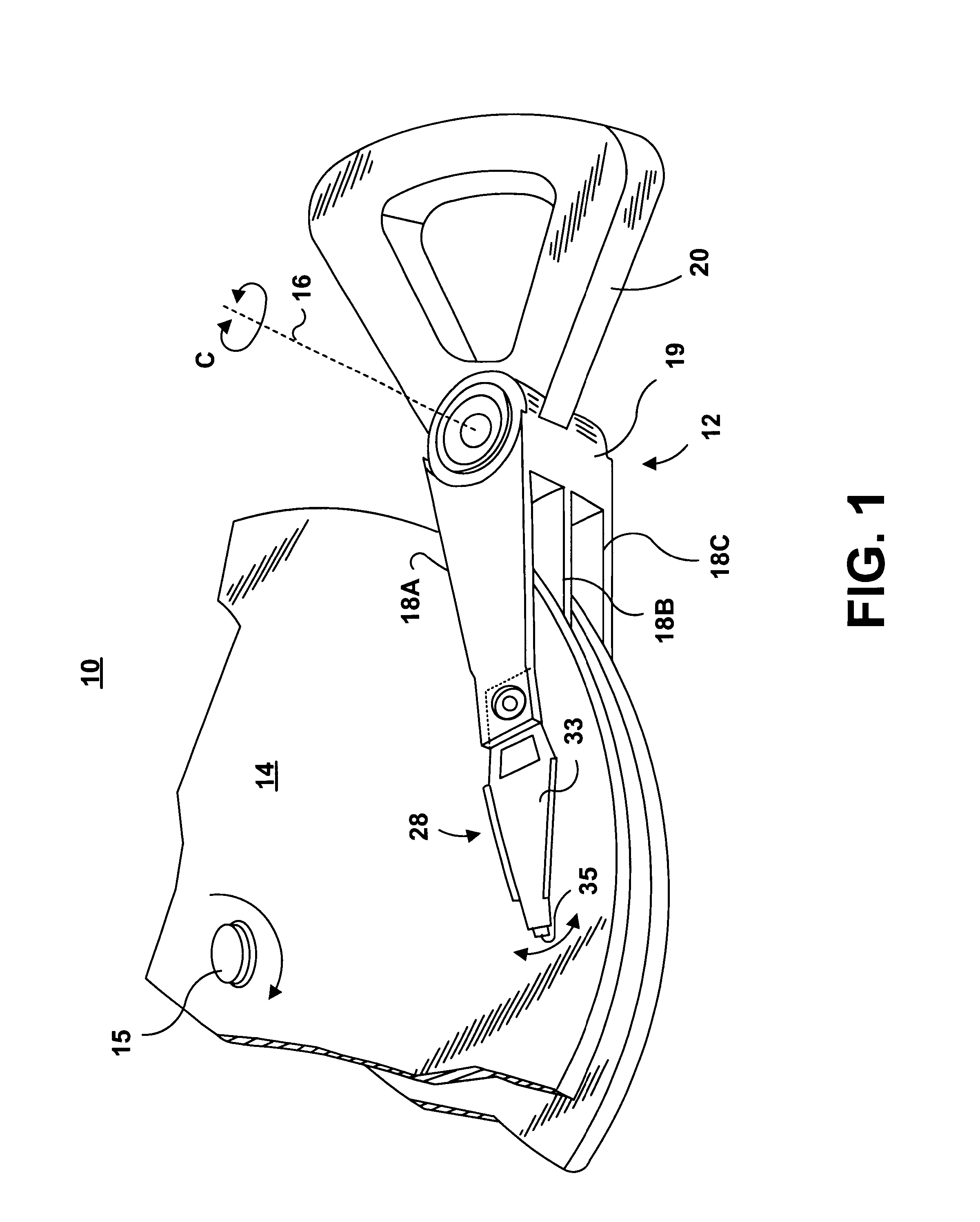

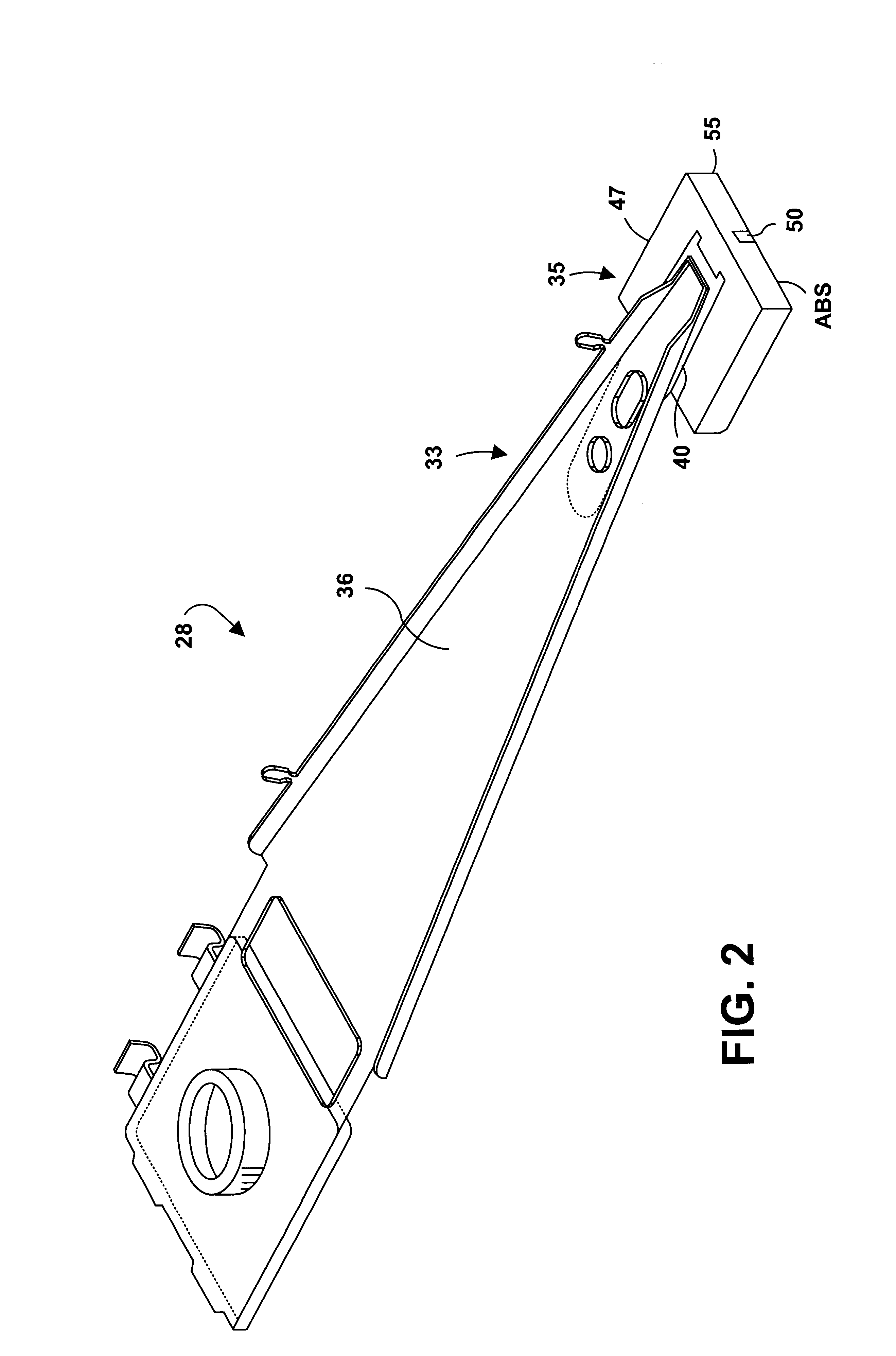

Hybrid diffuser for minimizing thermal pole tip protrusion and reader sensor temperature

InactiveUS6859343B1Reduces reader sensor temperatureImprove thermal conductivityManufacture head surfaceRecord information storageInvarInsulation layer

An enchance recording head design provides conduction and mechanical restraint control in order to minimize the pole tip protrusion and the head temperature resulting from the thermal heating of the magnetic recording head during operation. In one embodiment, the recording head includes a hybrid diffuser formed within an insulation layer, at a predetermined distance from the head write section. The hybrid diffuser is comprised of a thermal conduction layer with high thermal conductivity, such as gold or copper, and a mechanical restraint layer having near zero CTE, such as a 60-80% face-centered-cubic NiFe (Invar) material. The hybrid diffuser is recessed from the ABS to prevent the delamination of the hybrid diffuser due to the otherwise displacement incompatibility between the inner insulating layer and the hybrid diffuser at the ABS.

Owner:WESTERN DIGITAL TECH INC

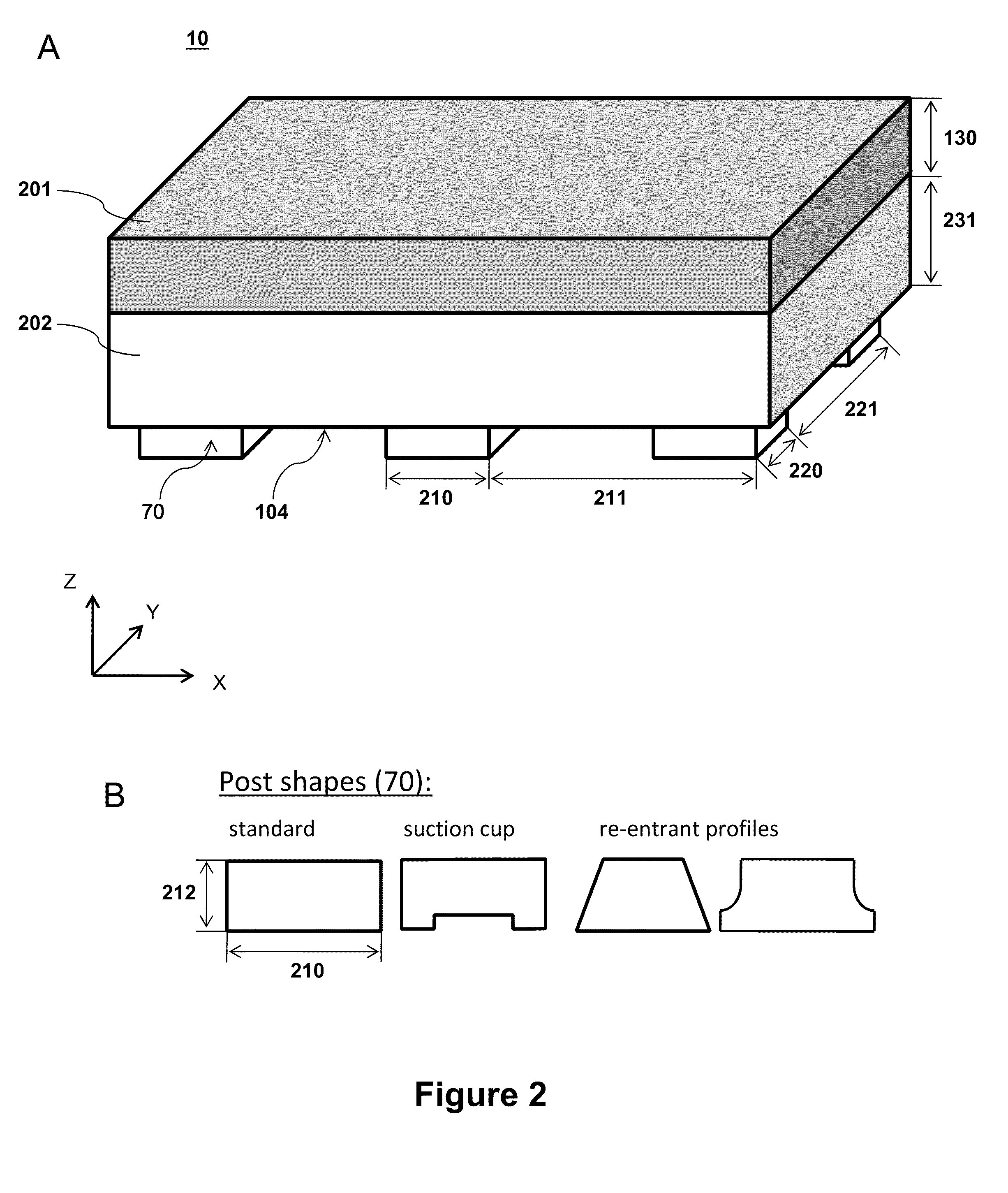

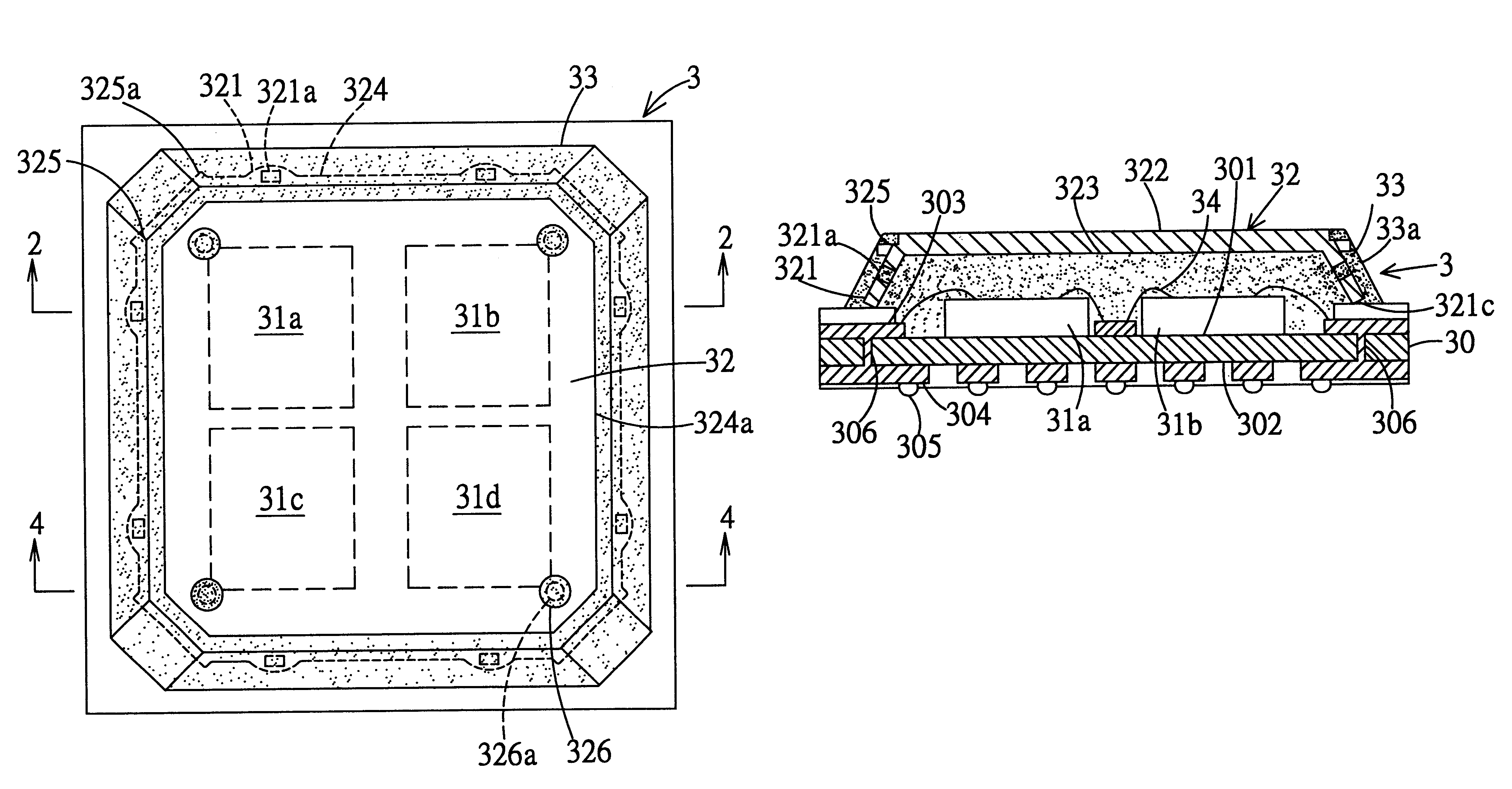

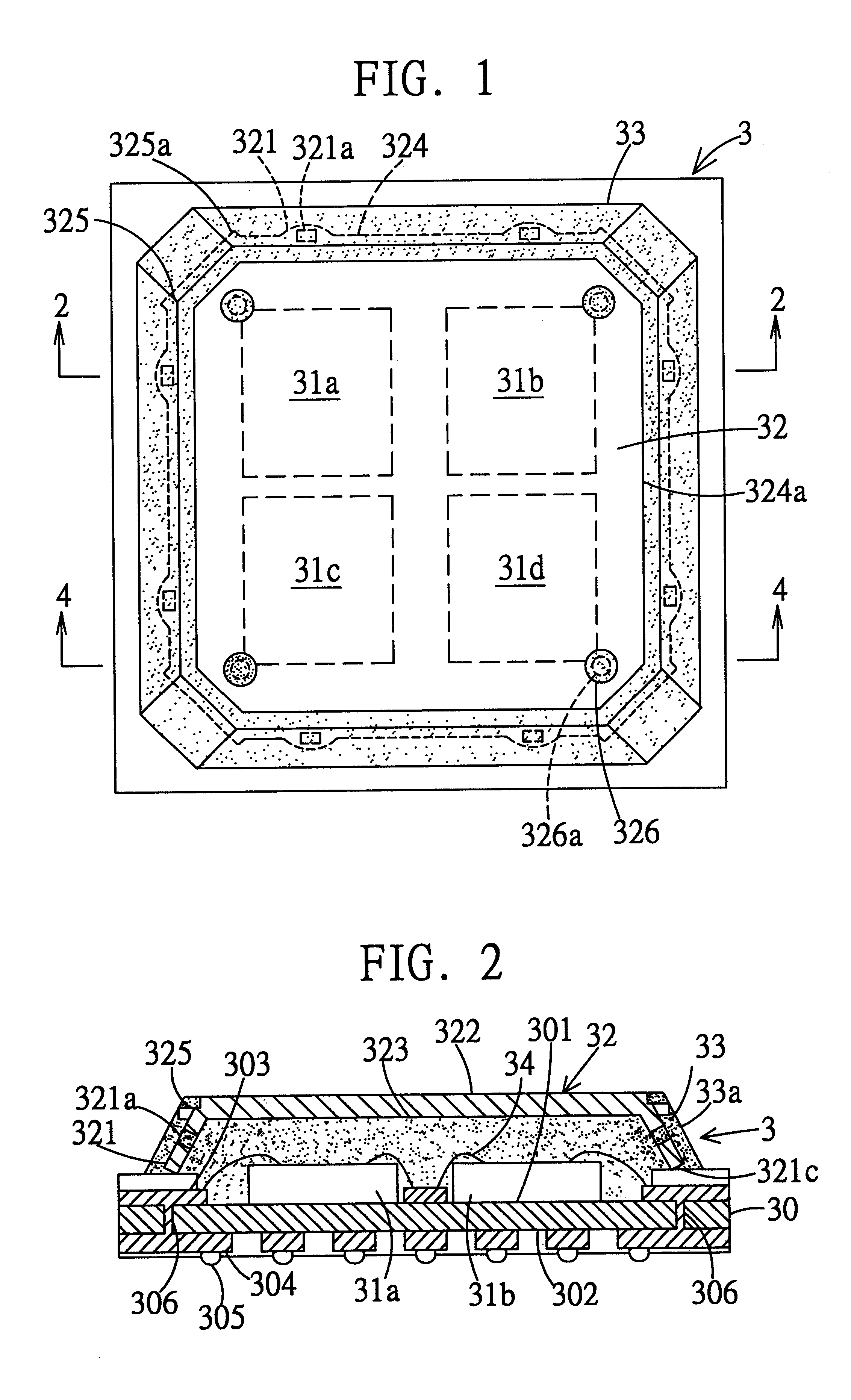

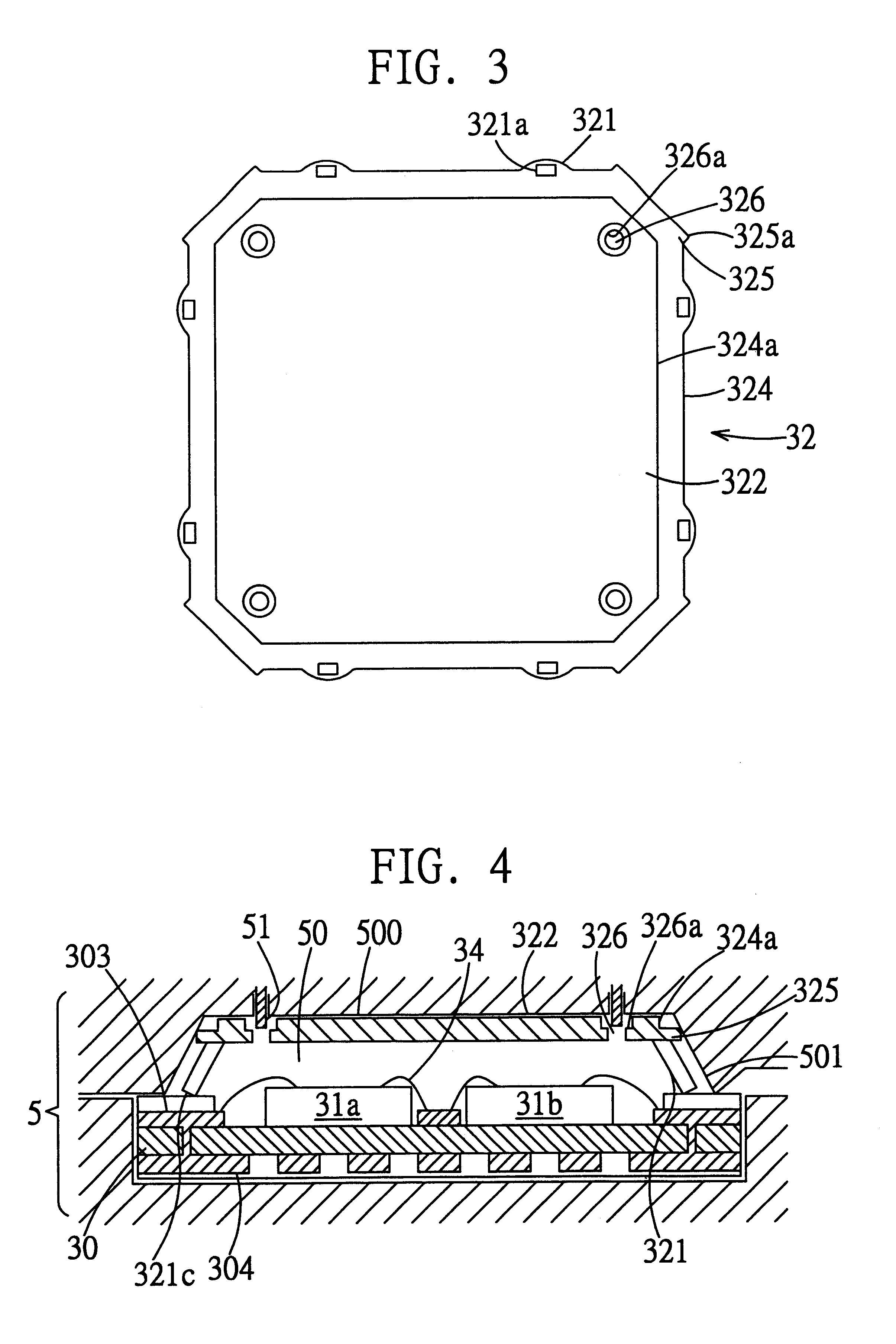

Semiconductor package having a heat sink with an exposed surface

InactiveUS6246115B1Precise positioningAvoid flashSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor package

An integrated circuit package with a fully-exposed heat sink is provided. The integrated circuit package includes a substrate having a first side being formed with first conductive traces and a second side being formed with second conductive traces. At least one chip is mounted on the substrate and electrically connected to the first conductive traces. A plurality of solder balls are provided at the terminal ends of the second conductive traces to allow external connection of the chip. The fully-exposed heat sink is mounted on the substrate. The heat sink is formed with a plurality of supportive legs arranged in such a manner as to allow a bottom surface of the heat sink to be separated from the chip and a top surface of the heat sink to be tightly attached to a cavity in a mold used to form an encapsulant for enclosing the chip. A plurality of positioning tongues are formed on the heat sink for securing the heat sink in position when performing a molding process for forming the encapsulant. With this integrated circuit package, no jig is required in the assembly of the integrated circuit package. Moreover, since there is no need to use adhesives to adhere the supportive legs onto the substrate, the integrated circuit package would not suffer from delamination as in the case of the prior art. The fully-exposed heat sink allows an increased heat-dissipating efficient as compared to the prior art.

Owner:SILICONWARE PRECISION IND CO LTD

Electrical Connector For A Window Pane Of A Vehicle

InactiveUS20070224842A1Reduce stress concentrationMinimizes mechanical stressElectric discharge tubesSoldered/welded conductive connectionsElectrical conductorCoupling

A window pane has a substrate formed from glass and includes an electrical device including an electrical conductor. An electrical connector is operatively connected to and in electrical communication with the conductor for transferring electrical energy to the conductor. An electrical connector is bonded to the electrical conductor and has a first interacting portion. A terminal is disposed adjacent to the electrical connector and has a second interacting portion for interacting with the first interacting portion to mechanically couple the electrical connector and the terminal. The substrate has a first coefficient of thermal expansion and the connector has a second coefficient of thermal expansion. A difference between the first and second coefficients of thermal expansion is equal to or less than 5×10−6 / ° C. Due to the mechanical coupling between the connector and the terminal, the terminal and connector are less prone to bending, breakage, or delamination than conventional connector structures.

Owner:AGC AUTOMOTIVE AMERICAS

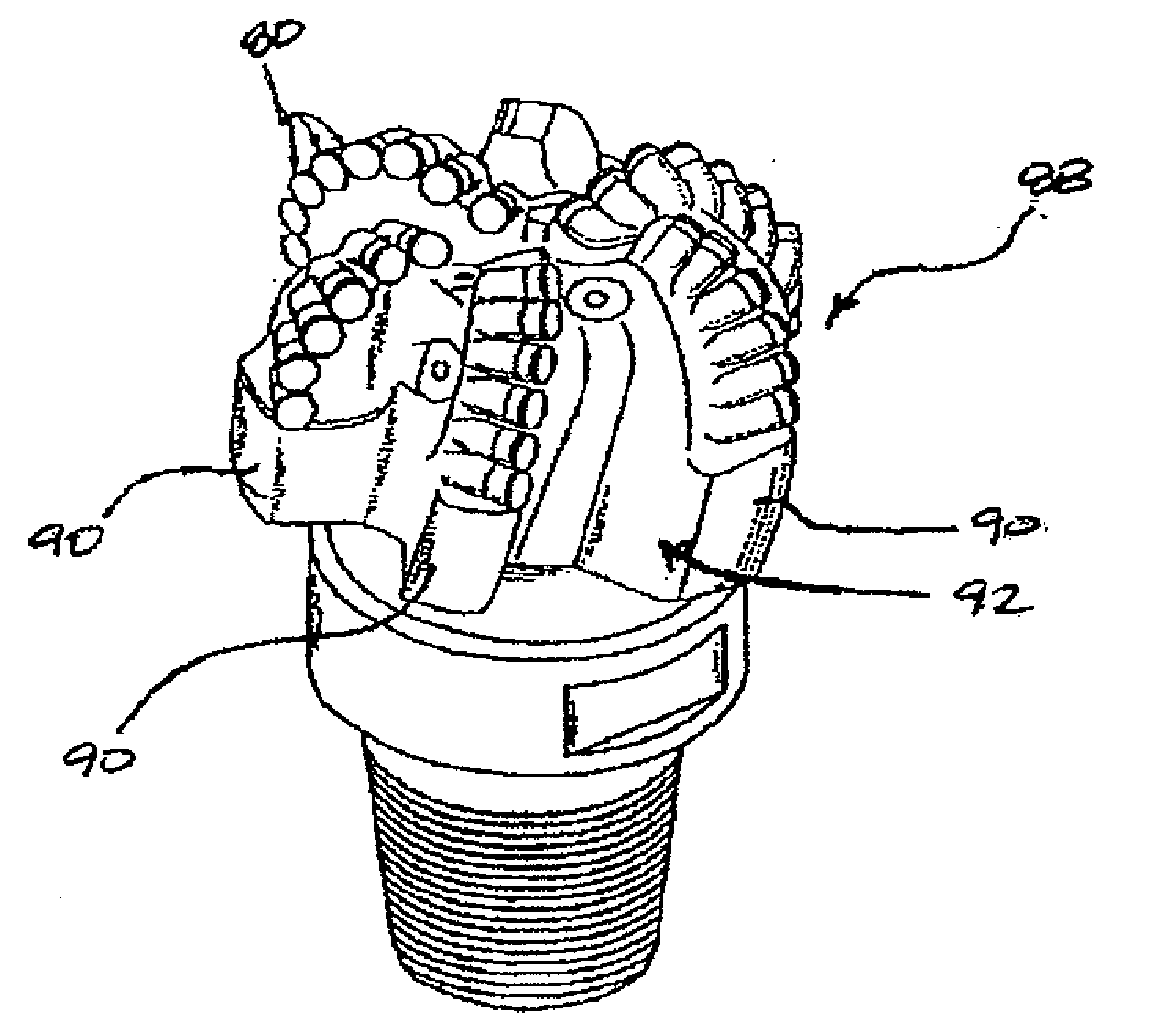

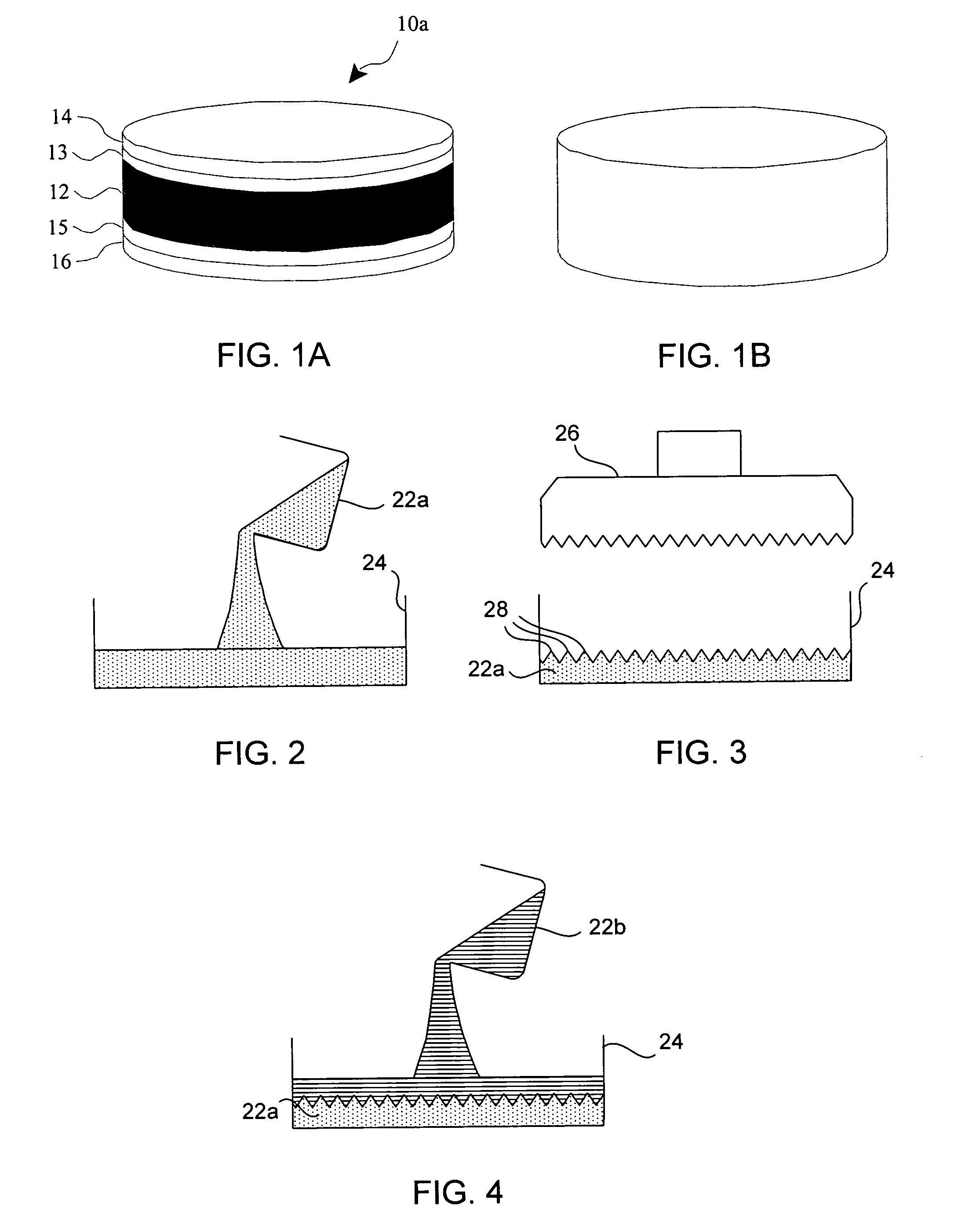

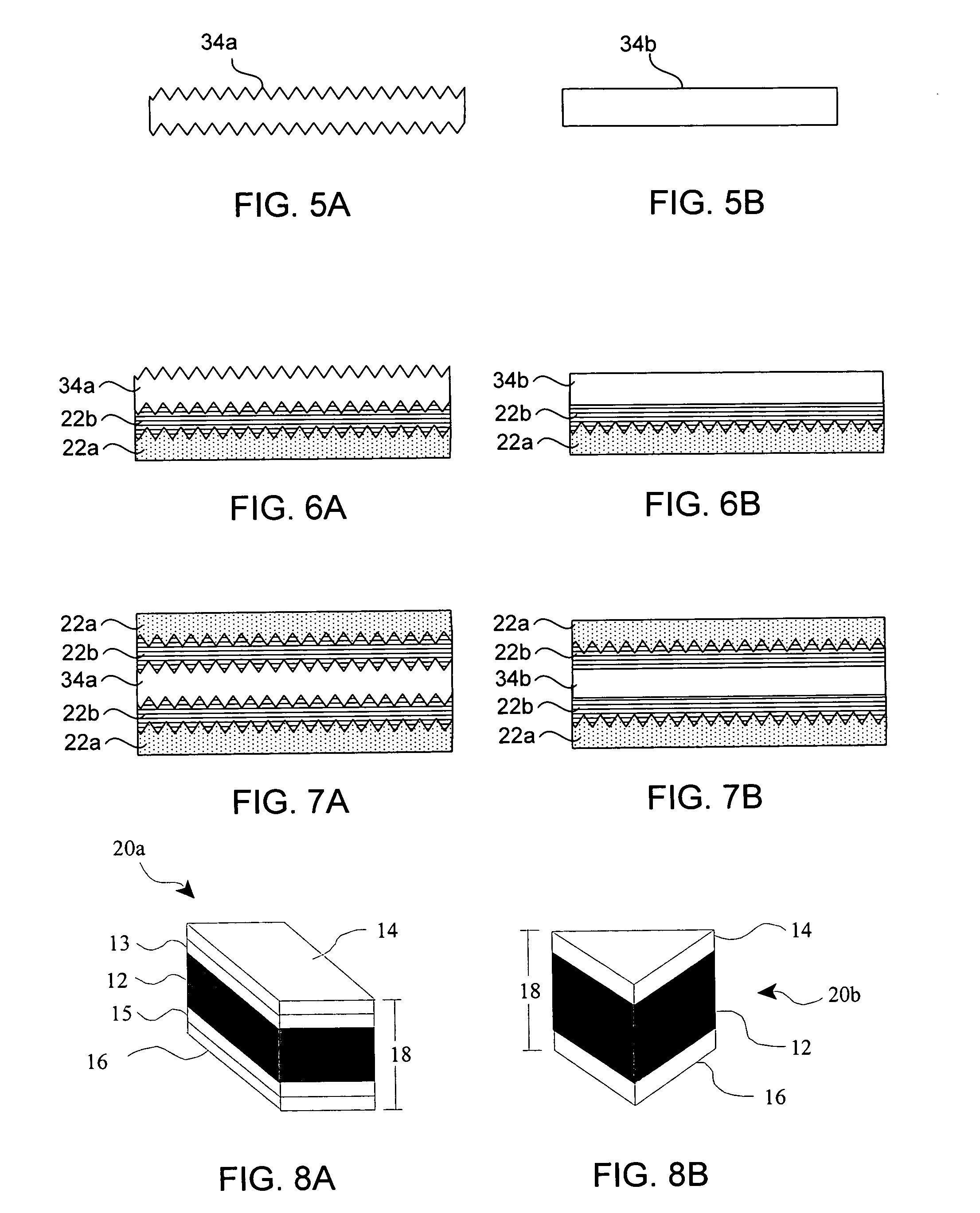

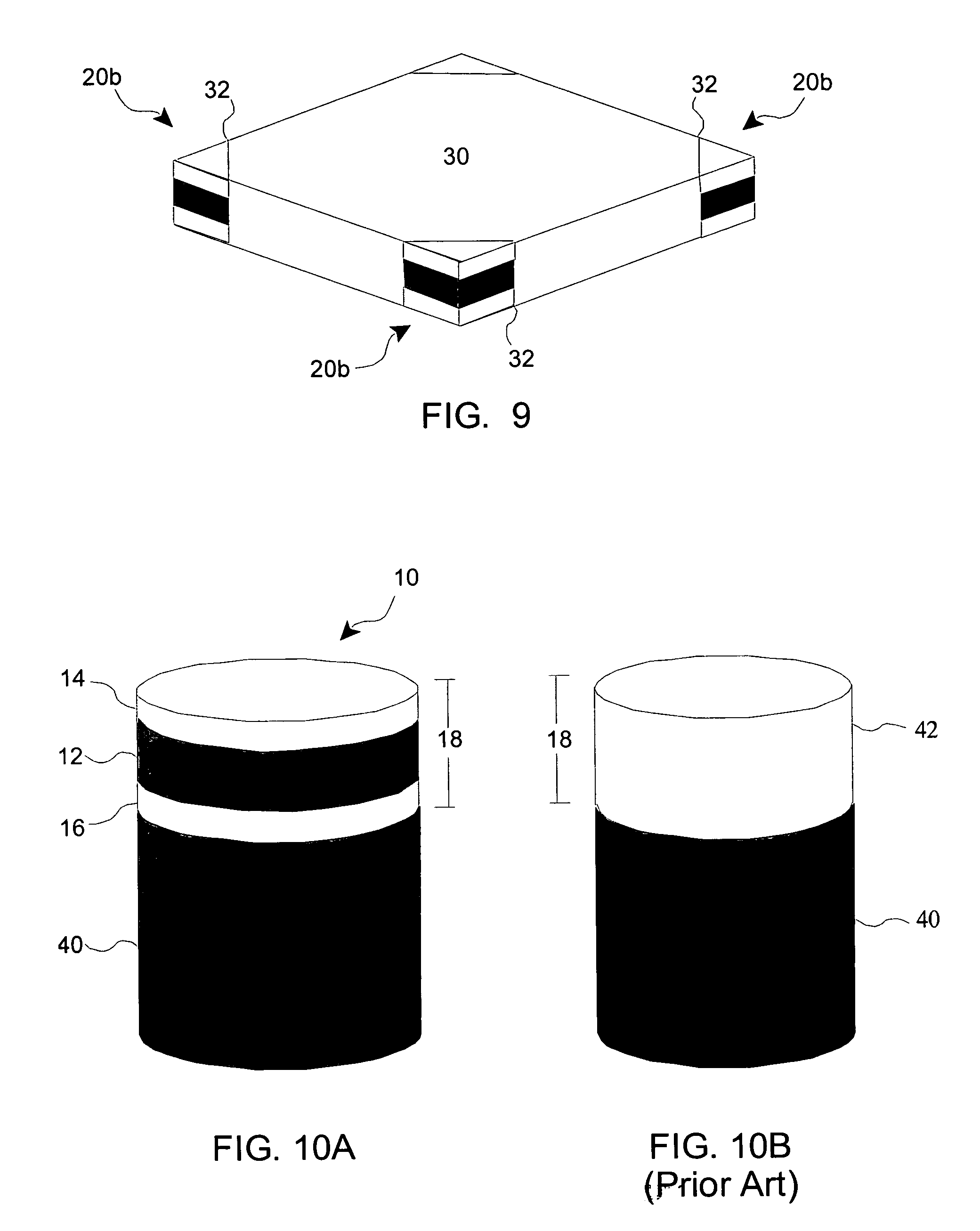

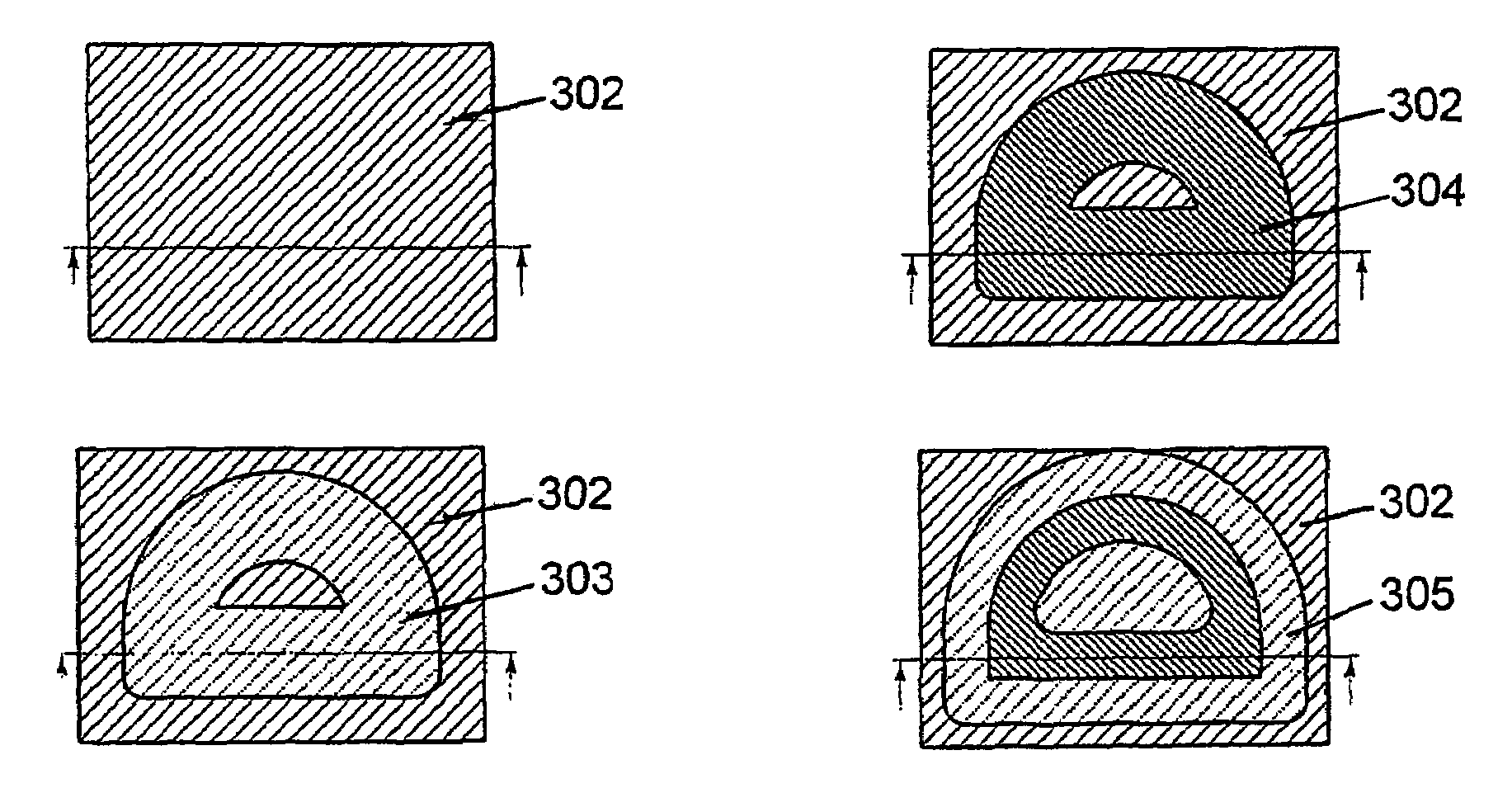

Thermally stable ultra-hard material compact constructions

InactiveUS20080142276A1Extend effective lifePigmenting treatmentDrill bitsSuperhard materialPolycrystalline diamond

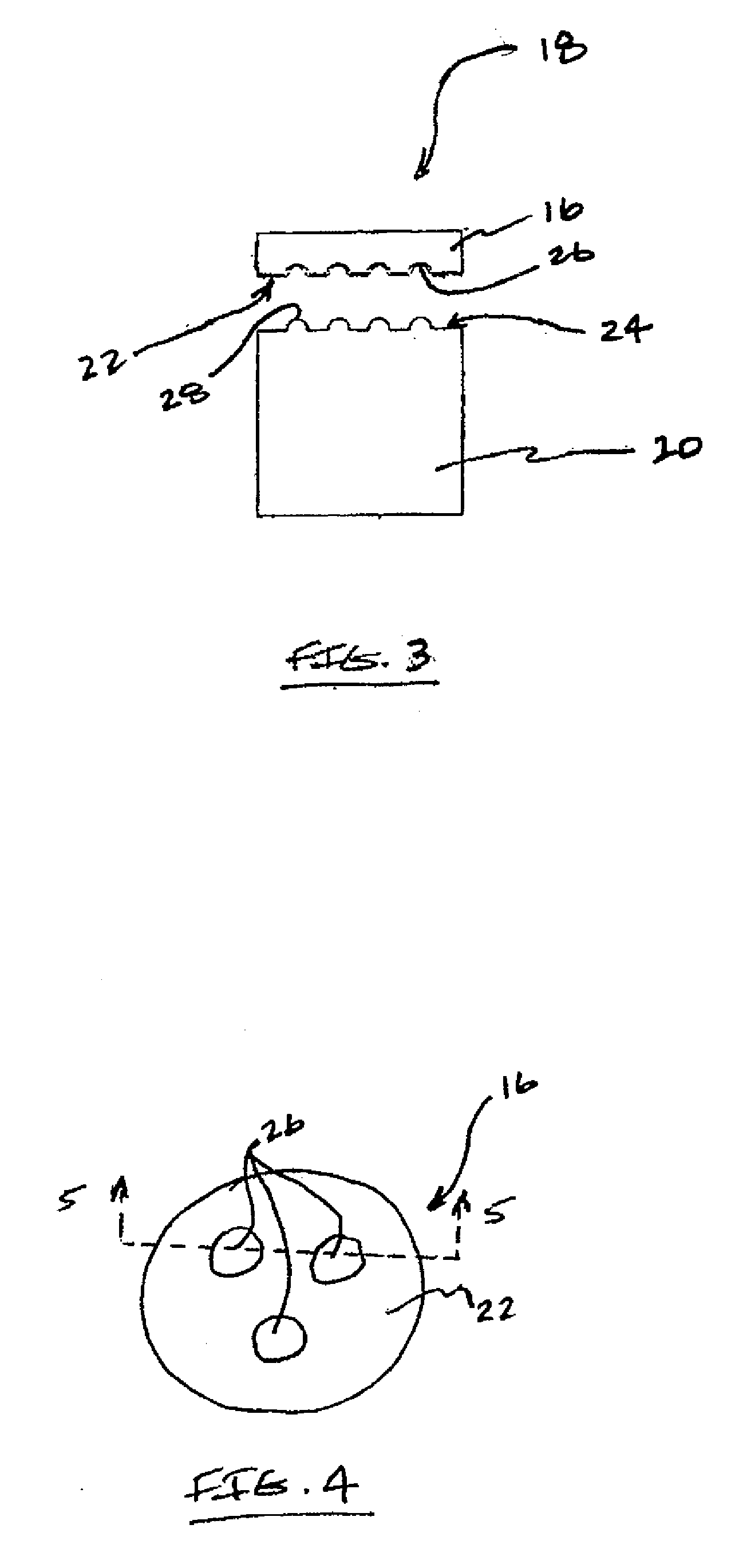

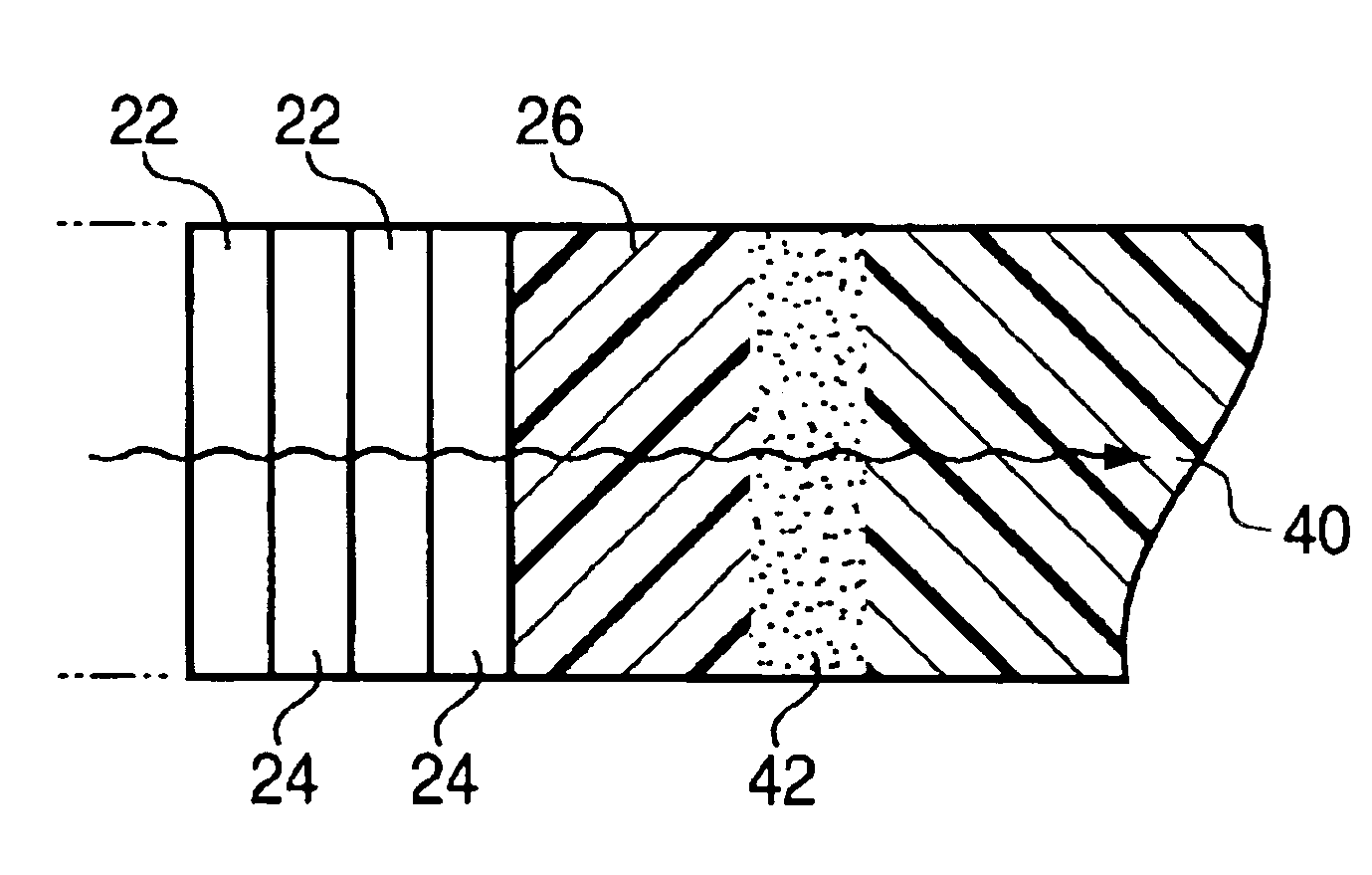

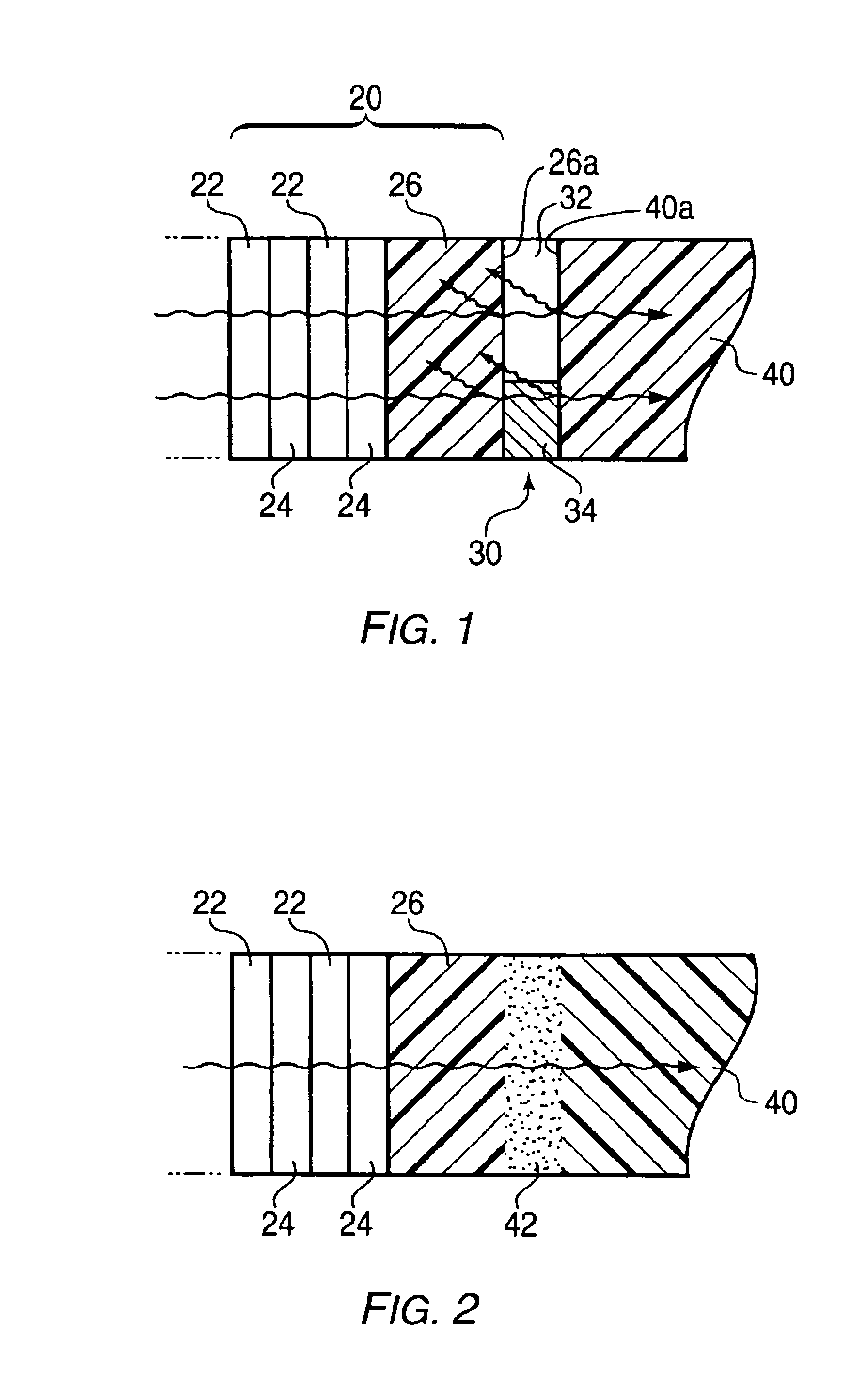

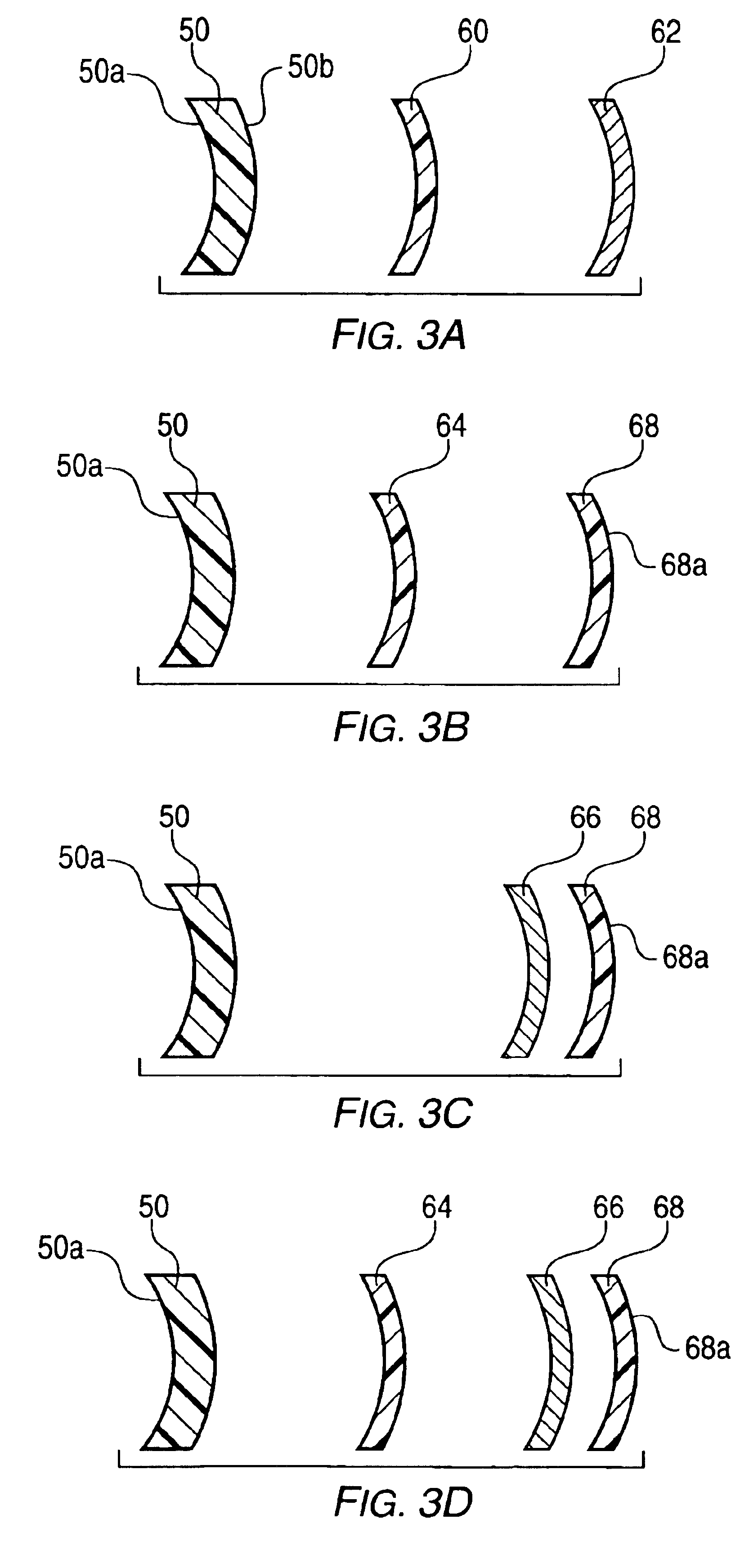

Thermally stable ultra-hard compact constructions comprise a polycrystalline diamond body substantially free of a catalyst material, and a substrate that is joined thereto. The substrate can be ceramic, metallic, cermet and combinations thereof, and can be joined to the body by a braze material or other material that forms an attachment bond at high pressure / high temperature conditions. The body and substrate are specially formed having complementary interfacing surface features to facilitate providing an improved degree of attachment therebetween. The complementary surface features can in the form of openings and projections, e.g., one of the body or substrate can comprise one or more openings, and the other of the body or substrate can comprise one or more projections, disposed within or extending from respective interfacing surfaces. The complementary surface features operate to resist unwanted delamination between the body and substrate, thereby extending effective service life of the construction.

Owner:SMITH INT INC

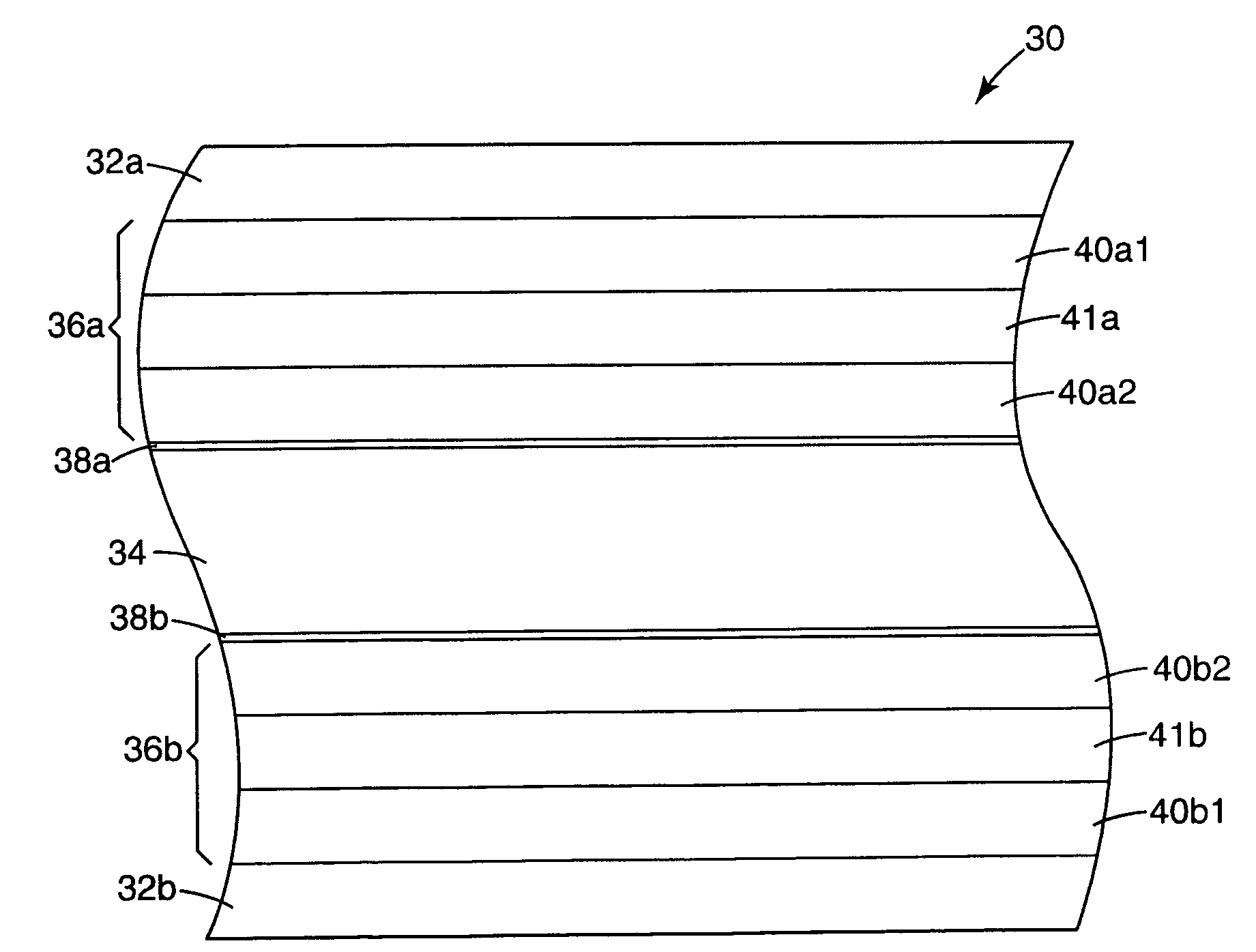

Substrate mounting for organic, dielectric, optical film

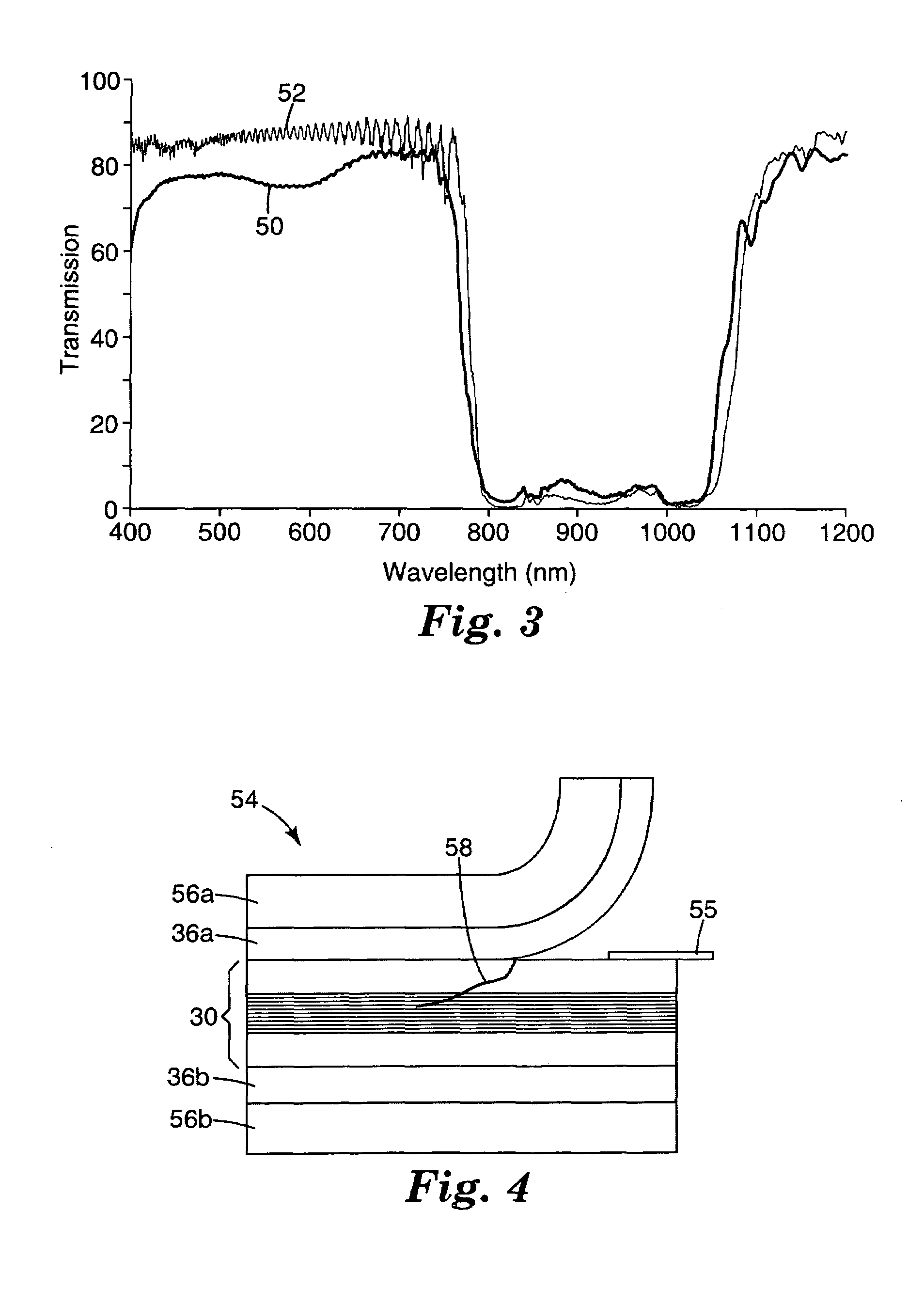

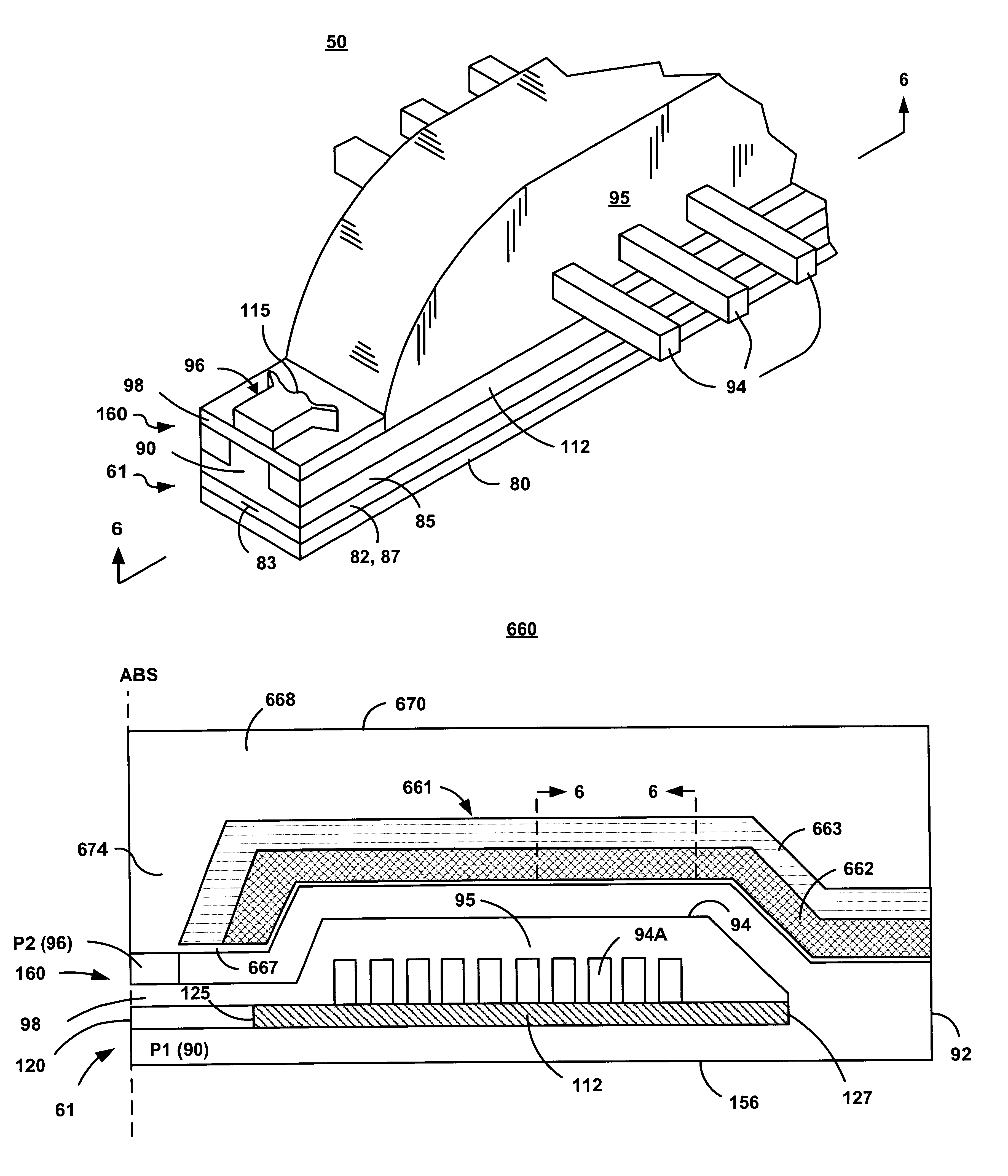

A method for optically coupling a thermoplastic material to an outer surface layer of an organic, dielectric, optical film and the resulting optical filter. Initially, a dielectric film is selected that includes (i) repeating optical layers of at least two polymers having different refractive indexes from each other, (ii) an exterior film surface, (iii) a refractive boundary along the exterior film surface, and (iv) a delamination threshold based on total thermal energy delivered to the film. A thermoplastic material which is miscible with the exterior film surface is fused to the refractive boundary with thermal energy below the delamination threshold to form a polydisperse region having a higher optical transmission than the refractive boundary. Add-on filters in the form of hardcoat layers, anti-reflection layers, holograms, metal dielectric stacks and combinations of these may be combined with the thermoplastic-film construct.

Owner:GENTEX CORP

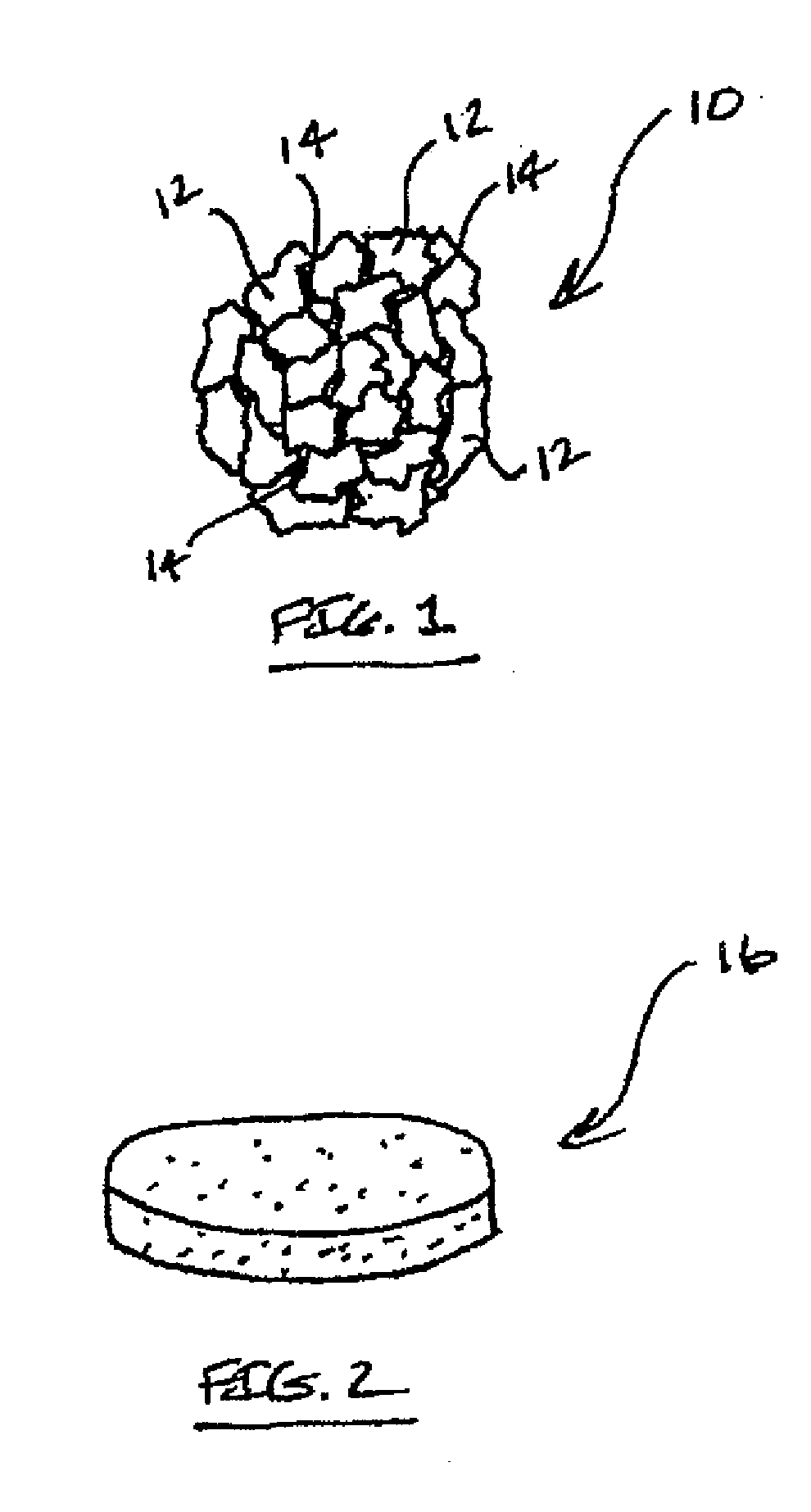

Doubled-sided and multi-layered PCBN and PCD abrasive articles

InactiveUS20050210755A1Improve propertiesIncreasing the thicknessPigmenting treatmentTool workpiece connectionWear particleHigh pressure

A doubled-sided PCBN and / or PCD compact can be produced using high pressure high temperature processes allowing for increased effective thickness of abrasive tools, decreased delamination, and increased useful service life. A polycrystalline compact can include a substrate having a first surface and a second surface which are non-contiguous. Additionally, a first polycrystalline layer can be attached to the first surface of the substrate and a second polycrystalline layer attached to the second surface of the substrate. The first and second polycrystalline layers can be attached to the substrate via an intermediate layer containing superabrasive particles. Such double-sided PCBN and PCD compacts allow for increased effective thickness of a tool without suffering from non-homogenous results typical of standard PCD and PCBN compacts, regardless of superabrasive particle size. Each polycrystalline layer can include superabrasive particles of varying particle sizes such that the final tool is tailored for specific abrading characteristics. Such doubled-sided PCBN and PCD compacts can be incorporated into a wide variety of abrasive tools for use in cutting, milling, grinding, polishing, drilling and other similar abrasive applications.

Owner:ADICO ASIA POLYDIAMOND

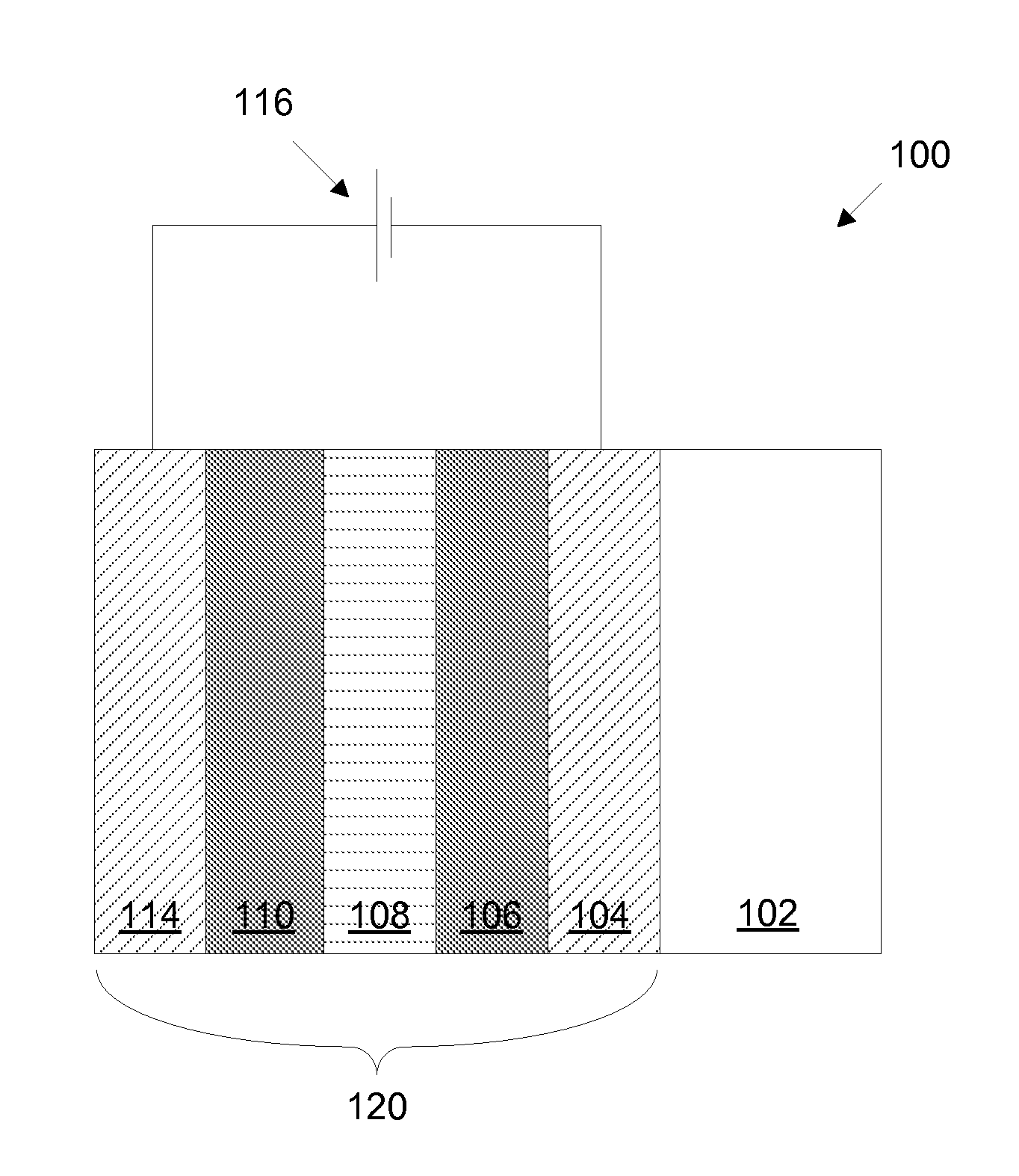

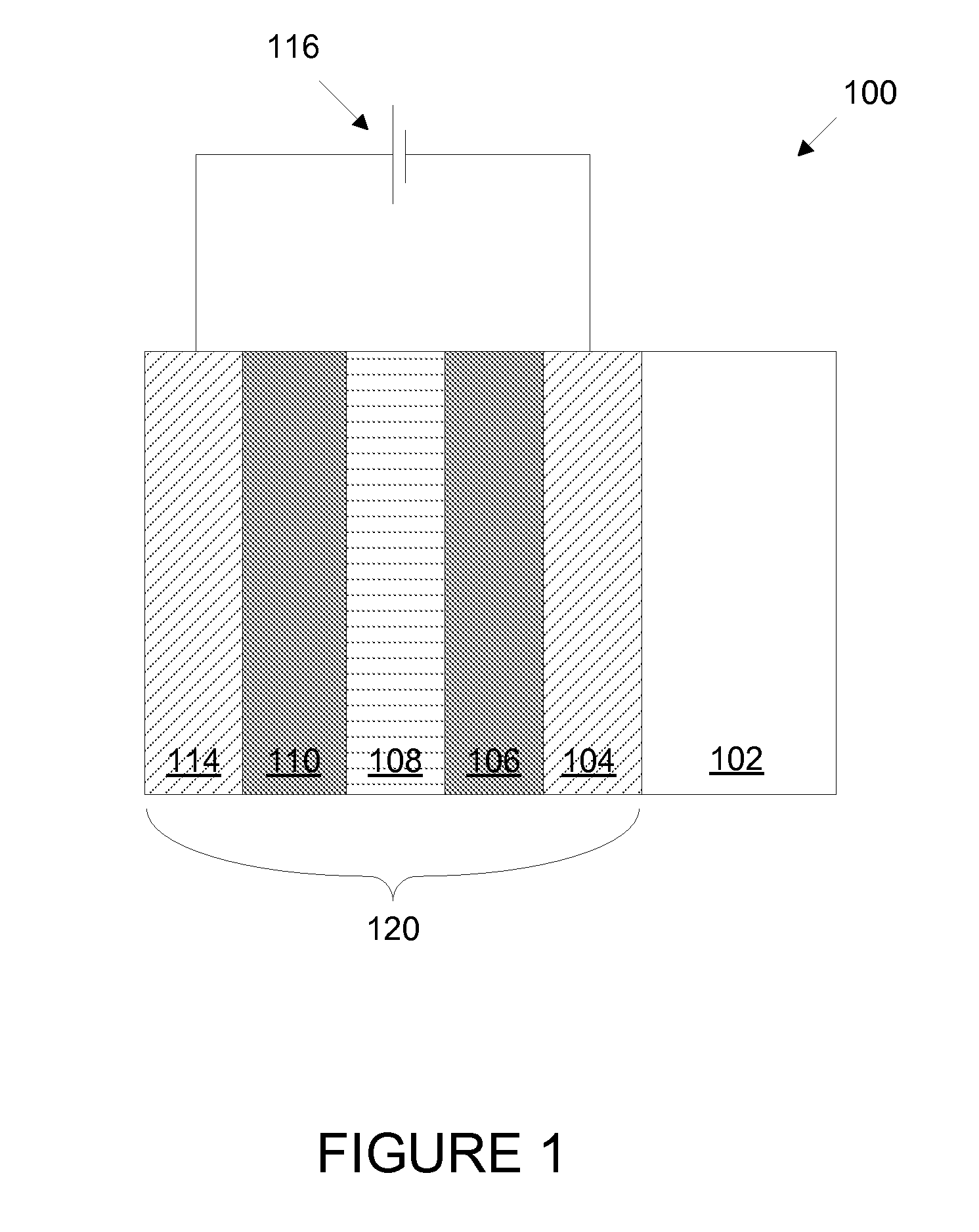

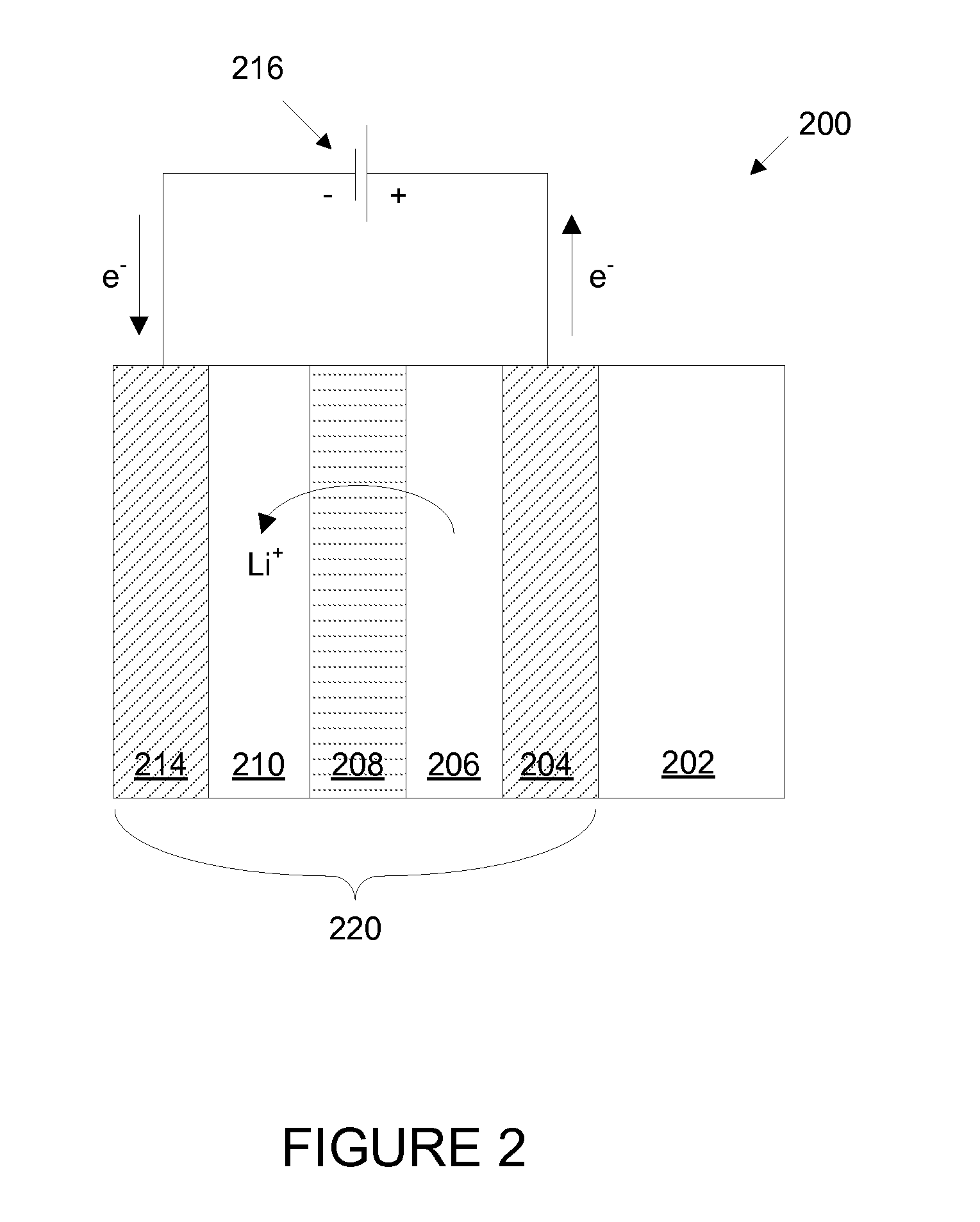

Fabrication of low defectivity electrochromic devices

Prior electrochromic devices frequently suffer from high levels of defectivity. The defects may be manifest as pin holes or spots where the electrochromic transition is impaired. This is unacceptable for many applications such as electrochromic architectural glass. Improved electrochromic devices with low defectivity can be fabricated by depositing certain layered components of the electrochromic device in a single integrated deposition system. While these layers are being deposited and / or treated on a substrate, for example a glass window, the substrate never leaves a controlled ambient environment, for example a low pressure controlled atmosphere having very low levels of particles. These layers may be deposited using physical vapor deposition.

Owner:VIEW INC

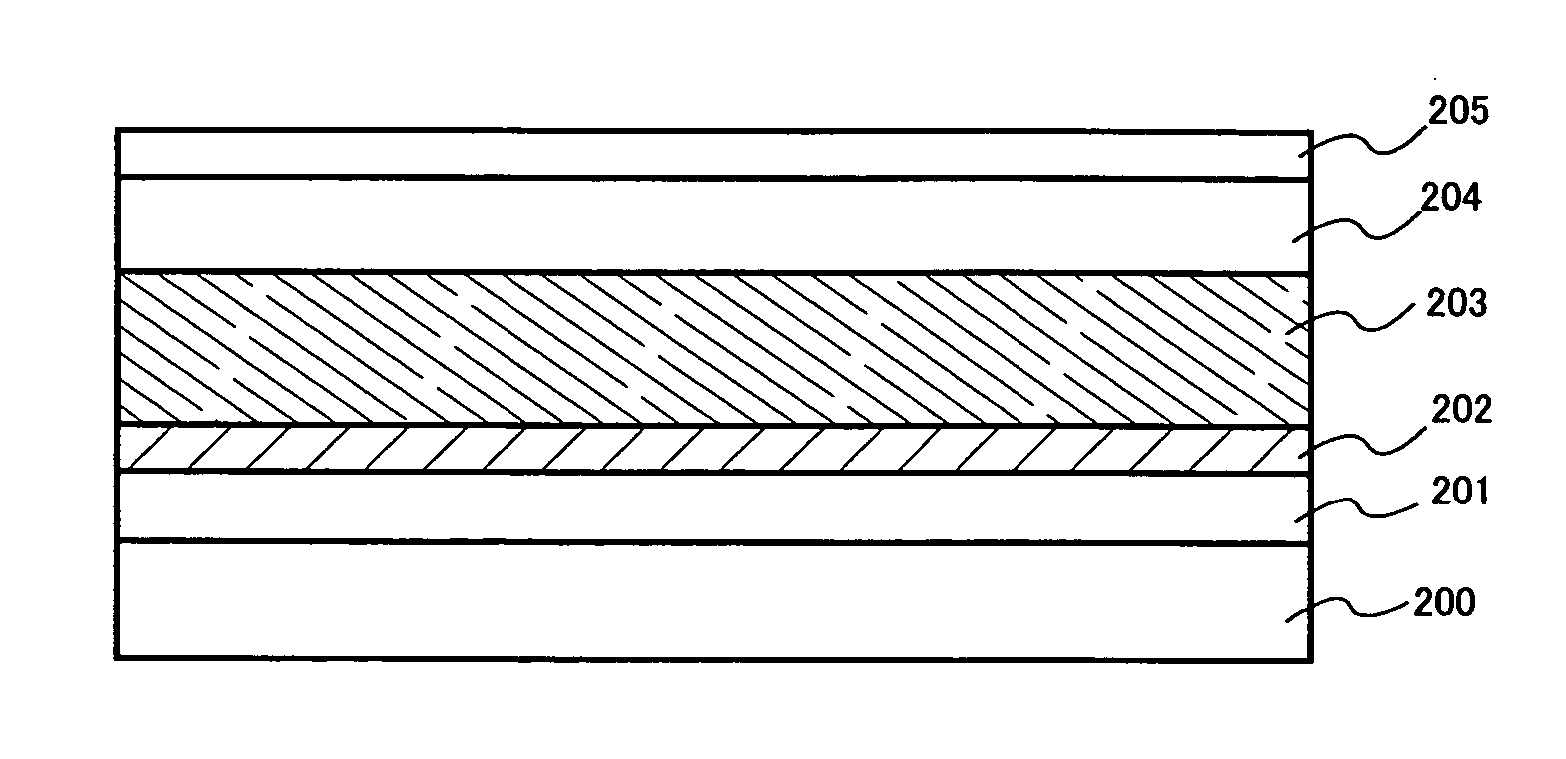

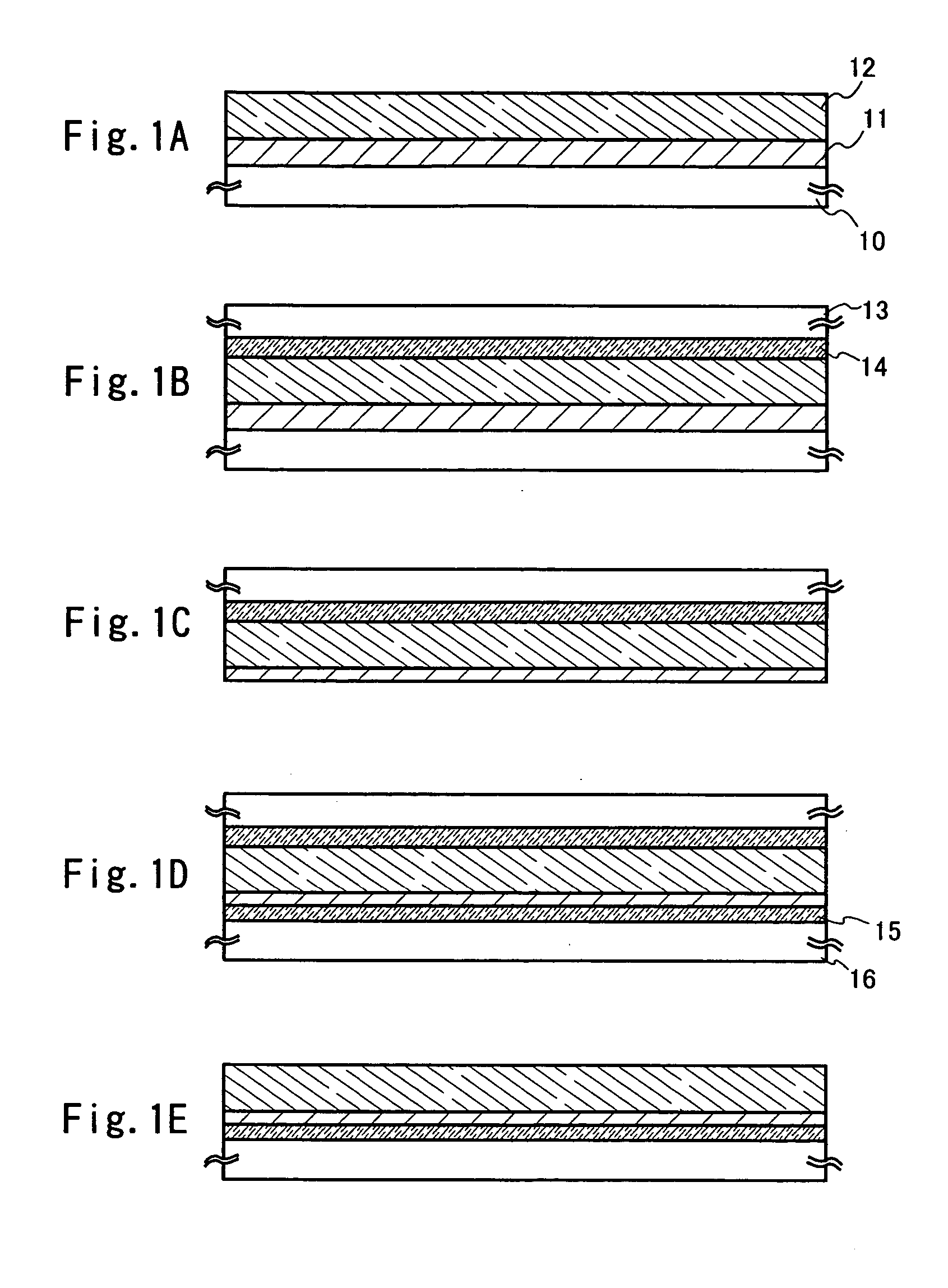

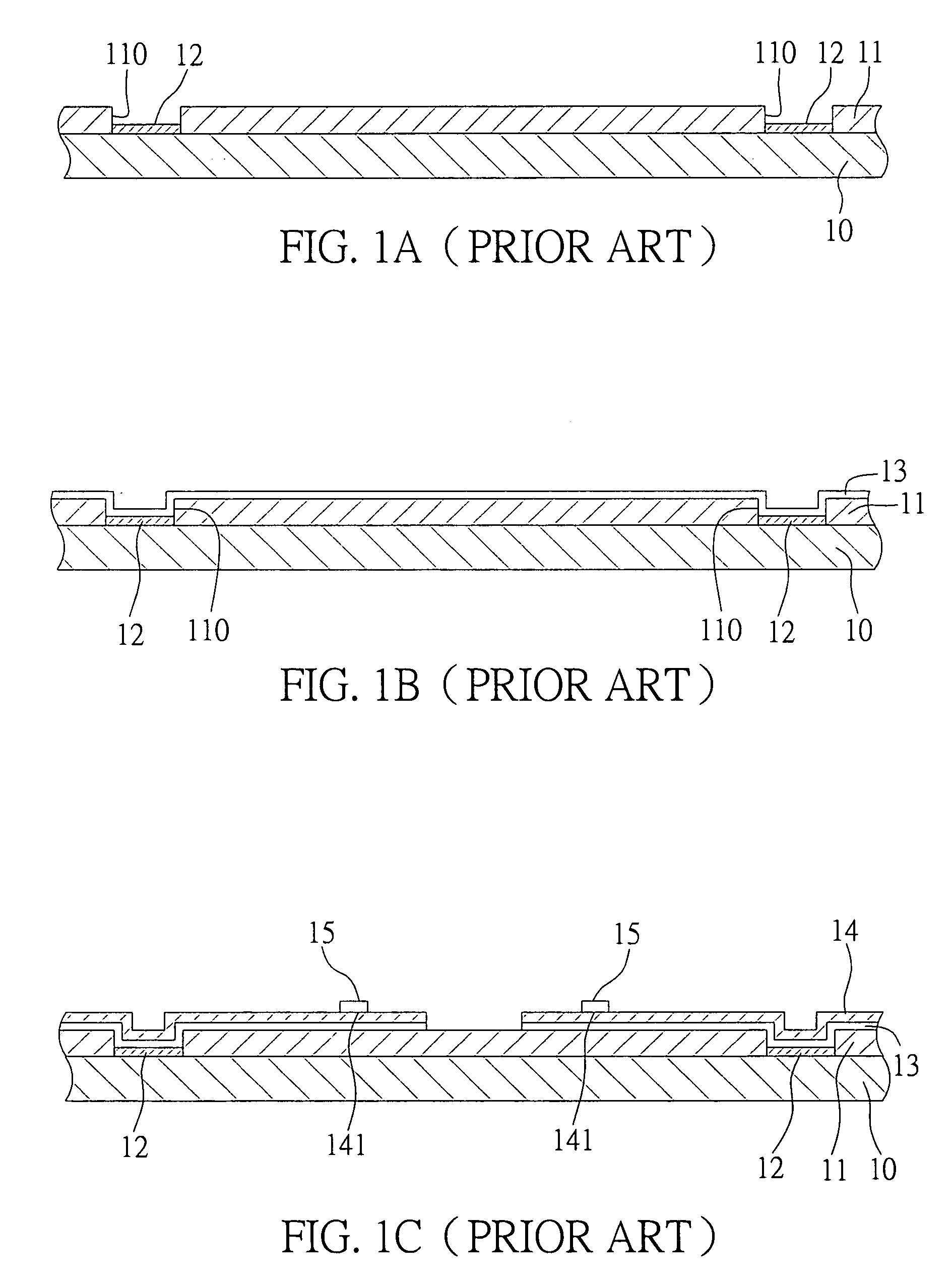

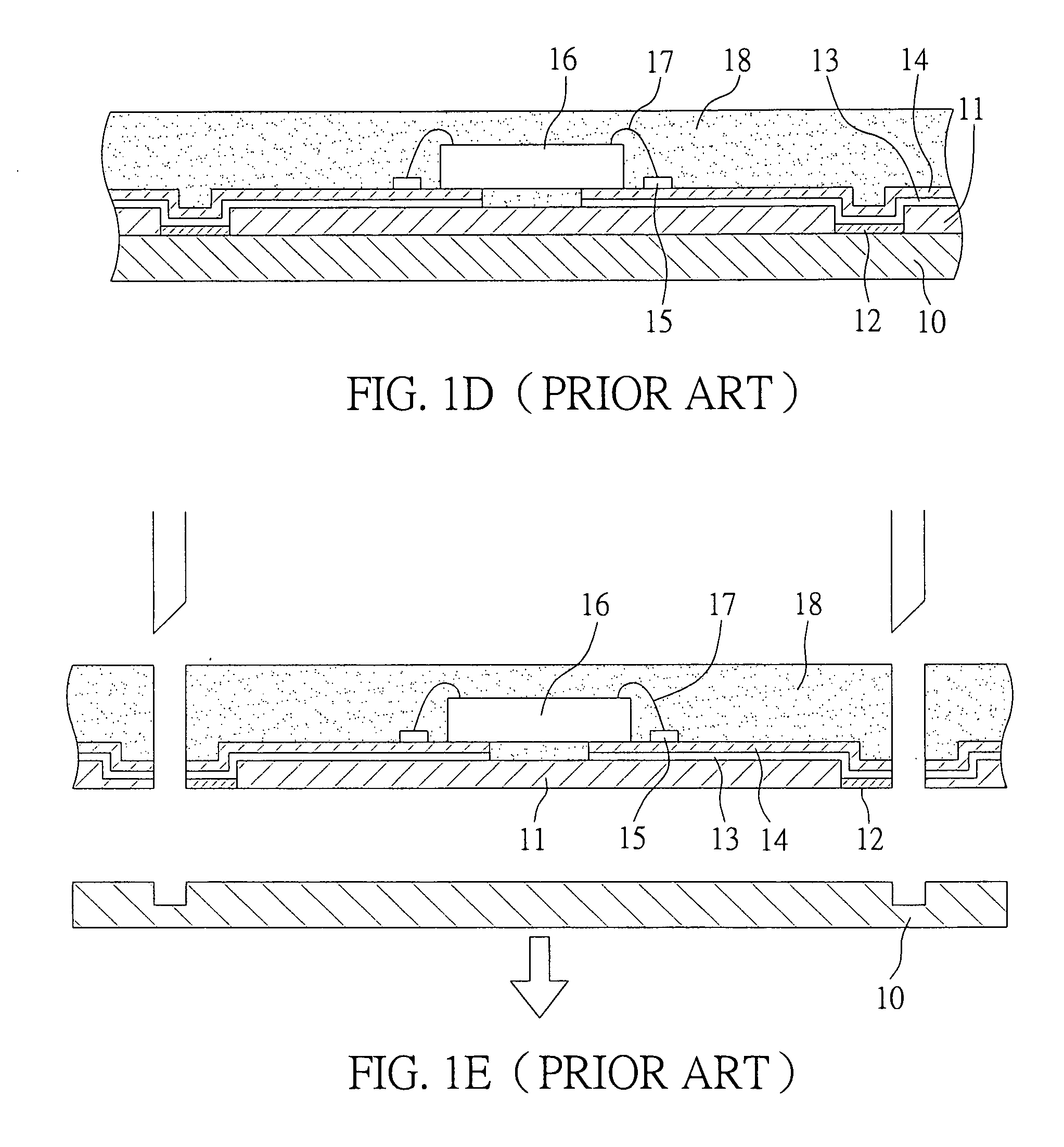

Semiconductor device and manufacturing method thereof, delamination method, and transferring method

A technique for forming a TFT element over a substrate having flexibility typified by a flexible plastic film is tested. When a structure in which a light-resistant layer or a reflective layer is employed to prevent the damage to the delamination layer, it is difficult to fabricate a transmissive liquid crystal display device or a light emitting device which emits light downward. A substrate and a delamination film are separated by a physical means, or a mechanical means in a state where a metal film formed over a substrate, and a delamination layer comprising an oxide film including the metal and a film comprising silicon, which is formed over the metal film, are provided. Specifically, a TFT obtained by forming an oxide layer including the metal over a metal film; crystallizing the oxide layer by heat treatment; and performing delamination in a layer of the oxide layer or at both of the interface of the oxide layer is formed.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device with crack prevention ring and method of manufacture thereof

ActiveUS20060012012A1High mechanical strengthAvoid crackingSemiconductor/solid-state device detailsSolid-state devicesDevice materialConductive materials

A method of forming a crack prevention ring at the exterior edge of an integrated circuit to prevent delamination and cracking during the separation of the integrated circuits into individual die. The crack prevention ring extends vertically into a semiconductor workpiece to at least a metallization layer of the integrated circuit. The crack prevention ring may be formed simultaneously with the formation of test pads of the integrated circuits. The crack prevention ring may be partially or completely filled with conductive material. An air pocket may be formed within the crack prevention ring beneath a passivation layer of the integrated circuit. The crack prevention ring may be removed during the singulation process. An optional seal ring may be formed between the crack prevention ring and the integrated circuit.

Owner:TAIWAN SEMICON MFG CO LTD

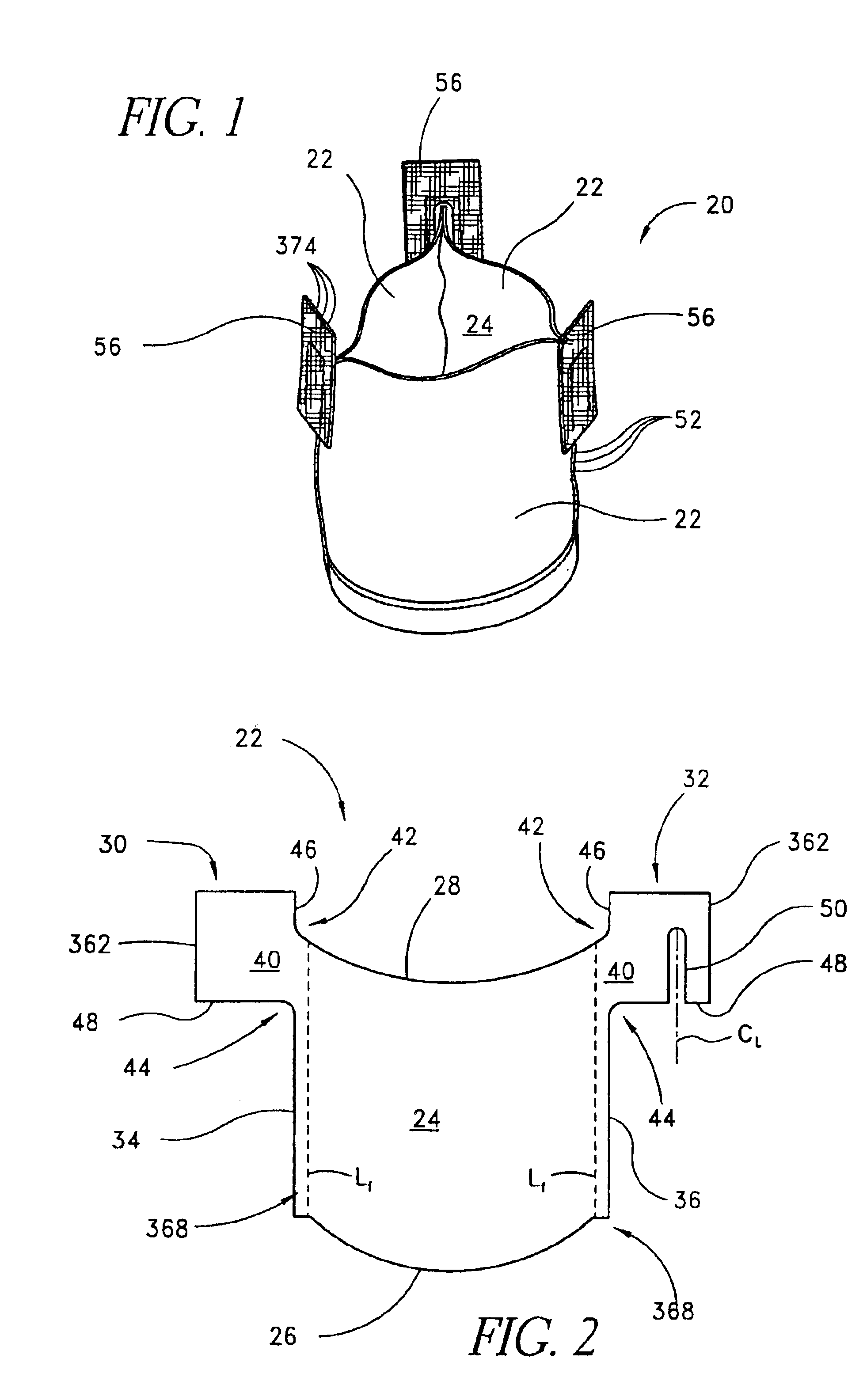

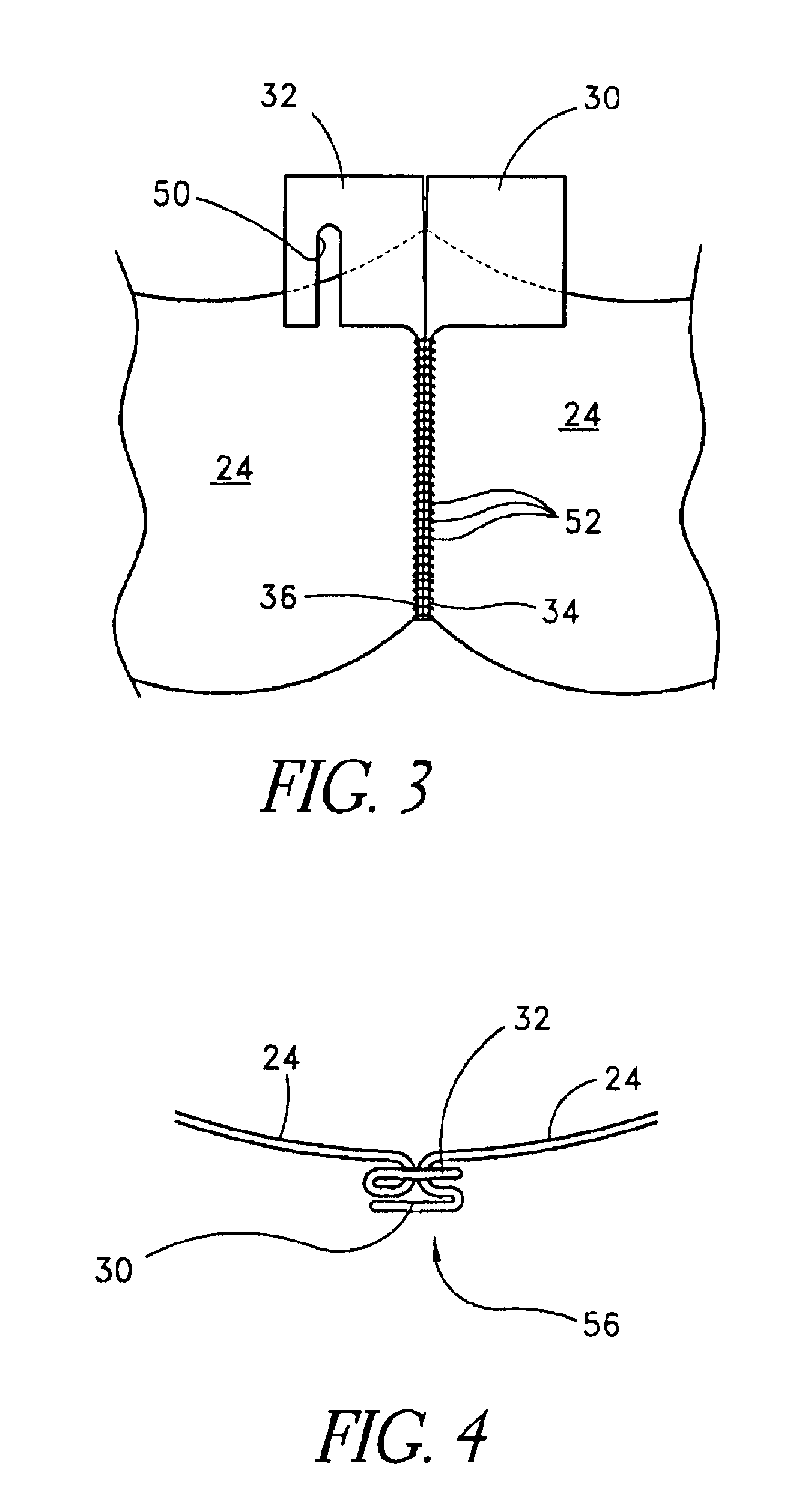

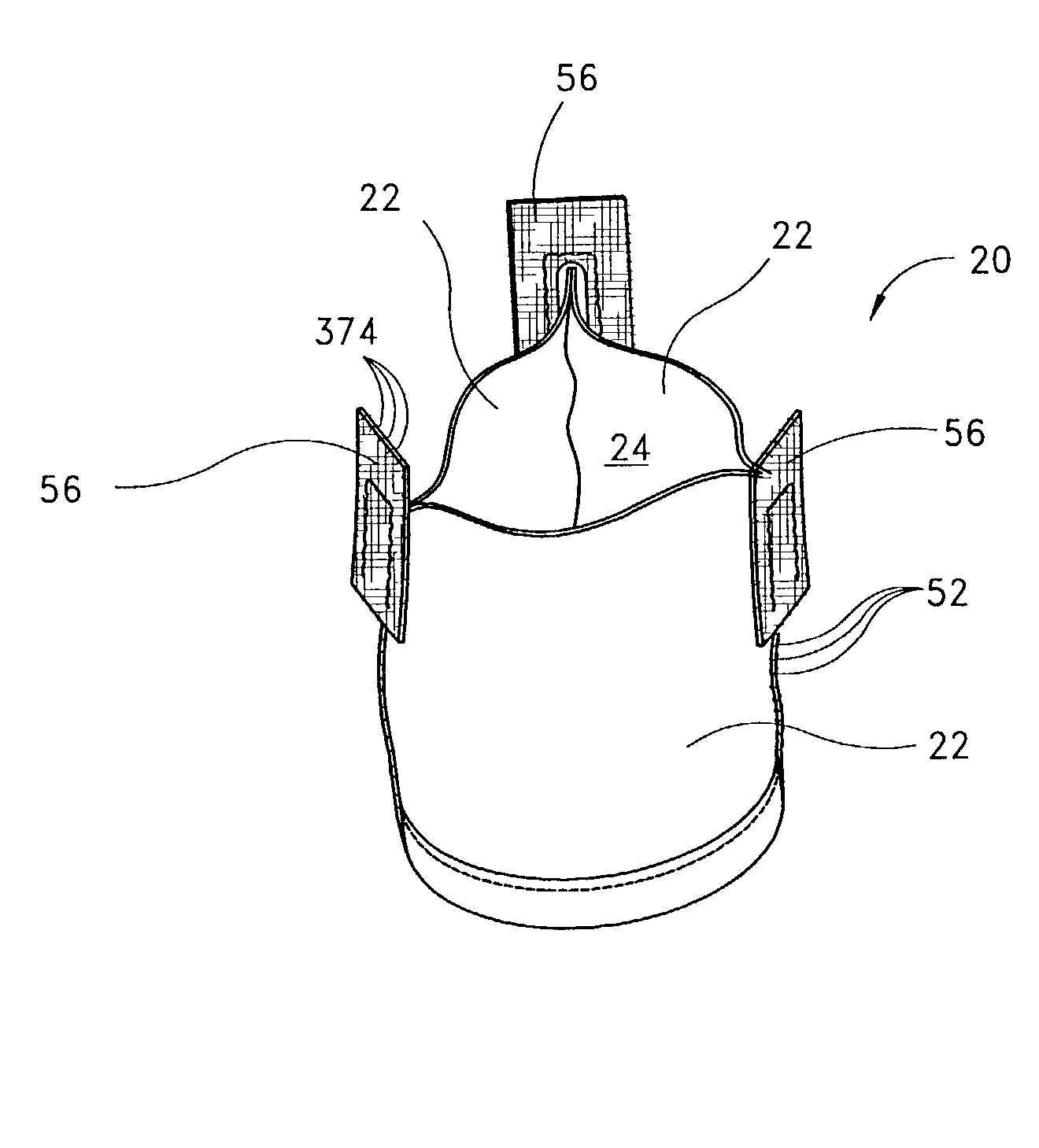

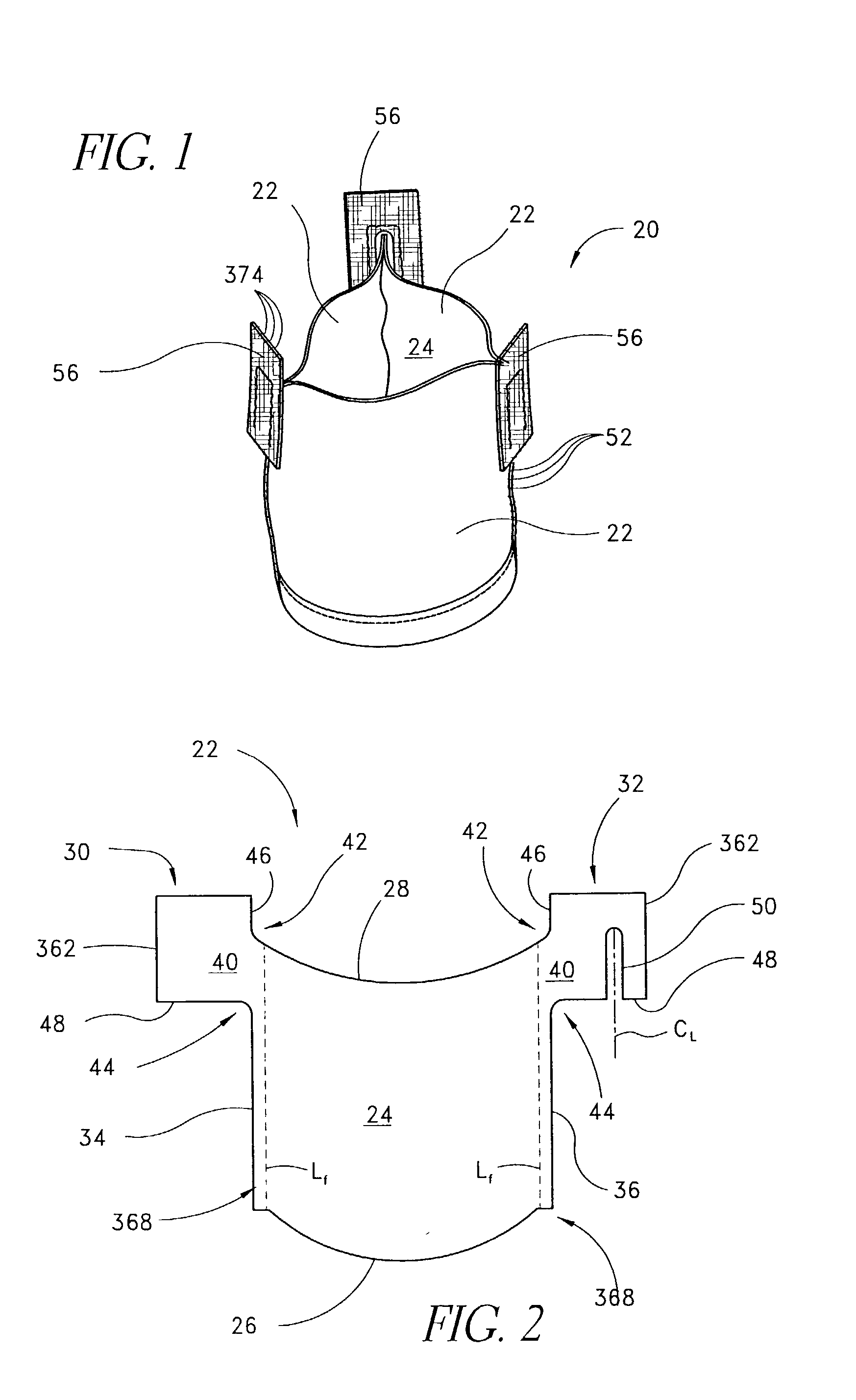

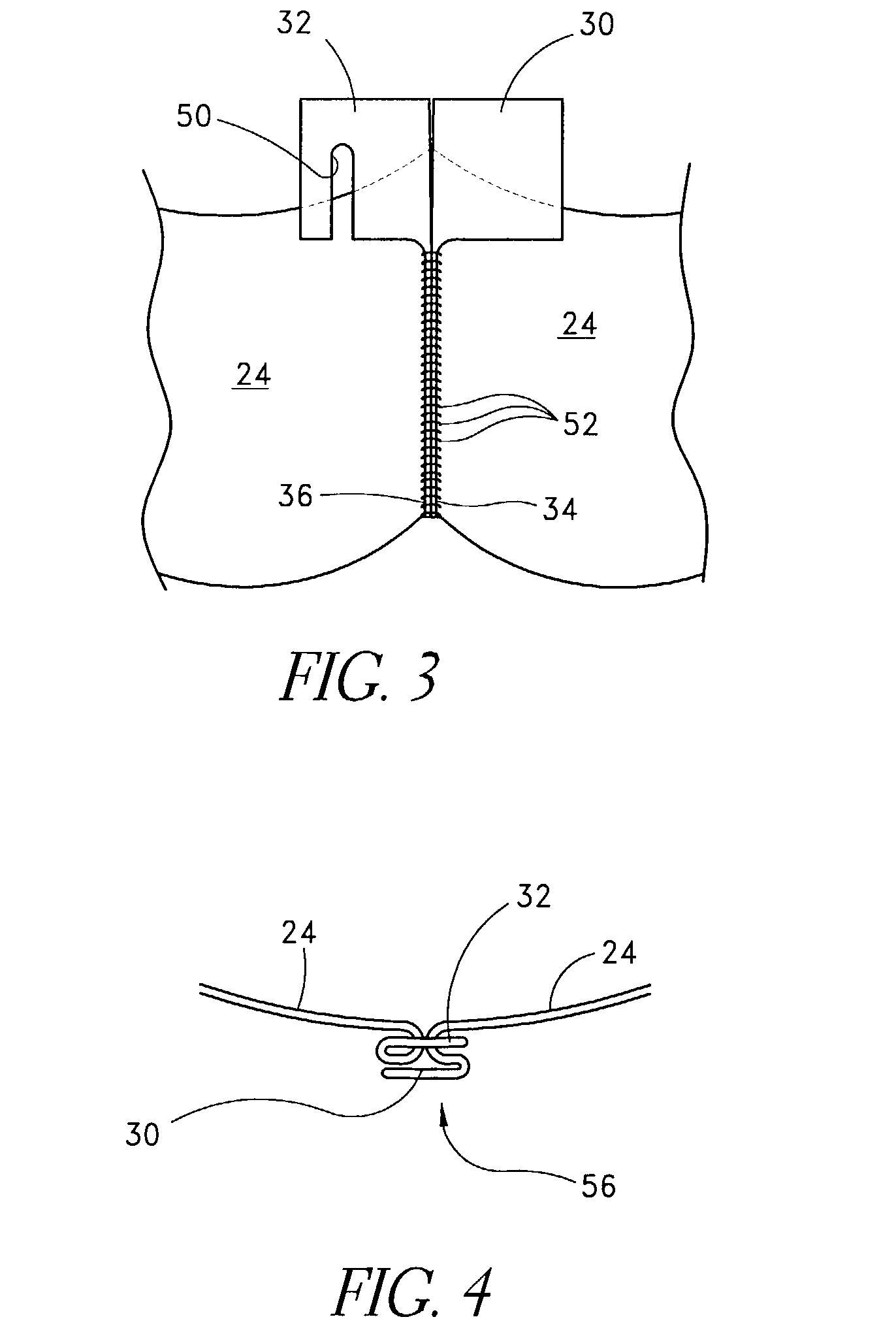

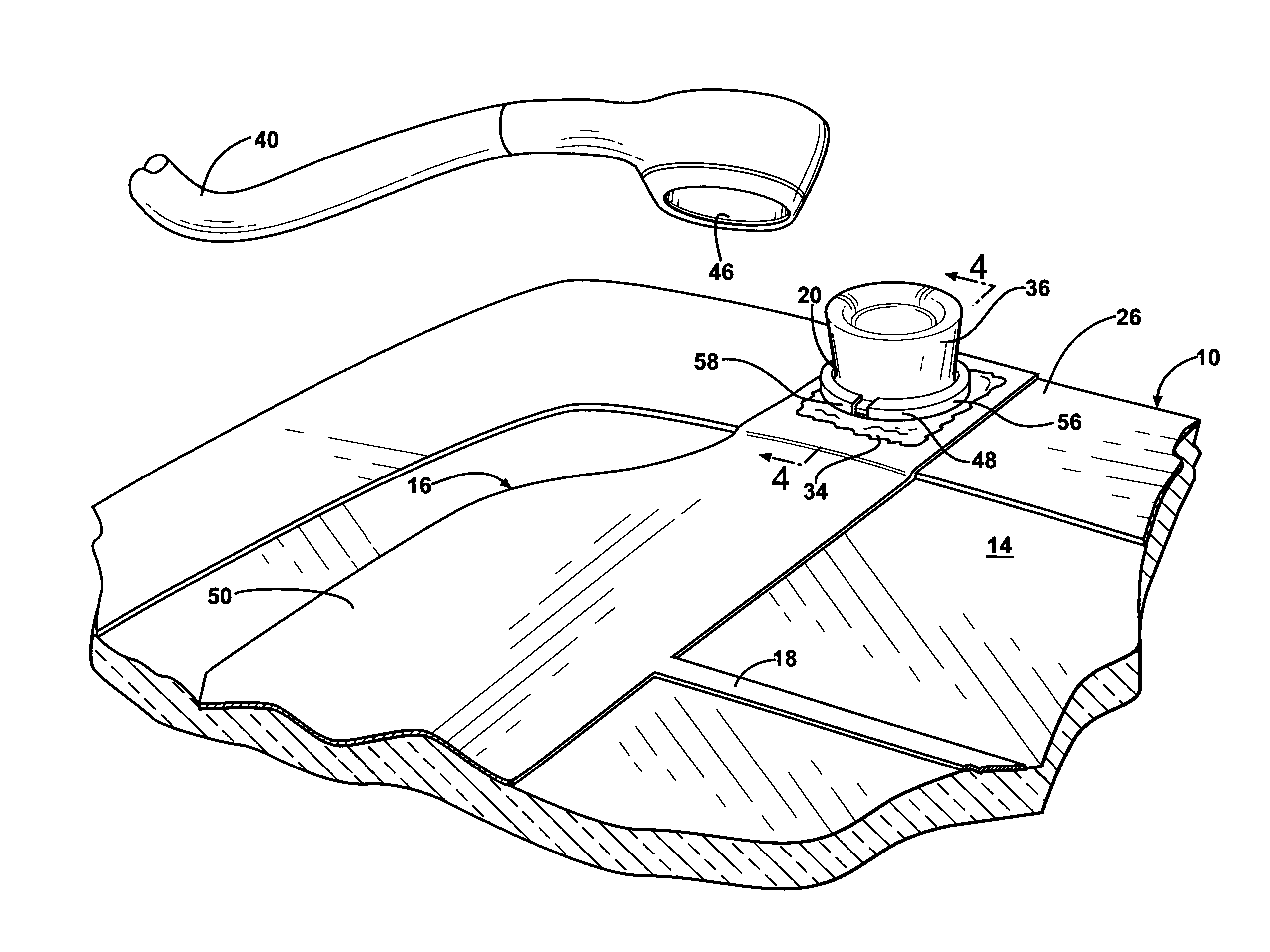

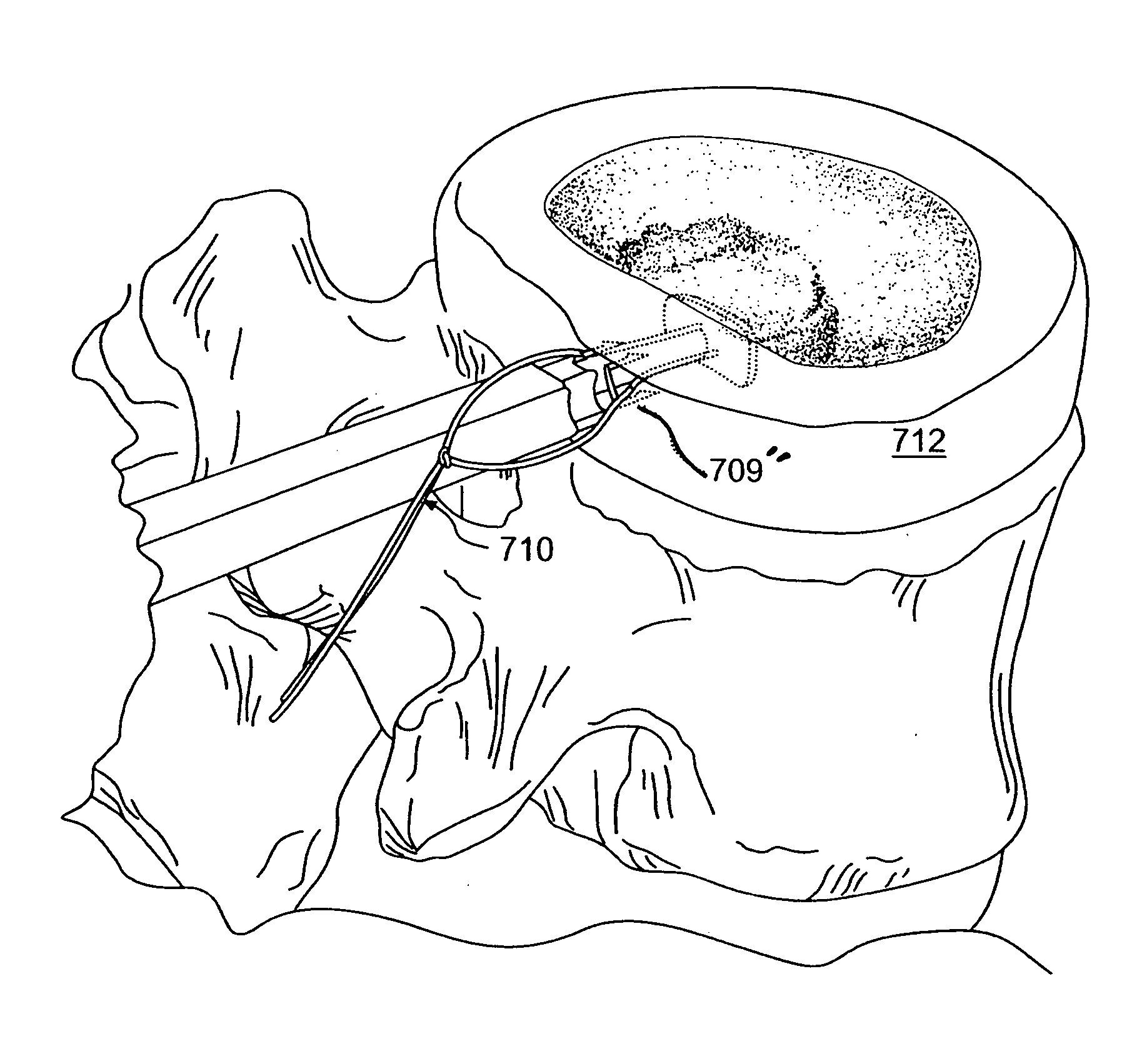

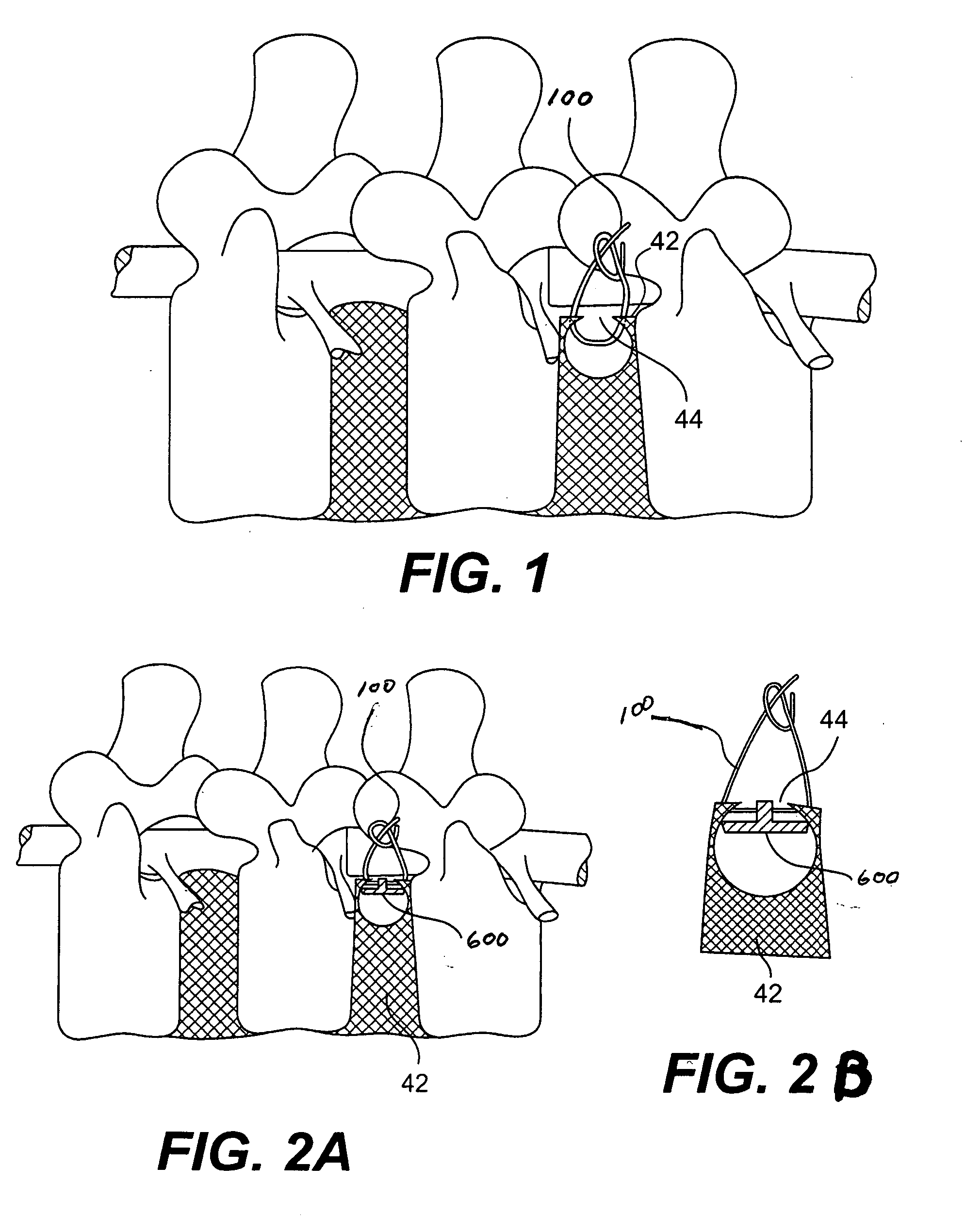

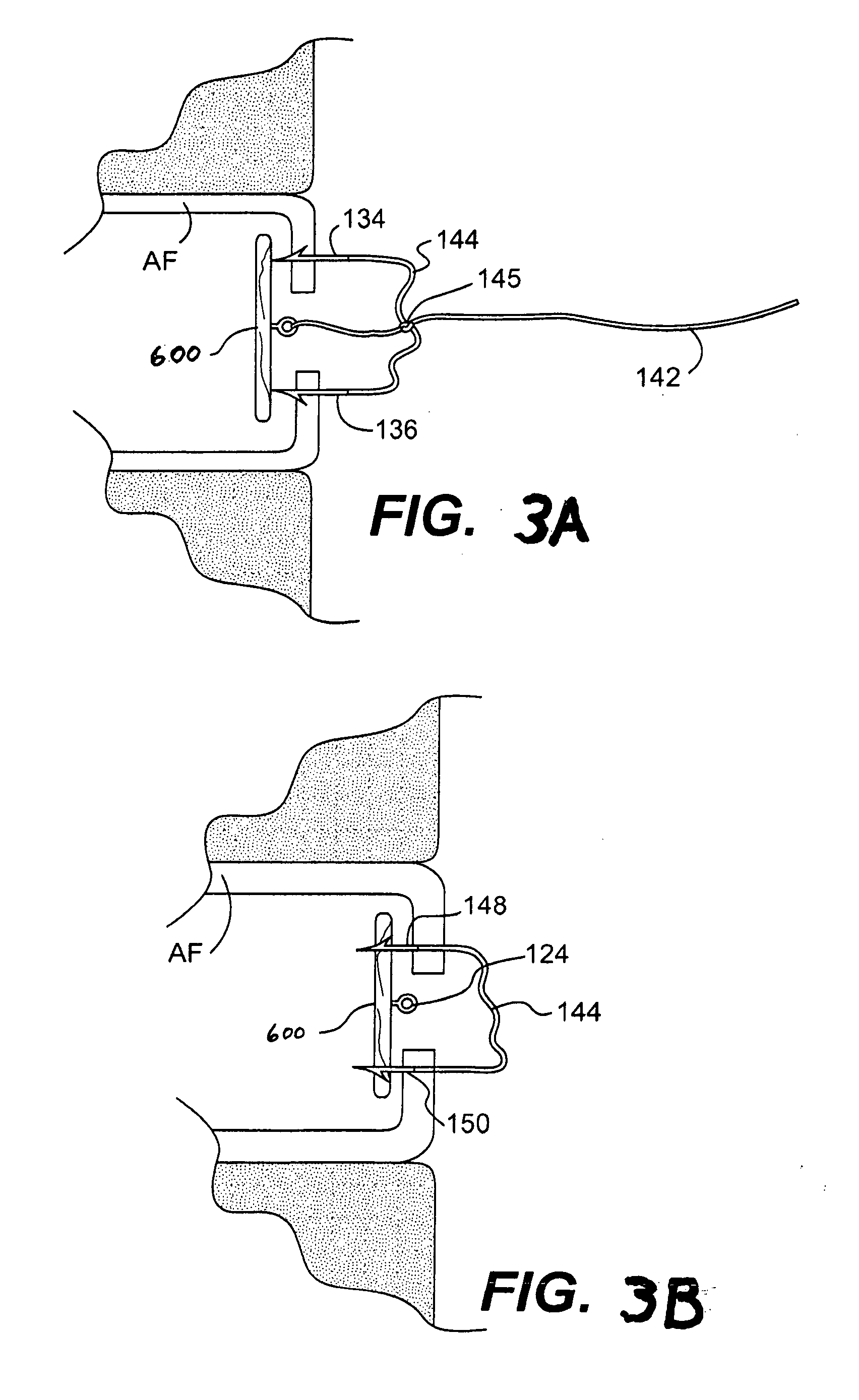

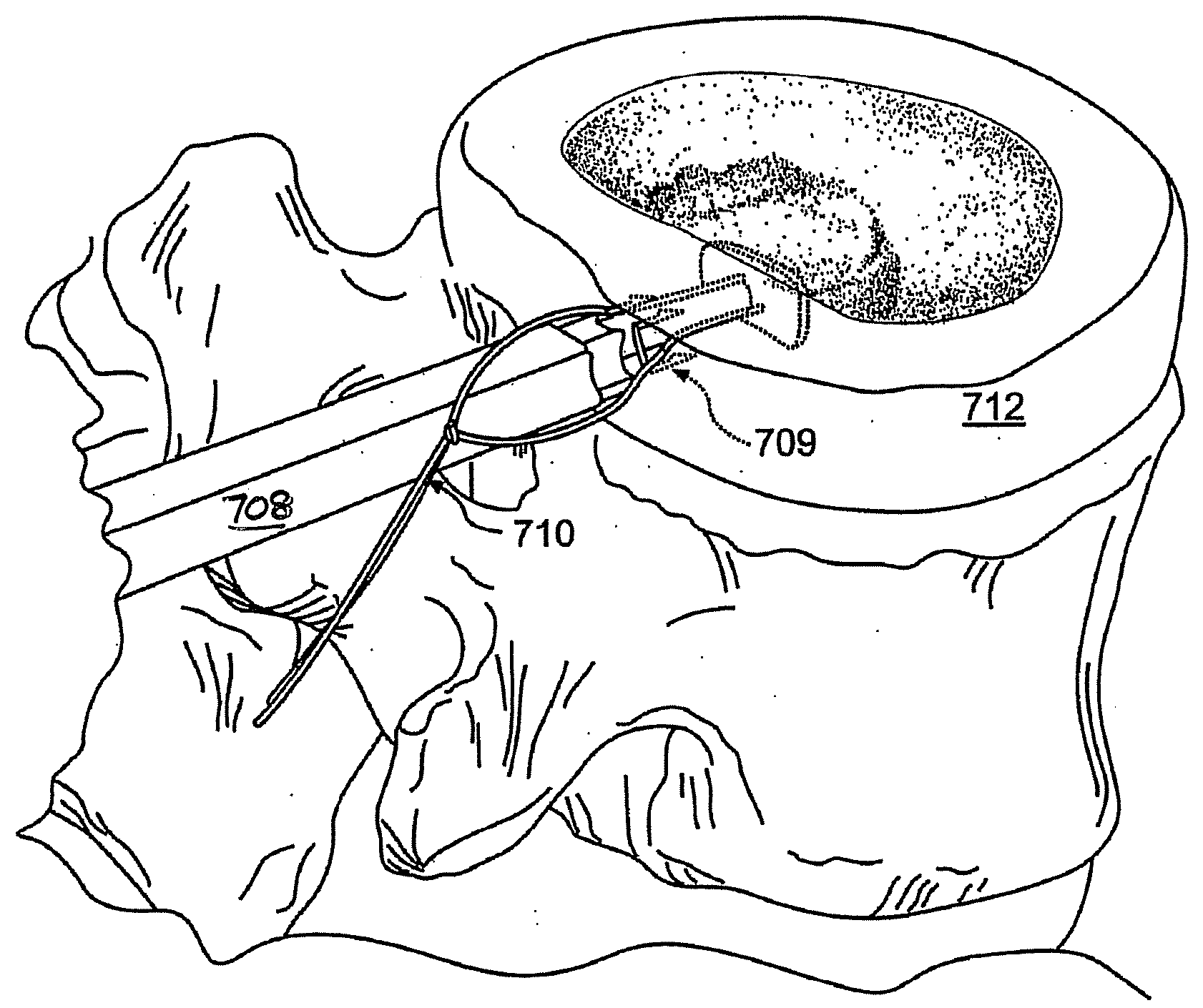

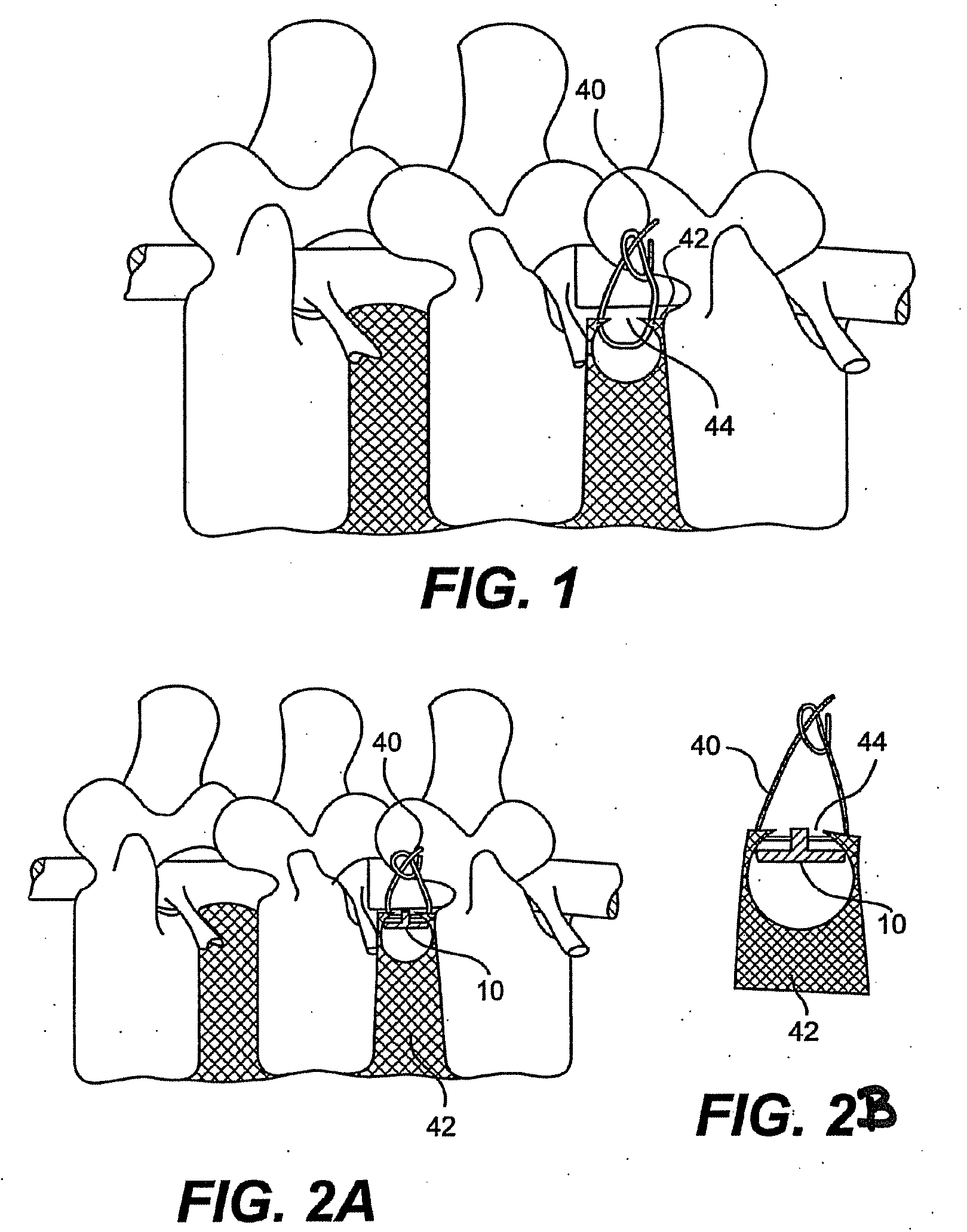

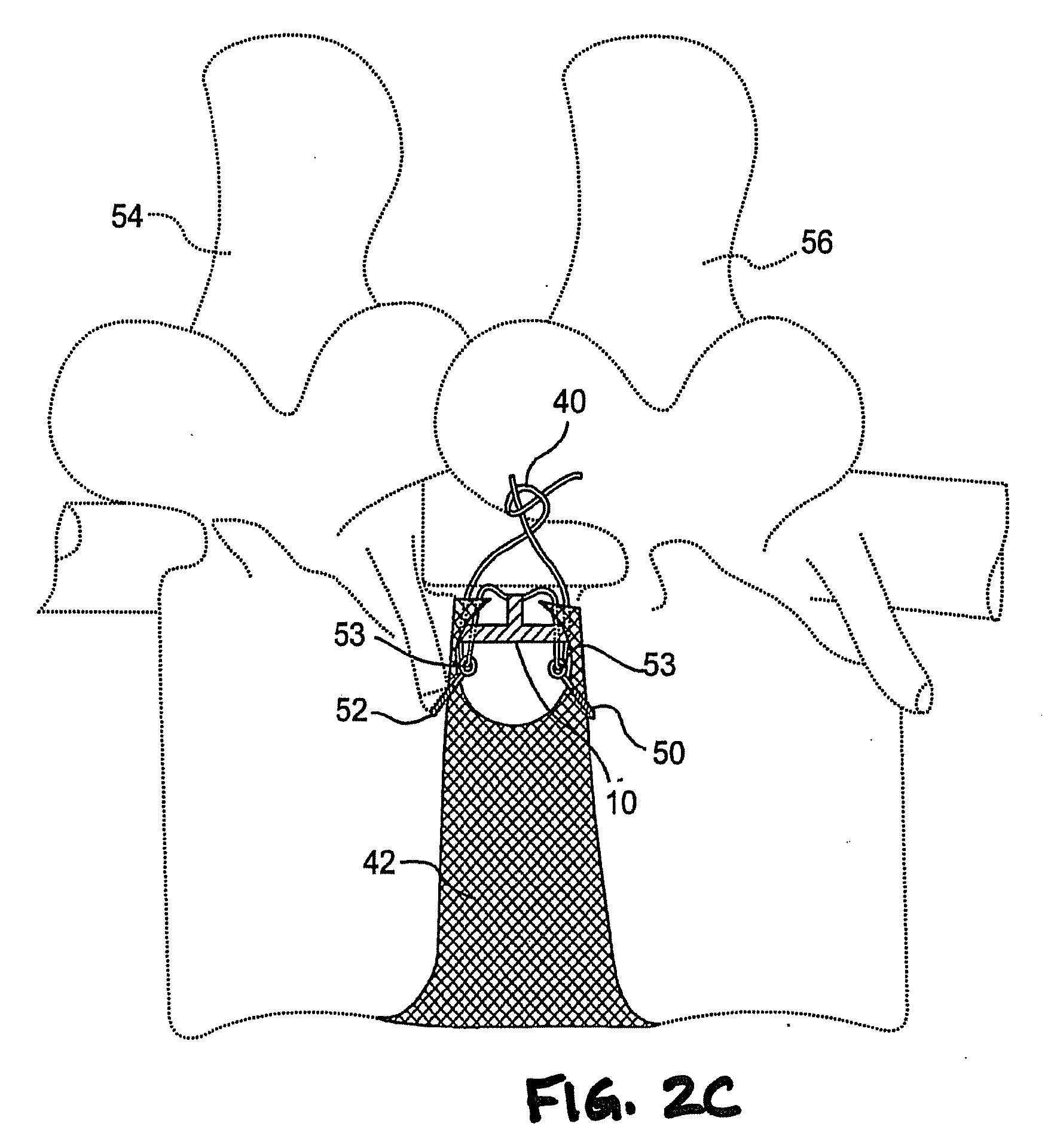

Apparatus and methods for the treatment of the intervertebral disc

InactiveUS20070100348A1Low failure rateRestore integritySuture equipmentsBone implantIntervertebral discBiomedical engineering

The present inventions provide apparatuses and methods for repairing or otherwise treating an intervertebral disc. The apparatus and methods in accordance with the present inventions may be used to treat or repair a tear, rent, incision, defect, aperture or delamination of the annulus fibrosus of an intervertebral disc. The apparatus and methods may employ fixation delivery apparatuses, fixation apparatuses, patch delivery tools and patches positioned in or on aspects of an intervertebral disc for treatment or repair of the intervertebral disc or its components.

Owner:KRT INVESTORS

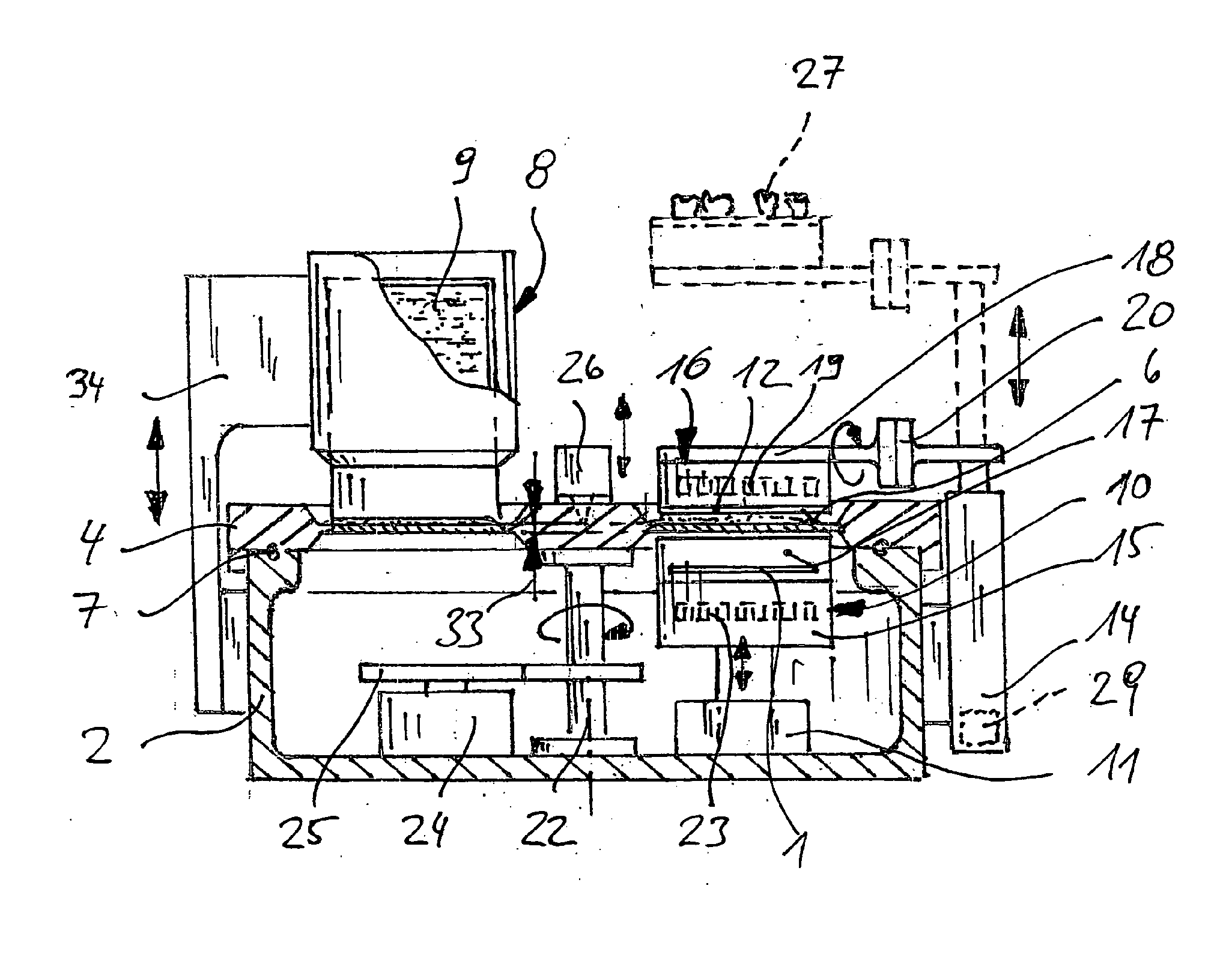

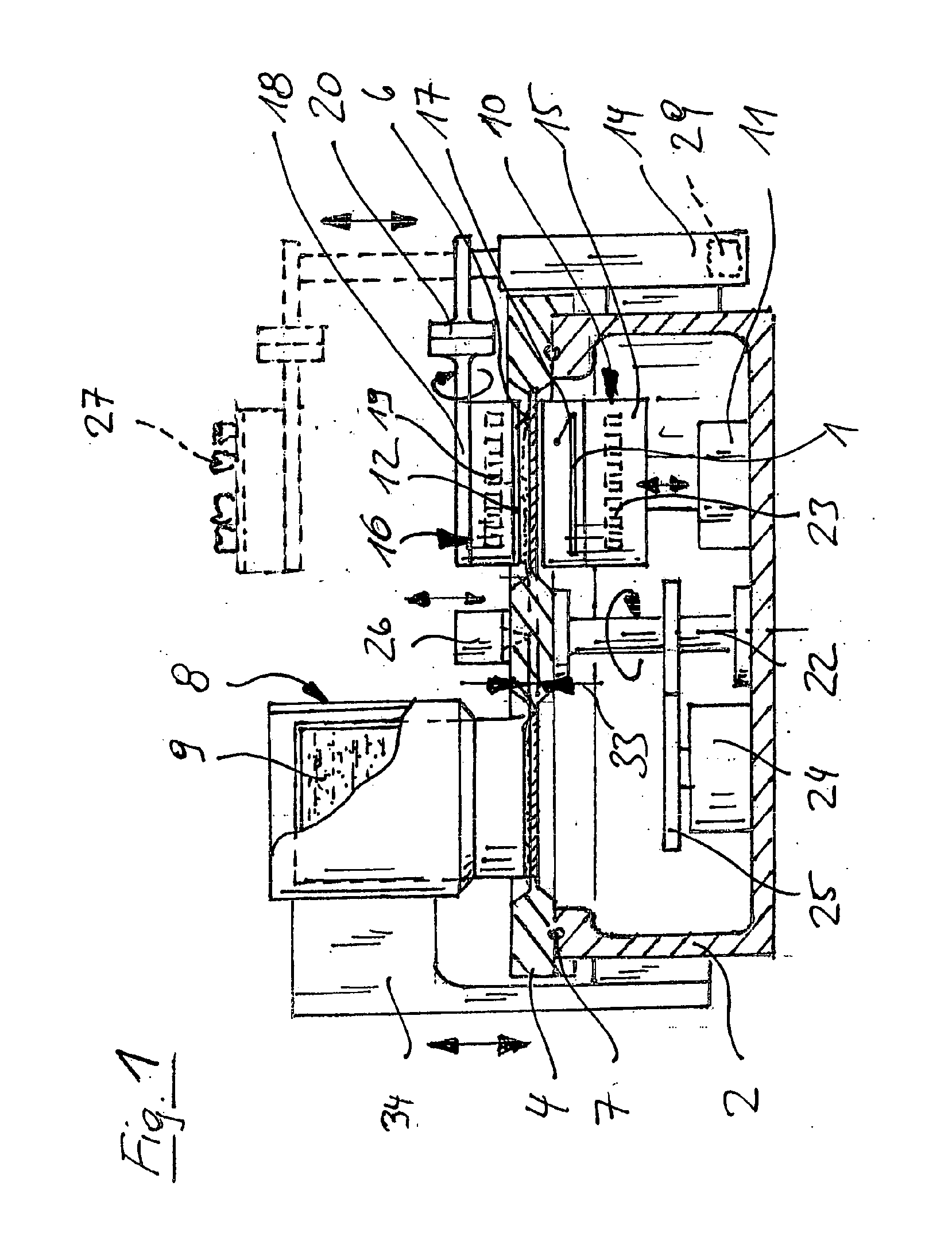

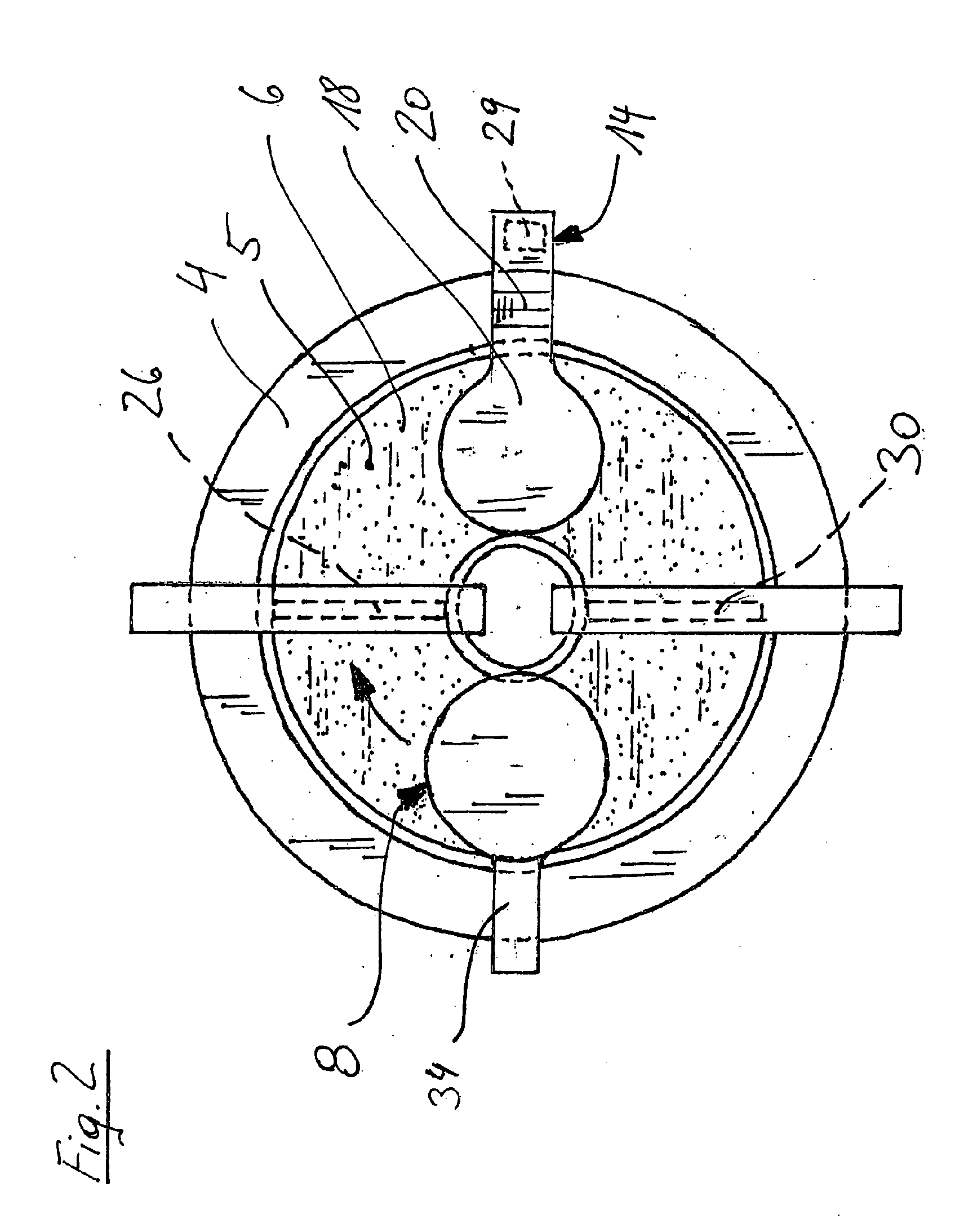

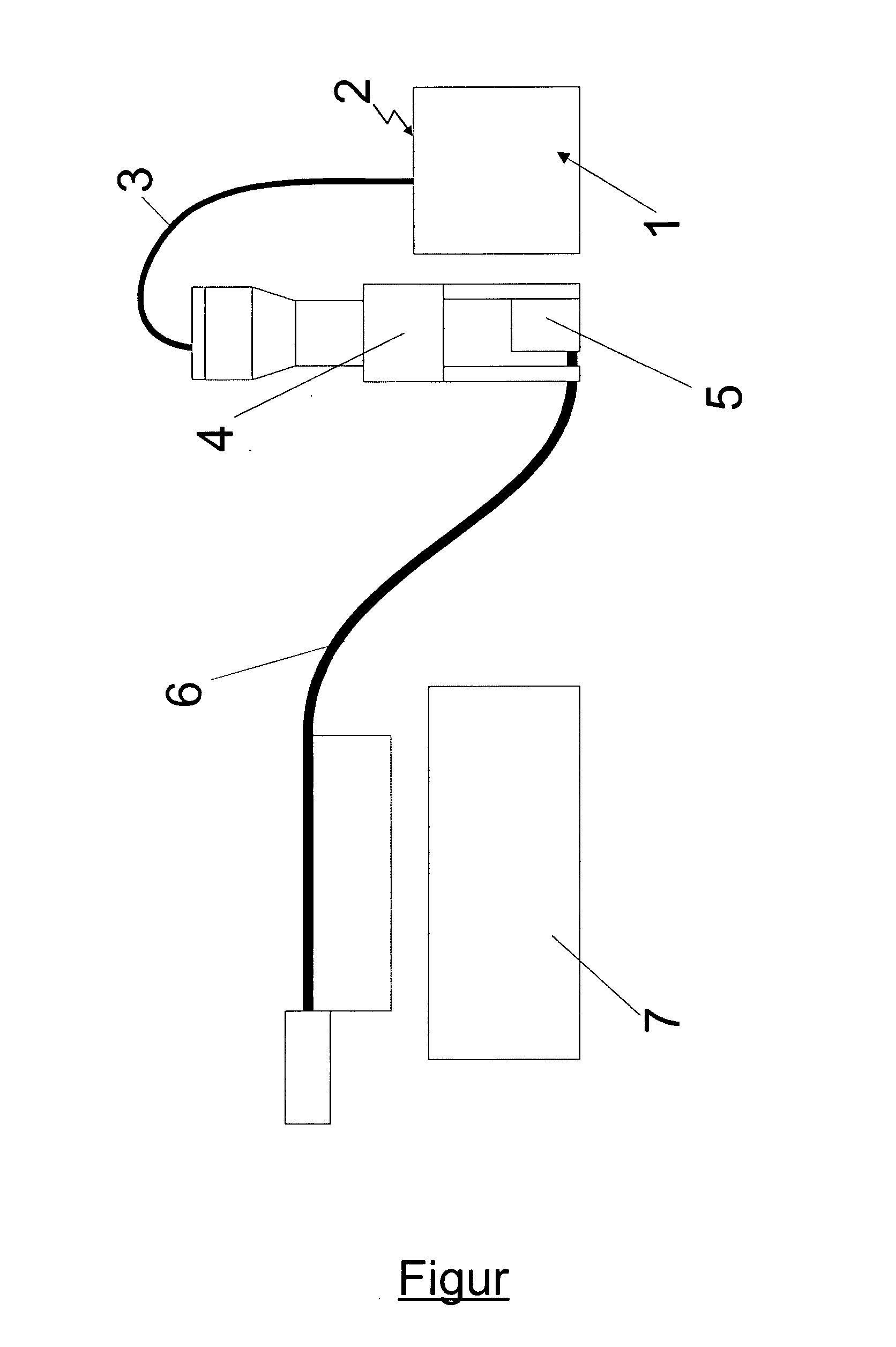

Device And Method For Processing Light-Polymerizable Material For Building Up An Object In Layers

ActiveUS20110309554A1High viscositySimple methodAdditive manufacturing apparatusTailstocks/centresControl cellStructural engineering

A method and a device for processing a light-polymerizable material (5, 55) for building up an object (27) in layers, using a lithography based generative manufacture having a construction platform (12) for building up the object (27), a projecting exposure unit (10, 60) that can be controlled for locally selected exposing of a surface on the construction platform (12, 62) to an intensity pattern having a prescribed shape, and a control unit (11, 61) prepared for polymerizing overlapping layers (28) on the construction platform (12, 62) in successive exposure steps, each having a prescribed geometry, by controlling the projecting exposure unit (10, 60), in order to thus successively build up the object (27) in the desired shape, said shape resulting from the sequence of layer geometries. The invention is characterized in that a further exposure unit (16, 66) for exposing the surface of the construction platform (12, 62) is provided on the side opposite the projecting exposure unit (10, 60), and that the construction platform (12, 62) is designed to be at least partially transparent to light, and that the control unit (11, 61) is designed for controlling the further exposure unit (16, 66) at least while building up the first layer (28), said layer adhering to the construction platform (12, 62), for exposing in the prescribed geometry.

Owner:VIENNA UNIVERSITY OF TECHNOLOGY +1

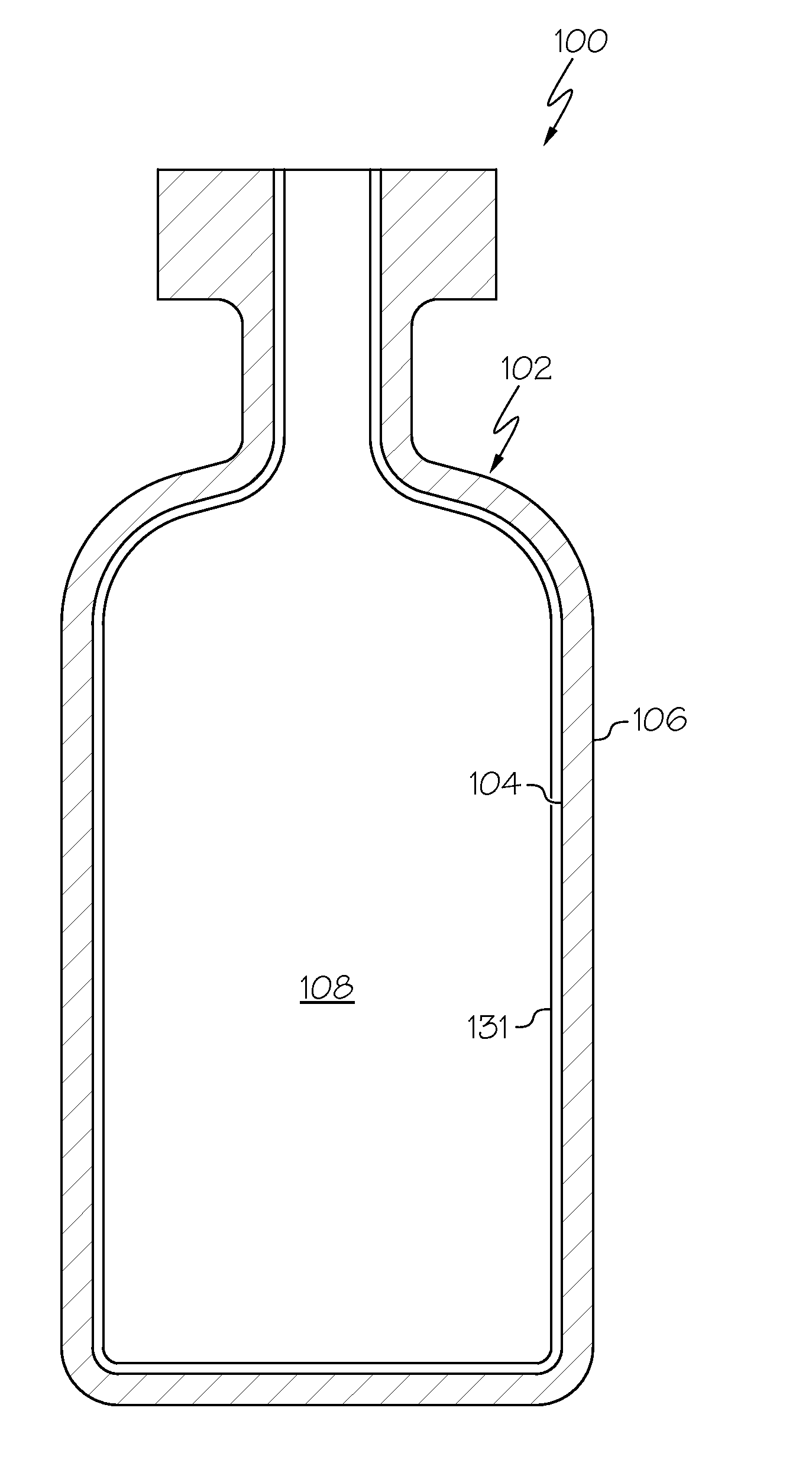

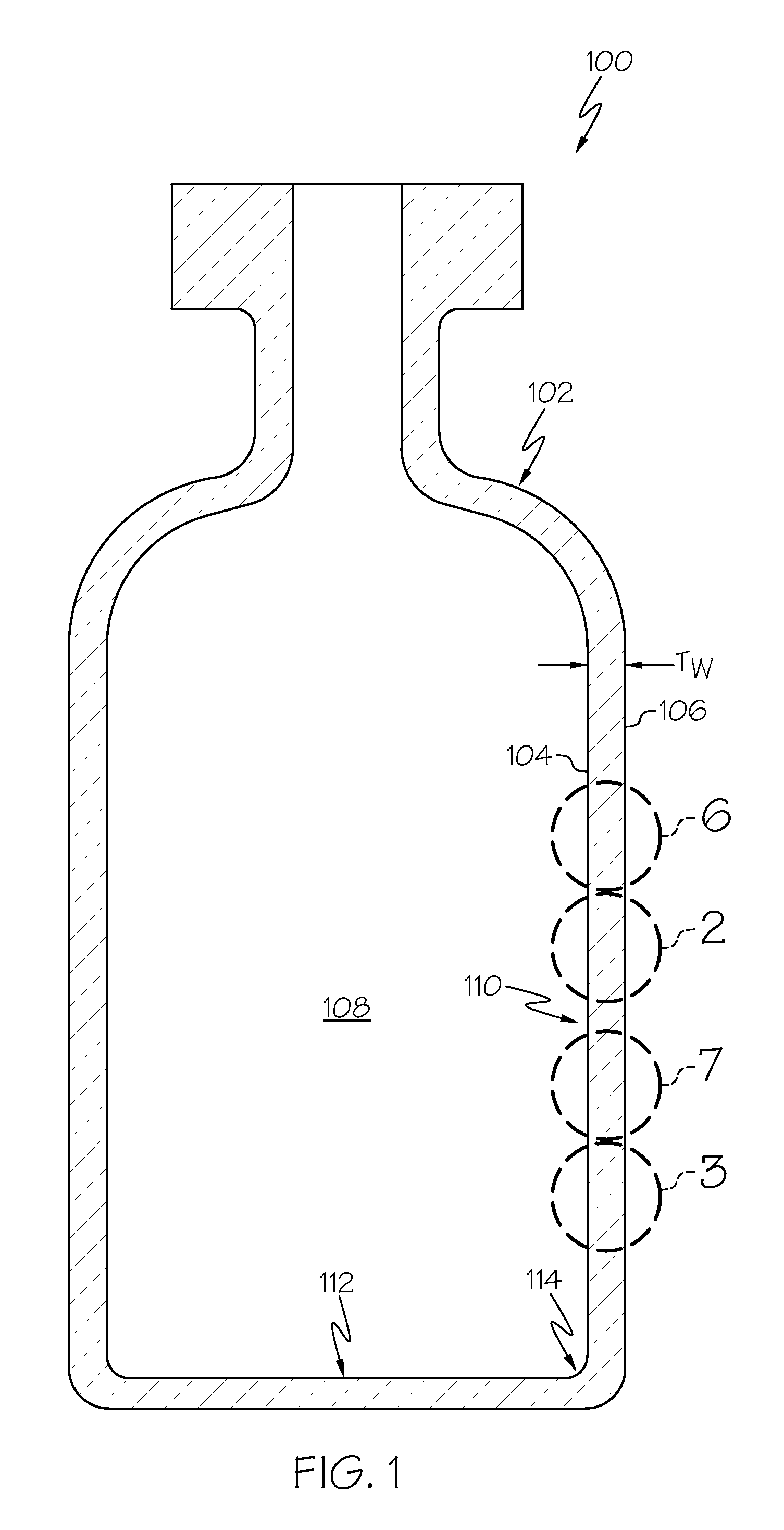

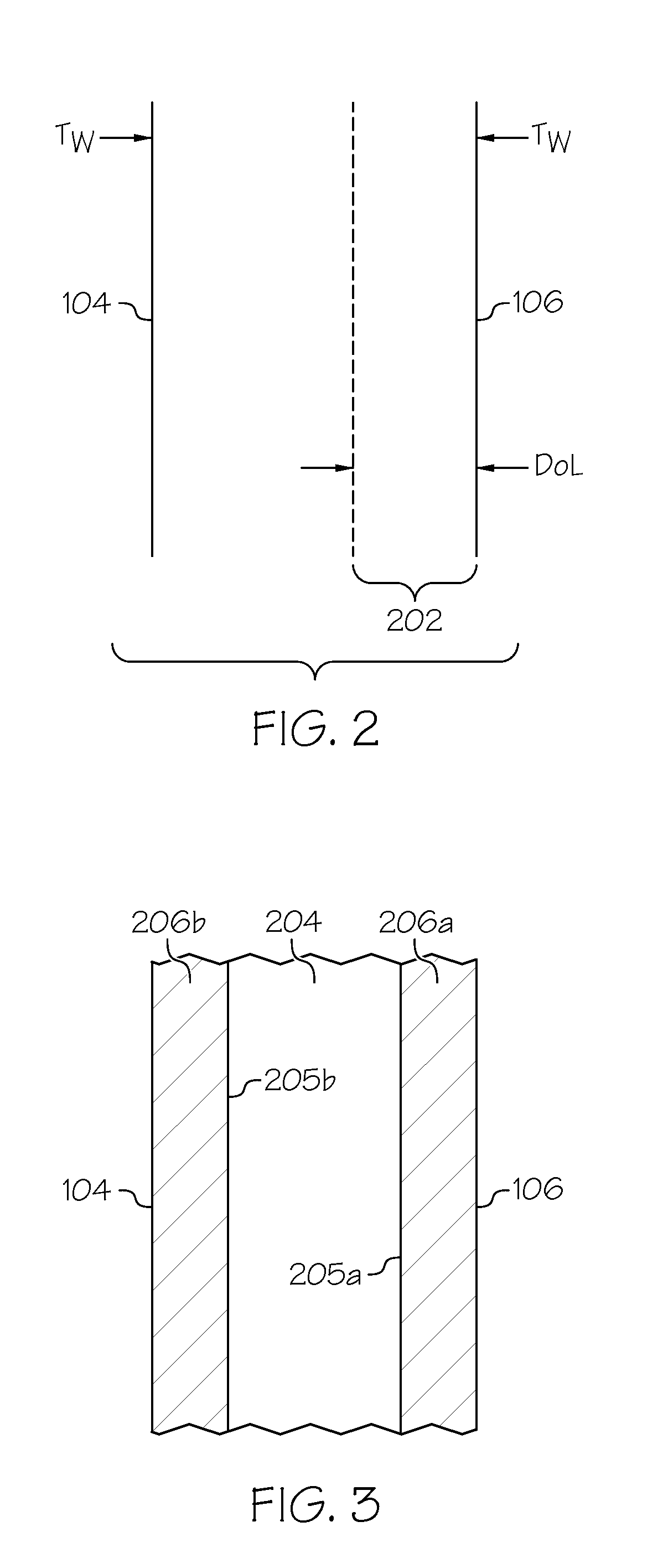

Strengthened glass containers resistant to delamination and damage

ActiveUS20140151370A1Pharmaceutical containersLarge containersUltimate tensile strengthMaterials science

The glass containers described herein are resistant to delamination, have improved strength, and increased damage resistance. In one embodiment, a glass container may include a body having an inner surface, an outer surface and a wall thickness extending between the outer surface and the inner surface. At least the inner surface of the body may have a delamination factor less than or equal to 10. The body may also have a compressively stressed layer extending from the outer surface of the body into the wall thickness. The compressively stressed layer may have a surface compressive stress greater than or equal to 150 MPa. A lubricous coating may be positioned around at least a portion of the outer surface of the body, such that the outer surface of the body with the lubricous coating has a coefficient of friction less than or equal to 0.7.

Owner:CORNING INC

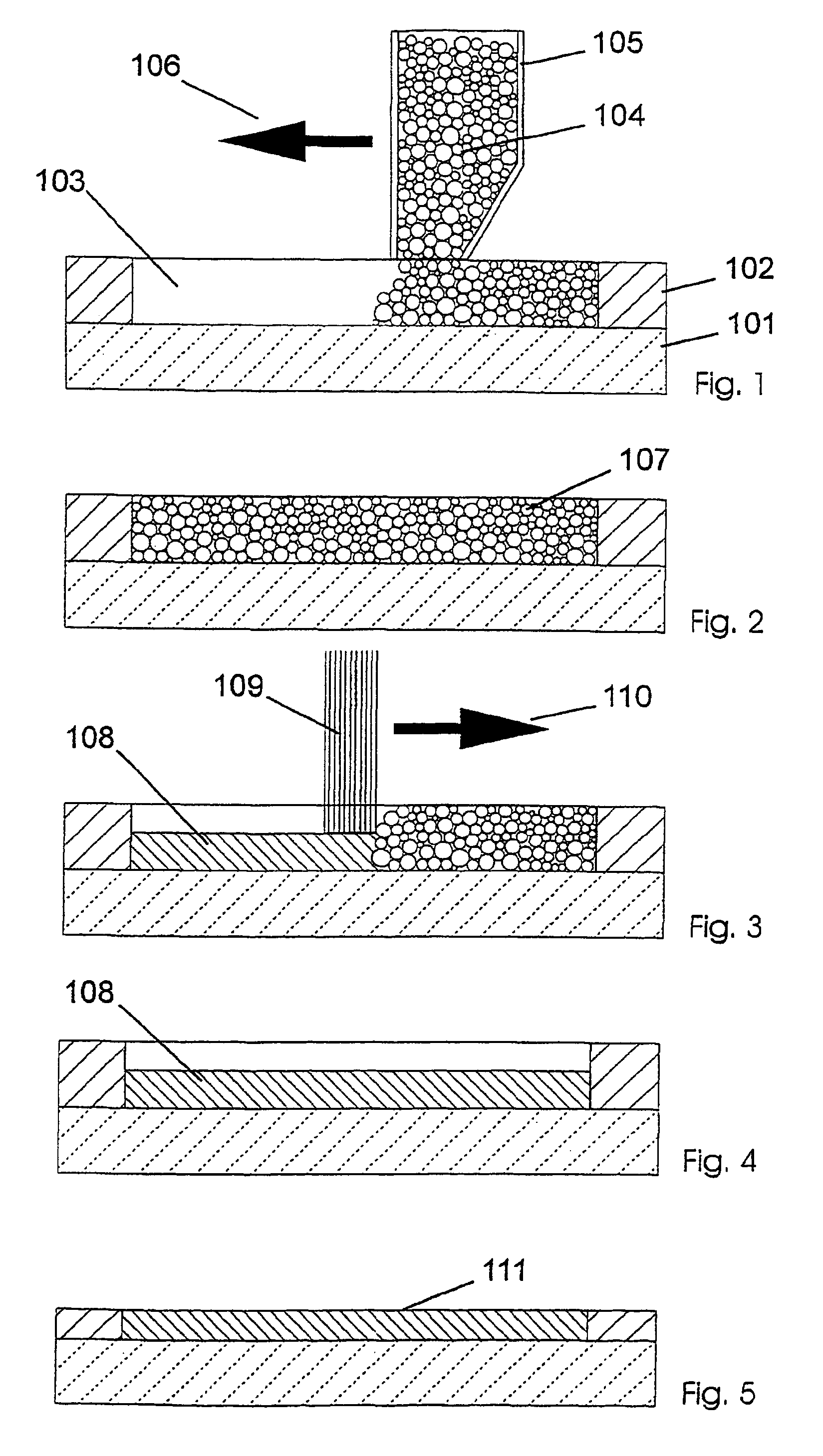

Method for producing a part and device for carrying out this method

InactiveUS7003864B2Faster machinabilityReduced tool wearMouldsWood working apparatusEngineeringRapid prototyping

The present invention relates to a method for producing a part (108, 200, 300), comprising the following steps:a) applying a first flat layer consisting of a support material (102, 202, 302), to a construction platform (101, 201, 301),b) introducing at least one recess (103, 203, 303) into the support material (102, 202, 302),c) filling the recess (103, 203, 303) with a construction material (104, 204, 304),d) applying a further layer of support material (102, 202, 302),e) repeating steps b) through d) until completion of the part (108, 200, 300), andf) removing the support material (102, 202, 302).This method is to provide a manufacturing method and a device that combine the advantages of the layerwise construction (rapid prototyping) with the advantages of machining (e.g. high-speed cutting) and particularly permit the production of sharp-edged contours.Furthermore, the present invention relates to a device for carrying out the method.

Owner:HERMLE MASCHENBAU

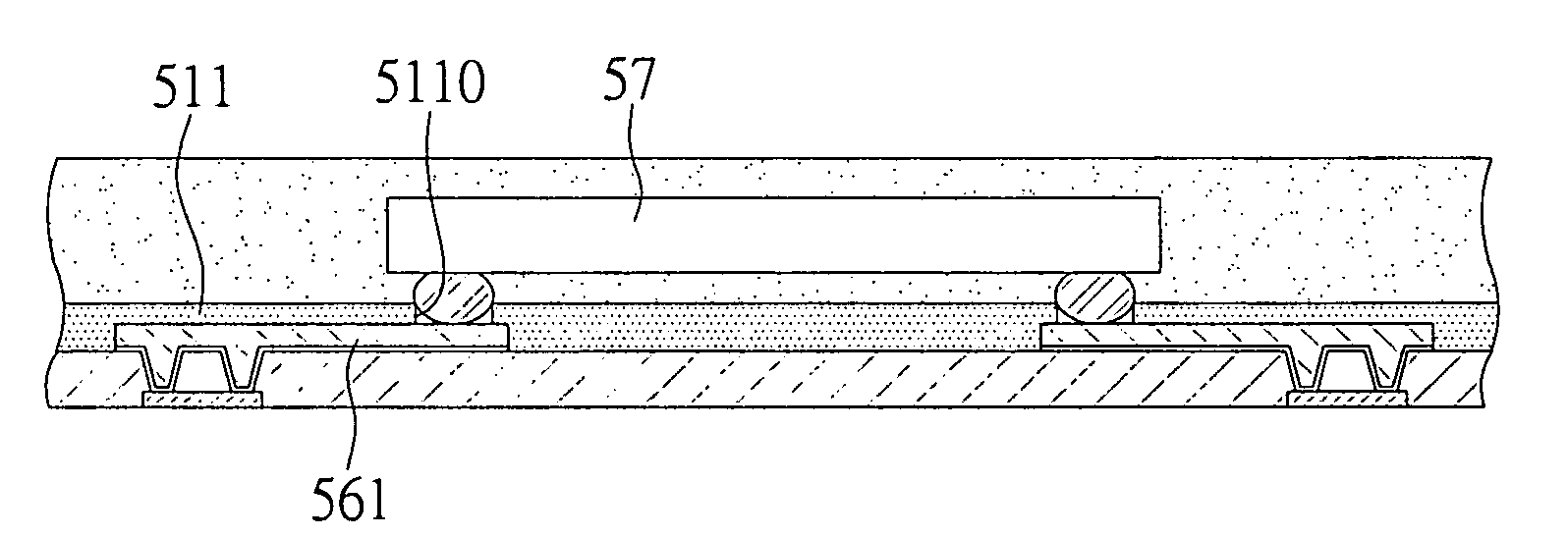

Semiconductor package and method for fabricating the same

InactiveUS20090102063A1Effective installationSmall sizeSemiconductor/solid-state device detailsSolid-state devicesManufacturing cost reductionResist

This invention provides a semiconductor package and a method for fabricating the same. The method includes: forming a first resist layer on a metal carrier; forming a plurality of openings penetrating the first resist layer; forming a conductive metal layer in the openings; removing the first resist layer; covering the metal carrier having the conductive metal layer with a dielectric layer; forming blind vias in the dielectric layer to expose a portion of the conductive metal layer; forming conductive circuit on the dielectric layer and conductive posts in the blind vias, such that the conductive circuit is electrically connected to the conductive metal layer via the conductive posts; electrically connecting at least one chip to the conductive circuit; forming an encapsulant for encapsulating the chip and the conductive circuit; and removing the metal carrier, thereby allowing a semiconductor package to be formed without a chip carrier. Given the conductive posts, both the conductive circuit and conductive metal layer are efficiently coupled to the dielectric layer to prevent delamination. Further, downsizing the blind vias facilitates the fabrication process and cuts the fabrication cost.

Owner:SILICONWARE PRECISION IND CO LTD

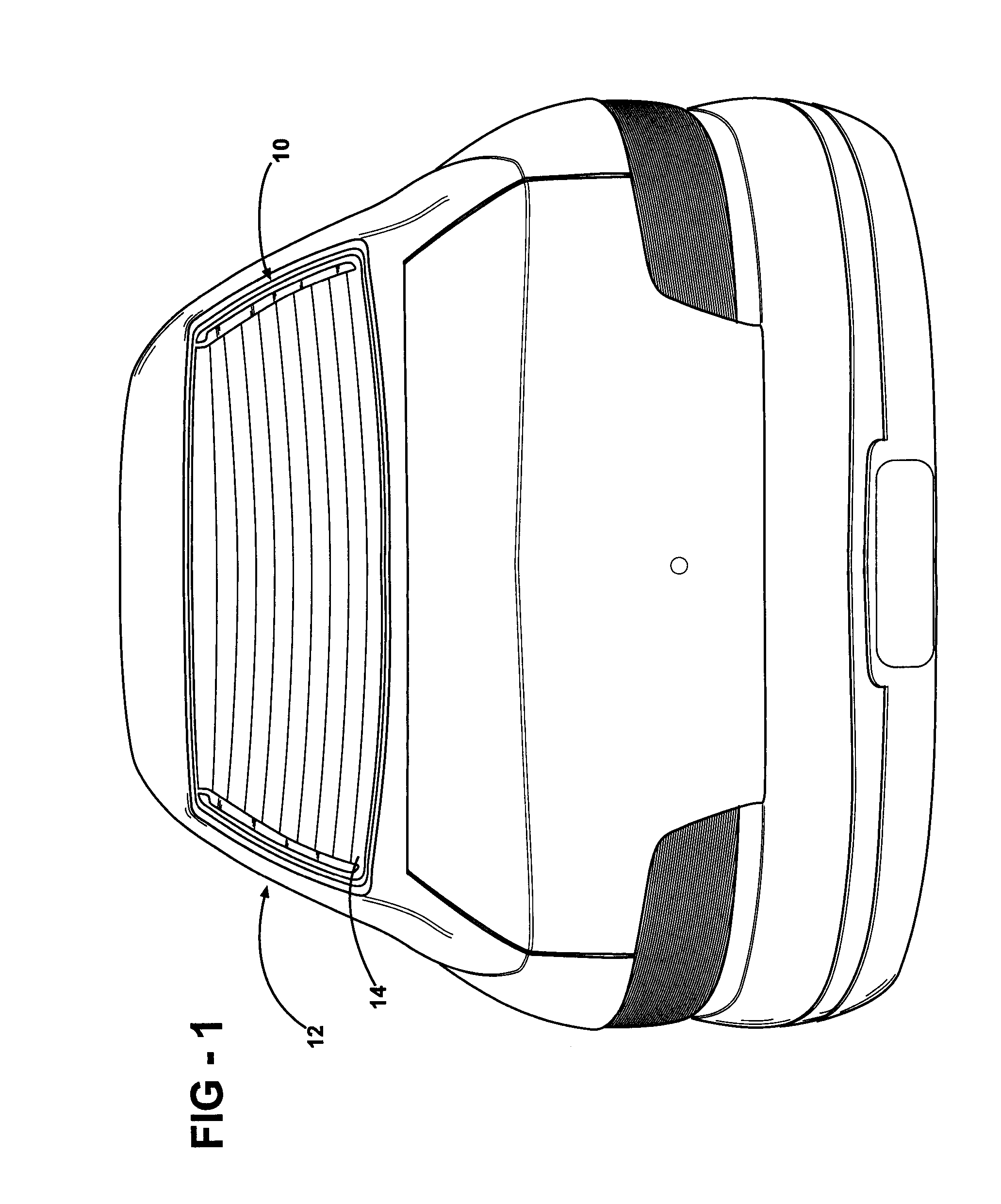

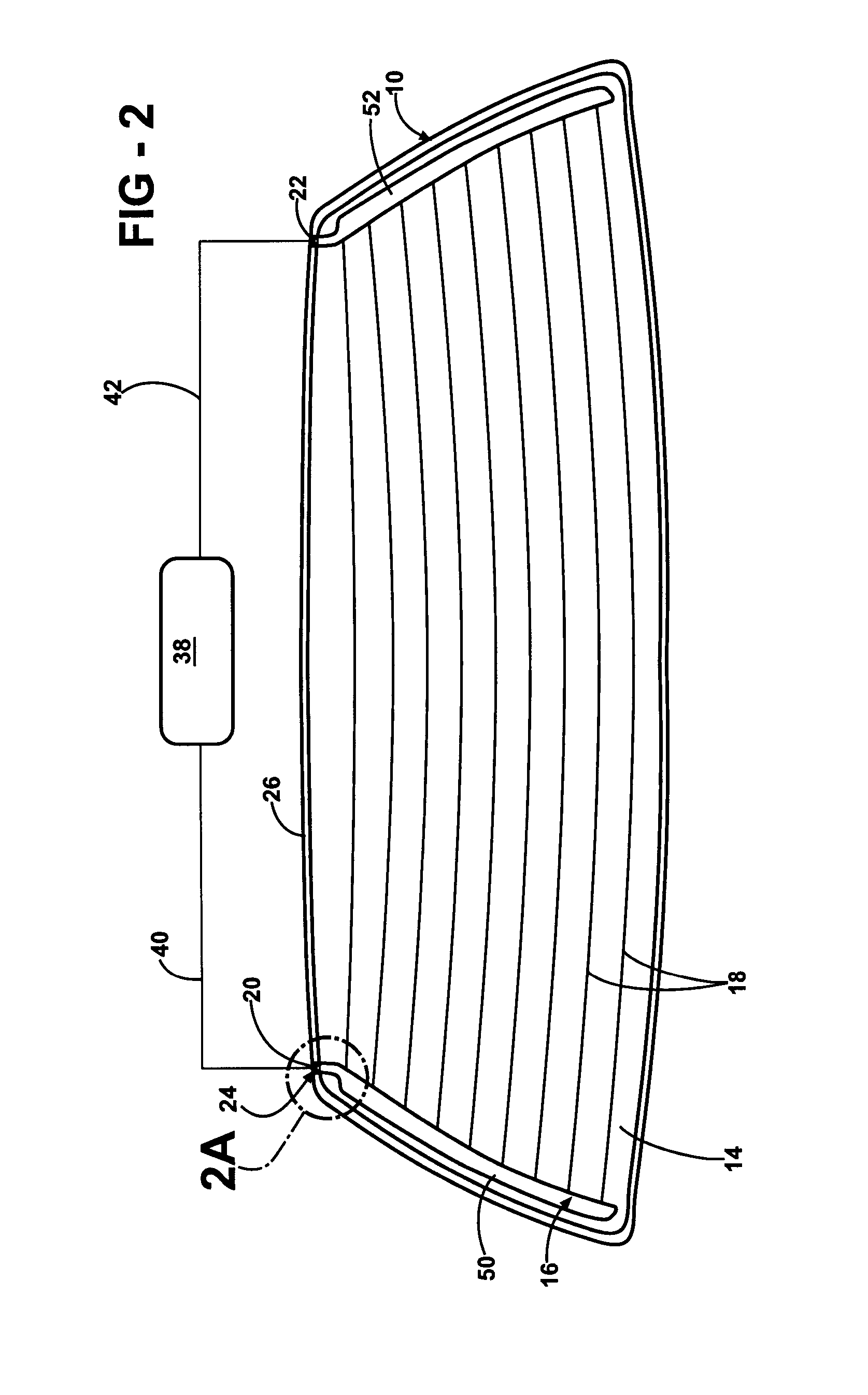

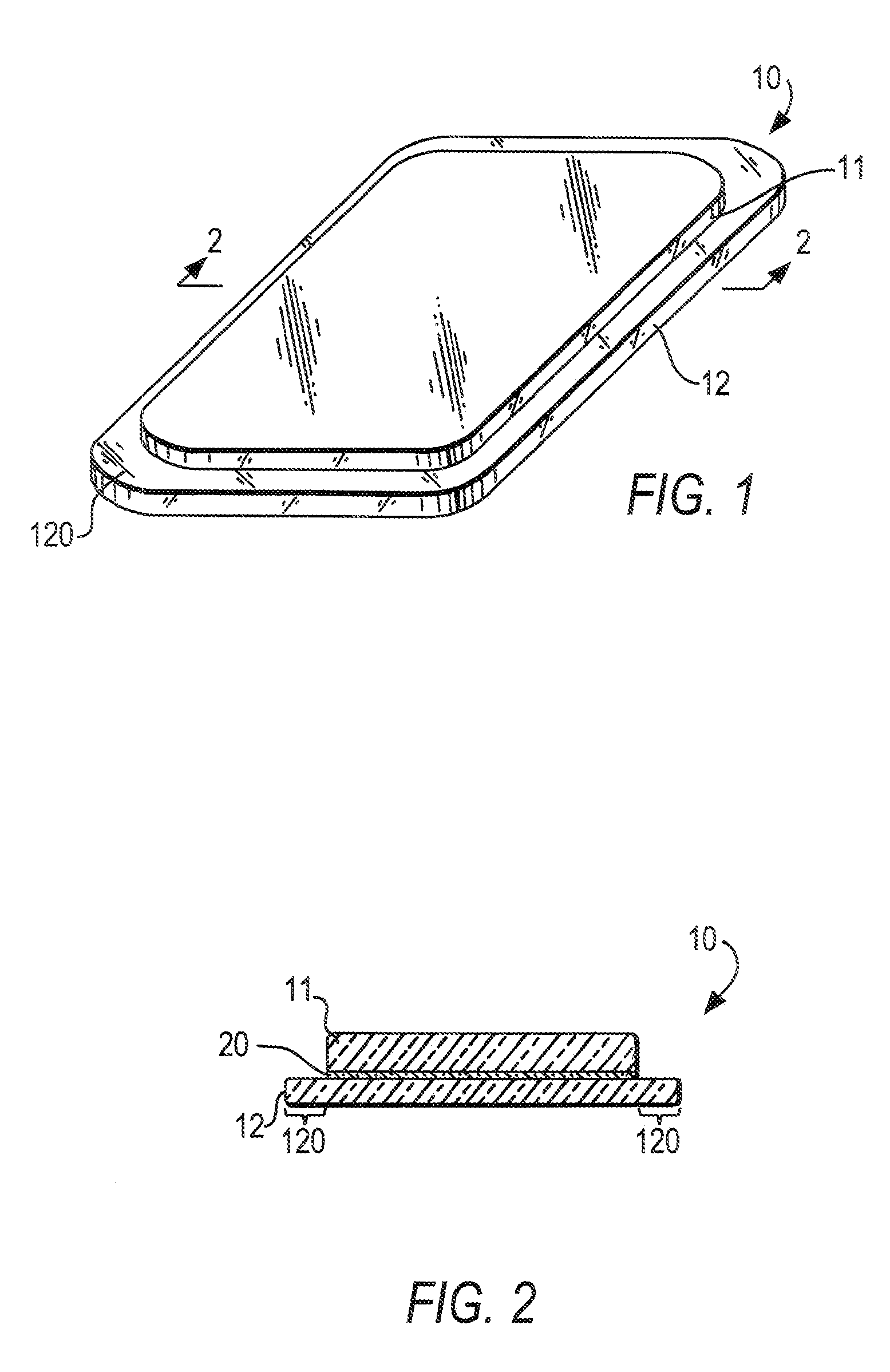

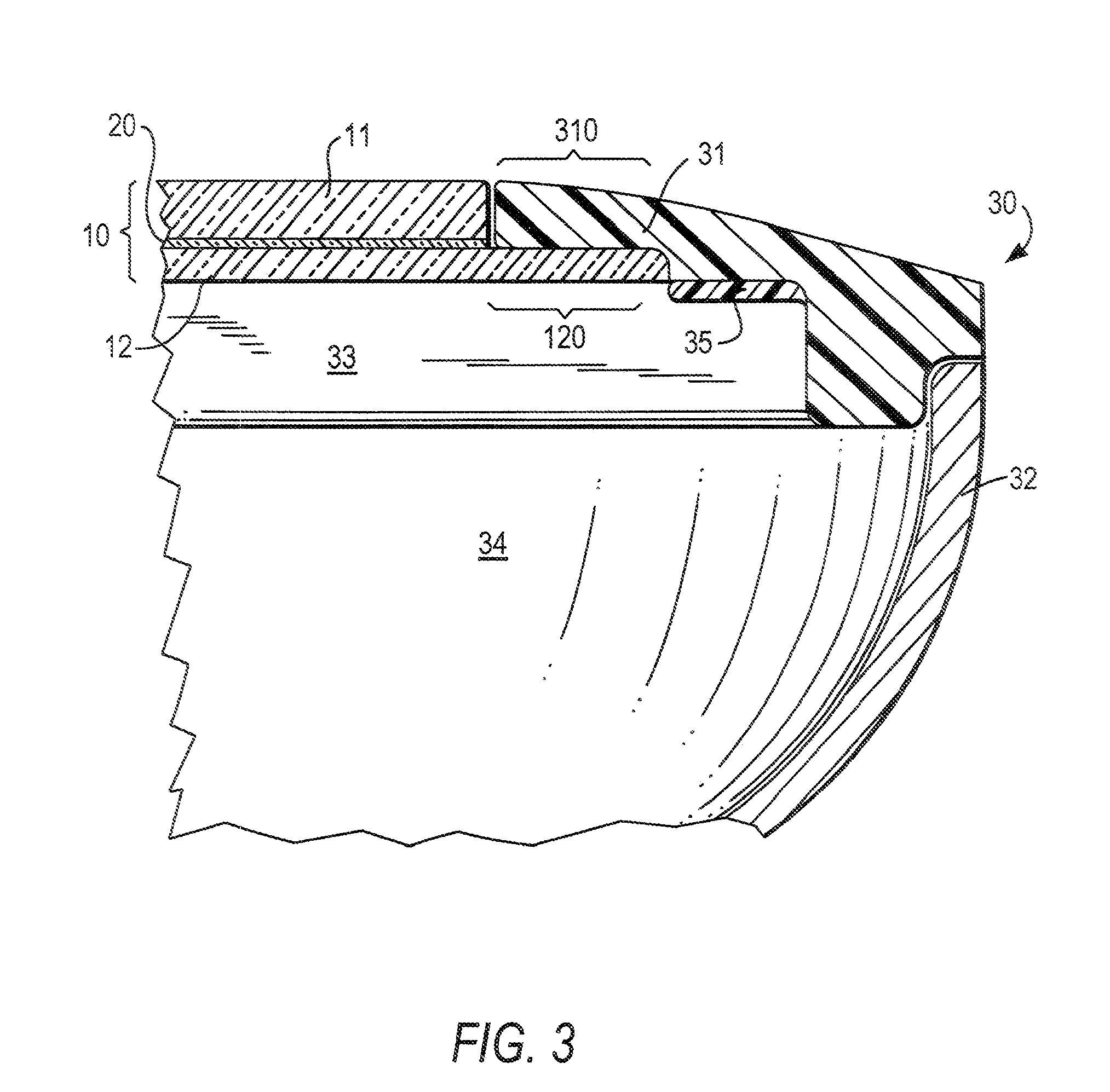

Laminated display window and device incorporating same

ActiveUS20090049773A1Resisting delaminationReduce sensitivityFire rescueSubstation equipmentAdhesiveEngineering

A laminated window assembly for a device, such as a handheld electronic device (e.g., a media player or mobile telephone), includes a window layer that preferably is glass, and a larger, substantially transparent lip-forming layer to which it is laminated, preferably by a substantially clear adhesive. Additional adhesive preferably is placed at at least portions of the edge of the window layer adjacent the lip-forming layer, especially at the corners, to resist delamination. Holes preferably are formed in the lip—e.g., at the corners—to resist the lip-forming layer peeling apart from the window layer forming layer. The holes preferably make up at most about 33% of the periphery of the window layer.

Owner:APPLE INC

Method and apparatus for the treatment of the intervertebral disc annulus

InactiveUS20090259260A1Shorten the lengthSuture equipmentsBone implantPresent methodIntervertebral disk

This disclosure presents methods and devices for treating a tear, rent, incision, defect, aperture or delamination of the annulus fibrosus of an intervertebral disc. The methods and devices can employ fixation delivery apparatuses, fixation apparatuses, patch delivery tools and patches positioned, at least in part, in or on aspects of an intervertebral disc for treatment of the intervertebral disc or its components. In some aspects, these techniques include the use of this includes a fixation apparatus that includes at least one bone anchor connected to at least one disc anchor by a shortenable elongate member.

Owner:KRT INVESTORS

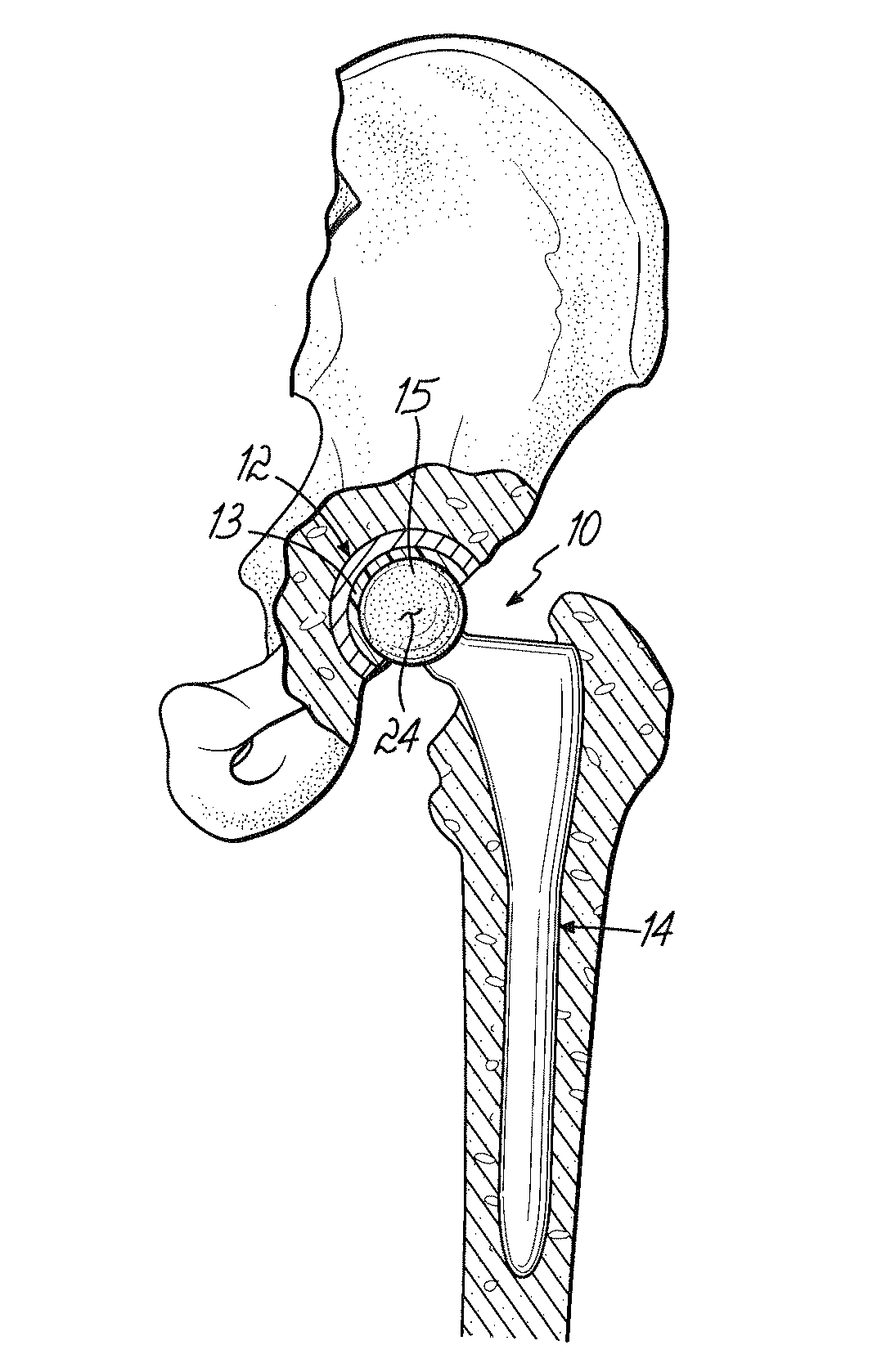

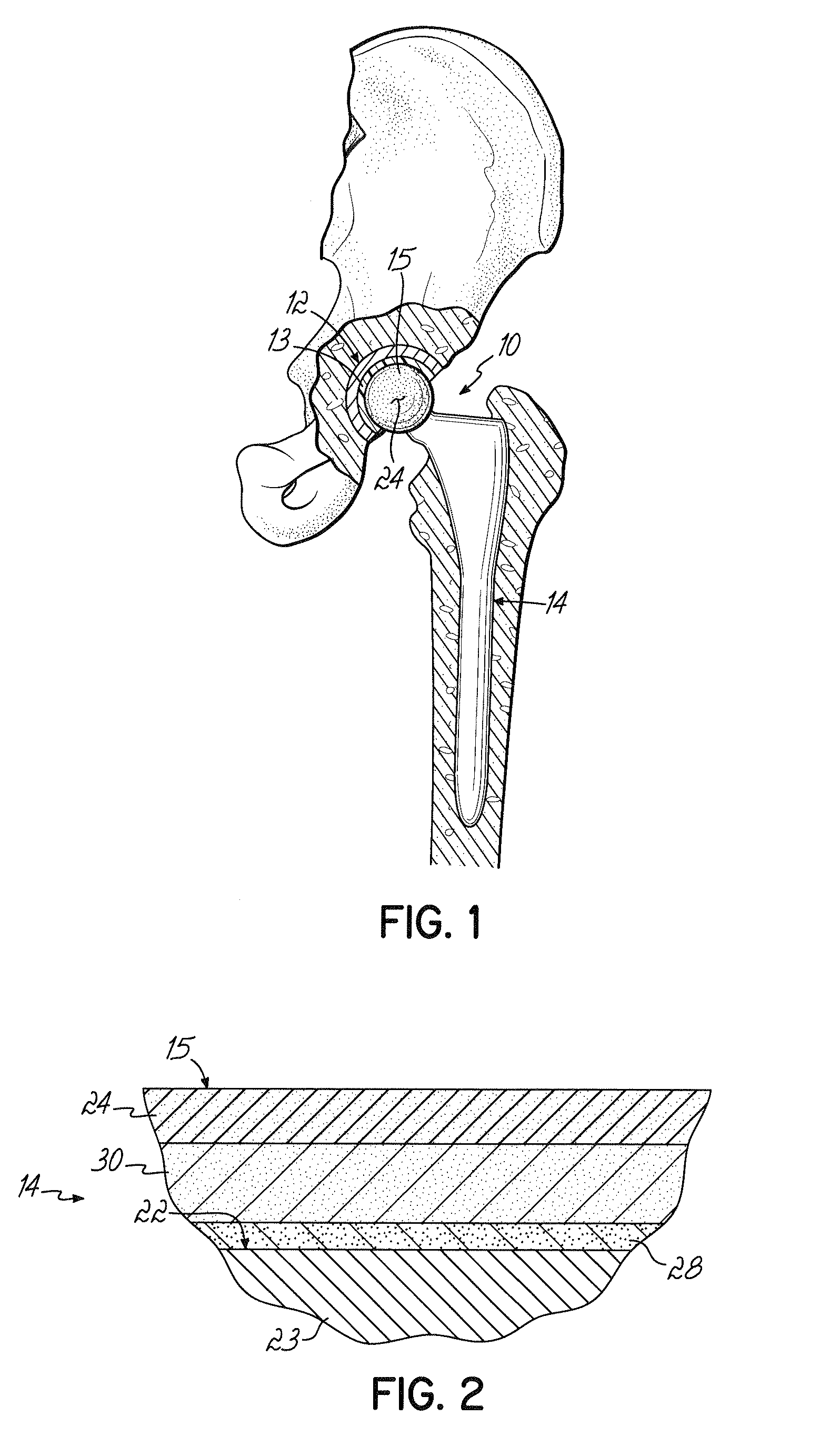

Titanium alloy with oxidized zirconium for a prosthetic implant

A prosthetic device having a generally fixed member formed from a low friction material such as ultra-high molecular weight polyethylene and an articulating titanium member, which includes an articular bearing surface. The articular surface is a zirconium oxide layer formed by applying a coating of zirconium onto the titanium member and heating this in an oxygen-containing environment. This causes the zirconium to oxidize and further causes the zirconium to migrate into the titanium member forming a titanium zirconium diffusion layer, which prevents delamination.

Owner:ZIMMER INC

Method for constructing patterns in a layered manner

ActiveUS20050167872A1Additive manufacturing apparatusMoulding toolsProduction modelMaterials science

A process to produce models in layers is described, whereby a first material and then selectively a second material is applied in layers on a building platform and these two application stages are repeated until a desired pattern is achieved. The two materials form a solid if a suitable mixture ratio is used and the first material is a material mixture. The material mixture is at least partially prepared prior to each application stage.

Owner:EXONE

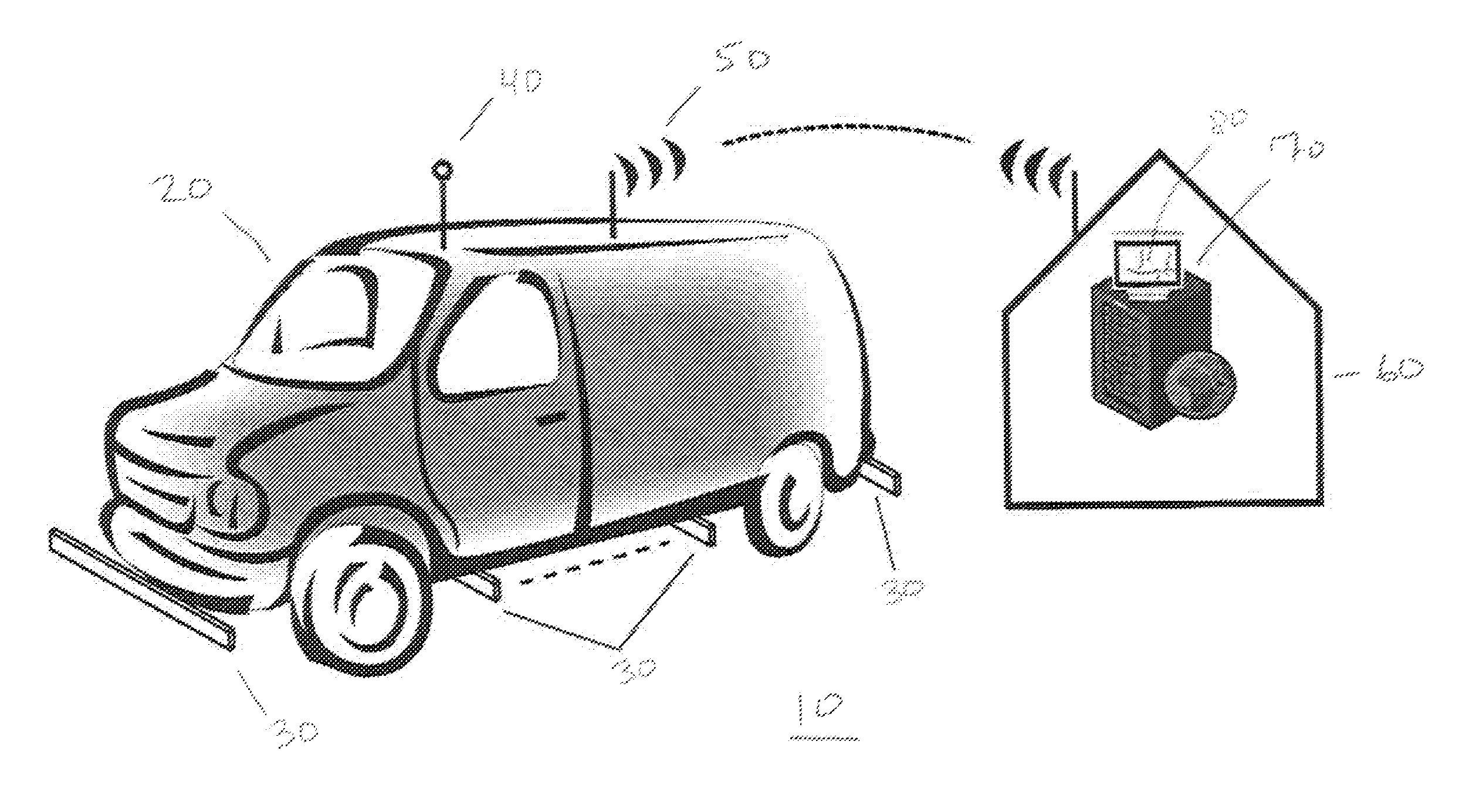

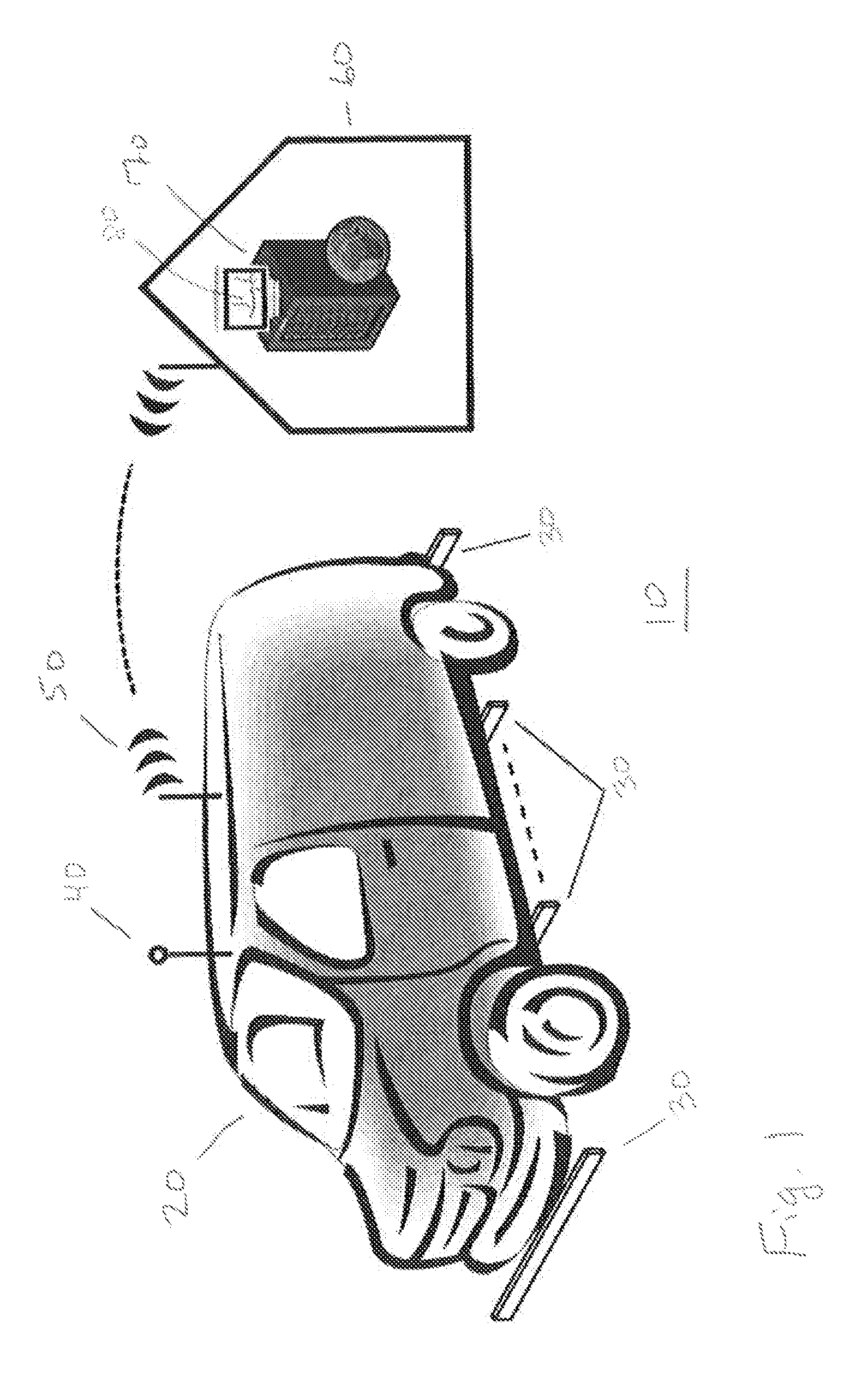

Roaming Mobile Sensor Platform For Collecting Geo-Referenced Data and Creating Thematic Maps

ActiveUS20130018575A1Improve securityTraffic can be stoppedInstruments for road network navigationRoad vehicles traffic controlRebar corrosionBridge deck

A roaming sensor system collects data on the condition of roads and bridge decks and identifies and maps defects, including cracks, potholes, debonding, tracking, delamination, surface ice, surface water, and rebar corrosion. Data are collected by a vehicle or a fleet of vehicles driven at normal traffic speeds. The vehicle is outfitted with sensors that collect data using acoustic surface waves, ground penetrating radar, mm wave surface radar, and / or video images. The data are transmitted to a control center for analysis and distribution.

Owner:NORTHEASTERN UNIV

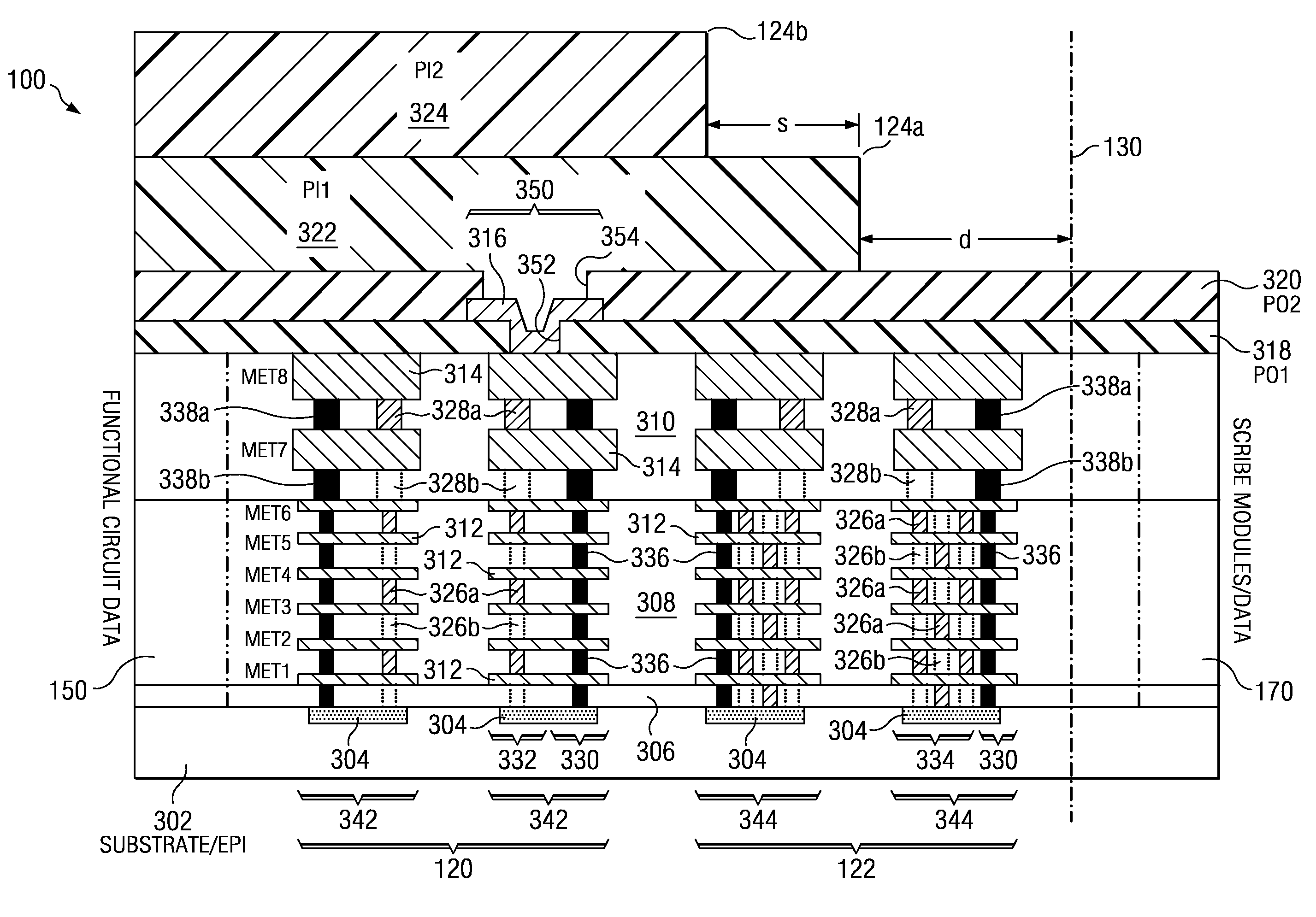

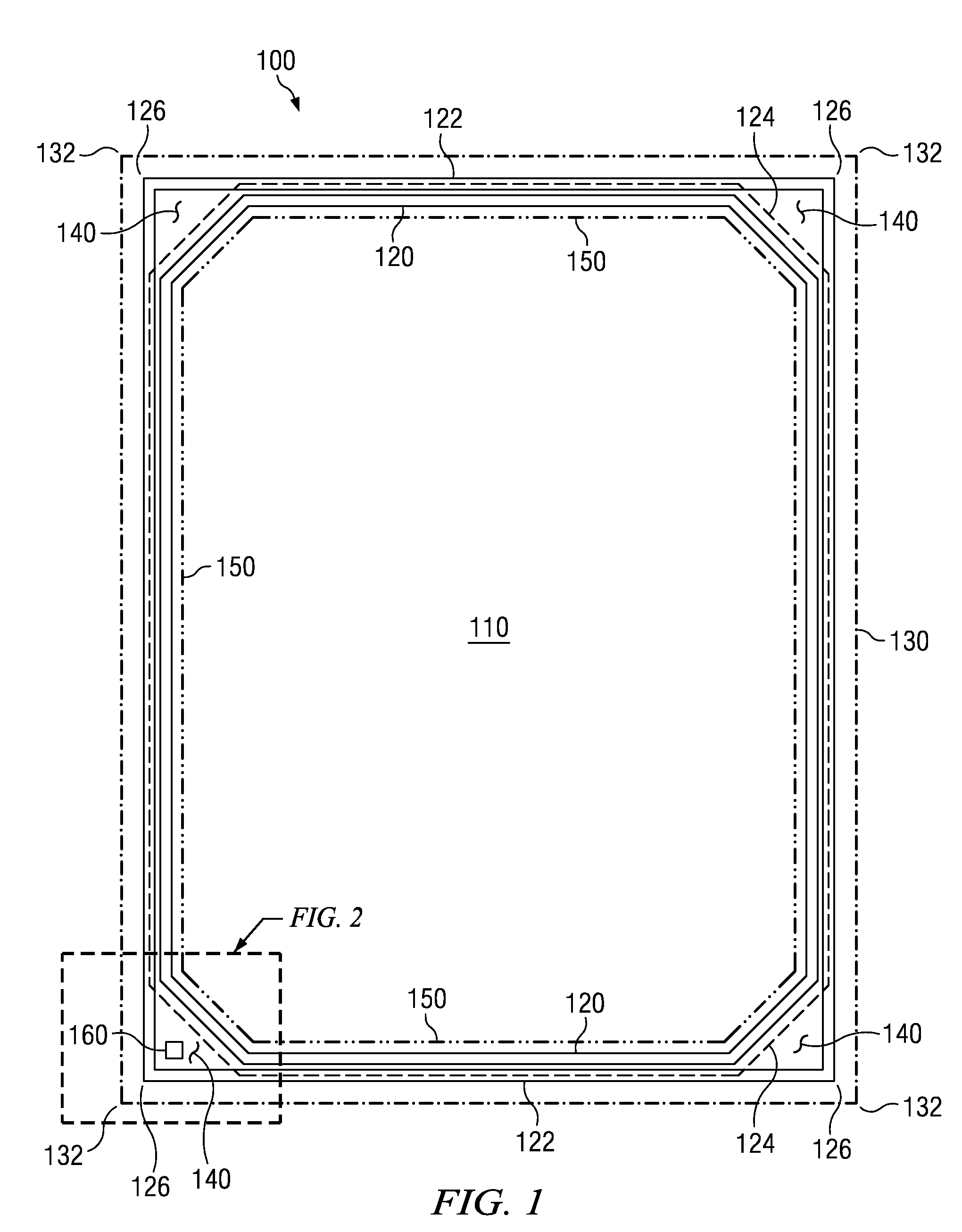

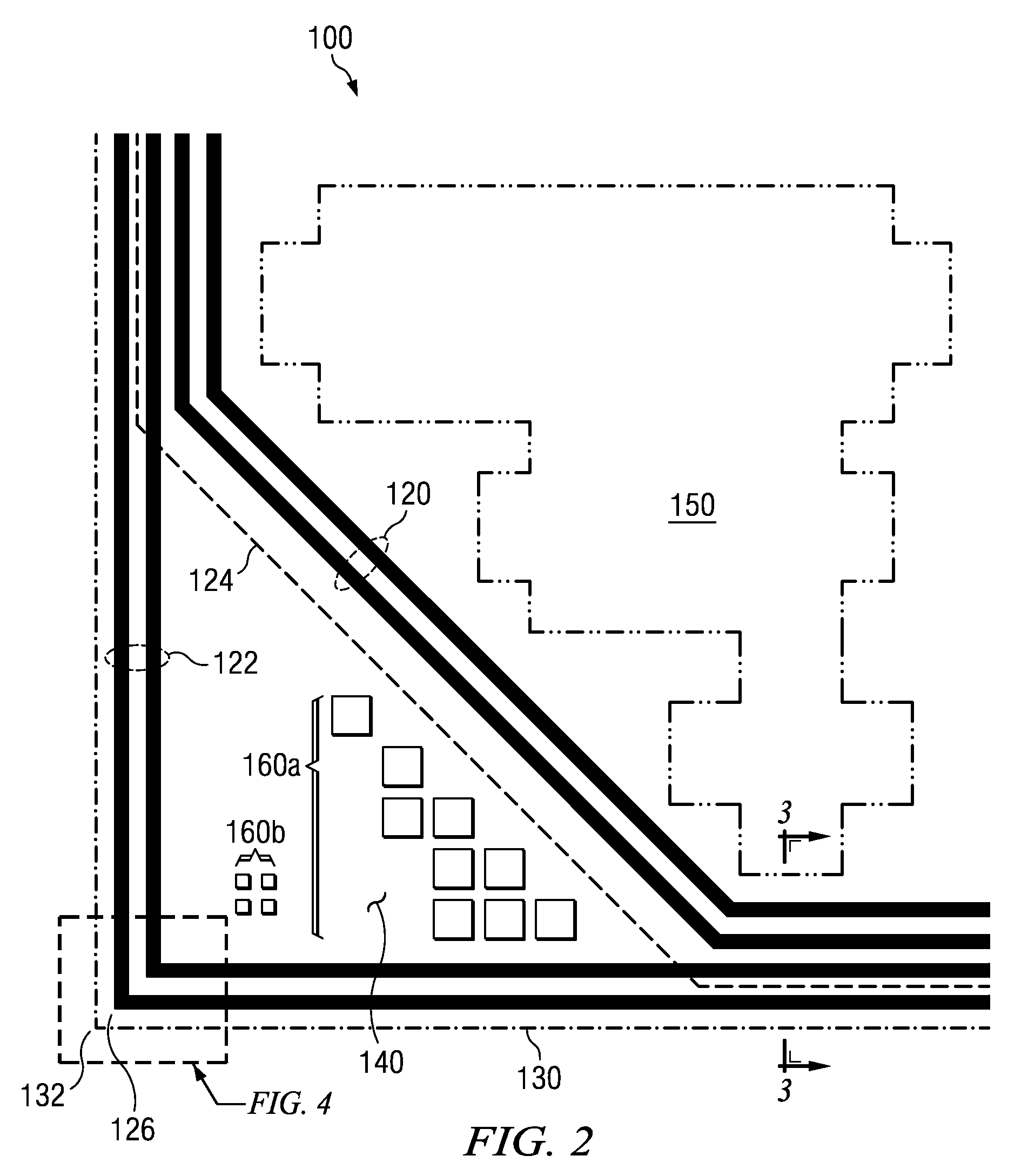

Environmental die seal enhancement for wafer level chip scale packages

ActiveUS20100078769A1Improve barrier propertiesImprove strength propertiesSemiconductor/solid-state device detailsSolid-state devicesMoisture penetrationEngineering

In a semiconductor device for use in a wafer level chip scale package (WLCSP) and a method for fabrication, an inner scribe seal is formed around a functional circuit area that does not extend all the way into the corners of the rectangular die, and an outer scribe seal follows the perimeter of the die and into the corners, with the outer scribe seal having a continuous barrier wall towards the die edges so that moisture penetration in dielectric layers of the die is minimized, and cracks and delamination are stopped near the die edges. Limiting the extent of the insulating layer or layers in the WLCSP to cover the functional circuit area also reduces the stresses caused by these layers near the die corners. Other features further enhance the strength and barrier properties of the scribe seals and the layers near the die corners, terminate cracks and delamination at various levels within the dielectric stack of the die and the die protective overcoat, and prevent damage during the WLCSP assembly process.

Owner:TEXAS INSTR INC

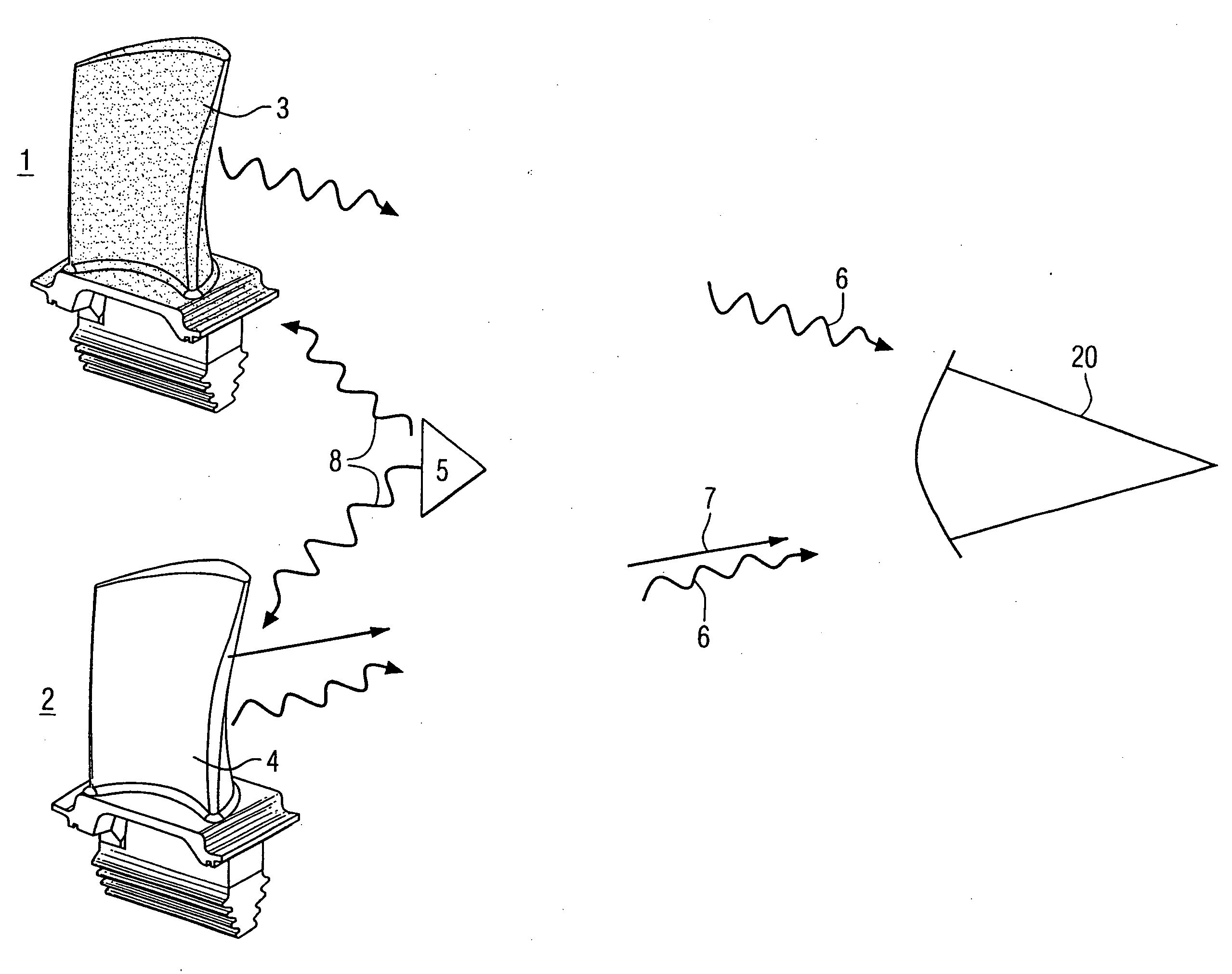

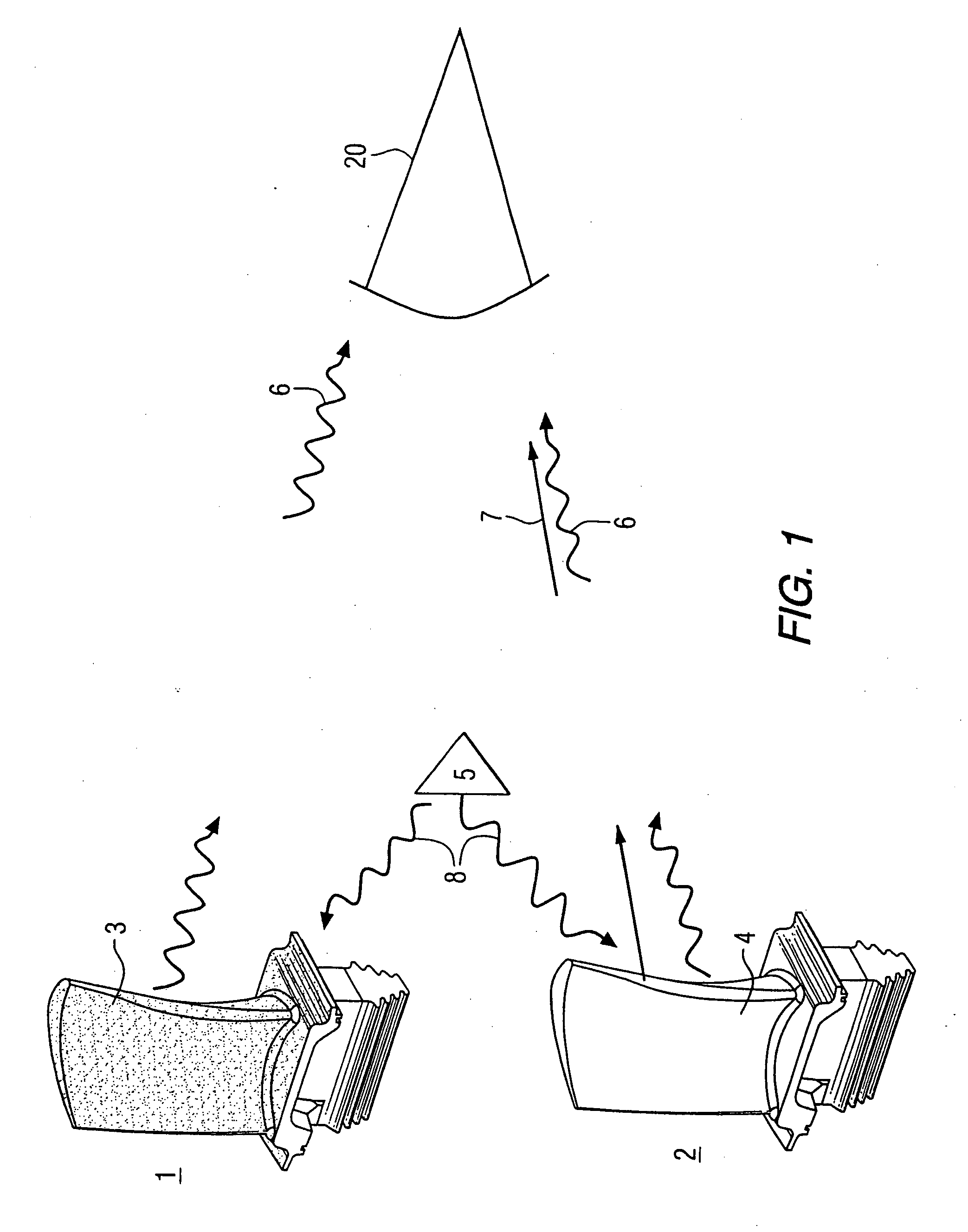

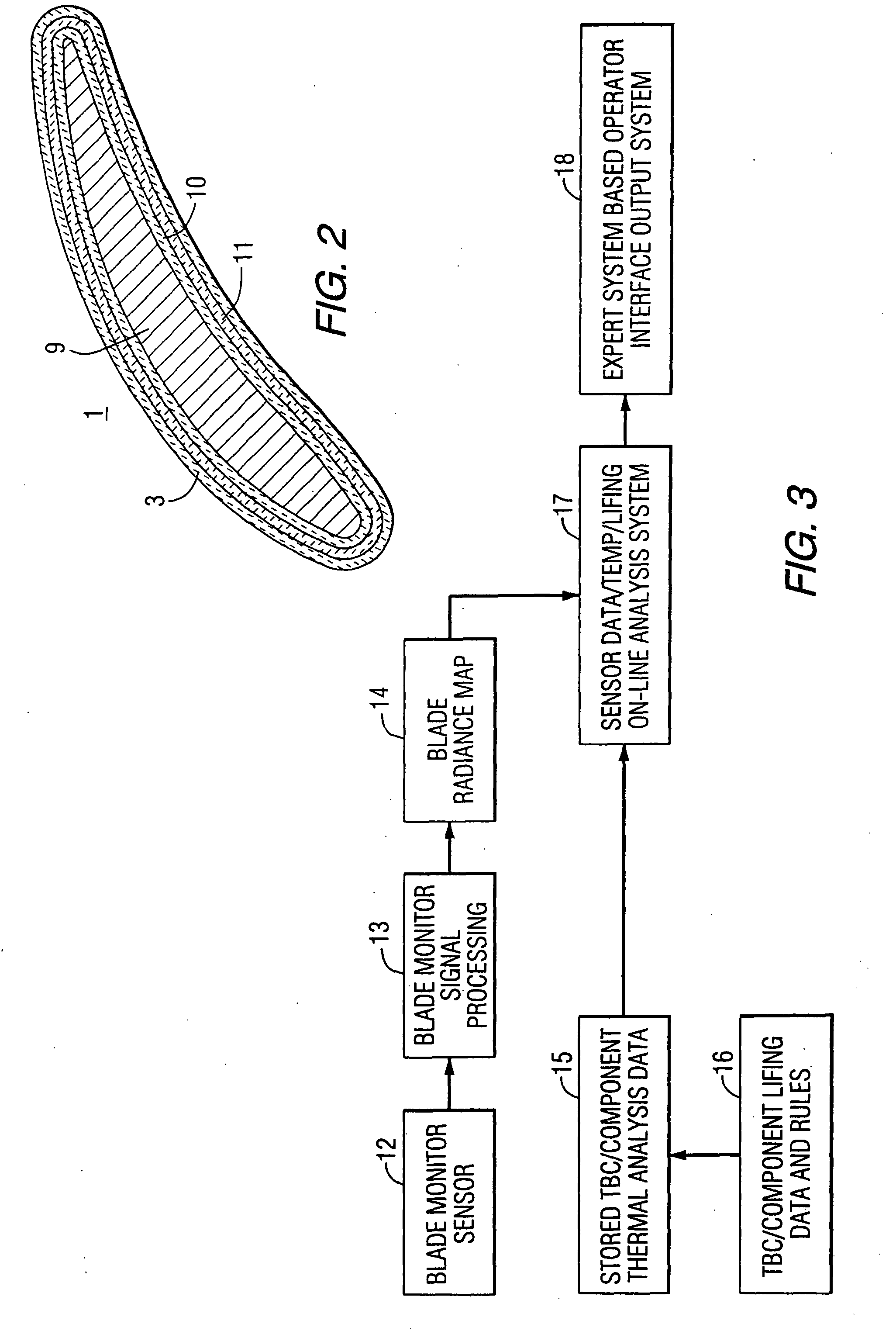

Method and apparatus for measuring on-line failure of turbine thermal barrier coatings

InactiveUS20090312956A1Detect degradationAvoid severe repairThermometer detailsPlug gaugesTurbine bladeEngineering

A method of remotely monitoring the radiant energy (6) emitted from a turbine component such as a turbine blade (1) having a low-reflective surface coating (3) which may be undergoing potential degradation is used to determine whether erosion, spallation, delamination, or the like, of the coating (3) is occurring.

Owner:SIEMENS ENERGY INC

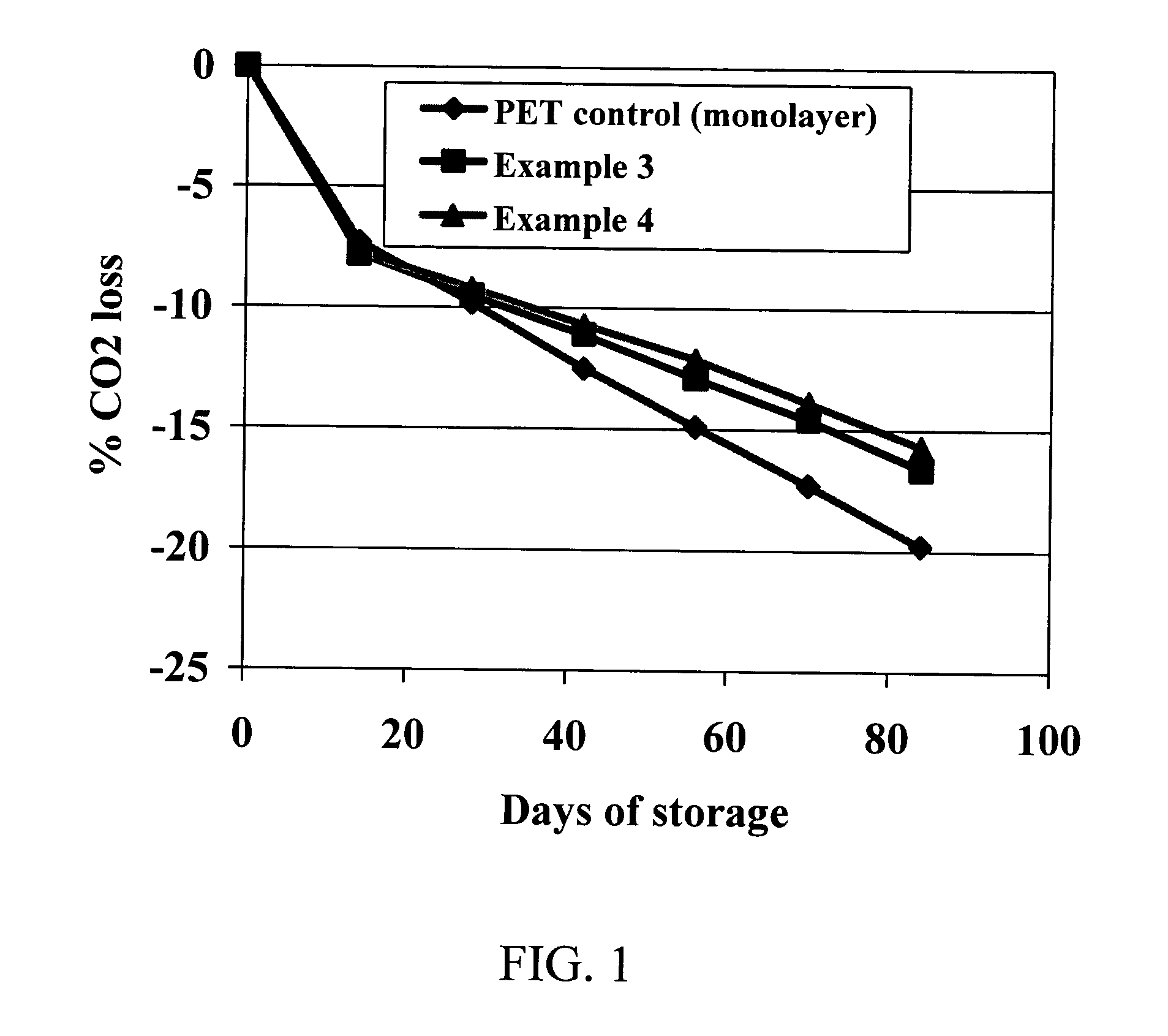

Delamination-resistant, barrier polyamide compositions for 3-layer pet beverage bottles

Gas barrier polyamide compositions exhibiting a low crystallization rate and good coinjection stretch blow moldability with polyethylene terephthalate (PET) to enable the fabrication of clear, high barrier multilayer PET bottles that have a long shelf life.

Owner:HONEYWELL INT INC

Stacked chip package using warp preventing insulative material and manufacturing method thereof

InactiveUS20070045836A1AdhesionHigh mechanical reliabilitySemiconductor/solid-state device detailsSolid-state devicesMechanical reliabilityPhotosensitive polymer

In a stacked chip configuration, and manufacturing methods thereof, the gap between a lower chip and an upper chip is filled completely using a relatively simple process that eliminates voids between the lower and upper chips and the cracking and delamination problems associated with voids. The present invention is applicable to both chip-level bonding and wafer-level bonding approaches. A photosensitive polymer layer is applied to a first chip, or wafer, prior to stacking the chips or stacking the wafers. The photosensitive polymer layer is partially cured, so that the photosensitive polymer layer is made to be structurally stable, while retaining its adhesive properties. The second chip, or wafer, is stacked, aligned, and bonded to the first chip, or wafer, and the photosensitive polymer layer is then cured to fully bond the first and second chips, or wafers. In this manner, adhesion between chips / wafers is greatly improved, while providing complete fill of the gap. In addition, mechanical reliability is improved and CTE mismatch is reduced, alleviating the problems associated with warping, cracking and delamination, and leading to an improvement in device yield and device reliability.

Owner:SAMSUNG ELECTRONICS CO LTD