Patents

Literature

450 results about "Photosensitive polymer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

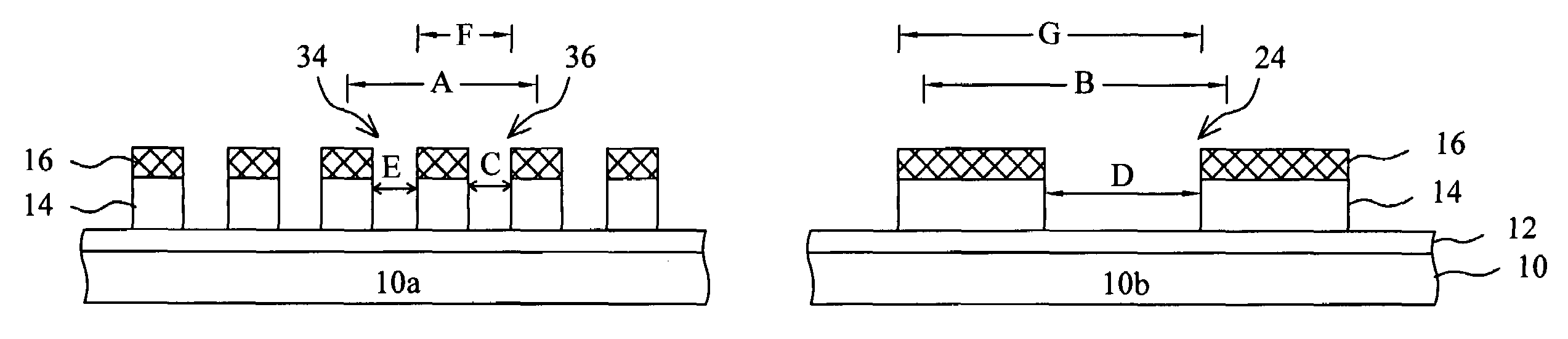

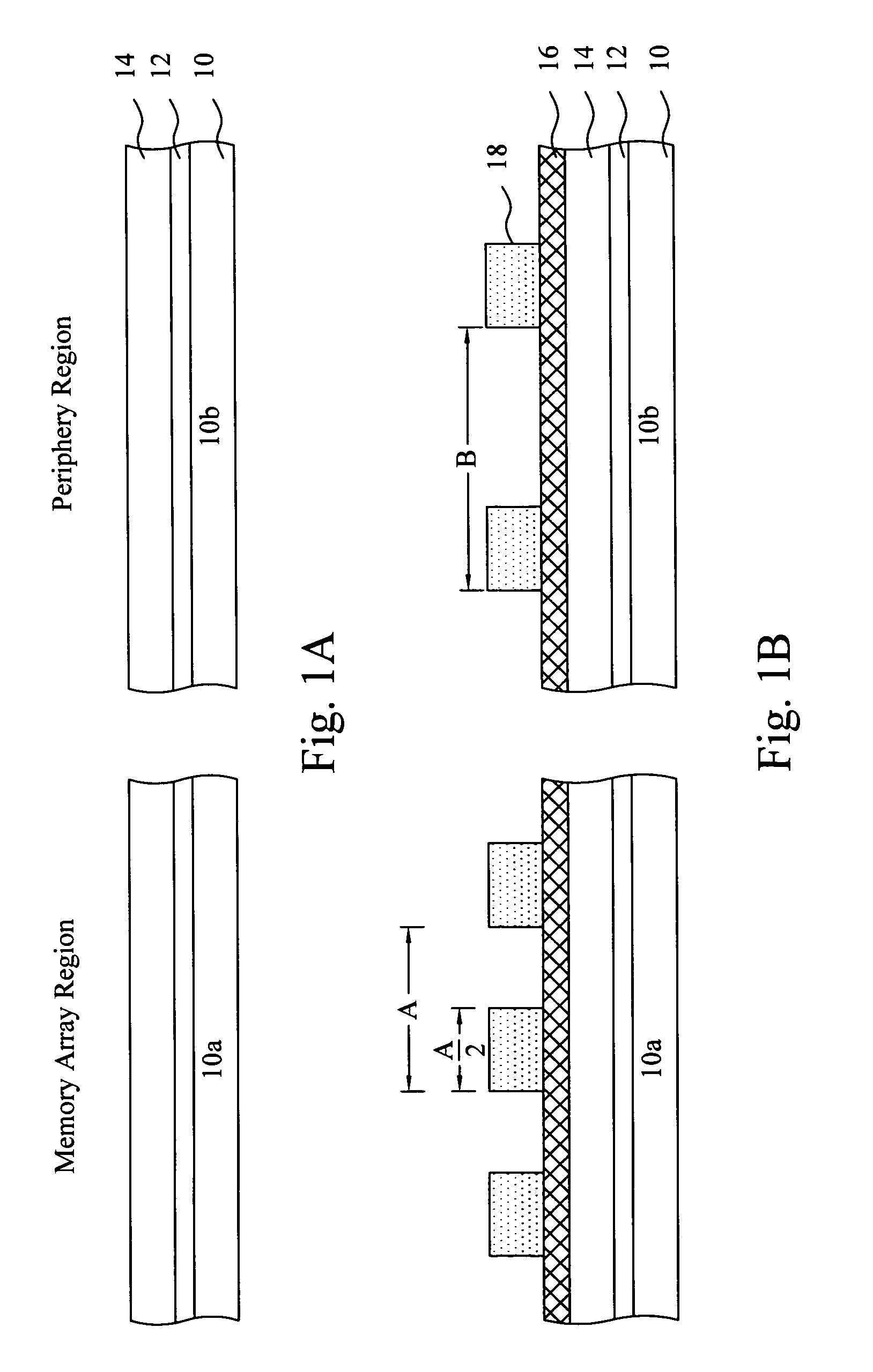

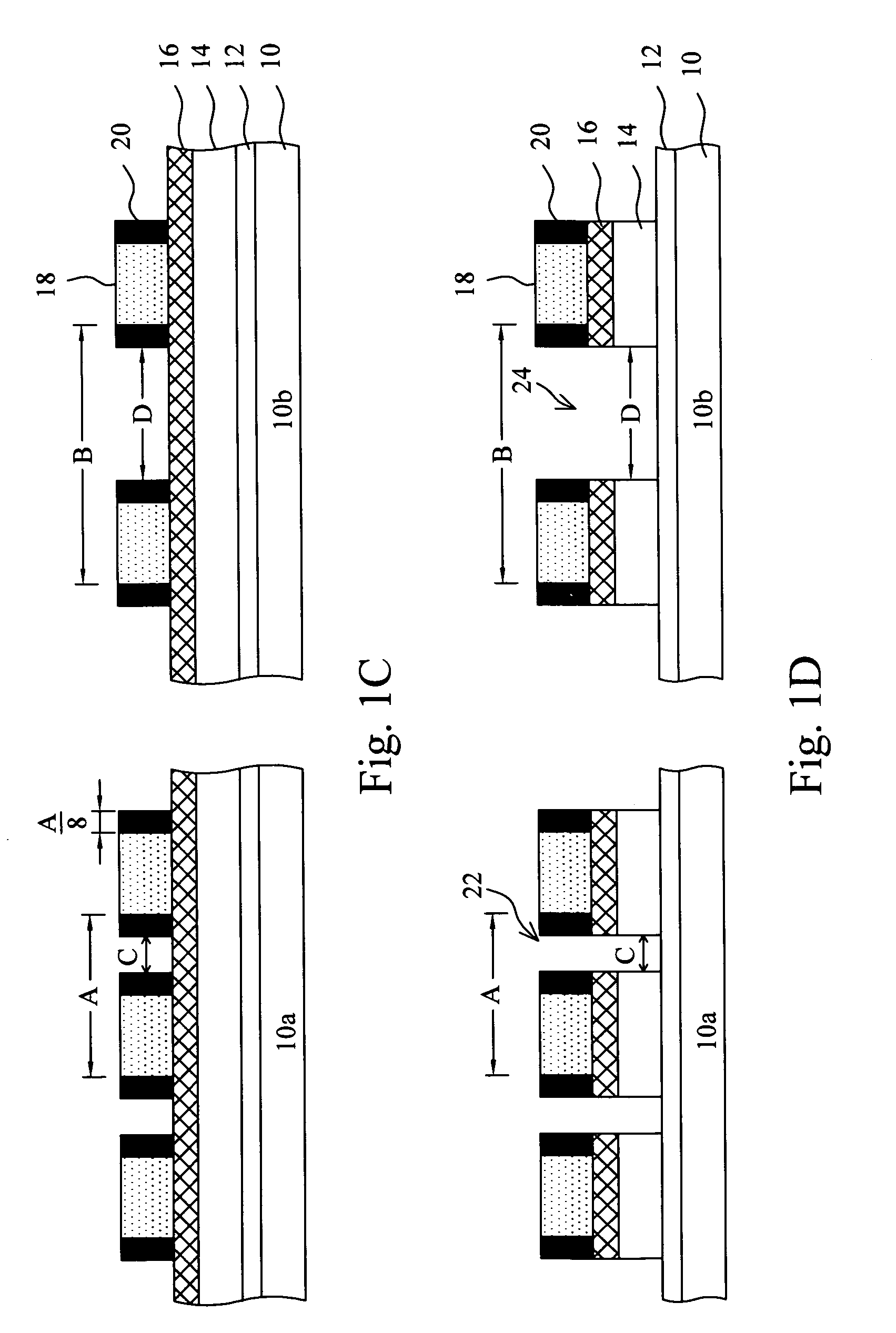

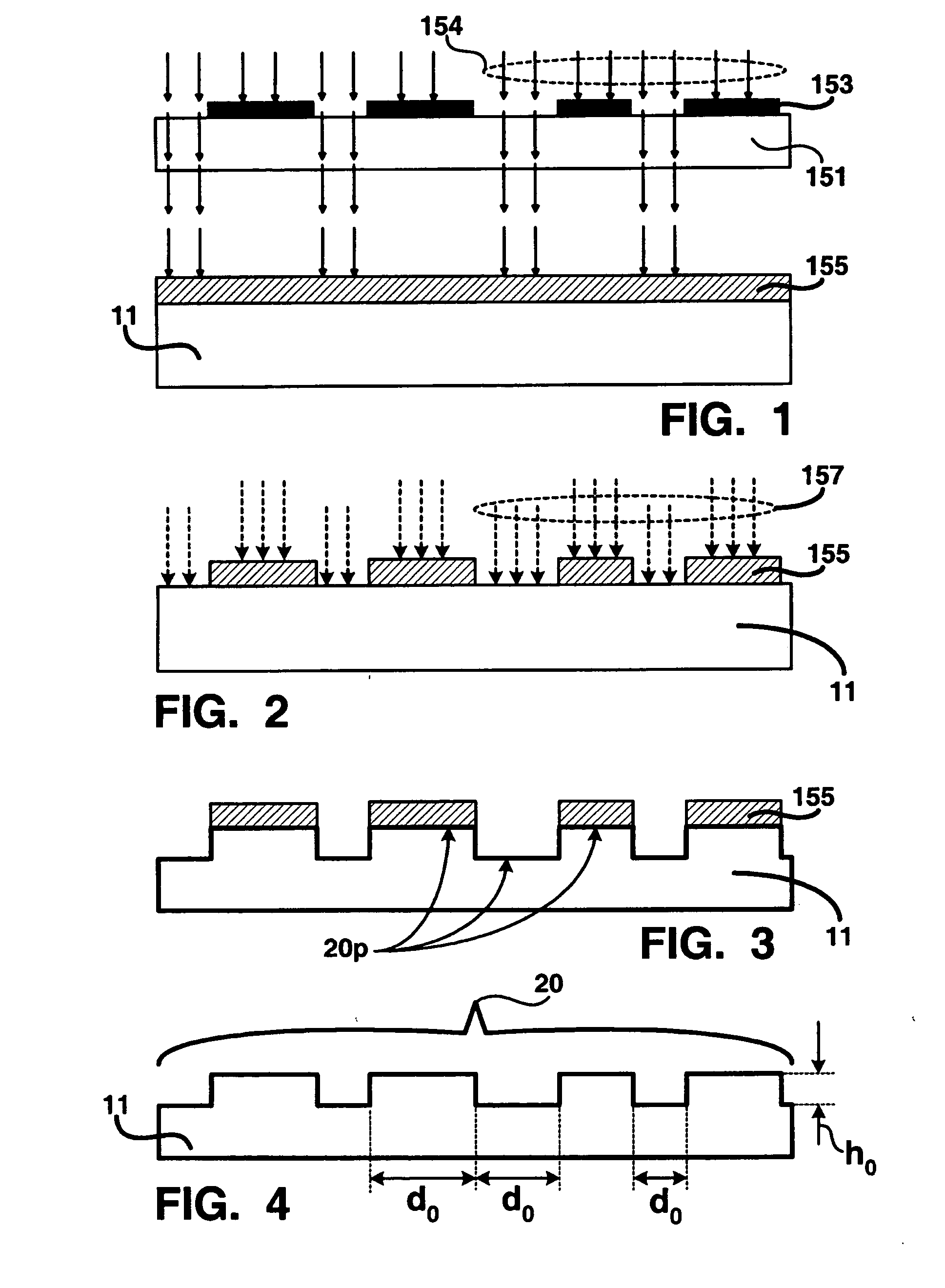

Method for defining a minimum pitch in an integrated circuit beyond photolithographic resolution

ActiveUS6955961B1Minimum polysilicon pitchSolid-state devicesSemiconductor/solid-state device manufacturingPhotosensitive polymerEngineering

A method for defining a minimum pitch in an integrated circuit beyond photolithographic resolution controls the defined pitches of the target layer by use of polymer spacer, photo-insensitive polymer plug and polymer mask during the process, so as to achieve the minimum pitch of the target layer beyond photolithographic resolution. Applied to memory manufacture, this method is capable of simultaneously overcoming the process difficulty of significant difference between polysilicon pitches in memory array region and periphery region.

Owner:MACRONIX INT CO LTD

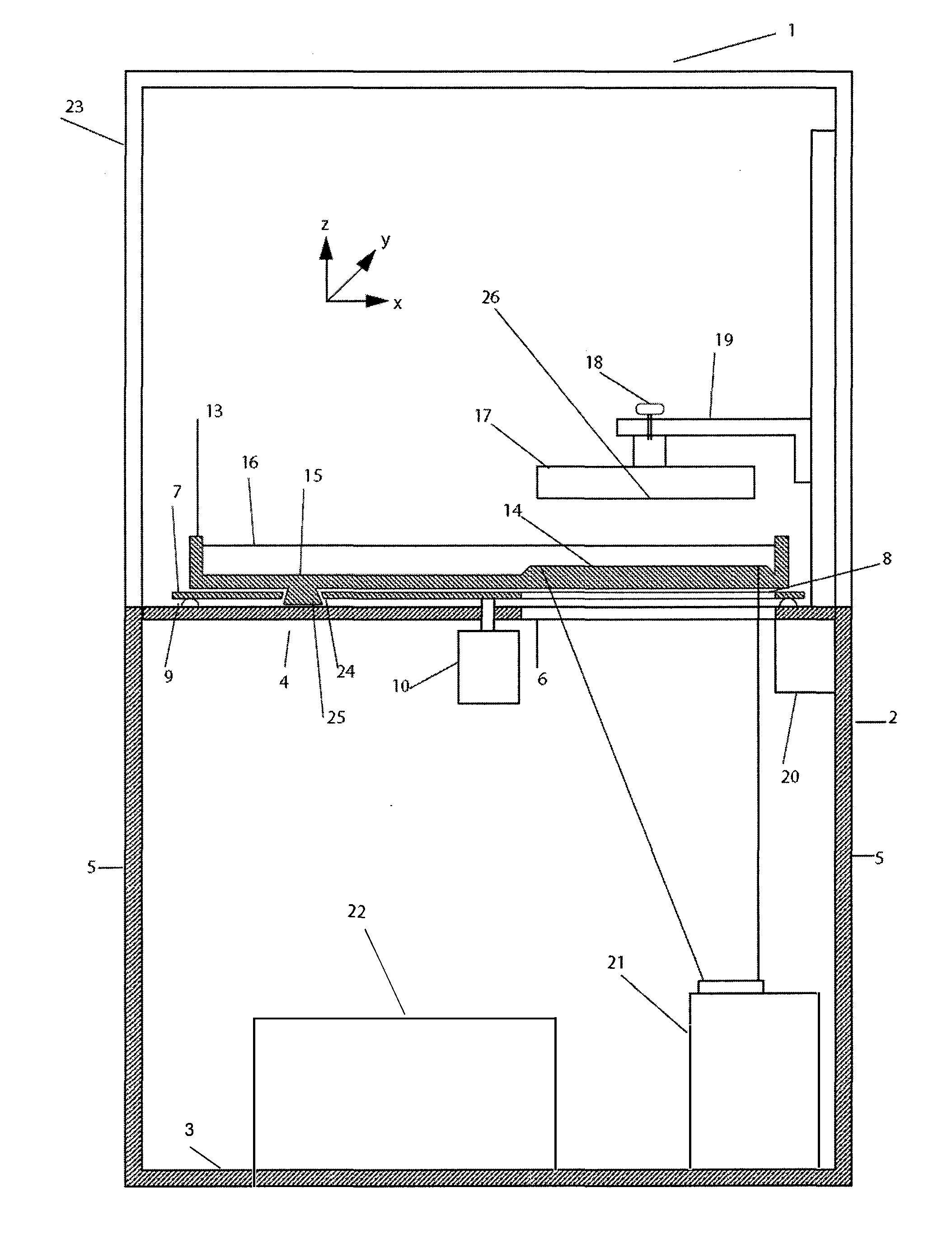

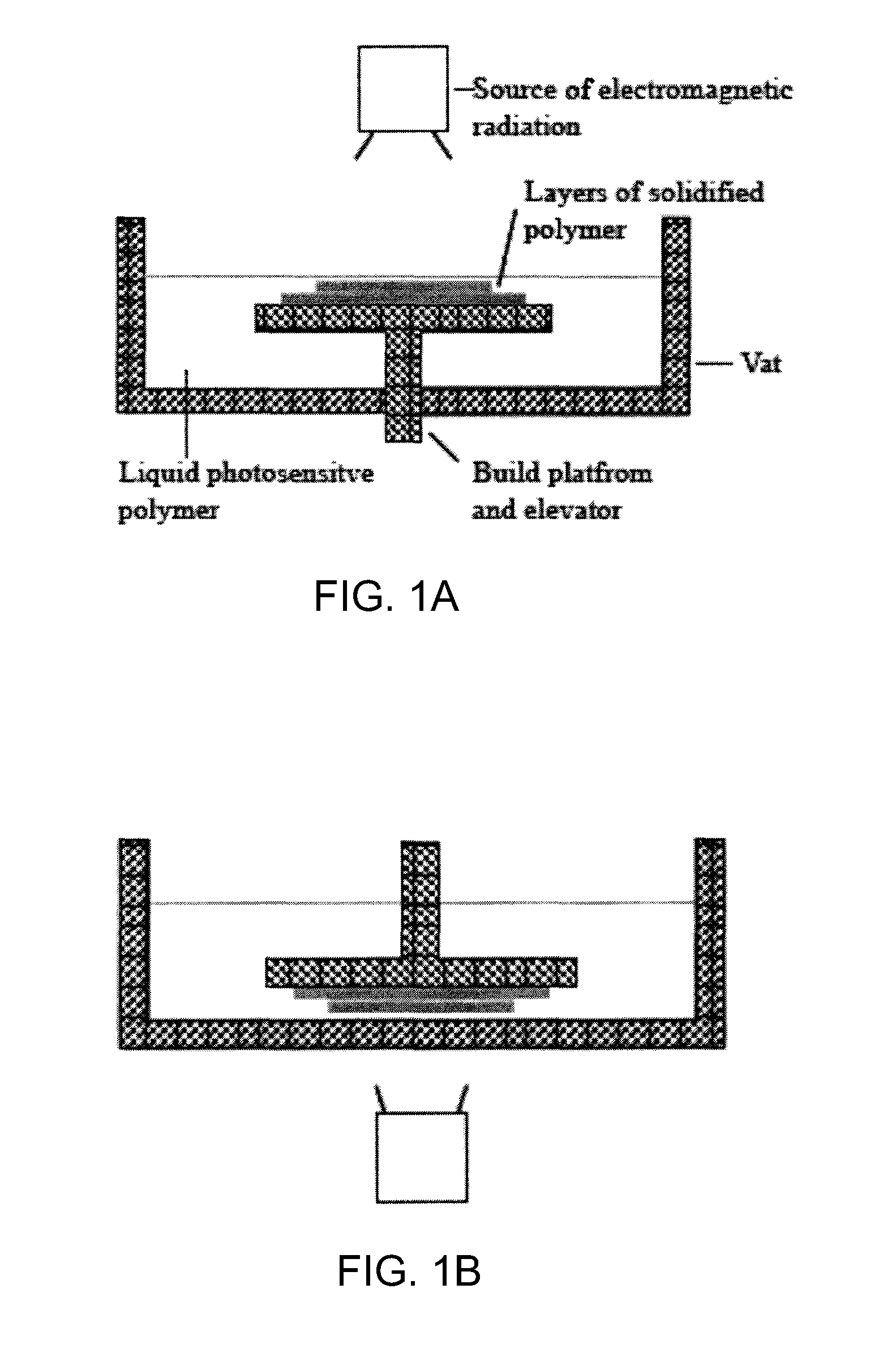

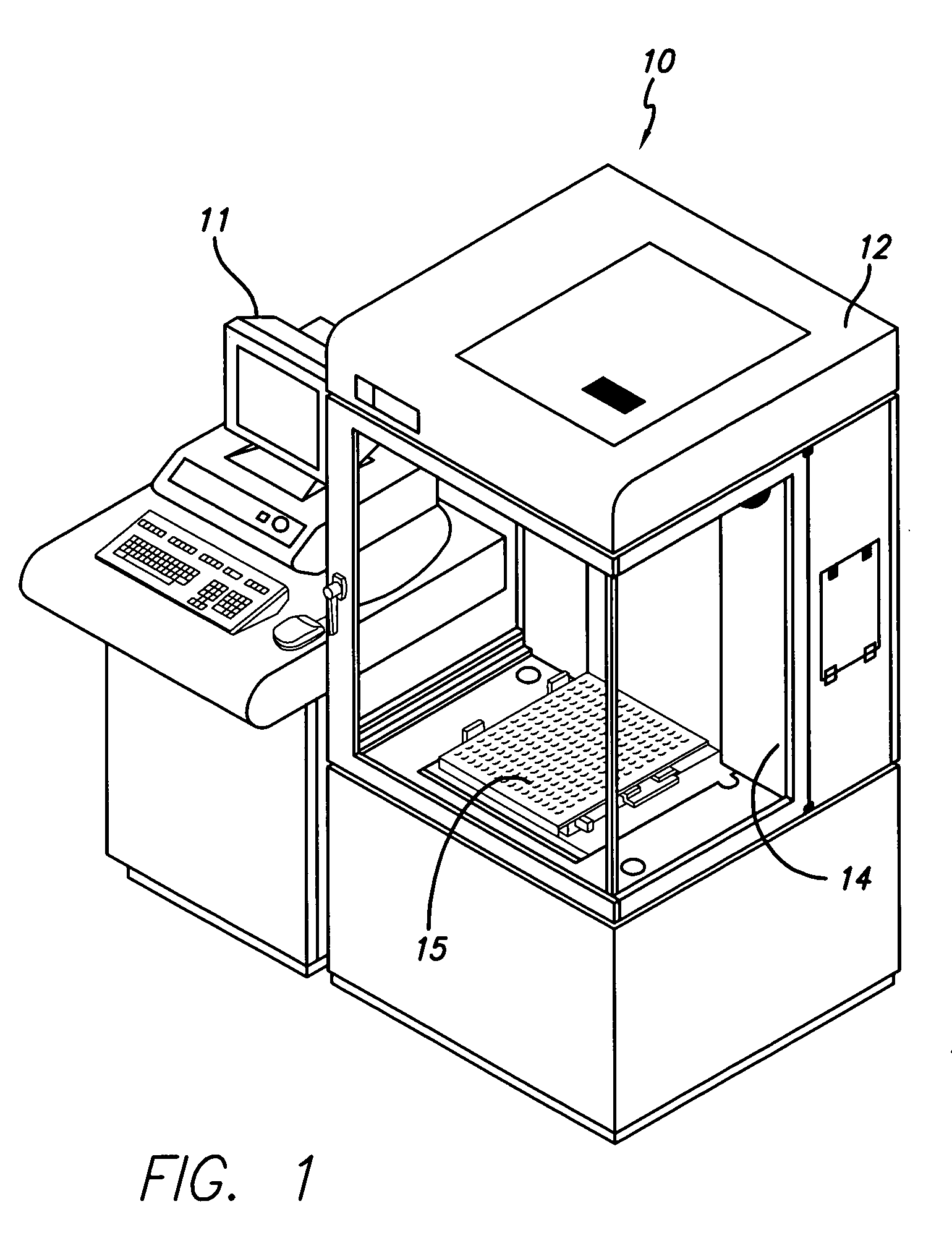

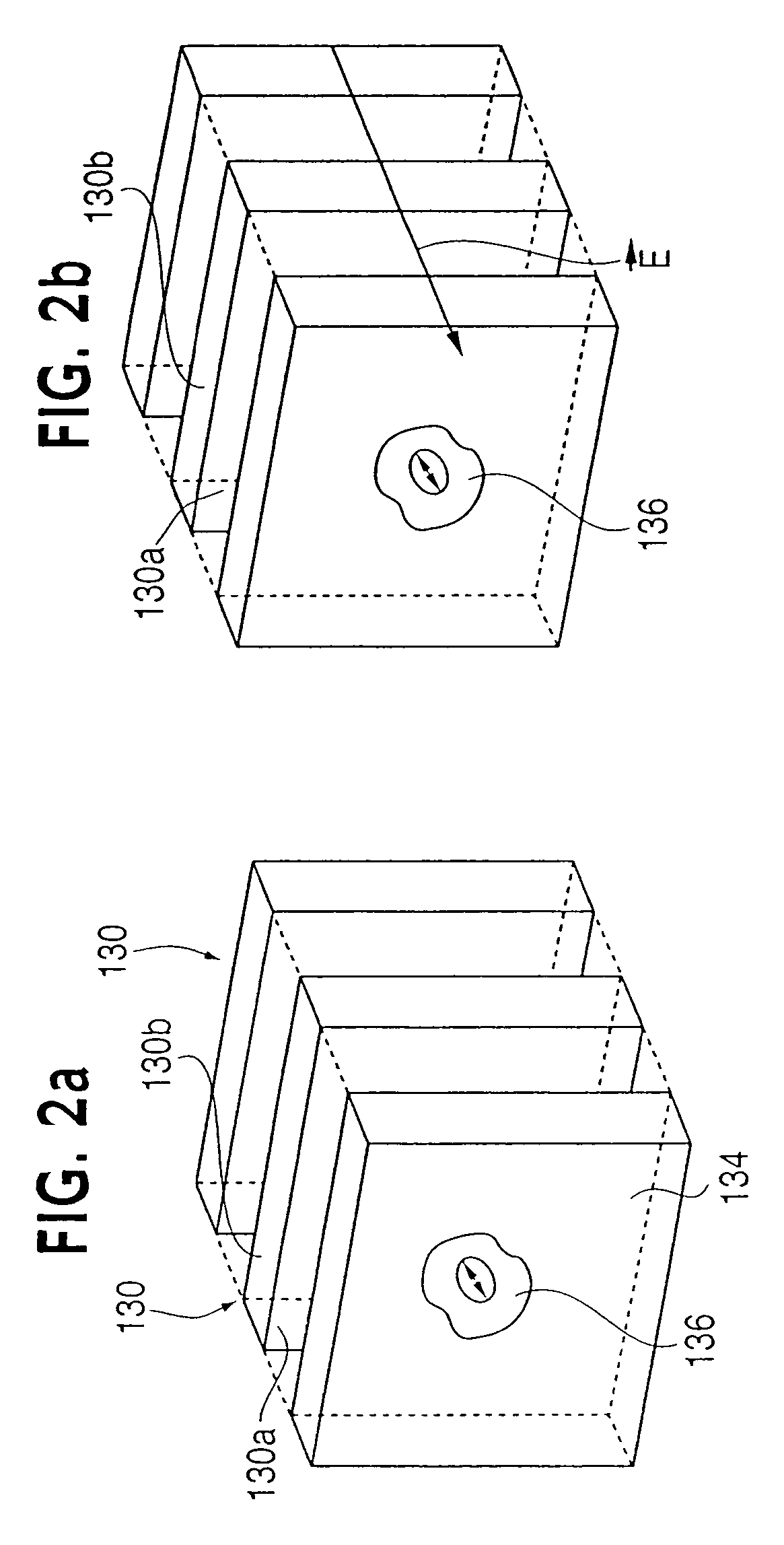

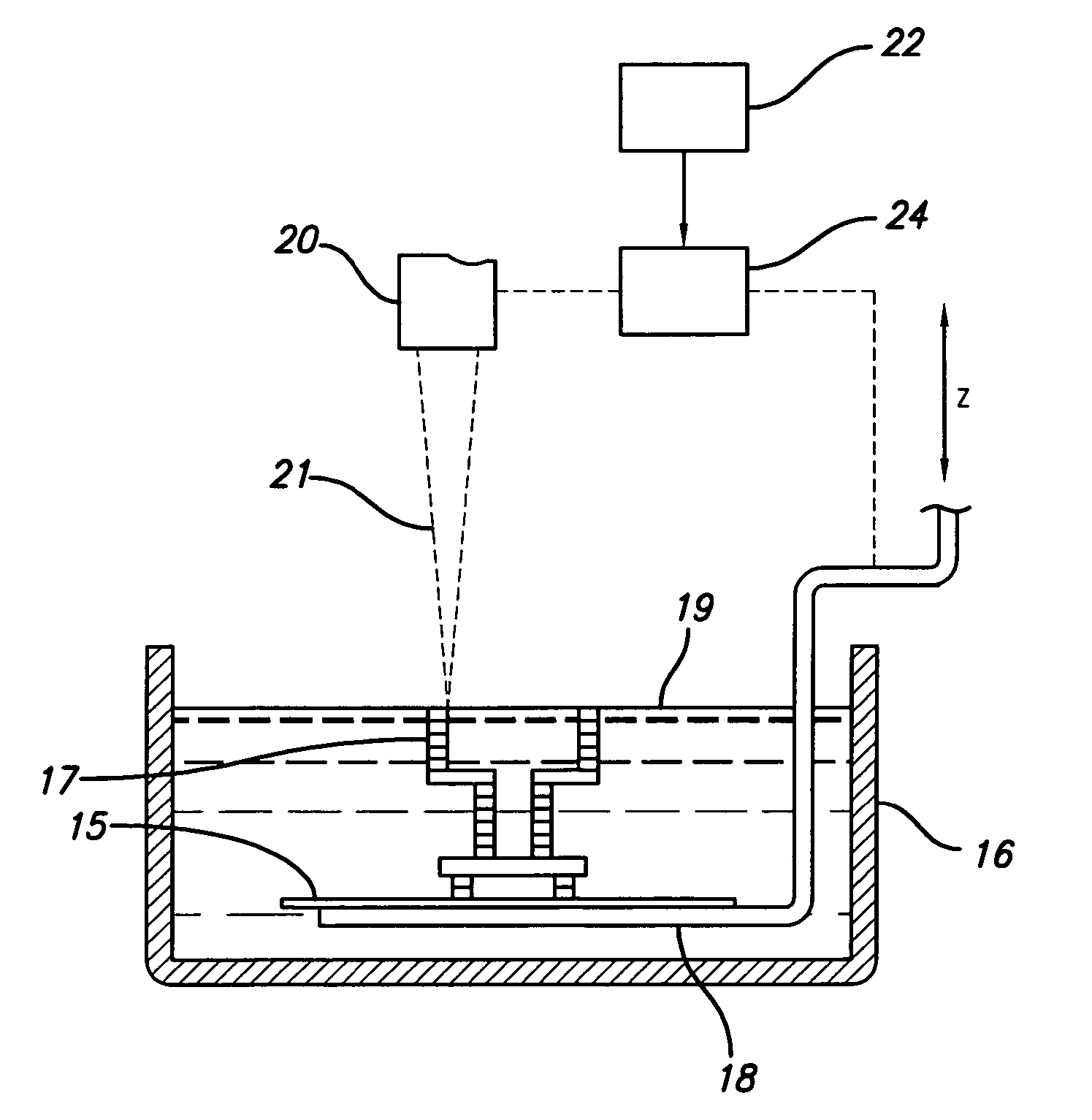

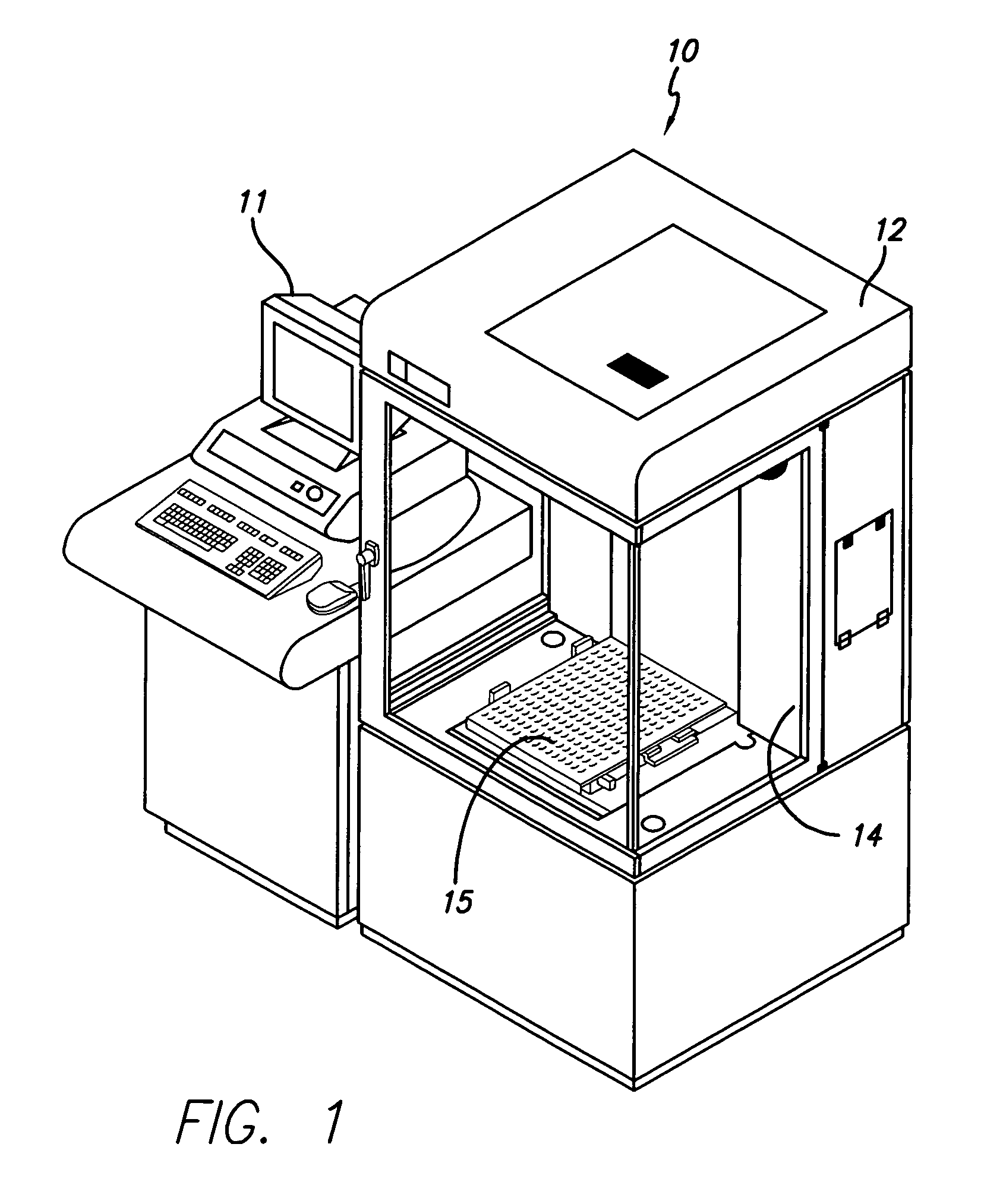

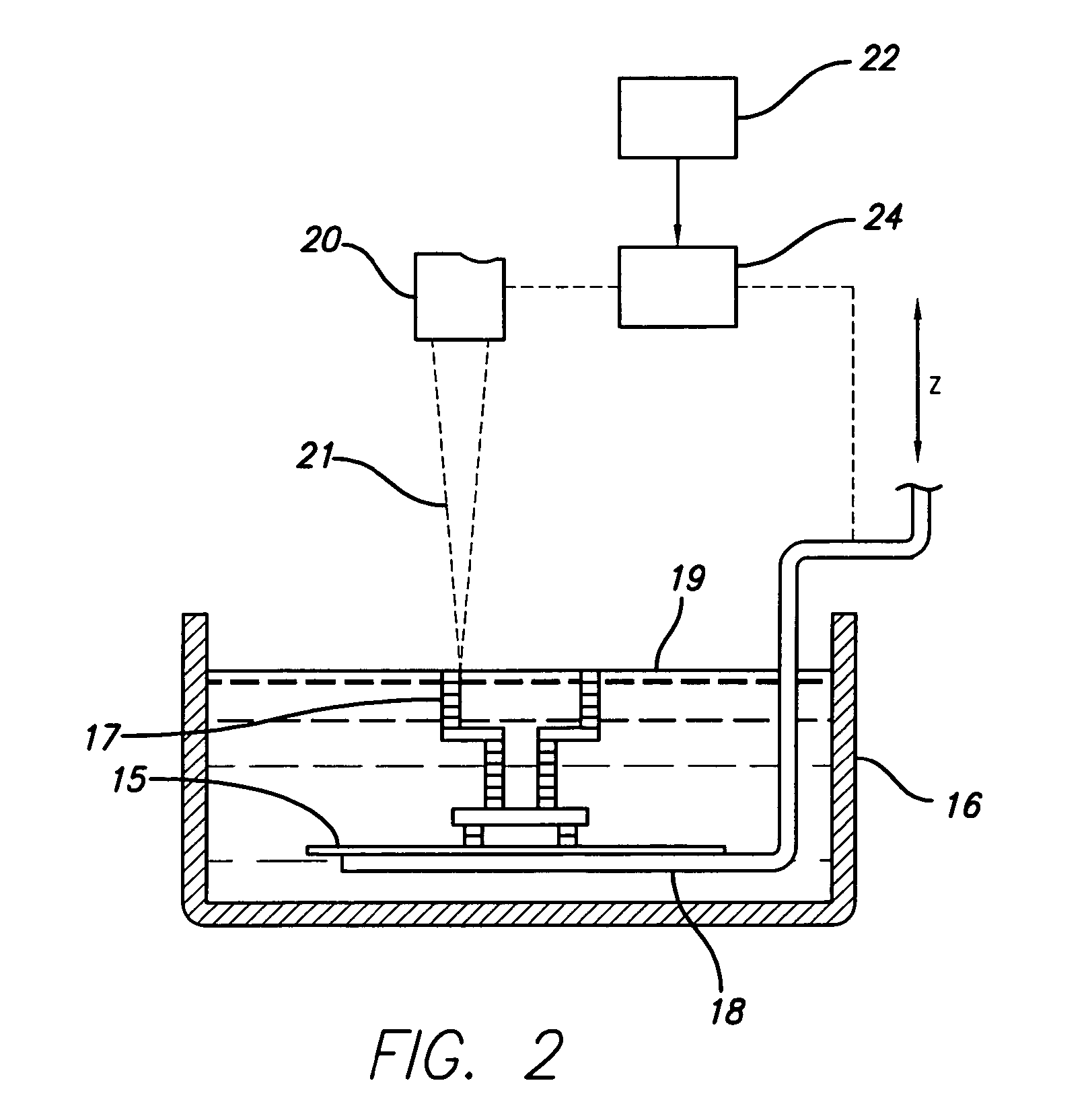

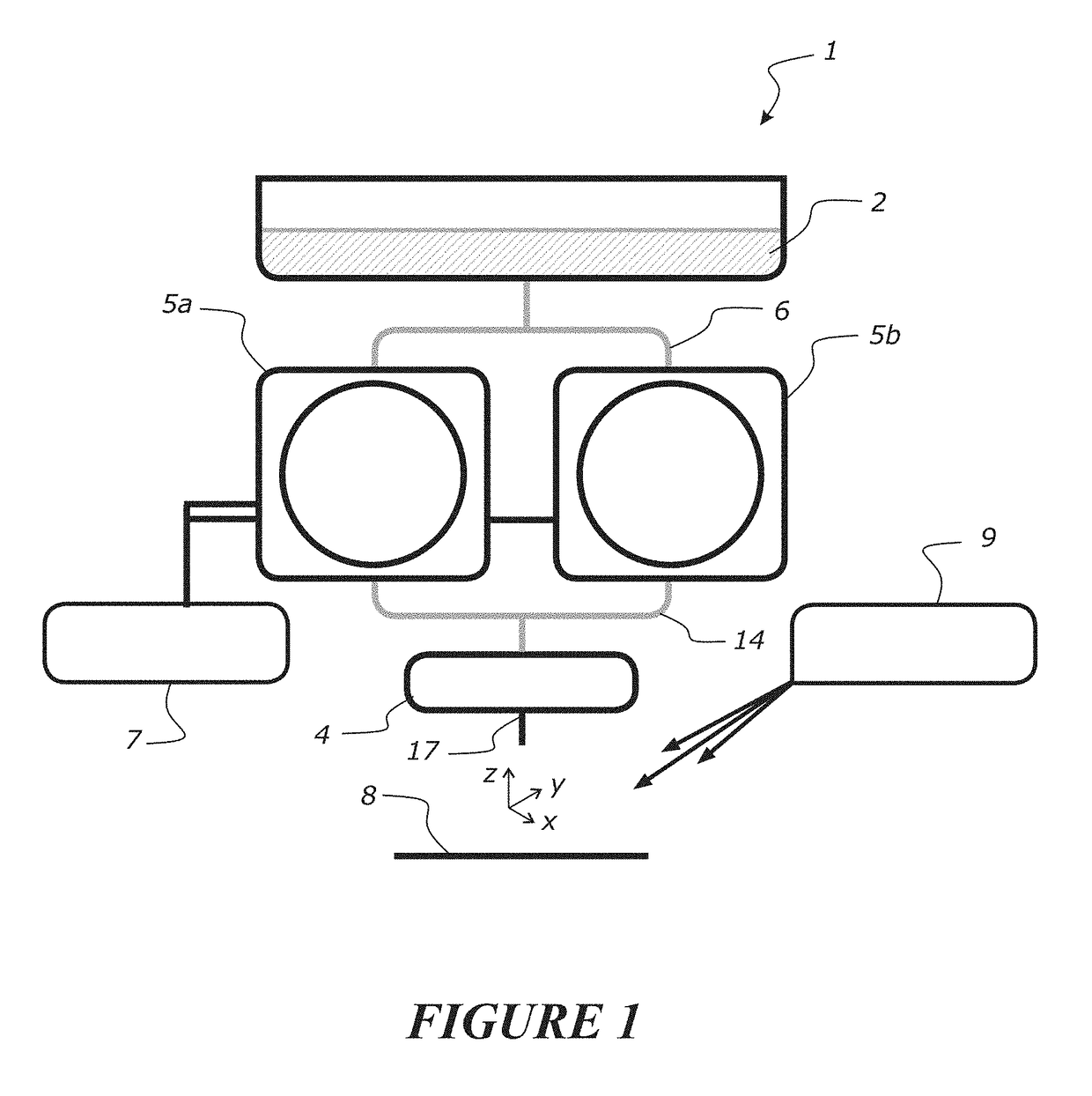

Apparatus for fabrication of three dimensional objects

ActiveUS20140339741A1Reduce power outputIncrease exposure timeManufacturing driving meansManufacturing enclosuresPhotosensitive polymerEngineering

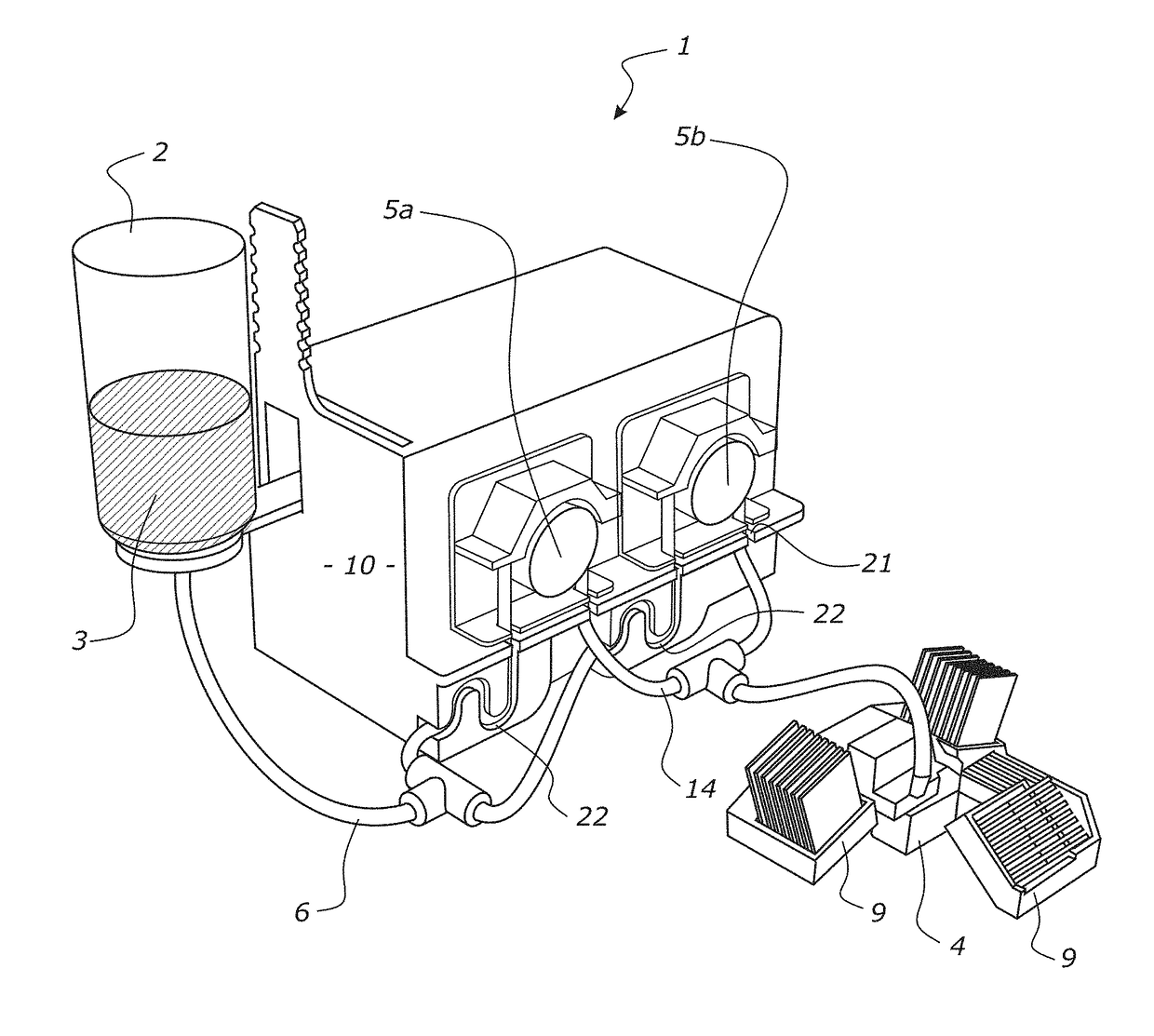

An apparatus for bottom-up fabrication of three dimensional objects, the apparatus comprising: a vat for a photosensitive polymer, the floor of the vat including a working surface arranged such that, in use, light incident on the working surface interacts with the photosensitive polymer at the working surface to fabricate a portion of the three dimensional object; a build platform capable of being inserted into the vat, the build platform having a planar surface; an elevator mechanism capable of adjusting the separation between the working surface of the vat and the planar surface of the build platform; and a rotation mechanism capable of varying the relative rotational position of the vat relative to the build platform, the relative rotation being about an axis which is normal to the working surface of the vat.

Owner:HOLO INC

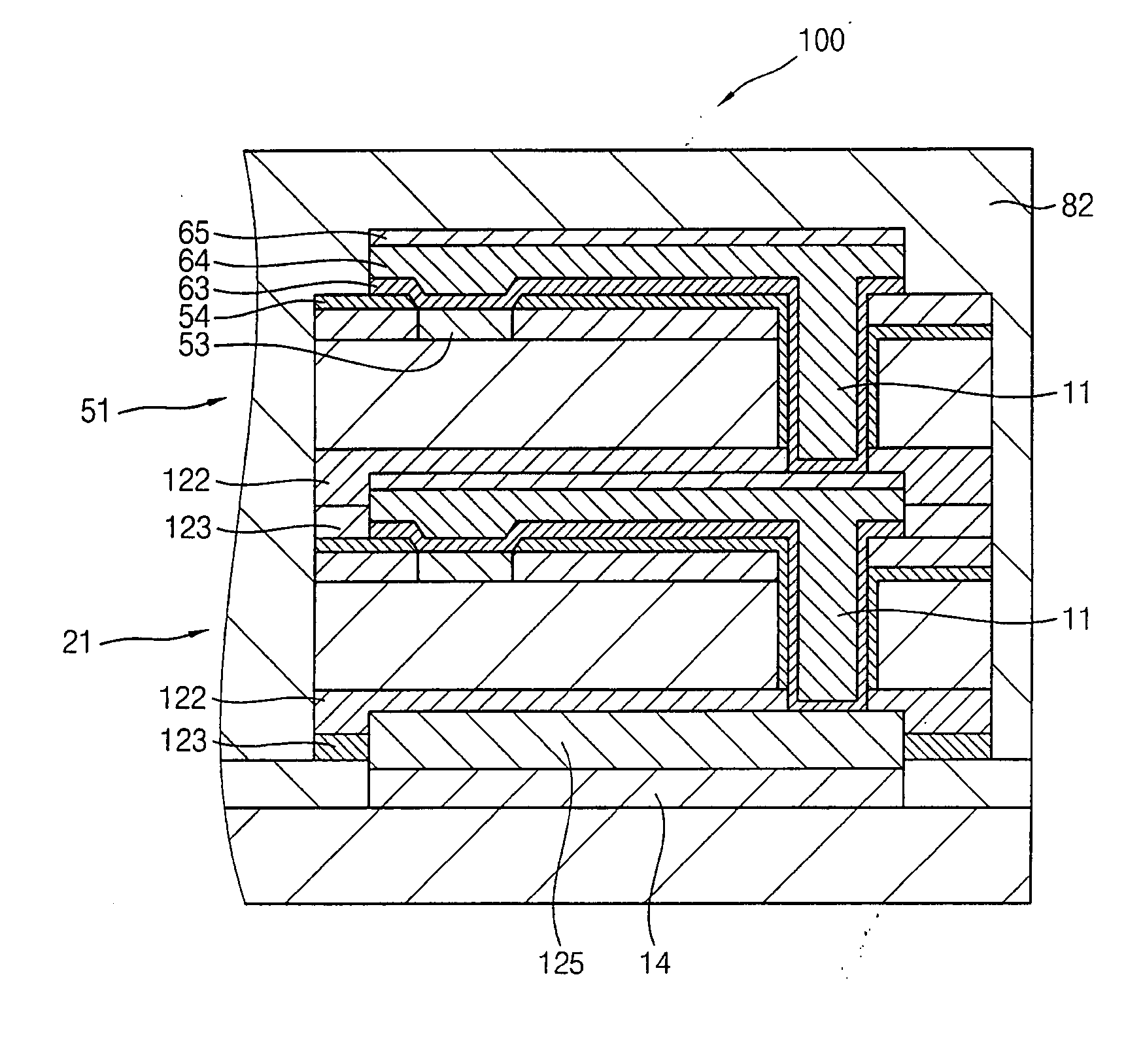

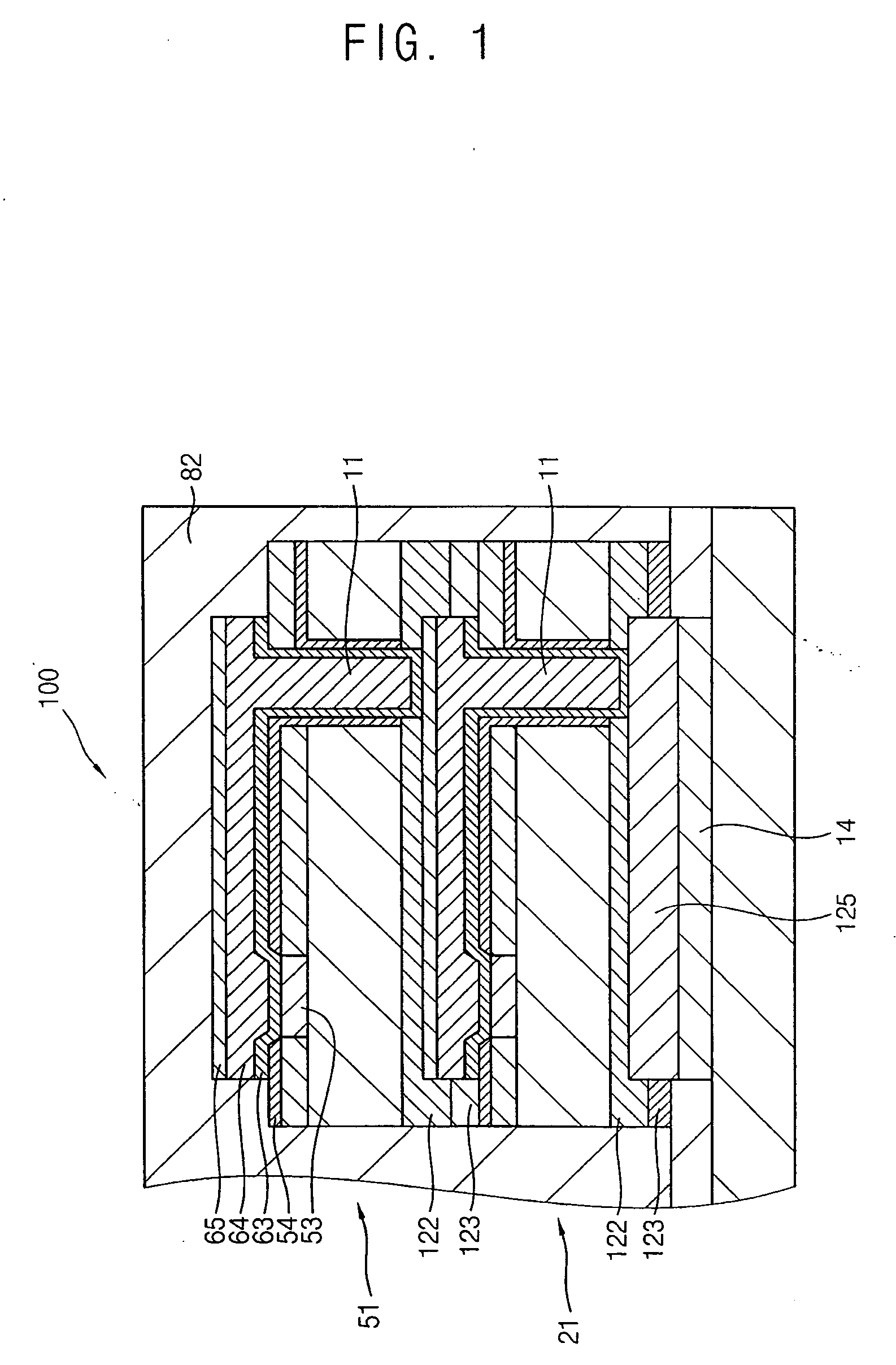

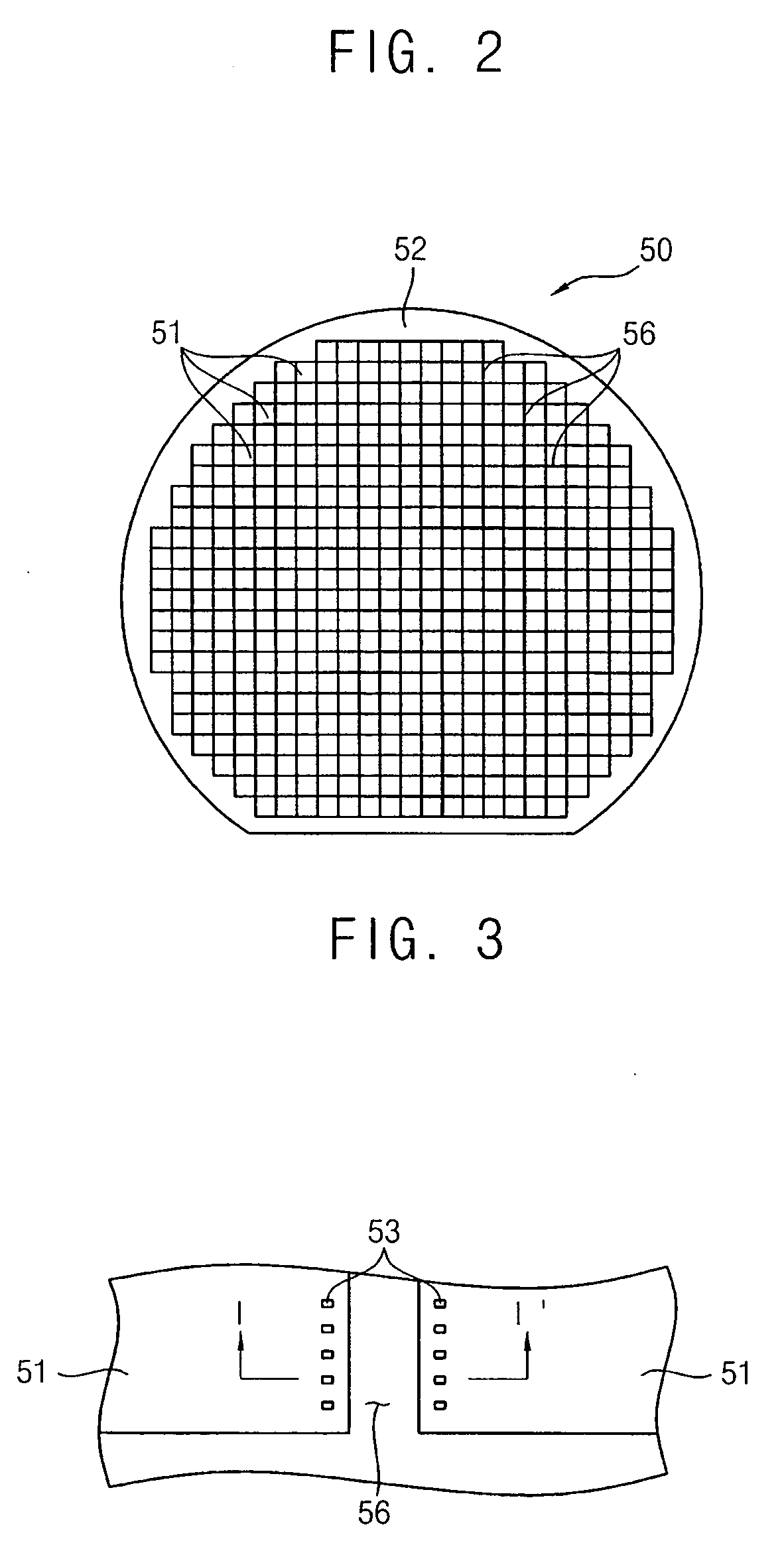

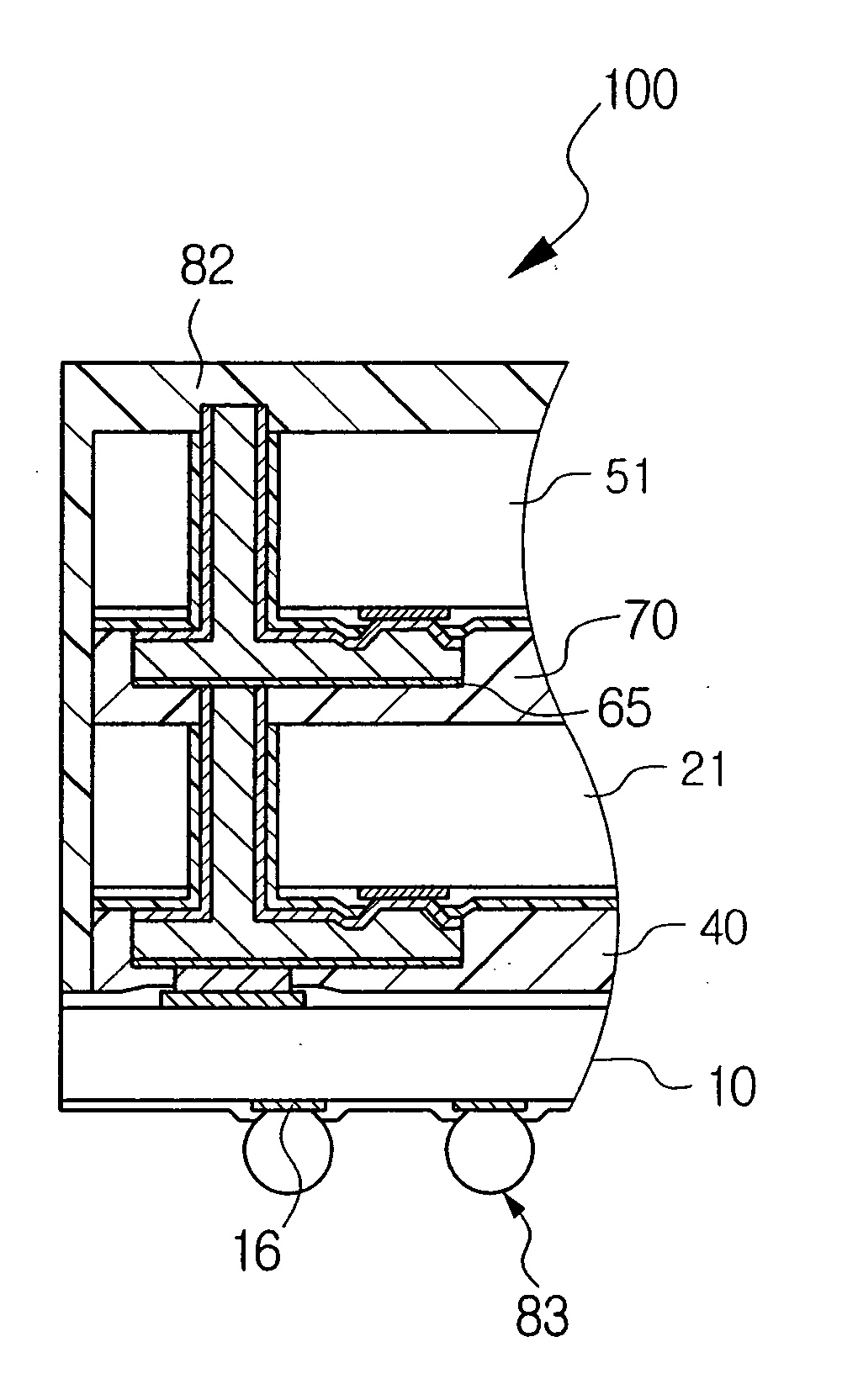

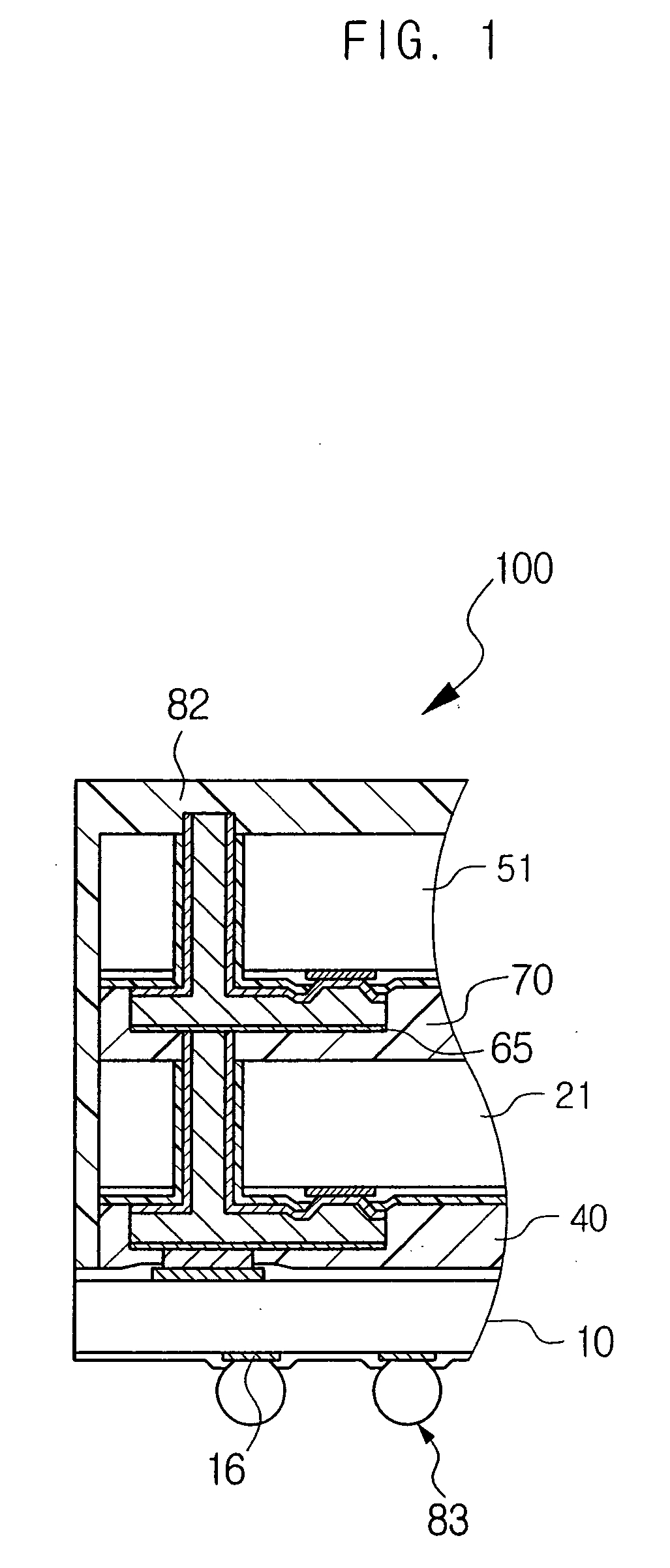

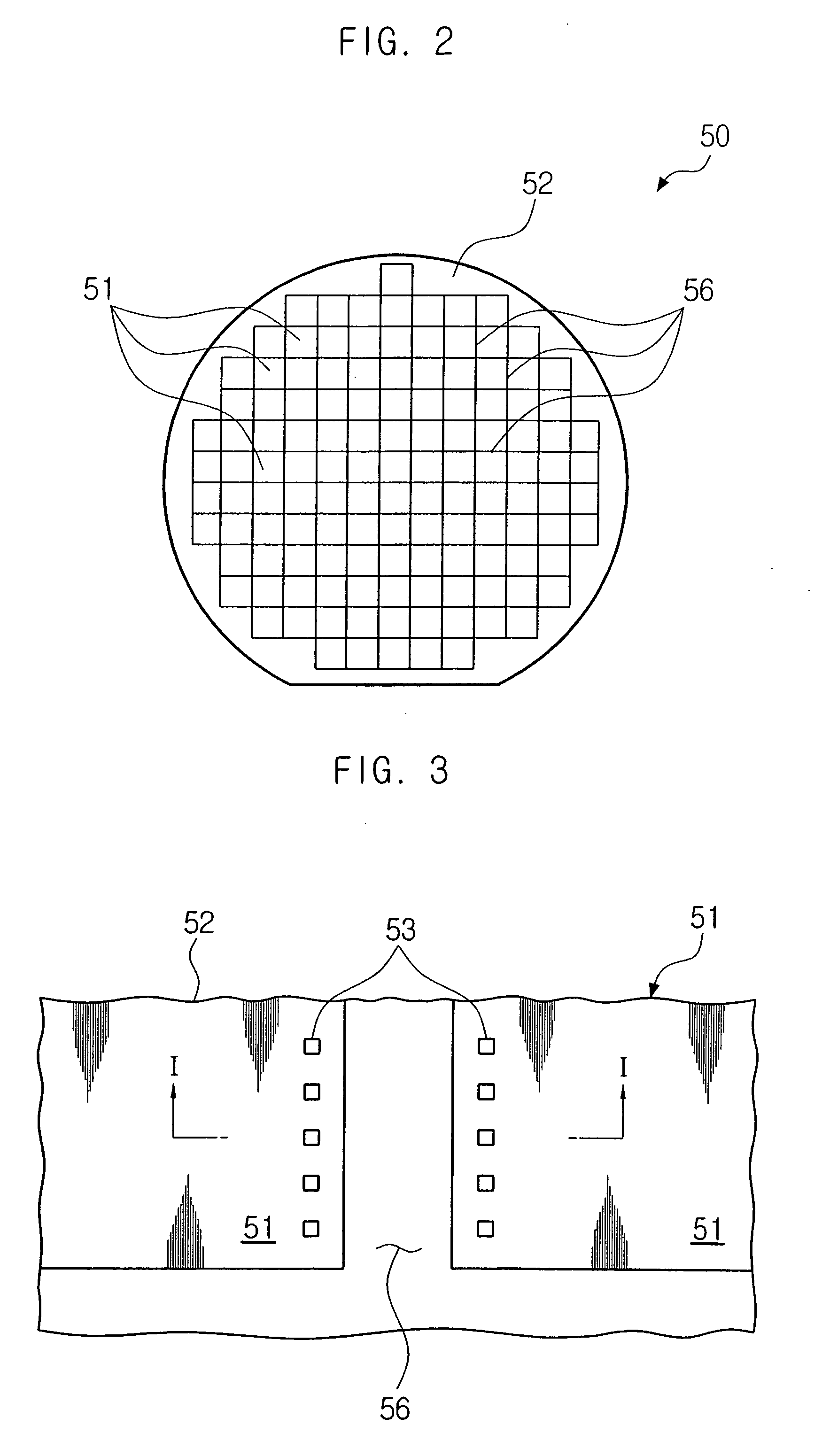

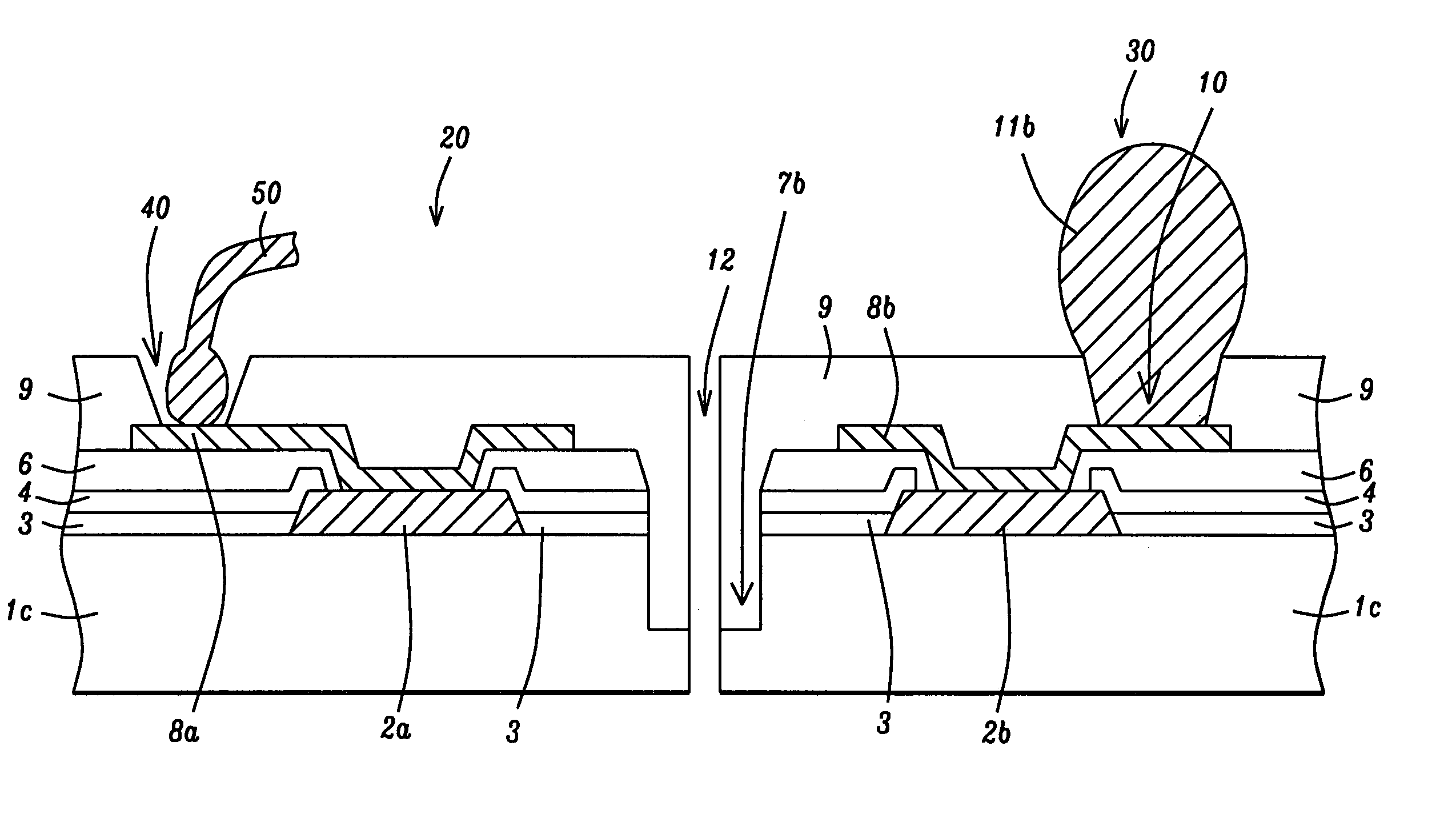

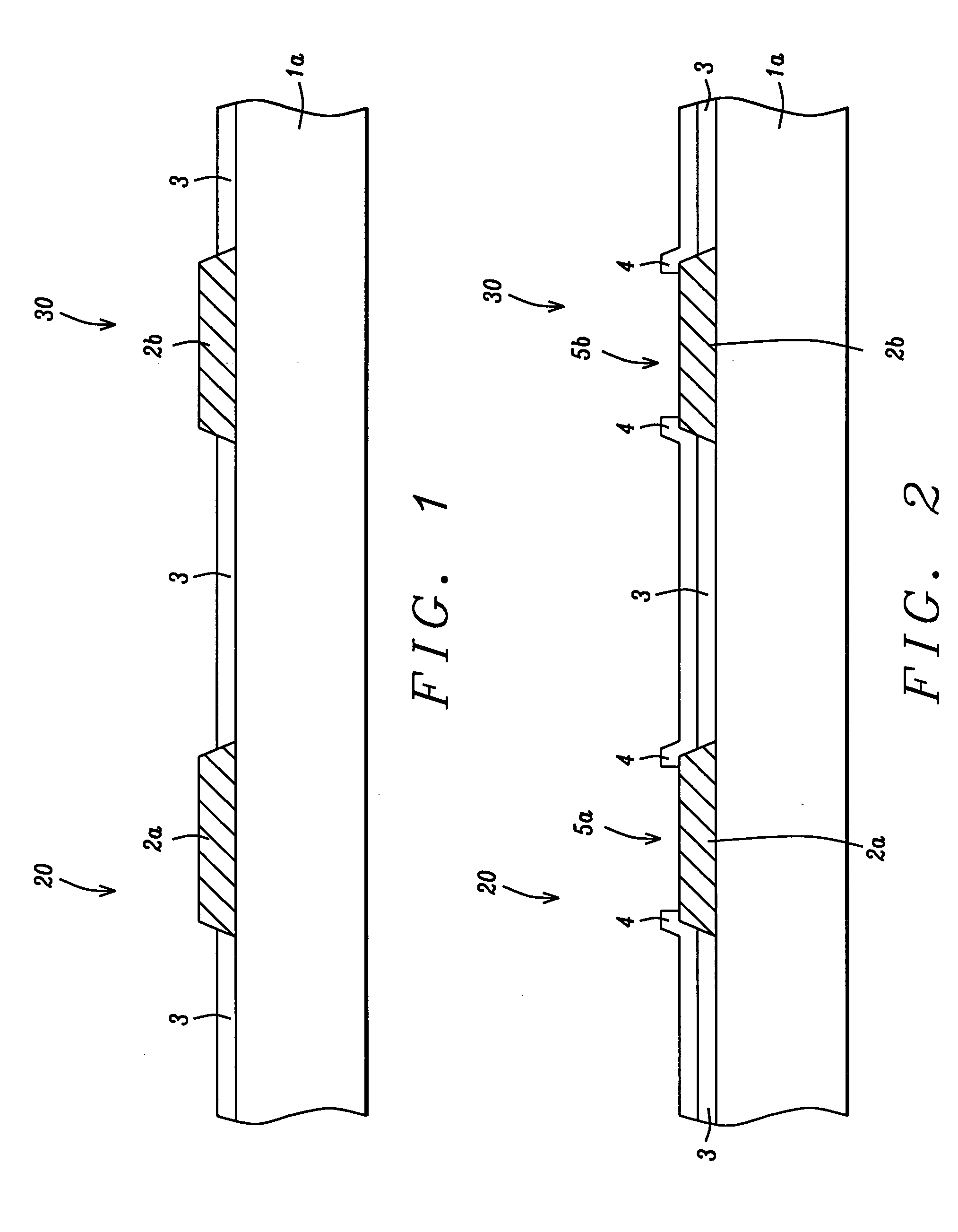

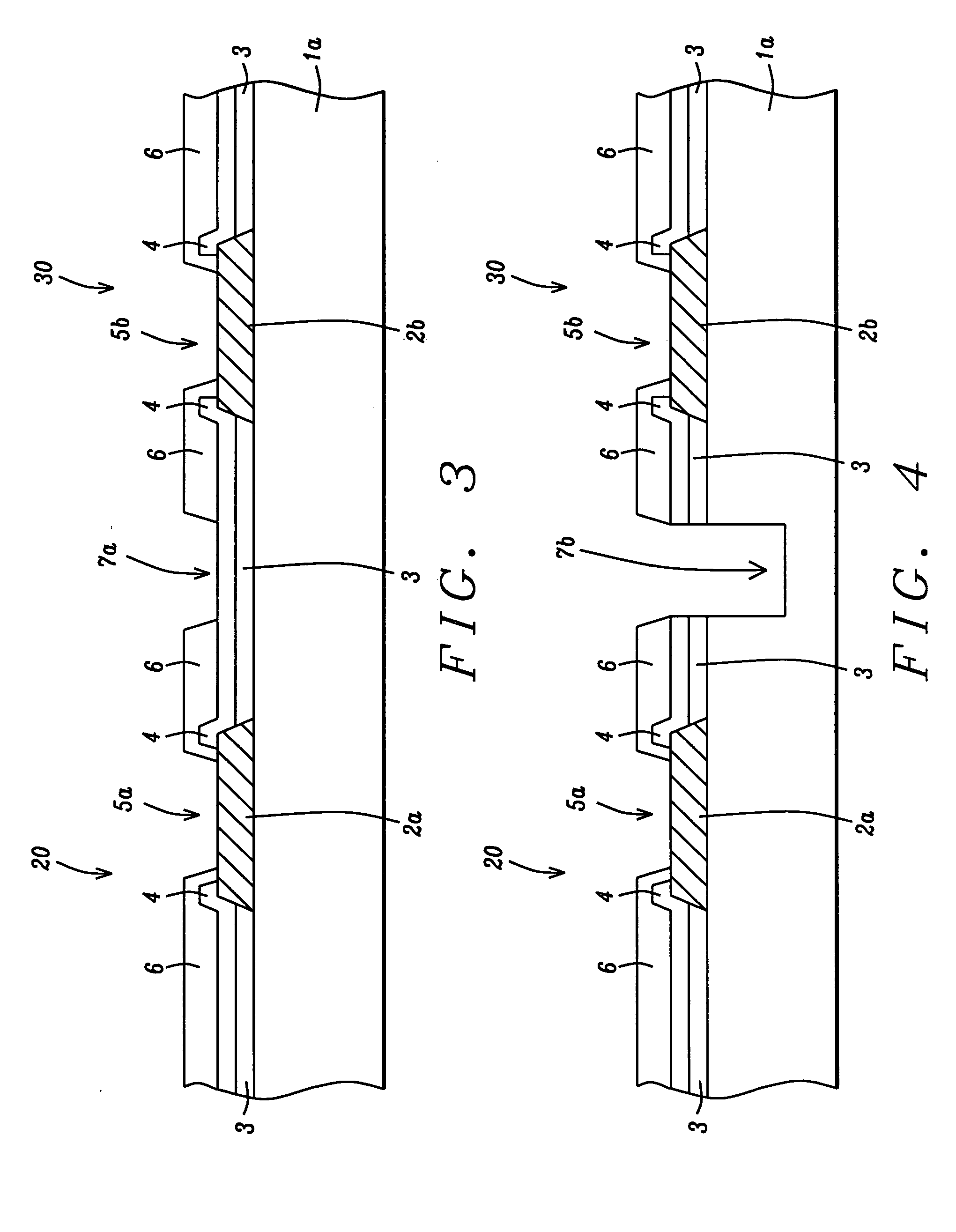

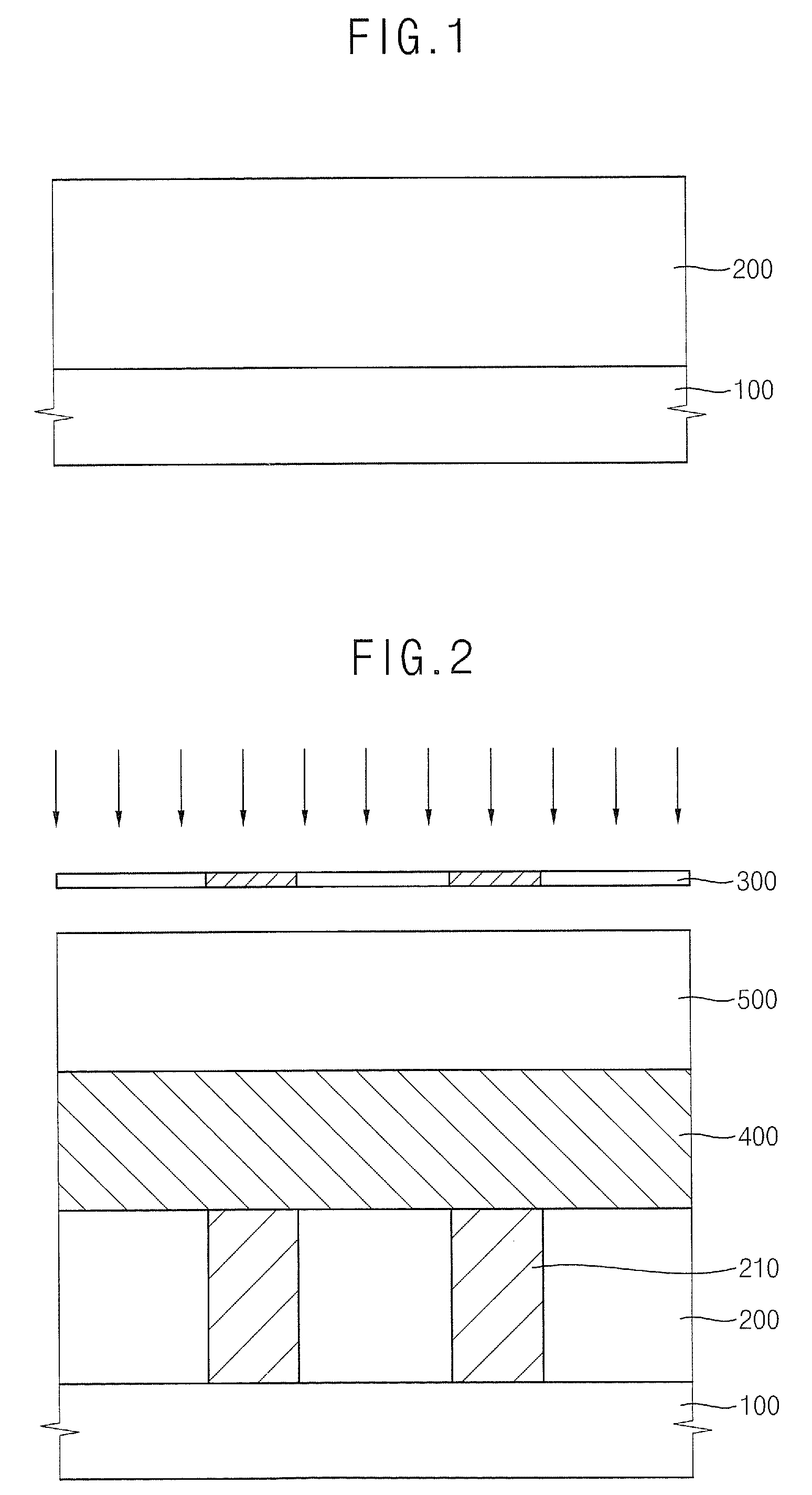

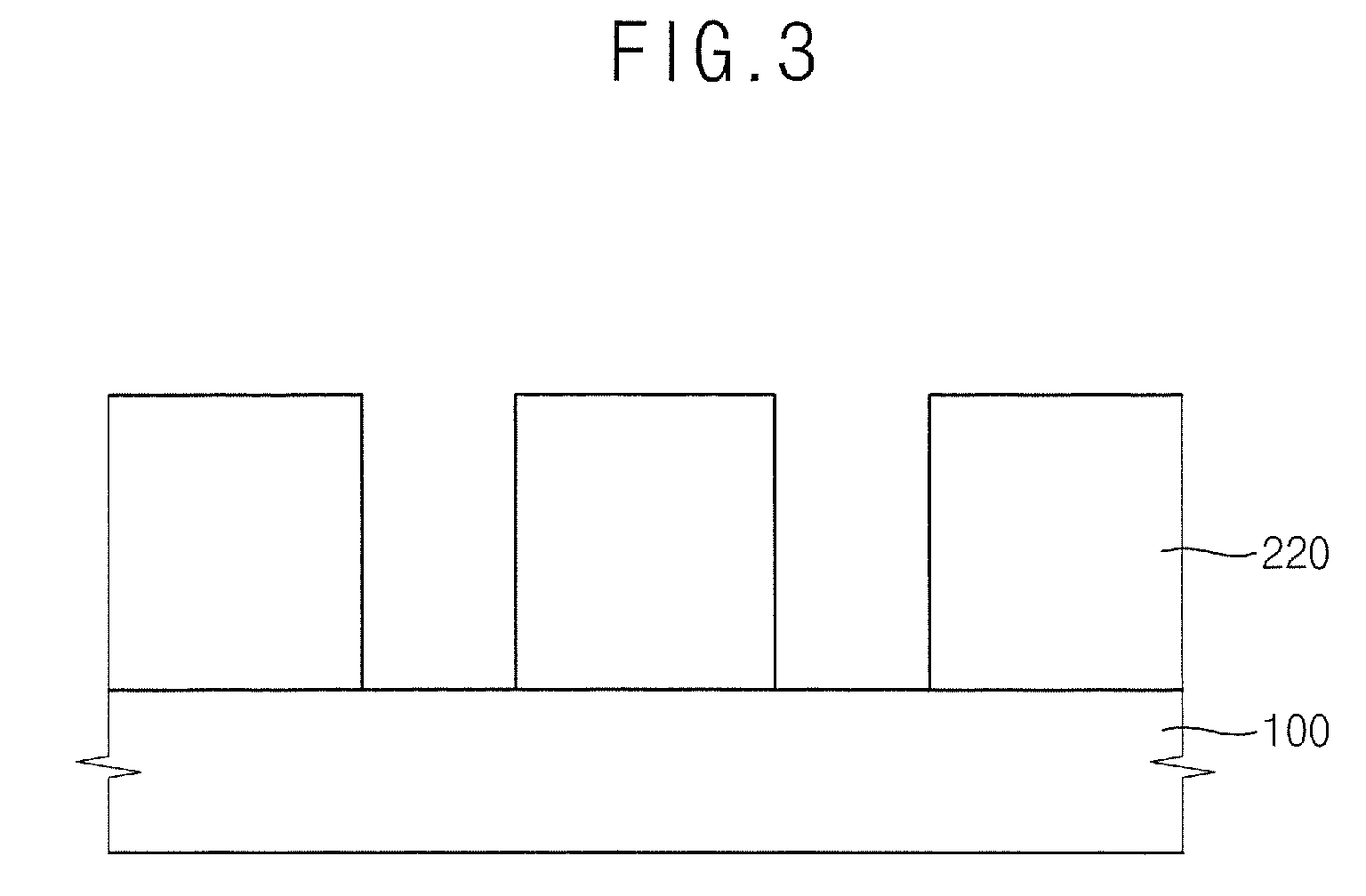

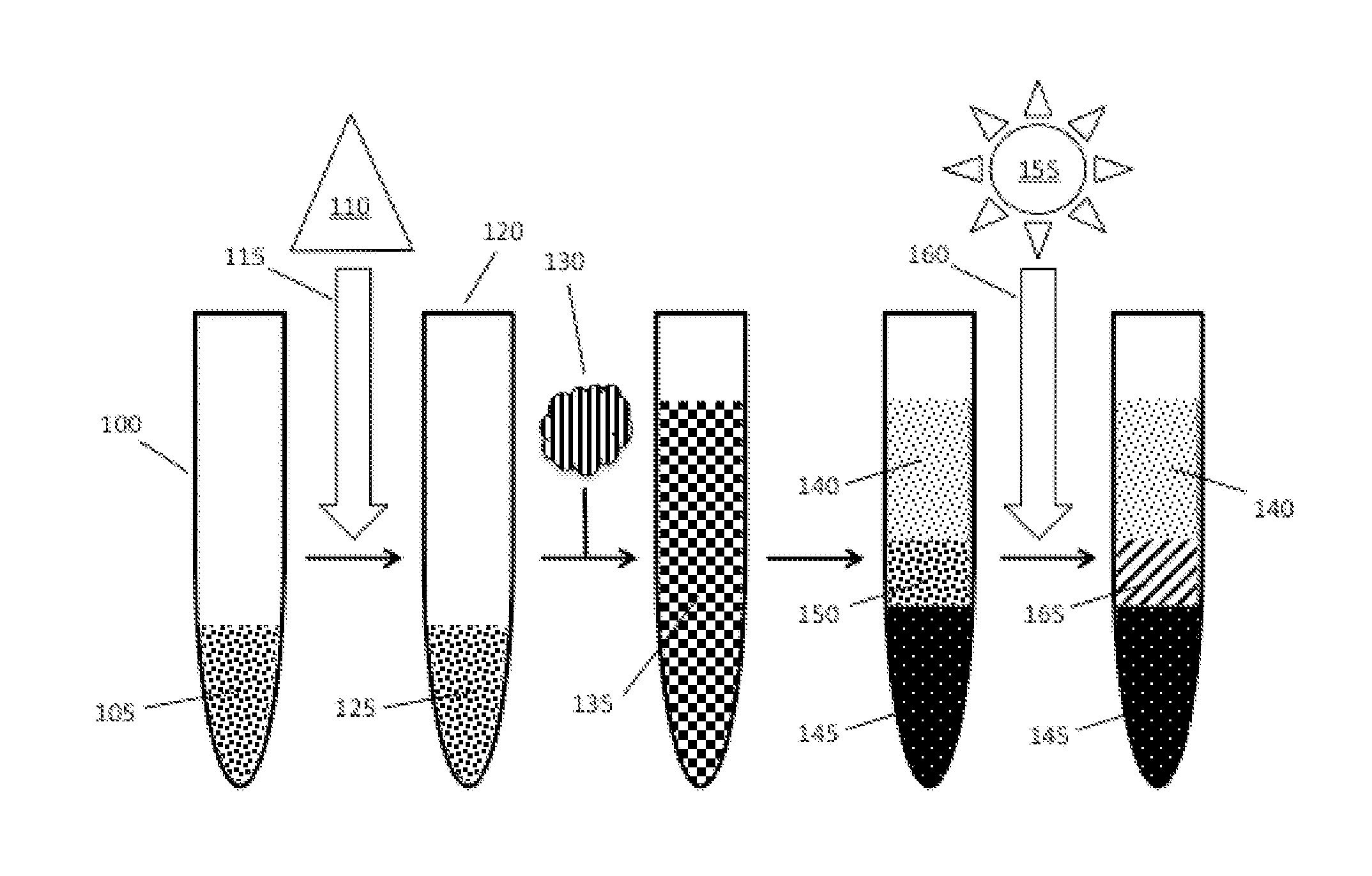

Stacked chip package using warp preventing insulative material and manufacturing method thereof

InactiveUS20070045836A1AdhesionHigh mechanical reliabilitySemiconductor/solid-state device detailsSolid-state devicesMechanical reliabilityPhotosensitive polymer

In a stacked chip configuration, and manufacturing methods thereof, the gap between a lower chip and an upper chip is filled completely using a relatively simple process that eliminates voids between the lower and upper chips and the cracking and delamination problems associated with voids. The present invention is applicable to both chip-level bonding and wafer-level bonding approaches. A photosensitive polymer layer is applied to a first chip, or wafer, prior to stacking the chips or stacking the wafers. The photosensitive polymer layer is partially cured, so that the photosensitive polymer layer is made to be structurally stable, while retaining its adhesive properties. The second chip, or wafer, is stacked, aligned, and bonded to the first chip, or wafer, and the photosensitive polymer layer is then cured to fully bond the first and second chips, or wafers. In this manner, adhesion between chips / wafers is greatly improved, while providing complete fill of the gap. In addition, mechanical reliability is improved and CTE mismatch is reduced, alleviating the problems associated with warping, cracking and delamination, and leading to an improvement in device yield and device reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

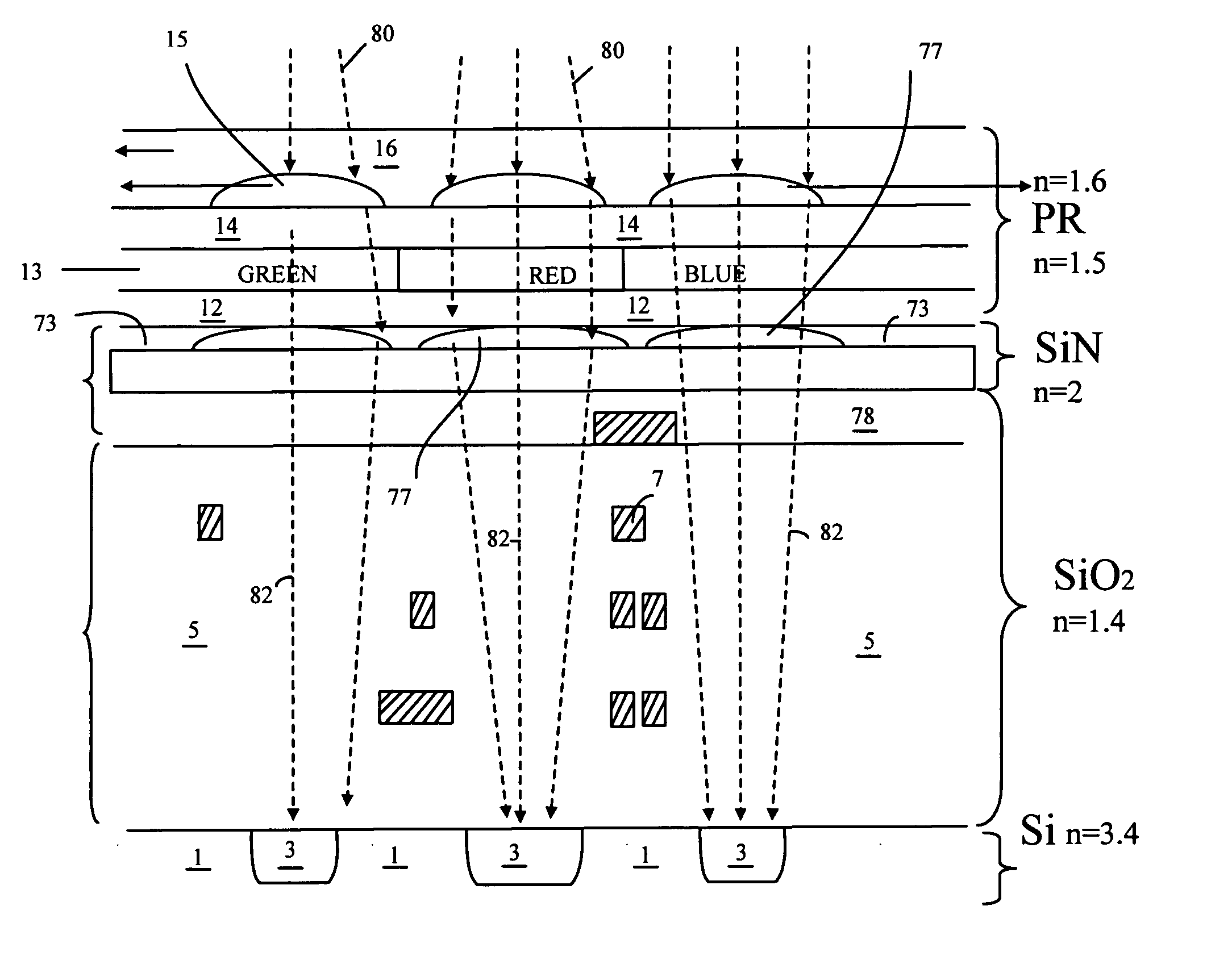

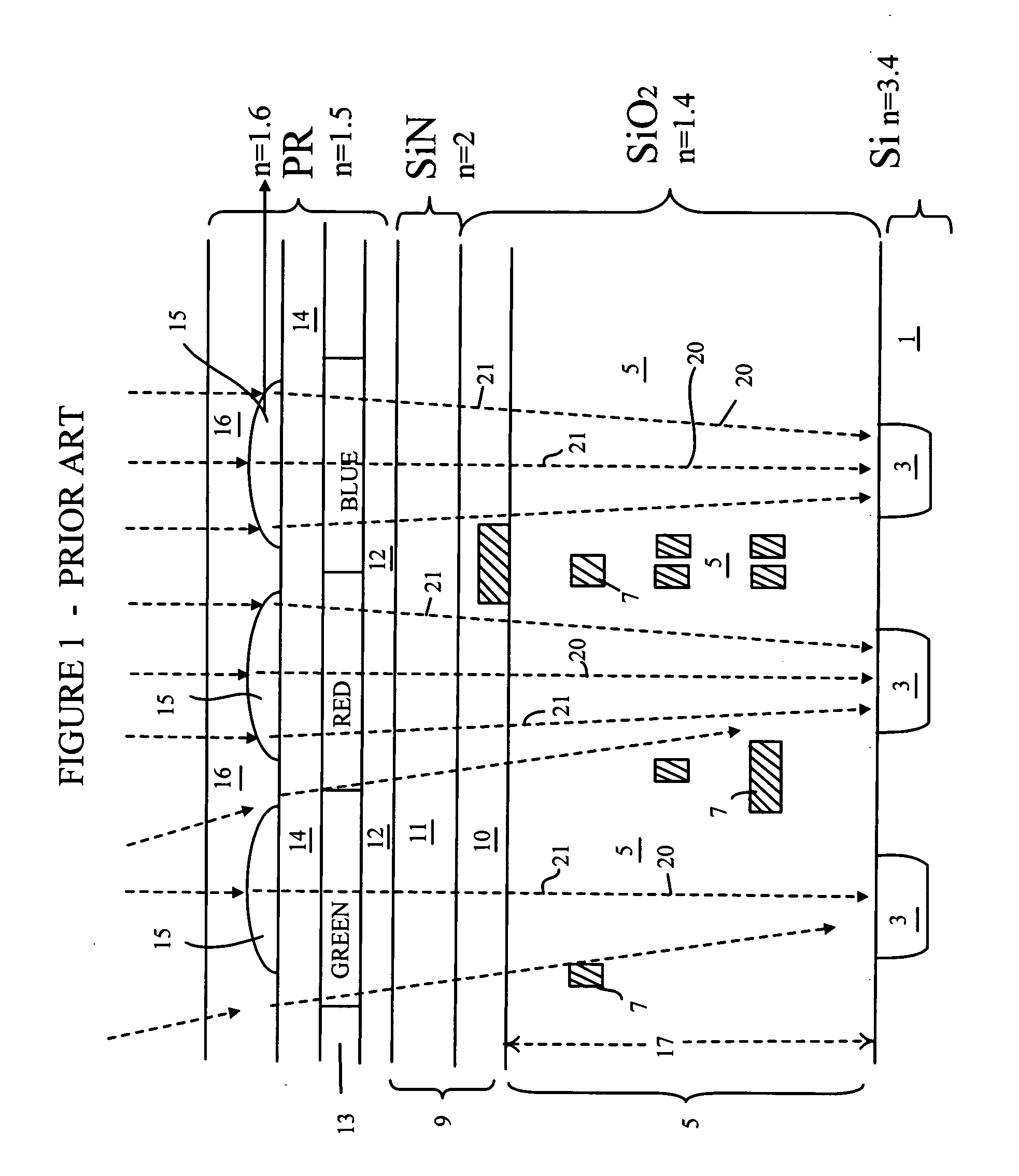

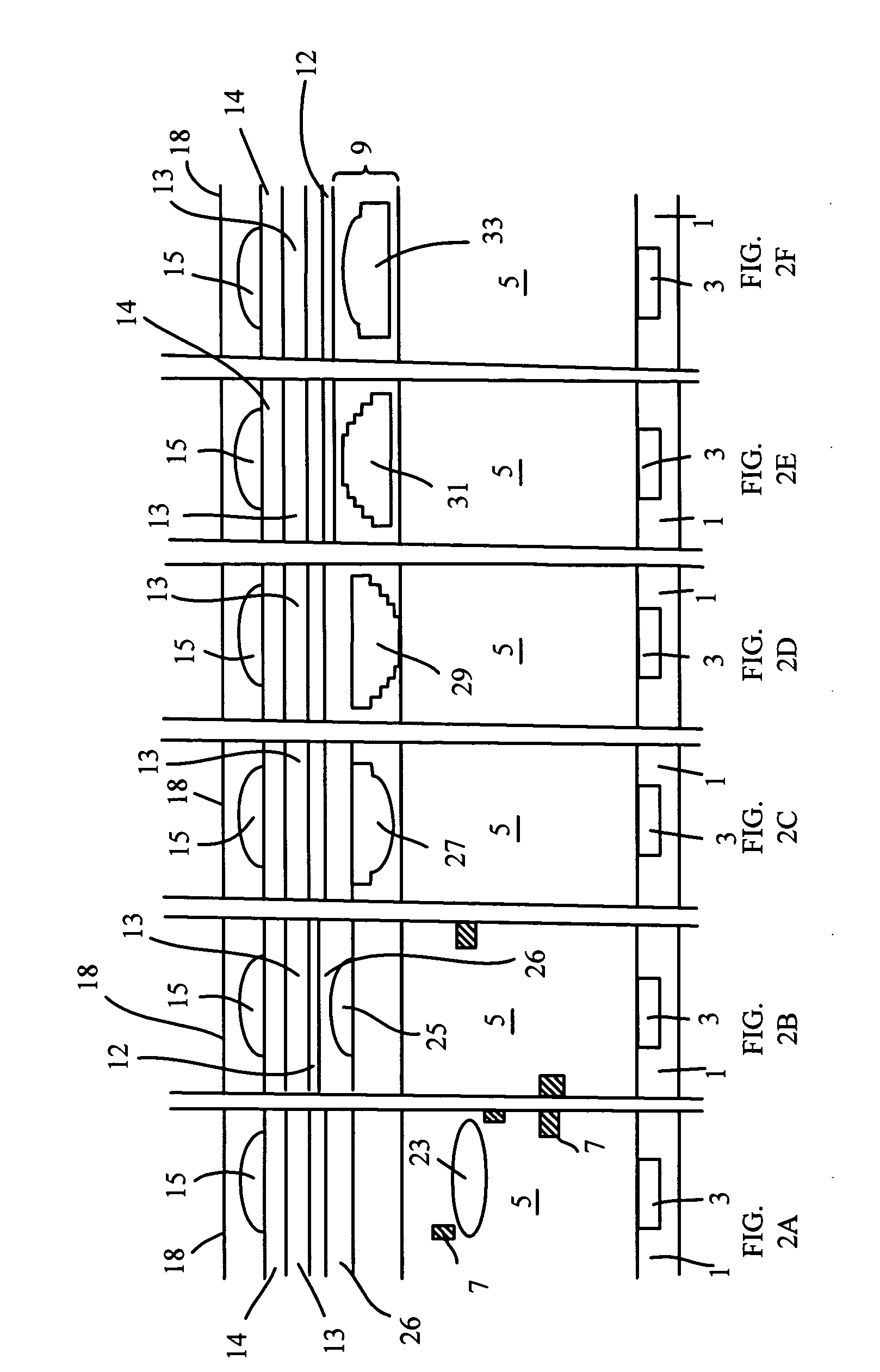

Lens structures suitable for use in image sensors and method for making the same

InactiveUS20050274968A1Solid-state devicesSemiconductor/solid-state device manufacturingResistPhotosensitive polymer

An image sensor includes a double-microlens structure with an outer microlens aligned over an inner microlens, both microlenses aligned over a corresponding photosensor. The inner or outer microlens may be formed by a silylation process in which a reactive portion of a photoresist material reacts with a silicon-containing agent. The inner or outer microlens may be formed by step etching of a dielectric material, the step etching process including a series of alternating etch steps including an anisotropic etching step and an etching step that causes patterned photoresist to laterally recede. Subsequent isotropic etching processes may be used to smooth the etched step structure and form a smooth lens. A thermally stable and photosensitive polymeric / organic material may also be used to form permanent inner or outer lenses. The photosensitive material is coated then patterned using photolithography, reflowed, then cured to form a permanent lens structure.

Owner:TAIWAN SEMICON MFG CO LTD

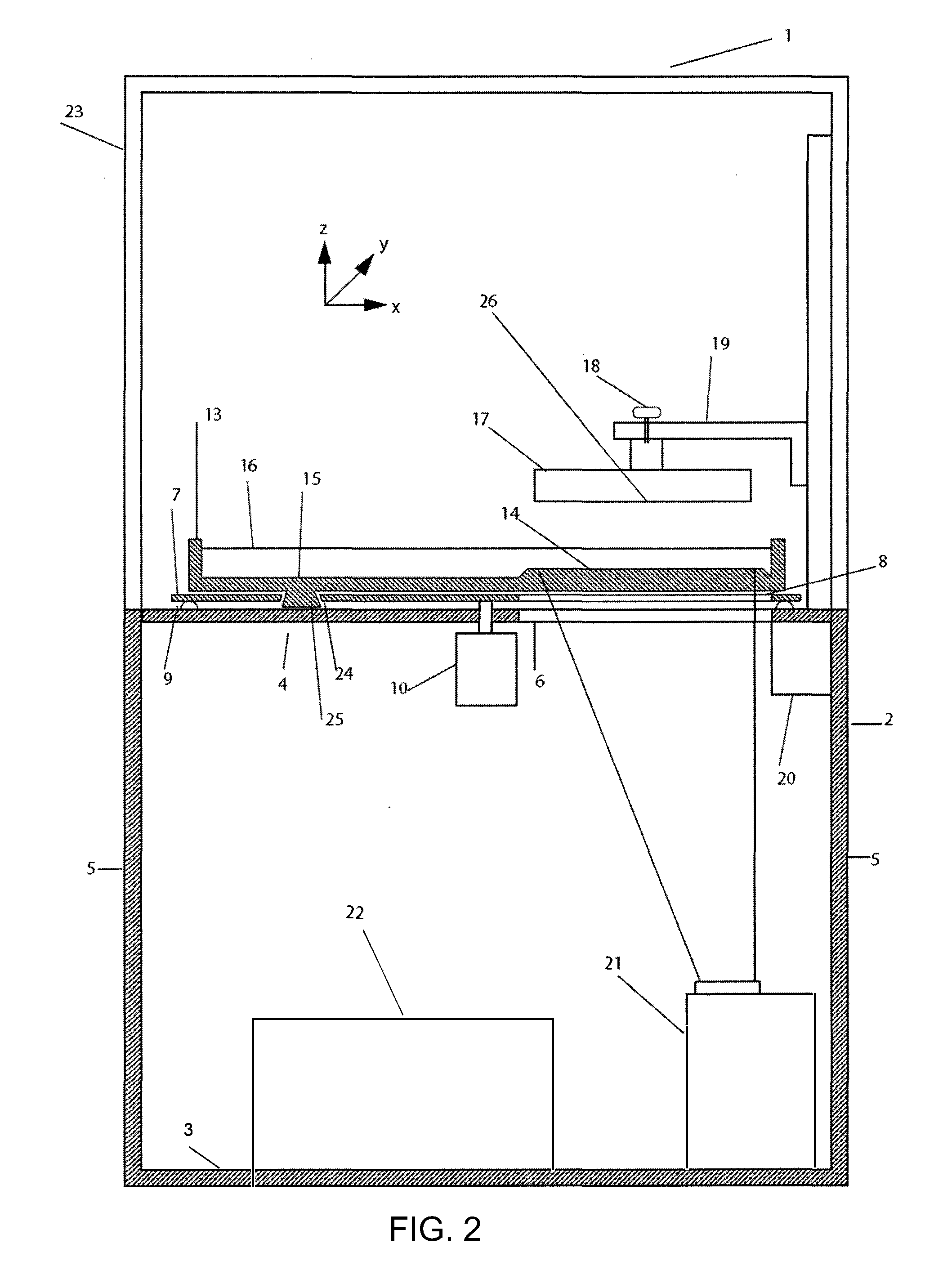

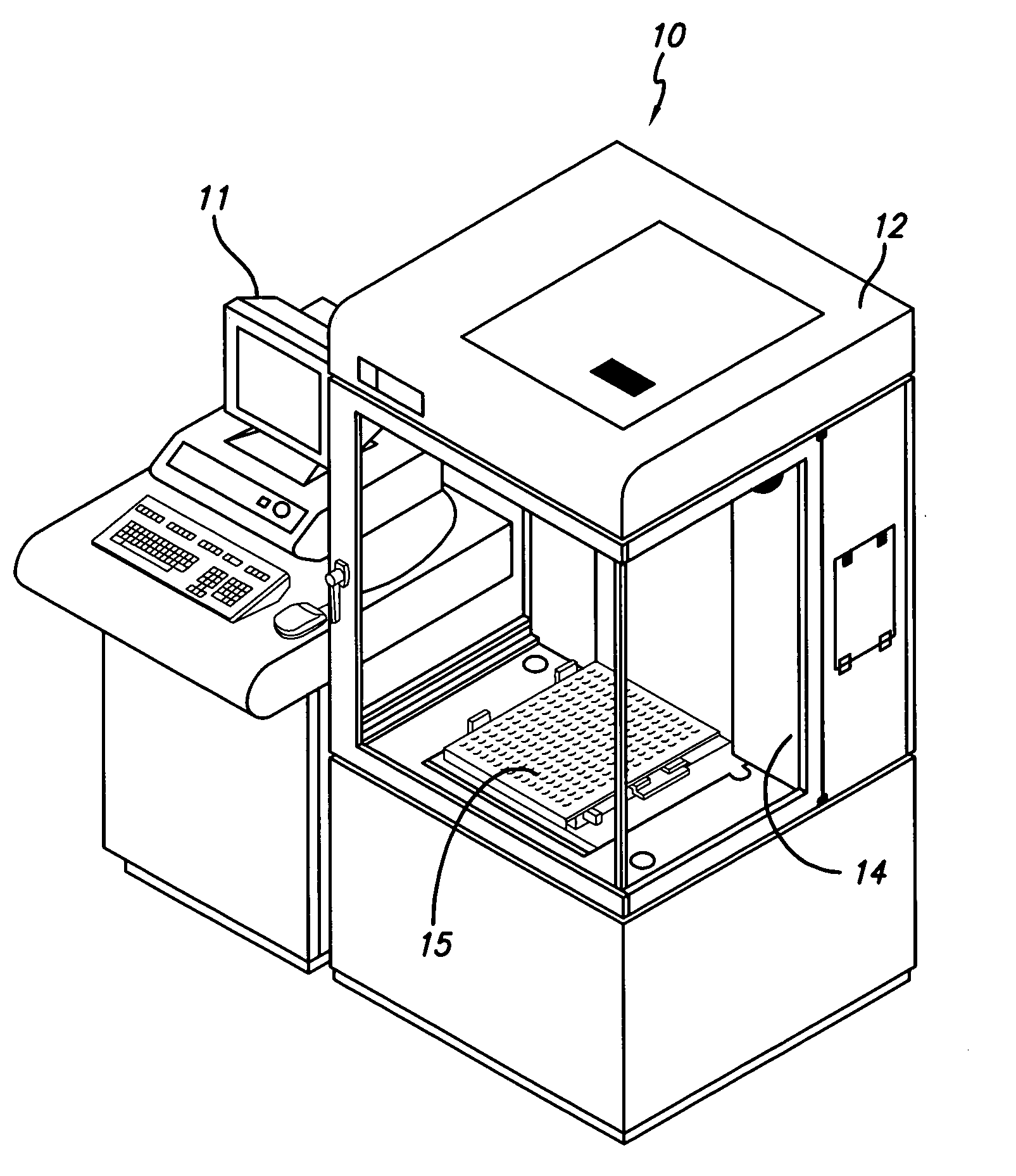

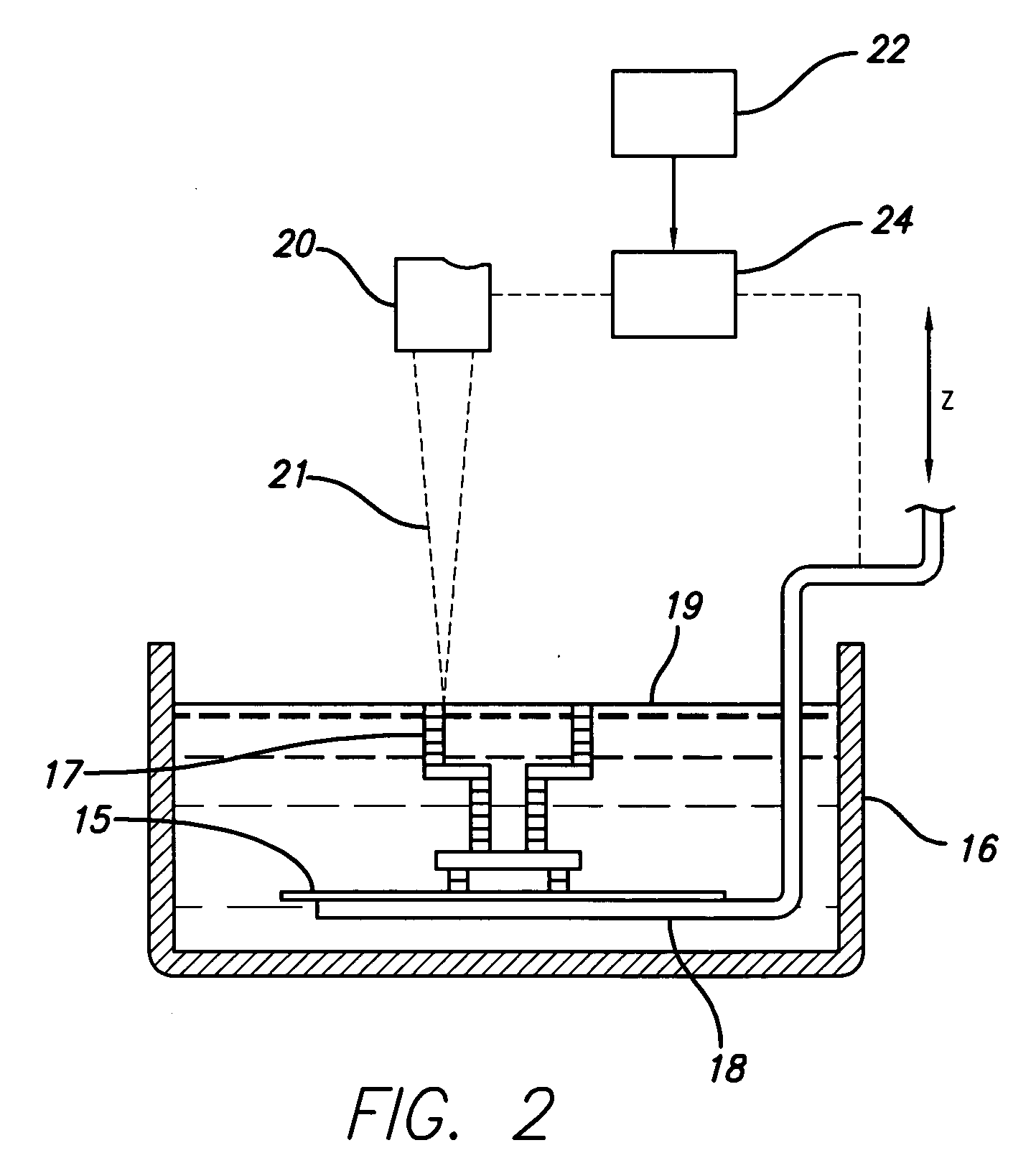

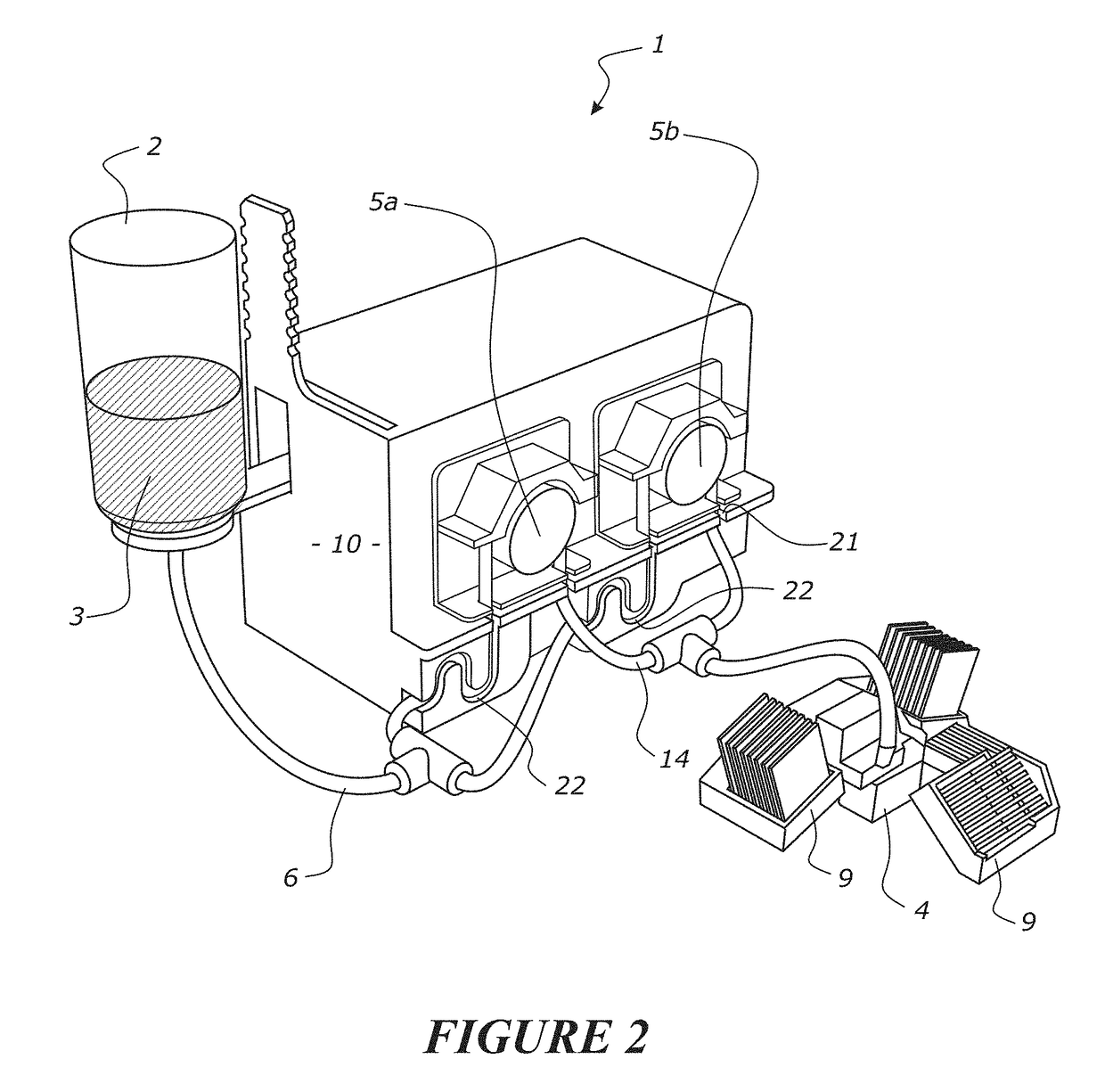

Stereolithographic apparatus

InactiveUS20060078638A1Simple processEasy and fast changingAdditive manufacturing apparatusAuxillary shaping apparatusPhotopolymerEngineering

An improved stereolithography apparatus for forming three-dimensional objects using multiple chambered resin vats and a quick disconnect mounting system to permit concurrent use of multiple photopolymer build materials and easy change over of resin vats is disclosed. The apparatus permits easy change over from multiple chambered vat use to single chamber vat use and vice versa or change over between multiple chambered vats.

Owner:3D SYST INC

Stacked chip package using photosensitive polymer and manufacturing method thereof

ActiveUS20070048969A1Reduce decreaseImprove device reliabilitySemiconductor/solid-state device detailsSolid-state devicesMechanical reliabilityPhotosensitive polymer

In a stacked chip configuration, and manufacturing methods thereof, the gap between a lower and an upper chip is filled completely using a relatively simple process that eliminates voids between the lower and upper chips and the cracking and delamination problems associated with such voids. The present invention is applicable to both chip-level bonding and wafer-level bonding approaches. A photosensitive polymer layer is applied to a first chip, or wafer, prior to stacking the chips or stacking the wafers. The photosensitive polymer layer is partially cured, so that the photosensitive polymer layer is made to be structurally stable, while retaining its adhesive properties. The second chip, or wafer, is stacked, aligned, and bonded to the first chip, or wafer, and the photosensitive polymer layer is then cured to fully bond the first and second chips, or wafers. In this manner, adhesion between chips / wafers is greatly improved, while providing complete gap fill. In addition, mechanical reliability is improved, alleviating the problems associated with cracking and delamination, and leading to an improvement in device yield and device reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

Switchable polymer-dispersed liquid crystal optical elements

InactiveUS7312906B2Increase the number ofDivision increaseNon-linear opticsOptical elementsAdditive ingredientPhotopolymer

Transmission and reflection type holograms may be formed utilizing a novel polymer-dispersed liquid crystal (PDLC) material and its unique switching characteristics to form optical elements. Applications for these switchable holograms include communications switches and switchable transmission, and reflection red, green, and blue lenses. The PDLC material offers all of the features of holographic photopolymers with the added advantage that the hologram can be switched on and off with the application of an electric field. The material is a mixture of a polymerizable monomer and liquid crystal, along with other ingredients, including a photoinitiator dye. Upon irradiation, the liquid crystal separates as a distinct phase of nanometer-size droplets aligned in periodic channels forming the hologram. The material is called a holographic polymer-dispersed liquid crystal (H-PDLC).

Owner:LEIDOS

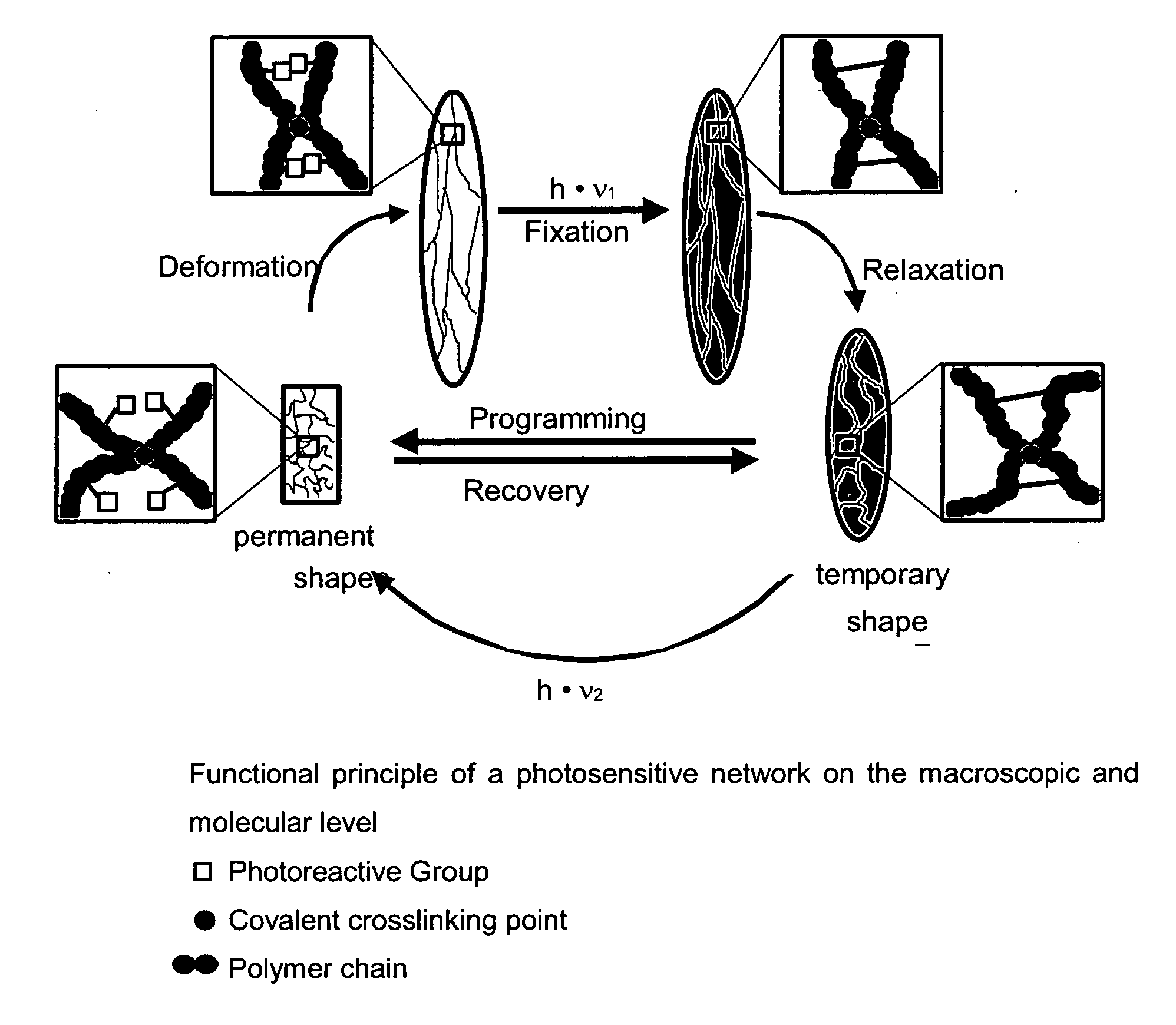

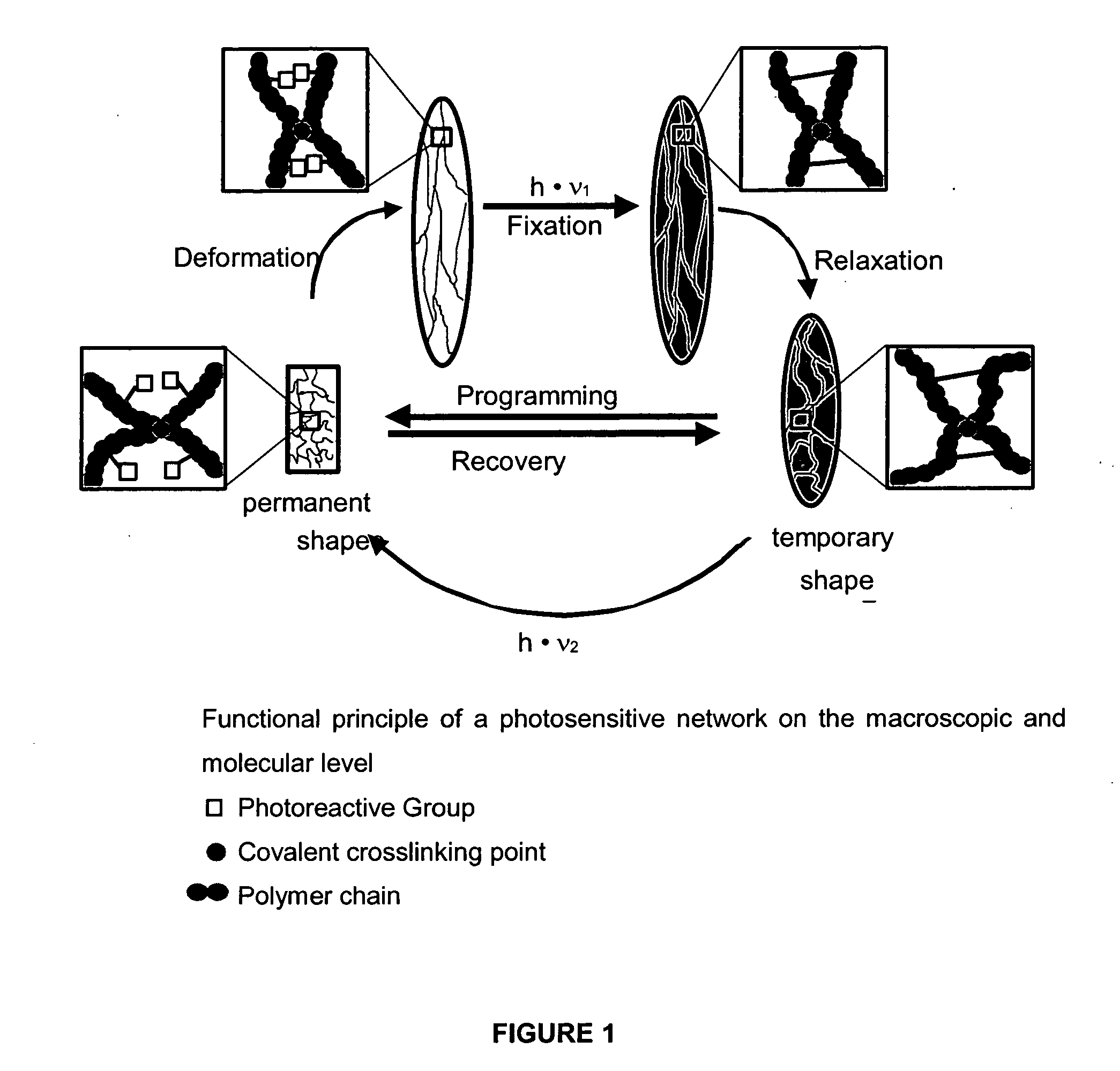

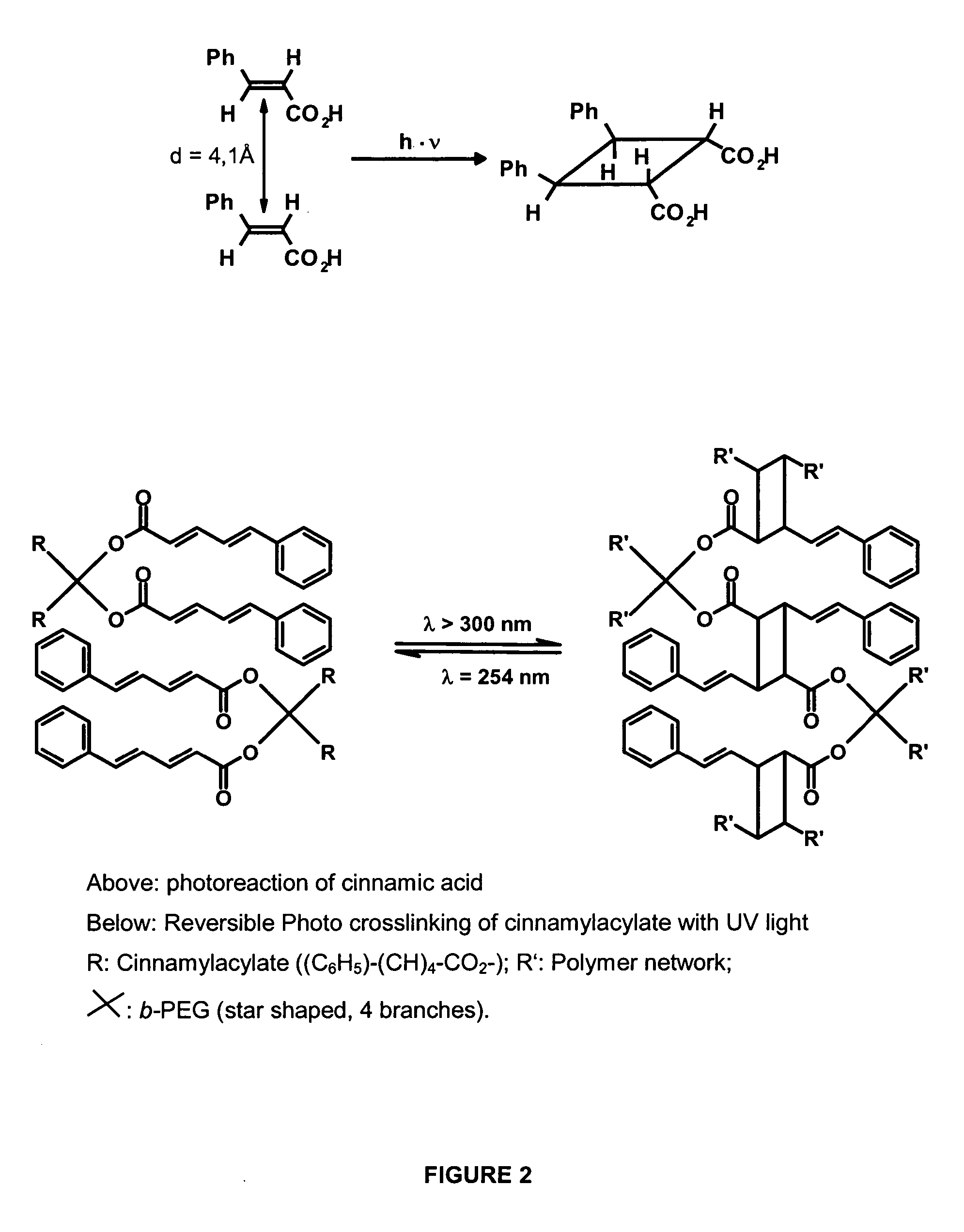

Photosensitive polymeric networks

ActiveUS20060257629A1High mechanical strengthOvercomes drawbackDecorative surface effectsDuplicating/marking methodsMedicinePhotosensitive polymer

Owner:HELMHOLTZ ZENT GEESTHACHT ZENT FUER MATERIAL UND KUESTENFORSCHUNG

Multiple vat leveling system

An improved apparatus for forming three-dimensional objects using multiple chambered resin vats and a photopolymer resin leveling system to permit concurrent use of multiple, photopolymer build materials and easy change over of resin vats is disclosed. The apparatus ensures the same level of photopolymer resin is maintained in each chamber during multiple chambered vat use.

Owner:3D SYST INC

Polymer encapsulated dicing lane (PEDL) technology for Cu/low/ultra-low k devices

InactiveUS20060079025A1Semiconductor/solid-state device detailsSolid-state devicesCopper interconnectLead bonding

A process for packaging semiconductor devices for flip chip and wire bond applications, wherein specific materials of the semiconductor devices are protected during device processing sequences and dicing procedures, has been developed. After definition of copper interconnect structures surrounded by a low k insulator layer, a protective, first photosensitive polymer layer comprised with a low dielectric constant is applied. After definition of openings in the first photosensitive polymer layer exposing portions of the top surface of the copper interconnect structures, a dicing lane opening is defined in materials located between copper interconnect structures. Conductive redistribution shapes are formed on the copper interconnect structures exposed in the openings in the first photosensitive polymer layer, followed by application of a protective, second photosensitive polymer layer. An opening is defined in the second photosensitive polymer layer exposing a portion of the top surface of a redistribution shape followed by placement of a solder ball in this opening. A reflow anneal procedure results in the solder ball wetting and overlying only the portion of the redistribution shape exposed in the opening in the second photosensitive polymer layer. Separation of the solder ball, flip chip regions from the non-solder ball, wire bond regions is accomplished via a dicing procedure performed in the dicing lane.

Owner:AGENCY FOR SCI TECH & RES

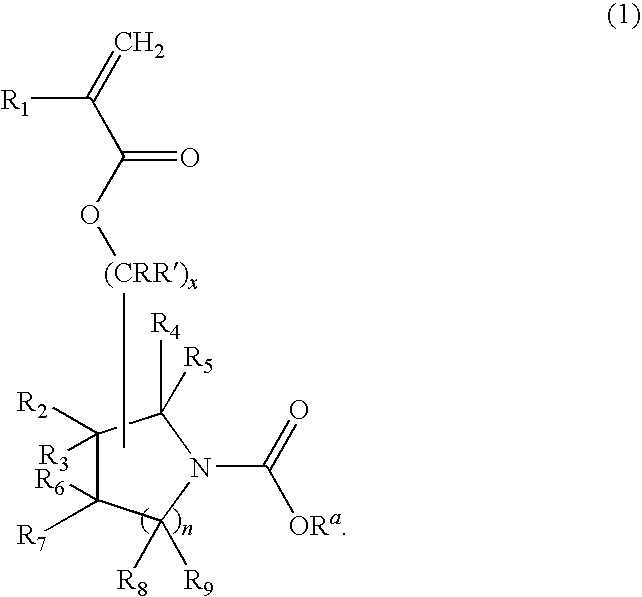

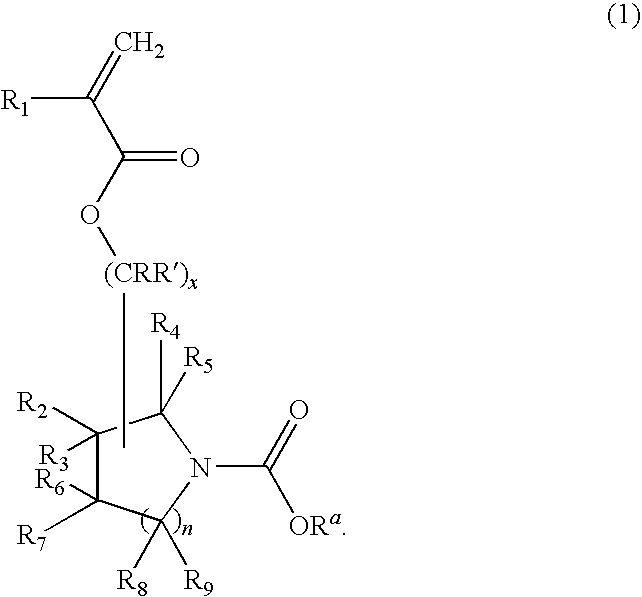

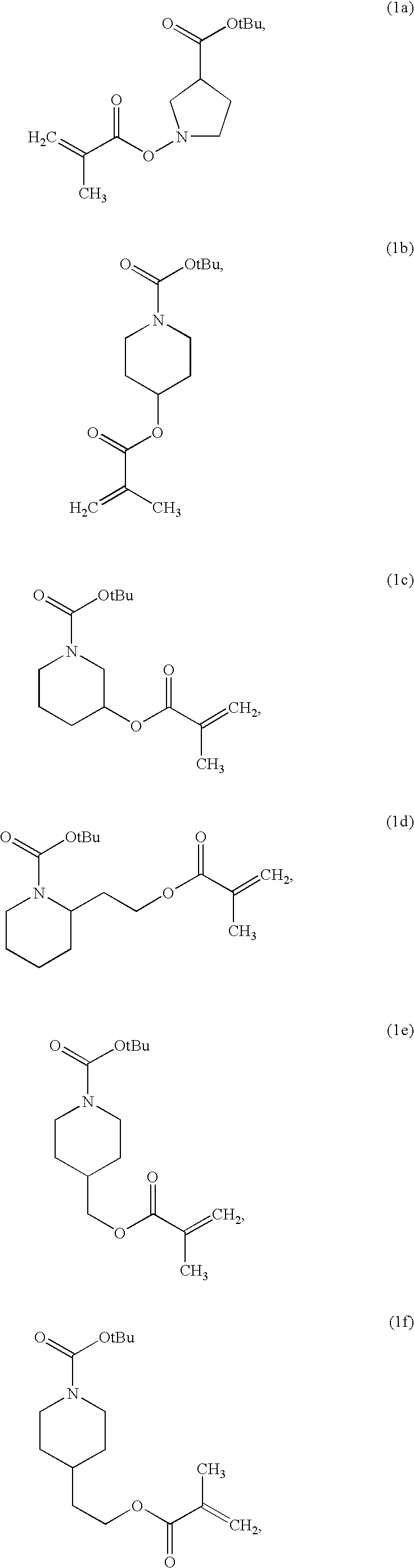

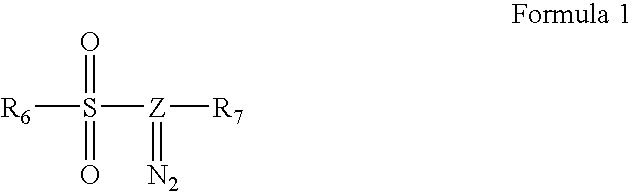

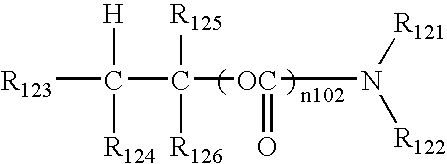

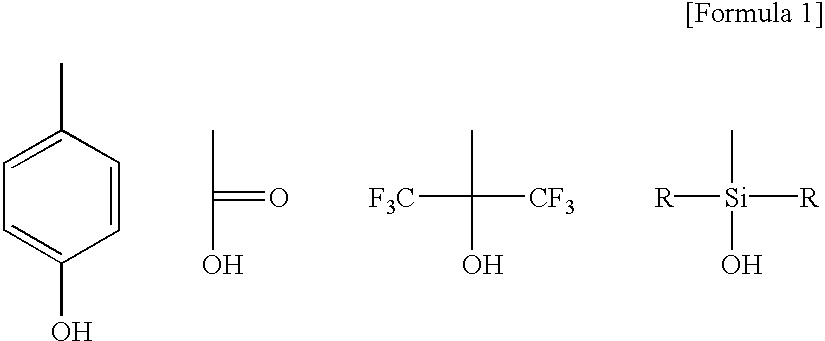

(Meth)acrylate compound, photosensitive polymer, and resist composition including the same

A (meth)acrylate compound having a nitrogen-containing cyclic group, a photosensitive polymer, and a resist composition including the same, the (meth)acrylate compound being represented by the following Chemical Formula 1:

Owner:CHEIL IND INC

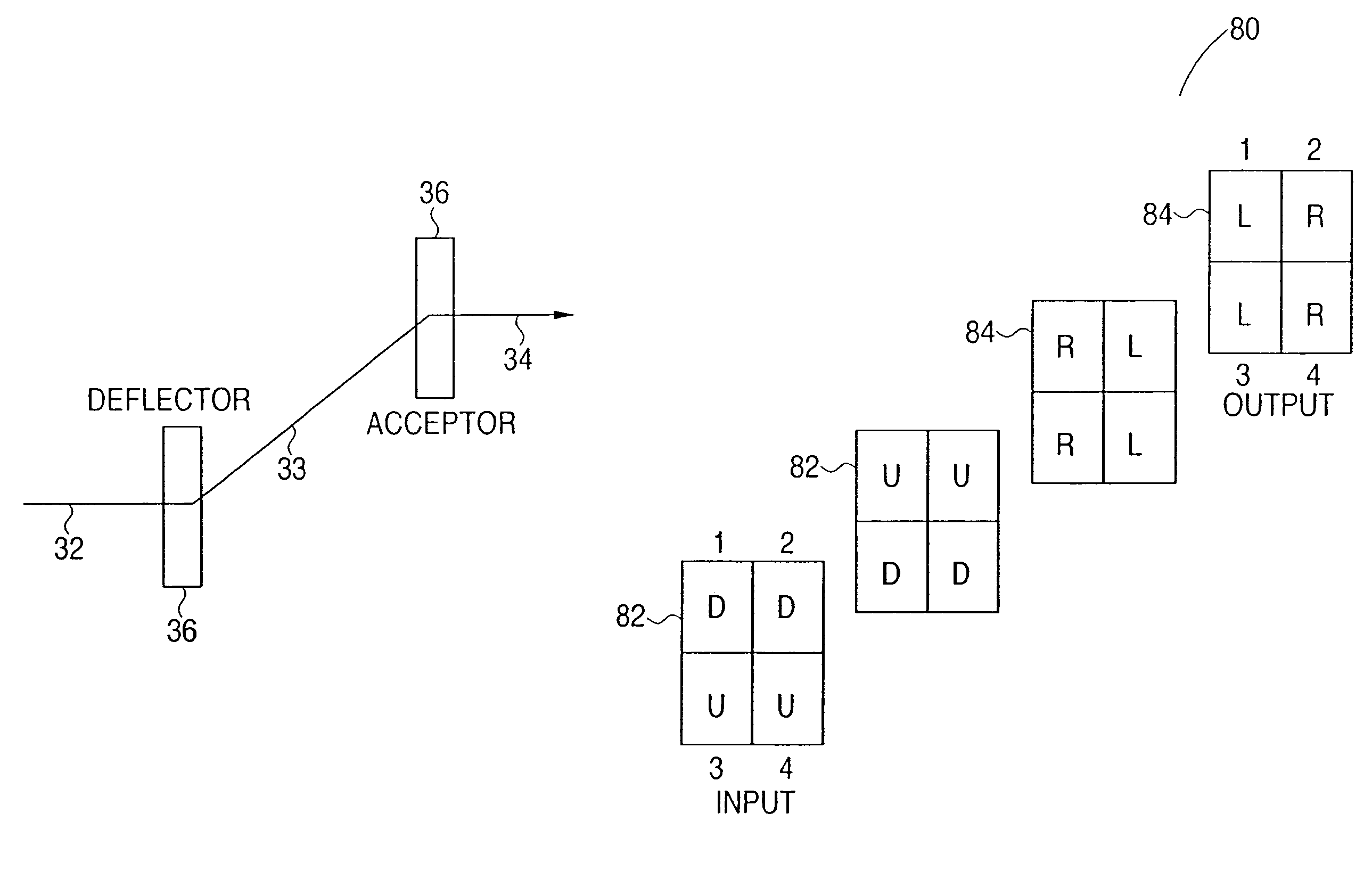

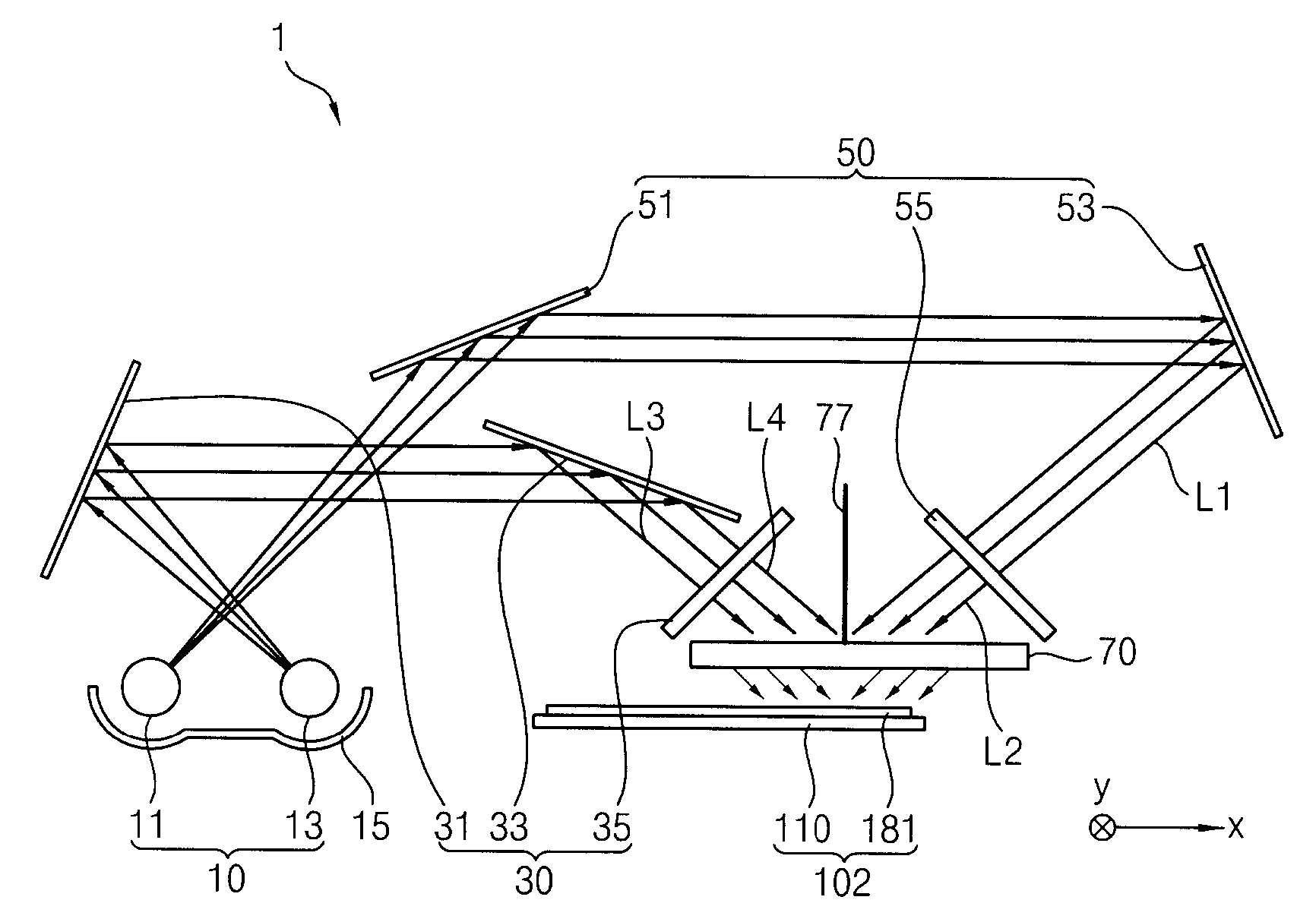

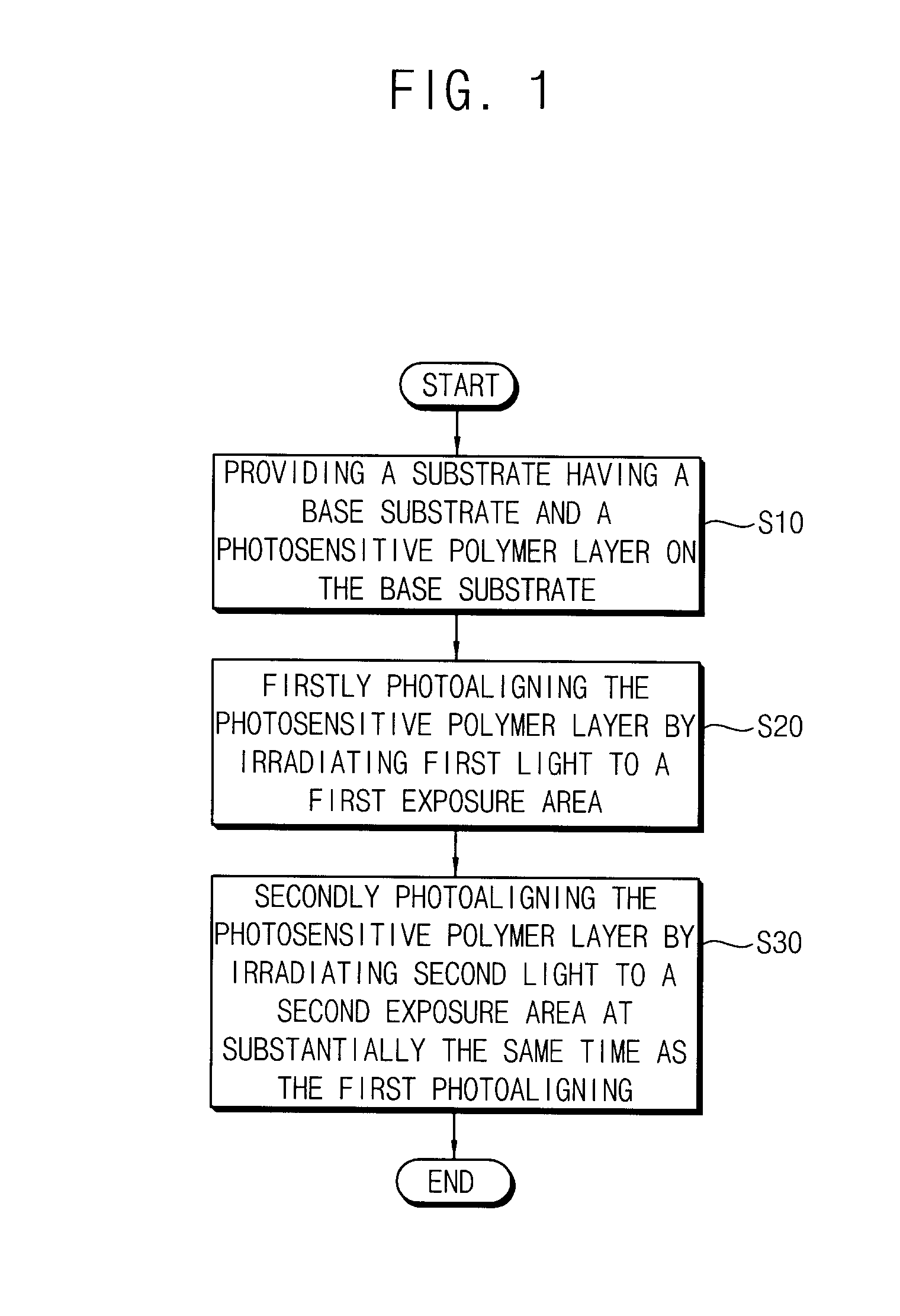

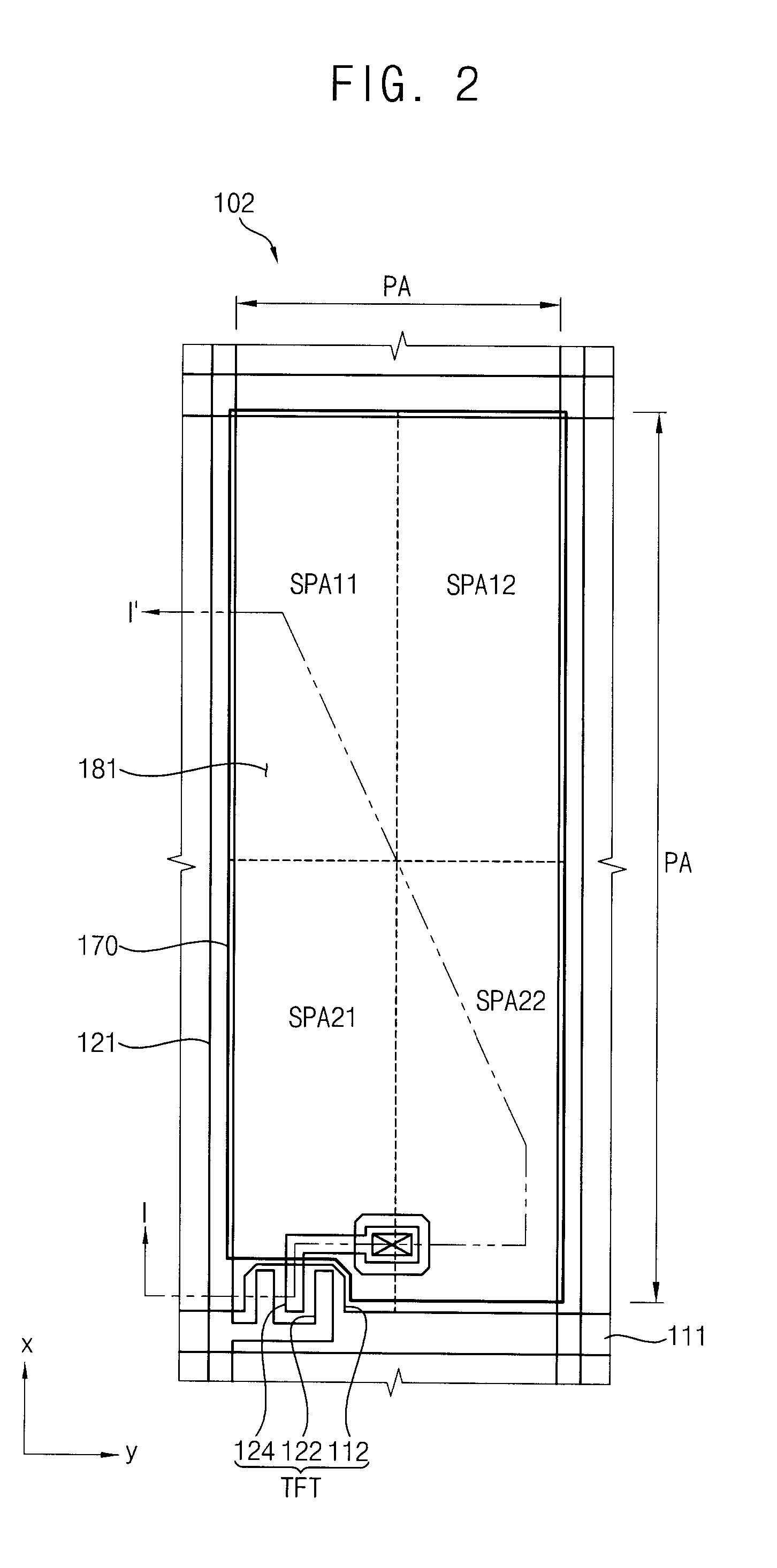

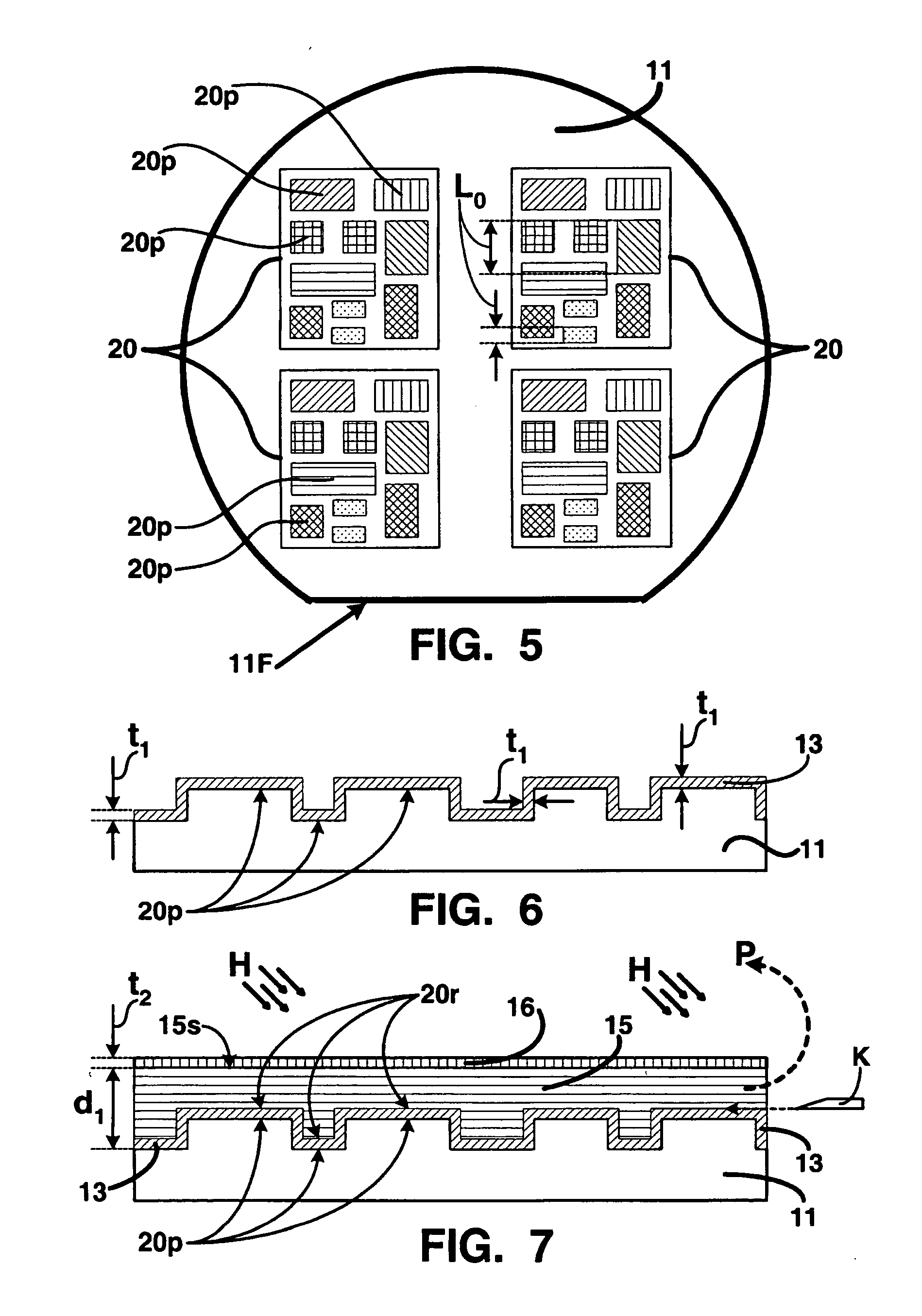

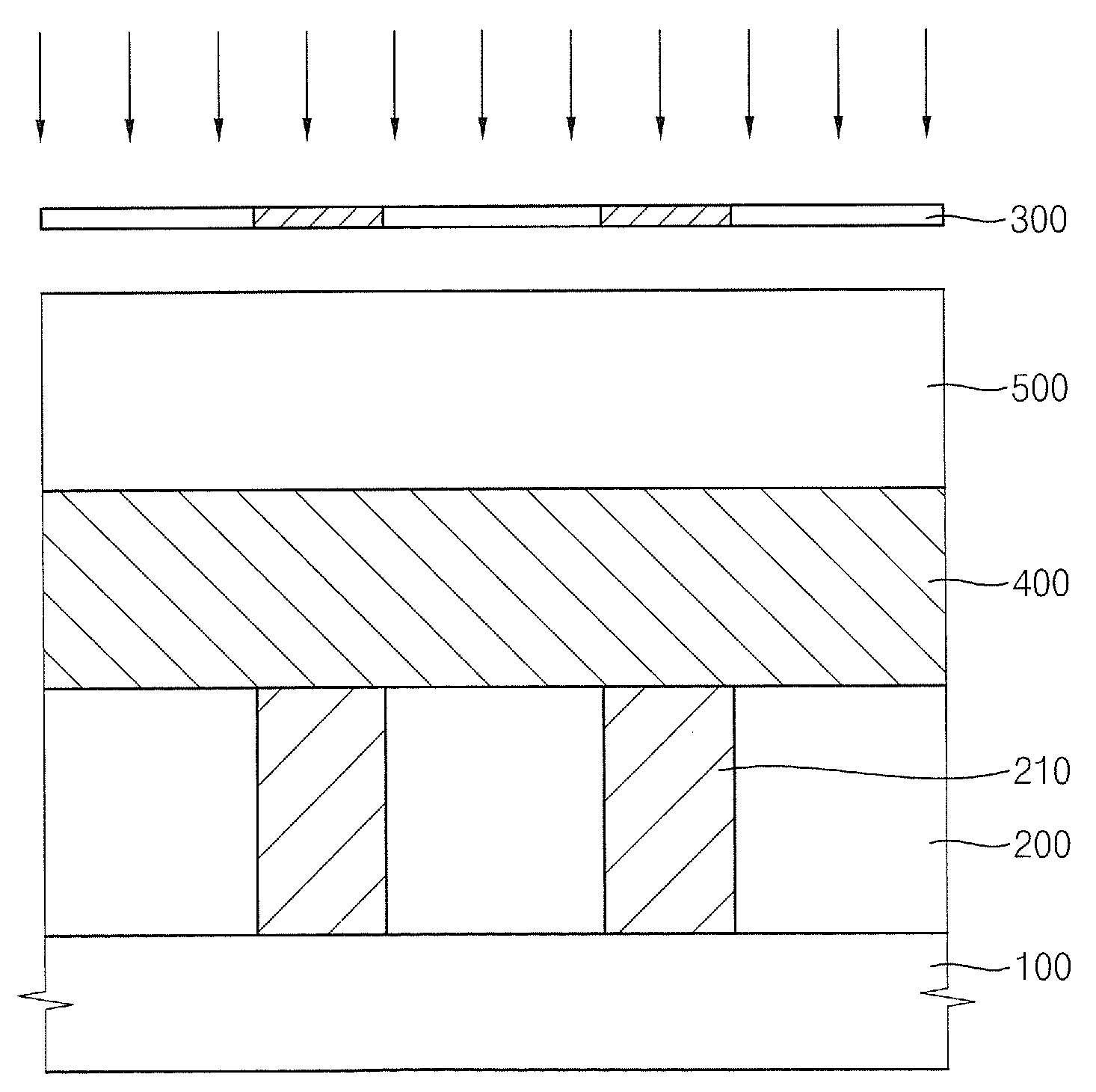

Method of forming an alignment layer, and apparatus for forming the alignment layer

ActiveUS20100035190A1Improve productivityReduce in quantityElectrographic process apparatusPhotomechanical exposure apparatusPhotosensitive polymerLight sensitive

A method of forming an alignment layer includes; providing a substrate having a base substrate and a photosensitive polymer layer disposed on the base substrate, the base substrate including a plurality of unit pixel areas, each of which is divided into a plurality of sub-pixel areas, photoaligning the photosensitive polymer layer by irradiating first light to a first exposure area of a first unit pixel area, the first light being inclined at a first angle with respect to the substrate in a first direction, and substantially simultaneously photoaligning the photosensitive polymer layer by irradiating second light to a second exposure area of a second unit pixel area at substantially the same time as the first light is irradiated to the first exposure area, the second light being inclined at a second angle with respect to the substrate in a second direction.

Owner:SAMSUNG DISPLAY CO LTD

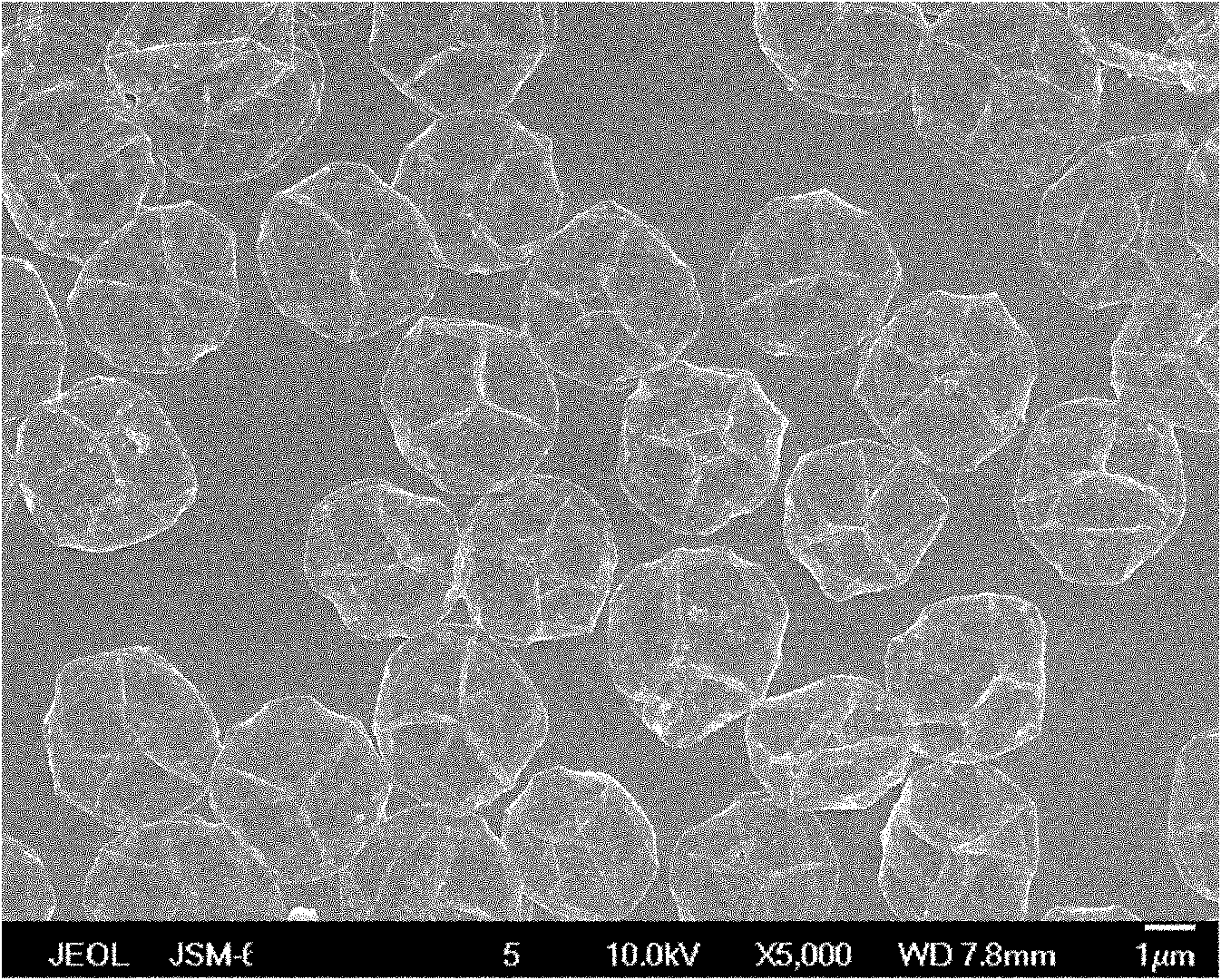

Method for hydrophilic modifying of poly-vinylidene fluoride film

The present invention belongs to the field of polymer film preparing technology, and is especially method of modifying hydrophilicity of polyvinylidene fluoride film. The method combines blending and surface grafting technology, and includes the first blending polyvinylidene fluoride and one other photosensitive polymer and preparing microporous or compact film, and the subsequent surface grafting hydrophilic monomer onto the surface of the blend film. The prepared modified film has excellent chemical stability and mechanical performance similar to that of microporous polyvinylidene fluoride film as well as improved surface hydrophilicity and antifouling performance.

Owner:FUDAN UNIV

Inorganic-containing photosensitive resin composition and method for forming inorganic pattern

InactiveUS6183935B1Good dispersionImprove stabilitySemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentColloidal silicaPhotosensitive polymer

An inorganic pattern is formed by coating an inorganic substance-containing photosensitive composition comprising a photosensitive polymer (A), a condensable organic metal compound or a condensate thereof (B) and an inorganic filler having a functional group (C) on a base, exposing the coated layer, and developing the exposed layer to form a pattern, baking the pattern give an inorganic pattern. The photosensitive polymer (A) may be constituted of an oligomer or polymer, and a photosensitizer, and the condensable organic metal compound (B) may have a photosensitive group. The inorganic filler may be a monodispersed colloidal silica having a mean particle size of 2 to 100 nm. The proportions of the components (B) and (C) relative to 1 part by weight of the component (A) on a solid basis are about 1 to 25 parts by weight and about 1 to 20 parts by weight, respectively. Even when the content of an inorganic component is high, an inorganic pattern of high resolution can be formed with the use of the above resin composition.

Owner:KRI INC

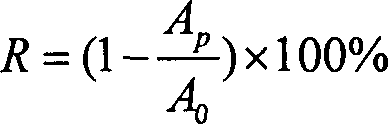

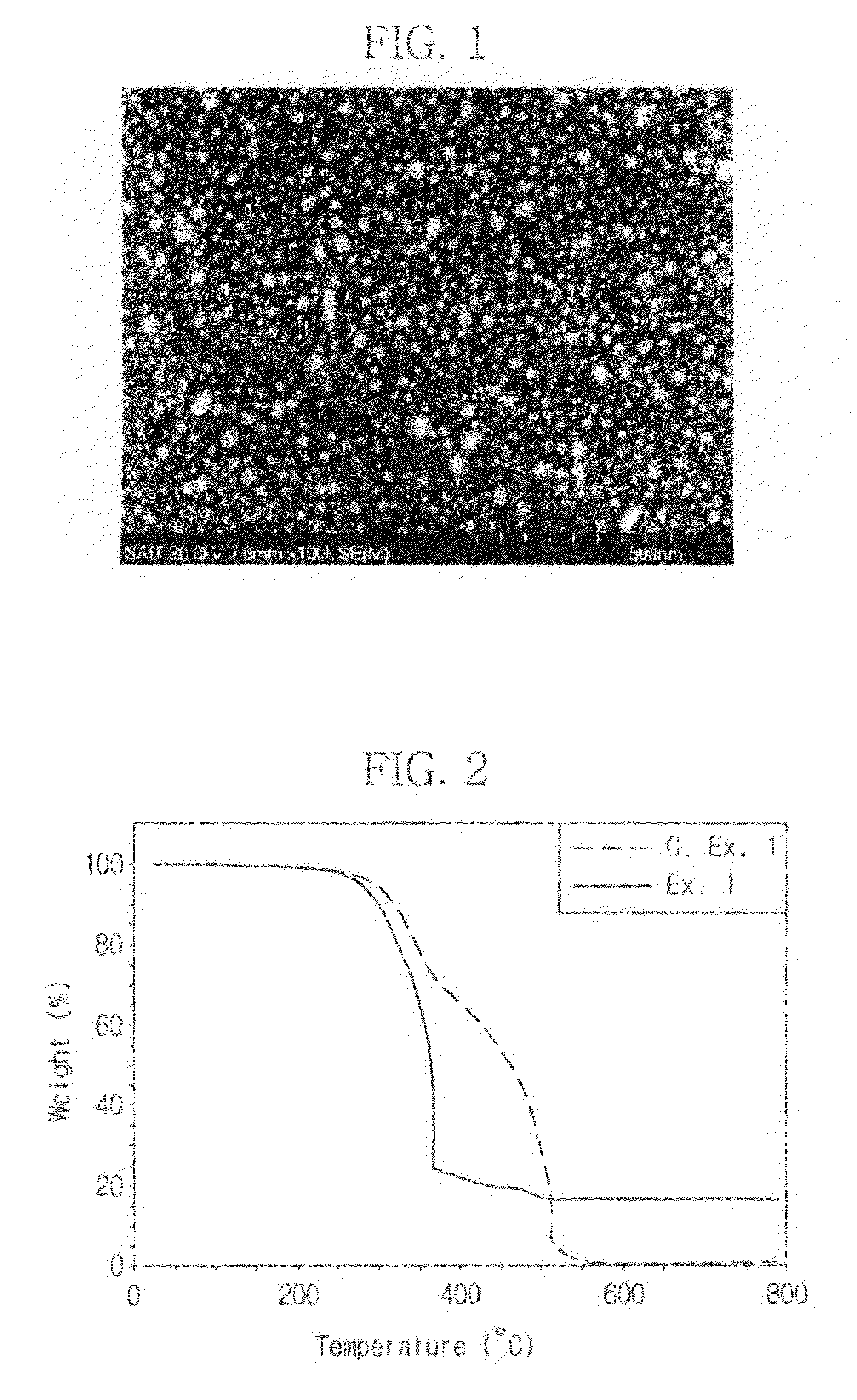

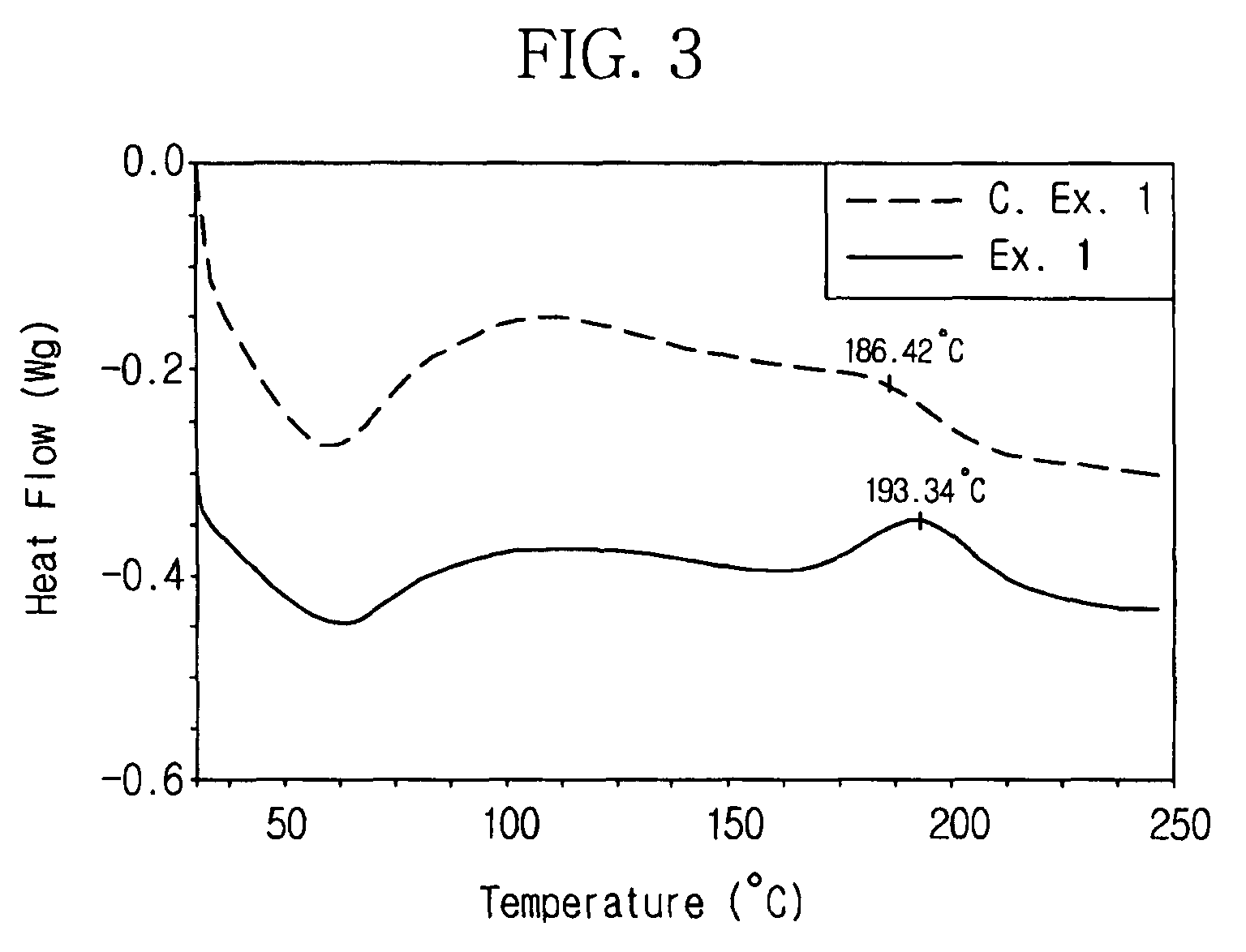

Composition for forming photosensitive polymer complex and method of preparing photosensitive polymer complex containing silver nanoparticles using the composition

InactiveUS7875416B2Improve conductivityHigh strengthRadiation applicationsPhotomechanical exposure apparatusEpoxyPhotosensitive polymer

A liquid-type composition for forming a photosensitive polymer complex and a method of preparing a photosensitive polymer complex containing silver nanoparticles using the same are provided. The composition for forming a photosensitive polymer complex includes a multifunctional epoxy resin, a photoacid generator, an organic solvent and a silver compound, or additionally includes a multifunctional acrylate resin and a photoinitiator, or an additive, e.g., a surfactant or a flow improver. This composition is applied, selectively exposed, and developed, thus preparing a photosensitive polymer complex, which contains silver nanoparticles uniformly dispersed and formed in the polymer pattern portion thereof through photo reduction and is therefore improved in terms of physical or chemical properties, e.g., heat resistance and wear resistance.

Owner:SAMSUNG ELECTRONICS CO LTD

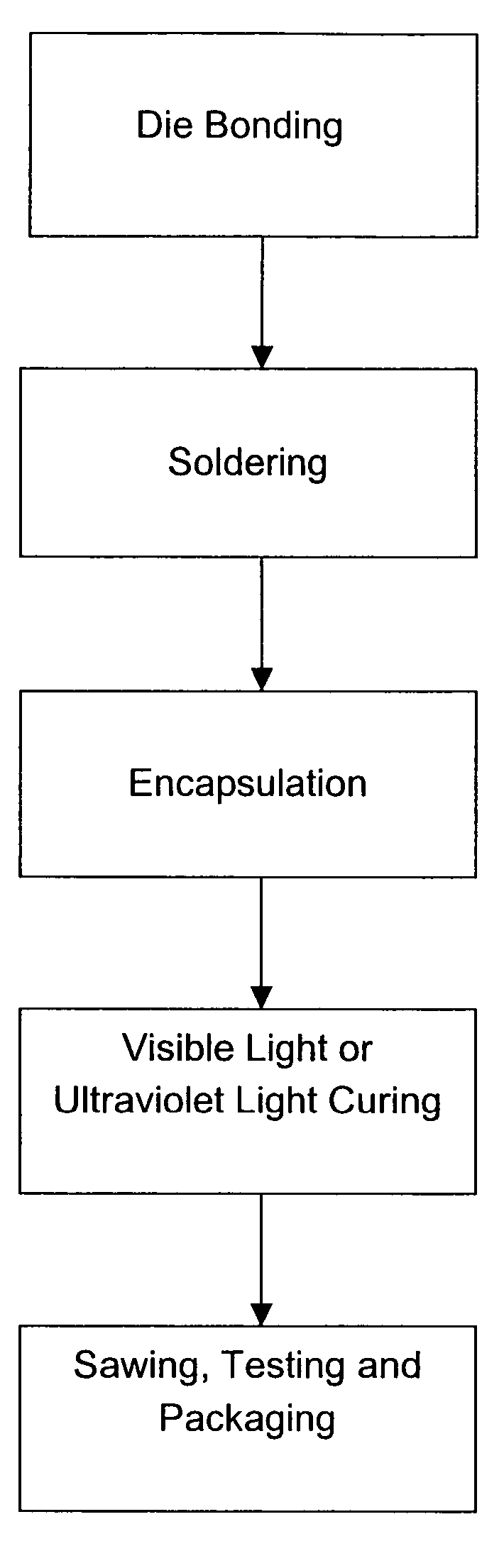

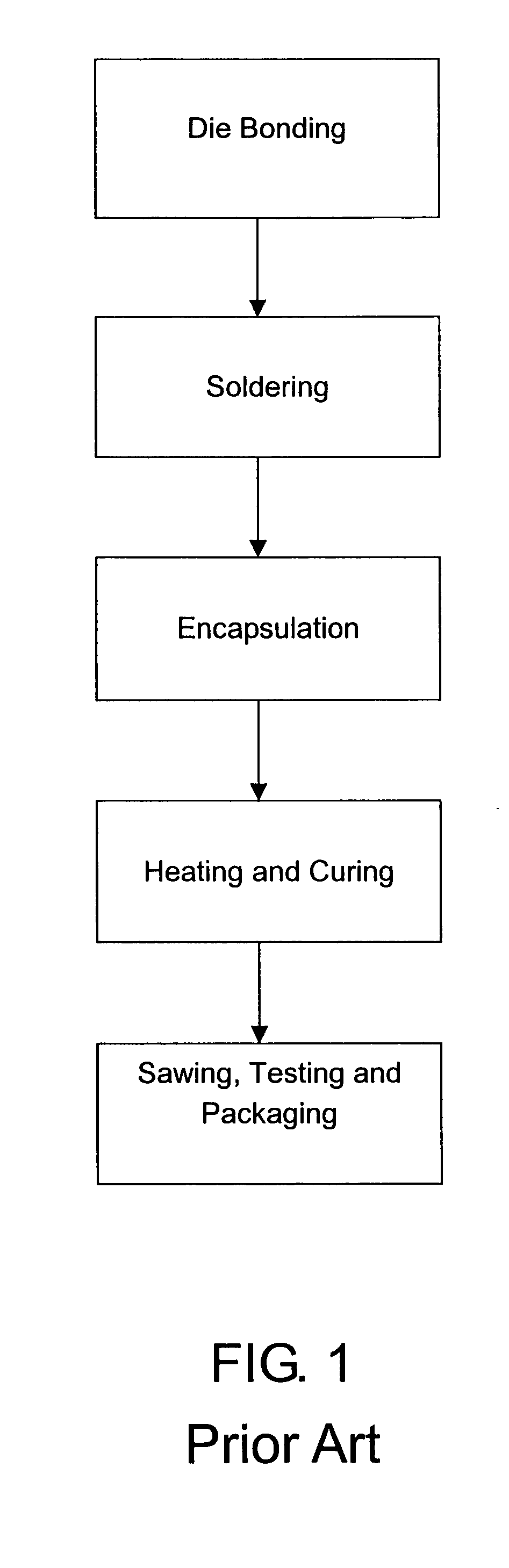

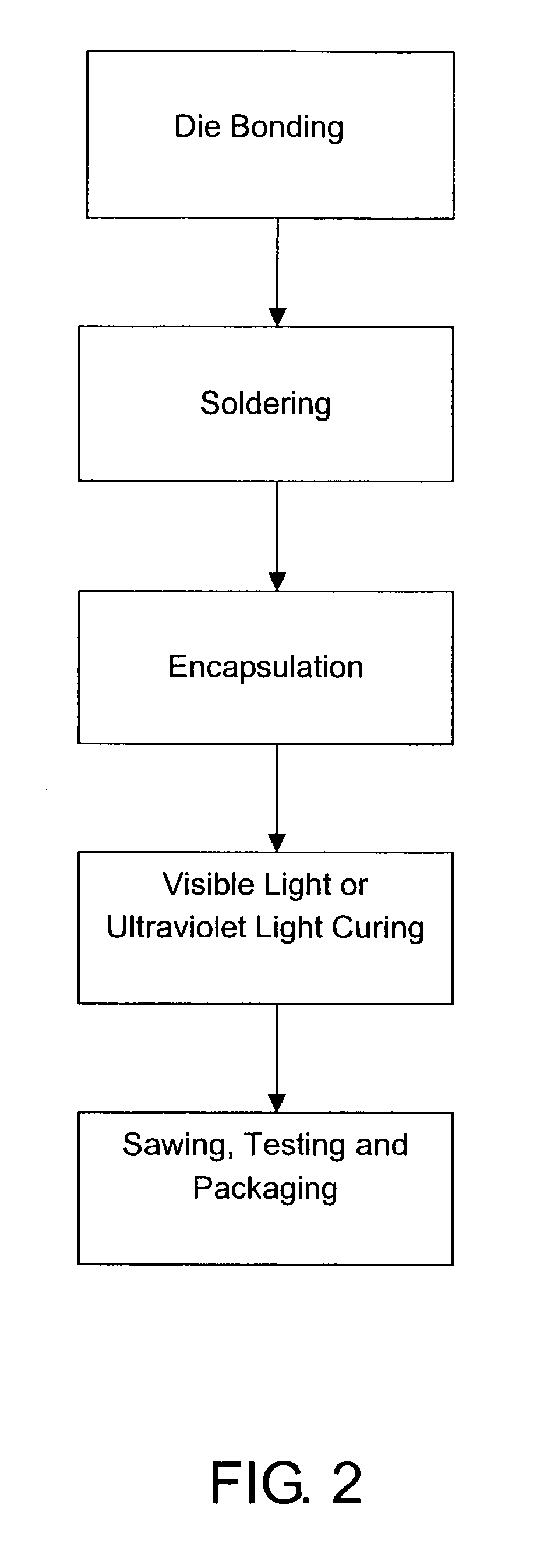

Light-emitting diode encapsulation material and manufacturing process

InactiveUS6958250B2Fast curingIncrease productivitySemiconductor/solid-state device detailsFibre treatmentInfraredPhotosensitive polymer

A light-emitting diode (LED) encapsulation material and manufacturing process comprising a photo-sensitive polymer constituting at least one of an Oligomer or a reactive Monomer, and a Photoinitiator. After a LED chip encapsulation, the photo-sensitive polymer is exposed to visible light or ultraviolet light, or electron beam, free of infrared rays, thereby triggering a free radical polymerization reaction of the photo-sensitive polymer, and rapid curing thereof under room temperature, eliminating the need for heating in a furnace during encapsulation manufacturing process of the light-emitting diode, while prompting rapid curing thereof, and thereby enhancing production efficiency.

Owner:YANG YUNG SHU

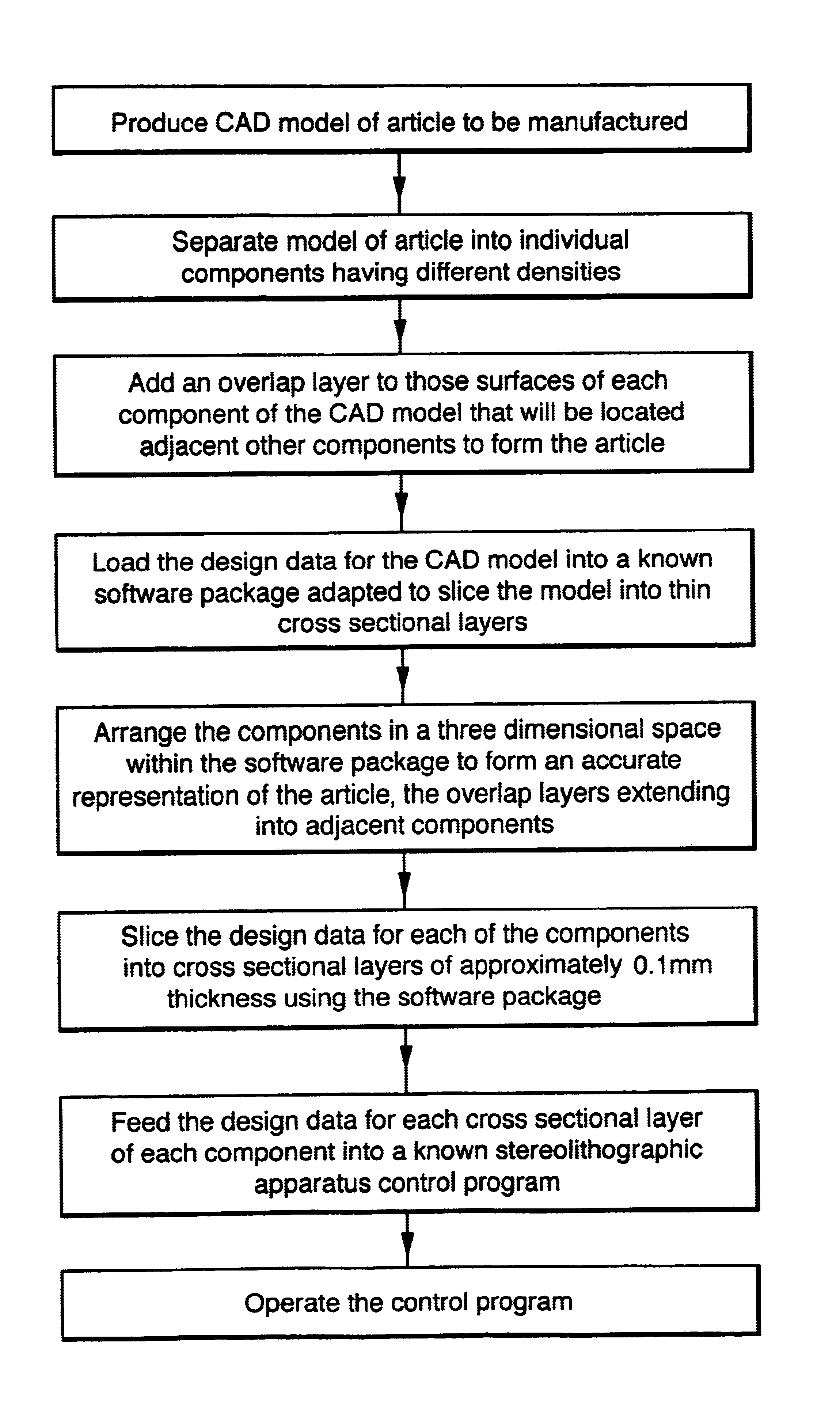

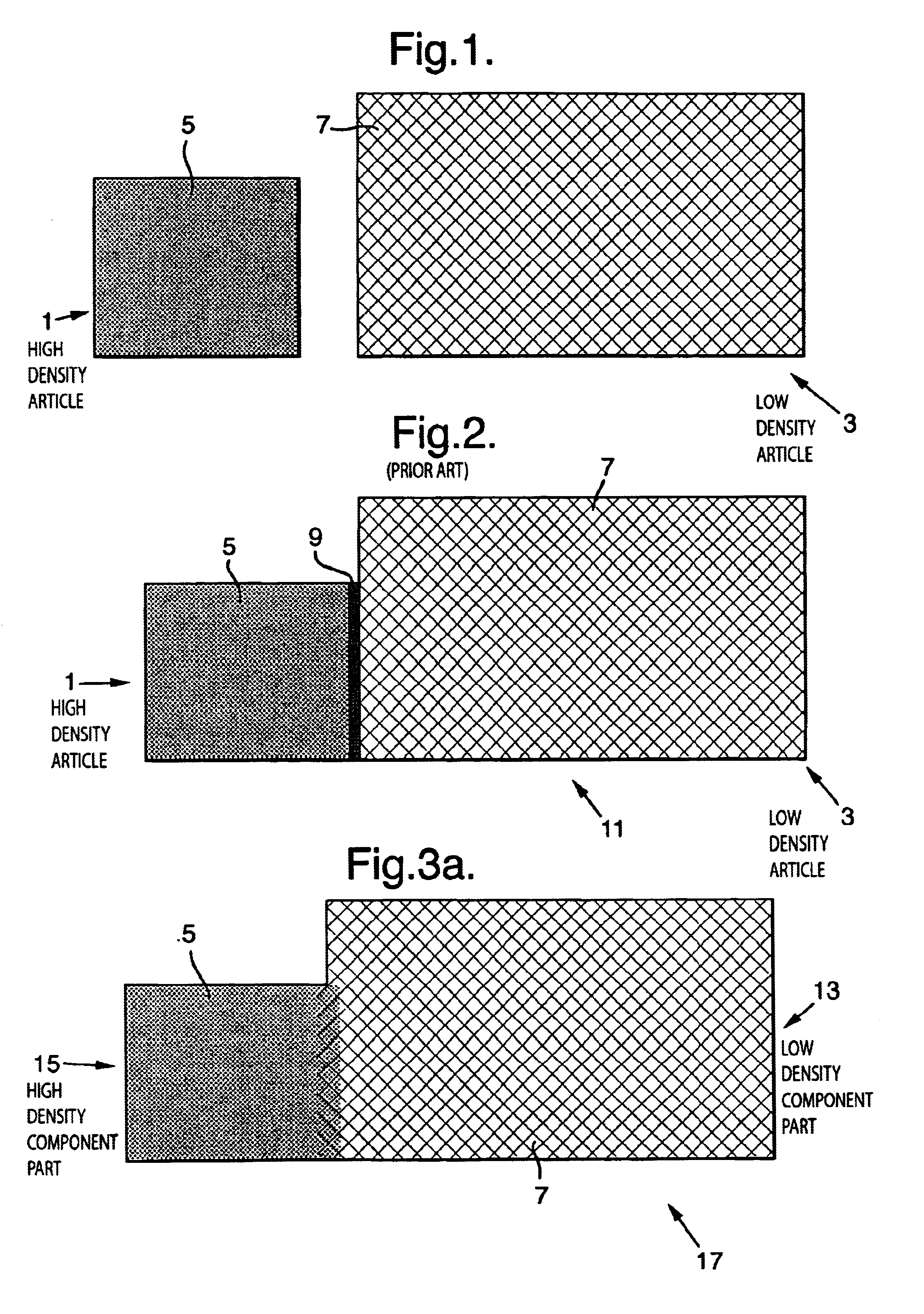

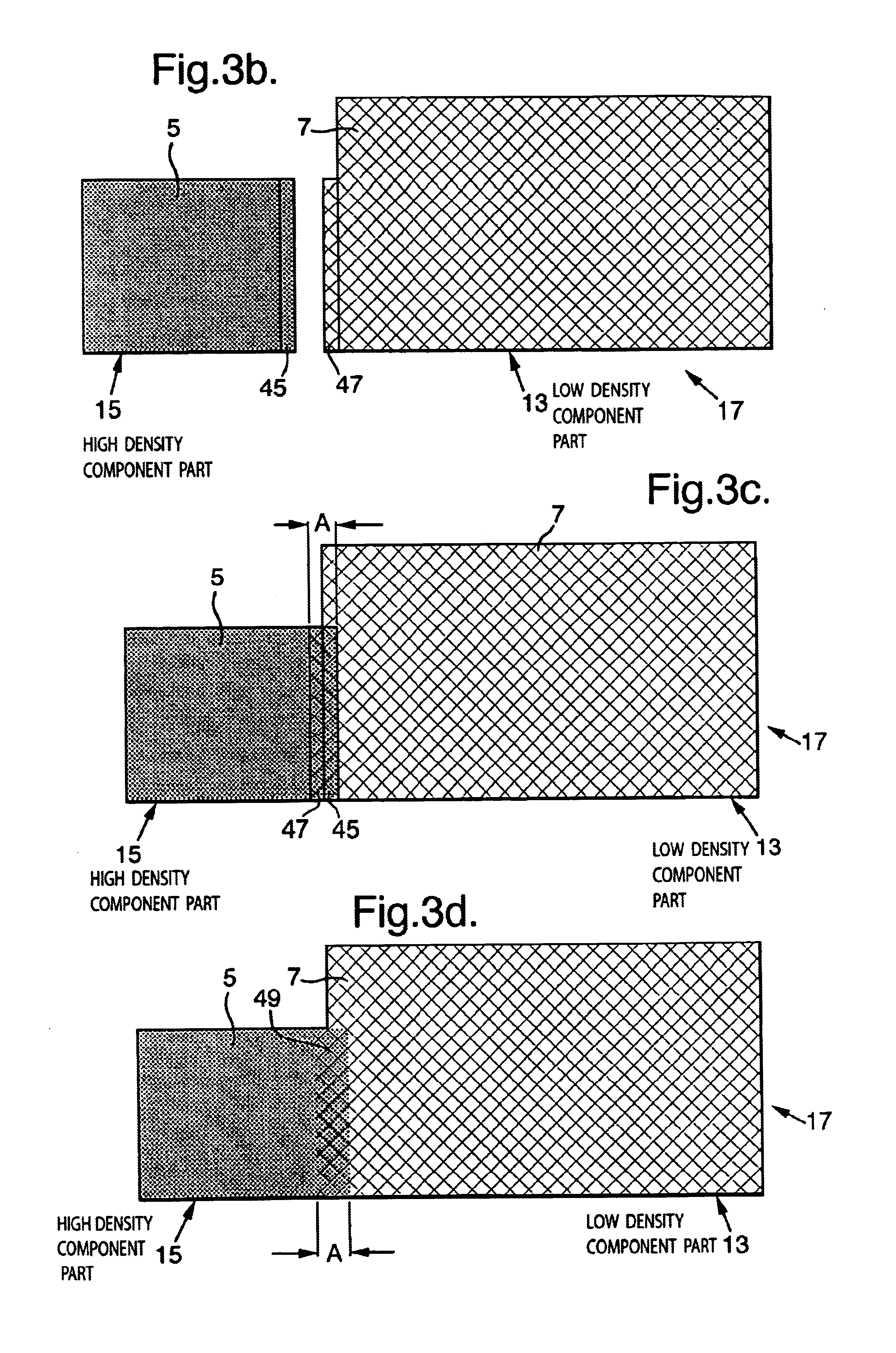

Stereolithographic method for combining components of varying densities

InactiveUS6792327B1Additive manufacturing apparatus3D object support structuresPhotosensitive polymerEngineering

A method of producing an article formed from a photosensitive polymer resin, the article having at least two different densities and the article being a unitary article having substantially no structural joint between regions of different density.

Owner:BAE SYSTEMS PLC

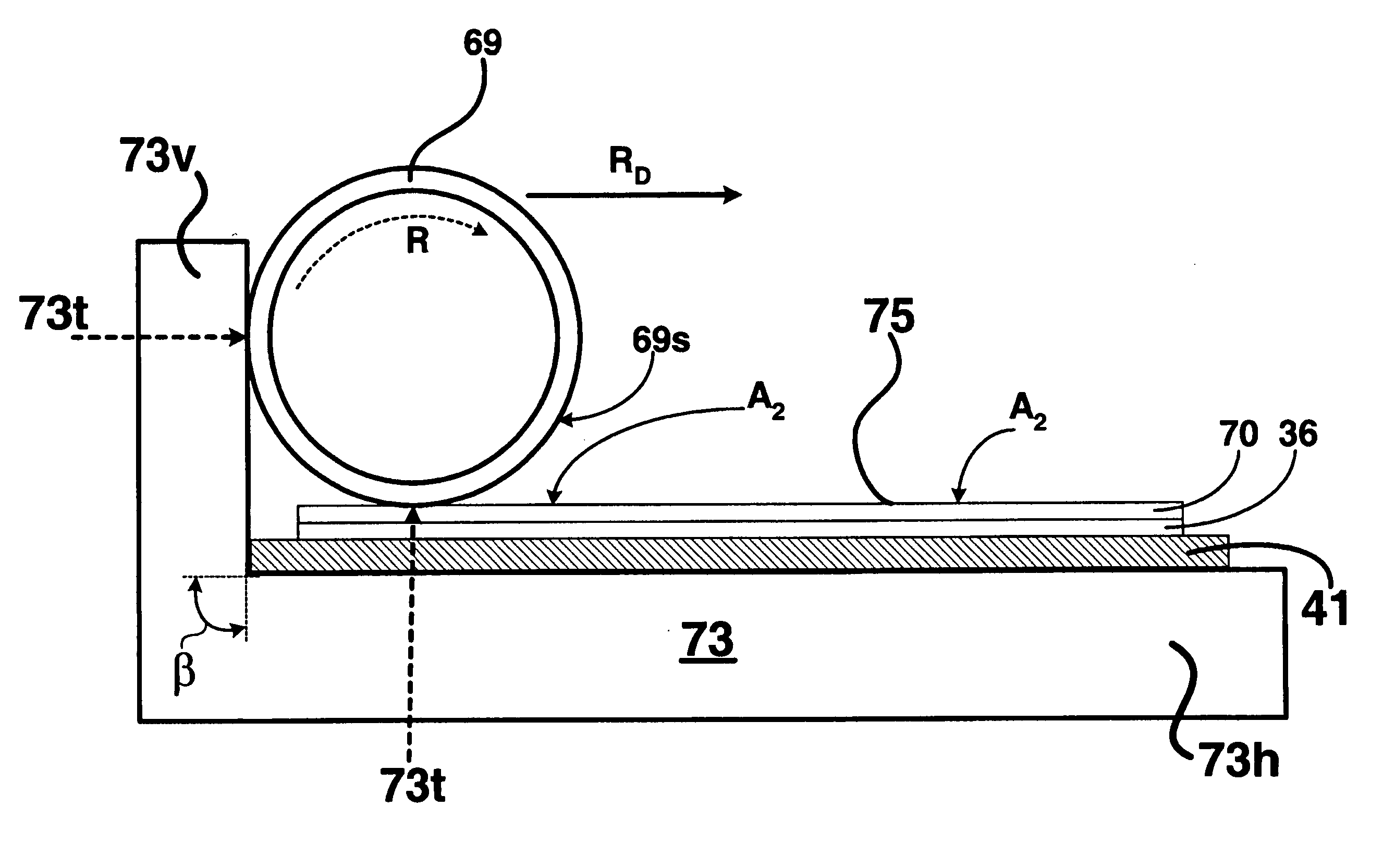

Apparatus for embossing a flexible substrate with a pattern carried by an optically transparent compliant media

An apparatus for embossing a flexible substrate with an optically transparent compliant media is disclosed. The complaint media includes an optically transparent imprint stamp with an imprint pattern therein. The flexible substrate is coated with a photopolymer material. The compliant media can be connected with an optically transparent belt material to form an embossing belt or connected with an optically transparent cylinder to from an embossing drum. A coated side of the flexible substrate is urged into contact with the imprint stamp and the imprint pattern is embossed in the photopolymer material and an ultraviolet light passing through the compliant media contemporaneously cures the photopolymer material during the embossing.

Owner:JEANS ALBERT H

Photoimageable, aqueous acid soluble polyimide polymers

A photoimageable, aqueous acid soluble polyimide polymer comprising an anhydride, including a substituted benzophenone nucleus, a diamine reacted with the anhydride to form a photosensitive polymer intermediate, and at least 60 Mole % of solubilizing amine reacted with the photosensitive polymer intermediate to form the photoimageable, aqueous acid soluble polyimide polymer. An emulsion for electrophoretic deposition of a coating of a photoimageable, aqueous acid soluble polyimide polymer comprises a dispersed phase, including the photoimageable aqueous acid soluble polyimide polymer, dissolved in an organic solvent and a dispersion phase including a coalescence promoter and water. The emulsion may be applied, by electrophoretic deposition, to a conductive structure to provide a photoimageable coating on the conductive structure. After exposing the coating to a pattern of radiation for photocrosslinking exposed parts of the photoimageable aqueous acid soluble polyimide polymer, an aqueous acid developer solution removes unexposed photoimageable aqueous acid soluble polyimide polymer to reveal a crosslinked polyimide polymer image of the radiation pattern.

Owner:3M INNOVATIVE PROPERTIES CO

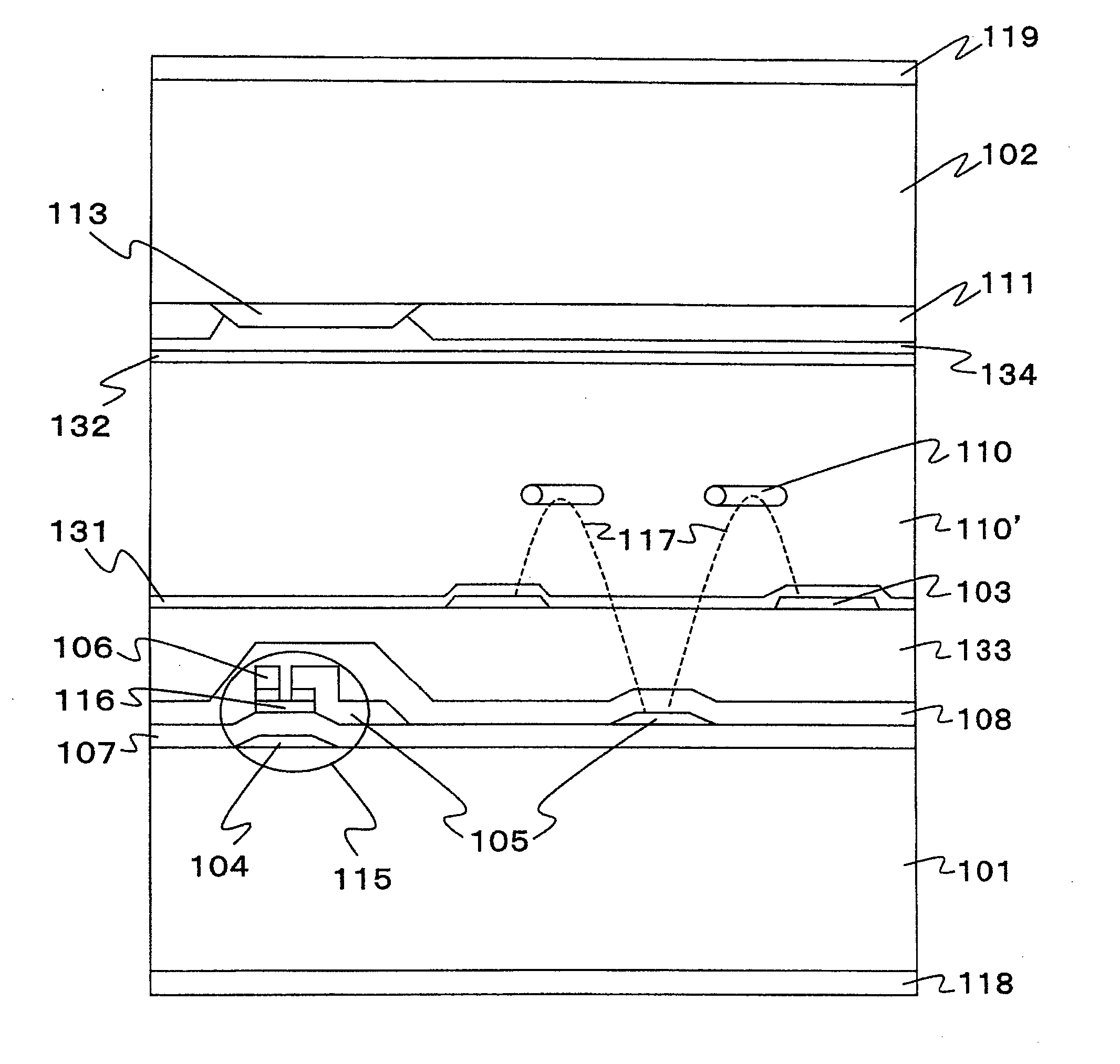

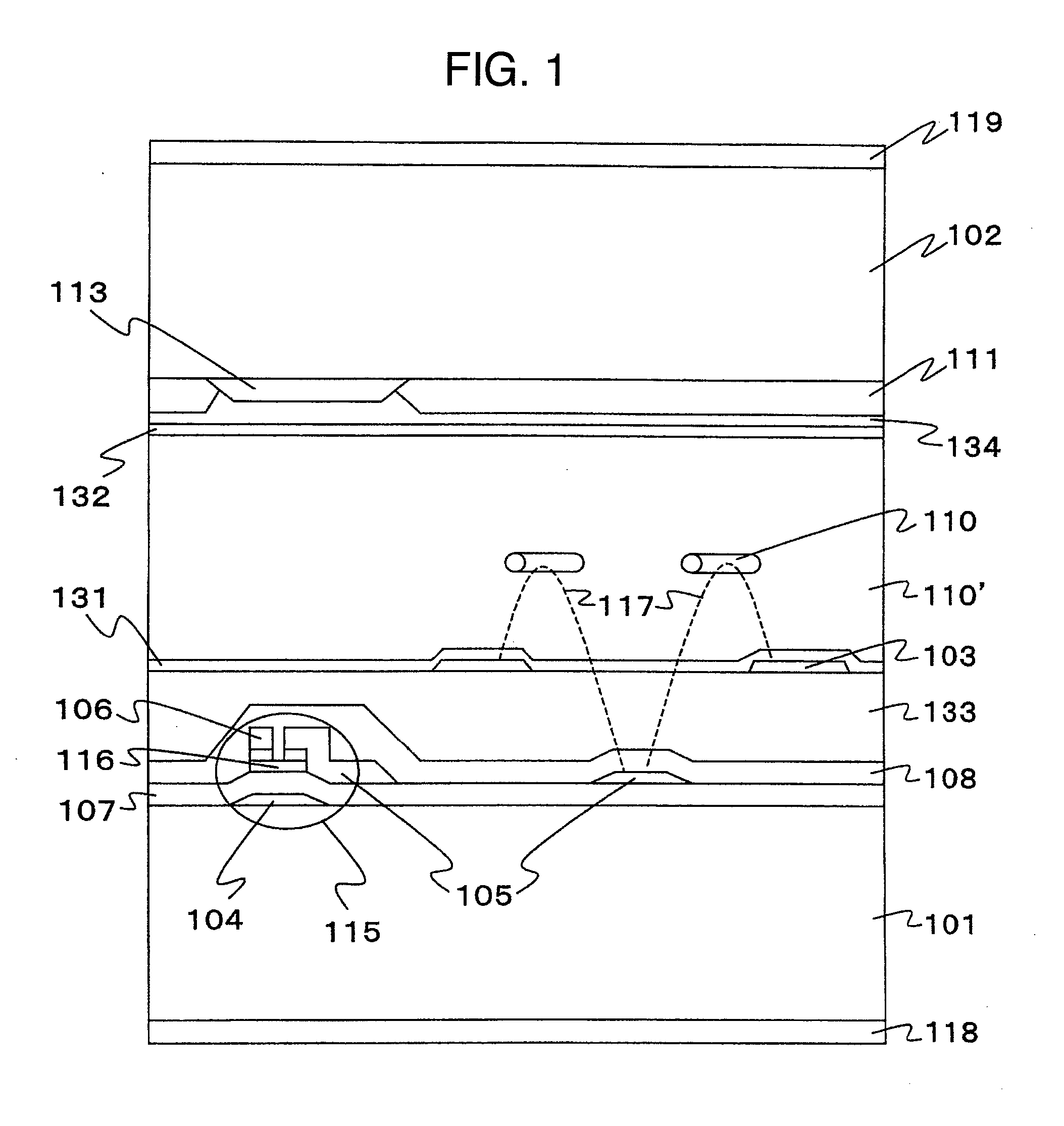

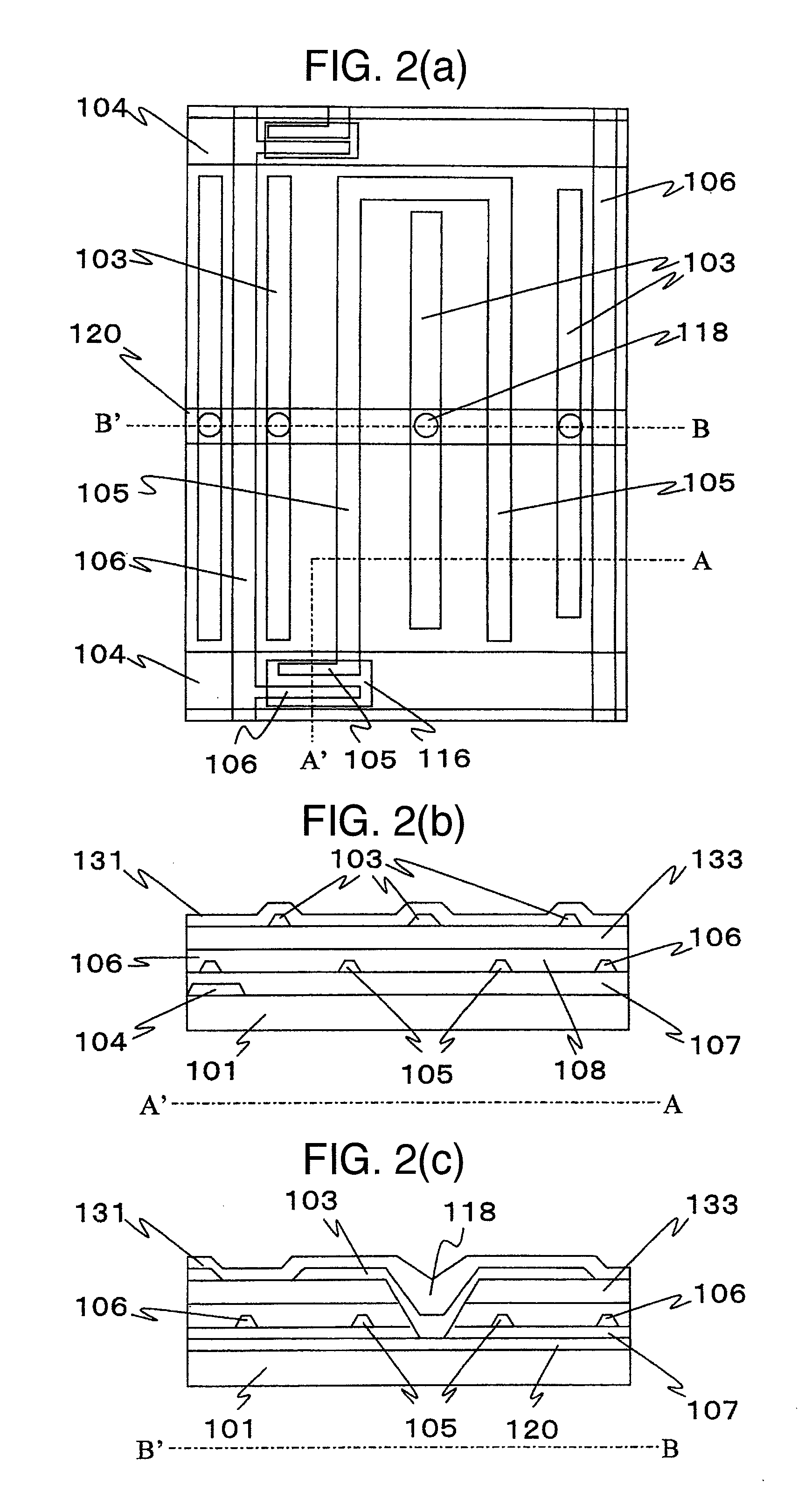

Liquid Crystal Display Device

ActiveUS20070160778A1Increase in degree of polarizationReduction of luminanceLiquid crystal compositionsNon-linear opticsLiquid-crystal displayPhotosensitive polymer

An object of the present invention is to provide a liquid crystal display device that has an excellent mass-productivity and gives an image improved by the reduction of the chromaticity difference between white display and black display, the reduction of coloring and luminance in black display, and the improvement of the contrast ratio. In the present invention, of a pair of alignment films 131 and 132 formed on a pair of substrates 101 and 102, respectively, the alignment film 132 formed on the glass substrate 102 on the observer side is made of a material obtained by adding a photoisomerized compound to a photosensitive polymer and has anisotropic absorption all over the visible light wavelength region (approximately 400 nm to 750 nm).

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

Two-photon absorbing optical recording material and two-photon absorbing optical recording and reproducing method

InactiveUS20050003133A1High sensitivityBig contrastPhotosensitive materialsLayered productsTwo-photon absorptionPhoto irradiation

A two-photon absorbing optical recording material comprising at least one two-photon absorbing compound and a recording component is provided. Recording is made on it by utilizing the two-photon absorption of the two-photon absorbing compound in the material, and then the material is irradiated with light to thereby detect the difference in the reflectance between the recorded area and the unrecorded area thereof, and the recorded information is thereby reproduced from the material, and also provided are a photosensitive polymer composition and a photon-mode recording method for the material.

Owner:FUJIFILM CORP +1

Apparatus and methods for printing three dimensional objects

InactiveUS20170210064A1Easy to operateAdditive manufacturing with liquids3D object support structuresPeristaltic pumpControl system

3D printing apparatus and methods involving a reservoir configured to store at least one photopolymer material for printing three-dimensional objects, a material dispensing head in fluid connection with the reservoir, one or more peristaltic pump(s) controlling transport of material from the reservoir to the material dispensing head, a control system controlling operation of the peristaltic pump(s), and a radiation source for curing the material. Pulsatility of the flow output from said peristaltic pump(s) is smoothed using a compensation procedure.

Owner:AUCKLAND UNISERVICES LTD

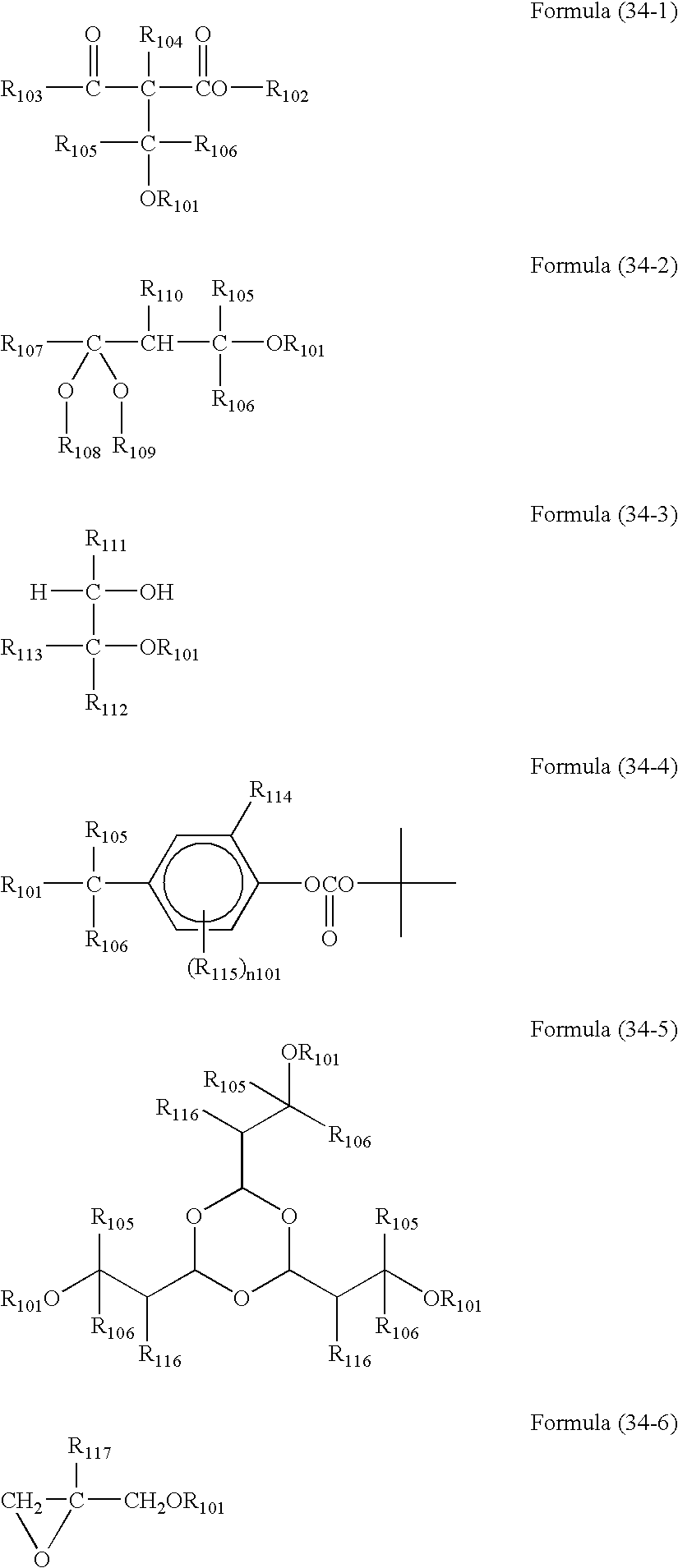

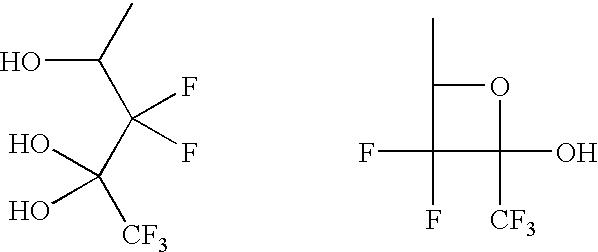

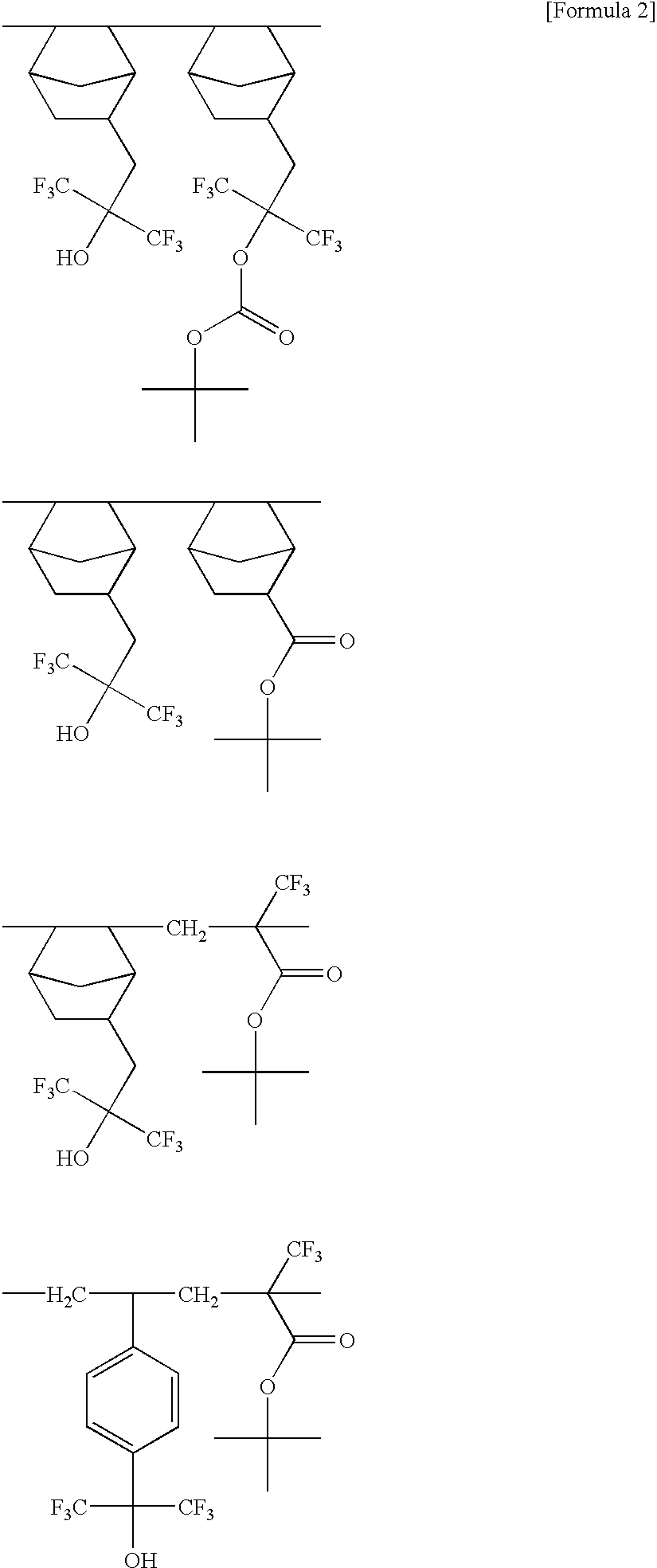

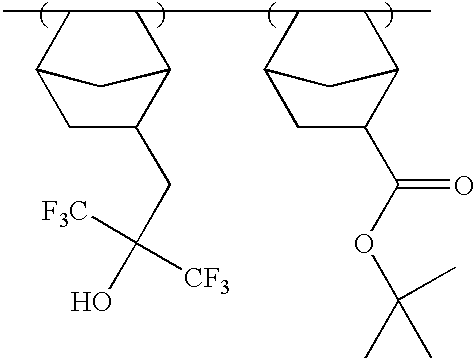

Fluorine-containing photosensitive polymer having hydrate structure and resist composition comprising the same

Provided are a fluorine-containing photosensitive polymer having a hydrate structure and a resist composition including the photosensitive polymer. The photosensitive polymer has an average molecular weight of about 3,000-100,000 with a repeating unit including a group having one of structural formulae below:

Owner:SAMSUNG ELECTRONICS CO LTD

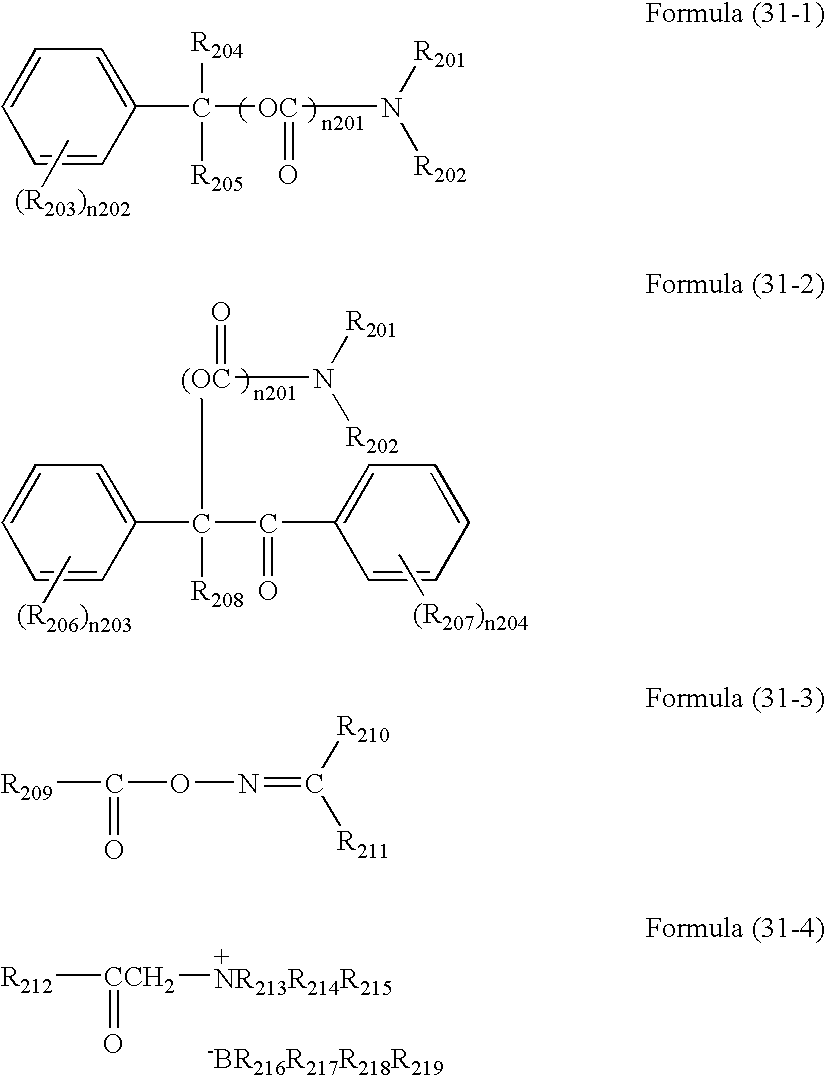

Method of forming a pattern using a photoresist composition for immersion lithography

ActiveUS20090176177A1High resolutionImprove hydrophilicityPhotosensitive materialsRadiation applicationsOrganic solventSide chain

A photoresist composition for immersion lithography and a method of forming a photoresist pattern using the photoresist composition are disclosed. The photoresist composition includes a photosensitive polymer including a cycloaliphatic group blocked with at least two cyclic acetal groups as a side chain, a photoacid generator and an organic solvent. The hydrophobic photoresist composition may be changed into the hydrophilic photoresist composition by an exposure process. Thus, before the exposure process, the photoresist composition may be insoluble in a liquid for the immersion lithography. After the exposure process, an exposure portion of a photoresist film formed using the photoresist composition may be effectively dissolved in a developing solution to form a uniform photoresist pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

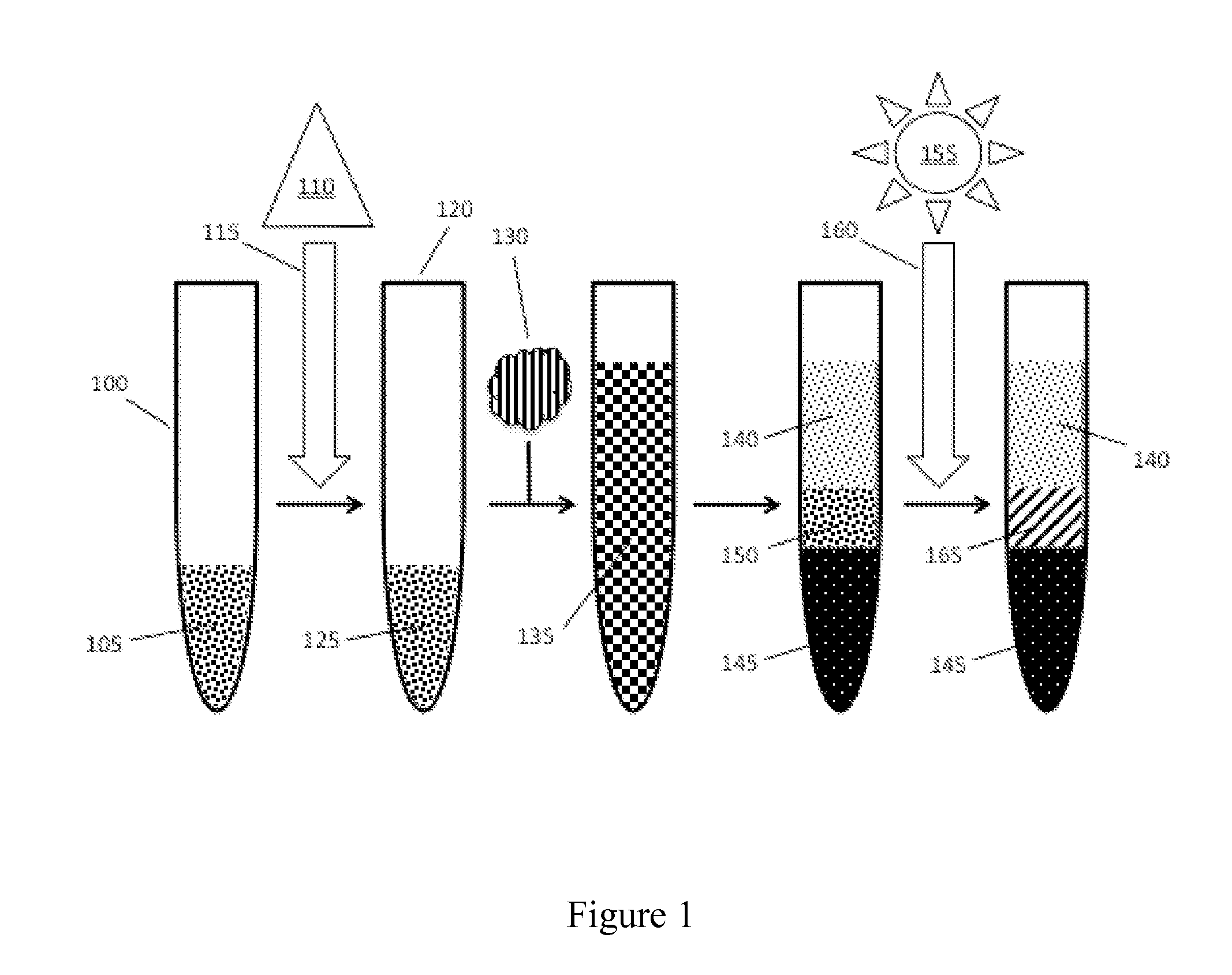

Sterilizable Photopolymer Serum Separator

ActiveUS20140113795A1Dispersed particle separationCentrifugal force sediment separationCentrifugationPhysical chemistry

Sterilizable separator tubes and methods of utilization of same are presented. Methods include providing a separator tube containing a separator substance that can be polymerized to a desired hardness following sterilization using radical generating radiation. The separator substance is formulated to have a density between that of the average densities of separable fractions derived from a sample fluid such as blood, and to be flowable. Upon centrifugation of a separator tube containing a fluid sample, the separator substance forms a barrier between the fractions. The barrier subsequently hardens to form a solid barrier when triggered by a suitable energy source.

Owner:UNIV OF MARYLAND +1

Vegetable oil based polyurethane acrylic ester, preparing process and use thereof

InactiveCN101497684AWide variety of sourcesEasy to makePolyurea/polyurethane coatingsSurface treatment compositionsAlkaneVegetable oil

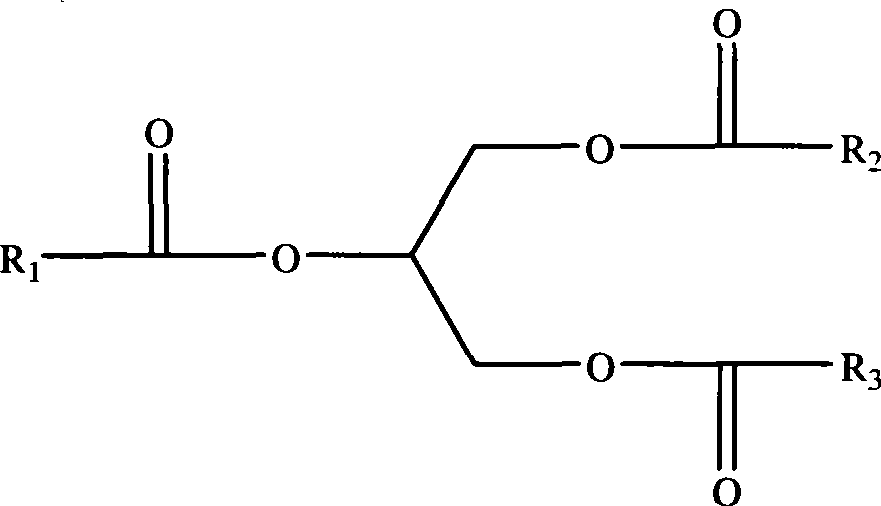

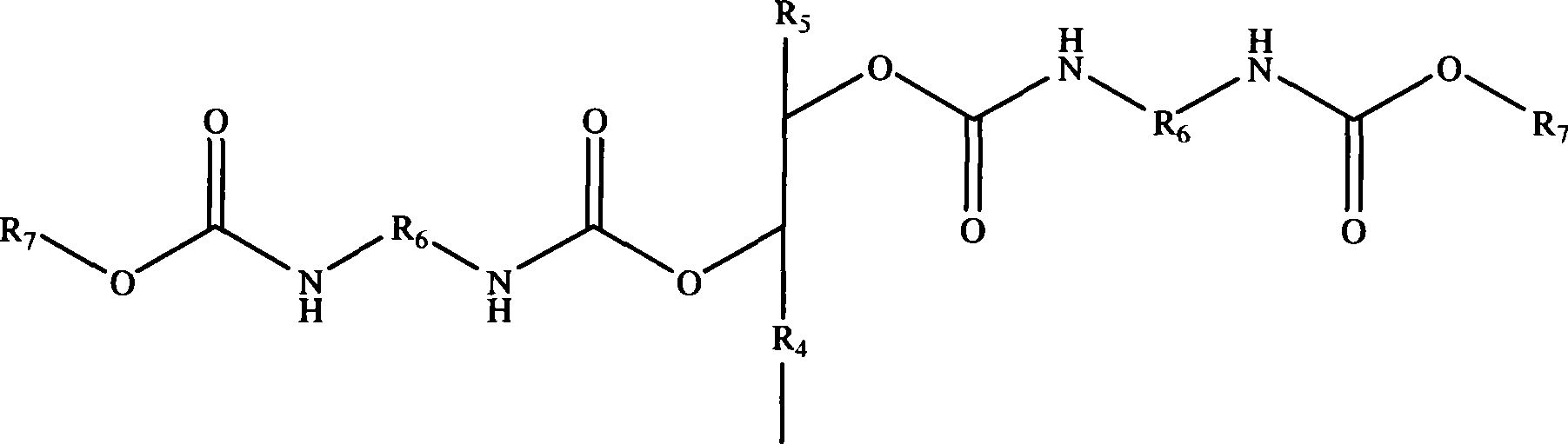

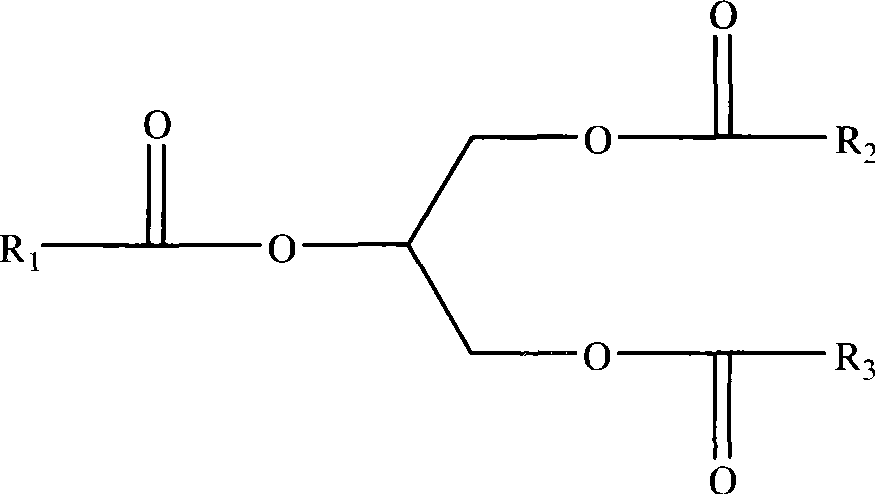

The invention relates to vegetable oil based polyurethane acrylic ester, belonging to the field of photosensitive polymer material. The vegetable oil based polyurethane acrylic ester is characterized in that the general chemical formula is Formula I, wherein R1, R2 and R3 are respectively chosen from alkane of C1-C18, at least one of the alkane is chosen from Formula II, R4 and R5 are respectively chosen from alkane of C1-C16, R6 is diphenyl methane-4,4'-diisocyanate, or hexamethylene diisocyanate, or isophorone diisocyanate or residue of 2,4-toluene diisocyanate with two isocyanate functional group removed, and R7 is 2-hydroxyethyl acrylate, or hydroxypropyl acrylate, or residue of pentaerythritol triacrylate with hydroxy functional group removed.

Owner:天津市天骄辐射固化材料有限公司

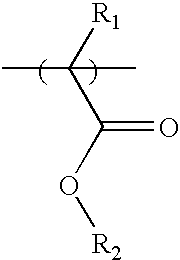

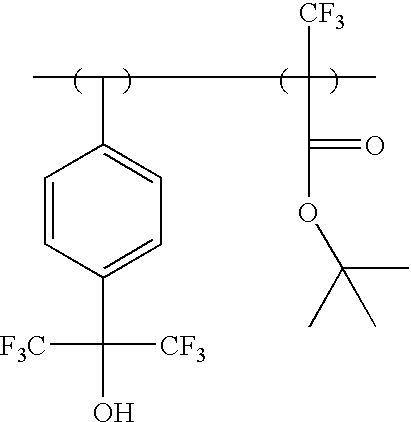

Photosensitive polymer having fluorinated ethylene glycol group and chemically amplified resist composition comprising the same

InactiveUS6844134B2High light transmittanceImprove adhesionPhotosensitive materialsRadiation applicationsResistHydrogen atom

A photosensitive polymer comprises a fluorinated ethylene glycol group and a chemically amplified resist composition including the photosensitive polymer. The photosensitive polymer has a weight average molecular weight of about 3,000-50,000 having a repeating unit as follows: wherein R1 is a hydrogen atom or methyl group, and R2 is a fluorinated ethylene glycol group having 3 to 10 carbon atoms.

Owner:SAMSUNG ELECTRONICS CO LTD

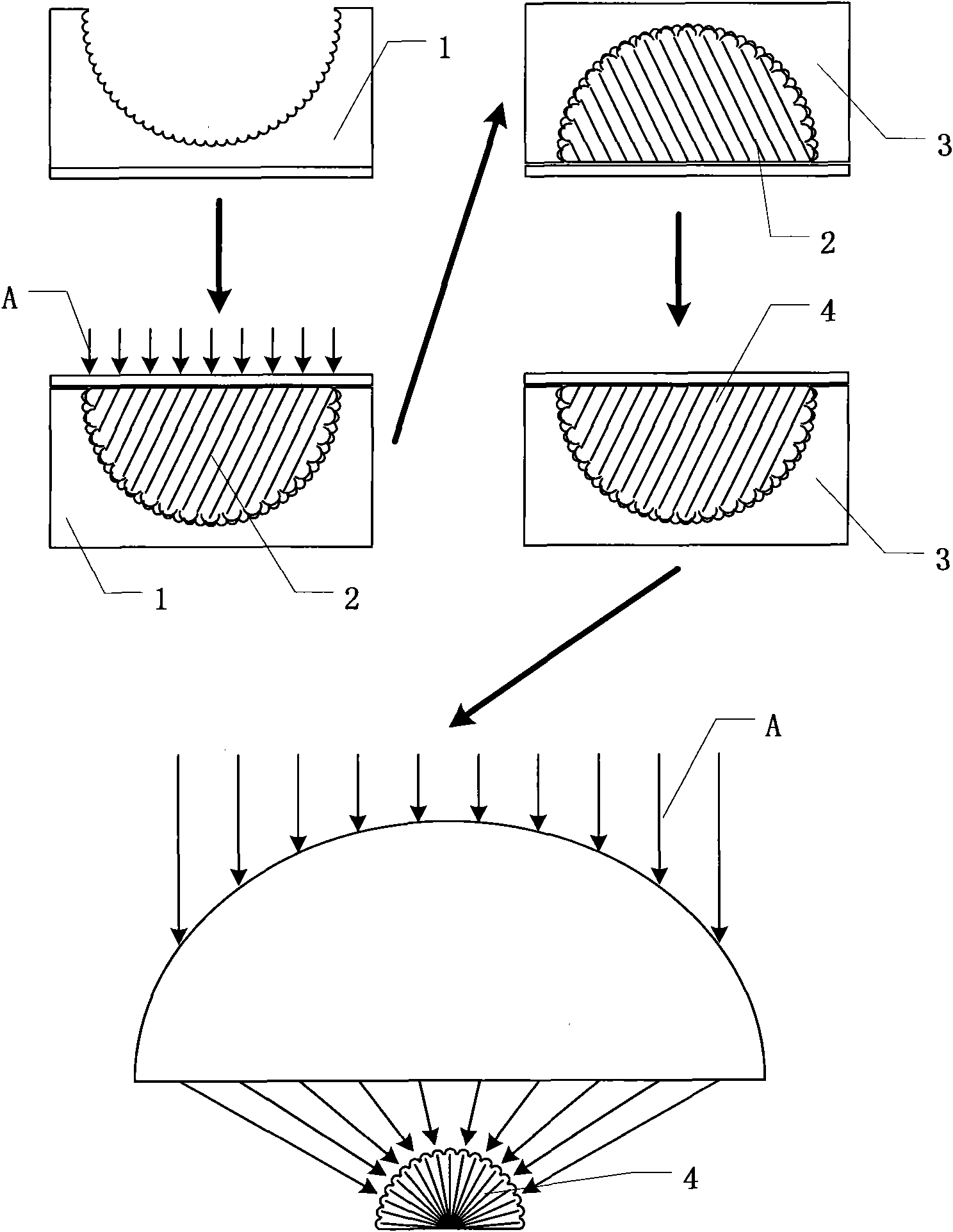

Method for manufacturing artificial bionic compound eyes

InactiveCN101672937AImprove machining accuracyOvercome light scattering effectPhotomechanical apparatusOptical articlesHigh volume manufacturingUltraviolet lights

The invention discloses a method for manufacturing artificial bionic compound eyes, comprising the steps of: firstly using femtosecond pulse bi-photon polymerization method to manufacture an inversioncurved surface micro lens mold; using ultraviolet nano impressing to manufacture into a three-dimensional curved surface micro lens template; then manufacturing an elastic mold on the three-dimensional curved surface micro lens template; sequentially accommodating photosensitive resin in the elastic mold, heating for baking into a photosensitive polymer mold with opposite polarity; and finally using the lens to focus ultraviolet lights and right irradiate to the photosensitive polymer mold placed on a substrate, manufacturing a light transmission channel by self-writing waveguide method, andmanufacturing into an artificial bionic compound eye. The invention overcomes limit of photoetching technology in aspect of three-dimensional micro-processing, improves processing precision of micro lens, can effectively reduce manufacture cost, enhance mass production capacity, and further promote application of artificial compound eyes in medical science, industry, military and other fields.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

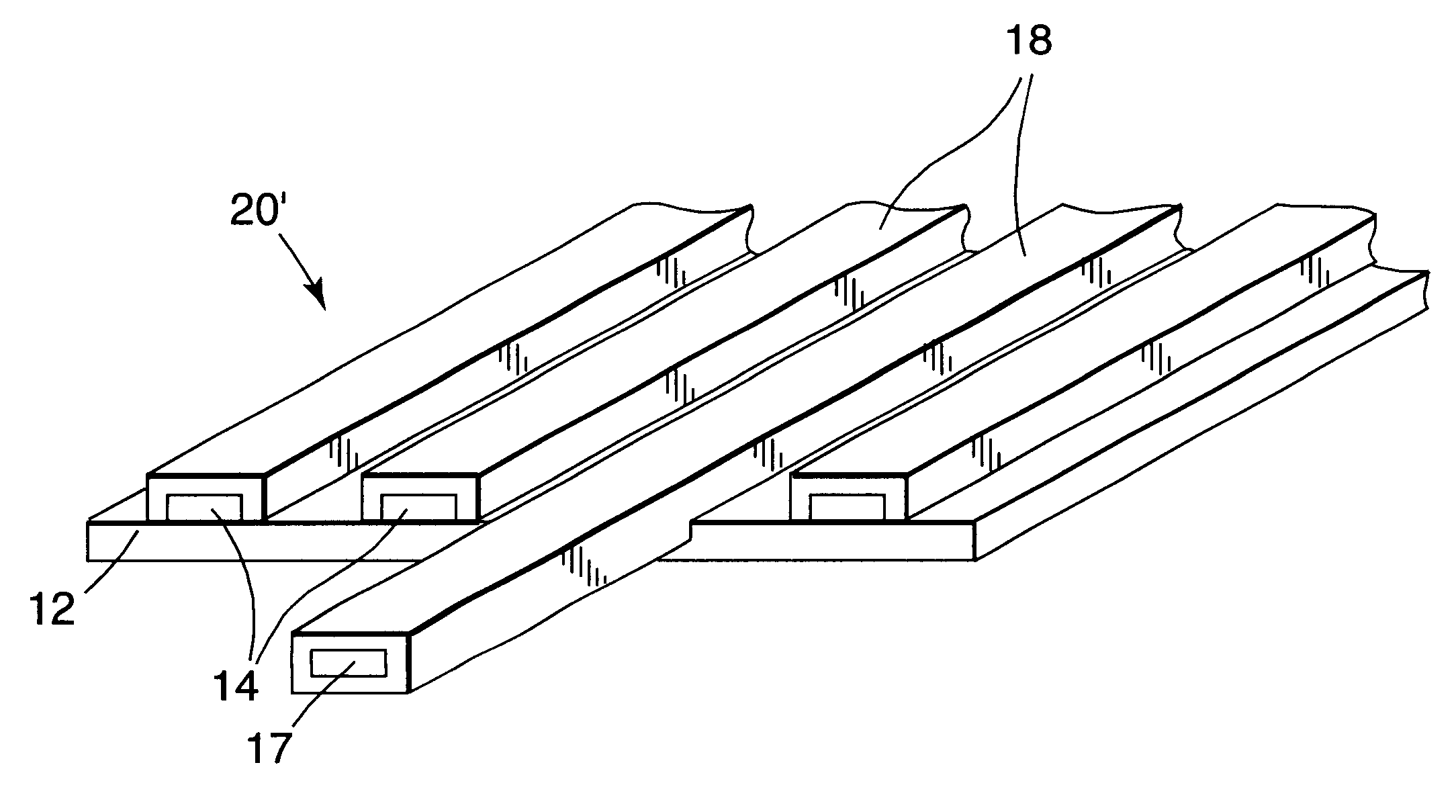

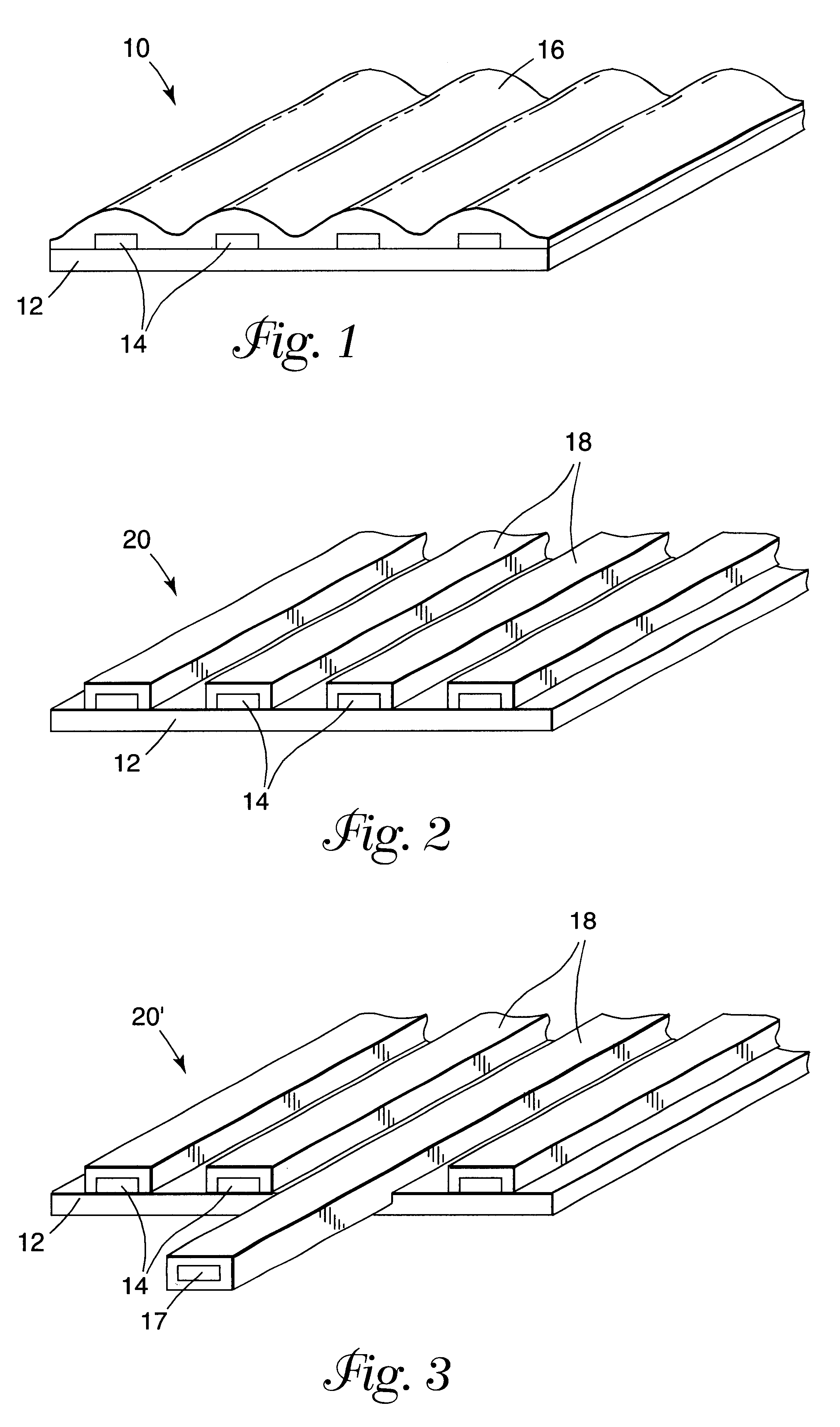

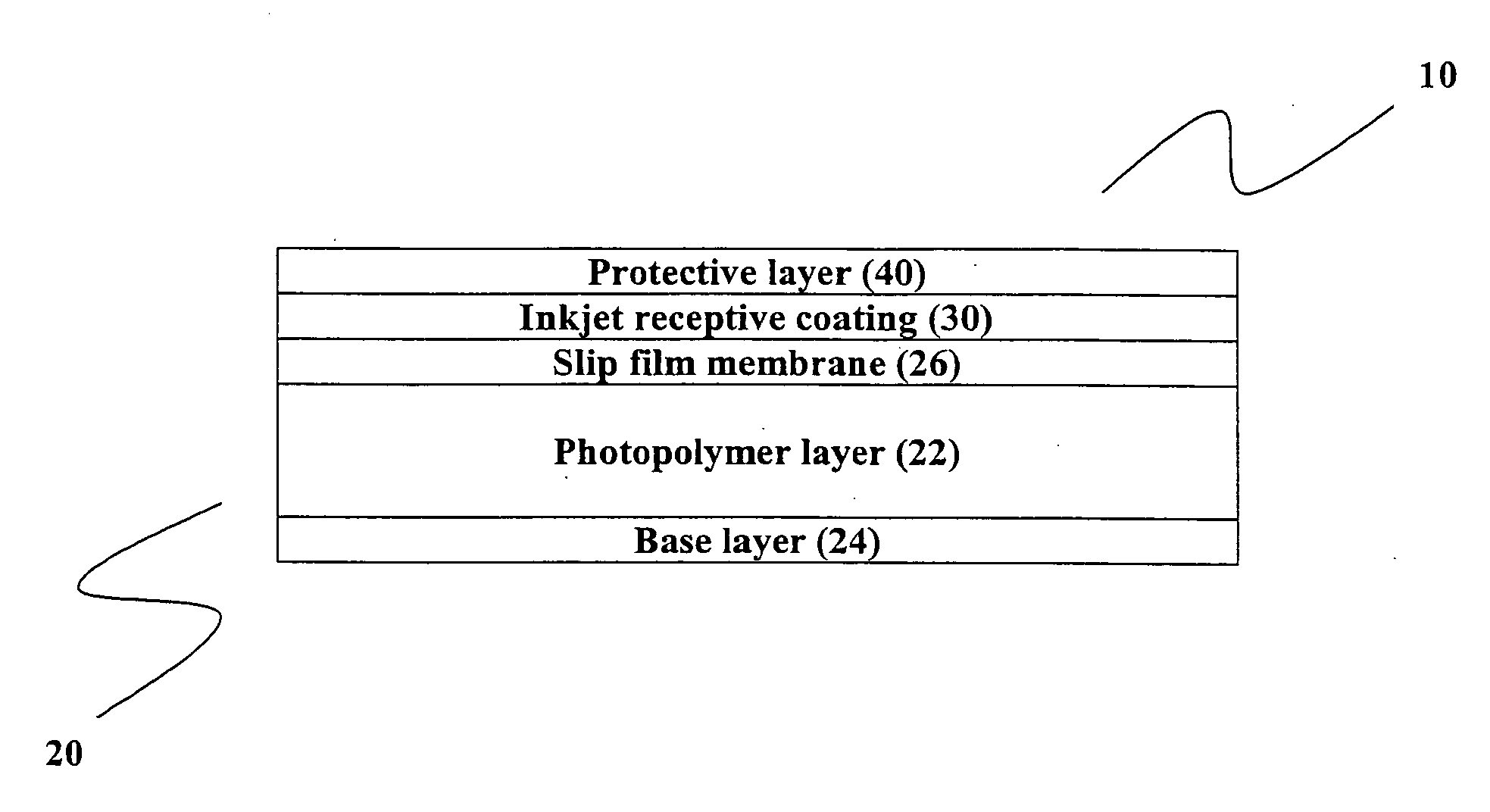

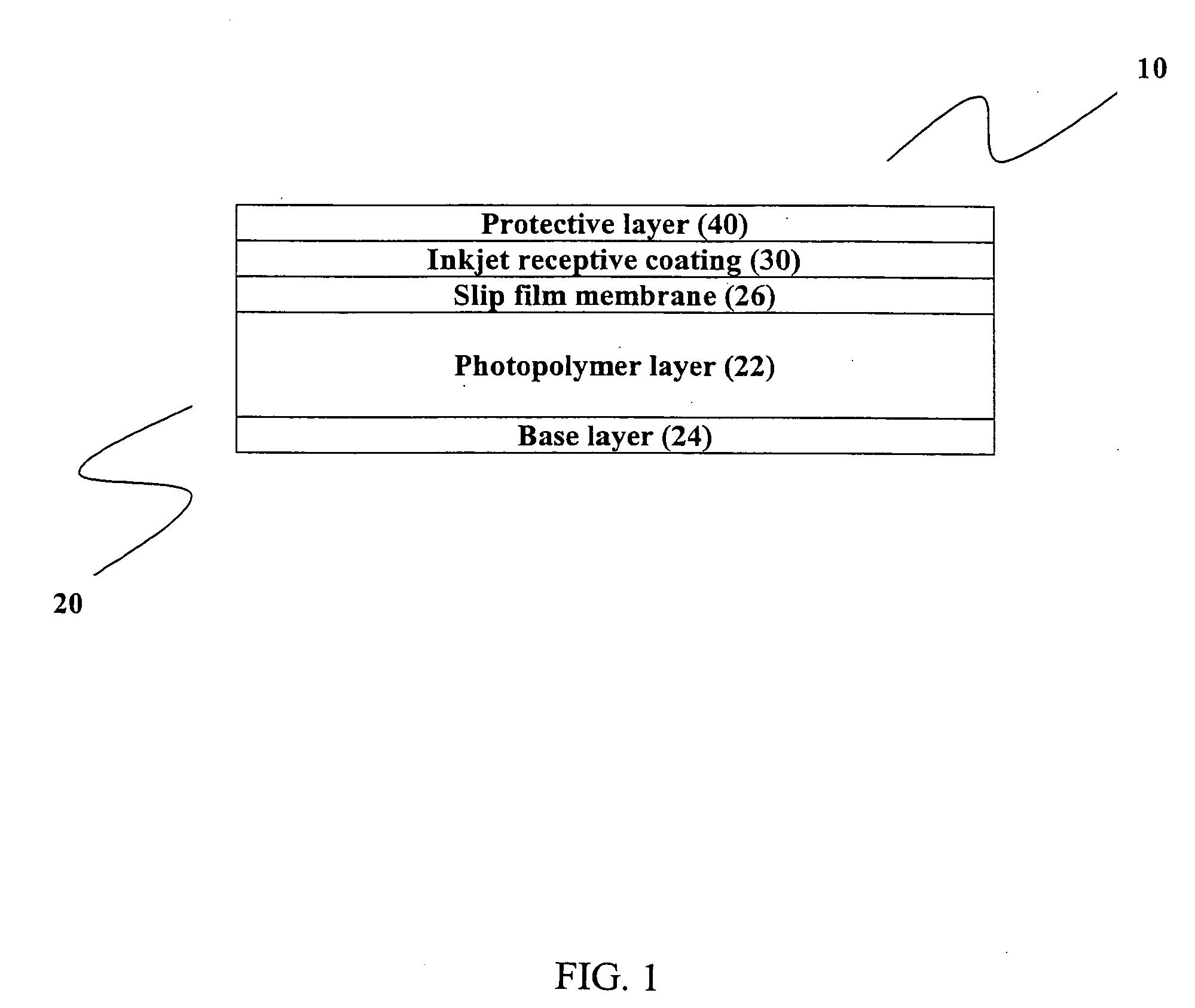

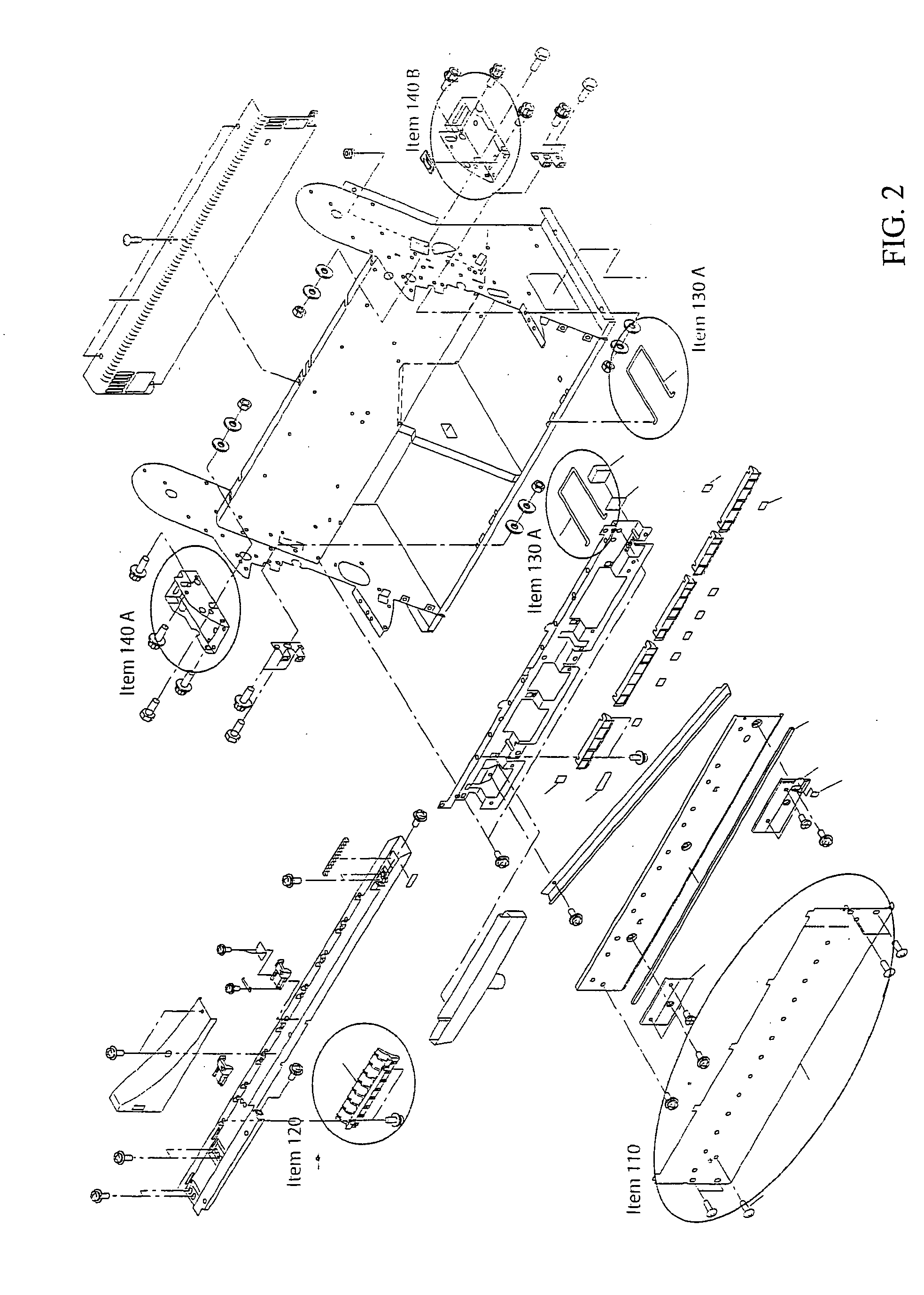

Photopolymer plate and method for imaging the surface of a photopolymer plate

InactiveUS20060073417A1Duplicating/marking methodsSemiconductor/solid-state device manufacturingPolymer substratePhotopolymer

A flexographic printing plate and a method for making a flexographic printing plate. According to one aspect, the method comprises the steps of providing a photopolymer substrate having a top surface pretreated with a non-gelatinous inkjet receptive coating; image-wise ink jetting an inkjet composition onto a portion of the pretreated surface of the photopolymer substrate to provide a photomask layer; exposing the photopolymer substrate to ultraviolet light to cure an unmasked portion of the photopolymer substrate; and processing the photopolymer substrate under conditions effective to render the cured unmasked portion of the photopolymer layer into a raised image surface suitable for use in a flexographic printing process.

Owner:HERMESDORF MARK

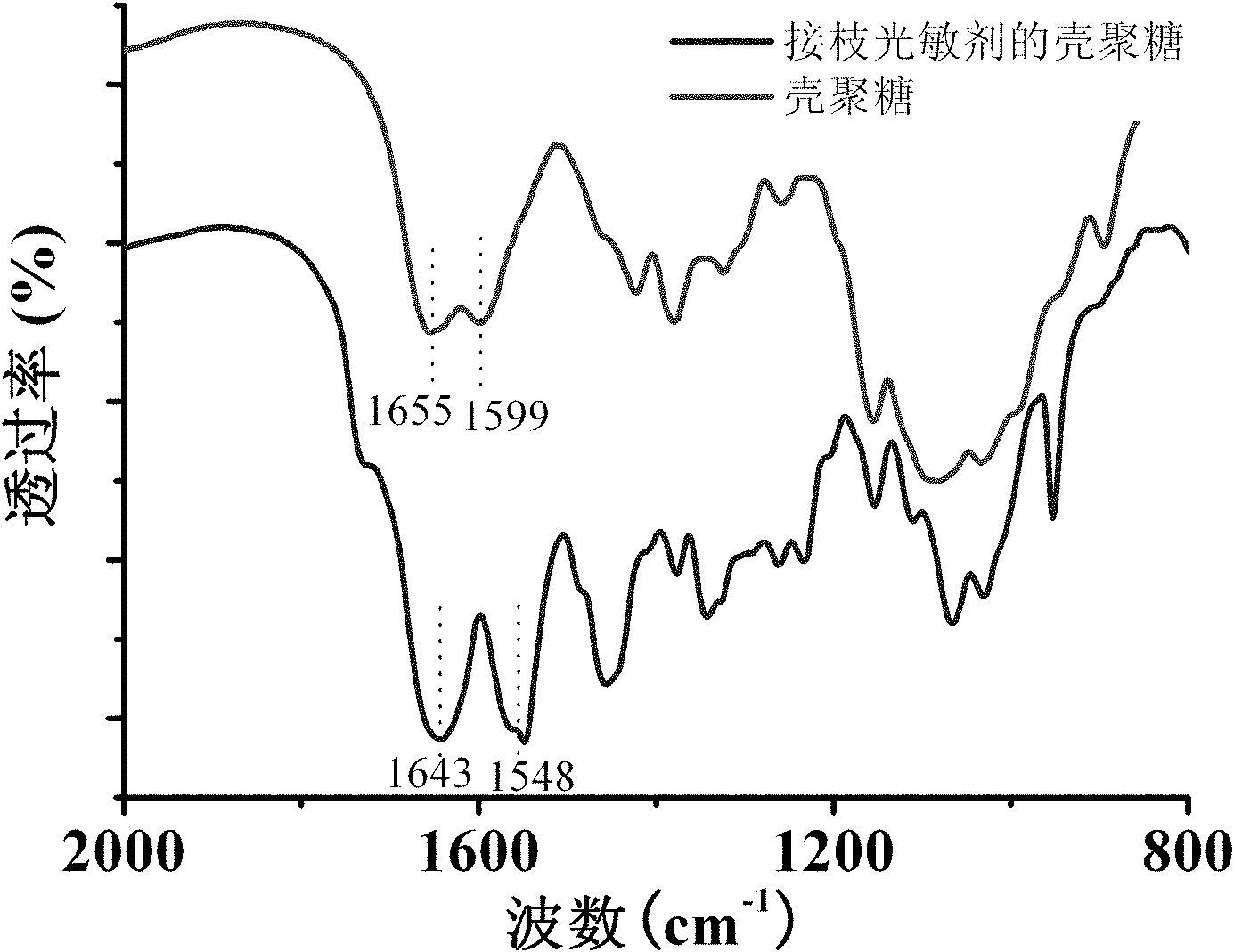

Photosensitive microcapsule used for photodynamic therapy and preparation method thereof

InactiveCN102133208AIncrease surface chargeEasy to assembleEnergy modified materialsPharmaceutical non-active ingredientsCancer cellMicrosphere

The invention discloses a photosensitive microcapsule used for photodynamic therapy and a preparation method thereof, belonging to the technical field of photosensitive polymer thin film materials. The photosensitive microcapsule is prepared by the following steps: firstly, preparing photosensitive polymer materials of photosensitizer molecule graft polymer, and then adopting the layer self assembly technology, assembling polyelectrolyte materials with opposite charges on a microballoon template, and preparing a hollow capsule assembled by a plurality of capsule walls, wherein materials of the capsule walls include natural polymer glycan (CHI) or glucan directly grafted with photosensitizer by chemical bonds. The photosensitive microcapsule has good biocompatibility, fixes photosensitive molecules, can kill cancer cells effectively, can be applied to (Photodynamic Therapy) PDT, and is good in water dispersion and uniform in particle size, high in single-state oxygen content yield under the illumination of beams with specific wavelength, simple in process and easy in operation.

Owner:BEIJING UNIV OF CHEM TECH