Stacked chip package using warp preventing insulative material and manufacturing method thereof

a technology of insulating material and chip package, which is applied in the direction of semiconductor/solid-state device details, semiconductor devices, electrical equipment, etc., can solve the problems of high process throughput, large volume, and high cost of modern applications, and achieve the effect of preventing warping of semiconductor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

second embodiment

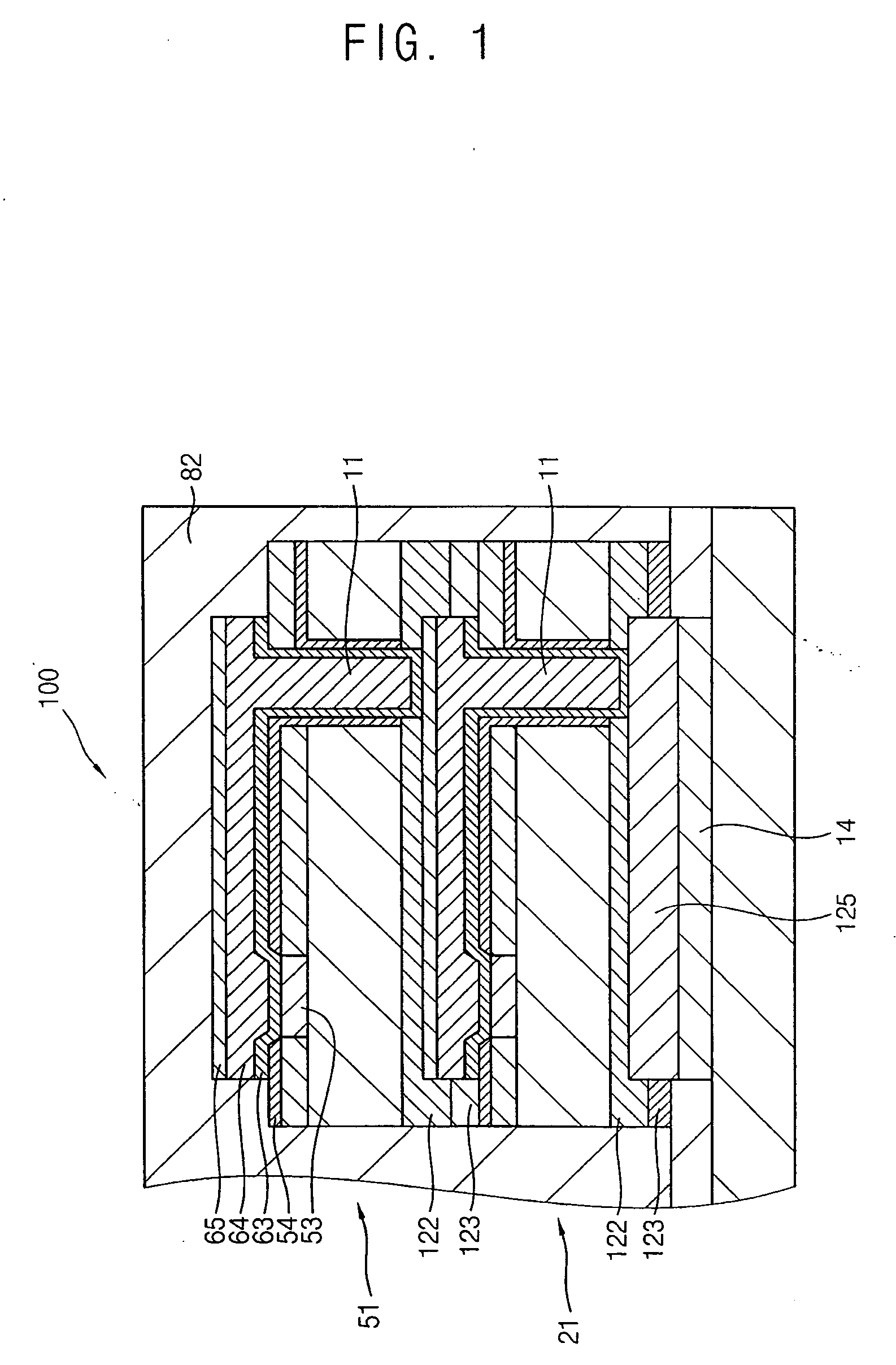

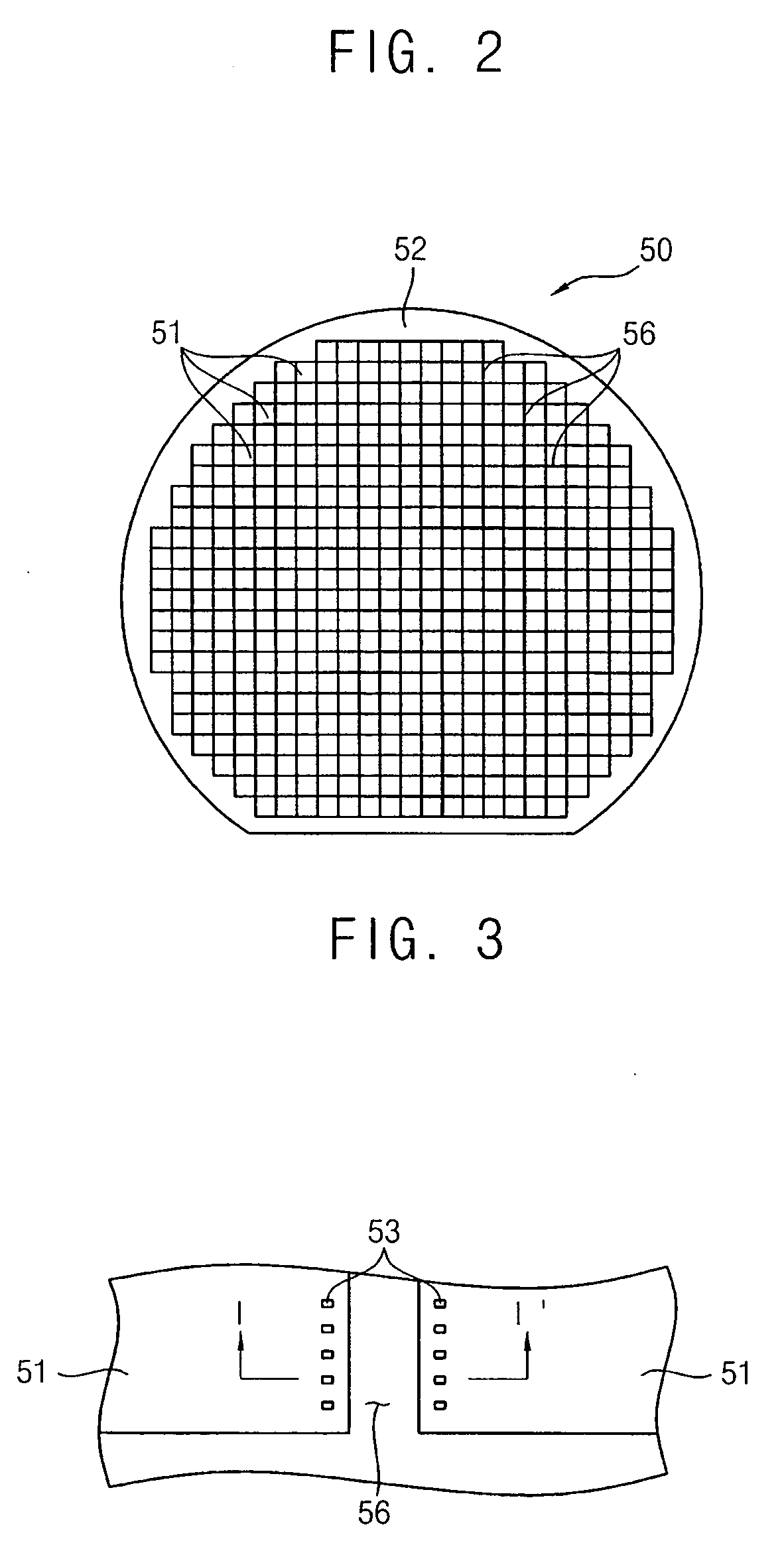

[0099] In a manner similar to the formation and dicing of the chips 51 from the common wafer 50, other chips can be formed and diced from another common wafer, in accordance with the second embodiment described above. For the purpose of the remainder of the present discussion, such other chips are referred to as first chips 21 that are formed and diced from a common first wafer 20, while chips 51 are referred to as second chips 51 that are formed and diced from a common second wafer 50.

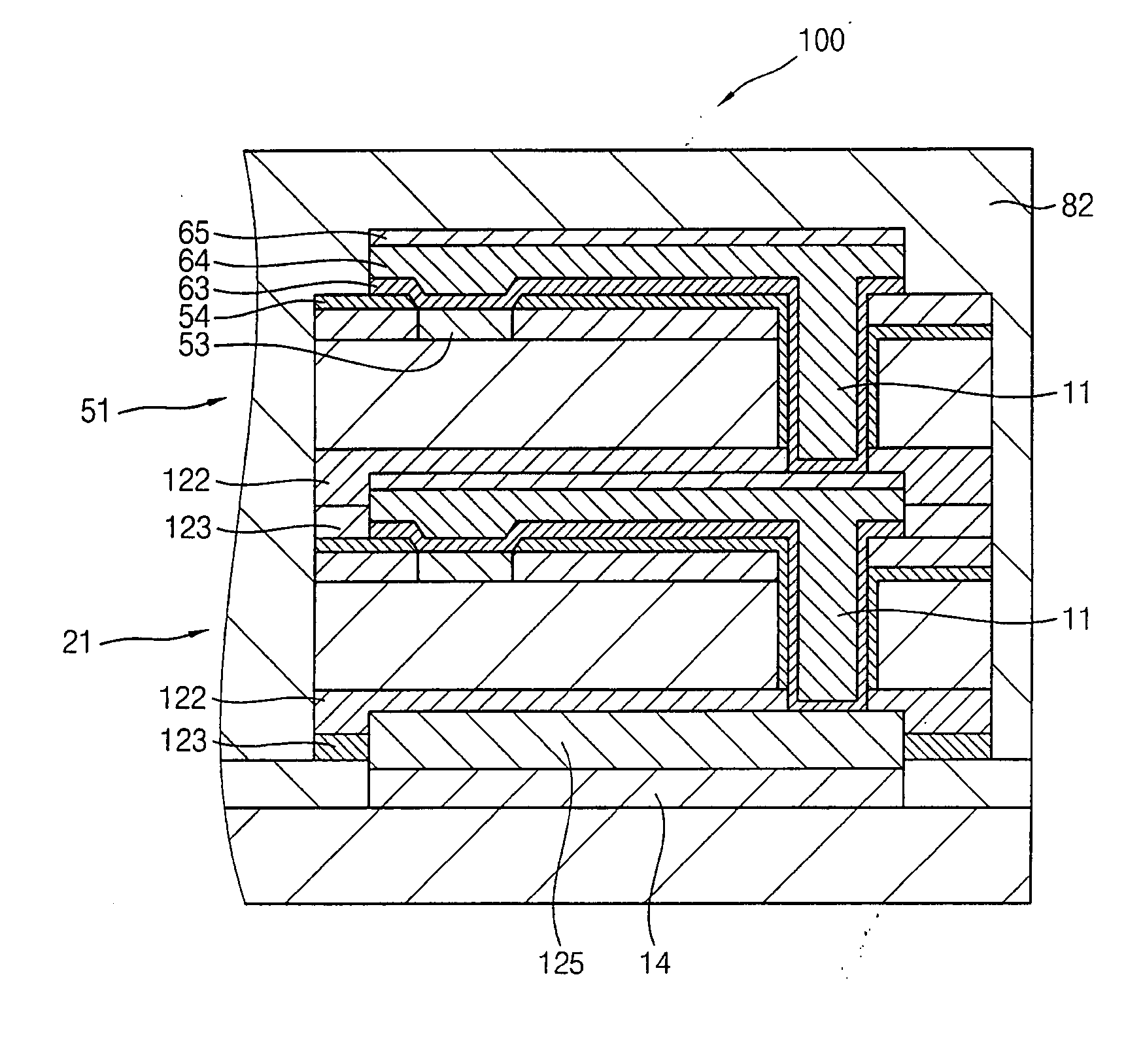

[0100] Referring to FIG. 22, a bottom surface of a separated first chip 21 is applied to a top surface of a printed circuit board 10, or other package substrate. The printed circuit board 10 includes a plurality of chip bonding pads 14, or landing pads, that serve as an interconnect location for conductive paths on the printed circuit board 10. The bonding pads 14 include optional conductive pads 125 on an upper surface thereof. The conductive pads 125 comprise, for example, a low melting point materi...

third embodiment

[0105]FIGS. 24 through 29 are sectional views of a method for fabricating a stacked chip package, in accordance with the present invention.

[0106] In the first and second embodiments above, separated chips are individually aligned and stacked on a substrate to form chip stack packages in a manner that is consistent with a chip level bonding configuration. In the following third embodiment, entire wafers including multiple chips, or segments of such wafers including multiple chips, are aligned and stacked, and applied to a substrate, prior to dicing of the chips in a manner that is consistent with a wafer level bonding configuration.

[0107] Referring to FIG. 24, a second wafer 50 is prepared in a manner similar to that of FIGS. 4 through 12 above to include a patterned insulator layer 122 and patterned adhesive layer 123, the adhesive layer comprising, for example, a photosensitive polymer material, as described above. The photosensitive polymer adhesive layer 123 is partially cured, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More