Patents

Literature

124436results about How to "High yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

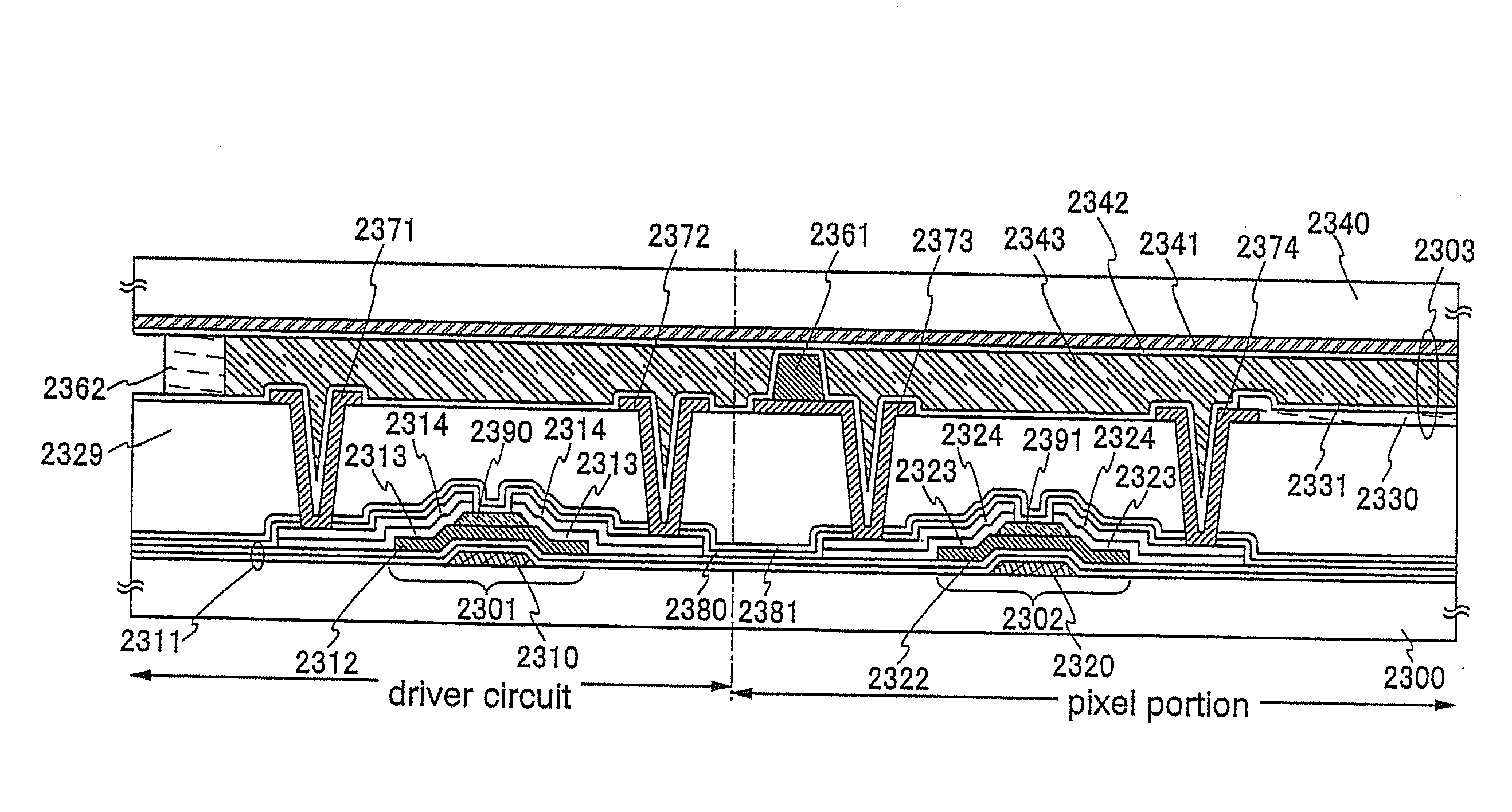

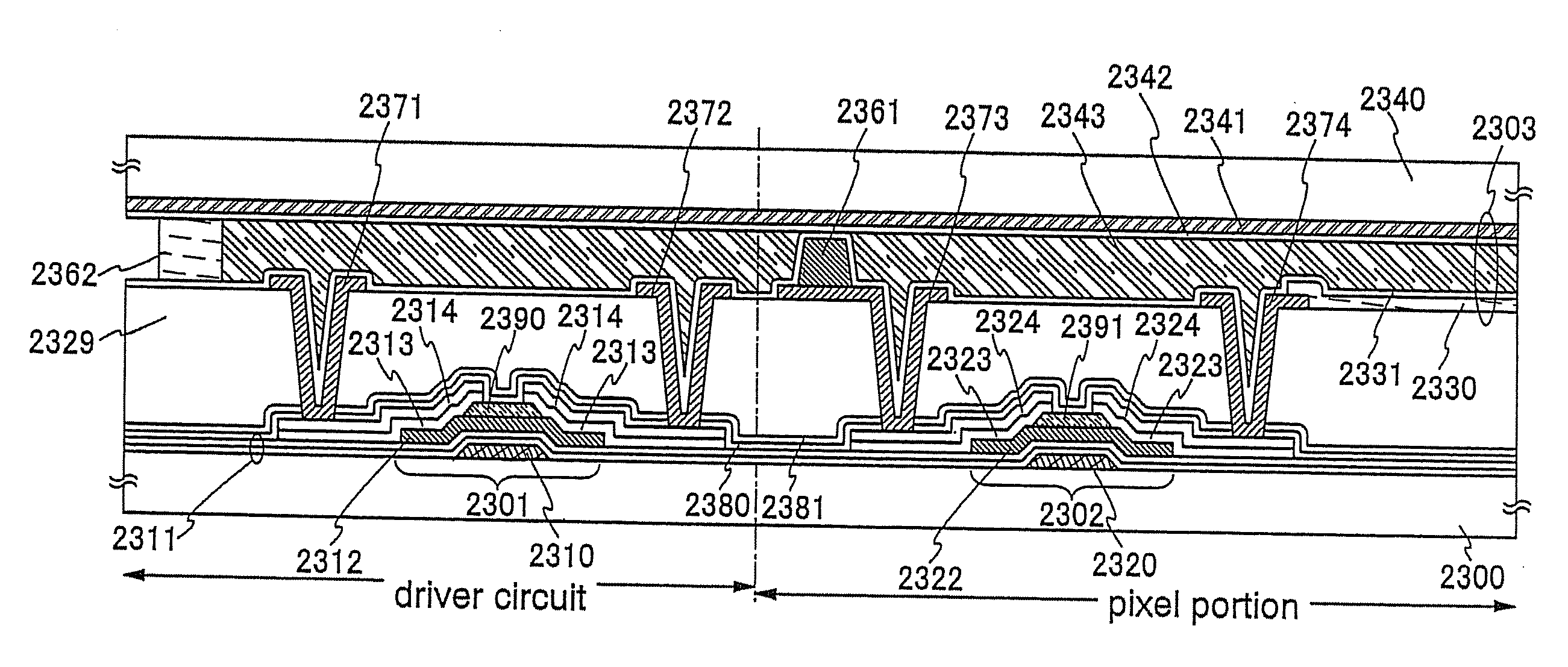

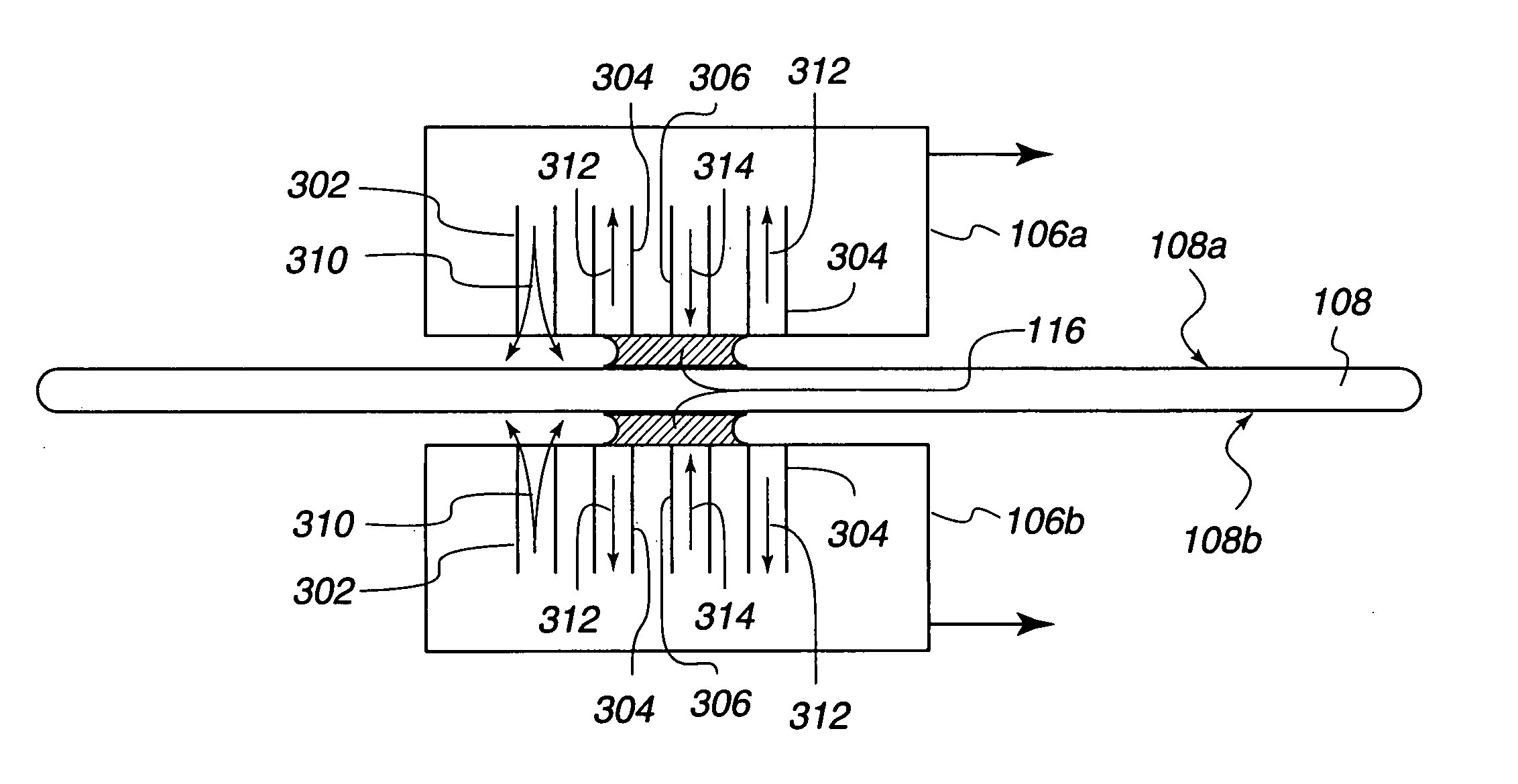

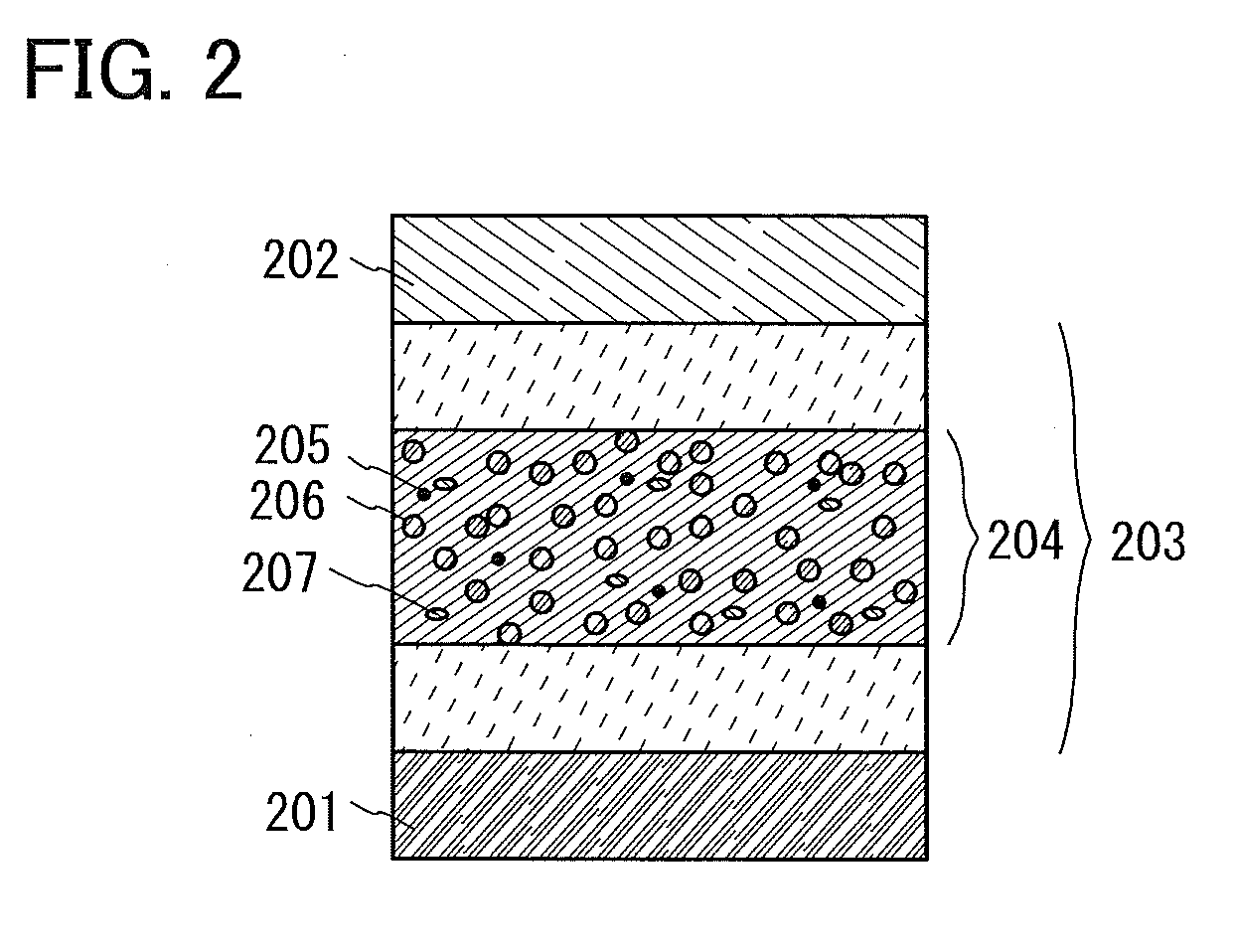

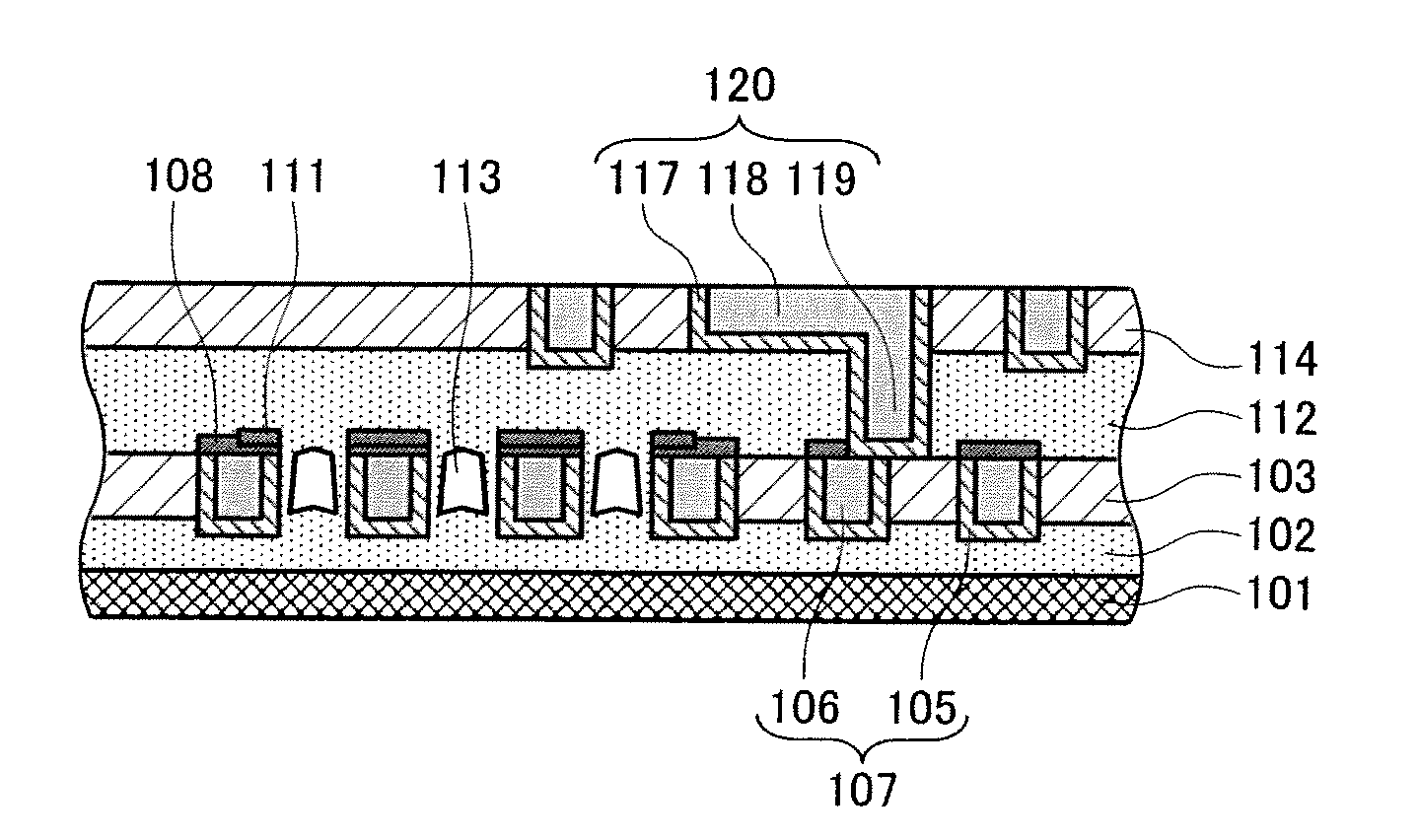

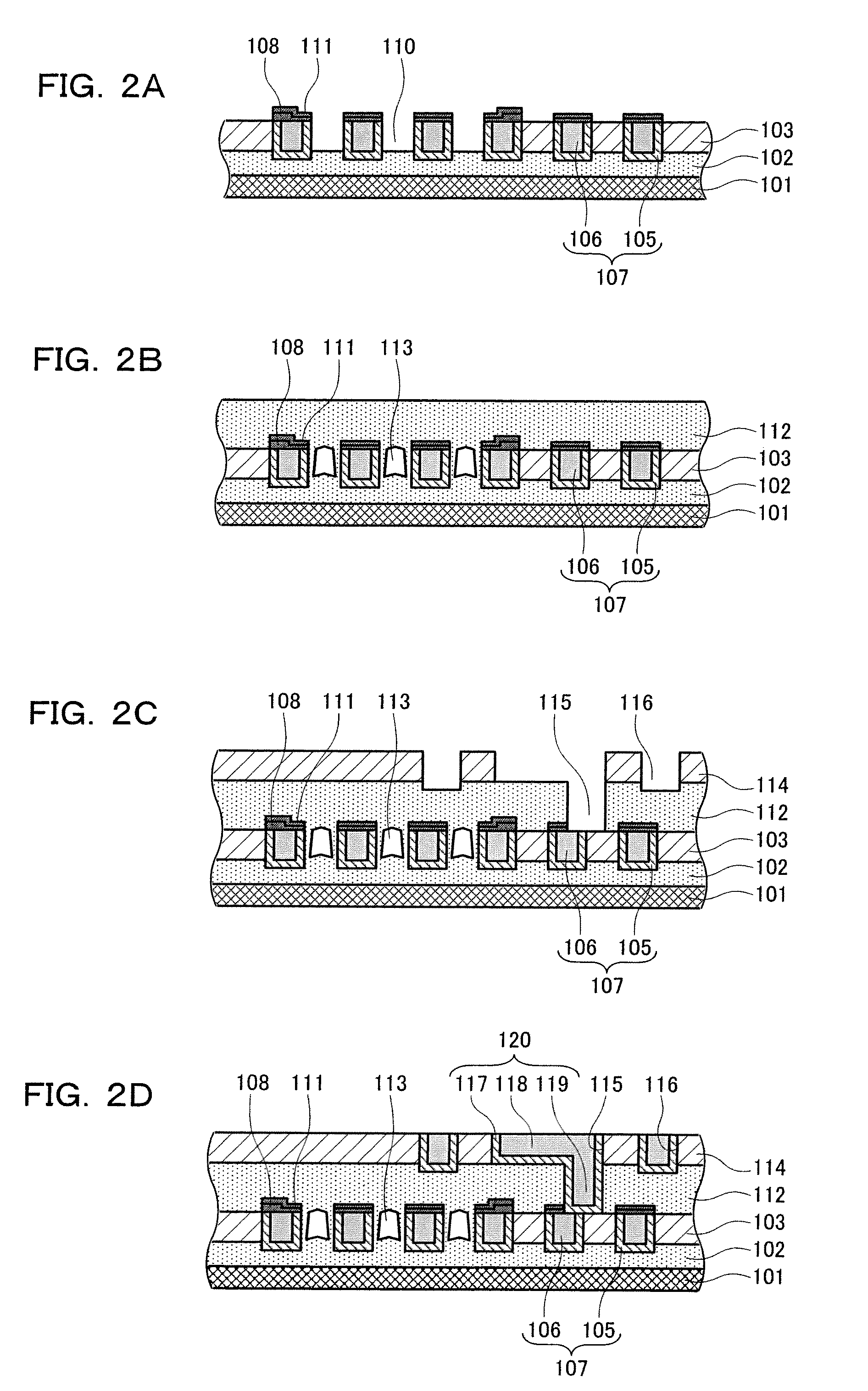

Semiconductor device, electronic device, and method of manufacturing semiconductor device

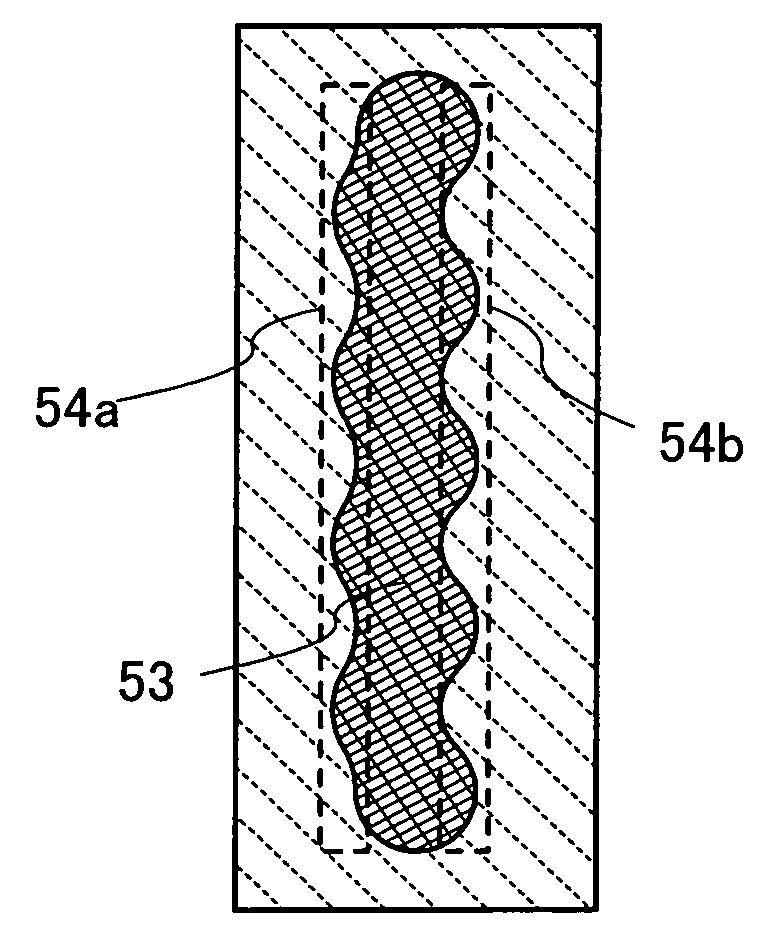

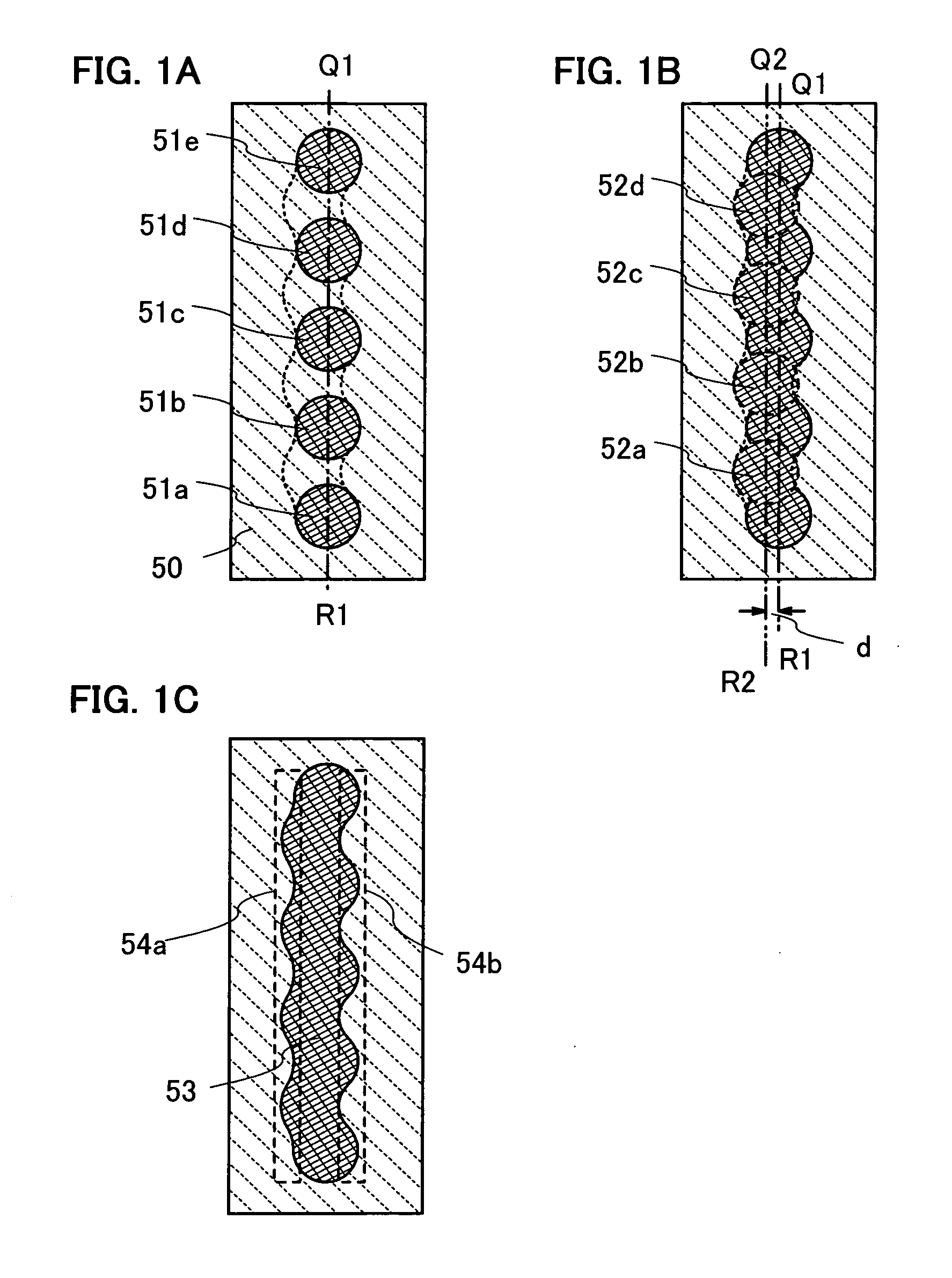

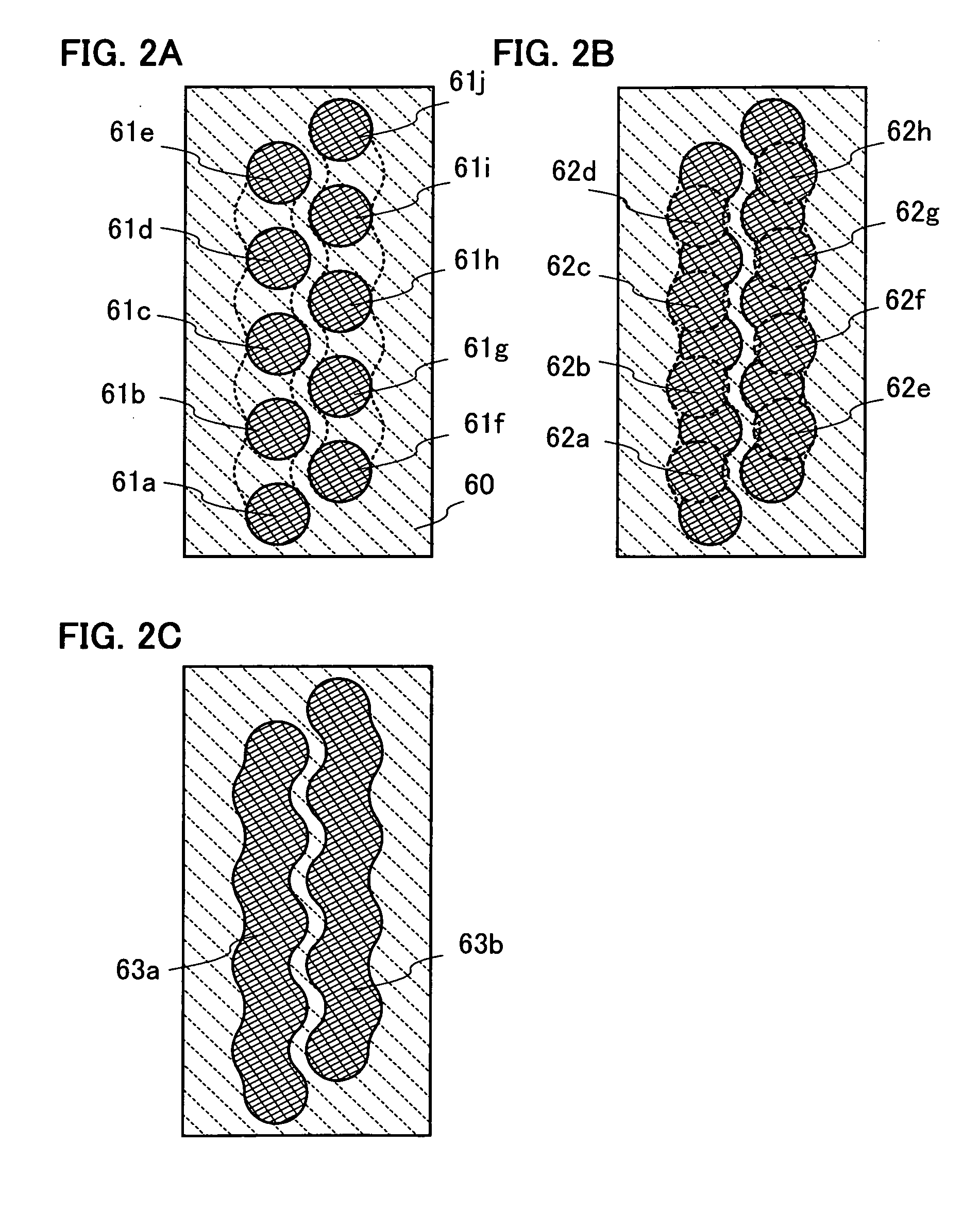

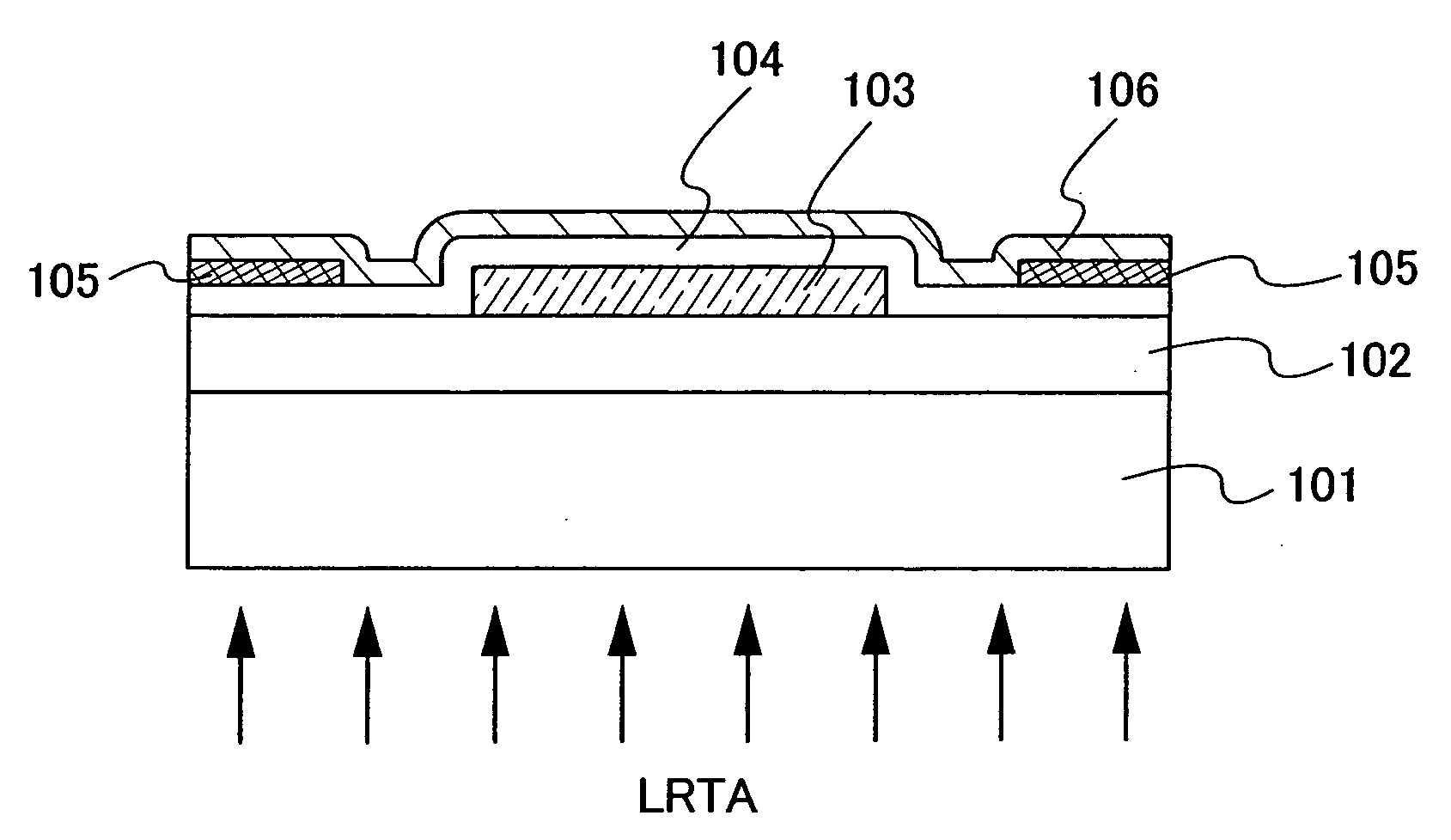

InactiveUS20060169973A1Stable formationImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialDisplay device

To provide a semiconductor device and a display device which can be manufactured through a simplified process and the manufacturing technique. Another object is to provide a technique by which a pattern of wirings or the like which is partially constitutes a semiconductor device or a display device can be formed with a desired shape with controllability.

Owner:SEMICON ENERGY LAB CO LTD

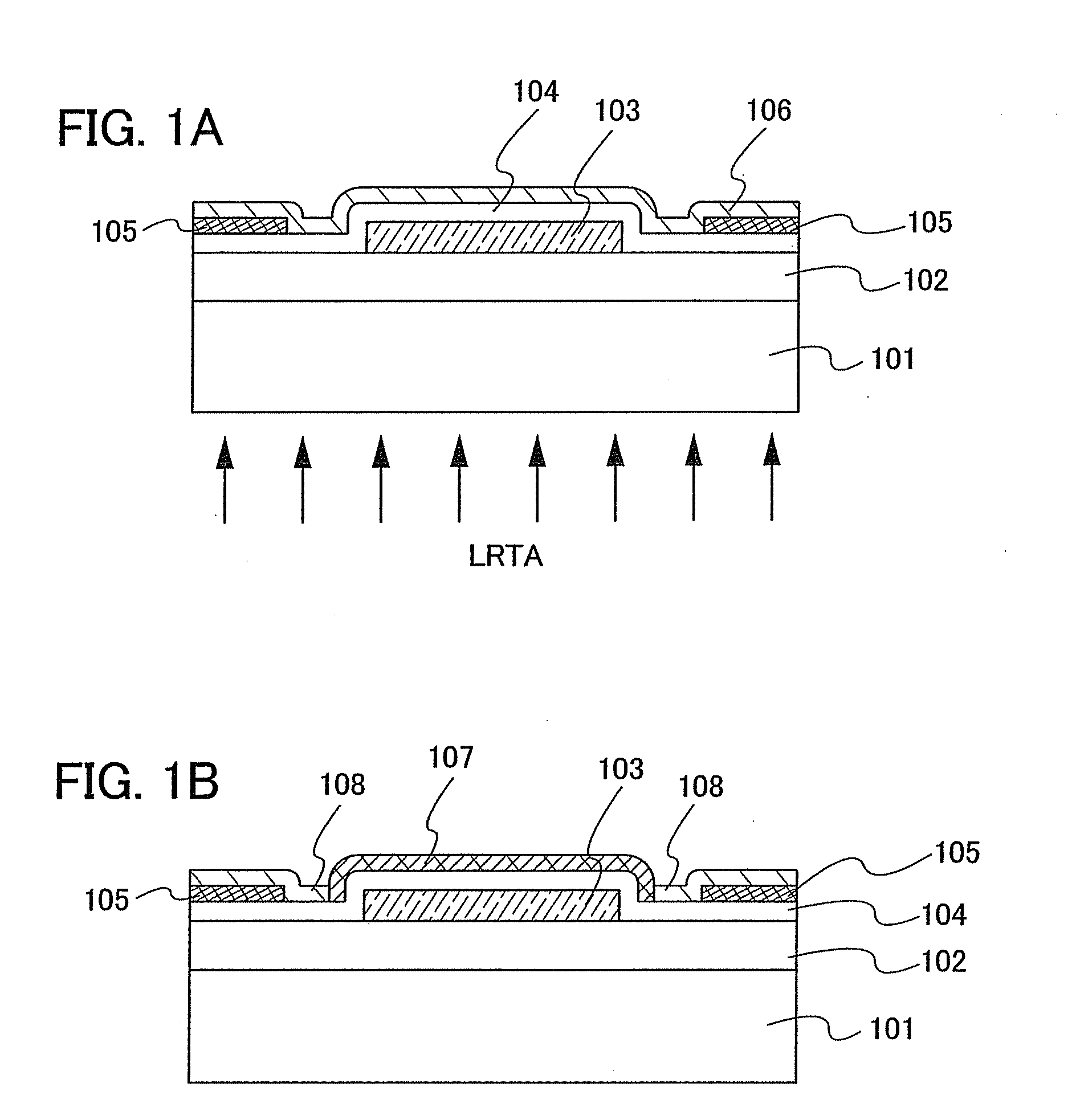

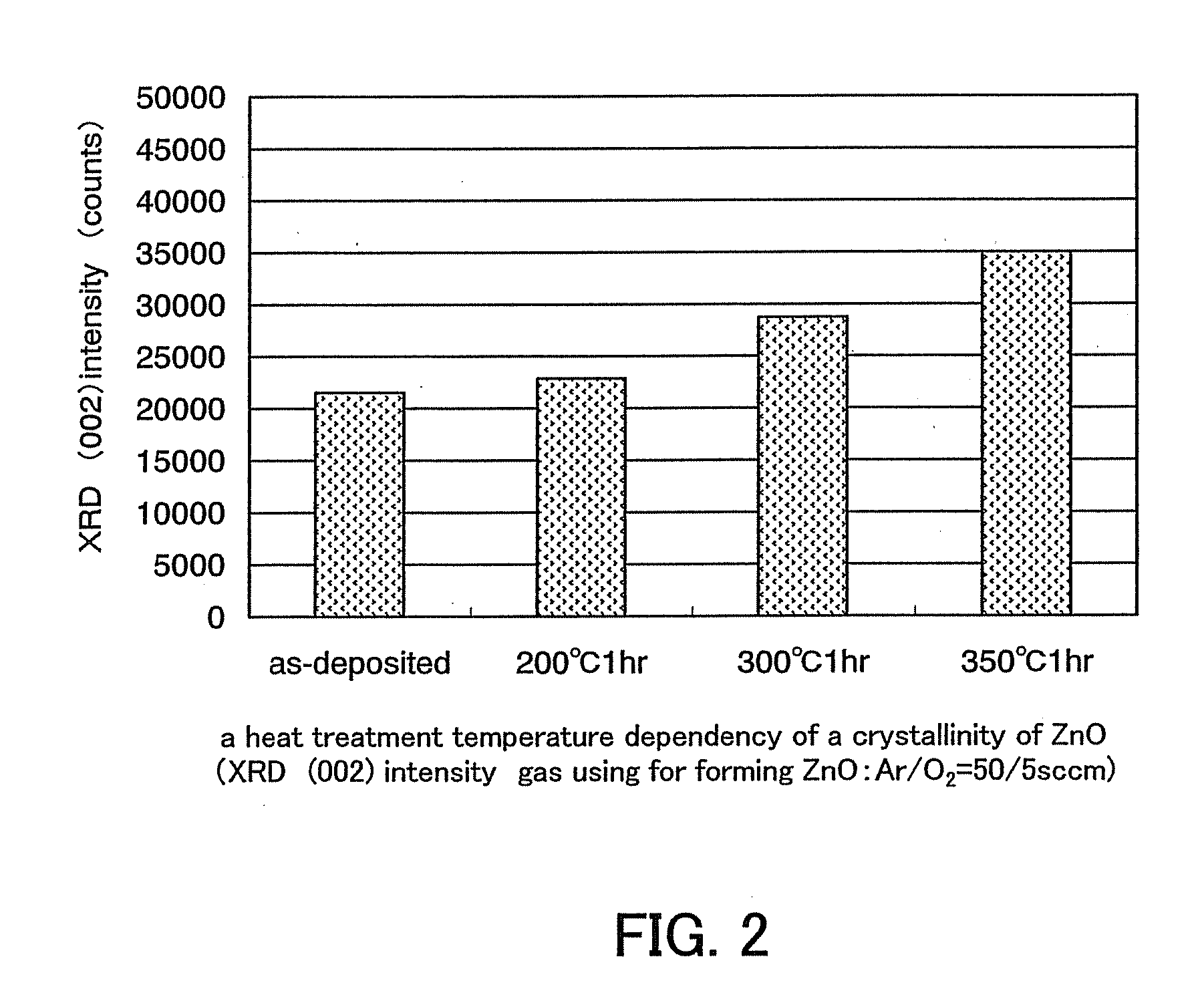

Semiconductor device and manufacturing method thereof

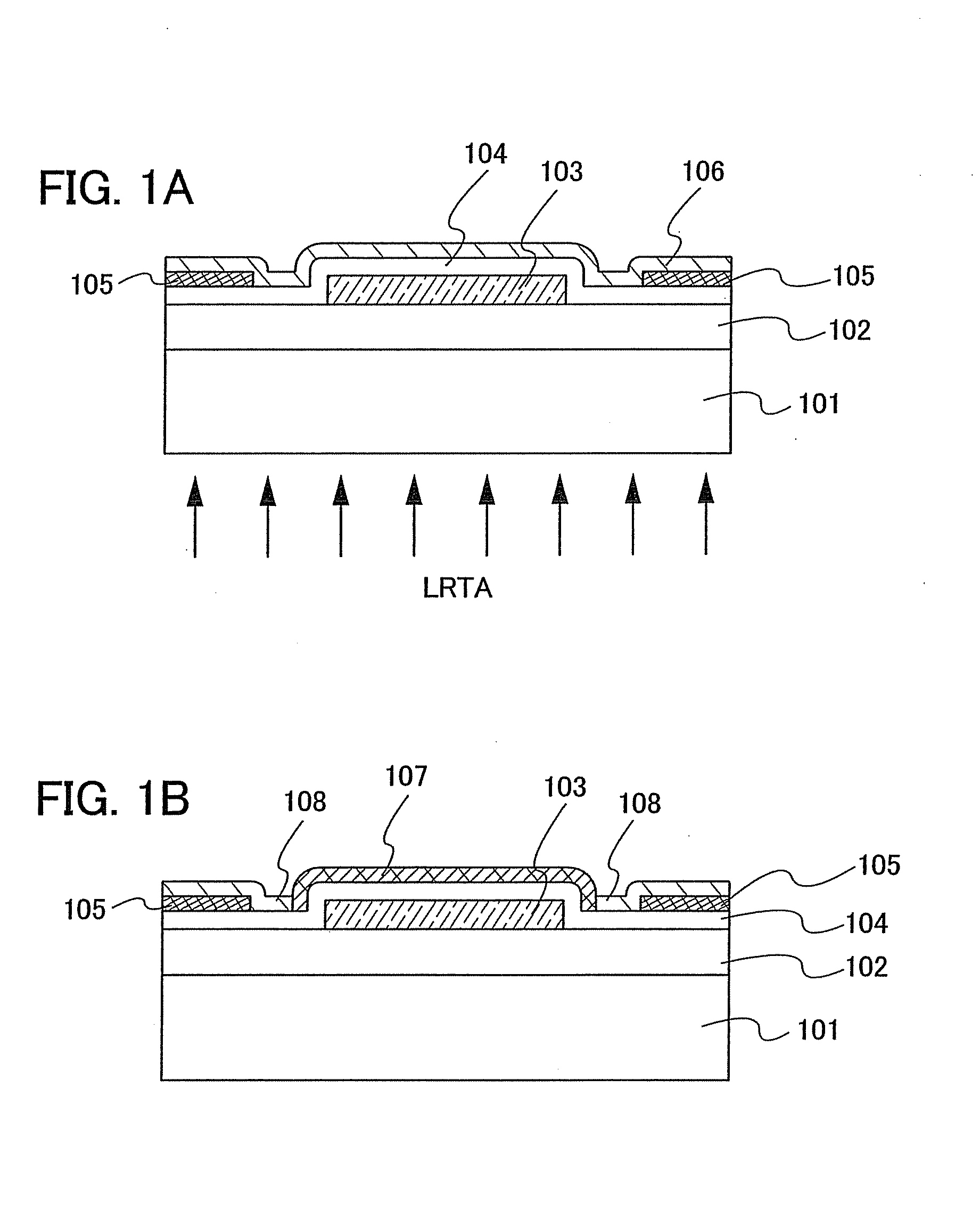

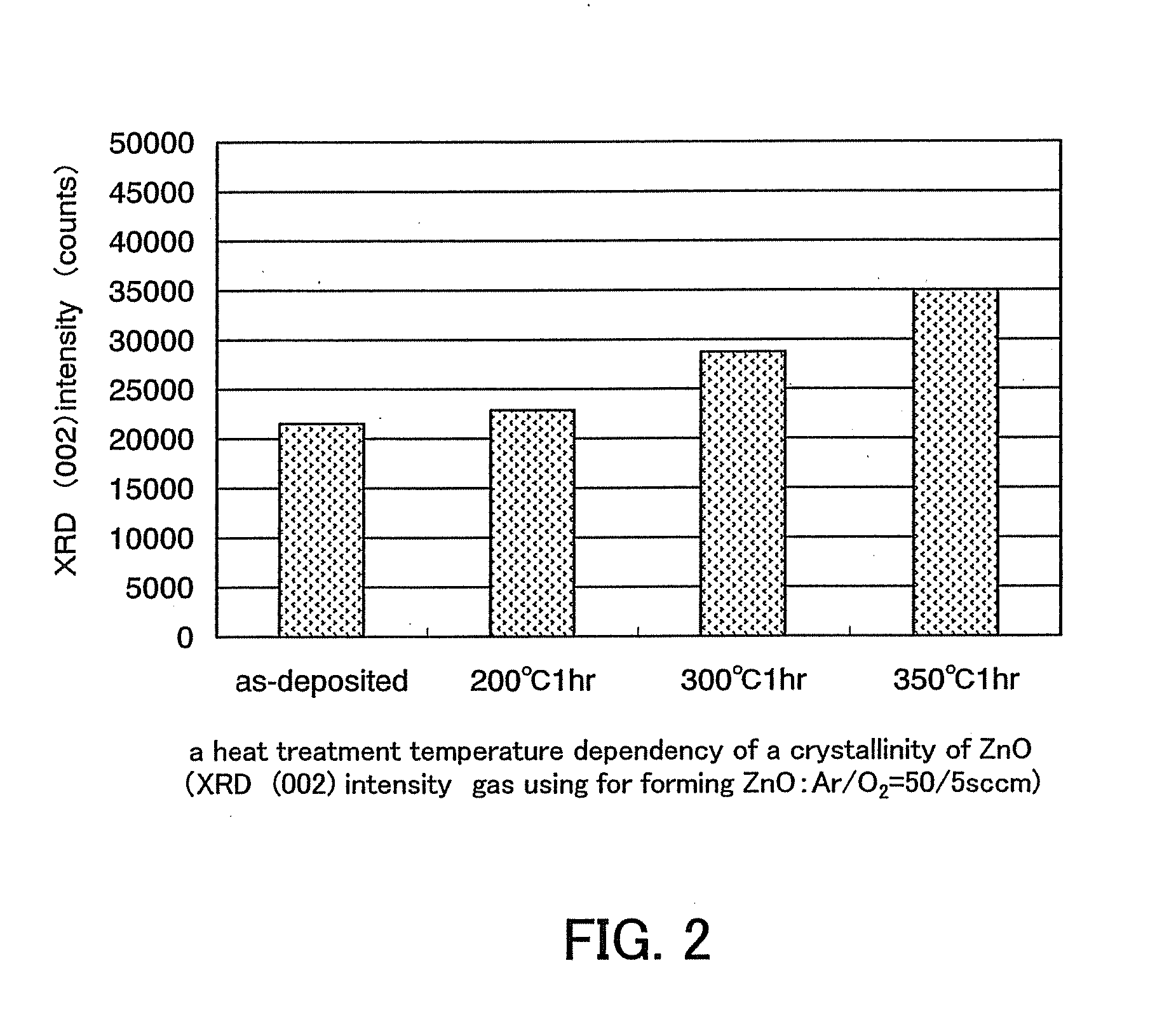

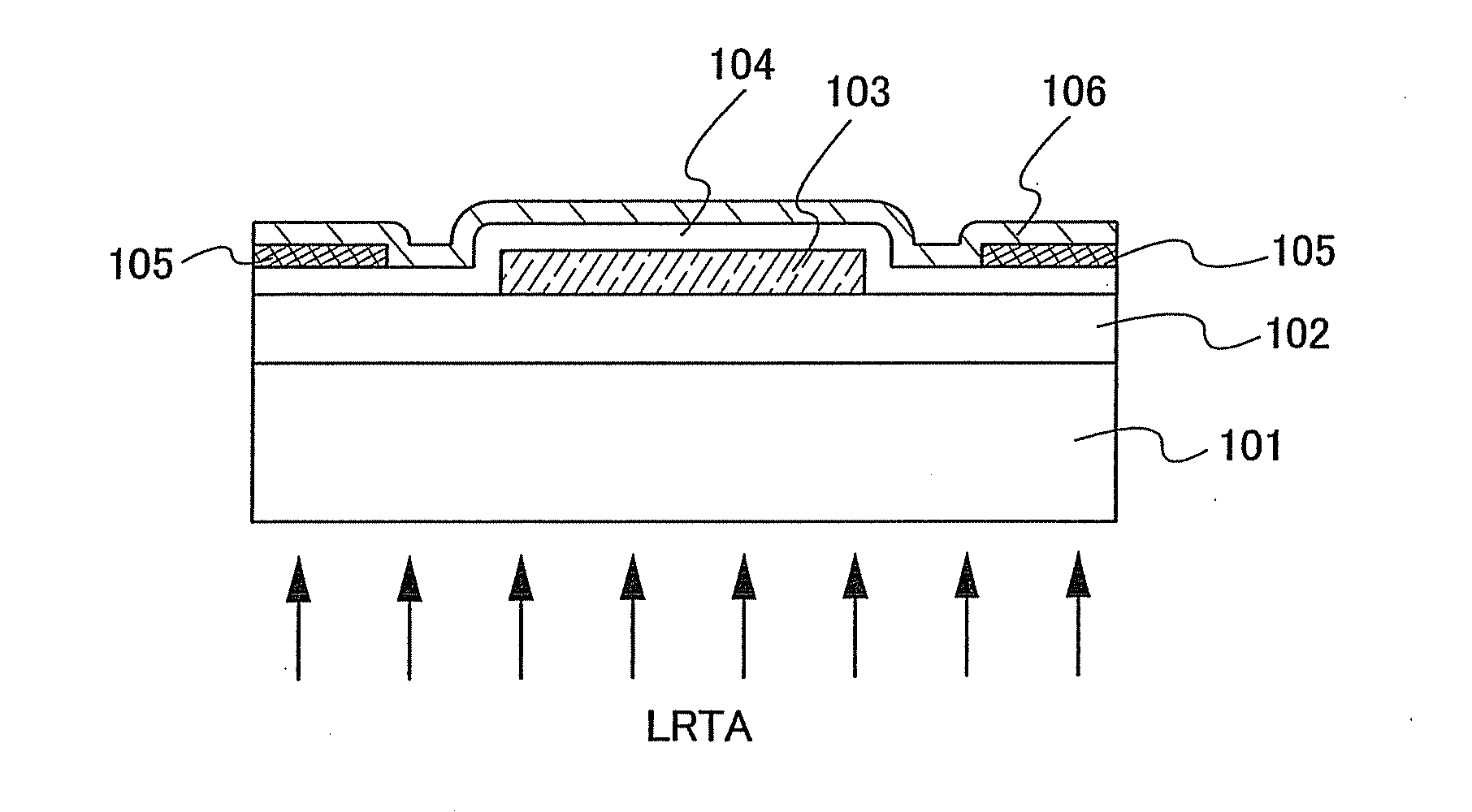

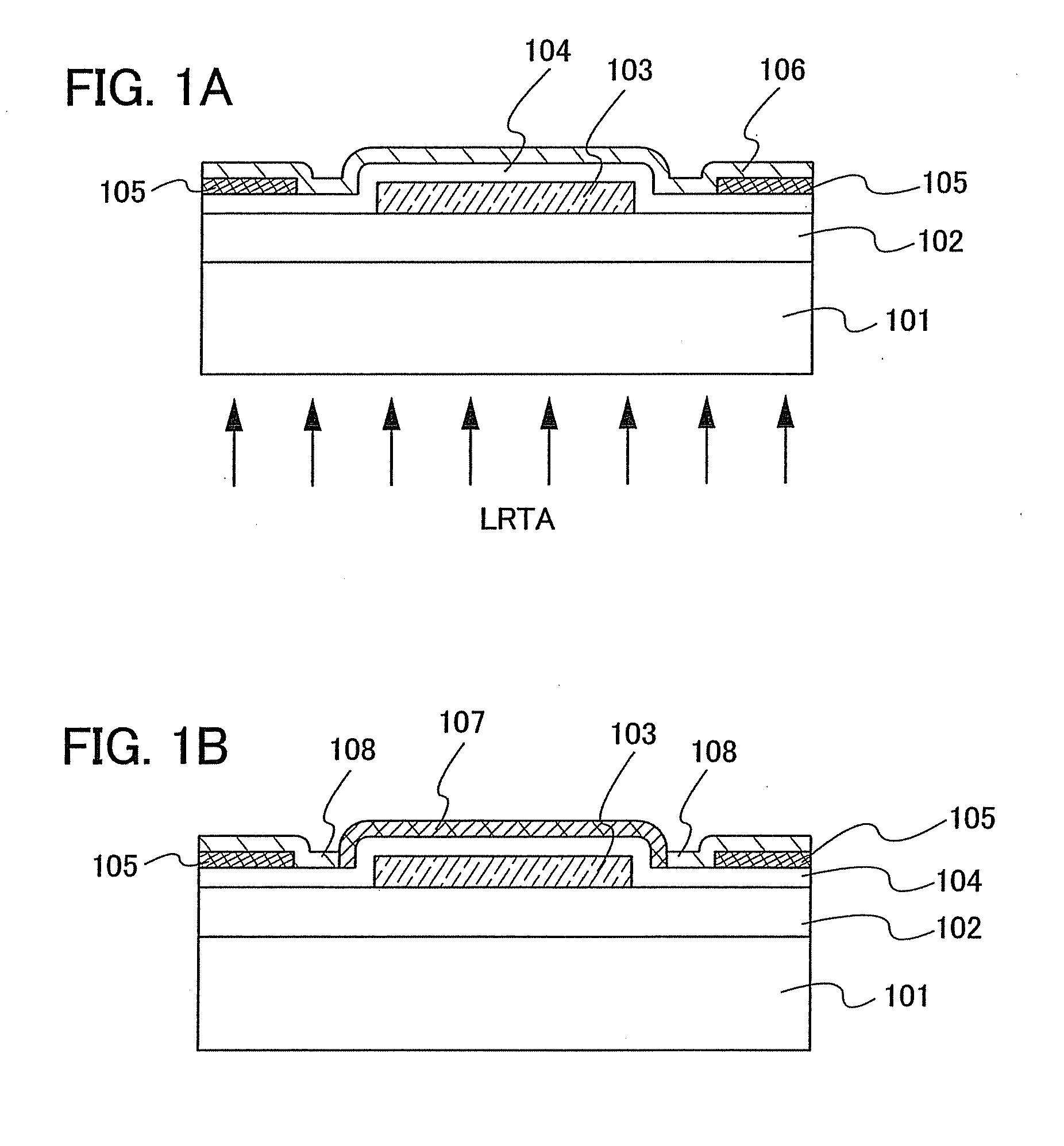

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:SEMICON ENERGY LAB CO LTD

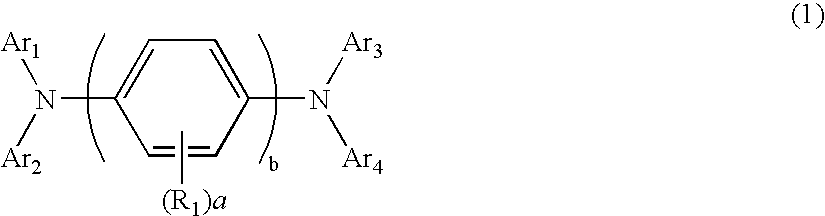

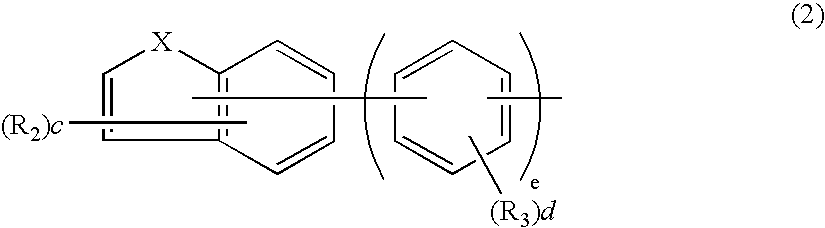

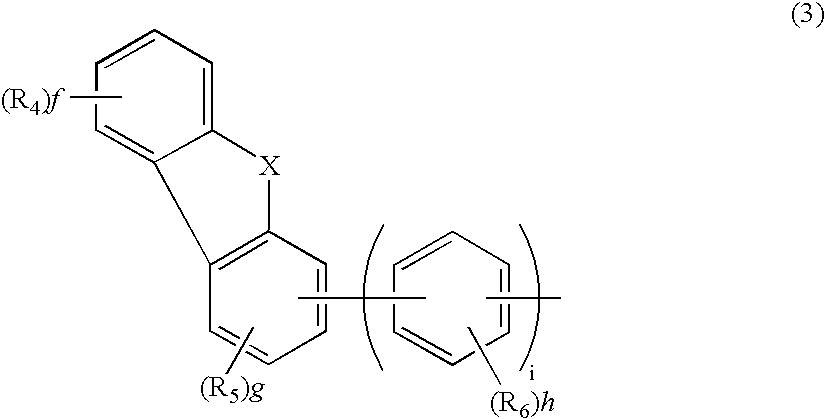

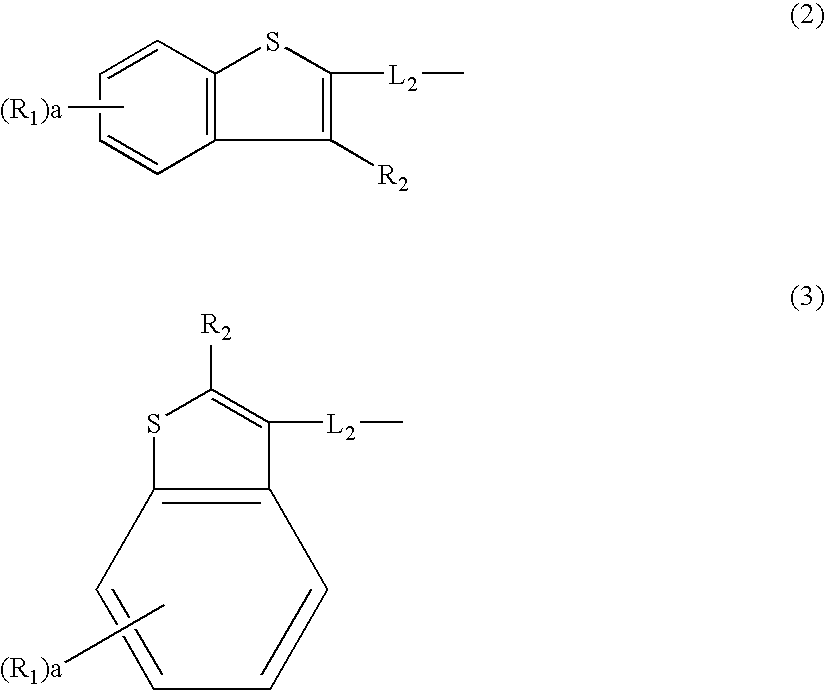

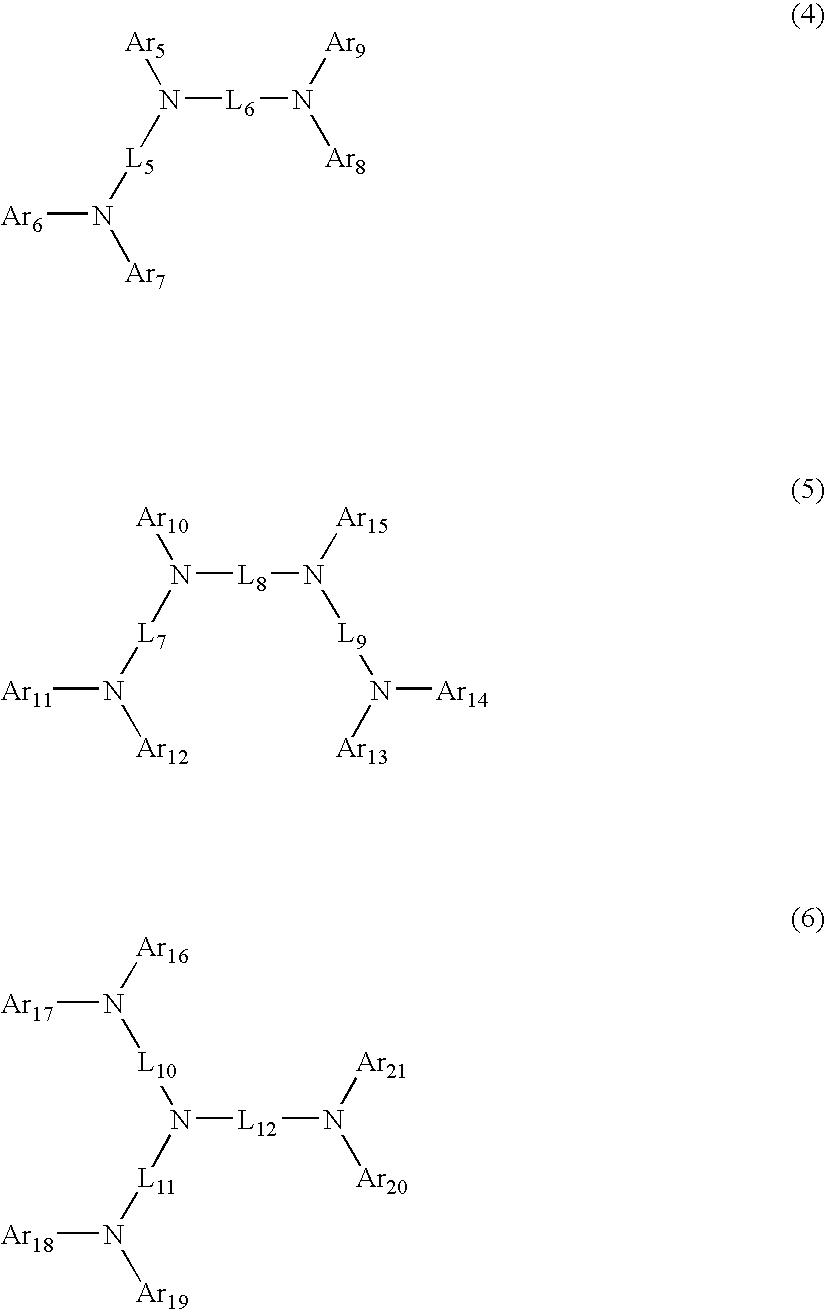

Aromatic amine derivative and electroluminescence device using the same

ActiveUS20070278938A1Improved in yield in producingLong life-timeOrganic chemistryDischarge tube luminescnet screensOrganic electroluminescencePerylene derivatives

Provided are a novel aromatic amine derivative having a specific structure and an organic electroluminescence device in which an organic thin layer comprising a single layer or plural layers including a light emitting layer is interposed between a cathode and an anode, wherein at leas one layer of the above organic thin layer contains the aromatic amine derivative described above in the form of a single component or a mixed component. Thus, the organic electroluminescence device is less liable to be crystallized in molecules, improved in a yield in producing the organic electroluminescence device and extended in a lifetime.

Owner:IDEMITSU KOSAN CO LTD

Aromatic amine derivatives and organic electroluminescent device using same

InactiveUS20080106190A1Less liableImproved in yield in producingOrganic chemistryDischarge tube luminescnet screensHole transport layerOrganic electroluminescence

The present invention provides a novel aromatic amine derivative having a specific structure and an organic electroluminescence device in which an organic thin film layer comprising a single layer or plural layers including at least a light emitting layer is interposed between a cathode and an anode, wherein at least one layer in the above organic thin film layer, particularly a hole transporting layer contains the aromatic amine derivative described above in the form of a single component or a mixed component. Use of the aromatic amine derivative described above materialize an organic electroluminescence device which reduces a driving voltage and makes molecules less liable to be crystallized and which enhances a yield in producing the organic EL device and has a long lifetime.

Owner:IDEMITSU KOSAN CO LTD

Process for producing oxime

InactiveUS7161036B2Speed up the conversion processHigh selectivityOrganic compound preparationOrganic chemistry methodsKetoneAmmonia

A process for producing an oxime is provided, wherein the process comprises the step of reacting a ketone, hydrogen peroxide and ammonia in the presence of a crystalline titanosilicate having MWW structure under the condition that the ammonia concentration in the liquid portion of the reaction mixture is about 1% by weight or more. By the process, an ammoximation reaction of the ketone can be carried out with a high conversion of the ketone and a high selectivity to the oxime corresponding to the ketone, thereby producing the oxime with a high yield.

Owner:SUMITOMO CHEM CO LTD

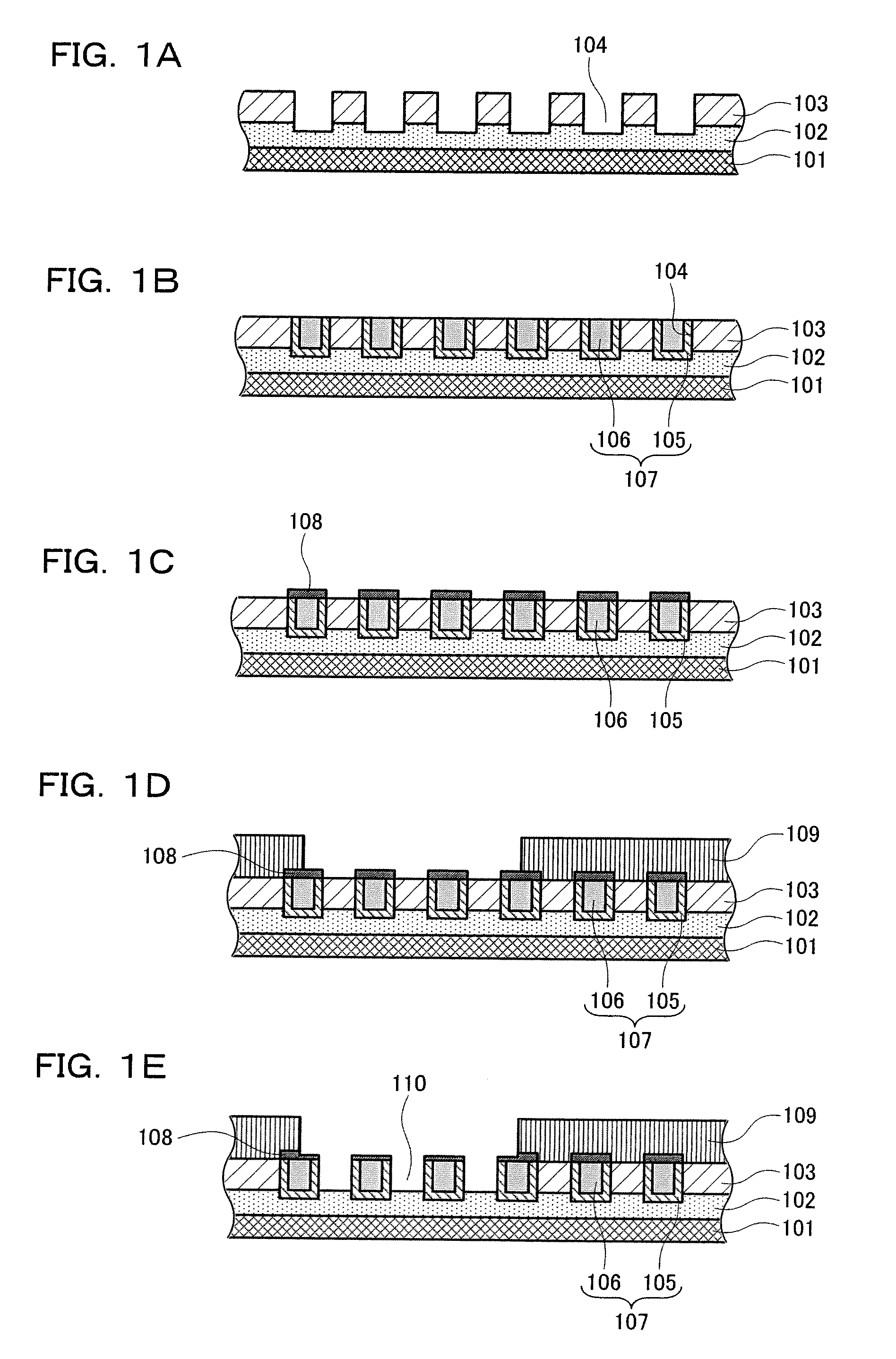

Semiconductor Device and Manufacturing Method Thereof

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor Device and Manufacturing Method Thereof

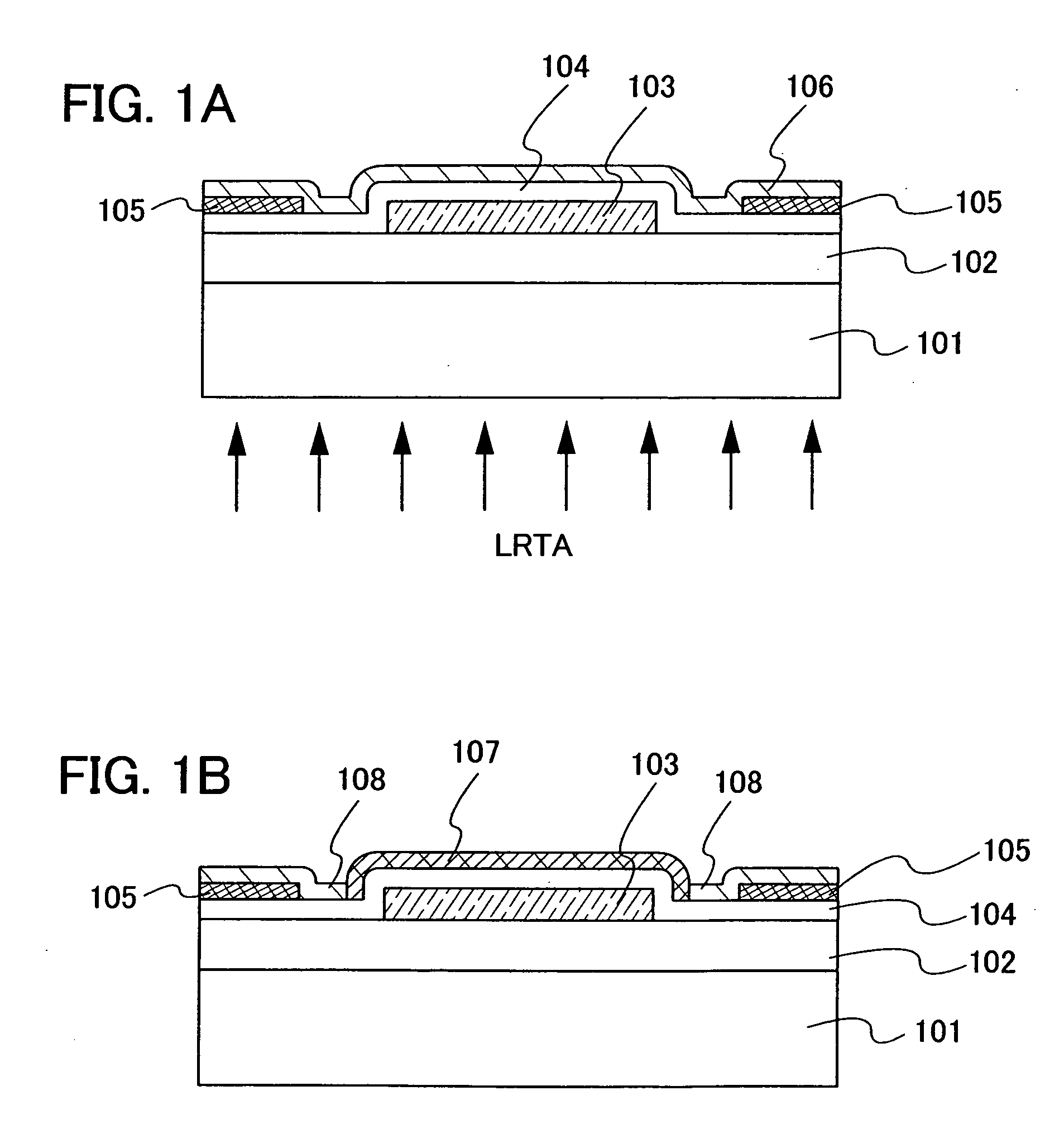

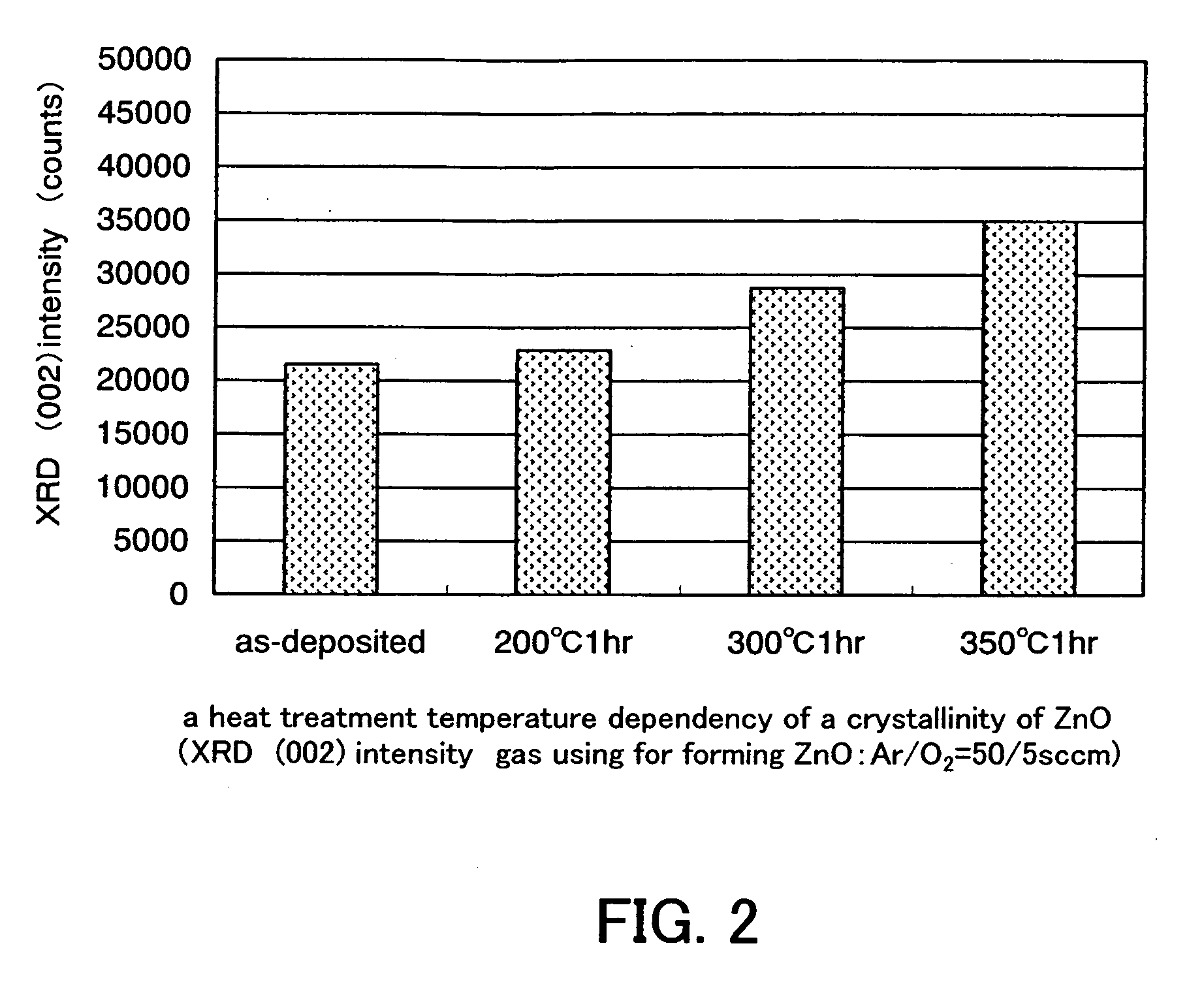

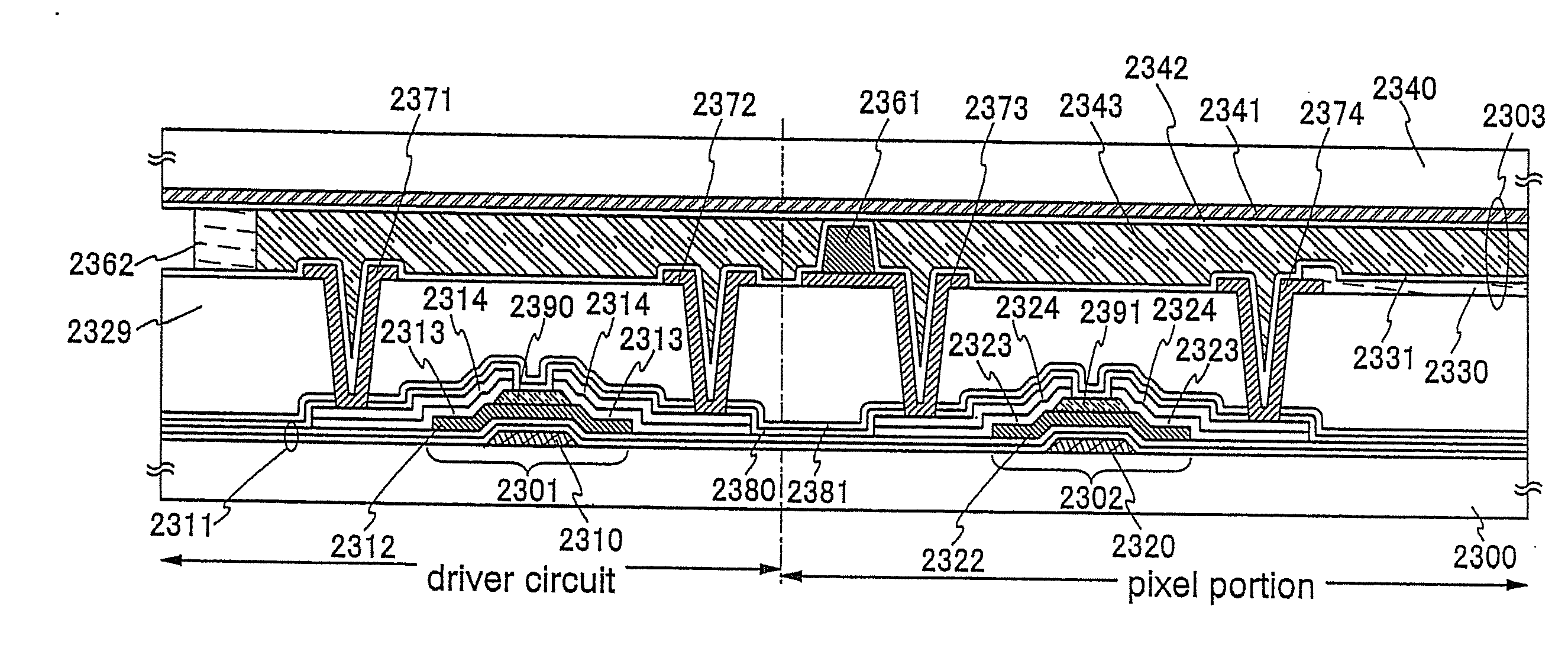

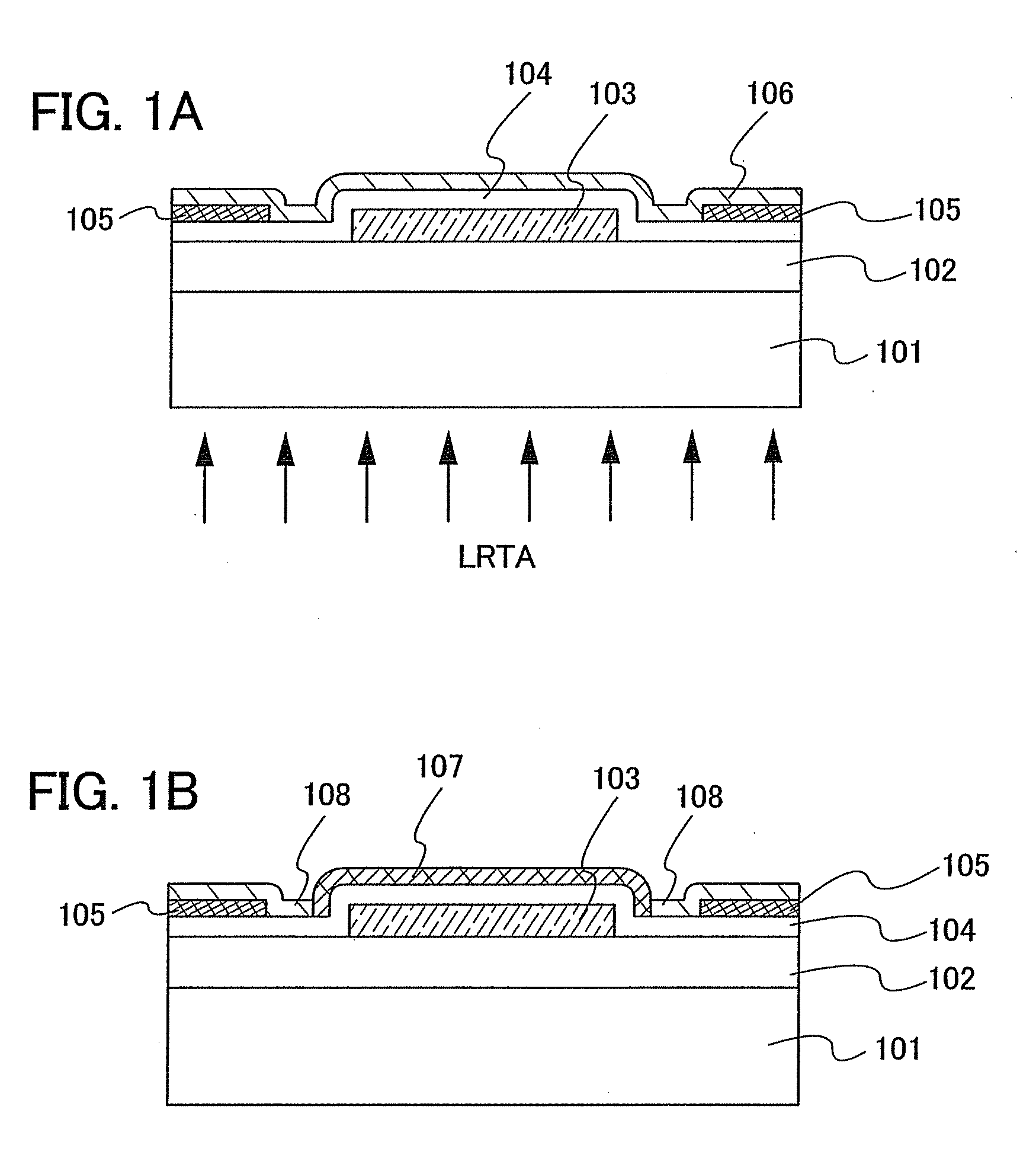

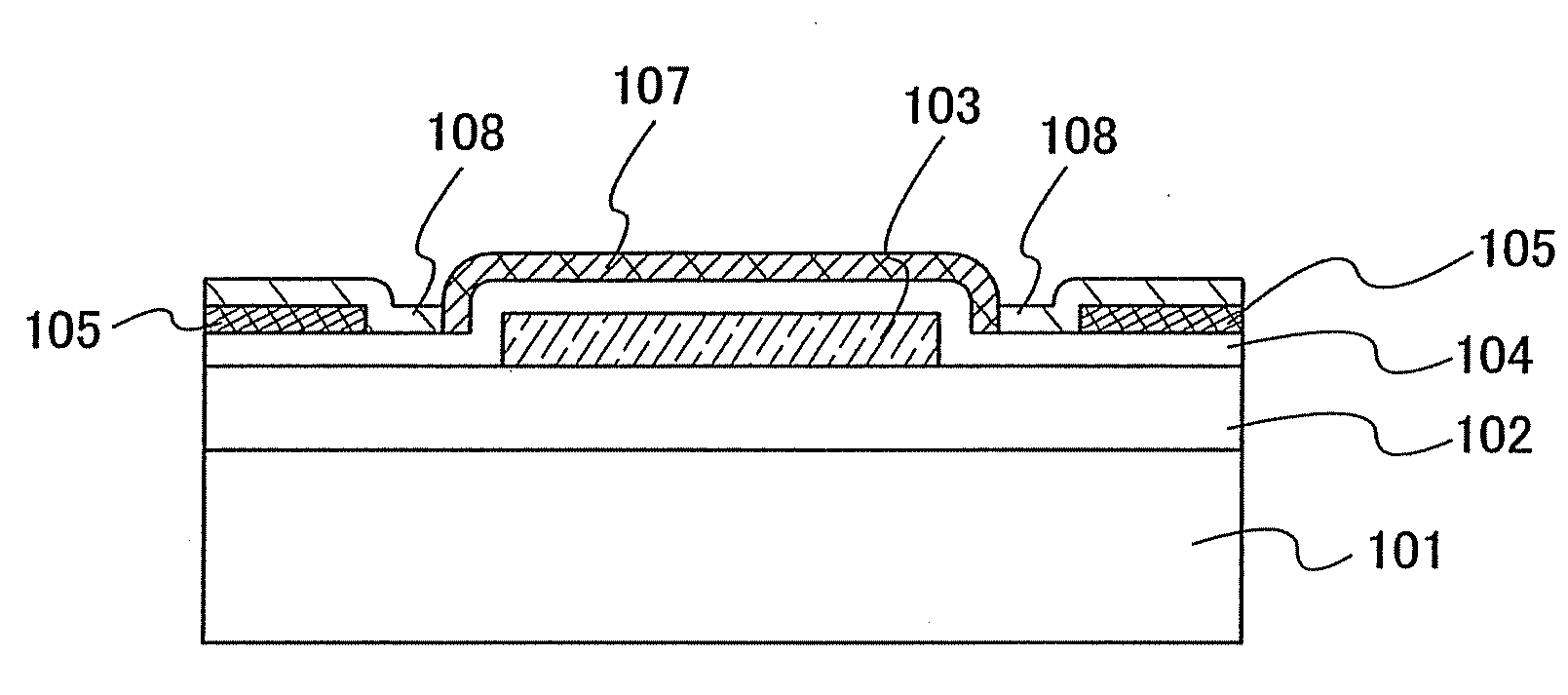

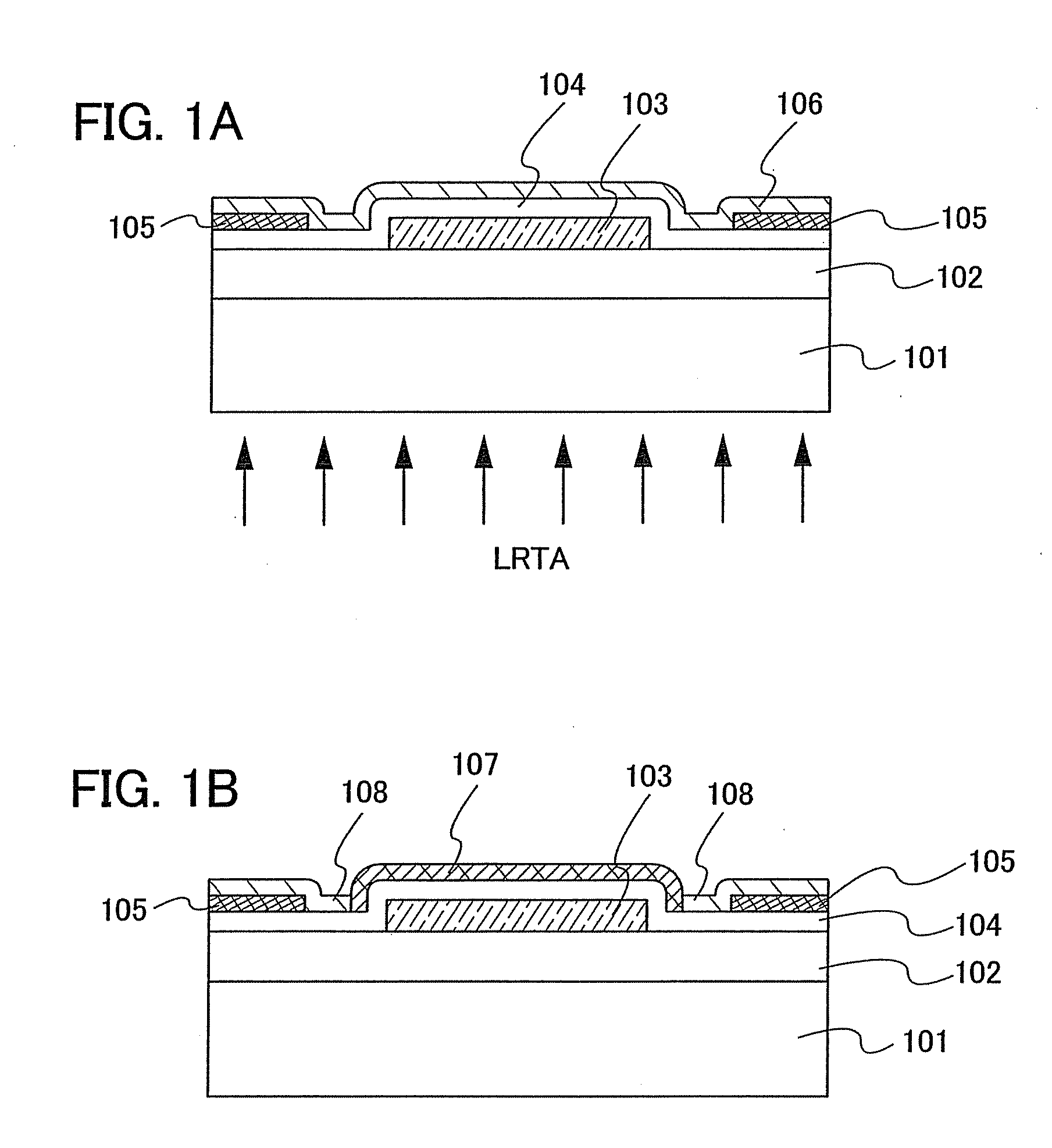

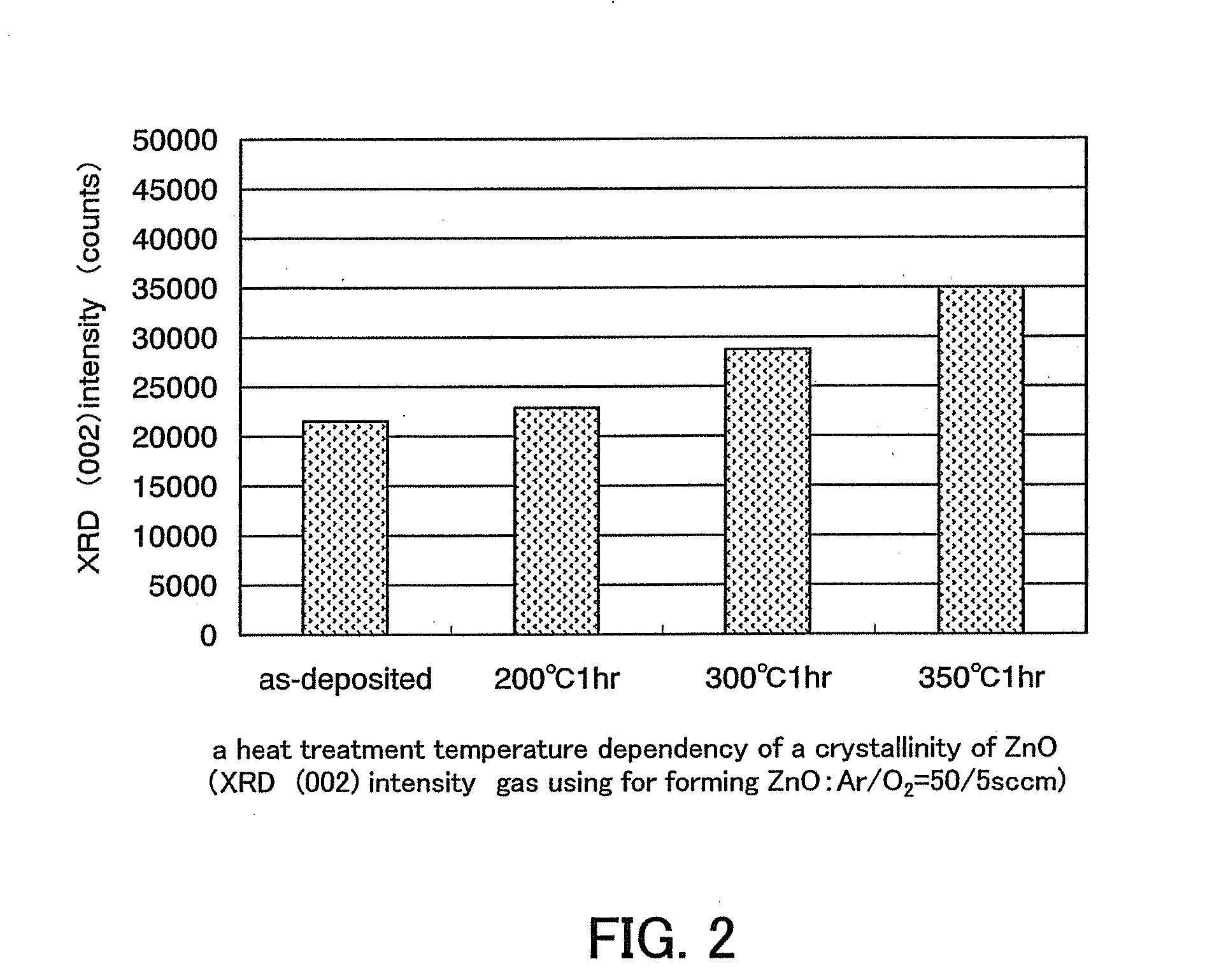

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor Device and Manufacturing Method Thereof

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor Device and Manufacturing Method Thereof

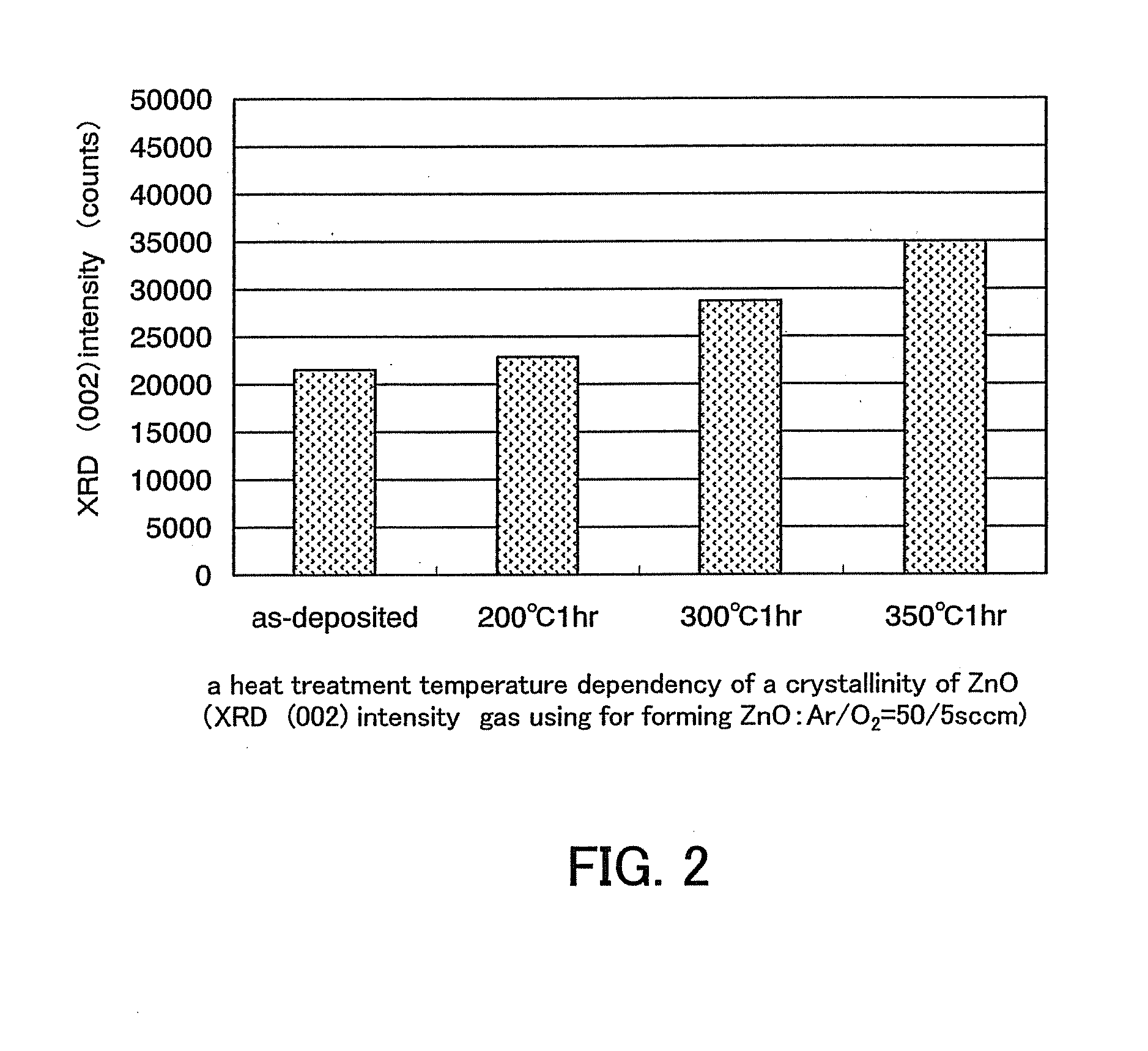

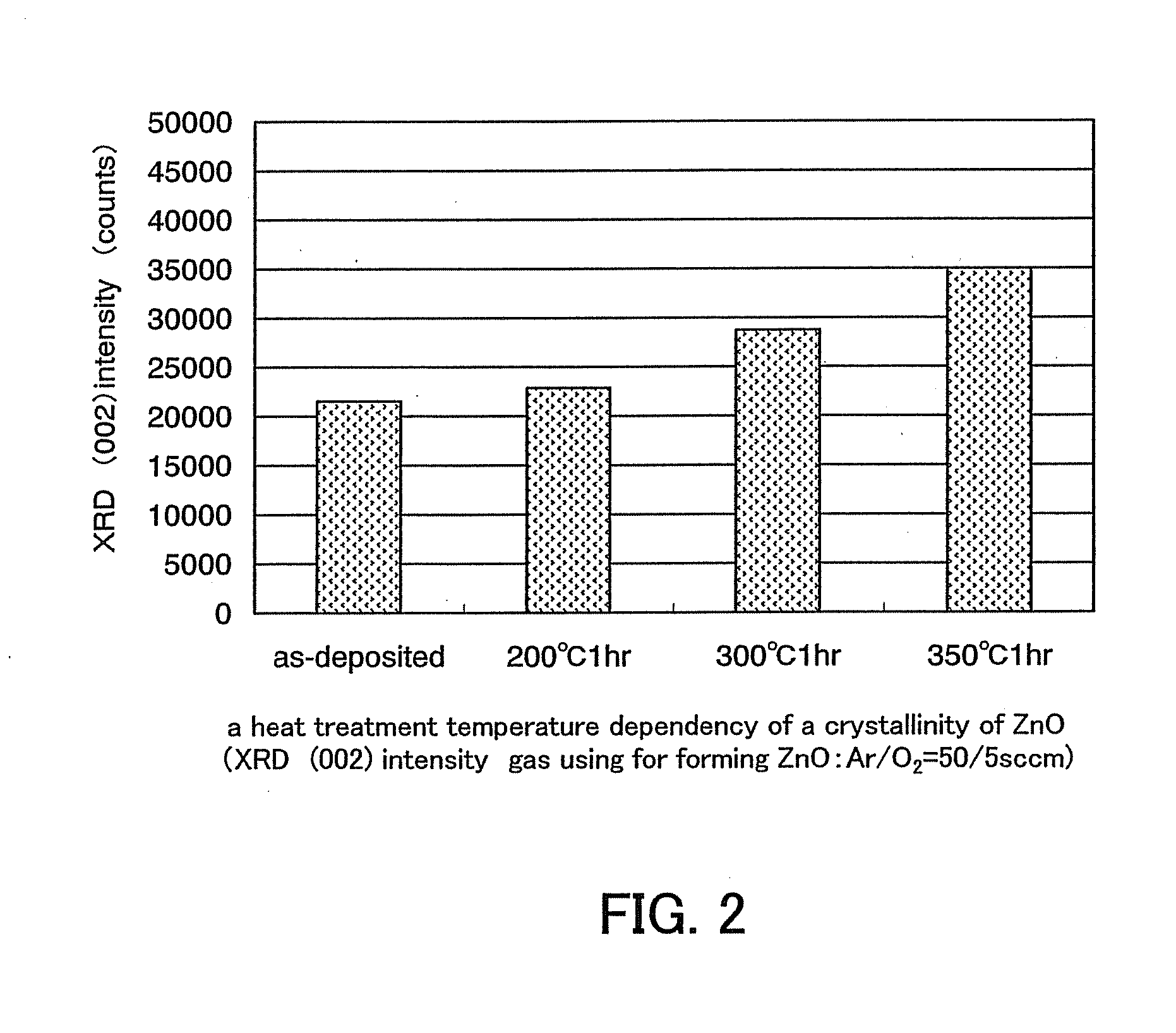

ActiveUS20080308797A1High yieldReduce the ratioTransistorDischarge tube luminescnet screensEngineeringZinc

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:SEMICON ENERGY LAB CO LTD

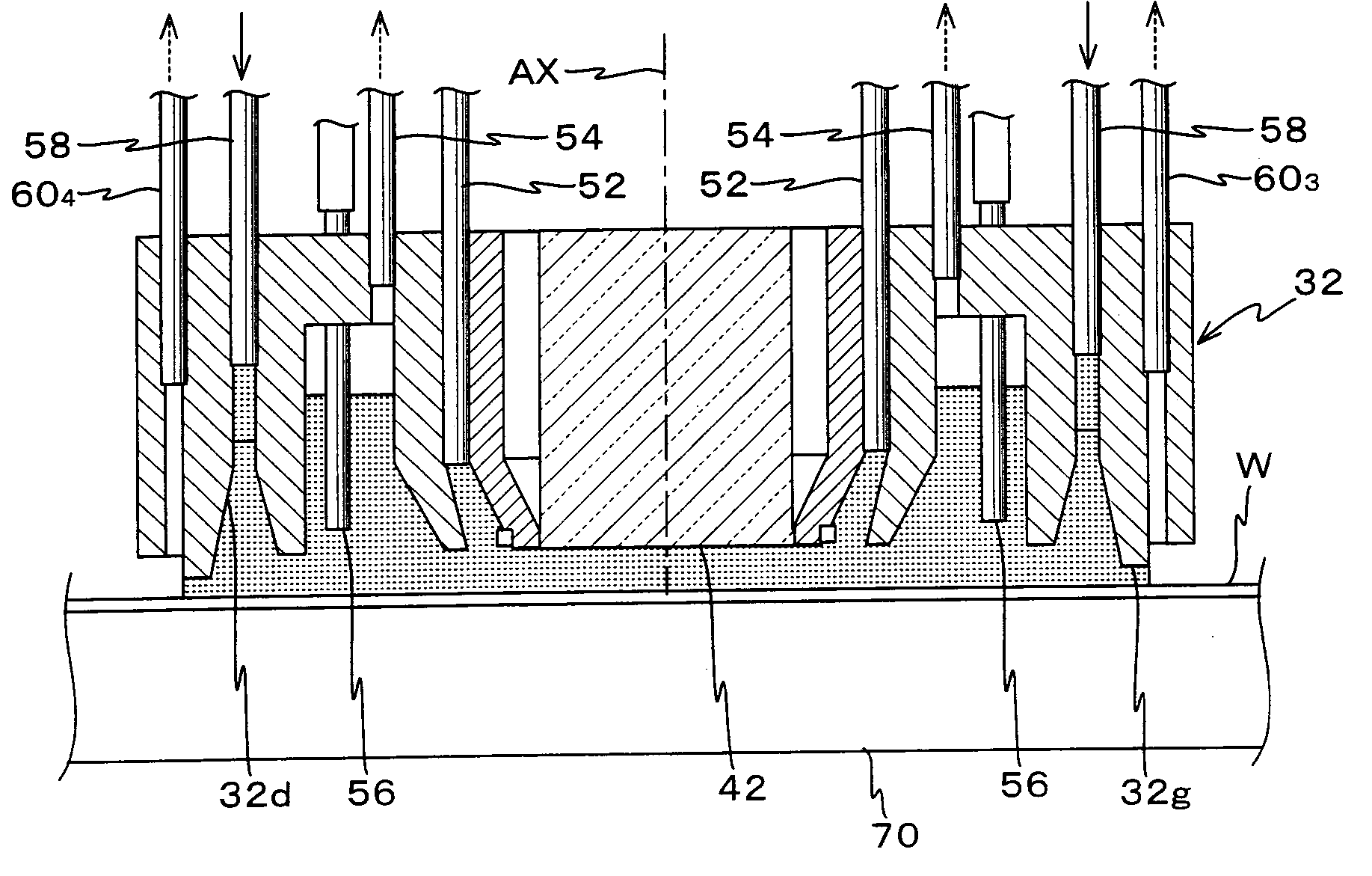

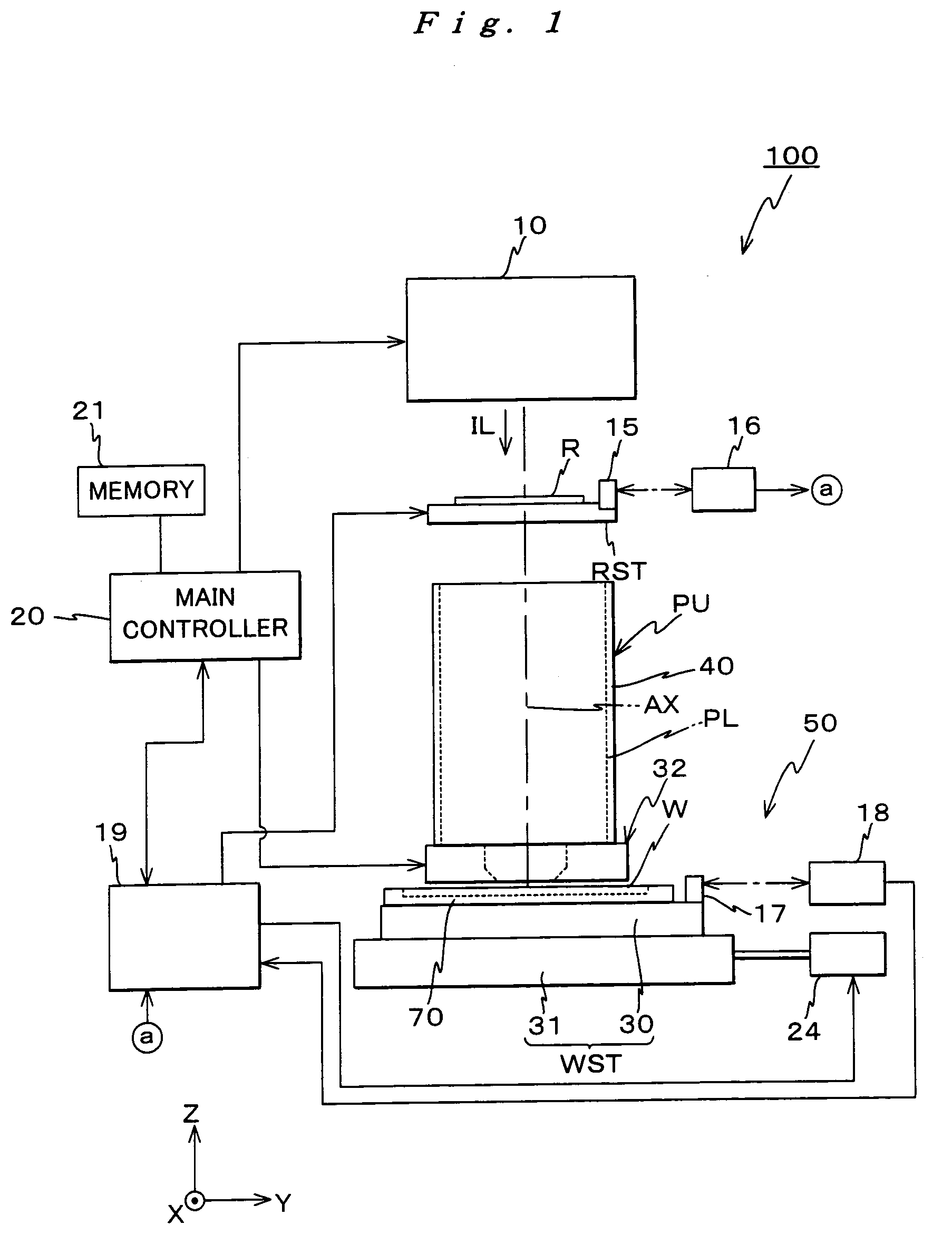

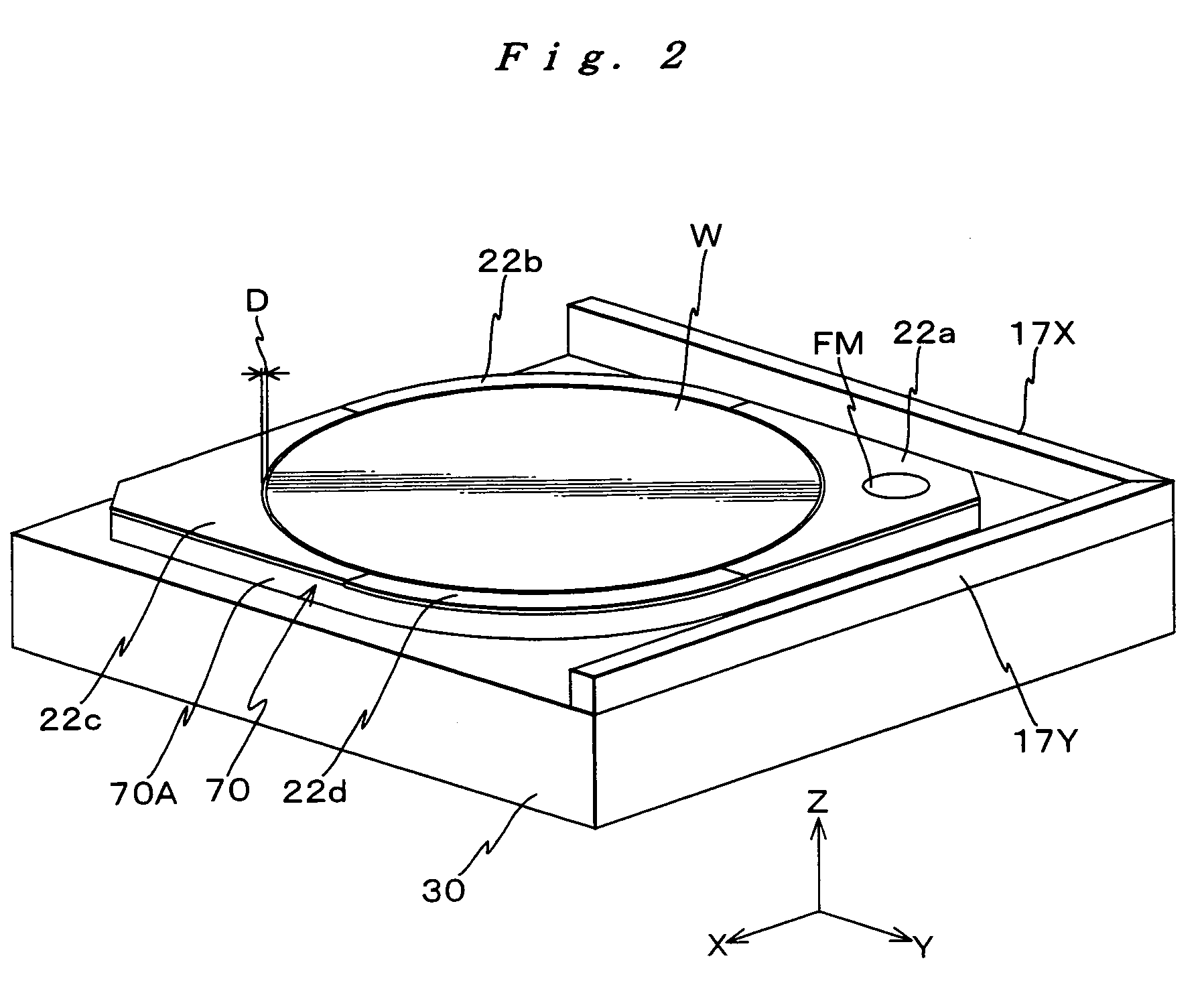

Exposure apparatus and device manufacturing method

InactiveUS20050259234A1Pressure of waterRaise transfer toSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusEngineeringElectrical and Electronics engineering

Liquid is supplied by a supply mechanism to a space between a lens and a wafer via a supply nozzle on one side of the lens, and the liquid is recovered by a recovery mechanism via a recovery pipe on the other side of the lens. When the supply and the recovery of the liquid are performed in parallel, a predetermined amount of liquid (exchanged at all times) is held between the lens and the substrate on the stage. Accordingly, when exposure (pattern transfer on the substrate) is performed in this state, an immersion method is applied and a pattern is transferred with good precision onto the substrate. In addition, in the case the liquid leaks out from under the lower edge of a peripheral wall, the liquid that could not be recovered is recovered by an auxiliary recovery mechanism via a slit. And, by such operations, the substrate is freed from the residual liquid on the substrate.

Owner:NIKON CORP

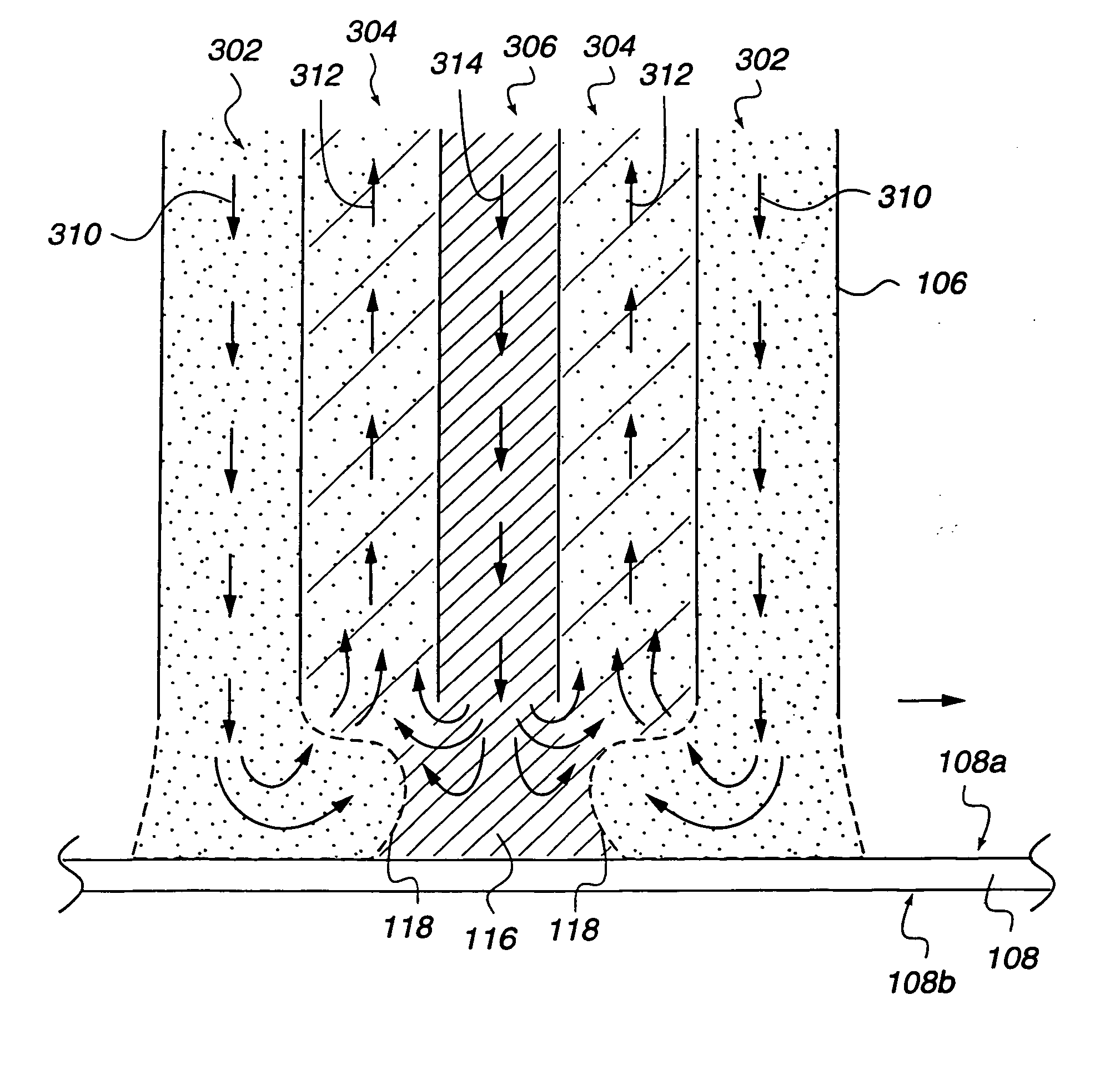

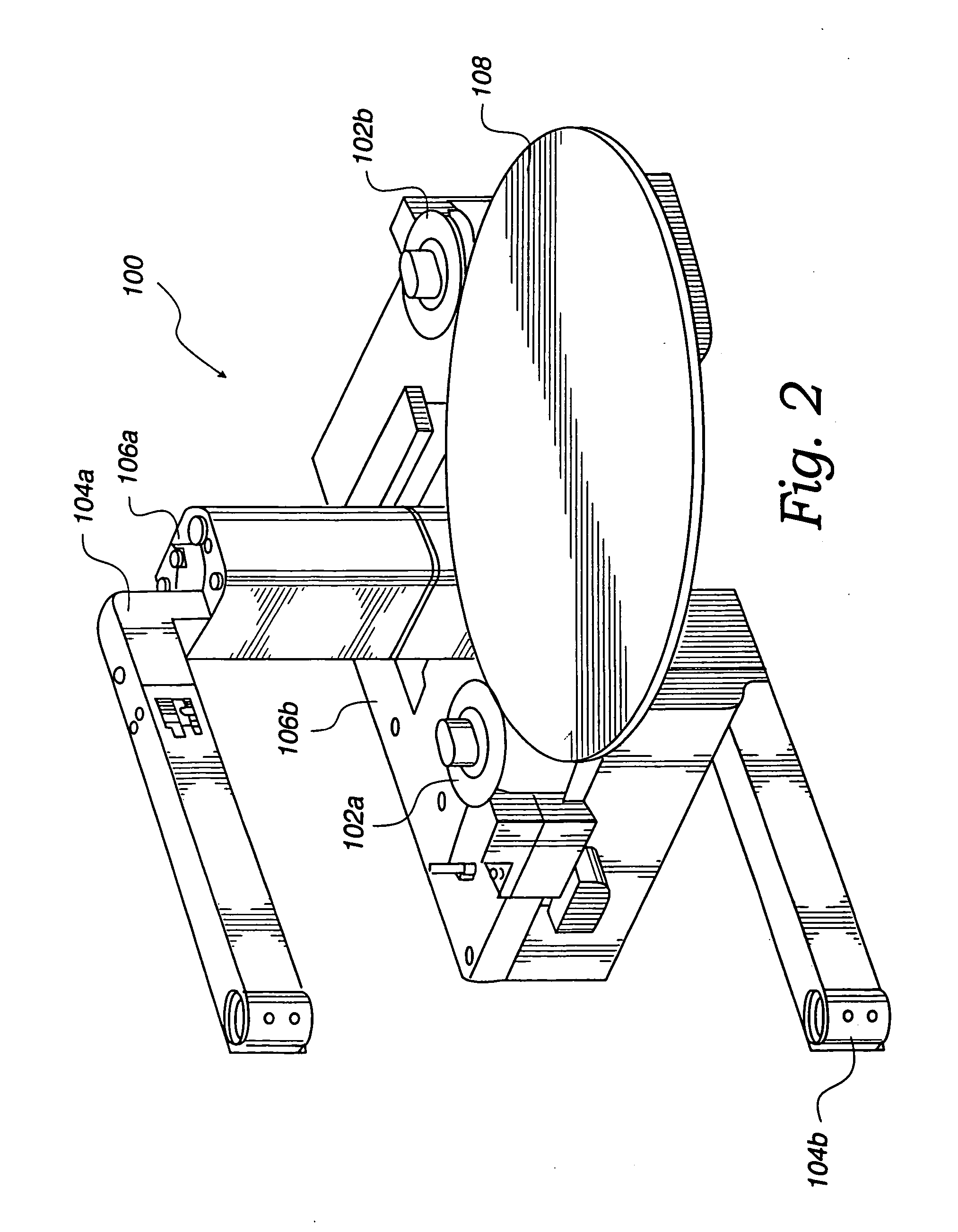

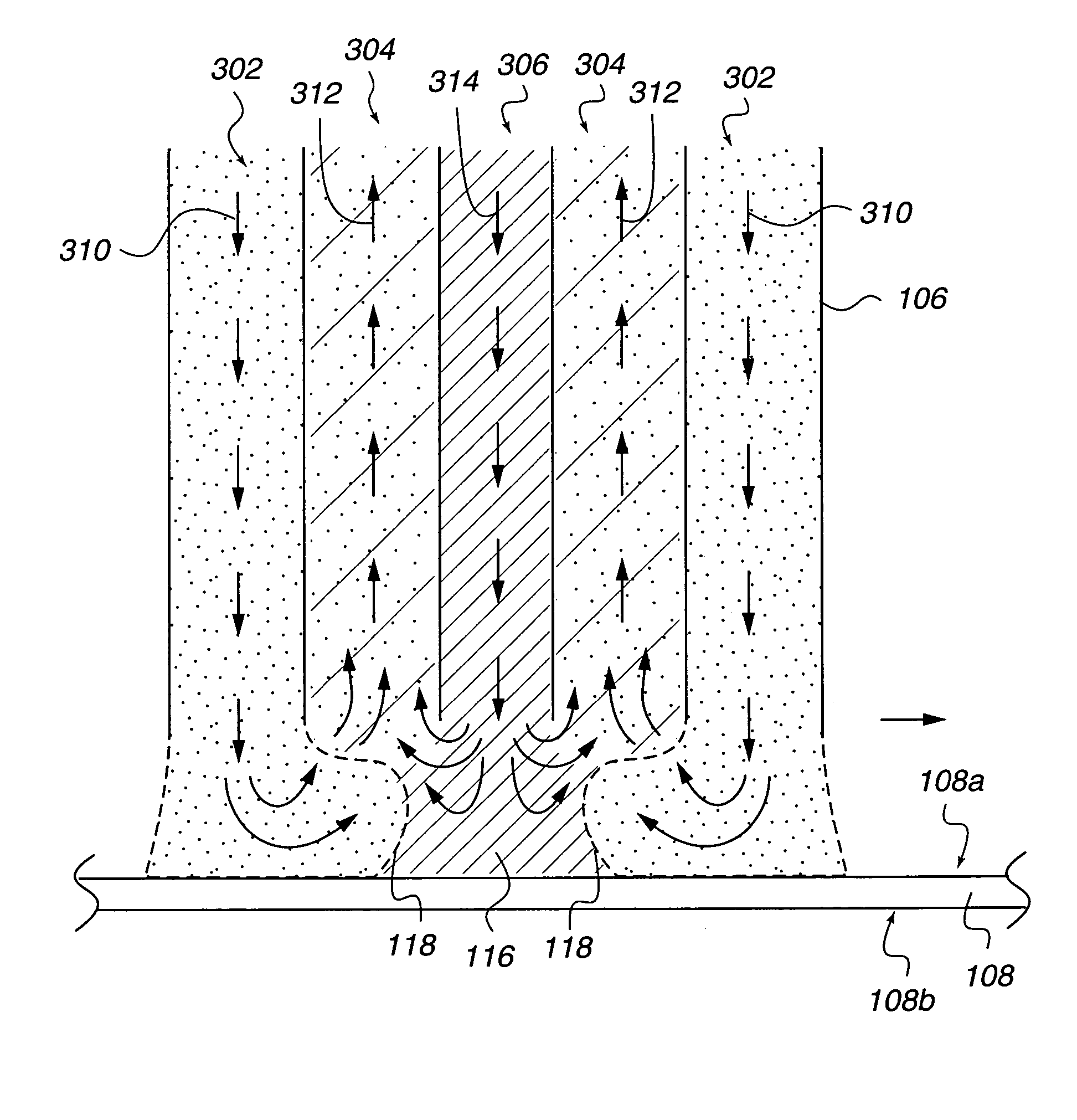

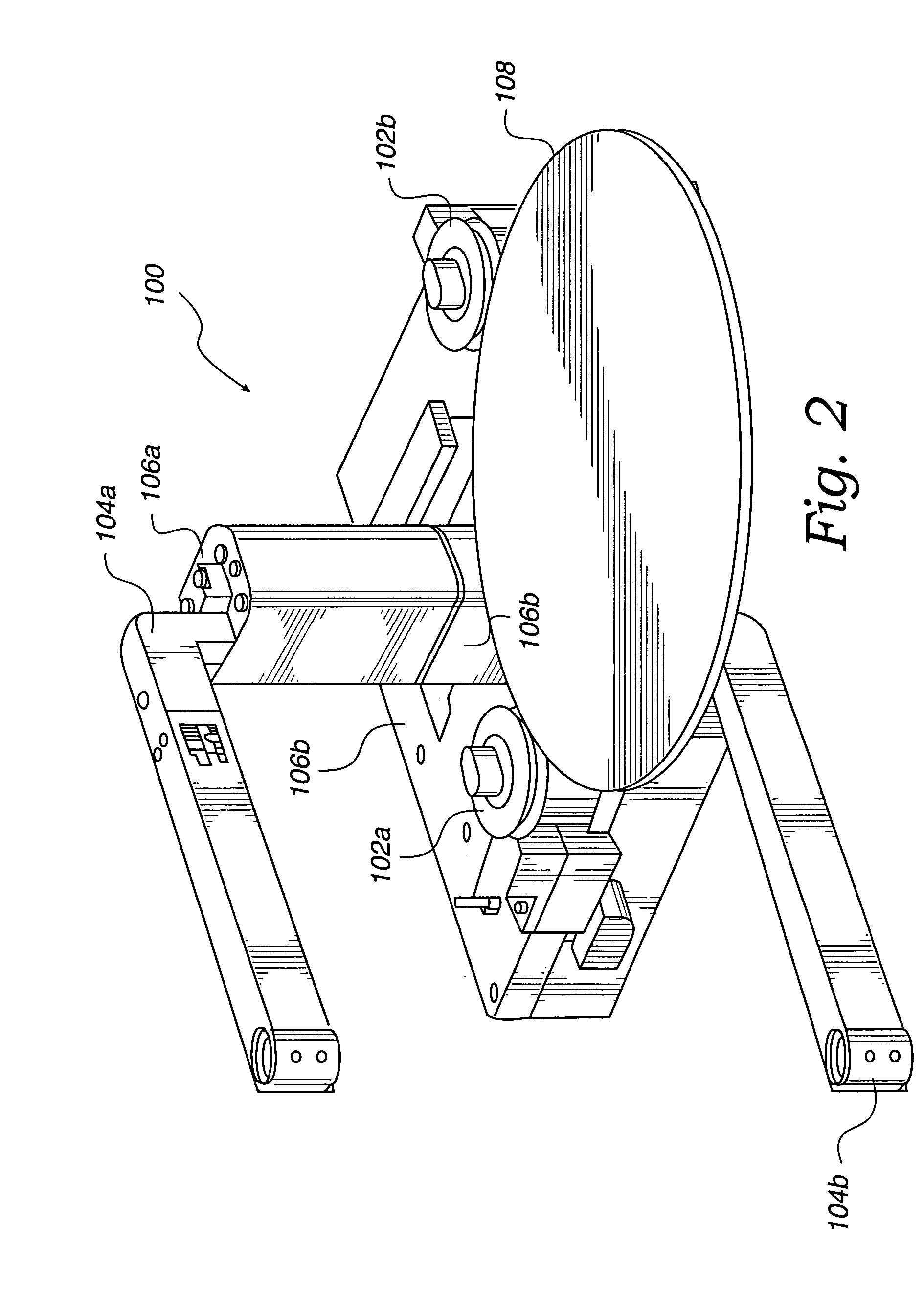

Apparatus and method for utilizing a meniscus in substrate processing

InactiveUS20050217703A1Process environment can be powerfully controlled and managedMore processedLiquid surface applicatorsSemiconductor/solid-state device manufacturingActive agentEngineering

An apparatus for processing a substrate is provided which includes a proximity head proximate to a surface of the substrate when in operation. The apparatus also includes an opening on a surface of the proximity head to a cavity defined in the proximity head where the cavity delivers an active agent to the surface of the substrate through the opening. The apparatus further includes a plurality of conduits on the surface of the proximity head that generates a fluid meniscus on the surface of the substrate surrounding the opening.

Owner:LAM RES CORP

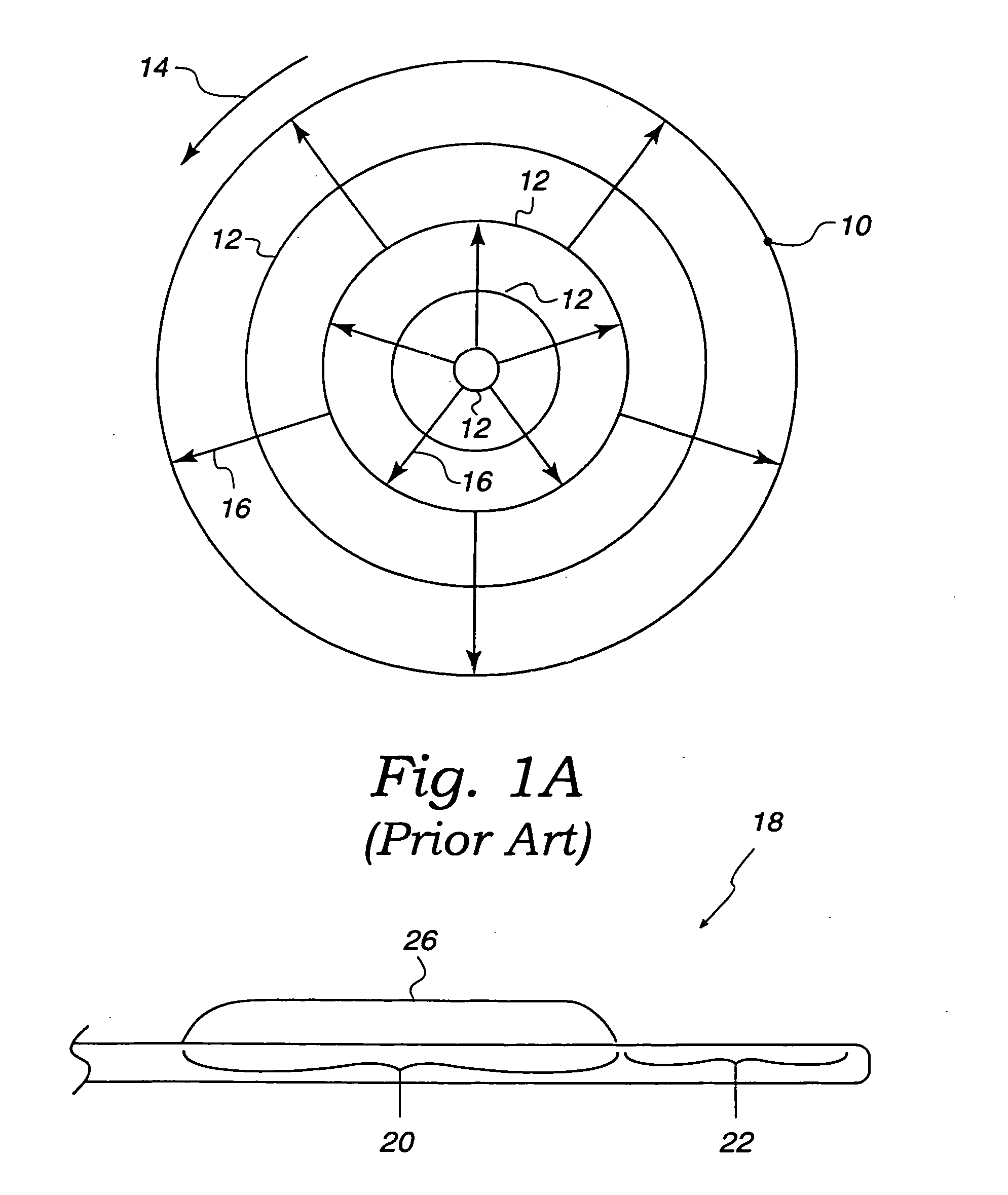

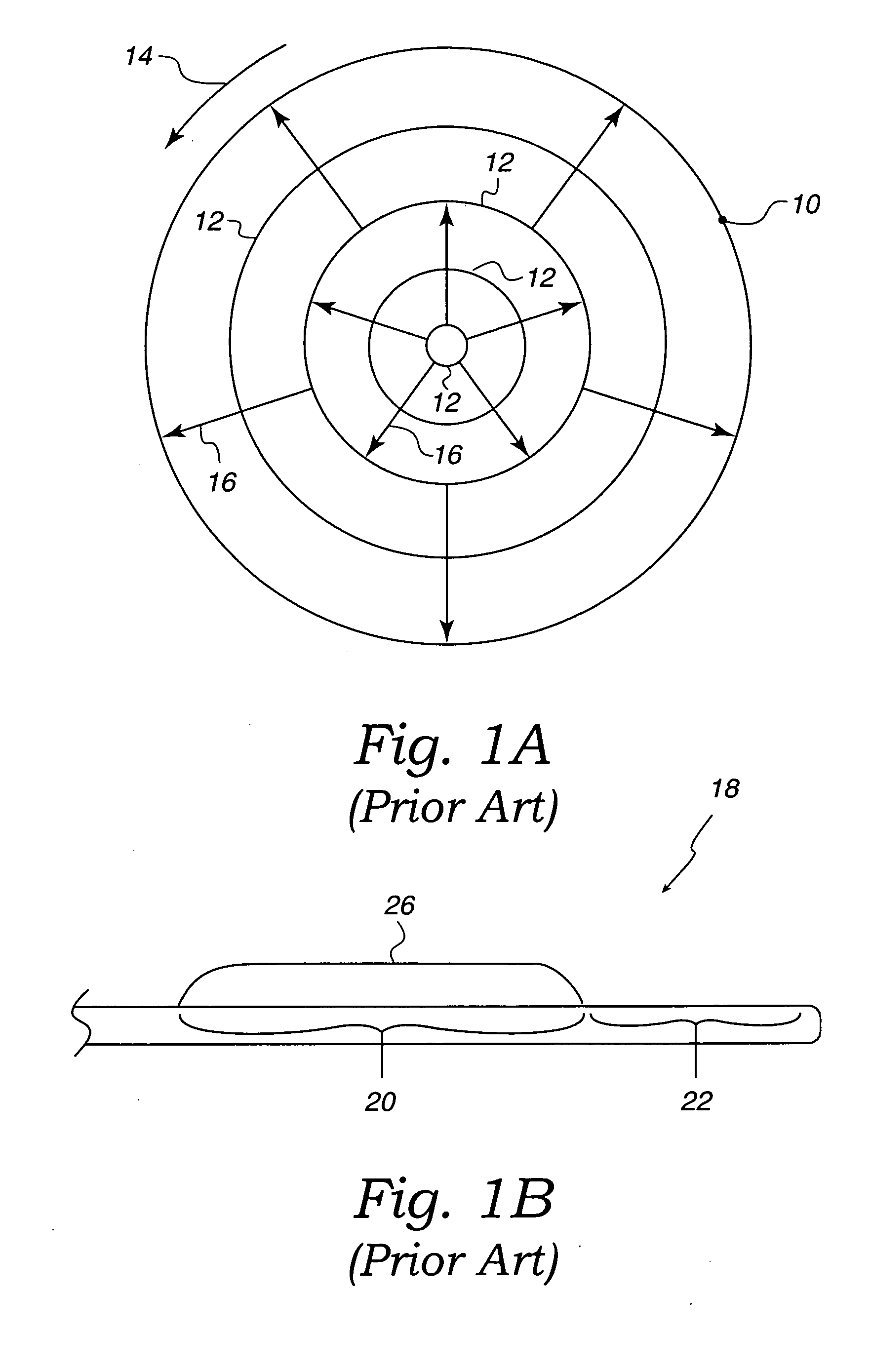

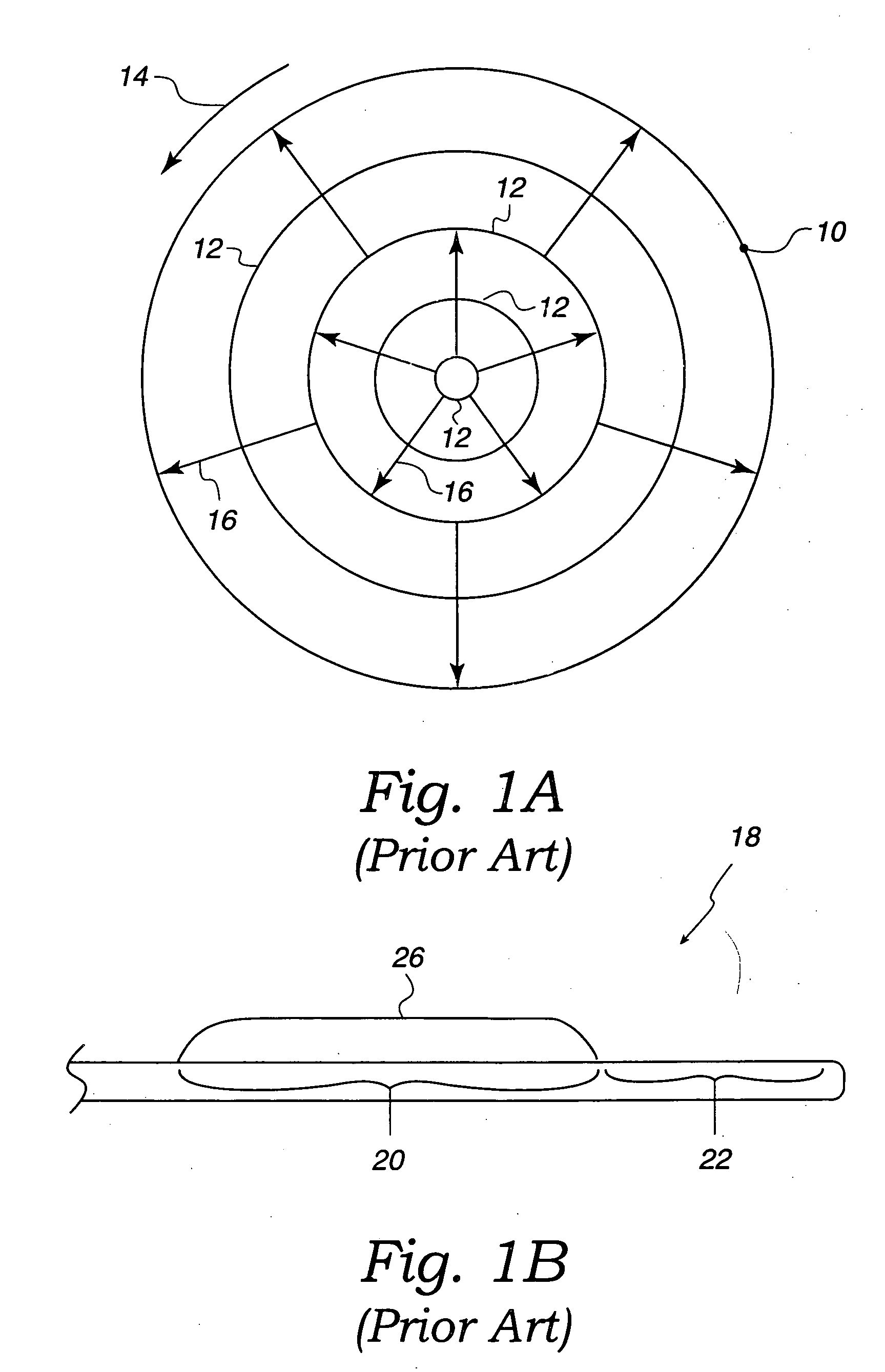

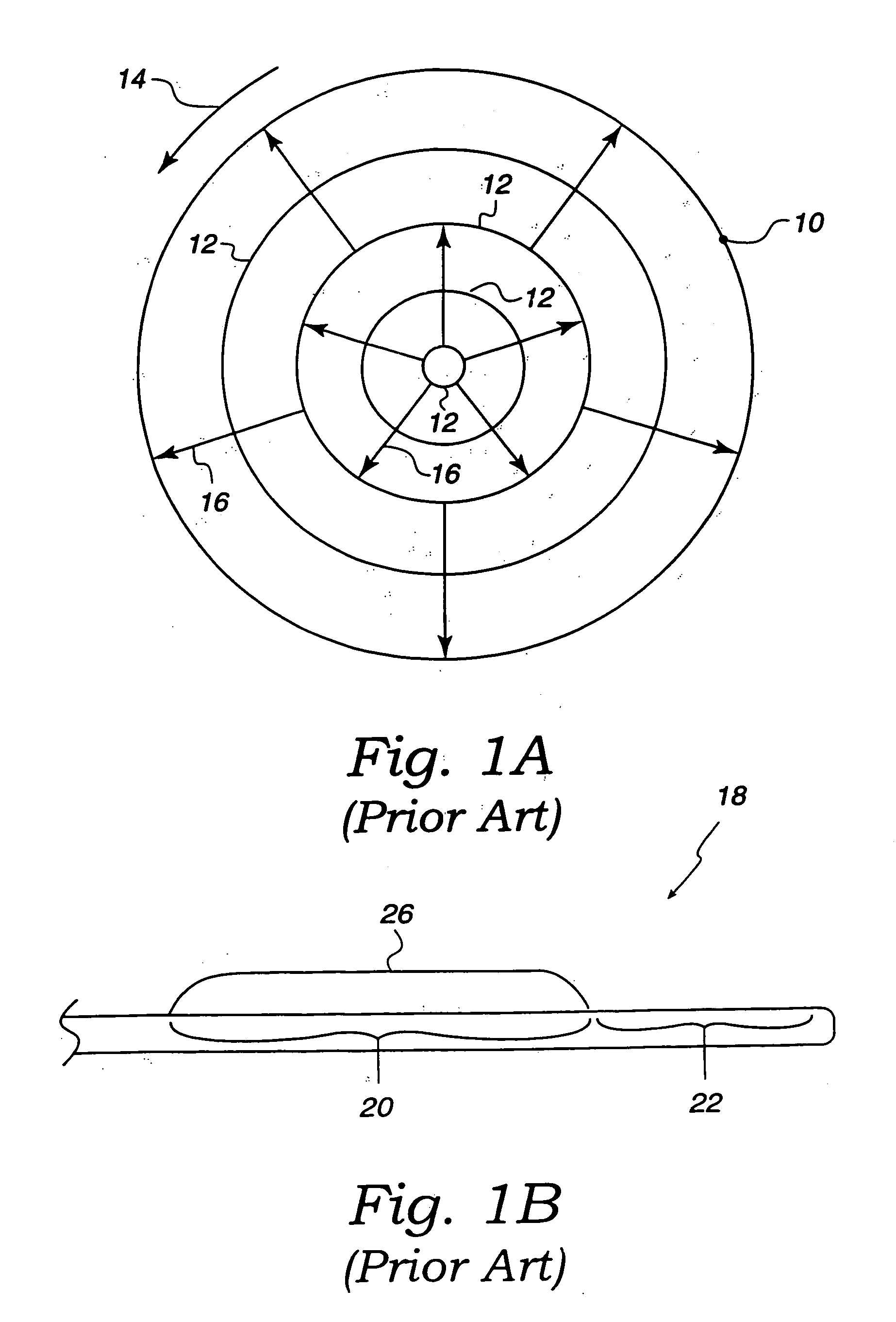

Concentric proximity processing head

InactiveUS20050217137A1Efficient processingImprove Wafer YieldDrying using combination processesDrying solid materials without heatEngineeringMeniscus

In one of the many embodiments, a method for processing a substrate is disclosed which includes generating a first fluid meniscus and a second fluid meniscus at least partially surrounding the first fluid meniscus wherein the first fluid meniscus and the second fluid meniscus are generated on a surface of the substrate.

Owner:LAM RES CORP

Semiconductor Device and Manufacturing Method Thereof

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:MOLECULAR DEVICES

Phobic barrier meniscus separation and containment

InactiveUS20050217135A1Improve Wafer YieldIncrease productionDrying using combination processesDrying solid materials with heatBiomedical engineeringMeniscus

In one of the many embodiments, a method for processing a substrate is provided which includes generating a first fluid meniscus and a second fluid meniscus on a surface of the substrate where the first fluid meniscus being substantially adjacent to the second fluid meniscus. The meniscus also includes substantially separating the first fluid meniscus and the second fluid meniscus with a barrier.

Owner:LAM RES CORP

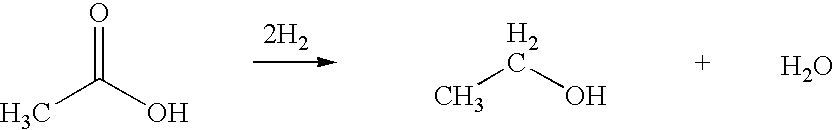

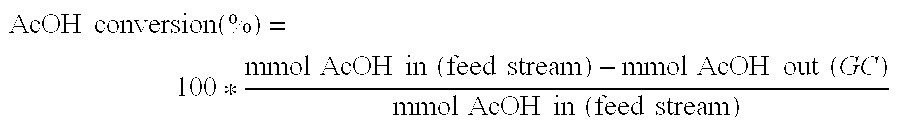

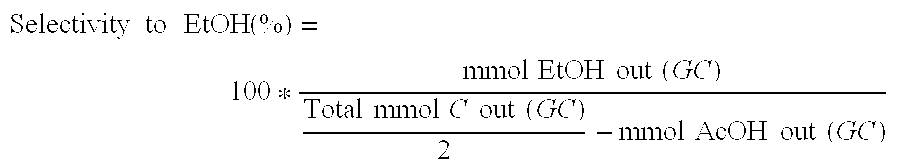

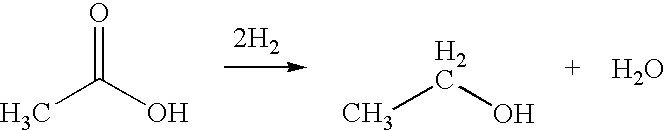

Ethanol production from acetic acid utilizing a cobalt catalyst

InactiveUS7608744B1High selectivityHigh yieldOrganic compound preparationOxygen compounds preparation by reductionAcetic acidPlatinum

A process for the selective production of ethanol by vapor phase reaction of acetic acid over a hydrogenating catalyst composition to form ethanol is disclosed and claimed. In an embodiment of this invention reaction of acetic acid and hydrogen over either cobalt and palladium supported on graphite or cobalt and platinum supported on silica selectively produces ethanol in a vapor phase at a temperature of about 250° C.

Owner:CELANESE INT CORP

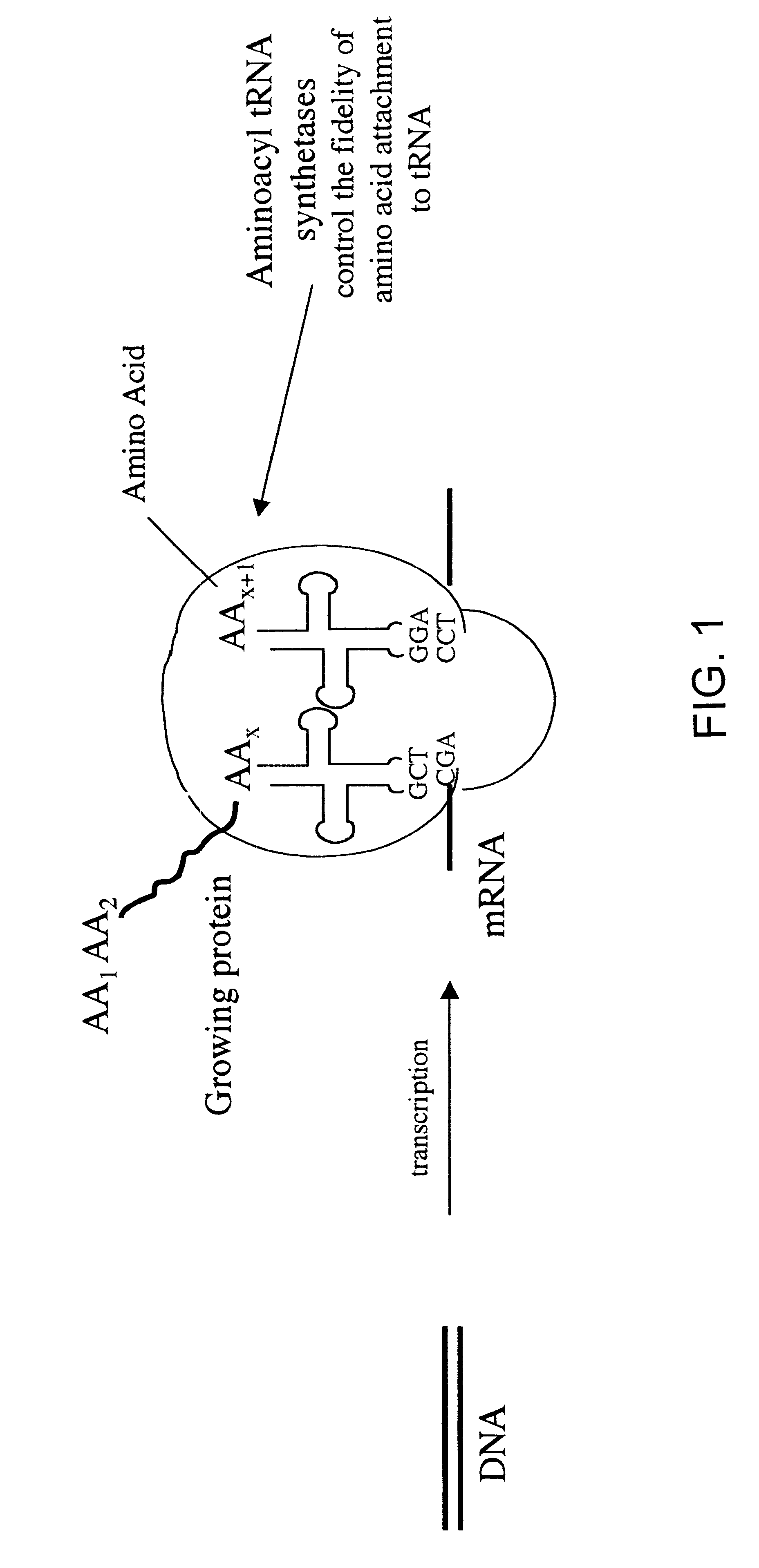

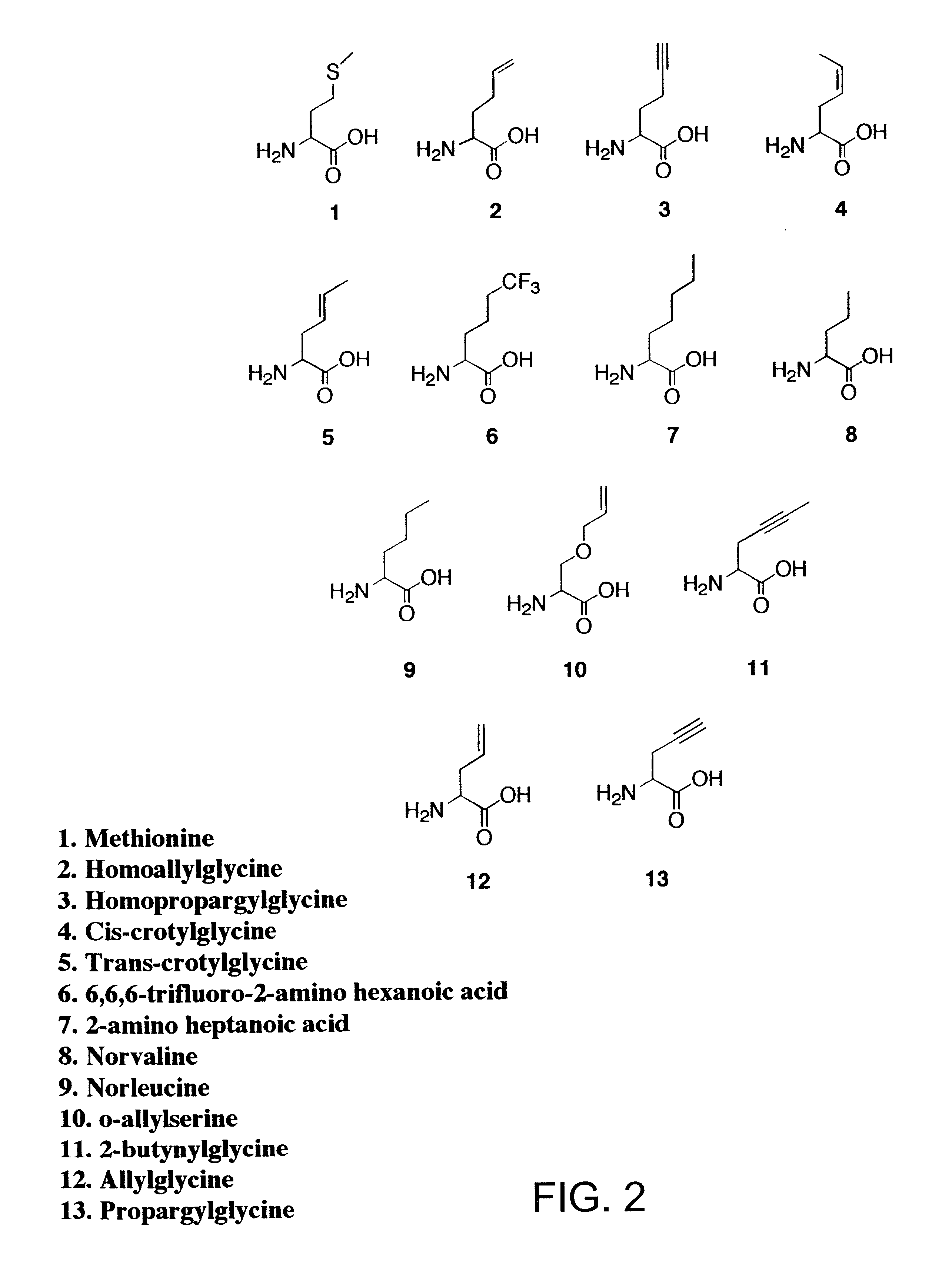

Overexpression of aminoacyl-tRNA synthetases for efficient production of engineered proteins containing amino acid analogues

InactiveUS6586207B2High yieldRapid and predictable approachBacteriaOxidoreductasesMethionine biosynthesisDihydrofolate reductase

Methods for producing modified polypeptides containing amino acid analogues are disclosed. The invention further provides purified dihydrofolate reductase polypeptides, produced by the methods of the invention, in which the methionine residues have been replaced with homoallyglycine, homoproparglycine, norvaline, norleucine, cis-crotylglycine, trans-crotylglycine, 2-aminoheptanoic acid, 2-butynylglycine and allylglycine.

Owner:CALIFORNIA INST OF TECH

Direct and selective production of ethanol from acetic acid utilizing a platinum/tin catalyst

InactiveUS7863489B2High selectivityHigh yieldOrganic compound preparationOxygen compounds preparation by reductionCalcium silicateAcetic acid

A process for the selective production of ethanol by vapor phase reaction of acetic acid over a hydrogenating catalyst composition to form ethanol is disclosed and claimed. In an embodiment of this invention reaction of acetic acid and hydrogen over a platinum and tin supported on silica, graphite, calcium silicate or silica-alumina selectively produces ethanol in a vapor phase at a temperature of about 250° C.

Owner:CELANESE INT CORP

Aqueous emulsion polymerization of fluorinated monomers using a perfluoropolyether surfactant

The invention relates to an aqueous emulsion polymerization of fluorinated monomers using perfluoropolyethers of the following formula (I) or (II). In particular, the perfluoropolyether surfactants correspond to formula (I) or (II) CF3—(OCF2)m—O—CF2—X (I) wherein m has a value of 1 to 6 and X represents a carboxylic acid group or salt thereof, CF3—O—(CF2)3—(OCF(CF3)—CF2)z—O-L-Y (II) wherein z has a value of 0, 1, 2 or 3, L represents a divalent linking group selected from —CF(CF3)—, —CF2— and —CF2CF2— and Y represents a carboxylic acid group or salt thereof. The invention further relates to an aqueous dispersion of a fluoropolymer having the aforementioned perfluoropolyether surfactant(s).

Owner:3M INNOVATIVE PROPERTIES CO

Organometallic Complex, Light-Emitting Element, Light-Emitting Device, Electronic Device, and Lighting Device

InactiveUS20140246656A1Improve efficiencyHigh sublimabilityGroup 5/15 element organic compoundsSolid-state devicesHydrogenEmission efficiency

As a novel substance having a novel skeleton, an organometallic complex having high emission efficiency and improved color purity is provided. The color purity is improved by reducing the half width of an emission spectrum. The organometallic complex is represented by General Formula (G1). In General Formula (G1), at least one of R1 to R4 represents a substituted or unsubstituted alkyl group having 1 to 4 carbon atoms, and the others each independently represent hydrogen or a substituted or unsubstituted alkyl group having 1 to 4 carbon atoms. Note that the case where all of R1 to R4 represent alkyl groups each having 1 carbon atom is excluded. Further, R5 to R9 each independently represent hydrogen or a substituted or unsubstituted alkyl group having 1 to 6 carbon atoms.

Owner:SEMICON ENERGY LAB CO LTD

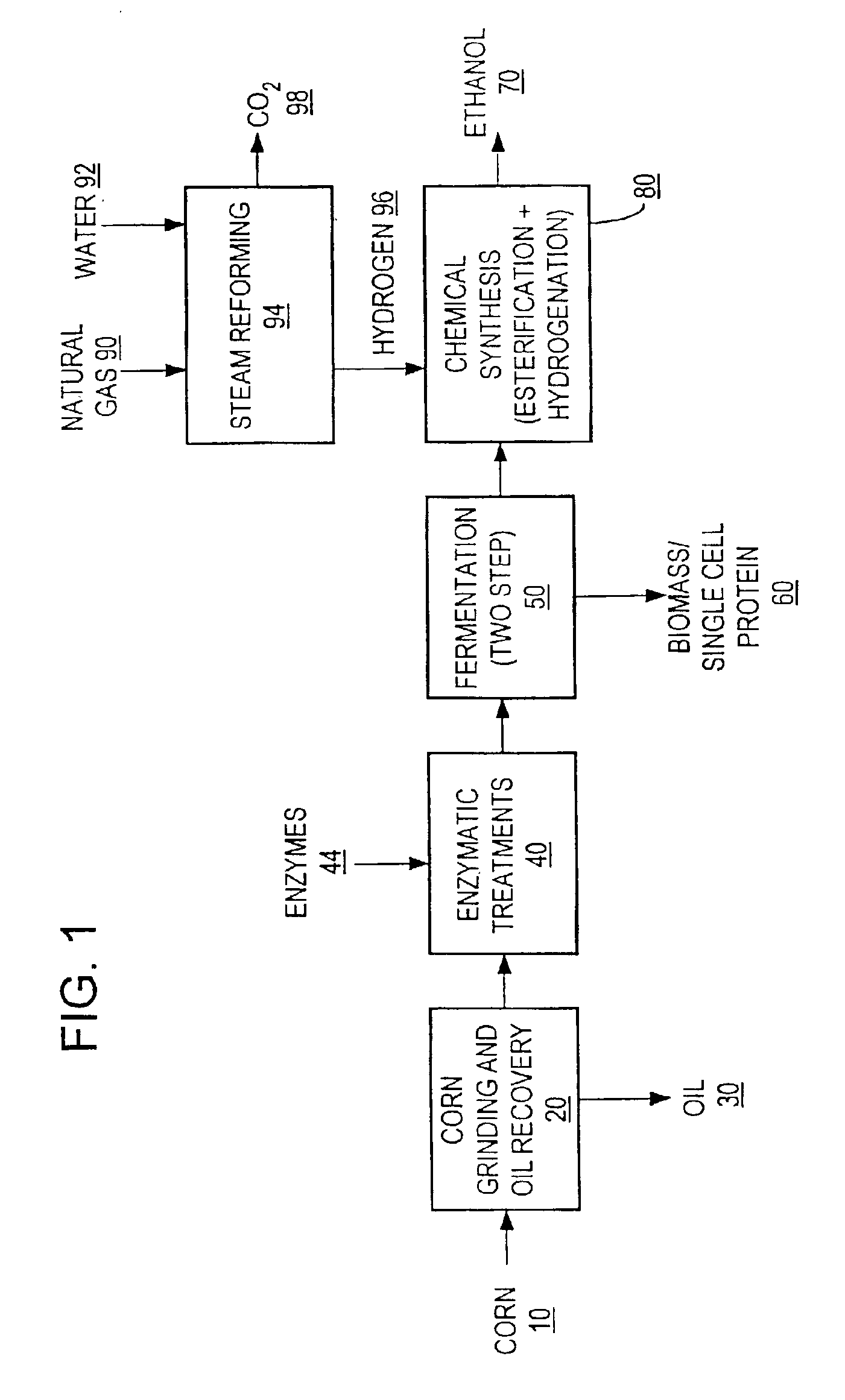

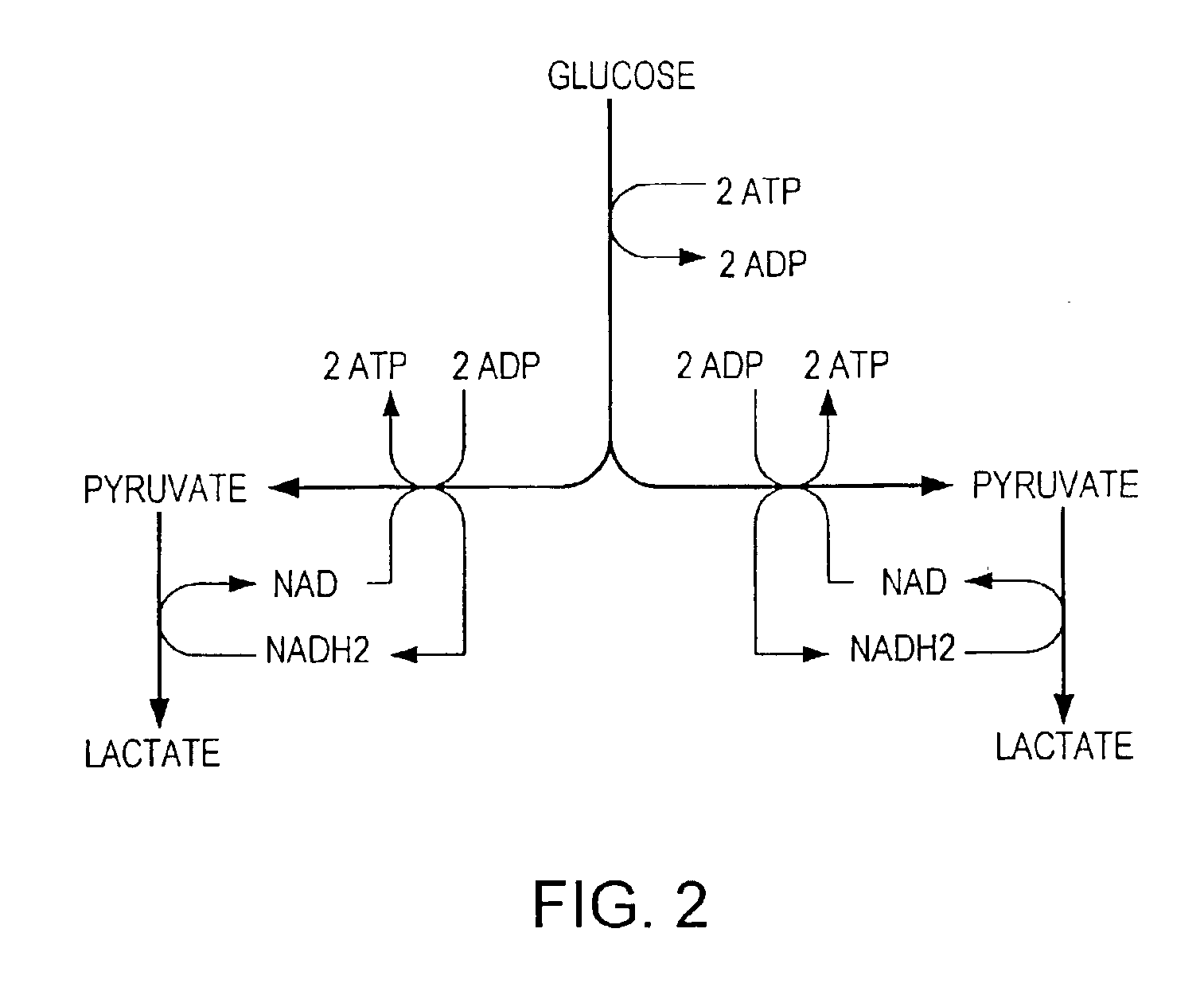

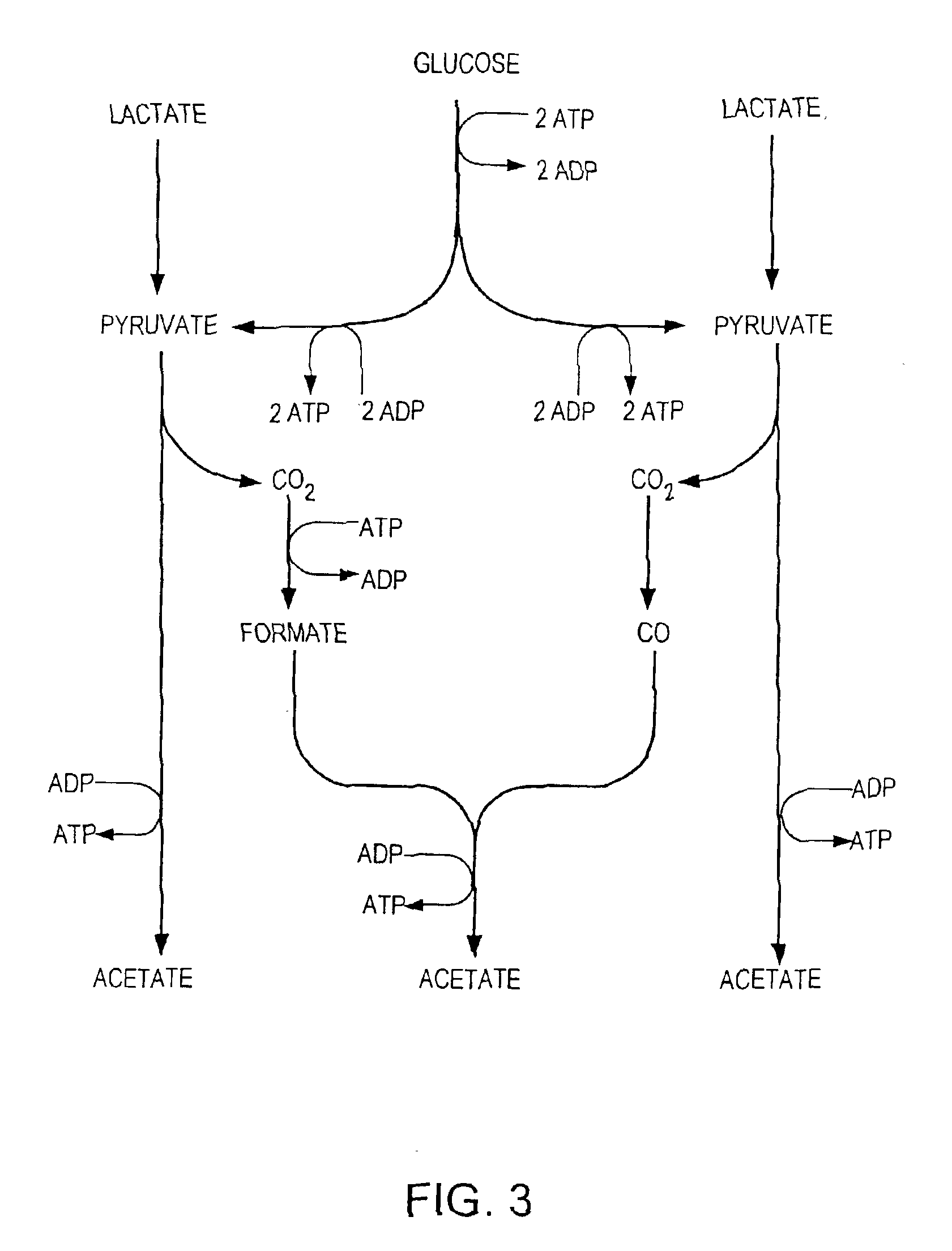

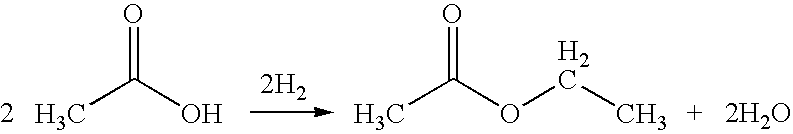

Process for producing ethanol

InactiveUS6927048B2High carbon yieldHigh protein concentrationOrganic compound preparationCarboxylic acid esters preparationAcetic acidHydrogenation reaction

A process for producing ethanol including a combination of biochemical and synthetic conversions results in high yield ethanol production with concurrent production of high value coproducts. An acetic acid intermediate is produced from carbohydrates, such as corn, using enzymatic milling and fermentation steps, followed by conversion of the acetic acid into ethanol using esterification and hydrogenation reactions. Coproducts can include corn oil, and high protein animal feed containing the biomass produced in the fermentation.

Owner:ZEACHEM

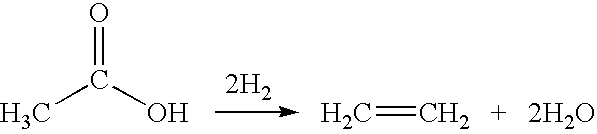

Process for catalytically producing ethylene directly from acetic acid in a single reaction zone

InactiveUS20100030001A1High selectivityHigh yieldHydrocarbonsBulk chemical productionAcetic acidHydrogen

A process for the selective production of ethylene by vapor phase reaction of acetic acid over a hydrogenating catalyst composition to form ethylene in a single reaction zone is disclosed and claimed. In an embodiment of this invention reaction of acetic acid and hydrogen over either a copper supported on iron oxide, copper-aluminum catalyst, cobalt supported on H-ZSM-5, ruthenium-cobalt supported on silica or cobalt supported on carbon selectively produces ethylene in a vapor phase at a temperature in the range of about 250° C. to 350° C.

Owner:CELANESE INT CORP

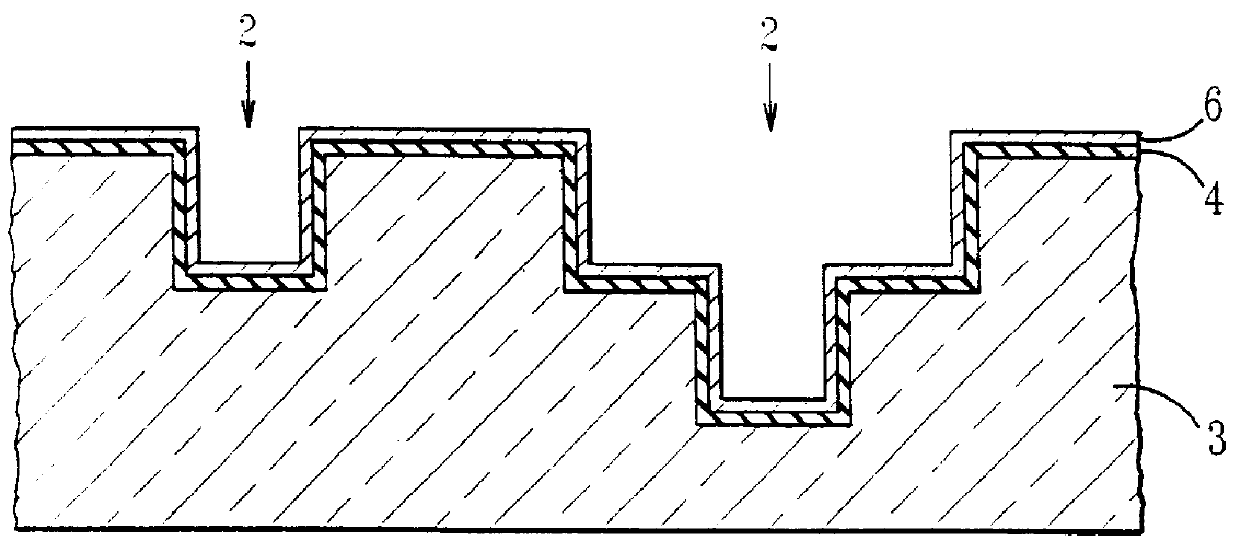

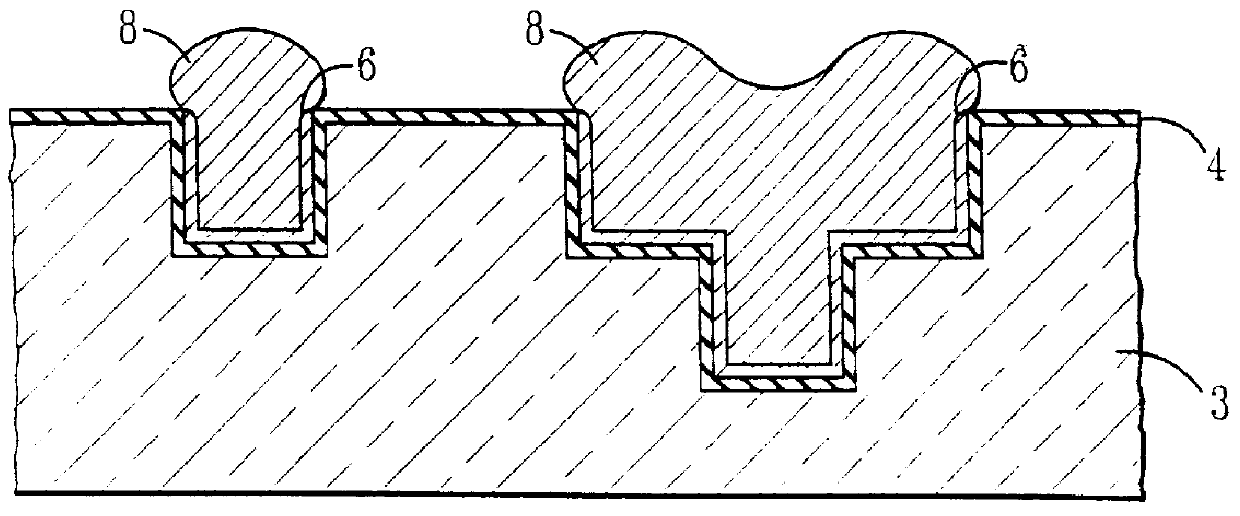

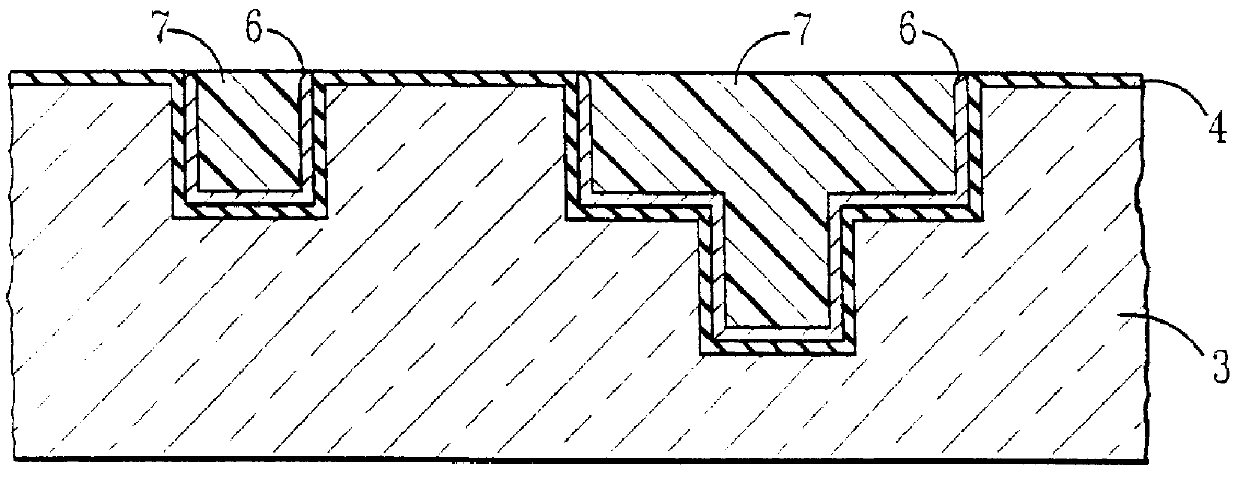

Method to selectively fill recesses with conductive metal

InactiveUS6140234AShorten the timeIncrease productionSolid-state devicesSemiconductor/solid-state device manufacturingResistSemiconductor structure

Recesses in a semiconductor structure are selectively plated by providing electrical insulating layer over the semiconductor substrate and in the recesses followed by forming a conductive barrier over the insulating layer; providing a plating seed layer over the barrier layer; depositing and patterning a photoresist layer over the plating seed layer; planarizing the insulated horizontal portions by removing the horizontal portions of the seed layer between the recesses; removing the photoresist remaining in the recesses; and then electroplating the patterned seed layer with a conductive metal using the barrier layer to carry the current during the electroplating to thereby only plate on the seed layer. In an alternative process, a barrier film is deposited over recesses in an insulator. Then, relatively thick resists are lithographically defined on the field regions, on top of the barrier film over the recesses. A plating base or seedlayer is deposited, so as to be continuous on the horizontal regions of the recesses in the insulator, but discontinuous on their surround wall. The recesses are then plated using the barrier film without seedlayers at the periphery of the substrate wafers for electrical contact. After electroplating, the resist is removed by lift-off process and exposed barrier film is etched by RIE method or by CMP. Also provided is a semiconductor structure obtained by the above processes.

Owner:GLOBALFOUNDRIES INC

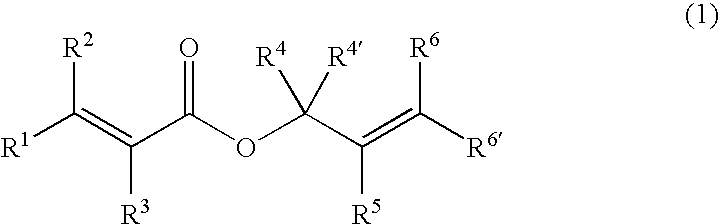

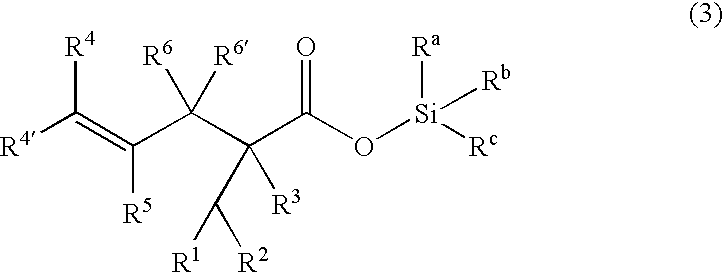

Processes of making gamma,delta-unsaturated carboxylic acid and silyl ester thereof, carboxyl group-containing organosilicon compound and process of making

ActiveUS7307178B2Few stepsHigh yieldSilicon organic compoundsPreparation from carboxylic acid esters/lactonesCarboxyl radicalPerylene derivatives

A γ,δ-unsaturated carboxylic acid silyl ester is prepared by reacting an α,β-unsaturated carboxylic acid ester with a hydrosilane or hydrosiloxane in the presence of tris(pentafluorophenyl)borane. γ,δ-Unsaturated carboxylic acid derivatives are readily prepared through fewer steps and in high yields.

Owner:SHIN ETSU CHEM CO LTD

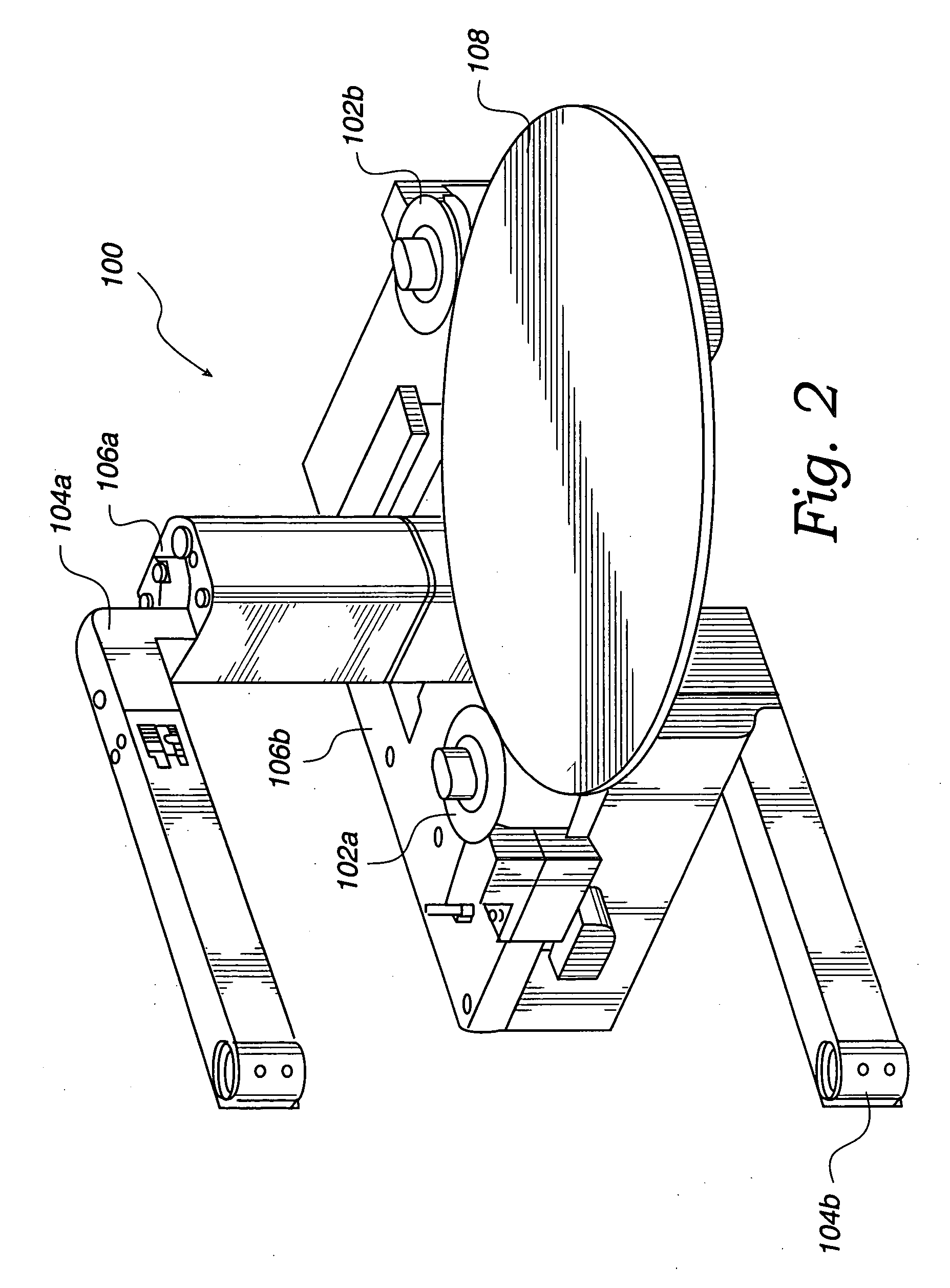

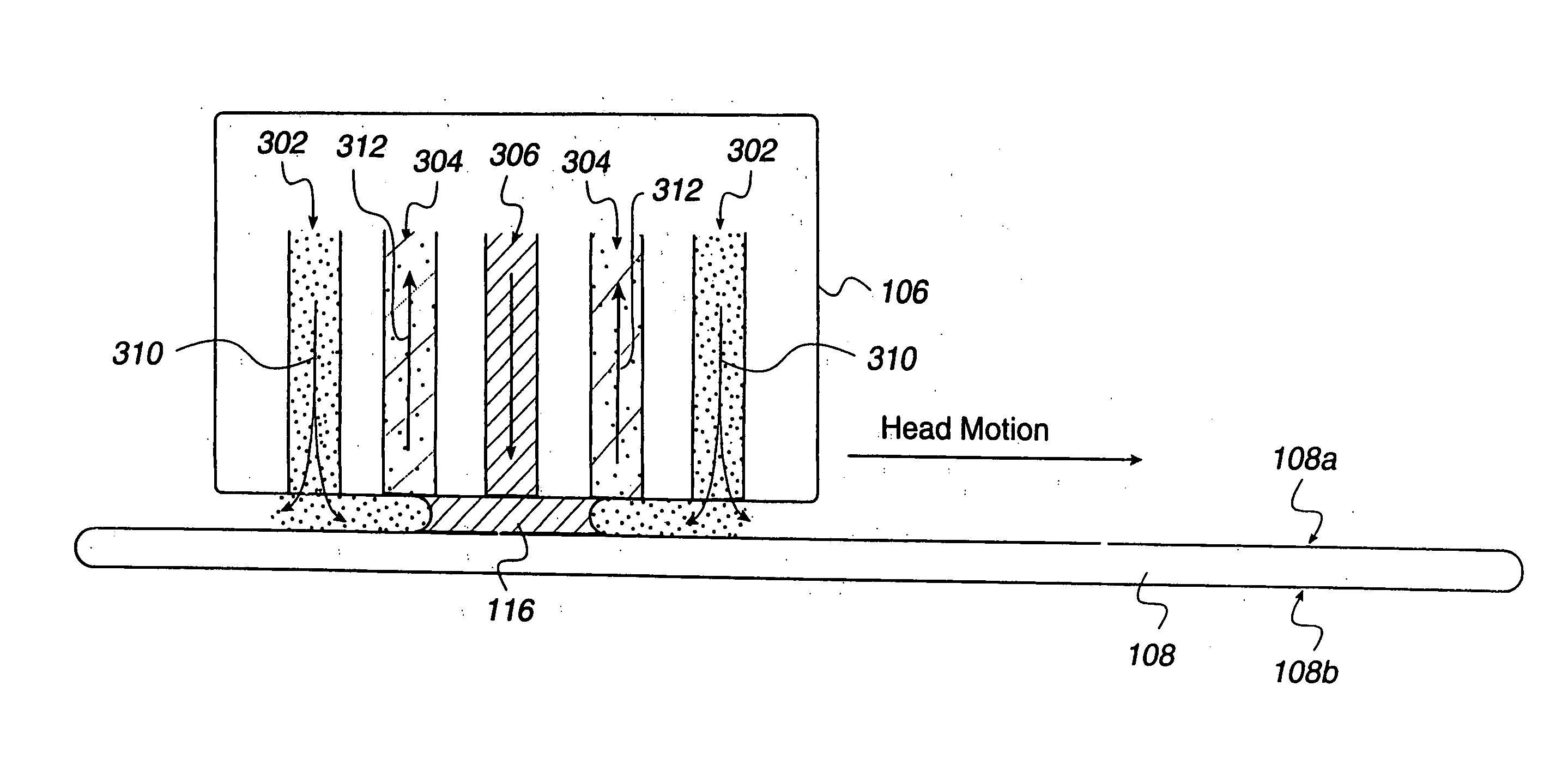

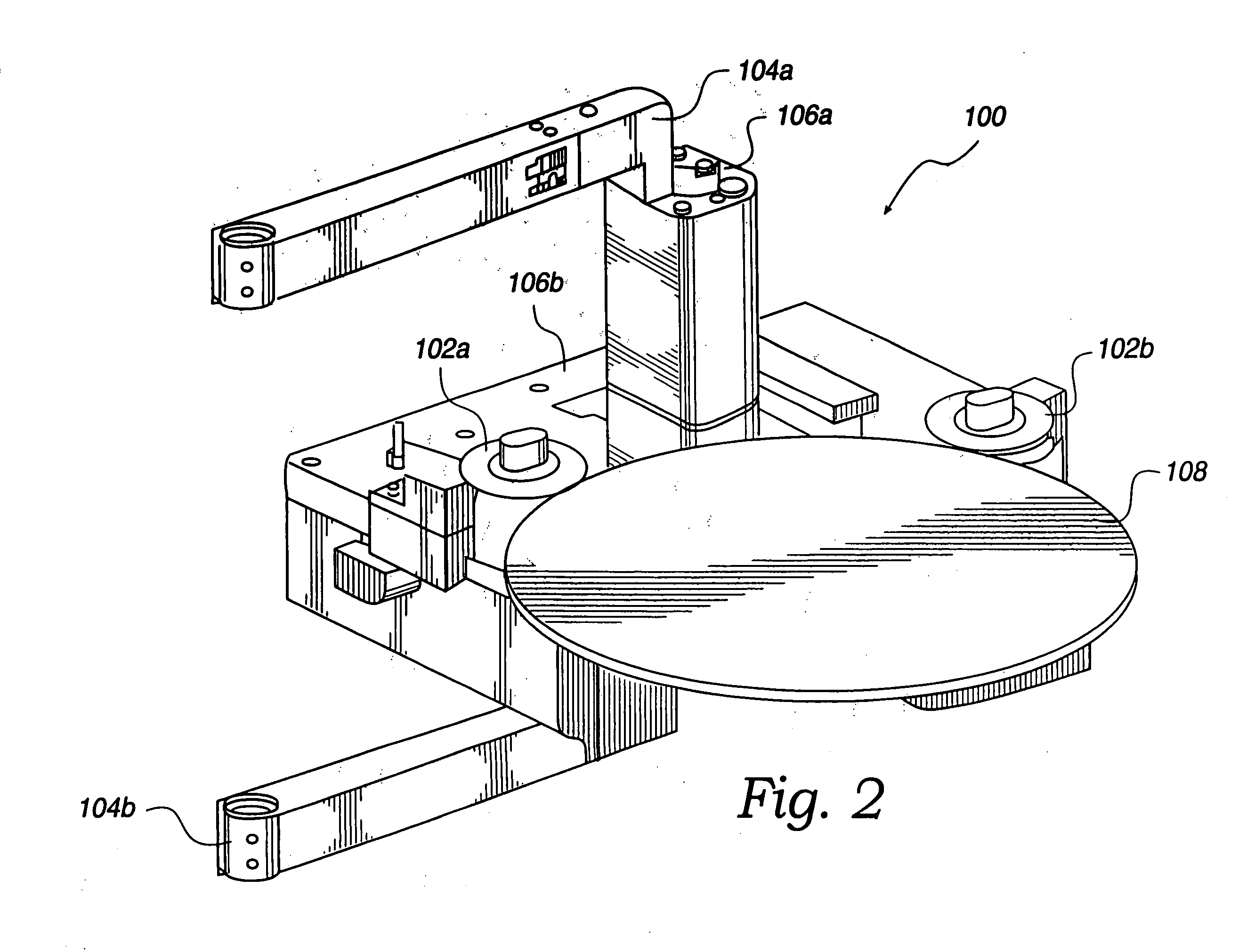

Method and apparatus for processing wafer surfaces using thin, high velocity fluid layer

InactiveUS20050145265A1Efficient processingReducing unwanted fluidElectrolysis componentsDrying solid materials without heatHigh velocityBiomedical engineering

Among the many embodiment, in one embodiment, a method for processing a substrate is disclosed which includes generating a fluid layer on a surface of the substrate, the fluid layer defining a fluid meniscus. The generating includes moving a head in proximity to the surface, applying a fluid from the head to the surface while the head is in proximity to the surface of the substrate to define the fluid layer, and removing the fluid from the surface through the proximity head by a vacuum. The fluid travels along the fluid layer between the head and the substrate at a velocity that increases as the head is in closer proximity to the surface.

Owner:LAM RES CORP

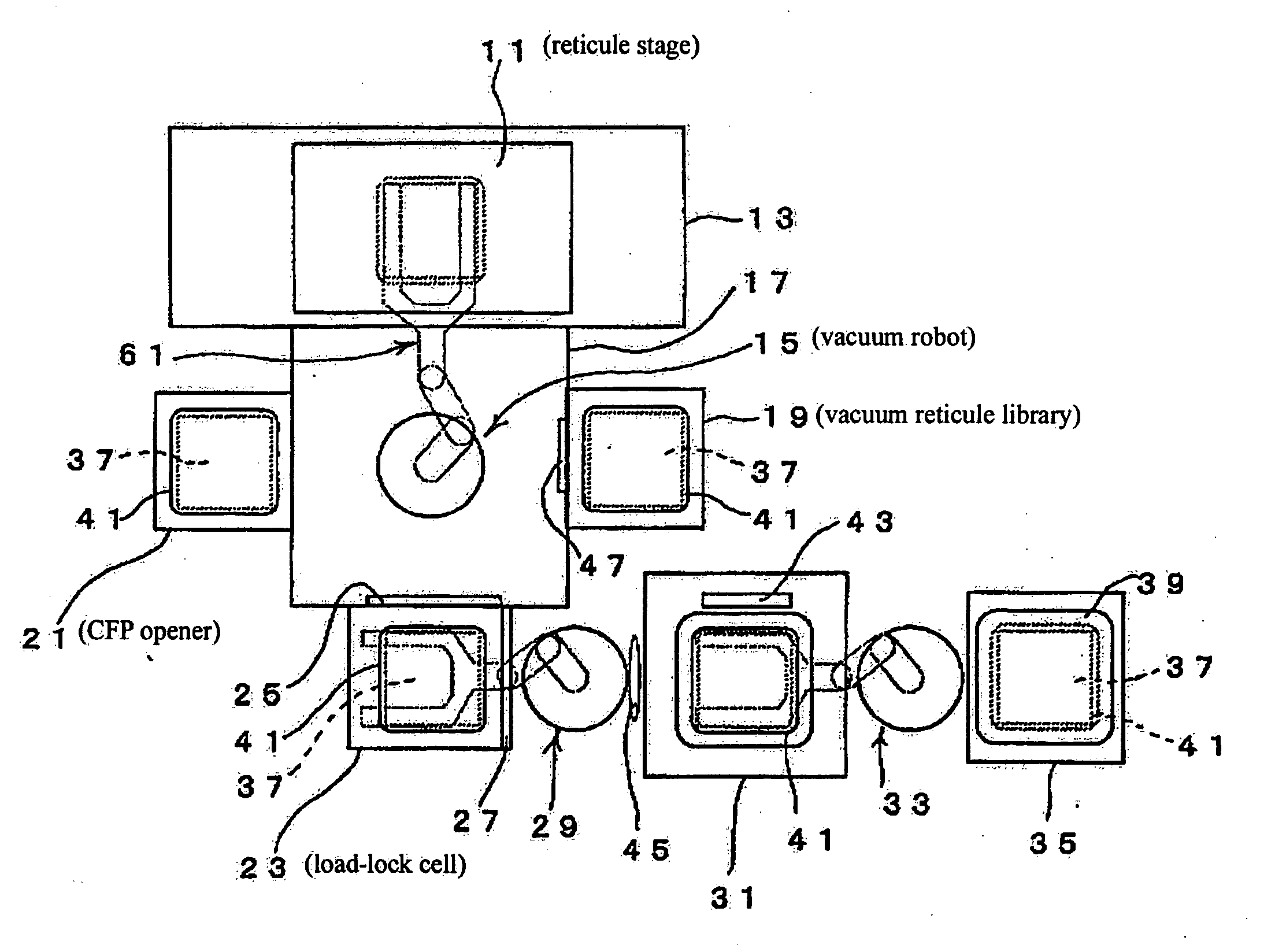

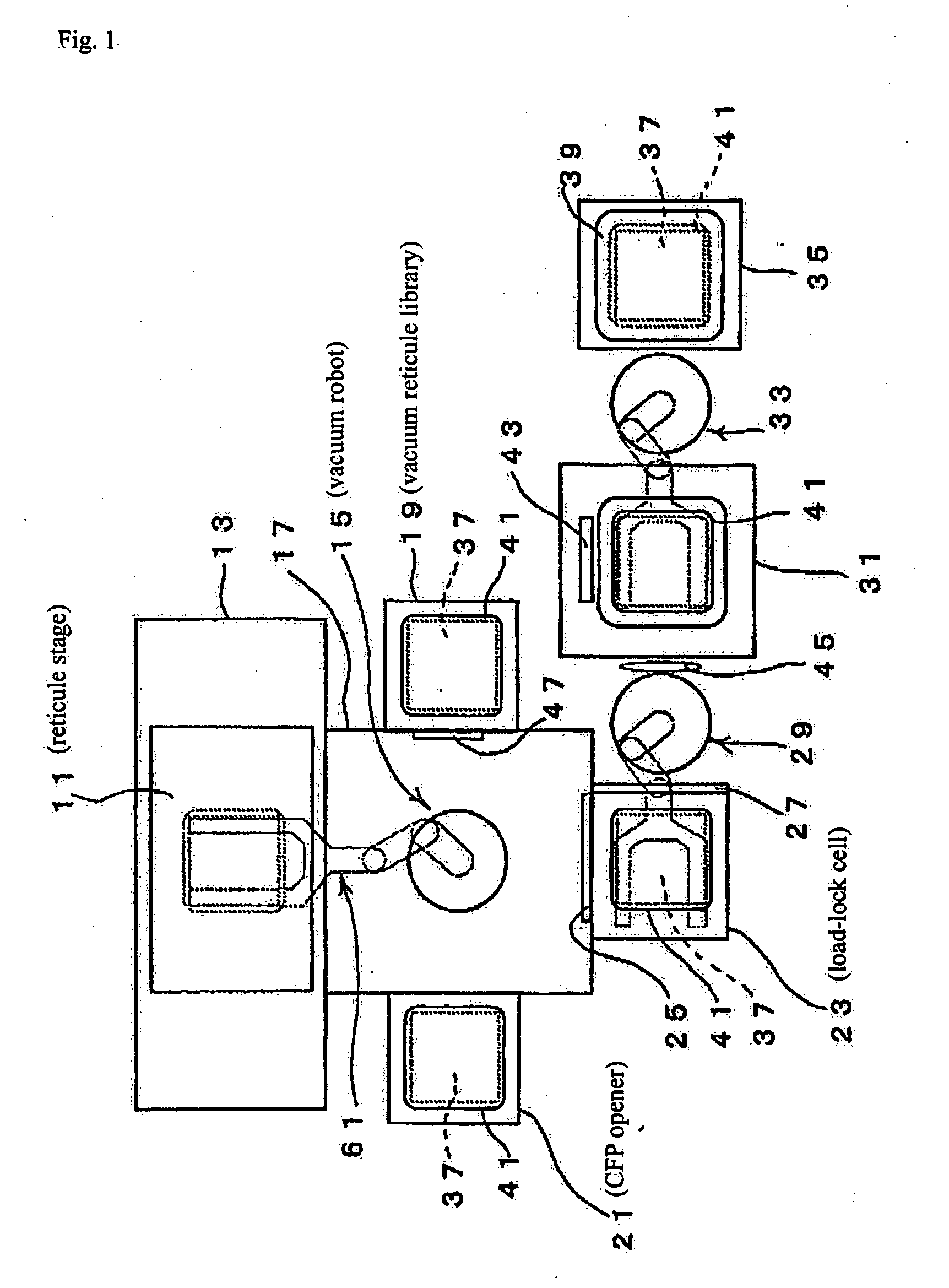

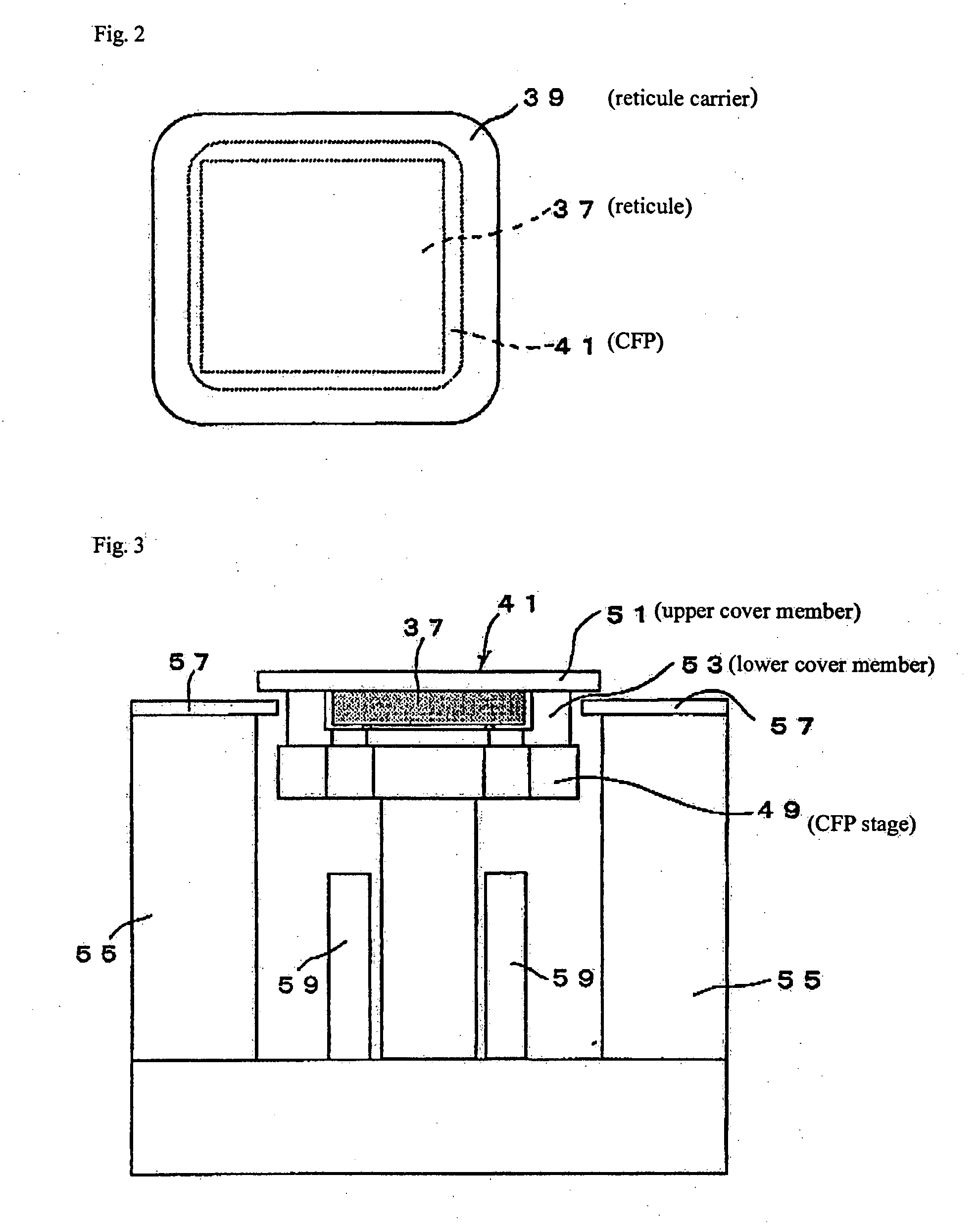

Substrate conveyor apparatus, substrate conveyance method and exposure apparatus

ActiveUS20060087638A1High yieldSmall contaminationNanoinformaticsSemiconductor/solid-state device manufacturingEngineering

Owner:NIKON CORP

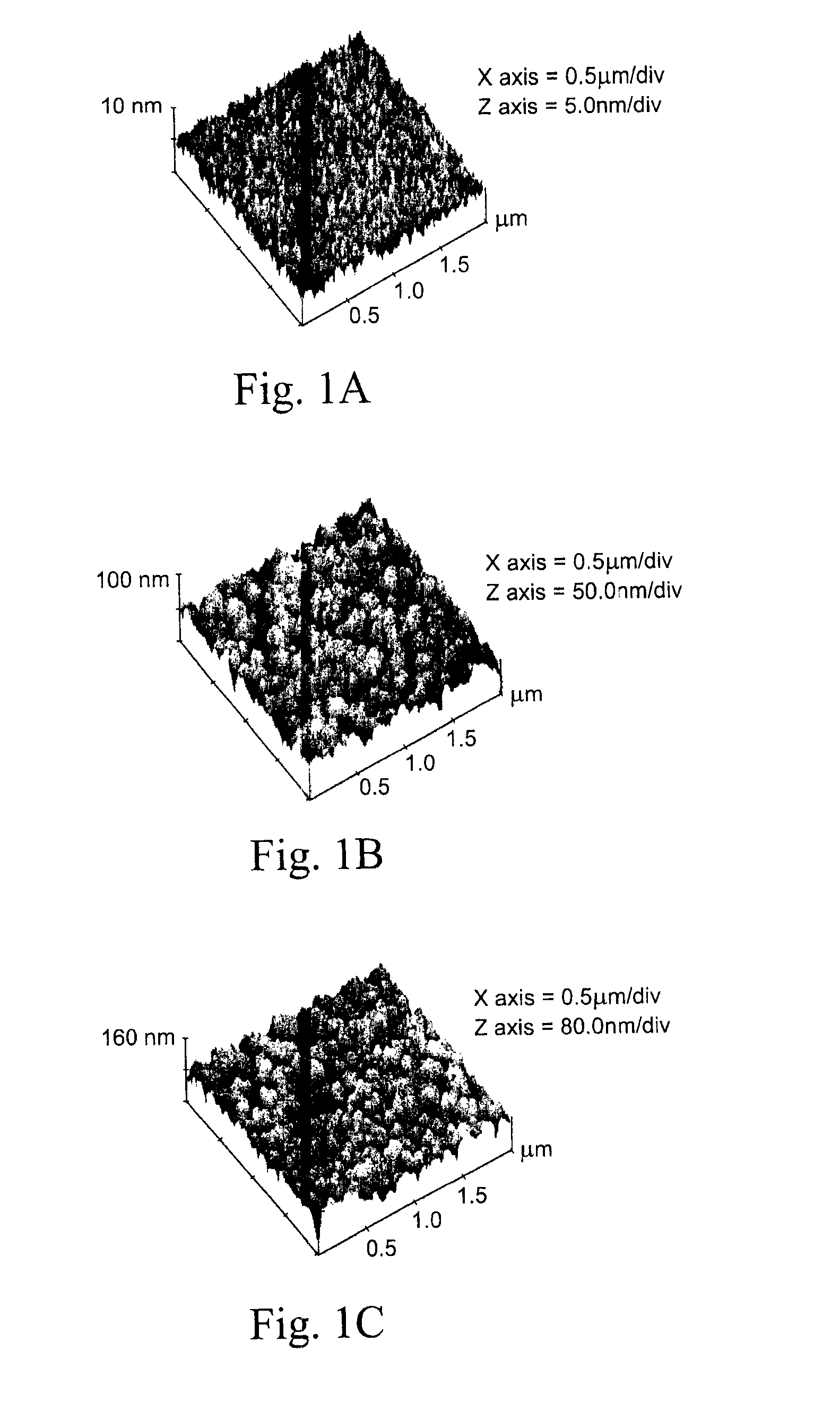

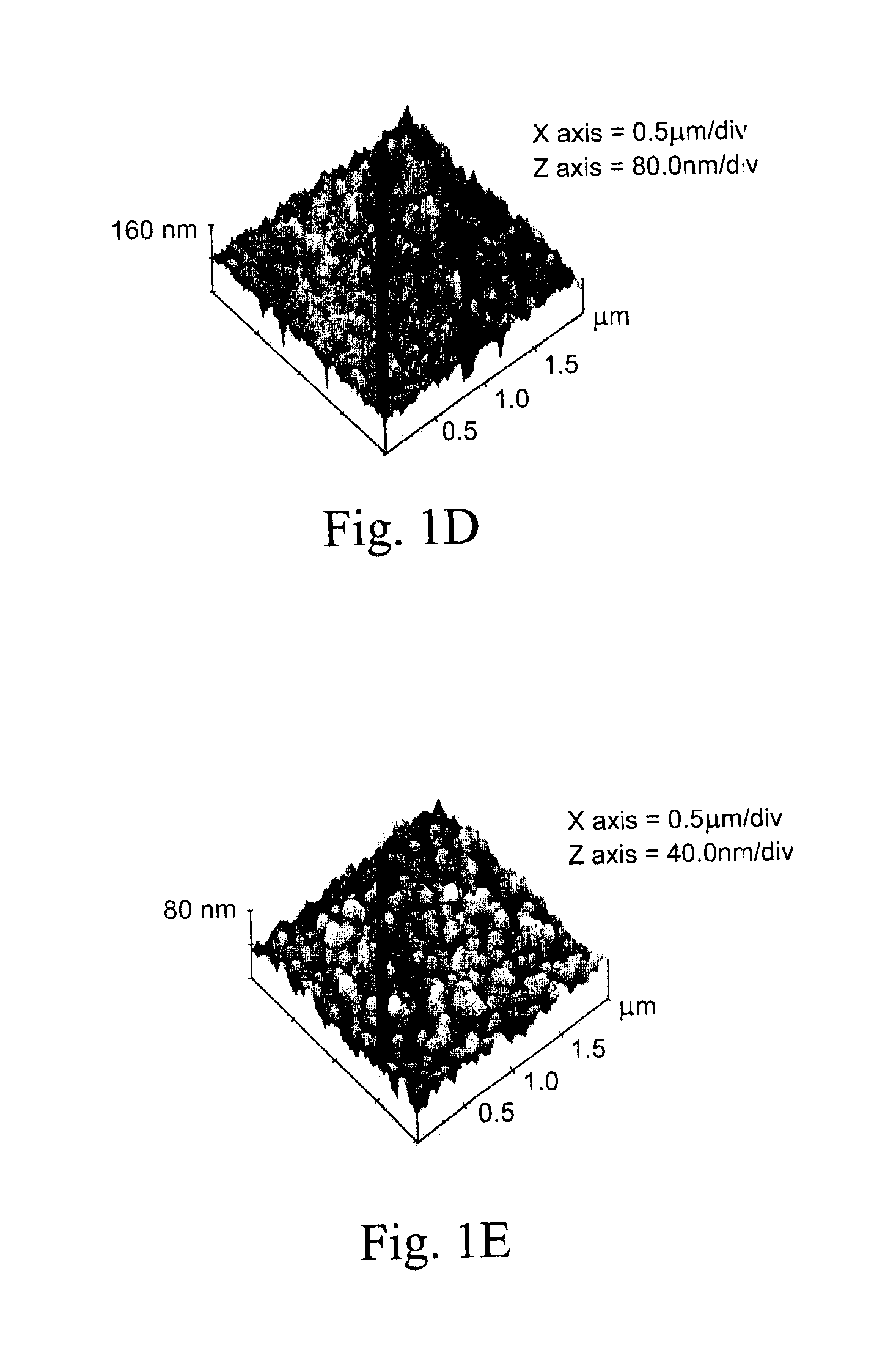

Method of preparing nano-structured surface coatings and coated articles

InactiveUS7892606B2Improve adhesionMore readily manufacturableMaterial nanotechnologyNanostructure manufactureCross-linkNano structuring

Owner:DSM IP ASSETS BV

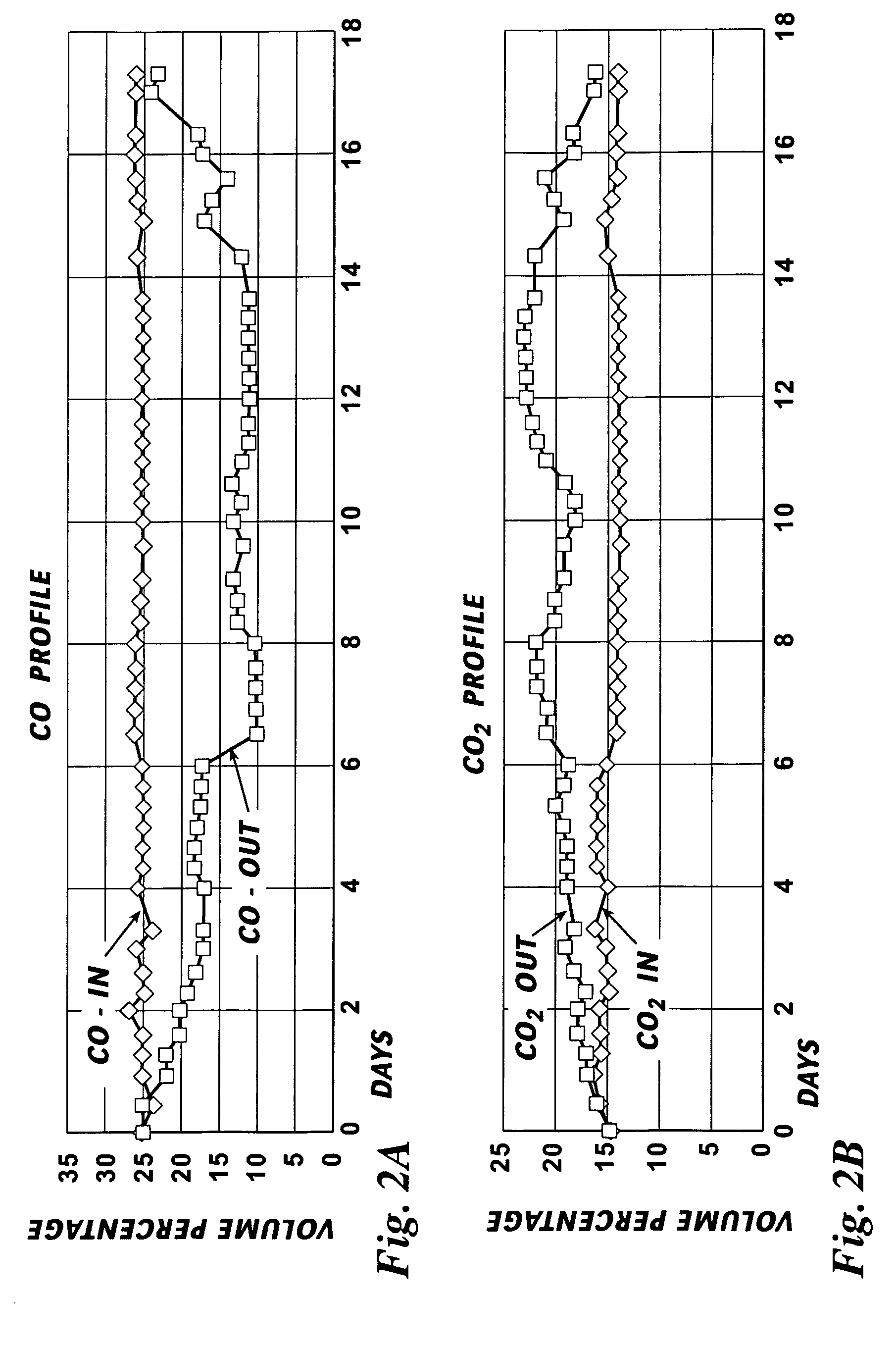

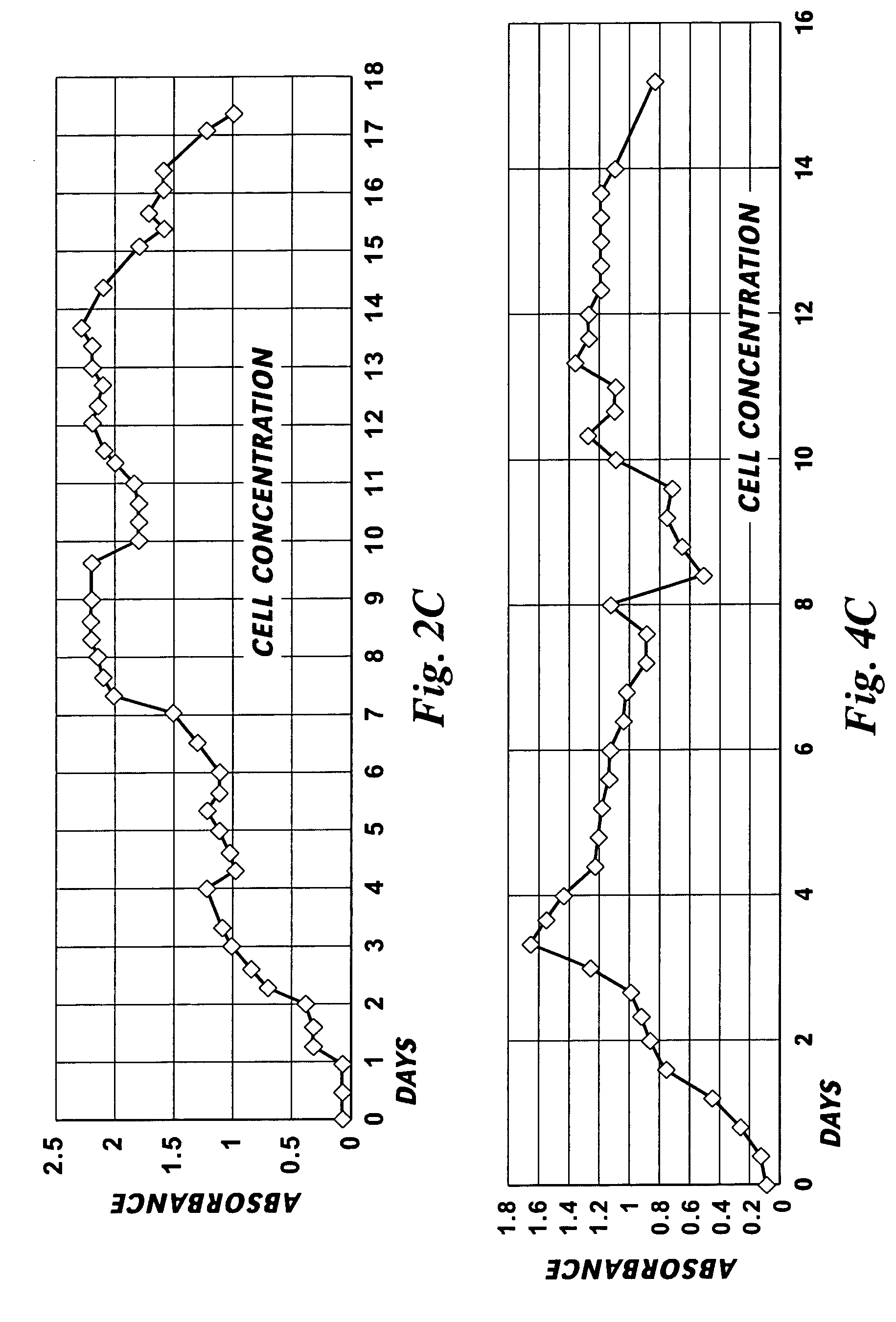

Indirect or direct fermentation of biomass to fuel alcohol

A novel clostridia bacterial species (Clostridium carboxidivorans, ATCC BAA-624, “P7”) is provided. P7 is capable of synthesizing, from waste gases, products which are useful as biofuel. In particular, P7 can convert CO to ethanol. Thus, this novel bacterium can transform waste gases (e.g. syngas and refinery wastes) into useful products. P7 also catalyzes the production of acetate and butanol. Further, P7 is also capable of directly fermenting lignocellulosic materials to produce ethanol and other substances.

Owner:THE BOARD OF RGT UNIV OF OKLAHOMA +1

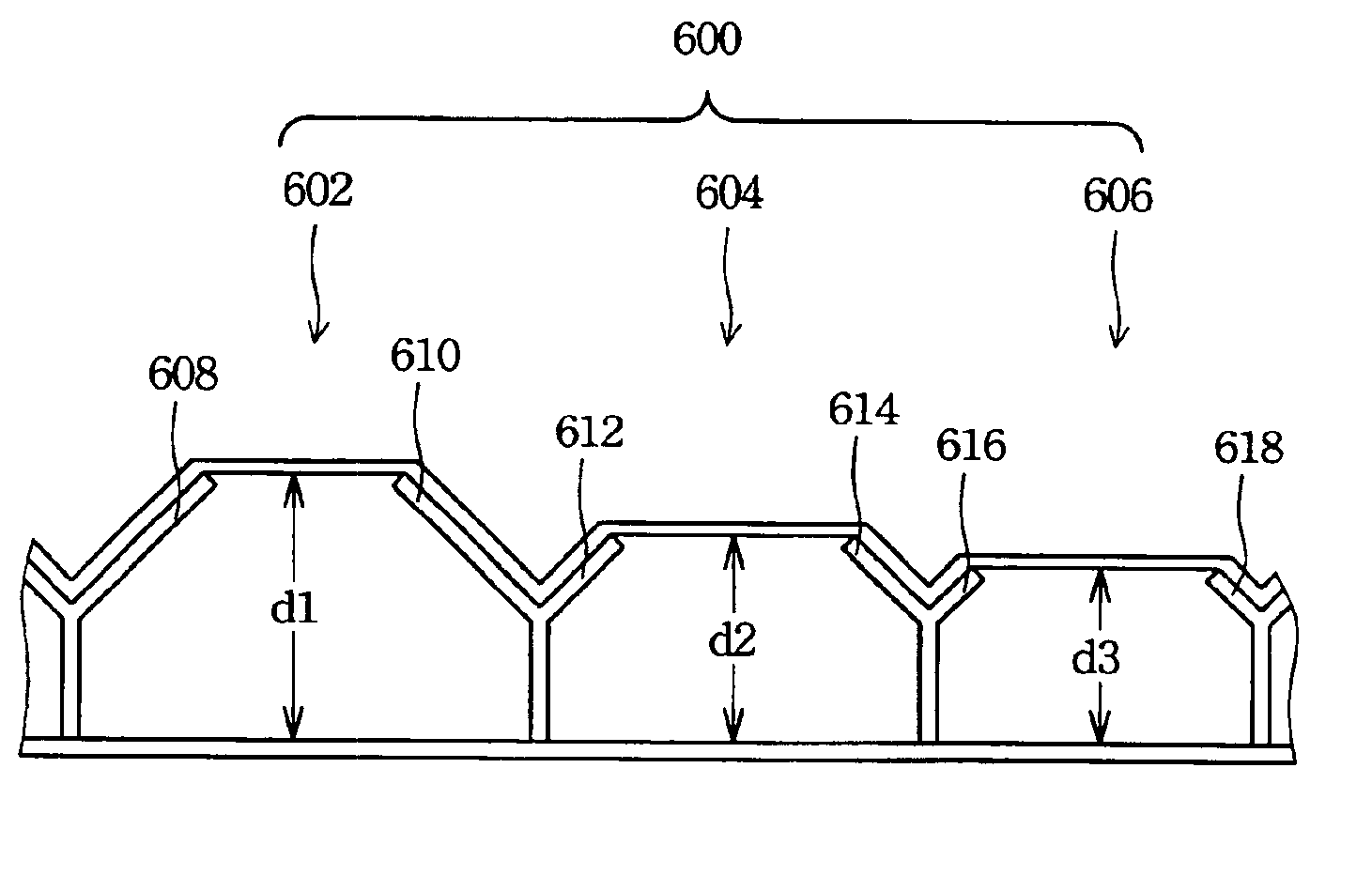

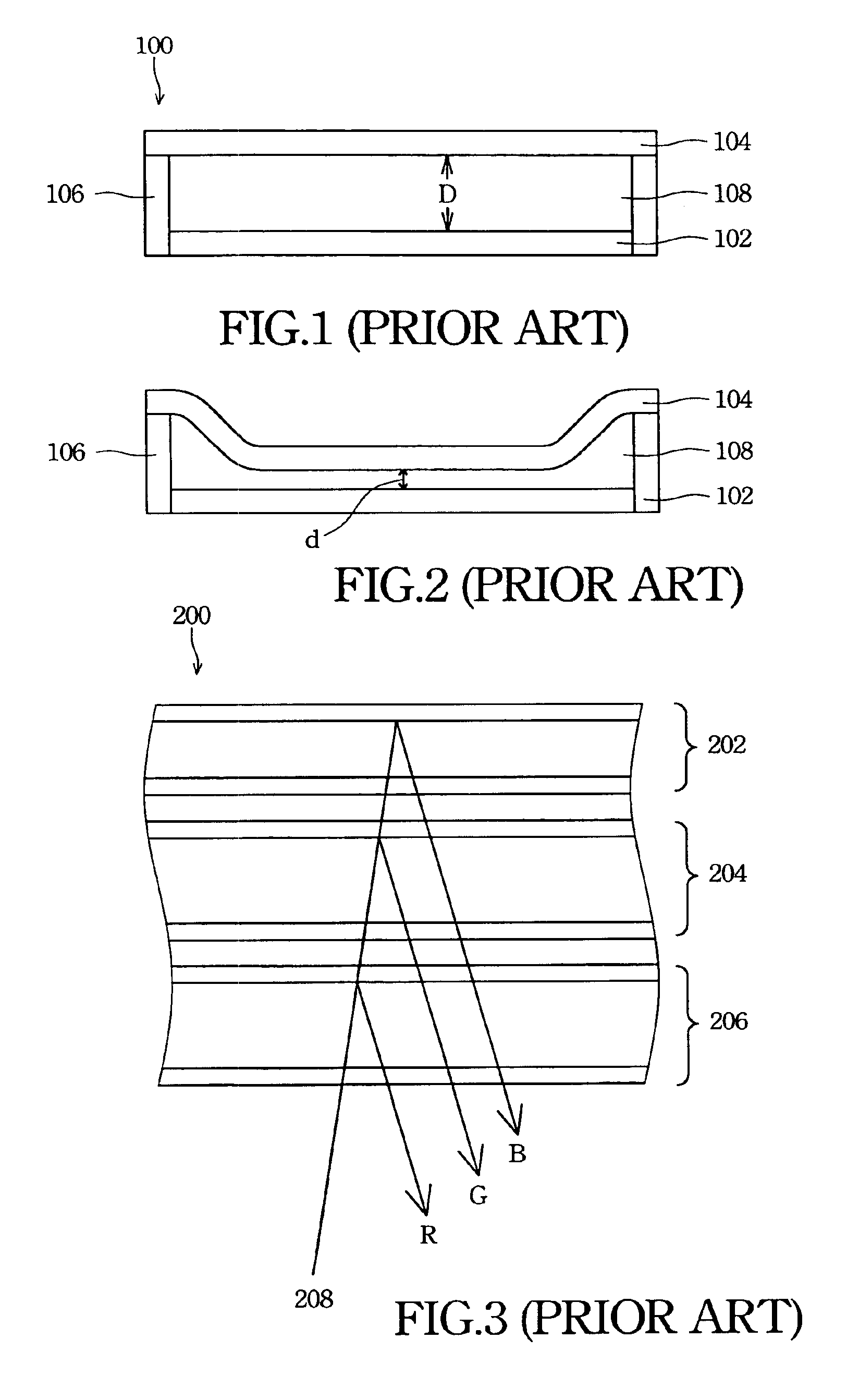

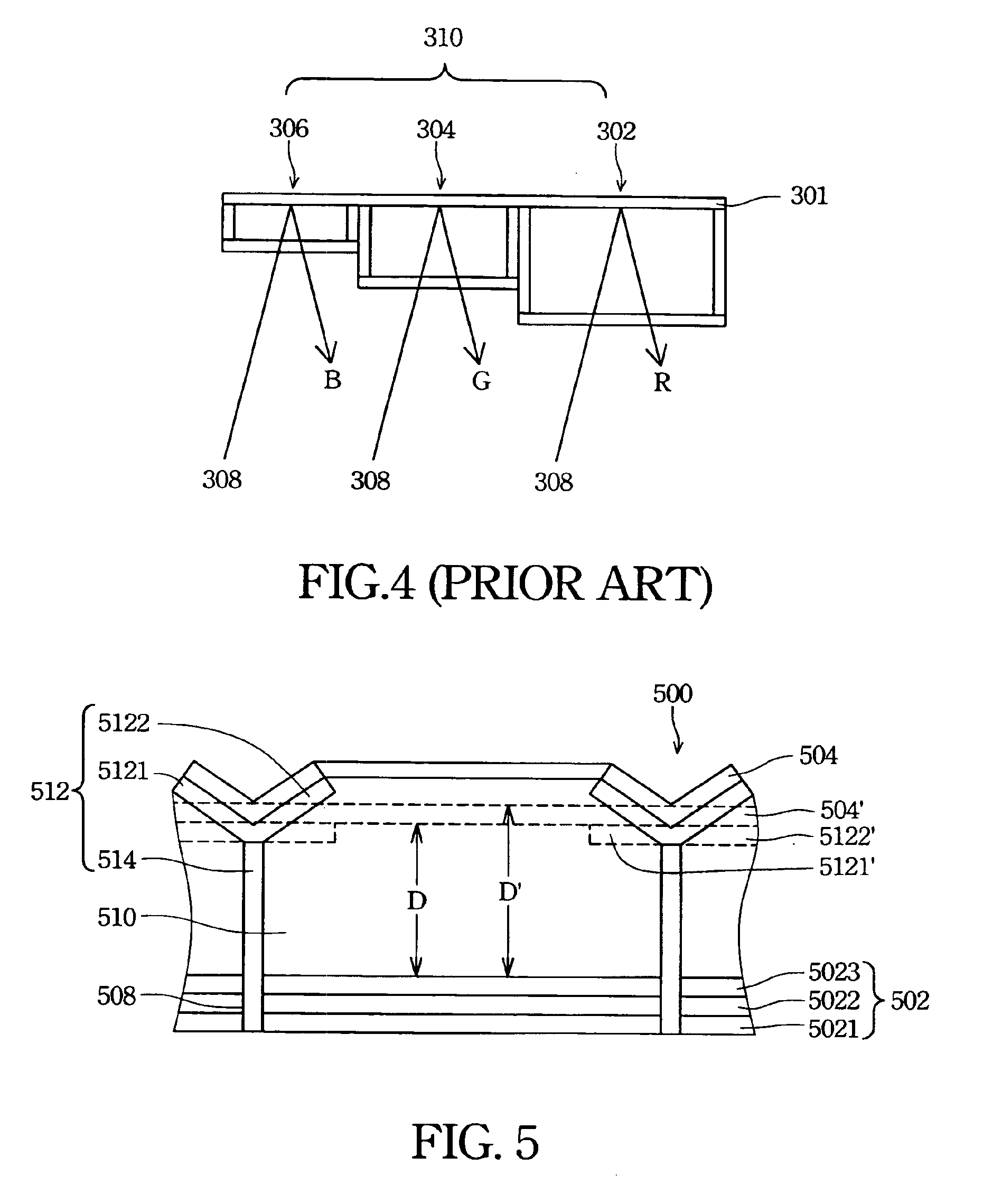

Structure of an optical interference display cell

A structure of an interference display cell is provided. The cell comprises a first plate and a second plate, wherein a support is located between the first plate and the second plate. The second plate is a deformable and reflective plate. An incident light from one side of the first plate is modulated and only specific frequency light reflects by the second plate. The frequency of the reflected light is related to the distance between the first plate and the second plate. The support has at least one arm. The arm's stress makes the arm hiking upward or downward. The distance between the first plate and the second plate is also changed. Therefore, the frequency of the reflected light is altered.

Owner:SNAPTRACK

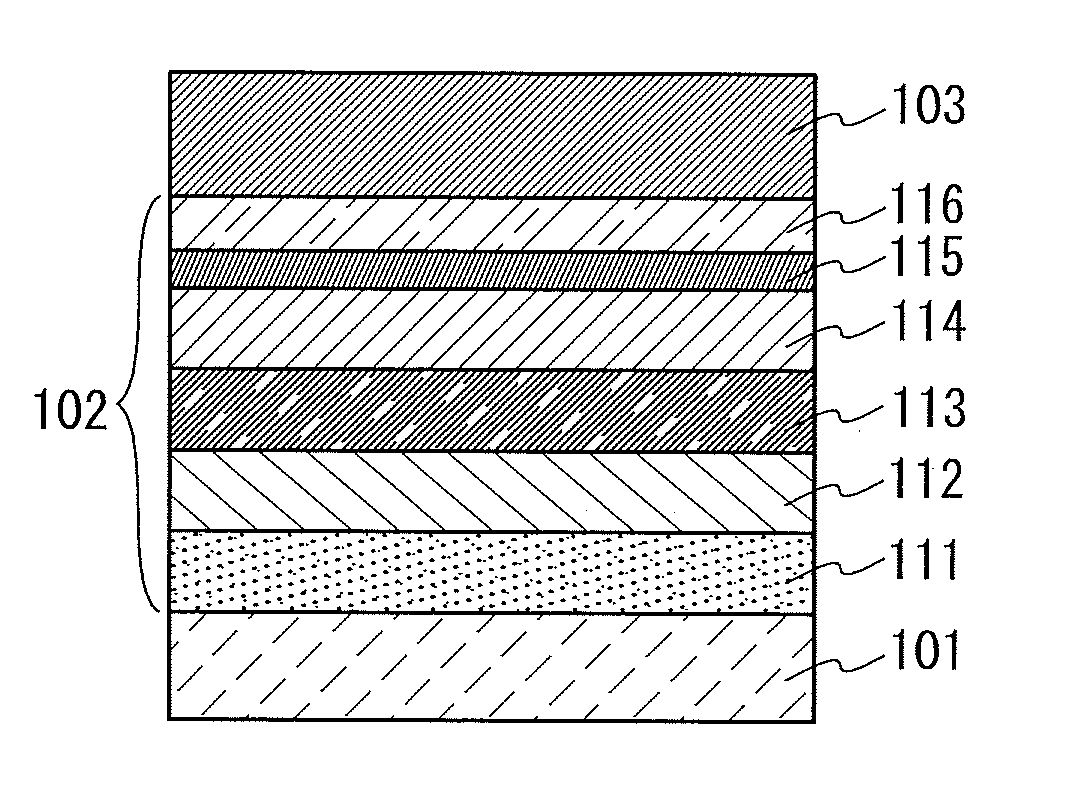

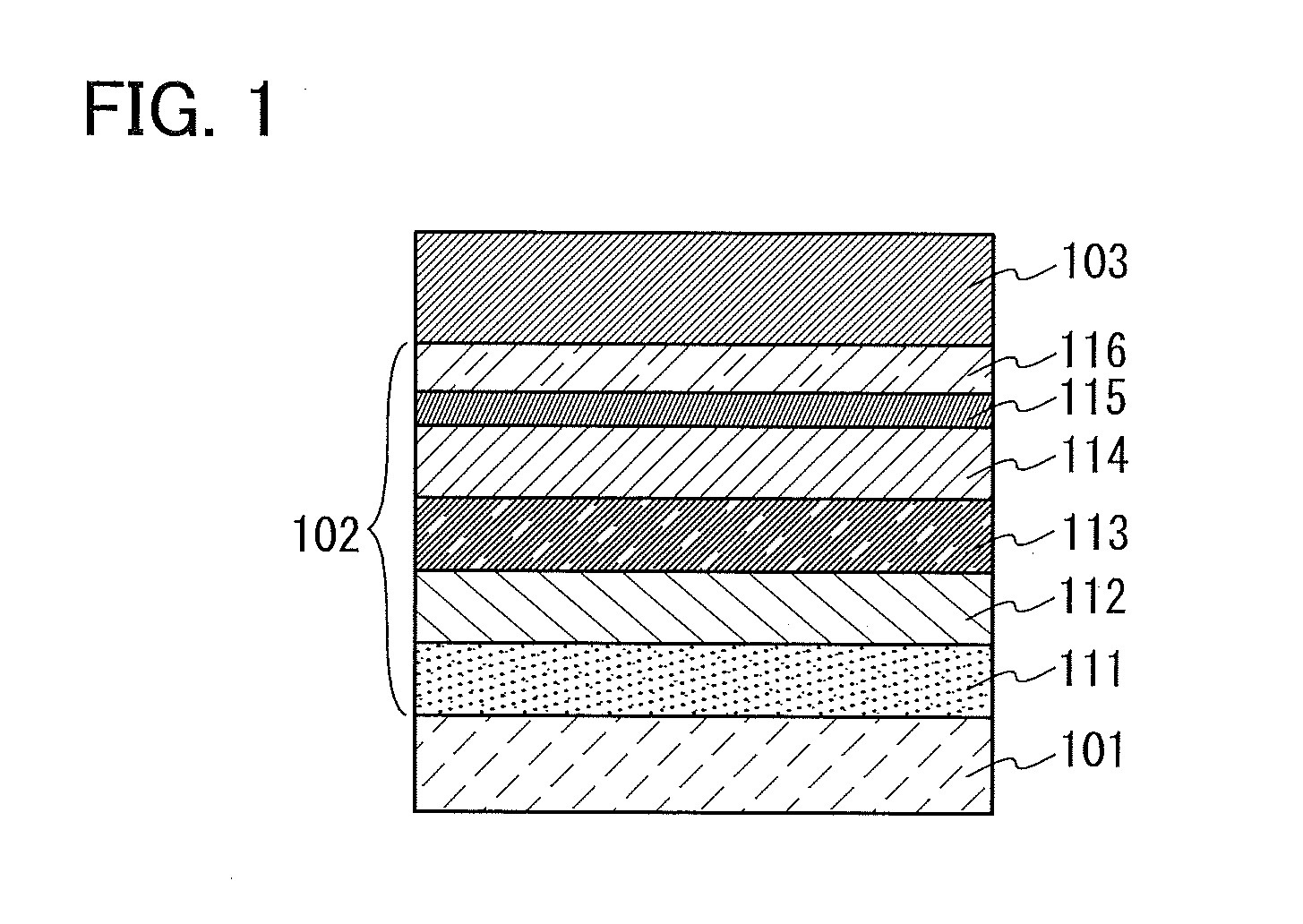

Method of manufacturing semiconductor device

ActiveUS20080299758A1Reduces yield and reliabilityReduce capacitySemiconductor/solid-state device detailsSolid-state devicesHigh densityDevice material

A high-density N-type diffusion layer 116 formed in a separation area 115 makes it possible to reduce a collector current flowing through a parasitic NPN transistor 102. Thus, a normal CMOS process can be used to provide a driving circuit and a data line driver which make it possible to improve resistance to possible noise occurring between adjacent terminals, while controlling a chip size.

Owner:PANNOVA SEMIC

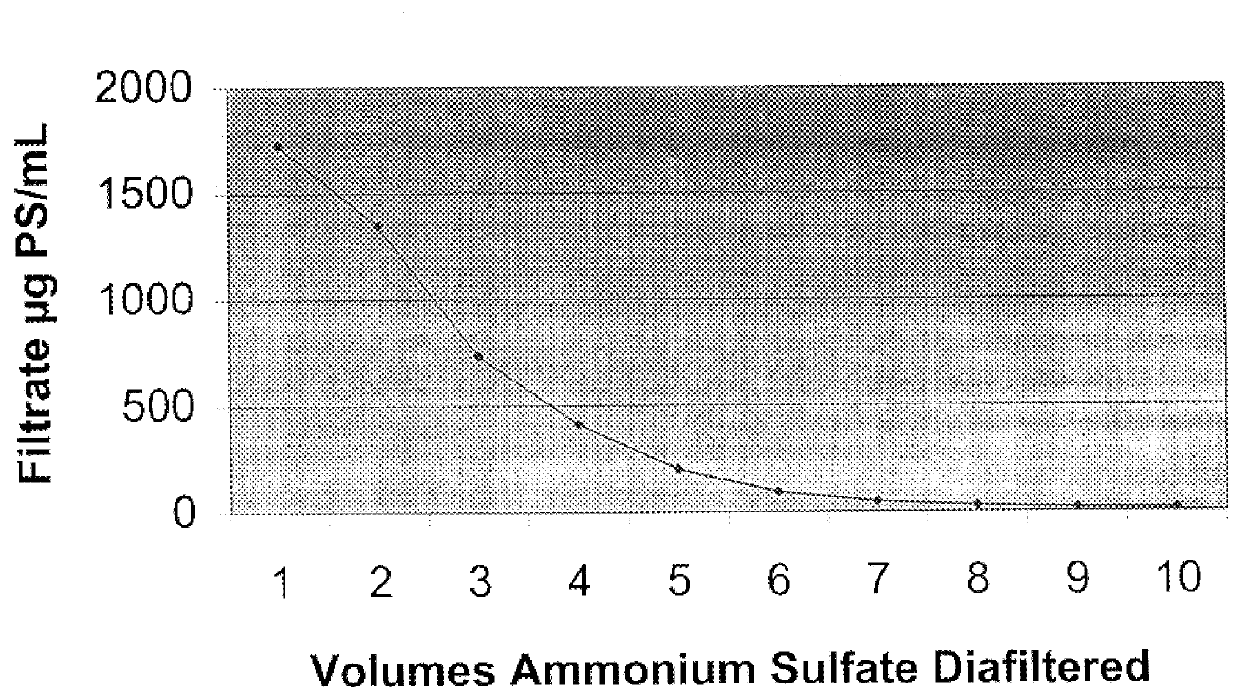

Purification of polysaccharide-protein conjugate vaccines by ultrafiltration with ammonium sulfate solutions

InactiveUS6146902AImprove scalabilityLevel of purityAntibacterial agentsSugar derivativesConjugate vaccineUltrafiltration

Disclosed and claimed are a method for the purification of polysaccharide-protein conjugate vaccines by ultrafiltration in a saturated solution of ammonium sulfate. The ultrafiltration method of the present invention provides an efficient, readily scalable method for removal of unbound polysaccharides from polysaccharide-protein vaccines, thereby improving the purity and consistency of the polysaccharide-protein vaccines.

Owner:AVENTIS PASTUER LTD