Patents

Literature

20942 results about "Electroplating" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electroplating is a process that uses an electric current to reduce dissolved metal cations so that they form a thin coherent metal coating on an electrode. The term is also used for electrical oxidation of anions on to a solid substrate, as in the formation of silver chloride on silver wire to make silver/silver-chloride electrodes. Electroplating is primarily used to change the surface properties of an object (such as abrasion and wear resistance, corrosion protection, lubricity, aesthetic qualities), but may also be used to build up thickness on undersized parts or to form objects by electroforming.

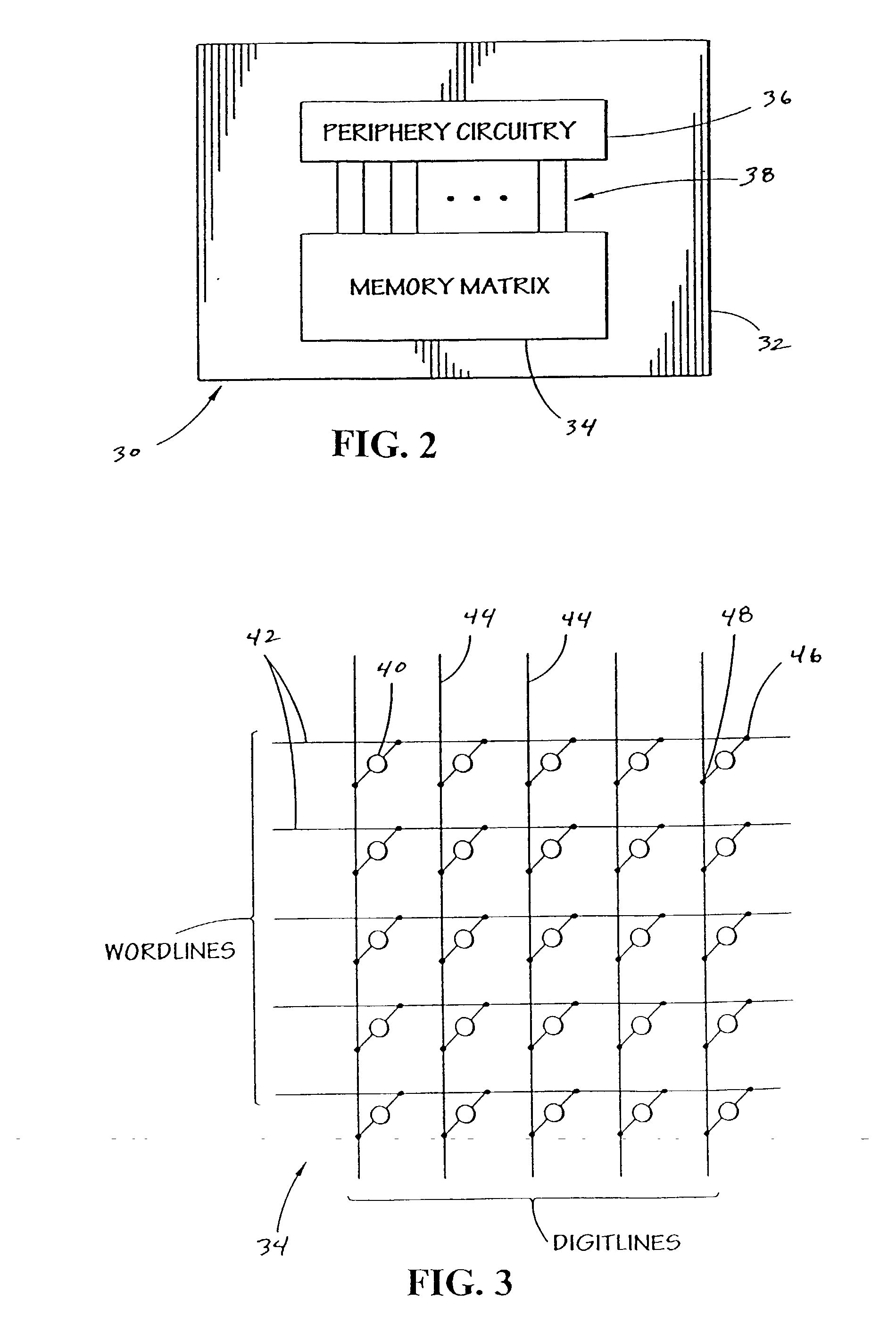

Method to selectively fill recesses with conductive metal

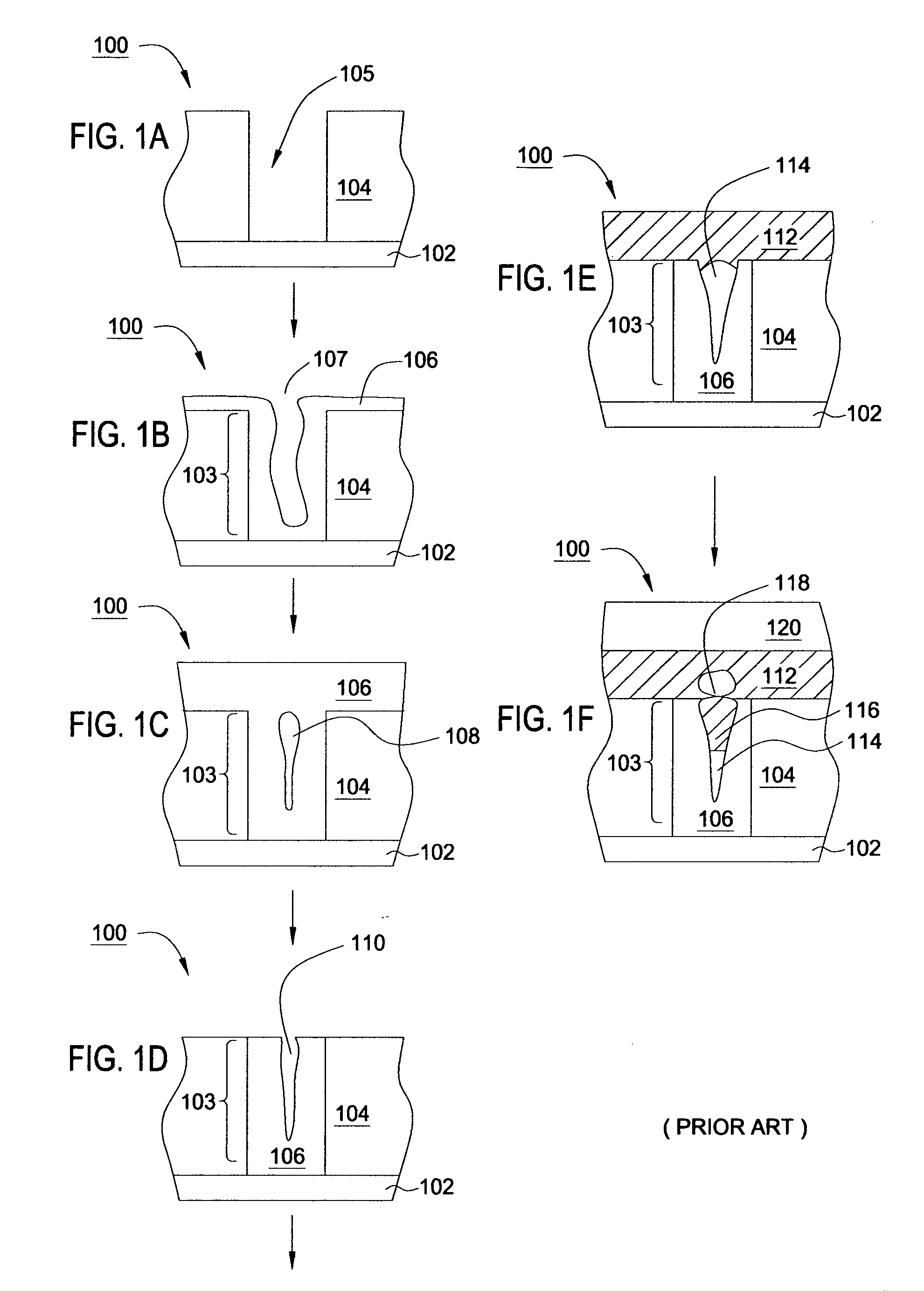

InactiveUS6140234AShorten the timeIncrease productionSolid-state devicesSemiconductor/solid-state device manufacturingResistSemiconductor structure

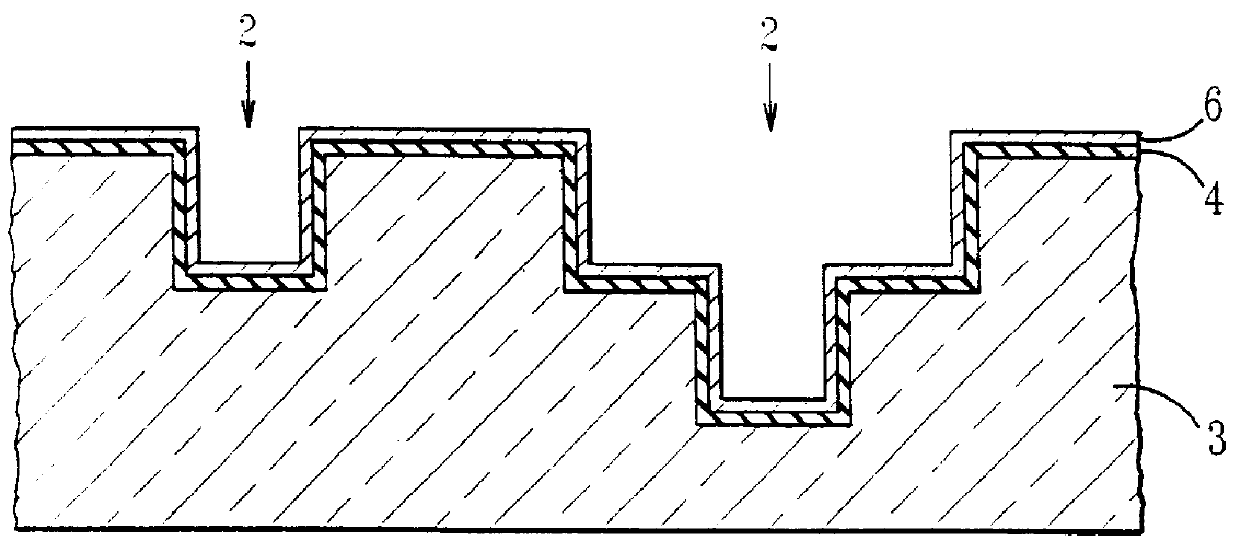

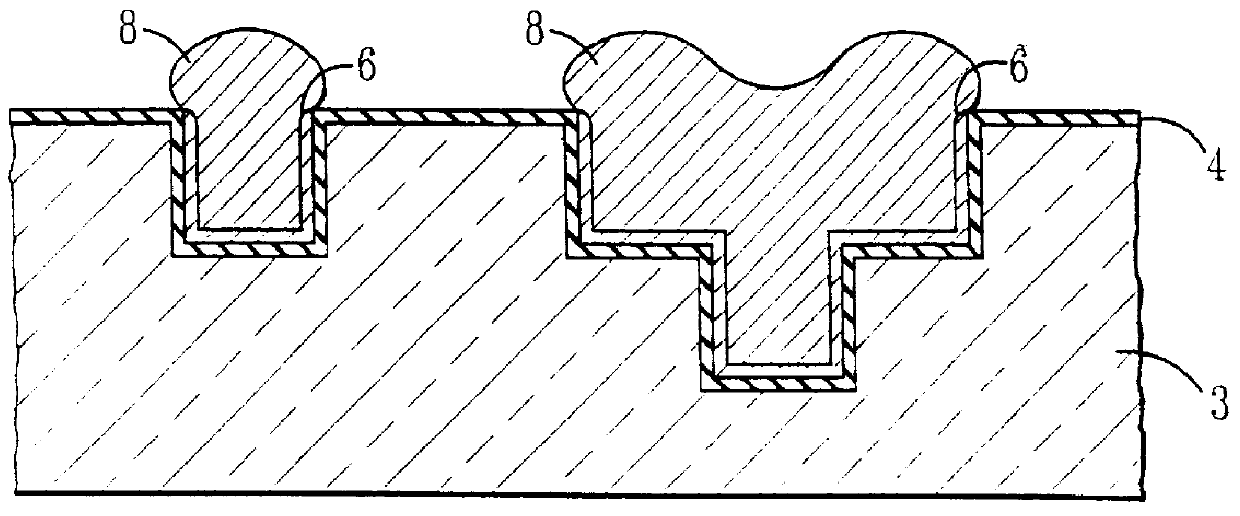

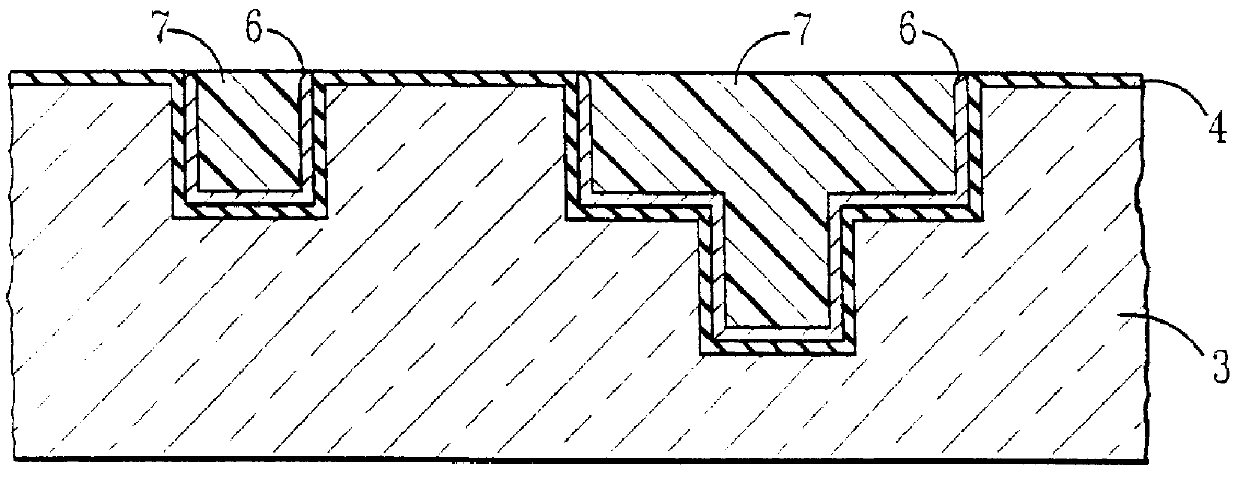

Recesses in a semiconductor structure are selectively plated by providing electrical insulating layer over the semiconductor substrate and in the recesses followed by forming a conductive barrier over the insulating layer; providing a plating seed layer over the barrier layer; depositing and patterning a photoresist layer over the plating seed layer; planarizing the insulated horizontal portions by removing the horizontal portions of the seed layer between the recesses; removing the photoresist remaining in the recesses; and then electroplating the patterned seed layer with a conductive metal using the barrier layer to carry the current during the electroplating to thereby only plate on the seed layer. In an alternative process, a barrier film is deposited over recesses in an insulator. Then, relatively thick resists are lithographically defined on the field regions, on top of the barrier film over the recesses. A plating base or seedlayer is deposited, so as to be continuous on the horizontal regions of the recesses in the insulator, but discontinuous on their surround wall. The recesses are then plated using the barrier film without seedlayers at the periphery of the substrate wafers for electrical contact. After electroplating, the resist is removed by lift-off process and exposed barrier film is etched by RIE method or by CMP. Also provided is a semiconductor structure obtained by the above processes.

Owner:GLOBALFOUNDRIES INC

Method of manufacturing a semiconductor package

InactiveUS7185426B1Printed circuit assemblingSemiconductor/solid-state device detailsElectrical conductorSemiconductor package

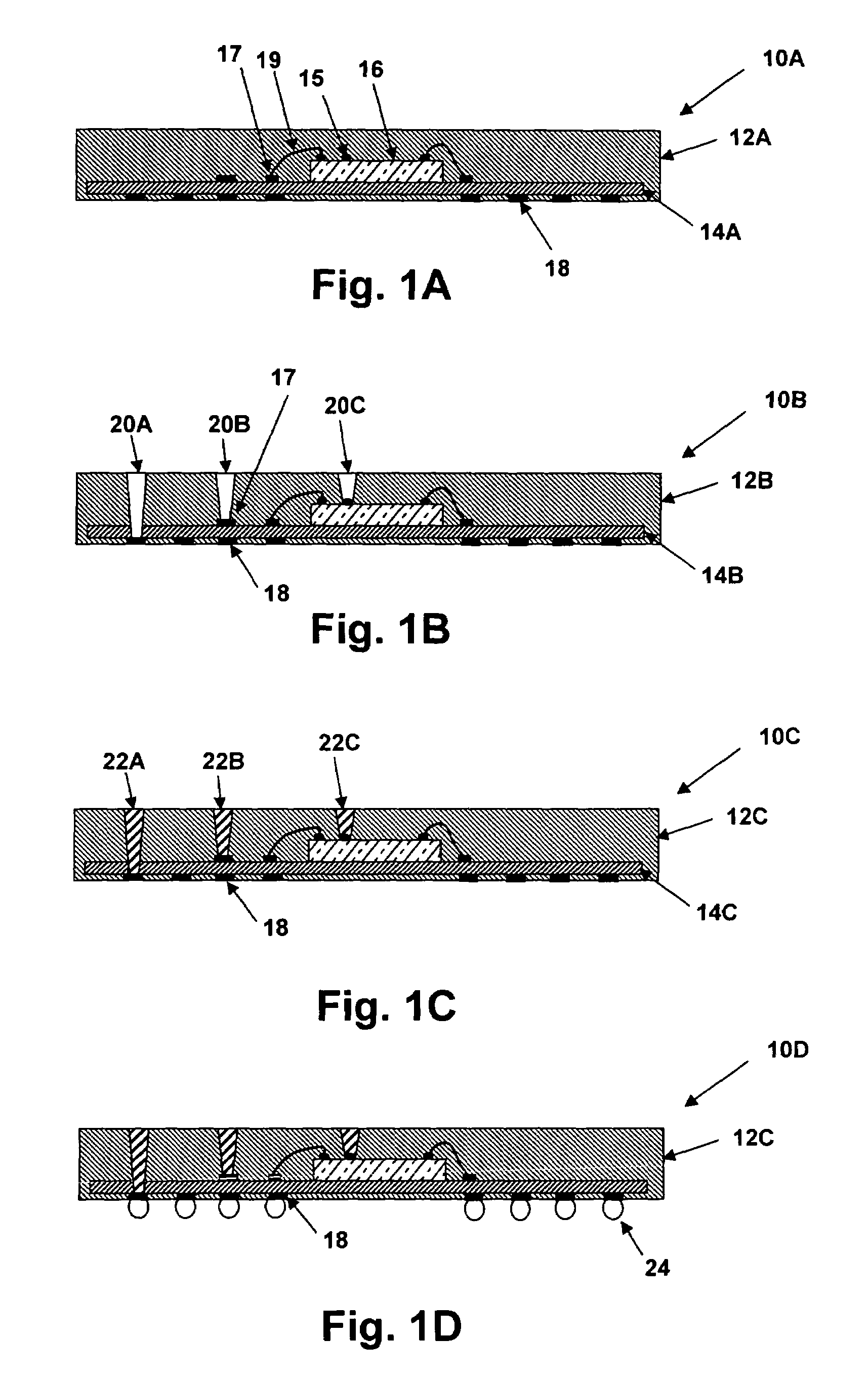

A semiconductor package including top-surface terminals for mounting another semiconductor package provides a three-dimensional circuit configuration that can provide removable connection of existing grid-array packages having a standard design. A semiconductor die is mounted on an electrically connected to a circuit substrate having terminals disposed on a bottom side for connection to an external system. The die and substrate are encapsulated and vias are laser-ablated or otherwise formed through the encapsulation to terminals on the top surface of the substrate that provide a grid array mounting lands to which another grid array semiconductor package may be mounted. The bottom side of the vias may terminate and electrically connect to terminals on the substrate, terminals on the bottom of the semiconductor package (through terminals) or terminals on the top of the semiconductor die. The vias may be plated, paste-filled, filled with a low melting point alloy and may have a conical profile for improved plating performance.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

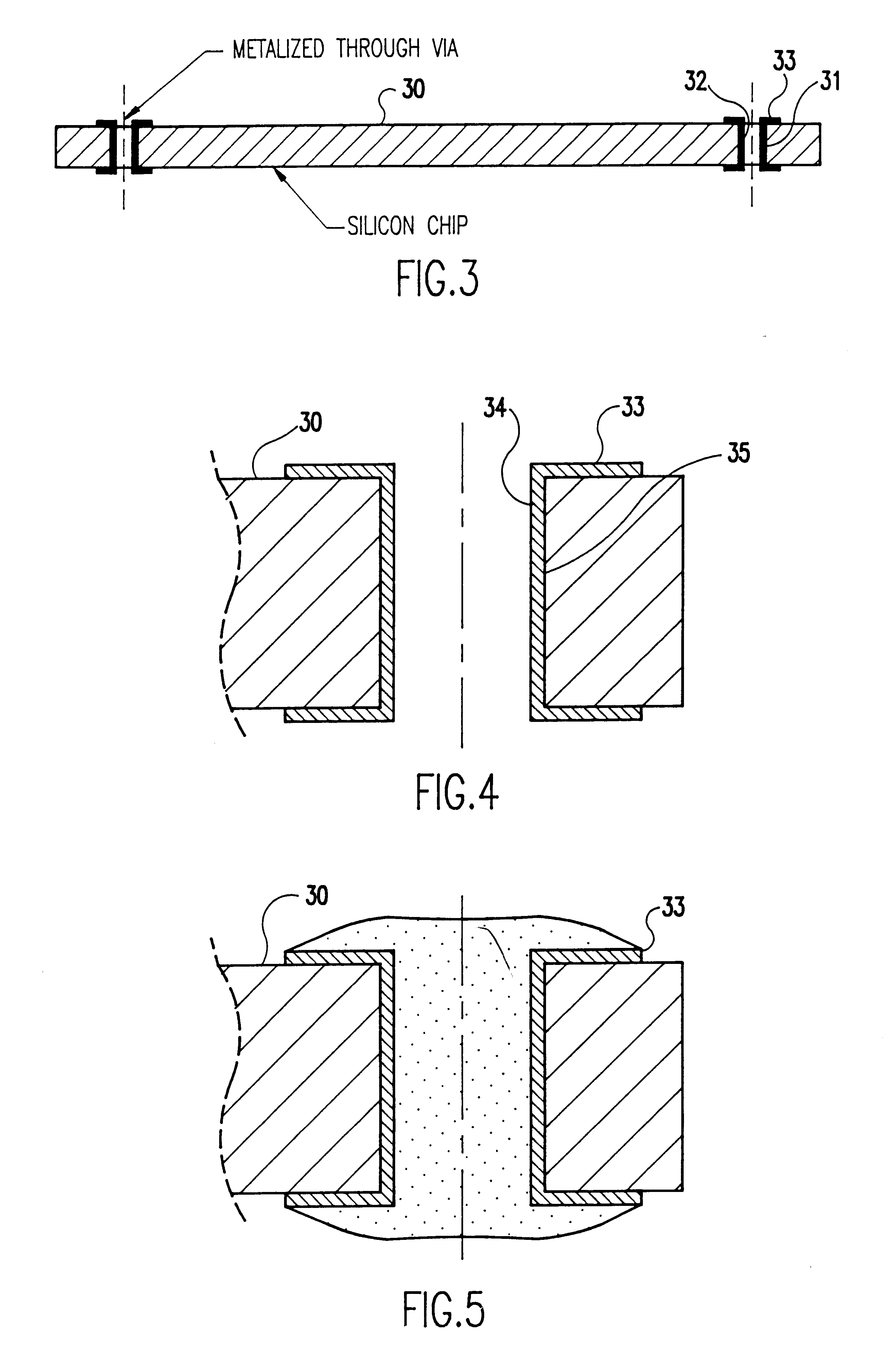

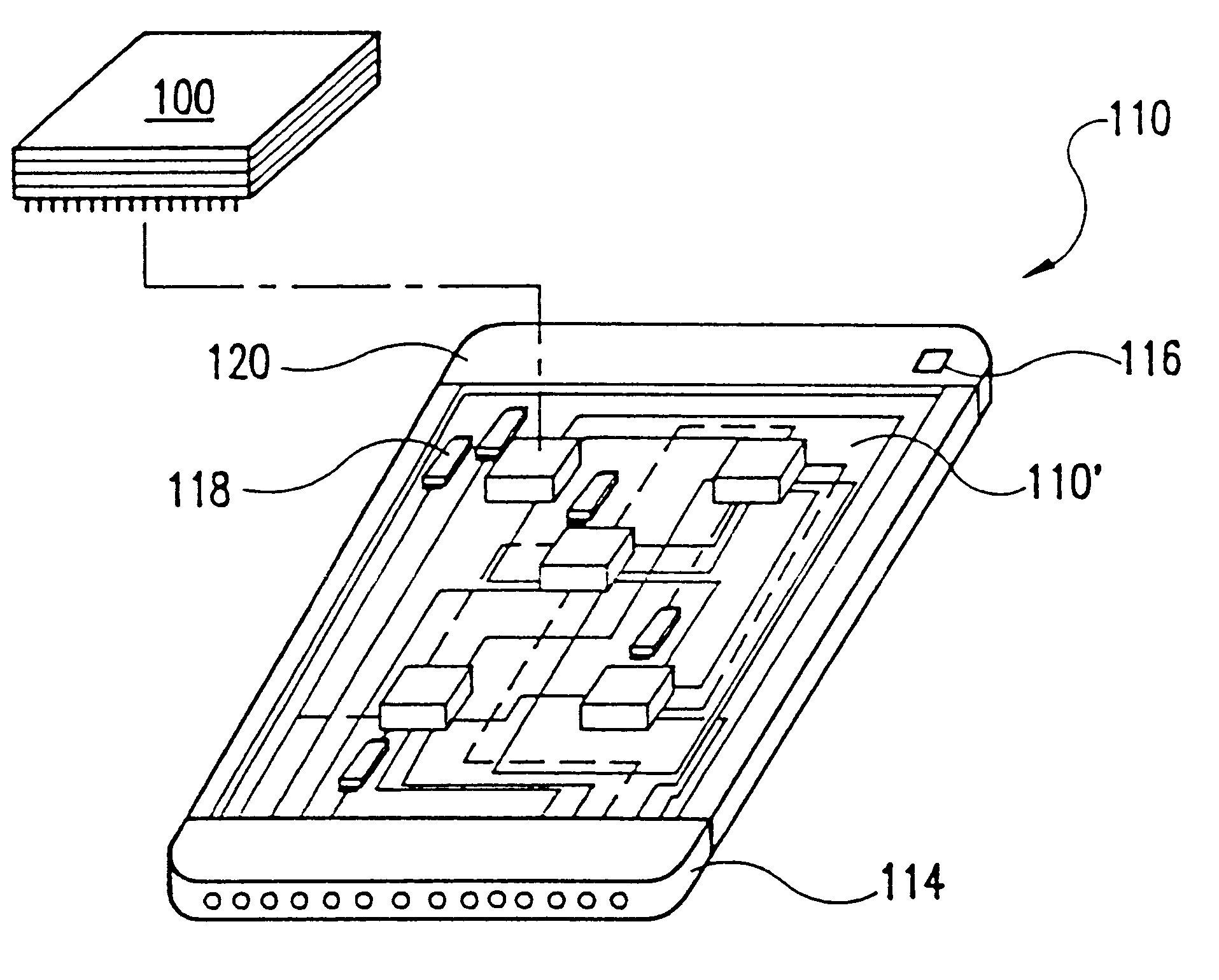

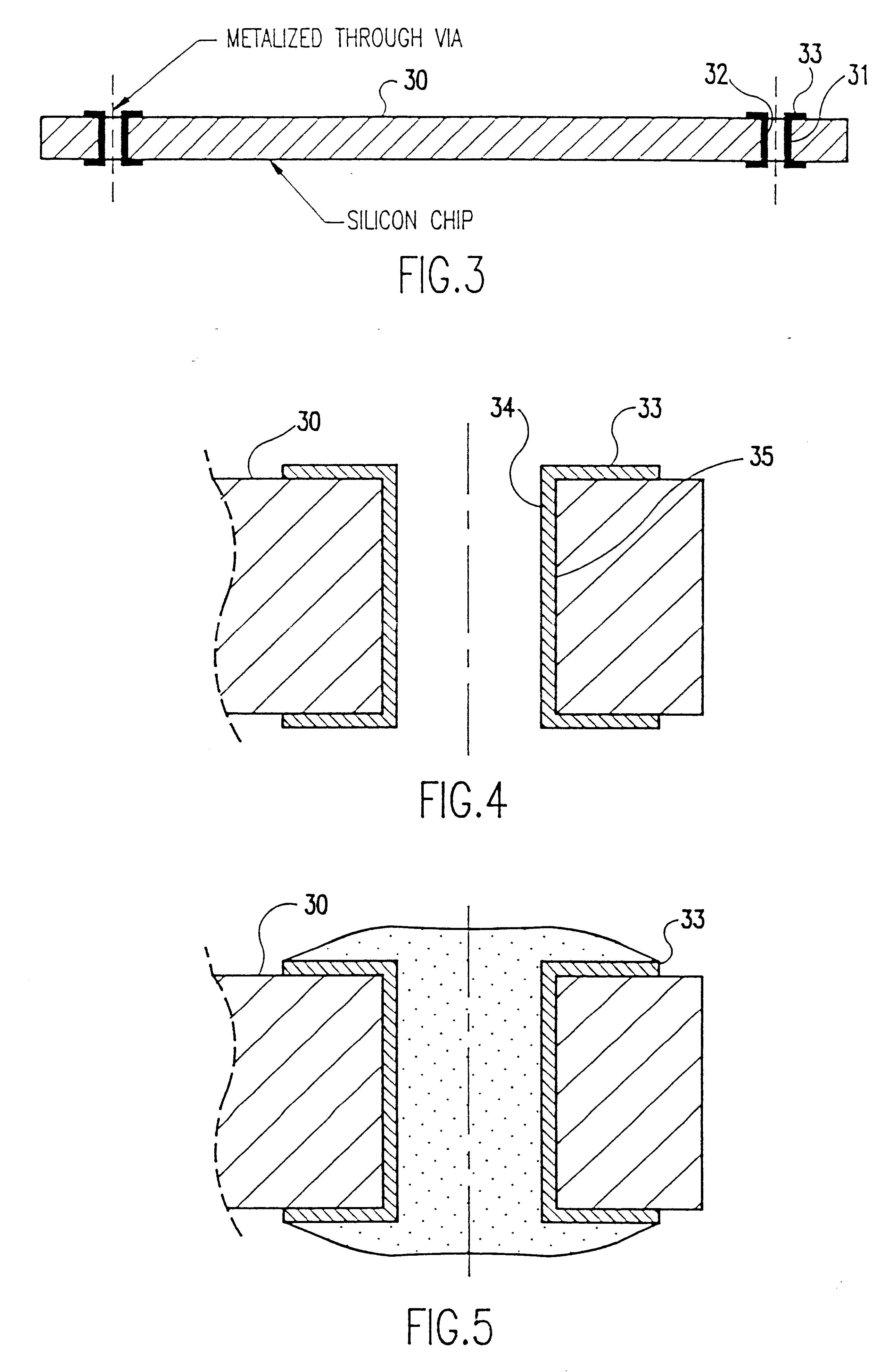

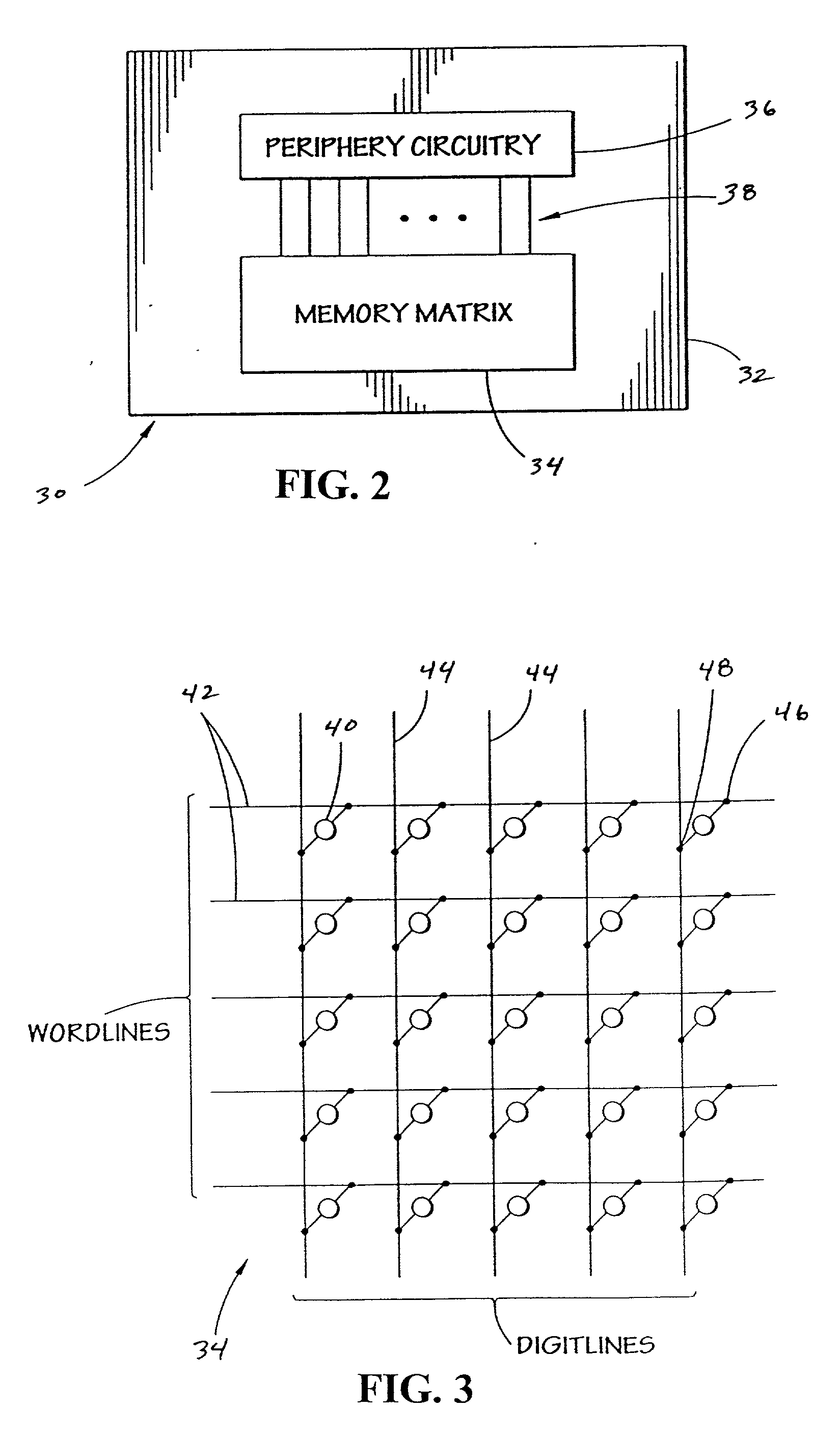

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6236115B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

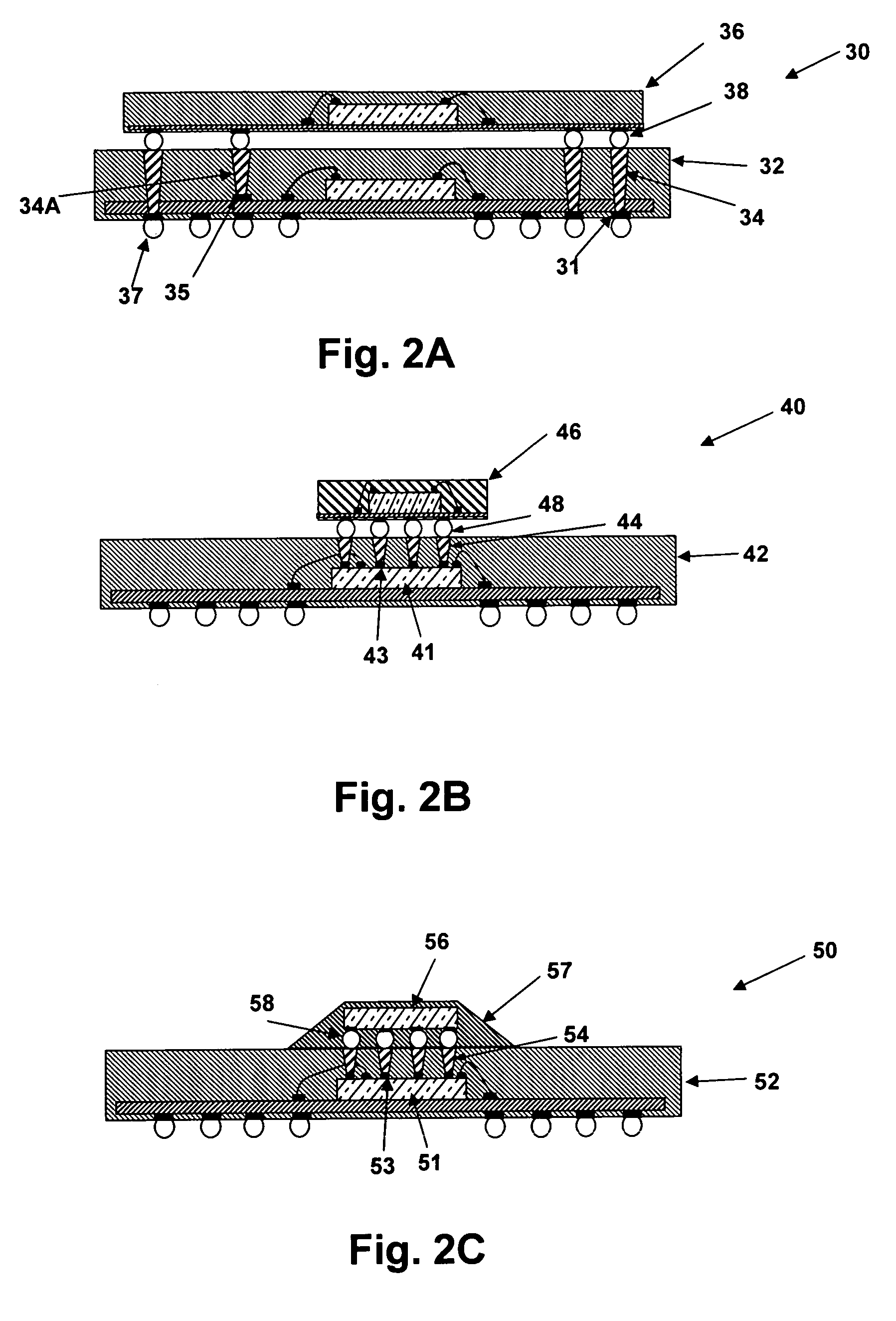

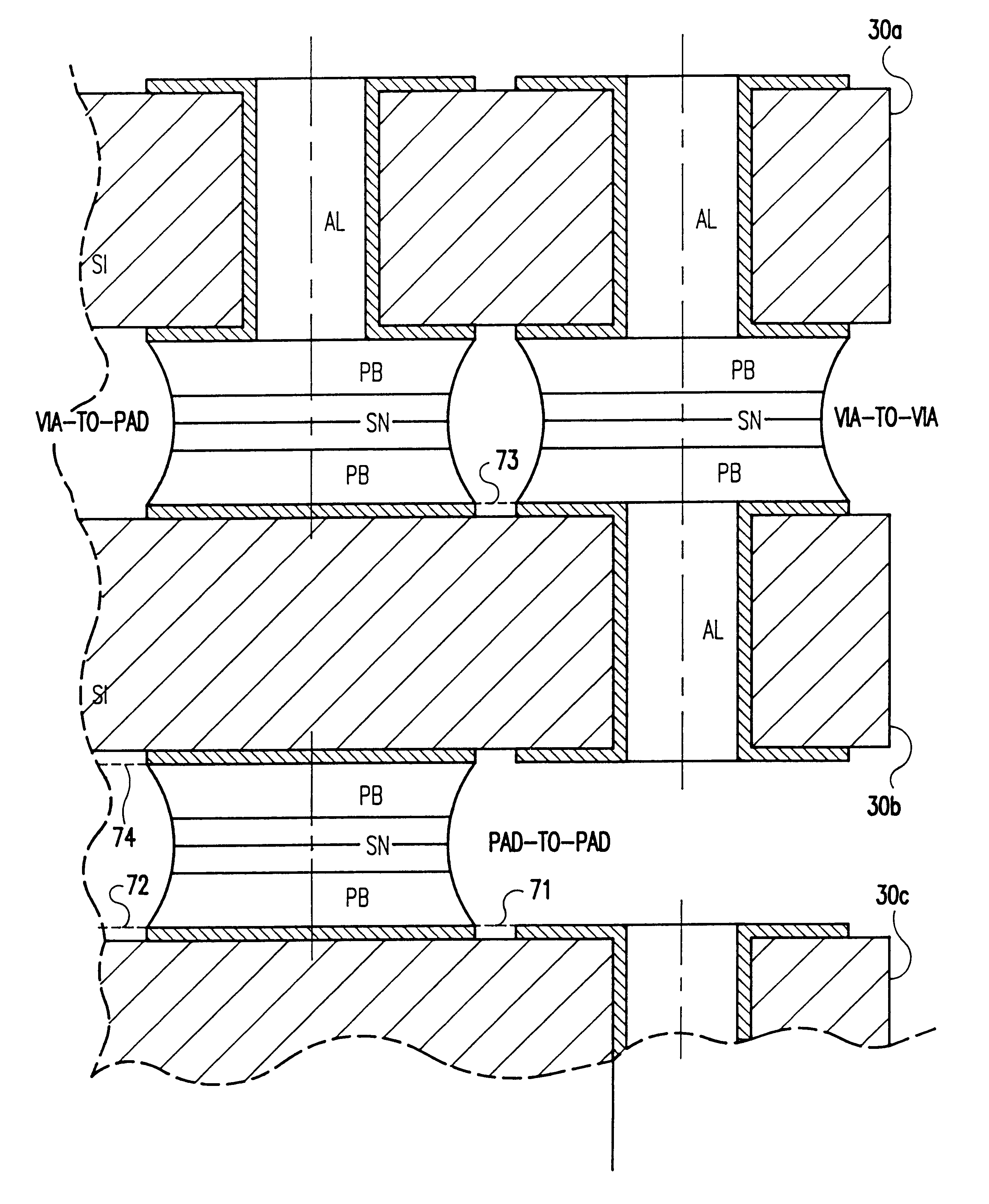

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:INT BUSINESS MASCH CORP

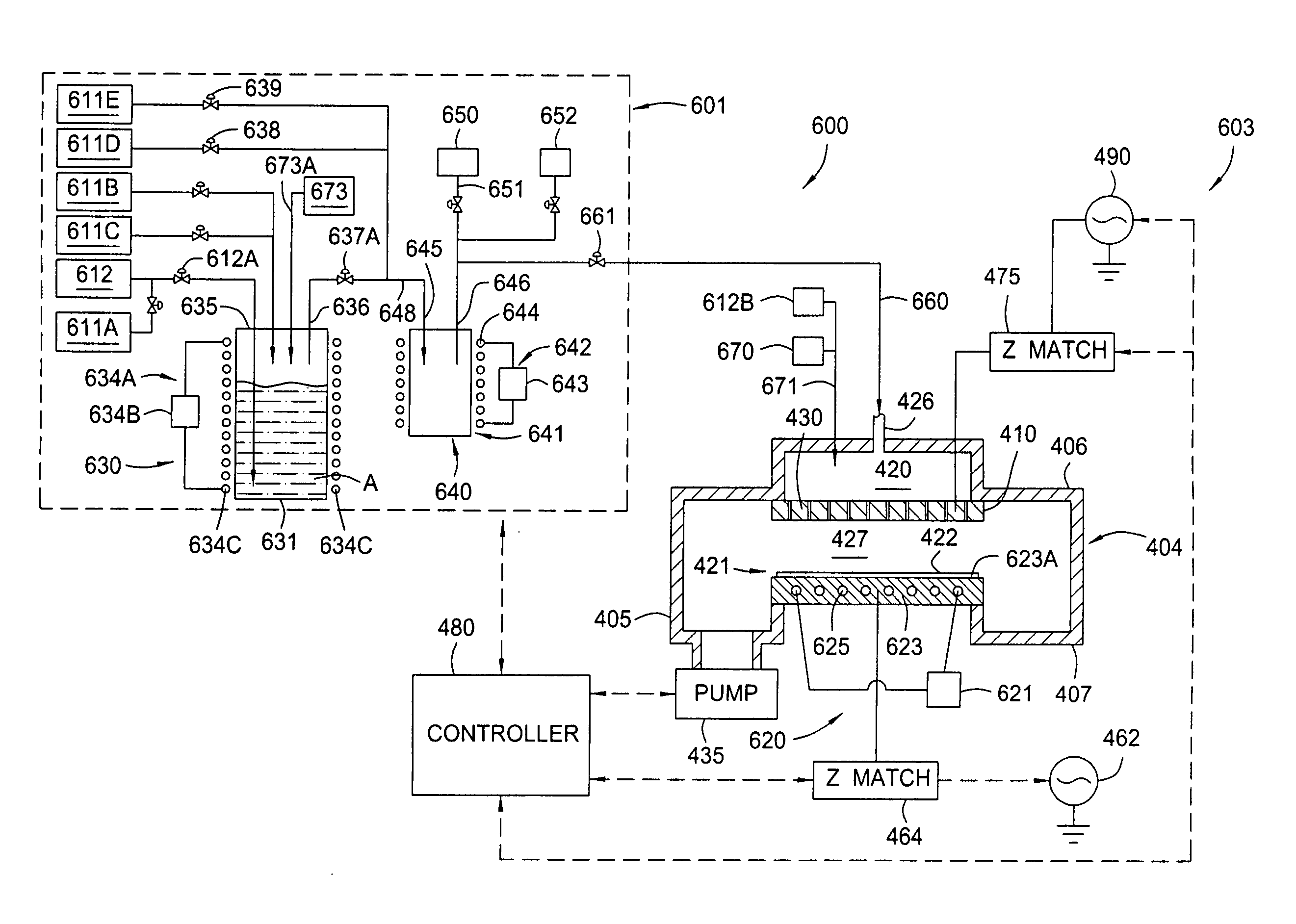

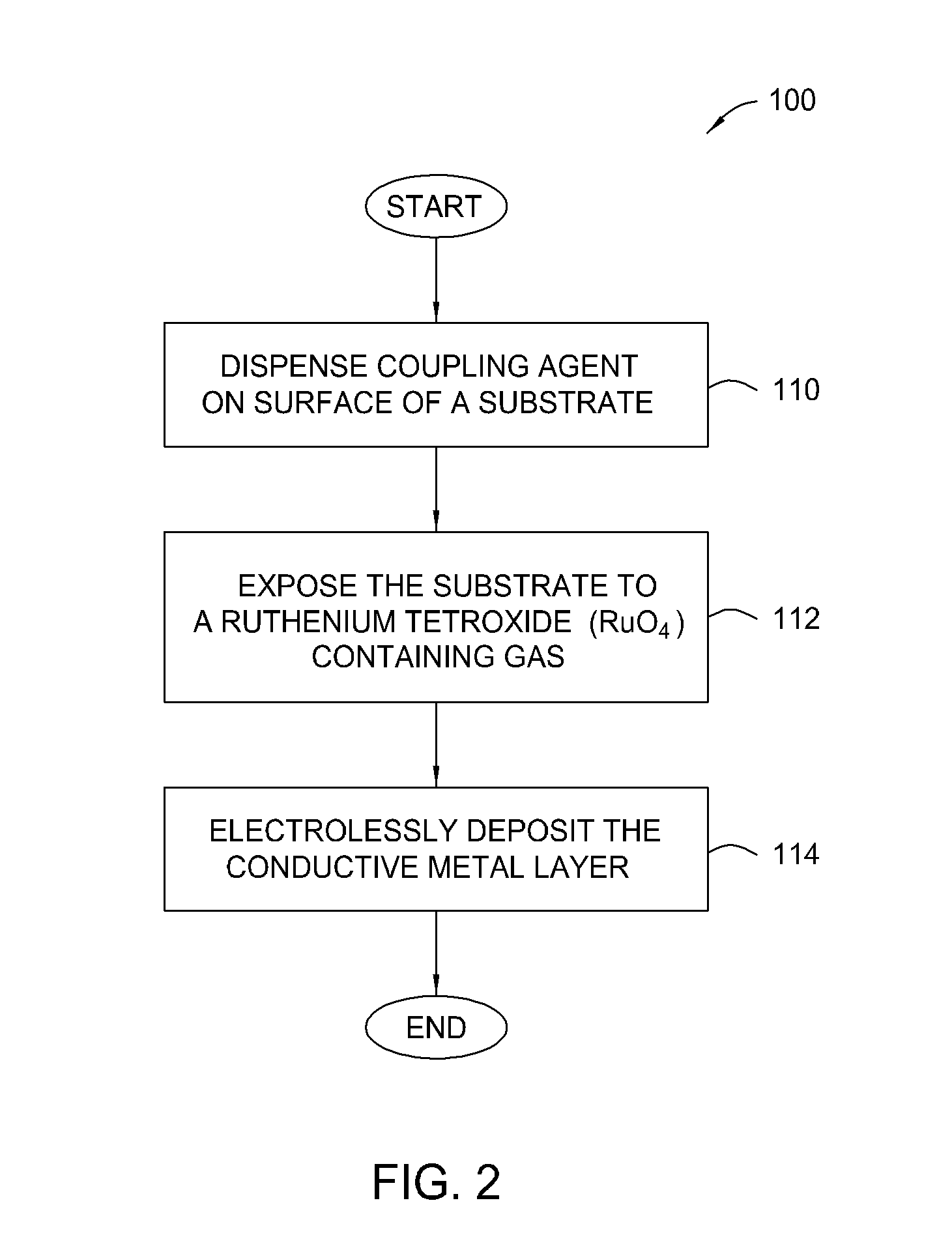

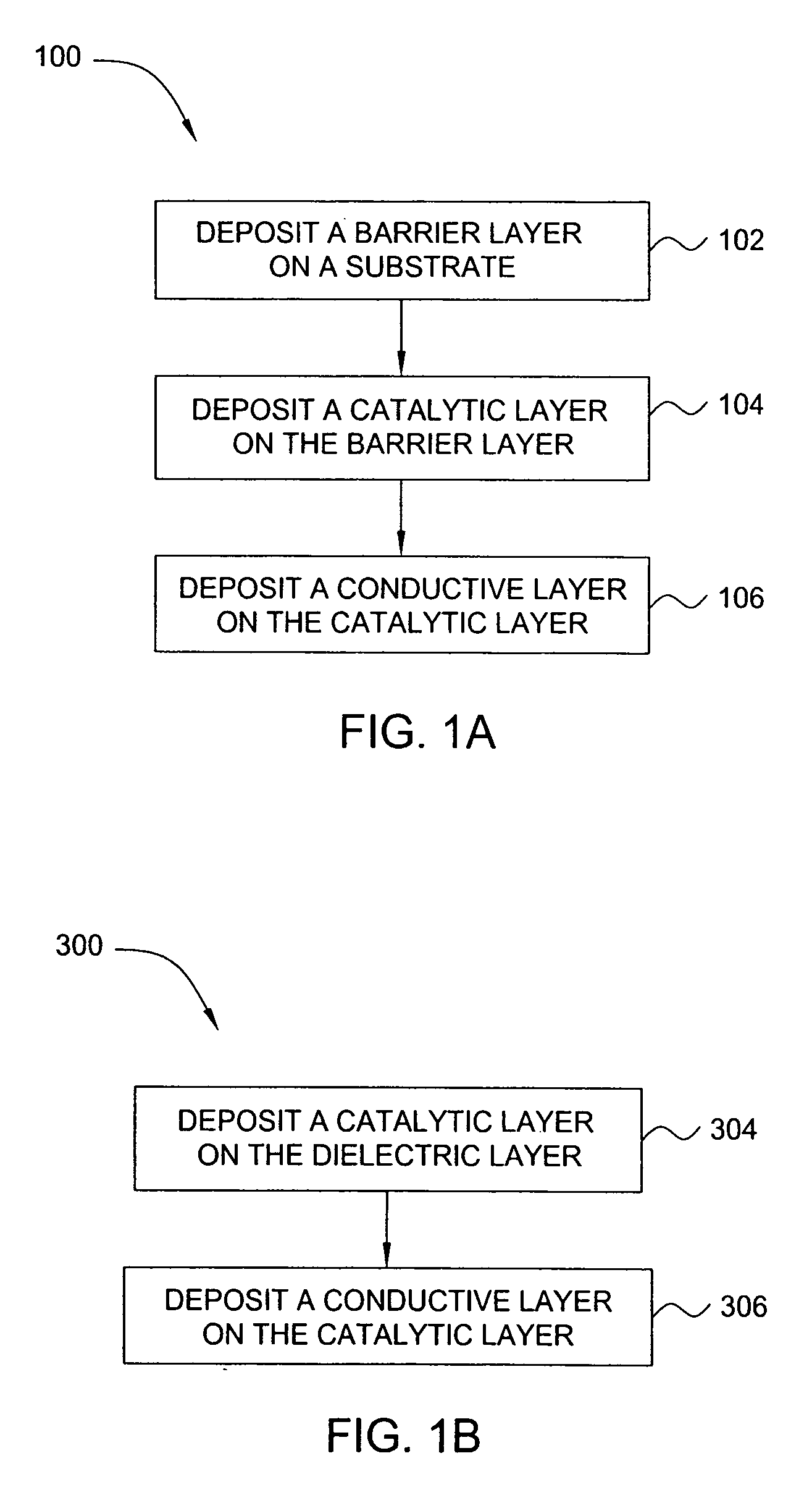

Ruthenium containing layer deposition method

ActiveUS20060165892A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingTemperature controlSource material

An exemplary apparatus and method of forming a ruthenium tetroxide containing gas to form a ruthenium containing layer on a surface of a substrate is described herein. The method and apparatus described herein may be especially useful for fabricating electronic devices that are formed on a surface of the substrate or wafer. Generally, the method includes exposing a surface of a substrate to a ruthenium tetroxide vapor to form a catalytic layer on the surface of a substrate and then filling the device structures by an electroless, electroplating, physical vapor deposition (PVD), chemical vapor deposition (CVD), plasma enhanced CVD (PECVD), atomic layer deposition (ALD) or plasma enhanced ALD (PE-ALD) processes. In one embodiment, the ruthenium containing layer is formed on a surface of a substrate by creating ruthenium tetroxide in an external vessel and then delivering the generated ruthenium tetroxide gas to a surface of a temperature controlled substrate positioned in a processing chamber. In one embodiment, a ruthenium tetroxide containing solvent formation process is used to form ruthenium tetroxide using a ruthenium tetroxide containing source material. In one embodiment, of a ruthenium containing layer is formed on a surface of a substrate, using the ruthenium tetroxide containing solvent. In another embodiment, the solvent is separated from the ruthenium tetroxide containing solvent mixture and the remaining ruthenium tetroxide is used to form a ruthenium containing layer on the surface of a substrate.

Owner:APPLIED MATERIALS INC

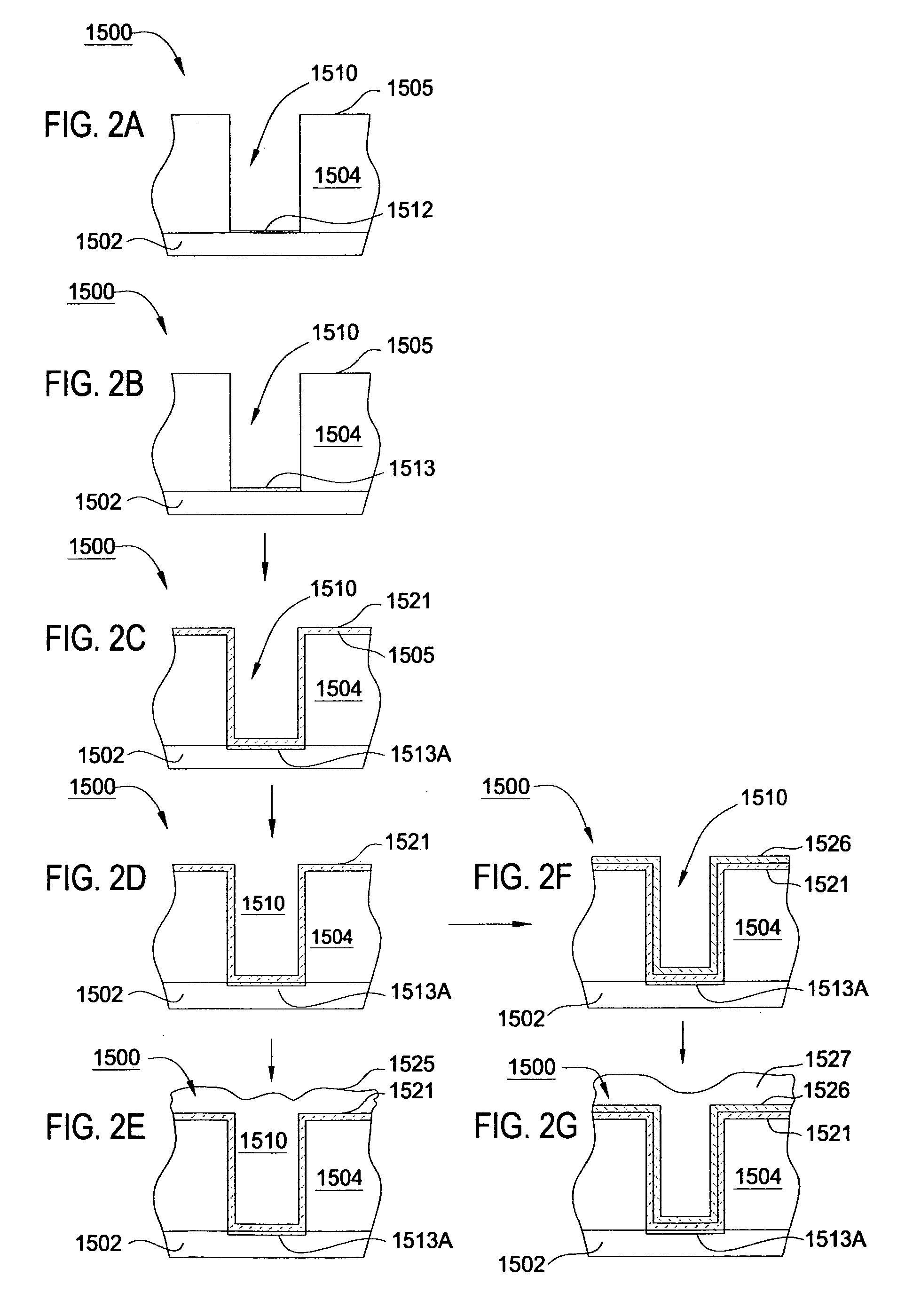

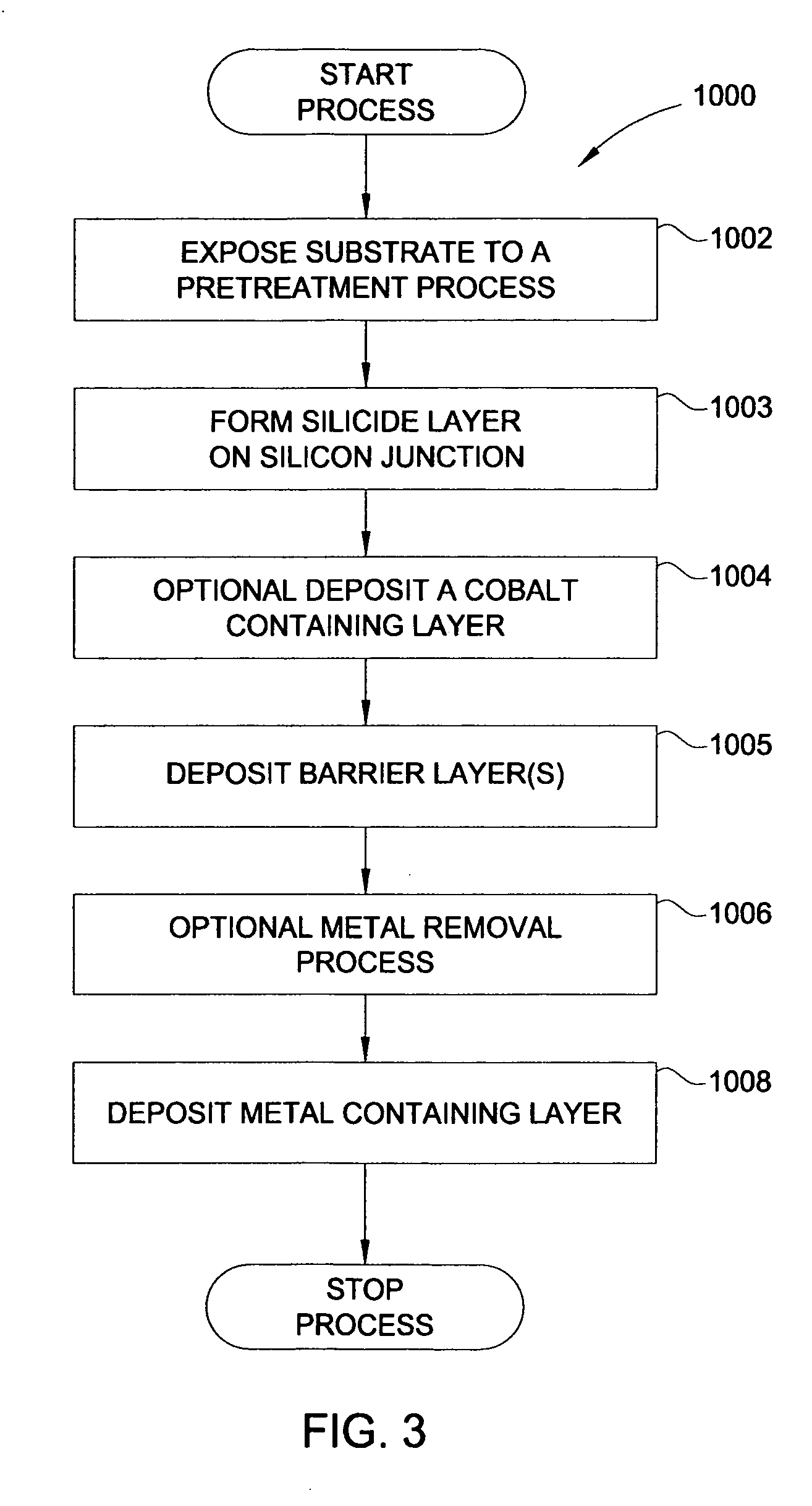

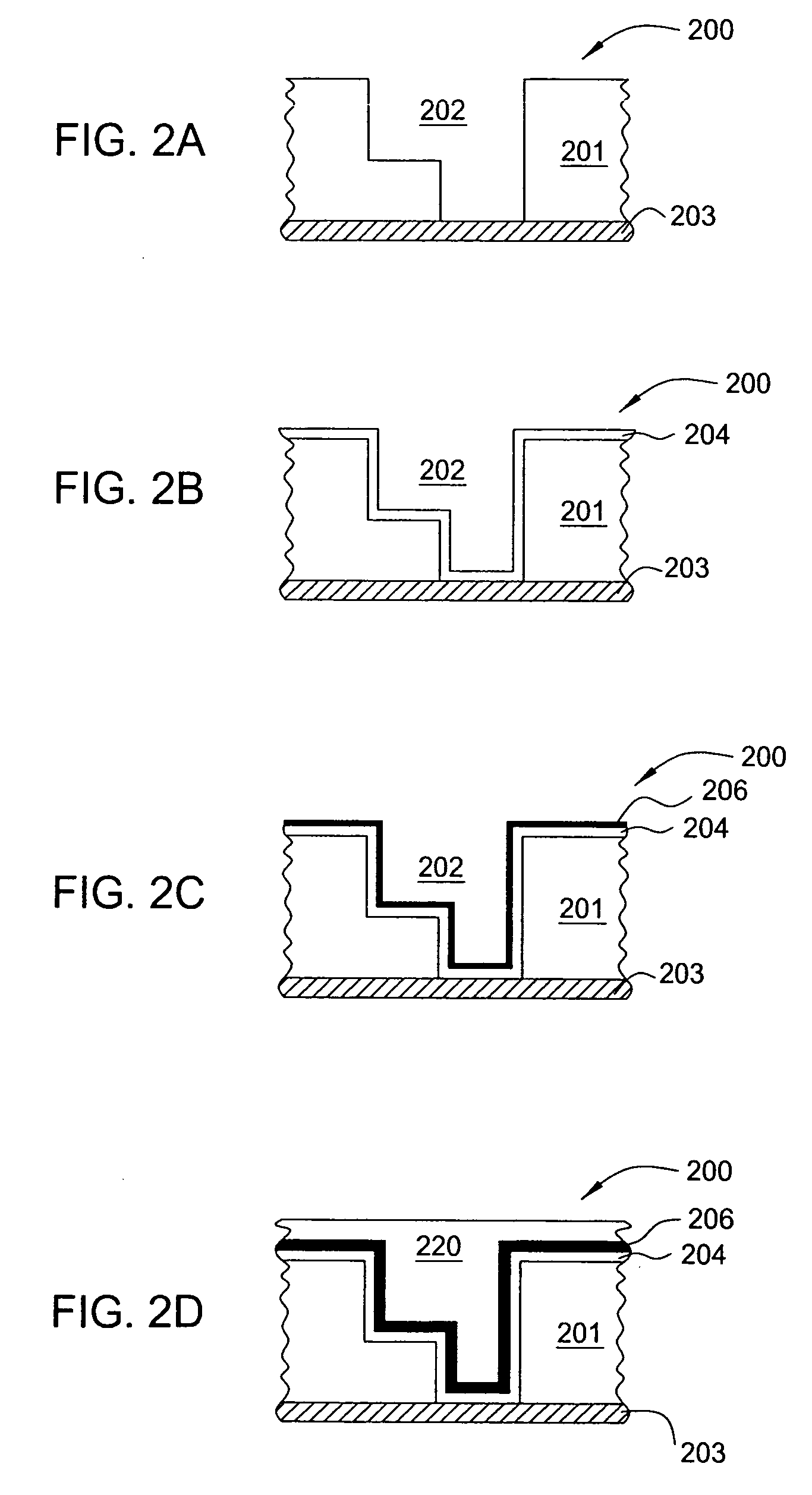

Contact metallization scheme using a barrier layer over a silicide layer

ActiveUS20060251800A1Material nanotechnologySemiconductor/solid-state device detailsDevice materialElectroless deposition

Embodiments of the invention generally provide methods of filling contact level features formed in a semiconductor device by depositing a barrier layer over the contact feature and then filing the layer using an PVD, CVD, ALD, electrochemical plating process (ECP) and / or electroless deposition processes. In one embodiment, the barrier layer has a catalytically active surface that will allow the electroless deposition of a metal on the barrier layer. In one aspect, the electrolessly deposited metal is copper or a copper alloy. In one aspect, the contact level feature is filled with a copper alloy by use of an electroless deposition process. In another aspect, a copper alloy is used to from a thin conductive copper layer that is used to subsequently fill features with a copper containing material by use of an ECP, PVD, CVD, and / or ALD deposition process. In one embodiment, a portion of the barrier layer is purposely allowed to react with traces of residual oxide at the silicon junction of the contact level feature to form a low resistance connection.

Owner:APPLIED MATERIALS INC

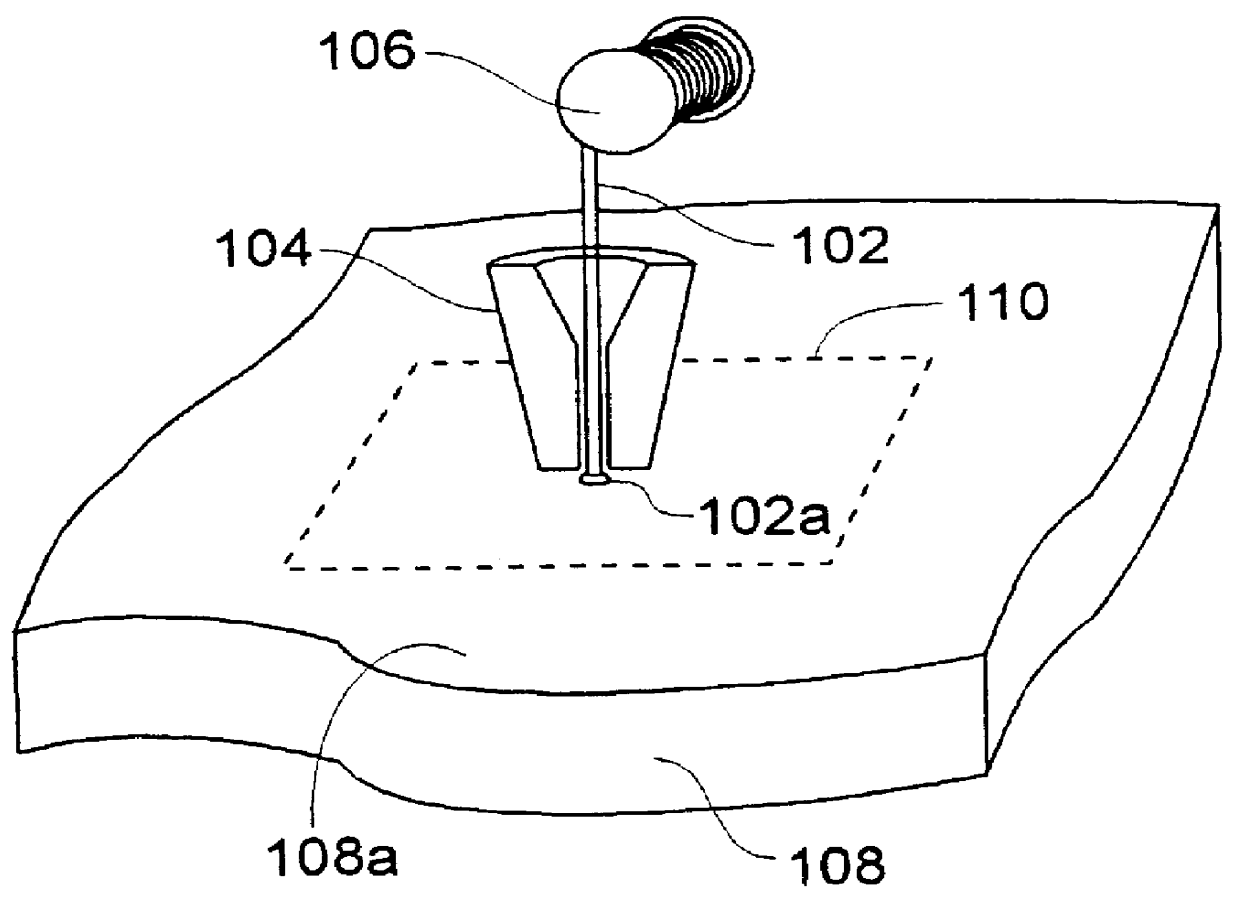

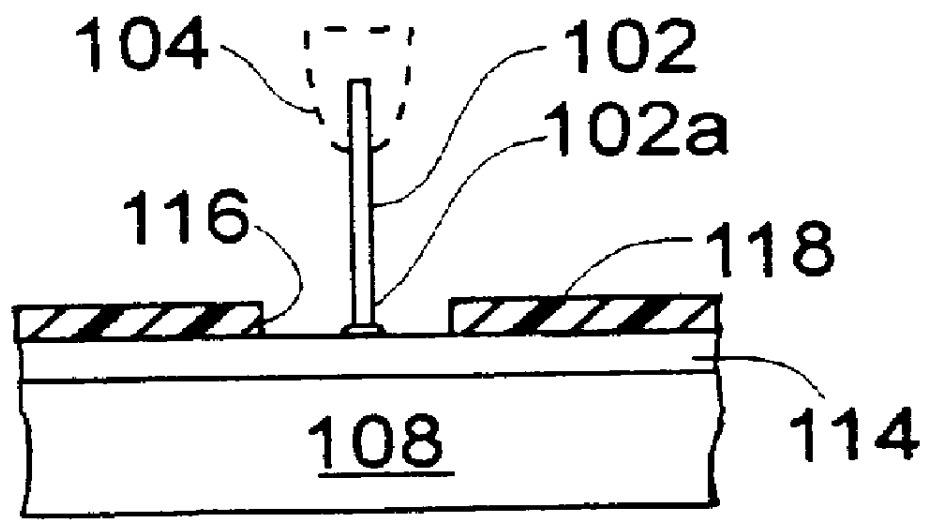

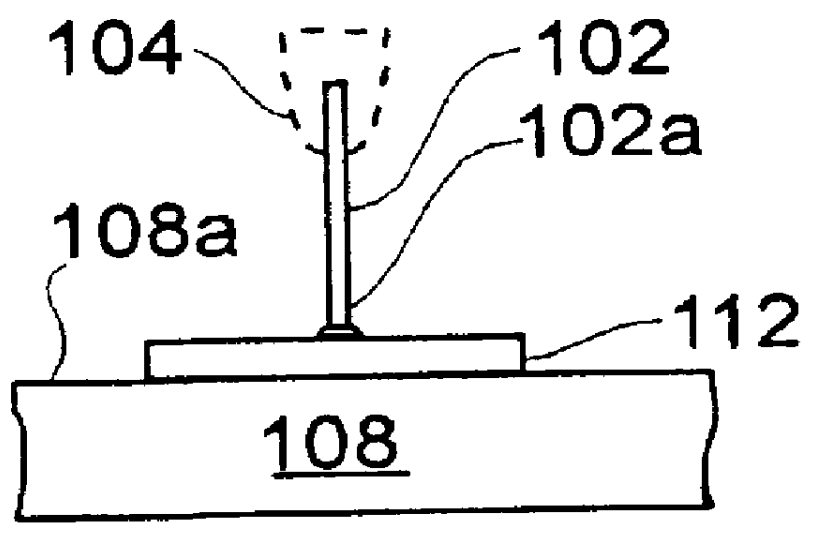

Method of modifying the thickness of a plating on a member by creating a temperature gradient on the member, applications for employing such a method, and structures resulting from such a method

InactiveUS6110823ASimple technologyTrend downSemiconductor/solid-state device testing/measurementFinal product manufactureEngineeringElectronic component

Contact structures exhibiting resilience or compliance for a variety of electronic components are formed by bonding a free end of a wire to a substrate, configuring thw wire into a wire stem having a springable shape, serving thw wire stem, and overcoating the wire stem with at least one layer of a material chosen primarily for its structural (resiliency, compliance) characteristics. A variety of techniques for configuring, serving, and overcoating the wire stem are disclosed. In an exemplary embodiment, a free end of a wire stem is bonded to a contact area on a substrate, the wire stem is configured to ahve a springable shape, the wire stem is served to be free-standing by an electrical discharge, and the free-standing wire stem is overcoating by plating.

Owner:FORMFACTOR INC

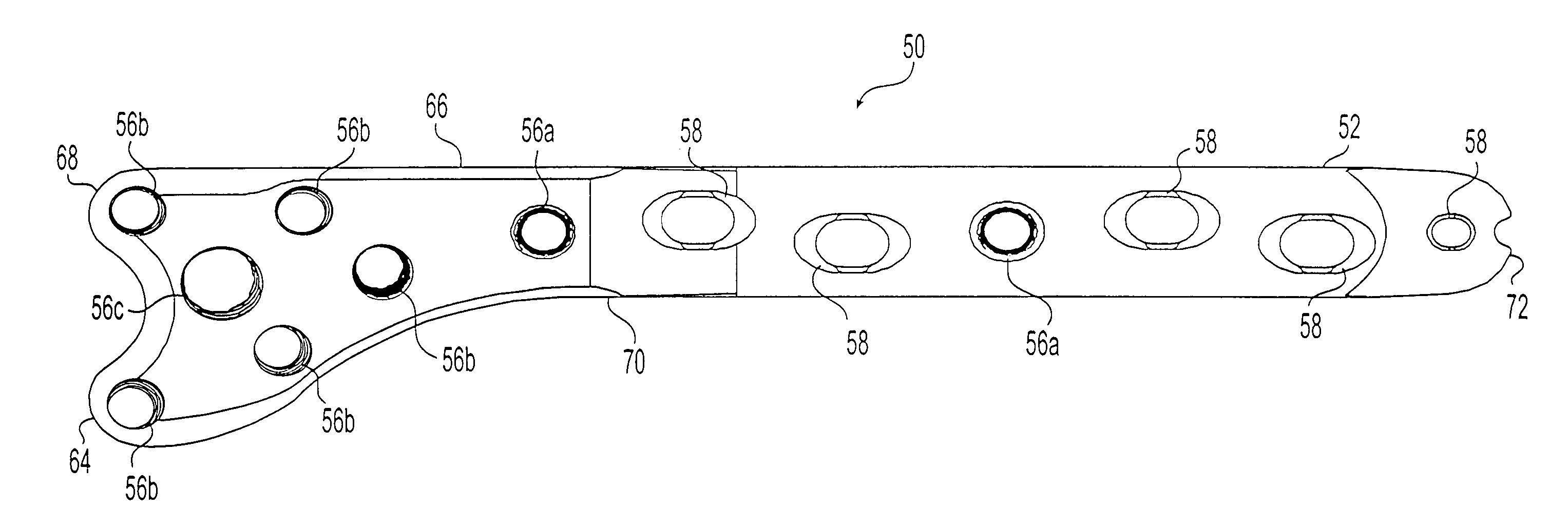

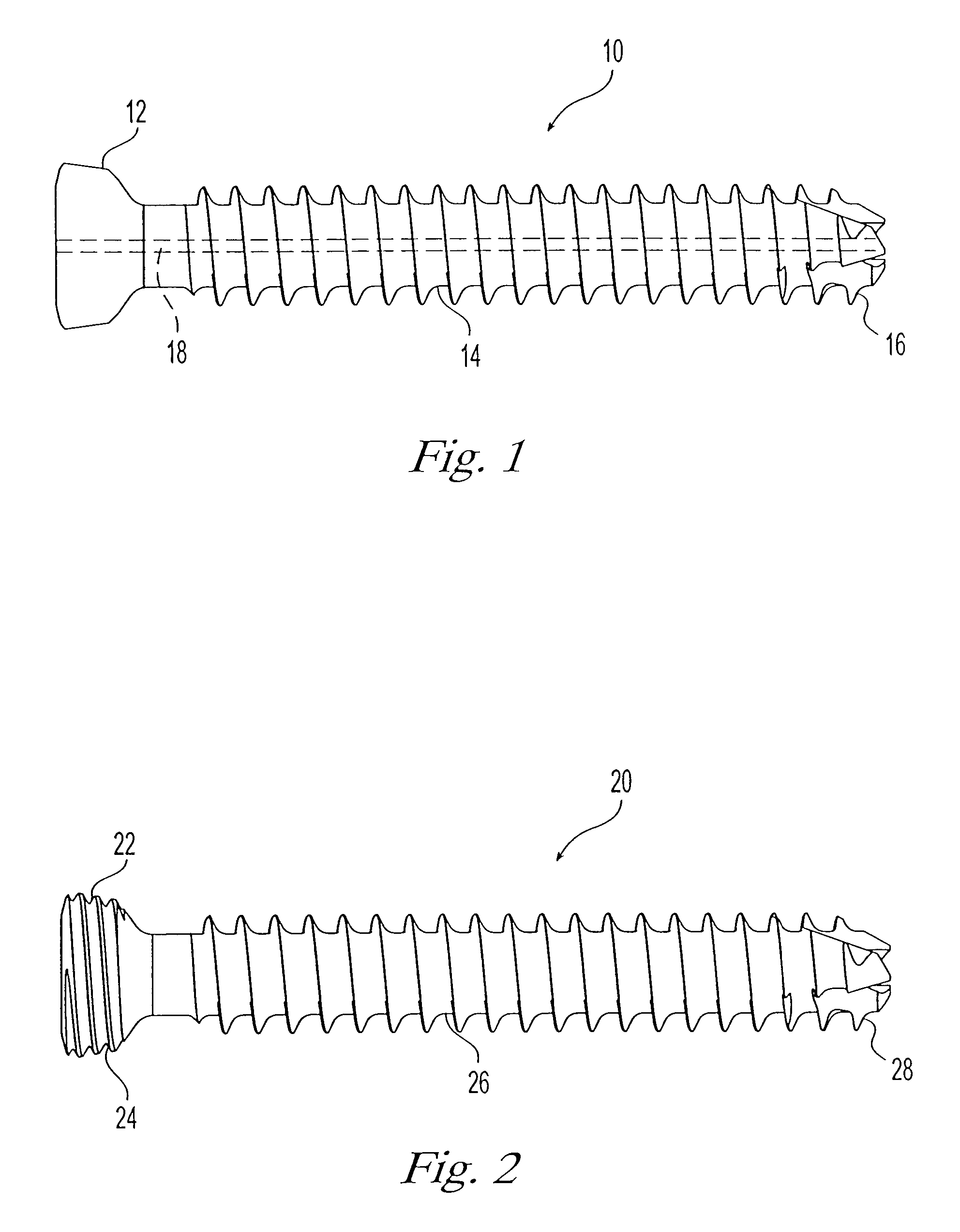

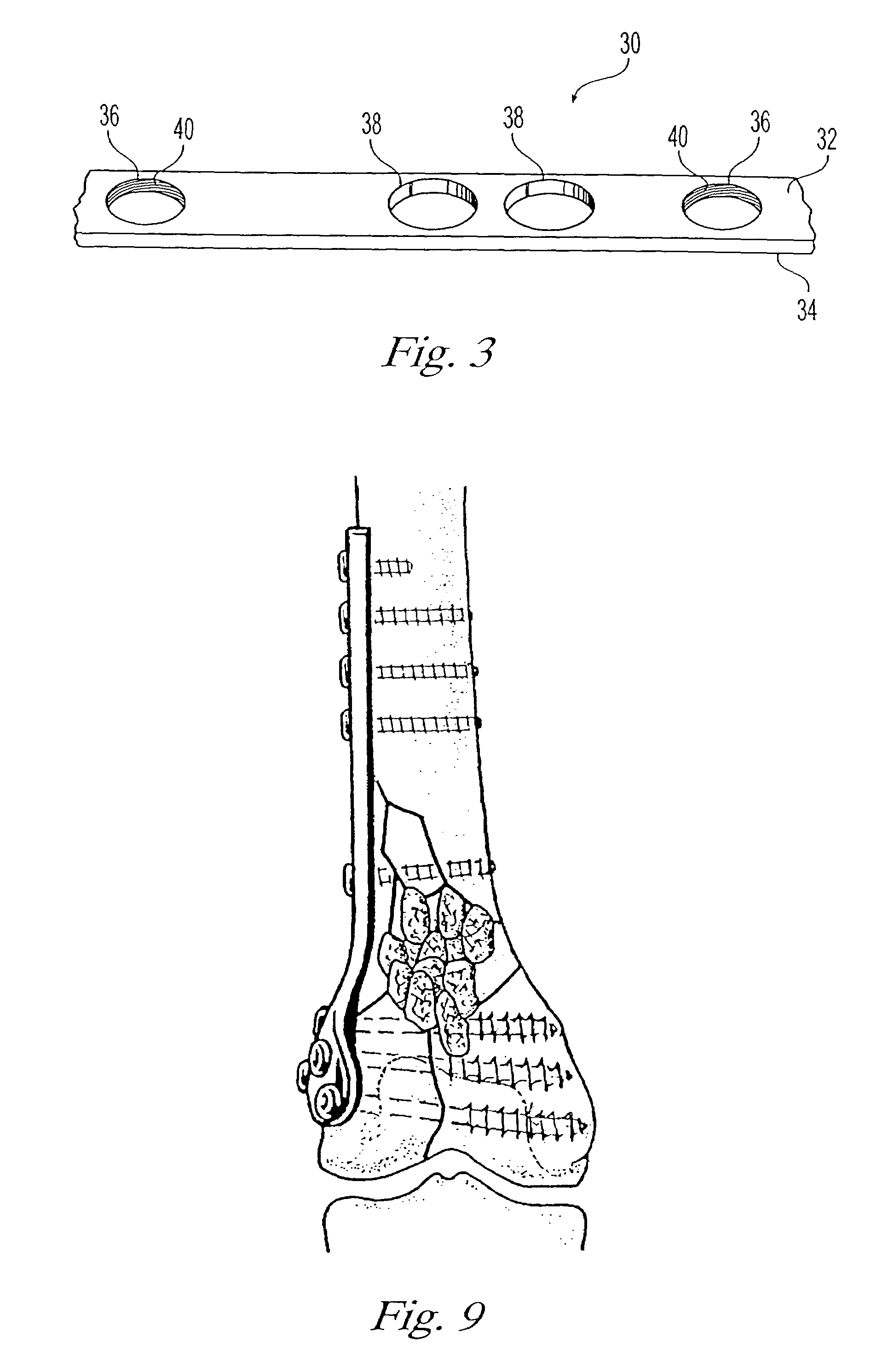

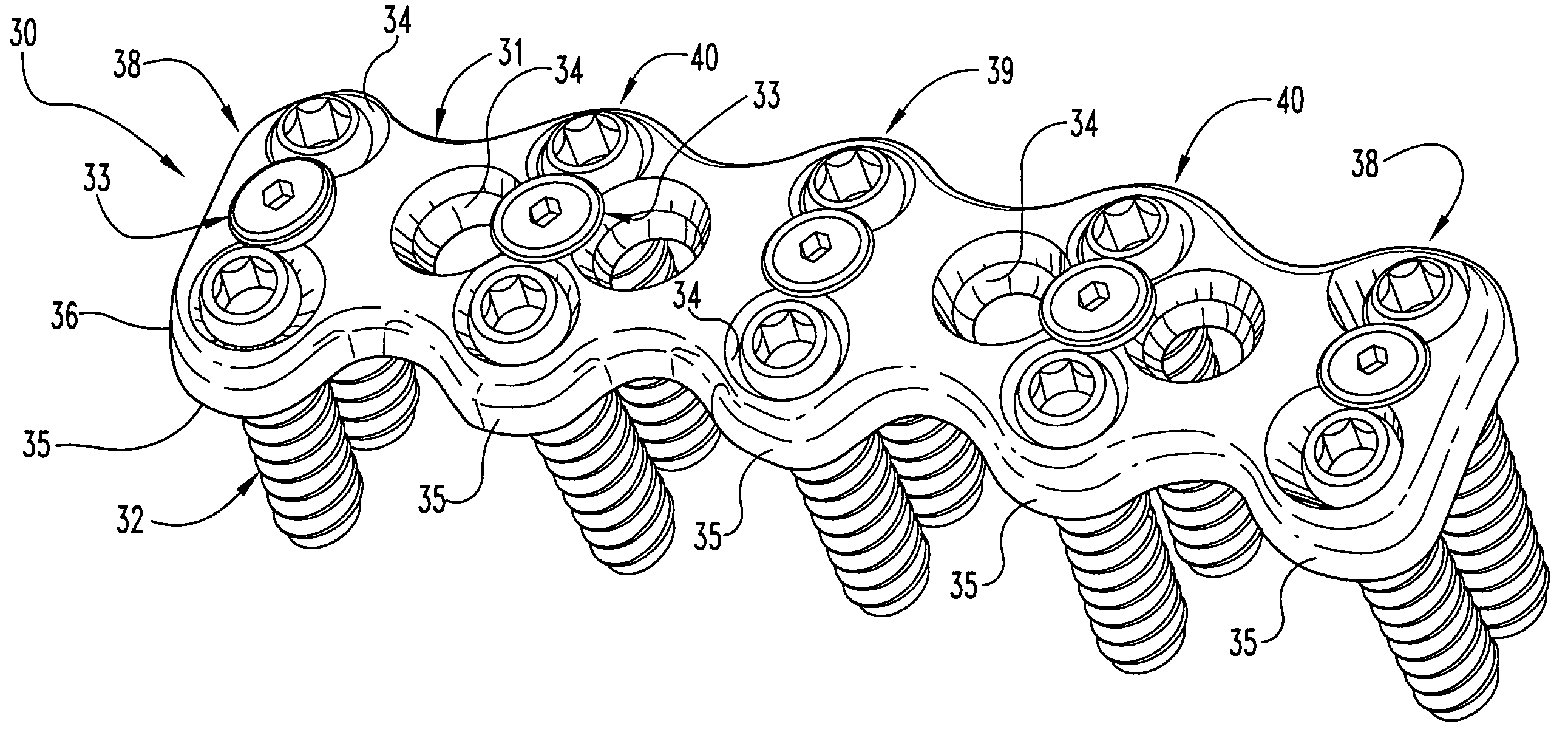

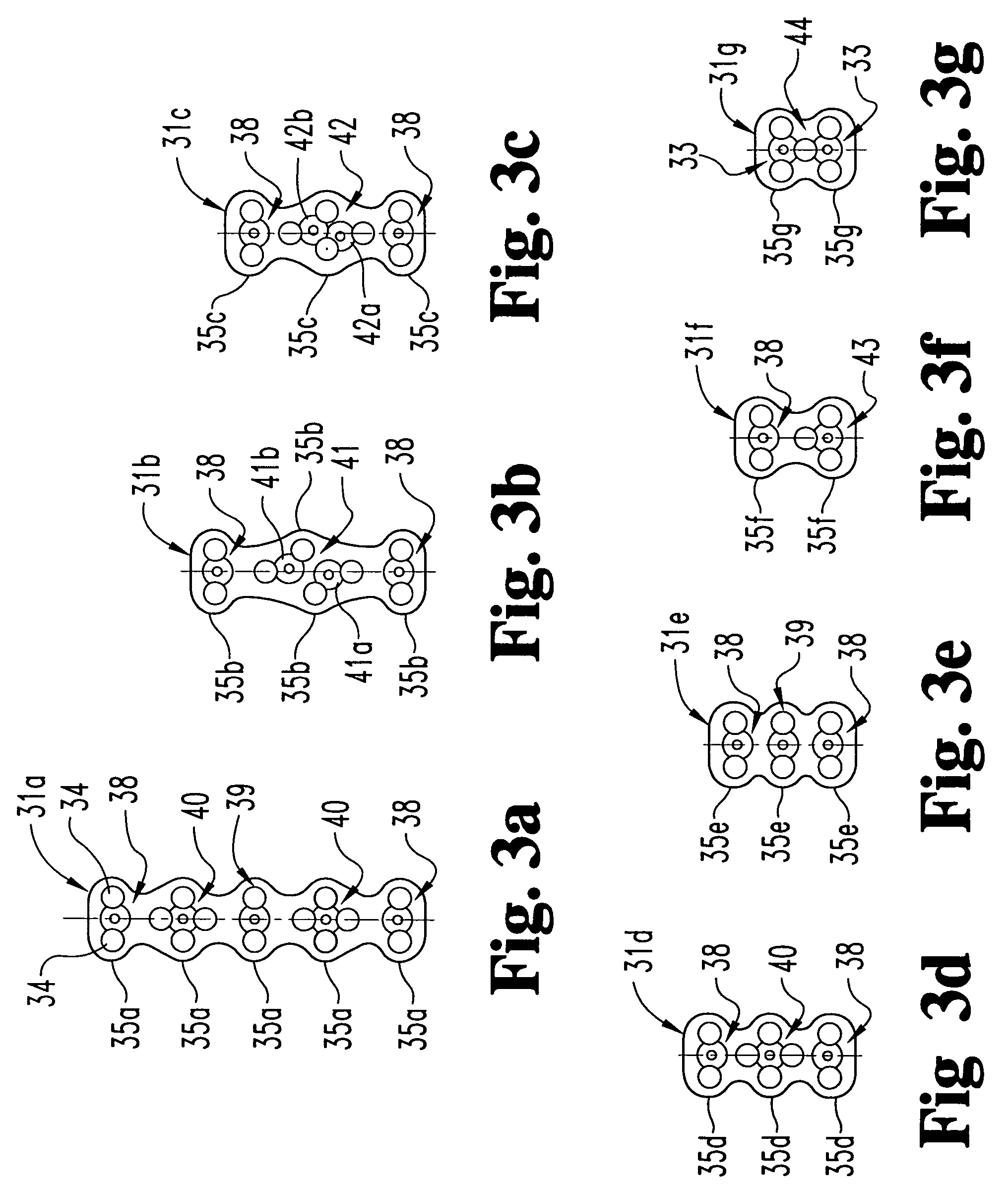

Bone plating system

The present invention relates to a bone plating system and method for fracture fixation of bone. The bone plating system includes a bone plate, at least one locking screw, and at least one non-locking screw. The bone plate has locking holes with threads and non-locking holes. The locking screws have a shaft with a thread for engaging bone and a head with a thread configured and dimensioned to mate with the thread of the locking holes. The non-locking screws have a thread for engaging bone and a non-threaded head. Both the locking and non-locking screws remain seated in their respective holes for substantially as long as the bone plate is implanted. The non-locking screws compress the bone plate against the bone and hold fracture reduction while the locking screws are secured to the plate at a fixed angular relationship. The mixed fixation achieved by this bone plating system and method is particularly useful for treatment of per-articular fractures.

Owner:DEPUY SYNTHES PROD INC

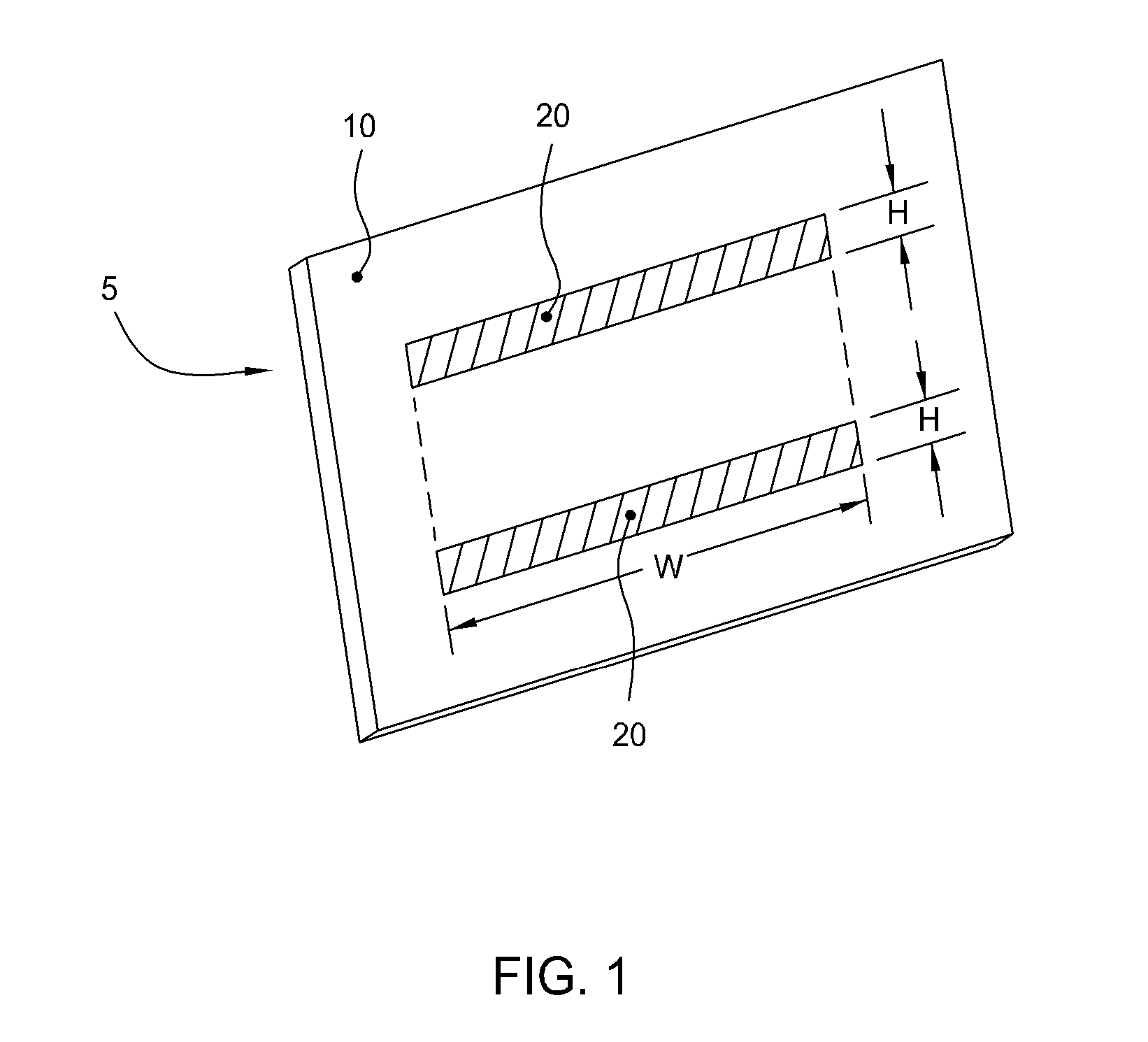

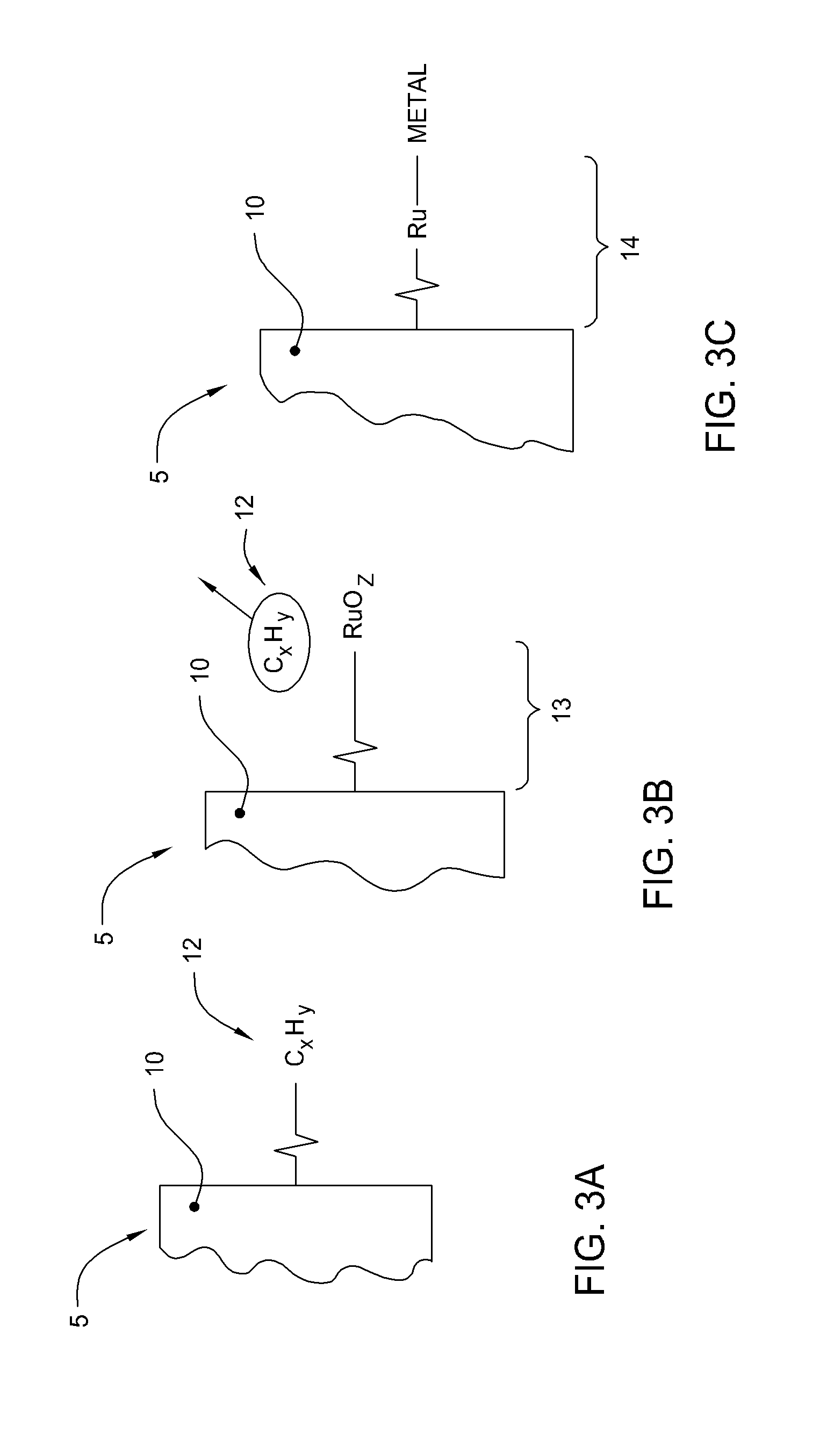

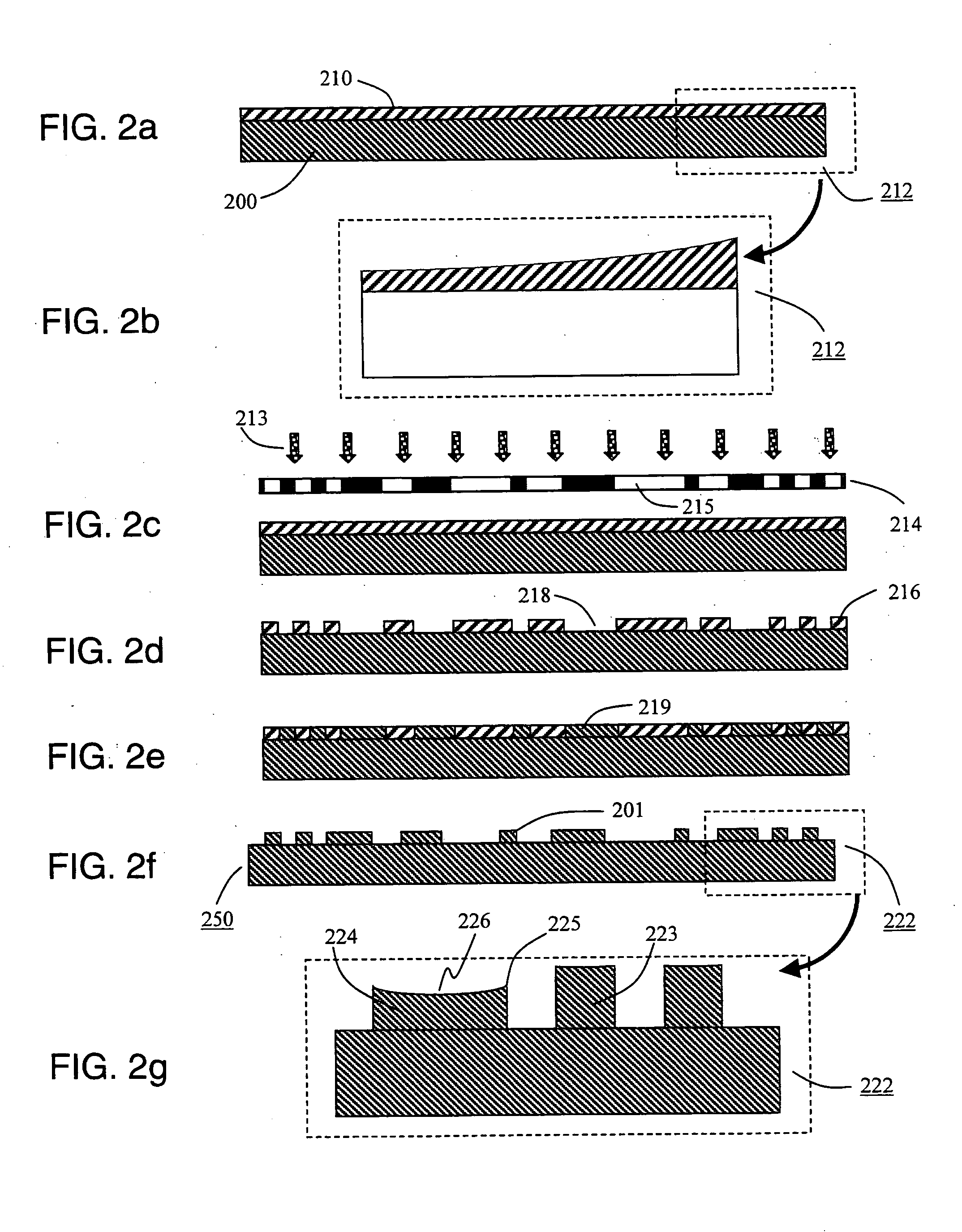

Patterned electroless metallization processes for large area electronics

The present invention generally provides an apparatus and method for selectively forming a metallized feature, such as an electrical interconnect feature, on a electrically insulating surface of a substrate. The present invention also provides a method of forming a mechanically robust, adherent, oxidation resistant conductive layer selectively over either a defined pattern or as a conformal blanket film. Embodiments of the invention also generally provide a new chemistry, process, and apparatus to provide discrete or blanket electrochemically or electrolessly platable ruthenium or ruthenium dioxide containing adhesion and initiation layers. In general, aspects of the present invention can be used for flat panel display processing, semiconductor processing, solar cell device processing, or any other substrate processing, being particularly well suited for the application of stable adherent coating on glass as well as flexible plastic substrates. This invention may be especially useful for the formation of electrical interconnects on the surface of flat panel display or solar cell type substrates where the line sizes are generally larger than semiconductor devices or where the formed feature are not generally as dense.

Owner:APPLIED MATERIALS INC

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6187678B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesThermal expansionPrism

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:IBM CORP

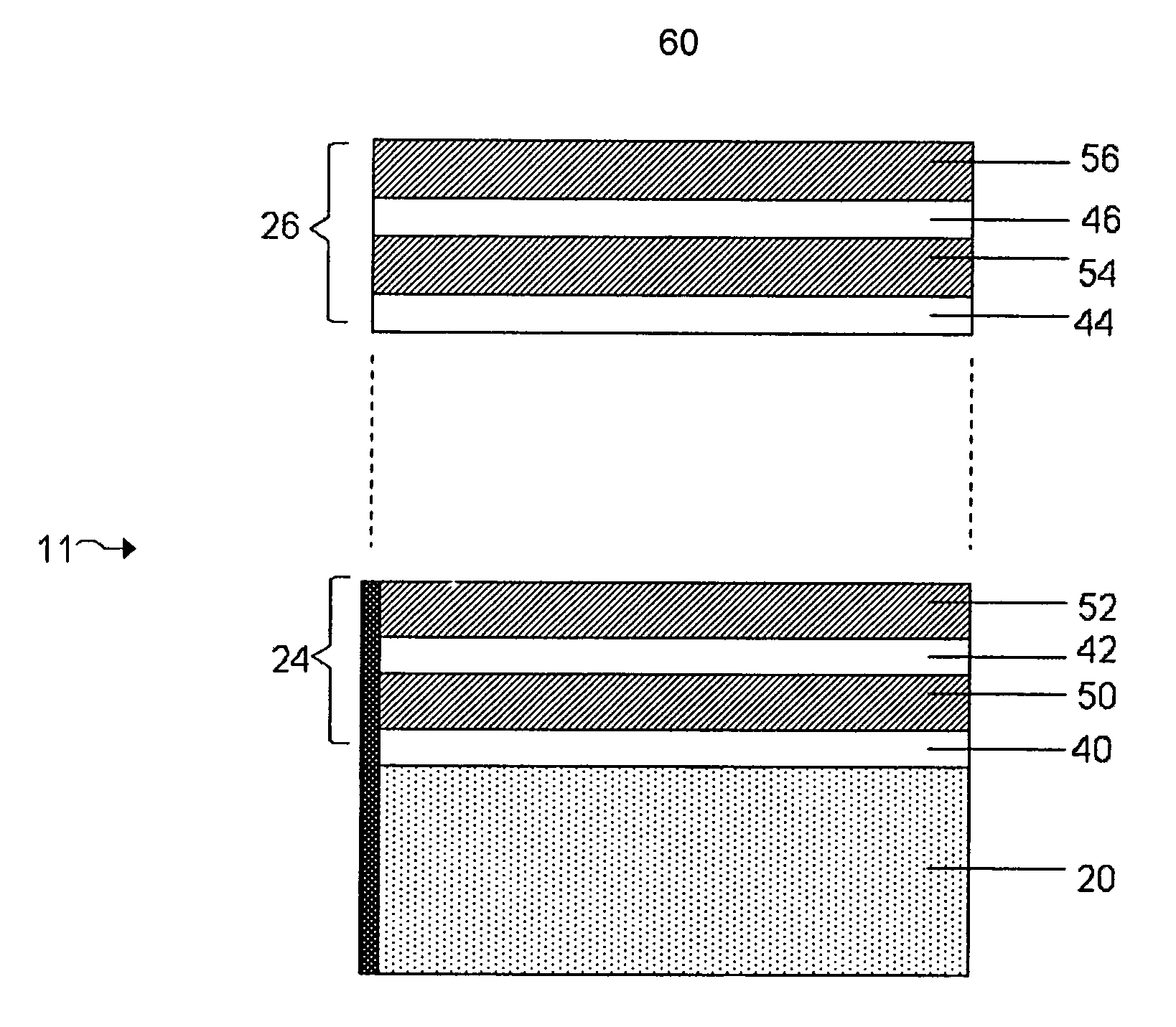

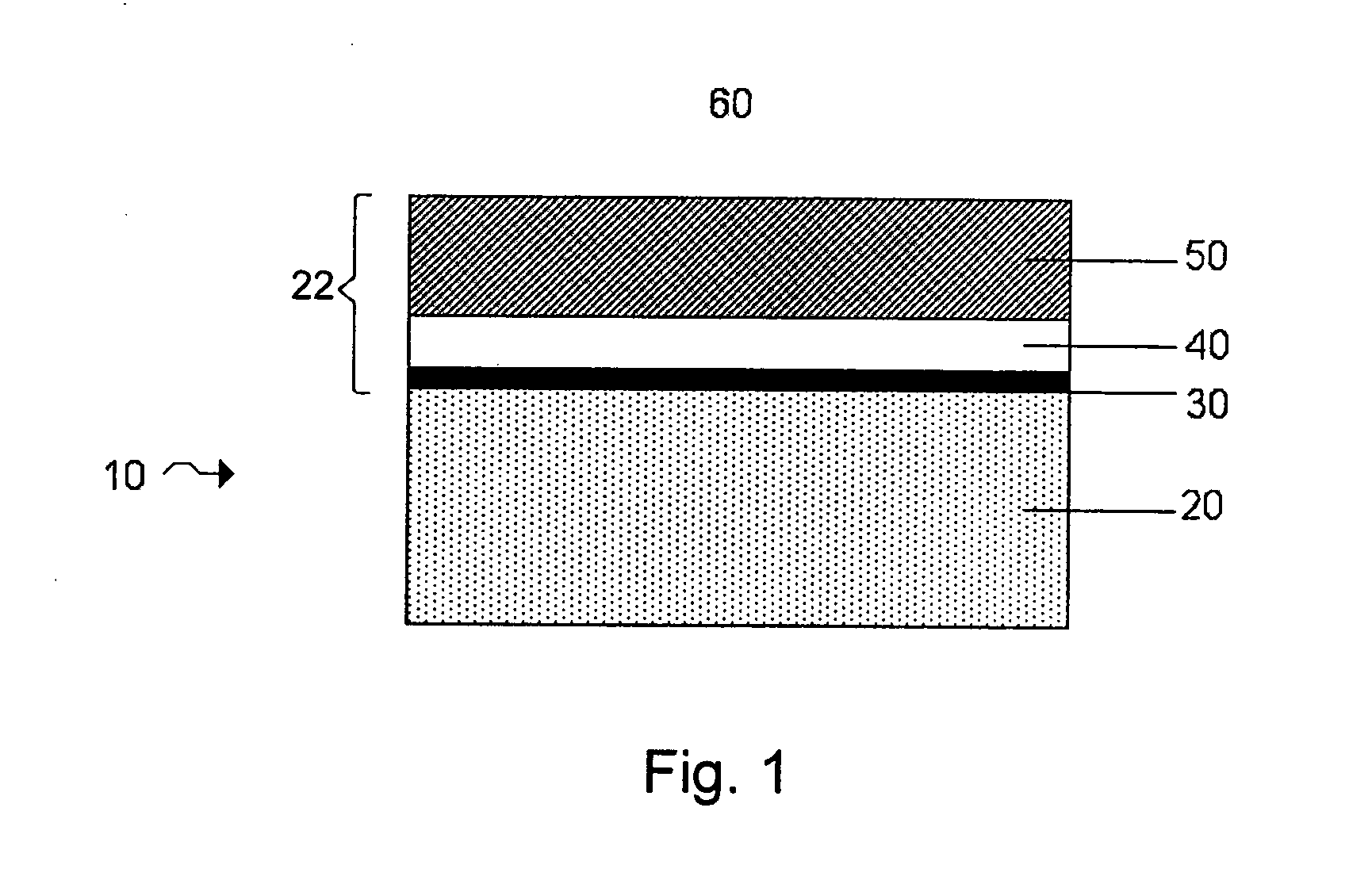

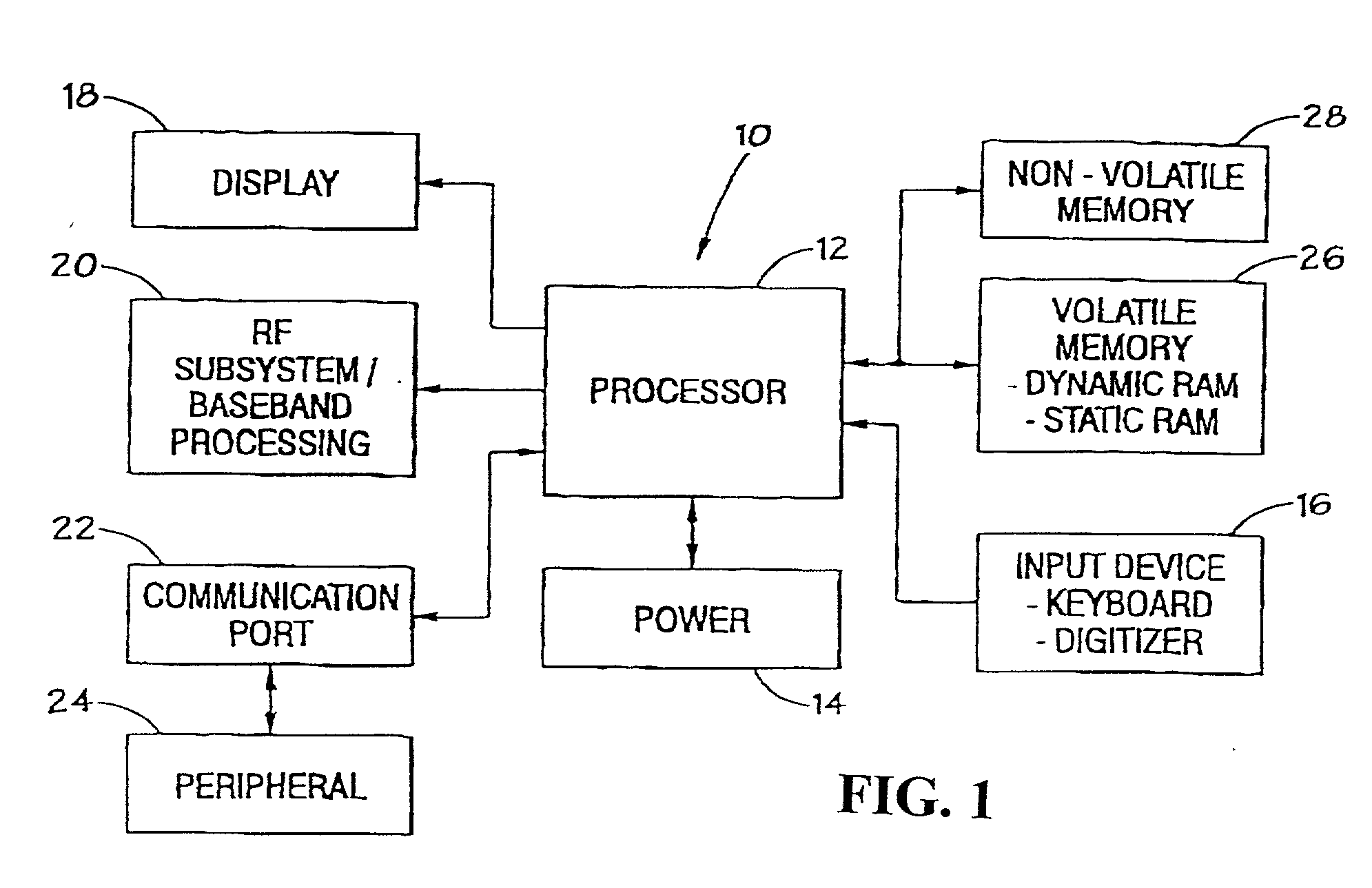

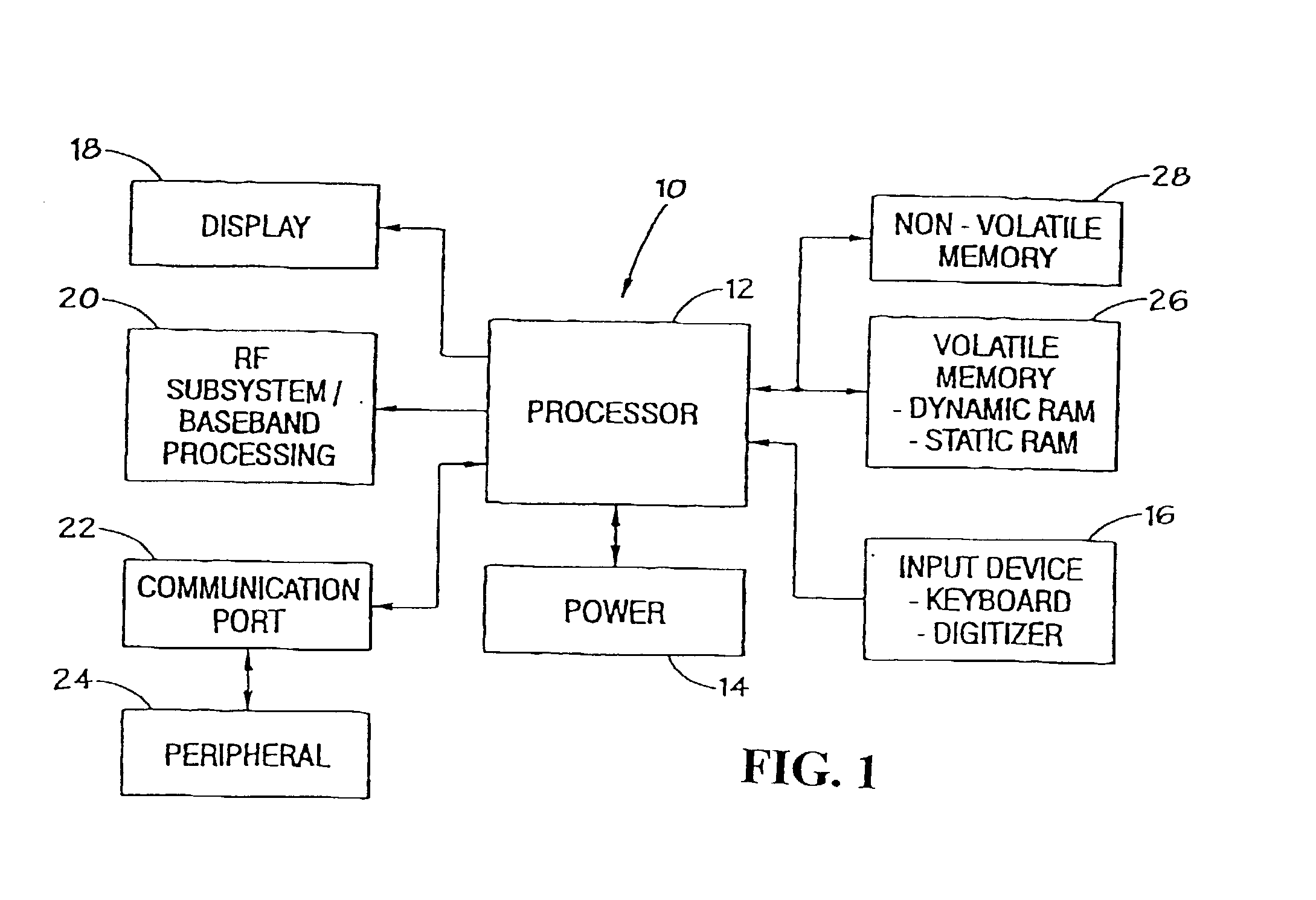

Rechargeable lithium/water, lithium/air batteries

InactiveUS20070221265A1Improve protectionEasy to controlFinal product manufacturePV power plantsHigh energyOptoelectronics

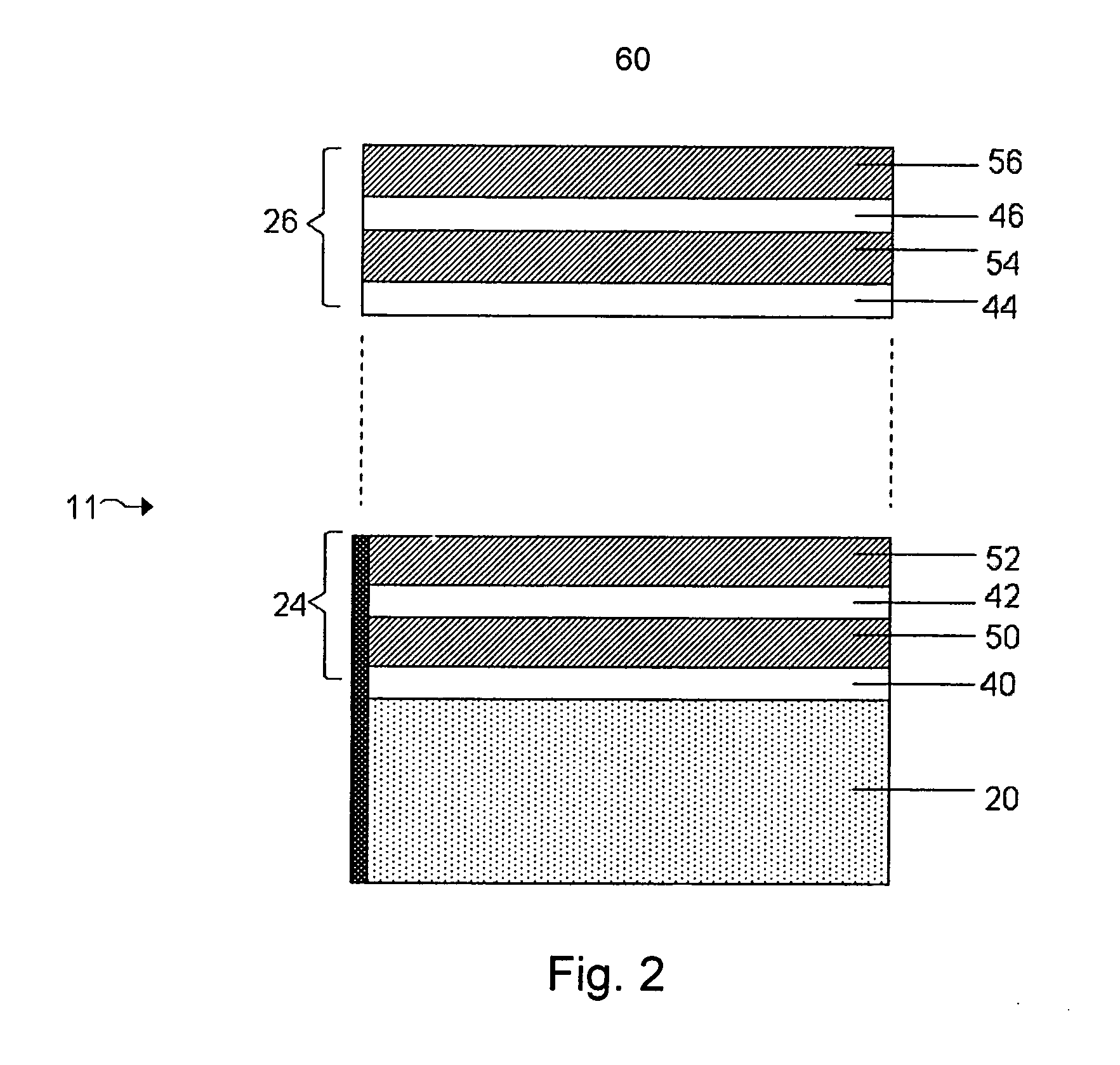

Electrochemical cells, and more specifically, rechargeable batteries comprising lithium anodes for use in water and / or air environments, as well as non-aqueous and non-air environments, are presented. In one embodiment, an electrochemical cell includes an anode comprising lithium and a multi-layered structure positioned between the anode and an electrolyte of the cell. A multi-layered structure can include at least a first single-ion conductive material layer (e.g., a lithiated metal layer), and at least a first polymeric layer positioned between the anode and the single-ion conductive material. The invention also can provide an electrode stabilization layer positioned within the electrode, i.e., between one portion and another portion of an electrode, to control depletion and re-plating of electrode material upon charge and discharge of a battery. Advantageously, electrochemical cells comprising combinations of structures described herein are not only compatible with environments that are typically unsuitable for lithium, but the cells may be also capable of displaying long cycle life, high lithium cycling efficiency, and high energy density.

Owner:SION POWER CORP

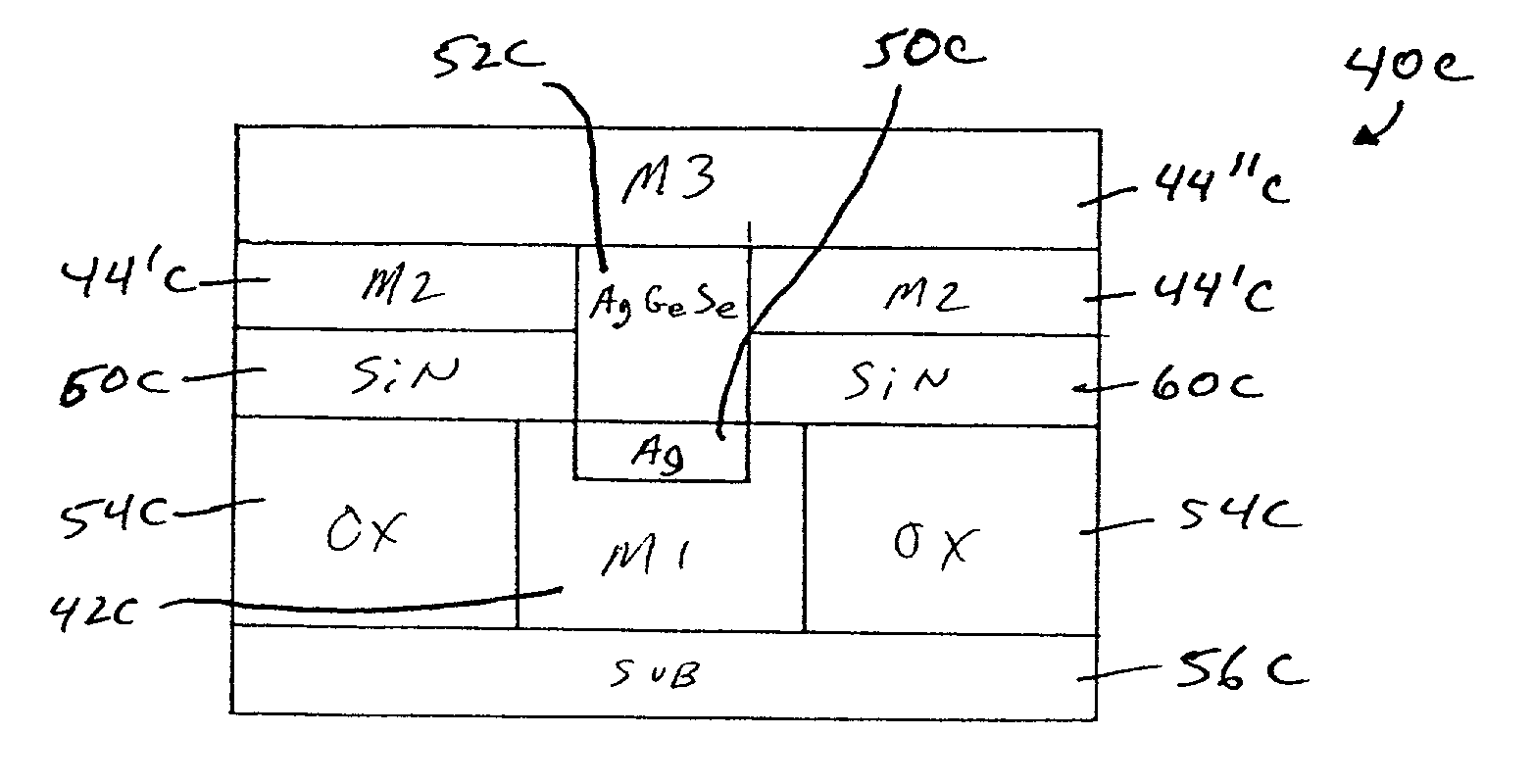

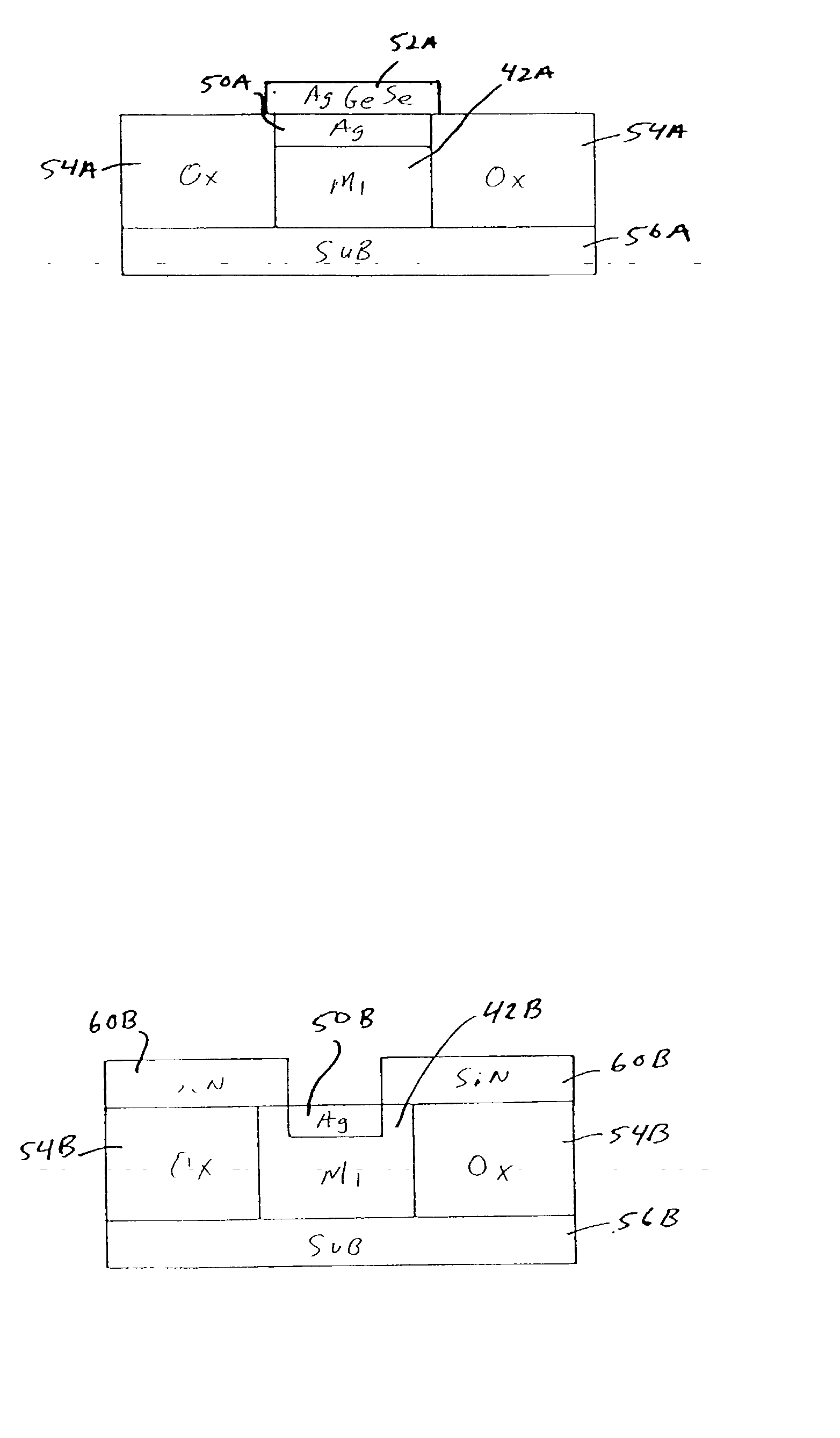

PCRAM memory cell and method of making same

InactiveUS20020168852A1Semiconductor/solid-state device manufacturingBulk negative resistance effect devicesConductive materialsCopper

An inverted PCRAM cell is formed by plating the bottom electrode, made of copper for example, with a conductive material, such as silver. Chalcogenide material is disposed over the plated electrode and subjected to a conversion process so that ions from the plated material diffuse into the chalcogenide material.

Owner:OVONYX MEMORY TECH LLC

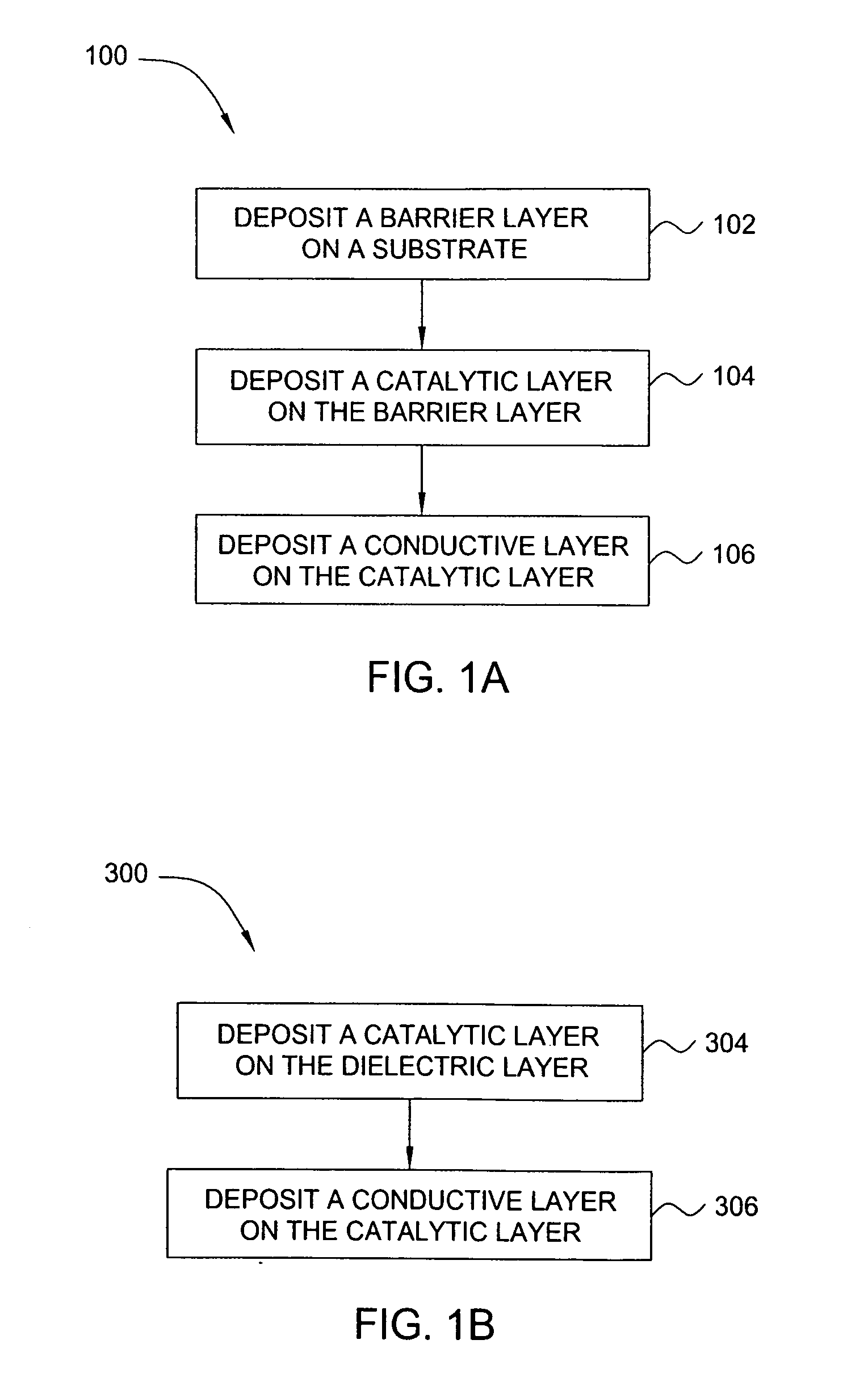

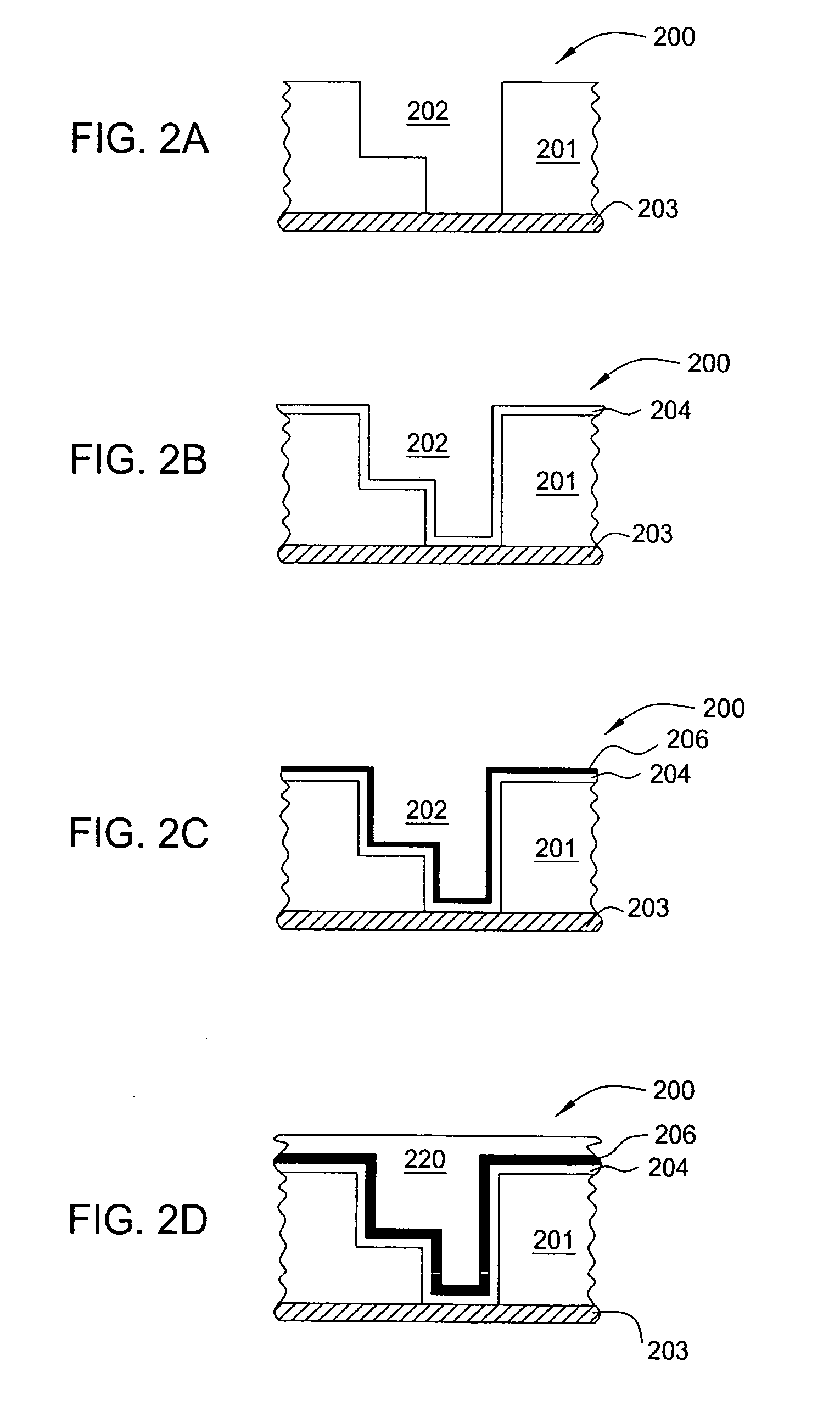

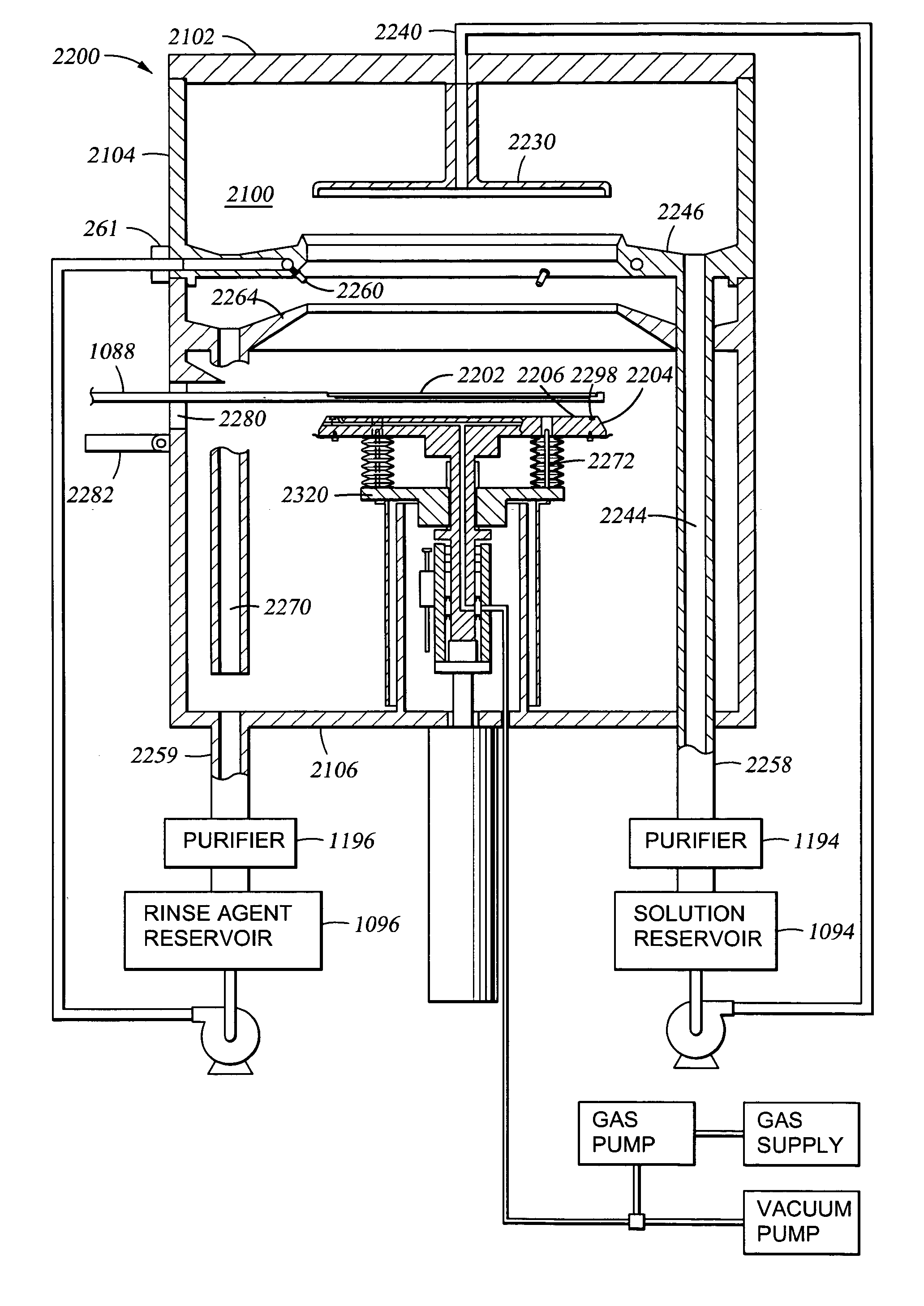

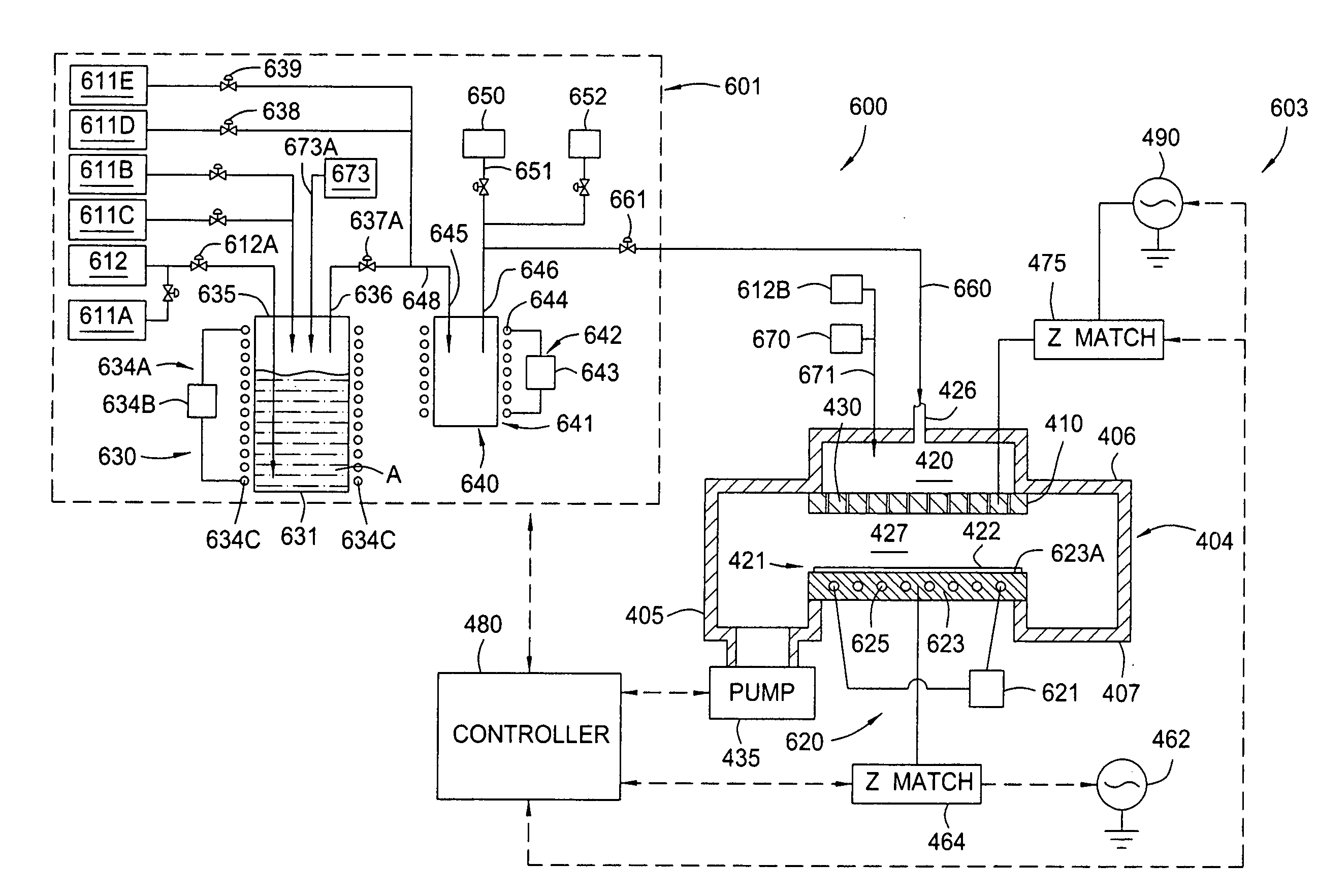

Electroless deposition apparatus

An apparatus and a method of depositing a catalytic layer comprising at least one metal selected from the group consisting of noble metals, semi-noble metals, alloys thereof, and combinations thereof in sub-micron features formed on a substrate. Examples of noble metals include palladium and platinum. Examples of semi-noble metals include cobalt, nickel, and tungsten. The catalytic layer may be deposited by electroless deposition, electroplating, or chemical vapor deposition. In one embodiment, the catalytic layer may be deposited in the feature to act as a barrier layer to a subsequently deposited conductive material. In another embodiment, the catalytic layer may be deposited over a barrier layer. In yet another embodiment, the catalytic layer may be deposited over a seed layer deposited over the barrier layer to act as a “patch” of any discontinuities in the seed layer. Once the catalytic layer has been deposited, a conductive material, such as copper, may be deposited over the catalytic layer. In one embodiment, the conductive material is deposited over the catalytic layer by electroless deposition. In another embodiment, the conductive material is deposited over the catalytic layer by electroless deposition followed by electroplating or followed by chemical vapor deposition. In still another embodiment, the conductive material is deposited over the catalytic layer by electroplating or by chemical vapor deposition.

Owner:APPLIED MATERIALS INC

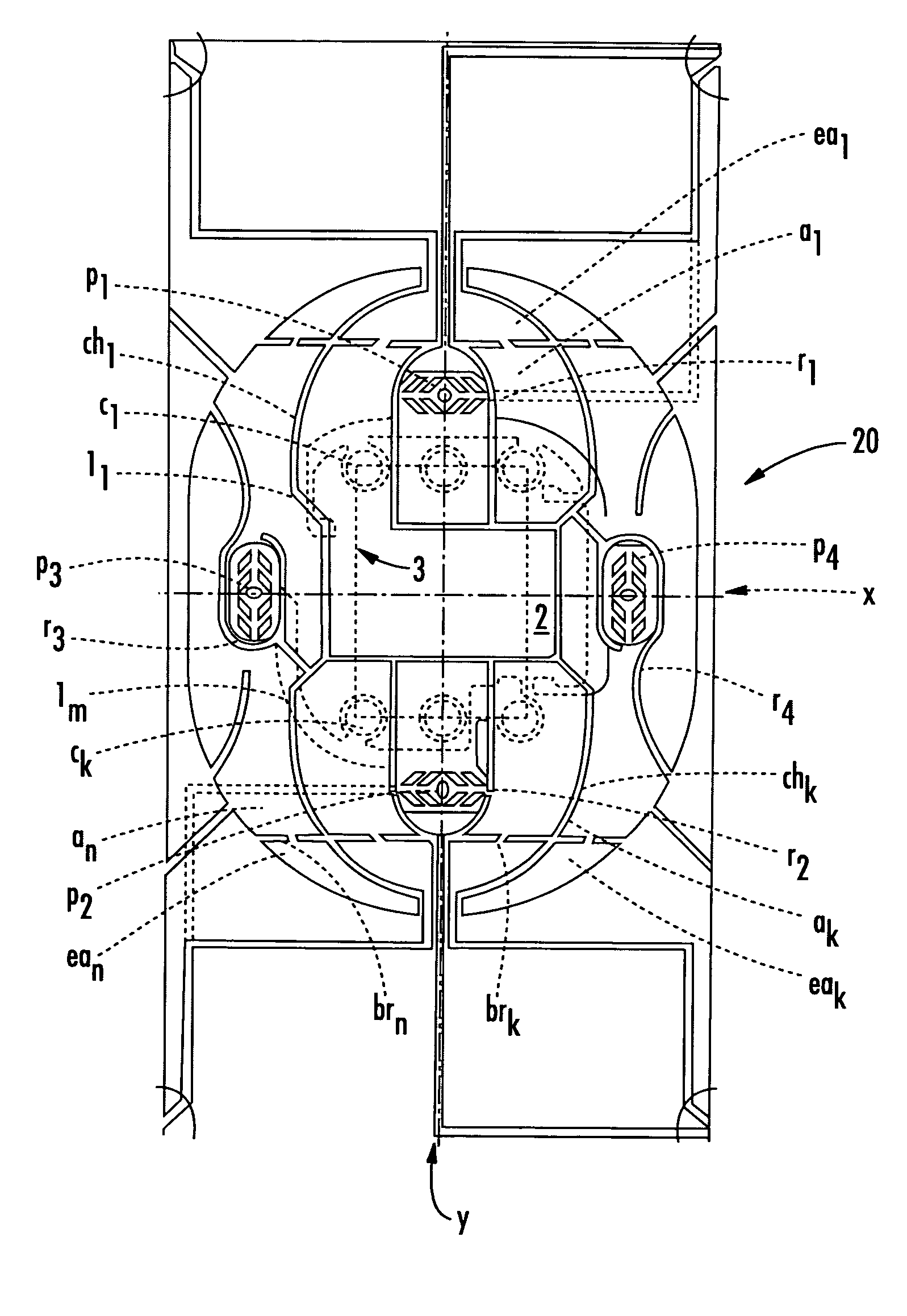

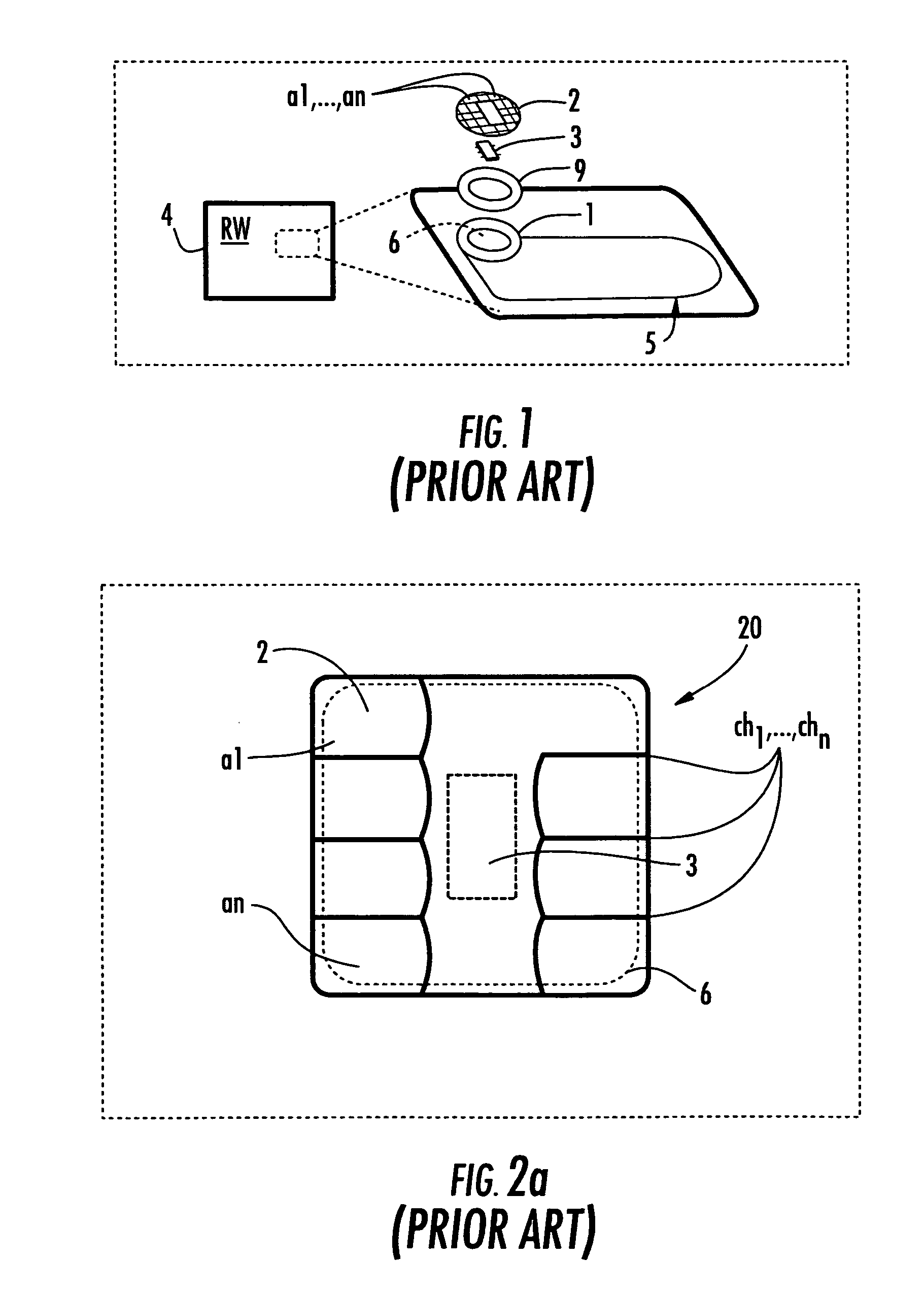

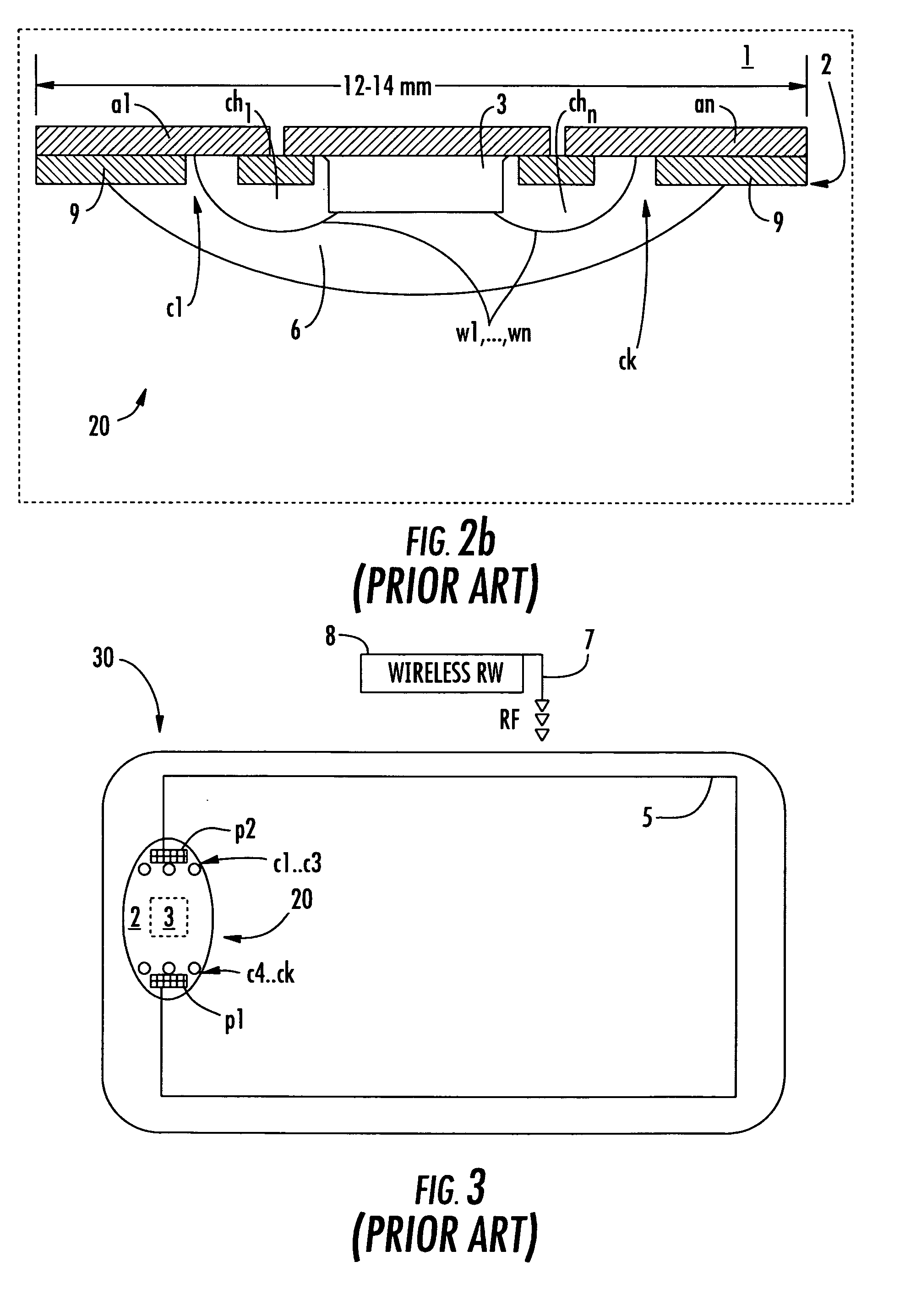

IC card with improved plated module

InactiveUS20070152072A1Reduce impactSmooth connectionSolid-state devicesRecord carriers used with machinesElectroplatingIntegrated circuit

An IC card includes a plated or protective module including a printed circuit having a plurality of conductive areas, delimited by a network of insulating channels, for covering an integrated circuit chip, a plastic support with a recess intended to host the plated module and the integrated circuit chip, with at least some of the conductive areas connected to corresponding contact points on the integrated circuit chip. A plurality of extended areas are linked to a corresponding conductive areas by one or more bridges. A couple of advanced extended areas form a rounded border of the plated module. Advanced extended areas are linked to conductive areas not connected to contact points. Advanced extended areas wrap around the extended areas and form the opposite rounded sides of the plated module.

Owner:STMICROELECTRONICS INT NV

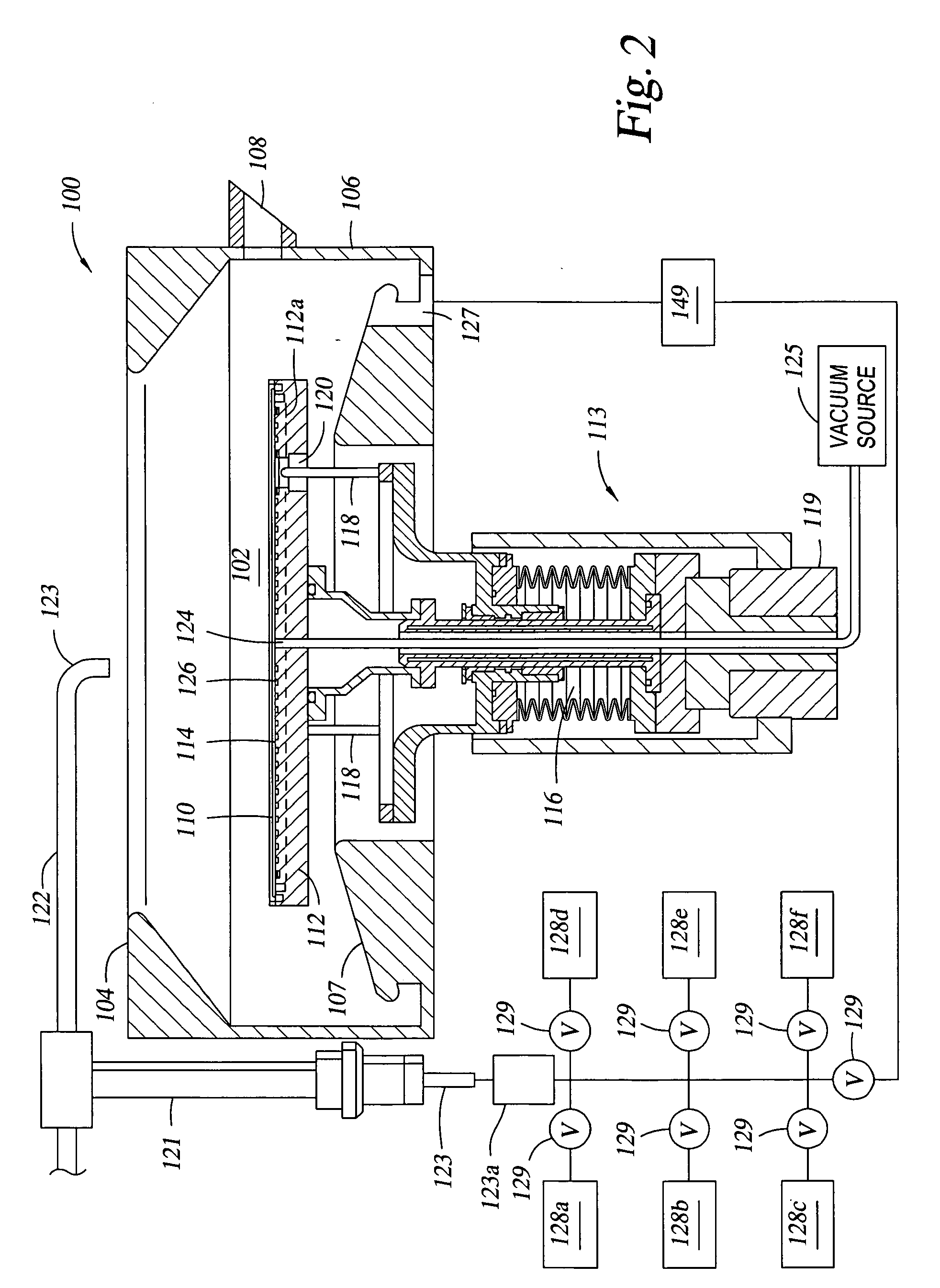

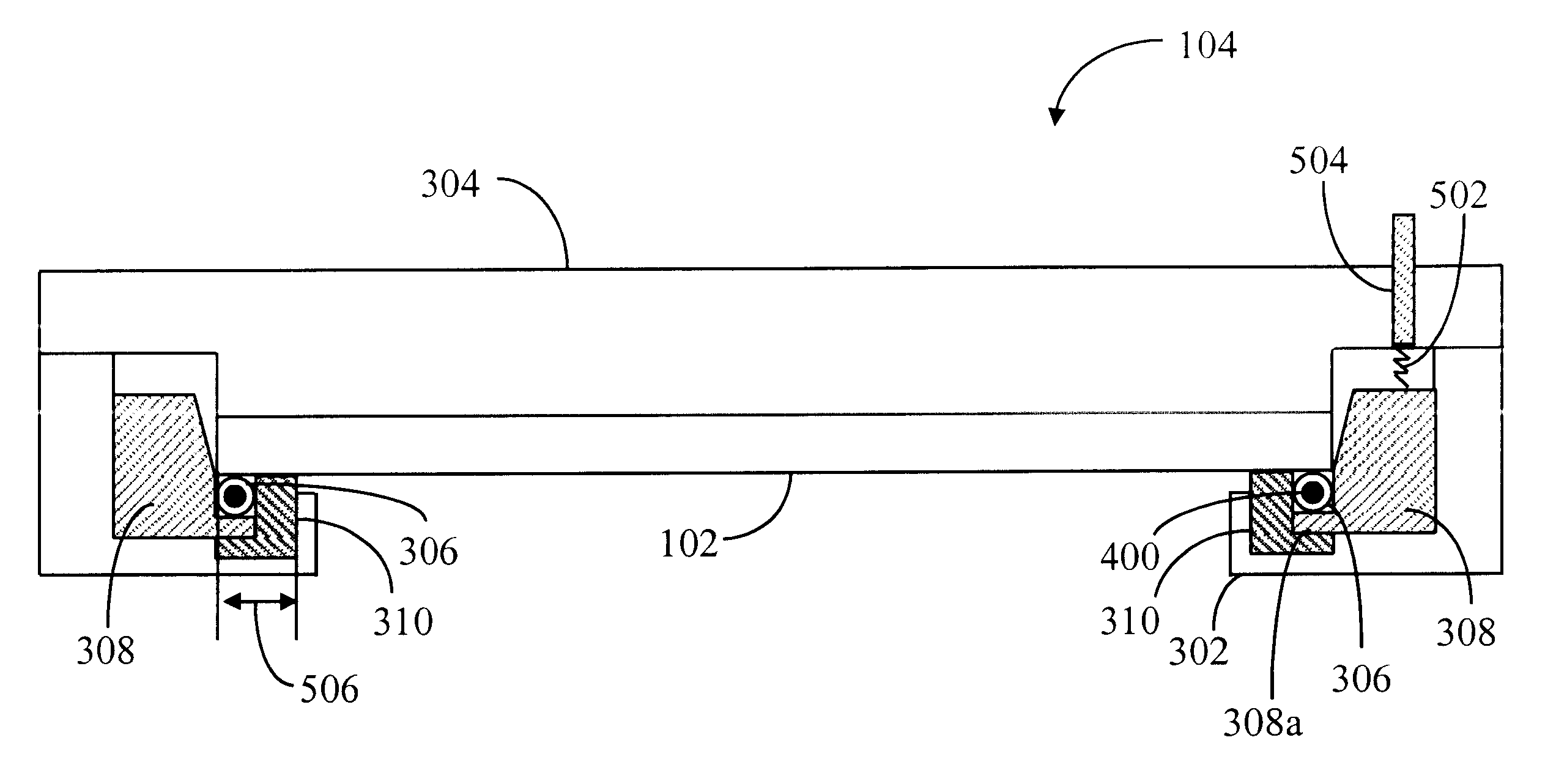

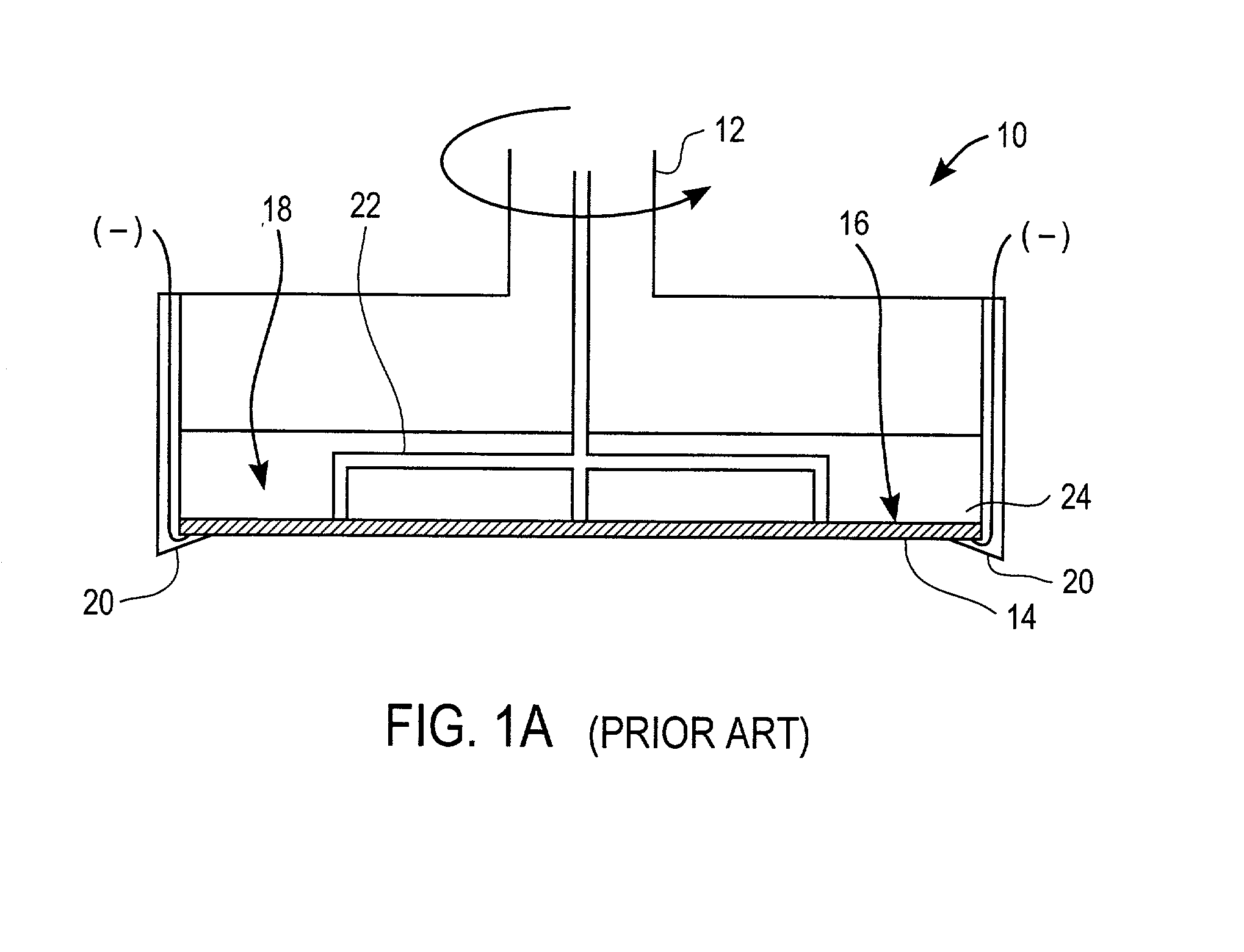

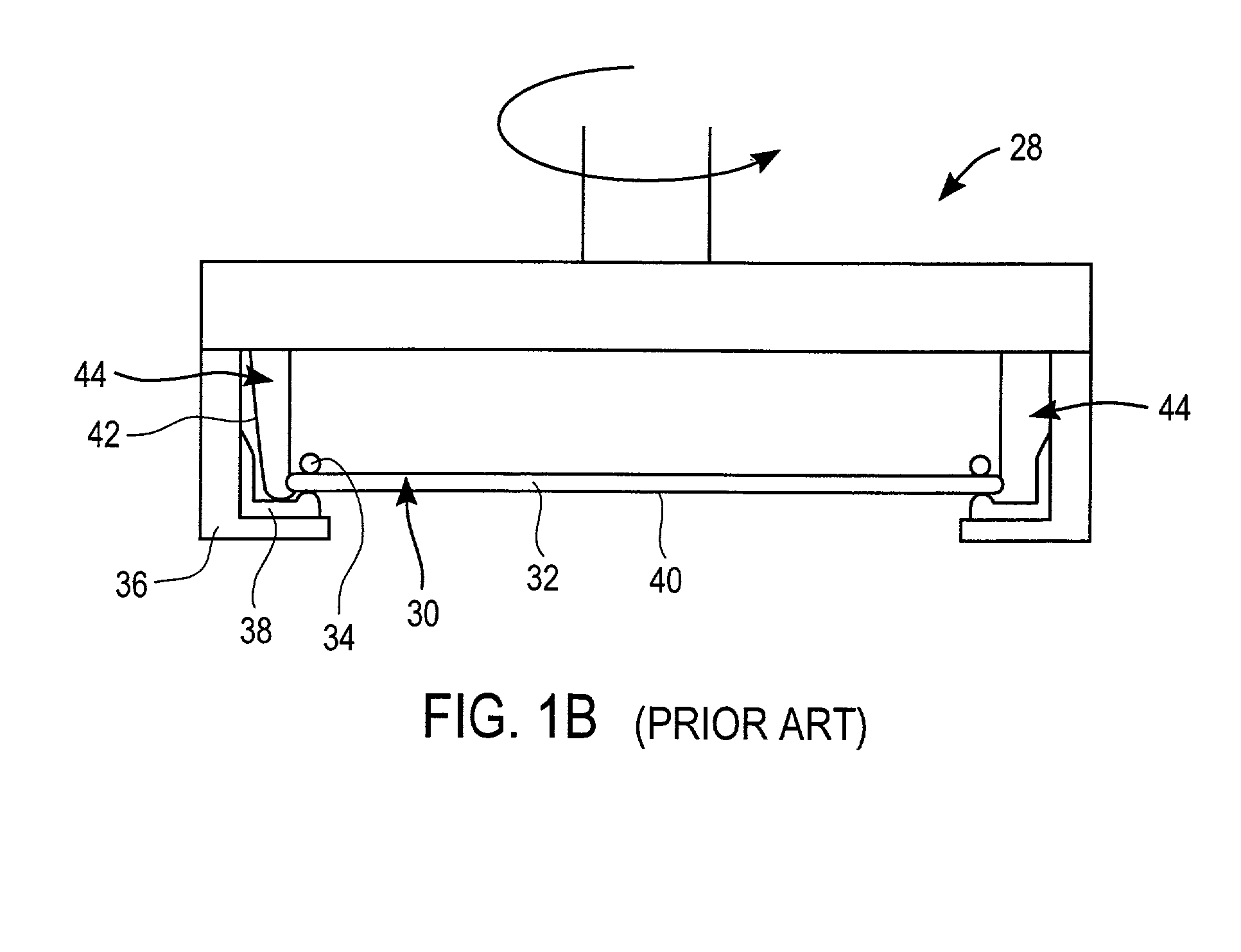

Methods and apparatus for holding and positioning semiconductor workpieces during electropolishing and/or electroplating of the workpieces

A wafer chuck for holding a wafer during electropolishing and / or electroplating of the wafer includes a top section, a bottom section, and a spring member. In accordance with one aspect of the present invention, the top section and the bottom section are configured to receive the wafer for processing. The spring member is disposed on the bottom section and configured to apply an electric charge to the wafer. In accordance with another aspect of the present invention, the spring member contacts a portion of the outer perimeter of the wafer. In one alternative configuration of the present invention, the wafer chuck further includes a seal member to seal the spring member from the electrolyte solution used in the electropolishing and / or electroplating process.

Owner:ACM RES

Ruthenium layer deposition apparatus and method

InactiveUS20060162658A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingTemperature controlSource material

An exemplary apparatus and method of forming a ruthenium tetroxide containing gas to form a ruthenium containing layer on a surface of a substrate is described herein. The method and apparatus described herein may be especially useful for fabricating electronic devices that are formed on a surface of the substrate or wafer. Generally, the method includes exposing a surface of a substrate to a ruthenium tetroxide vapor to form a catalytic layer on the surface of a substrate and then filling the device structures by an electroless, electroplating, physical vapor deposition (PVD), chemical vapor deposition (CVD), plasma enhanced CVD (PECVD), atomic layer deposition (ALD) or plasma enhanced ALD (PE-ALD) processes. In one embodiment, the ruthenium containing layer is formed on a surface of a substrate by creating ruthenium tetroxide in an external vessel and then delivering the generated ruthenium tetroxide gas to a surface of a temperature controlled substrate positioned in a processing chamber. In one embodiment, a ruthenium tetroxide containing solvent formation process is used to form ruthenium tetroxide using a ruthenium tetroxide containing source material. In one embodiment, of a ruthenium containing layer is formed on a surface of a substrate, using the ruthenium tetroxide containing solvent. In another embodiment, the solvent is separated from the ruthenium tetroxide containing solvent mixture and the remaining ruthenium tetroxide is used to form a ruthenium containing layer on the surface of a substrate.

Owner:APPLIED MATERIALS INC

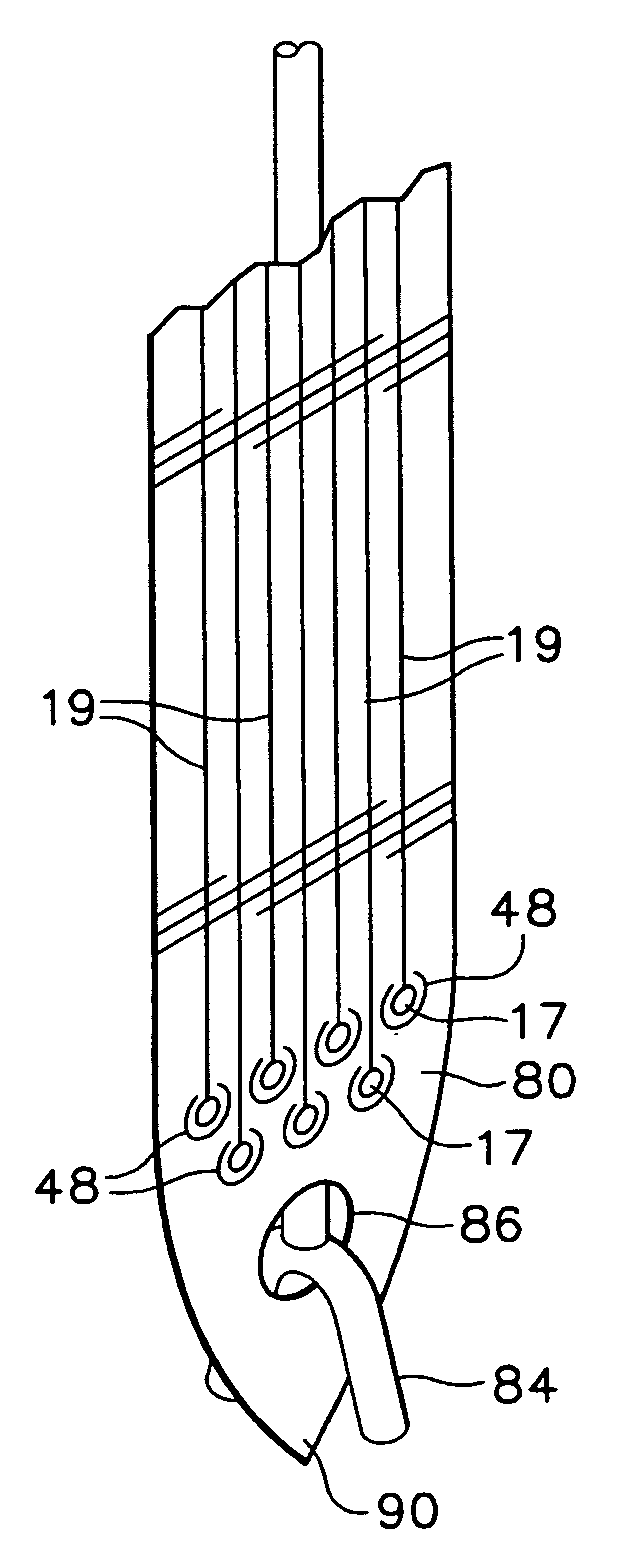

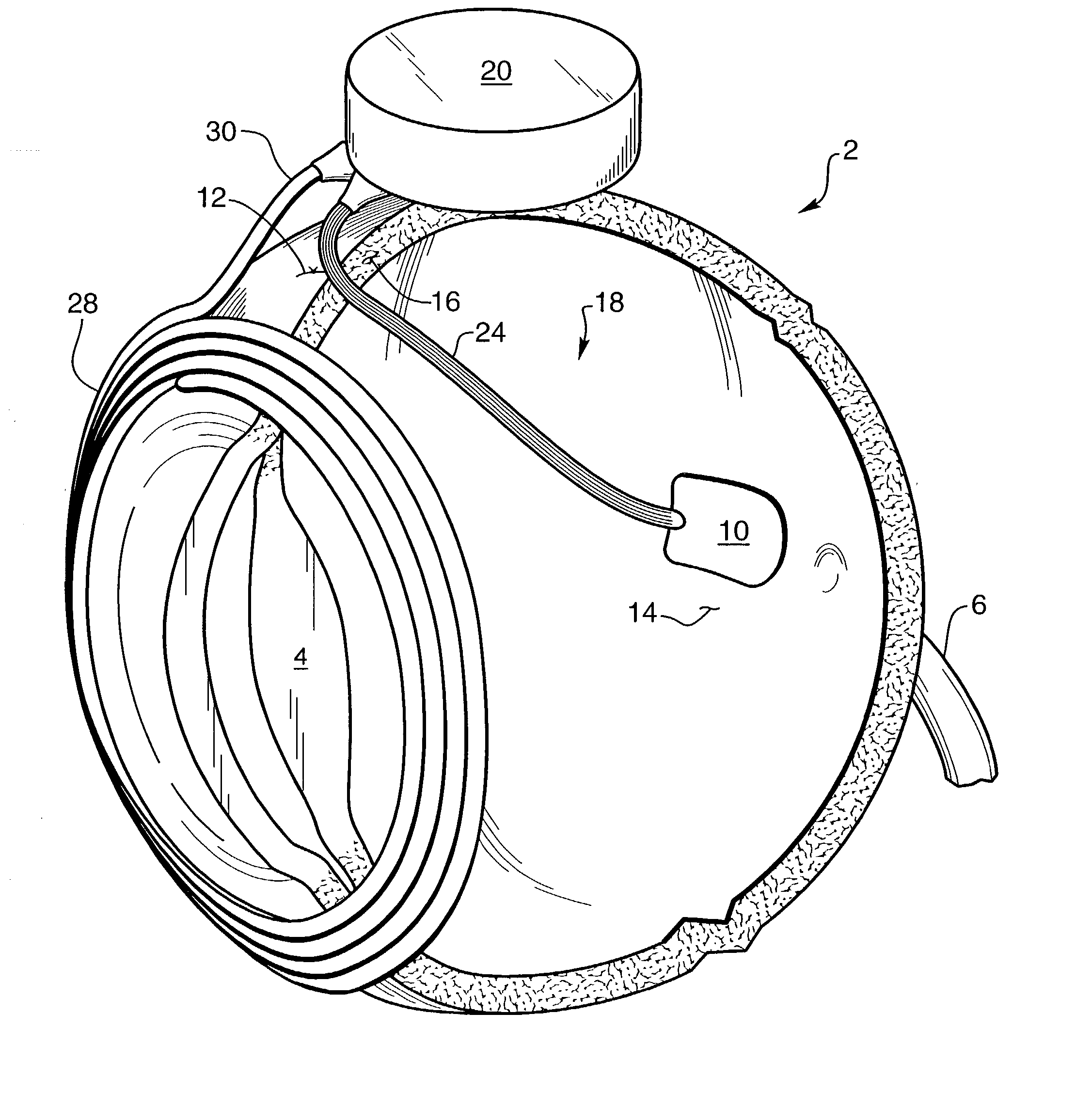

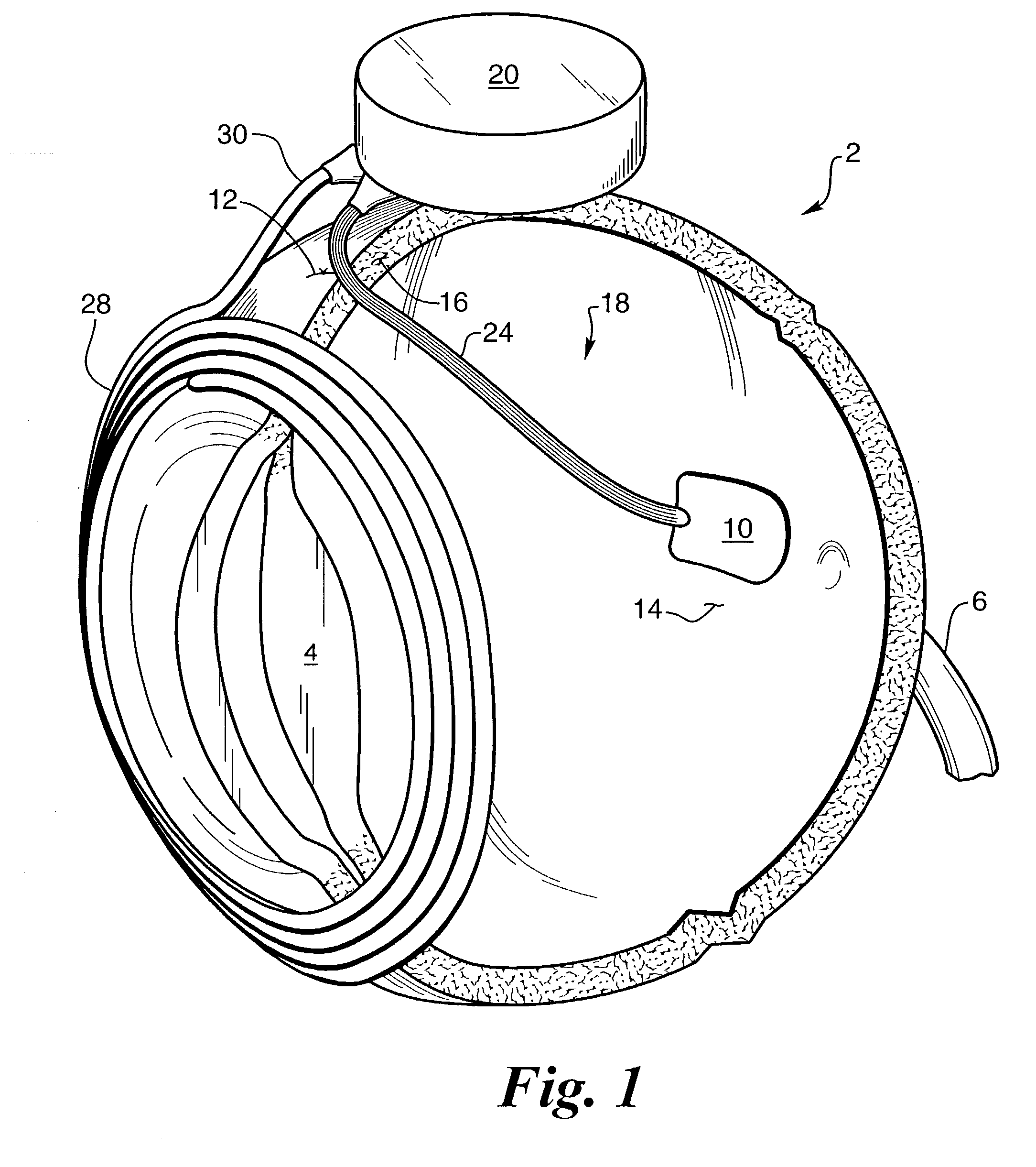

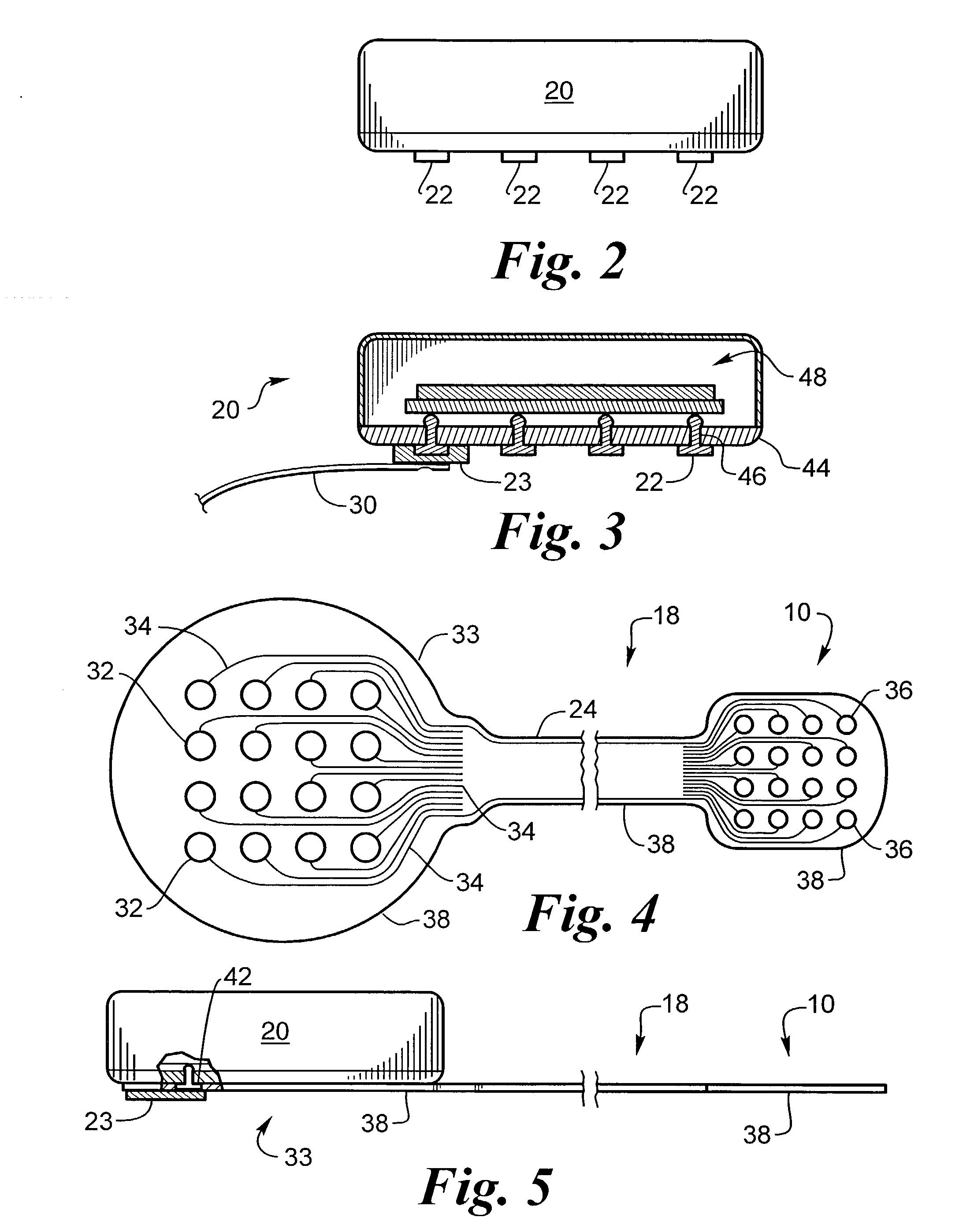

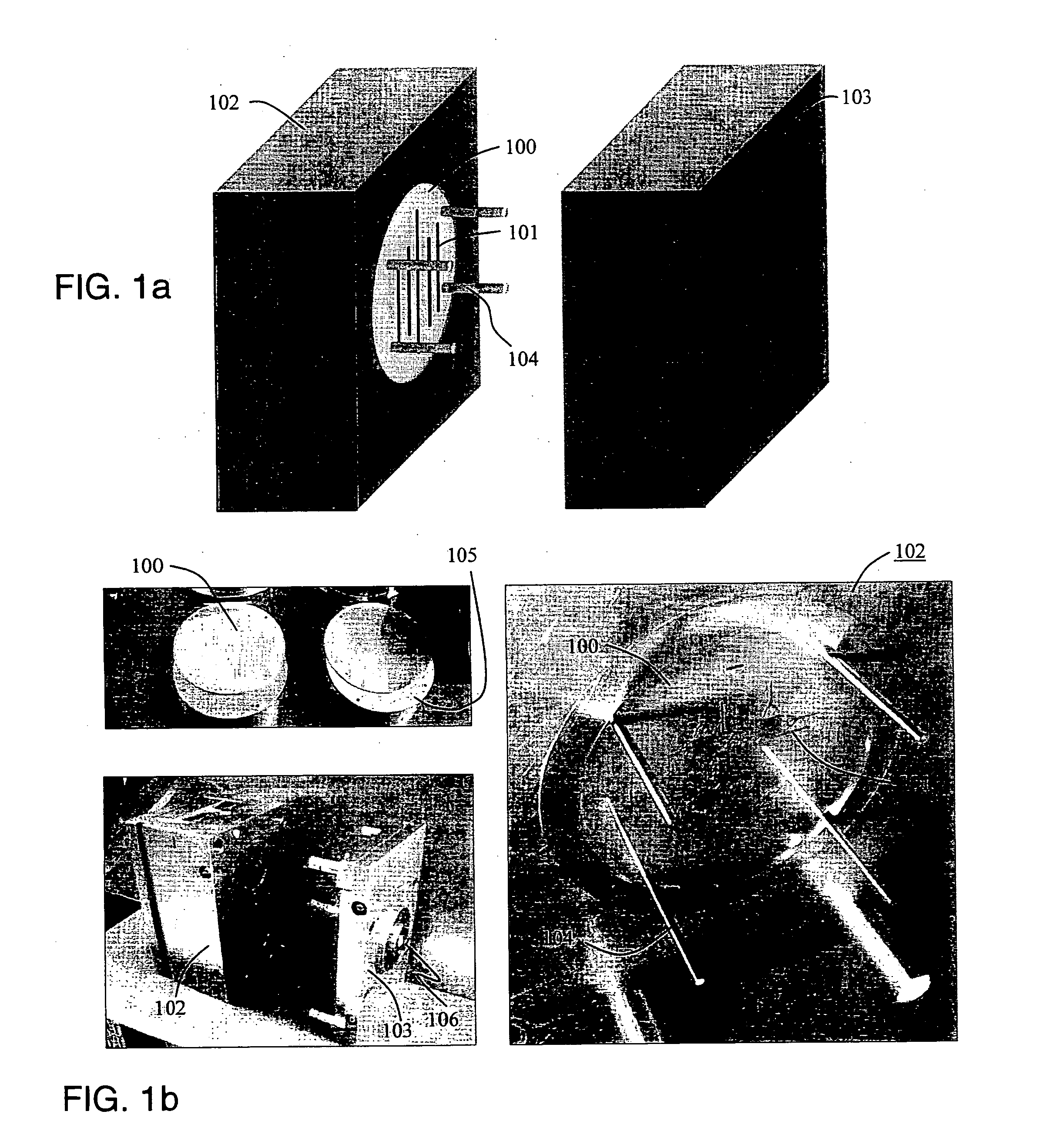

Flexible bio-probe assembly

A method of producing an electrode brain probe assembly, using a flexible substrate comprising a polymeric layer bearing a conductive material coating. Photolithography and electroplating are used to form a set of contacts and conductors on the polymeric layer of the flexible substrate. Also, the flexible substrate is shaped to have a distal end and to be at least 5 mm long, but less than 5 mm wide and less than 1 mm thick.

Owner:ADVANCED NEUROMODULATION SYST INC

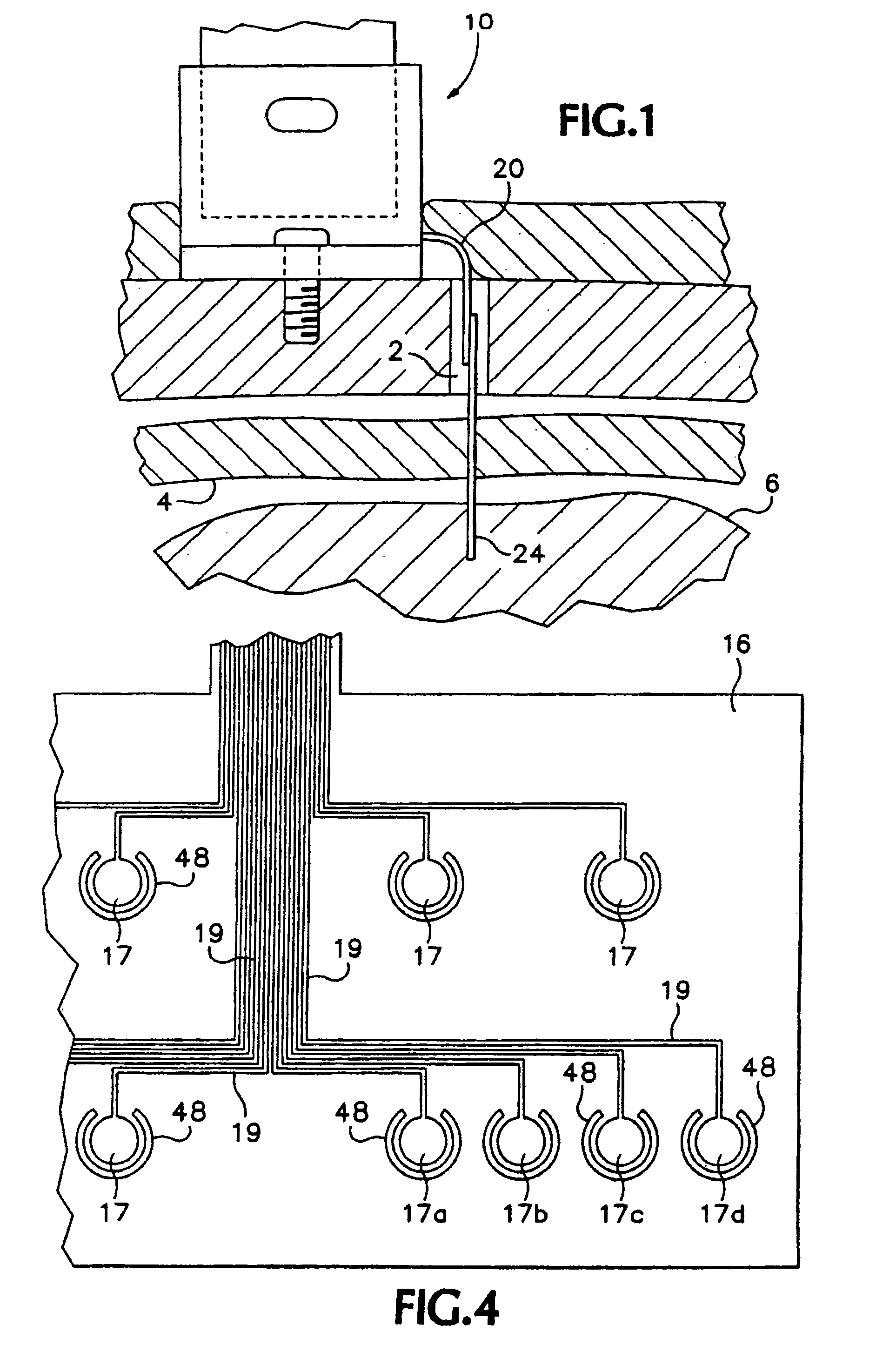

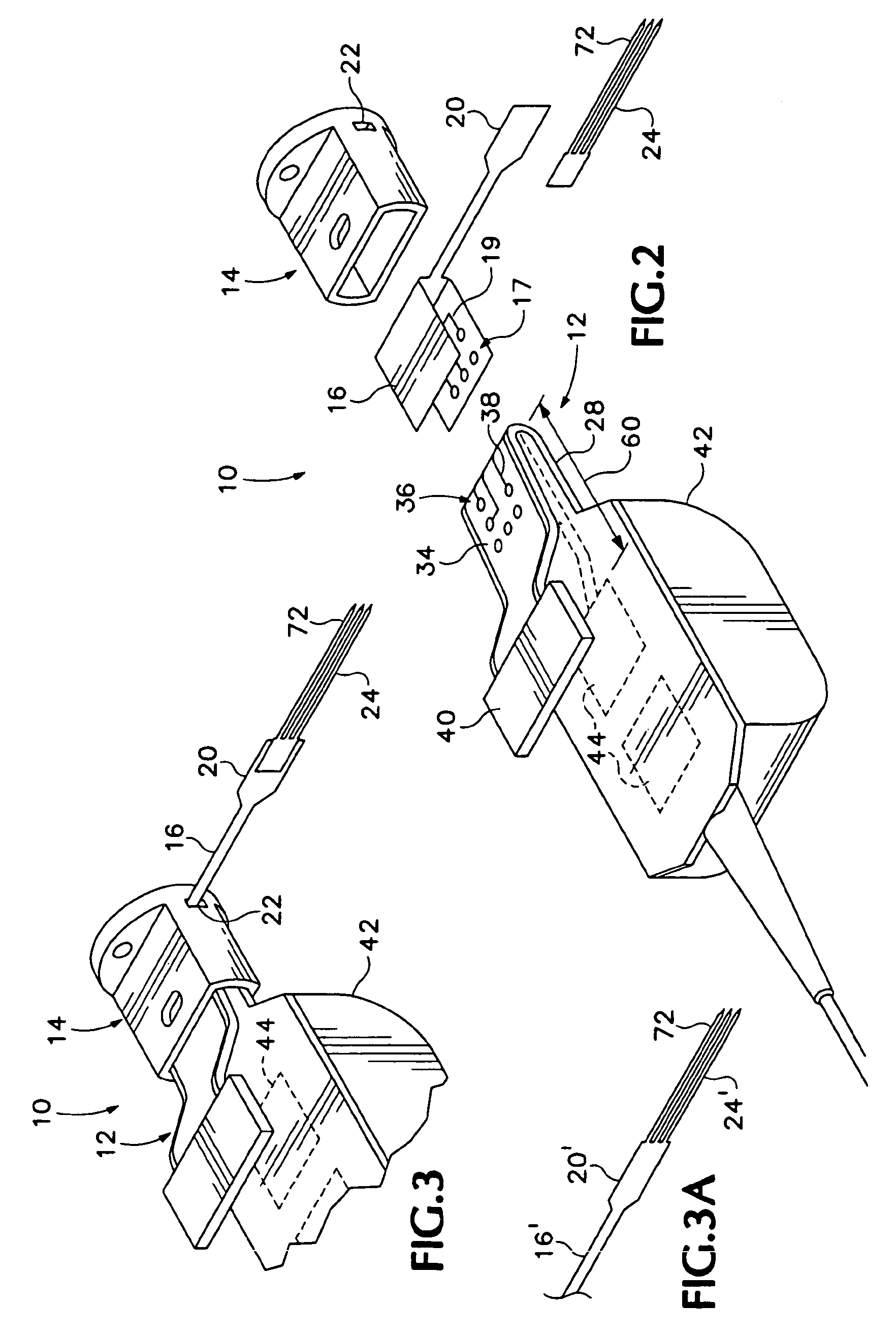

Biocompatible bonding method and electronics package suitable for implantation

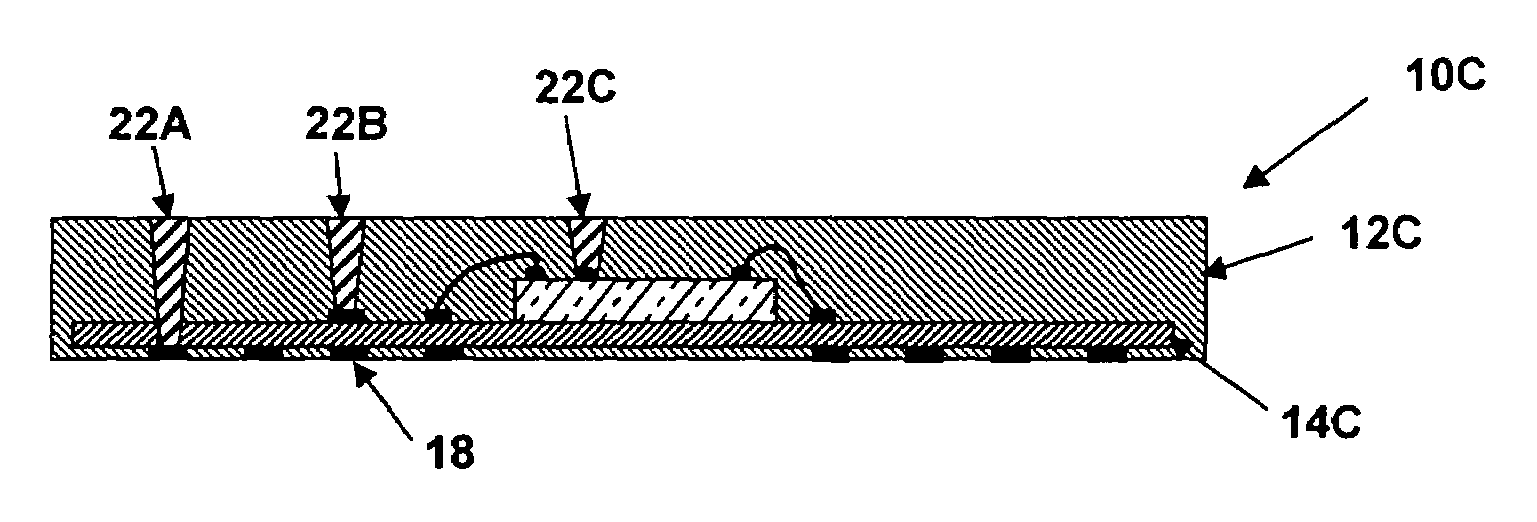

ActiveUS20030233134A1Uniform propertySemiconductor/solid-state device detailsSolid-state devicesFlexible circuitsHermetic seal

The invention is directed to a method of bonding a hermetically sealed electronics package to an electrode or a flexible circuit and the resulting electronics package, that is suitable for implantation in living tissue, such as for a retinal or cortical electrode array to enable restoration of sight to certain non-sighted individuals. The hermetically sealed electronics package is directly bonded to the flex circuit or electrode by electroplating a biocompatible material, such as platinum or gold, effectively forming a plated rivet-shaped connection, which bonds the flex circuit to the electronics package. The resulting electronic device is biocompatible and is suitable for long-term implantation in living tissue.

Owner:CORTIGENT INC +1

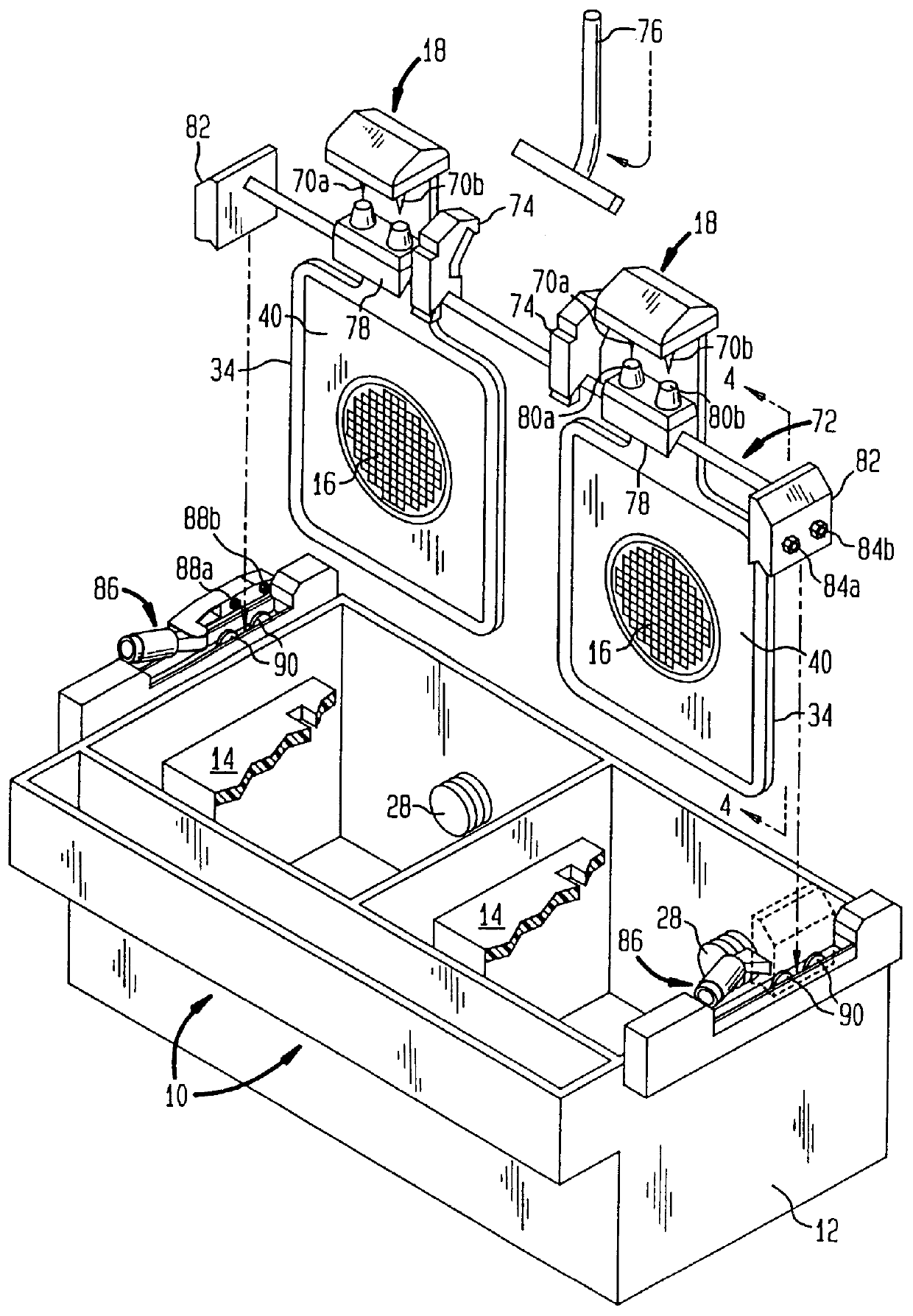

Electroplating workpiece fixture having liquid gap spacer

A fixture for supporting a workpiece during electroplating of a metal upon the workpiece in a conductive electroplating bath includes a non-conductive frame member for receiving the workpiece therein. The fixture further includes a current distribution means having a plurality of contacts. The plurality of contacts is disposed inwardly for providing an equally distributed electrical contact with an outer perimeter region of the workpiece. The workpiece is supported between the frame member and the current distribution means. Lastly, a thief electrode is perimetrically disposed about the workpiece and spaced a prescribed distance from the workpiece by a gap region. During plating of a metal upon the workpiece, the gap region between the thief and the workpiece is filled with the conductive electroplating bath. An electroplating apparatus having a fixture for supporting a workpiece during an electroplating process and a method of supporting the workpiece to be electroplated are also disclosed.

Owner:NOVELLUS SYSTEMS

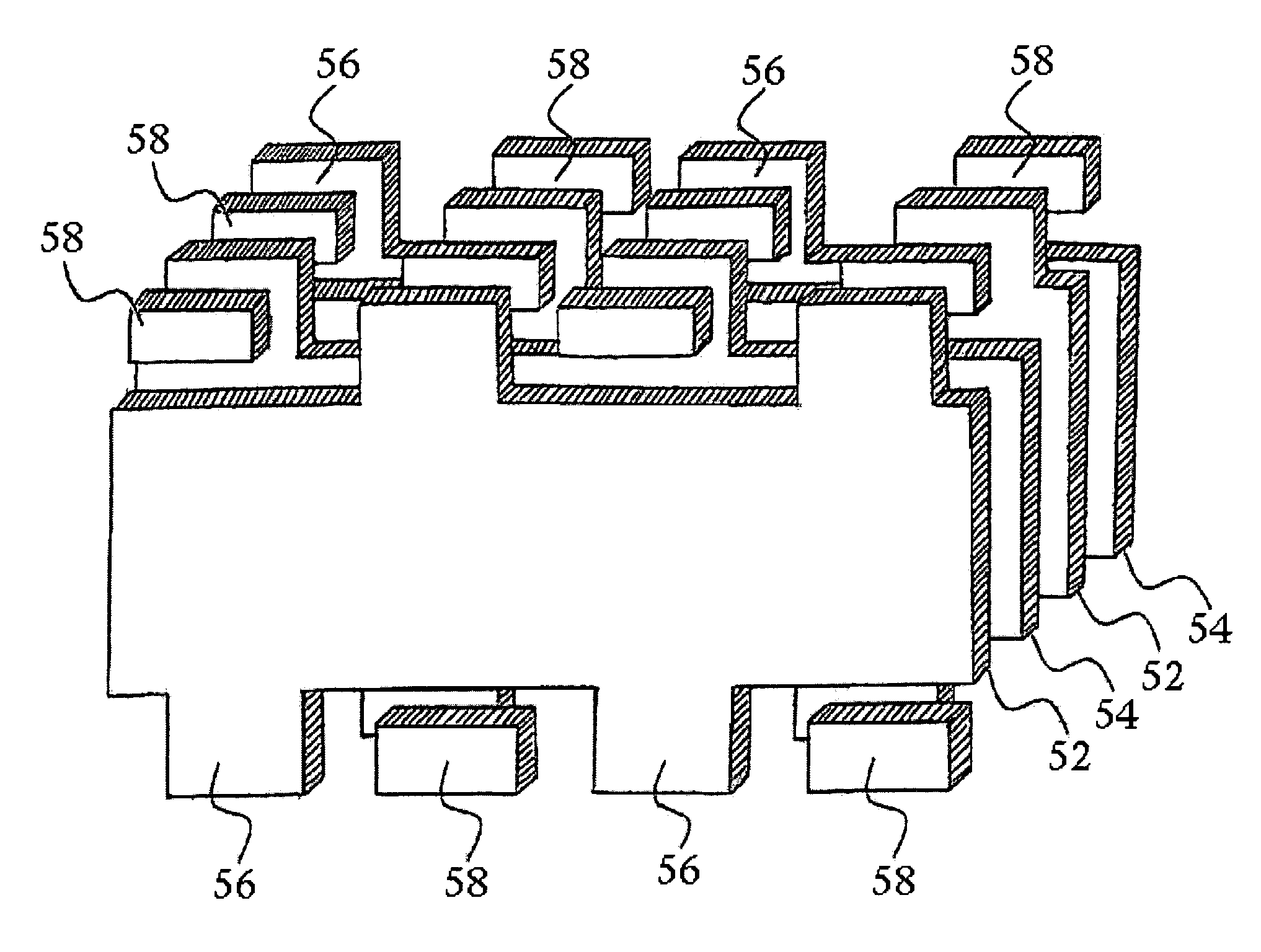

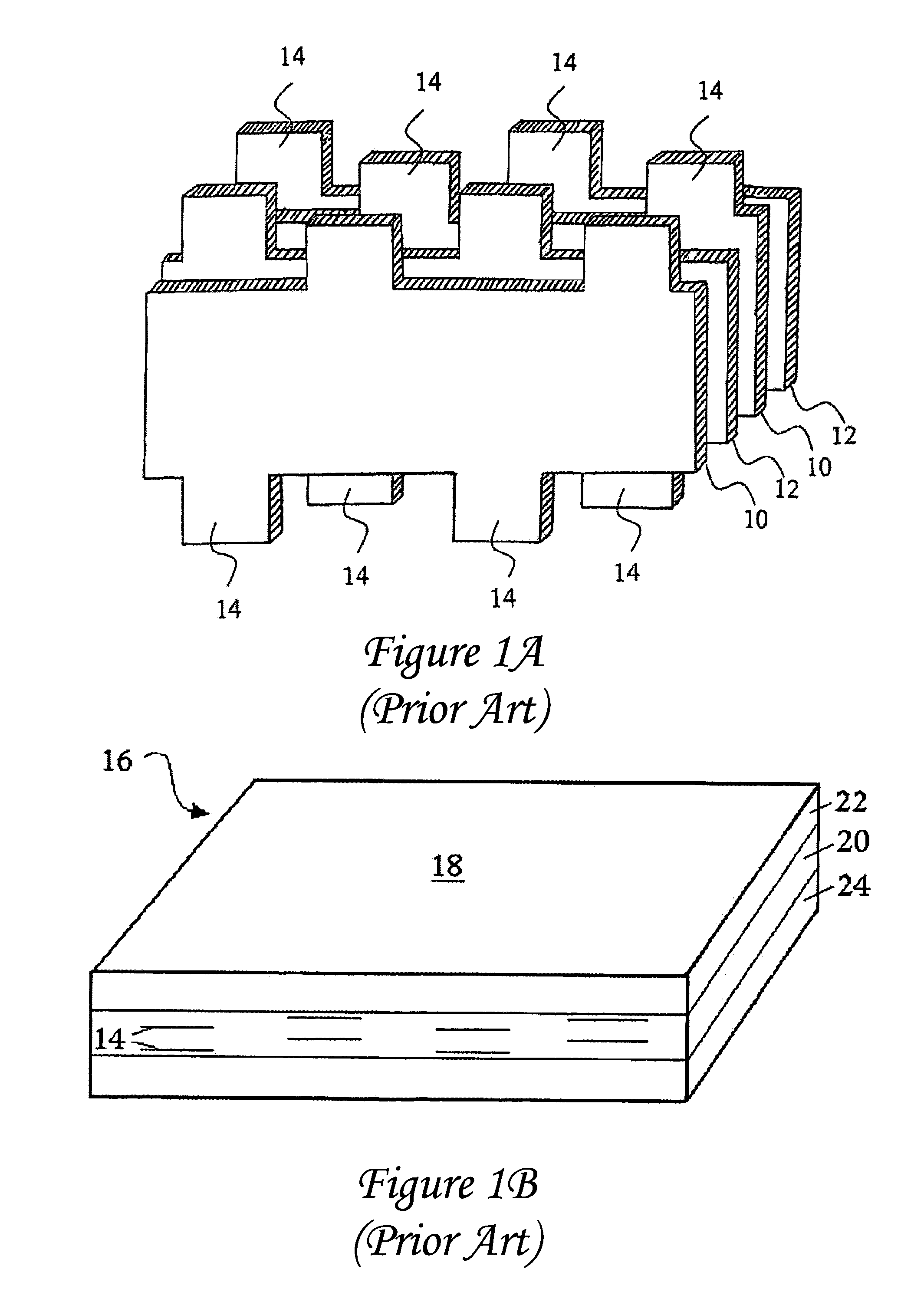

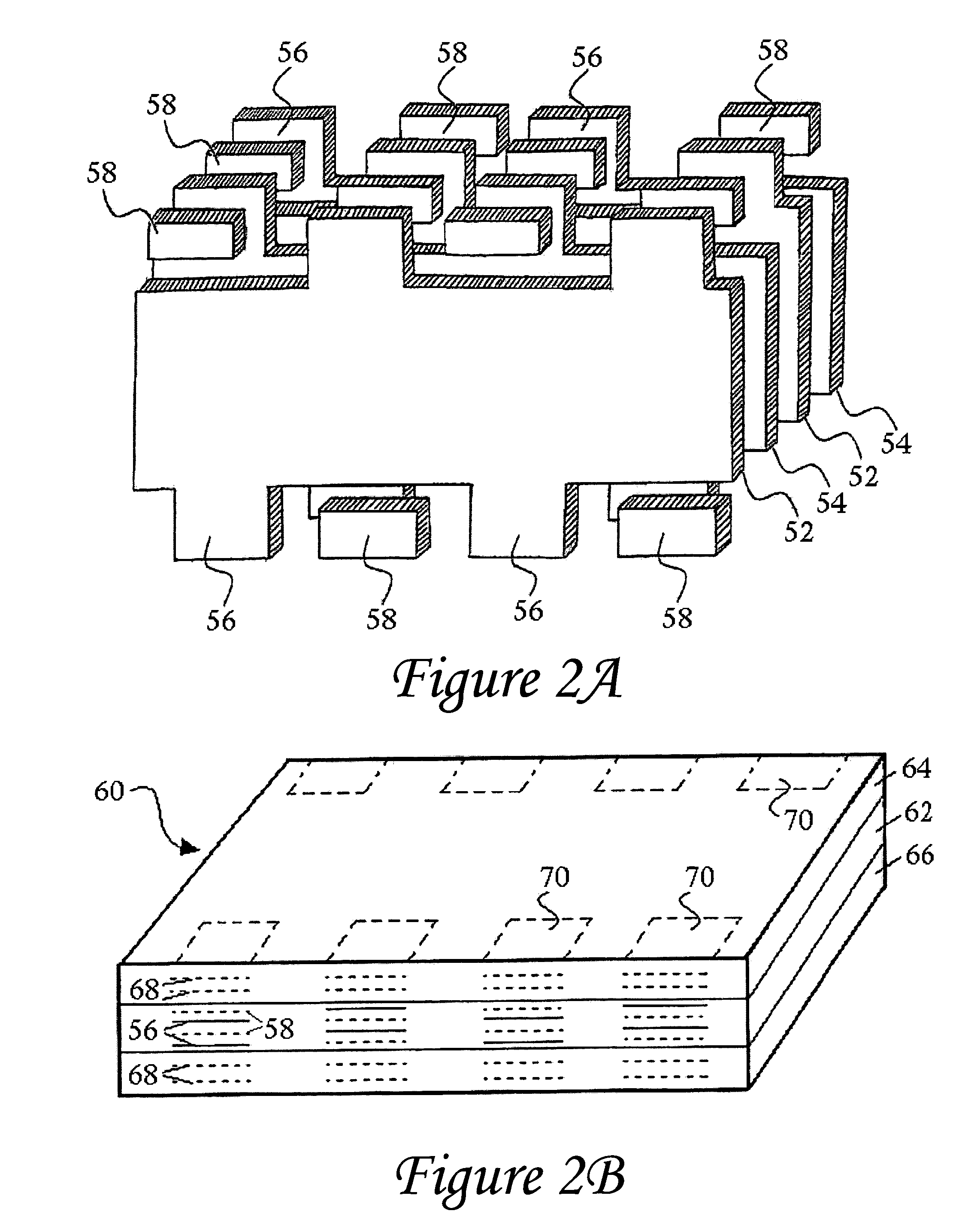

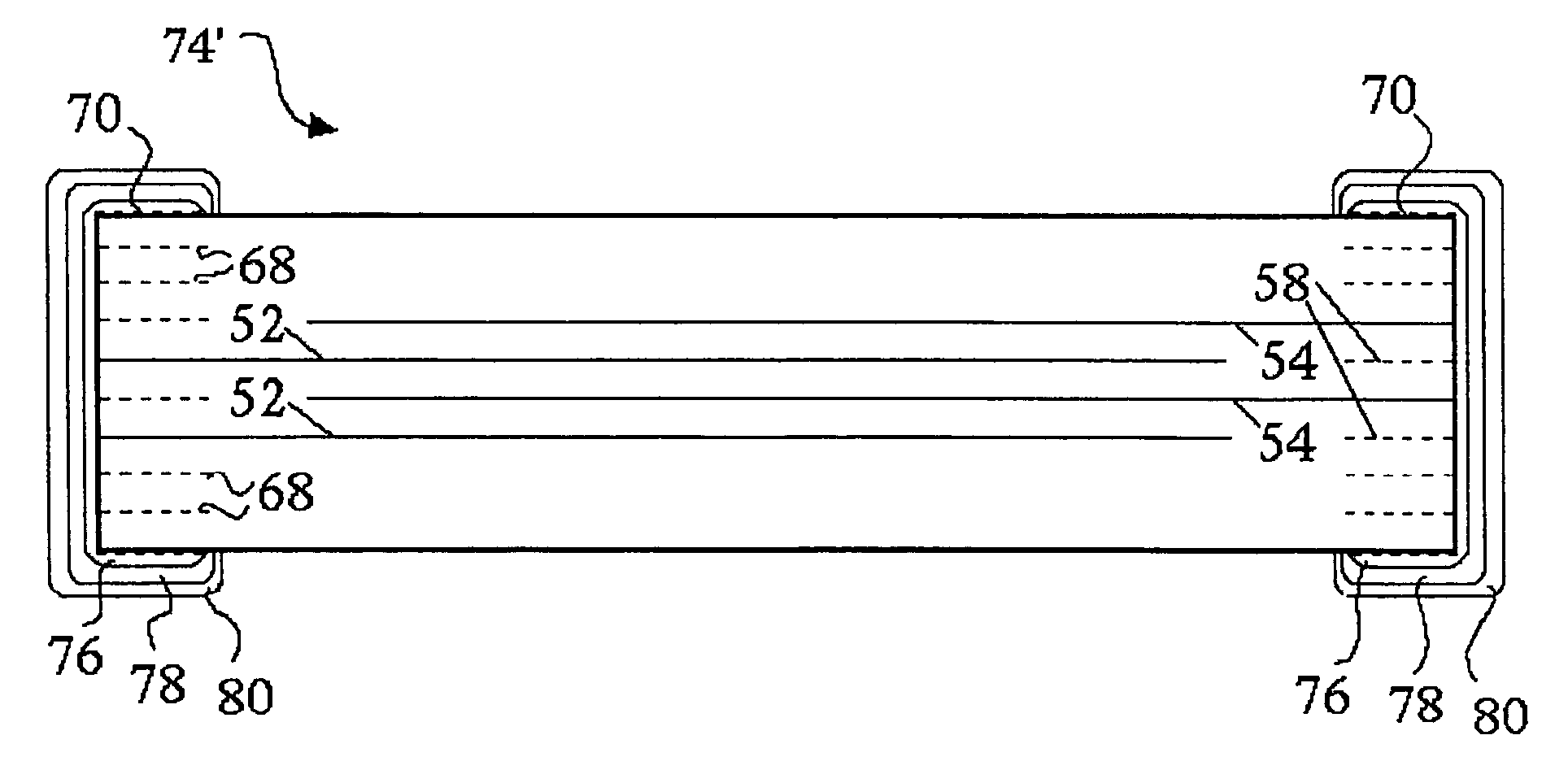

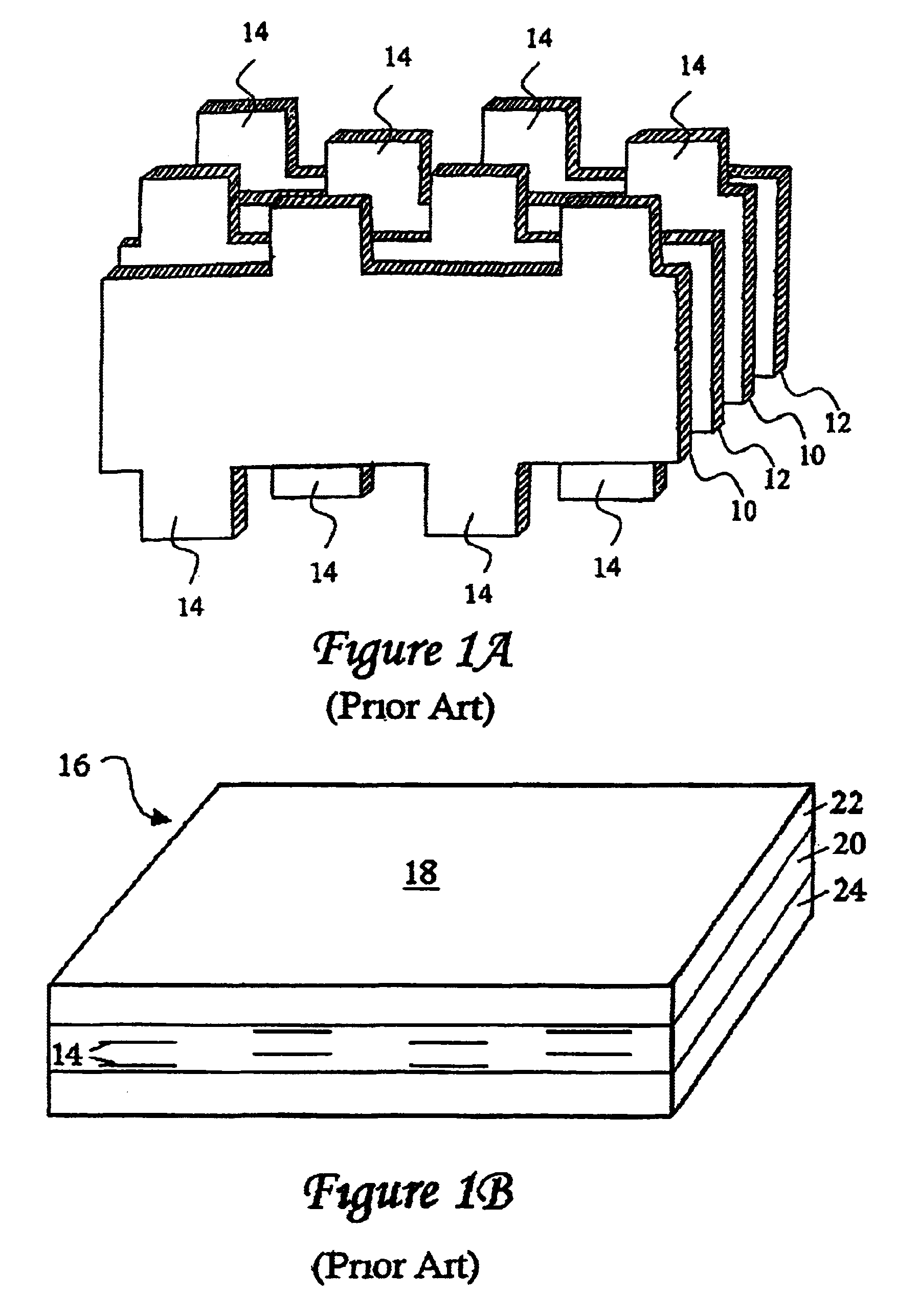

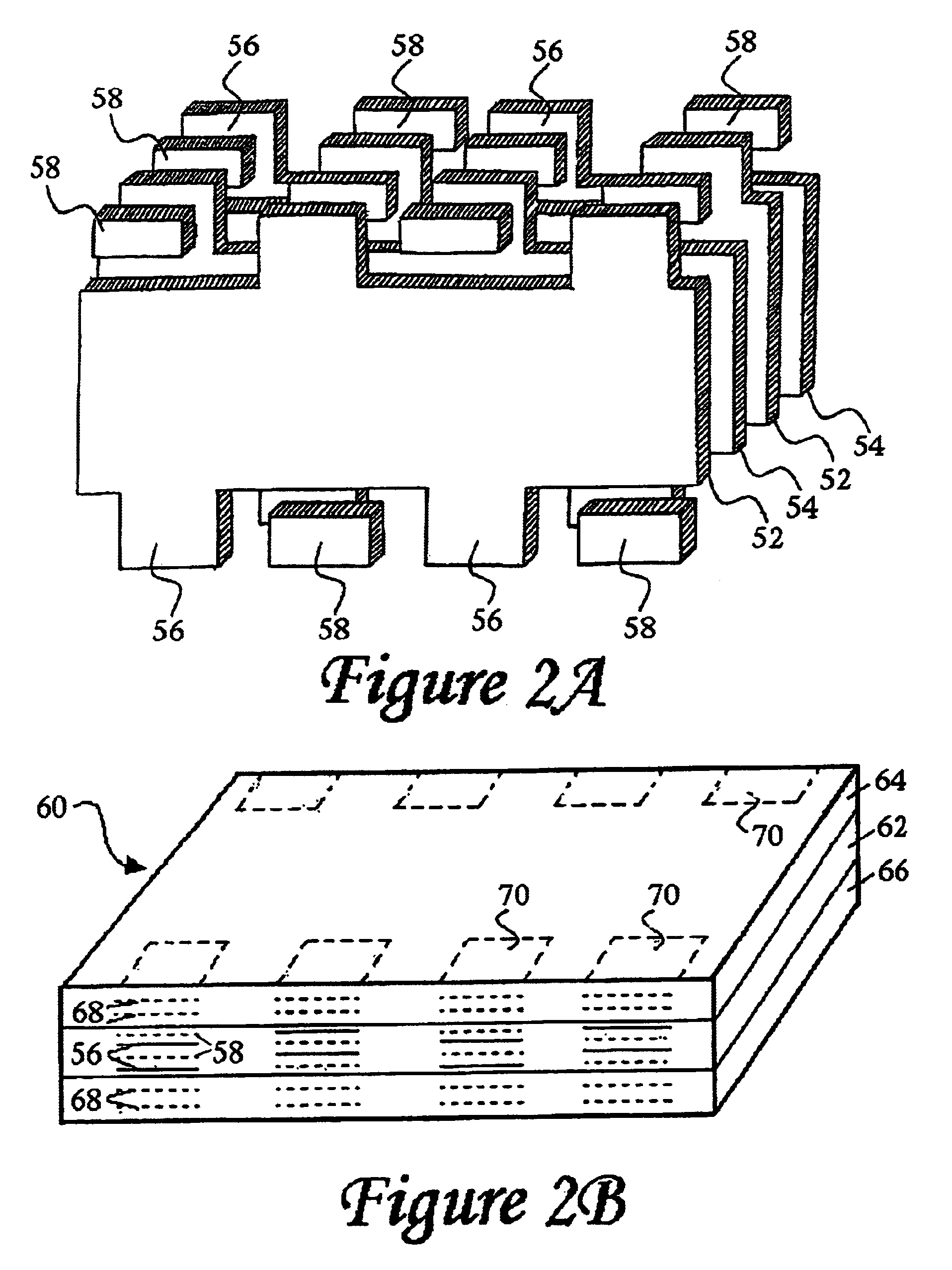

Plated terminations

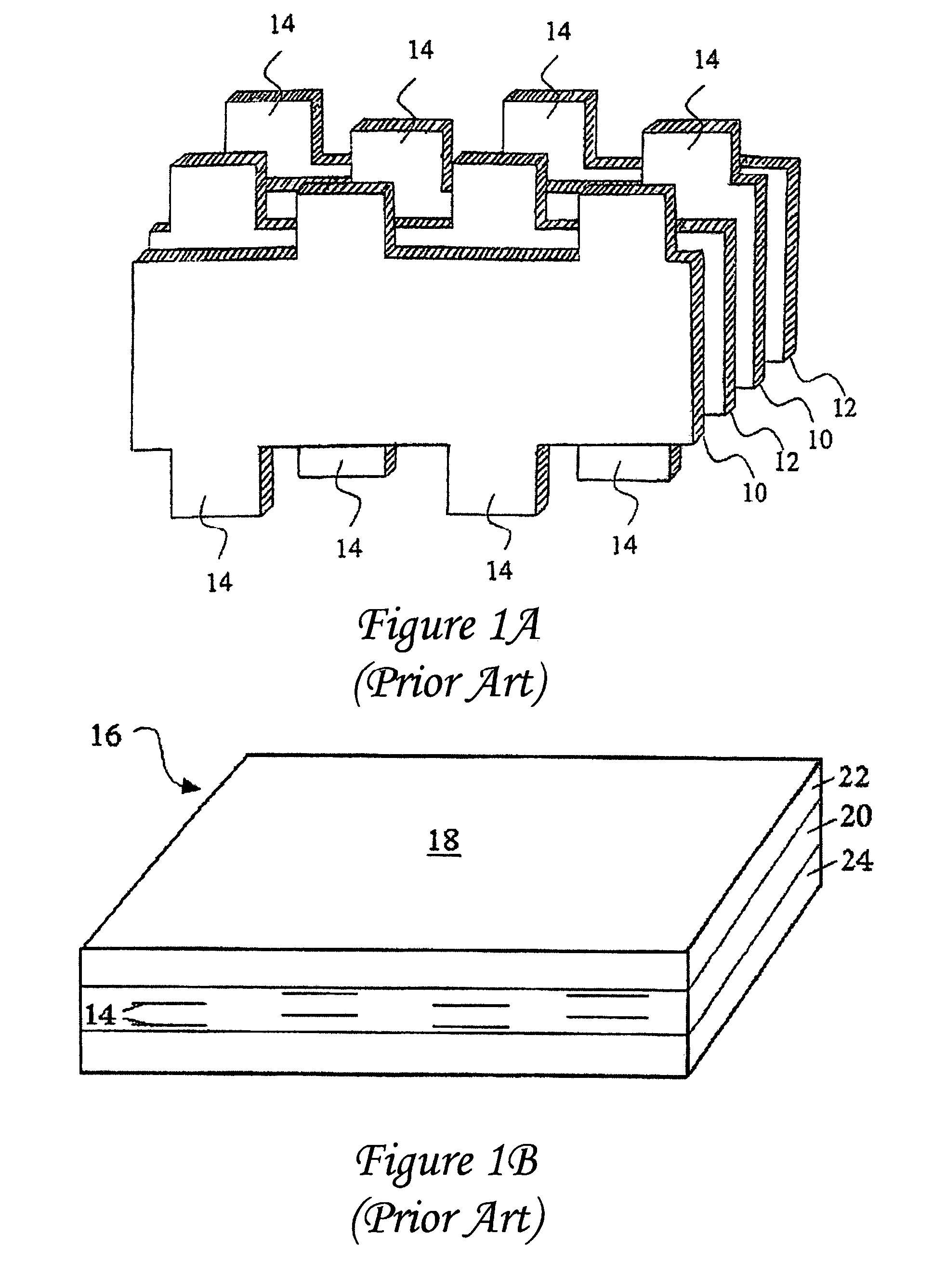

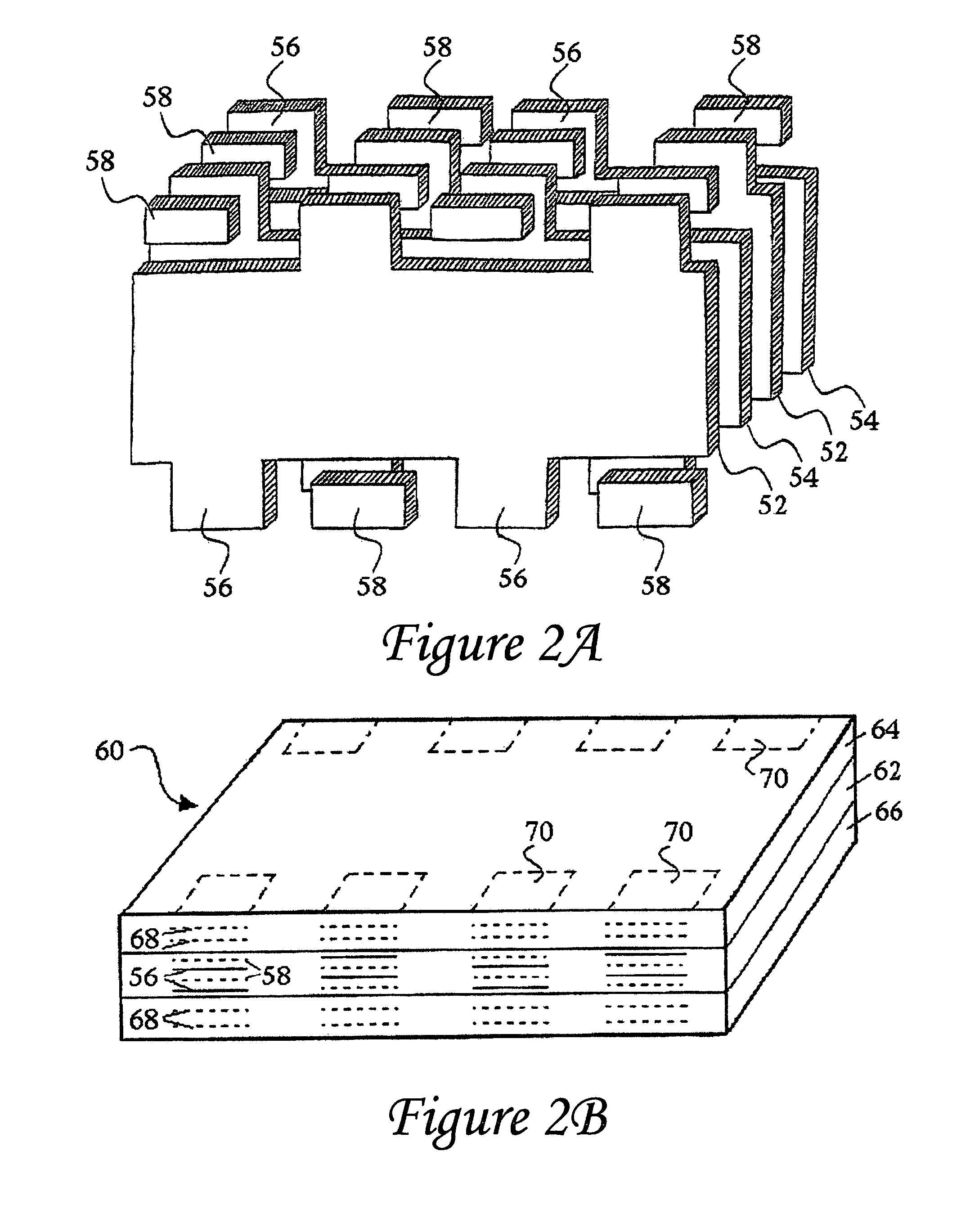

InactiveUS7177137B2Improved termination featureEliminate or greatly simplify thick-film stripesFixed capacitor electrodesFixed capacitor dielectricHigh densityEngineering

A multilayer electronic component includes a plurality of dielectric layers interleaved with a plurality of internal electrode elements and a plurality of internal anchor tabs. Portions of the internal electrode elements and anchor tabs are exposed along the periphery of the electronic component in one or more aligned columns. Each exposed portion is within a predetermined distance from other exposed portions in a given column such that bridged terminations may be formed by depositing one or more plated termination materials over selected of the respectively aligned columns. Internal anchor tabs may be provided and exposed in prearranged relationships with other exposed conductive portions to help nucleate metallized plating material along the periphery of a device. External anchor tabs or lands may be provided to form terminations that extend to top and / or bottom surfaces of the device. Selected of the conductive elements may be formed by a finite volume percentage of ceramic material for enhanced durability, and external lands may be thicker than internal conductive elements and / or may also be embedded in top and / or bottom component surfaces. A variety of potential internal electrode configurations are possible including ones configured for orientation-insensitive component mounting and for high density peripheral termination interdigitated capacitors.

Owner:KYOCERA AVX COMPONENTS CORP

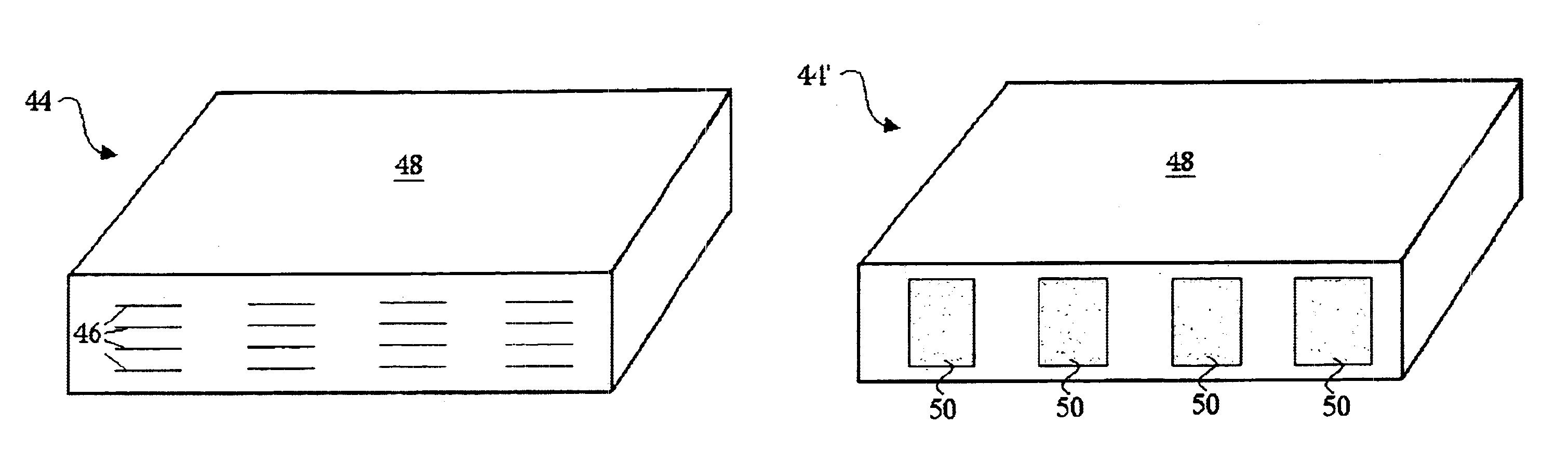

System and method of plating ball grid array and isolation features for electronic components

InactiveUS7463474B2Improved termination featureEliminate or greatly simplify thick-film stripesFixed capacitor dielectricStacked capacitorsEngineeringElectronic component

Owner:KYOCERA AVX COMPONENTS CORP

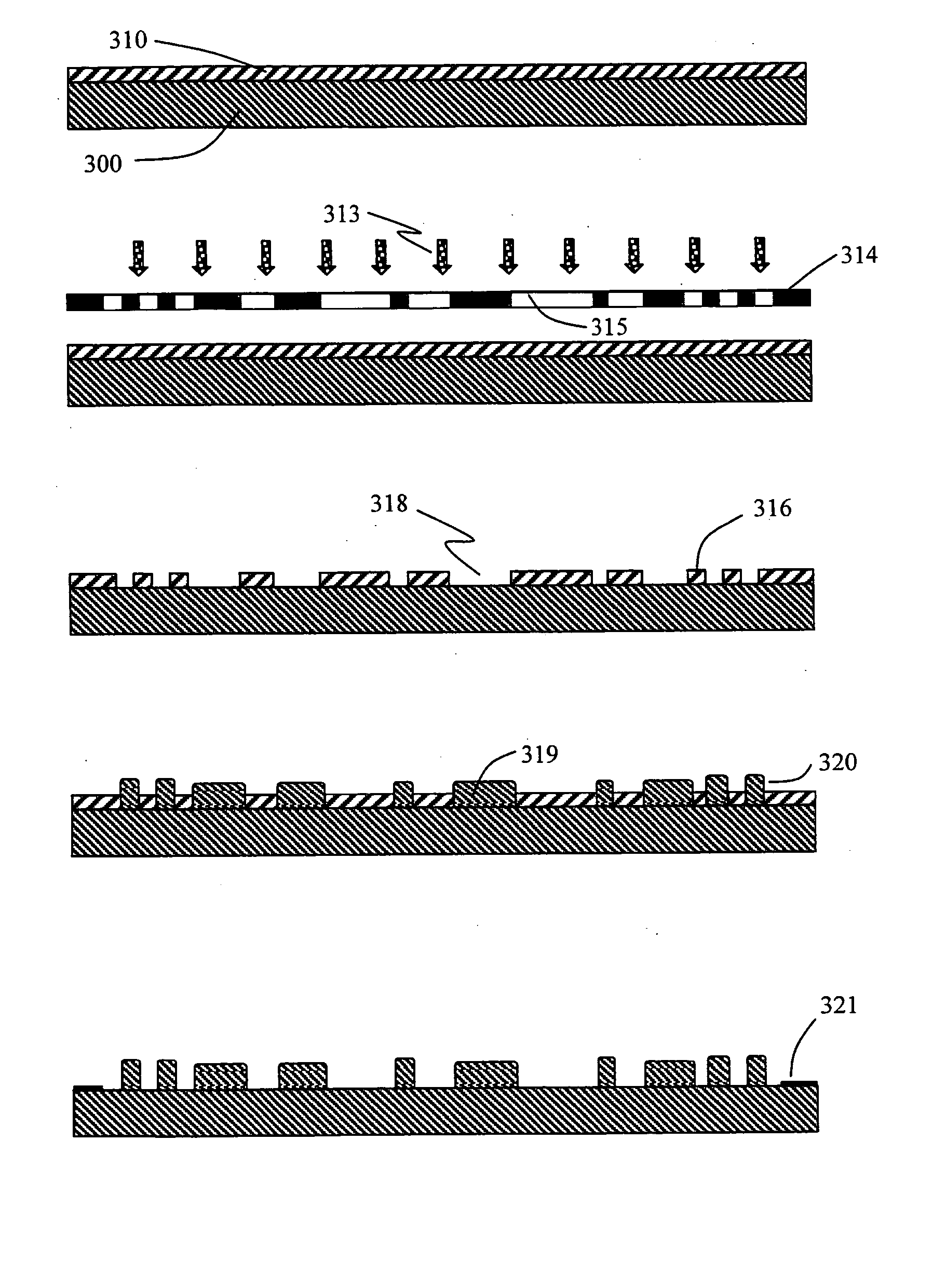

Microfabricated structures and processes for manufacturing same

InactiveUS20050067286A1Minimize surface roughnessEasy to controlElectroforming processesMicroelectromechanical systemsManufacturing technologyCompound (substance)

Various techniques for the fabrication of highly accurate master molds with precisely defined microstructures for use in plastic replication using injection molding, hot embossing, or casting techniques are disclosed herein. Three different fabrication processes used for master mold fabrication are disclosed wherein one of the processes is a combination of the other two processes. In an embodiment of the first process, a two-step electroplating approach is used wherein one of the metals forms the microstructures and the second metal is used as a sacrificial support layer. Following electroplating, the exact height of the microstructures is defined using a chemical mechanical polishing process. In an embodiment of the second process, a modified electroforming process is used for master mold fabrication. The specific modifications include the use of Nickel-Iron (80:20) as a structural component of the master mold, and the use of a higher saccharin concentration in the electroplating bath to reduce tensile stress during plating and electroforming on the top as well as sides of the dummy substrate to prevent peel off of the electroform. The electroforming process is also well suited towards the fabrication of microstructures with non-rectangular cross sectional profiles. Also disclosed is an embodiment of a simple fabrication process using direct deposition of a curable liquid molding material combined with the electroforming process. Finally, an embodiment of a third fabrication process combines the meritorious features of the first two approaches and is used to fabricate a master mold using a combination of the two-step electroplating plus chemical mechanical polishing approach and the electroforming approach to fabricate highly accurate master molds with precisely defined microstructures. The microstructures are an integral part of the master mold and hence the master mold is more robust and well suited for high volume production of plastic MEMS devices through replication techniques such as injection molding.

Owner:CINCINNATI UNIVERISITY OF THE

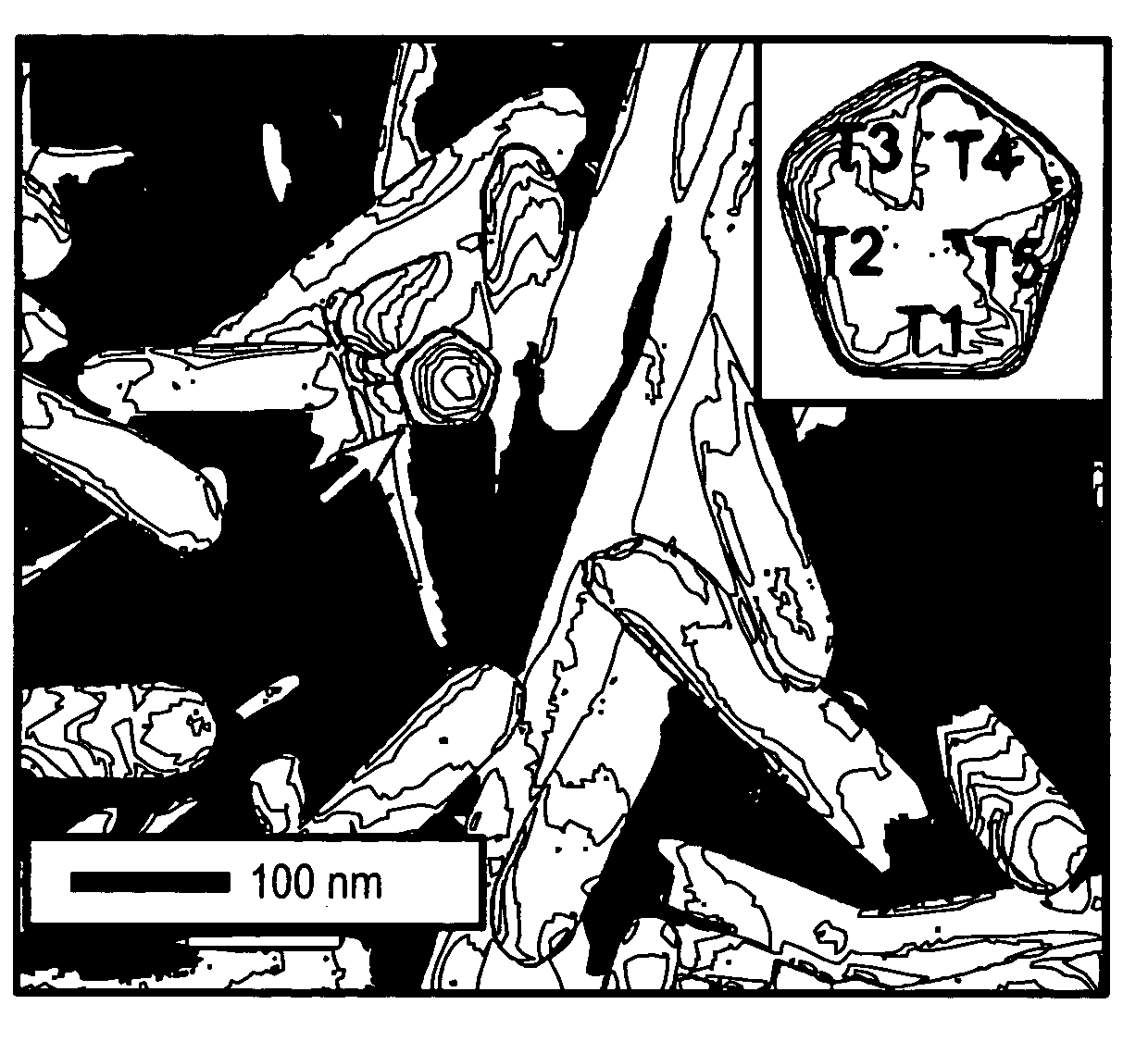

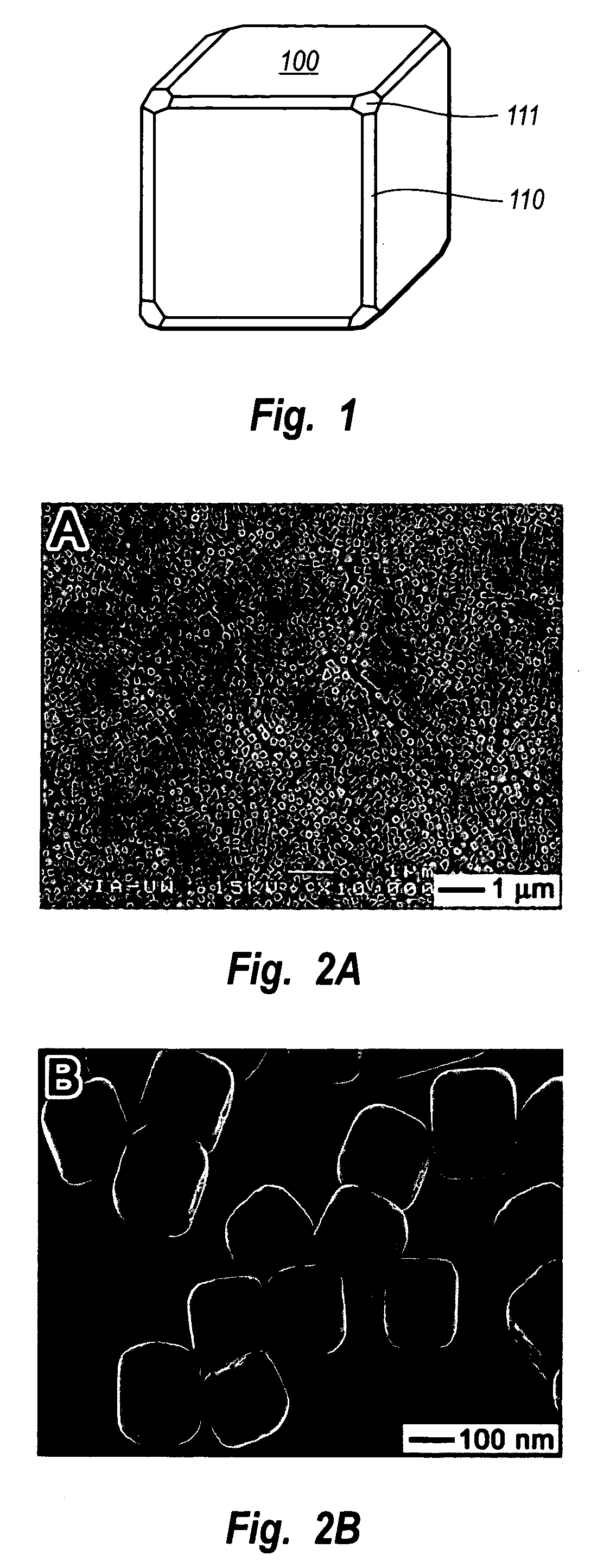

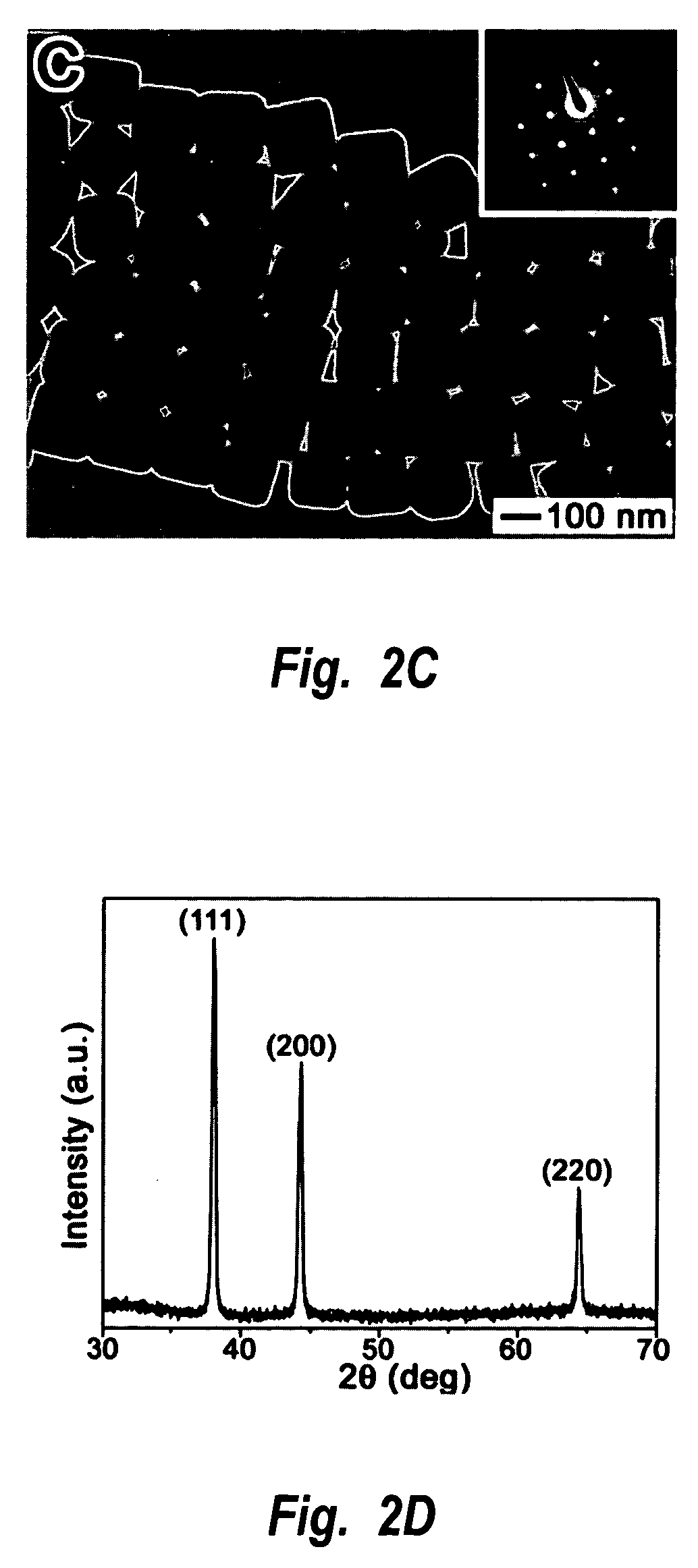

Methods of nanostructure formation and shape selection

Methods for forming nanostructures of various shapes are disclosed. Nanocubes, nanowires, nanopyramids and multiply twinned particles of silver may by formed by combining a solution of silver nitrate in ethylene glycol with a solution of poly(vinyl pyrrolidone) in ethylene glycol. Hollow nanostructures may be formed by reacting a solution of solid nanostructures comprising one of a first metal and a first metal alloy with a metal salt that can be reduced by the first metal or first metal alloy. Nanostructures comprising a core with at least one nanoshell may be formed by plating a nanostructure and reacting the plating with a metal salt.

Owner:UNIV OF WASHINGTON

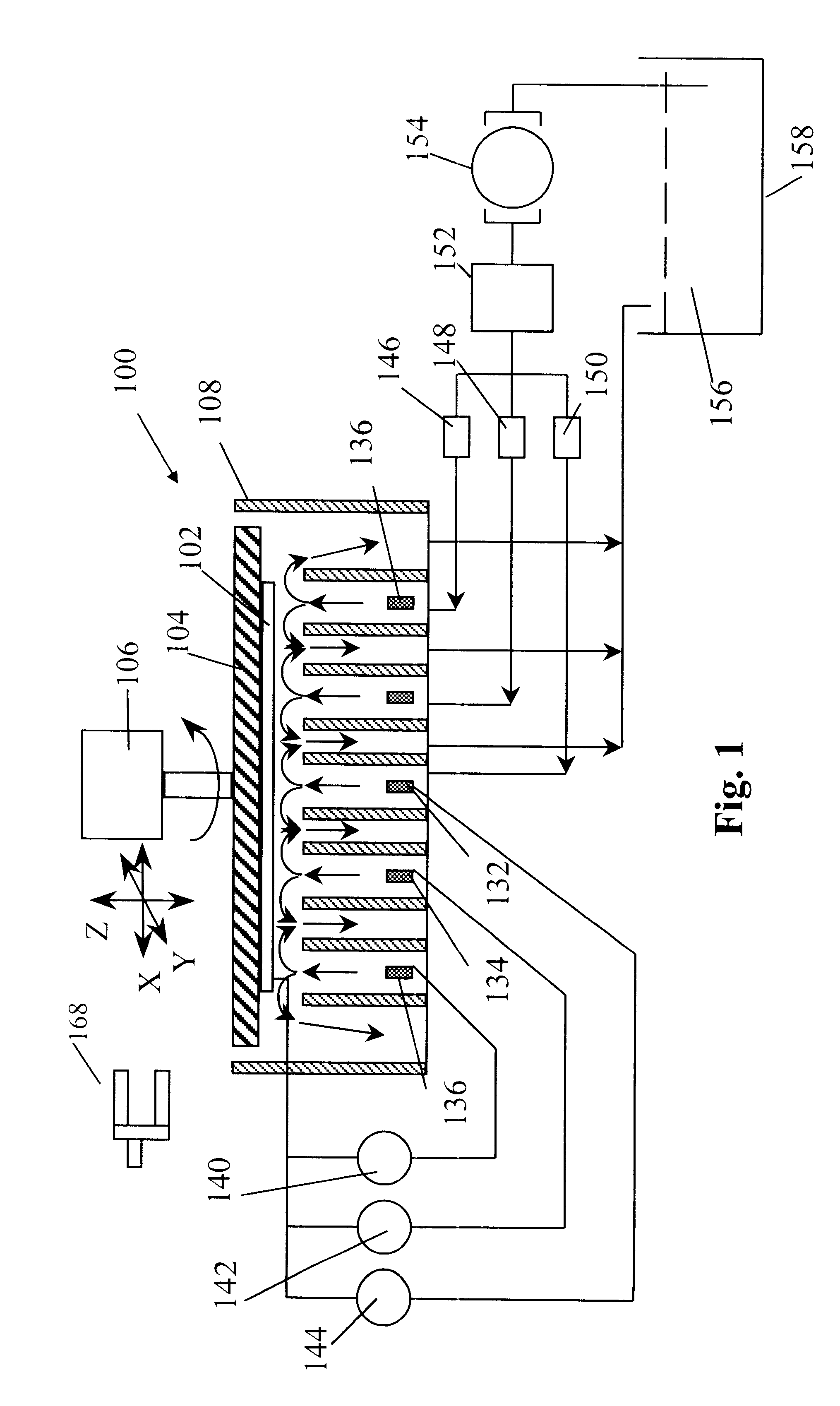

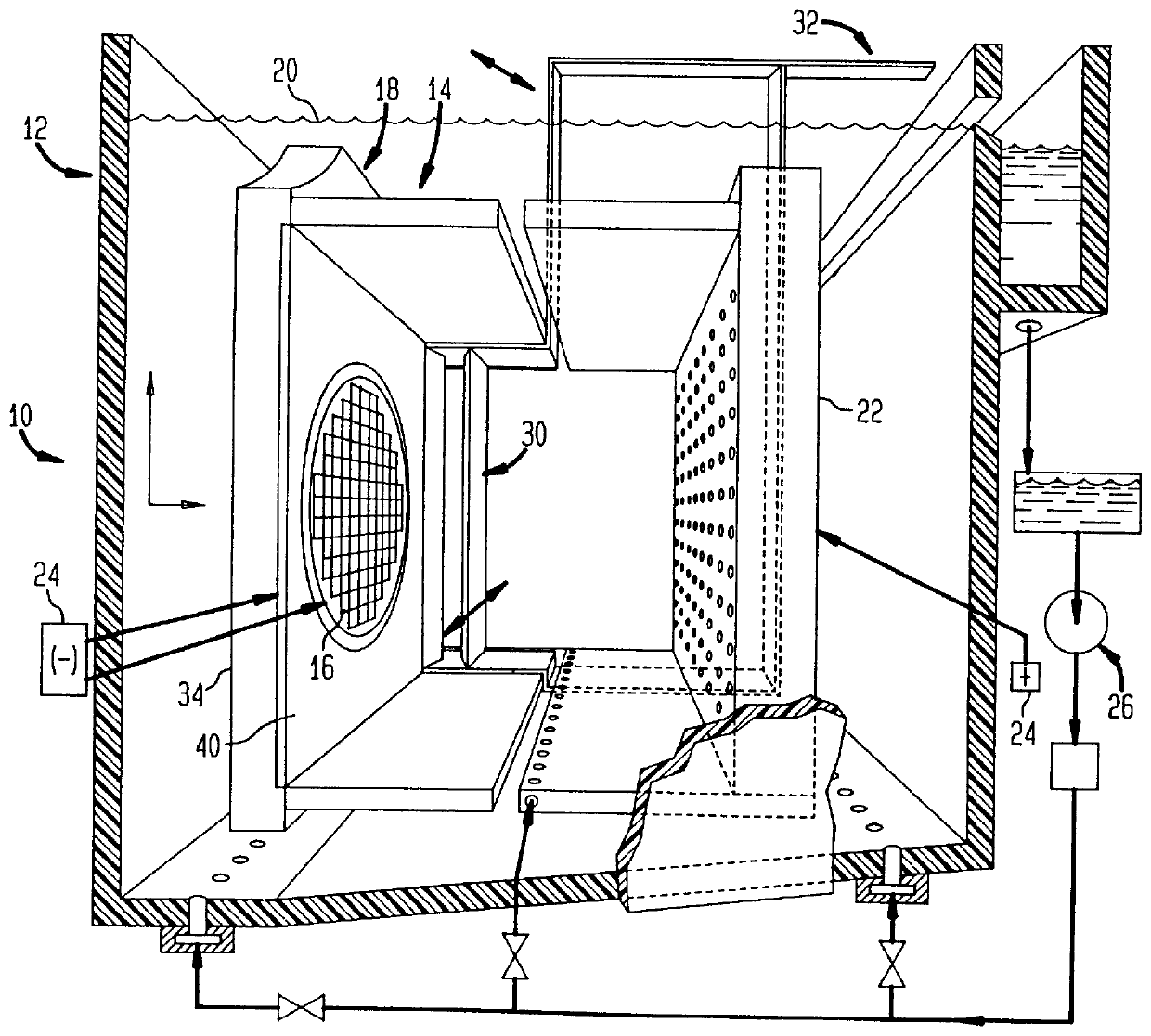

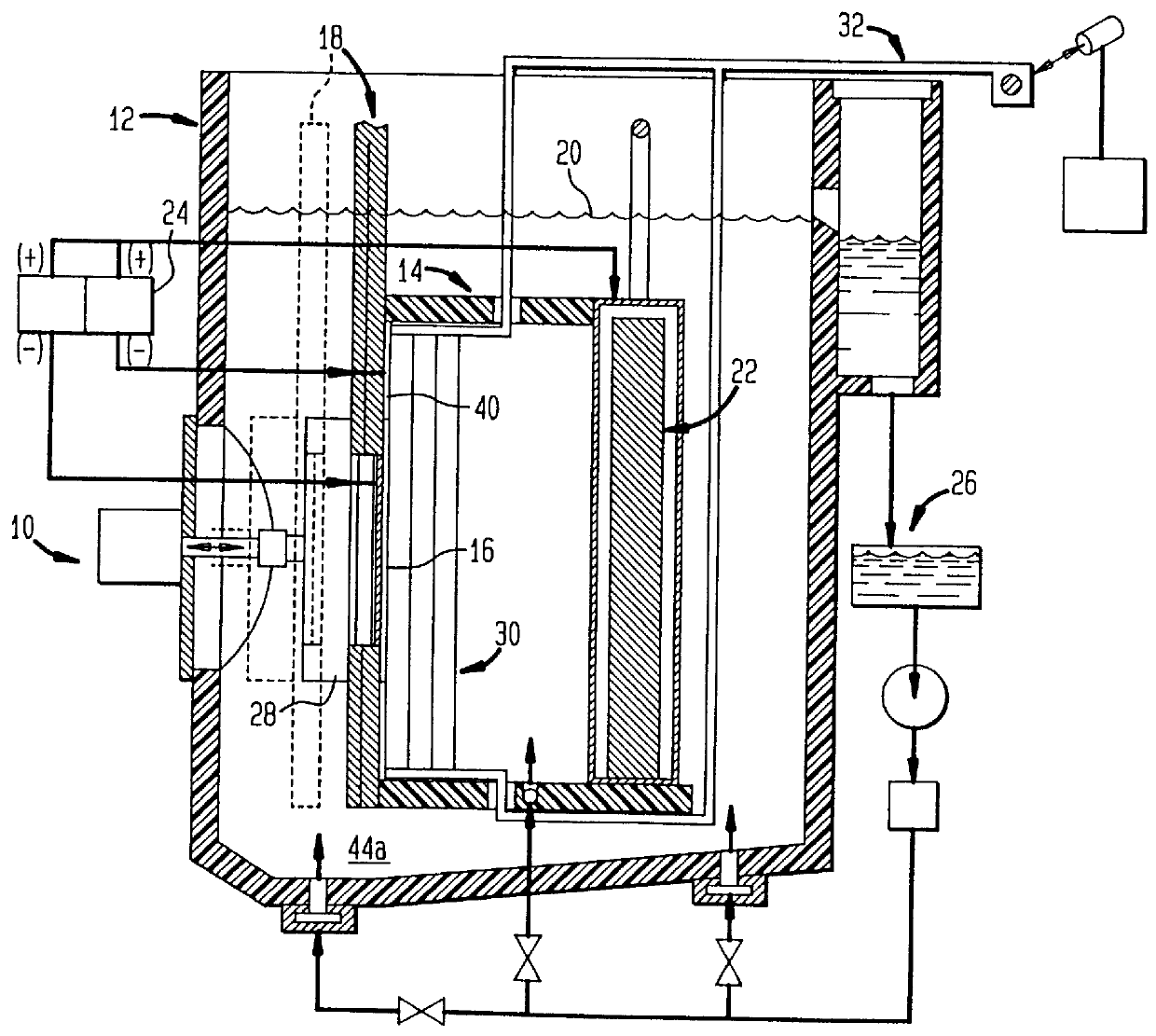

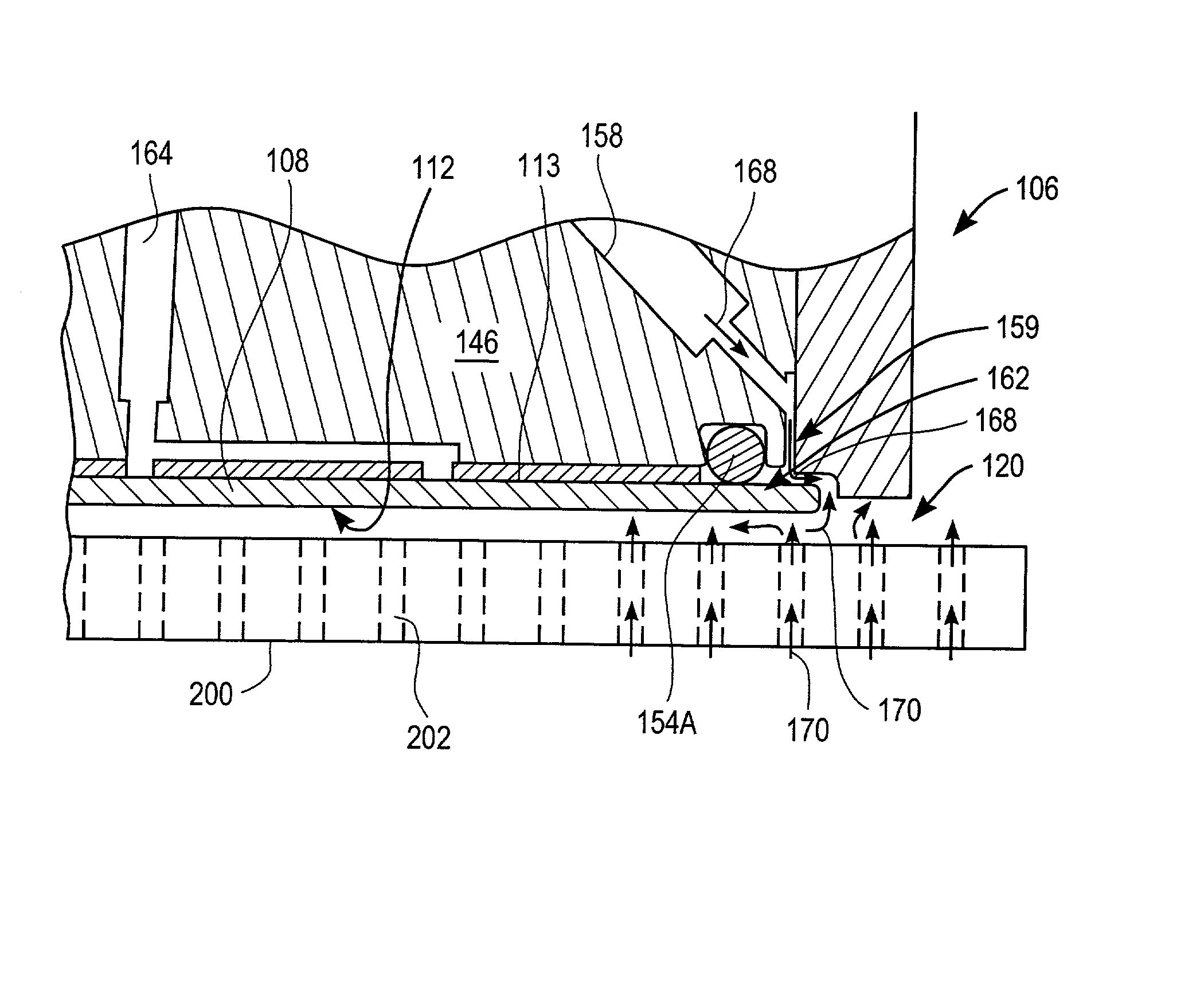

Method and apparatus for electroplating

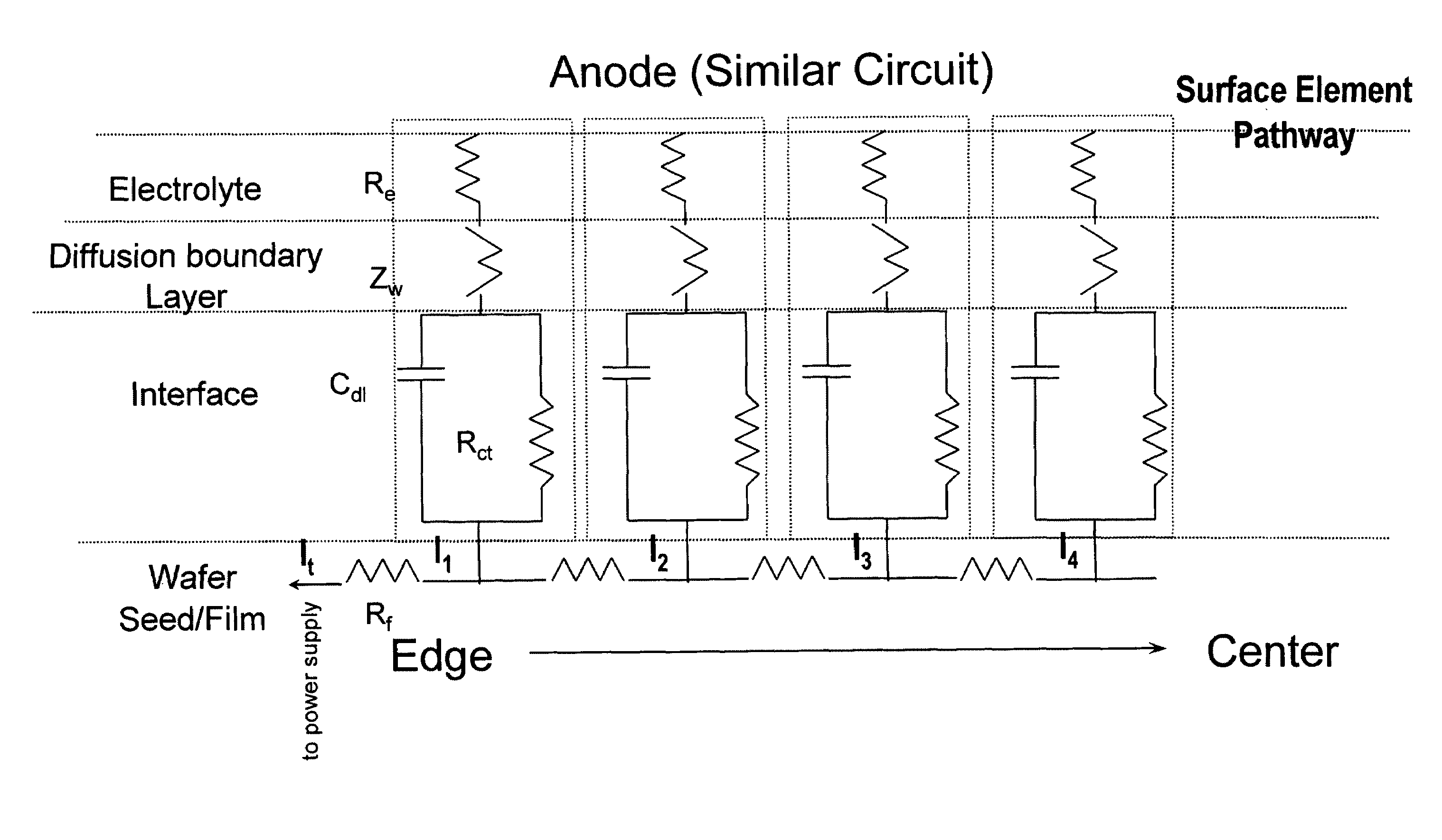

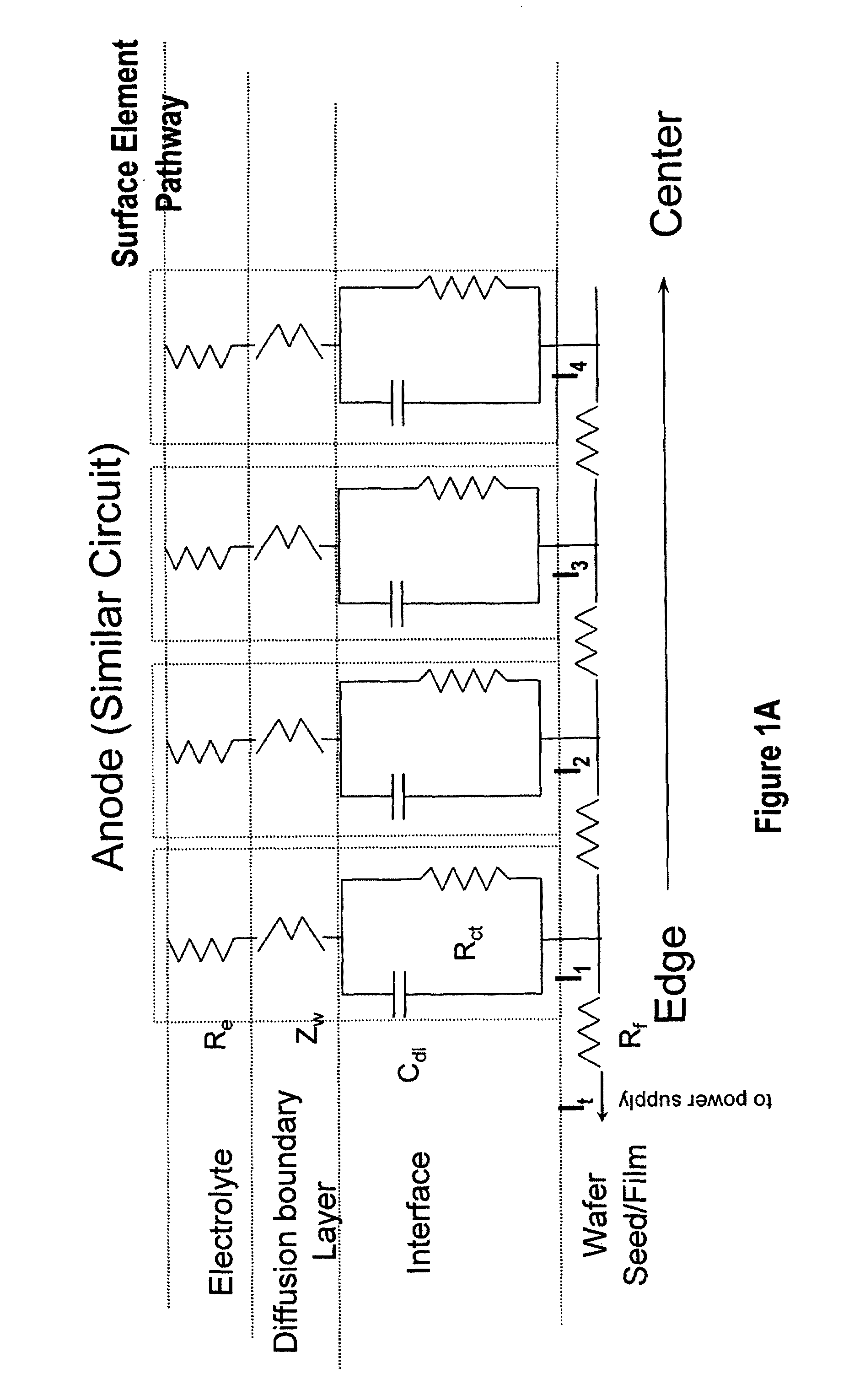

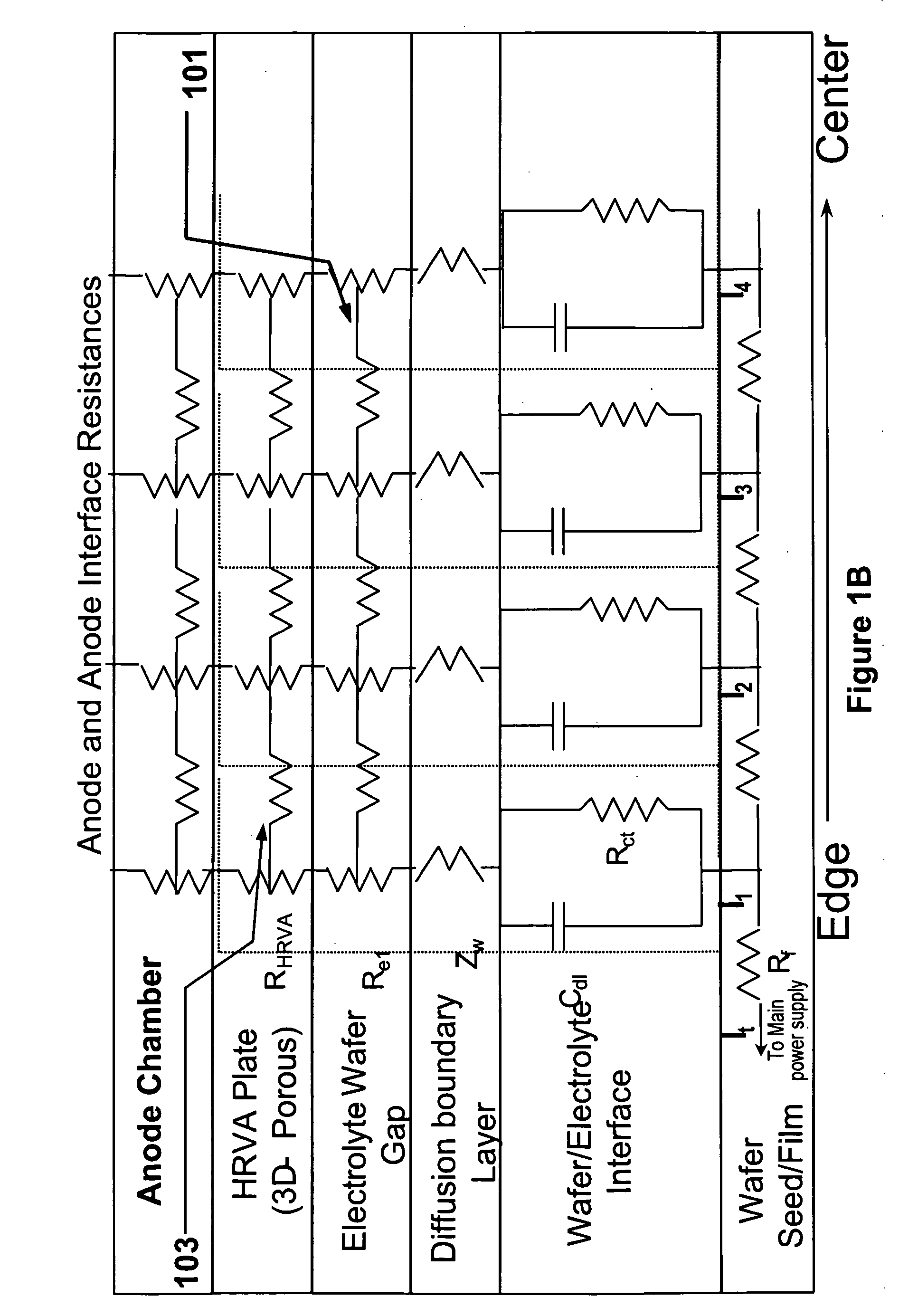

ActiveUS20100032310A1Improve uniformityImprovement becomes significantly less pronounced or non-existentCellsSemiconductor/solid-state device manufacturingElectrical resistance and conductancePower flow

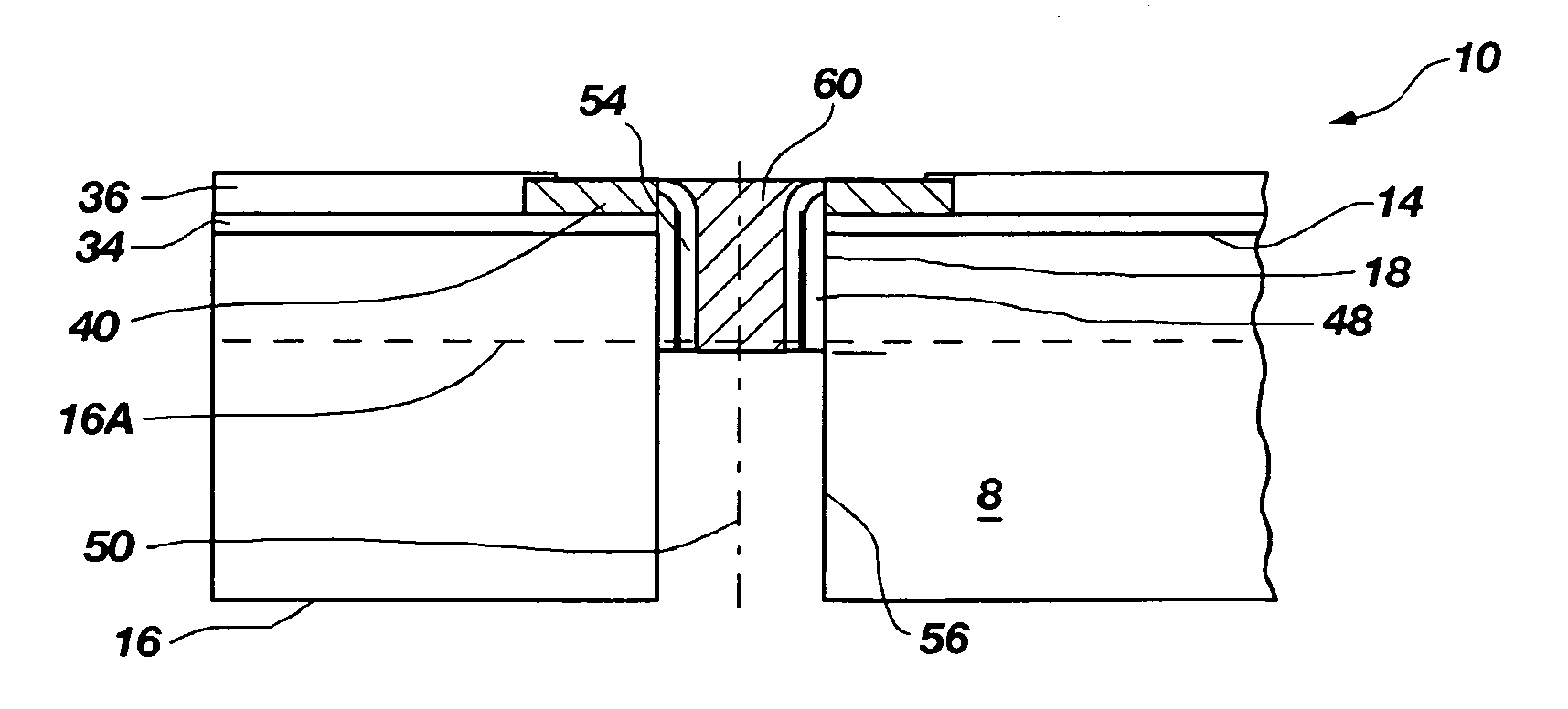

An apparatus for electroplating a layer of metal on the surface of a wafer includes an ionically resistive ionically permeable element located in close proximity of the wafer (preferably within 5 mm of the wafer surface) which serves to modulate ionic current at the wafer surface, and a second cathode configured to divert a portion of current from the wafer surface. The ionically resistive ionically permeable element in a preferred embodiment is a disk made of a resistive material having a plurality of perforations formed therein, such that perforations do not form communicating channels within the body of the disk. The provided configuration effectively redistributes ionic current in the plating system allowing plating of uniform metal layers and mitigating the terminal effect.

Owner:NOVELLUS SYSTEMS

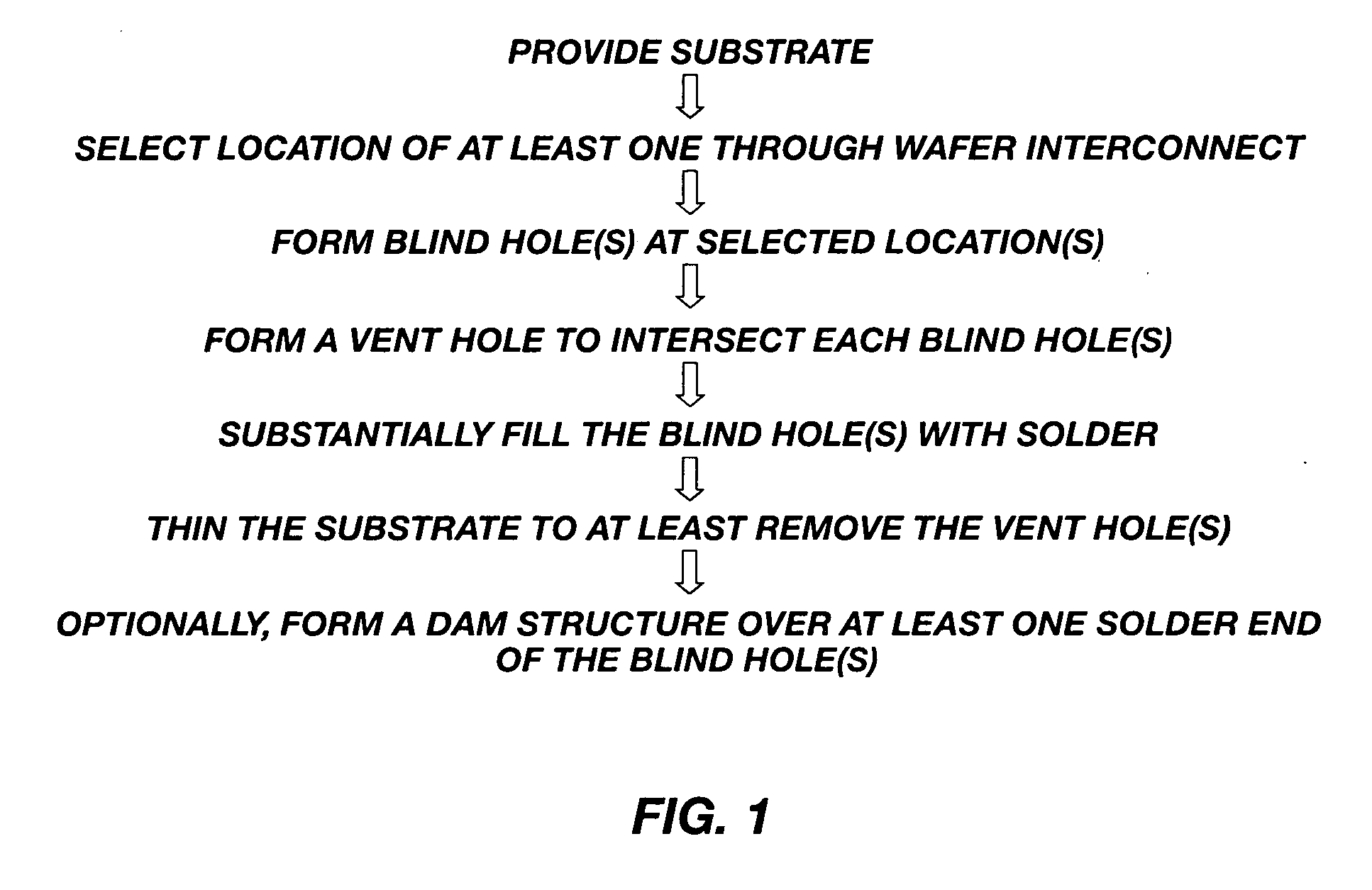

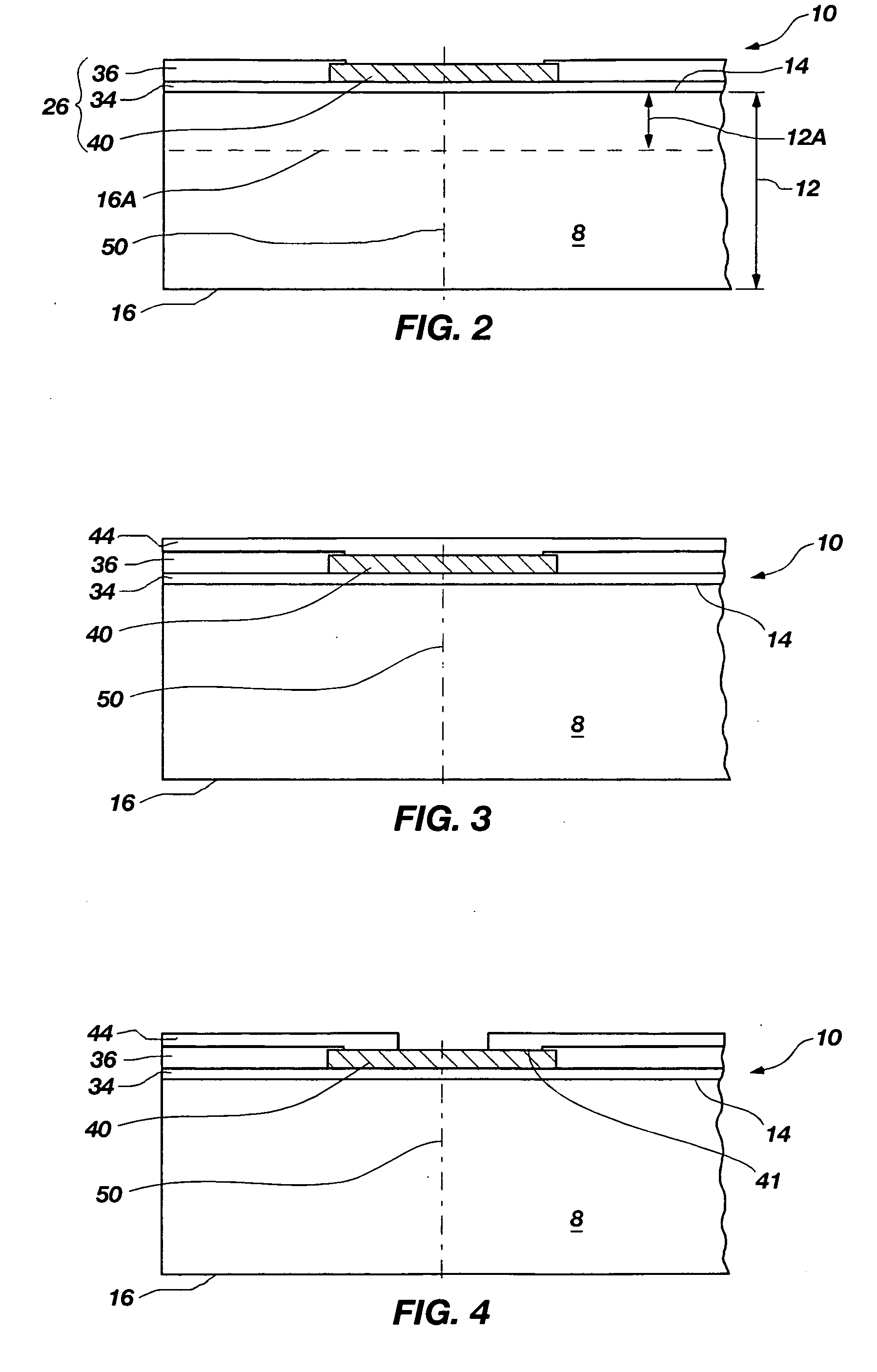

Methods for forming through-wafer interconnects, intermediate structures so formed, and devices and systems having at least one solder dam structure

ActiveUS20070045779A1Conveniently attachedEliminate cross-contaminationSemiconductor/solid-state device detailsSolid-state devicesVitrificationDevice material

A method for forming through-wafer interconnects (TWI) in a substrate of a thickness in excess of that of a semiconductor die such as a semiconductor wafer. Blind holes are formed from the active surface, sidewalls thereof passivated and coated with a solder-wetting material. A vent hole is then formed from the opposite surface (e.g., wafer back side) to intersect the blind hole. The blind hole is solder filled, followed by back thinning of the vent hole portion of the wafer to a final substrate thickness to expose the solder and solder-wetting material at both the active surface and the thinned back side. A metal layer such as nickel, having a glass transition temperature greater than that of the solder, may be plated to form a dam structure covering one or both ends of the TWI including the solder and solder-wetting material to prevent leakage of molten solder from the TWI during high temperature excursions. Intermediate structures of semiconductor devices, semiconductor devices and systems are also disclosed.

Owner:MICRON TECH INC

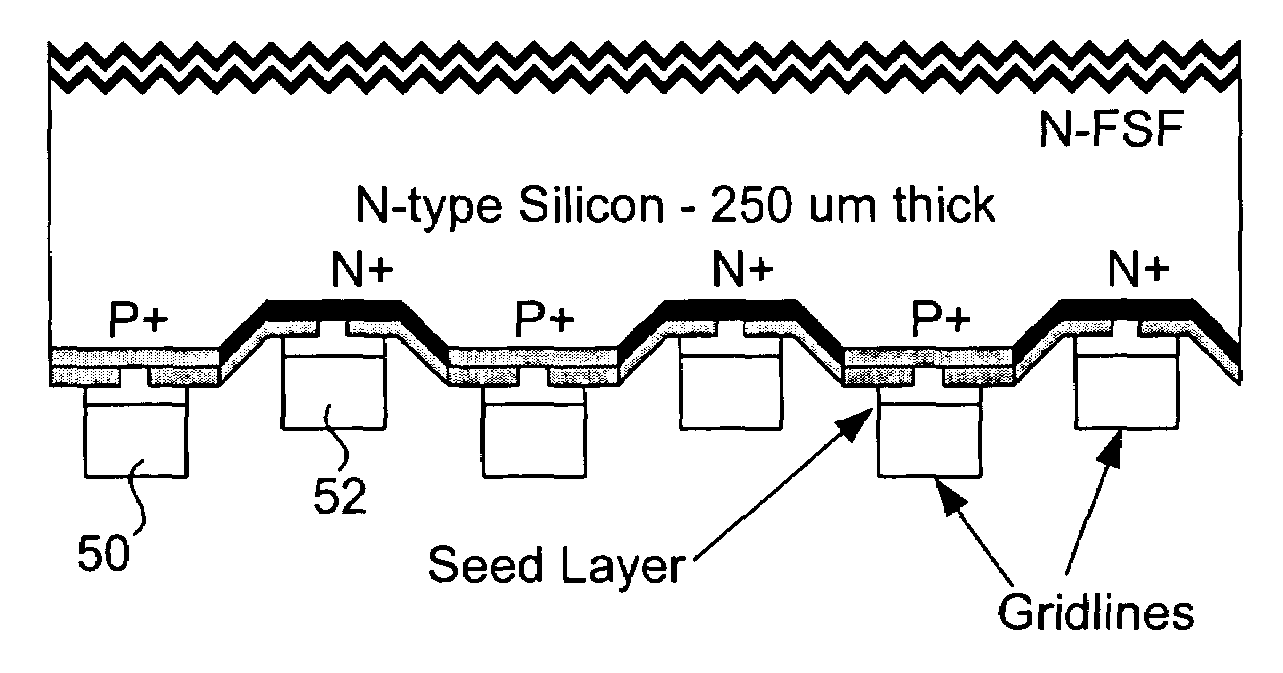

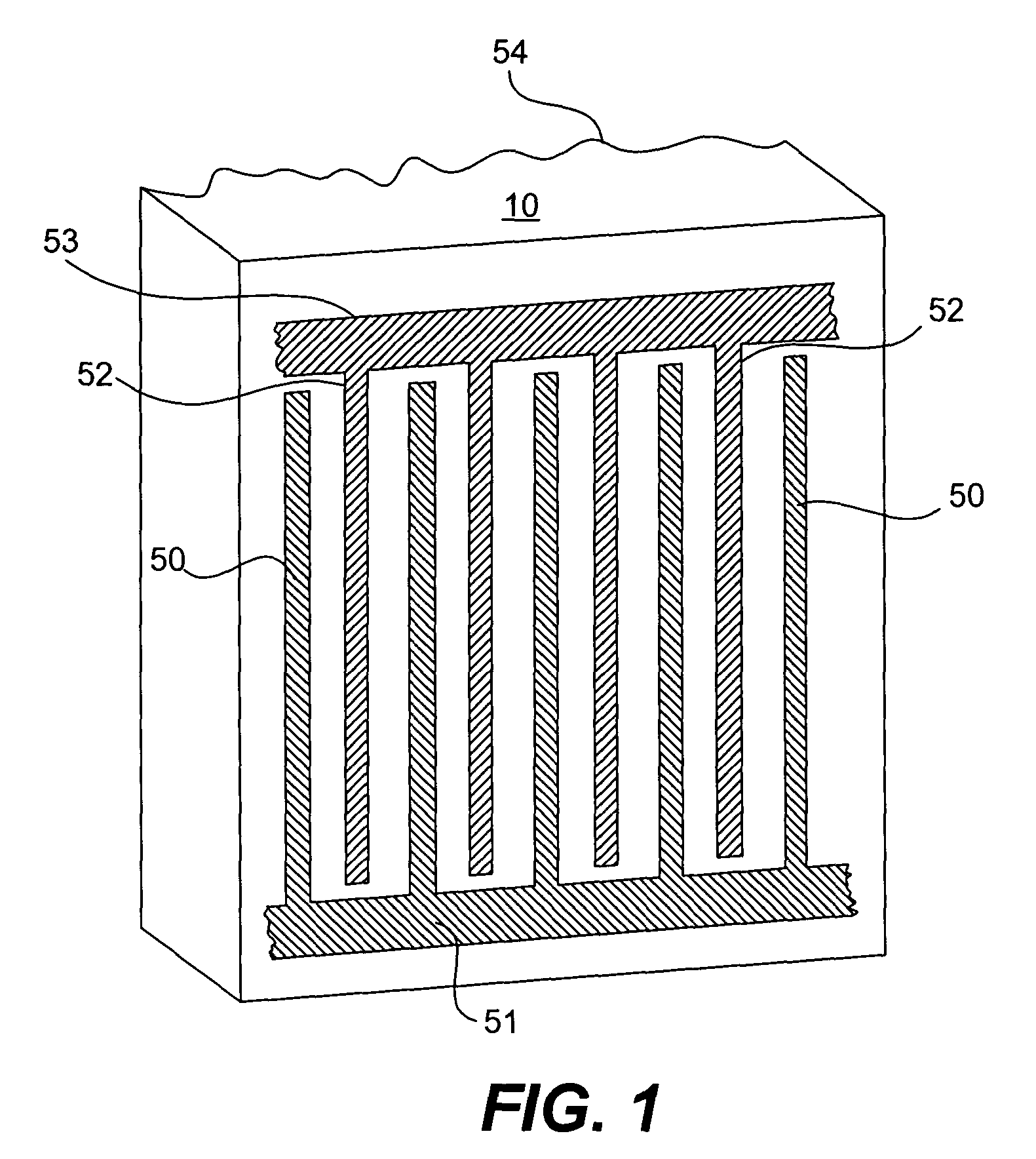

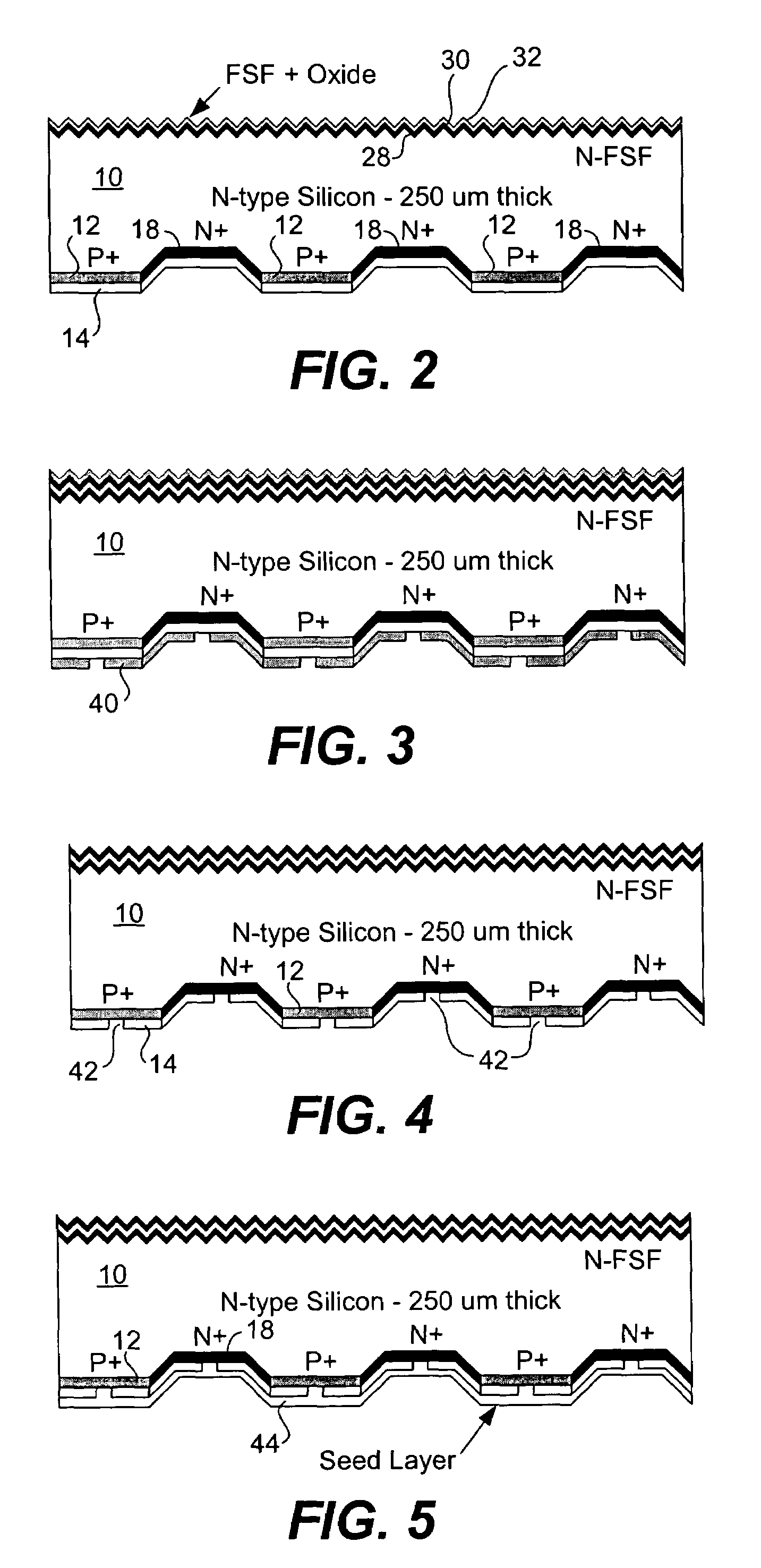

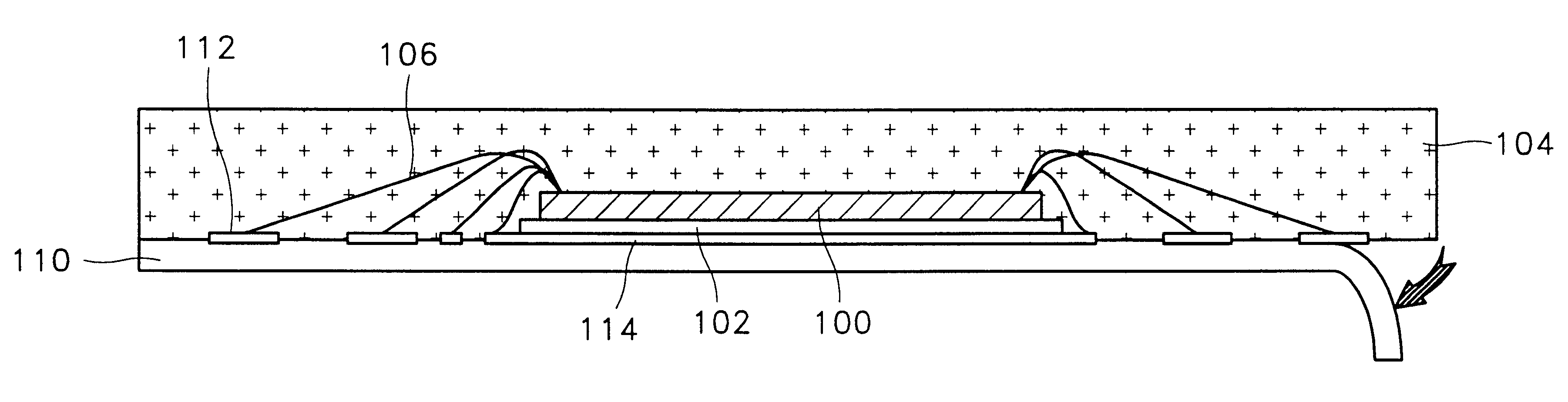

Metal contact structure for solar cell and method of manufacture

In a solar cell having p doped regions and n doped regions alternately formed in a surface of a semiconductor wafer in offset levels through use of masking and etching techniques, metal contacts are made to the p regions and n regions by first forming a base layer contacting the p doped regions and n doped regions which functions as an antireflection layer, and then forming a barrier layer, such as titanium tungsten or chromium, and a conductive layer such as copper over the barrier layer. Preferably the conductive layer is a plating layer and the thickness thereof can be increased by plating.

Owner:CREDIT SUISSE CAYMAN ISLANDS BRANCH +1

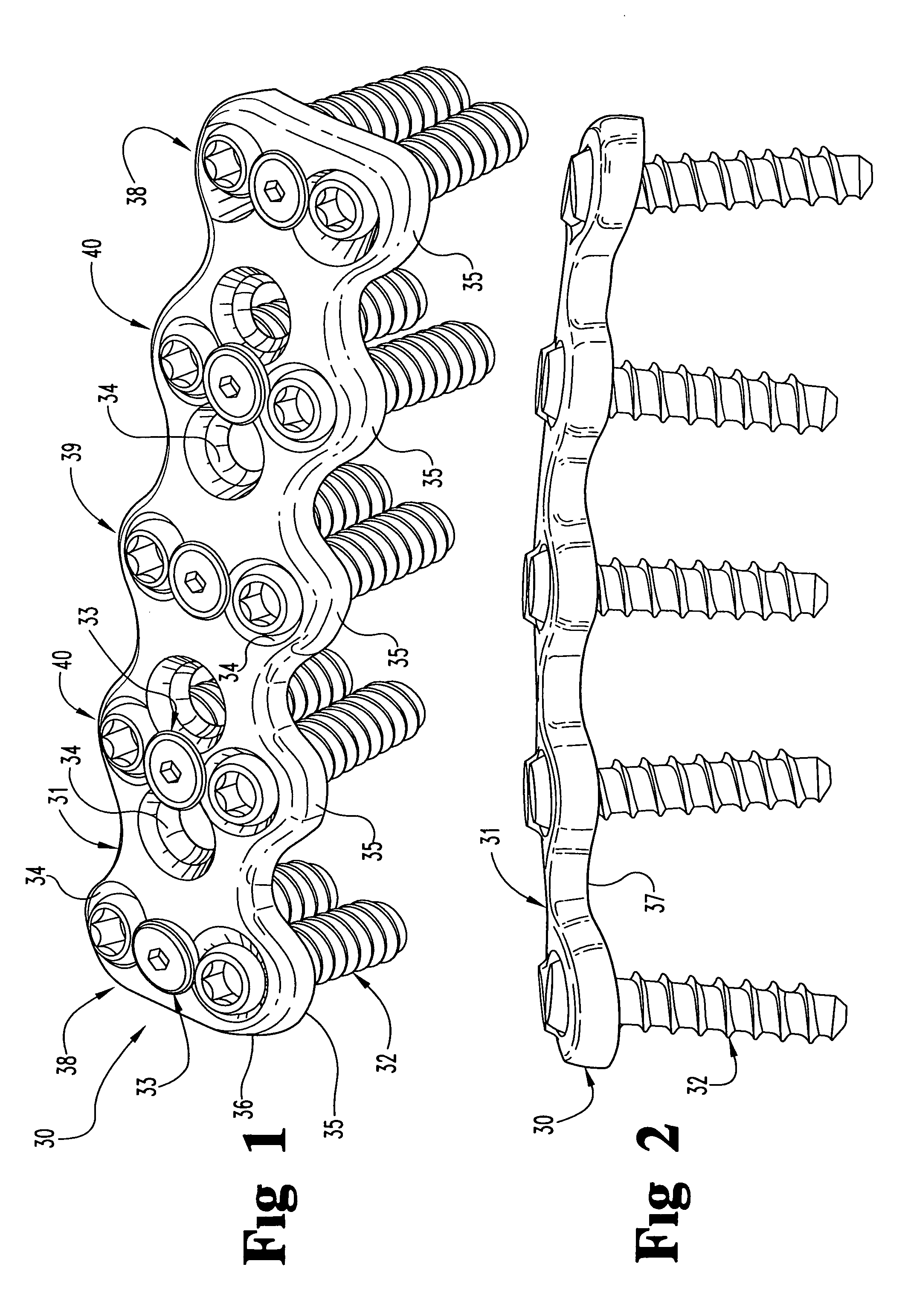

Anterior cervical plating system

In one embodiment of the invention, an anterior fixation system includes a plate defining a plurality of screw holes, a number of screws and a number of locking assemblies for fixing the screws to the plate. The system includes two bone screws a fixed angle screw and a variable angle screw, that are configured to extend through the same screw openings in the fixation plate. The surgeon can select either the fixed or variable angled screws to be implanted with a single plate and can place either type of screw into any of the screw holes along the plate. The fixation plate according to the invention can include several screw holes in various patterns that provide the surgeon with great flexibility in the placement of bone screws depending upon the spinal anatomy and pathology. The invention further contemplates a locking assembly to lock one or more bone screws within a respective screw hole. In one embodiment, the locking assembly includes a washer that is held to the plate by a staked locking screw. The washer includes an outer surface that overlaps one or more screw holes. The washer is initially loosely held to the plate by the locking screw so that various tools and bone screws can be passed through the screw holes. In one embodiment of the washer, the washer includes cut-outs corresponding to the screw holes, along with a notch and key configuration for setting the locking washer in its locked configuration.

Owner:SDGI HLDG

Plated terminations

InactiveUS6960366B2Improved termination featureEliminate and greatly simplifyResistor terminals/electrodesFinal product manufactureTermination problemEngineering

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on one or both of top and bottom surfaces of a monolithic structure can facilitate the formation of selective wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

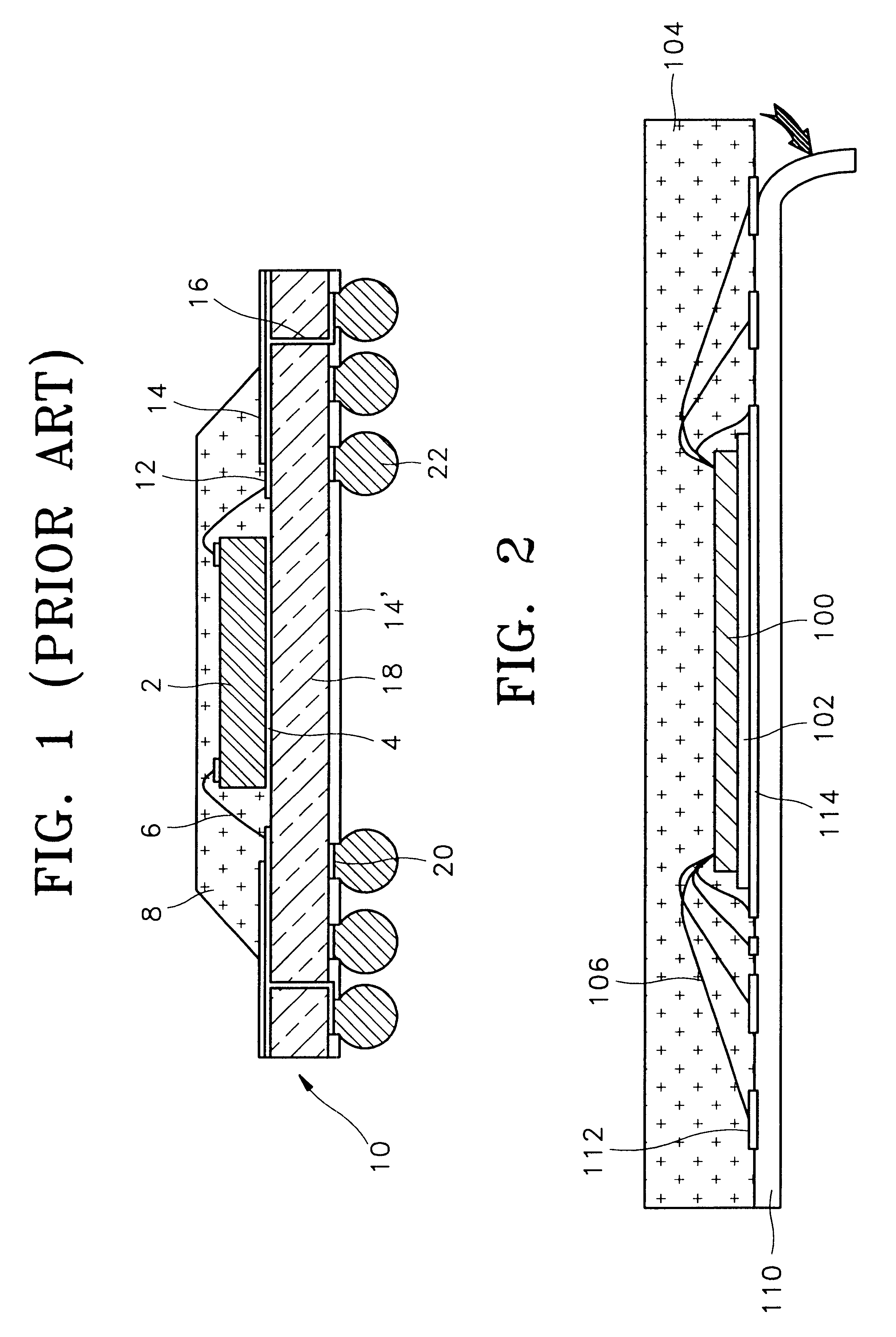

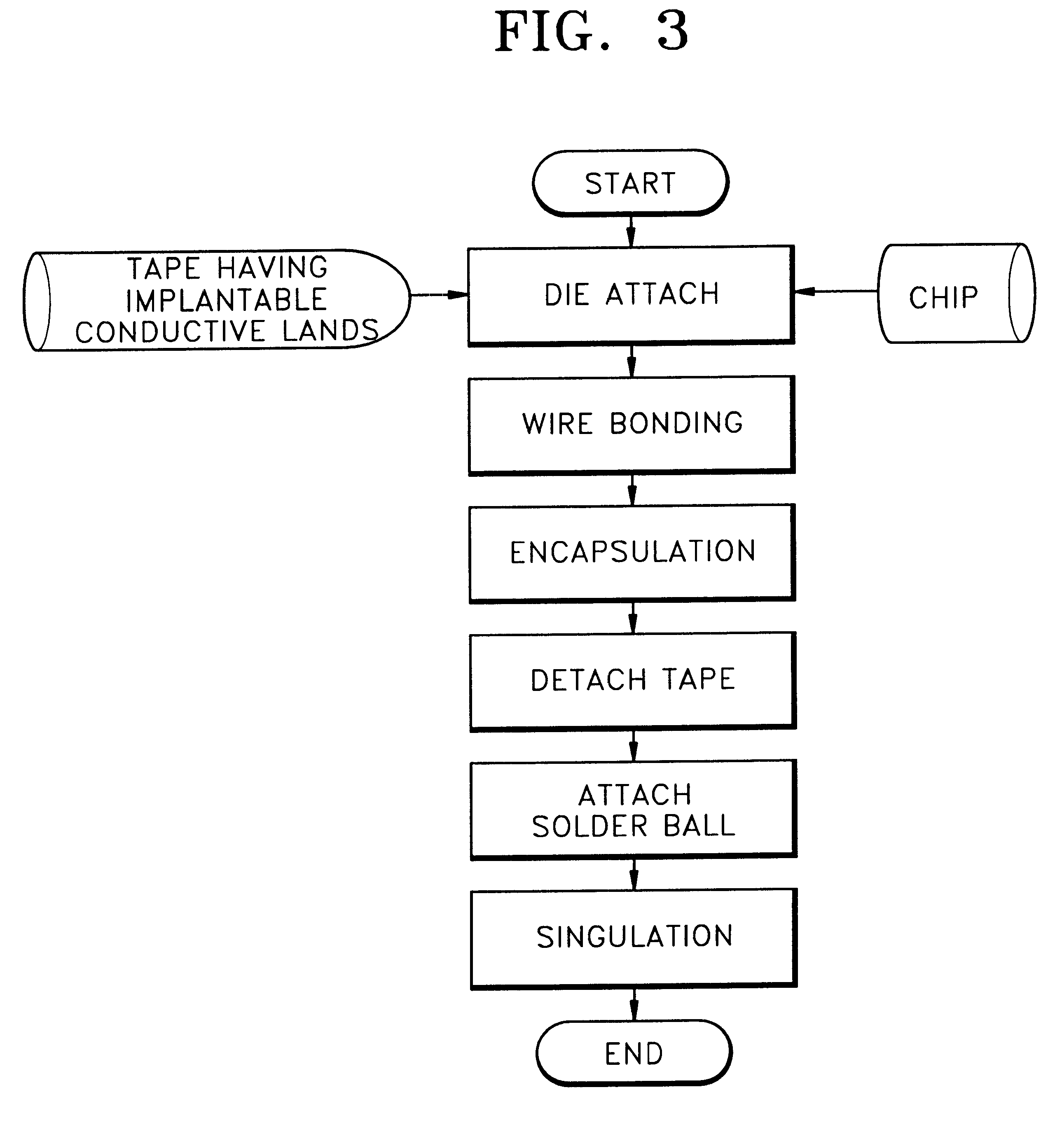

Tape having implantable conductive lands for semiconductor packaging process and method for manufacturing the same

InactiveUS6507096B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

Owner:KOSTAT SEMICON

PCRAM memory cell and method of making same

An inverted PCRAM cell is formed by plating the bottom electrode, made of copper for example, with a conductive material, such as silver. Chalcogenide material is disposed over the plated electrode and subjected to a conversion process so that ions from the plated material diffuse into the chalcogenide material.

Owner:MICRON TECH INC

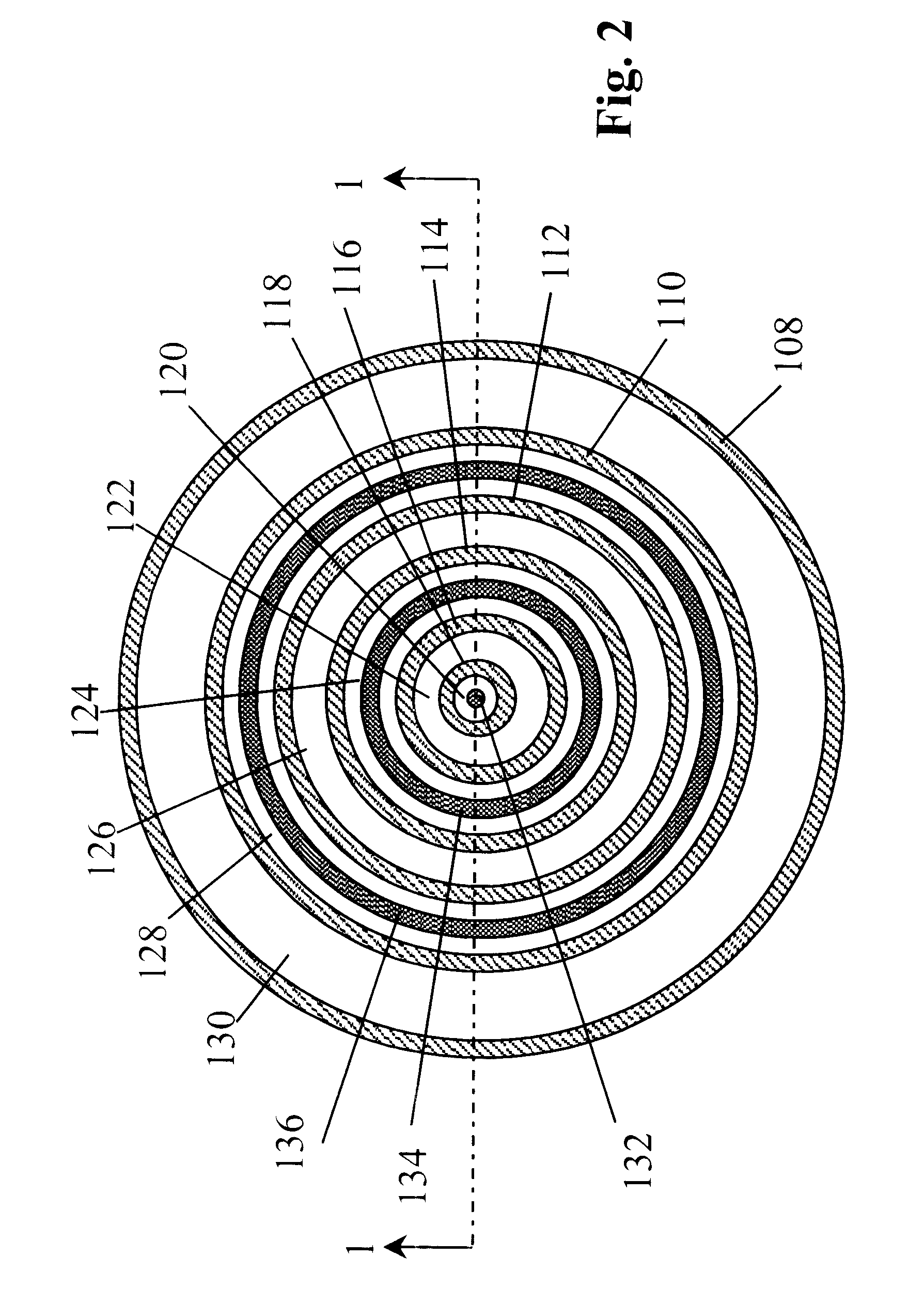

Method and apparatus of sealing wafer backside for full-face electrochemical plating

InactiveUS20030008602A1Efficient configurationMinimize irregularityEdge grinding machinesPolishing machinesMechanical engineeringElectroplating

The present invention provides a wafer carrier that includes a plurality of concentric sealing members that provide a seal, with the outer seal independently movable to allow cleaning of a peripheral backside of the wafer to occur while the wafer is still attached to the wafer carrier, and a plurality of vacuum openings that a re disposed only adjacent to an inner side of the inner seal at a location corresponding to the backside periphery of the wafer.

Owner:NOVELLUS SYSTEMS