Patents

Literature

7799 results about "Low resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

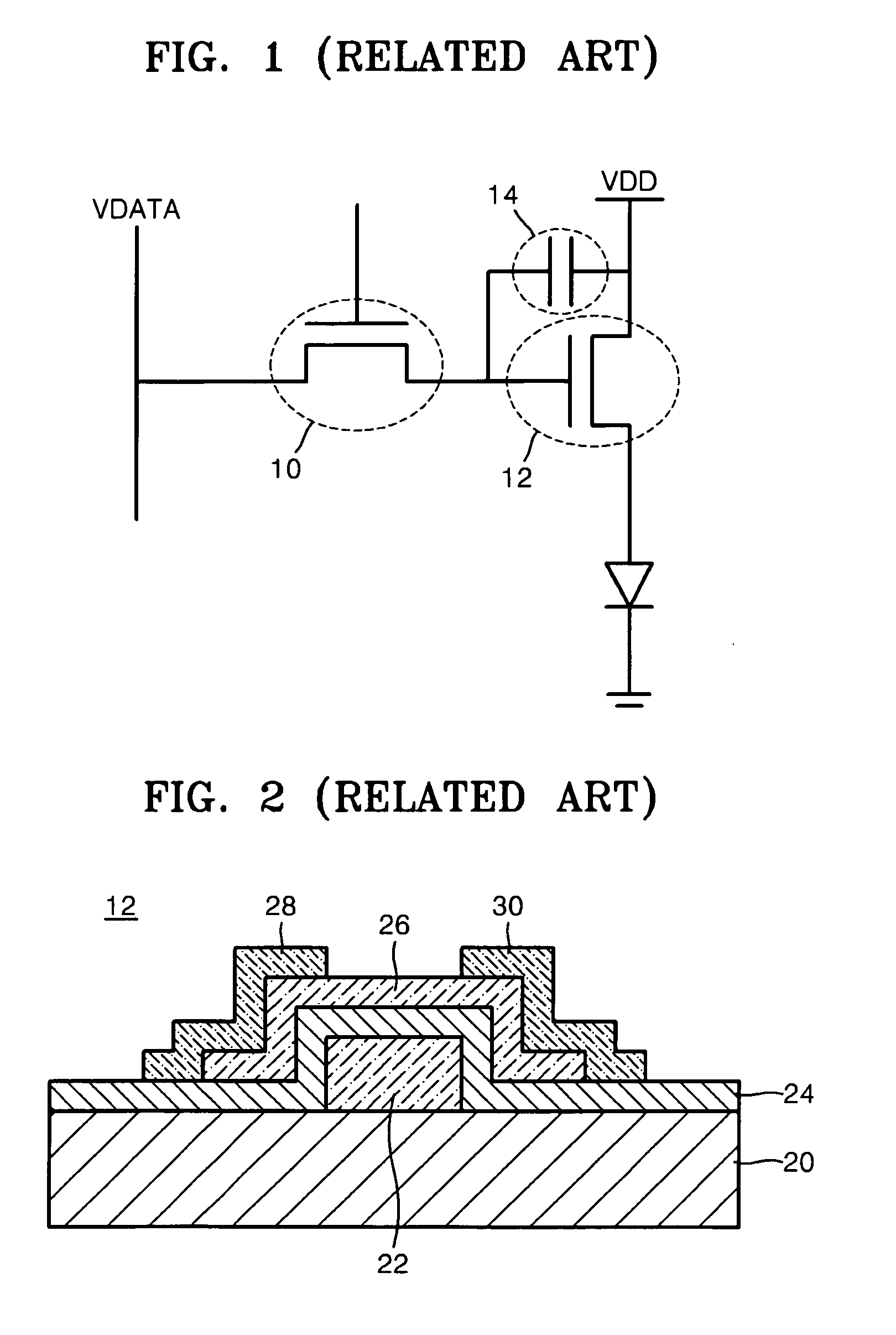

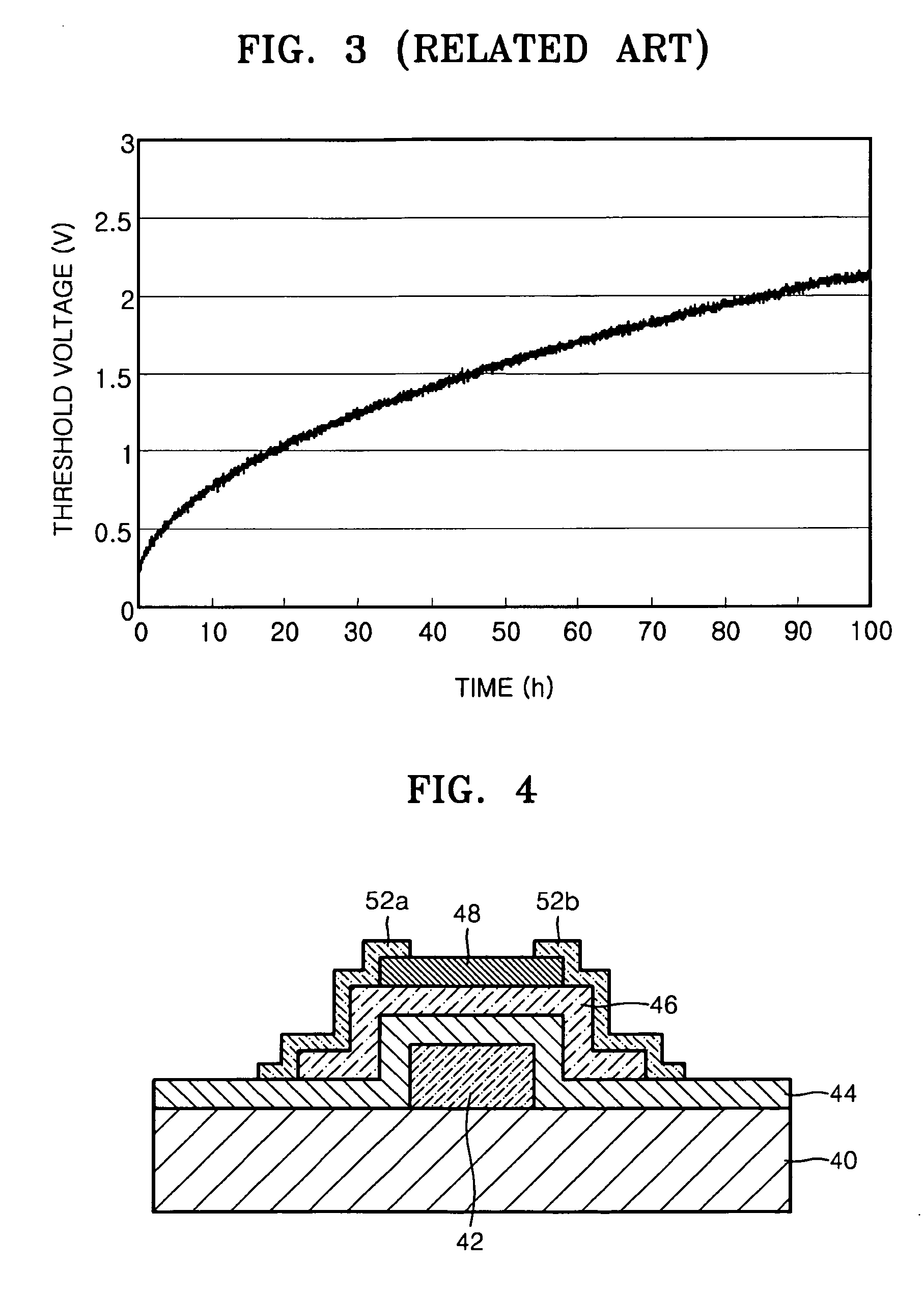

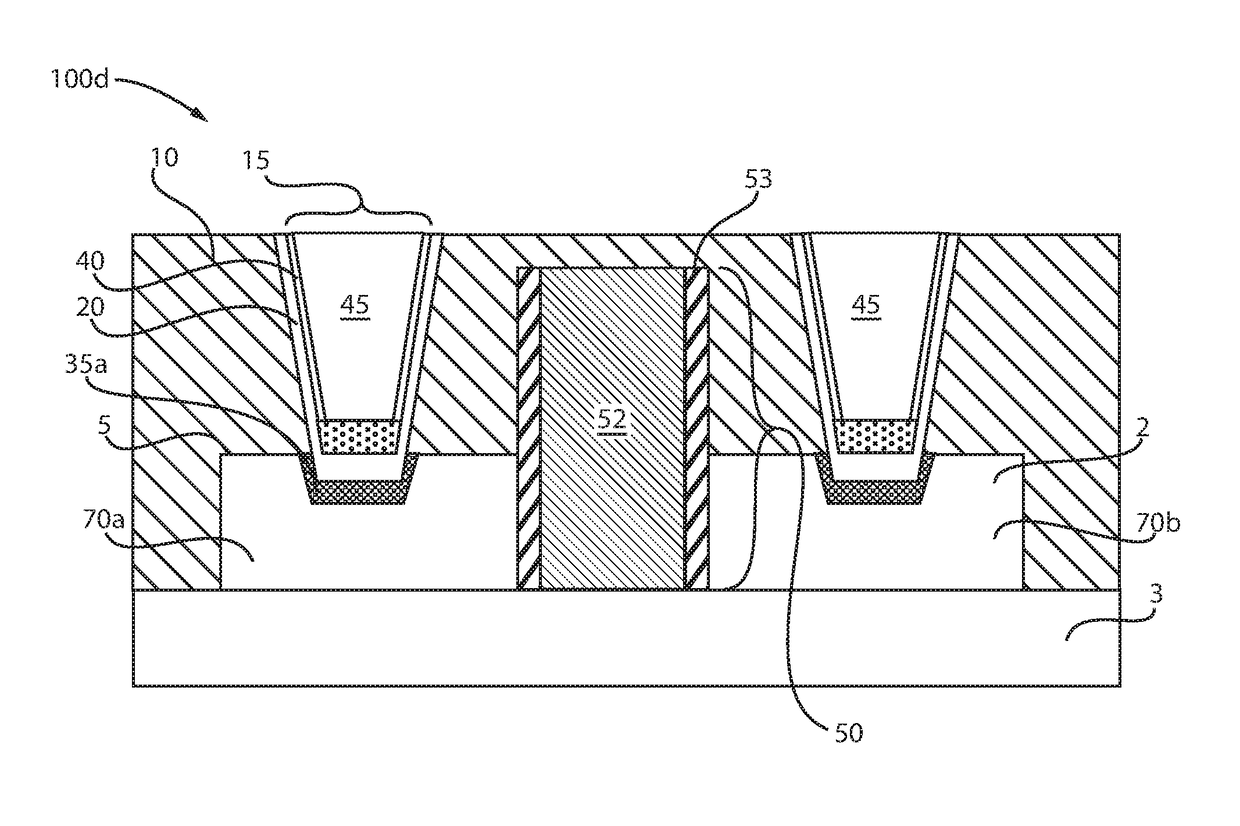

Thin film transistor, method of manufacturing the same, and flat panel display having the same

ActiveUS20080258141A1Improve stabilityUniform characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A thin film transistor (TFT), a method of manufacturing the TFT, and a flat panel display comprising the TFT are provided. The TFT includes a gate, a gate insulating layer that contacts the gate, a channel layer that contacts the gate insulating layer and faces the gate with the gate insulating layer therebetween, a source that contacts an end of the channel layer; and a drain that contacts an other end of the channel layer, wherein the channel layer is an amorphous oxide semiconductor layer, and each of the source and the drain is a conductive oxide layer comprising an oxide semiconductor layer having a conductive impurity in the oxide semiconductor layer. A low resistance metal layer can further be included on the source and drain. A driving circuit of a unit pixel of a flat panel display includes the TFT.

Owner:SAMSUNG ELECTRONICS CO LTD

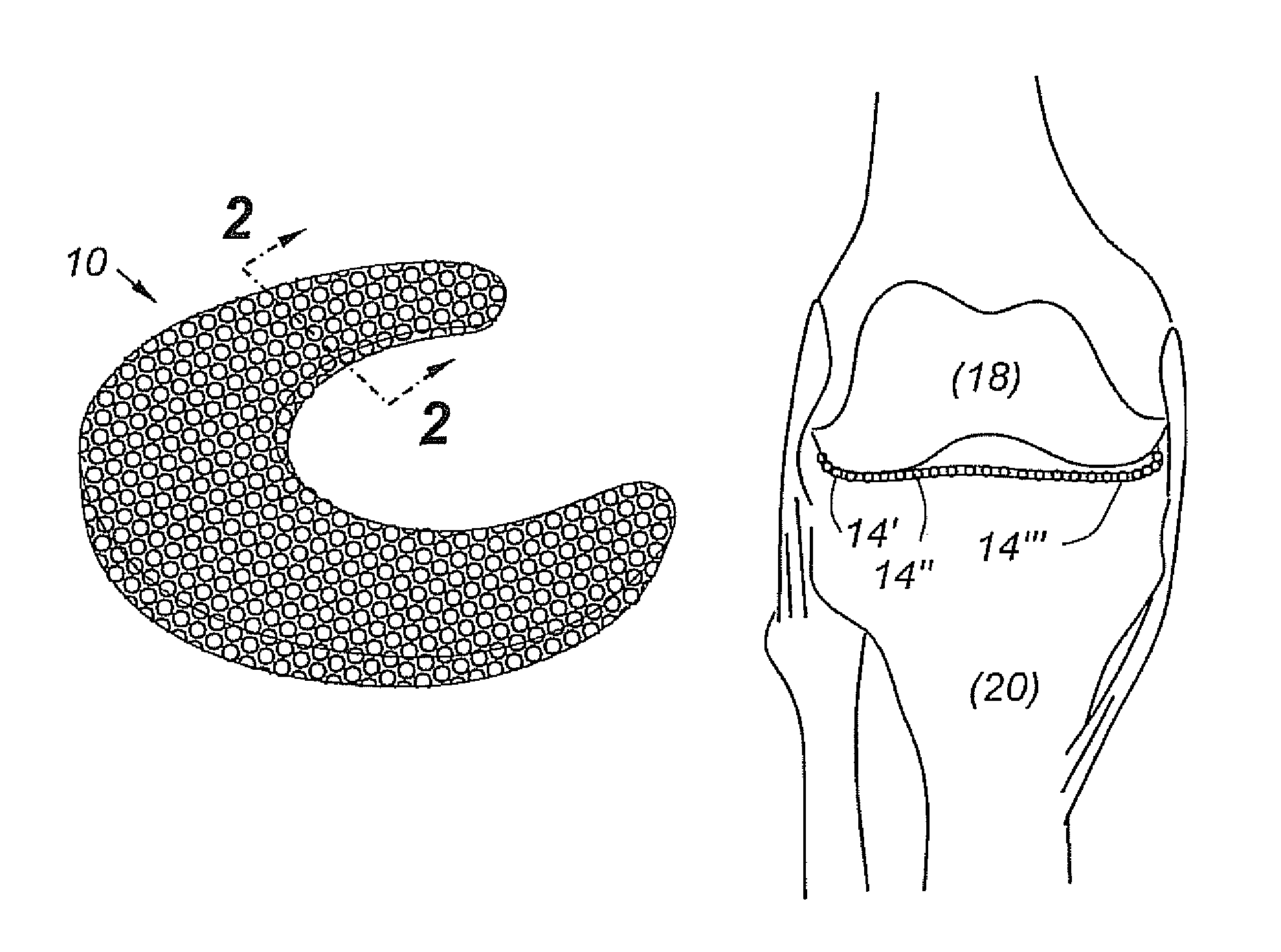

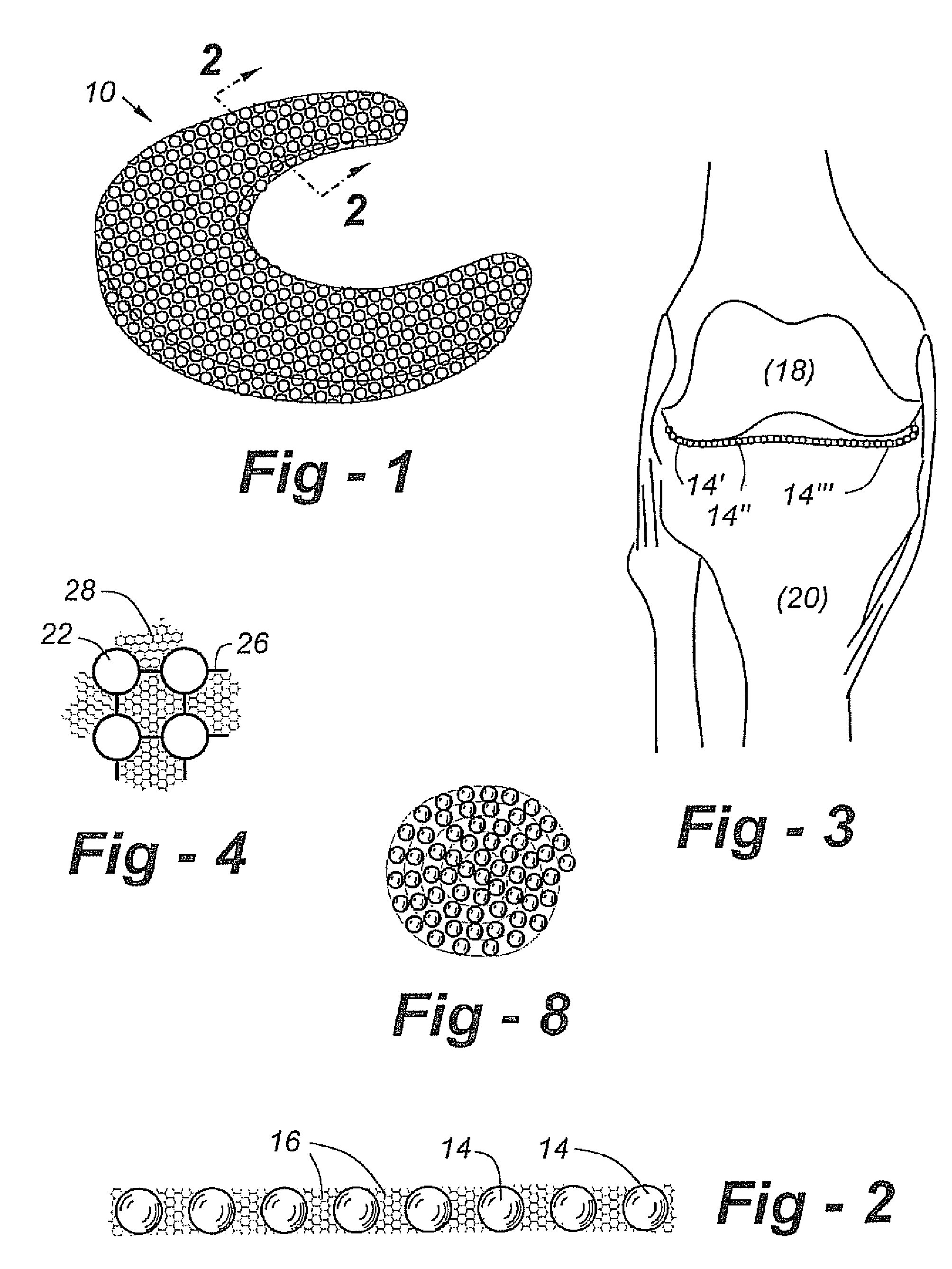

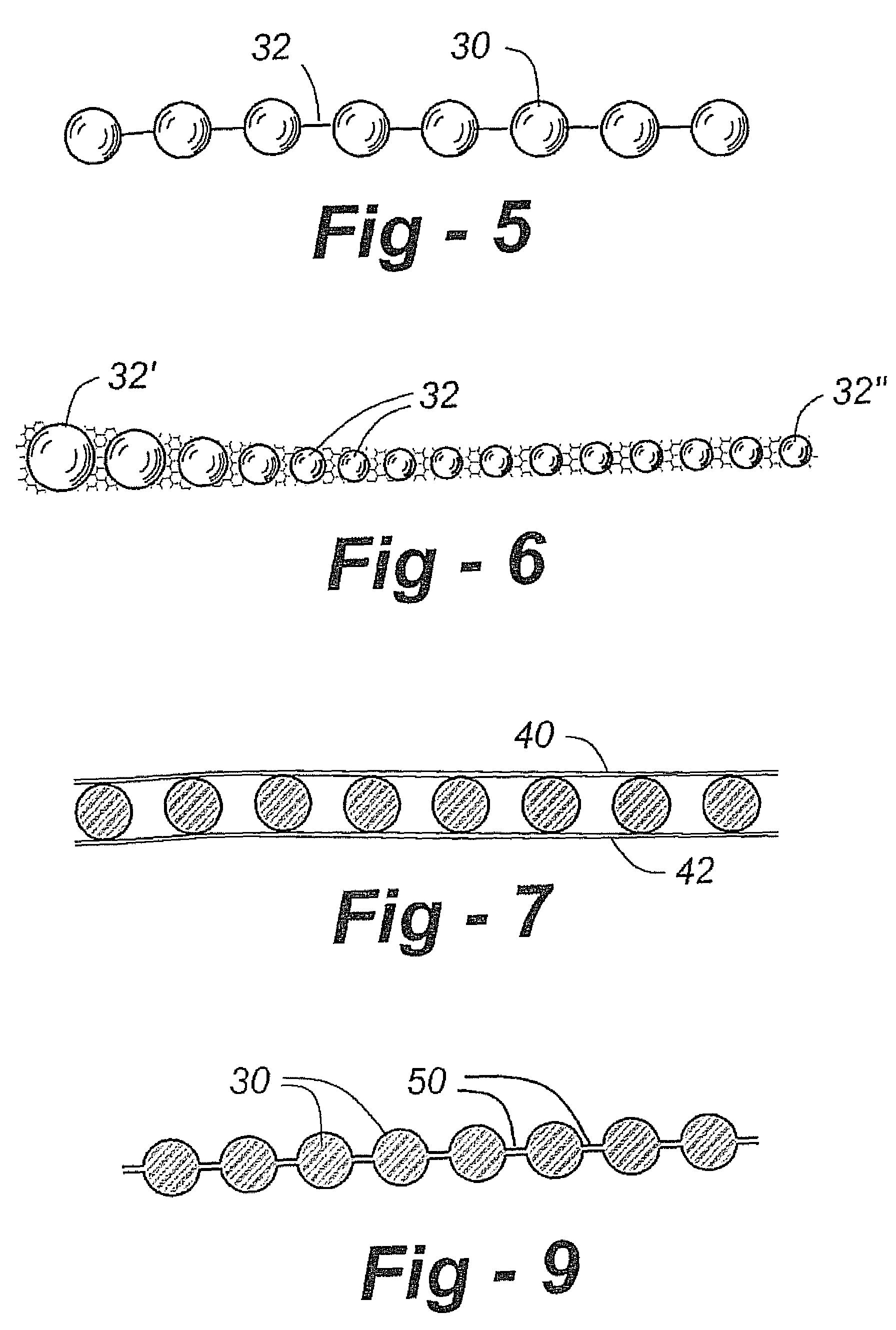

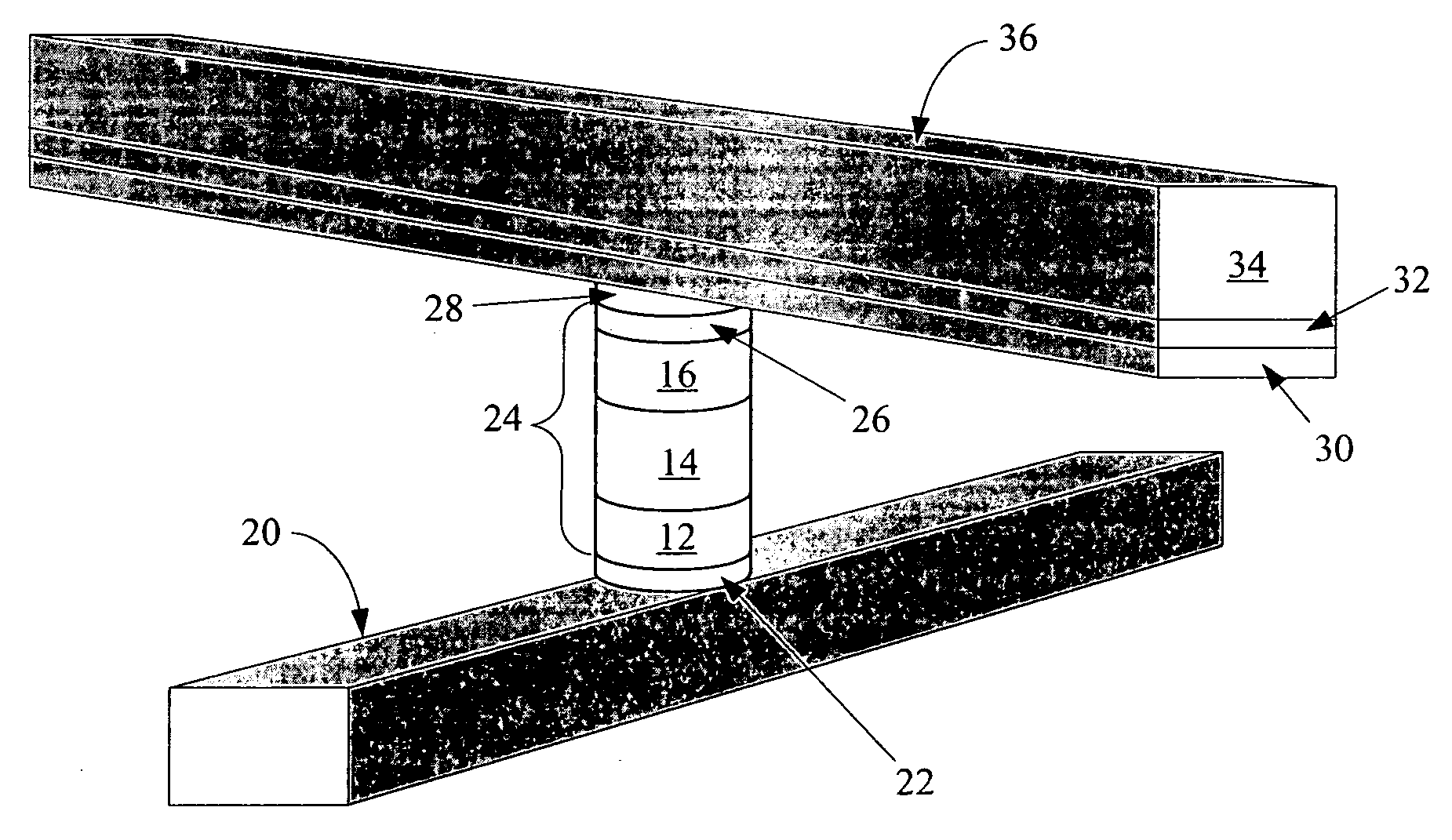

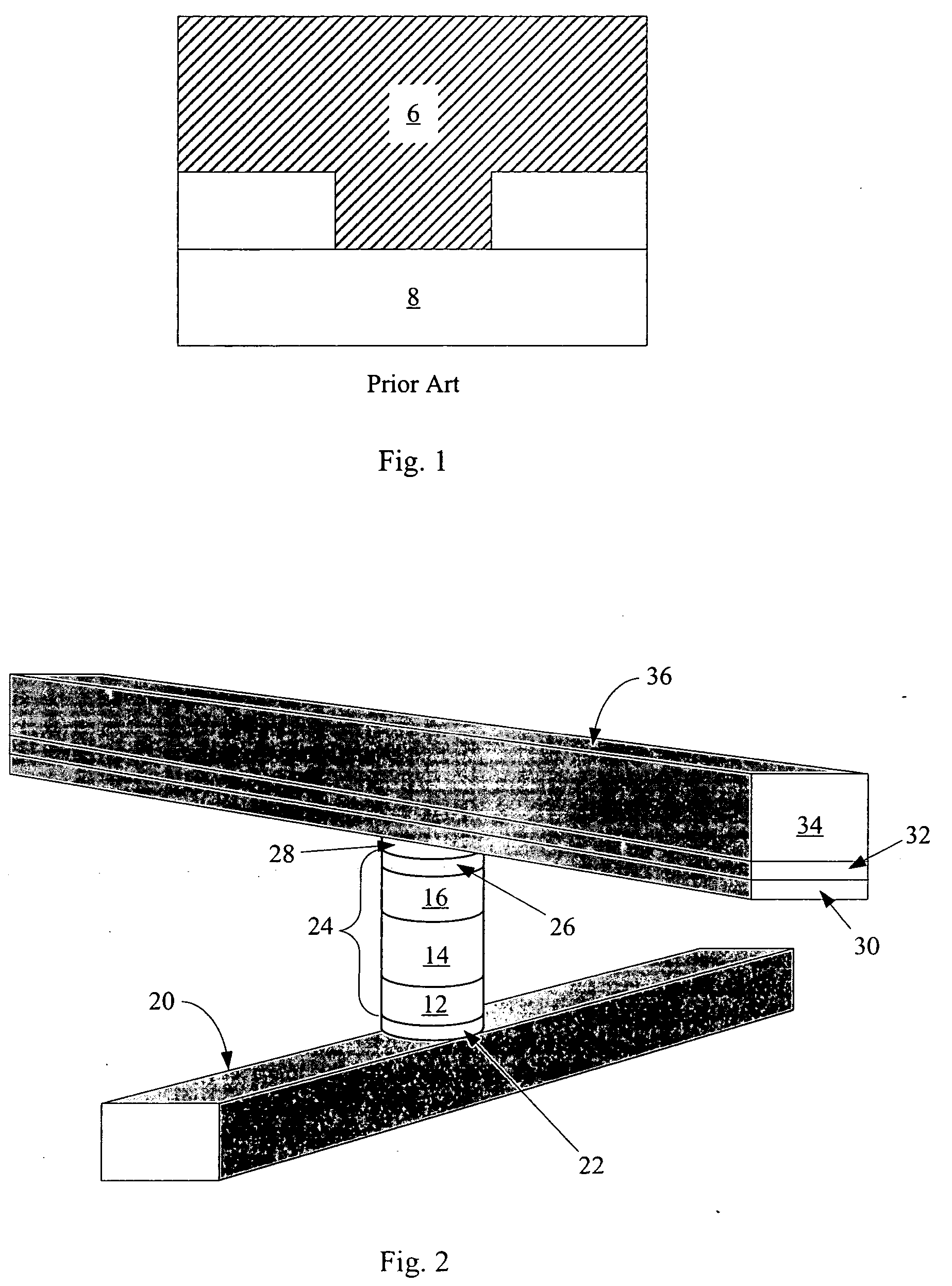

Prosthesis for replacement of cartilage

A cartilage replacement or repair prosthesis comprises a layer of streamlined elastomer elements, preferably in the form of spheres, supported in a matrix material so that the radially opposed surfaces of the spheres are positioned on opposite surfaces of the layer and make contact with the opposed surfaces of the femur and tibia and the forces exerted between these bones extend through the streamlined elements. The matrix material has a substantially lower resistance to deformation than the spheres to control the position of the spheres relative to one another without significantly restraining their load-responsive deformation under forces exerted between the femur and tibia. The layer, with its elastomeric inserts, is sufficiently thin and flexible to allow it to be rolled for arthroscopic insertion into a knee joint.

Owner:SUCCESSOR TRUSTEE OF THE EUGENE RIVIN LIVING TRUST +2

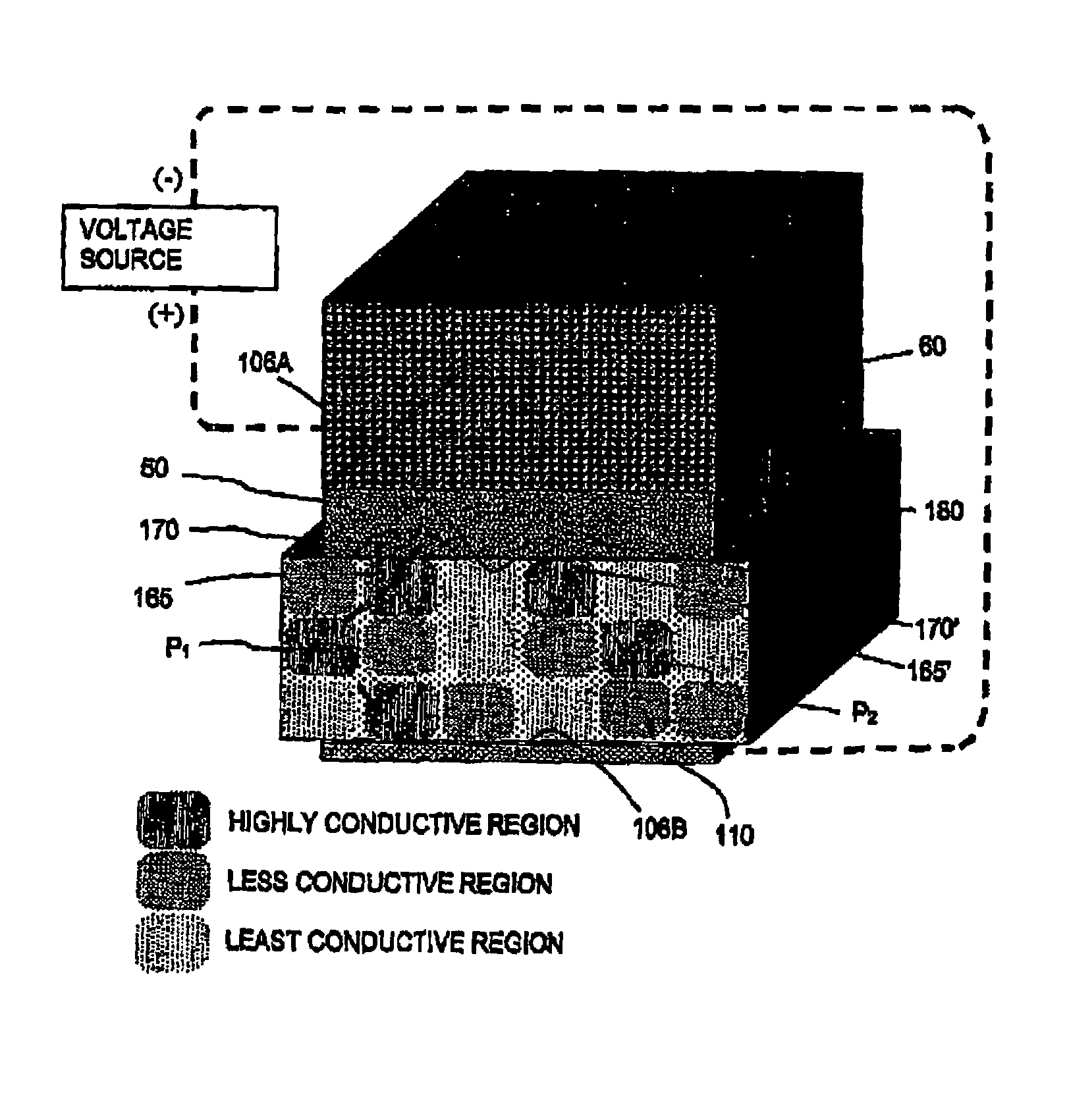

Surgical sealing surfaces and methods of use

ActiveUS7220951B2Fast transferHighly stable current-limitingDielectric heatingSurgical instruments for heatingOmni directionalSwitching time

Various embodiments provide compositions that exhibit positive temperature coefficient of resistance (PTCR) properties for use in thermal interactions with tissue—including thermal sensing and I2R current-limiting interactions. Embodiments also provide tissue-engaging surfaces having PTCR materials that provide very fast switching times between low resistance and high, current-limiting resistance. One embodiment provides a matrix for an electrosurgical energy delivery surface comprising a PTCR material and a heat exchange material disposed within an interior of the matrix. The PTCR material has a substantially conductive state and a substantially non-conductive state. The heat exchange material has a structure configured to have an omni-directional thermal diffusivity for exchanging heat with the PTCR material to cause rapid switching of the PTCR material between the conductive state and non-conductive state. Preferably, the structure comprises a graphite foam having an open cell configuration. The matrix can be carried by tissue contacting surfaces of various electrosurgical devices.

Owner:ETHICON ENDO SURGERY INC

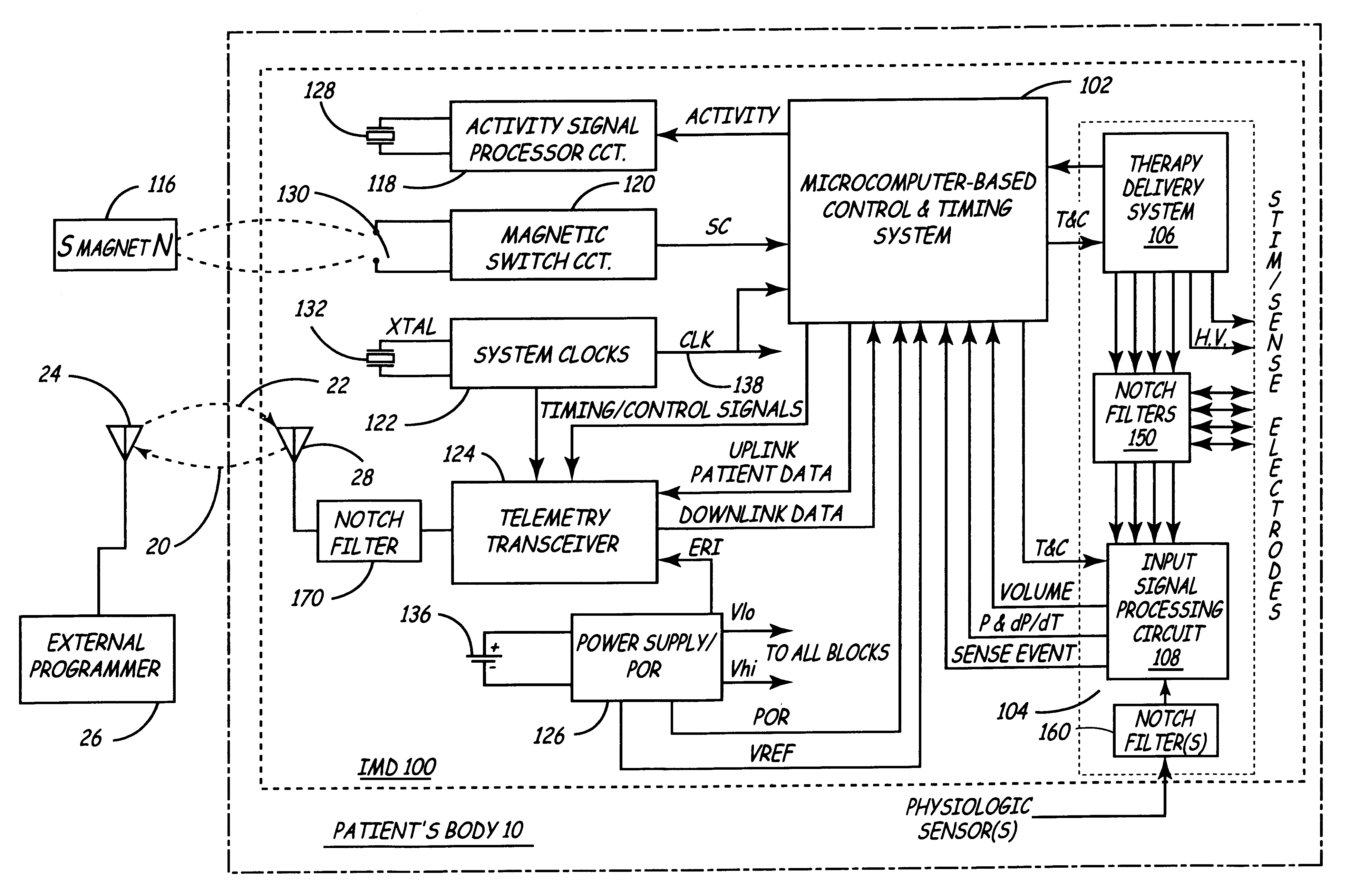

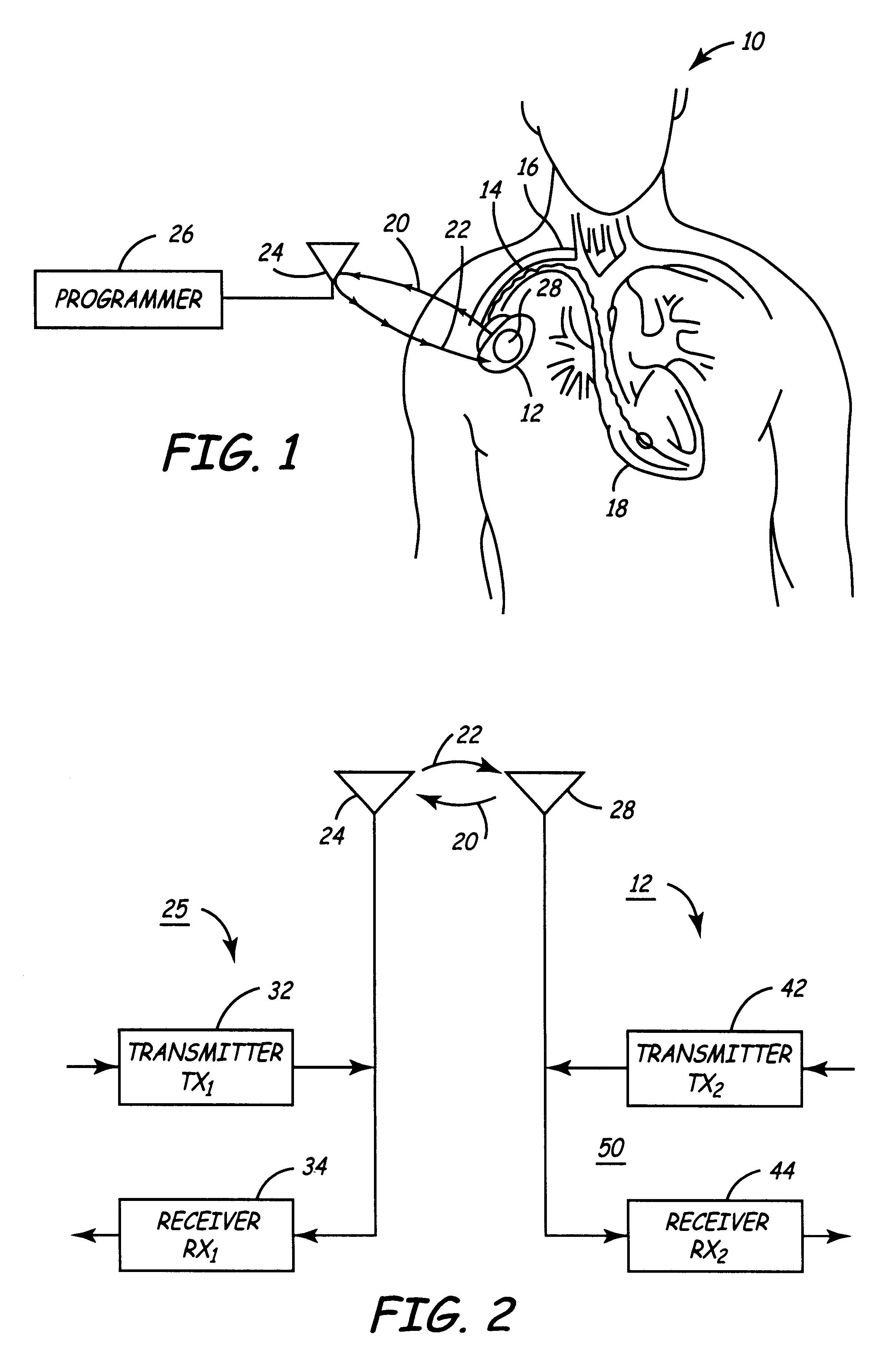

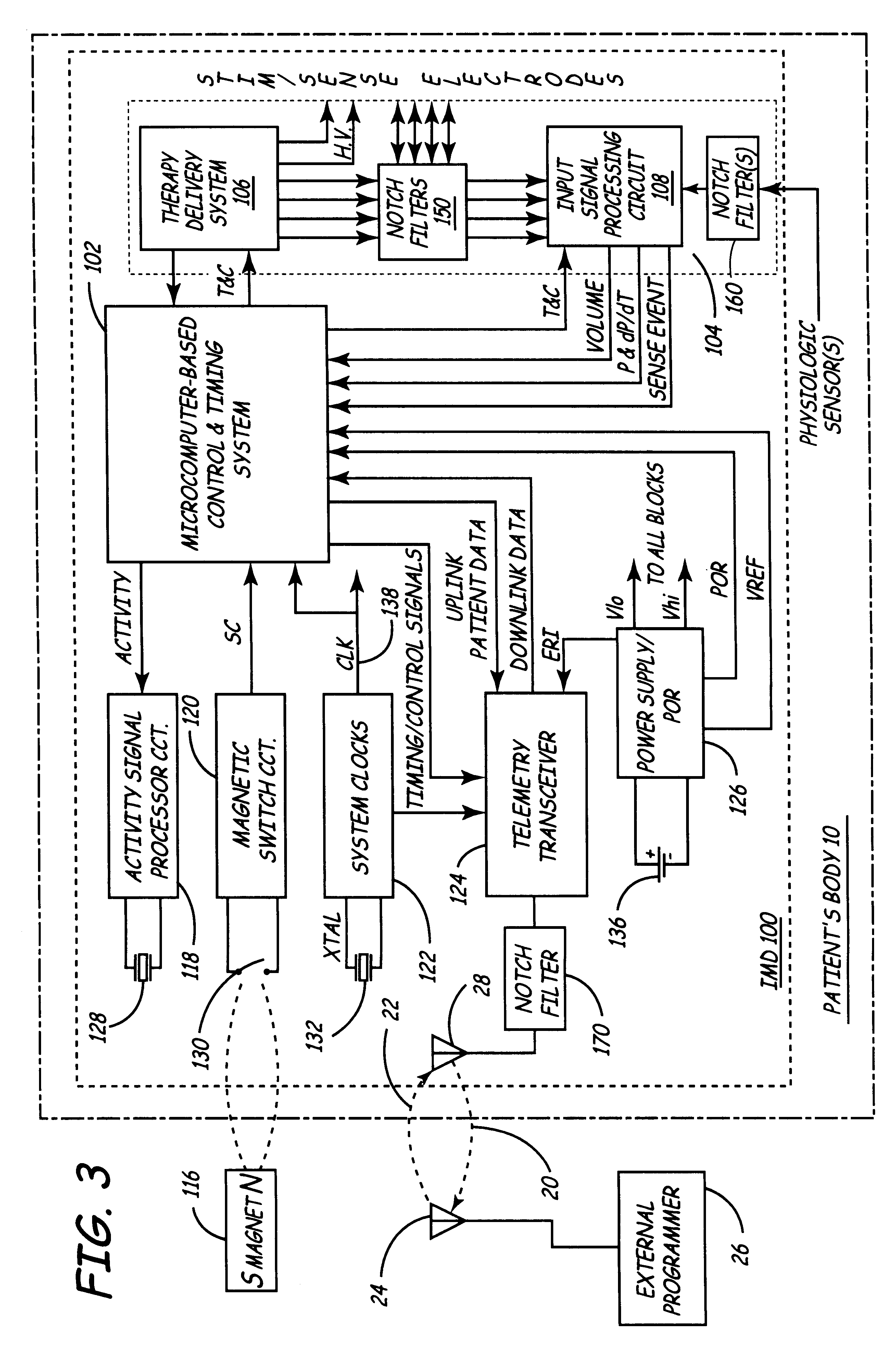

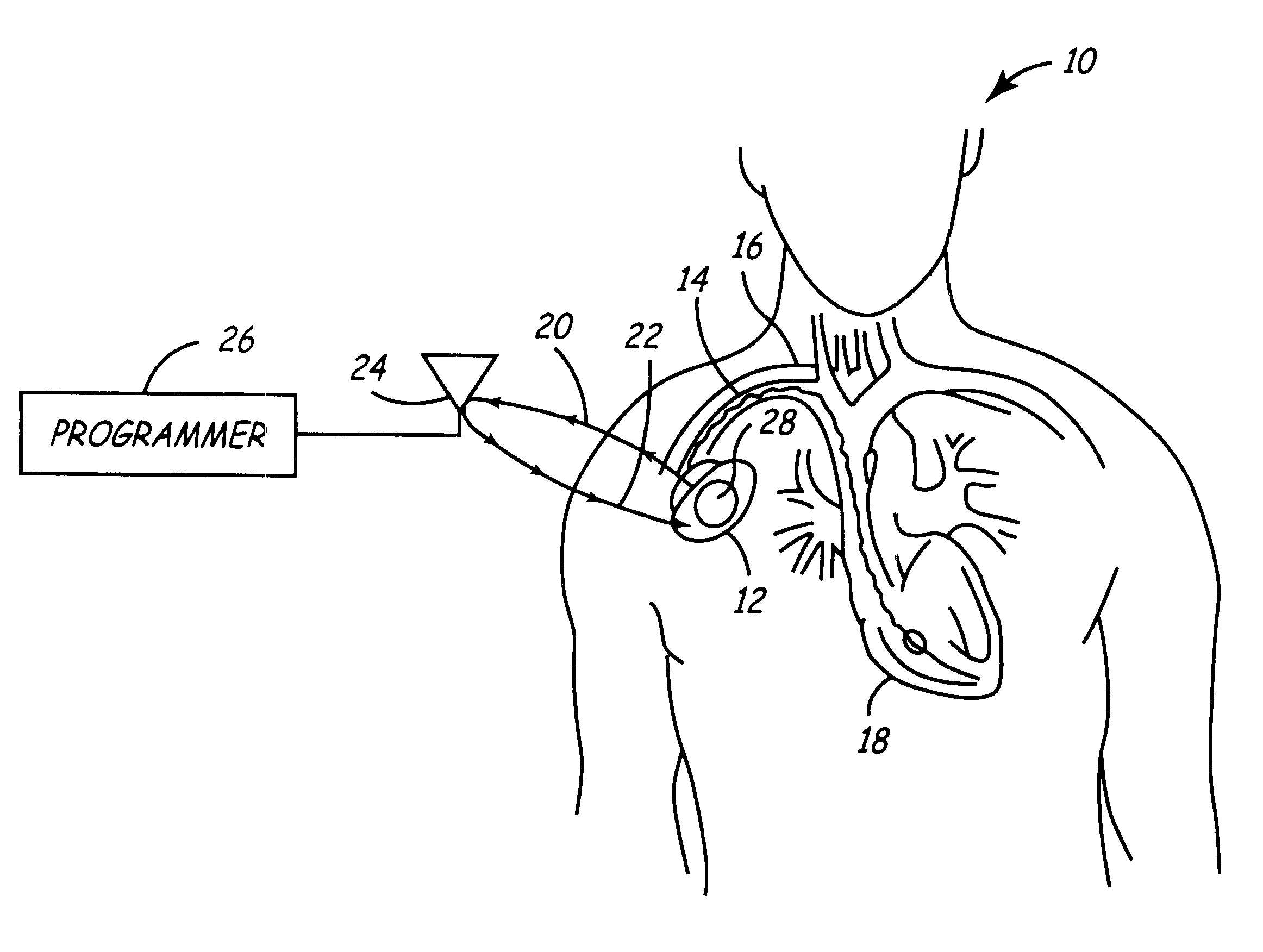

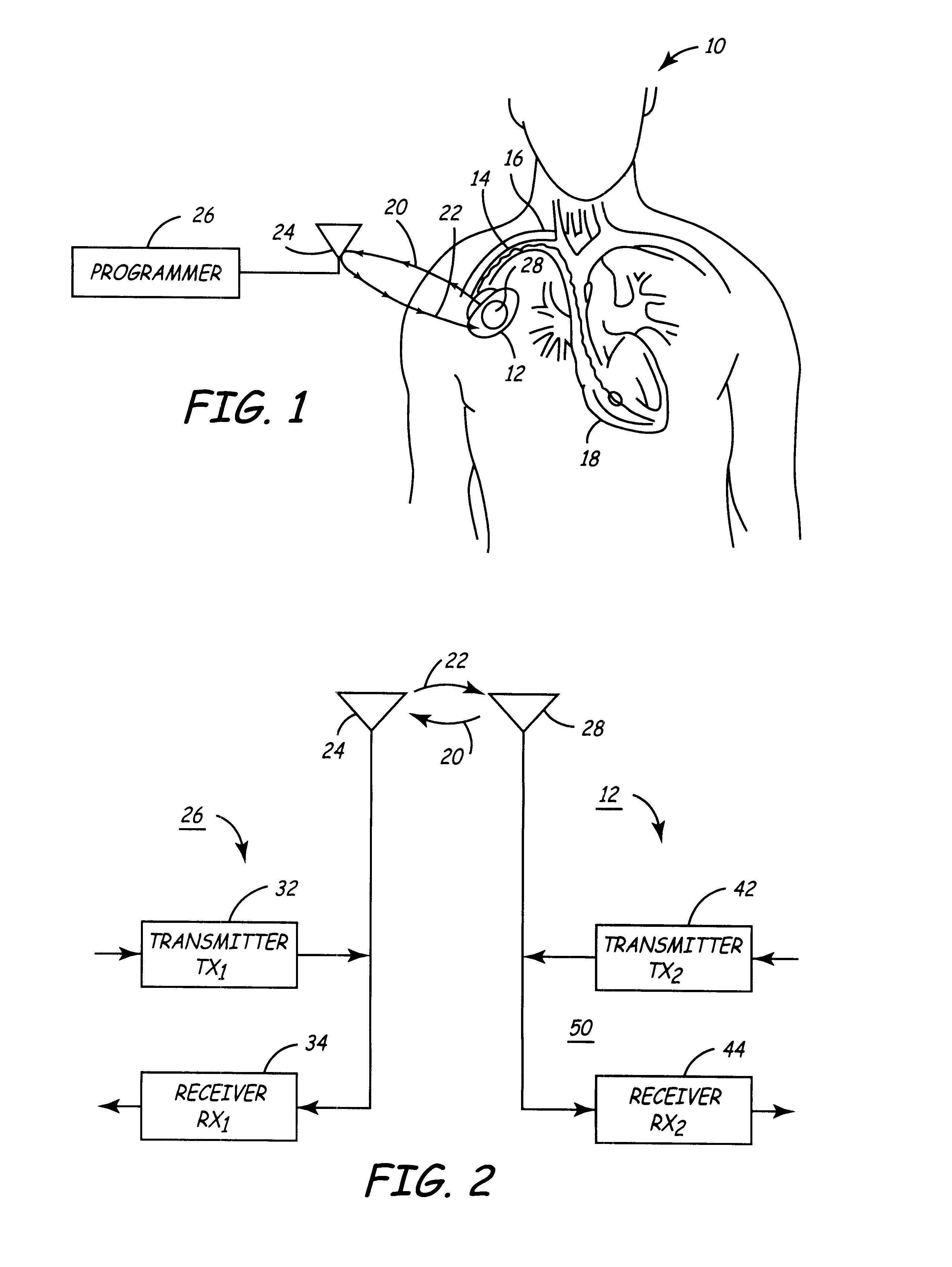

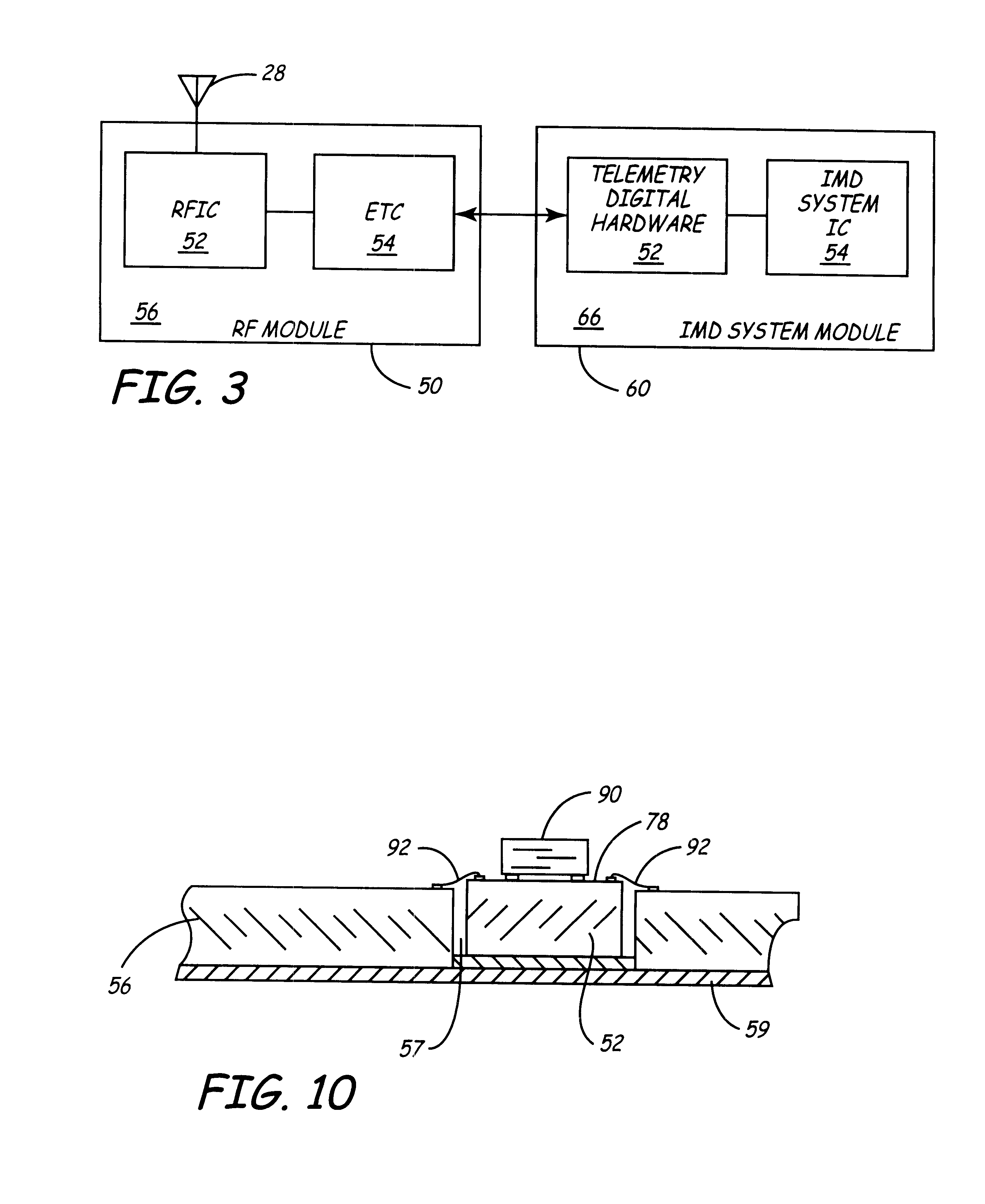

Implantable medical device incorporating integrated circuit notch filters

Implantable medical devices (IMDs) having sense amplifiers for sensing physiologic signals and parameters, RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming and interrogation commands to and from an external programmer or other medical device are disclosed. At least one IC chip and discrete components have a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include forming notch filters of MEMS structures or forming discrete circuit notch filters by one or more of: (1) IC fabricating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The IC fabricated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the IC chip substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

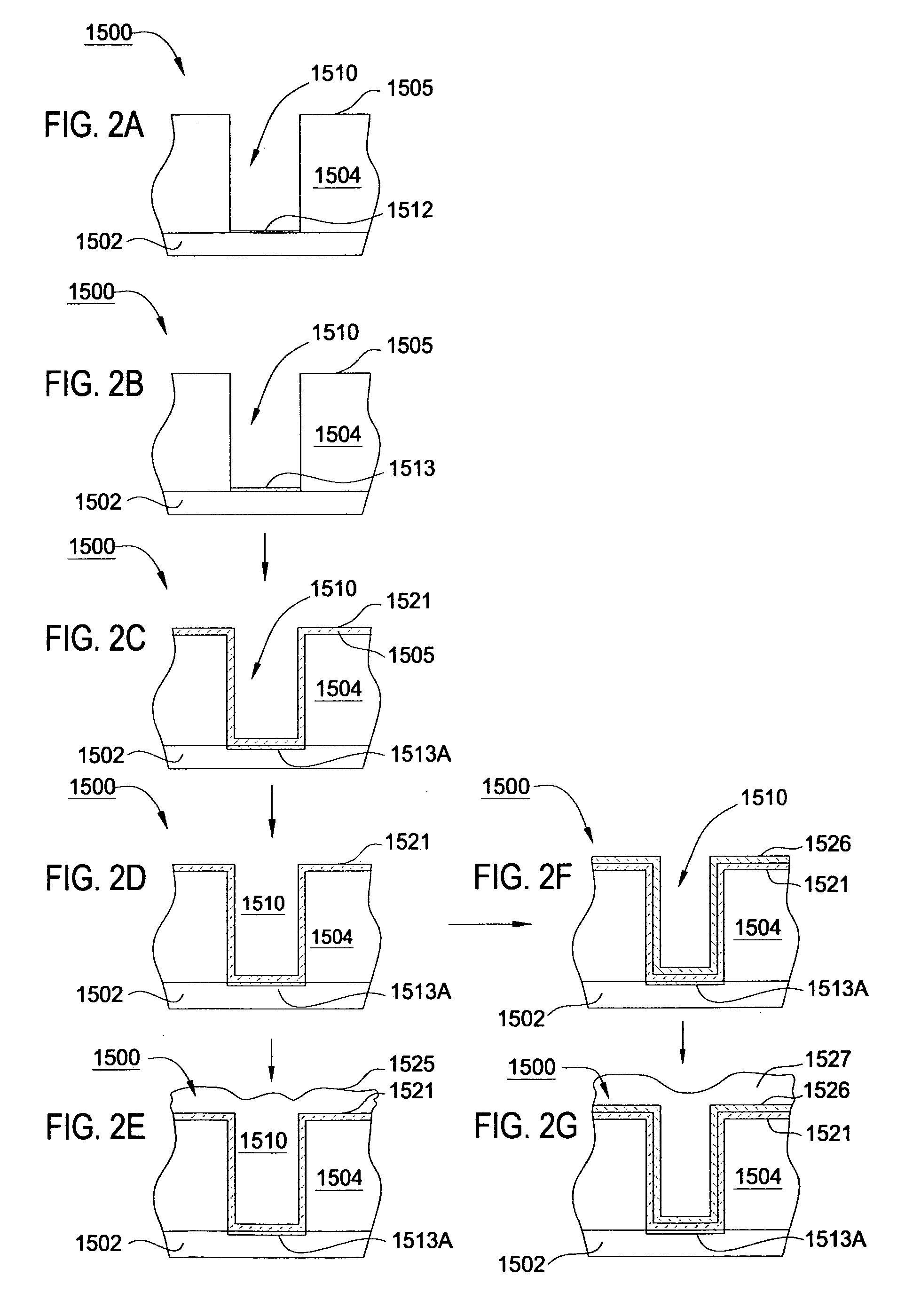

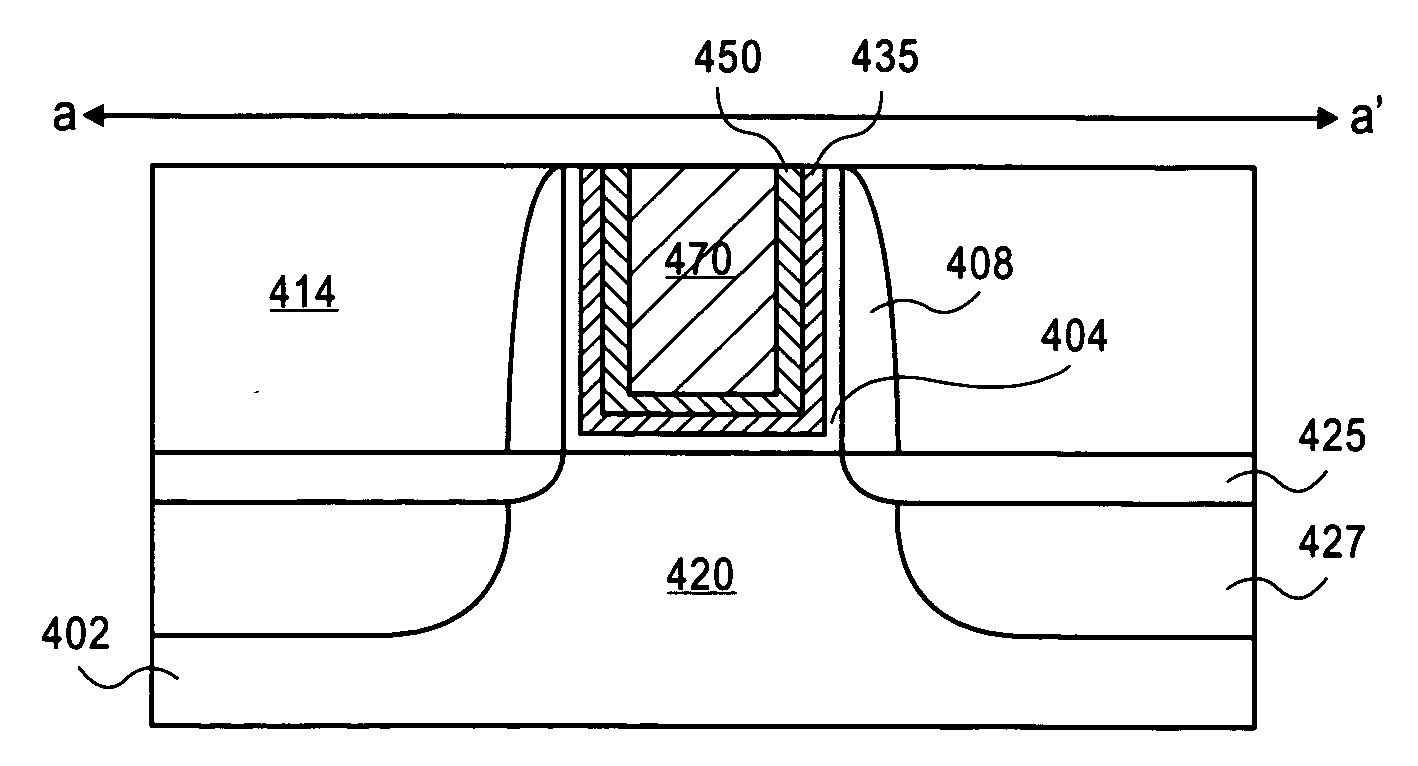

Semiconductor device and method of manufacturing thereof

InactiveUS20100001409A1Increase the cross-sectional areaLower interconnect resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorEngineering

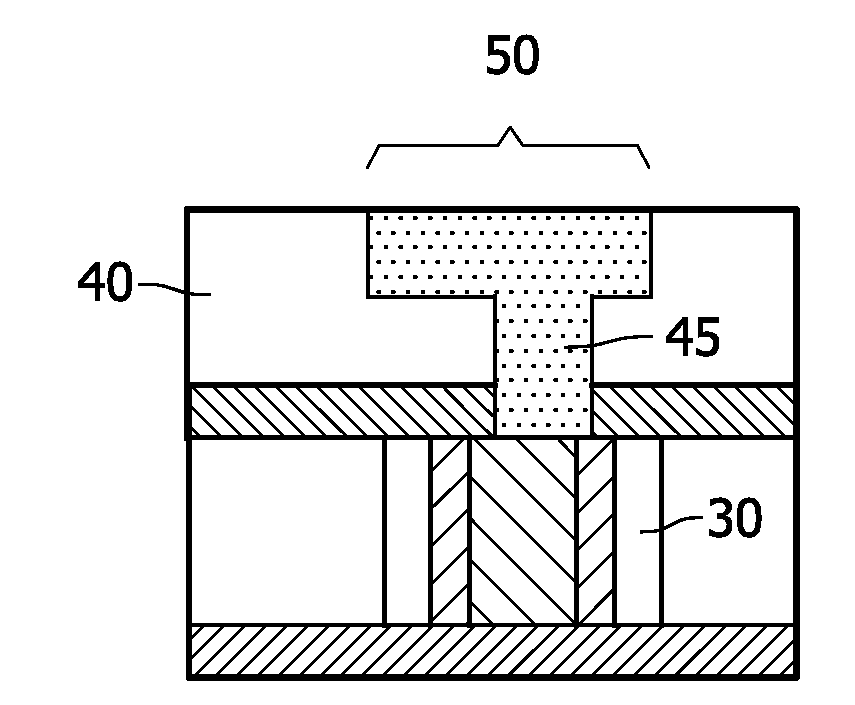

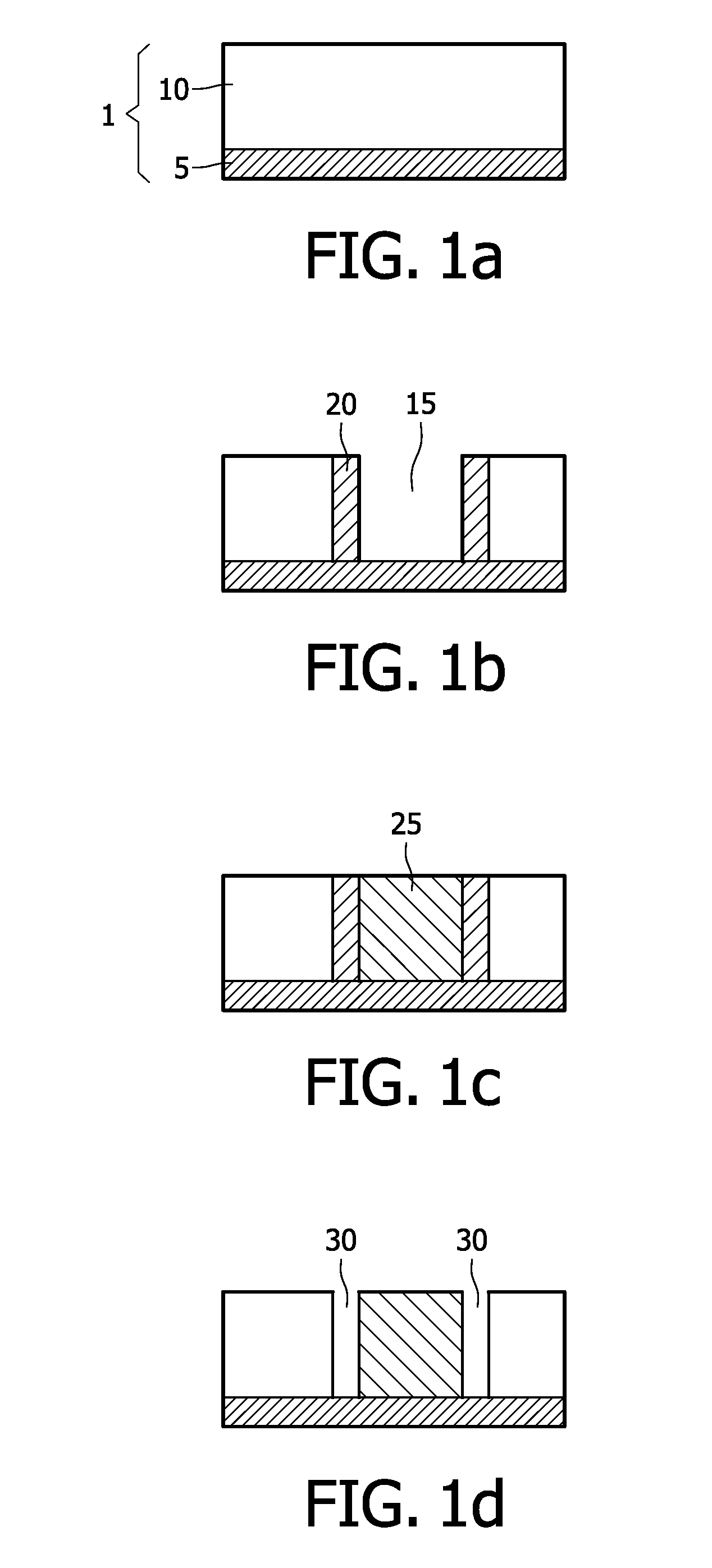

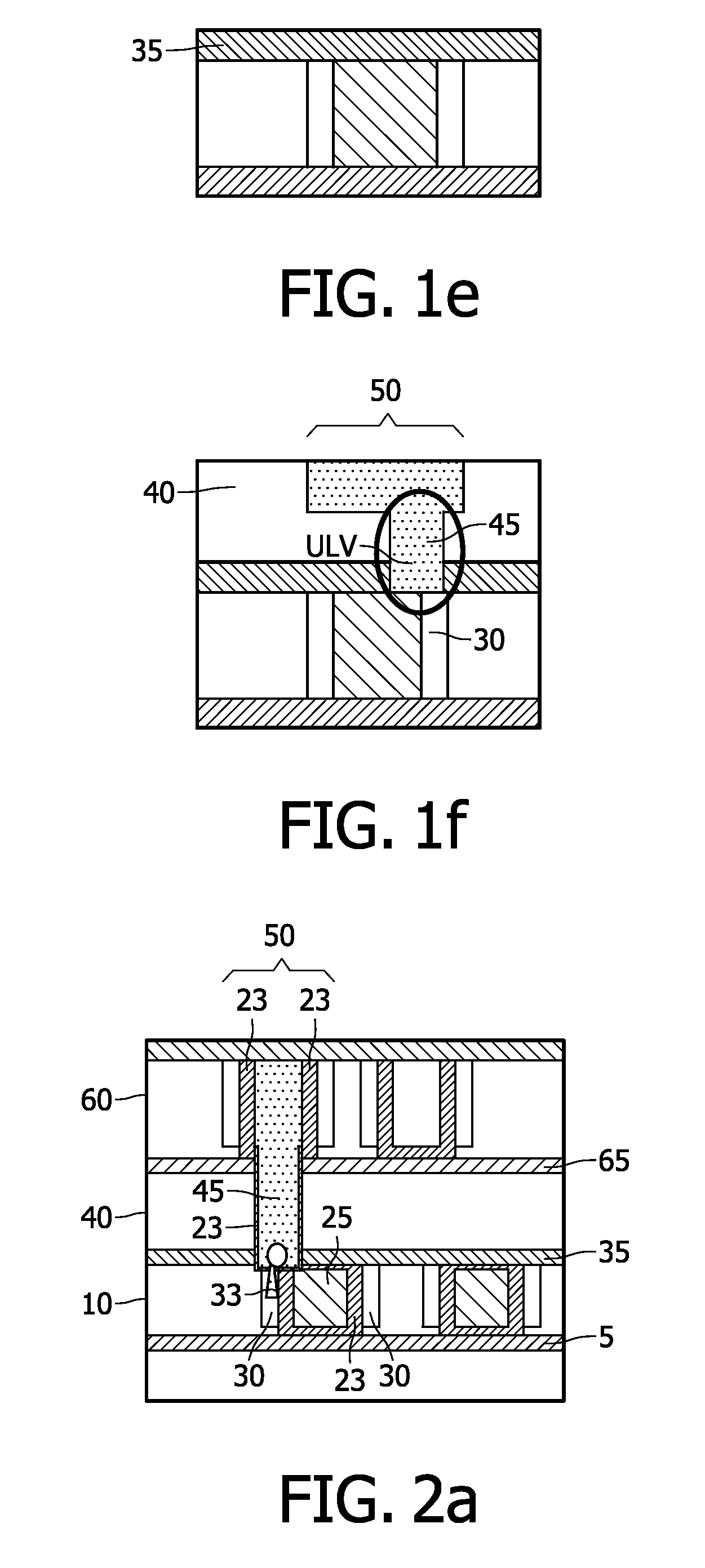

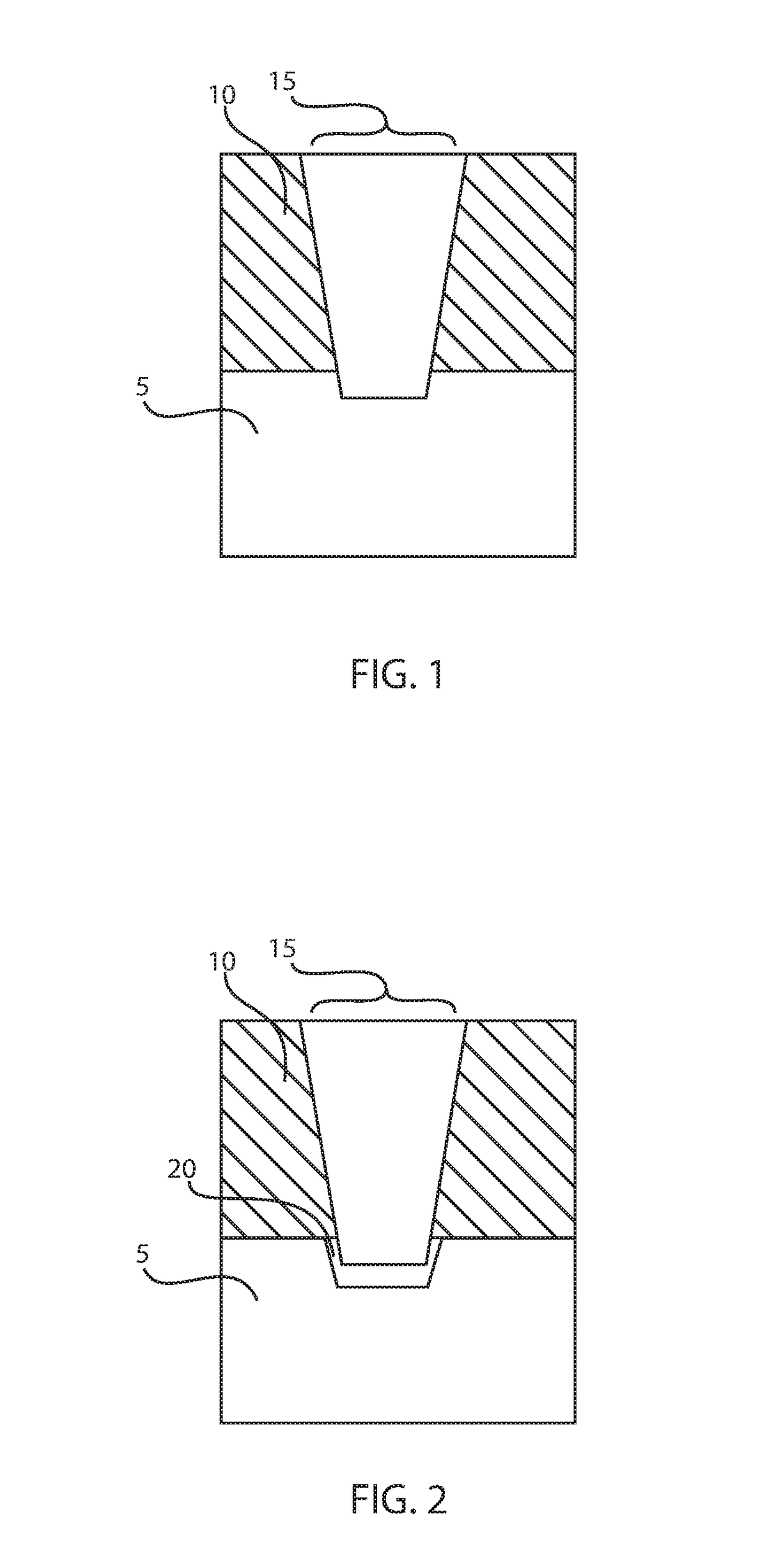

The invention relates to a semiconductor device comprising: a substrate (1), the substrate (1) comprising a body (5), the body (5) having a surface, the substrate (1) being provided with an insulating layer (10) on the surface of the body (1);—a conductor (25) with insulating sidewall spacers (22) located in the insulating layer (10), the conductor (25) having a current-flow direction during operation, the conductor (25) having a first width, the insulating sidewall spacers (22) each having a second width being smaller than the first width of the conductor (25), the first width and the second width being measured in a direction perpendicular to the current-flow direction of the conductor (25) and parallel to said surface, the conductor (25) having a first top surface extending parallel to said surface, the insulating sidewall spacers (22) having a second top surface, and airgaps (30) located in the insulating layer (10) adjacent to the insulating sidewall spacers (22), characterized in that the first top surface coincides with the second top surface, and in that the airgaps (30) extend from the surface of the body (5) to said first and second top surface. The invention further relates to a method of manufacturing such a semiconductor device. The semiconductor device according to the invention enables a lower resistance of the conductor while still providing a tolerance for unlanded vias.

Owner:NXP BV

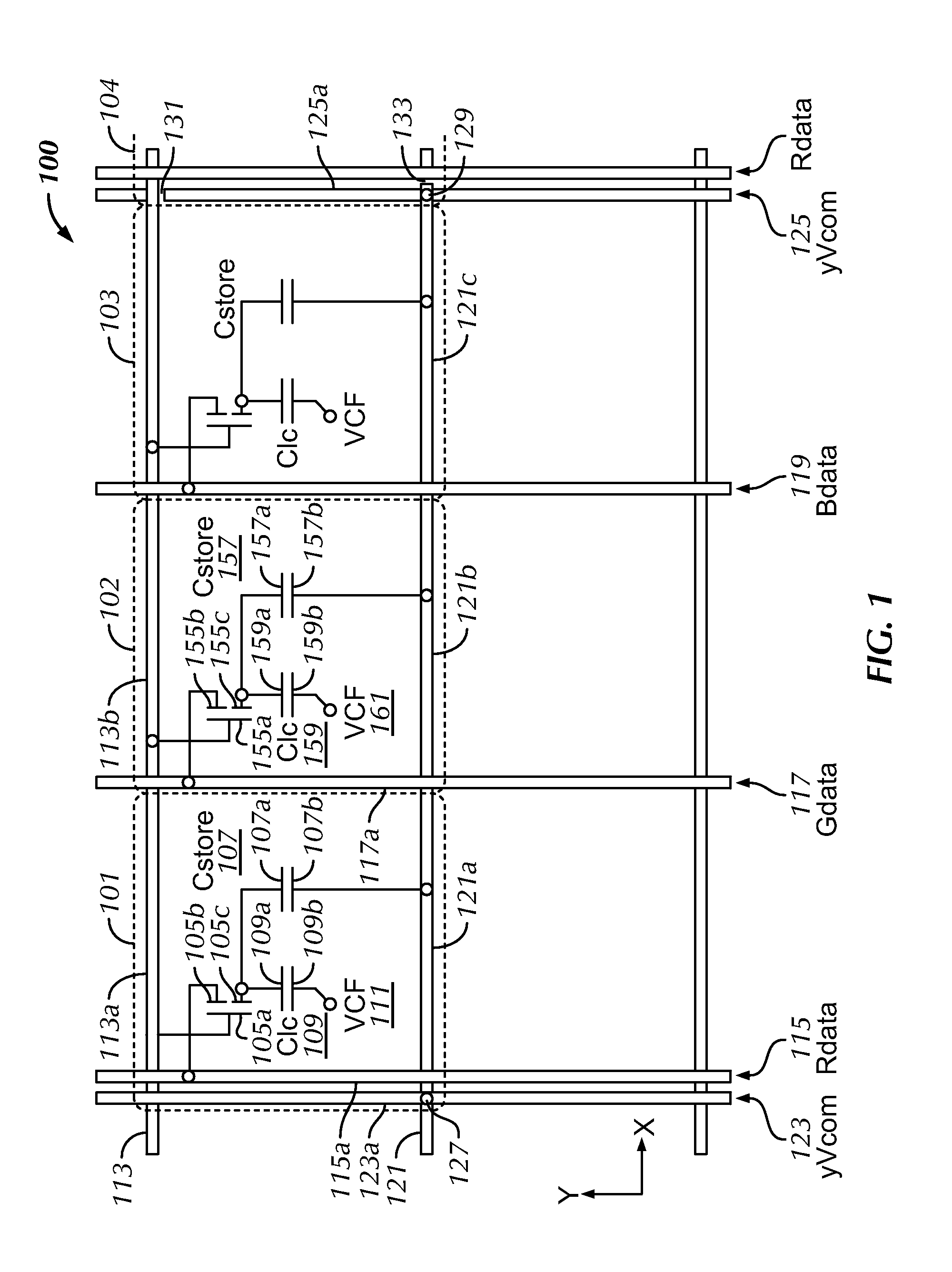

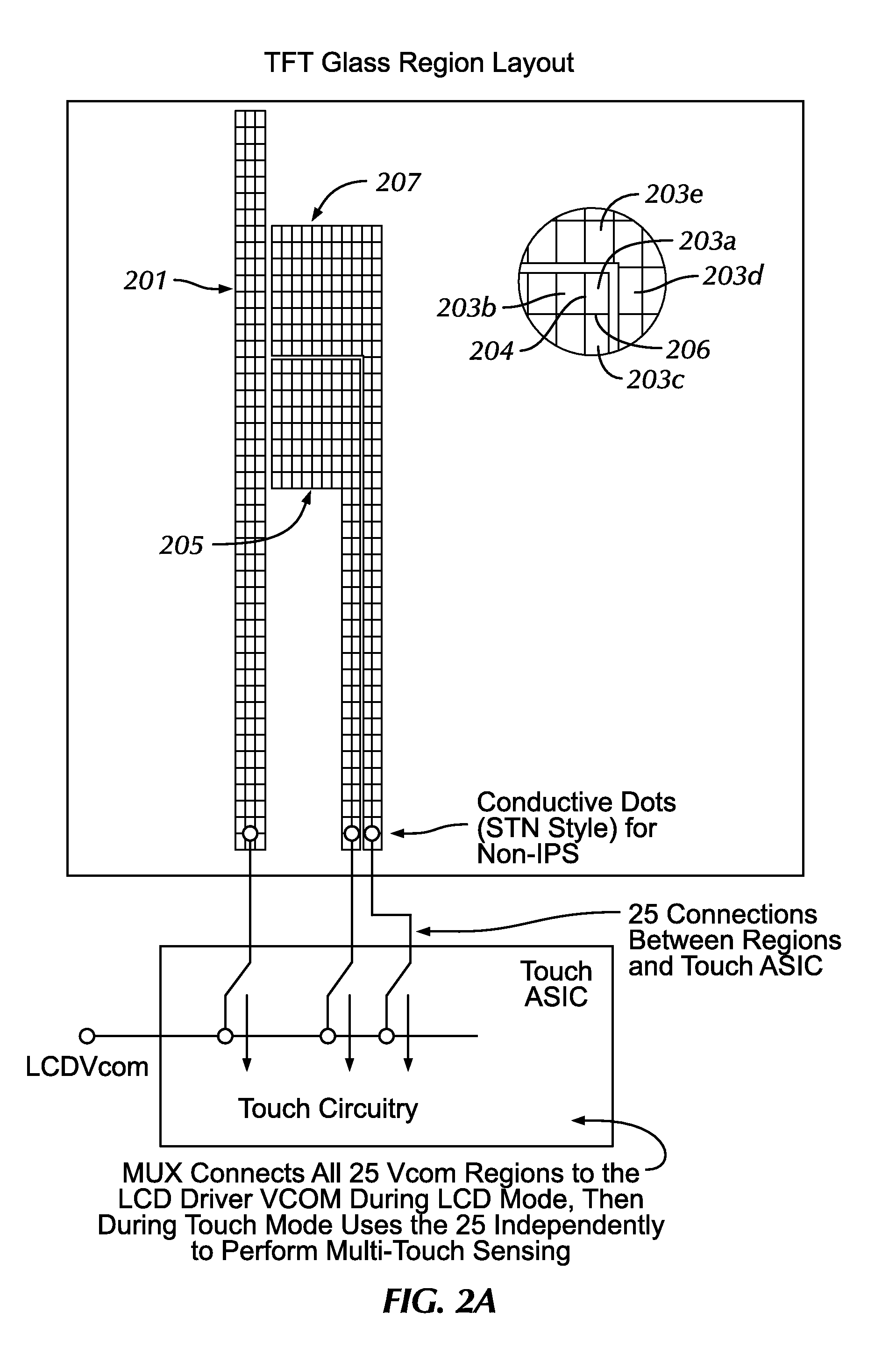

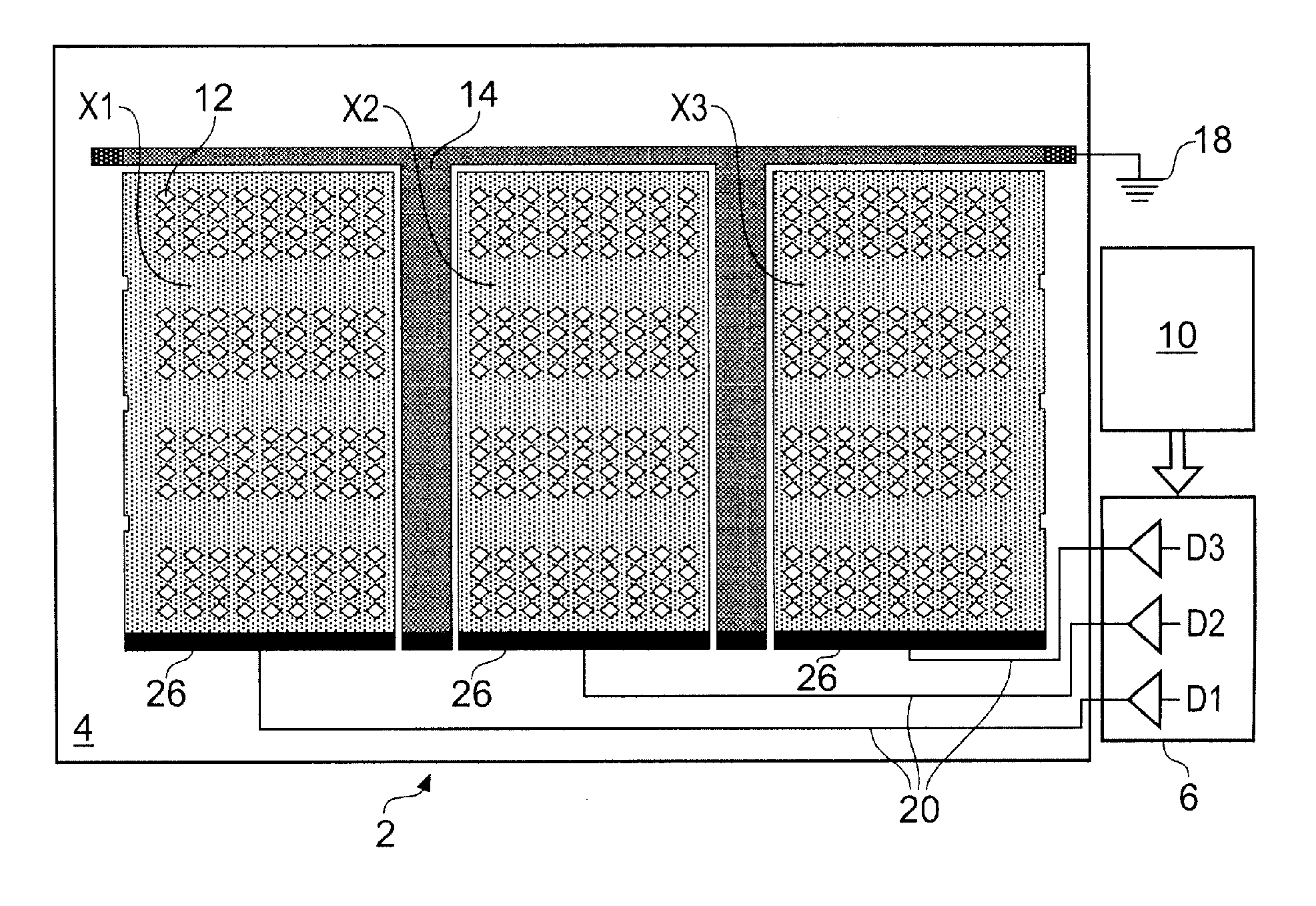

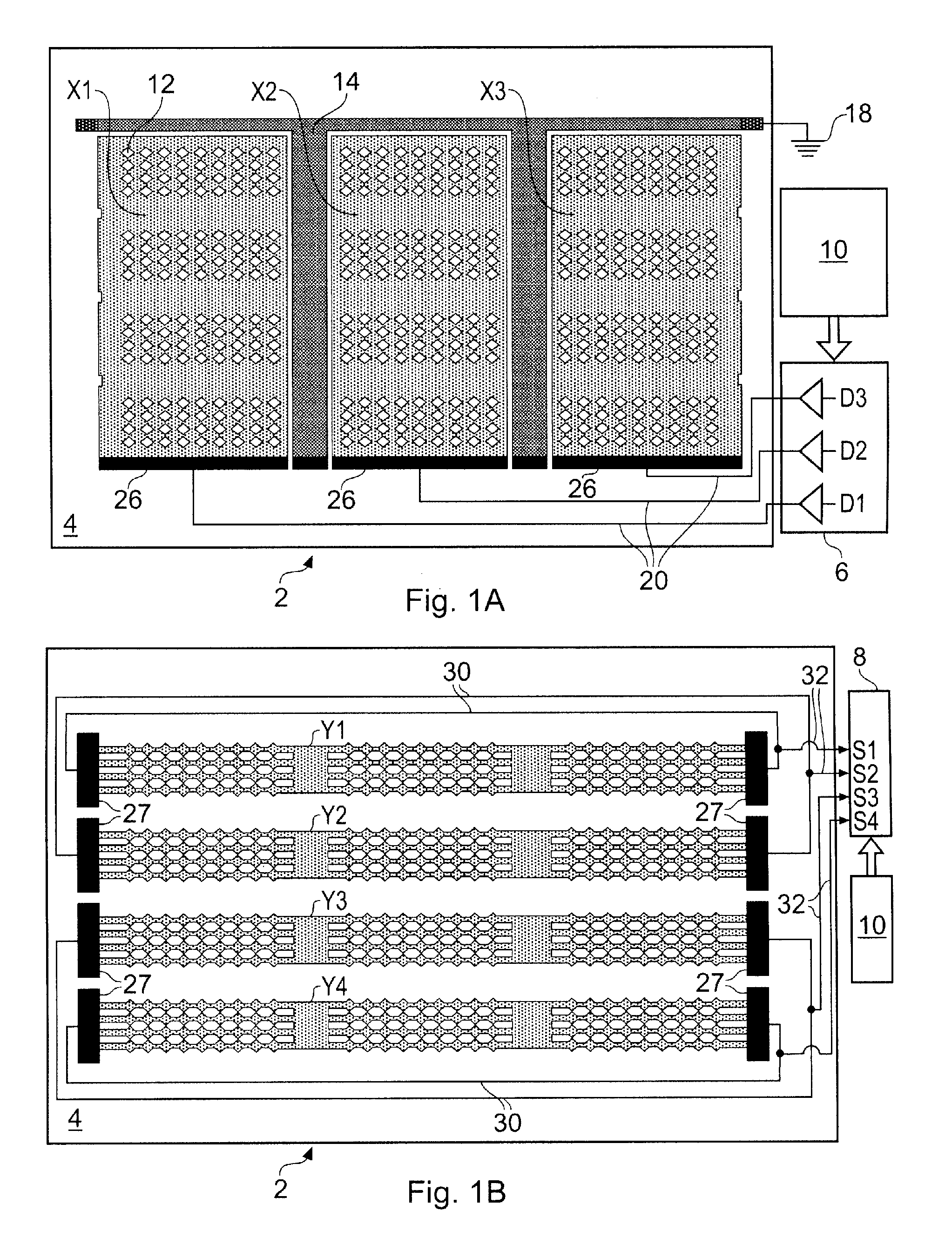

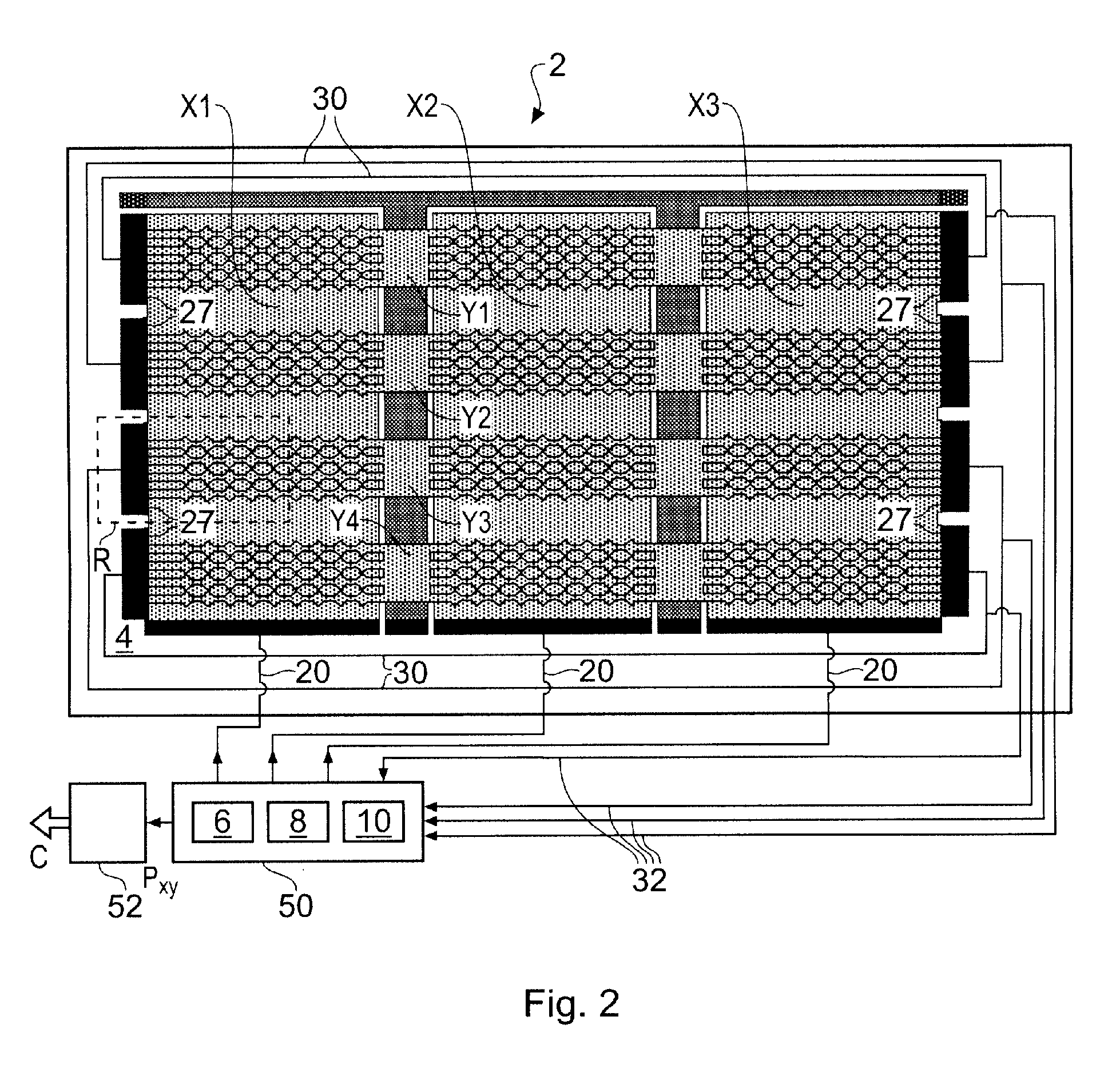

Display with dual-function capacitive elements

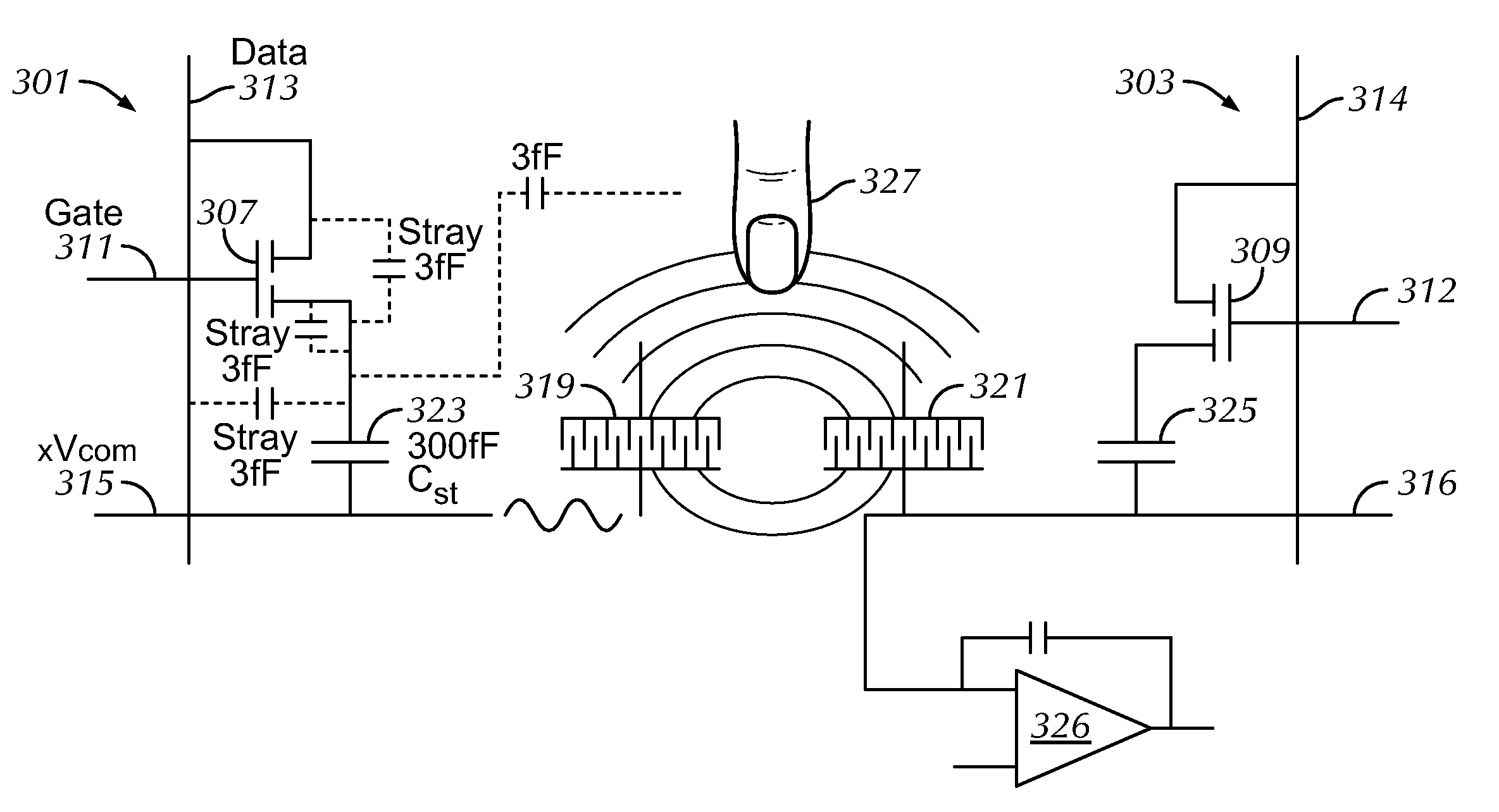

A touch screen including display pixels with capacitive elements is provided. The touch screen includes first common voltage lines connecting capacitive elements in adjacent display pixels, and a second common voltage line connecting first common voltage lines. The pixels can be formed as electrically separated regions by including breaks in the common voltage lines. The regions can include a drive region that is stimulated by stimulation signals, a sense region that receives sense signals corresponding to the stimulation signals. A grounded region can also be included, for example, between a sense region and a drive region. A shield layer can be formed of a substantially high resistance material and disposed to shield a sense region. A black mask line and conductive line under the black mask line can be included, for example, to provide low-resistance paths between a region of pixels and touch circuitry outside the touch screen borders.

Owner:APPLE INC

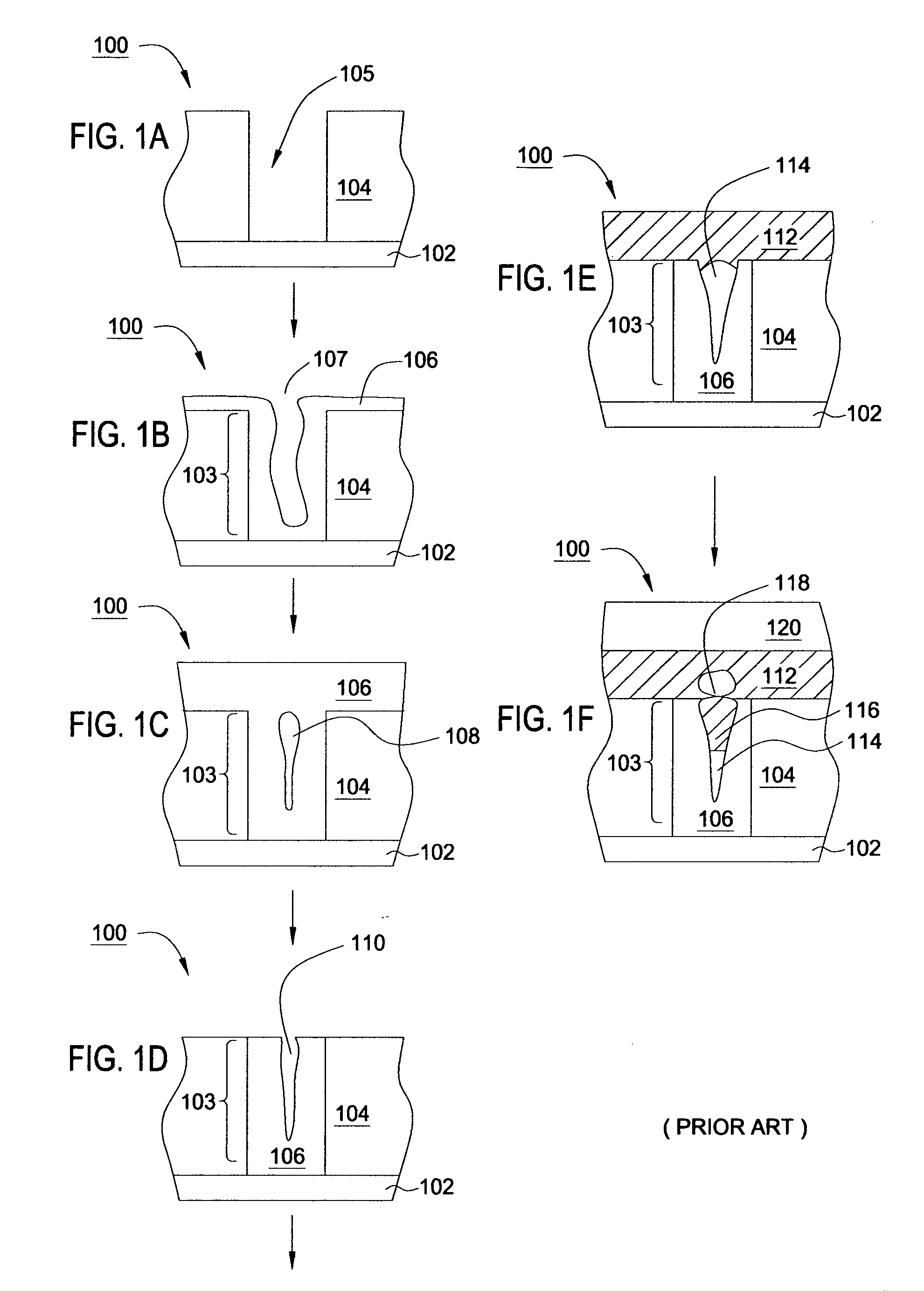

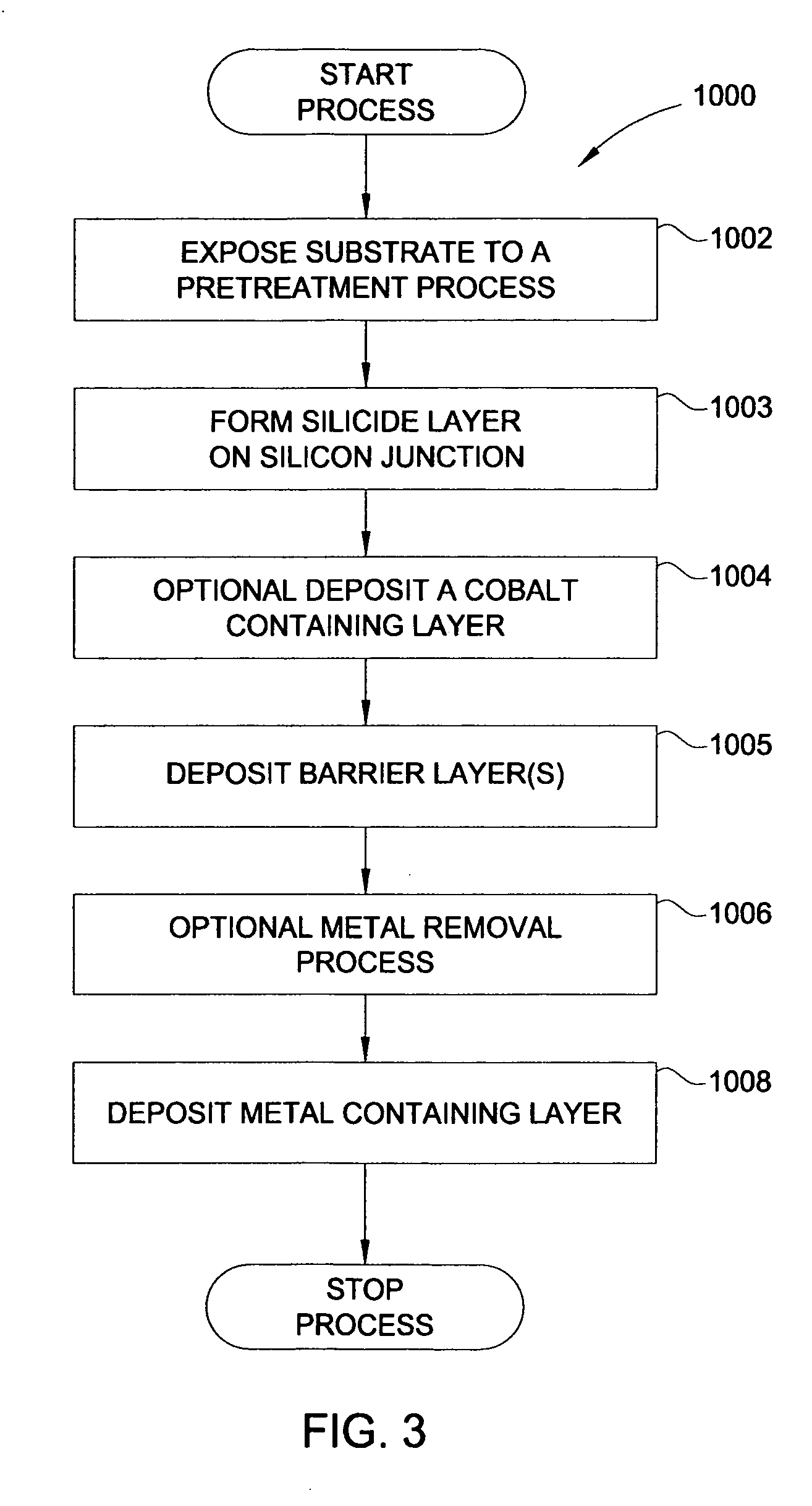

Contact metallization scheme using a barrier layer over a silicide layer

ActiveUS20060251800A1Material nanotechnologySemiconductor/solid-state device detailsDevice materialElectroless deposition

Embodiments of the invention generally provide methods of filling contact level features formed in a semiconductor device by depositing a barrier layer over the contact feature and then filing the layer using an PVD, CVD, ALD, electrochemical plating process (ECP) and / or electroless deposition processes. In one embodiment, the barrier layer has a catalytically active surface that will allow the electroless deposition of a metal on the barrier layer. In one aspect, the electrolessly deposited metal is copper or a copper alloy. In one aspect, the contact level feature is filled with a copper alloy by use of an electroless deposition process. In another aspect, a copper alloy is used to from a thin conductive copper layer that is used to subsequently fill features with a copper containing material by use of an ECP, PVD, CVD, and / or ALD deposition process. In one embodiment, a portion of the barrier layer is purposely allowed to react with traces of residual oxide at the silicon junction of the contact level feature to form a low resistance connection.

Owner:APPLIED MATERIALS INC

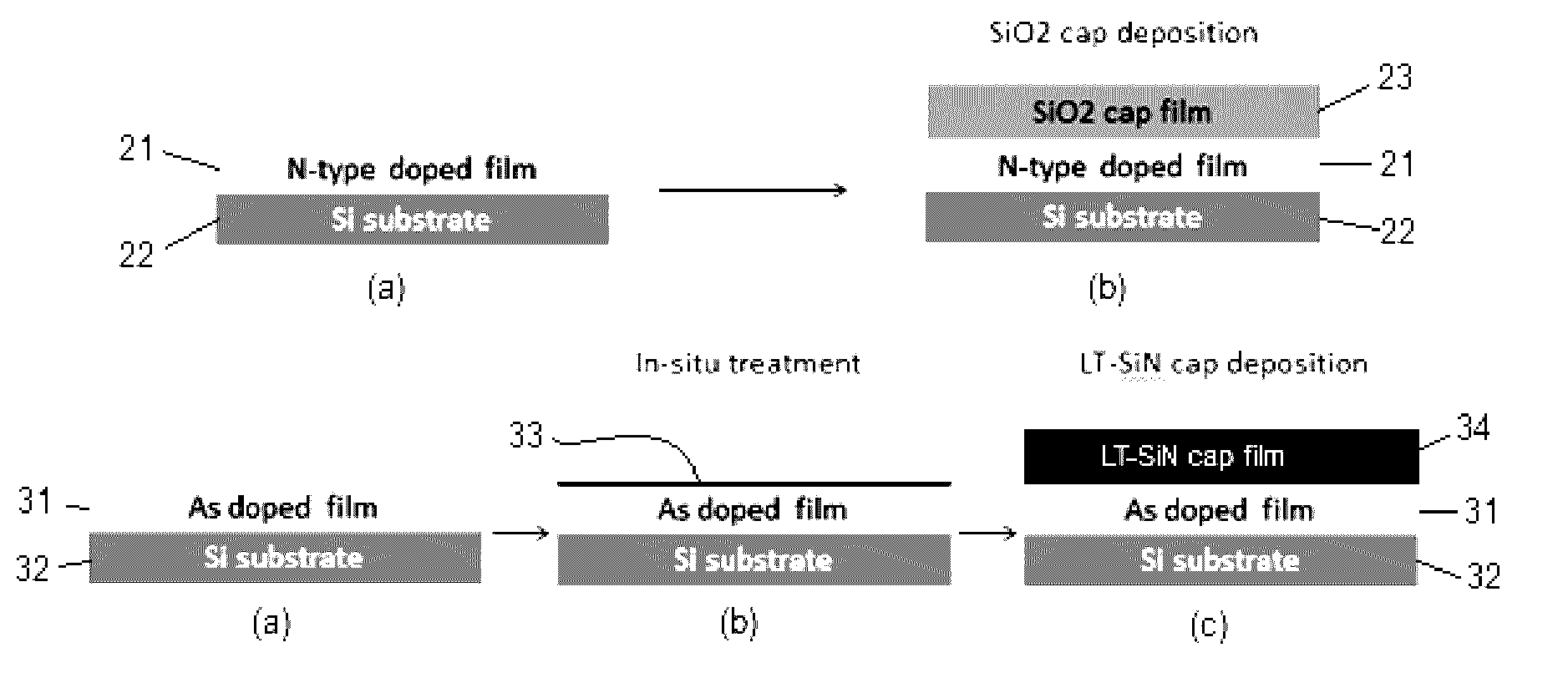

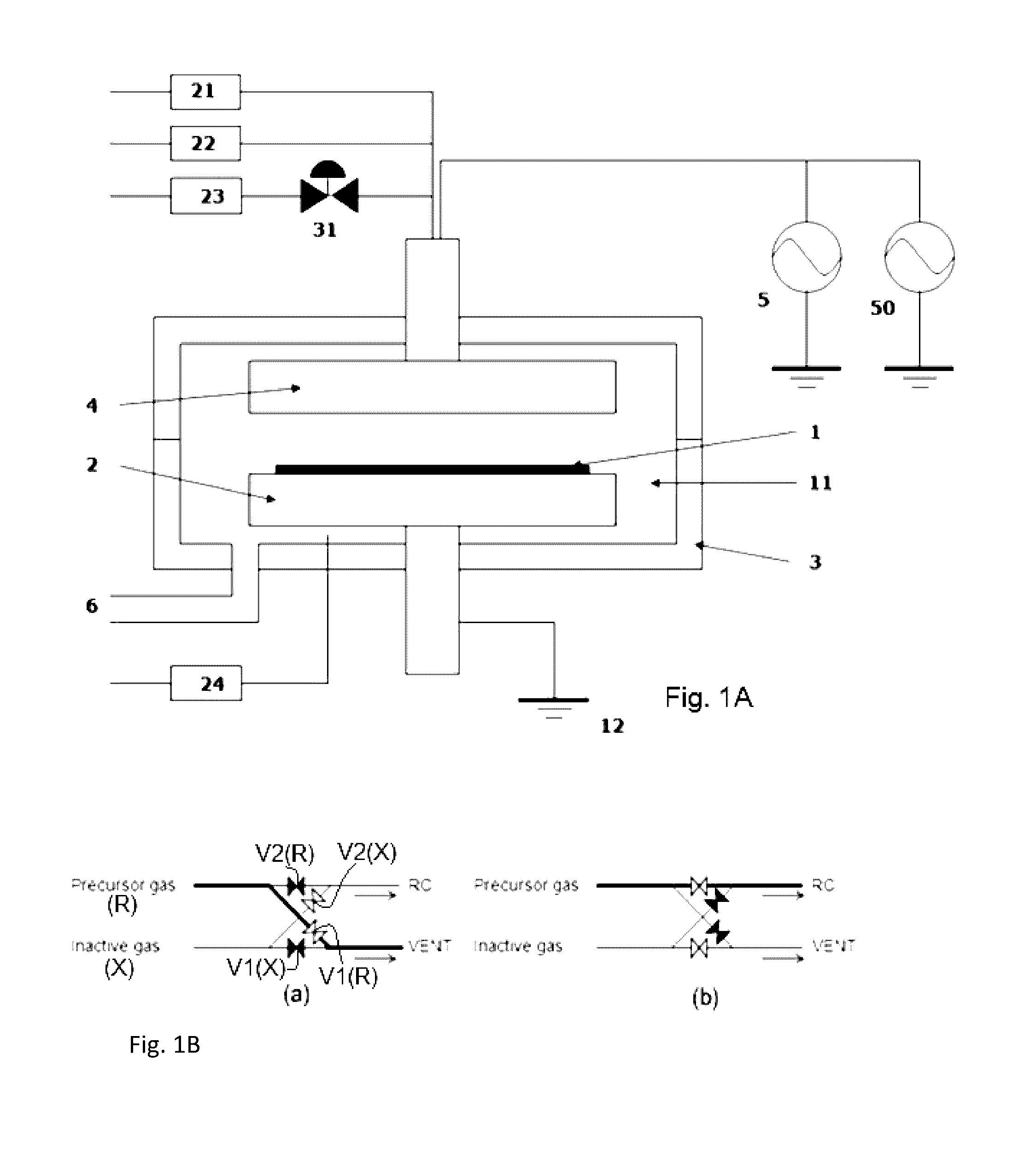

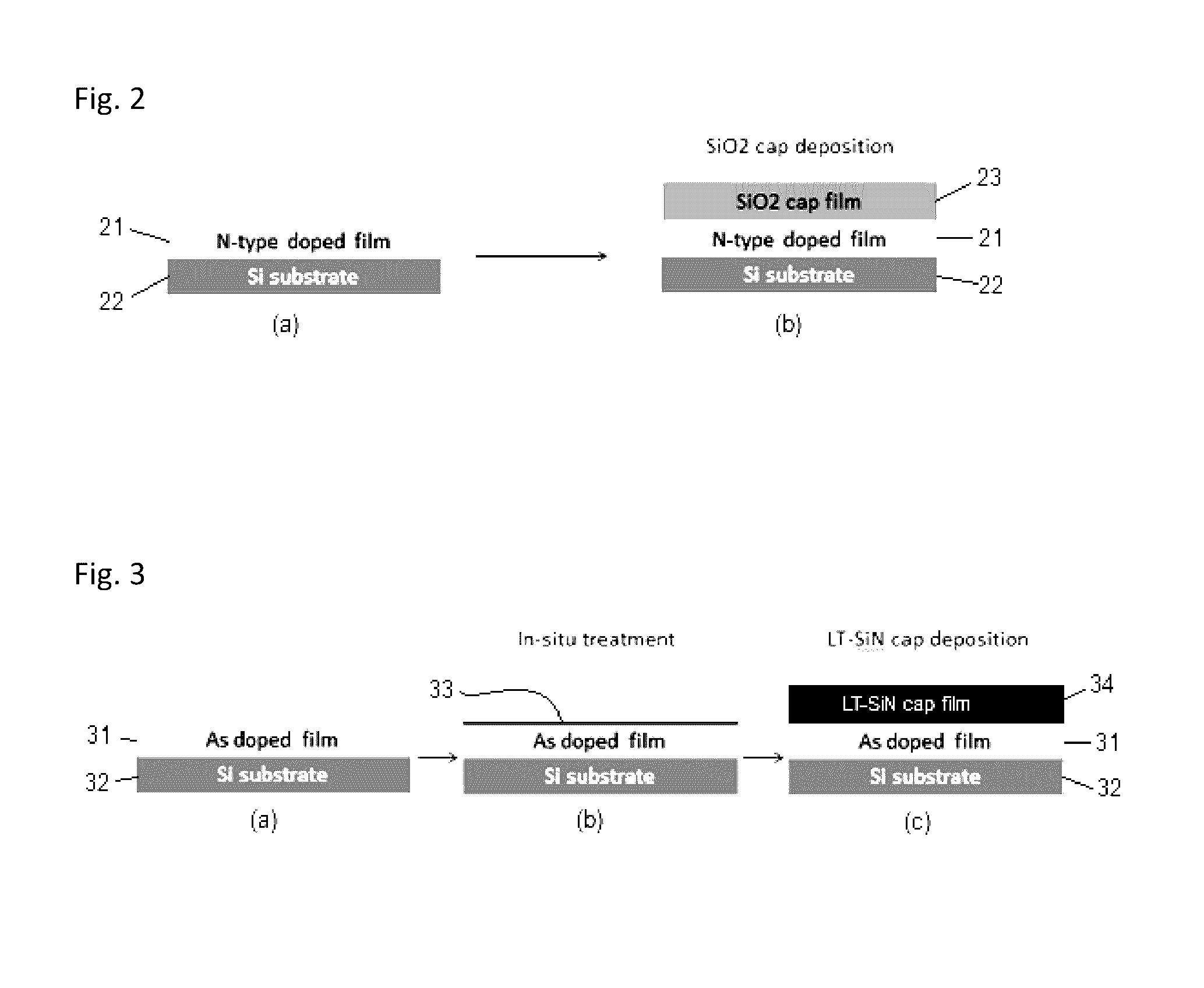

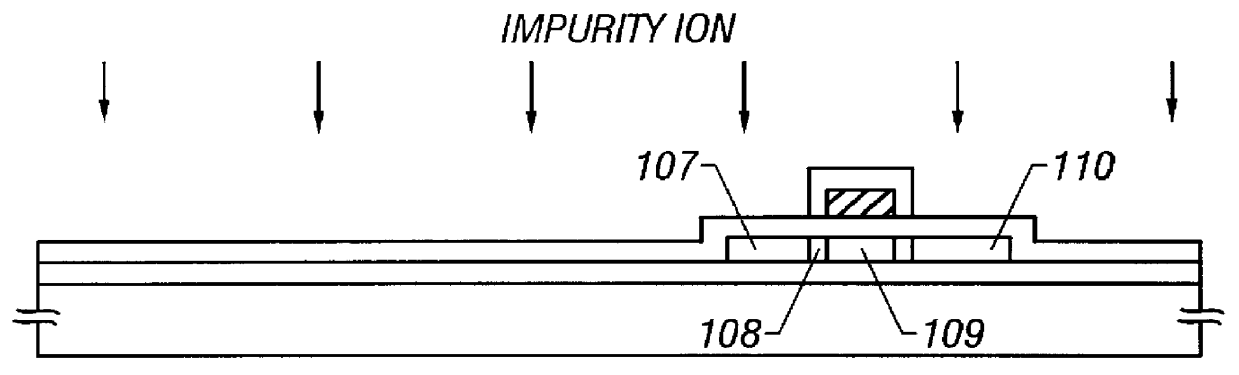

Method for forming film having low resistance and shallow junction depth

ActiveUS9478415B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilicon oxideLow resistance

A method for forming on a substrate a doped silicon oxide film with a cap film, includes: forming an arsenosilicate glass (ASG) film as an arsenic (As)-doped silicon oxide film on a substrate; continuously treating a surface of the ASG film with a treating gas constituted by Si, N, and H without excitation; and continuously forming a silicon nitride (SiN) film as a cap film on the treated surface of the ASG film.

Owner:ASM IP HLDG BV

Touch Sensitive Screen

ActiveUS20070062739A1Lower impedanceEfficient couplingTransmission systemsInput/output processes for data processingElectrical resistance and conductancePlastic materials

A capacitive sensor for determining the presence of an object, such as a user's finger or a stylus, is provided. The sensor comprises a substrate, for example made of transparent plastics material, such as PET, on which electrodes are deposited. A resistive drive electrode for example formed of transparent ITO, is arranged on one side of the substrate and a resistive sense electrode, which again may be of transparent ITO, is arranged on the other side of the substrate. Thus an overall transparent sensor may be provided. A shorting connection is also provided which is configured to connect between two locations on one of the electrodes. The electrodes are connected to respective drive and sense channels. By providing the shorting connection between two locations on one or other (or both) of the electrodes, a lower resistance connection is provided between other locations on the electrode and the corresponding drive or sense channel.

Owner:NEODRON LTD

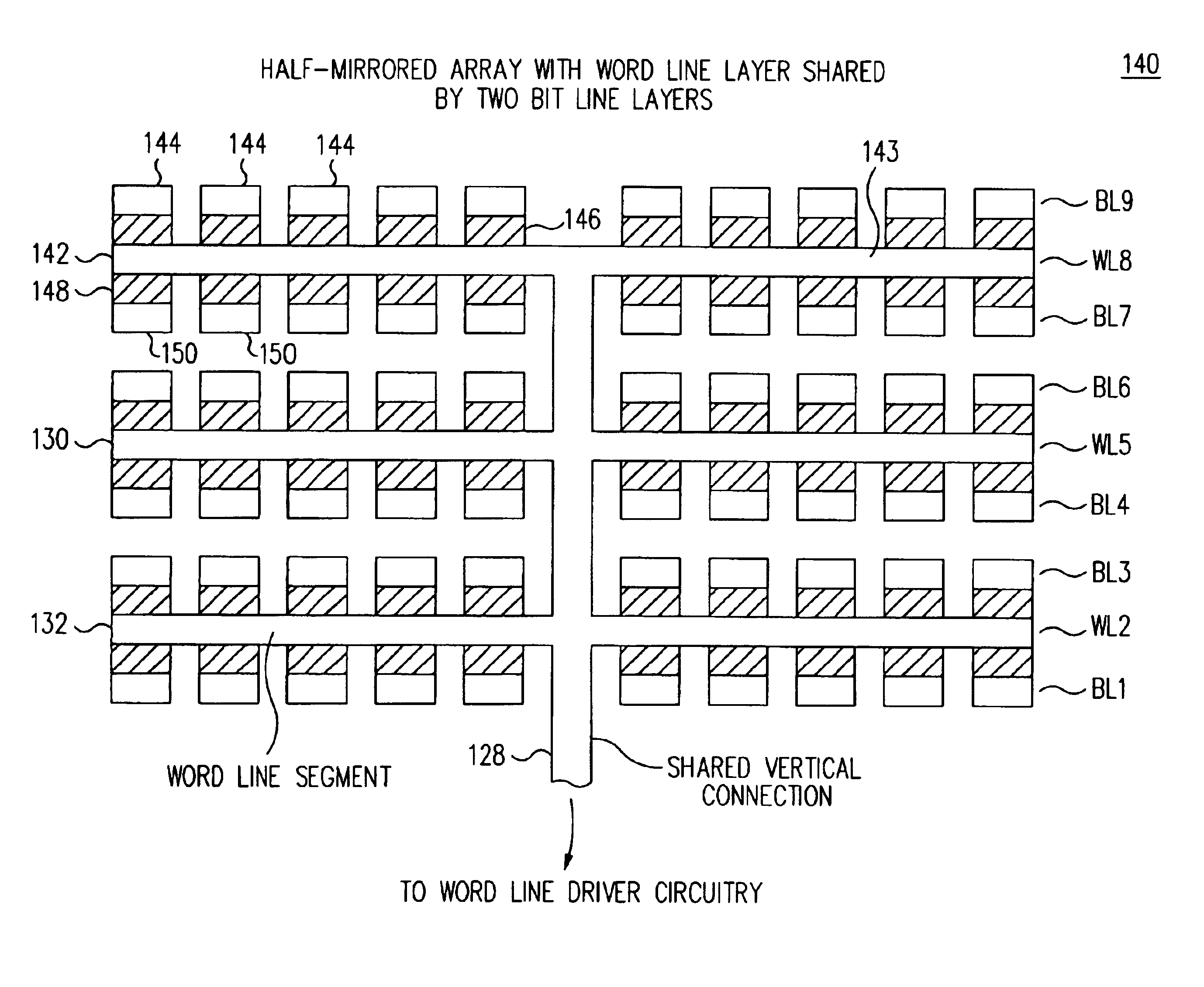

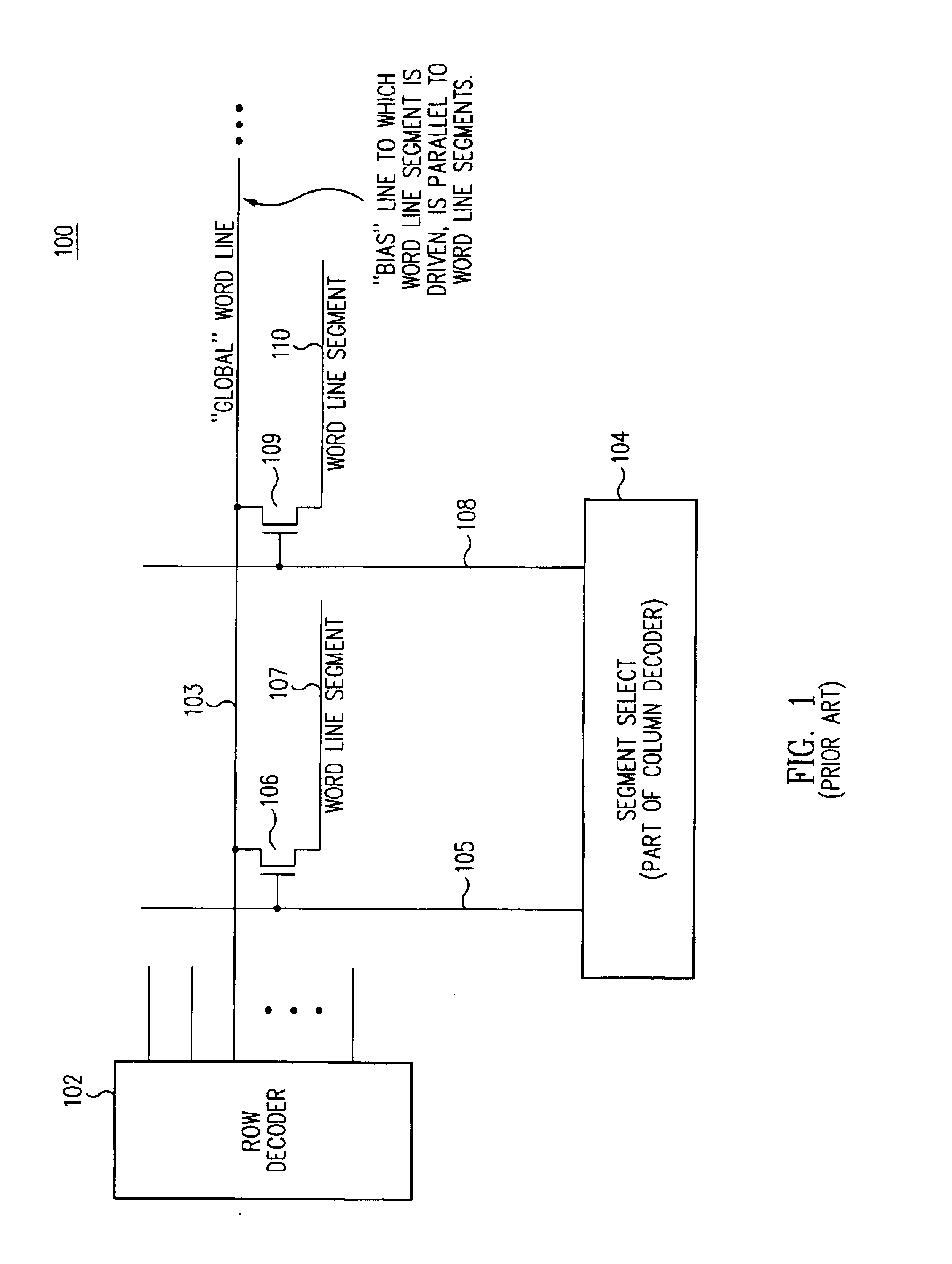

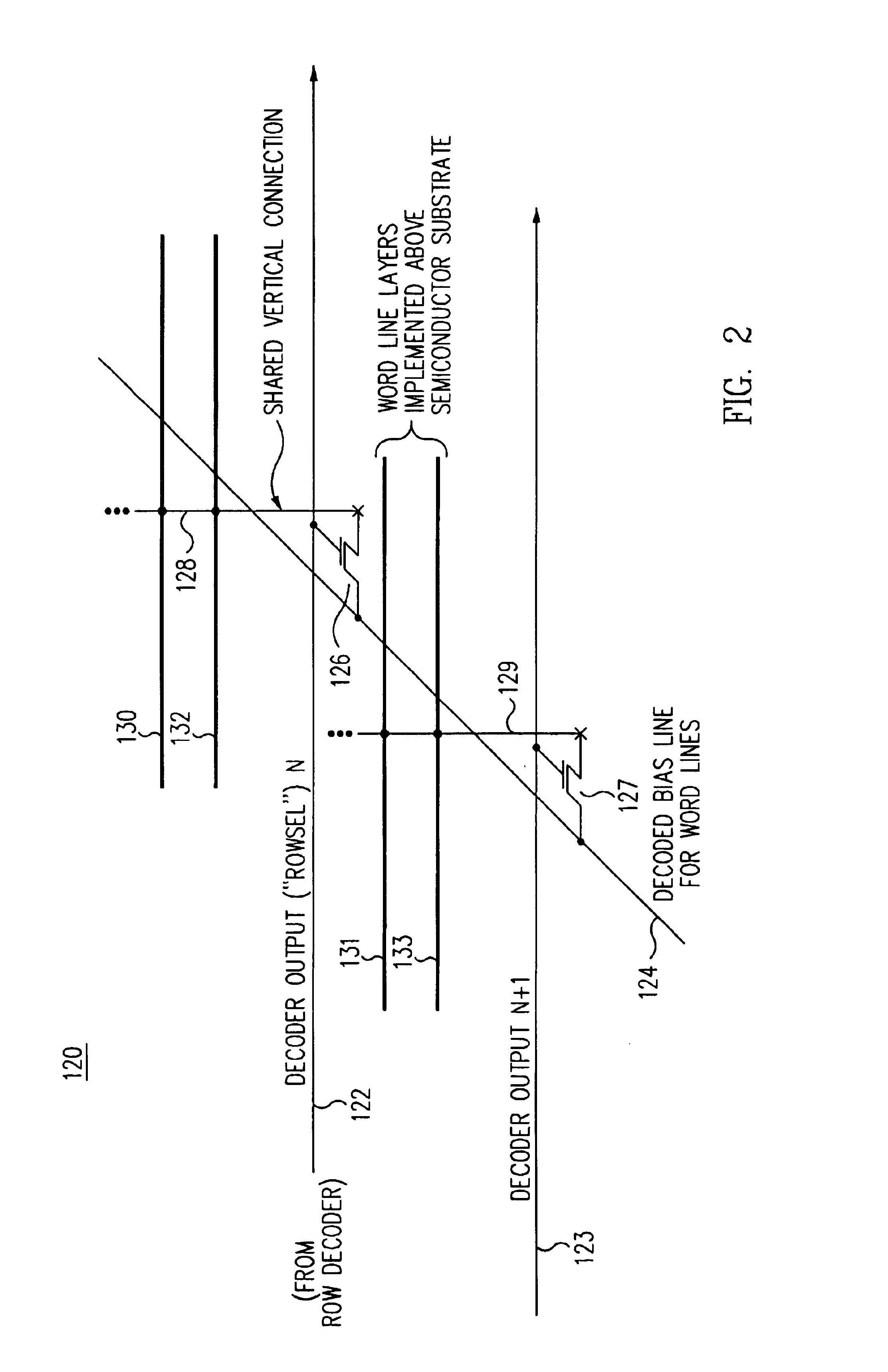

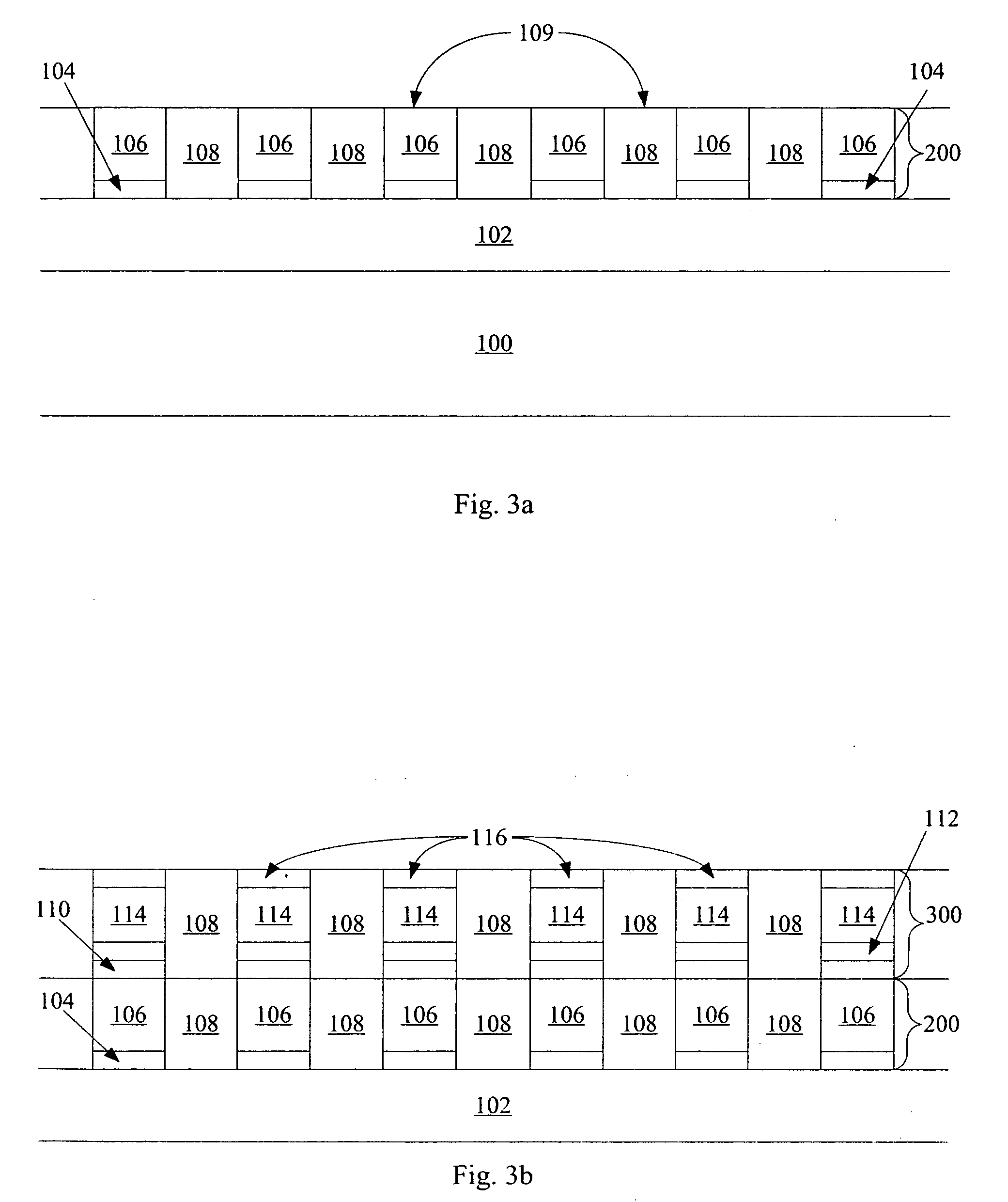

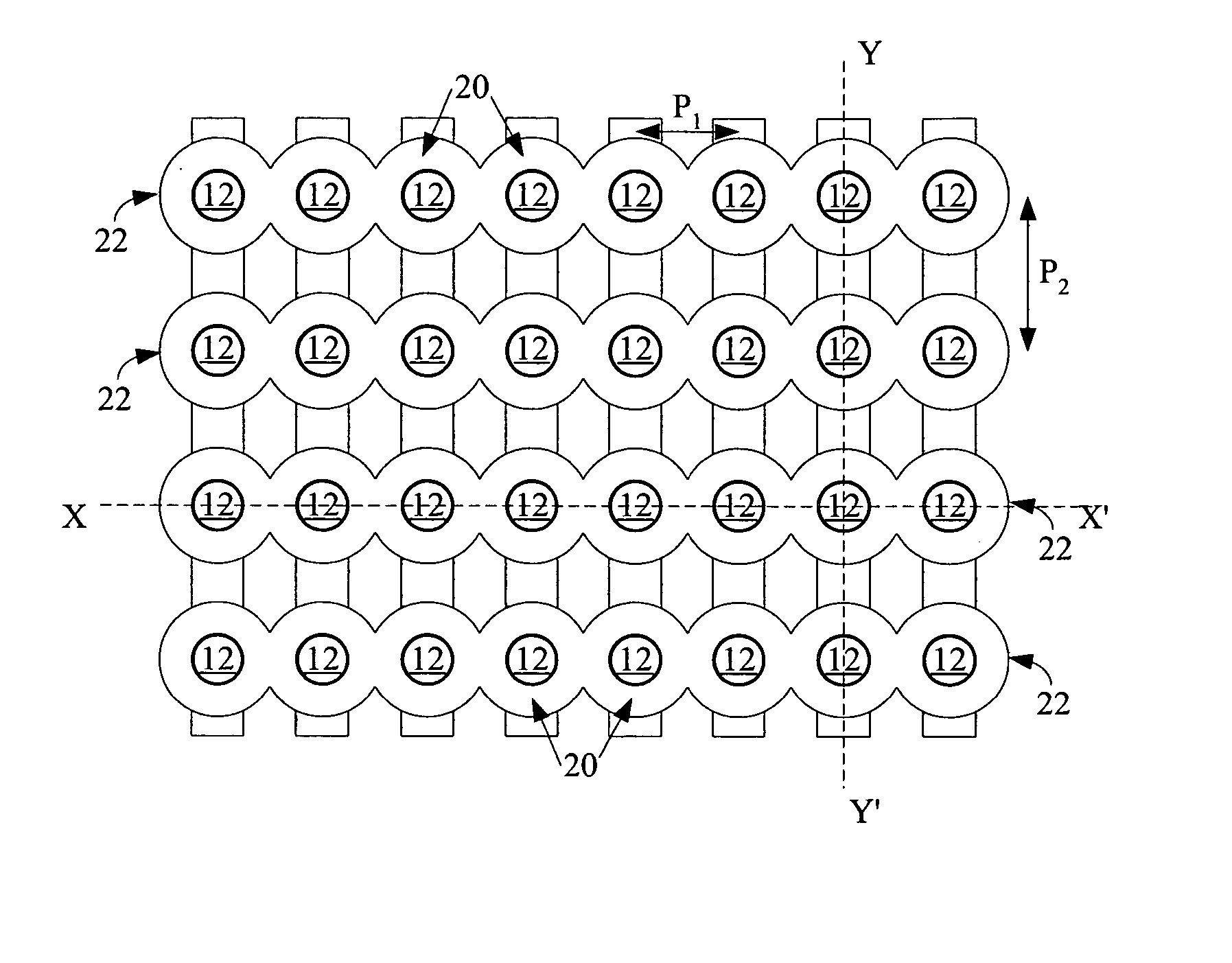

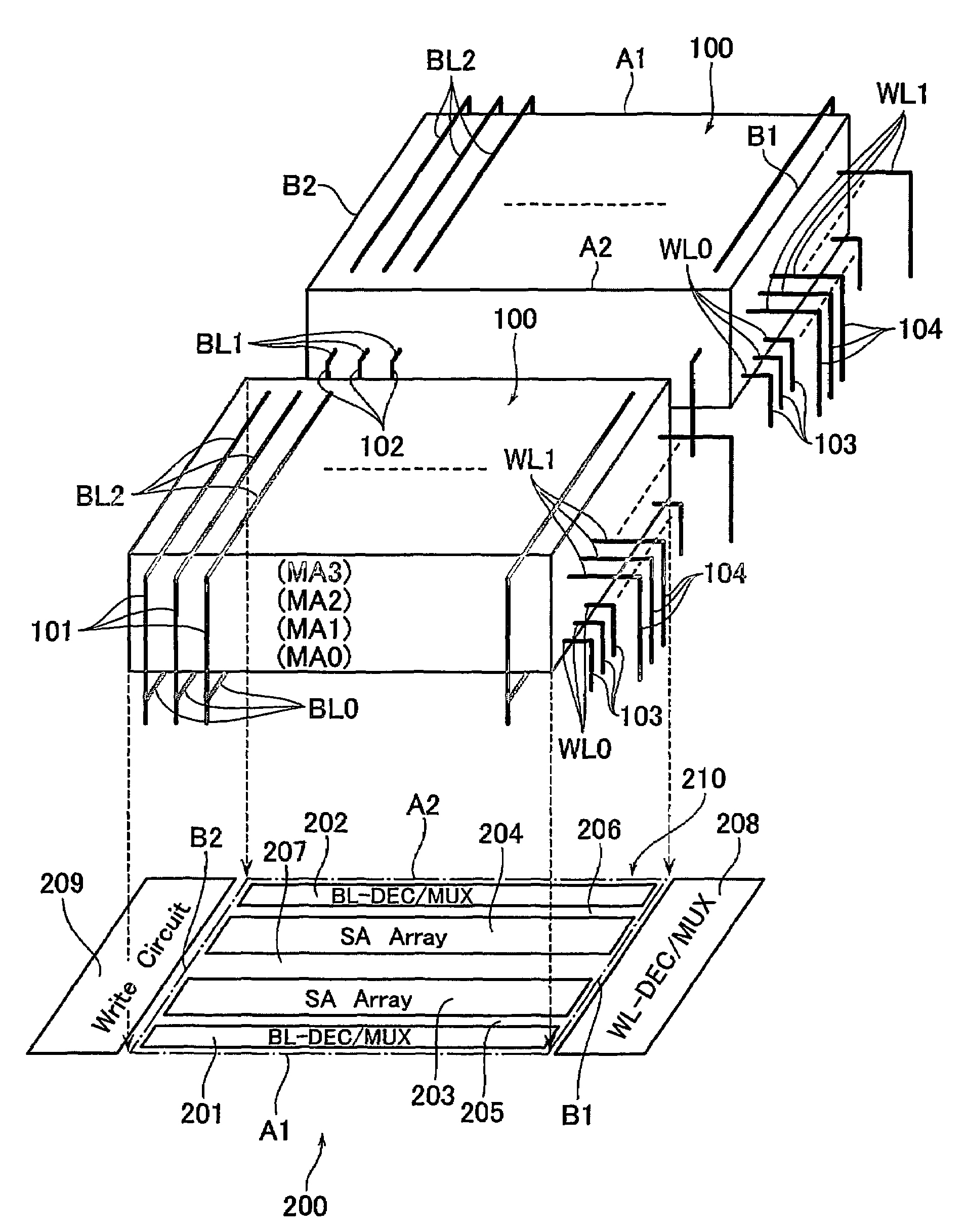

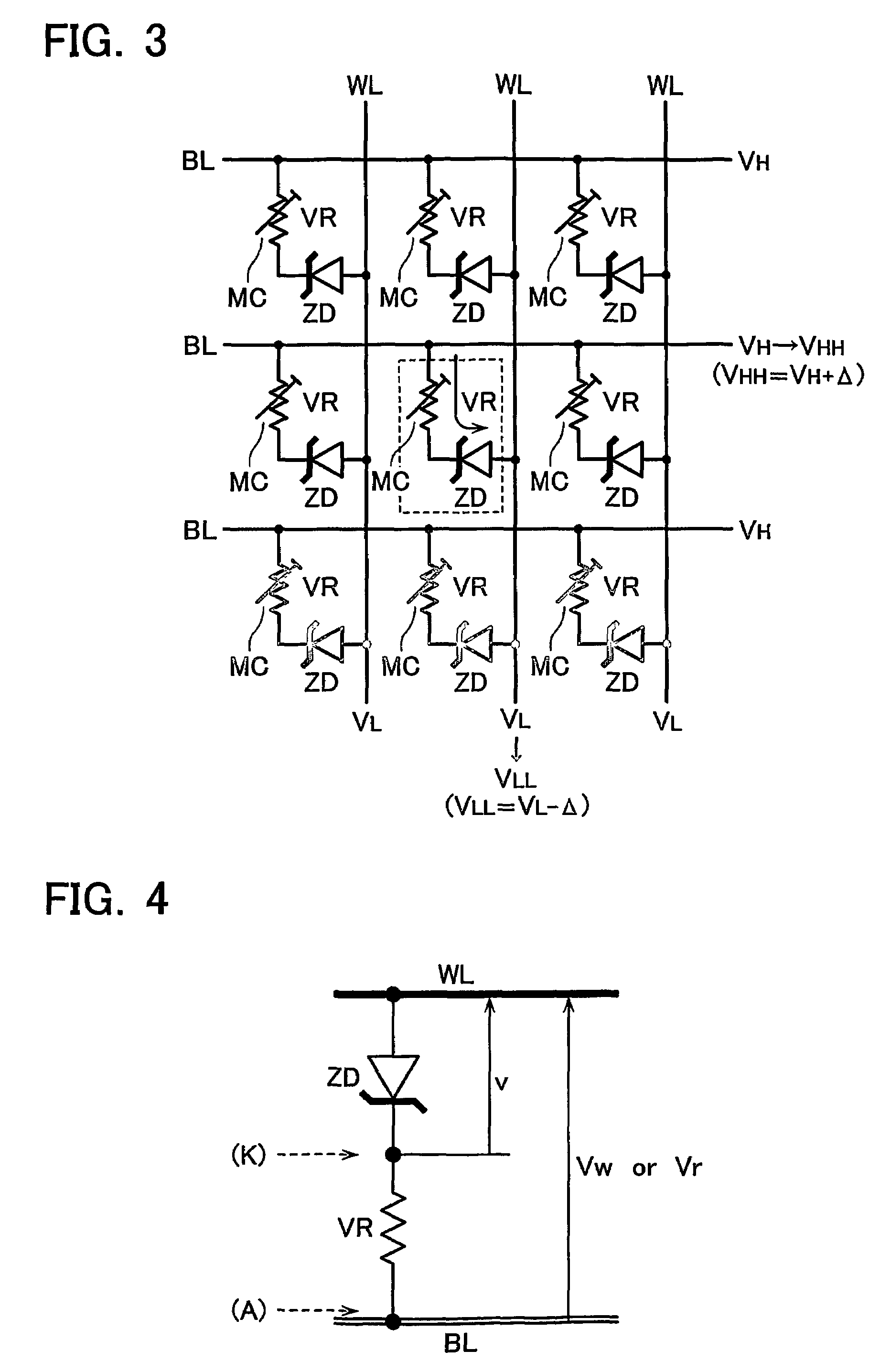

Word line arrangement having multi-layer word line segments for three-dimensional memory array

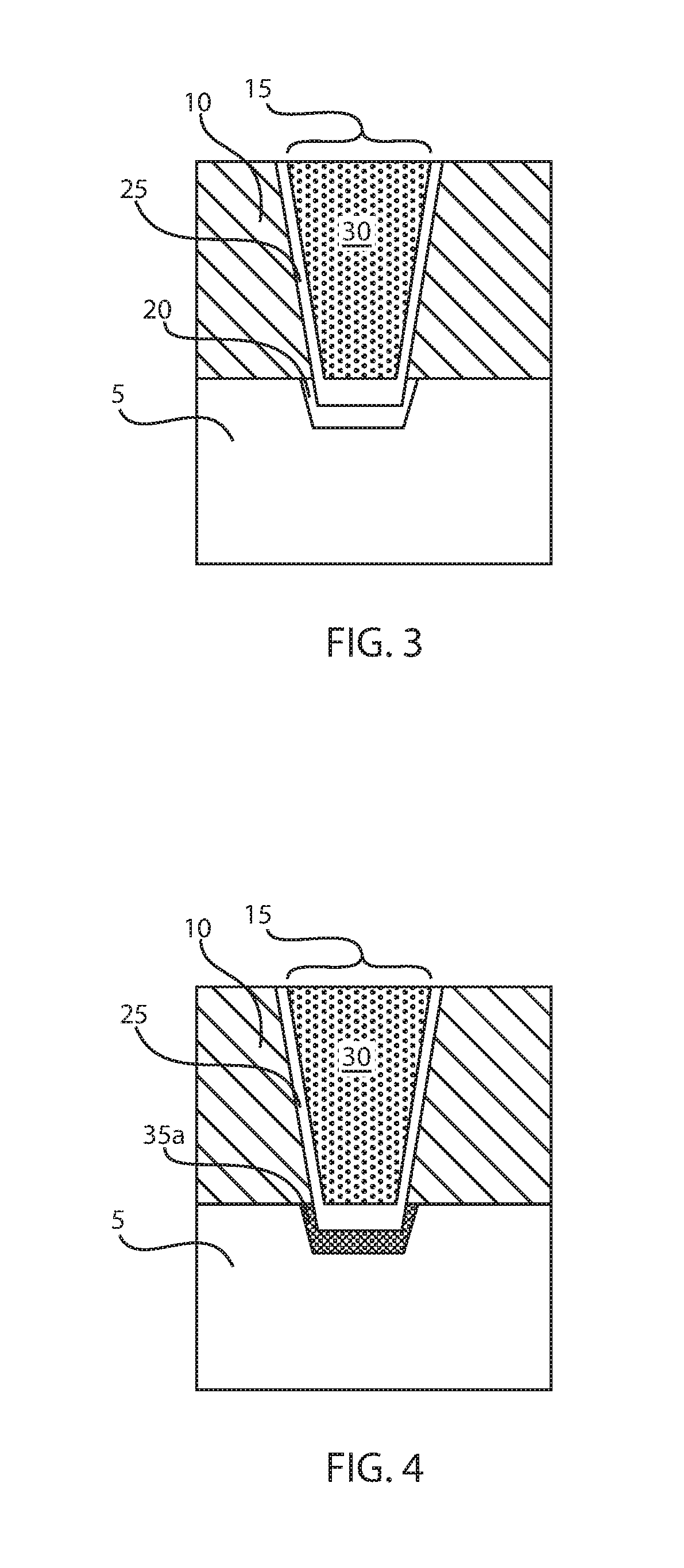

InactiveUS6879505B2Reduce stress timeDecreasing fan-outSolid-state devicesDigital storageDriver circuitLine driver

A three-dimensional (3D) passive element memory cell array provides short word lines while still maintaining a small support circuit area for efficiency. Short, low resistance word line segments on two or more word line layers are connected together in parallel to form a given word line without use of segment switch devices between the word line segments. A shared vertical connection preferably connects the word line segments together and connects to a word line driver circuit disposed generally below the array near the word line. Each word line driver circuit preferably couples its word line either to an associated one of a plurality of selected bias lines or to an unselected bias line associated with the driver circuit, which selected bias lines are themselves decoded to provide for an efficient multi-headed word line decoder.

Owner:SANDISK TECH LLC

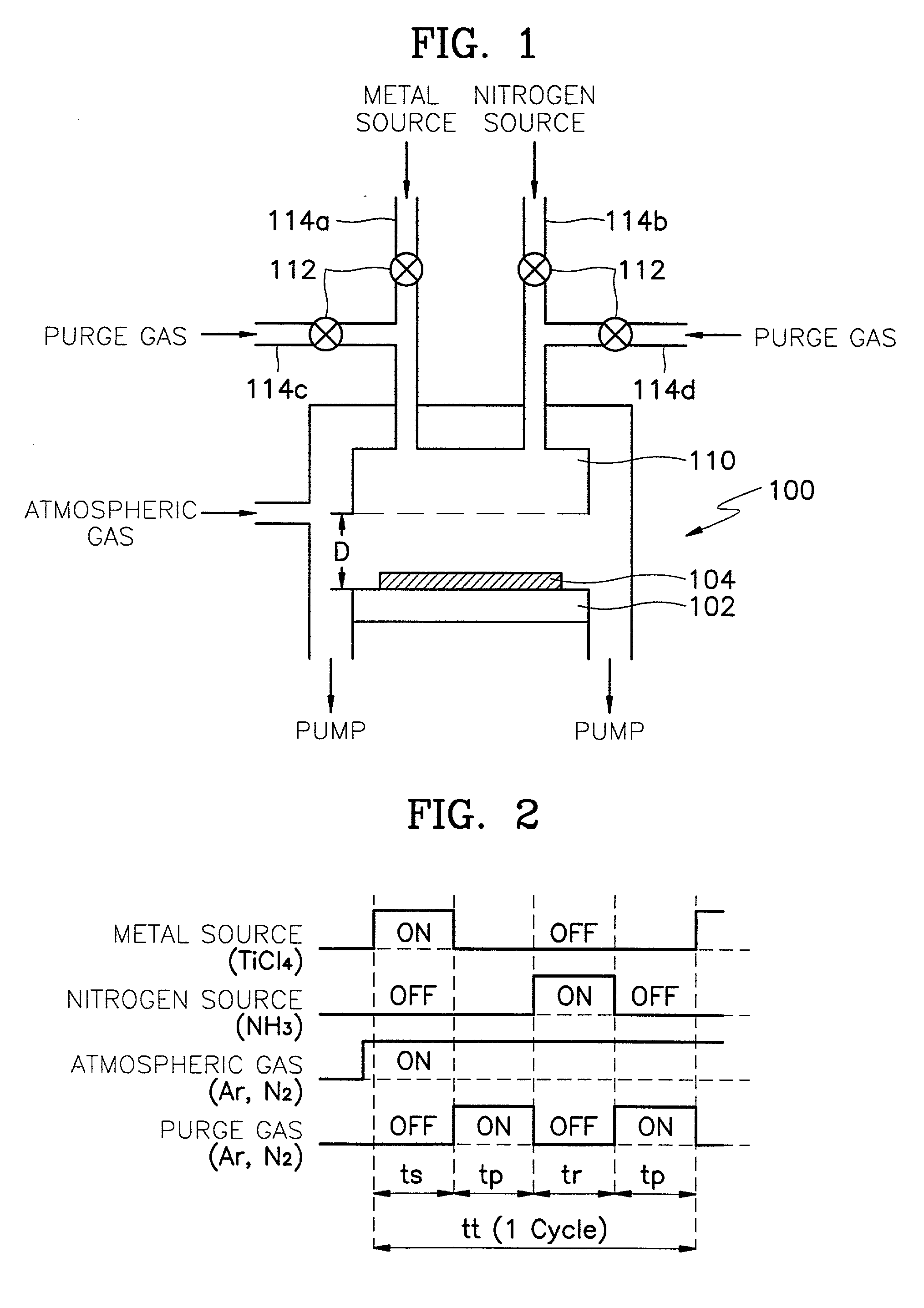

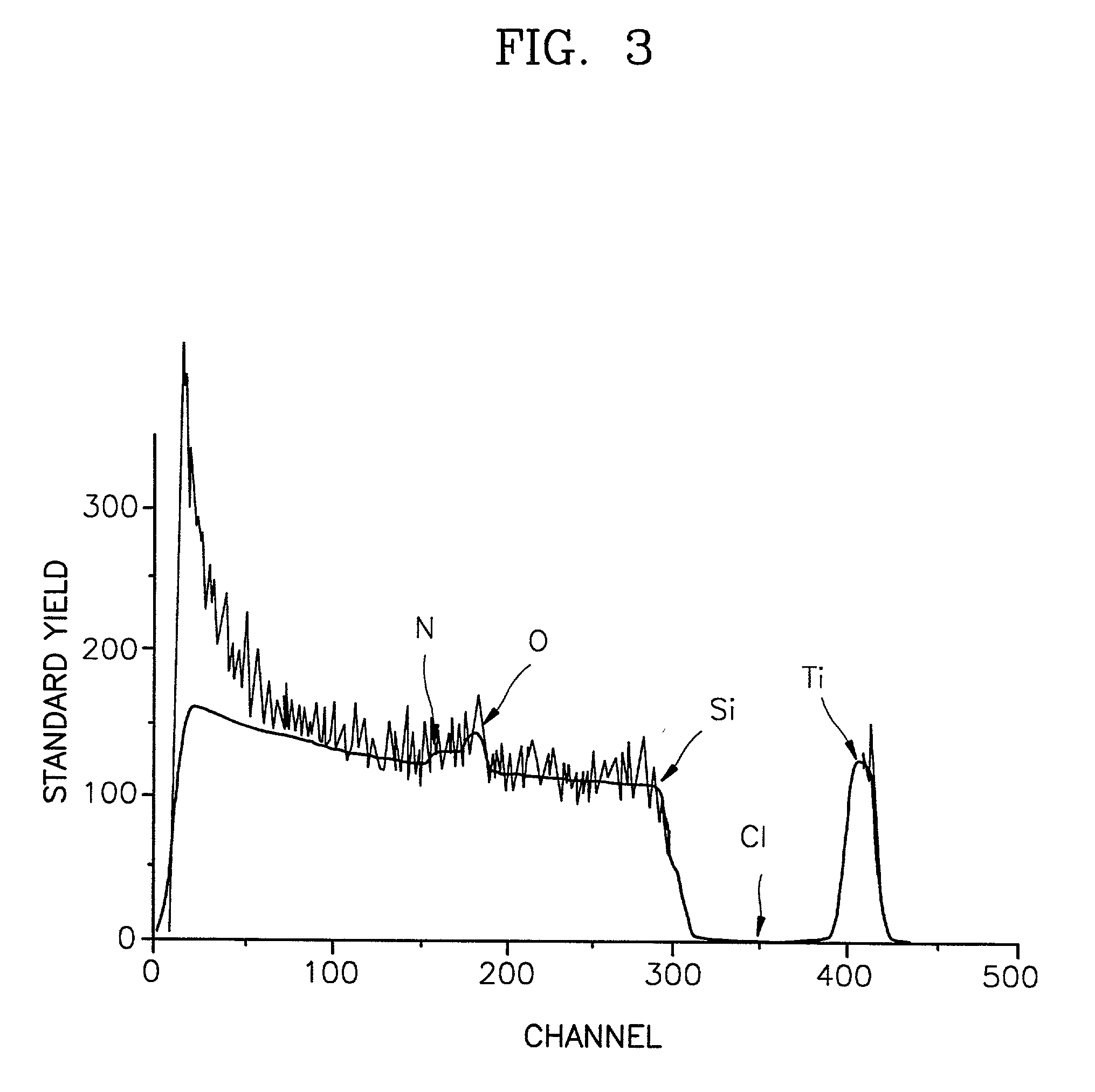

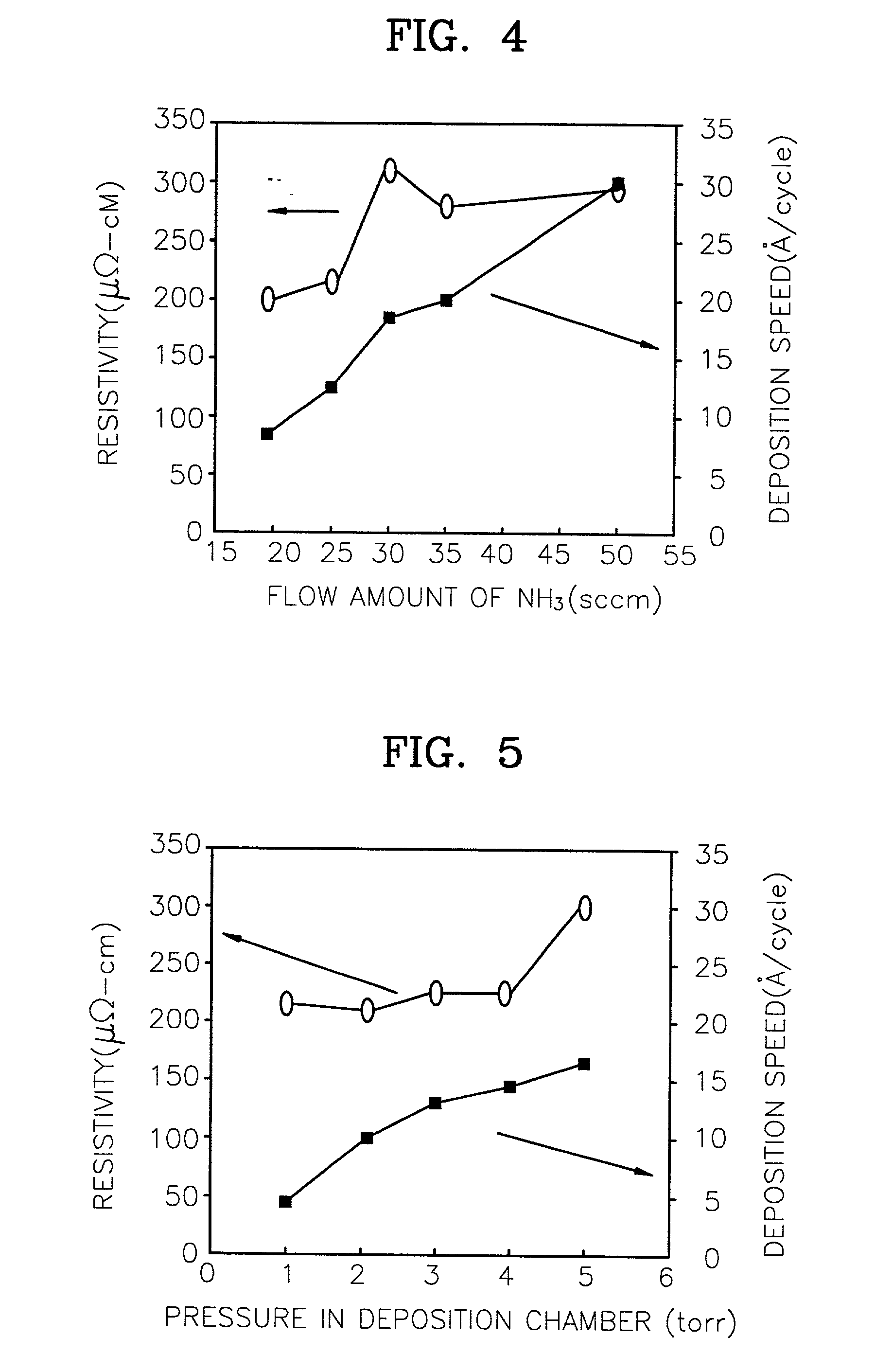

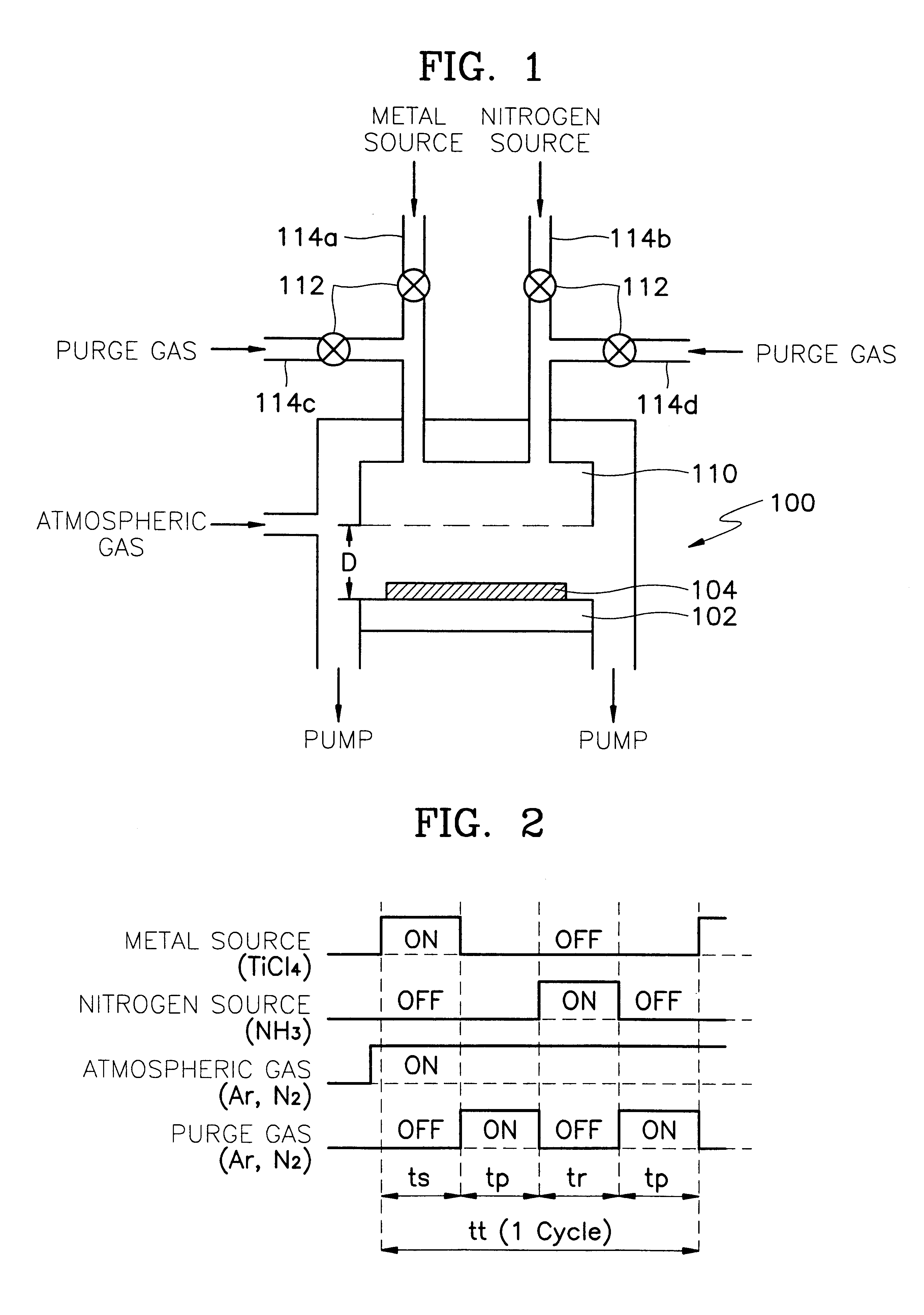

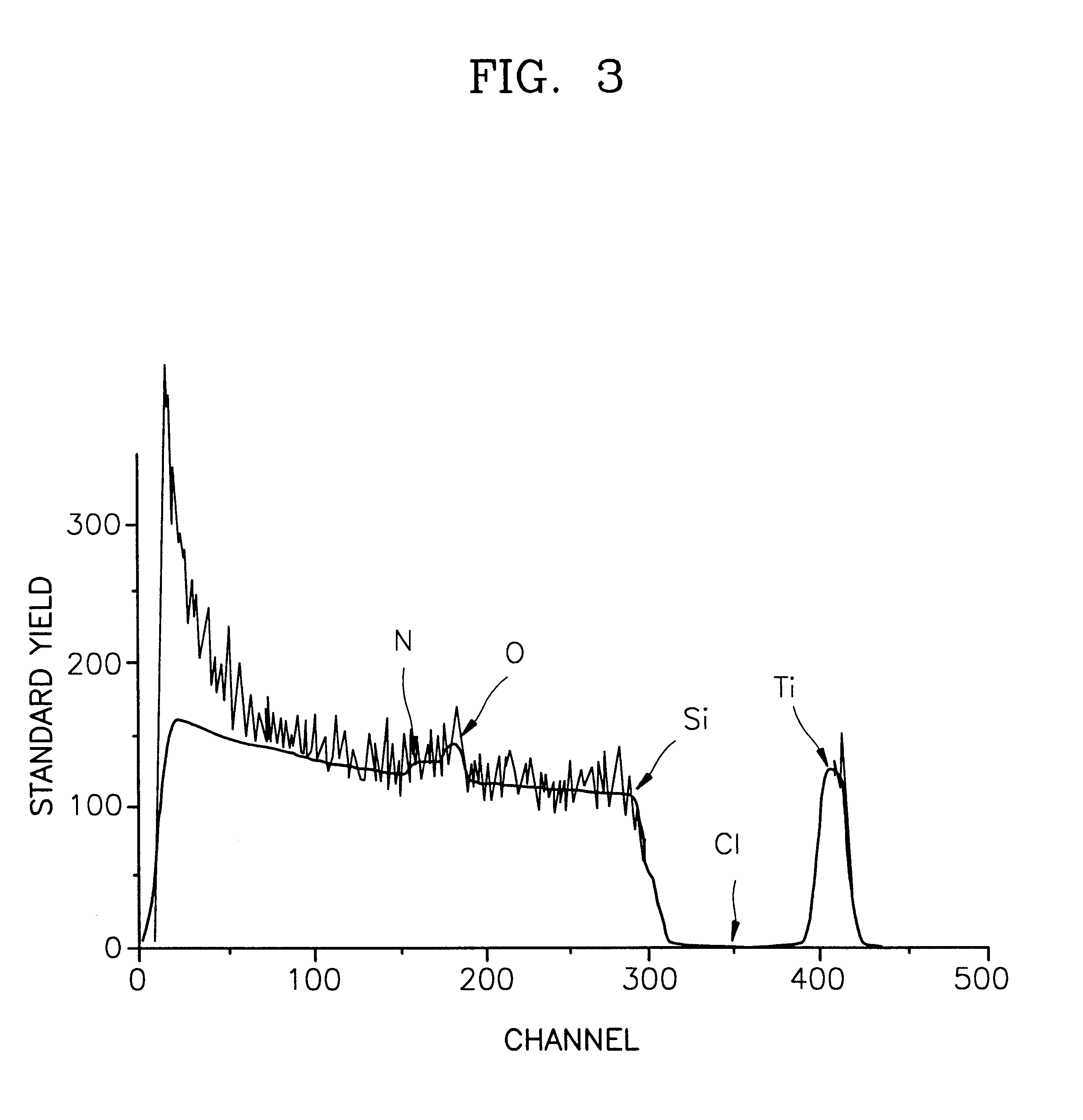

Method of forming metal nitride film by chemical vapor deposition and method of forming metal contact and capacitor of semiconductor device using the same

InactiveUS20010034097A1Good step coverageLow resistivitySemiconductor/solid-state device manufacturingCapacitorsChemical physicsDevice material

A method of forming a metal nitride film using chemical vapor deposition (CVD), and a method of forming a metal contact and a semiconductor capacitor of a semiconductor device using the same, are provided. The method of forming a metal nitride film using chemical vapor deposition (CVD) in which a metal source and a nitrogen source are used as a precursor, includes the steps of inserting a semiconductor substrate into a deposition chamber, flowing the metal source into the deposition chamber, removing the metal source remaining in the deposition chamber by cutting off the inflow of the metal source and flowing a purge gas into the deposition chamber, cutting off the purge gas and flowing the nitrogen source into the deposition chamber to react with the metal source adsorbed on the semiconductor substrate, and removing the nitrogen source remaining in the deposition chamber by cutting off the inflow of the nitrogen source and flowing the purge gas into the deposition chamber. Accordingly, the metal nitride film having low resistivity and a low content of Cl even with excellent step coverage can be formed at a temperature of 500° C. or lower, and a semiconductor capacitor having excellent leakage current characteristics can be manufactured. Also, a deposition speed, approximately 20 A / cycle, is suitable for mass production.

Owner:SAMSUNG ELECTRONICS CO LTD

Implantable medical device incorporating miniaturized circuit module

Implantable medical devices (IMDS) having RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming commands to and from an external programmer having an improved RF module configured to occupy small spaces within the IMD housing to further effect the miniaturization thereof. An RF module formed of an RF module substrate and at least one IC chip and discrete components has a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include: (1) integrating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The integrated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the RF module substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

Method of forming metal nitride film by chemical vapor deposition and method of forming metal contact and capacitor of semiconductor device using the same

InactiveUS6348376B2Good step coverageLow resistivitySemiconductor/solid-state device manufacturingCapacitorsDevice materialNitrogen source

A method of forming a metal nitride film using chemical vapor deposition (CVD), and a method of forming a metal contact and a semiconductor capacitor of a semiconductor device using the same, are provided. The method of forming a metal nitride film using chemical vapor deposition (CVD) in which a metal source and a nitrogen source are used as a precursor, includes the steps of inserting a semiconductor substrate into a deposition chamber, flowing the metal source into the deposition chamber, removing the metal source remaining in the deposition chamber by cutting off the inflow of the metal source and flowing a purge gas into the deposition chamber, cutting off the purge gas and flowing the nitrogen source into the deposition chamber to react with the metal source adsorbed on the semiconductor substrate, and removing the nitrogen source remaining in the deposition chamber by cutting off the inflow of the nitrogen source and flowing the purge gas into the deposition chamber. Accordingly, the metal nitride film having low resistivity and a low content of Cl even with excellent step coverage can be formed at a temperature of 500° C. or lower, and a semiconductor capacitor having excellent leakage current characteristics can be manufactured. Also, a deposition speed, approximately 20 A / cycle, is suitable for mass production.

Owner:SAMSUNG ELECTRONICS CO LTD

Low resistance contacts including intermetallic alloy of nickel, platinum, titanium, aluminum and type iv semiconductor elements

ActiveUS20180068950A1Semiconductor/solid-state device detailsSolid-state devicesPlatinumSemiconductor materials

A method of forming a contact to a semiconductor device is provided that forms an alloy composed of nickel (Ni), platinum (Pt), aluminum (Al), titanium (Ti) and a semiconductor material. The methods may include forming a nickel and platinum semiconductor alloy at a base of a via. A titanium layer having an angstrom scale thickness is deposited in the via in contact with the nickel platinum semiconductor alloy. An aluminum containing fill is deposited atop the titanium layer. A forming gas anneal including an oxygen containing atmosphere is applied to the structure to provide a contact alloy comprising nickel, platinum, aluminum, titanium and a semiconductor element from the contact surface of the semiconductor device.

Owner:IBM CORP

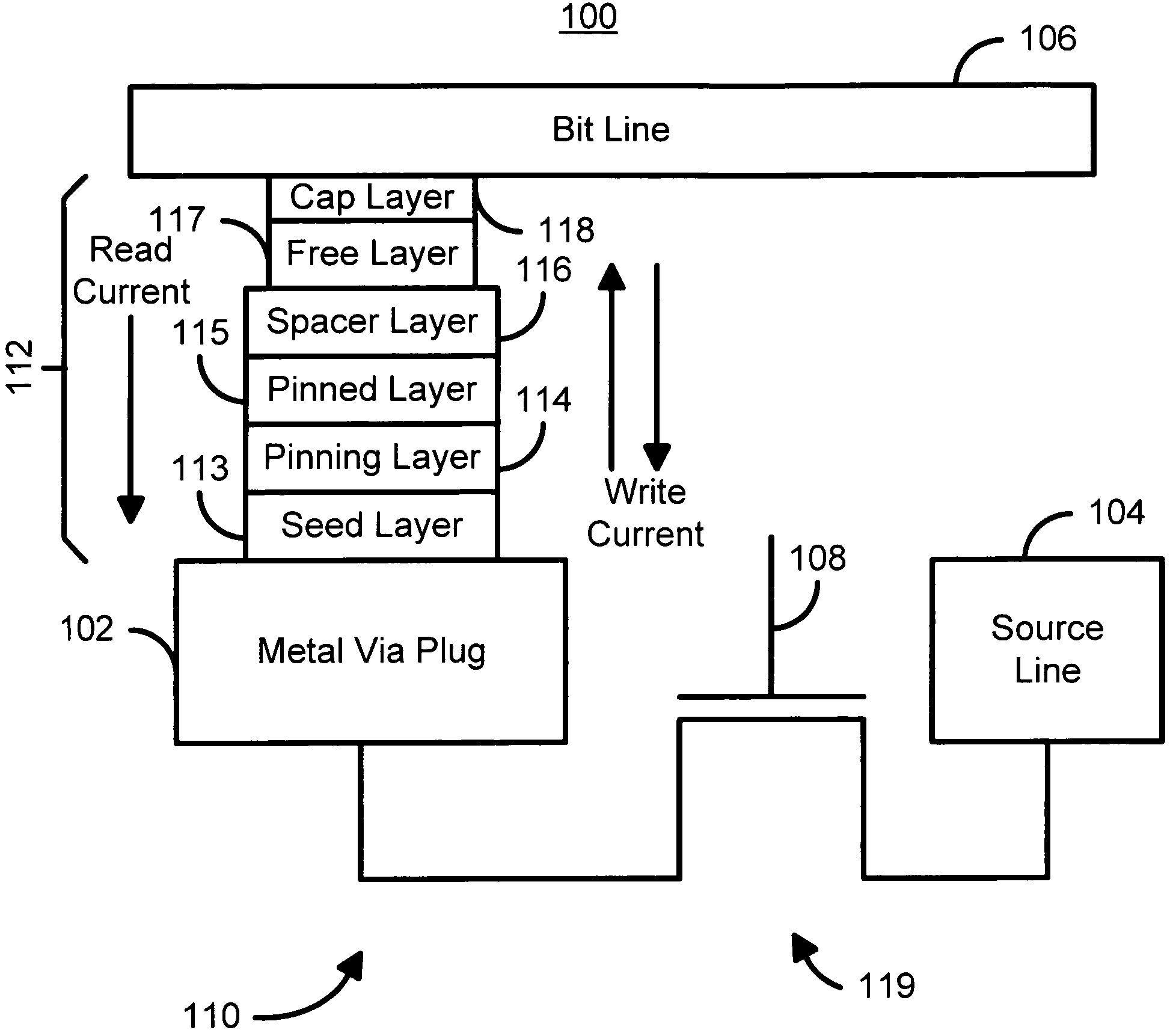

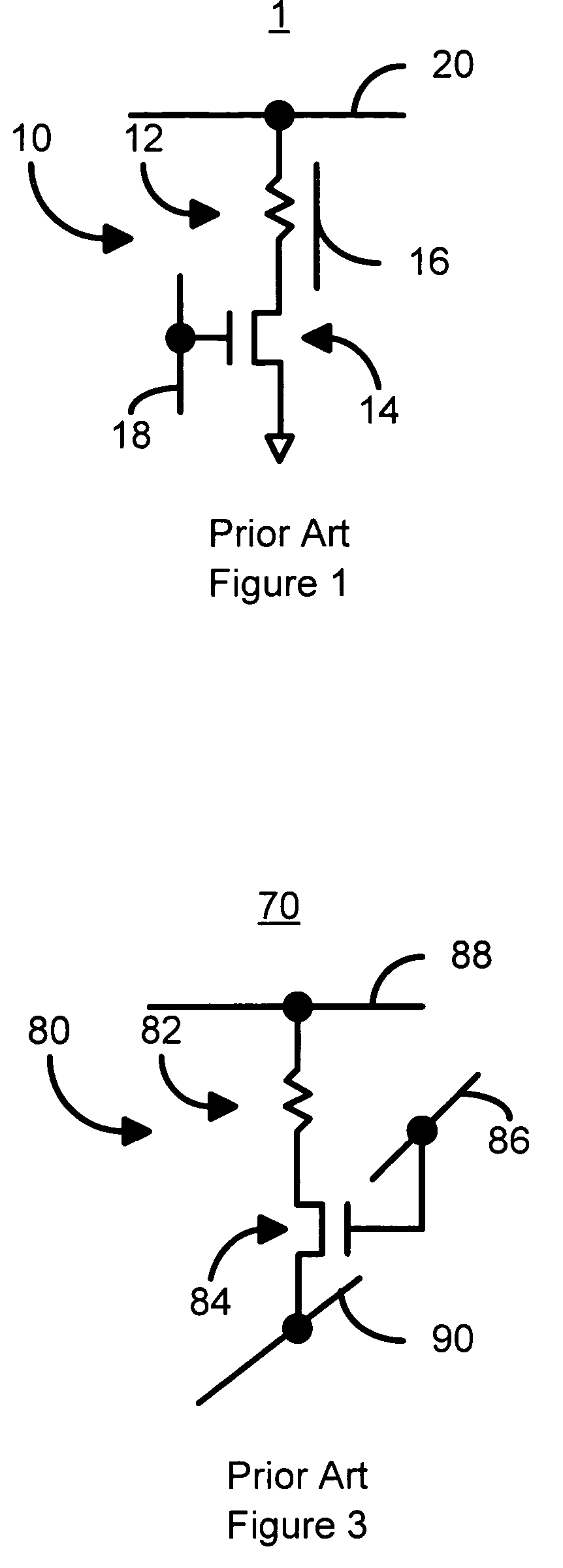

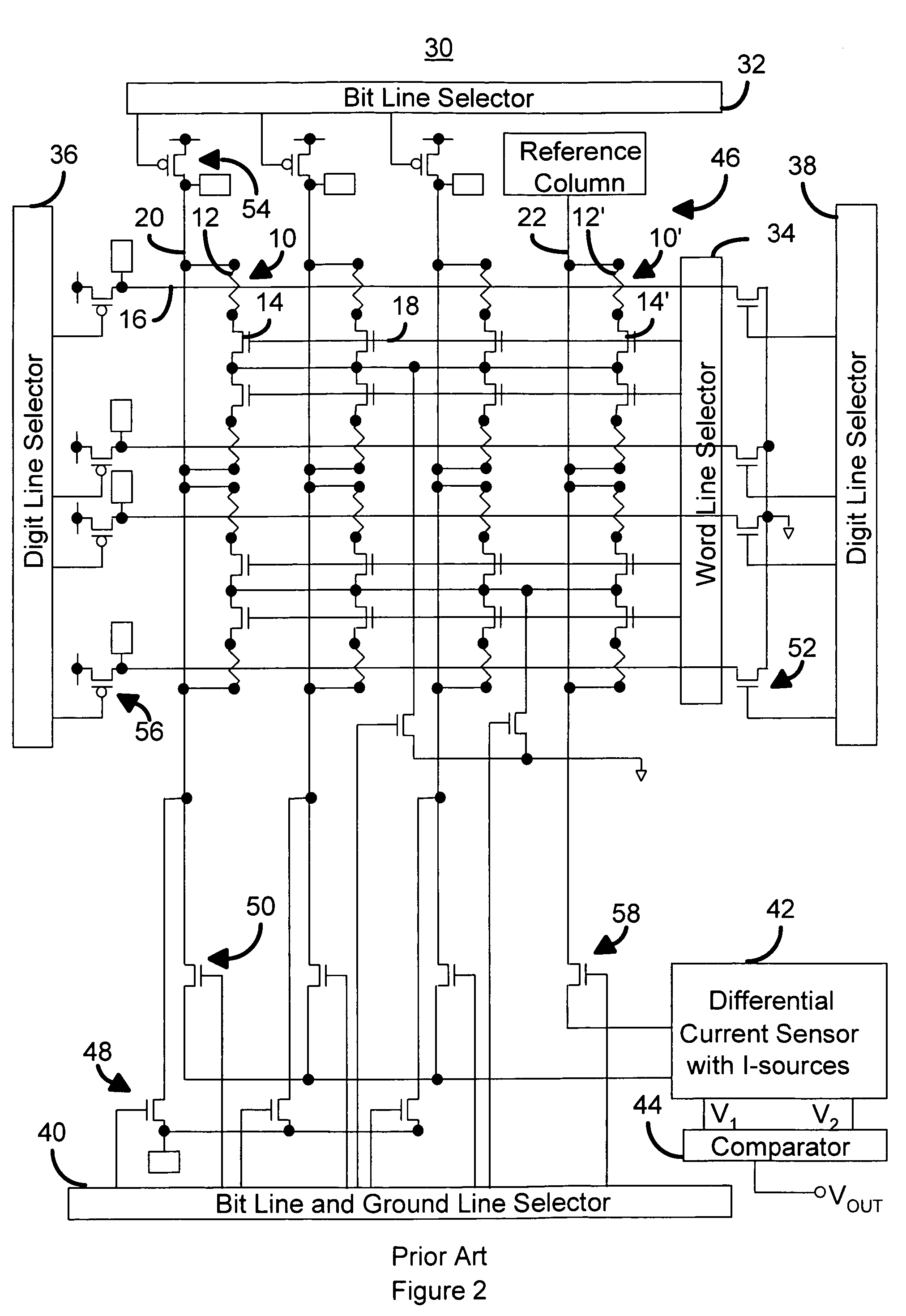

Current driven switching of magnetic storage cells utilizing spin transfer and magnetic memories using such cells having enhanced read and write margins

ActiveUS7379327B2Higher read and write marginDigital storageHigh resistanceElectrical resistance and conductance

A method and system for providing a magnetic memory. The magnetic memory includes magnetic storage cells in an array, bit lines, and source lines. Each magnetic storage cell includes at least one magnetic element. The magnetic element(s) are programmable by write currents driven through the magnetic element(s). Each magnetic element has free and pinned layer(s) and a dominant spacer. The magnetic memory is configured such that either the read current(s) flow from the free layer(s) to the dominant spacer if the maximum low resistance state read current divided by the minimum low resistance state write current is greater than the maximum high resistance state read current divided by the minimum high resistance state write current or the read current(s) flow from the dominant spacer to the free layer(s) if the maximum low resistance state read current divided by the minimum low resistance state write current is less than the maximum high resistance state read current divided by the minimum high resistance state write current.

Owner:SAMSUNG SEMICON +1

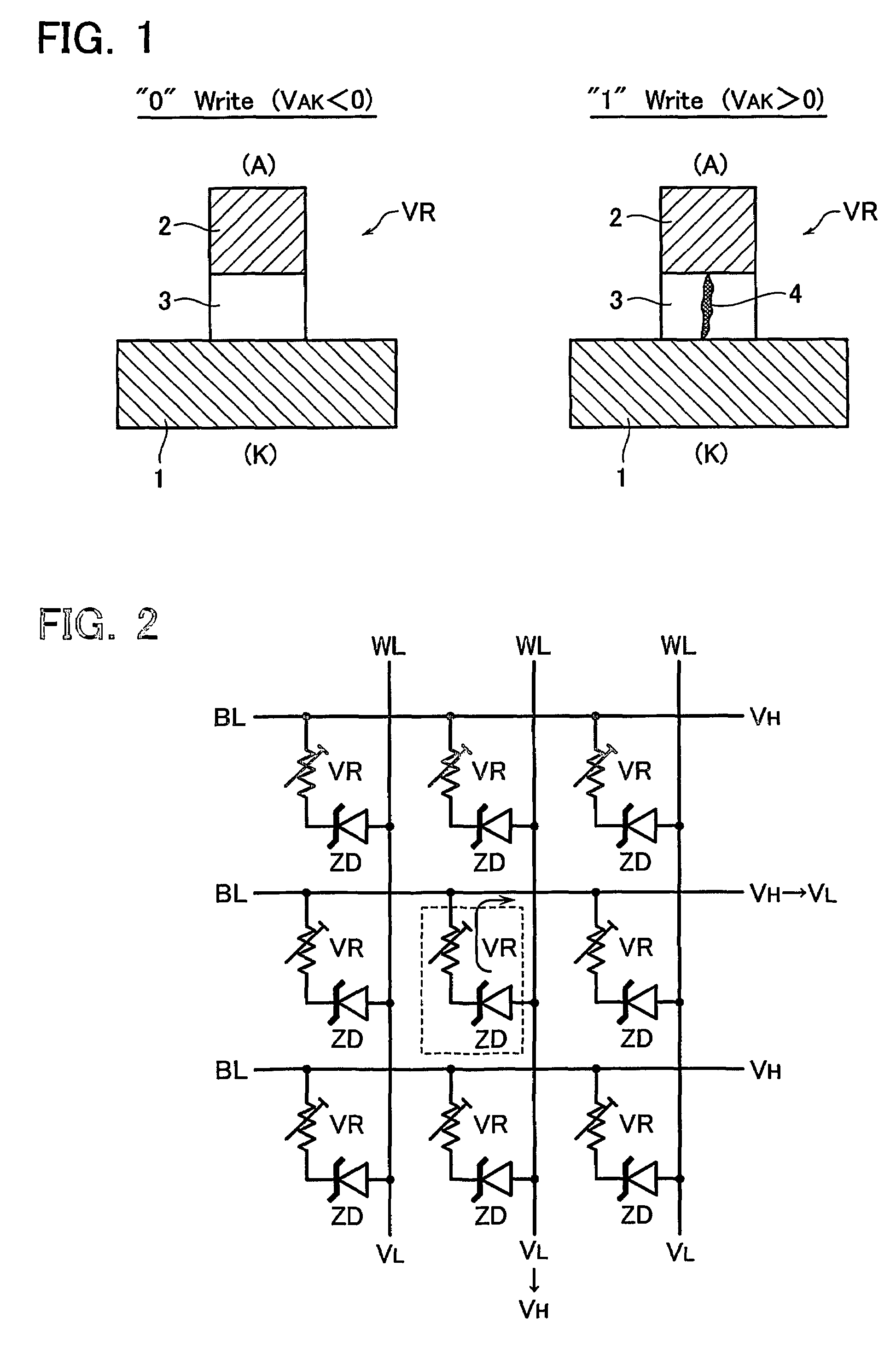

Non-volatile memory cell comprising a dielectric layer and a phase change material in series

The invention provides for a nonvolatile memory cell comprising a dielectric material in series with a phase change material, such as a chalcogenide. Phase change is achieved in chalcogenide memories by thermal means. Concentrating thermal energy in a relatively small volume assists this phase change. By applying high voltage across a dielectric layer, dielectric breakdown occurs, forming a low-resistance rupture region traversing the dielectric layer. This rupture region can serve to concentrate thermal energy in a phase-change memory cell. In a preferred embodiment, such a cell can be used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

Rewriteable memory cell comprising a transistor and resistance-switching material in series

InactiveUS20060273298A1Solid-state devicesBulk negative resistance effect devicesHigh resistanceEngineering

A nonvolatile memory cell is provided, the cell comprising a transistor in series with resistance-switching material, which can be switched between at least two stable resistance states, for example a high-resistance state and a low-resistance state. In preferred embodiments the transistor is a TFT, having a channel region not formed in a monocrystalline wafer substrate. In preferred embodiments the transistor may have either a vertically oriented channel or a laterally oriented channel. Either embodiment can be formed in a monolithic three dimensional memory array in which multiple memory levels can be formed above a single substrate, forming a highly dense nonvolatile memory array.

Owner:SANDISK TECH LLC

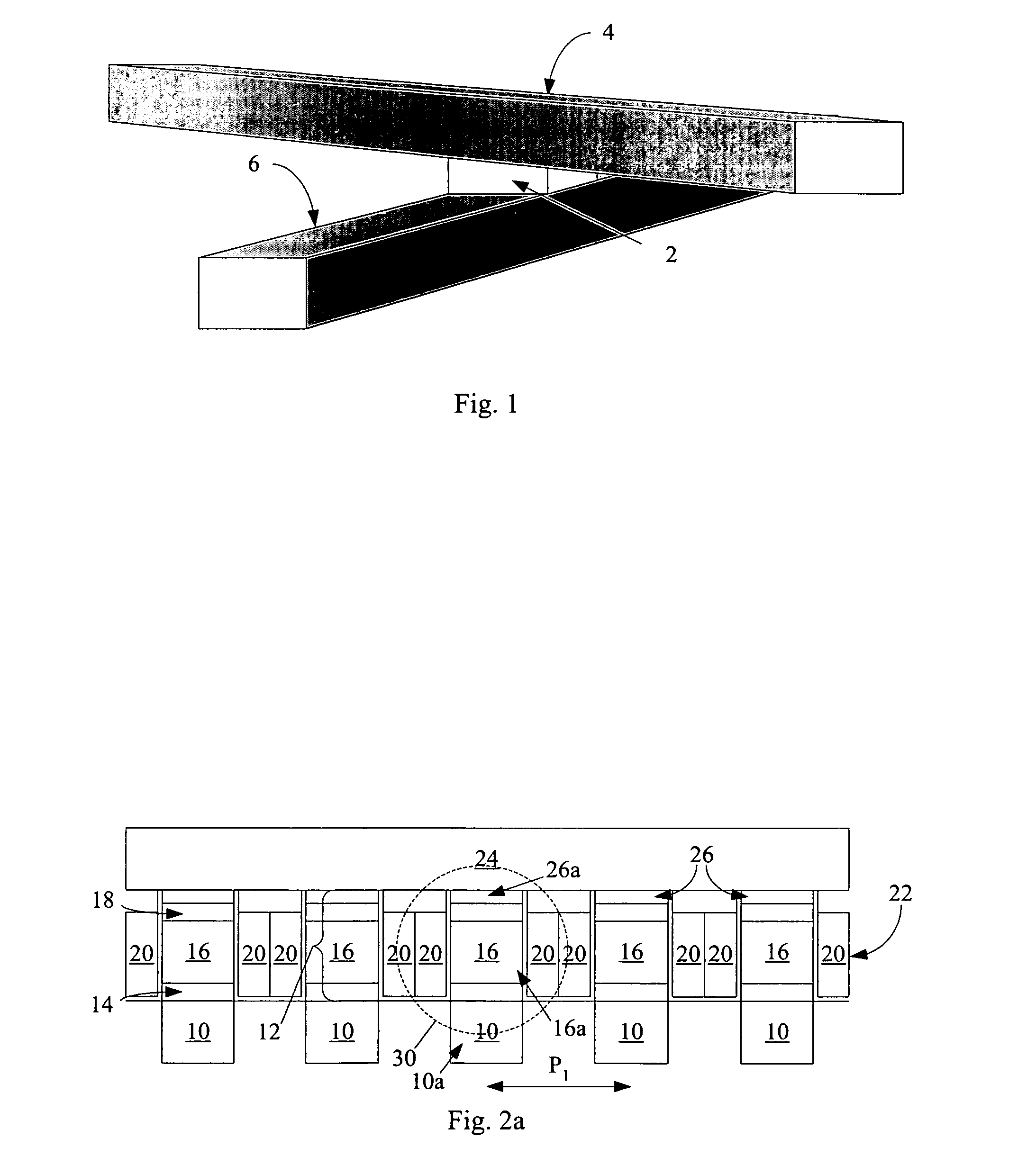

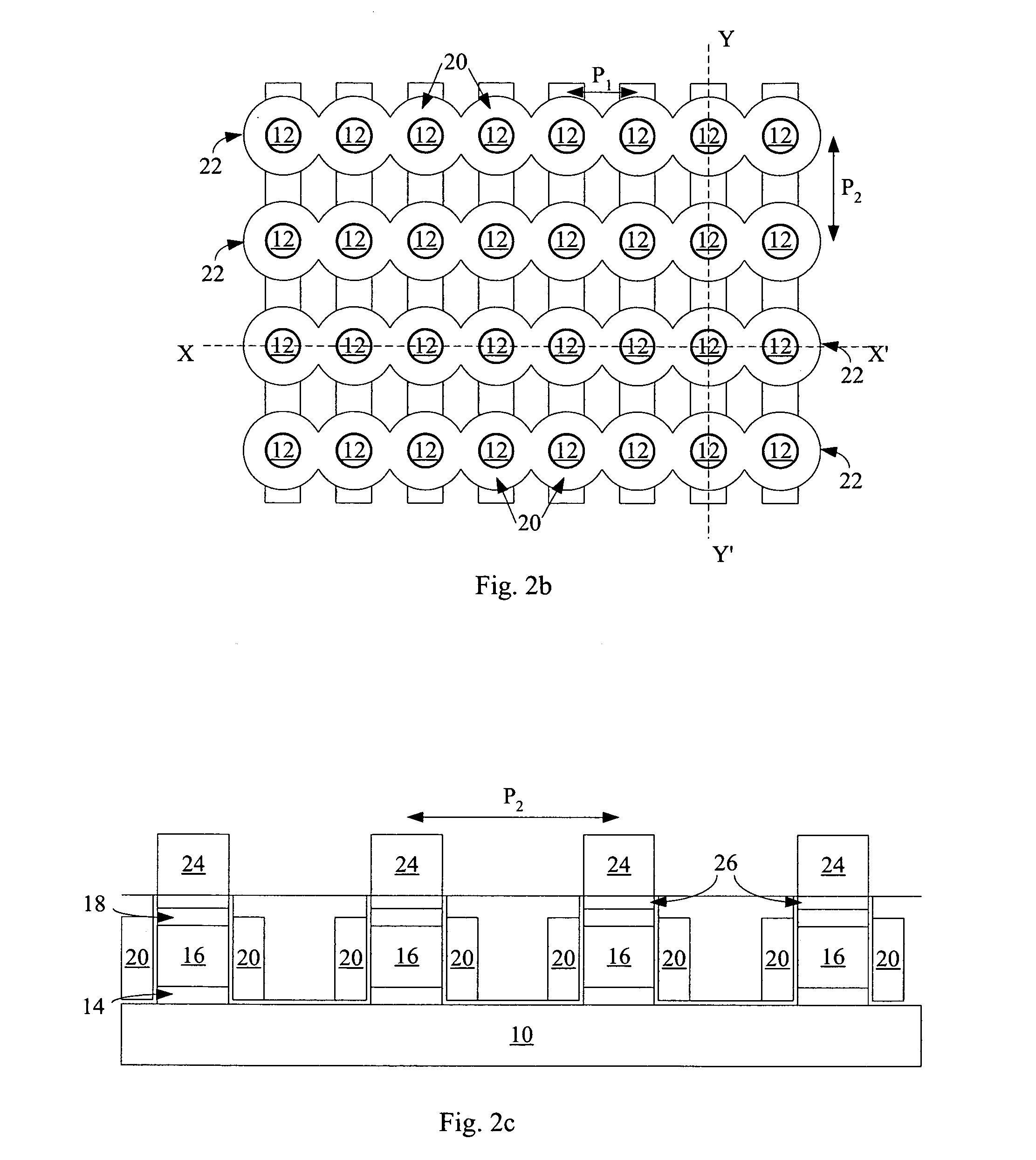

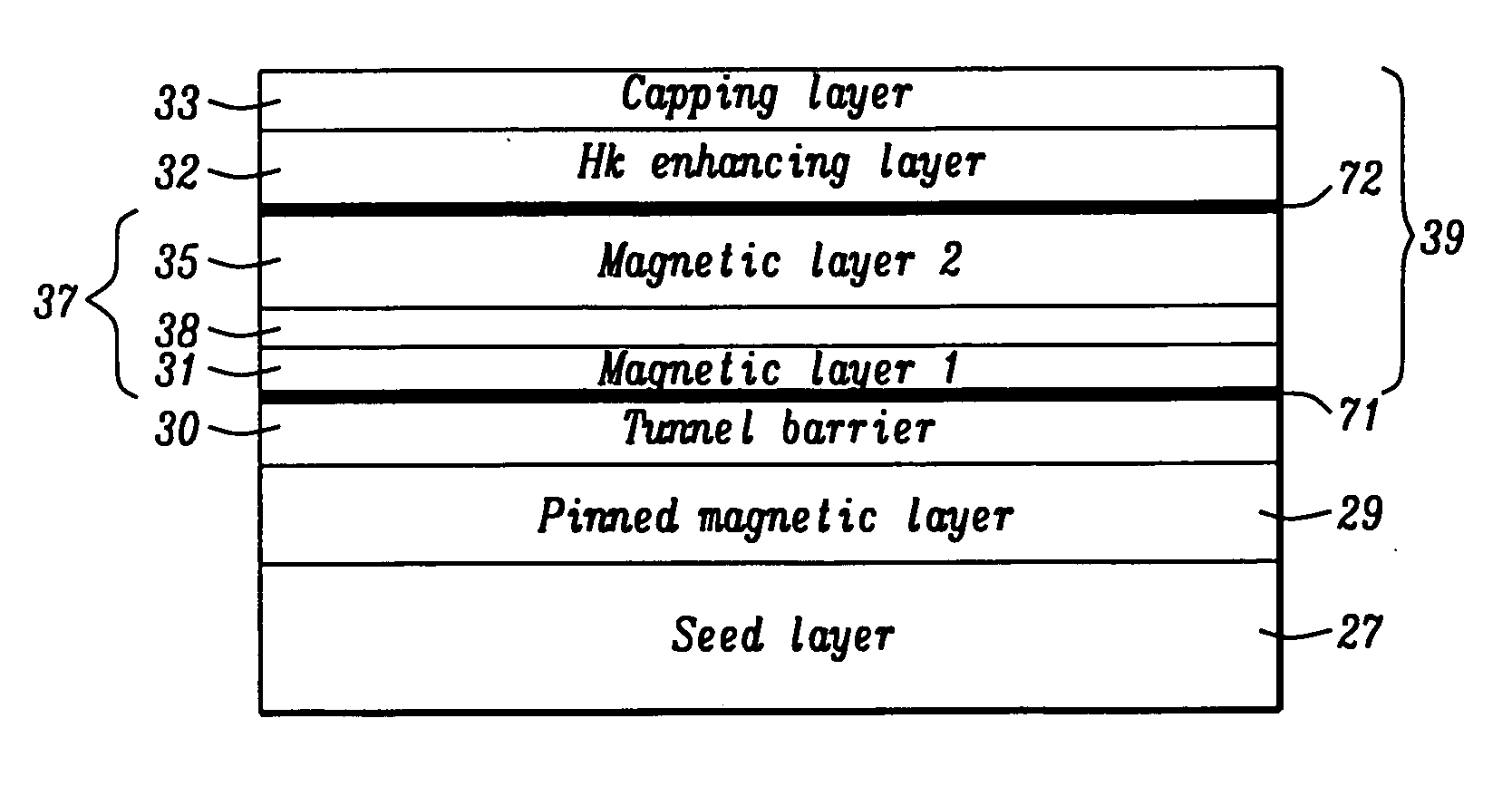

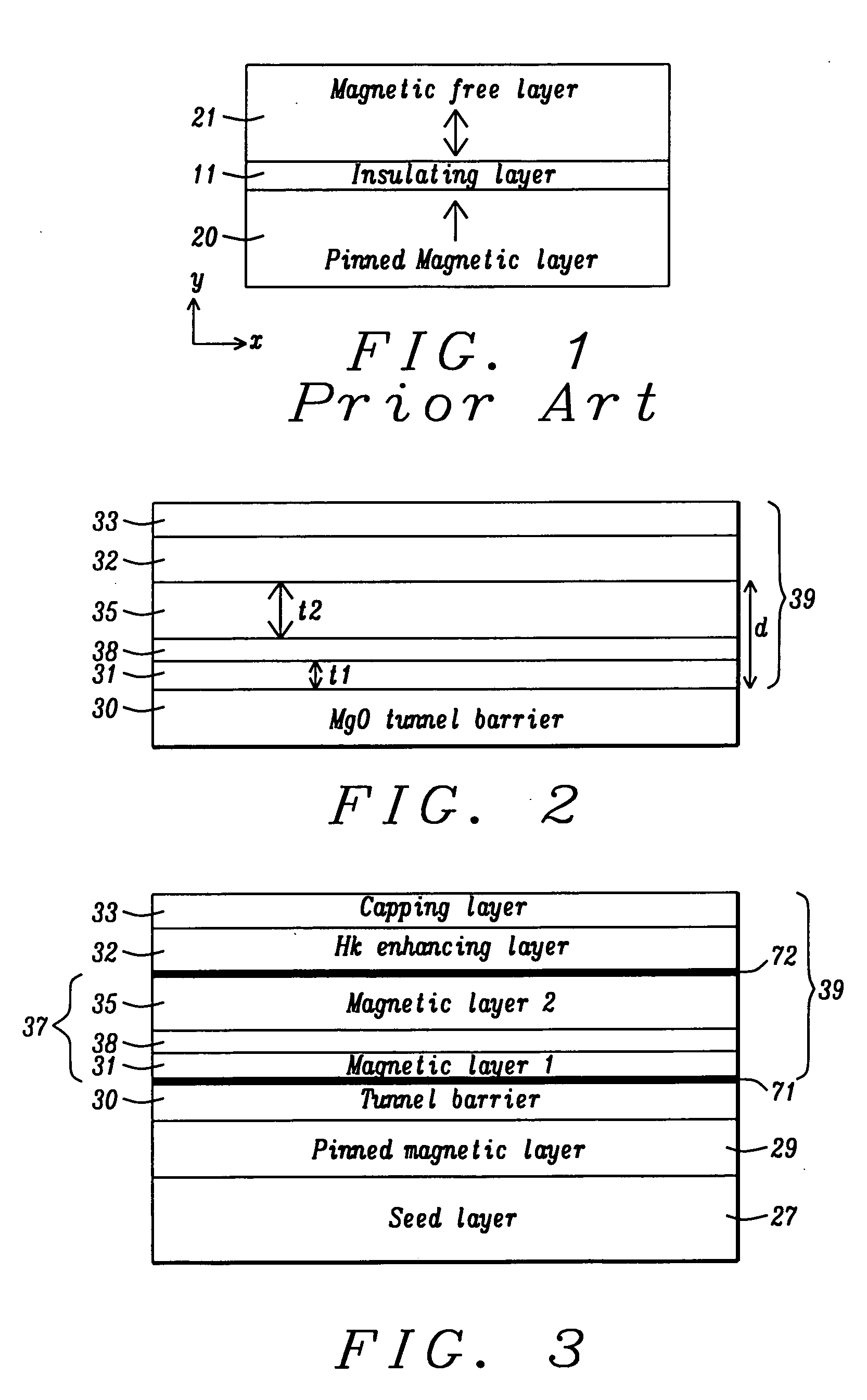

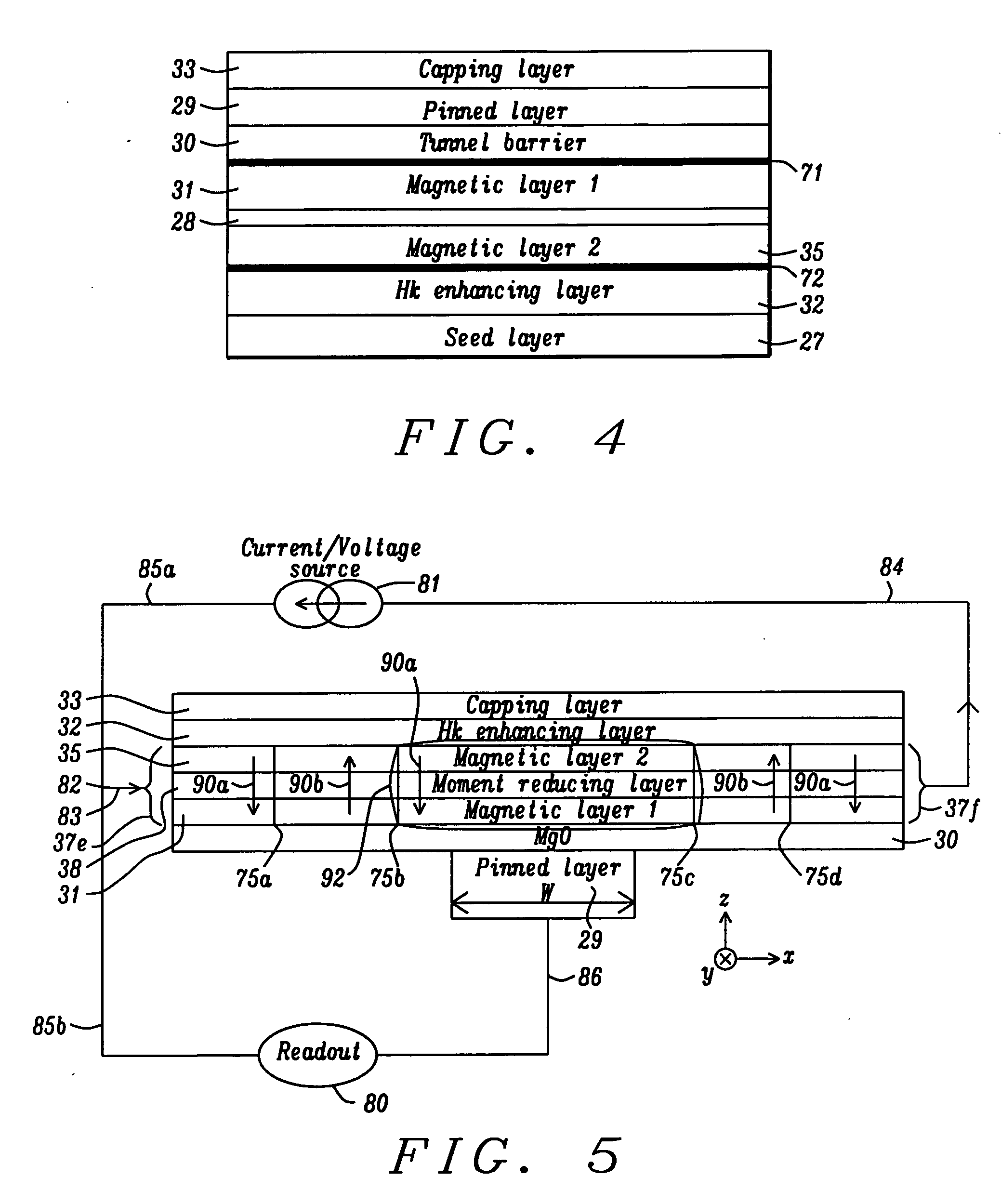

Multilayers having reduced perpendicular demagnetizing field using moment dilution for spintronic applications

ActiveUS20120280336A1Improve thermal stabilityHigh MR ratioMagnetic-field-controlled resistorsGalvano-magnetic material selectionPerpendicular anisotropyAlloy

A magnetic element is disclosed that has a composite free layer with a FM1 / moment diluting / FM2 configuration wherein FM1 and FM2 are magnetic layers made of one or more of Co, Fe, Ni, and B and the moment diluting layer is used to reduce the perpendicular demagnetizing field. As a result, lower resistance x area product and higher thermal stability are realized when perpendicular surface anisotropy dominates shape anisotropy to give a magnetization perpendicular to the planes of the FM1, FM2 layers. The moment diluting layer may be a non-magnetic metal like Ta or a CoFe alloy with a doped non-magnetic metal. A perpendicular Hk enhancing layer interfaces with the FM2 layer and may be an oxide to increase the perpendicular anisotropy field in the FM2 layer. The magnetic element may be part of a spintronic device or serve as a propagation medium in a domain wall motion device.

Owner:TAIWAN SEMICON MFG CO LTD

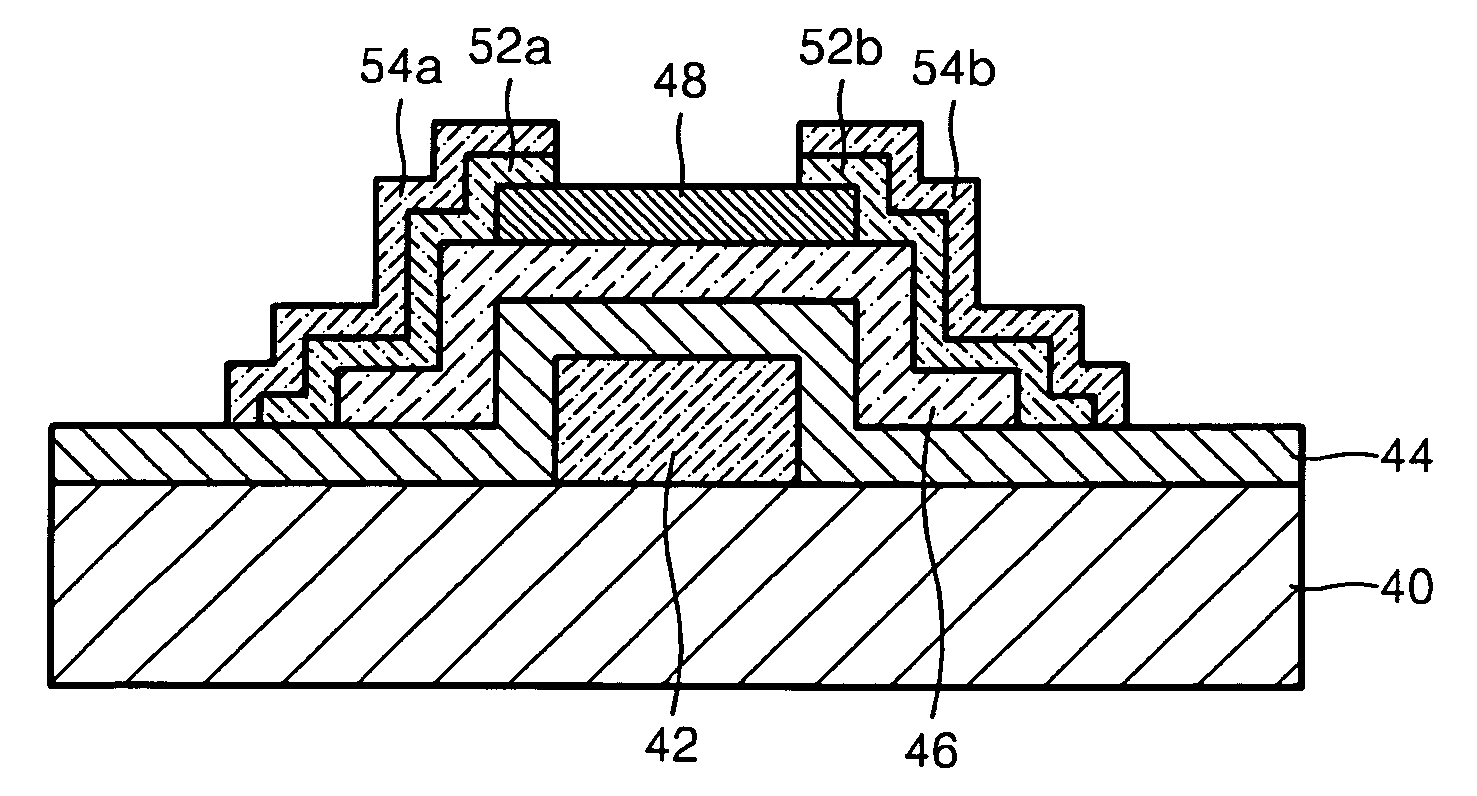

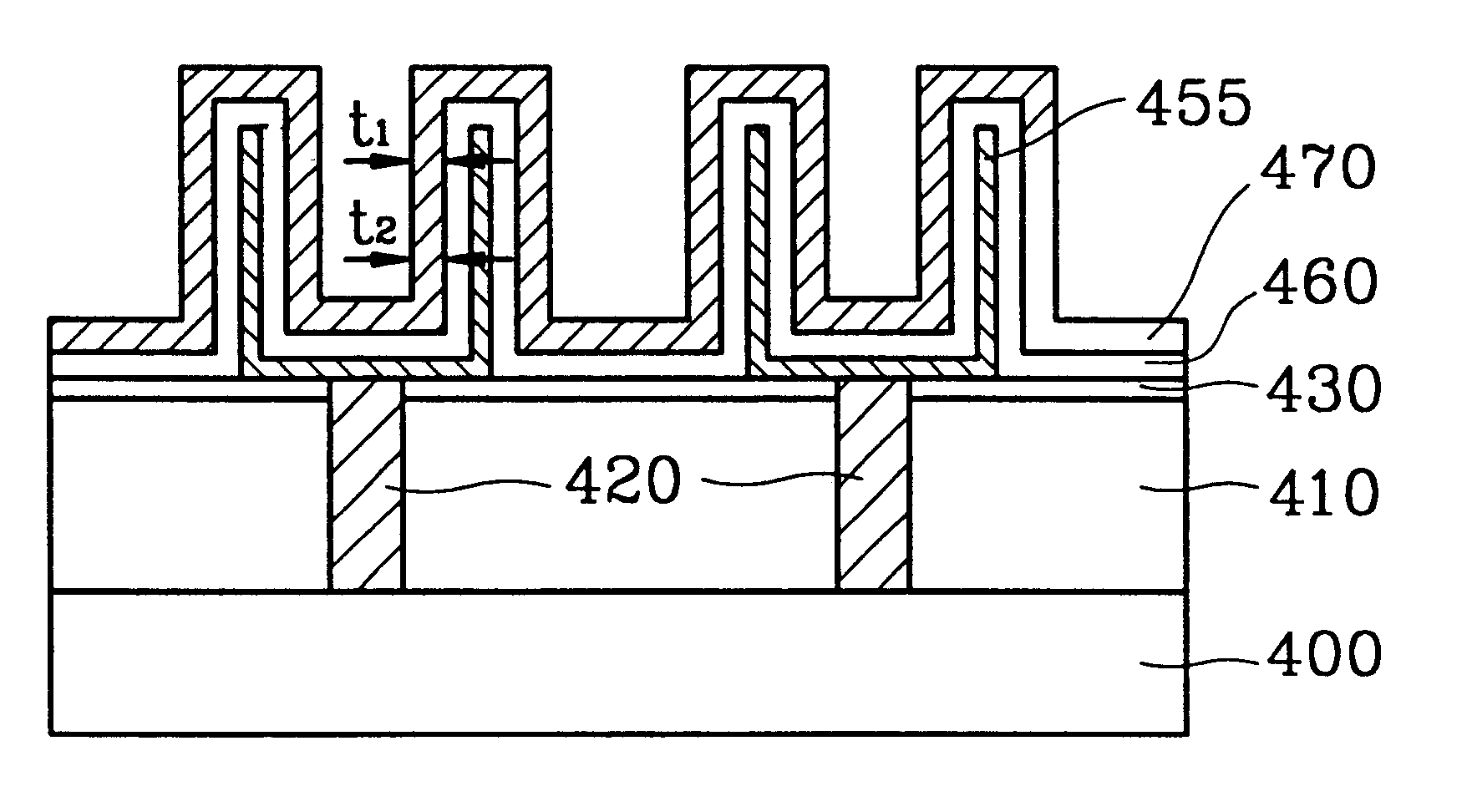

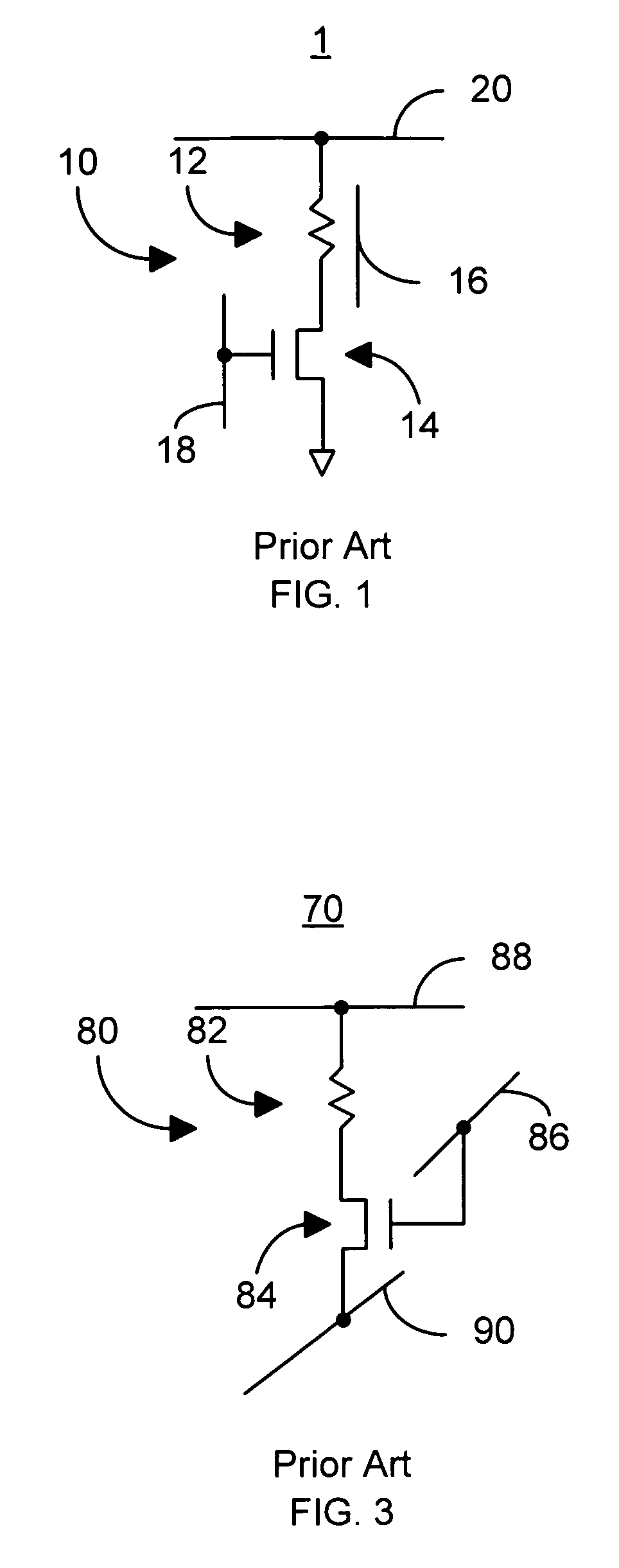

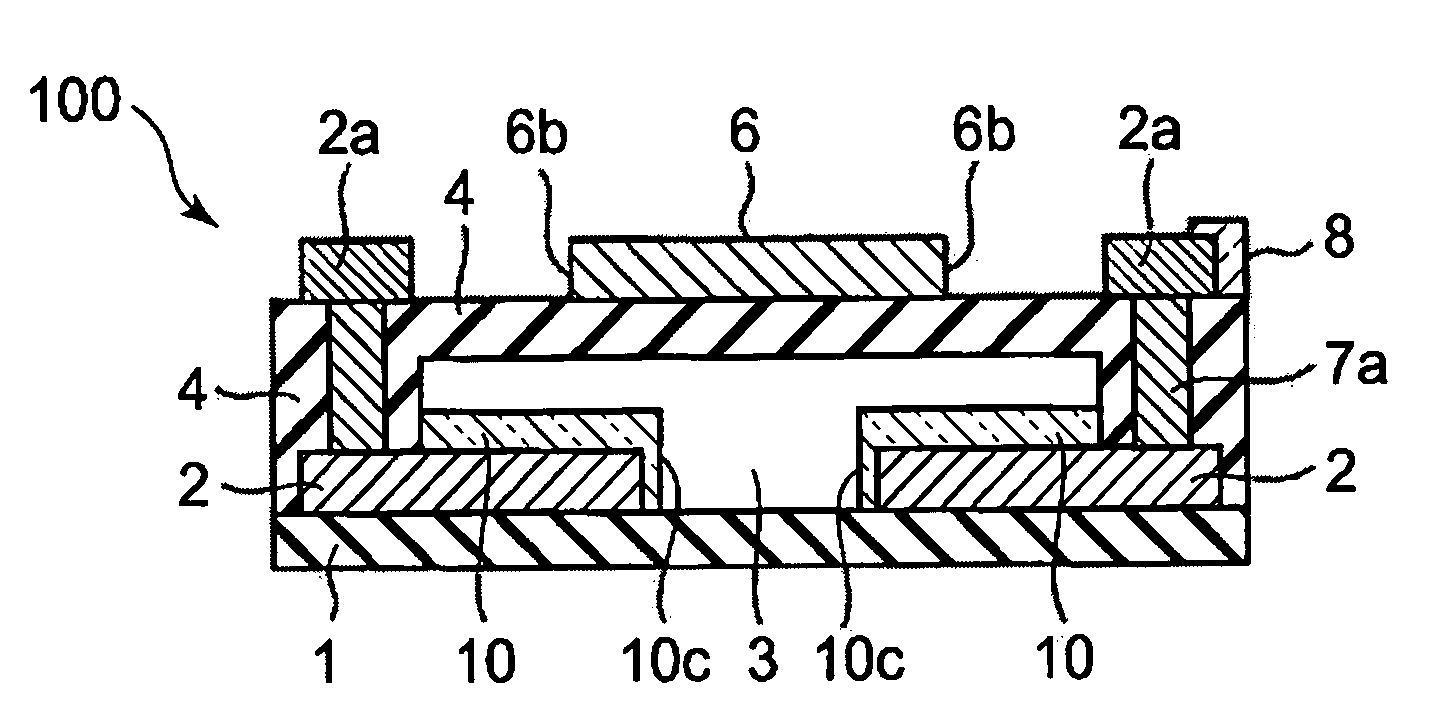

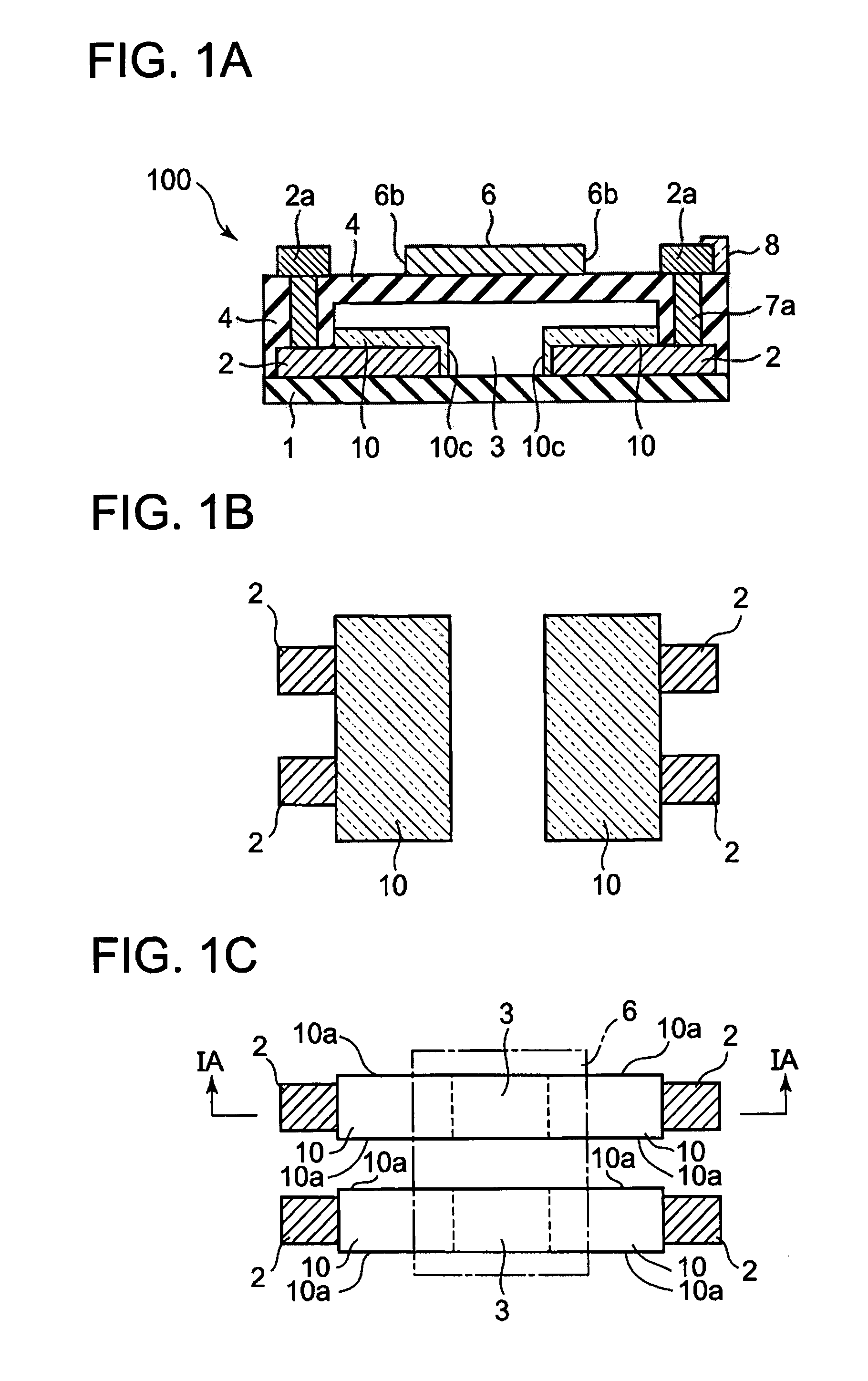

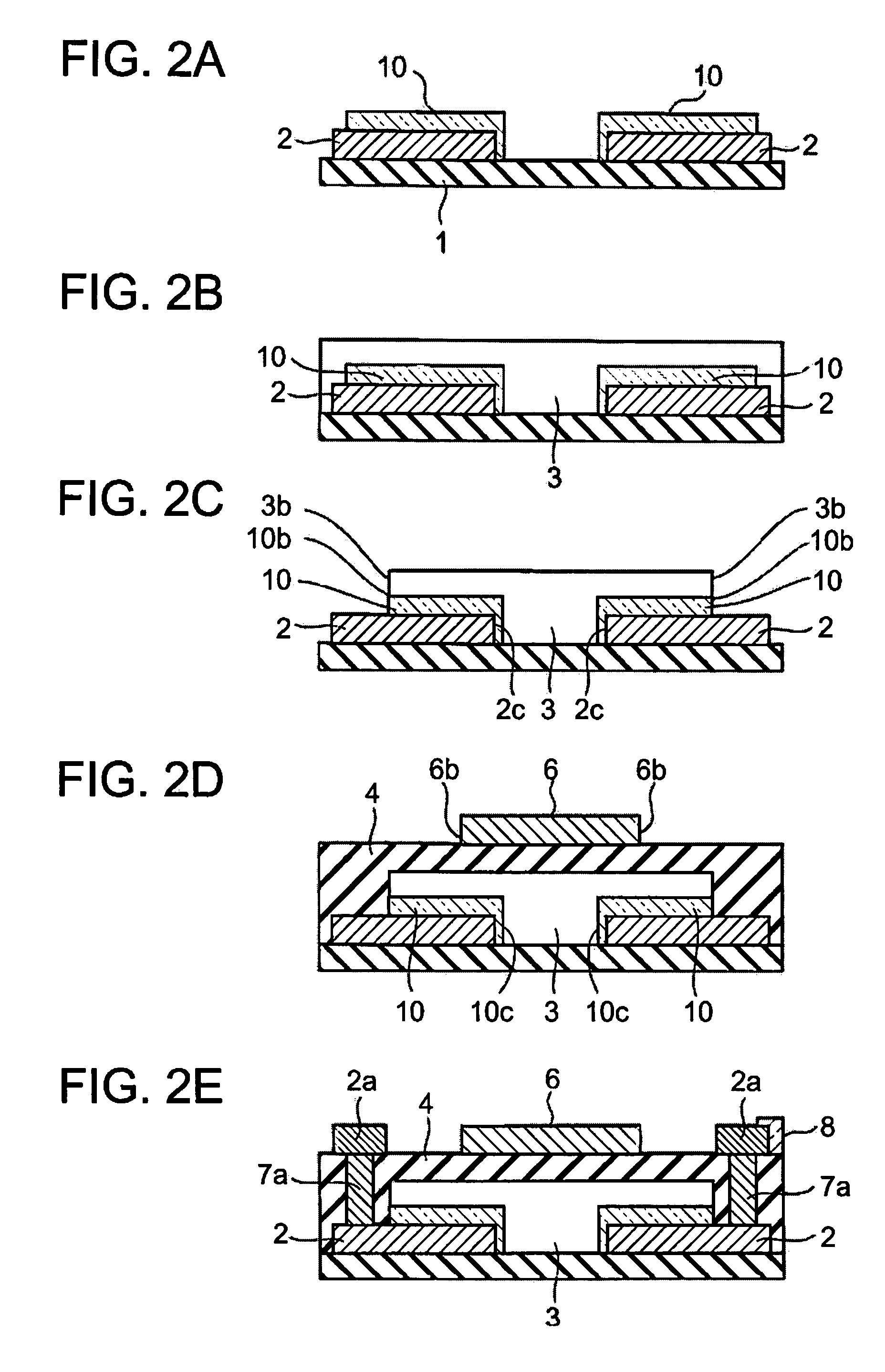

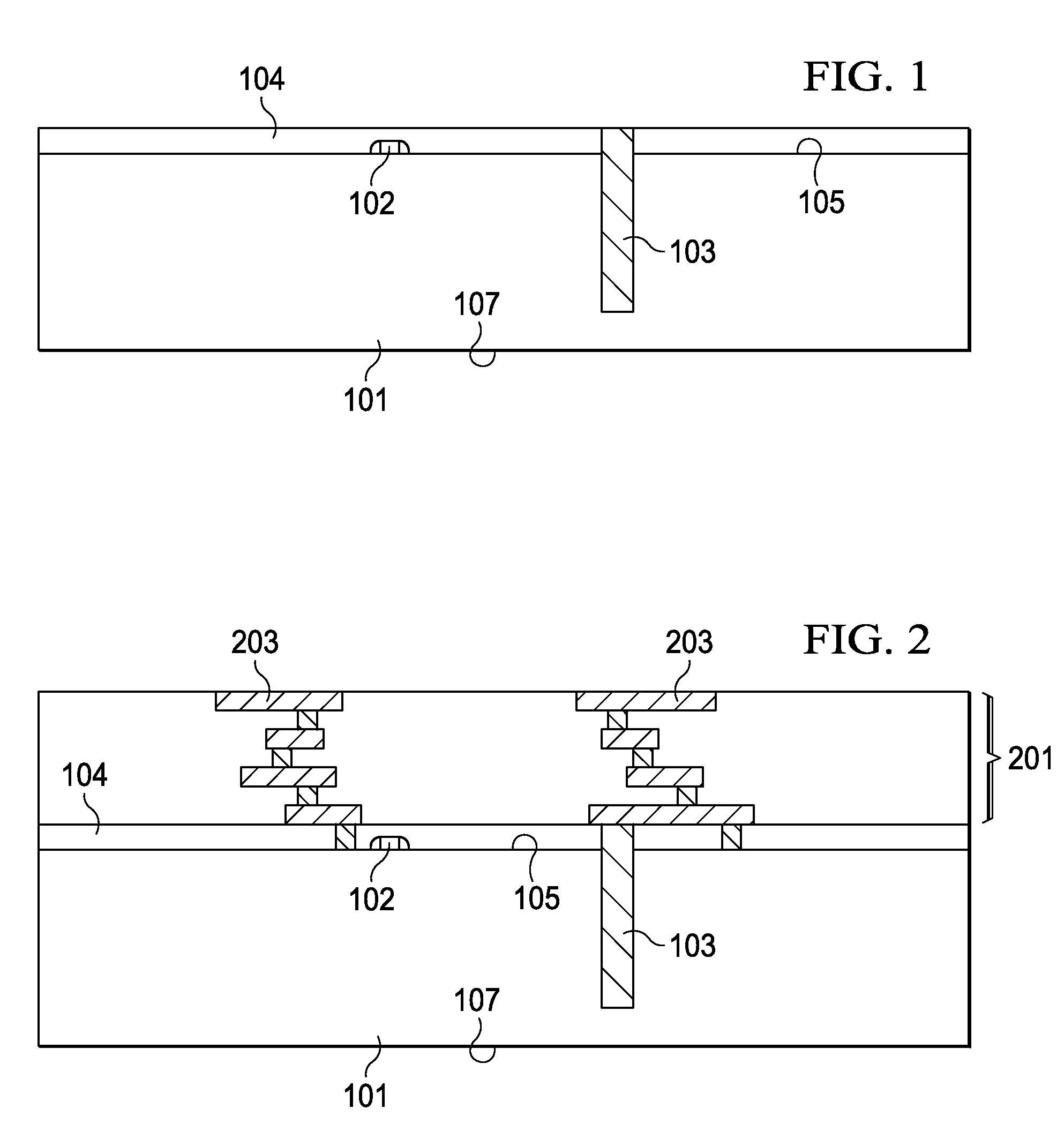

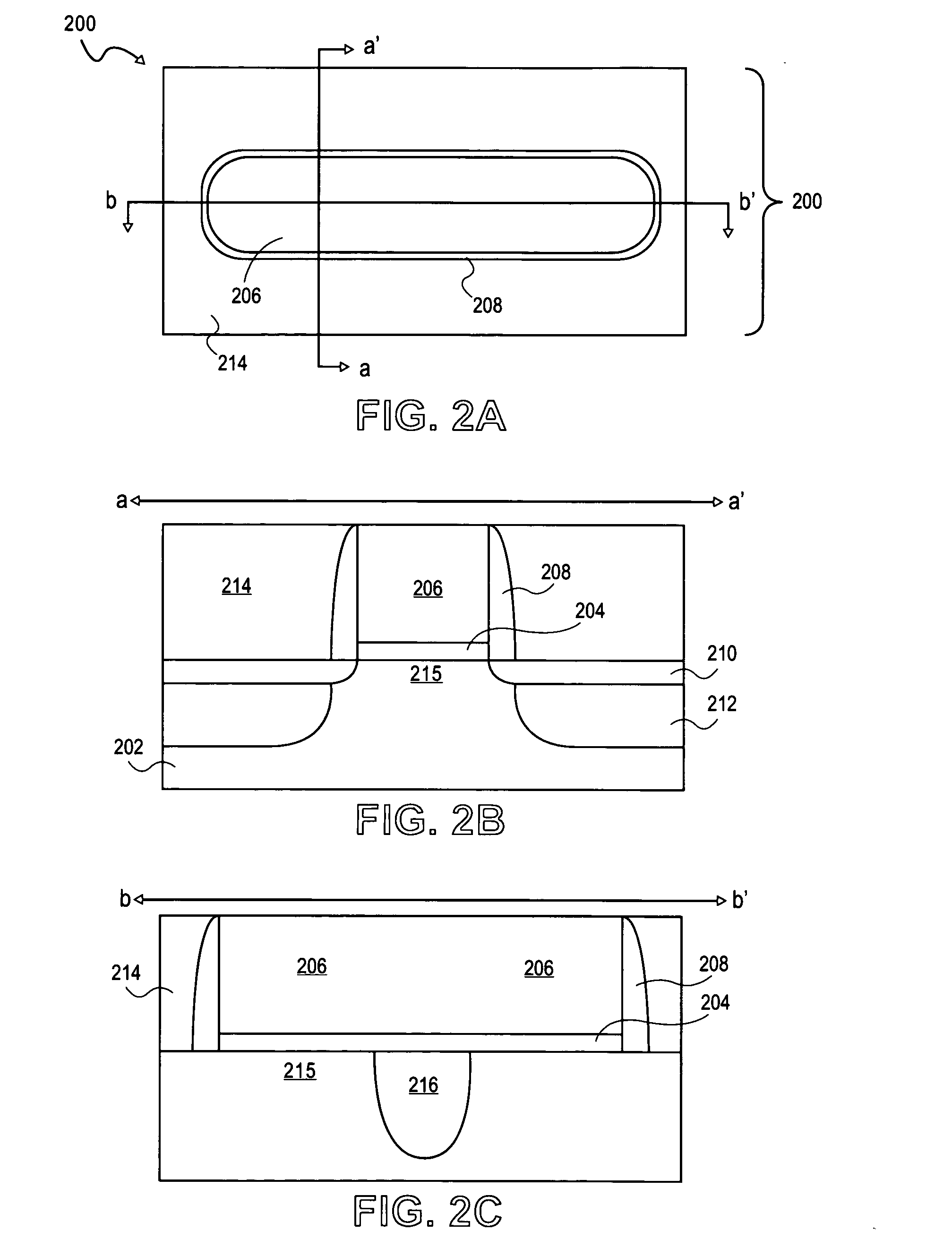

Thin film transistor including low resistance conductive thin films and manufacturing method thereof

InactiveUS7576394B2Decrease distance DHighly integratedSolid-state devicesSemiconductor/solid-state device manufacturingChannel widthSemiconductor

A thin film transistor includes a substrate, and a pair of source / drain electrodes (i.e., a source electrode and a drain electrode) formed on the substrate and defining a gap therebetween. A pair of low resistance conductive thin films are provided such that each coats at least a part of one of the source / drain electrodes. The low resistance conductive thin films define a gap therebetween. An oxide semiconductor thin film layer is continuously formed on upper surfaces of the pair of low resistance conductive thin films and extends along the gap defined between the low resistance conductive thin films so as to function as a channel. Side surfaces of the oxide semiconductor thin film layer and corresponding side surfaces of the low resistance conductive thin films coincide with each other in a channel width direction of the channel.

Owner:KOICHI IND PROMOTION CENT +1

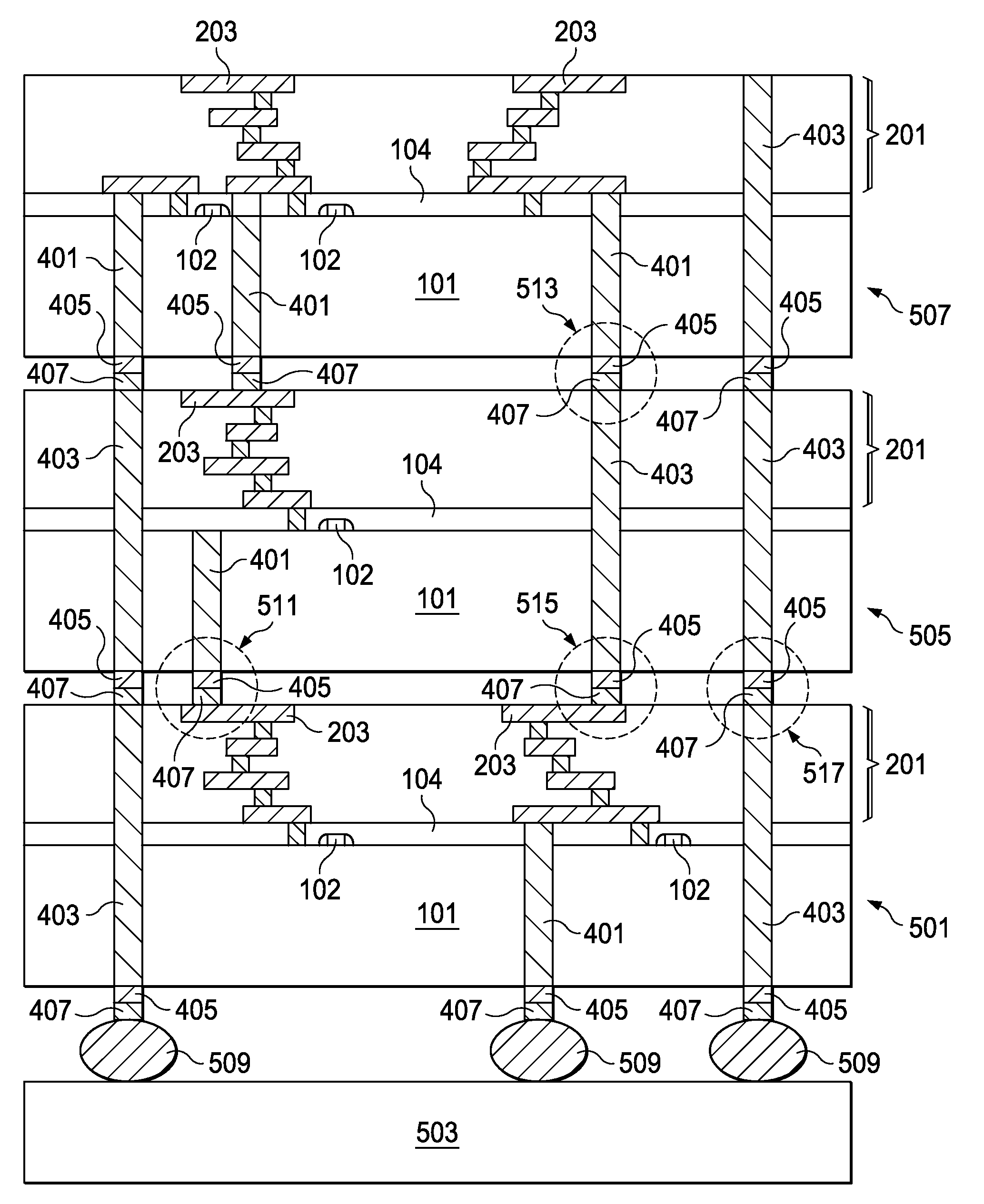

Three-Dimensional System-in-Package Architecture

ActiveUS20100225002A1Reduce resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSystem in package

A system and method for making semiconductor die connections with through-silicon vias (TSVs) are disclosed. A semiconductor die is manufactured with both via-first TSVs as well as via-last TSVs in order to establish low resistance paths for die connections between adjacent dies as well as for providing a low resistance path for feedthrough channels between multiple dies.

Owner:TAIWAN SEMICON MFG CO LTD

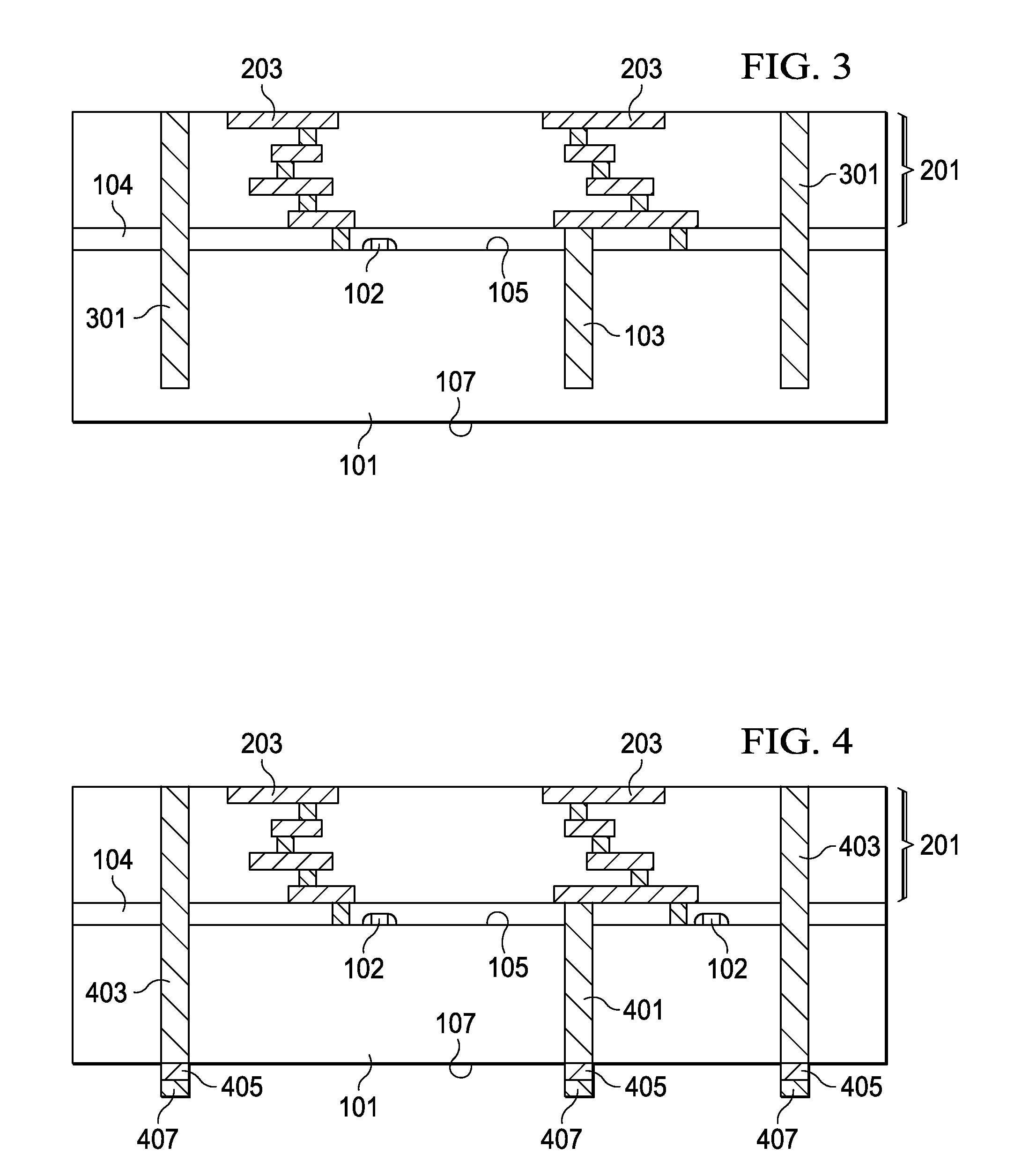

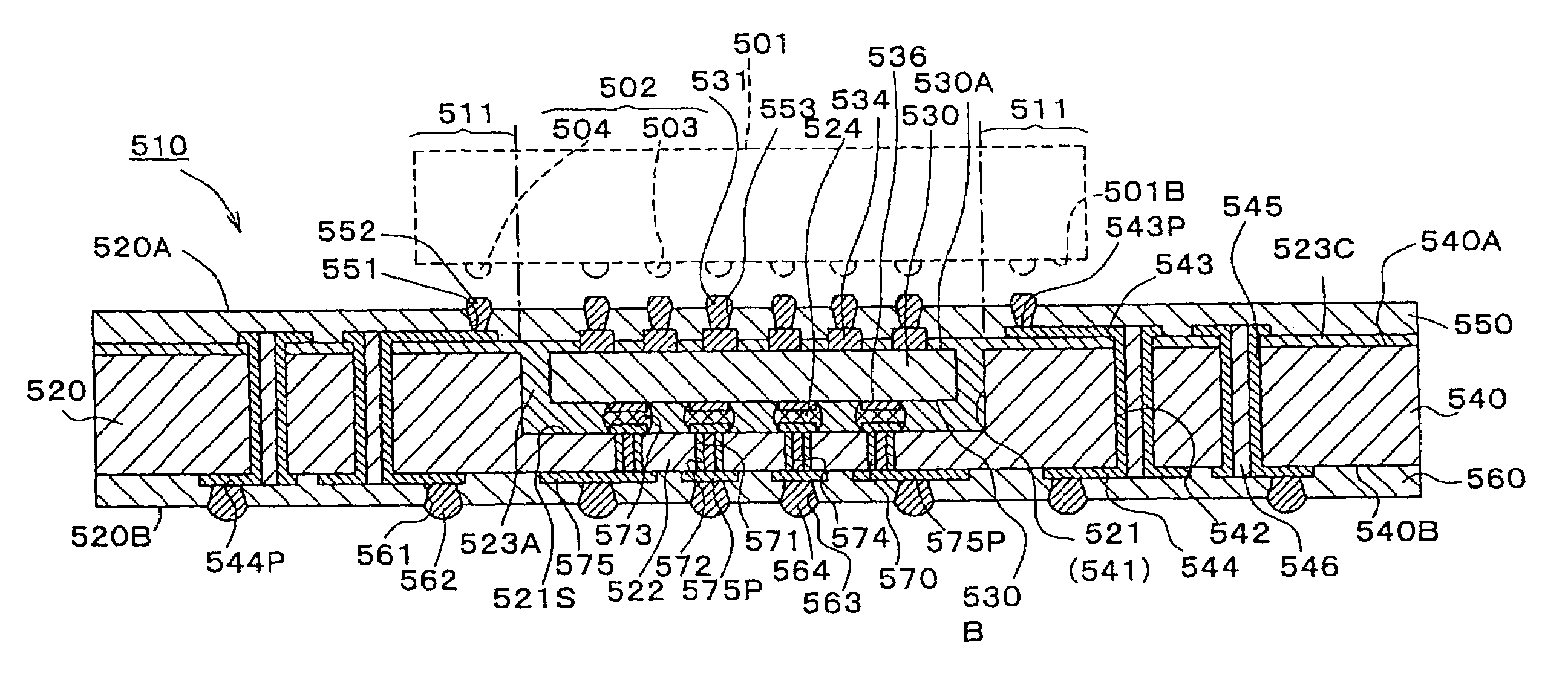

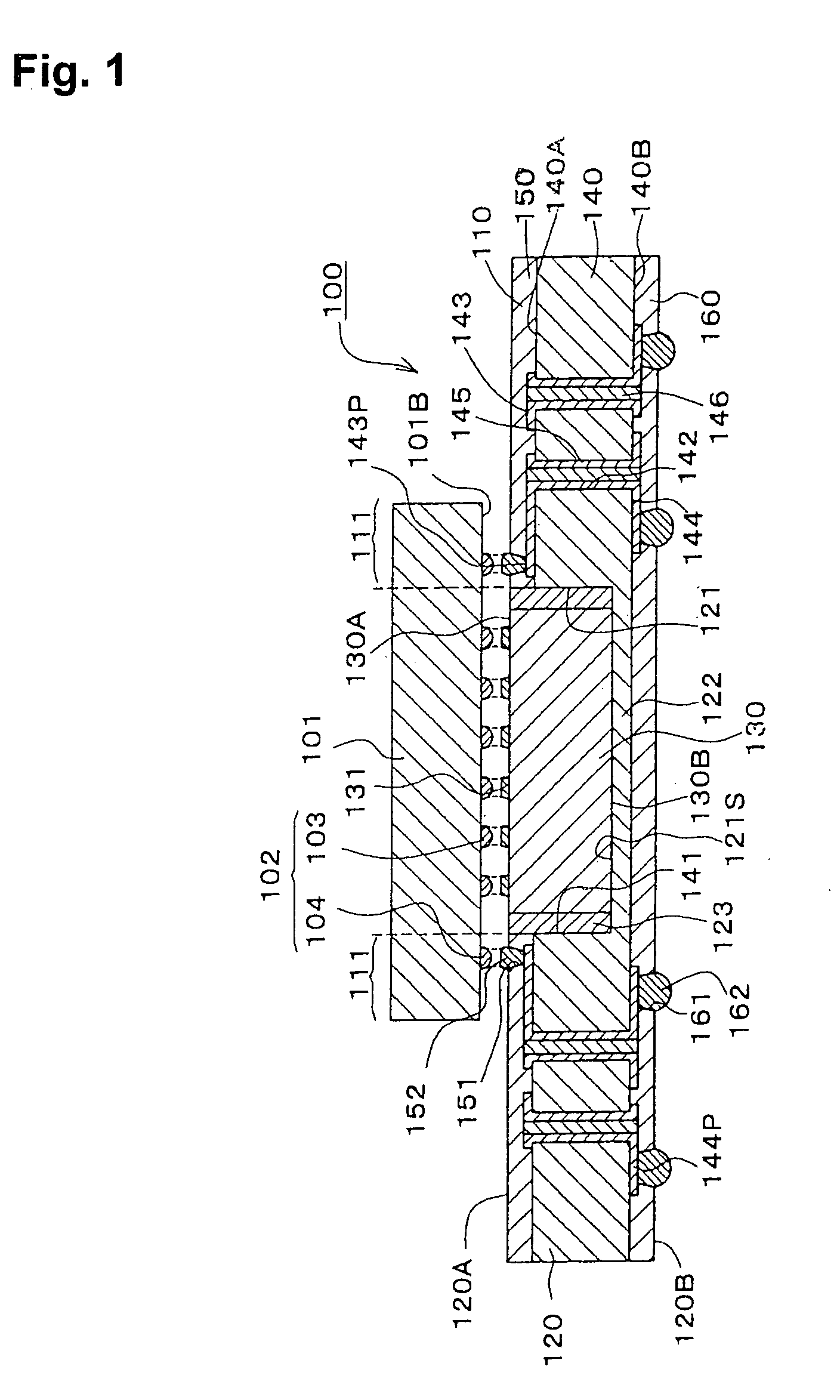

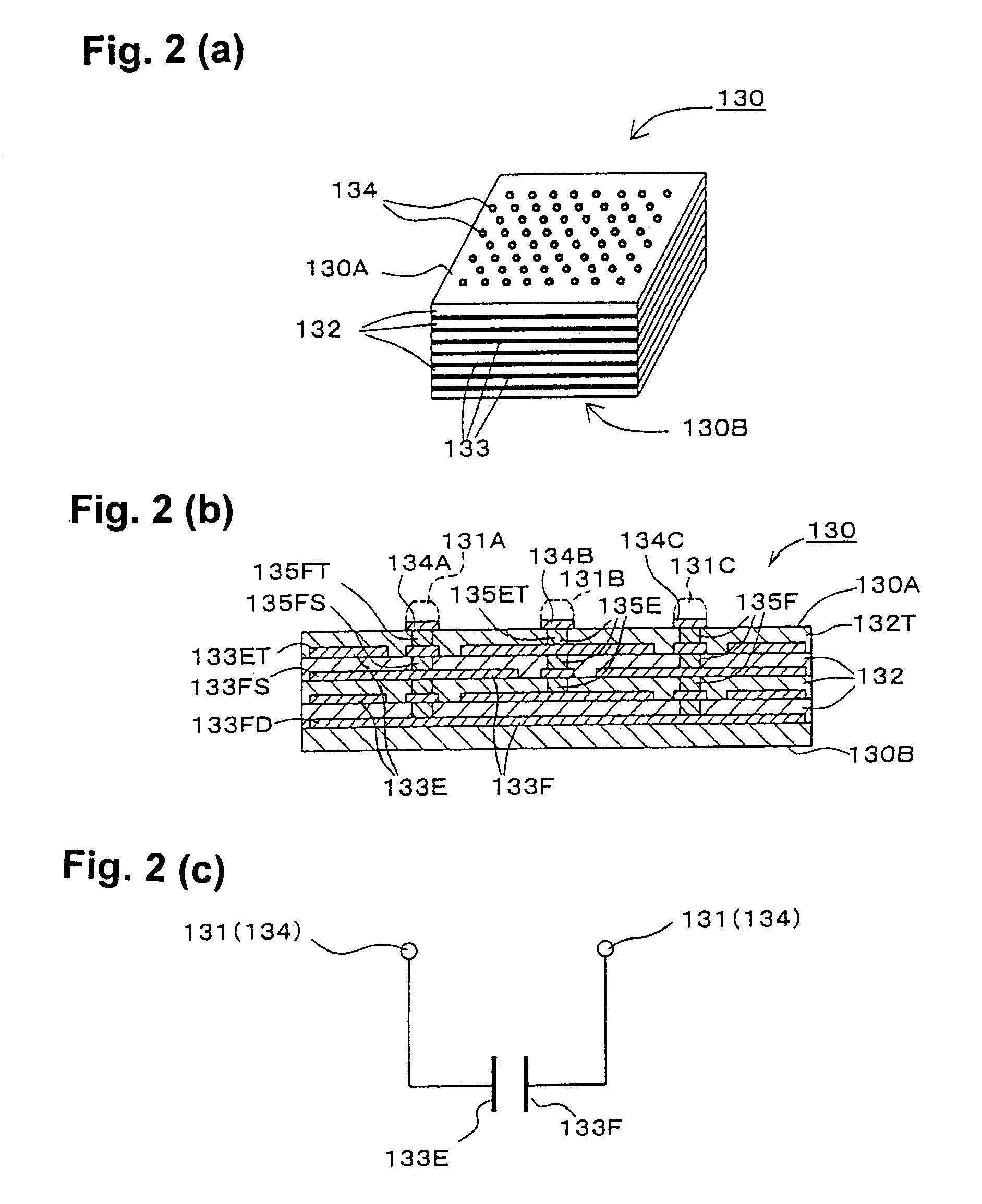

Capacitor-built-in type printed wiring substrate, printed wiring substrate, and capacitor

InactiveUS6952049B1Firmly connectedReliably eliminate noiseCross-talk/noise/interference reductionSemiconductor/solid-state device detailsLow inductanceEngineering

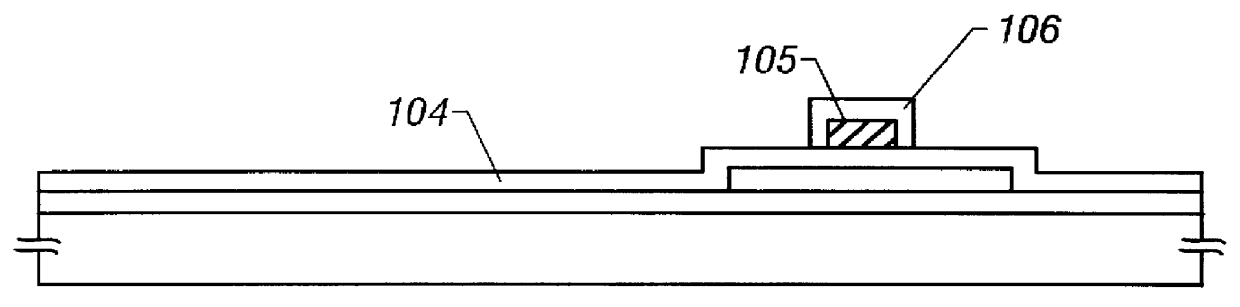

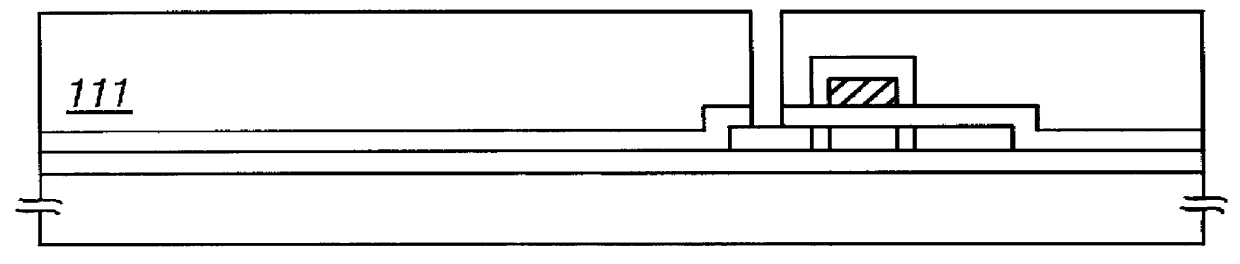

A capacitor-built-in-type printed wiring substrate which can reliably eliminate noise and attain extremely low resistance and low inductance in connections between an IC chip and the capacitor, and a printed wiring substrate and capacitor for use in the same. A capacitor-built-in-type printed wiring substrate 100 on which an IC chip is mounted includes a capacitor-built-in-type printed wiring substrate 110 and an IC chip 101 mounted on the capacitor-built-in-type printed wiring substrate 110. A printed wiring substrate 120 includes a number of connection-to-IC substrate bumps 152 and a closed-bottomed capacitor accommodation cavity 121 formed therein. A capacitor 130 is disposed in the cavity 121 and includes a pair of electrode groups 133E and 133F and a number of connection-to-IC capacitor bumps 131 connected to either one of the paired electrode groups 133E and 133F. The connection-to-IC capacitor bumps 131 are flip-chip-bonded to corresponding connection-to-capacitor bumps 103 on the IC chip 101. The connection-to-IC substrate bumps 152 are flip-chip-bonded to corresponding connection-to-substrate bumps 104 on the IC chip 101.

Owner:NGK SPARK PLUG CO LTD

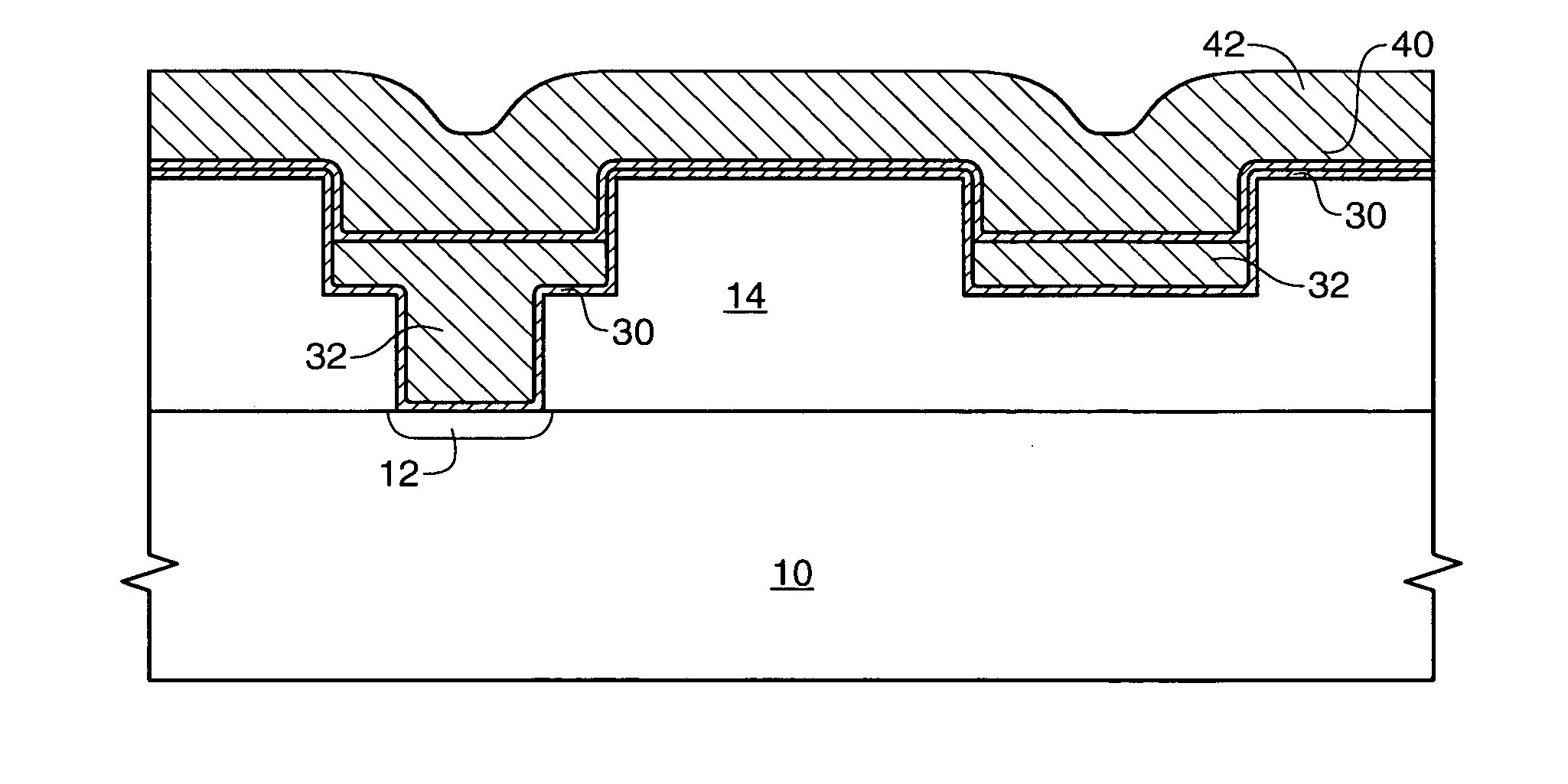

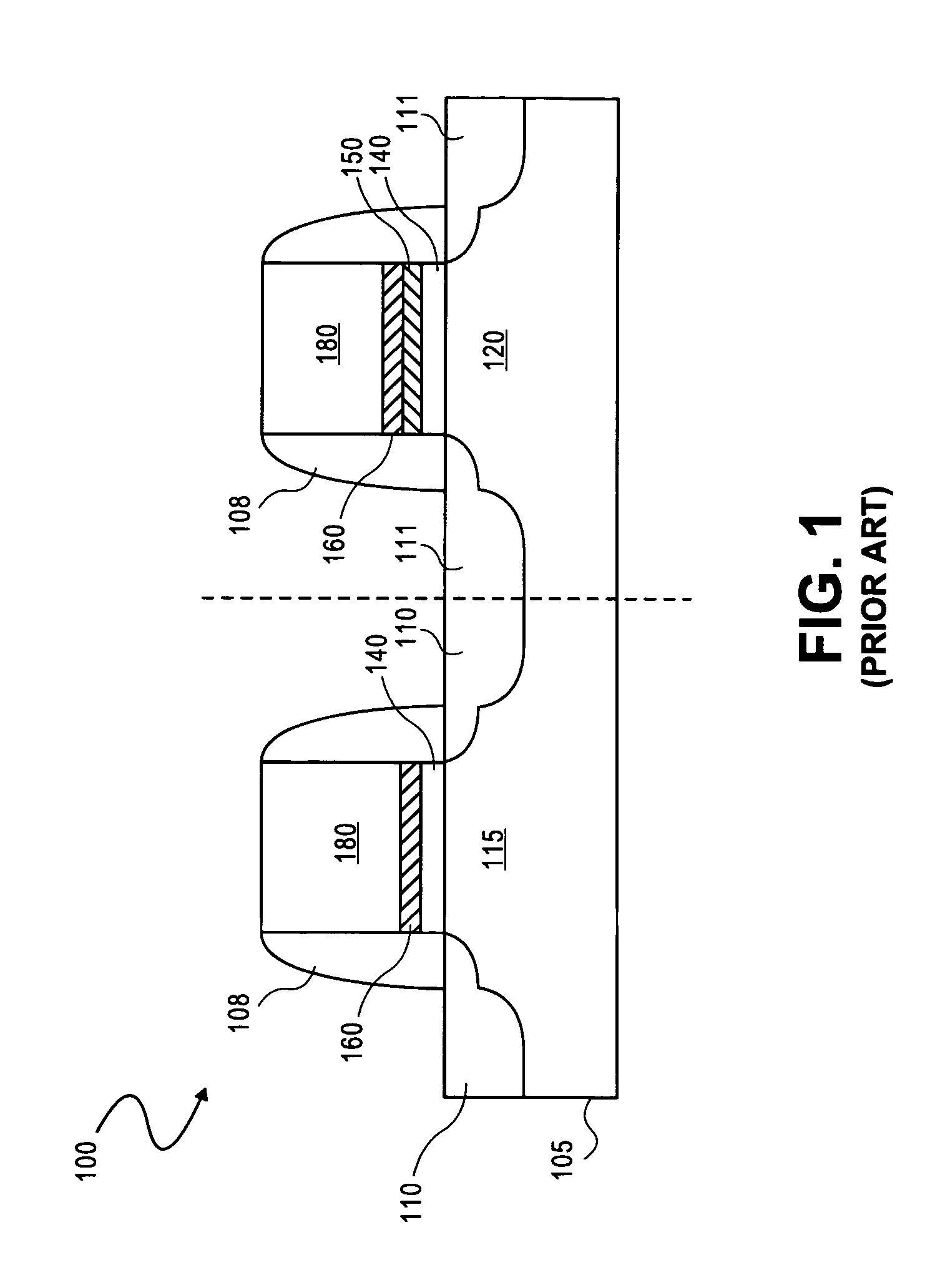

Method for forming a dual layer, low resistance metallization during the formation of a semiconductor device

InactiveUS20060097397A1Reduce the cross-sectional areaHigh resistance contactSemiconductor/solid-state device detailsSolid-state devicesDevice materialCopper

A method for providing a highly reliable, low resistance interconnect comprises forming a trench in a dielectric layer, forming a first liner in the trench then forming a resilient layer such as a tungsten layer within the trench. The resilient layer is etched back to remove the layer from a horizontal portion of the dielectric outside the trench and to recess the layer within the trench. Next, a second liner and a copper layer are formed in the trench over the resilient layer. The copper layer and exposed portions of the two liners are polished or etched back to result in the interconnect. Variations to this embodiment are also described.

Owner:MICRON TECH INC

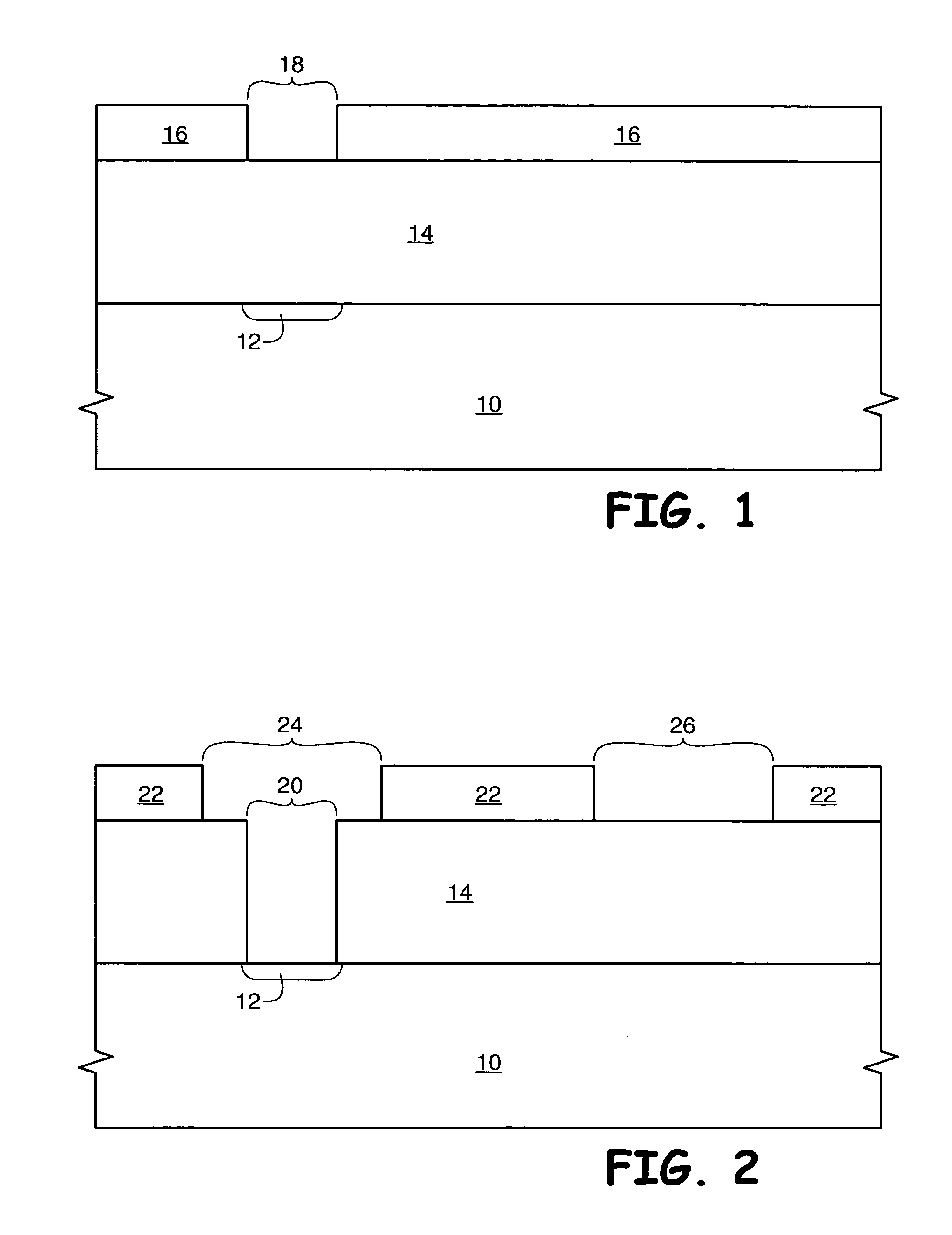

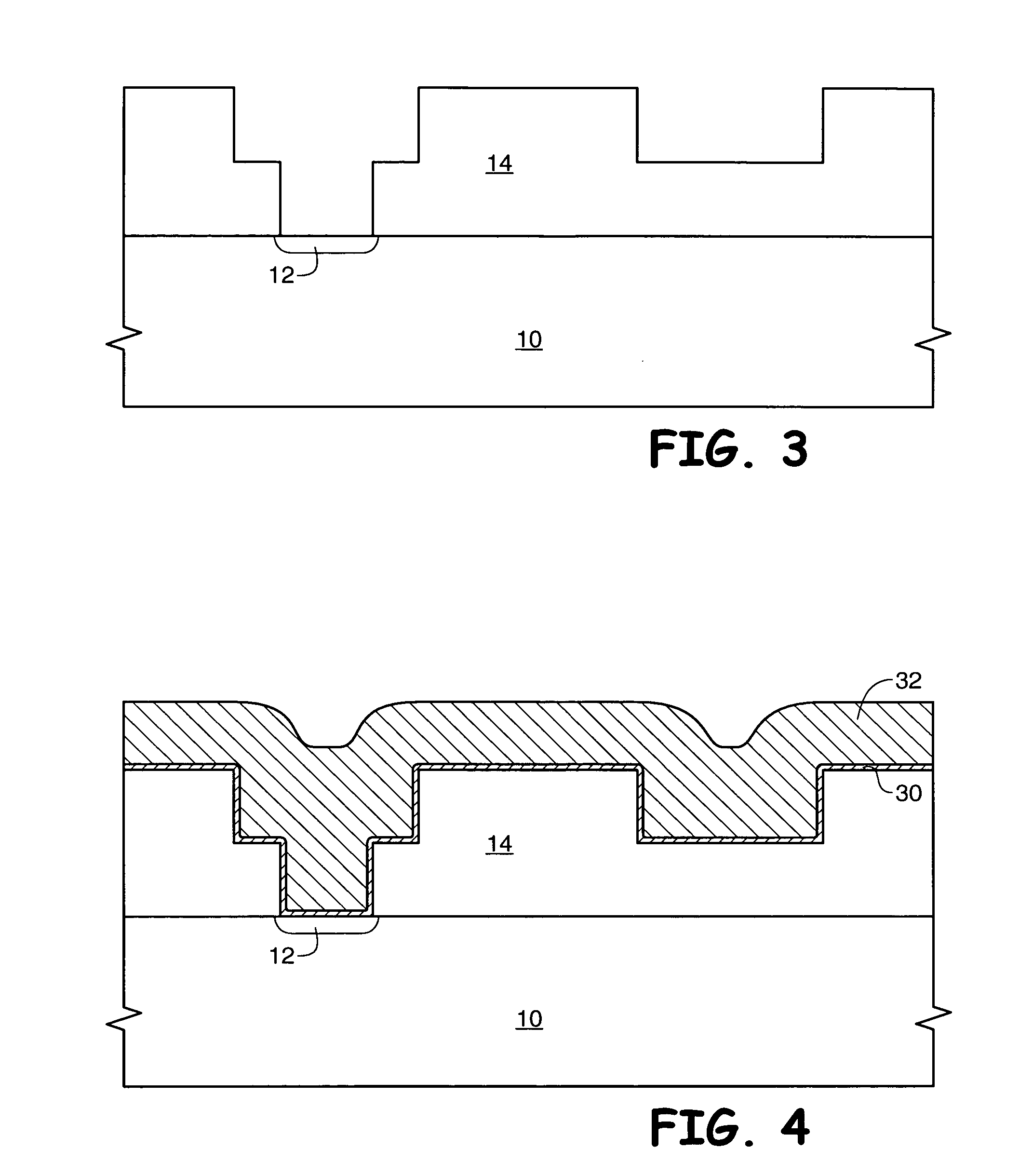

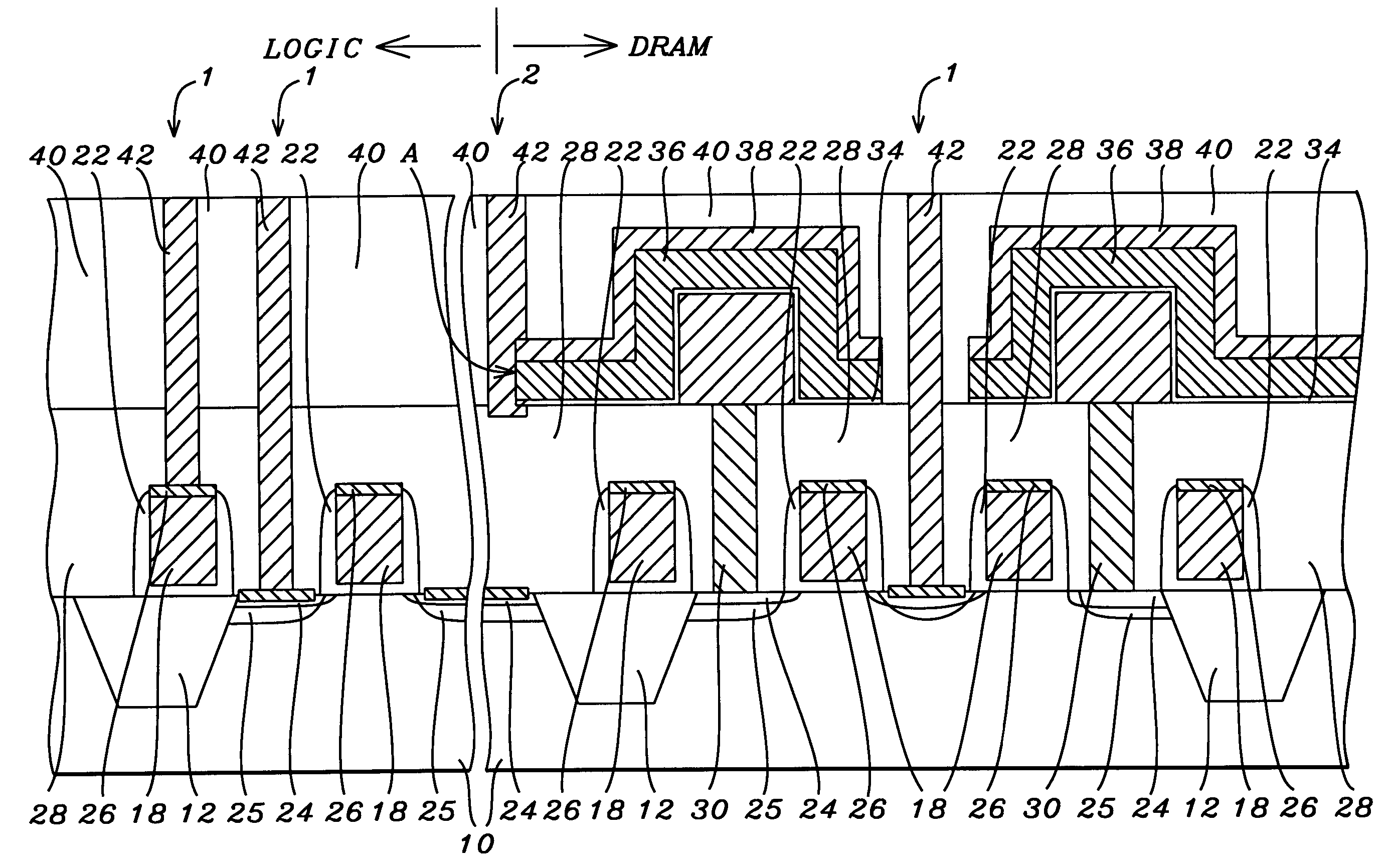

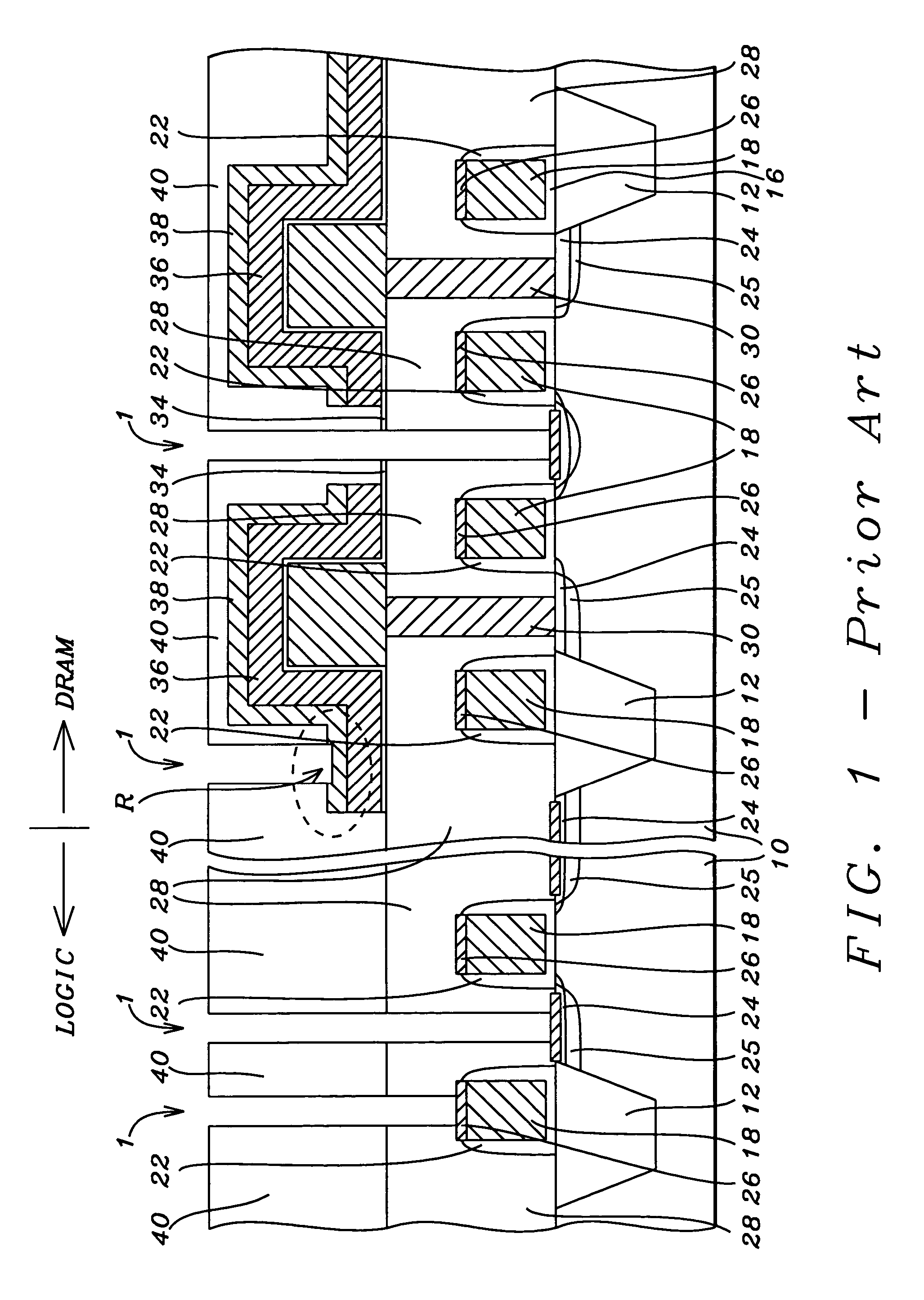

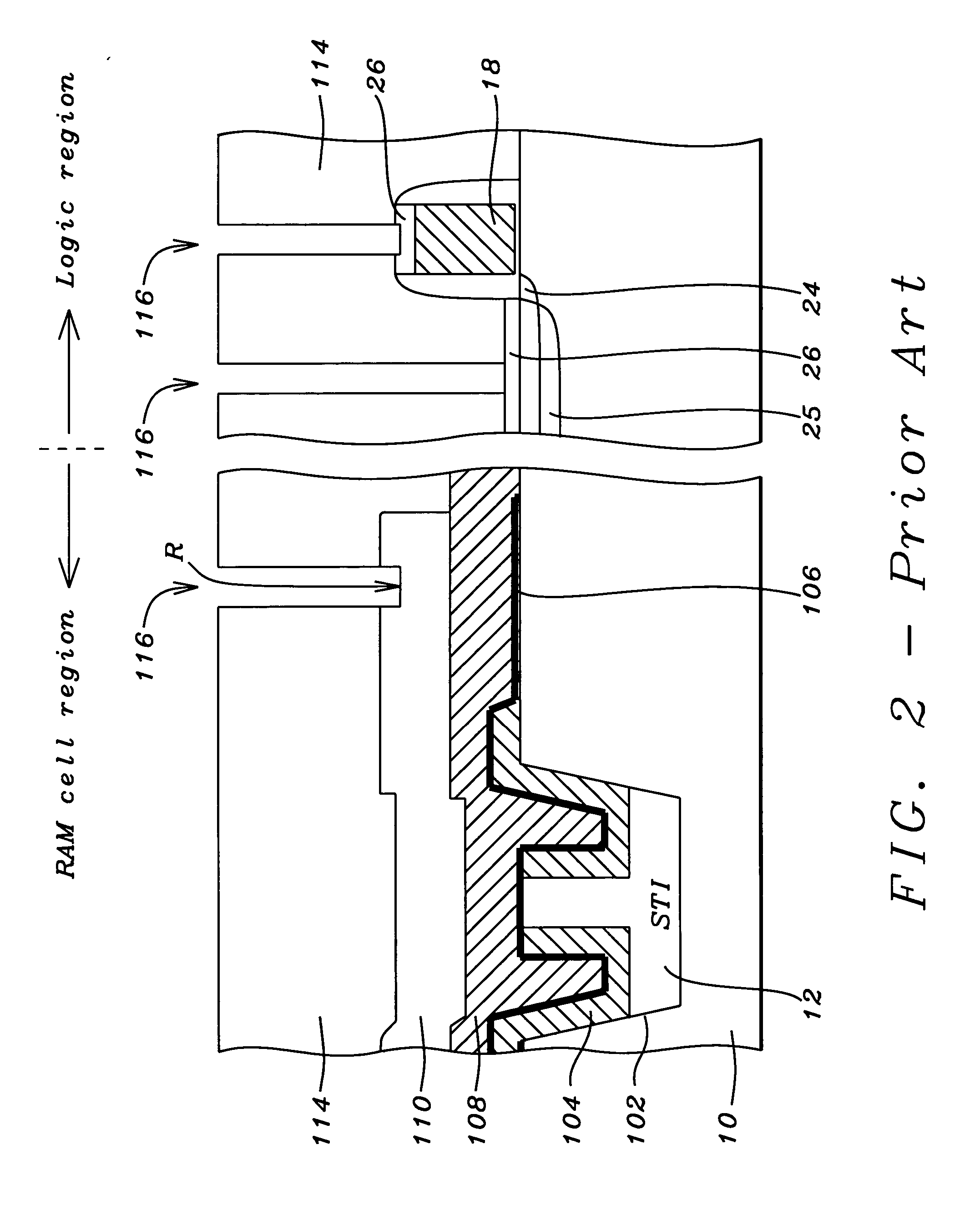

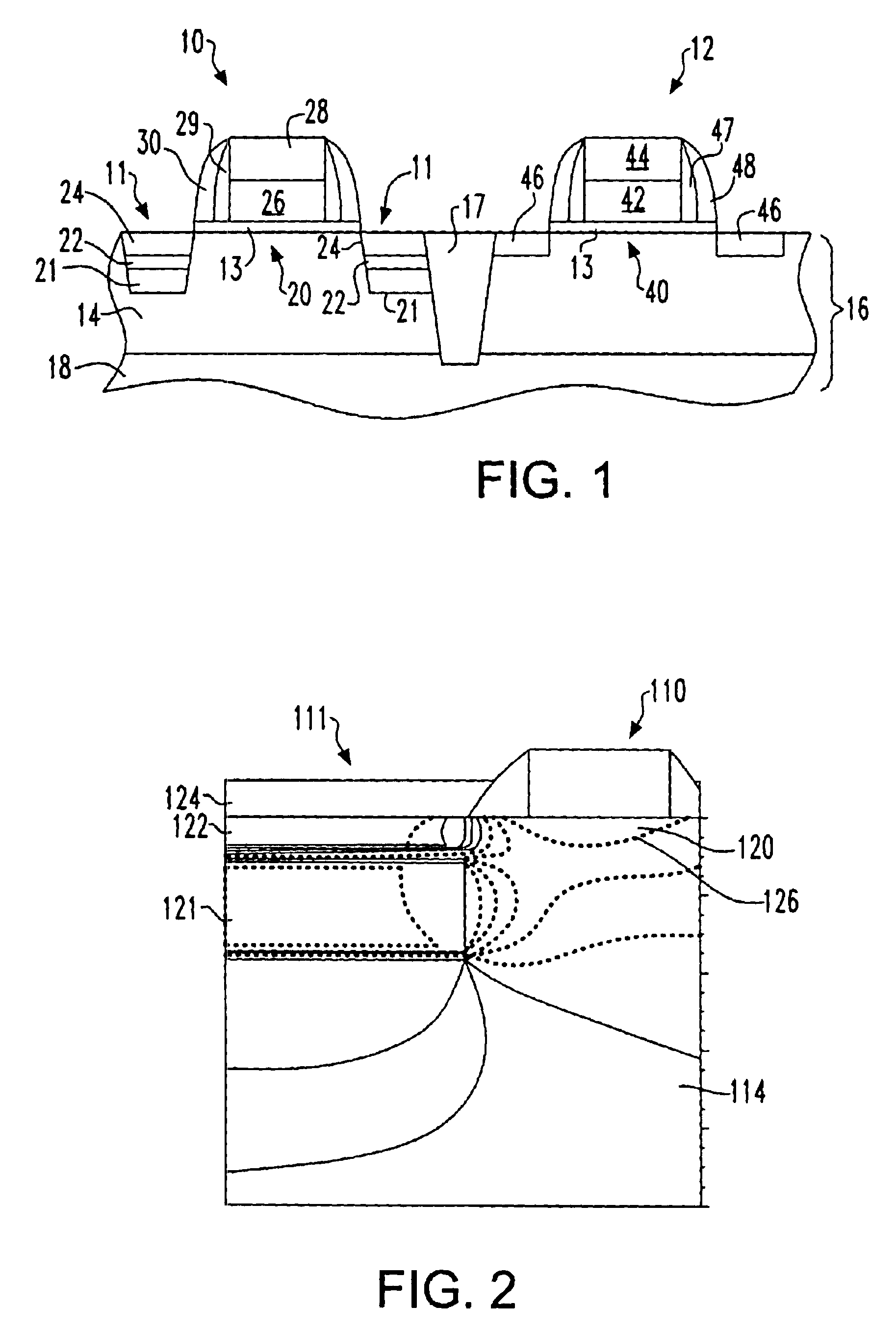

Structure for reducing leakage currents and high contact resistance for embedded memory and method for making same

ActiveUS20050093147A1More alignment toleranceReduce manufacturing costTransistorSemiconductor/solid-state device detailsDrain currentCapacitor

A method for fabricating an insulating layer having contact openings of varying depths for logic / DRAM circuits is achieved using a single mask and etch step. After forming stacked or trench capacitors, a planar insulating layer is formed. Contact openings are etched in the planar insulating layer to the substrate, and contact openings that extend over the edge of the stacked or trench capacitor top electrode, having an ARC, are etched using a novel mask design and a single etching step. This allows one to make contacts to the substrate without overetching while making low-resistance contacts to the sidewall of the capacitor top electrode. In the trench capacitor open areas are formed to facilitate making contact openings that extend over the top electrode. A series of contact openings that are skewed or elongated also improve the latitude in alignment tolerance.

Owner:TAIWAN SEMICON MFG CO LTD

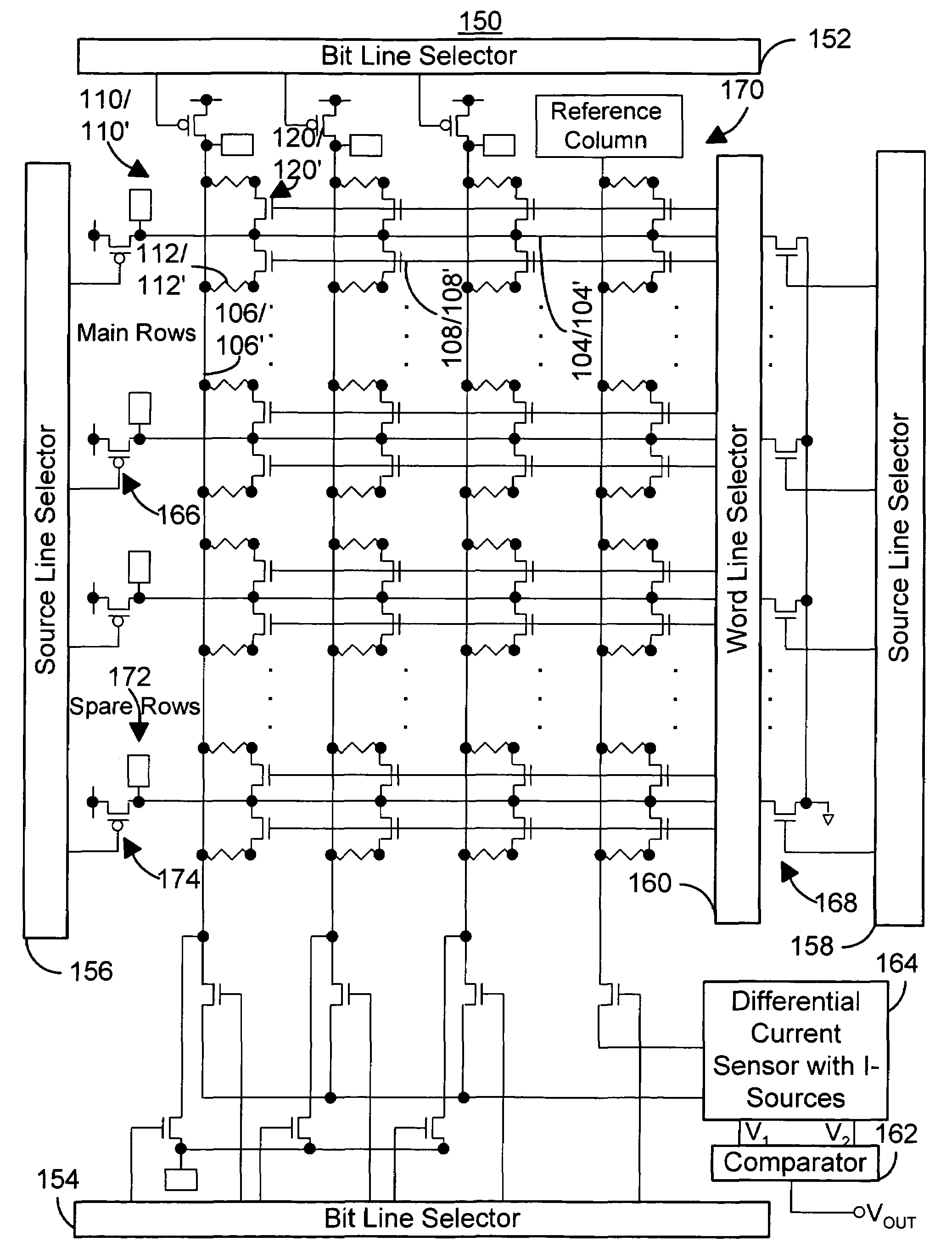

Current driven switched magnetic storage cells having improved read and write margins and magnetic memories using such cells

A method and system for providing a magnetic memory is described. The magnetic memory includes a plurality of magnetic storage cell and at least one bit line and a plurality of source lines corresponding to the plurality of magnetic storage cells. Each magnetic storage cell includes a magnetic element that is programmed to a high resistance state by a first write current driven through the magnetic element in a first direction and to a low resistance state by a second write current driven through the magnetic element in a second direction. The bit line(s) and the source lines are configured to drive the first write current through the magnetic element in the first direction, to drive the second write current through the magnetic element in the second direction, and to drive at least one read current through the magnetic element in a third direction that does not destabilize the low resistance state.

Owner:SAMSUNG SEMICON

Tunable gate electrode work function material for transistor applications

Described herein are metal gate electrode stacks including a low resistance metal cap in contact with a metal carbonitride diffusion barrier layer, wherein the metal carbonitride diffusion barrier layer is tuned to a particular work function to also serve as a work function metal for a pMOS transistor. In an embodiment, the work function-tuned metal carbonitride diffusion barrier prohibits a low resistance metal cap layer of the gate electrode stack from migrating into the MOS junction. In a further embodiment of the present invention, the work function of the metal carbonitride barrier film is modulated to be p-type with a pre-selected work function by altering a nitrogen concentration in the film.

Owner:TAHOE RES LTD

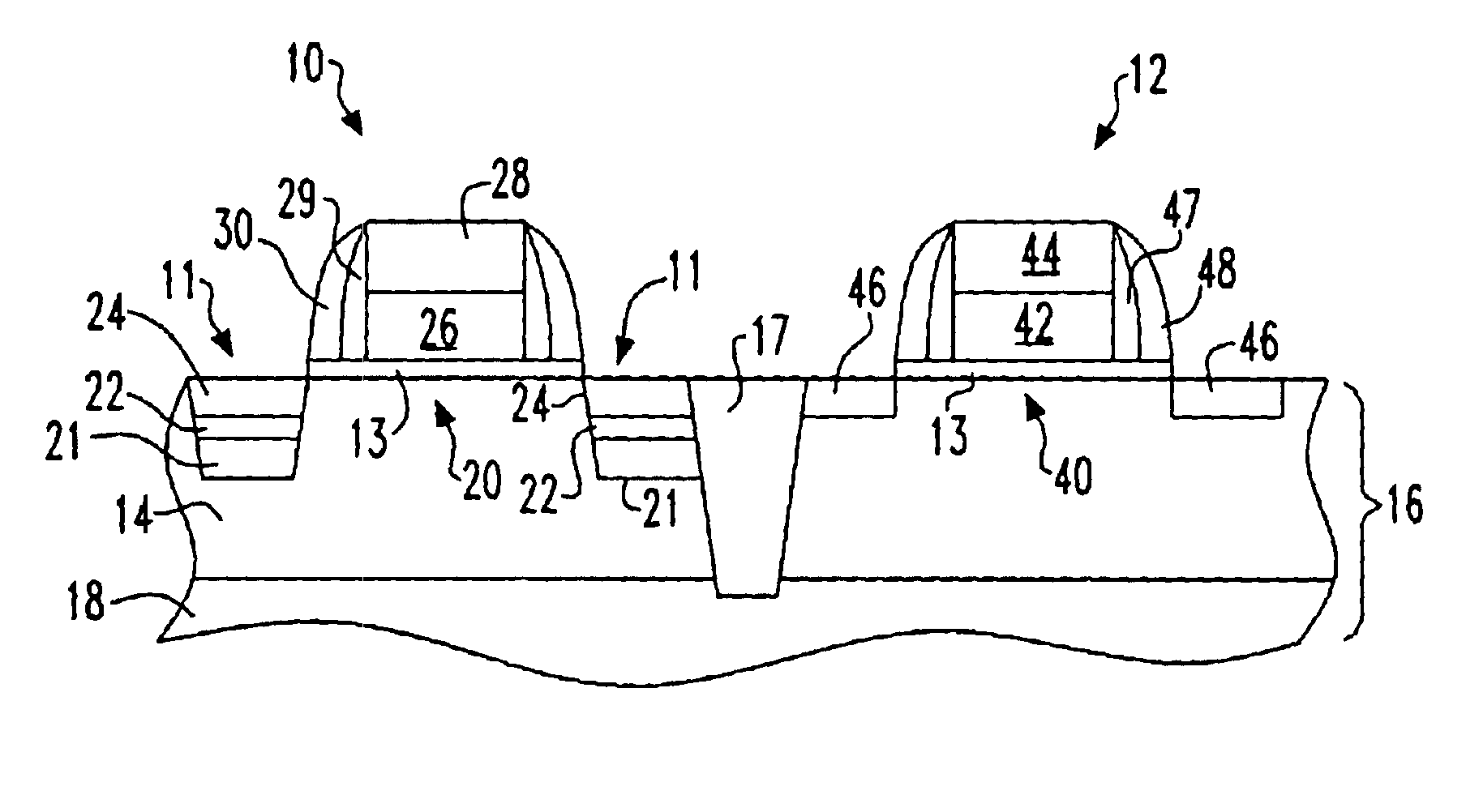

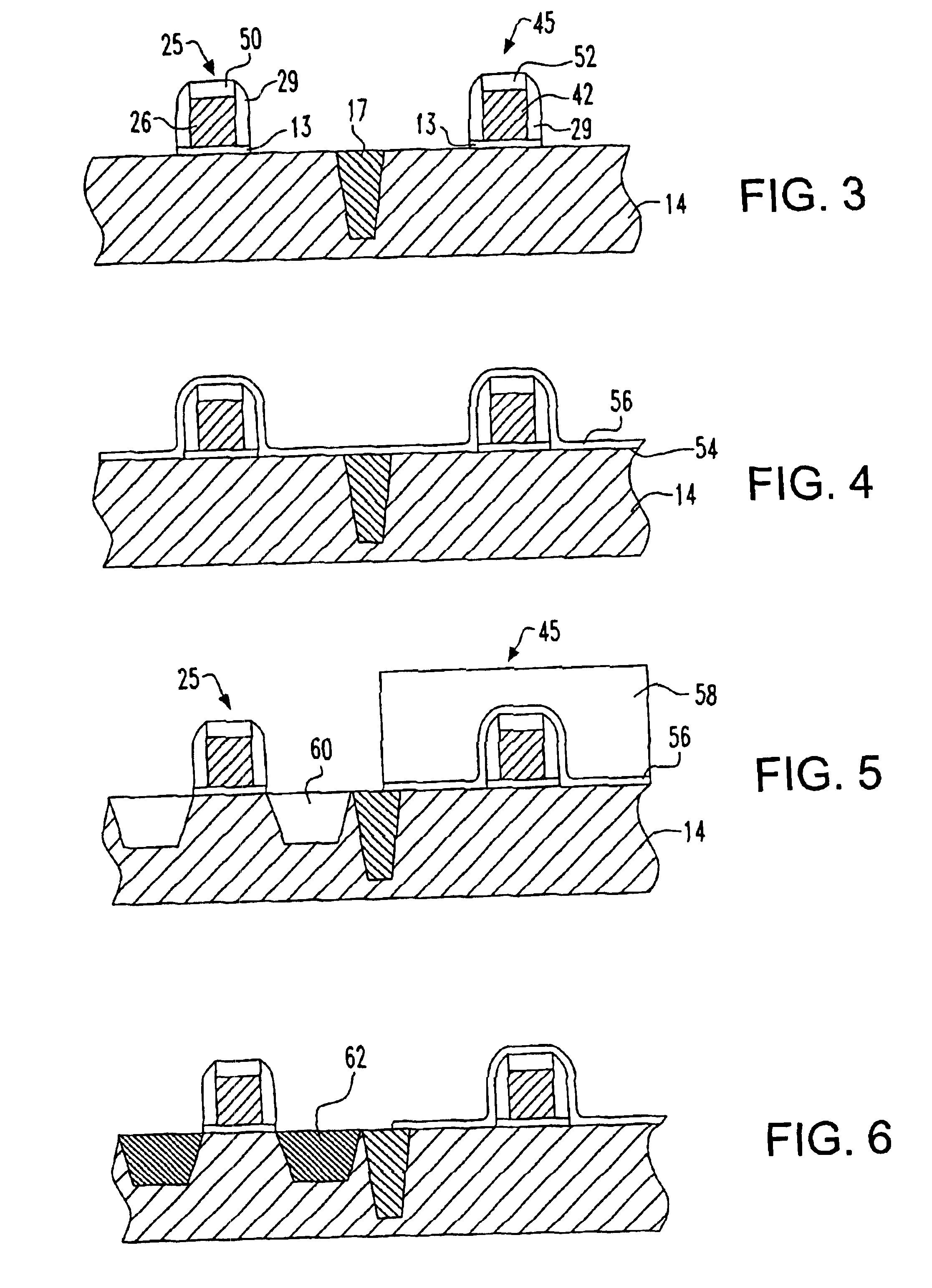

Structure and method of making strained semiconductor CMOS transistors having lattice-mismatched semiconductor regions underlying source and drain regions

Owner:SEMICON MFG INT (SHANGHAI) CORP

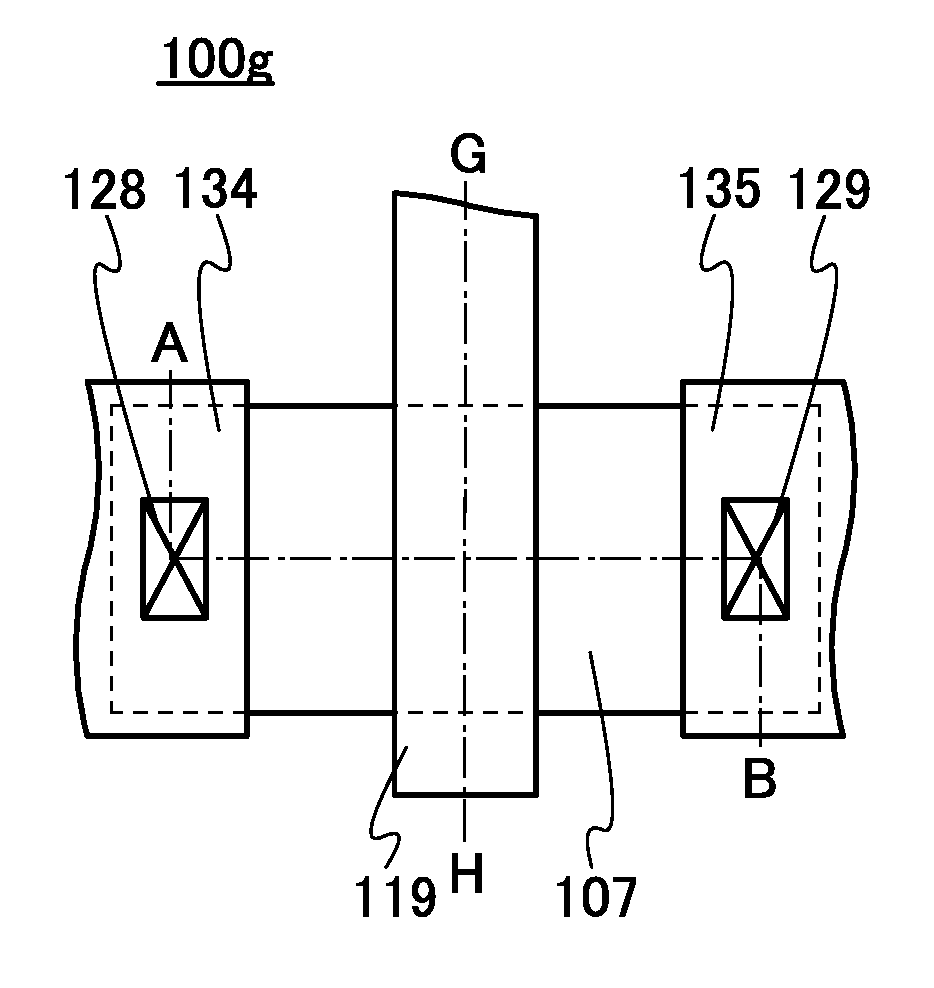

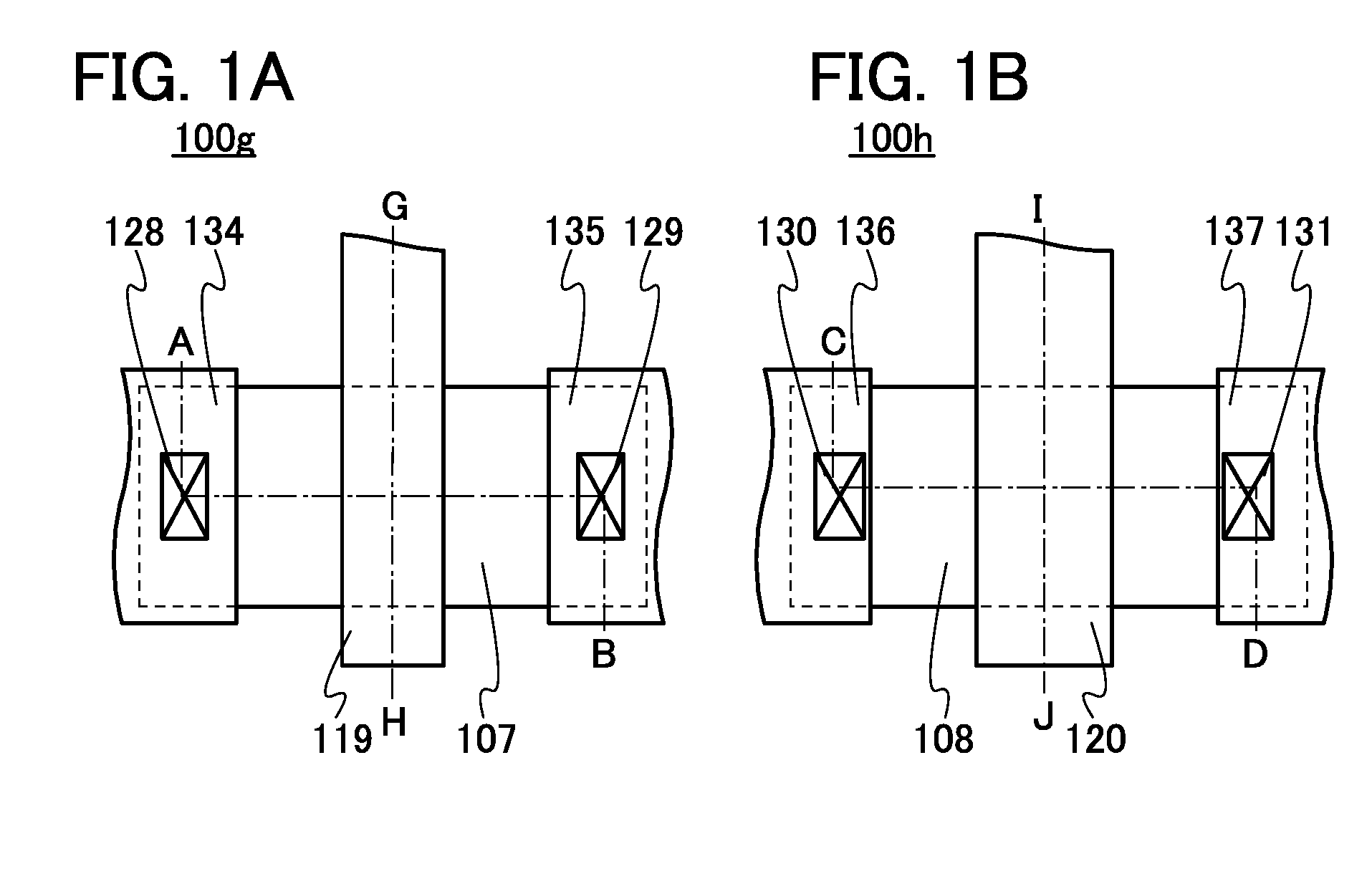

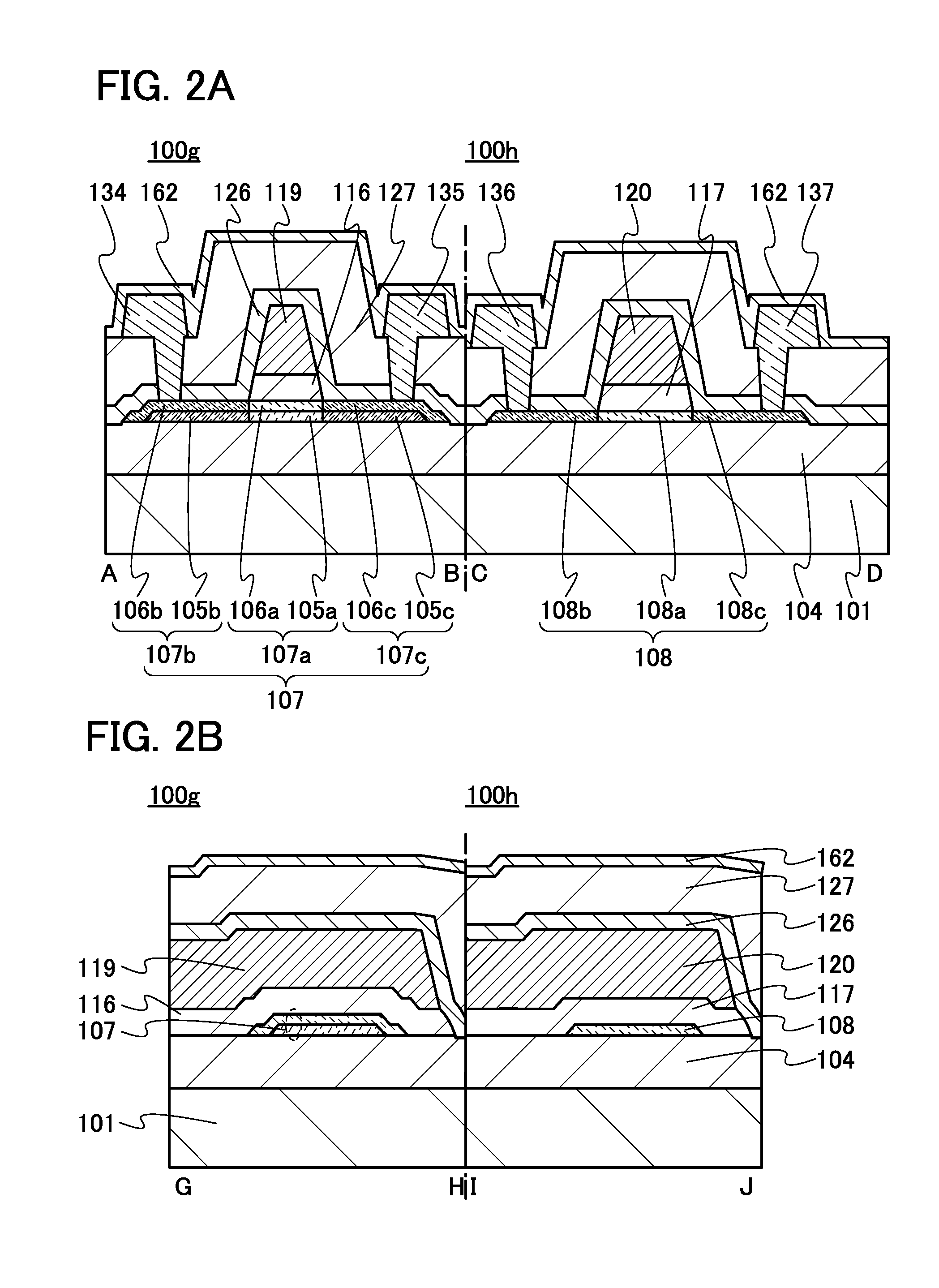

Semiconductor device

ActiveUS20150228803A1Stable semiconductor characteristicSimple manufacturing processTransistorSolid-state devicesDriver circuitHydrogen

The semiconductor device includes a first transistor provided in a driver circuit portion and a second transistor provided in a pixel portion; the first transistor and the second transistor have different structures. In an oxide semiconductor film of each of the transistors, an impurity element is contained in regions which do not overlap with a gate electrode. The regions of the oxide semiconductor film which contain the impurity element function as low-resistance regions. Furthermore, the regions of the oxide semiconductor film which contain the impurity element are in contact with a film containing hydrogen. Furthermore, the first transistor provided in the driver circuit portion may include the oxide semiconductor film in which a first film and a second film are stacked, and the second transistor provided in the pixel portion may include the oxide semiconductor film which differs from the first film in the atomic ratio of metal elements.

Owner:SEMICON ENERGY LAB CO LTD

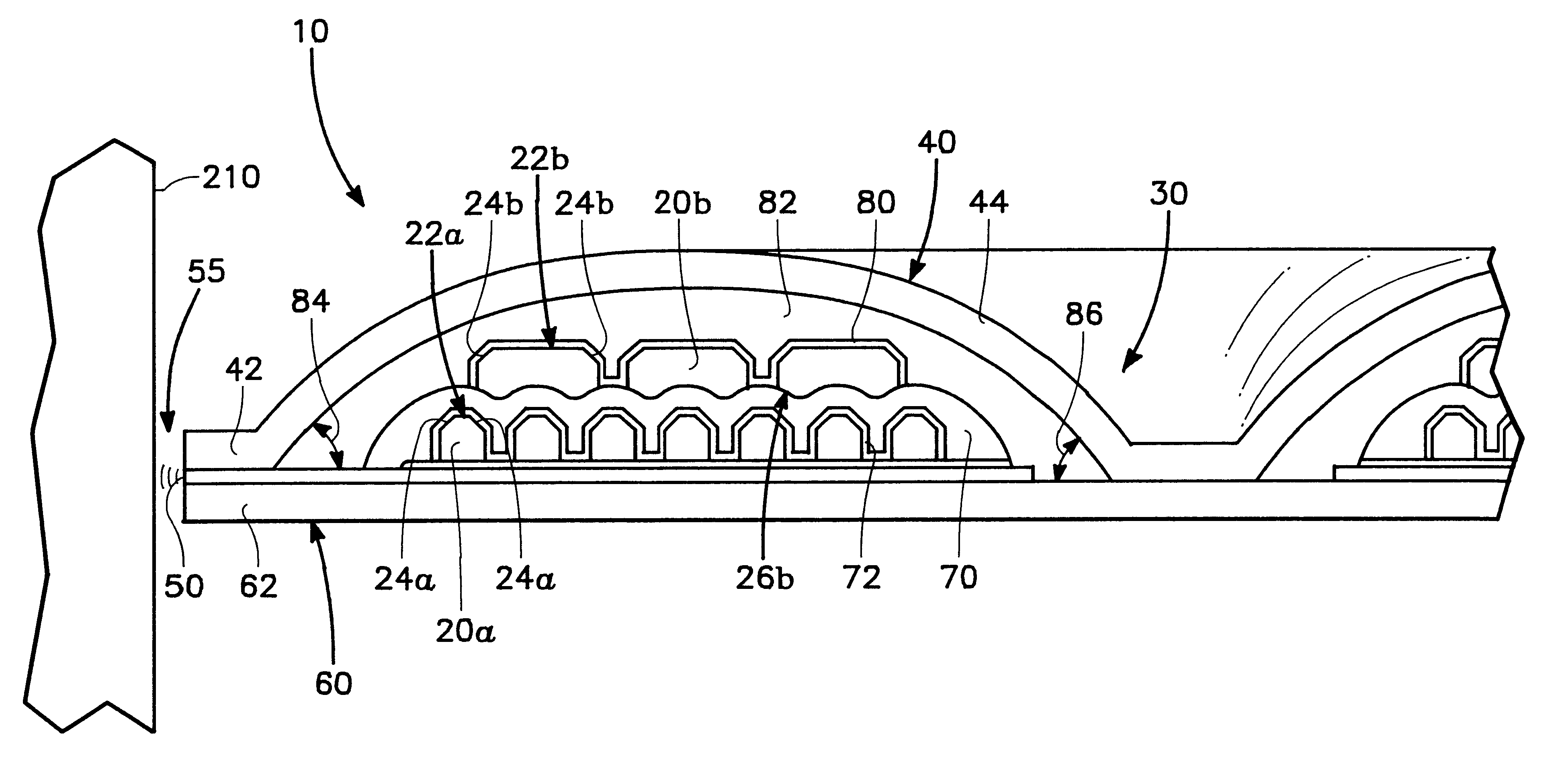

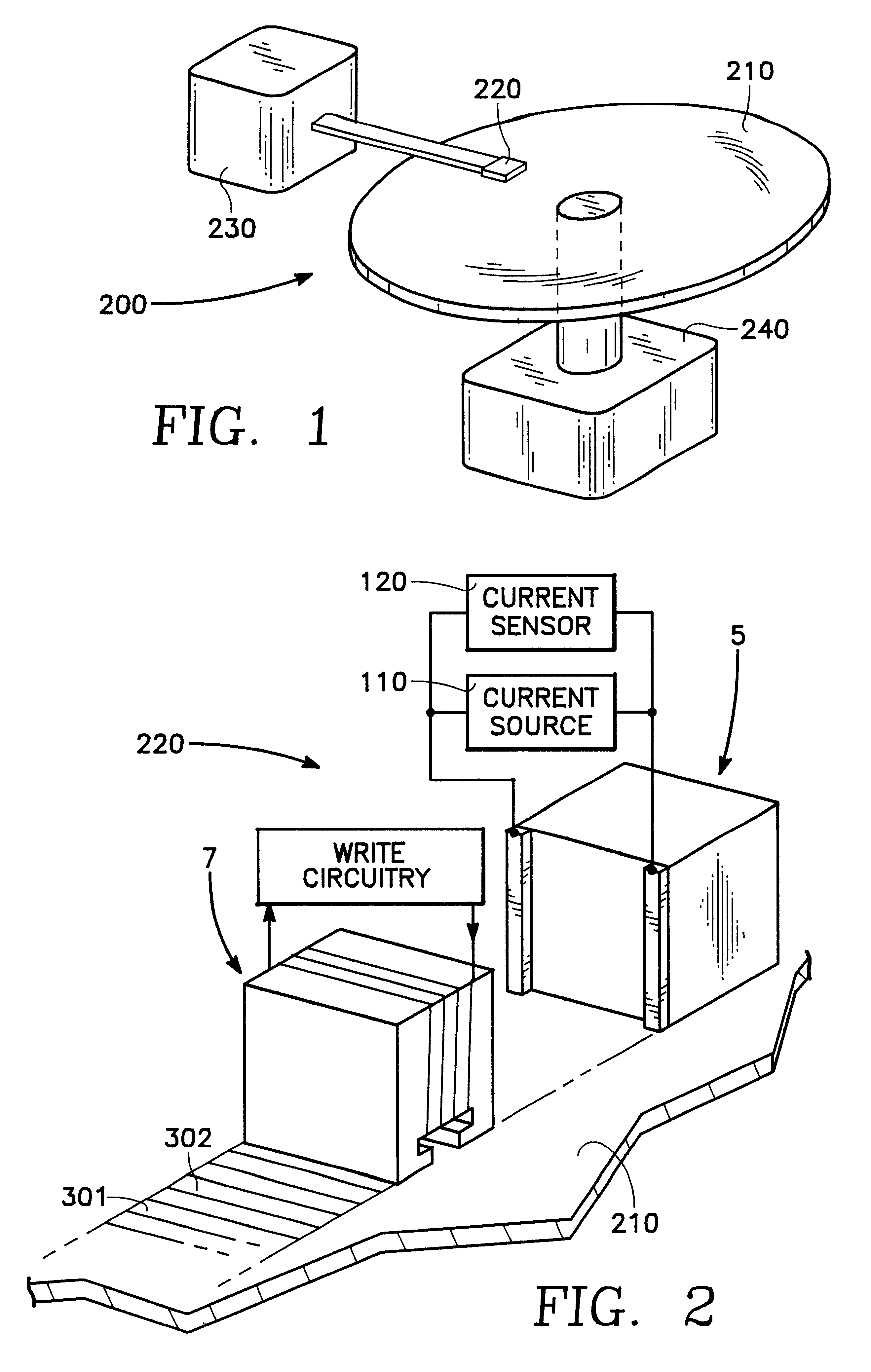

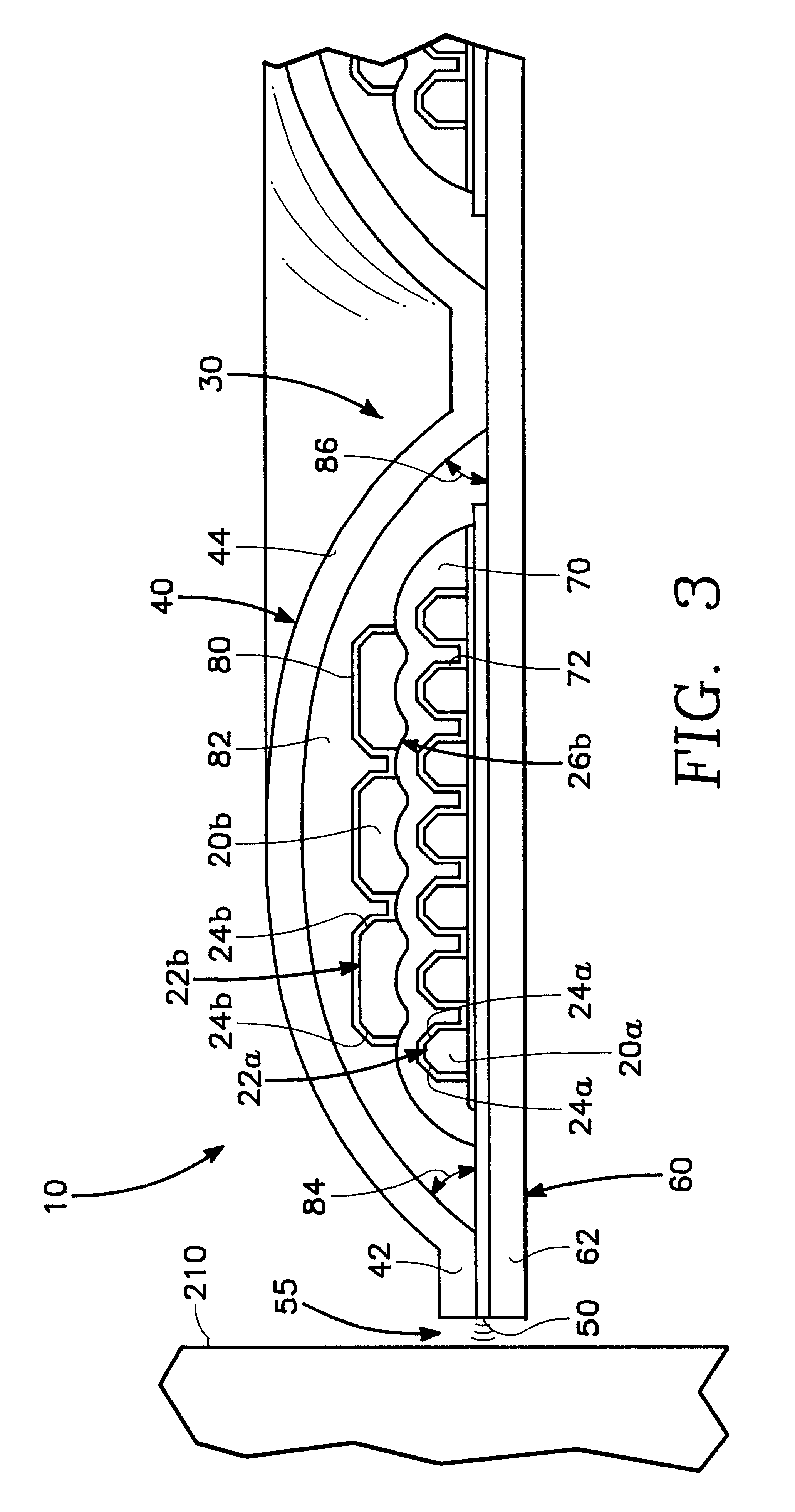

Low resistance coil structure for high speed writer

InactiveUS6333830B2Lower coil resistanceReduce dissipationConstruction of head windingsHeads using thin filmsElectrical conductorLower pole

The present invention provides a thin film write head having an upper and lower pole structures and conductor turns forming a winding for generating magnetic flux. The conductor is formed with a non-planar top surface. The winding of the present invention may be formed of lower and upper turns. The upper turns may be formed with a non-planar top surface, a non-planar bottom surface, or both. It is preferred that the bottom surface of the upper conductor turns be coherent with the non-planar top surface of the lower conductor turns. The non-planar top surface may be formed by removing corners formed during deposition between a generally planar top surface and abutting side walls. The corners may be removed by ion milling to form the non-planar top surface. The conductor may be copper with the non-planar top surface having sloping facets. The thin film write head of the present invention may be utilized to provide an improved data storage and retrieval apparatus. The preferred embodiment provides reduced coil resistance thereby reducing Johnson Thermal Noise and power dissipation. It also allows for reduced yoke length and reduced stack height while providing low apex angles to expand and improve yoke material deposition thereby improving head response and operational frequency.

Owner:WESTERN DIGITAL TECH INC

Semiconductor devices

InactiveUS6166396AQuality improvementLower resistanceTransistorSemiconductor/solid-state device detailsActive-matrix liquid-crystal displayElectrical conductor

In an active matrix liquid crystal display (LCD) device, a conductor line interconnecting a drain of each thin-film transistor and a corresponding pixel electrode constructed with indium tin oxide (ITO) is formed in a three-layer structure in which an aluminum film is sandwiched between a pair of titanium films. This construction prevents poor contact and deterioration of reliability because electrical contact is established between one titanium film and semiconductor and between the other titanium film and ITO. The aluminum film has low resistance which is essential for ensuring high performance especially in large-screen LCDs.

Owner:SEMICON ENERGY LAB CO LTD

Three-dimensional programmable resistance memory device with a read/write circuit stacked under a memory cell array

A programmable resistance memory device includes a semiconductor substrate, at least one cell array, in which memory cells are arranged and formed above the semiconductor substrate. Each of the memory cells has a stack structure of a programmable resistance element and an access element, the programmable resistance element storing a high resistance state or a low resistance state based on the polarity of voltage application in a non-volatile manner. The access element has a resistance value in an off-state in a certain voltage range that is ten time or more as high as that in a select state. A read / write circuit is formed on the semiconductor substrate and underlying the cell array for data reading and data writing in communication with the cell array.

Owner:KIOXIA CORP