Patents

Literature

2517 results about "Active surface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An active surface is a surface of a radio telescope that is under active computer control of its shape. Large (more than 10 m in diameter or length) radio telescopes always bend during operation, due to their enormous weight and the fact that even the strongest materials are not perfectly stiff. This bending, in the range of a few millimetres, does not affect low frequency operation much, but dramatically reduces the efficiency of the telescope at higher frequencies where the wavelengths are comparable to the distortion. Typically, the efficiency of a telescope drops appreciably when the deviation from the desired shape is more than 1/10 of the considered wavelength. An active surface uses numerous small actuators to move the surface panels with respect to the underlying frame, and thus maintain the correct shape.

Fingerprint-reading system

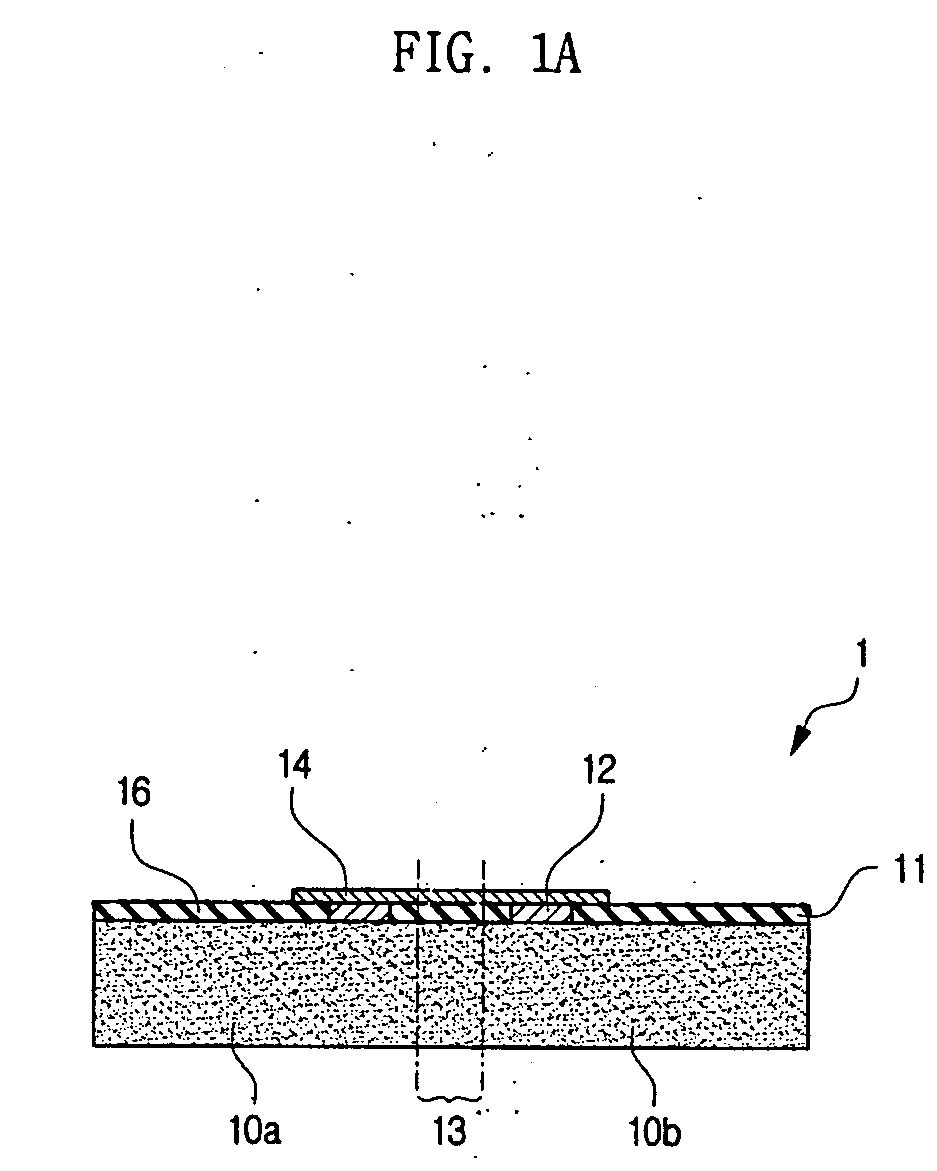

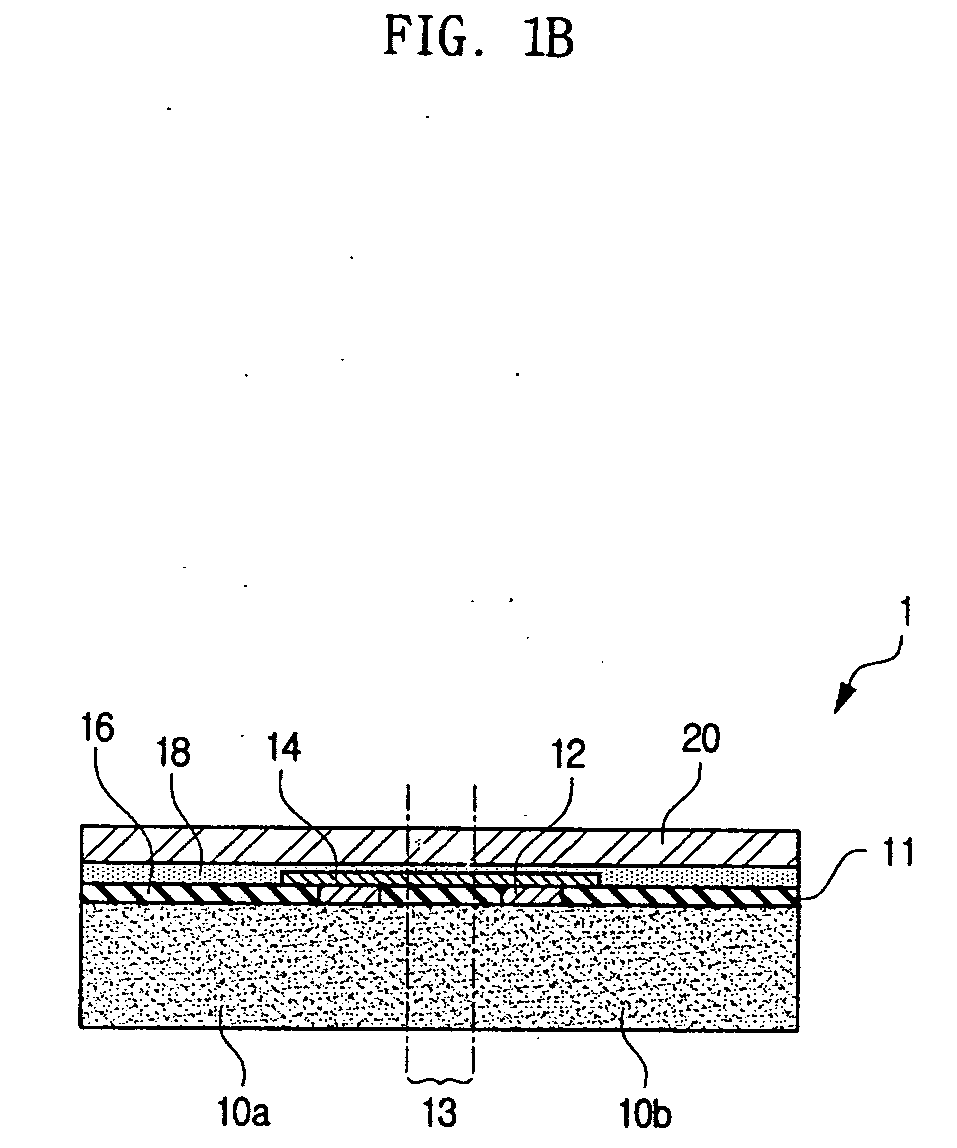

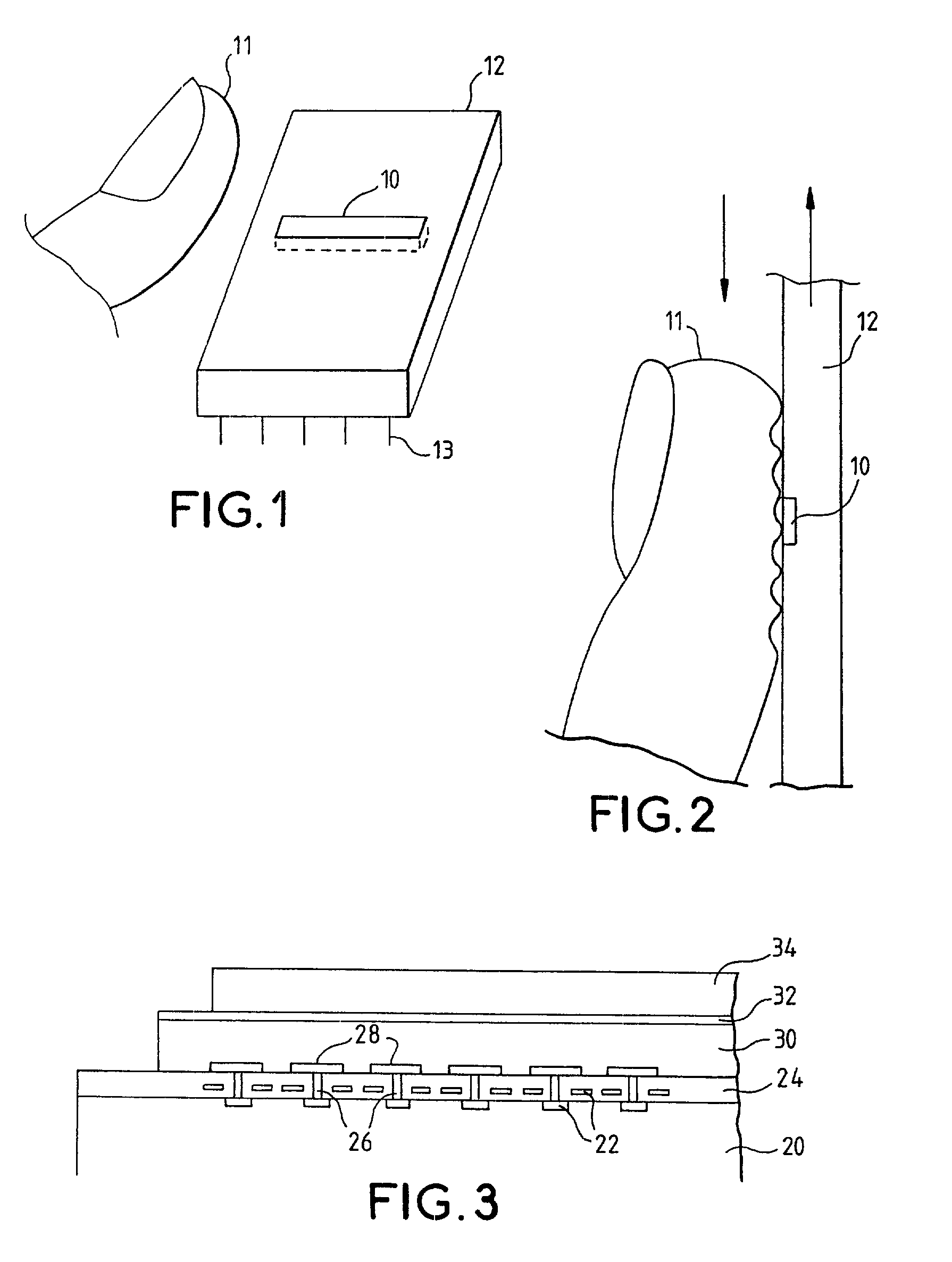

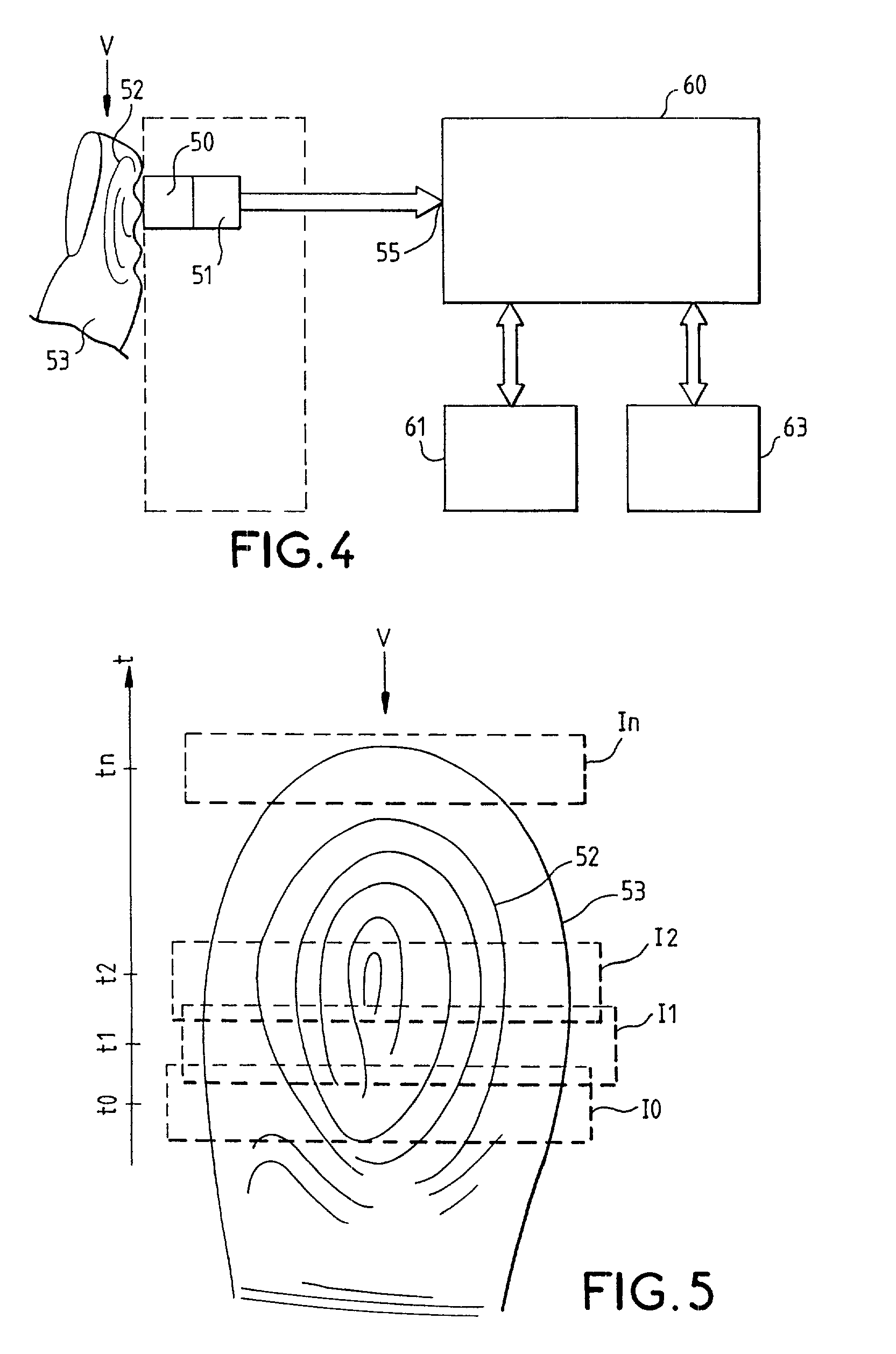

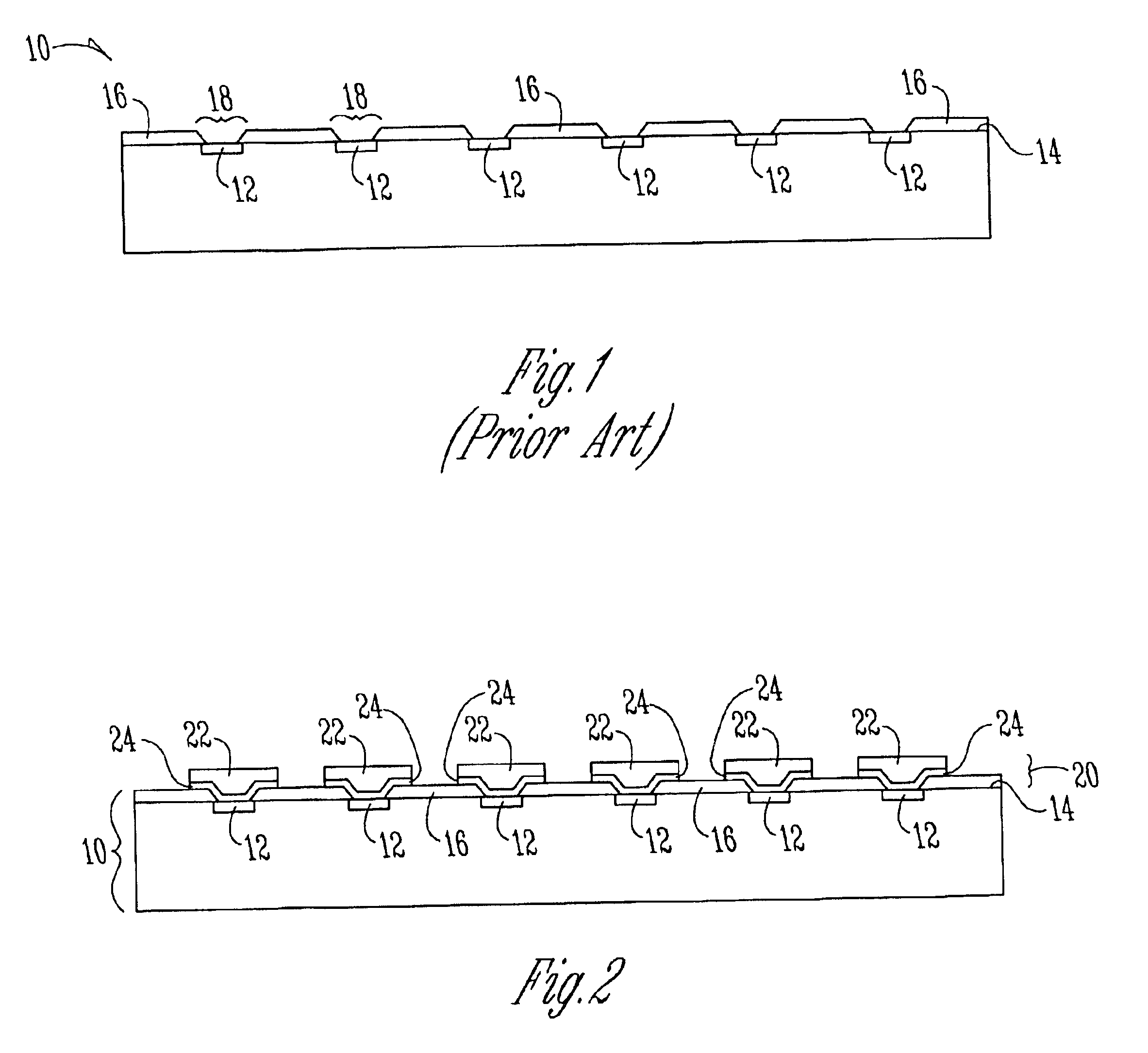

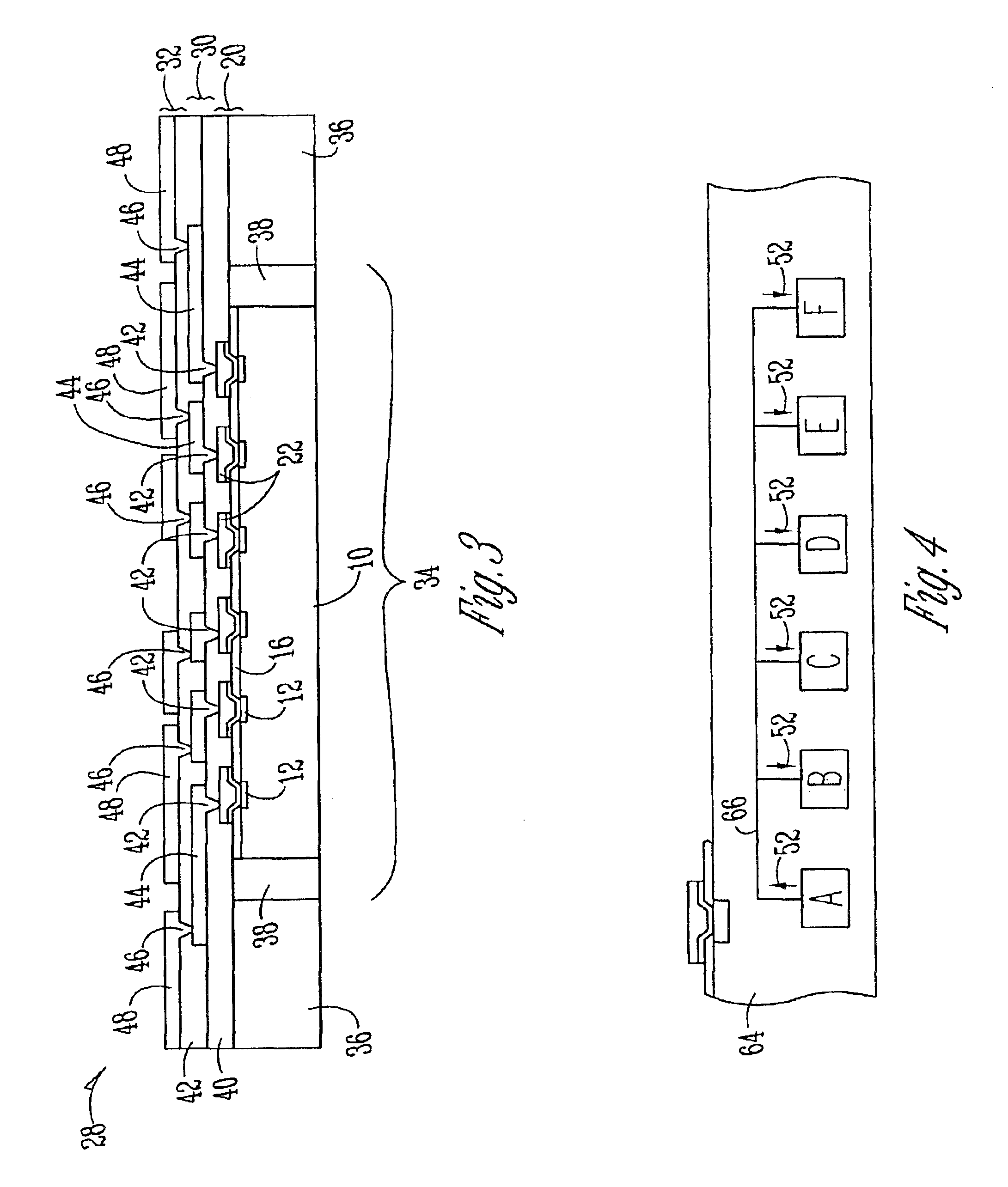

InactiveUS6289114B1Image analysisElectric/magnetic contours/curvatures measurementsEffective surfaceRelative motion

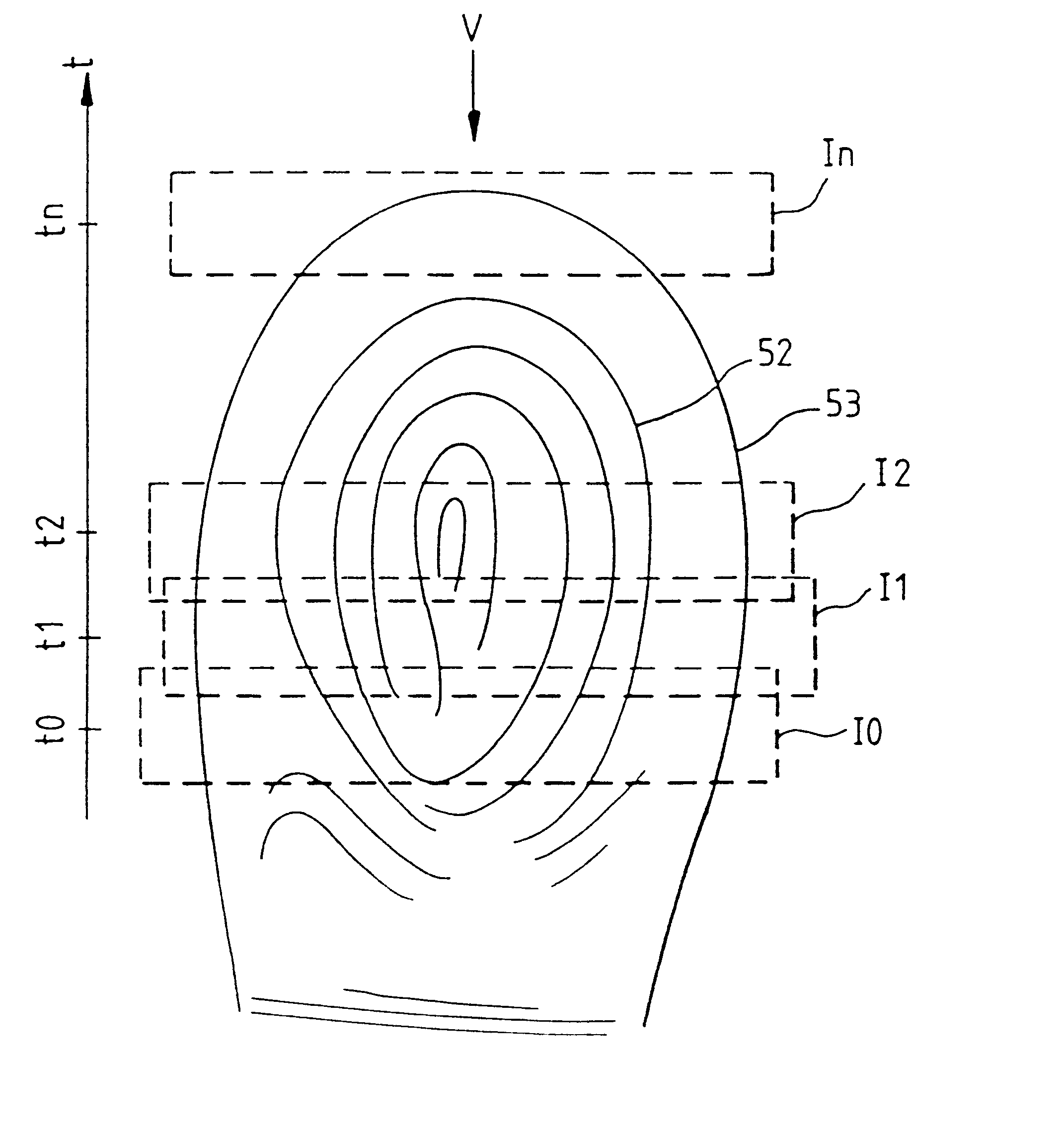

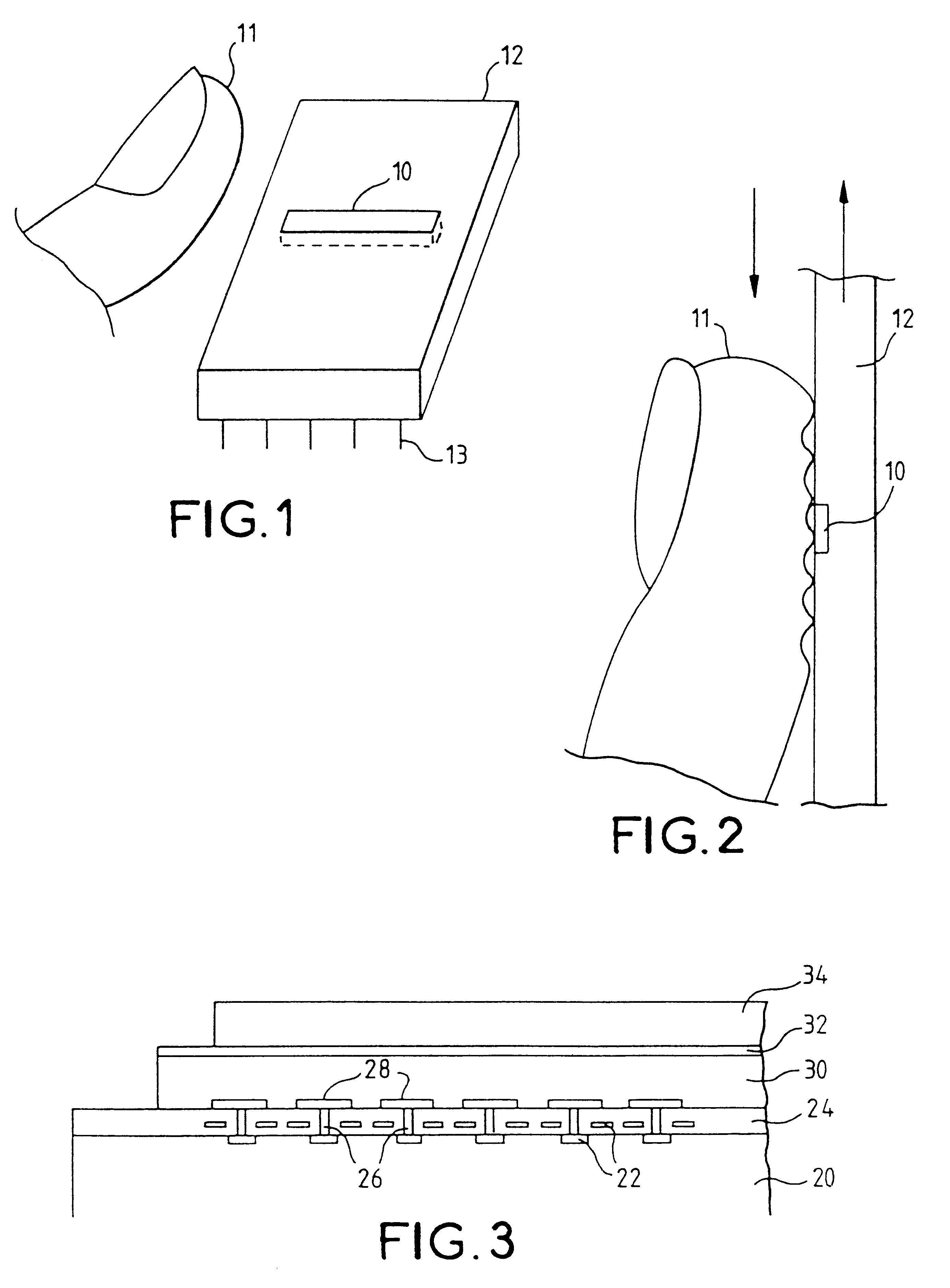

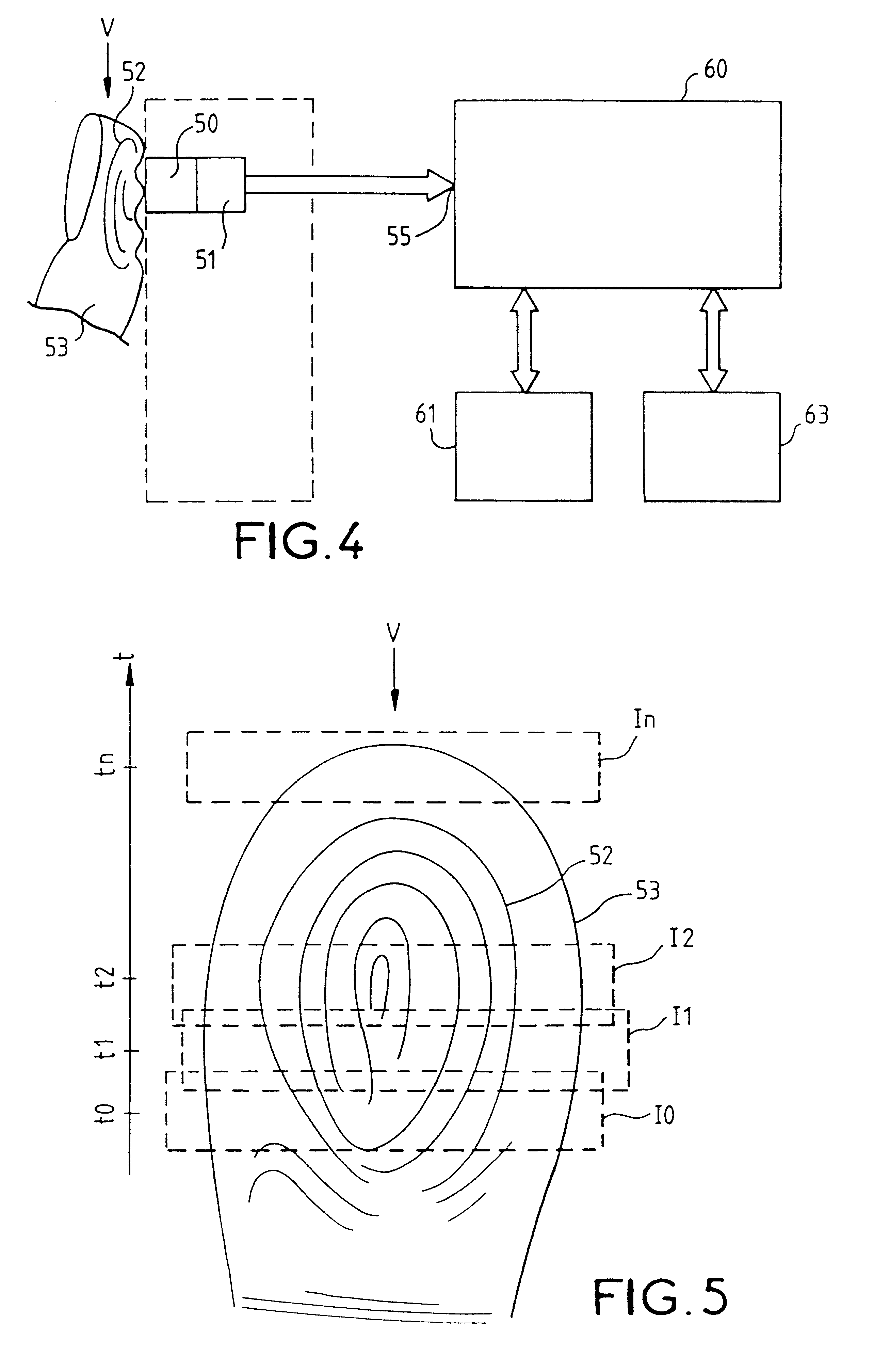

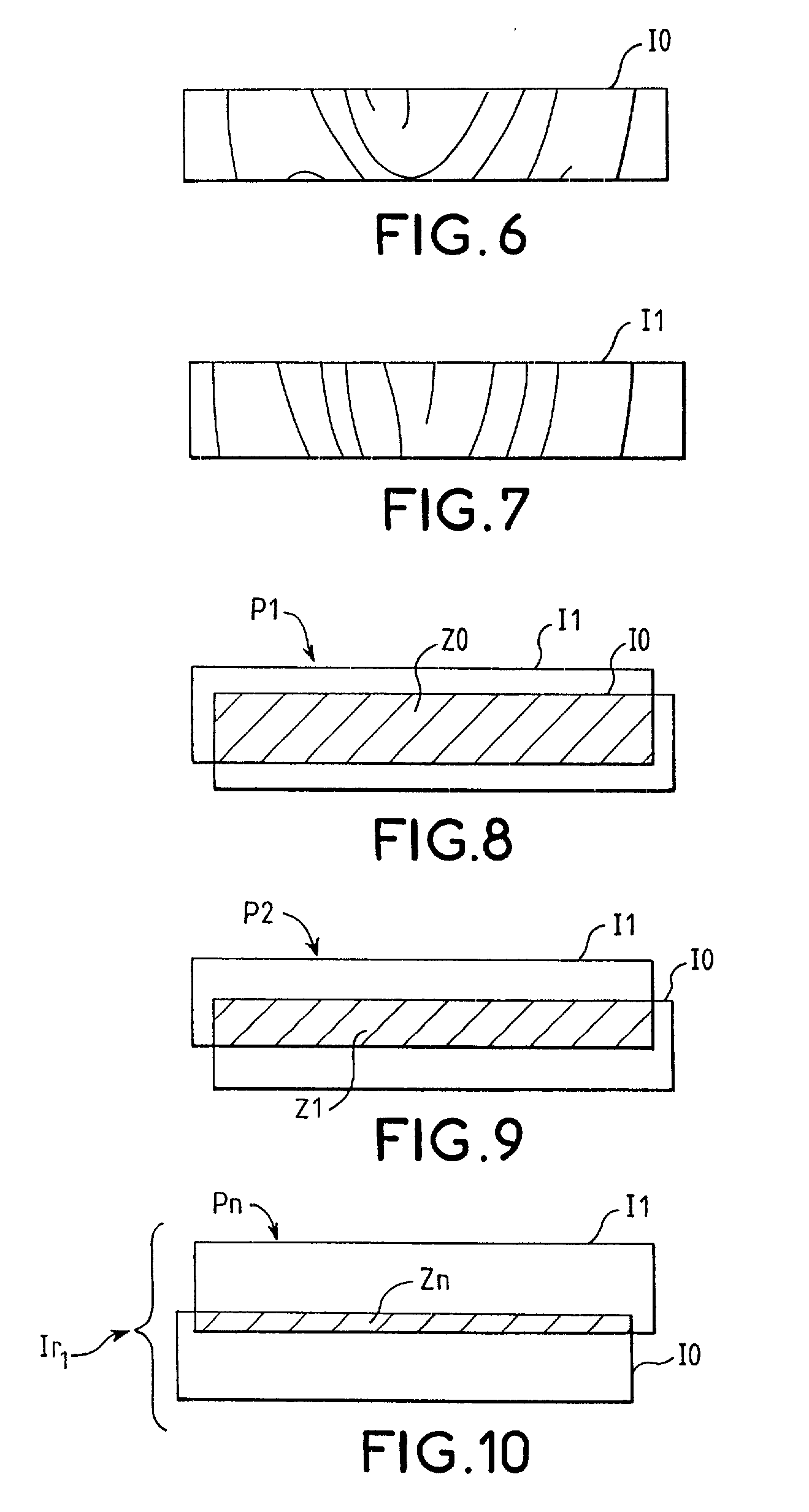

A fingerprint-reading system includes a fingerprint sensor having an active surface sensitive to the pressure and temperature of a finger. The surface area of this sensor is far smaller than the surface area of the fingerprint to be read. The reading is done when the sensor and the finger are in contact and in a relative motion of sliding of the sensor and the finger with respect to each other. The system reconstitutes a complete image of the fingerprint from the partial images given by the sensor during this motion.

Owner:APPLE INC

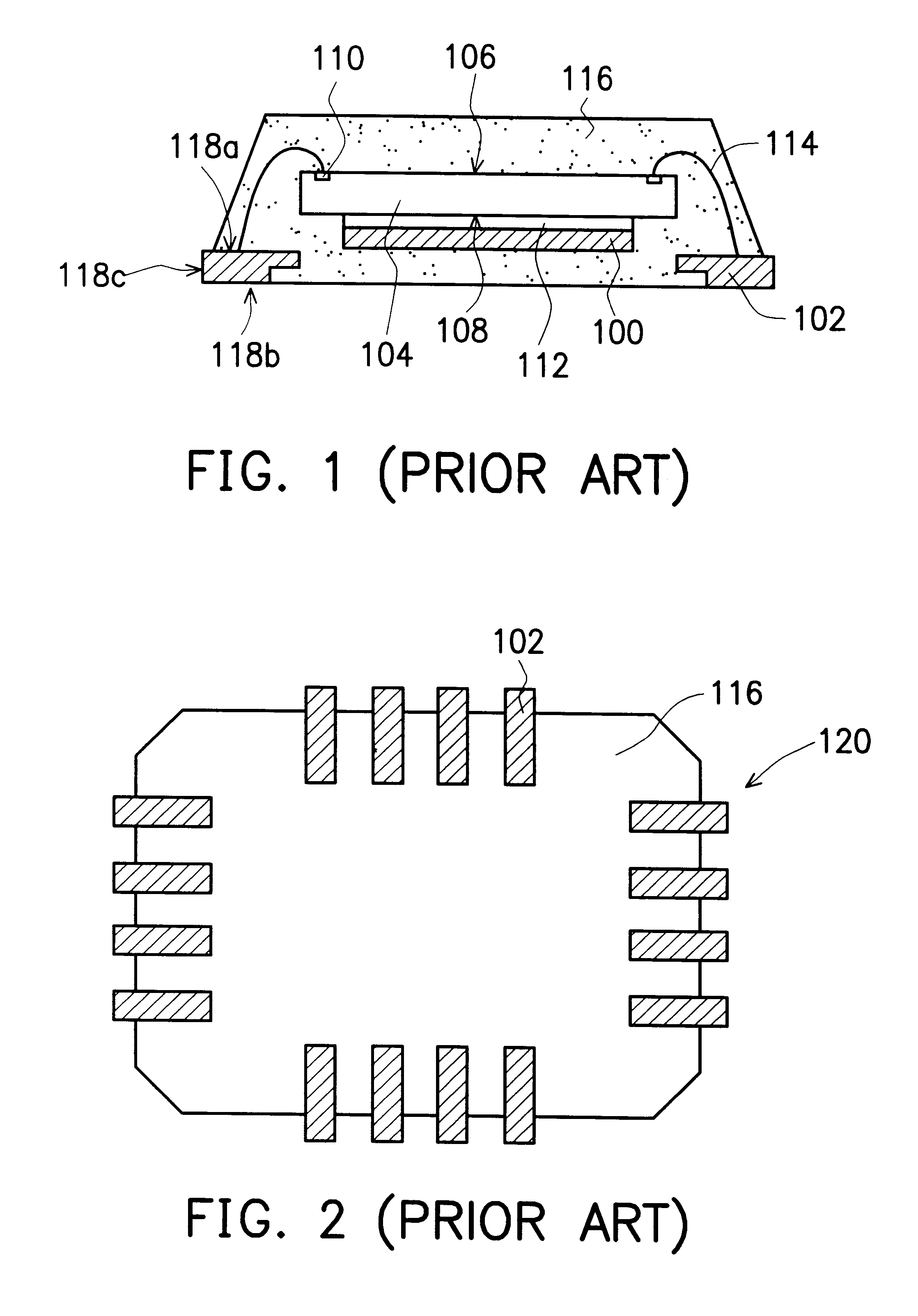

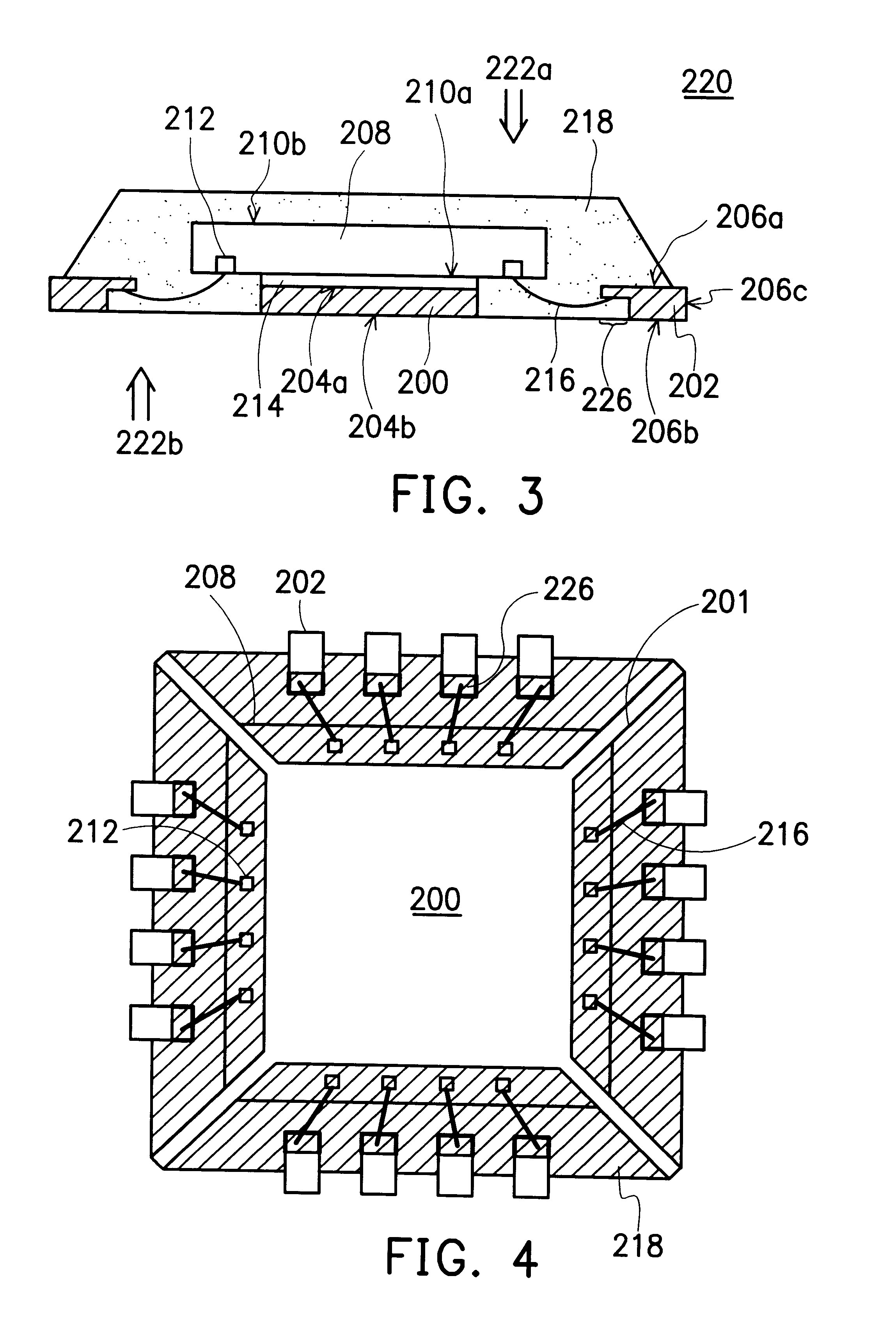

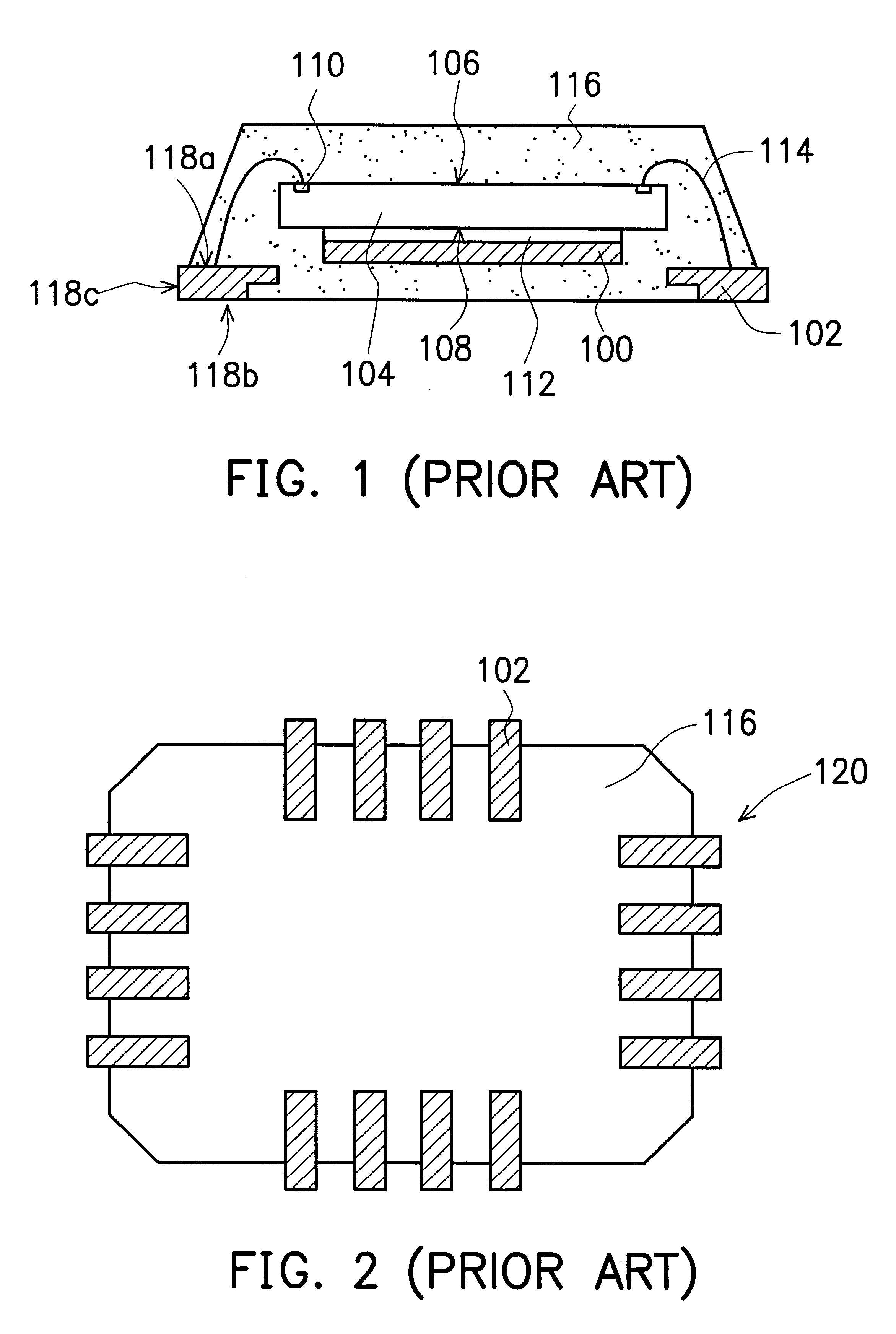

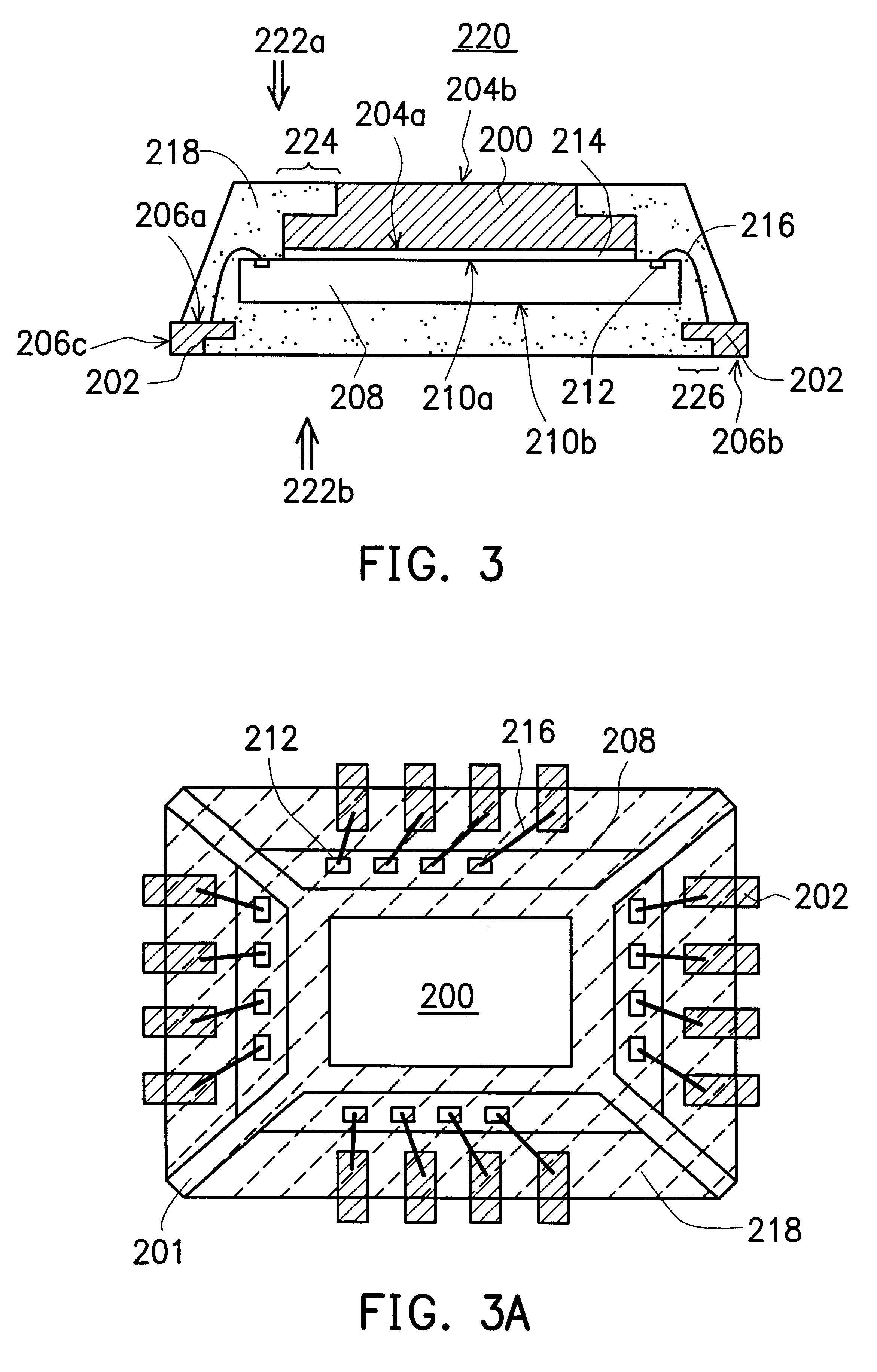

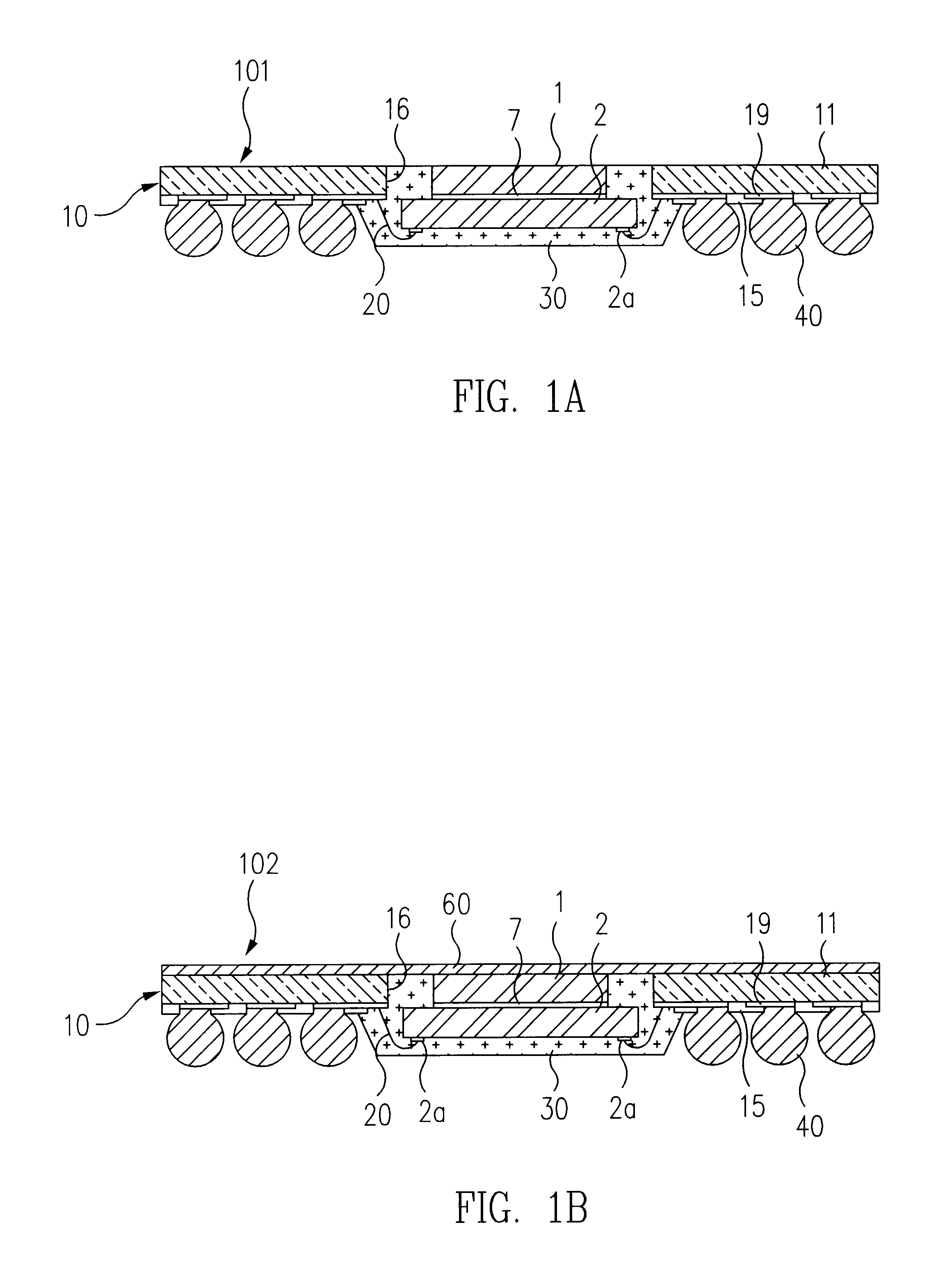

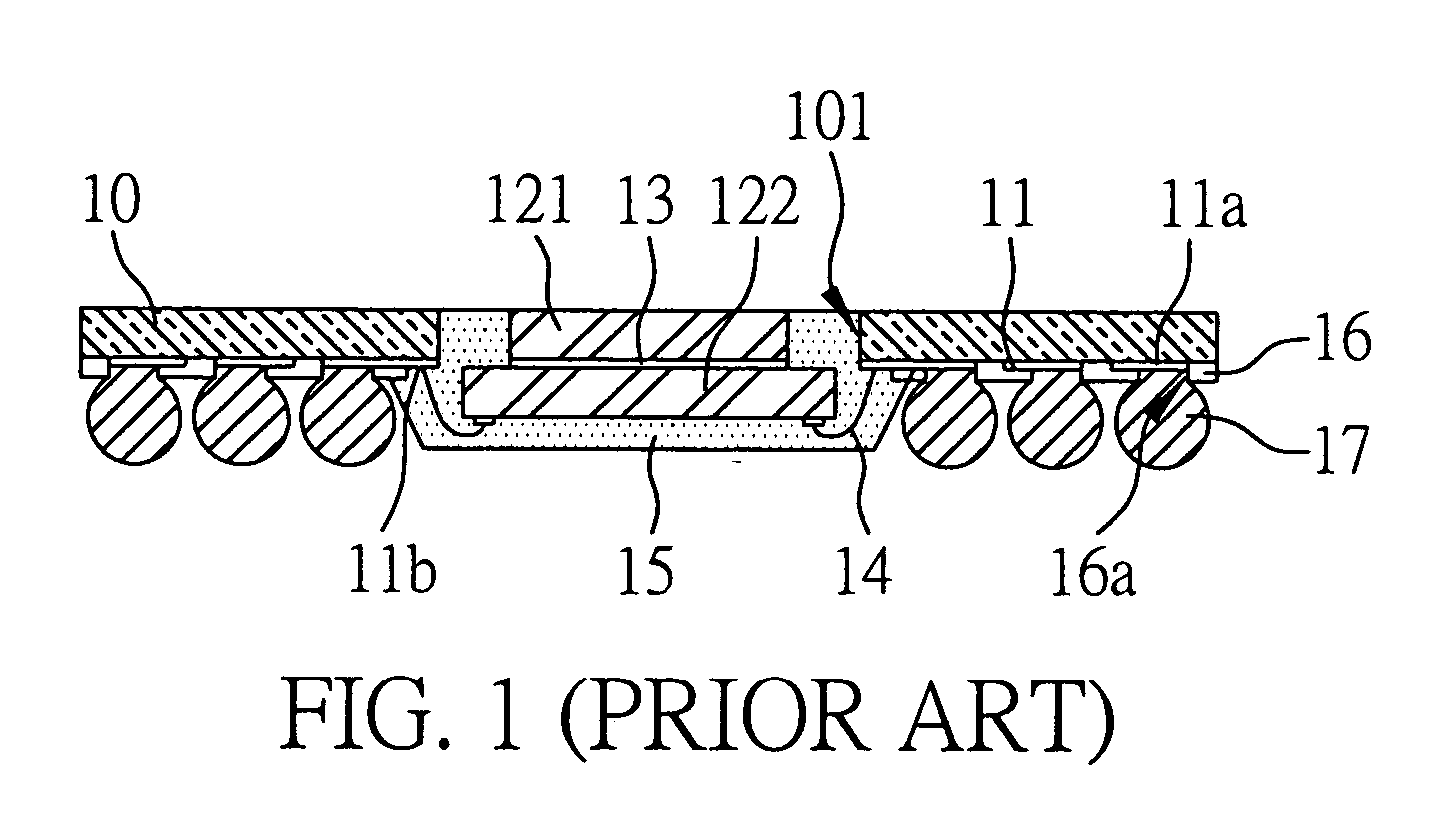

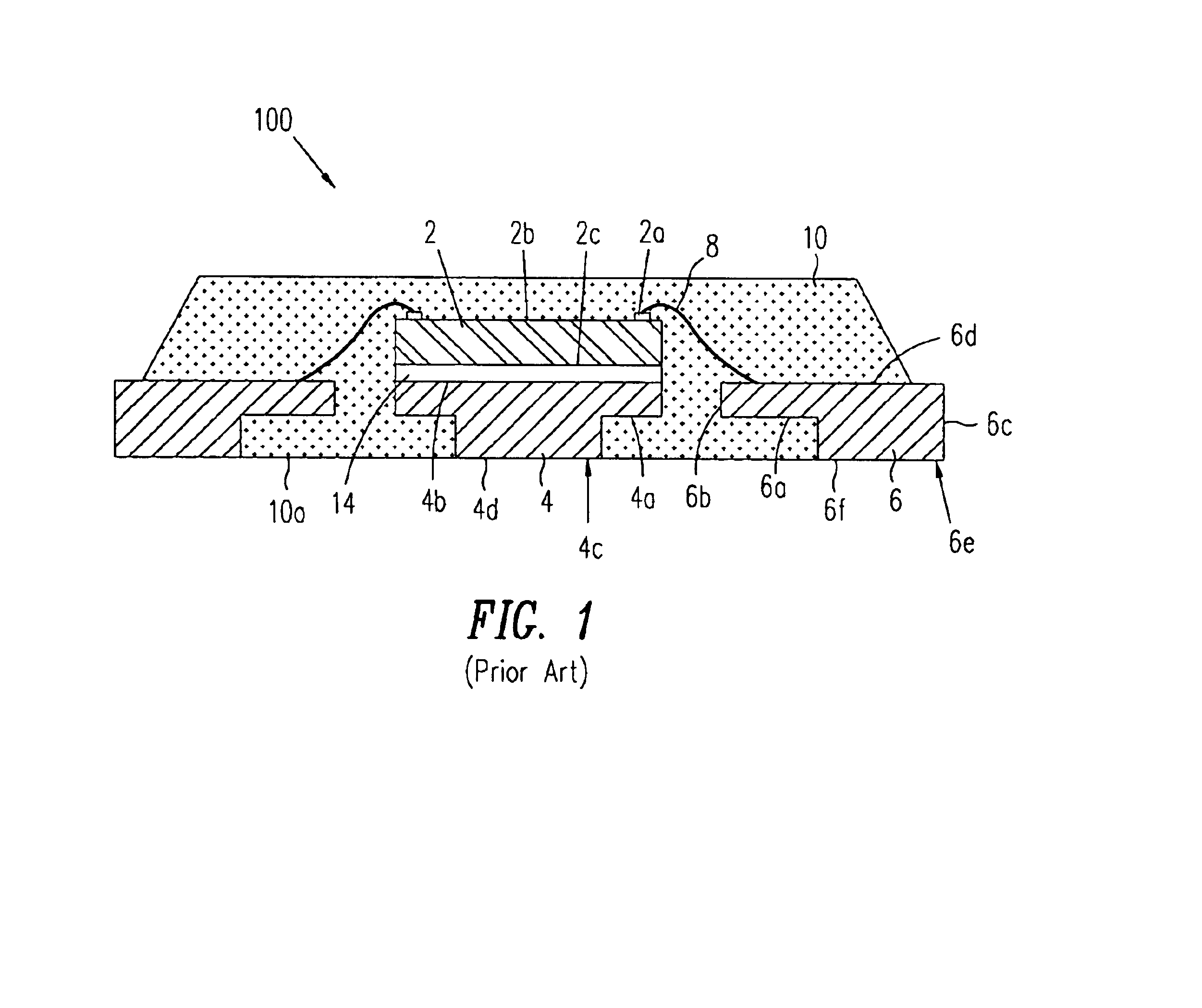

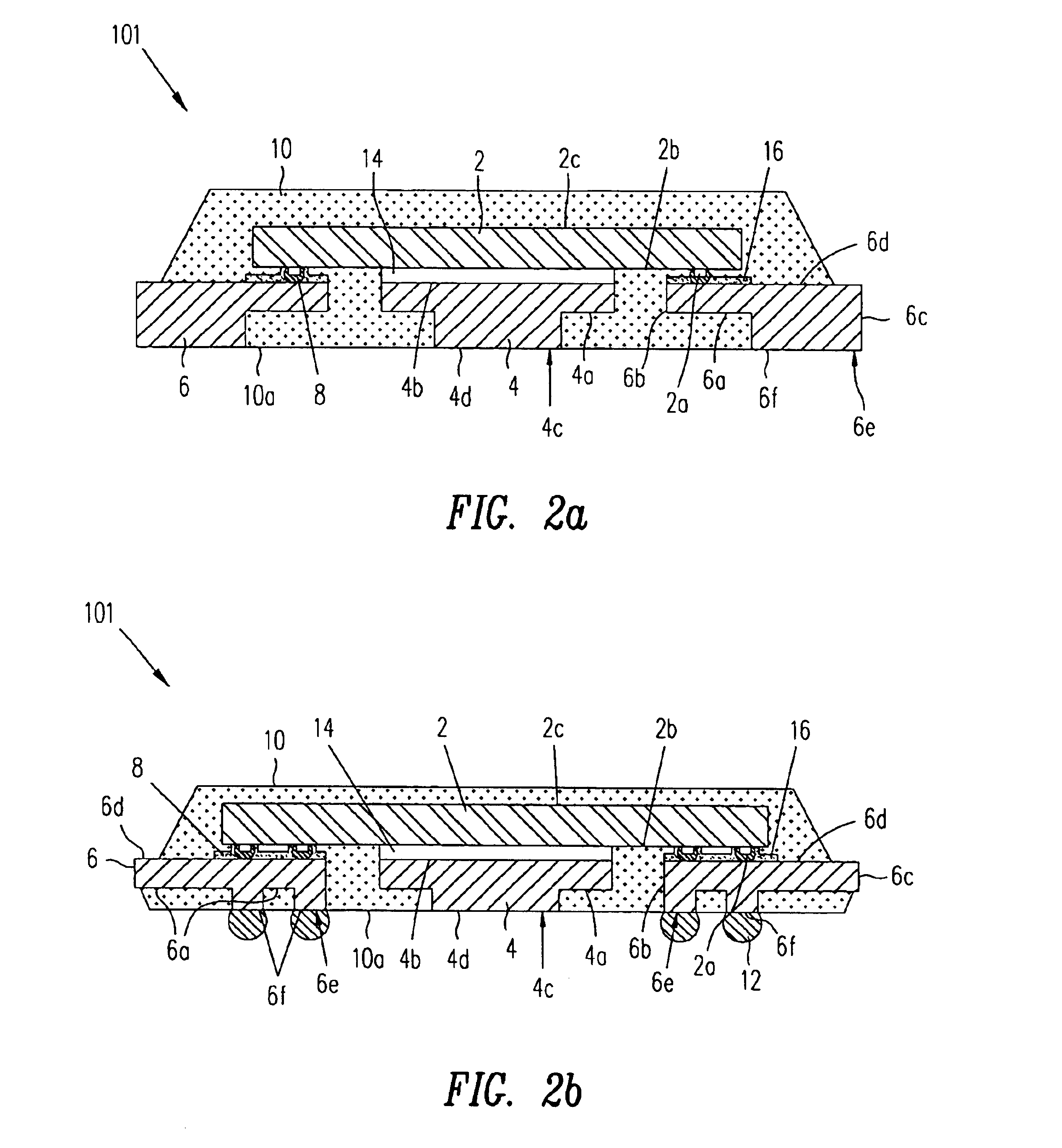

Thermally enhanced quad flat non-lead package of semiconductor

InactiveUS6198171B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductorWire bonding

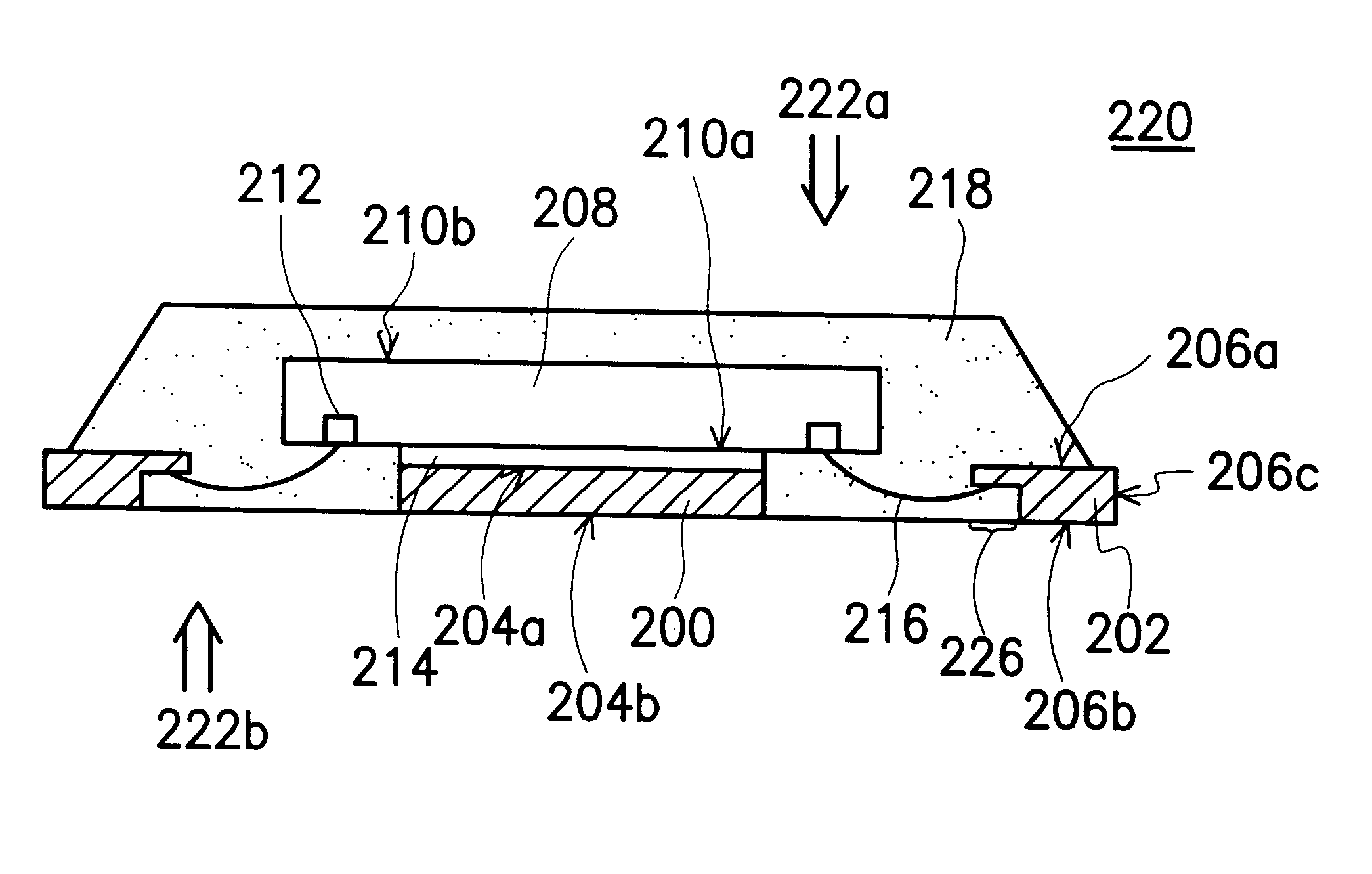

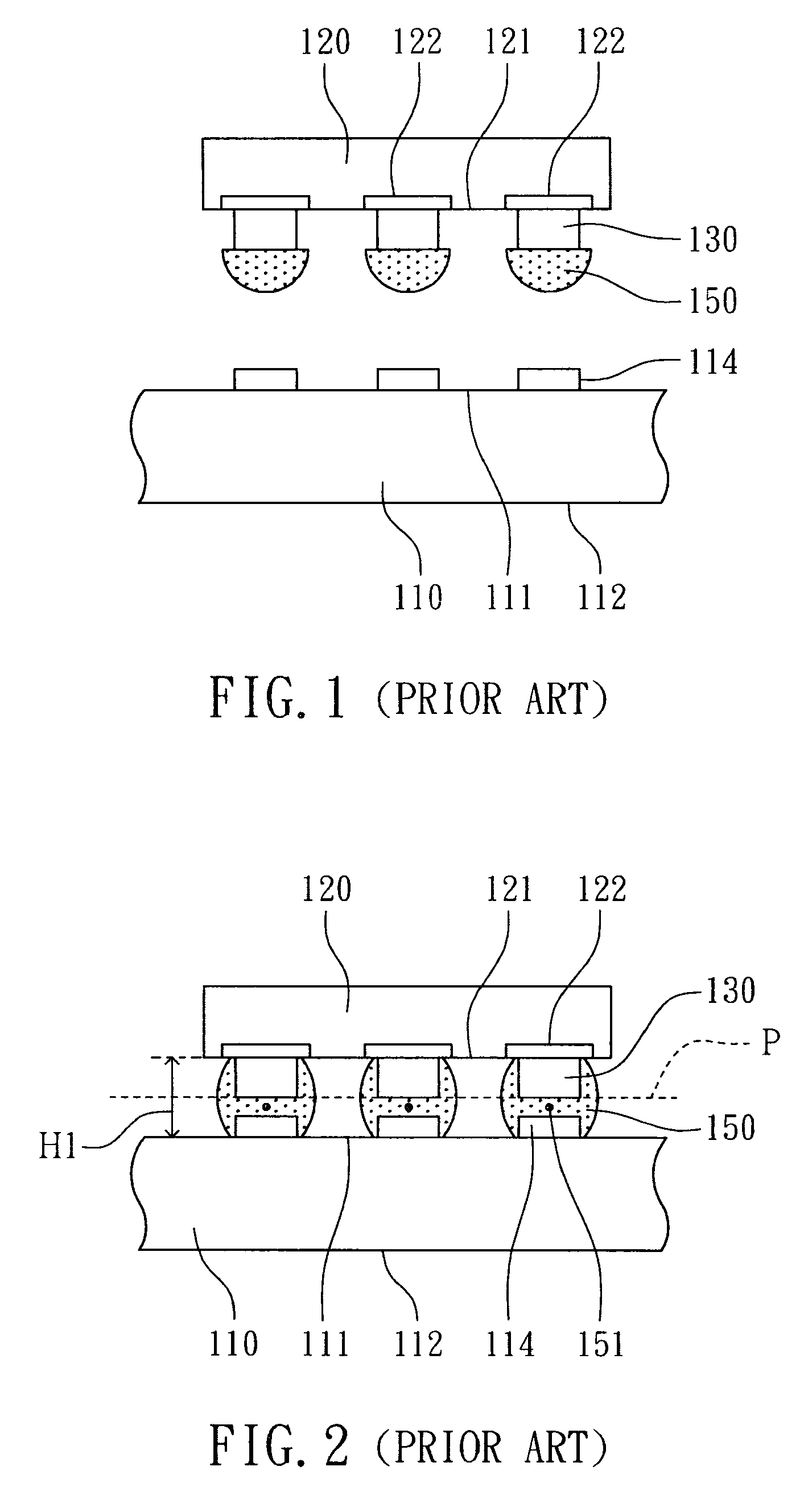

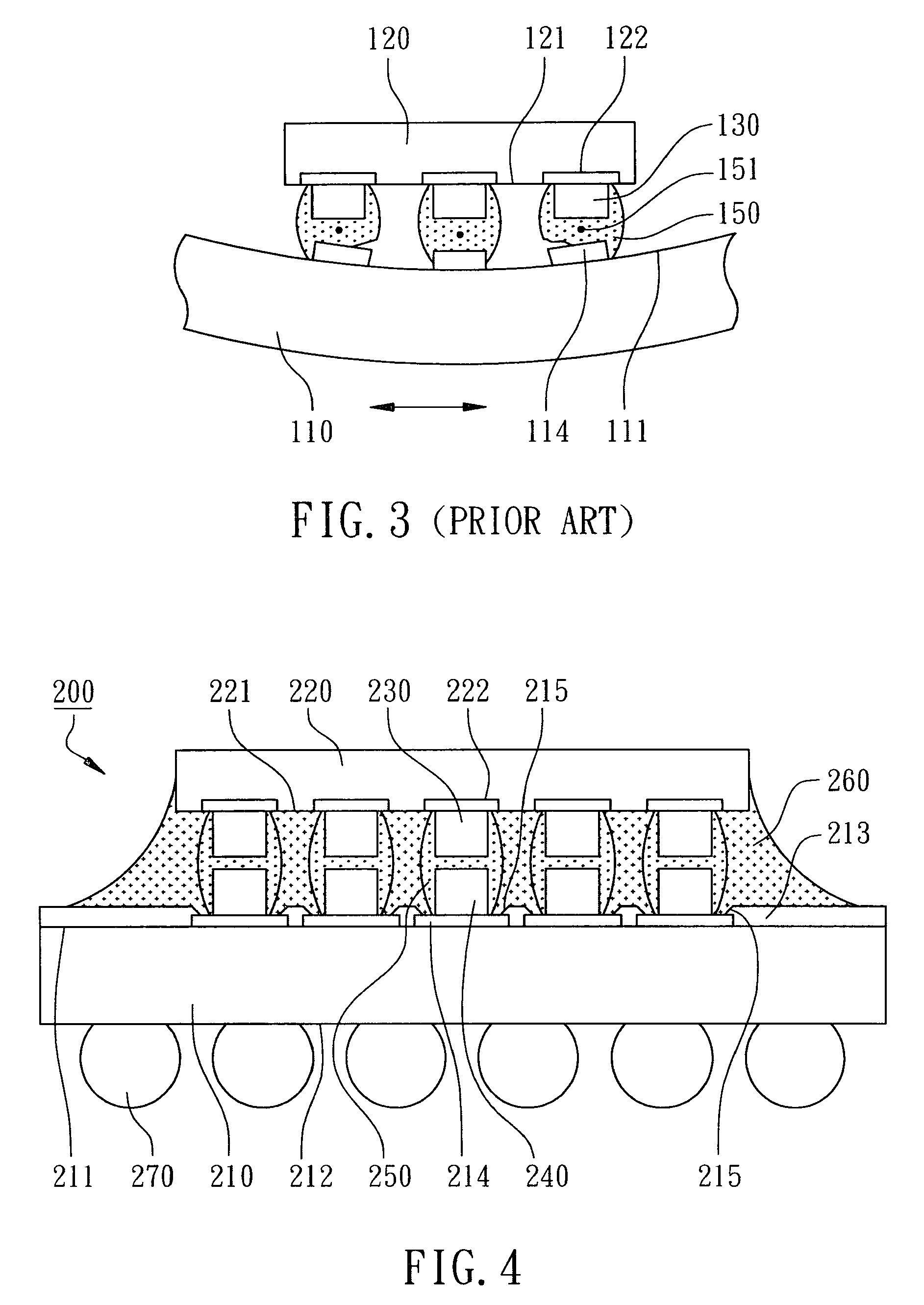

A thermally enhanced quad flat non-lead package of semiconductor comprises a chip a plurality of leads, and a molding compound. The chip has its active surface bonded to the top surface of the die pad, and the area of the die pad is smaller than that of the chip in order to expose the bonding pads on the active surface of the chip. The leads are disposed at the periphery of the die pad wherein the bottom surface of the lead has a stepped structure with a relatively thin portion to form a wire-bonding protruded zone. A plurality of bonding wires is used to electrically connect the wire-bonding protruded zone of the leads to the bonding pads of the chip. The molding compound encapsulates the chip, bonding wires, the die pad, and a portion of the surface of the leads, but exposes the bottom surface of the die pad. In this way, the encapsulating process makes the side surface of the lead, and the portion excluding the wire-bonding protruded zone of the bottom surface of the lead exposed in order to make the lead become the external connecting points of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

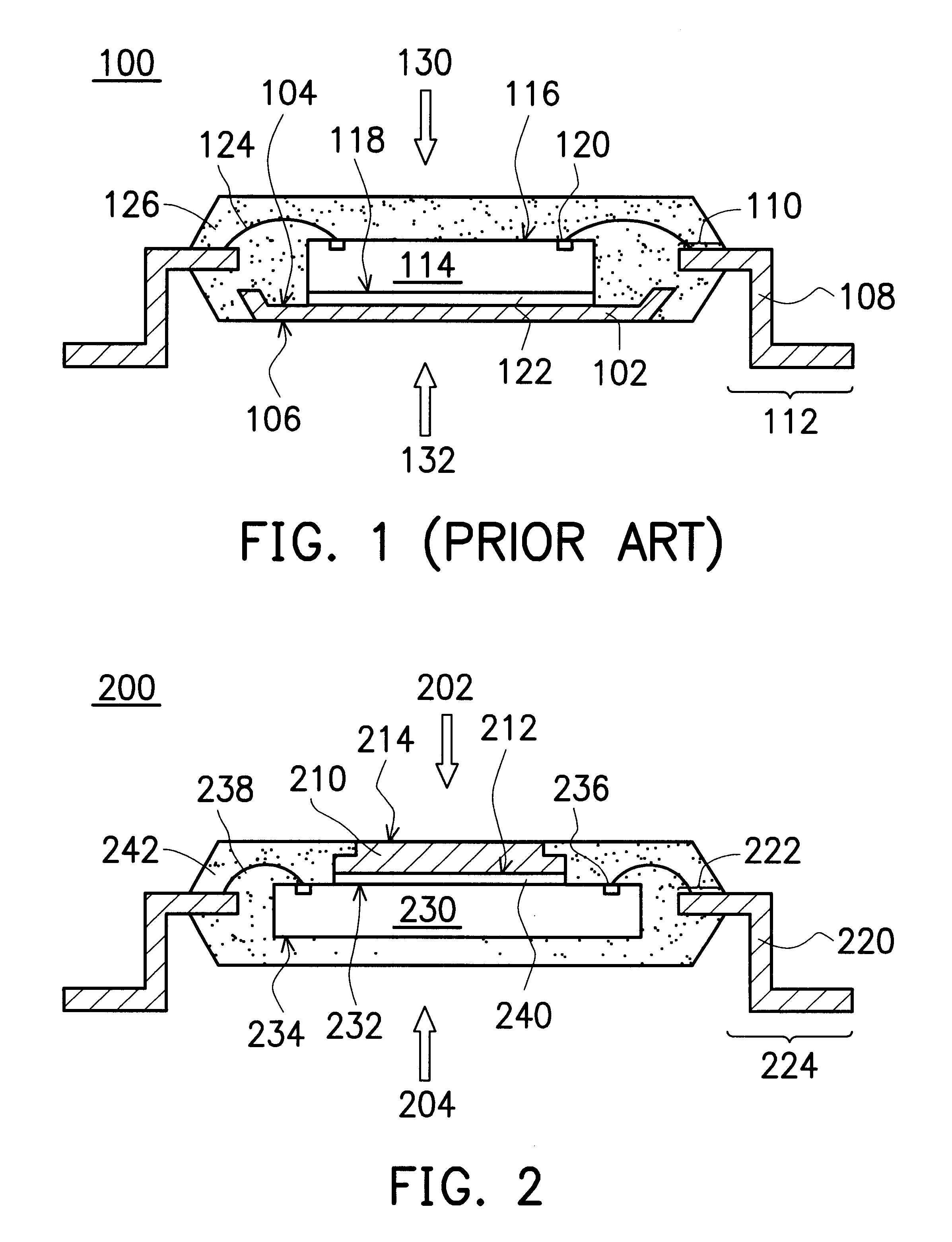

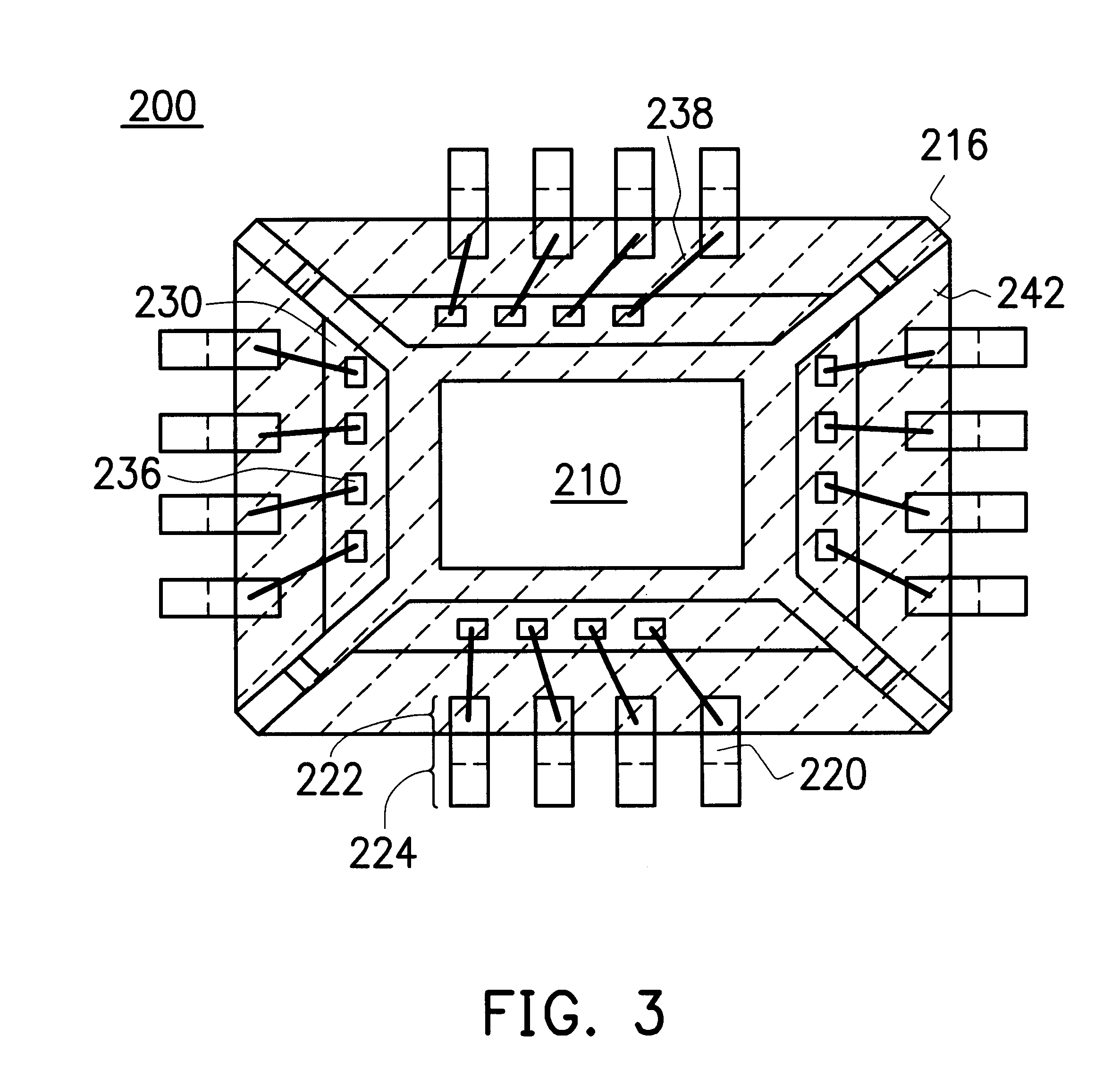

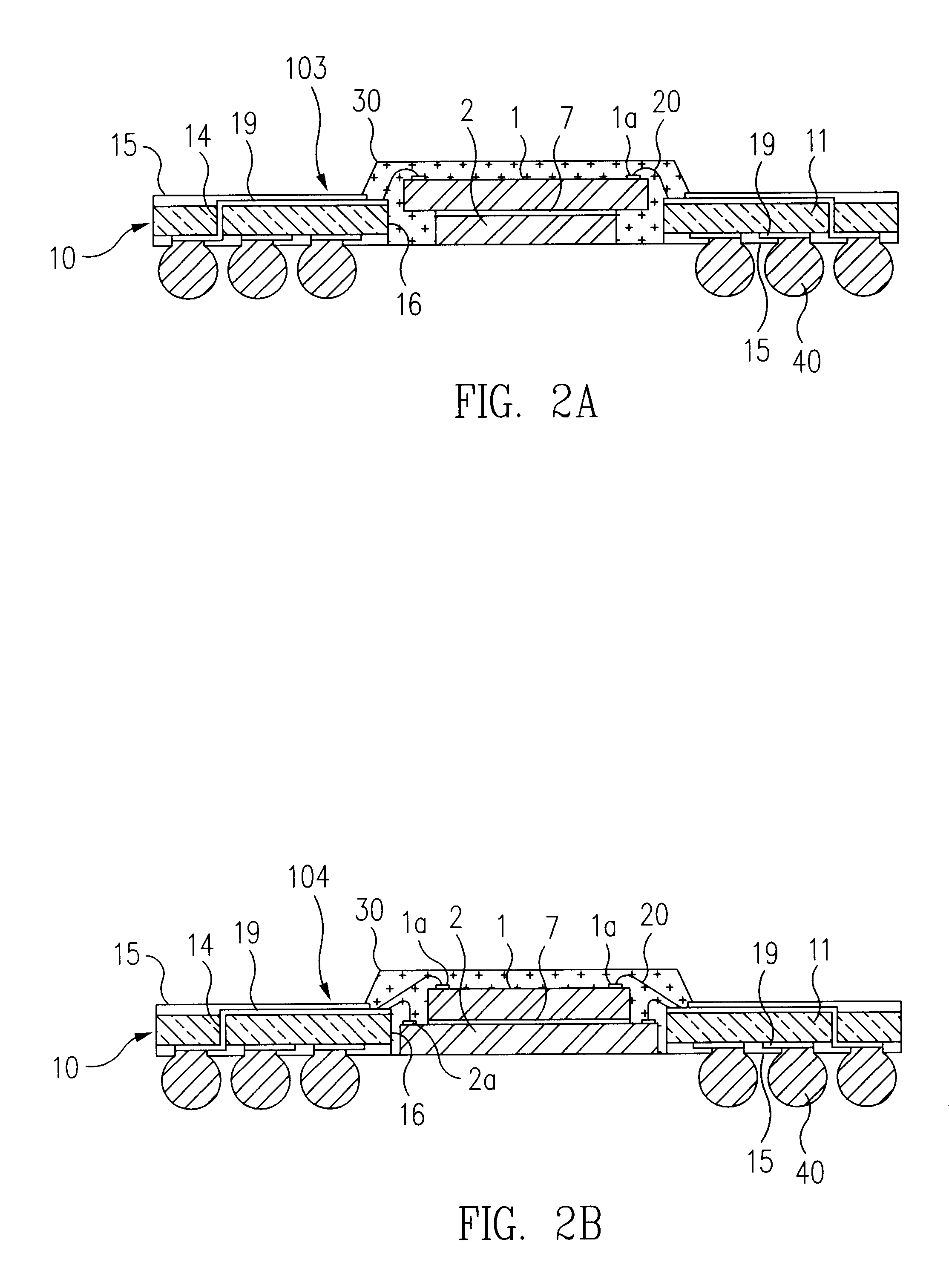

Quad flat non-lead package of semiconductor

InactiveUS6414385B1Semiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor package

A Quad Flat Non-Lead package of semiconductor comprises a chip, a plurality of leads, and a molding compound. The chip has its active surface bonded to the die pad, and the area of the die pad is smaller than that of the chip in order to expose the bonding pad on the active surface of the chip. The leads are disposed at the periphery of the die pad. A plurality of bonding wires is used to electrically connect the top surface of the leads to the bonding pads. The molding compound encapsulates the chip, the die pad, the bonding wires, and a portion of the surface of the leads. In this way, the encapsulating process make the side surface of the lead, and the portion excluding the wire-bonding protruded zone of the bottom surface of the lead exposed in order to make the leads become the external connections of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

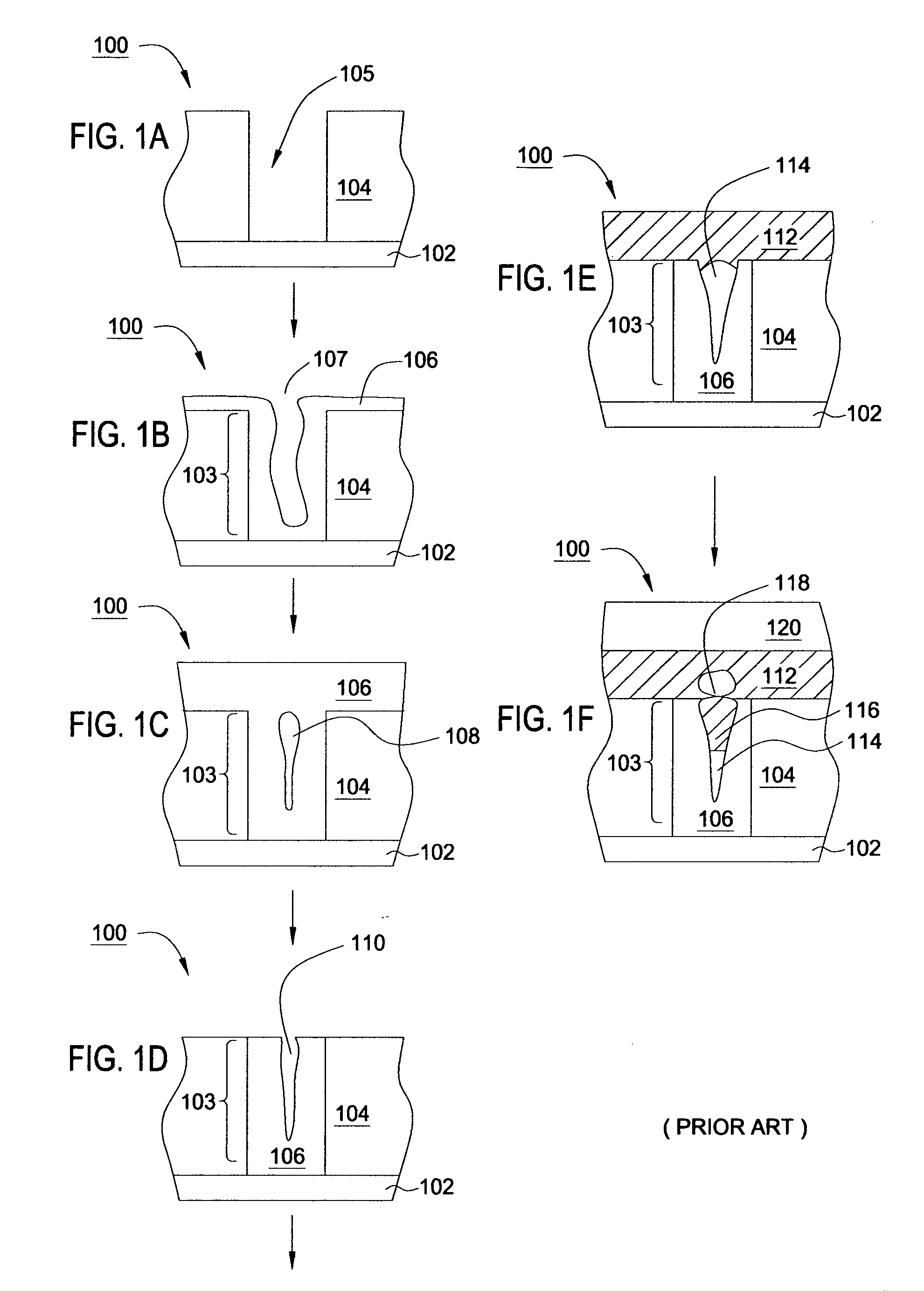

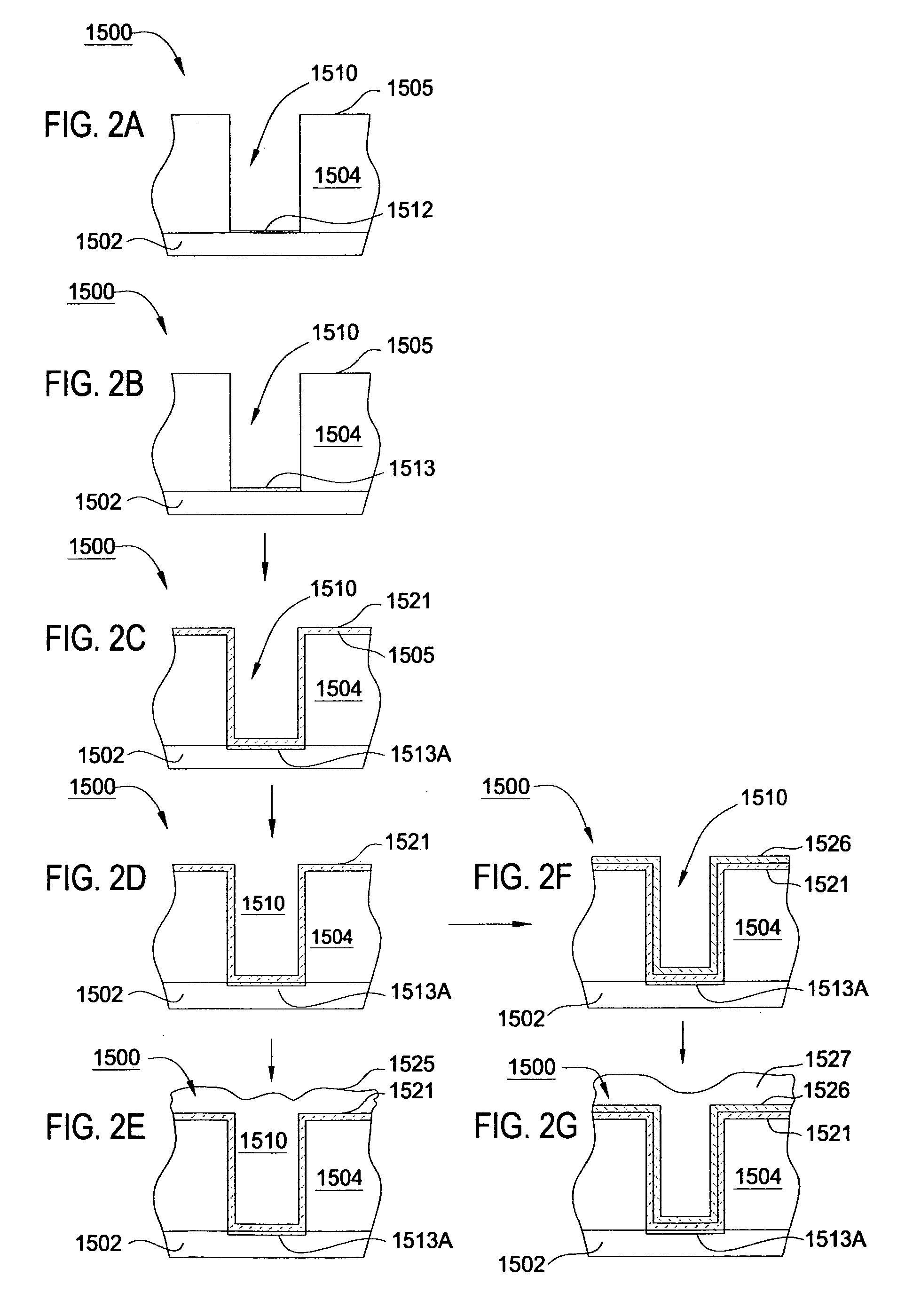

Contact metallization scheme using a barrier layer over a silicide layer

ActiveUS20060251800A1Material nanotechnologySemiconductor/solid-state device detailsDevice materialElectroless deposition

Embodiments of the invention generally provide methods of filling contact level features formed in a semiconductor device by depositing a barrier layer over the contact feature and then filing the layer using an PVD, CVD, ALD, electrochemical plating process (ECP) and / or electroless deposition processes. In one embodiment, the barrier layer has a catalytically active surface that will allow the electroless deposition of a metal on the barrier layer. In one aspect, the electrolessly deposited metal is copper or a copper alloy. In one aspect, the contact level feature is filled with a copper alloy by use of an electroless deposition process. In another aspect, a copper alloy is used to from a thin conductive copper layer that is used to subsequently fill features with a copper containing material by use of an ECP, PVD, CVD, and / or ALD deposition process. In one embodiment, a portion of the barrier layer is purposely allowed to react with traces of residual oxide at the silicon junction of the contact level feature to form a low resistance connection.

Owner:APPLIED MATERIALS INC

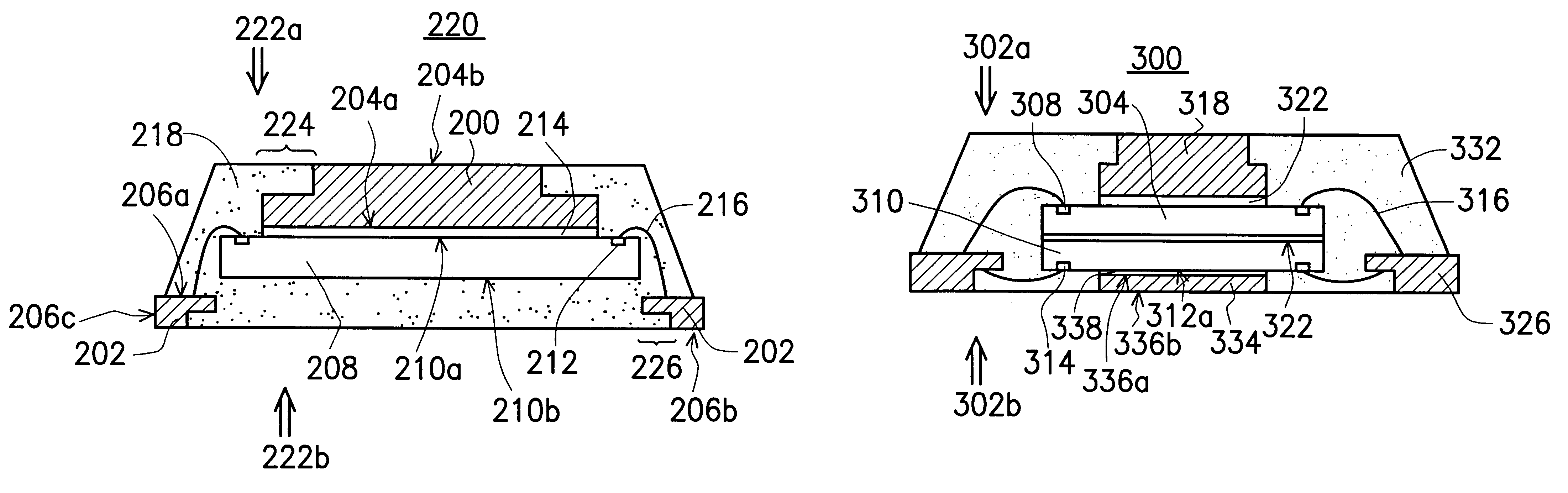

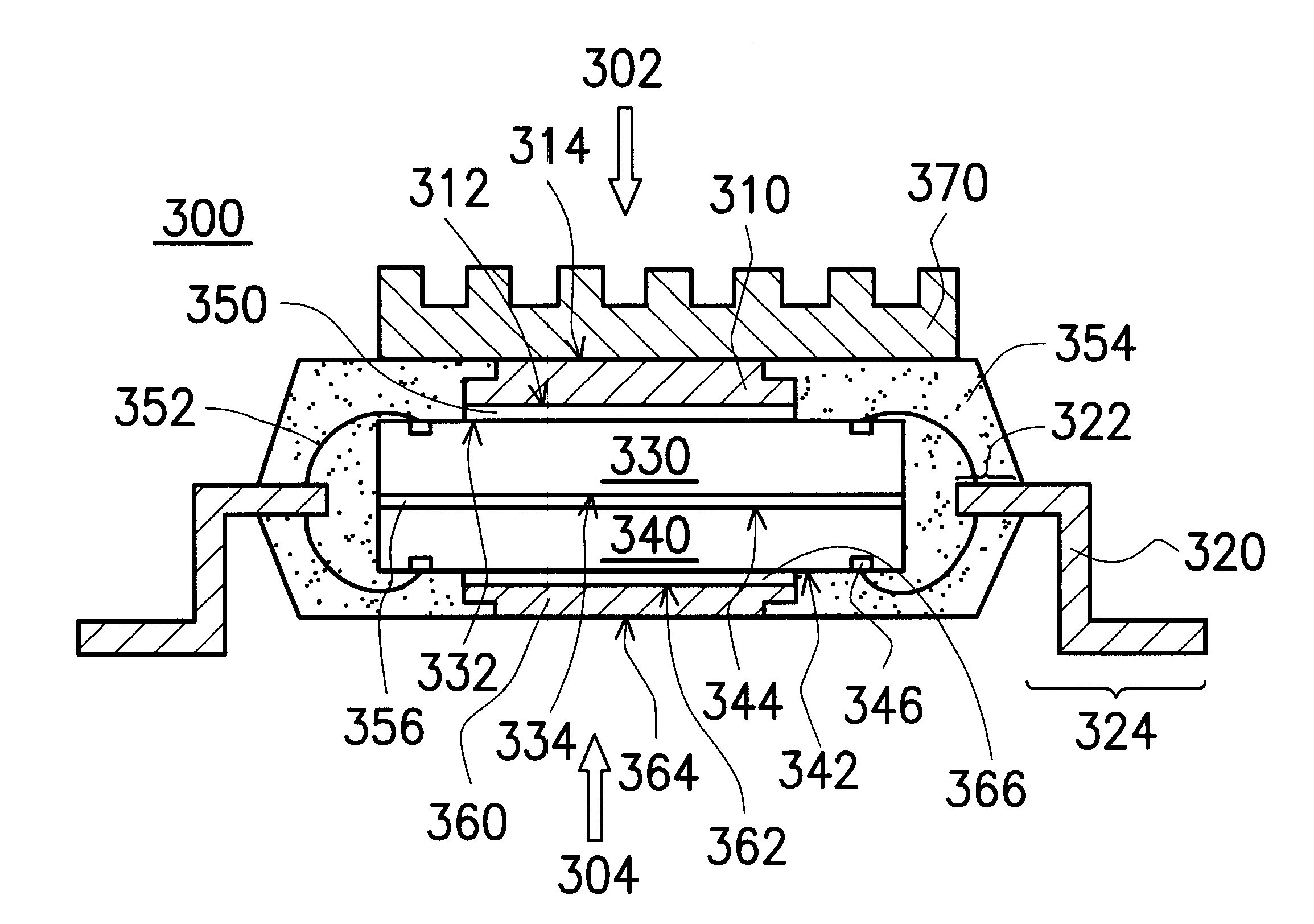

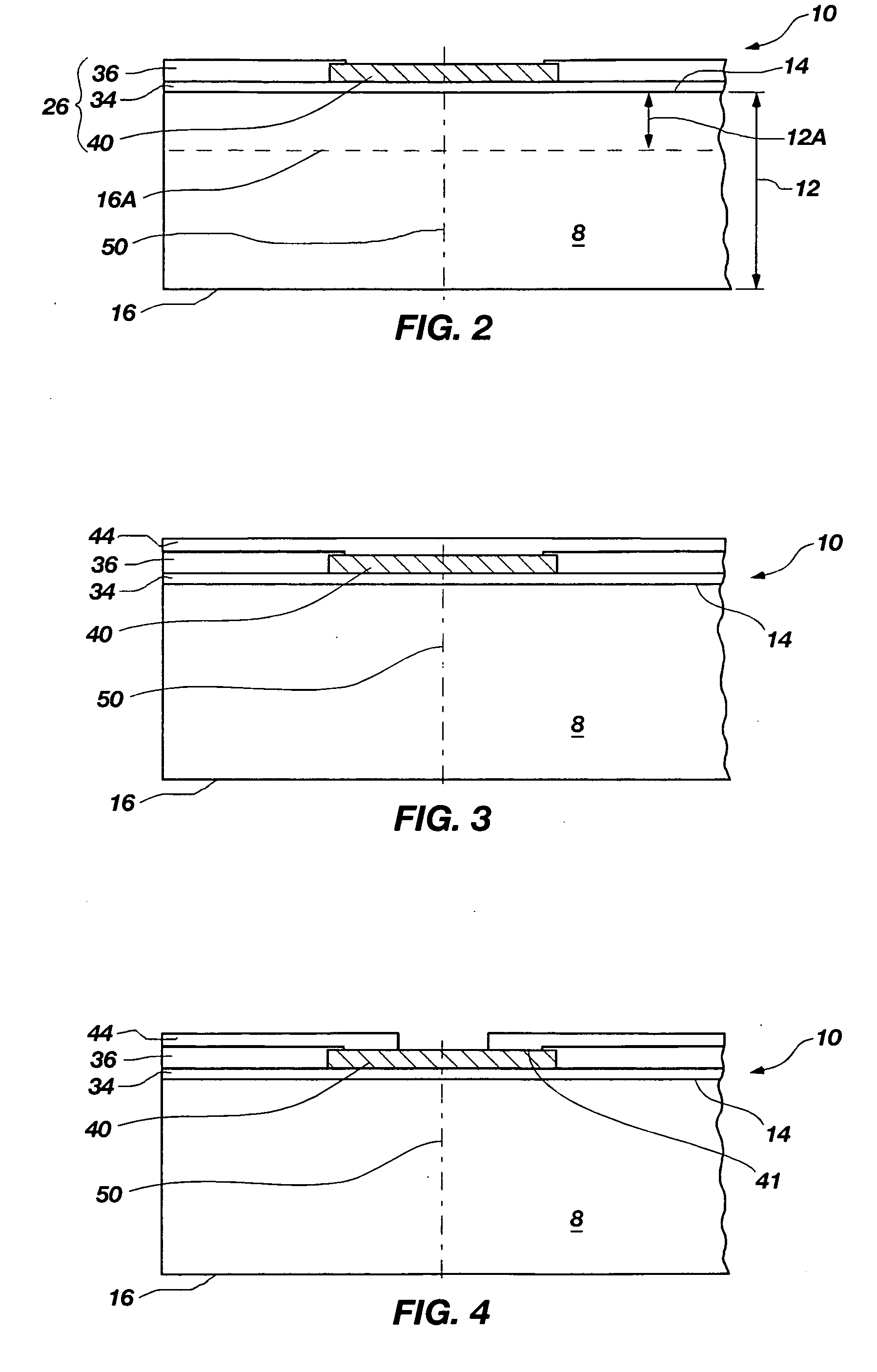

Semiconductor package having heat sink at the outer surface

InactiveUS6559525B2Easy to addImprove packaging efficiencySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageLead frame

A semiconductor package having heat sink at the outer surface is constructed on a lead frame. The package comprises a chip, a die pad, a plurality of leads, a plurality of bonding wires, and a molding compound. The die pad has a first surface and a second surface, and the chip has its active surface bonded to the first surface of the die pad. The area of the die pad is smaller than the area of the chip in order to expose the bonding pads on the active surface of the chip. The leads having an inner lead portions and an outer lead portions are disposed at the periphery of the die pad, and the inner lead portions are electrically connected to the bonding pads by a plurality of bonding wires. The molding compound encapsulates the chip, the die pad, the inner lead portions of the leads, and the bonding wires. The second surface of the die pad is exposed on the top surface of the package structure while the outer lead portion of the leads is exposed at the side edge of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

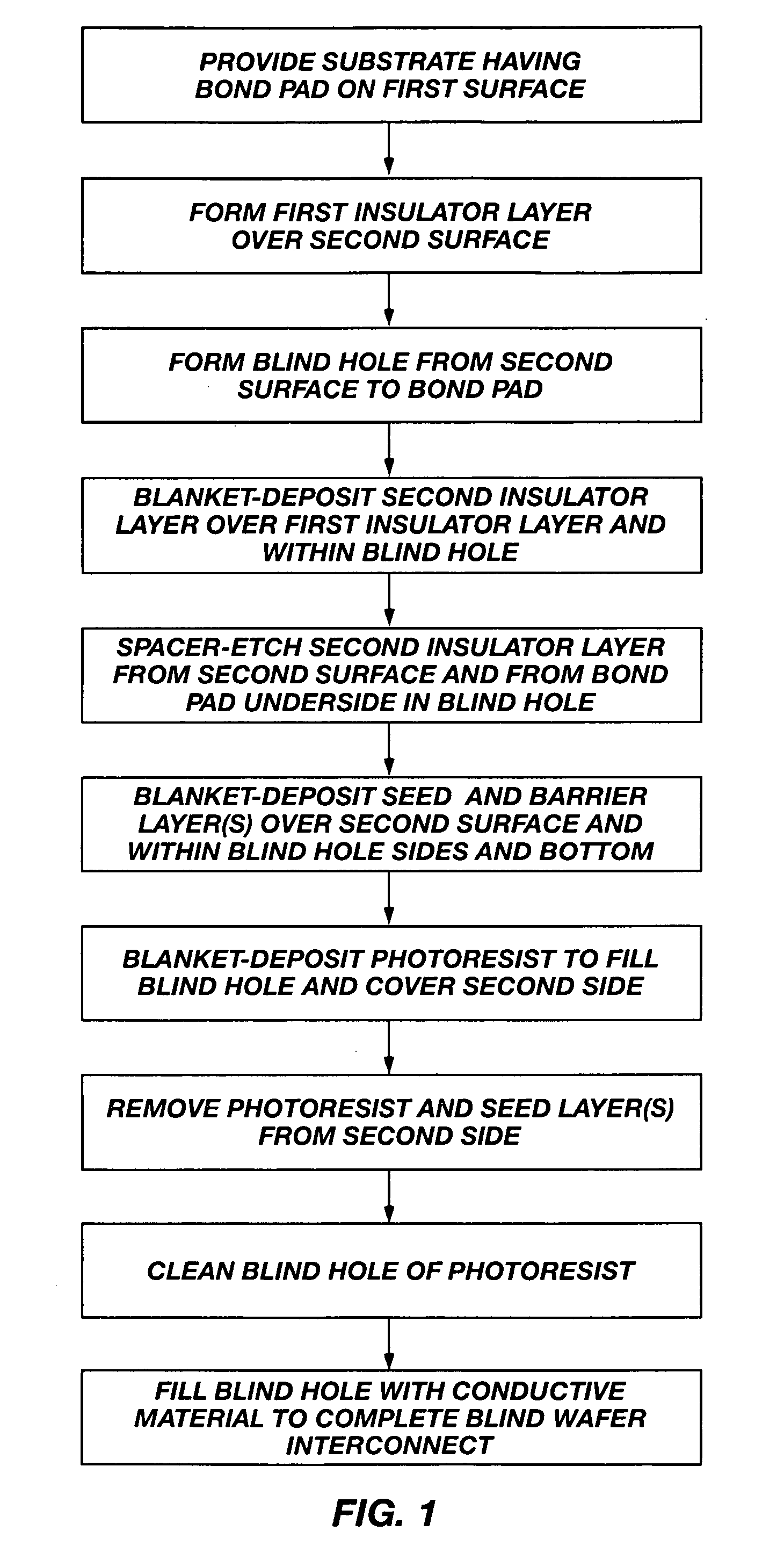

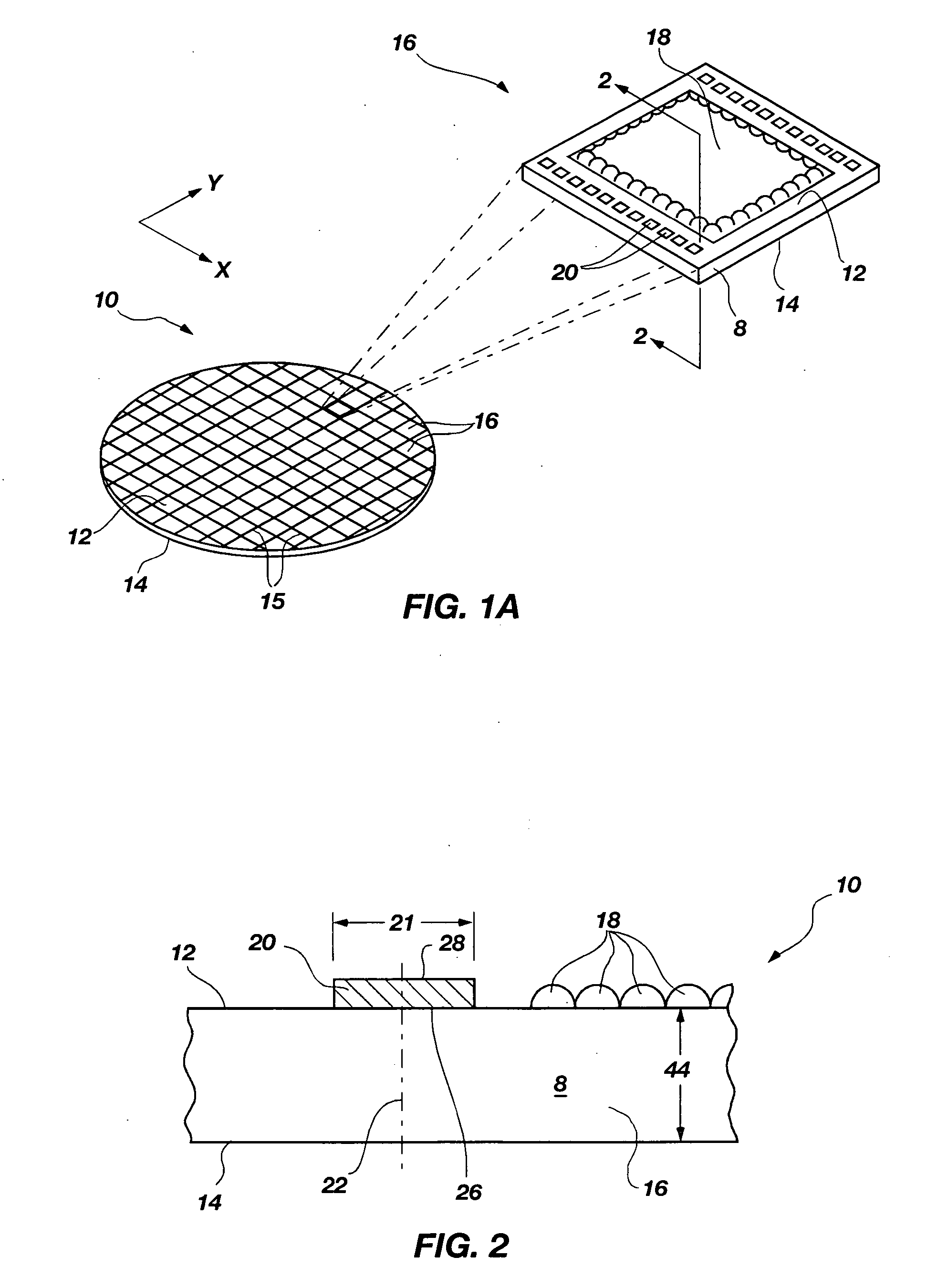

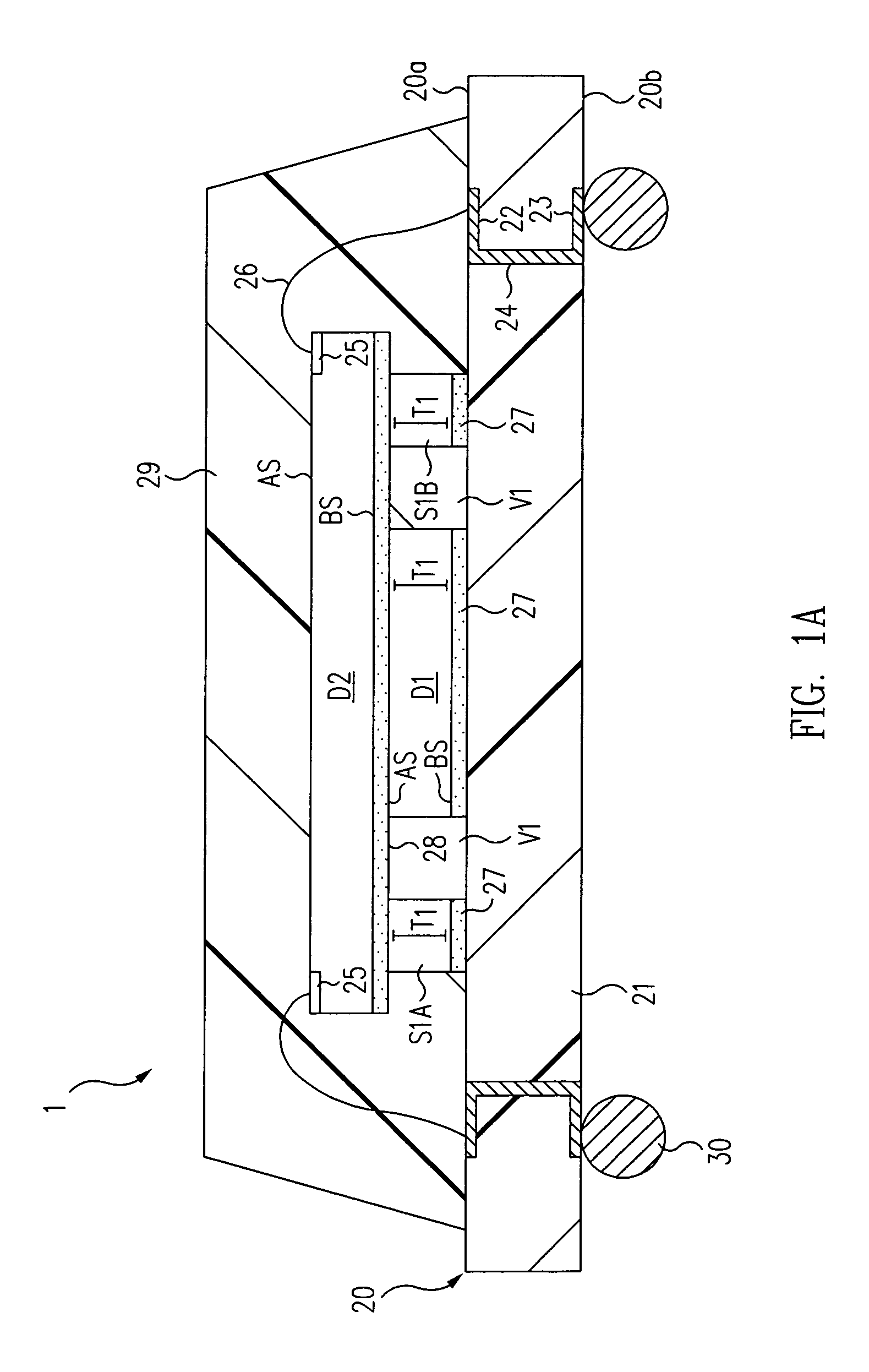

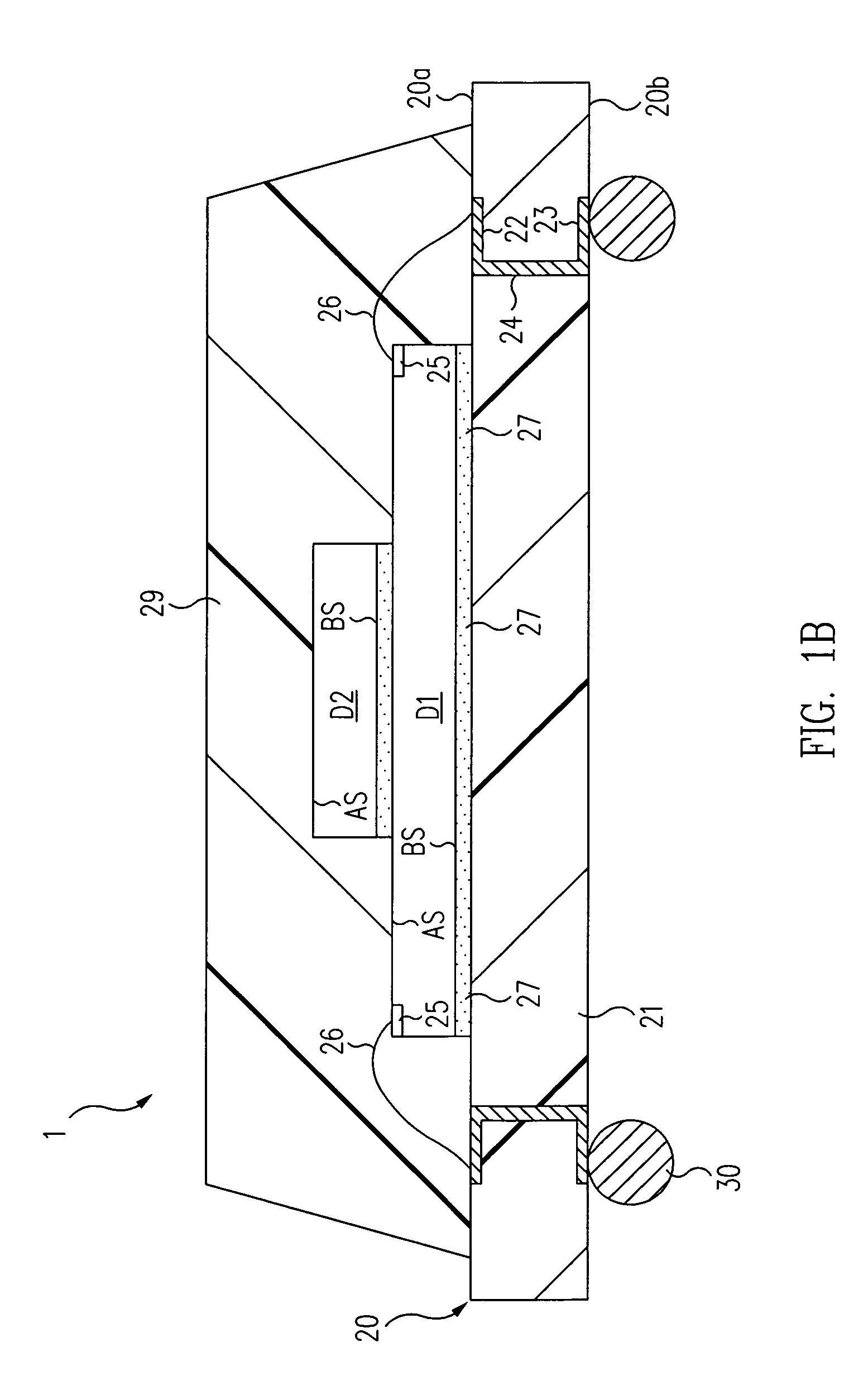

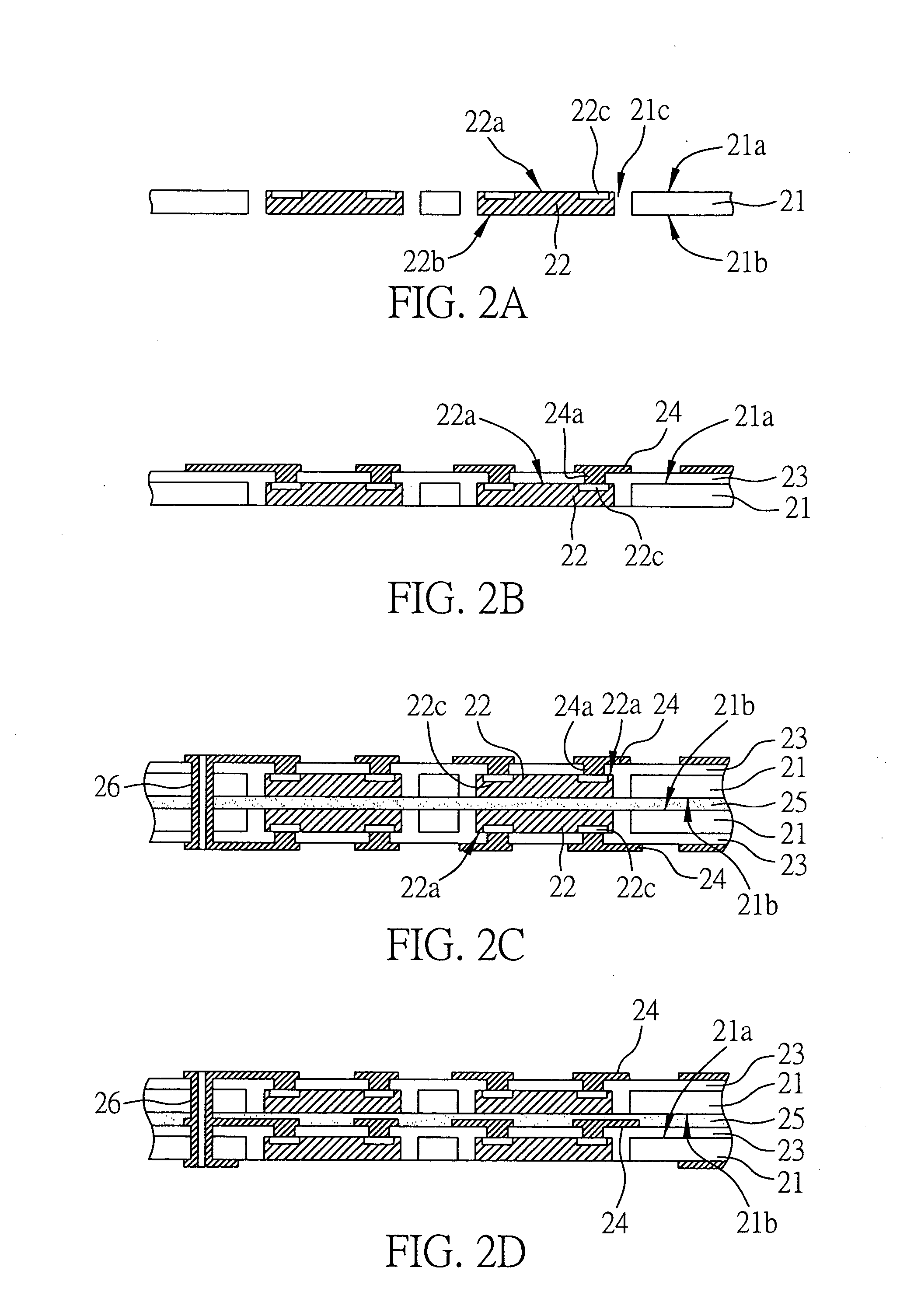

Methods of forming blind wafer interconnects, and related structures and assemblies

InactiveUS20070045780A1Reduce expensesReduce processing timeSemiconductor/solid-state device detailsSolid-state devicesResistSolder ball

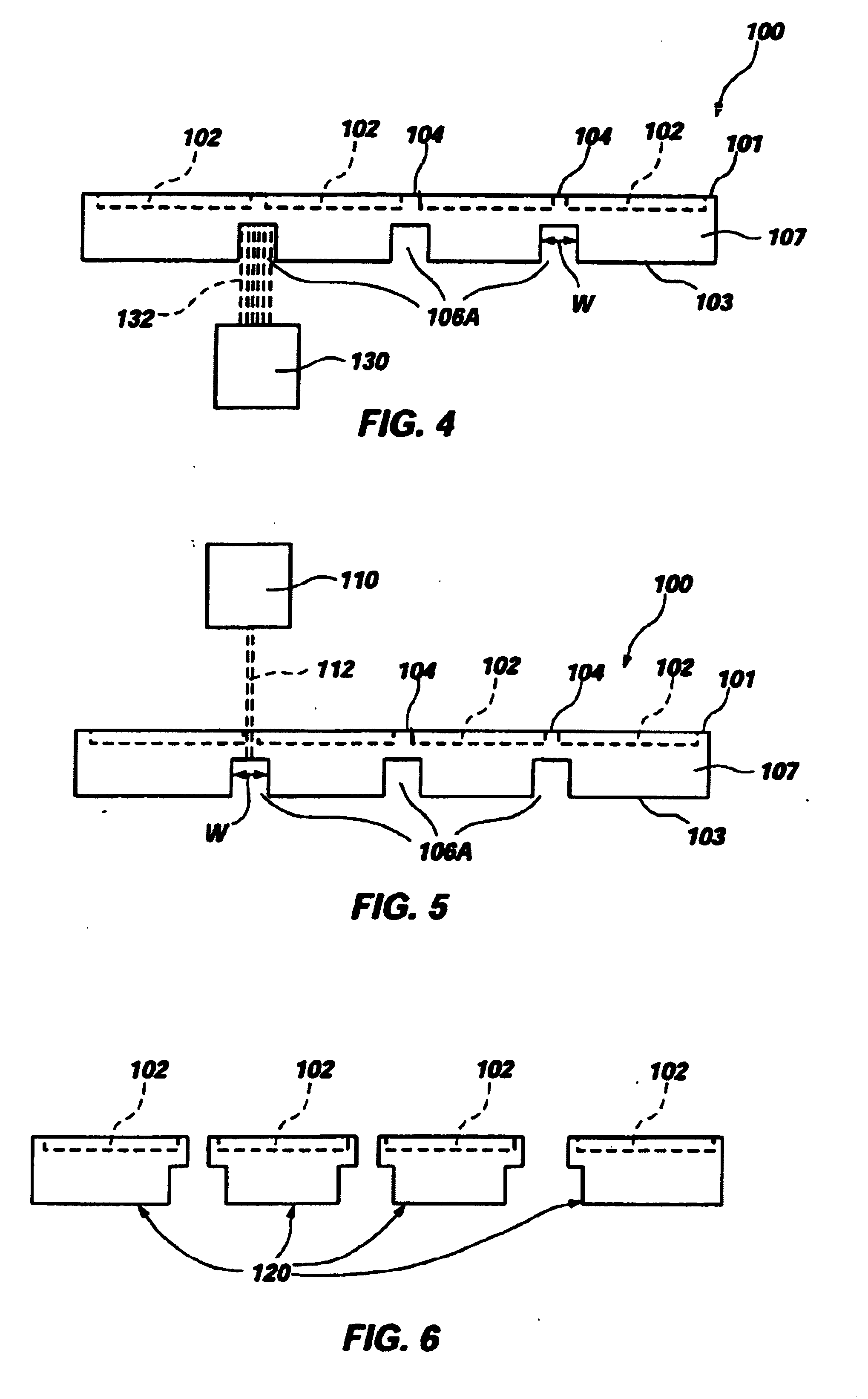

Methods for forming blind wafer interconnects (BWIs) from the back side of a previously thinned substrate structure such as a semiconductor wafer to the underside of a bond pad on its active surface includes the formation of a blind hole from the back side, application of a passivating layer therein, anisotropically etching to remove passivation material from the blind hole bottom, blanket-depositing at least one conductive layer within the blind hole and over the back side, blanket-depositing a resist in the blind hole and over the back side, planarizing the back side to remove resist and the at least one conductive layer, removing resist from the blind hole, and filling the blind hole with solder or other conductive material or a dielectric material. Variations in the methods include formation of a conductive pad adjacent the back side surface, disposition of a solder ball or other conductive structure on the BWI, or forming an end thereof in the form of an extended slug protruding from the back side (for ball-less attachment) as the outer terminus of the BWI.

Owner:ROUND ROCK RES LLC

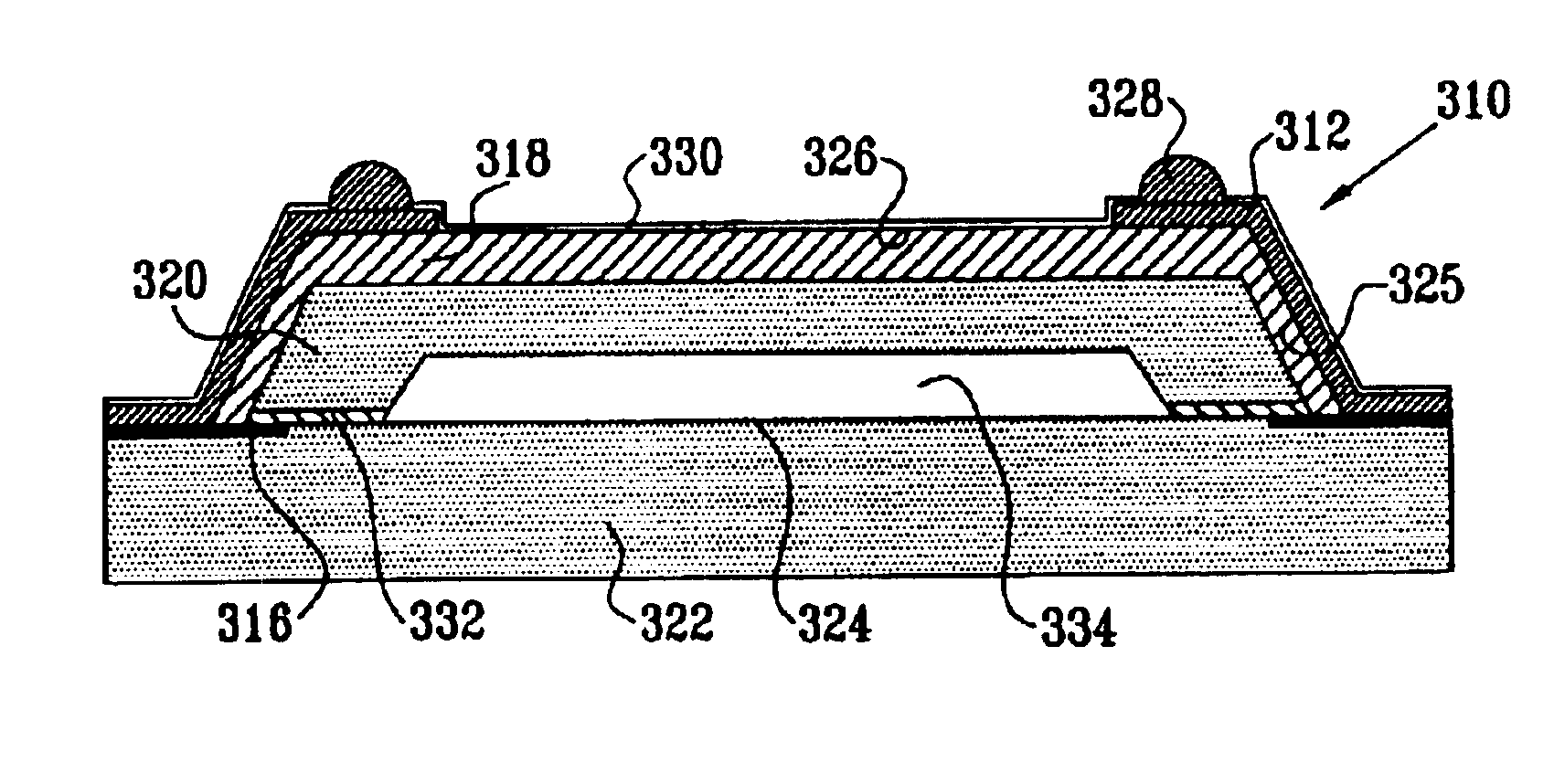

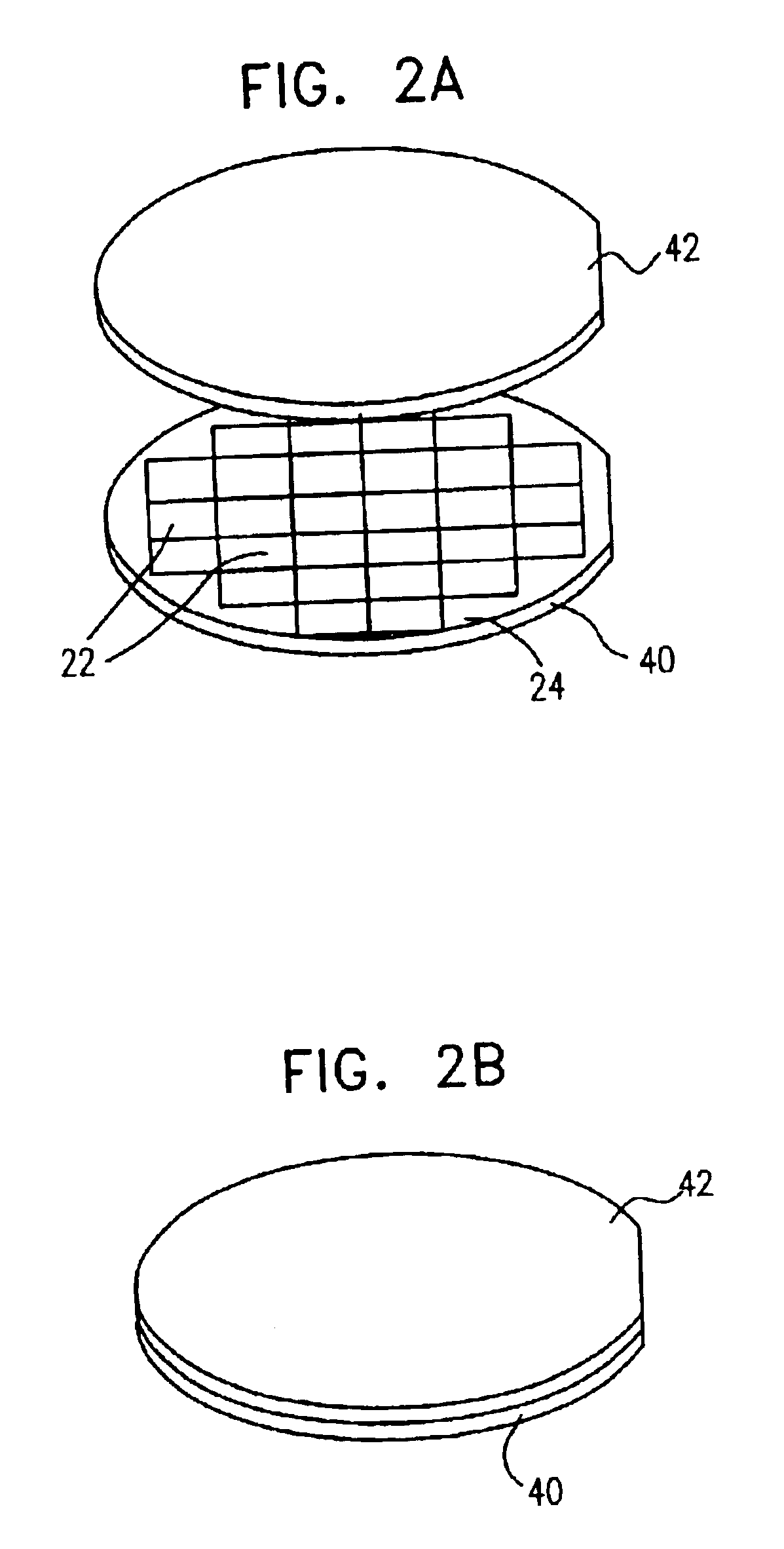

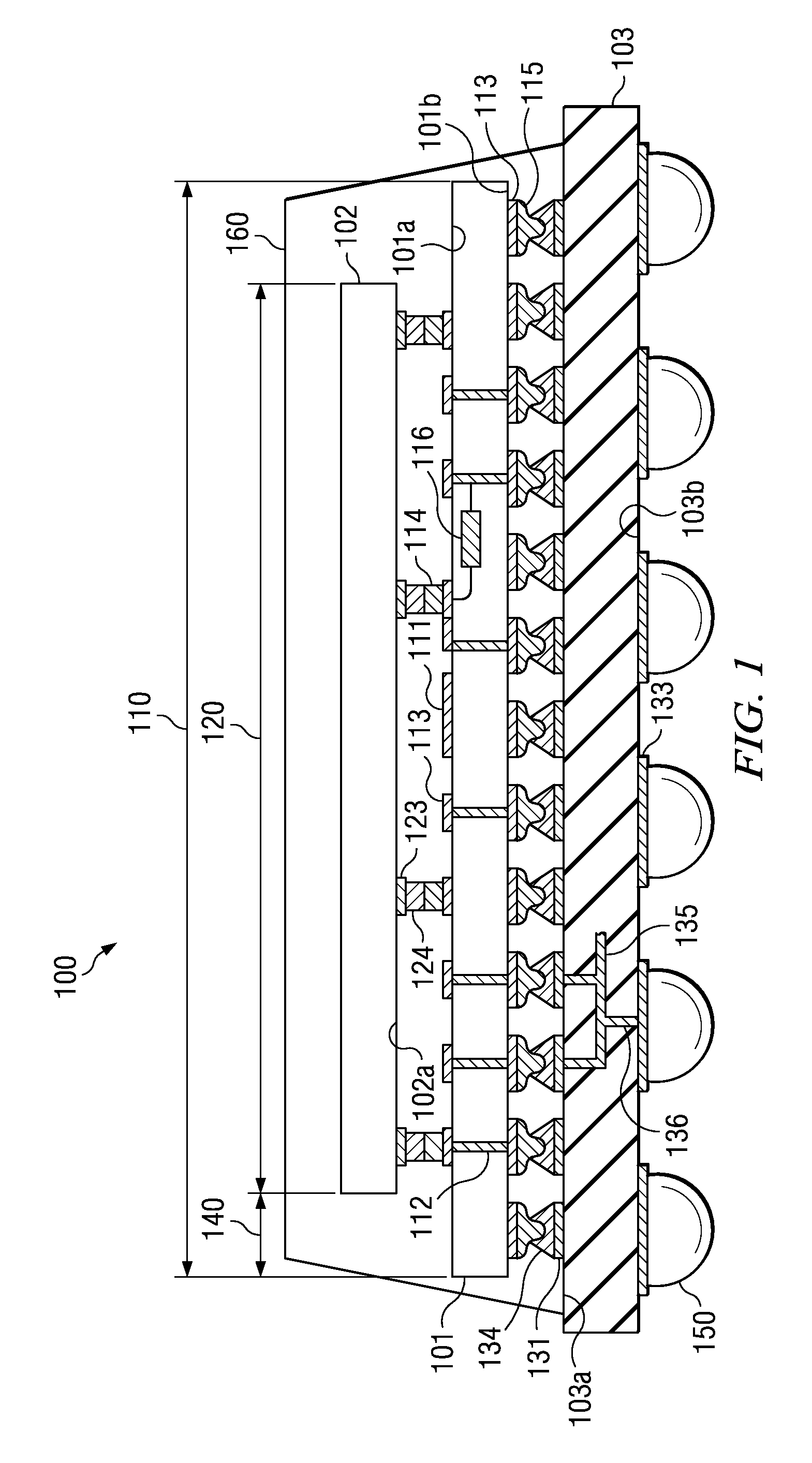

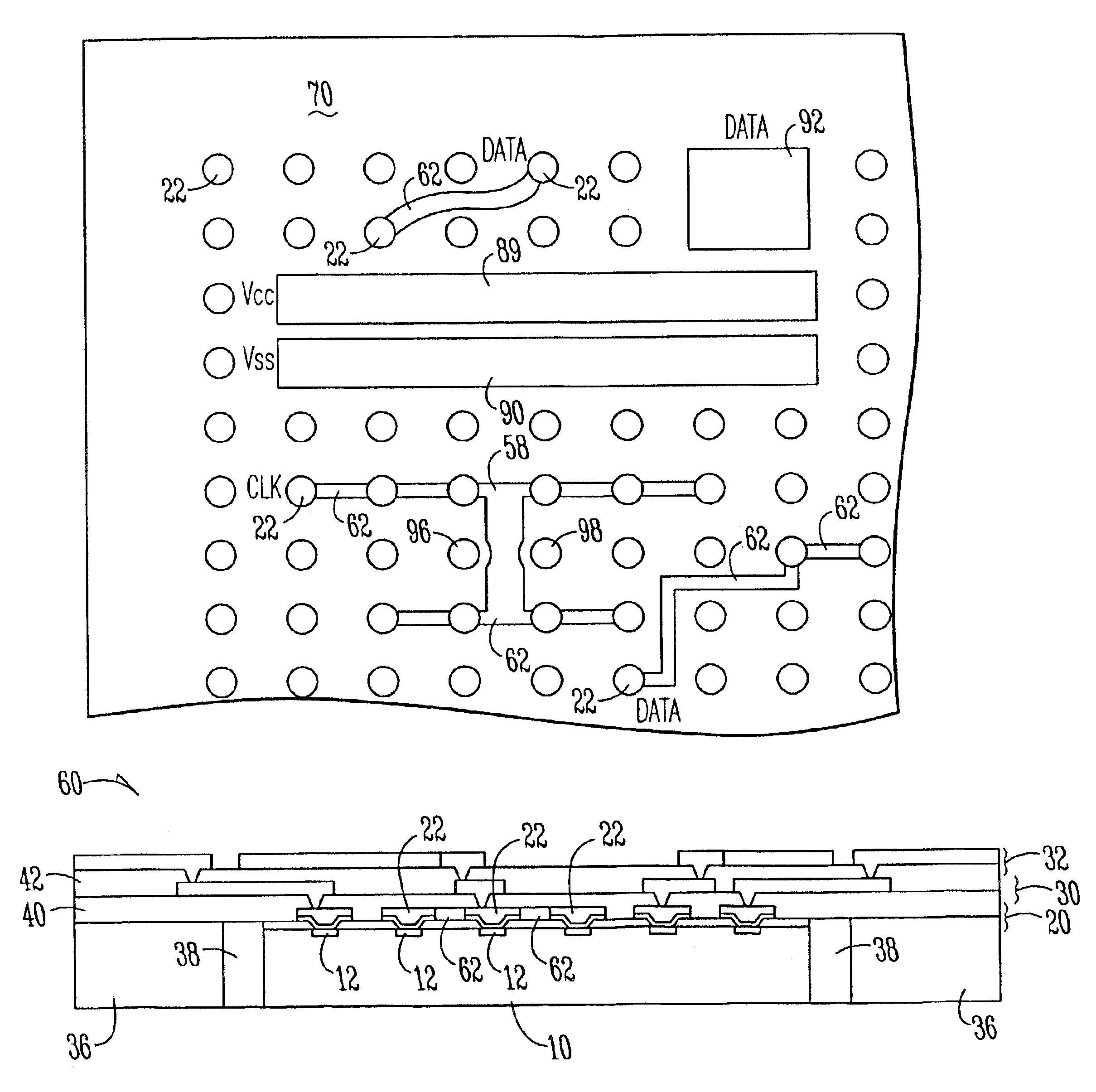

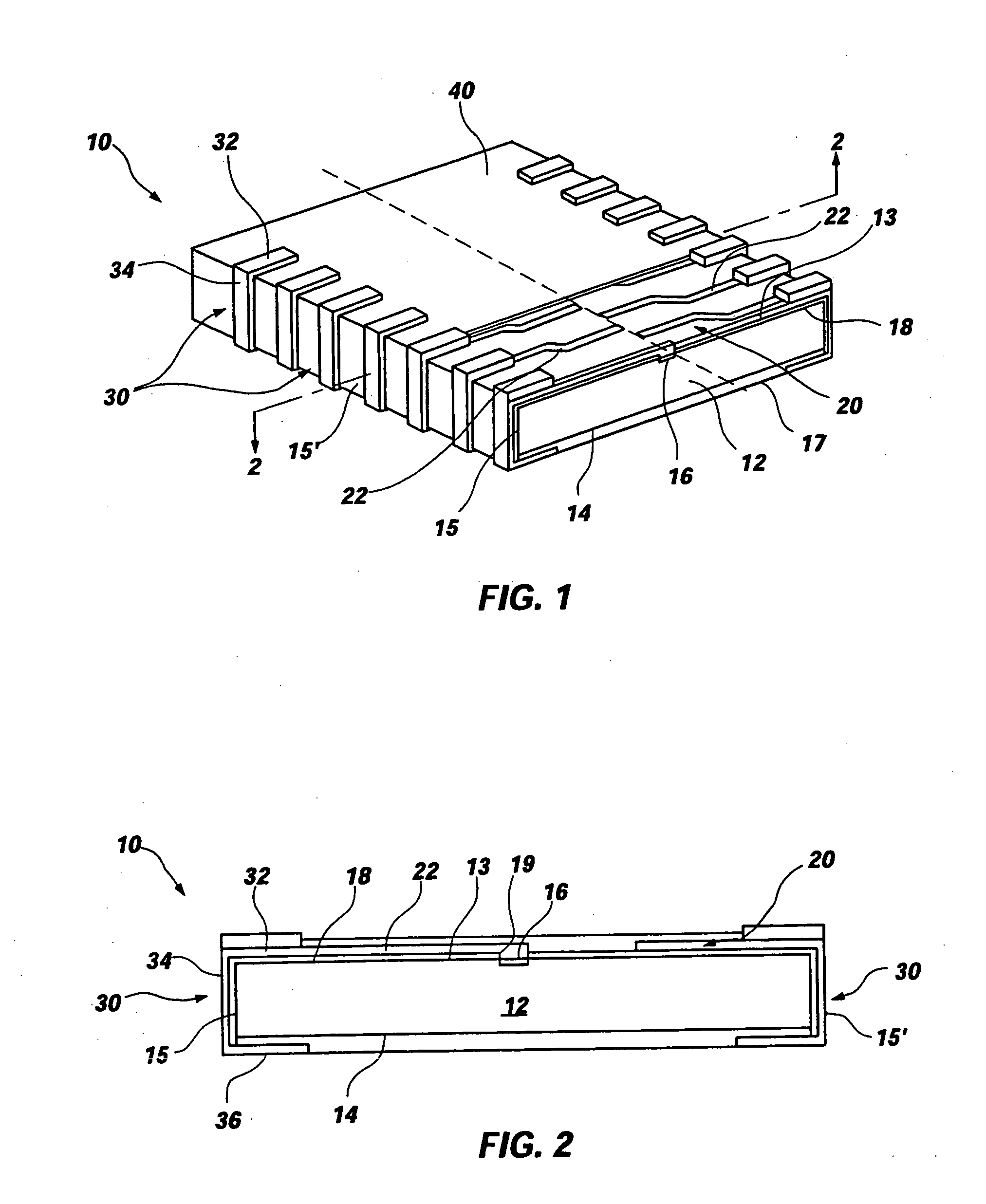

Methods and apparatus for packaging integrated circuit devices

InactiveUS6972480B2Semiconductor/solid-state device detailsSolid-state devicesEdge surfaceEngineering

An integrally packaged integrated circuit device including an integrated circuit die including a crystalline substrate having first and second generally planar surfaces and edge surfaces and an active surface formed on the first generally planar surface, at least one chip scale packaging layer formed over the active surface and at least one electrical contact formed over the at least one chip scale packaging layer, the at least one electrical contact being connected to circuitry on the active surface by at least one pad formed on the first generally planar surface.

Owner:INVENSAS CORP +1

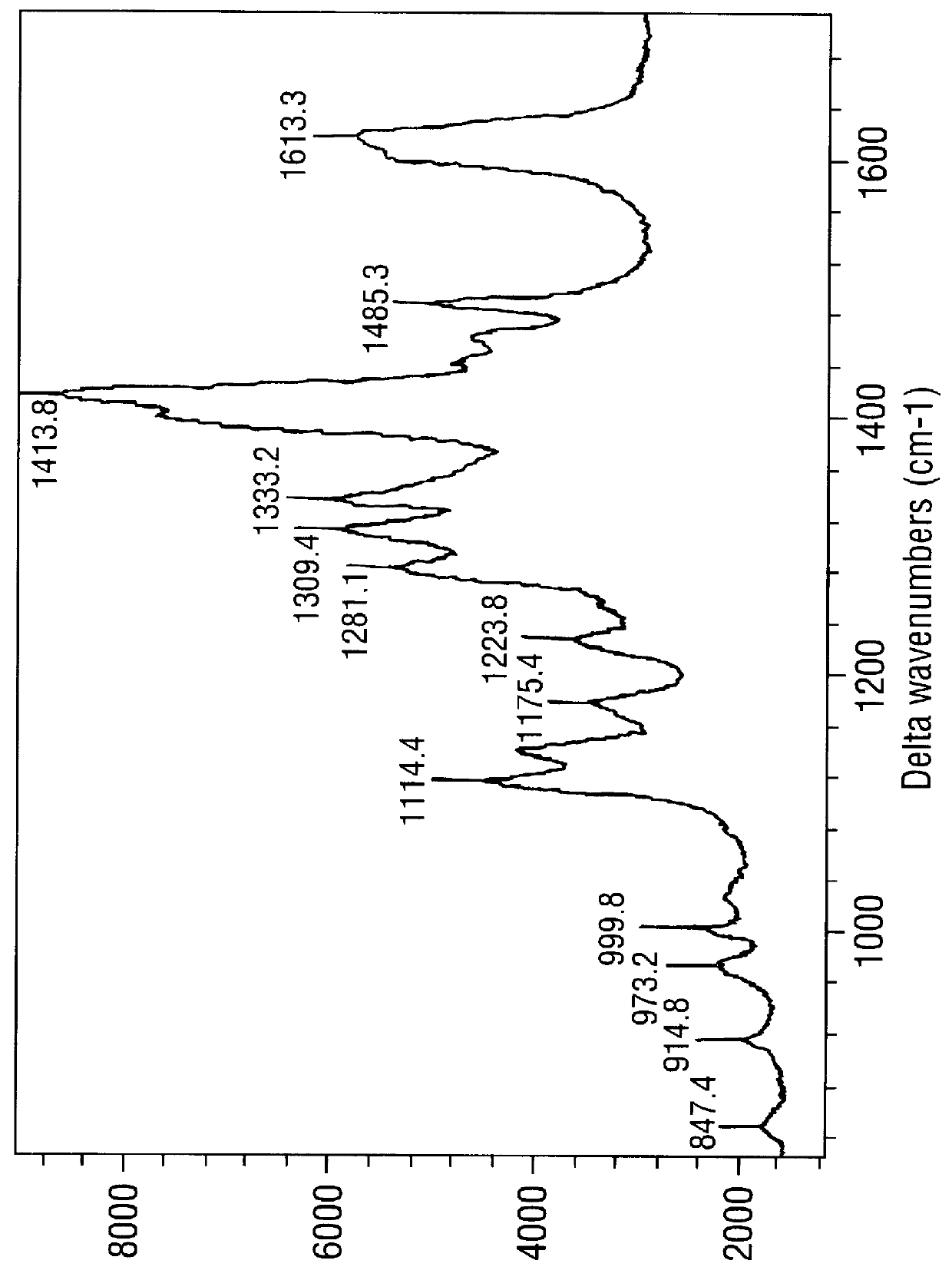

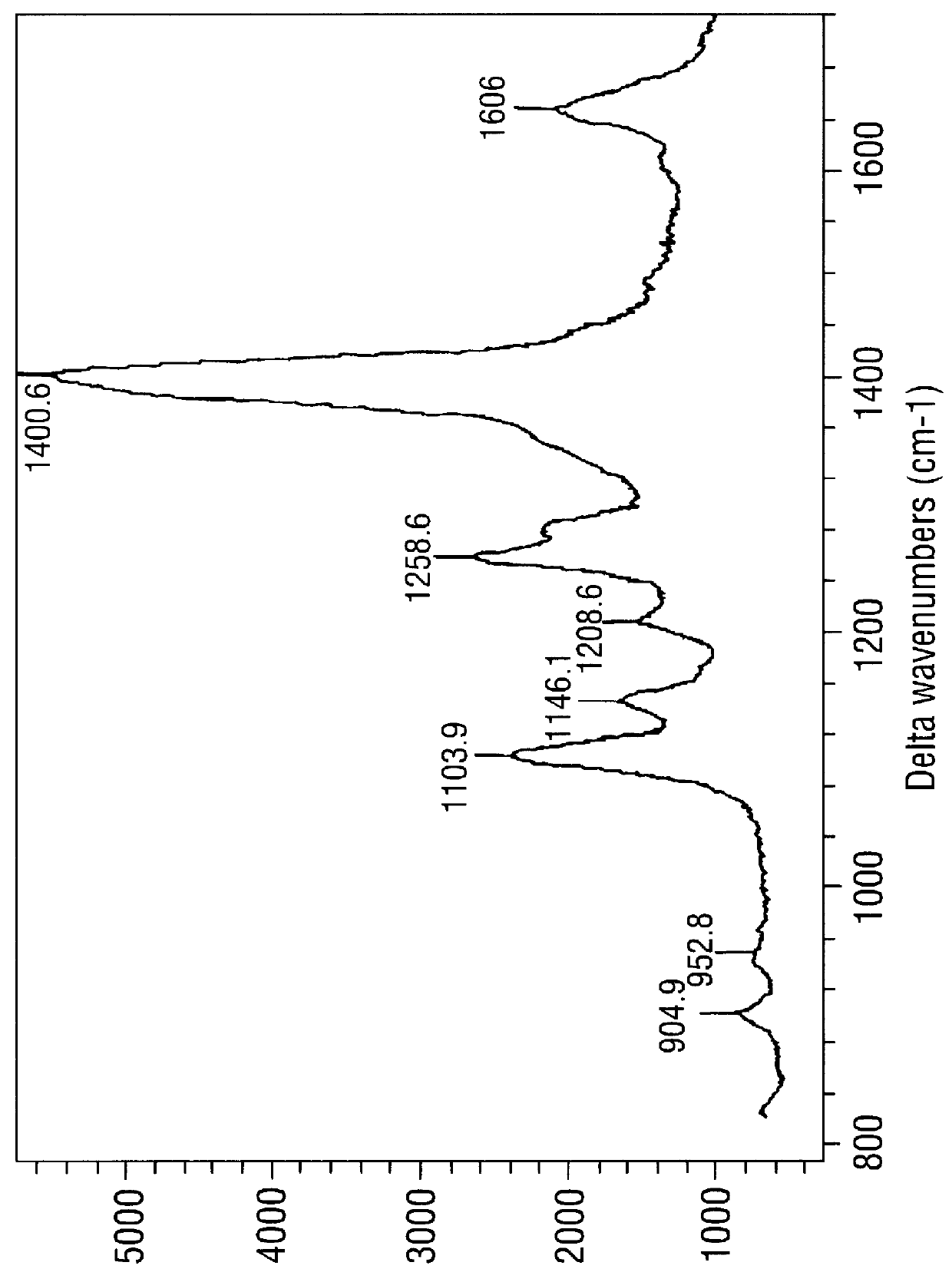

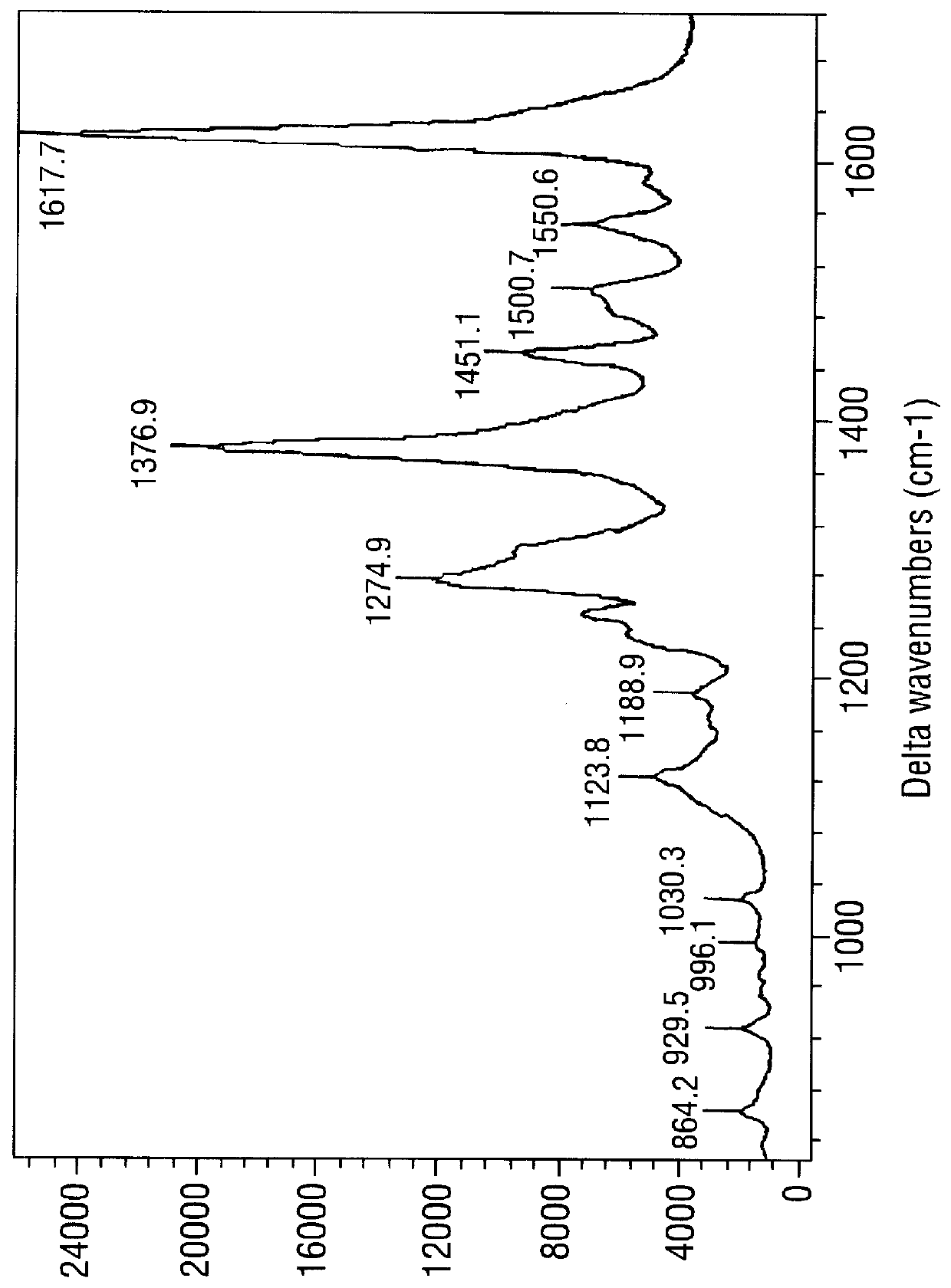

Detection of nucleic acids and nucleic acid units

InactiveUS6127120AReduce riskReducing operator timeSugar derivativesMicrobiological testing/measurementNucleotideBiology

PCT No. PCT / GB96 / 01830 Sec. 371 Date Apr. 21, 1998 Sec. 102(e) Date Apr. 21, 1998 PCT Filed Jul. 25, 1996 PCT Pub. No. WO97 / 05280 PCT Pub. Date Feb. 13, 1997The invention relates to the detection of target nucleic acids or nucleic acid units in a sample, by obtaining a SER(R)S spectrum for a SER(R)S-active complex containing, or derived directly from, the target. The complex includes at least a SER(R)S-active label, and optionally a target binding species containing a nucleic acid or nucleic acid unit. In this detection method, the concentration of the target present in the SER(R)S-active complex, or of the nucleic acid or unit contained in the target binding species in the SER(R)S-active complex, is no higher than 10-10 moles per liter. Additionally or alternatively, one or more of the following features may be used with the method: i) the introduction of a polyamine; ii) modification of the target, and / or of the nucleic acid or nucleic acid unit contained in the target binding species, in a manner that promotes or facilitates its chemi-sorption onto a SER(R)S-active surface; iii) inclusion of a chemi-sorptive functional group in the SER(R)S-active label. The invention also provides SER(R)S-active complexes for use in such a method, a kit for use in carrying out the method or preparing the complexes and a method for sequencing a nucleic acid which comprises the use of the detection method to detect at least one target nucleotide or sequence of nucleotides within the acid.

Owner:RENISHAW DIAGNOSTICS

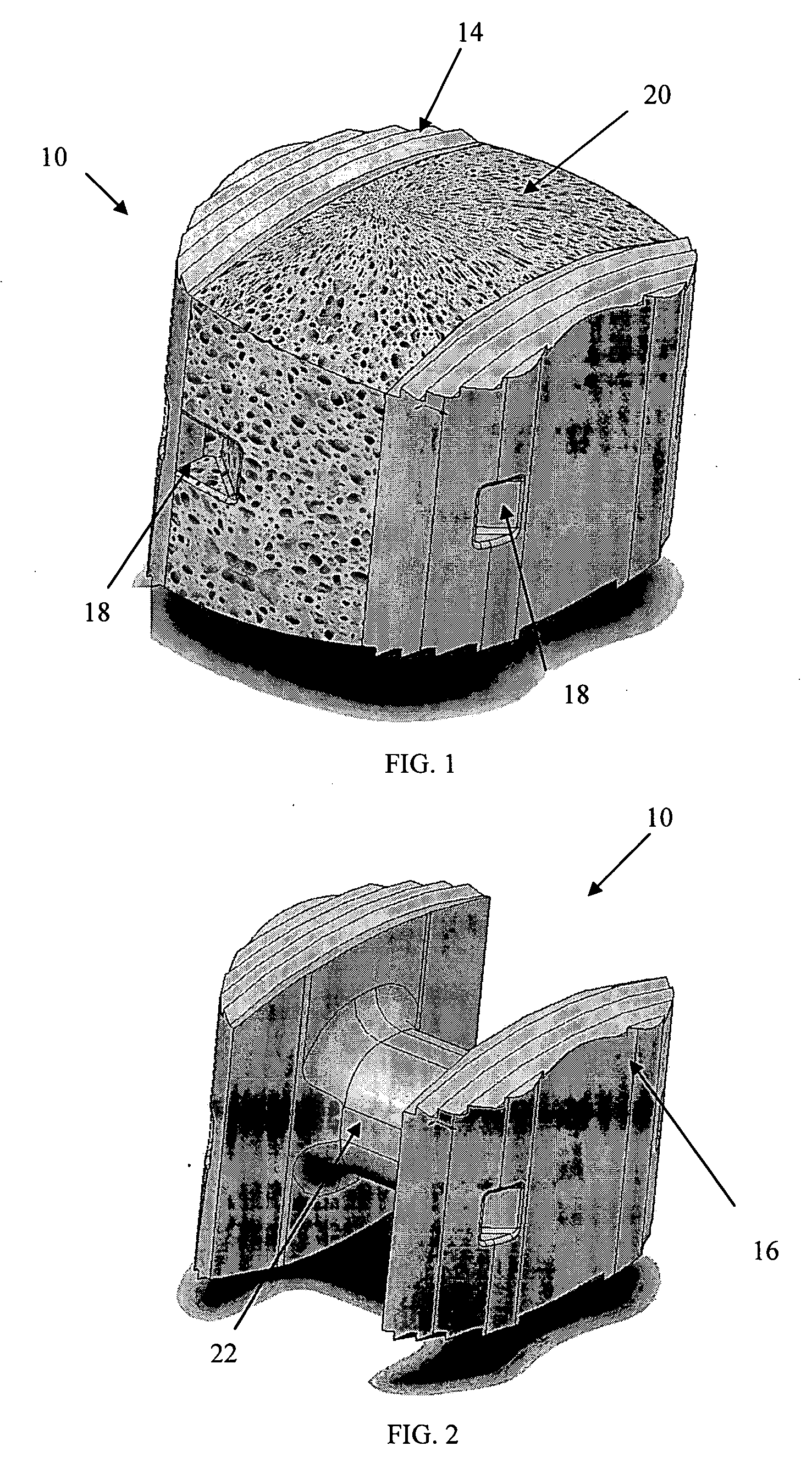

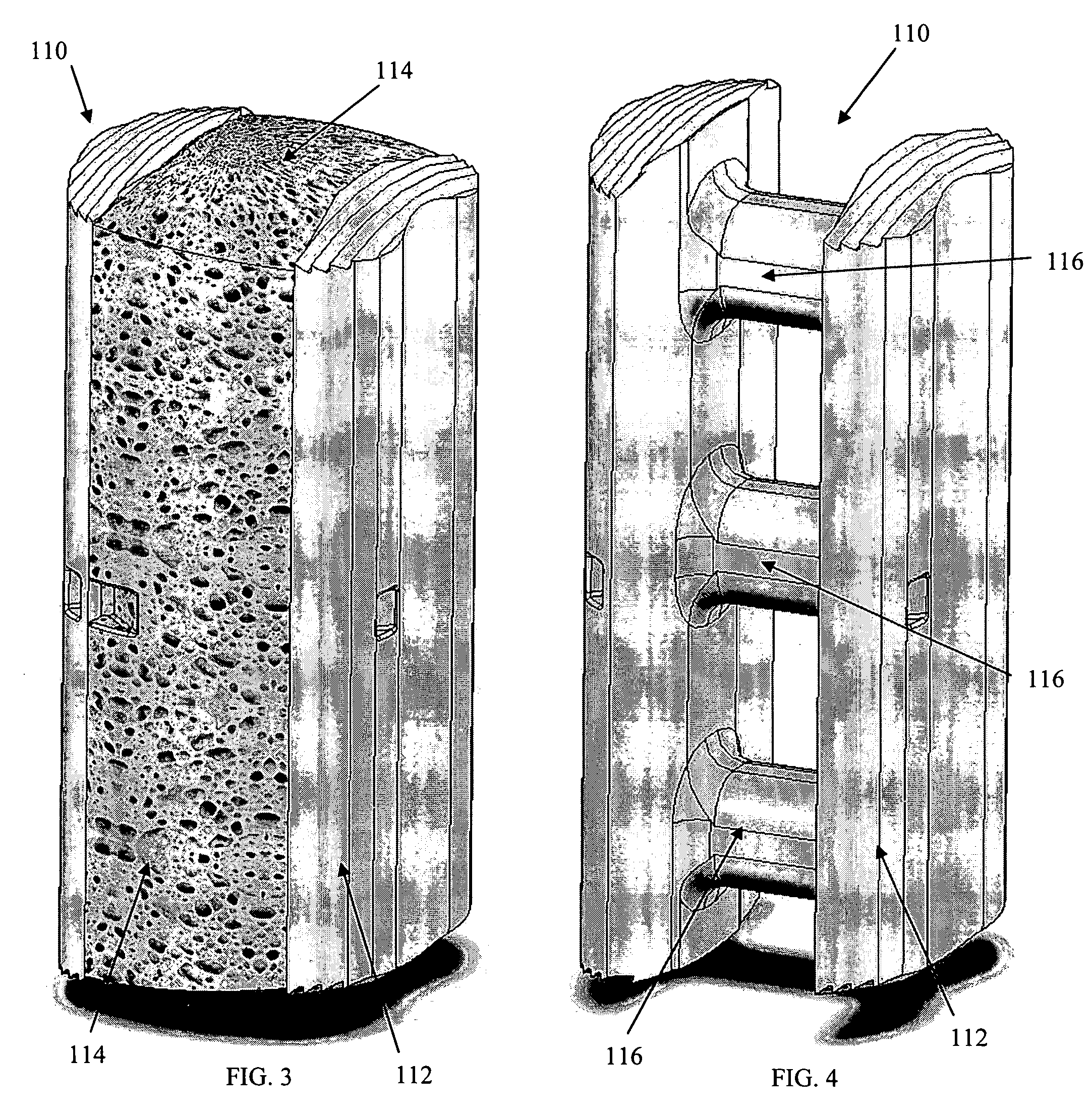

Radiolucent bone graft

An improved bone graft is provided for human implantation, bone graft includes a substrate block of high strength biocompatible material having a selected size and shape to fit the anatomical space, and a controlled porosity analogous to natural bone. The substrate block may be coated with a bio-active surface coating material such as hydroxyapatite or a calcium phosphate to promote bone ingrowth and enhanced bone fusion. Upon implantation, the bone graft provides a spacer element having a desired combination of mechanical strength together with osteoconductivity and osteoinductivity to promote bone ingrowth and fusion, as well as radiolucency for facilitated post-operative monitoring. The bone graft may additionally carry one or more natural or synthetic therapeutic agents for further promoting bone ingrowth and fusion.

Owner:AMEDICA A DELAWARE

Touch screen

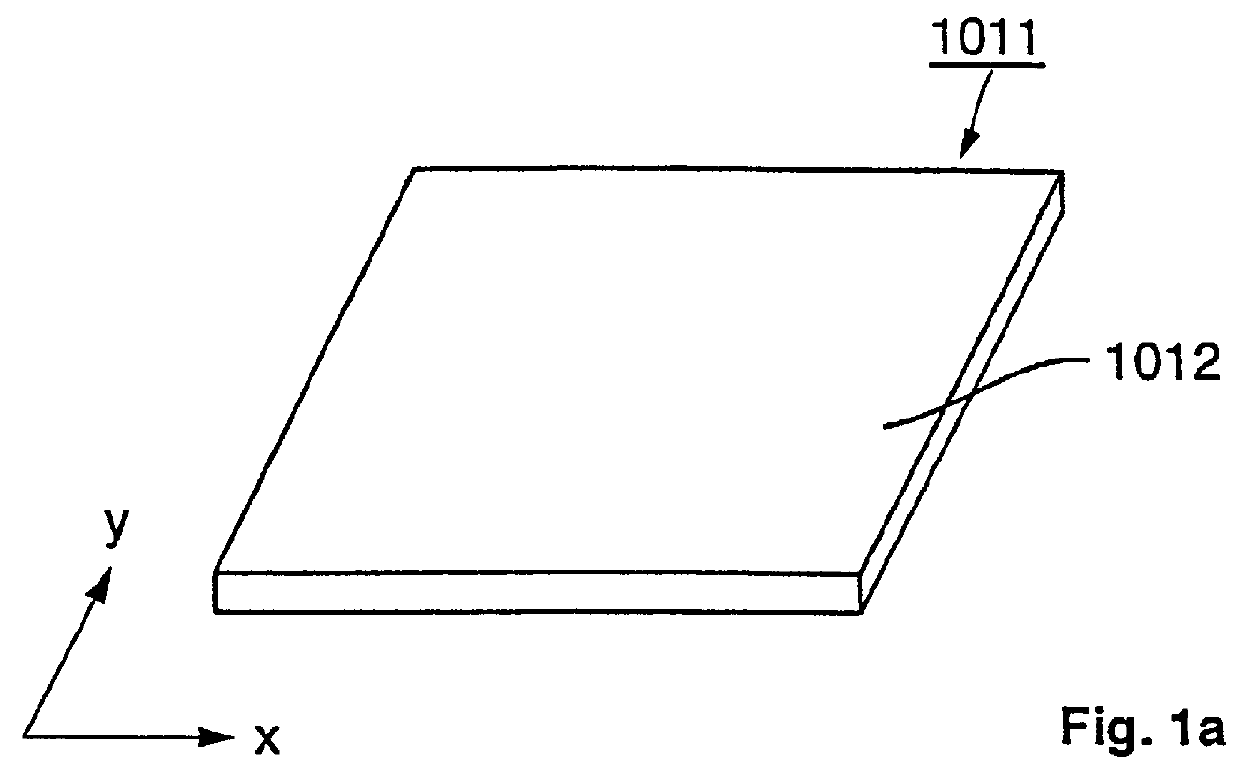

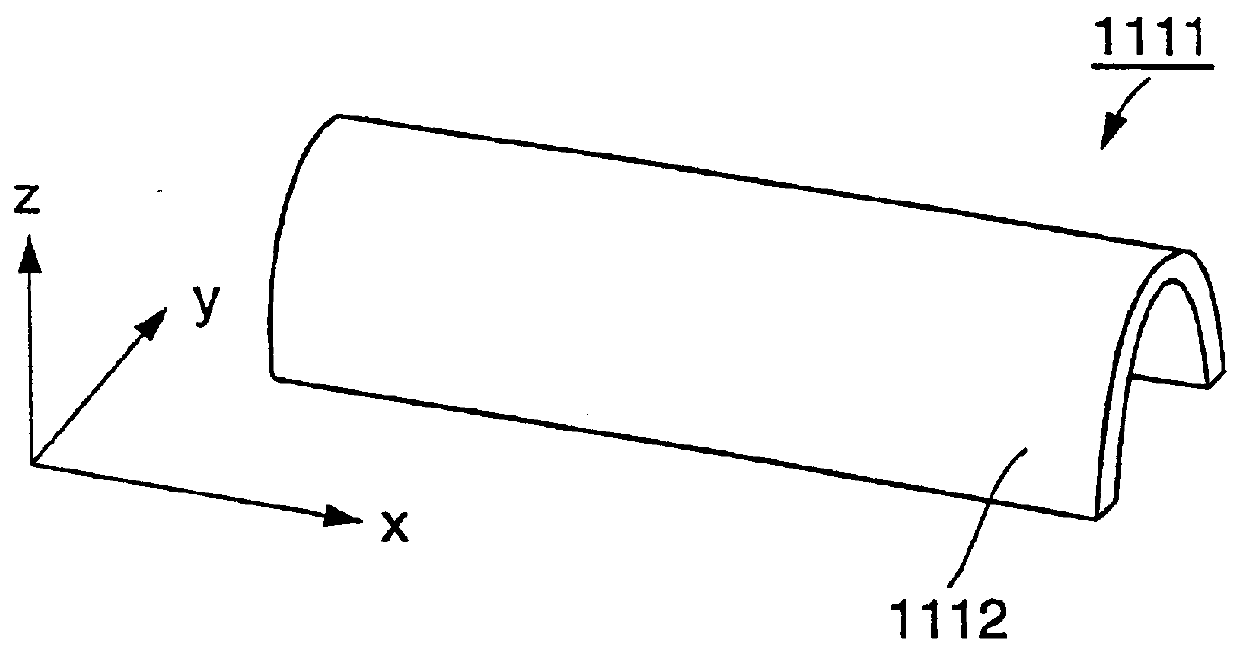

InactiveUS6072475AEasy to useSmall surface areaInput/output for user-computer interactionEmergency actuatorsTouch SensesHand held

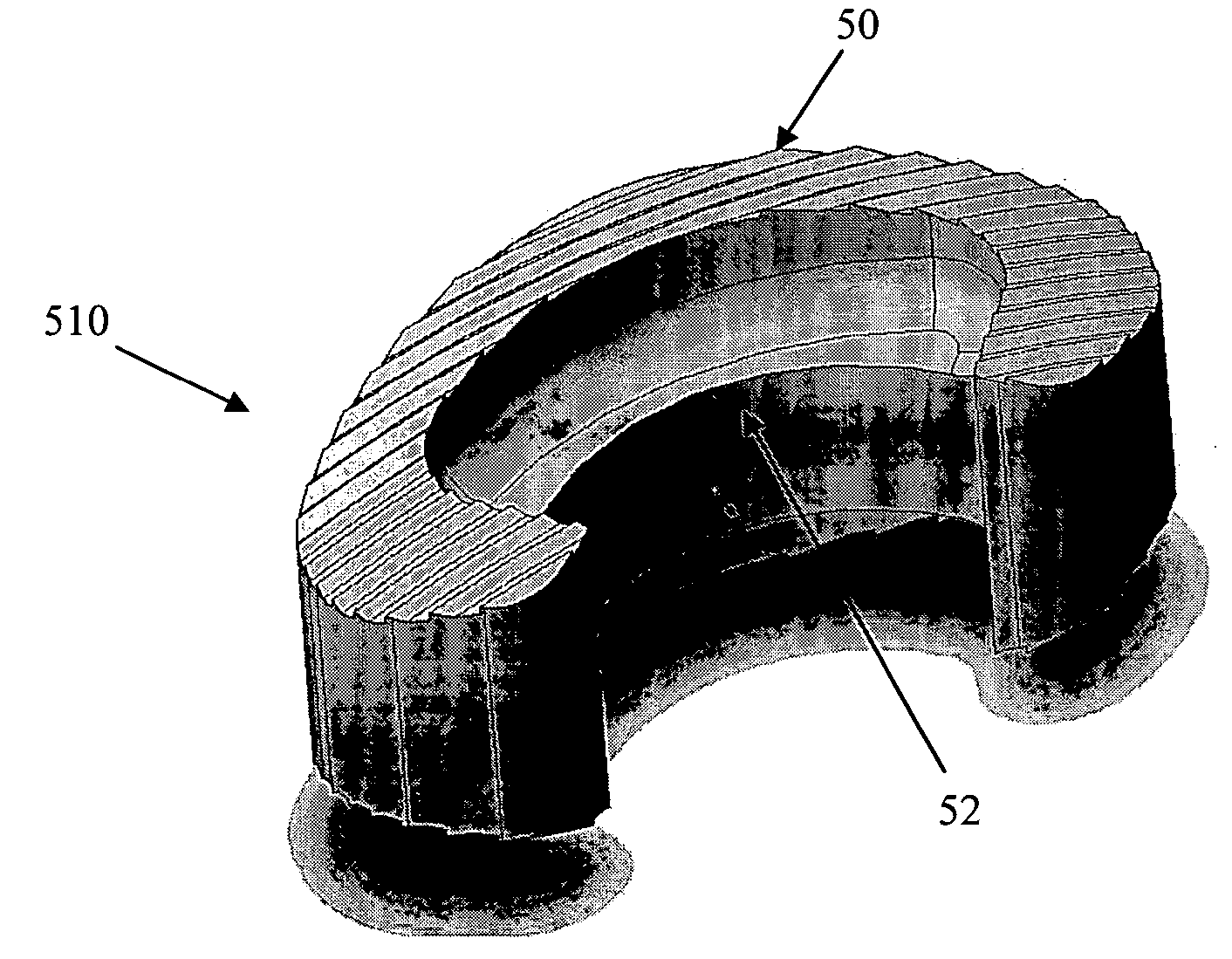

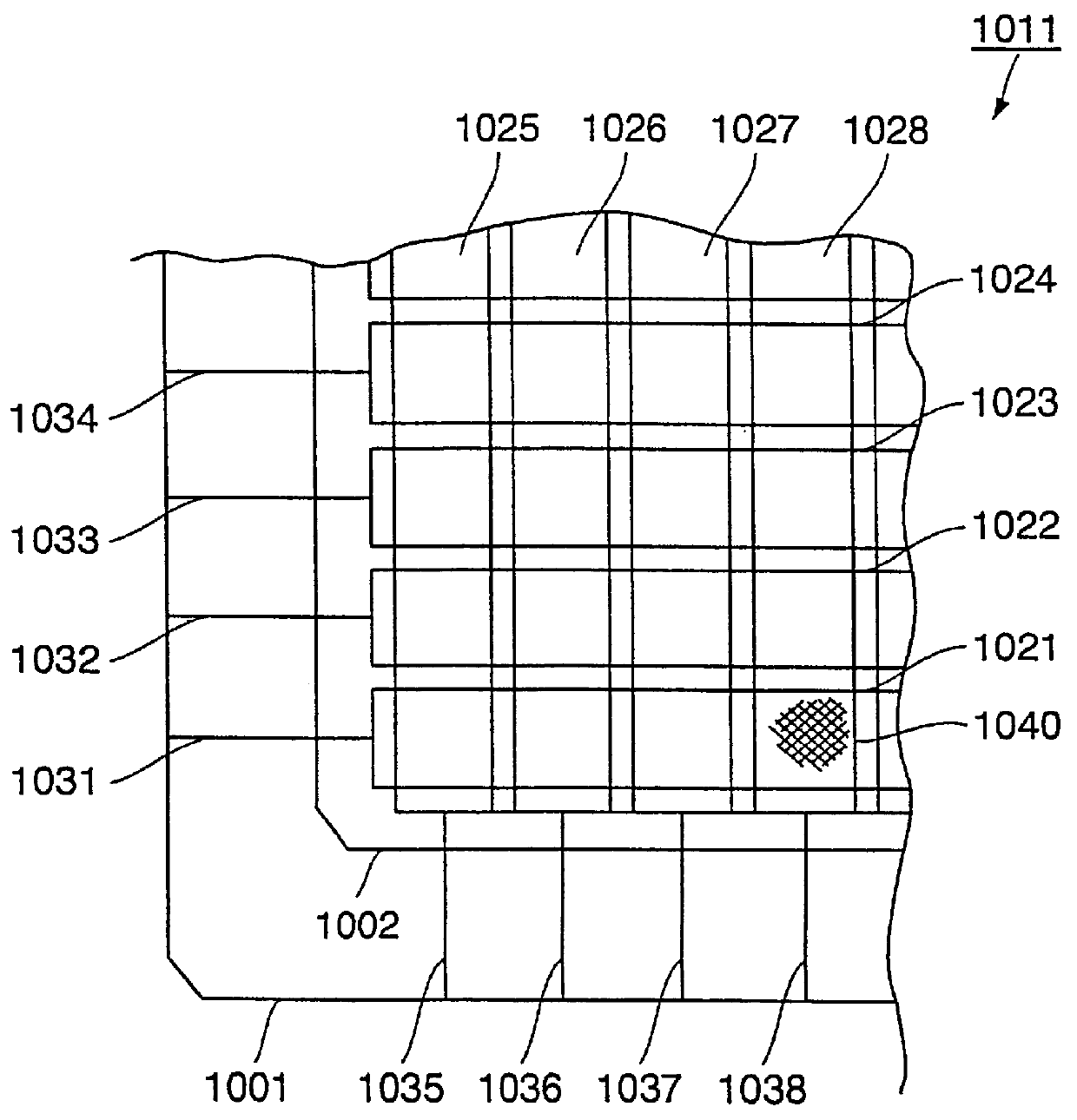

A touch screen 1111 having an active surface area 1112 which extends in three physical dimensions (x-, y- and z-dimensions) is provided. In the figure the active surface area has an U-shaped form. When a user slides his finger over the active surface area the tactile feedback gives him information about the position of the finger. The touch screen is activated when the active surface area senses a certain pressure from the finger. The use of the touch screen is facilitated especially when the user is on the move or when the touch screen is out of sight. Such use is common when operating hand-held terminals.

Owner:TELEFON AB LM ERICSSON (PUBL)

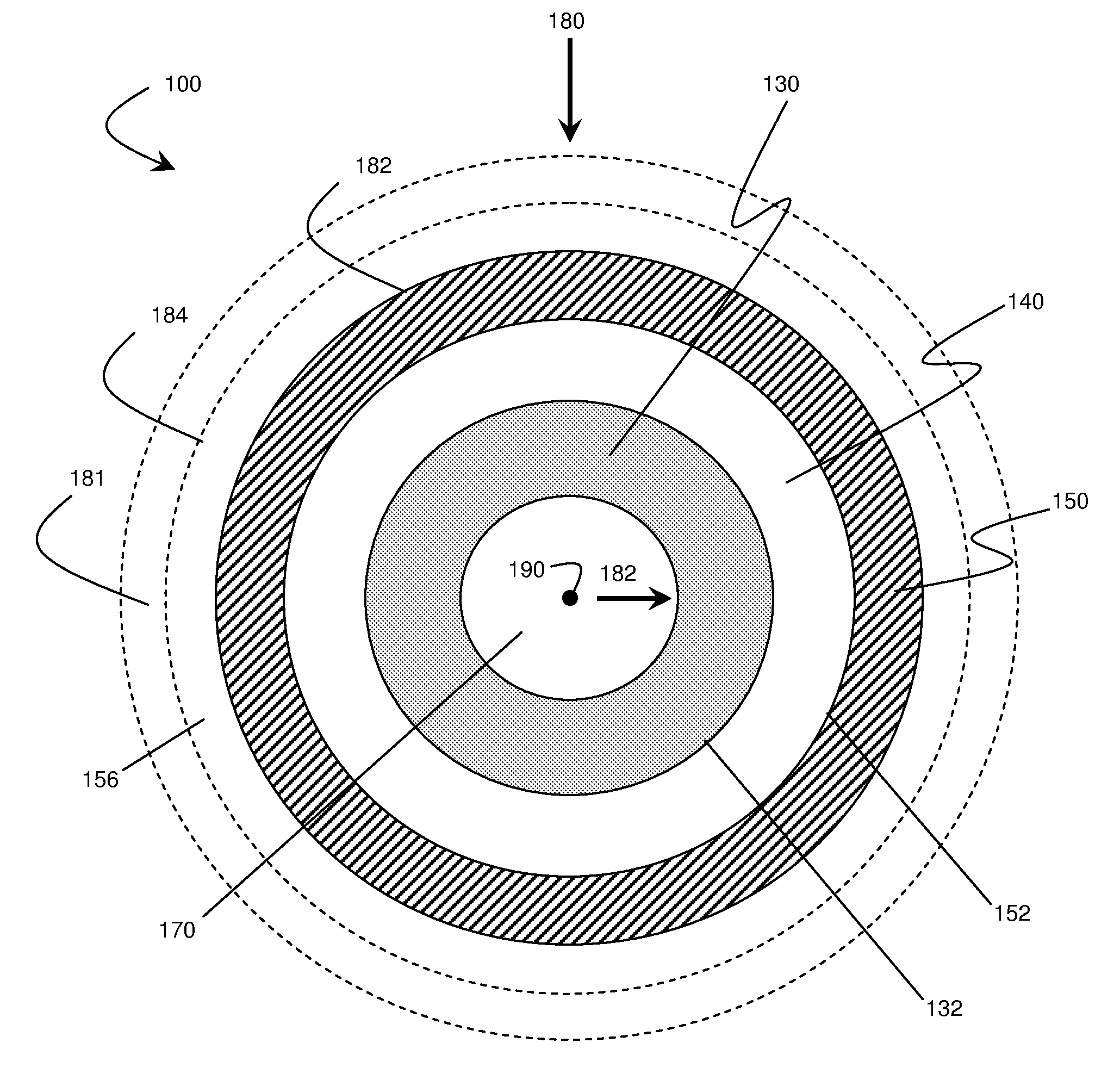

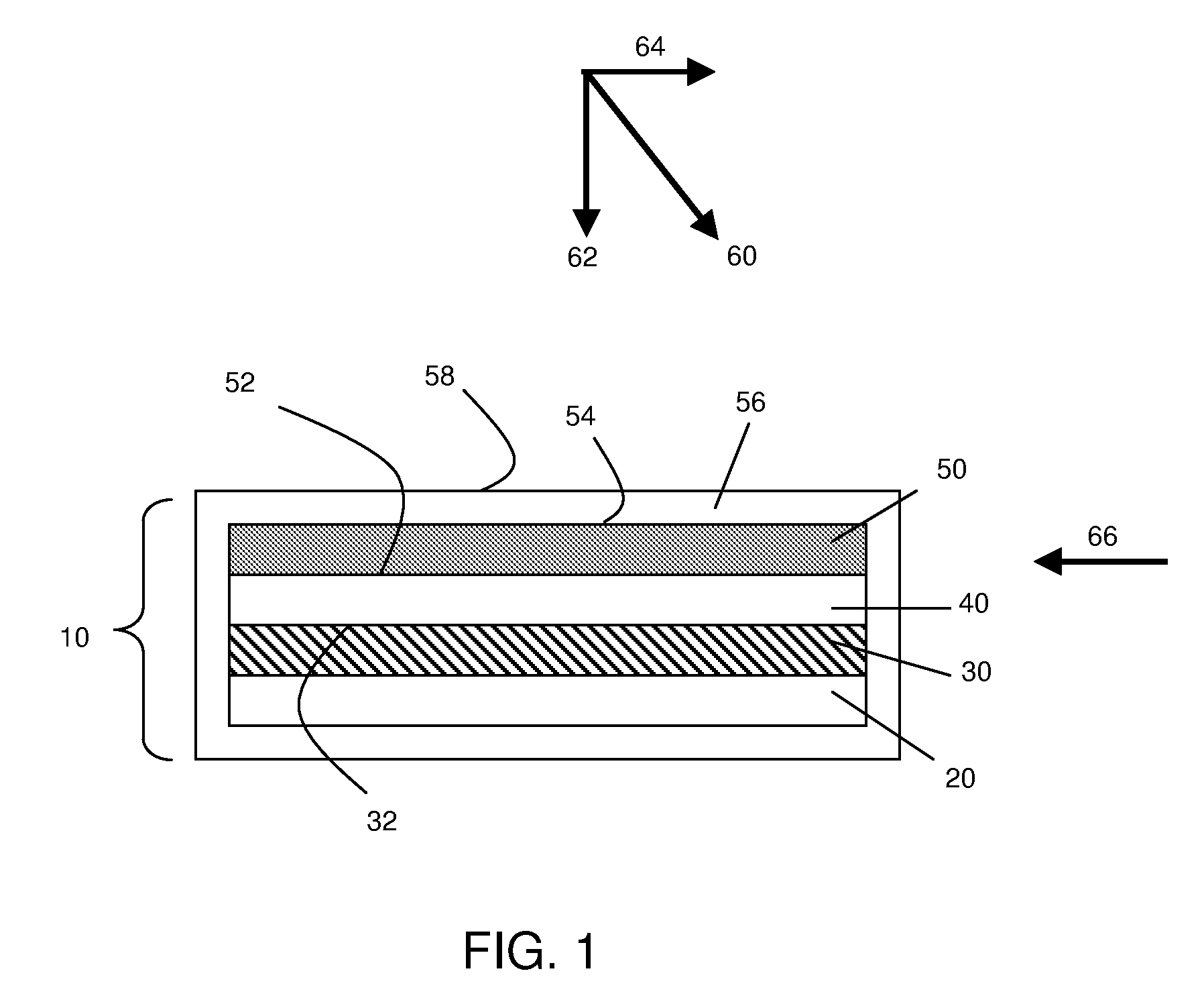

Application of force in electrochemical cells

ActiveUS20100035128A1Improve performancePrimary cell to battery groupingCell seperators/membranes/diaphragms/spacersRough surfaceChemical reaction

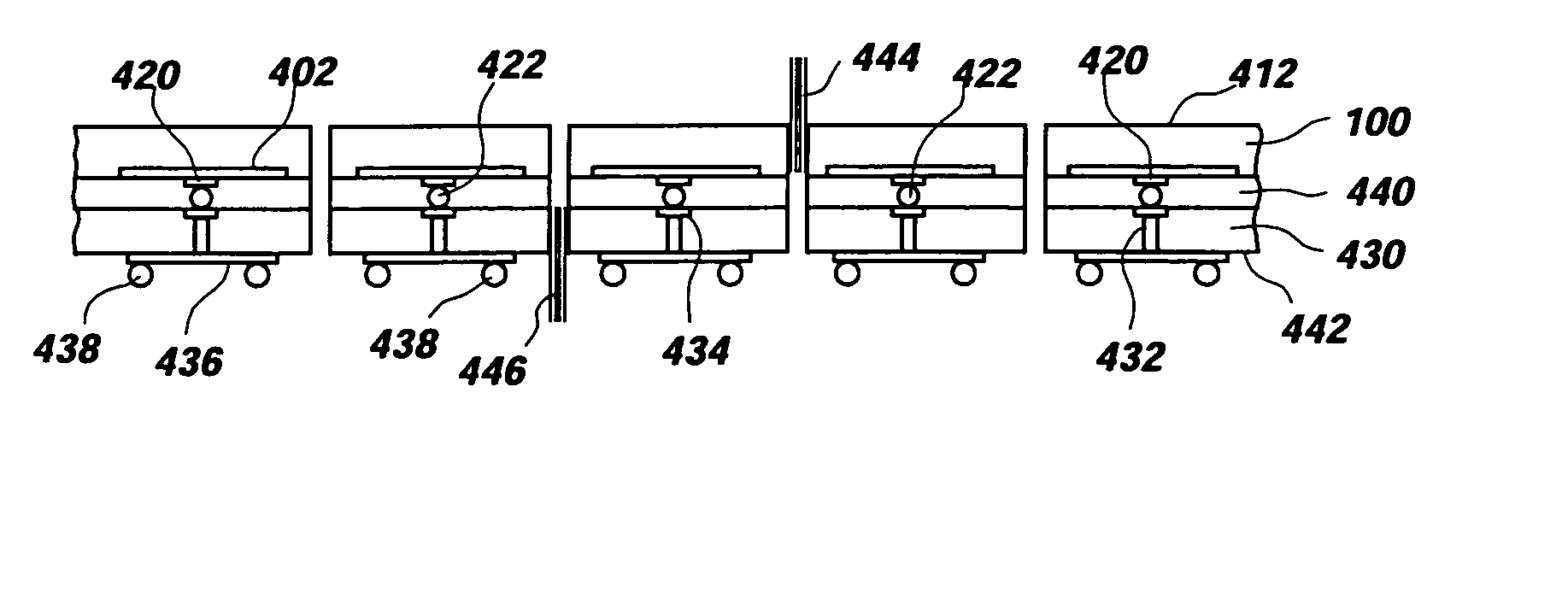

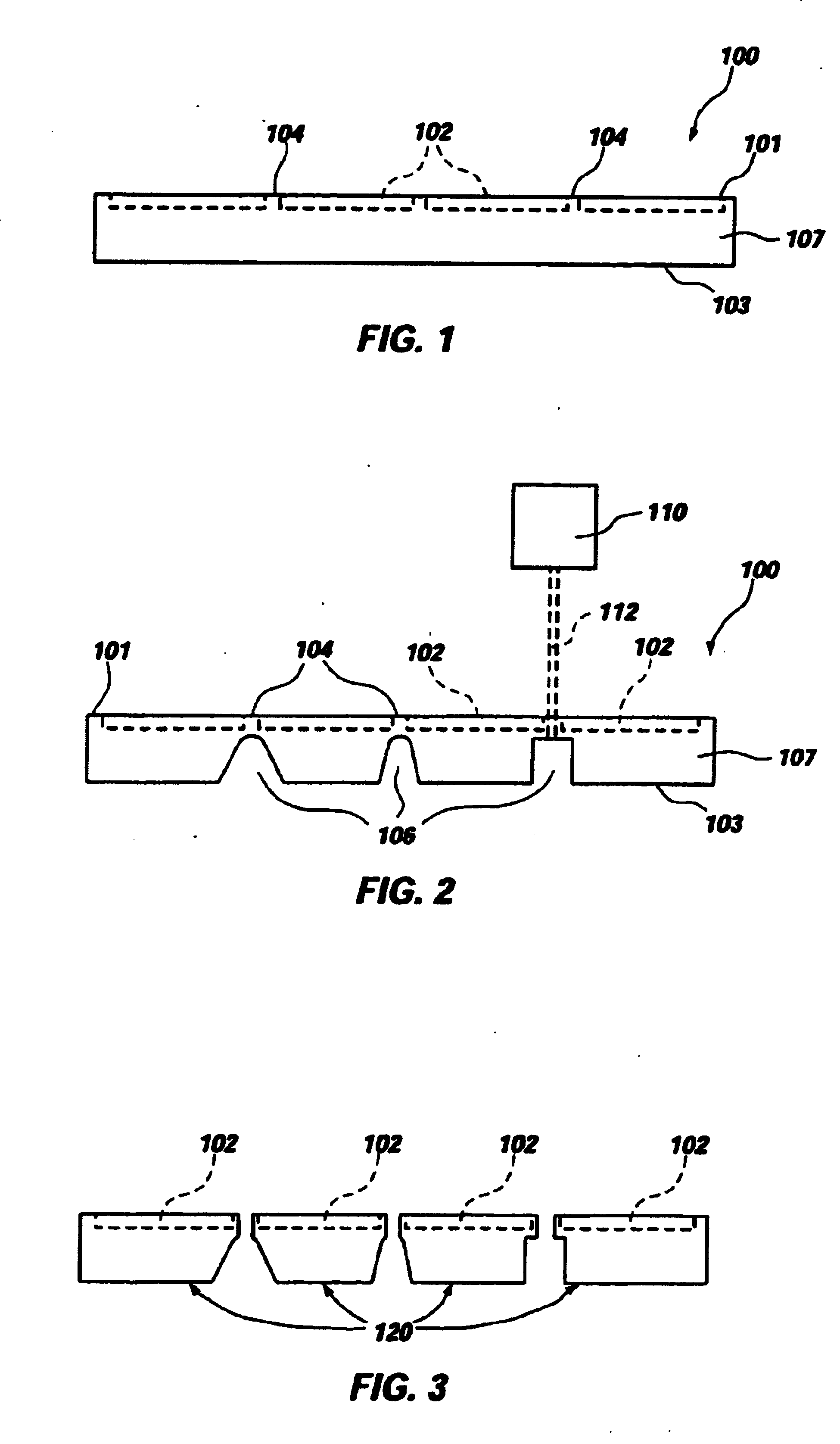

The present invention relates to the application of a force to enhance the performance of an electrochemical cell. The force may comprise, in some instances, an anisotropic force with a component normal to an active surface of the anode of the electrochemical cell. In the embodiments described herein, electrochemical cells (e.g., rechargeable batteries) may undergo a charge / discharge cycle involving deposition of metal (e.g., lithium metal) on a surface of the anode upon charging and reaction of the metal on the anode surface, wherein the metal diffuses from the anode surface, upon discharging. The uniformity with which the metal is deposited on the anode may affect cell performance. For example, when lithium metal is redeposited on an anode, it may, in some cases, deposit unevenly forming a rough surface. The roughened surface may increase the amount of lithium metal available for undesired chemical reactions which may result in decreased cycling lifetime and / or poor cell performance. The application of force to the electrochemical cell has been found, in accordance with the invention, to reduce such behavior and to improve the cycling lifetime and / or performance of the cell.

Owner:SION POWER CORP

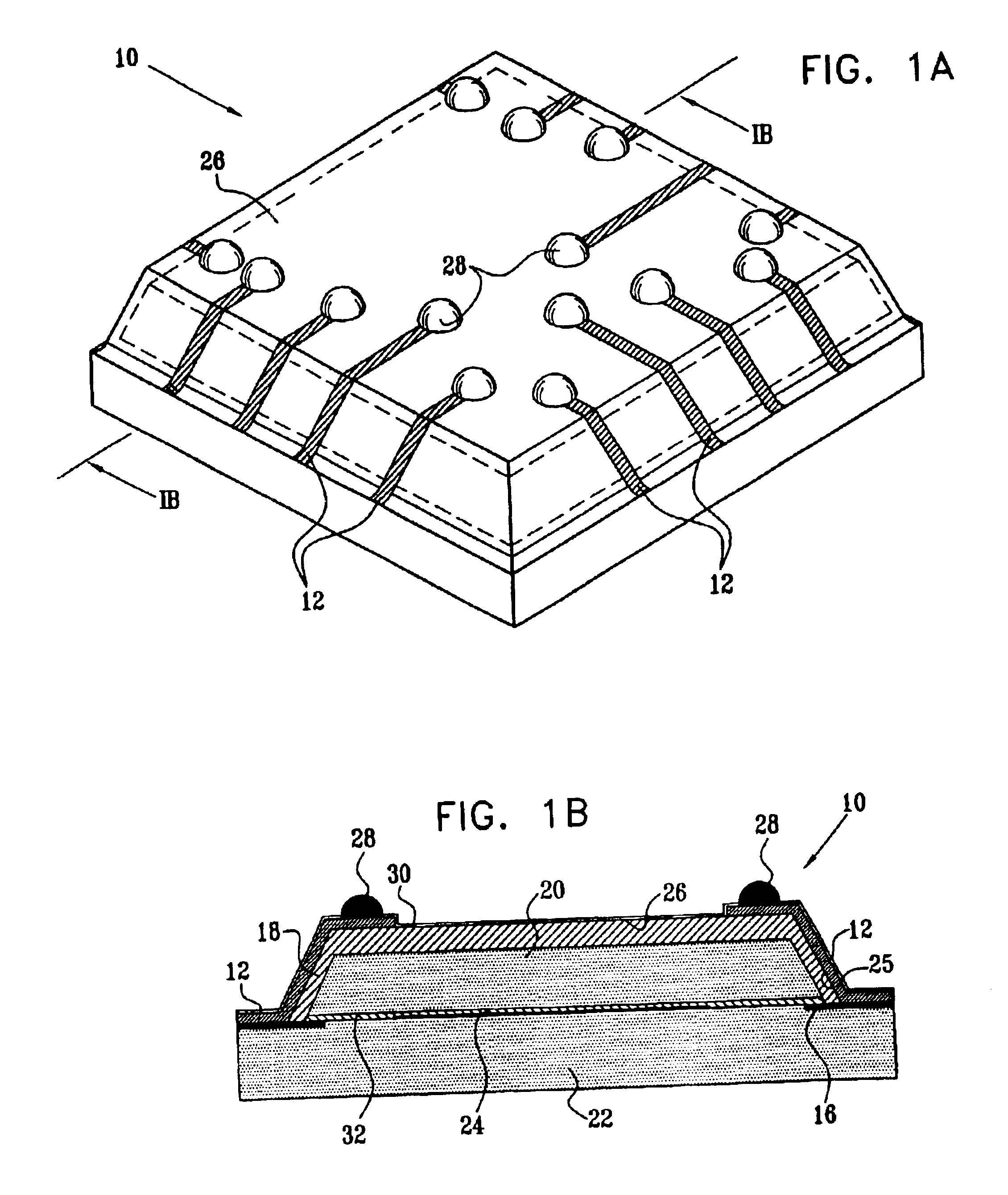

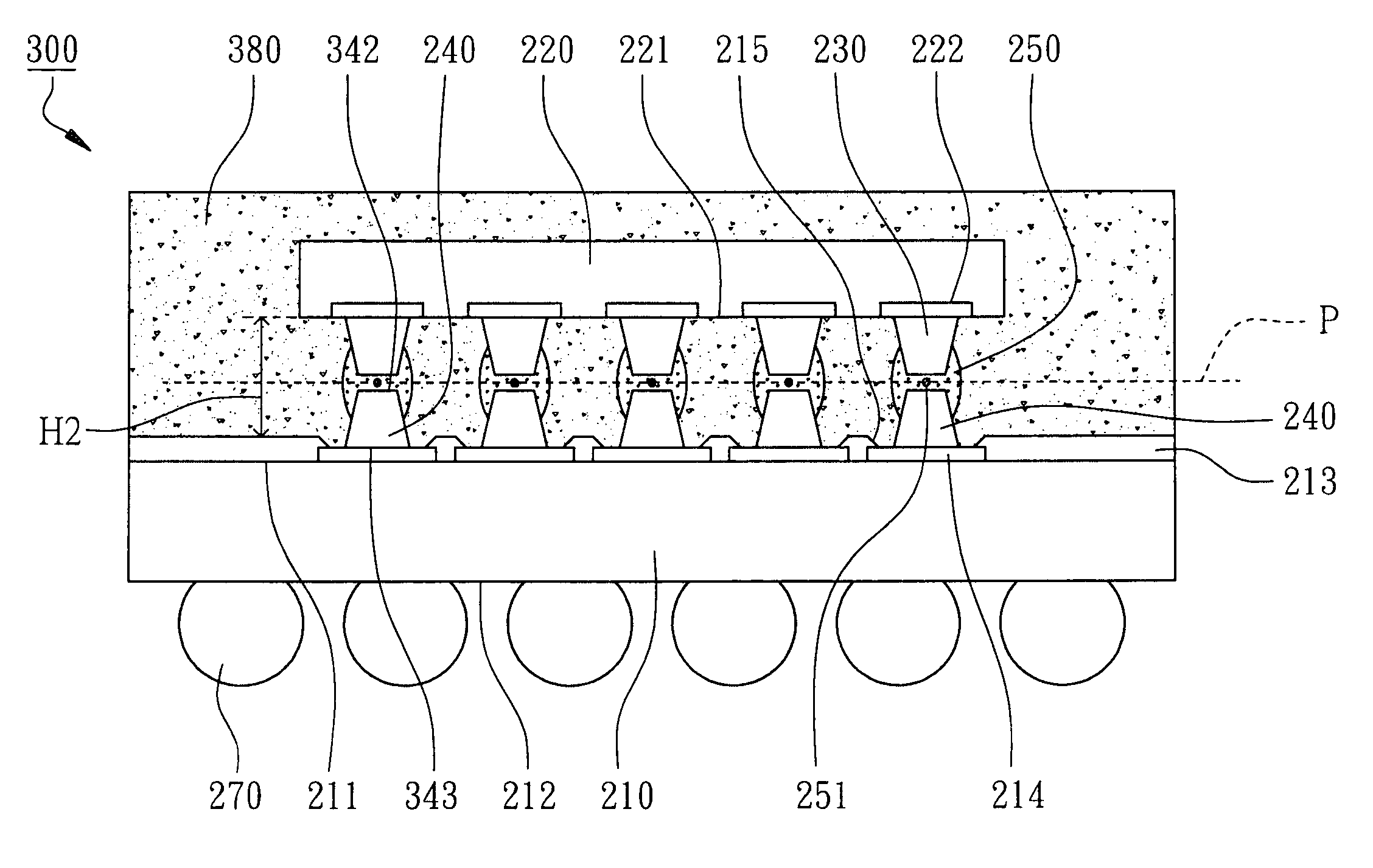

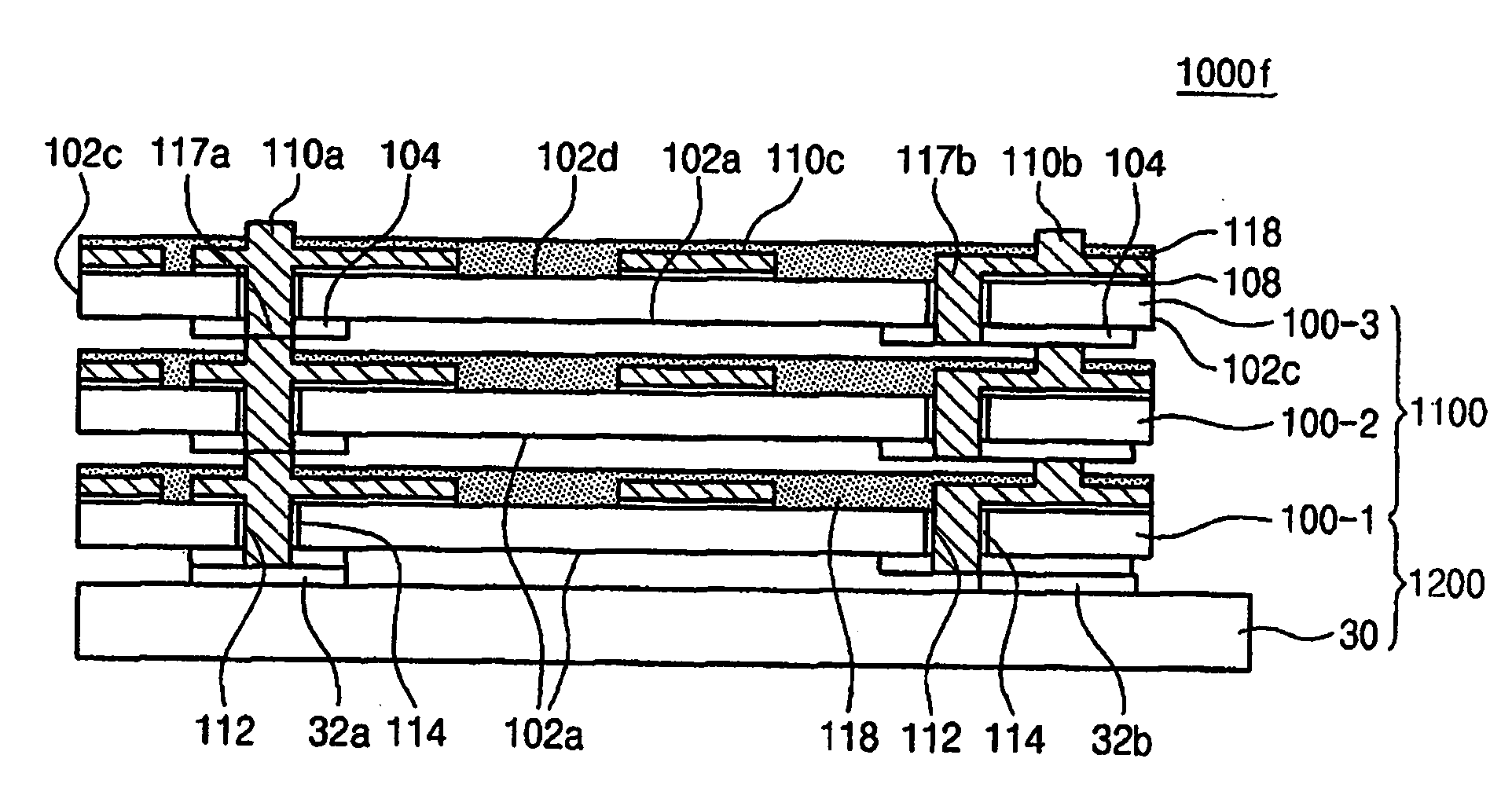

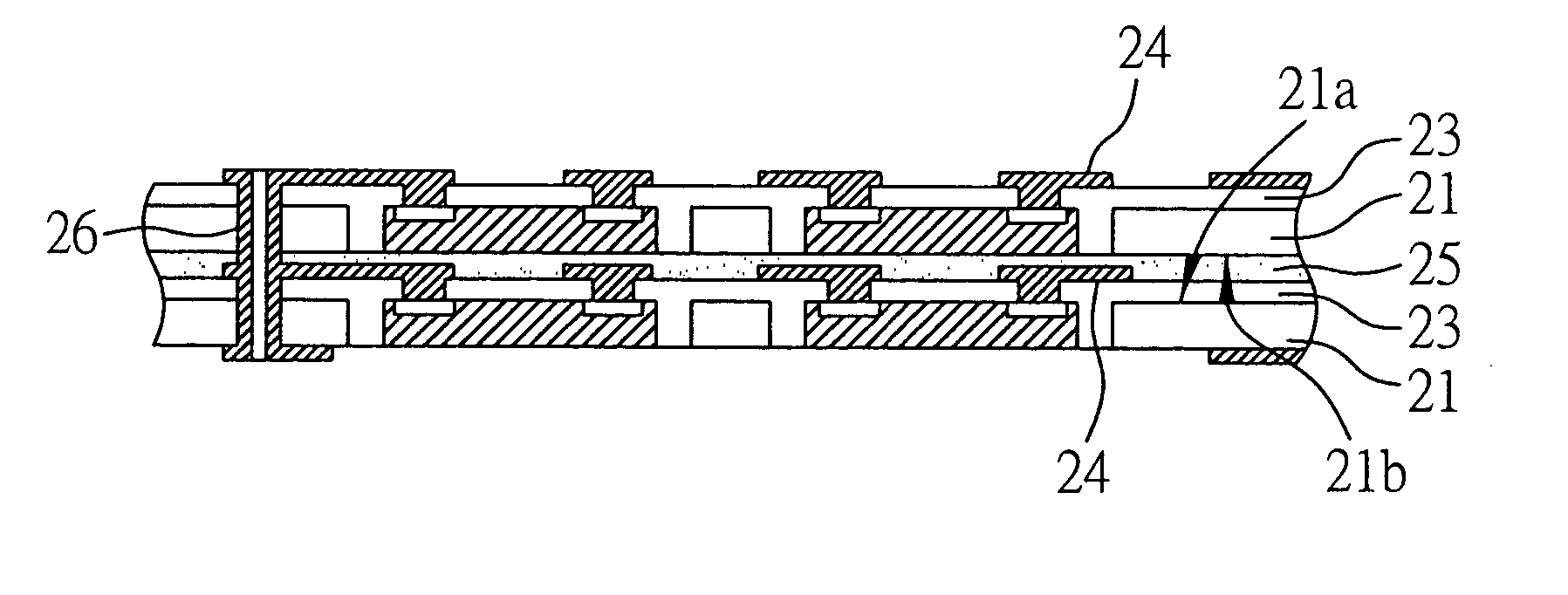

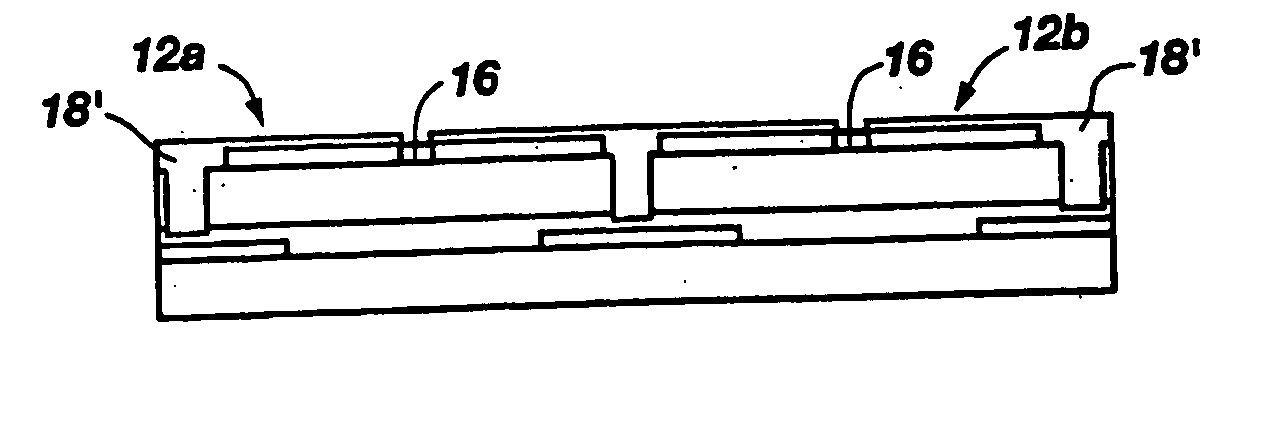

Stacked semiconductor die assembly having at least one support

ActiveUS6930378B1Low costShorten the timeSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A stack of semiconductor dies is disclosed. A first stack level includes a first semiconductor die and at least one first support that are attached to a substrate surface. A second level includes a second semiconductor die and at least one second support that are attached to the active surface of the first semiconductor die and to a coplanar surface of the first support(s). A third level includes a third semiconductor die attached to the active surface of the second semiconductor die and to a coplanar surface of the second support(s). The second and third semiconductor dies do not overlap bond pads of the first and second semiconductor dies, respectively. An adhesive film overlies the entire inactive surface of the second and third semiconductor dies, and attaches the second and third semiconductor dies to the immediately underlying active surface and support(s).

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

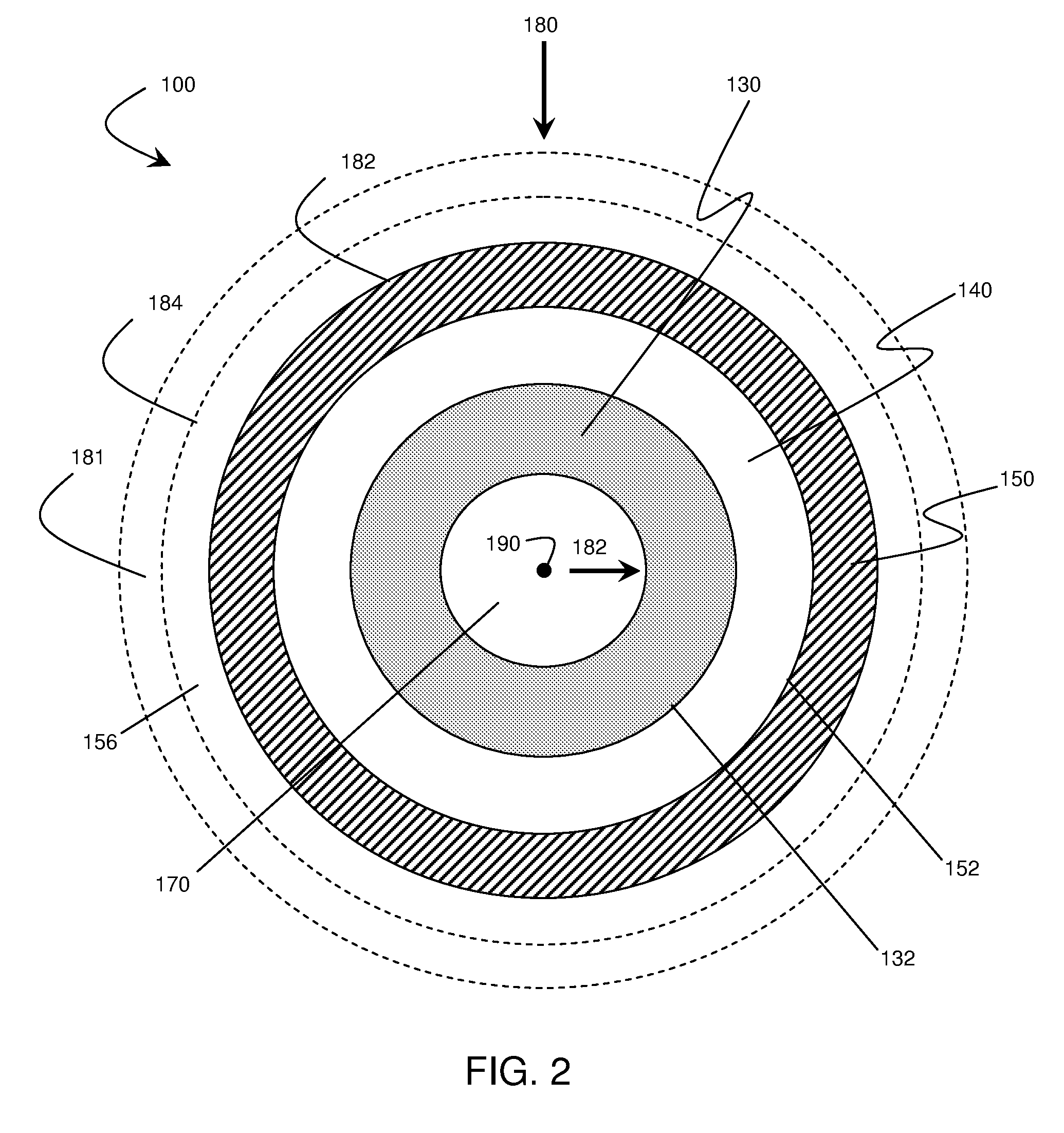

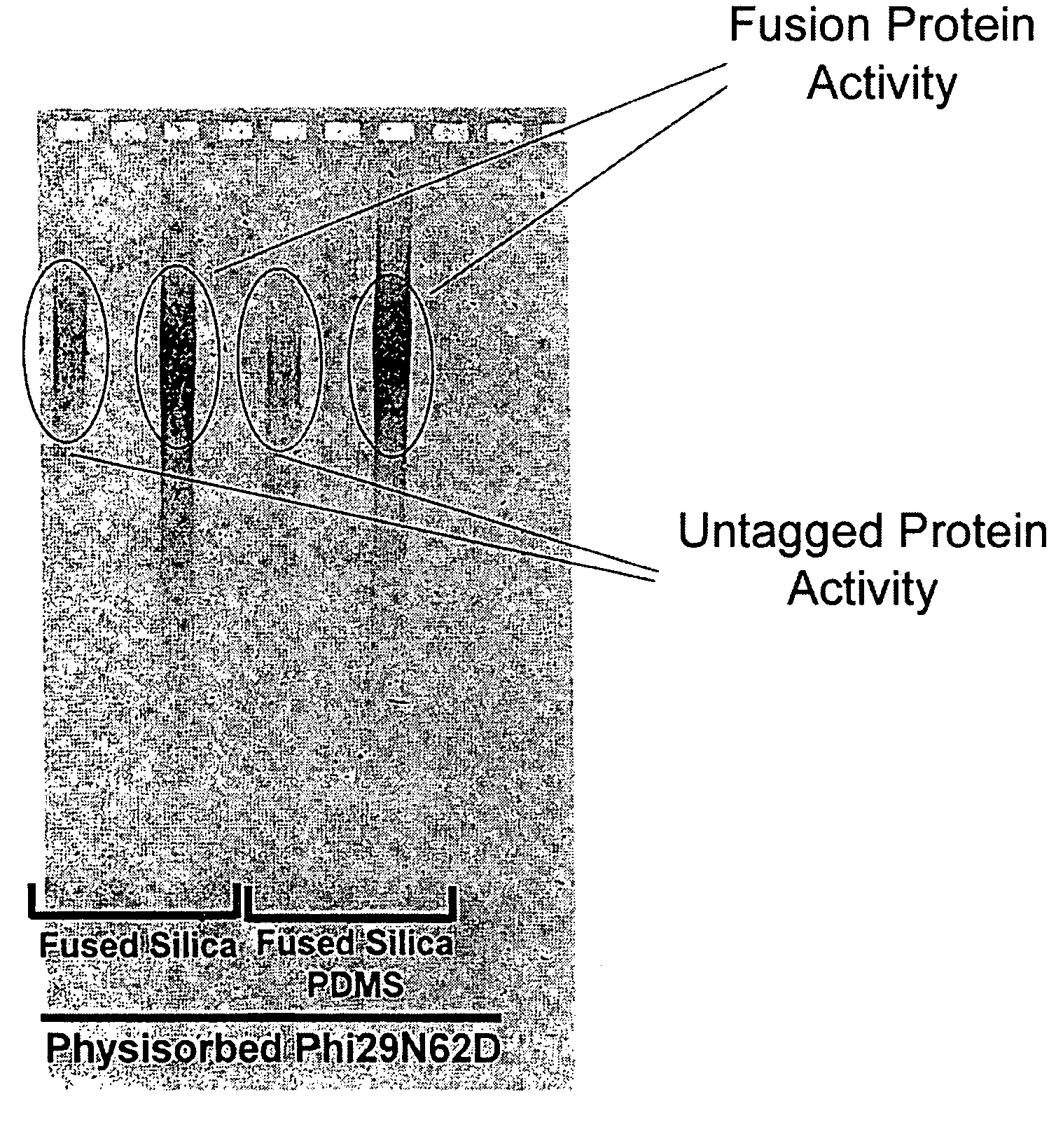

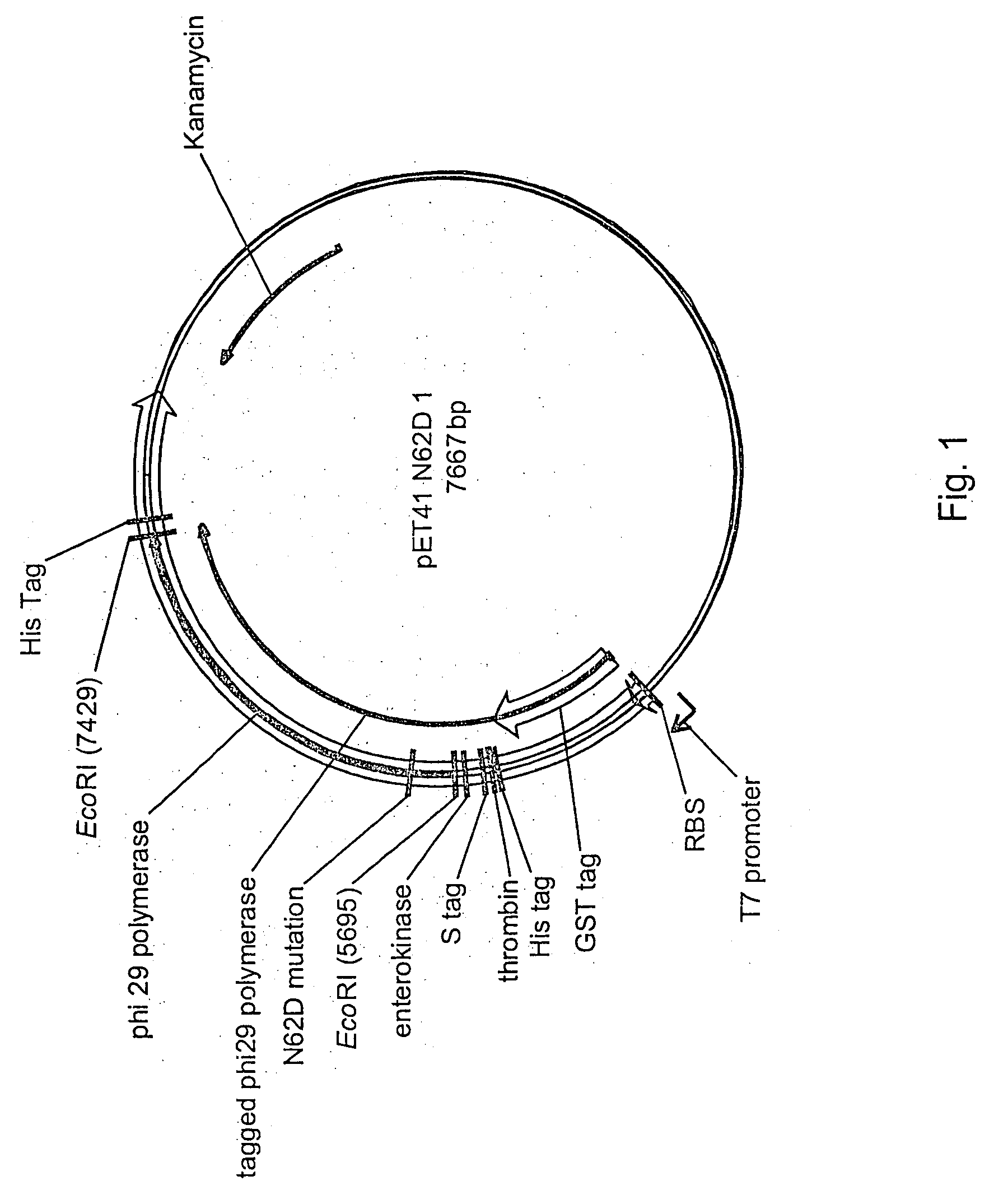

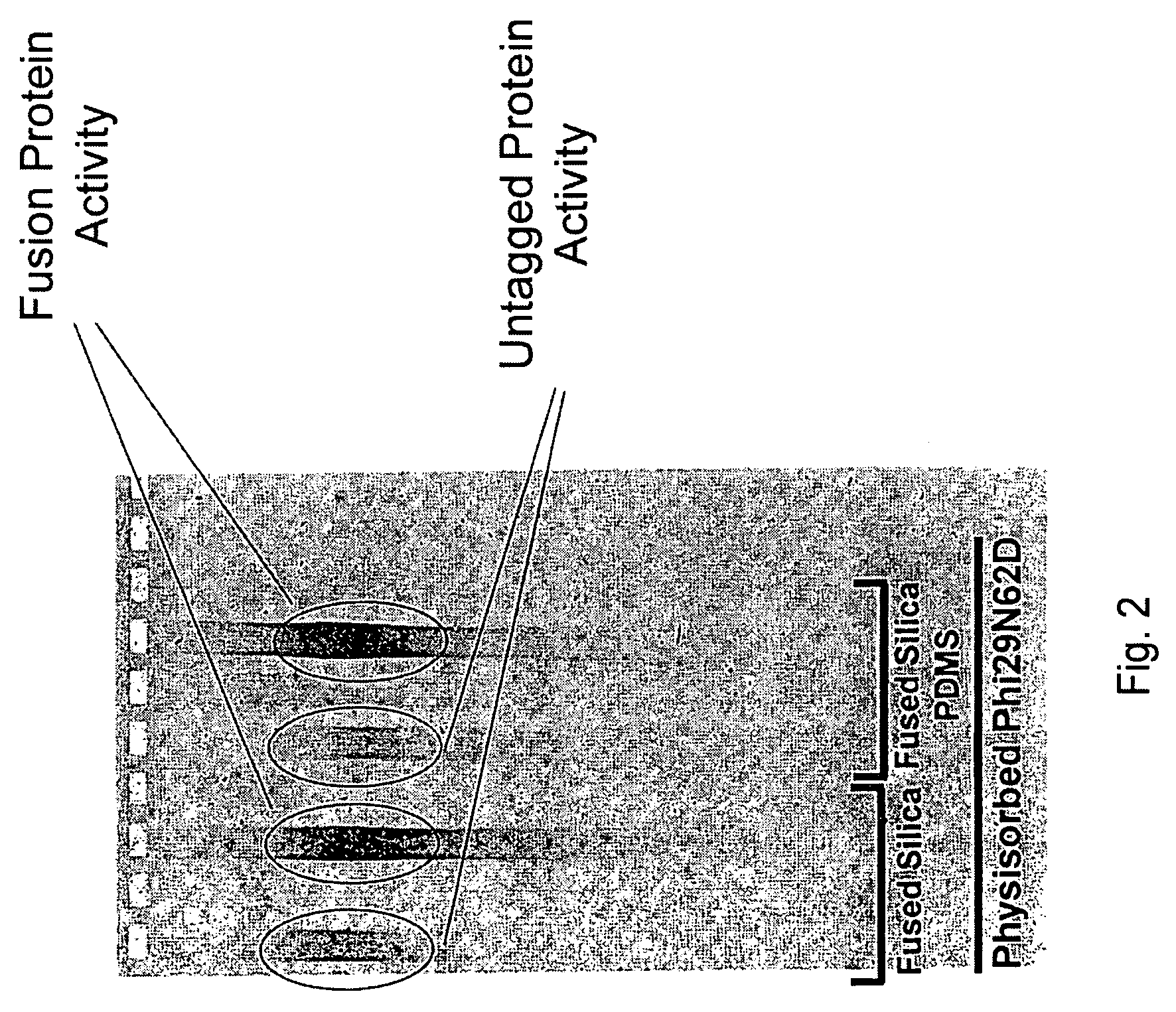

Active surface coupled polymerases

ActiveUS20080199932A1Without substantial loss of activityHigh binding affinityMicrobiological testing/measurementOn/in organic carrierPolymerase LBiomedical engineering

Active surface coupled polymerases, surfaces that include such polymerases, and methods of making and using surface-attached polymerases are provided.

Owner:PACIFIC BIOSCIENCES

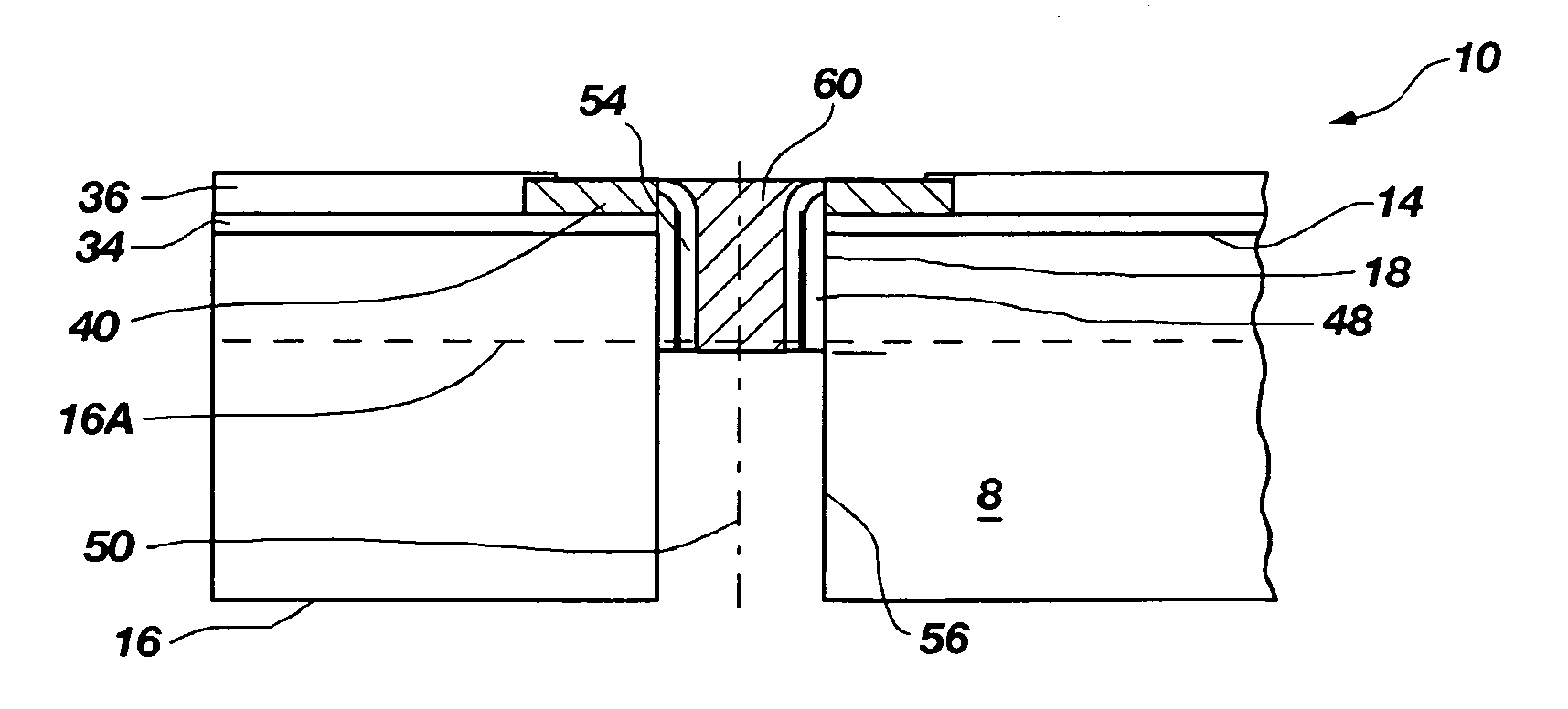

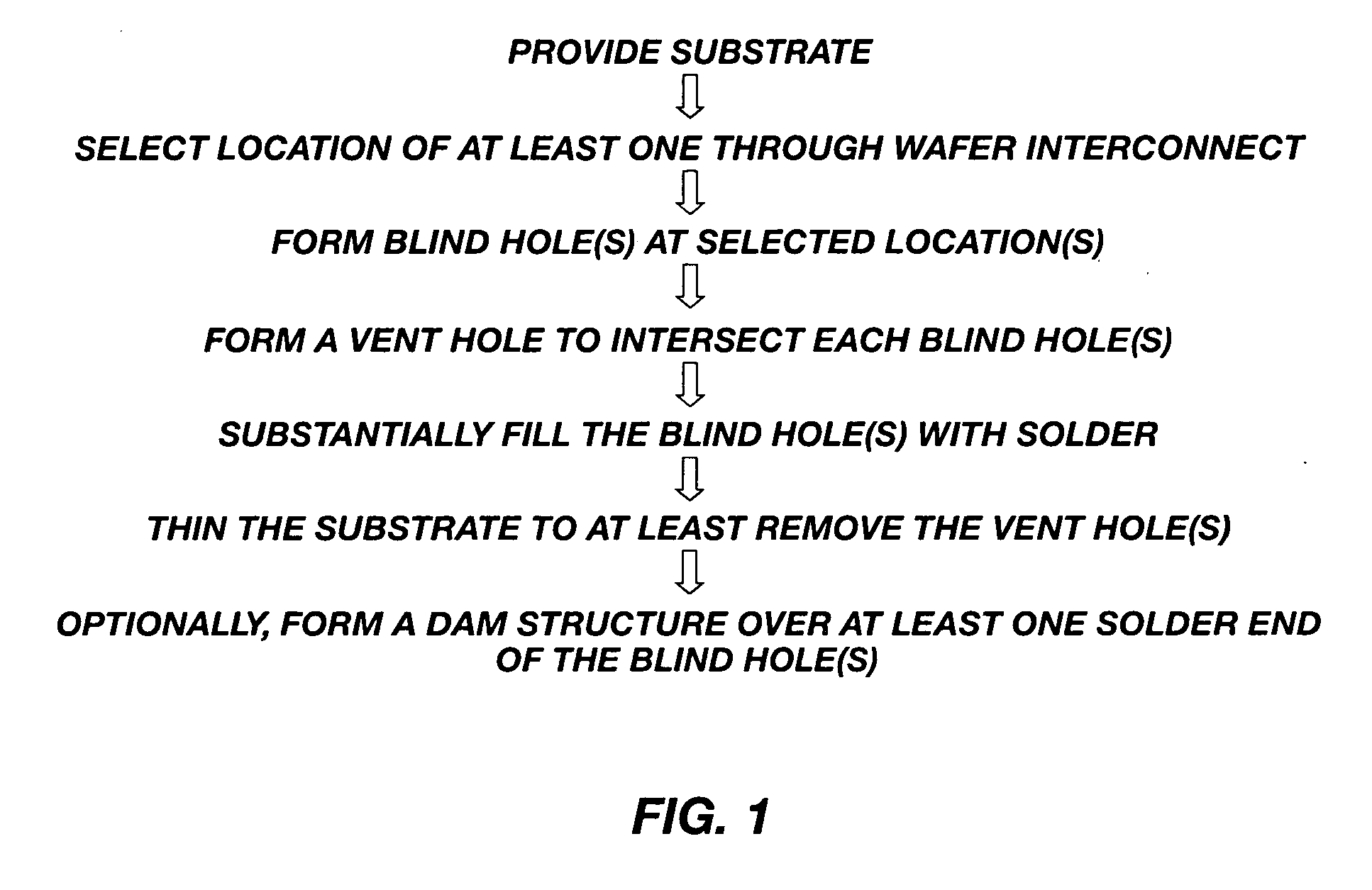

Methods for forming through-wafer interconnects, intermediate structures so formed, and devices and systems having at least one solder dam structure

ActiveUS20070045779A1Conveniently attachedEliminate cross-contaminationSemiconductor/solid-state device detailsSolid-state devicesVitrificationDevice material

A method for forming through-wafer interconnects (TWI) in a substrate of a thickness in excess of that of a semiconductor die such as a semiconductor wafer. Blind holes are formed from the active surface, sidewalls thereof passivated and coated with a solder-wetting material. A vent hole is then formed from the opposite surface (e.g., wafer back side) to intersect the blind hole. The blind hole is solder filled, followed by back thinning of the vent hole portion of the wafer to a final substrate thickness to expose the solder and solder-wetting material at both the active surface and the thinned back side. A metal layer such as nickel, having a glass transition temperature greater than that of the solder, may be plated to form a dam structure covering one or both ends of the TWI including the solder and solder-wetting material to prevent leakage of molten solder from the TWI during high temperature excursions. Intermediate structures of semiconductor devices, semiconductor devices and systems are also disclosed.

Owner:MICRON TECH INC

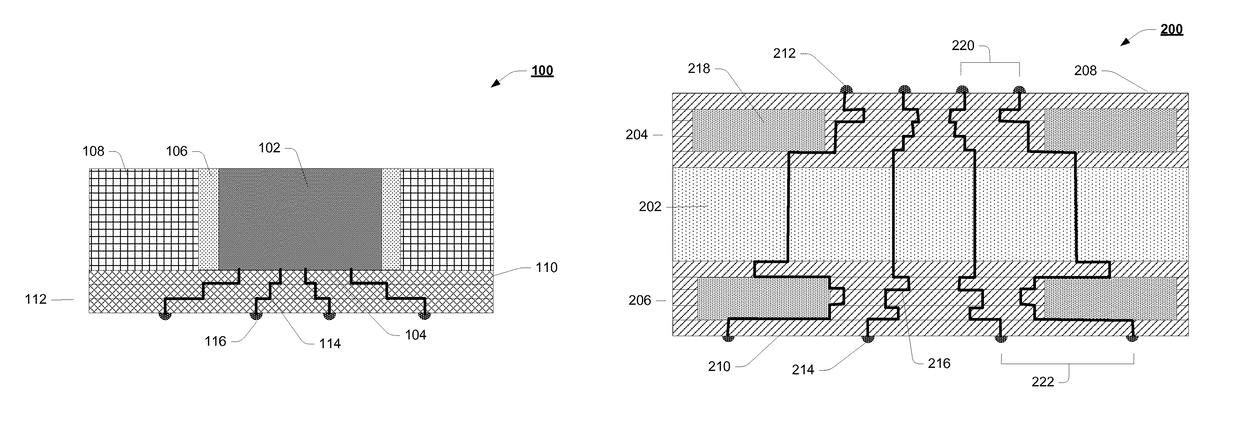

Integrated circuit packages including high density bump-less build up layers and a lesser density core or coreless substrate

In some embodiments, integrated circuit packages including high density bump-less build up layers and a lesser density core or coreless substrate are presented. In this regard, an apparatus is introduced having a first element including a microelectronic die having an active surface and at least one side, an encapsulation material adjacent said at least one microelectronic die side, wherein said encapsulation material includes at least one surface substantially planar to said microelectronic die active surface, a first dielectric material layer disposed on at least a portion of said microelectronic die active surface and said encapsulation material surface, a plurality of build-up layers disposed on said first dielectric material layer, and a plurality of conductive traces disposed on said first dielectric material layer and said build-up layers and in electrical contact with said microelectronic die active surface; and a second element coupled to the first element, the second element including a substrate having a plurality of dielectric material layers and conductive traces to conductively couple conductive contacts on a top surface with conductive contacts on a bottom surface, said conductive contacts on said top surface conductively coupled with said conductive traces of said first element. Other embodiments are also disclosed and claimed.

Owner:INTEL CORP

Pillar-to-pillar flip-chip assembly

ActiveUS7569935B1Reduce thermal stressPrevent peelingFinal product manufactureSemiconductor/solid-state device detailsSolder maskSolder ball

A pillar-to-pillar flip-chip assembly primarily comprises a substrate, a chip disposed on the substrate, a plurality of first copper pillars on the bonding pads of the chip, a plurality of second copper pillars on the bump pads of the substrate, and a soldering material. A first height of the first copper pillars protruding from the active surface of the chip is the same as a second height of the second copper pillars from the solder mask on the substrate. When the soldering material electrically and mechanically connects the first copper pillars to the second copper pillars, a plurality of central points of the soldering material are formed on an equal-dividing plane between the chip and the substrate to reduce the direct stresses exerted at the soldering material to avoid peeling or breaks from the bump pads. Moreover, each of conventional solder balls is replaced with two soldered copper pillars to meet the lead-free requirements with higher reliability and lower costs.

Owner:POWERTECH TECHNOLOGY

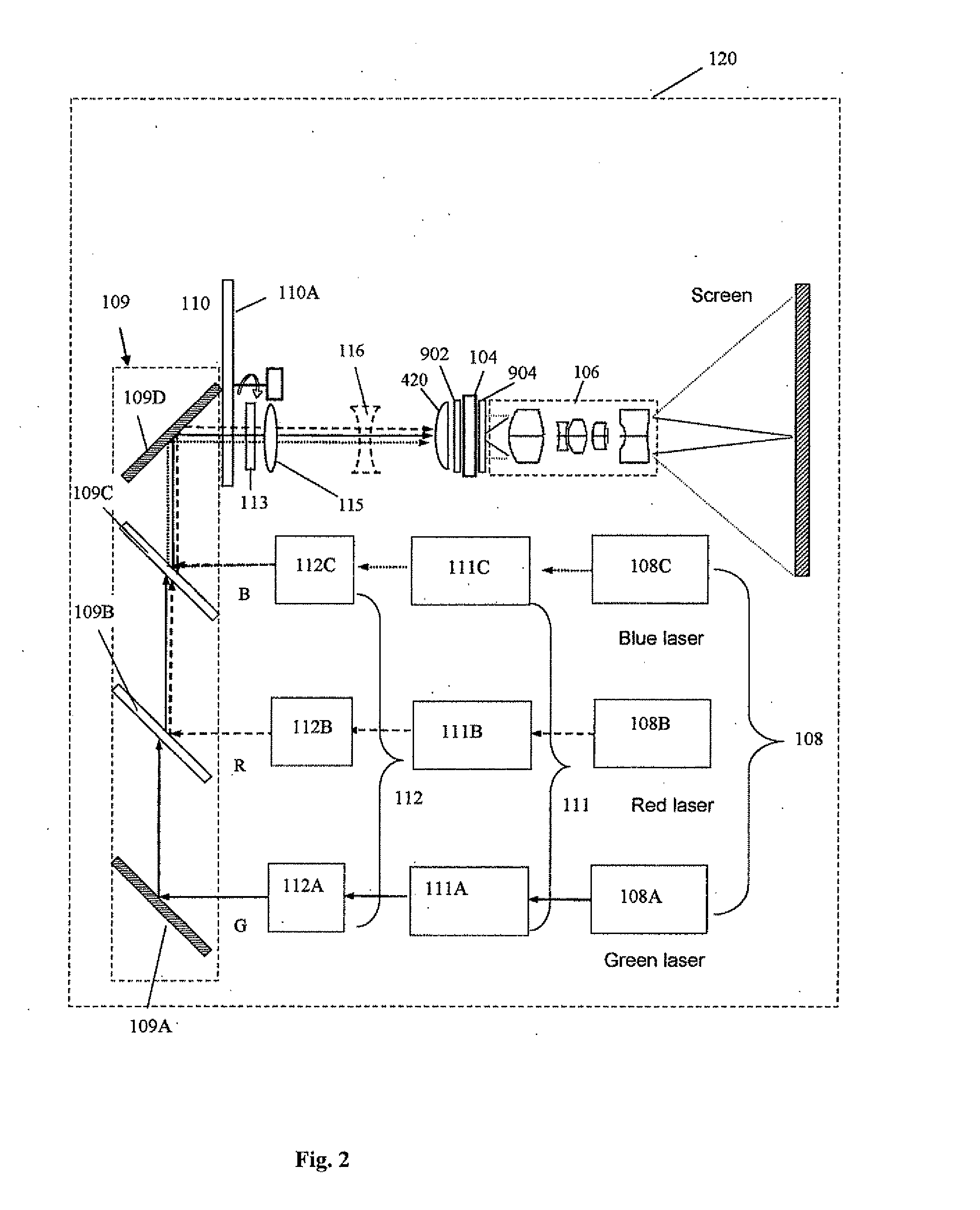

Micro-projector

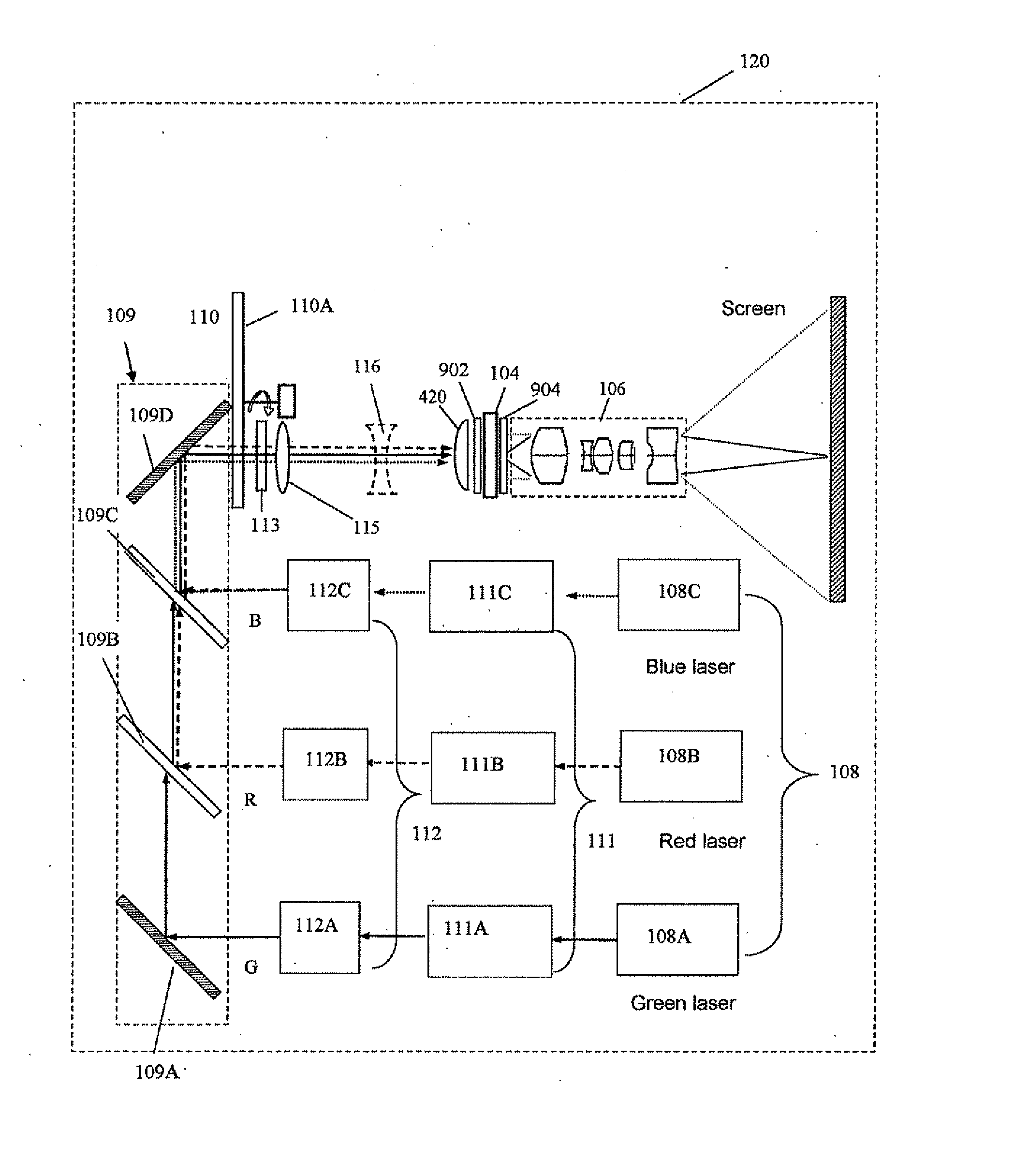

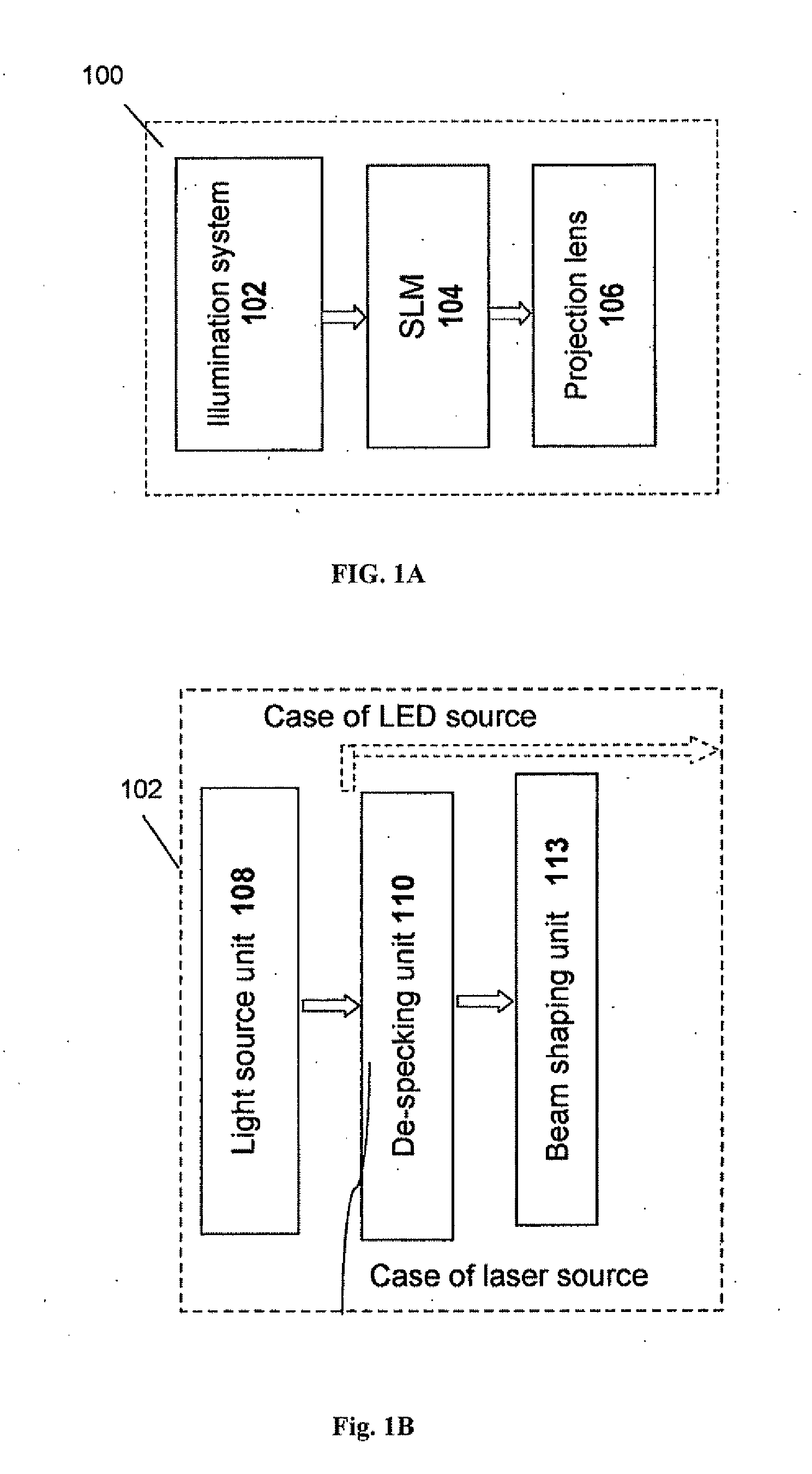

InactiveUS20110037953A1Increase brightnessQuality improvementTelevision system detailsPrismsDisplay deviceLaser source

The present invention provides a projection display comprising an illumination system comprising at least one laser source unit and configured and operable for producing one or more light beams; a spatial light modulating (SLM) system accommodated at output of the illumination system and comprising one or more SLM units for modulating light incident thereon in accordance with image data; and a light projection optics for imaging modulated light onto a projection surface. The illumination system comprises at least one beam shaping unit comprising a Dual Micro-lens Array (DMLA) arrangement formed by front and rear micro-lens arrays (MLA) located in front and rear parallel planes spaced-apart along an optical path of light propagating towards the SLM unit, the DMLA arrangement being configured such that each lenslet of the DMLA directs light incident thereon onto the entire active surface of the SLM unit, each lenslet having a geometrical aspect ratio corresponding to an aspect ratio of said active surface of the SLM unit.

Owner:EXPLAY

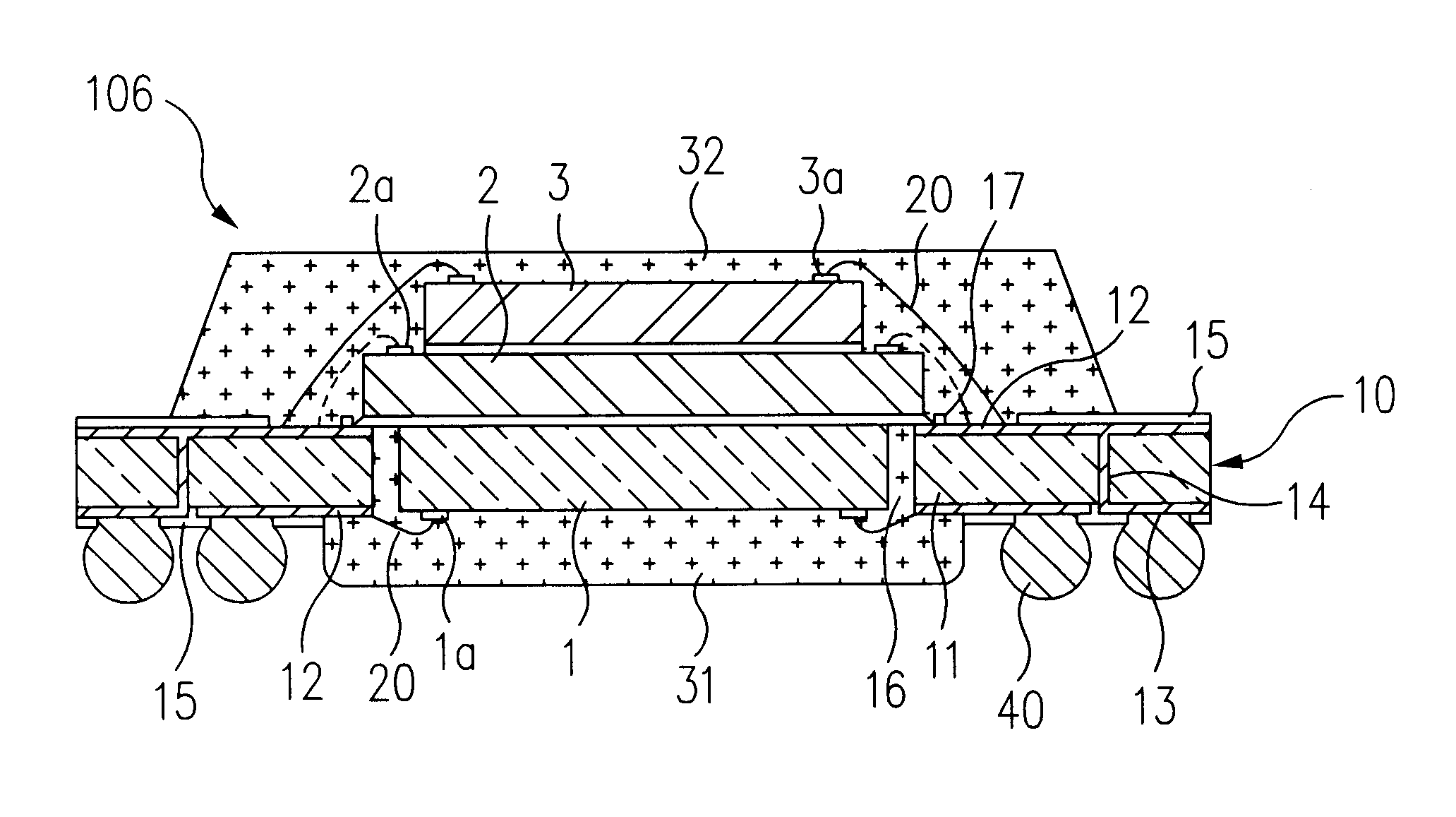

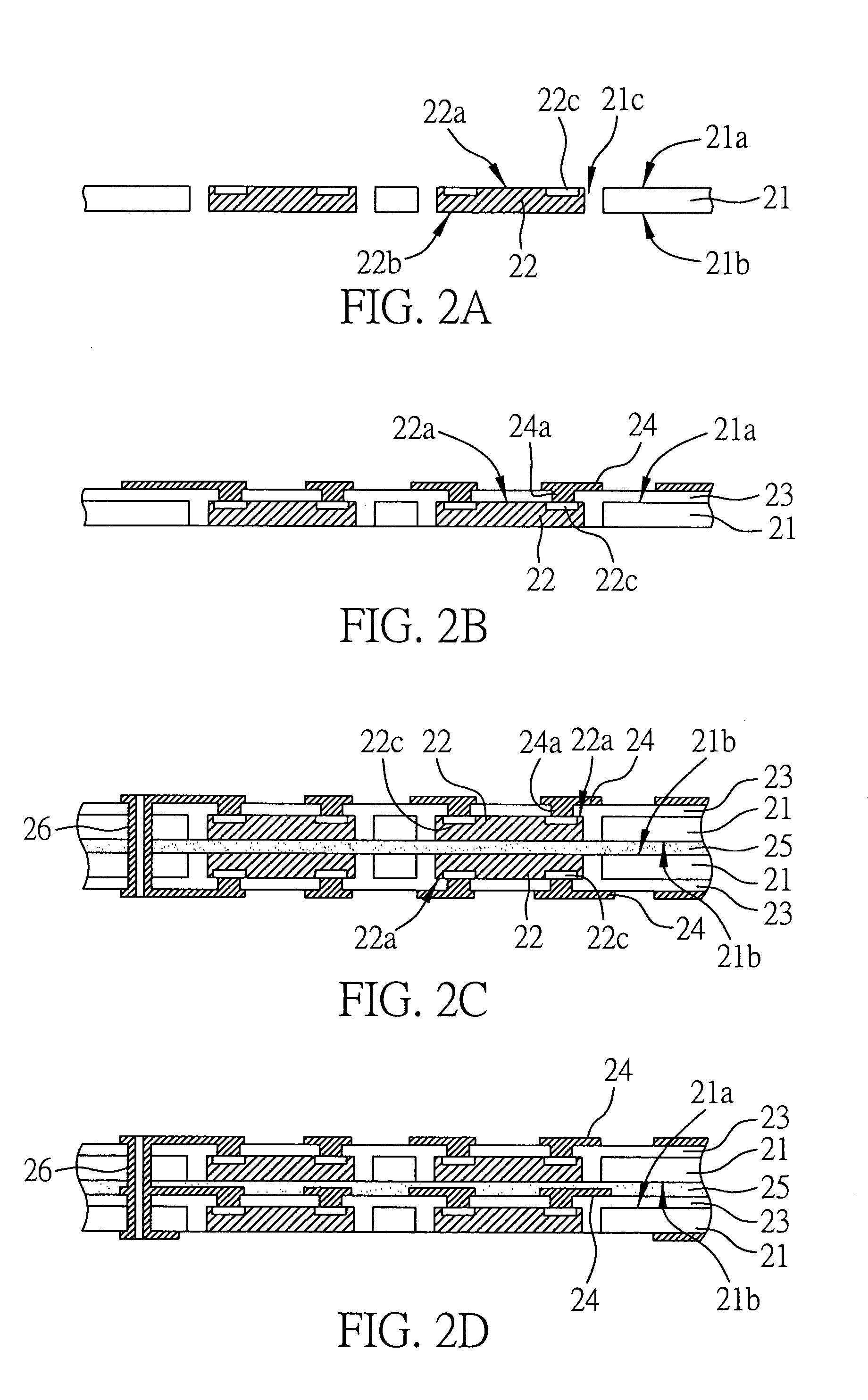

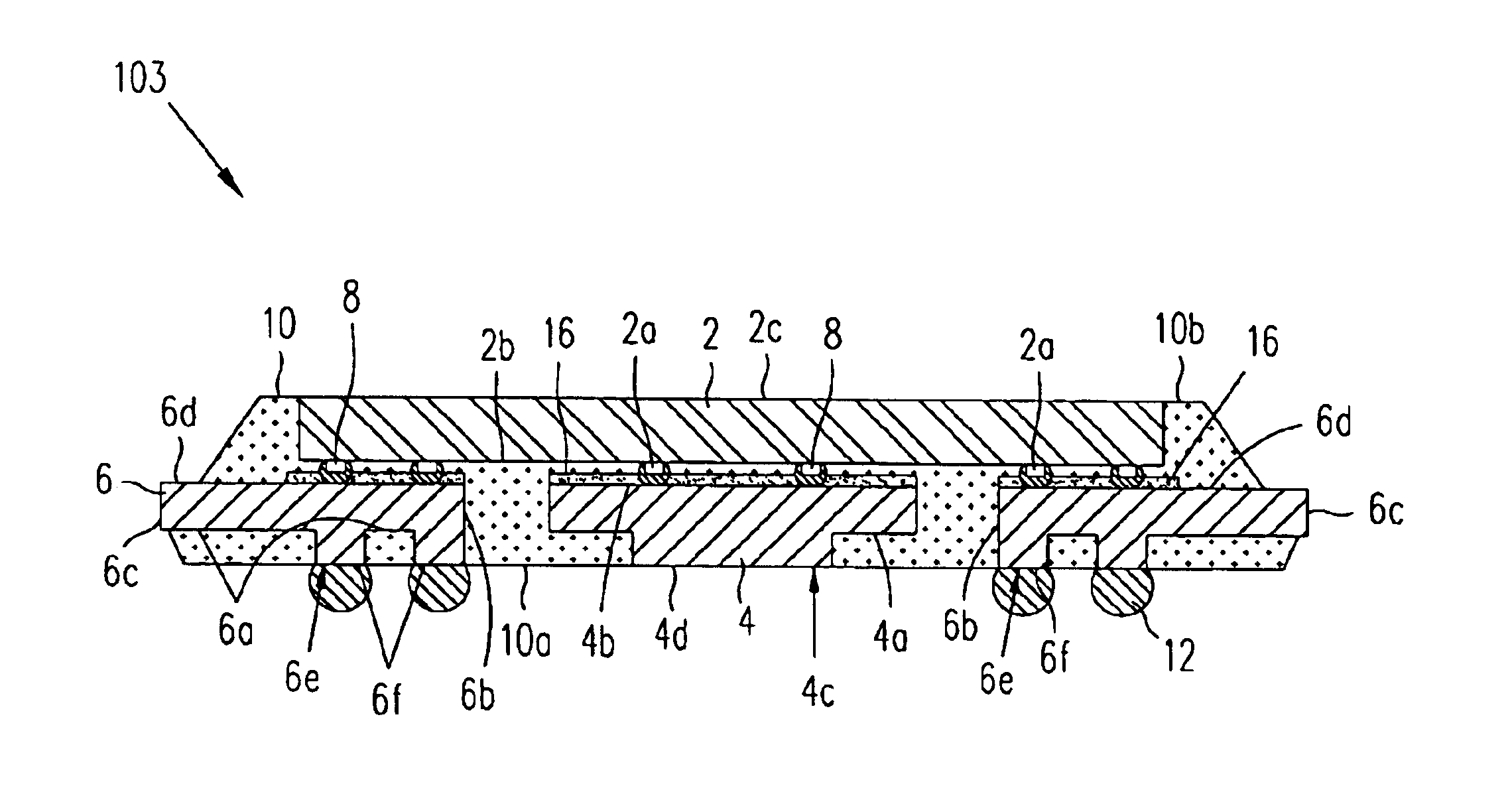

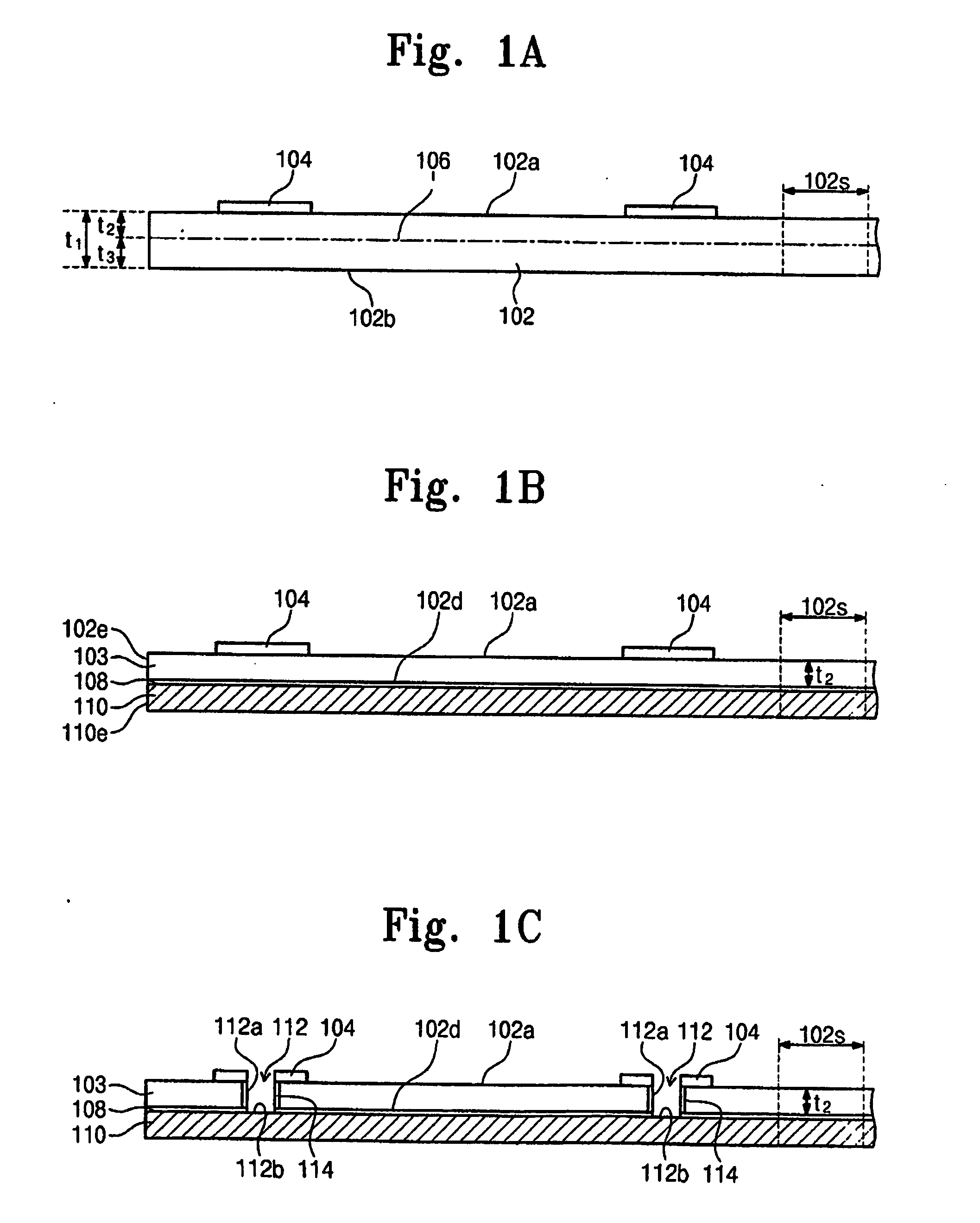

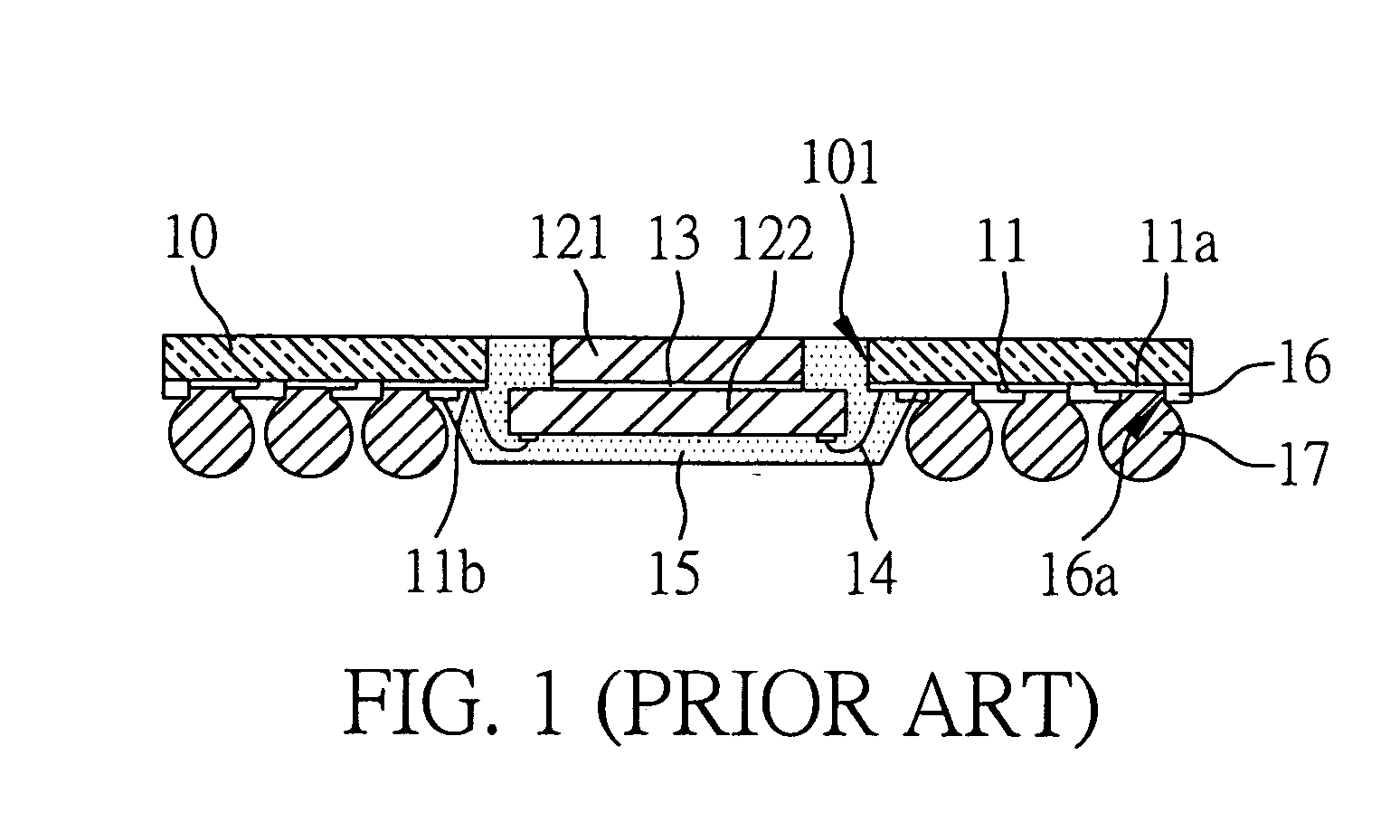

Semiconductor package and method for fabricating the same

InactiveUS6798049B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package and method for fabricating the same is disclosed. In one embodiment, the semiconductor package includes a circuit board, at least two semiconductor chips, electric connection means, an encapsulant, and a plurality of conductive balls. The circuit board has a resin layer and a circuit pattern. The resin layer is provided with an opening at its center portion. The circuit pattern is formed on at least one of upper and lower surfaces of the resin layer and includes one or more bond fingers and ball lands exposed to the outside. The semiconductor chips have a plurality of input / output pads on an active surface thereof. The semiconductor chips are stacked at a position of the opening of the circuit board, with at least one of the chips being within the opening. Alternatively, both chips are in the opening. The electric connection means connects the input / output pads of the semiconductor chips to the bond fingers of the circuit board. The encapsulant surrounds the semiconductor chips so as to protect the chips from the external environment. The conductive balls are fusion-bonded on the ball lands of the circuit board.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Methods and apparatus relating to singulating semiconductor wafers and wafer scale assemblies

ActiveUS20050202651A1Increase distanceAvoid excessive widthSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Methods relating to the singulation of dice from semiconductor wafers. Trenches or channels are formed in the bottom surface of a semiconductor wafer, corresponding in location to the wafer streets. The trenches may be formed by etching or through an initial laser cut. The wafer is then singulated along the streets with a laser preferably having a beam narrower than the trenches. Multiple, laterally spaced lasers may be used in combination during a single pass to perform simultaneous singulating cuts. Additional edge protection for integrated circuitry on the active surface of the semiconductor dice may be provided by forming trenches or channels along the streets in the active surface instead of the bottom surface, disposing protective material along the streets and within the trenches prior to singulation and cutting through the wafer, leaving protective material on the sidewalls of the channels.

Owner:MICRON TECH INC

Method for manufacturing wafer level chip scale package using redistribution substrate

InactiveUS20060079019A1Increase widthIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringChip-scale package

The present invention provides a method for manufacturing a wafer level chip scale package using a redistribution substrate, which has patterned bump pairs connected by redistribution lines and formed on a transparent insulating substrate. The redistribution substrate is produced separately from a wafer and then bonded to the wafer. One part of each bump pair is in contact with a chip pad on the active surface of the wafer, and the other part coincides with one of holes formed in the wafer. Conductive lines are formed in the holes and on the non-active surface of the wafer. External connection terminals are formed on the conductive lines at the non-active surface.

Owner:EPWORKS

Fingerprint-reading system

InactiveUS20010026636A1Image analysisElectric/magnetic contours/curvatures measurementsEffective surfaceRelative motion

Owner:APPLE INC

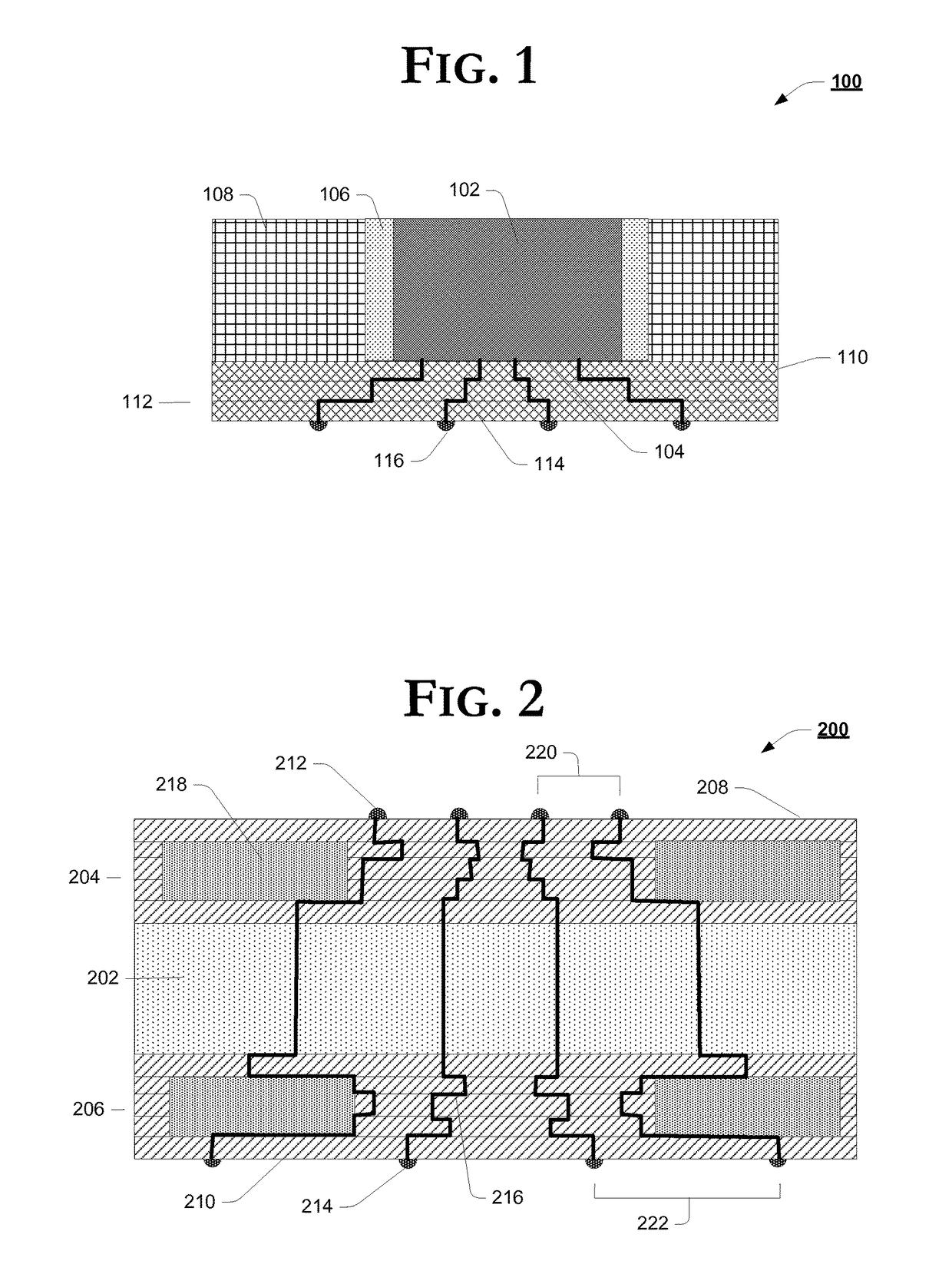

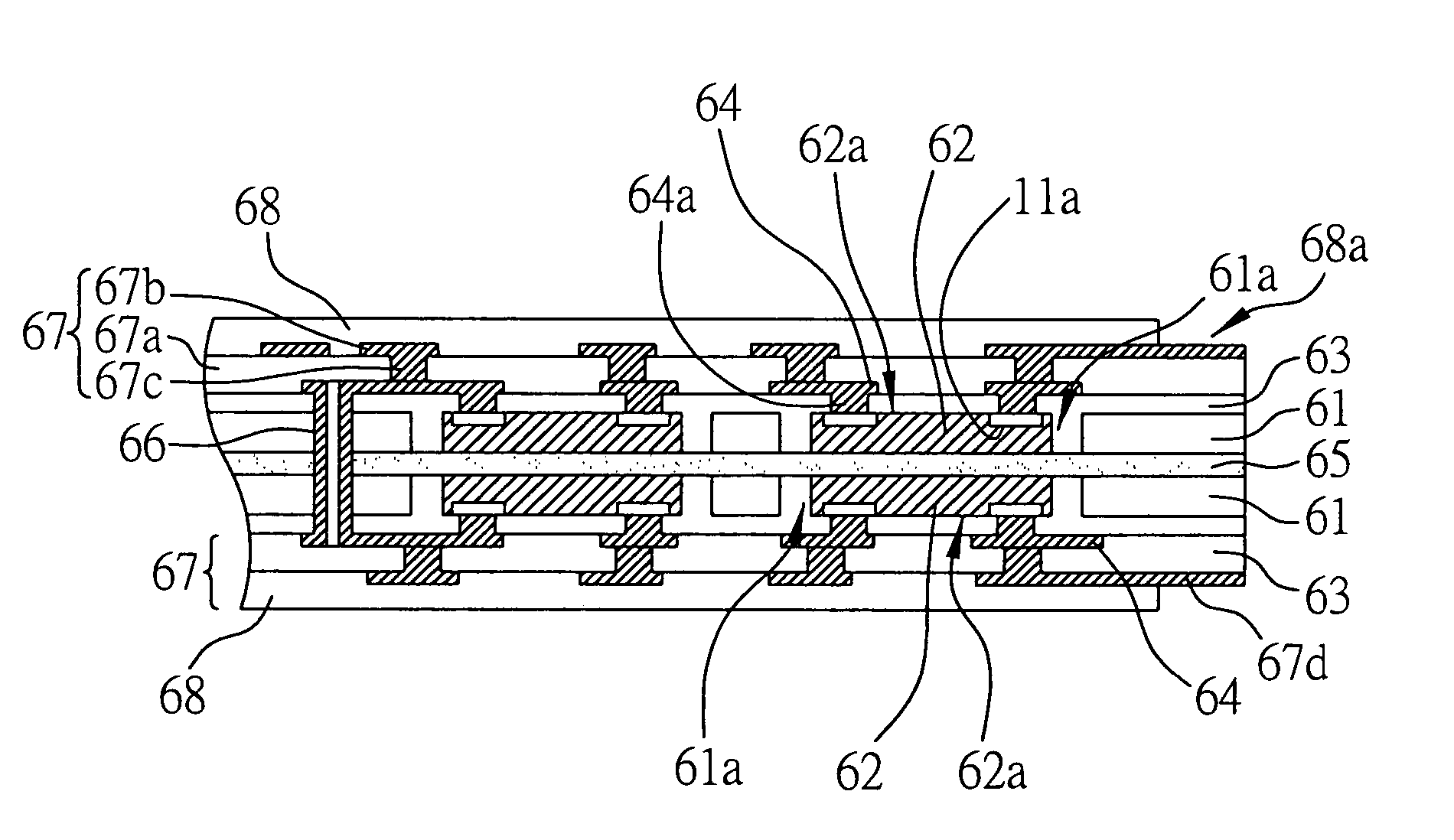

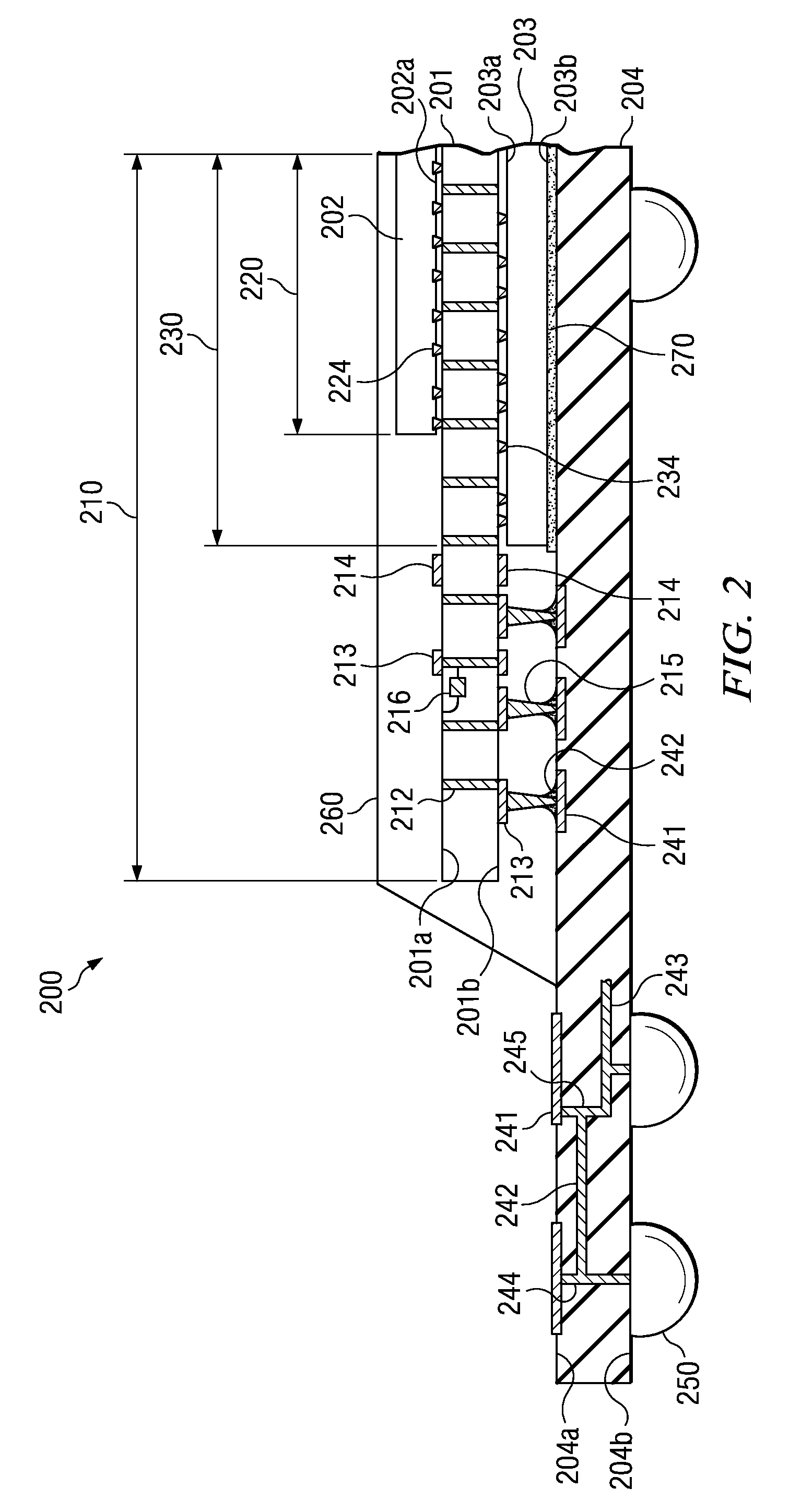

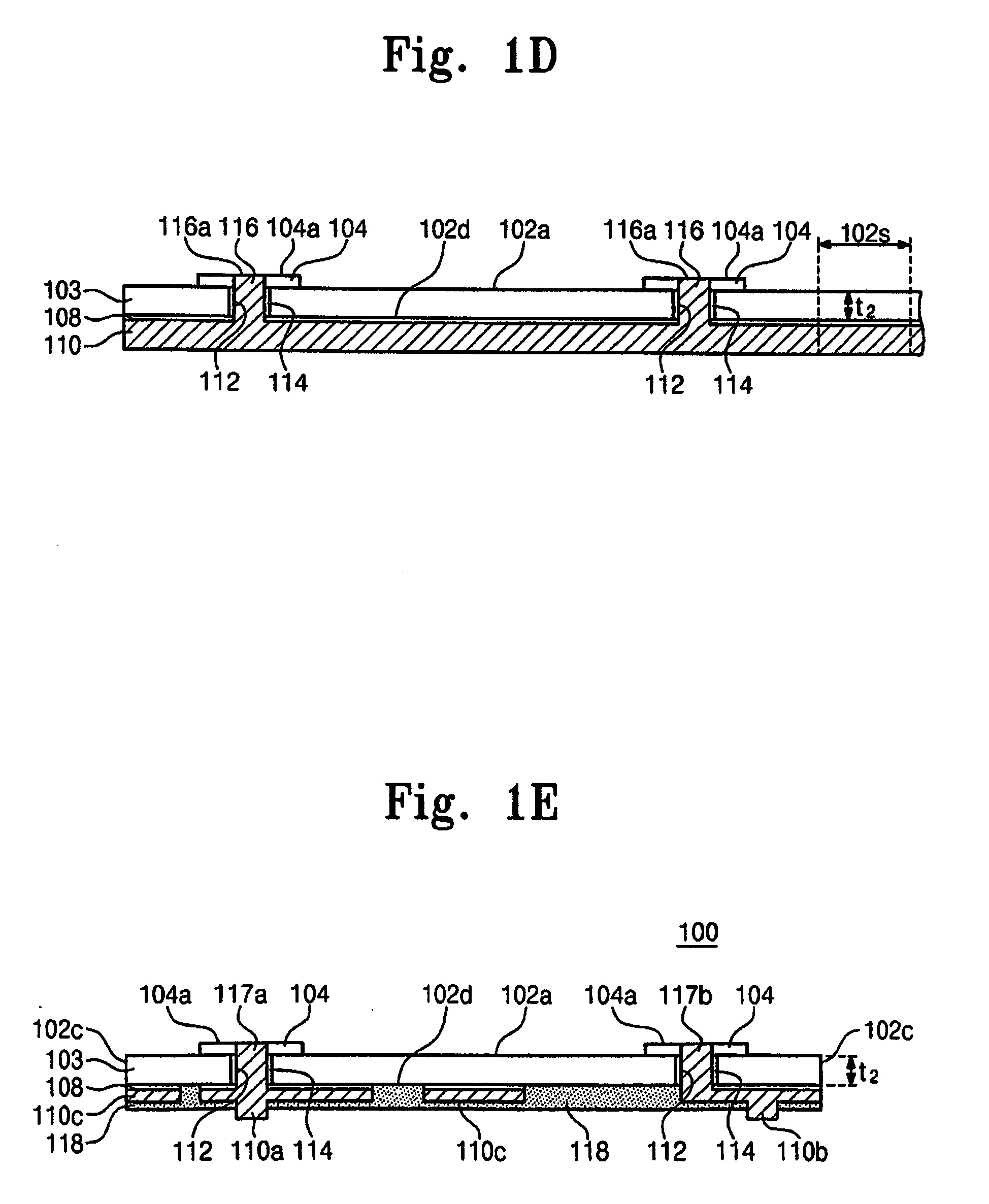

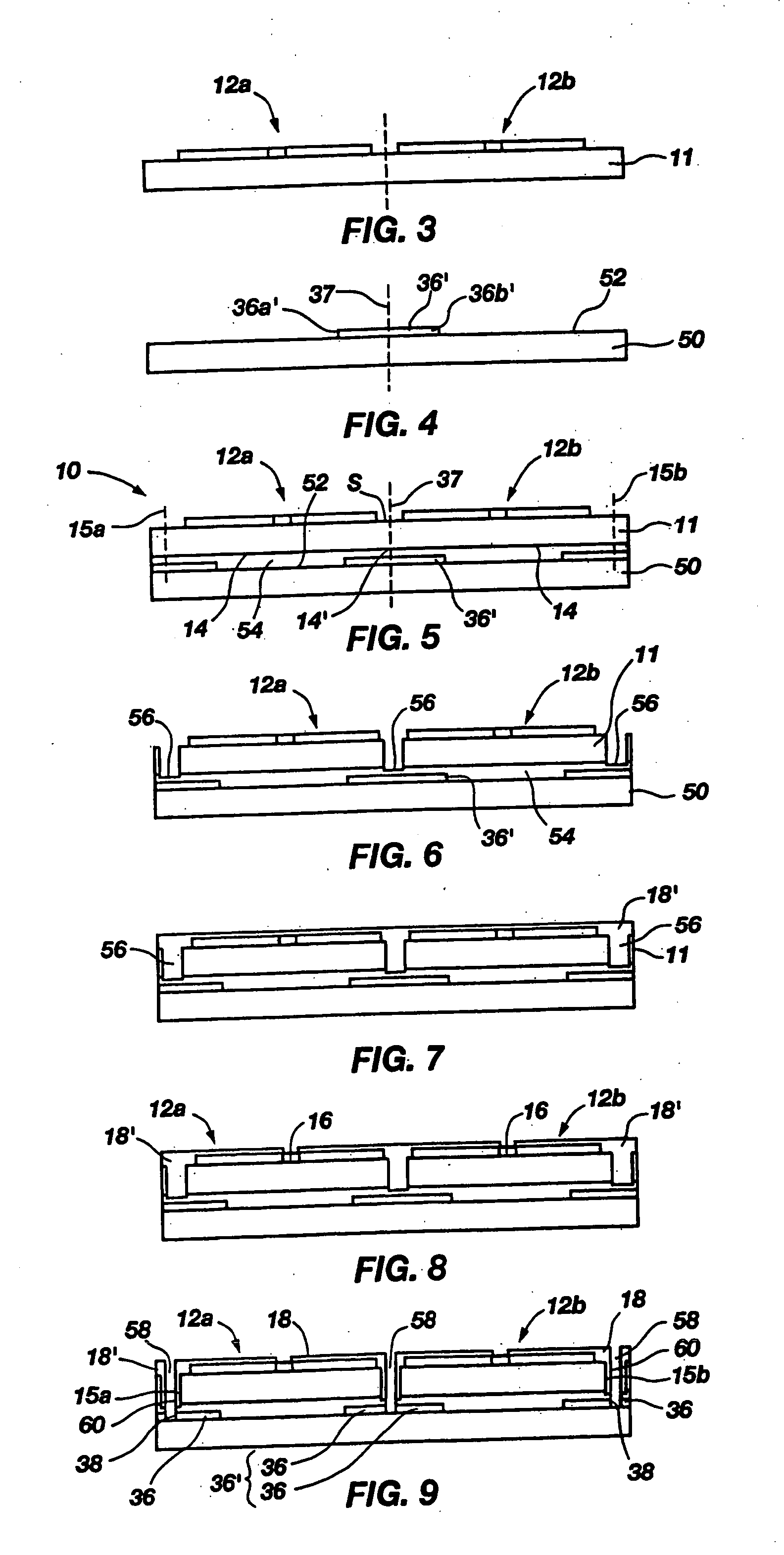

Stack structure with semiconductor chip embedded in carrier

ActiveUS7321164B2Easy to changeSmall sizeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

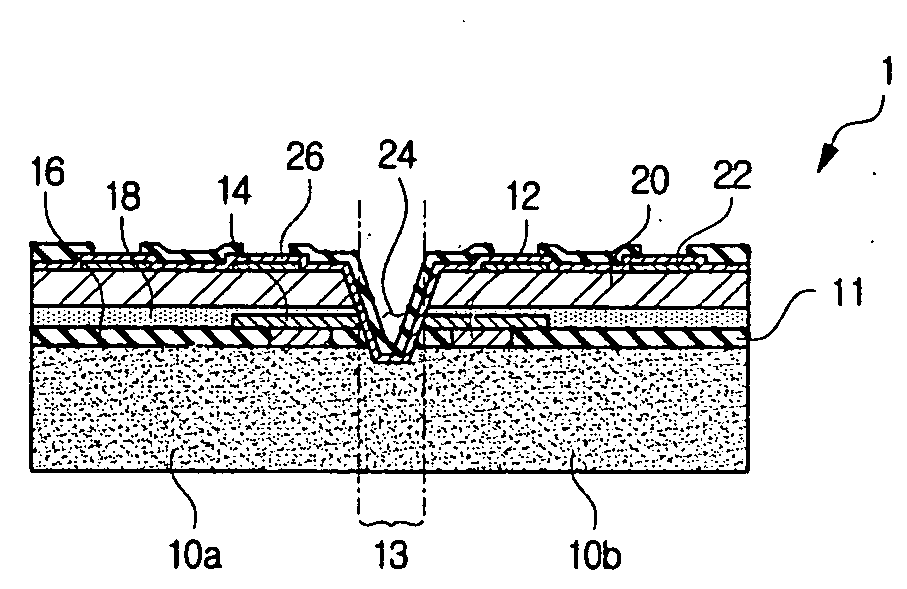

A stack structure with semiconductor chips embedded in carriers comprises two carriers stacking together as a whole, at least two semiconductor chips having active surfaces with electrode pads and inactive surfaces corresponding thereto placed in the cavities of the carriers, at least one dielectric layer formed on the active surface of the semiconductor chip and the surface of the carrier, at least a conductive structure formed in the opening of the dielectric layer, and at least a circuit layer formed on the surface of the dielectric layer wherein the circuit layer is electrically connected to the electrode pad by the conductive structure, so as to form a three-dimensional module to increase the storage capacity dramatically and integrate the semiconductor chips in the carriers for efficiently reducing the size of the module, so that the combinations can be changed flexibly to form the required storage capacity according to the demands.

Owner:PHOENIX PRECISION TECH CORP

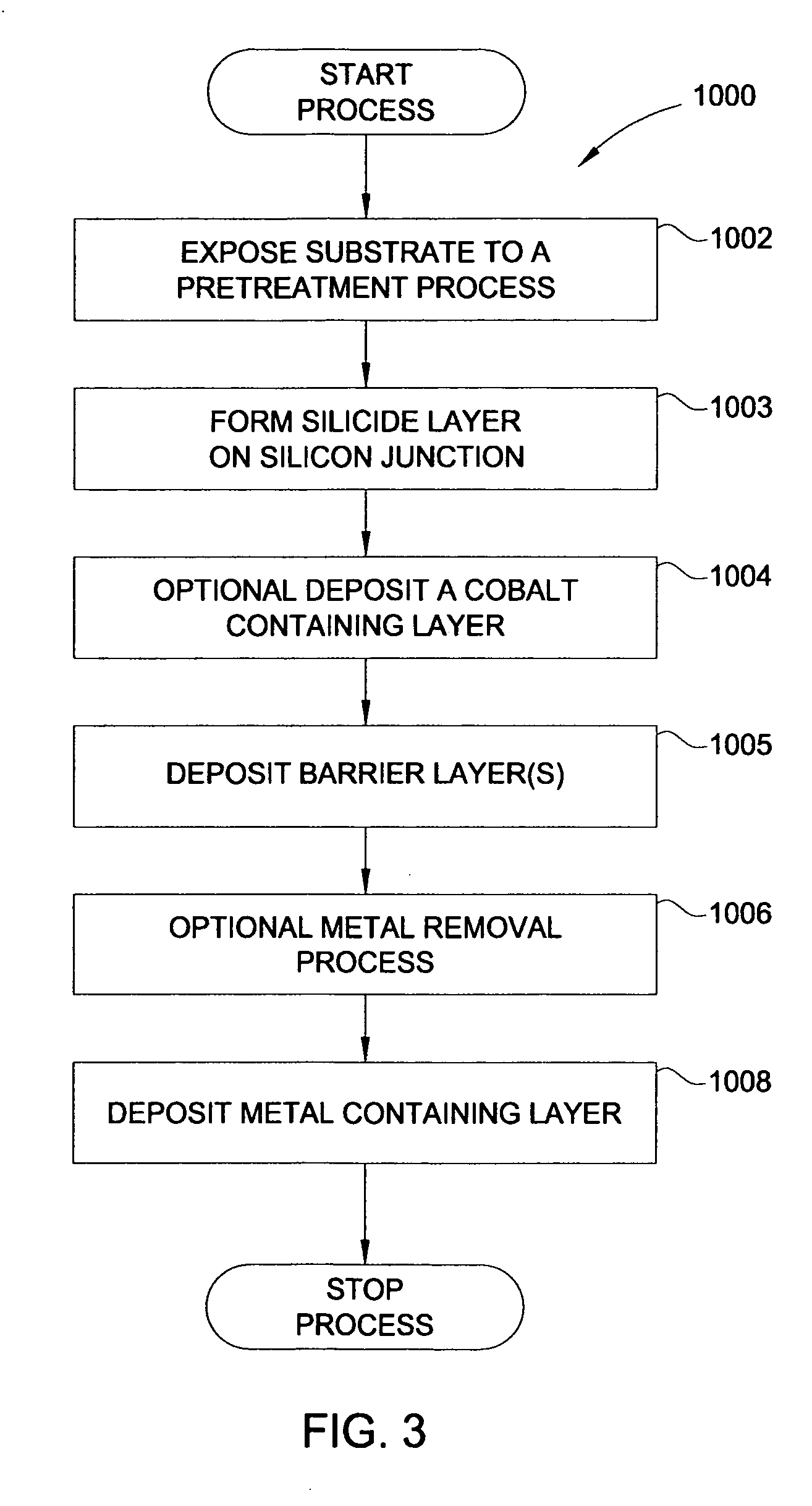

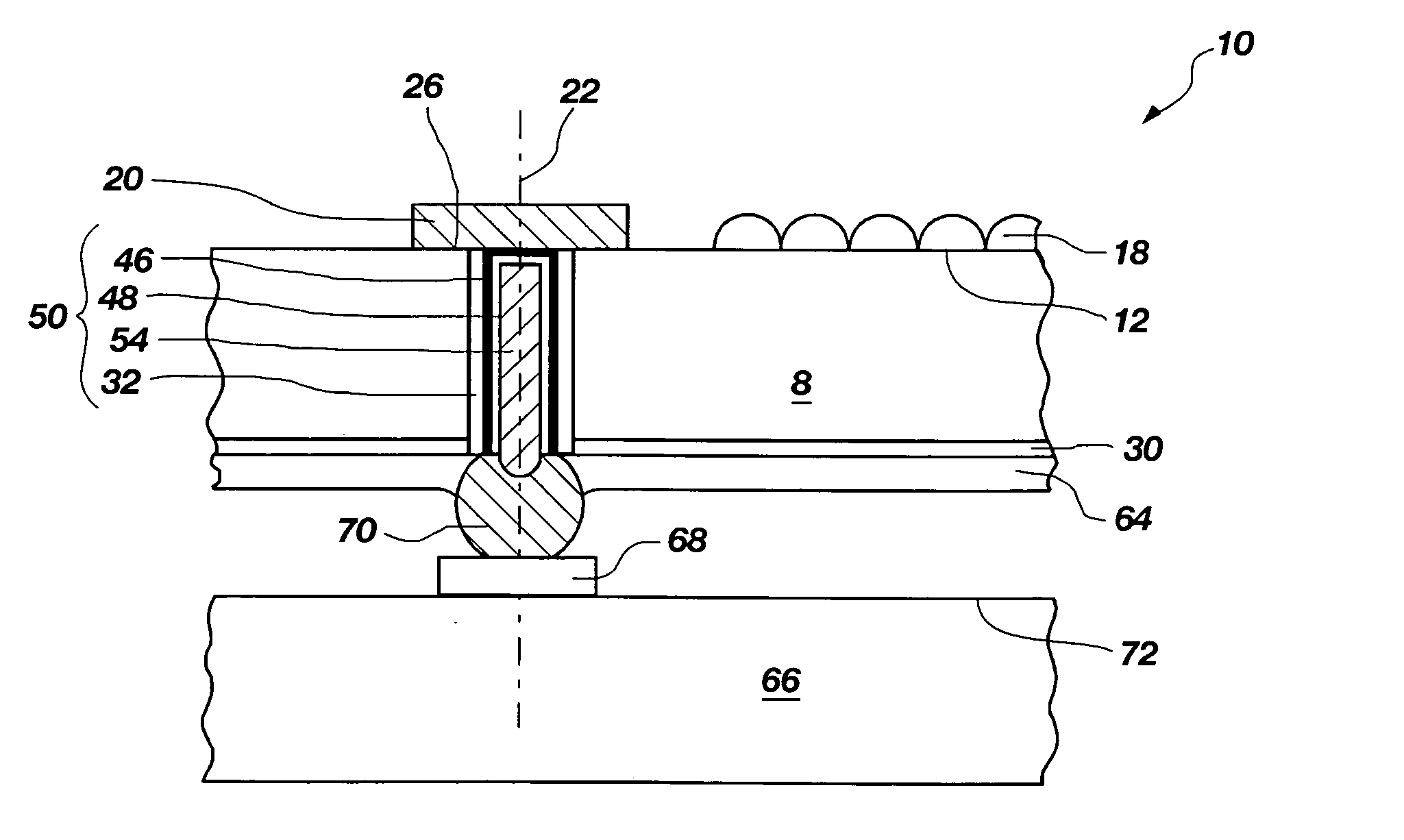

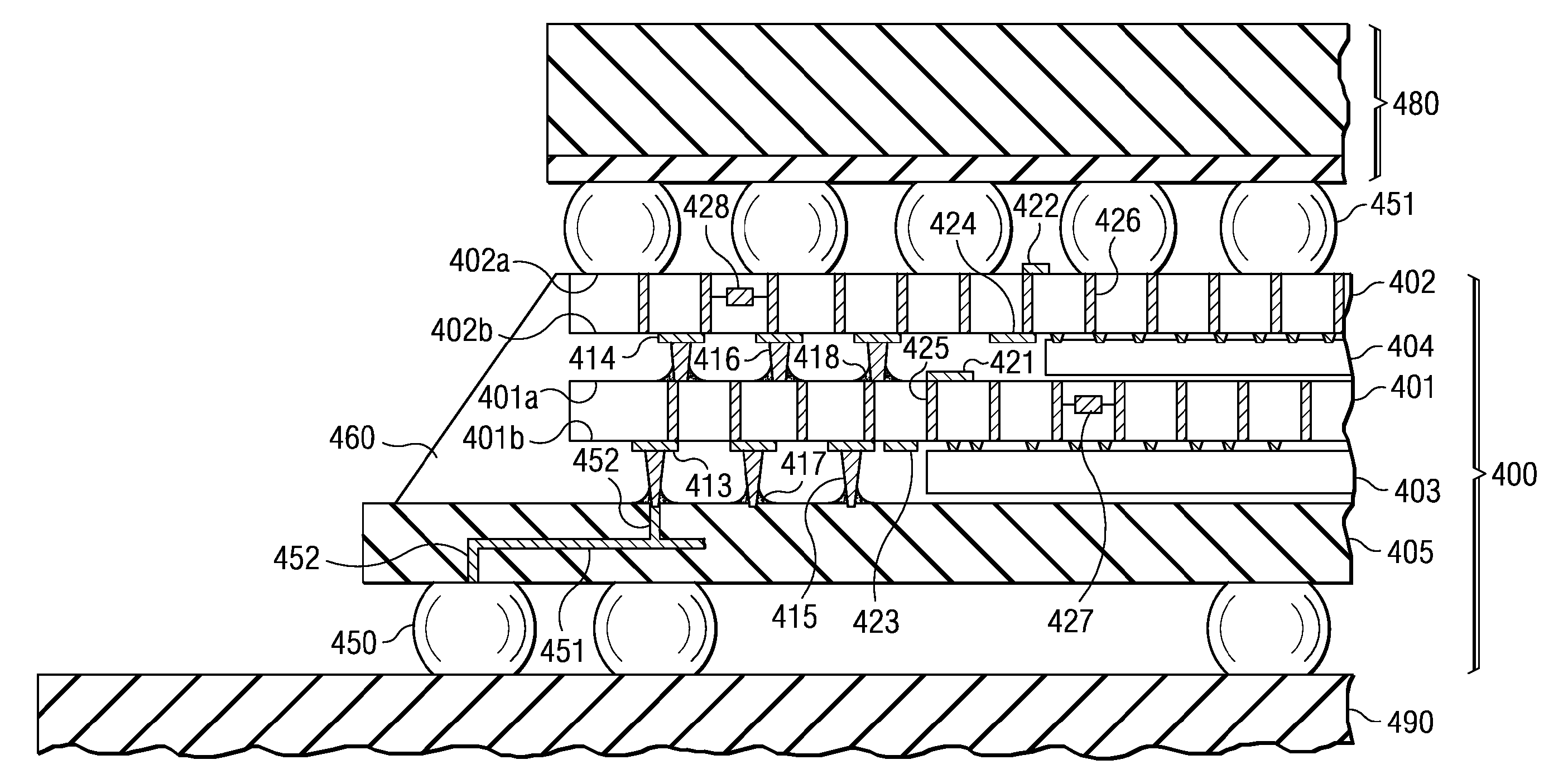

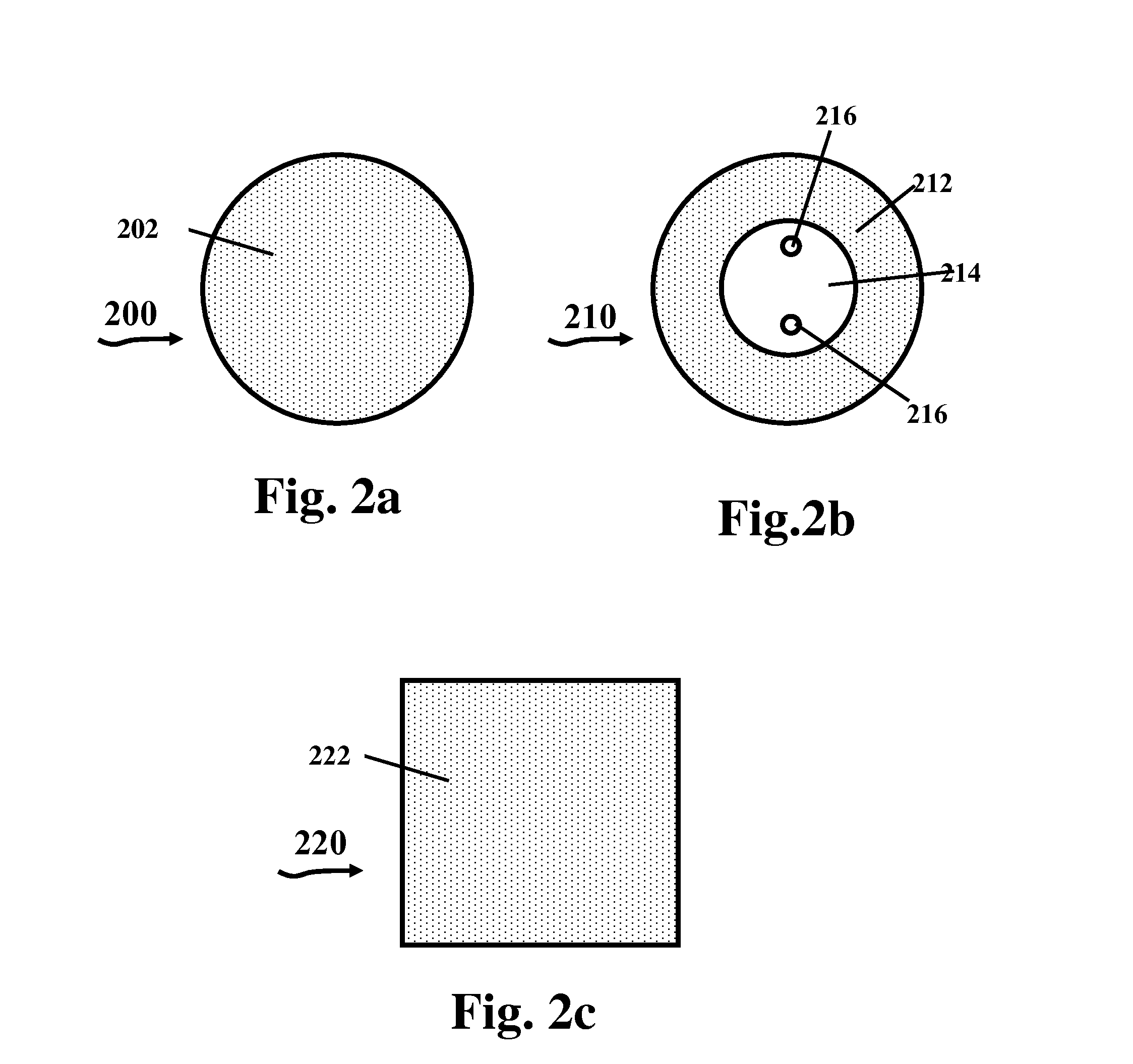

Packaged system of semiconductor chips having a semiconductor interposer

ActiveUS20070235850A1Increase powerIncrease speedSemiconductor/solid-state device detailsSolid-state devicesChip sizeInterposer

A semiconductor system (200) of one or more semiconductor interposers (201) with a certain dimension (210), conductive vias (212) extending from the first to the second surface, with terminals and attached non-reflow metal studs (215) at the ends of the vias. A semiconducting interposer surface may include discrete electronic components or an integrated circuit. One or more semiconductor chips (202, 203) have a dimension (220, 230) narrower than the interposer dimension, and an active surface with terminals and non-reflow metal studs (224, 234). One chip is flip-attached to the first interposer surface, and another chip to the second interposer surface, so that the interposer dimension projects over the chip dimension. An insulating substrate (204) has terminals and reflow bodies (242) to connect to the studs of the projecting interposer.

Owner:TEXAS INSTR INC

Semiconductor package

InactiveUS6858919B2Lesser mounting heightLesser footprintSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package is disclosed that bonds a semiconductor chip to a leadframe using a flip chip technology. An exemplary semiconductor package includes a semiconductor chip having a plurality of input-output pads at an active surface thereof. A plurality of leads are superimposed by the bond pads and active surface of the semiconductor chip. The leads have at least one exposed surface at a bottom surface of the package body. A plurality of conductive connecting means electrically connect the input-output pads of the chip to the leads. A package body is formed over the semiconductor chip and the conductive connecting means. The bottom surface portions of the leads are exposed to the outside.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Method of fabricating a 3-D device and device made thereby

ActiveUS20090032966A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

A method of fabricating a semiconductor device includes providing a semiconductor substrate having an active surface, thinning the substrate by removing material from a second surface of the substrate opposite the active surface, bonding a metal carrier to the second surface of the thinned substrate, forming a via opening in the thinned substrate, forming a conductive member in the via opening, and patterning the metal carrier bonded to the second surface of the thinned substrate to form a metal pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

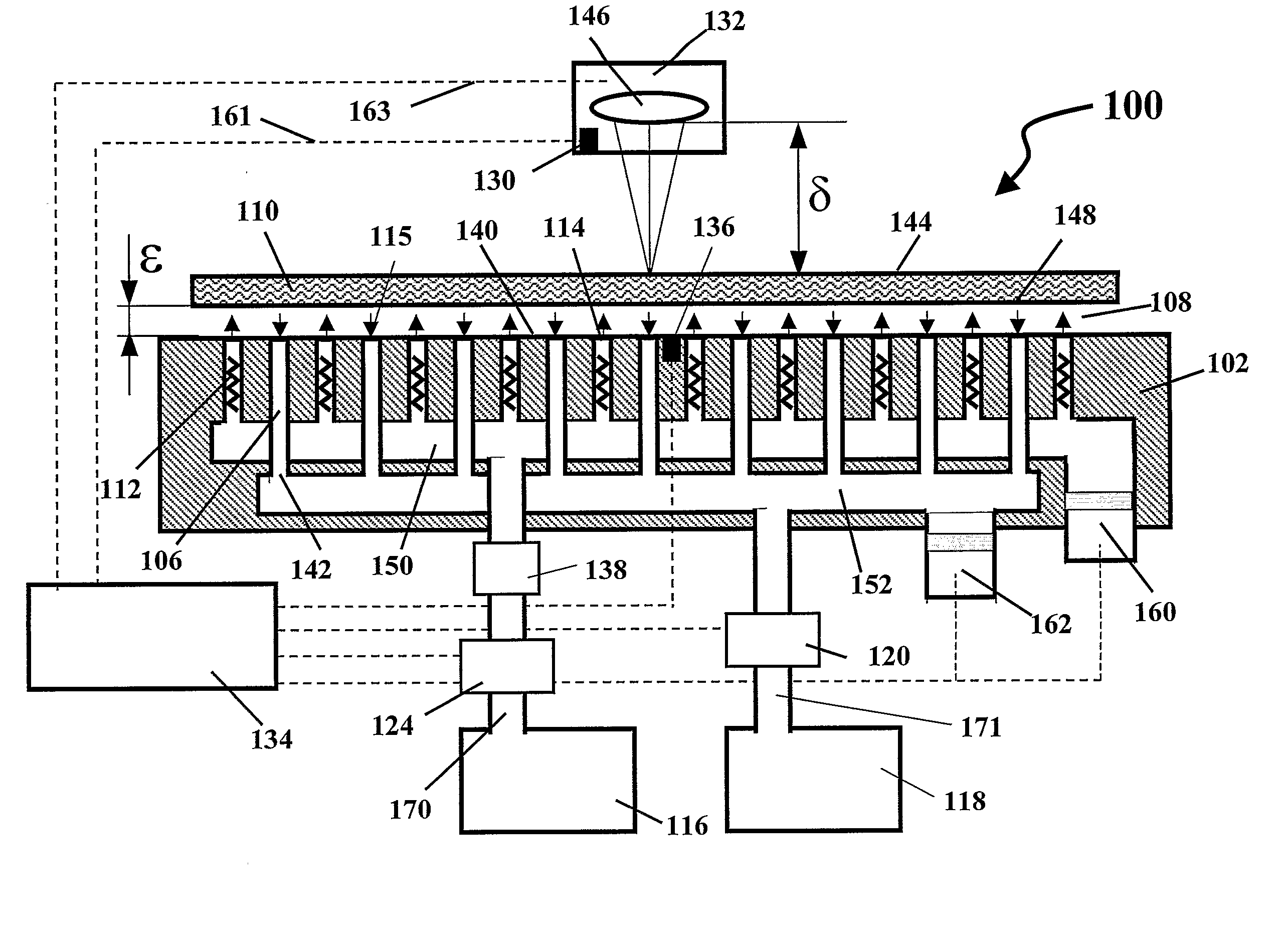

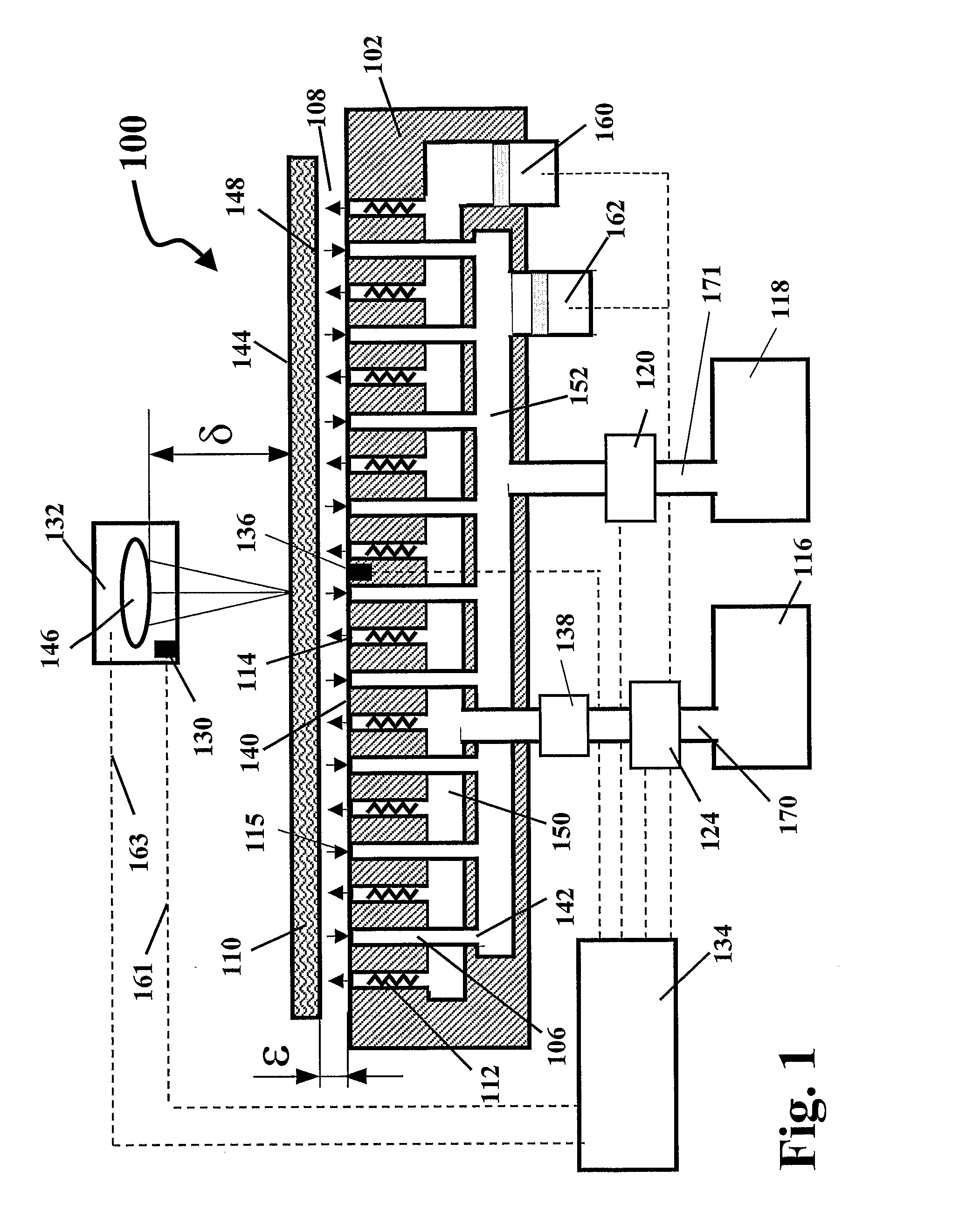

Non-contact support platforms for distance adjustment

An apparatus for supporting a stationary or moving substantially flat object without physical contact on an fluid-cushion. The object floats on a fluid cushion gap, the apparatus aimed for globally or locally adjusting the gap. The apparatus comprising: a first platform for supporting the object without contact, the platform having a substantially flat active surface comprised of one or more sectors, each sector comprising at least one of a plurality of basic cells, each basic cell having at least one of a plurality of pressure outlets fluidically connected through a pressure flow restrictors to a higher-pressure manifold associated with the sector in which the basic cell lies, the higher-pressure manifold is fluidically connected through main supply pipeline to pressurized fluid supply and at least one of a plurality of fluid-evacuation channels fluidically connected to a lower-pressure manifold associated with the sector in which the basic cell lies having main evacuation pipeline; wherein the flow restrictor characteristically exhibiting fluidic return spring behavior; and wherein at least one pressure control valve is interposed with at least one of the two main pipelines of at least one sector for controlling pressure levels of at least one of the two manifolds of that sector.

Owner:COREFLOW SCI SOLUTIONS

Integrated thermoelectric cooling devices and methods for fabricating same

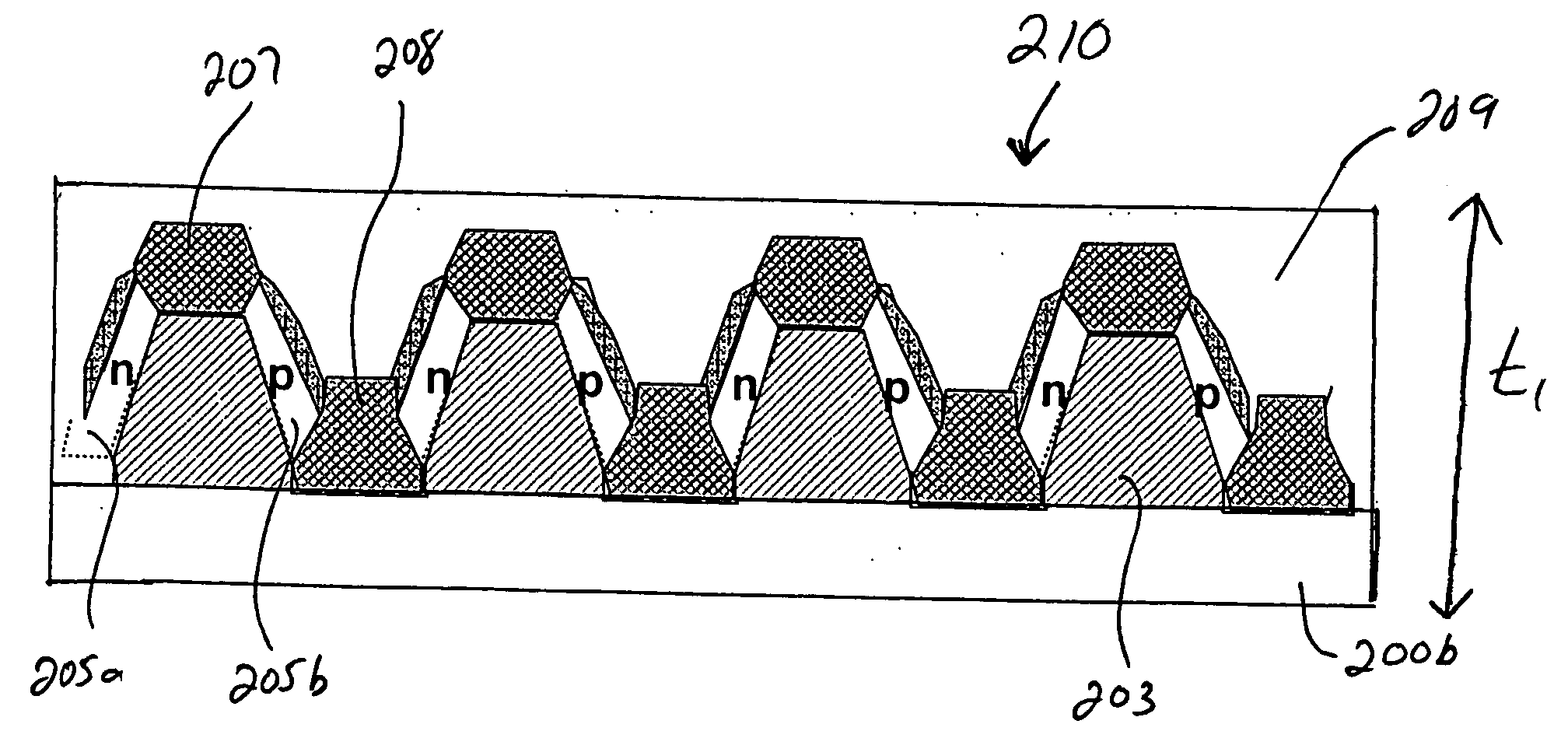

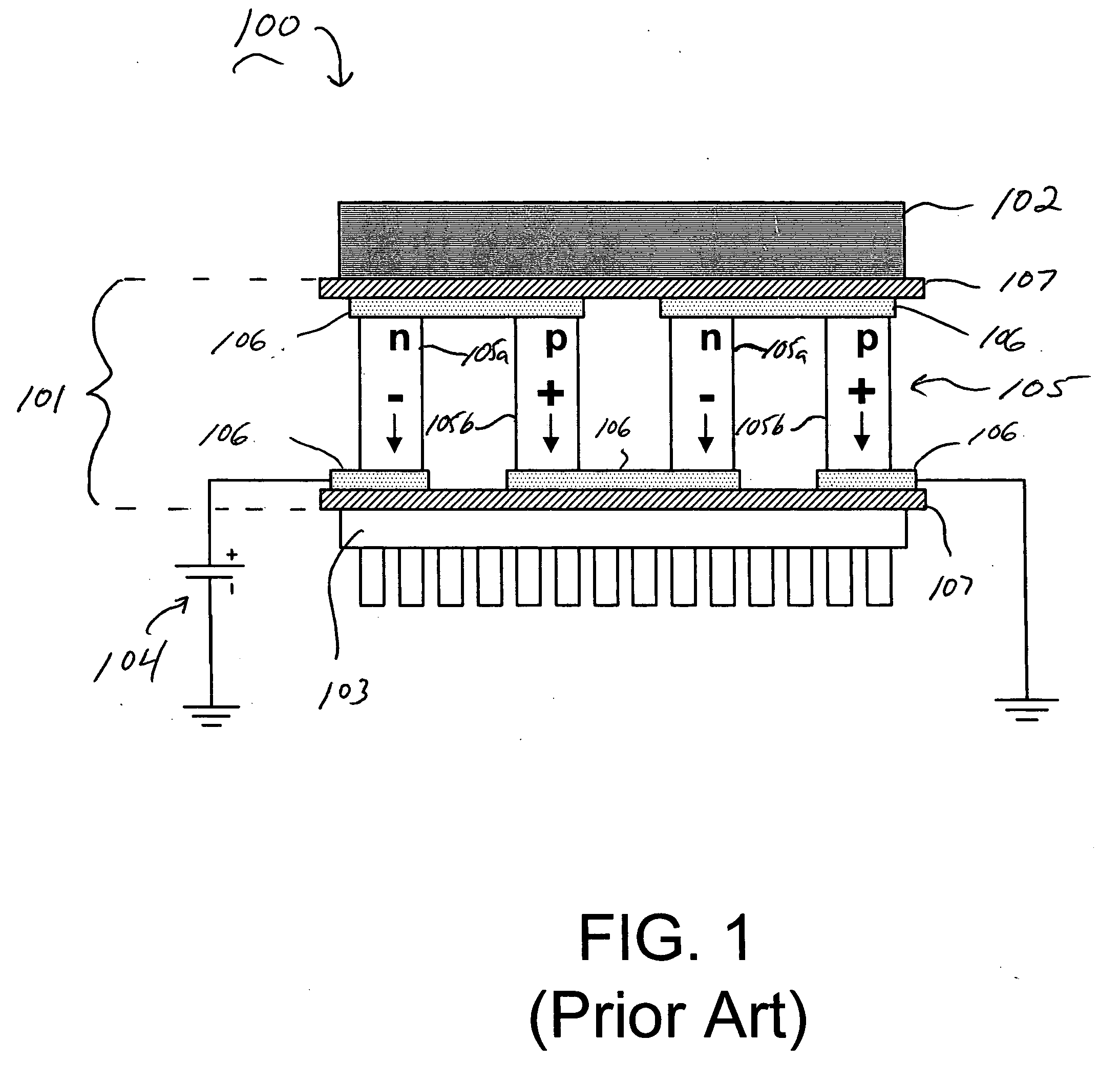

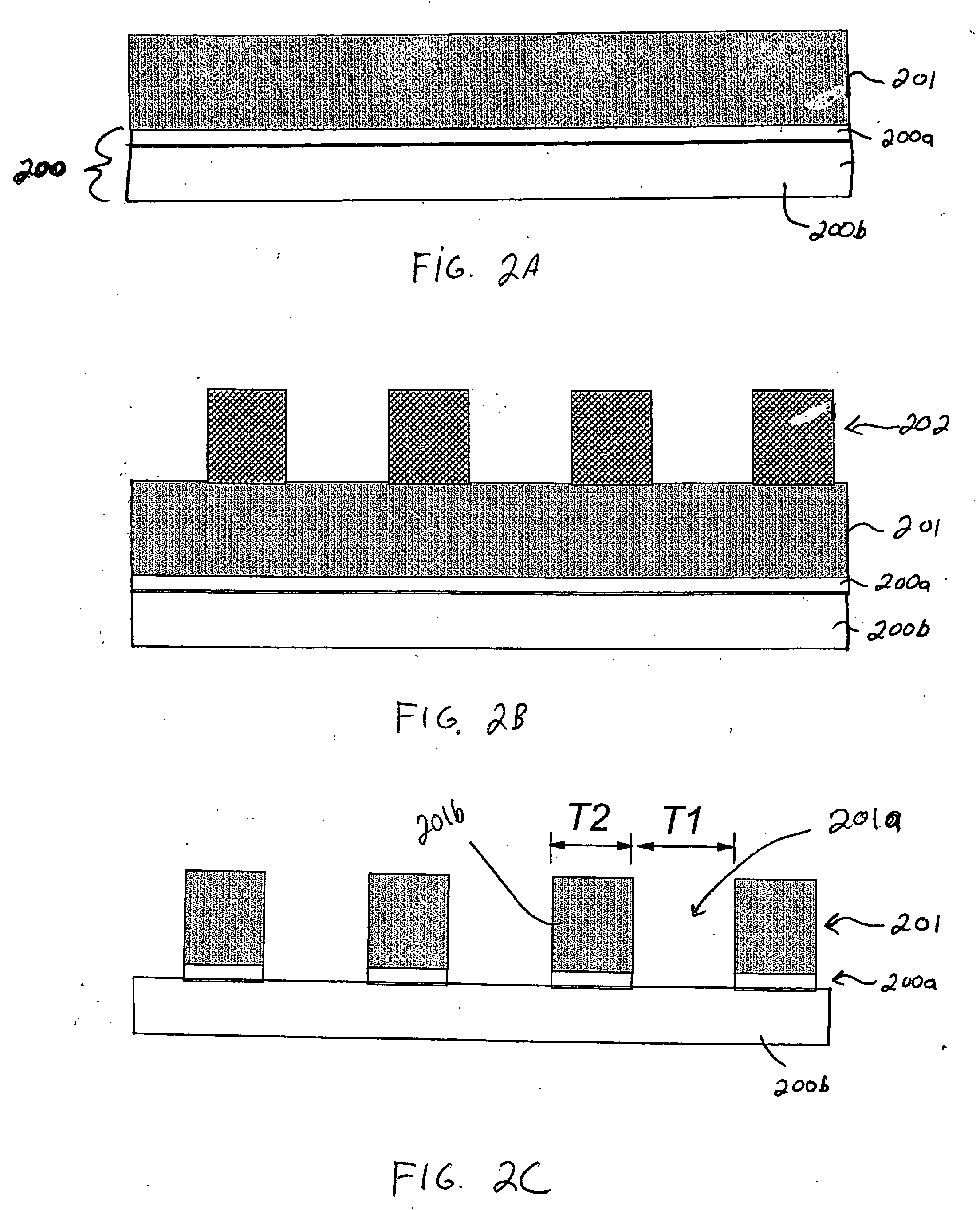

ActiveUS20060102223A1Reduced dimensionIncrease heatThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentThermoelectric coolingHigh density

Semiconductor integrated thermoelectric devices are provided, which are formed having high-density arrays of thermoelectric (TE) elements using semiconductor thin-film and VLSI (very large scale integration) fabrication processes. Thermoelectric devices can be either separately formed and bonded to semiconductor chips, or integrally formed within the non-active surface of semiconductor chips, for example.

Owner:GLOBALFOUNDRIES US INC

Microelectronic device having signal distribution functionality on an interfacial layer thereof

InactiveUS6894399B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringDistribution function

A microelectronic device includes a microelectronic die having an interfacial metal layer deposited over an active surface thereof to perform a signal distribution function within the device. The microelectronic die is fixed within a package core to form a die / core assembly. One or more metallization layers may then be built up over the die / core assembly as part of a packaging scheme. The interfacial metal layer can be applied either before or after the die is fixed within the package core. In one approach, the interfacial layer is applied during wafer-level processing.

Owner:INTEL CORP

Stack structure with semiconductor chip embedded in carrier

ActiveUS20070035015A1Good flexibilitySmall sizeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipDielectric layer

A stack structure with semiconductor chips embedded in carriers comprises two carriers stacking together as a whole, at least two semiconductor chips having active surfaces with electrode pads and inactive surfaces corresponding thereto placed in the cavities of the carriers, at least one dielectric layer formed on the active surface of the semiconductor chip and the surface of the carrier, at least a conductive structure formed in the opening of the dielectric layer, and at least a circuit layer formed on the surface of the dielectric layer wherein the circuit layer is electrically connected to the electrode pad by the conductive structure, so as to form a three-dimensional module to increase the storage capacity dramatically and integrate the semiconductor chips in the carriers for efficiently reducing the size of the module, so that the combinations can be changed flexibly to form the required storage capacity according to the demands.

Owner:PHOENIX PRECISION TECH CORP

Castellated chip-scale packages and methods for fabricating the same

ActiveUS20050067680A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A method for fabricating a chip-scale package includes securing a device substrate that carries at least two adjacent semiconductor devices to a sacrificial substrate. The sacrificial substrate may include conductive elements on a surface thereof, which are located so as to align along a street between each adjacent pair of semiconductor devices on the device substrate. The device substrate is then severed along each street and the newly formed peripheral edge of each semiconductor device coated with dielectric material. If the sacrificial substrate includes conductive elements, they may be exposed between adjacent semiconductor devices and subsequently serve as lower sections of contacts. Peripheral sections of contacts are formed on the peripheral edge. Upper sections of the contacts may also be formed over the active surfaces of the semiconductor devices. Once the contacts are formed, the sacrificial substrate is substantially removed from the back sides of the semiconductor devices.

Owner:MICRON TECH INC