Patents

Literature

14118 results about "Semiconductor package" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A semiconductor package is a metal, plastic, glass, or ceramic casing containing one or more discrete semiconductor devices or integrated circuits. Individual components are fabricated on semiconductor wafers (commonly silicon) before being diced into die, tested, and packaged. The package provides a means for connecting the package to the external environment, such as printed circuit board, via leads such as lands, balls, or pins; and protection against threats such as mechanical impact, chemical contamination, and light exposure. Additionally, it helps dissipate heat produced by the device, with or without the aid of a heat spreader. There are thousands of package types in use. Some are defined by international, national, or industry standards, while others are particular to an individual manufacturer.

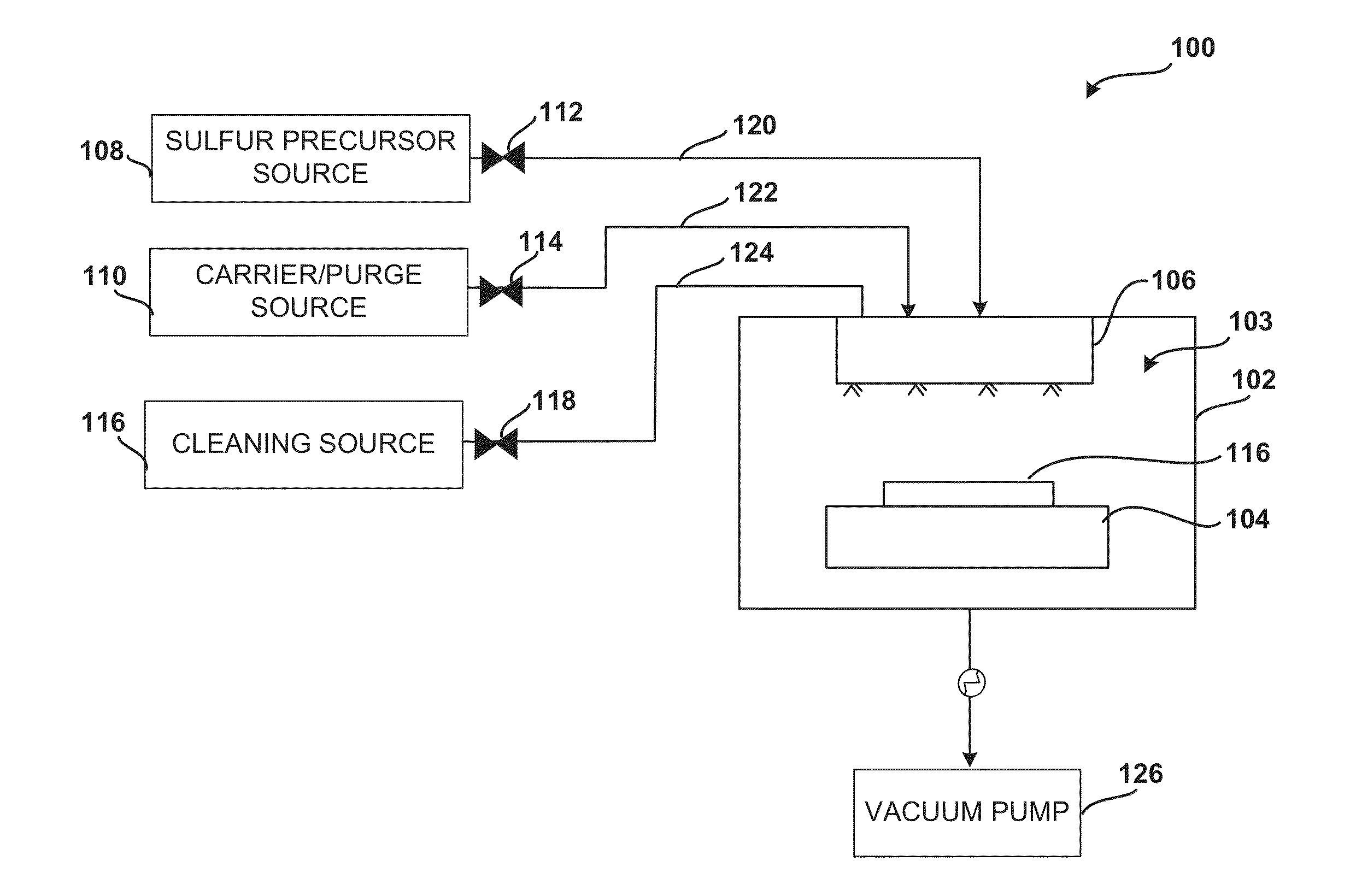

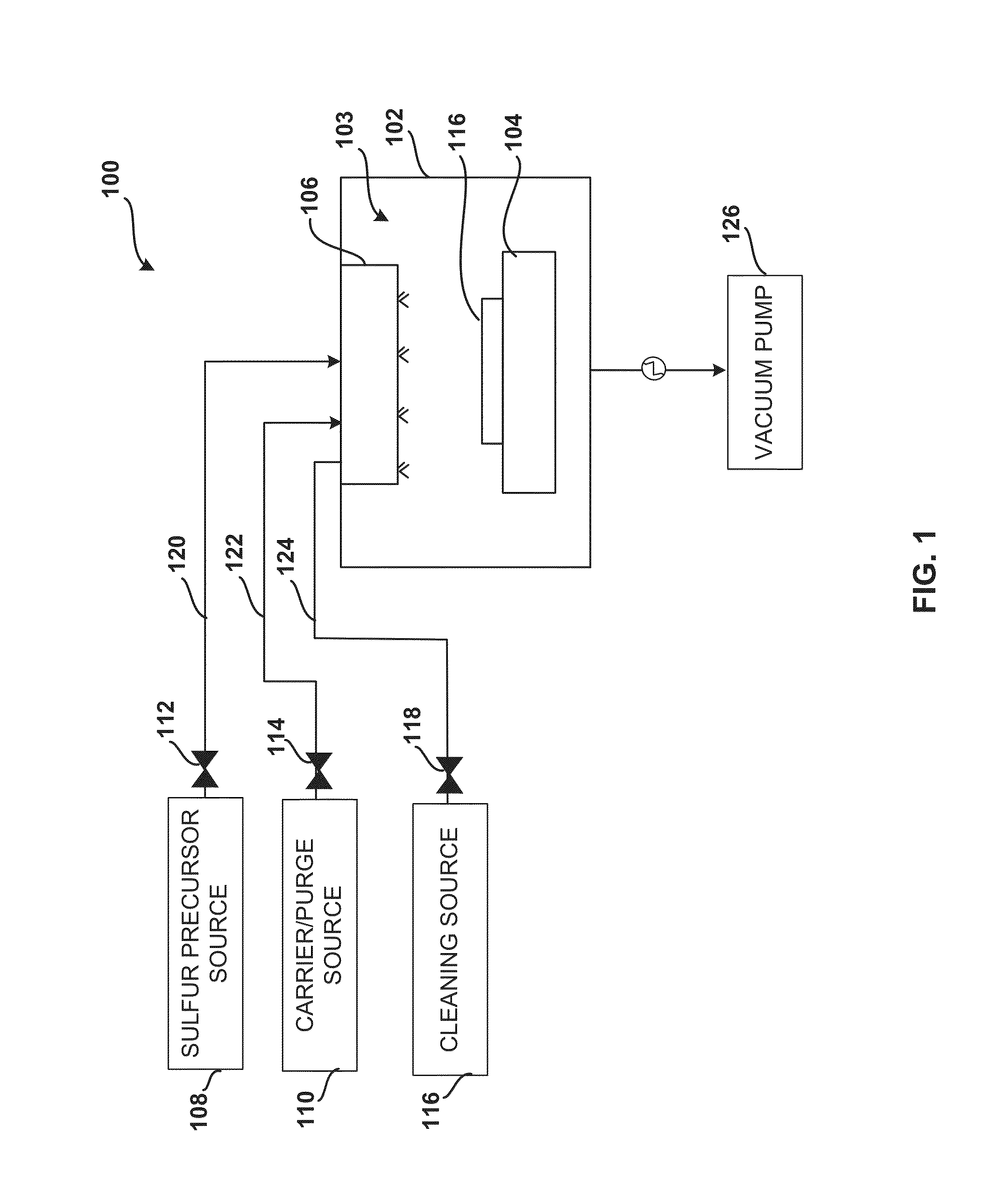

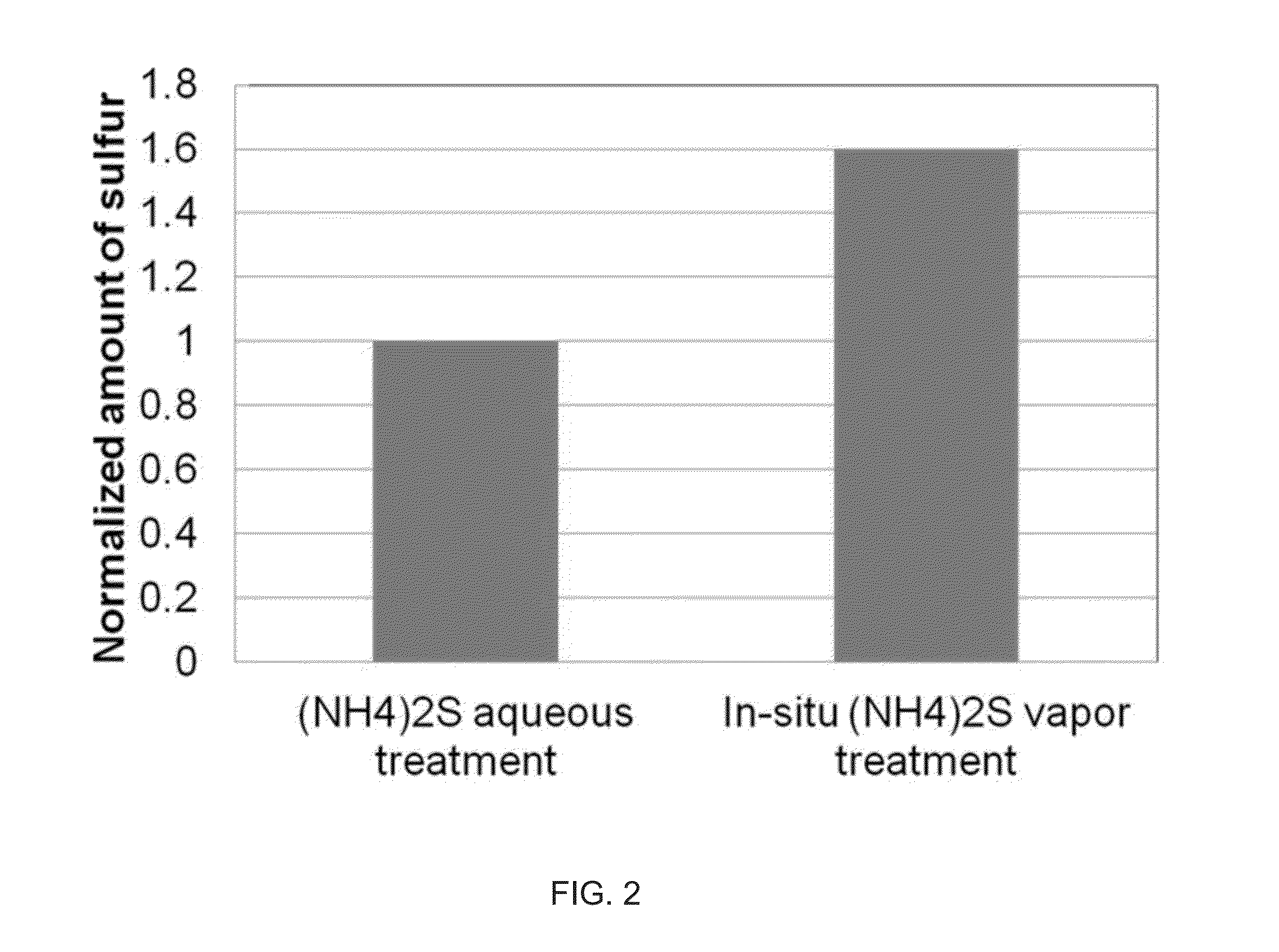

System and method for gas-phase sulfur passivation of a semiconductor surface

ActiveUS20140027884A1Semiconductor/solid-state device detailsSolid-state devicesGas phaseDevice form

Improved methods and systems for passivating a surface of a high-mobility semiconductor and structures and devices formed using the methods are disclosed. The method includes providing a high-mobility semiconductor surface to a chamber of a reactor and exposing the high-mobility semiconductor surface to a gas-phase sulfur precursor to passivate the high-mobility semiconductor surface.

Owner:ASM IP HLDG BV

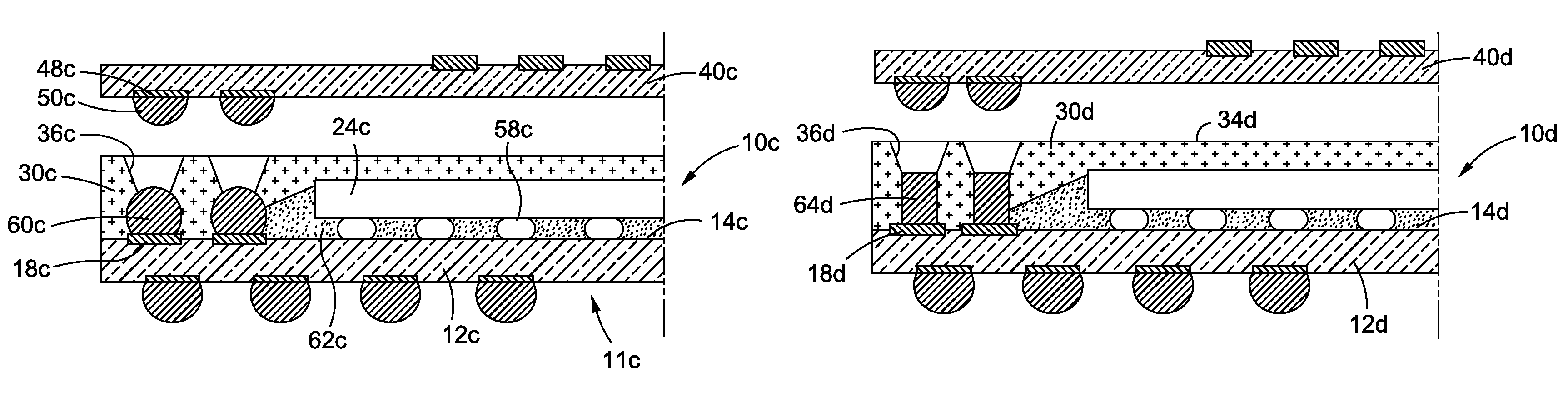

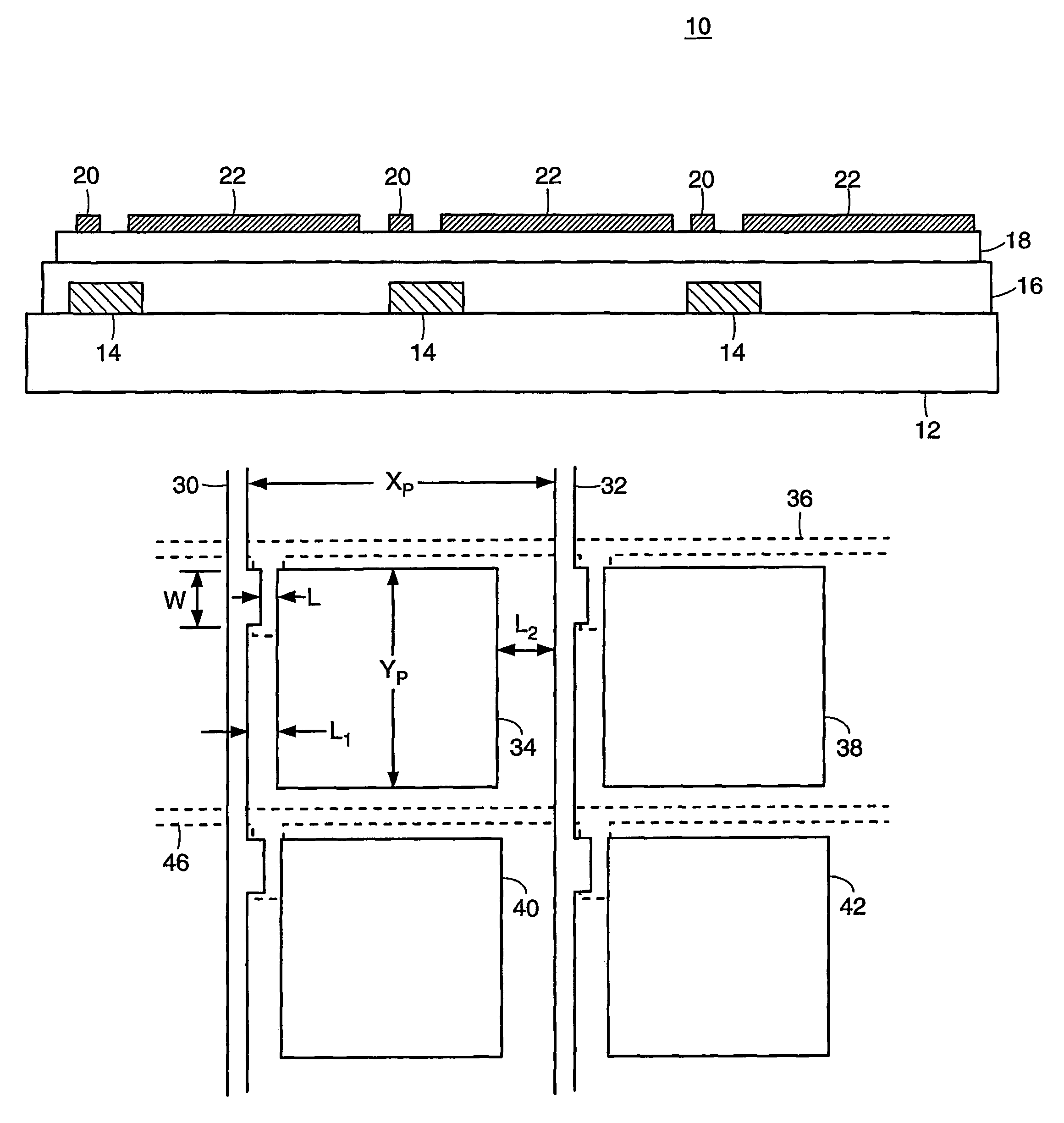

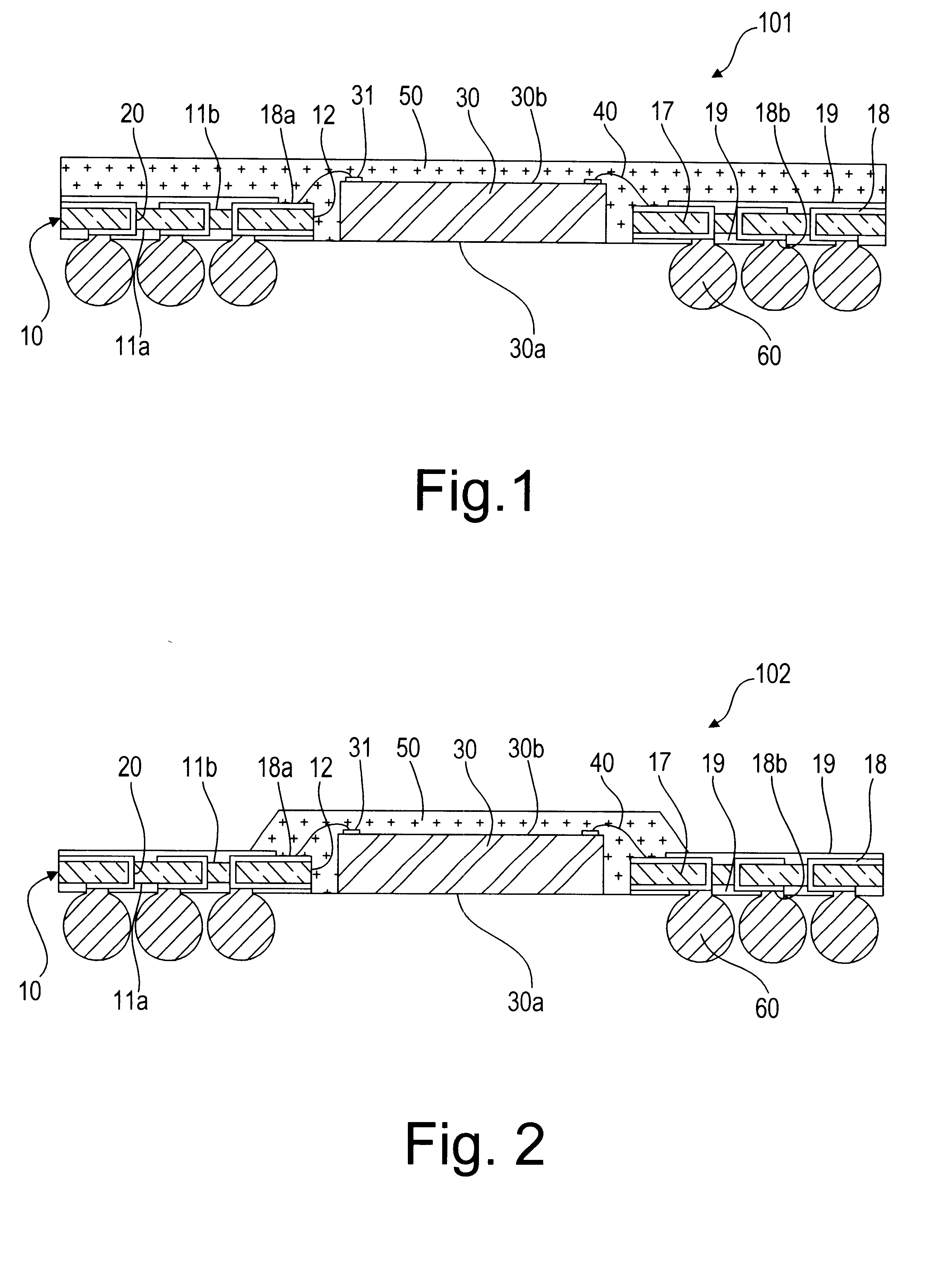

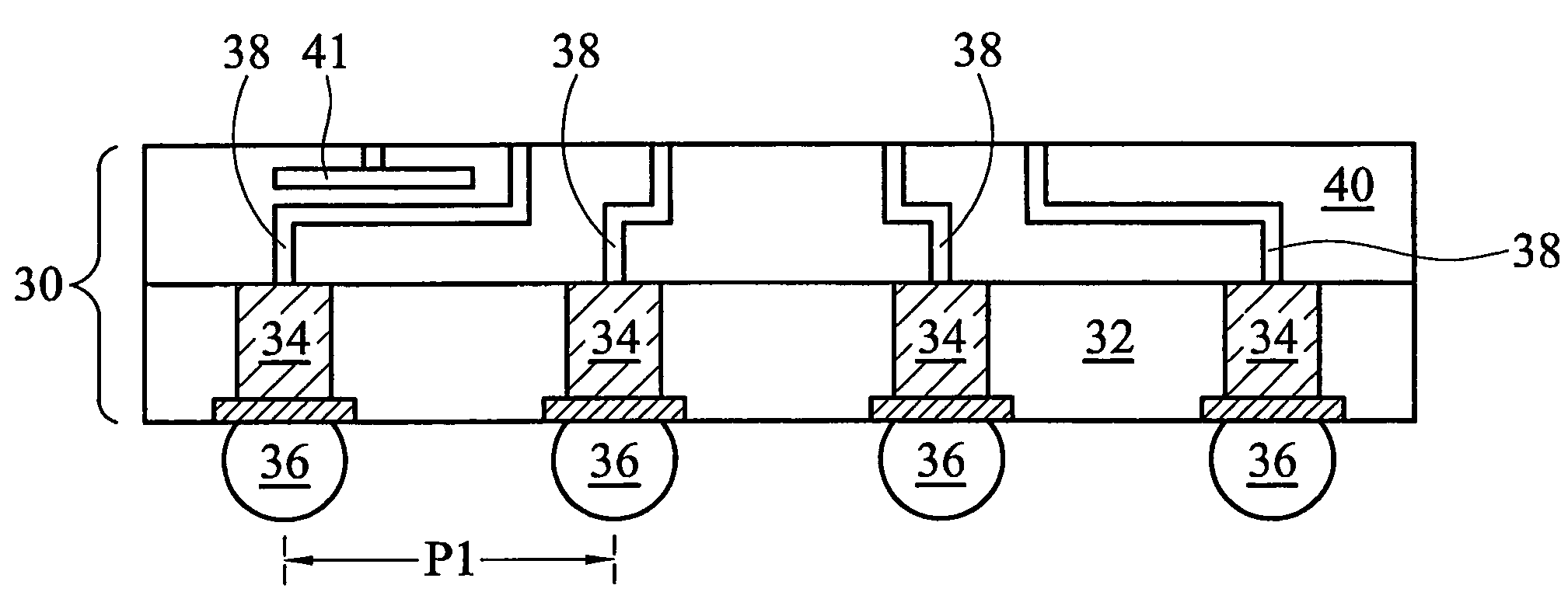

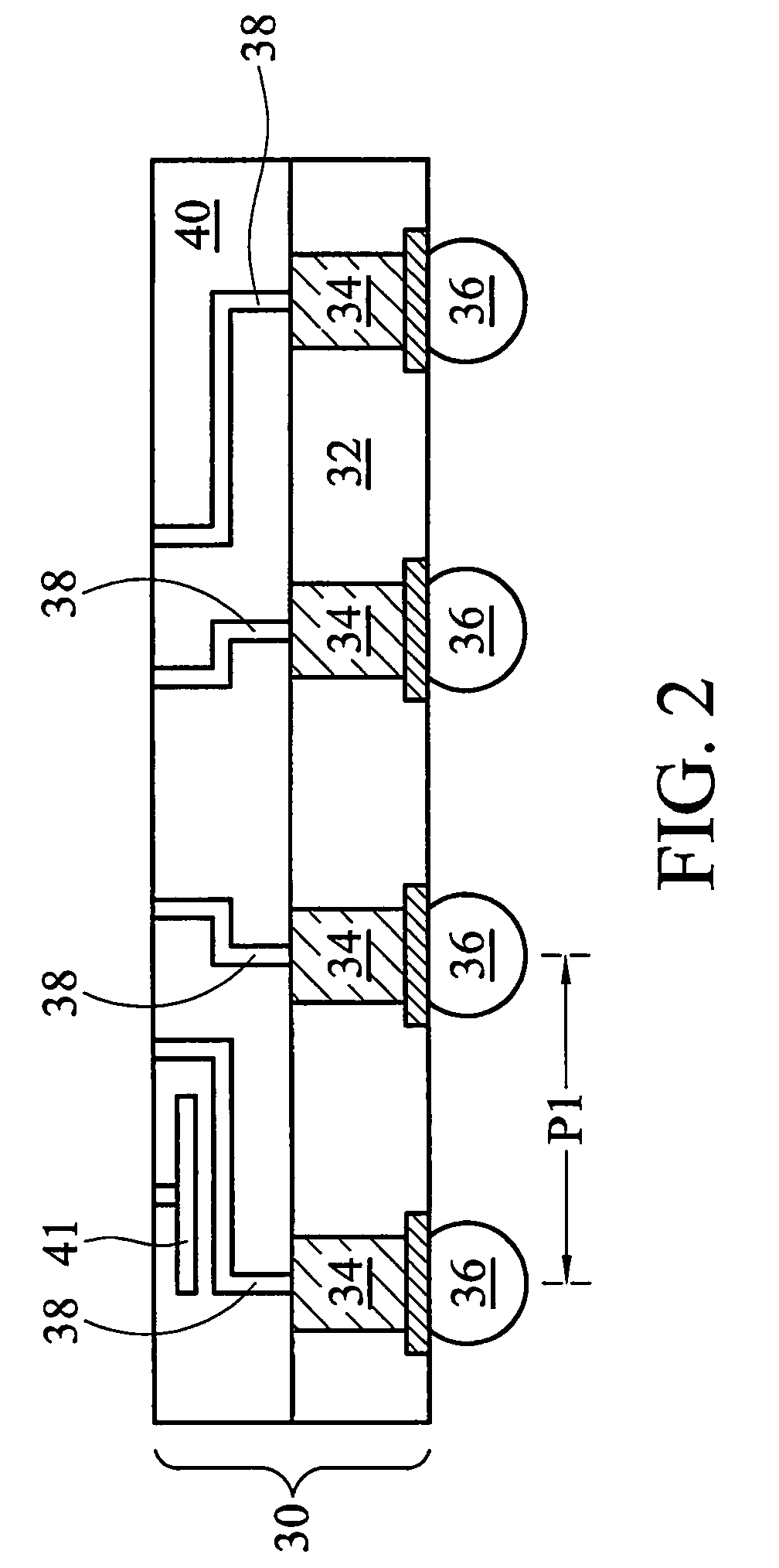

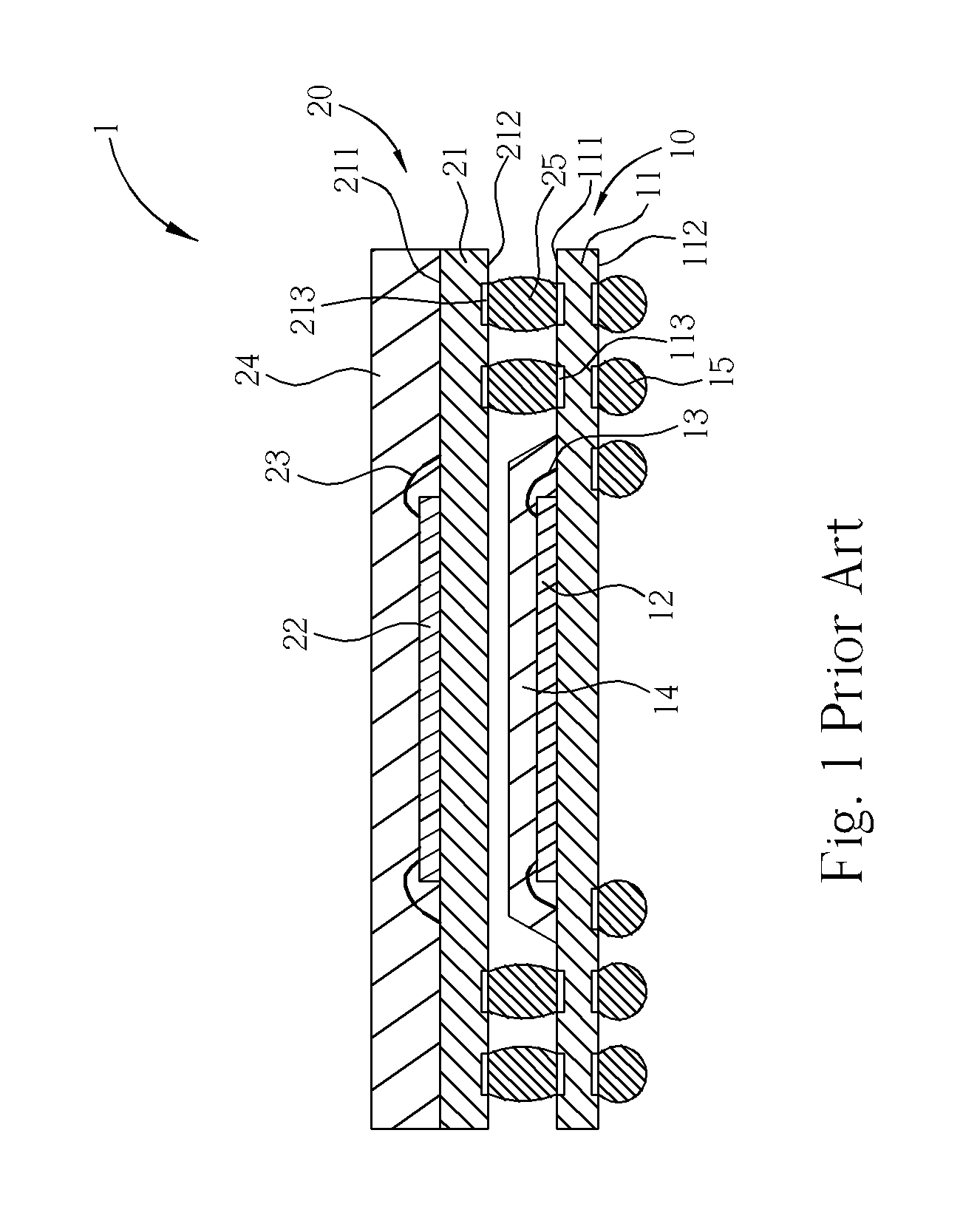

Thin stacked interposer package

ActiveUS7777351B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectronic component

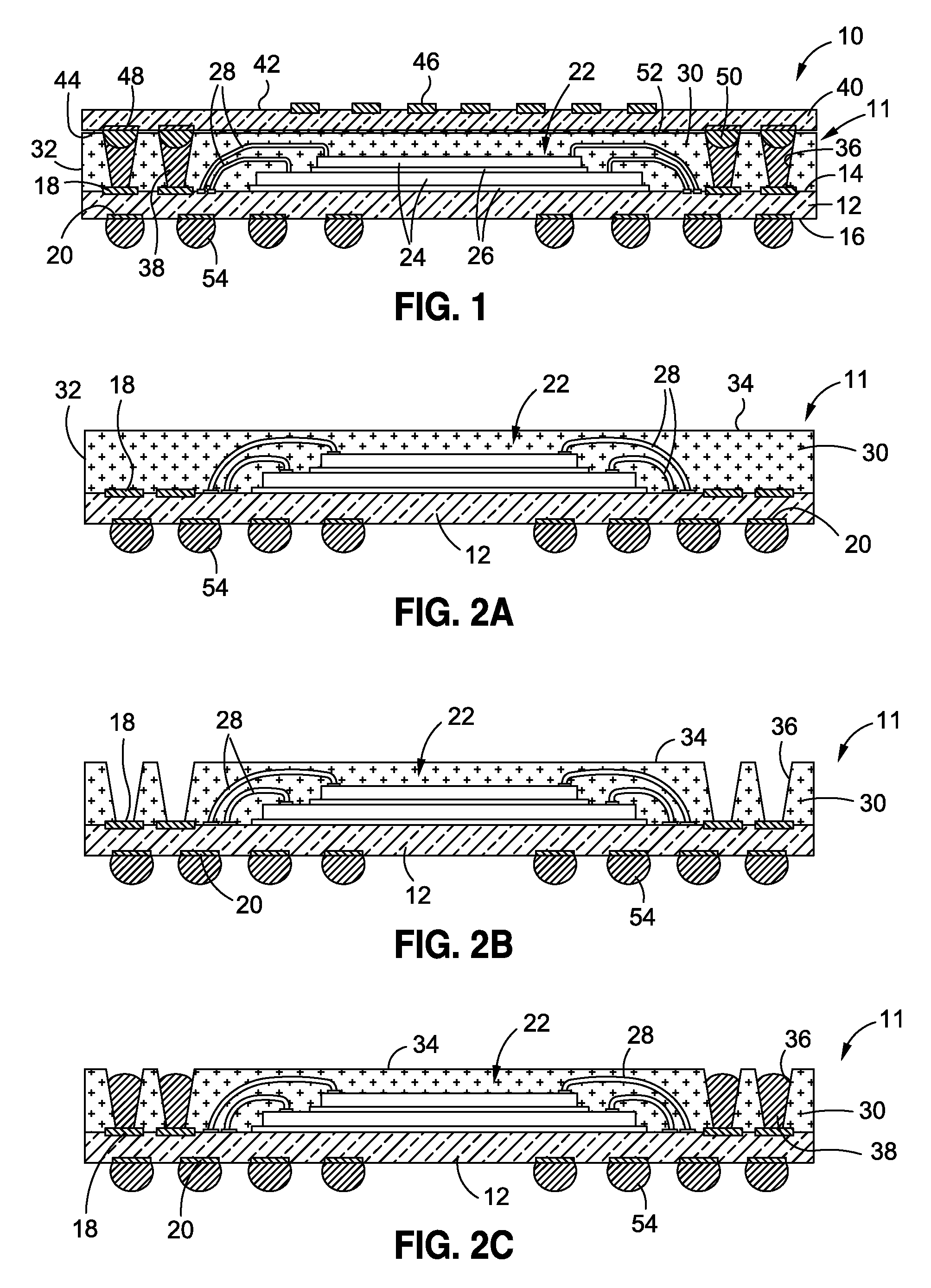

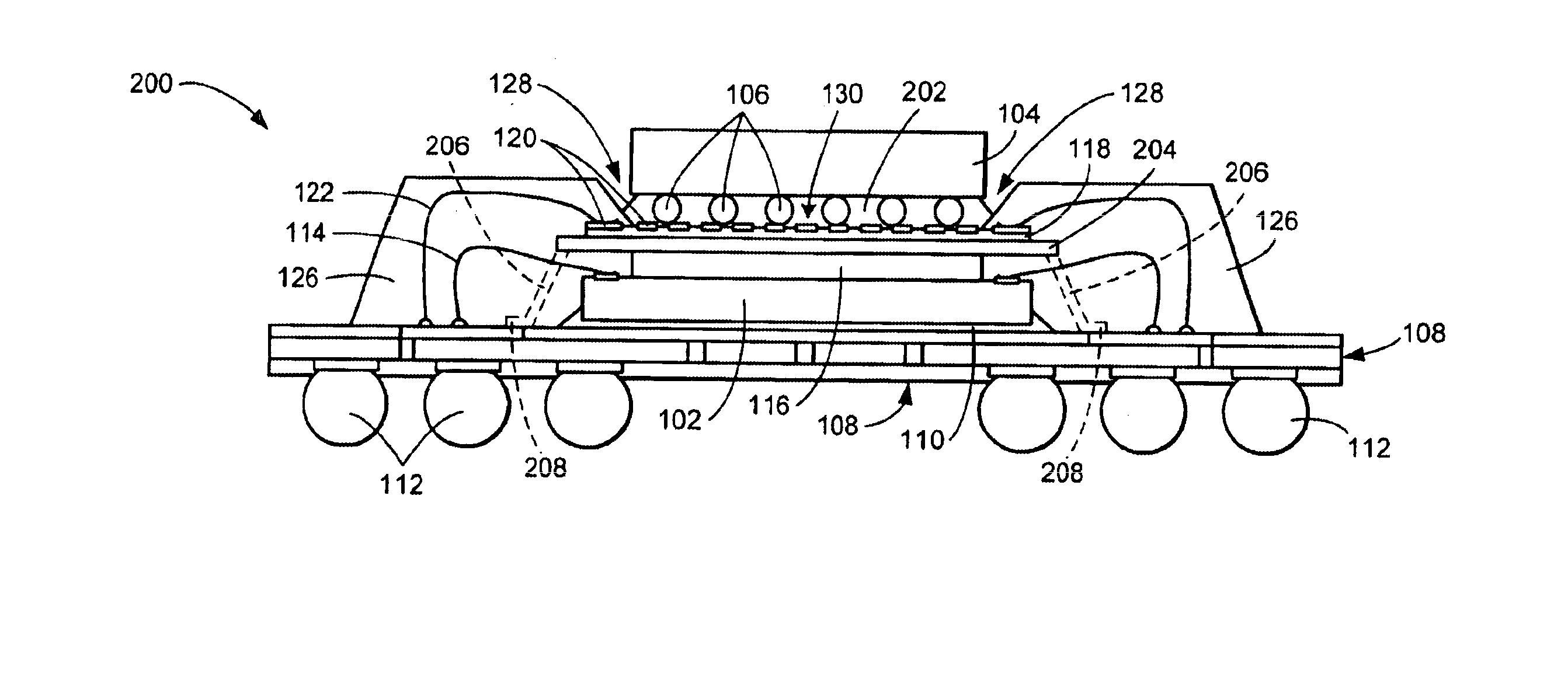

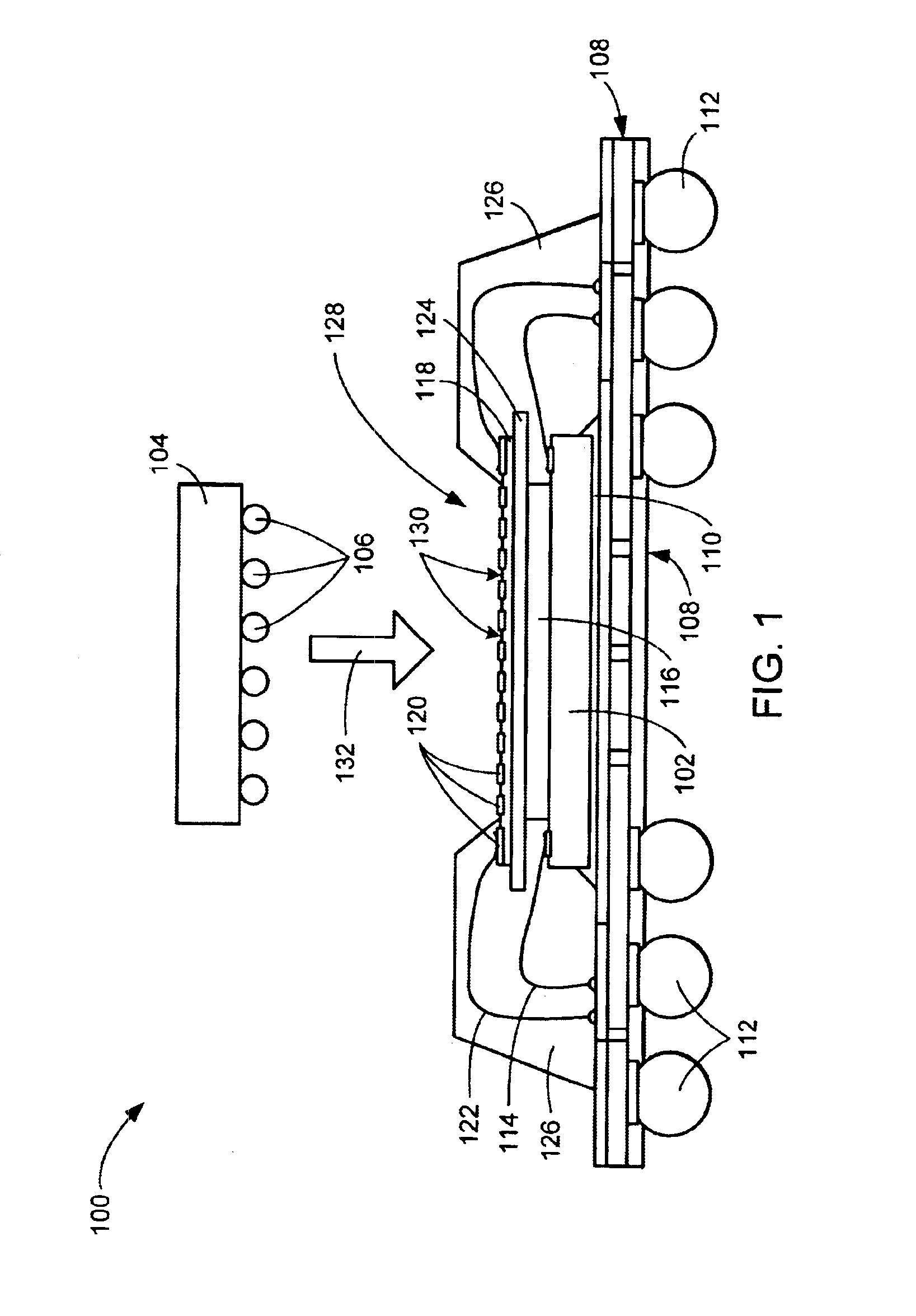

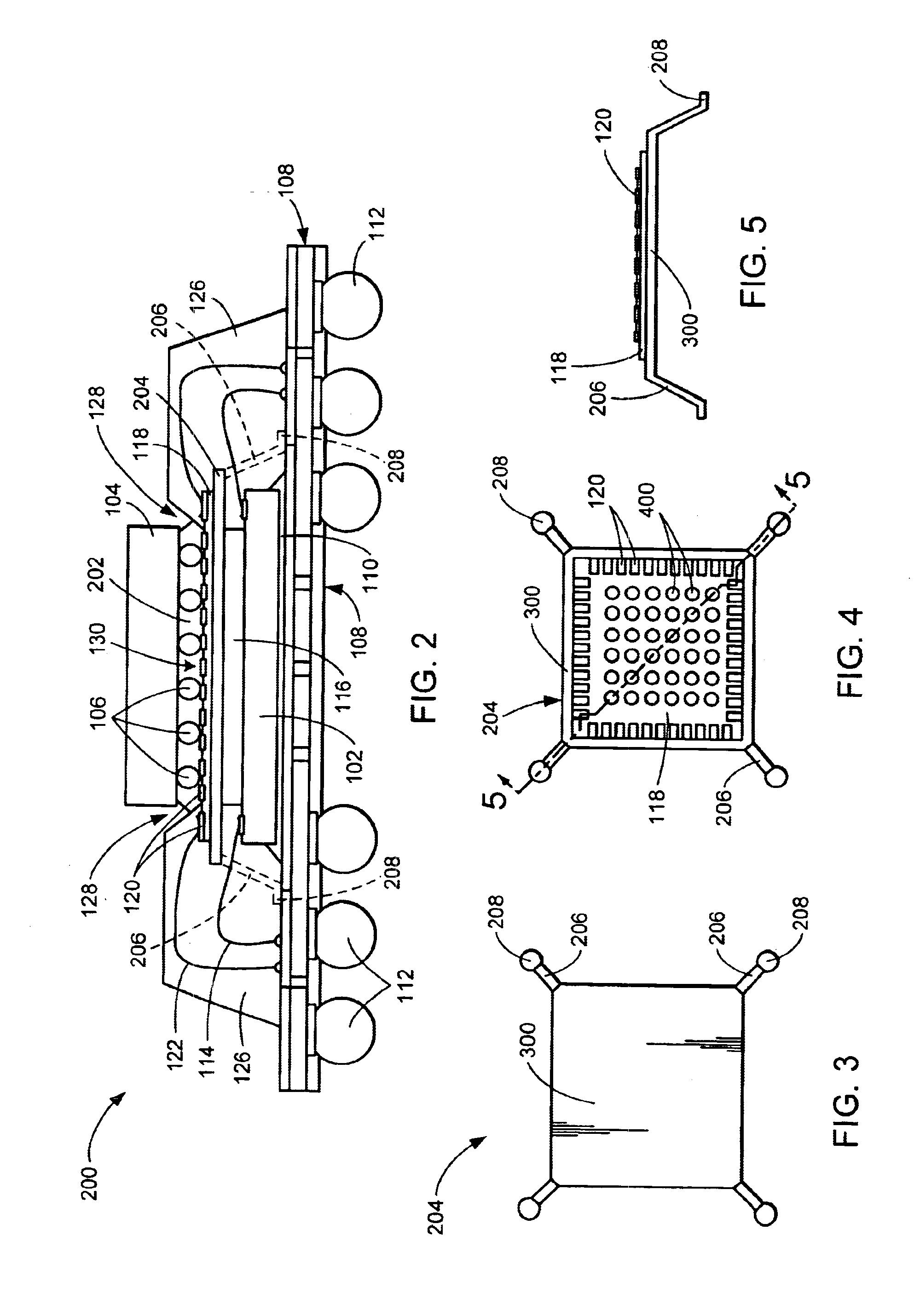

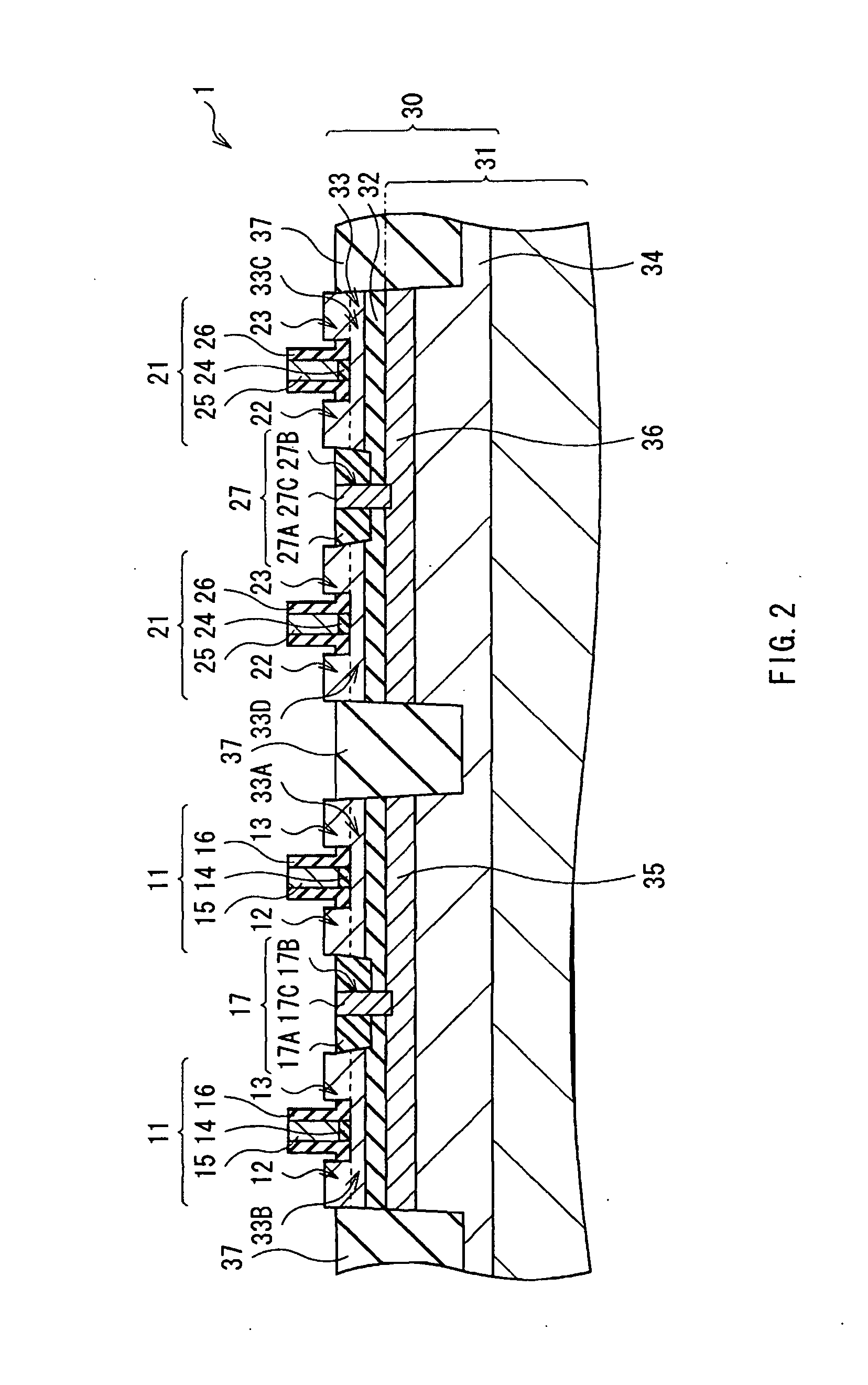

The present invention comprises a semiconductor package comprising a bottom semiconductor package substrate which is populated with one or more electronic components. The electronic component(s) of the bottom substrate are covered or encapsulated with a suitable mold compound which hardens into a package body of the semiconductor package. The package body is provided with one or more vias through the completion of laser drilling process, such via(s) providing access to one or more corresponding conductive contacts of the bottom substrate. These vias are either lined or partially filled with a conductive metal material. Subsequently, a top semiconductor package substrate (which may optionally be populated with one or more electronic components) is mounted to the package body and electrically connected to the conductive metal within the via(s) of the package body.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

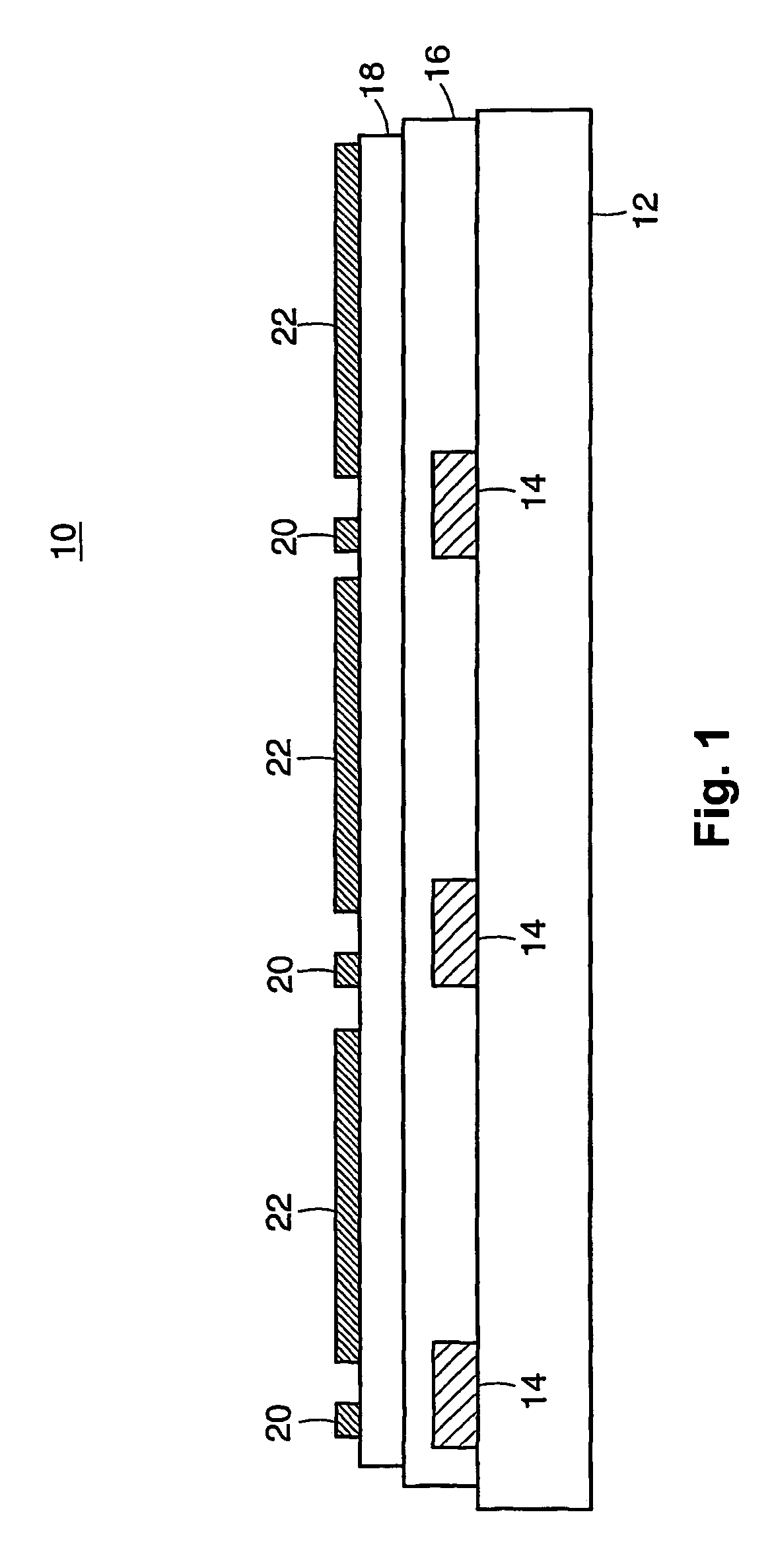

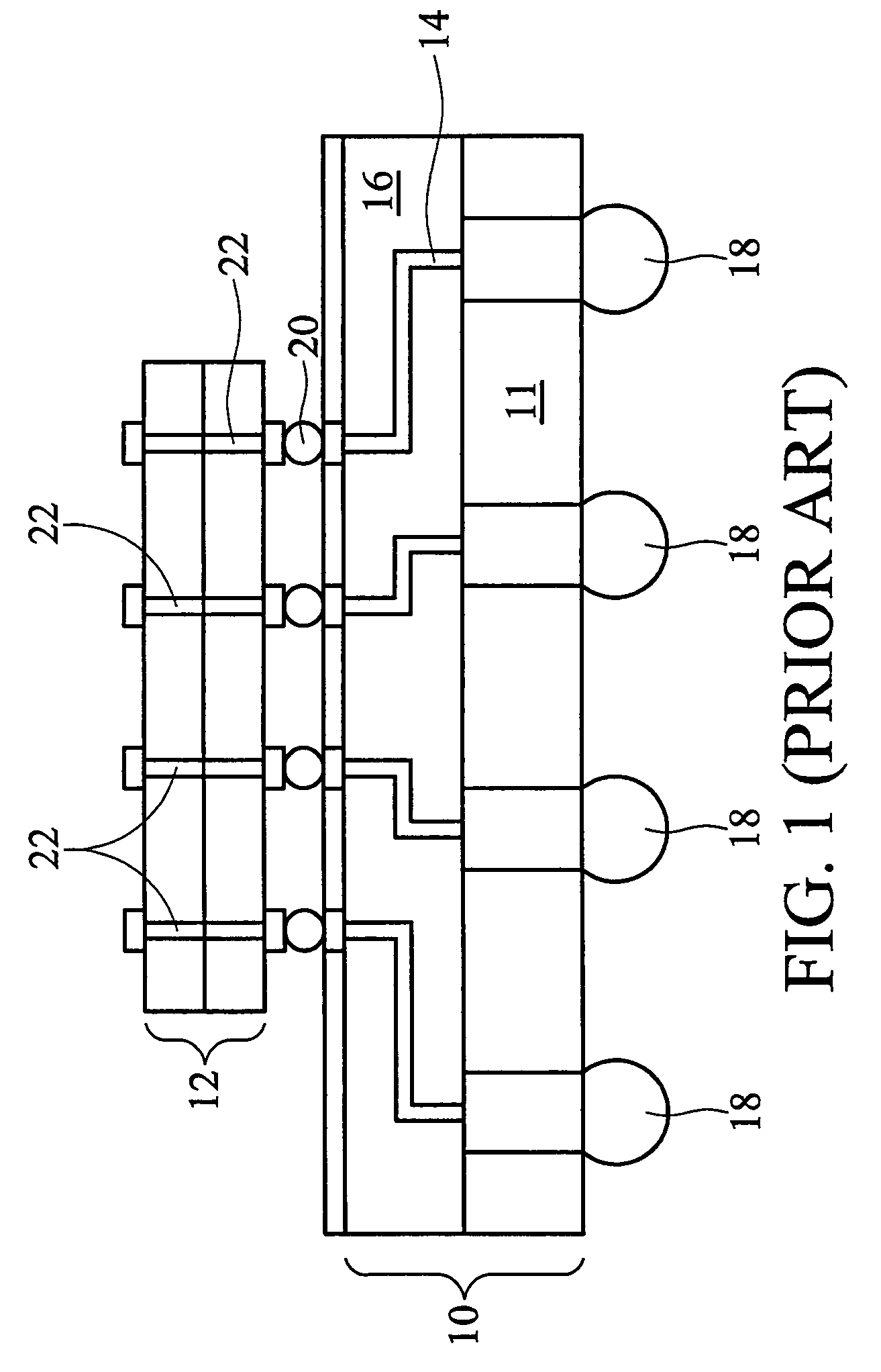

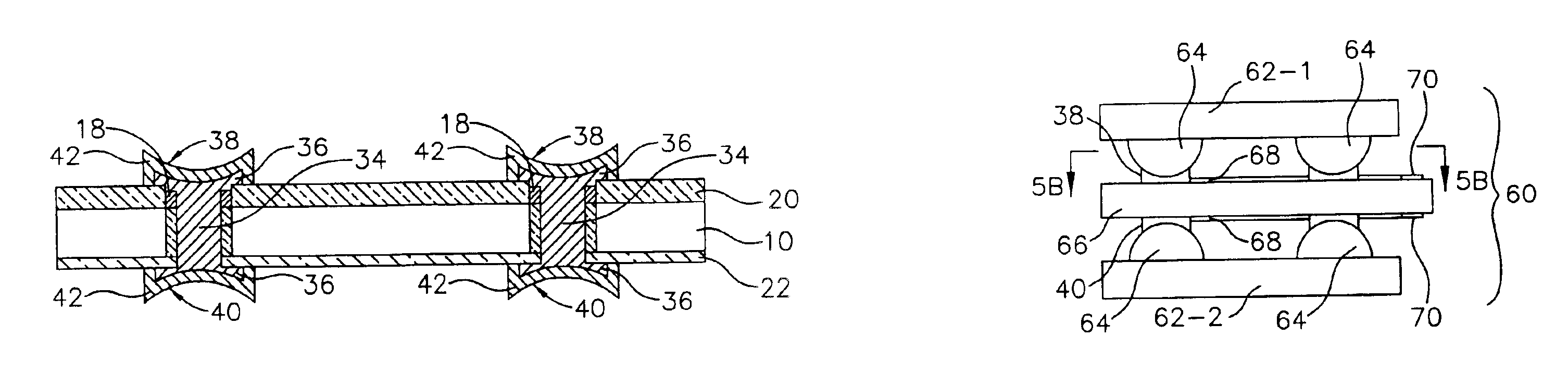

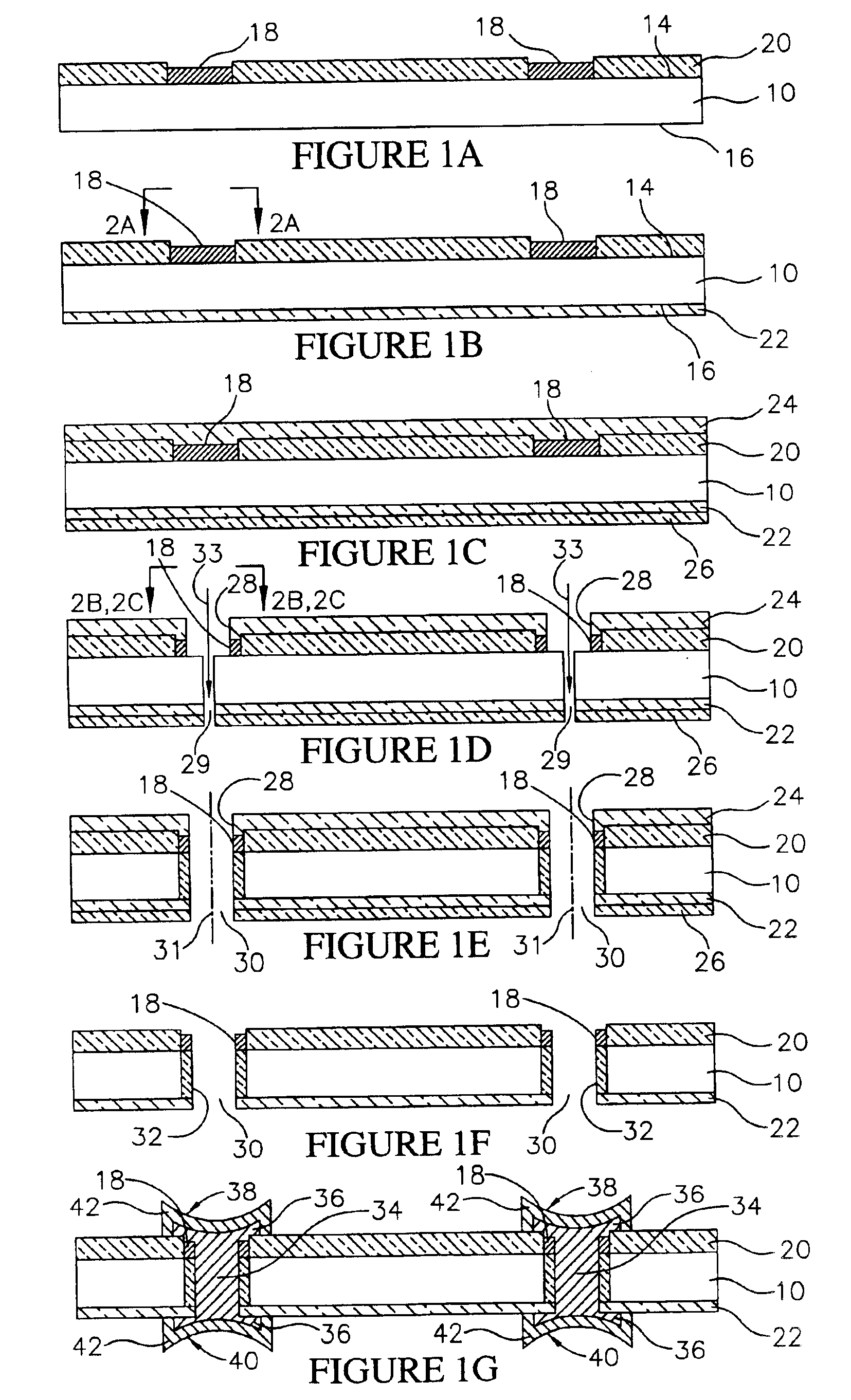

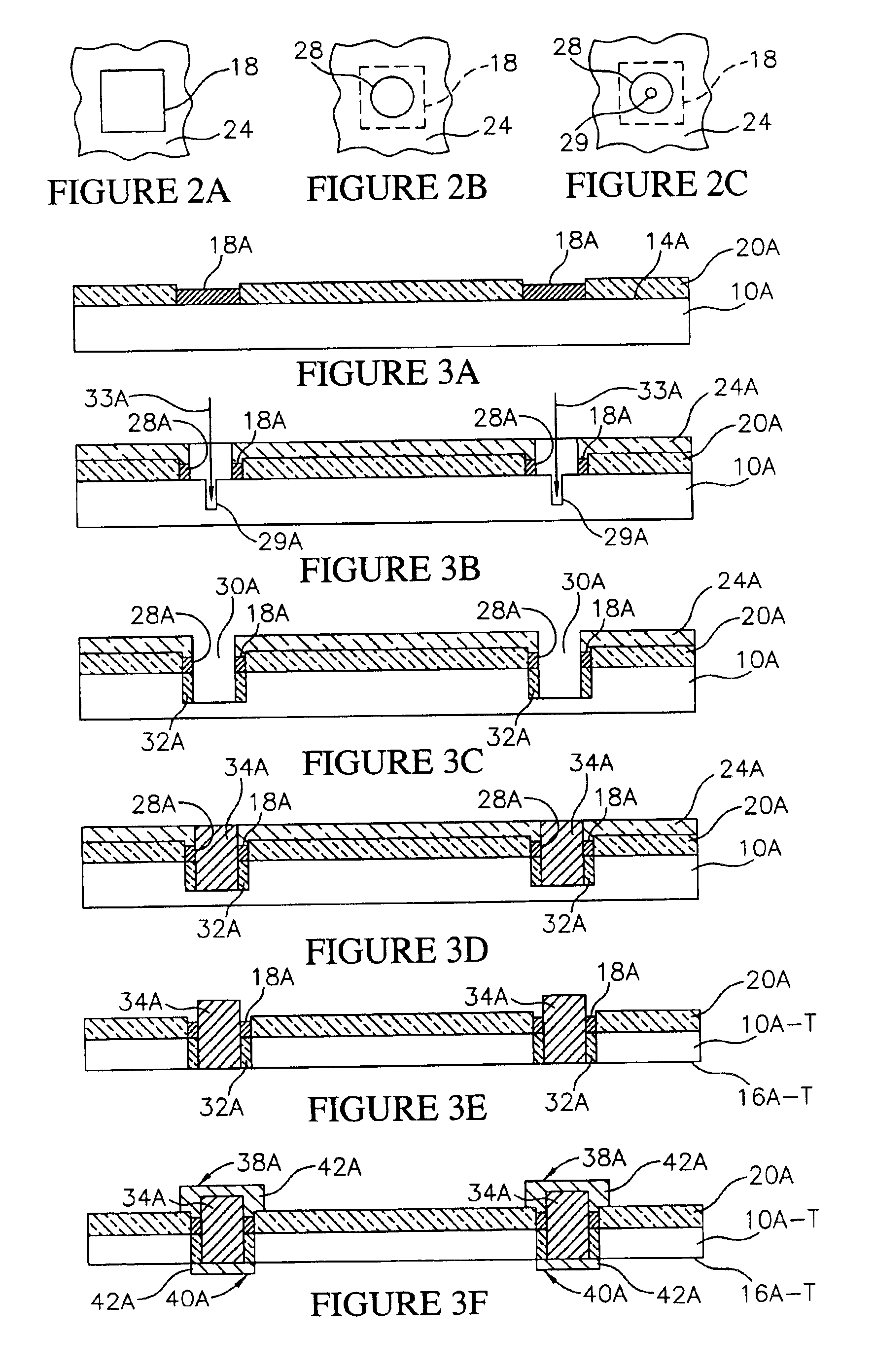

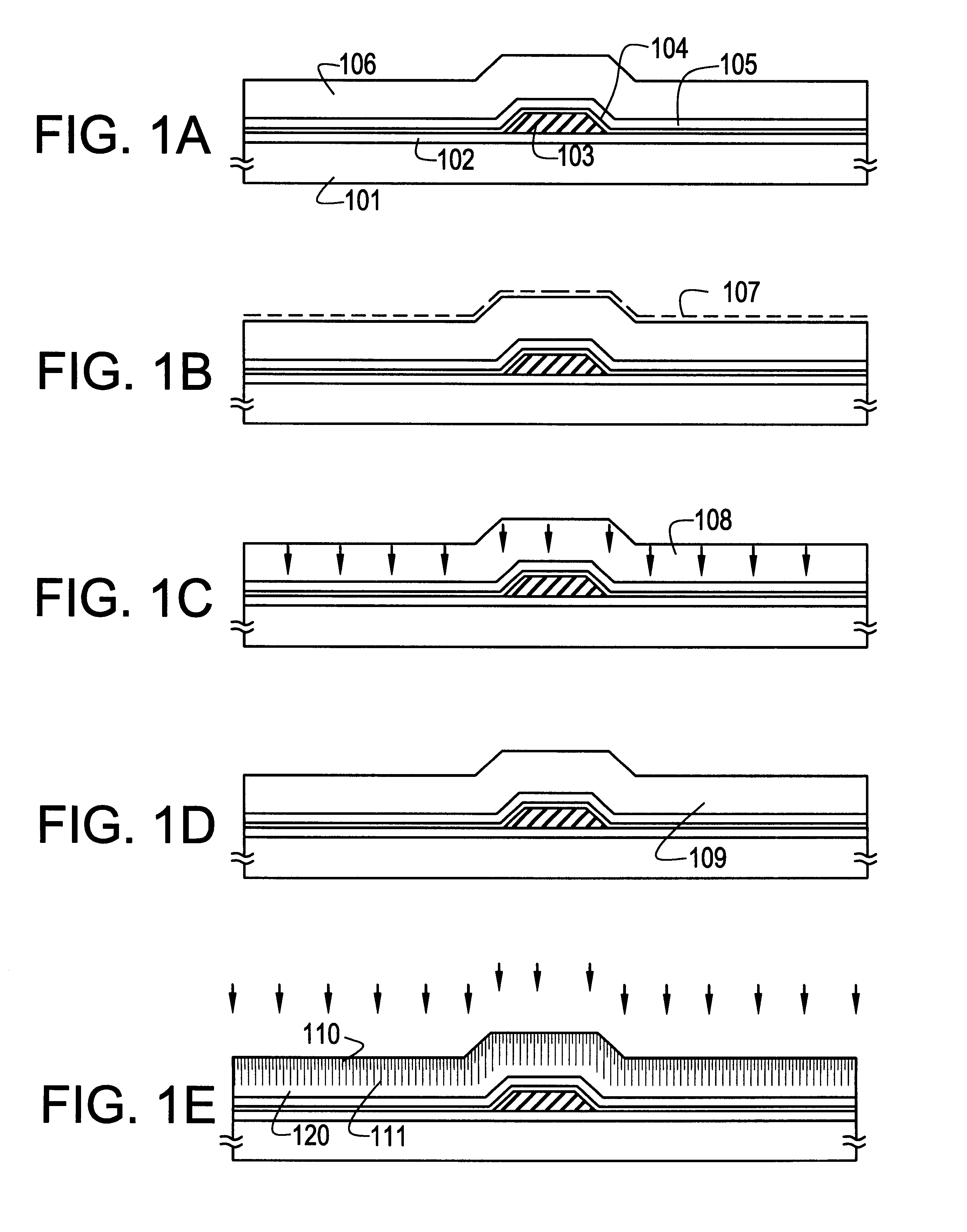

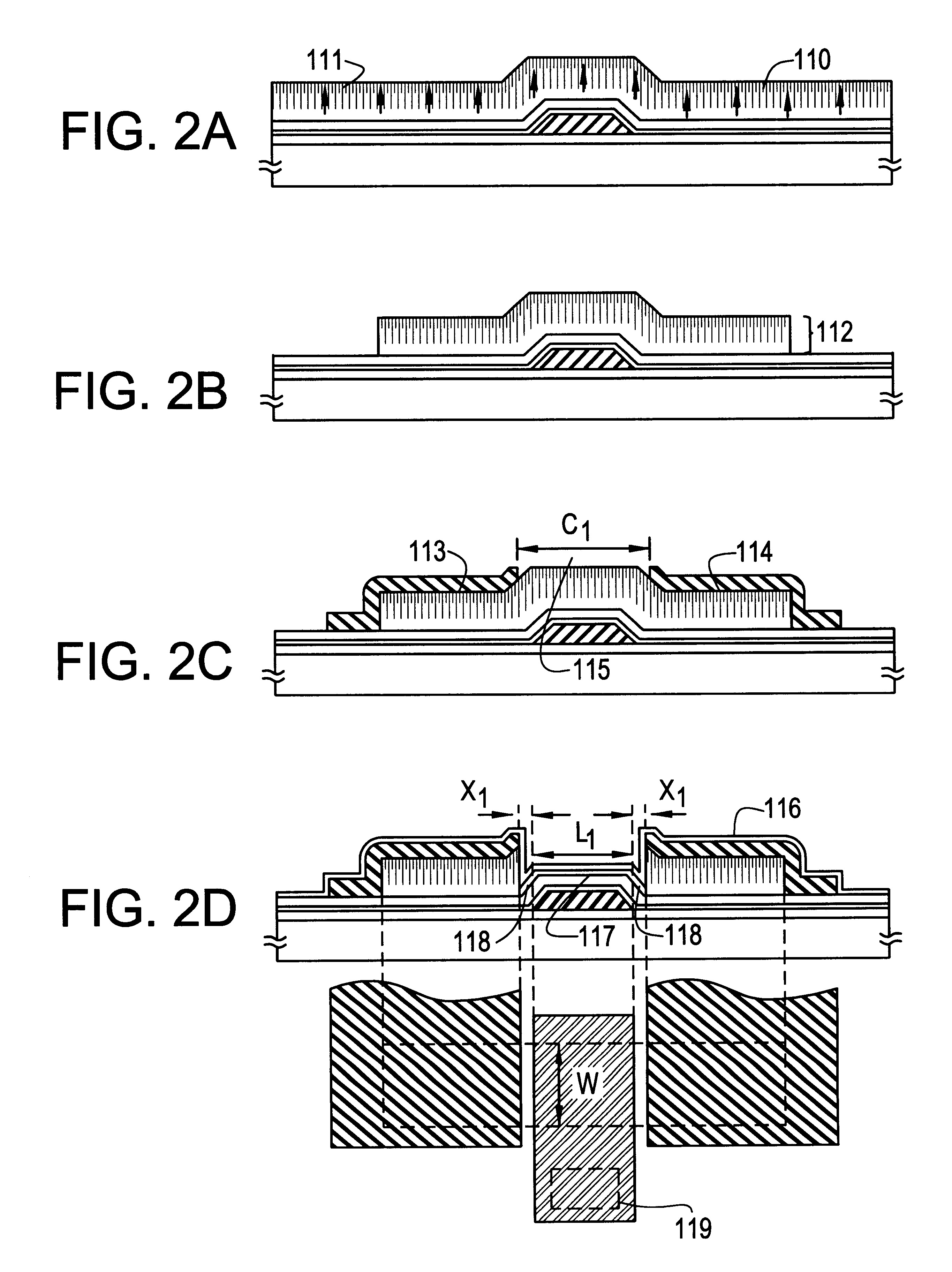

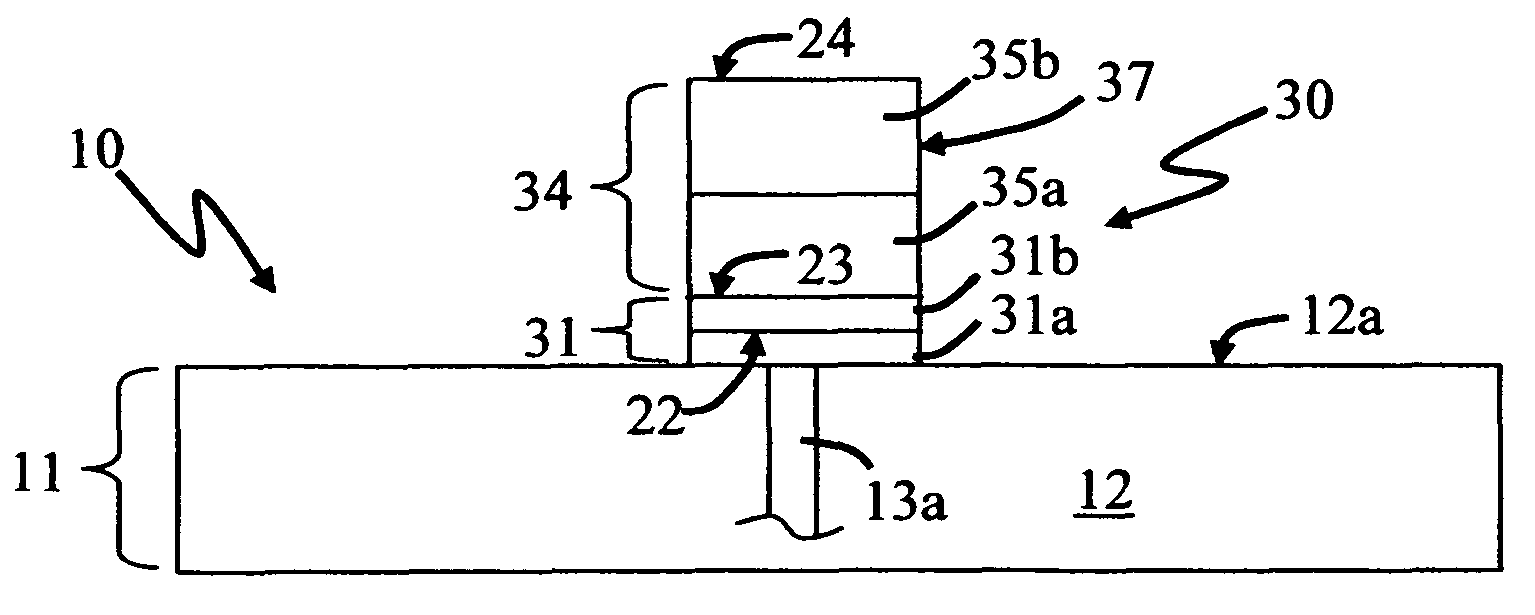

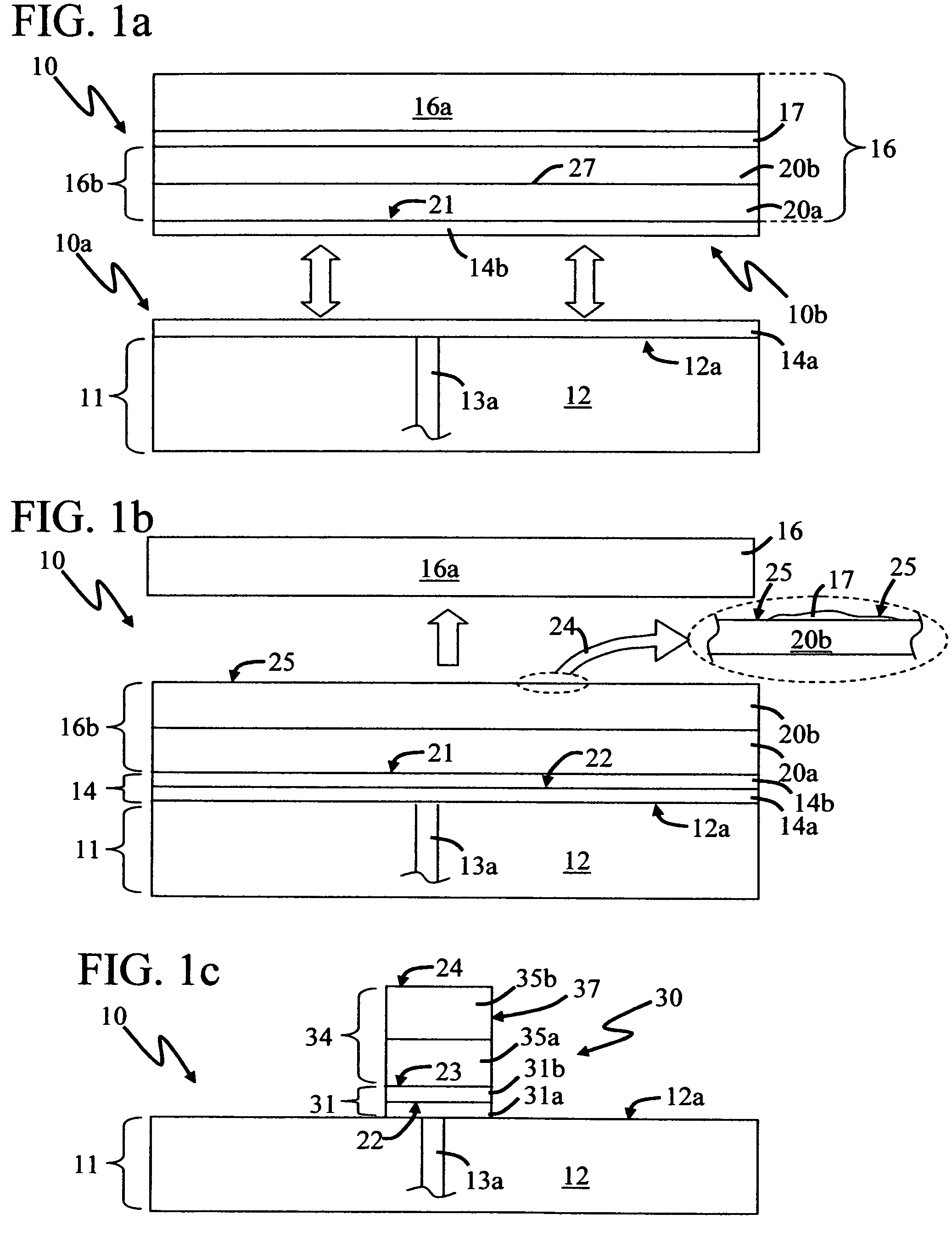

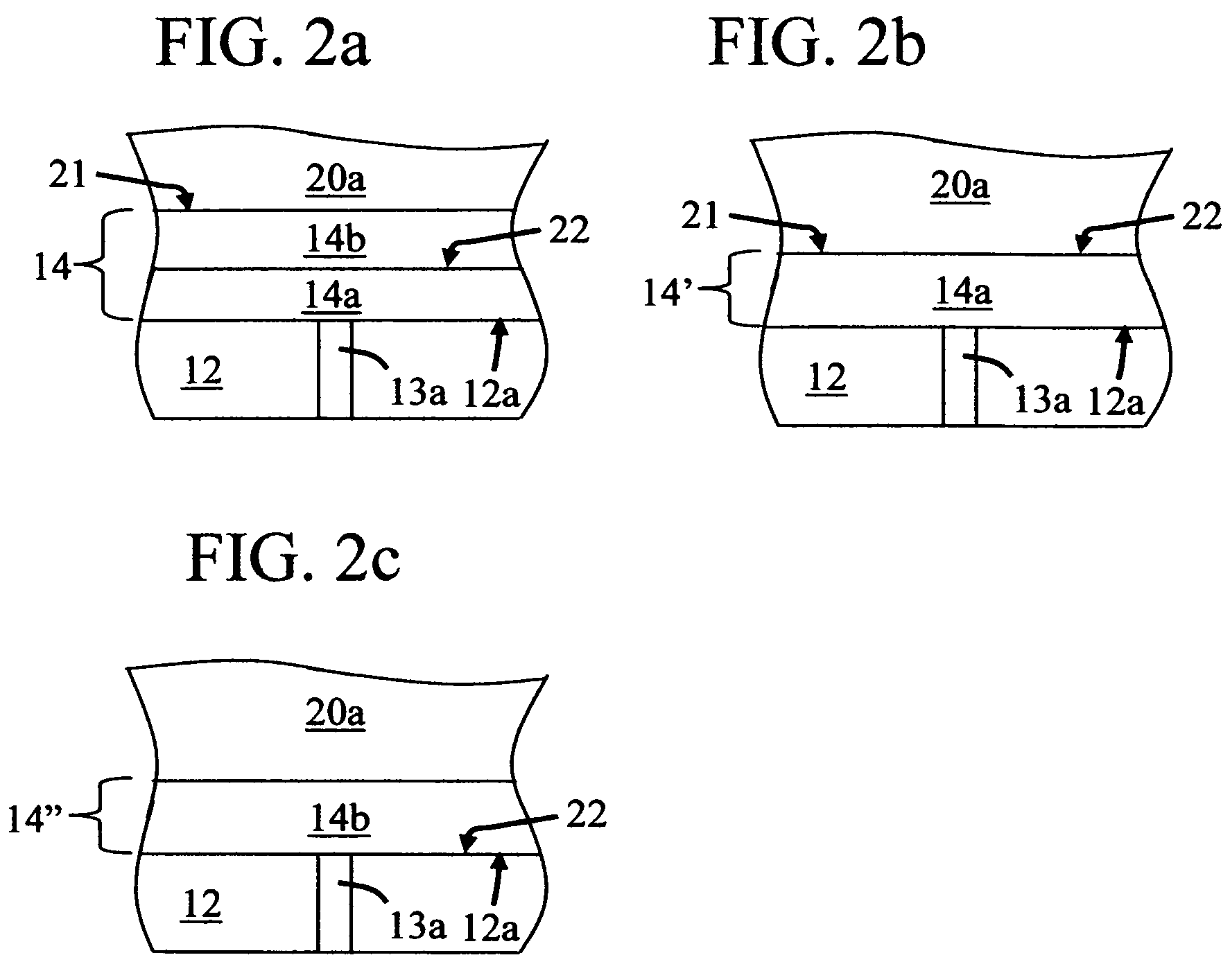

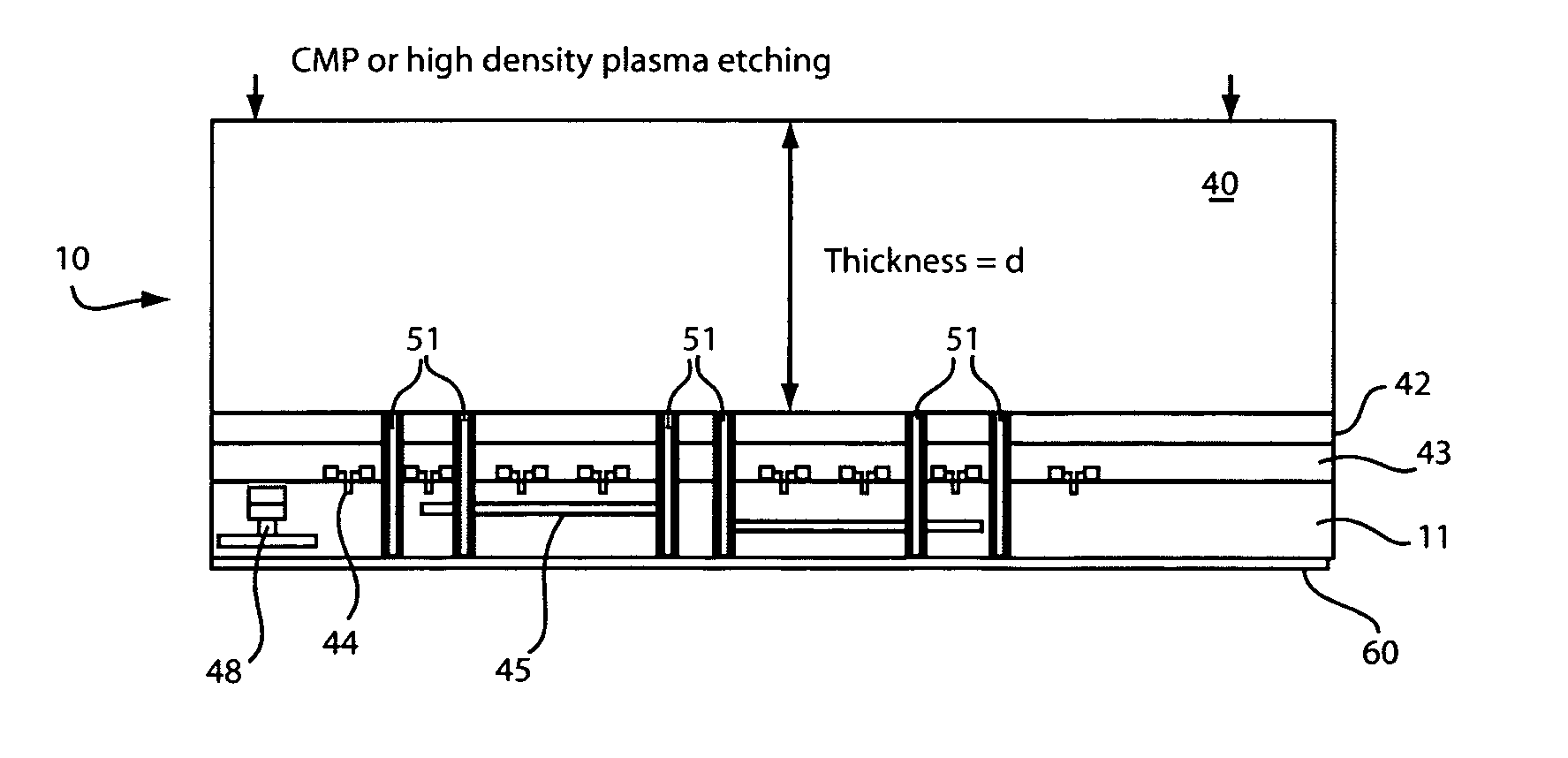

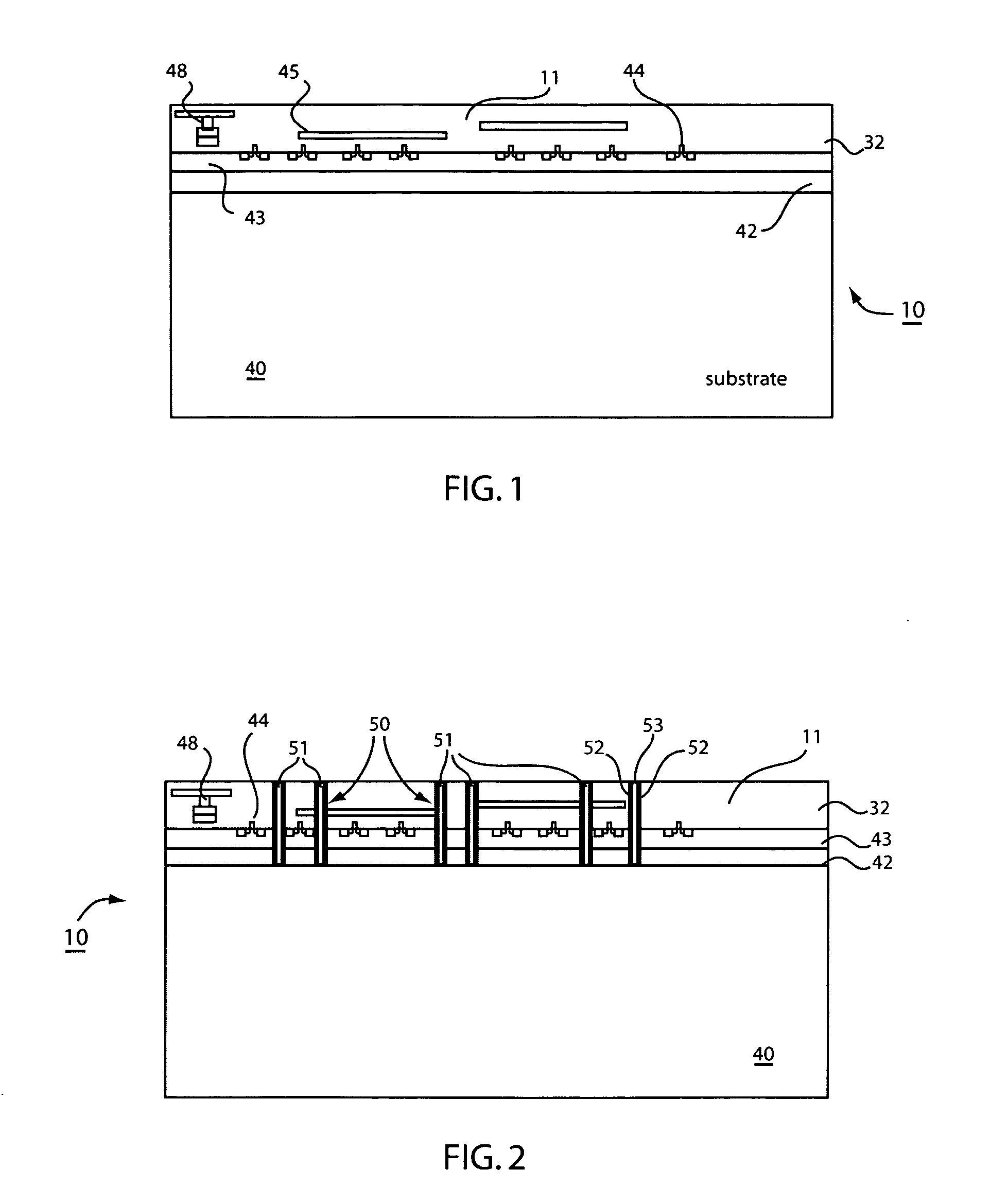

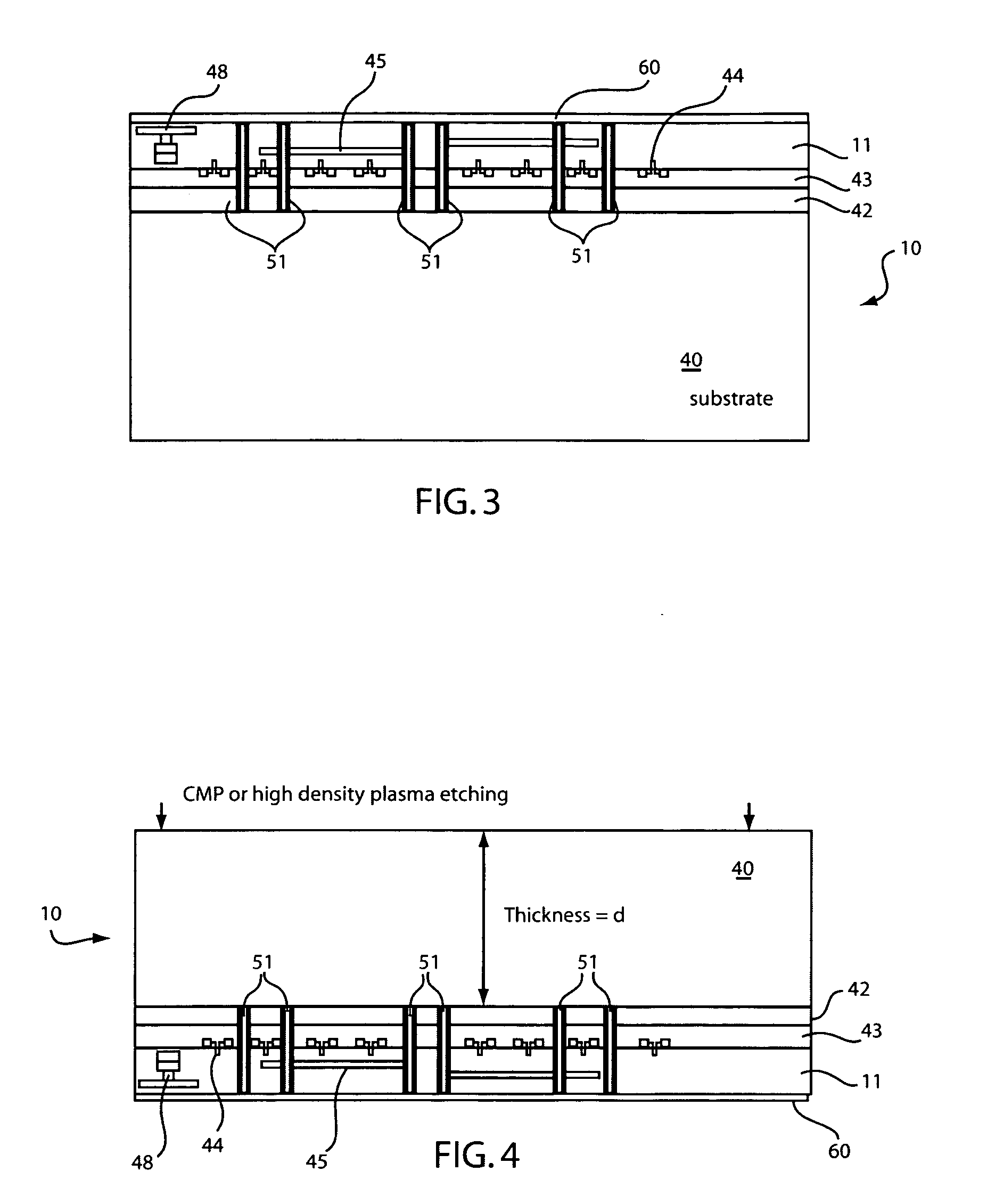

Method of manufacturing a semiconductor package

InactiveUS7185426B1Printed circuit assemblingSemiconductor/solid-state device detailsElectrical conductorSemiconductor package

A semiconductor package including top-surface terminals for mounting another semiconductor package provides a three-dimensional circuit configuration that can provide removable connection of existing grid-array packages having a standard design. A semiconductor die is mounted on an electrically connected to a circuit substrate having terminals disposed on a bottom side for connection to an external system. The die and substrate are encapsulated and vias are laser-ablated or otherwise formed through the encapsulation to terminals on the top surface of the substrate that provide a grid array mounting lands to which another grid array semiconductor package may be mounted. The bottom side of the vias may terminate and electrically connect to terminals on the substrate, terminals on the bottom of the semiconductor package (through terminals) or terminals on the top of the semiconductor die. The vias may be plated, paste-filled, filled with a low melting point alloy and may have a conical profile for improved plating performance.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

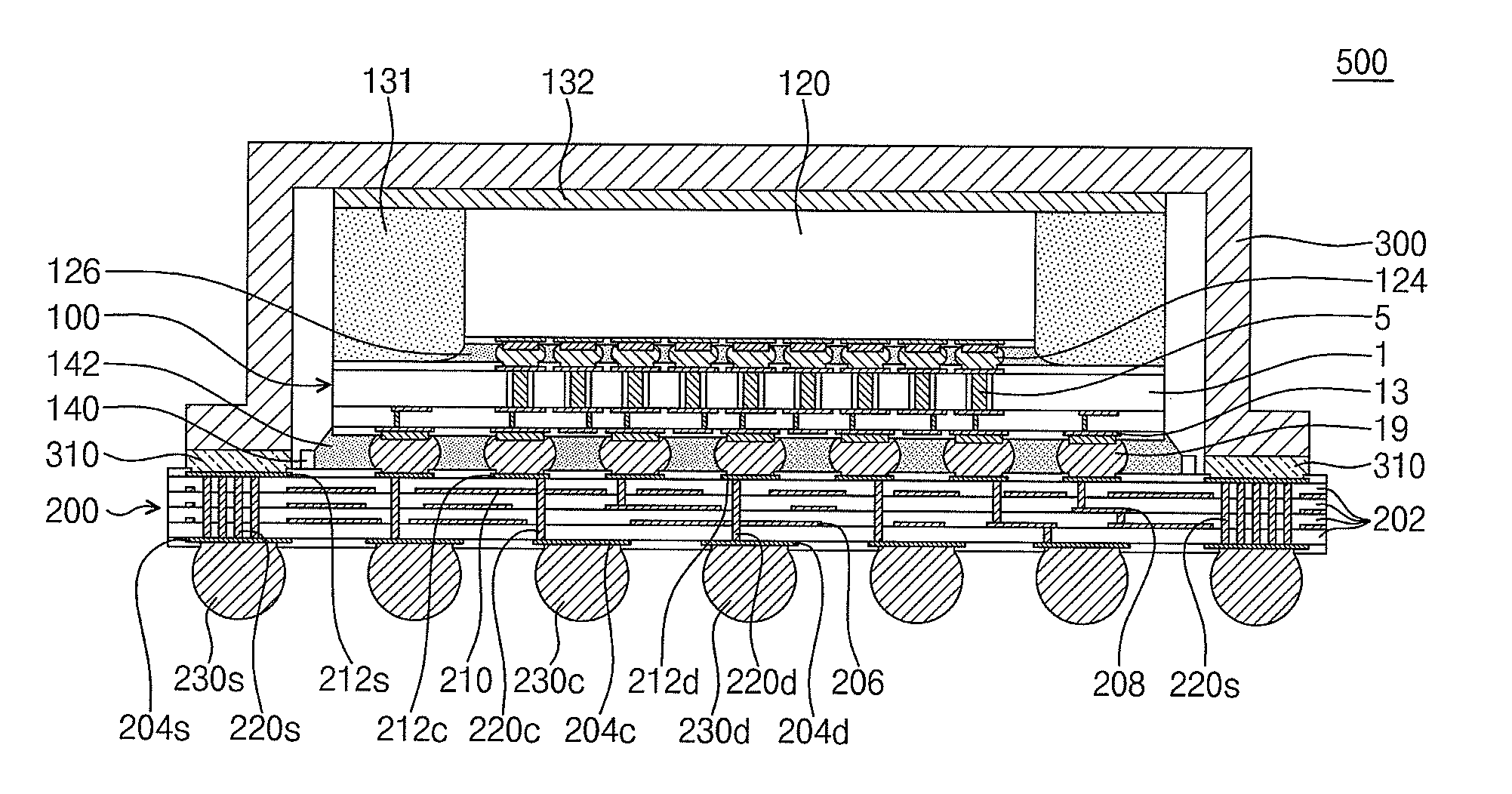

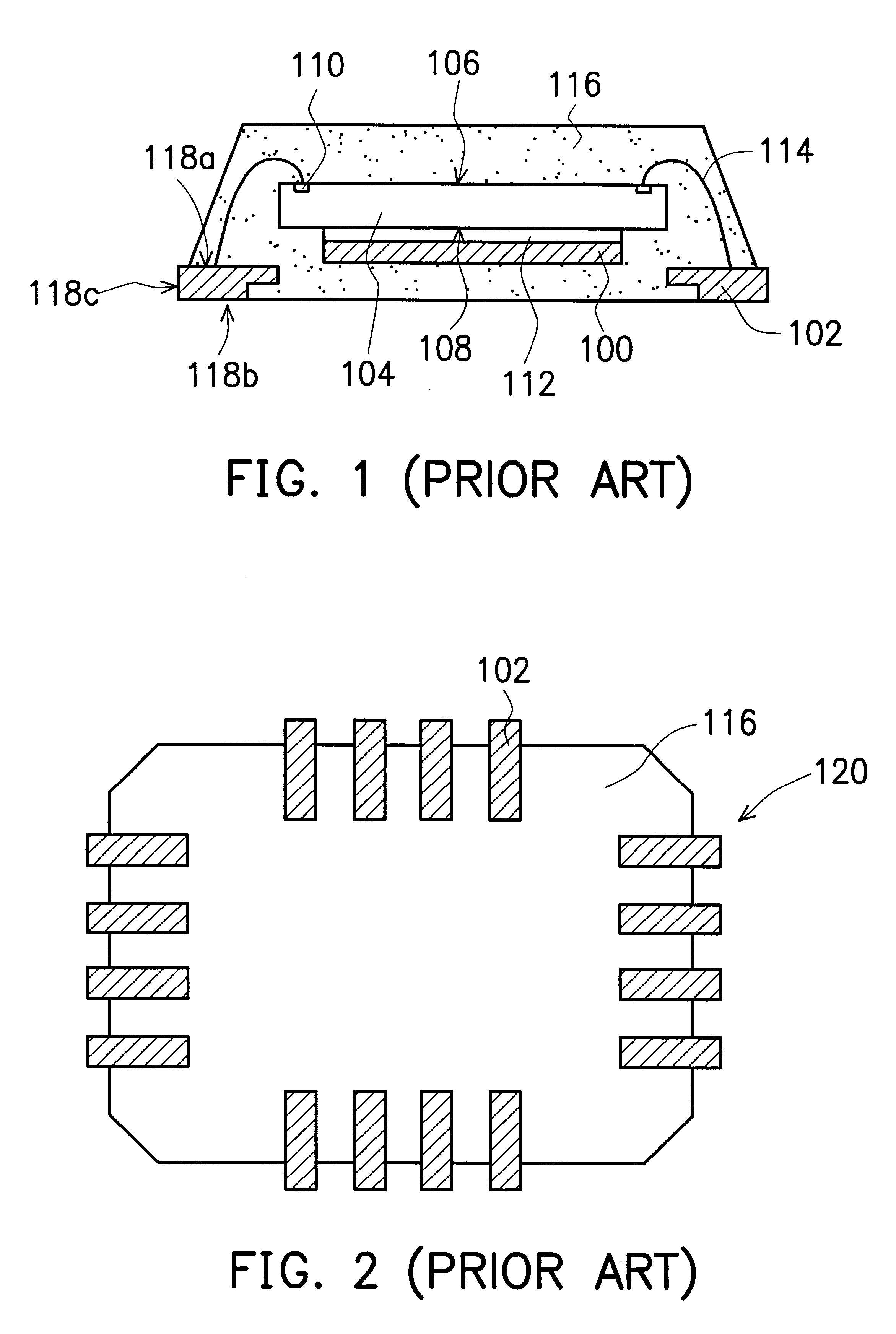

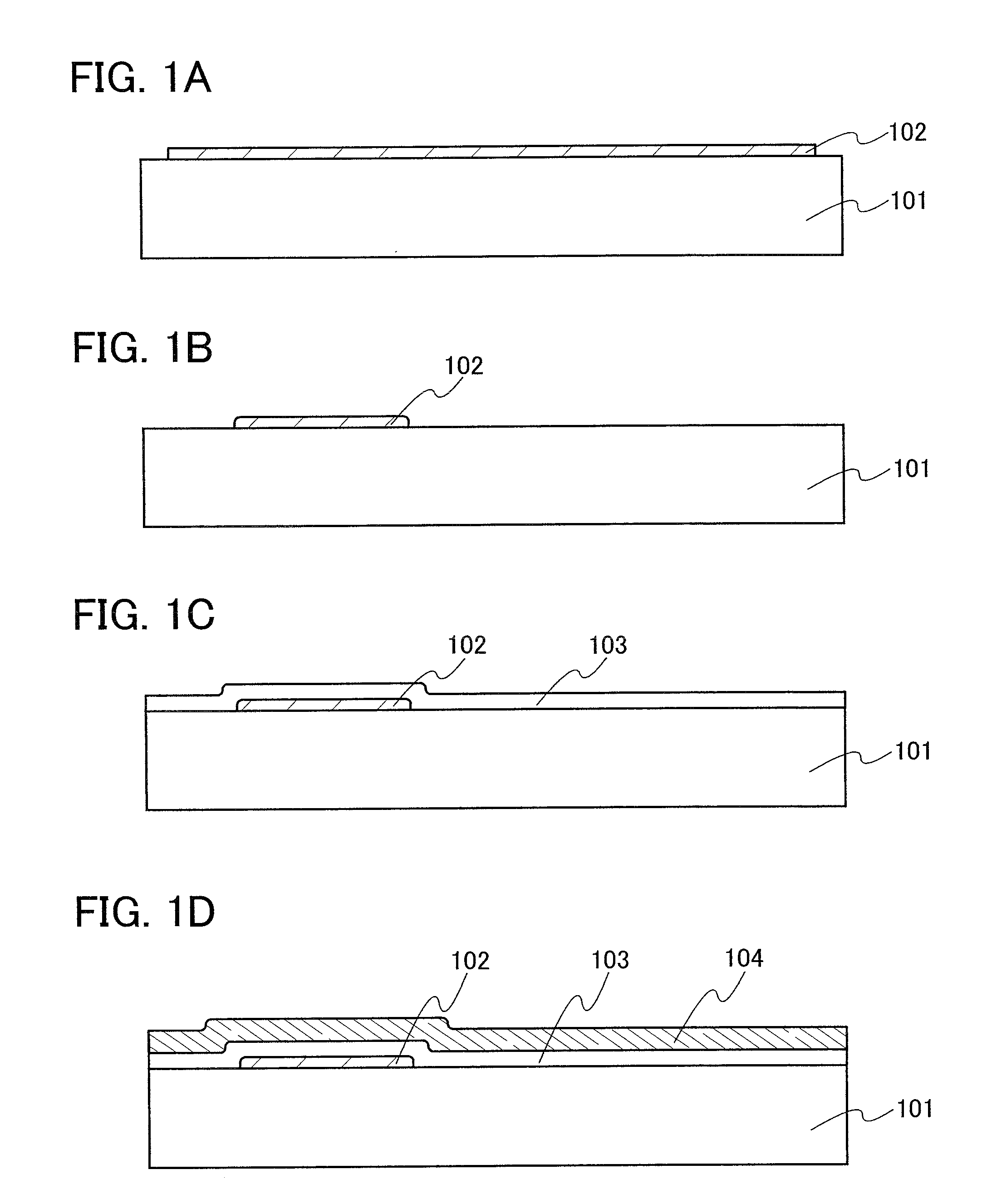

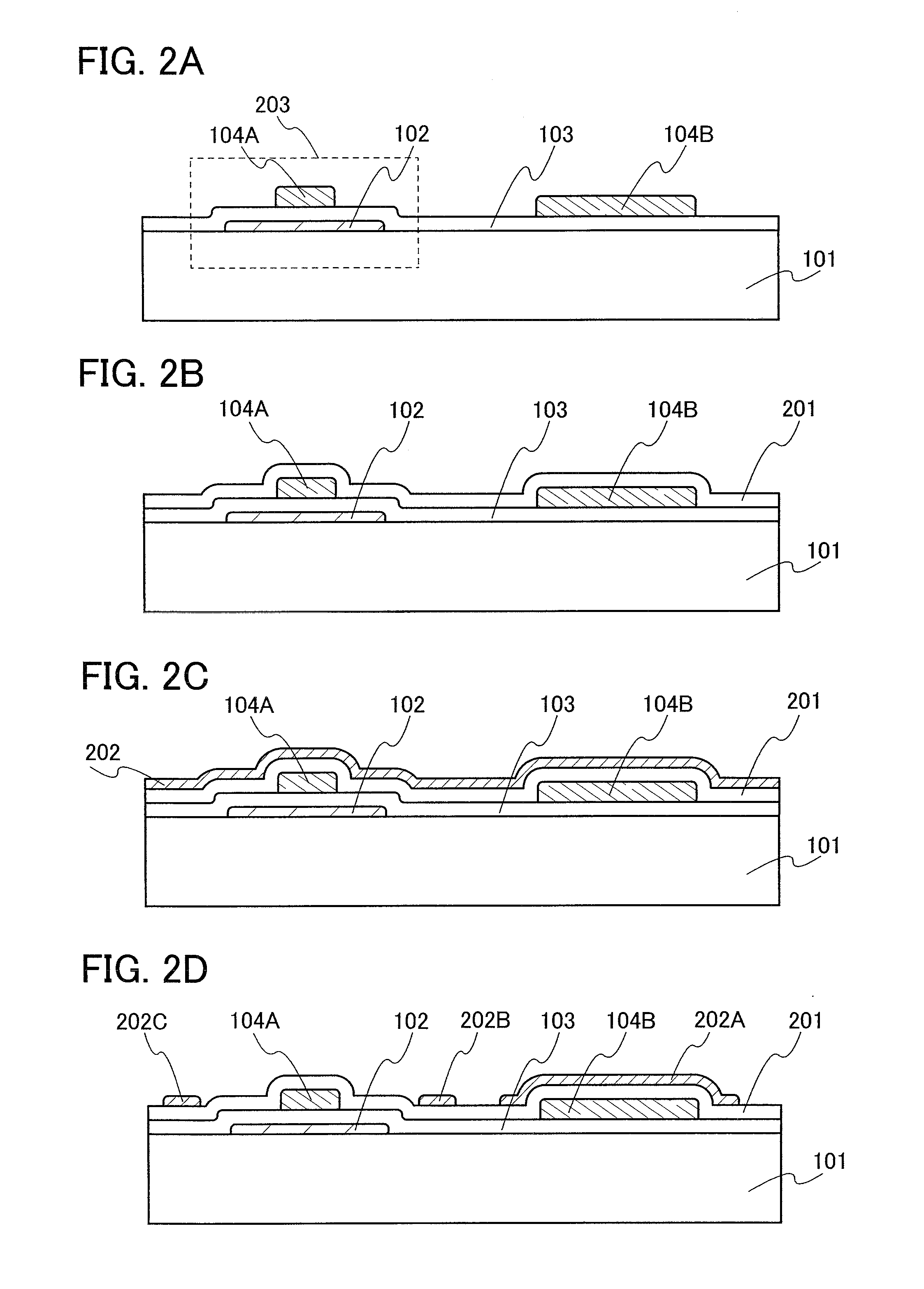

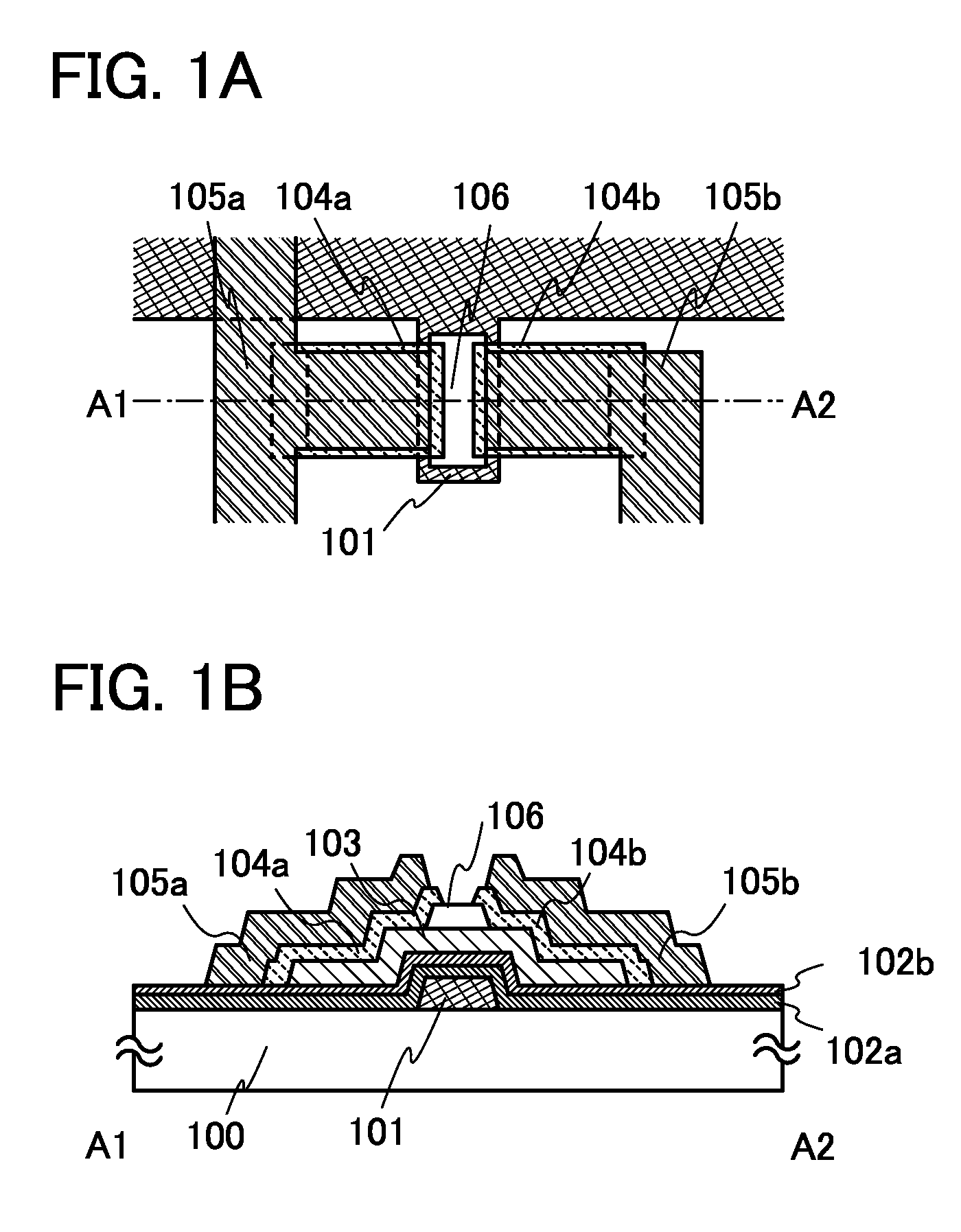

Minimally-patterned semiconductor devices for display applications

InactiveUS7030412B1Potential greatly variesSolid-state devicesSemiconductor devicesSemiconductor electrodeTransistor array

A thin-film transistor array comprises at least first and second transistors. Each transistor comprises a source electrode, a drain electrode a semiconductor electrode, a gate electrode, and a semiconductor layer. The semiconductor layer is continuous between the first and second transistors. The semiconductor layer is preferably unpatterned. In various display applications, the geometry of the transistors is selected to provide acceptable leakage currents. In a preferred embodiment, the transistor array is employed in an encapsulated electrophoretic display.

Owner:E INK CORPORATION

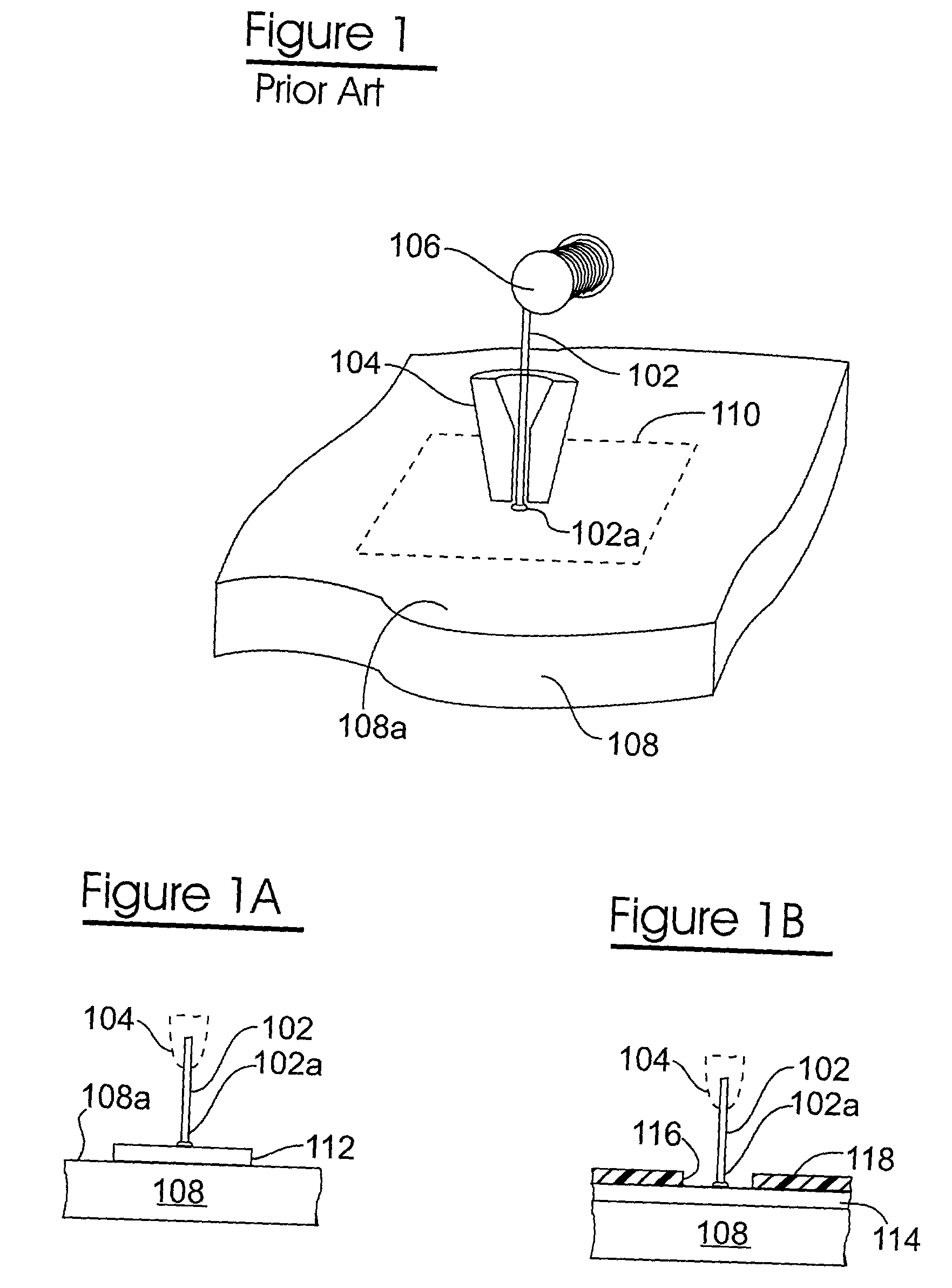

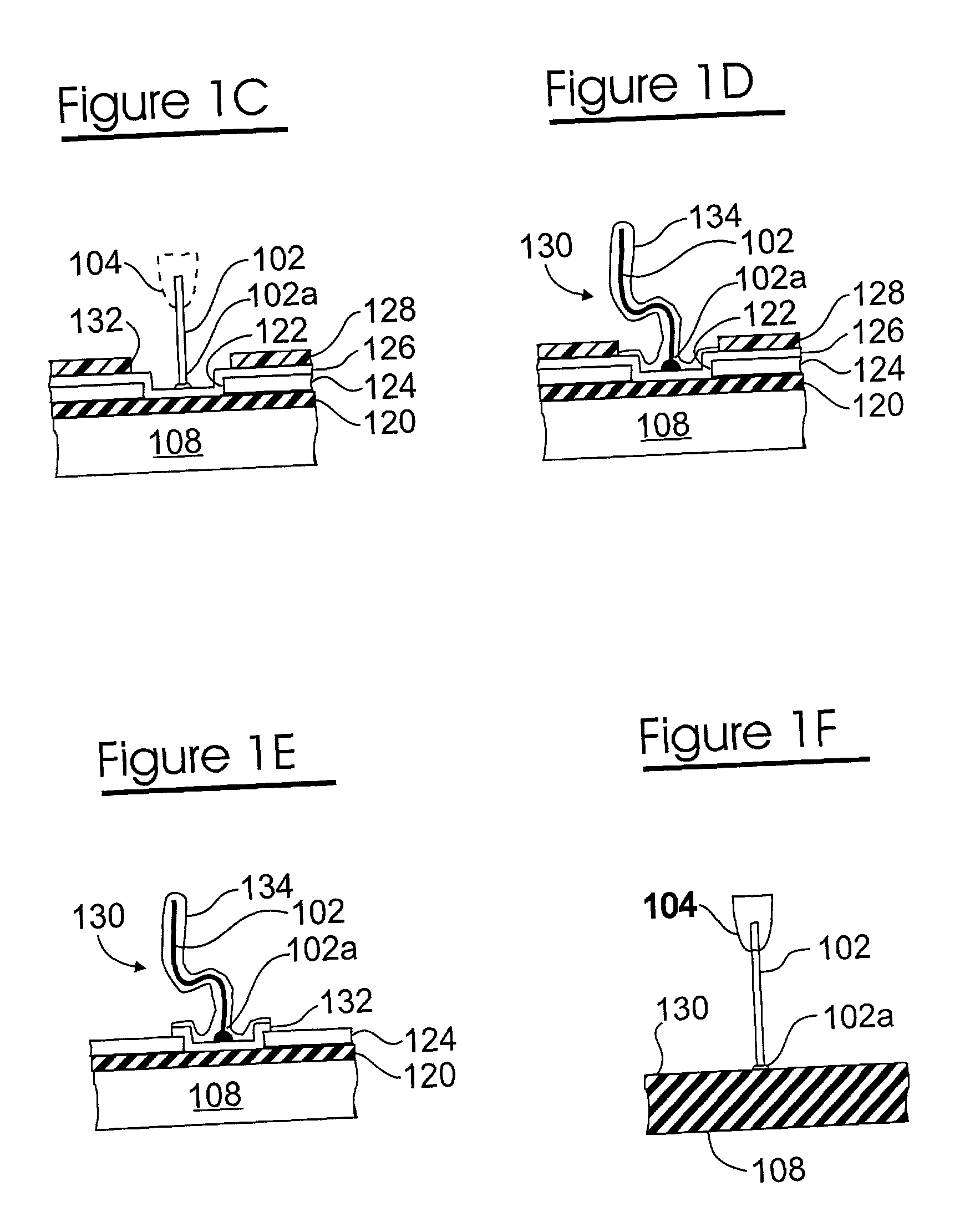

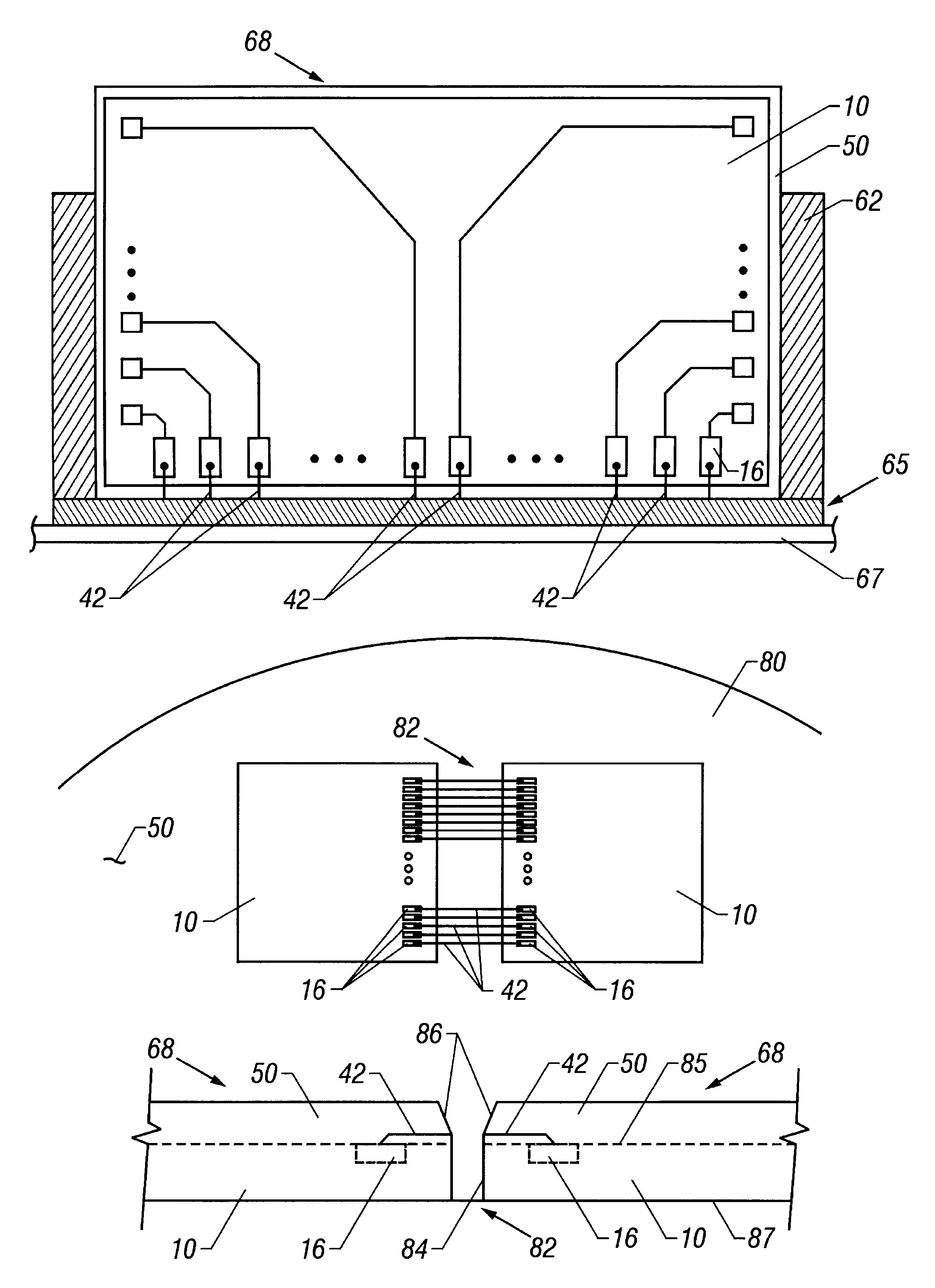

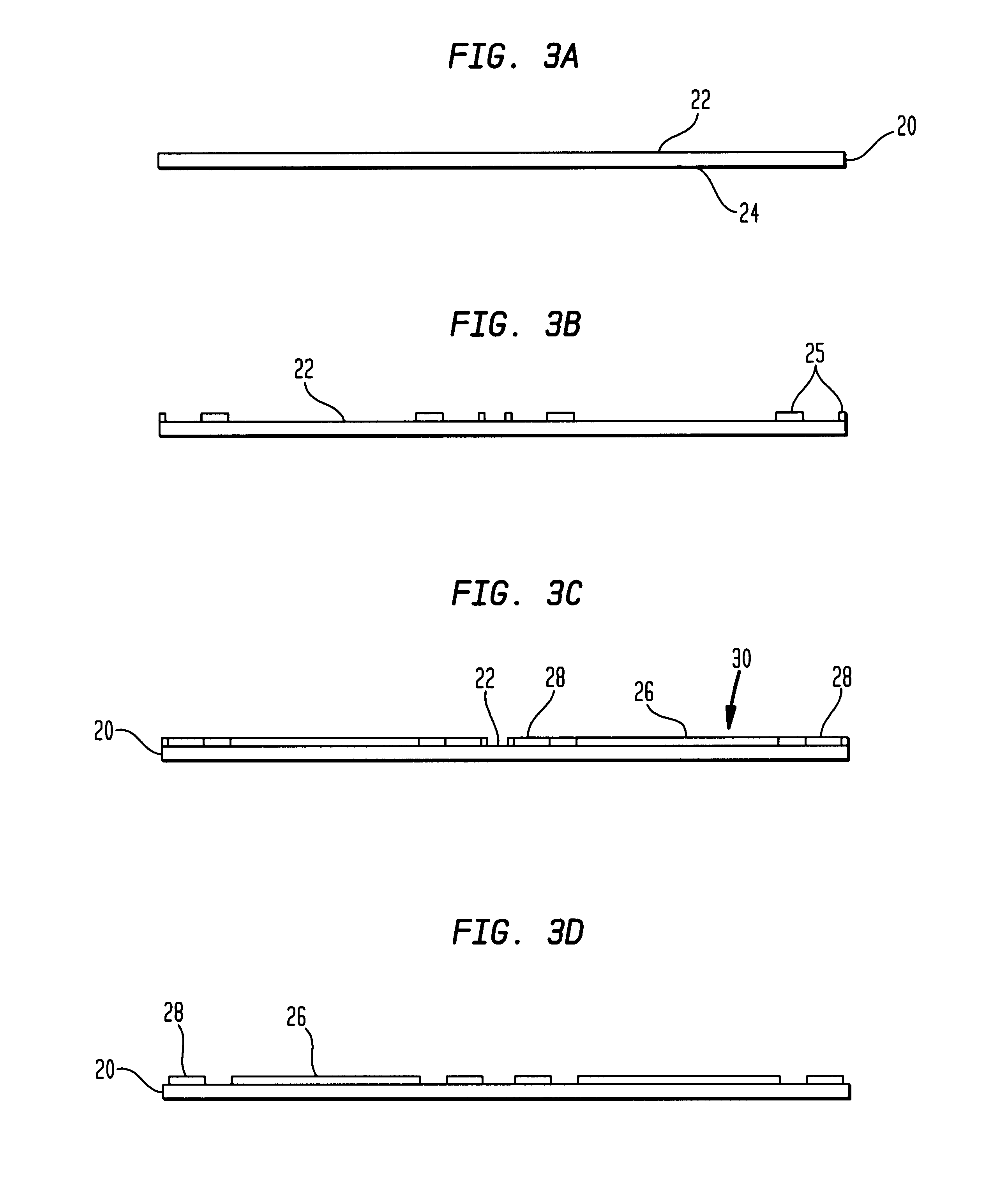

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

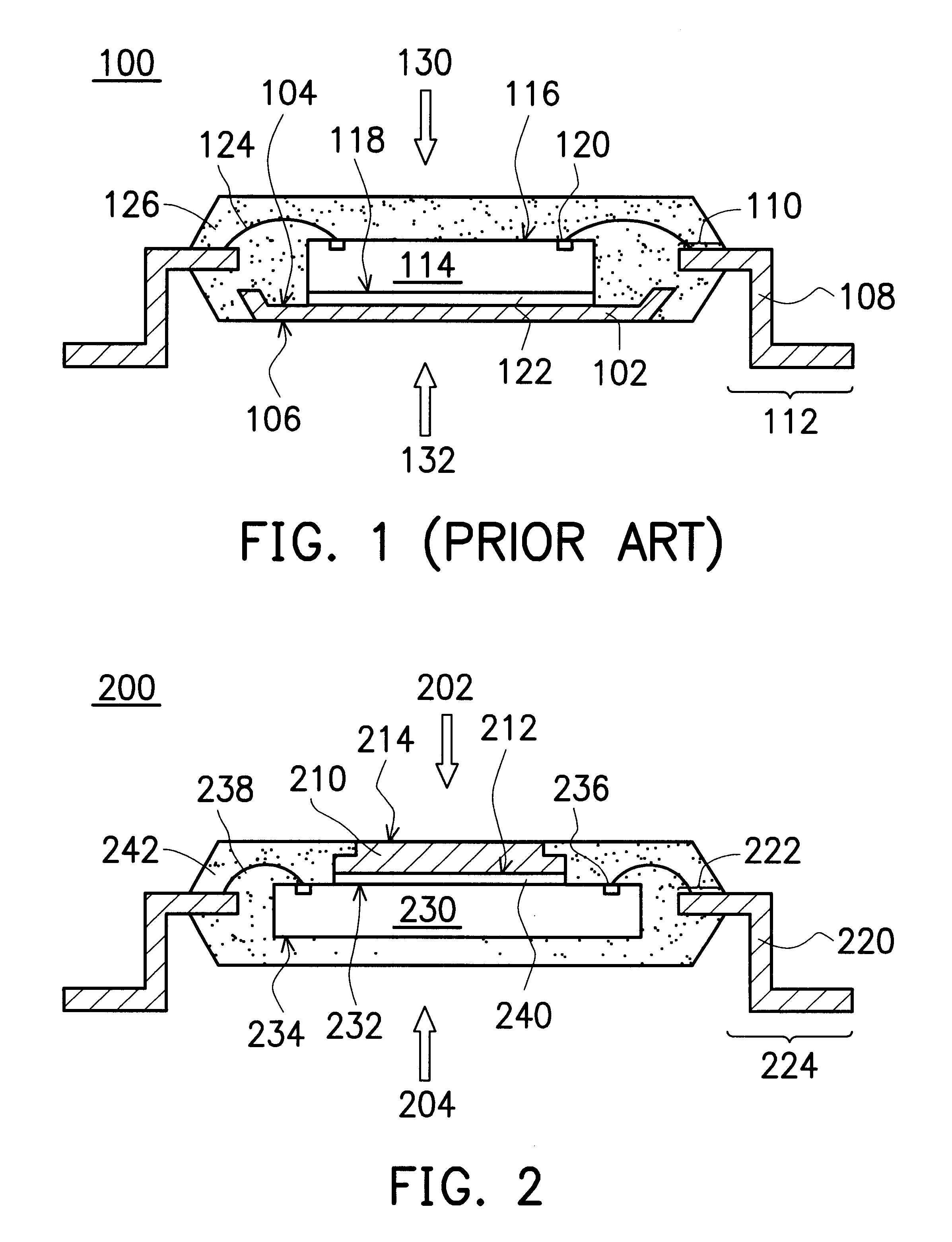

Semiconductor package and method for fabricating the same

InactiveUS6395578B1Improve cooling effectUniform encapsulationSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

Semiconductor packages having a thin structure capable of easily discharging heat from a semiconductor chip included therein, and methods for fabricating such semiconductor packages, are disclosed. An embodiment of a semiconductor package includes a semiconductor chip having a first major surface and a second major surface, the semiconductor chip being provided at the second major surface with a plurality of input / output pads; a circuit board including a resin substrate having a first major surface and a second major surface, a first circuit pattern formed at the first major surface and provided with a plurality of ball lands, a second circuit pattern formed at the second major surface and provided with a plurality of bond fingers connected with he ball lands by conductive via holes through the resin substrate, cover coats respectively coating the first and second circuit patterns while allowing the bond fingers and the ball lands to be exposed therethrough, and a central through hole adapted to receive the semiconductor chip therein; electrical conductors that electrically connect the input / output pads of the semiconductor chip with the bond fingers of the circuit board, respectively; a resin encapsulate that covers the semiconductor chip, the electrical conductors, and at least part of the circuit board; and, a plurality of conductive balls fused on the ball lands of the circuit board, respectively.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

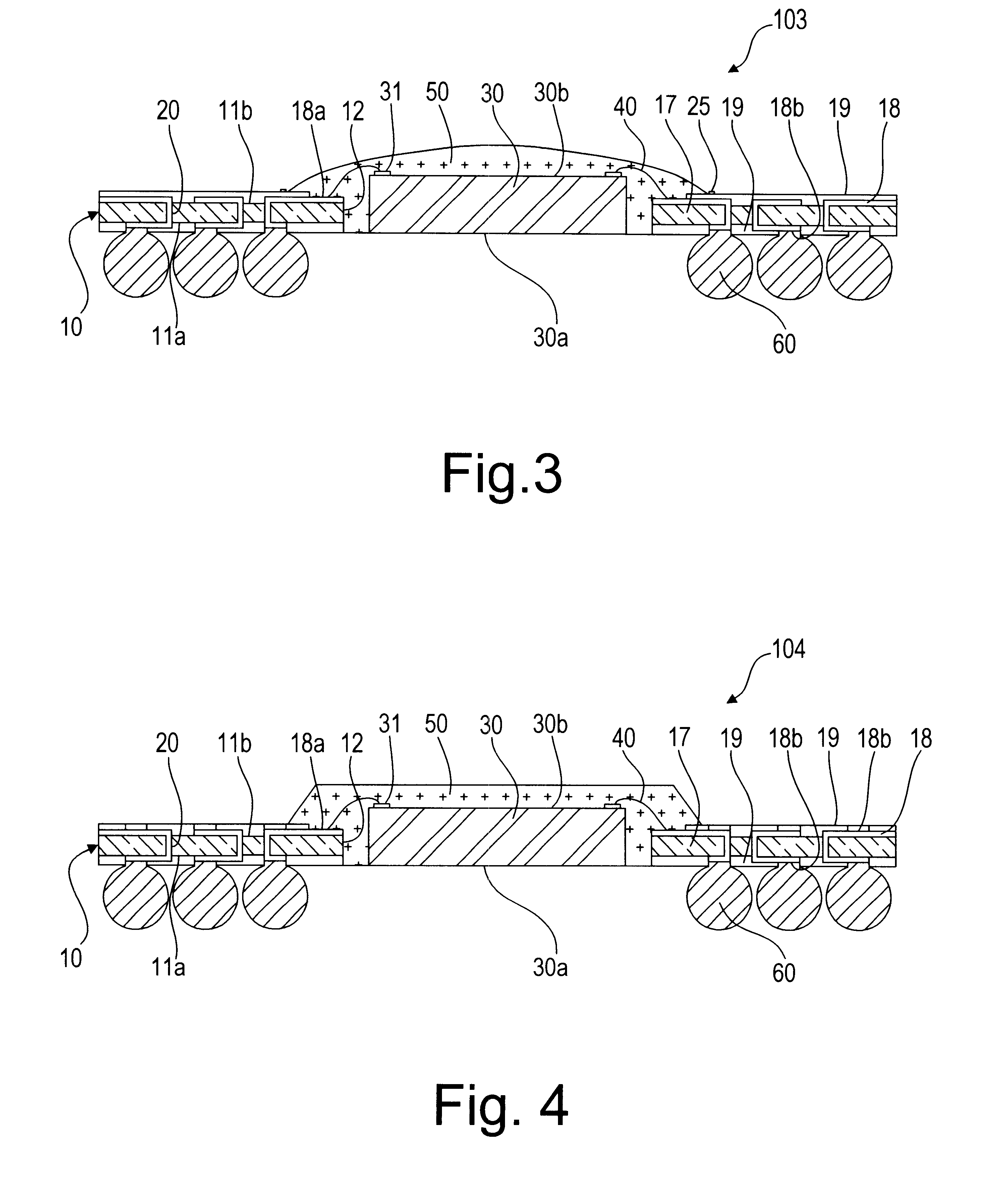

Semiconductor package and method of forming the same

InactiveUS20120119346A1Semiconductor/solid-state device detailsSolid-state devicesElectromagnetic wave transmissionSemiconductor chip

Disclosed are a semiconductor package and a method of manufacturing the same. The semiconductor package comprises a package cap which is capable of radiating high temperatures and performs a shield function preventing transmission of electromagnetic waves into and / or out of the semiconductor package. The semiconductor package including the package cap prevents chip malfunctions and improves device reliability. The package cap is positioned to cover first and second semiconductor chips of a semiconductor package.

Owner:SAMSUNG ELECTRONICS CO LTD

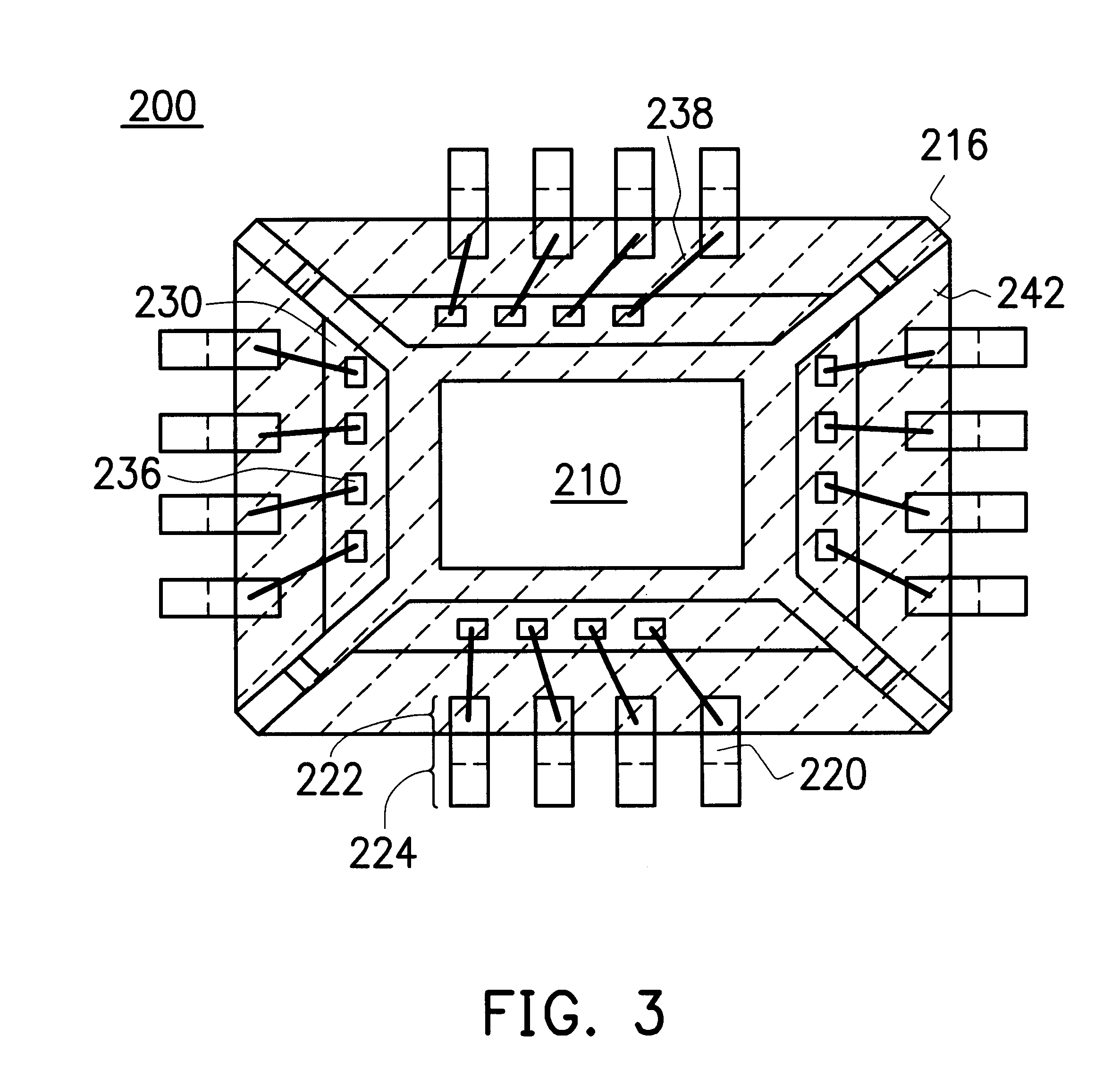

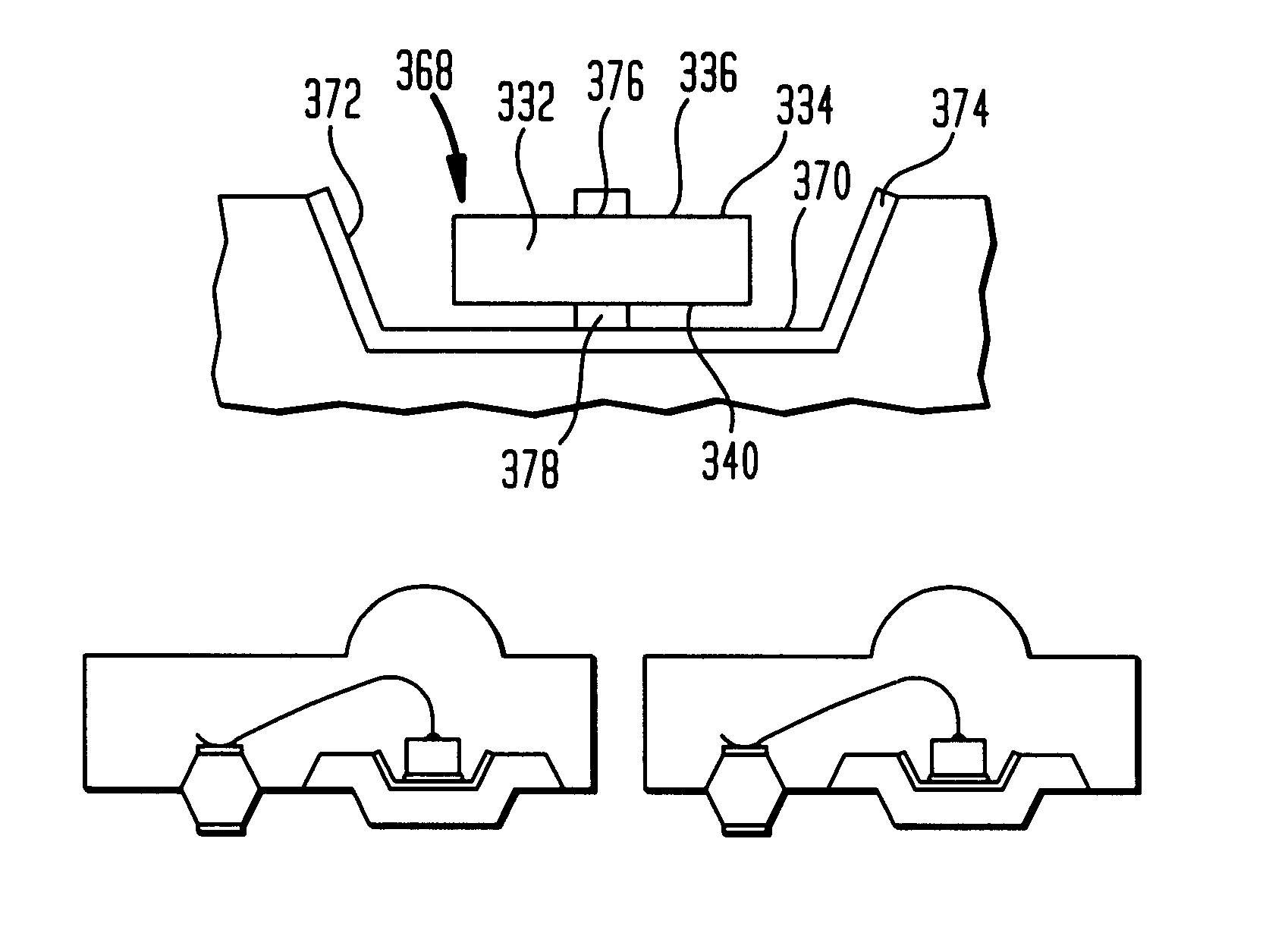

Quad flat non-lead package of semiconductor

InactiveUS6414385B1Semiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor package

A Quad Flat Non-Lead package of semiconductor comprises a chip, a plurality of leads, and a molding compound. The chip has its active surface bonded to the die pad, and the area of the die pad is smaller than that of the chip in order to expose the bonding pad on the active surface of the chip. The leads are disposed at the periphery of the die pad. A plurality of bonding wires is used to electrically connect the top surface of the leads to the bonding pads. The molding compound encapsulates the chip, the die pad, the bonding wires, and a portion of the surface of the leads. In this way, the encapsulating process make the side surface of the lead, and the portion excluding the wire-bonding protruded zone of the bottom surface of the lead exposed in order to make the leads become the external connections of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

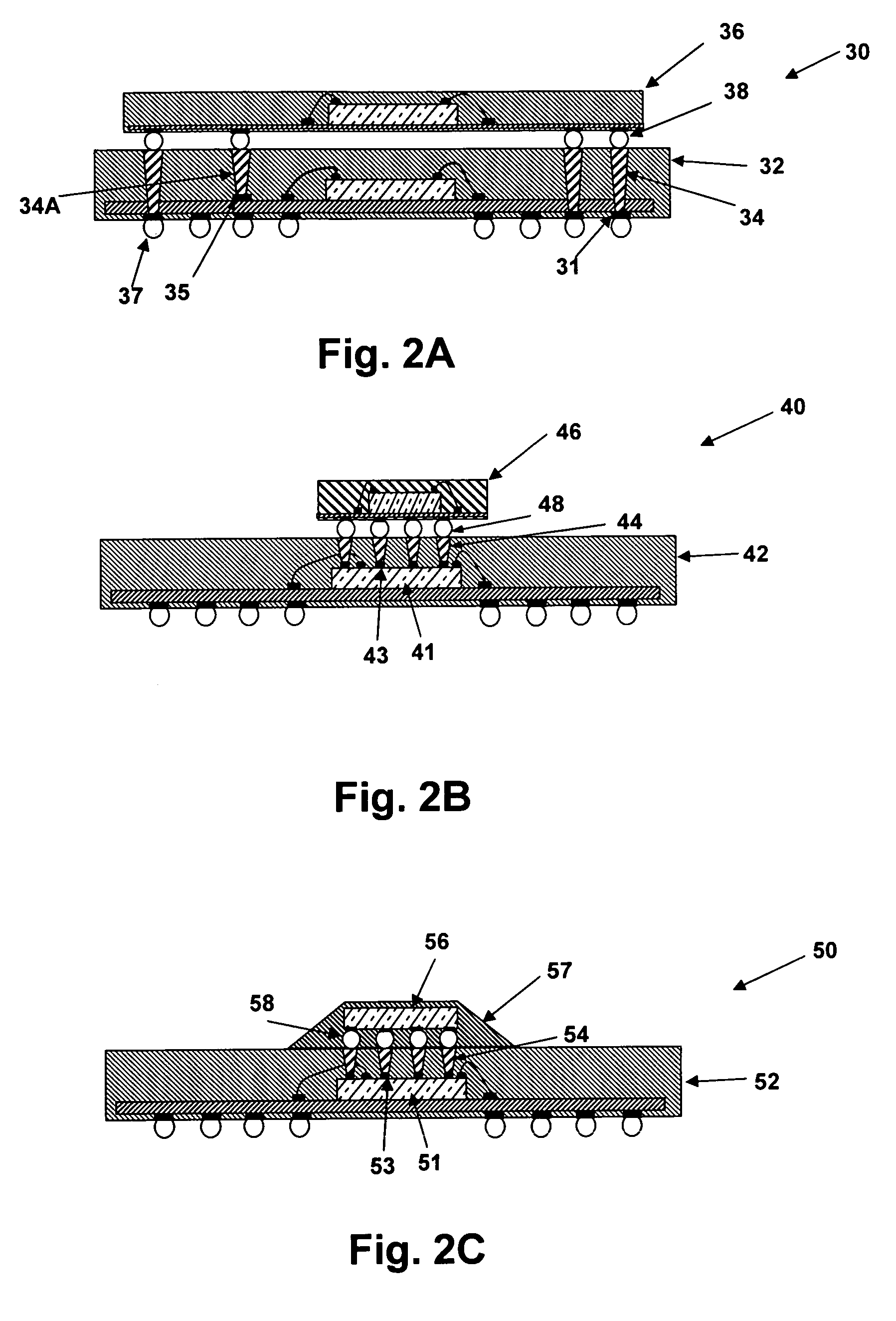

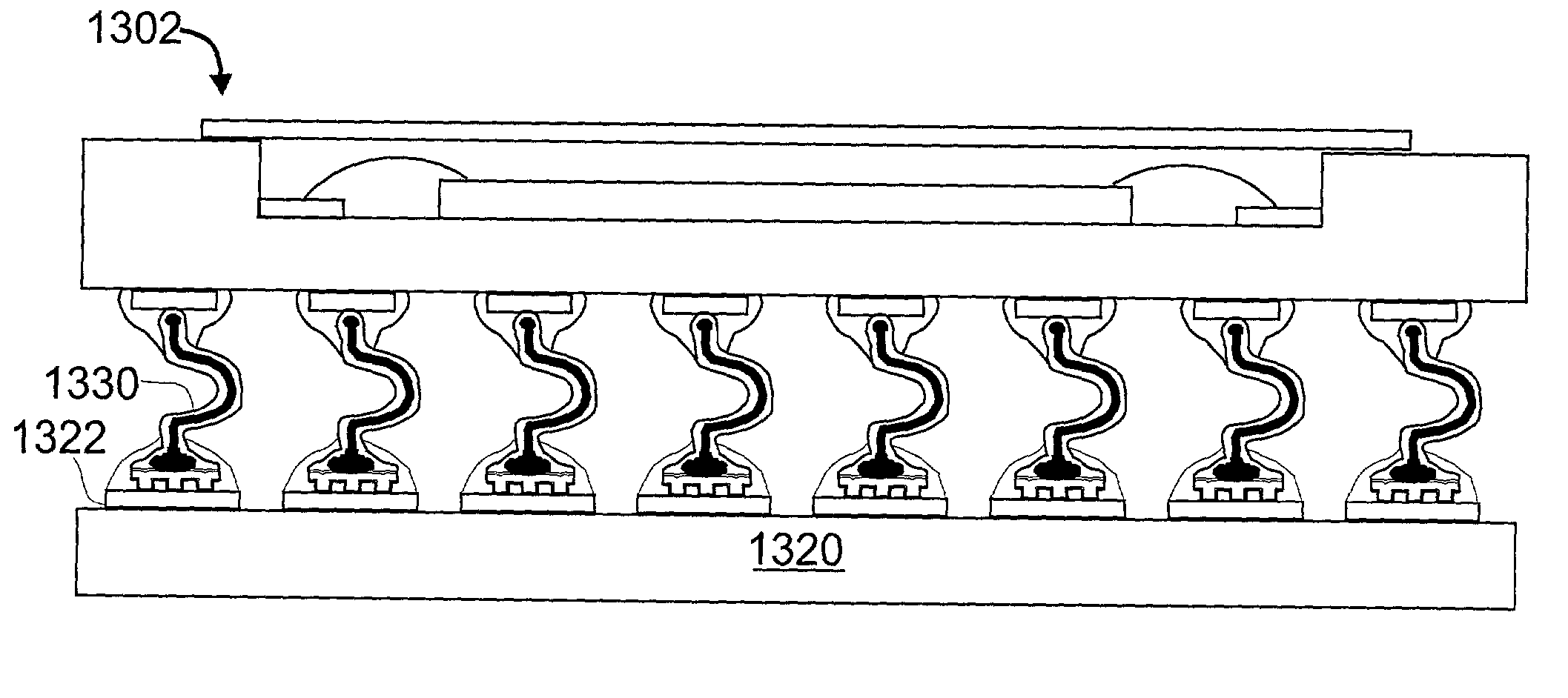

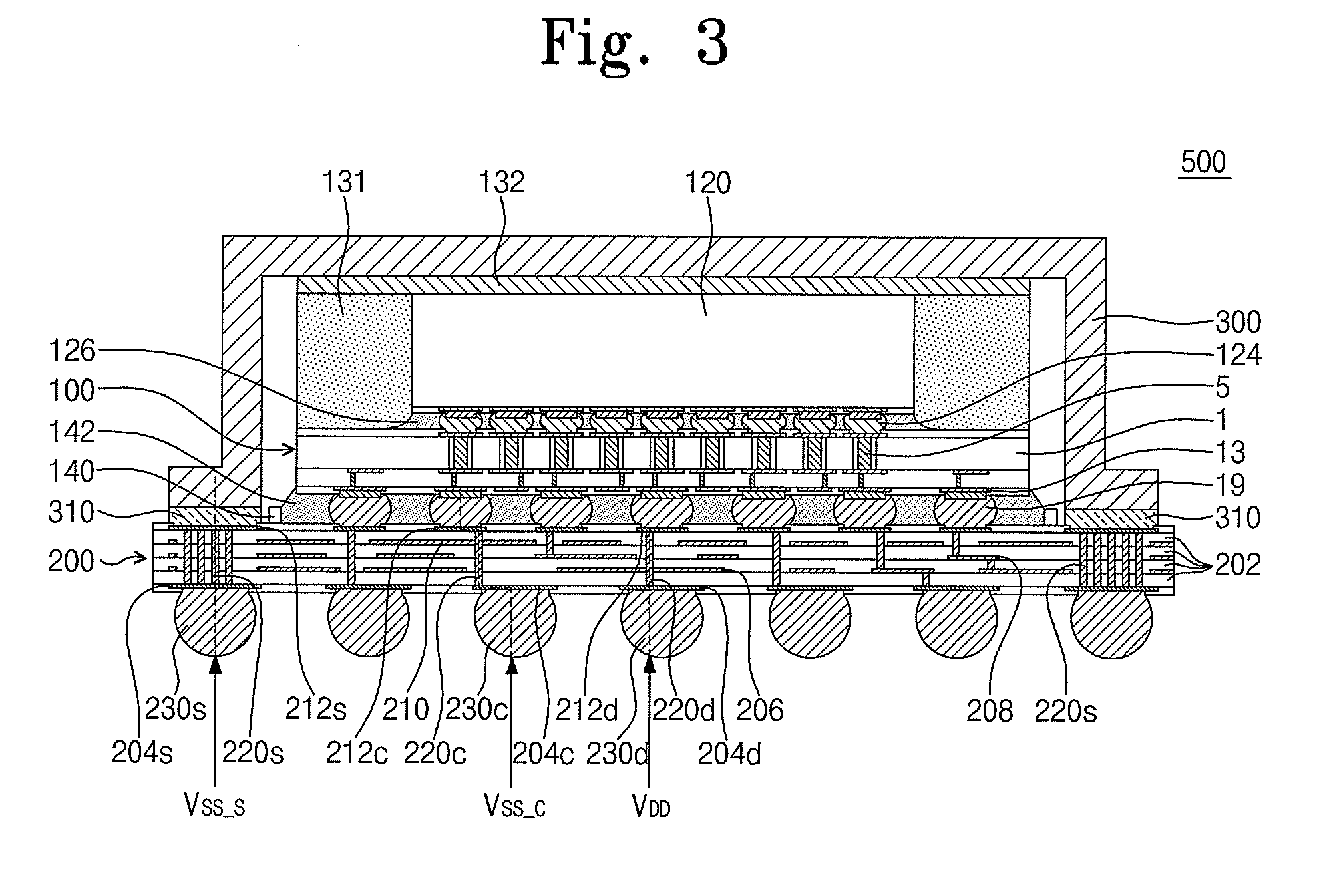

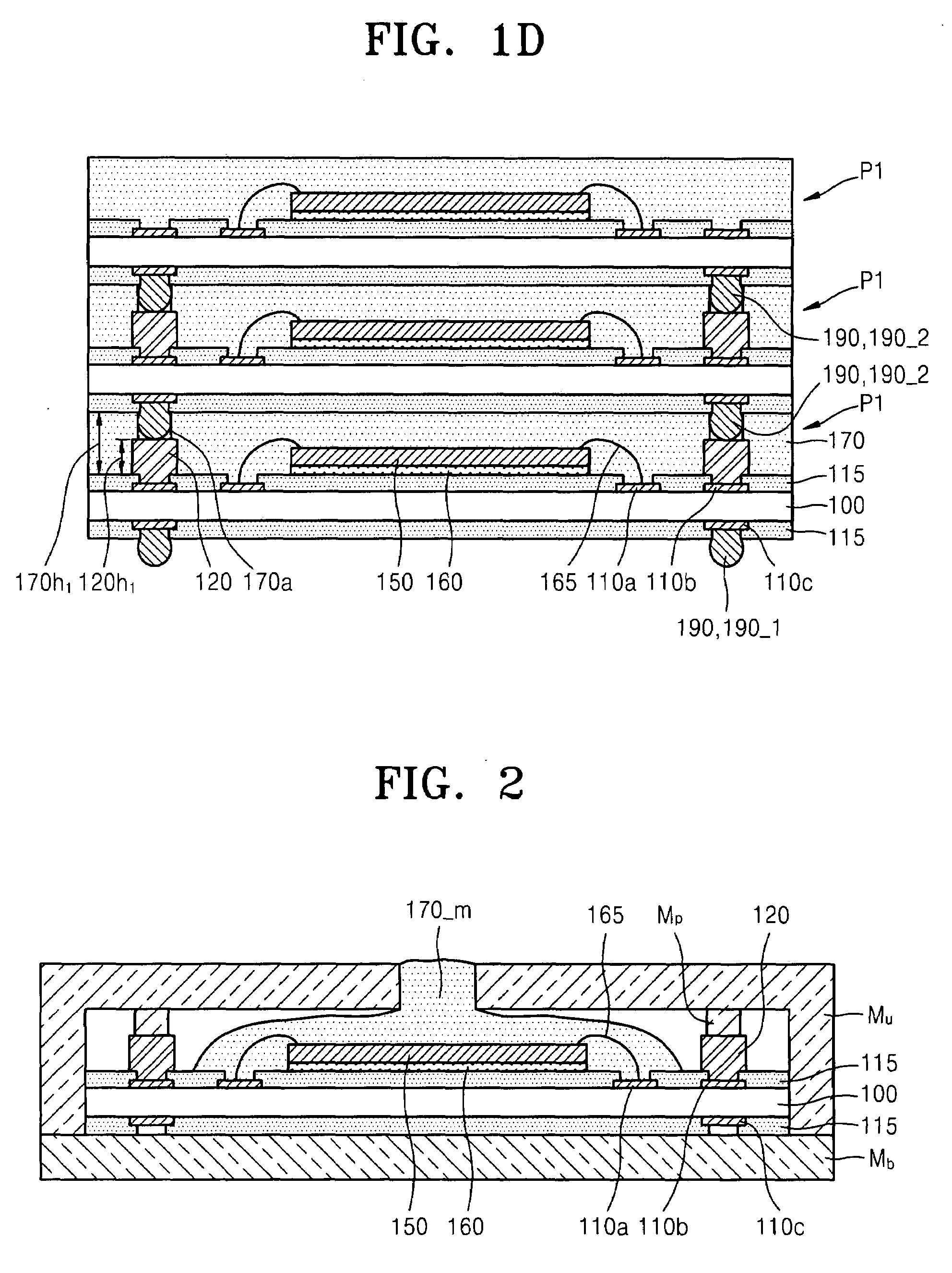

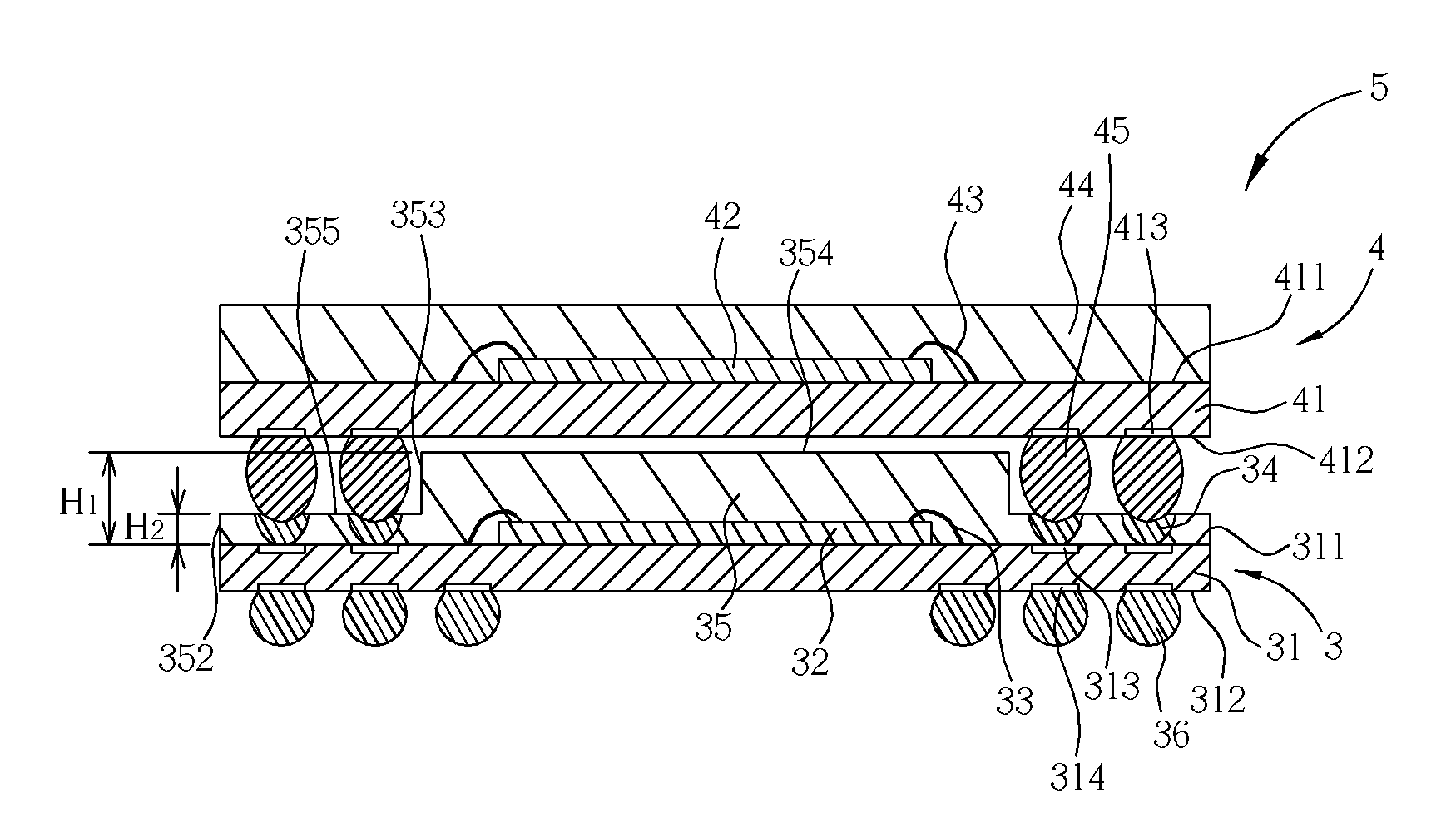

Stacked semiconductor packages and method for the fabrication thereof

ActiveUS6861288B2High densitySemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor package

A method for fabricating a stacked semiconductor package includes providing a substrate and mounting a first semiconductor device on the substrate. An interposer is supported above the first semiconductor device opposite the substrate. The interposer is electrically connected to the substrate. A second semiconductor device is then mounted on the interposer.

Owner:STATS CHIPPAC LTD

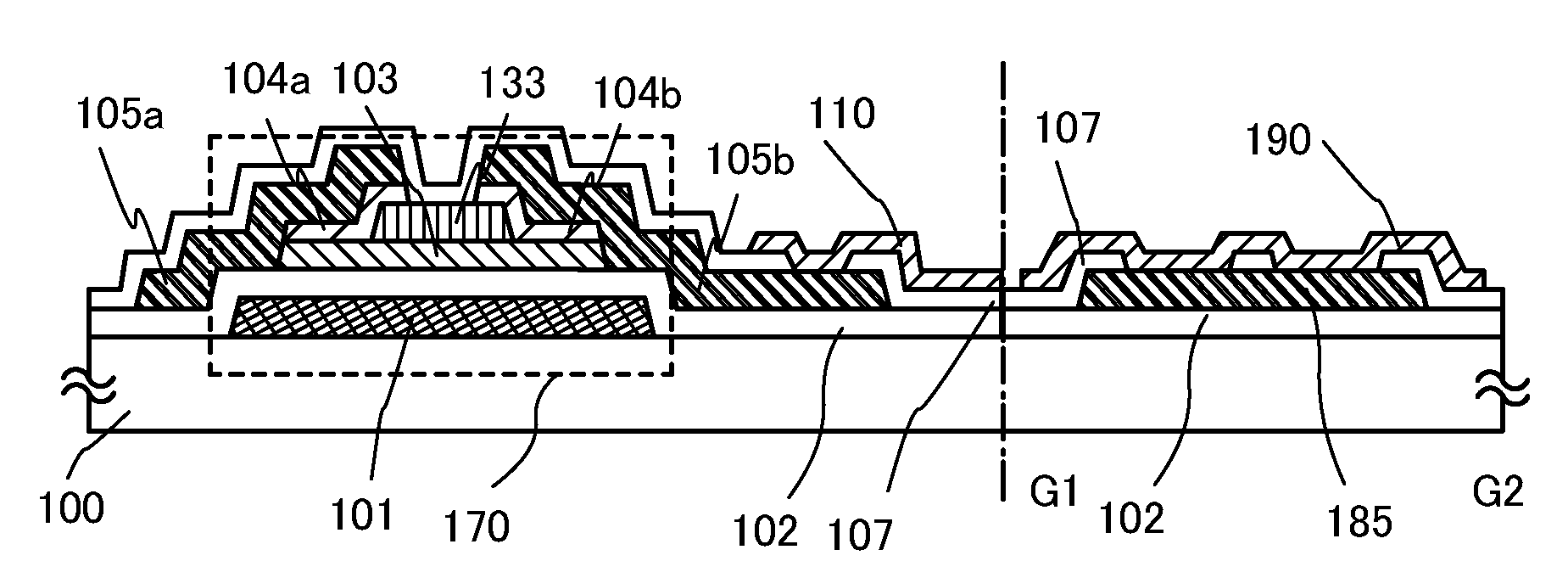

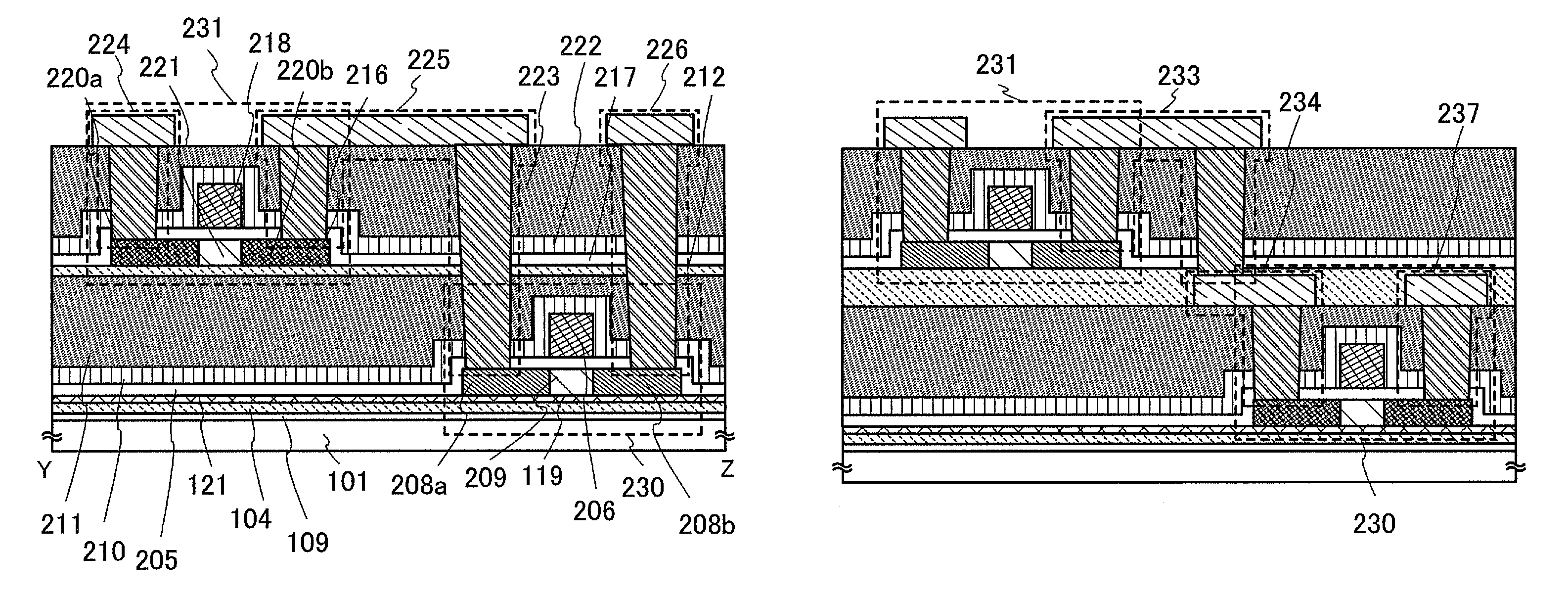

Semiconductor device

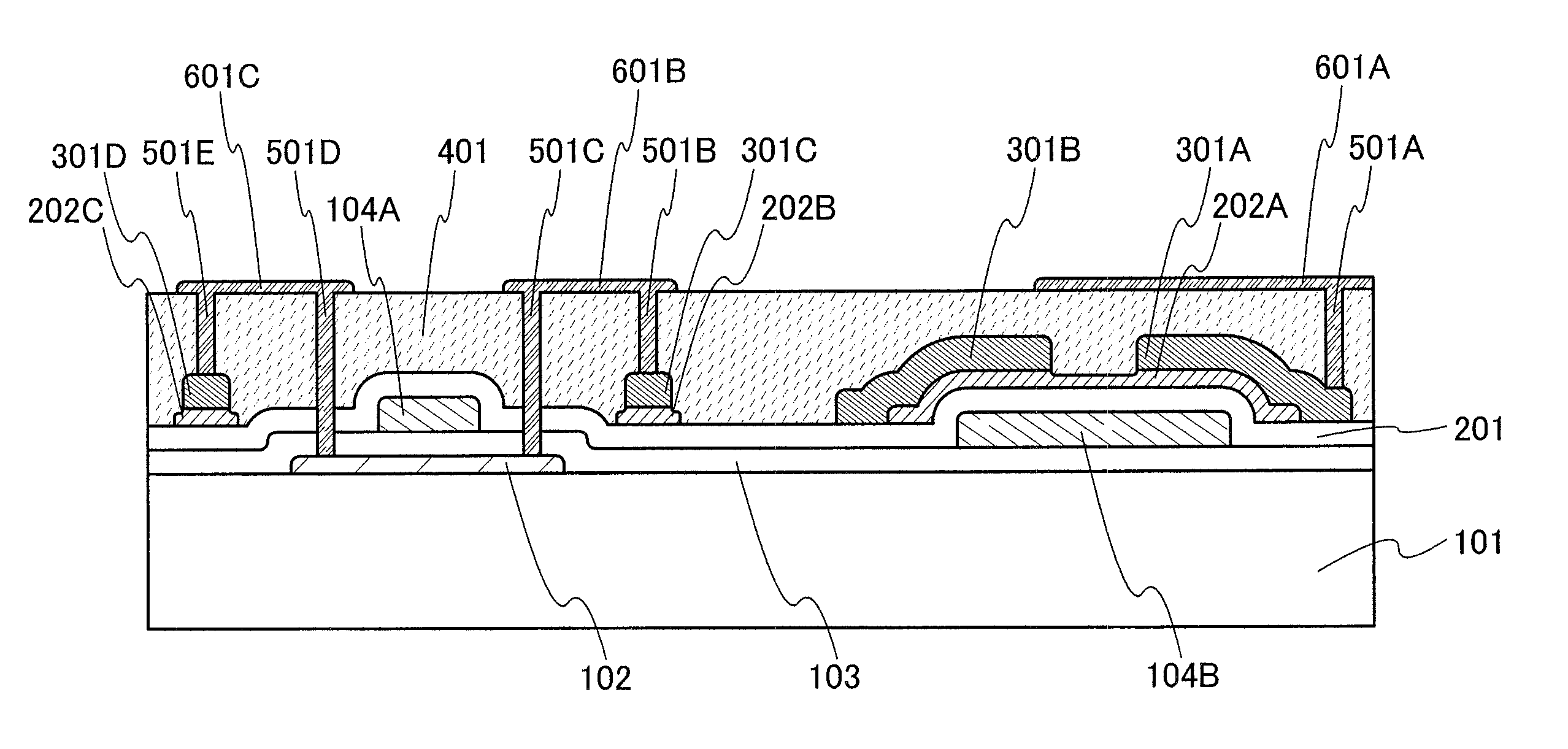

InactiveUS20100193785A1Low costReduce power consumptionTransistorSolid-state devicesSemiconductor packageSingle crystal

It is an object to provide a semiconductor device which has a large size and operates at high speed. A top gate transistor which includes a semiconductor layer of single-crystal and a bottom gate transistor which includes a semiconductor layer of amorphous silicon (microcrystalline silicon) are formed over the same substrate. Then, gate electrodes of each transistor are formed with the same layer, and source and drain electrodes are also formed with the same layer. Thus, manufacturing steps are reduced. In other words, two types of transistors can be manufactured by adding only a few steps to the manufacturing process of a bottom gate transistor.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor package having heat sink at the outer surface

InactiveUS6559525B2Easy to addImprove packaging efficiencySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageLead frame

A semiconductor package having heat sink at the outer surface is constructed on a lead frame. The package comprises a chip, a die pad, a plurality of leads, a plurality of bonding wires, and a molding compound. The die pad has a first surface and a second surface, and the chip has its active surface bonded to the first surface of the die pad. The area of the die pad is smaller than the area of the chip in order to expose the bonding pads on the active surface of the chip. The leads having an inner lead portions and an outer lead portions are disposed at the periphery of the die pad, and the inner lead portions are electrically connected to the bonding pads by a plurality of bonding wires. The molding compound encapsulates the chip, the die pad, the inner lead portions of the leads, and the bonding wires. The second surface of the die pad is exposed on the top surface of the package structure while the outer lead portion of the leads is exposed at the side edge of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

Method and apparatus for a semiconductor package for vertical surface mounting

InactiveUS6291894B1Electrically conductive connectionsDigital data processing detailsDevice materialSurface mounting

A method for packaging a semiconductor device includes connecting a plurality of wire leads to a corresponding plurality of electrical connection pads on the semiconductor device, covering at least a portion of the semiconductor device and at least a portion of each of the wire leads with an encapsulating material, and removing a portion of the encapsulating material and a portion of each of the wire leads to form a packaged semiconductor device wherein each of the wire leads has an exposed portion only at an end. The invention also includes a packaged semiconductor device having an integrated circuit device with a plurality of electrical connection pads, a plurality of wire leads coupled to the plurality of electrical connection pads, and a covering of encapsulating material covering at least a portion of the integrated circuit device and covering each of the wire leads, wherein each of the wire leads has an exposed end. The present invention contemplates wire bonding and encapsulation of individual die as well as multiple die on a single wafer.

Owner:MICRON TECH INC

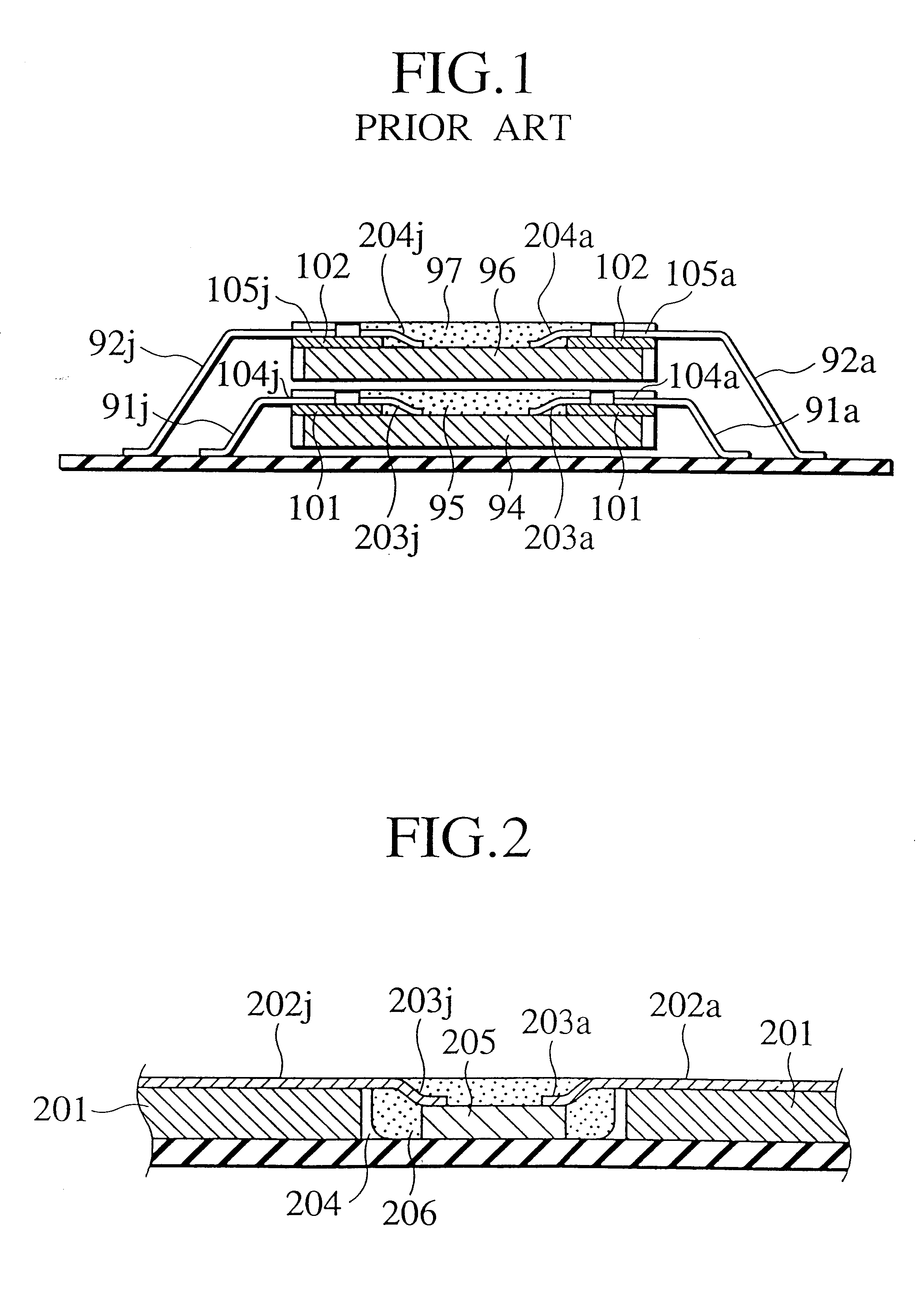

Stack type semiconductor package and method of fabricating the same

InactiveUS20080017968A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A stack type semiconductor package, and a method of fabricating the same are provided. The stack type semiconductor package may include a lower unit package and an upper unit package. The lower unit package may include a substrate, and a semiconductor chip on an upper surface of the substrate. A bump may be on an upper surface of the substrate, and a protecting layer, covering the semiconductor chip, may be formed. The protecting layer may include a via hole partially exposing the bump. The upper unit package may be on the protecting layer, and may include an internal connection solder ball on a lower surface of the upper unit package. The internal connection solder ball may be inserted into the via hole and connected to the bump.

Owner:SAMSUNG ELECTRONICS CO LTD

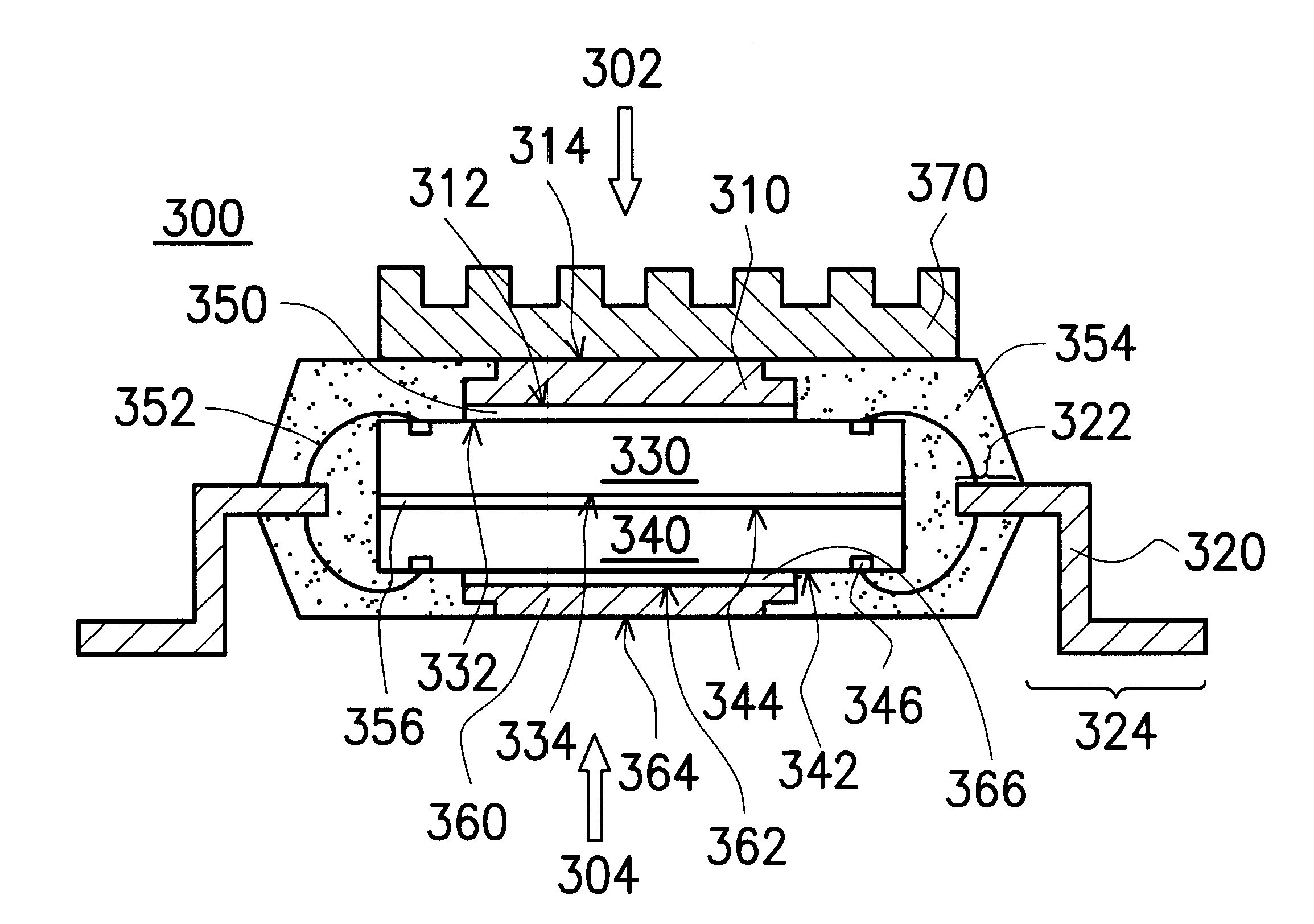

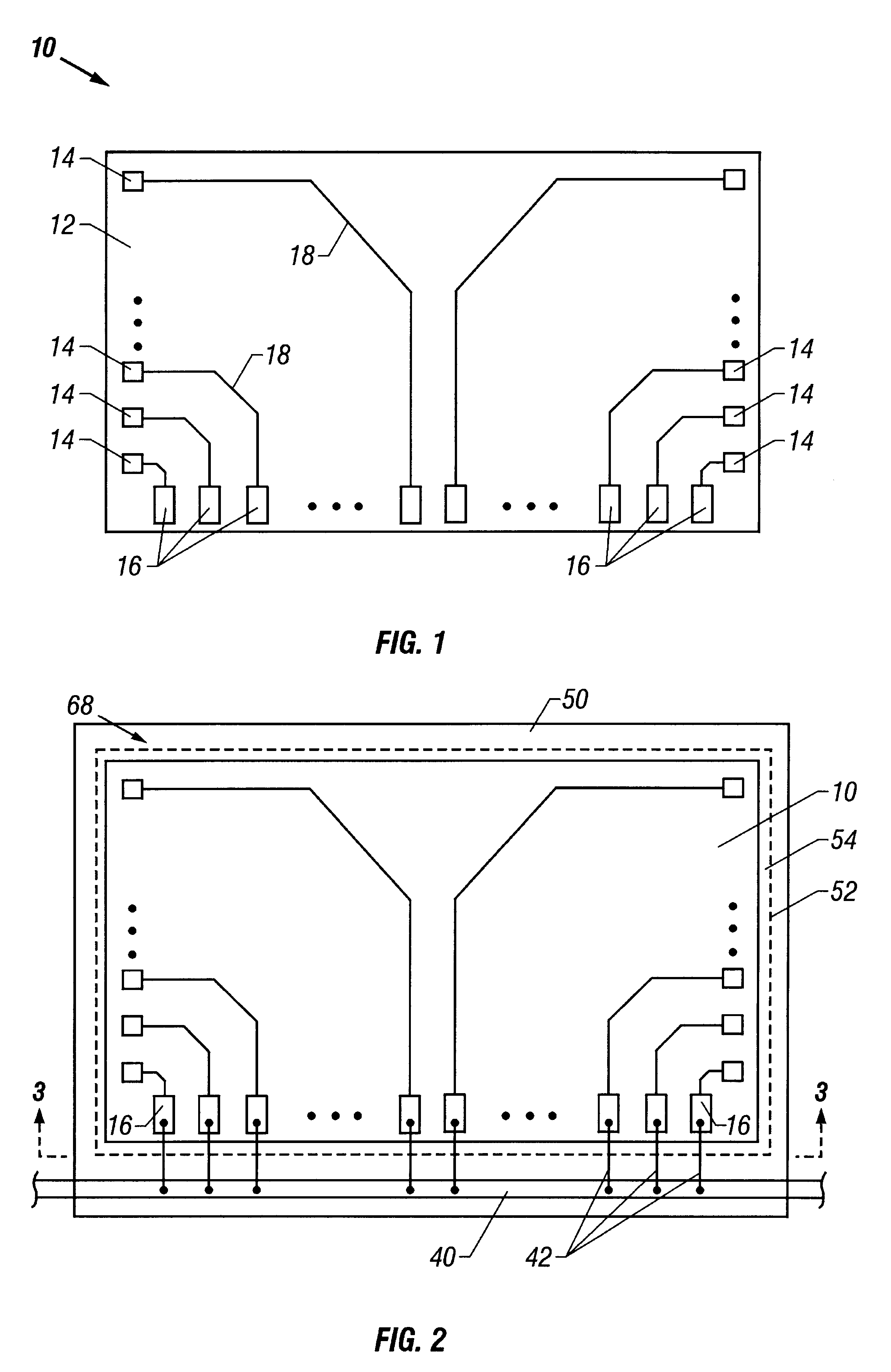

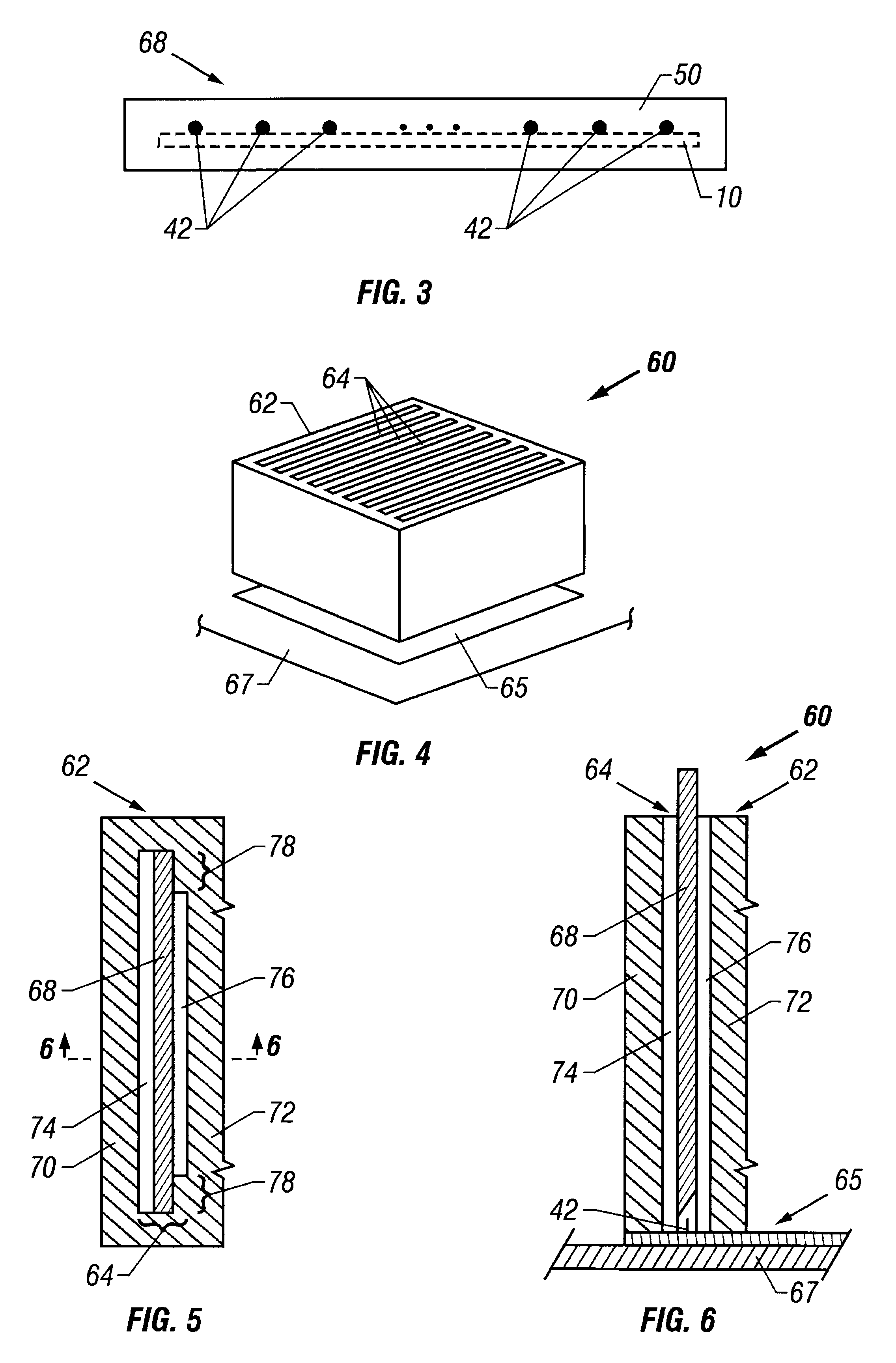

Semiconductor packages having light-sensitive chips

InactiveUS6583444B2Readily flexEasy to moveSemiconductor/solid-state device detailsSolid-state devicesProgrammable read-only memorySemiconductor package

A method of making a microelectronic package includes providing a sacrificial layer having a first surface and providing an optoelectronic element having a front face including one or more contacts and a rear surface and securing the rear surface of the optoelectronic element over the first surface of the sacrificial layer. The one or more contacts are then electrically interconnected with one or more conductive pads on the sacrificial layer and a curable and at least partially transparent encapsulant is provided over the first surface of the sacrificial layer so as to encapsulate the optoelectronic element and the conductive pads. The encapsulant is then cured the sacrificial layer is at least partially removed so as to leave said one or more conductive pads on a bottom surface of the encapsulant, the bottom surface of the encapsulant defining the bottom of the package. The optoelectronic element may include a light sensitive chip such as an ultraviolet-erasable programmable read-only memory (UV EPROM) or a light emitting chip, such as a light emitting diode (LED).

Owner:TESSERA INC

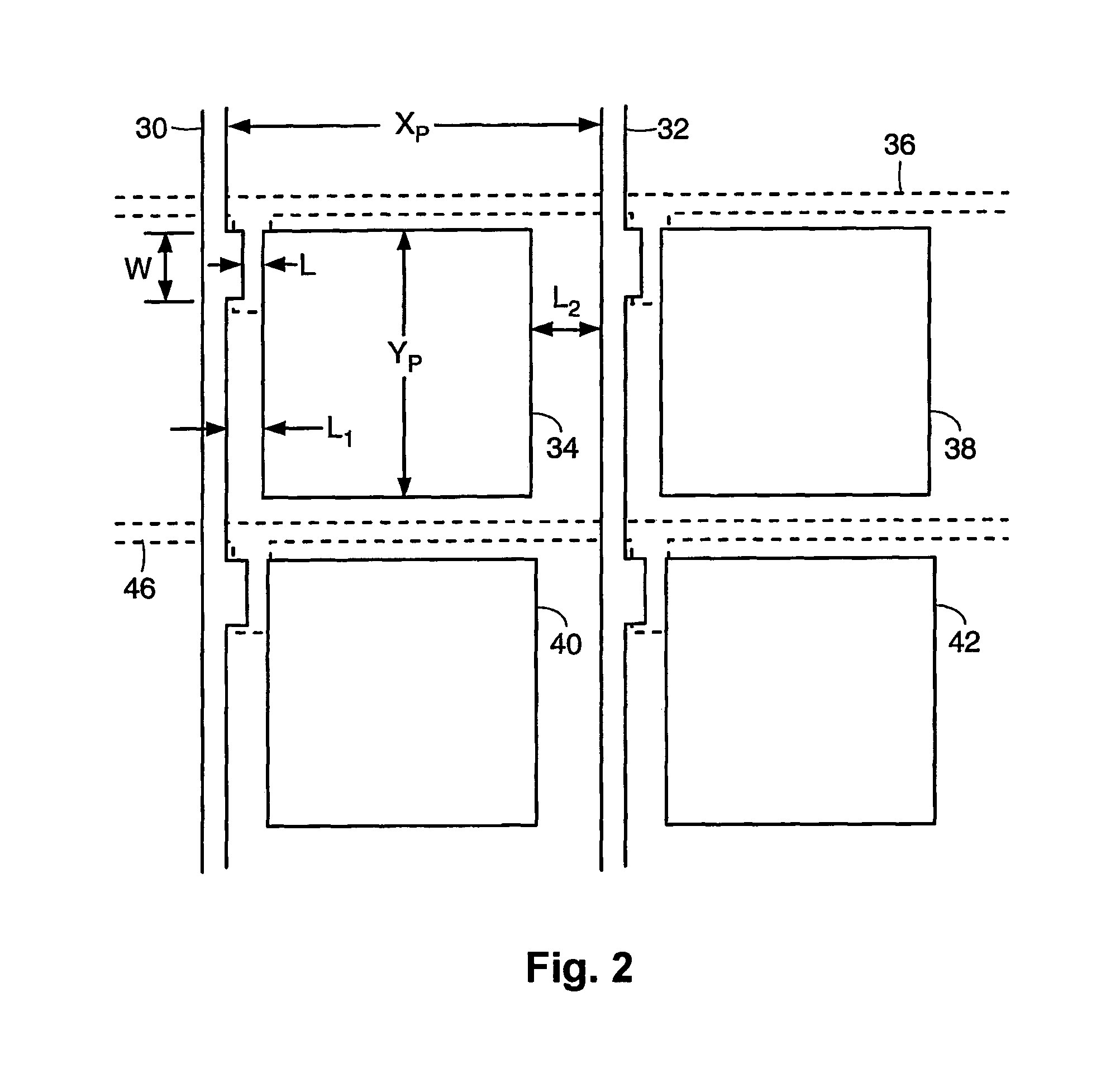

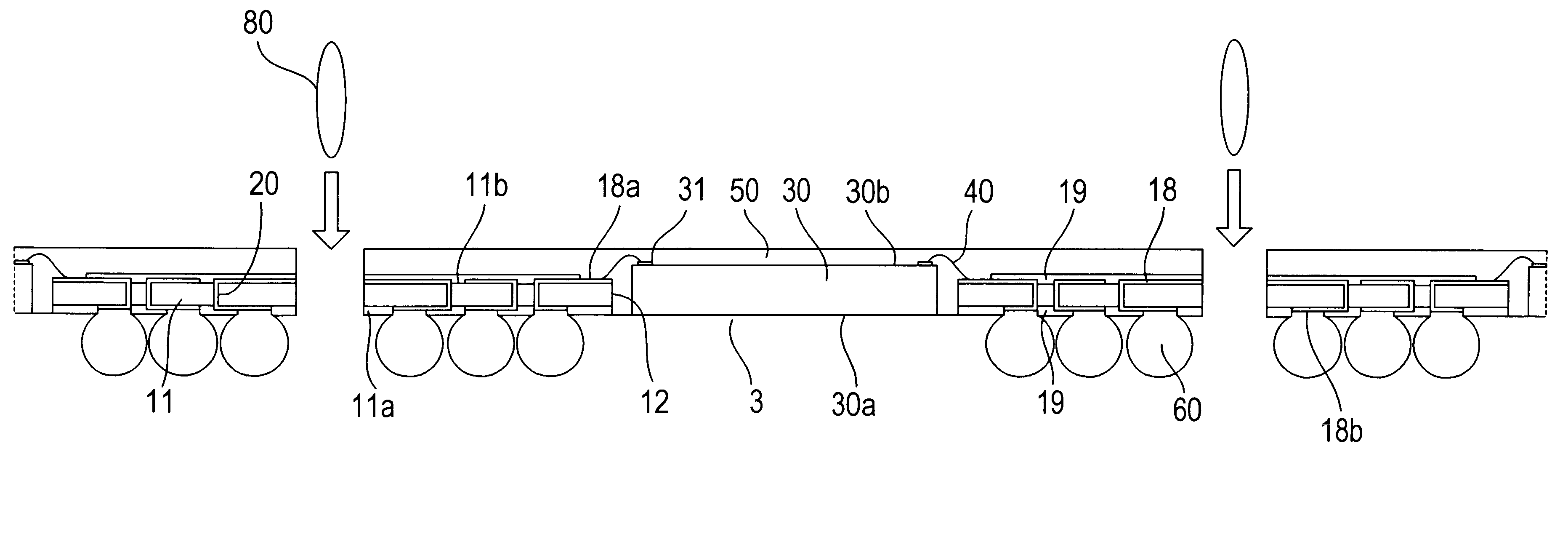

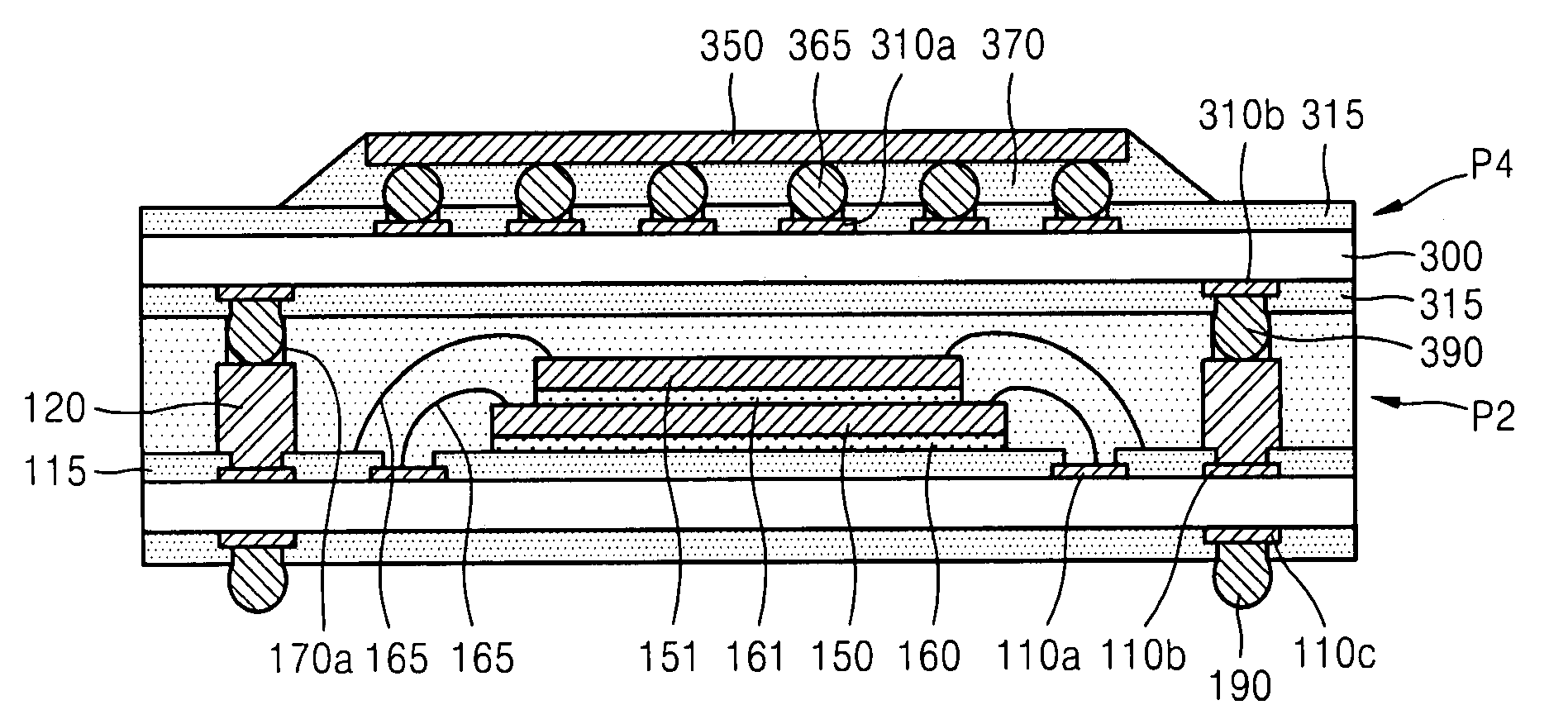

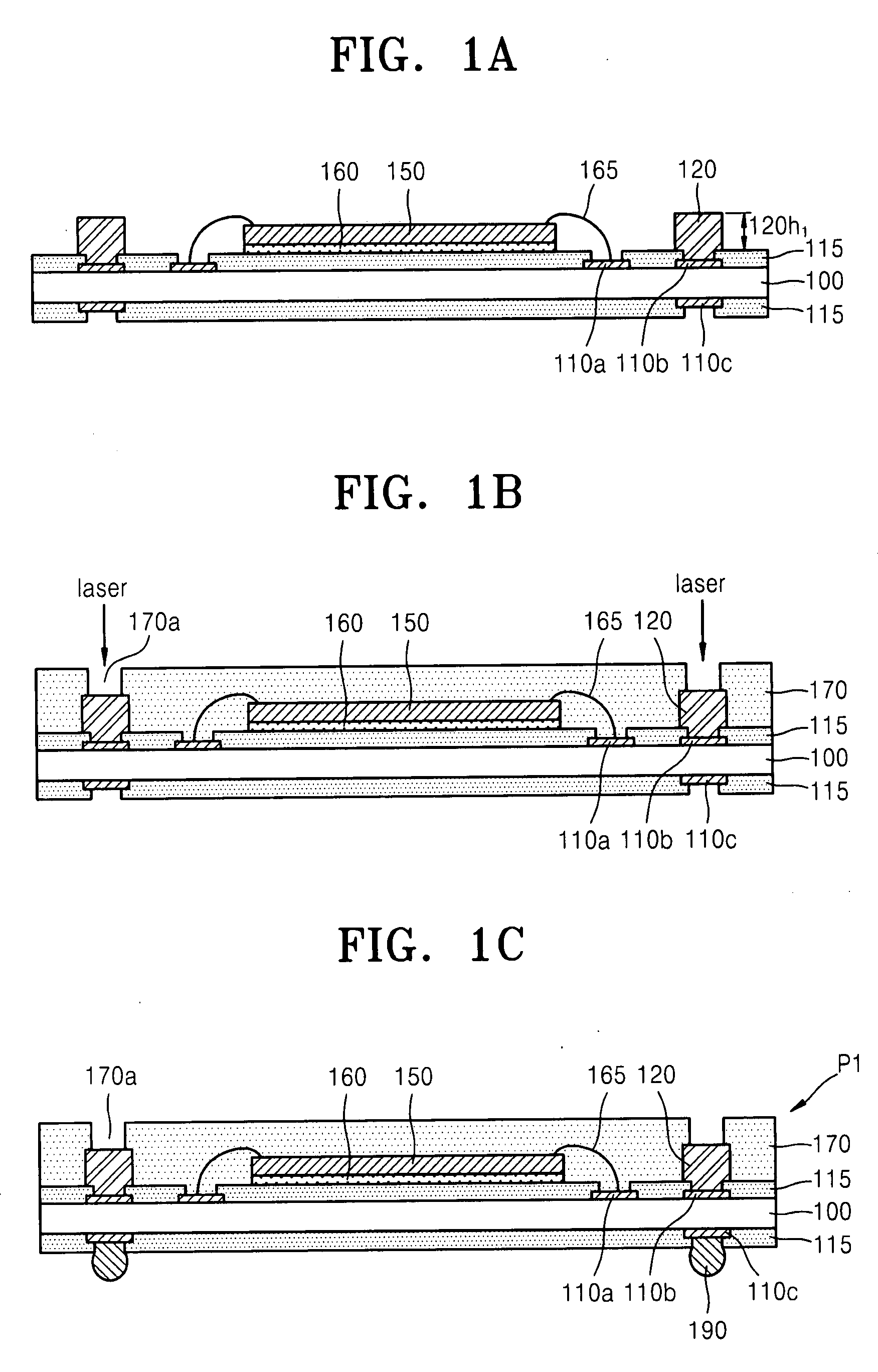

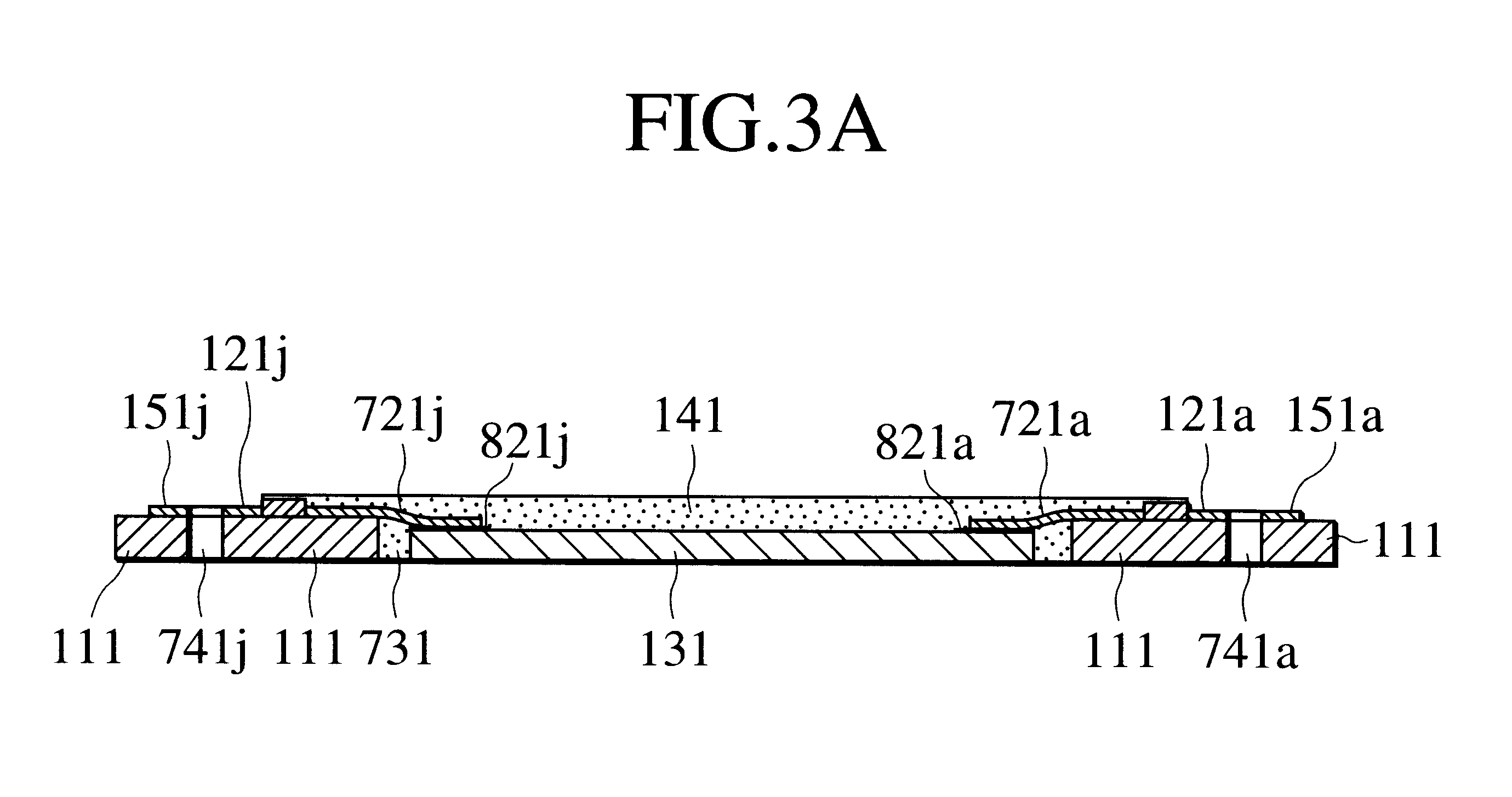

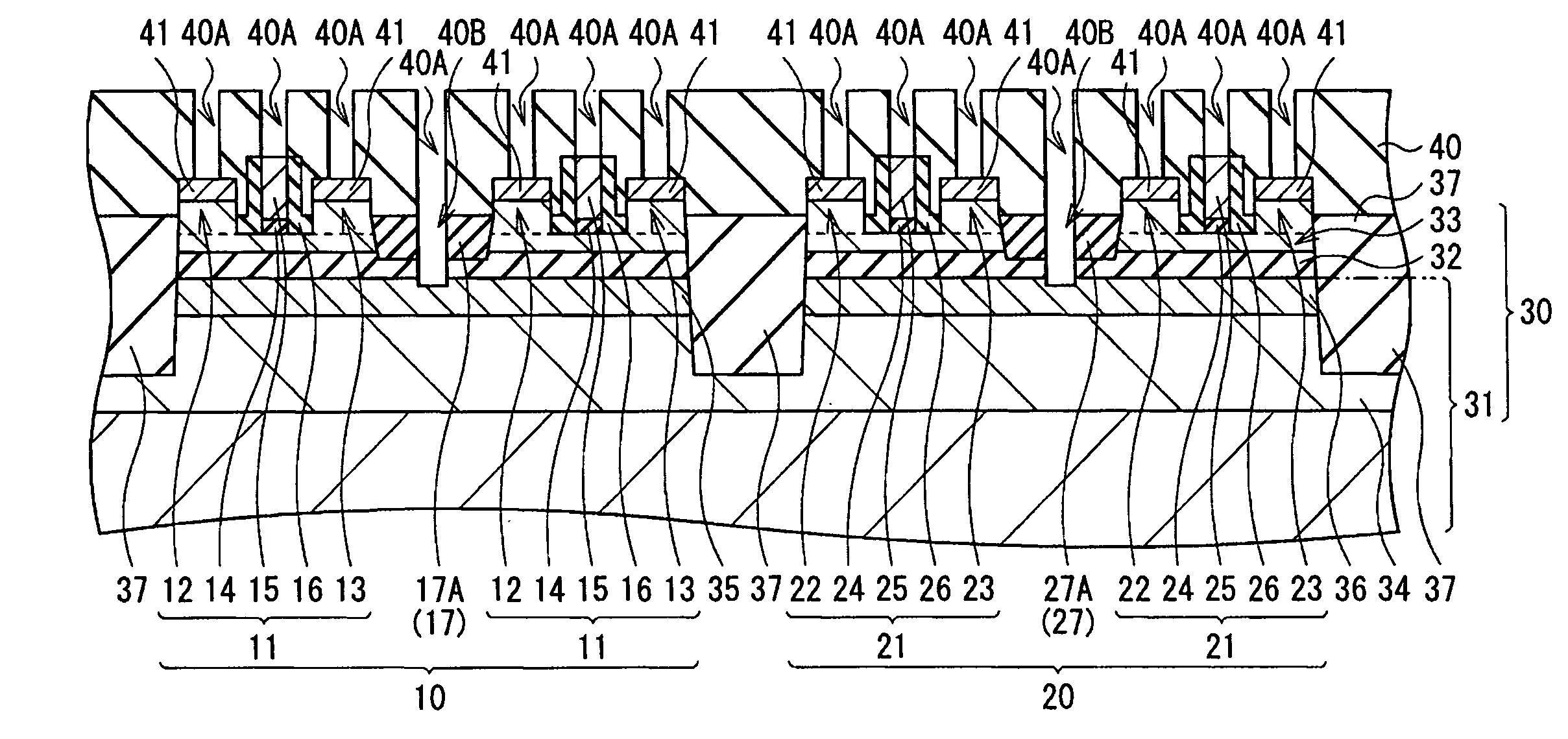

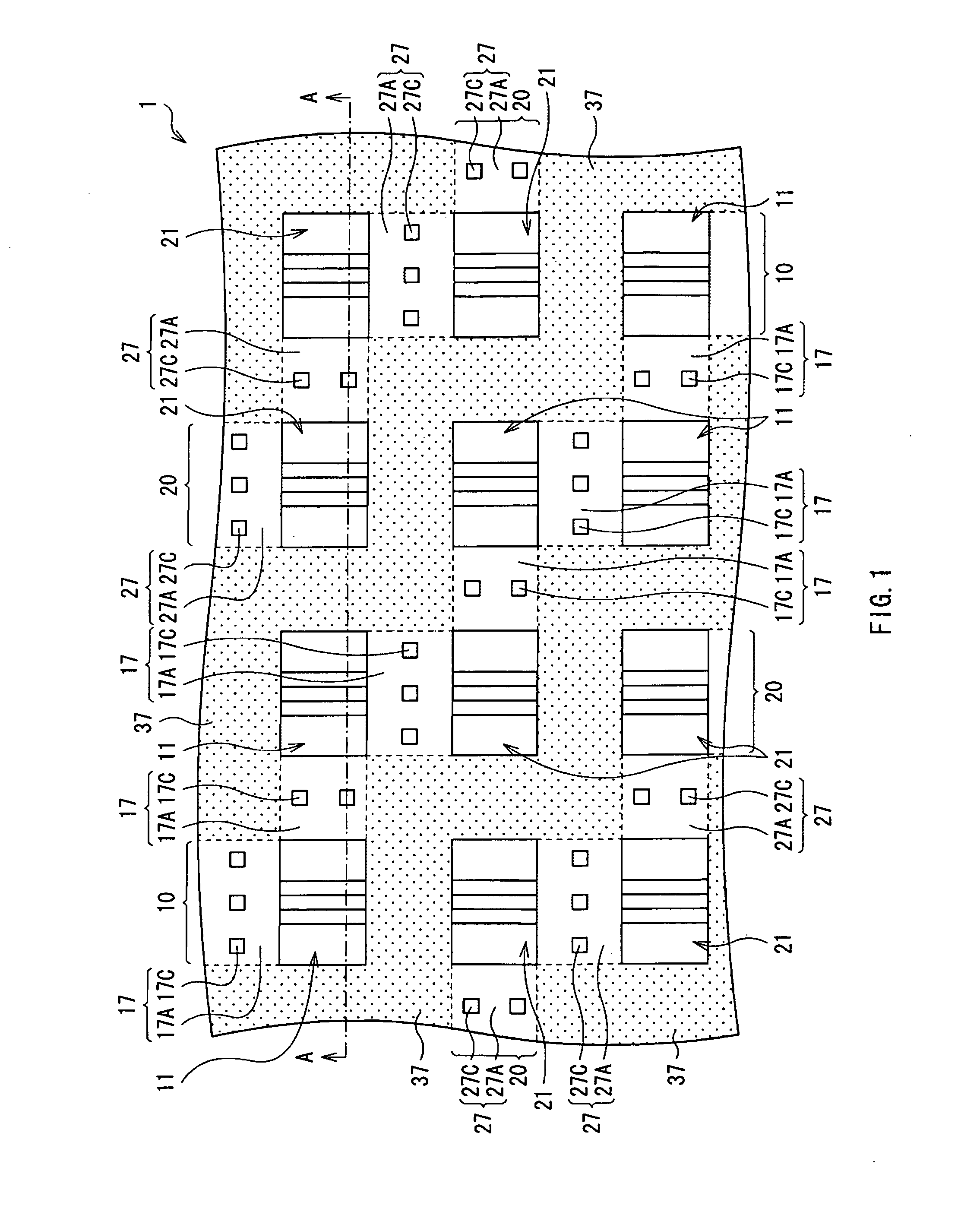

Package having very thin semiconductor chip, multichip module assembled by the package, and method for manufacturing the same

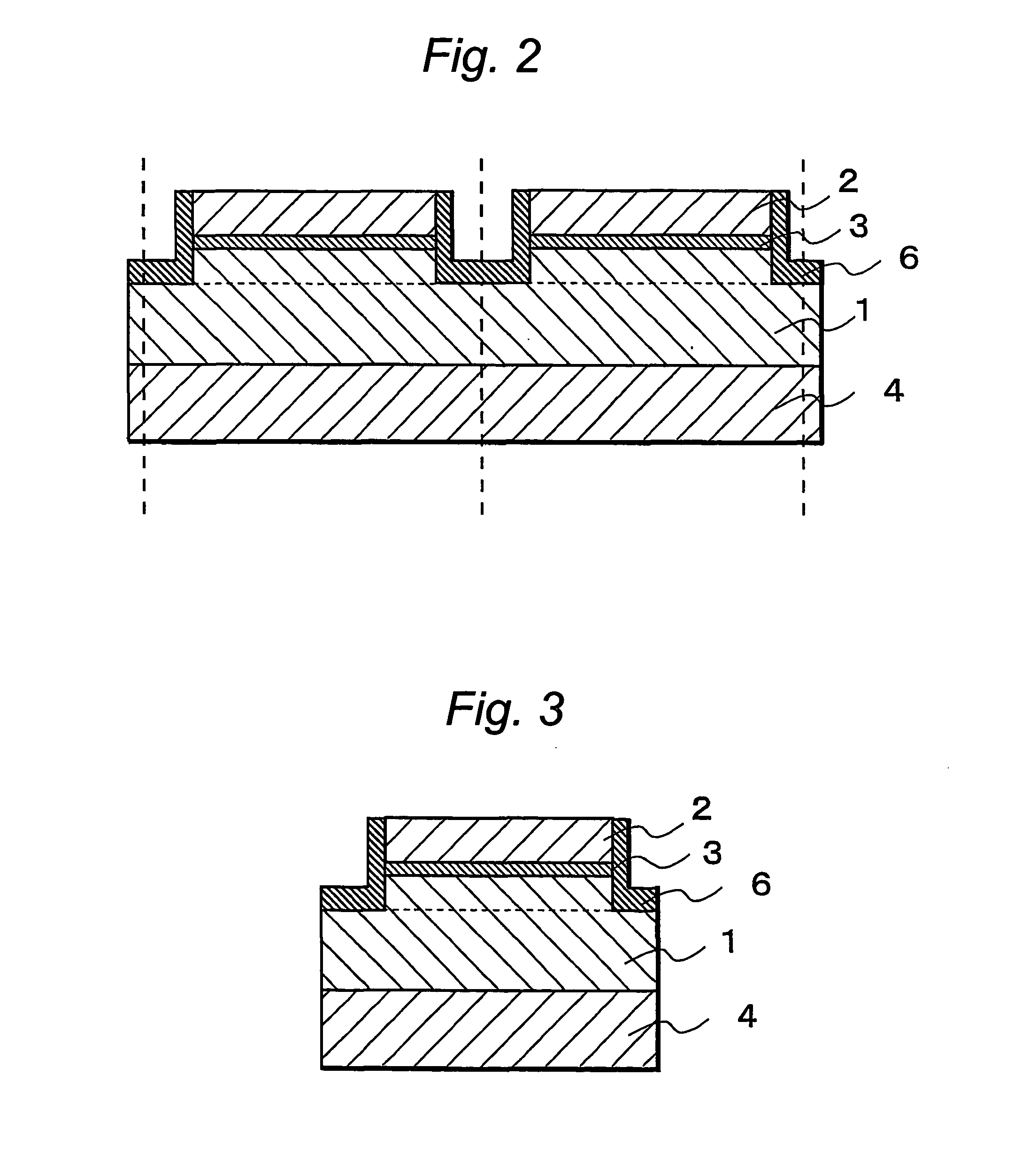

InactiveUS6239496B1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor package

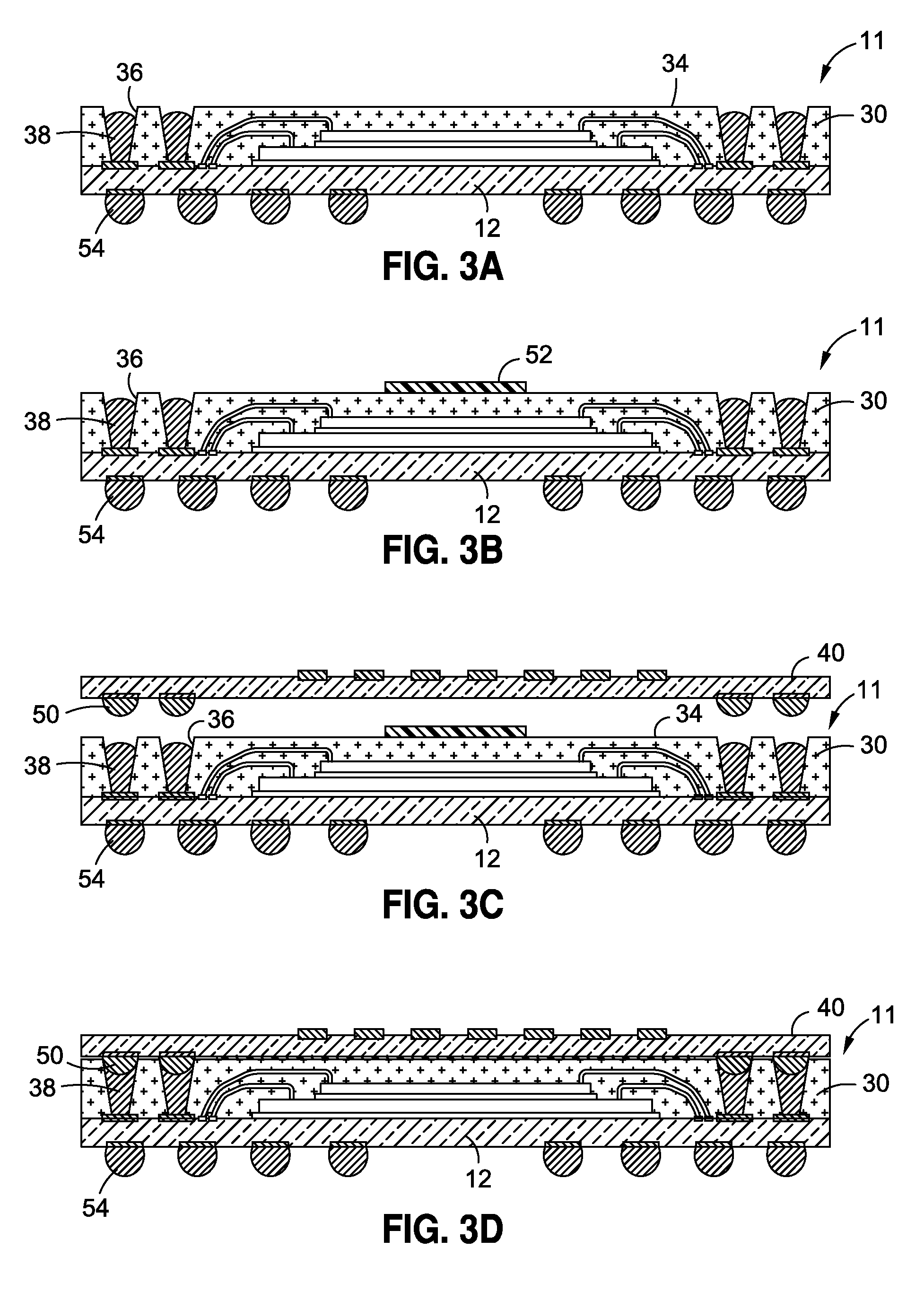

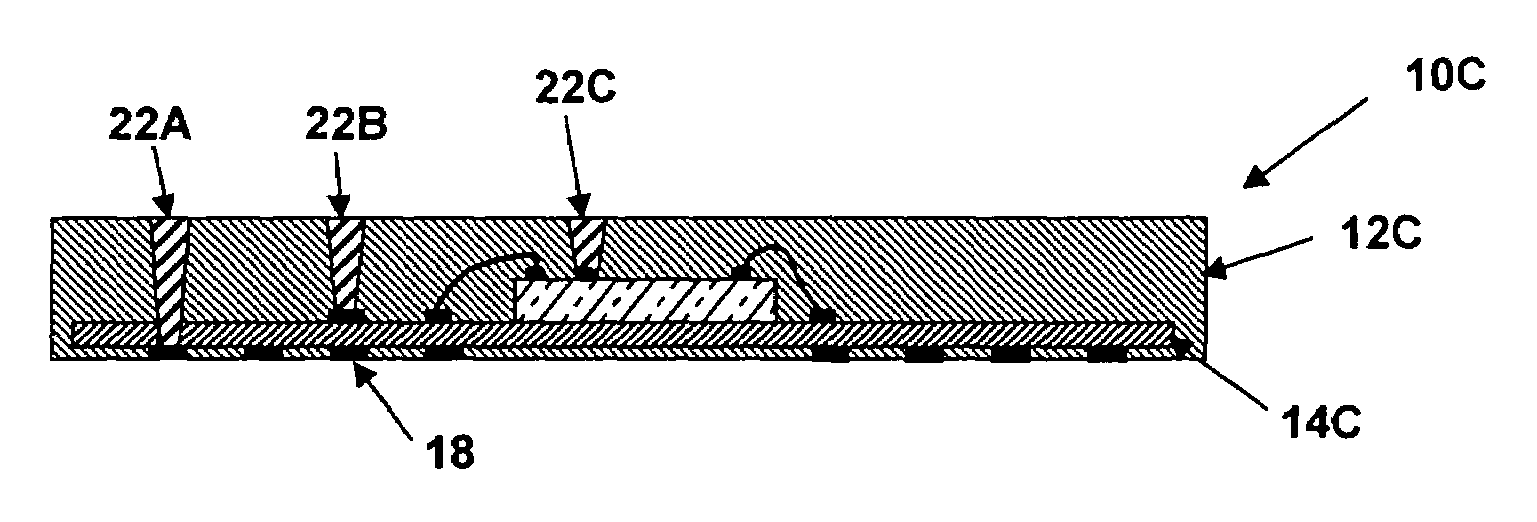

A semiconductor package of this invention has an insulating substrates, wiring layers disposed on the surface of the insulating substrate, a semiconductor chip disposed in a device hole provided in the insulating substrate, inner-joint-conductors for connecting at least part of the bonding pads on the surface of the semiconductor chip to the corresponding inner-joint-conductors and connection lands connected to the wiring layers. The device hole is provided so that it goes through the center of the insulating substrate. The semiconductor chip is thinner than the insulating substrate. Then, this semiconductor chip is disposed in the device hole such that a bottom thereof is flush with a bottom plane of the insulating substrate. Further, this invention provides a MCM in which plural pieces of the thin semiconductor packages are laminated. In the MCM, the semiconductor packages are laminated such that top and bottom faces of the thin silicon chip are inverted. Predetermined connection lands are electrically connected to each other through a connecting conductor. This MCM has a high mechanical strength in its stacked structure and there is a low possibility that crack may occur in the package due to stress in the bending direction.

Owner:KK TOSHIBA

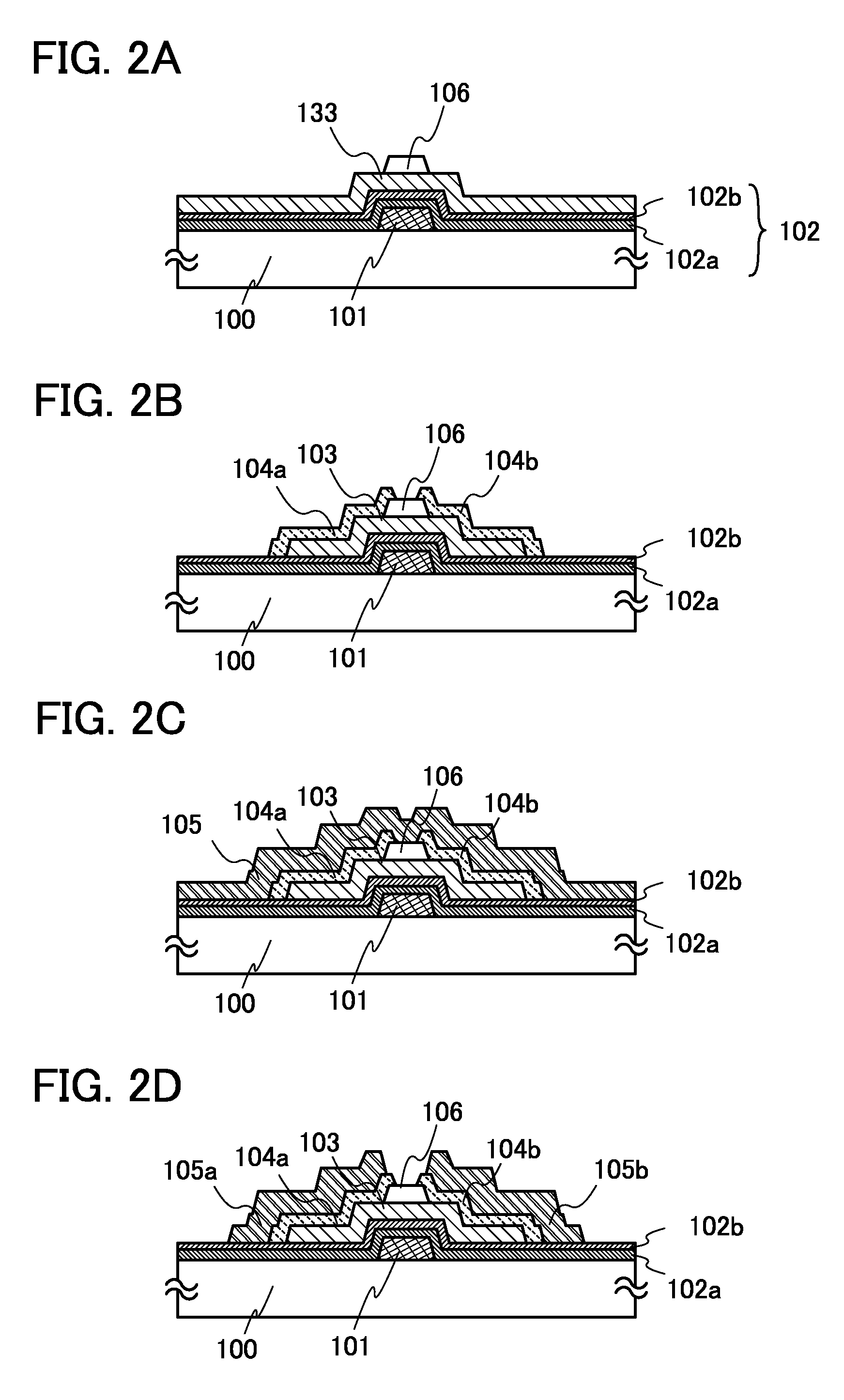

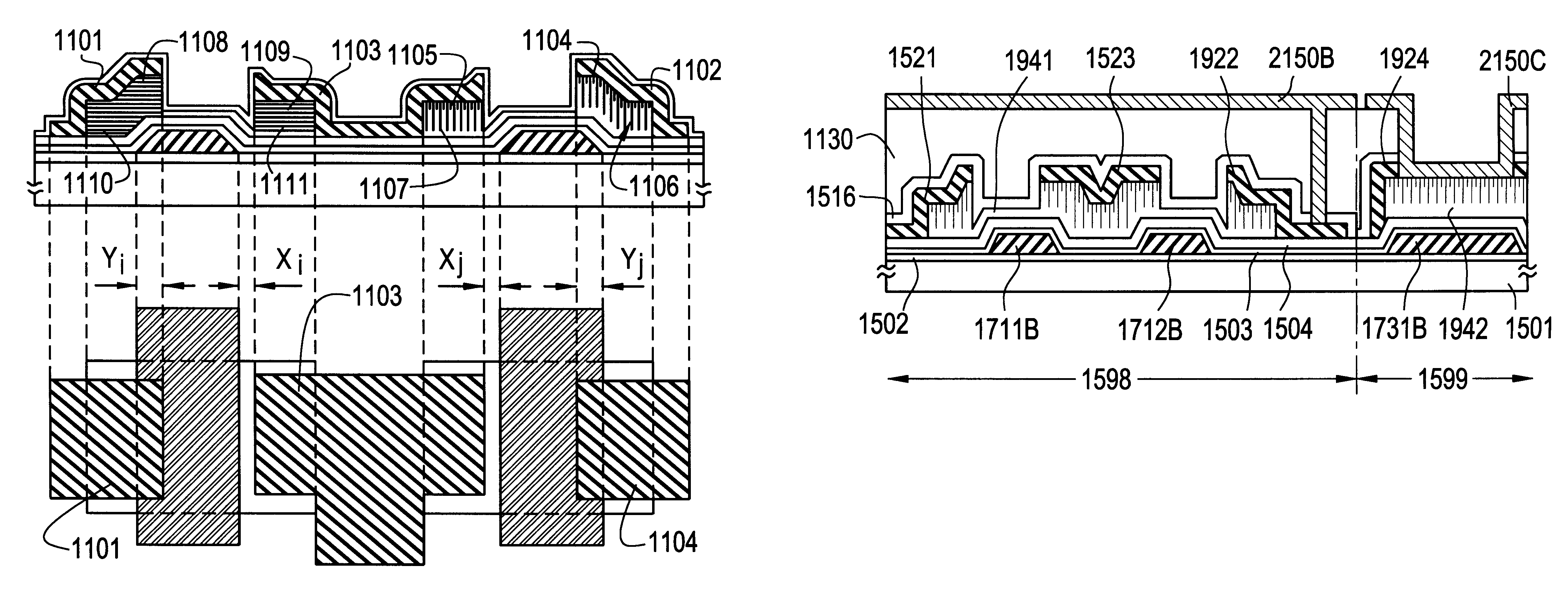

Semiconductor device and manufacturing method thereof

ActiveUS20100025677A1Small amount of photocurrentReduce parasitic capacitanceTransistorElectroluminescent light sourcesProduction rateCharge carrier

To provide a semiconductor device including a thin film transistor having excellent electric characteristics and high reliability and a manufacturing method of the semiconductor device with high mass productivity. The summary is that an inverted-staggered (bottom-gate) thin film transistor is included in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer, a channel protective layer is provided in a region that overlaps a channel formation region of the semiconductor layer, and a buffer layer is provided between the semiconductor layer and source and drain electrodes. An ohmic contact is formed by intentionally providing the buffer layer having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

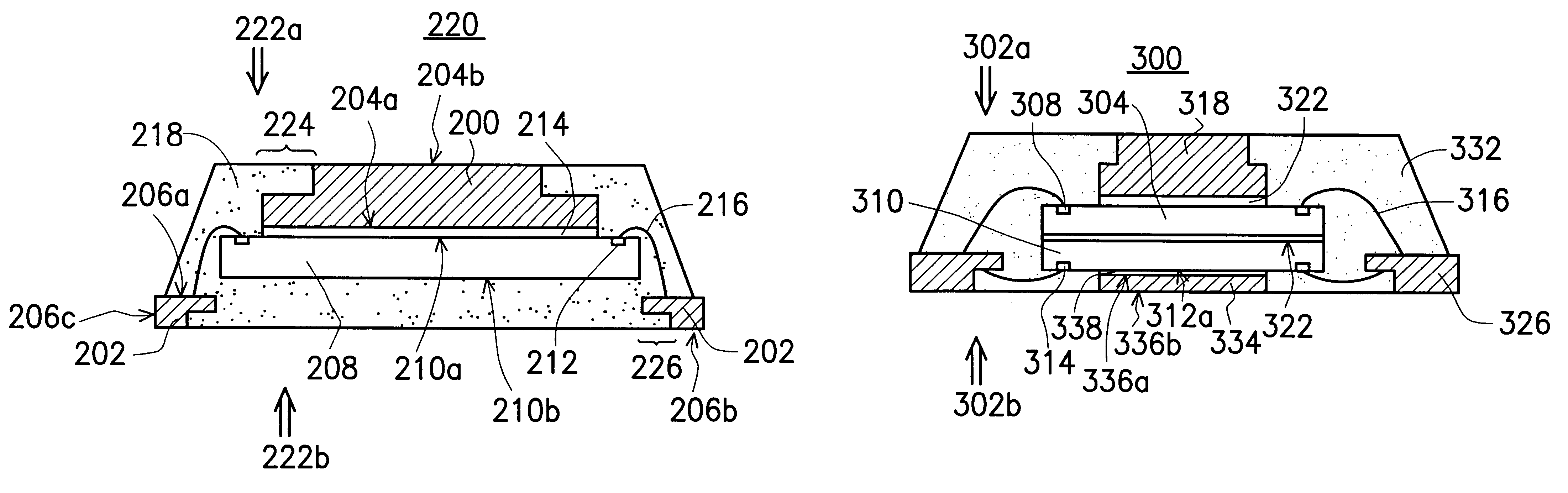

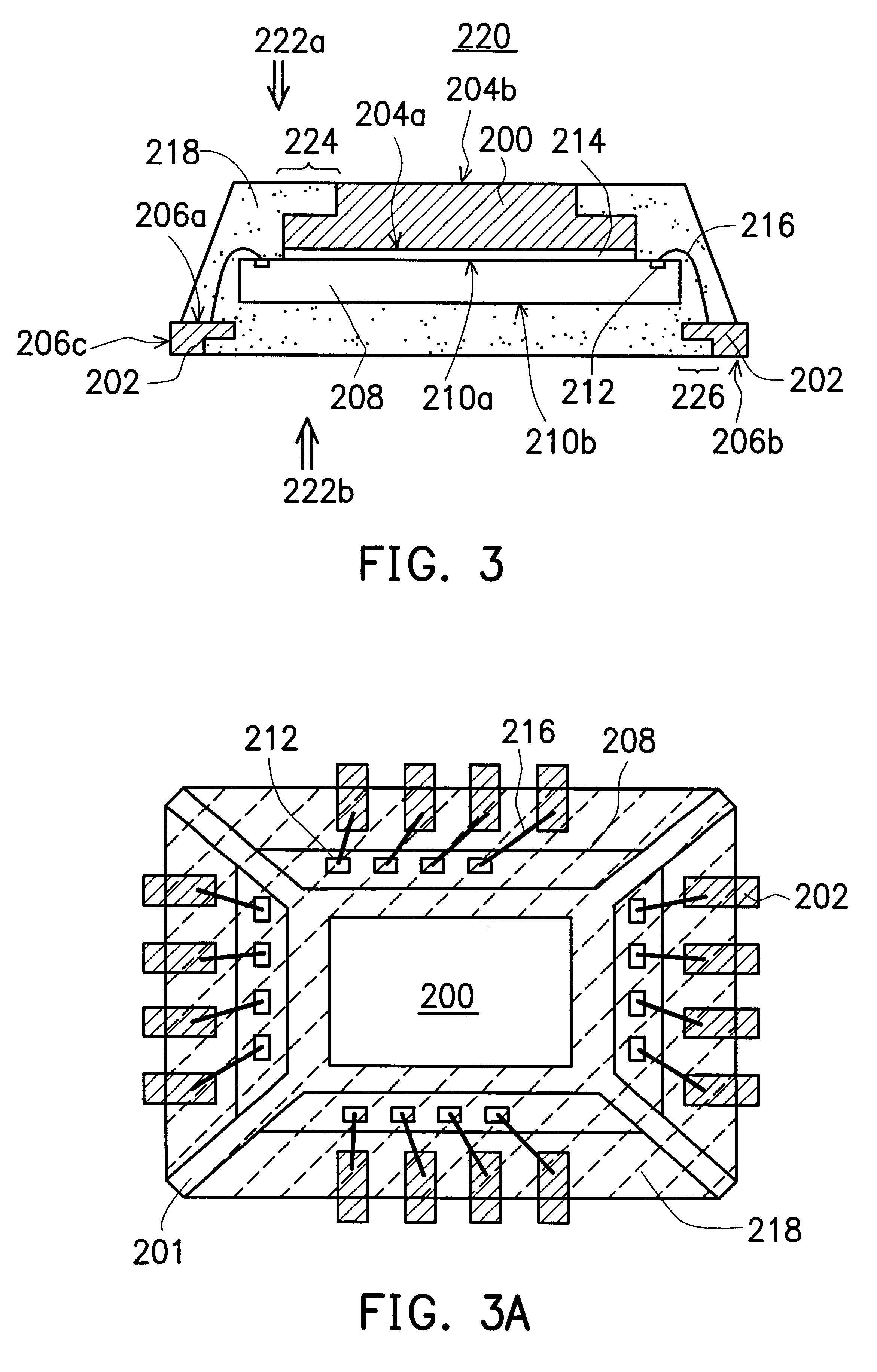

Low-cost and ultra-fine integrated circuit packaging technique

ActiveUS7576435B2Improved feasibility of formingReduce bondingSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor chip

A semiconductor package structure and the methods for forming the same are provided. The semiconductor package structure includes an interposer; a first plurality of bonding pads on a side of the interposer; a semiconductor chip; and a second plurality of bonding pads on a side of the semiconductor chip. The first and the second plurality of bonding pads are bonded through metal-to-metal bonds.

Owner:ADVANCED MFG INNOVATIONS INC

Semiconductor component and interconnect having conductive members and contacts on opposing sides

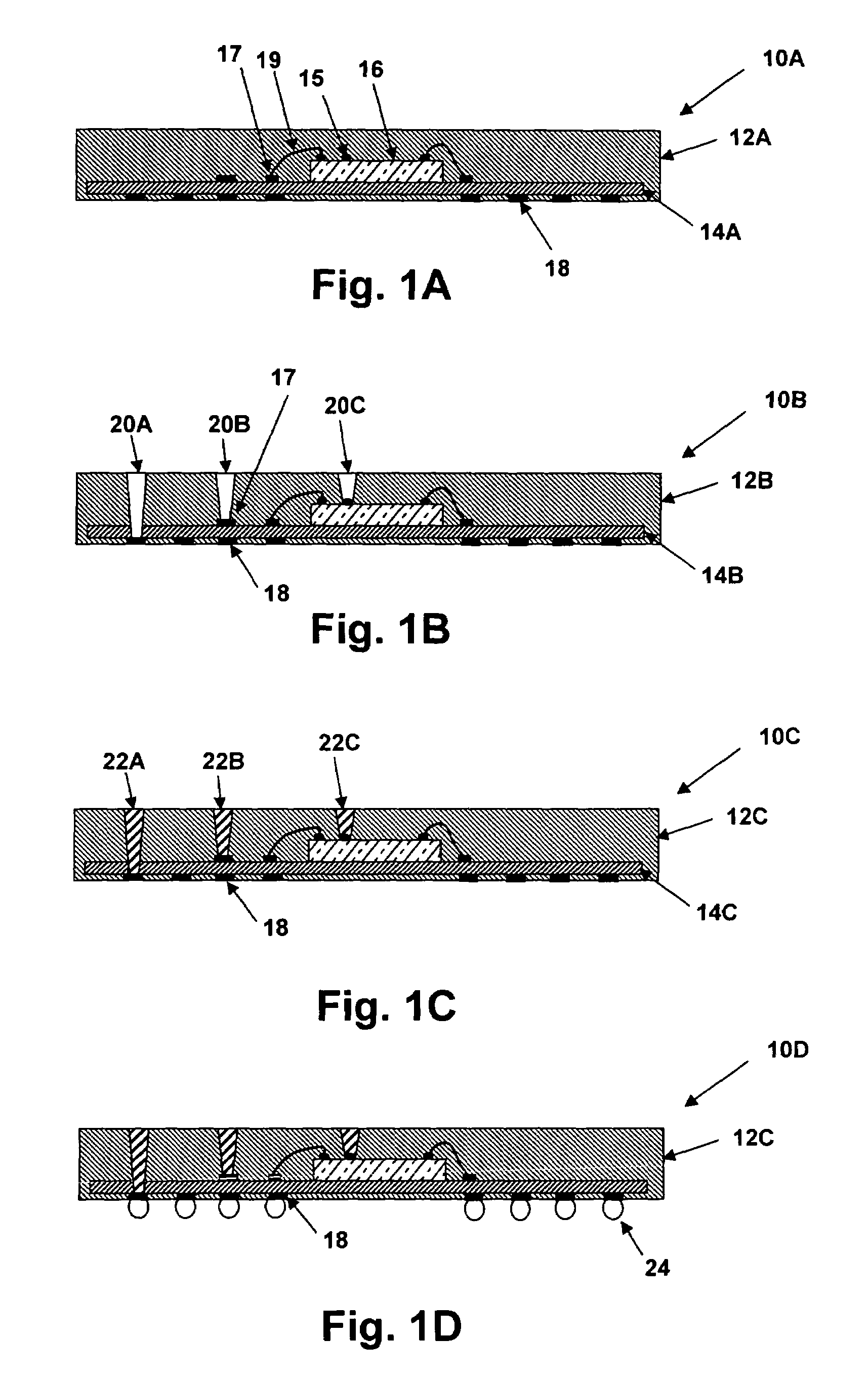

InactiveUS6903443B2Easy to manufactureSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageElectronic assemblies

A method for fabricating semiconductor components and interconnects includes the steps of providing a substrate, such as a semiconductor die, forming external contacts on opposing sides of the substrate by laser drilling vias through the substrate, and forming conductive members in the vias. The conductive members include enlarged terminal portions that are covered with a non-oxidizing metal. The method can be used to fabricate stackable semiconductor packages having integrated circuits in electrical communication with the external contacts. The method can also be used to fabricate interconnects for electrically engaging packages, dice and wafers for testing or for constructing electronic assemblies.

Owner:ROUND ROCK RES LLC

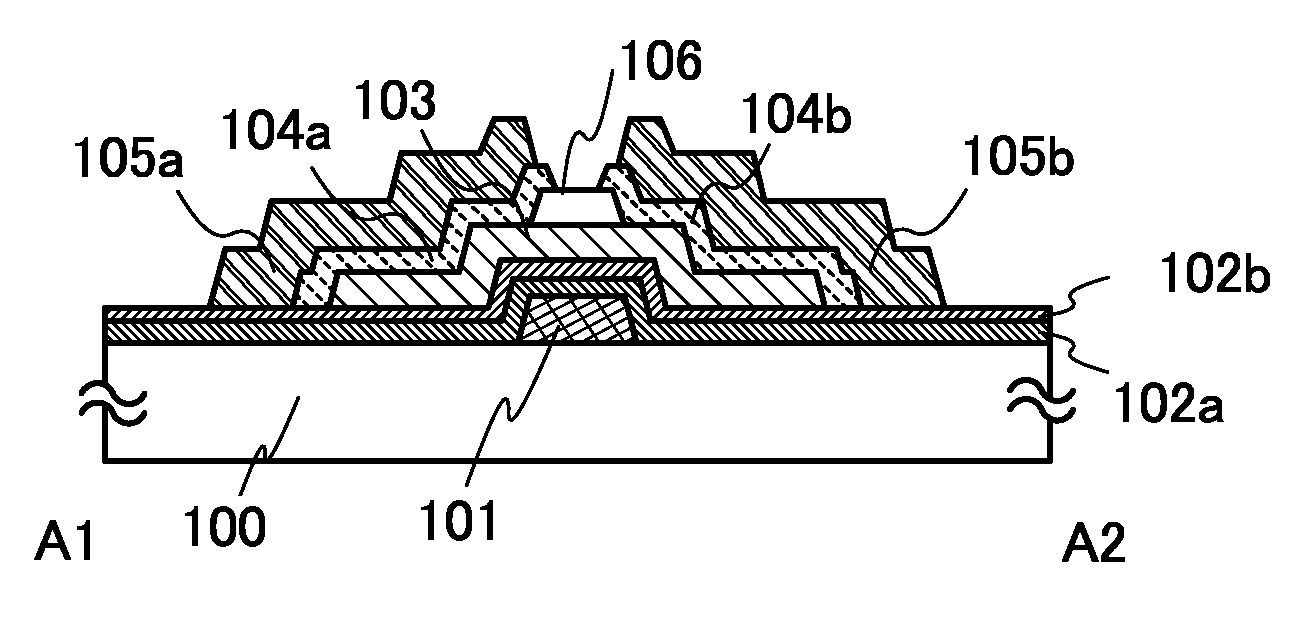

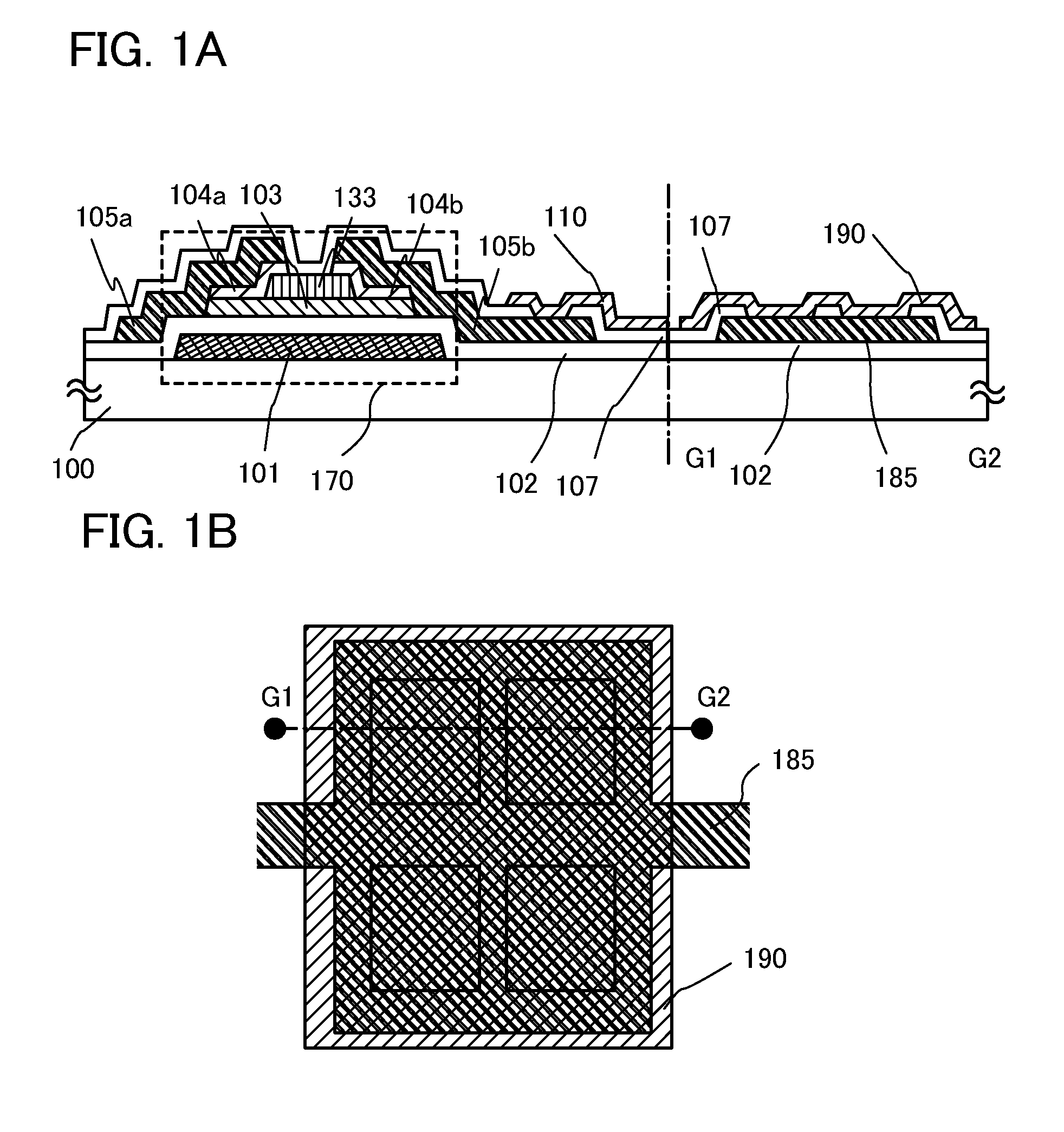

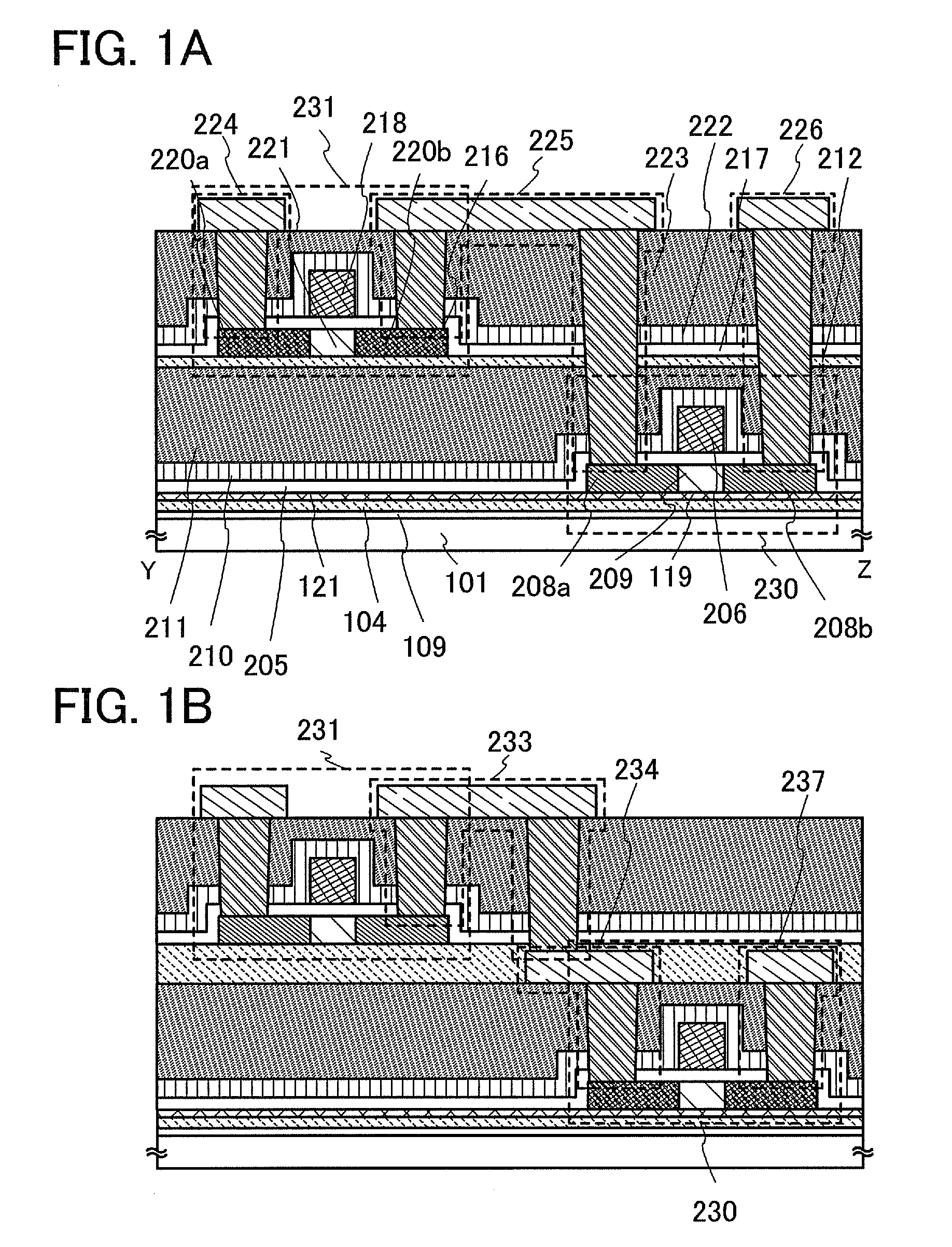

Semiconductor device

ActiveUS20100072467A1Increasing the thicknessAvoid separationTransistorElectroluminescent light sourcesDisplay deviceSemiconductor package

A display device includes a pixel portion in which a pixel is arranged in a matrix, the pixel including an inverted staggered thin film transistor having a combination of at least two kinds of oxide semiconductor layers with different amounts of oxygen and having a channel protective layer over a semiconductor layer to be a channel formation region overlapping a gate electrode layer and a pixel electrode layer electrically connected to the inverted staggered thin film transistor. In the periphery of the pixel portion in this display device, a pad portion including a conductive layer made of the same material as the pixel electrode layer is provided. In addition, the conductive layer is electrically connected to a common electrode layer formed on a counter substrate.

Owner:SEMICON ENERGY LAB CO LTD

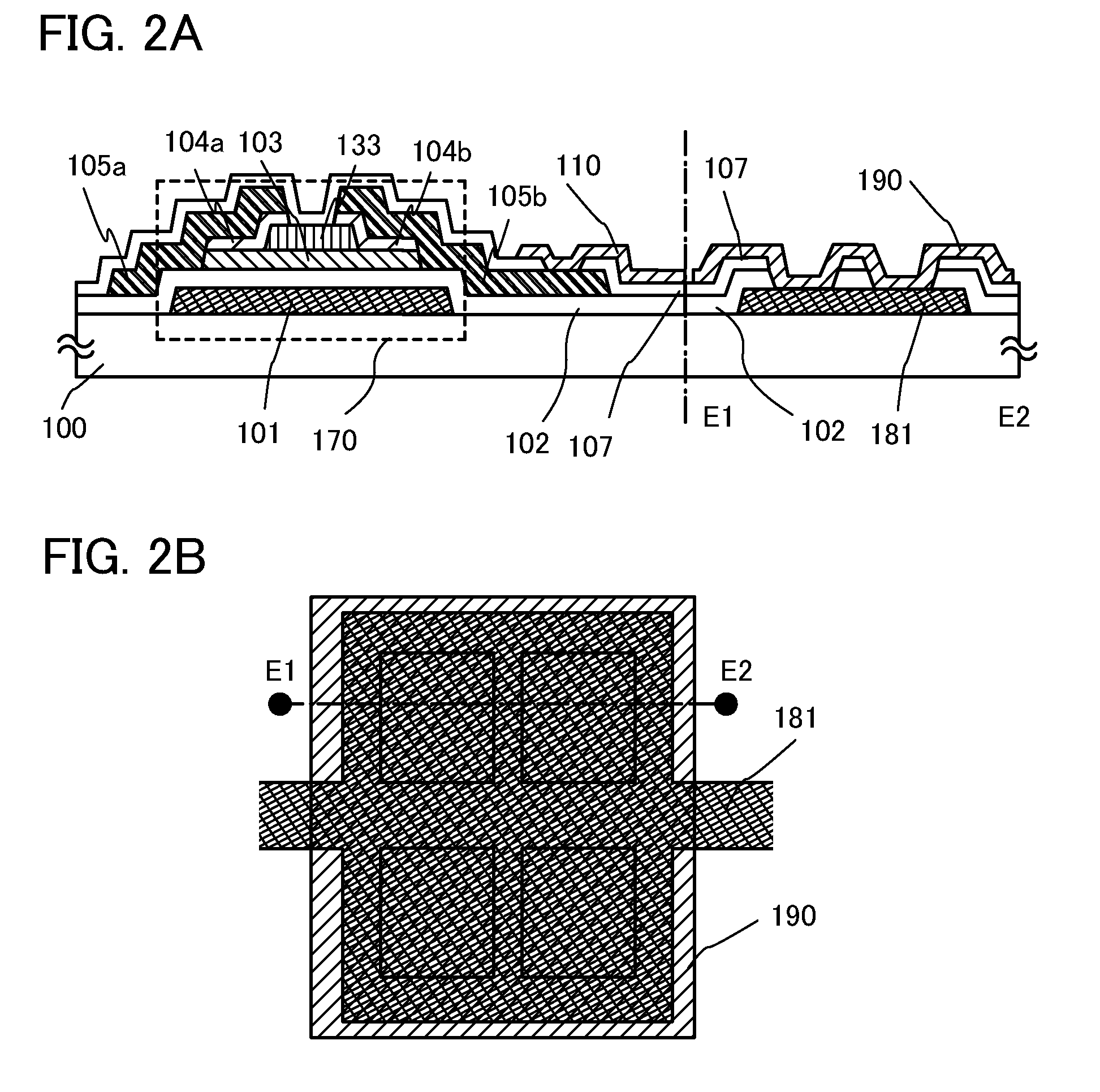

Semiconductor device and fabrication method thereof

To provide a semiconductor device having high mass production performance and high reliability and reproducibility by simple fabrication steps, in a constitution of a semiconductor device of a bottom gate type formed by a semiconductor layer having a crystal structure, source and drain regions are constituted by a laminated layer structure comprising a first conductive layer (n+ layer), a second conductive layer (n- layer) having resistance higher than the first conductive layer and an intrinsic or a substantially intrinsic semiconductor layer (i layer) in which the n- layer functions as an LDD region and the i layer functions as an offset region in a film thickness direction.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

InactiveUS8044464B2Guaranteed high speed operationReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packagePlane orientation

Owner:SEMICON ENERGY LAB CO LTD

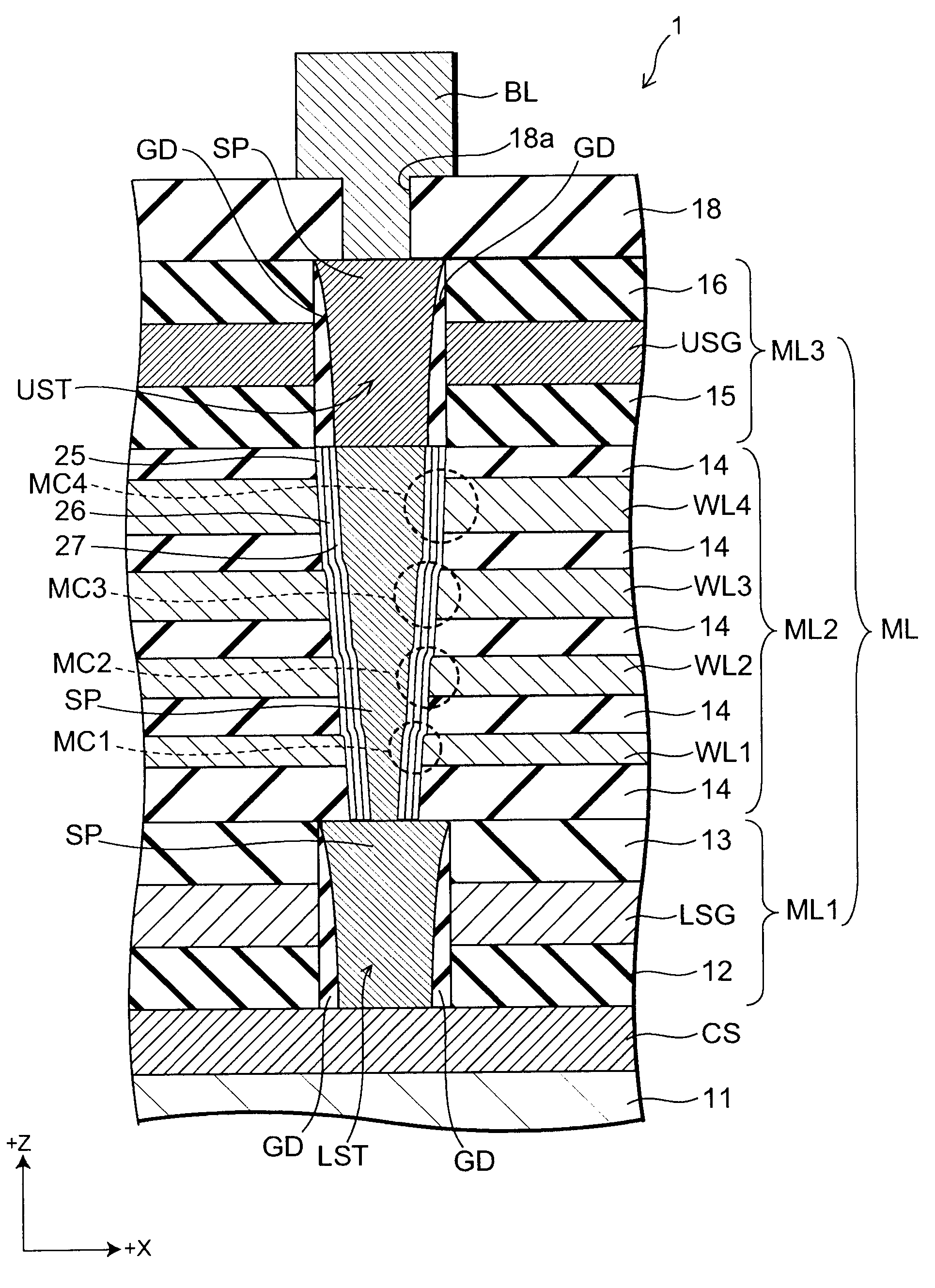

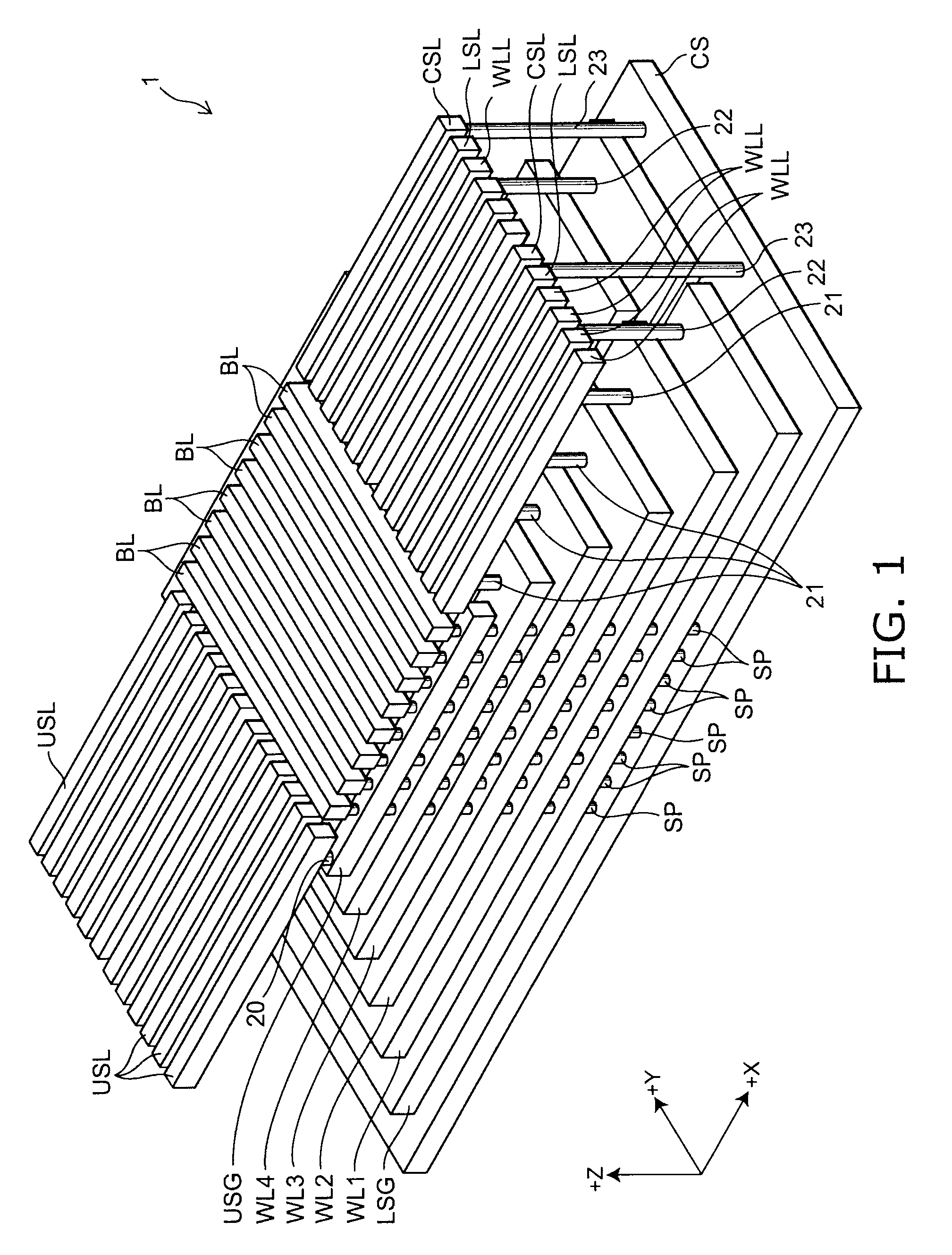

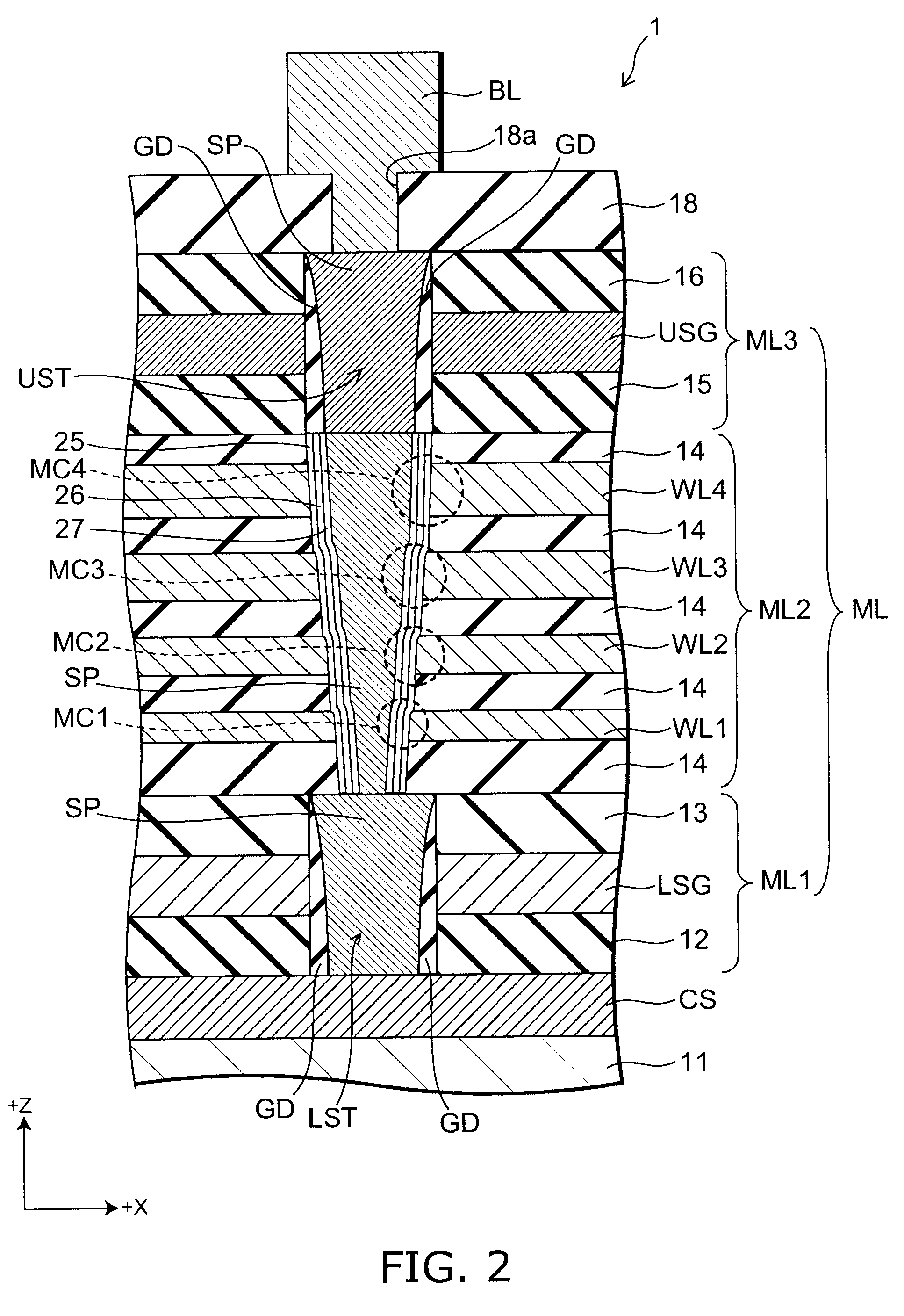

Semiconductor memory device

A semiconductor memory device includes: a semiconductor substrate; a stacked body provided on the semiconductor substrate and having a plurality of insulator layers and a plurality of conductive layers alternately stacked; a semiconductor layer provided inside a through-hole formed so as to pass through the stacked body and extending in a stacking direction of the insulator layers and the conductive layers; and a charge trap layer provided between the conductive layer and the semiconductor layer. A lower part in the semiconductor layer is narrower than an upper part therein, and at least the lowermost layer in the conductive layers is thinner than the uppermost layer therein.

Owner:KIOXIA CORP

Three-dimensional integrated circuit structure

InactiveUS7888764B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureSemiconductor package

Owner:BESANG

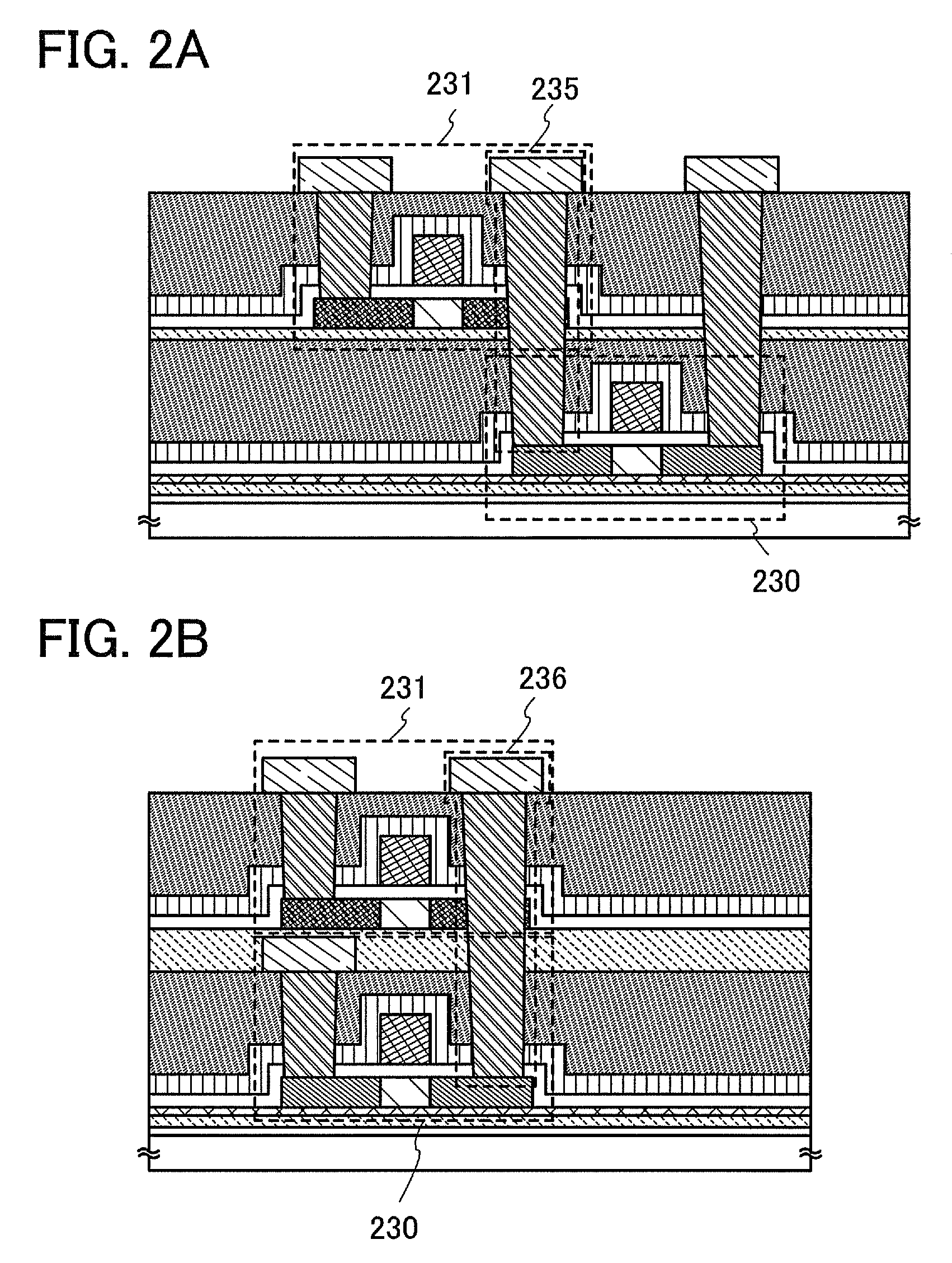

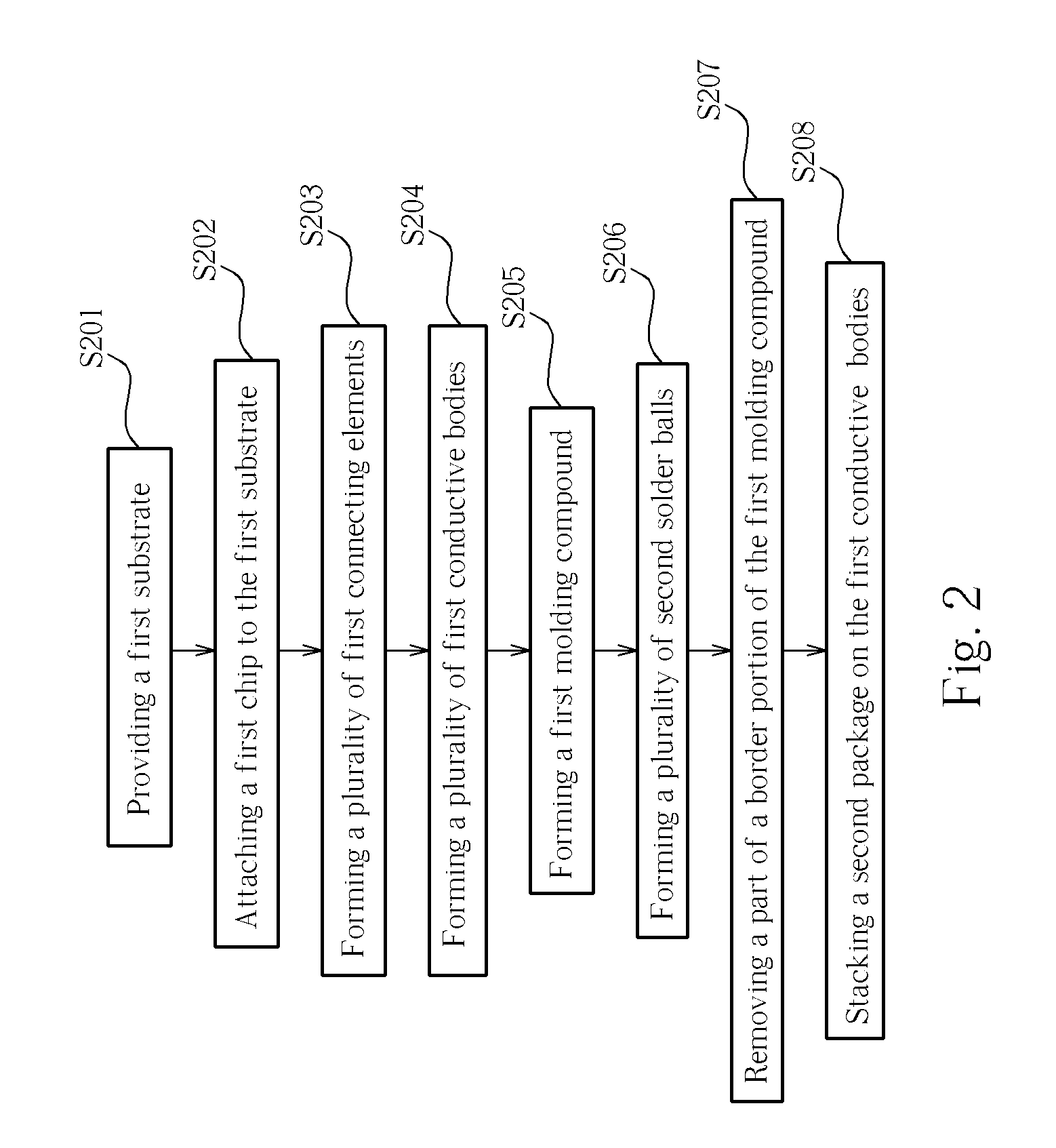

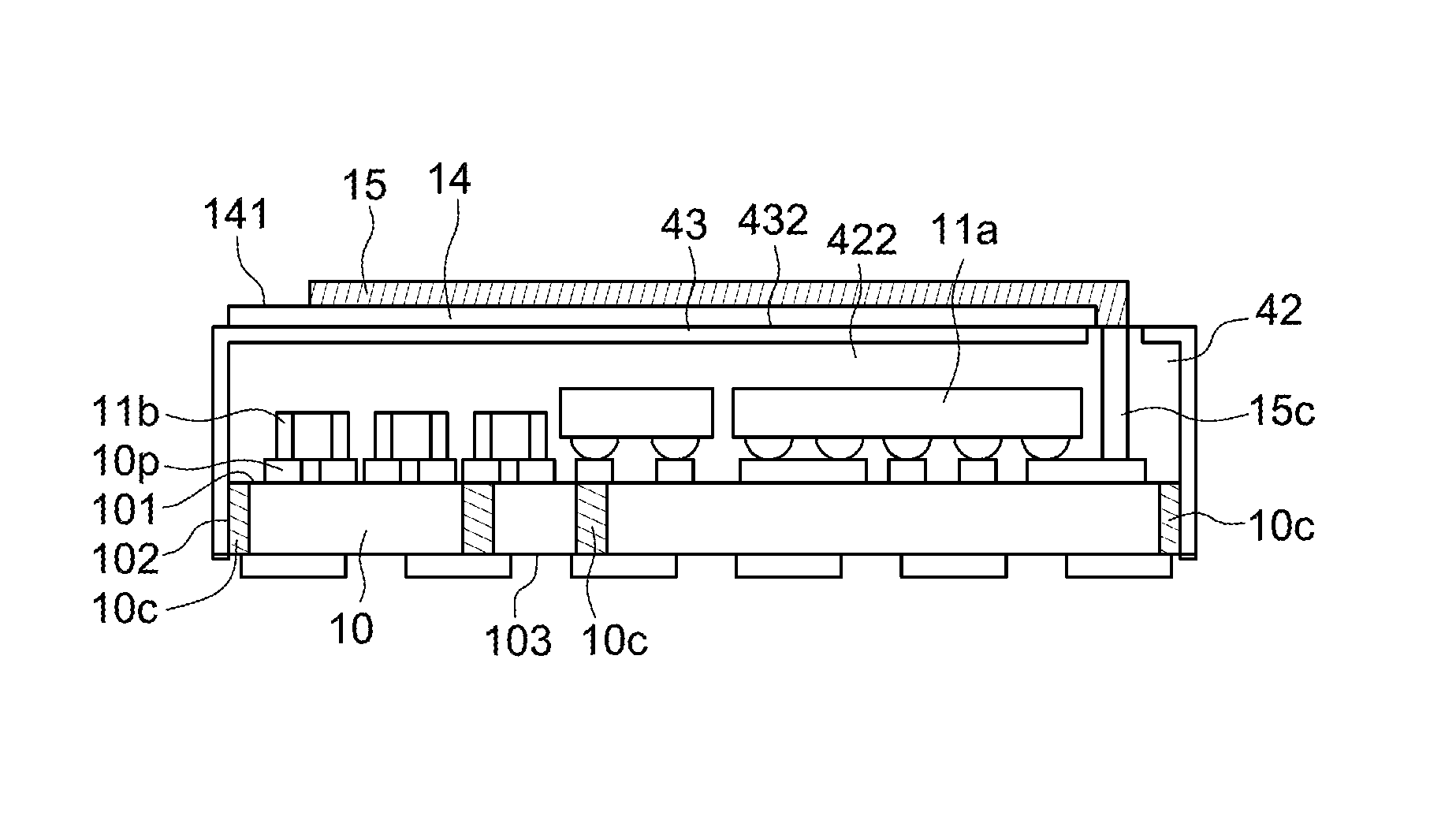

Semiconductor package and semiconductor device

InactiveUS20080073769A1Low production costSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageSemiconductor device

The present invention relates to a semiconductor package and a semiconductor device and a method of making the same. The method of making the semiconductor package comprises: providing a substrate; attaching a chip to a surface of the substrate; forming a plurality of connecting elements for electrically connecting the chip and the substrate; forming a plurality of first conductive bodies on the surface of the substrate; forming a molding compound for encapsulating the surface of the substrate, the chip, the connecting elements and the first conductive bodies; and removing a part of a border portion of the molding compound, so that the molding compound has two heights and one end of each first conductive bodies is exposed. Thereby, the molding compound covers the entire surface of the substrate, so that the bonding pads on the surface of the substrate will not be polluted.

Owner:ADVANCED SEMICON ENG INC

Semiconductor device

ActiveUS20100200919A1Suppression of short channel effectsSpeed up the flowTransistorSemiconductor/solid-state device detailsSemiconductor packageImpurity

The invention provides a semiconductor device capable of suppressing a short channel effect and fluctuation in a threshold. The semiconductor device includes: a plurality of first transistors formed in a first region in a semiconductor layer in a multilayer substrate having, on a semiconductor substrate, an insulating layer and the semiconductor layer in order from the semiconductor substrate; a plurality of second transistors formed in a second region in the semiconductor layer; a first impurity layer formed in a region opposed to the first region in the semiconductor substrate; a second impurity layer formed in a region opposed to the second region in the semiconductor substrate; and a first isolation part that isolates the first and second regions from each other and electrically isolates the first and second impurity layers from each other to a degree that at least current flowing between the first and second impurity layers is interrupted.

Owner:SONY CORP

Circuit board for direct flip chip attachment

InactiveUS20090212317A1Semiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageLaser cutting

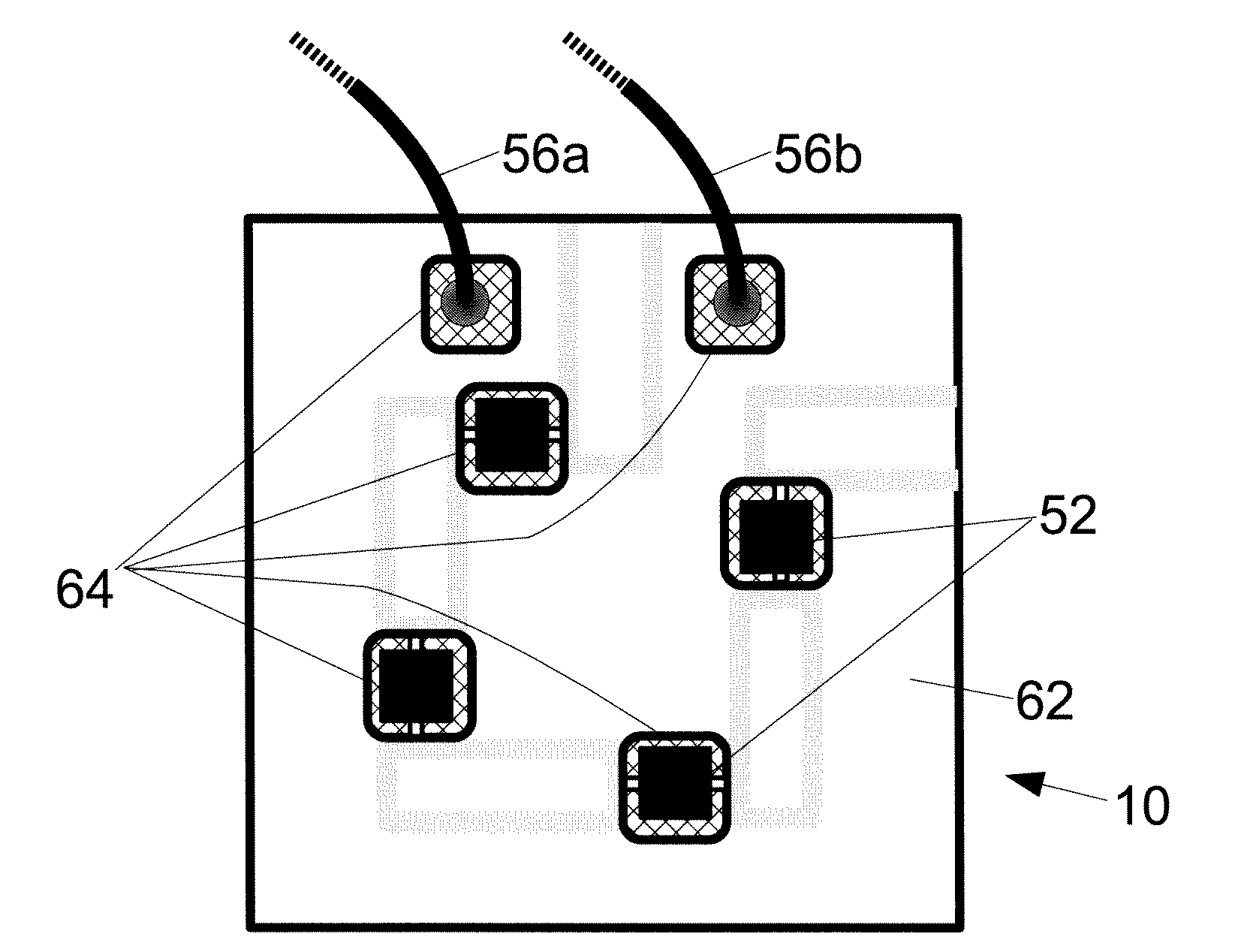

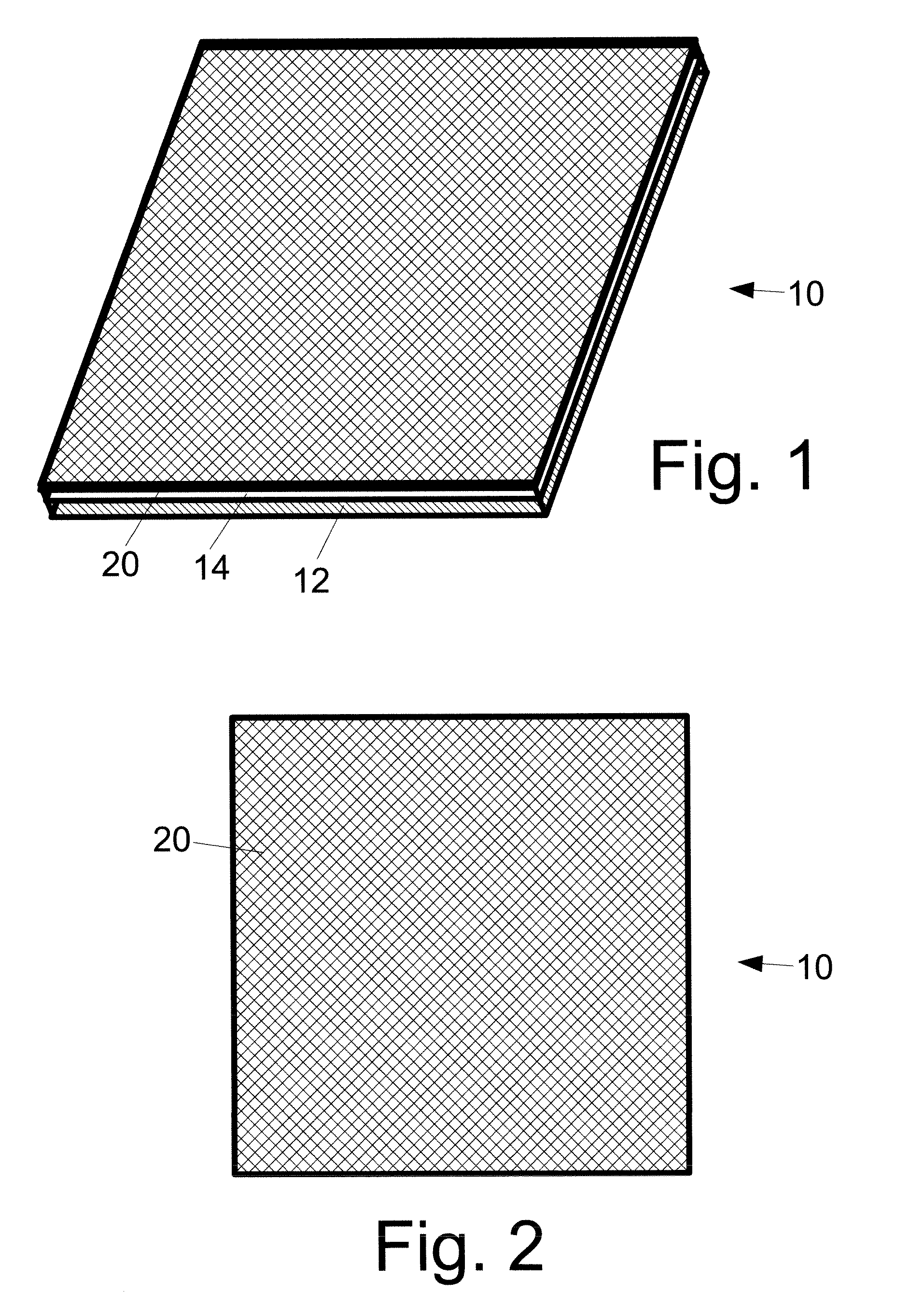

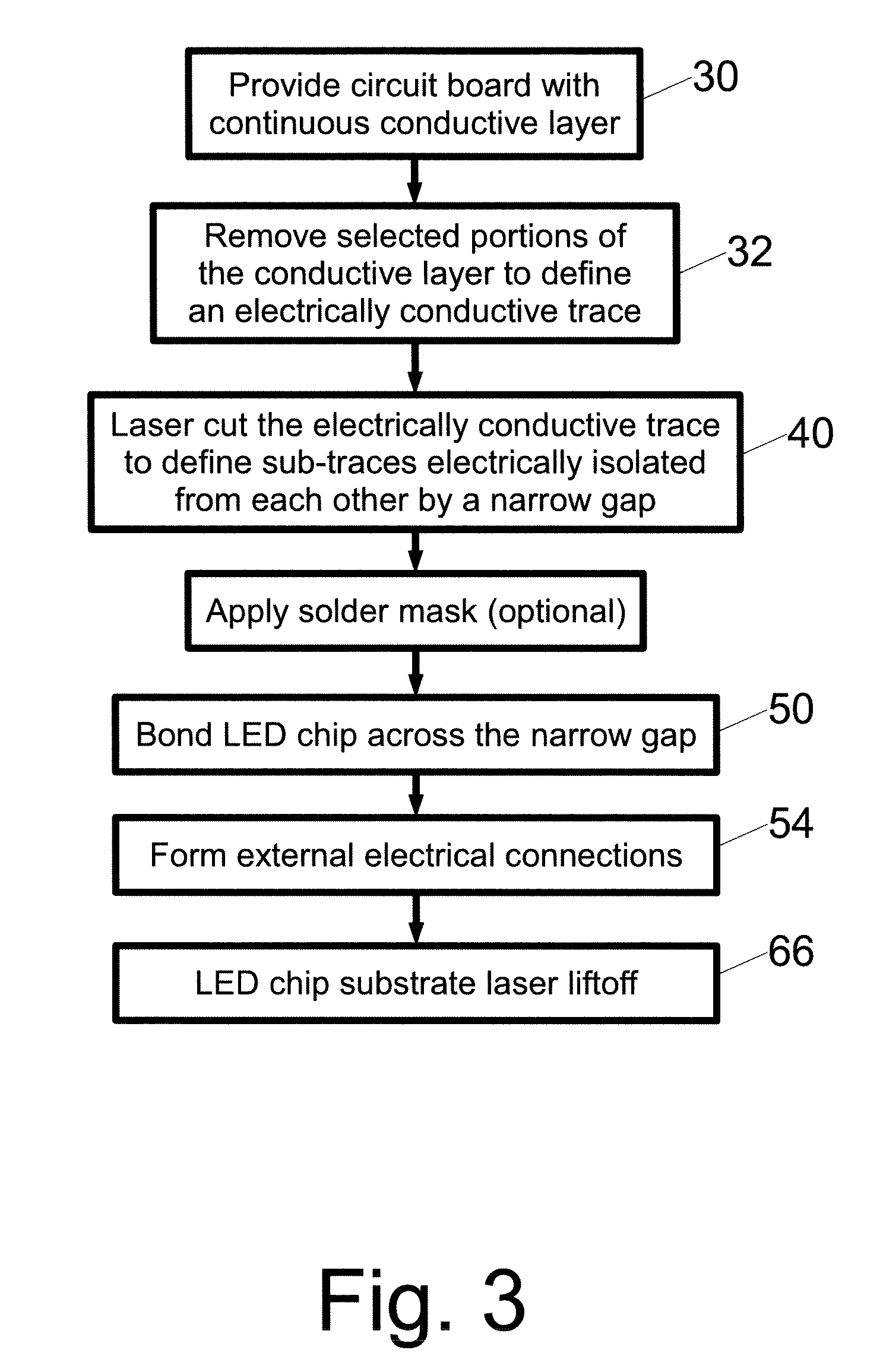

A packaging method comprises: forming a circuit board by forming a substantially continuous conductive layer on an insulating board and removing selected portions of the continuous conductive layer to define an electrically conductive trace; laser cutting the electrically conductive trace to define sub-traces electrically isolated from each other by a laser-cut gap formed by the laser cutting; and bonding a light emitting diode (LED) chip to the circuit board across or adjacent to the laser-cut gap, the bonding including operatively electrically connecting an electrode of the LED chip to one of the sub-traces without using an interposed submount. A semiconductor package comprises an LED chip flip-chip bonded to sub-traces of an electrically conductive trace of a circuit board, the sub-traces being electrically isolated from each other by a narrow gap of less than or about 100 microns.

Owner:LUMINATION

Device and method for fabricating double-sided SOI wafer scale package with through via connections

ActiveUS20060105496A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package includes an SOI wafer having a first side including an integrated circuit system, and a second side, opposite the first side, forming at least one cavity. At least one chip or component is placed in the cavity. A through buried oxide via connects the chip(s) to the integrated circuit system.

Owner:GLOBALFOUNDRIES US INC

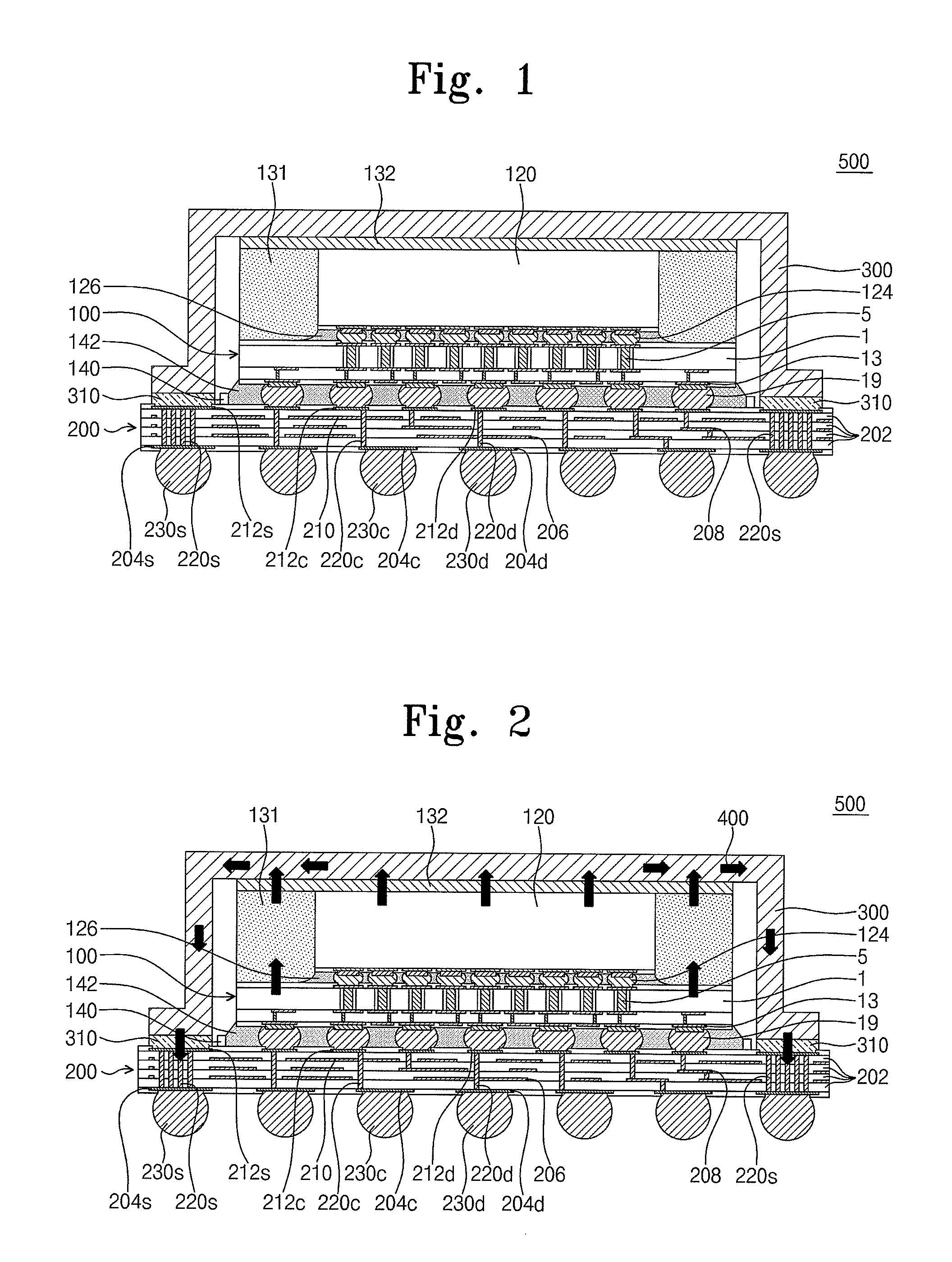

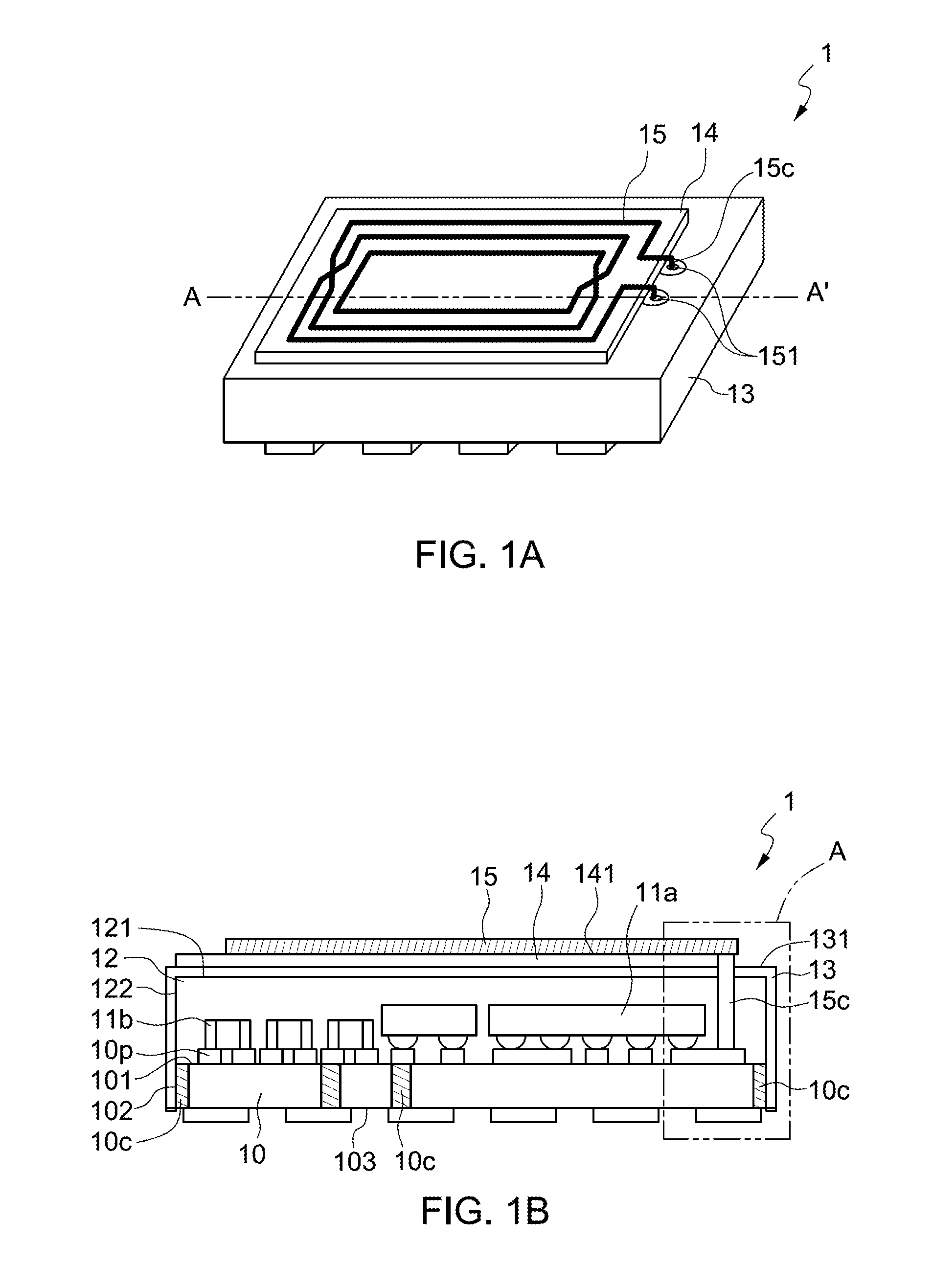

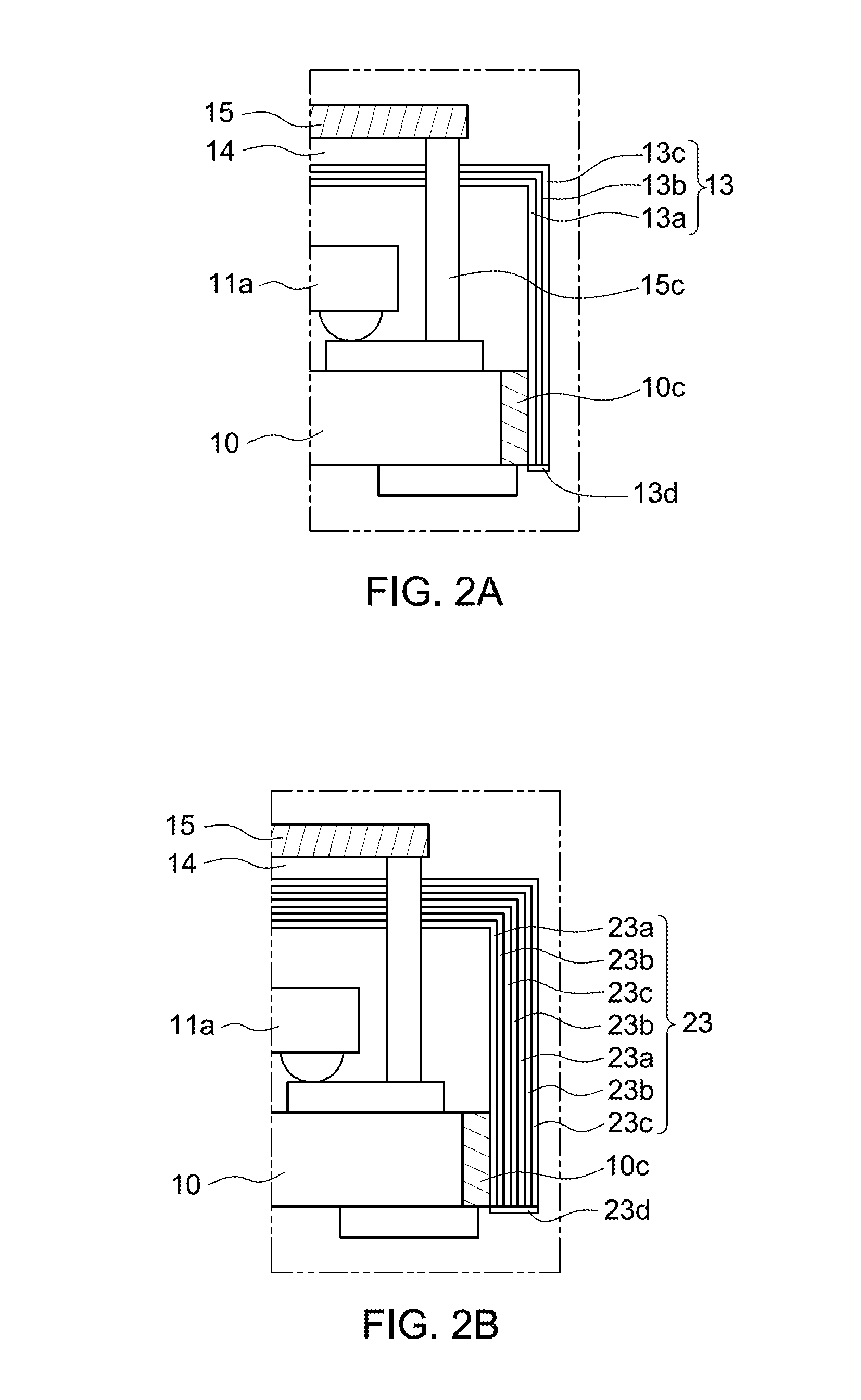

Semiconductor device package integrated with coil for wireless charging and electromagnetic interference shielding, and method of manufacturing the same

ActiveUS9461001B1Batteries circuit arrangementsSemiconductor/solid-state device detailsElectricityElectromagnetic interference

The present disclosure relates to a semiconductor device package which includes a carrier, an electronic component, conductive elements, a package body, a shield, a magnetic insulating layer, and a patterned conductive layer. The carrier has a top surface on which the electronic component is disposed. The conductive elements are disposed on the top surface of the carrier. The package body is disposed on the top surface of the carrier and encapsulates the electronic component and a portion of each of the conductive elements. The shield is disposed on the package body and covers an exterior of the package body. The magnetic insulating layer is disposed on a top surface of the shield. The patterned conductive layer is disposed on the magnetic insulating layer. Each of the conductive elements electrically connects the patterned conductive layer to the electronic component.

Owner:ADVANCED SEMICON ENG INC

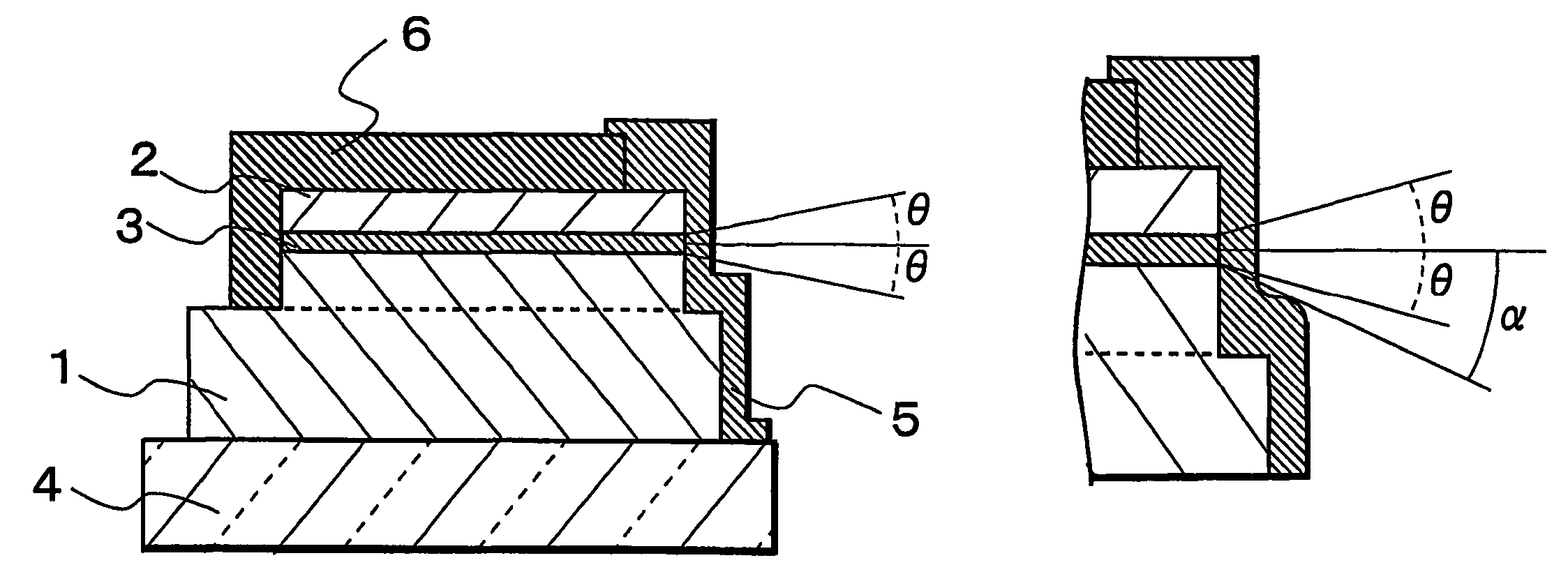

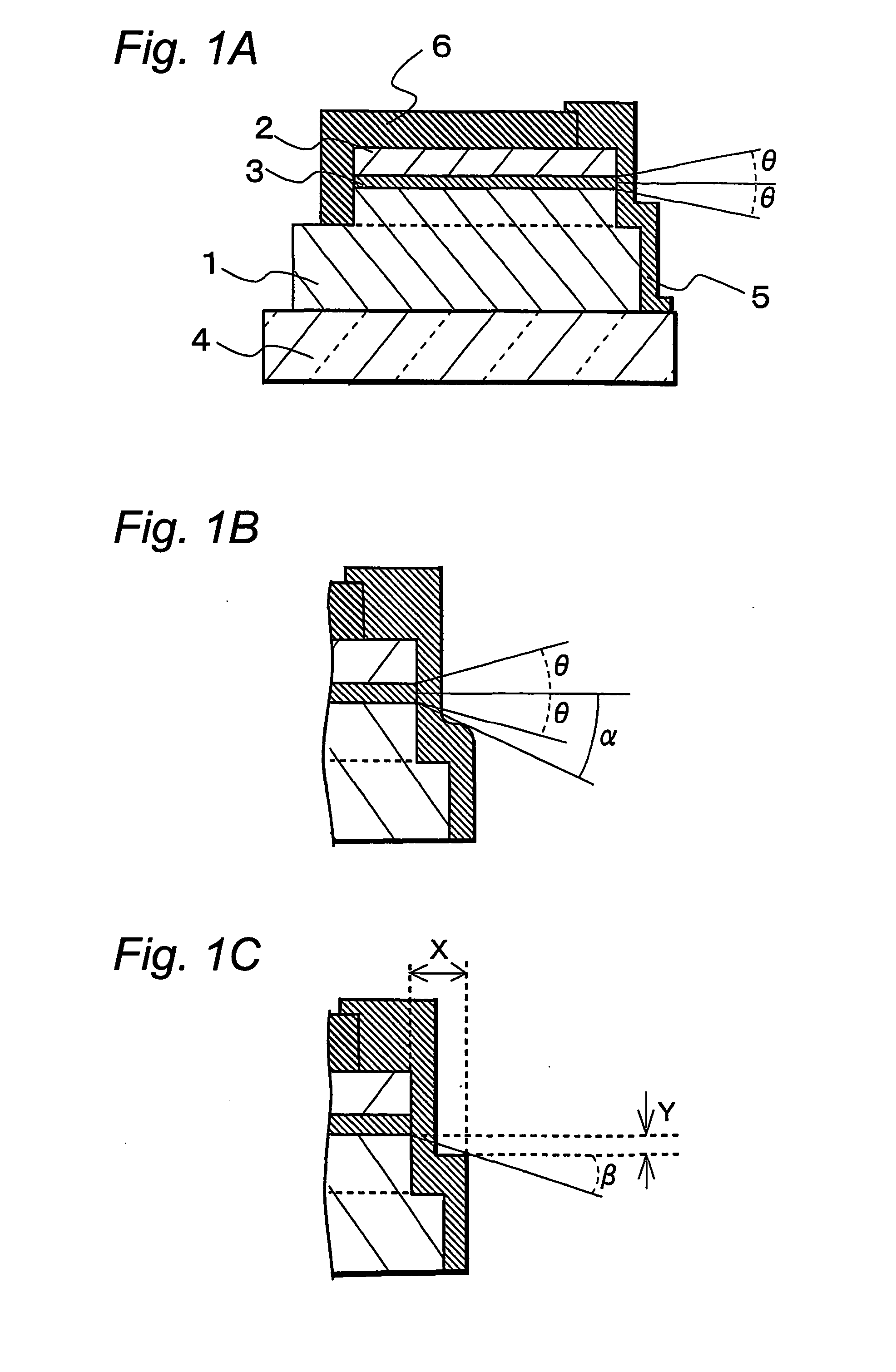

Semicondutor laser device and its manufacturing method

InactiveUS20040233950A1Efficient executionLaser optical resonator constructionSemiconductor laser structural detailsTectorial membraneSemiconductor package

A semiconductor laser device have, on a substrate, a semiconductor layer including an active layer sandwiched between an n-type layer and a p-type layer, the semiconductor layer having a sonator face formed by etching and a projection projecting out in an emission direction relatively to the resonator face, wherein a protective film is formed to extend from the resonator face to an end face of the projection, and, an emission critical angle, which is the largest angle at which light emitted from the resonator face can be radiated without being blocked by the projection and the protective film formed on the projection, is larger than an emission half-angle of an emission distribution in a vertical direction of a laser beam emitted from the resonator face.

Owner:NICHIA CORP

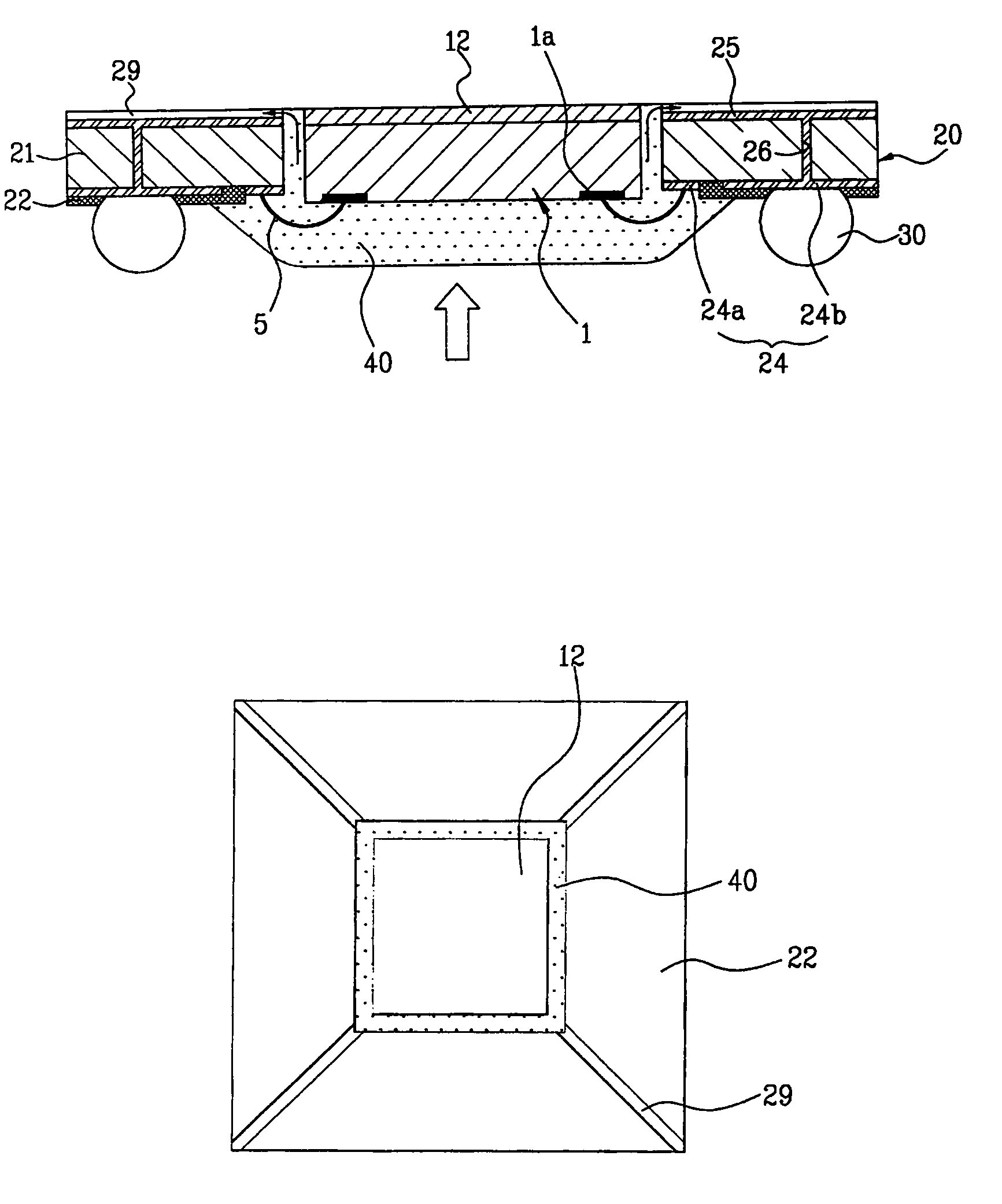

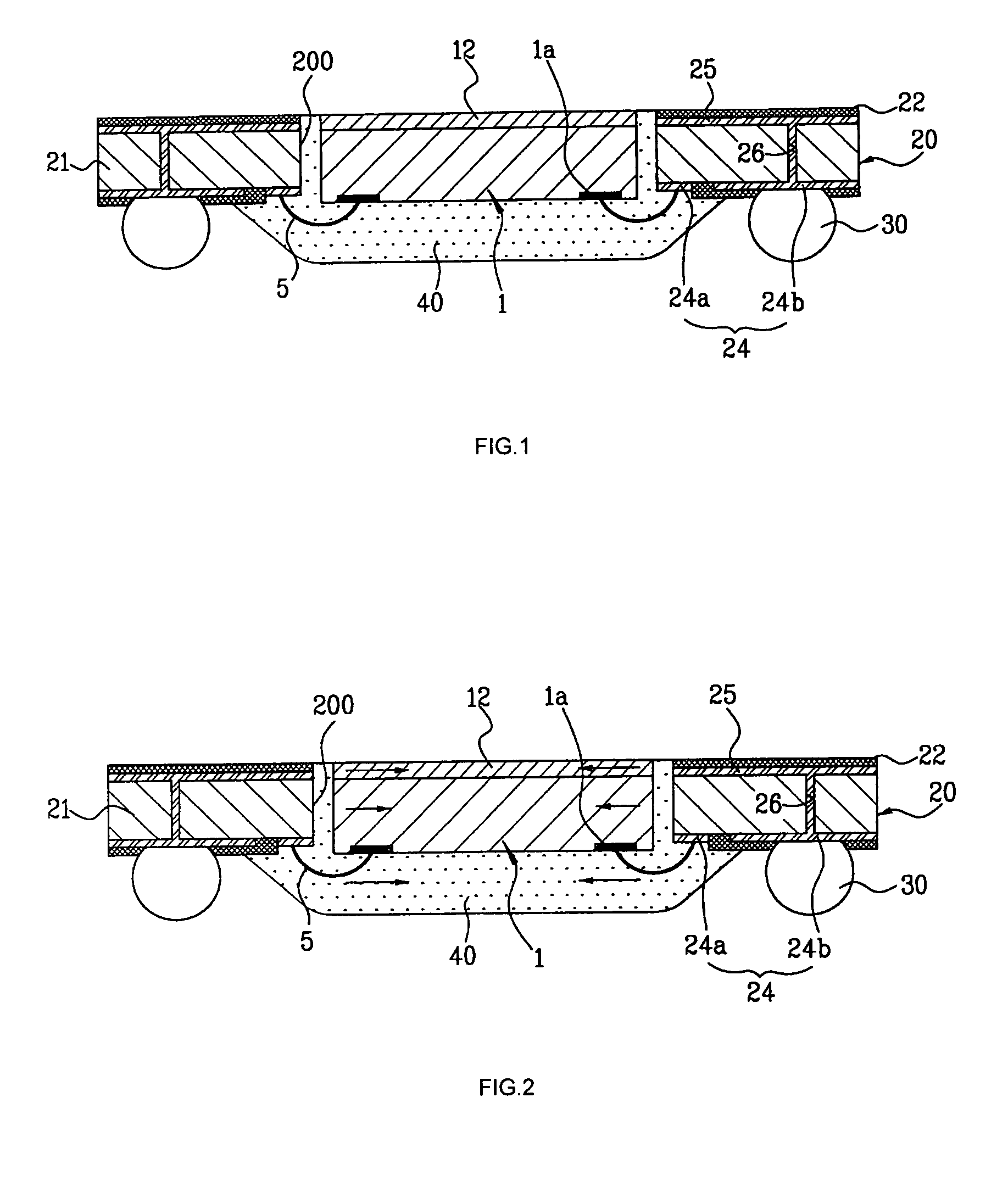

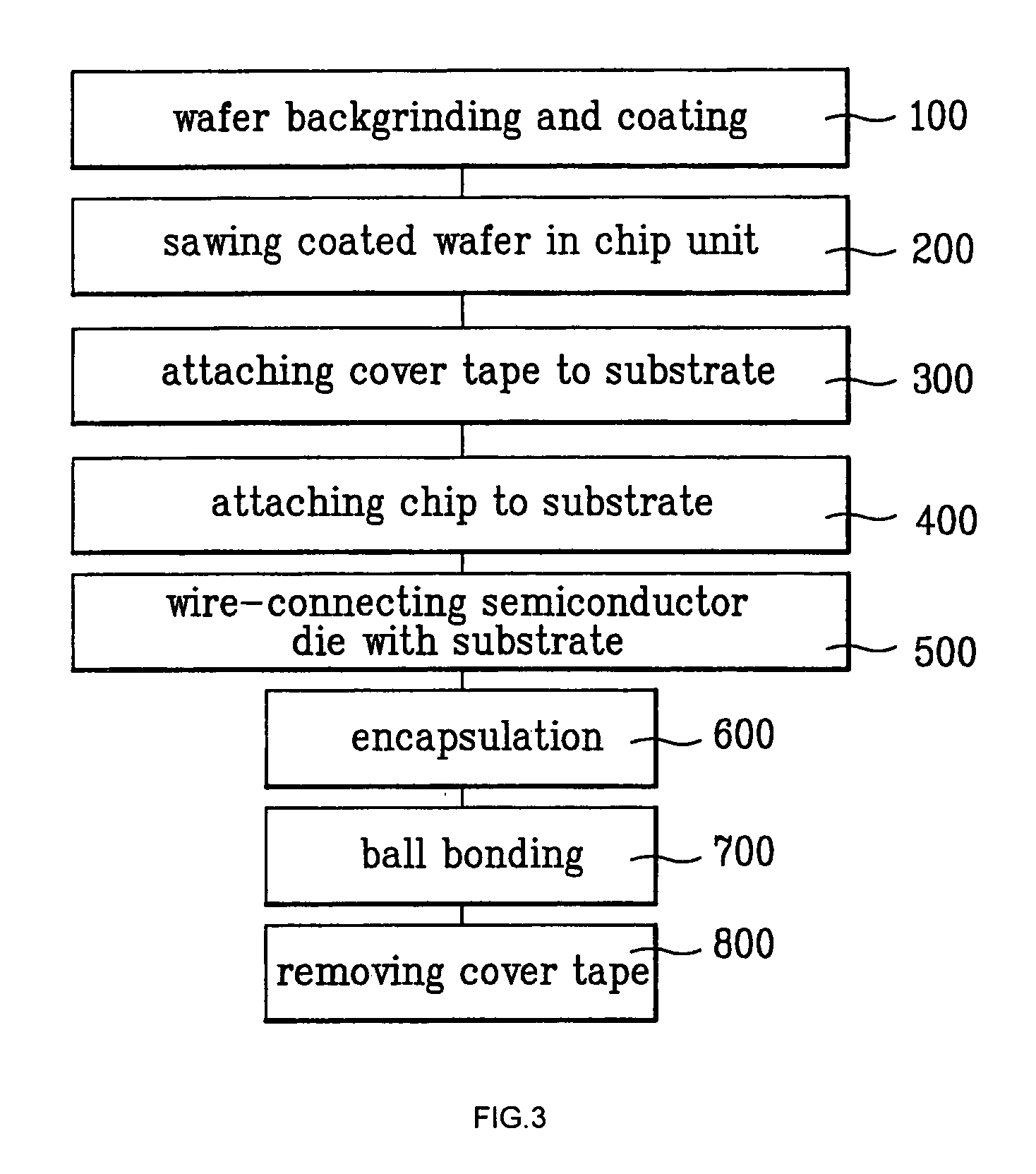

Semiconductor package and method of manufacturing the same which reduces warpage

InactiveUS7042072B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package and method of producing the same has a semiconductor die having a first face and a second face. A coating material is coupled to the second face of the semiconductor die. A substrate having a cavity is provided wherein the semiconductor die is placed within the cavity. An encapsulant is used to encapsulate the second face of the semiconductor die placed in the cavity. Connection members are provided to couple the semiconductor die and the substrate in order to transfer signals between the semiconductor die and the substrate. Terminal members are couple to the substrate to connect the semiconductor package to an external device. In the semiconductor package, a thermal expansion coefficient of the coating material C and a thermal expansion coefficient of the encapsulant E should be approximately equal in value in order to limit the problems associated with warpage.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD