Patents

Literature

118 results about "EPROM" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

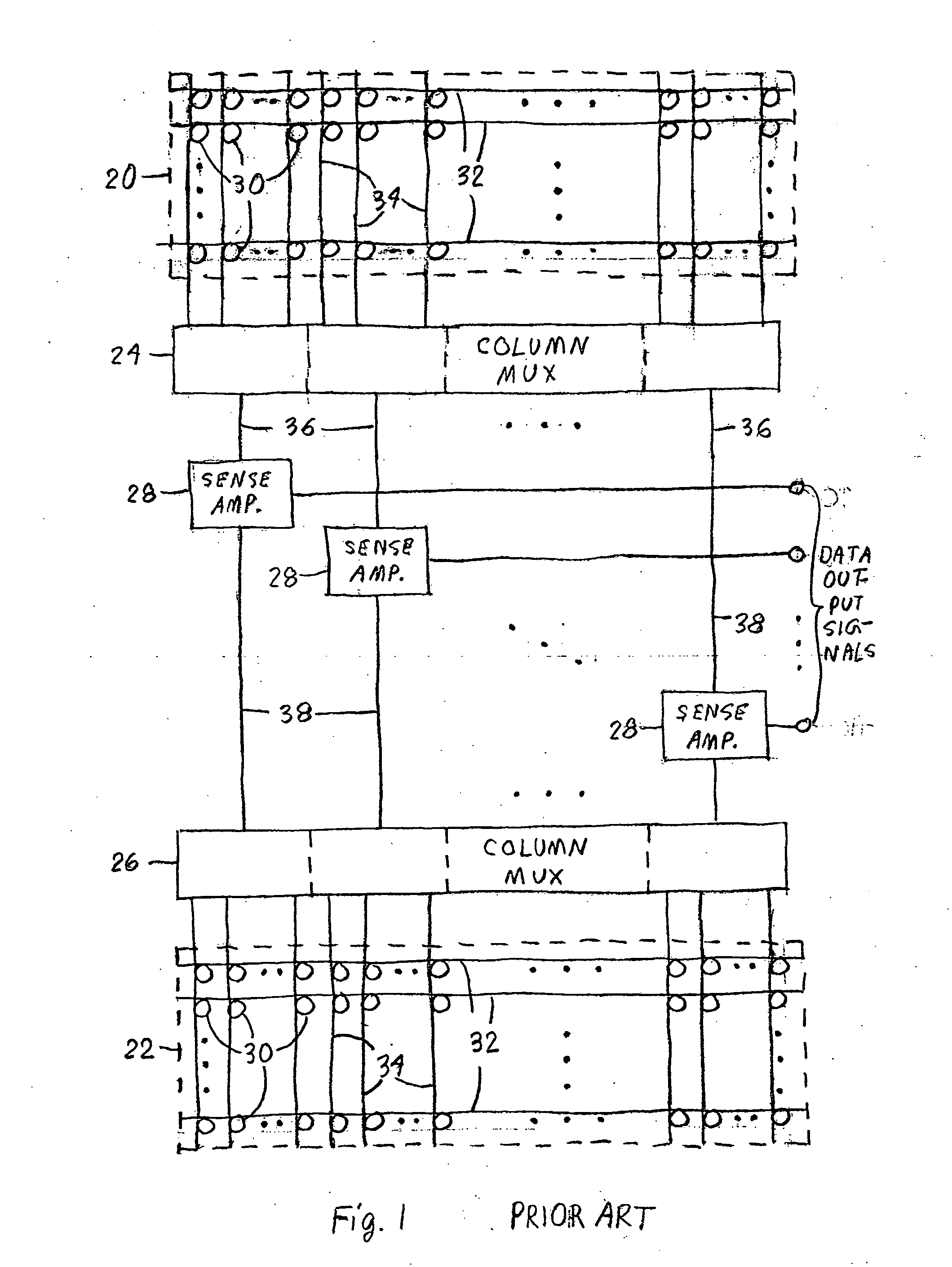

An EPROM (rarely EROM), or erasable programmable read-only memory, is a type of programmable read-only memory (PROM) chip that retains its data when its power supply is switched off. Computer memory that can retrieve stored data after a power supply has been turned off and back on is called non-volatile. It is an array of floating-gate transistors individually programmed by an electronic device that supplies higher voltages than those normally used in digital circuits. Once programmed, an EPROM can be erased by exposing it to strong ultraviolet light source (such as from a mercury-vapor lamp). EPROMs are easily recognizable by the transparent fused quartz window in the top of the package, through which the silicon chip is visible, and which permits exposure to ultraviolet light during erasing.

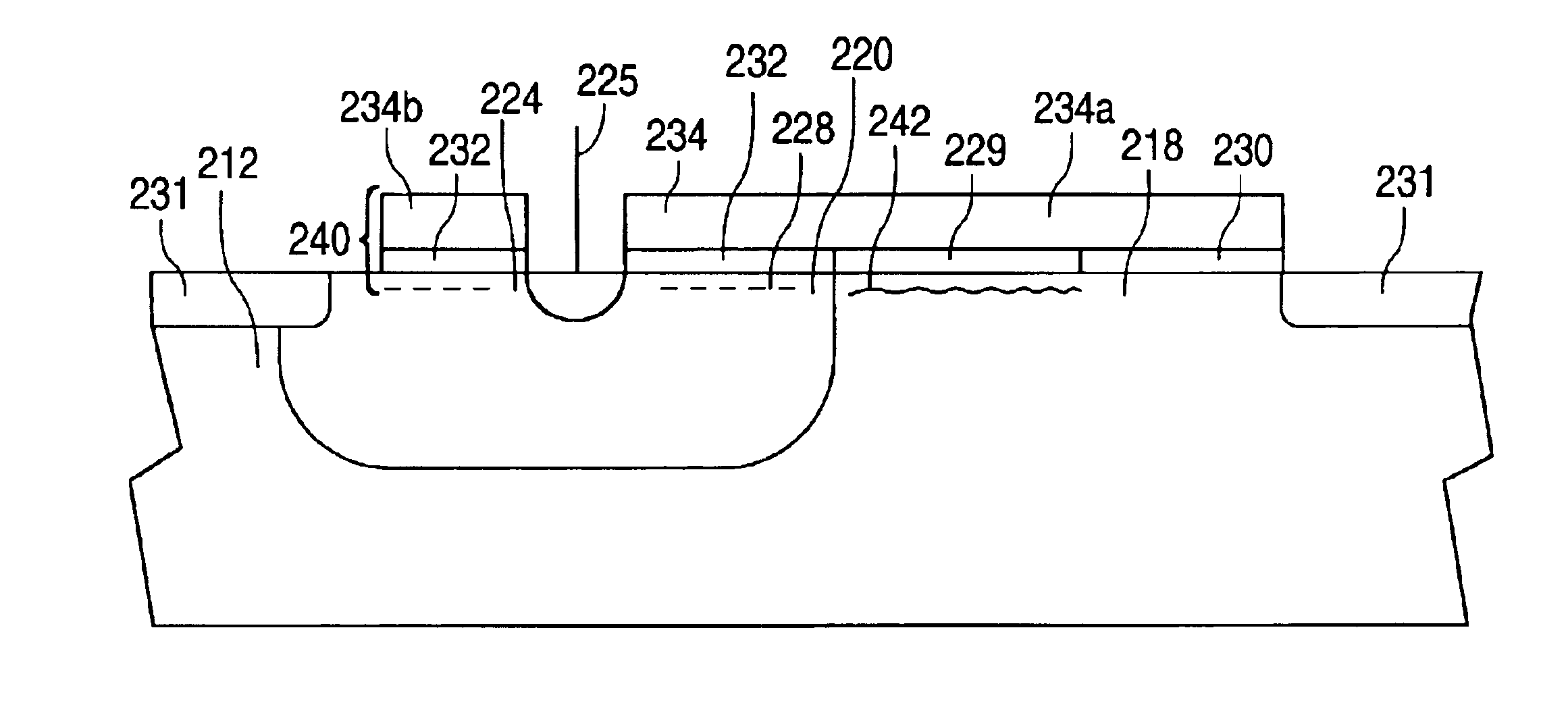

Highly compact EPROM and flash EEPROM devices

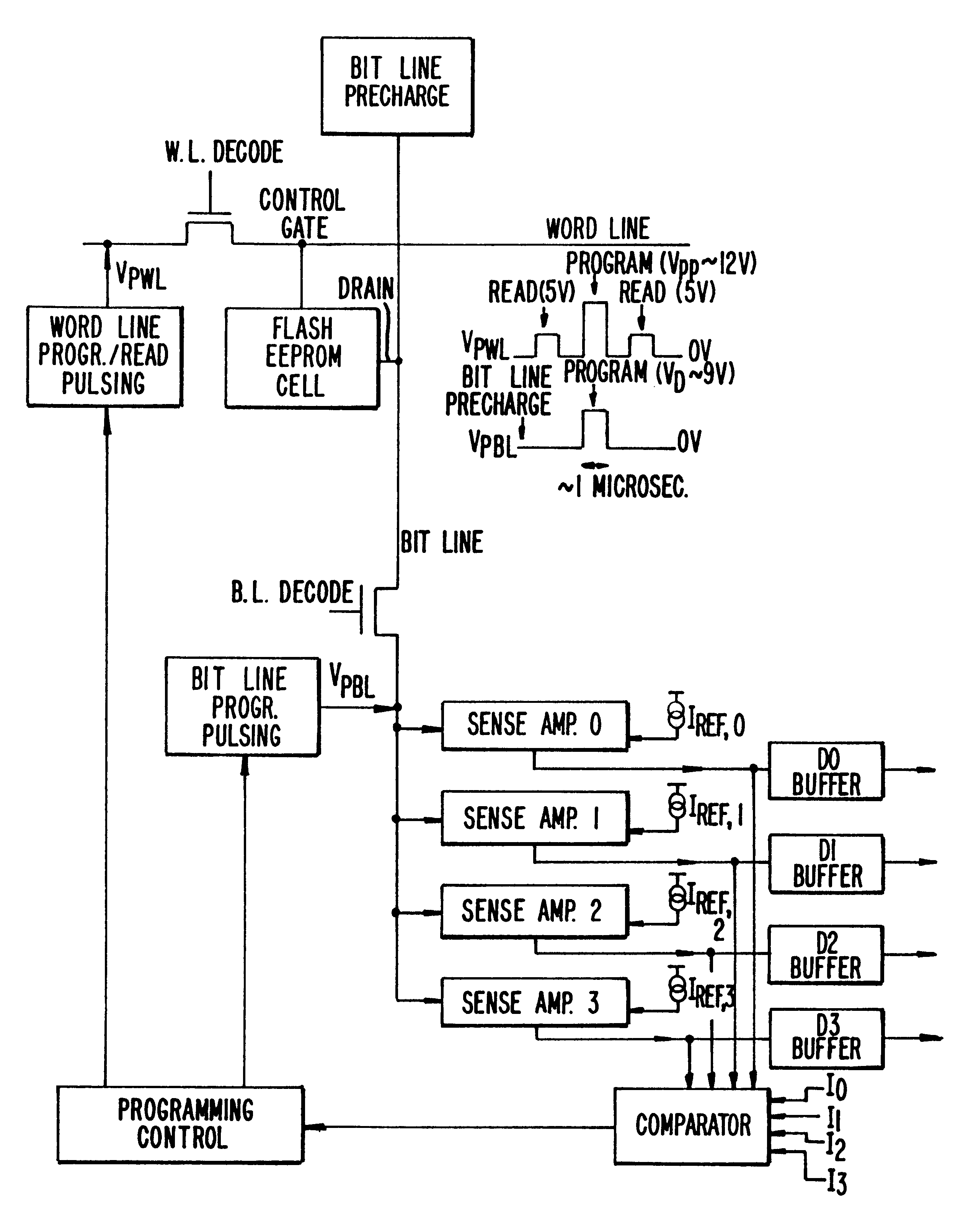

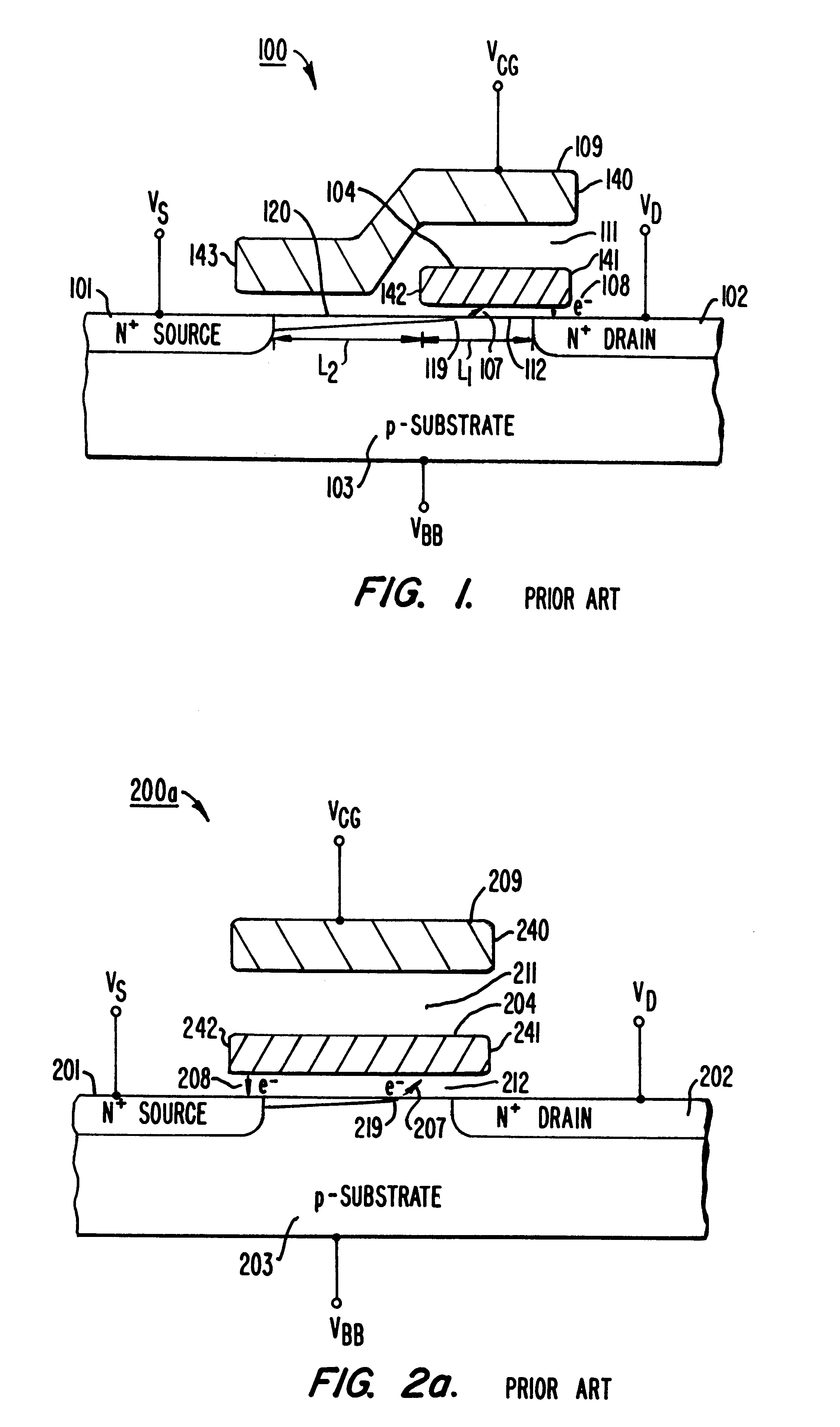

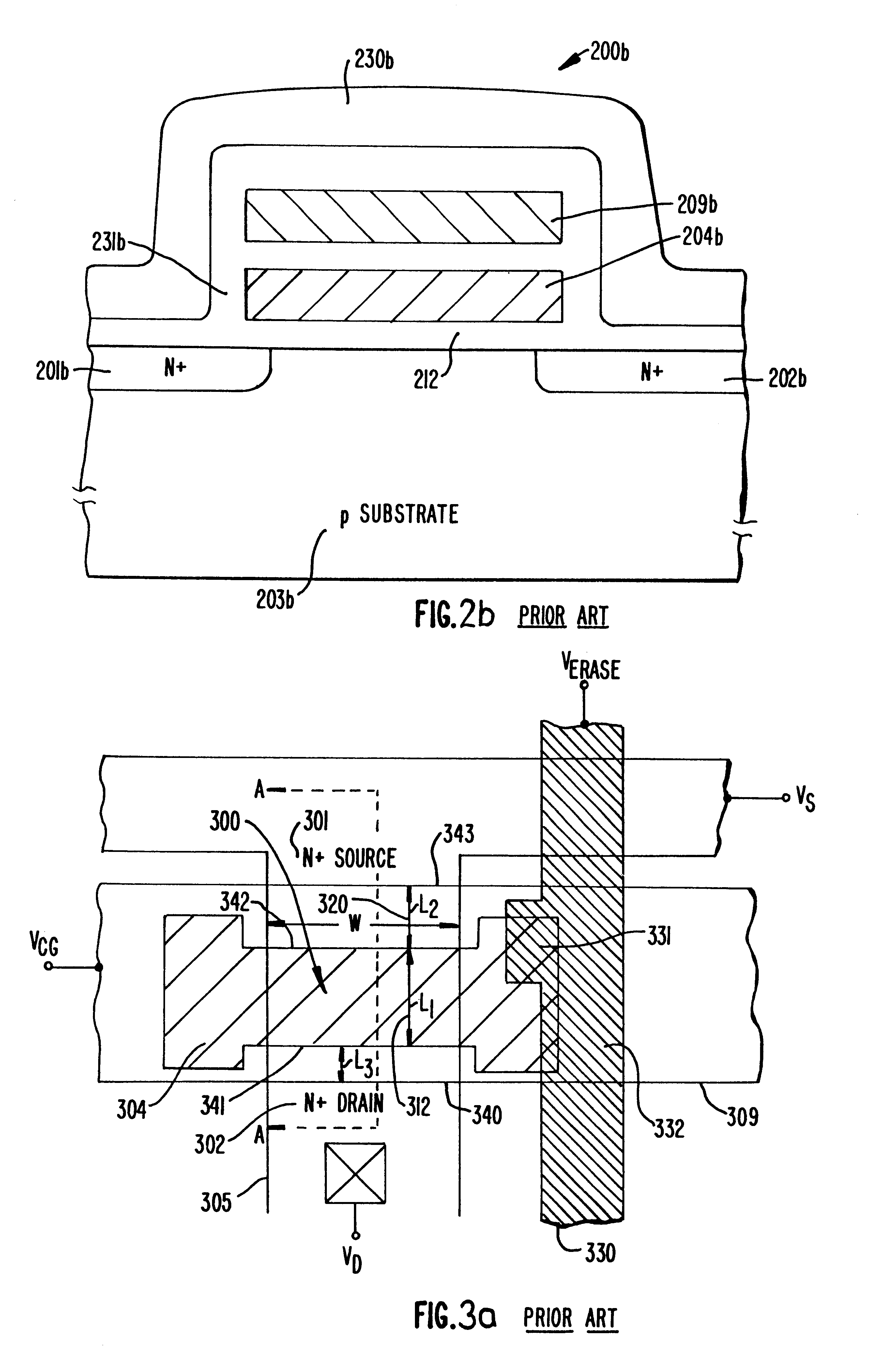

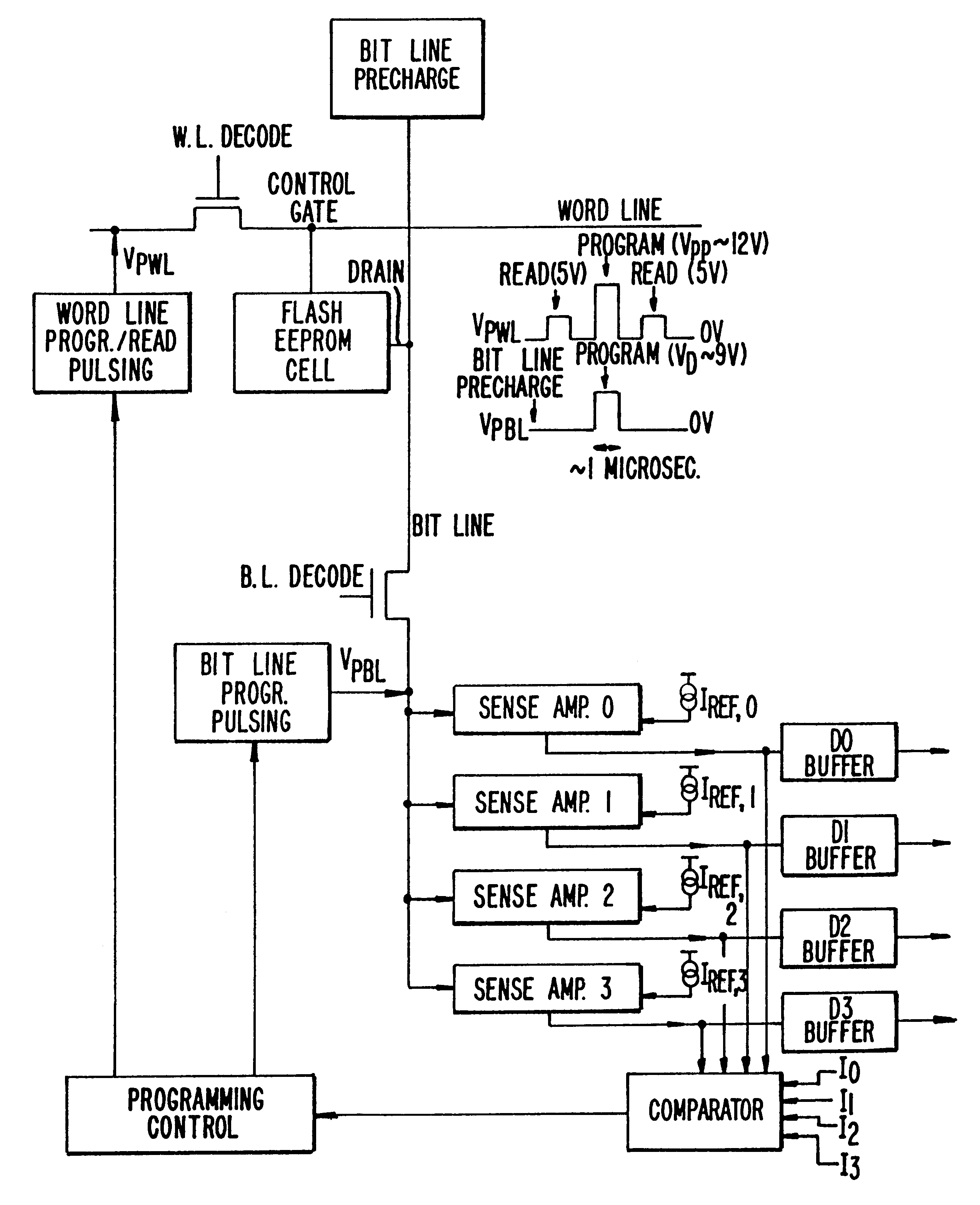

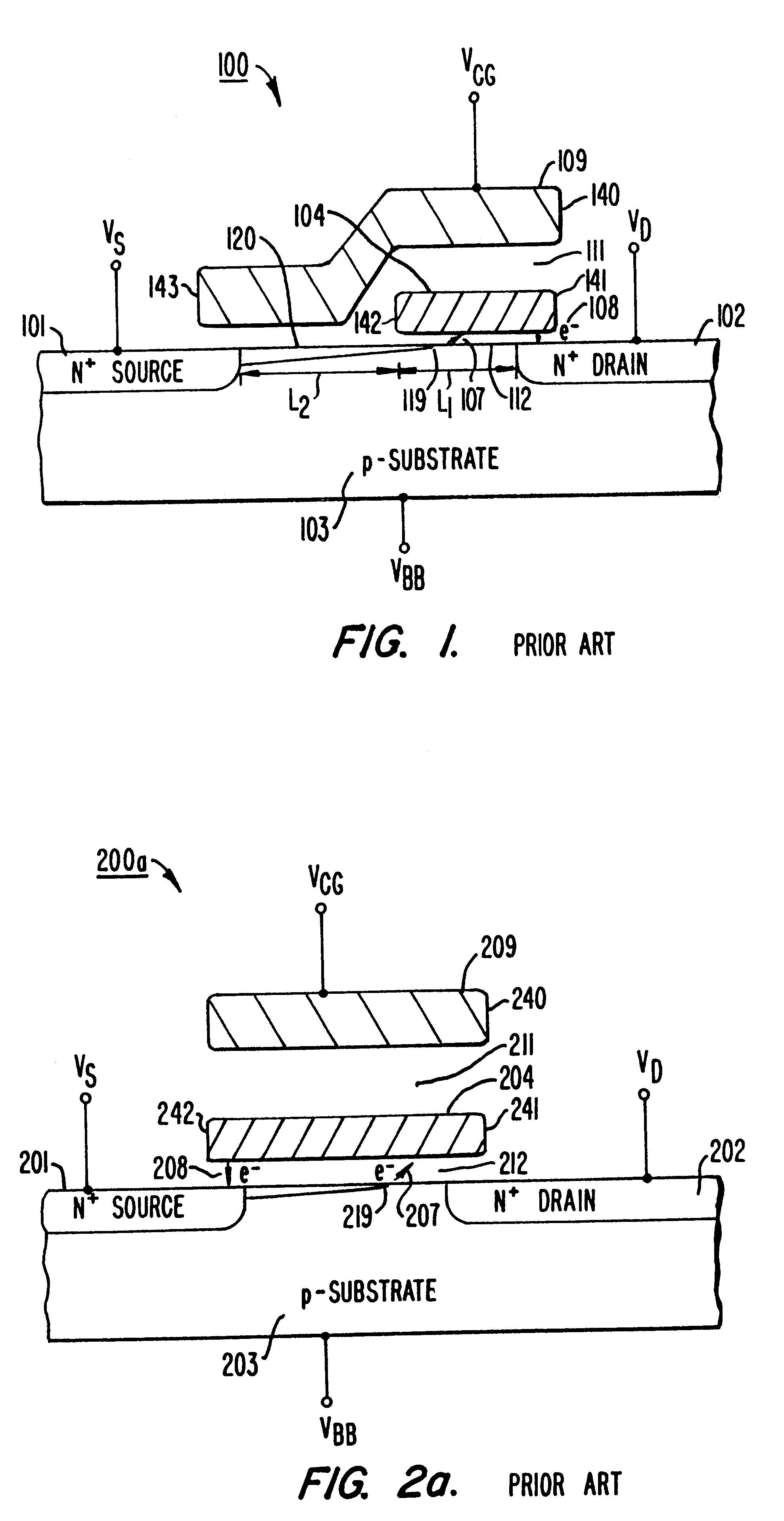

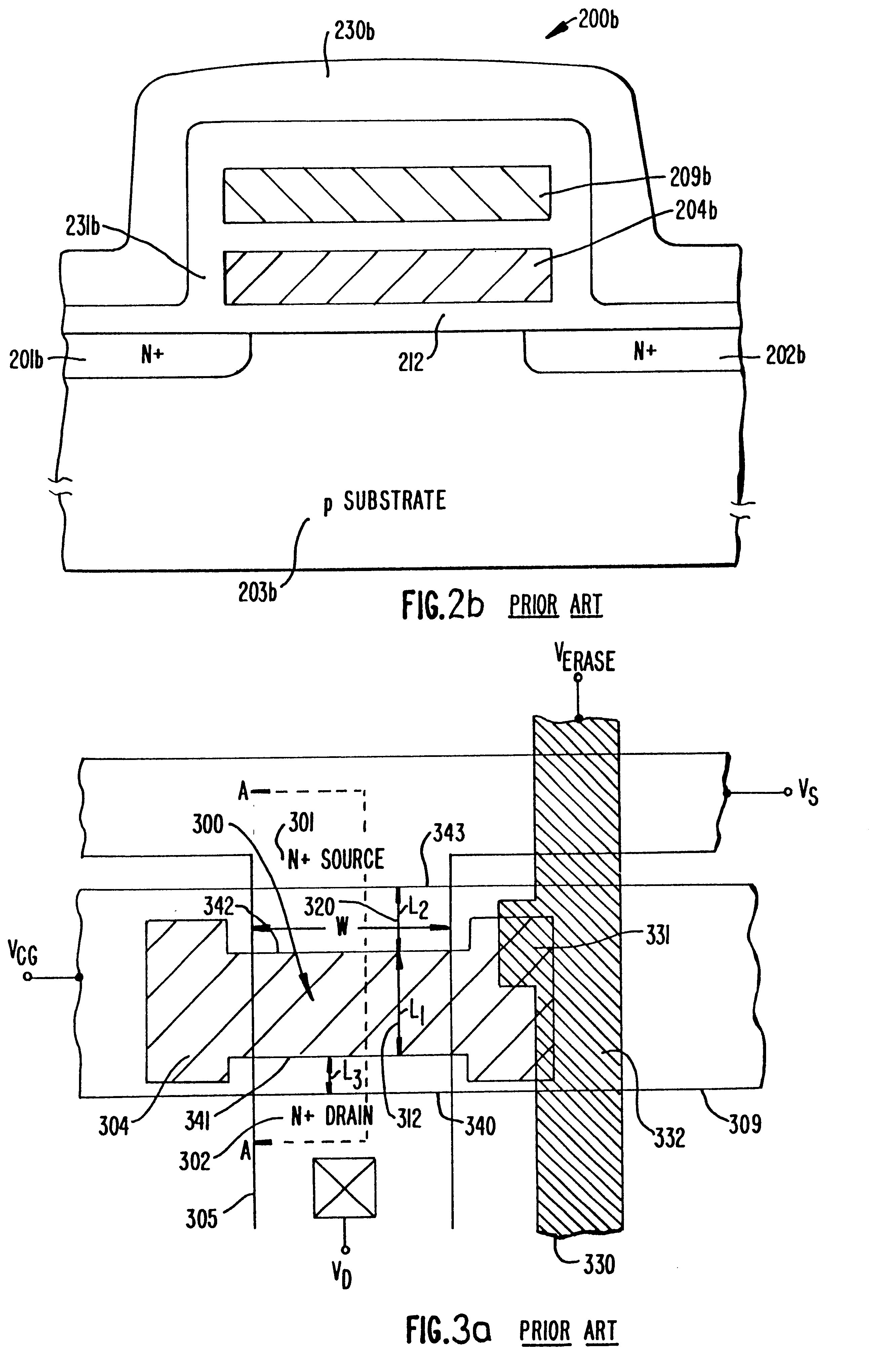

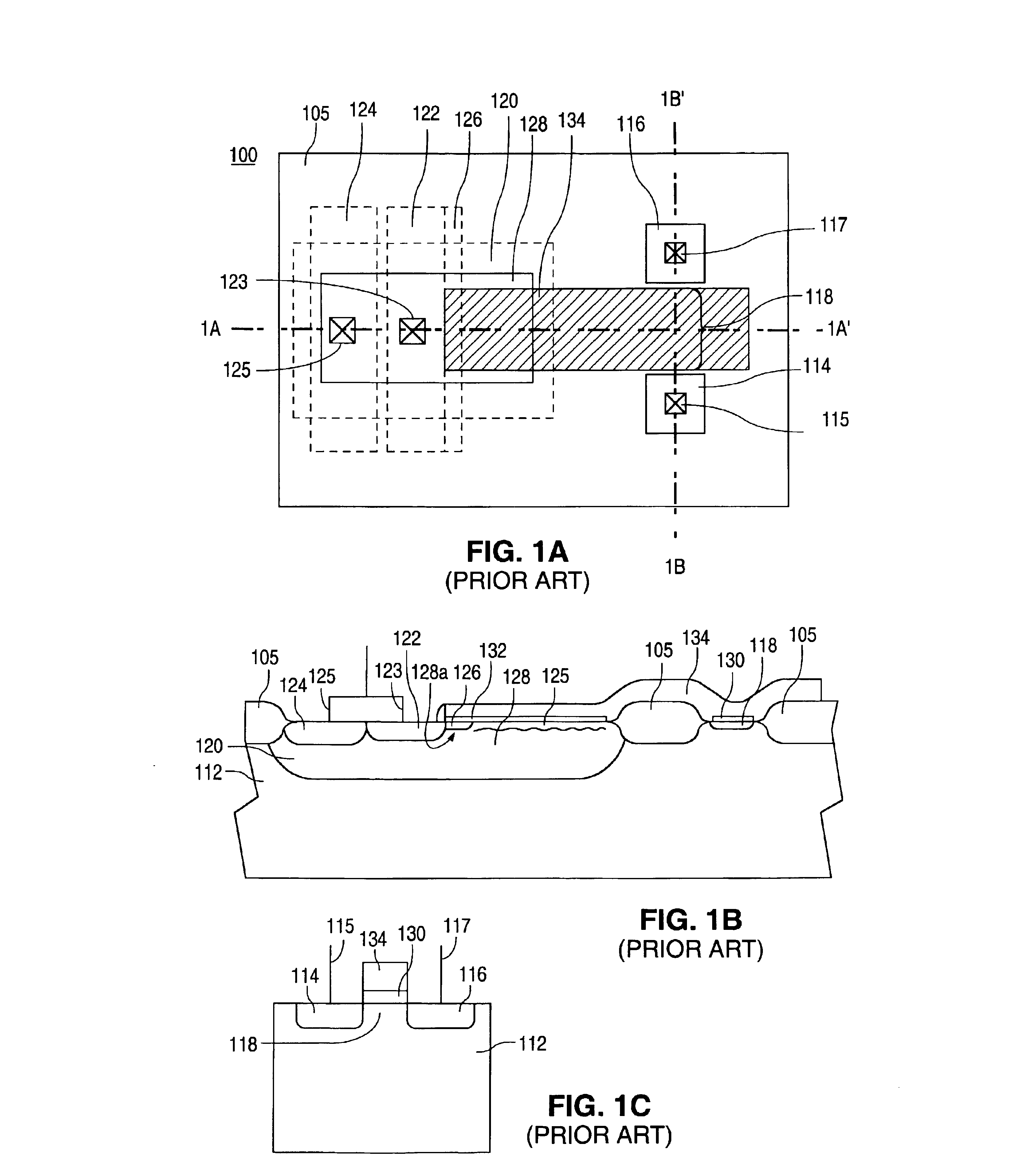

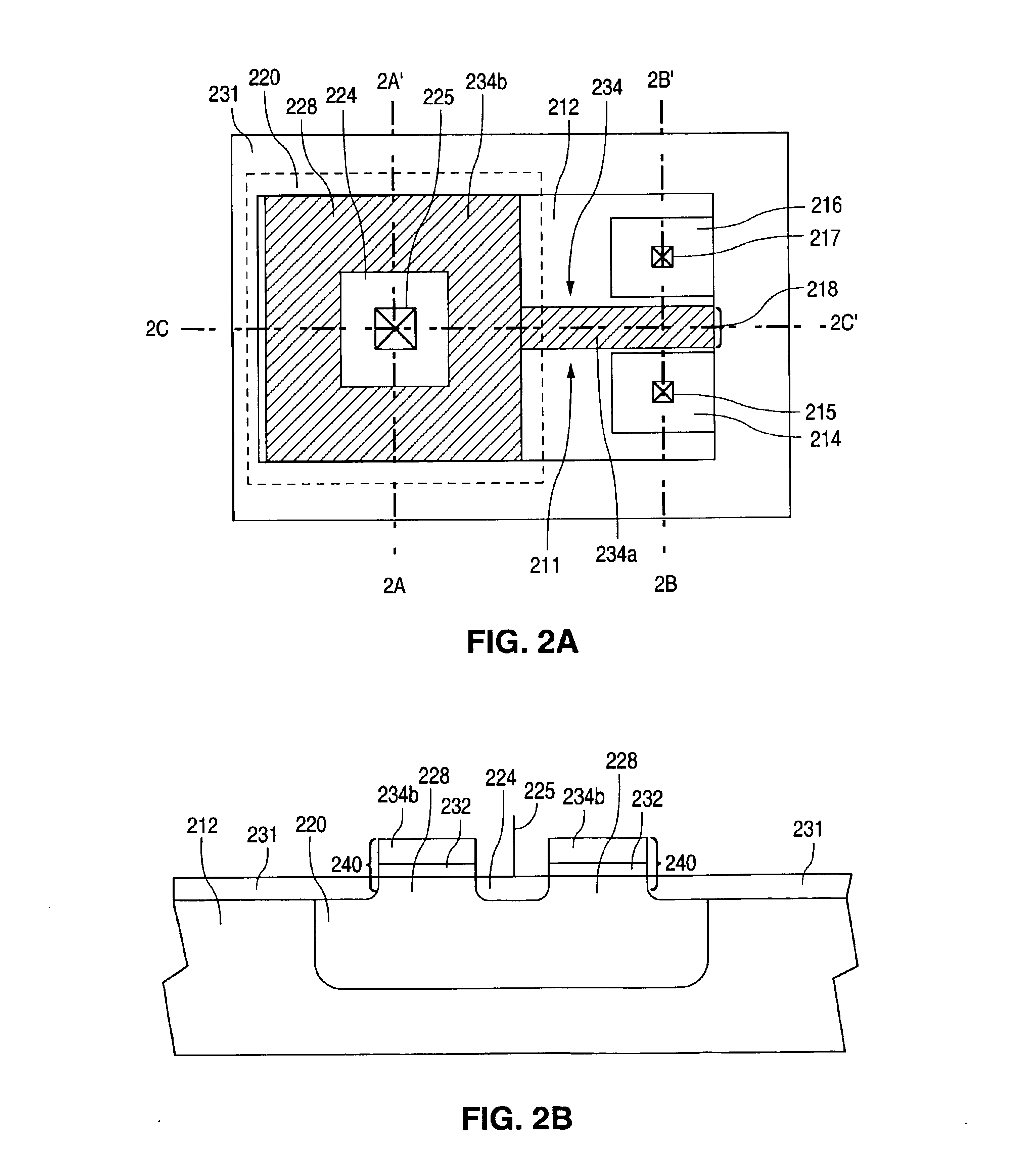

Structures, methods of manufacturing and methods of use of electrically programmable read only memories (EPROM) and flash electrically erasable and programmable read only memories (EEPROM) include split channel and other cell configurations. An arrangement of elements and cooperative processes of manufacture provide self-alignment of the elements. An intelligent programming technique allows each memory cell to store more than the usual one bit of information. An intelligent erase algorithm prolongs the useful life of the memory cells. Use of these various features provides a memory having a very high storage density and a long life, making it particularly useful as a solid state memory in place of magnetic disk storage devices in computer systems.

Owner:SANDISK TECH LLC

Highly compact EPROM and flash EEPROM devices

Structures, methods of manufacturing and methods of use of electrically programmable read only memories (EPROM) and flash electrically erasable and programmable read only memories (EEPROM) include split channel and other cell configurations. An arrangement of elements and cooperative processes of manufacture provide self-alignment of the elements. An intelligent programming technique allows each memory cell to store more than the usual one bit of information. An intelligent erase algorithm prolongs the useful life of the memory cells. Use of these various features provides a memory having a very high storage density and a long life, making it particularly useful as a solid state memory in place of magnetic disk storage devices in computer systems.

Owner:SANDISK TECH LLC

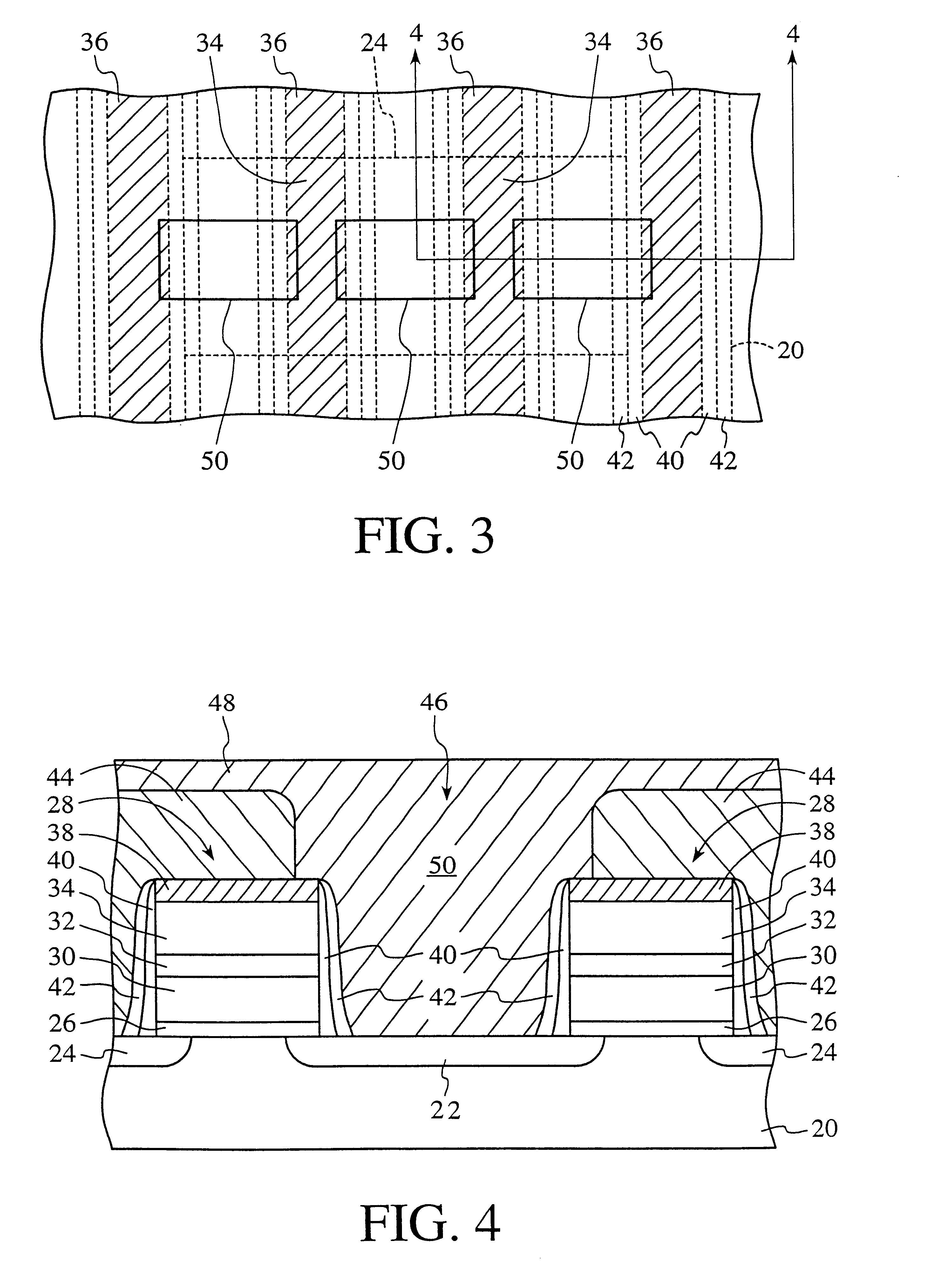

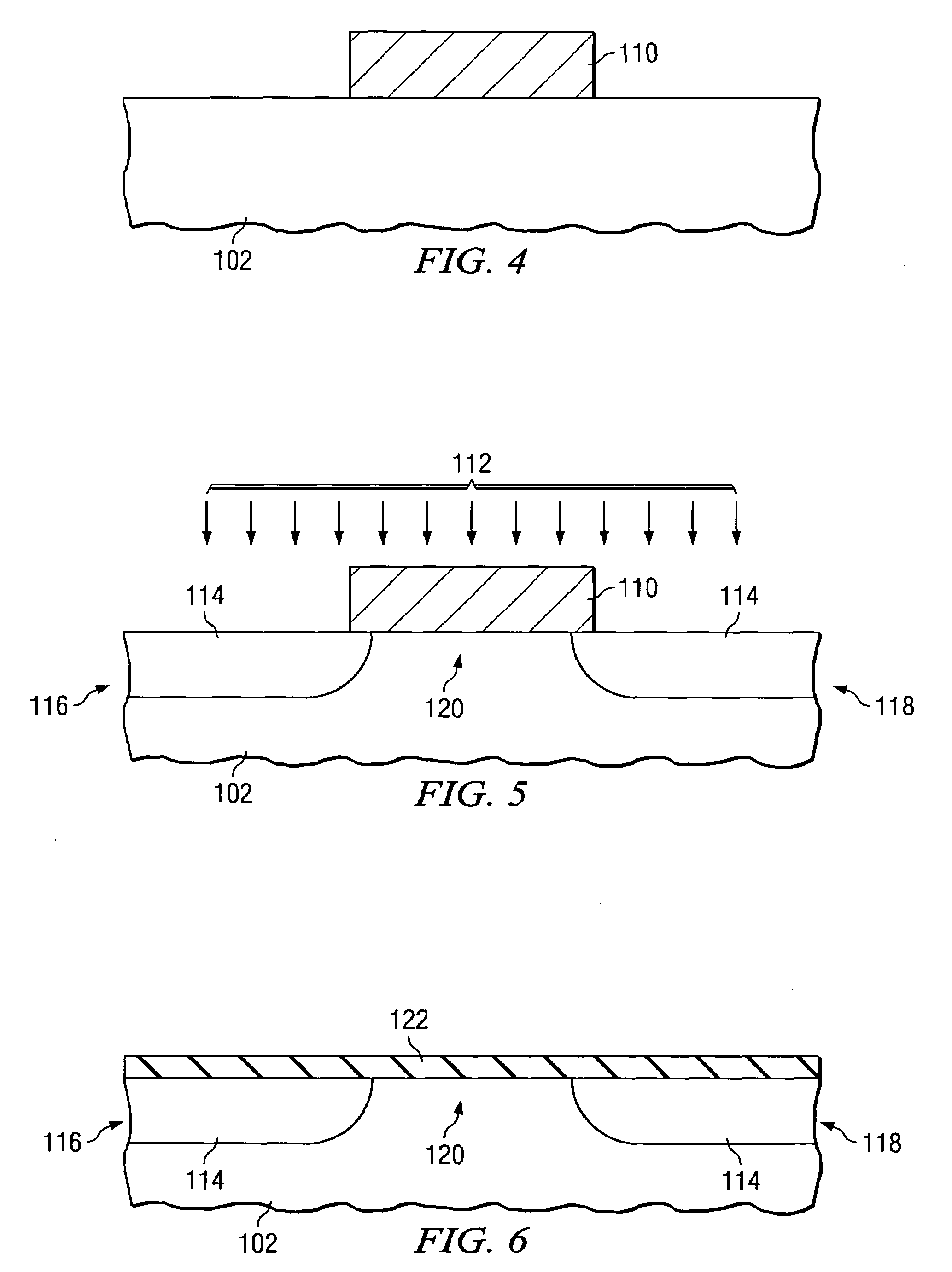

High density programmable read-only memory employing double-wall spacers

InactiveUS6255205B1Reduce areaHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingHigh densityProgrammable read-only memory

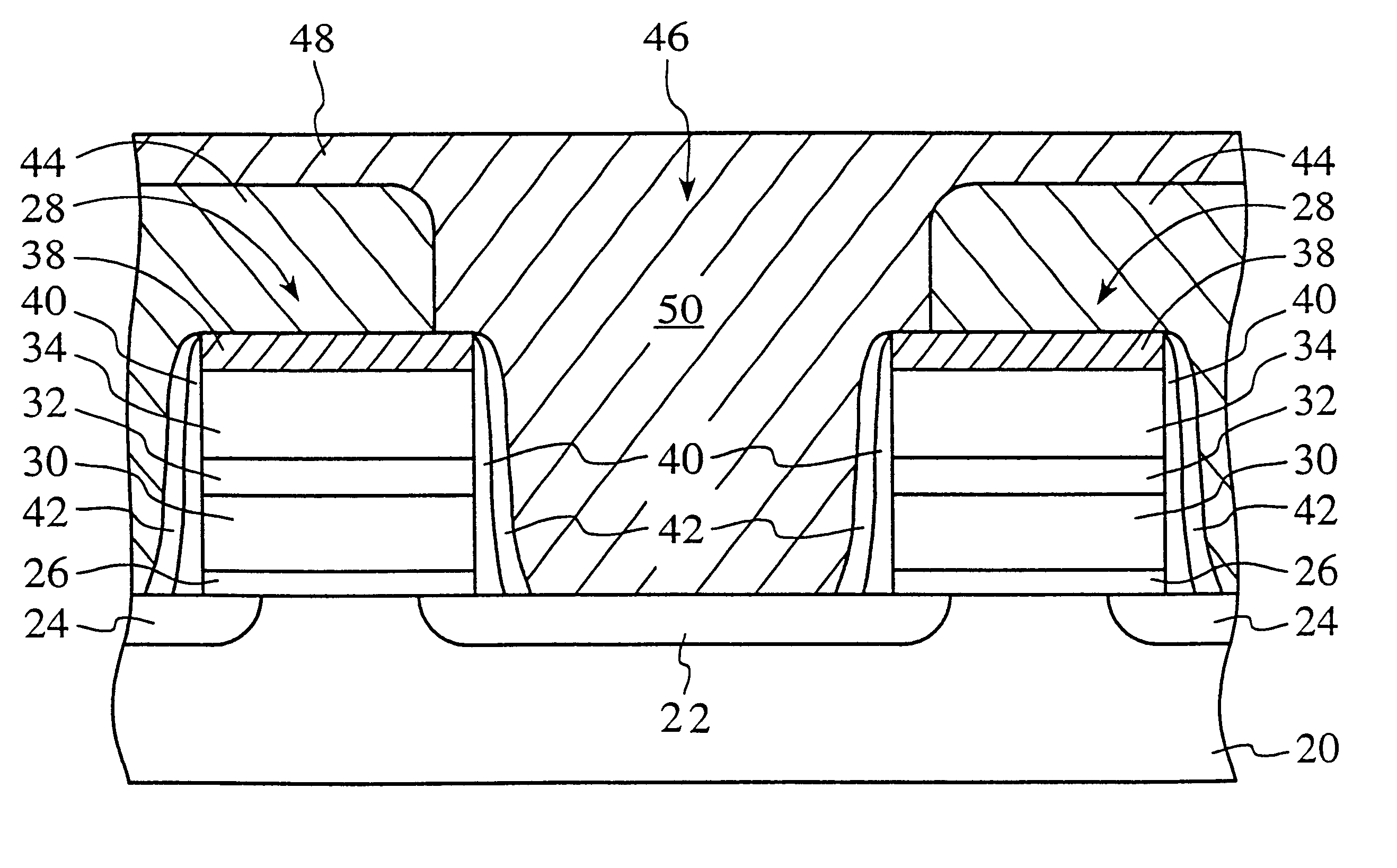

The present invention provides an EPROM and a method for forming the same having increased density. The invention does so by reducing the area required for formation of a contact. Specifically, a storage cell for an electrically programmable read-only memory having a pair of spaced-apart gate structures, with a double wall spacer structure disposed on opposite sides of each gate structure.

Owner:PROMOS TECH INC

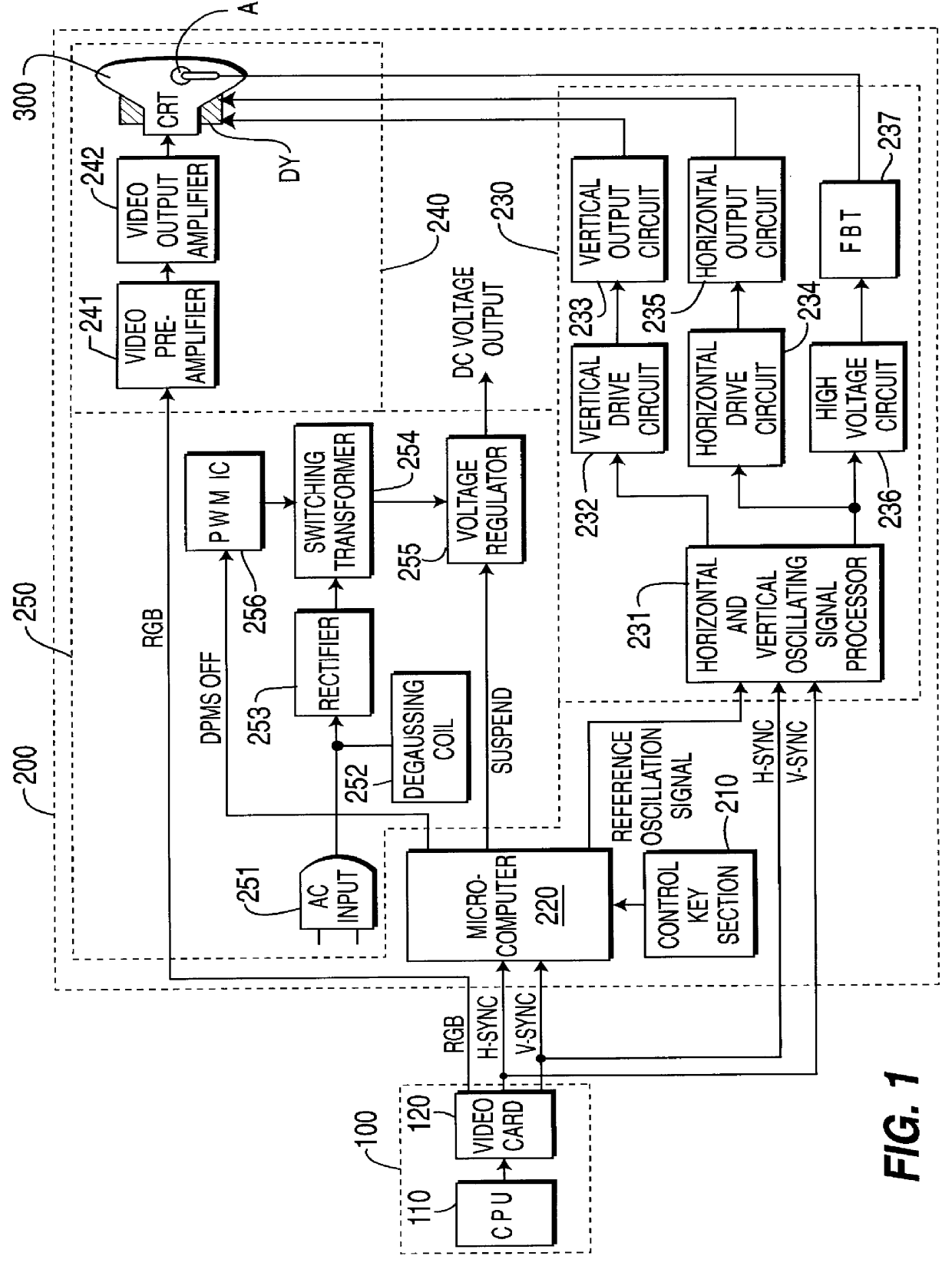

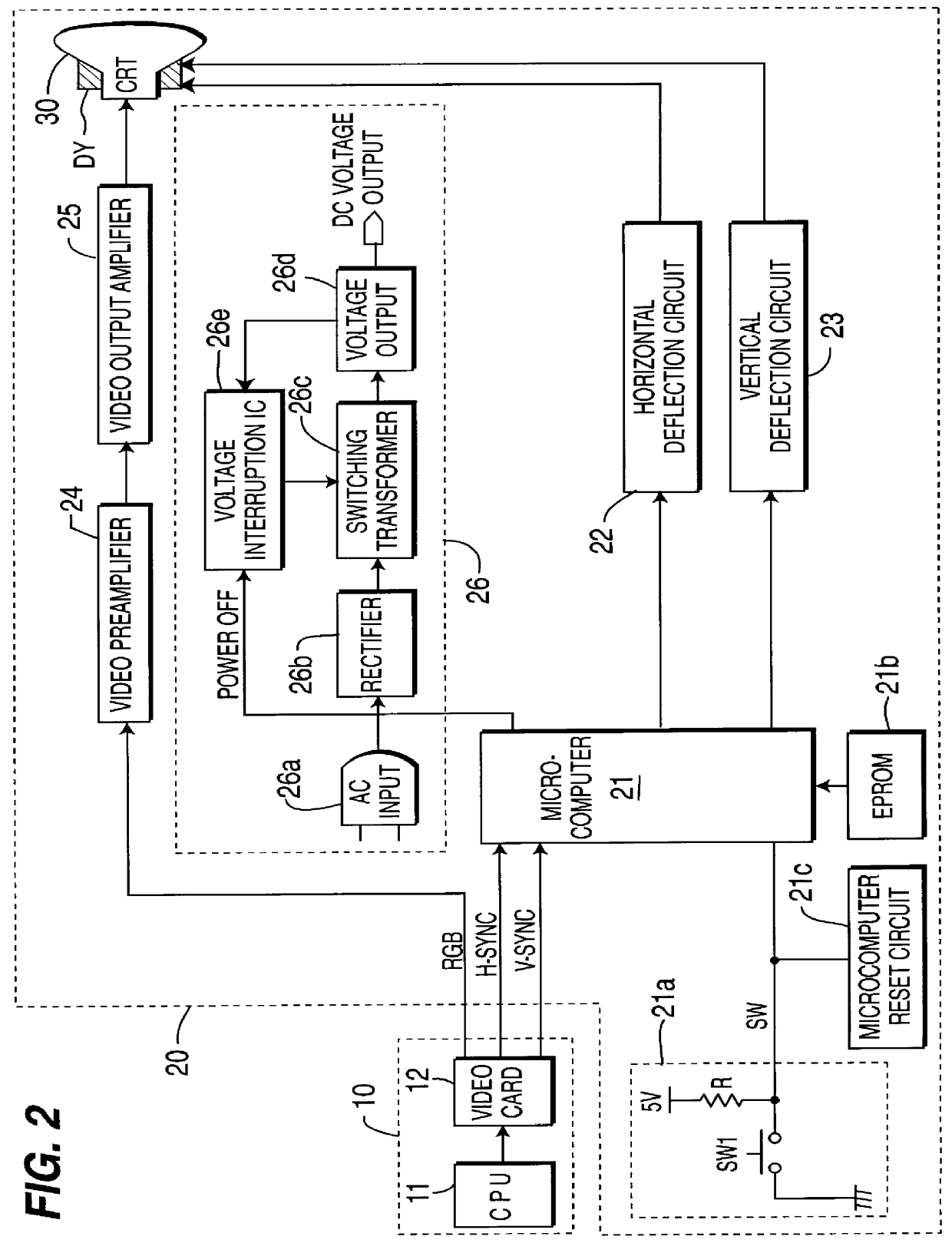

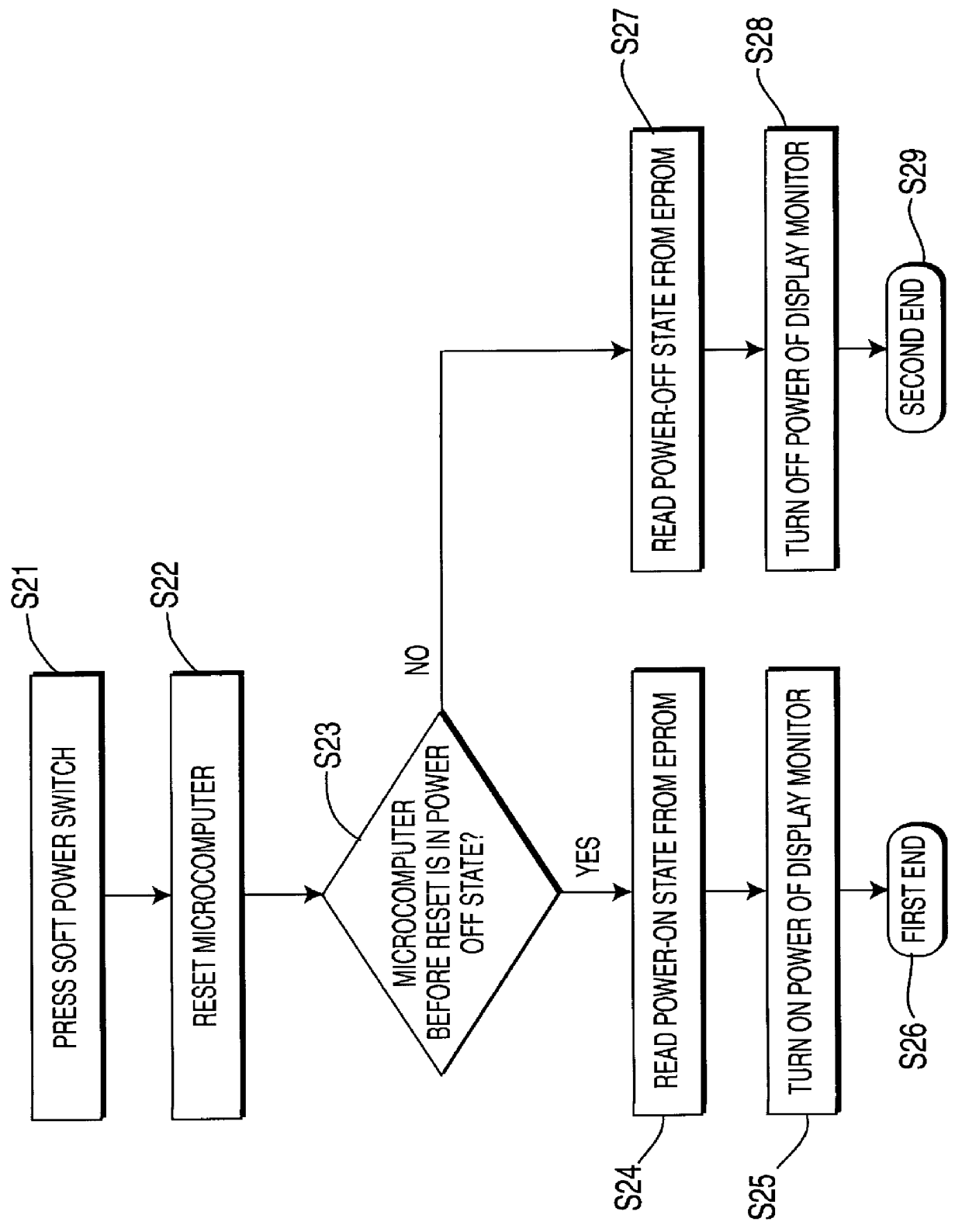

Power switching device and method of display monitor through reset of microcomputer

InactiveUS6119225AReduce power consumptionVolume/mass flow measurementDetecting faulty computer hardwareMicrocomputerEPROM

A method and device which powerswitches a display monitor through the reset of a microcomputer is adapted to interrupt the latch up caused during the use of a soft power key by reading the power state of the display monitor before latch up from a memory, and switching the power state to the state before the latch up of the display monitor. The device includes: a soft power key section for generating a reset signal; an EPROM for storing data concerning the power on / off state of the display monitor before the operation of the soft power key section; a microcomputer for generating a power-off signal with the use of the soft power key section and, if a latch up occurs during the use of the soft power key section, reading the power on / off state data stored in the EPROM and switching the power state of the display monitor to the state before the latch up; and a power supply circuit section controlled according to the presence of the power-off signal generated by the microcomputer, and switching the output of a DC voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

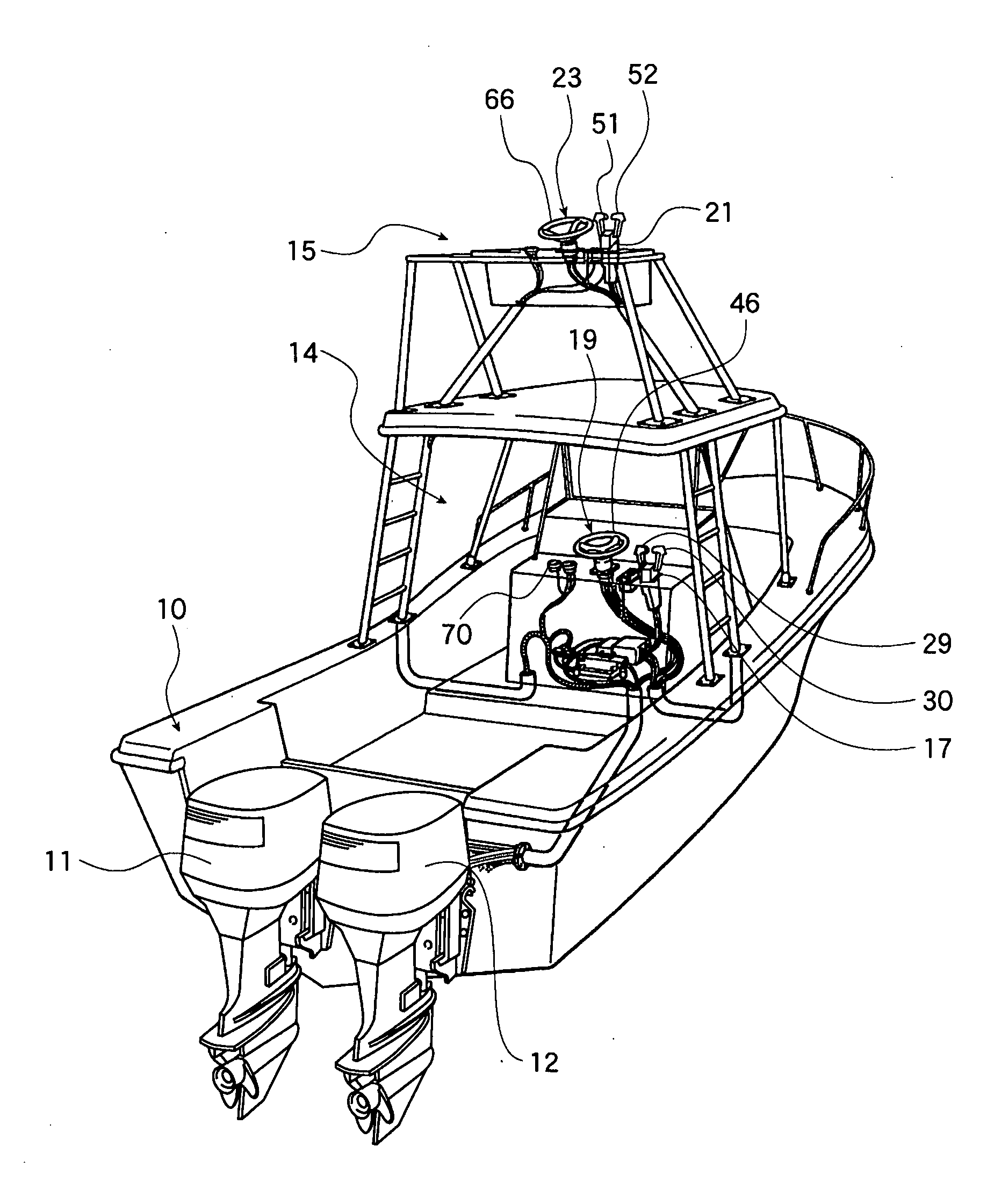

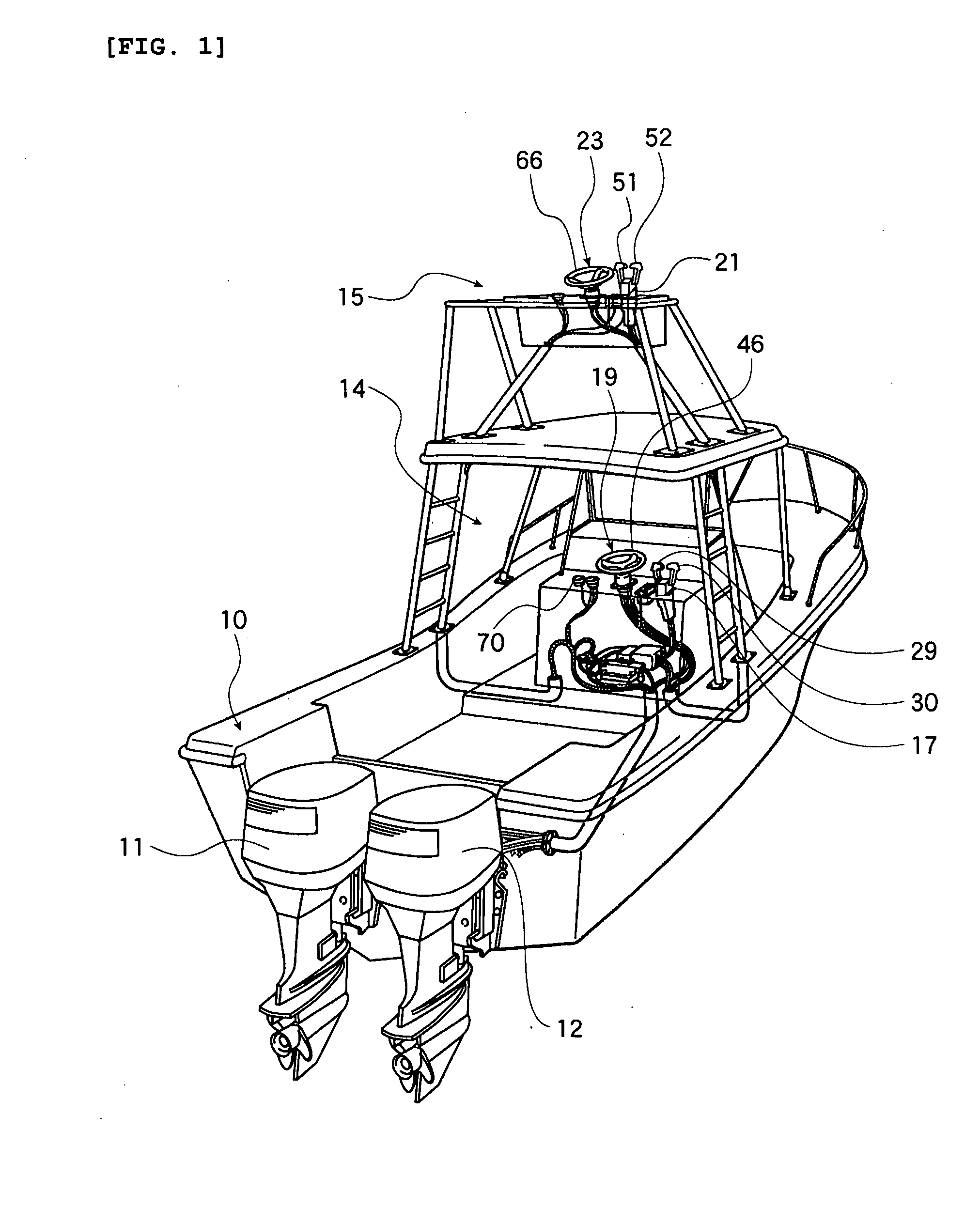

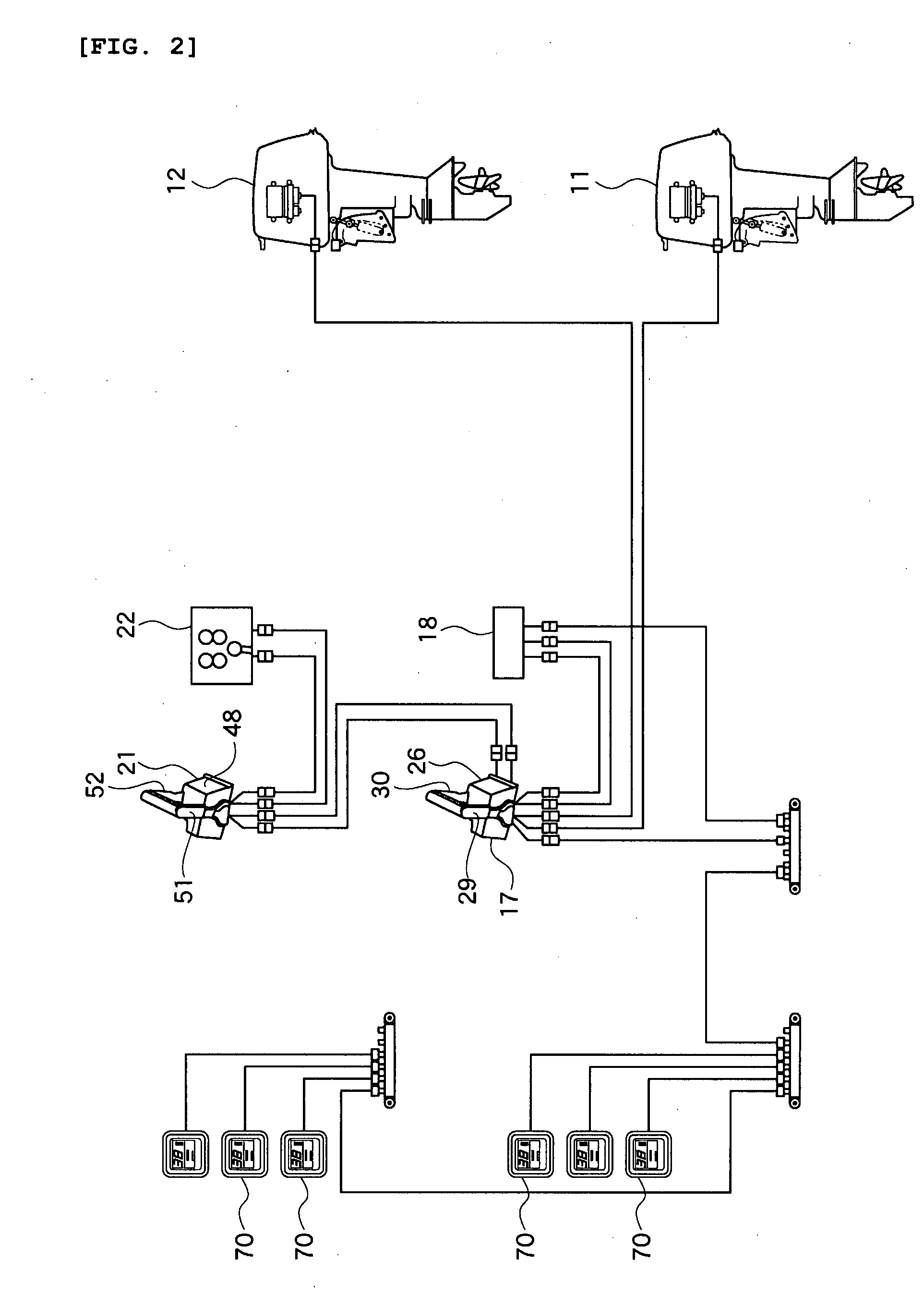

Remote control system for a watercraft

A remote control system for controlling a propulsion unit of a watercraft includes a plurality of remote controller side ECUs, all of which have the same construction in one embodiment. Each remote controller side ECU includes ECU discriminating terminal sections and an ECU determining section for determining a role of each remote controller side ECU based upon signals provided by the ECU discriminating terminal sections. The ECU determining section determines a role of the particular remote controller side ECU based upon the signals provided by the ECU discriminating terminal sections when the remote controller side ECU starts operating. The ECU determining section also reads out the most proper one of first through sixth exclusive use sections, which define the function of the ECU's role. A determination result is stored in first, second and third EPROMs so as to be used to determine the role.

Owner:YAMAHA MARINE KK

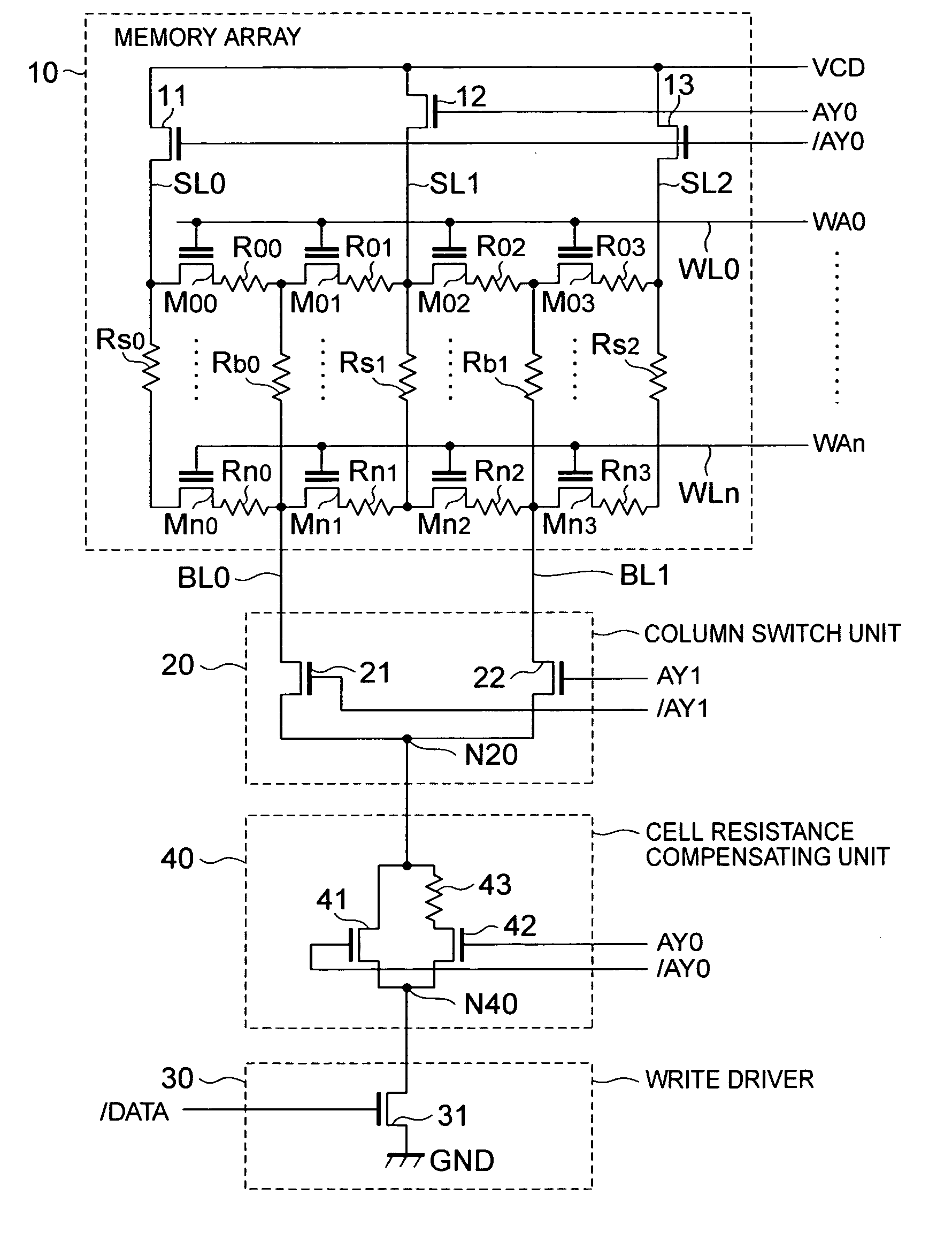

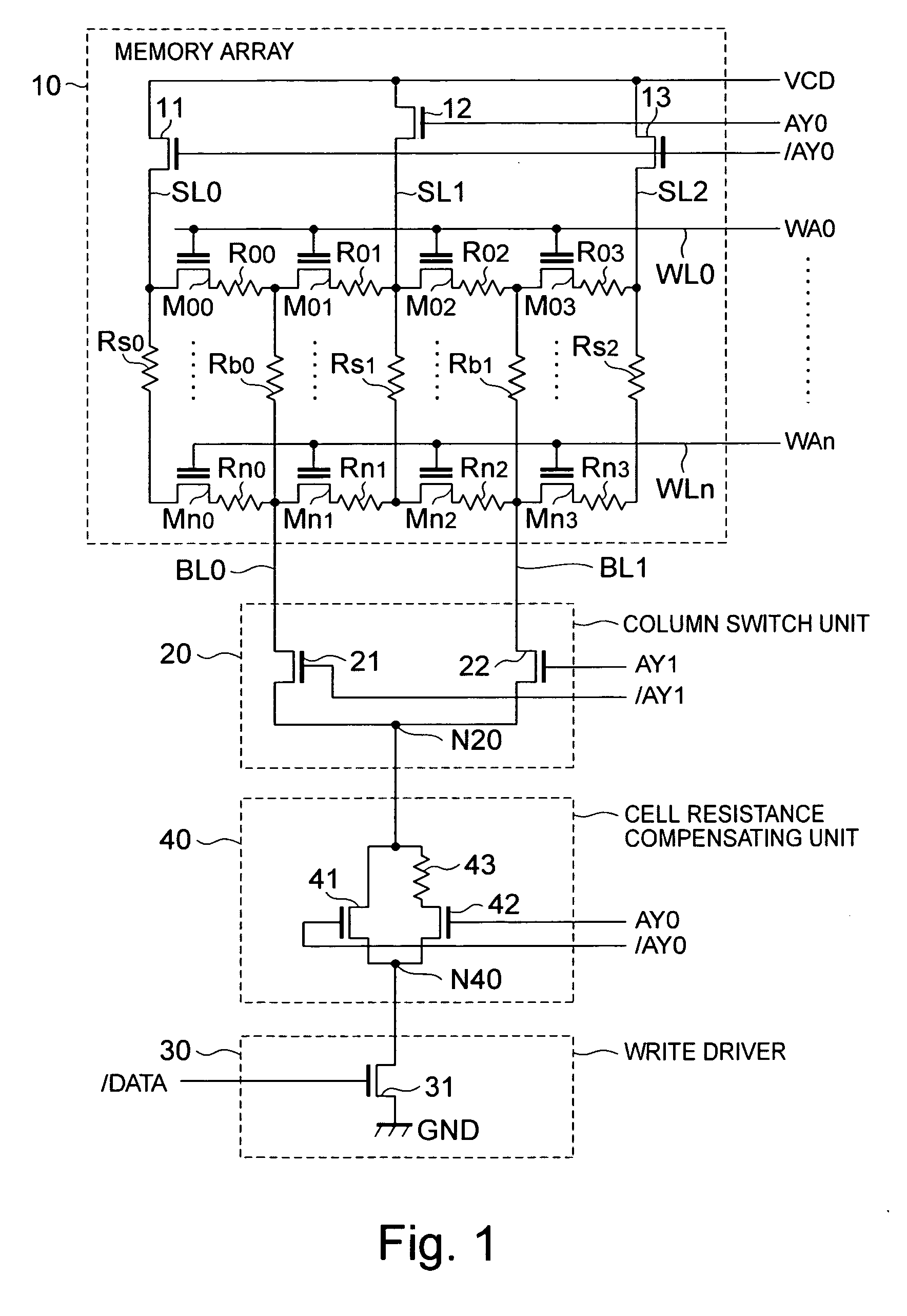

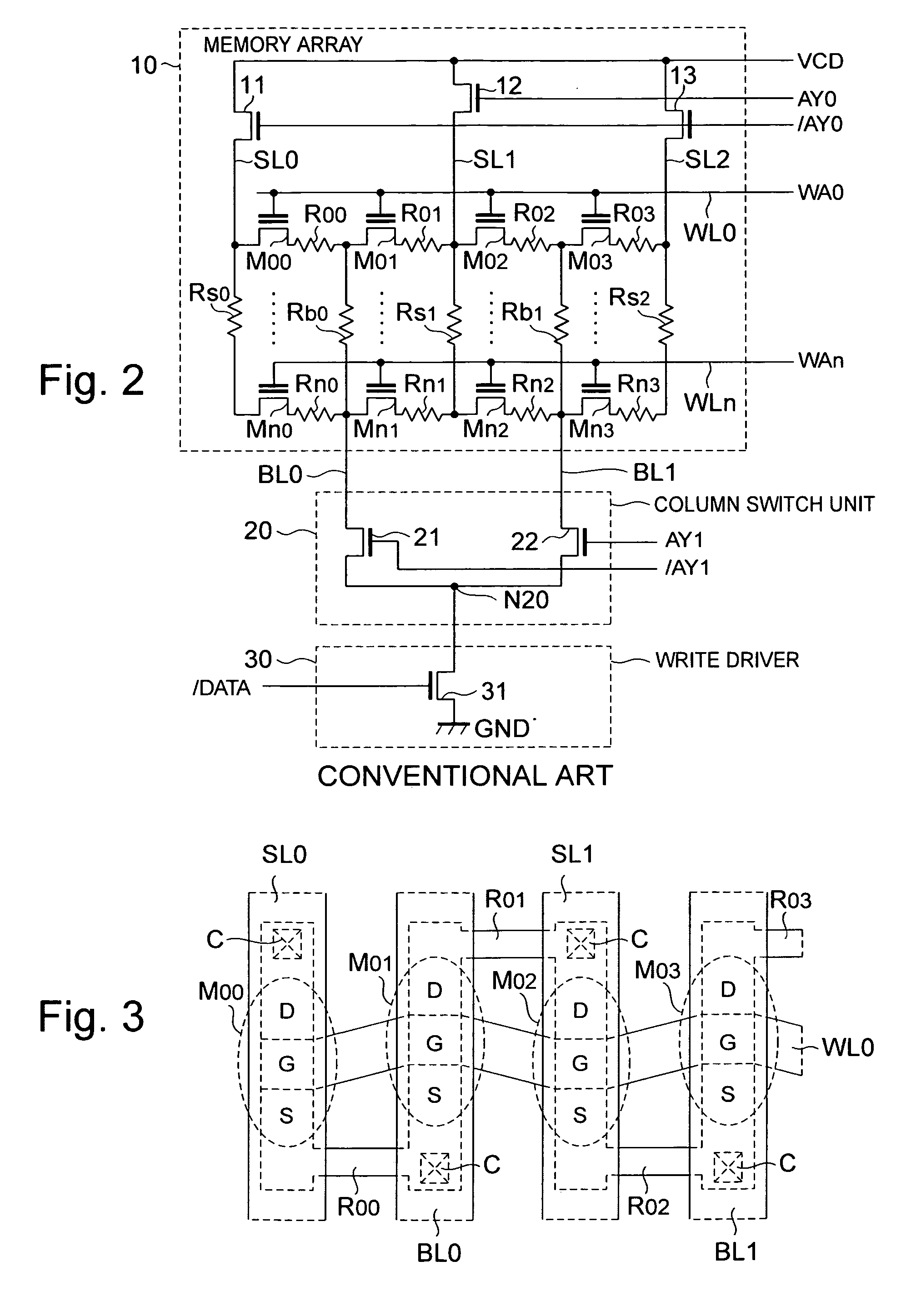

Nonvolatile semiconductor memory device and data writing method

InactiveUS20070070710A1Uniform valueEliminate variationRead-only memoriesDigital storageEPROMSemiconductor memory

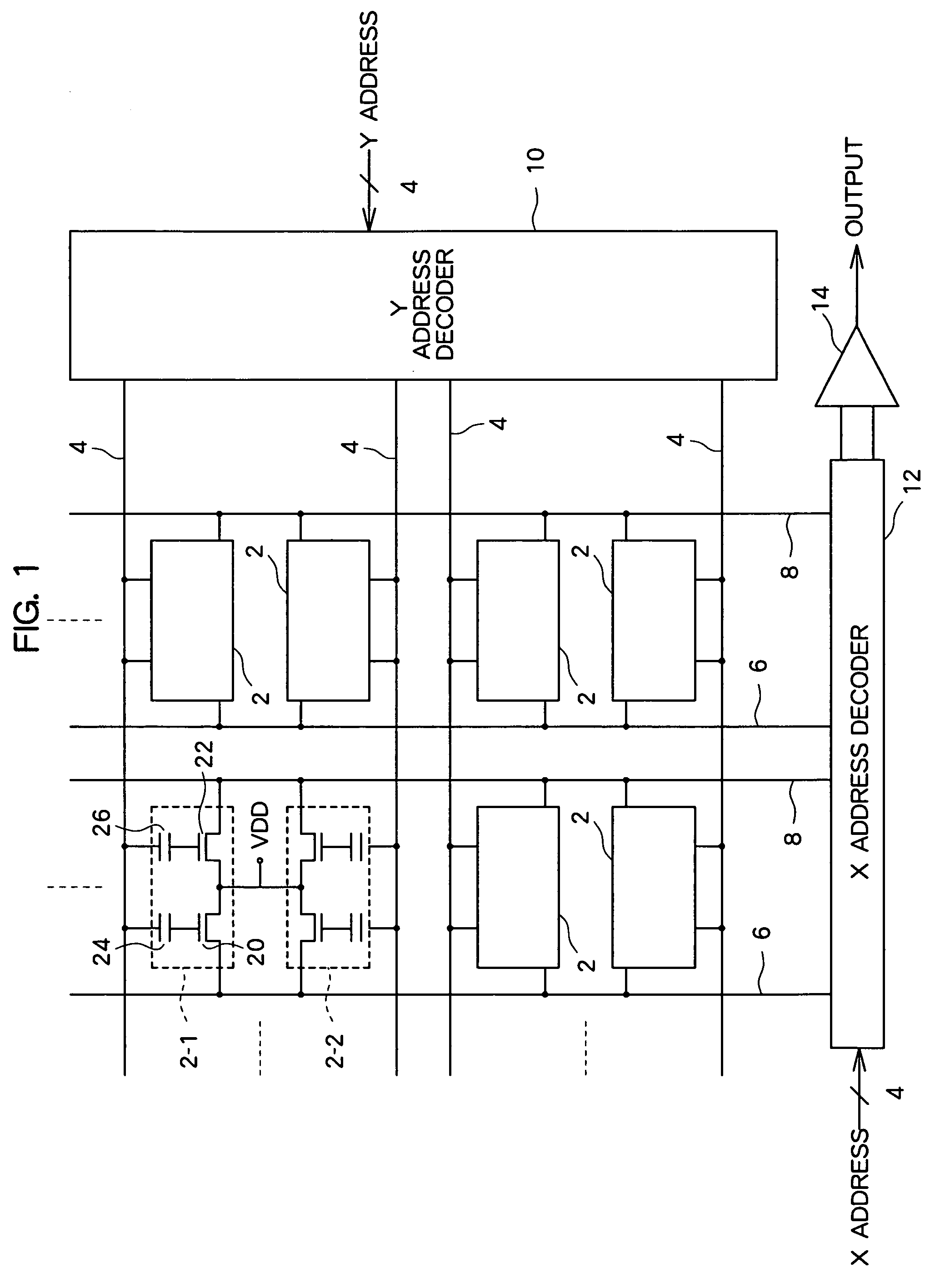

The present invention aims to eliminate variations in threshold voltage subsequent to the writing of data in an EPROM. When a parasitic resistance between the source of a memory cell (M00) of an even-numbered row and its corresponding bit line (BL0) is larger by a resistance (R00) than a parasitic resistance between the source of a memory cell (M01) of an odd-numbered row and its corresponding bit line (BL0), a cell resistance compensating unit (40) having a compensating resistor (43) whose resistance value is equal to the resistance (R00) is provided between the bit line (BL0) and a ground potential (GND). When the memory cell (M00) is selected by a drain cell power-supply switching address ( / AY0), a transistor (41) is turned on by the same signal ( / AY0). When the memory cell (M01) is selected by a drain cell power-supply switching address (AY0), a transistor (42) is turned on by the same signal (AY0). The resistor (43) is inserted for the transistor (42), and resistance values from the sources of the memory cells (M00, M01) to the ground potential (GND) become equal to each other. Thus, variations in threshold voltage subsequent to the writing of data can be suppressed.

Owner:OKI ELECTRIC IND CO LTD

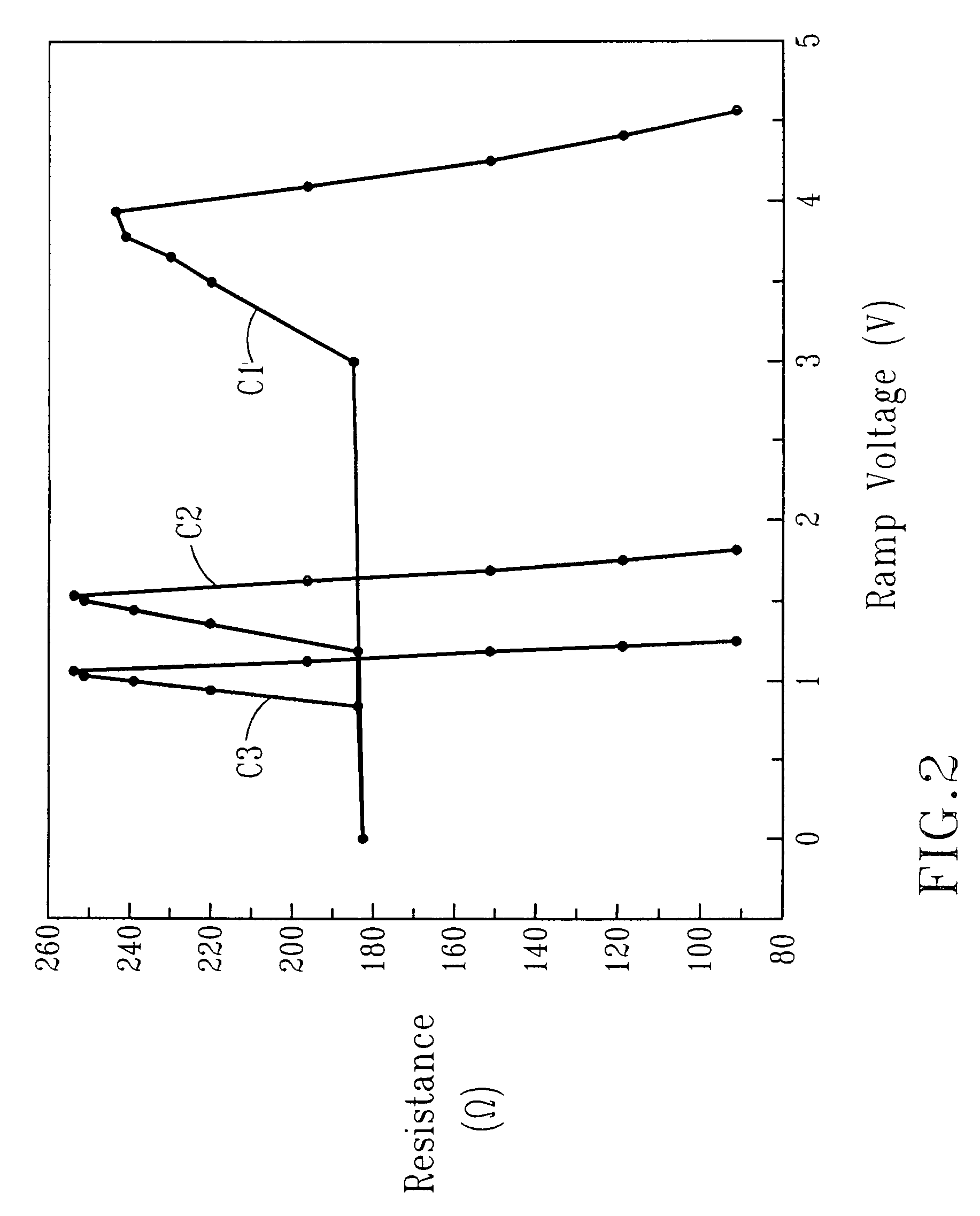

Phase-change TaN resistor based triple-state/multi-state read only memory

ActiveUS7381981B2Without consuming extra die surface areaIncrease information densitySolid-state devicesRead-only memoriesElectrical resistance and conductanceEPROM

The present invention relates to a nonvolatile memory such as, for example a ROM or an EPROM, in which the information density of the memory is increased relative to a conventional nonvolatile memory that includes two logic state devices. Specifically, the nonvolatile memory of the present invention includes a SiN / TaN / SiN thin film resistor embedded within a material having a thermal conductivity of about 1 W / m-K or less; and a non-linear Si-containing device coupled to the resistor. Read and write circuits and operations are also provided in the present application.

Owner:INT BUSINESS MASCH CORP

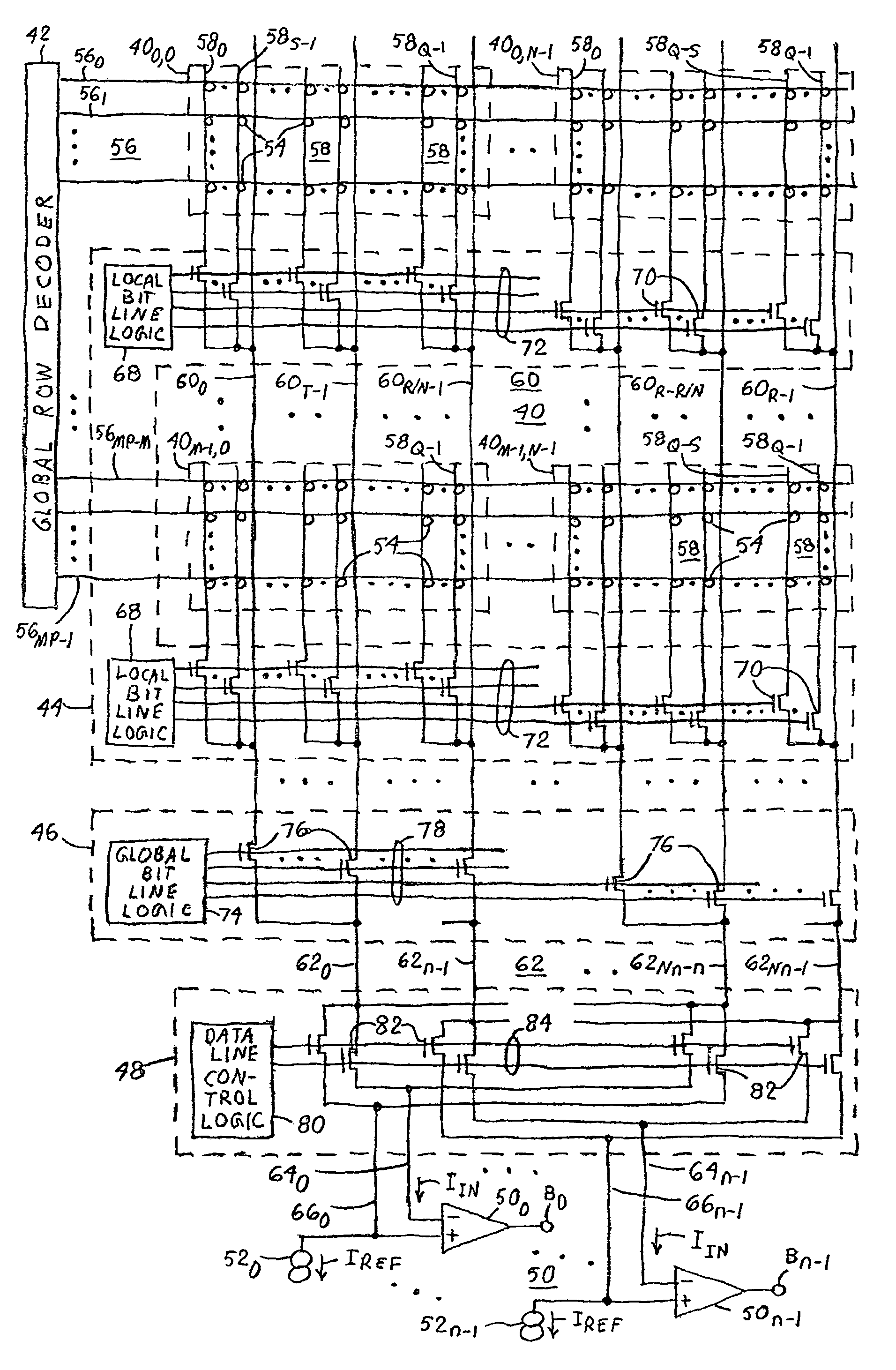

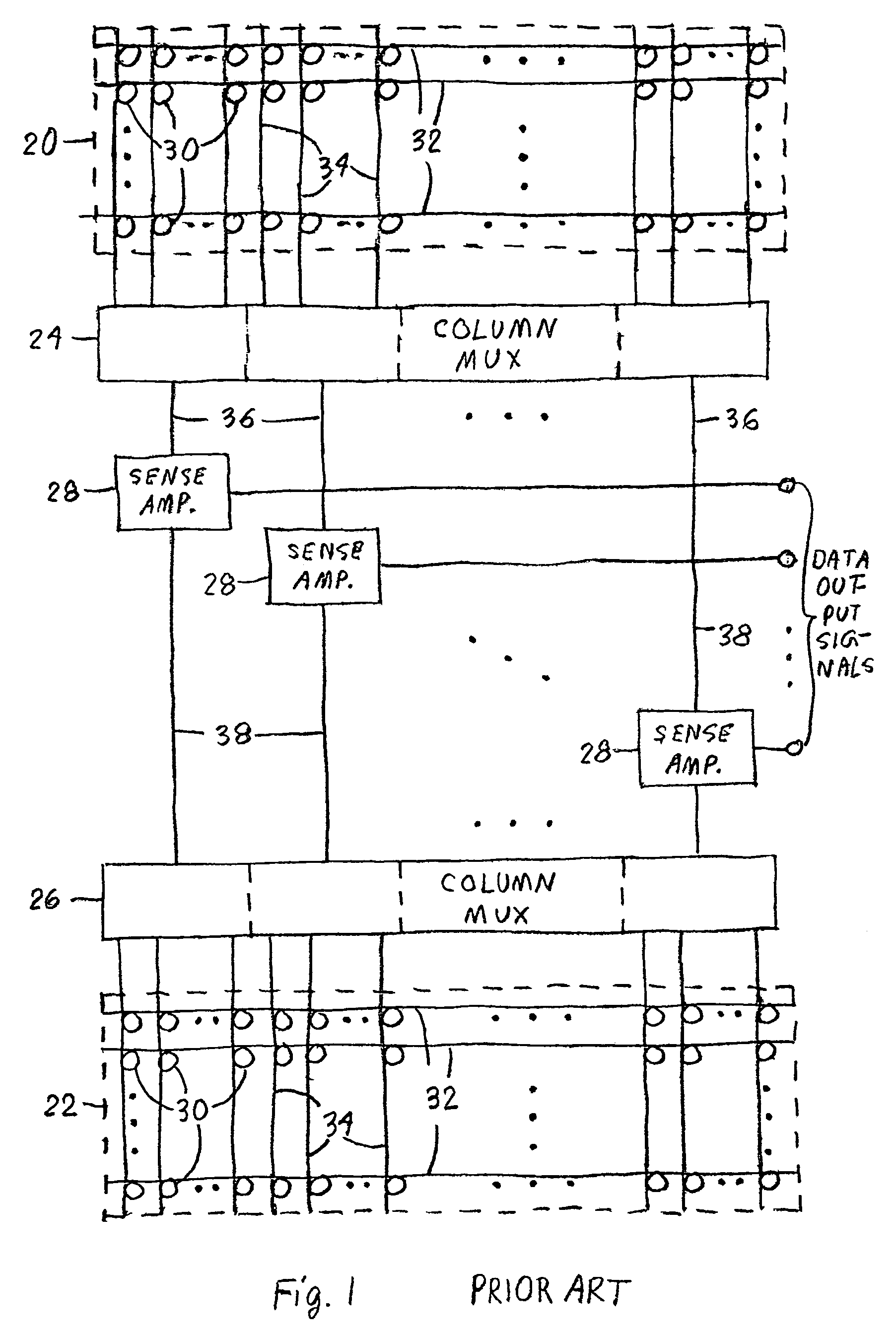

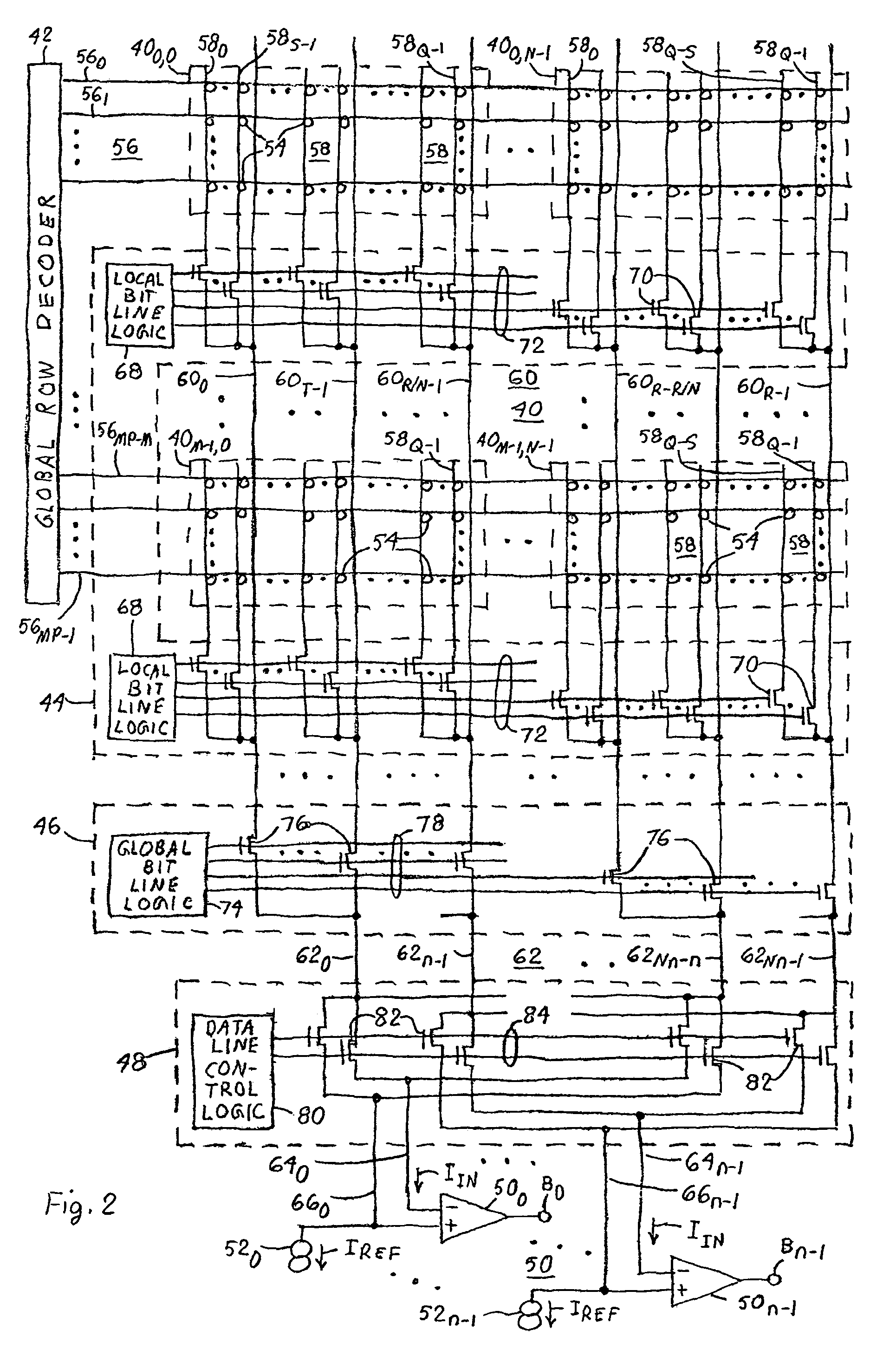

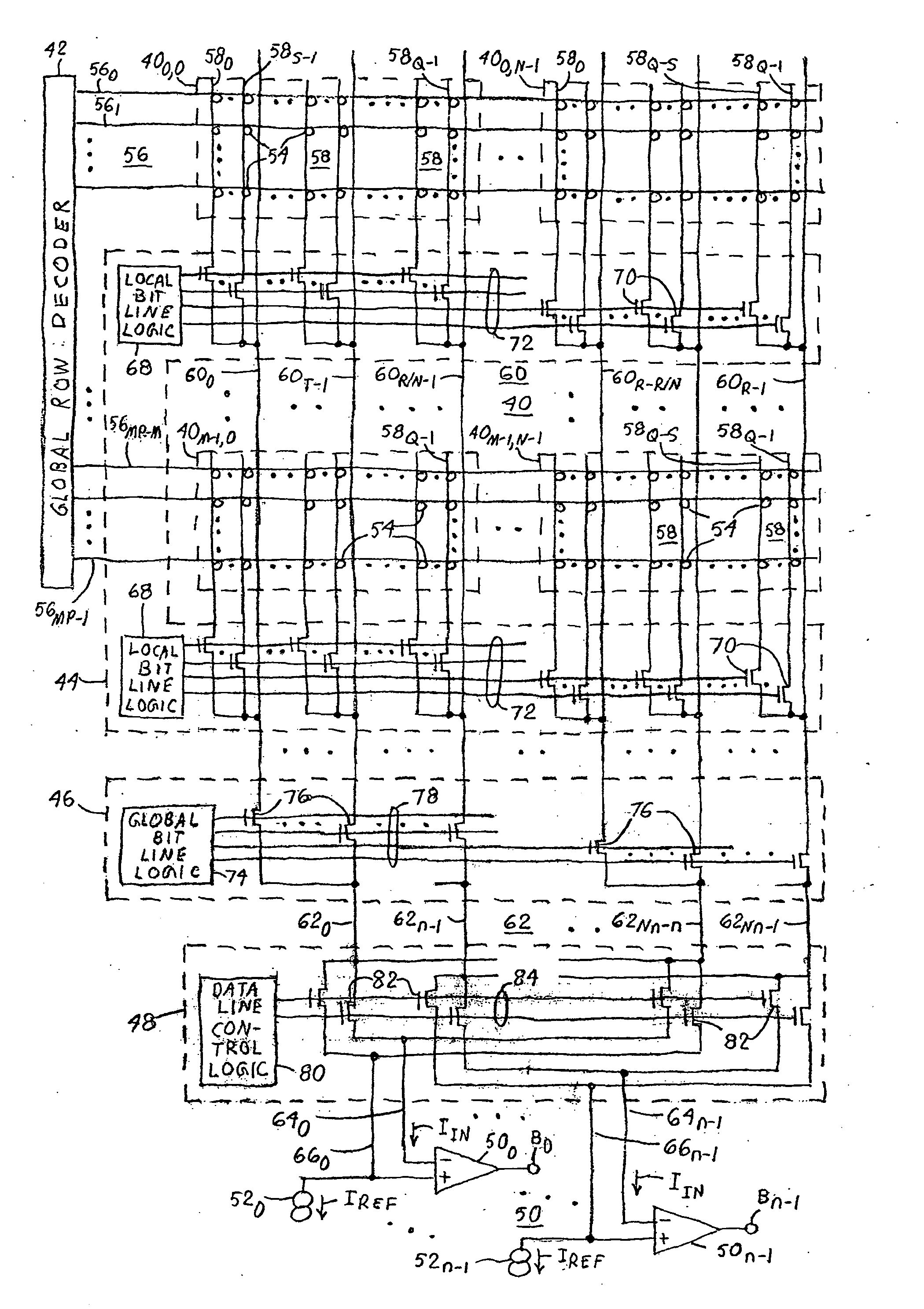

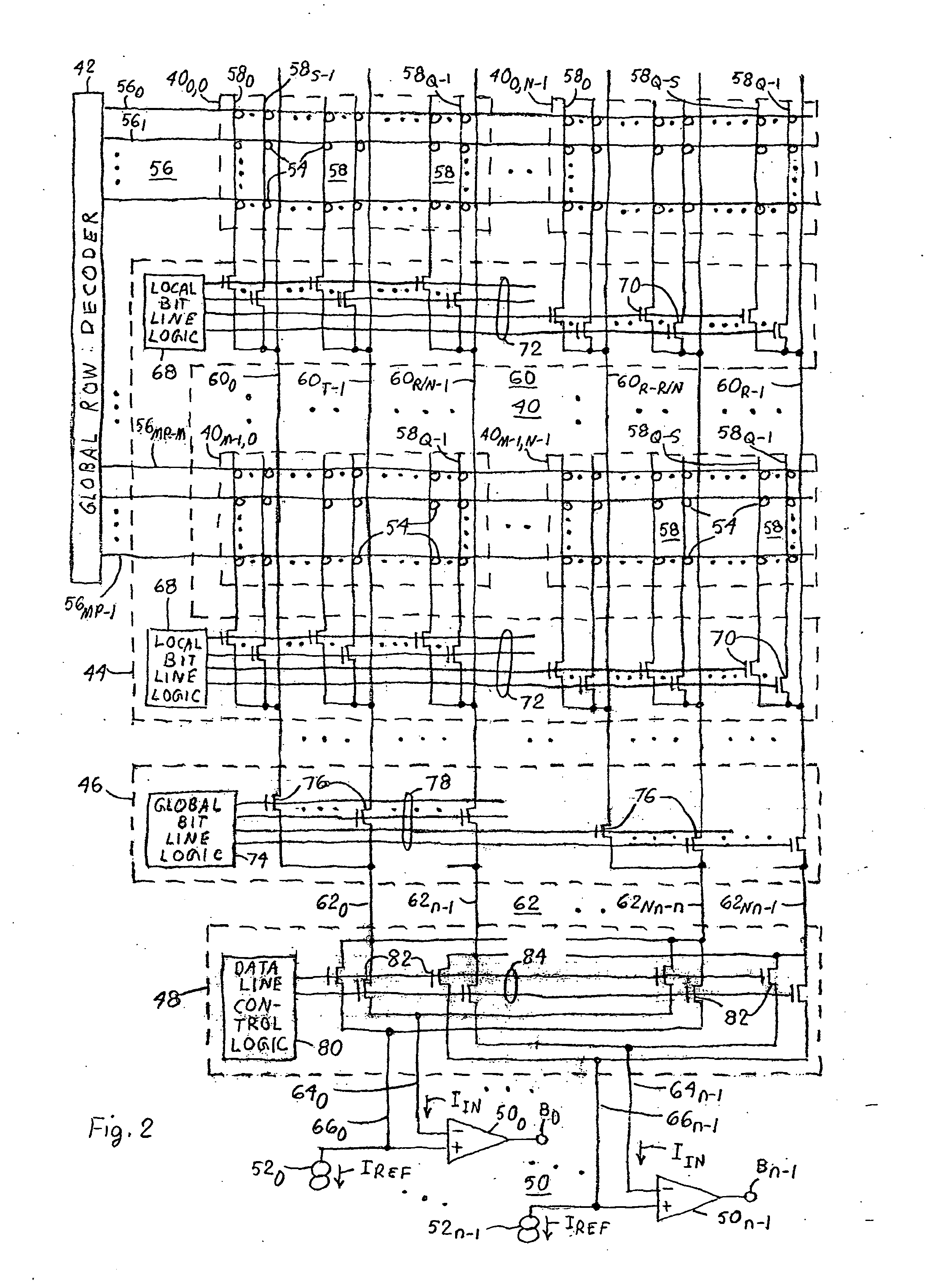

Electronic memory having impedance-matched sensing

InactiveUS7126853B2Accurate dataReduce sensitivityRead-only memoriesDigital storageLow noiseBit line

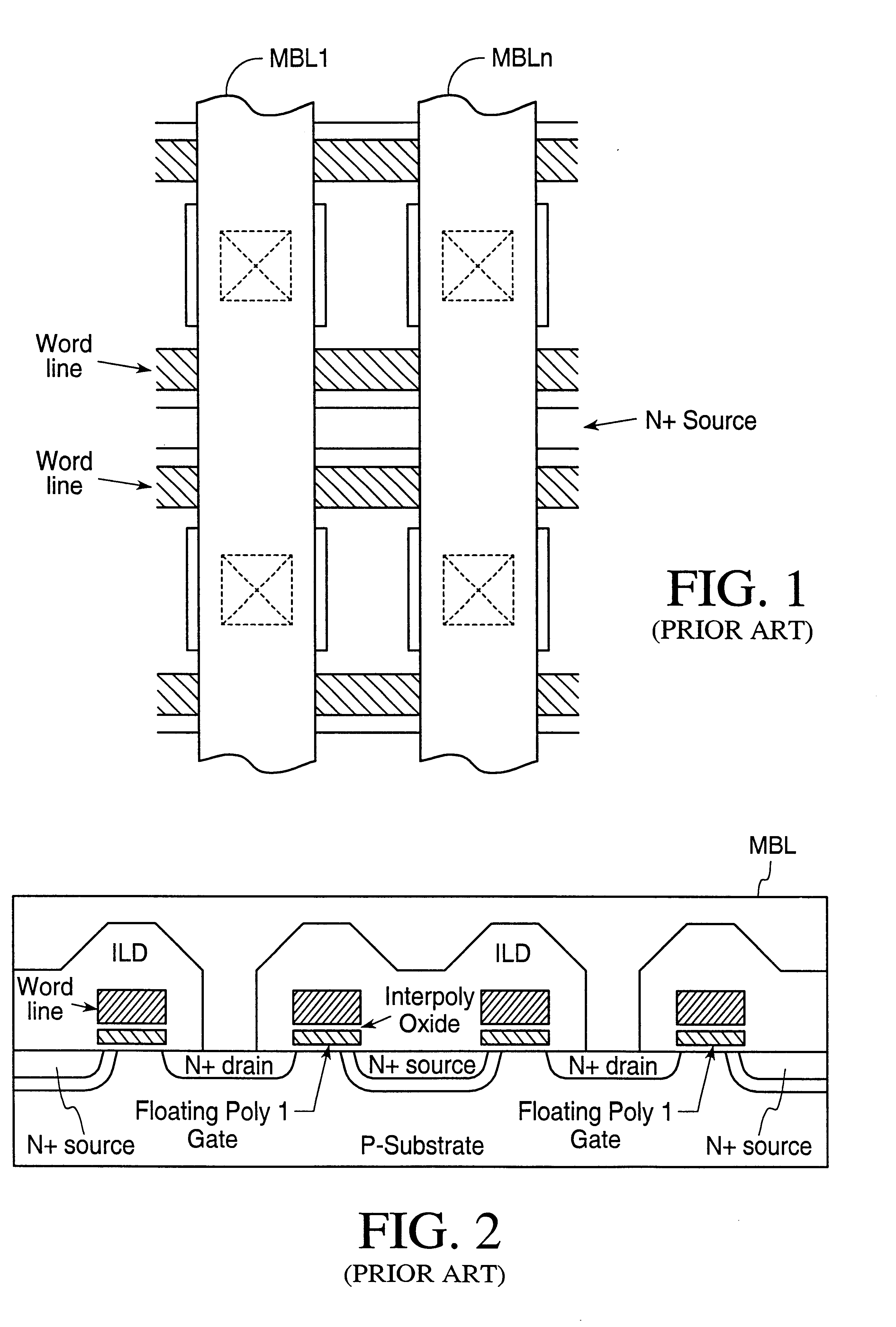

An electronic memory, typically a flash EPROM, contains an array of memory sections (40), each containing an array of memory cells (54). Global bit lines (60) fully traverse the memory. Local bit lines (58) partially traverse the memory. Data stored in the memory is sensed with an arrangement that utilizes impedance matching to achieve high sensing accuracy with low noise sensitivity. The impedance matching may be provided solely from the sections and lines of the memory or partially from a separate reference memory section (102) that contains reference memory cells (104).

Owner:PROMOS TECH INC

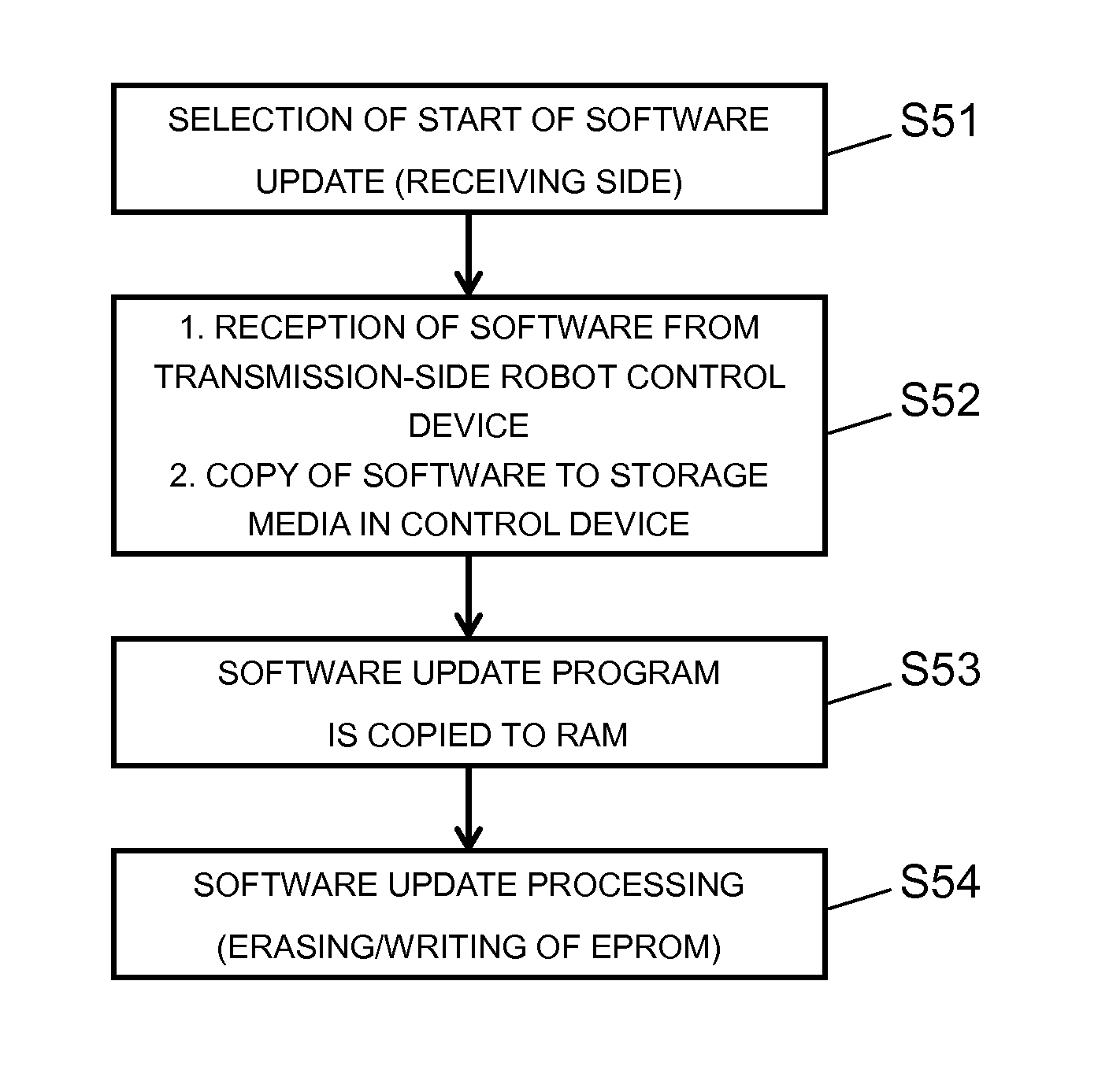

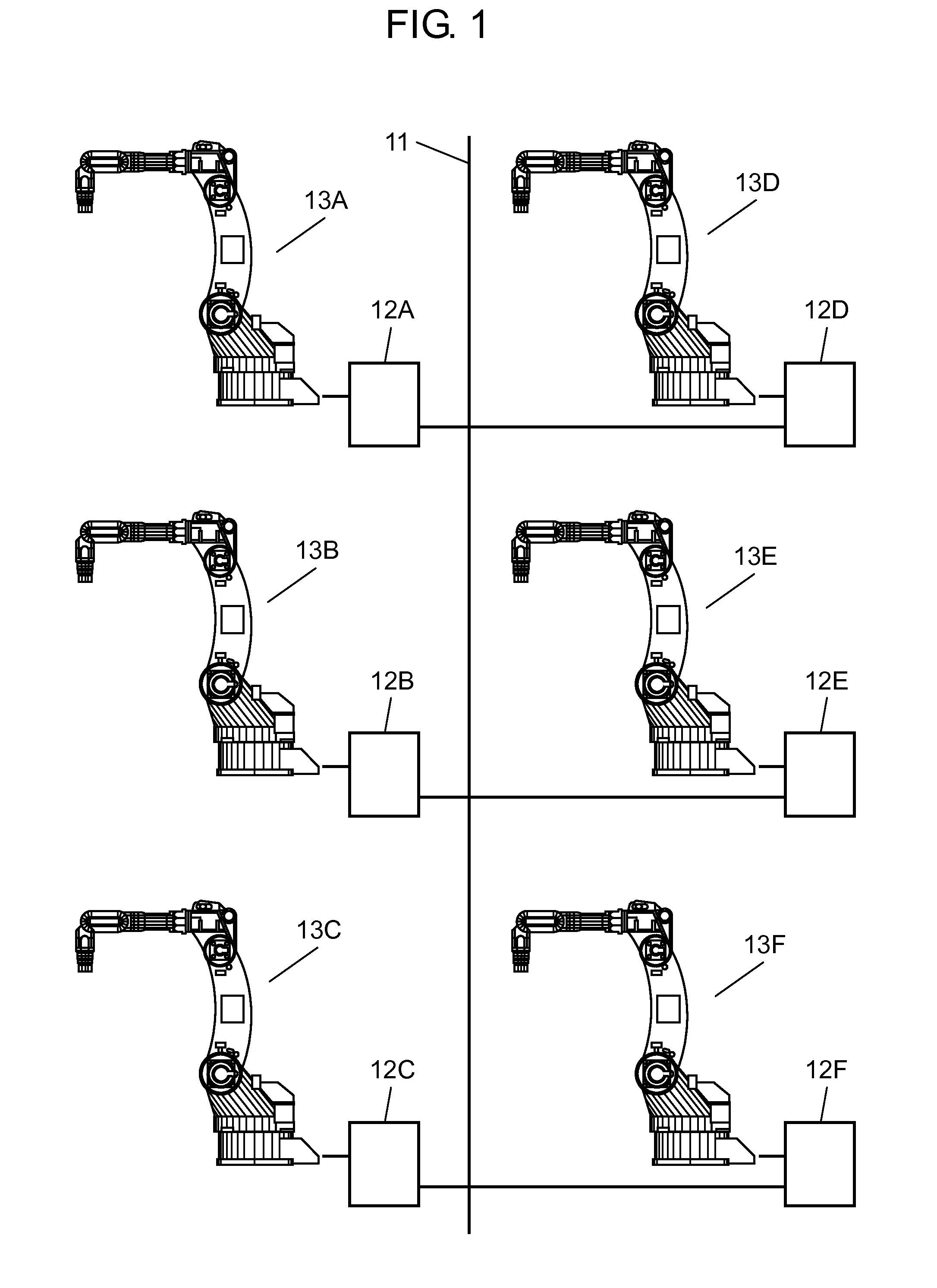

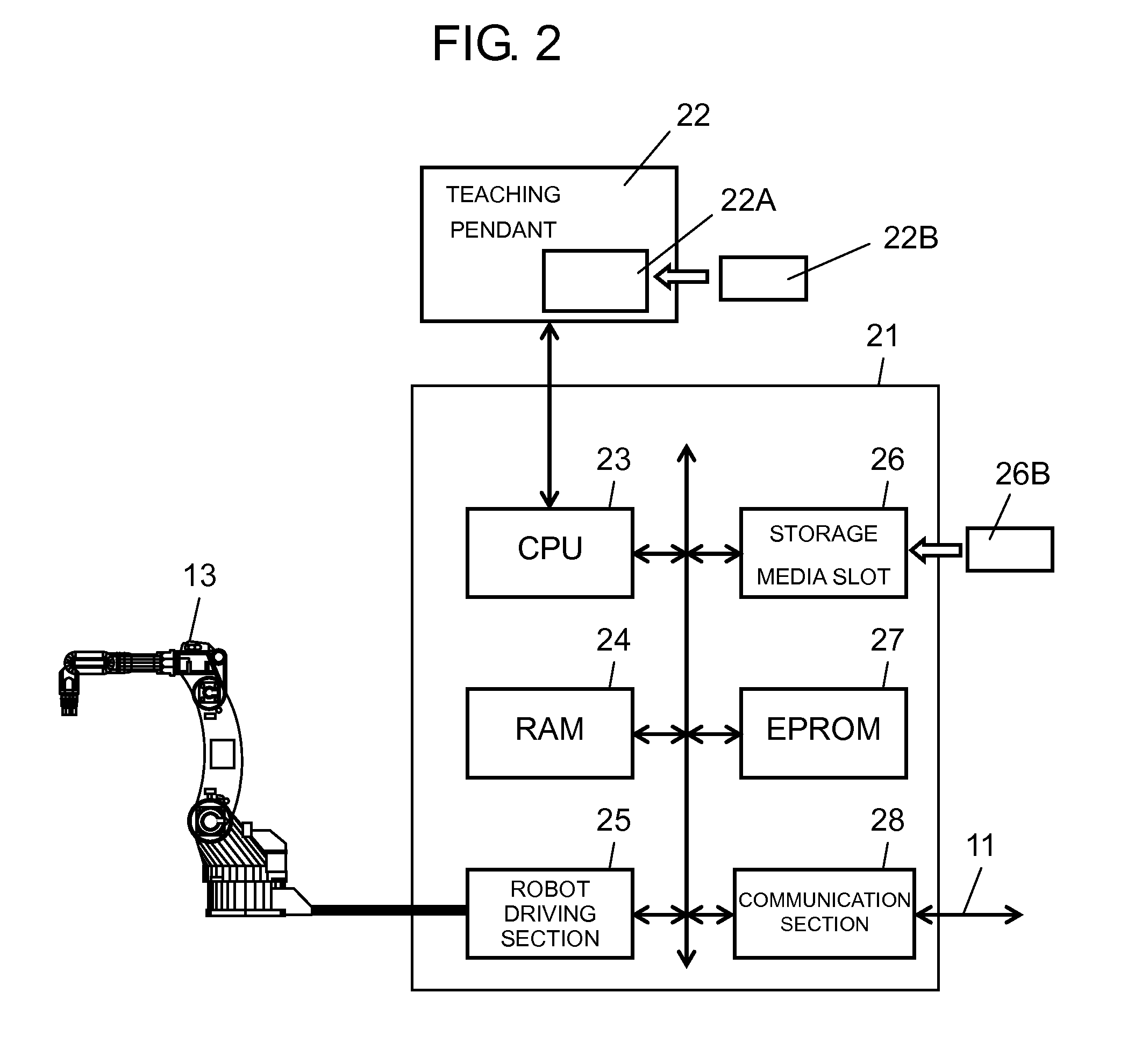

Robot system, robot control device, and software update method of robot system

InactiveUS20100325623A1Increase speedHigh-speed performanceProgramme-controlled manipulatorSpecific program execution arrangementsRobotic systemsEPROM

A transmission-side robot control device (21) and a receiving-side robot control device (21) each include an EPROM (27) which stores a software update program and robot motion control software, a RAM (24) which stores the software update program read from the first storage section (27), and storage media (26B) which stores update software. An external terminal or a host computer for software update is not needed, and a plurality of robot control devices can be standardized to have even an old version. It is not necessary to check a version currently stored, and the update can be performed at high speed.

Owner:PANASONIC CORP

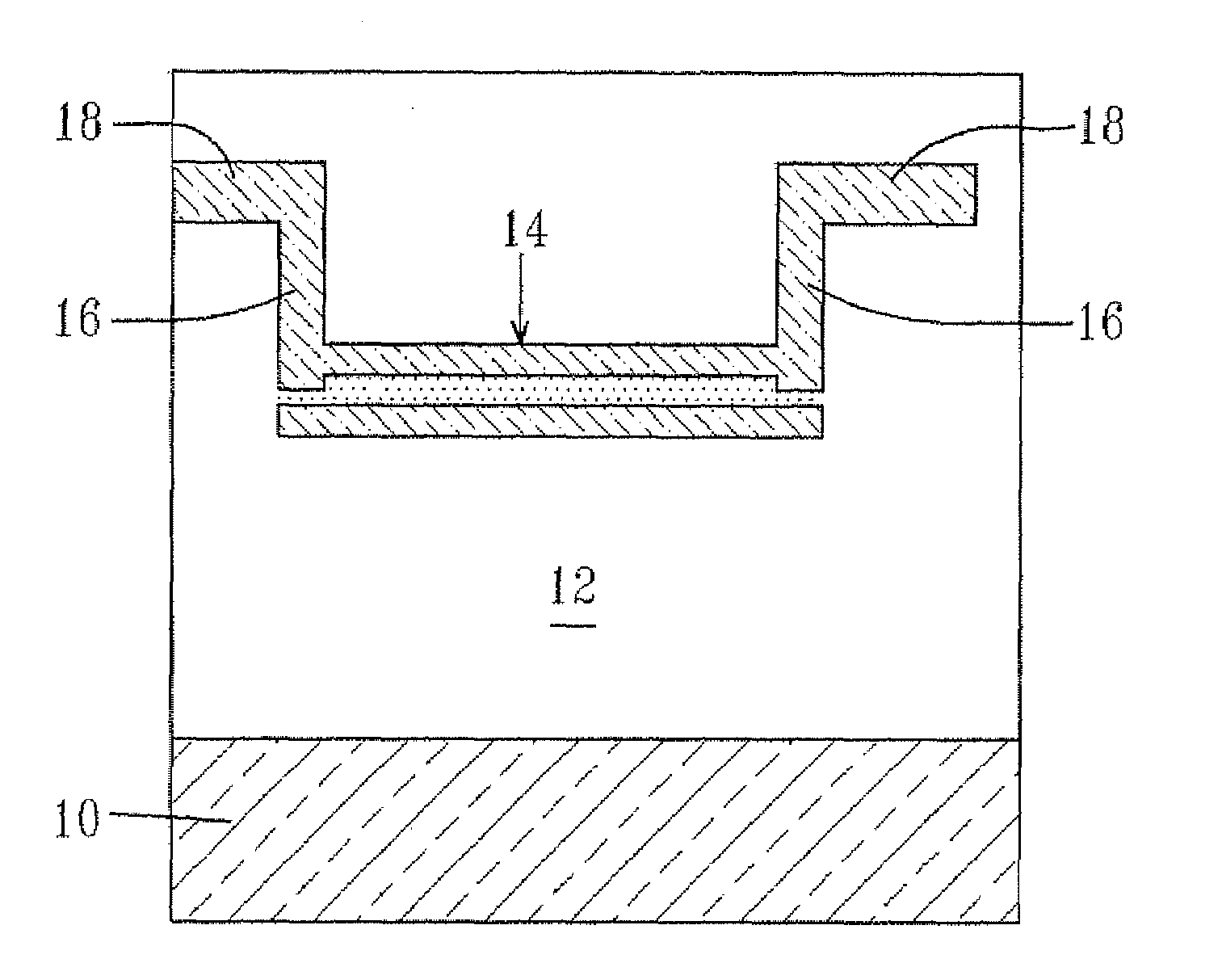

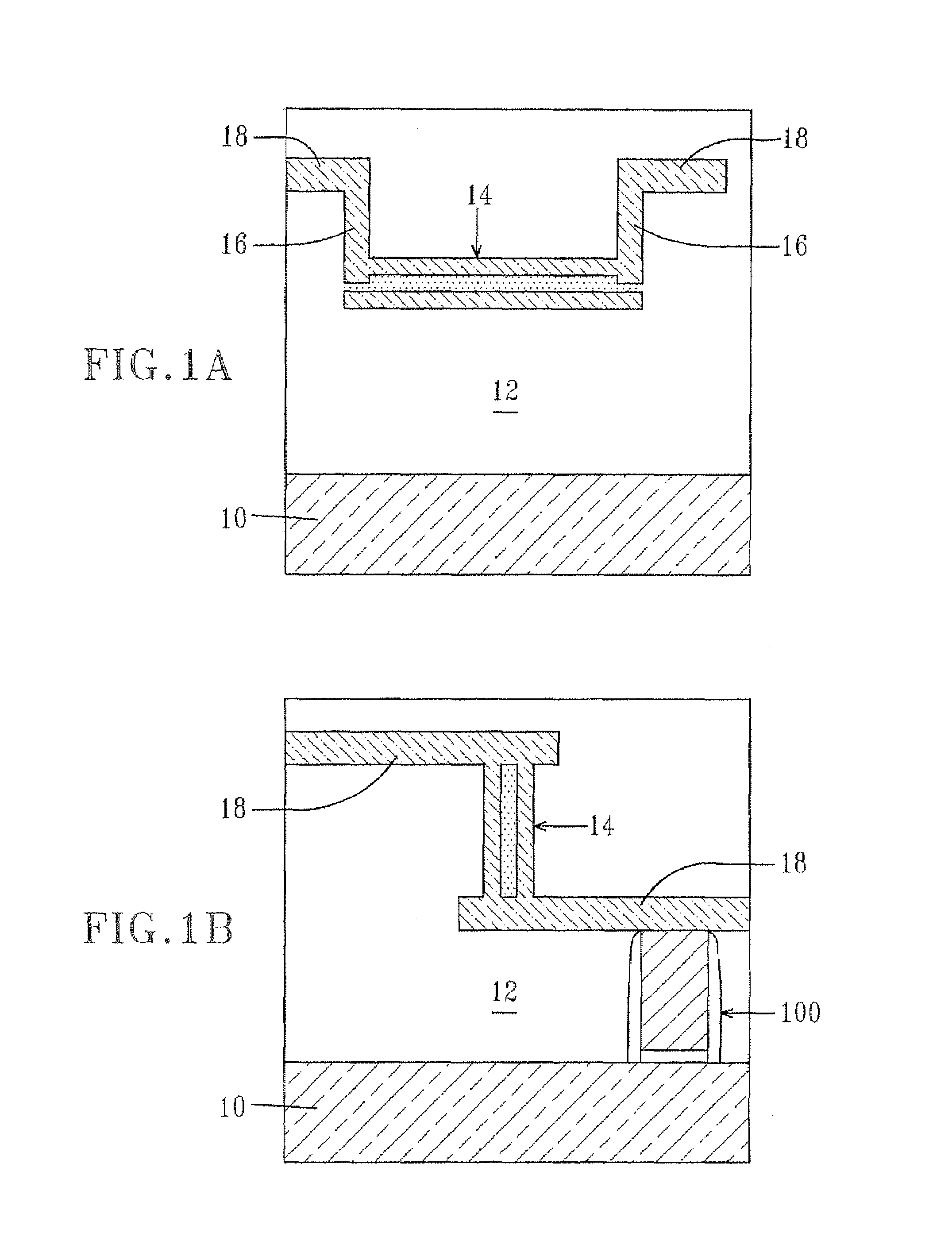

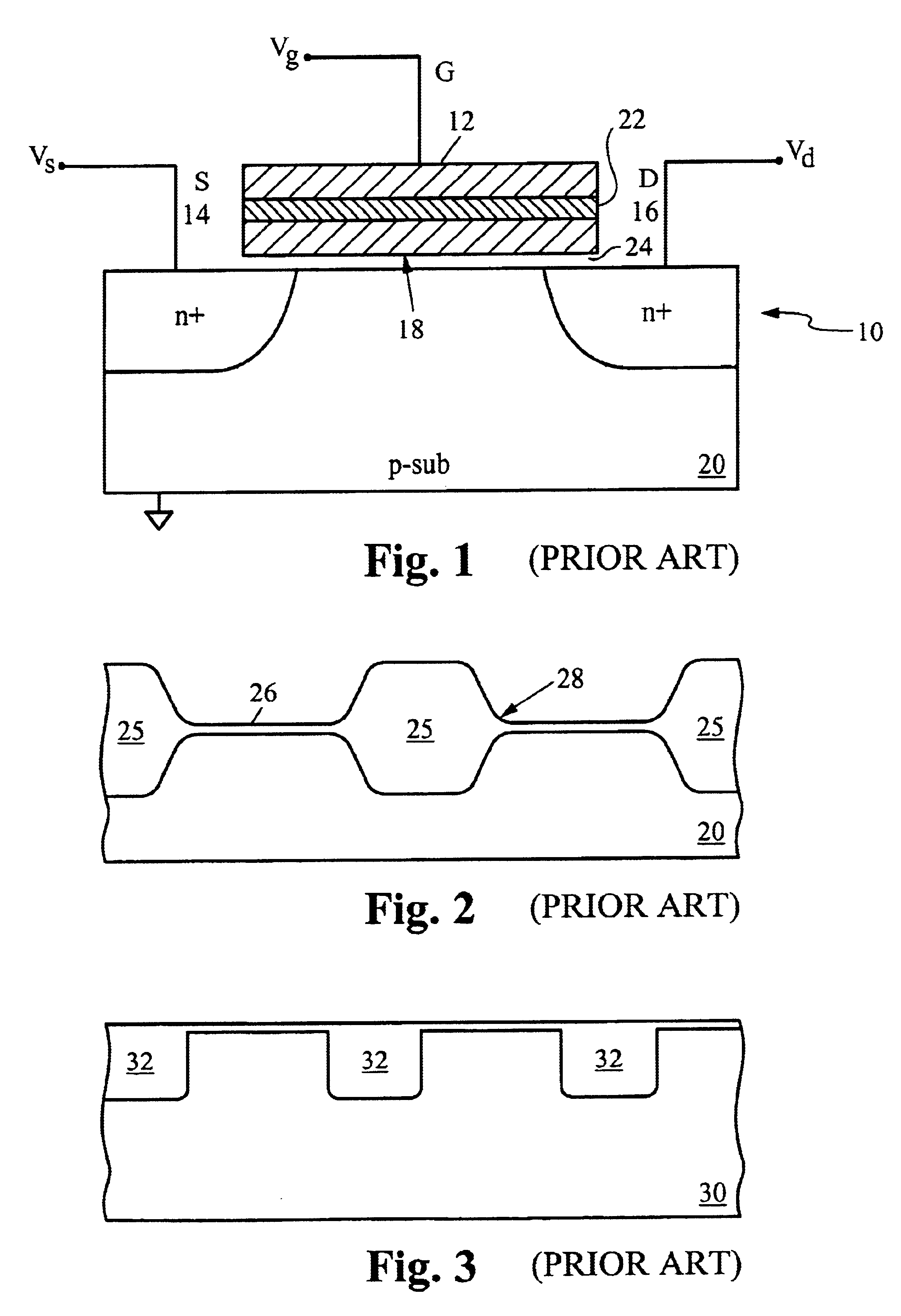

Single poly EPROM cell having smaller size and improved data retention compatible with advanced CMOS process

Leakage of a single-poly EPROM cell is prevented by eliminating field oxide isolating the source, channel, and drain from the control gate n-well, and by replacing field oxide surrounding the cell with a heavily doped surface isolation region. The EPROM cell also utilizes a floating gate having an open-rectangular floating gate portion over the control gate region, and a narrow floating gate portion over the channel and intervening silicon substrate. The surface area of the open-rectangular floating gate portion ensures a high coupling ratio with the control gate region. The small width of the narrow floating gate portion prevents formation of a sizeable leakage path between the n-well and the source, channel, and drain. To conserve surface area, the EPROM cell also eliminates the p+ contact region and the PLDD region in the control gate well of the conventional EPROM design. This is permitted because the VTp implant step is masked, permitting the control gate region to operate in accumulation mode during application of 5V programming voltages.

Owner:NAT SEMICON CORP

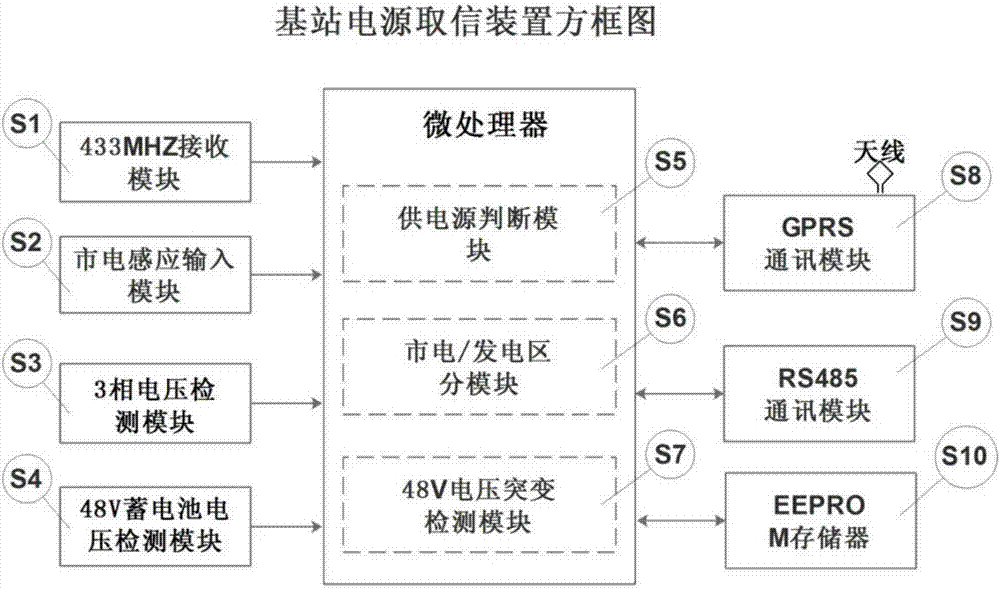

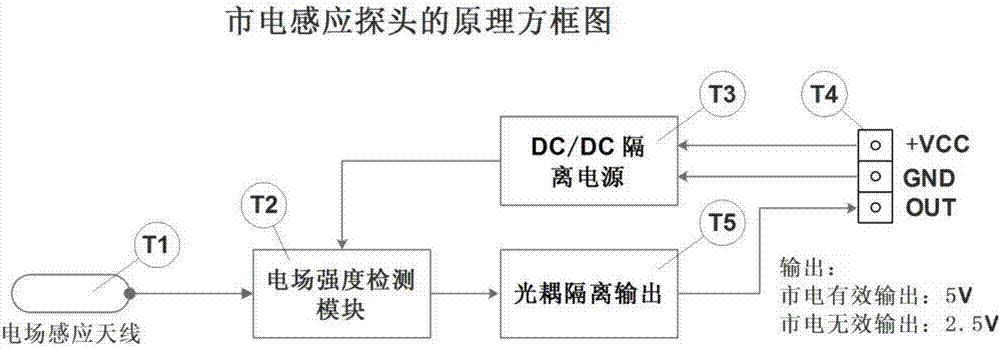

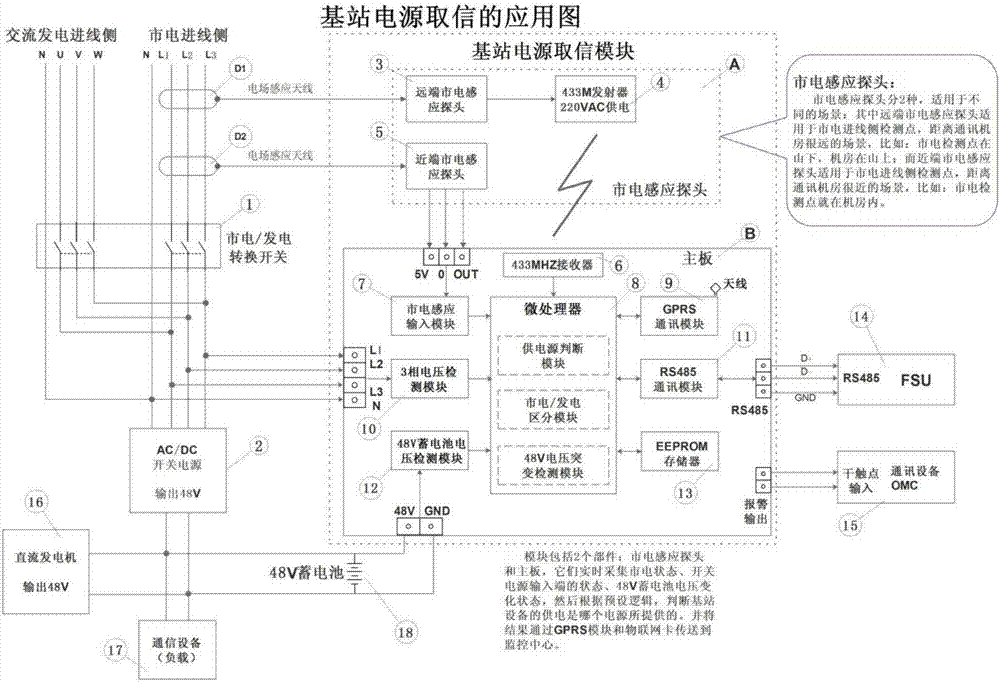

Method and device for monitoring communication base station power supply state

PendingCN107091995APrevent false billingAvoid interferenceSpectral/fourier analysisFrequency measurement arrangementEPROMHarmonics

The invention discloses a method and device for monitoring communication base station power supply state. The method and device comprises a mains supply inductive probe, a three-phase alternating voltage detection module, a 48 V accumulator voltage detection module, a power supply judgment module and a GPRS communication module. The power supply judgment module is characterized in that through detection of the jitter rate of alternating voltage frequency and the harmonic wave amplitude and the mains supply state of the incoming line side of an AC / DC switch power, whether the base station power supply is a mains supply or an electricity generator or a suspected mains supply is judged, the power supply starting and ending moments of different powers are judged through detection of 48 V accumulator voltage mutation direction, and whether or not the voltage of the mains supply input side is abnormal is detected through the mains supply inductive probe; whether the current power supplying for a base station is a mains supply or an alternating current generator or a direct current generator or an accumulator and the corresponding power supply starting and ending time are precisely monitored, and the monitoring results are stored in an EPROM and transmitted to a cloud server of a mobile oil engine management system for data statistics through the GPRS communication module.

Owner:DONGGUAN TUANCHENG AUTOMATION EQUIP CO LTD

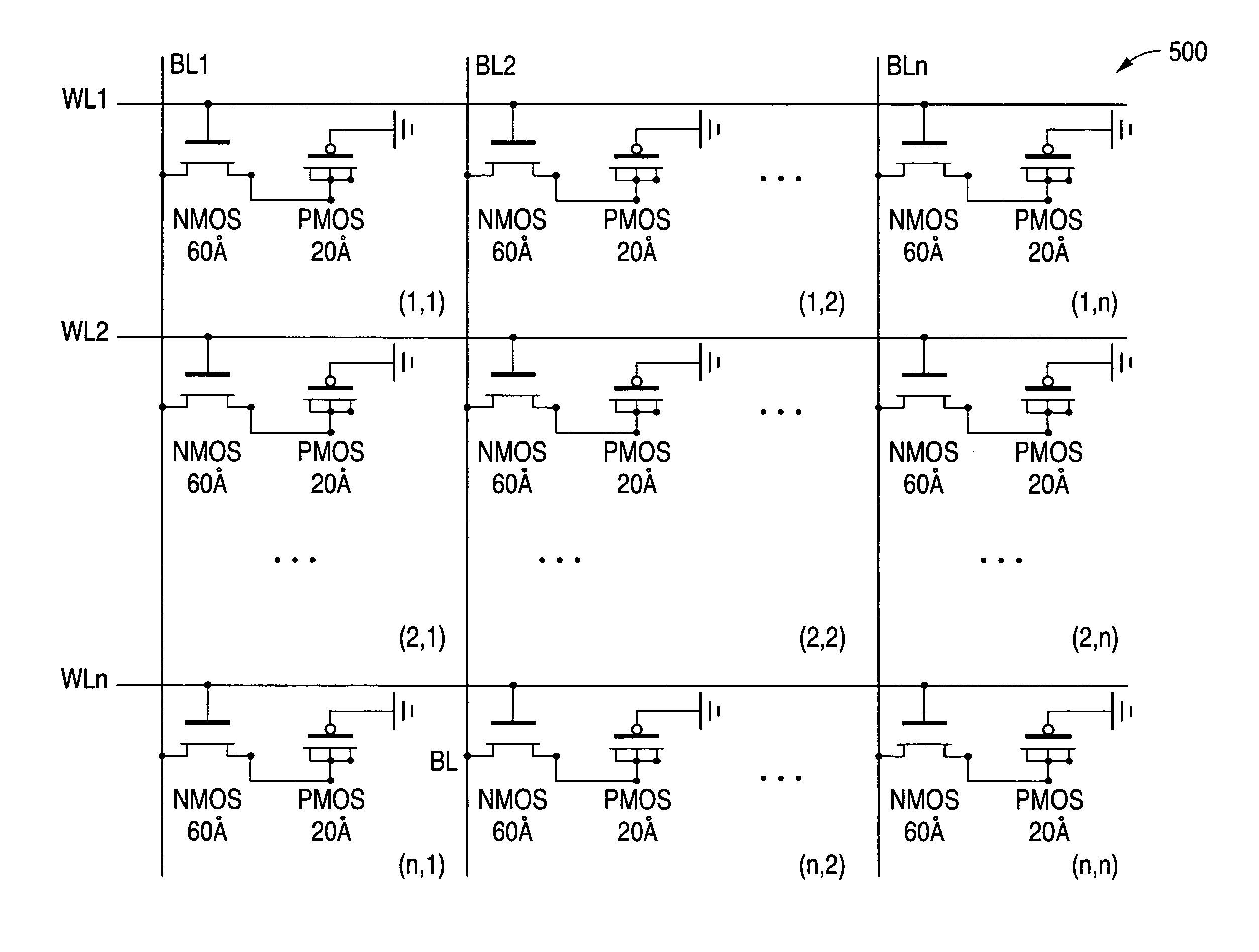

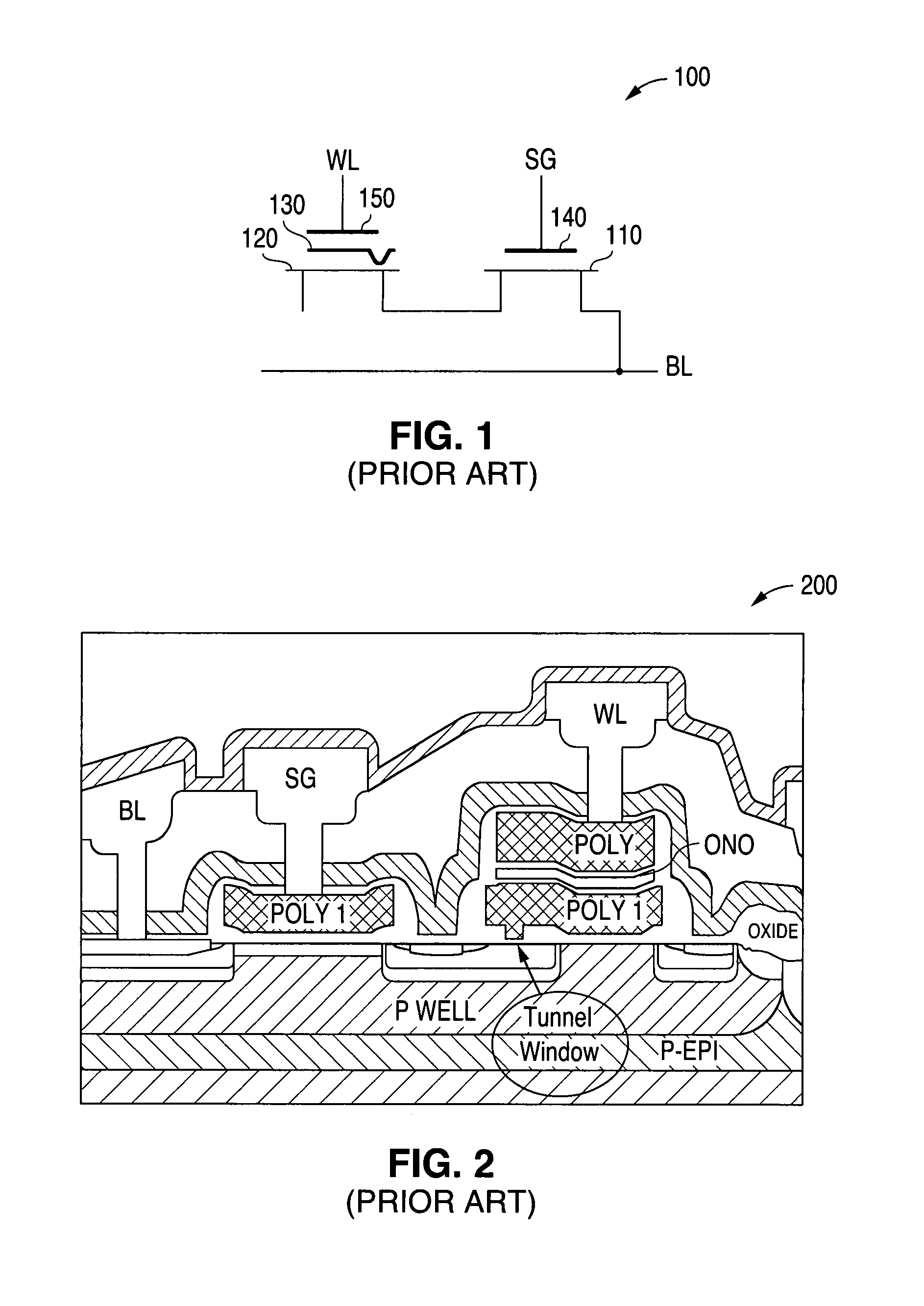

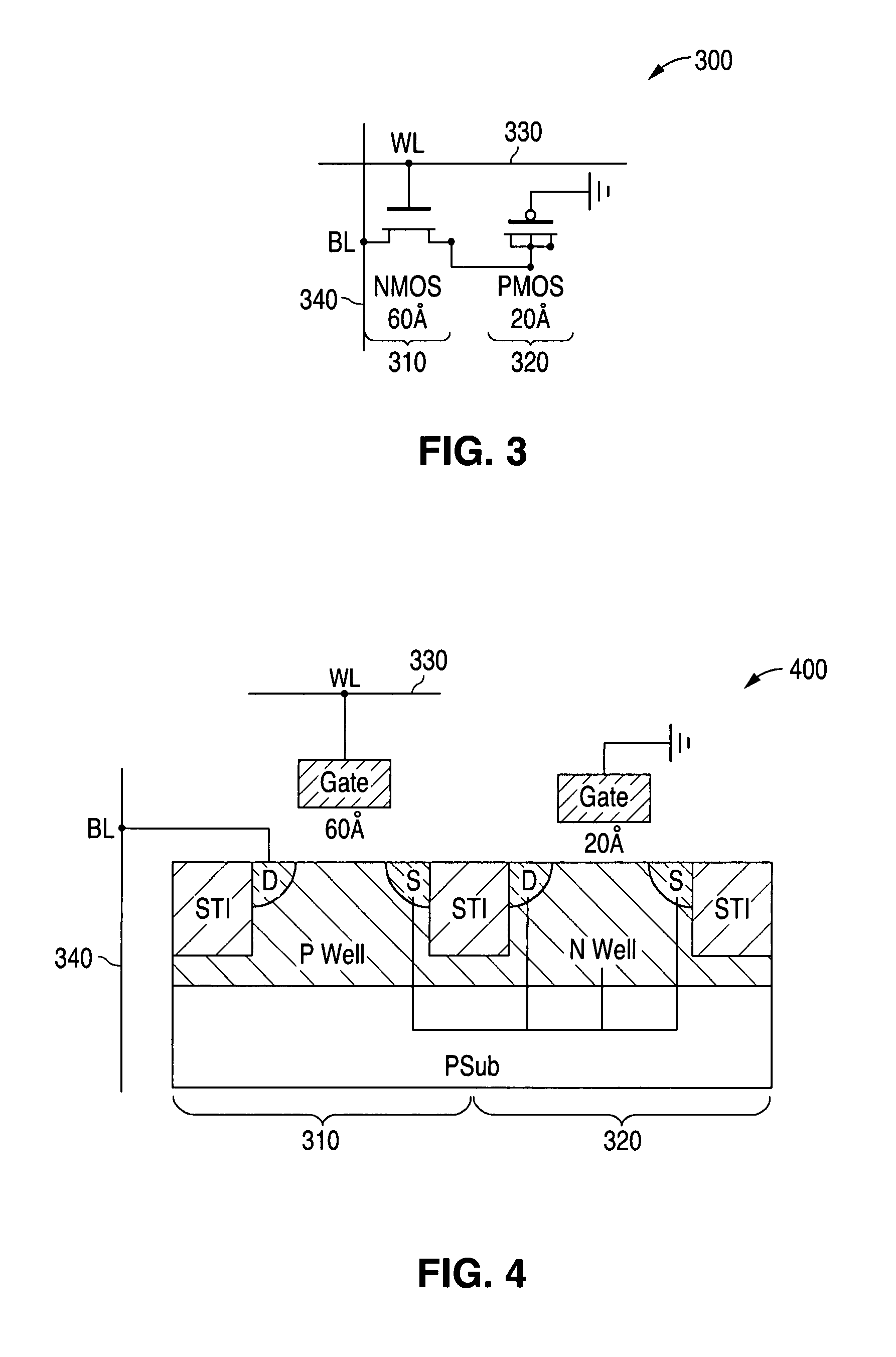

System and method for providing an EPROM with different gate oxide thicknesses

A system and method are disclosed for providing an electrically programmable read only memory (EPROM) in which each memory cell comprises an NMOS select transistor with a thick gate oxide and a PMOS breakdown transistor with a thin gate oxide. The source of the NMOS transistor and the source, drain and N well of the PMOS transistor are connected. The gate of the PMOS transistor is grounded. Under the control of the NMOS transistor, a programming voltage pulse is passed to the N well of the PMOS transistor of a selected memory cell. The magnitude of the voltage is sufficient to break the thin gate oxide of the PMOS transistor without damaging the NMOS transistor. Because the memory state of the memory cell depends on the breakdown status of the PMOS transistor, the data may be retained in the memory cell for an unlimited period of time.

Owner:NAT SEMICON CORP

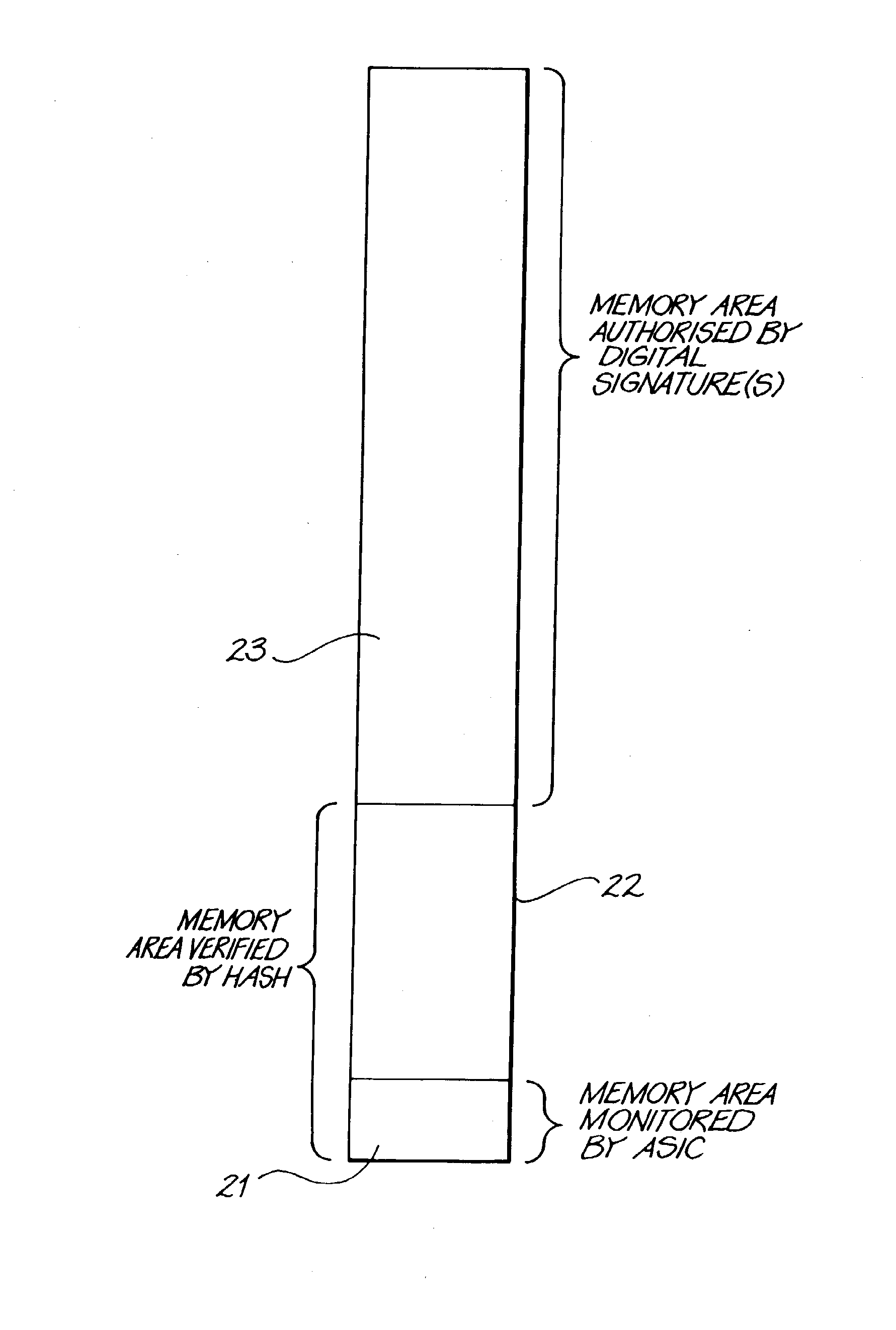

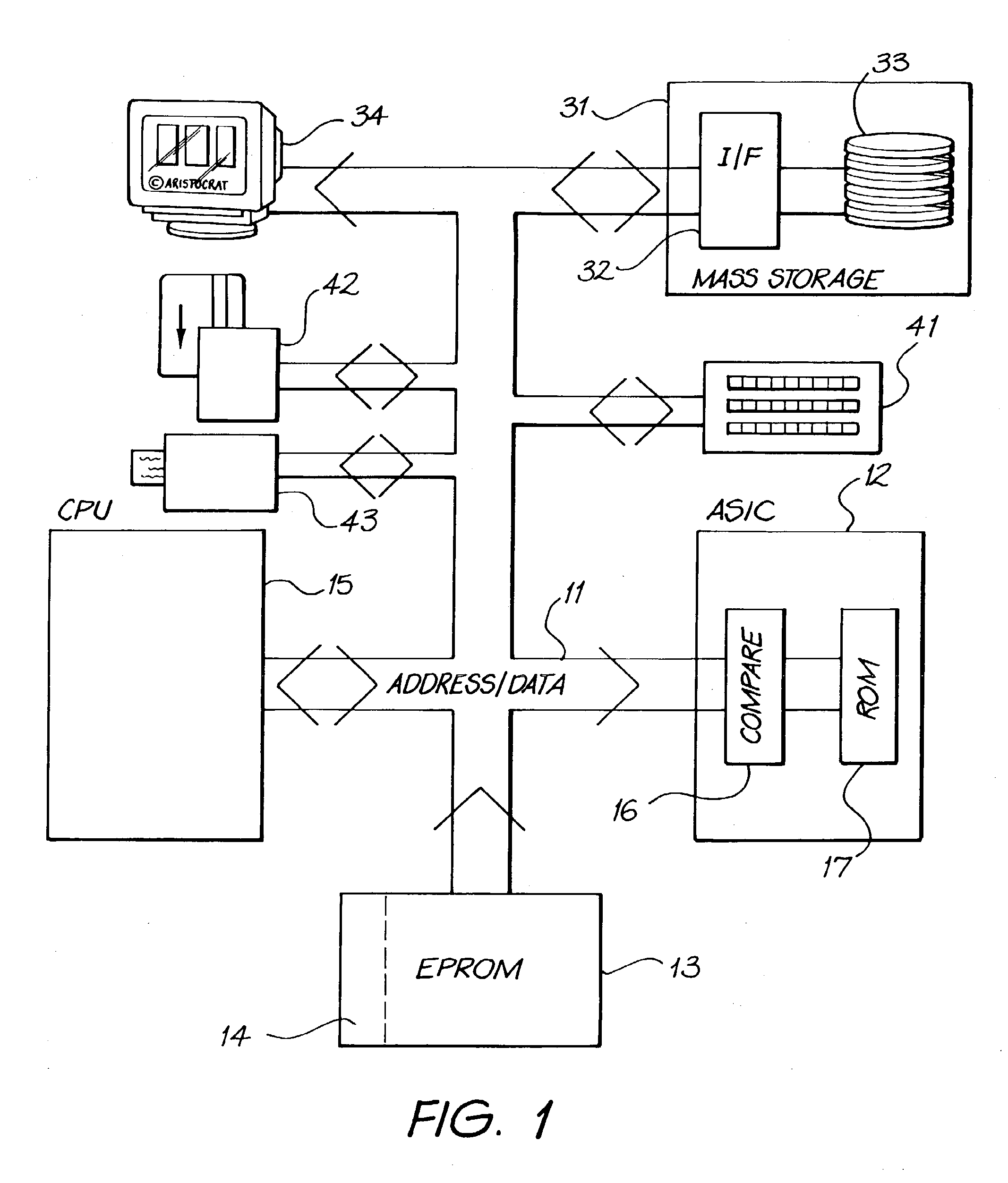

Gaming Security System

InactiveUS20120272071A1Implement securityImprove securityIndoor gamesMemory loss protectionEPROMCritical function

Verification of software to be run in a secure environment is performed by comparing a critical portion of the executable boot program code in an EPROM with code stored in a logic circuit. The comparison may be performed before the code to be verified is run or while it is running. in the event that the validation fails certain critical functions of the platform are inhibited to prevent fraudulent operation of the platform. The system is particularly applicable to gaming machines to avoid cheating.

Owner:ARISTOCRAT TECH AUSTRALIA PTY LTD

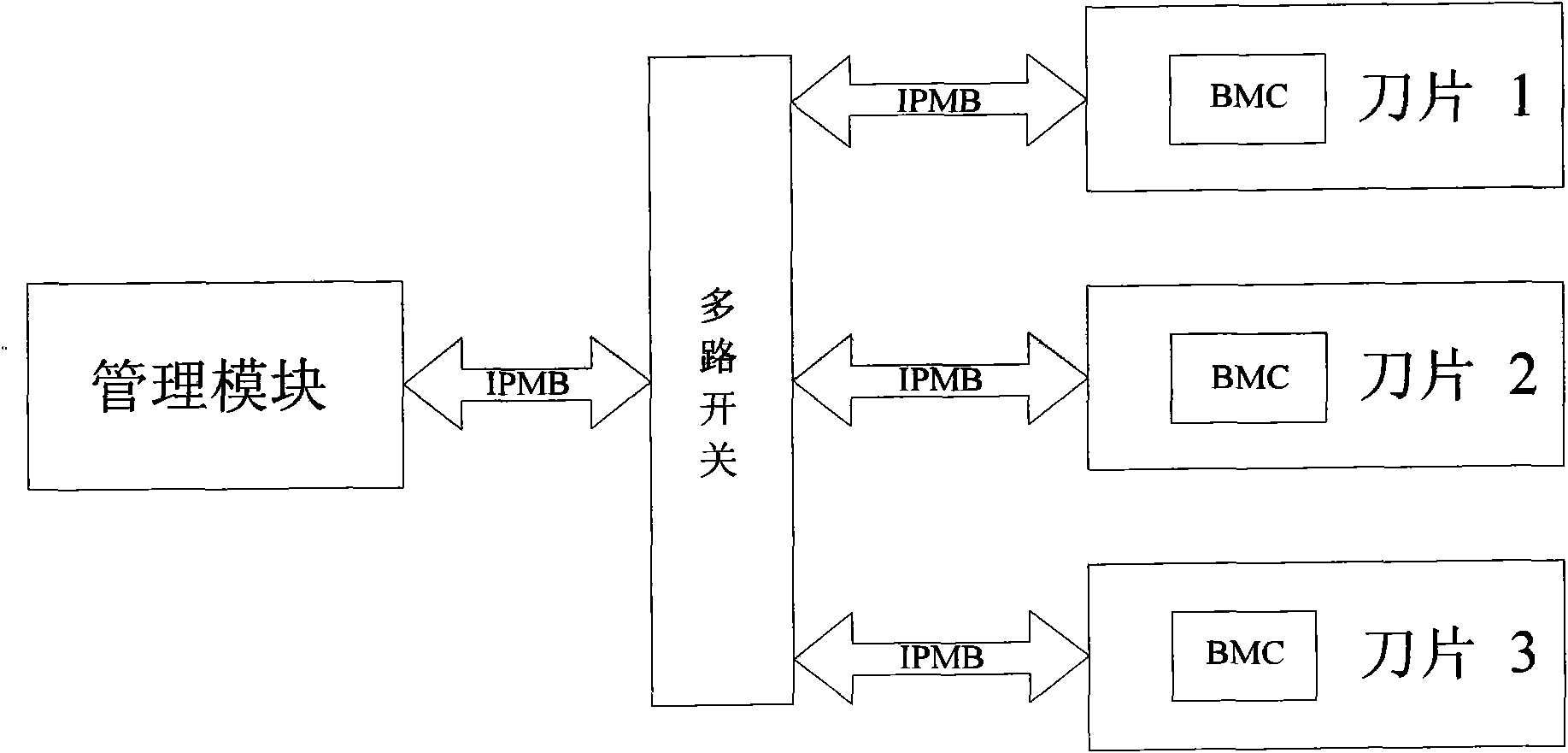

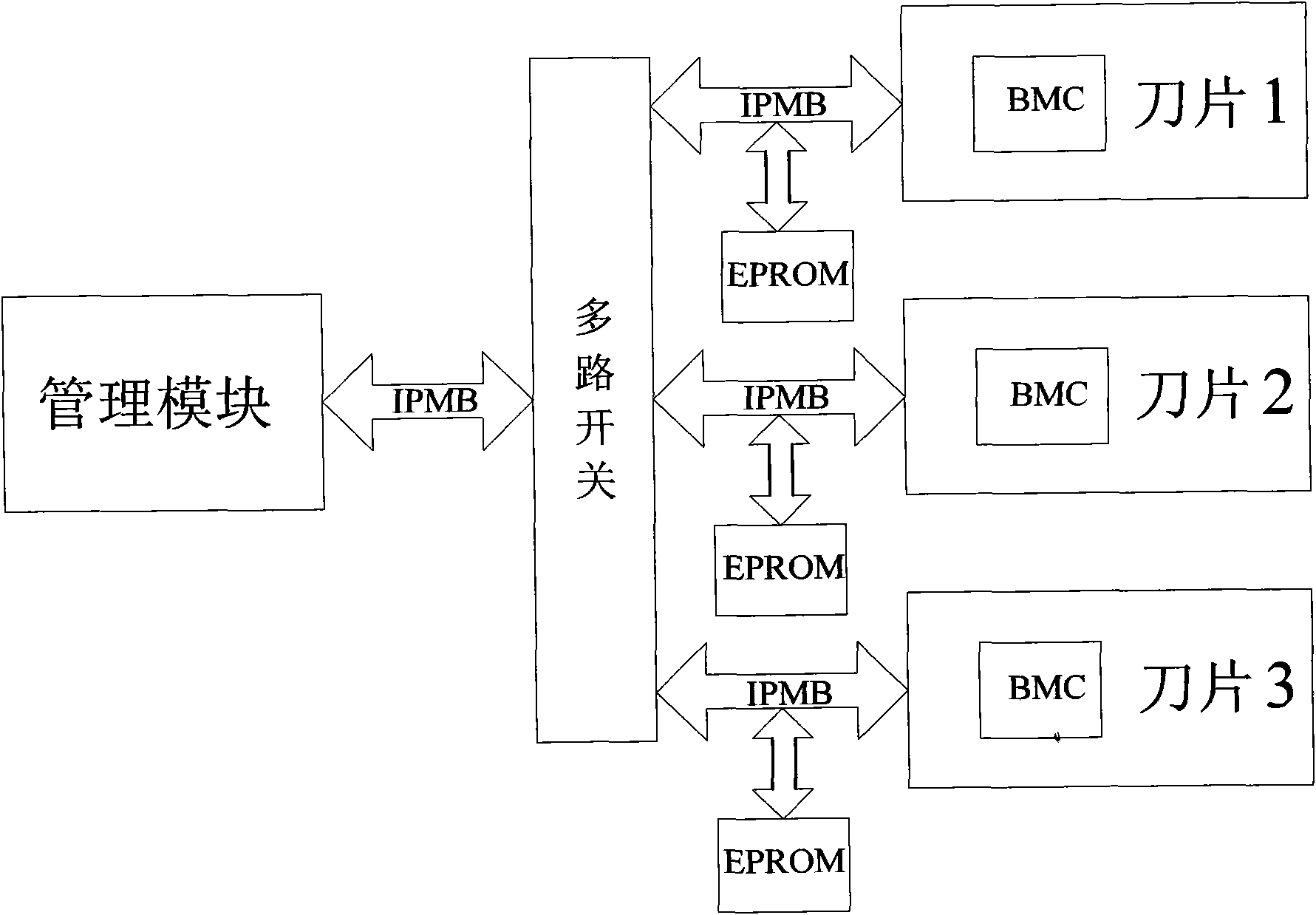

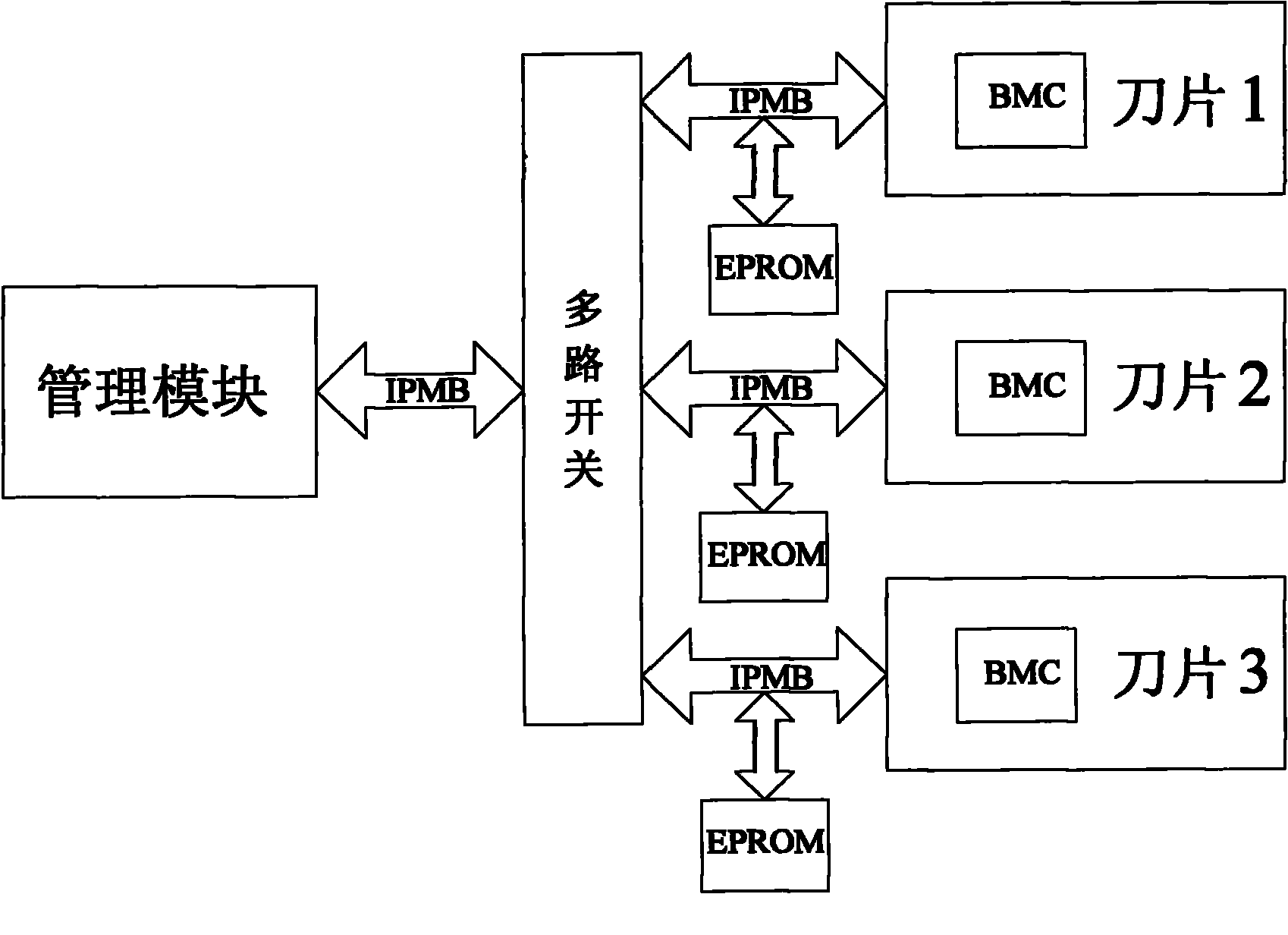

Method for determining intelligent platform management bus (IPMB) addresses of block multiplexer channels (BMC) of blade servers

InactiveCN101980180AFlexible modificationImprove securityElectric digital data processingProgrammable read-only memoryEPROM

The invention discloses a method for determining the IPMB addresses of BMCs of blade servers and belongs to the technical field of blade server communication. The method adopts a structure which comprises management module and blade servers, wherein the management module performs data interaction with the BMC of each blade server through an IPMB bus. The structure is characterized in that: each IPMB bus is provided with an electrically programmable read-only-memory (EPROM) for storing the IPMB address of the BMCs of the blade servers; the management module writes the specified IPMB addresses of the BMCs of the blade servers in the EPROMs in the buses when starting for the first time; and when inserted, the blade servers can configure the IPMB addresses of the BMCs of the blade servers by reading the IPMB addresses in the EPROMs. The management module can change the IPMB addresses of the BMCs of the blade servers flexibly according to needs, thereby improving the safety of the IPMB addresses.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

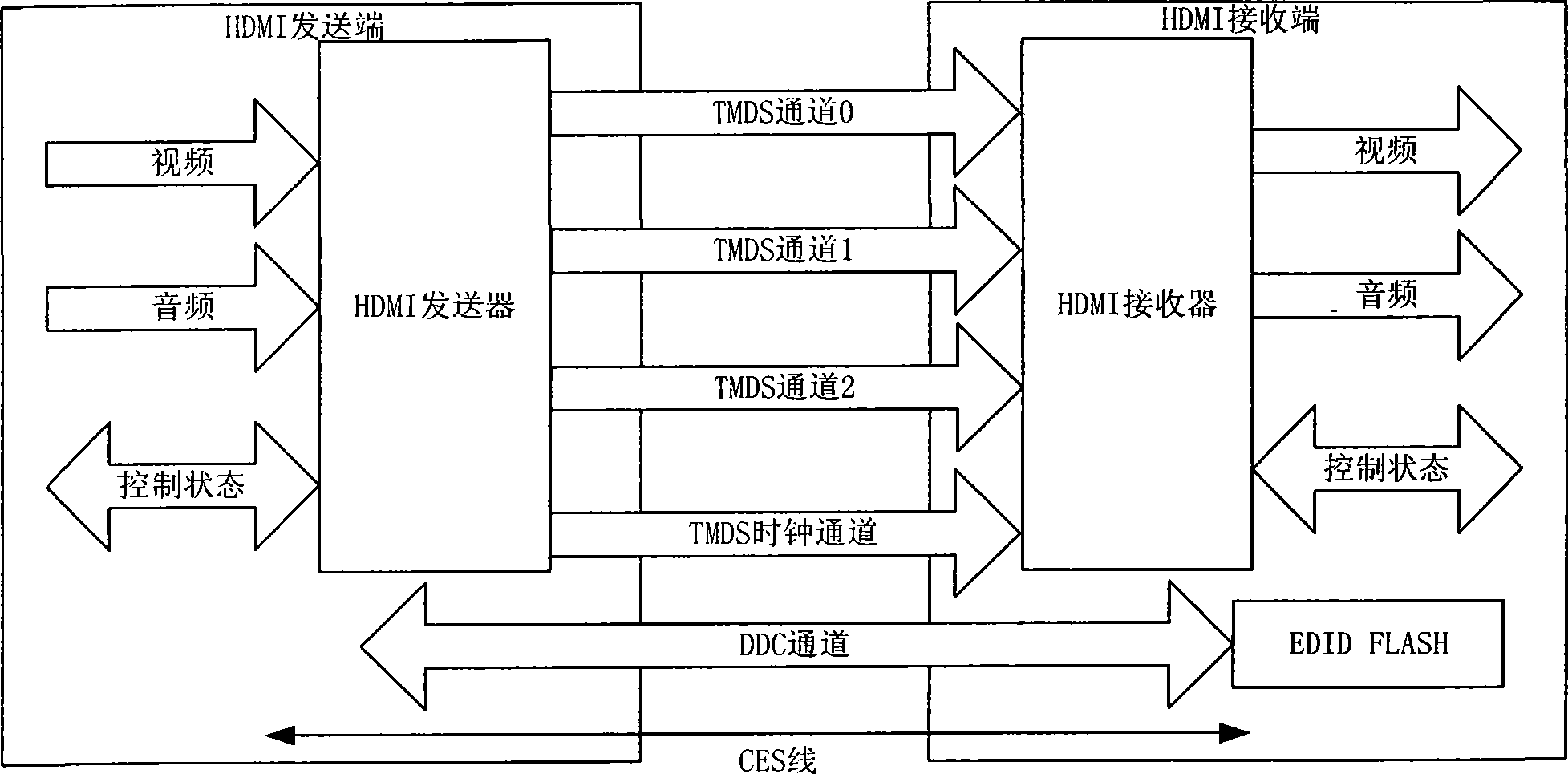

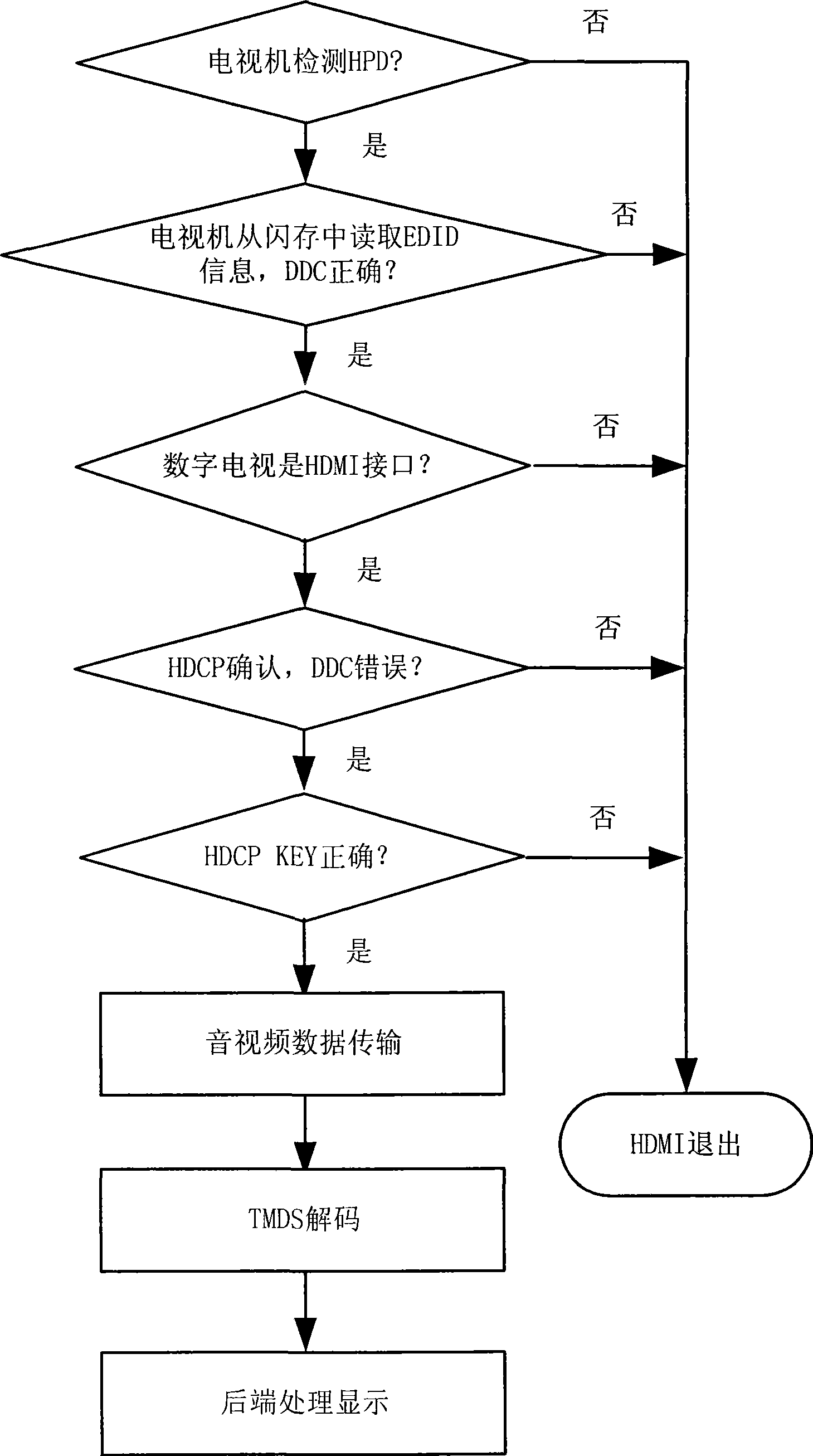

Expanded display recognition data and information writing method for high-resolution multimedia interface

The present invention discloses an expanded display identification data information writing-into method of high definition multimedia interface. The method comprises the following steps: allocating one part of space in the flash memory of flat panel TV memory, writing the source information of expanded display identification data into the flash memory with a binary format, exchanging collocation information between a transmitting end and a receiving end of high definition multimedia interface through display data channel, confirming the setting and function displayed by the terminal of receiving end, determining the audio / video data transmission format between the transmitting end and the receiving end, and selecting the optimal matching video / audio display format. The invention does not require additionally an EPROM for storing the EDID information, realizes the same function with least component and saves the hardware cost. The invention is suitable to apply in the flat panel display field.

Owner:KONKA GROUP

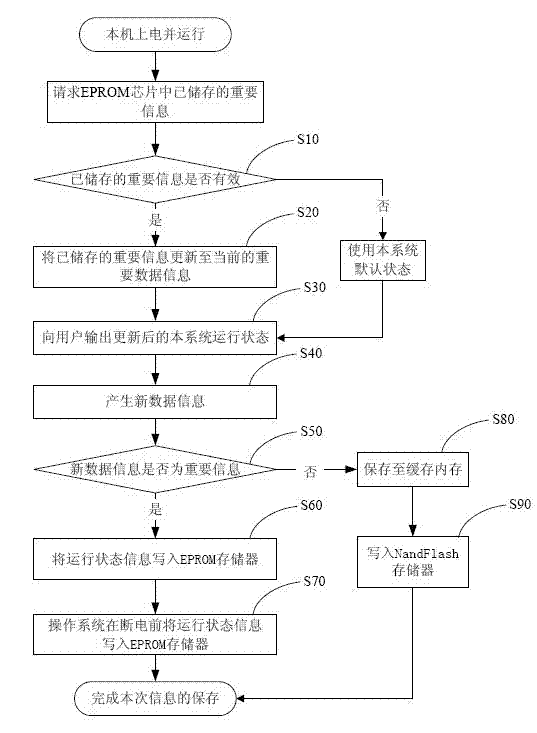

Vehicle navigation system and information storing method thereof

InactiveCN103206961AClear logical management hierarchyKeep foreverInstruments for road network navigationEPROMData information

The present invention relates to a vehicle navigation system and information storing method thereof. An EPROM memory capable of repeatedly erasing and writing is arranged inside the system, and is used for storing important data information of the system. When the system is in an operation process, the important data information in the EPROM memory can be real-timely called, the current operation status of a navigation device can be updated according to the important data information, and the updated operation status information is written into the EPROM memory if the navigation device operation status is changed. The method for storing information has a clear logic management level, and can permanently store related setting information of the navigation device into the EPROM memory, effectively avoiding the shortcoming of information losing because of the voltage drop in the unit.

Owner:HUIZHOU DESAY SV AUTOMOTIVE

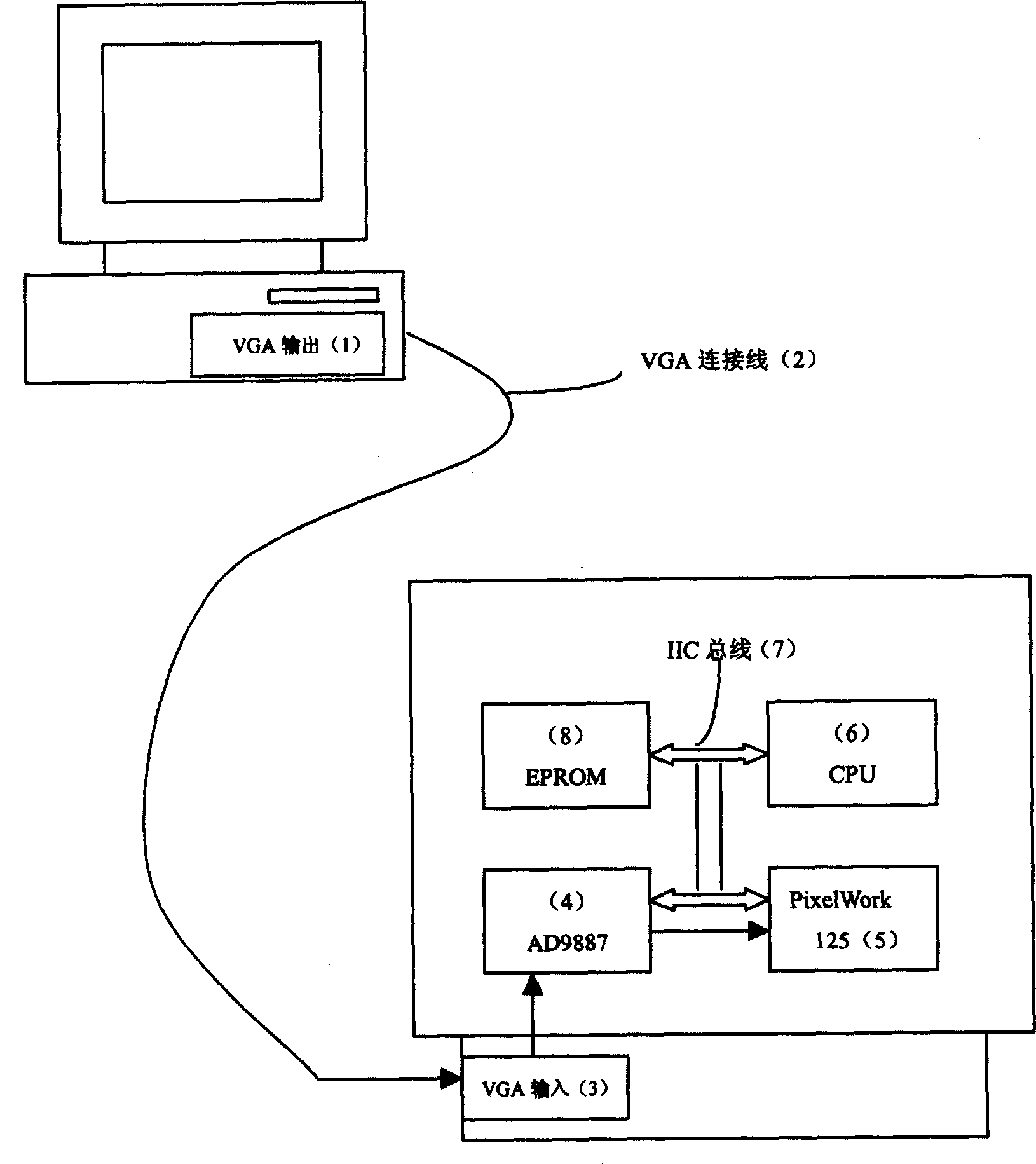

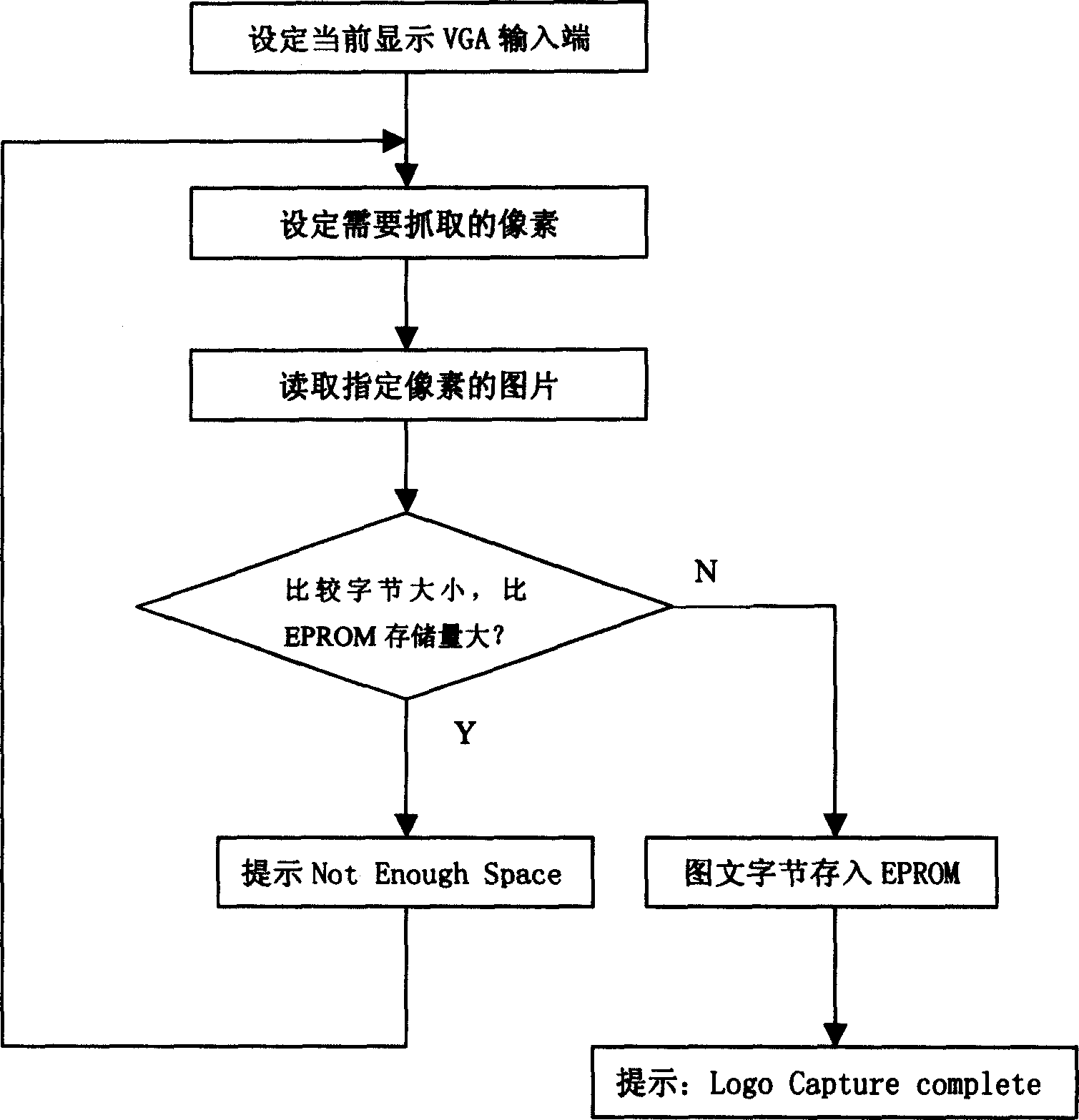

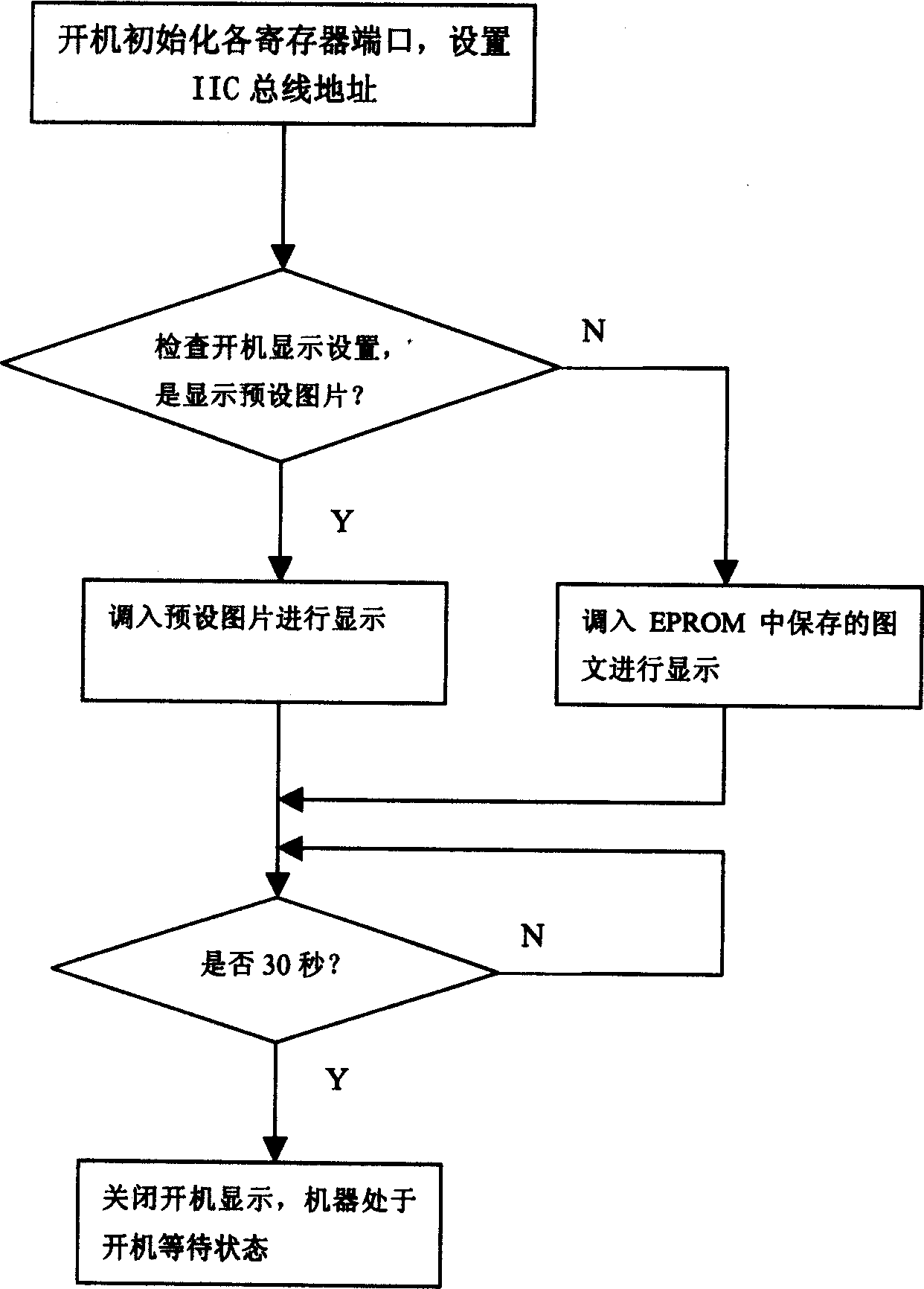

A digital optical display back projection with online alteration of start-up display frame and method thereof

InactiveCN1547392ARealize random online changesPersonalizedTelevision system detailsColor television detailsEPROMText mode

The invention discloses a kind of television which can change the start image online and the method, the user can display any image and text on the start image according to the demands. The computer VGA output interface is connected with the VGA input interface of the lightshow back projecting television, when the computer is powered on, it loads the image and text mode, makes the VGA input end of the lightshow and back projecting television display the preset image and text. The microprocessor of the lightshow back projecting television is controlled to act through the OSD menu of the television, reads the preset image and text on the VGA inputting end, and stores them in the EPROM. The television read the image and text file in the EPROM, and reduces the into R, G, and B data, they are inputted into the display driving circuit, the image and text can be displayed on the television screen, realizes the online change of the start image.

Owner:SHENZHEN SKYWORTH RGB ELECTRONICS CO LTD

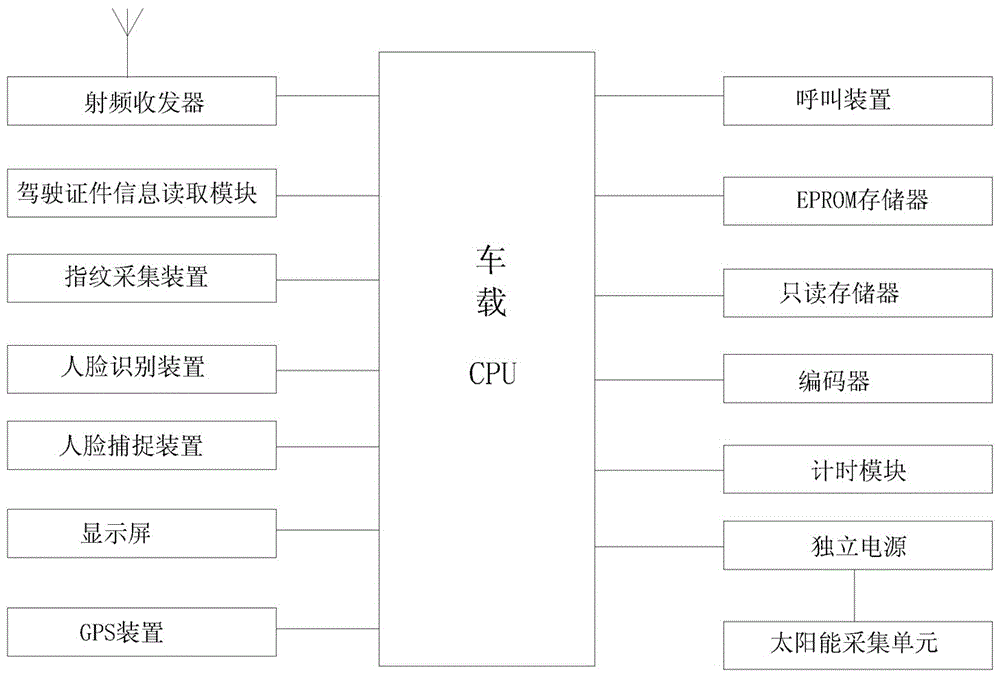

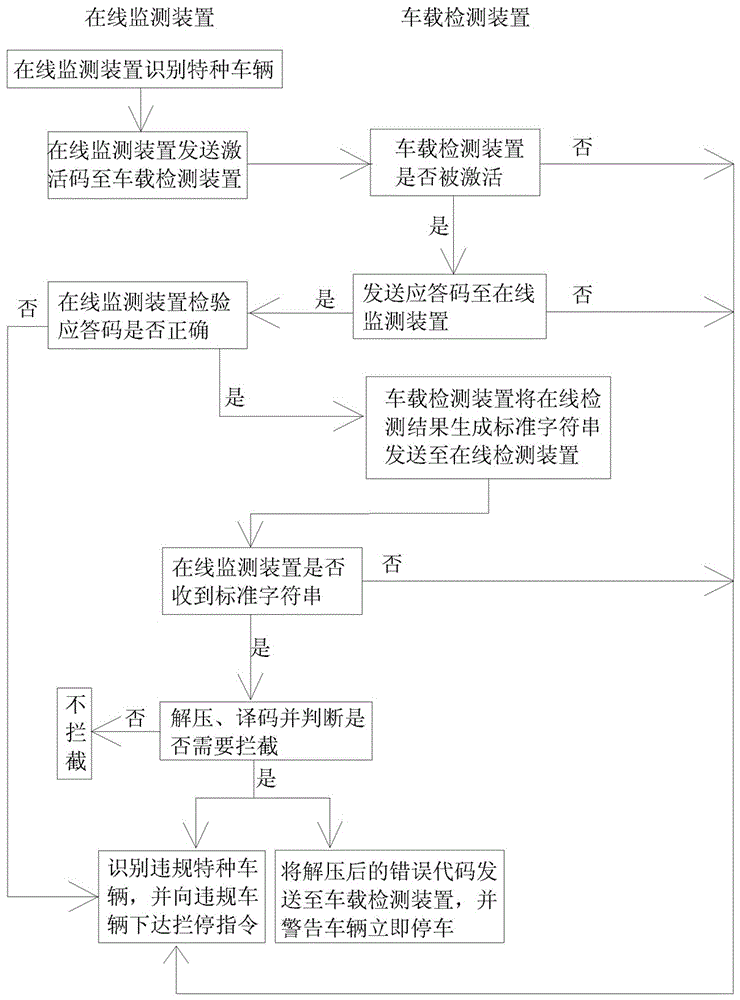

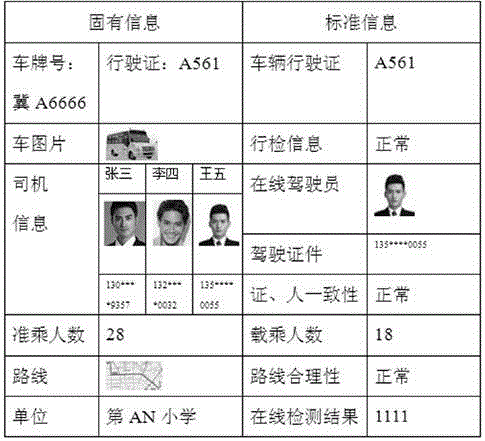

Vehicle-mounted detection device and method for realizing rapid screening of violation special vehicle

The invention relates to a vehicle-mounted detection device and method for realizing rapid screening of a violation special vehicle, and solves the technical problem that vehicle potential safety hazard checking and driver qualification verification of a special vehicle cannot be rapidly realized at the same time. An automatic routing inspection module is arranged in a special vehicle, an instant on-line monitoring module is arranged at a road side, and the device is characterized in that the on-line monitoring module structure includes a CPU and an EPROM (Electrically Programmable Read-Only-Memory), a ROM (Read-Only-Memory), a radio frequency transceiver, a timing circuit or / and a GPS module, a driving license information reading device, a fingerprint acquisition device or / and face recognition device, and an encoder is additionally arranged in the structure, and automatic, rapid and instant on-line screening of a violation special vehicle by a system is realized.

Owner:苏州德亚交通技术有限公司

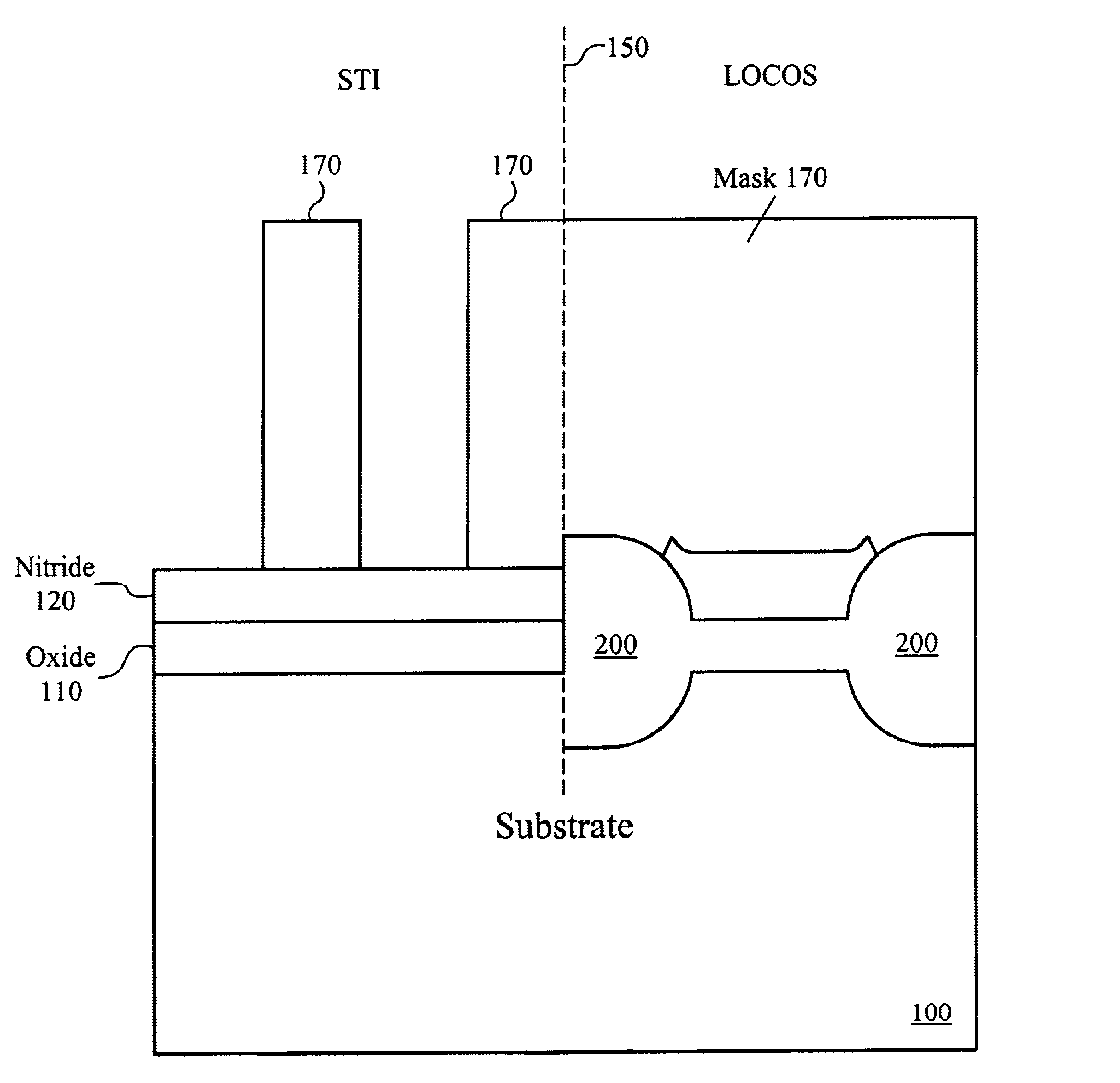

Method of and apparatus for integrating flash EPROM and SRAM cells on a common substrate

InactiveUS6921688B2Solid-state devicesSemiconductor/solid-state device manufacturingEPROMEngineering

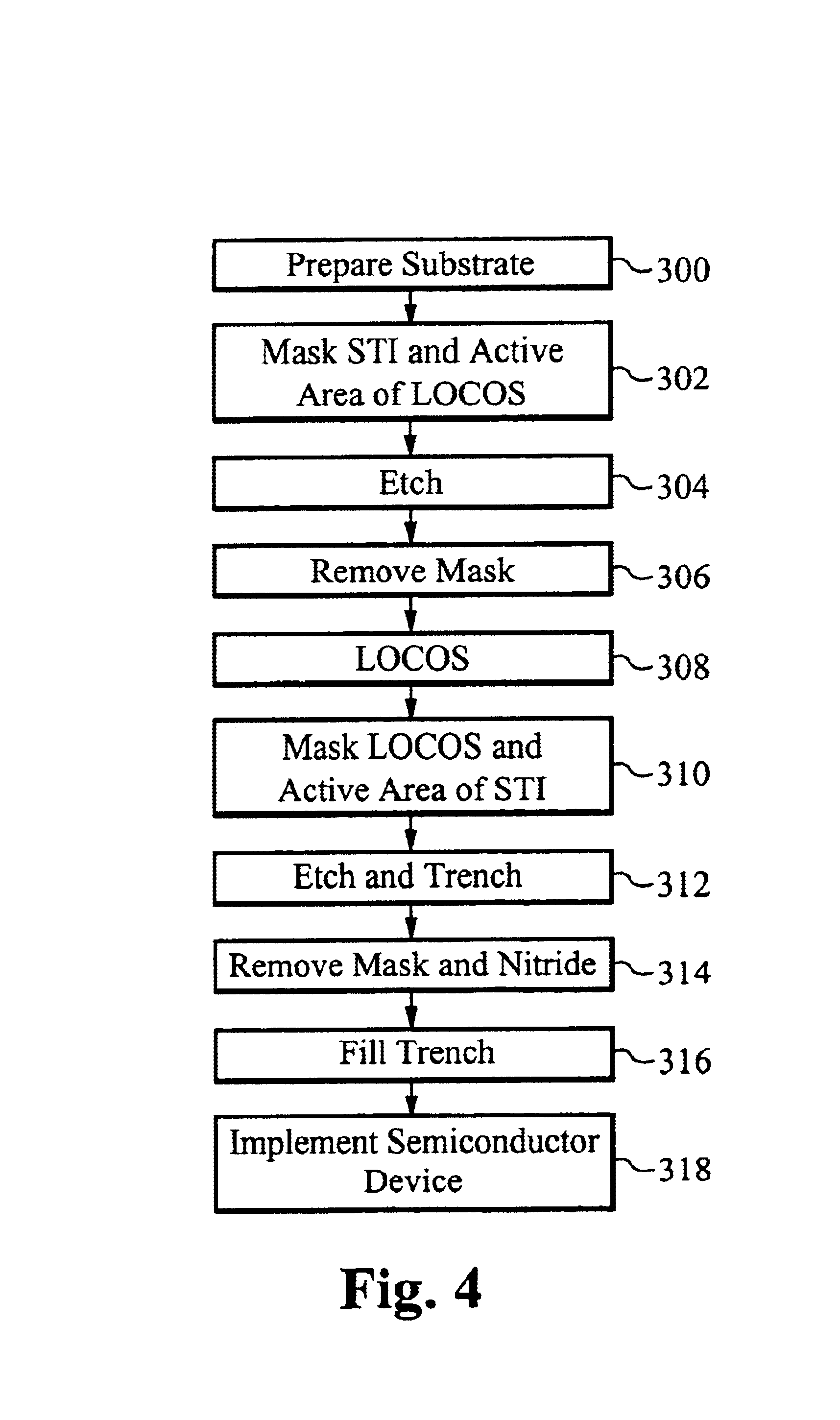

A system for and a method of integrating SRAM cells and flash EPROM cells onto a single silicon substrate includes an area on the silicon substrate where a local oxidation of silicon (LOCOS) isolation technique is implemented and another area on the same silicon substrate where a shallow trench isolation (STI) technique is implemented. Further, this system and method also include flash EPROM cells implemented within the area of the substrate utilizing the LOCOS isolation technique and SRAM cells implemented within the area of the substrate utilizing the STI technique. Preferably, the LOCOS isolation technique is first implemented to define a flash area of the silicon substrate on which the flash EPROM cell is implemented. Before the LOCOS isolation technique is implemented, an SRAM area is masked. After the LOCOS isolation technique has been fully implemented, the flash area is then preferably masked and the STI technique is implemented in order to define the SRAM area of the silicon substrate on which the SRAM cell is implemented. After the STI technique is implemented, the flash EPROM and the SRAM cells are preferably formed. Thus, the SRAM cells and the flash EPROM cells are both implemented on the common silicon substrate, but yet are appropriately isolated from each other, as well as from other additional devices which may be further implemented on the same silicon substrate, while providing the advantages of respective isolation schemes for the two cells.

Owner:ACACIA PATENT ACQUISITION

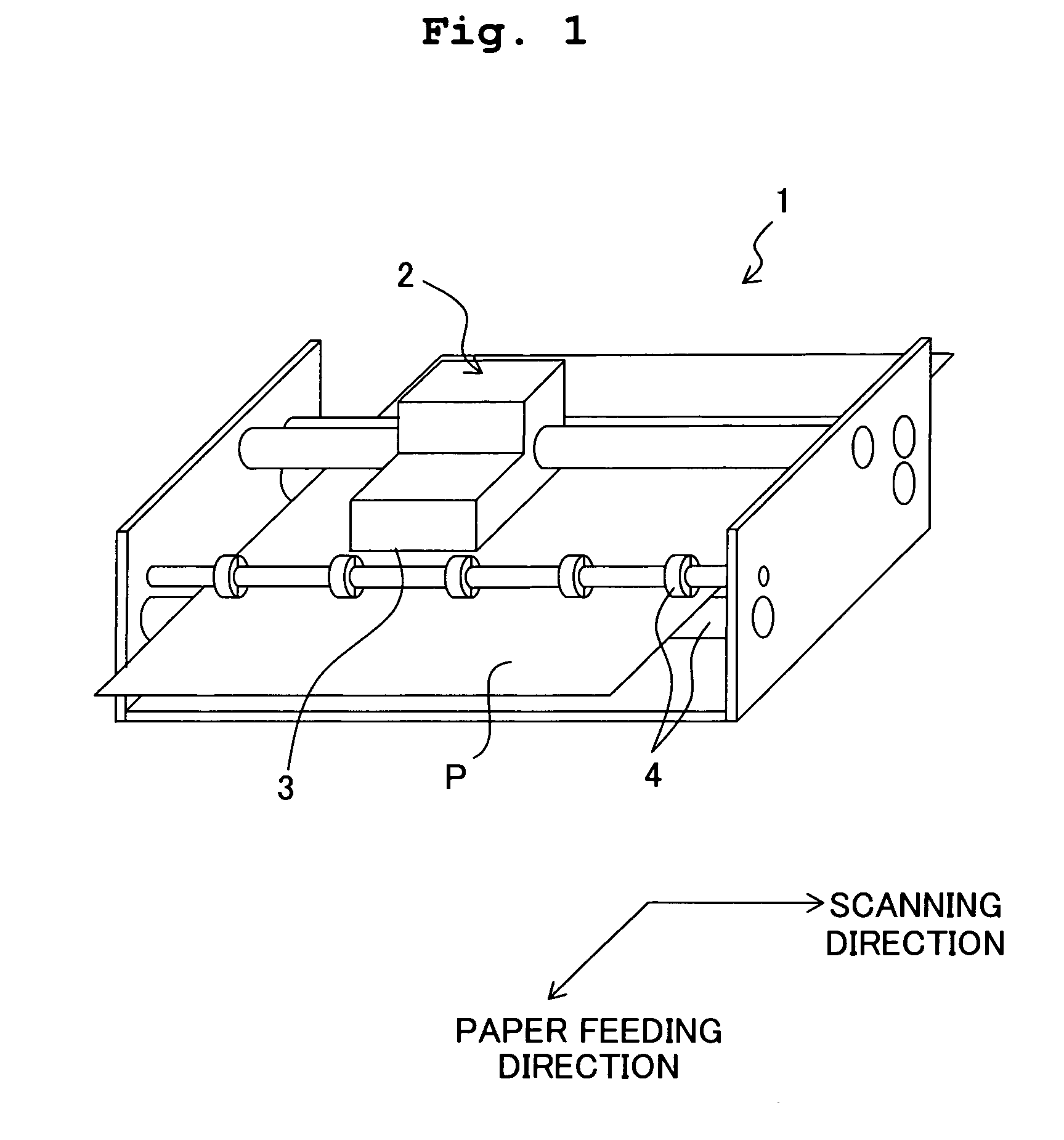

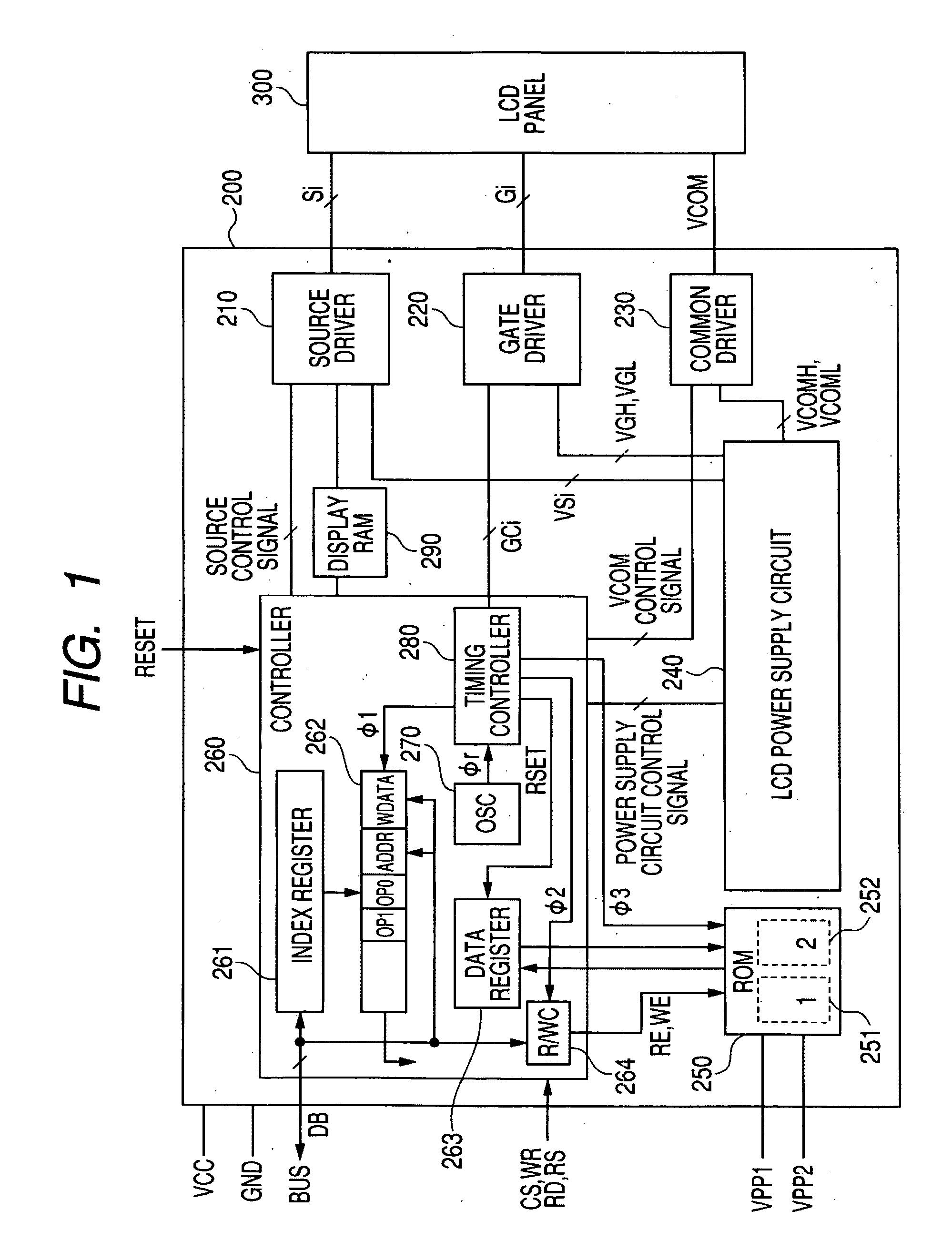

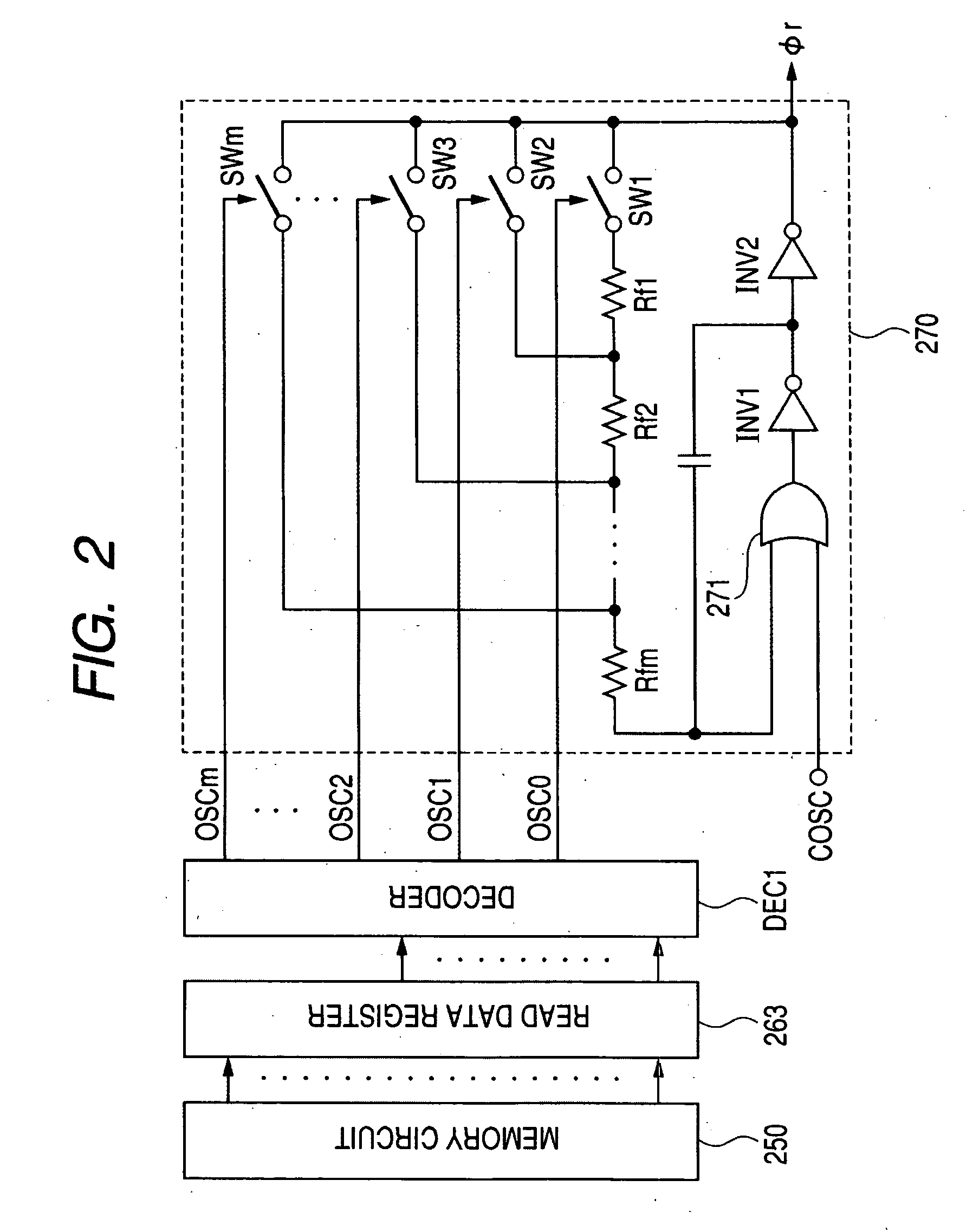

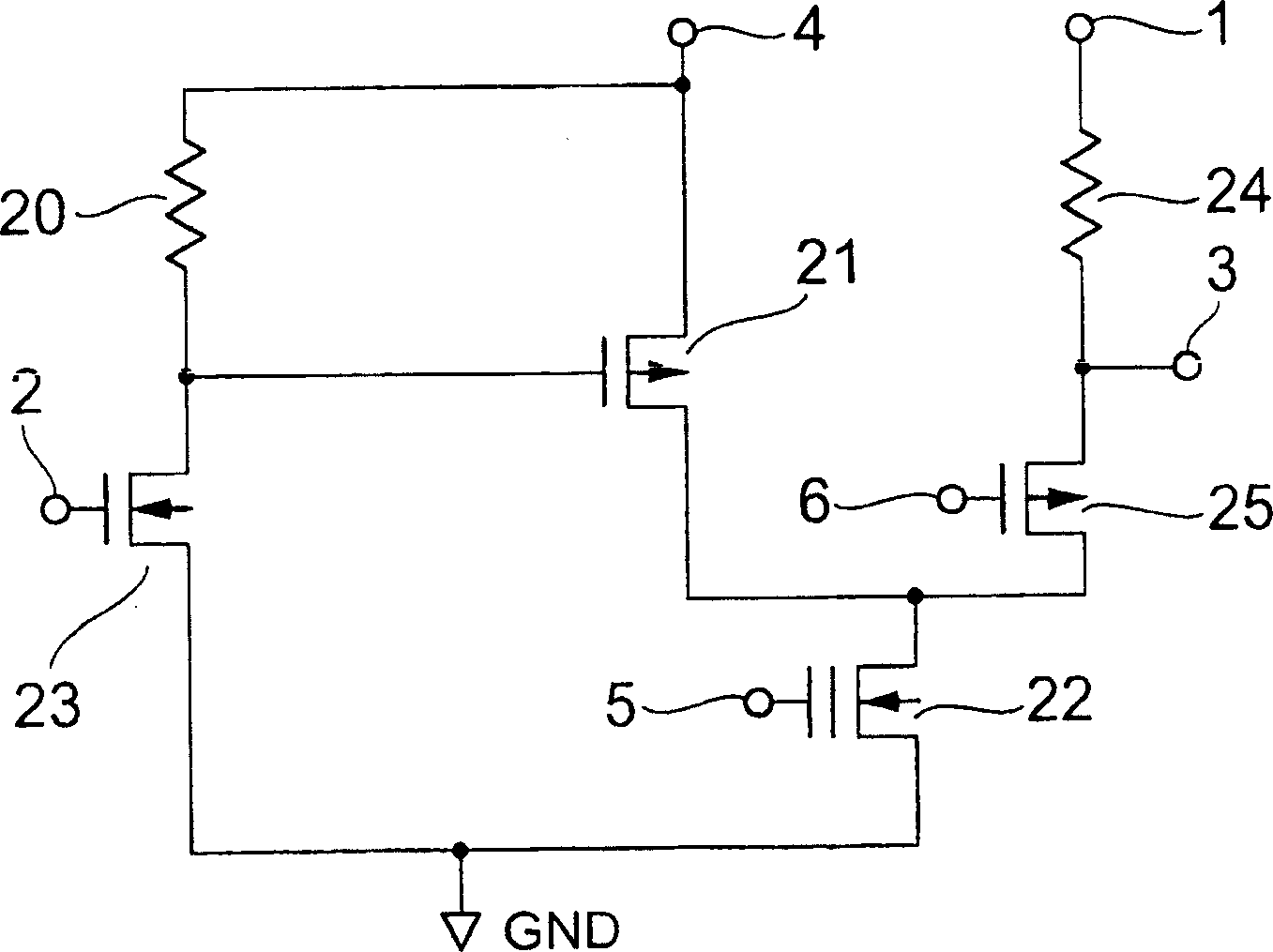

Semiconductor integrated circuit device for driving liquid crystal display

ActiveUS20060267903A1Reduce in quantityMiniaturizationSolid-state devicesCathode-ray tube indicatorsEPROMLiquid-crystal display

Owner:SYNAPTICS JAPAN GK

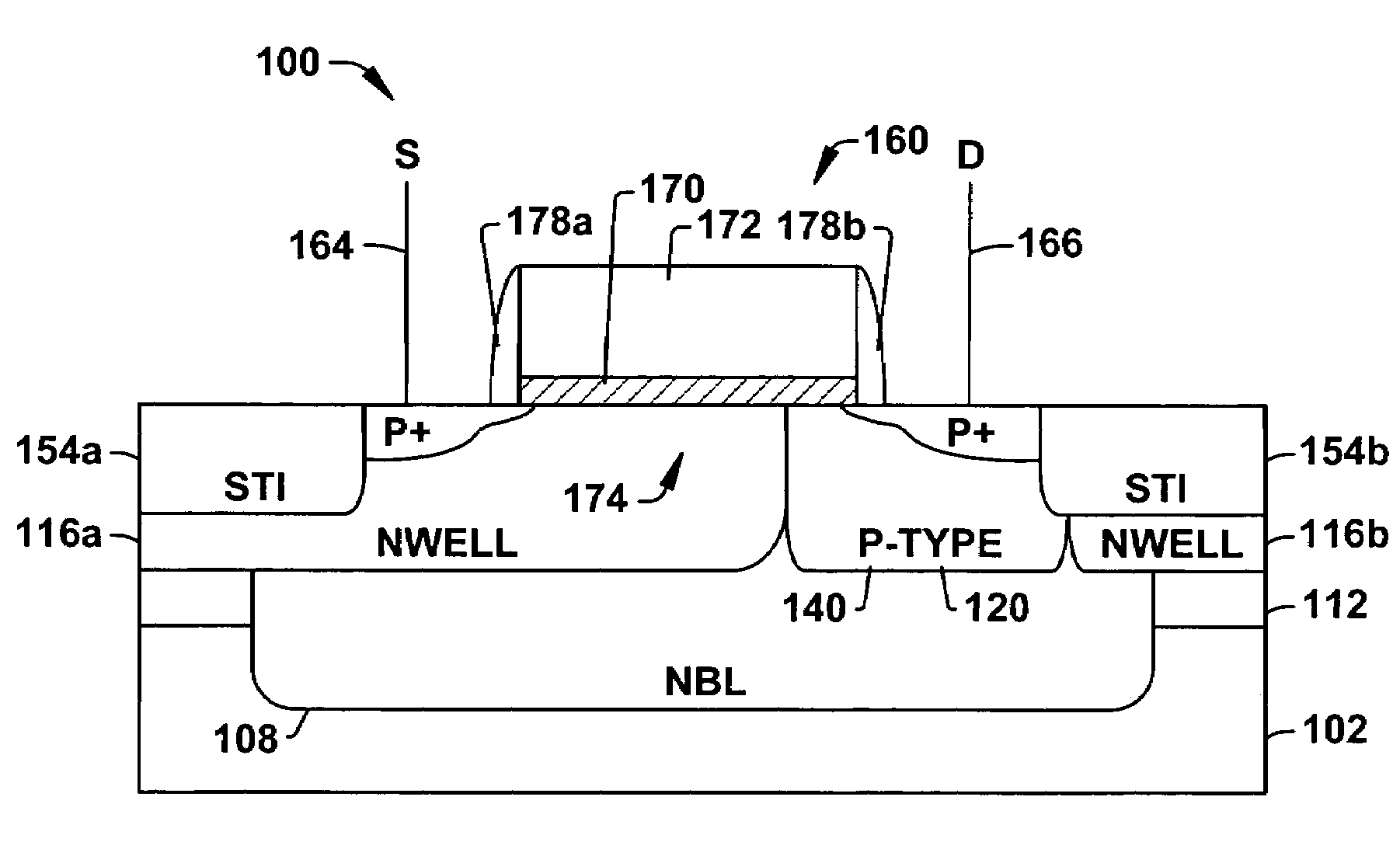

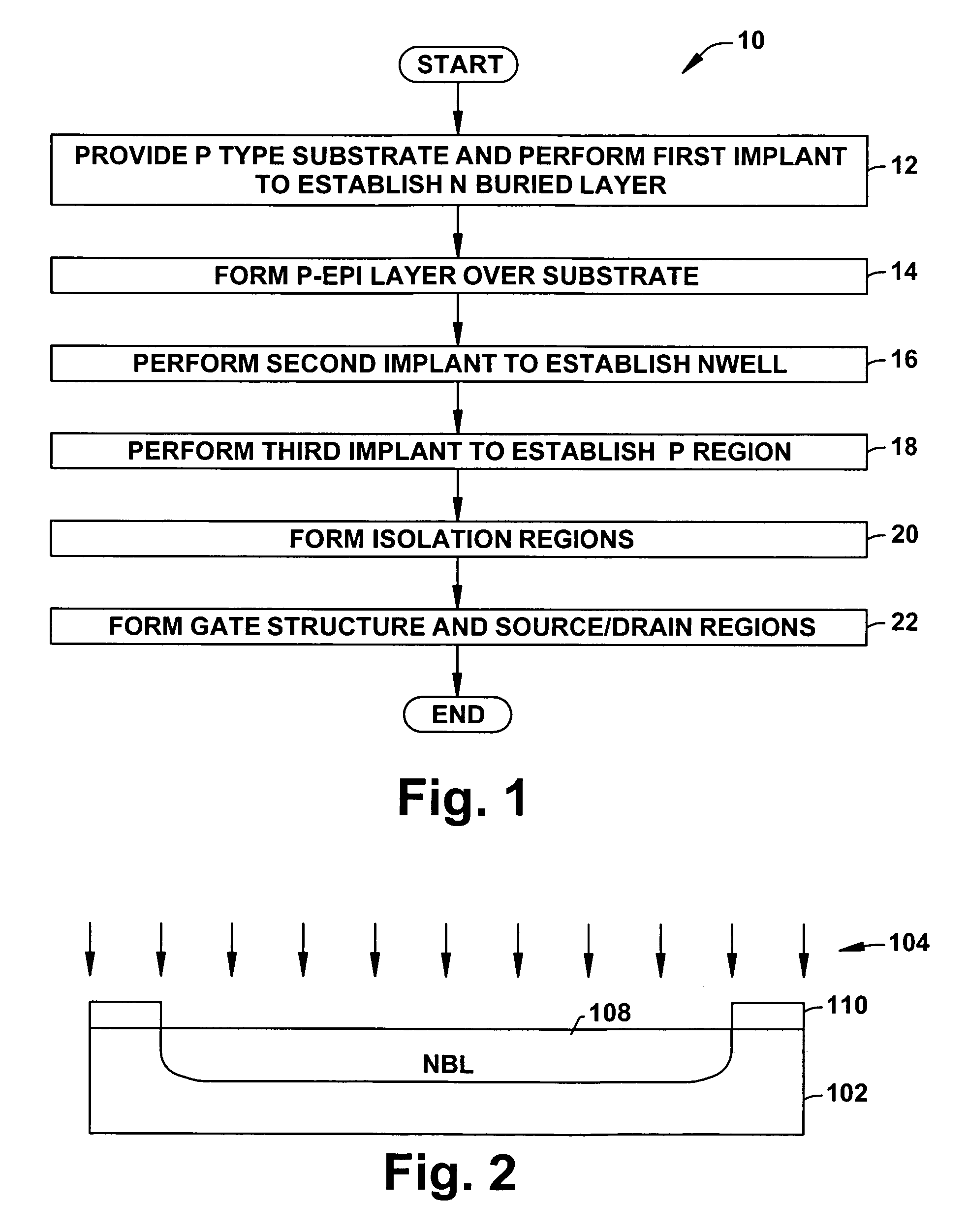

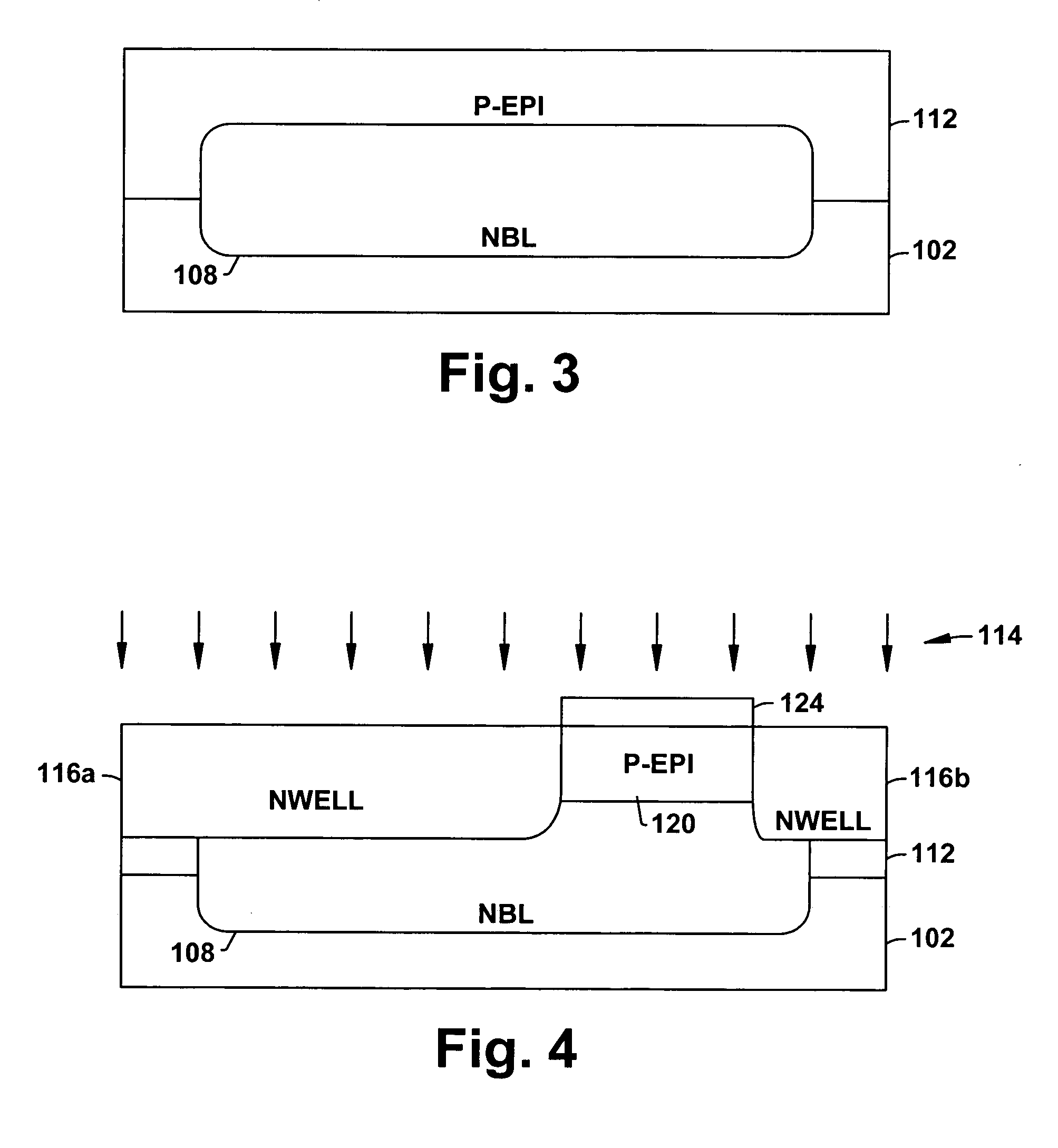

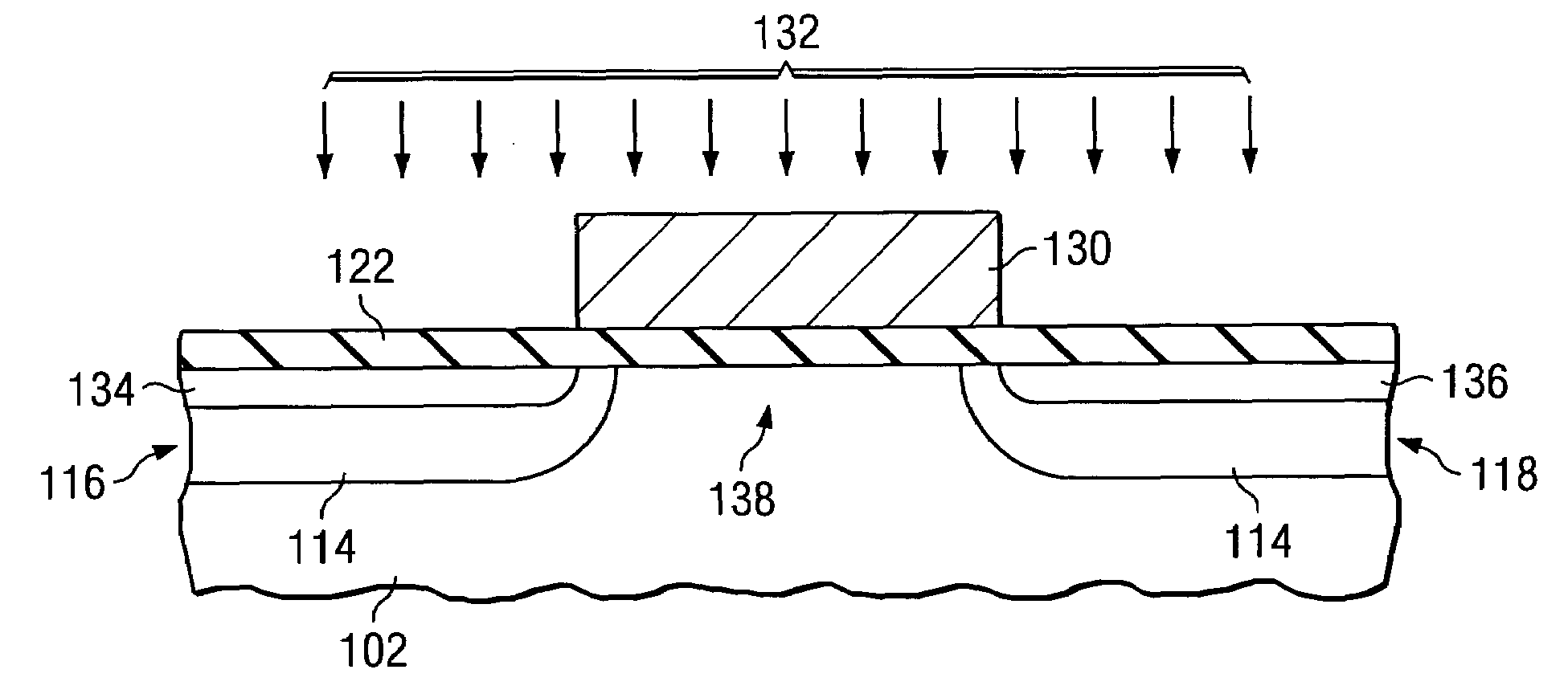

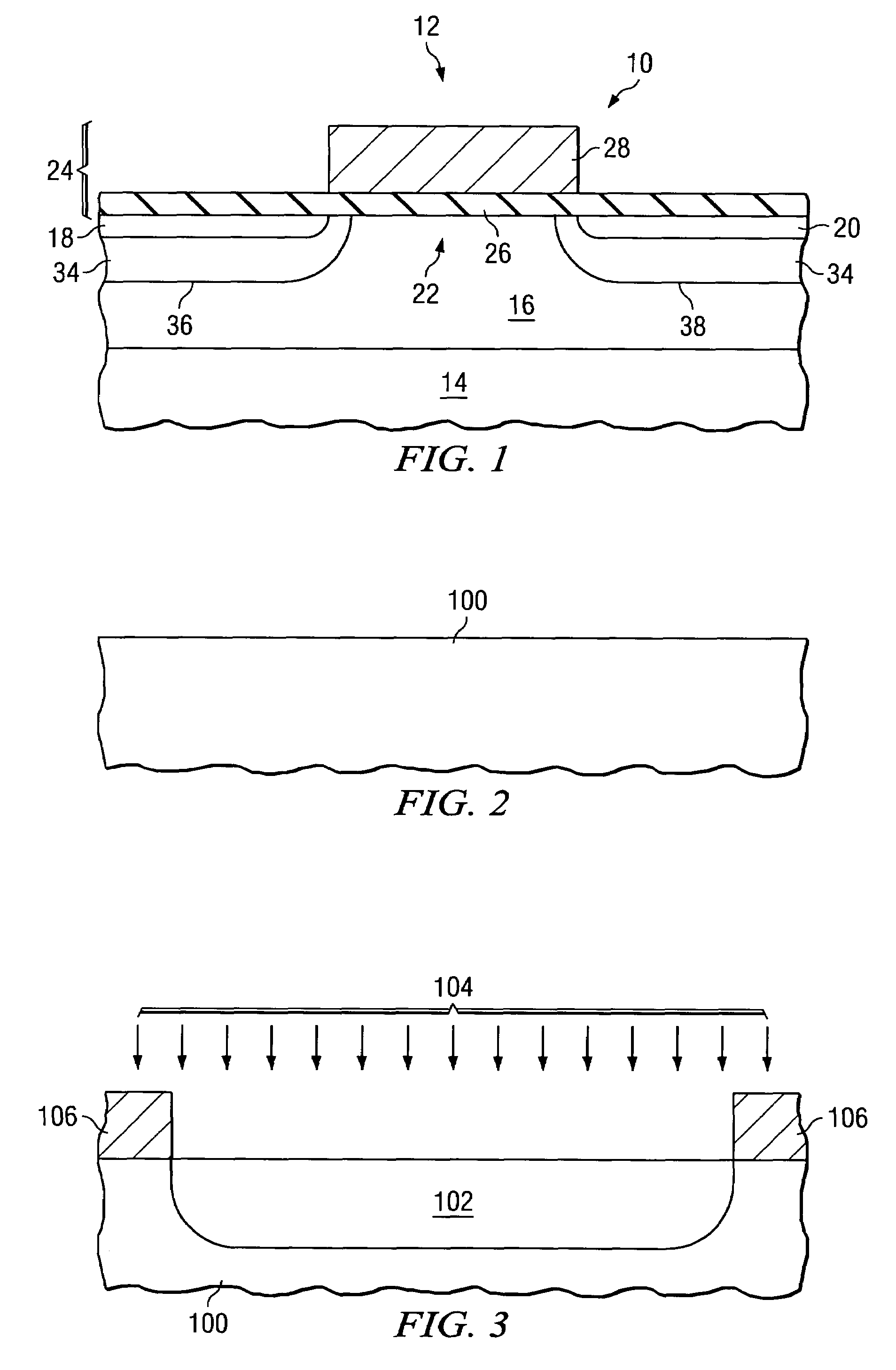

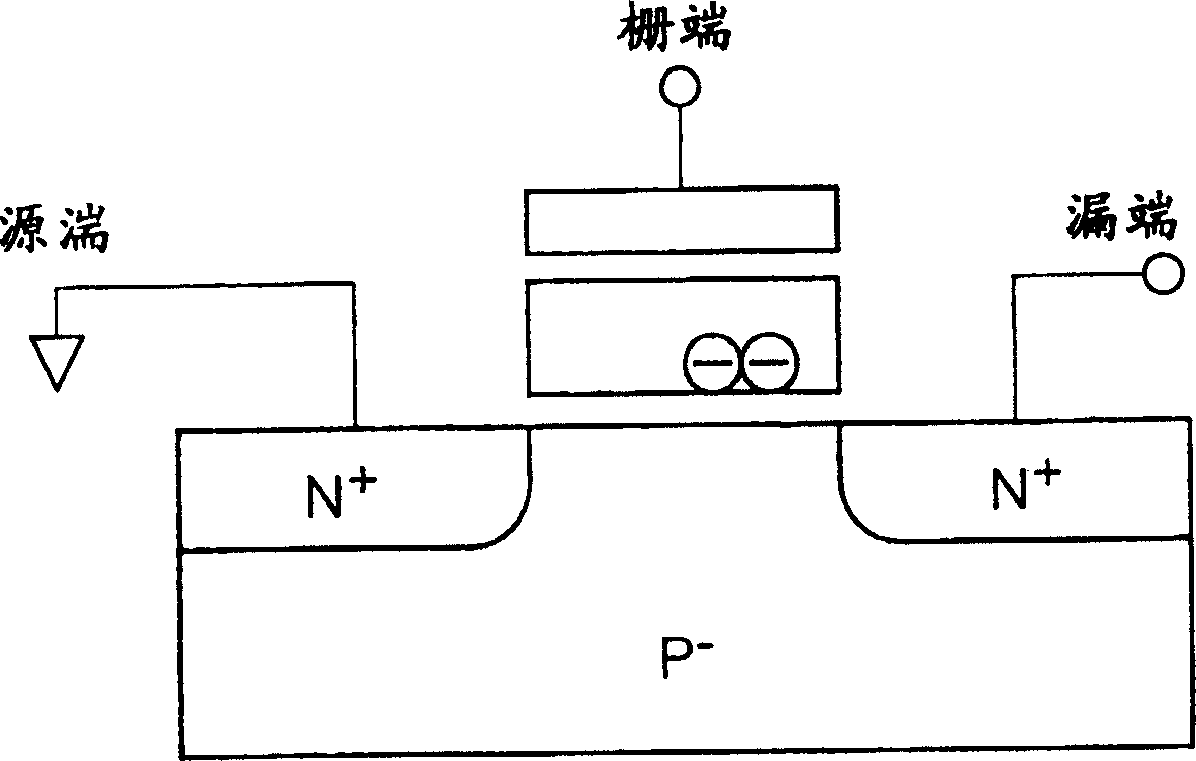

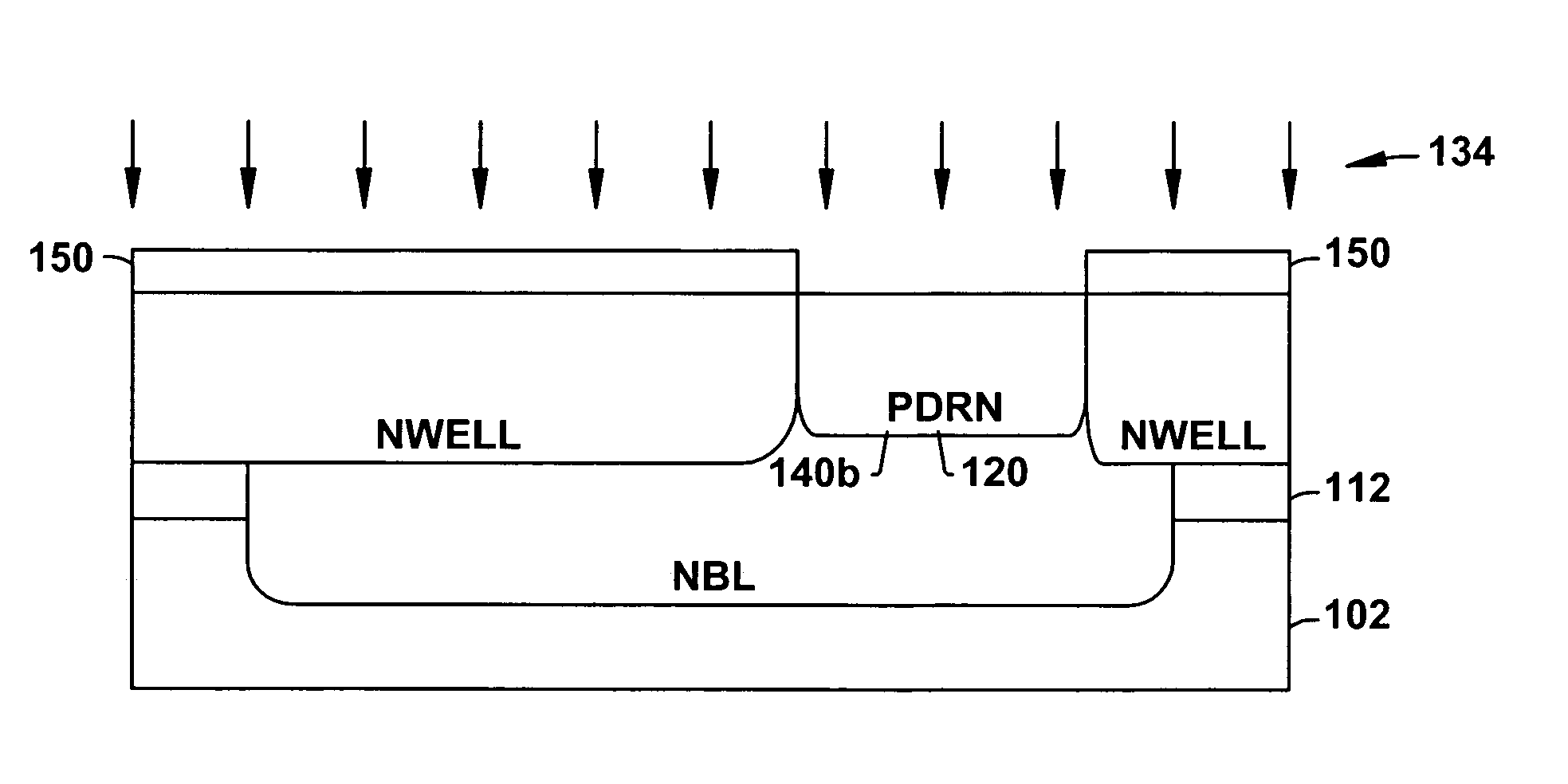

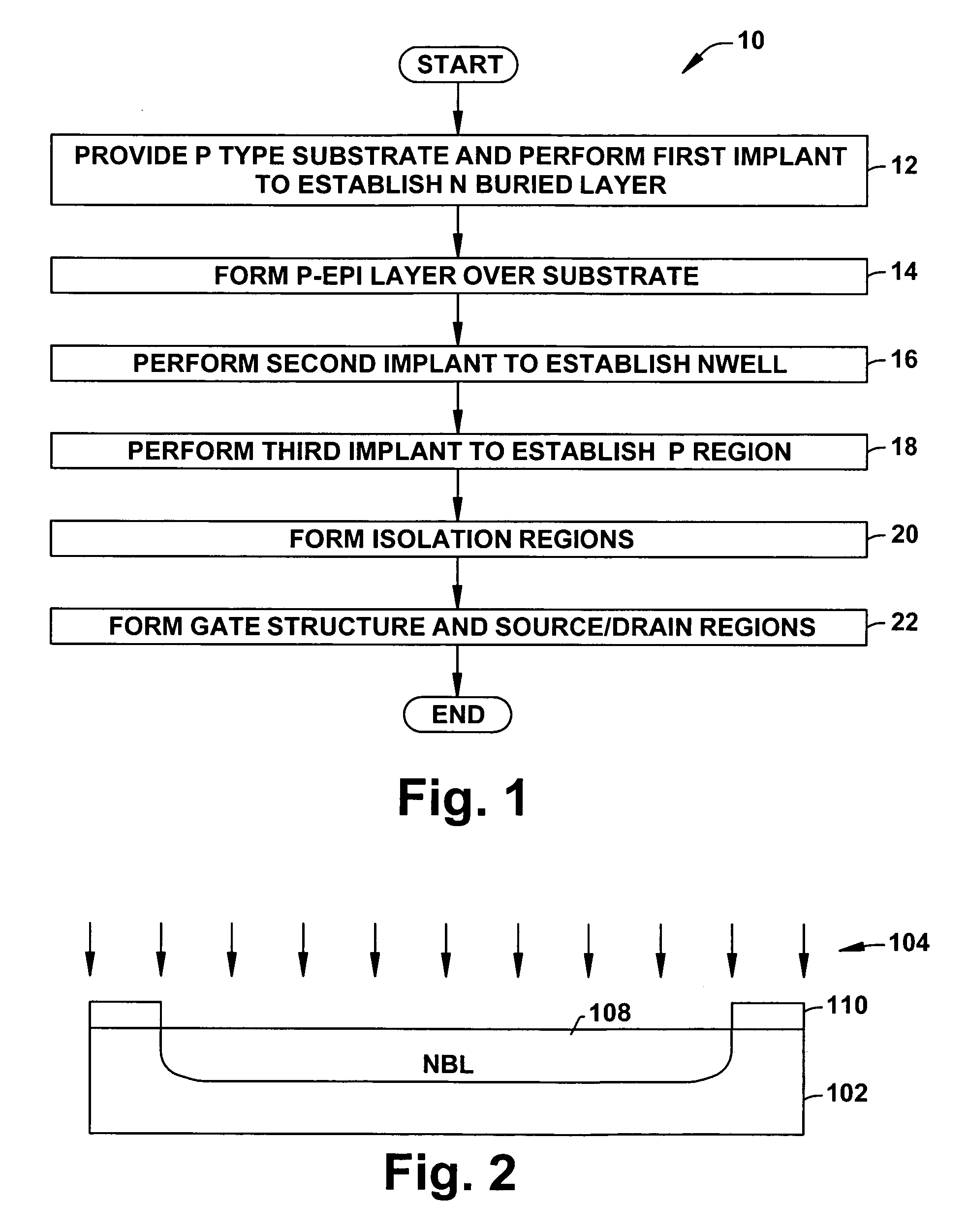

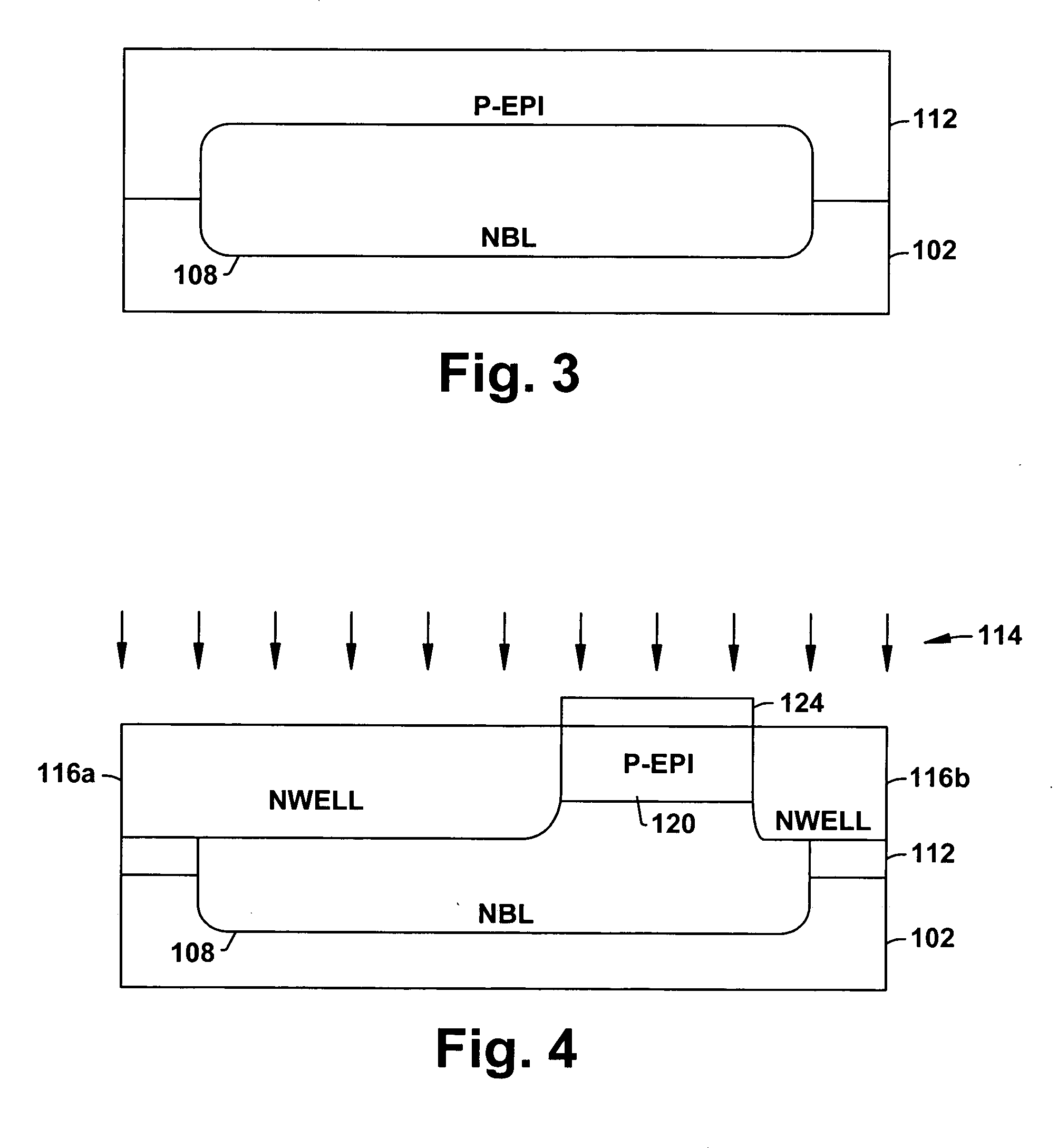

One time programmable EPROM for advanced CMOS technology

A one time programmable (OTP) electrically programmable read only memory (EPROM) transistor (100) having an increased breakdown voltage (BVdss) is disclosed. The increased breakdown voltage reduces the probability that the OTP EPROM (100) will breakdown during a programming operation by maintaining a breakdown voltage above a programming voltage. The breakdown voltage is, at least partially, increased by forming a p-doped region (140) within a semiconductor substrate (102), and forming a drain region (166) of the OTP EPROM (100) within the p-doped region (140).

Owner:TEXAS INSTR INC

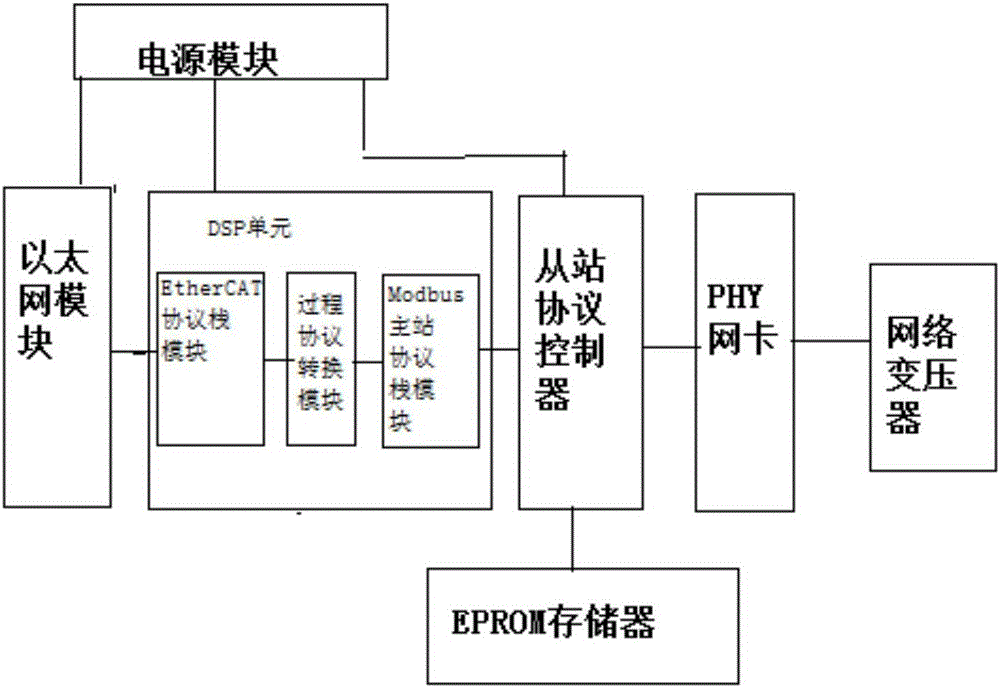

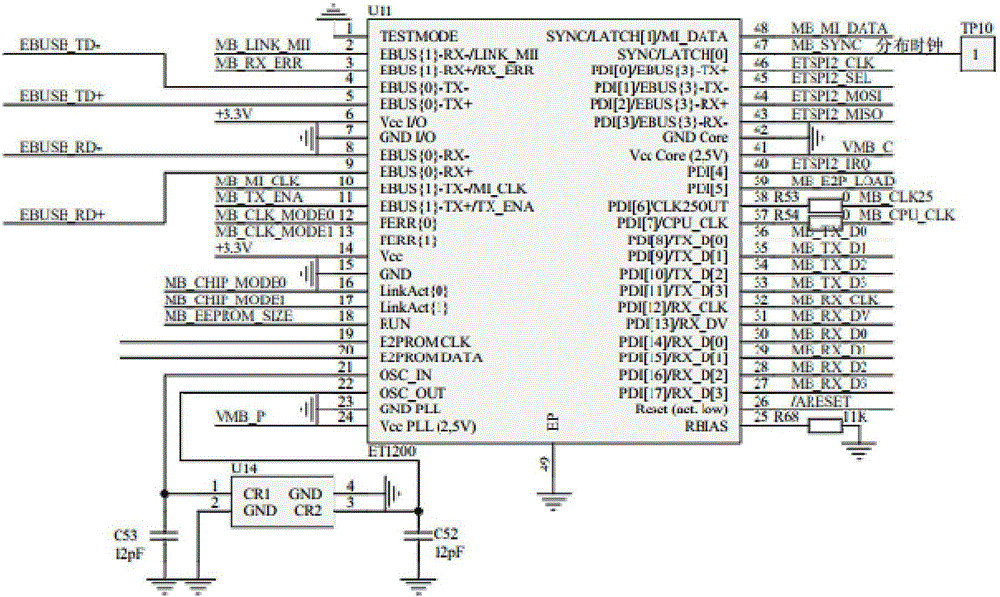

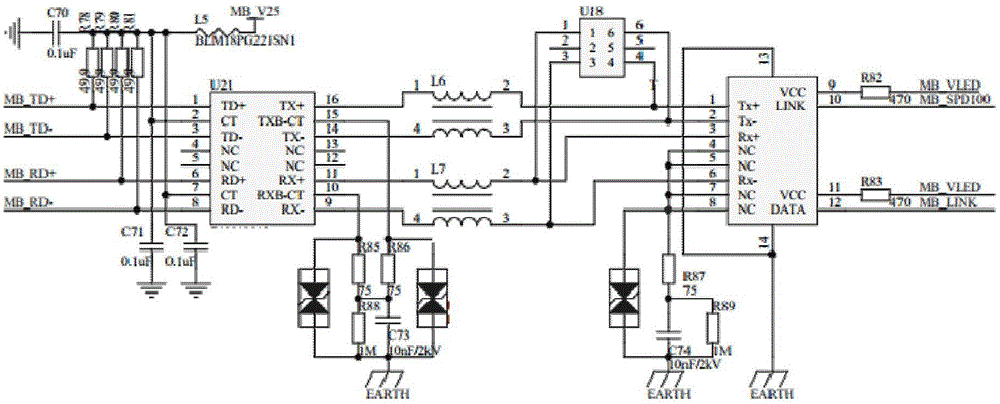

Communication device for converting industry Ethernet slave station into Modbus master station

PendingCN105978896AReasonable designSolve the problem of joining the EtherCAT industrial Ethernet control networkTransmissionCommunication interfaceIndustrial Ethernet

The invention provides a communication device for converting an industry Ethernet slave station into a Modbus master station. The device comprises a DSP unit, a slave station protocol controller, an Ethernet module, an EPROM memory and a power source module, wherein the DSP unit is connected with the slave station protocol controller through a serial port, the DSP unit is connected with the Ethernet module through the serial port, the slave station protocol controller is connected with the EPROM memory, the power source module is used for supplying power for the slave station protocol controller, the DSP unit and the Ethernet module; the slave station protocol controller is connected with a PHY network card through a PHY interface thereon, the PHY network card is connected with the RJ45 interface through a network transformer. The communication unit provided by the invention has the features of high-speed computing and high-speed conversion, and is capable of efficiently the operation of adding power electronic equipment only with the Modbus communication interface into an EtherCAT control looped network.

Owner:RENERGY ELECTRIC TIANJIN

Fabrication of an OTP-EPROM having reduced leakage current

ActiveUS7244651B2Improve operating profitReduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingEPROMBiomedical engineering

The leakage current of an OTP-EPROM cell formed using buried channel PMOS technology can be reduced. The reduction in leakage current of the OTP-EPROM can be achieved by blocking implantation of the Vtp implant into a channel region of an n-well that substantially underlies a floating gate structure. The Vtp implant can be blocked by providing a mask overlying the surface of the channel region of the n-well during implantation of the Vtp implant.

Owner:TEXAS INSTR INC

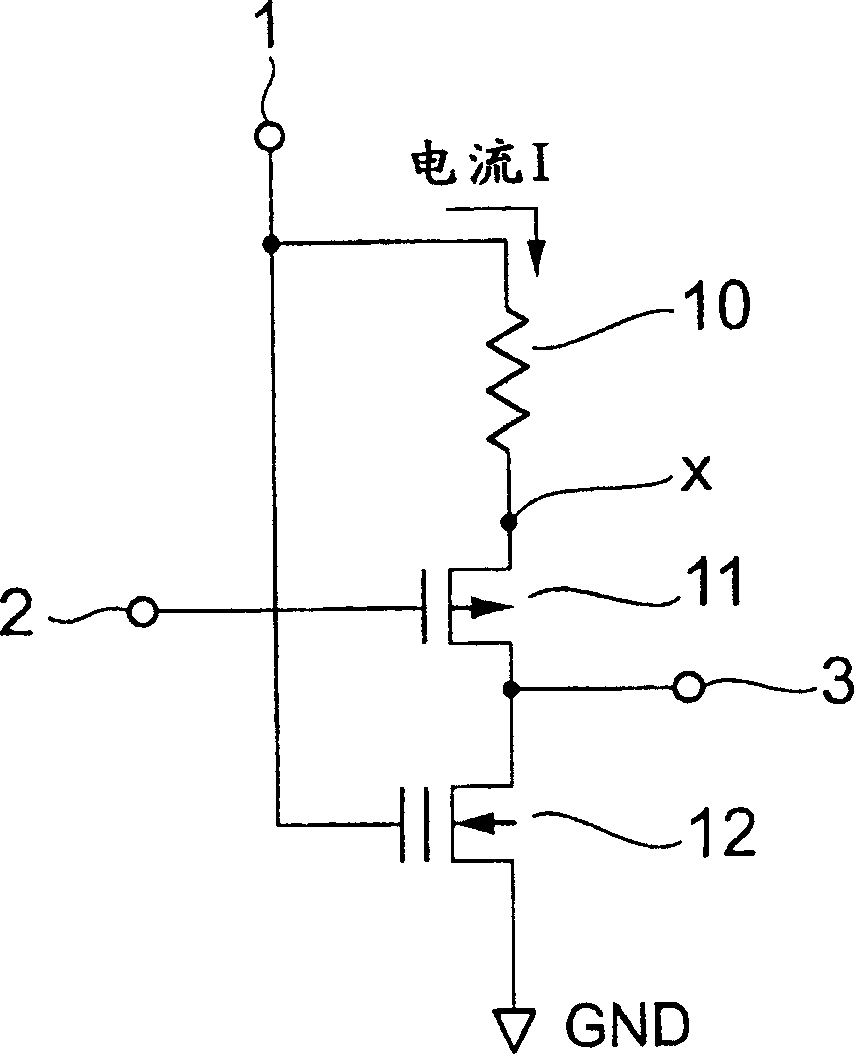

Non-volatile memory circuit and semiconductor device

The invention executes writing / reading in / from an EPROM without adding any signal terminal by generating an EPROM writing voltage by resistance in a trimming circuit having the EPROM. When writing to the EPROM is executed, a drop voltage by resistance is set as a writing voltage by a power supply voltage terminal. Thus, the writing / reading in / from the EPROM is executed without disposing any writing terminal.

Owner:SEIKO INSTR INC

One time programmable EPROM for advanced CMOS technology

A one time programmable (OTP) electrically programmable read only memory (EPROM) transistor (100) having an increased breakdown voltage (BVdss) is disclosed. The increased breakdown voltage reduces the probability that the OTP EPROM (100) will breakdown during a programming operation by maintaining a breakdown voltage above a programming voltage. The breakdown voltage is, at least partially, increased by forming a p-doped region (140) within a semiconductor substrate (102), and forming a drain region (166) of the OTP EPROM (100) within the p-doped region (140).

Owner:TEXAS INSTR INC

Electronic memory having impedance-matched sensing

ActiveUS20050036389A1Accurate dataReduce sensitivityRead-only memoriesDigital storageBit lineLow noise

An electronic memory, typically a flash EPROM, contains an array of memory sections (40), each containing an array of memory cells (54). Global bit lines (60) fully traverse the memory. Local bit lines (58) partially traverse the memory. Data stored in the memory is sensed with an arrangement that utilizes impedance matching to achieve high sensing accuracy with low noise sensitivity. The impedance matching may be provided solely from the sections and lines of the memory or partially from a separate reference memory section (102) that contains reference memory cells (104).

Owner:PROMOS TECH INC

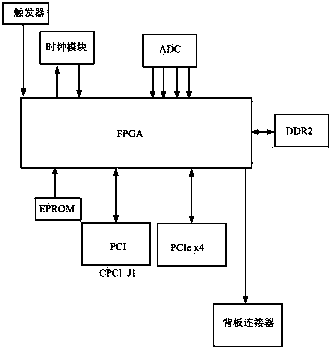

High speed data collecting module

InactiveCN103678195AReduce upload timeImprove signal processing capabilitiesElectric digital data processingEPROMFpga implementations

The invention discloses a high speed data collecting module which comprises an FPGA. The FPGA is connected with an ADC data collecting module and a clock distribution module. The ADC data collecting module is connected with the clock distribution module. The FPGA is further connected with an EPROM, a CPCI bus and a CPCIe bus. The ADC data collecting module is used for sampling data and transmitting the data to the FPGA to be further recognized and sorted, and then the data are transmitted to the CPCI bus and the CPCIe bus through the FPGA. The signal processing capability can be improved, data uploading time is shortened, and the high speed data collecting module is fast and convenient to use.

Owner:CHENGDU GUORONG TECH

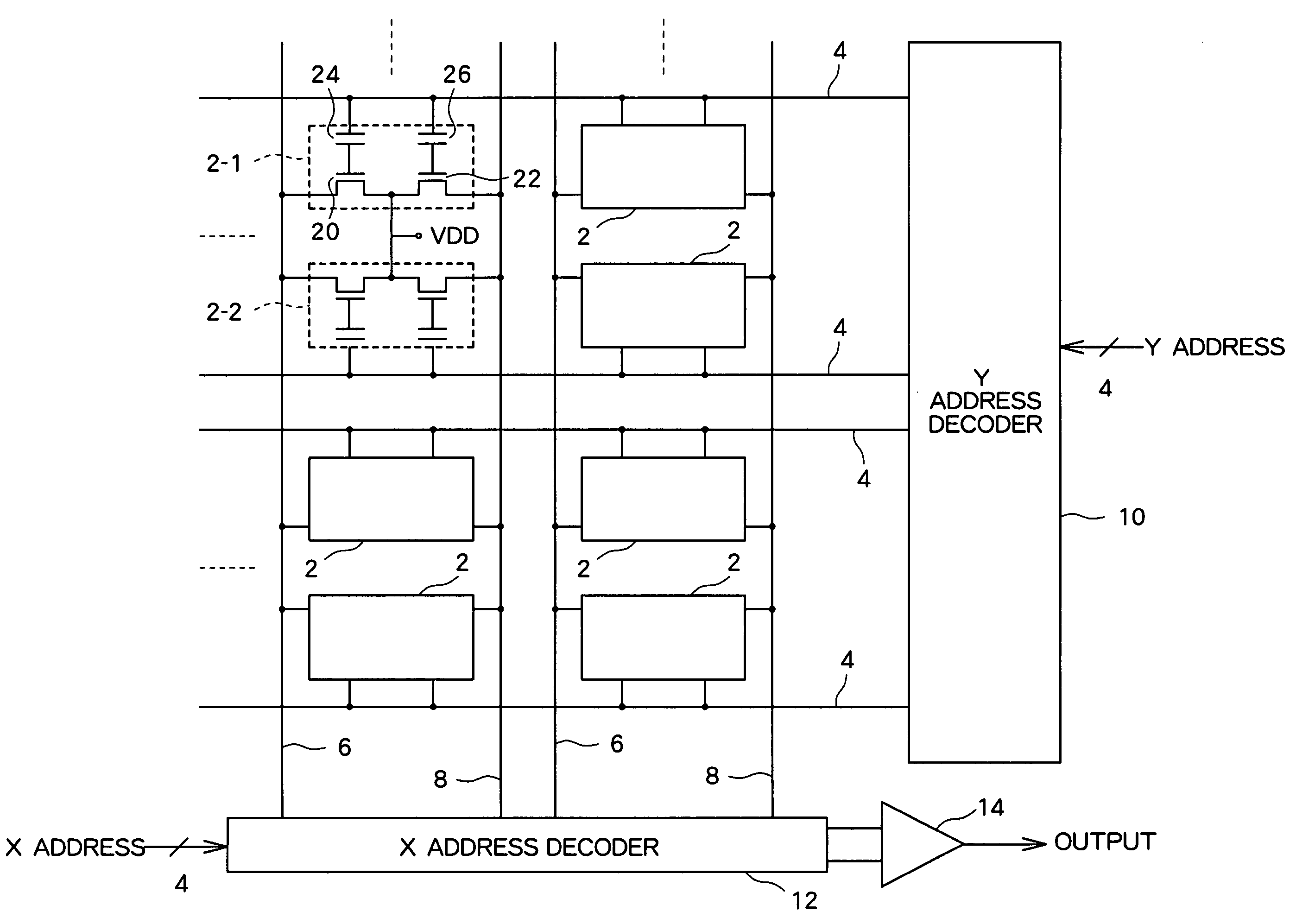

Ultraviolet erasable semiconductor memory device

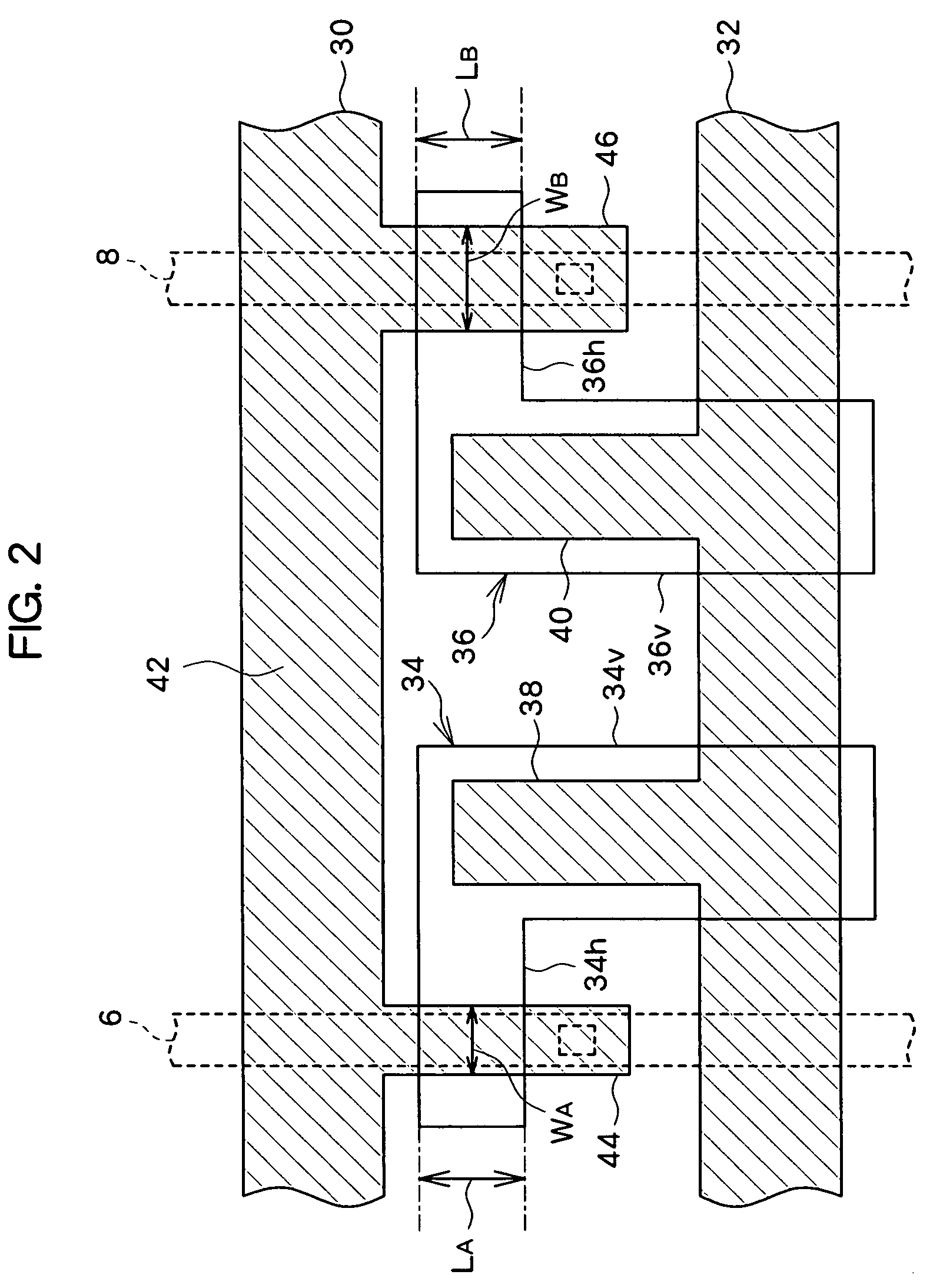

Each memory cell of an EPROM contains two MOSFETs and a data of each memory cell is read out by detecting a current difference between the two MOSFETs by using a differential amplifier. In such constitution as described above, even when the data is erased by irradiating an ultraviolet ray, a stable output of the differential amplifier can be obtained and, therefore, confirmation of an initialized state can be facilitated. Specifically, a channel width WA of one of the two MOSFETs constituting the memory cell is formed narrower than a channel width WB of the other. By such arrangement as described above, in an initialized state in which the ultraviolet ray is irradiated, a data signal current value IHA of the MOSFET having the channel width WA becomes smaller than a data signal current value IHB flowing in the MOSFET having the channel width WB. Accordingly, the output of the differential amplifier is fixed in accordance with a current magnitude relation of IHA<IHB, to thereby define a data “0”. On the other hand, in writing a data “1”, charges are injected in a floating gate electrode of the MOSFET having the channel width WB to raise a threshold voltage Vt and, then, the MOSFET is set in an “off” state.

Owner:SEMICON COMPONENTS IND LLC

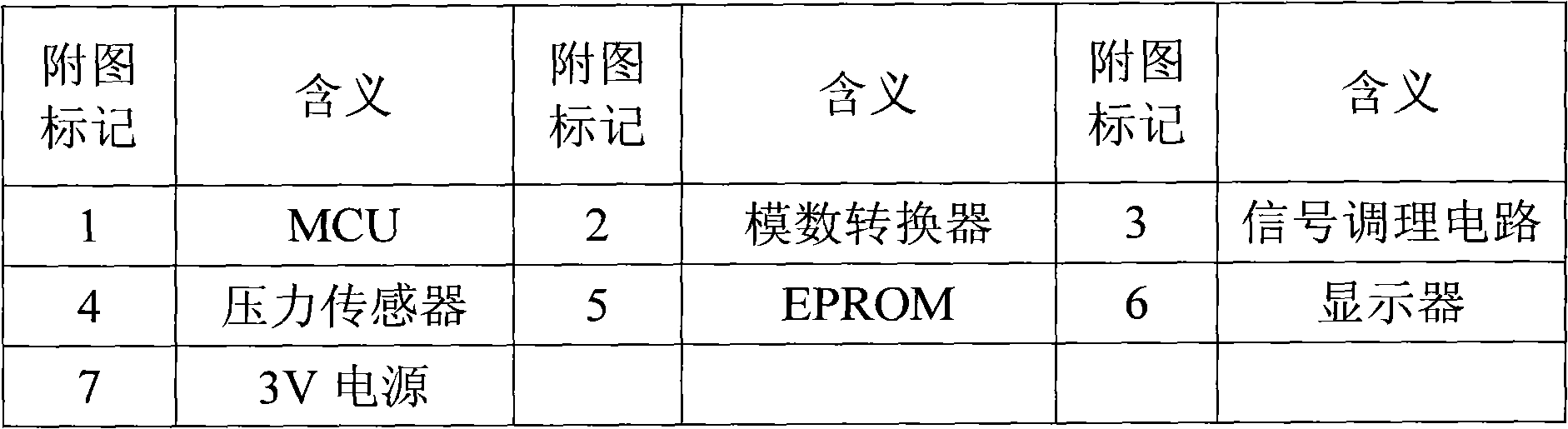

Digital manometer for accurately measuring pressure to be measured

InactiveCN102095547ALower crystal frequencyReduce the introduction of errorFluid pressure measurement by electric/magnetic elementsEPROMPower consumption

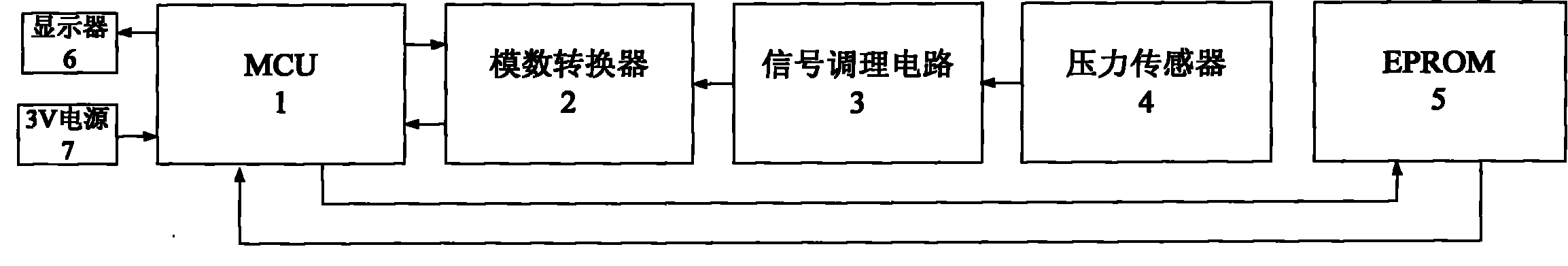

The invention relates to a digital manometer for accurately measuring pressure to be measured, comprising a MCU (Microprogrammed Control Unit) and a pressure sensor. The pressure sensor is connected with a signal conditioning circuit, the signal conditioning circuit is connected to an analog-to-digital converter, and the analog-to-digital converter is connected to the MCU which is also connected to an EPROM (Electrically Programmable Read-Only Memory), a power supply of 3V and a monitor. By adopting the MCU for low-voltage power supply, the oscillator frequency of the MCU is decreased, the system power supply is automatically switched off to decrease power consumption when no measurement is carried out; a high-linearity 14-bit analog-to-digital converter is adopted to add a temperature comprehension circuit to a pressure transmitter and reduce environmental introduce errors; and errors nonlinearly introduced by the pressure sensor are corrected through the technologies of zero point correction and multi-point correction when data is processed and measured so as to prolong service life to the maximum extend.

Owner:苏州工业园区广福汽保机电设备有限公司

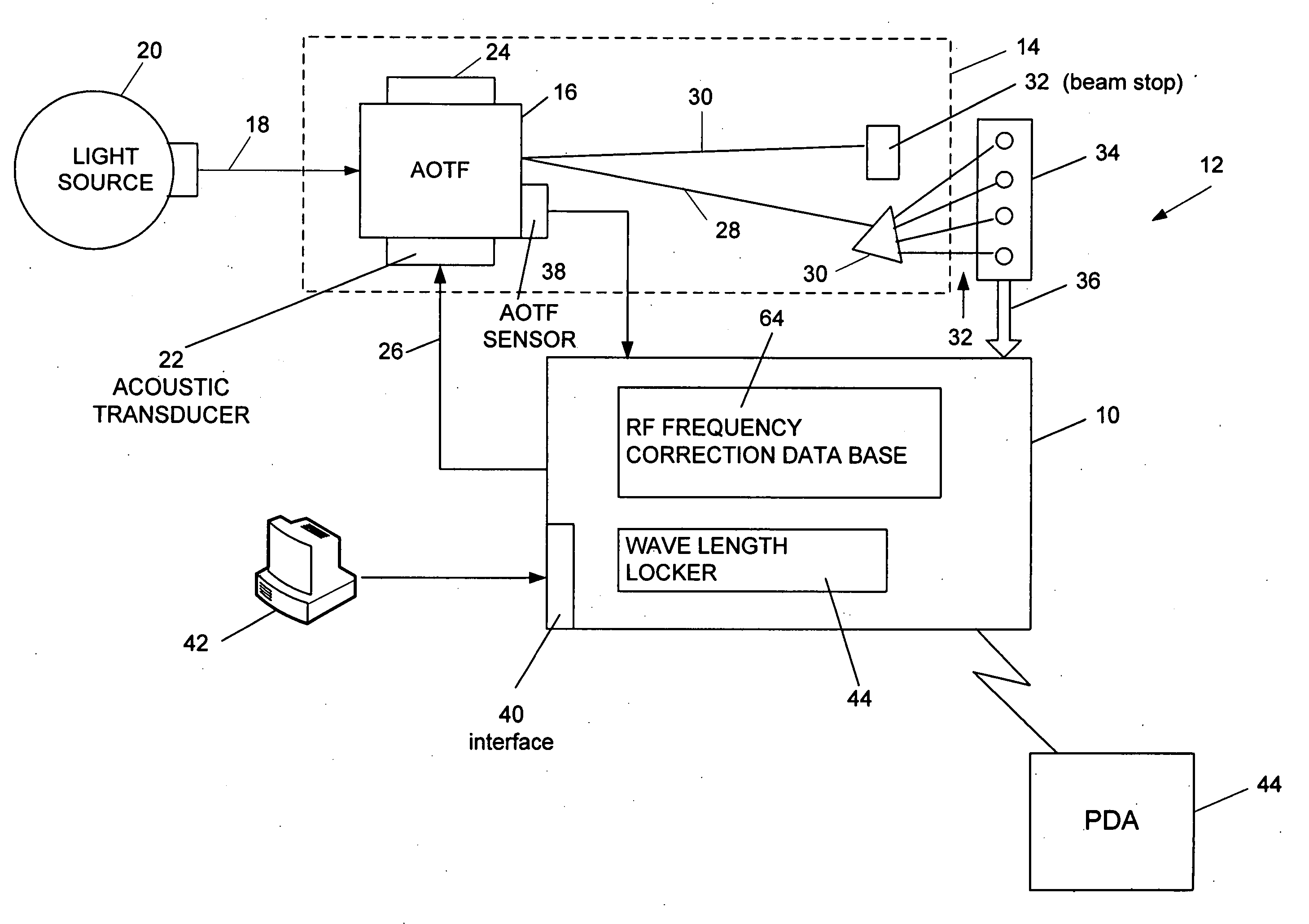

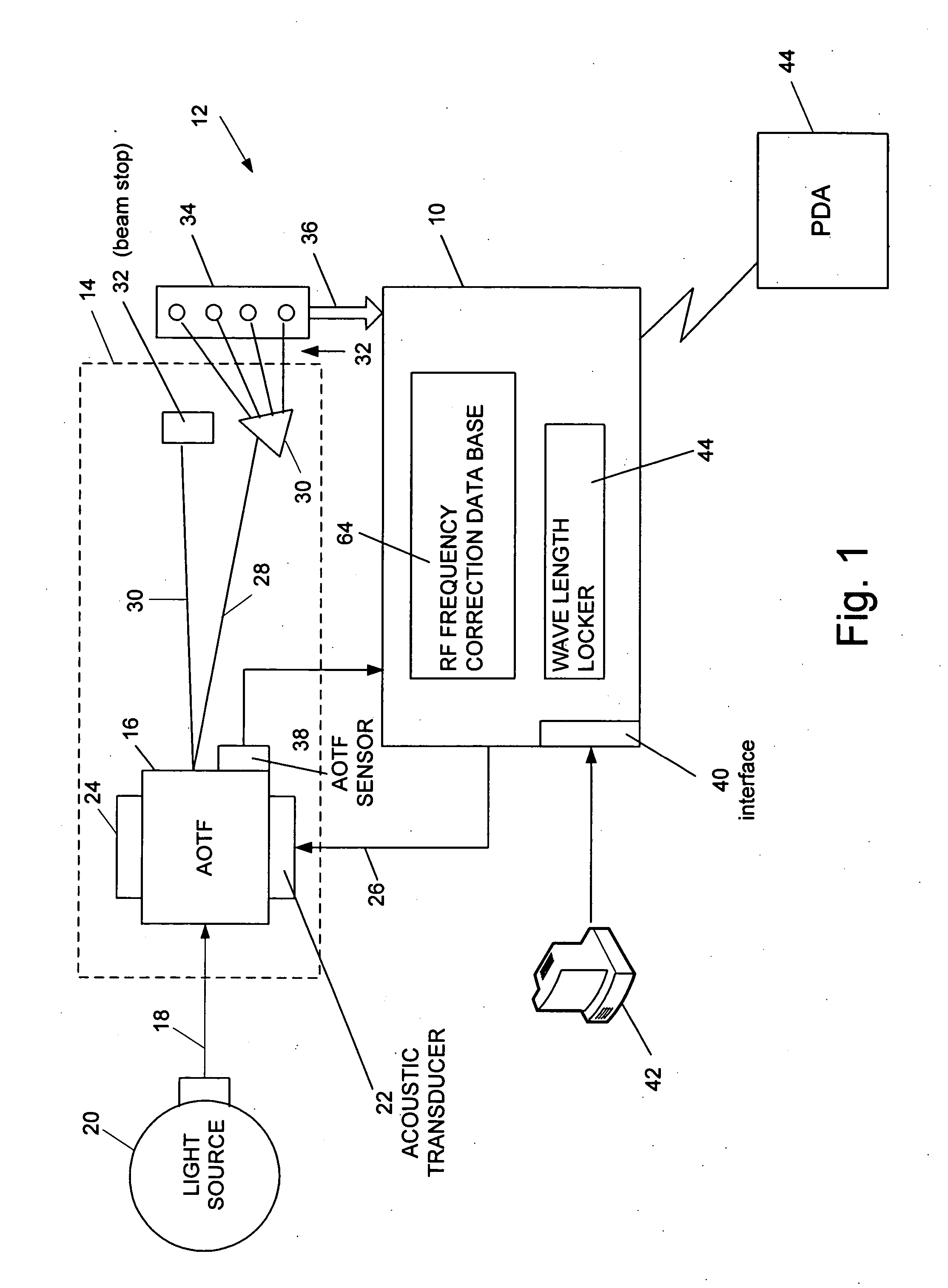

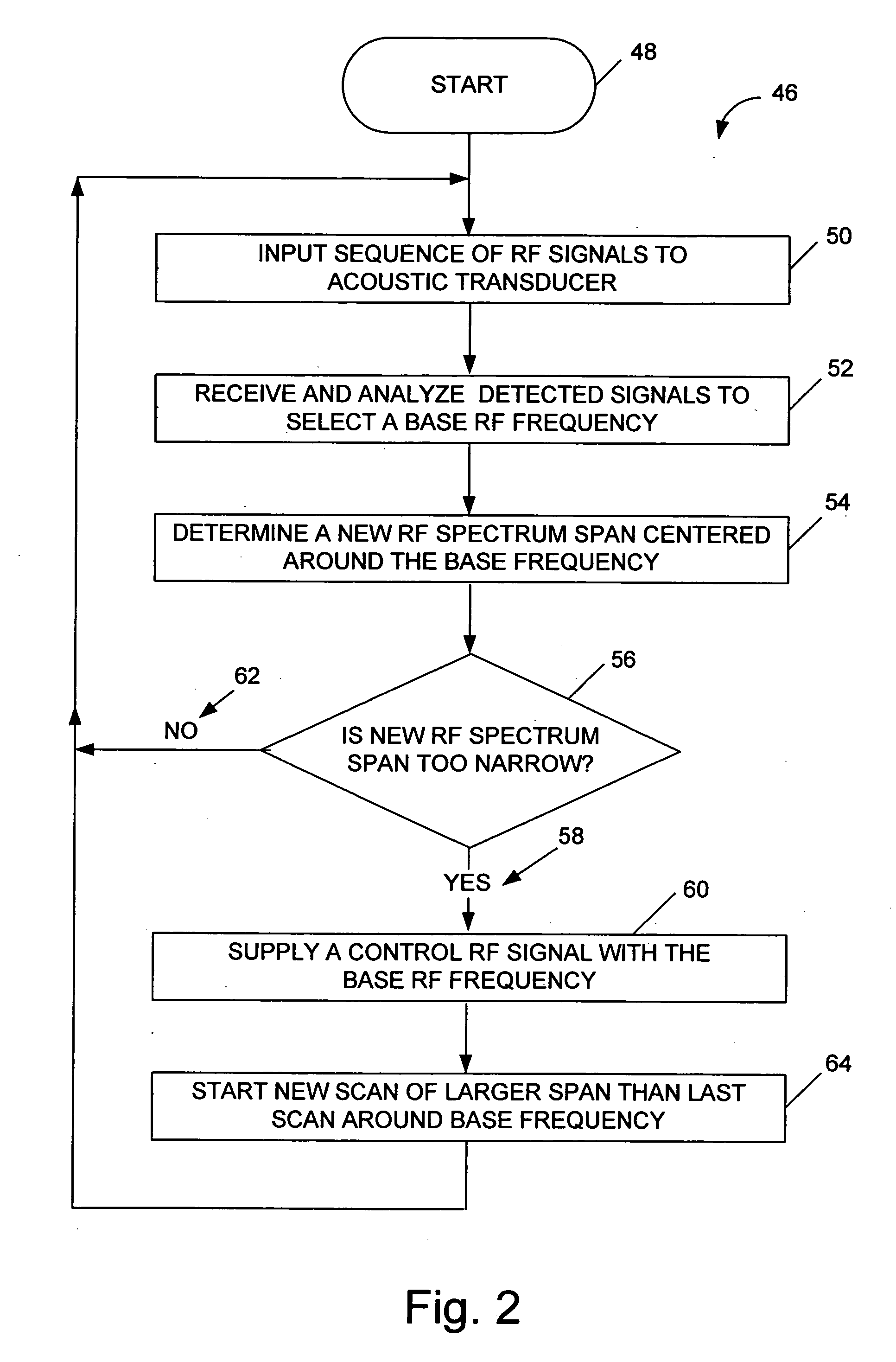

Pillsbury Winthrop Shaw Pittman

AOTF controller that monitors output power of a plurality of wavelengths of an AOTF and scans the frequency of corresponding RF input signals to an AOTF acoustic transducer and searches for the RF frequency corresponding to each desired wavelength that provides maximum optical output for each wavelength. The controller includes a plurality of sensor inputs for monitoring the power of each wavelength output from the AOTF, and alternatively, also monitors other AOTF parameters such as temperature and / or reads AOTF identification performance data that can be stored in a EPROM on a AOTF housing. The controller includes facility for input of modulation data, and in response to the data modulates the corresponding wavelength parameter such as power. A USB bus is provided for input of programming to the controller, and for output of performance data from the controller.

Owner:CRYSTAL TECH