Patents

Literature

2632 results about "Voltage pulse" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

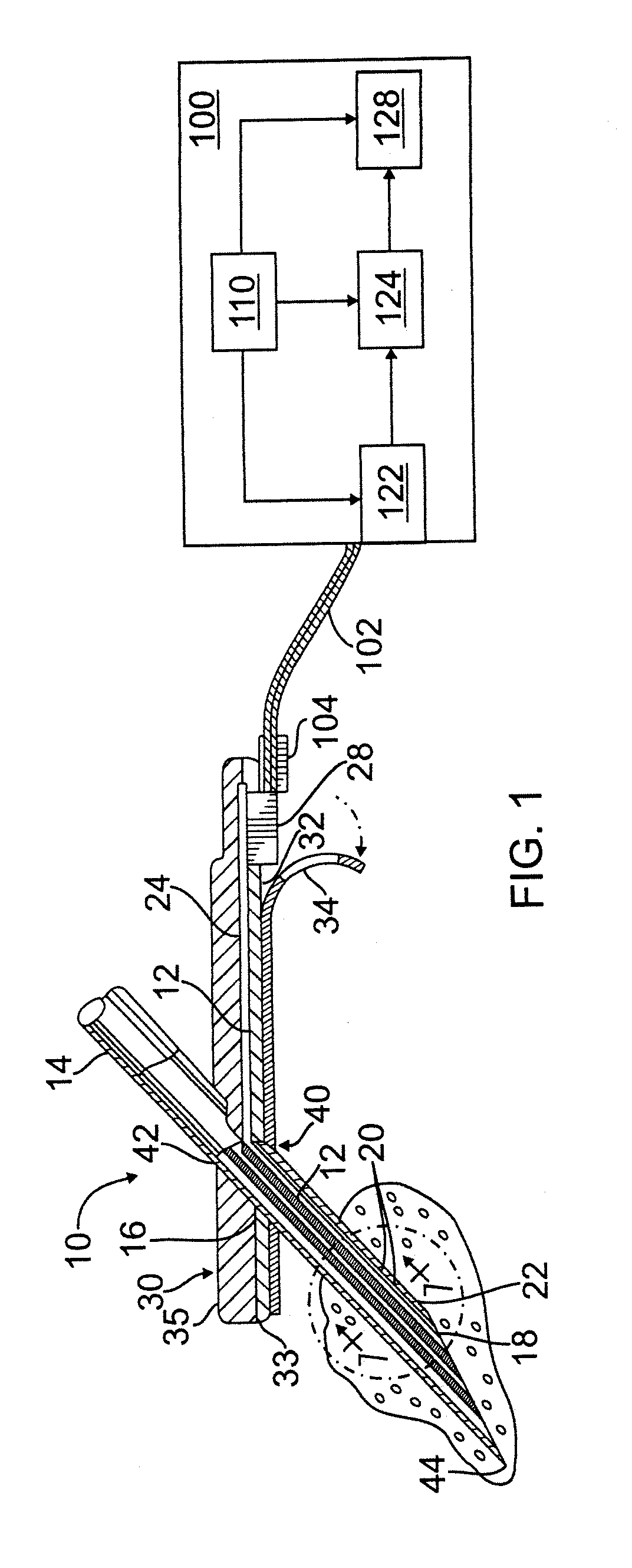

Transducer for embedded bio-sensor using body energy as a power source

InactiveUS20050261563A1Improve accuracyAccurate measurementTelemedicineEndoradiosondesMuscle tissueVoltage pulse

Provided is a bio-sensor system which utilizes radio frequency identification technology and which includes a remote transponder in wireless communication with an implantable on-chip transponder. A power supply collects alternating current voltage pulses from an electro-active polymer generator embedded in muscle tissue for generating power for the on-chip transponder. The power supply is specifically adapted to provide a stable and precise sensor reference voltage to a sensor assembly to enhance the accuracy of measurements of a physiological parameter of a patient. The remote transponder receives data representative of the physiological parameter such as glucose concentration levels. The data is processed and transmitted to the remote transponder by the on-chip transponder. The precision and stability of the sensor reference voltage is enhanced by the specific circuit architecture of a glucose sensor to allow for relatively accurate measurement of glucose concentration levels without the use of a microprocessor.

Owner:JAMM TECH INC

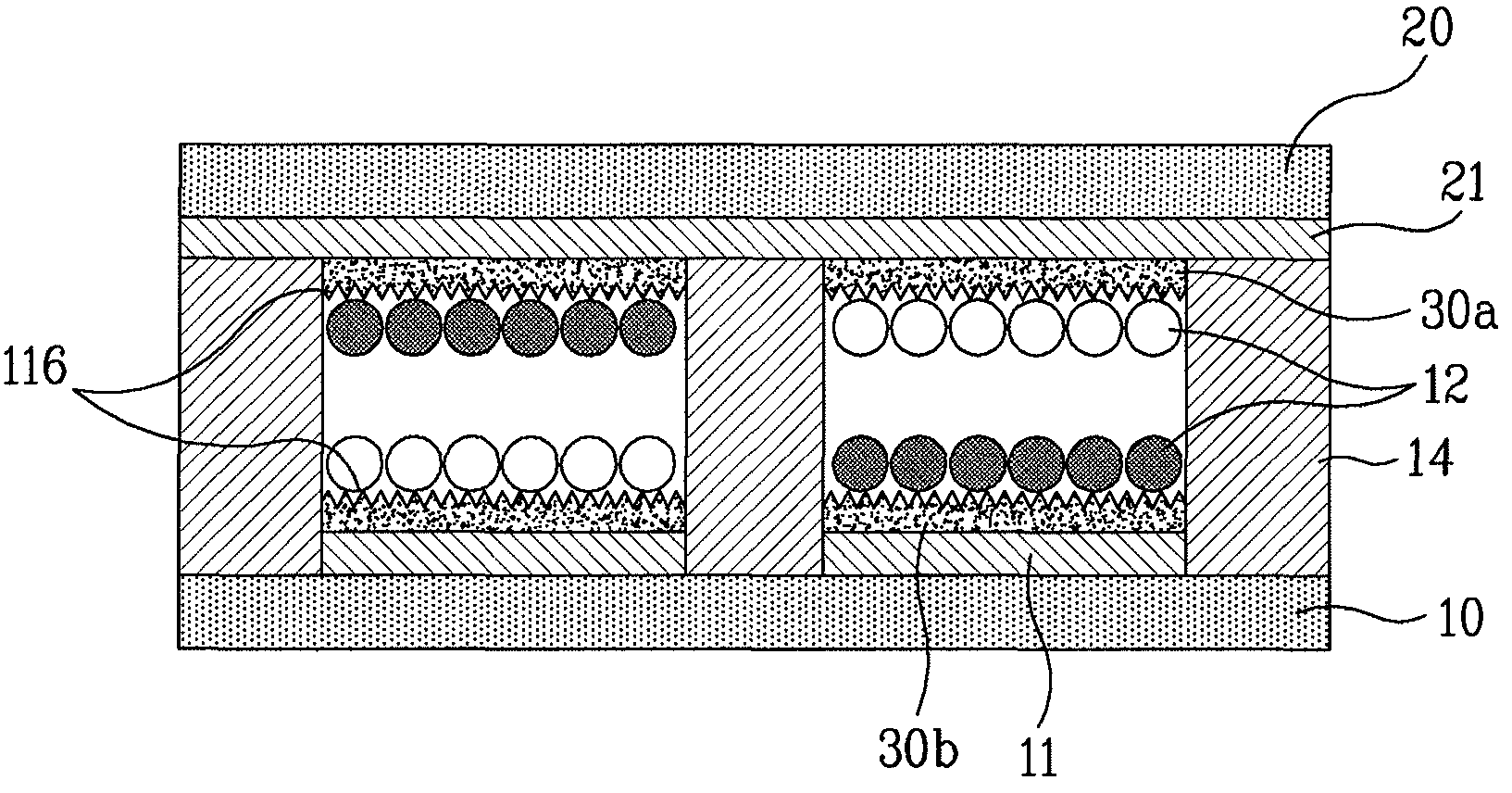

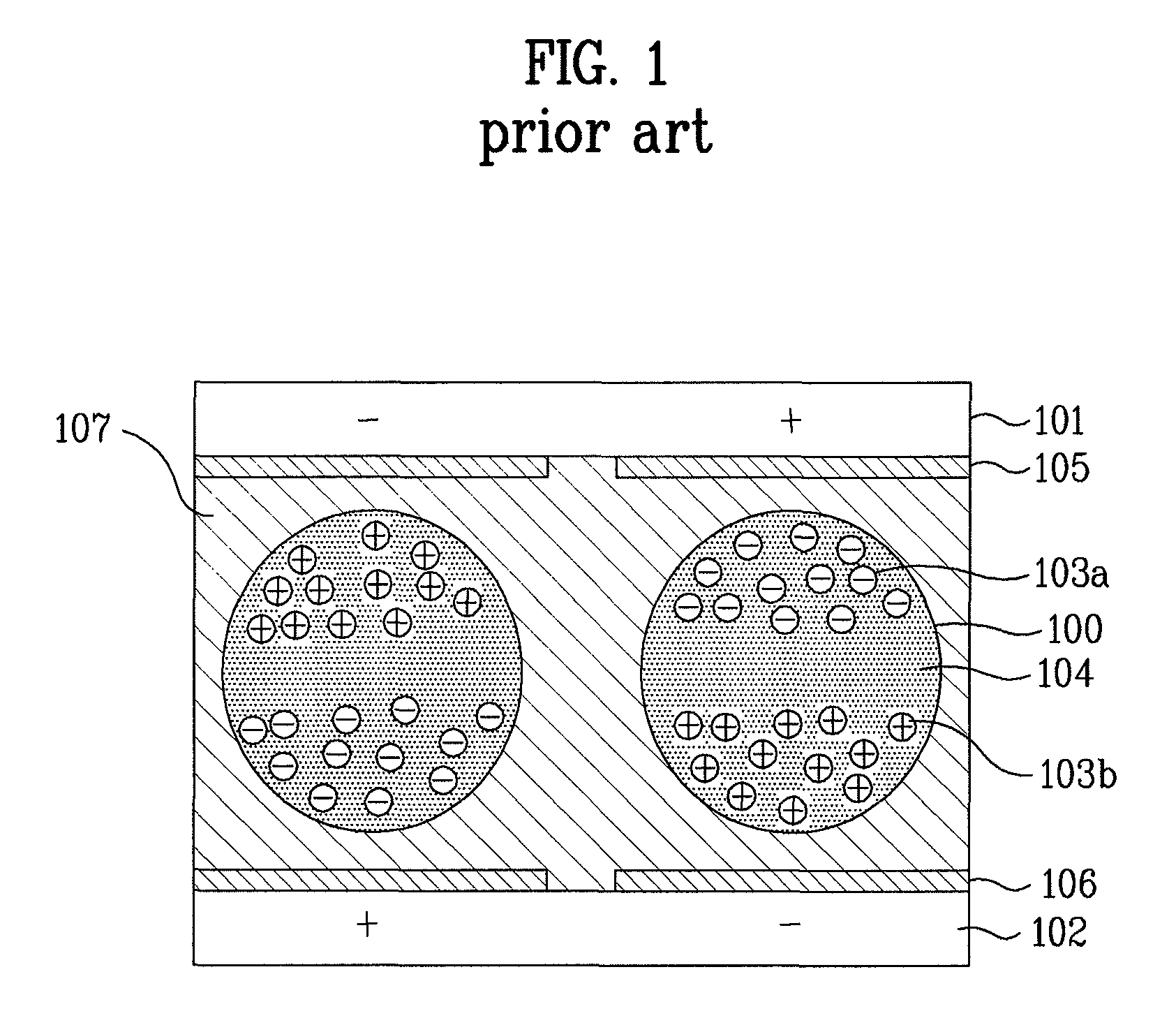

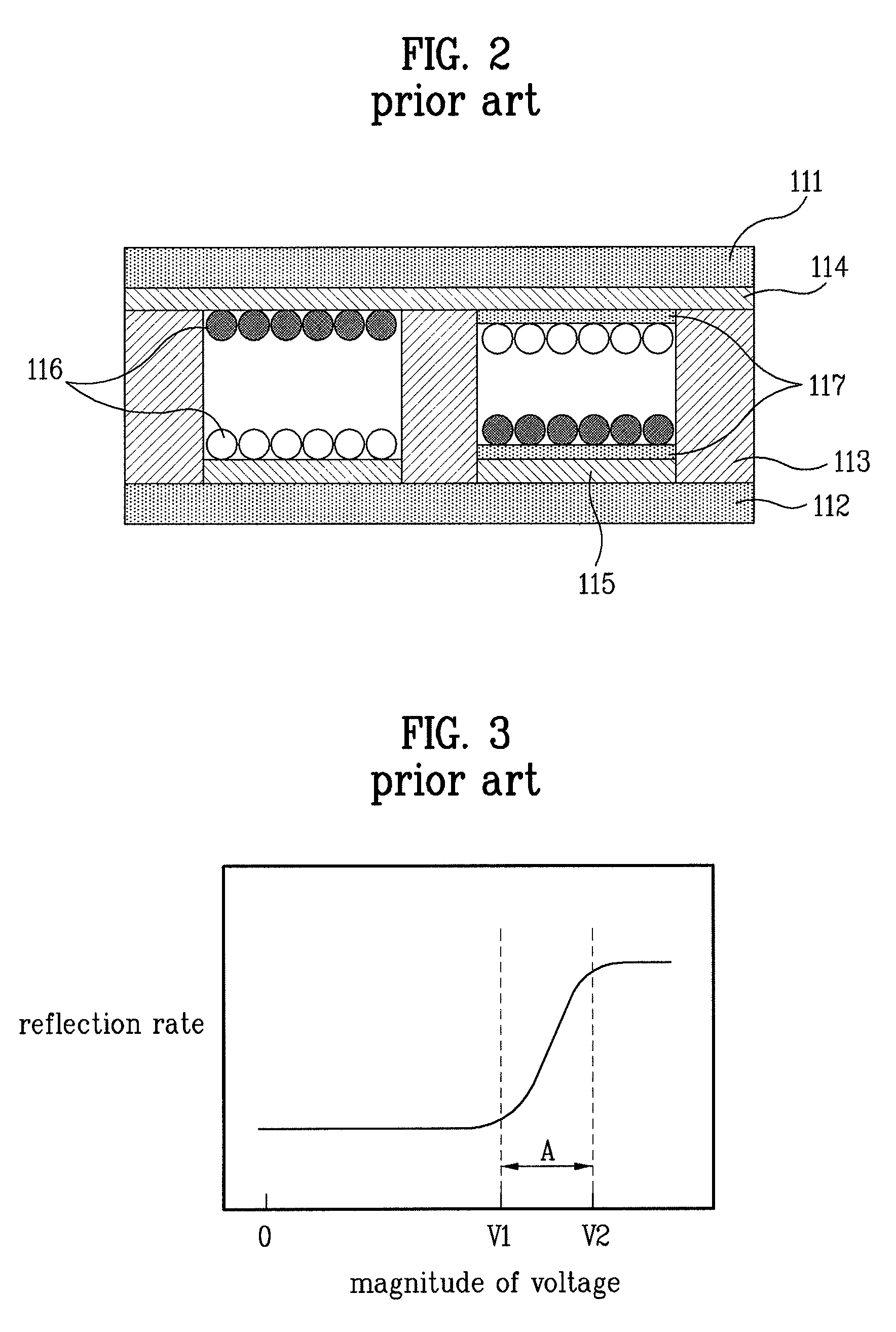

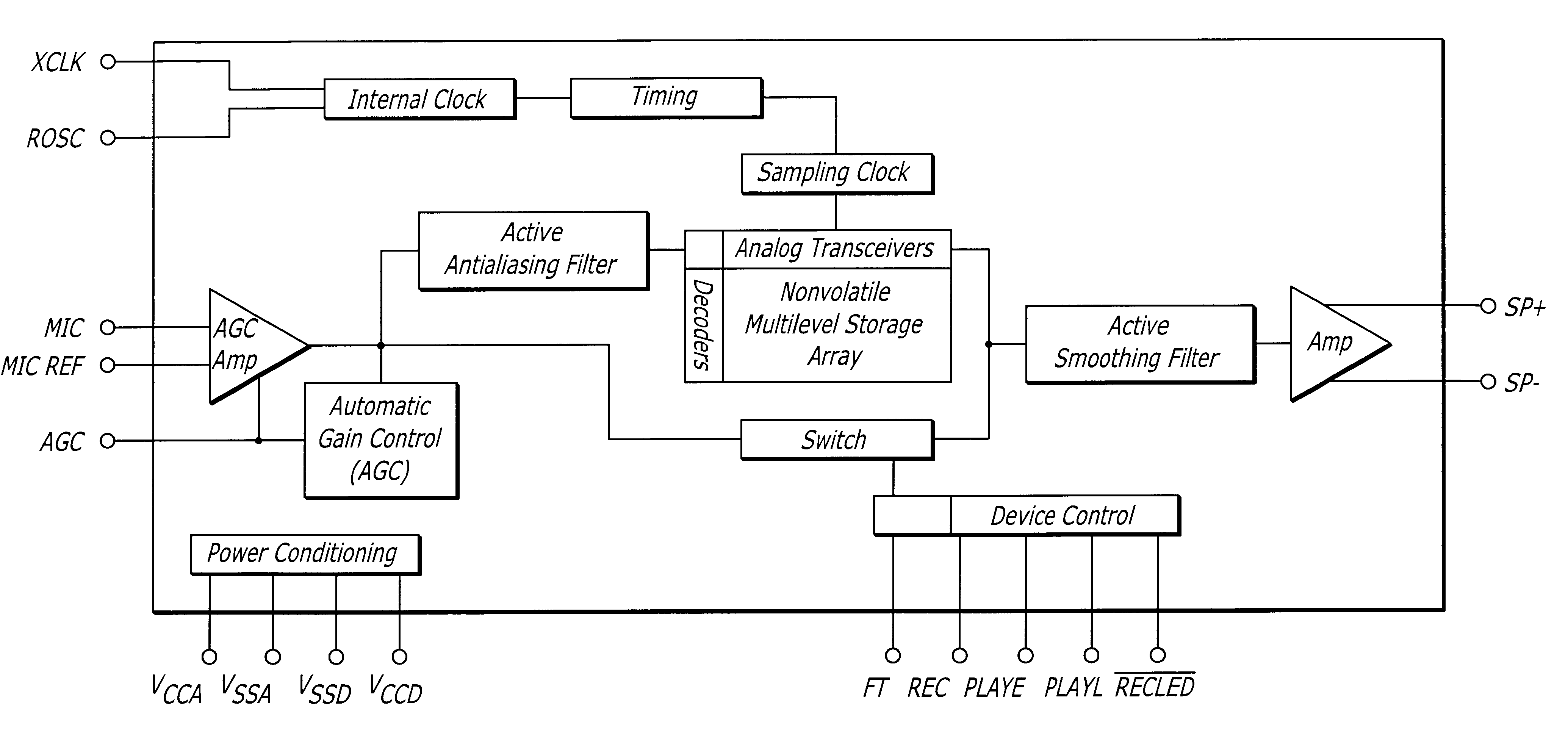

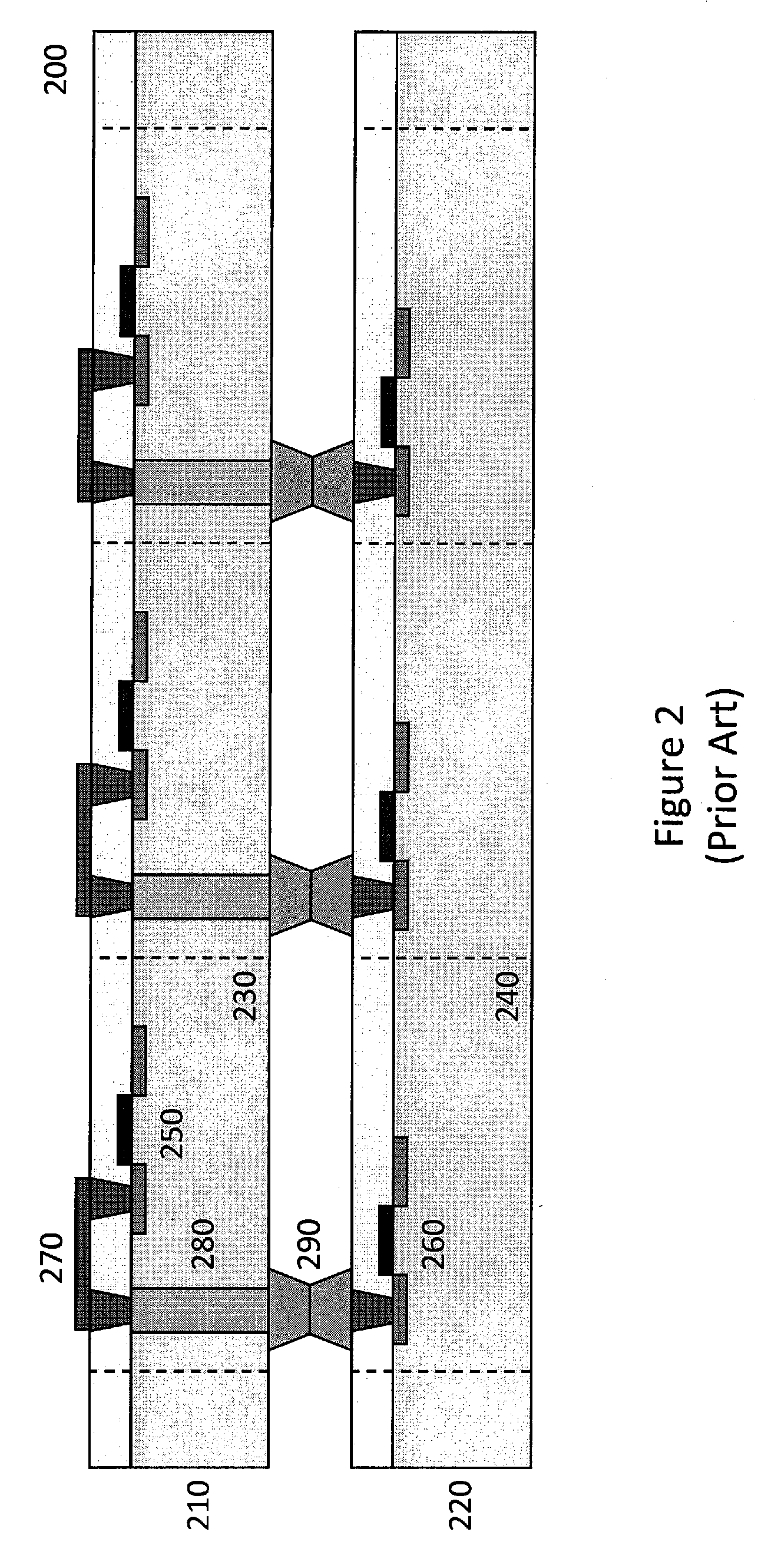

Electronic paper display device, manufacturing method and driving method thereof

InactiveUS7751115B2Quick responseReduce voltageStatic indicating devicesNon-linear opticsVoltage pulseElectrophoresis

An electronic paper display device, a manufacturing method and a driving method thereof are disclosed. Micro protrusion members are formed at electrodes or at insulating layers. Consequently, the electrophoretic particles are prevented from being securely attached to an upper or the lower structure, and therefore, the quality of pictures is improved, and the contrast ratio of the pictures is increased. The relative sizes and the injection amounts of two kinds of electrophoretic particles are changed such that the relative sizes and the injection amounts of the electrophoretic particles are different from each other. Consequently, the driving voltage is lowered by excessively electrifying the electrophoretic particles of one kind. Protrusions are formed at the corresponding electrode such that a relatively large electric field is distributed around the electrode at which electrophoretic particles are located in the initial stage of voltage application. Consequently, the electrophoretic particles are easily separated from the electrode and moved even at low driving voltage. As such, the voltage level of the driving voltage pulse is lowered. Consequently, it is possible to further increase the response speed of the driving devices and to lower the internal voltage of the devices, thereby reducing the costs related to the driving devices.

Owner:LG ELECTRONICS INC

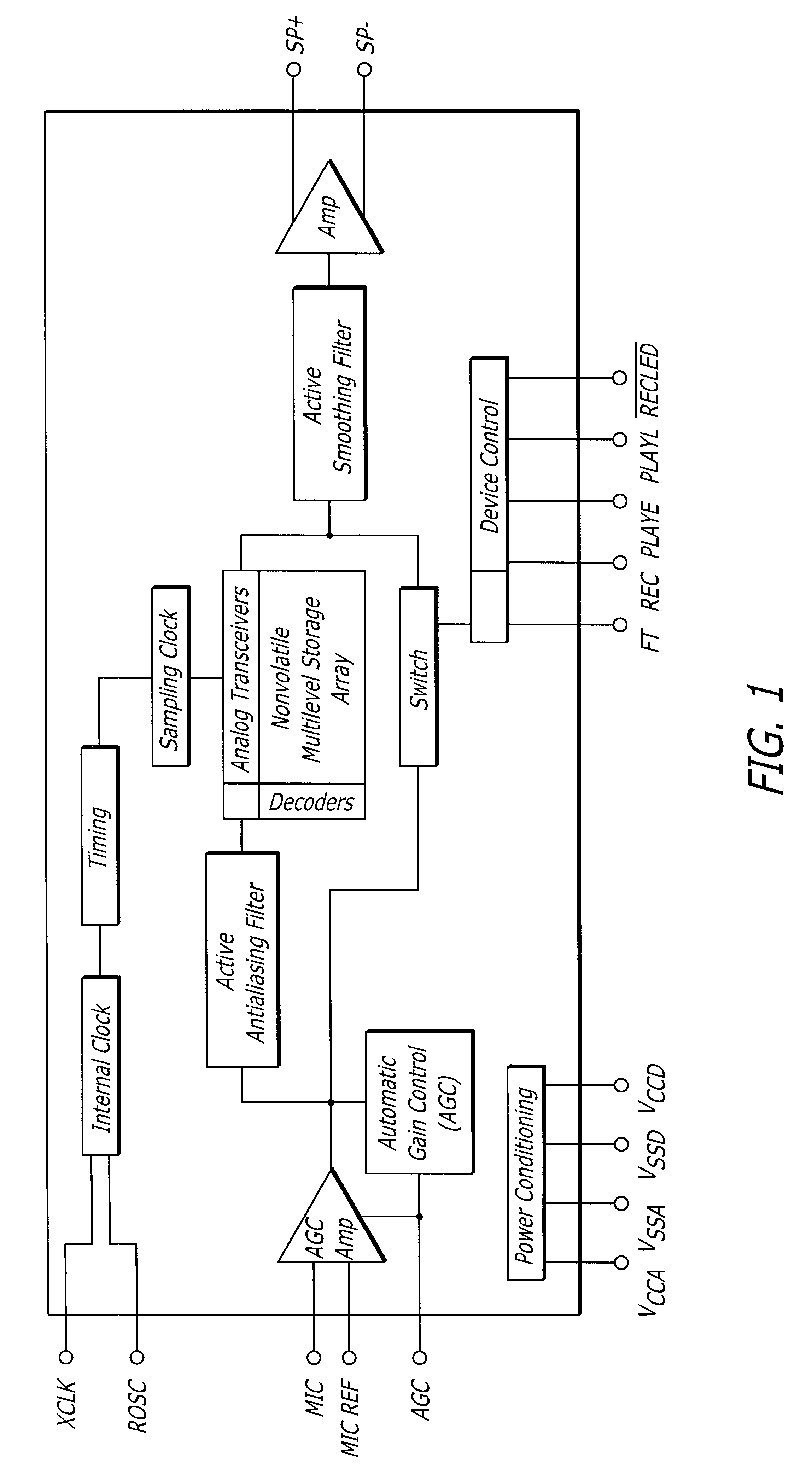

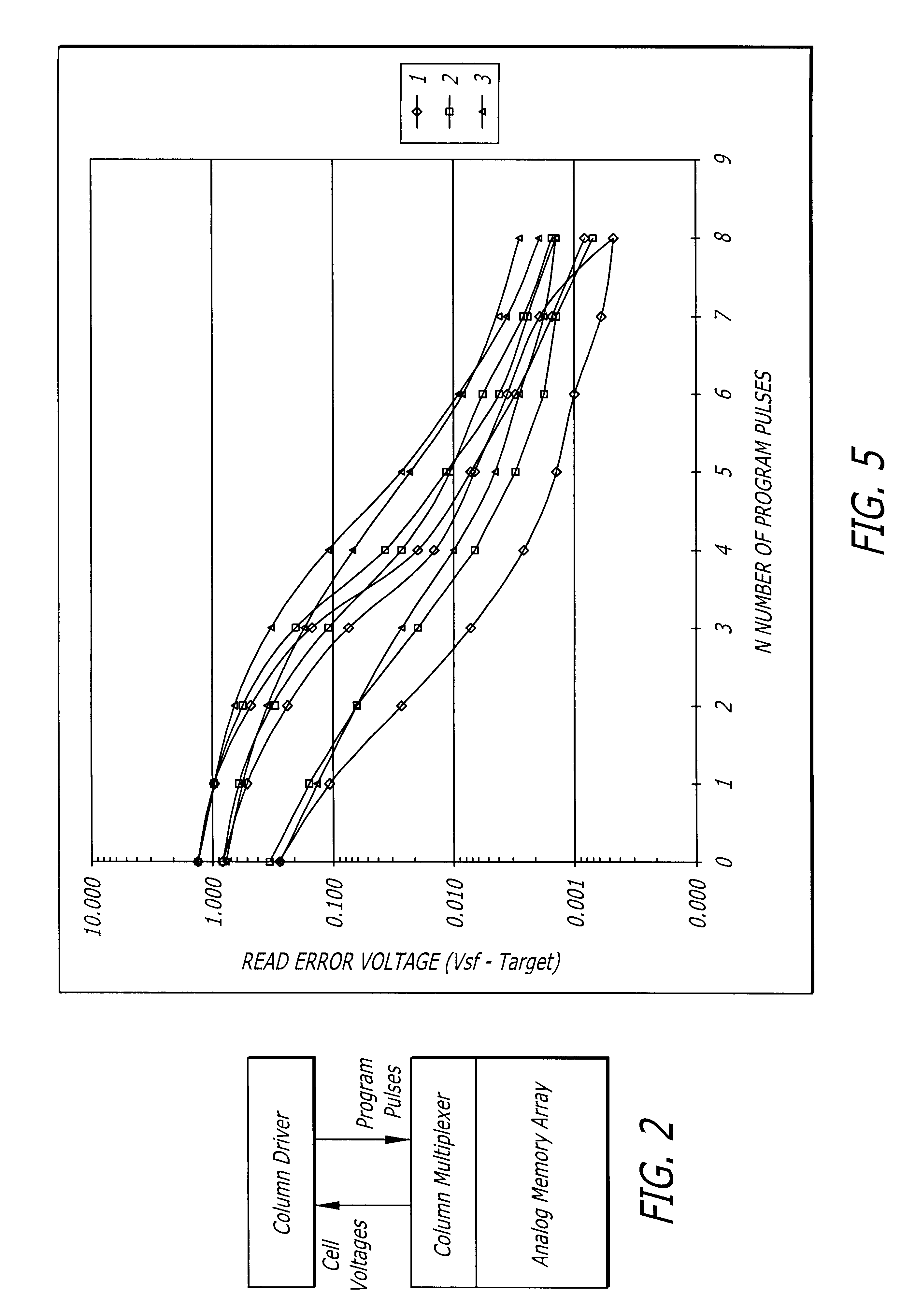

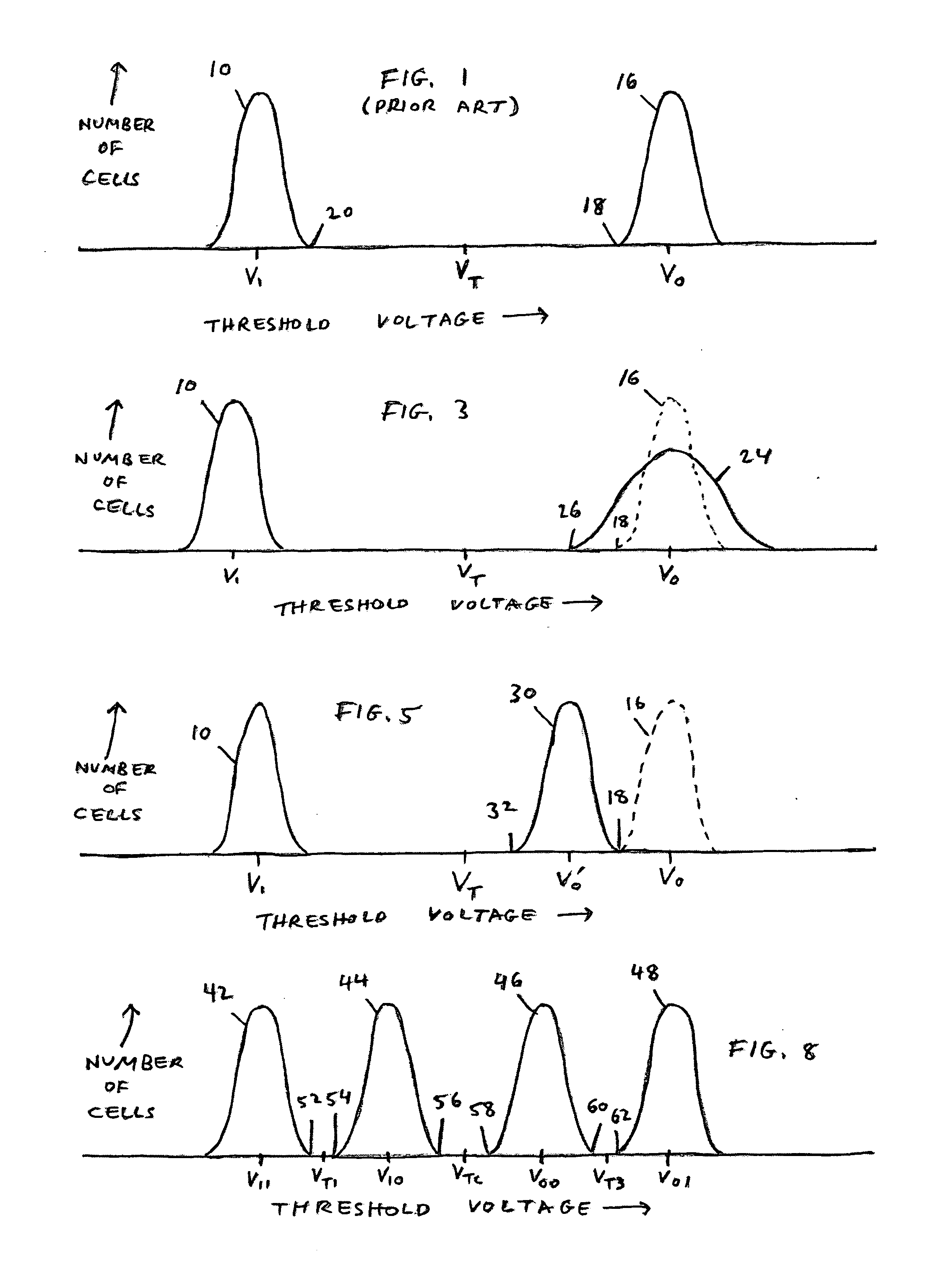

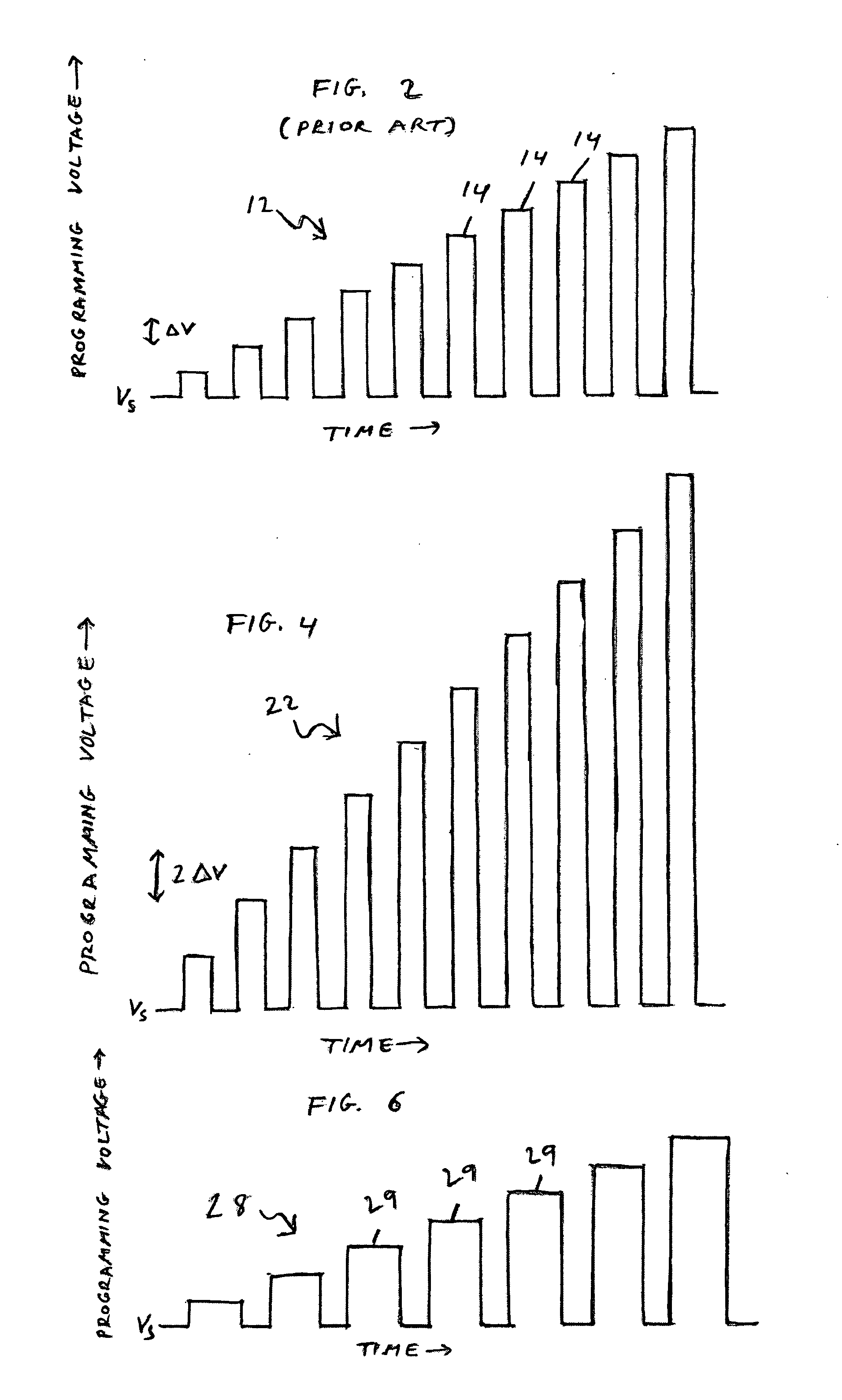

Adaptive programming method and apparatus for flash memory analog storage

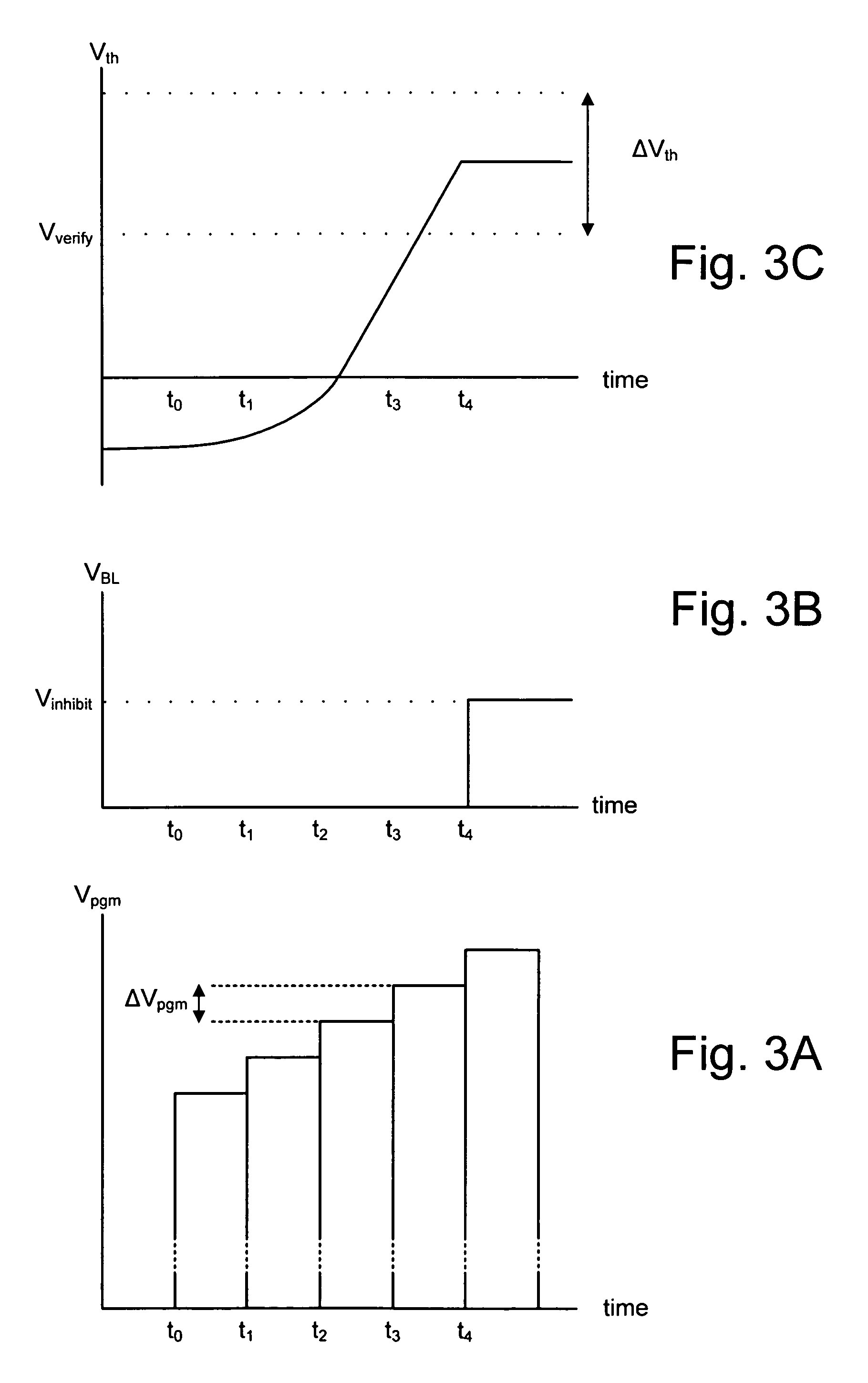

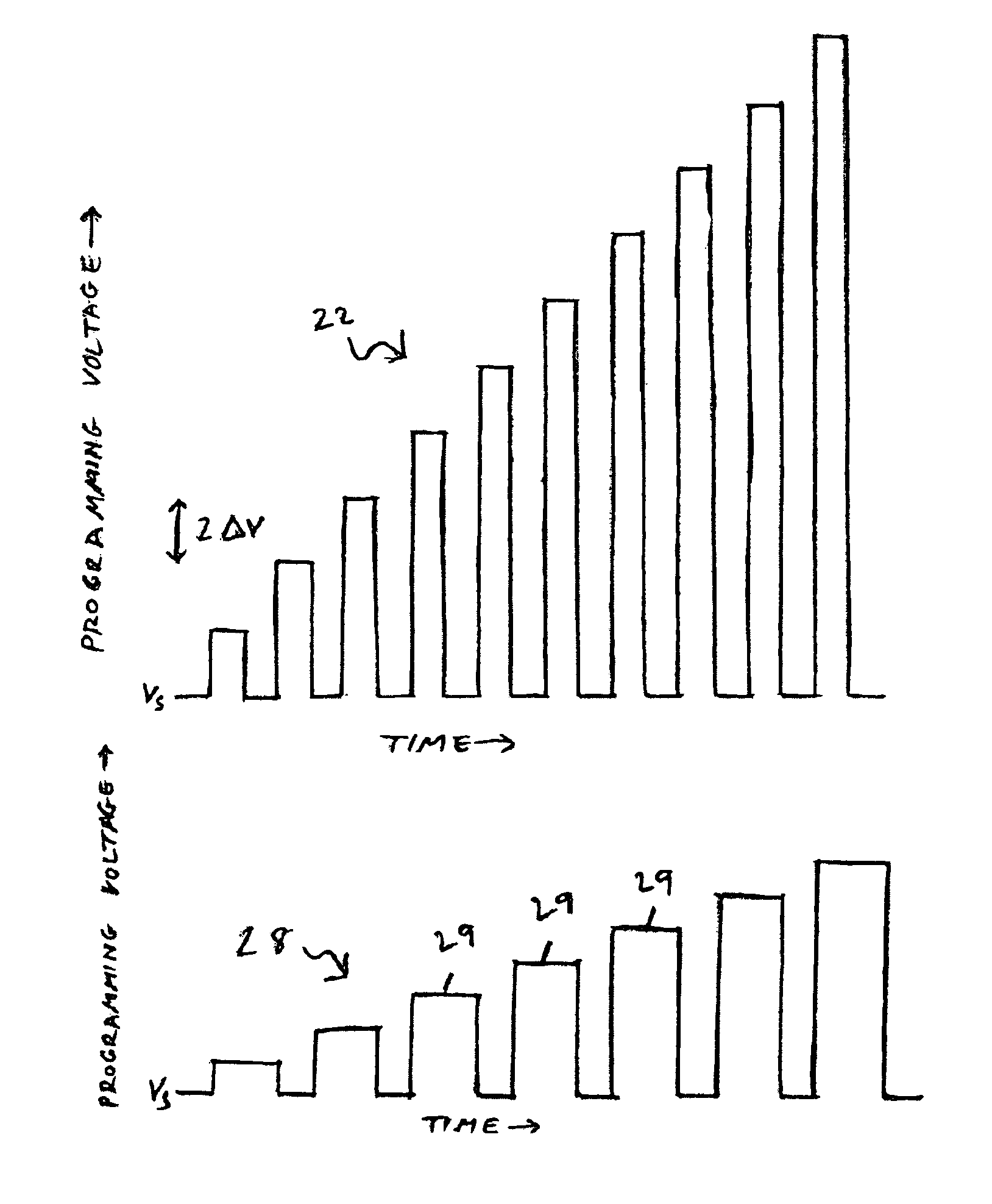

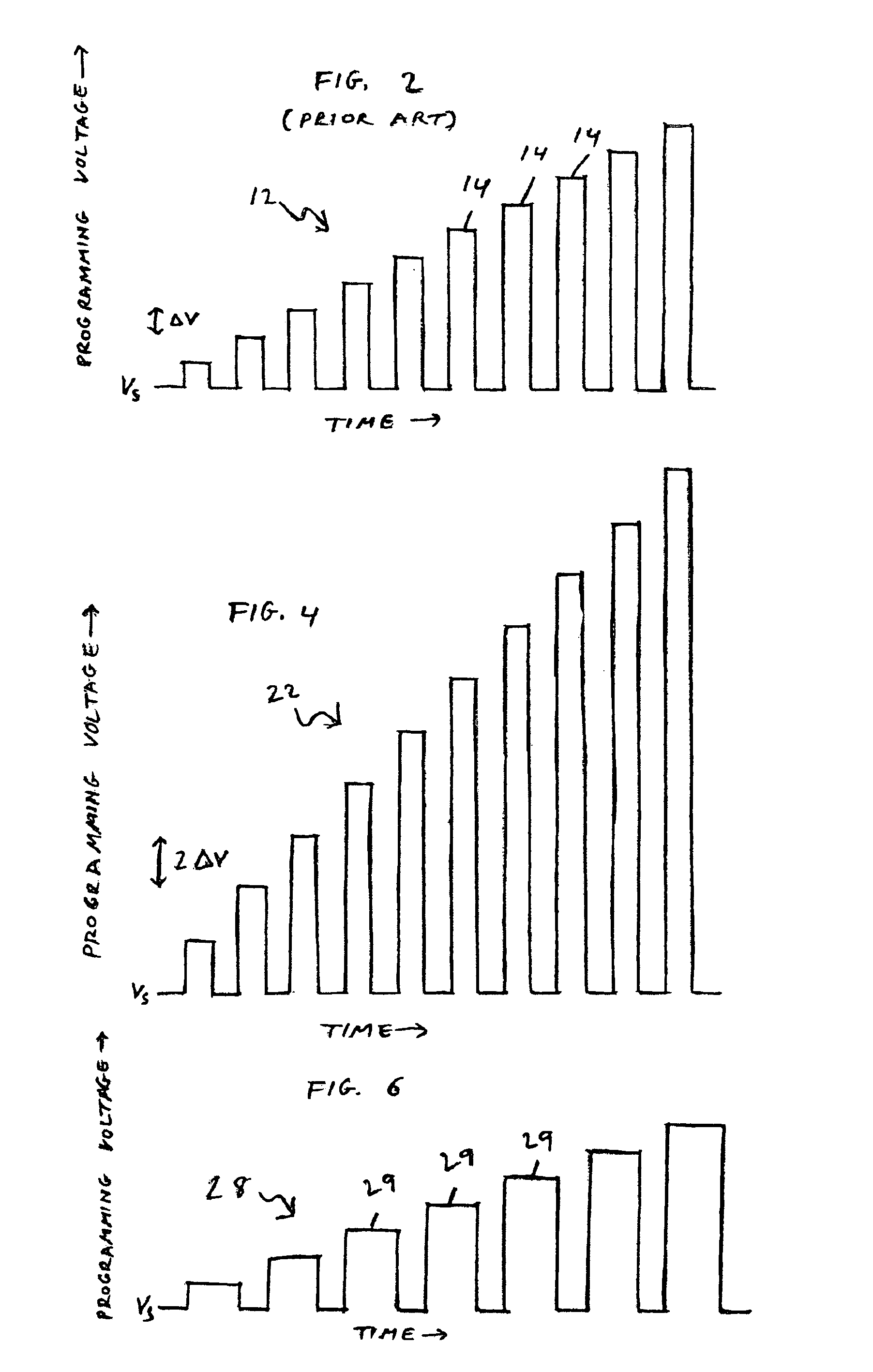

Adaptive programming method and apparatus for flash memory analog storage. The present invention method is to adjust the voltage of the programming pulse each time based on the result of the previous pulse. The expected change in the programmed value is compared to the measured change, and the difference used to improve the model of that cell after each programming pulse. The algorithm is "adaptive" because the voltage of each pulse is adapted to whatever the cell needs. If the cell is programming too slowly, the voltage is increased dramatically to make it faster. Conversely if the results show that a particular cell is programming too fast, the next voltage pulse is increased by only a small amount (or even decreased if necessary). Because the response of the cell is non-linear, a special analog circuit is used to calculate the optimum voltage for each pulse. As one alternative, a digital calculation may also be used to program the cells. Because of the programming speed of the exemplary method, a voice signal may be sampled and stored in flash memory one cell at a time. Variable programming parameters other than voltage may be used if desired.

Owner:WINBOND ELECTRONICS CORP

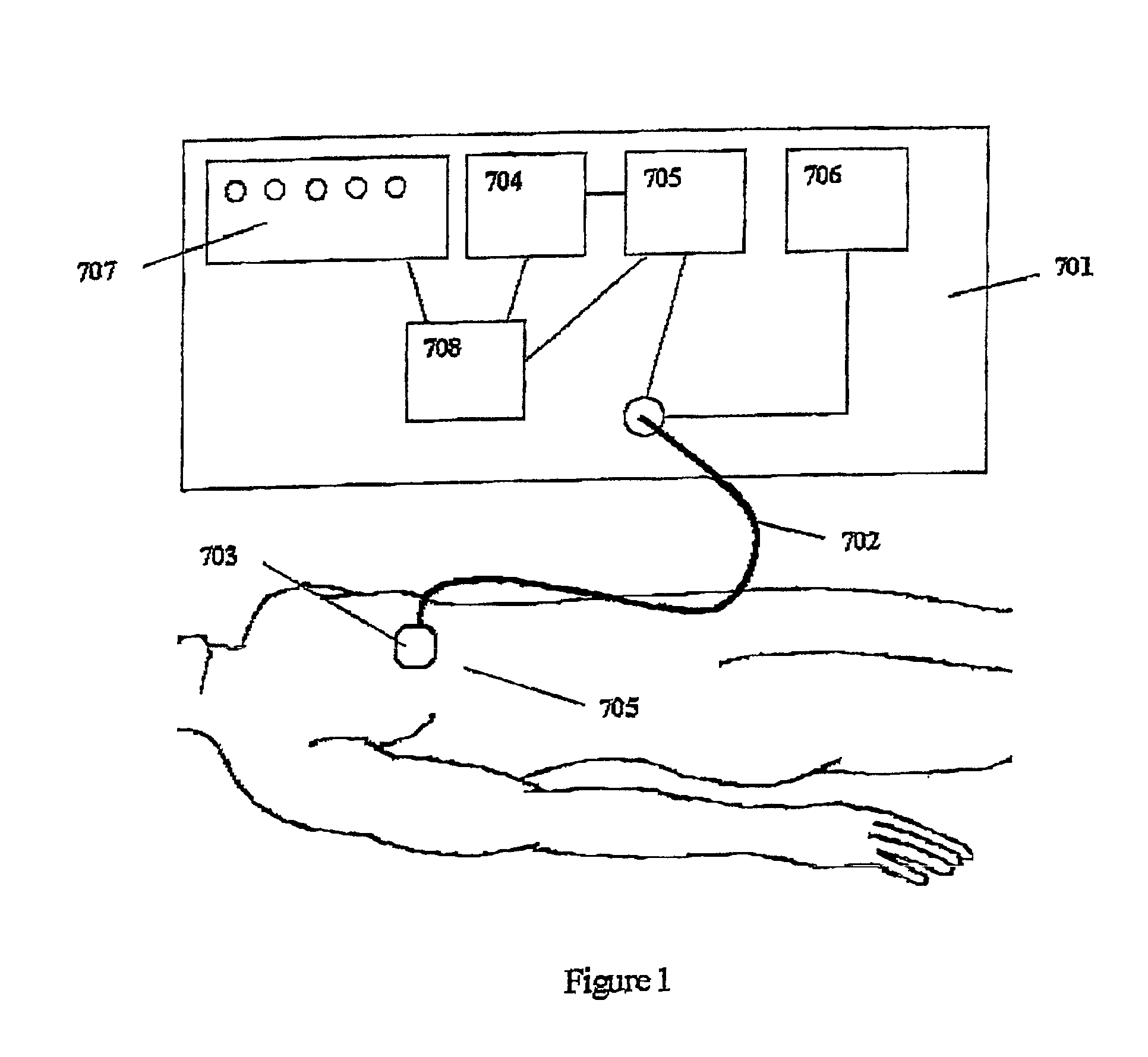

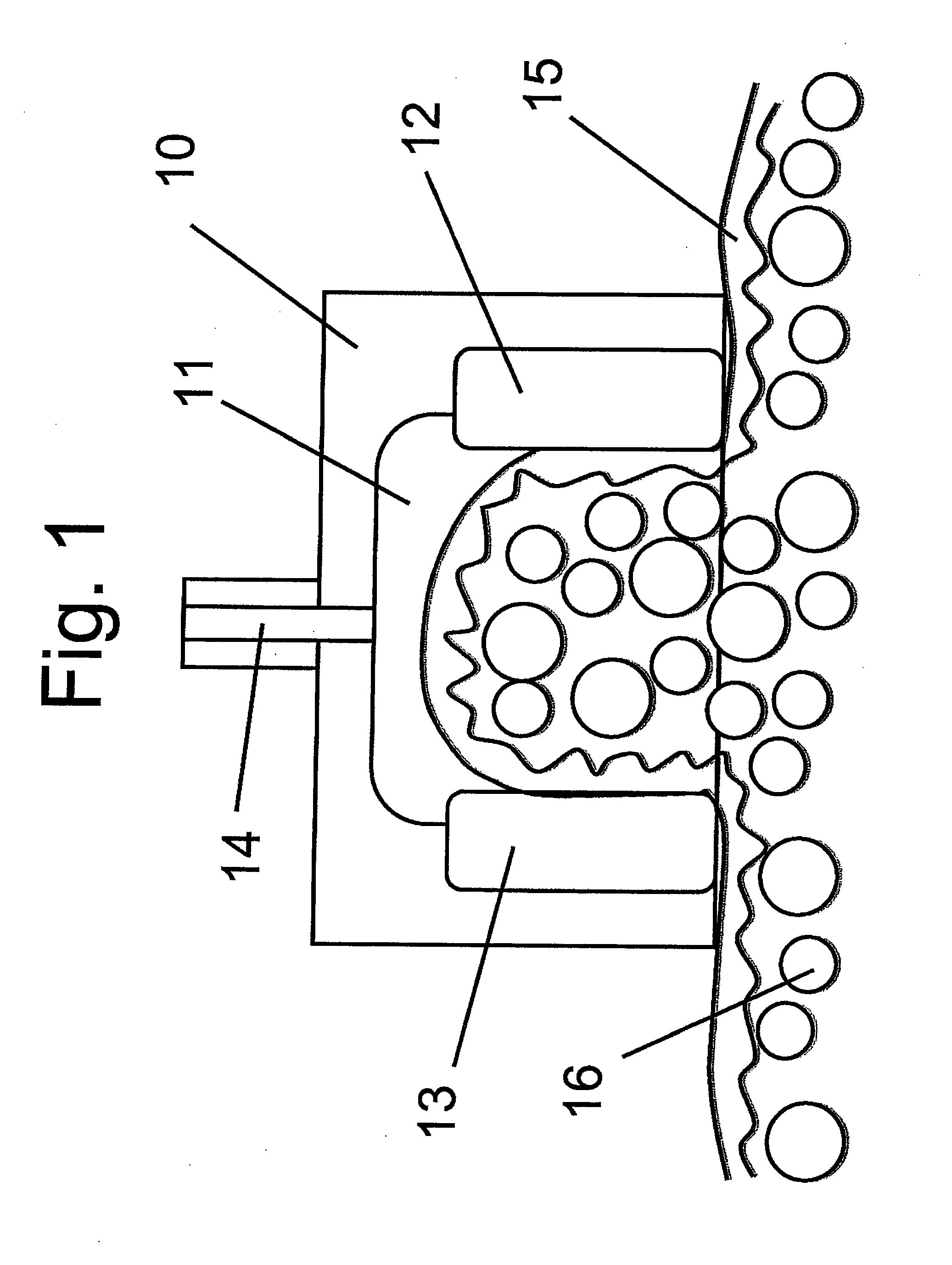

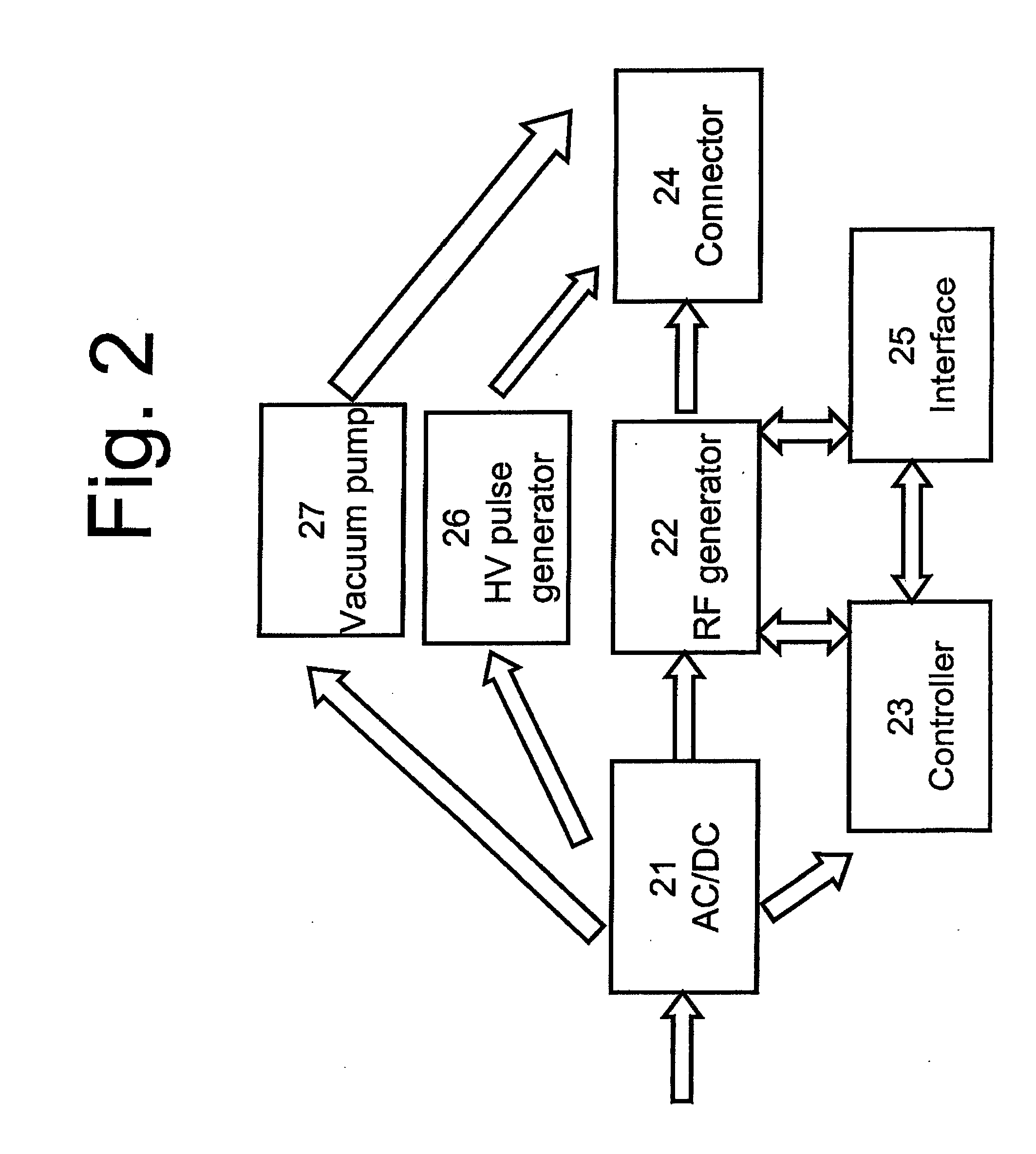

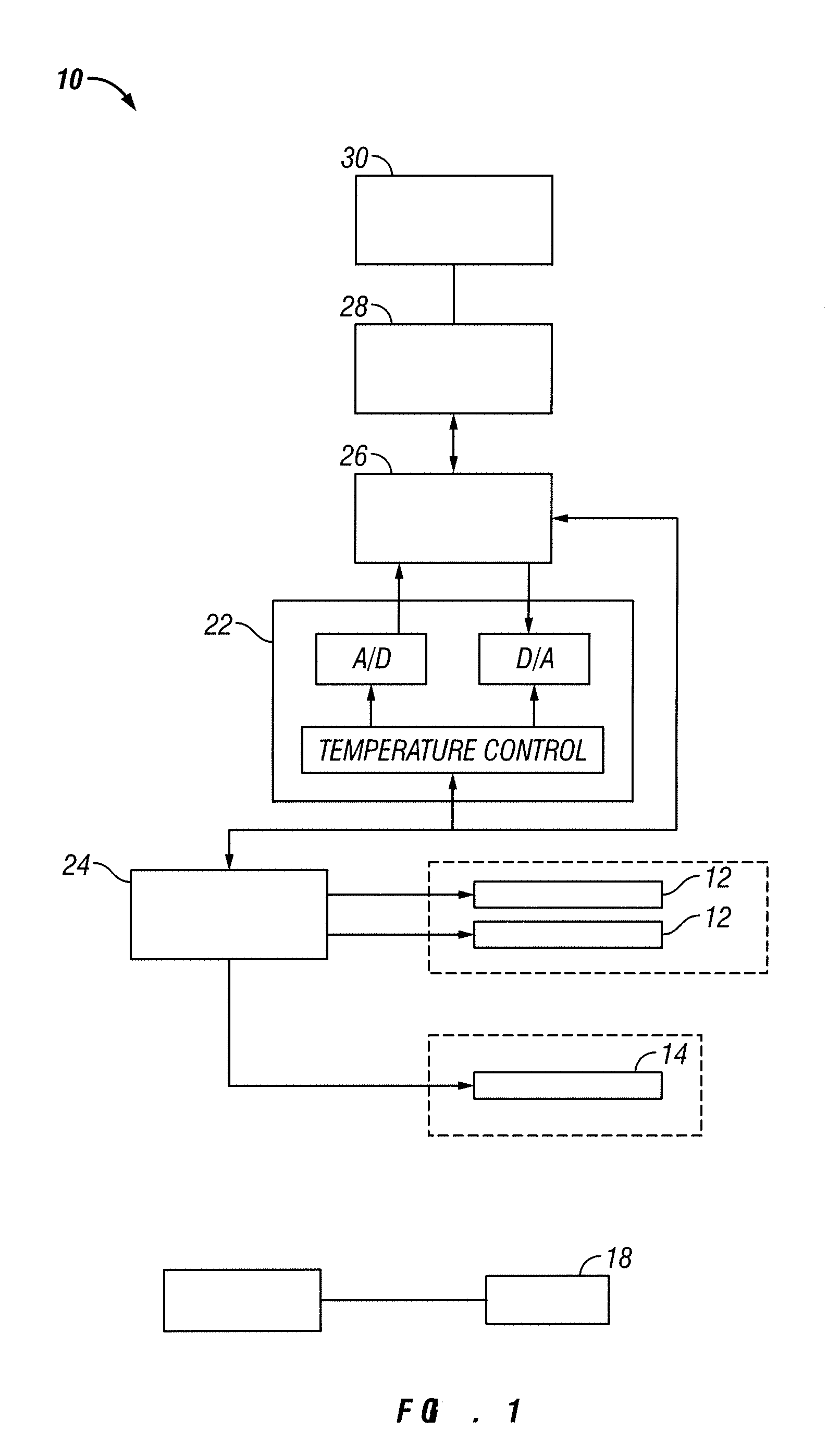

System and method for skin treatment using electrical current

InactiveUS6889090B2Improve permeabilityHigh calorific valueElectrotherapyTherapeutic coolingSkin treatmentsVoltage pulse

A system and method for selective thermal treatment of skin irregularities. The system comprises one or more RF electrodes that are adapted to apply RF energy to the skin. An RF pulse generator generates voltage pulses in the RF range at the electrodes, where the voltage pulses have a duration of 2-500 ms. The method comprises applying RF electrodes to the skin and generating voltage pulses at the electrodes in the RF range, where the pulses have a duration in the range of 2-500 ms.

Owner:SYNERON MEDICAL LTD

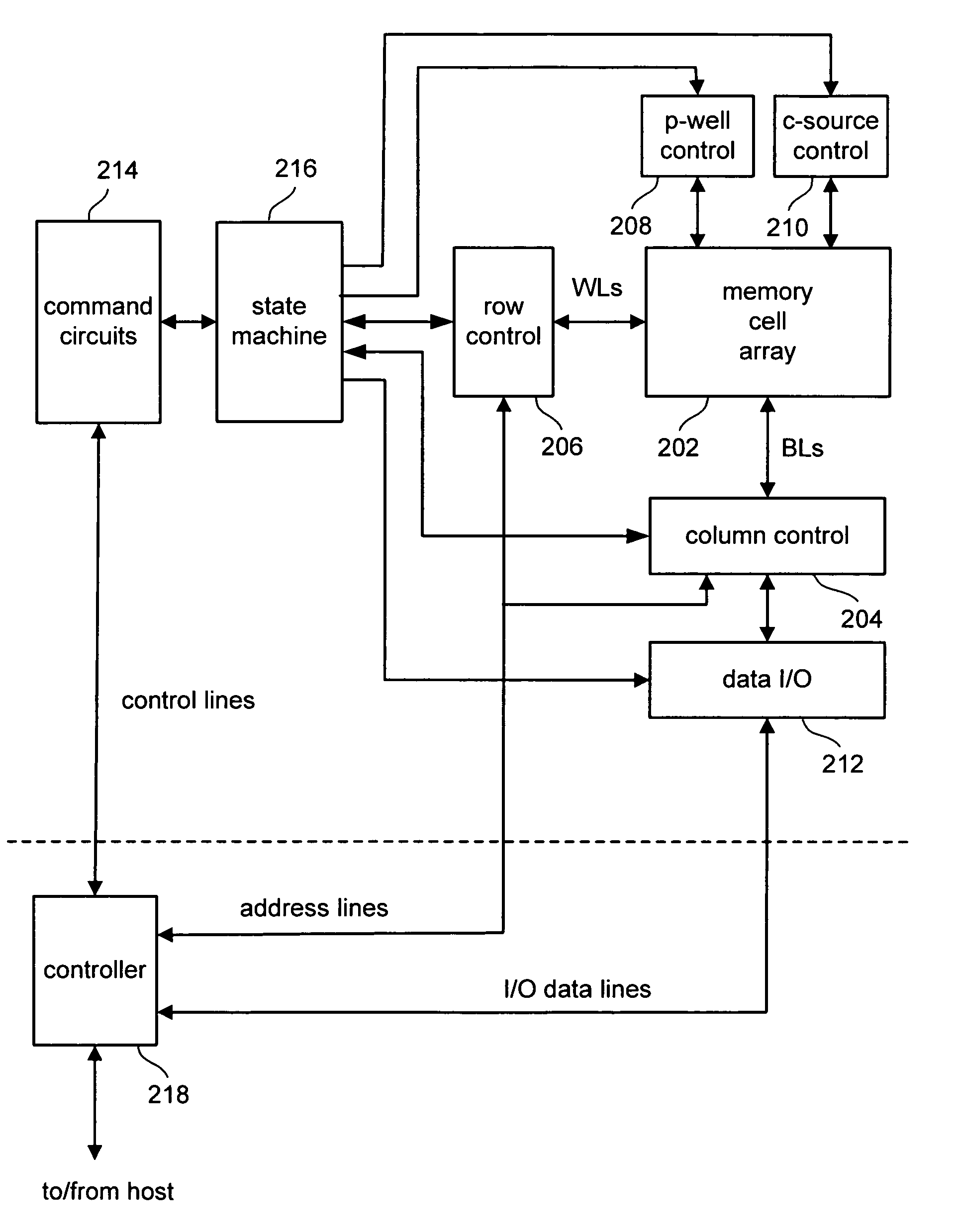

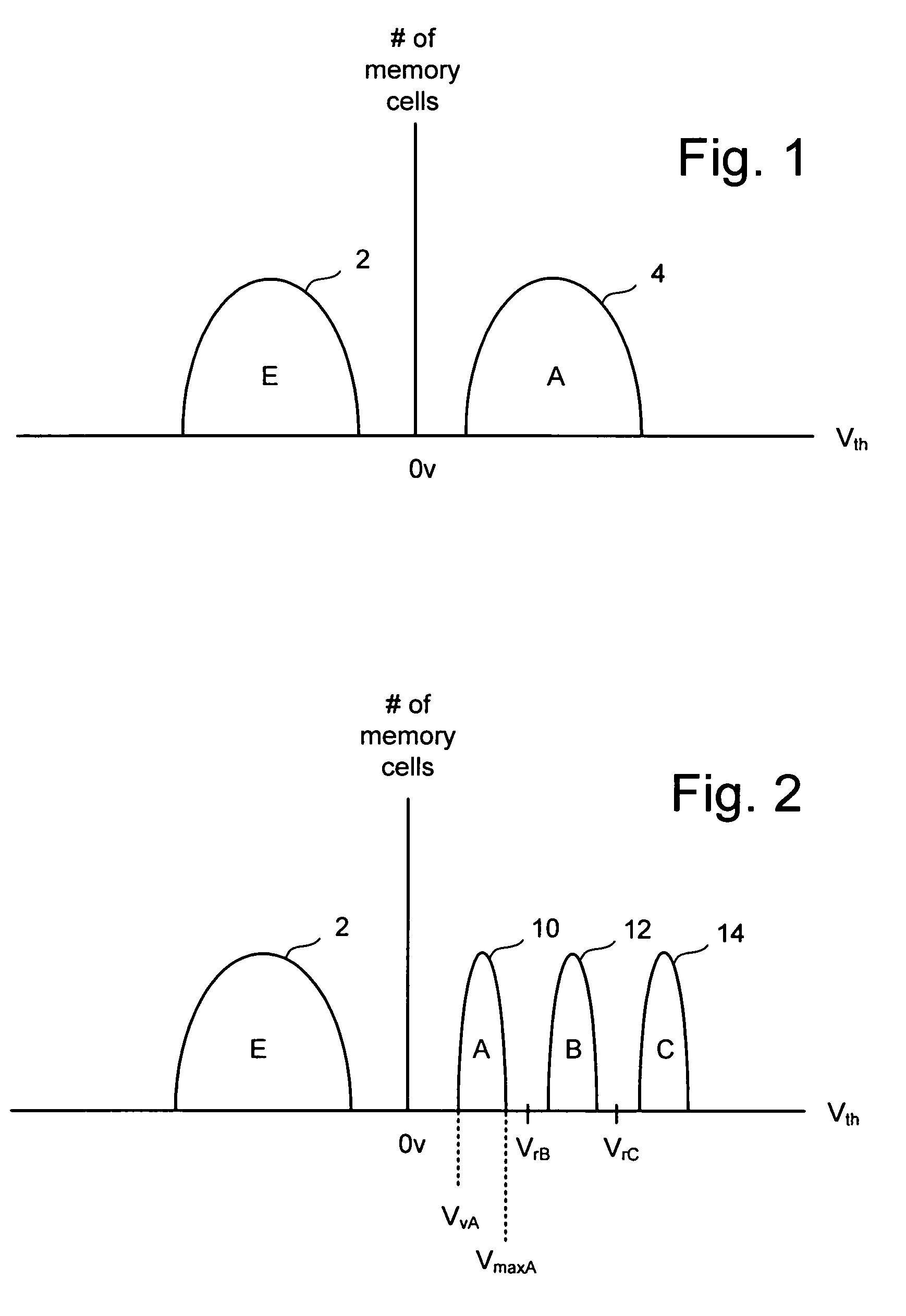

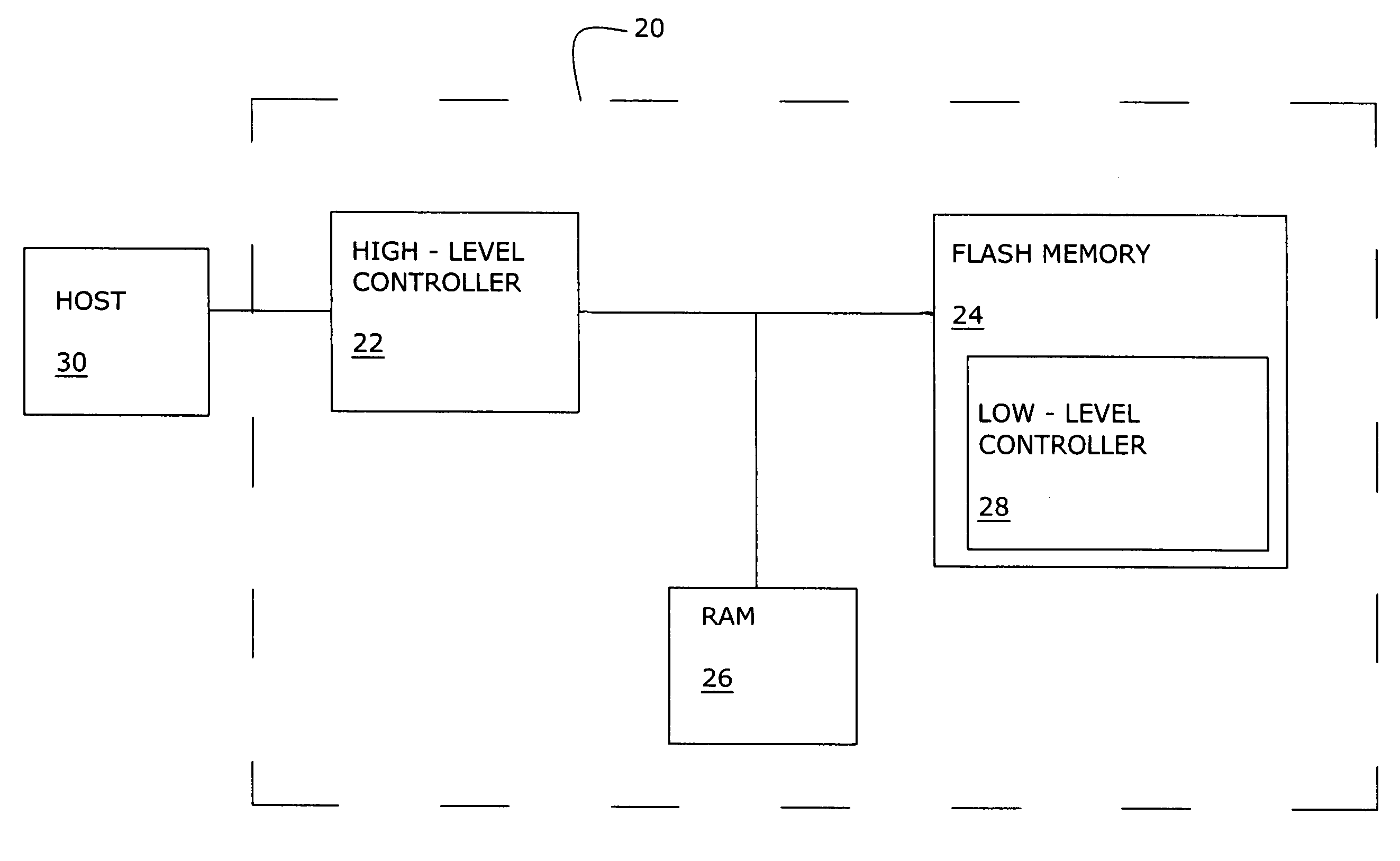

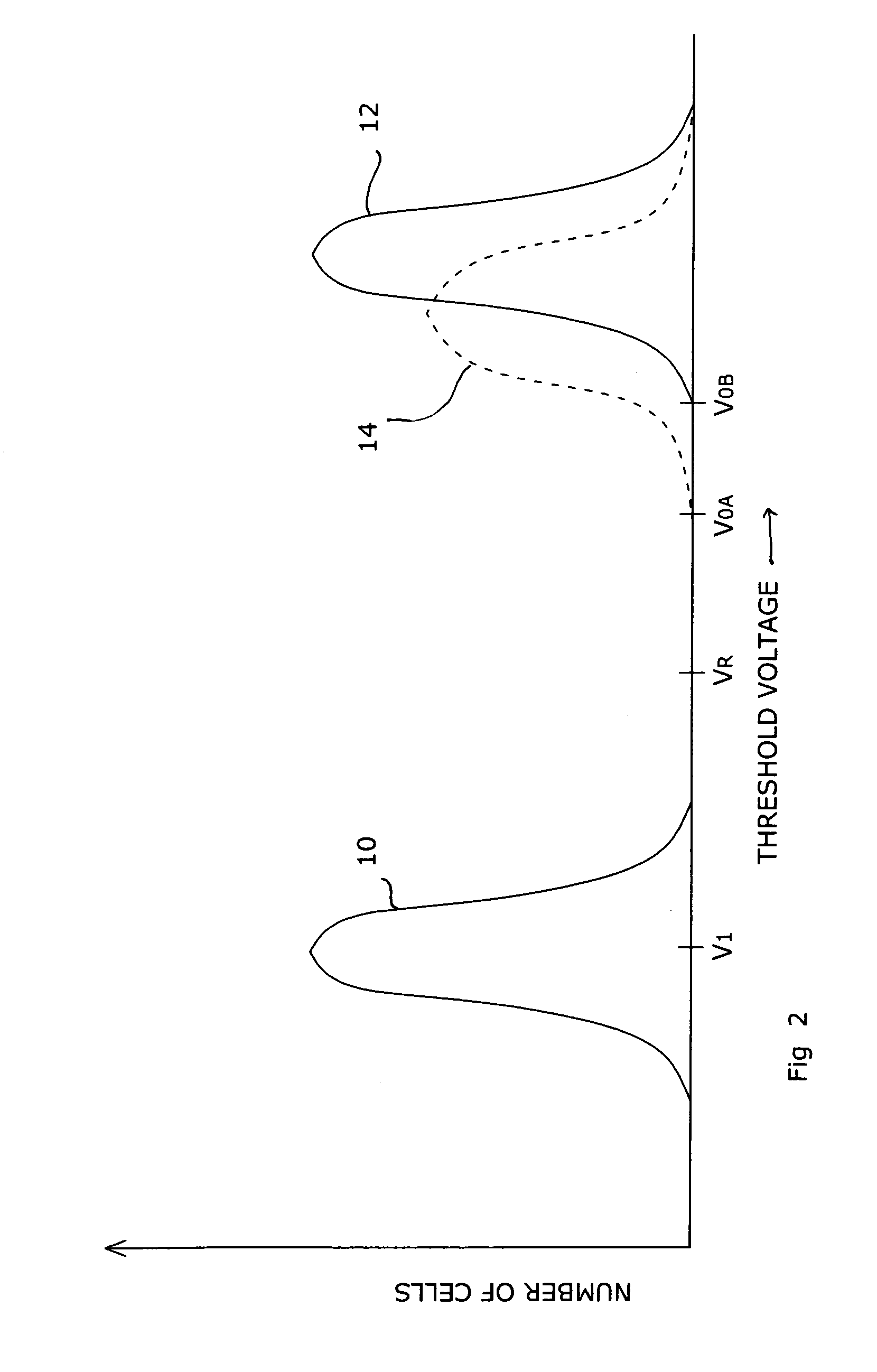

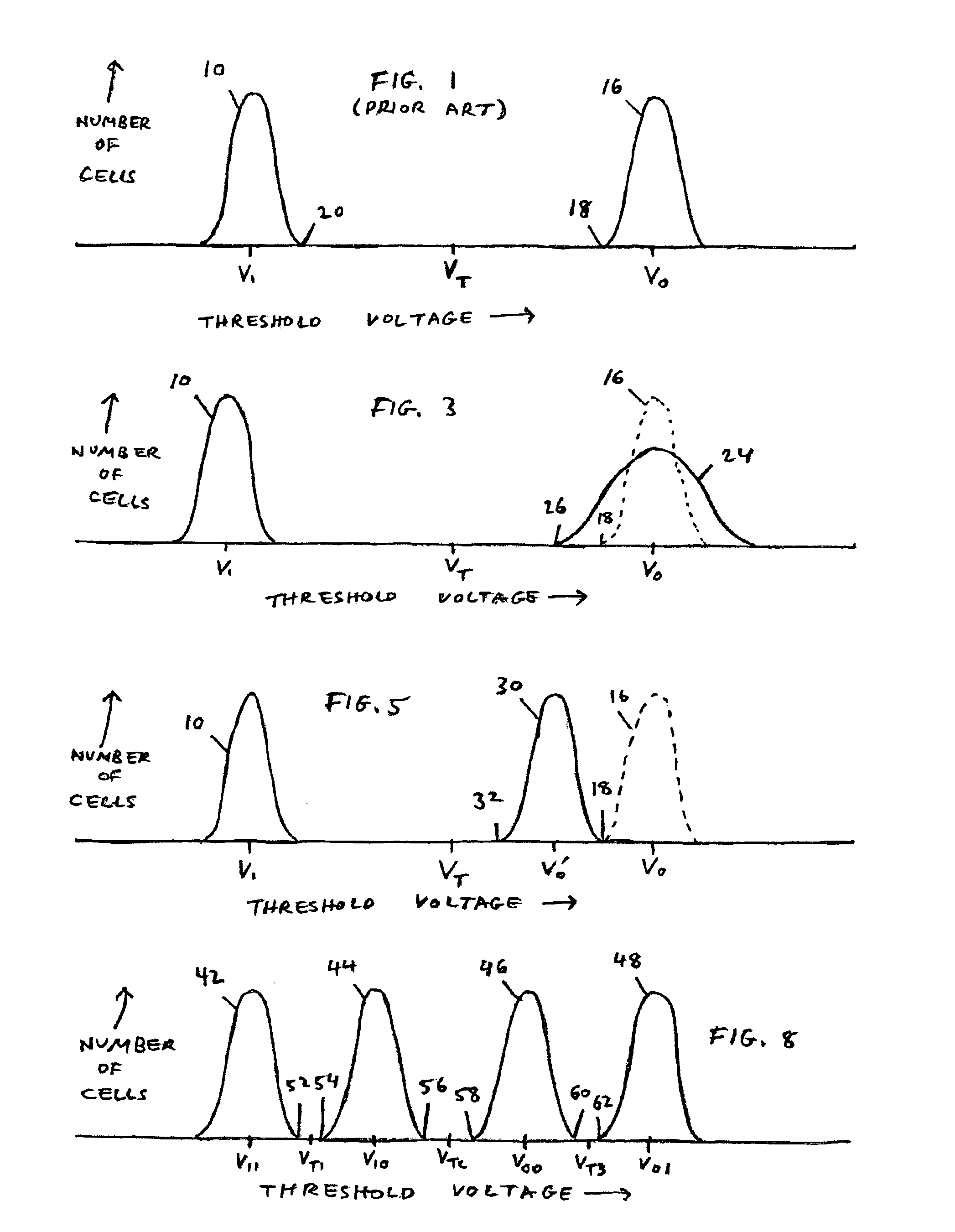

Faster programming of higher level states in multi-level cell flash memory

A program voltage signal implemented as a series of increasing program voltage pulses is applied to a set of non-volatile storage elements. Different increment values can be used when programming memory cells to different memory states. A smaller increment value can be used when programming memory cells to lower threshold voltage memory states and a larger increment value used when programming memory cells to higher threshold voltage memory states such as the highest memory state in an implementation. When non-volatile storage elements of a set are programmed to different memory states under simultaneous application of a single program voltage signal, programming can be monitored to determine when lower state programming is complete. The increment value can then be increased to complete programming to the highest memory state. Coarse / fine programming methodology can be incorporated for the highest memory state when the increment value is increased to maintain the threshold distribution within a reasonable range.

Owner:SANDISK TECH LLC

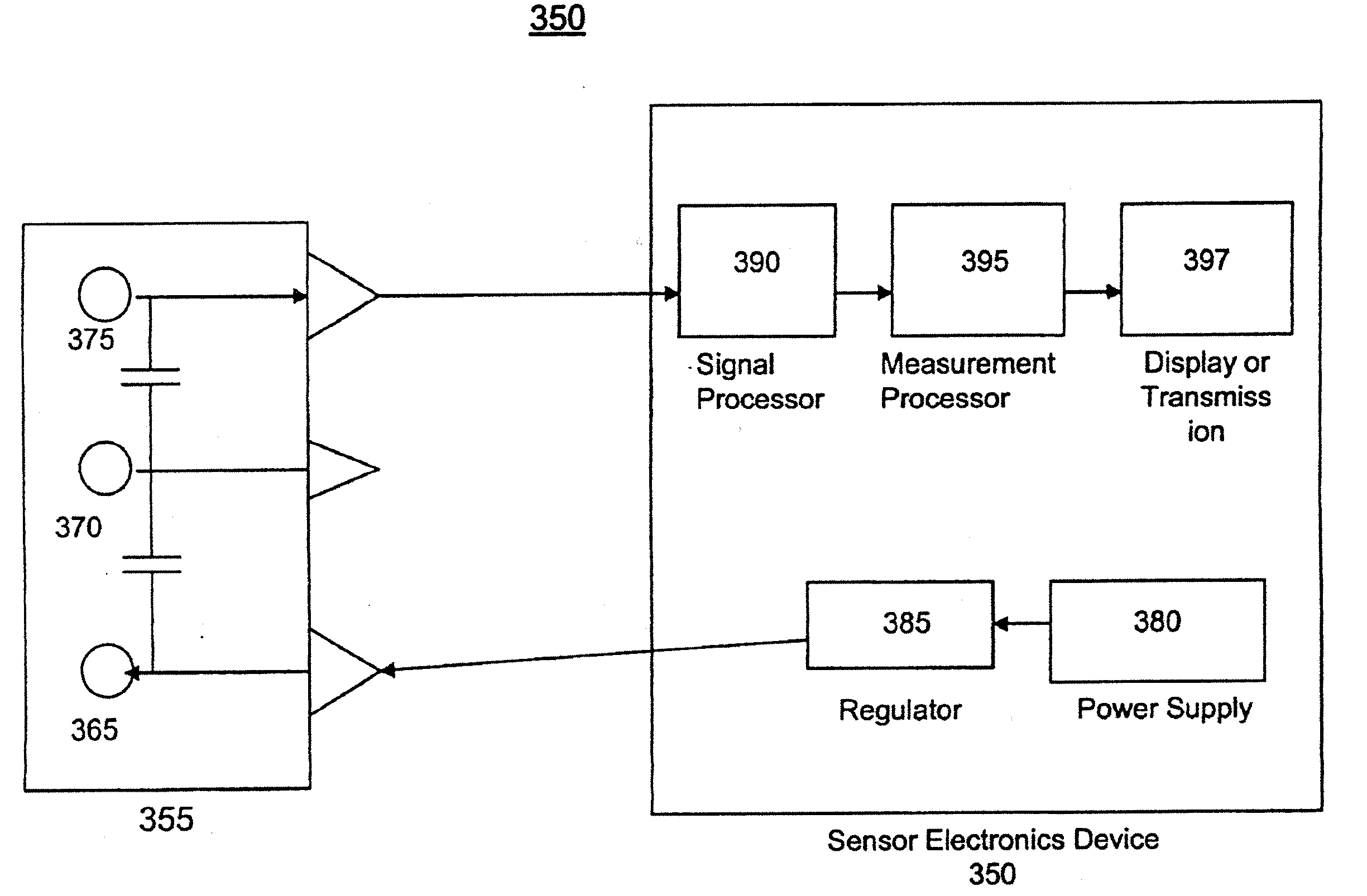

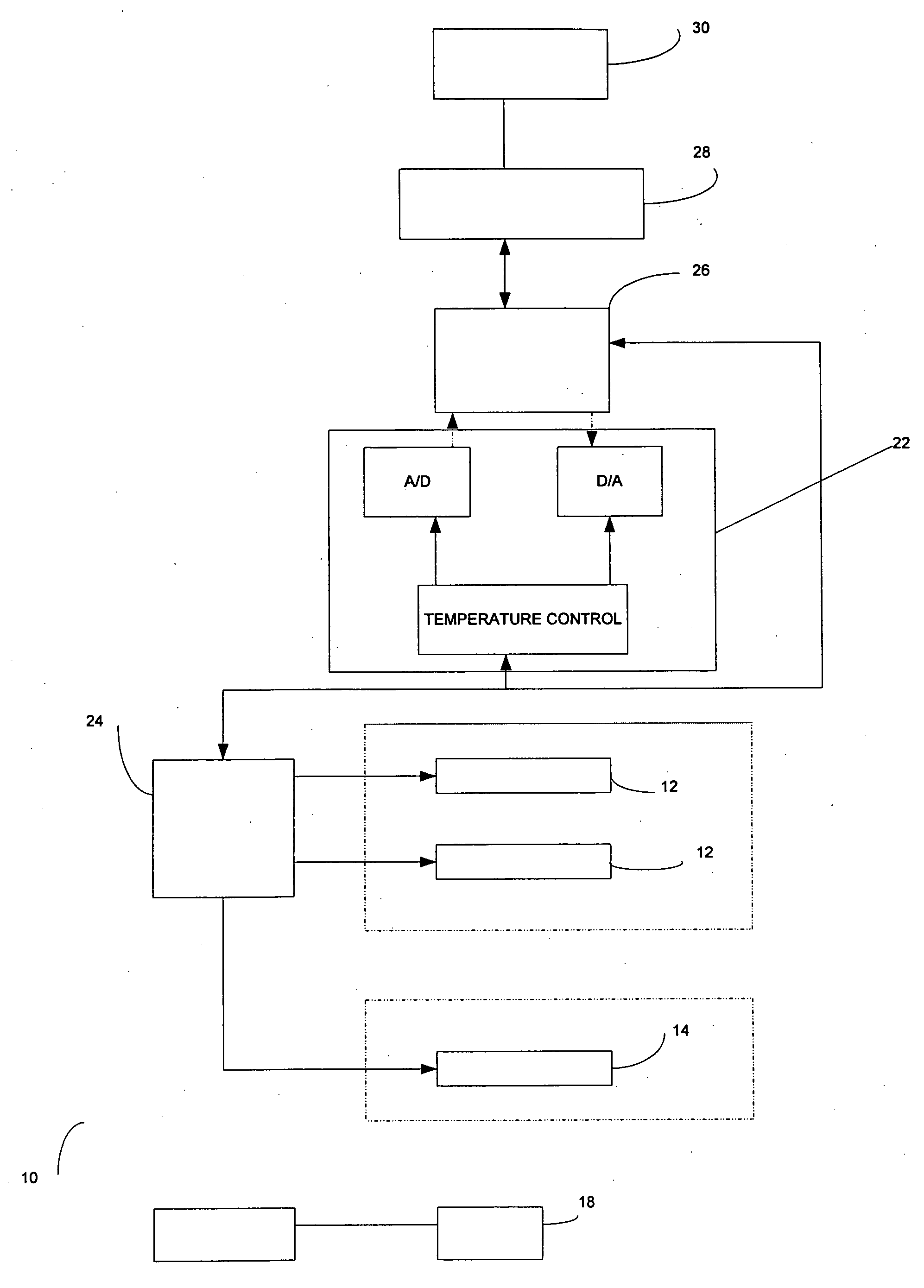

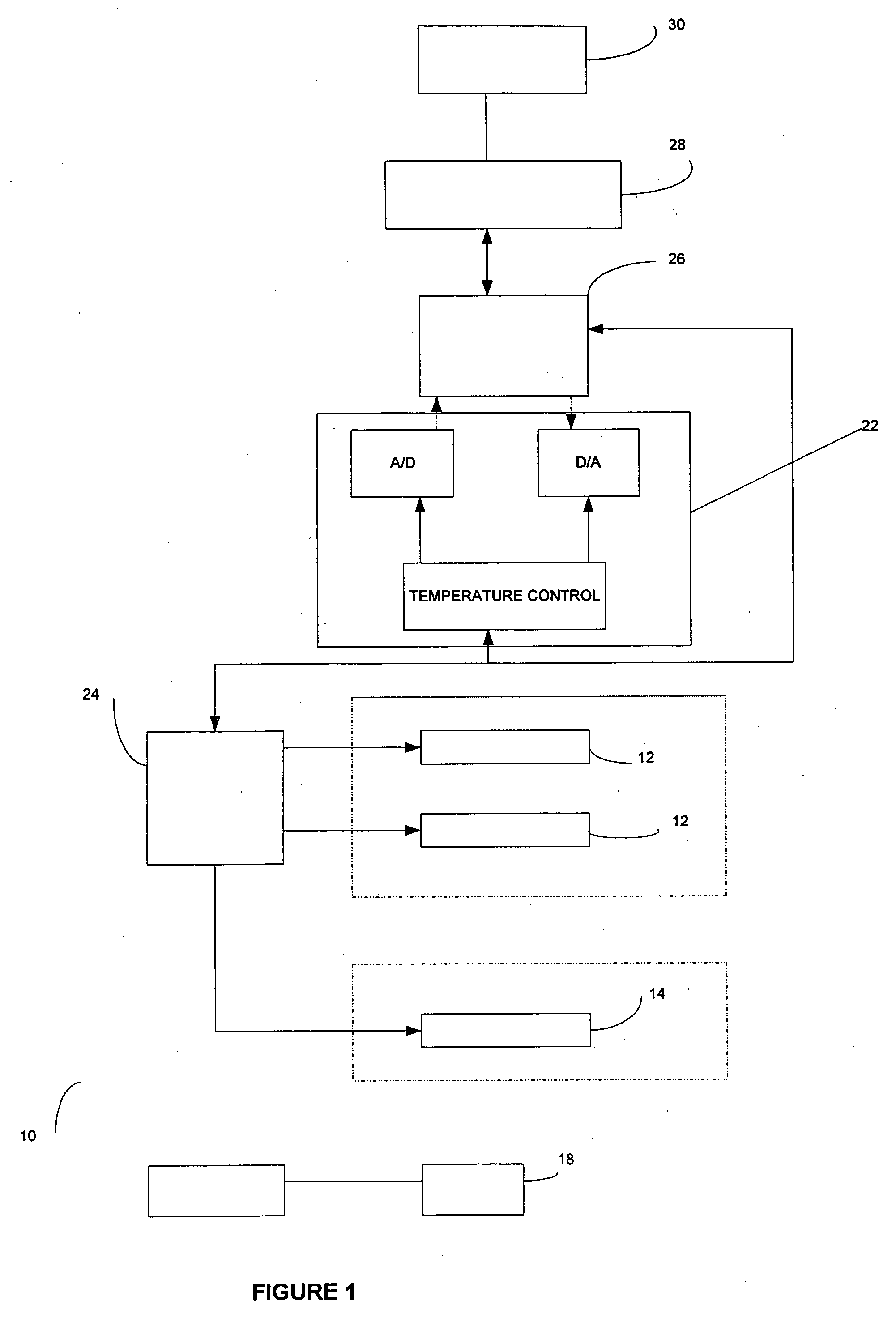

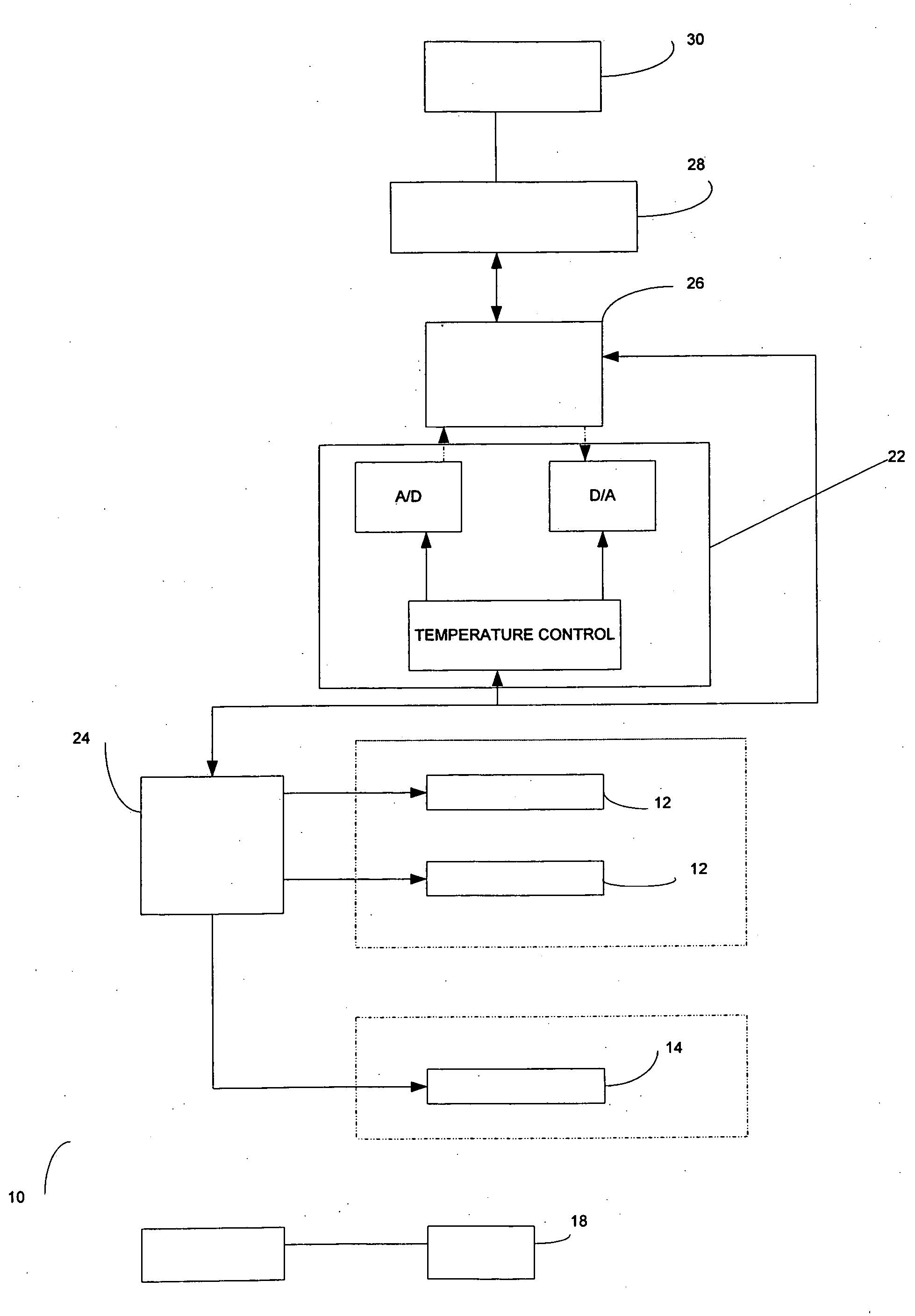

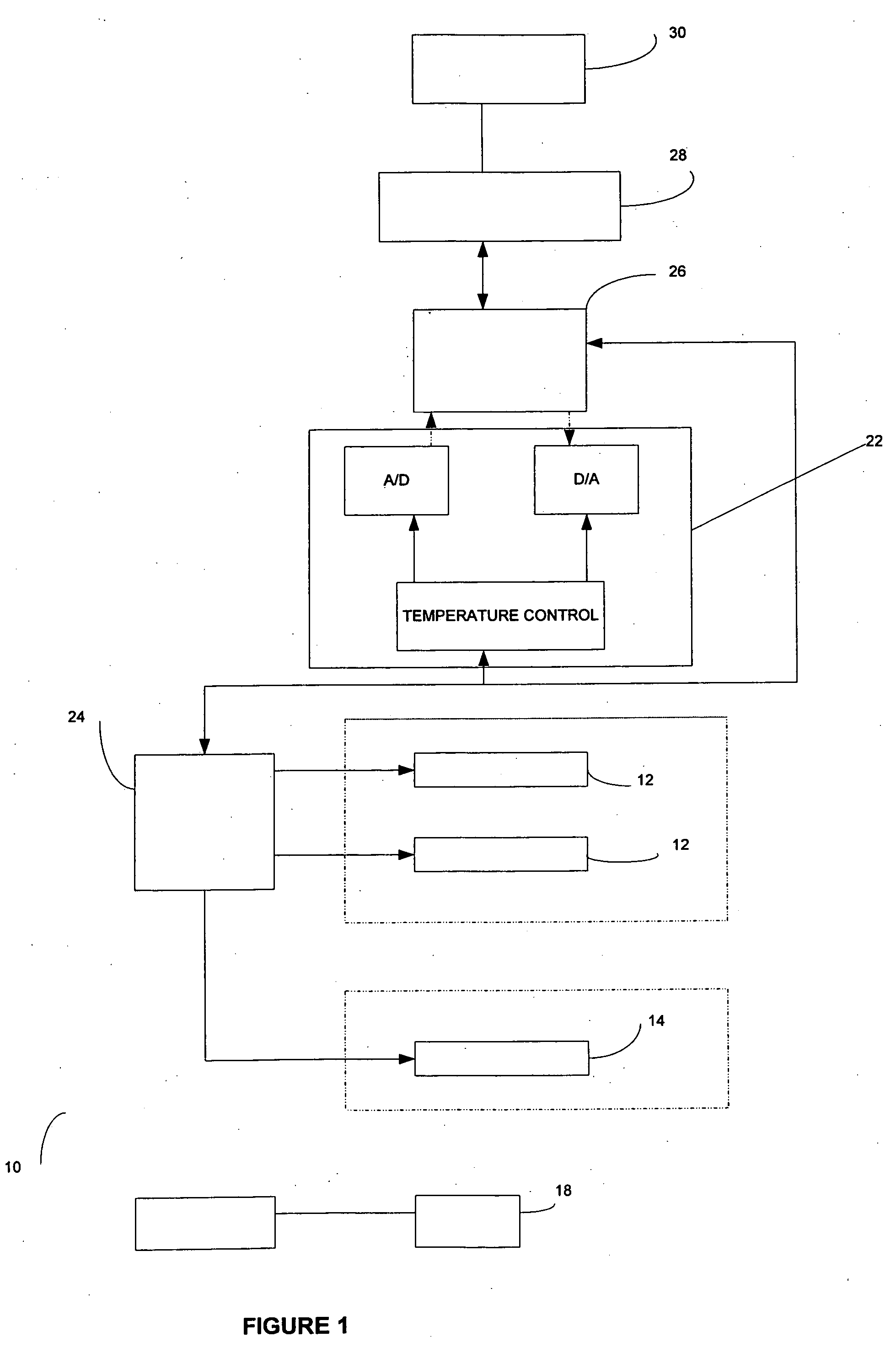

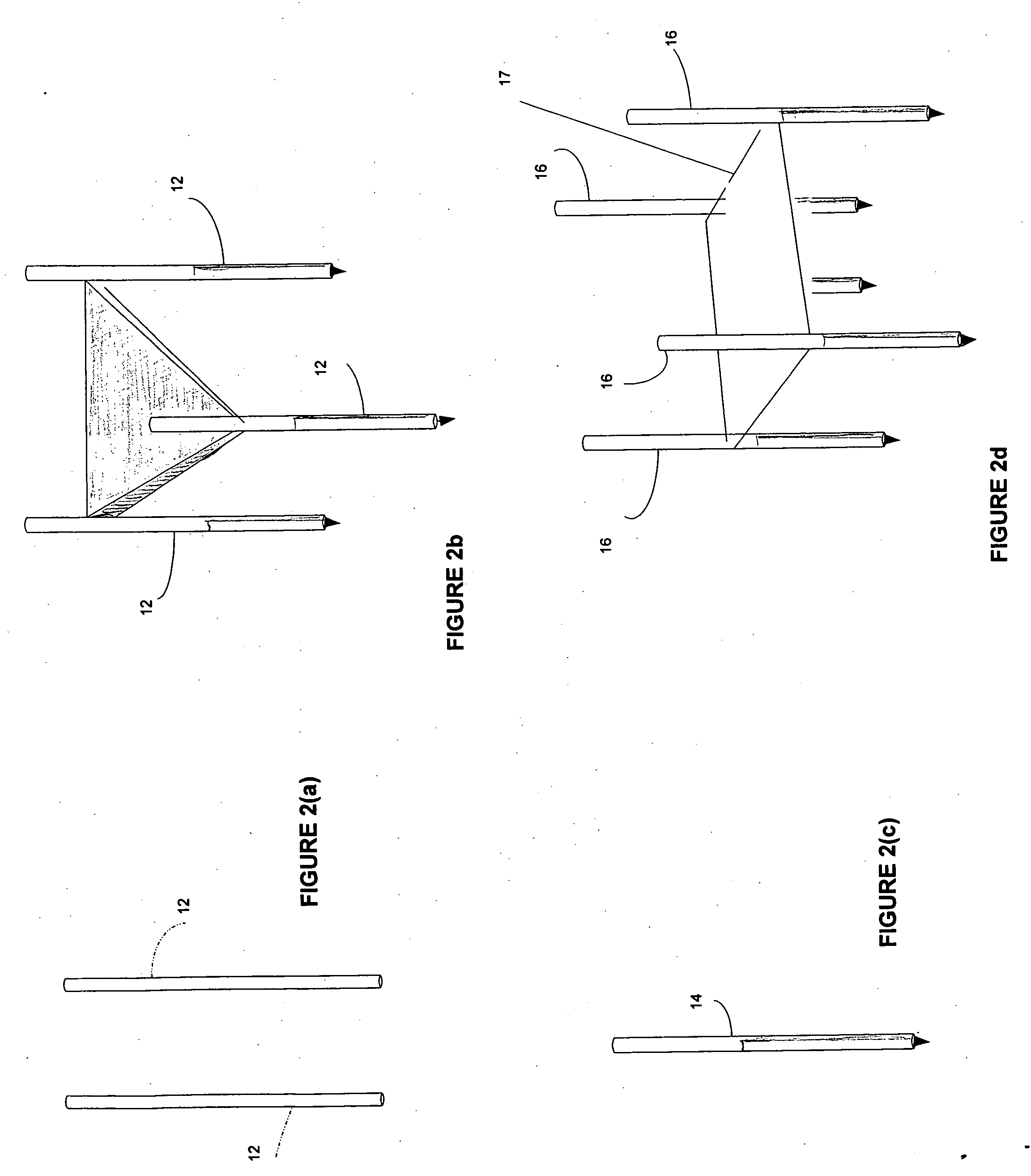

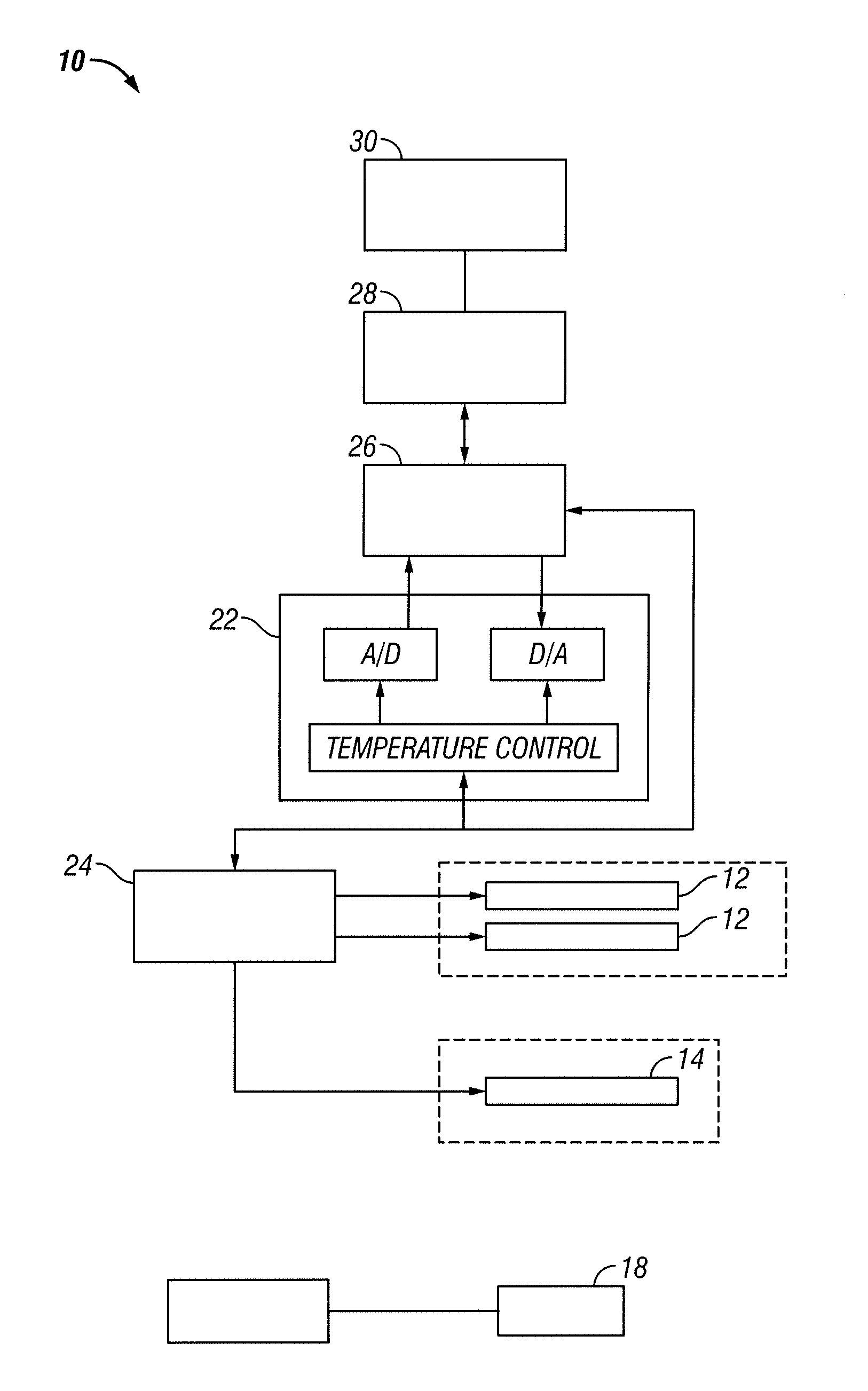

Methods and systems for observing sensor parameters

ActiveUS20110230741A1Testing/calibration apparatusResistance/reactance/impedenceVoltage pulseMonitors blood glucose

The invention disclosed herein provides methods and materials for observing the state of a sensor, for example those used by diabetic patients to monitor blood glucose levels. Typically a voltage such as a voltage pulse is applied to the sensor in order to solicit a current response from which for example, factors such as impedance values can be derived. Such values can then be used as indicators of a sensor's state, for example the state of sensor hydration, sensor noise, sensor offset, sensor drift or the like.

Owner:MEDTRONIC MIMIMED INC

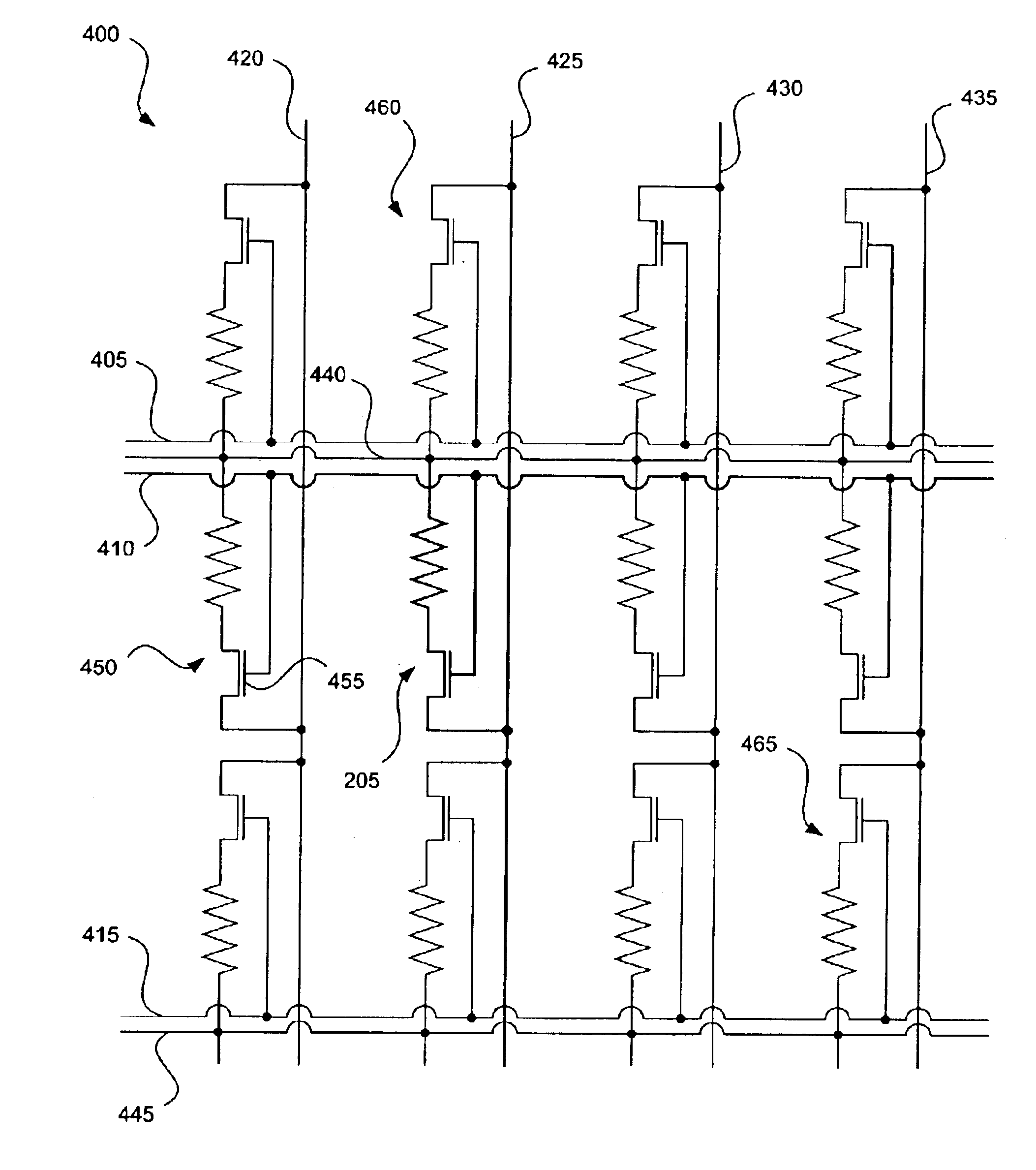

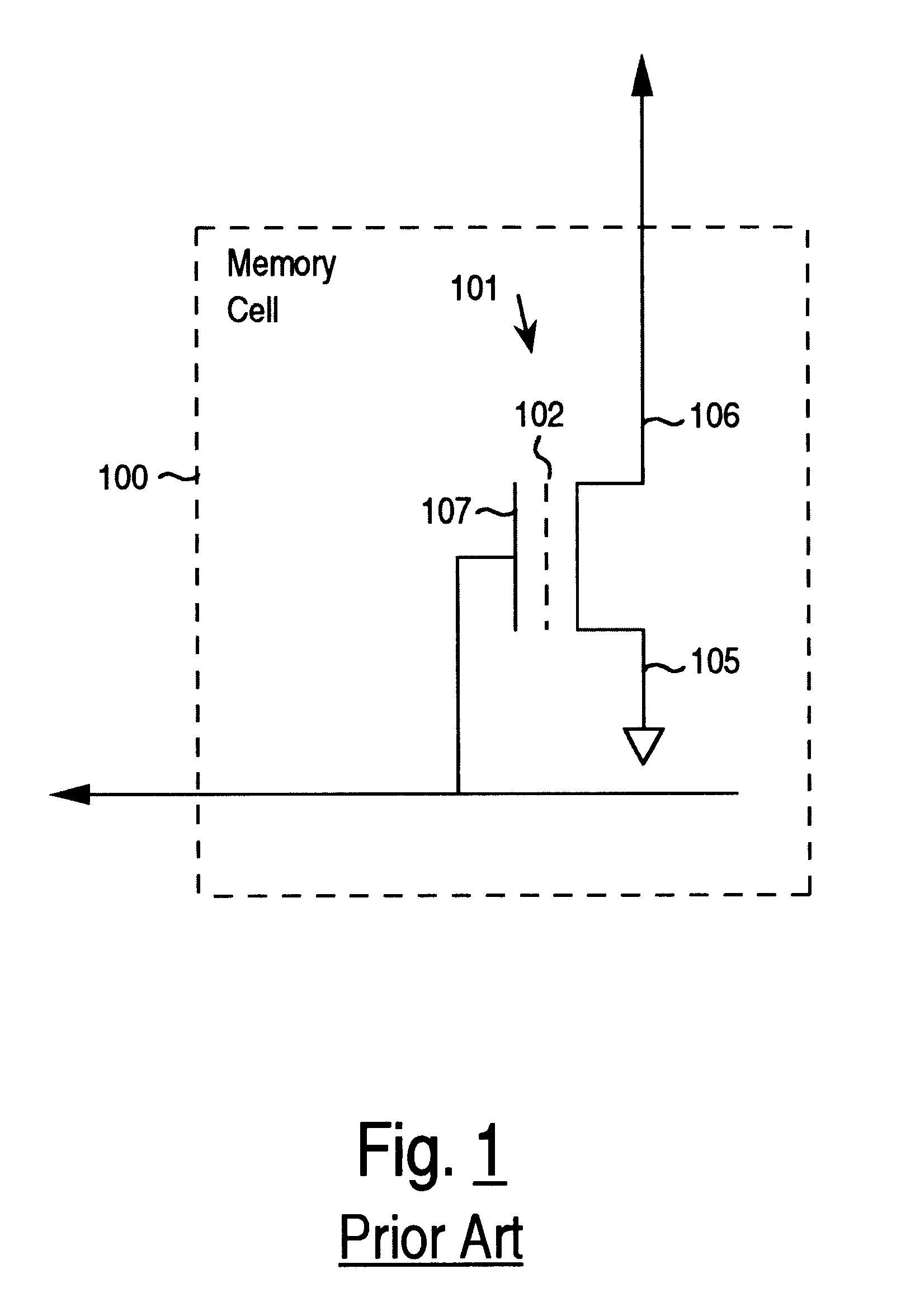

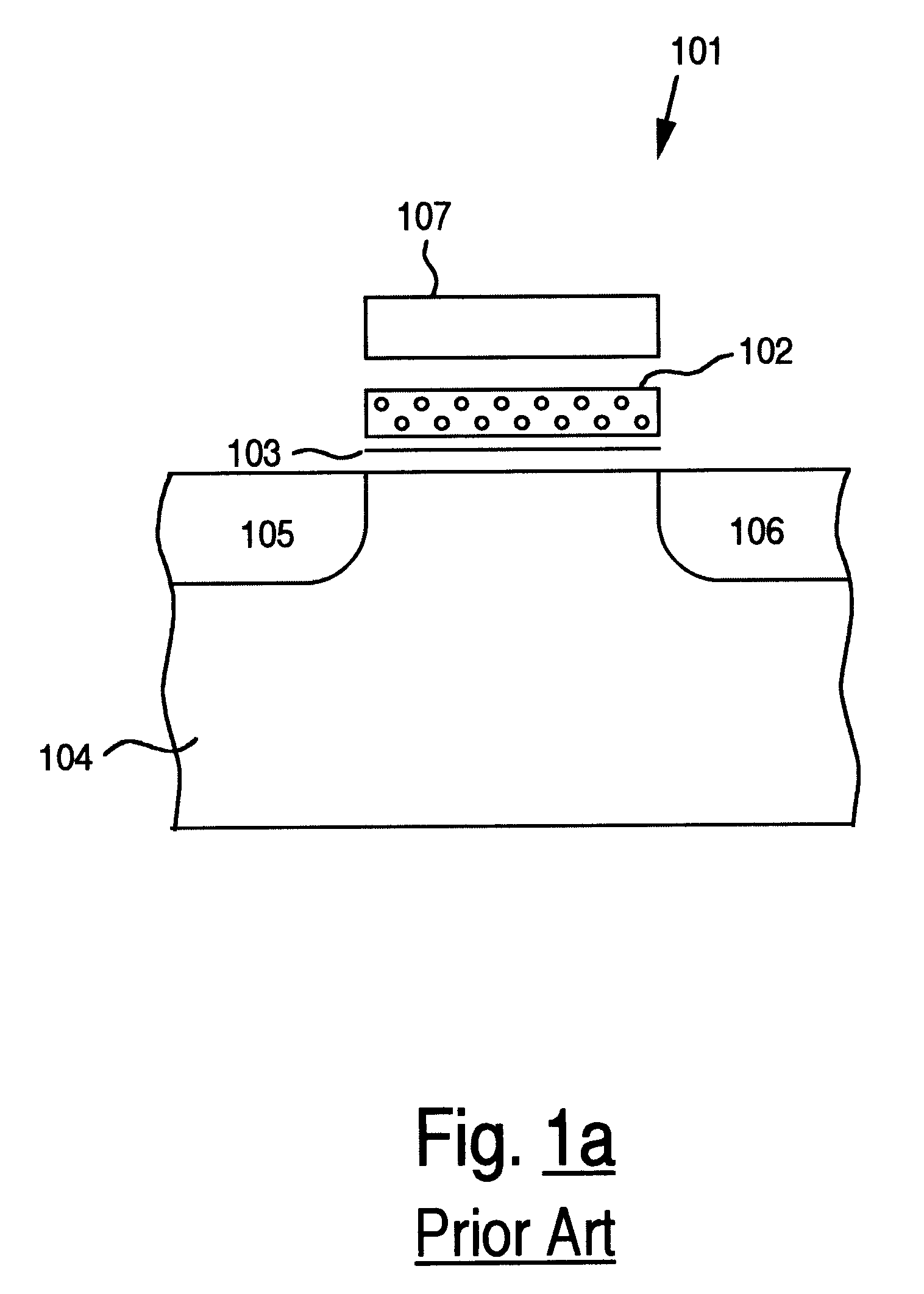

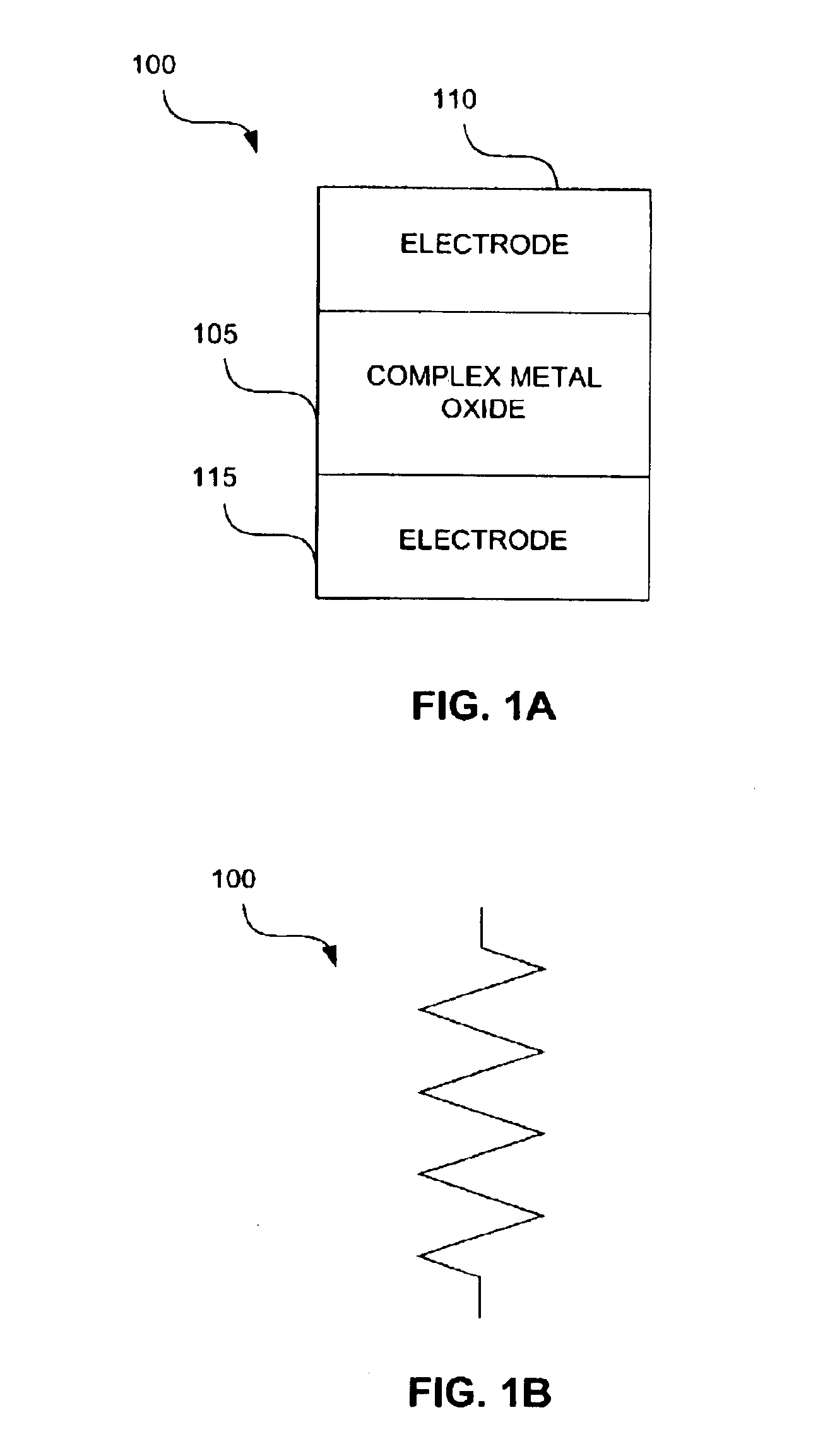

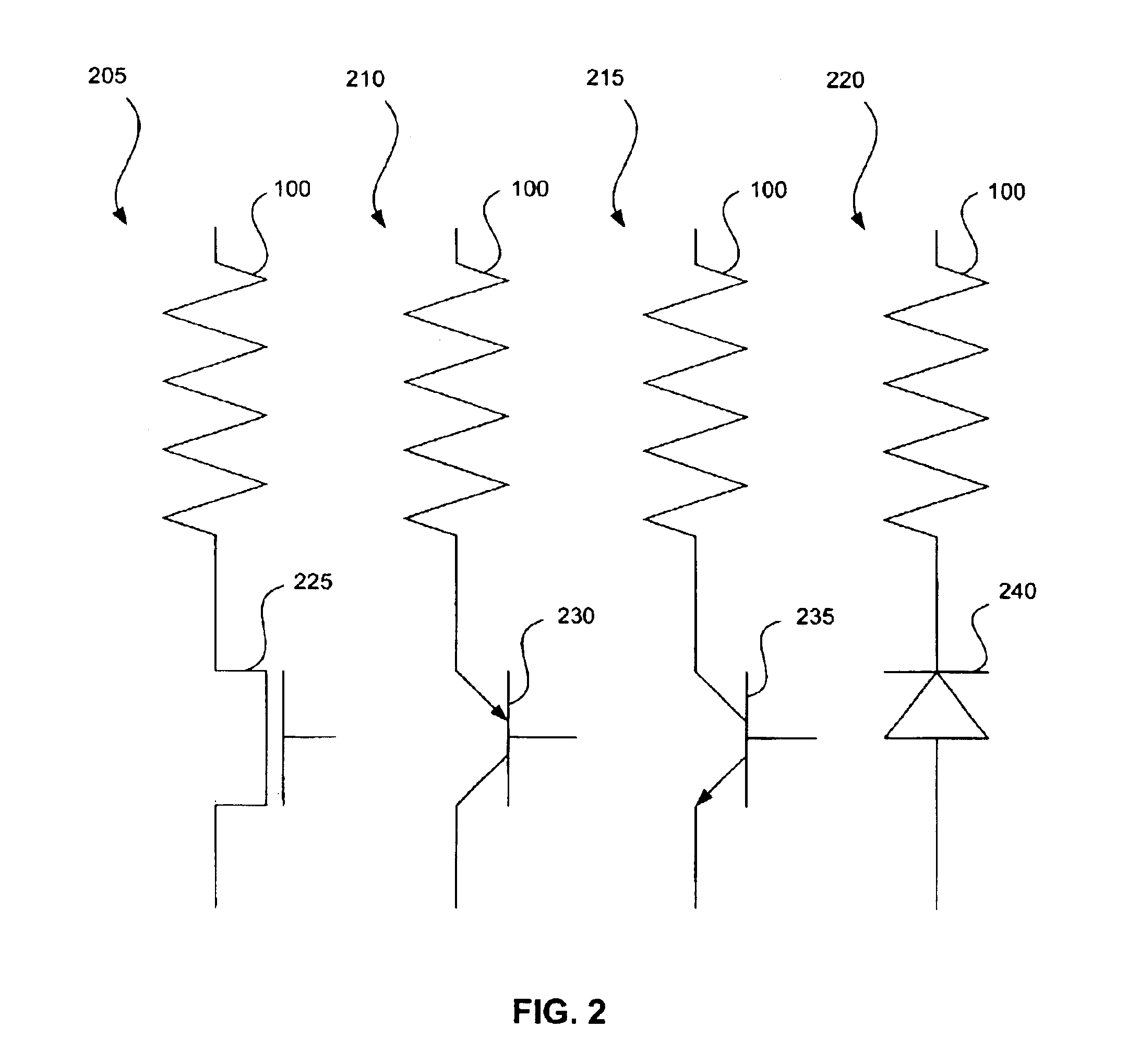

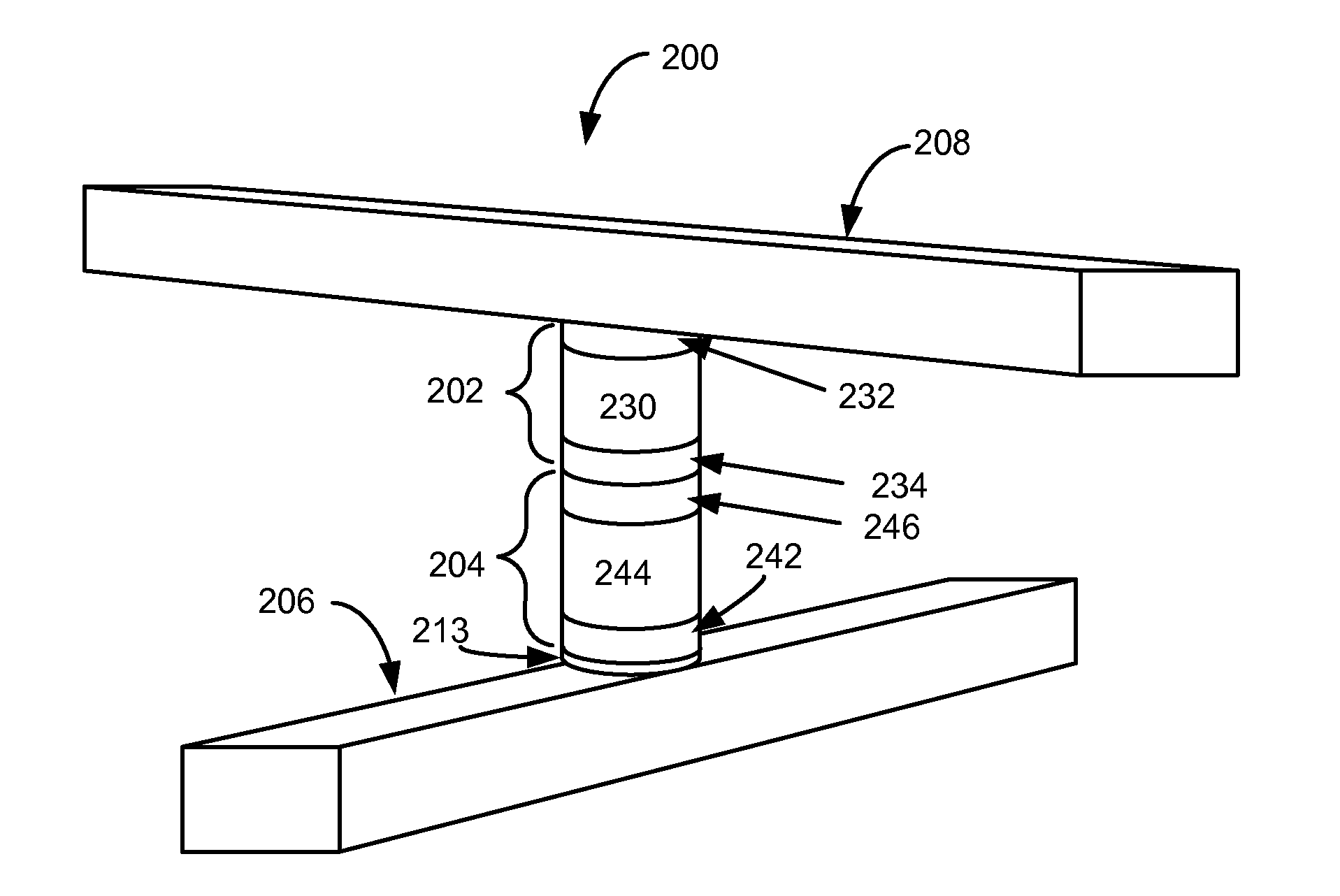

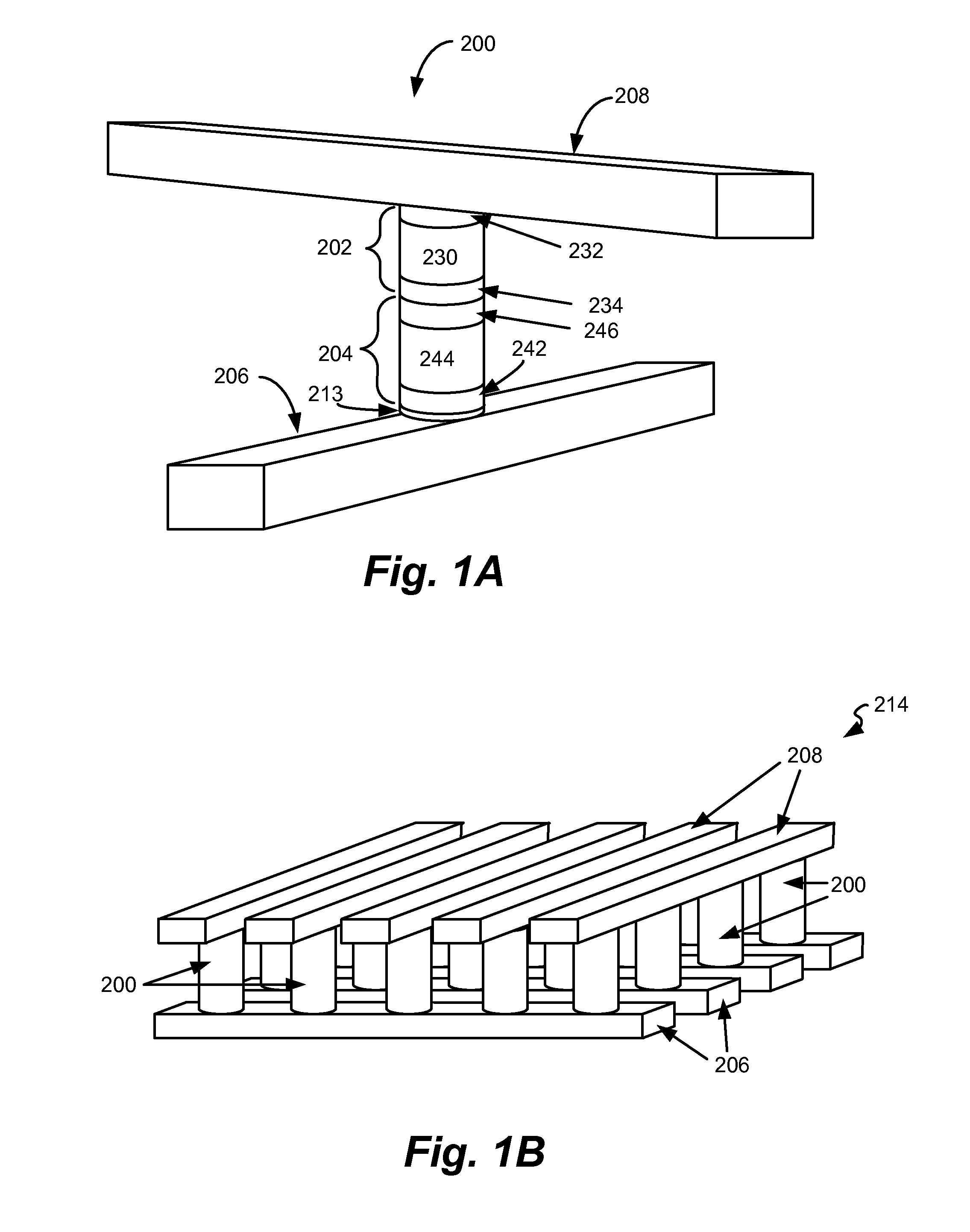

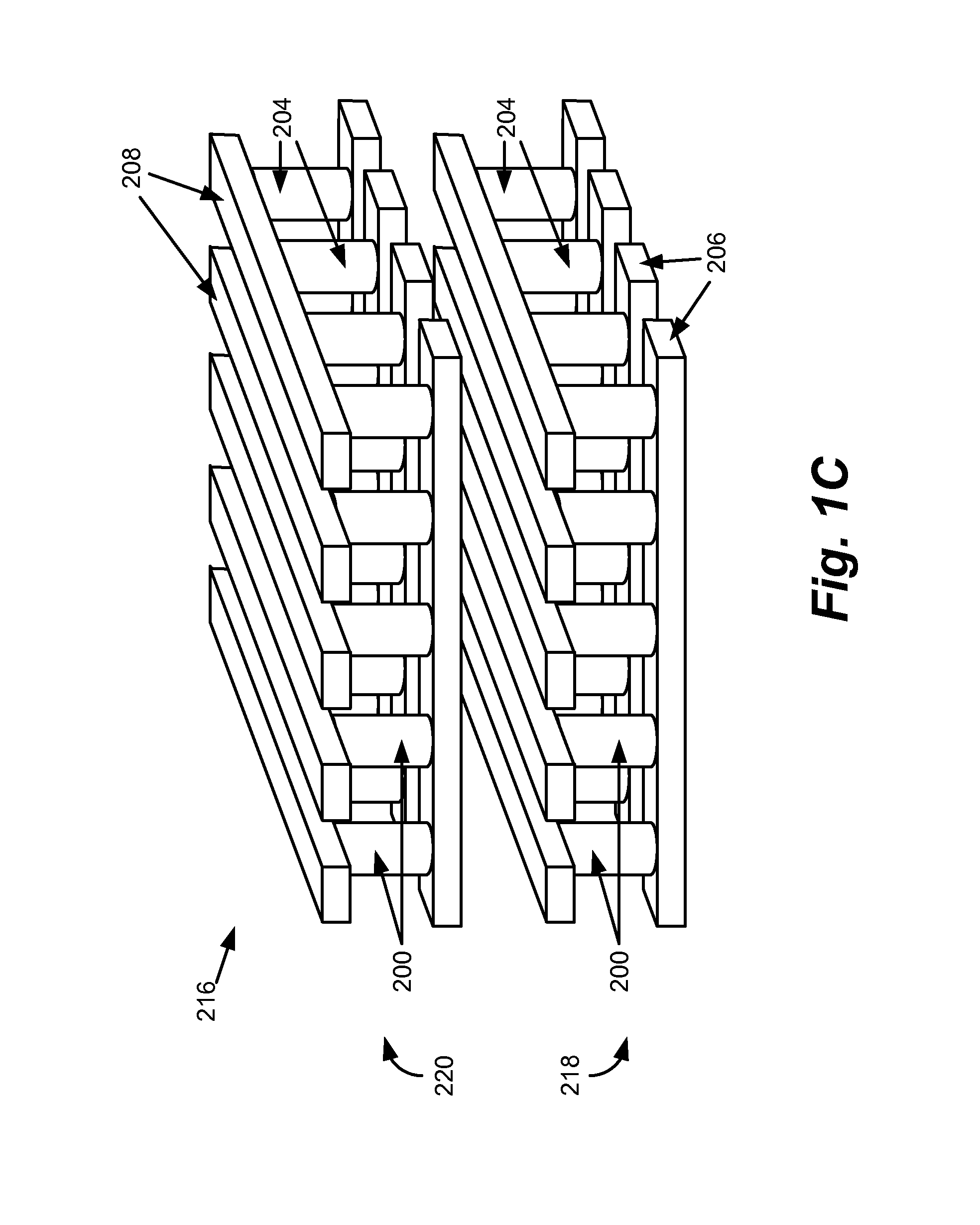

Non-volatile memory with a single transistor and resistive memory element

Non-volatile memory cell with a single semiconductor device per memory cell. The present invention generally allows for a plurality of memory cells to be formed on a semiconductor substrate that supports a semiconductor device. A multi-resistive state material layer that changes its resistive state between a low resistive state and a high resistive state upon application of a voltage pulse is formed above the substrate, generally at a very high temperature. While the layers fabricated between the substrate and the multi-resistive state material use materials that can withstand high temperature processing, the layers fabricated above the multi-resistive state material do not need to withstand high temperature processing.

Owner:UNITY SEMICON

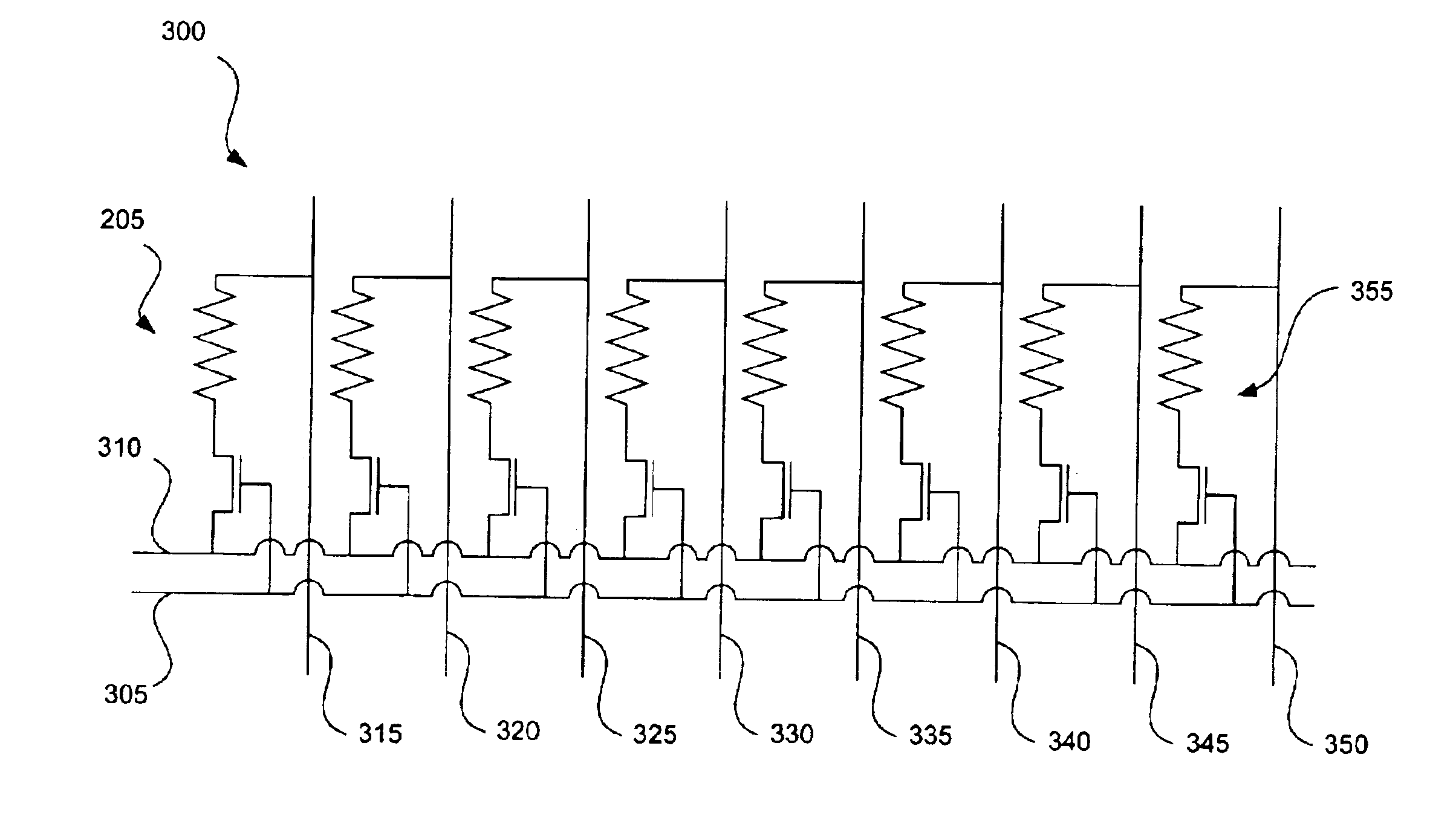

Staircase program verify for multi-level cell flash memory designs

InactiveUS6538923B1Improve performanceAvoid programmingRead-only memoriesDigital storageComputer architectureVoltage pulse

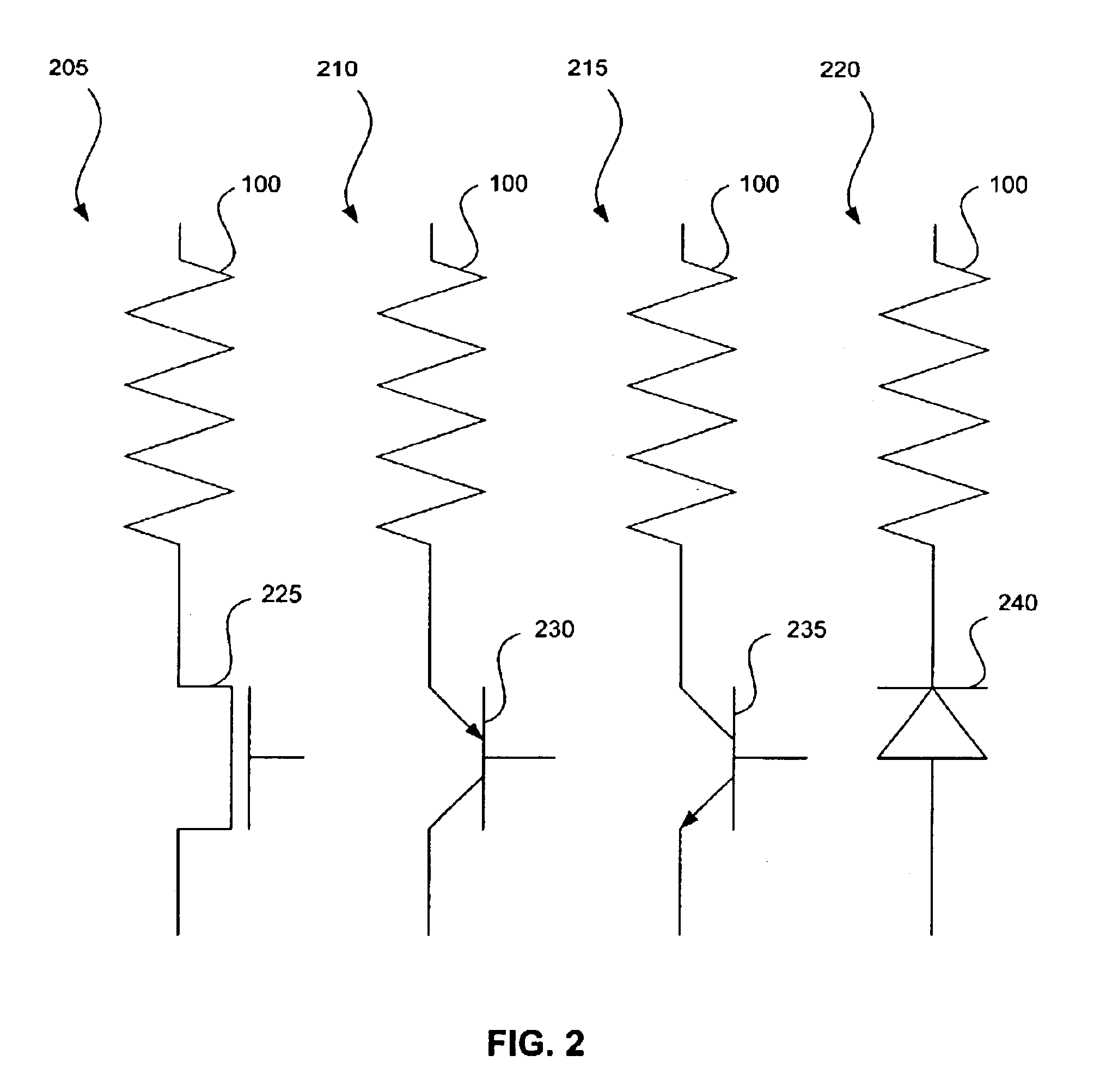

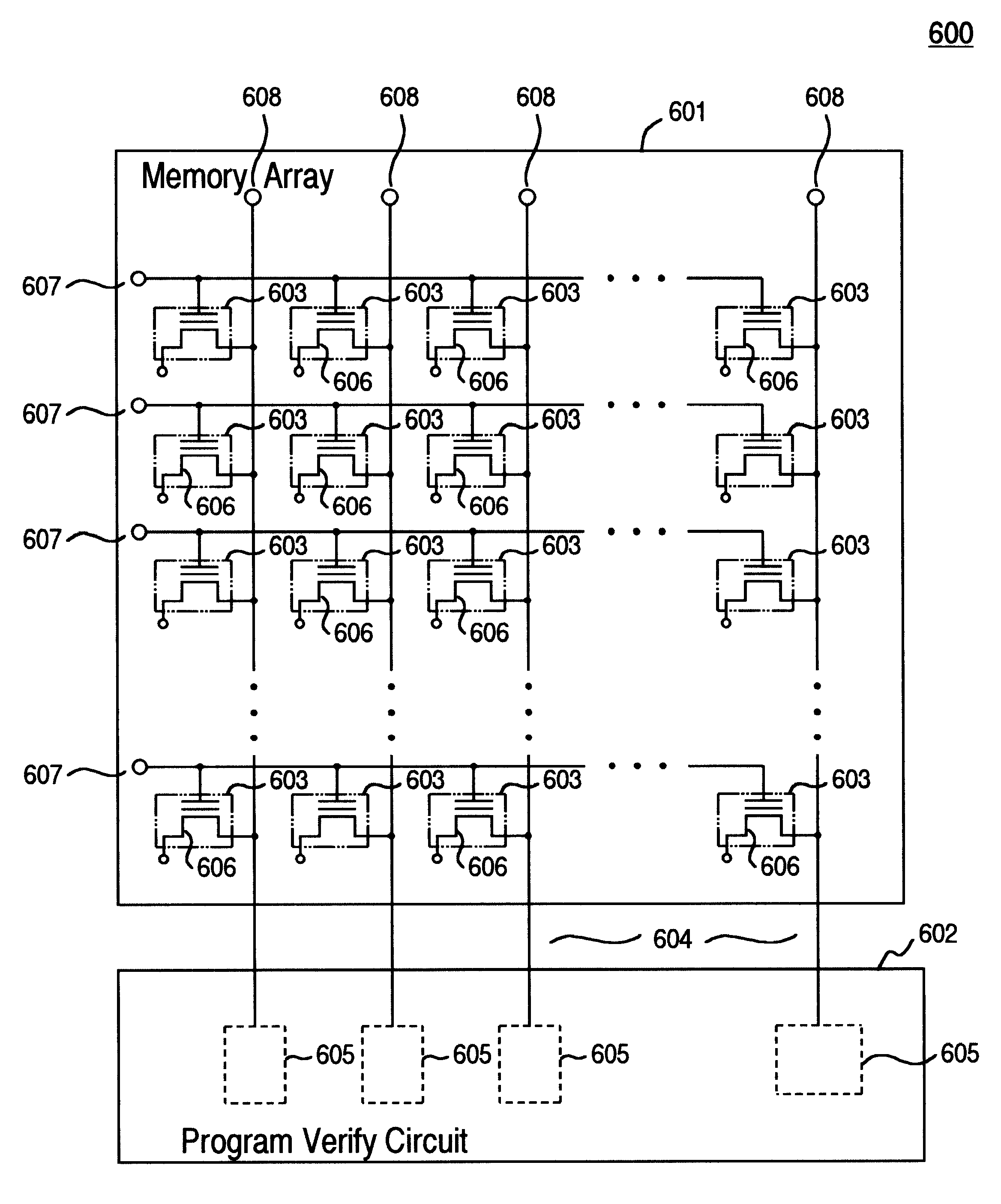

A system for concurrently verifying programming of logical data in a multi-level-cell (MLC) flash memory device having a plurality of memory cells each configured to store N bits of logical data where N>=2. The MLC flash memory device has a plurality of memory cells capable of being storing N-bits of data in one of 2N distinct data storage levels, each data storage level corresponding to a discrete N-bit combination of logical data. The data storage levels include a default level, called the erased level, and 2N-1 program levels, including a lowest program level, 2N-2 intermediate program levels and a highest program level. For each memory cell to be verified as programmed, an N-bit combination of data to be verified is loaded into a program-verify circuit and a stepped voltage pulse having 2N-1 steps is applied to each memory cell. The stepped voltage pulse includes an initial step, at least one intermediate step and a final step with the initial step substantially equal to a program-verify voltage for the highest program level of the MLC flash memory within a the highest program level, each successive intermediate step is substantially equal to a program-verify voltage corresponding to an intermediate program level and the final step of the voltage pulse is substantially equal to a program-verify voltage for the lowest program level. Concurrently with the application of the stepped voltage pulse to each memory cell, the data storage level is verified as substantially within a program level corresponding to the N-bit combination for the memory cell. Subsequent to verifying the data storage level for a memory cell, the verified memory cell is inhibited form further application of a program pulse.

Owner:MONTEREY RES LLC

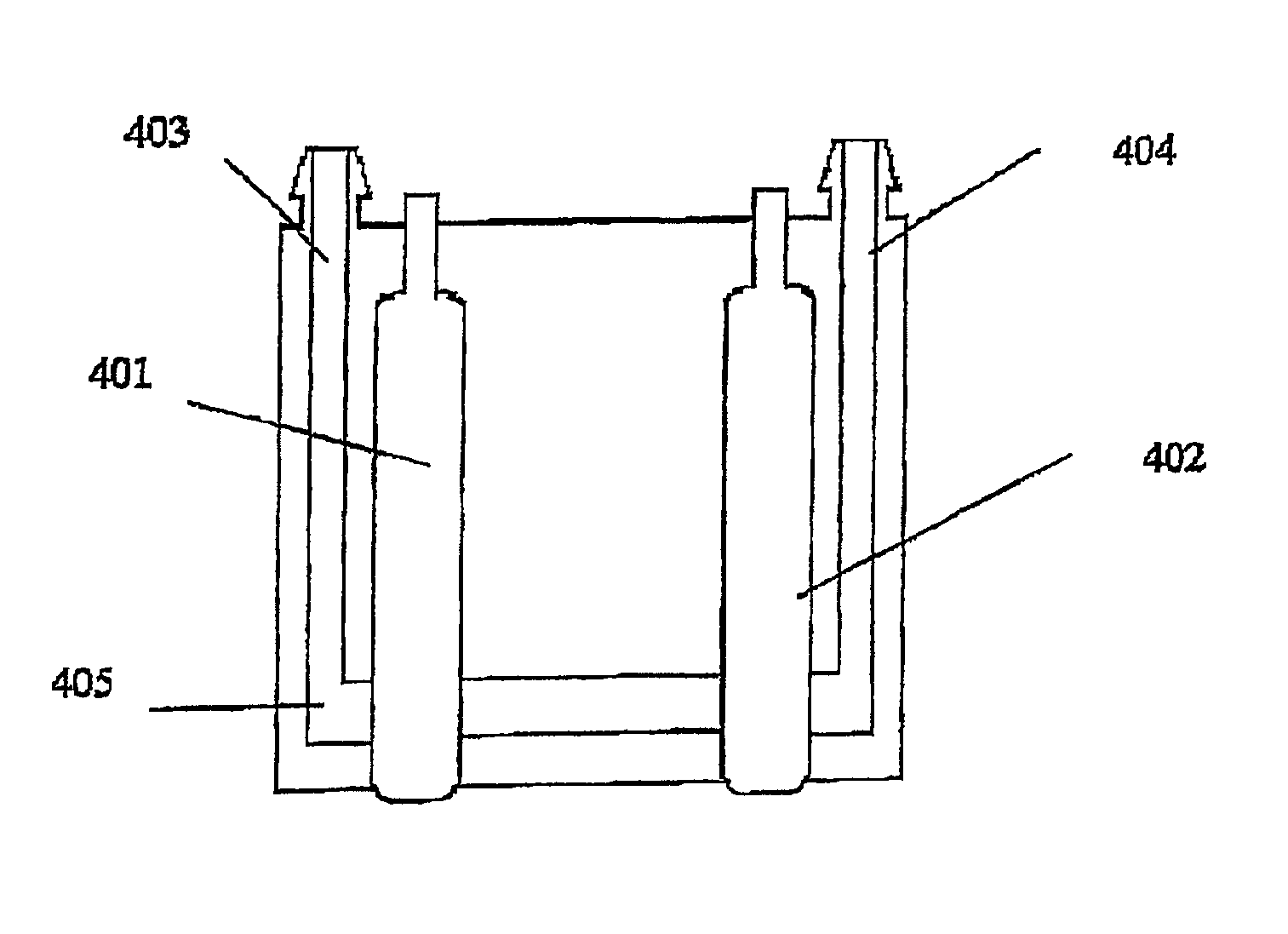

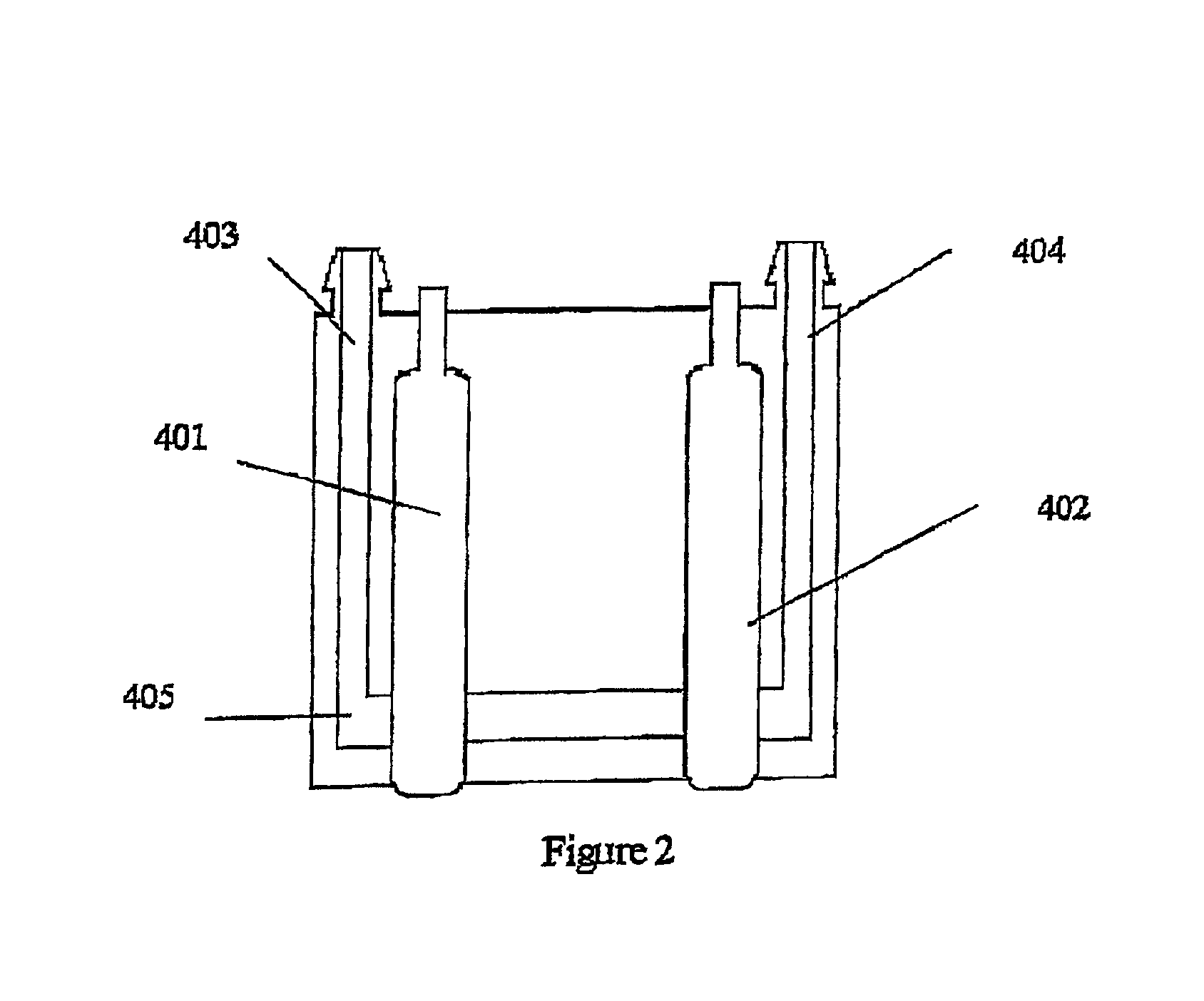

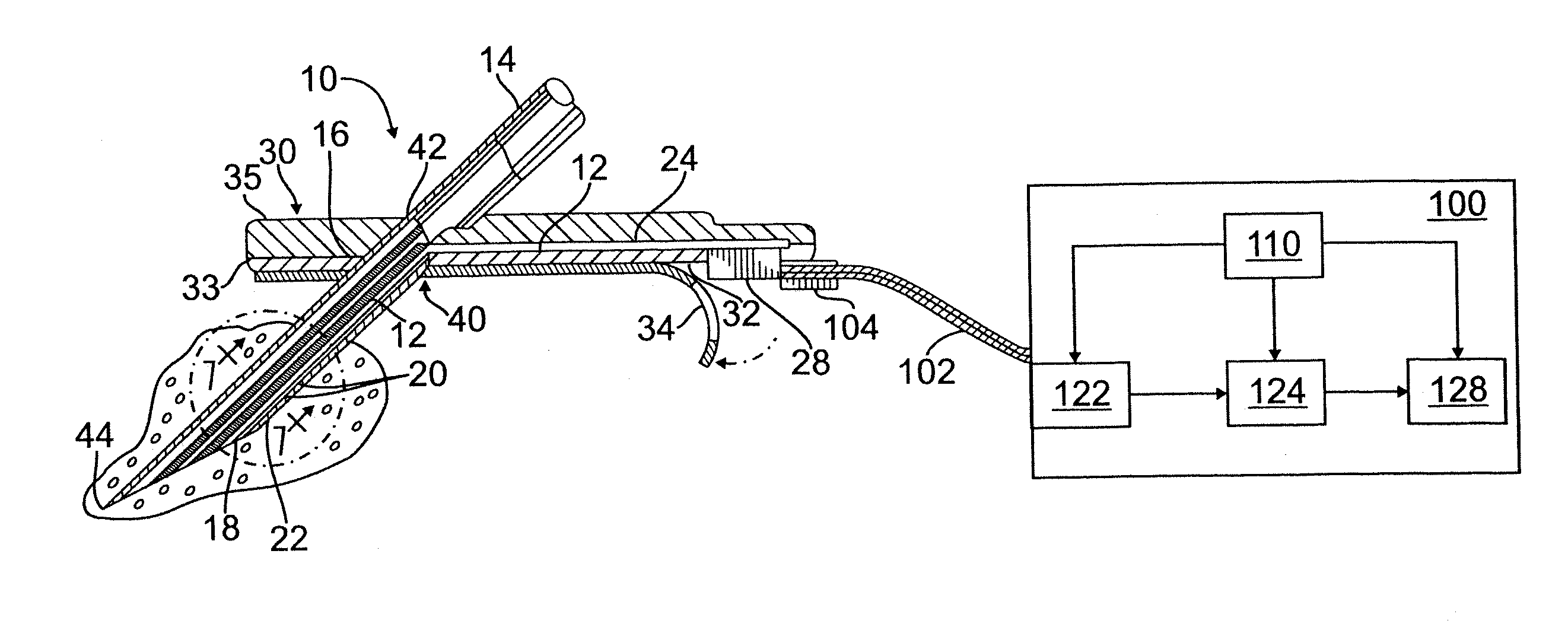

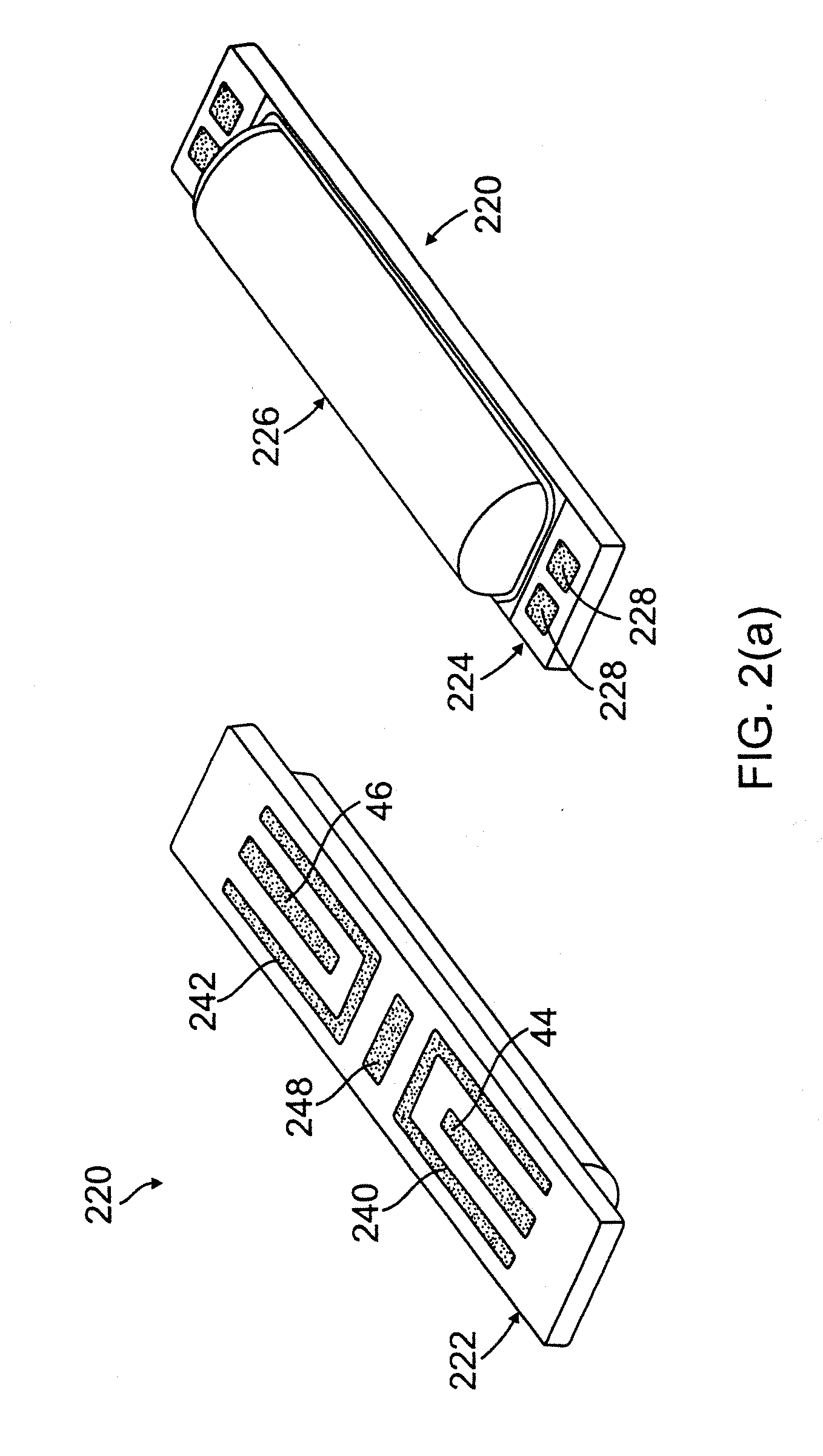

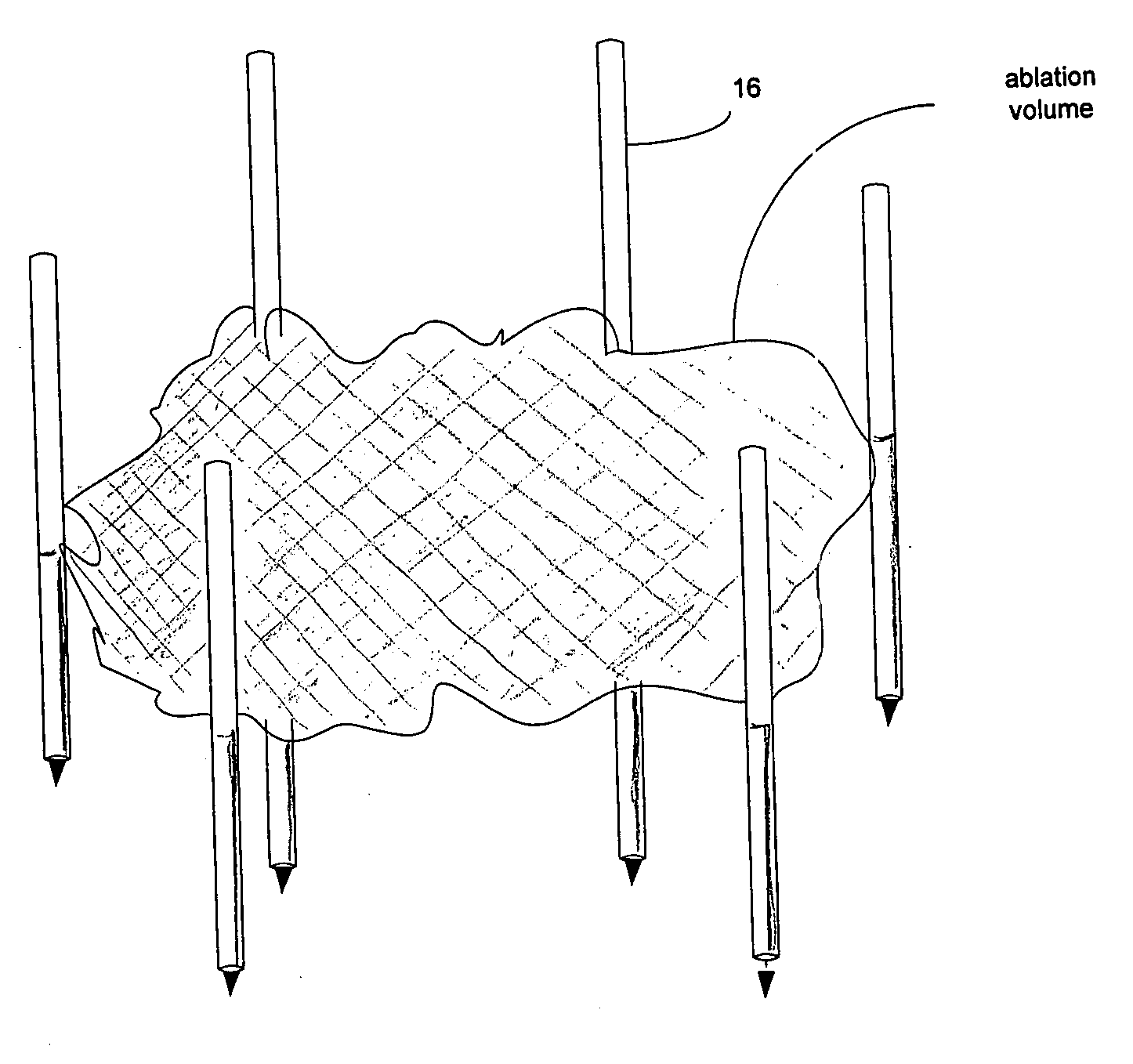

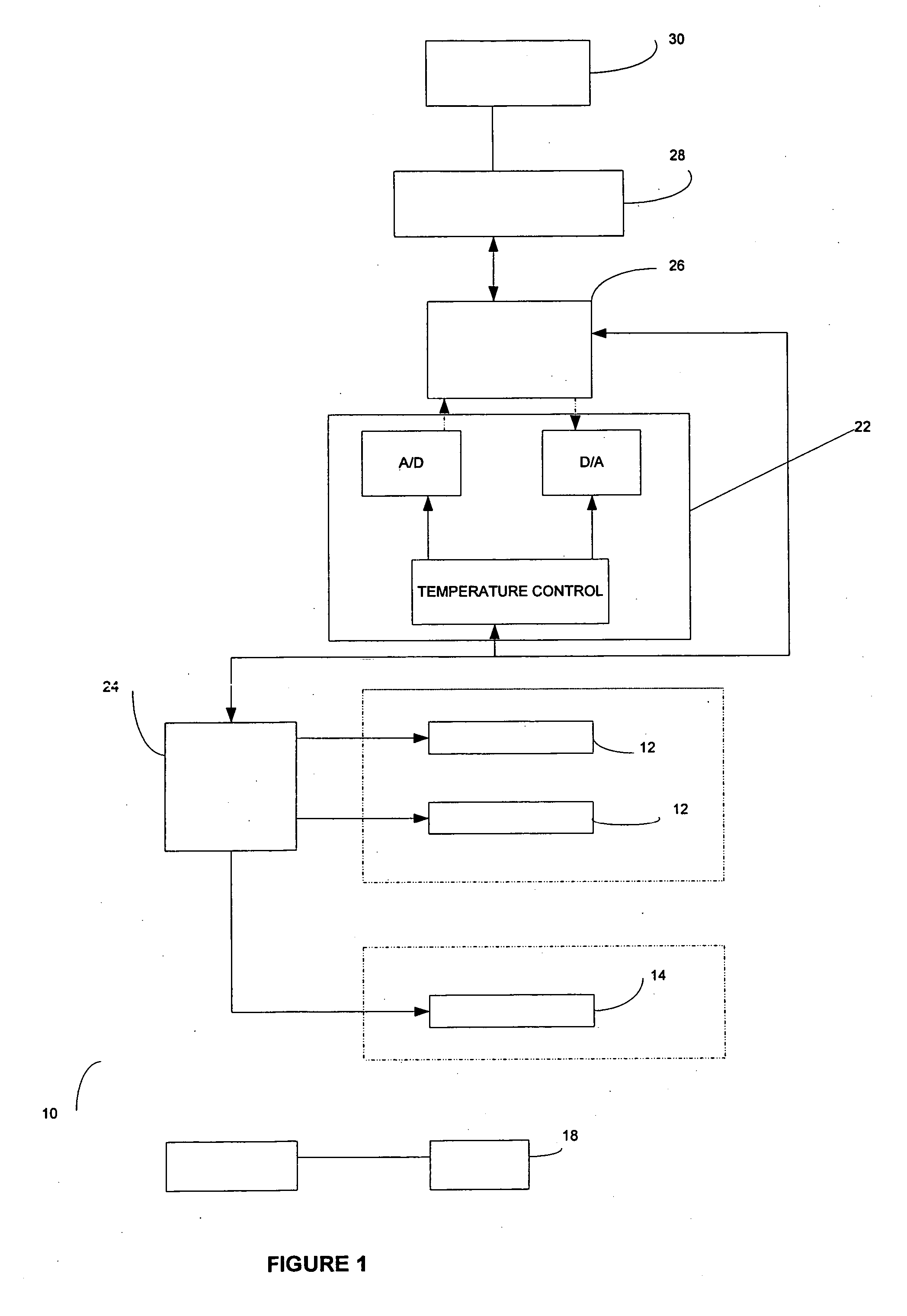

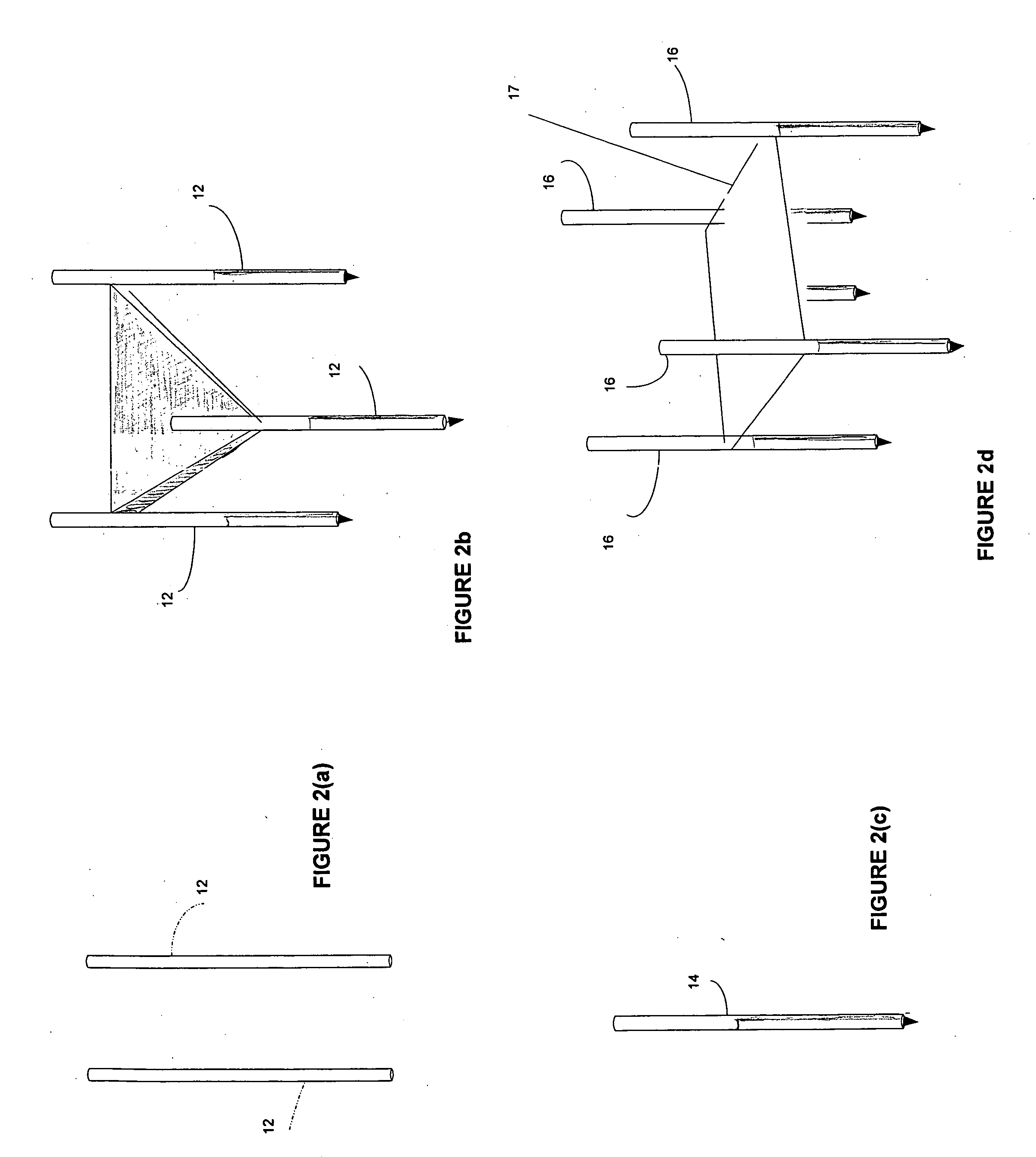

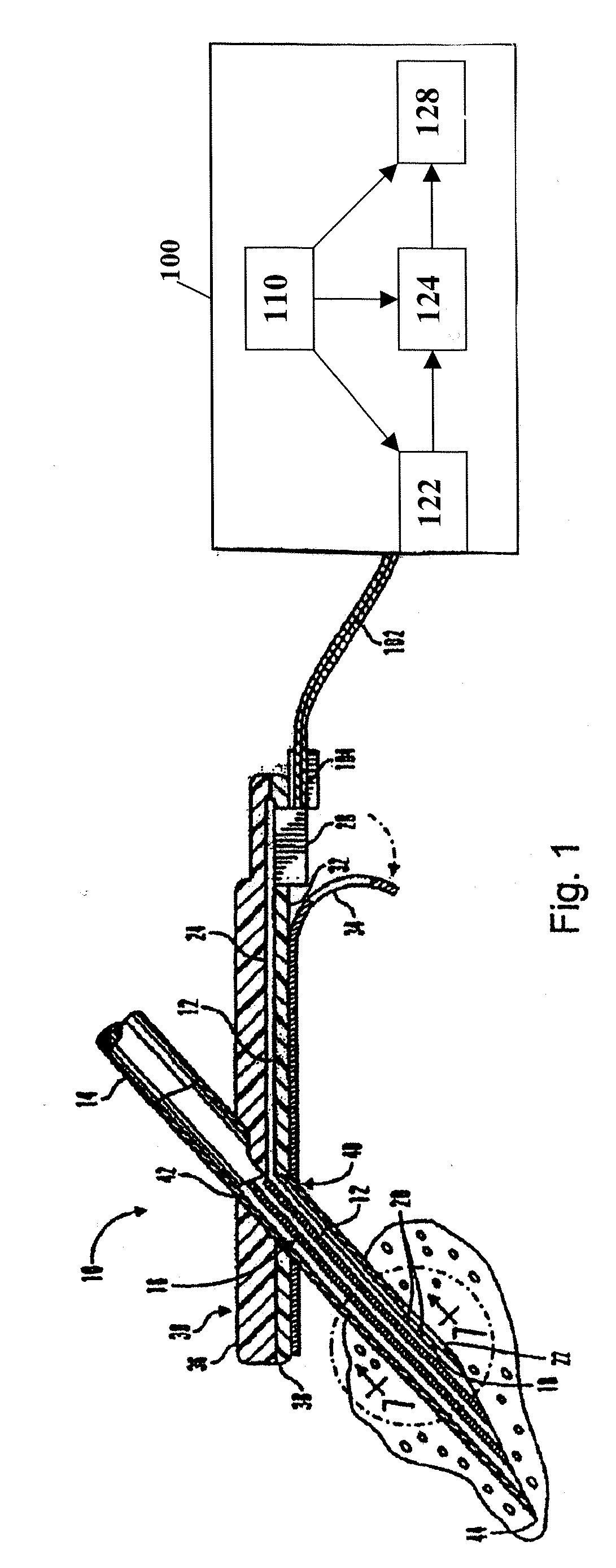

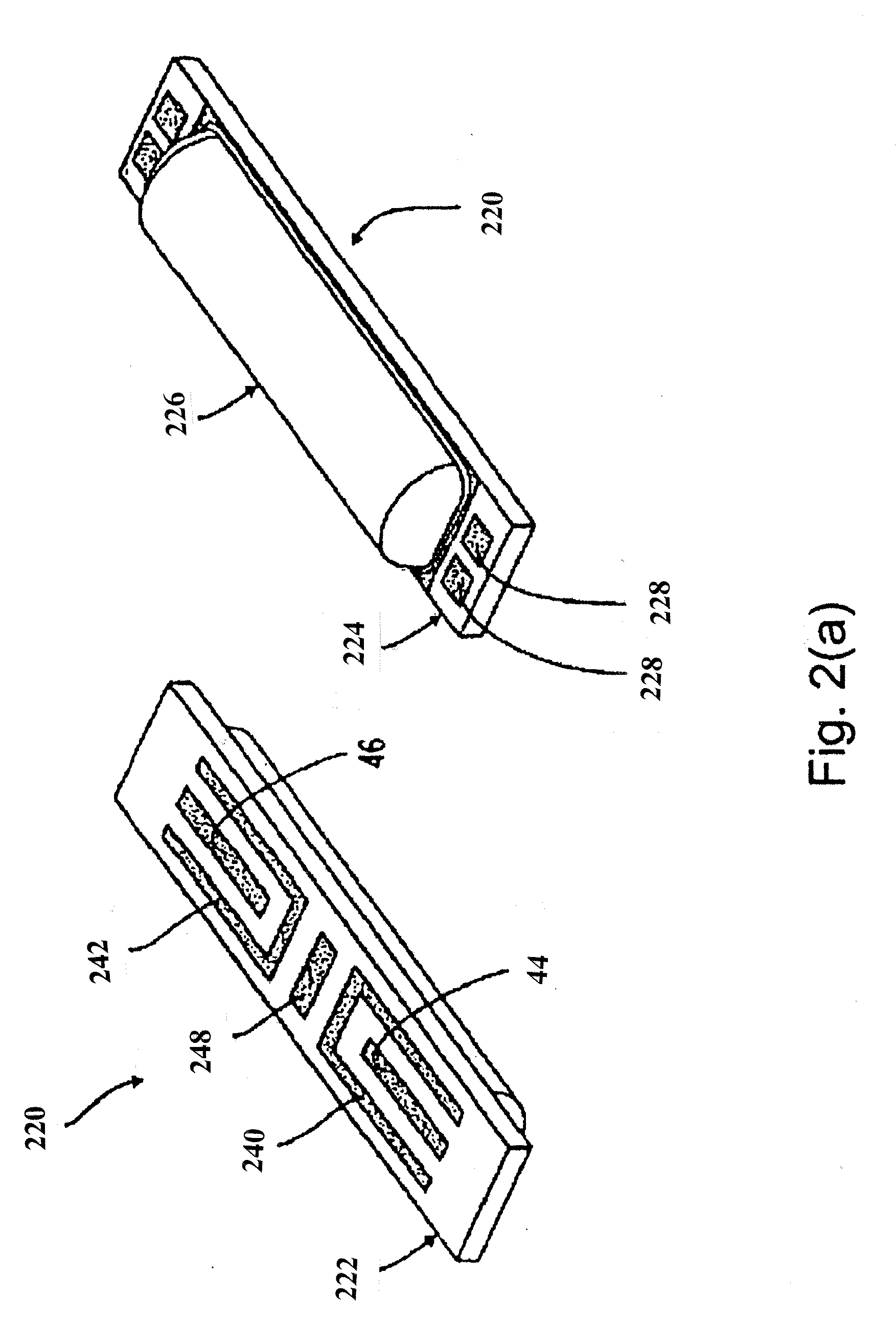

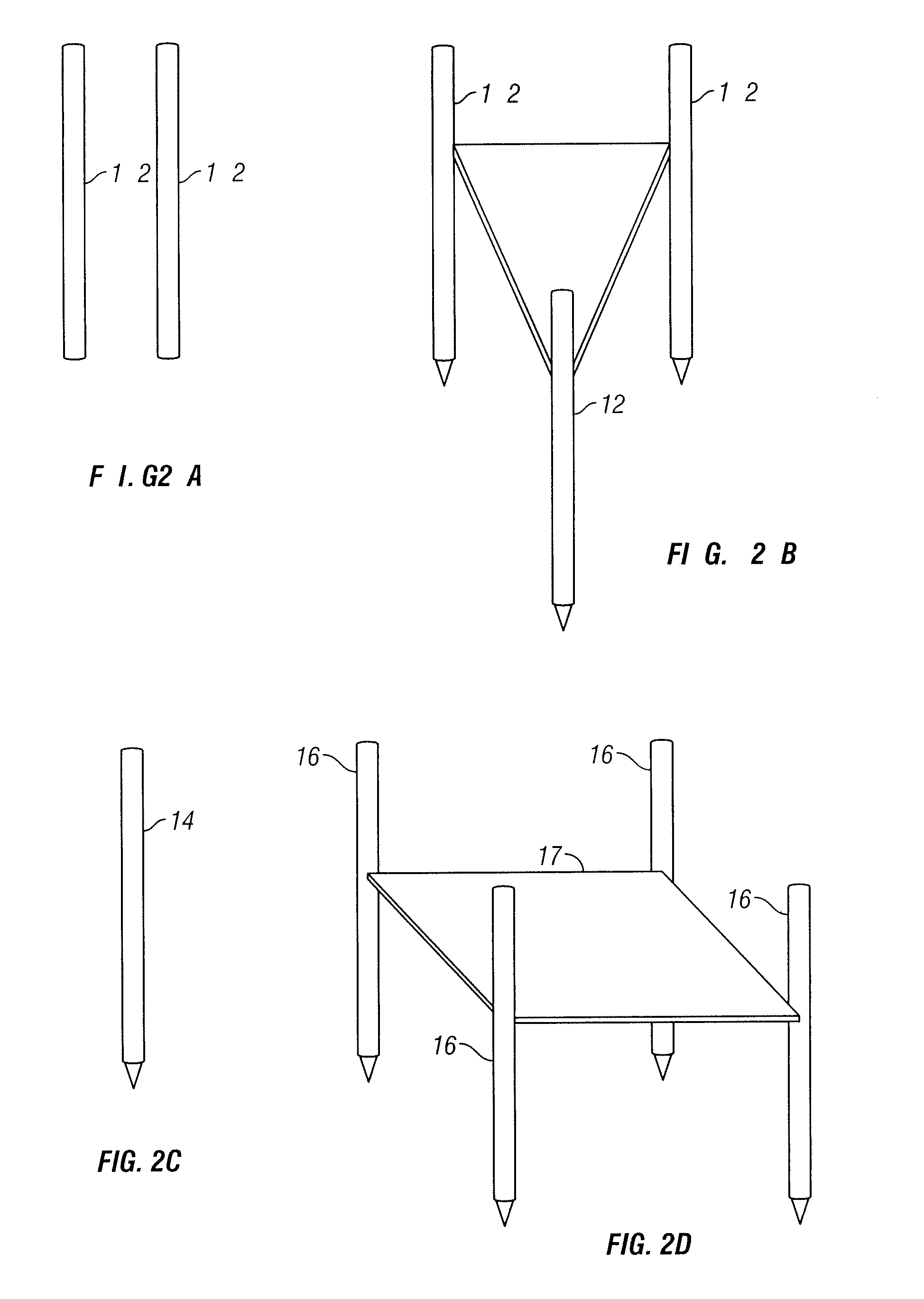

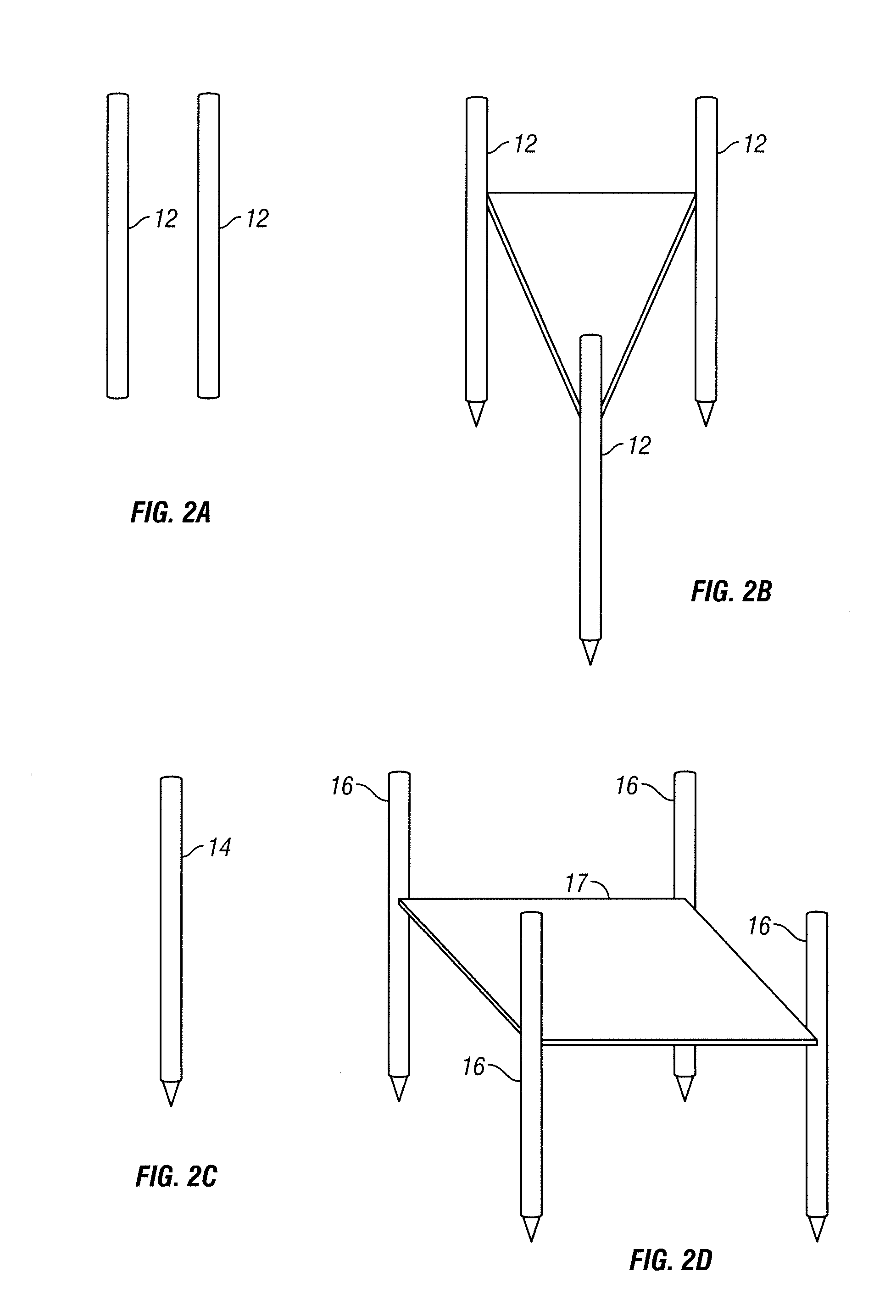

Methods and systems for treating fatty tissue sites using electroporation

InactiveUS20060293725A1Sufficient electricityElectrotherapySurgical instrument detailsVoltage pulseBiomedical engineering

A system is provided for treating fatty tissue sites of a patient. At least first and second mono-polar electrodes are configured to be introduced at or near the fatty tissue site of the patient. A voltage pulse generator is coupled to the first and second mono-polar electrodes. The voltage pulse generator is configured to apply sufficient electrical pulses between the first and second mono-polar electrodes to induce electroporation of cells in the fatty tissue site, to create necrosis of cells of the fatty tissue site, but insufficient to create a thermal damaging effect to a majority of the fatty tissue site. The system can be incorporated into standard liposuction devices or used simultaneously to treat and remove the tissue.

Owner:ANGIODYNAMICS INC

Methods and systems for observing sensor parameters

InactiveUS20100169035A1Resistance/reactance/impedenceCurrent/voltage measurementVoltage pulseEngineering

The invention disclosed herein provides methods and materials for observing the state of a sensor, for example those used by diabetic patients to monitor blood glucose levels. Typically a voltage such as a voltage pulse is applied to the sensor in order to solicit a current response from which for example, factors such as impedance values can be derived. Such values can then be used as indicators of a sensor's state, for example the state of sensor hydration, sensor noise, sensor offset, sensor drift or the like.

Owner:MEDTRONIC MIMIMED INC

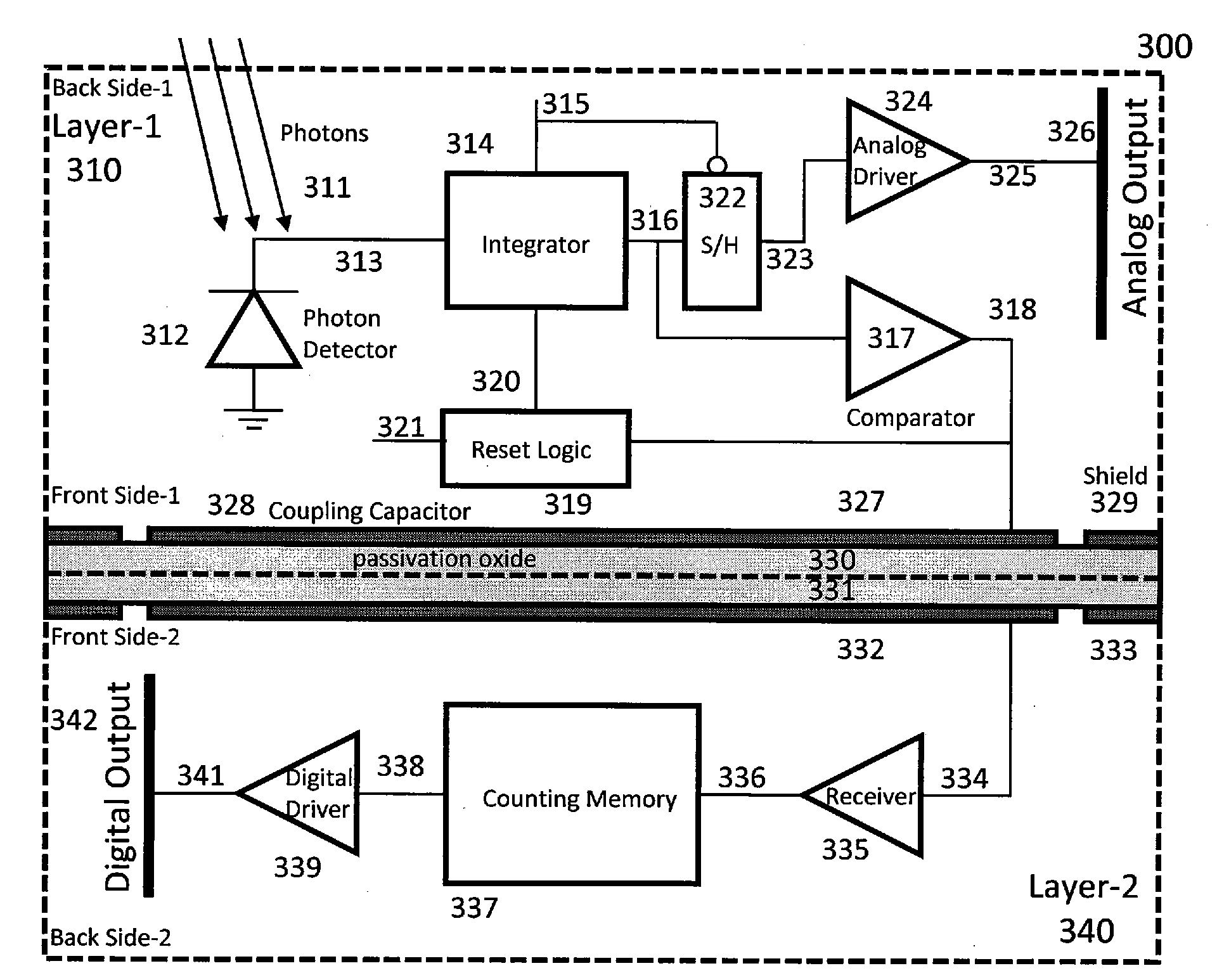

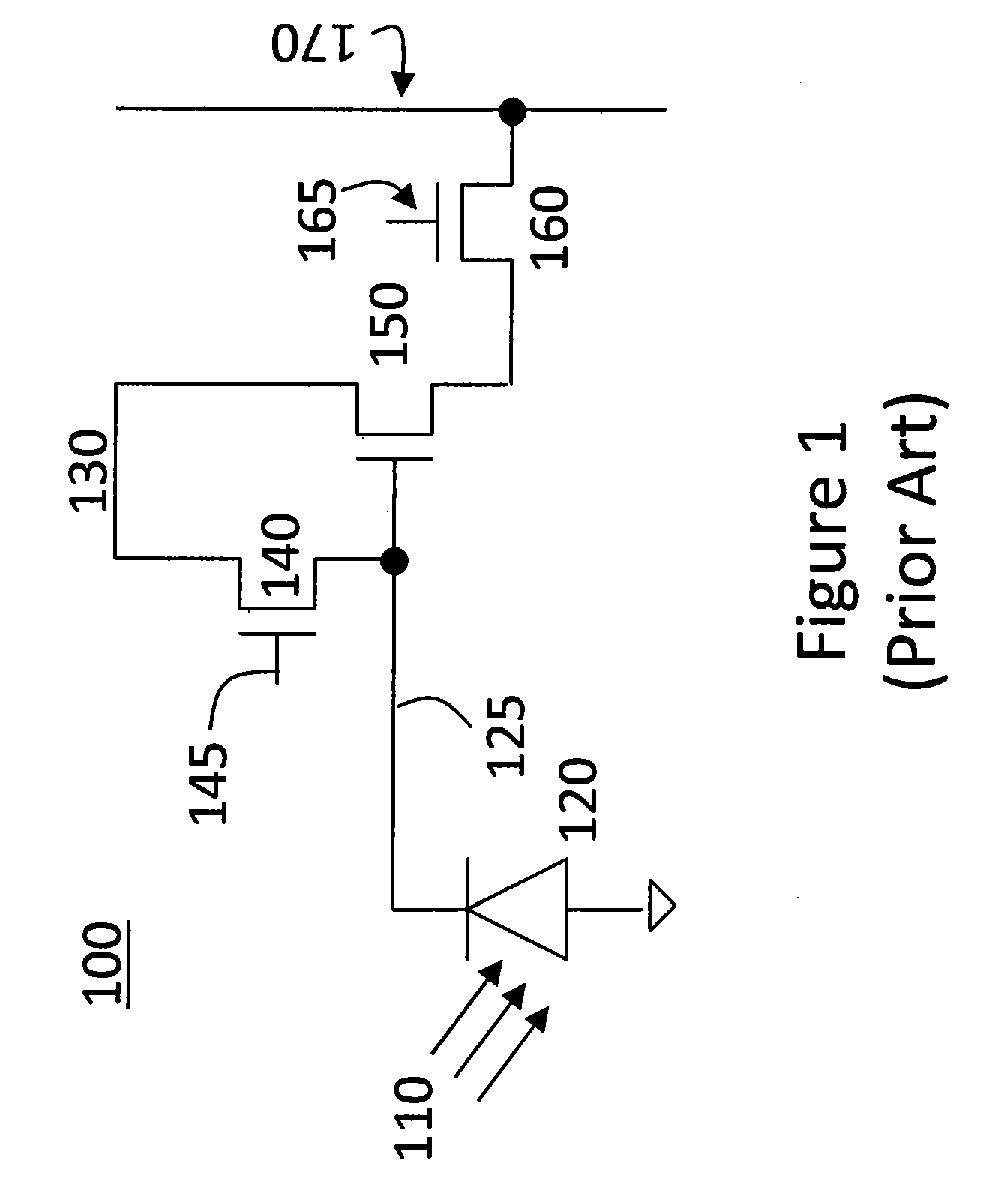

Method and apparatus for backside illuminated image sensors using capacitively coupled readout integrated circuits

InactiveUS20100140732A1Improve dynamic rangeImprove scanning rateTelevision system detailsSolid-state devicesCapacitanceIntegrator

The images sensor includes a readout circuit capacitatively coupled to a memory circuit. The readout circuit includes: (i) a photon detector to receive a plurality of photons and to provide a charge signal corresponding to the received photons, (ii) a resettable integrator that is reset multiple times over a single exposure time and provides an analog representation of the incident photons during the last integration cycle, and (iii) a comparator that monitors the integrator output and generates a reset pulse when the integrator reaches a built-in threshold value. The memory circuit includes: (i) a receiver circuit that detects the output of the digital driver in the front-end readout circuit via capacitive coupling and generates a digital voltage pulse for each received signal, and (ii) a digital counting memory to count the received pulses to provide a coarse digital representation of how many times the integrator is reset.

Owner:TELEDYNE SCI & IMAGING

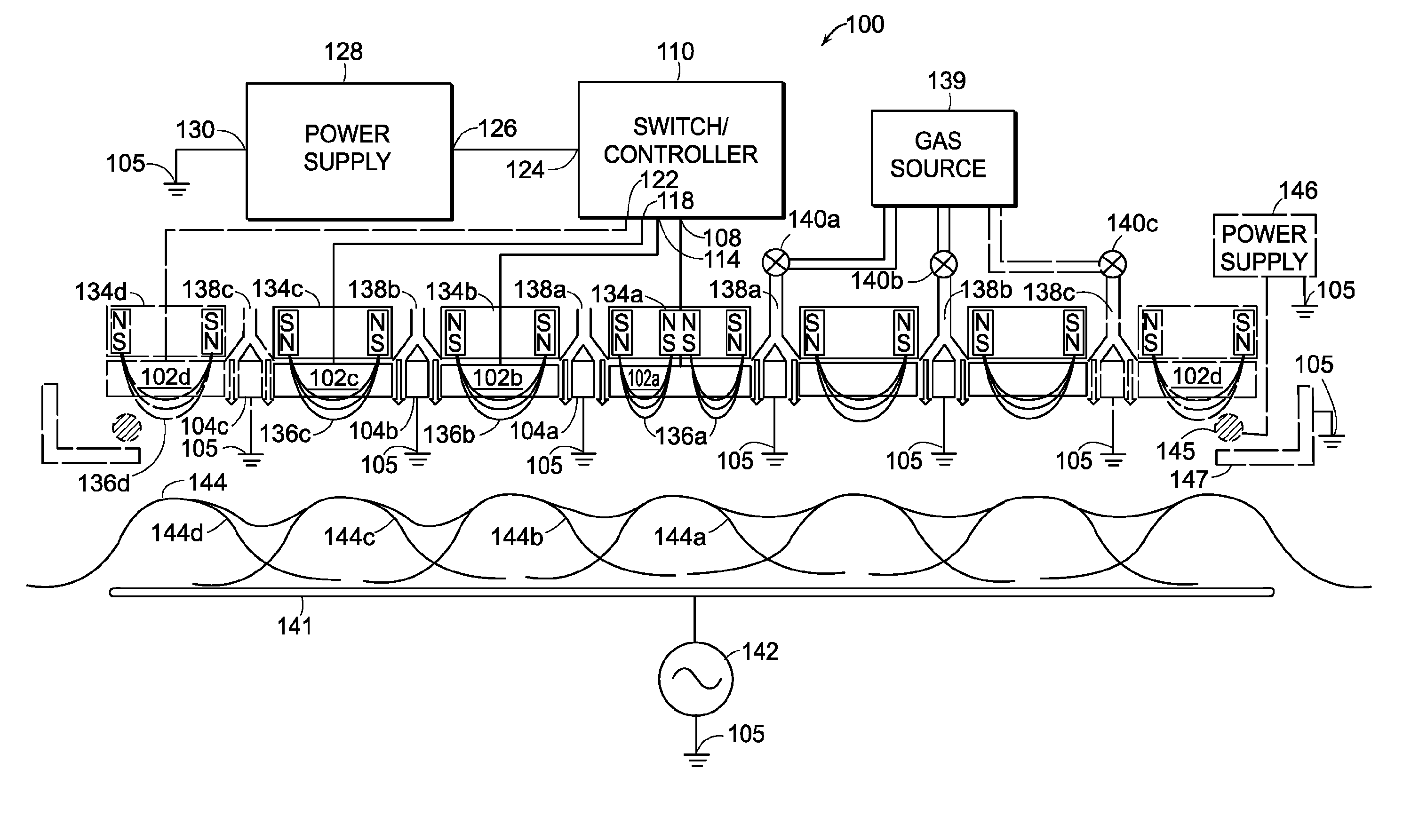

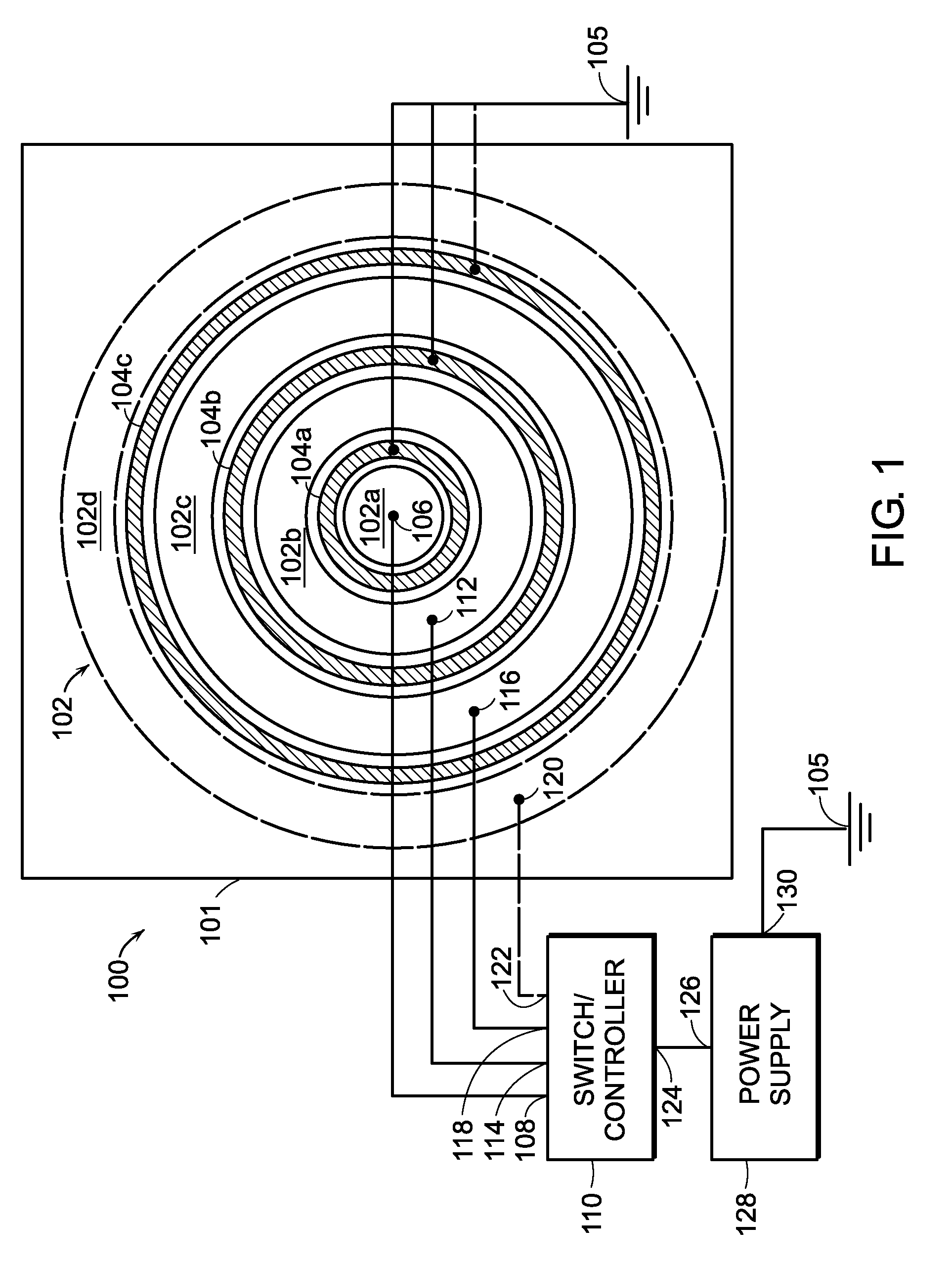

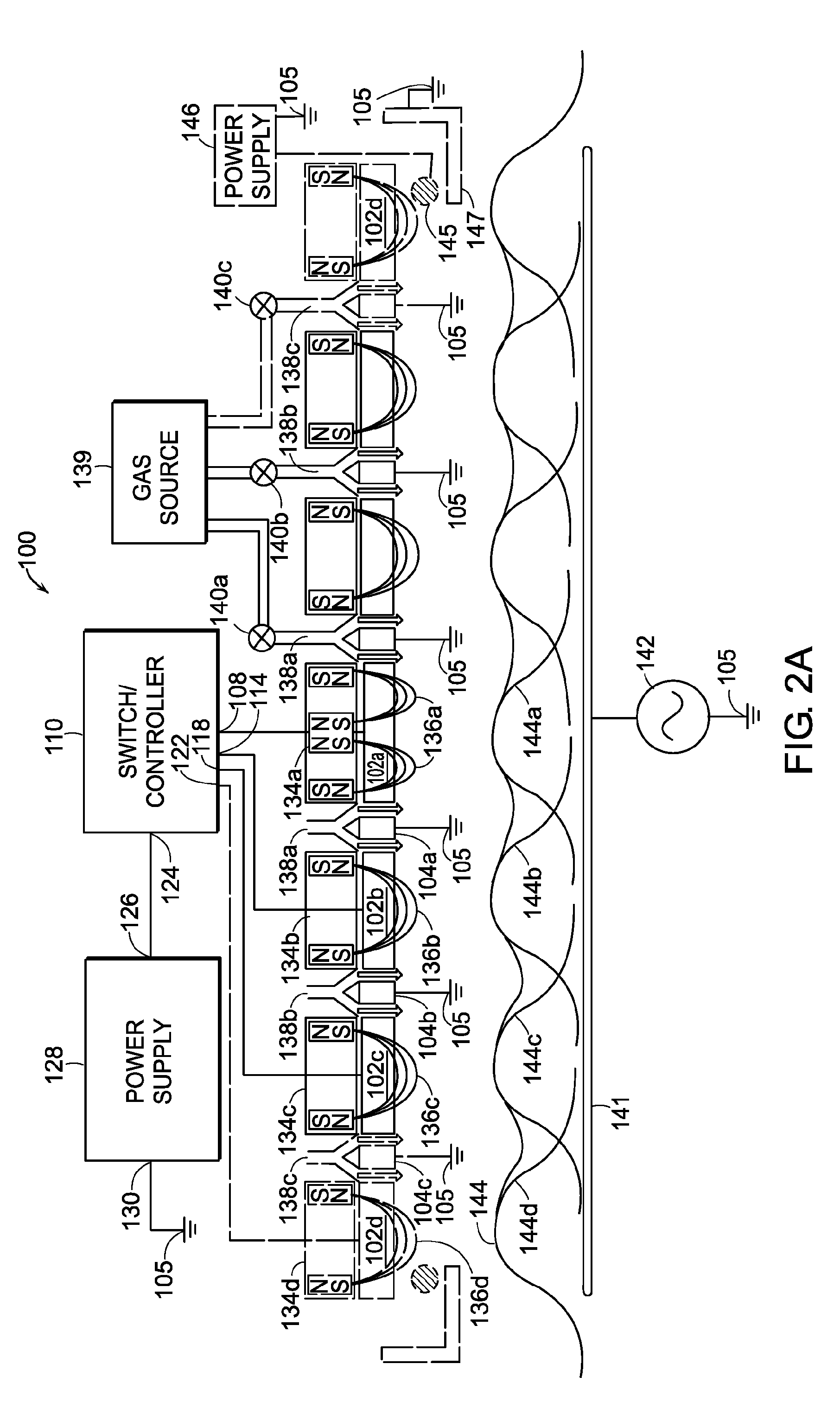

Plasma source with segmented magnetron cathode

A plasma source includes a chamber for containing a feed gas. An anode is positioned in the chamber. A segmented magnetron cathode comprising a plurality of electrically isolated magnetron cathode segments is positioned in the chamber proximate to the anode. A power supply is electrically connected to an electrical in-put of a switch. A respective one of the plurality of electrical out-puts of the switch is electrically connected to a respective one of the plurality of magnetron cathode segments. The power supply generates a train of voltage pulses that ignites a plasma from the feed gas. Individual voltage pulses in the train of voltage pulses are routed by the switch in a predetermined sequence to at least two of the plurality of magnetron cathode segments.

Owner:ZOND

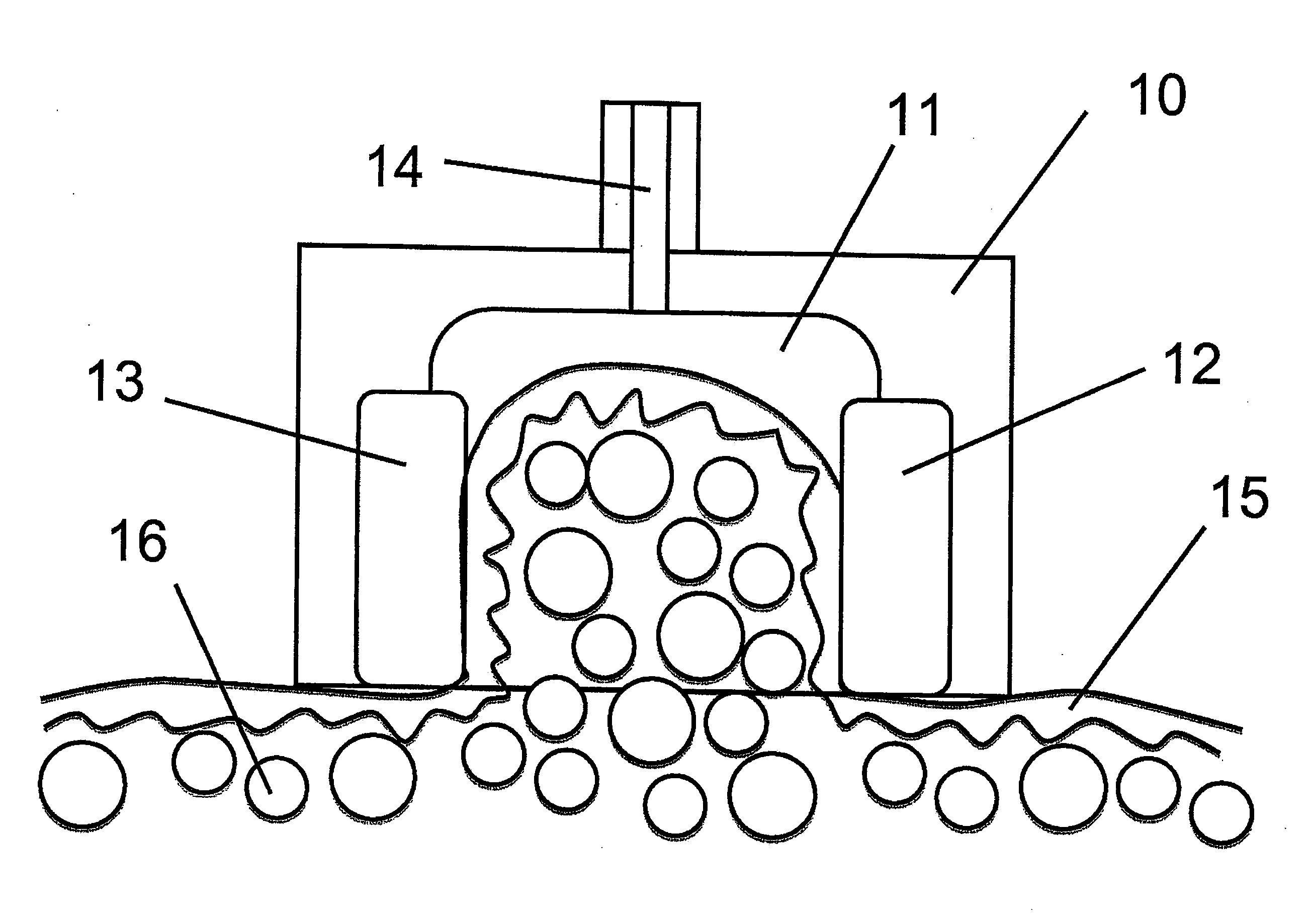

Method and device for fat treatment

InactiveUS20110112520A1Good electrode couplingEvenly distributedElectrotherapySurgical instruments for heatingVoltage pulseTissue heating

A method and apparatus for fat destruction and body contouring. The method comprises pre-heating treated tissue and applying a high voltage pulse to destroy adipose tissue. The device includes an energy source for tissue heating and an HV pulse generator for applying voltage pulsed in the range of 200V to 5 kV.

Owner:INVASIX

Memory array of a non-volatile ram

InactiveUS6859382B2Control flowSolid-state devicesRead-only memoriesVoltage pulseArray data structure

Non-volatile memory cell with a single semiconductor device per memory cell. The present invention generally allows for a plurality of memory cells to be formed on a semiconductor substrate that supports a semiconductor device. A multi-resistive state material layer that changes its resistive state between a low resistive state and a high resistive state upon application of a voltage pulse is formed above the substrate, generally at a very high temperature. While the layers fabricated between the substrate and the multi-resistive state material use materials that can withstand high temperature processing, the layers fabricated above the multi-resistive state material do not need to withstand high temperature processing.

Owner:UNITY SEMICON

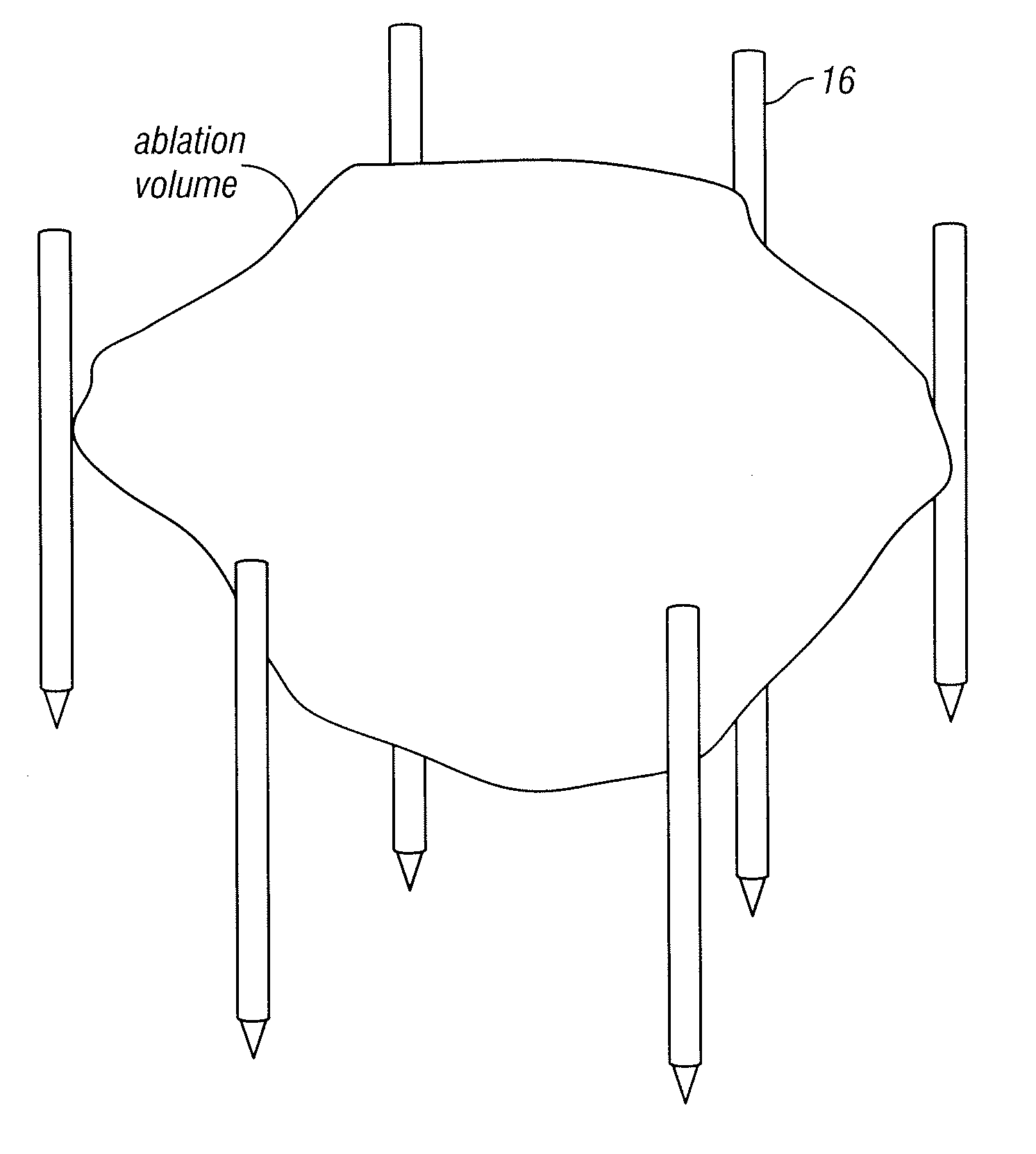

Methods and systems for treating tumors using electroporation

InactiveUS20060293731A1Create insufficiencySurgical needlesSurgical instrument detailsVoltage pulseTumor tissue

A system is provided for treating tumor tissue sites of a patient. At least first and second mono-polar electrodes are configured to be introduced at or near the tumor tissue site of the patient. A voltage pulse generator is coupled to the first and second mono-polar electrodes. The voltage pulse generator is configured to apply sufficient electrical pulses between the first and second mono-polar electrodes to induce electroporation of cells in the tumor tissue site, to create necrosis of cells of the tumor tissue site, but insufficient to create a thermal damaging effect to a majority of the tumor tissue site.

Owner:ANGIODYNAMICS INC

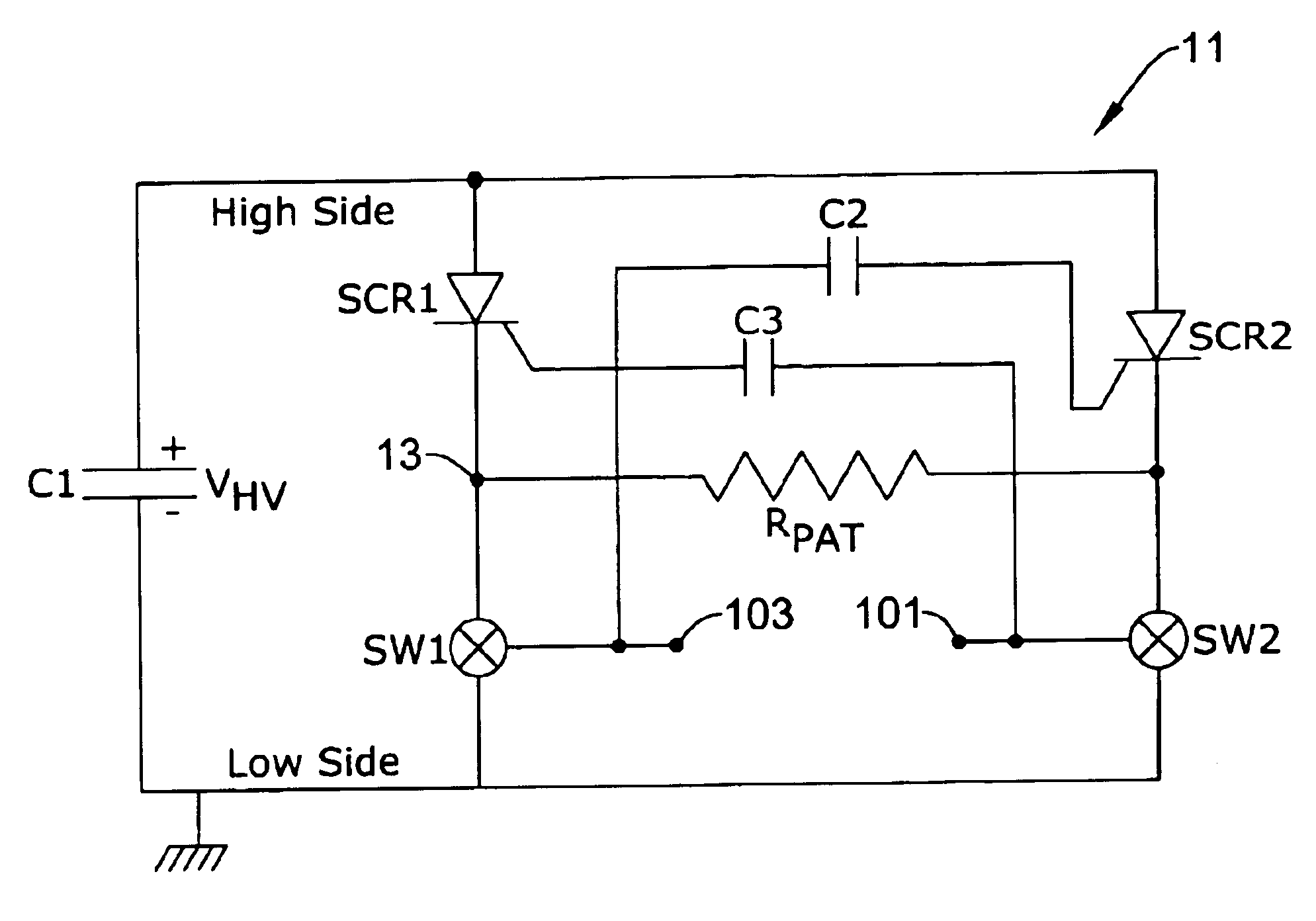

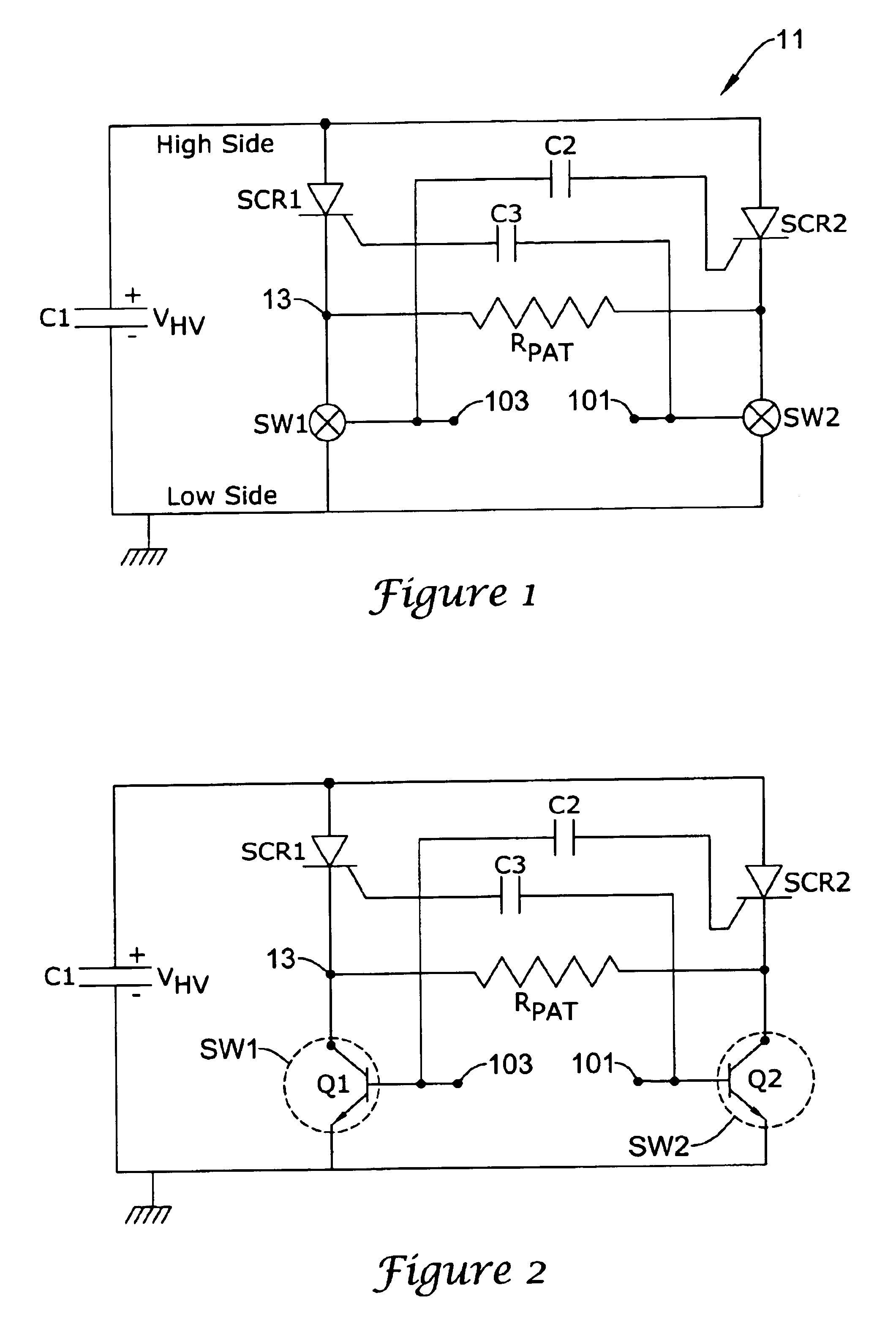

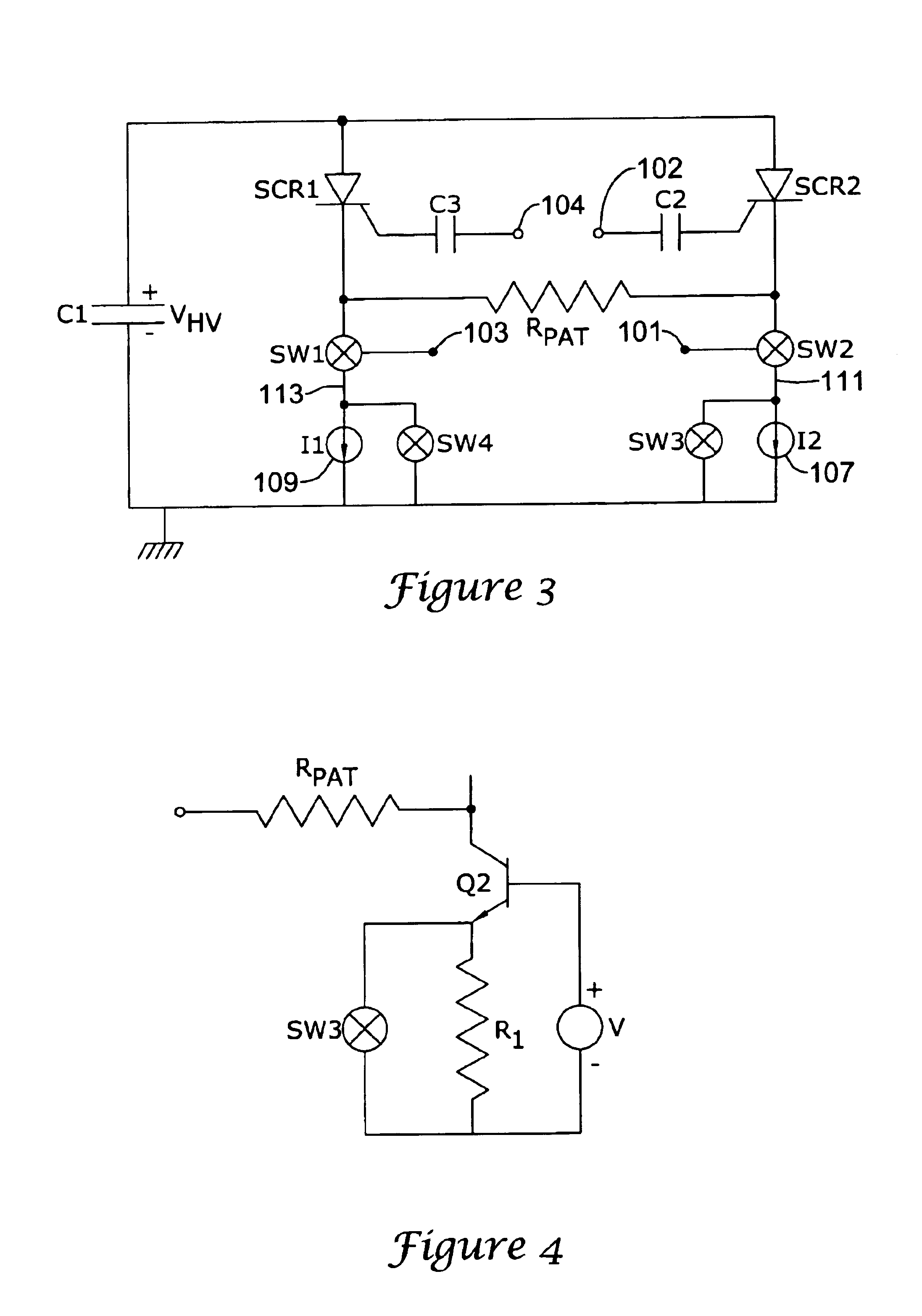

Simplified defibrillator output circuit

High side driver circuitry for a defibrillator circuit employs respective capacitors connected to respective gates of silicon controlled rectifiers serving as high side switches. Applying a voltage pulse to a selected capacitor turns on the associated SCR. Positive turn-on of the high side SCRs is insured by inserting a constant current source into the low side activation current path at start-up.

Owner:CAMERON HEALTH

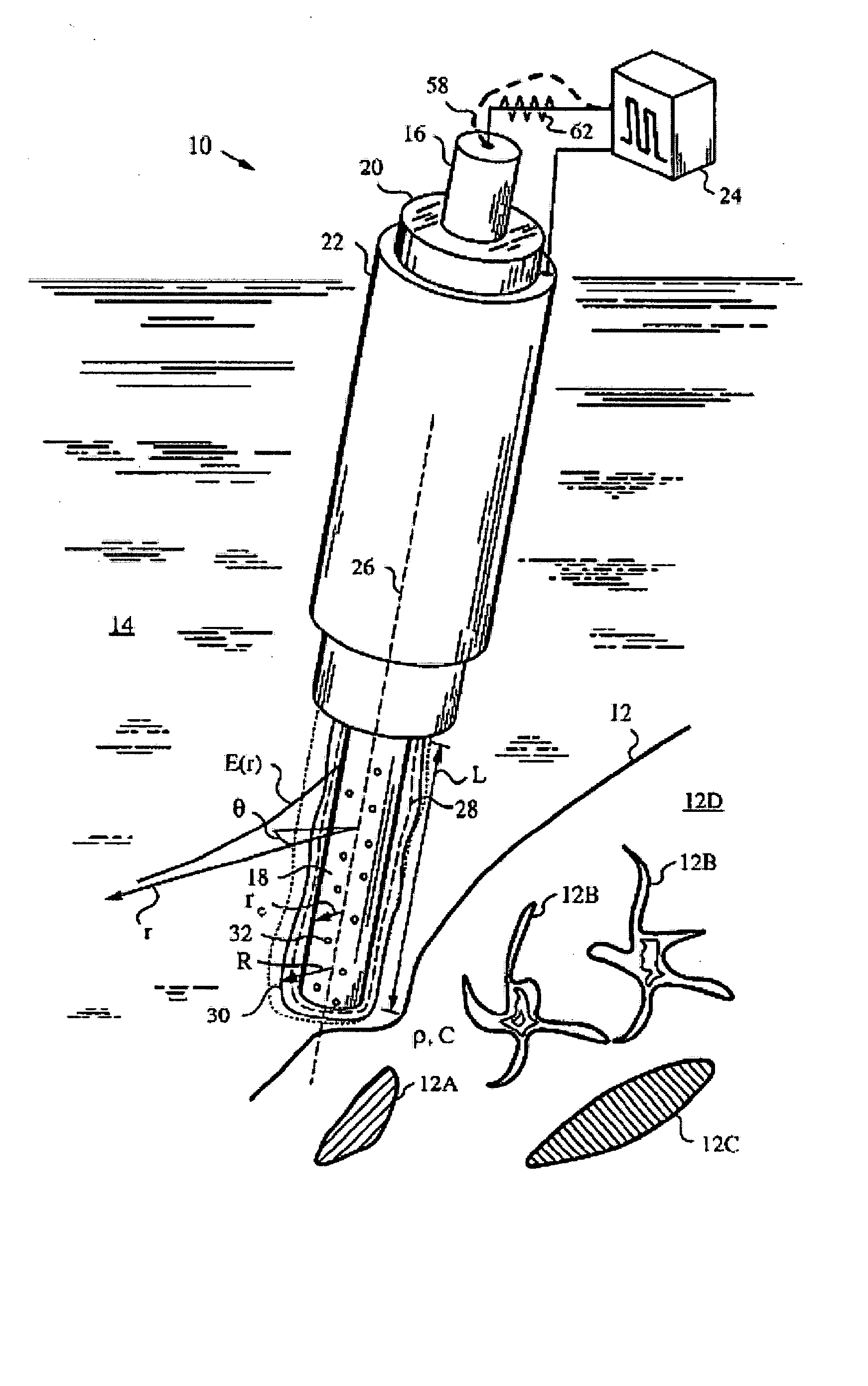

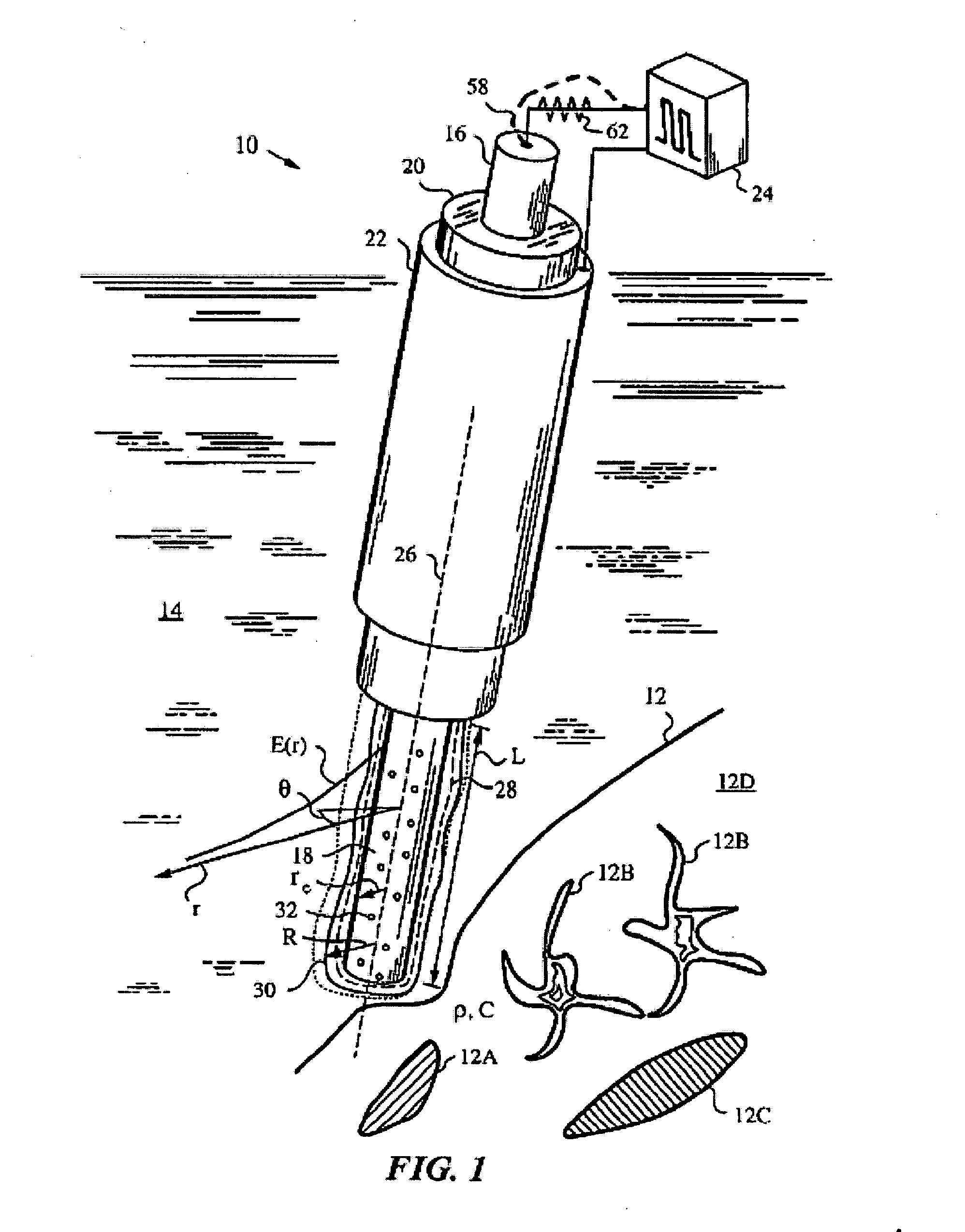

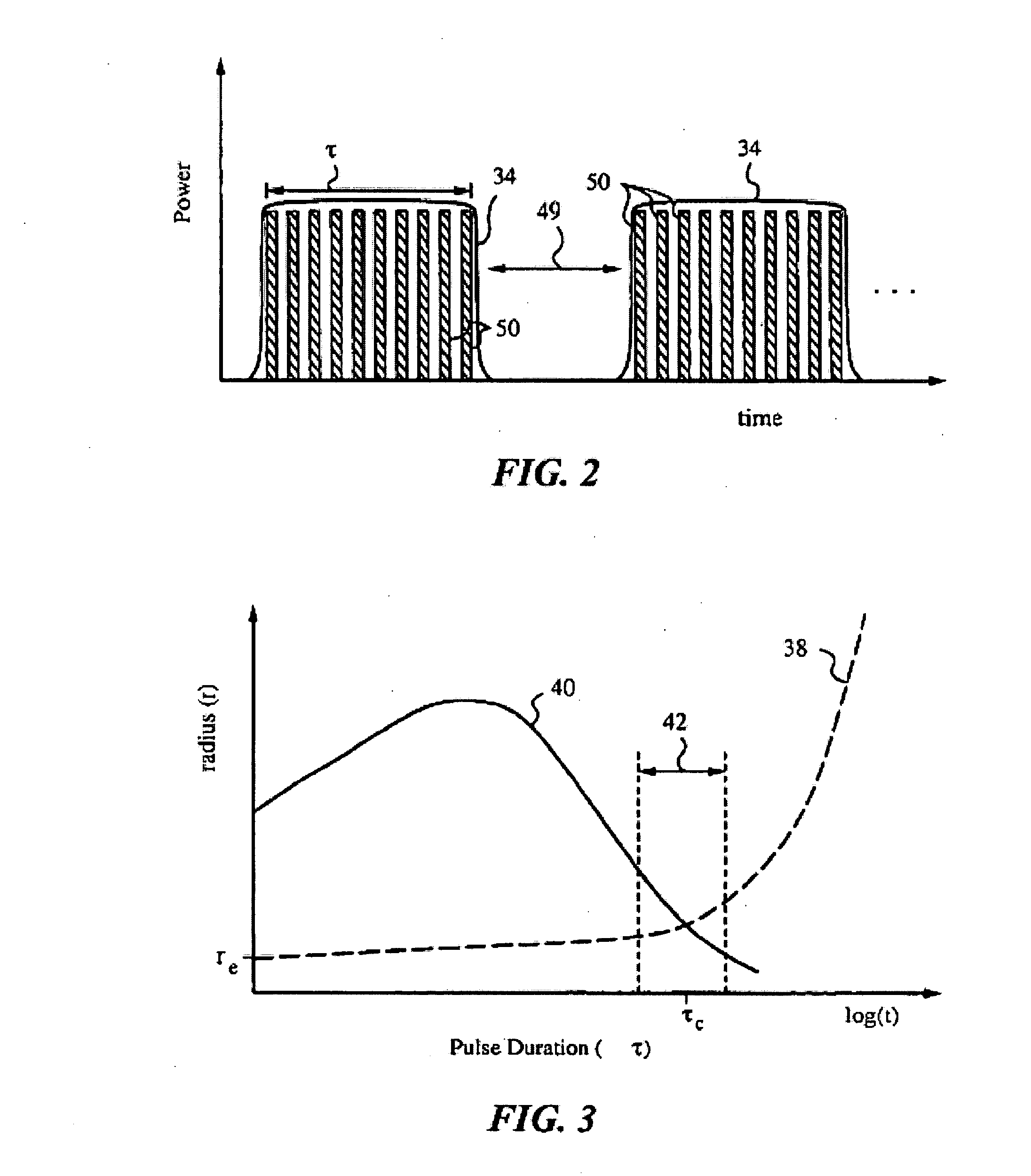

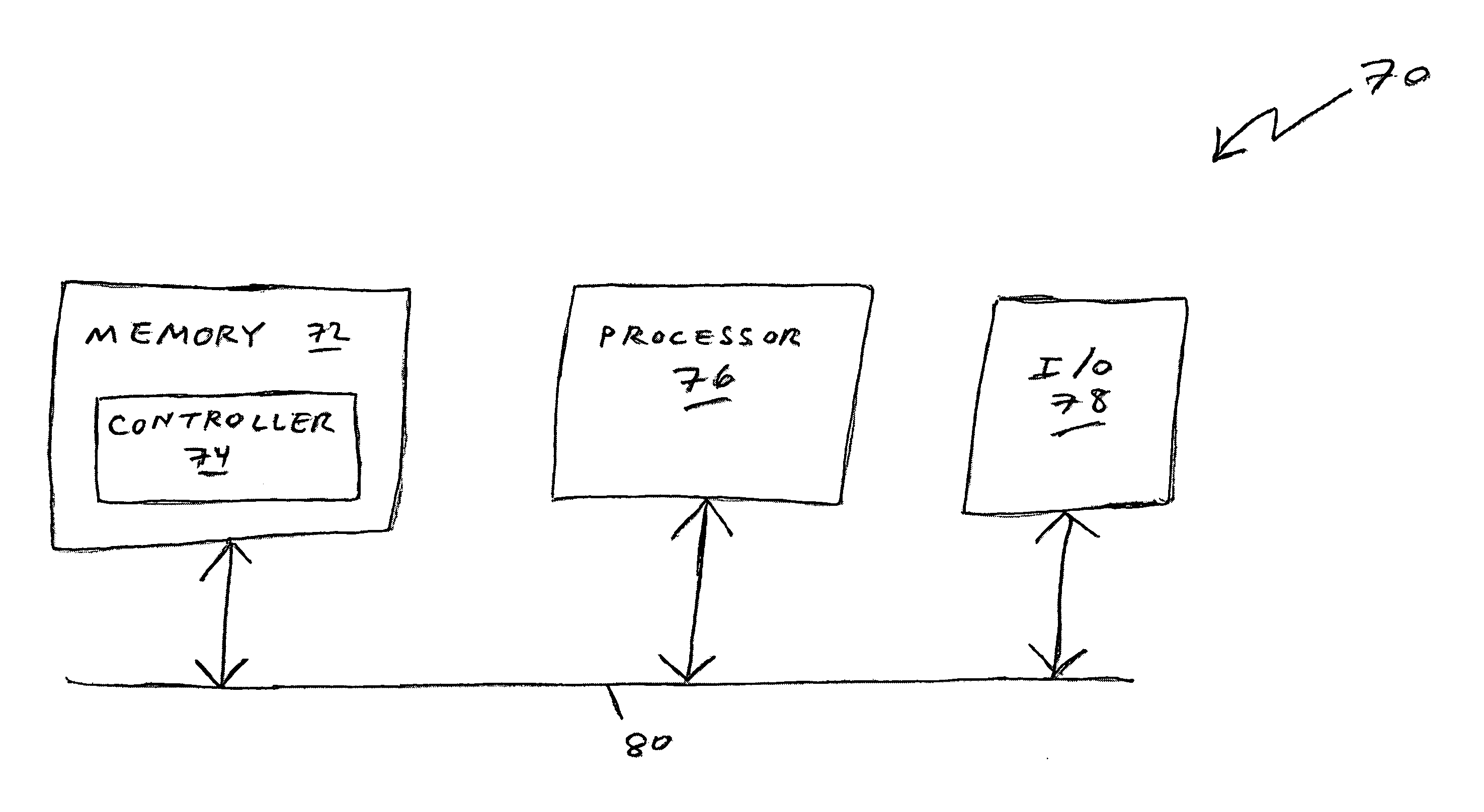

Method and apparatus for plasma-mediated thermo-electrical ablation

ActiveUS20080039832A1Efficient thermal ablationMinimize damage zoneSurgical instruments for heatingVoltage pulseBlood plasma

Described herein are methods and apparatus for cutting a material including biological tissue. The apparatus has a cutting electrode with an elongate cutting portion. A voltage pulse waveform (typically comprising repeated bursts of minipulses) having a low or very low duty-cycle is applied to the cutting electrode to cut the tissue or other material by producing a vapor cavity around the cutting portion of the electrode and ionizing a gas inside the vapor cavity to produce a plasma. A low duty cycle cutting waveform may prevent heat accumulation in the tissue, reducing collateral thermal damage. The duration of the burst of minipulses typically ranges from 10 μs to 100 μs, and the rep rate typically ranges from 1 KHz to 10 Hz, as necessary. The apparatus and method of invention may cut biological tissue while decreasing bleeding and maintaining a very shallow zone of thermal damage.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Method of archiving data

ActiveUS20050024941A1Impact reliabilityShort program timeMemory loss protectionMemory adressing/allocation/relocationVoltage pulseLong term data

A method and system for archiving data. The data are classified according to their desired lifetime and then archived in a memory using a storage method whose reliability is in accordance with the desired lifetime. For example, when storing data in the cells of an EPROM, short-term data could be archived using larger programming voltage pulse increments than for long-term data, using a lower target threshold voltage than for long-term data, using wider programming voltage pulses than for long-term data, using higher starting programming voltages than for long-term data, using fewer programming voltage pulses than for long term data, using lower maximum programming voltages than for long term data, or using more levels per cell than for long-term data.

Owner:WESTERN DIGITAL ISRAEL LTD

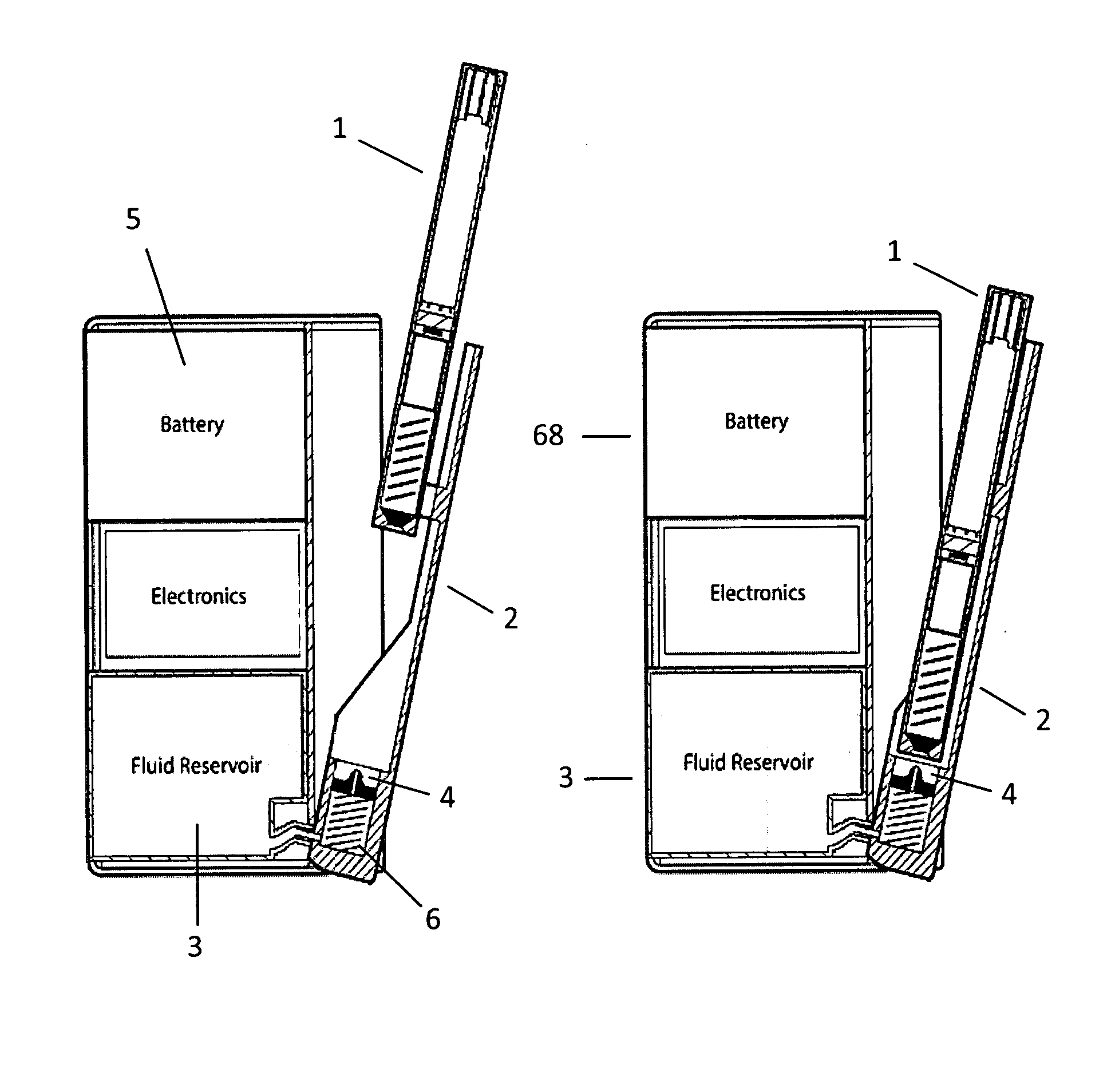

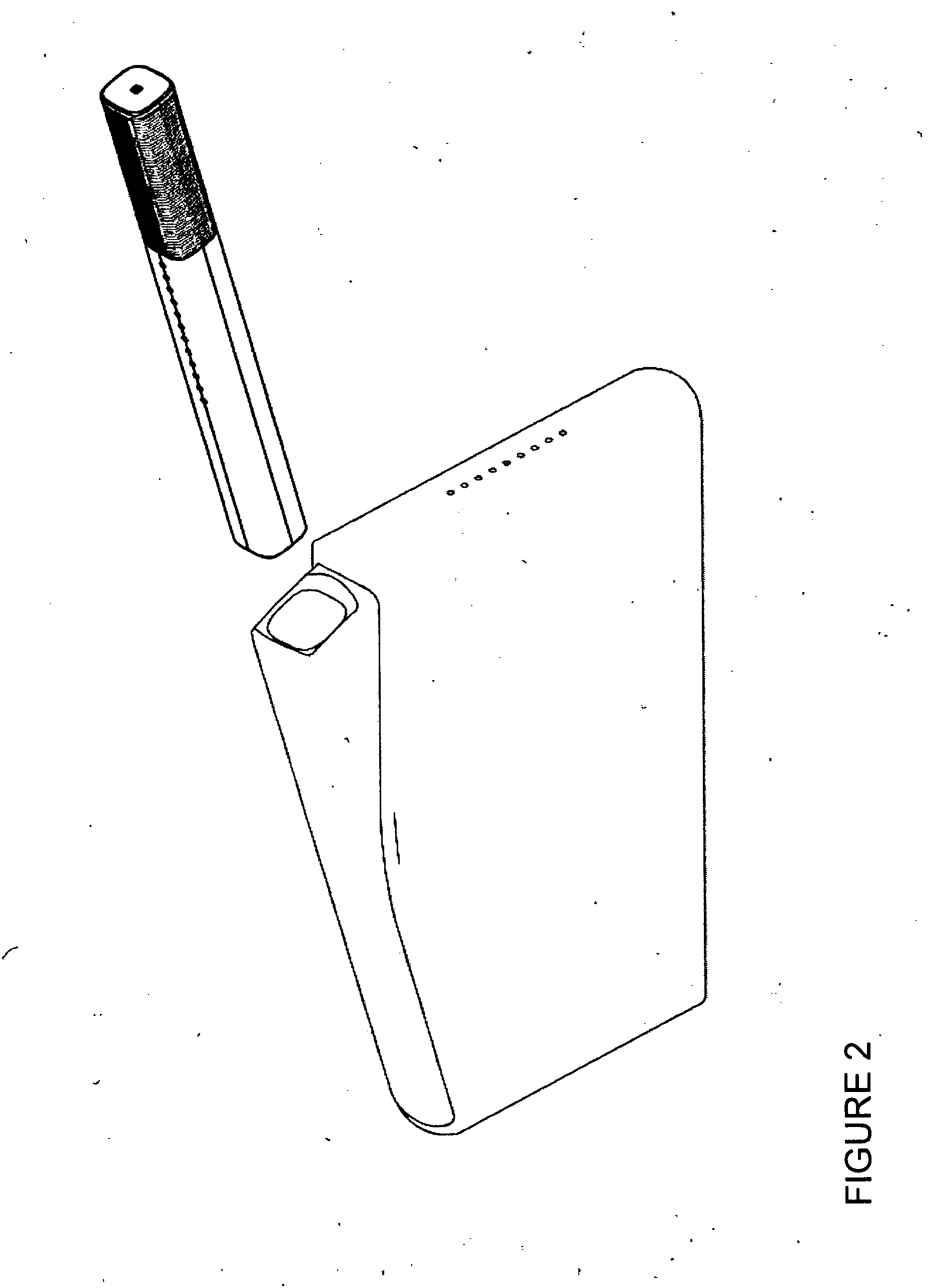

Electronic vaporiser system

An electronic cigarette vaporiser system includes a piezo-electric pump (6) with multiple piezo-actuators, in which a microcontroller independently adjusts the phase or timing or power of each voltage pulse that triggers a piezo-actuator. The microcontroller continuously or regularly monitors the efficiency or performance of the entire pump (6) and adjusts the phase, timing, or power delivered to each piezo-actuator relationship until or so that the optimum pumping performance is achieved.

Owner:AYR LTD

Methods and systems for treating restenosis sites using electroporation

A system is provided for reducing restenosis. A catheter apparatus is provided with at least first and second mono-polar electrodes positioned at an inflatable balloon. The balloon is sized to be positioned and expanded at a restenosis site. A voltage pulse generator is coupled to the first and second mono-polar electrodes. The voltage pulse generator is configured to apply an electric field, in a controlled manner, to the restenosis site in an amount sufficient to produce electroporation of the restenosis site, and below an amount that causes thermal damage to the restenosis site.

Owner:ANGIODYNAMICS INC

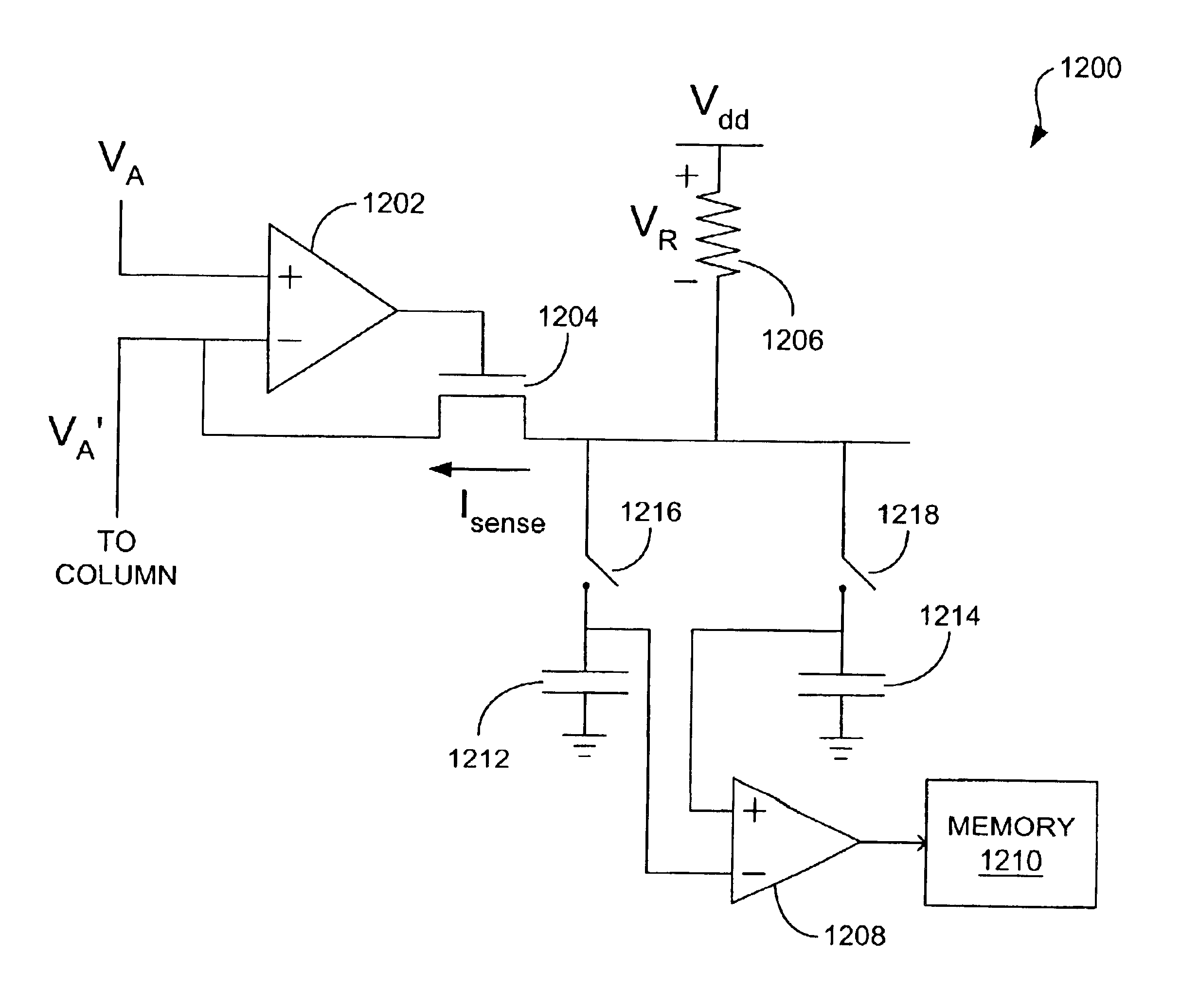

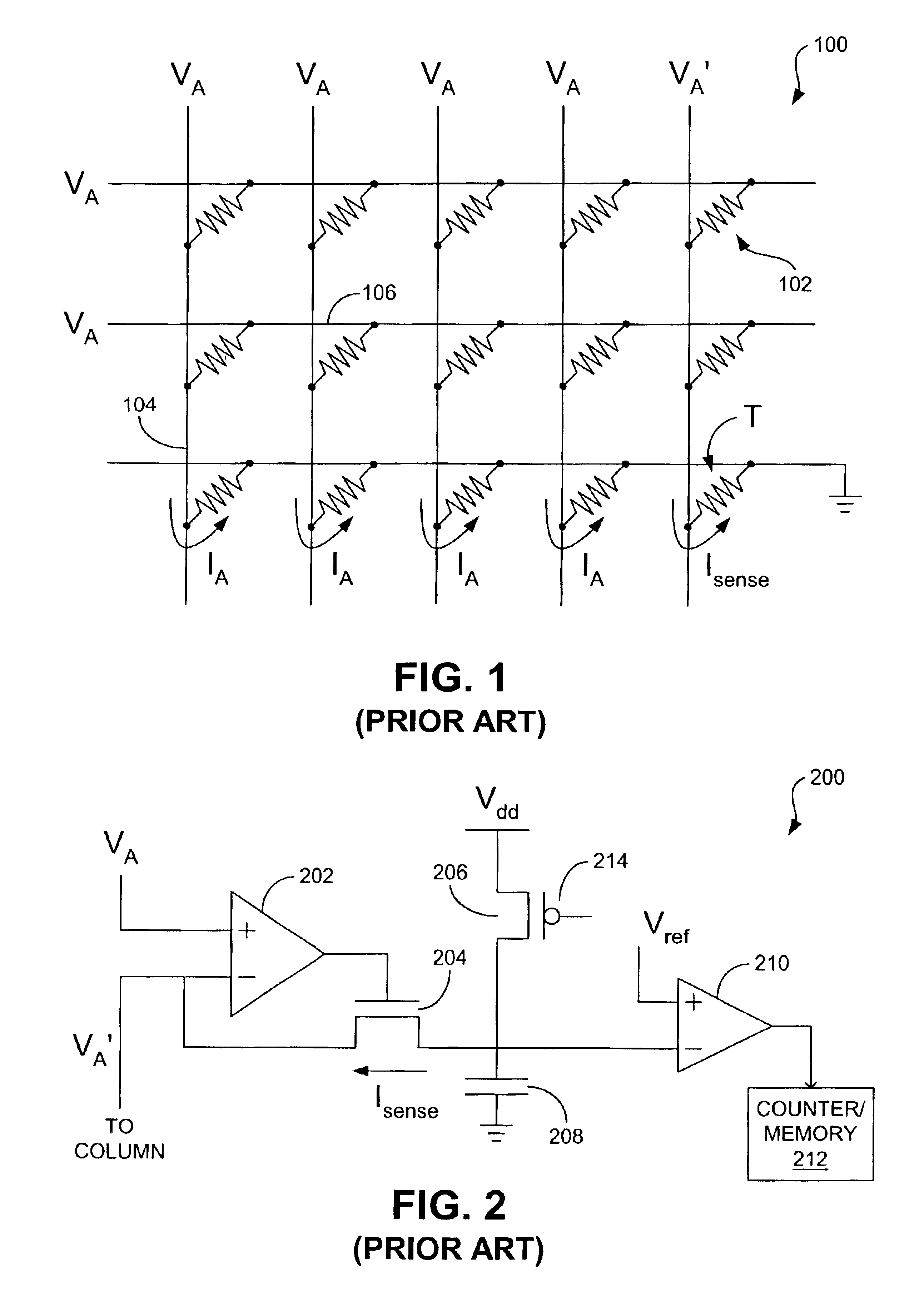

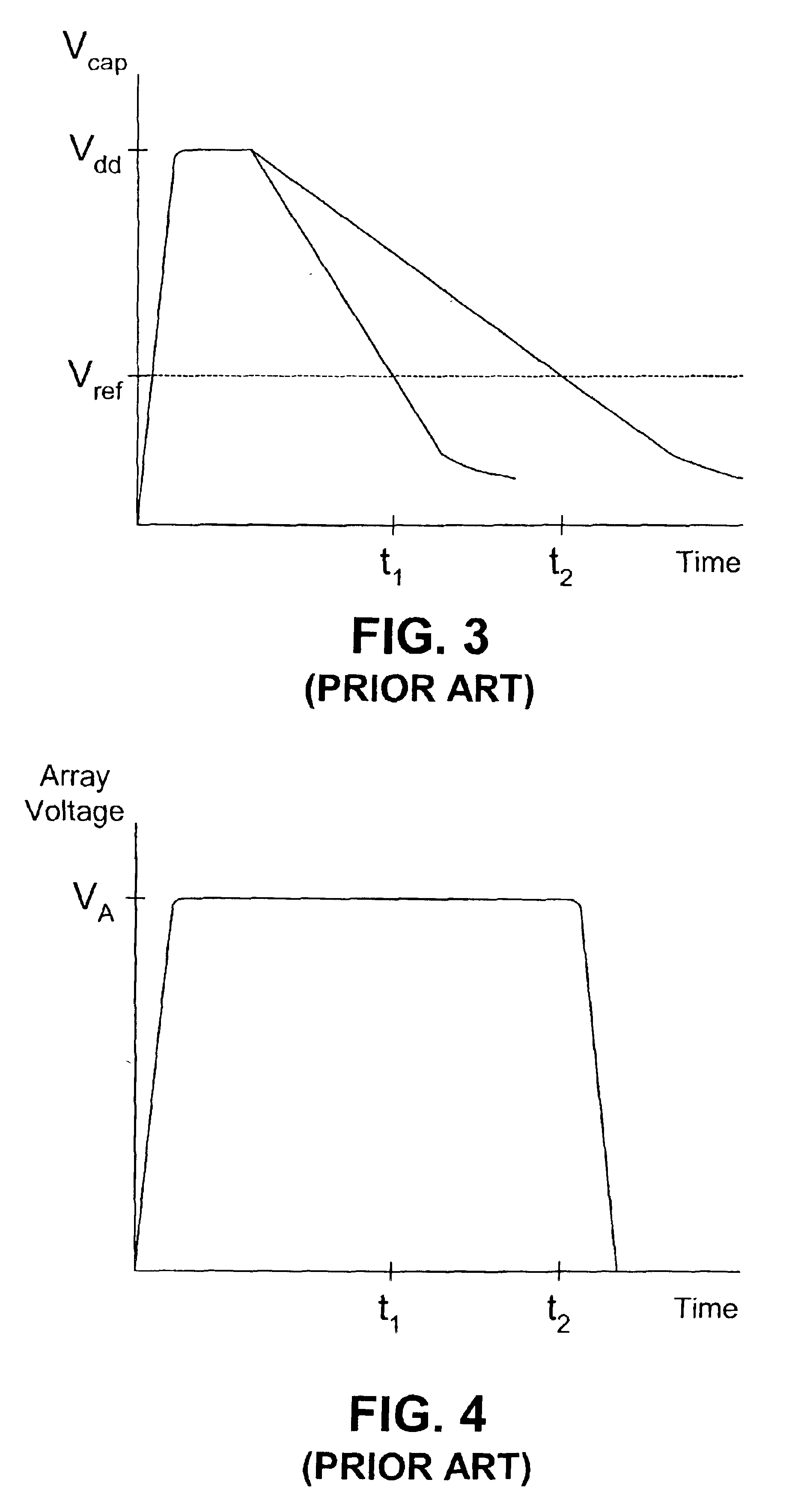

Power-saving reading of magnetic memory devices

Power-saving reading of magnetic memory devices. In one arrangement, a method includes pulsing a voltage on the array, and obtaining a voltage value indicative of a memory state of the target memory cell from the voltage pulse using a sensing circuit that is electrically connected to the target memory cell. In another arrangement, a method includes pulsing an array voltage on a plurality of row and column conductors of the array, connecting a sensing circuit to a conductor that is electrically coupled to the target memory cell, the sensing circuit including a sense element, and determining the voltage drop across the sense element of the sensing circuit during the voltage pulse, the voltage drop being indicative of a memory state of the target memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

Step soft program for reversible resistivity-switching elements

A method and system for forming, resetting, or setting memory cells is disclosed. One or more programming conditions to apply to a memory cell having a reversible resistivity-switching element may be determined based on its resistance. The determination of one or more programming conditions may also be based on a pre-determined algorithm that may be based on properties of the memory cell. The one or more programming conditions may include a programming voltage and a current limit. For example, the magnitude of the programming voltage may be based on the resistance. As another example, the width of a programming voltage pulse may be based on the resistance. In some embodiments, a current limit used during programming is determined based on the memory cell resistance.

Owner:SANDISK TECH LLC

Two-phase programming of a flash memory

Owner:WESTERN DIGITAL ISRAEL LTD

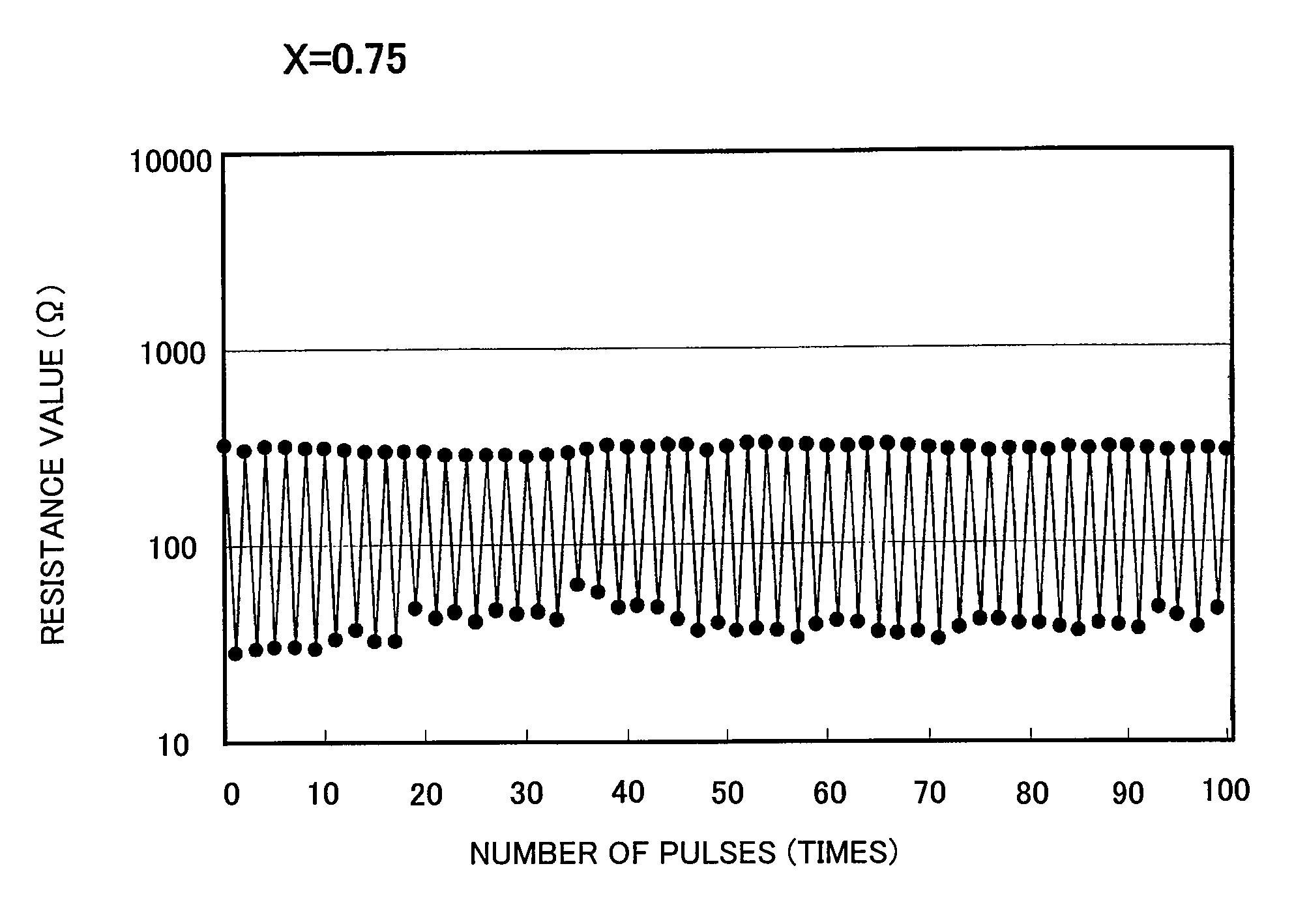

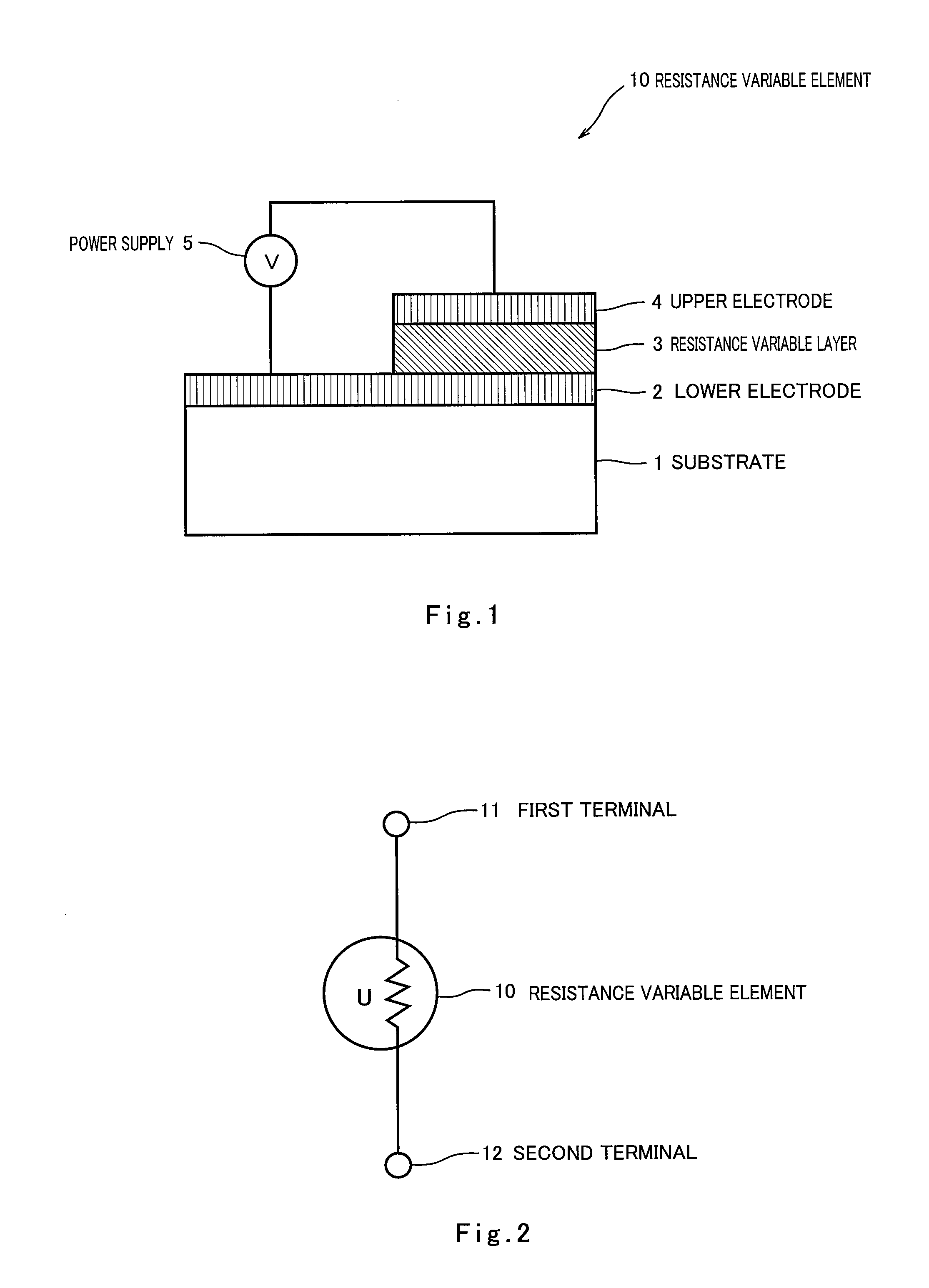

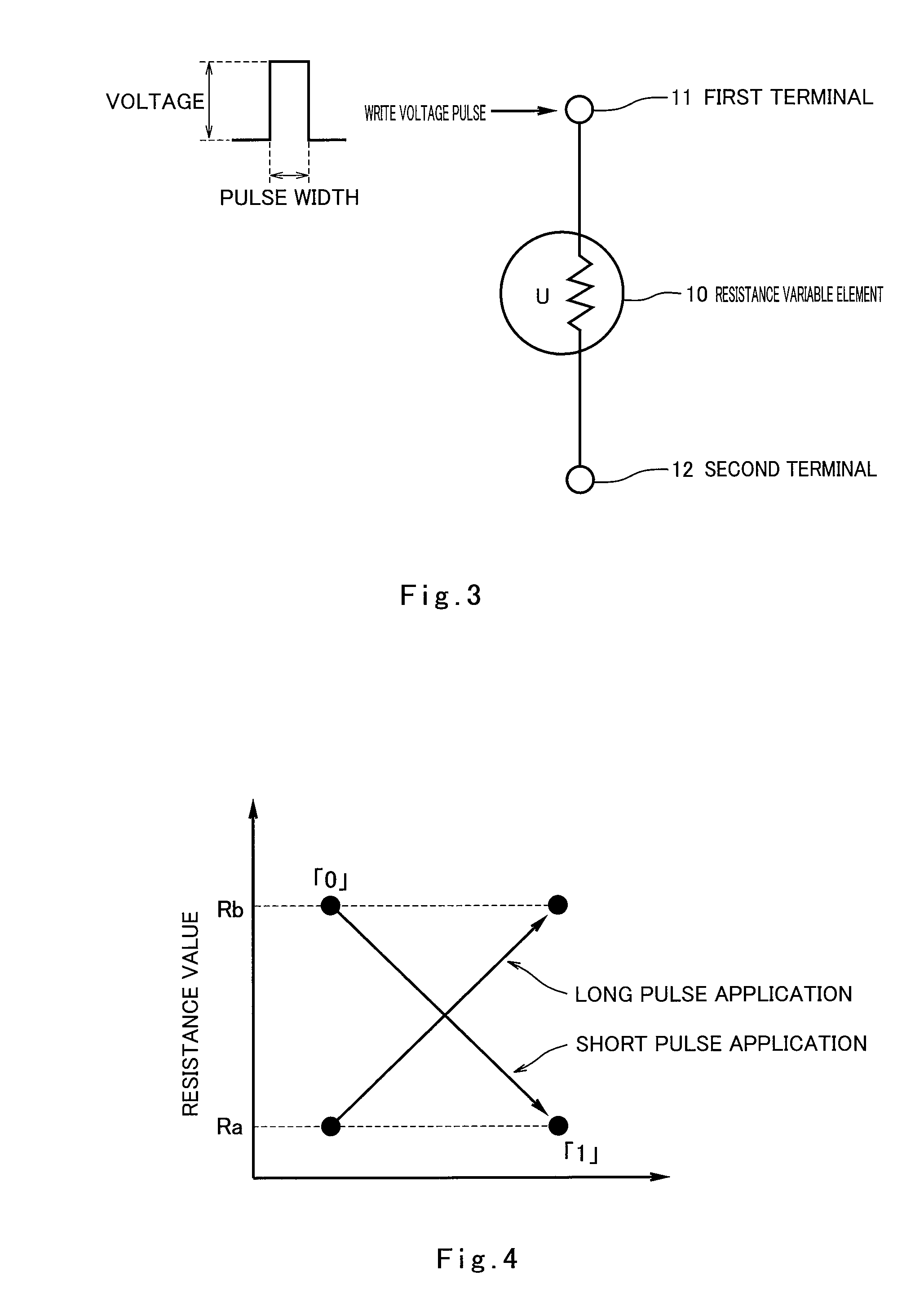

Resistance variable element and resistance variable memory apparatus

InactiveUS8018760B2Same polaritySolid-state devicesRead-only memoriesVoltage pulseElectrical polarity

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Methods and systems for treating tumors using electroporation

InactiveUS20080015571A1Surgical needlesSurgical instrument detailsAbnormal tissue growthVoltage pulse

A system is provided for treating tumor tissue sites of a patient. At least first and second mono-polar electrodes are configured to be introduced at or near the tumor tissue site of the patient. A voltage pulse generator is coupled to the first and second mono-polar electrodes. The voltage pulse generator is configured to apply sufficient electrical pulses between the first and second mono-polar electrodes to induce electroporation of cells in the tumor tissue site, to create necrosis of cells of the tumor tissue site, but insufficient to create a thermal damaging effect to a majority of the tumor tissue site.

Owner:ANGIODYNAMICS INC

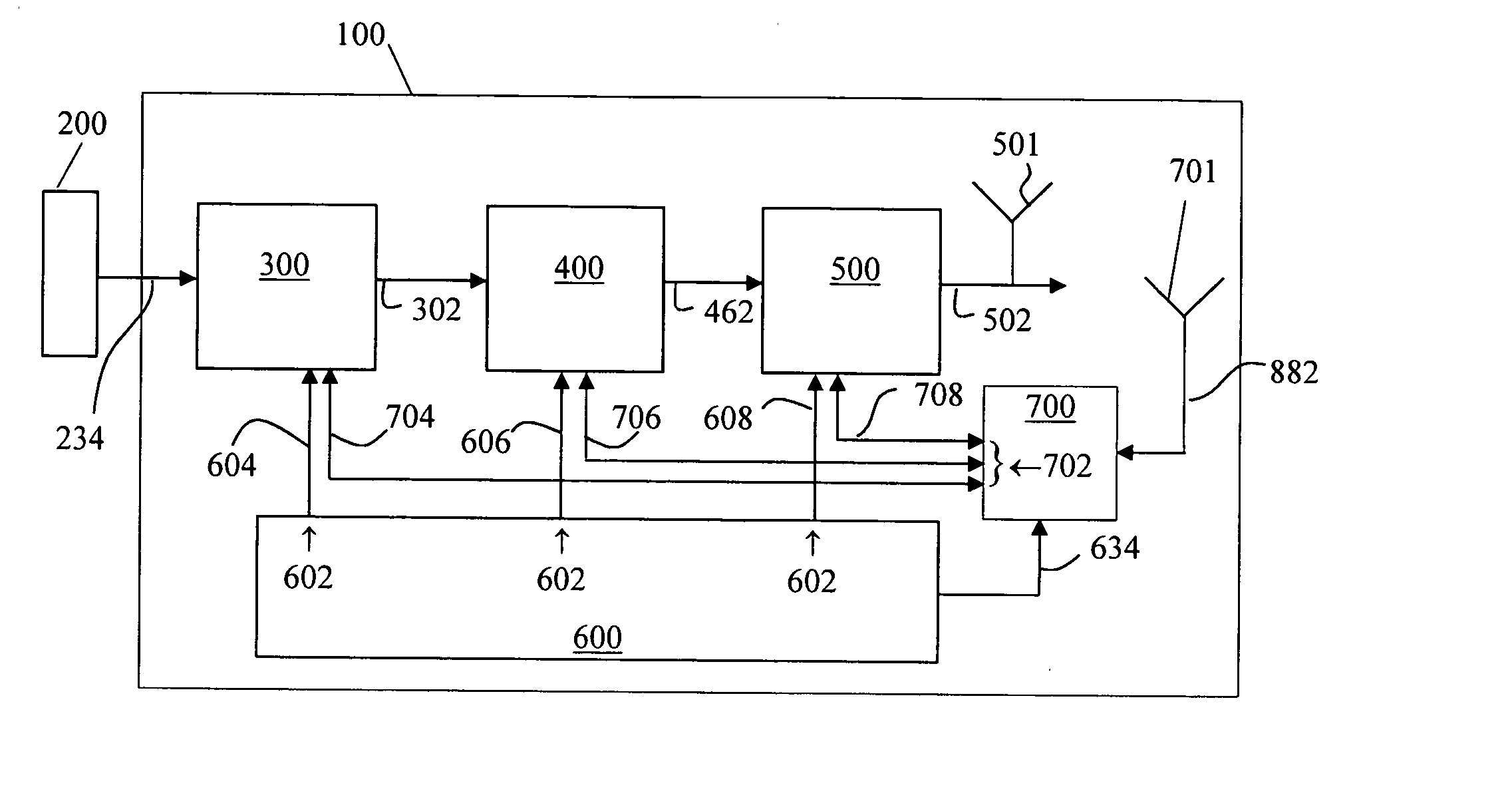

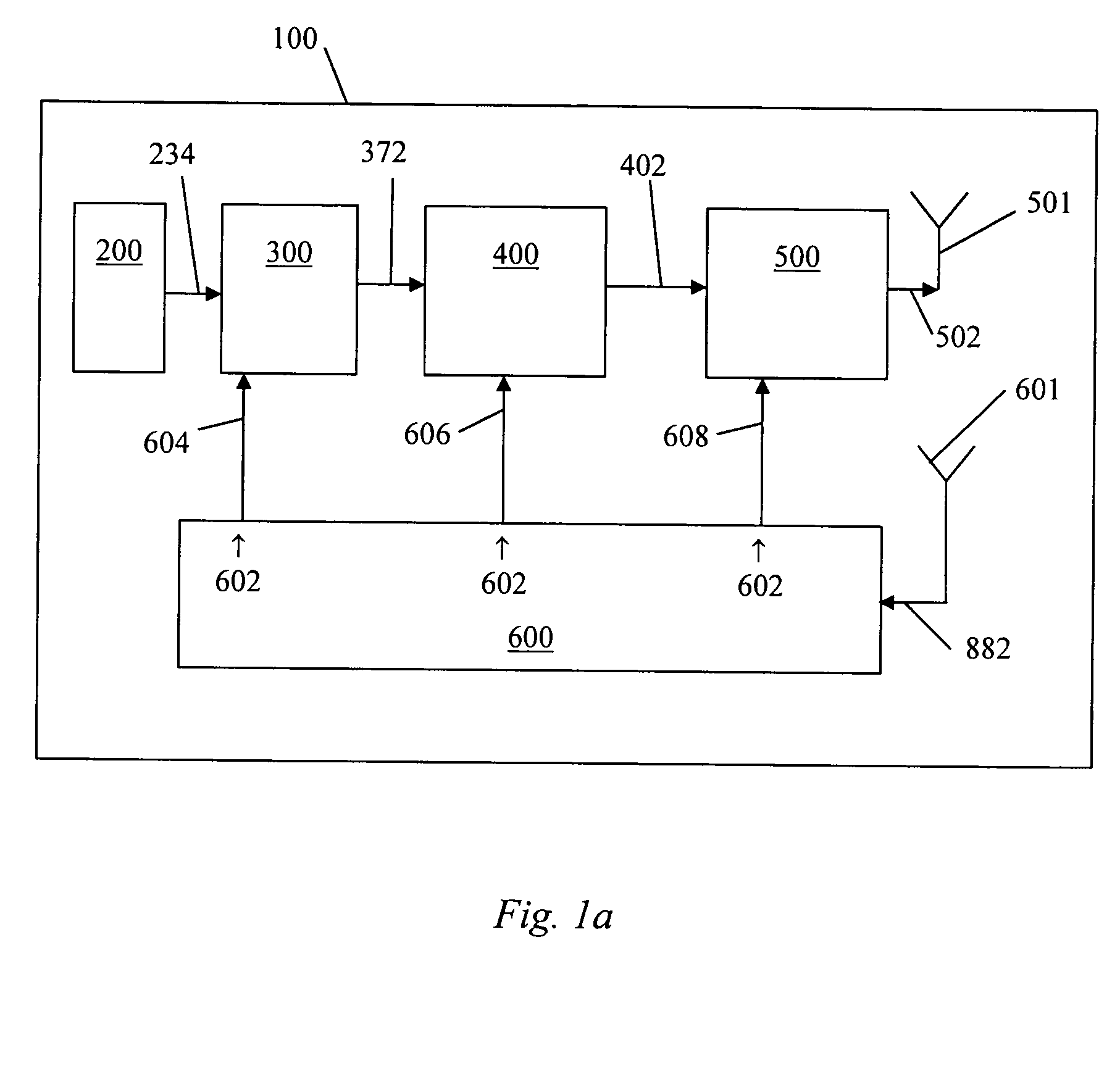

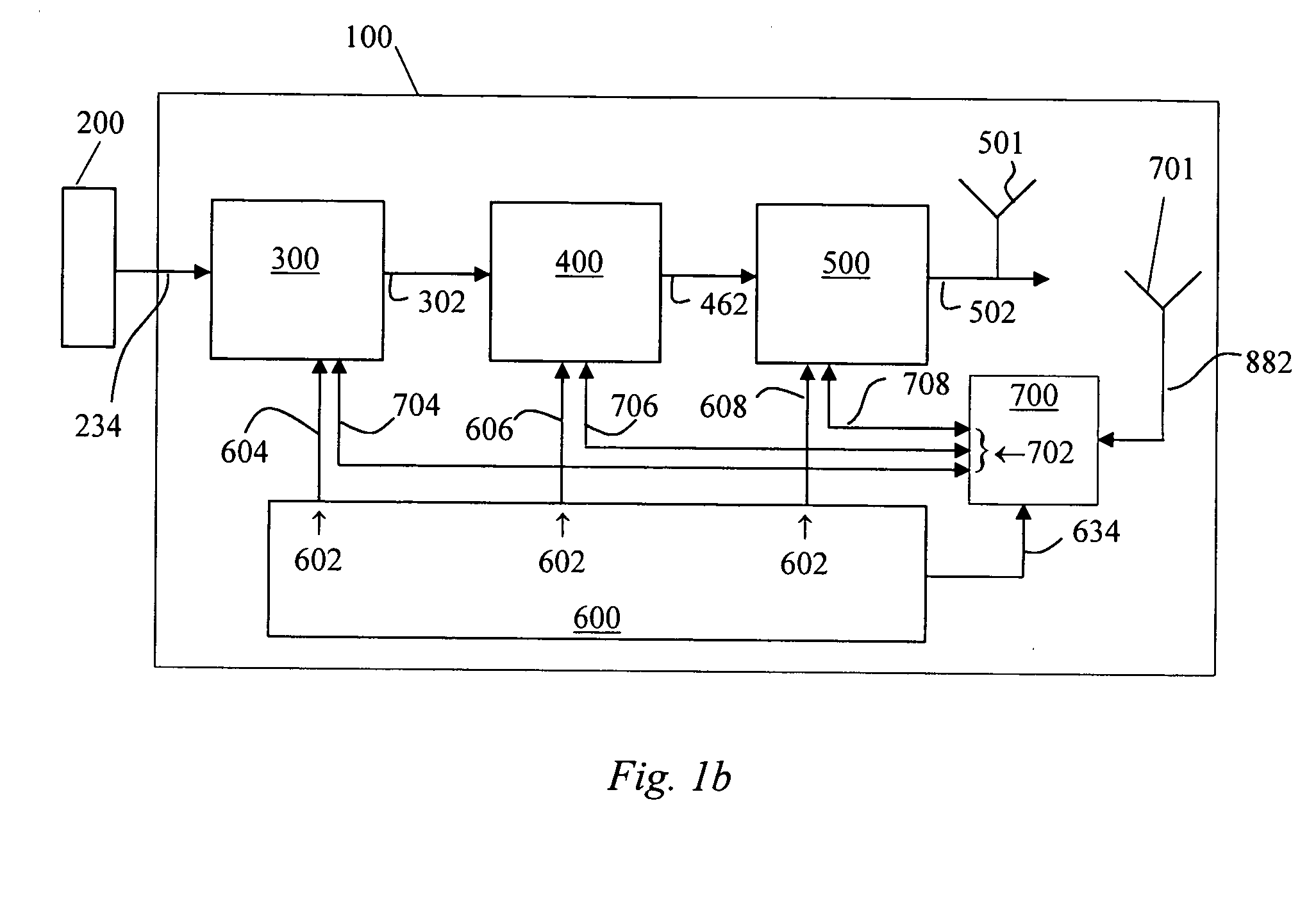

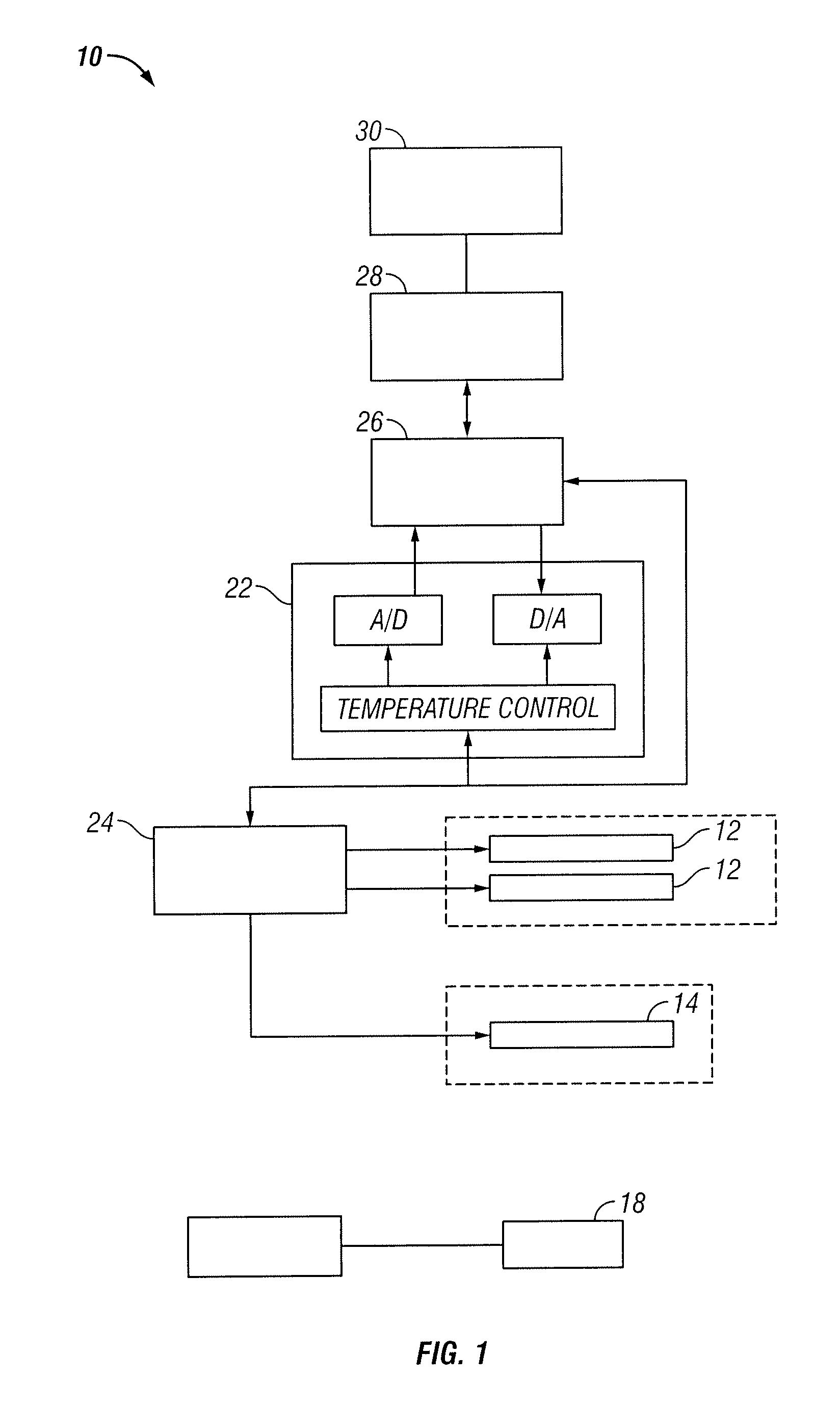

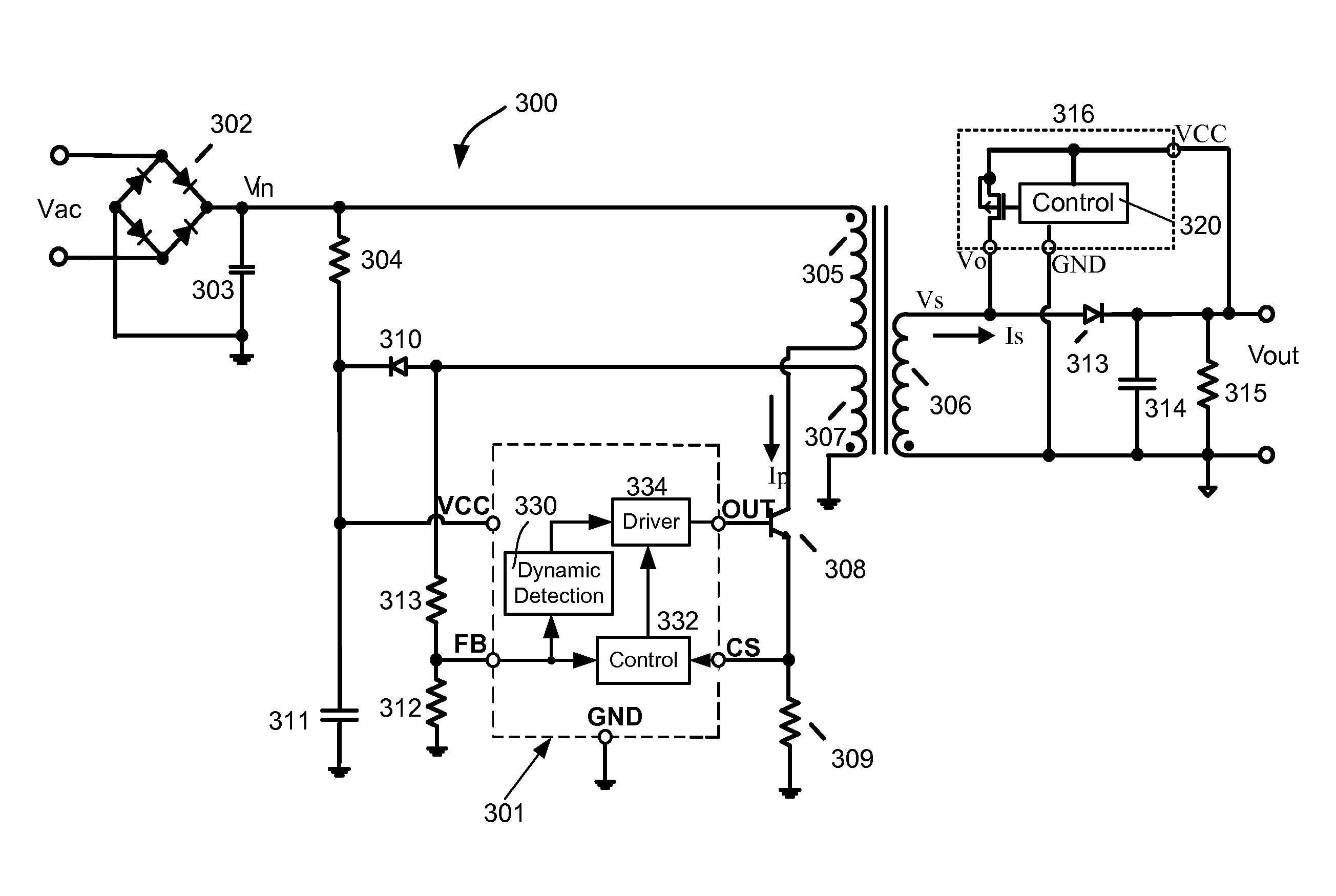

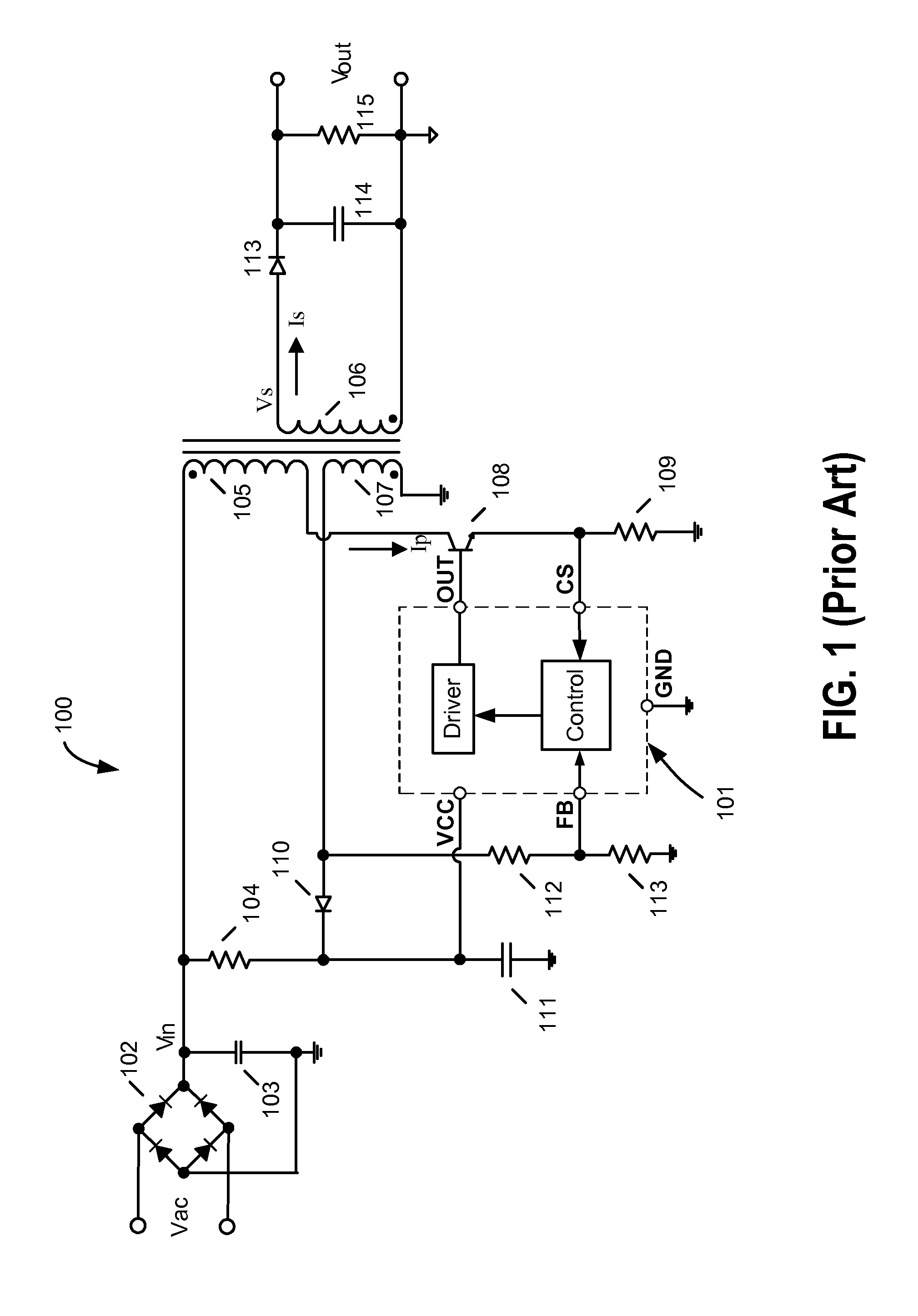

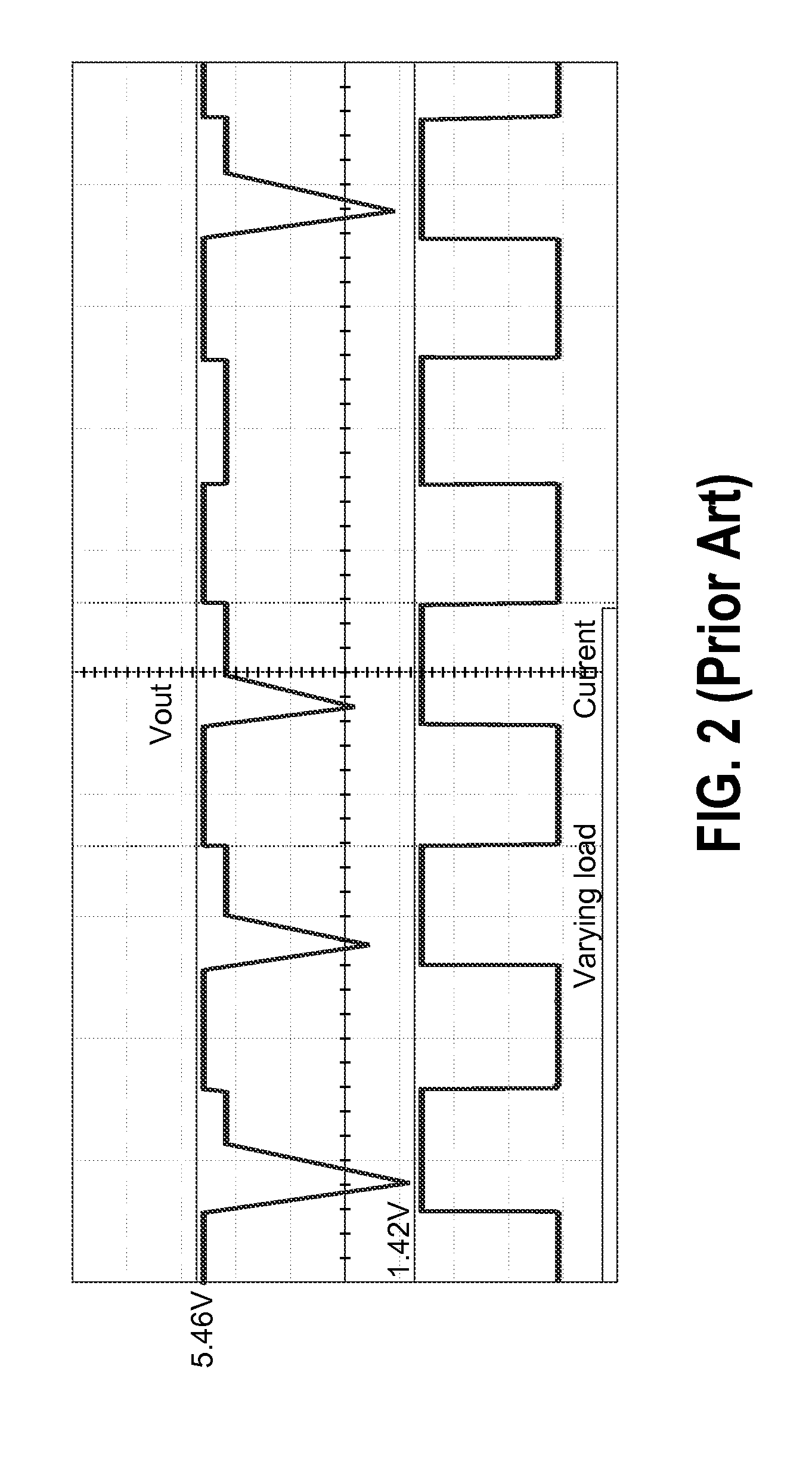

Control circuits and methods for switching mode power supplies

ActiveUS20110096573A1Reducing output voltage undershootReduce voltageDc-dc conversionElectric variable regulationVoltage pulsePower switching

Circuits and method for sensing a system output voltage change and transmitting an electrical signal to an auxiliary winding on the primary side. In an embodiment, a primary side controller detects the electrical signal and turns a power switch on and off to transfer energy from a primary winding to a secondary winding. A secondary side controller generates a voltage pulse at a terminal of the secondary winding when the system output voltage is below a reference voltage. The secondary side controller includes an input terminal connected to a system output, an output terminal connected to a terminal of the secondary winding, and a ground terminal connected to a ground potential of the system output.

Owner:BCD SHANGHAI MICRO ELECTRONICS CO LTD

Different methods applied for archiving data according to their desired lifetime

InactiveUS6903972B2Memory loss protectionMemory adressing/allocation/relocationVoltage pulseLong term data

Owner:WESTERN DIGITAL ISRAEL LTD

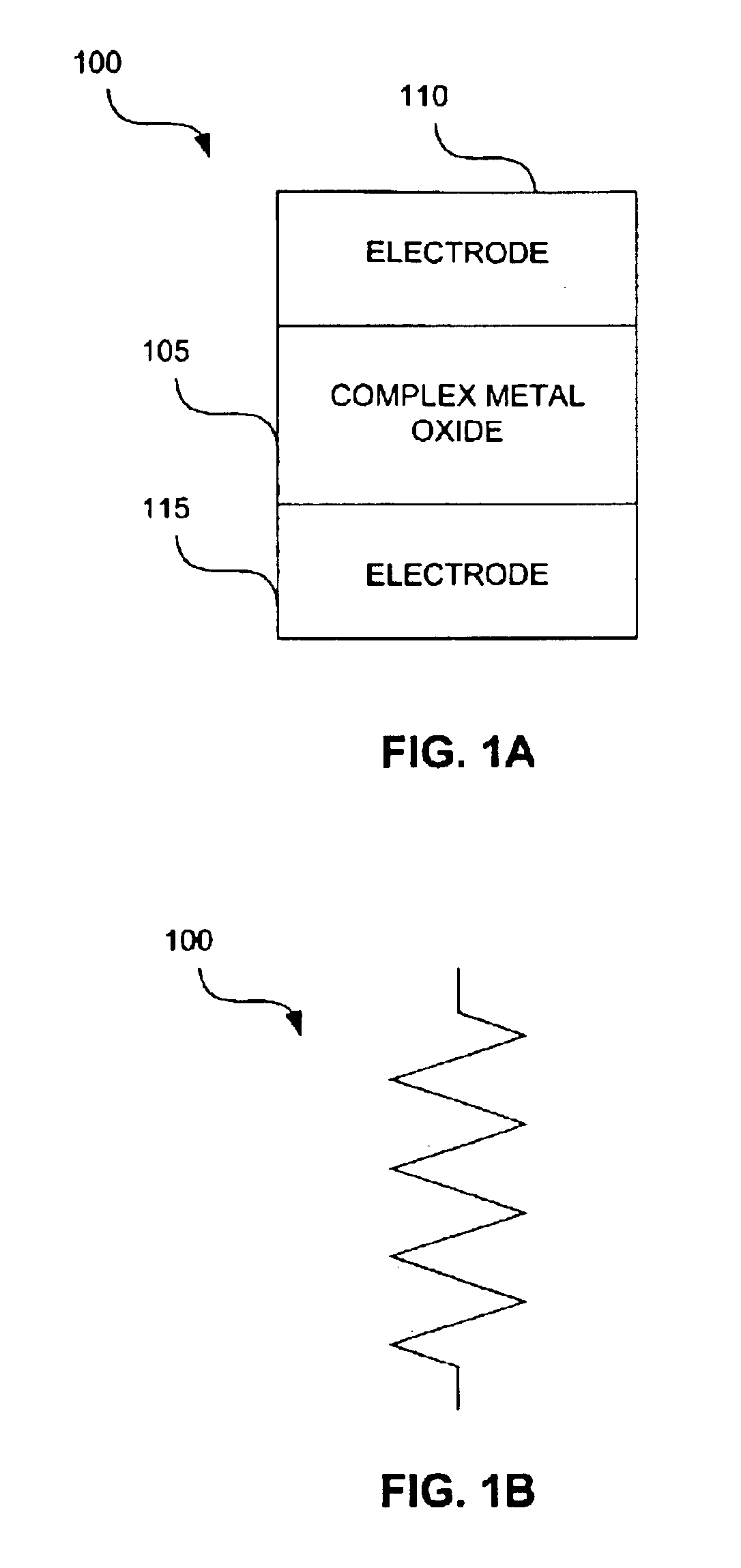

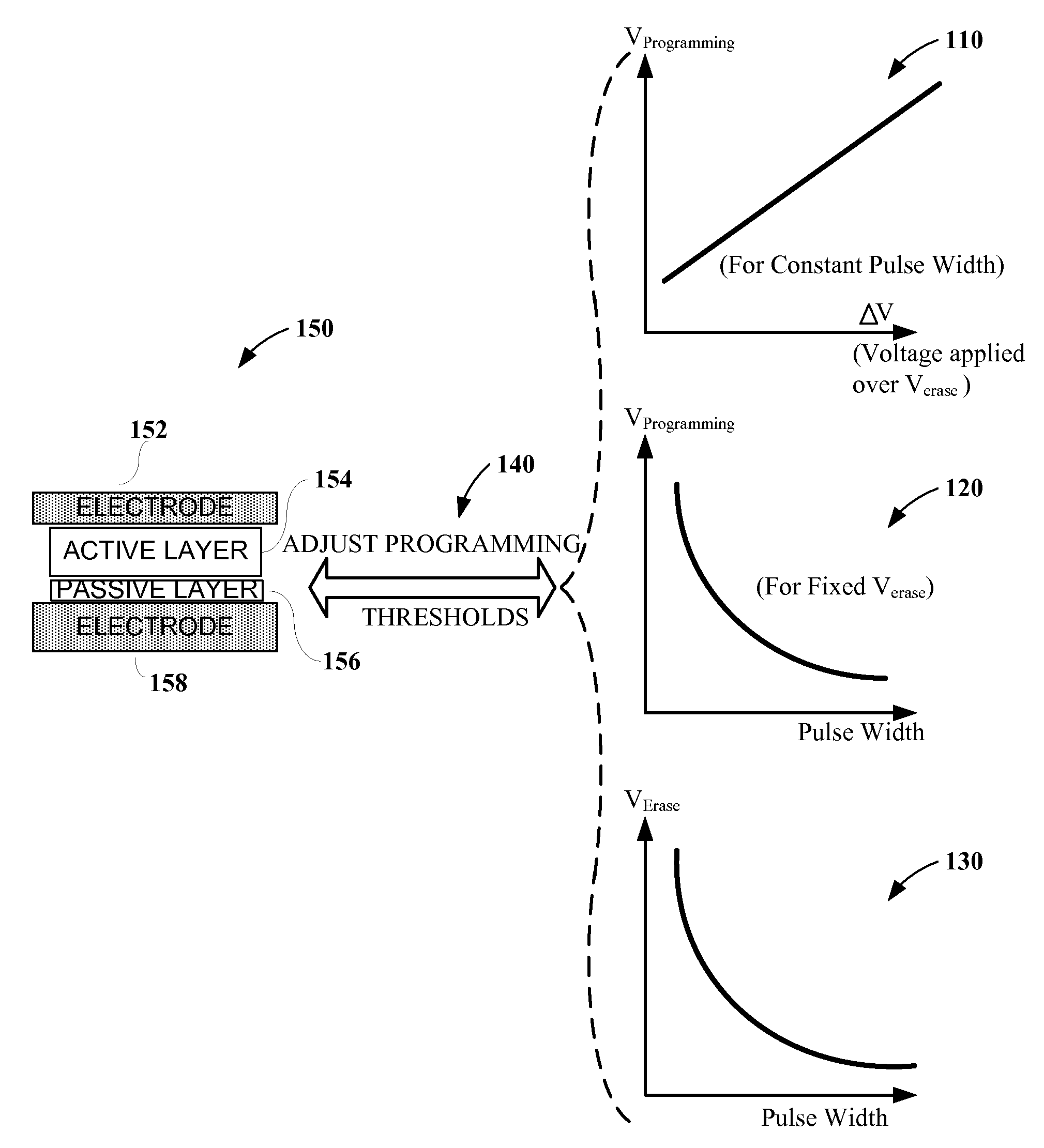

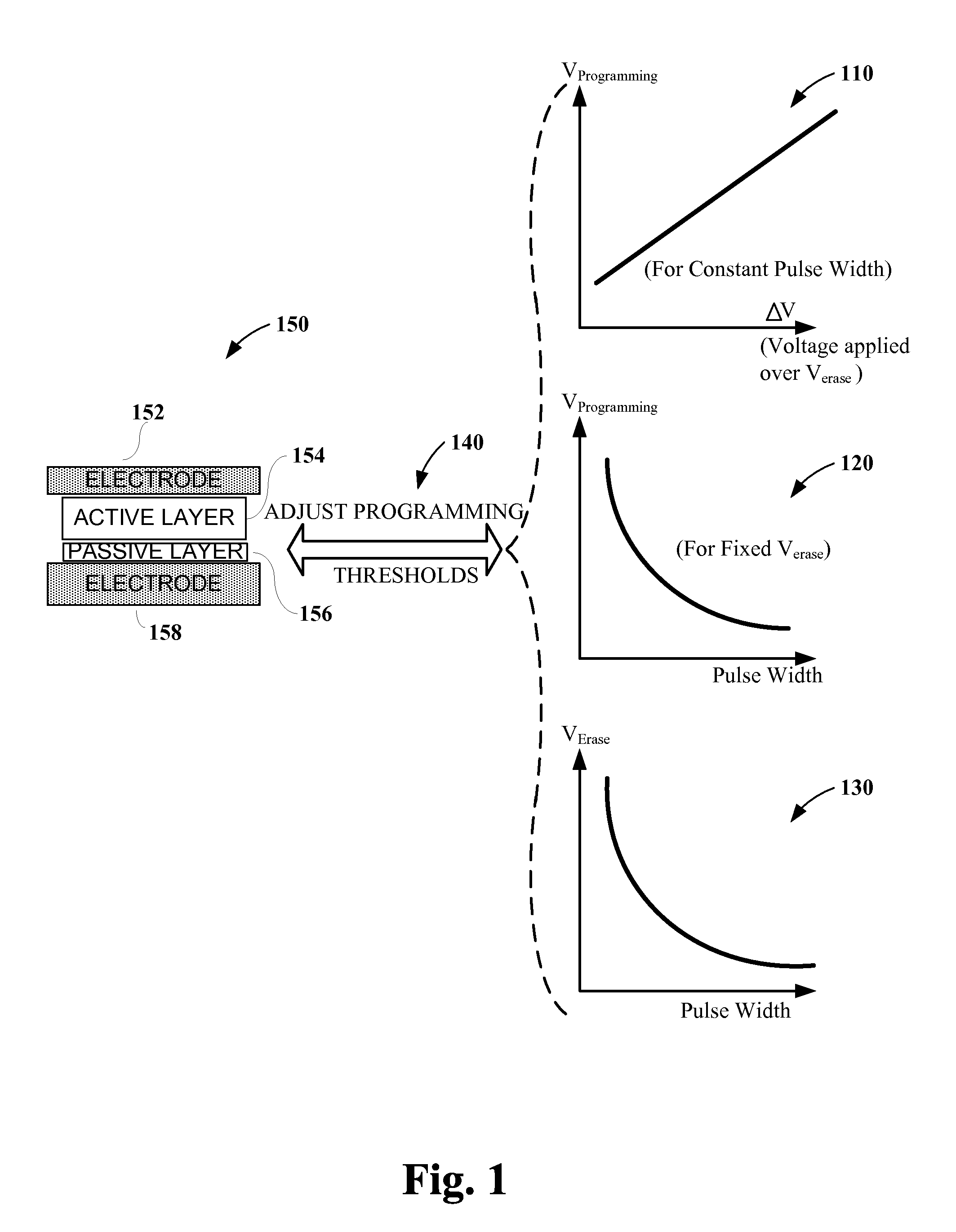

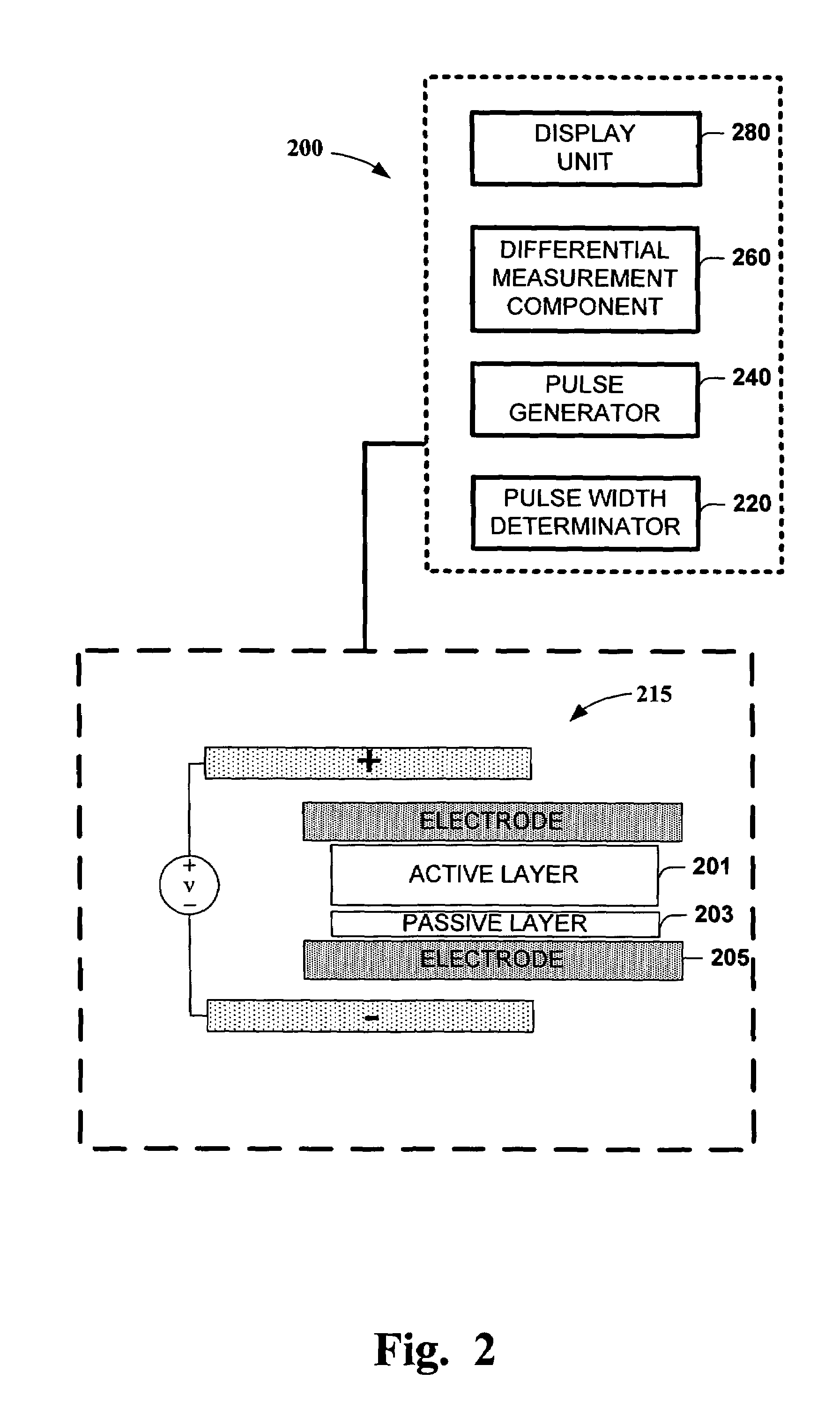

Systems and methods for adjusting programming thresholds of polymer memory cells

InactiveUS7289353B2Increase flexibilityImprove performanceNanoinformaticsNavigation by terrestrial meansTime domainVoltage pulse

Systems and methodologies are provided for adjusting threshold associated with a polymer memory cell's operation by applying thereupon a regulated electric field and / or voltage pulse width, during a post fabrication stage. Such customization of programming thresholds can typically be obtained at any cycle of programming the memory cell, to increase flexibility in circuit design. Accordingly, the present invention supplies both a current-voltage domain, and / or a frequency-time domain, to facilitate adjusting the program thresholds of the polymer memory cell.

Owner:MONTEREY RES LLC

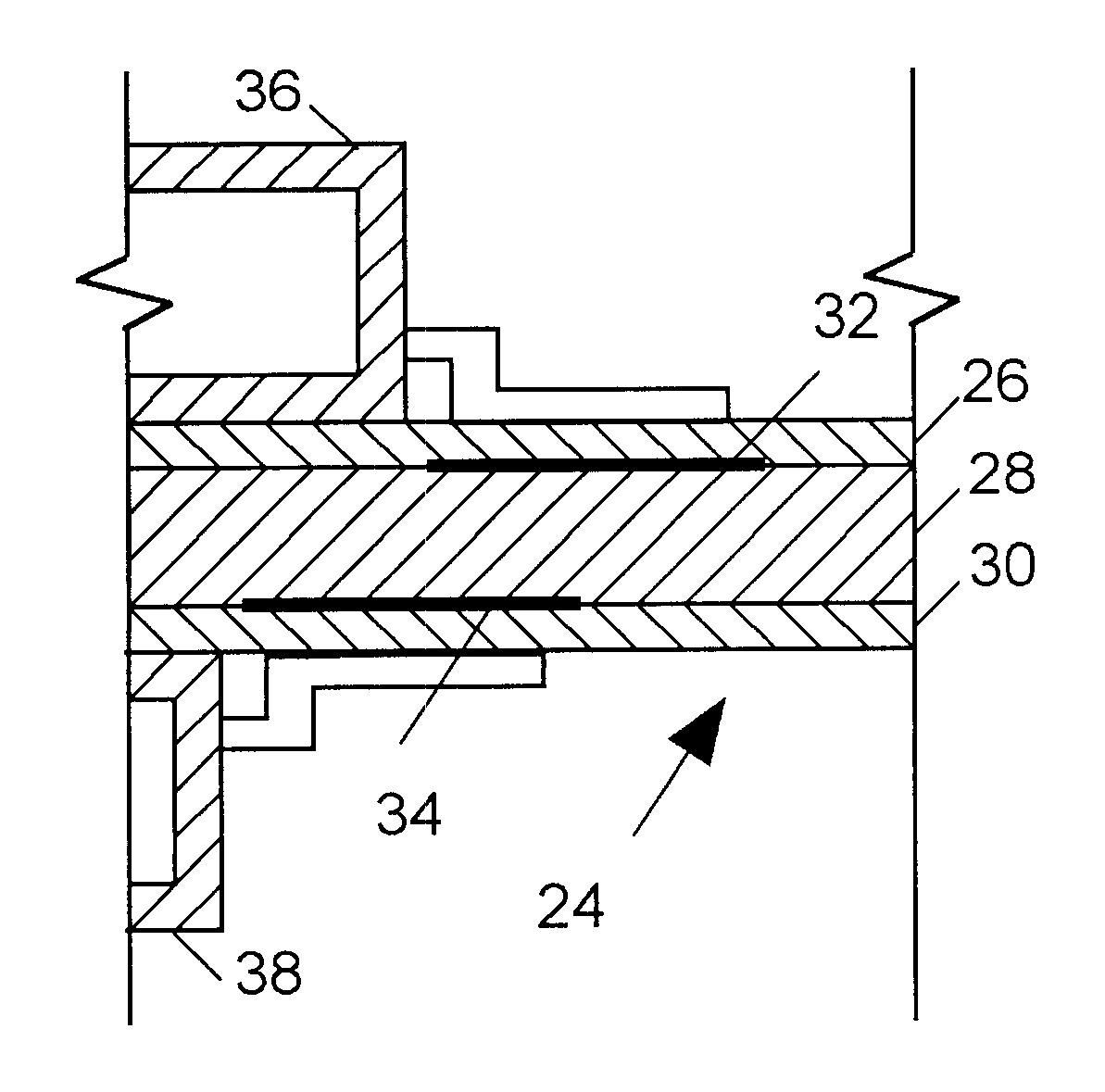

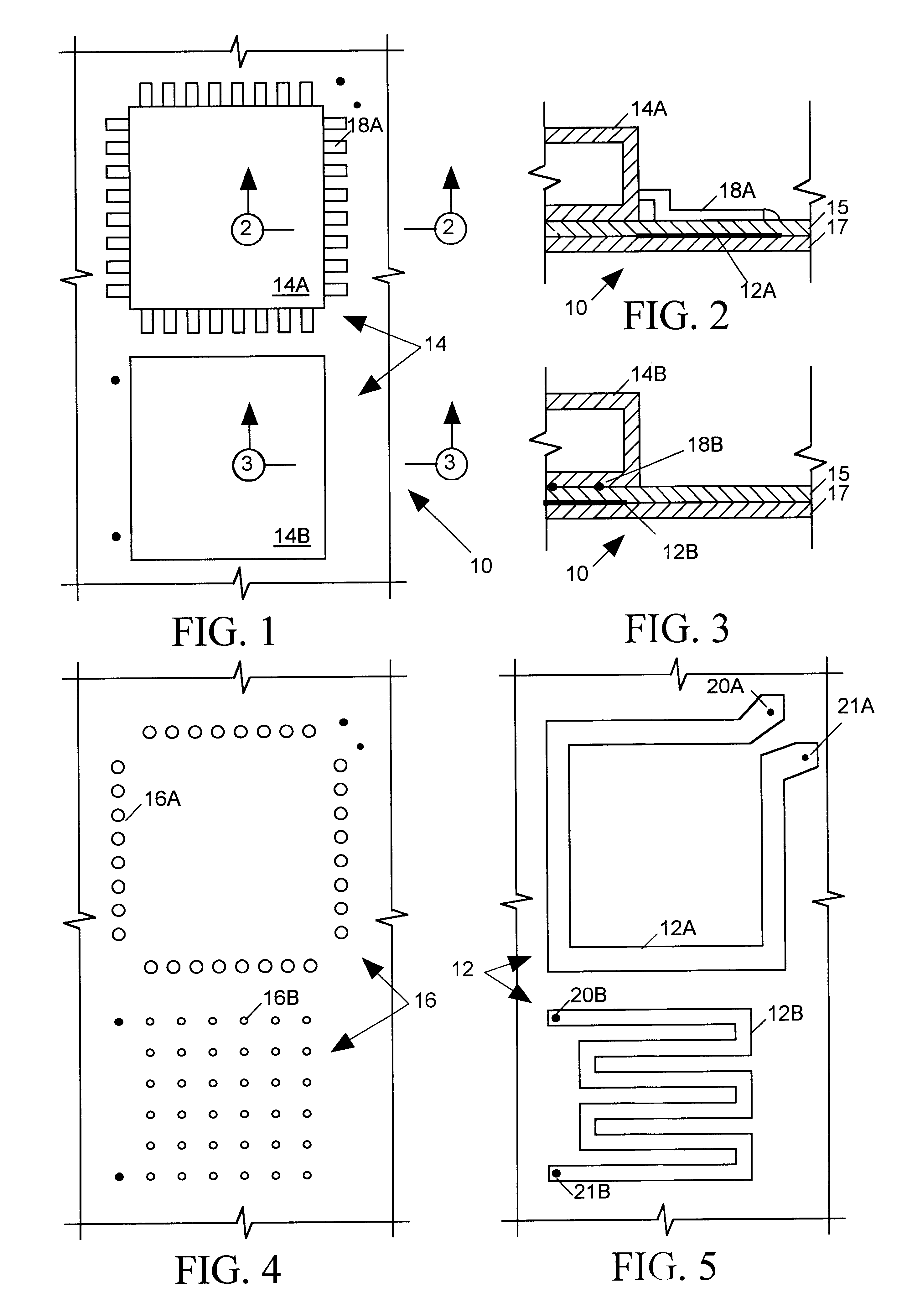

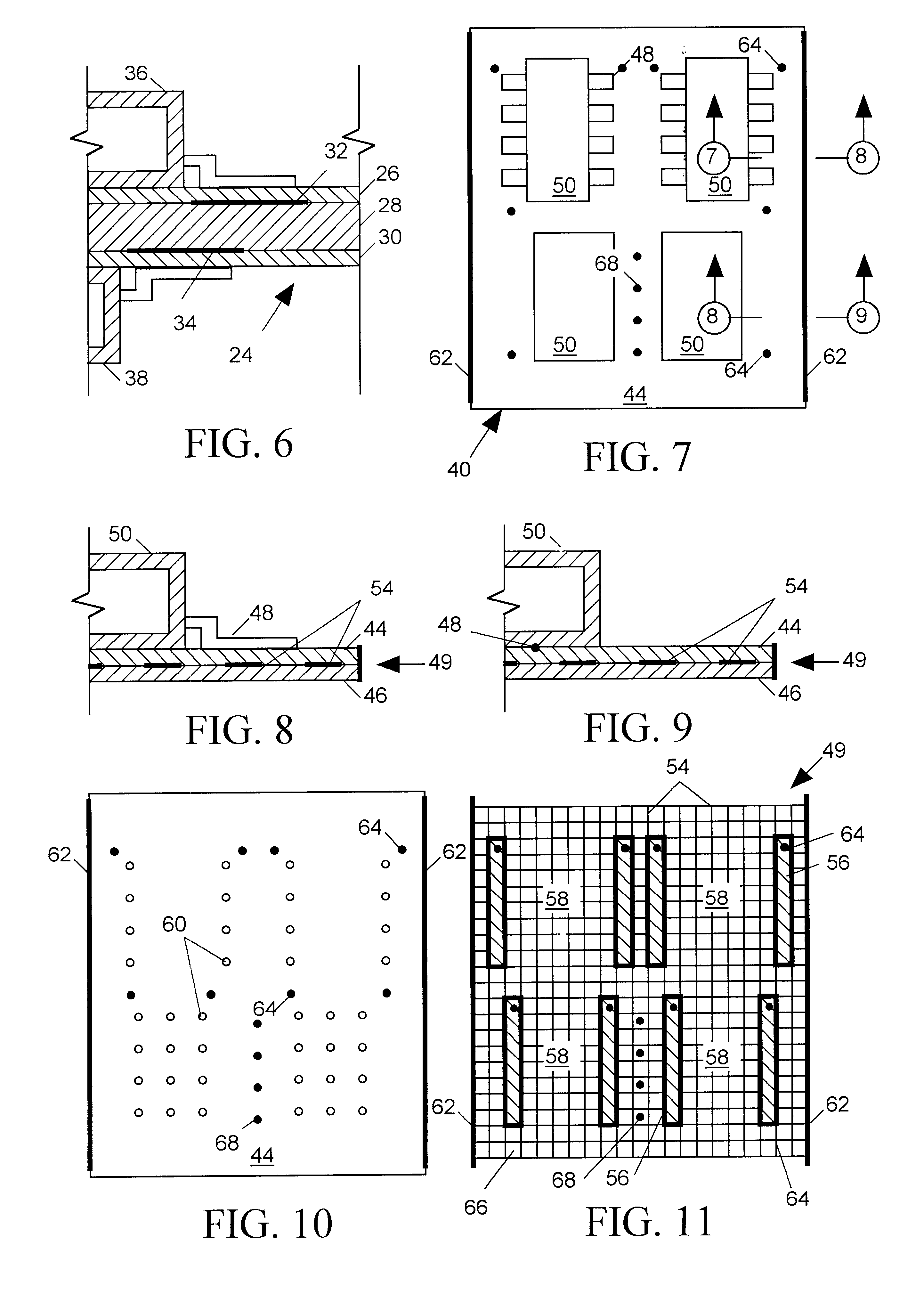

Self-heating circuit board

InactiveUS6396706B1Inexpensive and convenientSemiconductor/solid-state device detailsSolid-state devicesVoltage pulseAdhesive

Separate heating elements are embedded in a printed circuit board near integrated circuit (IC) packages or other parts mounted on the circuit board. Each heating element supplies heat to the part residing near it in response to an input voltage pulse. The heating elements are used to selectively melt solder or adhesives attaching the parts to the circuit board so that they can be easily removed or to temporarily melt solder or cure adhesive when the parts are mounted on the circuit board. The heating elements are also used to supply heat to IC packages for regulating their operating temperatures.

Owner:MA ZHONGXIN +1

Systems for Treating Tissue Sites Using Electroporation

Owner:RUBINSKY BORIS +2