Patents

Literature

461 results about "Circuit architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

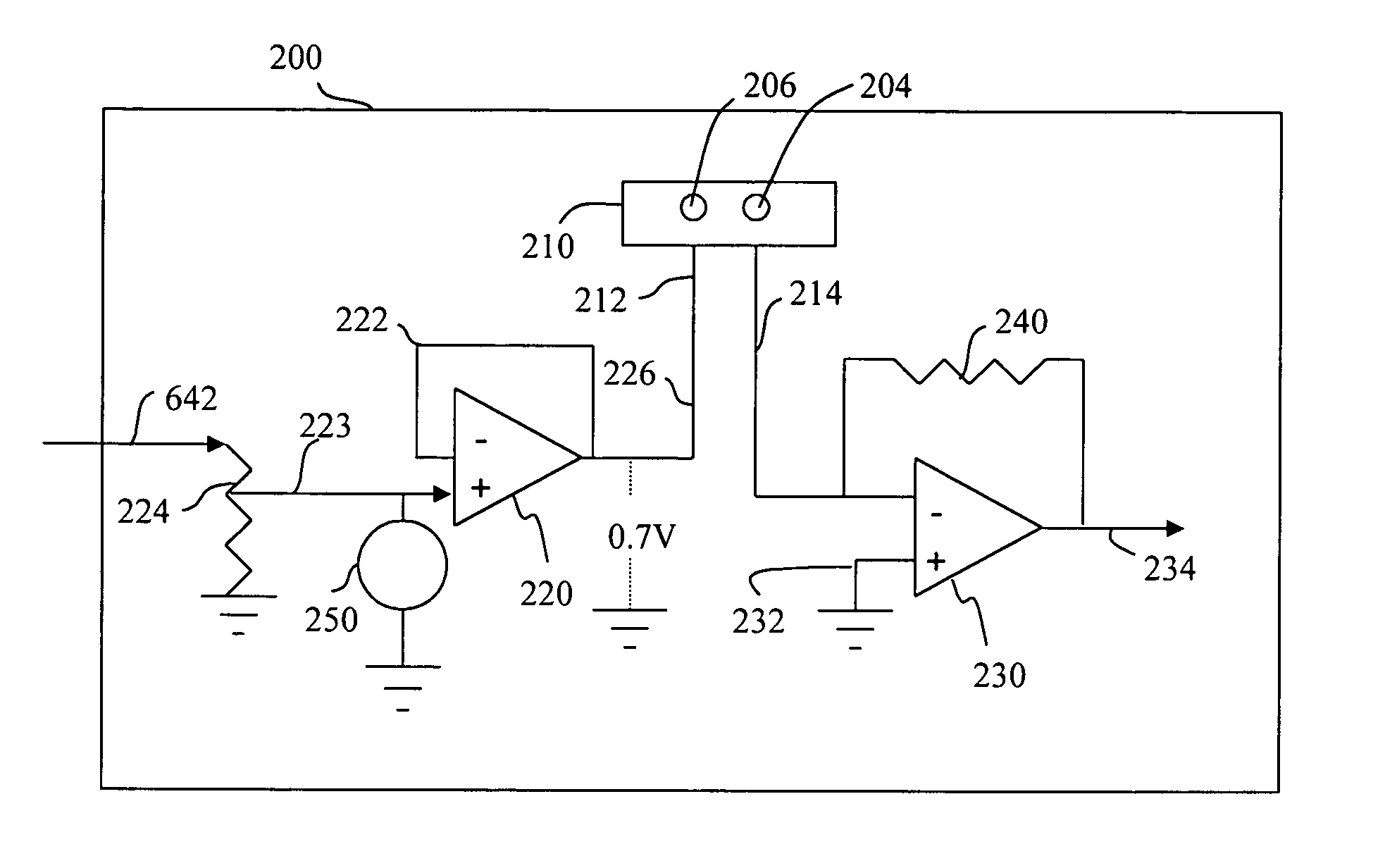

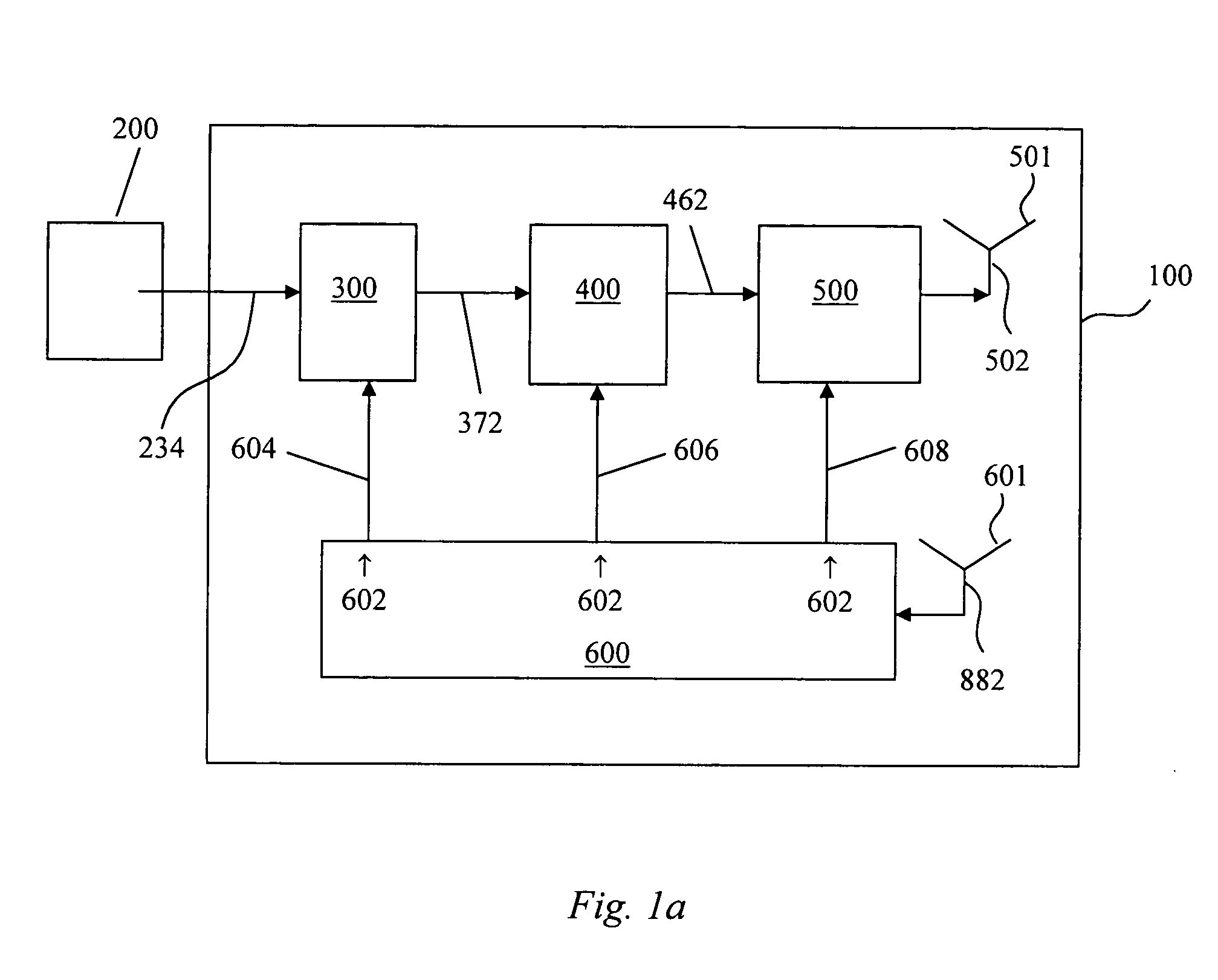

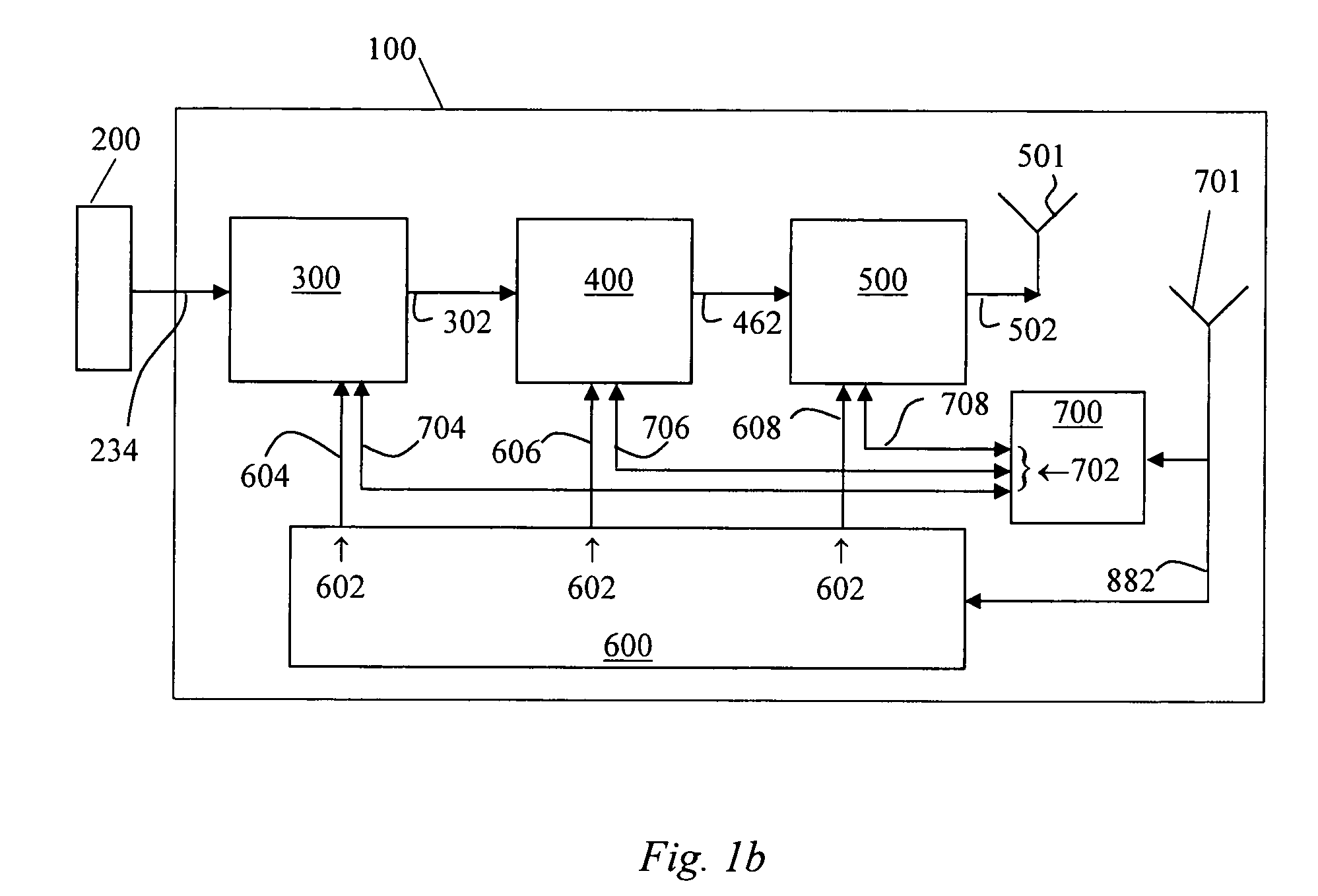

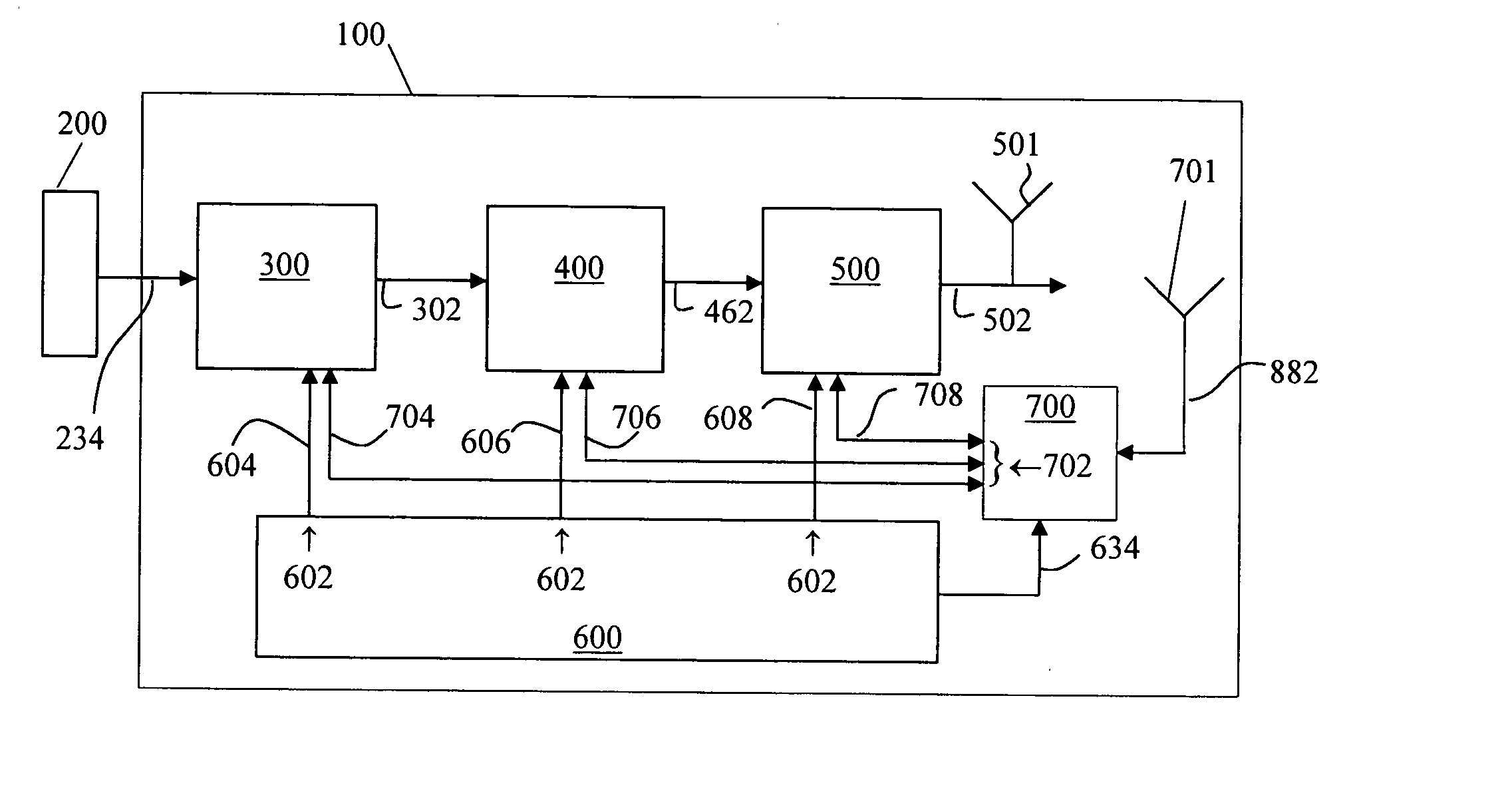

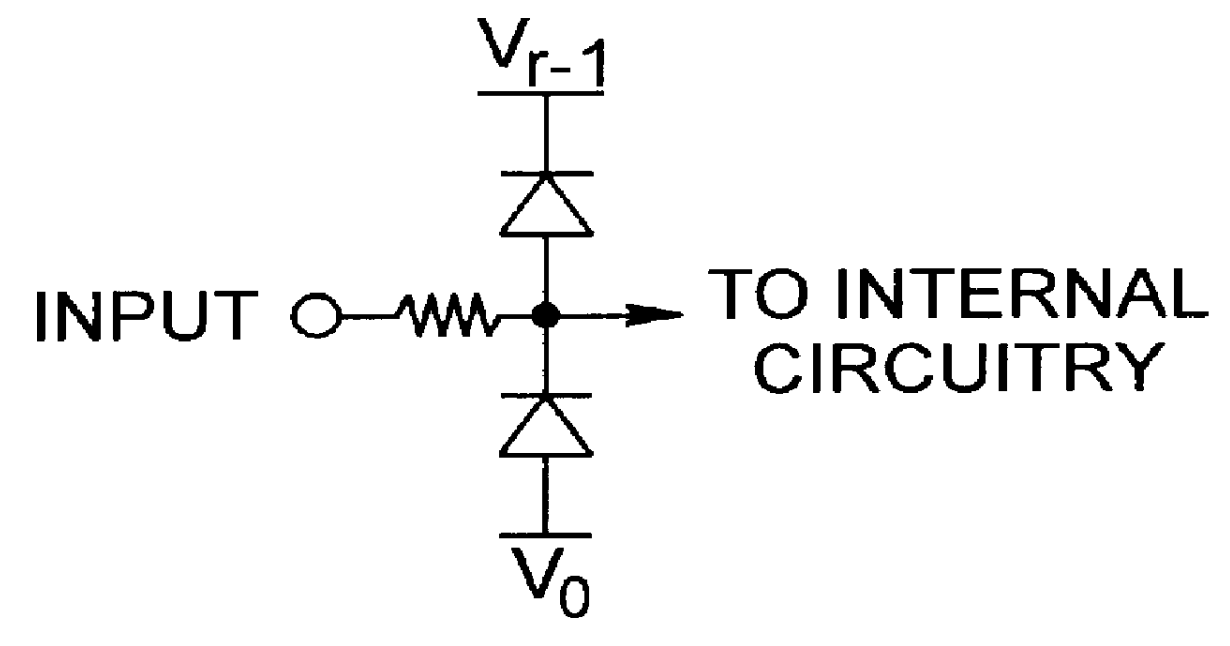

Embedded bio-sensor system

InactiveUS7125382B2Improve accuracyAccurate measurementTelemedicineEndoradiosondesGlucose sensorsConcentrations glucose

Provided is a bio-sensor system which utilizes radio frequency identification technology and which includes a remote transponder in wireless communication with an implantable passively-powered on-chip transponder. The bio-sensor system is specifically adapted to provide a substantially stable and precise sensor reference voltage to a sensor assembly that is included with the on-chip transponder. The remote transponder is also configured to remotely receive data representative of a physiological parameter of the patient as well as identification data and may enable readout of one or more of the physiological parameters that are measured, processed and transmitted by the on-chip transponder upon request by the remote transponder. The precision and stability of the sensor reference voltage is enhanced by the specific circuit architecture of the glucose sensor to allow for relatively accurate measurement of the physiological parameter such as measurement of glucose concentration by a glucose sensor without the use of a microprocessor.

Owner:JAMM TECH INC

Transducer for embedded bio-sensor using body energy as a power source

InactiveUS20050261563A1Improve accuracyAccurate measurementTelemedicineEndoradiosondesMuscle tissueVoltage pulse

Provided is a bio-sensor system which utilizes radio frequency identification technology and which includes a remote transponder in wireless communication with an implantable on-chip transponder. A power supply collects alternating current voltage pulses from an electro-active polymer generator embedded in muscle tissue for generating power for the on-chip transponder. The power supply is specifically adapted to provide a stable and precise sensor reference voltage to a sensor assembly to enhance the accuracy of measurements of a physiological parameter of a patient. The remote transponder receives data representative of the physiological parameter such as glucose concentration levels. The data is processed and transmitted to the remote transponder by the on-chip transponder. The precision and stability of the sensor reference voltage is enhanced by the specific circuit architecture of a glucose sensor to allow for relatively accurate measurement of glucose concentration levels without the use of a microprocessor.

Owner:JAMM TECH INC

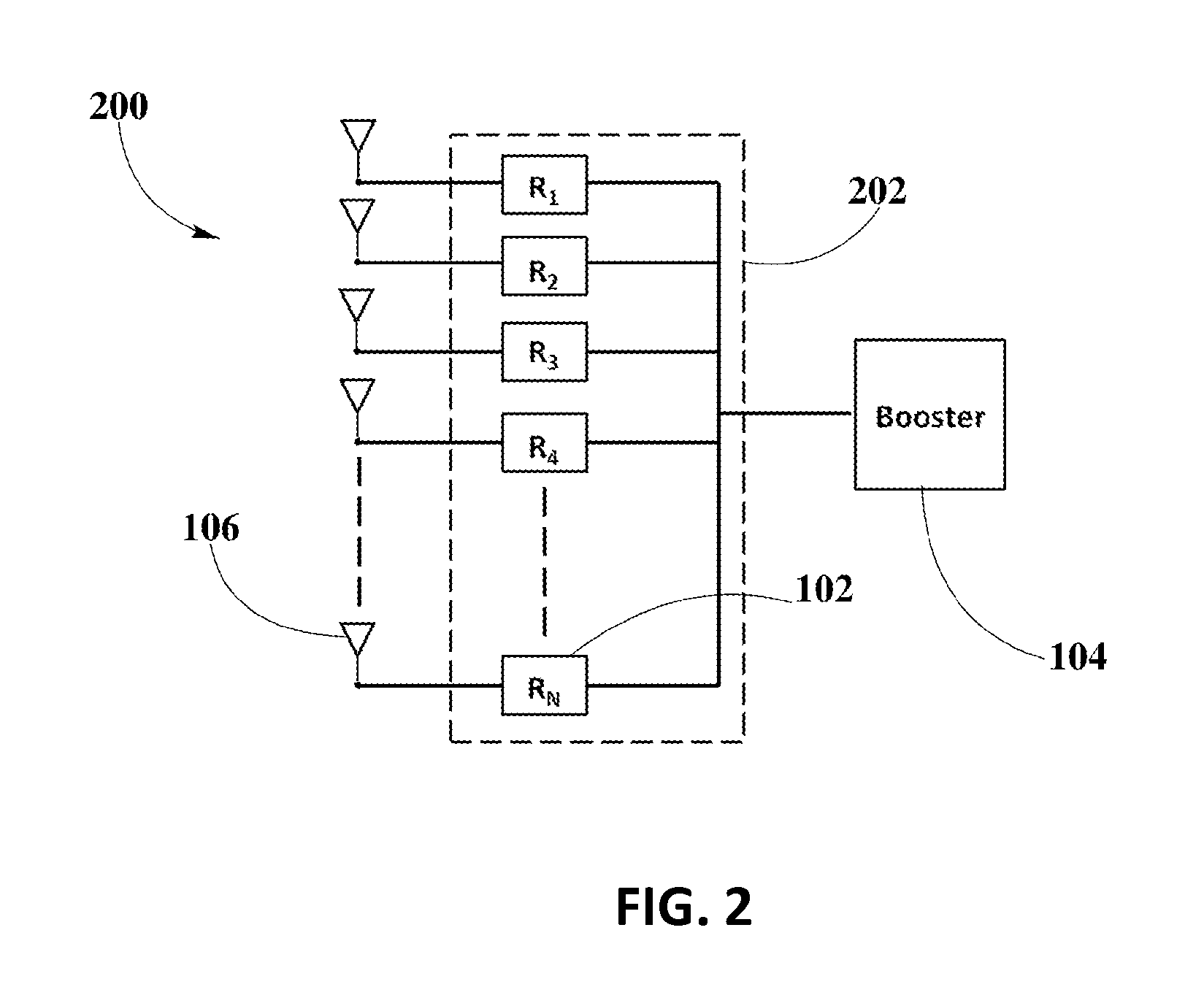

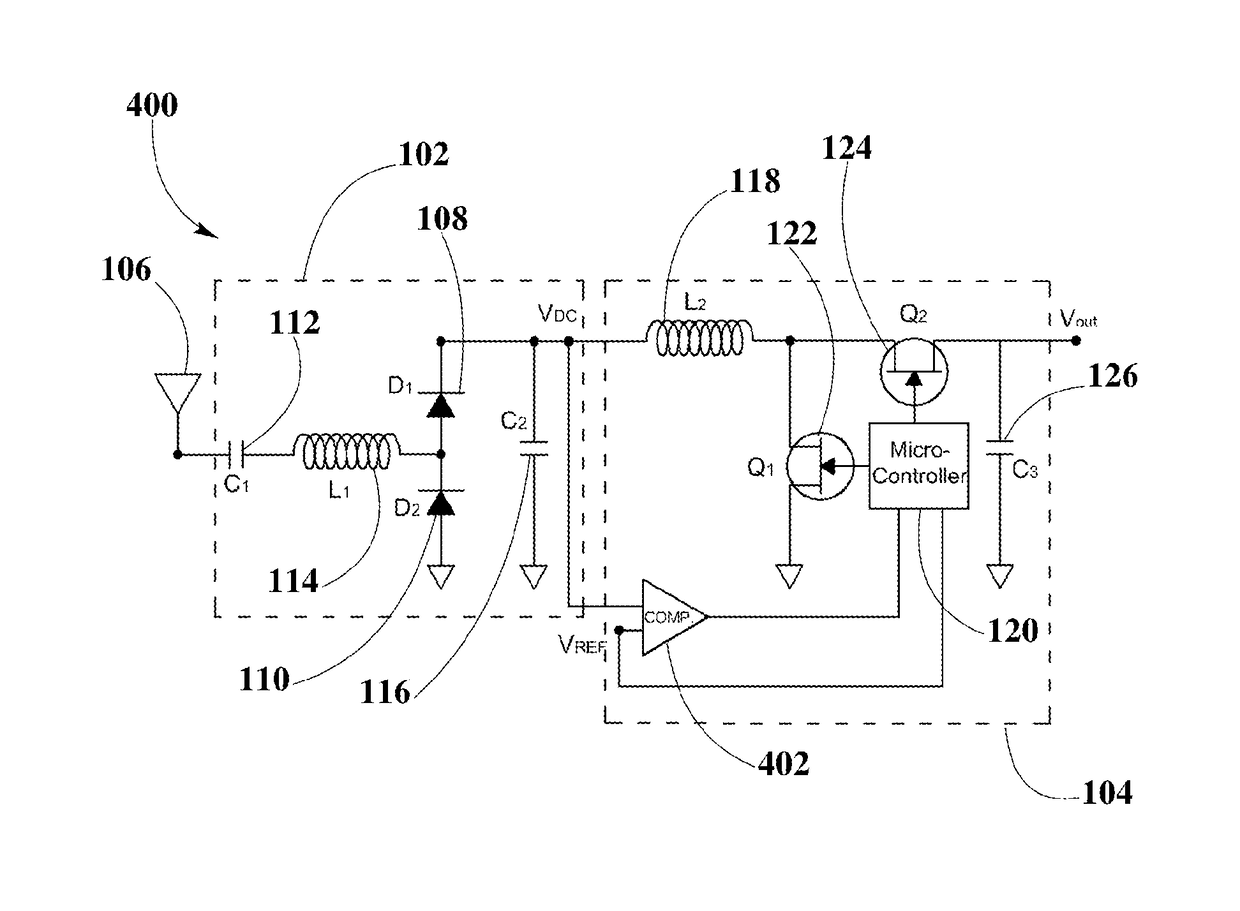

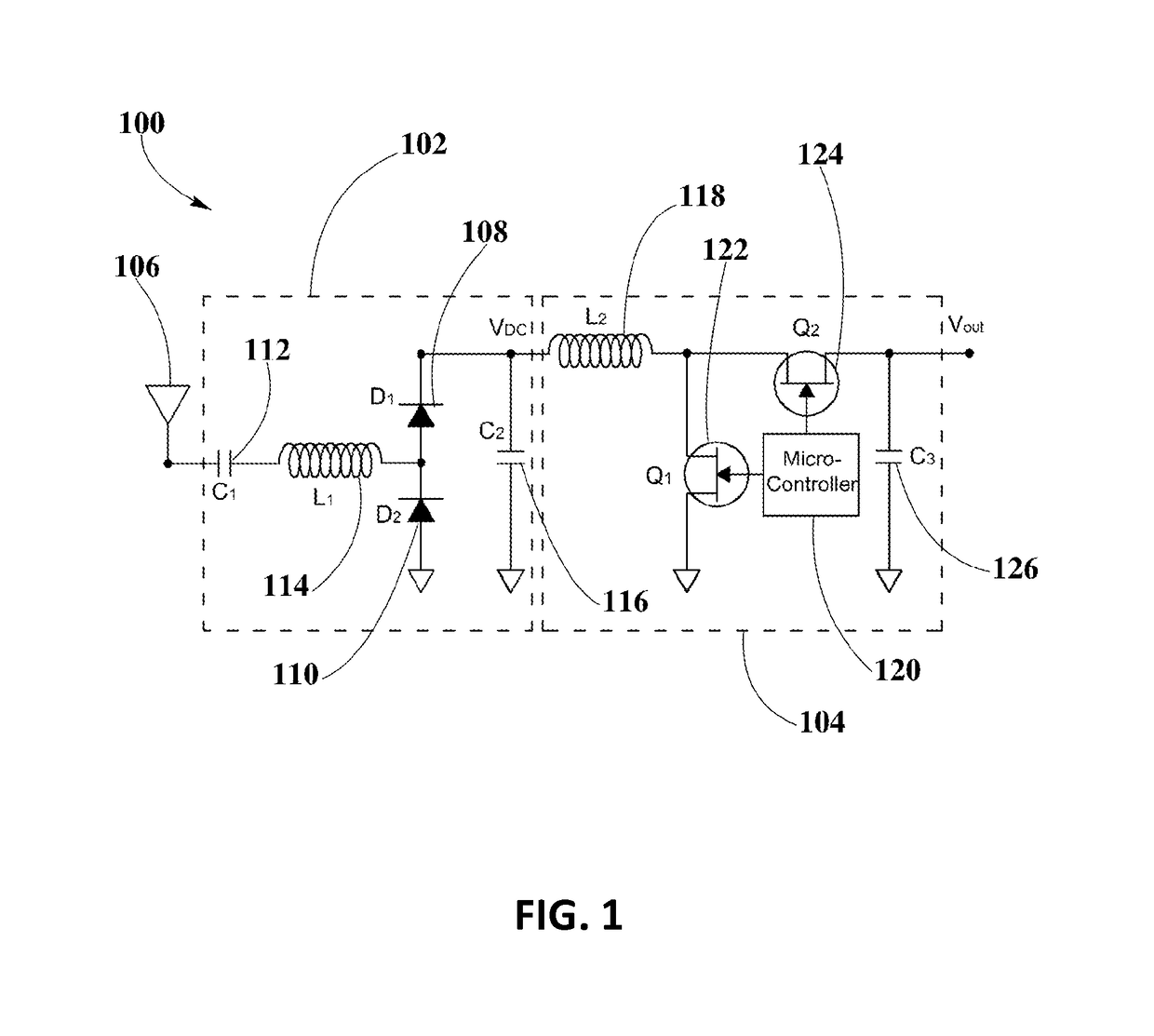

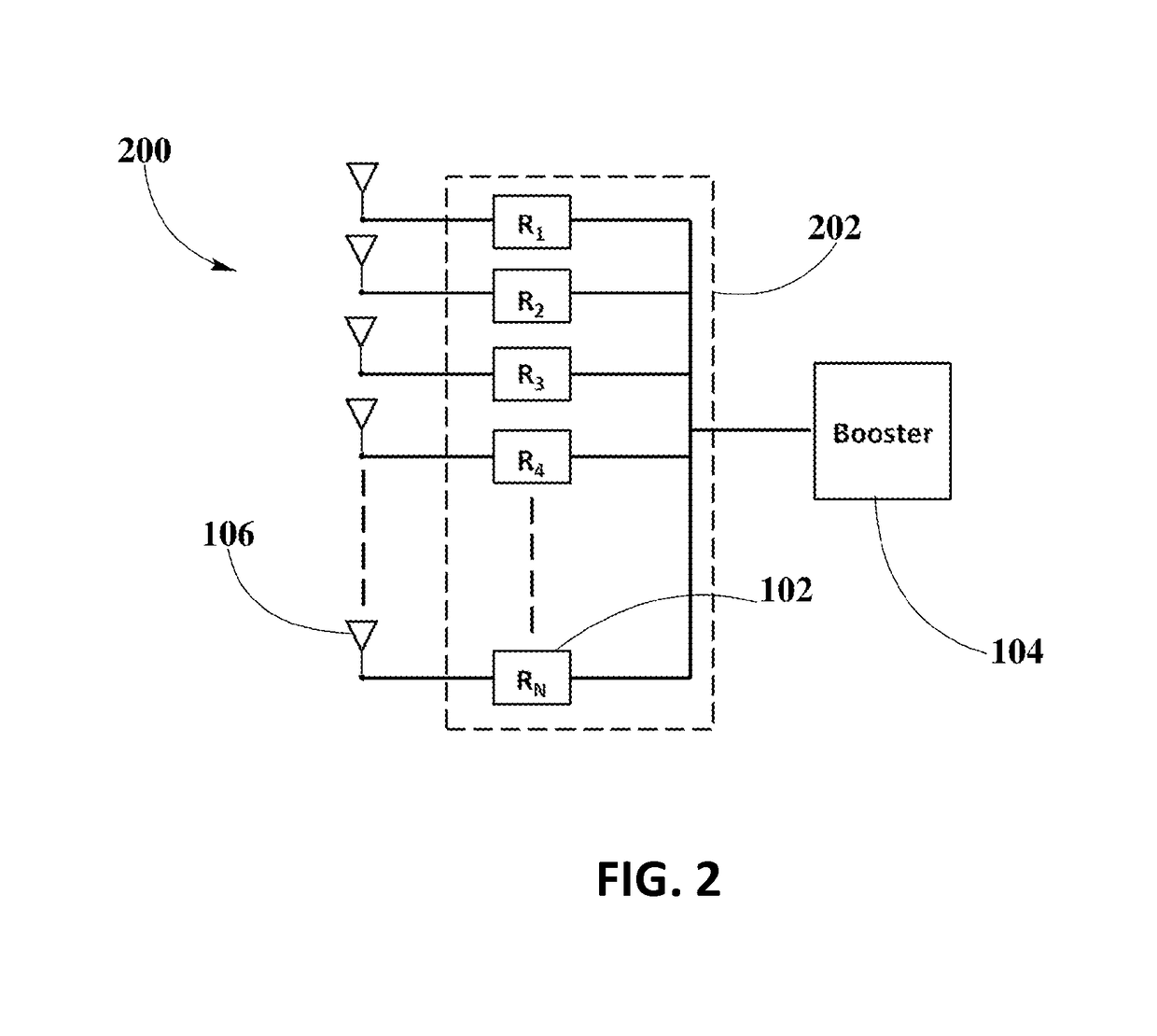

Integrated Rectifier and Boost Converter for Wireless Power Transmission

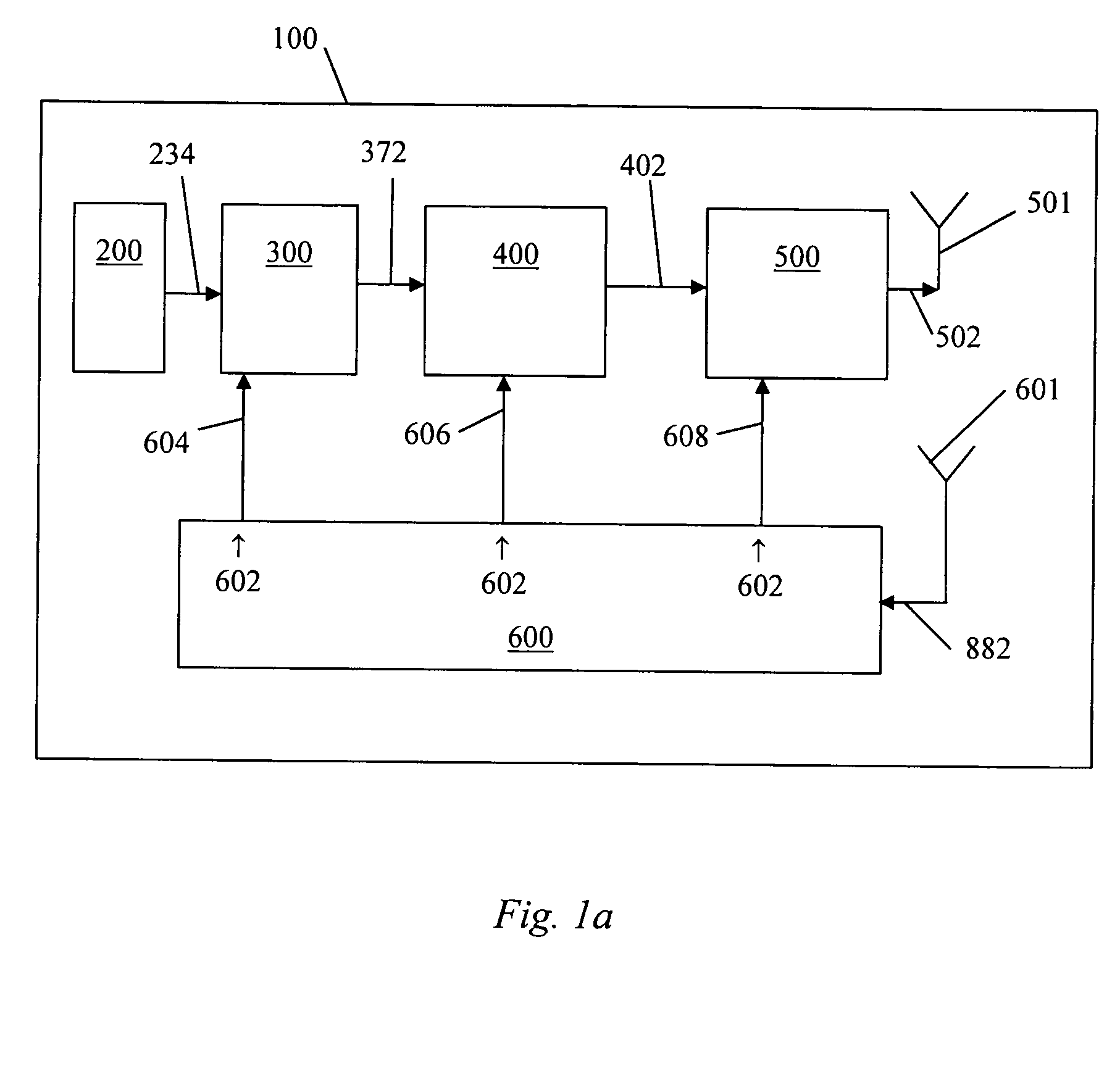

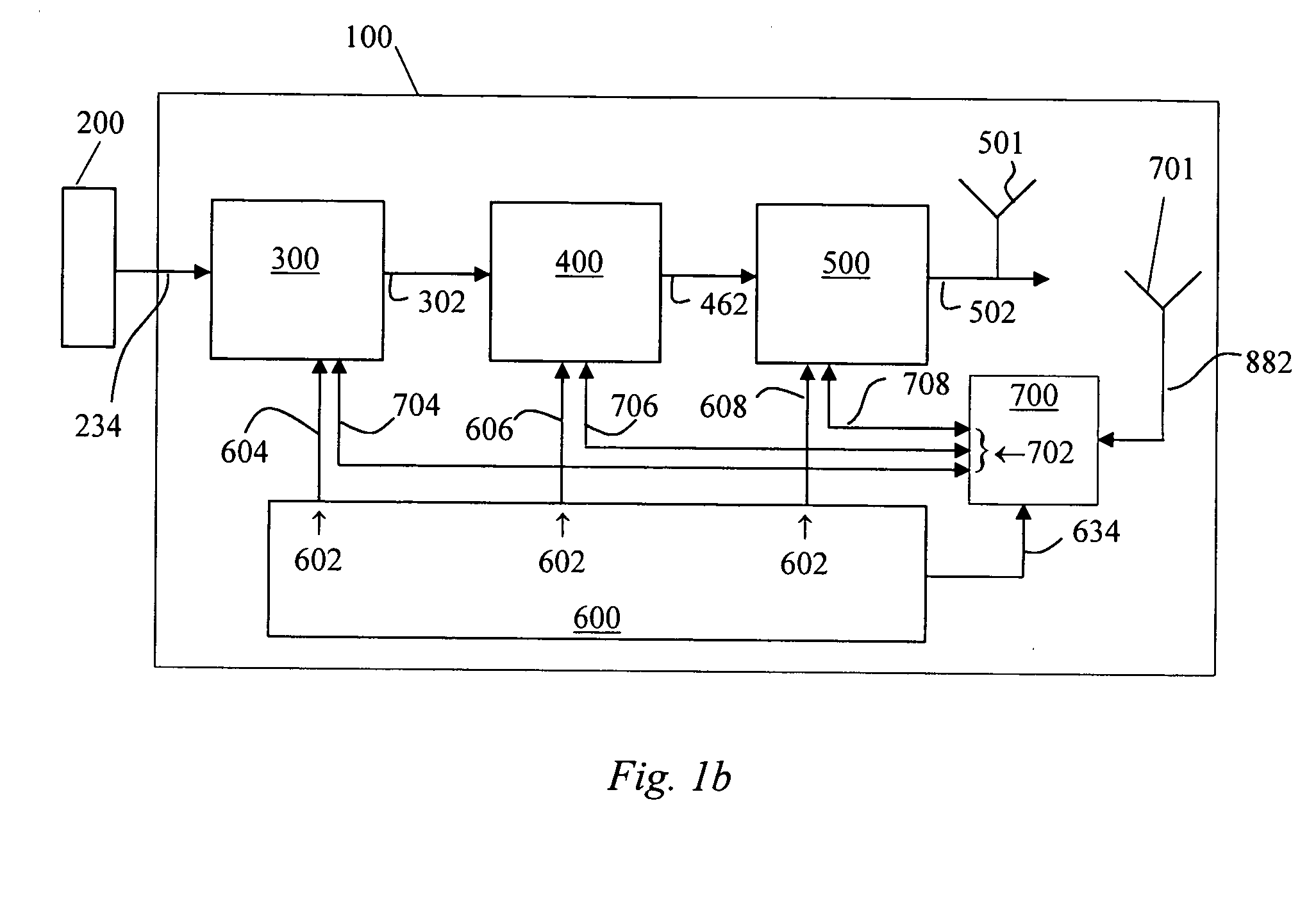

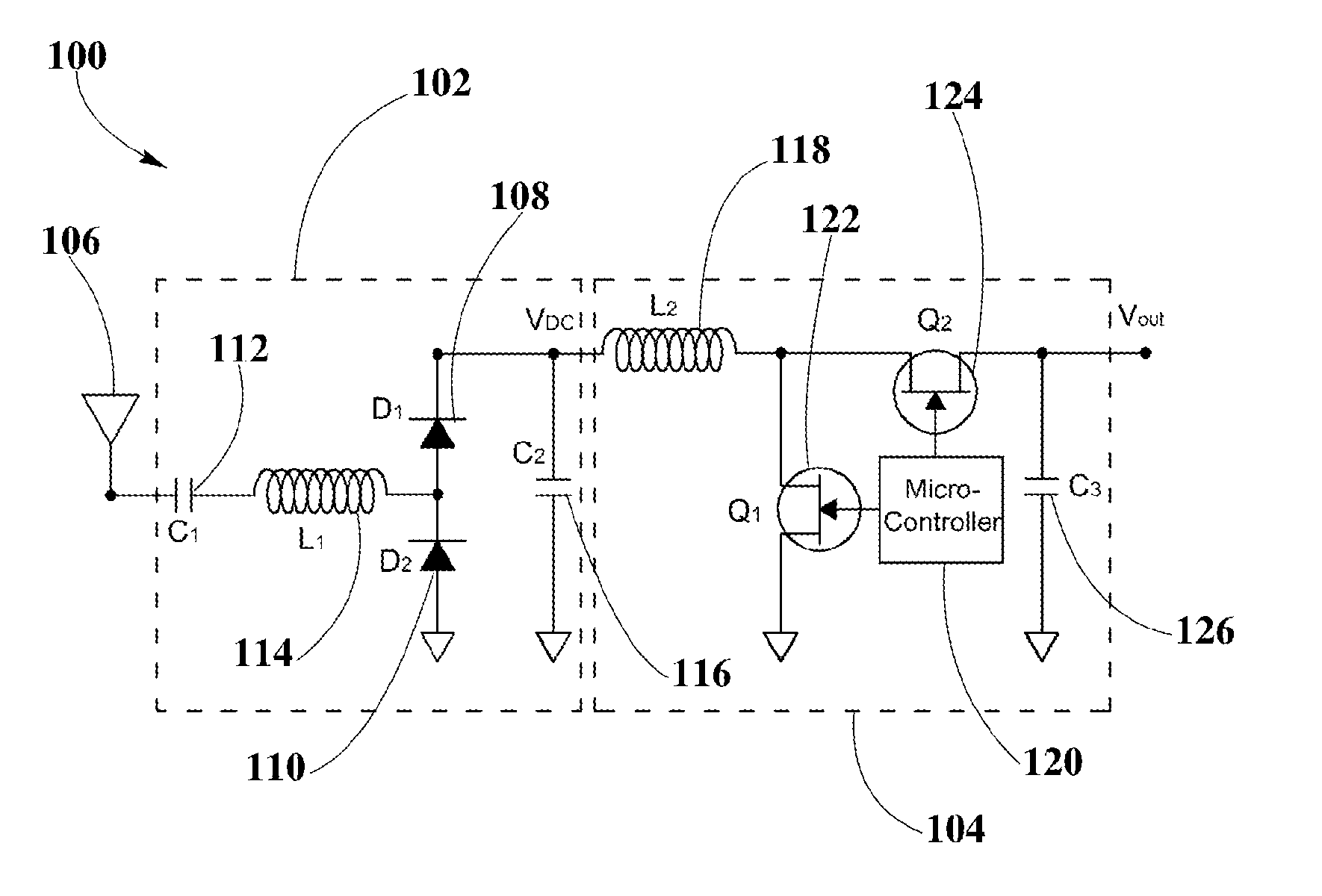

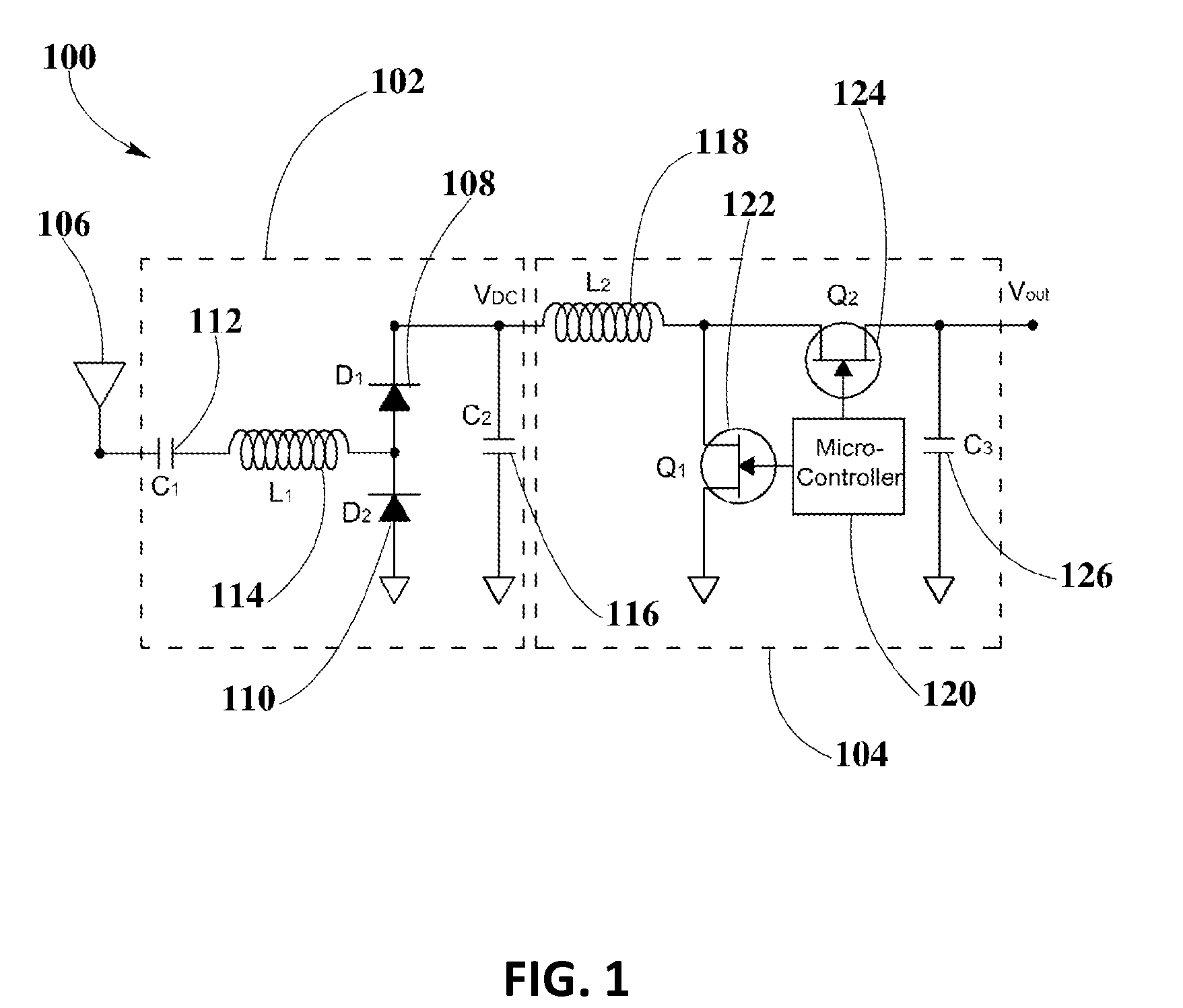

ActiveUS20150326142A1Reduce power consumptionIncrease wireless power transmission efficiencyAc-dc conversion without reversalElectromagnetic wave systemElectric power transmissionBoost controller

A novel integrated rectifier and boost converter circuit architecture is disclosed. The rectifier architecture includes a plurality of identical half-bridge rectifiers connected to receiving antennas to convert wireless AC power into DC power. The integrated rectifier may be coupled in series with a charging inductor in a boost converter. The inductor may discharge upon operation of two micro-controller-driven switching transistors using predetermined threshold and timing scheme to turn on / off. The rectifier architecture may provide high power densities, improve efficiency at larger load currents, and may be enabled in an integrated circuit with eight RF signal inputs, eight half-bridge rectifiers, and eight DC outputs ganged together as single feed into the boost converter. The rectifier circuit topology may include a comparator driven by the boost controller with a proprietary algorithm which suits control for a maximum power point tracking functionality, and an external micro-controller for additional control of the boost converter.

Owner:ENERGOUS CORPORATION

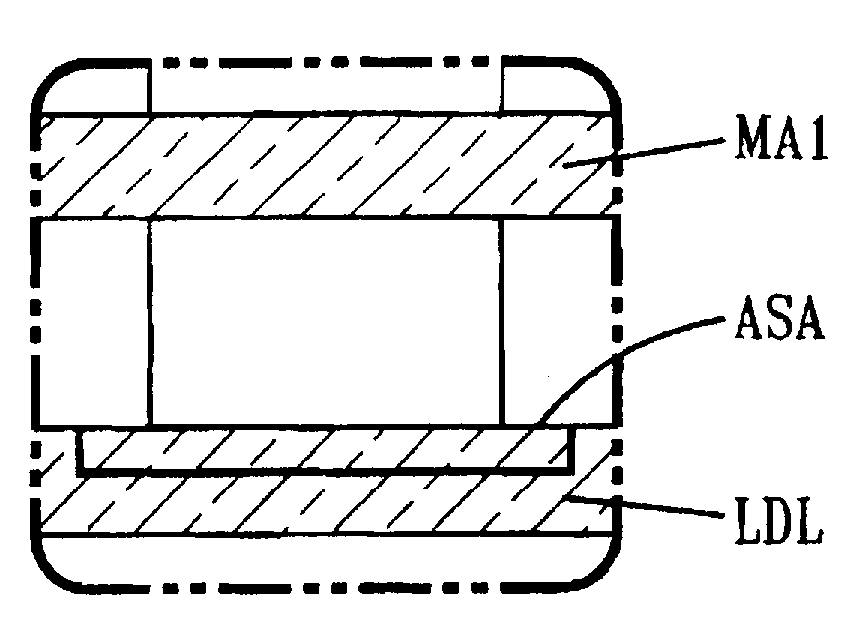

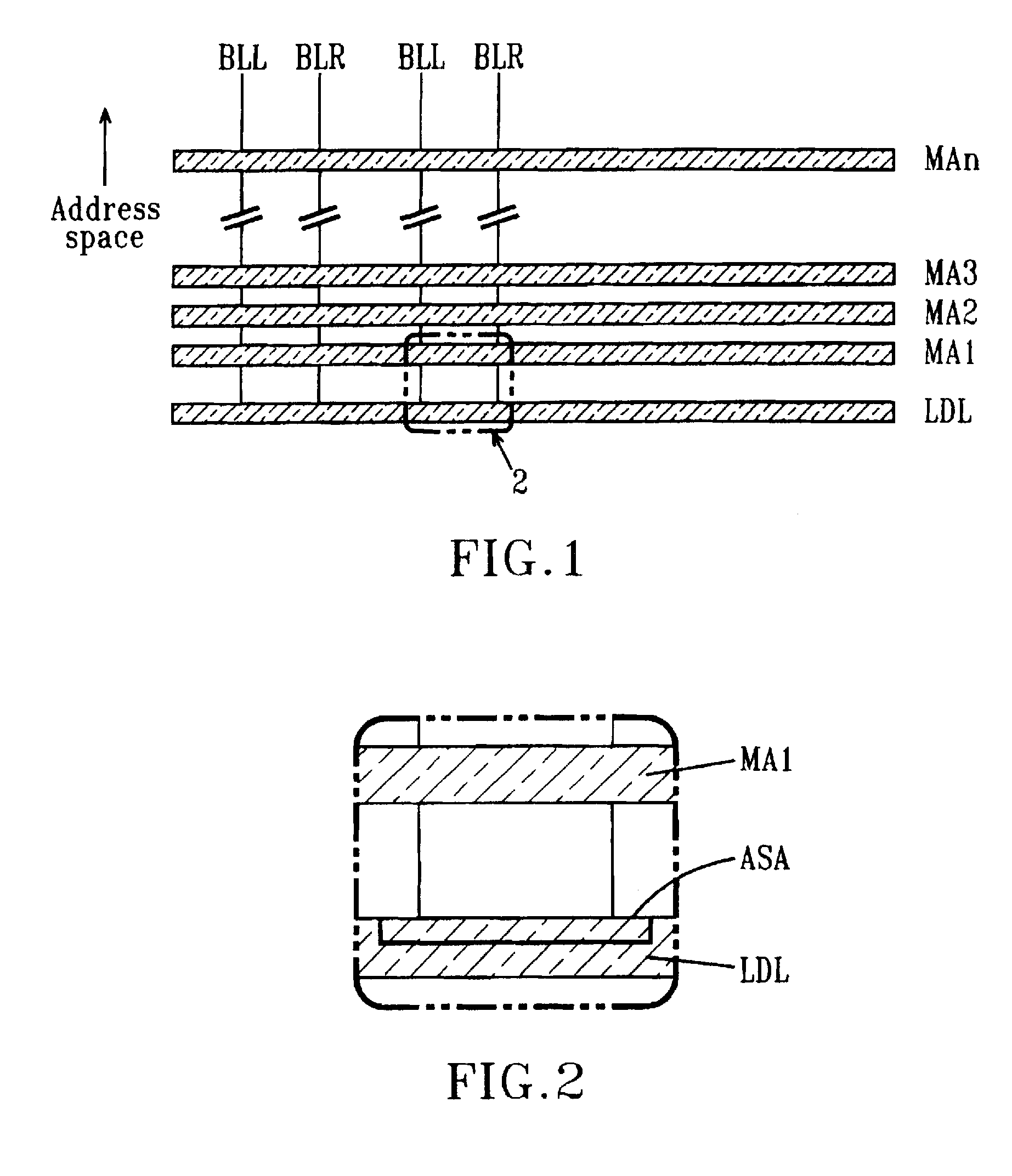

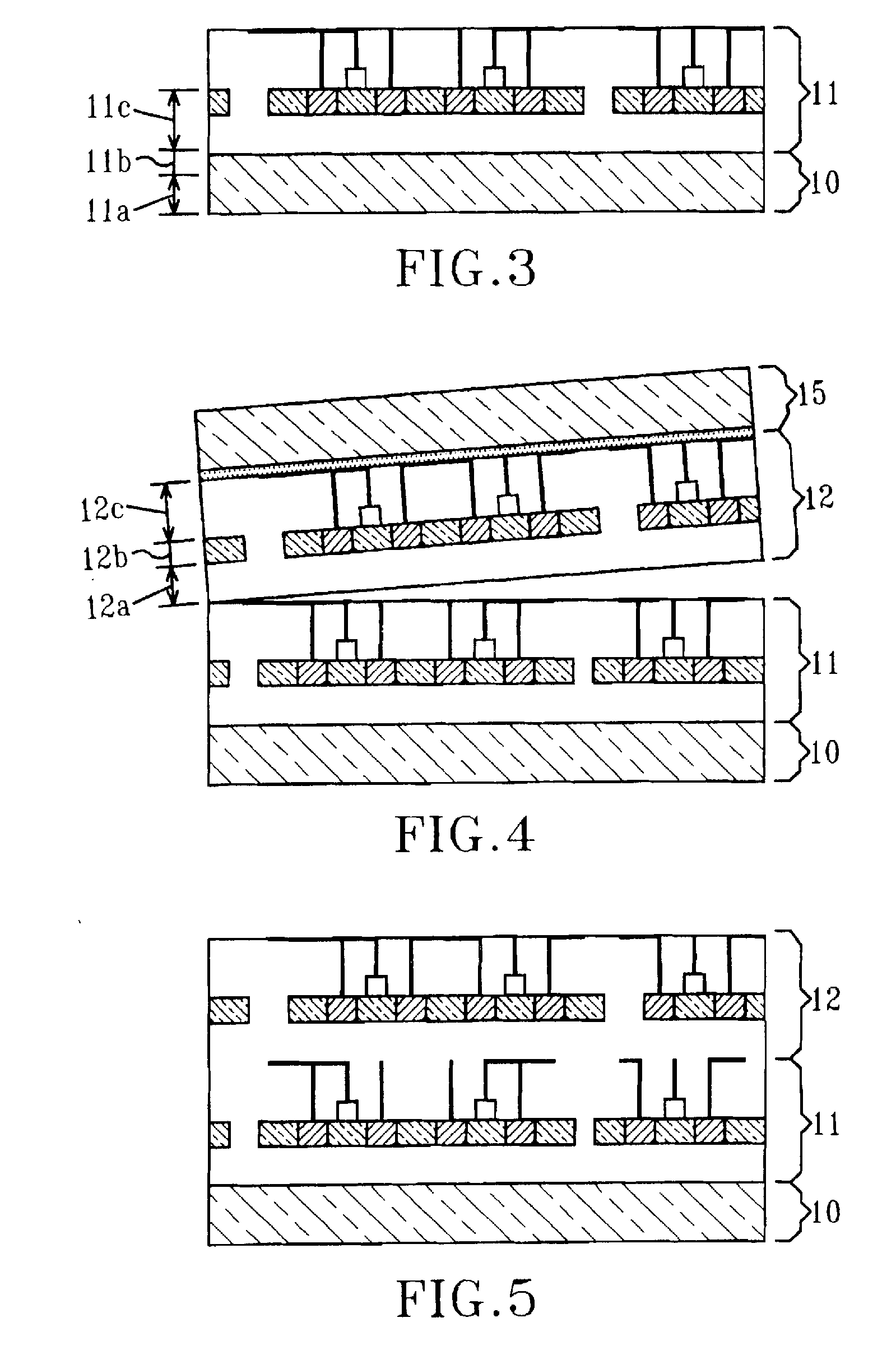

Structure comprising 3-dimensional integrated circuit architecture, circuit structure, and instructions for fabrication thereof

ActiveUS20070283298A1Allow optimizationSolid-state devicesSemiconductor/solid-state device manufacturingAudio power amplifierPerformance enhancement

A design structure comprising an integrated circuit architecture, circuit structure, and / or instructions for fabrication thereof. The circuit structure includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

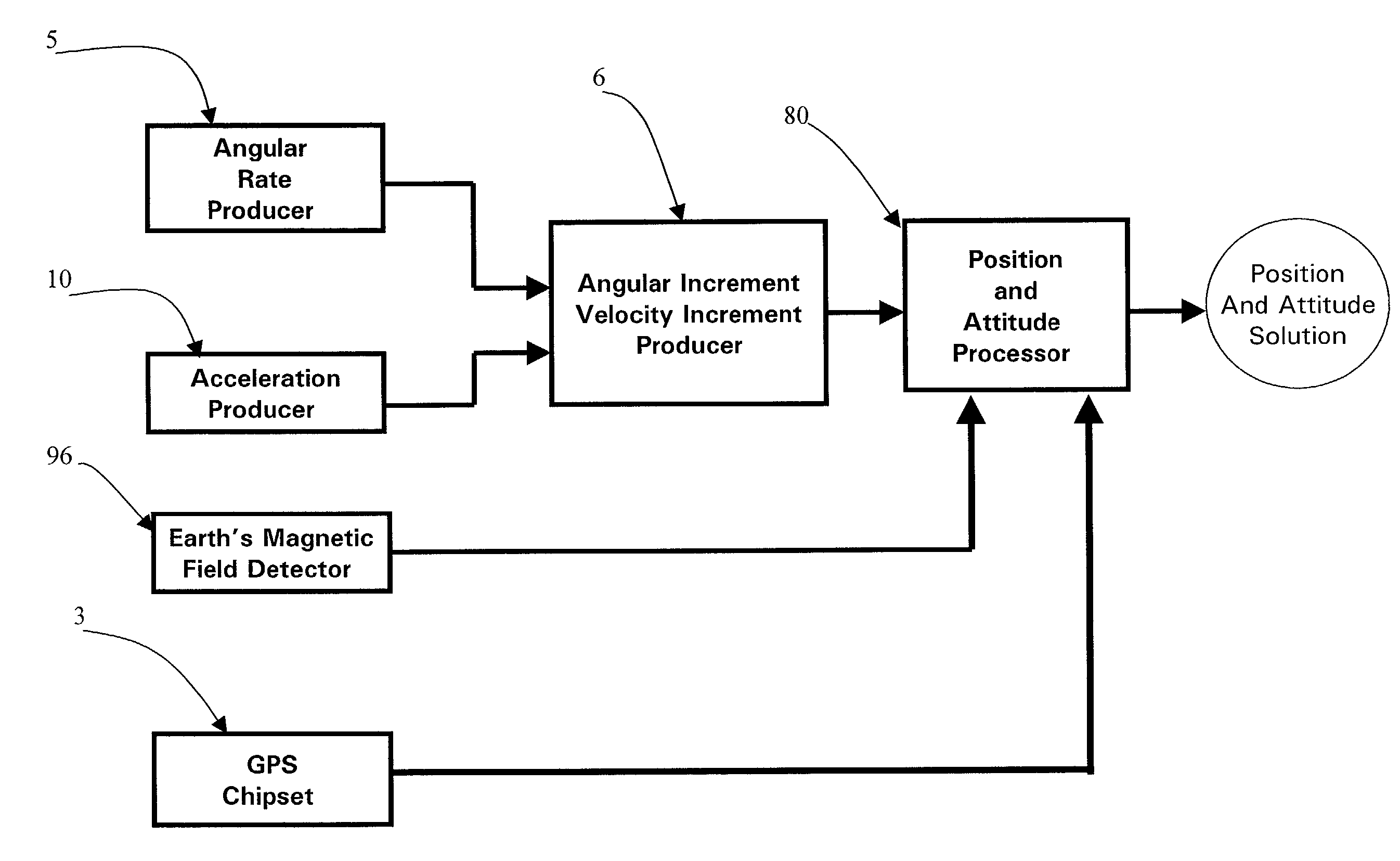

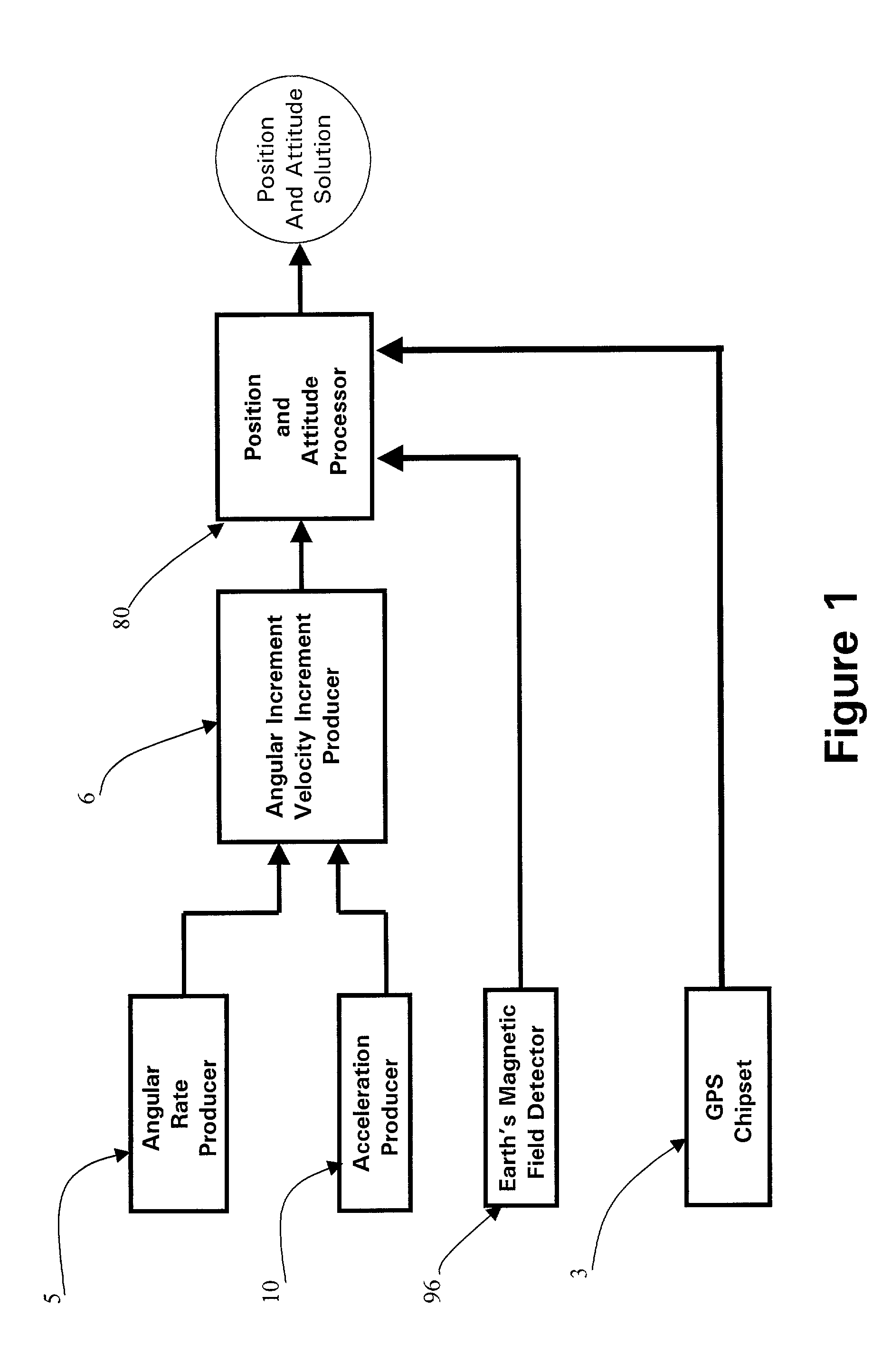

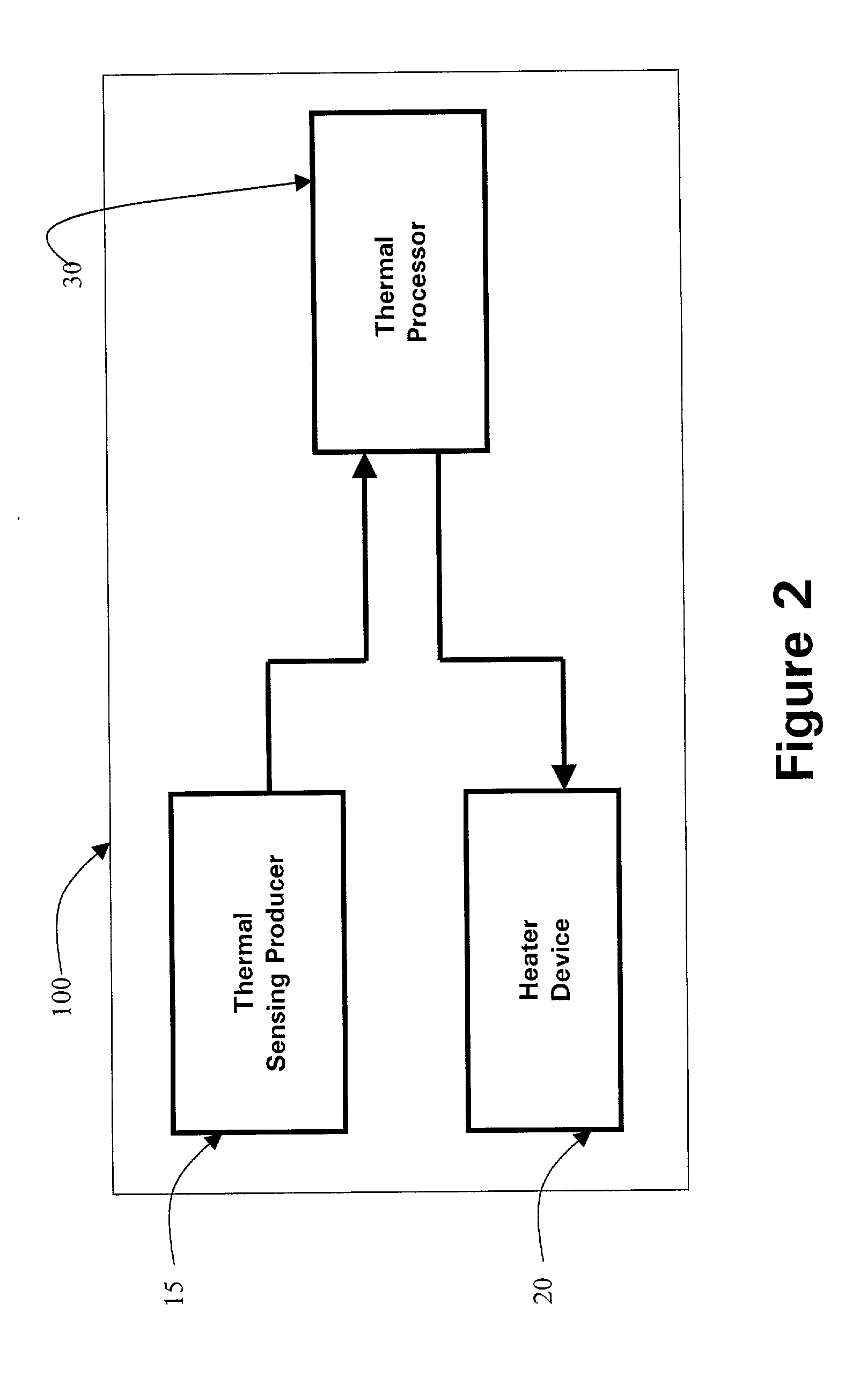

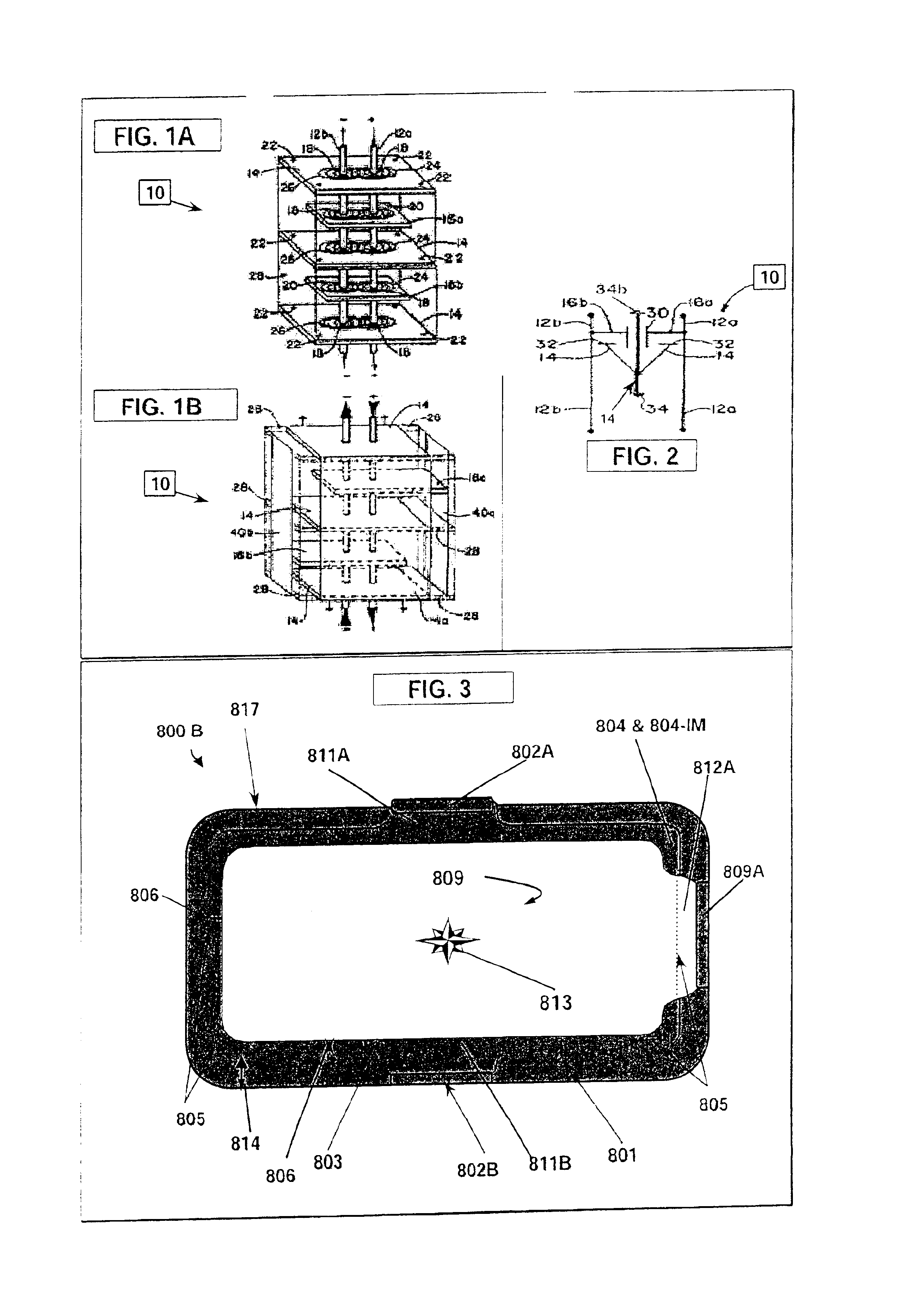

Micro integrated global positioning system/inertial measurement unit system

InactiveUS20020008661A1Precise positioningInstruments for road network navigationPosition fixationCarrier signalClosed loop

A micro integrated Global Positioning System (GPS) / Inertial Measurement Unit (IMU) System, which is adapted to apply to output signals proportional to rotation and translational motion of a carrier and GPS measurements of the carrier, respectively from angular rate sensors, acceleration sensors, and GPS chipset, is employed with MEMS angular rate and acceleration sensors and GPS chipset. Compared with a conventional IMU / GPS system, the system of the present invention uses an integrated processing scheme by means of digital closed loop control of the dither driver signals for MEMS angular rate sensors, a feedforward open-loop signal processing scheme of the IMU, digital temperature control and compensation, the earth's magnetic field-based heading damping, robust error estimator, and compact sensor and circuit architecture and dramatically shrinks the size of mechanical and electronic hardware and power consumption, meanwhile, obtains highly accurate motion measurements.

Owner:AMERICAN GNC

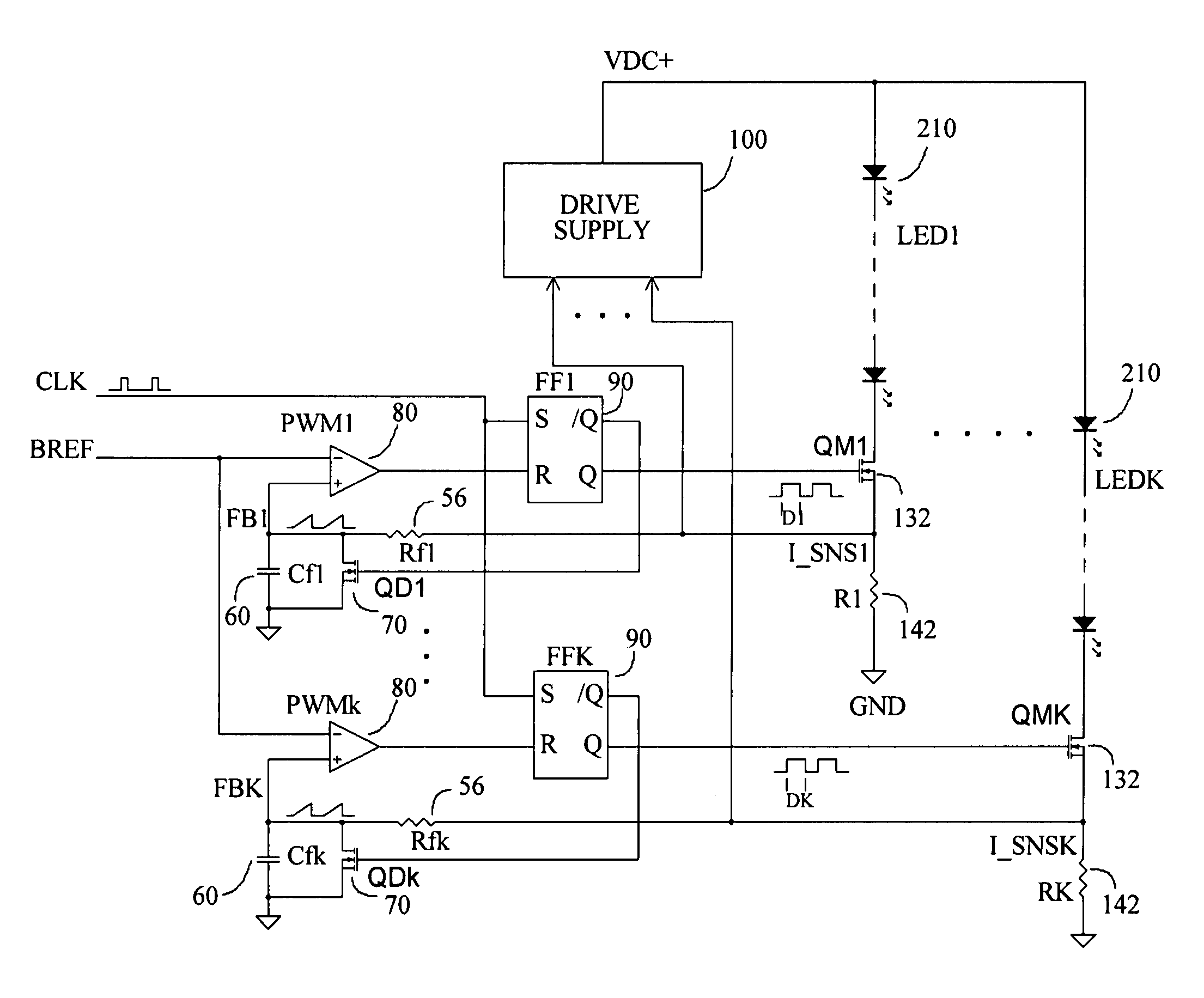

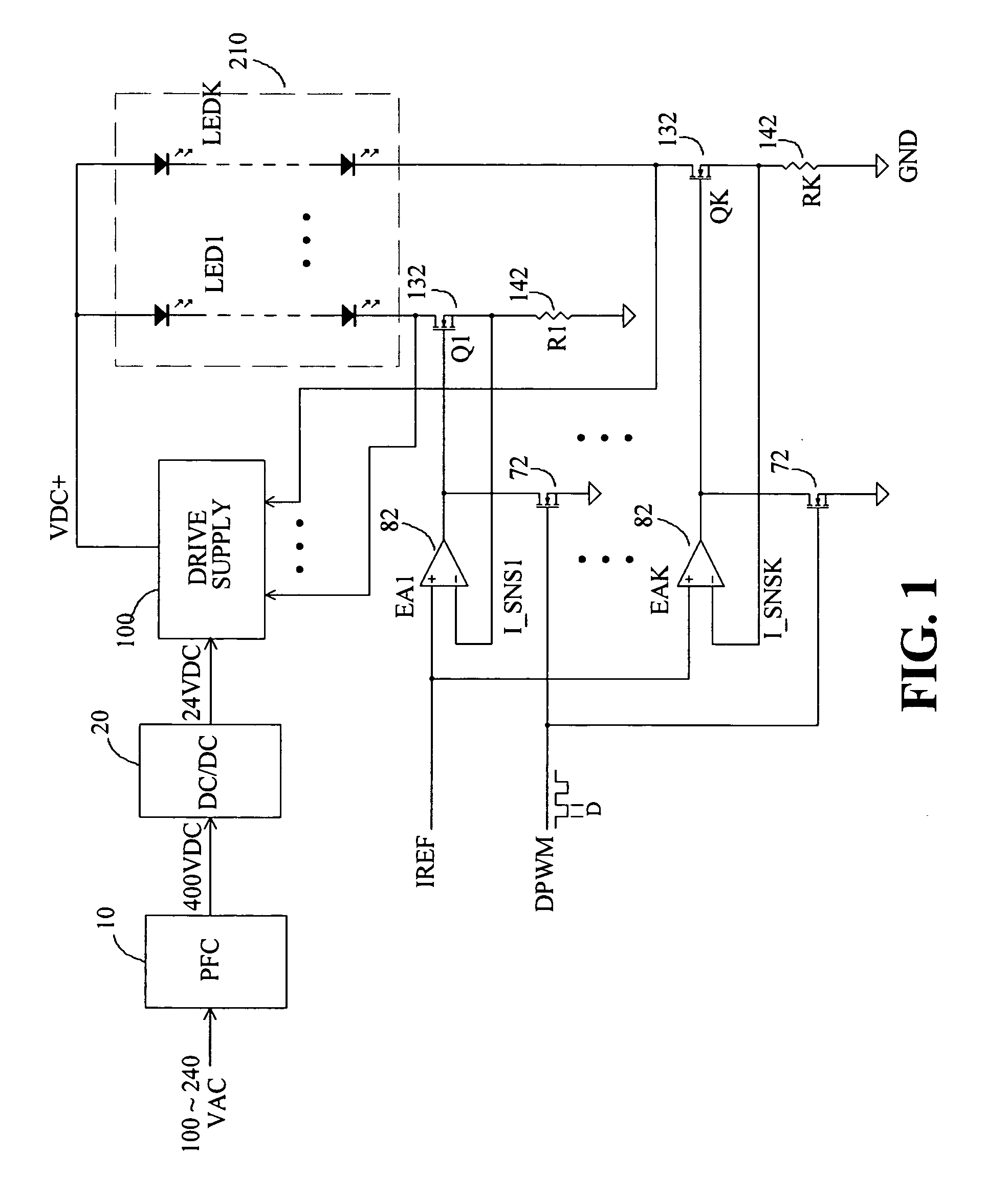

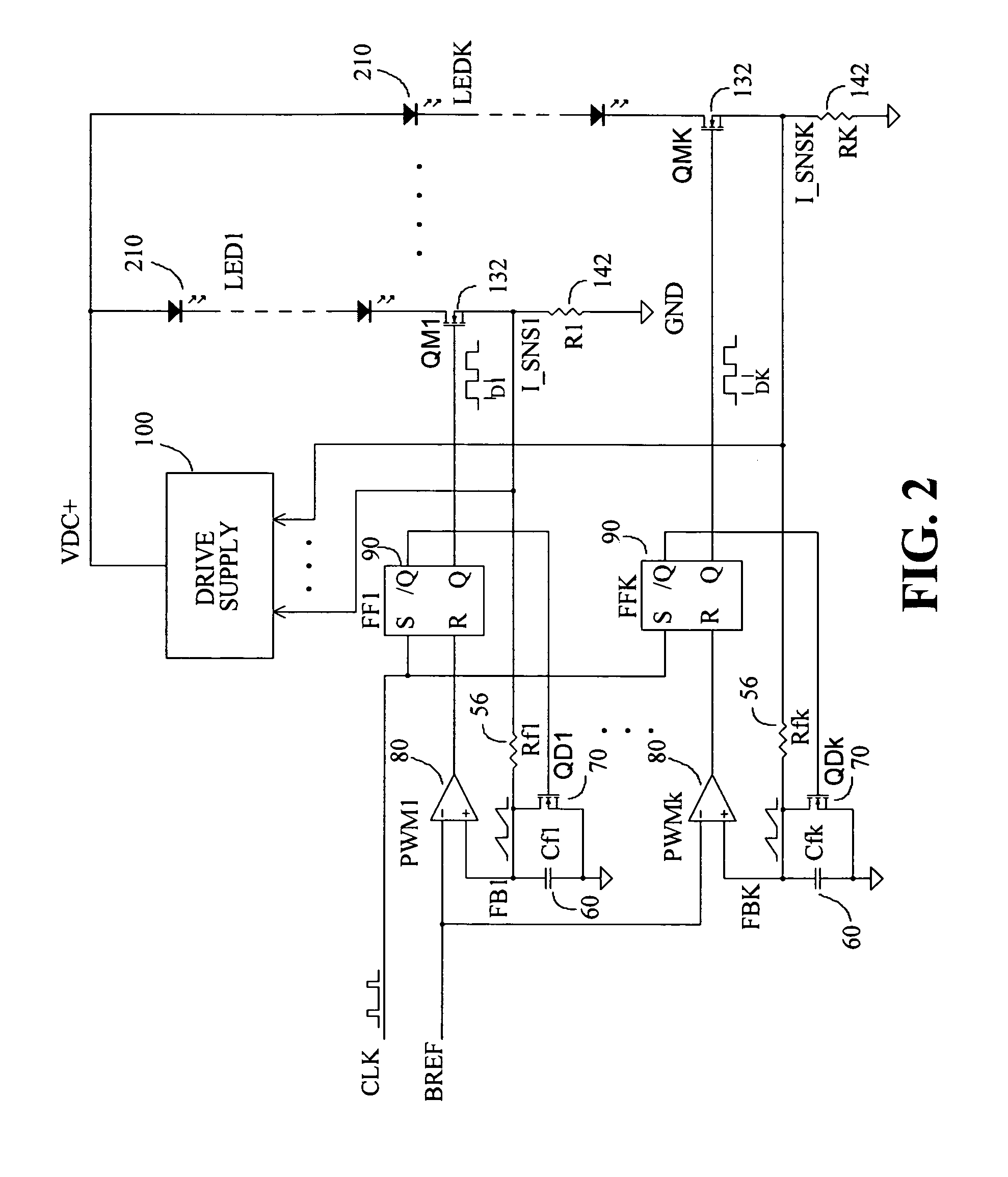

Method and apparatus for driving multiple LED devices

InactiveUS20110068700A1High efficiency circuit operationSimplified power conversion processElectrical apparatusElectroluminescent light sourcesBalancing networkEngineering

A series of methods of driving multiple LED devices with high efficiency balancing technique is disclosed. The regulation of the LED current is accomplished by switching operation to compensate the difference of the LED operating voltage. Reactive components are also employed to construct non-dissipative balancing networks to drive multiple LED strings with low losses. Additionally, a series of concept is presented to drive the LED devices from PFC voltage directly with low cost circuit architecture.

Owner:SUNTEC ENTERPRISES

Integrated rectifier and boost converter for wireless power transmission

ActiveUS9806564B2Reduce power consumptionReduce heat lossAc-dc conversion without reversalEfficient power electronics conversionConvertersBoost controller

A novel integrated rectifier and boost converter circuit architecture is disclosed. The rectifier architecture includes a plurality of identical half-bridge rectifiers connected to receiving antennas to convert wireless AC power into DC power. The integrated rectifier may be coupled in series with a charging inductor in a boost converter. The inductor may discharge upon operation of two micro-controller-driven switching transistors using predetermined threshold and timing scheme to turn on / off. The rectifier architecture may provide high power densities, improve efficiency at larger load currents, and may be enabled in an integrated circuit with eight RF signal inputs, eight half-bridge rectifiers, and eight DC outputs ganged together as single feed into the boost converter. The rectifier circuit topology may include a comparator driven by the boost controller with a proprietary algorithm which suits control for a maximum power point tracking functionality, and an external micro-controller for additional control of the boost converter.

Owner:ENERGOUS CORPORATION

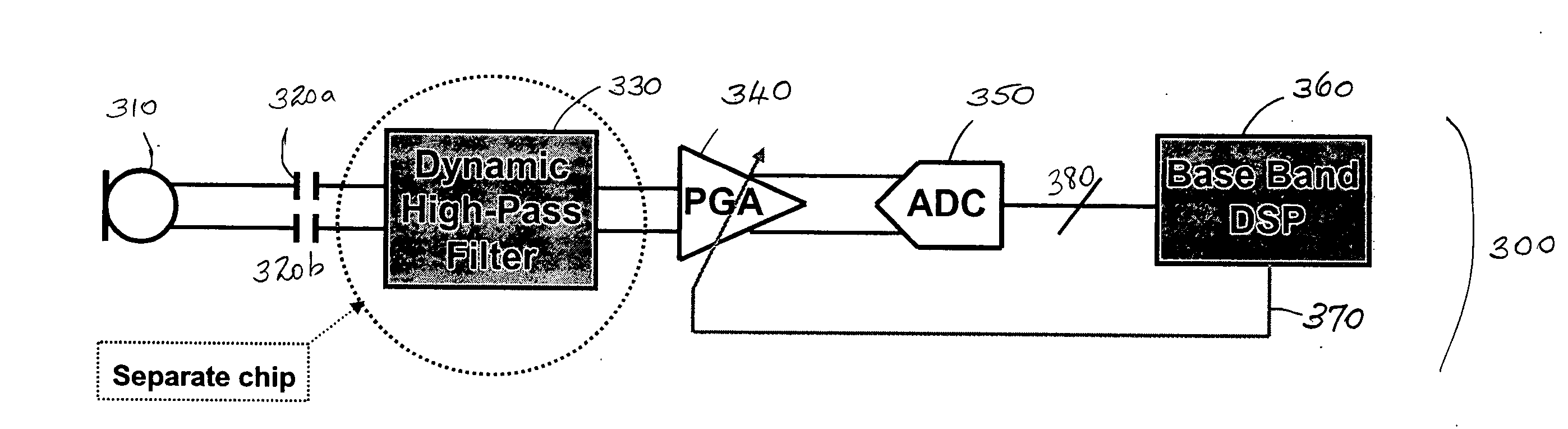

Low frequency noise reduction circuit architecture for communications applications

ActiveUS20080069373A1Economical yet effective high-pass filterAchieve adaptiveFrequency response correctionTransmission noise suppressionCapacitanceLow noise

A noise reduction circuit for reducing the effects of low frequency noise such as wind noise in communications applications is described. In one embodiment, the noise reduction circuit features a high pass filter formed by exploiting the existing off-chip AC coupling capacitances in making the connection to the source of audio signals. The filter may be adaptive to environmental low frequency noise level through programming the shunt resistances. A low-noise wide dynamic range programmable gain amplifier is also described. Adaptive equalization of the audio signal is also described through the utilization of programmable front-end resistors and a back-end audio equalizer.

Owner:AVAGO TECH INT SALES PTE LTD

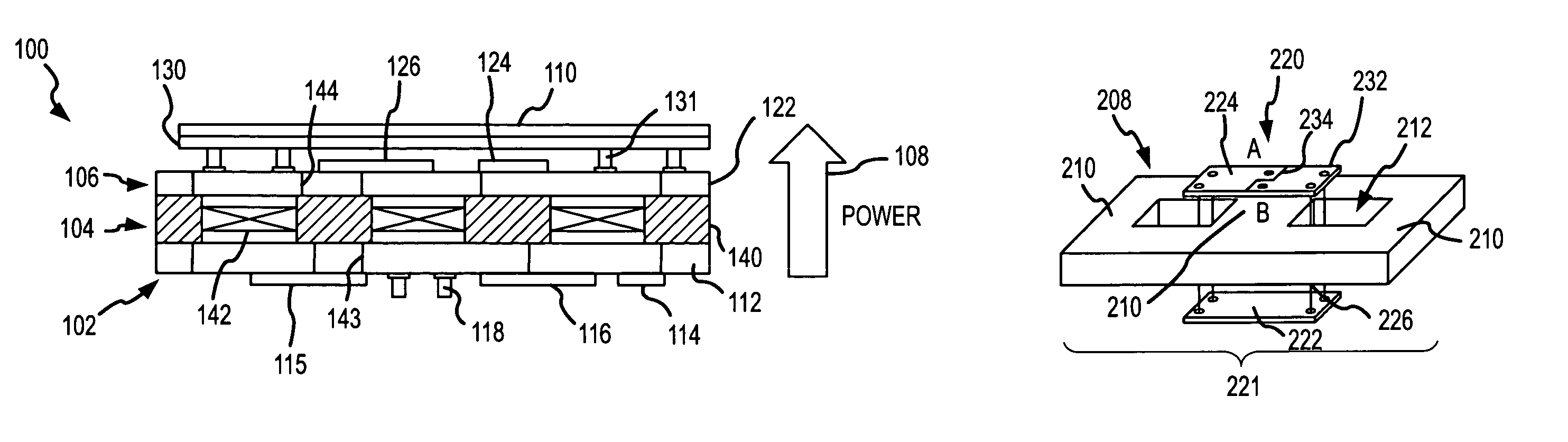

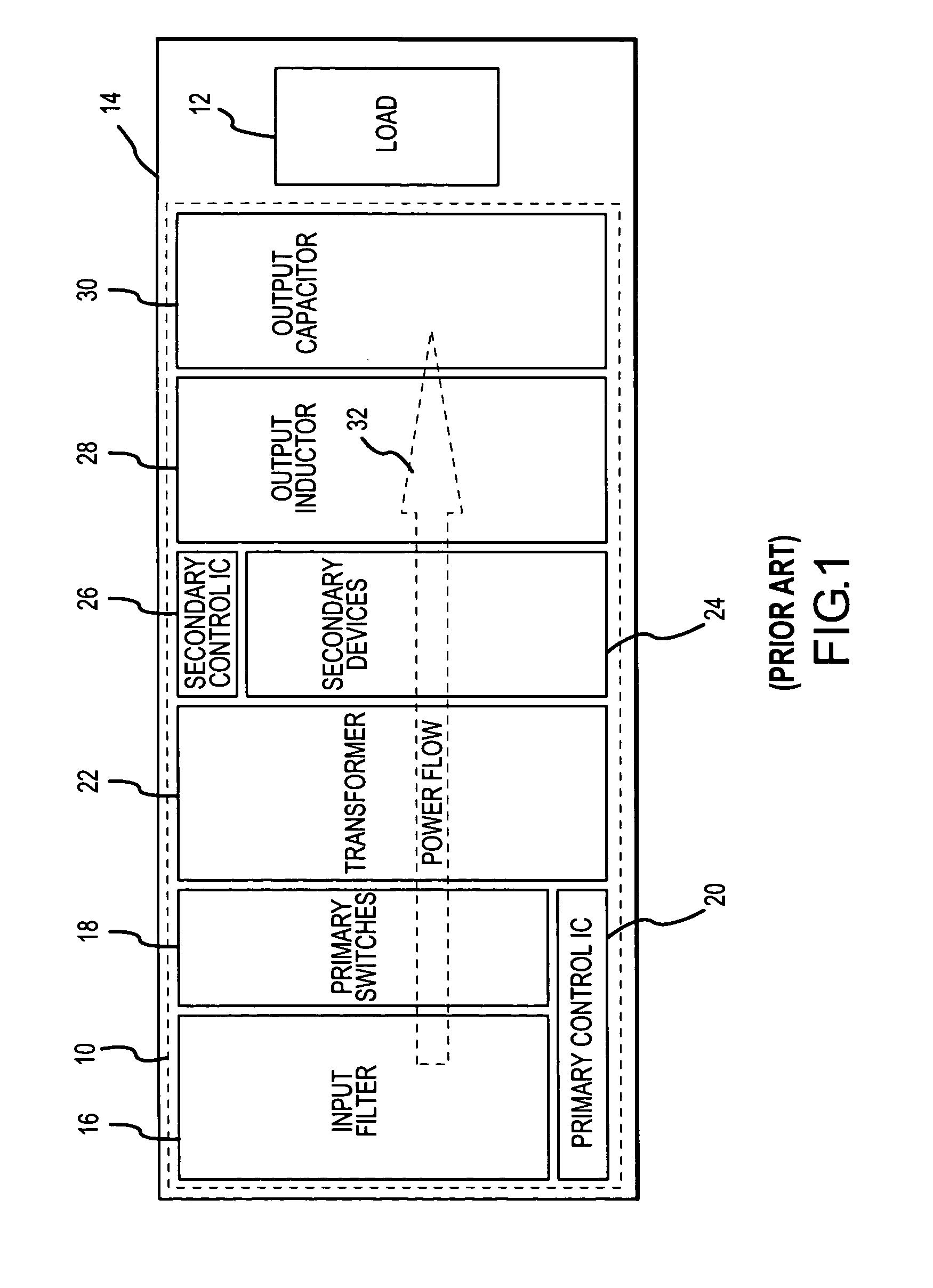

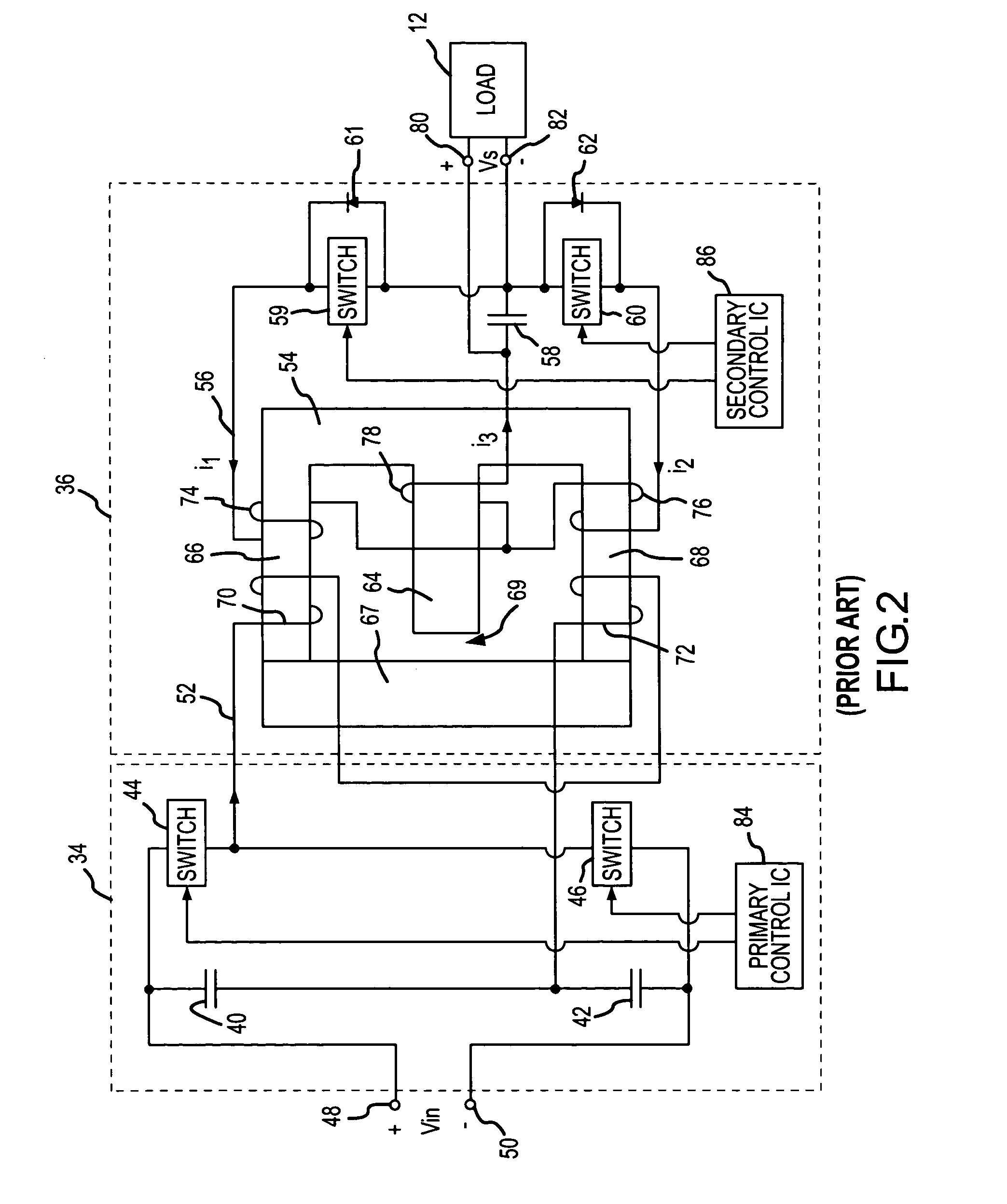

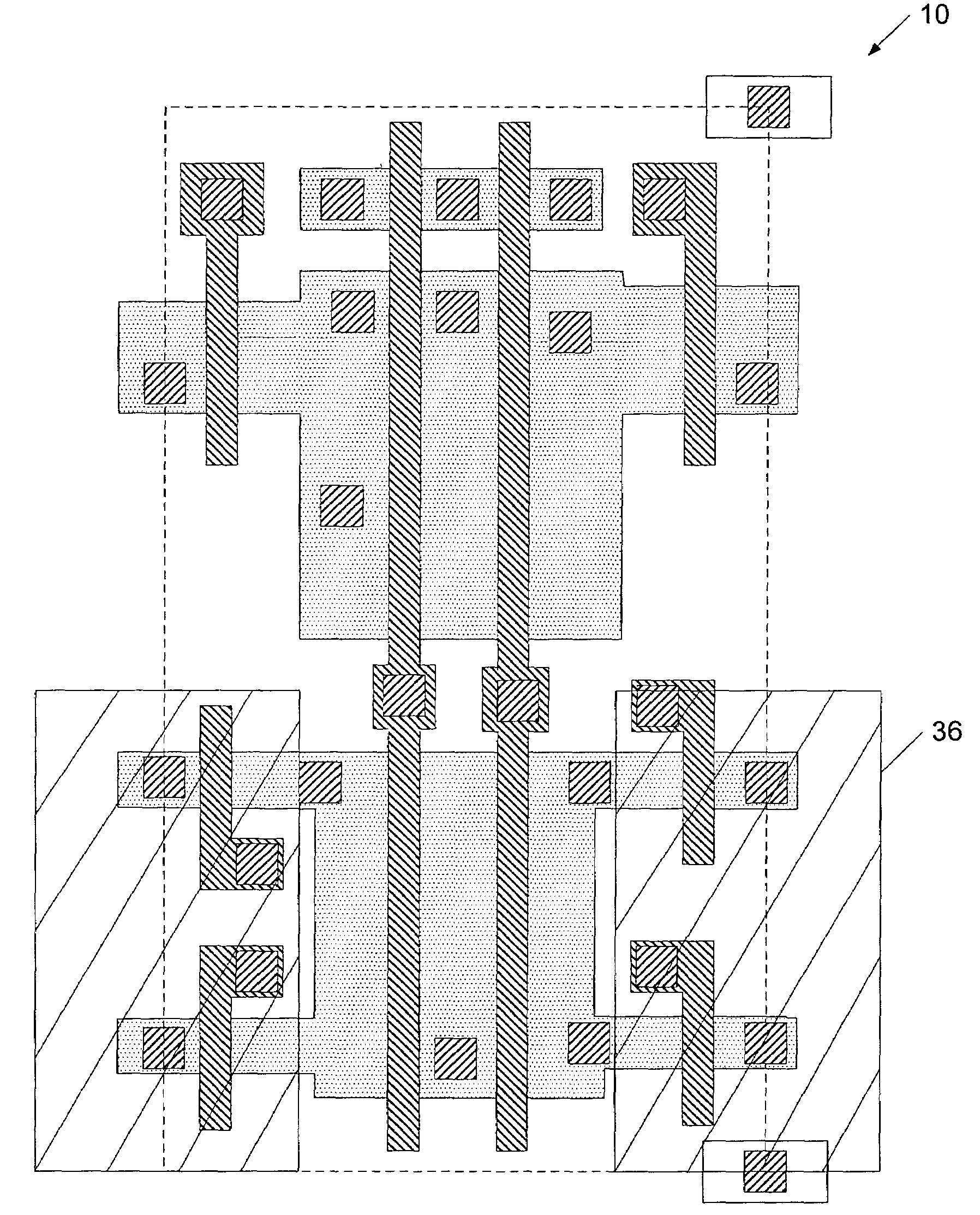

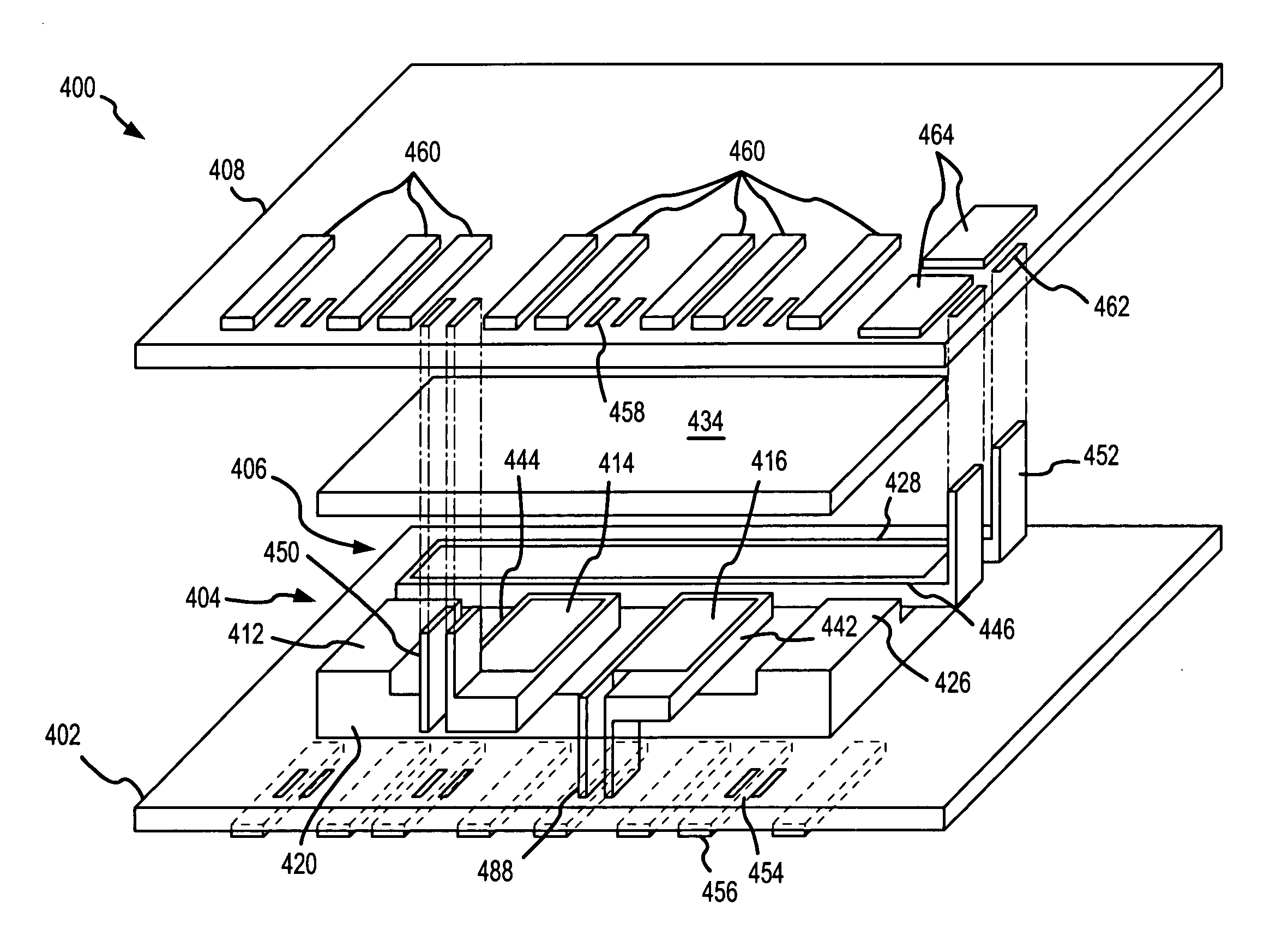

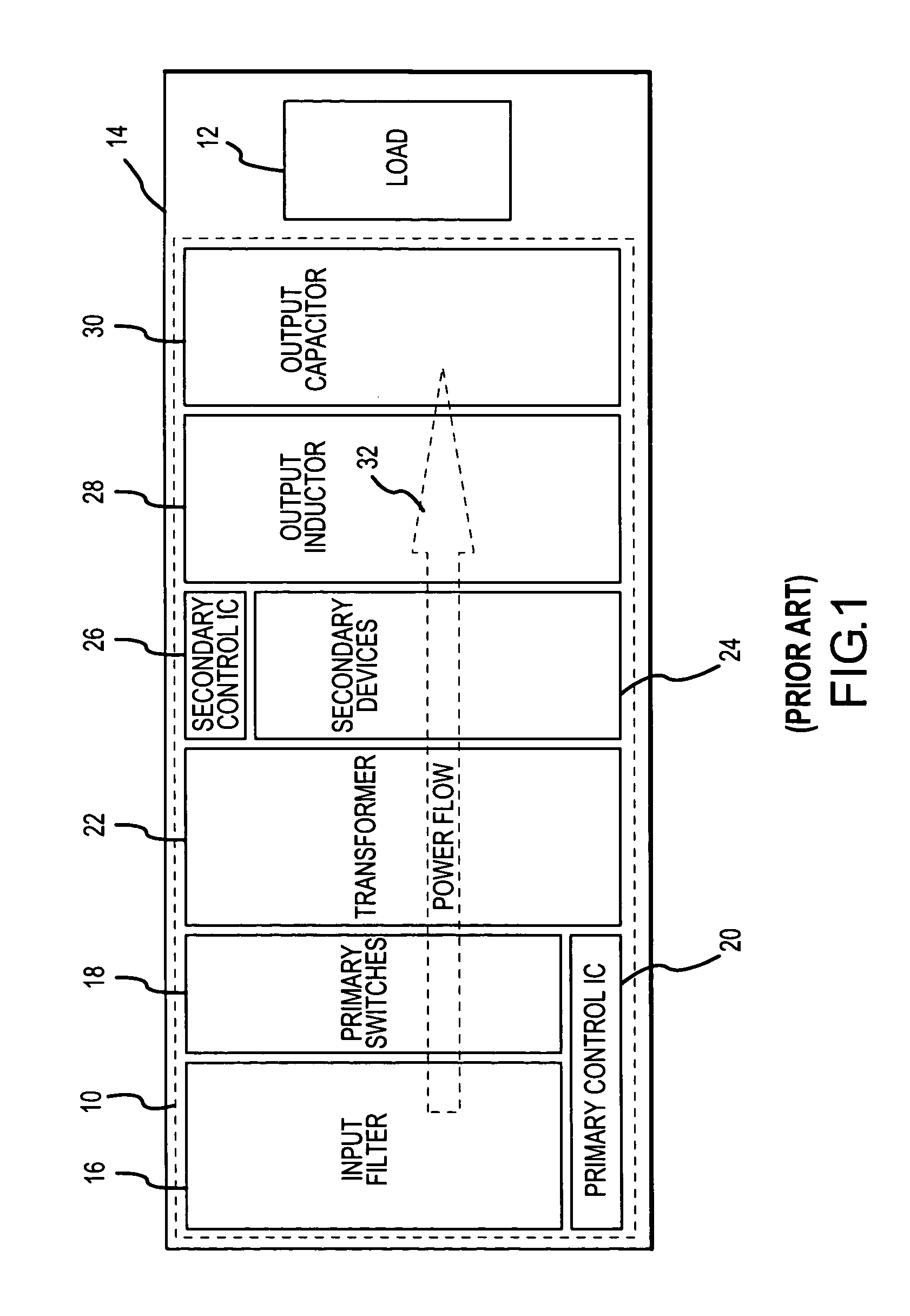

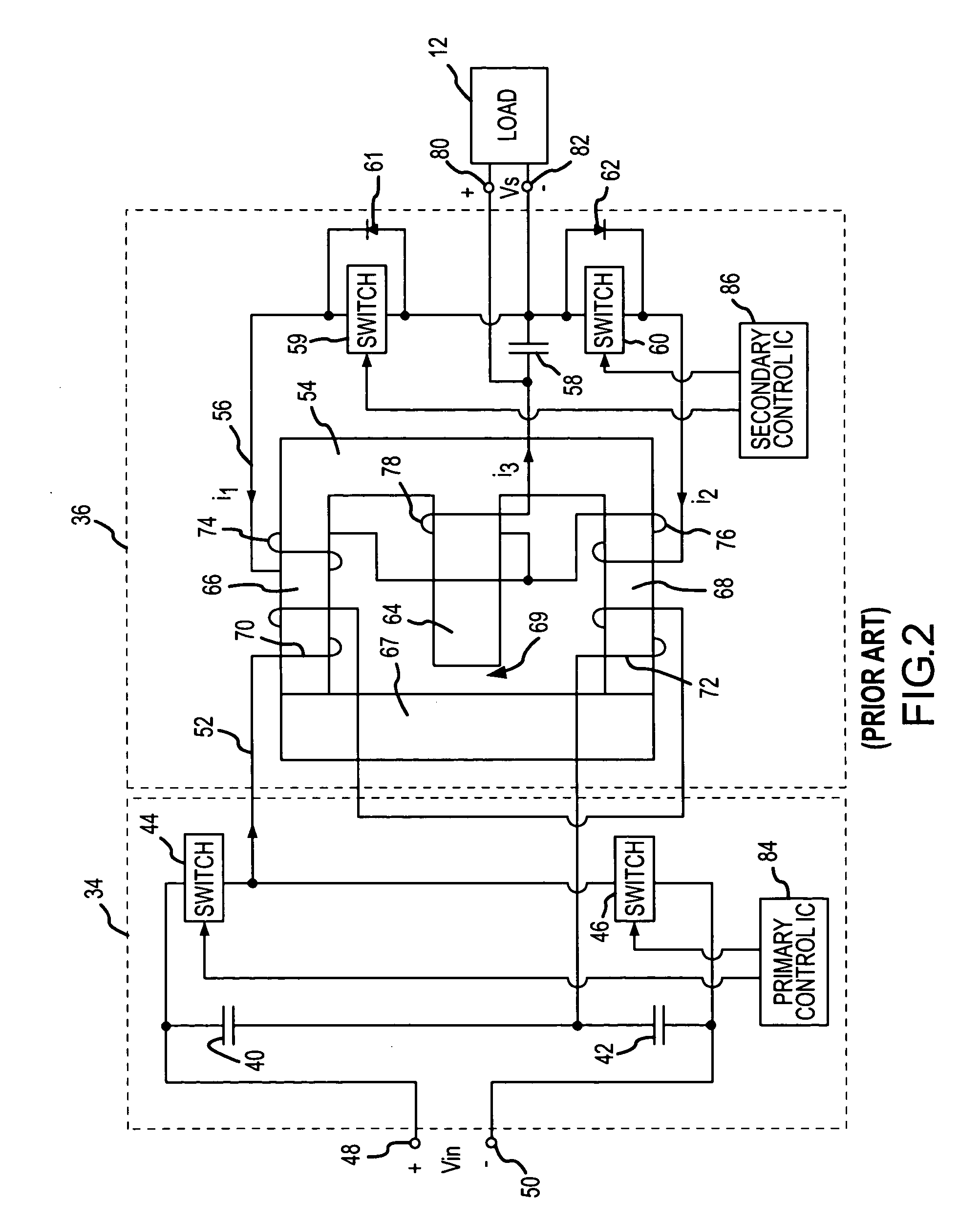

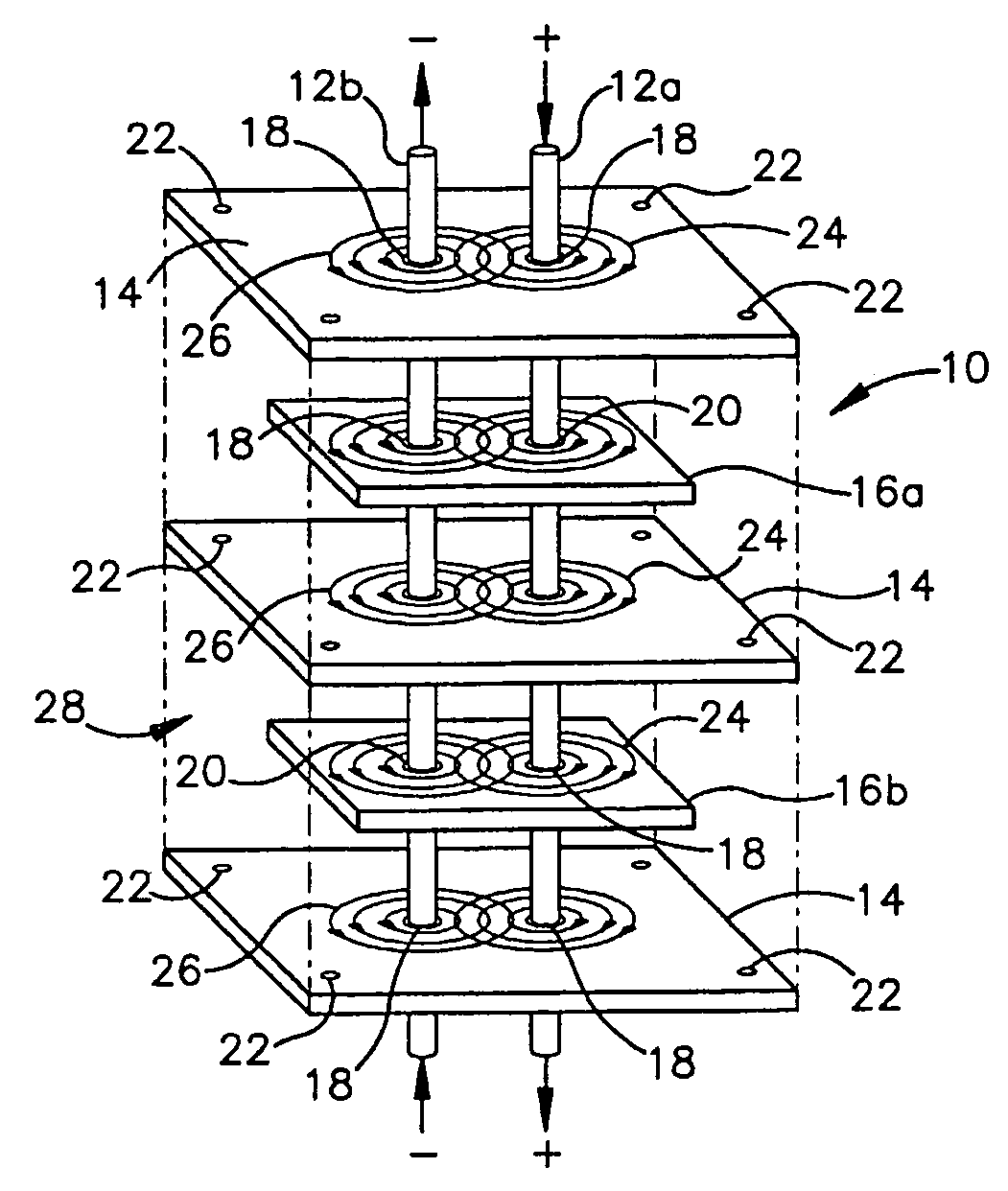

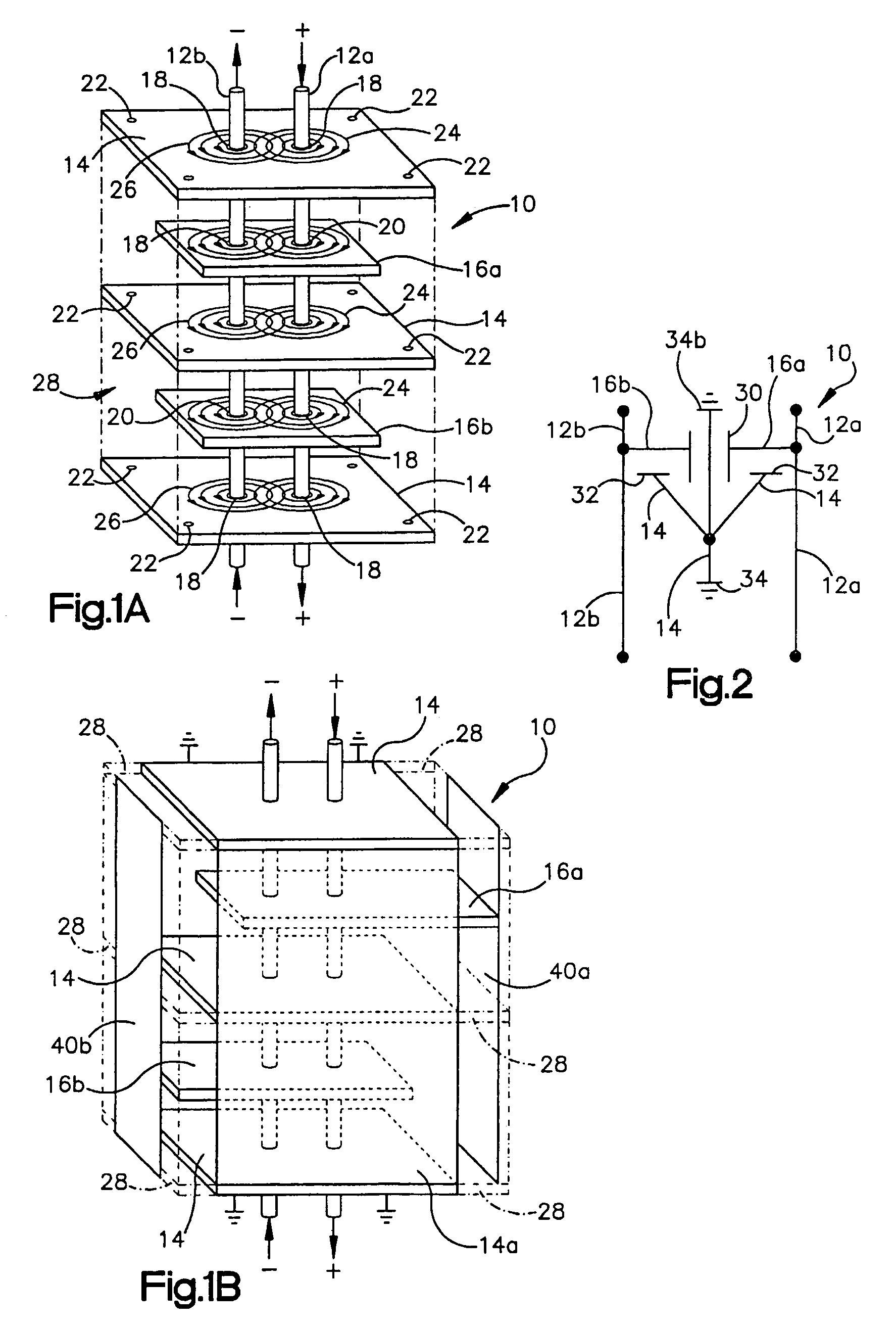

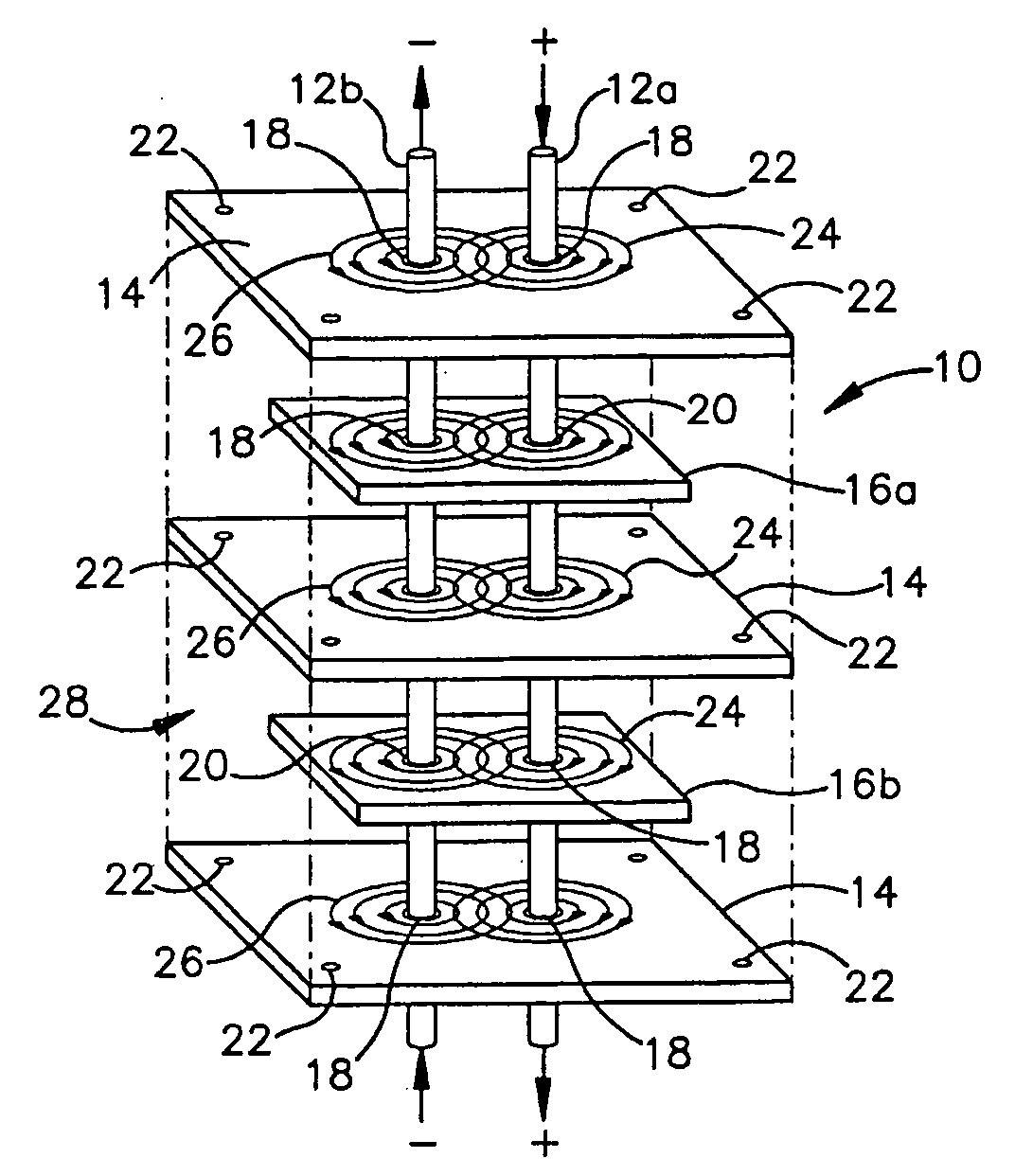

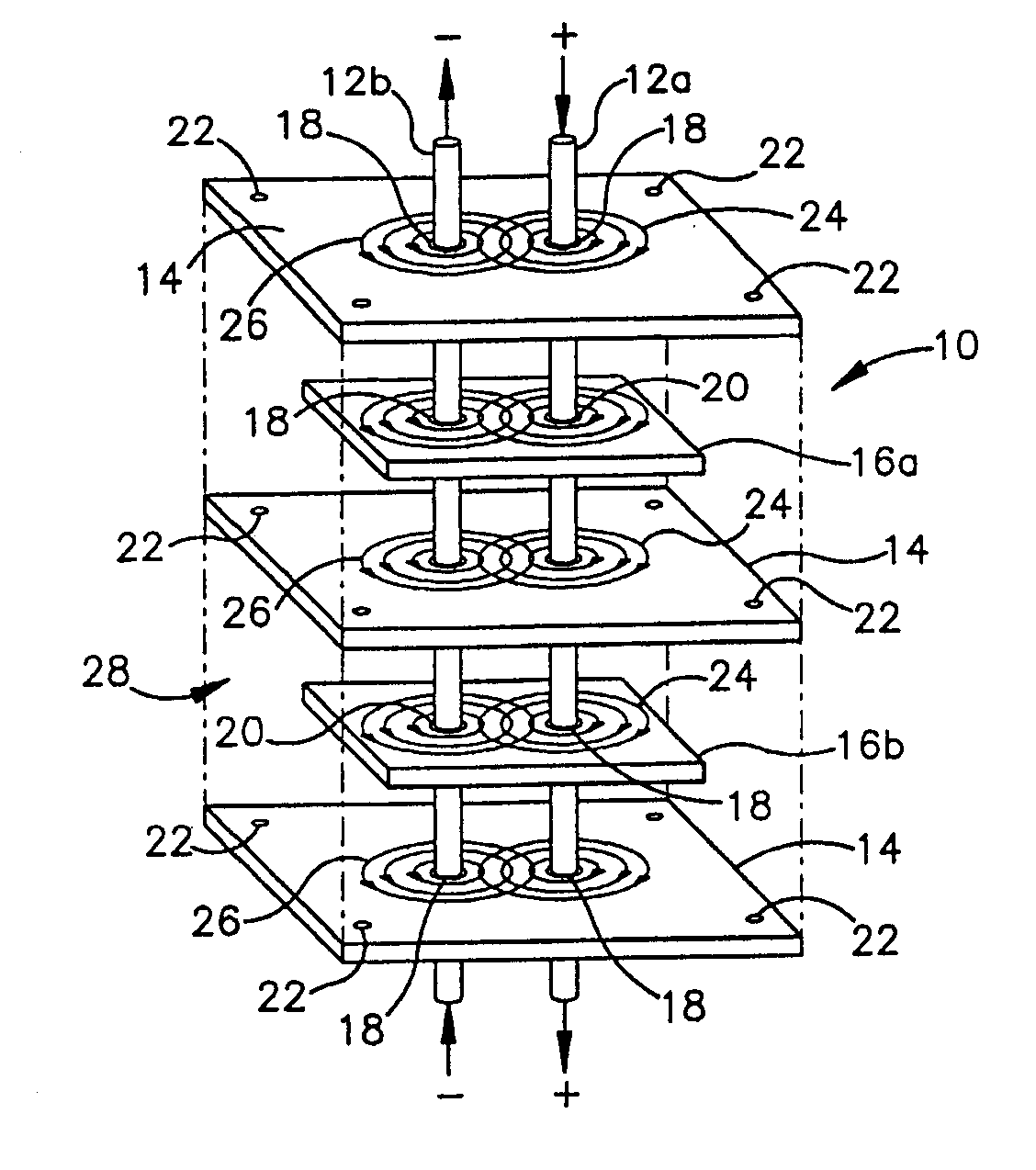

Vertically packaged switched-mode power converter

ActiveUS7012414B1Tight regulationFast transient responseTransformersConversion constructional detailsElectrical resistance and conductanceCellular architecture

A vertically packaged cellular power converter solves the problems associated with conventional designs and paves the way for a cellular circuit architecture with ultra-low interconnect resistance and inductance. The vertical packaging results in a power flow in the vertical direction (from the bottom to the top) with very short internal interconnects, thereby minimizing the associated conduction losses and permitting high conversion efficiency at high currents. The cellular architecture is ideally suited for generating multiple supply voltages.

Owner:MYPAQ HLDG LTD

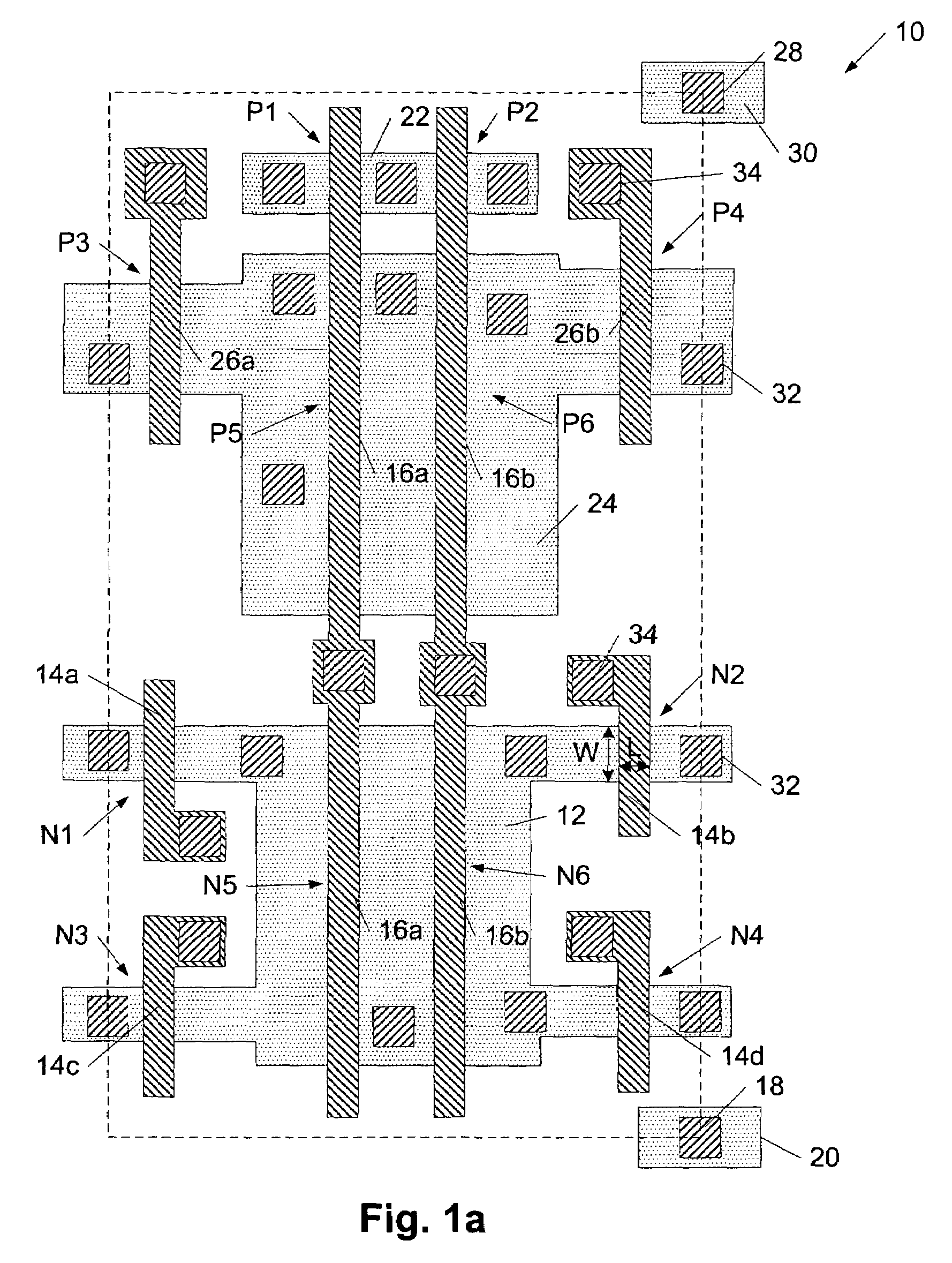

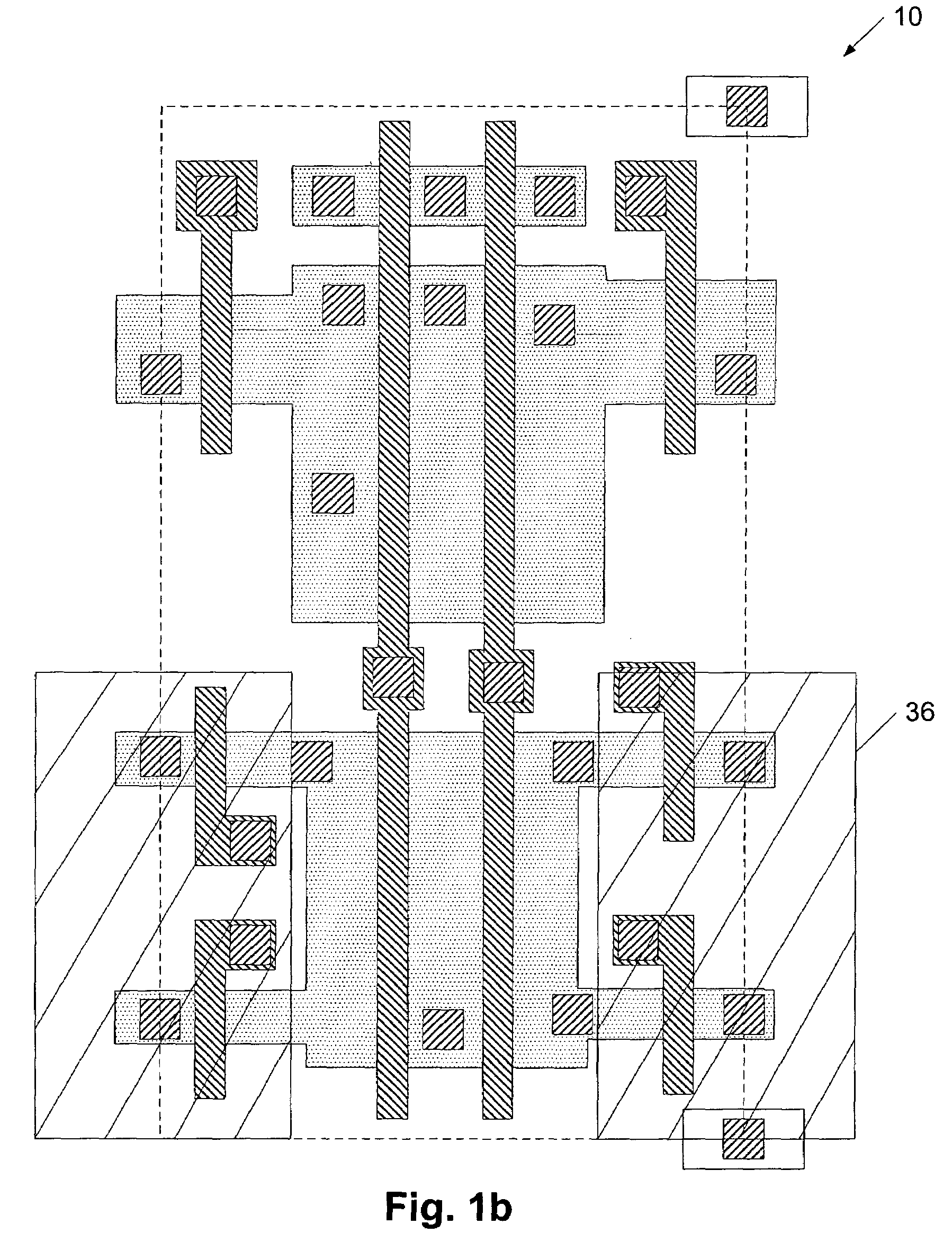

Basic cell architecture for structured application-specific integrated circuits

A basic cell circuit architecture having plurality of cells with fixed transistors configurable for the formation of logic devices and / or single / dual port memory devices within a structured ASIC is provided. Different configurations of ensuing integrated circuits are achieved by forming variable interconnect layers above the fixed structures. The circuit architecture can achieve interconnection of transistors within a single cell and / or across multiple cells. The interconnection can be configured to form basic logic gates as well as more complex digital and analog subsystems. In addition, each cell contains a layout of transistors that can be variably coupled to achieve a memory device, such as a SRAM device. By having the capability of forming either a logic circuit element, a memory device, or both, the circuit architecture is both memory-centric and logic-centric, and more fully adaptable to modern-day SoCs.

Owner:AVAGO TECH INT SALES PTE LTD

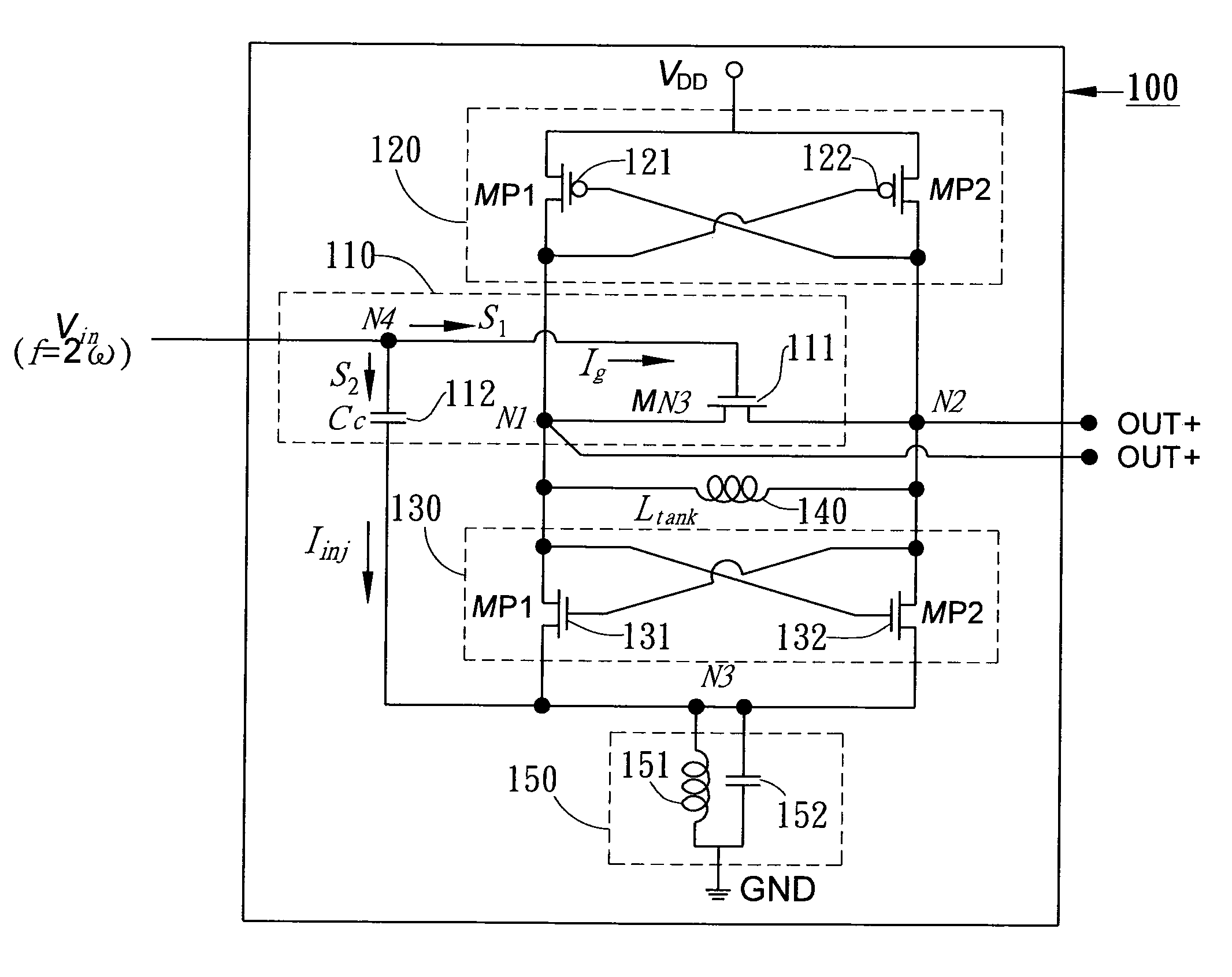

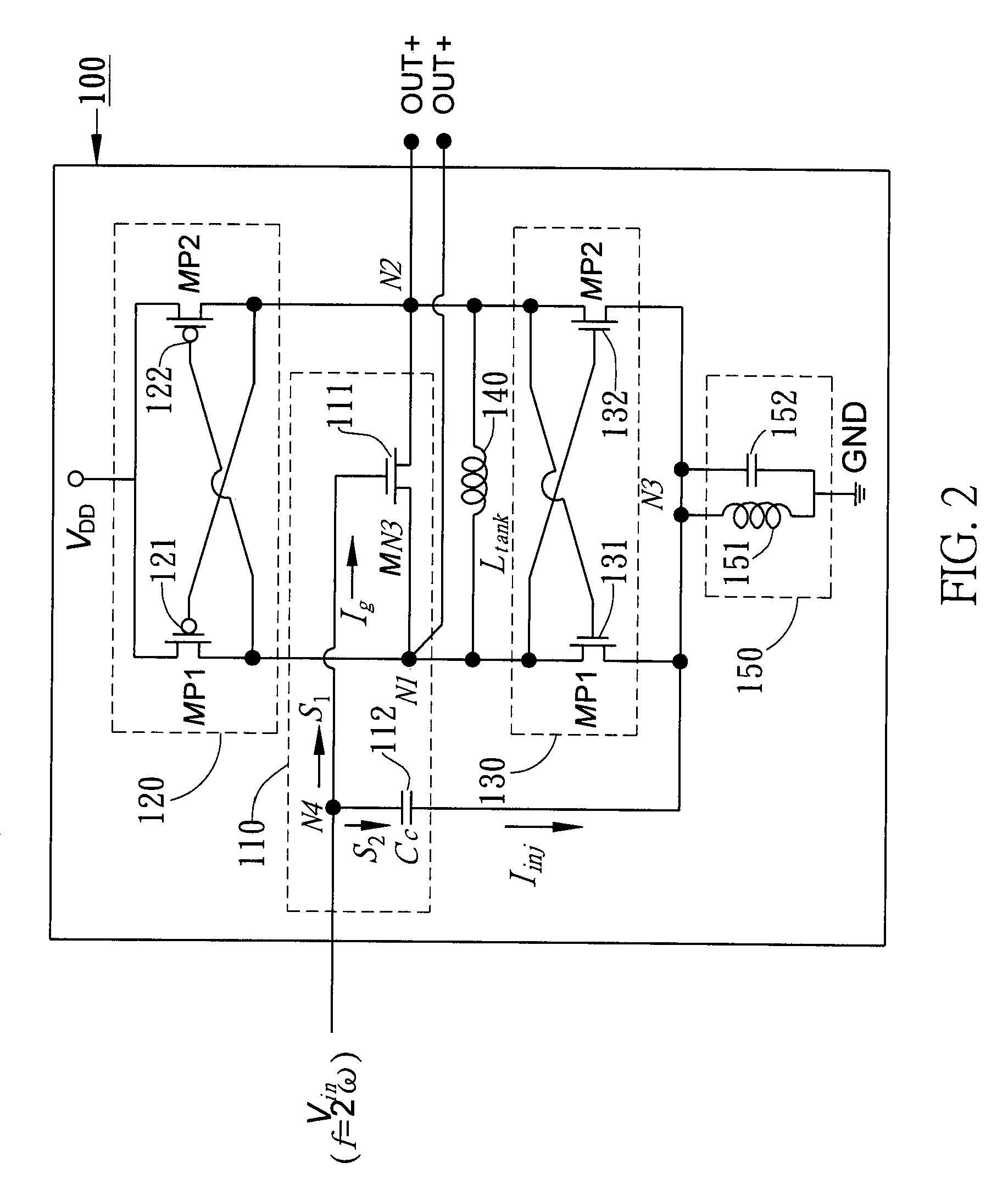

Dual-injection locked frequency dividing circuit

InactiveUS7656205B2Reduce power consumptionCounting chain pulse countersPulse counters with static storageDual injectionSignal processing circuits

A dual-injection locked frequency dividing circuit is proposed, which is designed for integration to a gigahertz signal processing circuit system for providing a frequency dividing function to gigahertz signals. The proposed circuit architecture is characterized by the provision of a dual-injection interface module on the input end for dividing the input signal into two parts for use as two injection signals, wherein the first injection signal is rendered in the form of a voltage signal and injected through a direct injection manner to the internal oscillation circuitry, while the second injection signal is rendered in the form of an electrical current and injected through a resonant circuit to the internal oscillation circuitry. This feature allow the proposed frequency dividing circuit to have broad frequency locking range and low power consumption.

Owner:NAT TAIWAN UNIV

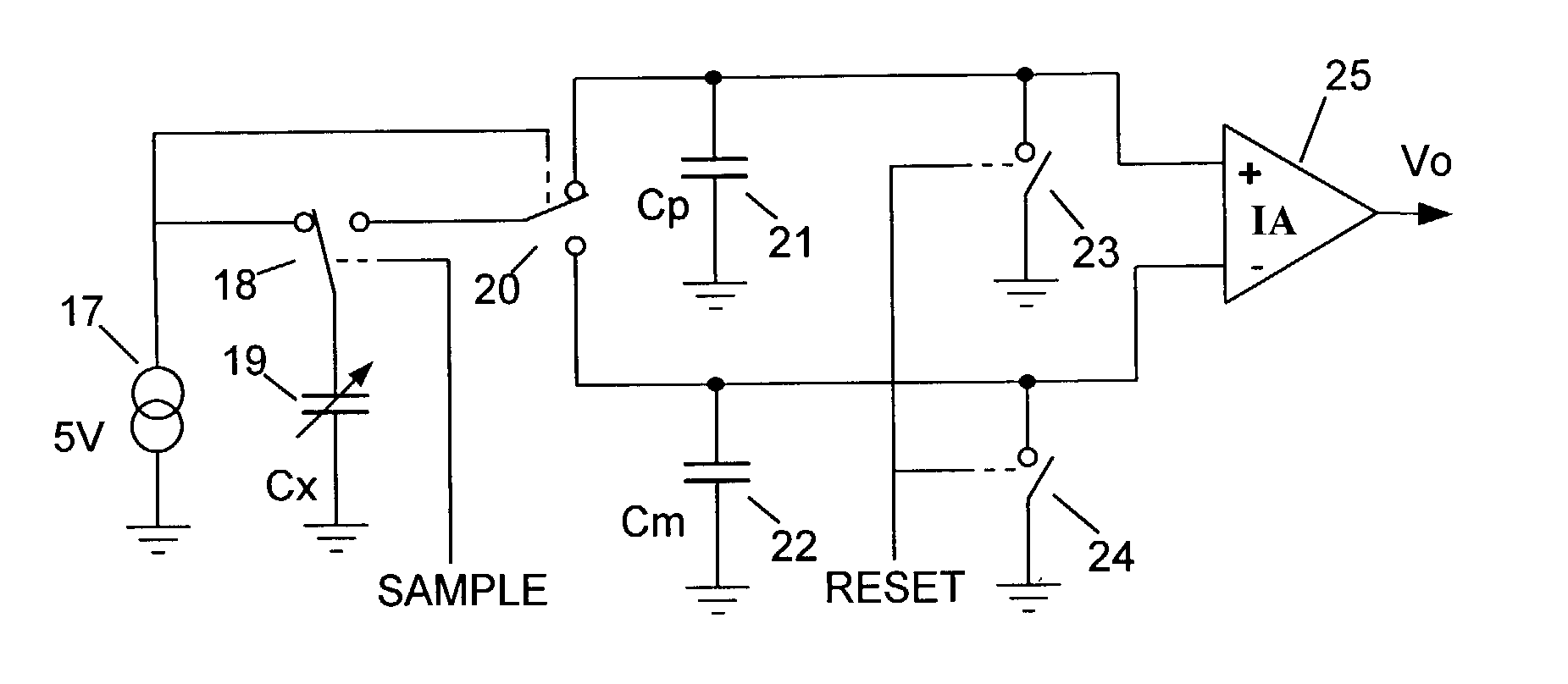

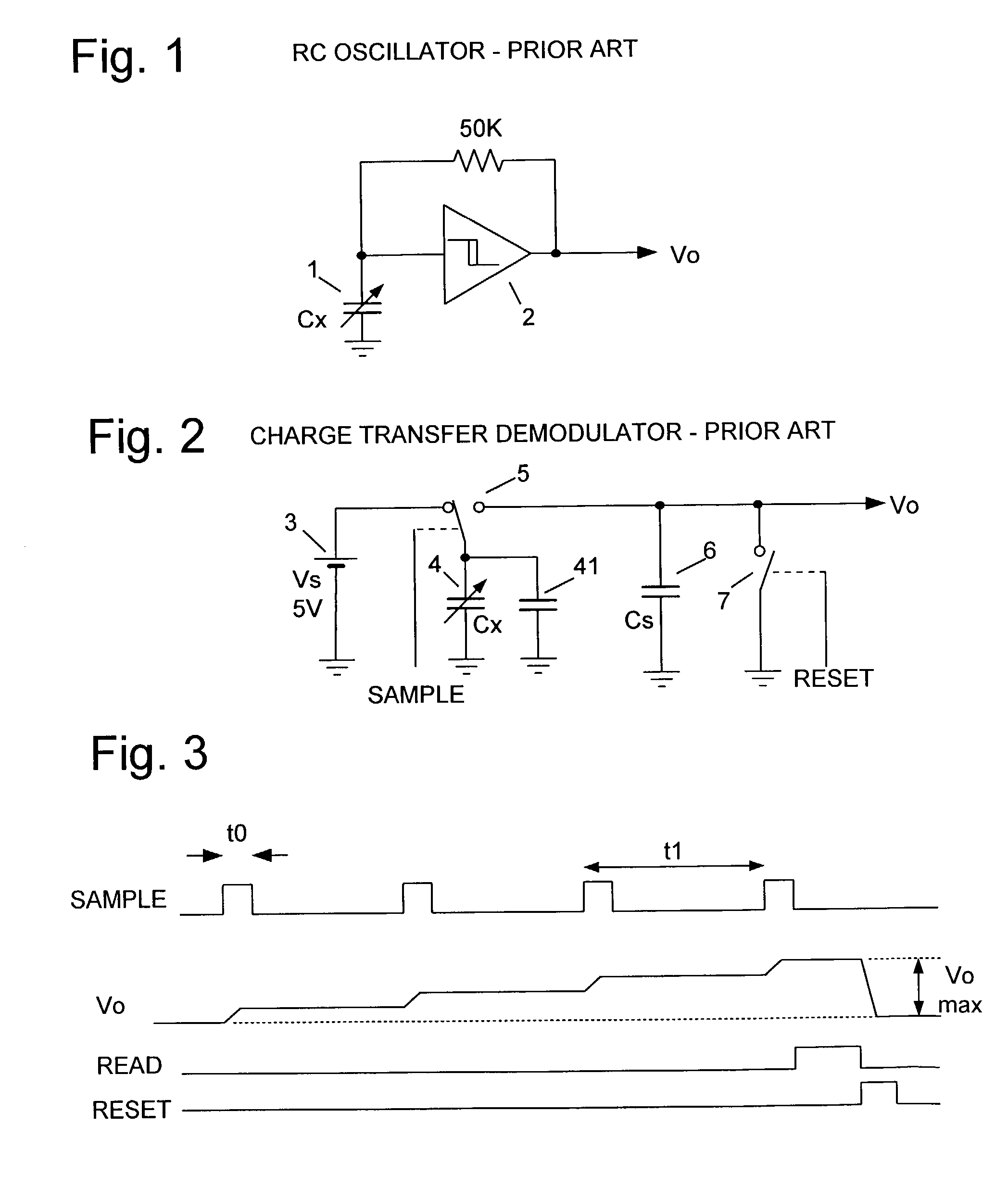

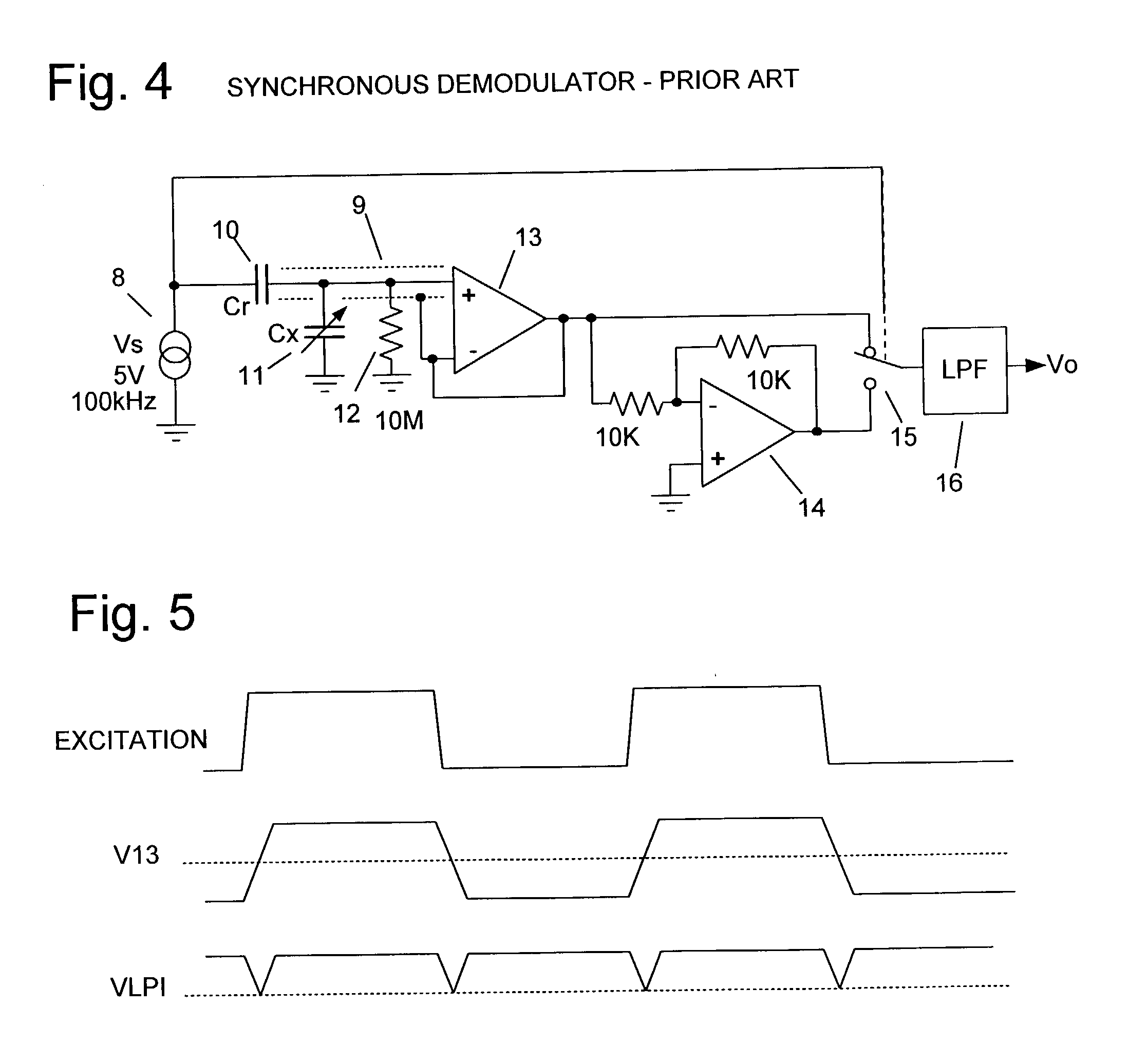

Capacitive sensor circuit with good noise rejection

InactiveUS20040004488A1Improved noise suppressionResistance/reactance/impedenceConverting sensor output electrically/magneticallyNoise suppressionImpedance sensor

This invention describes the deficiencies of current art for sensitive impedance sensors, particularly capacitive sensors, and describes several circuits that improve measurement of small value capacitances, especially in the presence of noise. It also shows various circuit architectures optimized for different capacitive sensing tasks. The circuits also describe a novel method to linearize a conventional charge-transfer capacitive sense circuit and a novel method to eliminate the effect of stray capacitance in charge-transfer capacitive sensors.

Owner:BAXTER LARRY K

Vertically packaged switched-mode power converter

ActiveUS20060038549A1Tight regulationFast transient responseTransformersConversion constructional detailsCellular architectureElectrical resistance and conductance

A vertically packaged cellular power converter solves the problems associated with conventional designs and paves the way for a cellular circuit architecture with ultra-low interconnect resistance and inductance. The vertical packaging results in a power flow in the vertical direction (from the bottom to the top) with very short internal interconnects, thereby minimizing the associated conduction losses and permitting high conversion efficiency at high currents. The cellular architecture is ideally suited for generating multiple supply voltages.

Owner:MYPAQ HLDG LTD

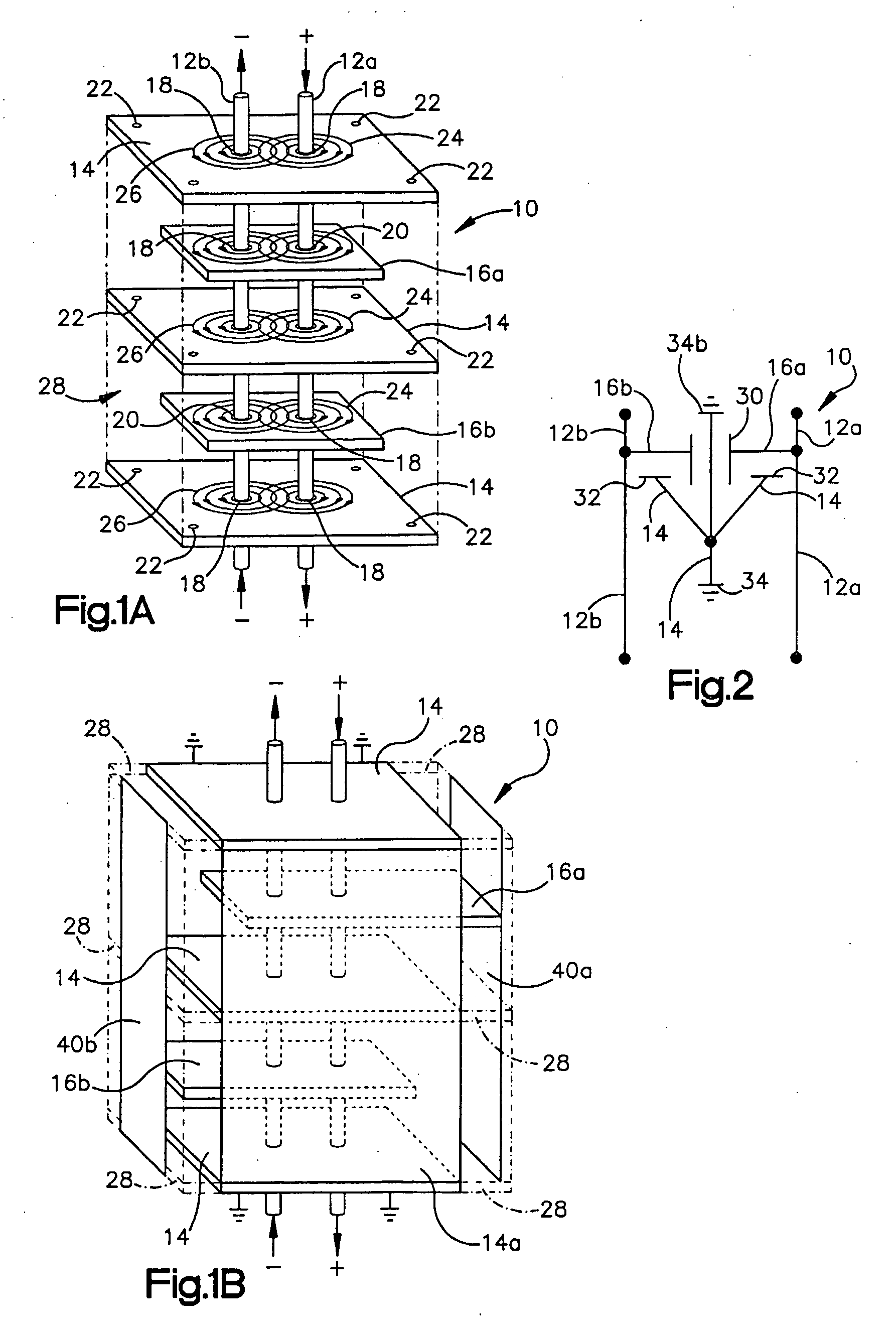

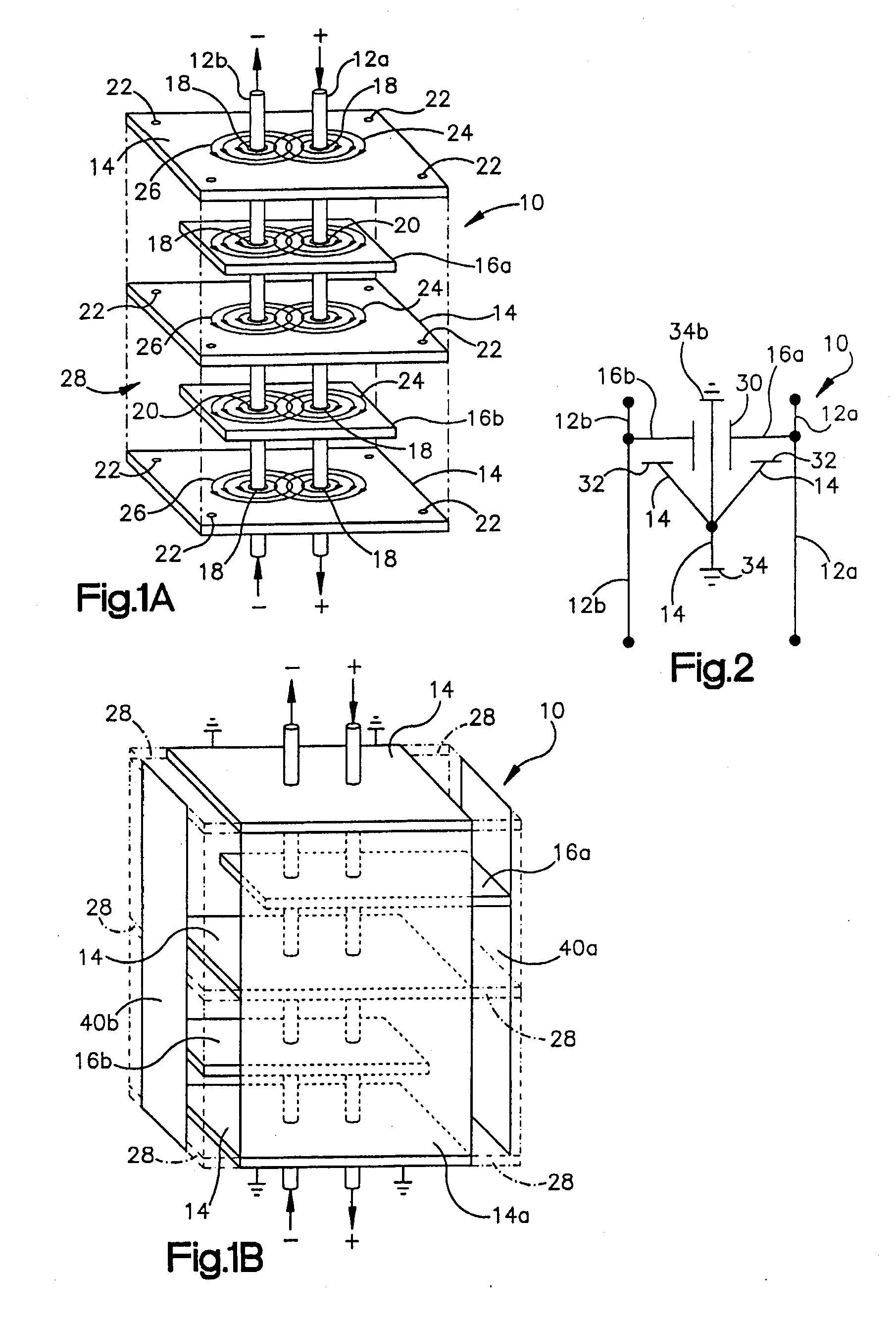

Universial energy conditioning interposer with circuit architecture

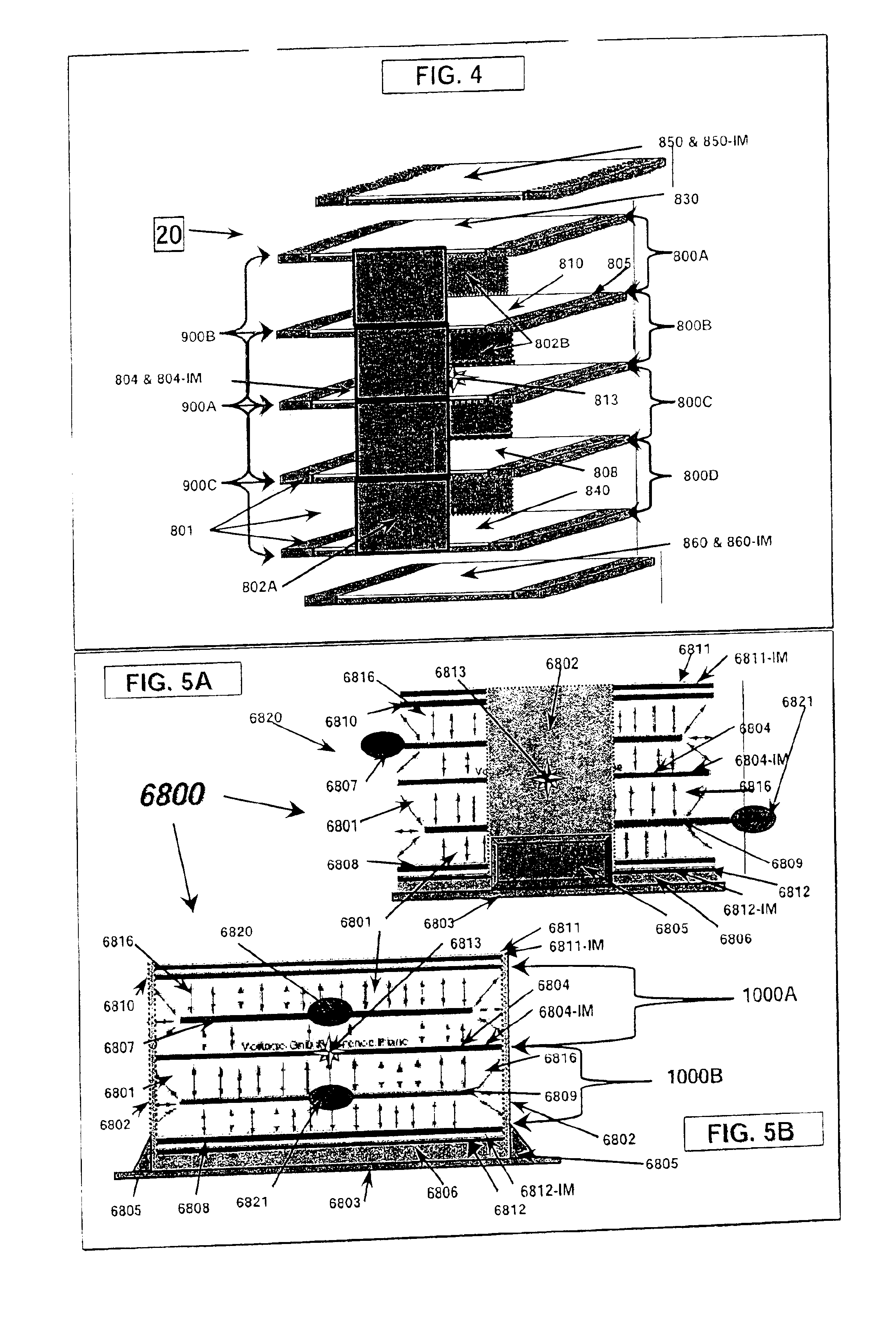

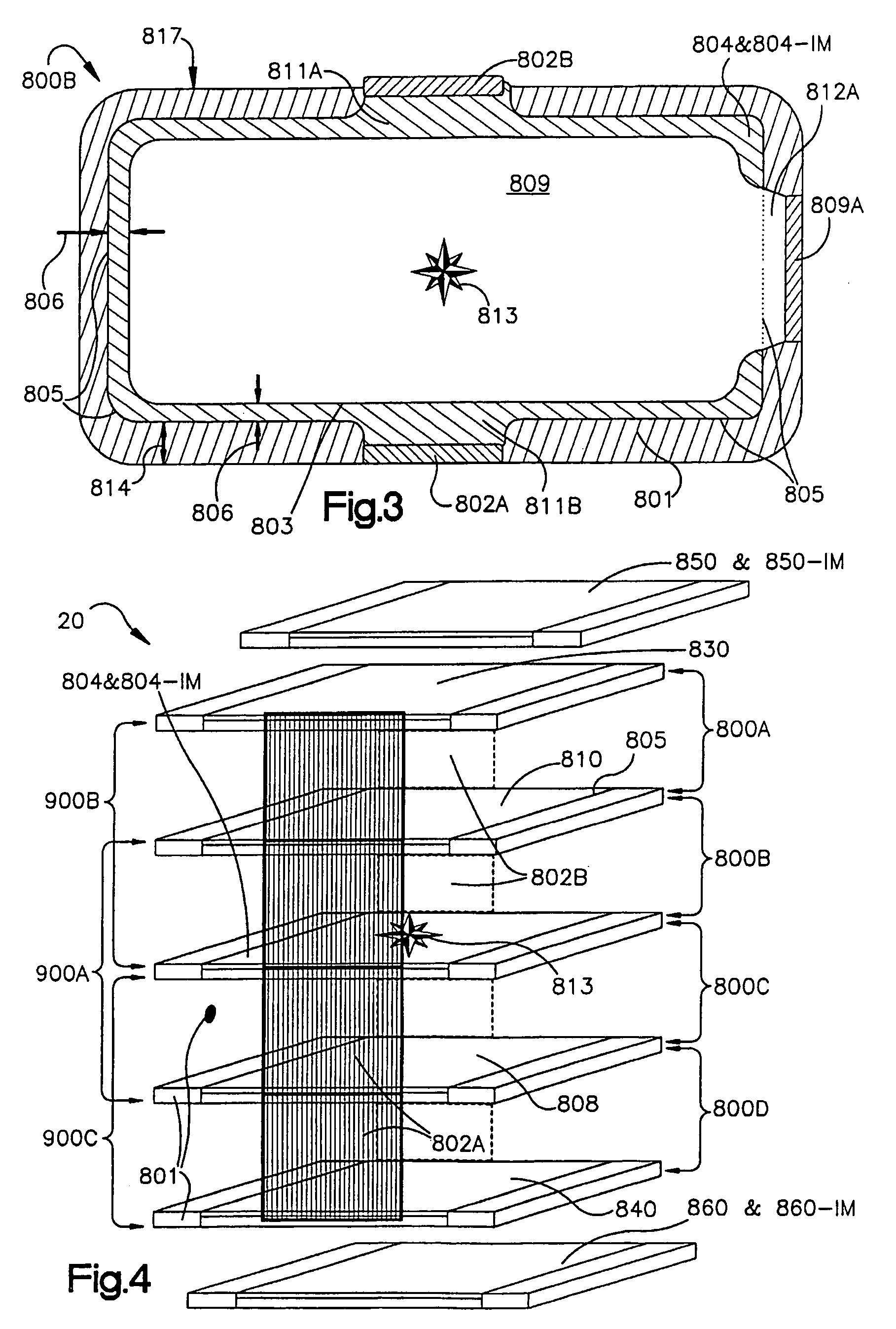

InactiveUS7110227B2Solve and reduce industry problemSolve and reduce and obstacleMagnetic/electric field screeningSemiconductor/solid-state device detailsEnergy regulationInterposer

The present invention relates to an interposer substrate for interconnecting between active electronic componentry such as but not limited to a single or multiple integrated circuit chips in either a single or a combination and elements that could comprise of a mounting substrate, substrate module, a printed circuit board, integrated circuit chips or other substrates containing conductive energy pathways that service an energy utilizing load and leading to and from an energy source. The interposer will also possess a multi-layer, universal multi-functional, common conductive shield structure with conductive pathways for energy and EMI conditioning and protection that also comprise a commonly shared and centrally positioned conductive pathway or electrode of the structure that can simultaneously shield and allow smooth energy interaction between grouped and energized conductive pathway electrodes containing a circuit architecture for energy conditioning as it relates to integrated circuit device packaging. The invention can be employed between an active electronic component and a multilayer circuit card. A method for making the interposer is not presented and can be varied to the individual or proprietary construction methodologies that exist or will be developed.

Owner:X2Y ATTENUATORS L L C

Universal energy conditioning interposer with circuit architecture

InactiveUS7301748B2Cost effectiveSolve or reduce industry problems and obstaclesImpedence networksSemiconductor/solid-state device detailsEnergy regulationInterposer

The present invention relates to an interposer substrate for interconnecting between active electronic componentry such as but not limited to a single or multiple integrated circuit chips in either a single or a combination and elements that could comprise of a mounting substrate, substrate module, a printed circuit board, integrated circuit chips or other substrates containing conductive energy pathways that service an energy utilizing load and leading to and from an energy source. The interposer will also possess a multi-layer, universal multi-functional, common conductive shield structure with conductive pathways for energy and EMI conditioning and protection that also comprise a commonly shared and centrally positioned conductive pathway or electrode of the structure that can simultaneously shield and allow smooth energy interaction between grouped and energized conductive pathway electrodes containing a circuit architecture for energy conditioning as it relates to integrated circuit device packaging. The invention can be employed between an active electronic component and a multilayer circuit card. A method for making the interposer is not presented and can be varied to the individual or proprietary construction methodologies that exist or will be developed.

Owner:X2Y ATTENUATORS L L C

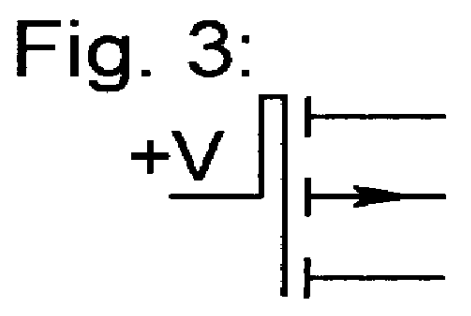

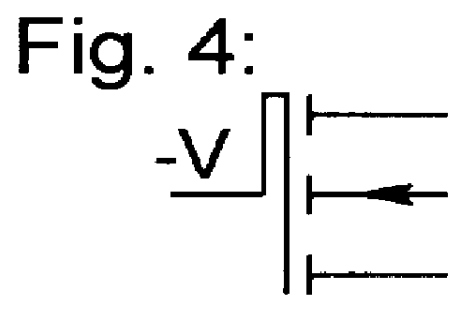

Multiple-valued logic circuit architecture; supplementary symmetrical logic circuit structure (SUS-LOC)

InactiveUS6133754AEasy to copyEasy transferPower consumption reductionLogic circuits characterised by logic functionMany-valued logicLogic synthesis

Circuit structure and resulting circuitry for multiple-valued logic. The circuit structure allows the design and fabrication of any r-valued logic function of n-places where r is an integer greater than 1 and n is an integer greater than 0. This structure is called SUpplementary Symmetrical LOgic Circuit structure (SUS-LOC). In circuits incorporating SUS-LOC, circuit branches are realized that uniquely deliver circuit response and output. For some circuits, and due to the operating characteristics of the switch elements, additional circuit elements, or stages, must be incorporated to prevent "back biasing." SUS-LOC is fully active. Only active elements perform logic synthesis and those components not directly related to logic synthesis, such as resistors and / or other passive loads, are relegated the task of circuit protection. The fabrication of r-valued, multi-valued, or multiple-valued logic circuits, designed using the definitions of the SUS-LOC structure can be accomplished with known techniques, materials, and equipment.

Owner:OMNIBASE LOGIC

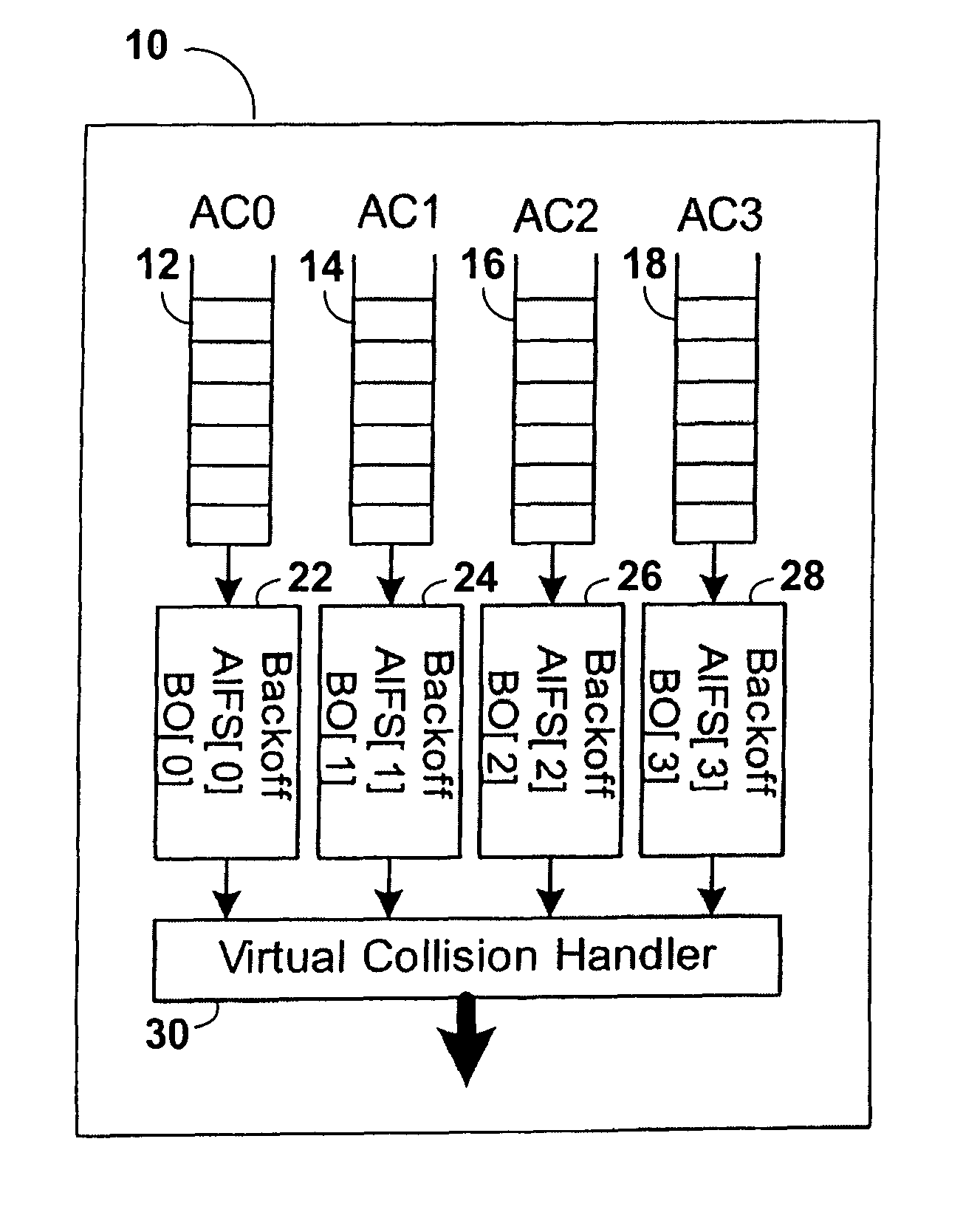

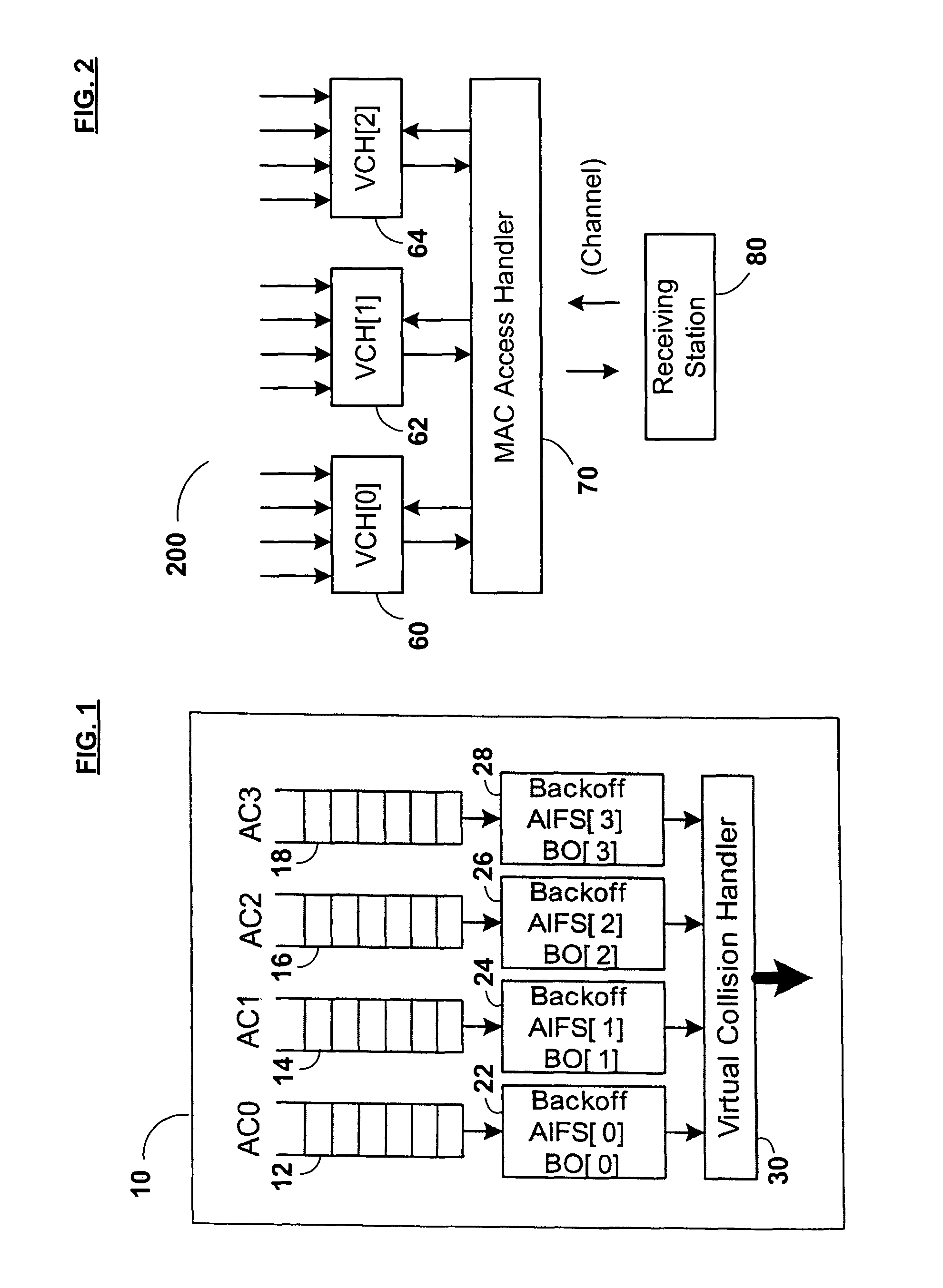

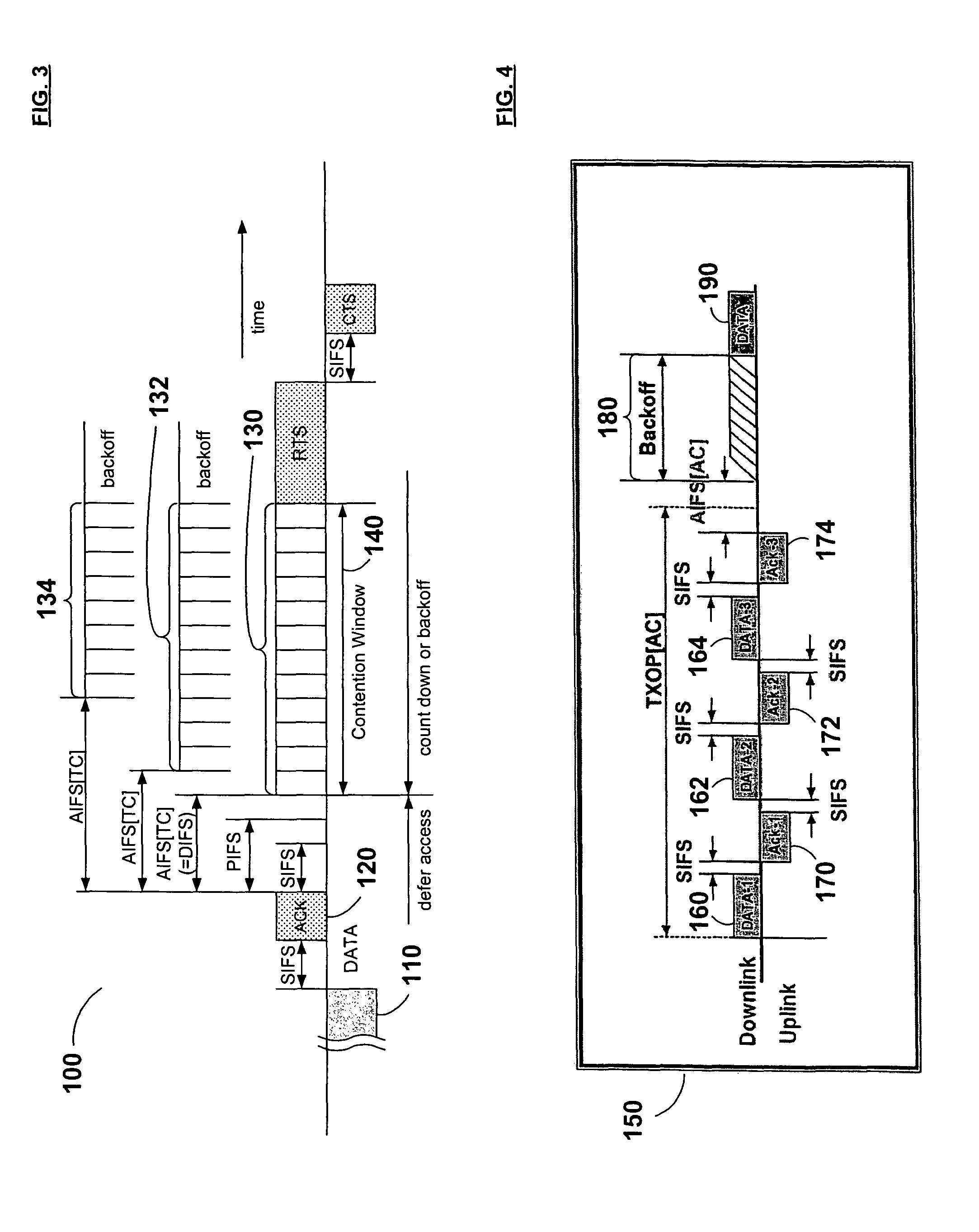

Circuits, architectures, systems, methods, algorithms and software for reducing contention and/or handling channel access in a network

InactiveUS7826438B1Improve efficiencyImprove reliabilityError preventionTime-division multiplexSpecific timeTransmitter

Methods, circuits and architectures for managing channel access and / or reducing contention in network transmissions where such transmissions may not be acknowledged within a certain time period, computer programs adapted to implement such methods, and systems and networks including such circuits / architectures. When the information is not so acknowledged, the methods generally include (1) waiting for a predetermined time period before attempting to retransmit the information, and / or (2) retransmitting the information. The action taken may depend on the priority of the information. The circuit and / or architecture generally includes (a) a transmitter, (b) a priority detector, and when the information is not acknowledged within a certain time period, (c) logic for (i) retransmitting the information having a first priority and (ii) waiting before attempting to retransmit information having a second priority. The present invention has particular advantage in wireless networks and advantageously improves network transmission efficiency, reliability and / or performance.

Owner:NXP USA INC

Digital imaging and pulse detection pixel

An imaging and pulse detection array includes: a plurality of pixels connected to a controller, the controller being configured to generate an image based on an image signal originating from each pixel in the plurality of pixels and configured to detect a pulse on at least one of the pixels in the plurality of pixels, and each of the pixels in the plurality of pixels including an imaging circuit and a pulse detection circuit, the imaging circuit and the pulse detection circuit including a shared circuit architecture, and wherein the imaging circuit and the pulse detection circuit include a shared portion.

Owner:HAMILTON SUNDSTRAND CORP

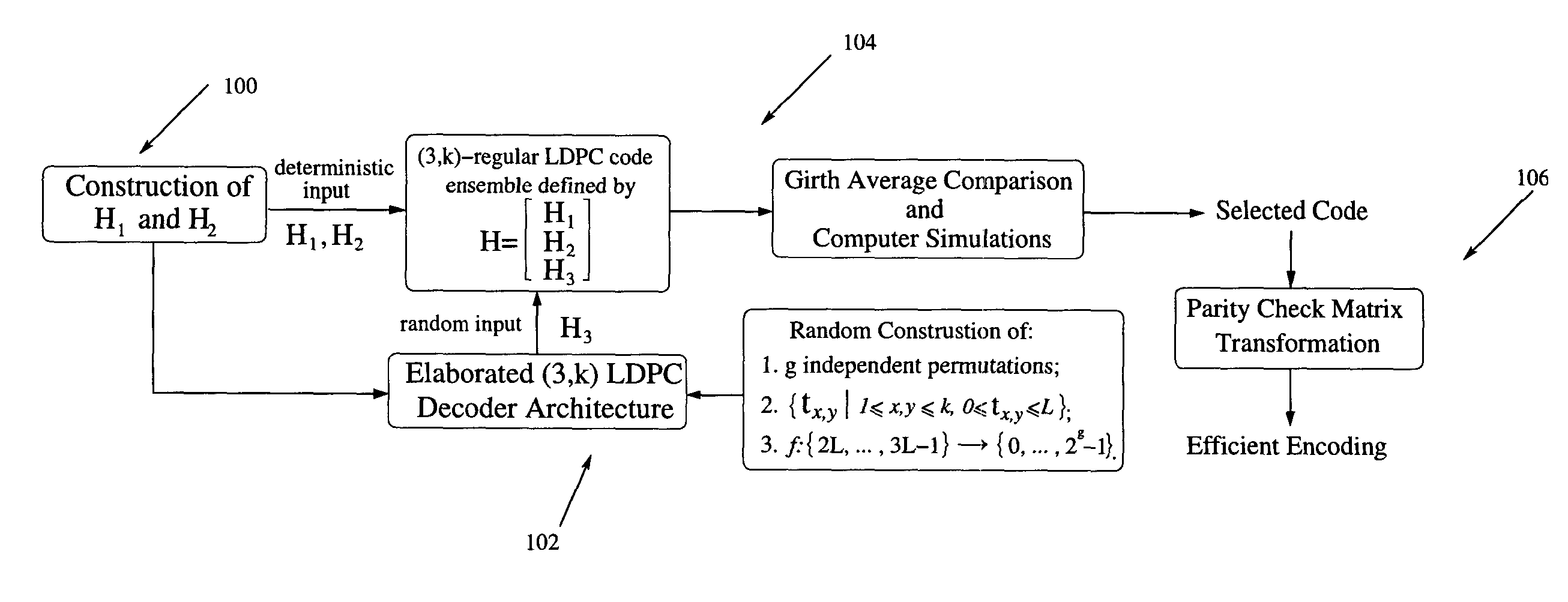

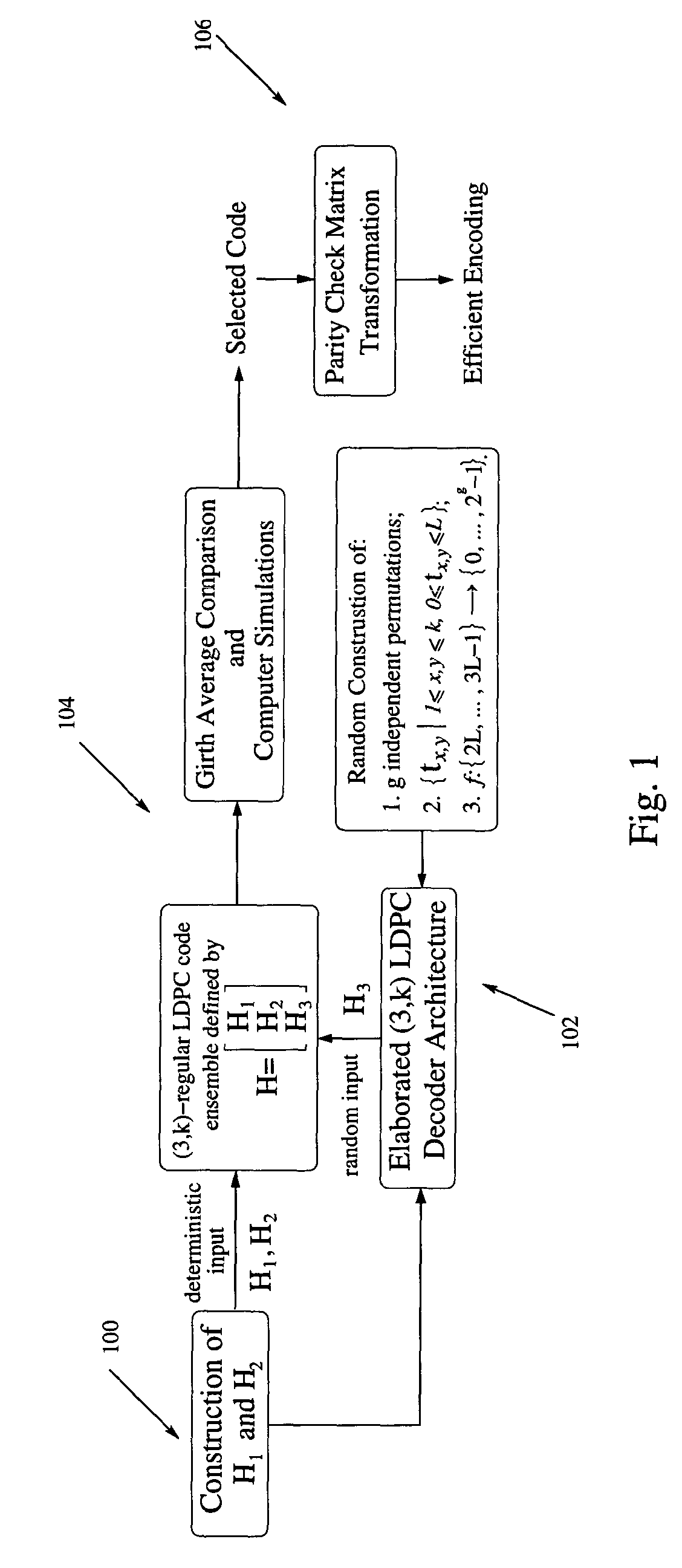

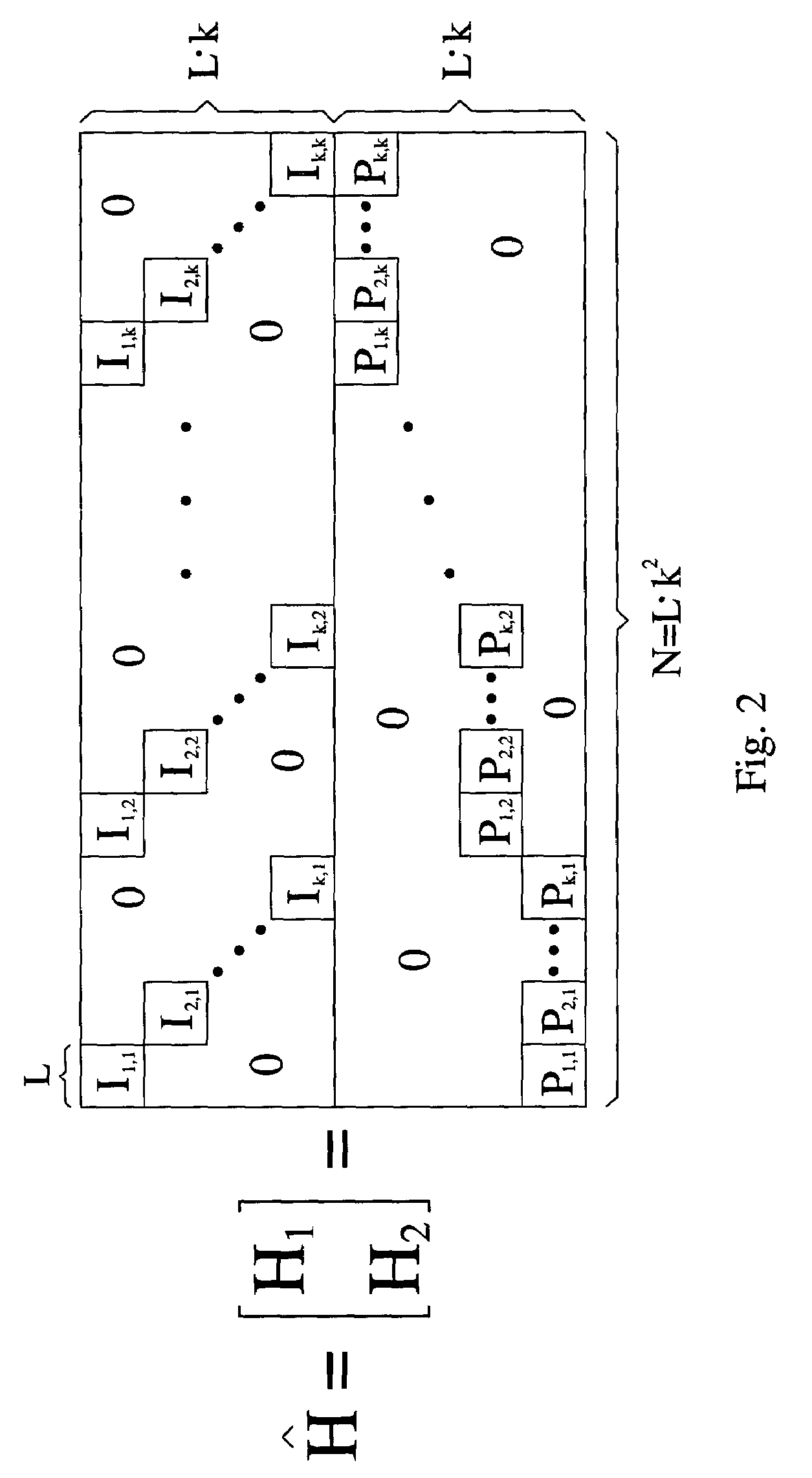

LDPC code and encoder/decoder regarding same

InactiveUS7120856B2Reduce complexityAccurate fitInterconnection arrangementsError detection/correctionEncoder decoderComputer architecture

A joint code-encoder-decoder design approach and circuit architecture design for (3,k)-regular LDPC coding system implementation. The joint design process relies on a high girth (2,k)-regular LDPC code construction. The decoder realizes partly parallel decoding. The encoding scheme only contains multiplications between sparse matrices and vector and multiplication between a very small dense matrix and vector.

Owner:LEANICS CORP

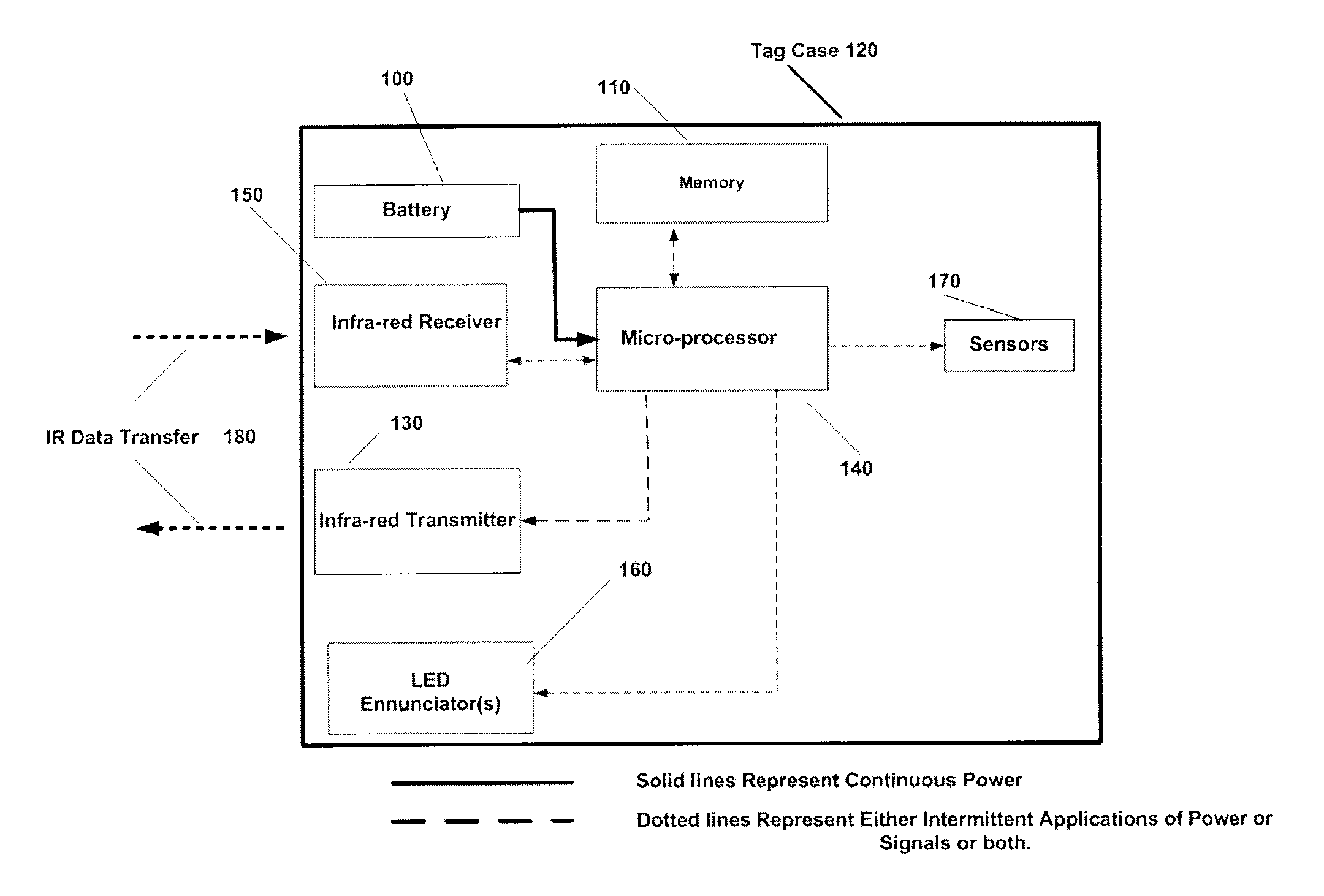

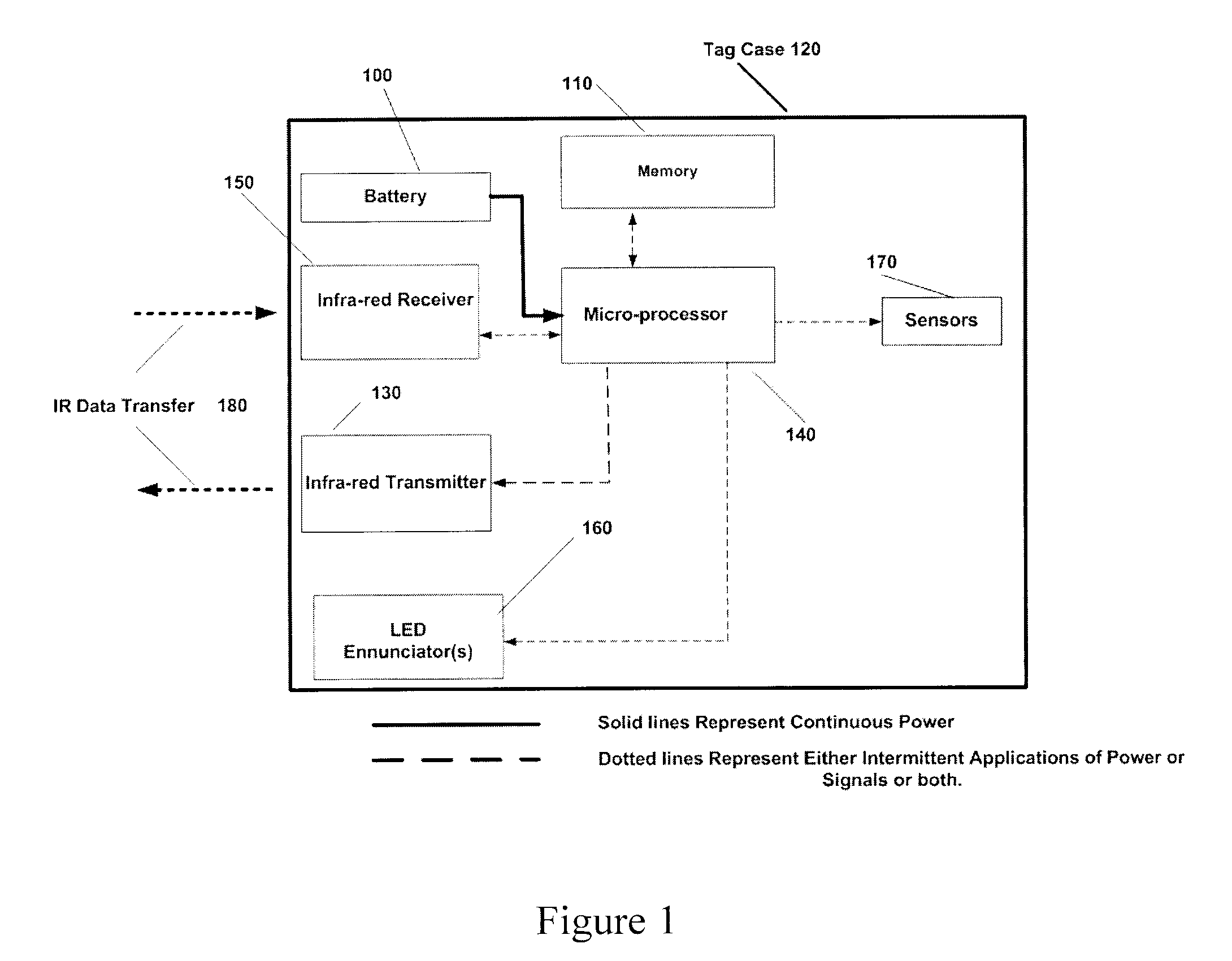

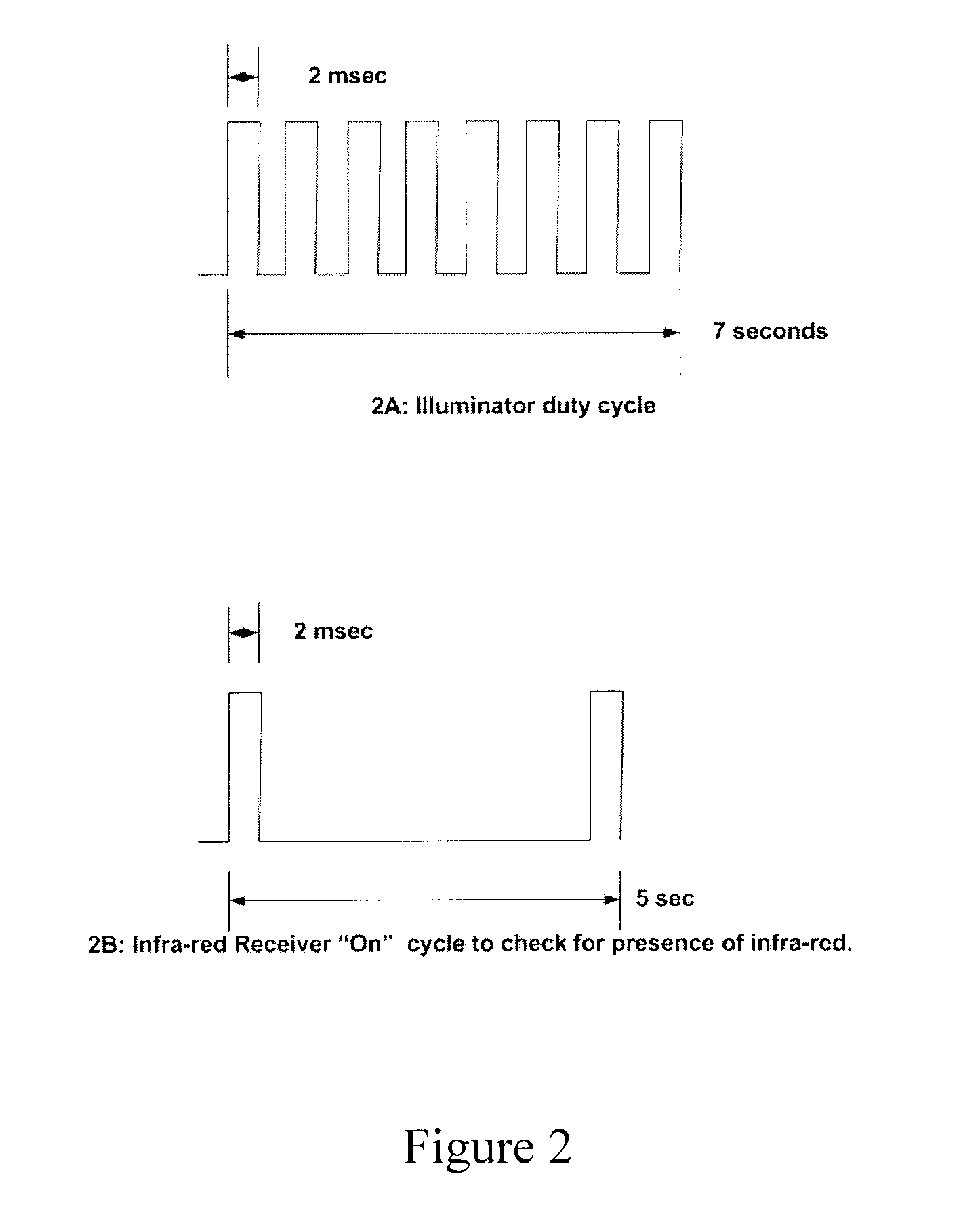

RFID tag power conservation system and method

InactiveUS20080218351A1Extend battery lifeSave batteryVolume/mass flow measurementElectric testing/monitoringEngineeringPulse cycle

Active multi-modal RFID tags, illuminator / tag / reader systems, circuit architecture and operational algorithms for battery power conservation that extends tag battery life from a typical 6 months to >5 years. The inventive system is particularly useful in asset and person tracking / inventory systems where power conservation is critical. The tag is configured with a micro-processor operational instruction set algorithm, modifiable on the fly via RF or IR, to synchronize a periodic tag awaken / sense envelope that overlaps the illuminator trigger pulse cycle and put the tag into deep, power conservation sleep for N periods of illuminator cycles. When the tag sees an illuminator signal with a different ID, or no illuminator signal at all, it transmits that anomaly via RF to a reader. This means the object or person with which the tag is associated has been moved out of the original illuminator field of view, permitting near real time investigation and tracking.

Owner:INNOVATION LAW GROUP

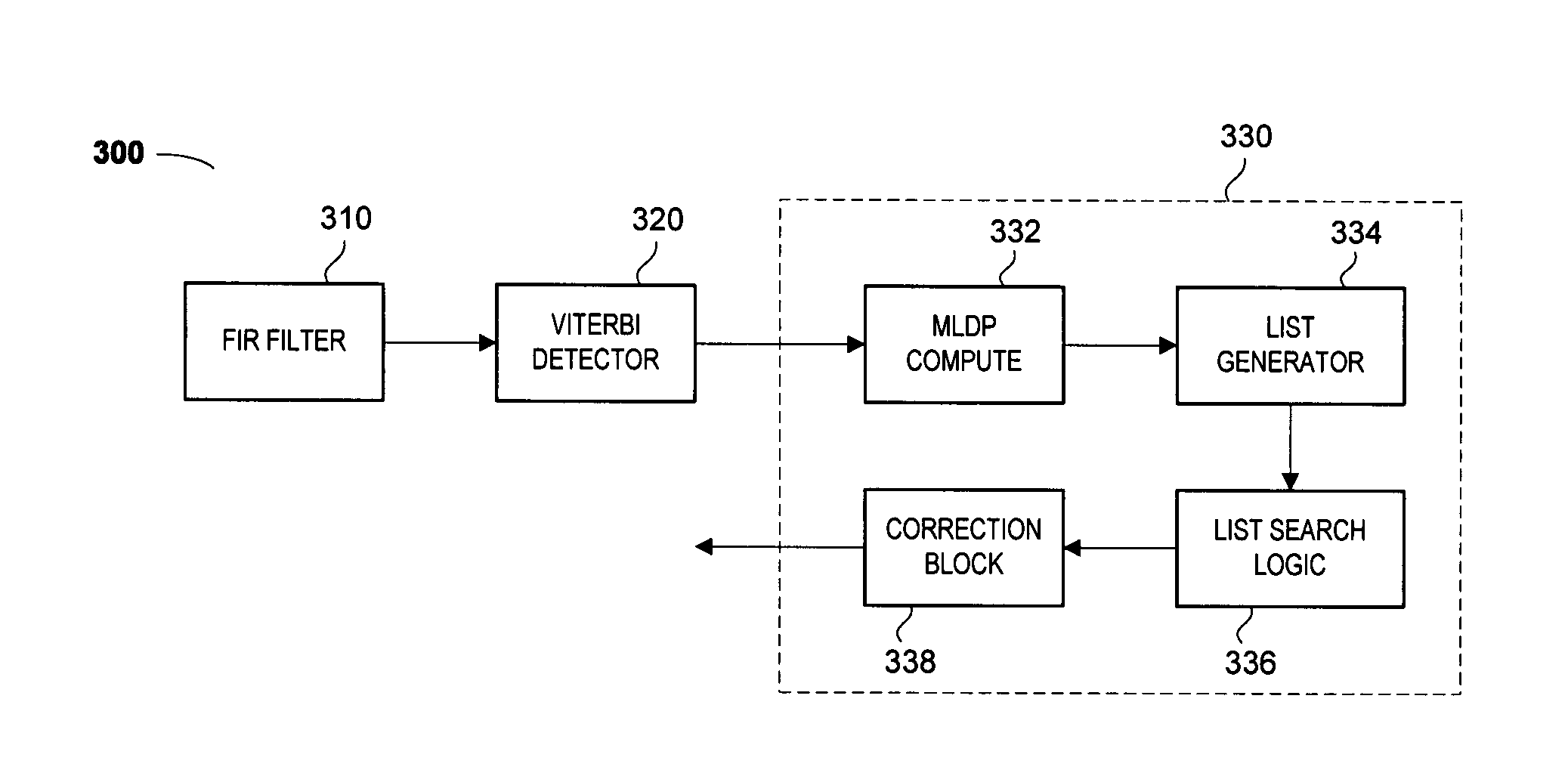

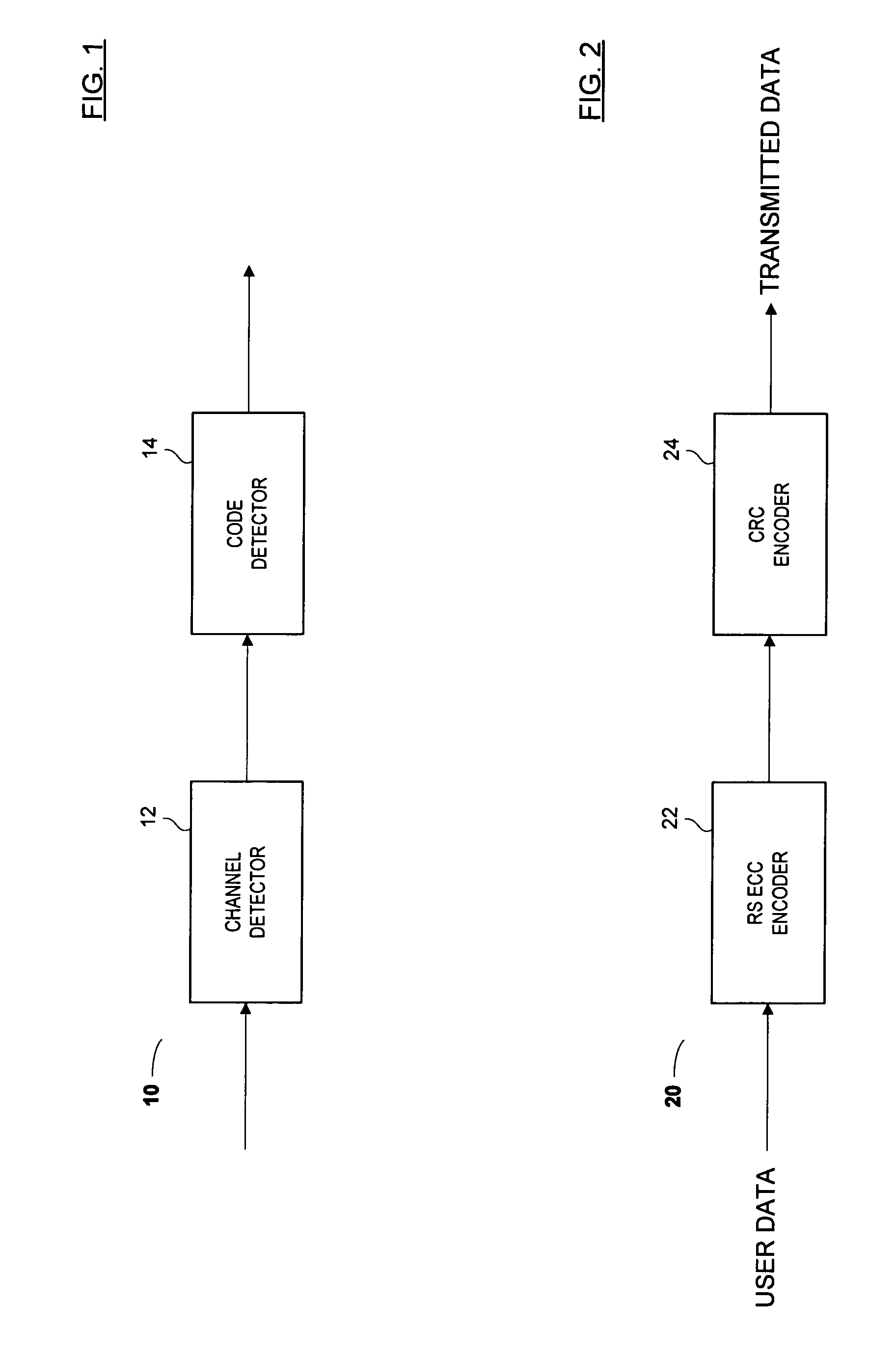

Methods and algorithms for joint channel-code decoding of linear block codes

ActiveUS7571372B1Facilitates PP implementationNot set it lowCode conversionRecord information storageError checkAlgorithm

Circuits, architectures, methods and algorithms for joint channel-code decoding of linear block codes, and more particularly, for identifying and correcting one or more errors in a code word and / or for encoding CRC (or parity) information. In one aspect, the invention focuses on use of (i) remainders, syndromes or other polynomials and (ii) Gaussian elimination to determine and correct errors. Although this approach may be suboptimal, the present error checking and / or detection scheme involves simpler computations and / or manipulations than conventional schemes, and is generally easier to implement logically. Since the complexity of parity-based error correction schemes increases disproportionately to the number of potential error events, the present invention meets a long-felt need for a scheme to manage error detection and / or correction in systems (such as magnetic recording applications) where there may be a relatively large number of likely error events, thereby advantageously improving reliability and / or performance in channel communications.

Owner:MARVELL ASIA PTE LTD

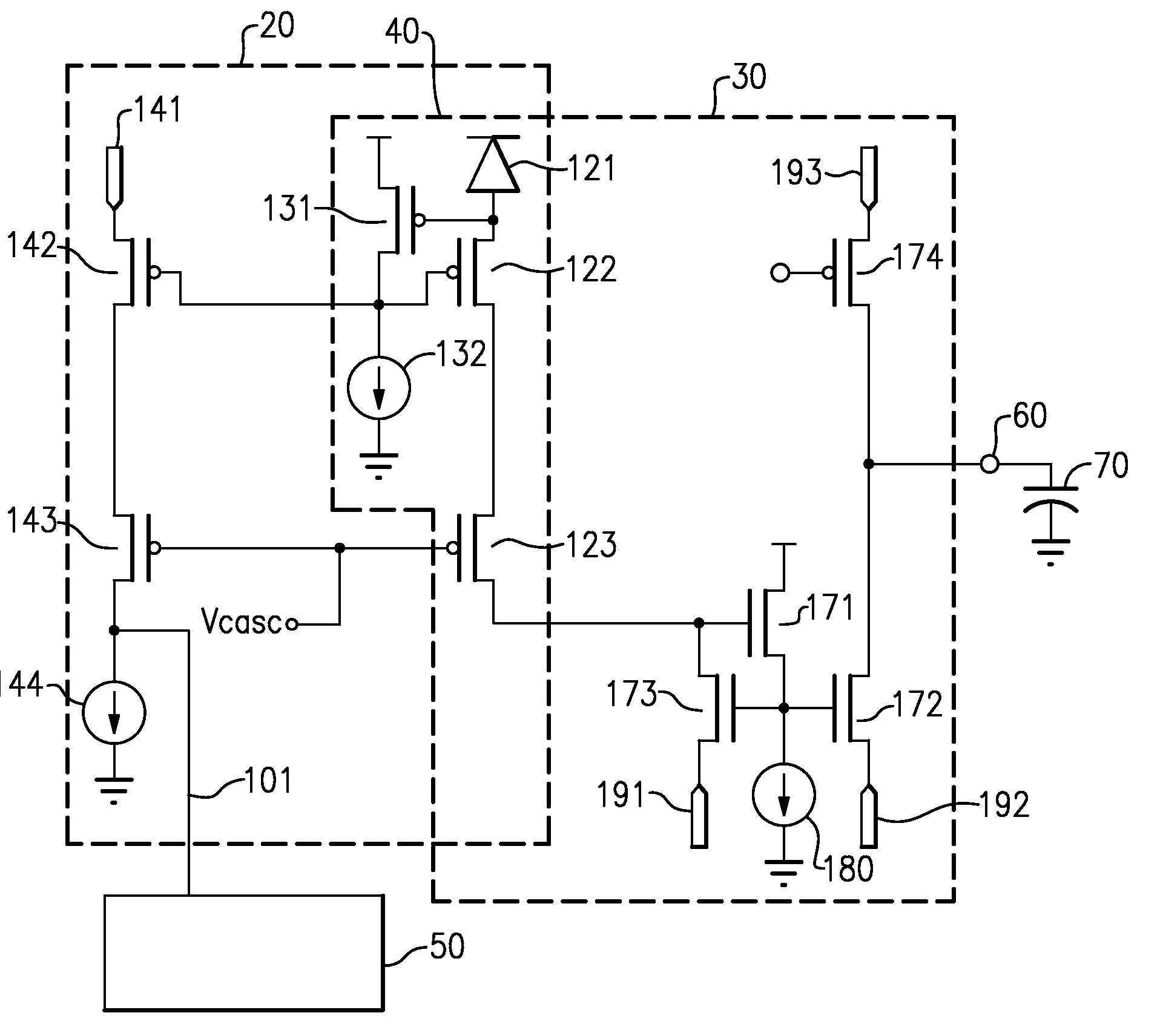

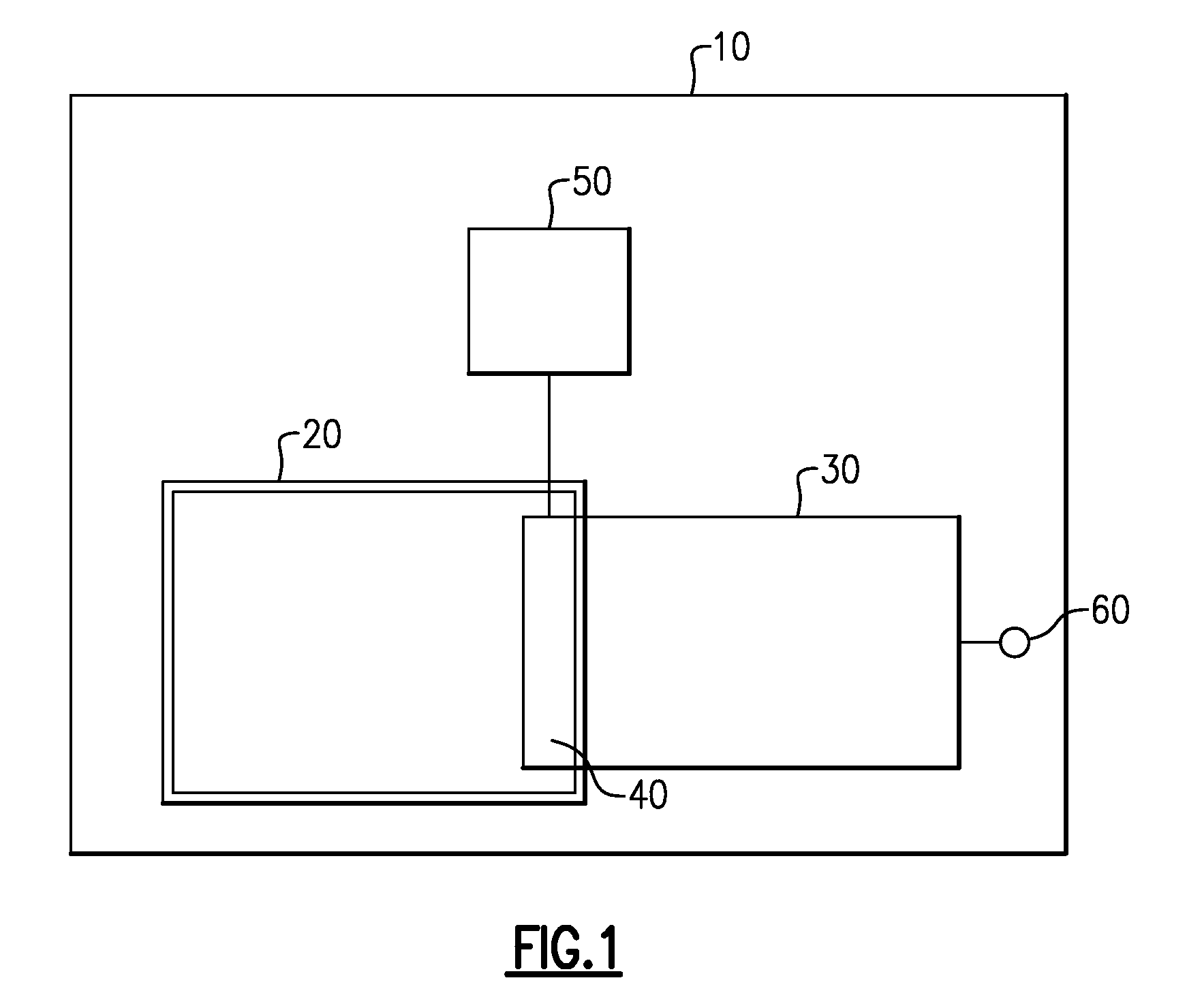

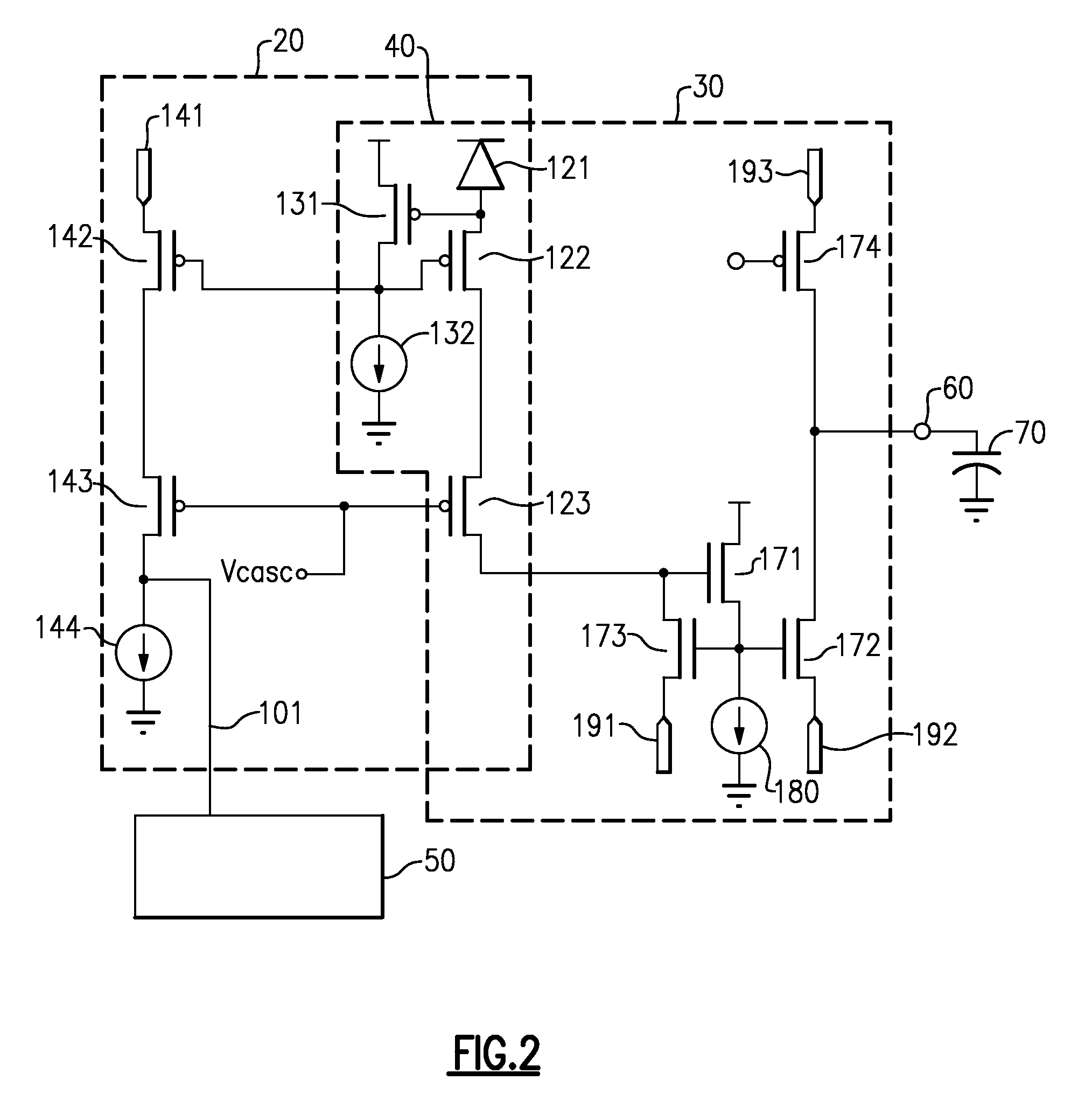

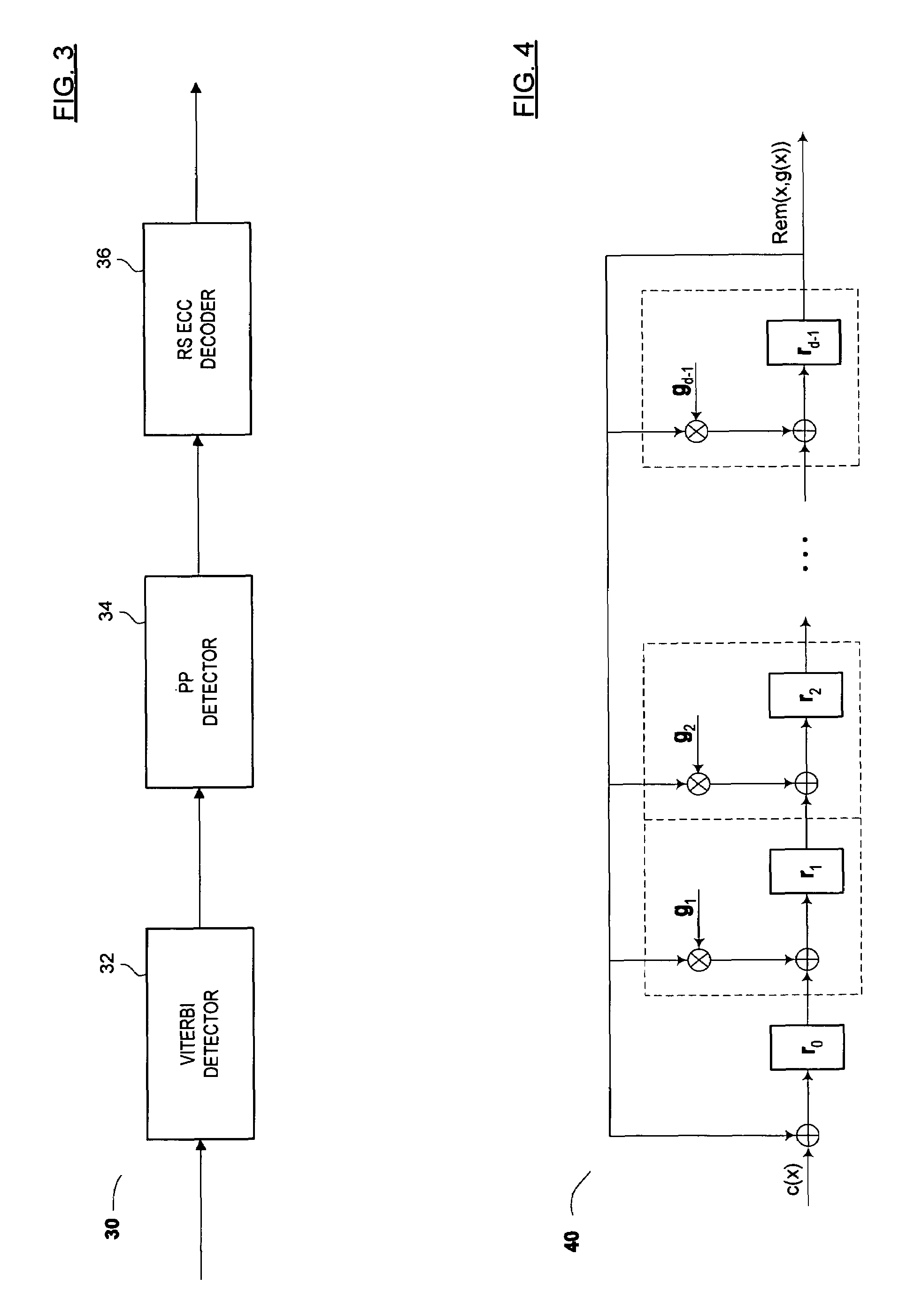

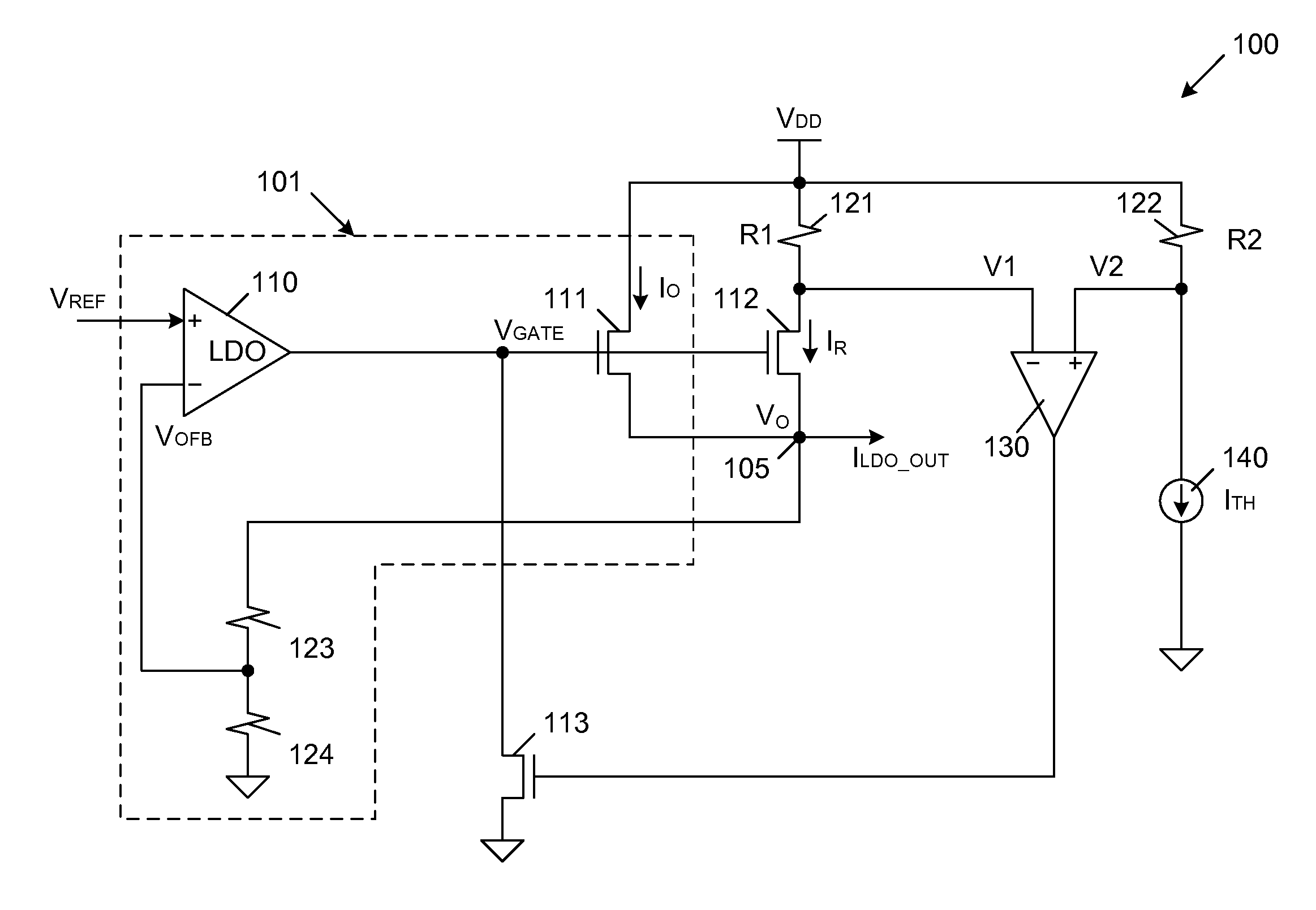

Current Limit Circuit Architecture For Low Drop-Out Voltage Regulators

InactiveUS20130293986A1Reduce output voltageSimple designEmergency protective arrangements for limiting excess voltage/currentElectric variable regulationLinear regulatorEngineering

A current limiting circuit for a linear regulator includes an output stage transistor and a replica transistor, which have gates coupled to receive an output voltage from a linear amplifier and sources coupled to load circuitry. A drain of the output stage transistor is coupled to a VDD supply terminal, while a drain of the replica transistor is coupled to the VDD supply terminal through a first resistor. The output stage transistor and replica transistor are operated in saturation, such that proportional currents flow through these transistors. The voltage drop across the first resistor provides a first voltage, which is applied to a second amplifier. A reference voltage is also applied to the second amplifier. When the first voltage becomes less than the reference voltage, a feedback transistor is enabled to pull down the output voltage of the linear amplifier, thereby limiting the output current supplied to the load circuitry.

Owner:TOWER SEMICONDUCTOR

Universal energy conditioning interposer with circuit architecture

InactiveUS20050286198A1Solve and reduce industry problemSolve and reduce and obstacleImpedence networksSemiconductor/solid-state device detailsEnergy regulationInterposer

The present invention relates to an interposer substrate for interconnecting between active electronic componentry such as but not limited to a single or multiple integrated circuit chips in either a single or a combination and elements that could comprise of a mounting substrate, substrate module, a printed circuit board, integrated circuit chips or other substrates containing conductive energy pathways that service an energy utilizing load and leading to and from an energy source. The interposer will also possess a multi-layer, universal multi-functional, common conductive shield structure with conductive pathways for energy and EMI conditioning and protection that also comprise a commonly shared and centrally positioned conductive pathway or electrode of the structure that can simultaneously shield and allow smooth energy interaction between grouped and energized conductive pathway electrodes containing a circuit architecture for energy conditioning as it relates to integrated circuit device packaging. The invention can be employed between an active electronic component and a multilayer circuit card. A method for making the interposer is not presented and can be varied to the individual or proprietary construction methodologies that exist or will be developed.

Owner:X2Y ATTENUATORS L L C

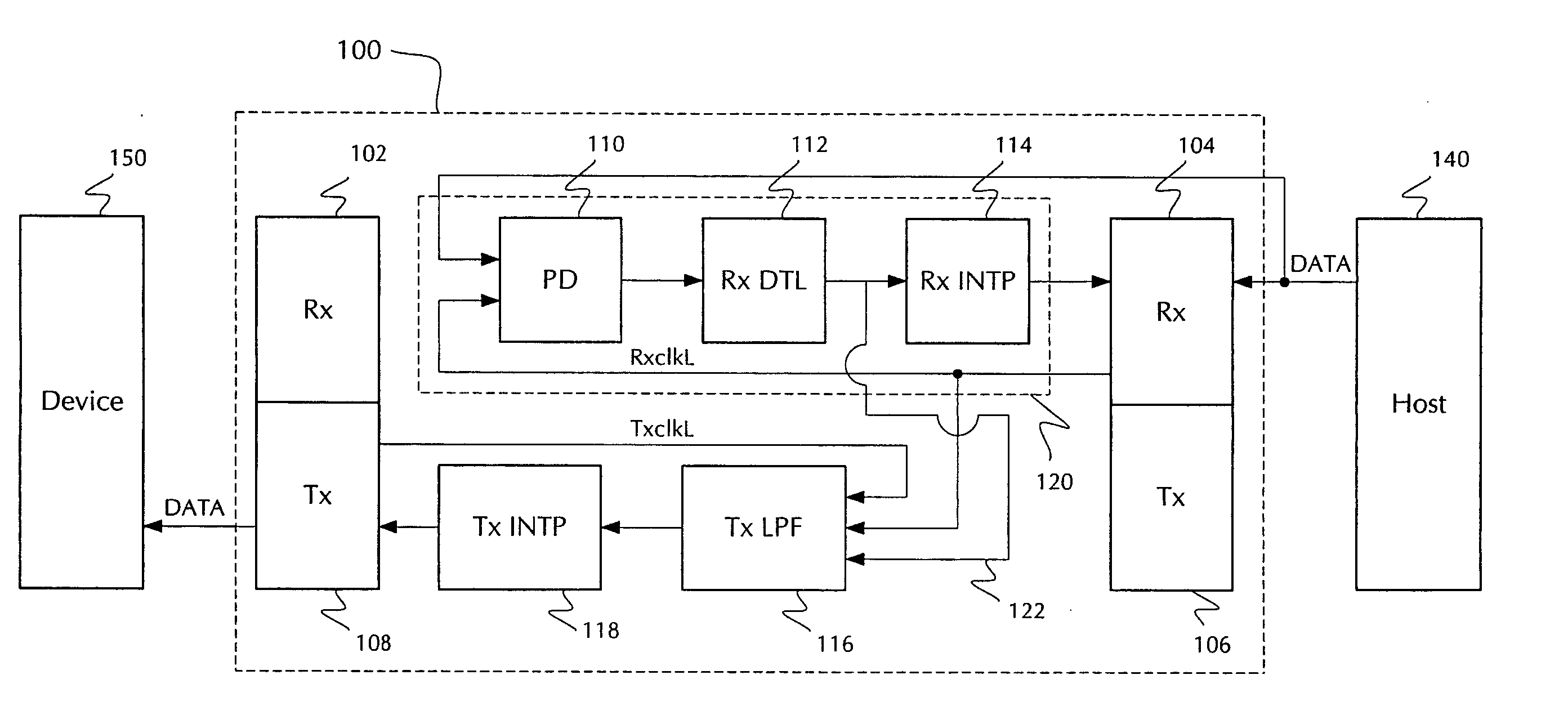

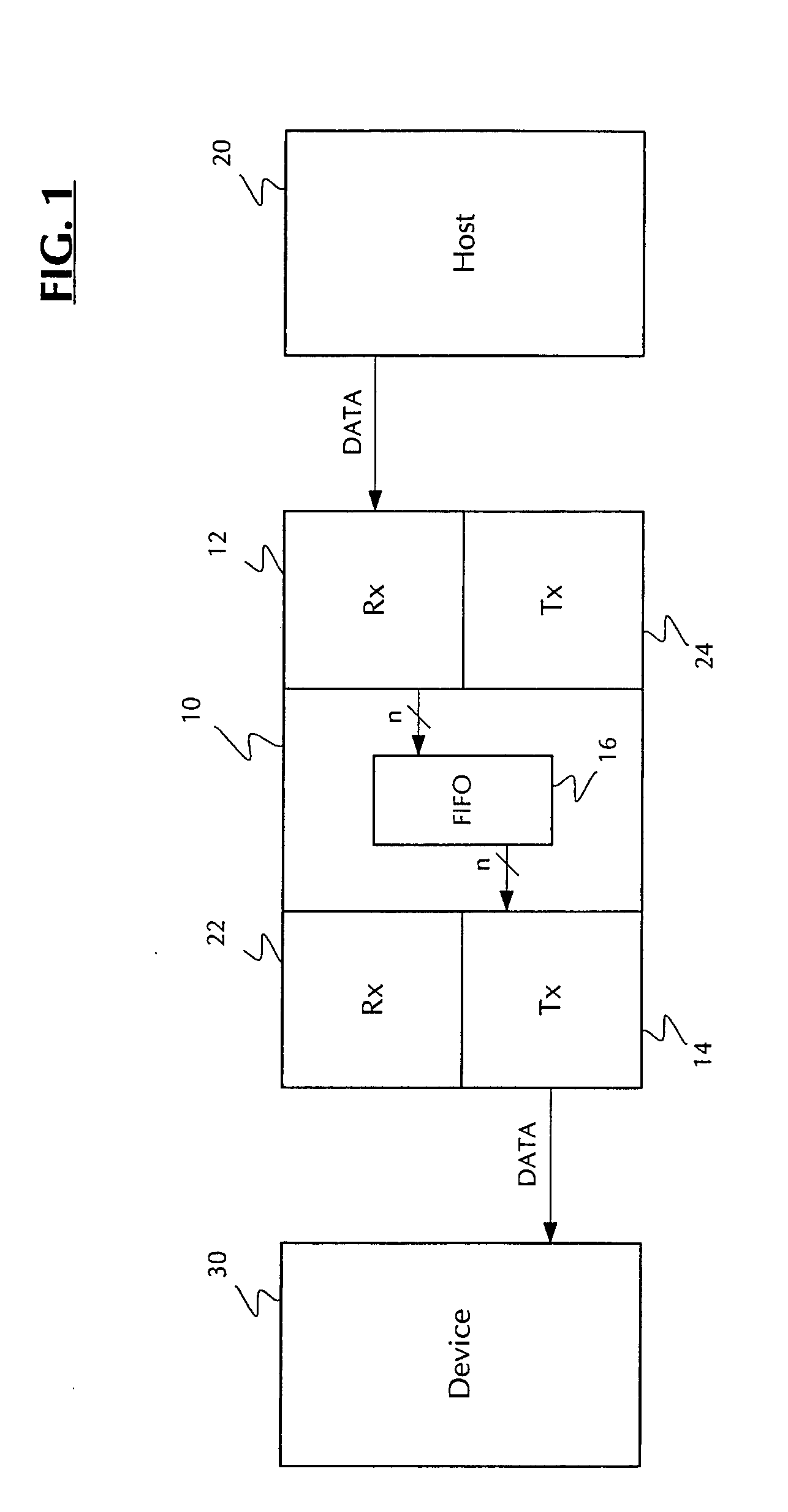

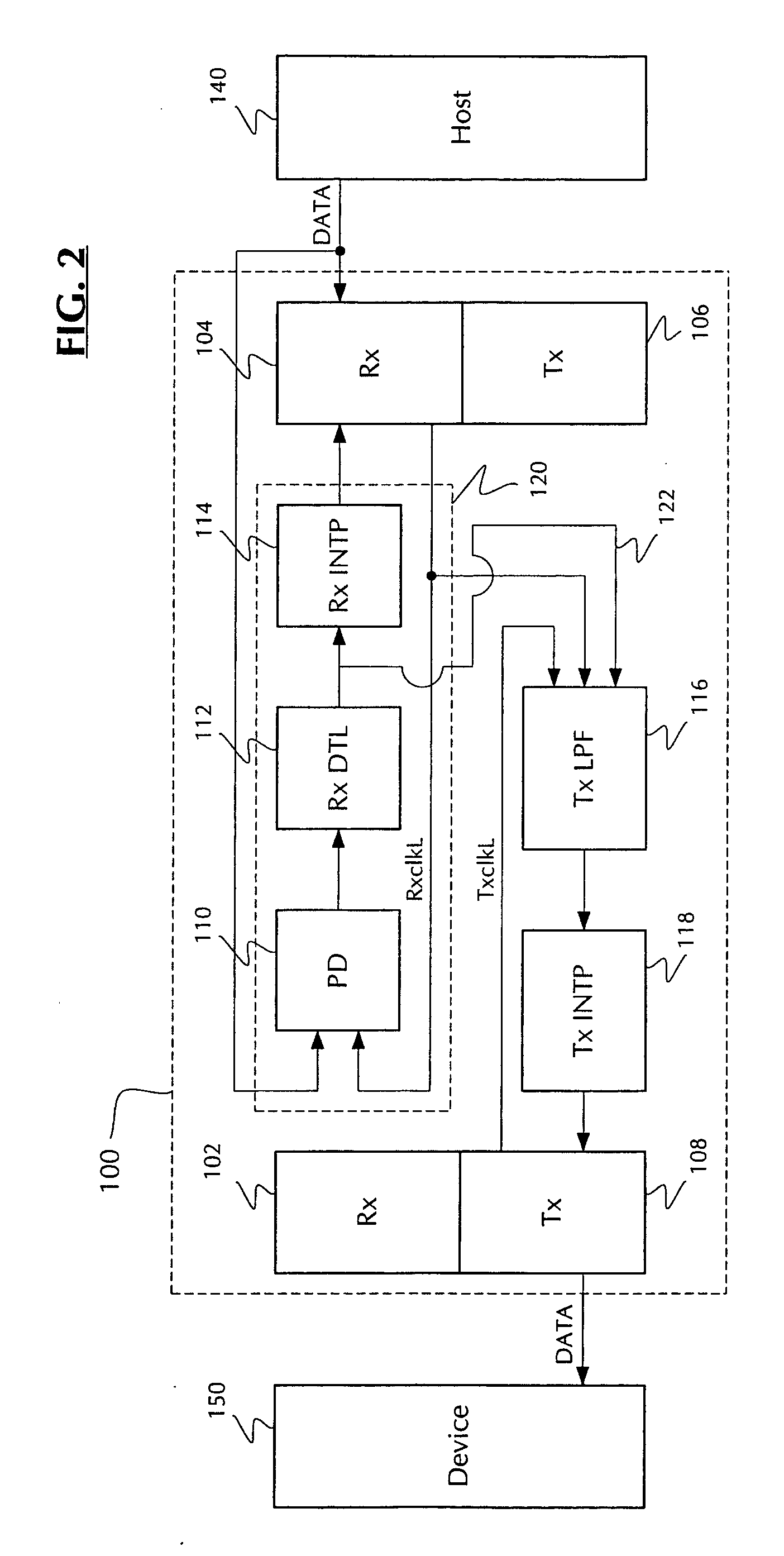

Architectures, circuits, systems and methods for reducing latency in data communications

ActiveUS20050034009A1Reduce in quantityReduce needPulse transformerError detection/correctionData streamTransceiver

Circuits, architectures, systems and methods for facilitating data communications and / or reducing latency in data communications. The architecture includes a clock recovery loop receiving data from a host device and providing a recovered clock signal, a filter circuit receiving recovered clock signal information and providing a control signal that adjusts the transmitter clock in response to recovered clock signal information and the two clock signals, and a transmitter receiving the control signal and transmitting data to a destination device in accordance with the transmitter clock. The circuitry generally includes a clock alignment block receiving first and second periodic signals and providing a control signal in response thereto, a filter for first periodic signal information, and a logic circuit configured to combine the control signal and the filtered information, thereby providing an adjustment signal for the second periodic signal. The systems generally relate to those that include the present architecture and / or circuit. The method generally includes determining a phase difference between first and second periodic signals, one of the periodic signals being recovered from a data stream; adjusting the other periodic signal in response to the phase difference and filtered information from the recovered periodic signal; and transmitting the data stream in accordance with said adjusted periodic signal. The present invention advantageously eliminates a FIFO memory in the data path, thereby reducing transceiver latency and improving system performance.

Owner:MARVELL ASIA PTE LTD

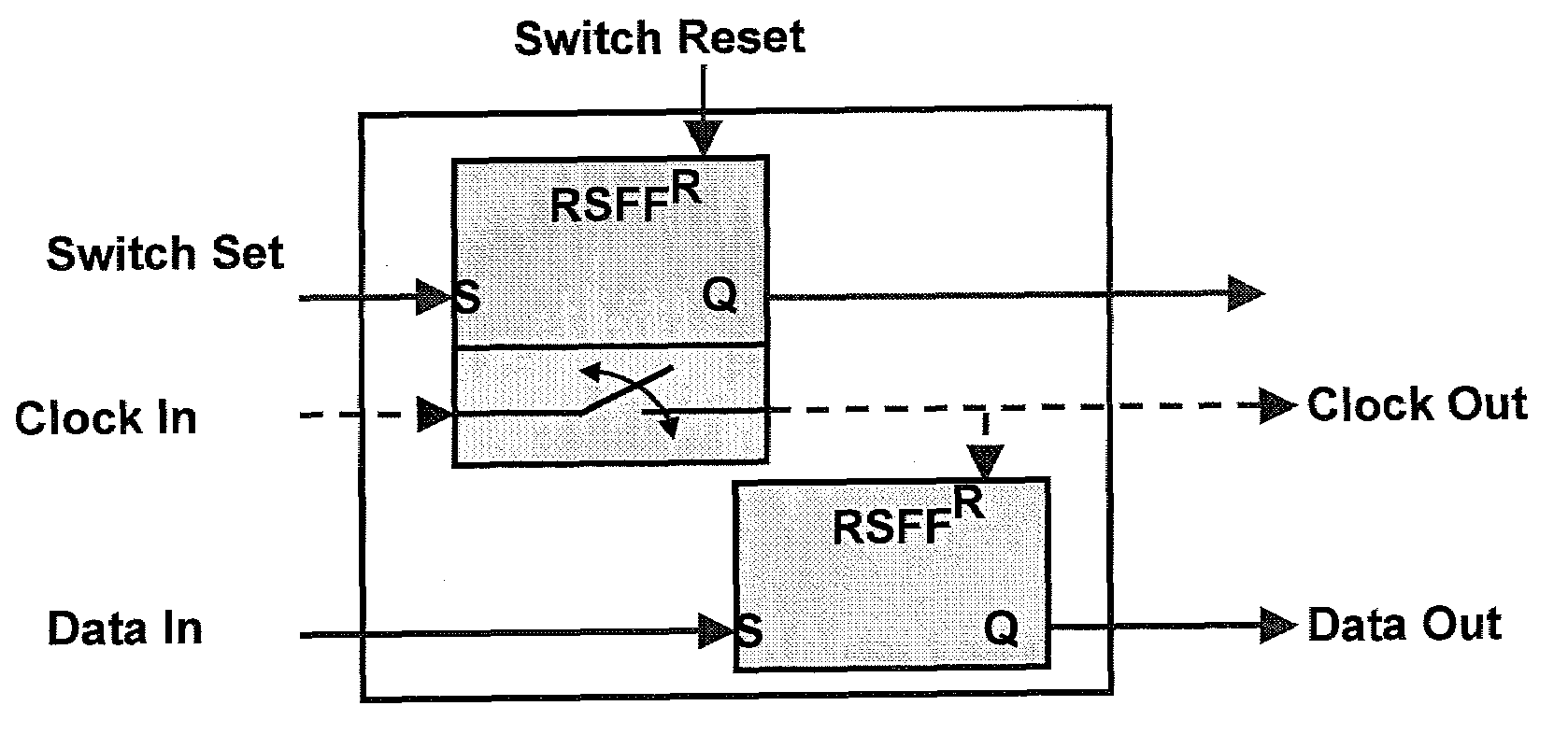

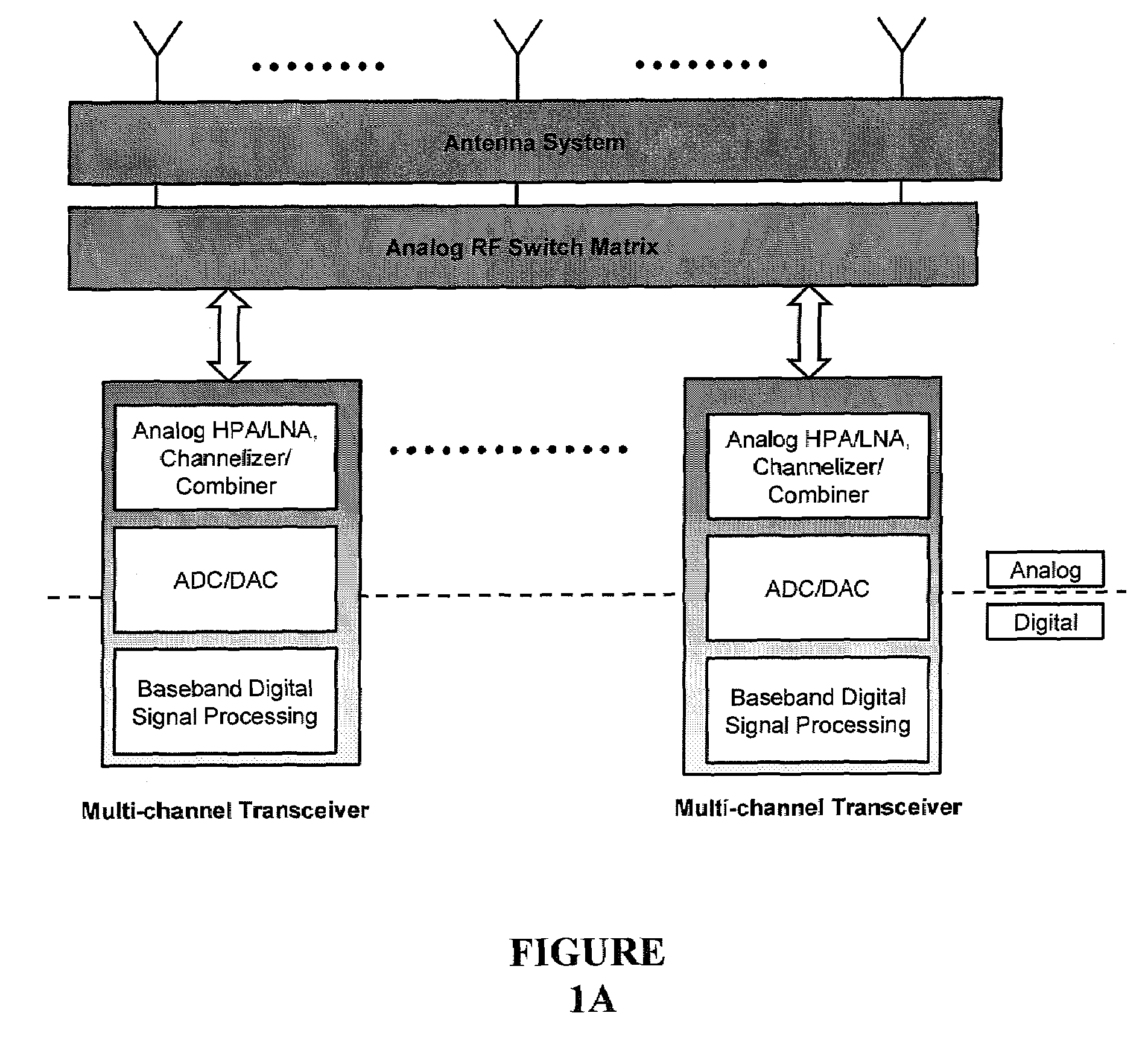

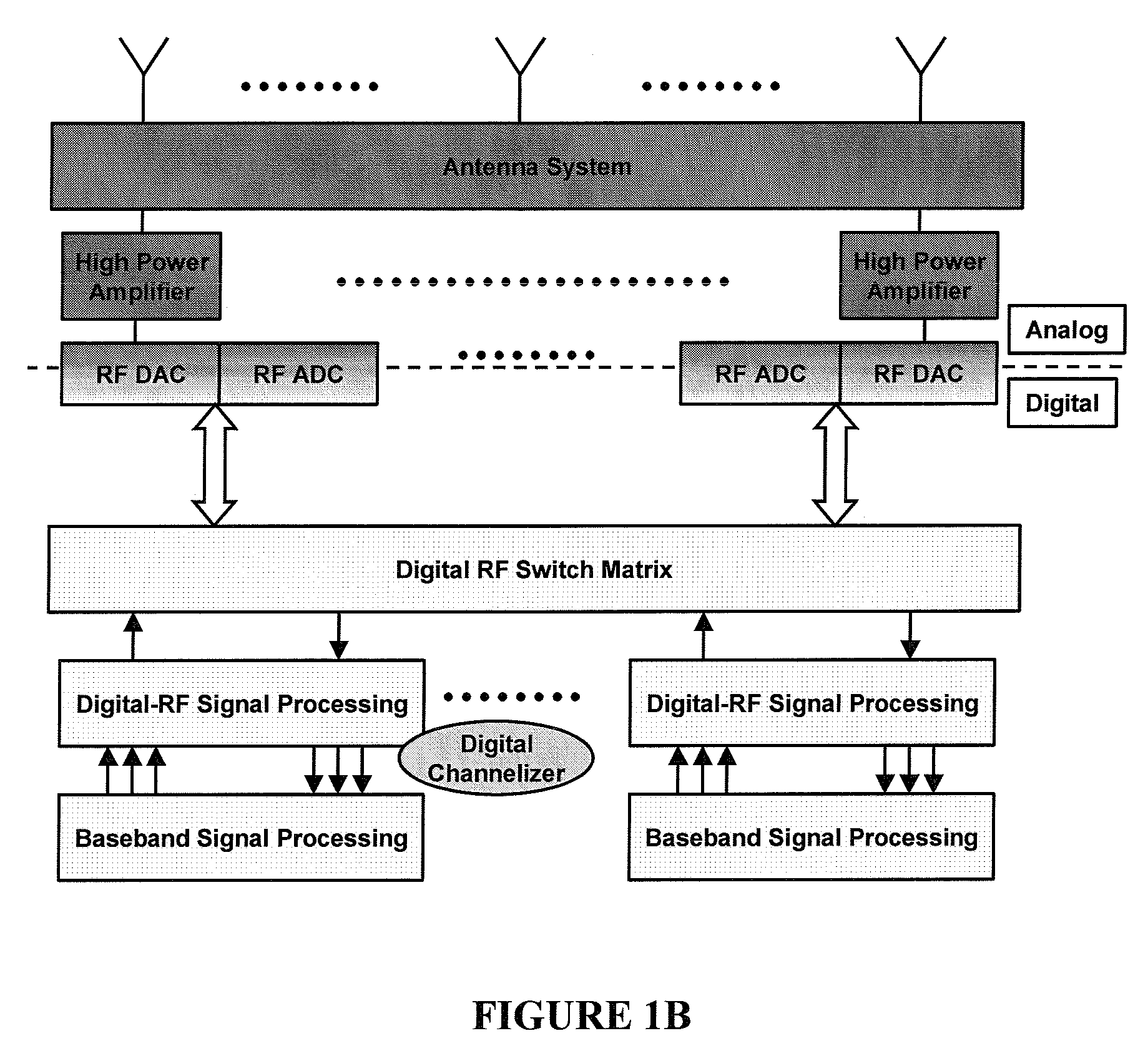

Digital routing switch matrix for digitized radio-frequency signals

InactiveUS7362125B2Efficient executionPrecise processingElectronic switchingSubstation equipmentMulti bandTransceiver

Routing and distribution of radio-frequency (RF) signals is commonly achieved in the analog domain. However, improved performance and simplified circuit architectures may be obtained by first digitizing the RF signal, and then carrying out all routing in the digital domain. A new generation of scalable digital switches has been developed, which routes both the data and clock signals together, this being necessary to maintain the integrity of the digitized RF signal. Given the extremely high switching speeds necessary for these applications (tens of GHz), this is implemented using Rapid-Single-Flux-Quantum (RSFQ) logic with superconducting integrated circuits. Such a digital switch matrix may be applied to either the receiver or transmitter components of an advanced multi-band, multi-channel digital transceiver system, and is compatible with routing of signals with different clock frequencies simultaneously within the same switch matrix.

Owner:HYPRES

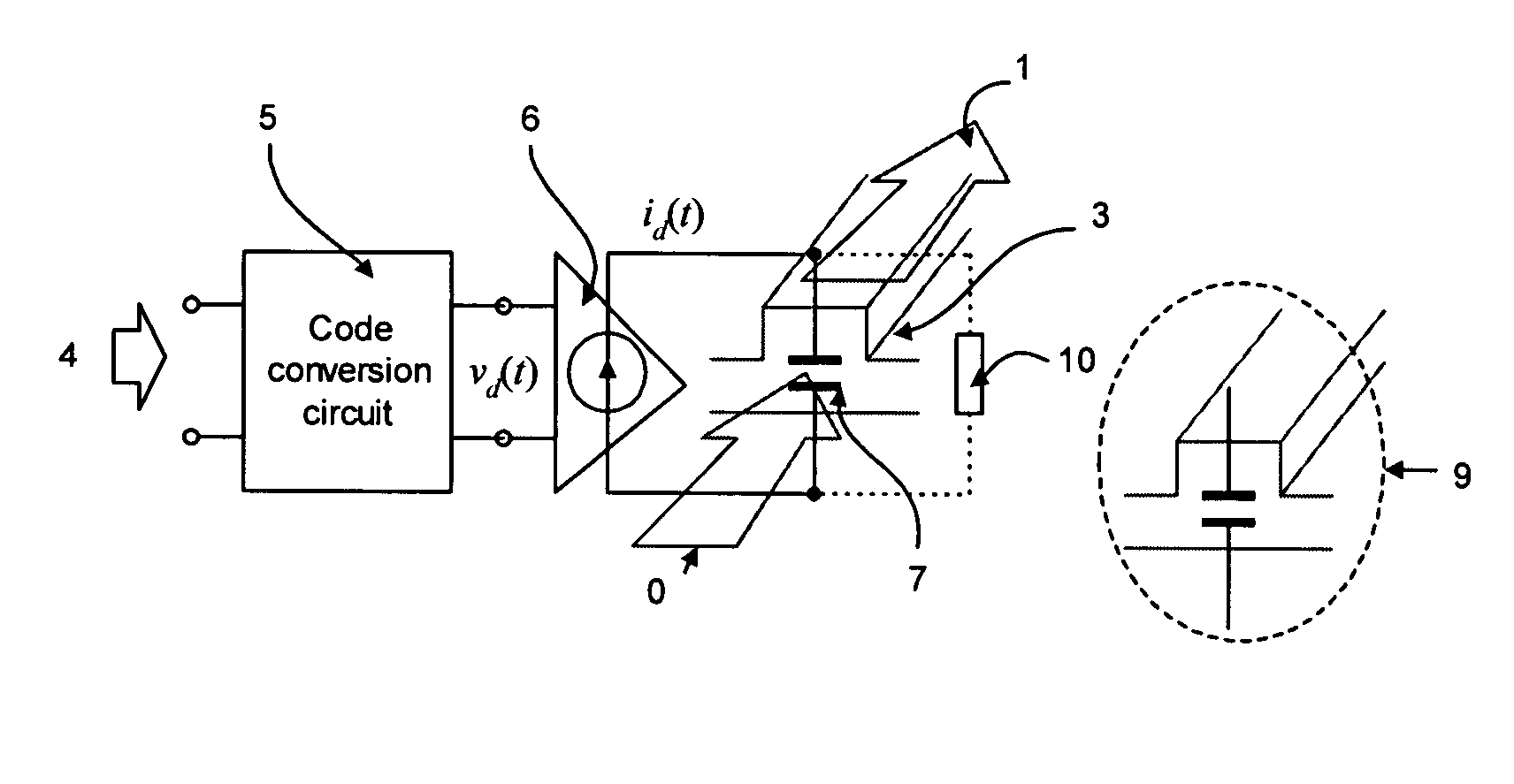

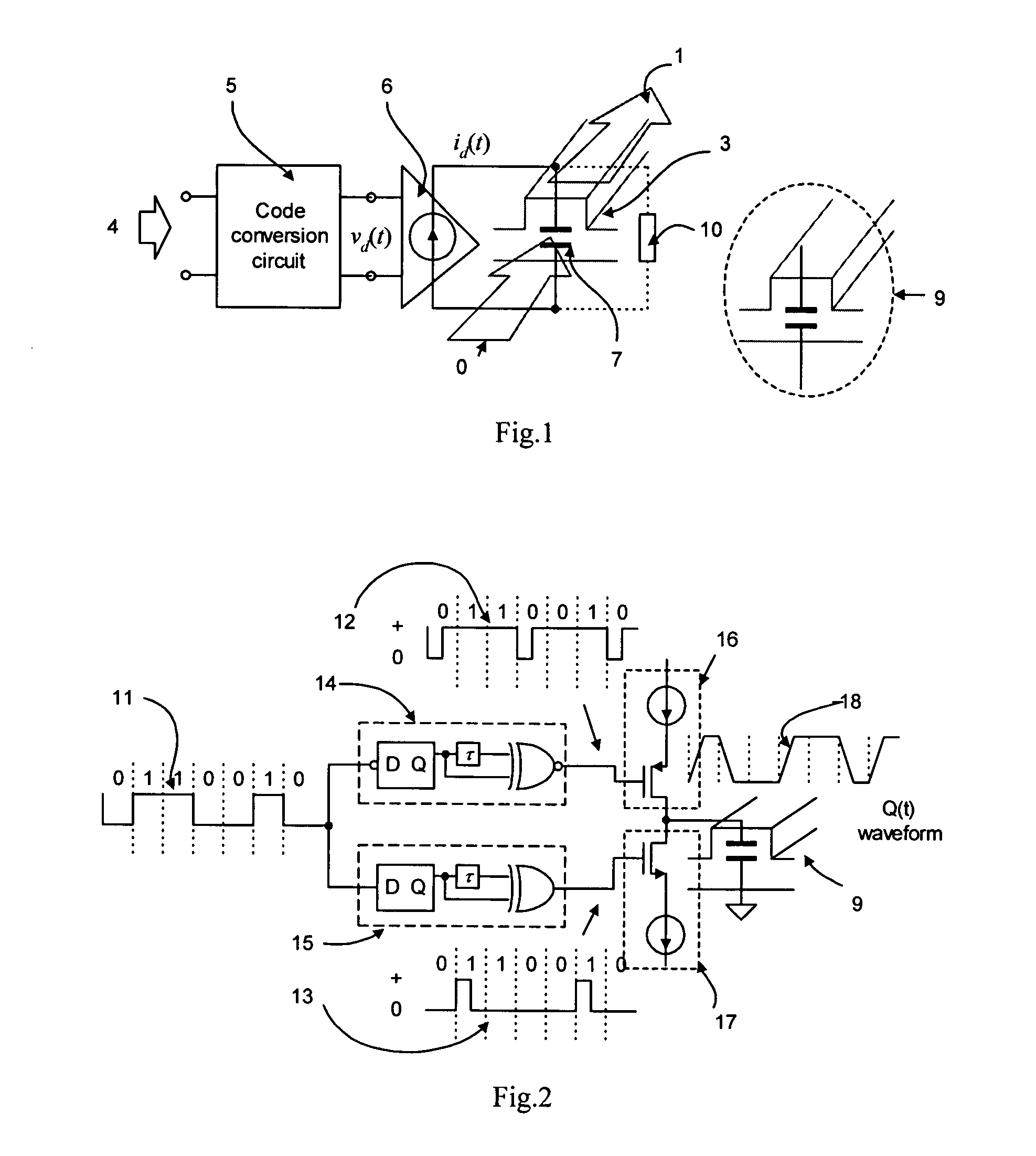

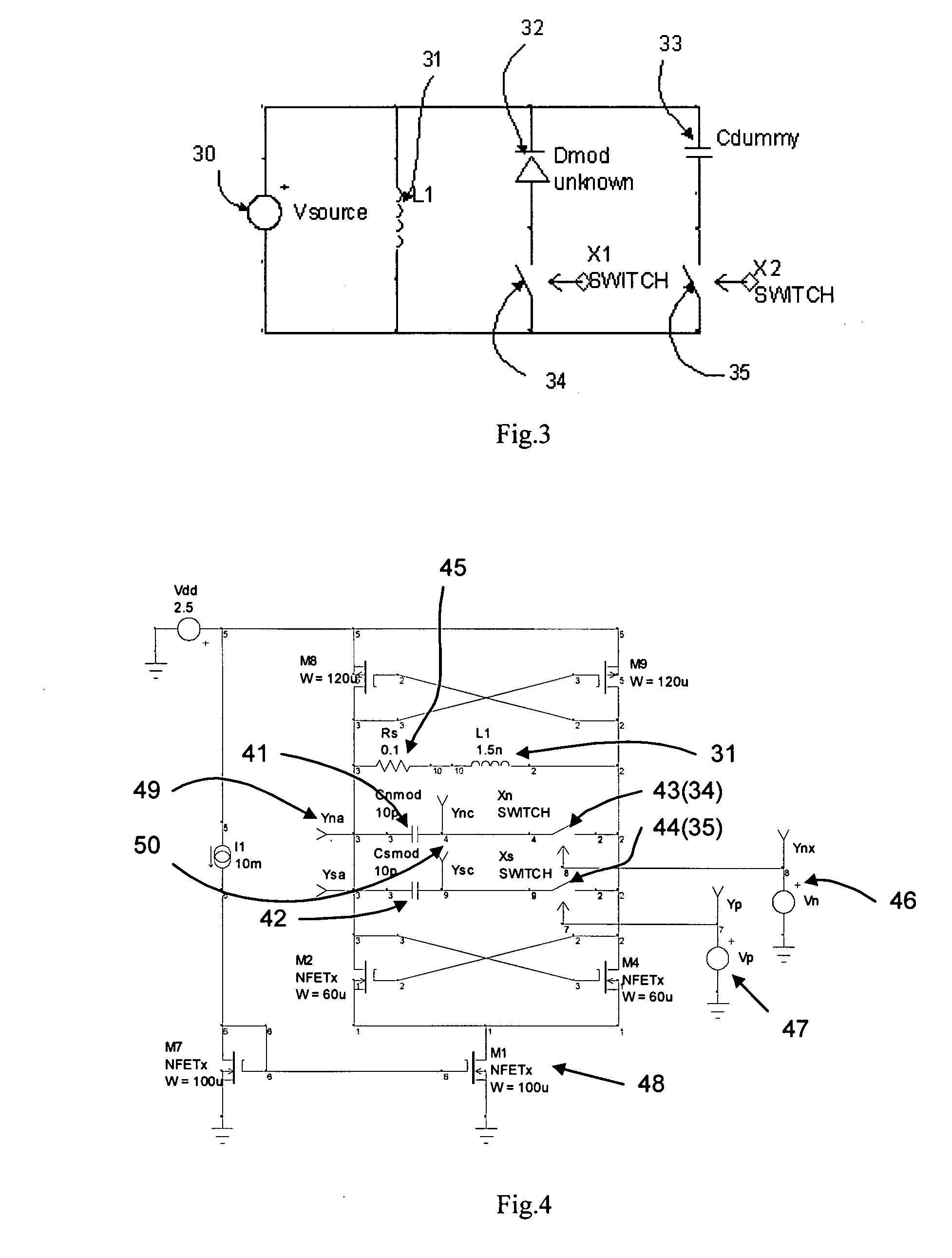

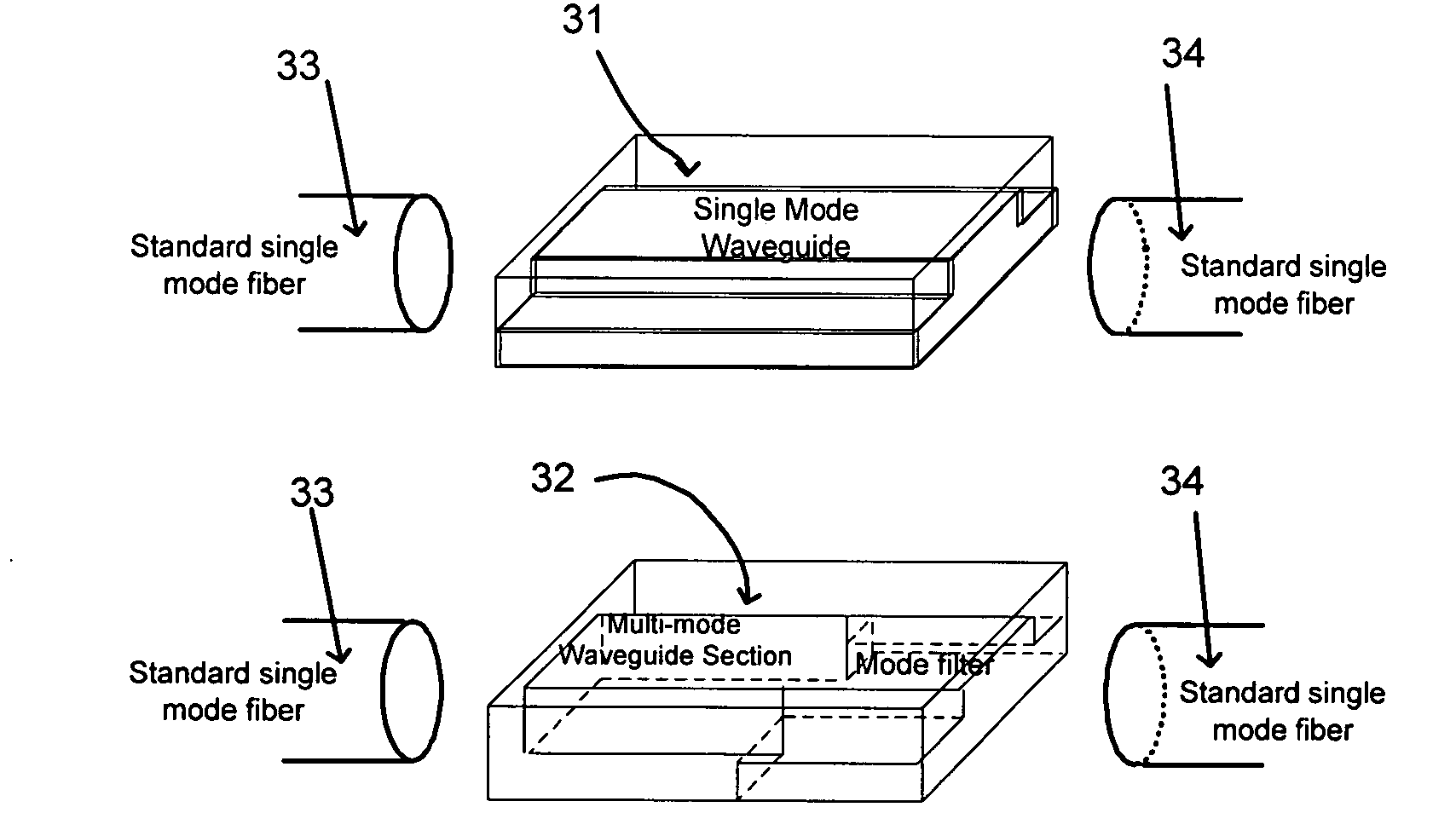

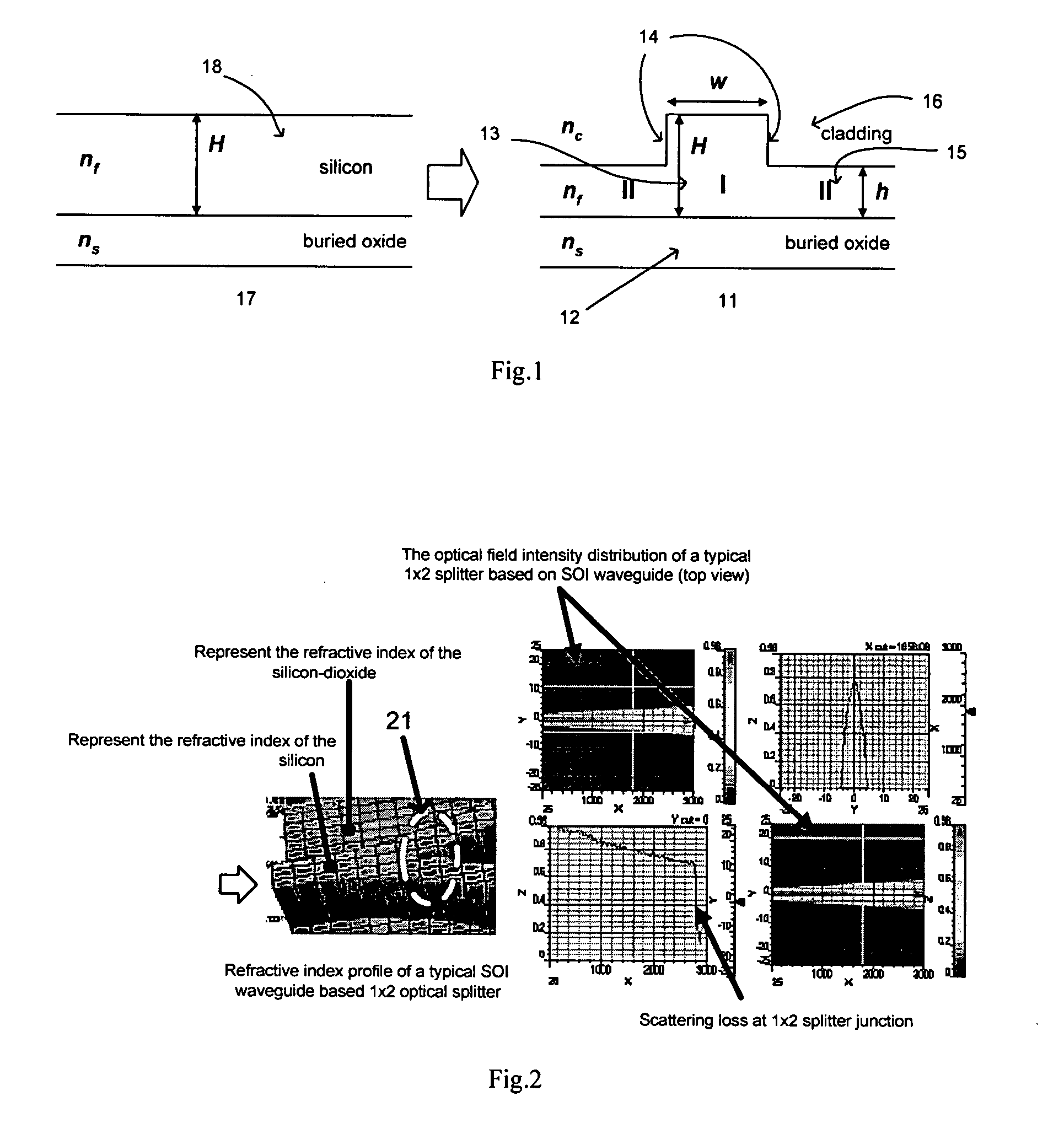

Circuit architecture for electro-optic modulation based on free carrier dispersion effect and the waveguide capacitor structures for such modulator circuitry using CMOS or Bi-CMOS process

ActiveUS20070292073A1Improve performanceOptical waveguide light guideNon-linear opticsHemt circuitsElectro-optic modulator

New circuit architecture for electro-optic modulator based on free-carrier dispersion effect is invented, in which the waveguide capacitor of the modulator is embed in the circuits and physically layout together with transistors, the switching of the modulator occurs in transistors, and as the result, the electro-optical modulation occurs in the waveguide capacitor. The invented modulator is not one physical device, it is actually a circuit. Several circuit design techniques are imported, leading to several new modulator circuits that have very high operation speed and very small power consumption. Several new waveguide capacitor structures are also invented that allow high efficient modulator circuits to be built.

Owner:LI BING

Universal Energy Conditioning Interposer with Circuit Architecture

InactiveUS20080158746A1Easy to adaptProvide protectionImpedence networksSemiconductor/solid-state device detailsInterposerHemt circuits

Owner:X2Y ATTENUATORS L L C

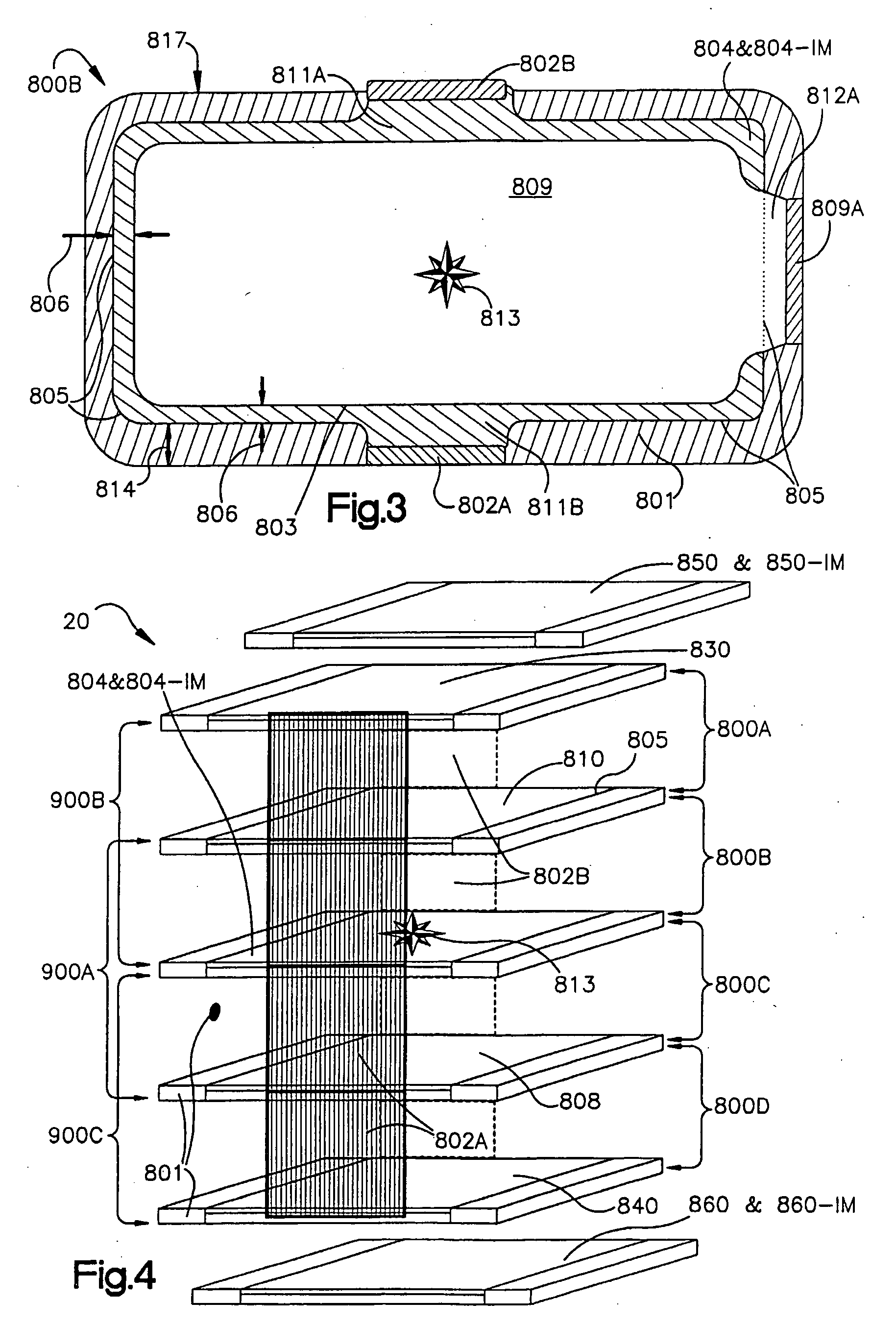

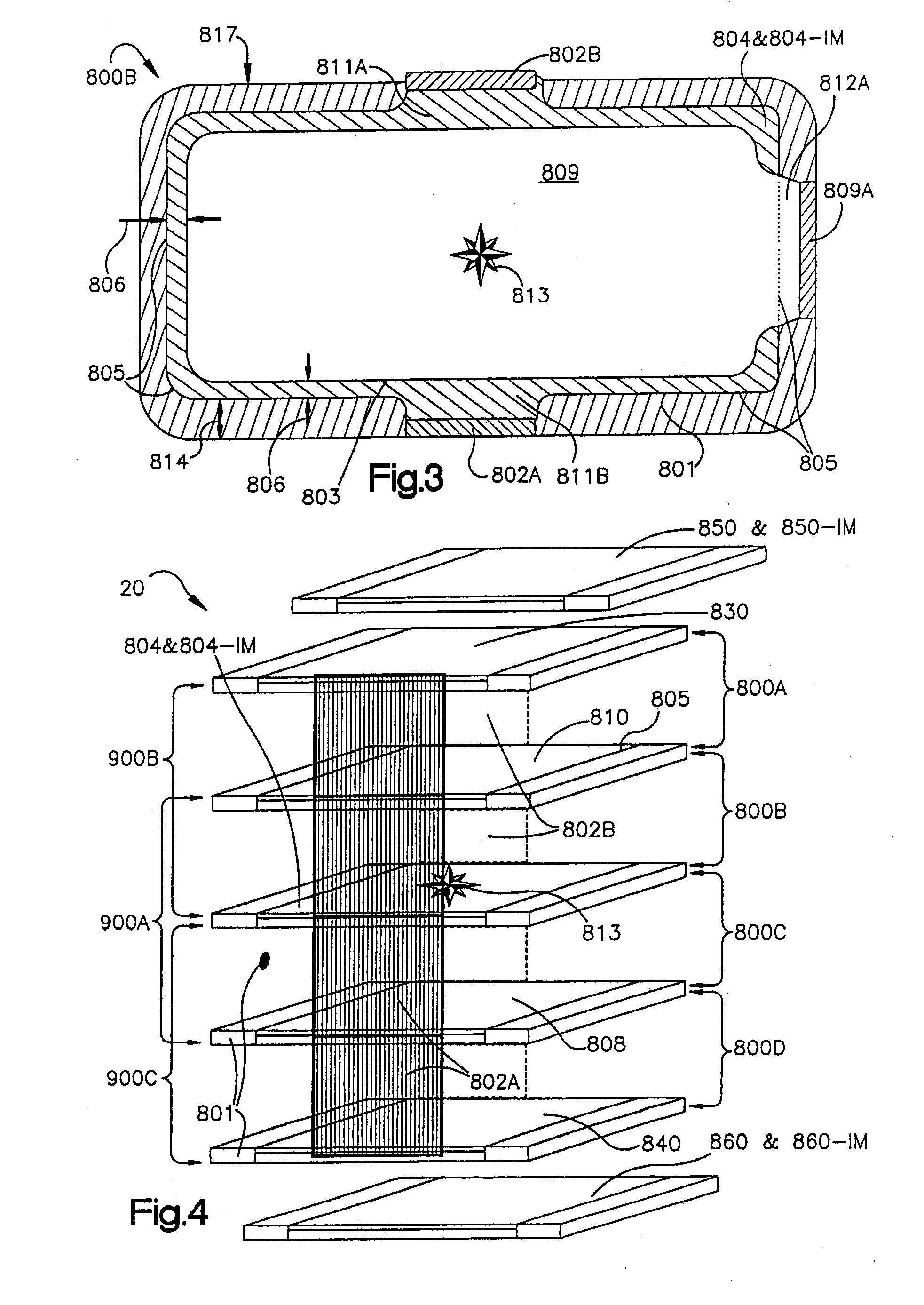

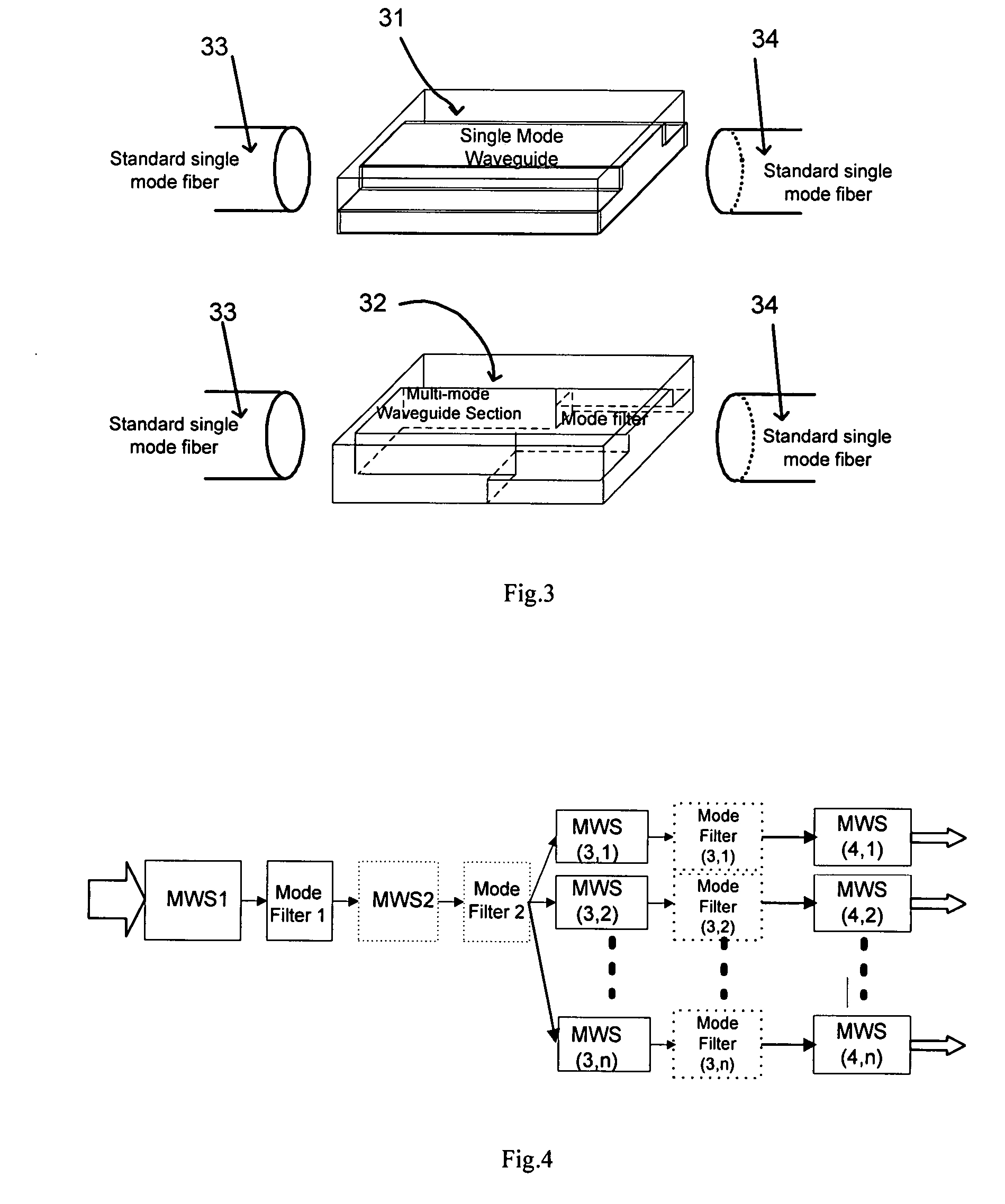

Single mode photonic circuit architecture and a new optical splitter design based on parallel waveguide mode conversion

ActiveUS20080002928A1Increase contrastSmall bend radiusNanoopticsCoupling light guidesRefractive indexWaveguide mode

The new single mode circuit (SMC) architecture is invented for photonic integrated circuits (PIC). This architecture allows using multimode waveguides or structures to construct a single mode operated PIC. The multimode sections used in such SMC based PIC possess strong lateral confinement so that the PIC can have high circuit density and high optical performance at the same time. A parallel mode converter structure is also invented here. Based on this parallel mode converter, a low loss optical splitter can be constructed for high index contrast waveguide system.

Owner:LI BING

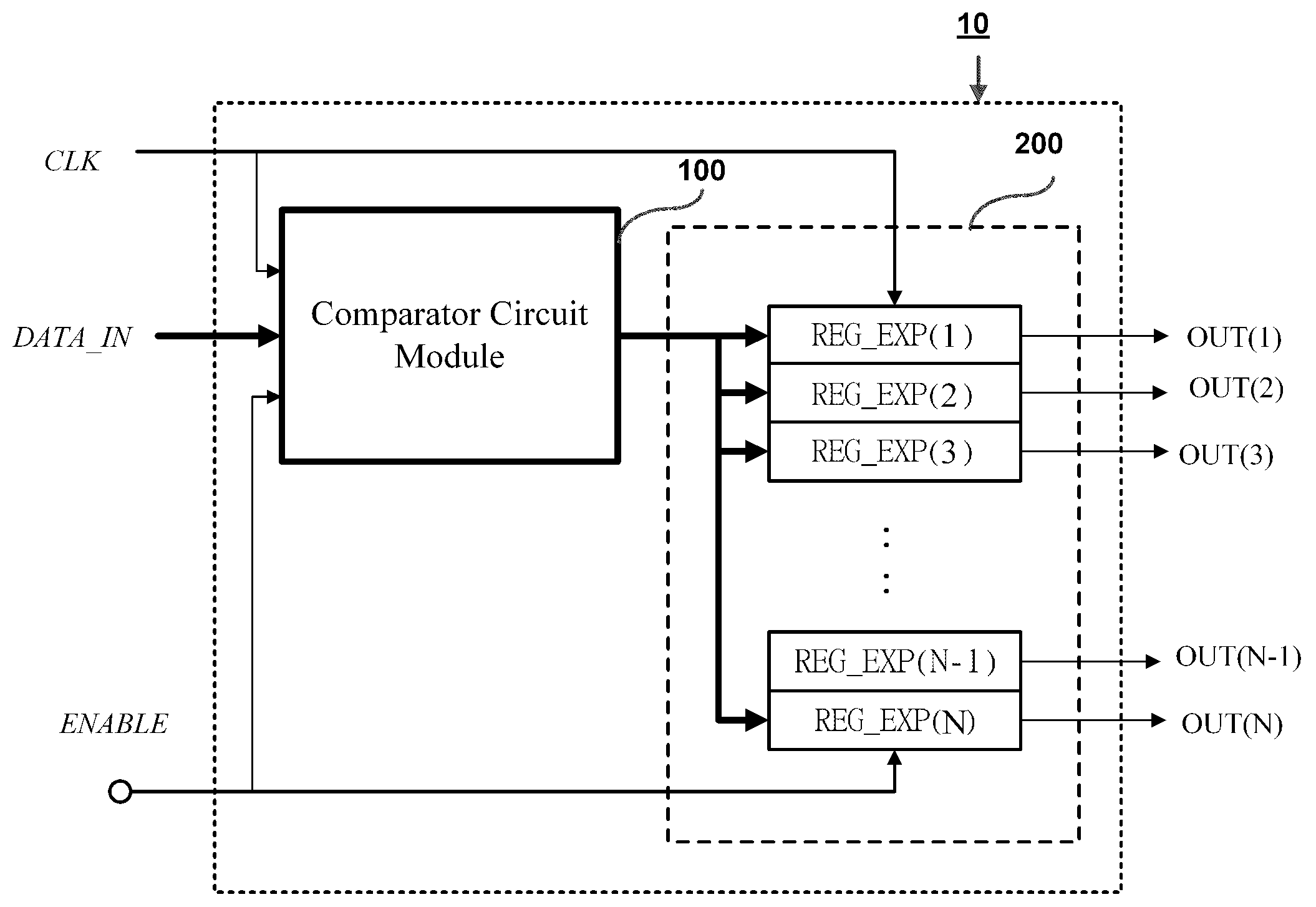

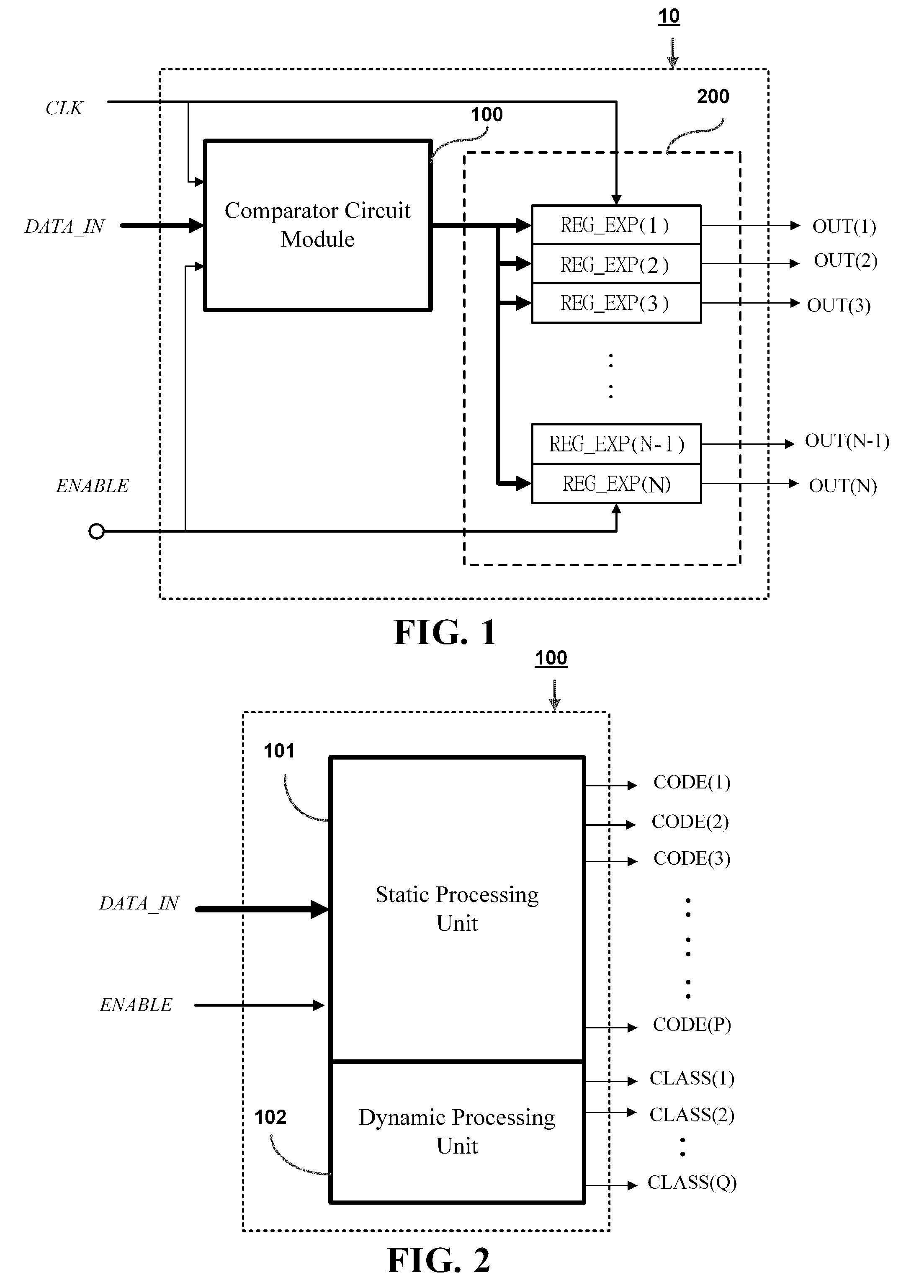

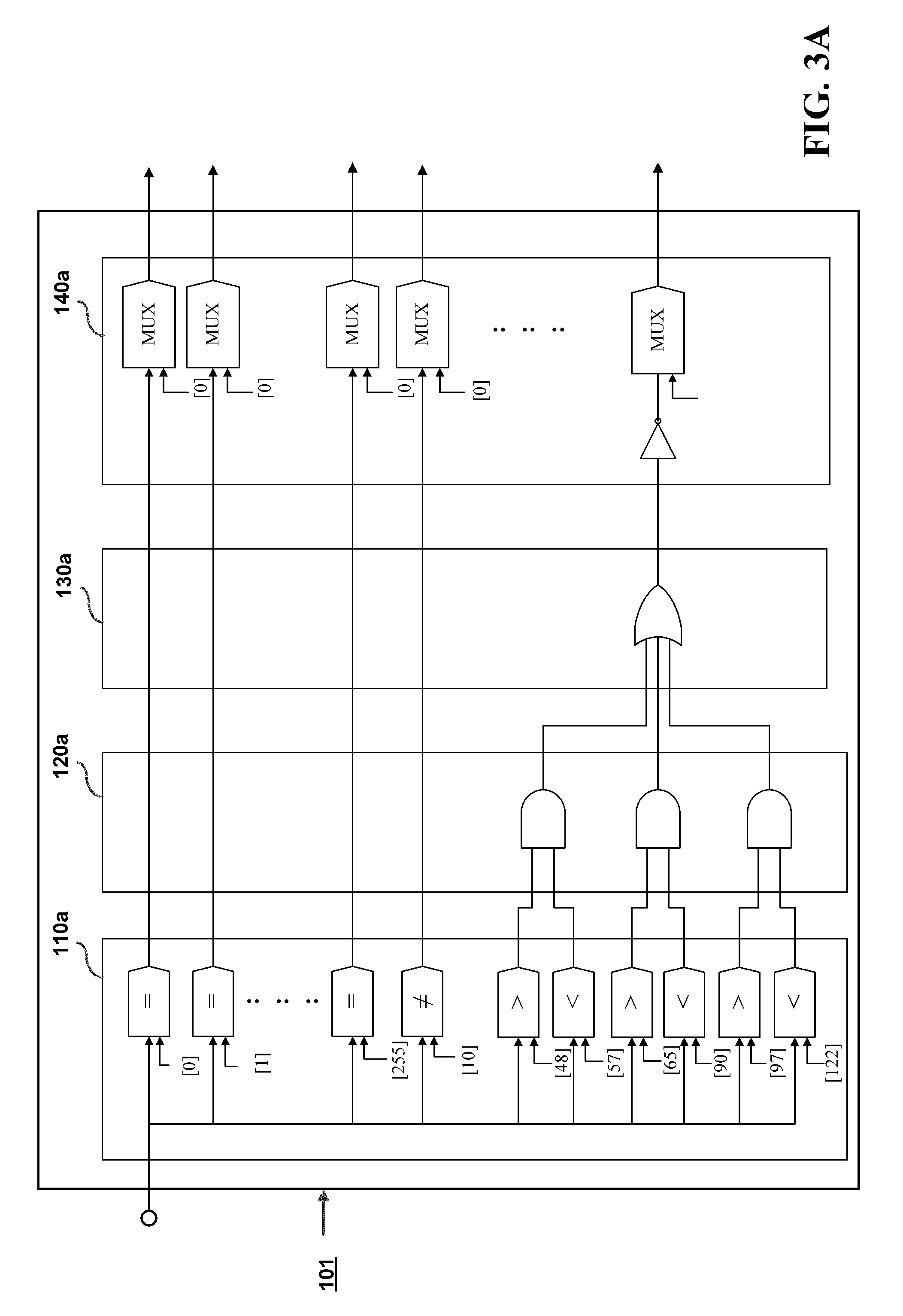

Regular expession pattern matching circuit based on a pipeline architecture

InactiveUS20100158394A1Improve processing speedIncrease speedDigital data information retrievalCharacter and pattern recognitionData packComputer architecture

A regular expression pattern matching circuit based on a pipeline architecture is proposed, which is designed for integration to a data processing system, such as a computer platform, a firewall, or a network intrusion detention system (NIDS), for checking whether an input code sequence (such as a network data packet) is matched to specific patterns predefined by regular expressions. The proposed circuit architecture includes an incremental improvement on an old combination of a comparator circuit module and an NDFA (non-deterministic finite-state automata) circuit module, where the incremental improvement comprises a data signal delay circuit module installed to the comparator circuit module and an enable signal delay circuit module installed to the NDFA circuit module to thereby constitute a multi-sage pipeline architecture that allows a faster processing speed than the prior art.

Owner:NAT TAIWAN UNIV

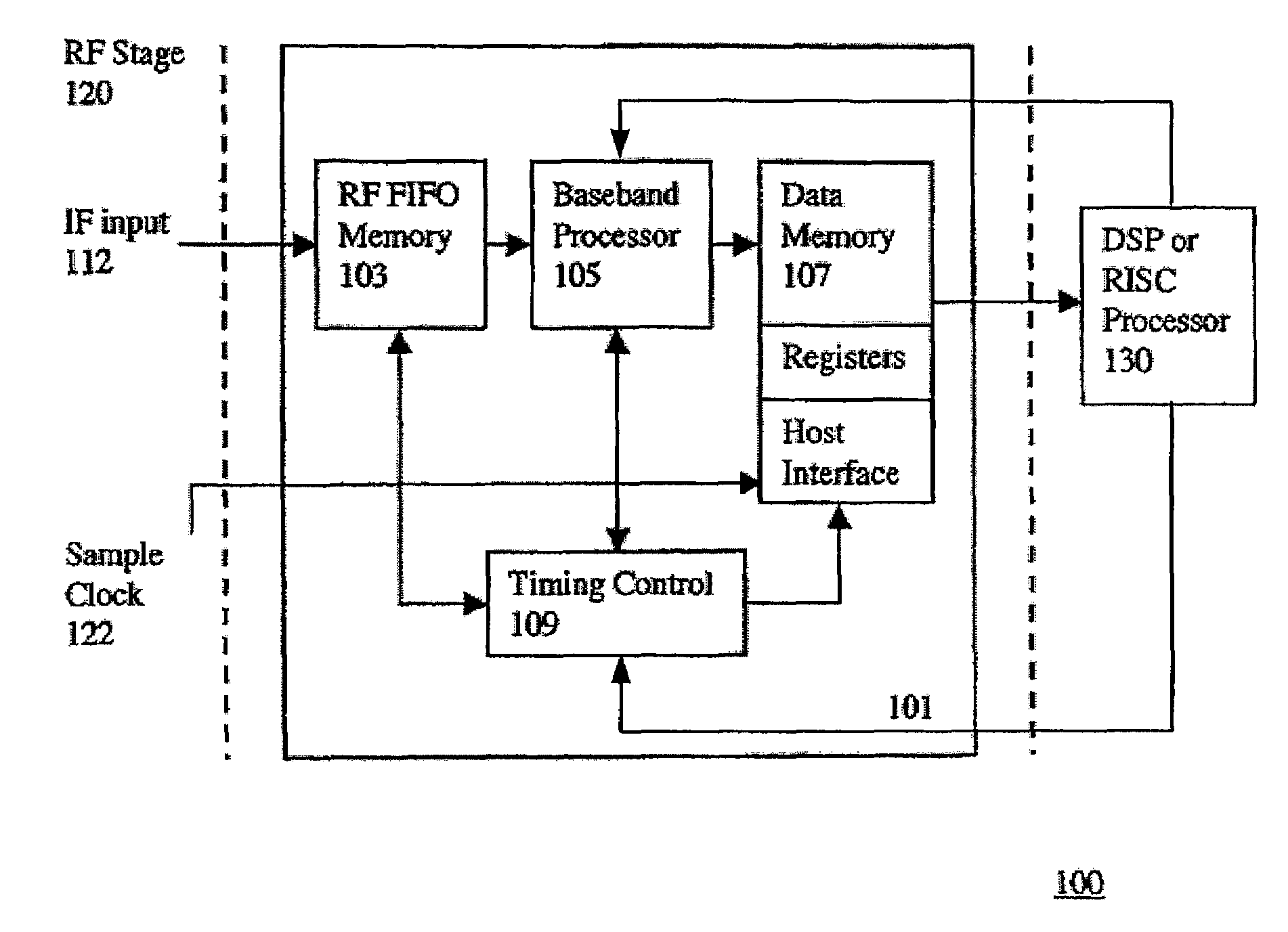

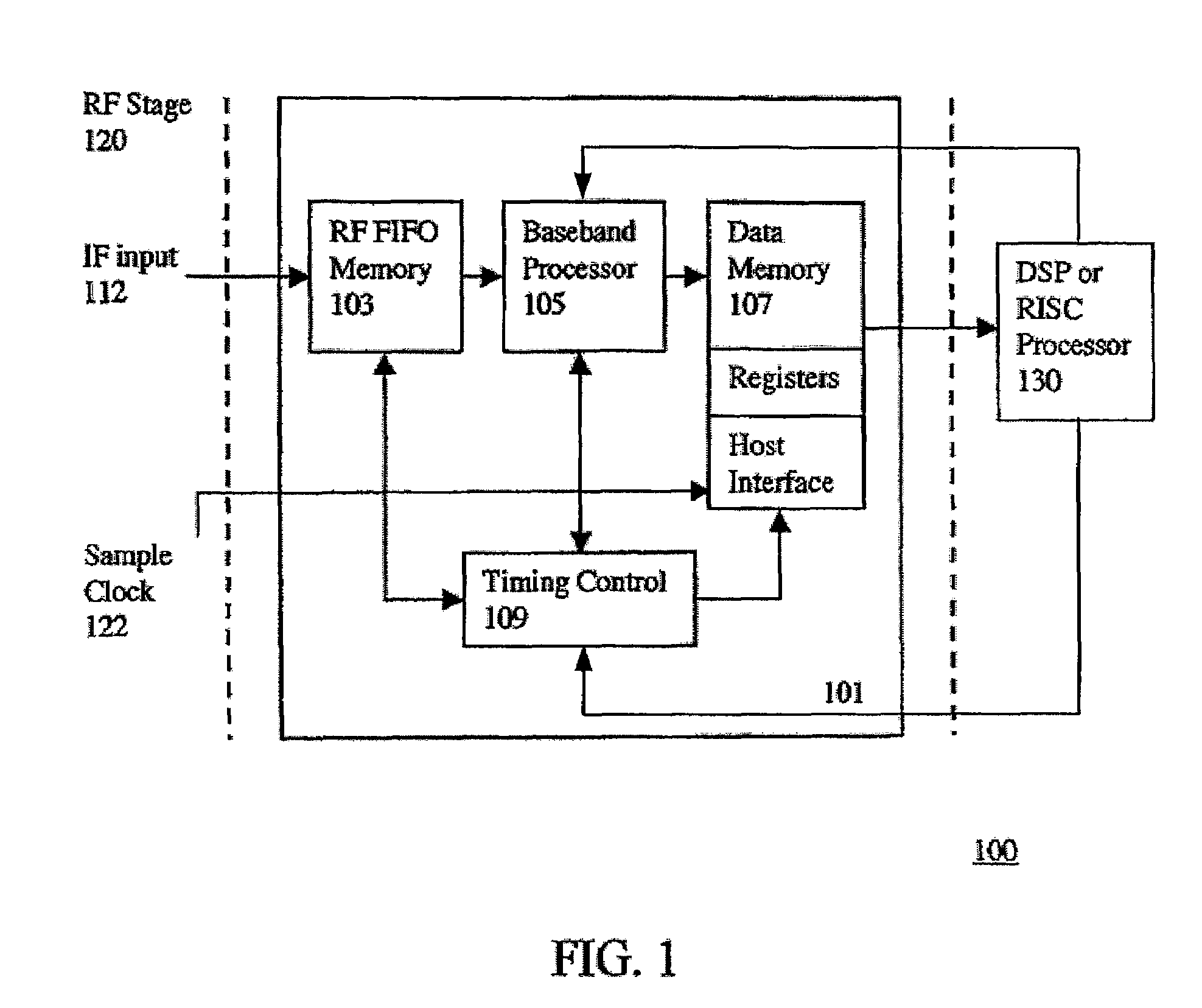

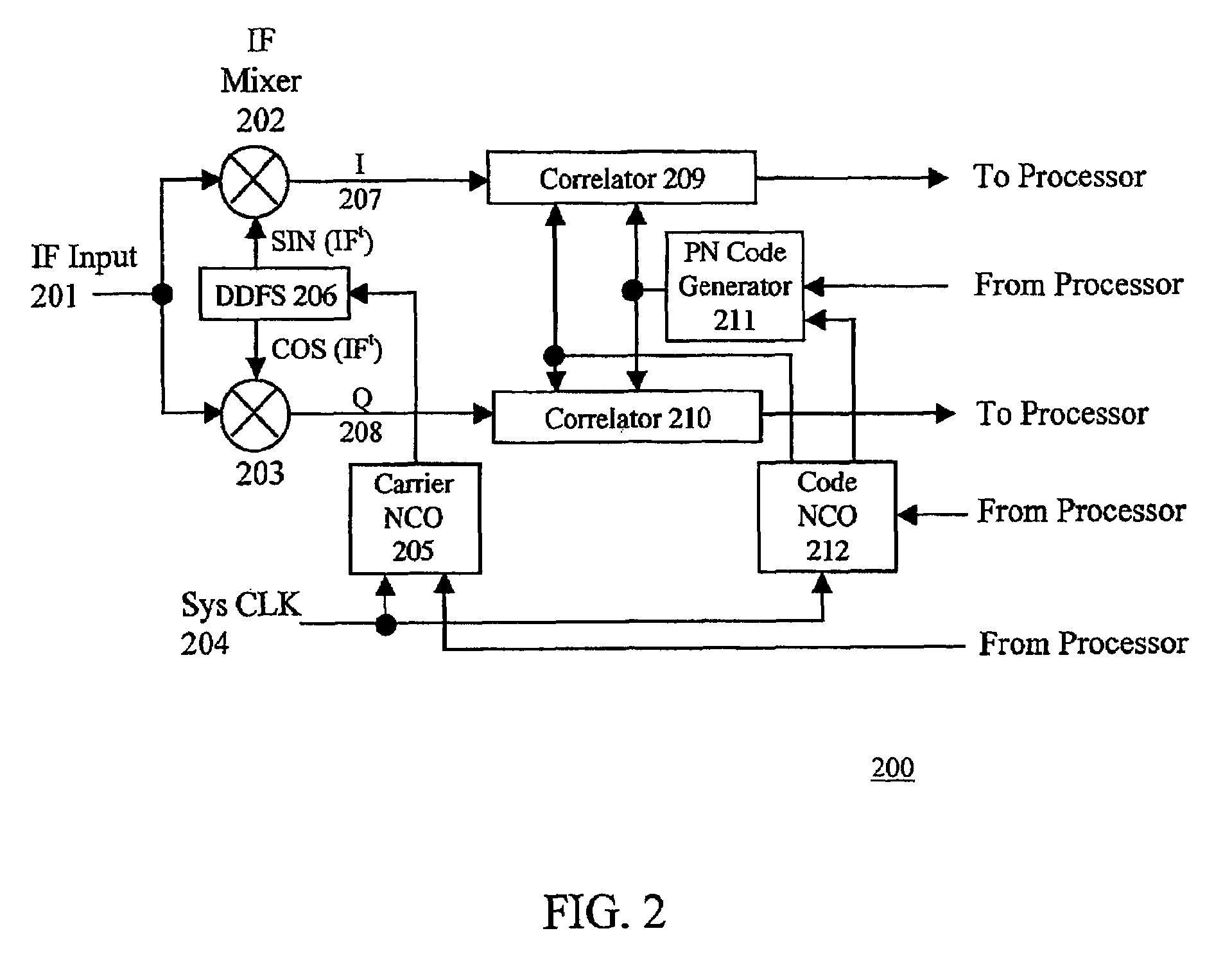

Efficient and flexible GPS receiver baseband architecture

ActiveUS7428259B2Minimize the numberEfficient powerColor television with pulse code modulationColor television with bandwidth reductionNCOSNumerically controlled oscillator

The present invention provides a new baseband integrated circuit (IC) architecture for direct sequence spread spectrum (DSSS) communication receivers. The baseband IC has a single set of baseband correlators serving all channels in succession. No complex parallel channel hardware is required. A single on-chip code Numerically Controlled Oscillator (NCO) drives a pseudorandom number (PN) sequence generator, generates all code sampling frequencies, and is capable of self-correct through feedback from an off-chip processor. A carrier NCO generates corrected local frequencies. These on-chip NCOs generate all the necessary clocks. This architecture advantageously reduces the total hardware necessary for the receiver and the baseband IC thus can be realized with a minimal number of gate count. The invention can accommodate any number of channels in a navigational system such as the Global Positioning System (GPS), GLONASS, WAAS, LAAS, etc. The number of channels can be increased by increasing the circuit clock speed.

Owner:CSR TECH HLDG