Patents

Literature

2636 results about "Chipset" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

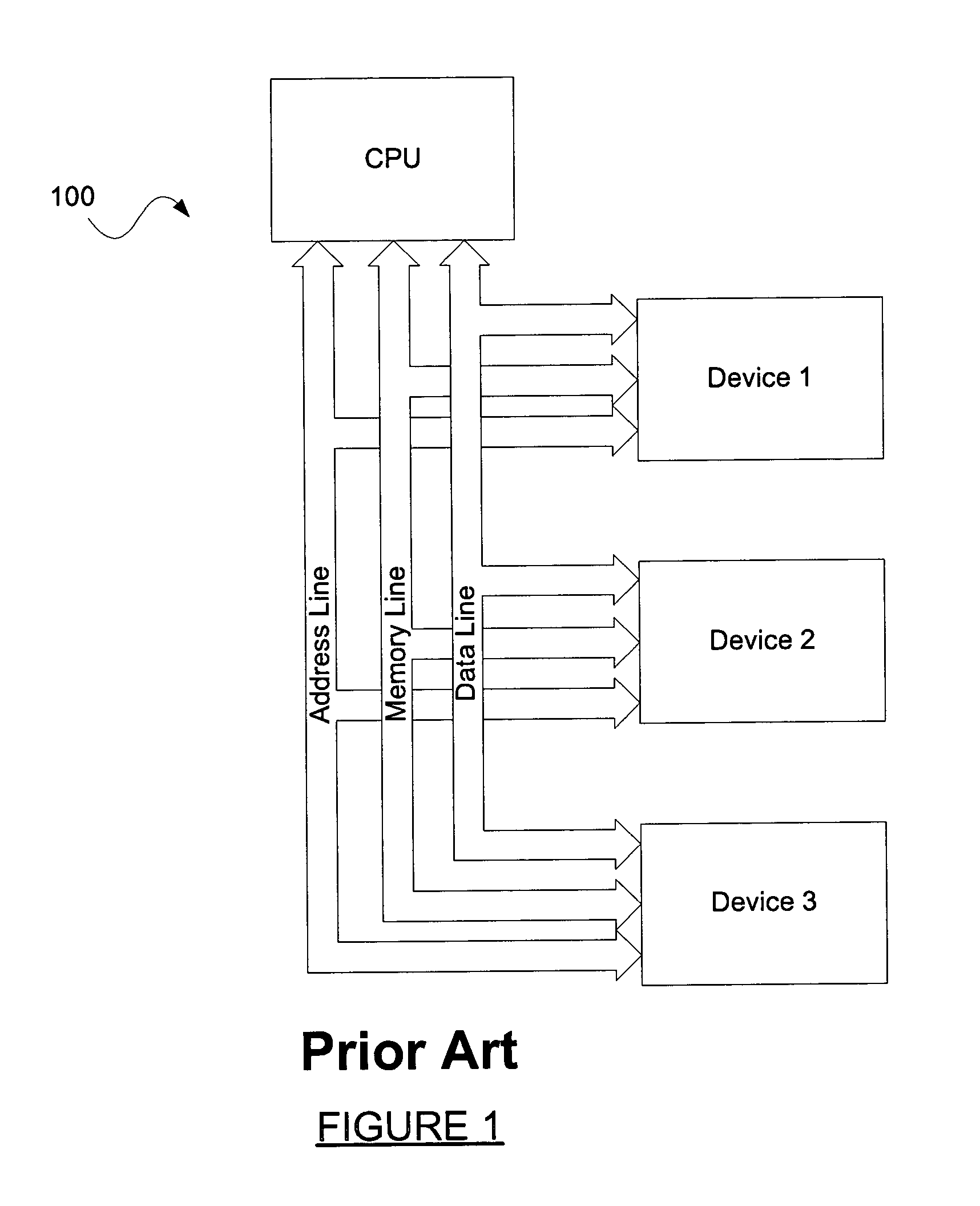

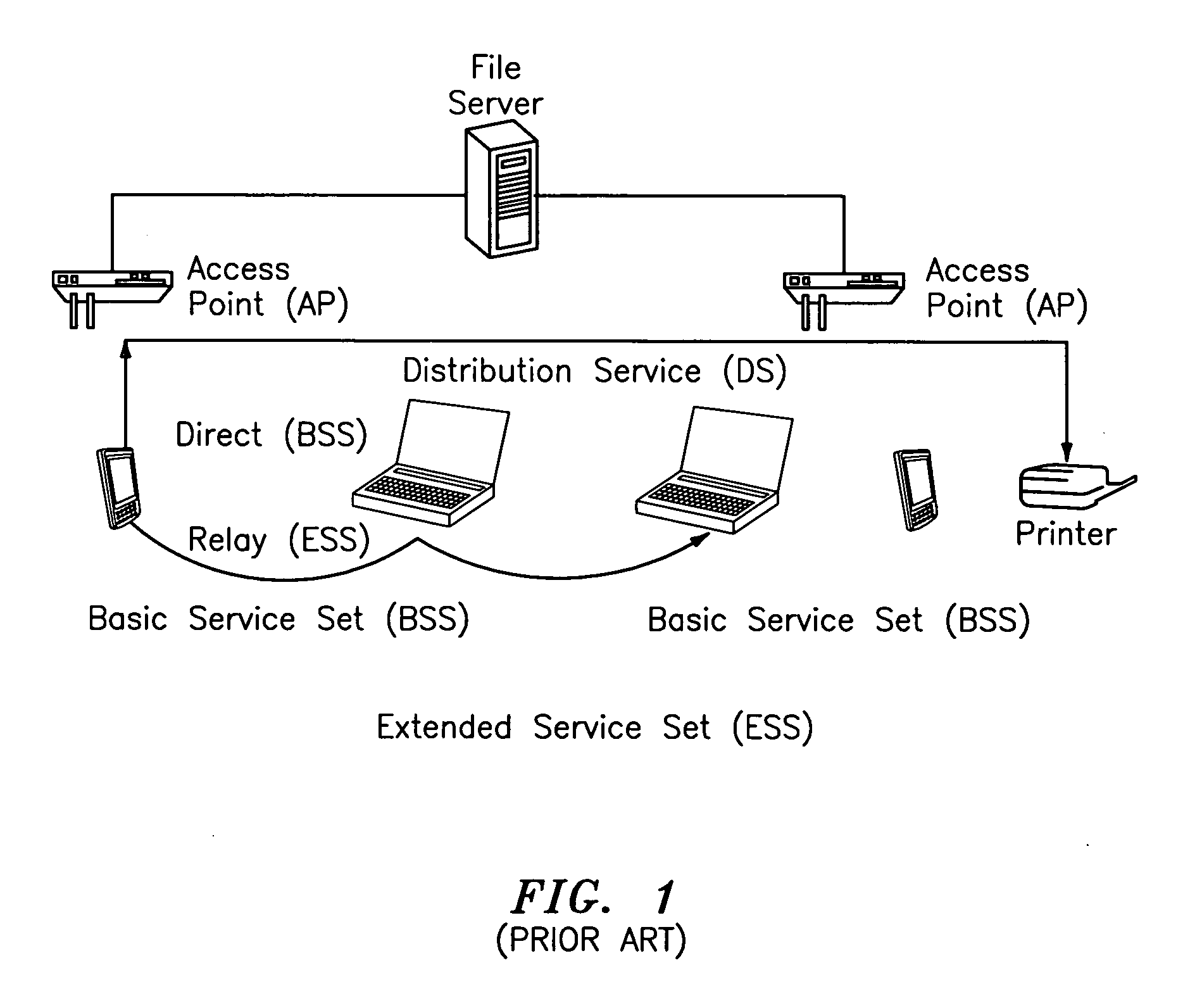

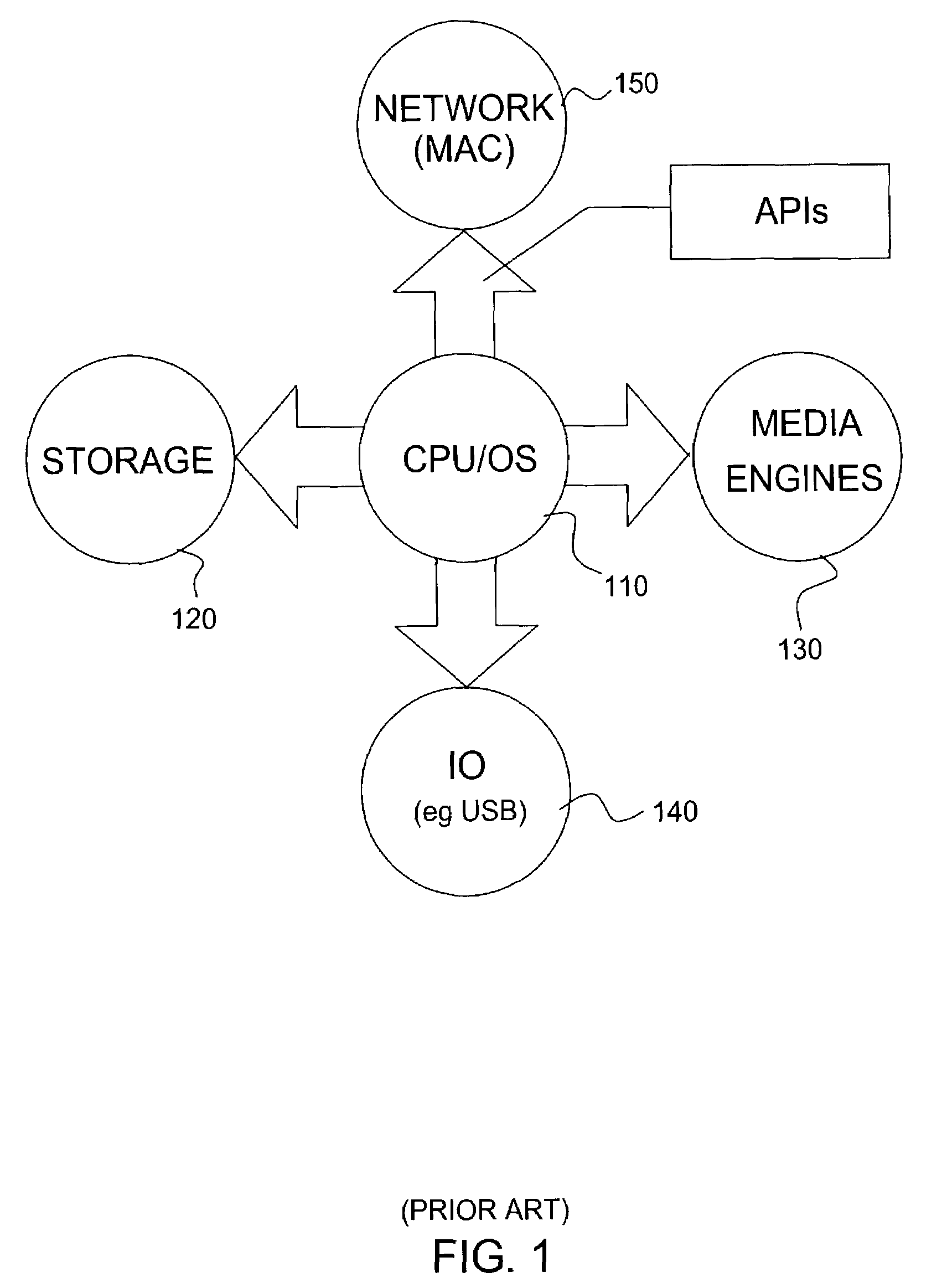

In a computer system, a chipset is a set of electronic components in an integrated circuit known as a "Data Flow Management System" that manages the data flow between the processor, memory and peripherals. It is usually found on the motherboard. Chipsets are usually designed to work with a specific family of microprocessors. Because it controls communications between the processor and external devices, the chipset plays a crucial role in determining system performance.

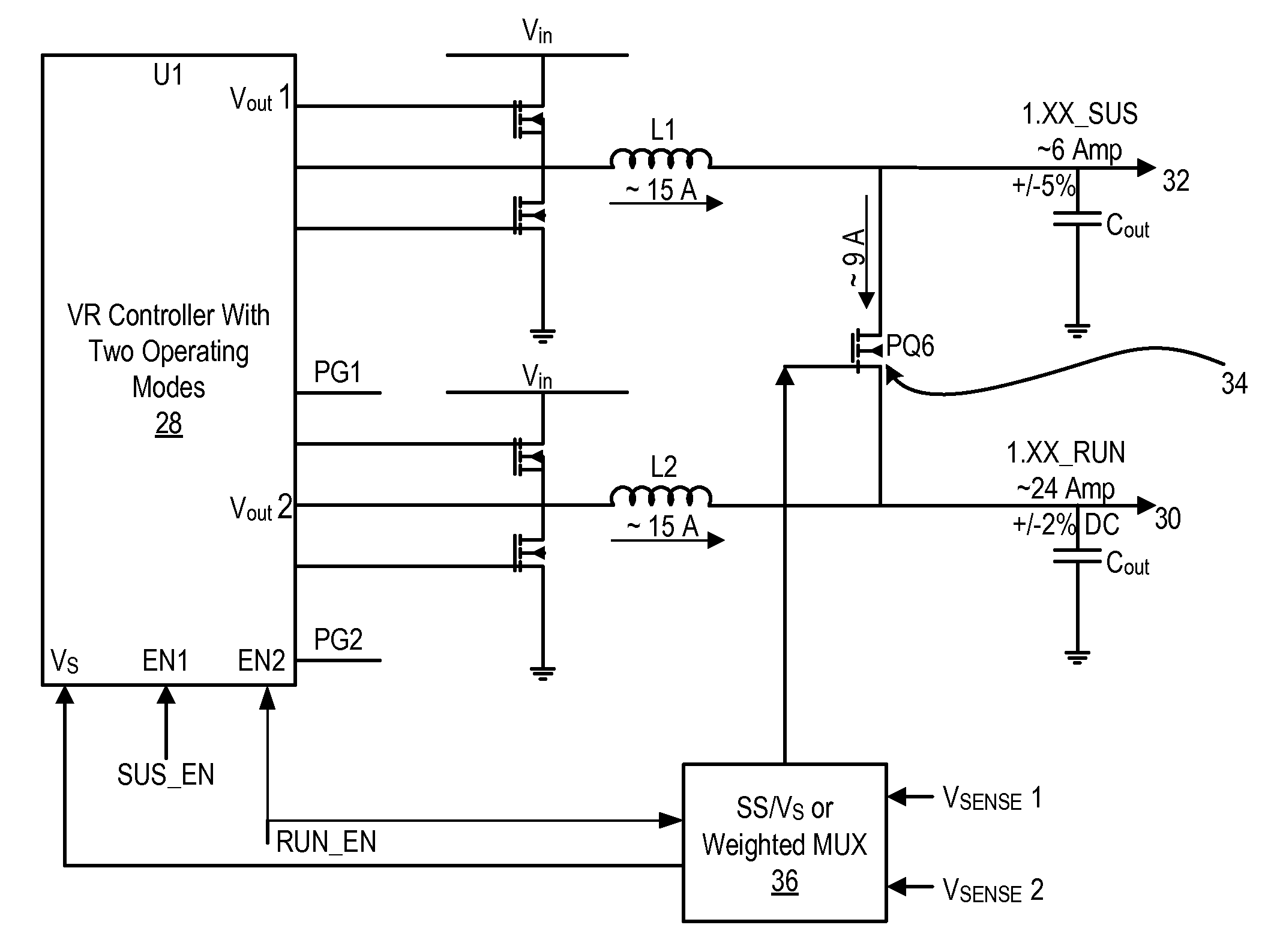

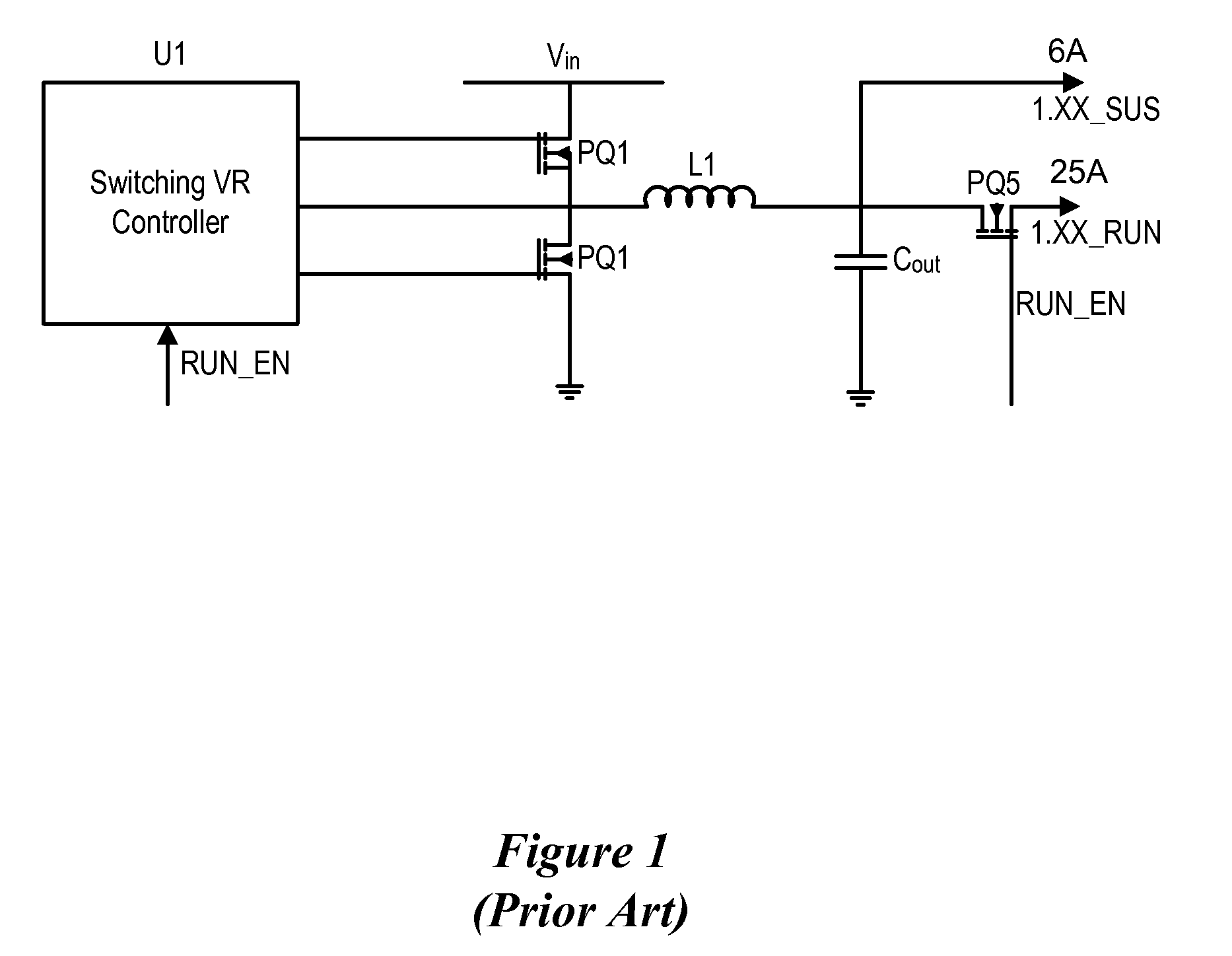

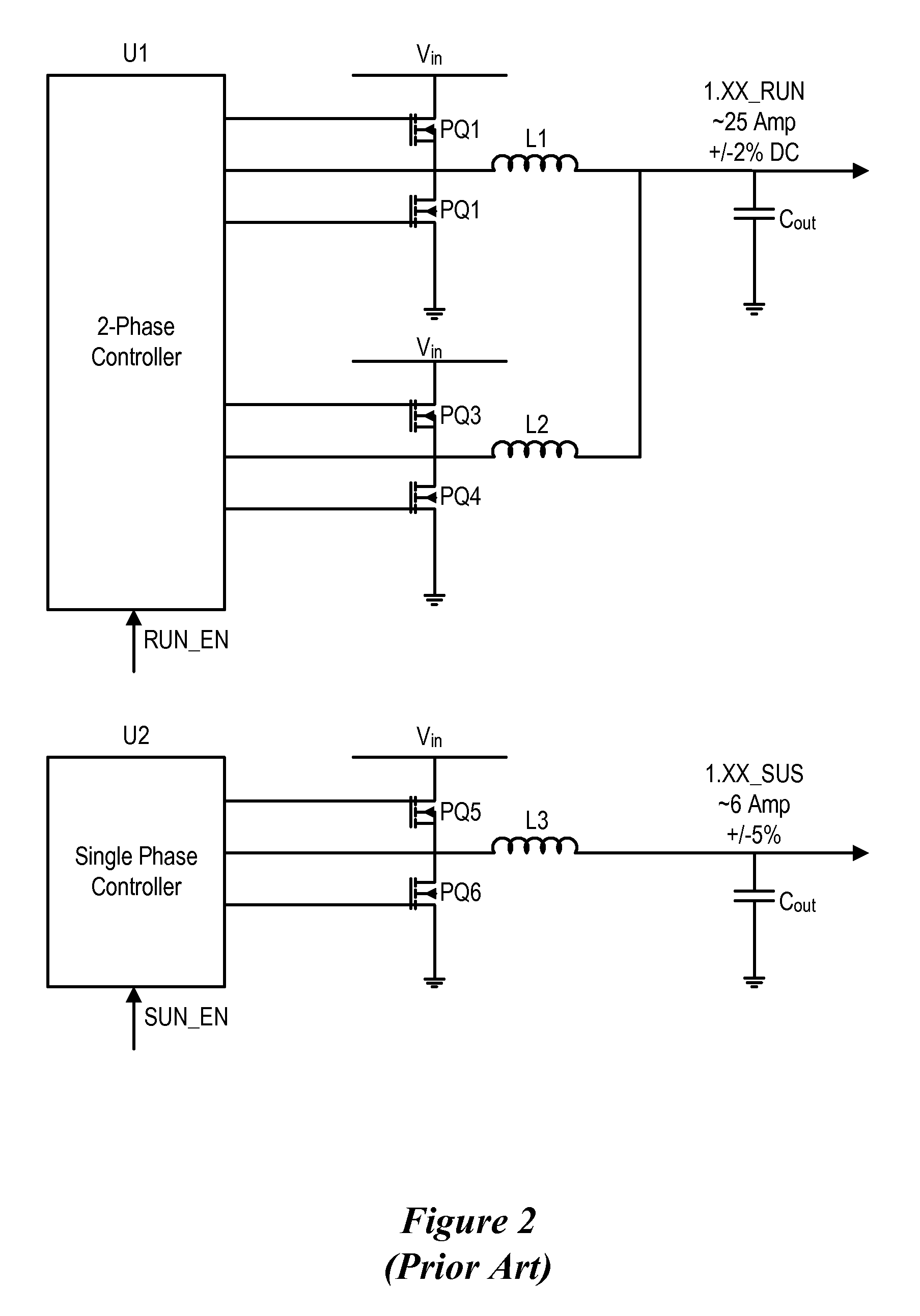

System and method for powering an information handling system in multiple power states

ActiveUS8063619B2Reduce disadvantagesReduce problemsElectric signal transmission systemsDc network circuit arrangementsMOSFETVoltage regulation

Power is supplied to an information handling system chipset with a single voltage regulator having dual phases. A first phase of the voltage regulator provides power to a low power state power rail in an independent mode to support a low power state, such as a suspend or hibernate state. A second phase of the voltage regulator provides power to a run power state power rail in combination with the first phase by activation of a switch, such as a MOSFET load switch, that connects the low power state power rail and the run power state power rail. Voltage sensed from both power rails is applied to control voltage output so that the run power state power rail is maintained within more precise constraints than the low power state power rail.

Owner:DELL PROD LP

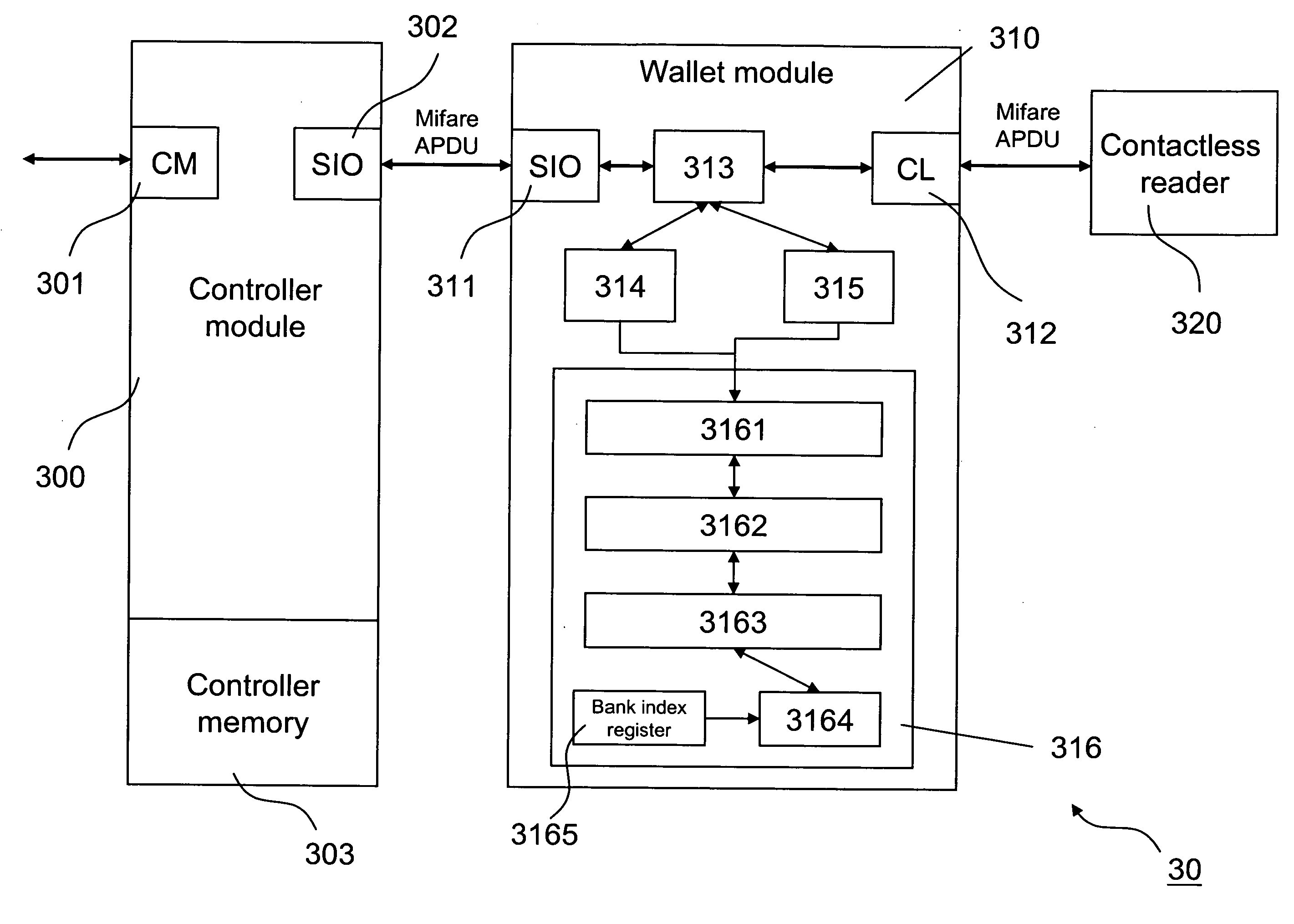

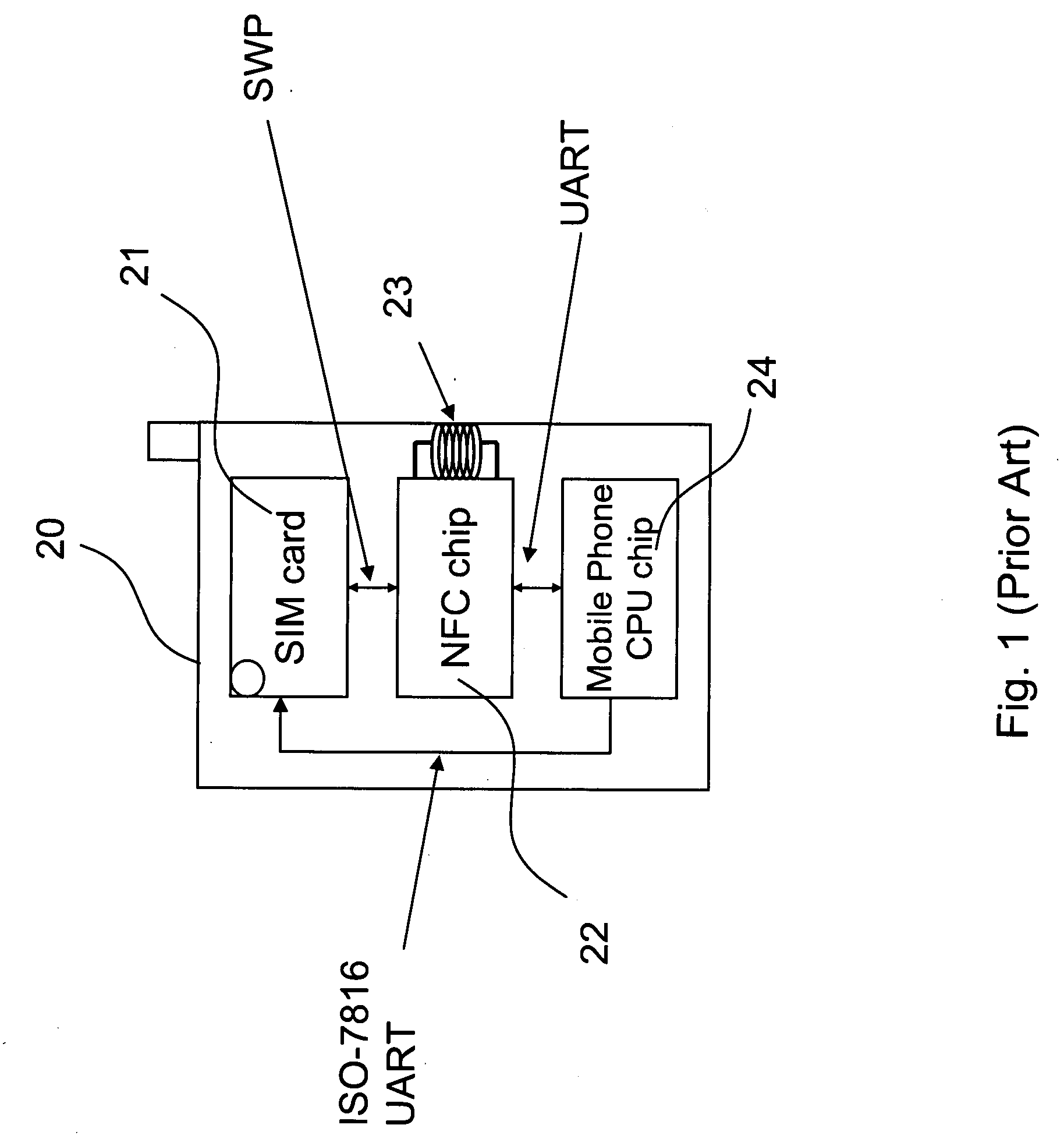

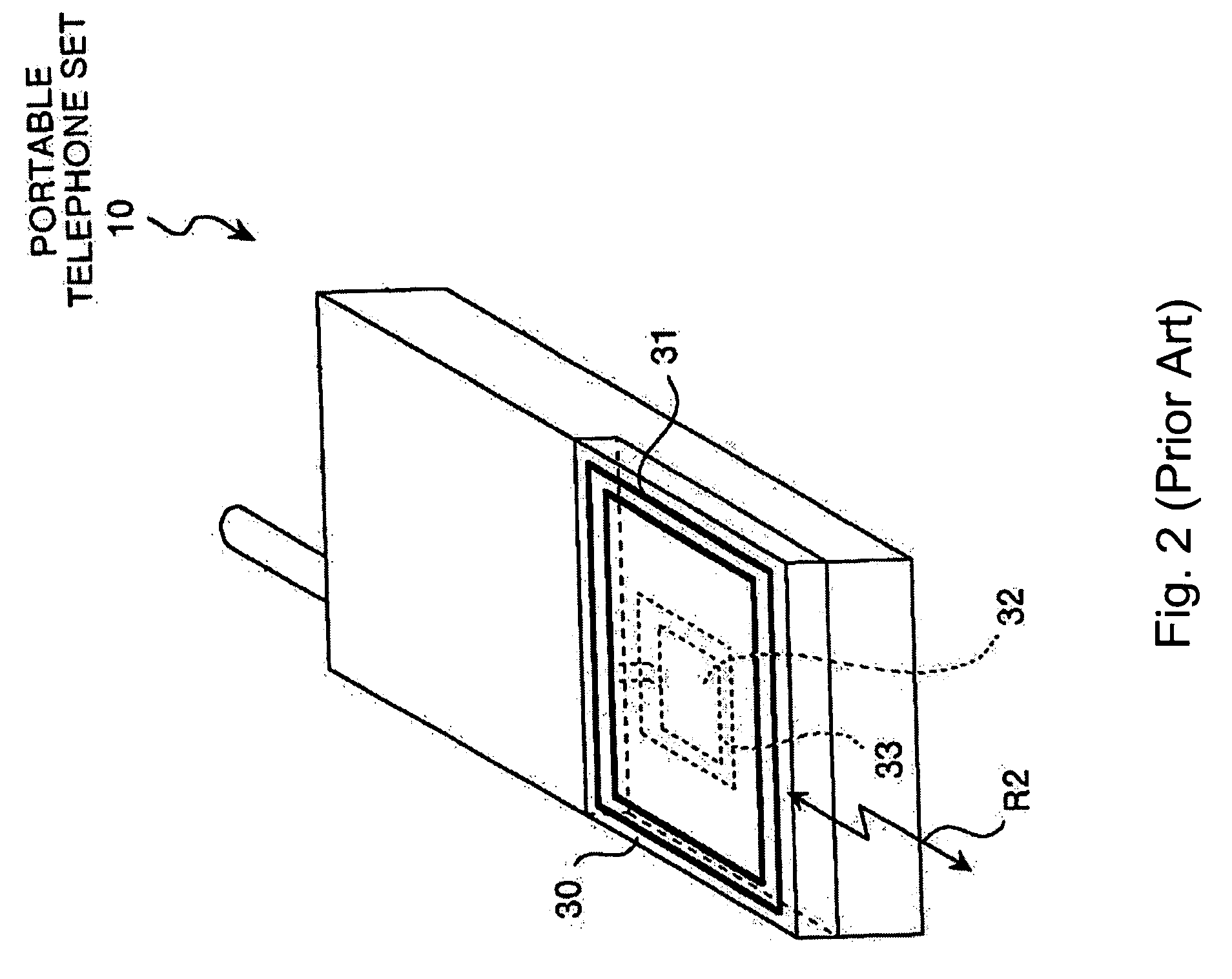

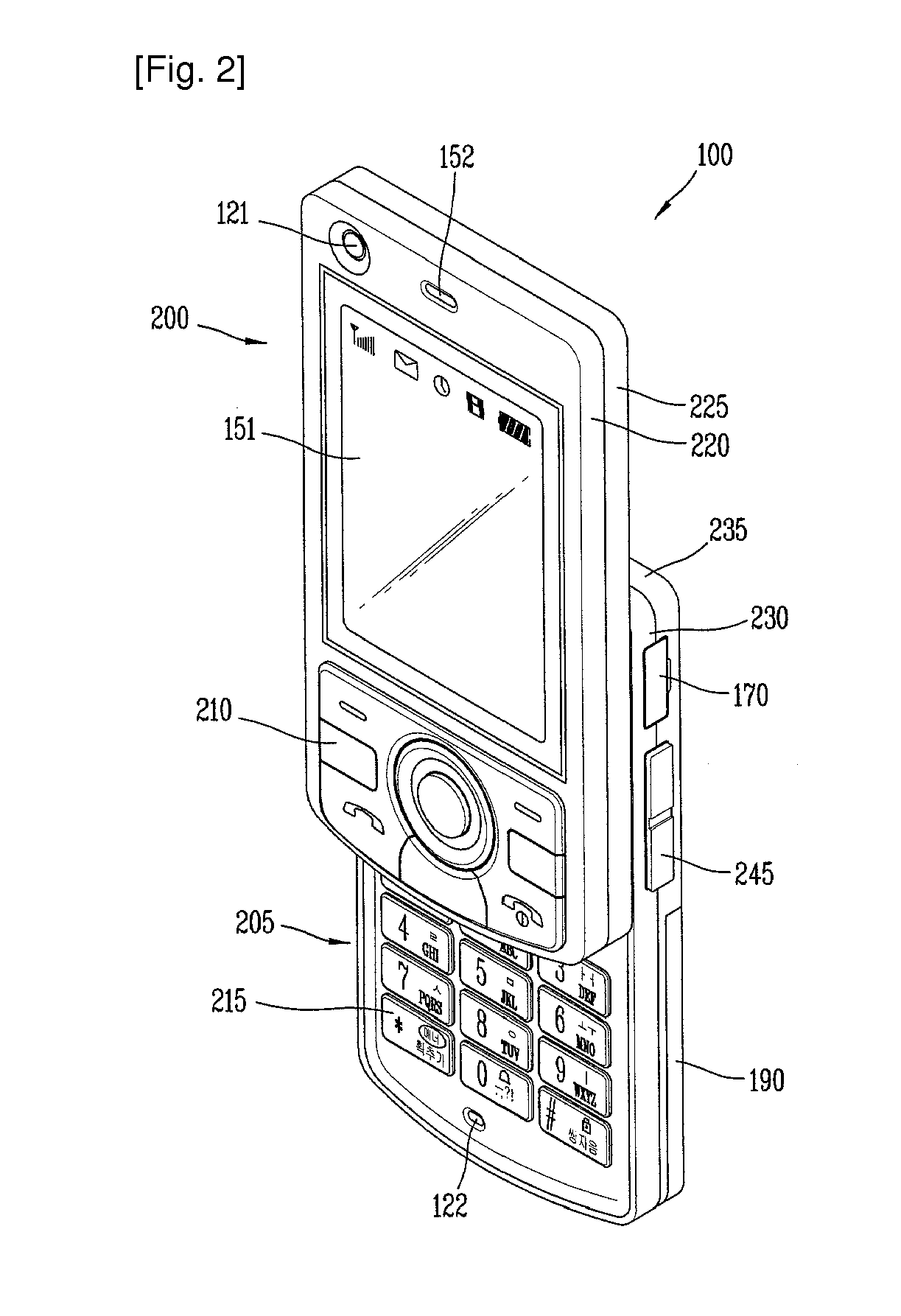

Chipset for mobile wallet system

ActiveUS20070293155A1Small sizeLow costPayment architectureSubstation equipmentComputer hardwareChipset

The invention presents a chipset for a mobile wallet system in a communication terminal having a SIM socket and a RFID antenna. The chipset includes a wallet module and a controller module. The wallet module has a contactless interface port coupled to the RFID antenna and a wallet memory for storing wallet applications. The controller module, connected to the SIM socket of the communication terminal, has a controller memory stored with SIM function software, mobile wallet application software and software to control the wallet module. The controller module is powered through the SIM socket, and the wallet module is powered through the SIM socket and the RFID antenna.

Owner:SILICON STORAGE TECHNOLOGY

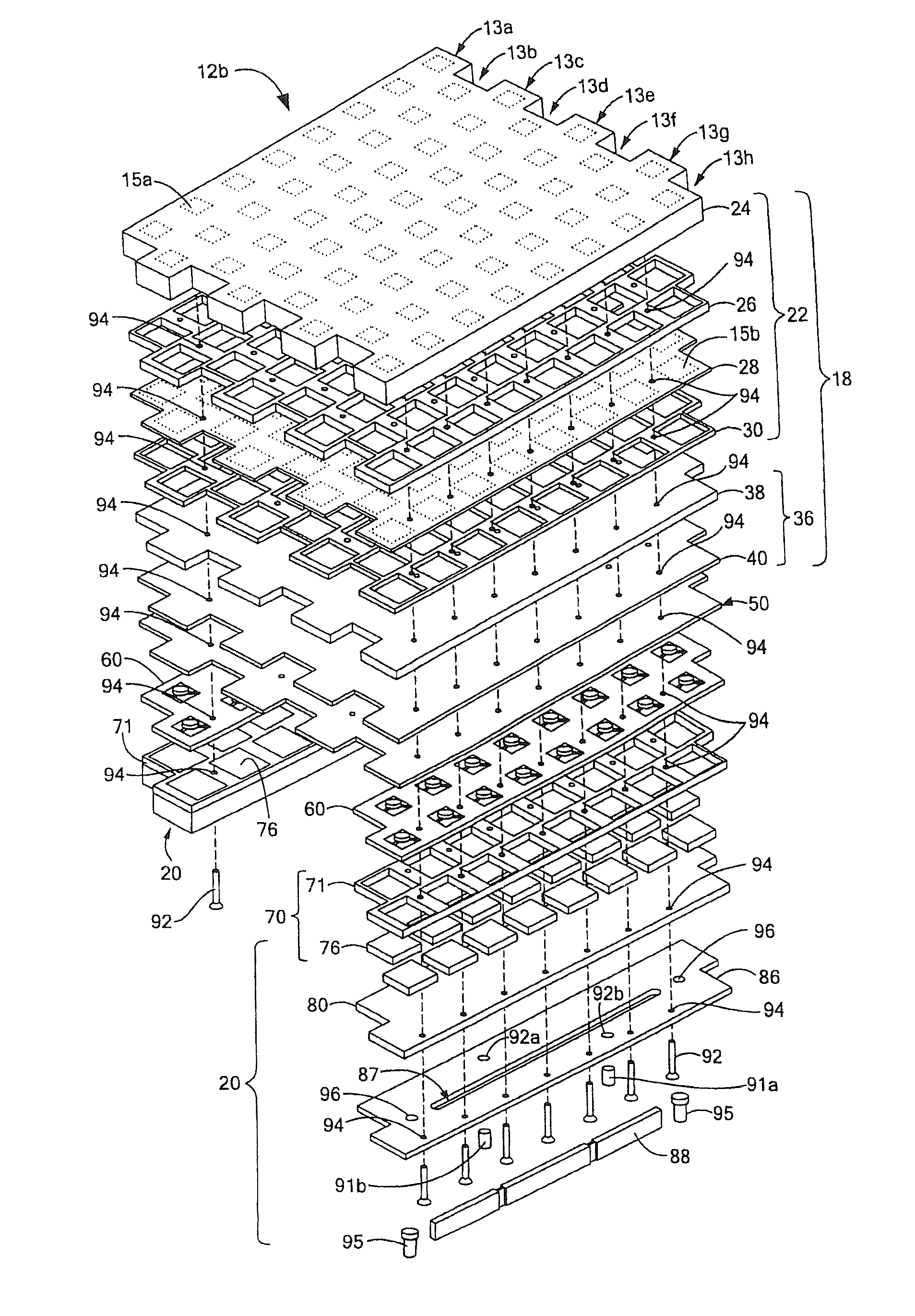

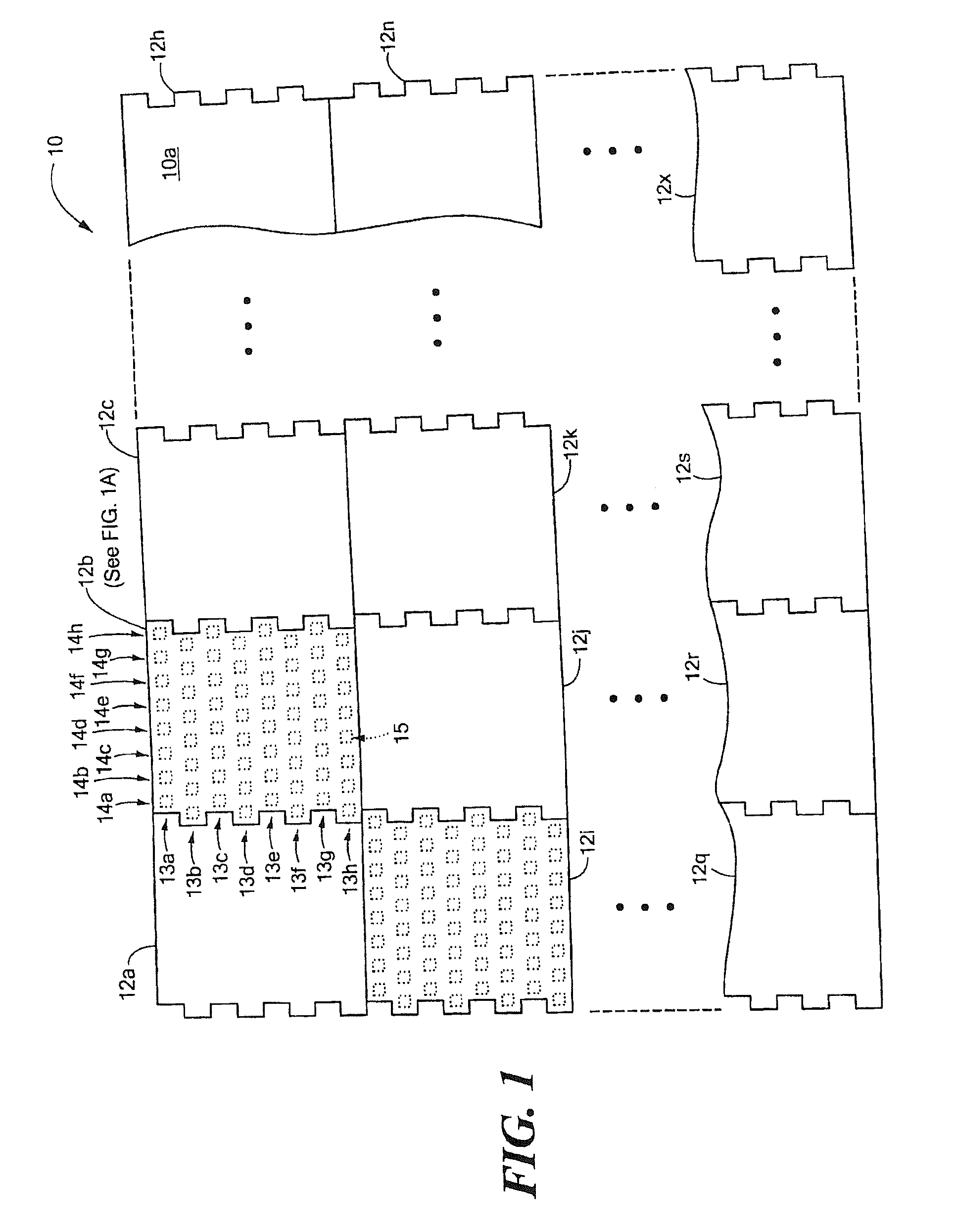

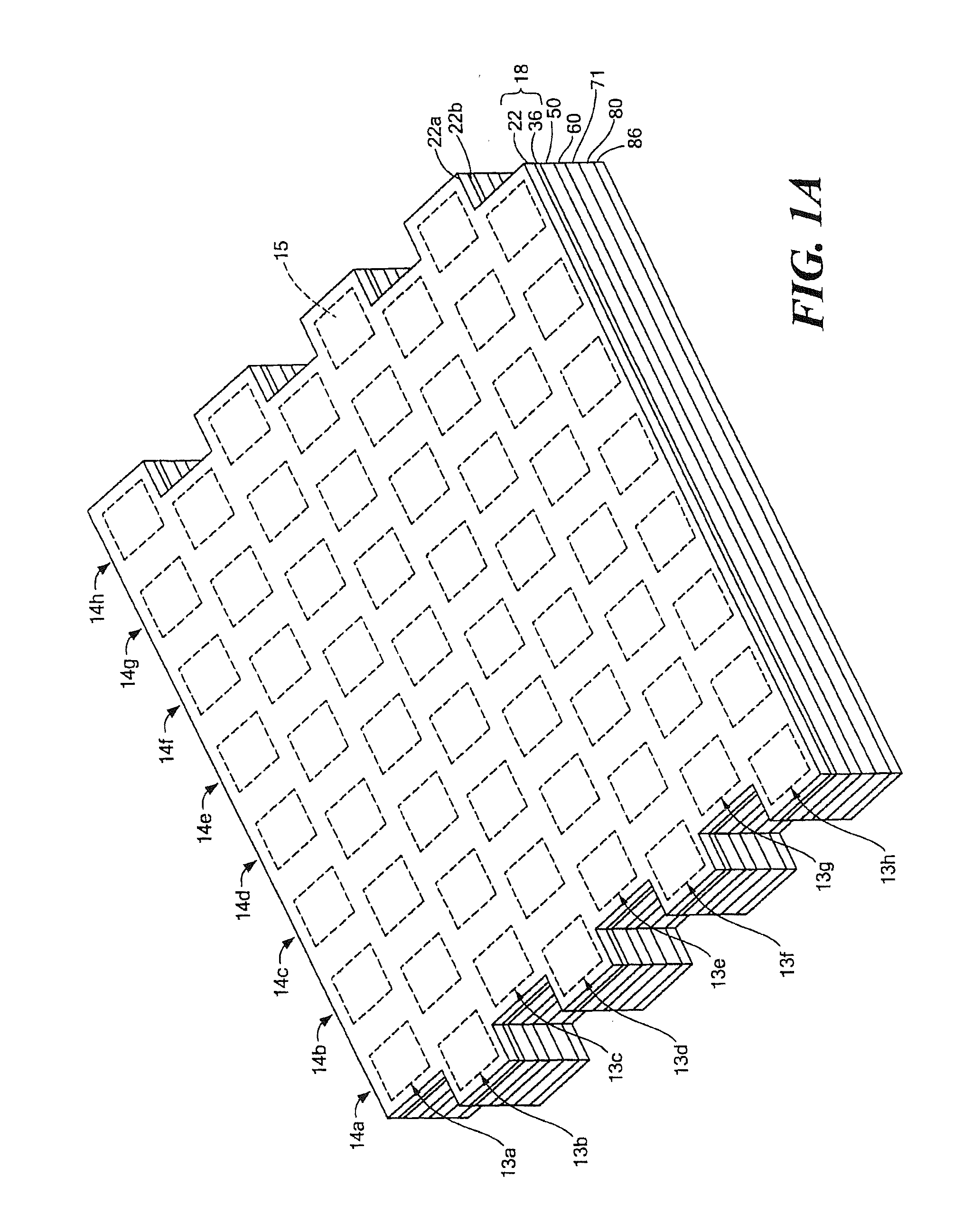

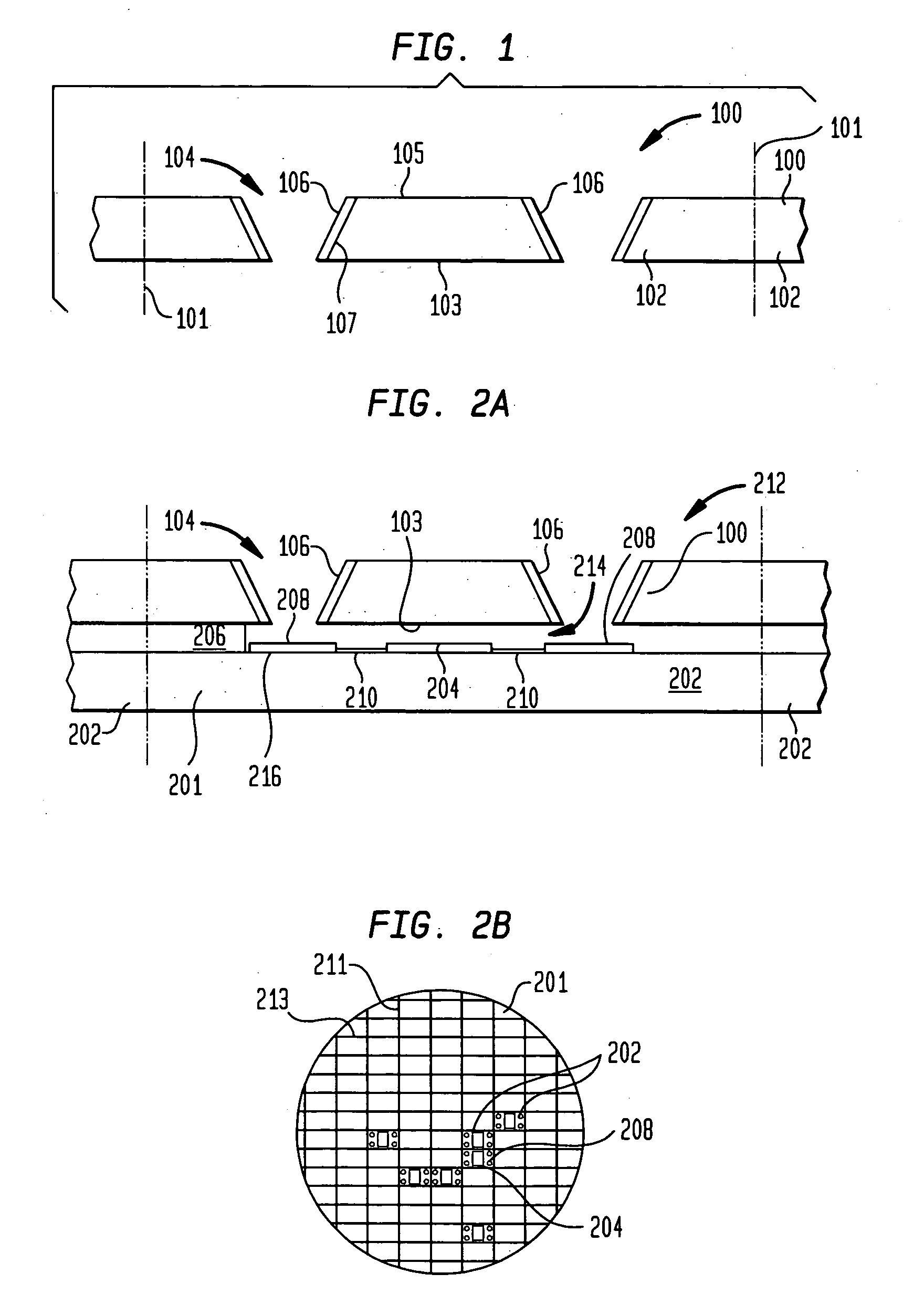

Panel Array

ActiveUS20100066631A1Low insertion lossEliminate needAntenna arrays manufactureModular arraysHemt circuitsChipset

A mixed-signal, multilayer printed wiring board fabricated in a single lamination step is described. The PWB includes one or more radio frequency (RF) interconnects between different circuit layers on different circuit boards which make up the PWB. The PWB includes a number of unit cells with radiating elements and an RF cage disposed around each unit cell to isolate the unit cell. A plurality of flip-chip circuits are disposed on an external surface of the PWB and a heat sink can be disposed over the flip chip components.

Owner:RAYTHEON CO

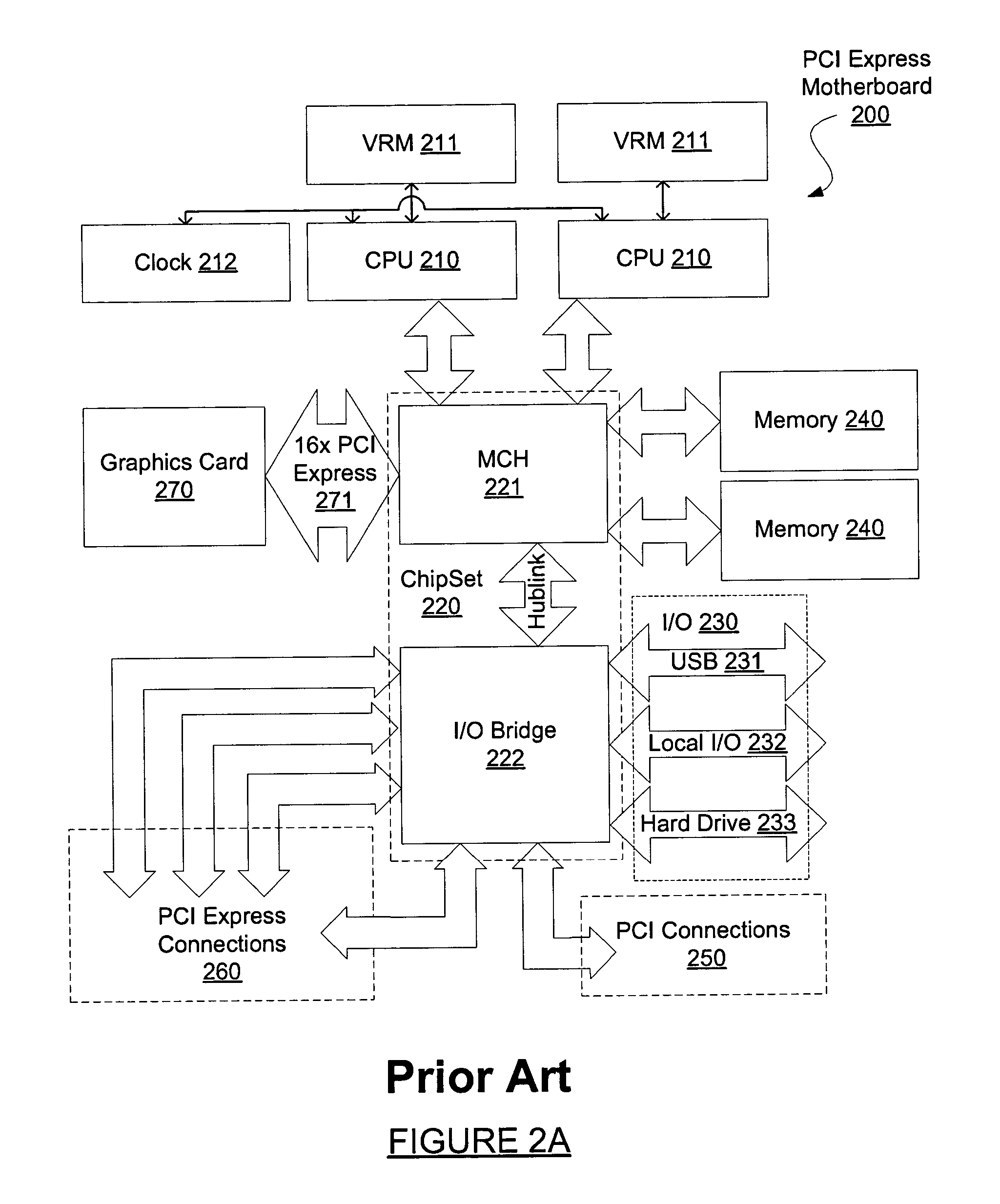

Motherboard for supporting multiple graphics cards

ActiveUS20050088445A1Cathode-ray tube indicatorsMultiple digital computer combinationsGraphicsScalable system

The present invention provides a motherboard that uses a high-speed, scalable system bus such as PCI Express® to support two or more high bandwidth graphics slots, each capable of supporting an off-the-shelf video controller. The lanes from the motherboard chipset may be directly routed to two or more graphics slots. For instance, the chipset may route (1) thirty-two lanes into two ×16 graphics slots; (2) twenty-four lanes into one ×16 graphics slot and one ×8 graphics slot (the ×8 slot using the same physical connector as a ×16 graphics slot but with only eight active lanes); or (3) sixteen lanes into two ×8 graphics slots (again, physically similar to a ×16 graphics slot but with only eight active lanes). Alternatively, a switch can convert sixteen lanes coming from the chipset root complex into two ×16 links that connect to two ×16 graphics slots. Each and every embodiment of the present invention is agnostic to a specific chipset.

Owner:DELL MARKETING

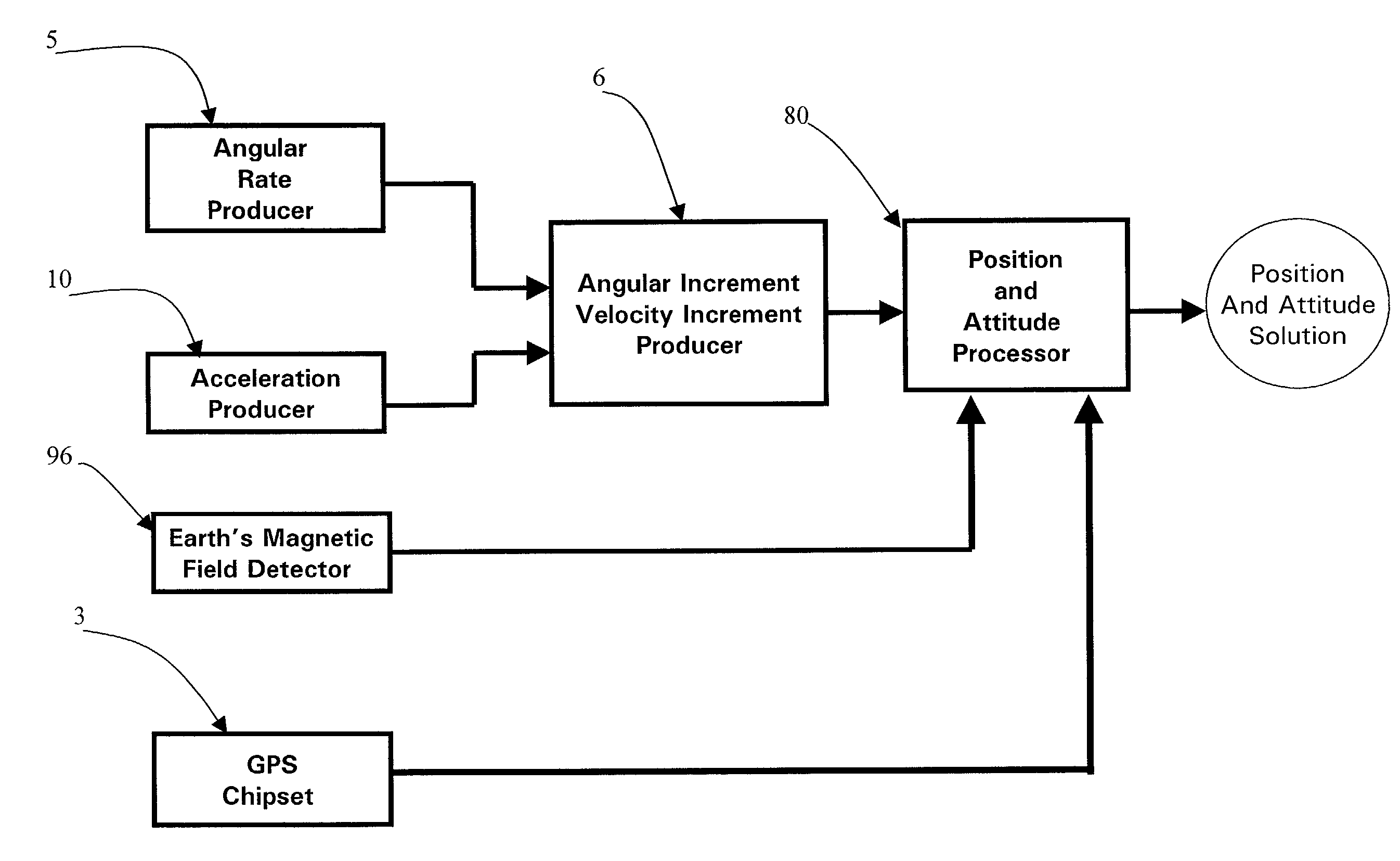

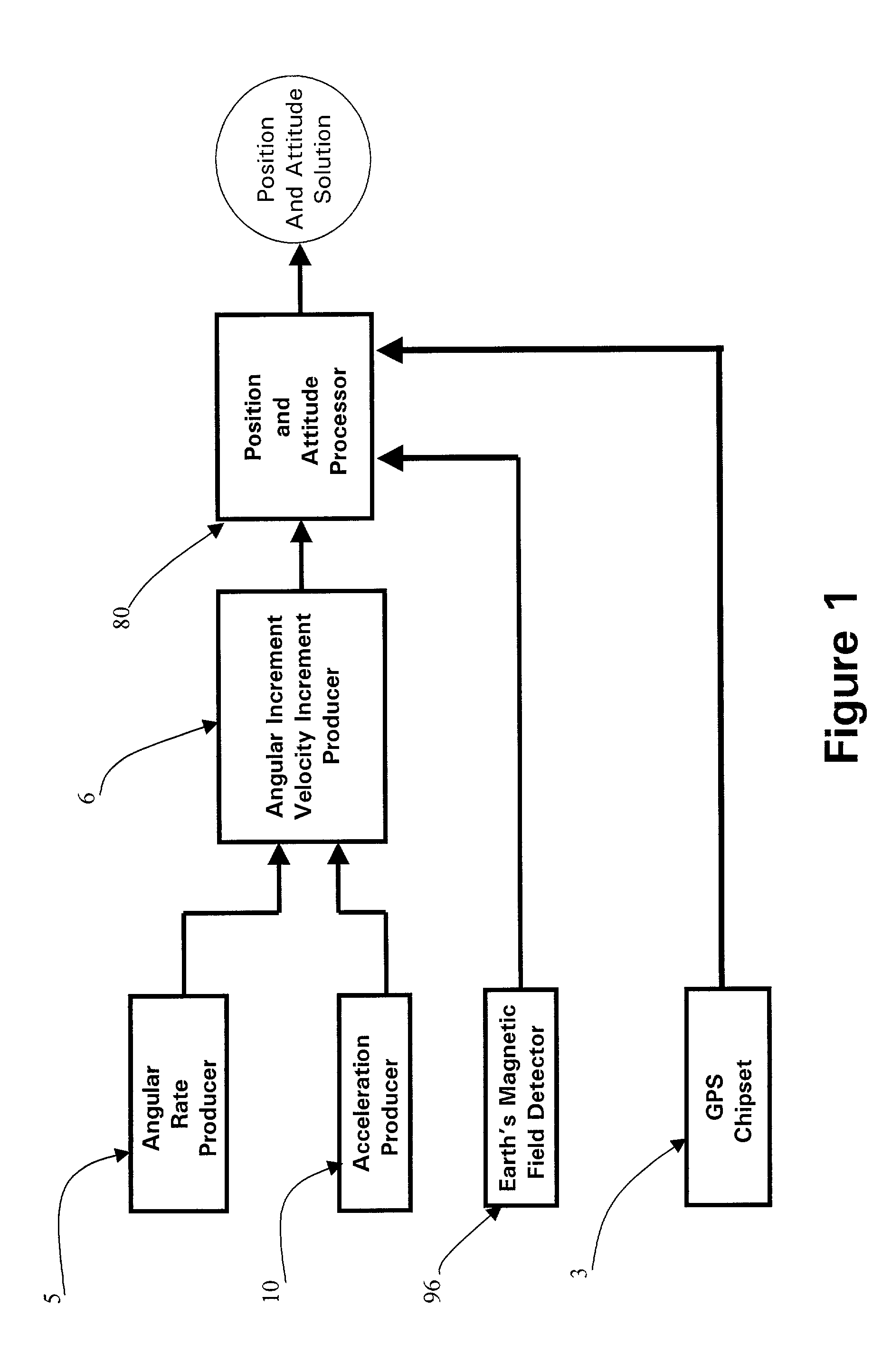

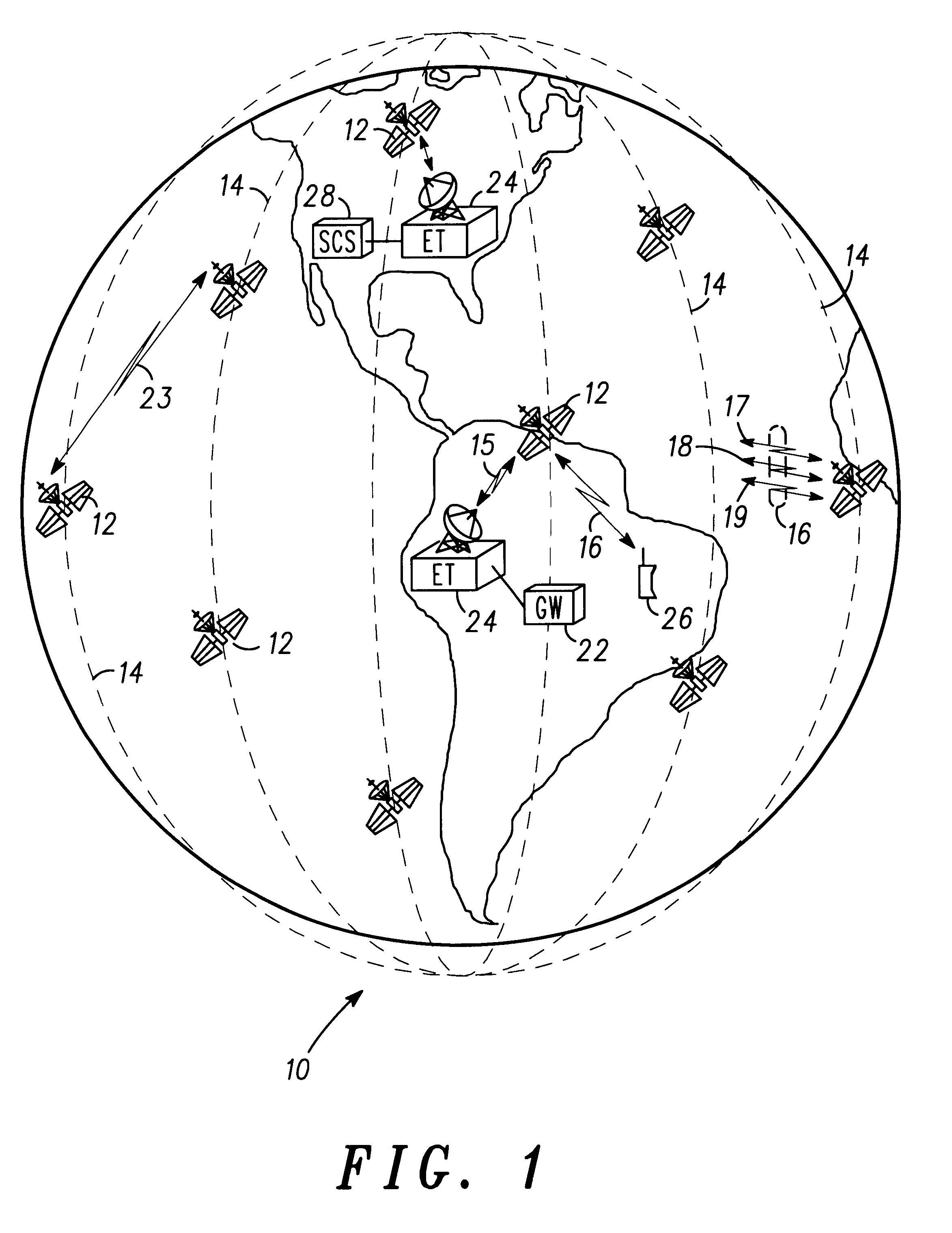

Micro integrated global positioning system/inertial measurement unit system

InactiveUS20020008661A1Precise positioningInstruments for road network navigationPosition fixationCarrier signalClosed loop

A micro integrated Global Positioning System (GPS) / Inertial Measurement Unit (IMU) System, which is adapted to apply to output signals proportional to rotation and translational motion of a carrier and GPS measurements of the carrier, respectively from angular rate sensors, acceleration sensors, and GPS chipset, is employed with MEMS angular rate and acceleration sensors and GPS chipset. Compared with a conventional IMU / GPS system, the system of the present invention uses an integrated processing scheme by means of digital closed loop control of the dither driver signals for MEMS angular rate sensors, a feedforward open-loop signal processing scheme of the IMU, digital temperature control and compensation, the earth's magnetic field-based heading damping, robust error estimator, and compact sensor and circuit architecture and dramatically shrinks the size of mechanical and electronic hardware and power consumption, meanwhile, obtains highly accurate motion measurements.

Owner:AMERICAN GNC

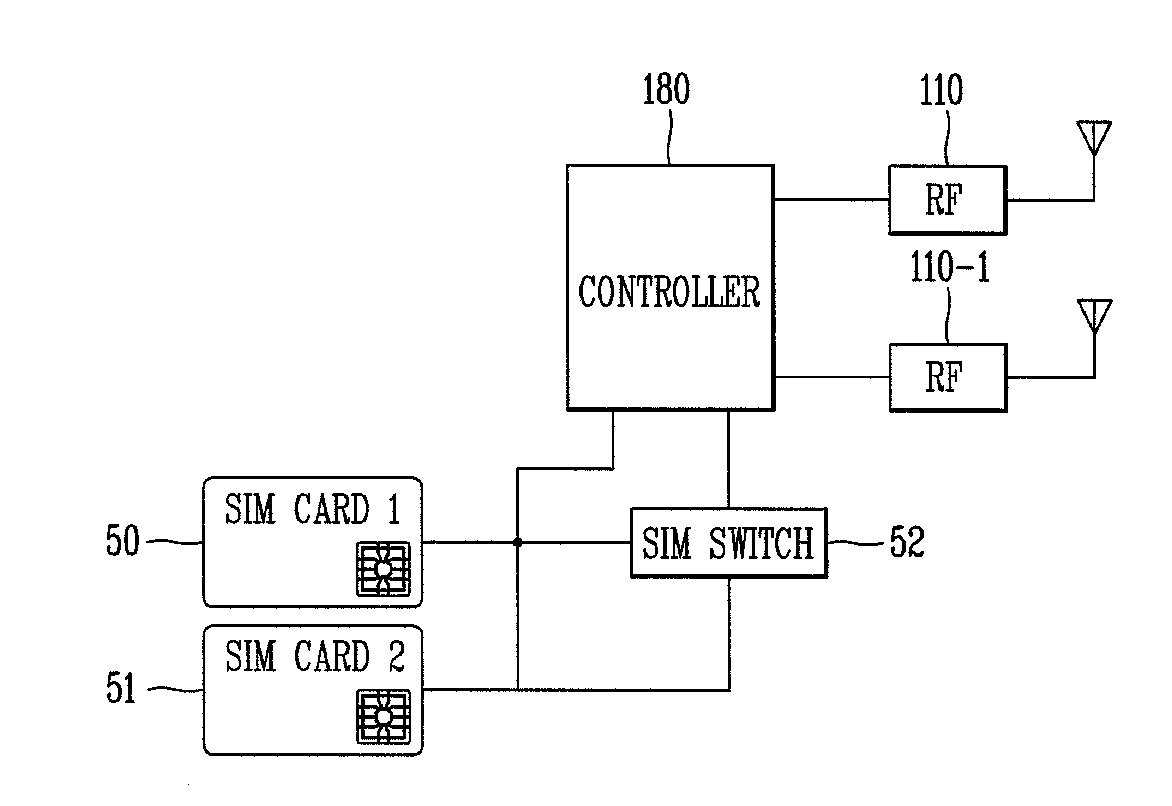

Dual sim mobile terminal and operating method thereof

ActiveUS20120135715A1Reduce probabilityAccounting/billing servicesUnauthorised/fraudulent call preventionEngineeringChipset

Disclosed herein is a dual SIM terminal and an operating method thereof for supporting dual standby and single talk using a single baseband. The dual SIM mobile terminal may include a controller which is a single chipset, a dual SIM, and two radio frequency (RF) units, thereby having an effect capable of providing a service at the same level as a dual SIM using two mobile terminals even with one mobile terminal. Furthermore, dual SIM switching is performed according to a state of the network, a pricing system, and a user's setting, thereby providing the user's desired service.

Owner:LG ELECTRONICS INC

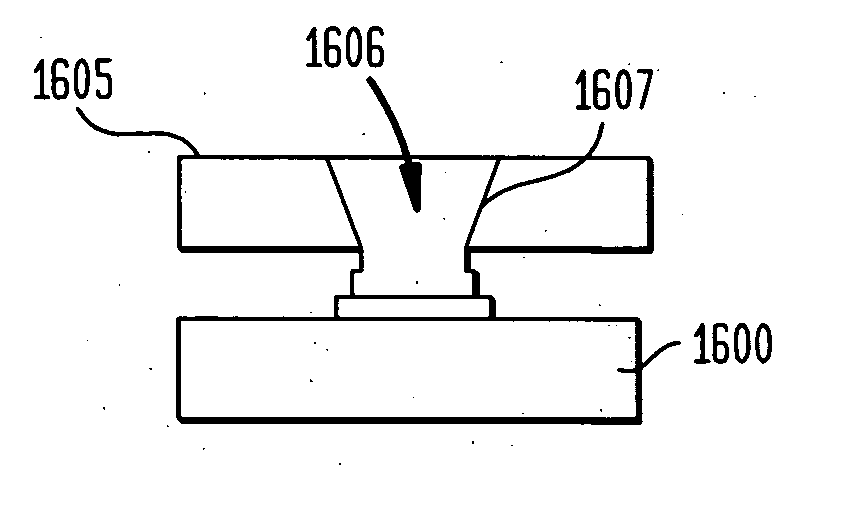

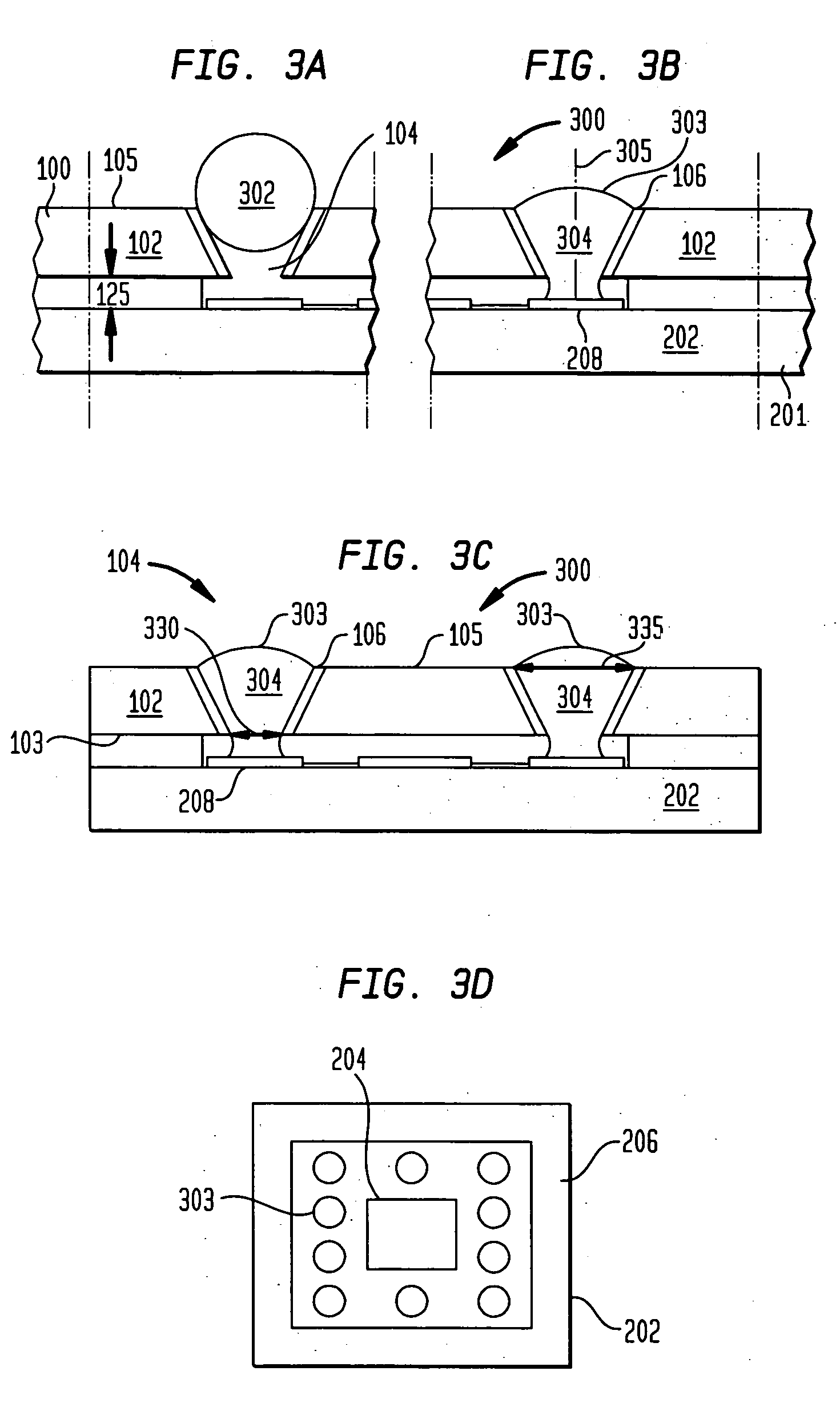

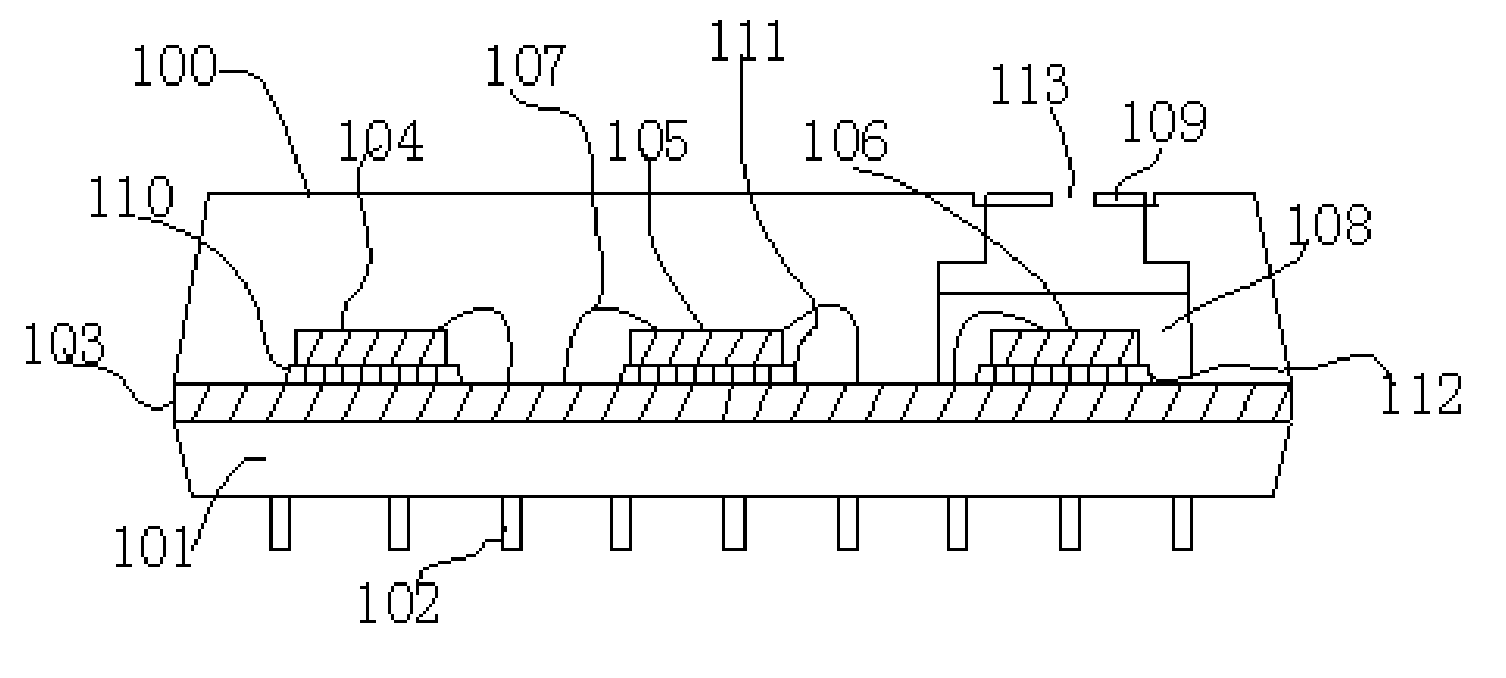

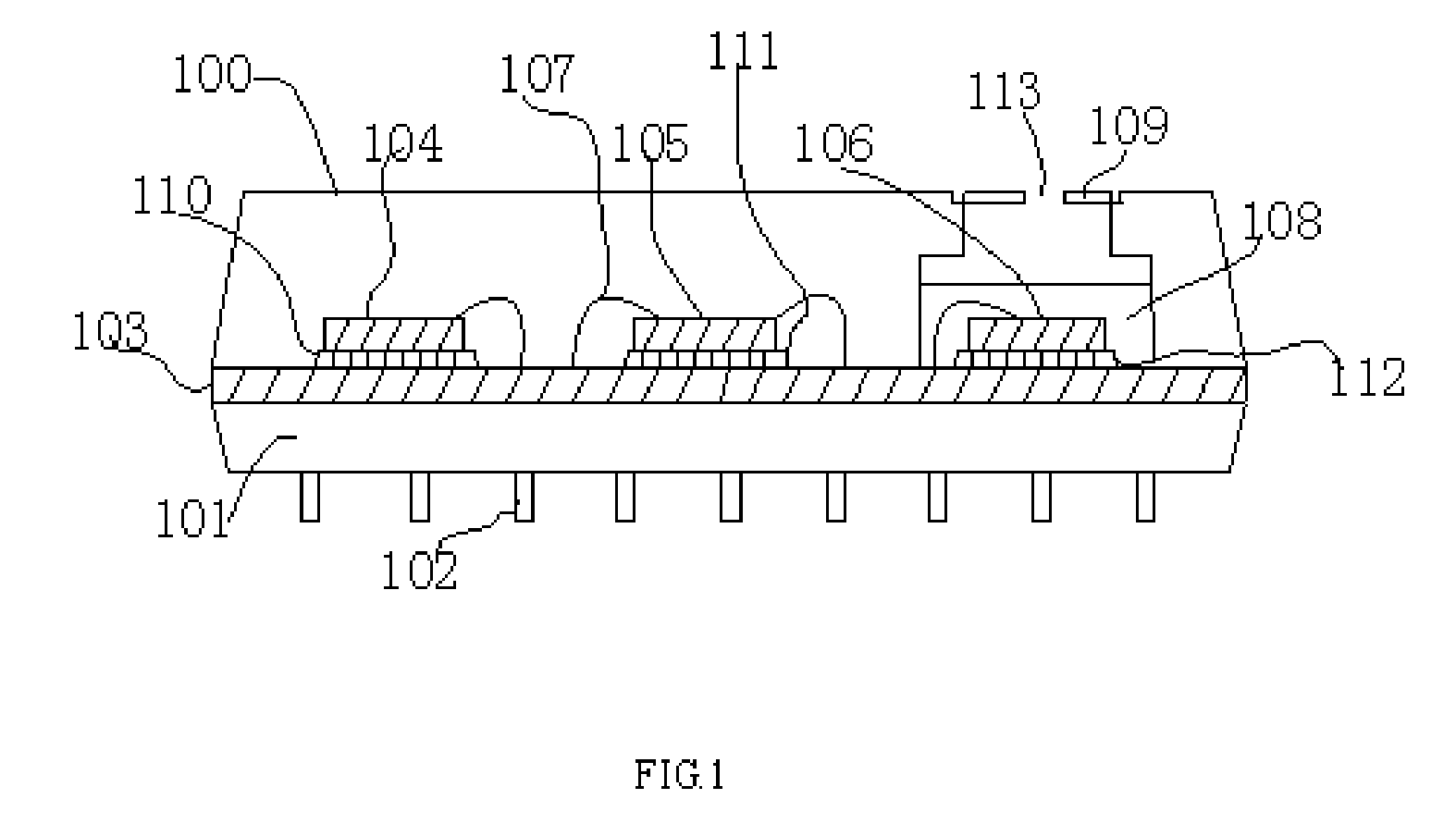

Structure and method of making capped chips including vertical interconnects having stud bumps engaged to surfaces of said caps

InactiveUS20050067688A1Impedence networksSemiconductor/solid-state device detailsEngineeringBiomedical engineering

A capped chip is provided which includes a chip and a cap member, the chip having a front surface and a plurality of bond pads exposed at the front surface, the cap member having a bottom surface facing the front surface of the chip and having a top surface opposite the front surface. A plurality of through holes extend from the bottom surface of the cap member to the top surface. The capped chip assembly further includes a plurality of metallic interconnects extending from the bond pads at least partially through the through holes, the metallic interconnects including stud bumps joined to the bond pads, the stud bumps contacting and engaging at least one of (i) the top surface of the cap member surrounding the through holes and (ii) inner surfaces of the through holes.

Owner:TESSERA INC

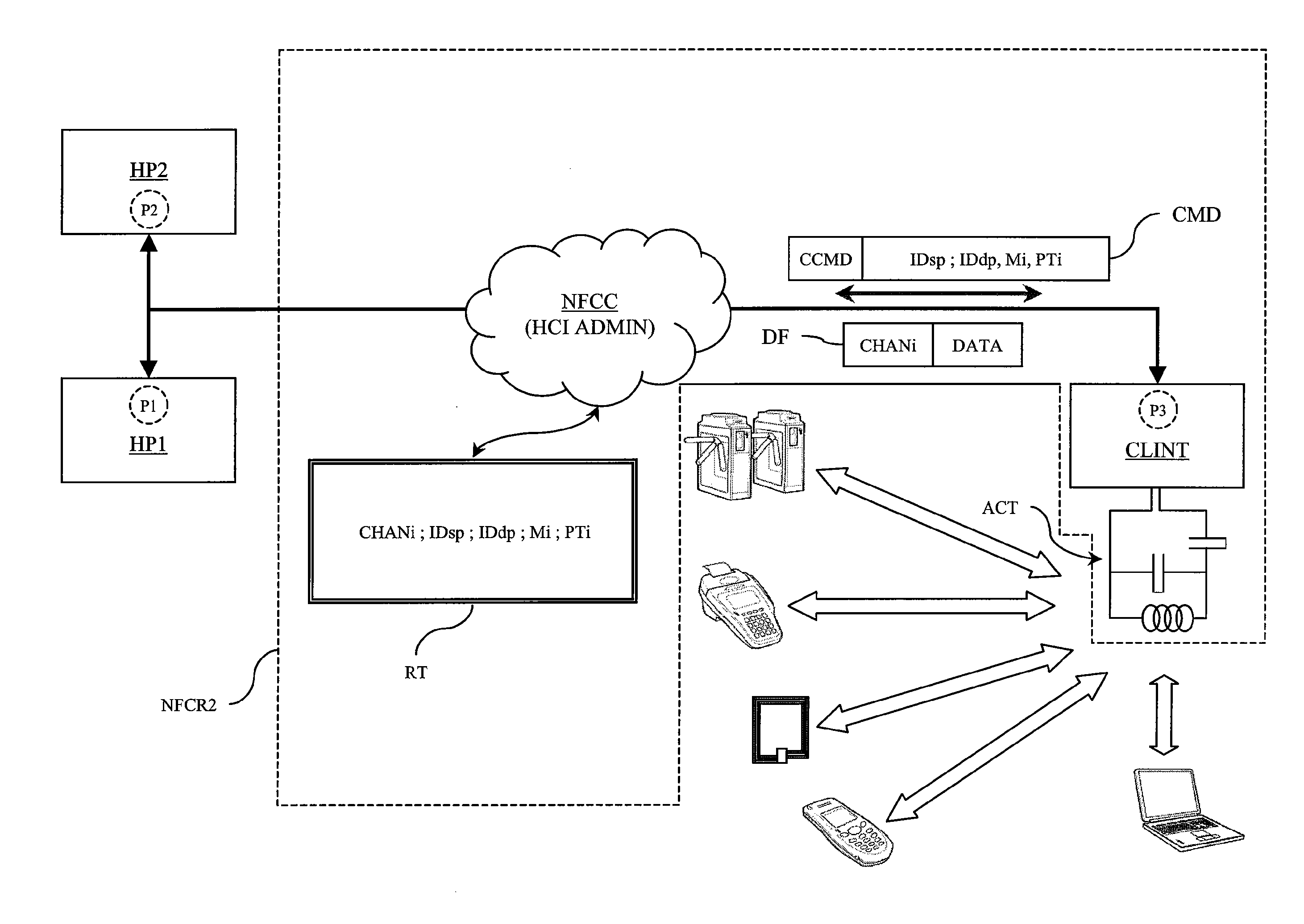

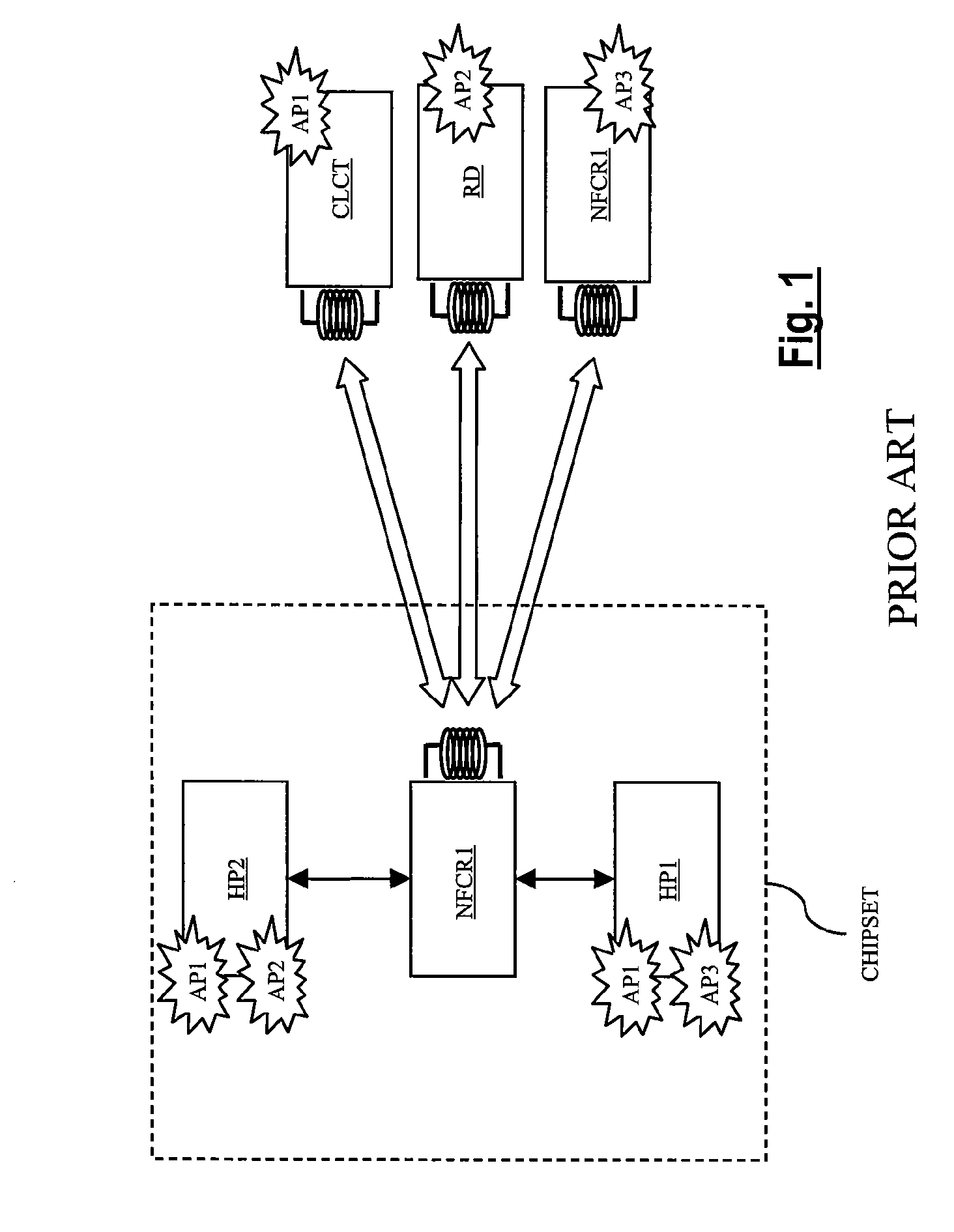

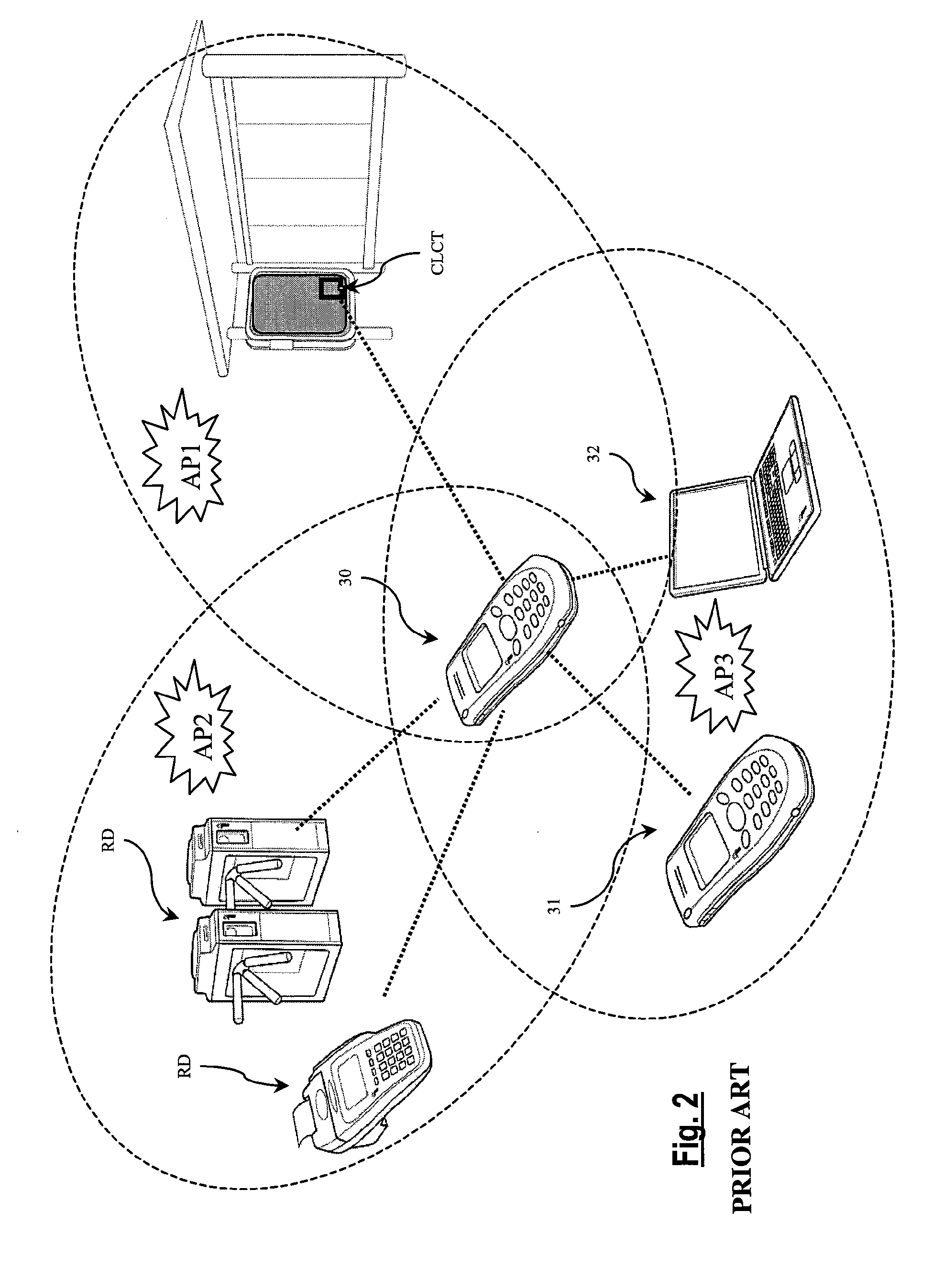

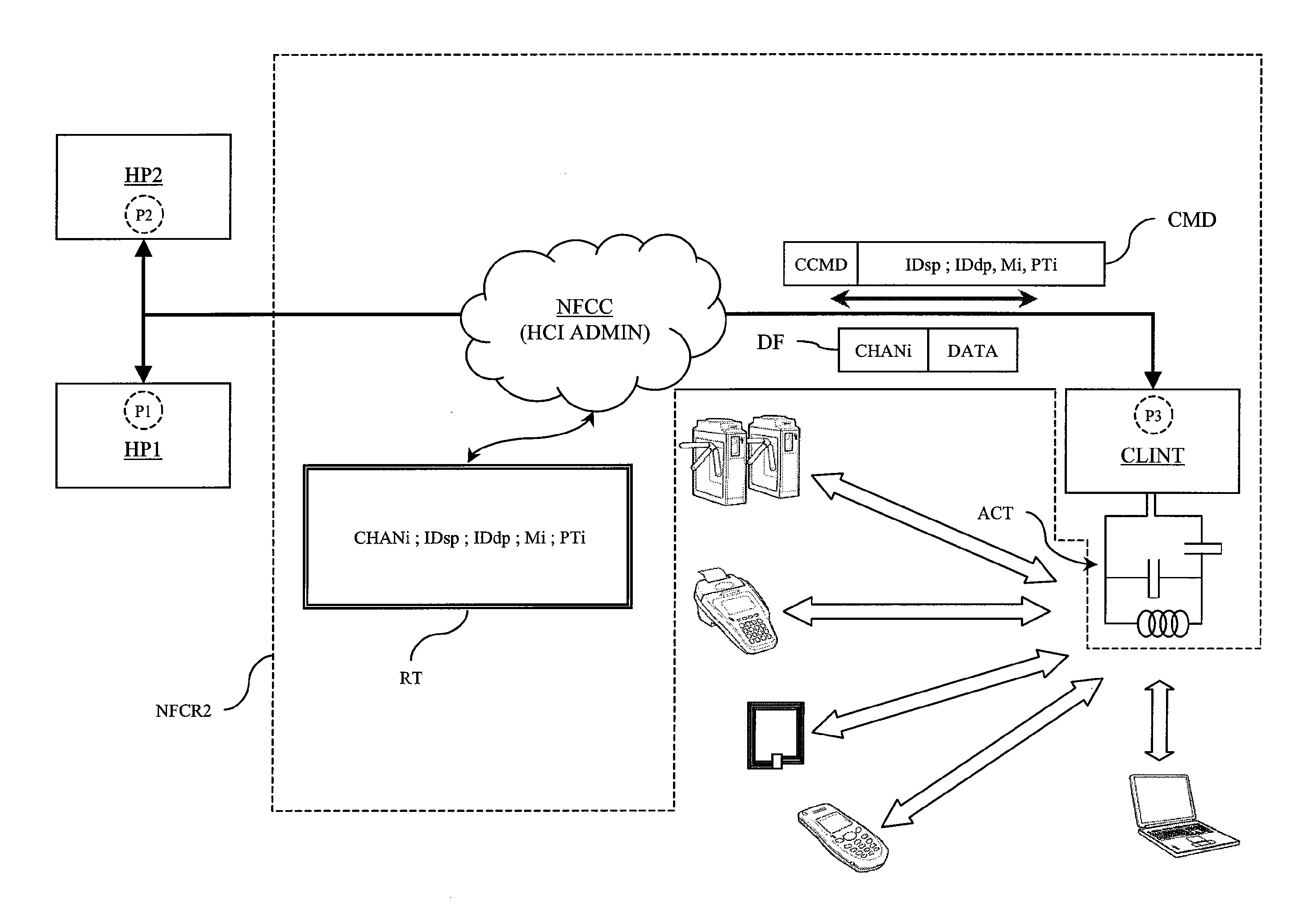

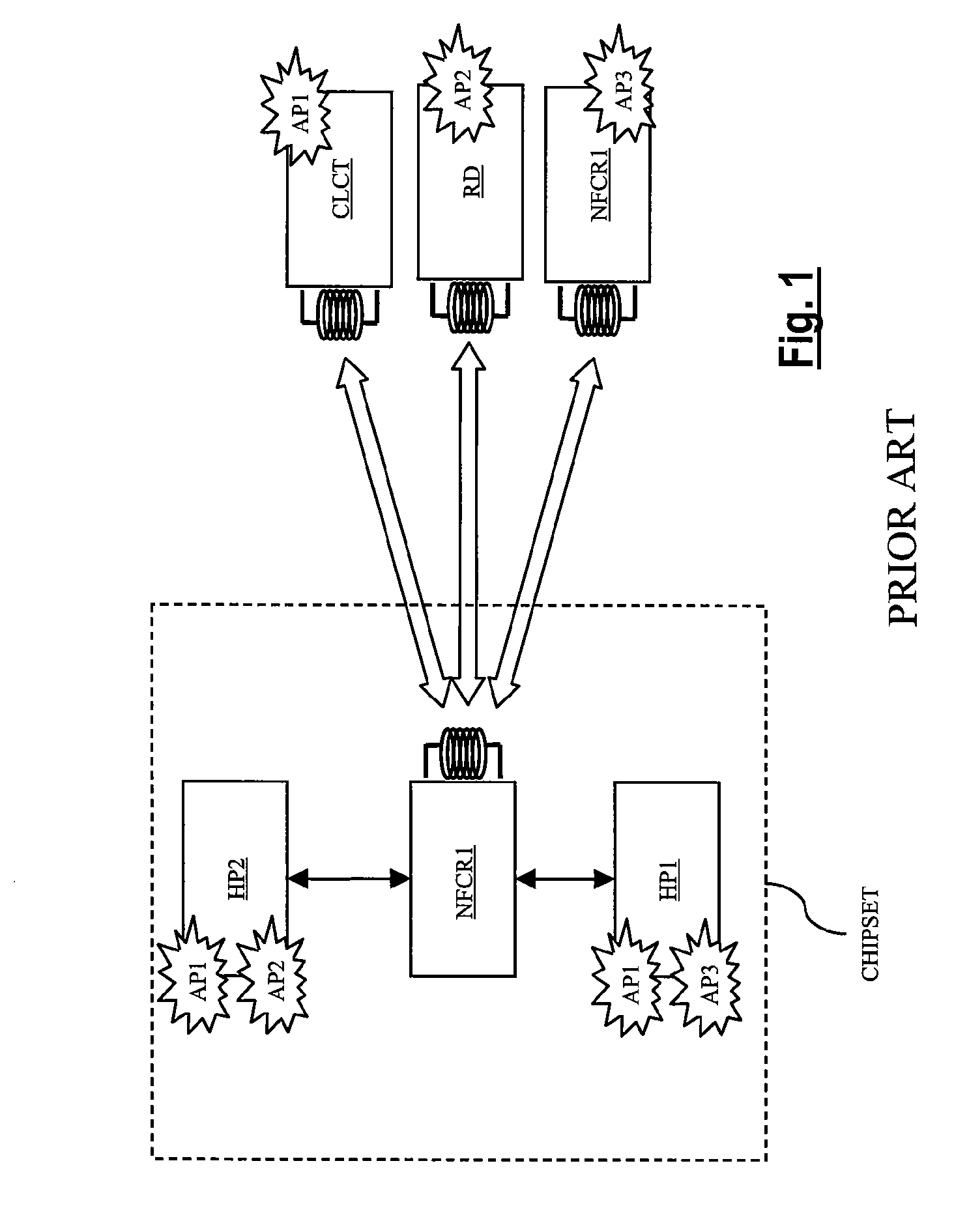

Method for routing incoming and outgoing data in an NFC chipset

A method for routing data in a chipset comprising at least two host processors and one RFID-type contactless data send / receive interface configurable according to several operating modes and according to several contactless communication protocols includes routing, to at least one of the host processors, data received by the contactless data send / receive interface via a contactless data transmission channel. The method further includes determining a destination point of the data in a host processor using as criteria to determine the destination point the operating mode and the contactless communication protocol used by the contactless data send / receive interface to create the contactless data transmission channel through which the data are received.

Owner:VERIMATRIX INC

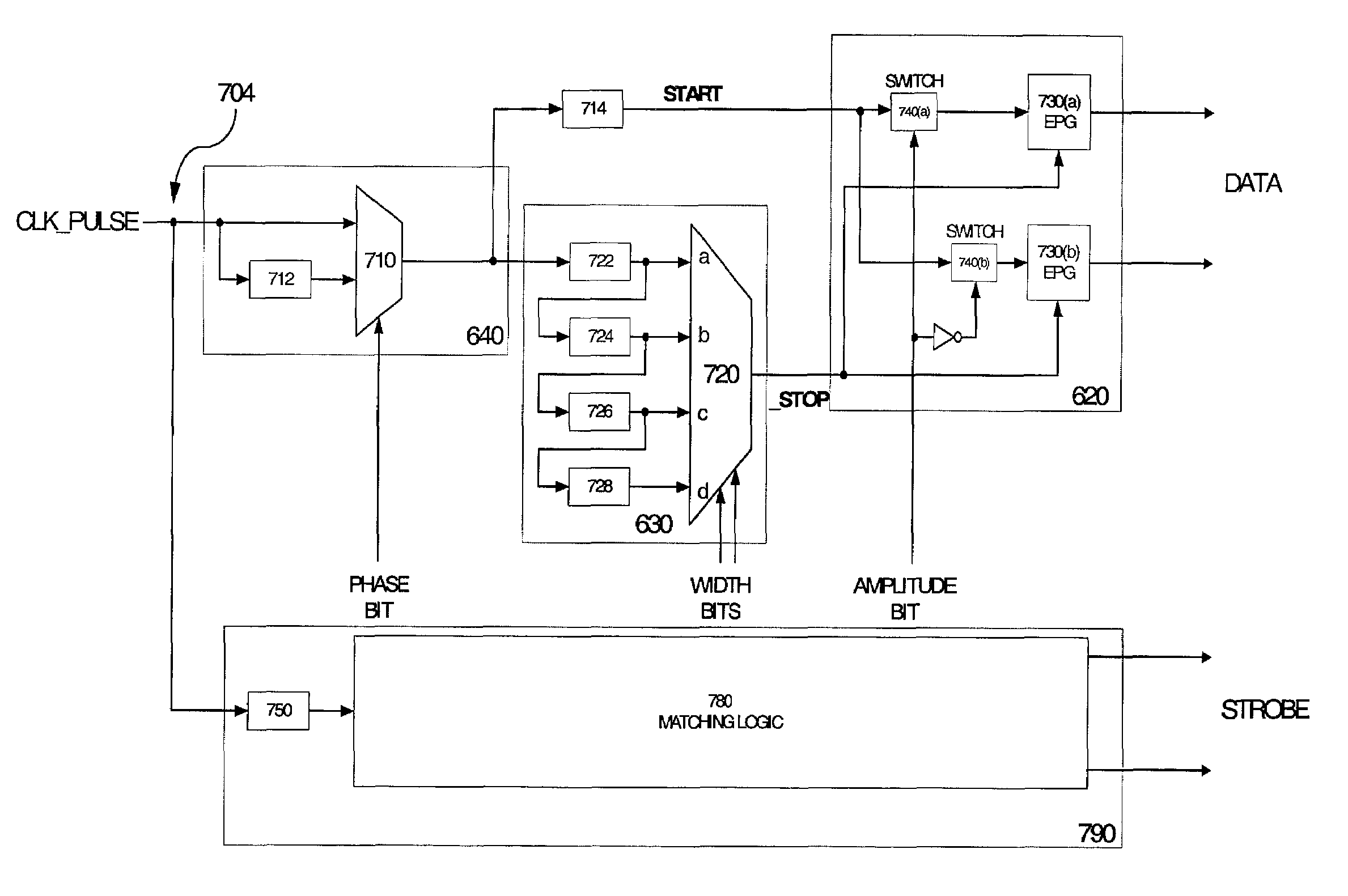

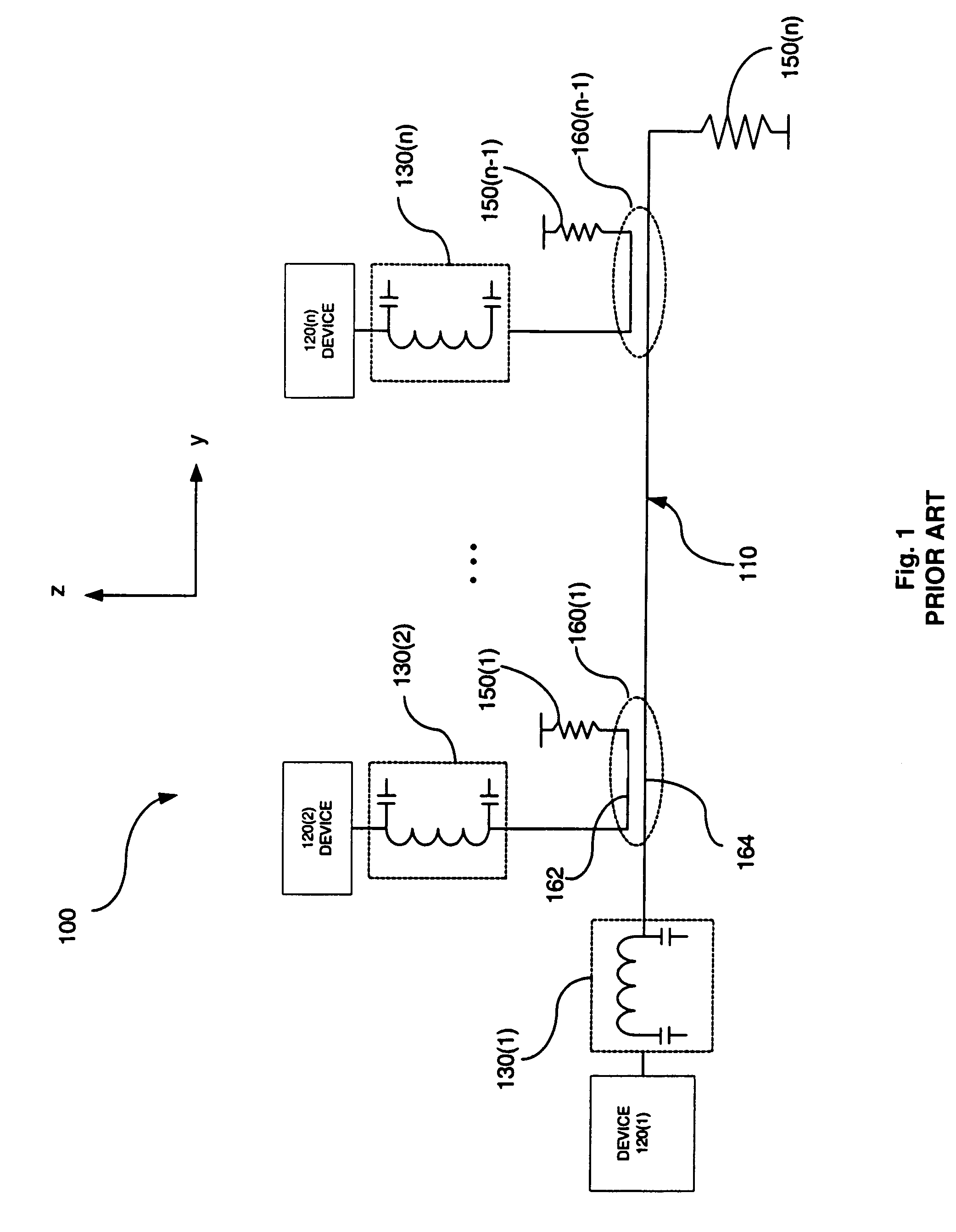

Symbol-based signaling device for an electromagnetically-coupled bus system

InactiveUS7075996B2Printed circuit assemblingLine impedence variation compensationComplementary pairChipset

The present invention provides a chipset for transferring data through an electromagnetically coupled bus system. The chipset includes a modulator, a matching circuit and a demodulator. The modulator modifies a clock to encode multiple bits in a complementary pair of symbols. The matching circuit modifies the clock signal to generate a complementary pair of reference signals that is transmitted with the complementary symbol pair, and the demodulator decodes a second set of bits from selected properties of a complementary pair of transferred symbols.

Owner:INTEL CORP

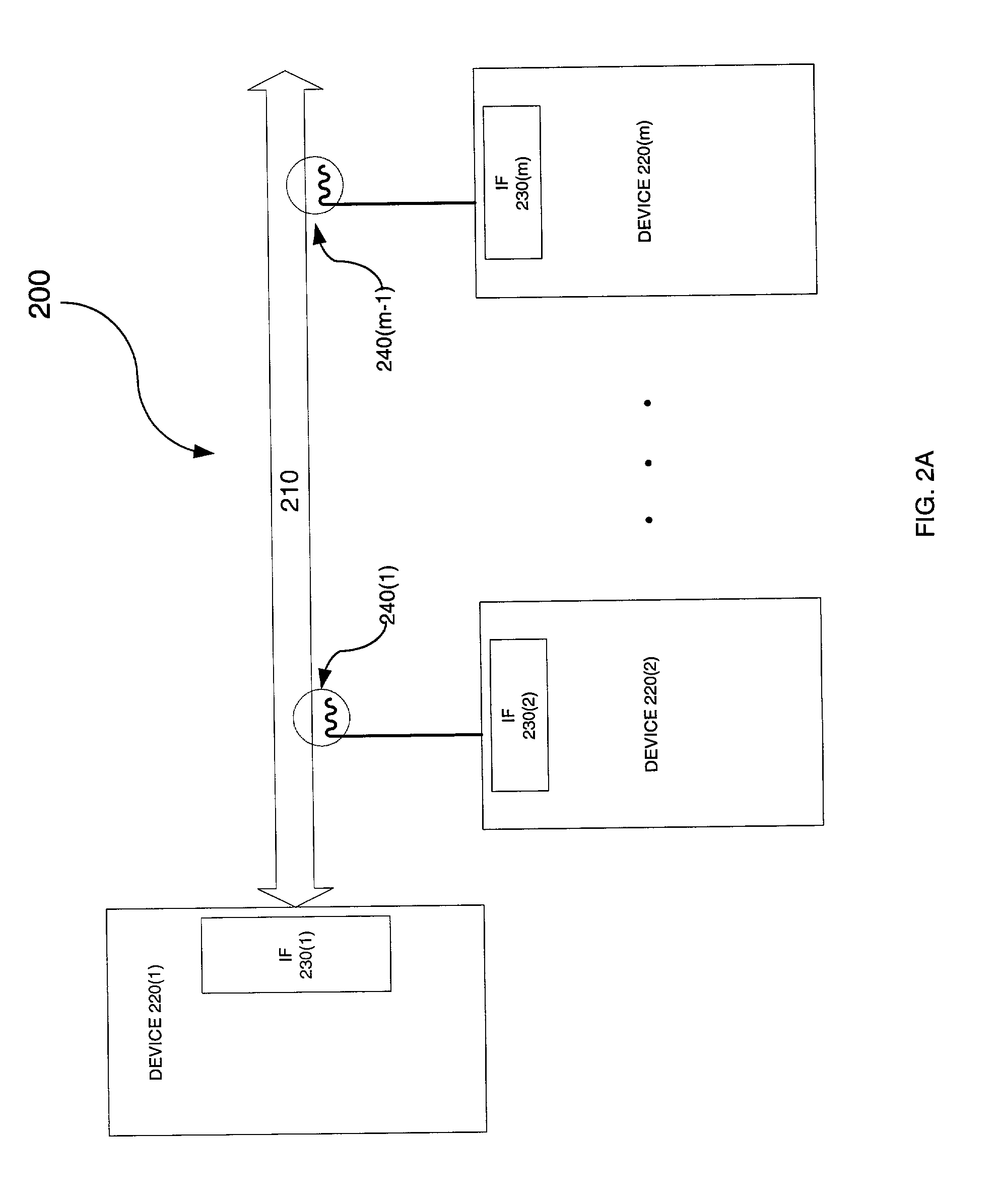

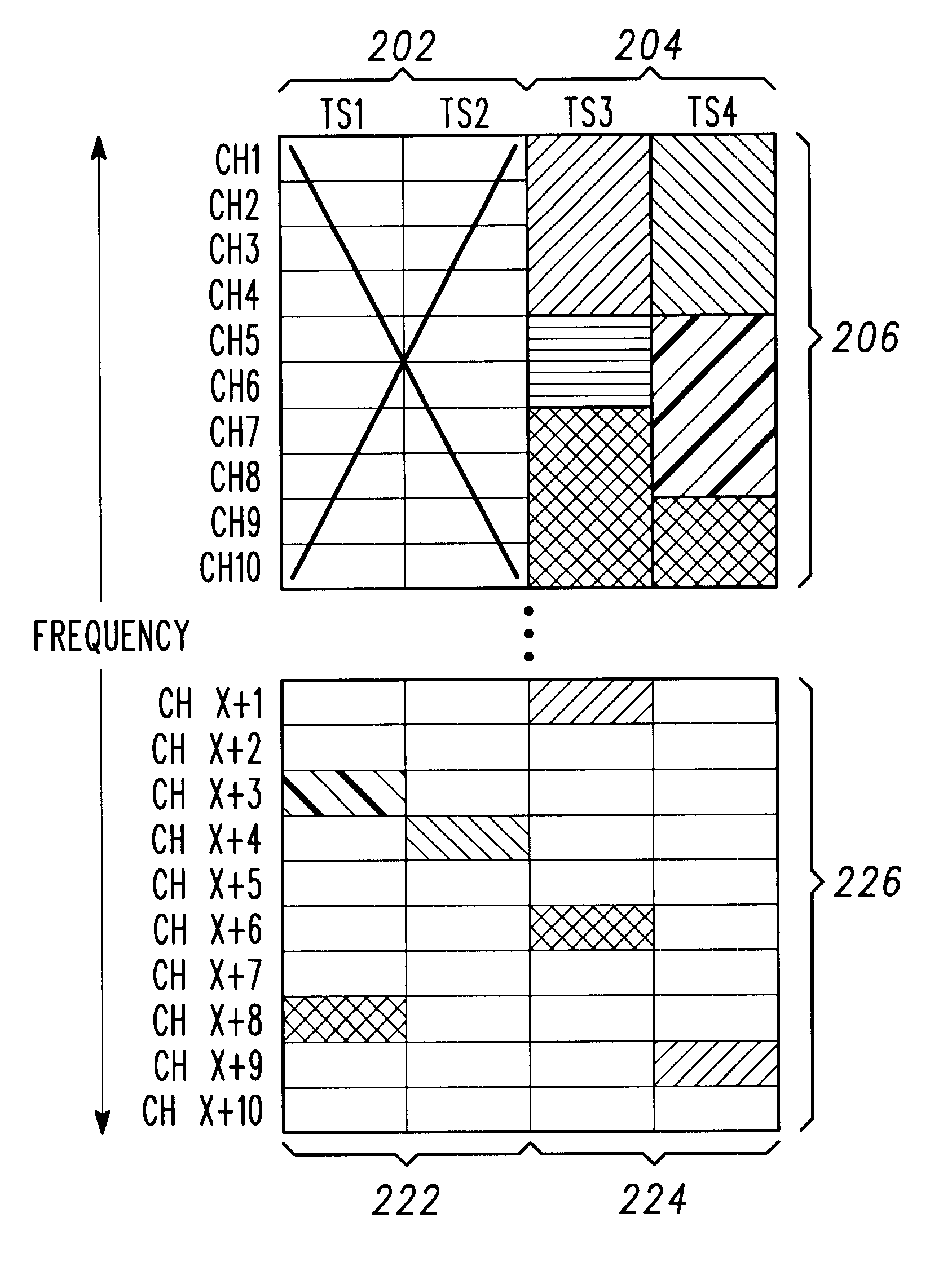

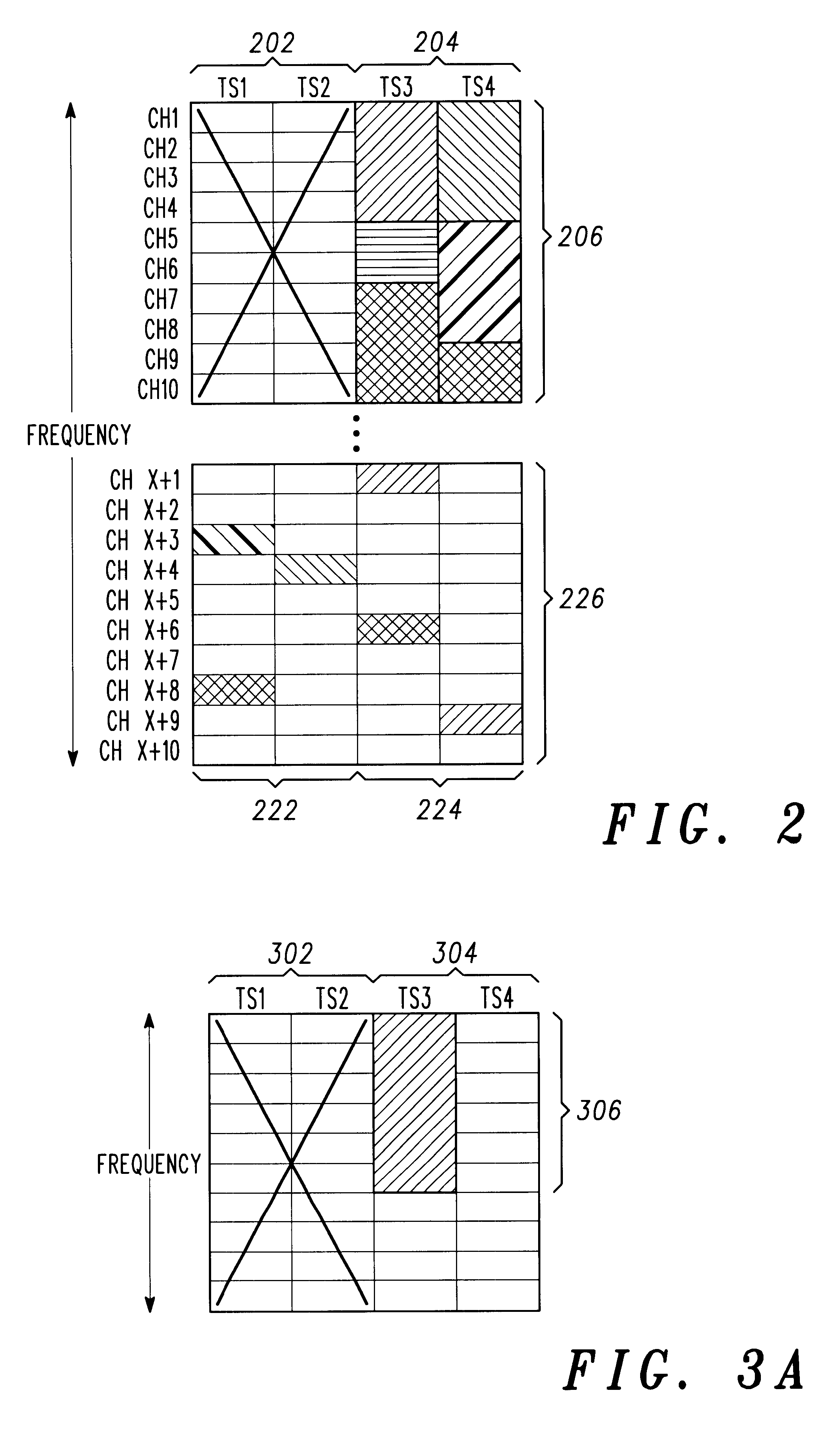

Channel management technique for asymmetric data services

InactiveUS6571102B1Network traffic/resource managementNetwork topologiesData terminalCommunications system

A narrowband communication system provides wideband data services in a secondary service band. This limits the impact on primary services in peak traffic regions in that the primary service band is not required to download wideband data from a communication node (e.g., a satellite) to a mobile terminal. The narrowband communication system implements a handoff protocol (400) that rate negotiates a channel bandwidth of an active connection (404) to the amount of channels that are available in a new cell. The narrowband communication system preempts (414) lower priority subscribers when a higher priority (408) high-speed data terminal requires access to the system and a requested channel assignment is not available (412). The complexity of a high-speed data terminal communication chipset is reduced by a receiver design that minimizes the range of frequencies that are required to be demodulated.

Owner:CDC PROPRIETE INTELLECTUELLE

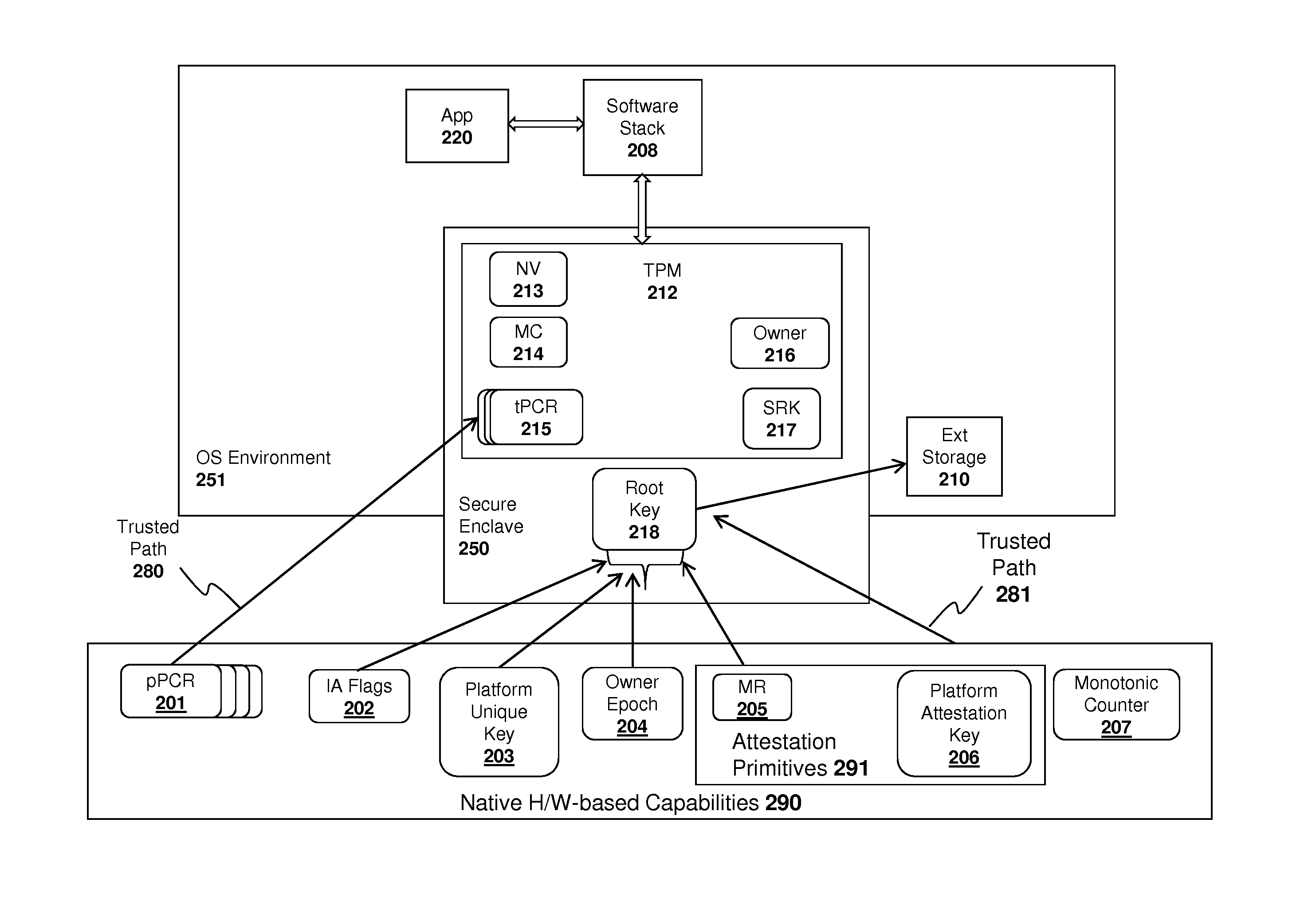

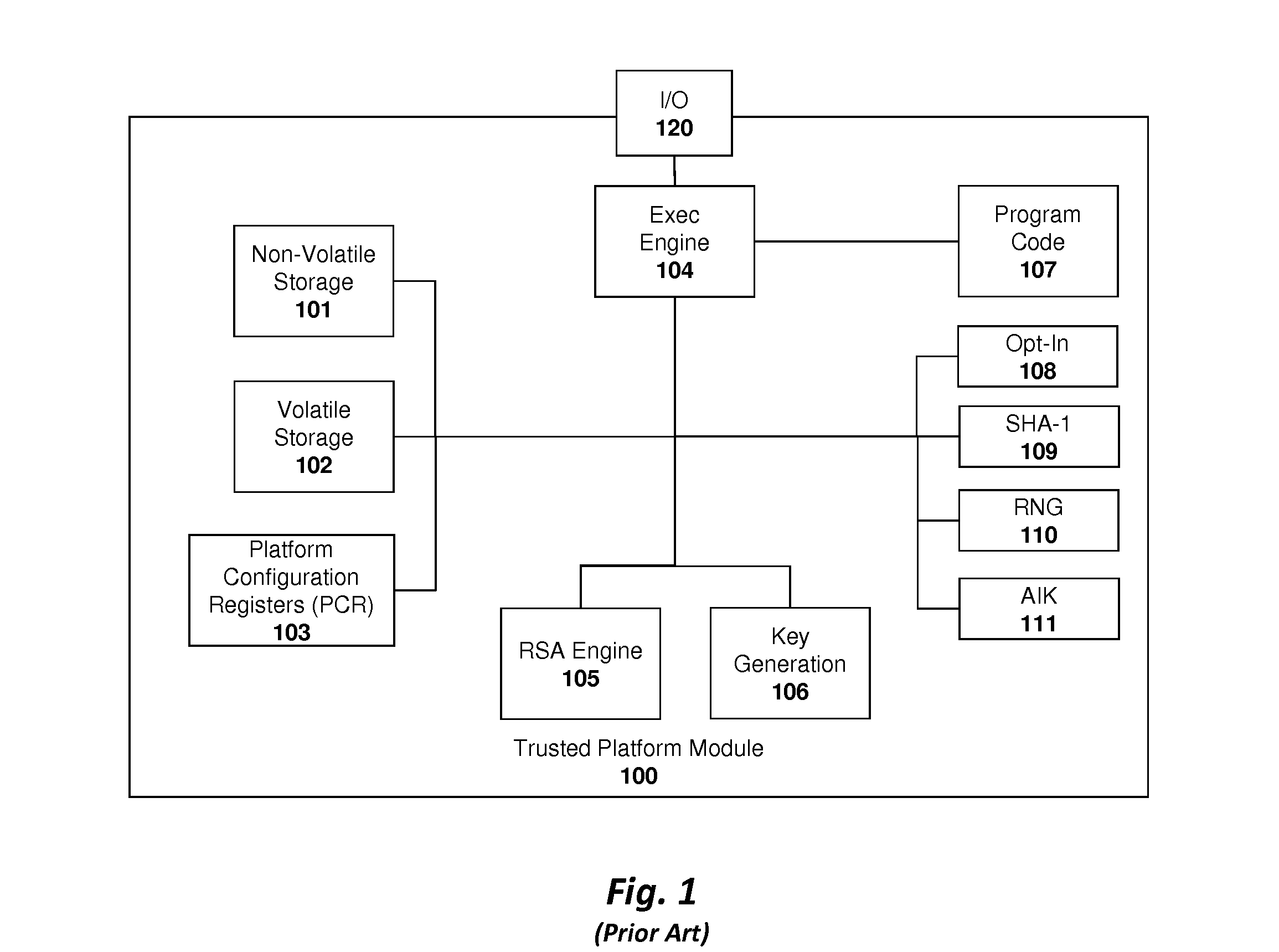

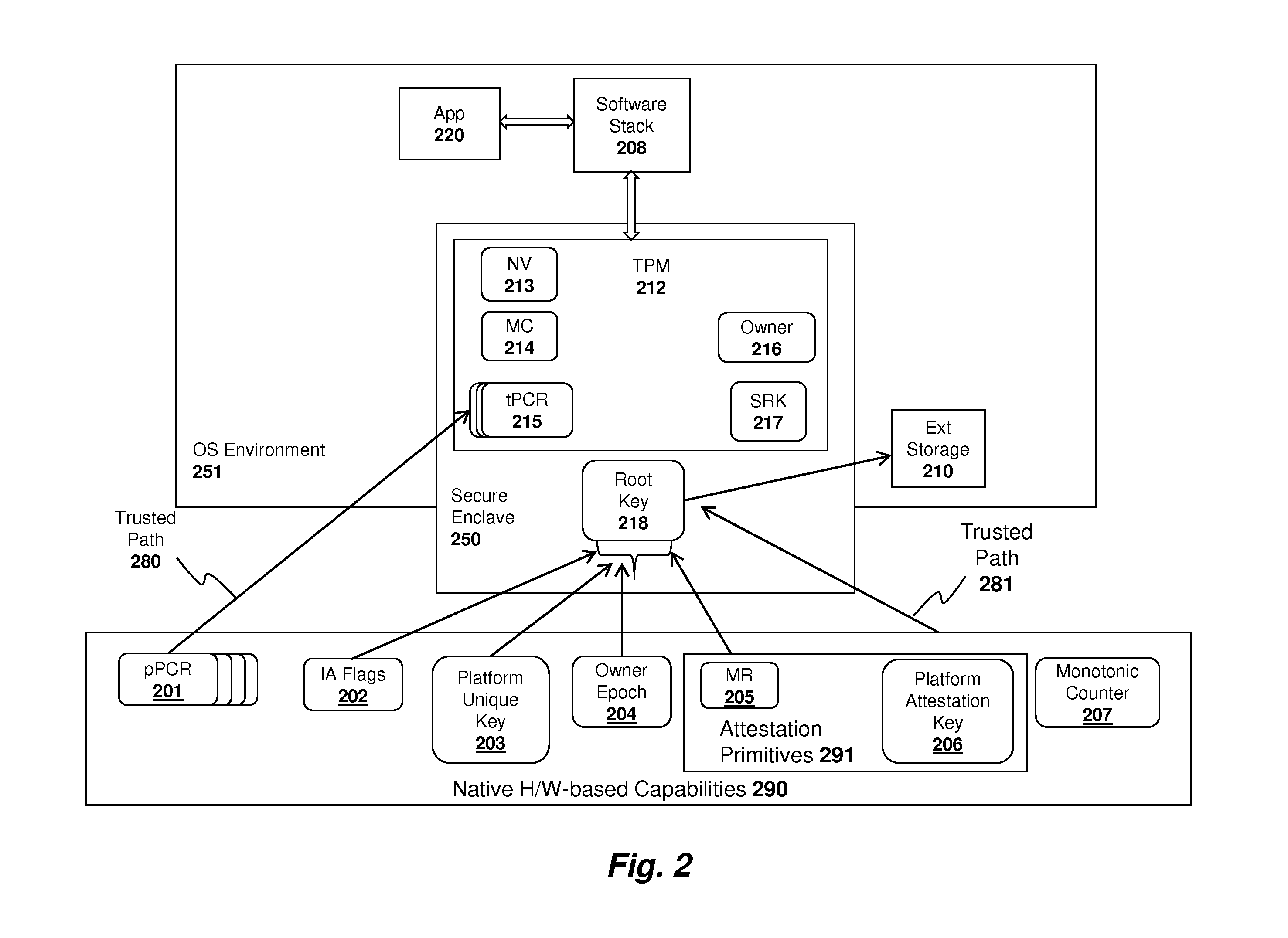

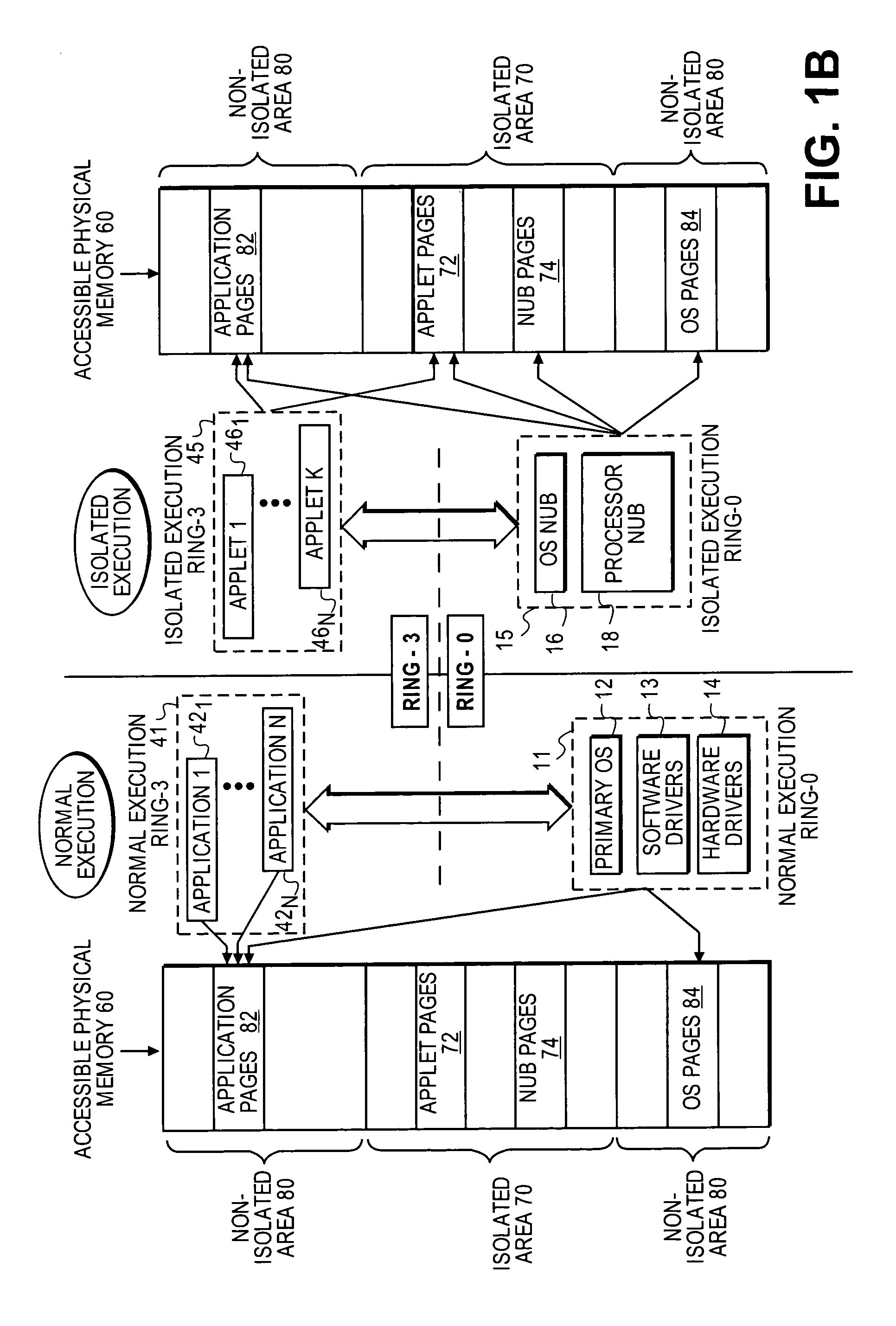

System and method for implementing a trusted dynamic launch and trusted platform module (TPM) using secure enclaves

ActiveUS20120163589A1Public key for secure communicationInternal/peripheral component protectionTrusted Platform ModuleControl register

An apparatus and method are described for implementing a trusted dynamic launch and trusted platform module (TPM) using a secure enclave. For example, a computer-implemented method according to one embodiment of the invention comprises: initializing a secure enclave in response to a first command, the secure enclave comprising a trusted software execution environment which prevents software executing outside the enclave from having access to software and data inside the enclave; and executing a trusted platform module (TPM) from within the secure enclave, the trusted platform module securely reading data from a set of platform control registers (PCR) in a processor or chipset component into a memory region allocated to the secure enclave.

Owner:INTEL CORP

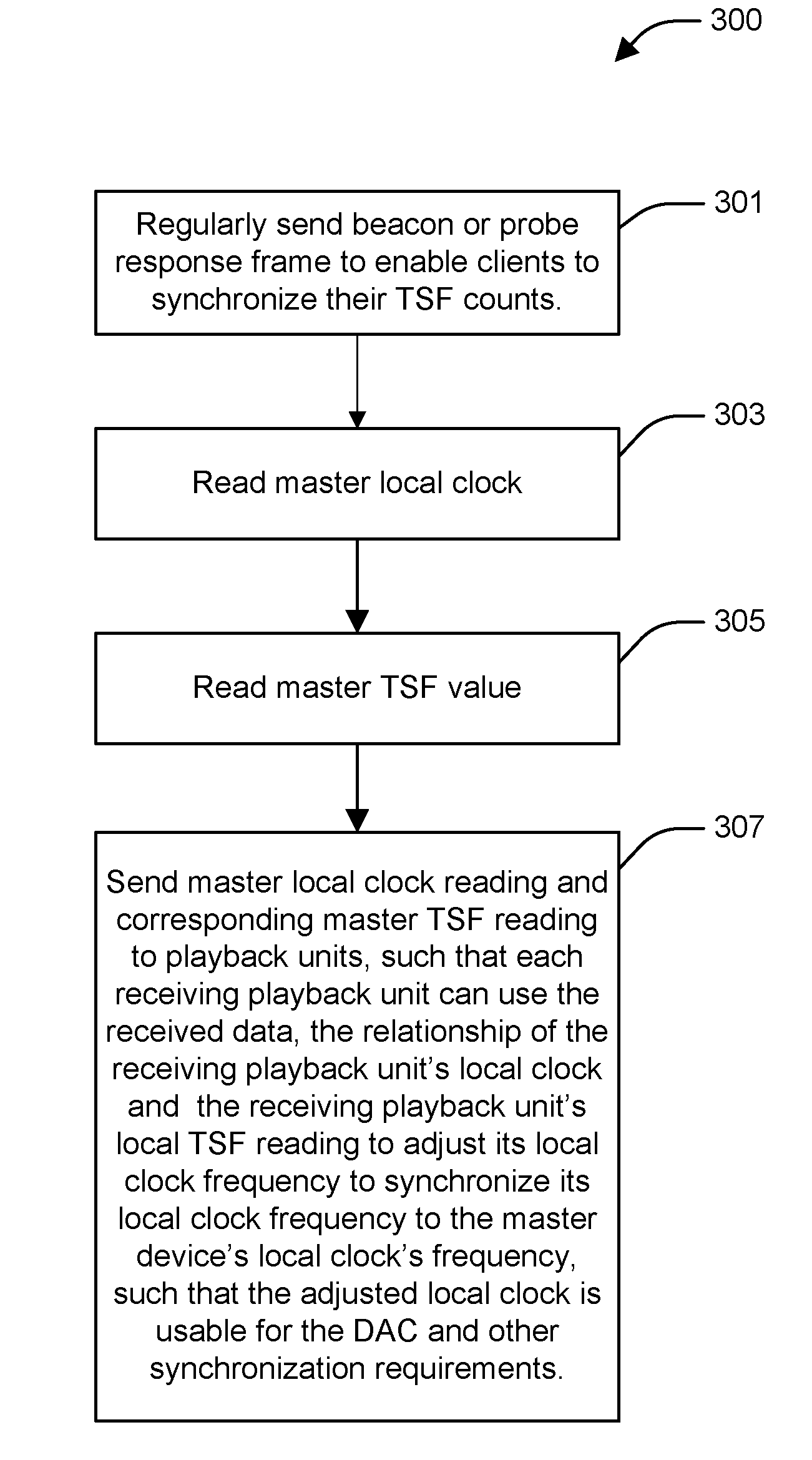

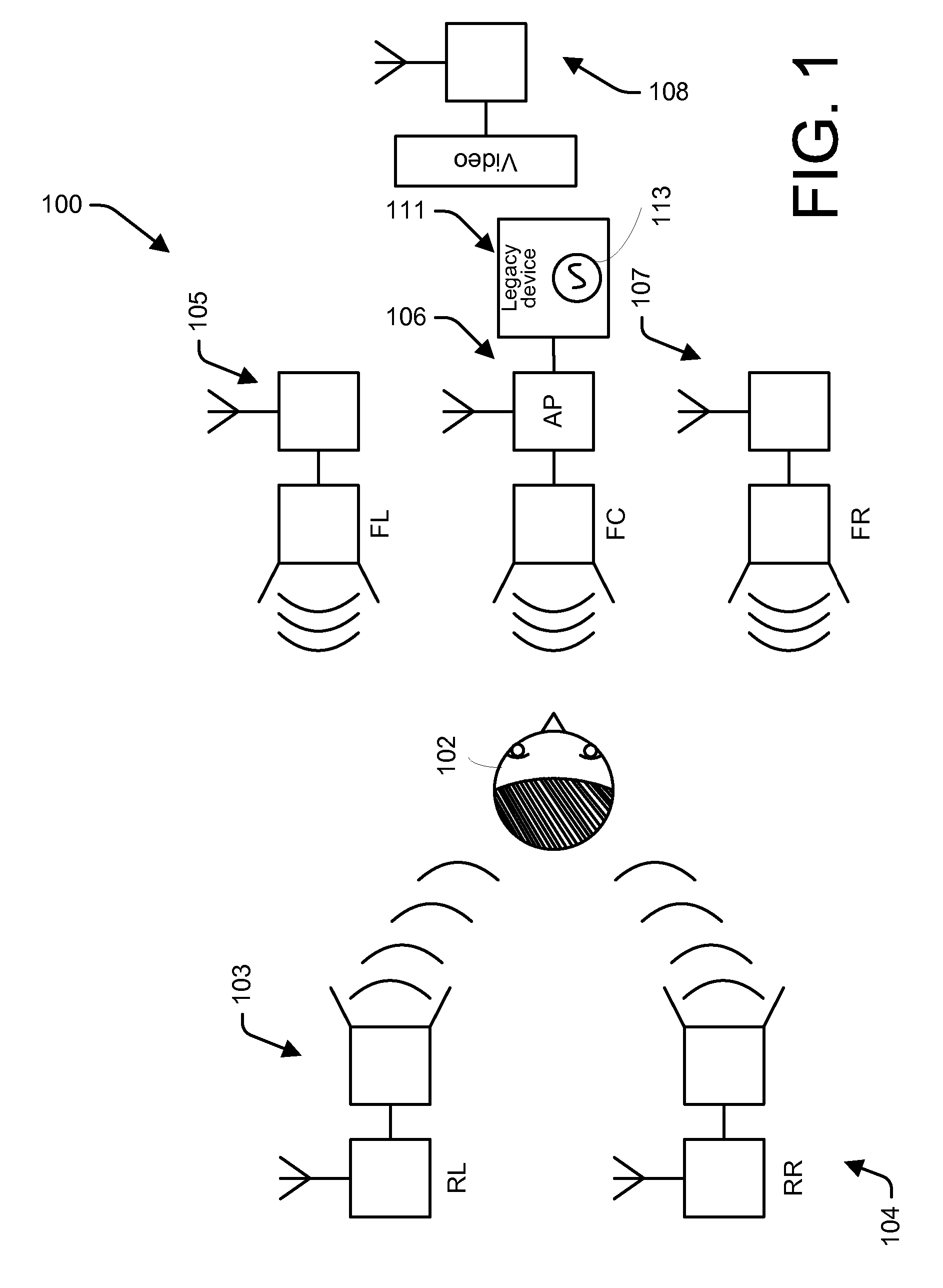

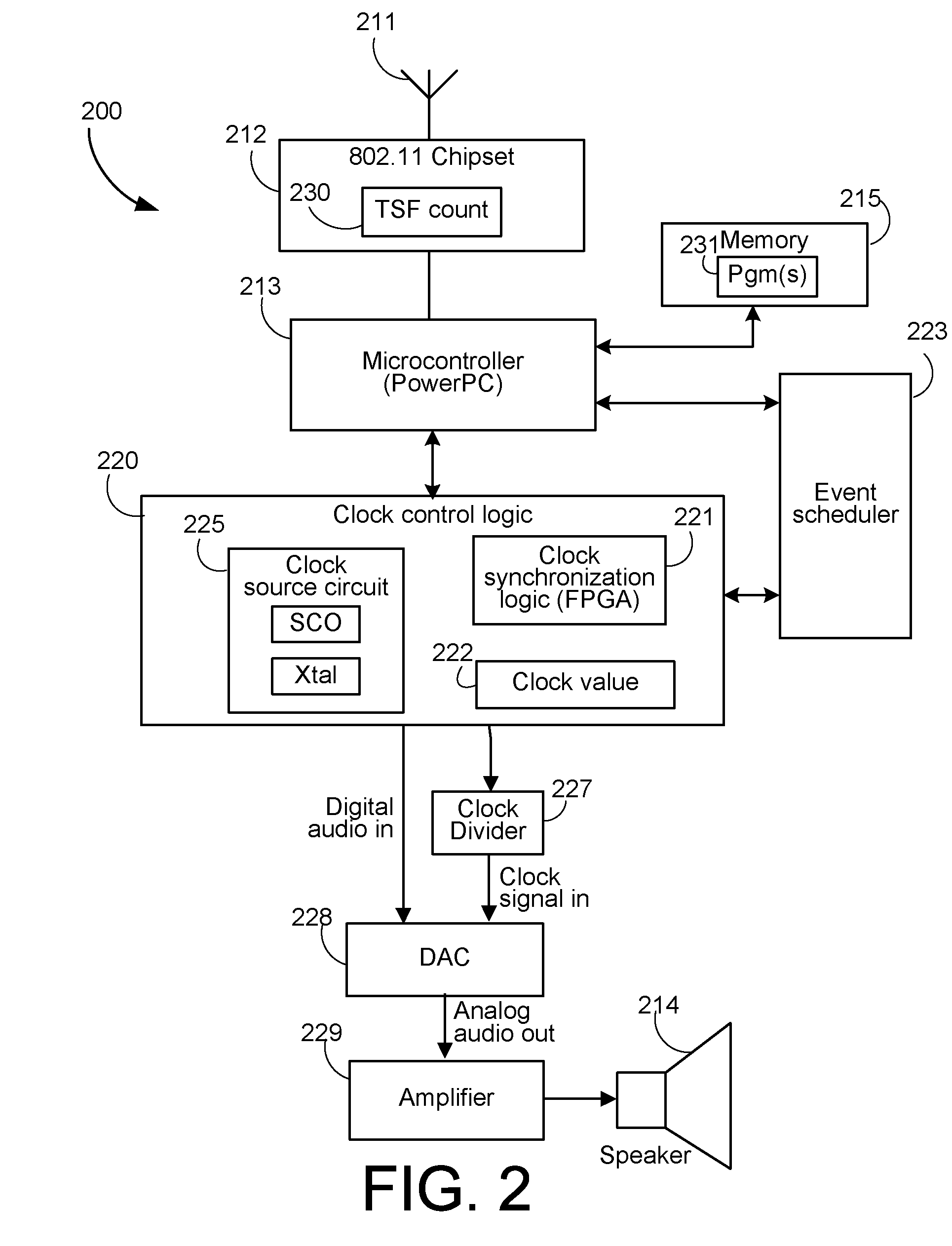

Media data synchronization in a wireless network

ActiveUS20070226530A1Network topologiesTime-division multiplexTiming Synchronization FunctionChipset

A method of keeping global time in a wireless network, the method comprising the steps of: using a first 802.11 chip set to read a Time Synchronization Function (TSF) to provide an initial time base; using an interconnected clock control circuit to read the TSF time directly from the 802.11 chip set and to implement a local clock based on time values read from the TSF function.

Owner:D & M HOLDINGS INC

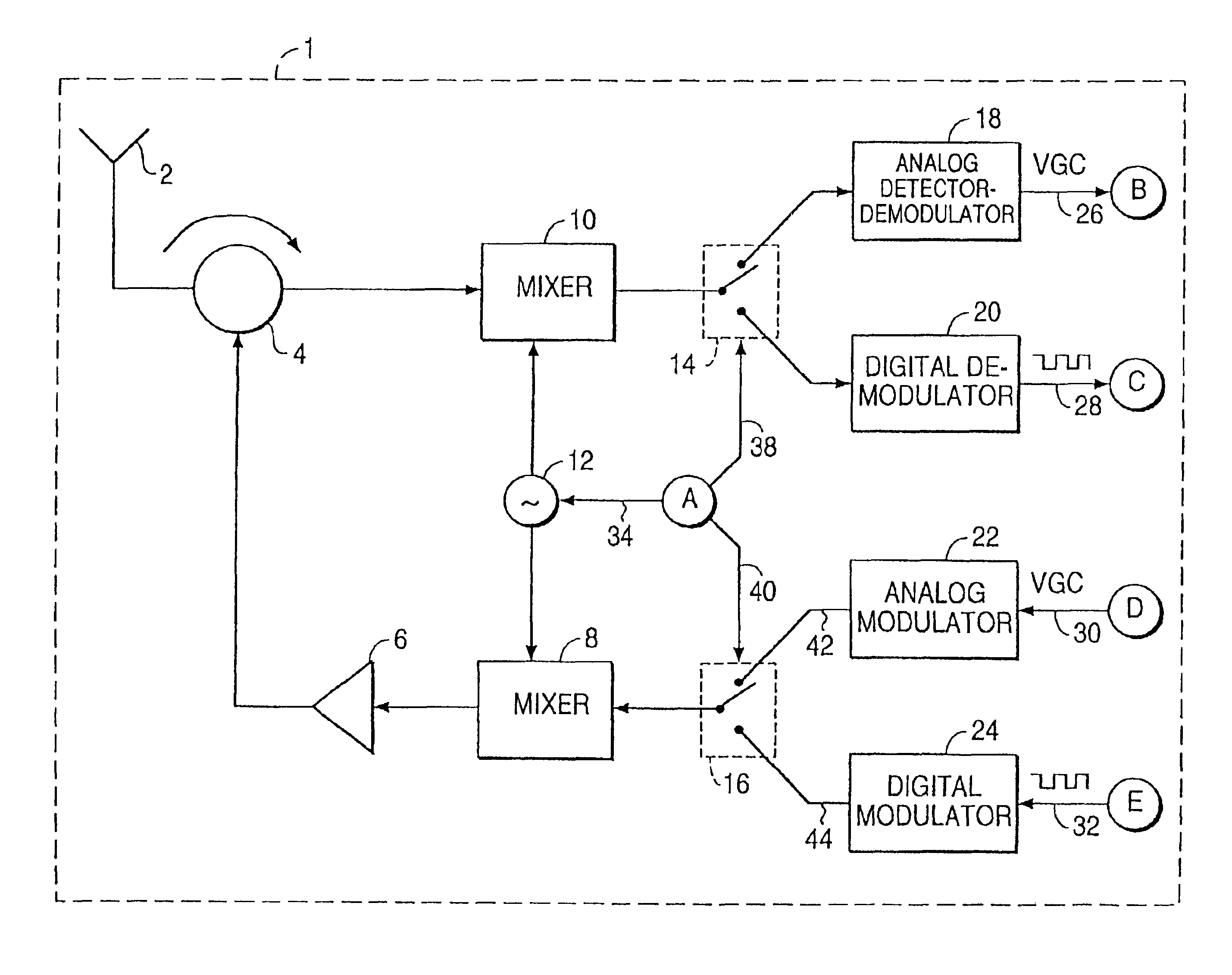

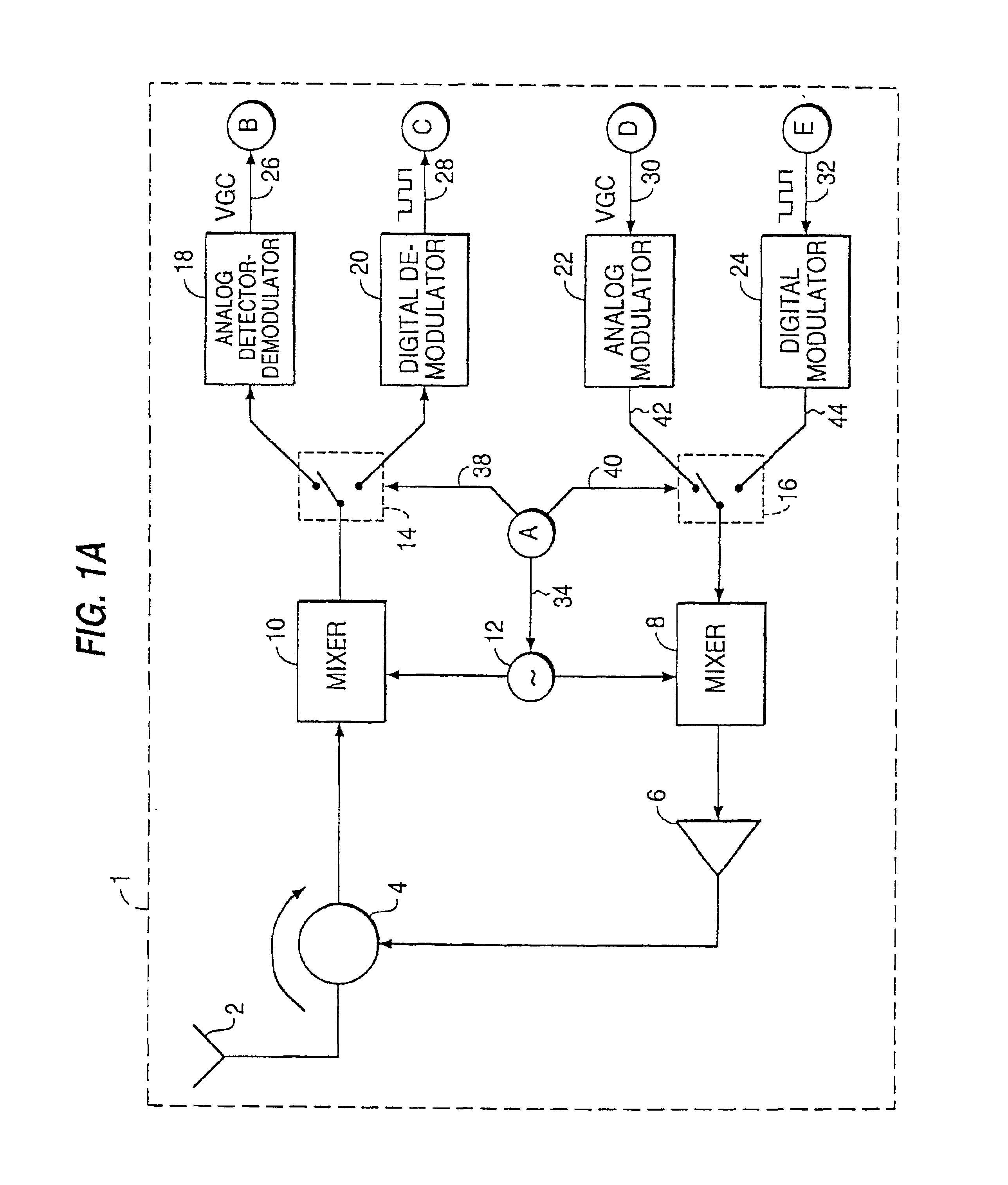

Adaptive omni-modal radio apparatus and methods

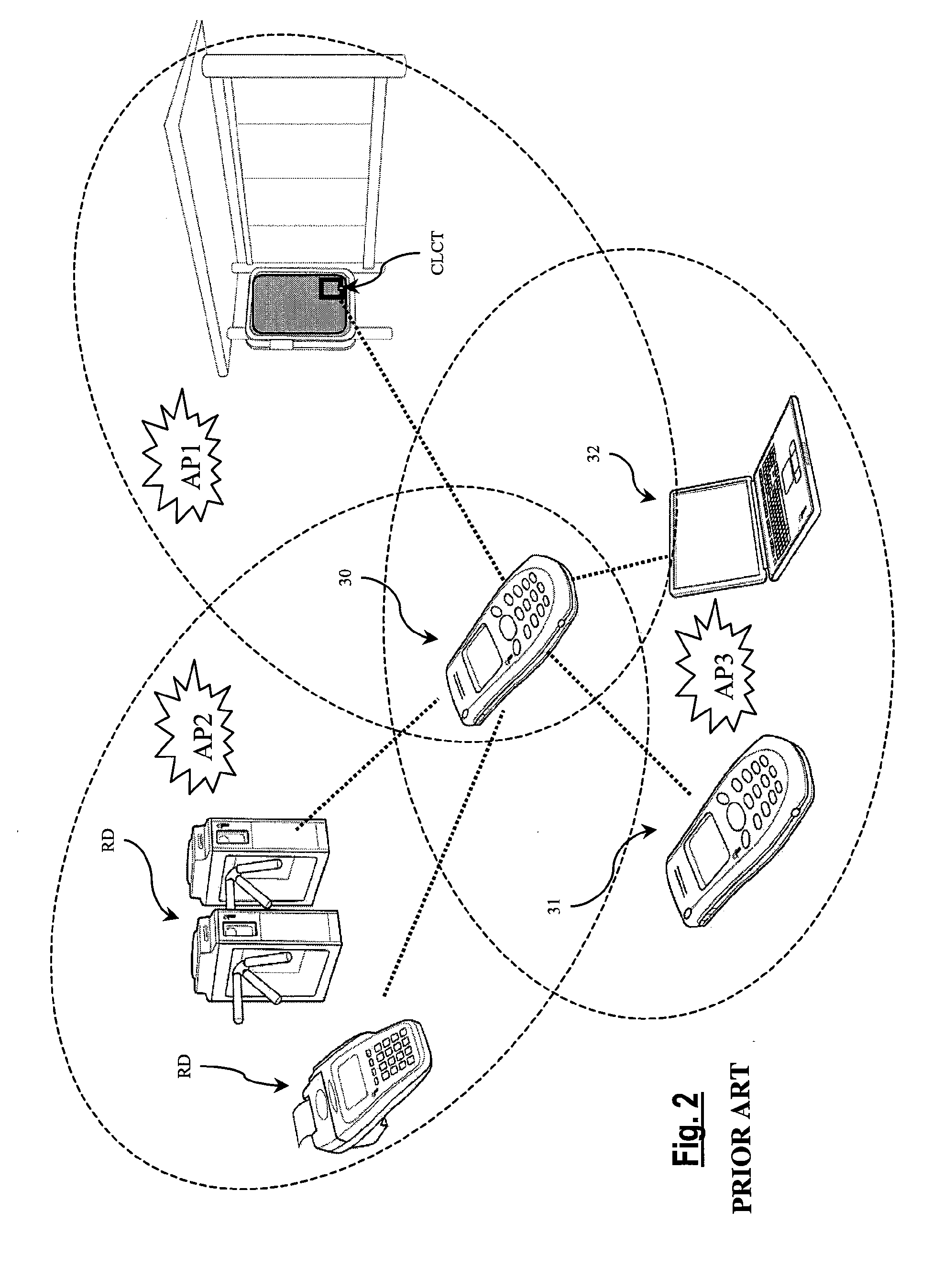

InactiveUS6934558B1Easily and conveniently identifyIntense competitionMetering/charging/biilling arrangementsAccounting/billing servicesTransmission protocolTransceiver

A frequency and protocol agile wireless communication product, and chipset for forming the same, including a frequency agile transceiver, a digital interface circuit for interconnecting the radio transceiver with external devices, protocol agile operating circuit for operating the radio transceiver in accordance with one of the transmission protocols as determined by a protocol signal and an adaptive control circuit for accessing a selected wireless communication network and for generating the frequency control signal and the protocol control signal in response to a user defined criteria Among the possible user defined criteria would be (1) the cost of sending a data message, (2) the quality of transmission link (signal strength, interference actual or potential), (3) the potential for being bumped off of the system (is service provider at near full capacity), (4) the security of transmnission, (5) any special criteria which the user could variably program into his omni-modal wireless product based on the user's desires or (6) any one or more combinations of the above features that are preprogrammed, changed or overridden by the user. The disclosed invention allows wireless service providers to broadcast electronically as part of any “handshaking” procedure with a omni-modal wireless product information such as (1) rate information and (2) information regarding system operating characteristics such as percent of system capacity in use and / or likelihood of being dropped. The disclosed invention creates a user oriented source enrollment and billing service in the wireless data market by establishing uniform standard for “handshakes” to occur between cell service providers and omni-modal wireless products. In addition, the disclosed invention can be implemented on a standard chip or chipset including a radio transceiver specifically designed to be used in all types of omni-modal wireless products.

Owner:ANTON INNOVATIONS INC

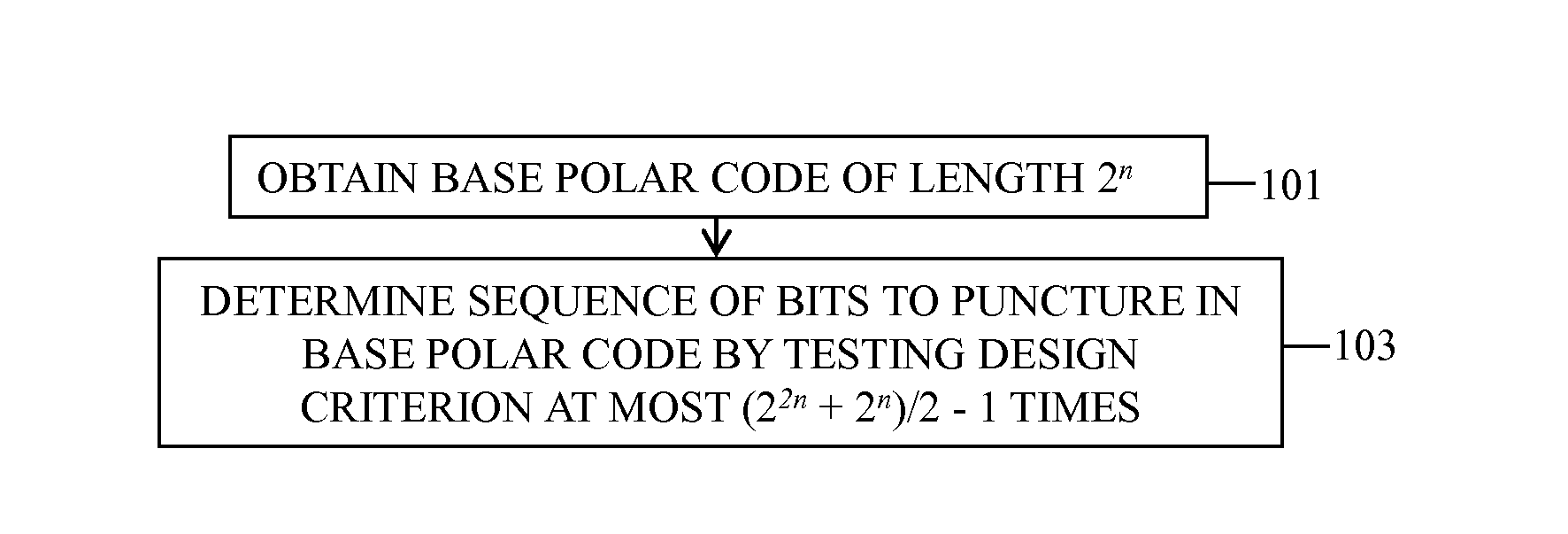

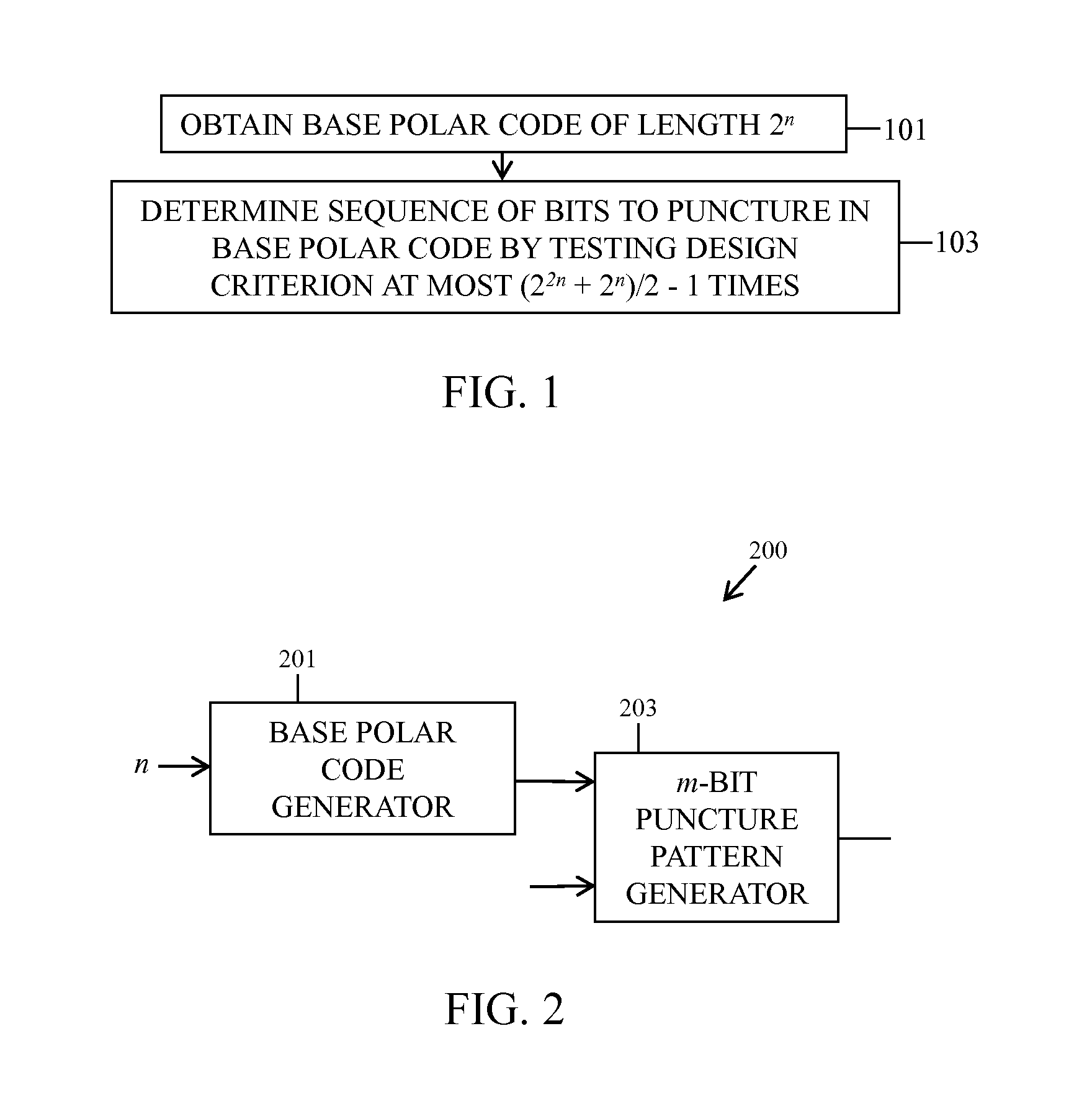

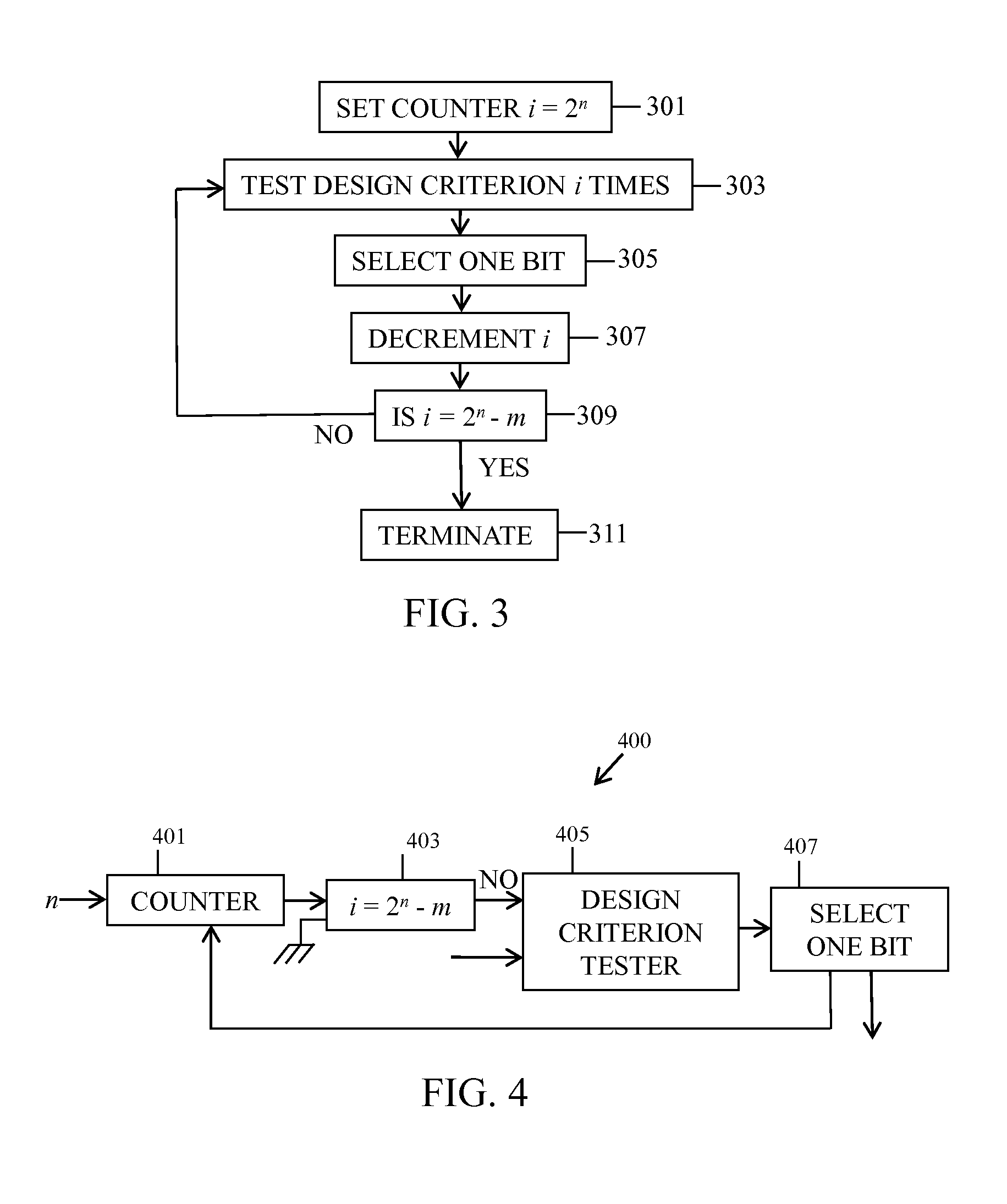

HARQ rate-compatible polar codes for wireless channels

ActiveUS20160285479A1Error prevention/detection by using return channelCode conversionTelecommunicationsChipset

A method, apparatus, and chipset are provided for constructing hybrid automatic repeat request (HARQ) rate-compatible polar codes for communication channels. The method includes constructing, in a terminal, a base polar code of length 2n; and determining a sequence of m<2n bits to puncture in the base polar code by testing a predetermined criterion at most (22n+2n) / 2−1 times.

Owner:SAMSUNG ELECTRONICS CO LTD

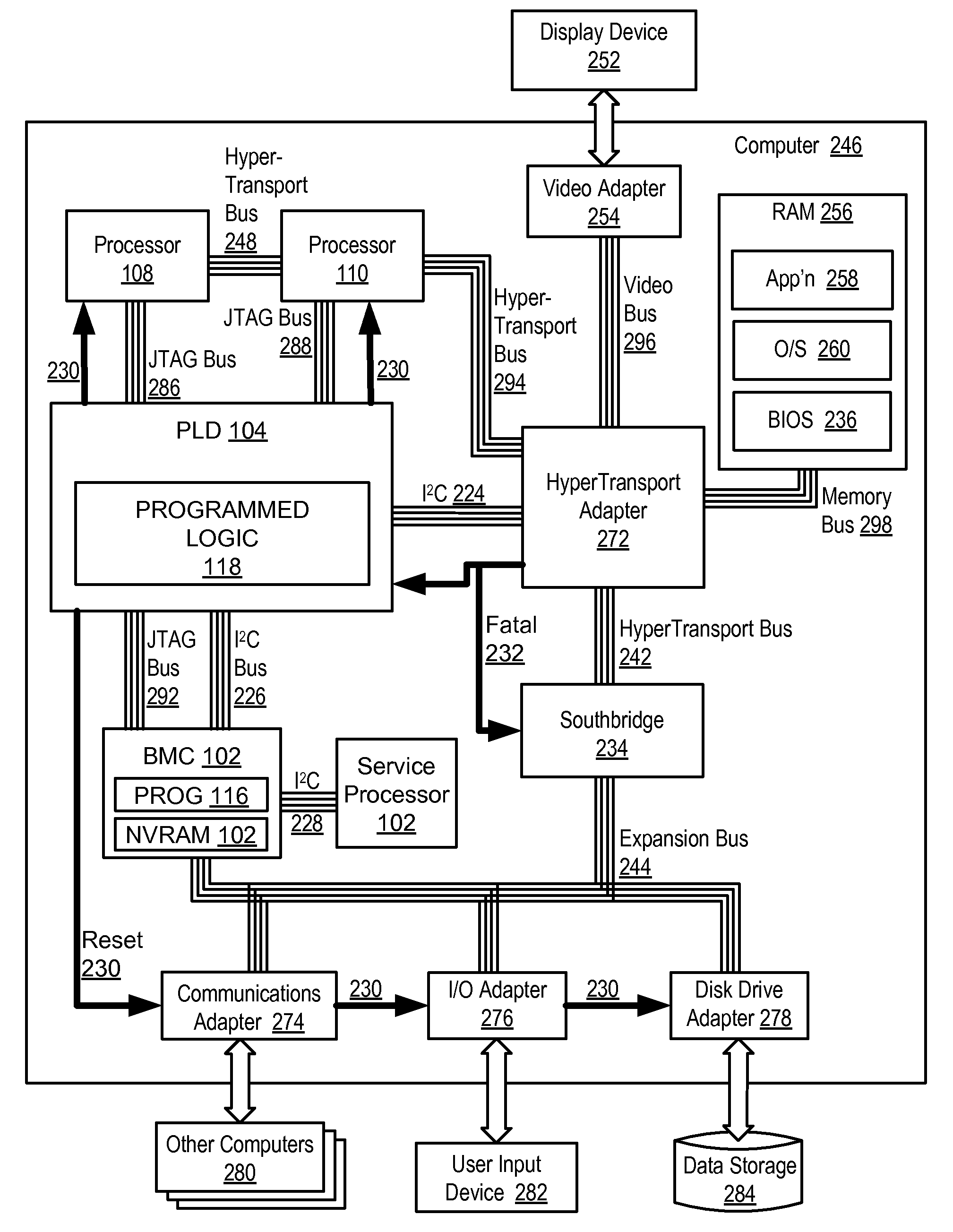

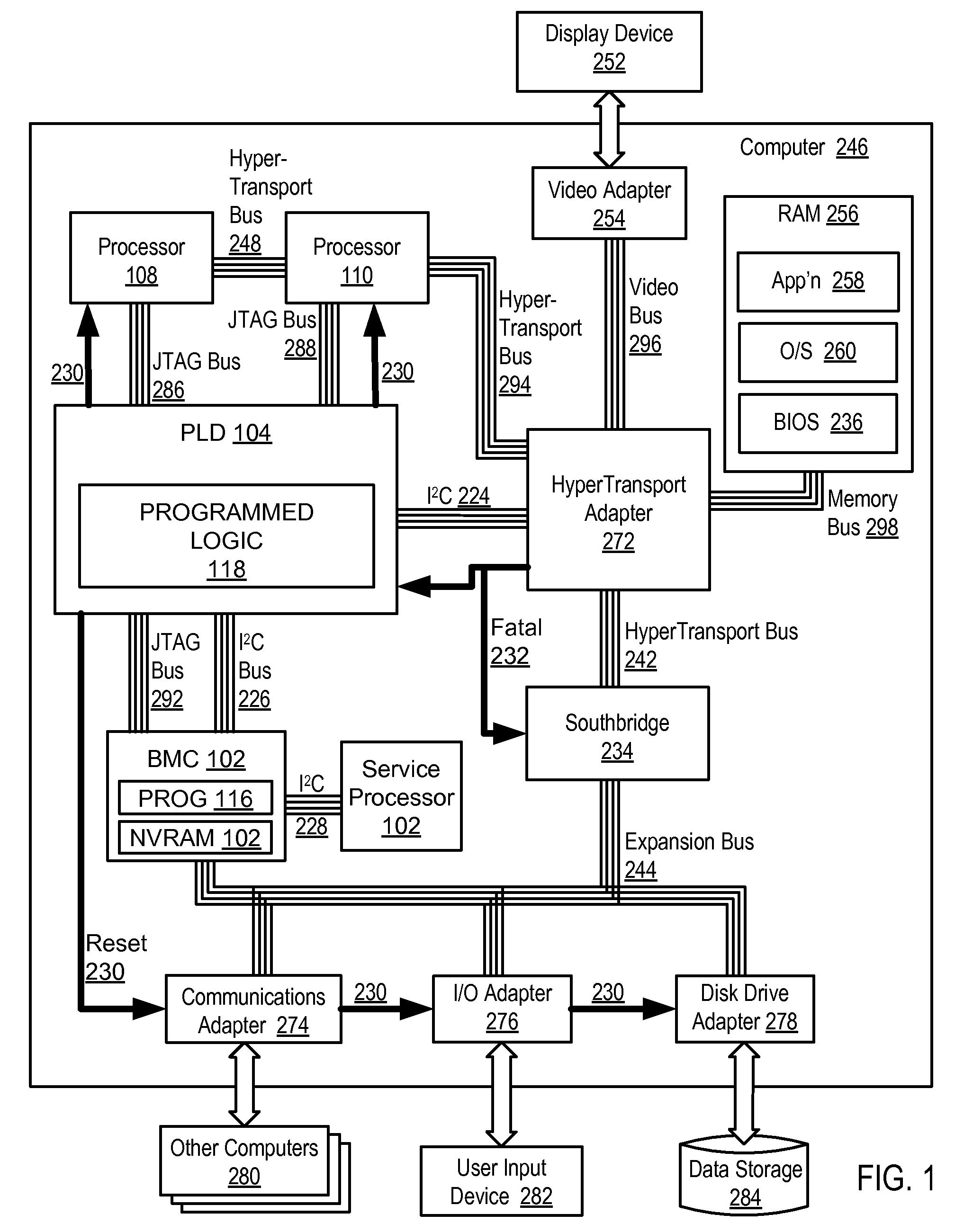

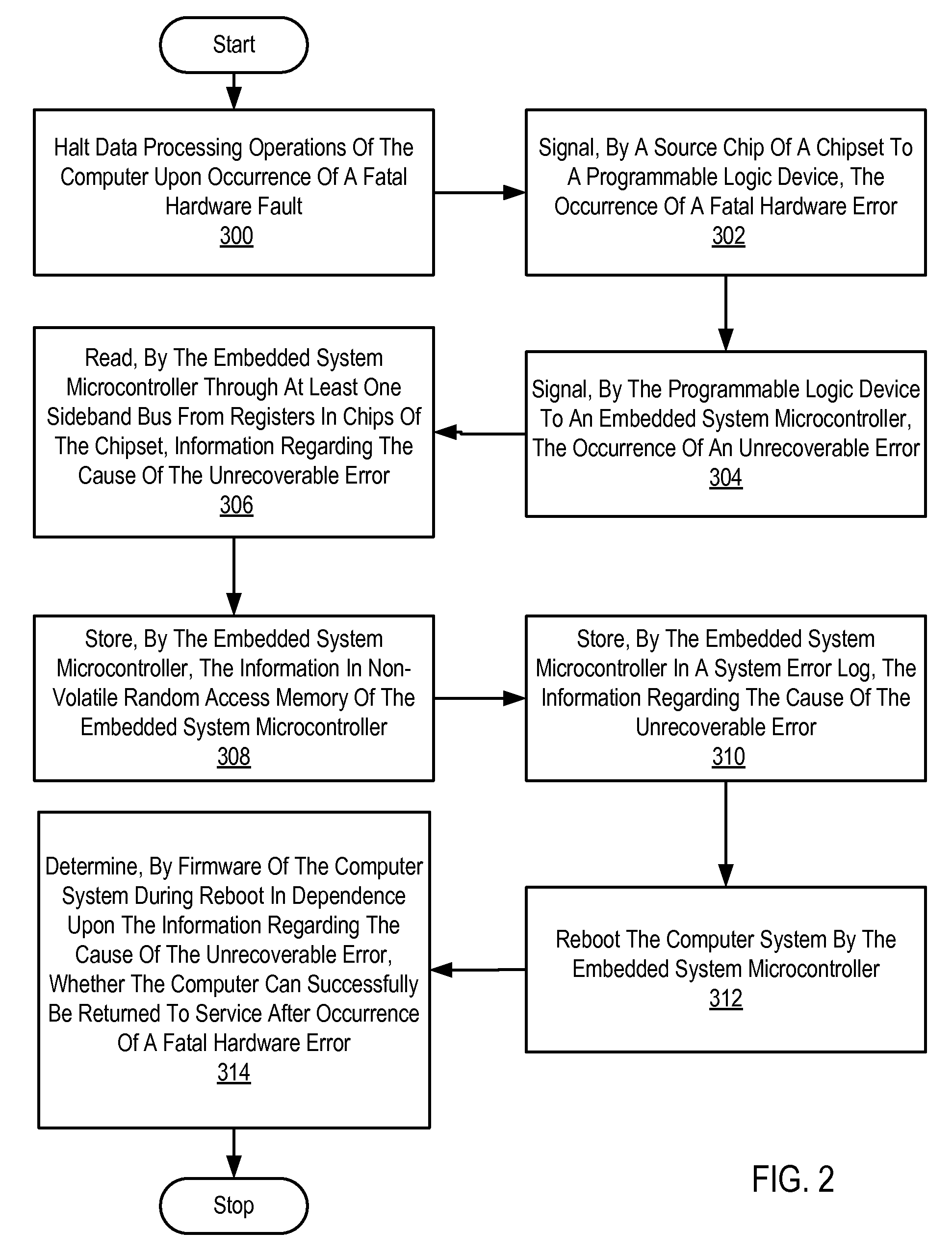

Handling Fatal Computer Hardware Errors

Methods and apparatus are disclosed for handling fatal computer hardware errors on a computer that include halting data processing operations of the computer upon occurrence of a fatal hardware error; signaling by a source chip of a chipset to the programmable logic device the occurrence of a fatal hardware error; signaling by the programmable logic device to an embedded system microcontroller the occurrence of a fatal hardware error; reading by the embedded system microcontroller through at least one sideband bus from registers in chips of the chipset information regarding the cause of the fatal hardware error; and storing by the embedded system microcontroller the information in non-volatile random access memory of the embedded system microcontroller.

Owner:IBM CORP

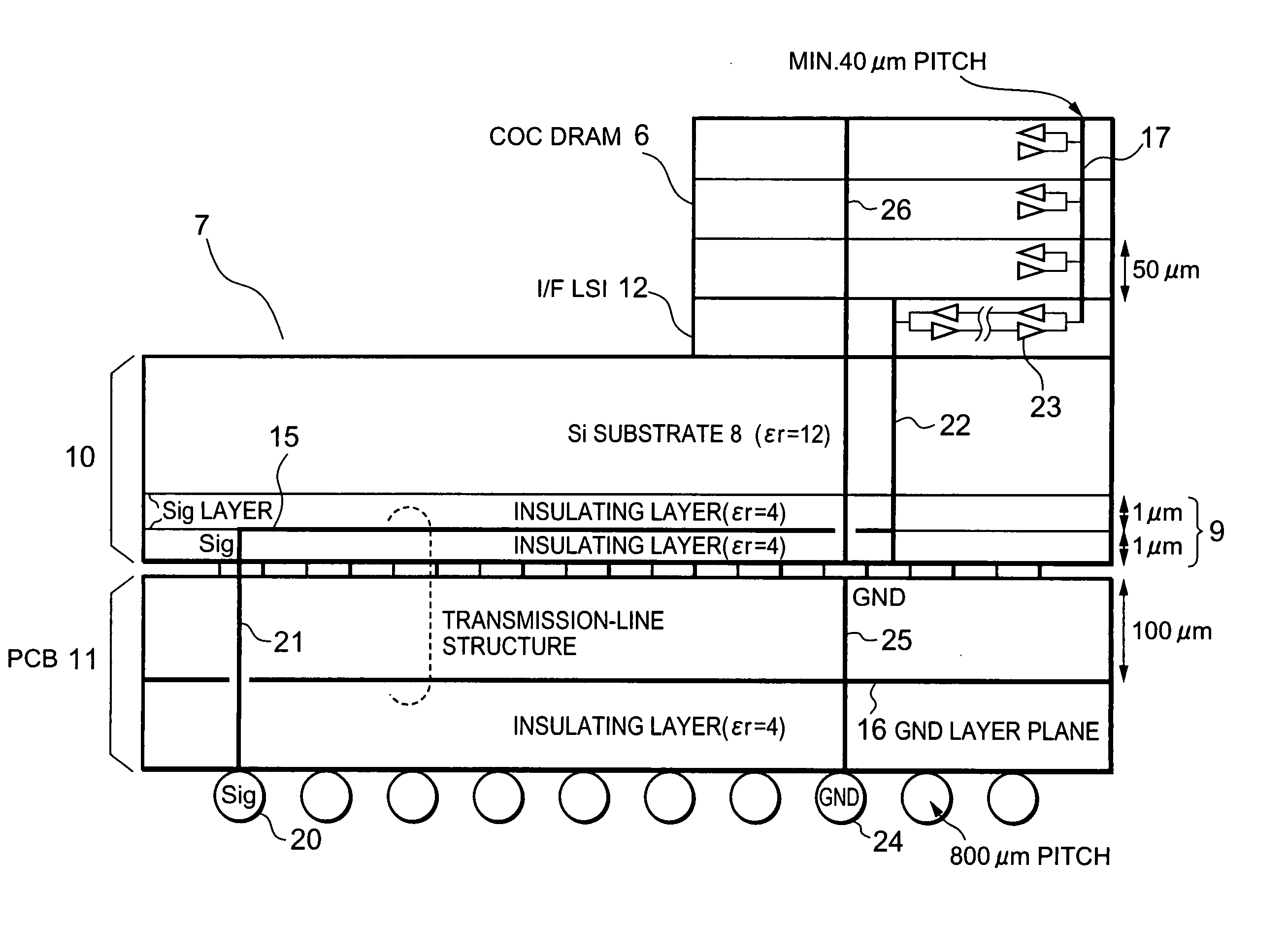

Semiconductor integrated circuit device

InactiveUS20050139977A1Easy impedance matchingReduce signalingTransistorSemiconductor/solid-state device detailsInterposerChipset

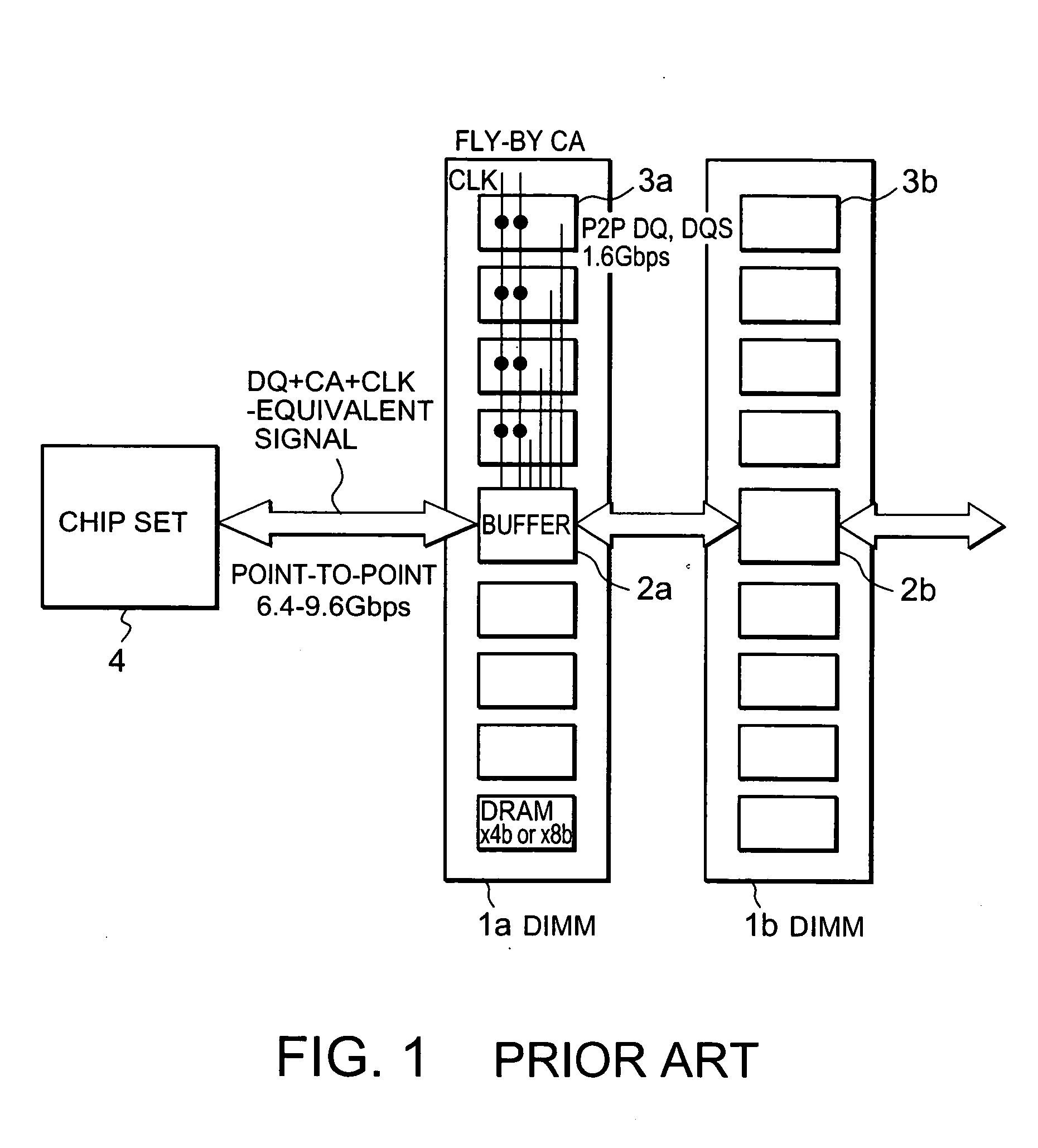

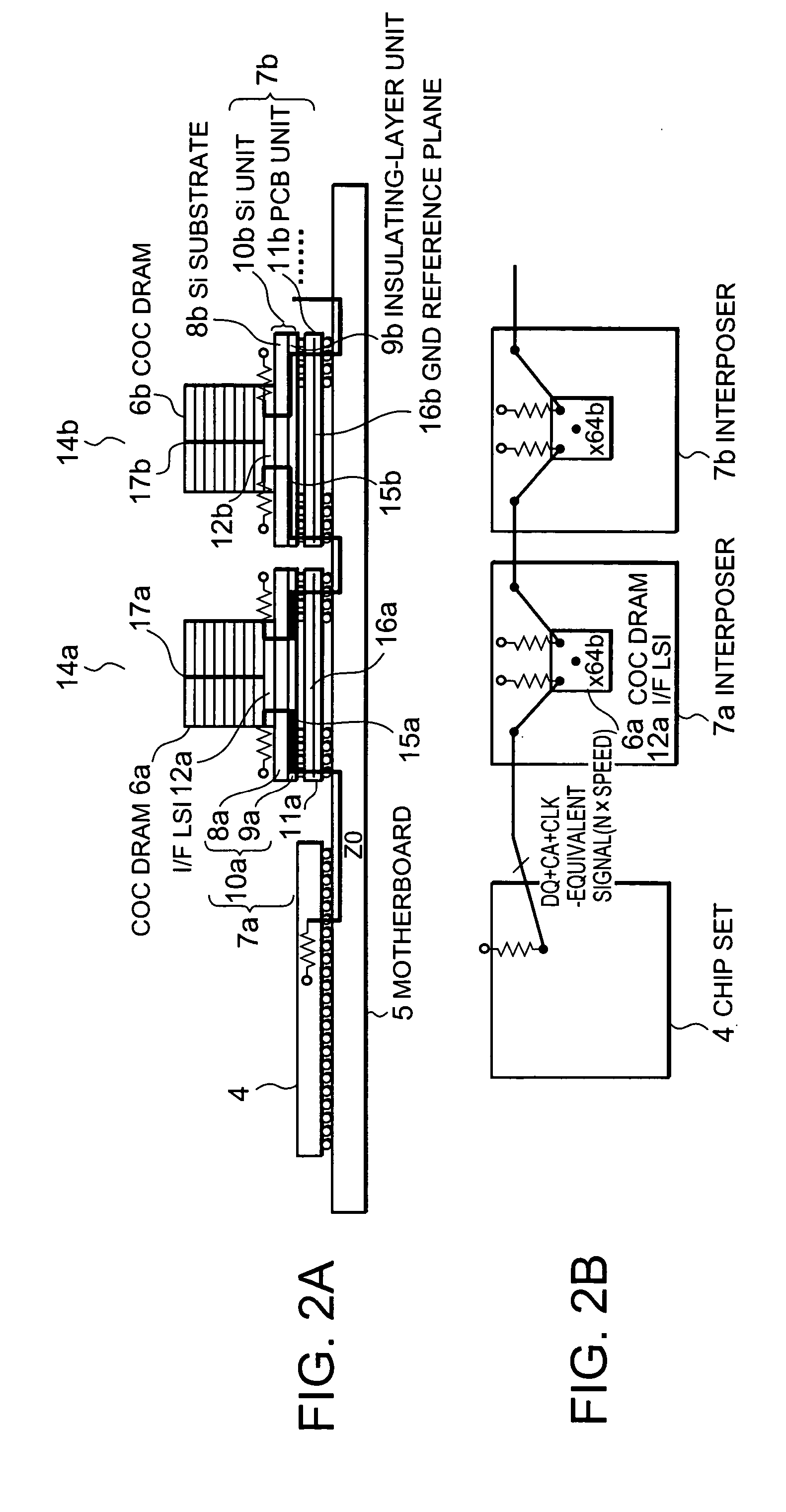

A COC DRAM including a plurality of stacked DRAM chips is mounted on a motherboard by using an interposer. The interposer includes a Si unit and a PCB. The Si unit includes a Si substrate and an insulating-layer unit in which wiring is installed. The PCB includes a reference plane for the wiring in the Si unit. The wiring topology between a chip set and the COC DRAM is the same for every signal. Accordingly, a memory system enabling a high-speed operation, low power consumption, and large capacity is provided.

Owner:PS4 LUXCO SARL

An Intelligent Integrated Sensor Of Tire Pressure Monitoring System (TPMS)

InactiveUS20060185429A1Precise size controlAccurate identificationSolid-state devicesTyre measurementsAccelerometerEngineering

A single integrated sensing chip with multi-functions for tire pressure monitor system (TPMS) comprises: a pressure sensor, an accelerometer, a temperature sensor, and an ASIC (Applied Specific Integrated Circuit) that implements signal conditioning and digitalizes pressure output. The accelerometer incorporated for vehicle motion is used to determine centrifugal acceleration or three-axial acceleration of the rotating wheel, and used for the TPMS sensor wake-up from “power down” mode, or when the velocity of the vehicle is higher than certain speed threshold, which is more robust and lower in cost than the mechanical vibration switch and is naturally integrated with the electronic control unit. The accelerometer can be used for regular motion sensing to monitor the dynamic stability. The integrated sensor system can be packaged into one plastic package first, and then surface mounted to the printed circuit board, or the multi-function single chip can be wafer bonded on the wafer level first and diced into many individual chips, with each chip being directly attached on to the printed circuit board by wire bonding or flip-chip assembly.

Owner:WUHAN FINEMEMS

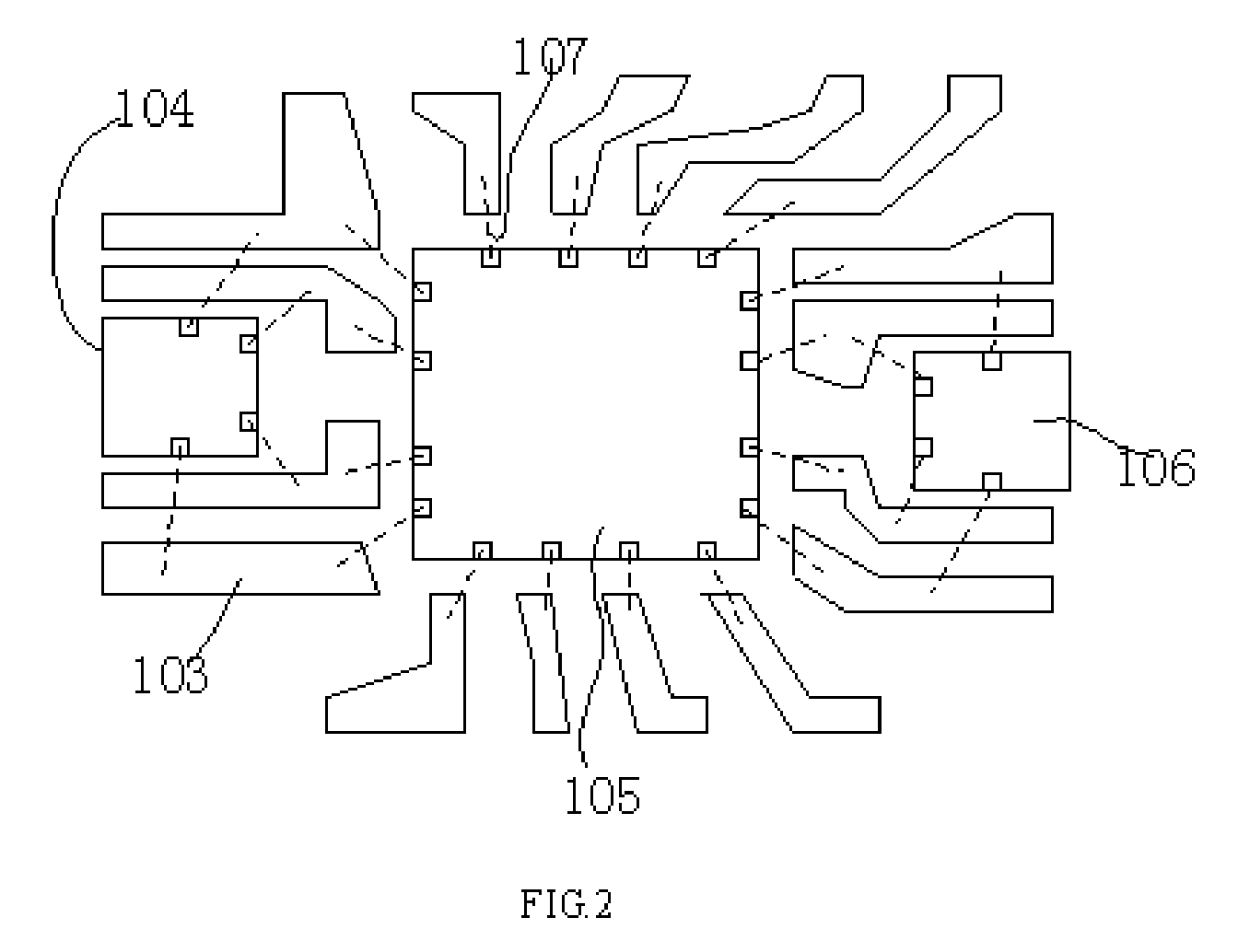

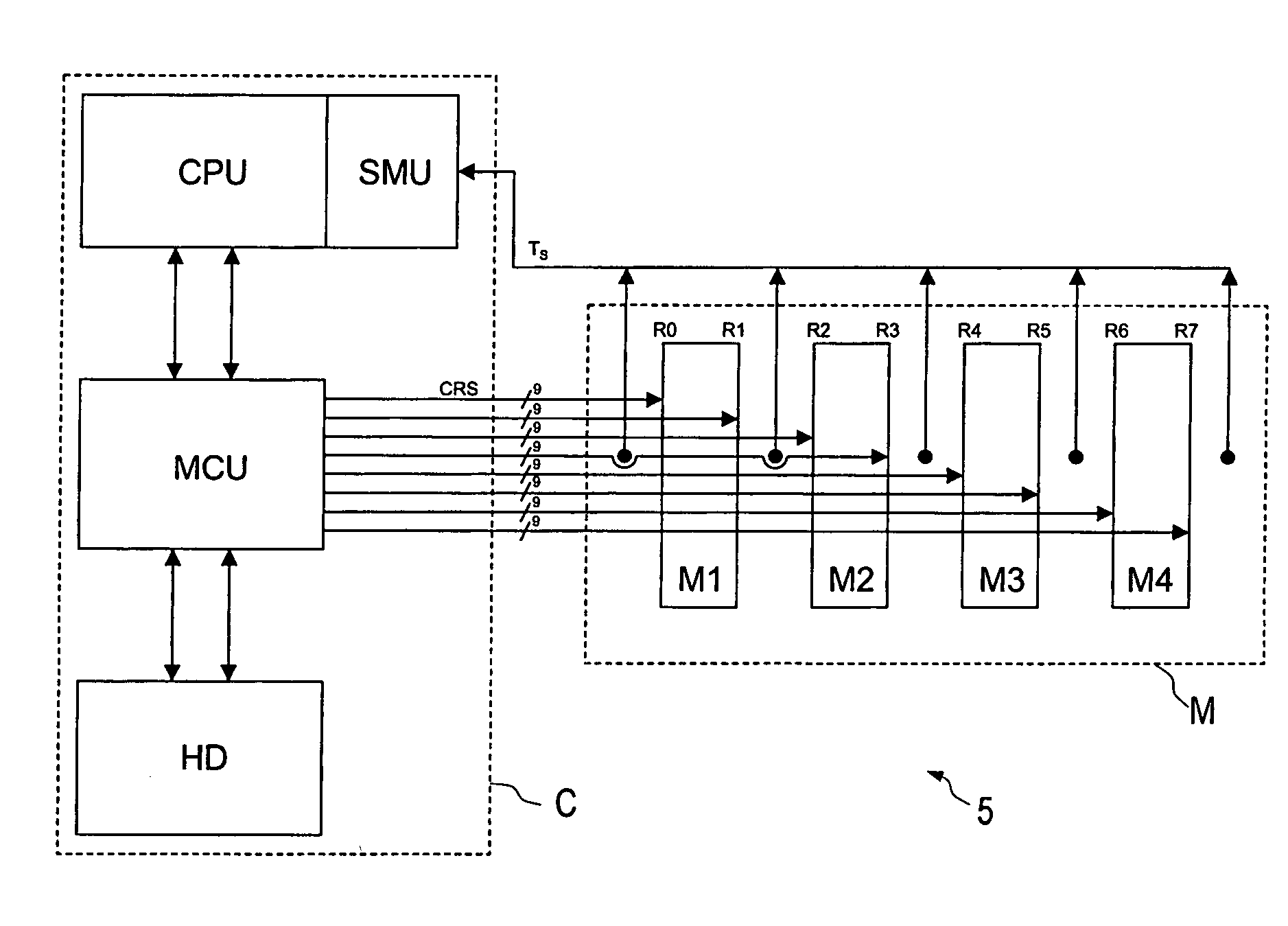

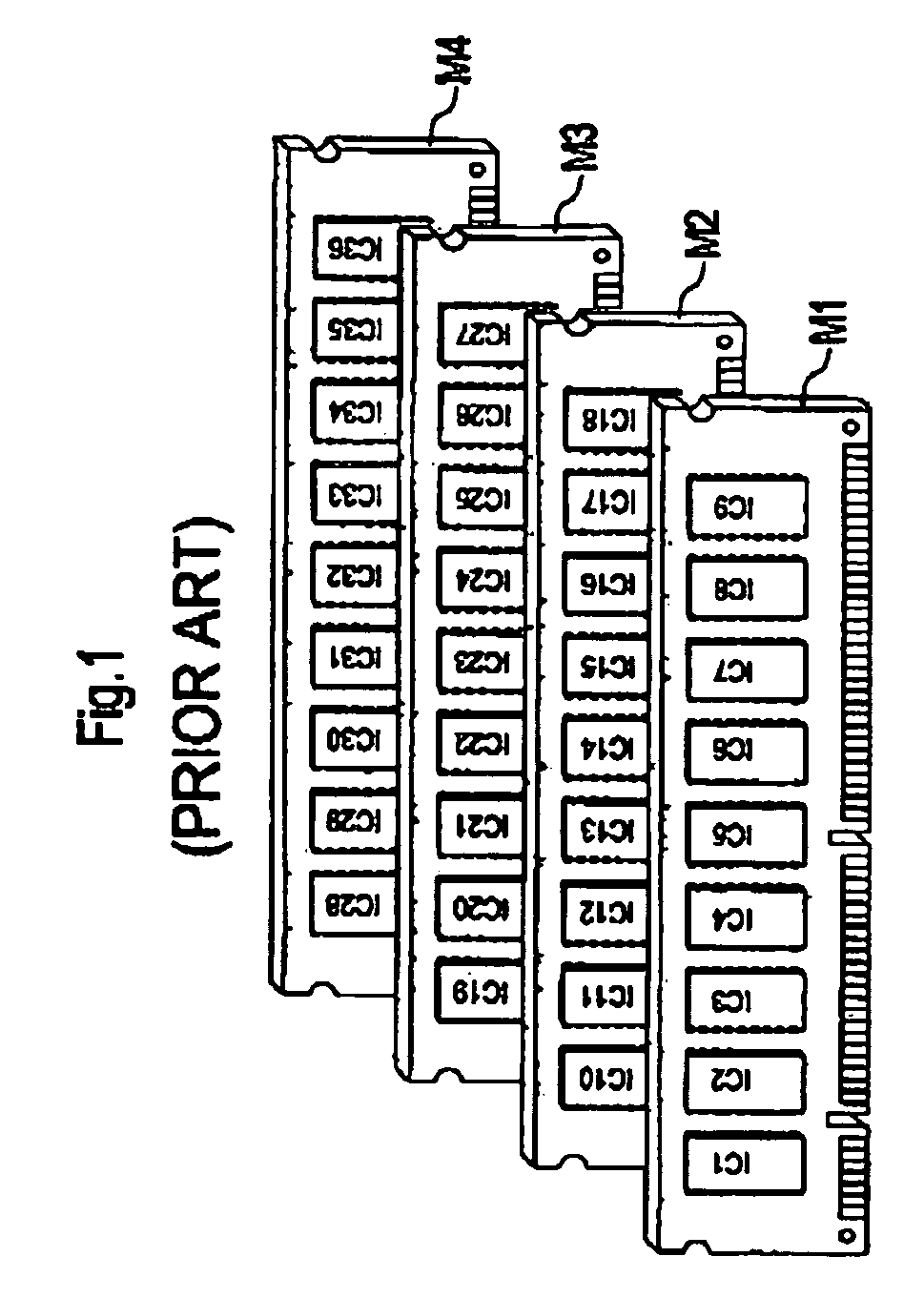

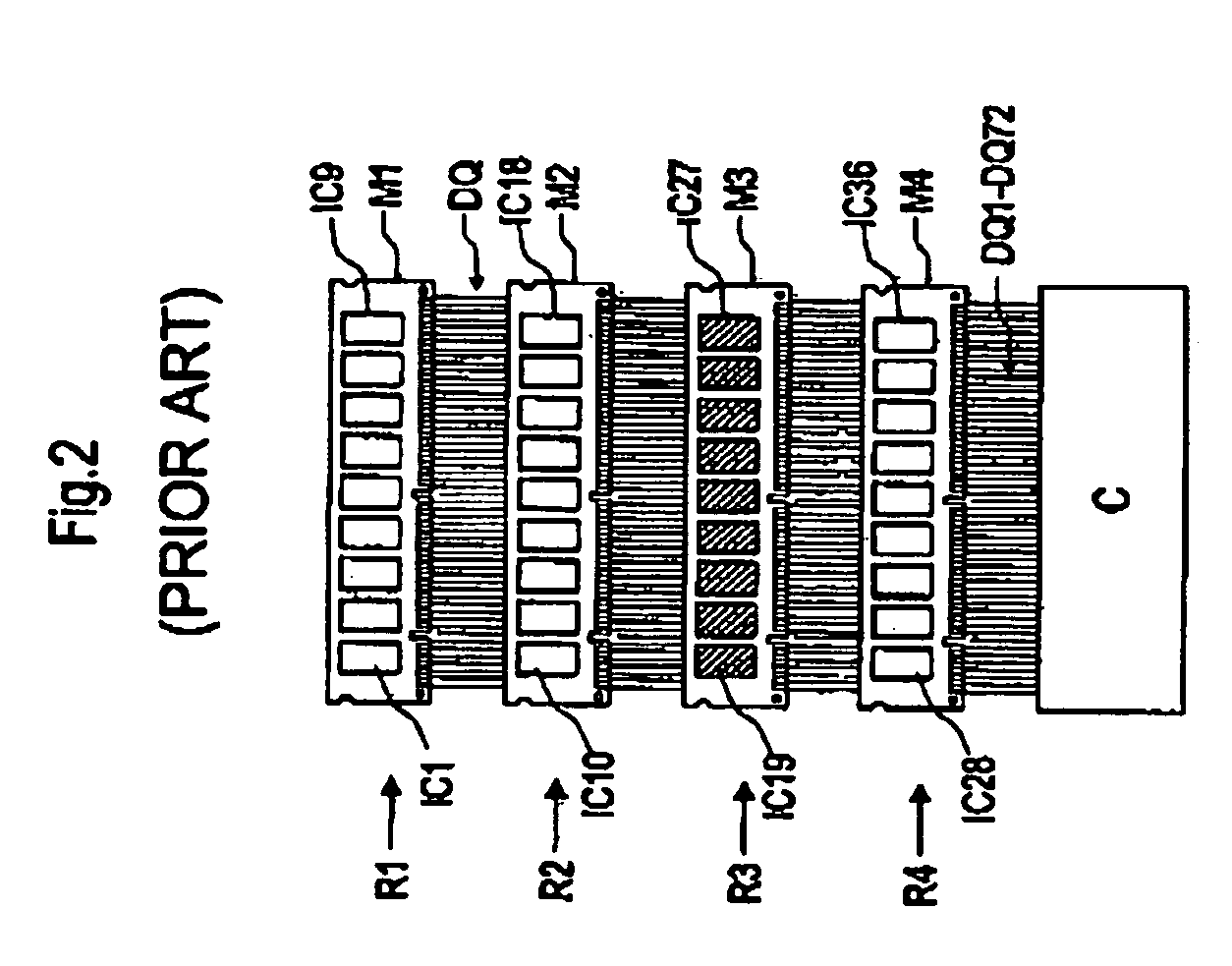

Method for controlling semiconductor chips and control apparatus

InactiveUS6986118B2Increase choiceEasy to operateDigital computer detailsData resettingMemory chipSemiconductor chip

The invention relates to a method for operating semiconductor chips, particularly memory chips, which are arranged in groups on modules which are connected to a common data bus wherein each semiconductor chip on each module is connected to at least one data line in the common data bus comprising the following method steps:a) selecting a group of semiconductor chips from the semiconductor chips arranged on the modules based on a prescribed selection criterion independently of module, the selected group of semiconductor chips using data lines in the common data bus over the entire bus width;b) activating the semiconductor chips in the selected group; andc) performing data interchange between the data lines in the common data bus and the selected group of semiconductor chips.

Owner:POLARIS INNOVATIONS

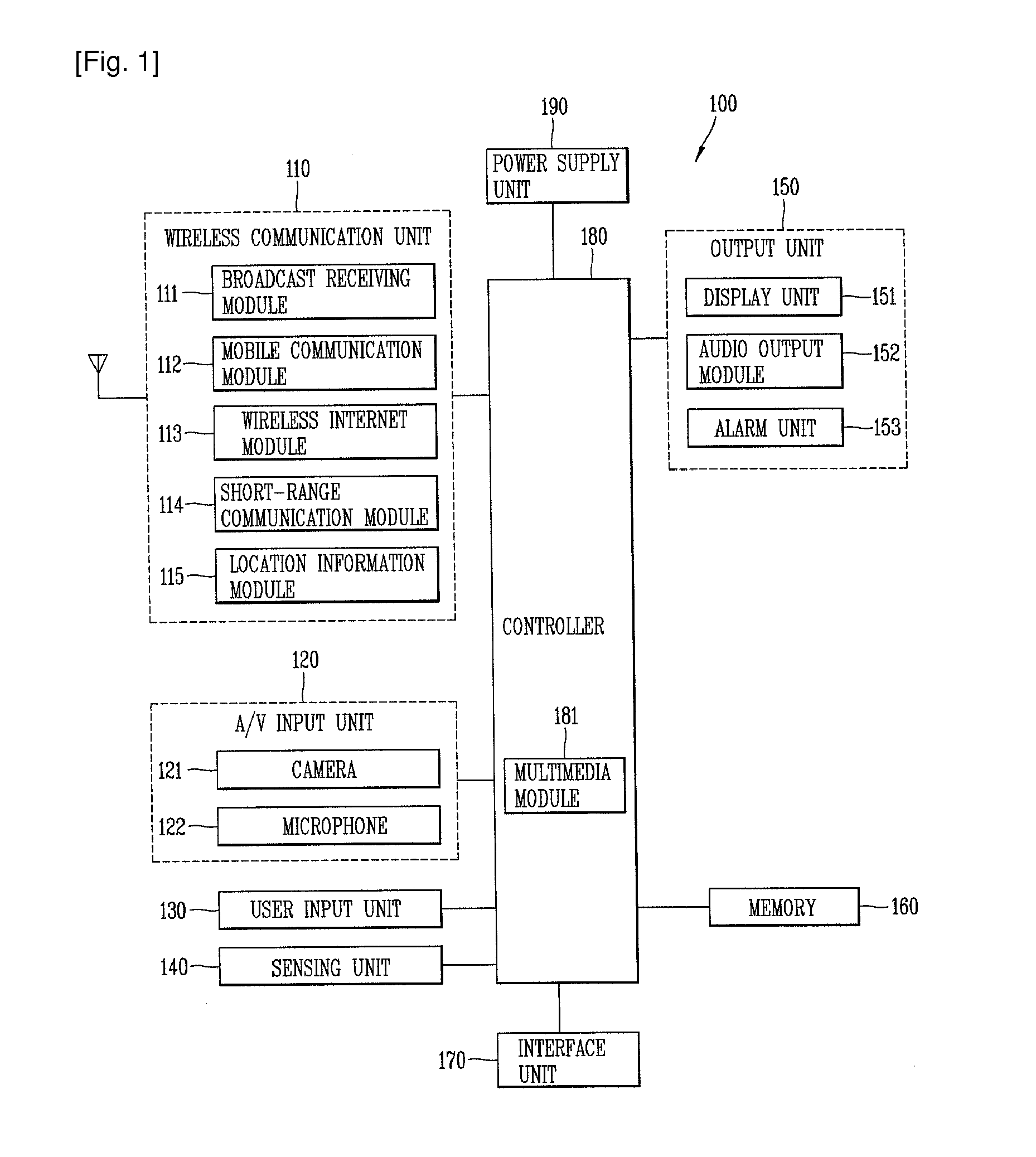

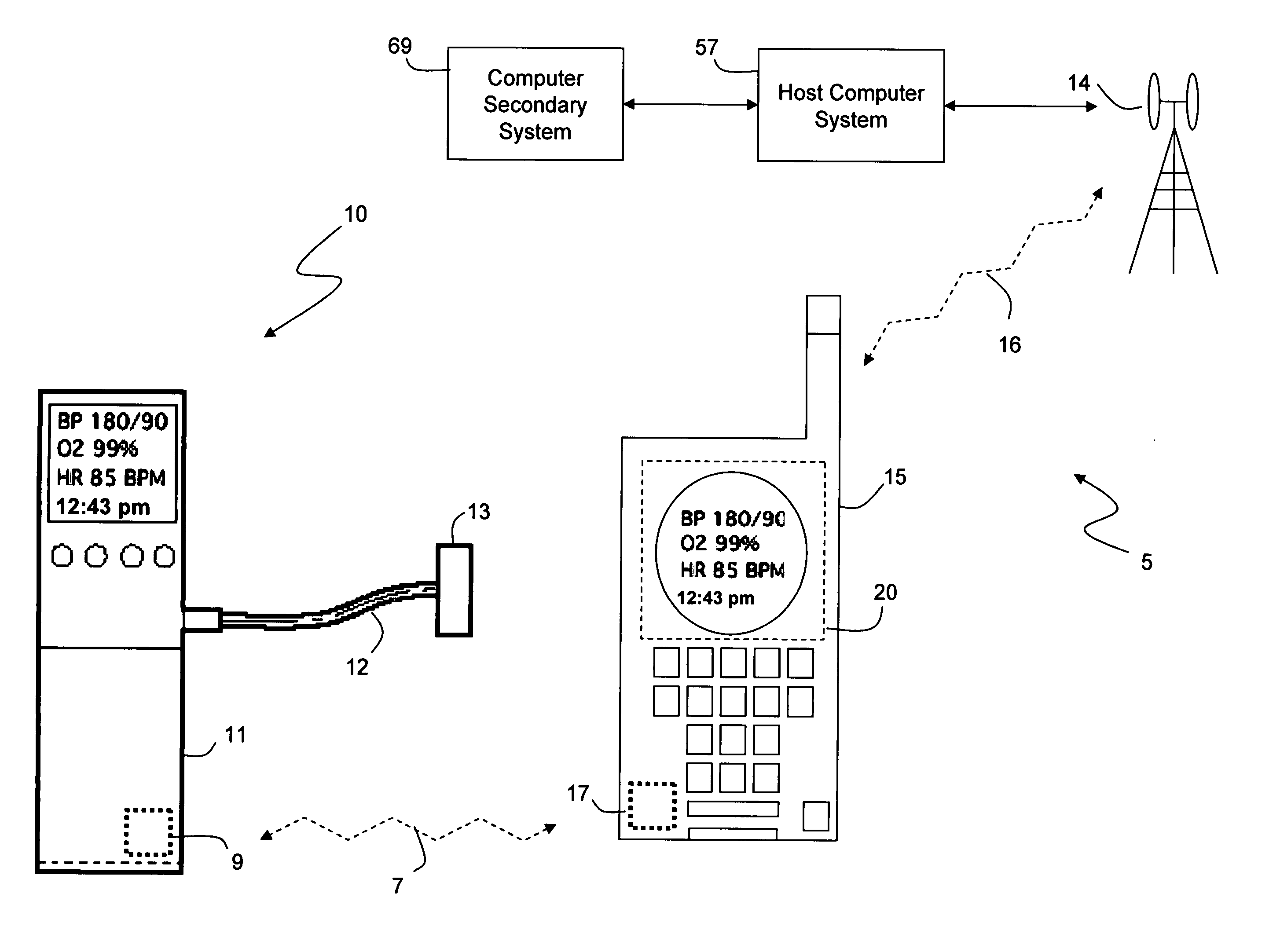

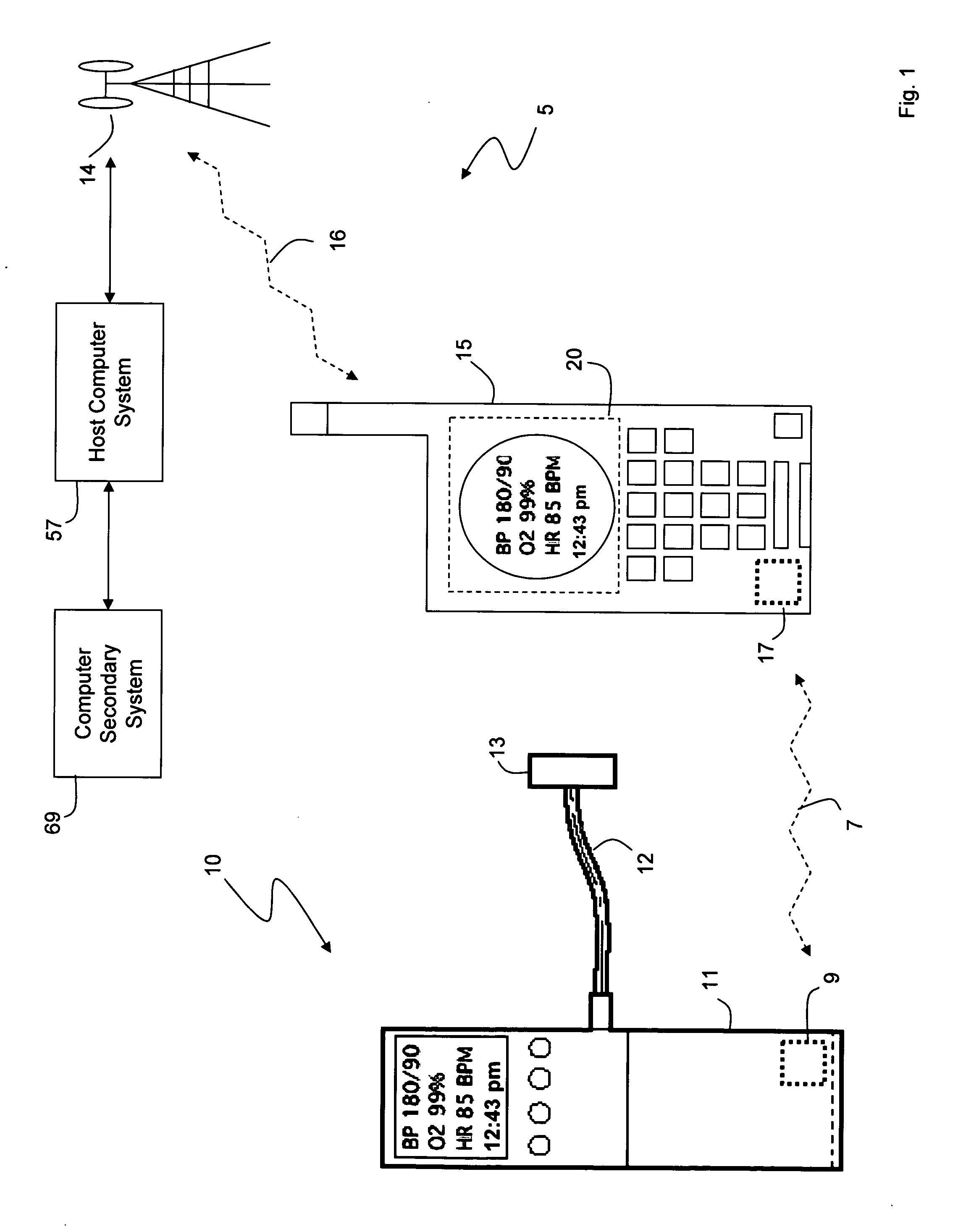

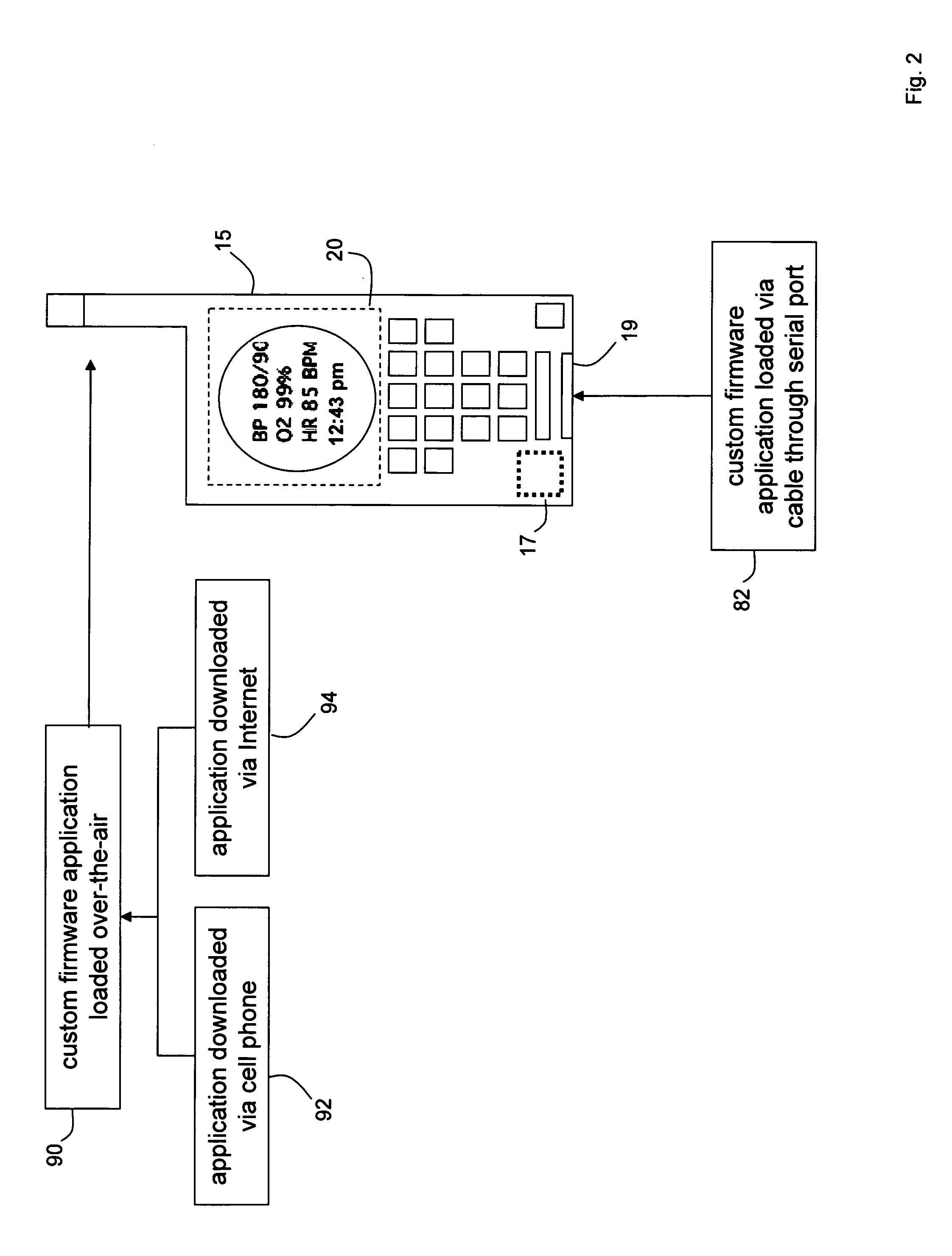

Cuffless blood-pressure monitor and accompanying wireless mobile device

InactiveUS20050228300A1Easy can be wornNon-invasive measurementEvaluation of blood vesselsCatheterMonitor blood pressureComputerized system

The present invention provides a system for monitoring blood pressure that preferably includes: 1) a blood-pressure monitor featuring a measuring component that generates blood-pressure information and a first short-range wireless component configured to wirelessly transmit the blood-pressure information; 2) a mobile device featuring a chipset that includes i) an embedded second short-range wireless component configured to receive the blood-pressure information; and ii) a long-range wireless component configured to transmit the blood-pressure information over a wireless network; and 3) a computer system configured to receive and display the blood-pressure information.

Owner:TRIAGE WIRELESS

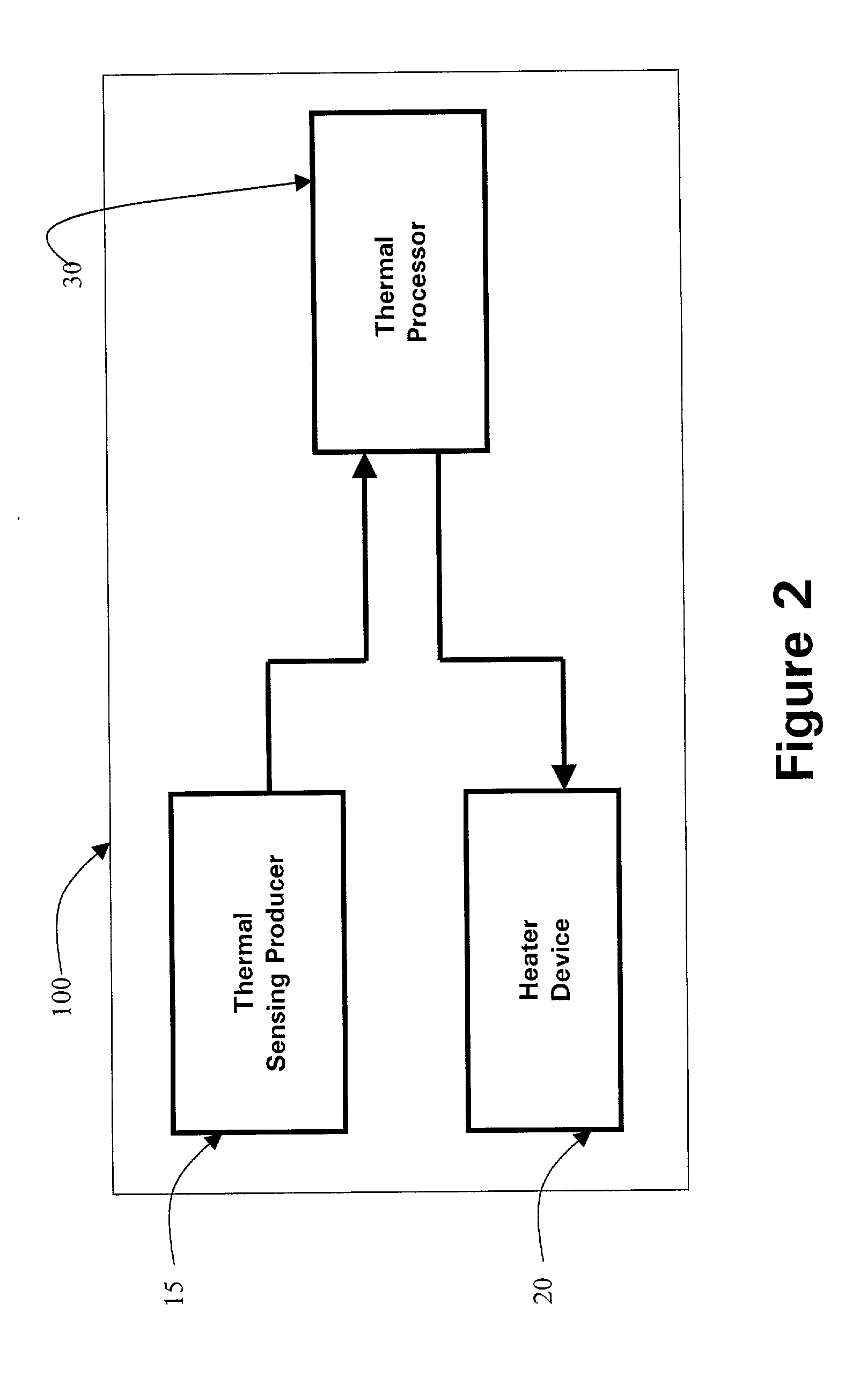

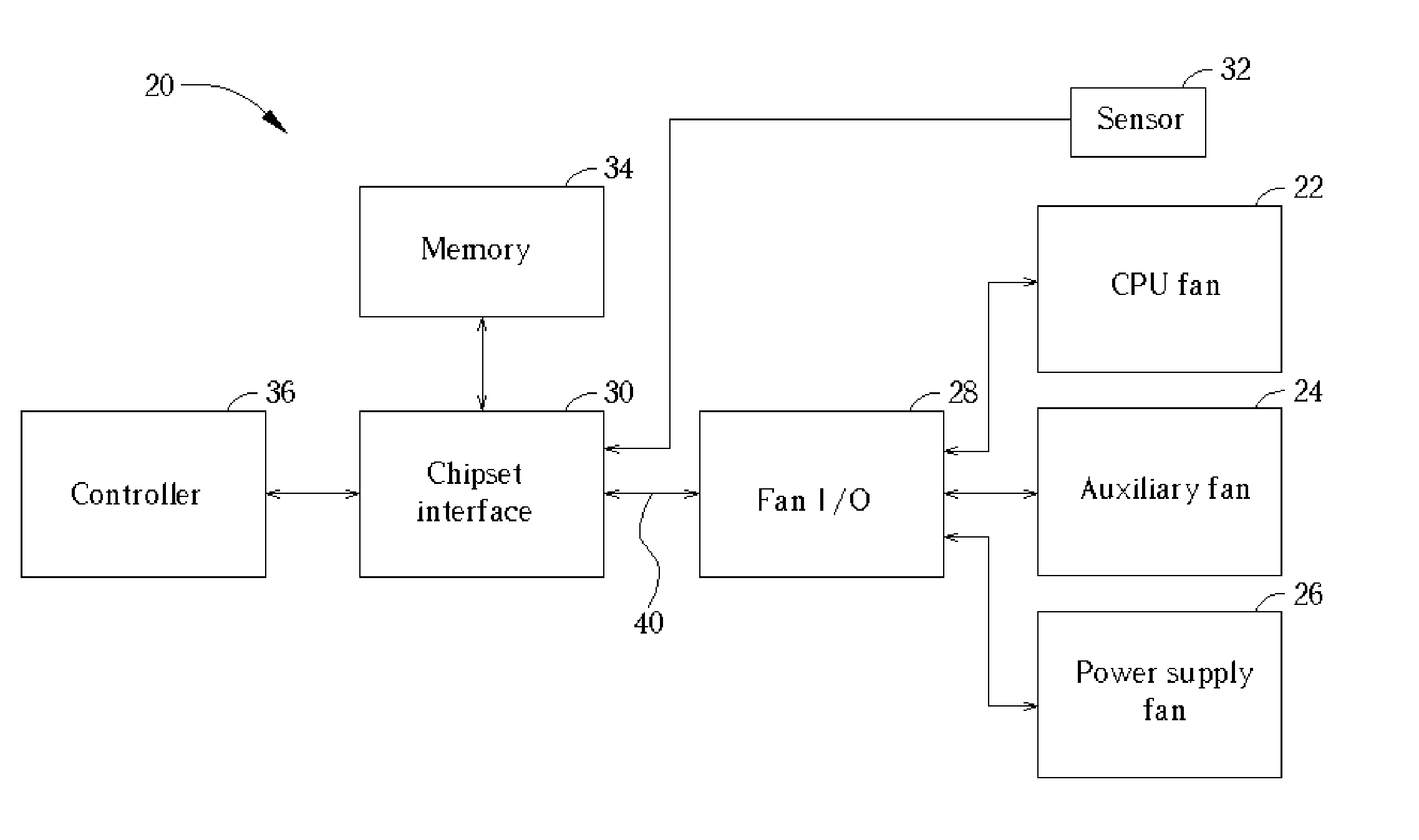

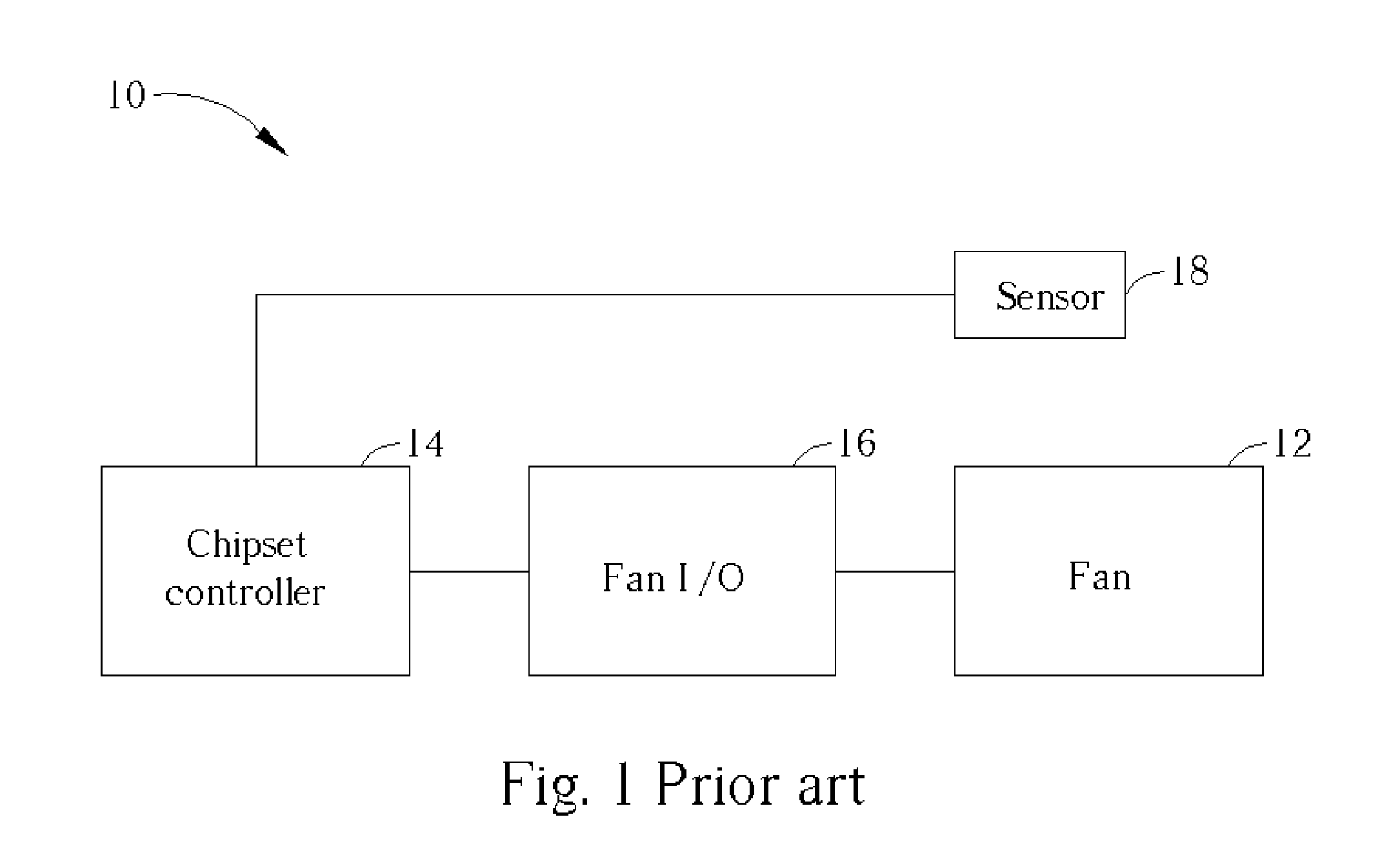

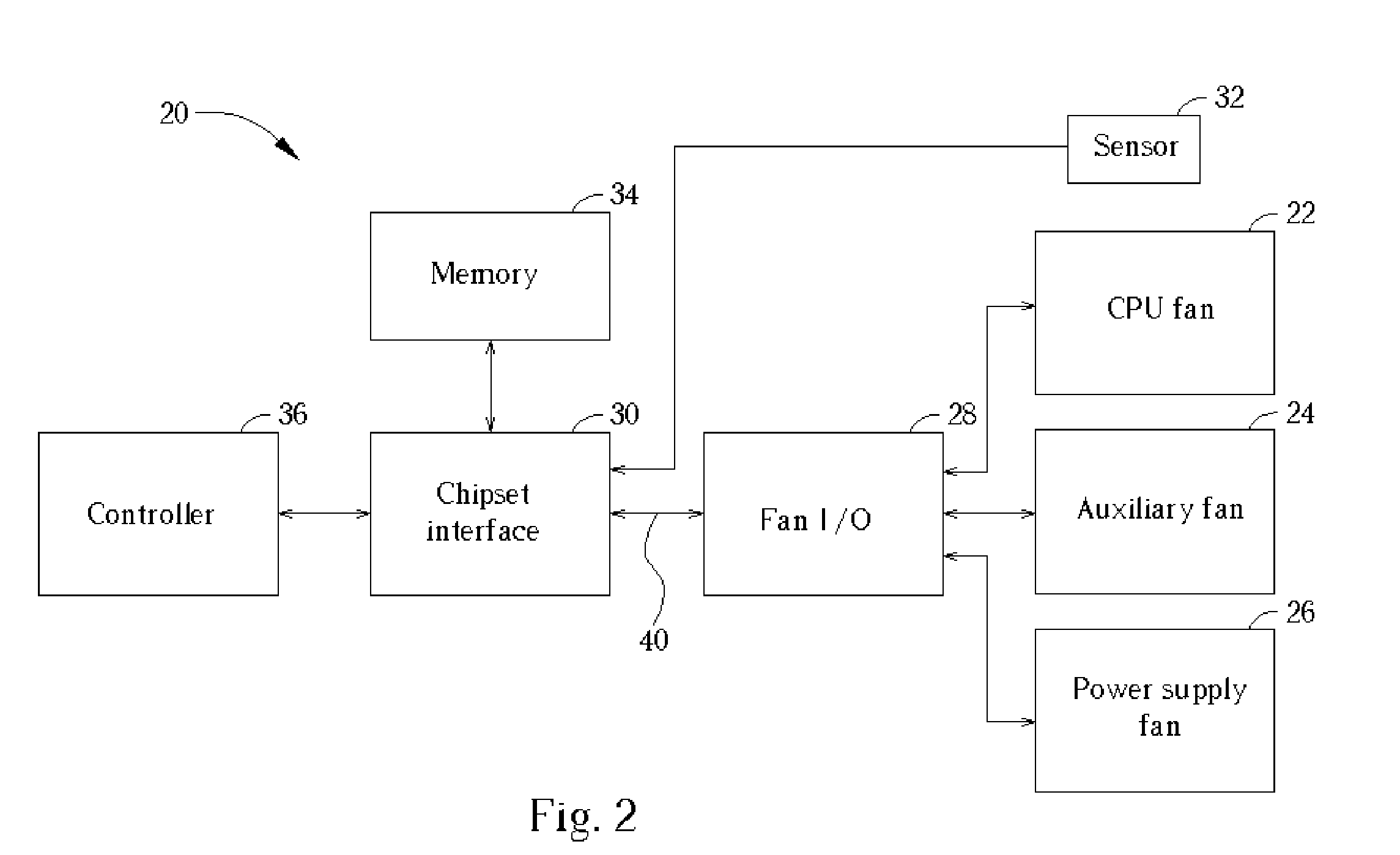

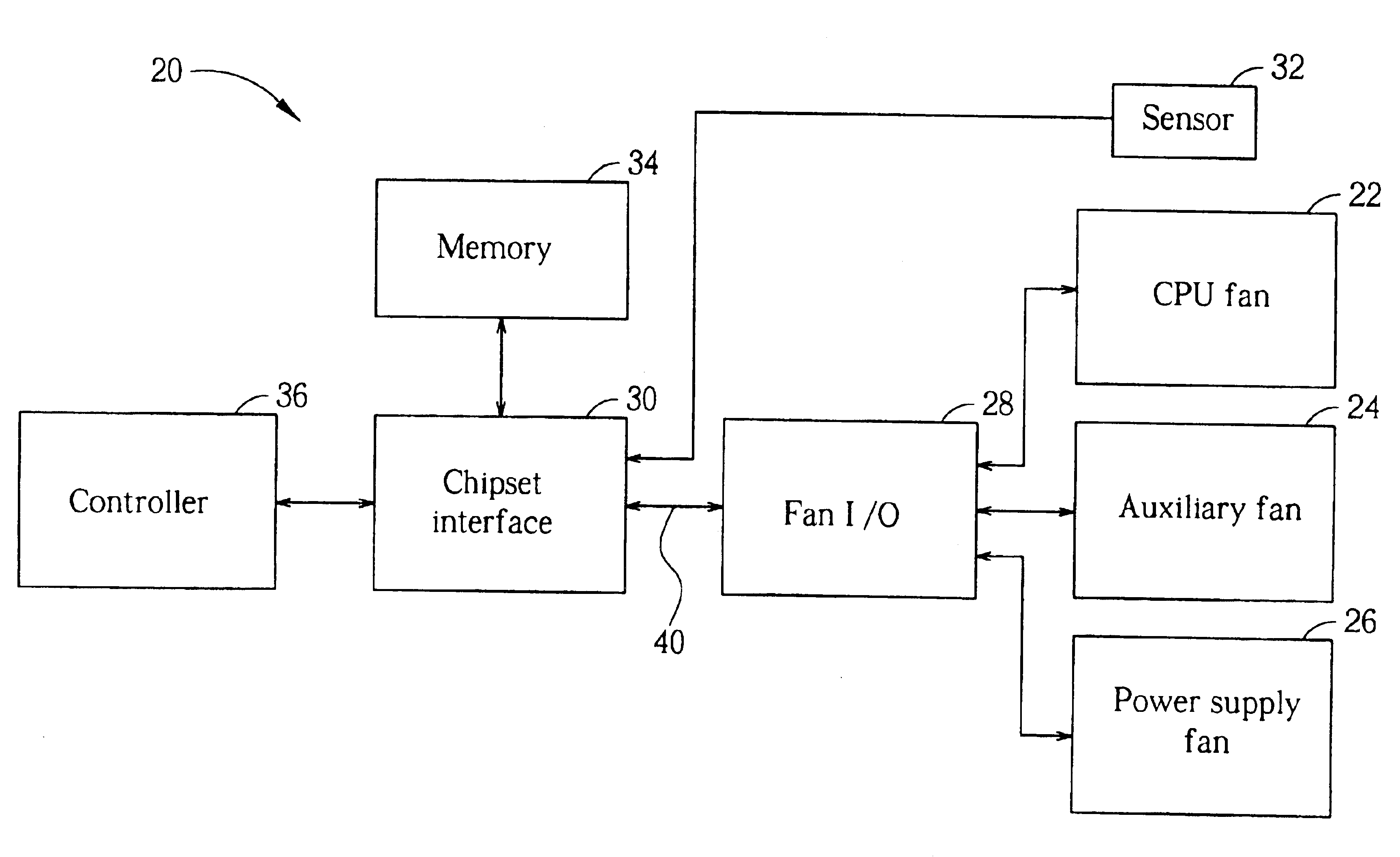

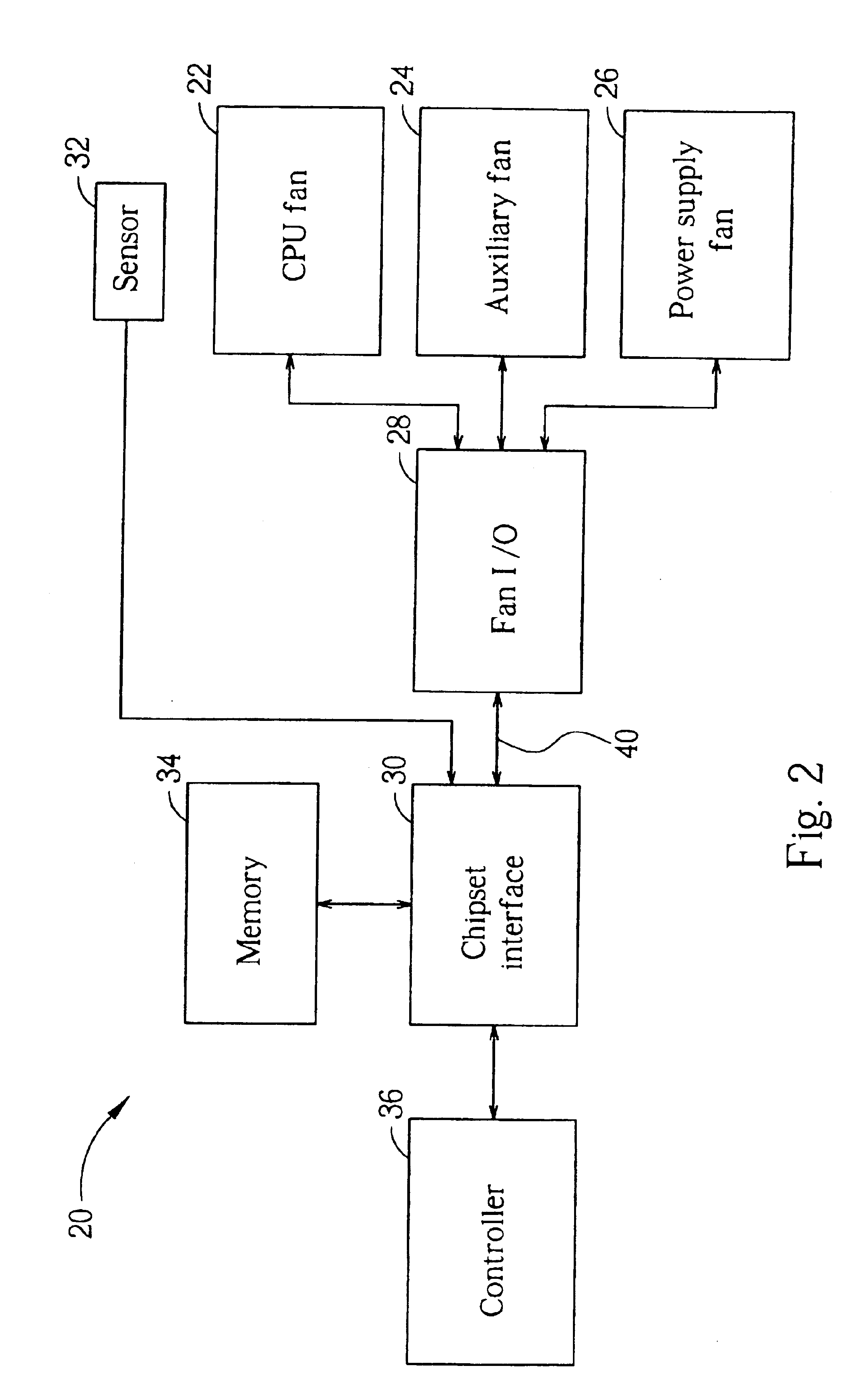

Cooling system for computing device

InactiveUS20050030171A1Minimize noise levelImprove performanceEnergy efficient ICTError detection/correctionClock rateControl signal

A cooling system includes a cooling fan, a fan input-output module for transmitting a control signal for controlling the rotational speed of the fan, a clock rate, and an operating voltage, and a chipset interface for generating the fan control signal based on a change in a vital temperature of the computer system. Further provided is a controller for receiving the vital temperature and forwarding the vital temperature to the chipset interface, and a temperature transducer for generating the vital temperature and outputting the vital temperature to the controller. The chipset interfacemonitors a rotational speed of the cooling fan, and monitors a vital temperature of the computer system. The chipset interface then sets the fan power based on a change in the vital temperature. When the vital temperature decreases, the fan power is reduced to slow the fan, and when the vital temperature increases, the fan power is increased to speed the fan.

Owner:AOPEN

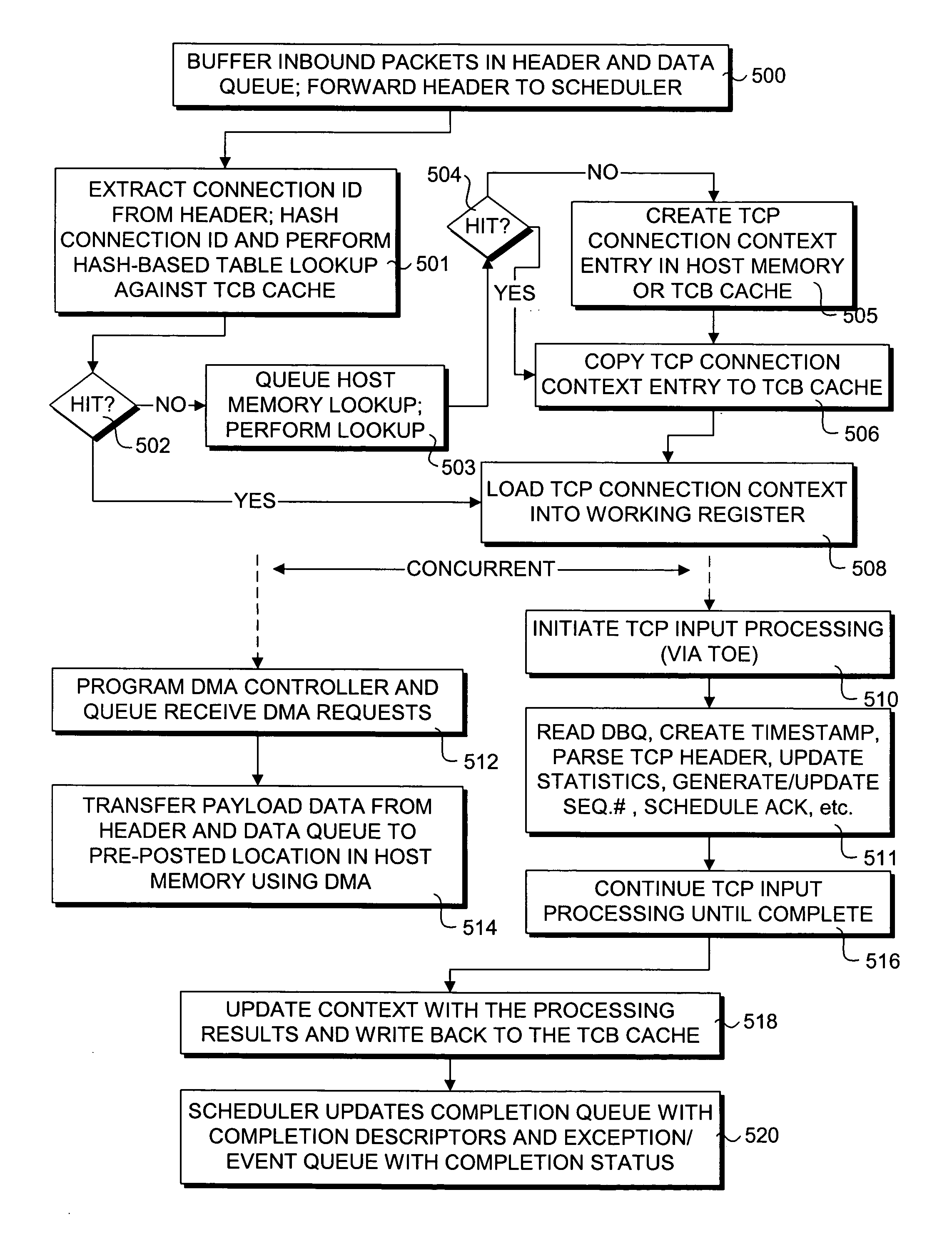

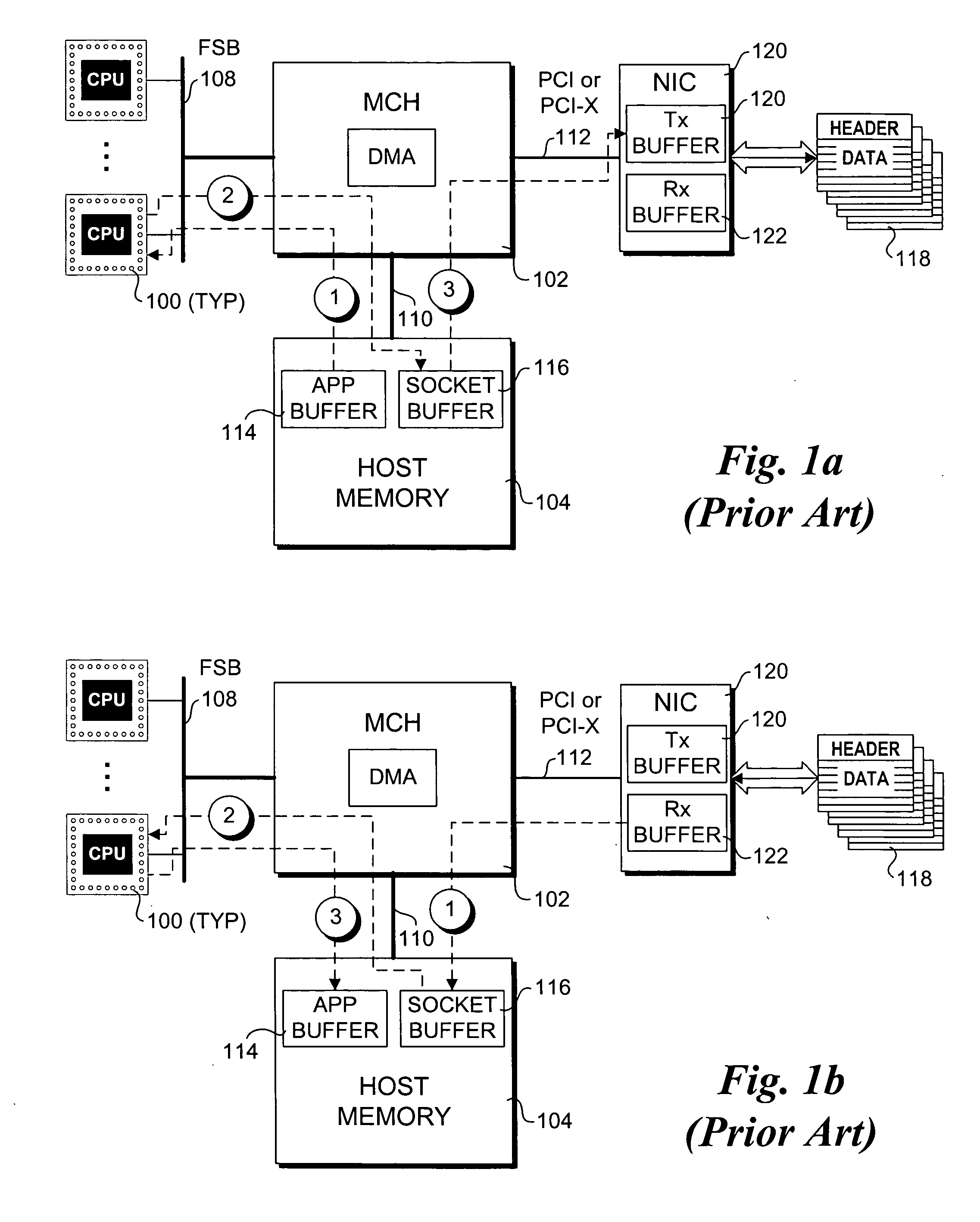

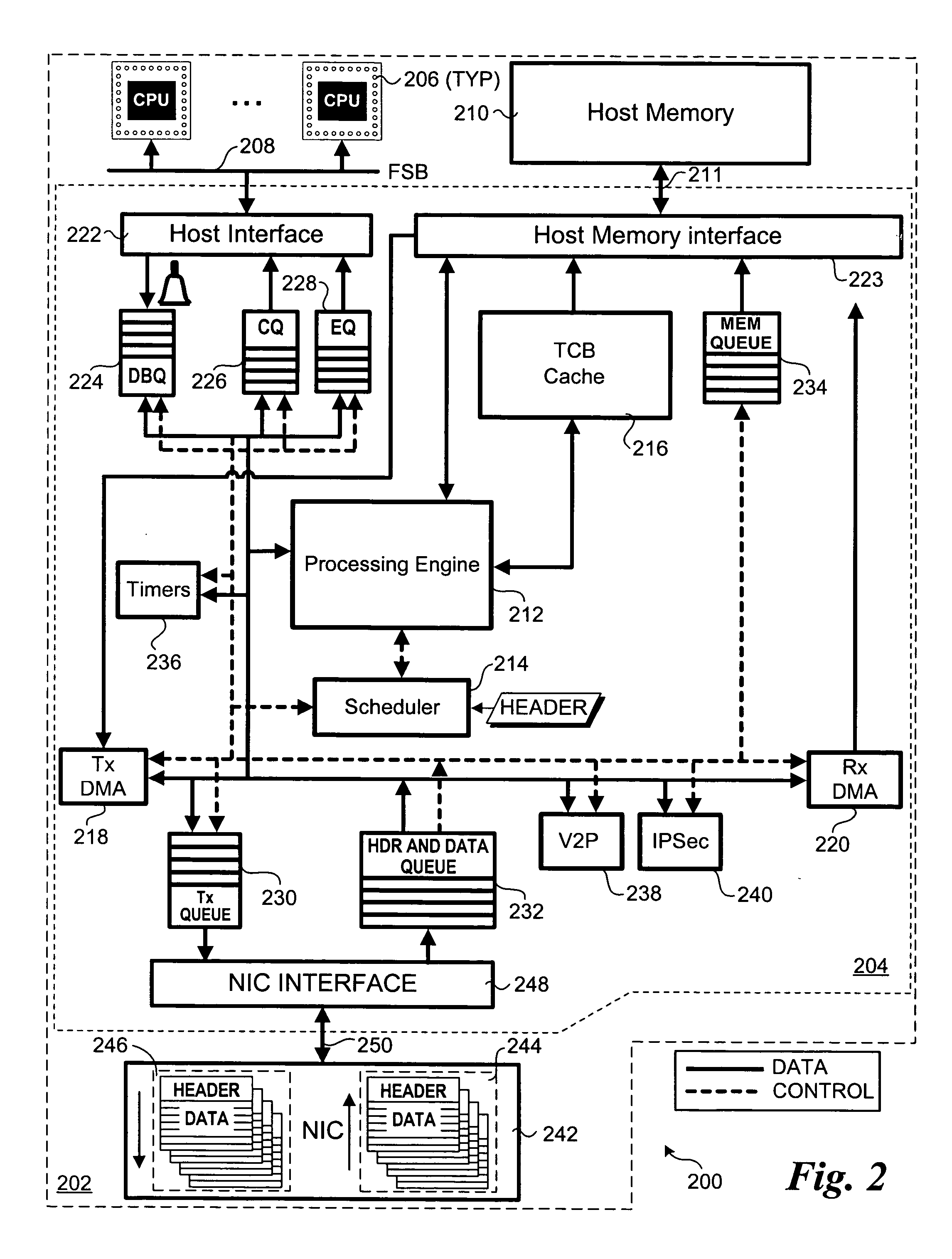

Hardware-based multi-threading for packet processing

Methods and apparatus for processing transmission control protocol (TCP) packets using hardware-based multi-threading techniques. Inbound and outbound TCP packet are processed using a multi-threaded TCP offload engine (TOE). The TOE includes an execution core comprising a processing engine, a scheduler, an on-chip cache, a host memory interface, a host interface, and a network interface controller (NIC) interface. In one embodiment, the TOE is embodied as a memory controller hub (MCH) component of a platform chipset. The TOE may further include an integrated direct memory access (DMA) controller, or the DMA controller may be embodied as separate circuitry on the MCH. In one embodiment, inbound packets are queued in an input buffer, the headers are provided to the scheduler, and the scheduler arbitrates thread execution on the processing engine. Concurrently, DMA payload data transfers are queued and asynchronously performed in a manner that hides memory latencies. In one embodiment, the technique can process typical-size TCP packets at 10 Gbps or greater line speeds.

Owner:TAHOE RES LTD

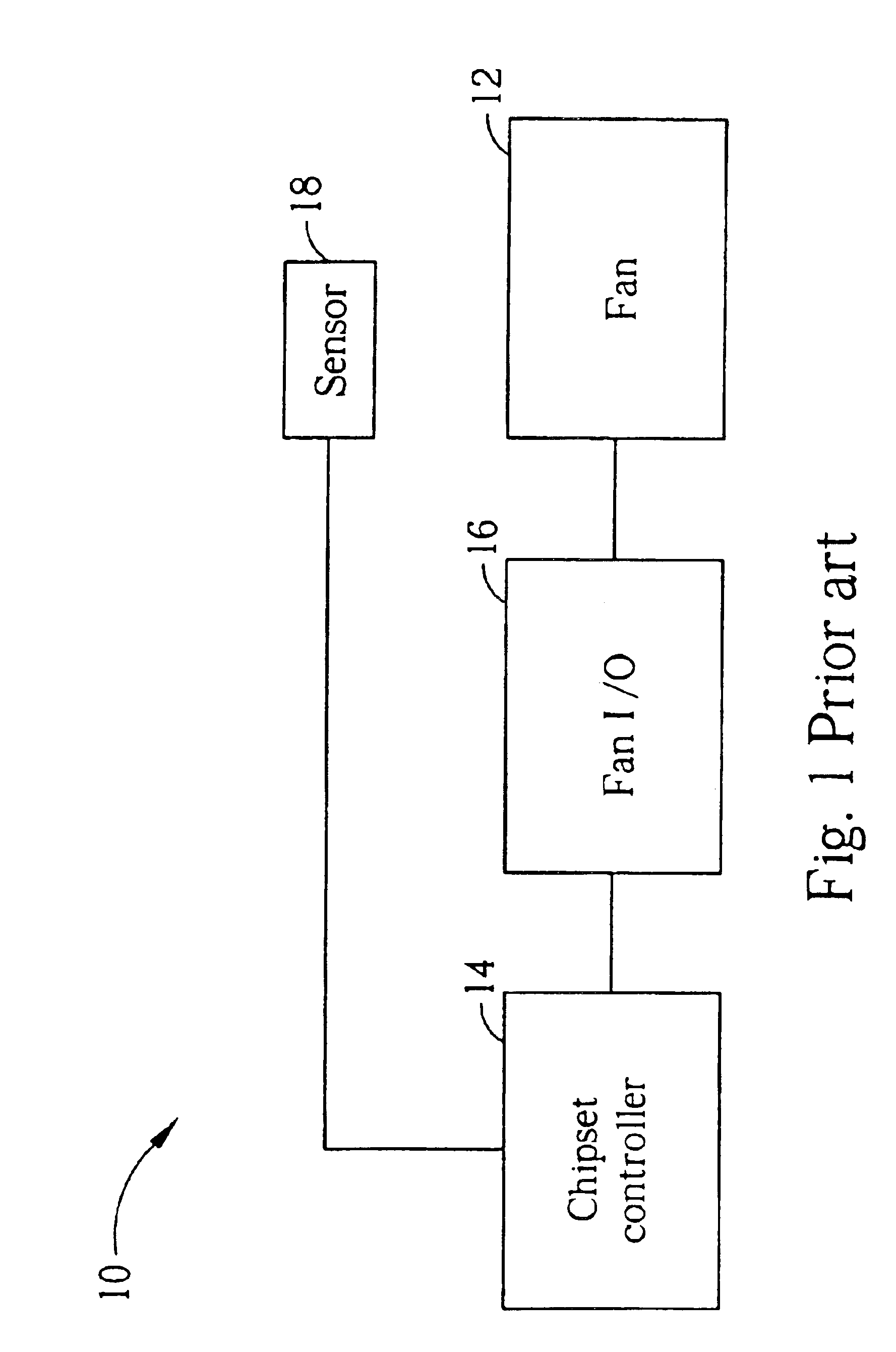

Computer cooling system

InactiveUS6935130B2Easy to controlReduce fan speedEnergy efficient ICTDigital data processing detailsControl signalTransducer

A cooling system includes a cooling fan, a fan input-output module for transmitting a control signal to the fan for controlling the rotational speed of the fan, and a chipset interface for generating the fan control signal based on a change in a vital temperature of the computer system. Further provided is a controller for receiving the vital temperature and forwarding the vital temperature to the chipset interface, and a temperature transducer for generating the vital temperature and outputting the vital temperature to the controller. The chipset interface monitors a rotational speed of the cooling fan, and monitors a vital temperature of the computer system. The chipset interface then sets the fan power based on a change in the vital temperature. When the vital temperature decreases, the fan power is reduced to slow the fan, and when the vital temperature increases, the fan power is increased to speed the fan.

Owner:AOPEN

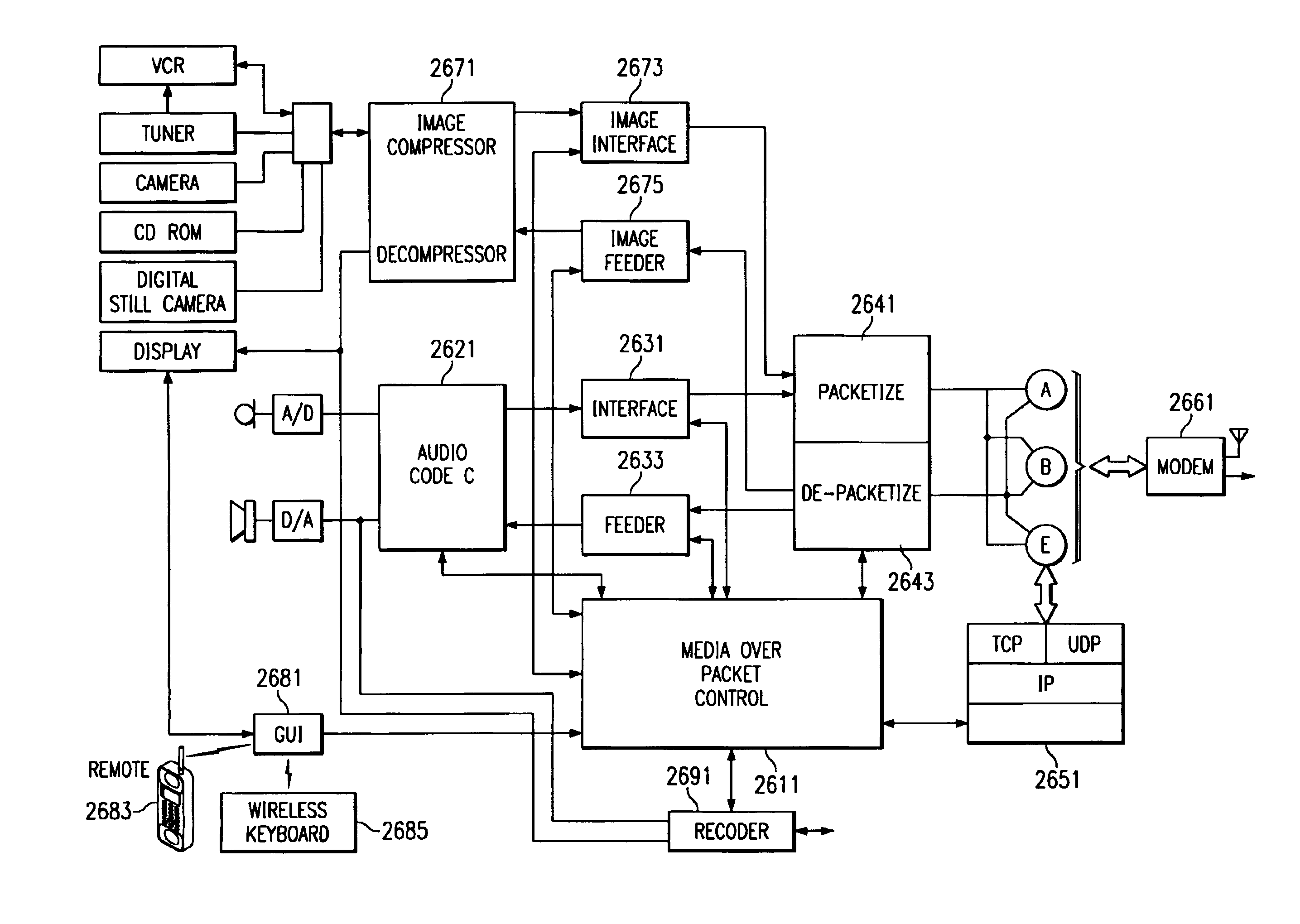

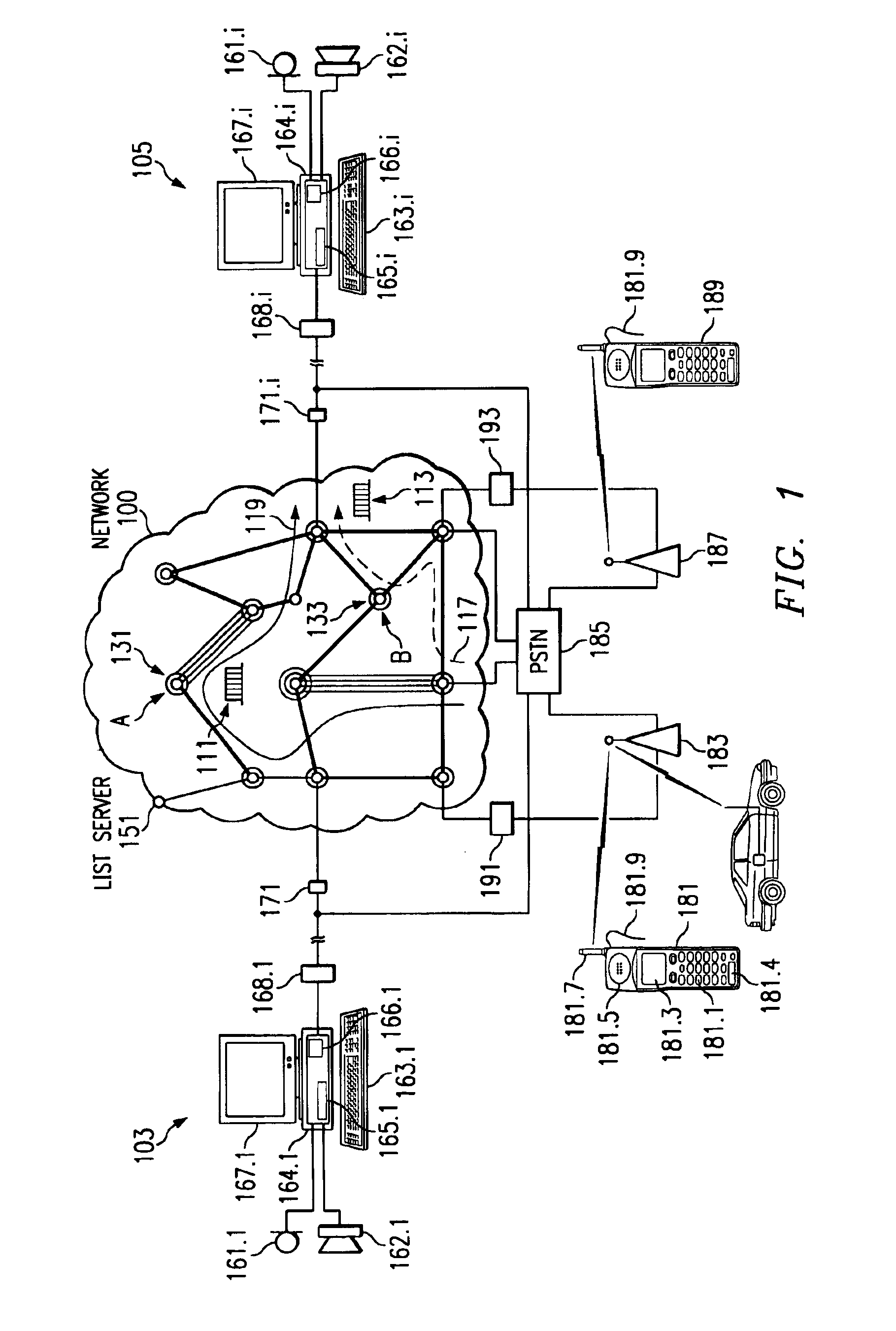

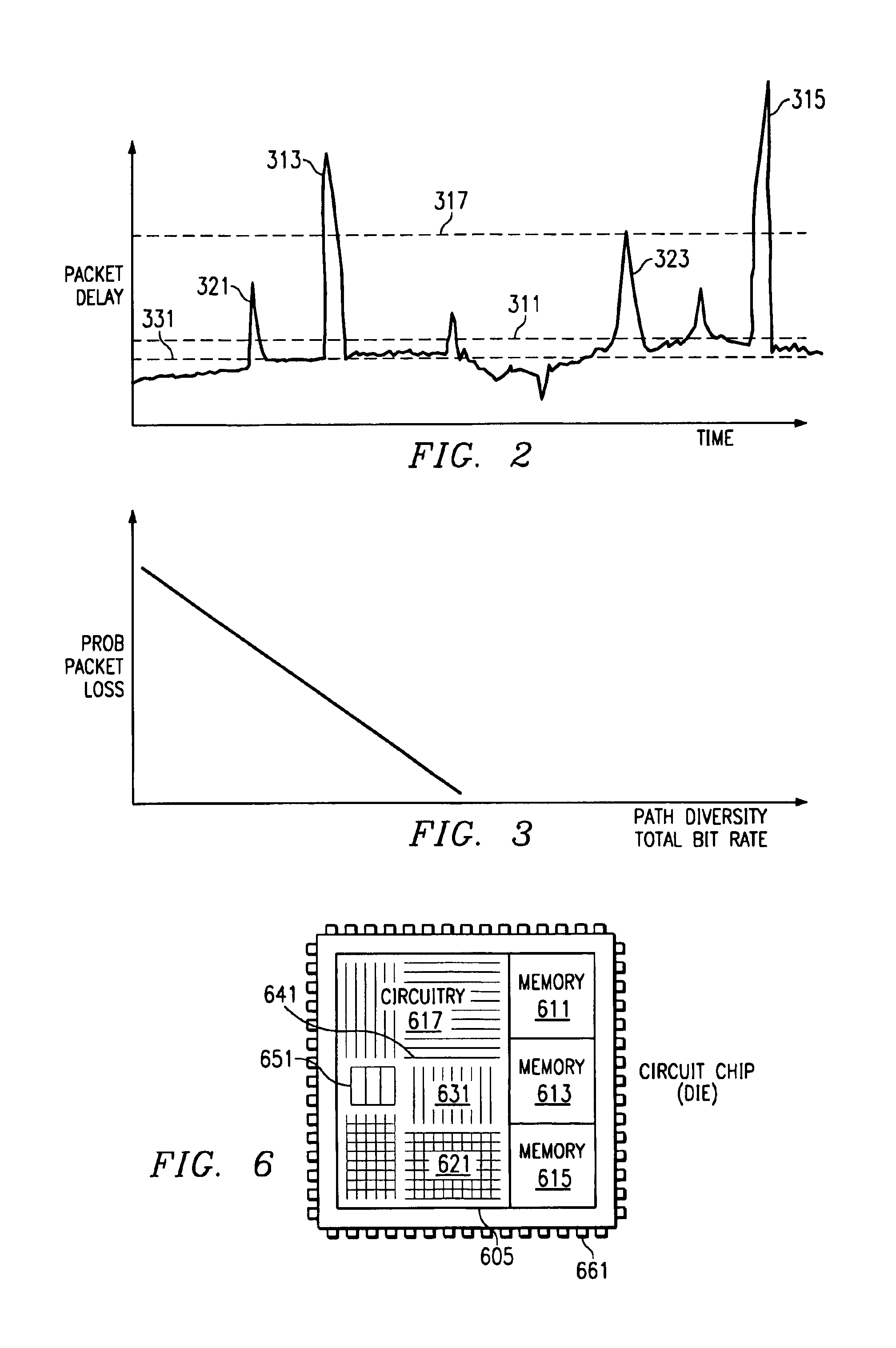

Integrated circuits, systems, apparatus, packets and processes utilizing path diversity for media over packet applications

In one form of the invention, a process of sending real-time information from a sender computer (103) to a receiver computer (105) coupled to the sender computer (103) by a packet network (100) wherein packets (111,113) sometimes become lost, includes steps of directing (441) packets (111) containing the real-time information from the sender computer (103) by at least one path (119) in the packet network (100) to the receiver computer (105), and directing packets (113) containing information dependent on the real-time information from the sender computer (103) by at least one path diversity path (117) in the packet network (100) to the same receiver computer (105).Other forms of the invention encompass other processes, improved packets and packet ensembles (111,113), integrated circuits (610), chipsets (DSP 1721, MCU), computer cards (1651), information storage articles (1511,1611), systems, computers (103,105), gateways (191,193), routers (131,133), cellular telephone handsets (181,189), wireless base stations (183,187), appliances (1721,1731,1741), and packet networks (100), and other forms as disclosed and claimed.

Owner:TEXAS INSTR INC

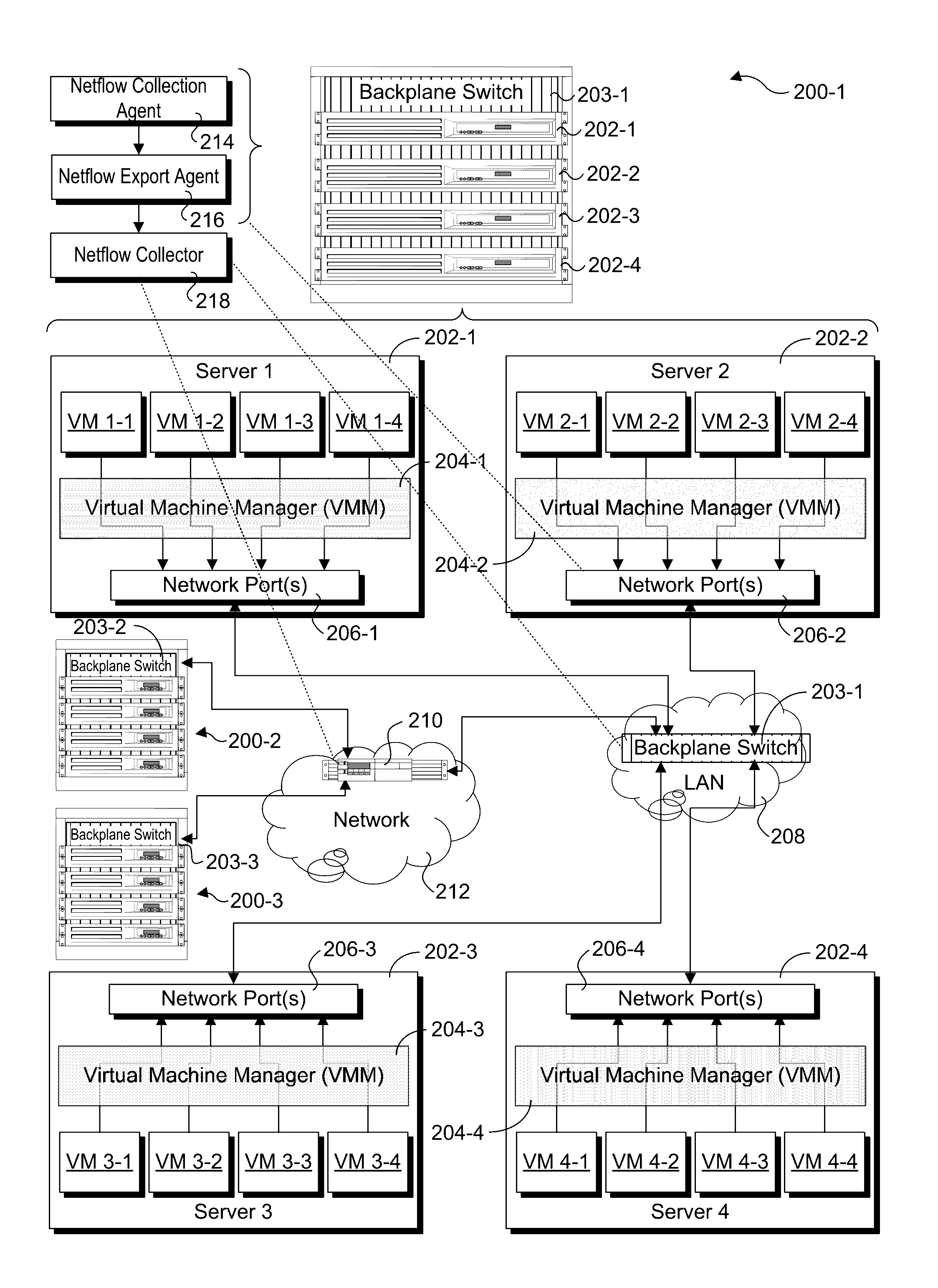

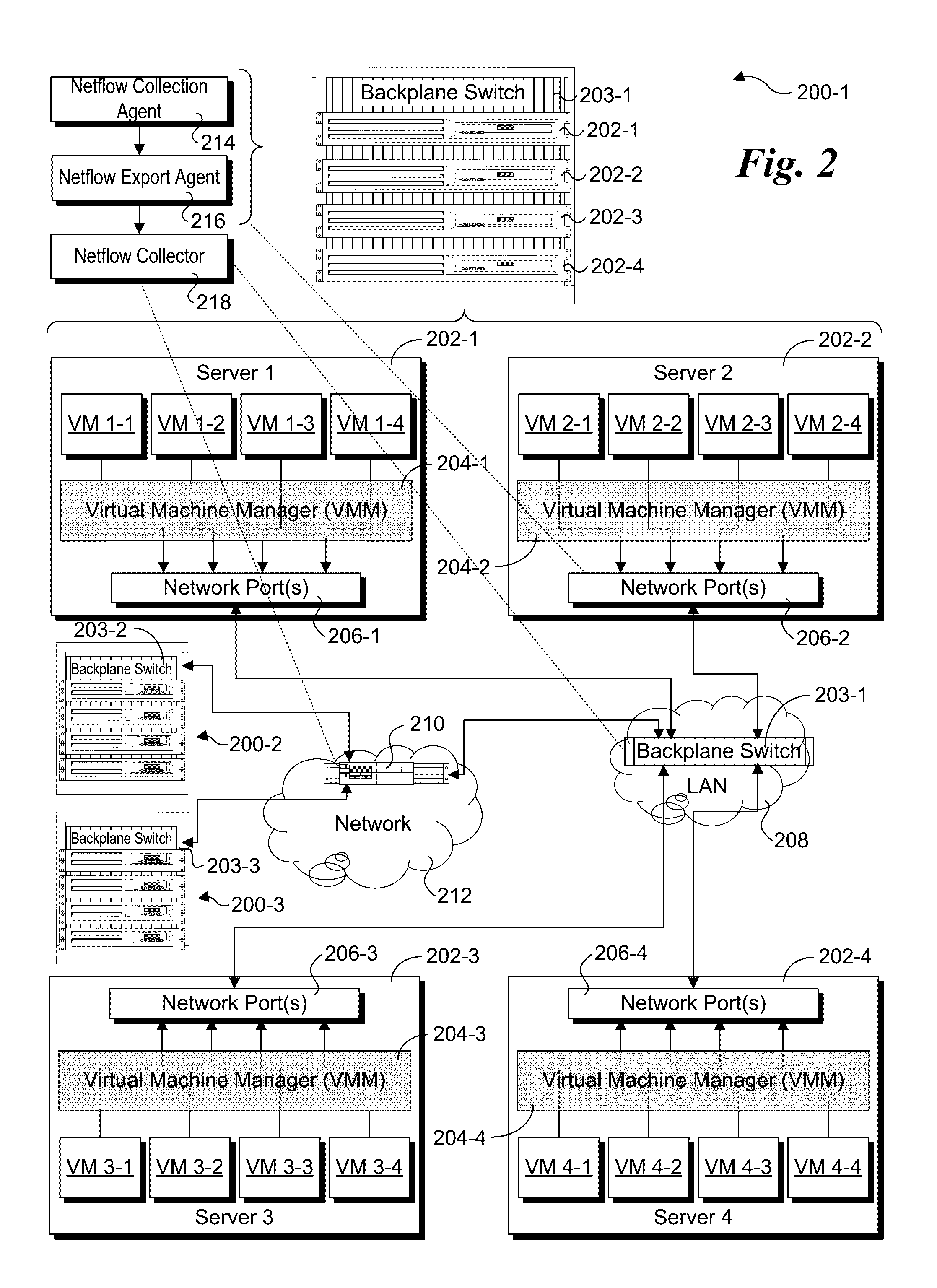

Netflow collection and export offload using network silicon

Methods and apparatus for collection of Netflow data and export offload using network silicon. In accordance with aspects of the embodiments, the Netflow export and collection functions are offloaded to the network silicon in the chipset, System on a Chip (SoC), backplane switch, disaggregated switch, virtual switch (vSwitch) accelerator, and Network Interface Card / Controller (NIC) level. For apparatus implementing virtualized environments, one or both of the collection and export functions are implemented at the Physical Function (PF) and / or Virtual Function (VF) layers of the apparatus.

Owner:INTEL CORP

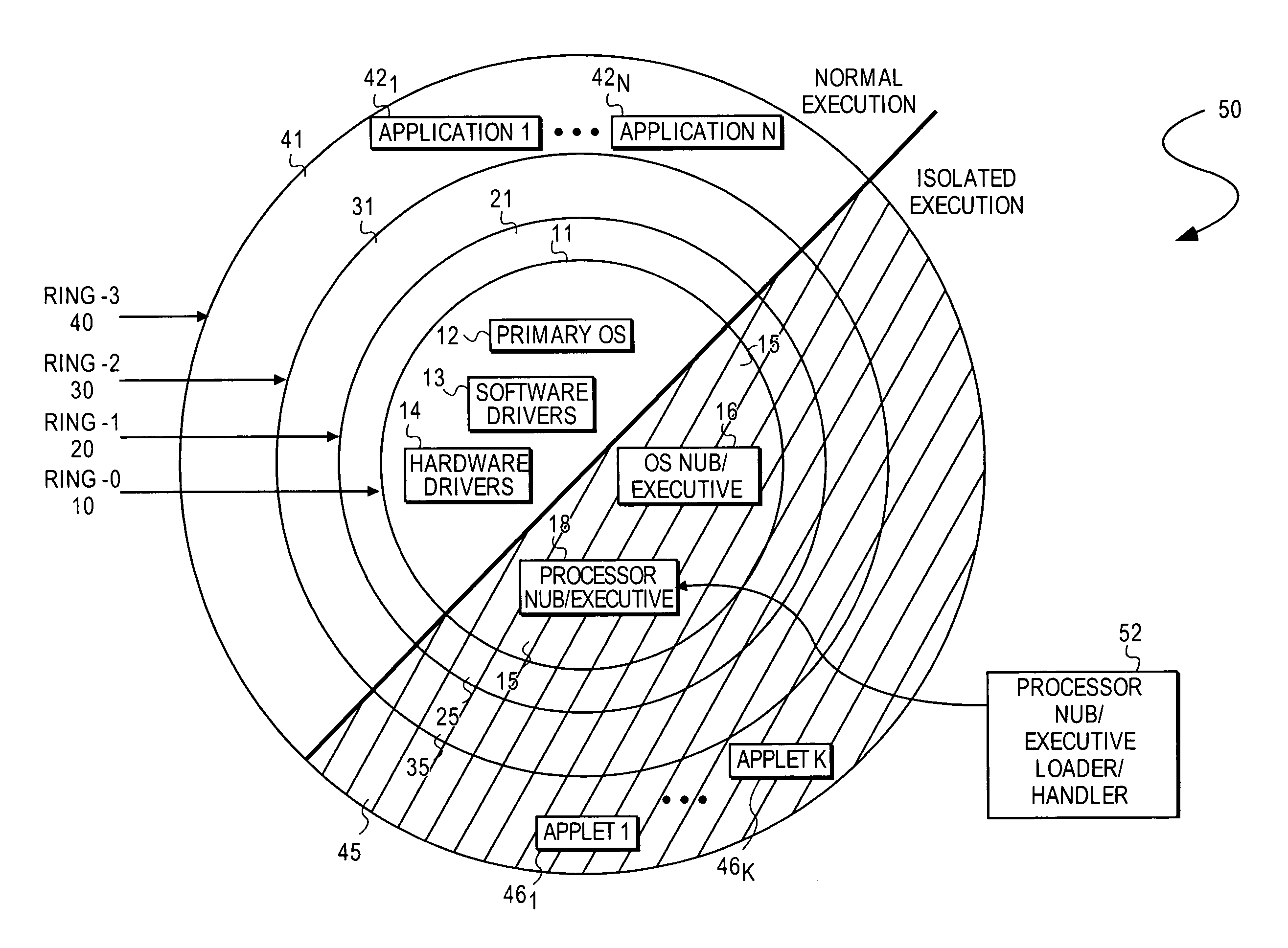

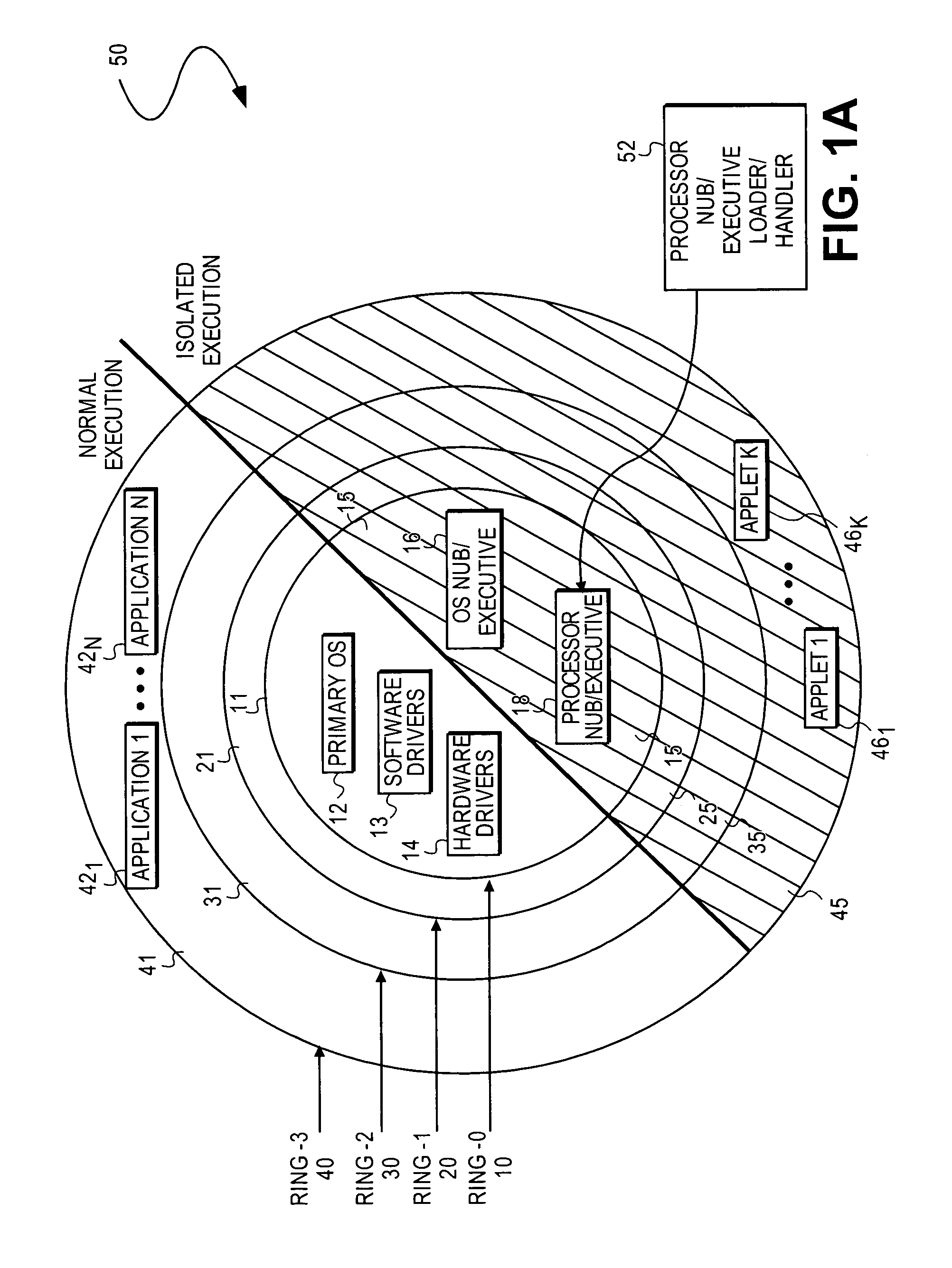

Managing a secure environment using a chipset in isolated execution mode

InactiveUS7013484B1Digital data processing detailsAnalogue secracy/subscription systemsComputer hardwareChipset

A chipset is initialized in a secure environment for an isolated execution mode by an initialization storage. The secure environment has a plurality of executive entities and is associated with an isolated memory area accessible by at least one processor. The at least one processor has a plurality of threads and operates in one of a normal execution mode and the isolated execution mode. The executive entities include a processor executive (PE) handler. PE handler data corresponding to the PE handler are stored in a PE handler storage. The PE handler data include a PE handler image to be loaded into the isolated memory area after the chipset is initialized. The loaded PE handler image corresponds to the PE handler.

Owner:ALIBABA GRP HLDG LTD

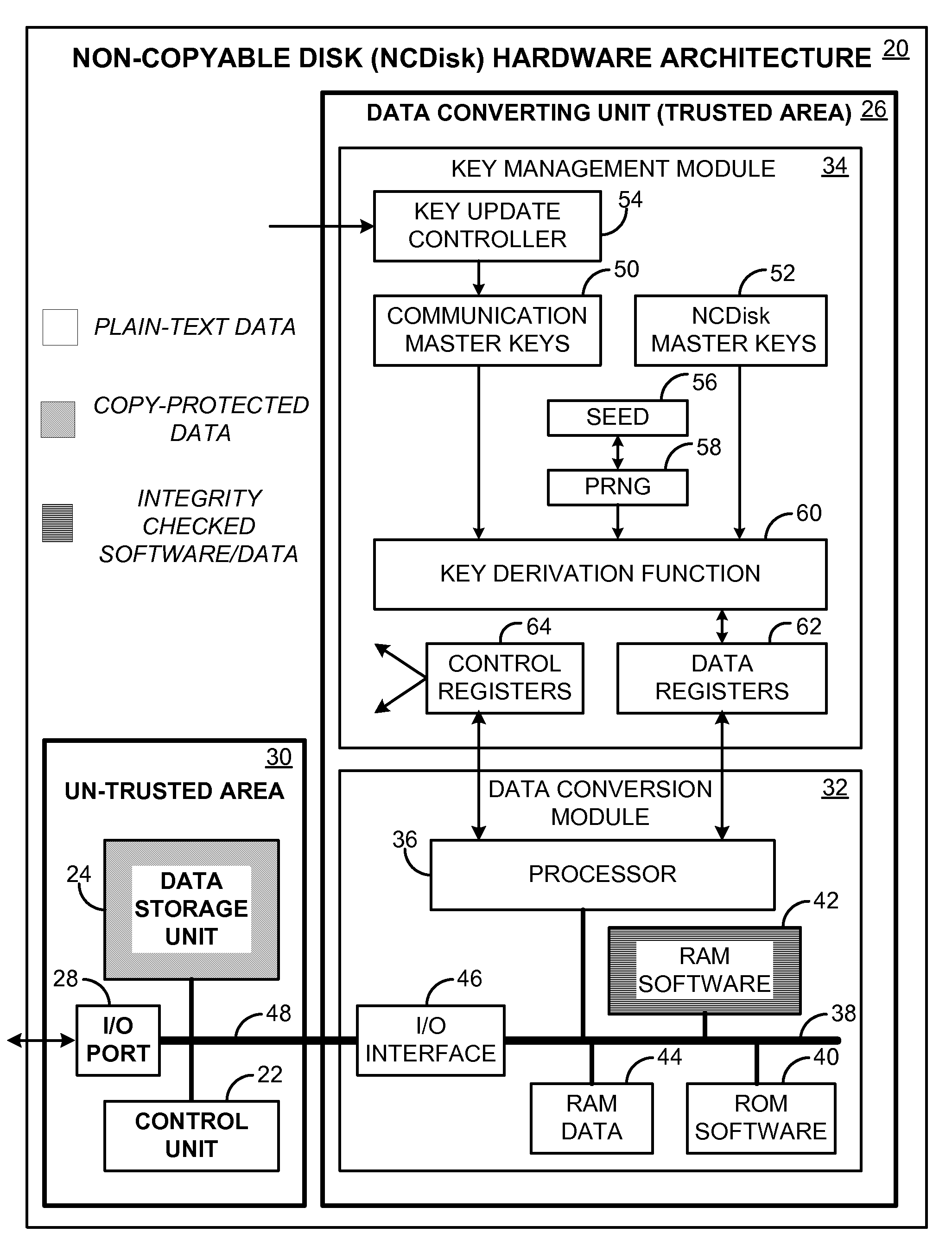

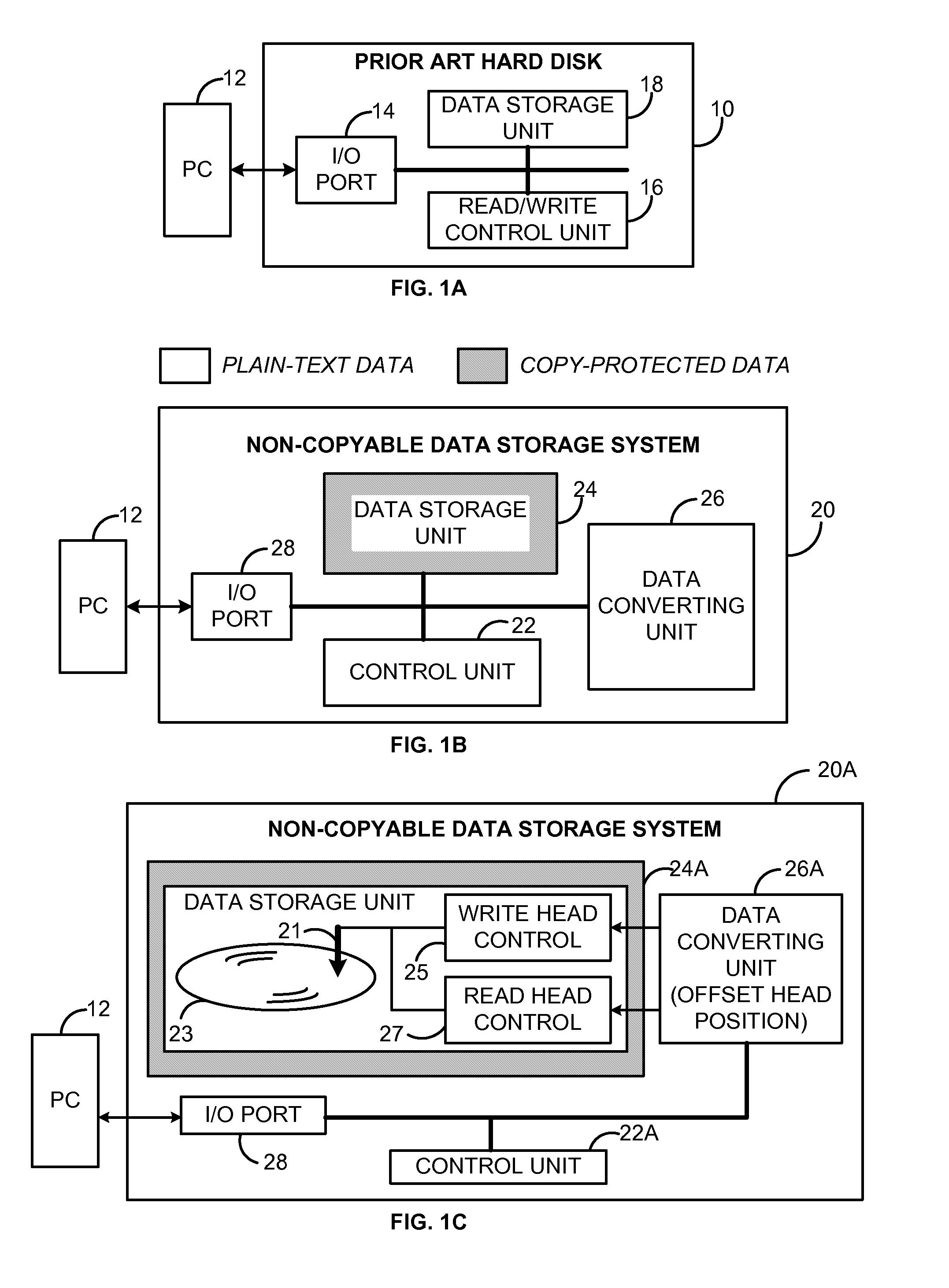

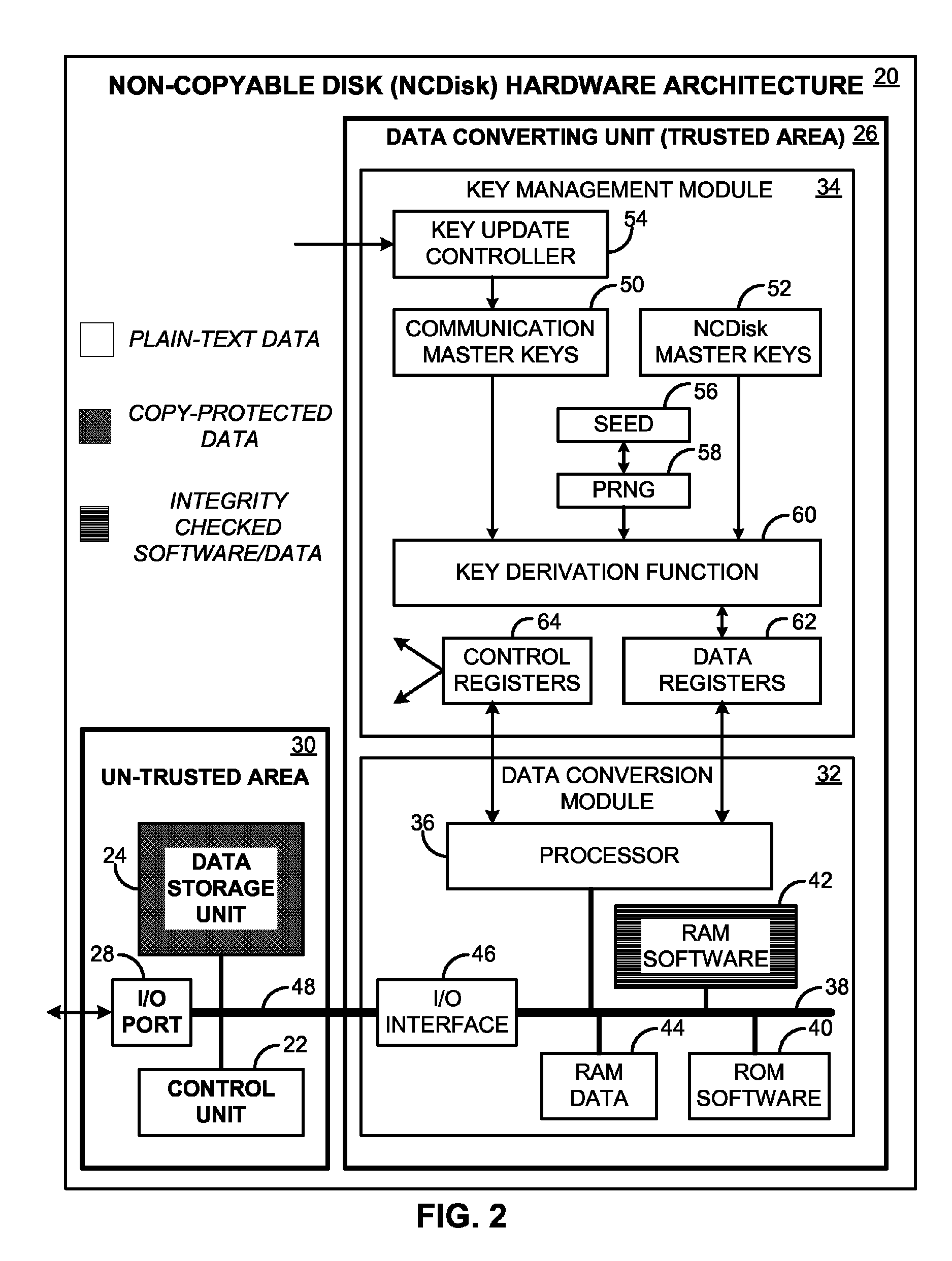

Secure data storage for protecting digital content

InactiveUS8452988B2The implementation process is simpleConvenient for userKey distribution for secure communicationUnauthorized memory use protectionDigital dataPaper data storage

Owner:WANG MICHAEL SUJUE

Method and apparatus for flexible spectrum usage in communications systems

InactiveUS20110096703A1Reduce distractionsReduce overlapRadio transmissionDuplex signal operationFrequency spectrumTransceiver

Methods and apparatuses are disclosed that provide flexible use of a shared radio resource. An apparatus determines from monitoring signal energy on a shared radio resource whether other transmitters are present. A predetermined set of time division duplex (TDD) signaling patterns are identified. A correlation is performed between signal energy received on the shared radio resource and the predetermined TDD signaling patterns. The apparatus may then determine a TDD signaling pattern that may reduce or avoid interference with any other transmitters using the shared resource. The shared radio resource may be, for example, a shared frequency spectrum. Efficient allocation of radio resources among apparatuses such as radio transceivers, without fixed time references or predetermined patterns, may be obtained. The radio transceivers may be base stations or mobile user equipment in a wireless communications system. The apparatus may be an integrated circuit, a portion thereof, or chipset.

Owner:NOKIA TECHNOLOGLES OY

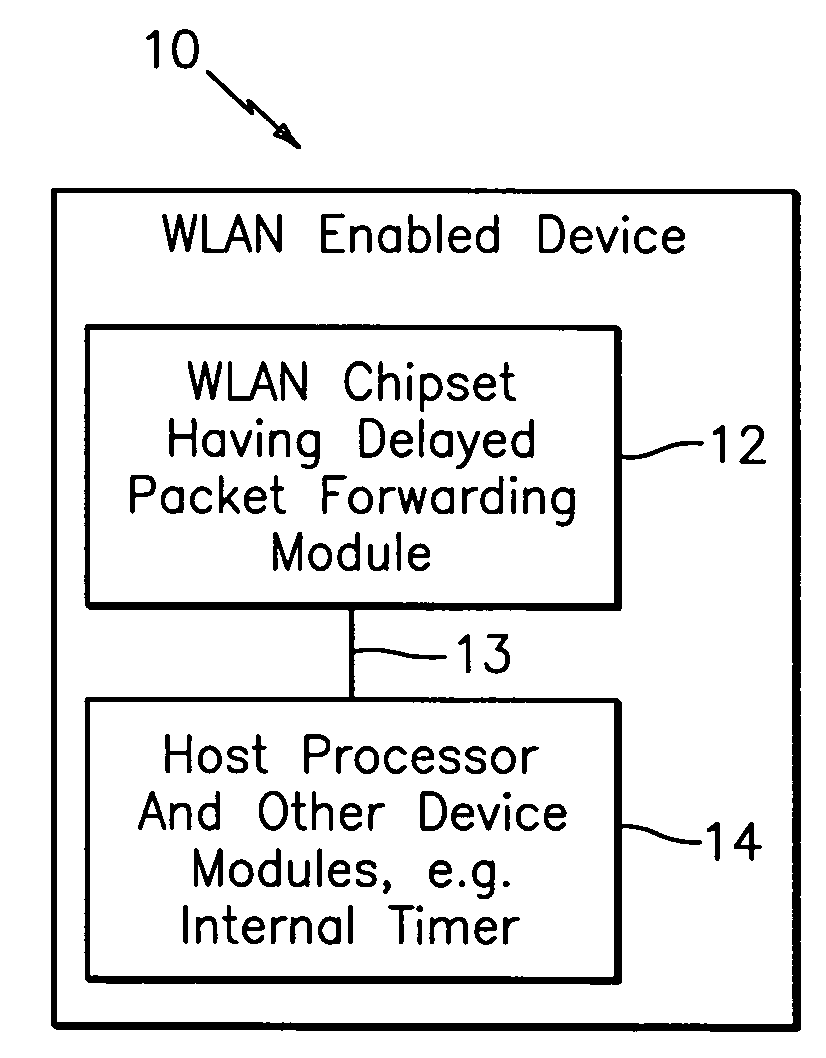

Delayed host wakeup for wireless communications device

InactiveUS20070238437A1Good power savingReduce power consumptionPower managementEnergy efficient ICTSleep stateNetwork packet

A new and unique method or apparatus for power savings in a node, point, terminal or device in a wireless local area network (WLAN), or other suitable network, featuring one or more steps for delaying forwarding one or more data packets from a WLAN chipset to a host processor based on information received by the WLAN chipset about whether the host processor is in a sleep state. The host processor has a clock request pin to indicate when it is in the sleep state. The WLAN chipset has a pin that is connected to a sleep state signal of the host processor so that the WLAN chipset knows when it can wake up the host processor or not. The WLAN chipset has an internal threshold timer to fulfil latency requirements for delivering packets to the host processor.

Owner:NOKIA CORP

Method for routing incoming and outgoing data in an NFC chipset

A method for routing data in a chipset comprising at least two host processors and one RFID-type contactless data send / receive interface configurable according to several operating modes and according to several contactless communication protocols includes routing, to at least one of the host processors, data received by the contactless data send / receive interface via a contactless data transmission channel. The method further includes determining a destination point of the data in a host processor using as criteria to determine the destination point the operating mode and the contactless communication protocol used by the contactless data send / receive interface to create the contactless data transmission channel through which the data are received.

Owner:VERIMATRIX INC

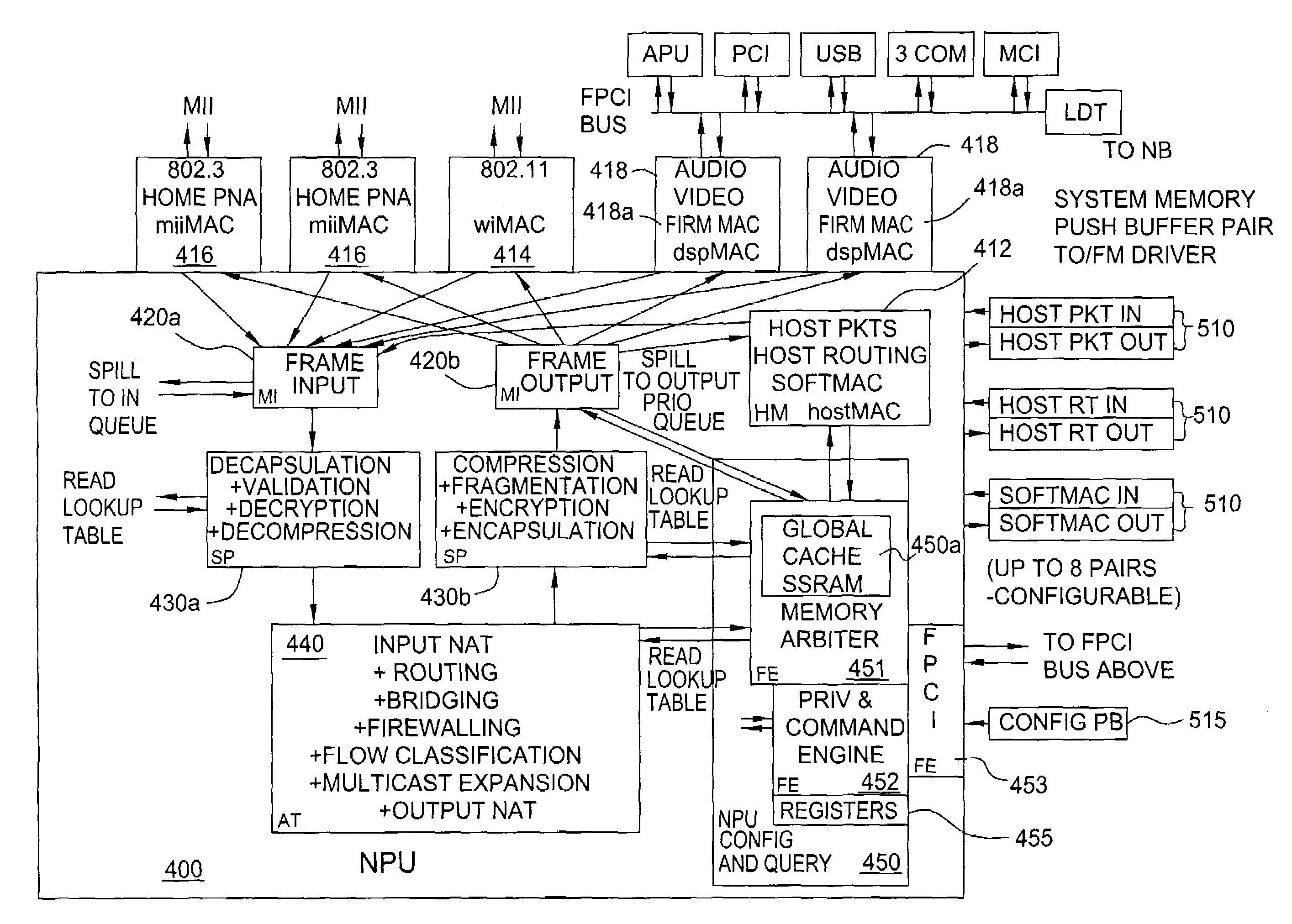

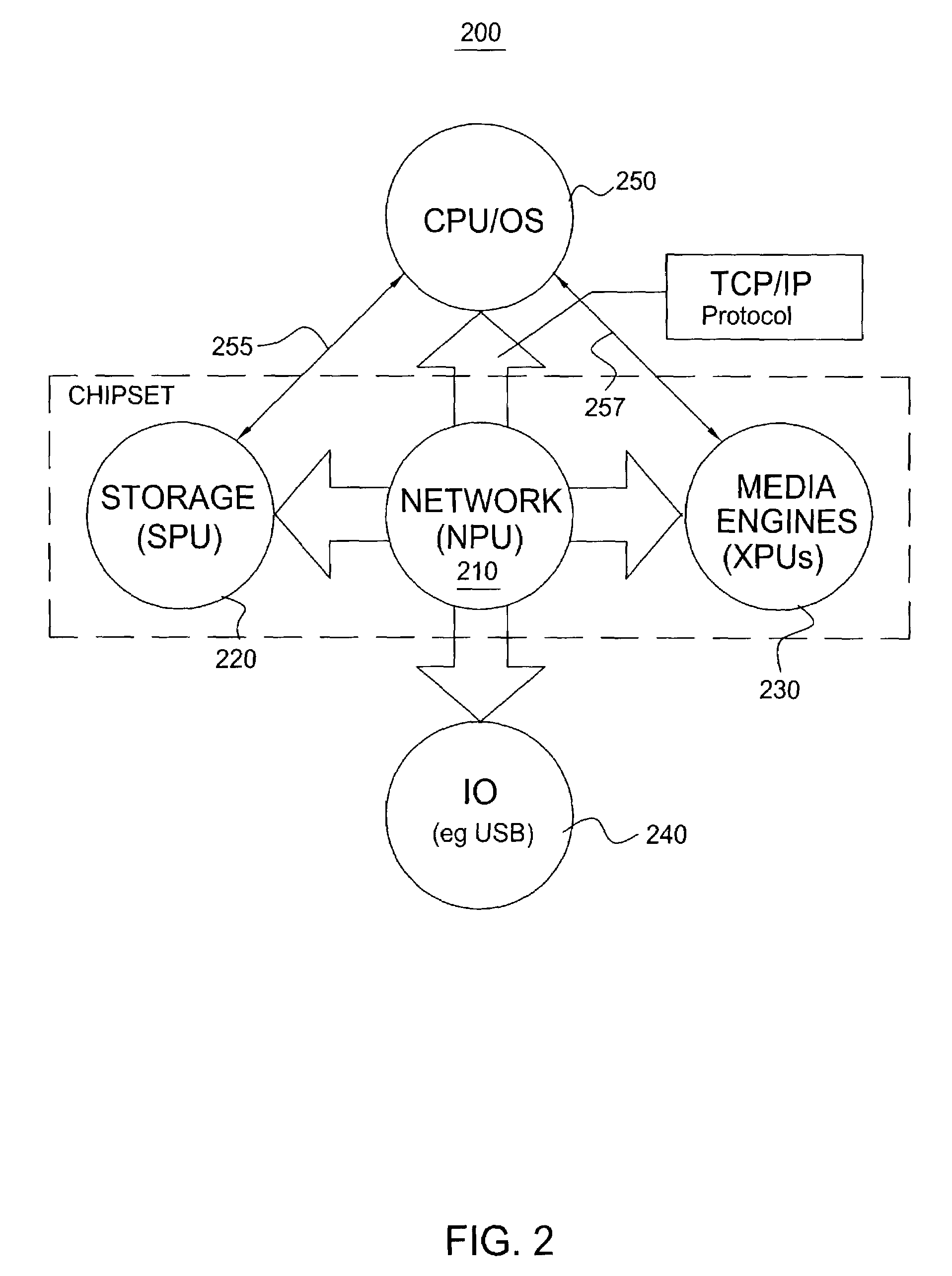

Internet protocol (IP) router residing in a processor chipset

ActiveUS7324547B1Effective serviceEasily configure networkLoop networksNetwork connectionsTTEthernetNetwork processing unit

A novel network architecture that integrates the functions of an internet protocol (IP) router into a network processing unit (NPU) that resides in a host computer's chipset such that the host computer's resources are perceived as separate network appliances. The NPU appears logically separate from the host computer even though, in one embodiment, it is sharing the same chip.

Owner:NVIDIA CORP