Patents

Literature

329 results about "Complementary pair" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

COMPLEMENTARY PAIRING. Complementary pairing is such a specific type of pairing in which the sequence of bases in one strand determines the sequence of bases on the opposite strand. For example, in the structure of DNA wherever adenine appears in one strand, a thymine appears opposite to it on the other strand.

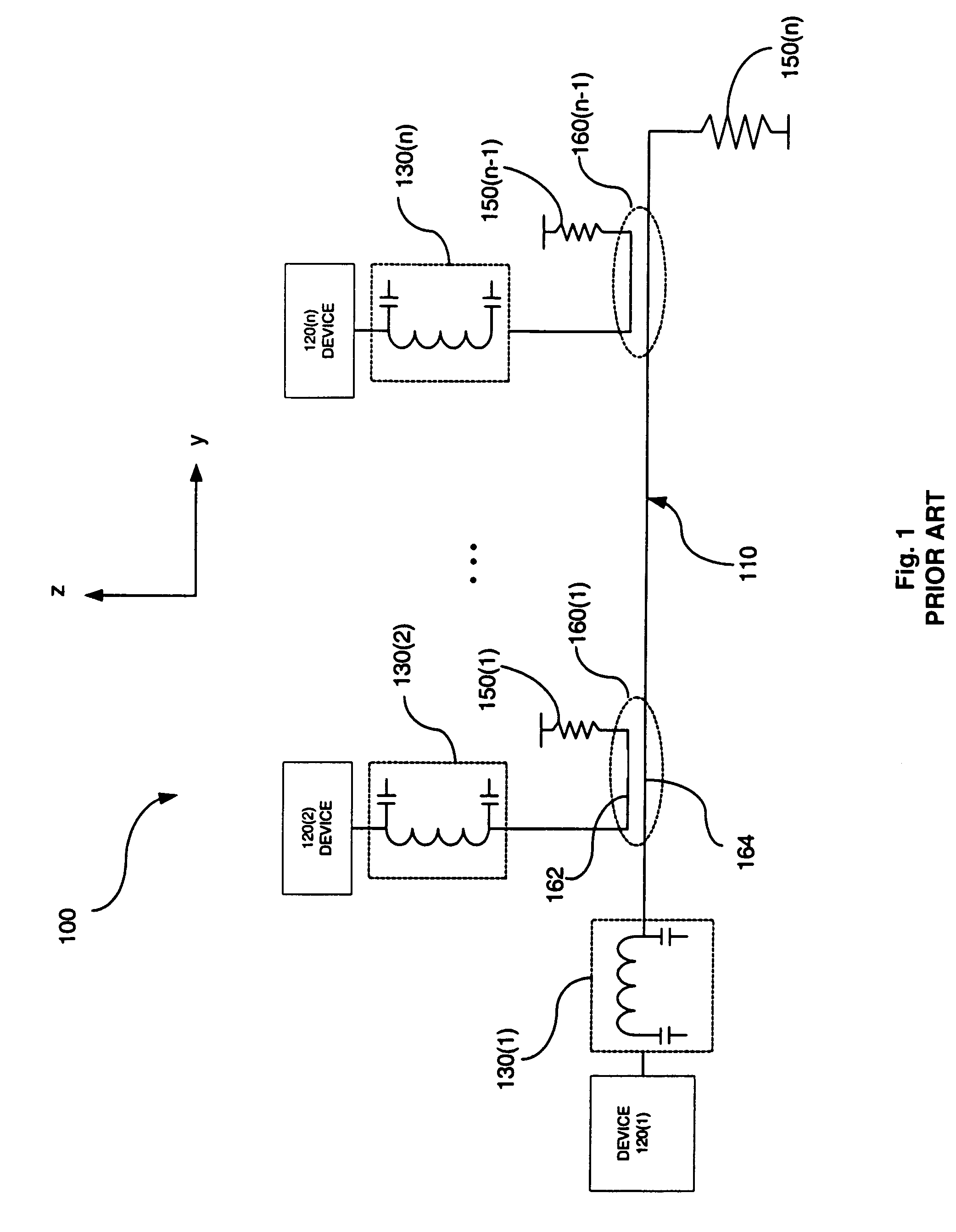

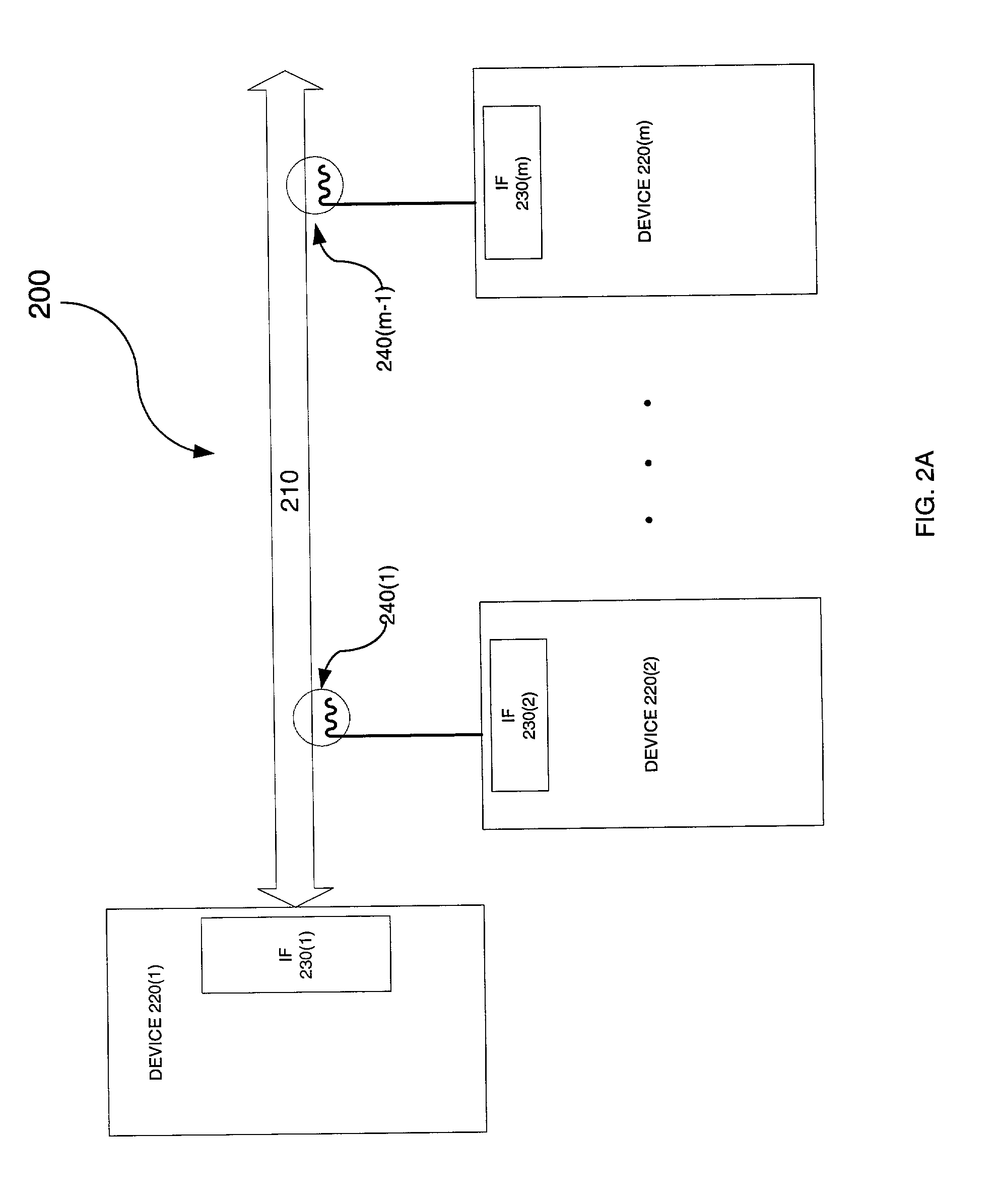

Symbol-based signaling device for an electromagnetically-coupled bus system

InactiveUS7075996B2Printed circuit assemblingLine impedence variation compensationComplementary pairChipset

The present invention provides a chipset for transferring data through an electromagnetically coupled bus system. The chipset includes a modulator, a matching circuit and a demodulator. The modulator modifies a clock to encode multiple bits in a complementary pair of symbols. The matching circuit modifies the clock signal to generate a complementary pair of reference signals that is transmitted with the complementary symbol pair, and the demodulator decodes a second set of bits from selected properties of a complementary pair of transferred symbols.

Owner:INTEL CORP

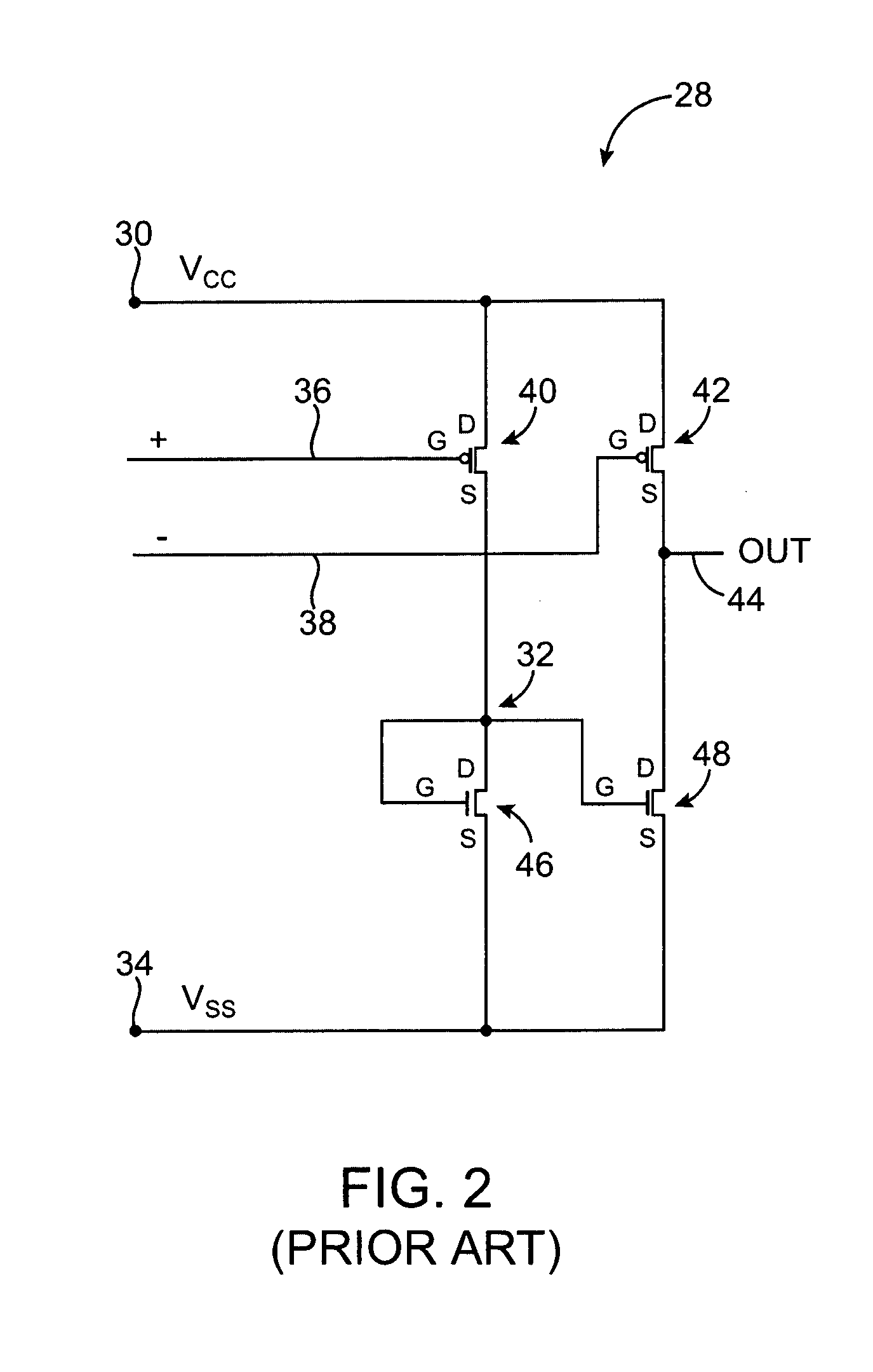

Overvoltage/undervoltage tolerant transfer gate

InactiveUS6163199AMassage combsLogic circuits characterised by logic functionOvervoltageComplementary pair

A transfer gate or pass gate circuit for transferring logic signals between nodes for a range of available high-potential supply levels. The primary transfer gate is designed to protect against potentials that either exceed either a high-potential or a low-potential level or that undershoot such potential levels. For overshoot (overvoltage) tolerance, this is achieved by coupling a NMOS transistor in parallel with a pair of PMOS transistors that are coupled in series. All three transistors are located between two nodes, either of which can be the input or the output of the transfer gate. The NMOS transistor is designed to be larger than the PMOS transistors and carries most of the transfer capability. The smaller PMOS transistors are designed to eliminate potential drops that would otherwise occur with a single NMOS transistor or with a complementary pair of transistors. For undershoot (undervoltage) tolerance, a PMOS transistor is coupled in parallel with a pair of NMOS transistors that are coupled in series.

Owner:SEMICON COMPONENTS IND LLC

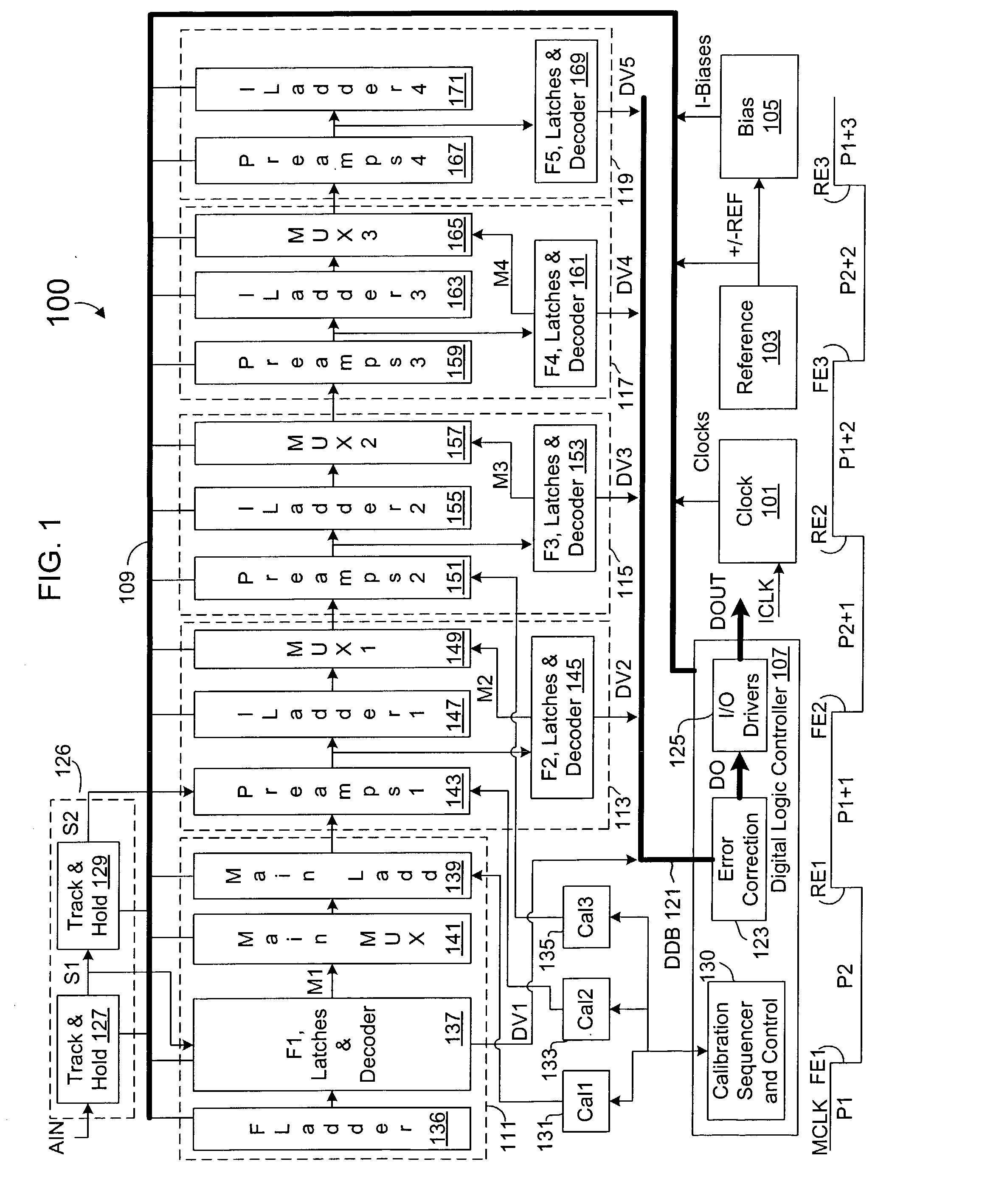

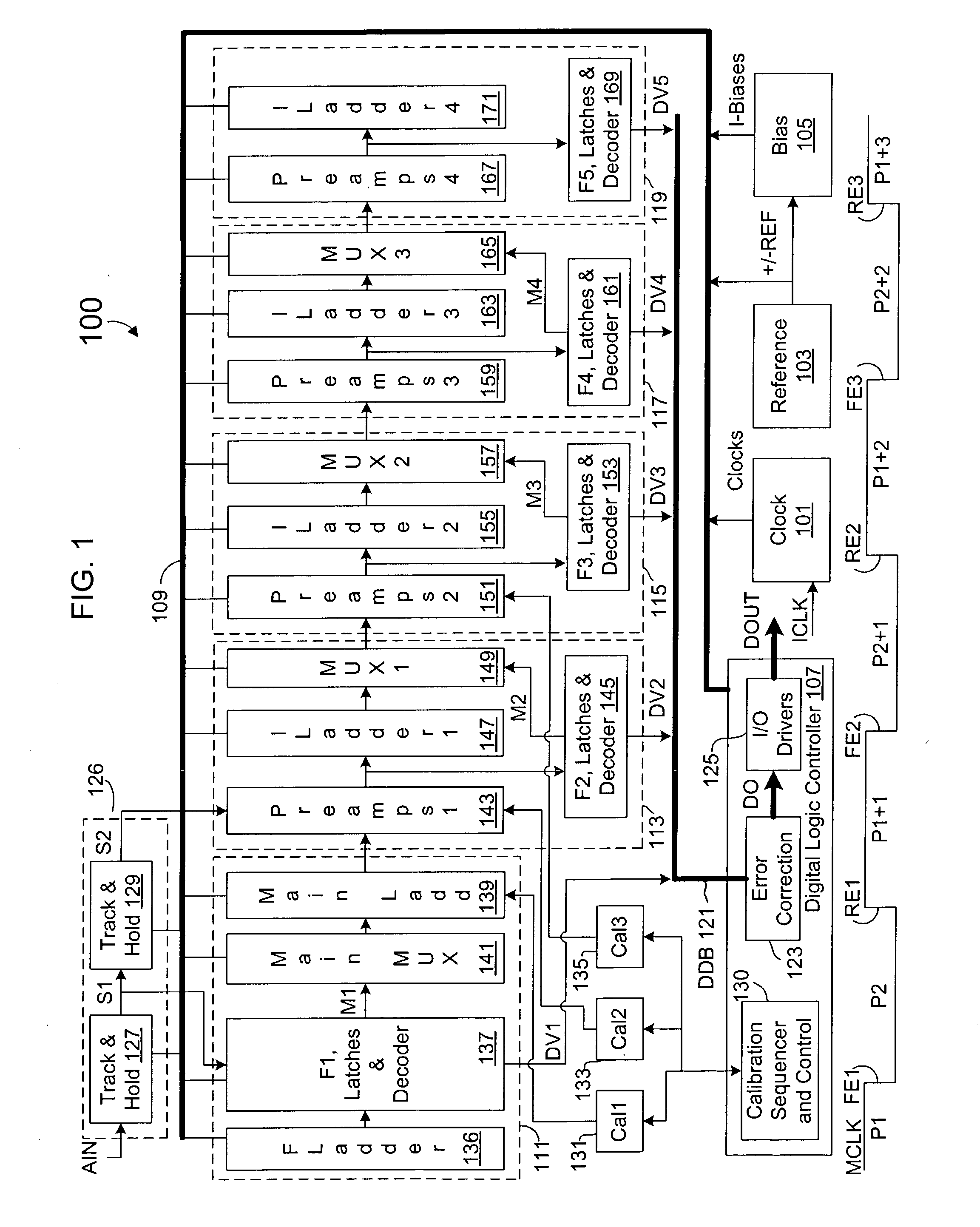

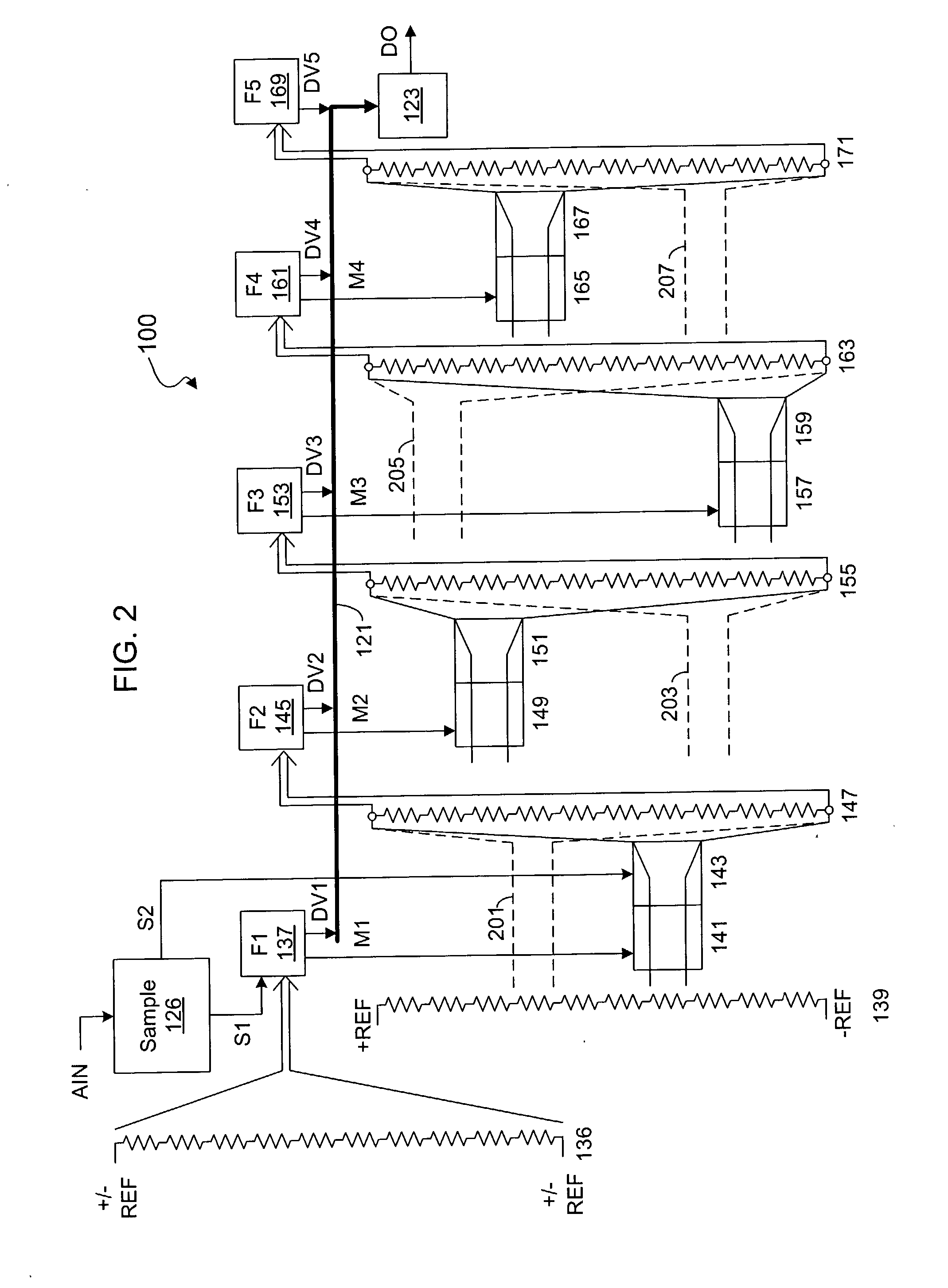

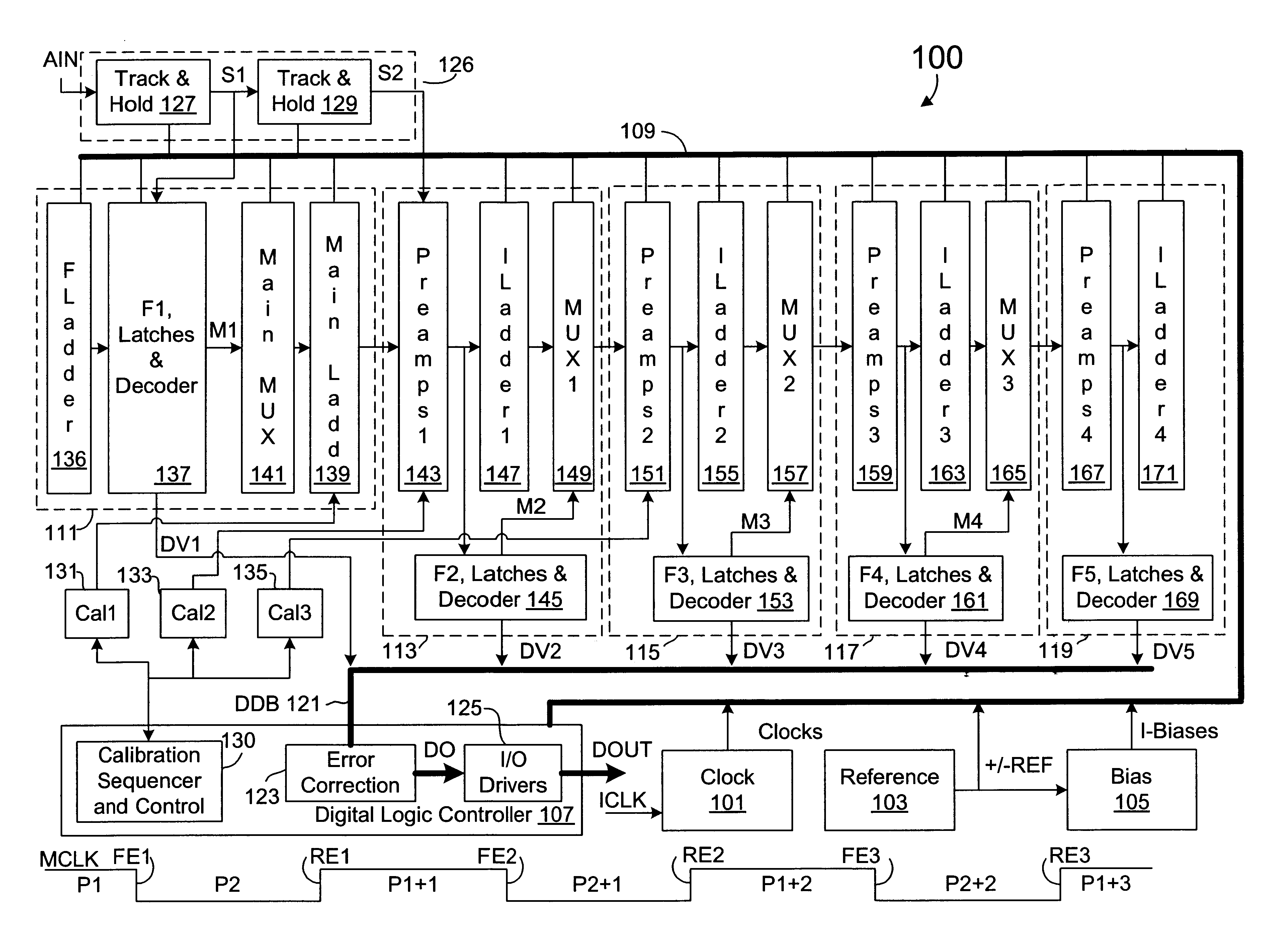

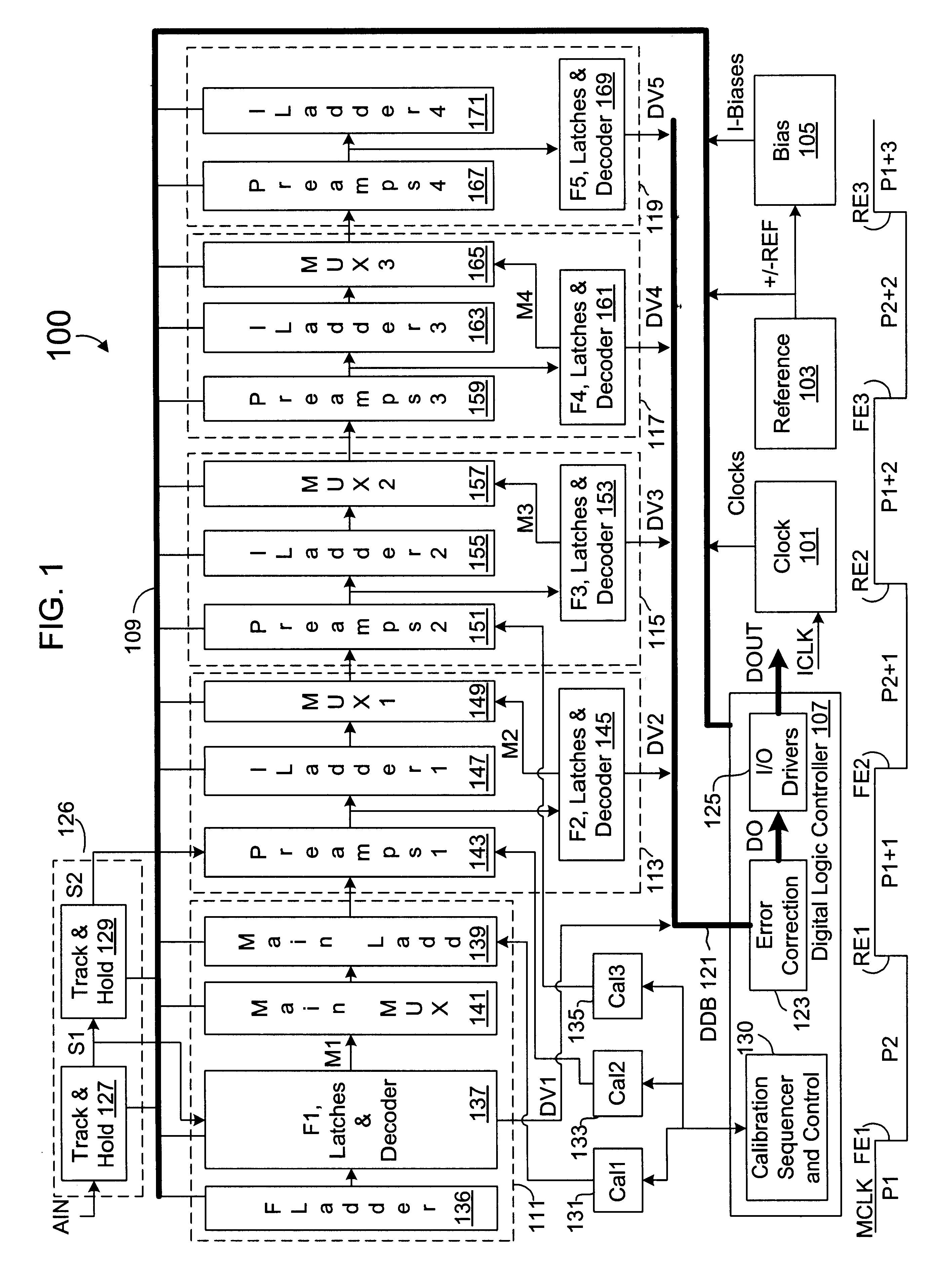

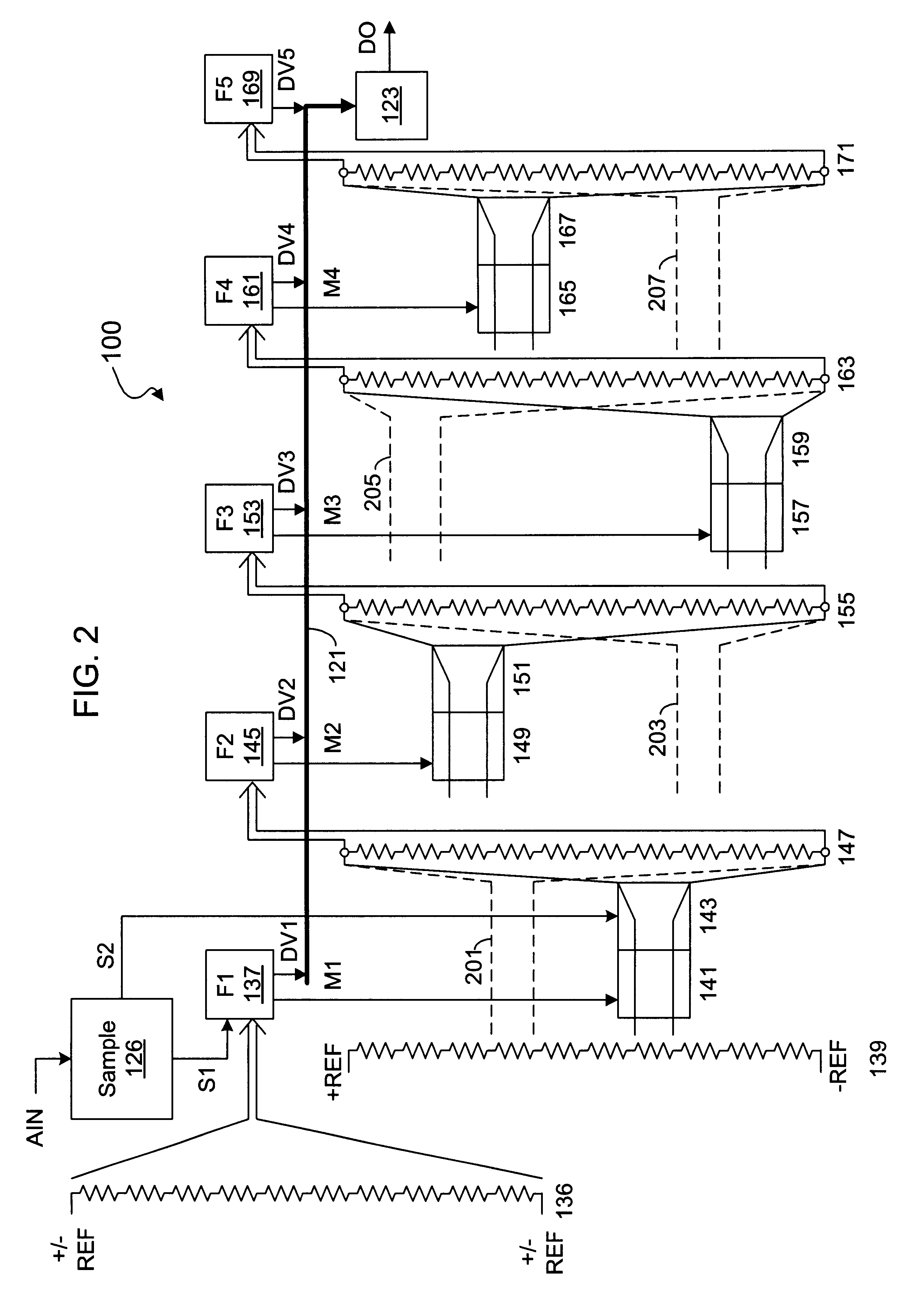

Calibration of resistor ladder using difference measurement and parallel resistive correction

InactiveUS20030151532A1Electric signal transmission systemsAnalogue-digital convertersDifferential measurementComplementary pair

A calibration system and method for a resistor ladder that employs relative measurement and adjustment between pairs of resistors. The system includes a resistor tree of complementary pairs of programmable resistors coupled to the resistor ladder, a measurement circuit that measures voltage differences between complementary pairs of programmable resistors, and control logic. The control logic controls the measurement circuit to measure a voltage difference between each complementary pair of programmable resistors and adjusts the relative resistance of each complementary pair of programmable resistors to equalize voltage. The measurement is facilitated by a sigma-delta ADC that converts a measured voltage difference into a bit stream. The programmable resistors are implemented with binary weighted resistors that are digitally adjusted one LSB at a time. Lower and upper adjustment thresholds may be employed to avoid unnecessary over-adjustments while maintaining a requisite level of accuracy.

Owner:INTERSIL INC

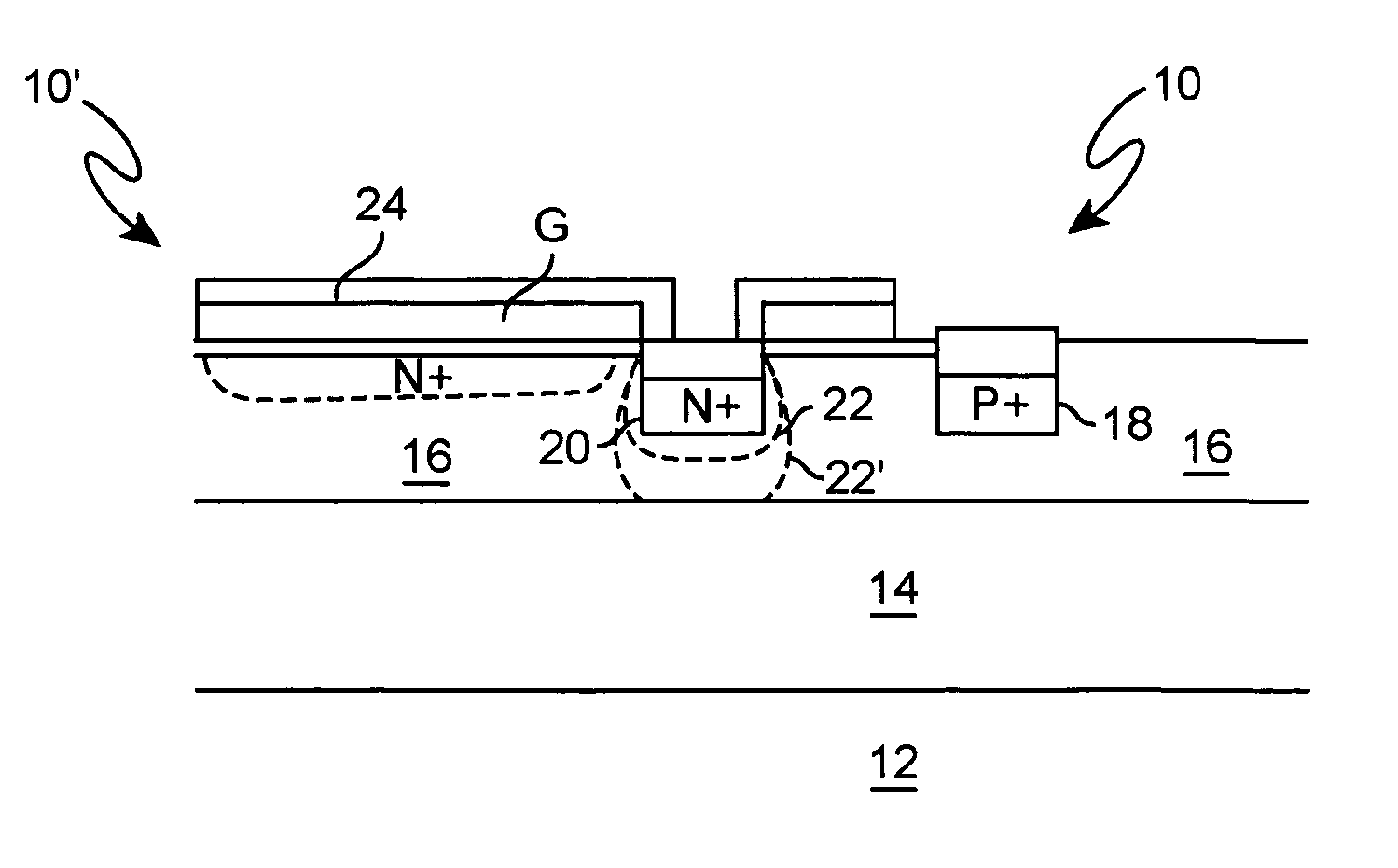

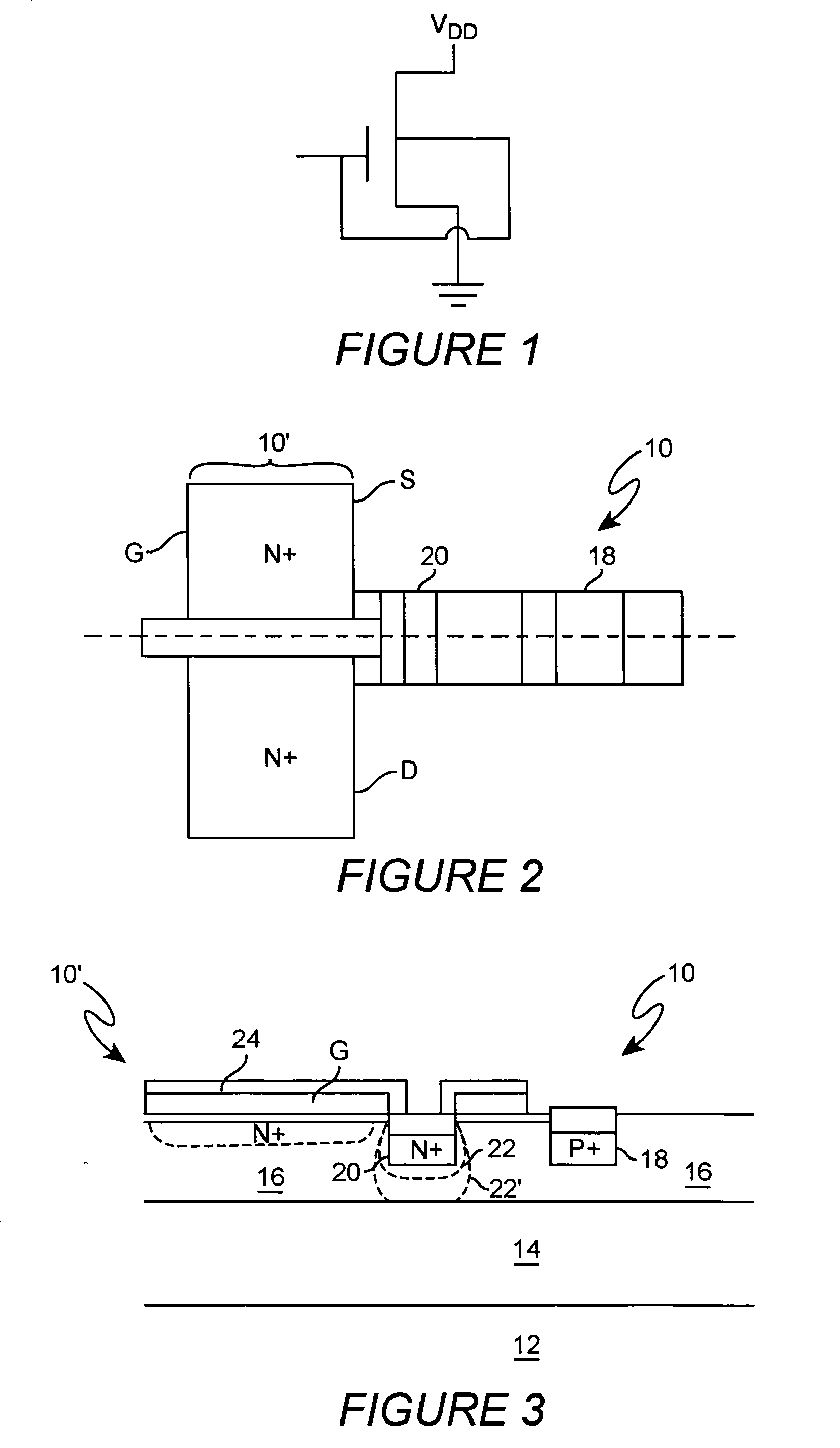

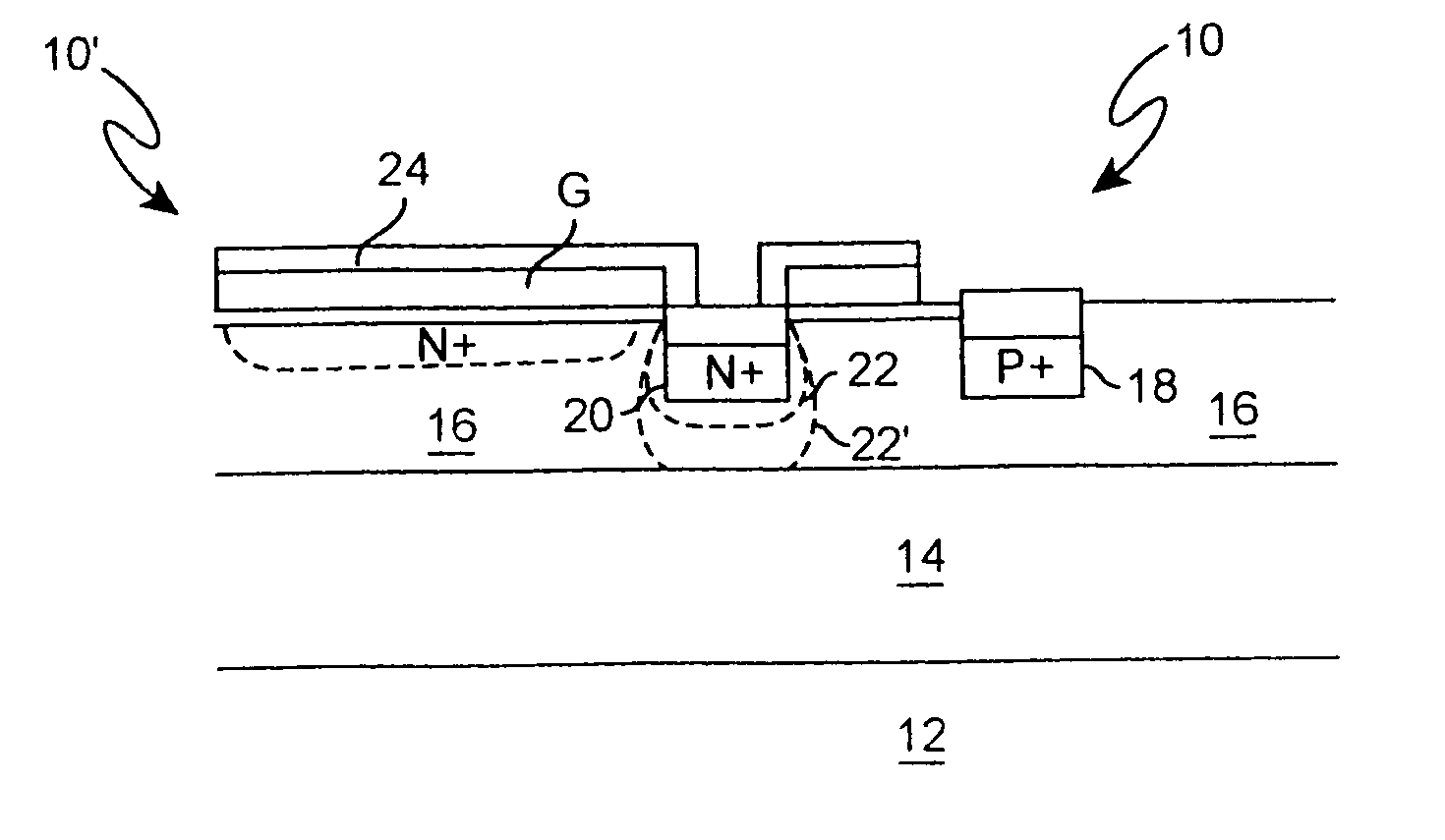

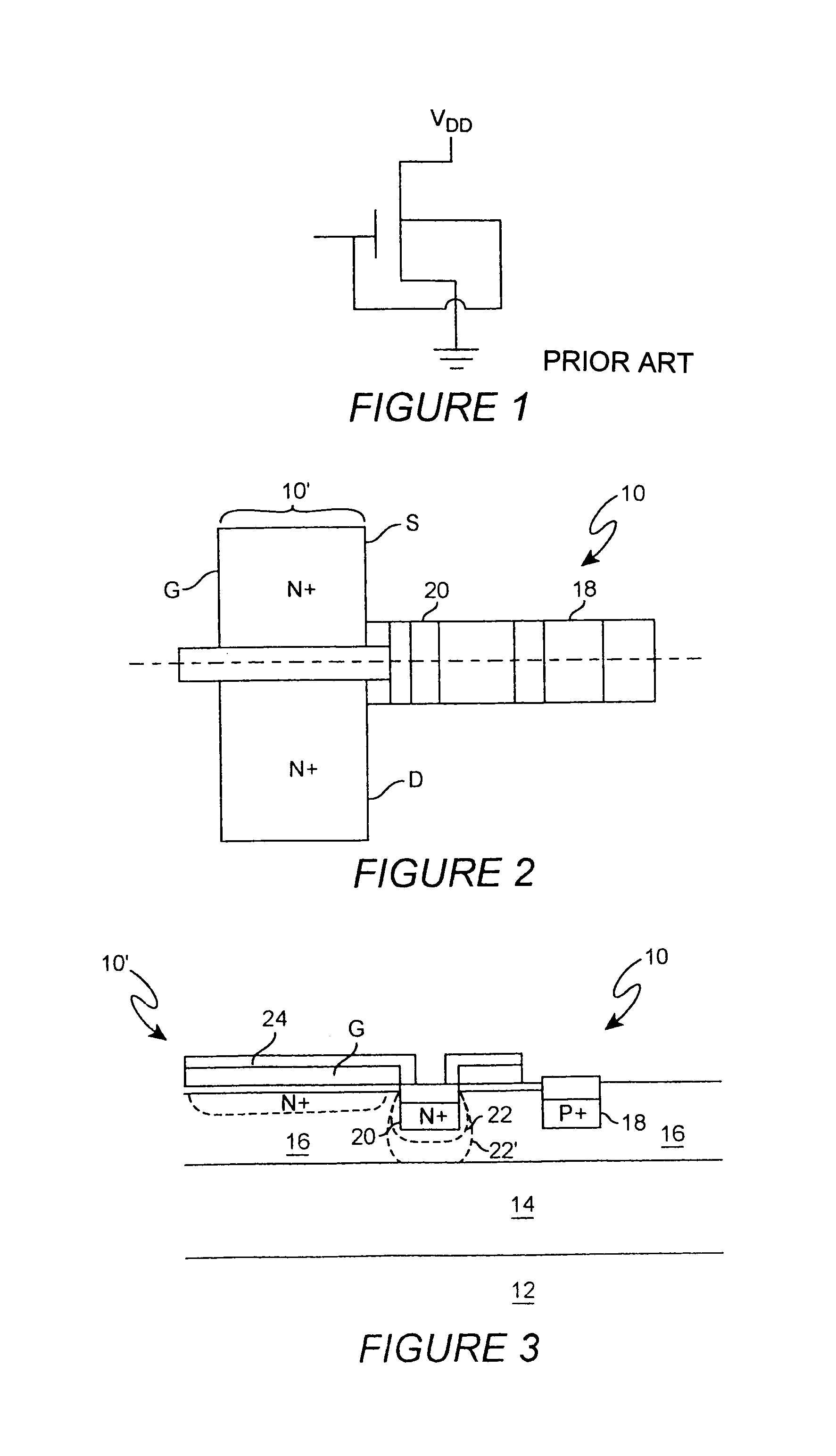

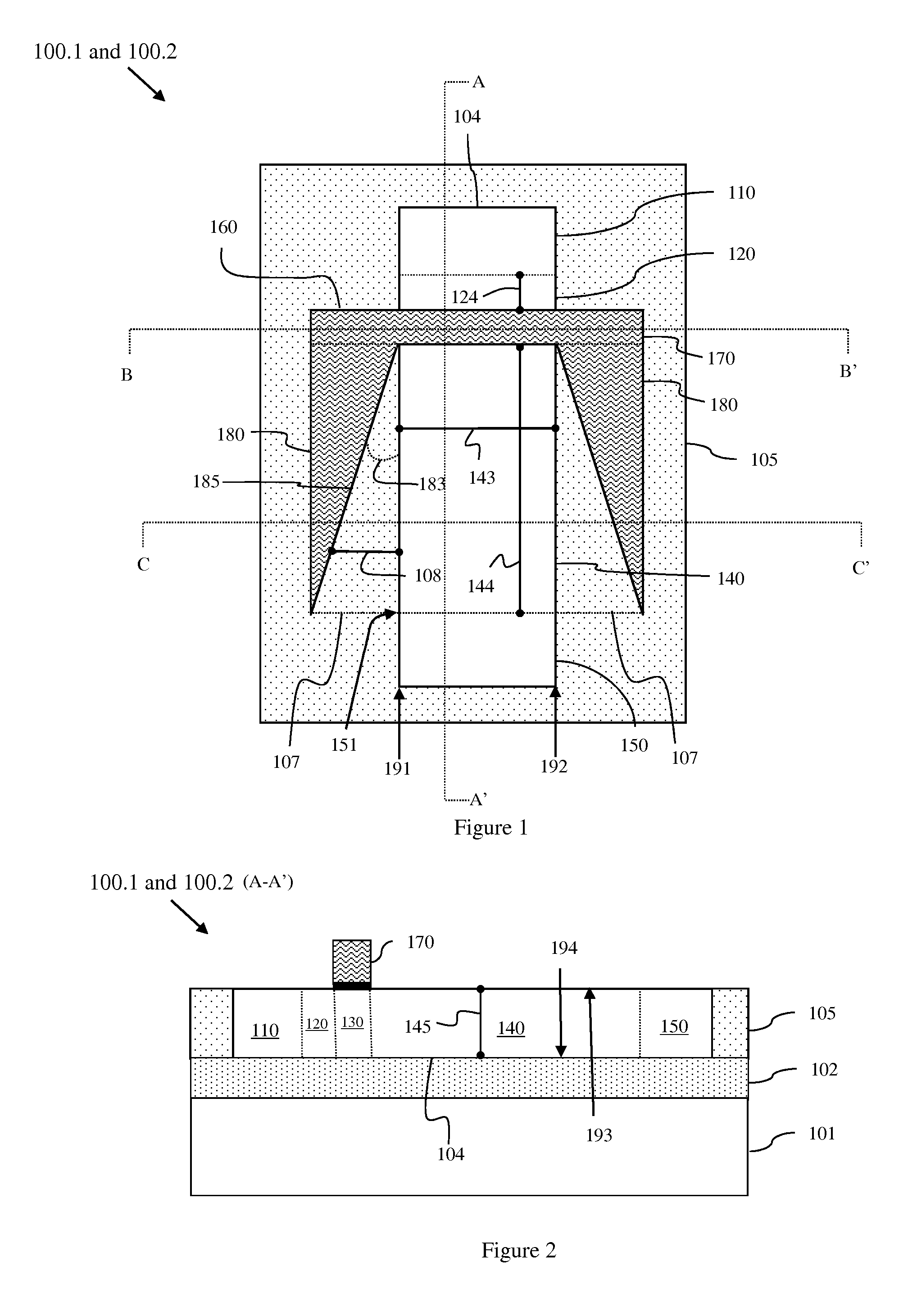

Dynamic threshold voltage MOSFET on SOI

ActiveUS20050121699A1Improve performanceReduce manufacturing costTransistorSolid-state devicesMOSFETFloating body effect

Provision of a body control contact adjacent a transistor and between the transistor and a contact to the substrate or well in which the transistor is formed allows connection and disconnection of the substrate of the transistor to and from a zero (ground) or substantially arbitrary low voltage in accordance with control signals applied to the gate of the transistor to cause the transistor to exhibit a variable threshold which maintains good performance at low supply voltages and reduces power consumption / dissipation which is particularly advantageous in portable electronic devices. Floating body effects (when the transistor substrate in disconnected from a voltage source in the “on” state) are avoided since the substrate is discharged when the transistor is switched to the “off” state. The transistor configuration can be employed with both n-type and p-type transistors which may be in complementary pairs.

Owner:GLOBALFOUNDRIES US INC

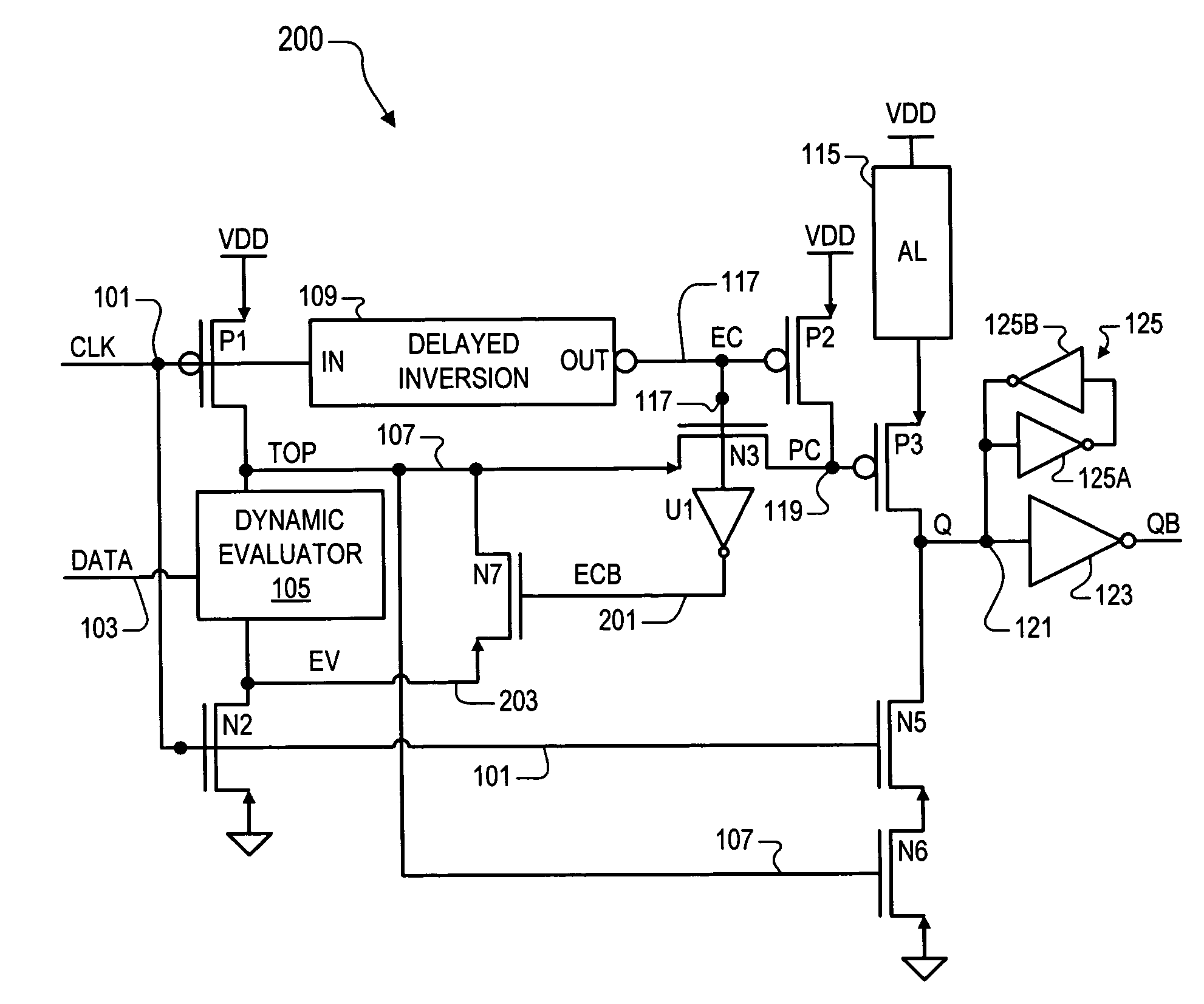

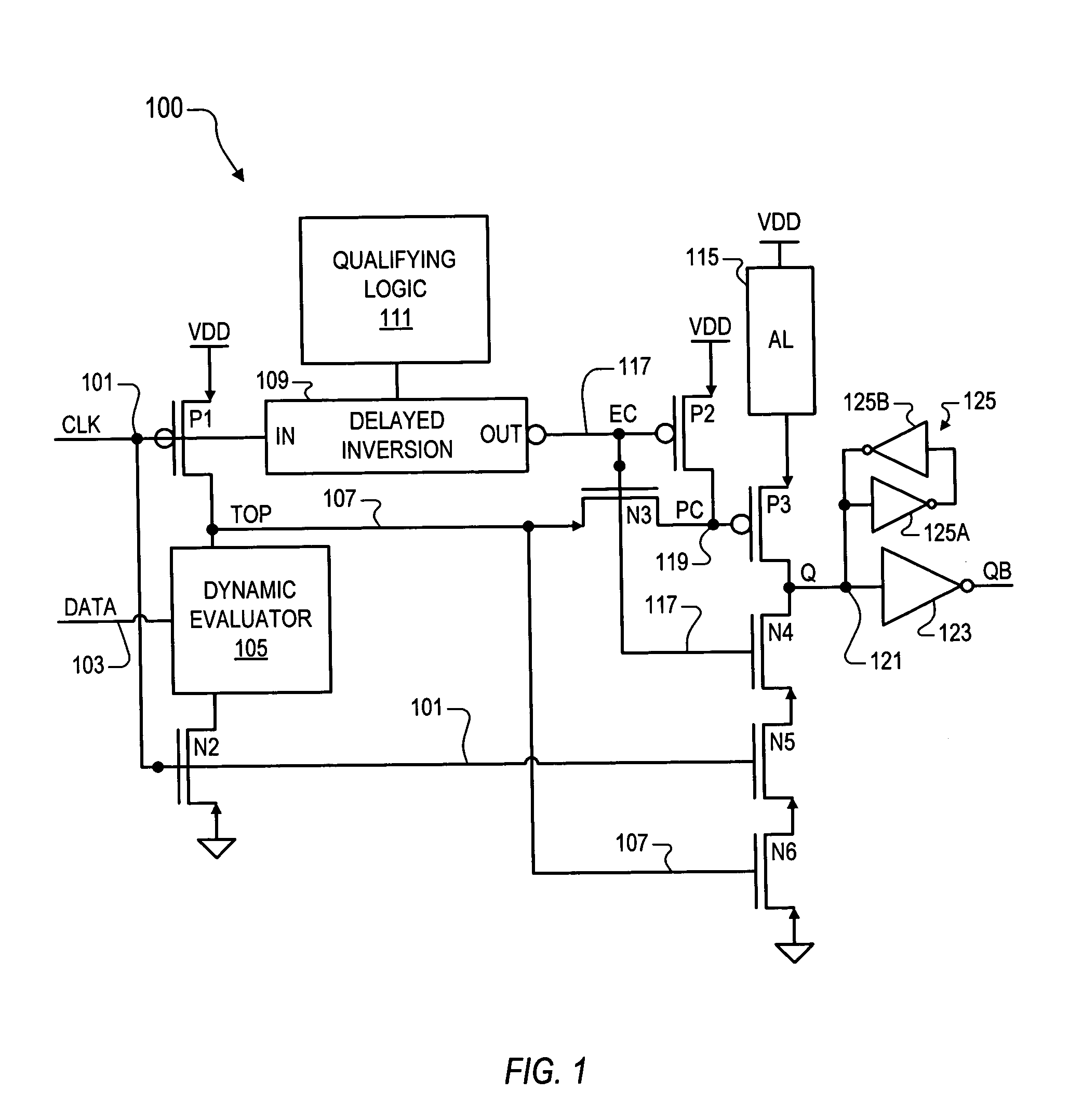

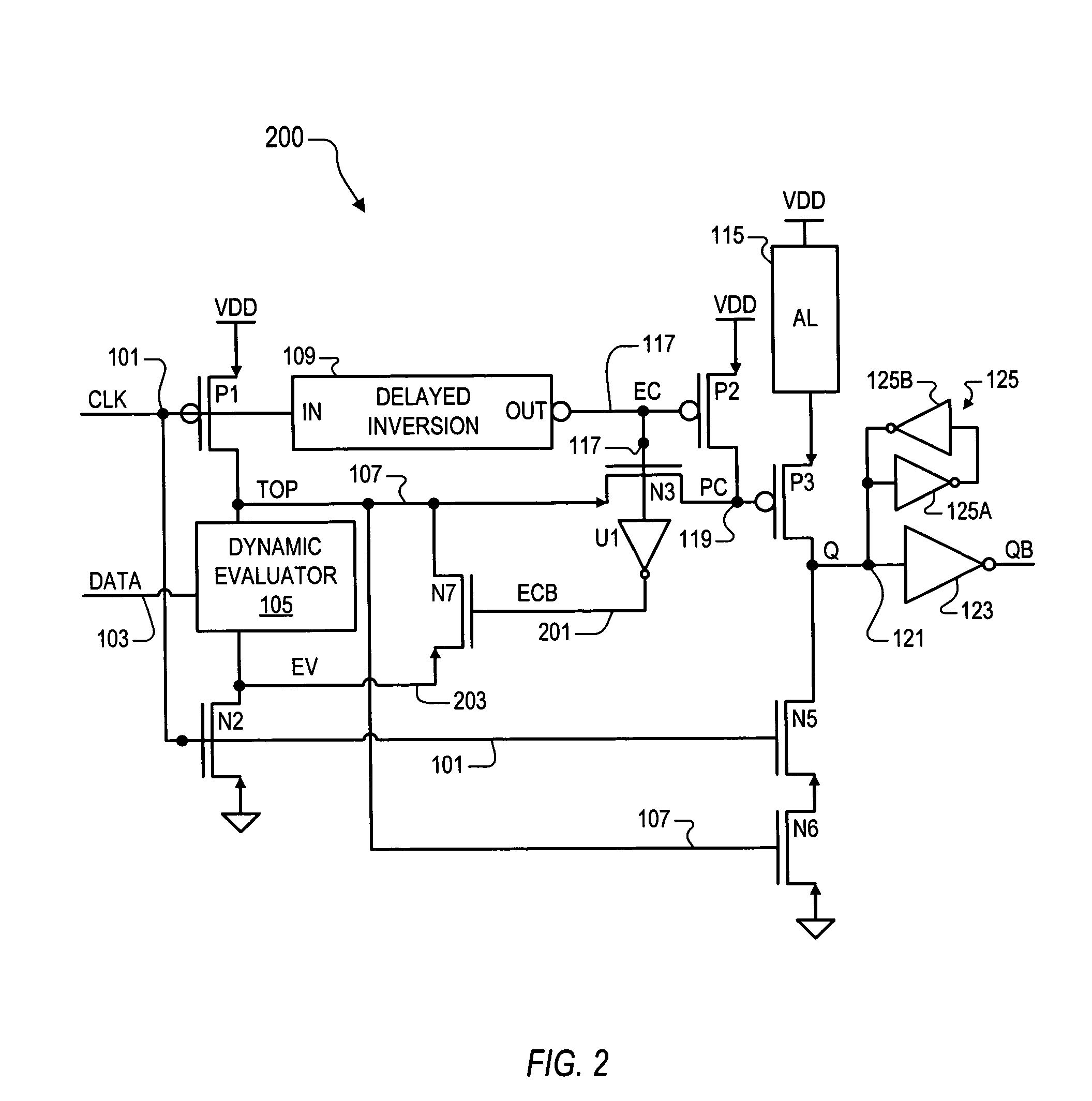

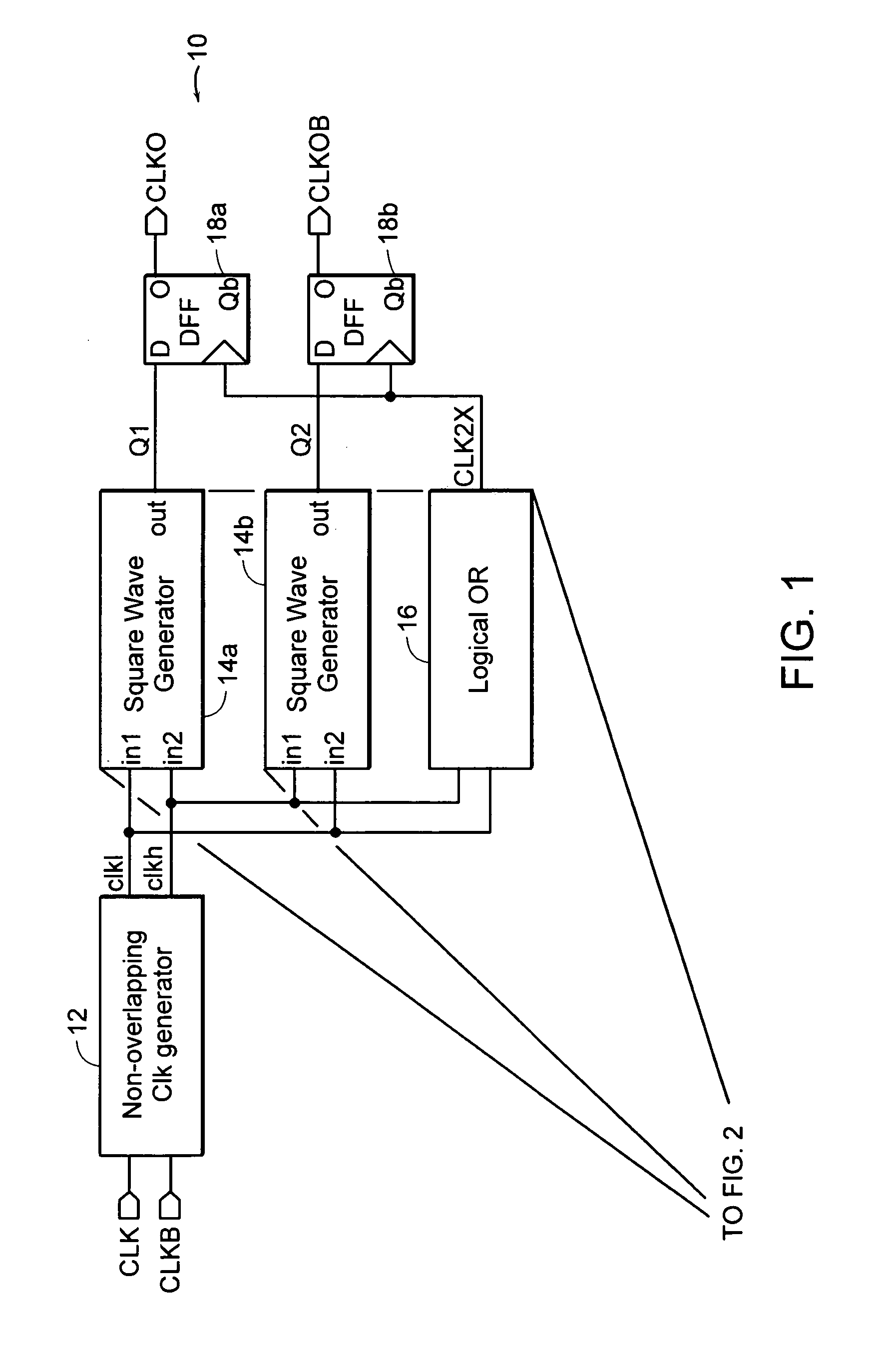

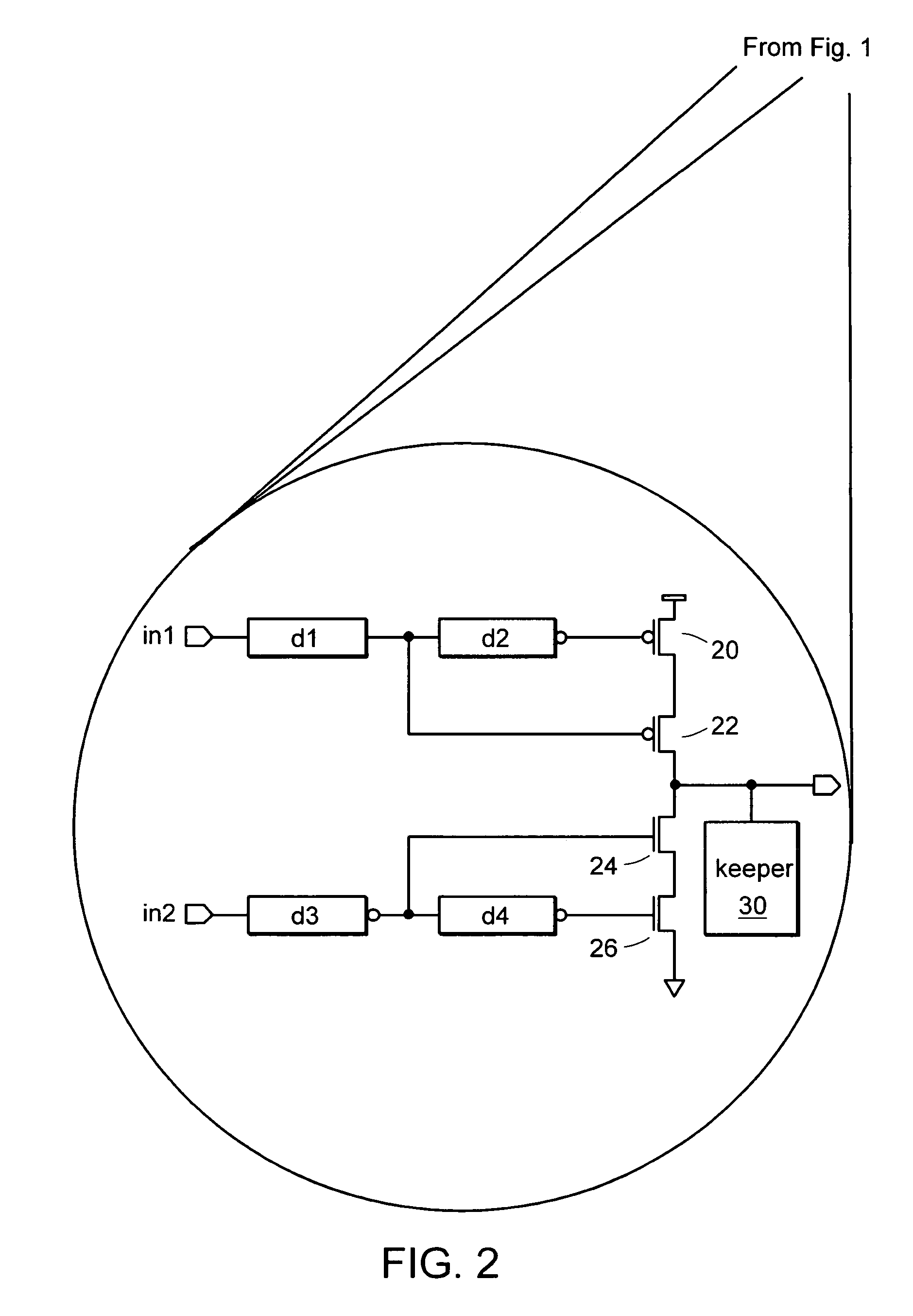

Dynamic logic register

ActiveUS20050046446A1Prevent of data signalAvoid dataDigital storageLogic circuitsPre-chargeData signal

A dynamic logic register including a complementary pair of evaluation devices, delayed inversion logic, a dynamic evaluator, latching logic, and a keeper circuit coupled to the output. The evaluation devices are responsive to a clock signal and provide a pre-charged node and an evaluation node. The delayed inversion logic outputs a complete signal that is a delayed and inverted version of the clock signal. The dynamic evaluator, coupled between the pre-charged and evaluation nodes, evaluates a logic function based on a data signal during an evaluation period between operative edges of the clock and complete signals. The latching logic enables the state of an output node to be determined by the state of the pre-charged node during the evaluation period and otherwise clamps the pre-charged node to prevent perturbations of the data signal from propagating to the output node.

Owner:VIA TECH INC

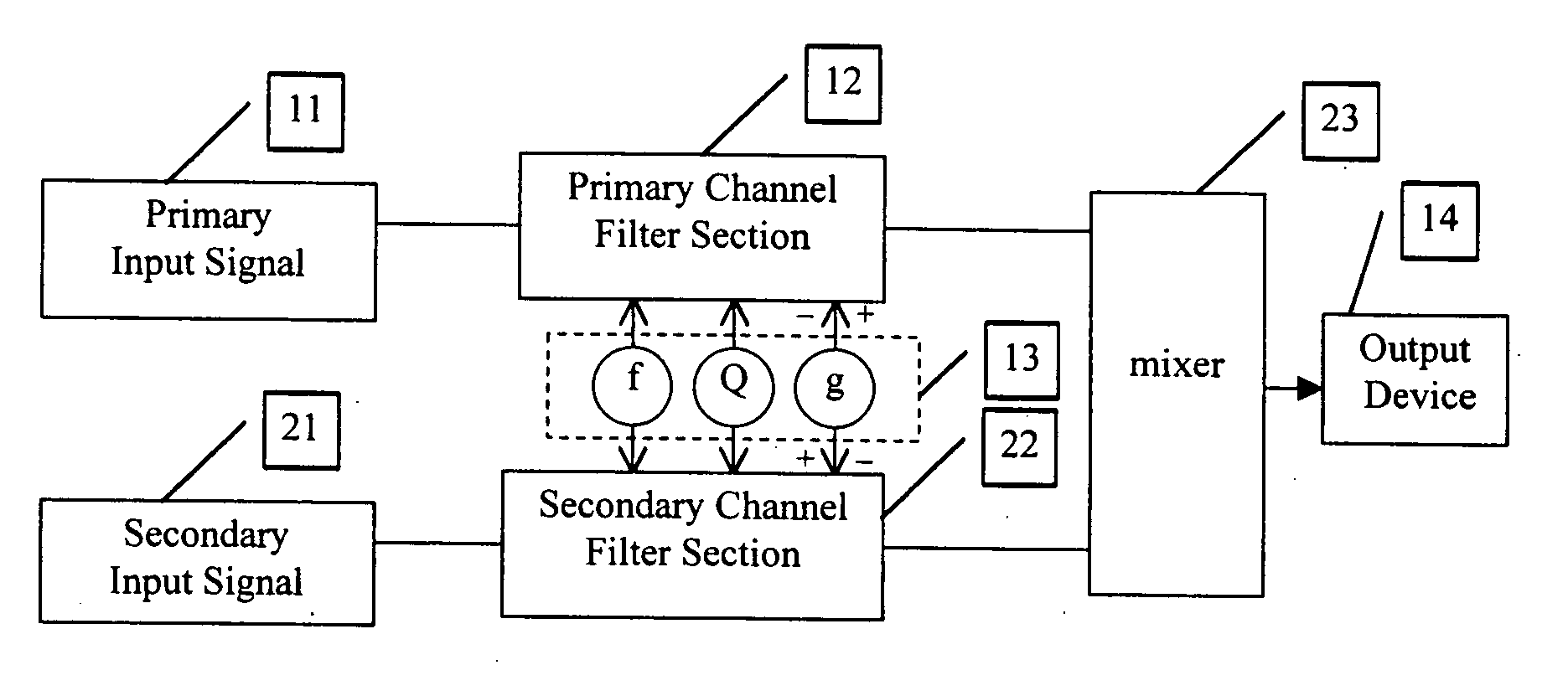

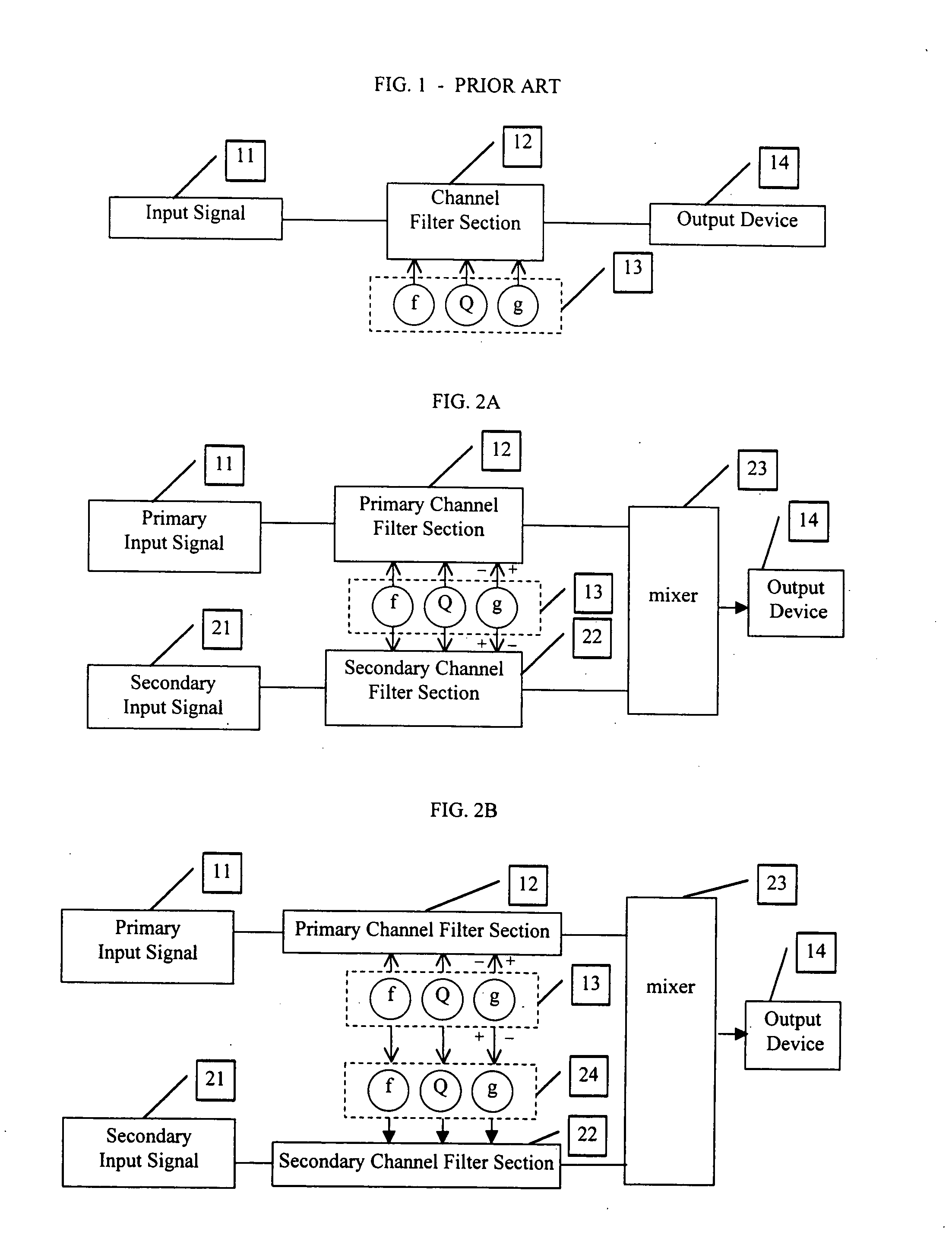

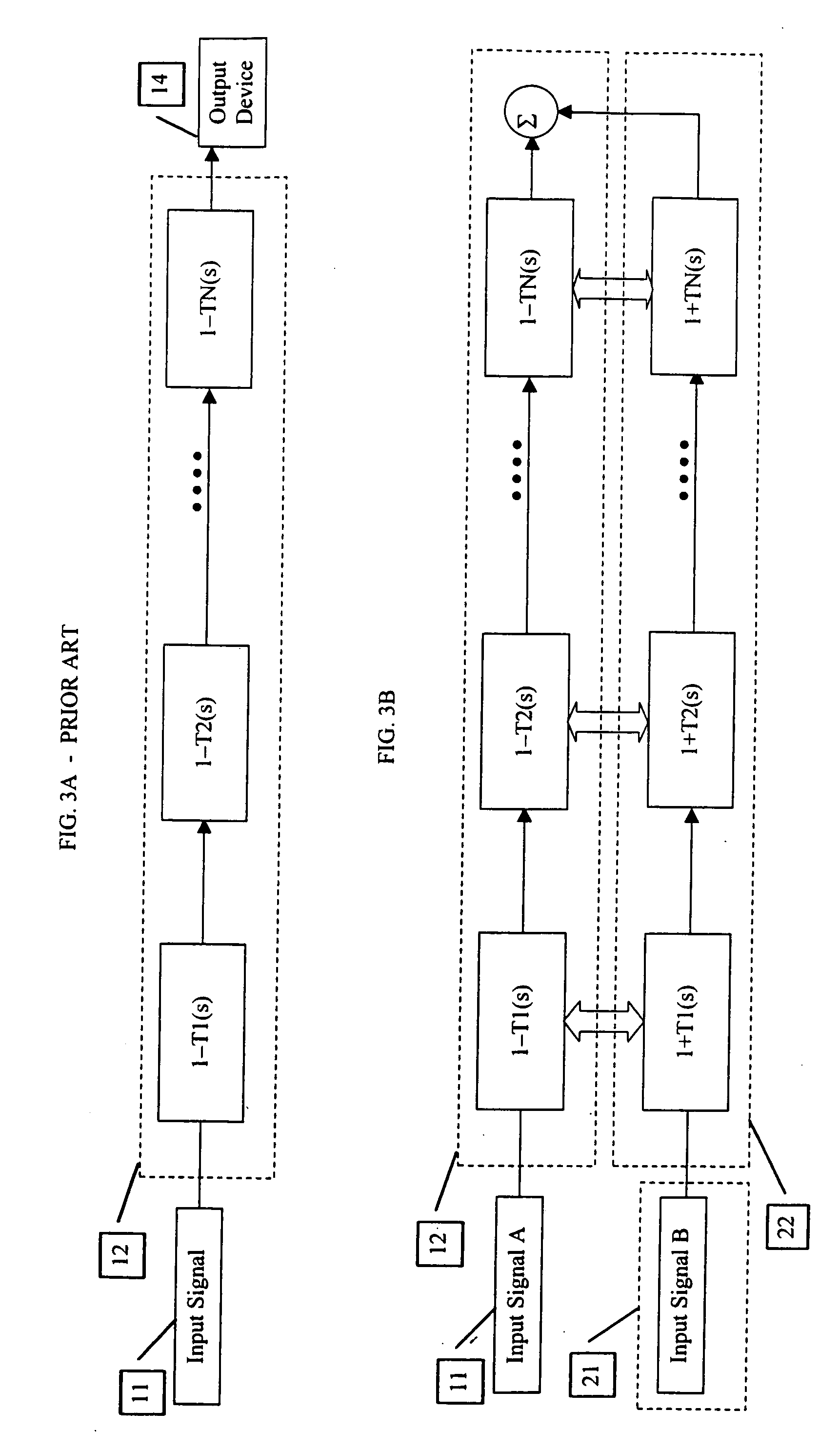

Complementary-pair equalizer

InactiveUS20060072768A1Weaken energyHigh energyTransmission noise suppressionTwo-channel systemsComplementary pairSignal processing

A method and apparatus are described which reduce the presence of an unwanted signal. According to one embodiment, a first signal is provided from a desired location that includes an unwanted signal while a second signal is provided from an alternate location (e.g., one where the unwanted signal is less of a proportion of the total signal). The first and alternate signals are provided to respective signal processors. A level for a selected frequency band of the first and alternate signals is adjusted so that an increase in one results in a decrease in the other. Doing so allows the frequency band that includes the unwanted signal to be reduced in the desired first signal and filled in with a similar frequency band from the alternate signal.

Owner:SCHWARTZ STEPHEN R +2

Dynamic threshold voltage MOSFET on SOI

ActiveUS7045873B2Improve performanceReduce manufacturing costTransistorSolid-state devicesMOSFETFloating body effect

Provision of a body control contact adjacent a transistor and between the transistor and a contact to the substrate or well in which the transistor is formed allows connection and disconnection of the substrate of the transistor to and from a zero (ground) or substantially arbitrary low voltage in accordance with control signals applied to the gate of the transistor to cause the transistor to exhibit a variable threshold which maintains good performance at low supply voltages and reduces power consumption / dissipation which is particularly advantageous in portable electronic devices. Floating body effects (when the transistor substrate in disconnected from a voltage source in the “on” state) are avoided since the substrate is discharged when the transistor is switched to the “off” state. The transistor configuration can be employed with both n-type and p-type transistors which may be in complementary pairs.

Owner:GLOBALFOUNDRIES U S INC

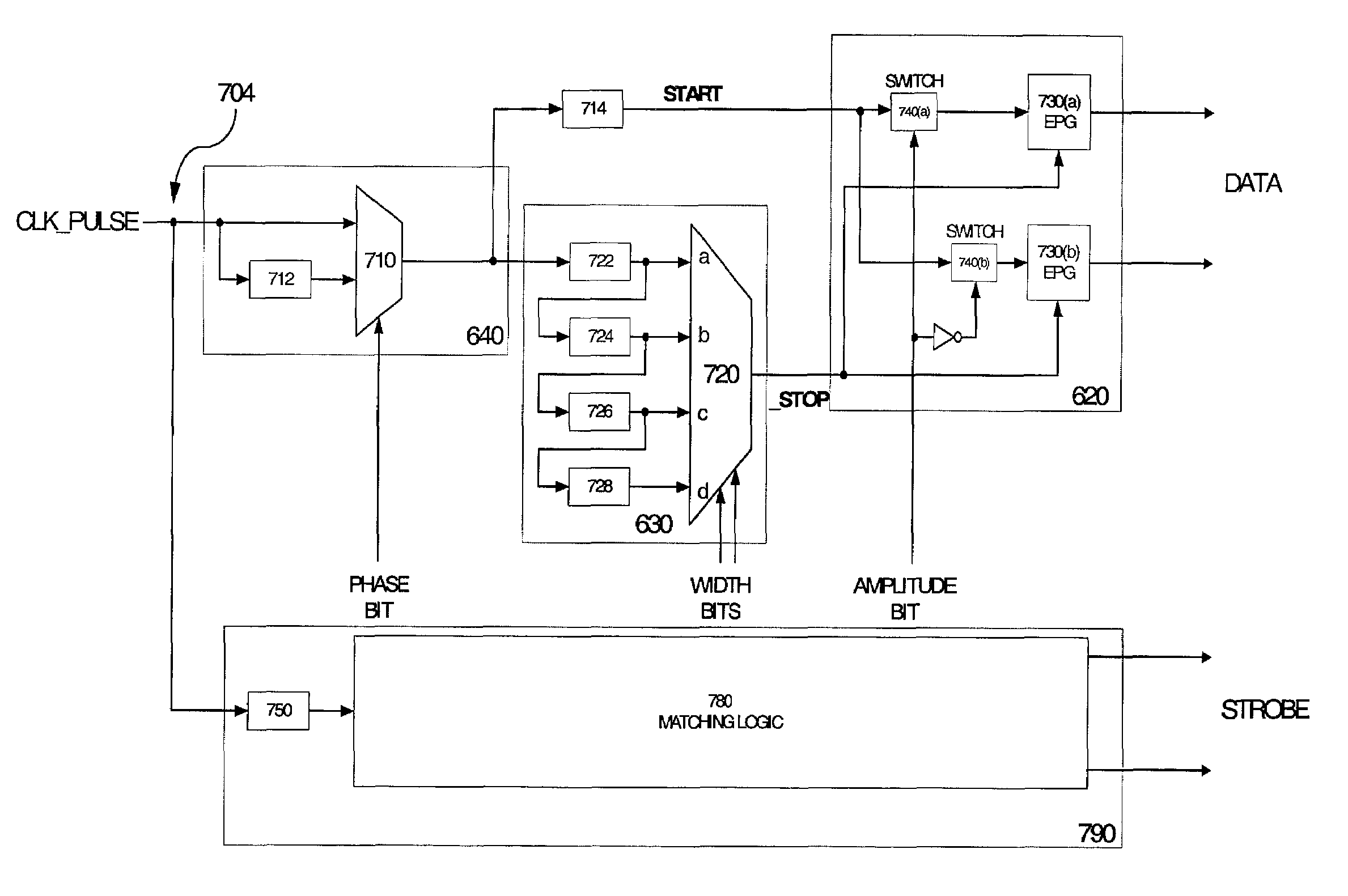

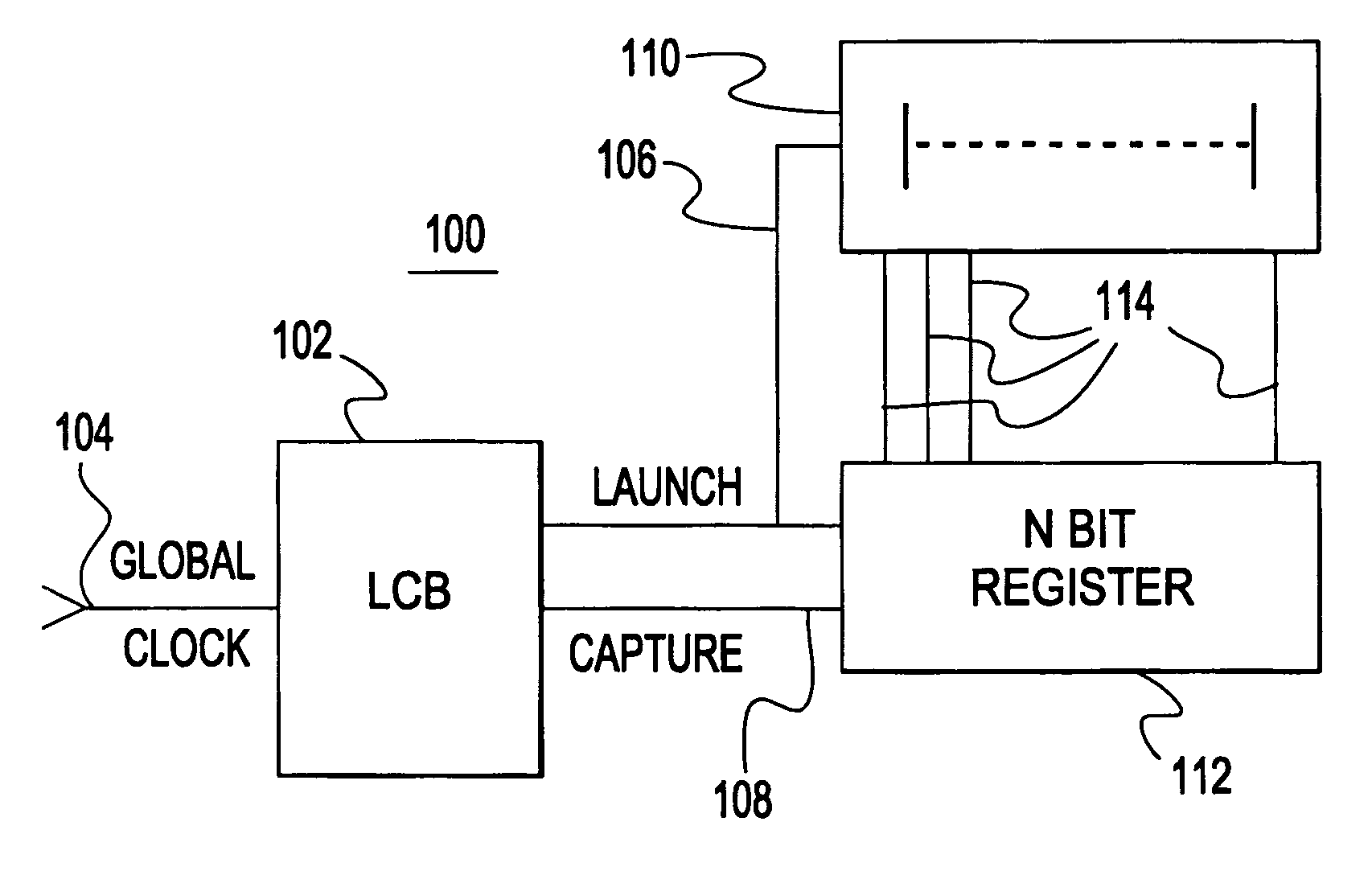

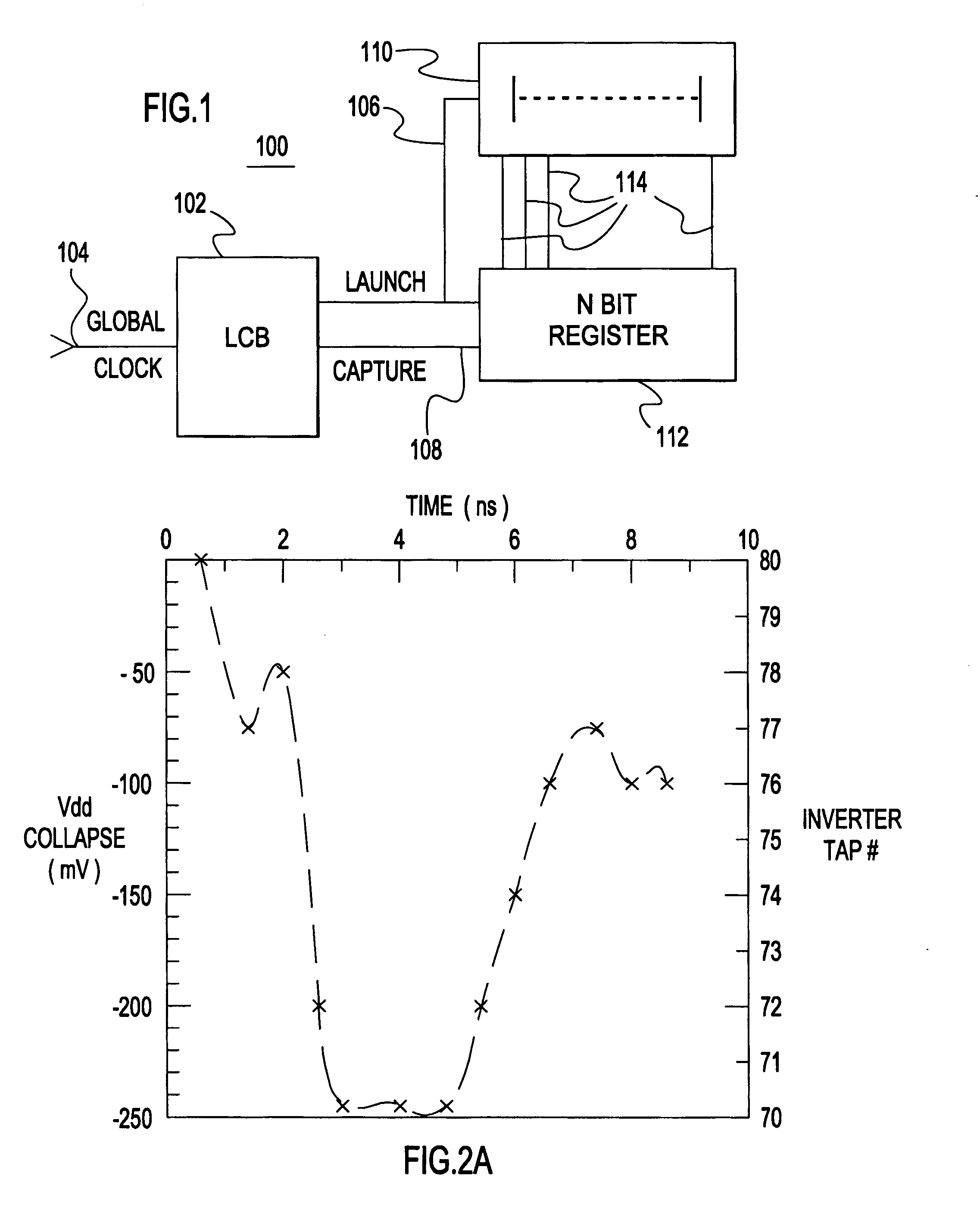

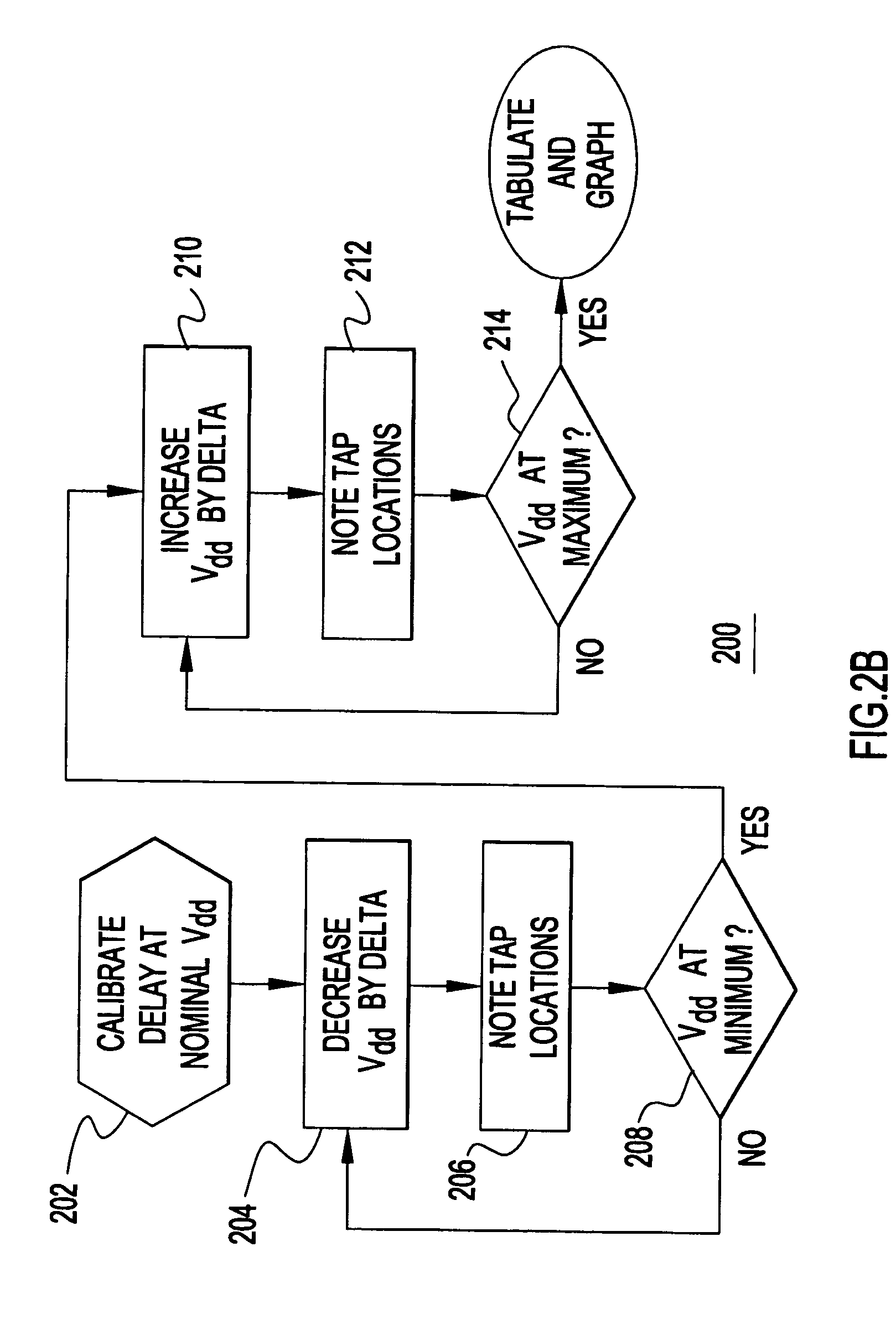

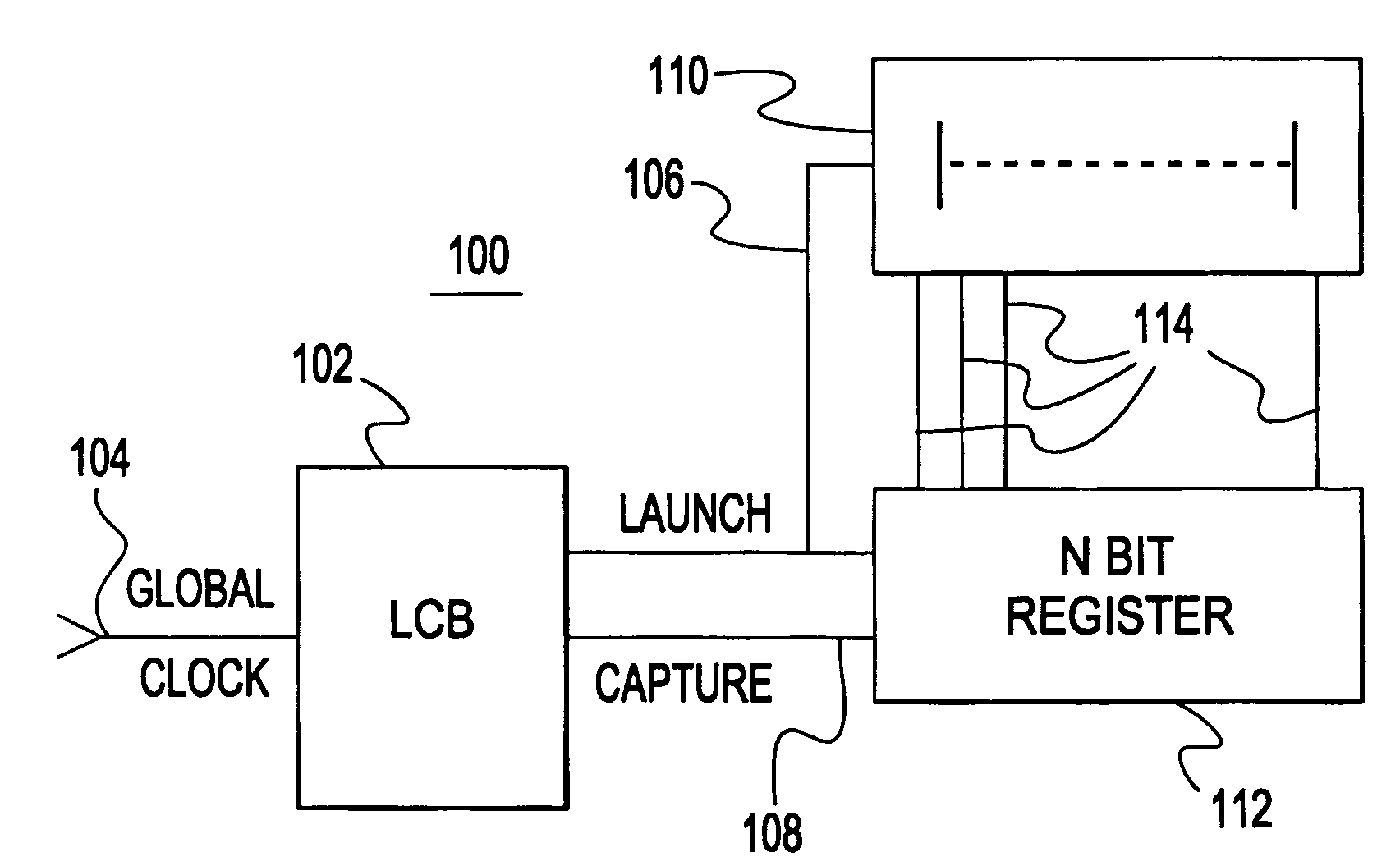

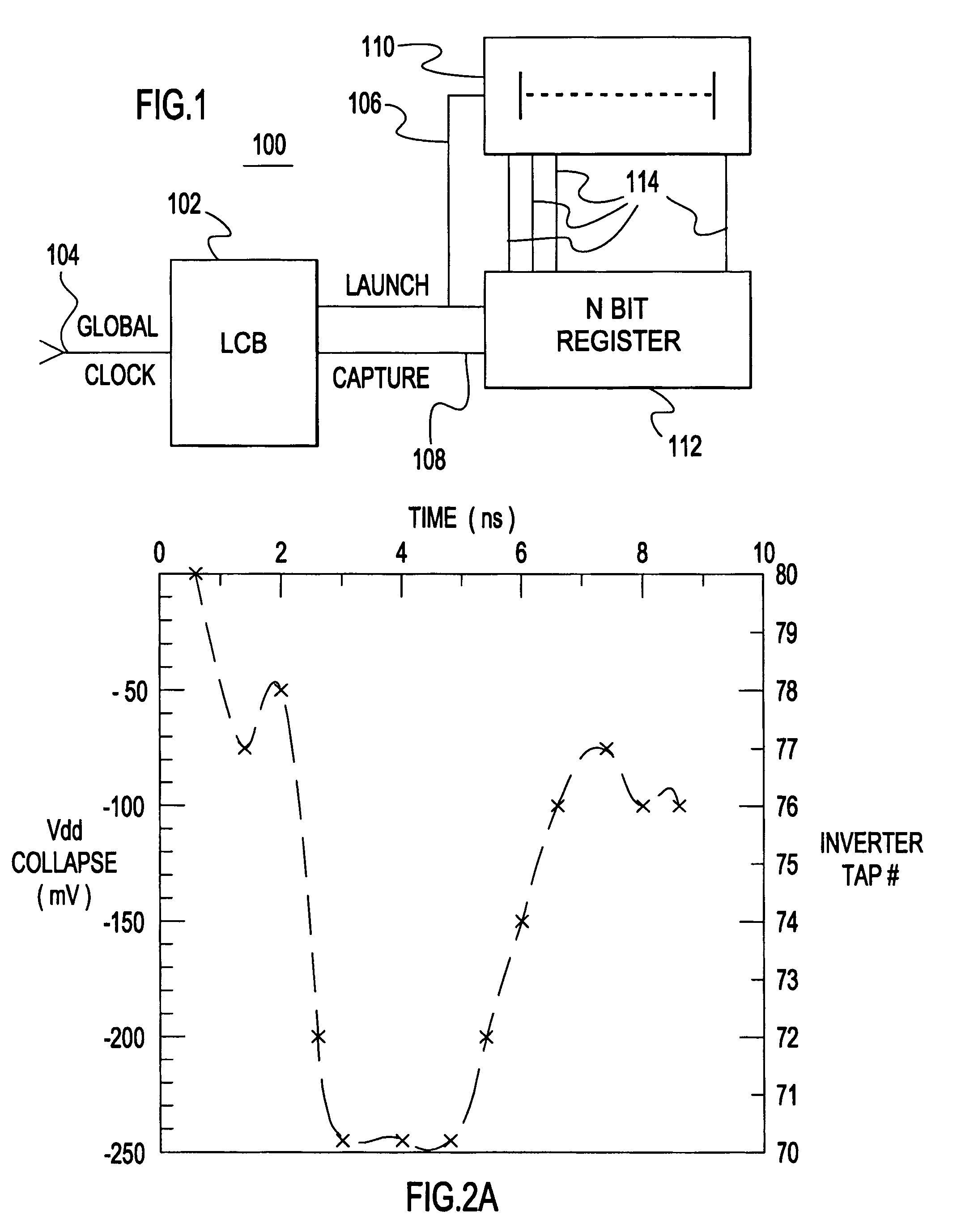

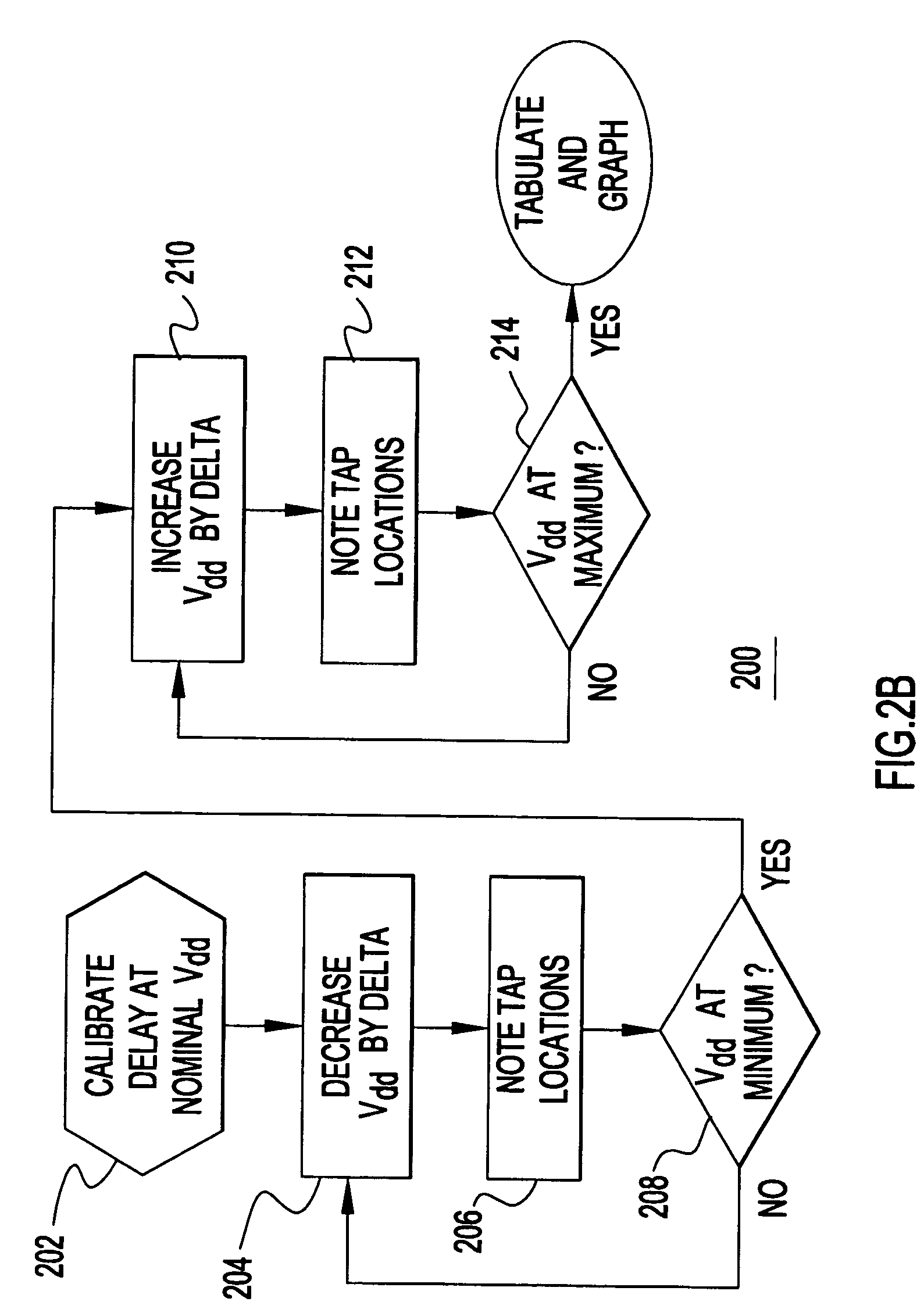

Built in self test circuit for measuring total timing uncertainty in a digital data path

InactiveUS20050107970A1Accurately determineAccurate recoveryDigital circuit testingElectromechanical unknown time interval measurementDigital dataCoupling

A circuit for measuring timing uncertainty in a clocked digital path and in particular, the number of logic stages completed in any clock cycle. A local clock buffer receives a global clock and provides a complementary pair of local clocks. A first local (launch) clock is an input to a delay line, e.g., 3 clock cycles worth of series connected inverters. Delay line taps (inverter outputs) are inputs to a register that is clocked by the complementary clock pair to capture progression of the launch clock through the delay line and identify any variation (e.g., from jitter, VDD noise) in that progression. Global clock skew and across chip gate length variation can be measured by cross coupling launch clocks from a pair of such clock buffers and selectively passing the local and remote launch clocks to the respective delay lines.

Owner:GLOBALFOUNDRIES INC

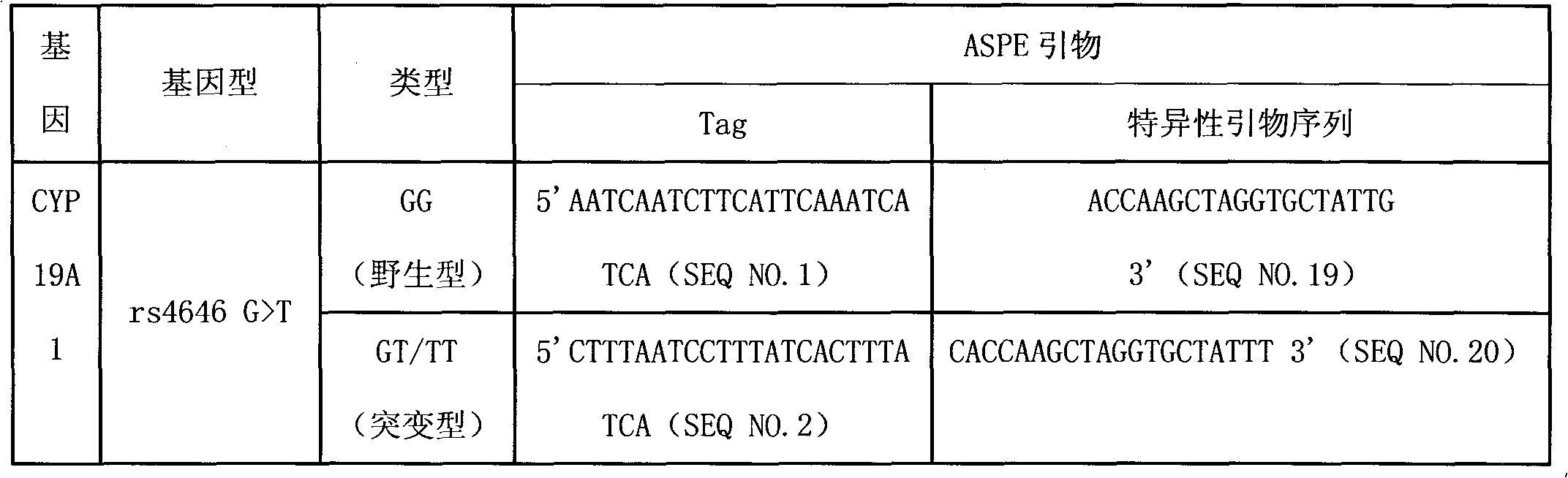

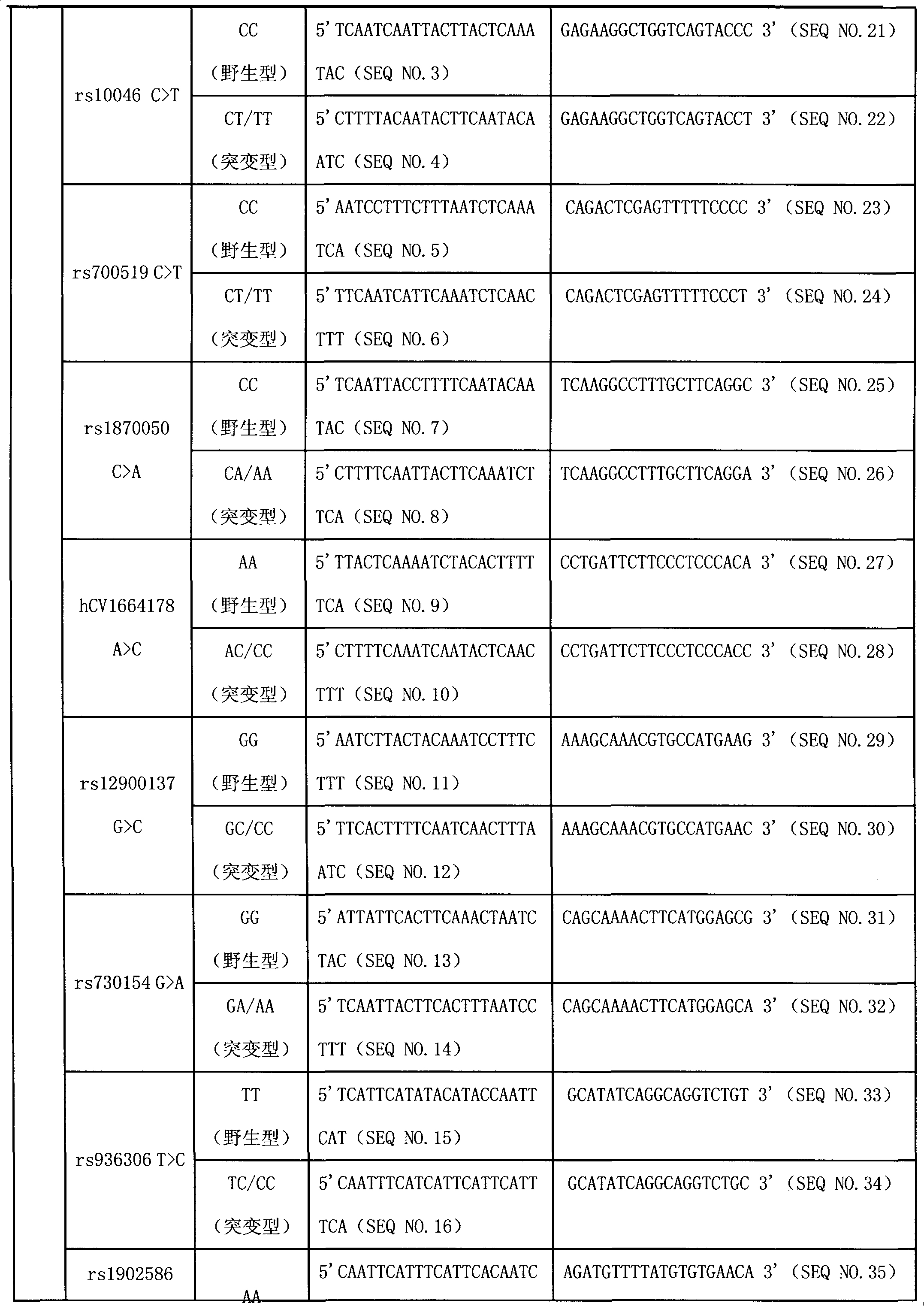

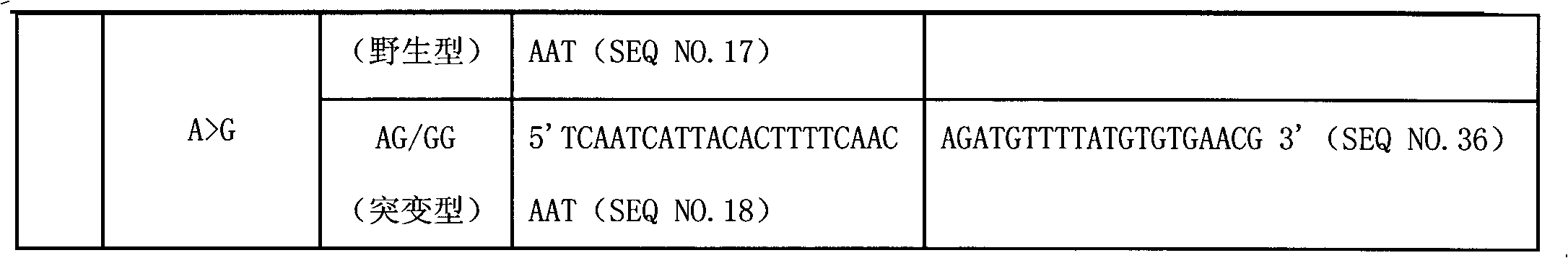

Liquid phase chip for CYP19A1 gene SNP (Single Nucleotide Polymorphism) detection and detection method thereof

ActiveCN101781684AImprove signal-to-noise ratioImplement parallel detectionMicrobiological testing/measurementType specificWild type

The invention discloses a liquid phase chip for CYP19A1 gene SNP (Single Nucleotide Polymorphism) detection, which comprises wild type and mutant type specific ASPE primers designed targeting CYP19A1 gene SNPs of rs4646, rs10046C>T, rs700519C>T, rs1870050C>A, hCV1664178A>C, rs12900137G>C, rs730154G>A, rs936306T>C and rs1902586A>G, microballoon spheres respectively coated with specific anti-tag sequences and primers used for amplifying CYP19A1 gene SNPs with target sequences to be detected. Each ASPE primer comprises a tag sequence at 5' end and a specific primer sequence at 3' end, wherein the specific primers are selected from SEQ ID NO. 19-36 and the tag sequences are selected from SEQ ID NO.1-18; and the anti-tag sequences can be correspondingly in complementary pairing with the tag sequences. The invention also discloses a CYP19A1 gene SNP detection method. The coincidence rate of the detection method provided by the invention and a sequencing method is as high as 100%; and the prepared liquid phase chip for CYP19A1 gene SNP (Single Nucleotide Polymorphism) detection has excellent signal-to-noise rate, and basically no cross reaction exists between a design probe and the anti-tag sequences.

Owner:SUREXAM BIO TECH

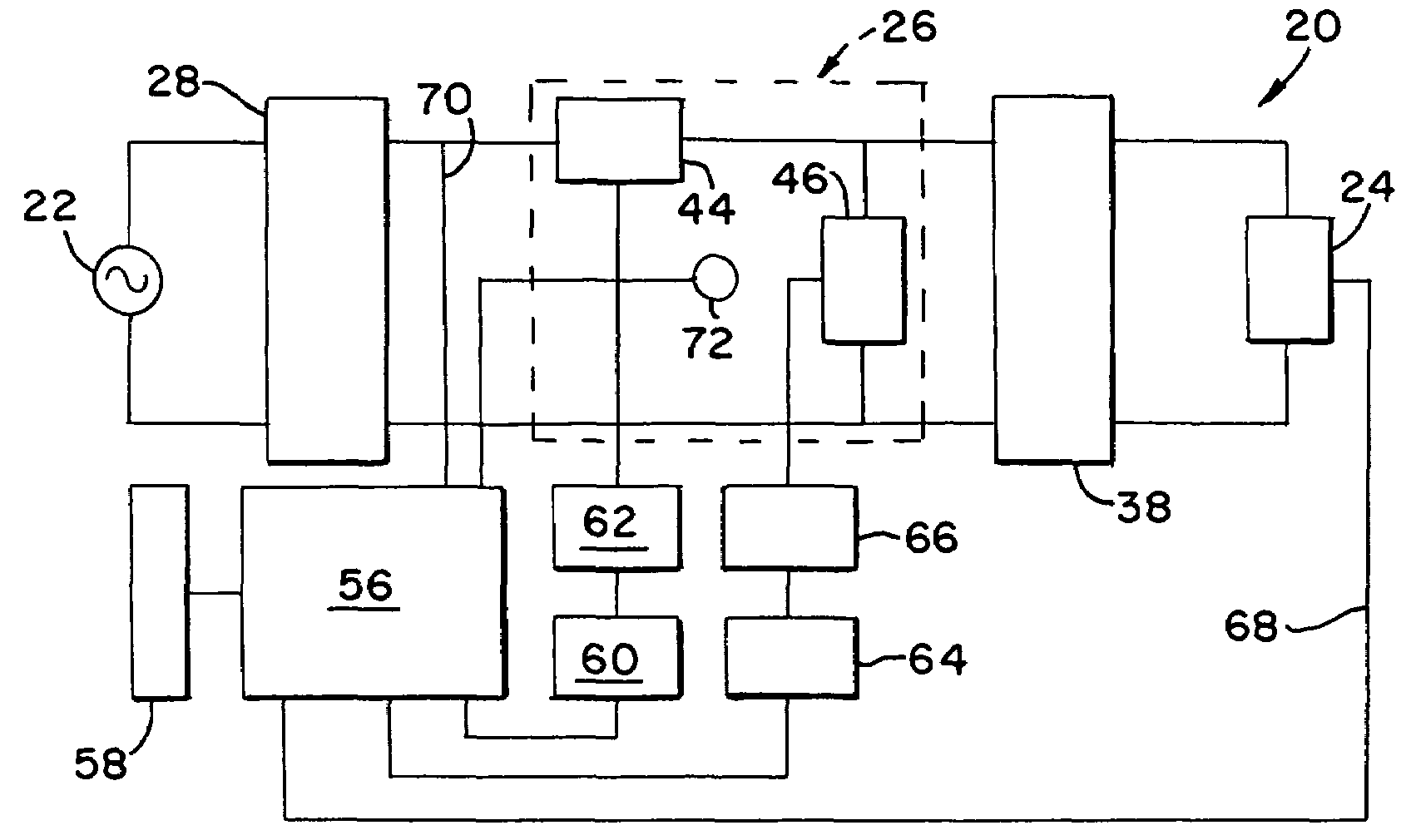

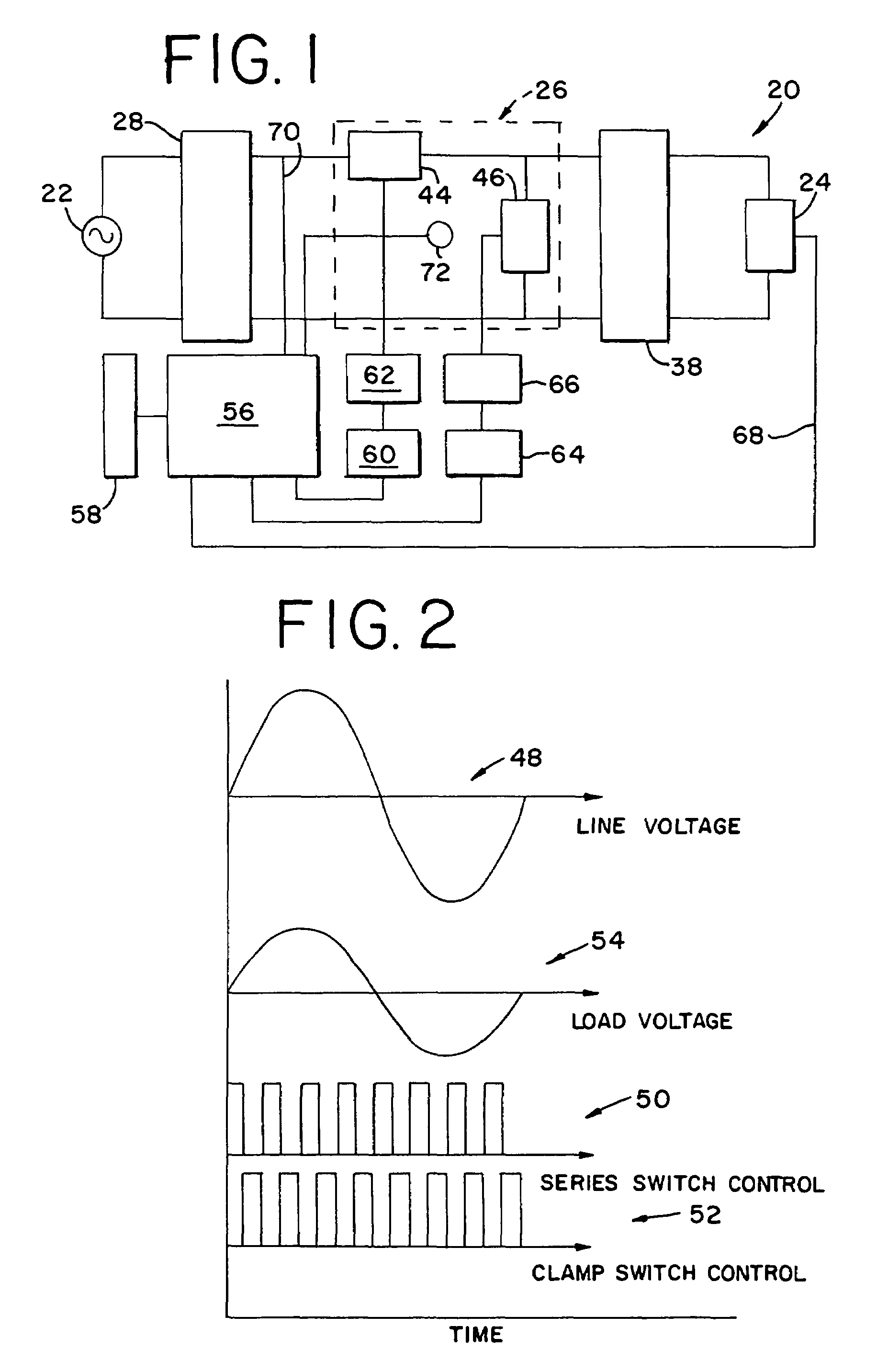

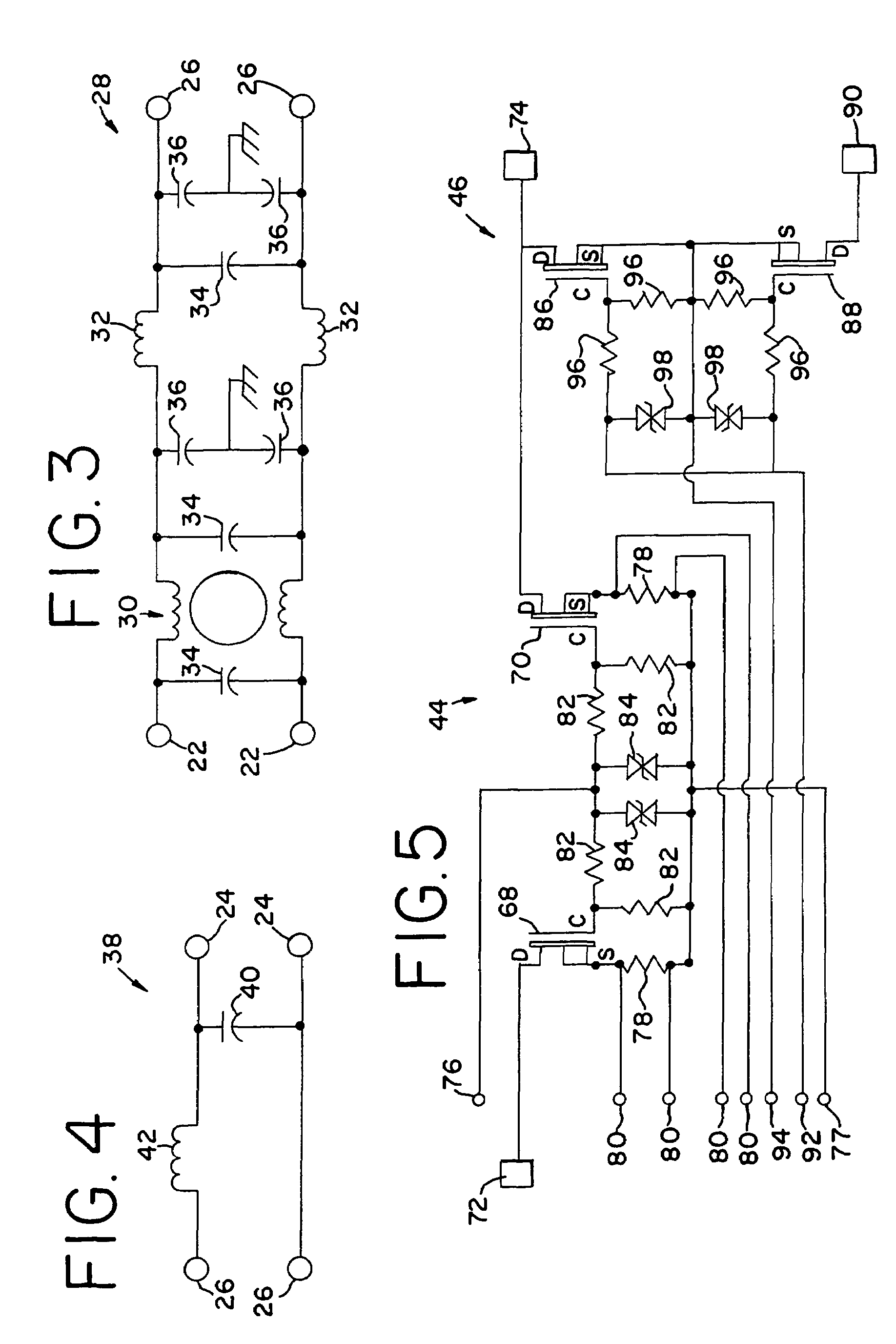

Sinewave dimmer control method

InactiveUS7019469B1Efficient couplingMaximizes efficient power transferElectric light circuit arrangementAc-ac conversionMOSFETControl signal

An input line filter separates an ac sinusoidal power source from a power switching stage having a series switching section and a clamp switching section. Both the series switching section and a clamp switching section include complementary pairs of high power and high speed MOSFETs. The series switching section is connected in series between the input line filter and the inductor of an output load filter between the power switching stage and a load. The clamp switching section is connected to shunt the inductor and load. Synchronous operation is achieved by alternately operating the series and clamp switching sections to conductive conditions at a high pulse width modulation frequency. The duty cycle is selected to provide a sinusoidal output waveform with a desired amplitude. A microprocessor based programmable controller provides control signals for alternate conduction of the series and clamp switching sections. A dead time interval stored in memory in the controller separates the control signals for reliable and efficient operation. The dead time interval may be constant, or may be varied in accordance with load power variations.

Owner:ELECTRONIC THEATRE CONTROLS

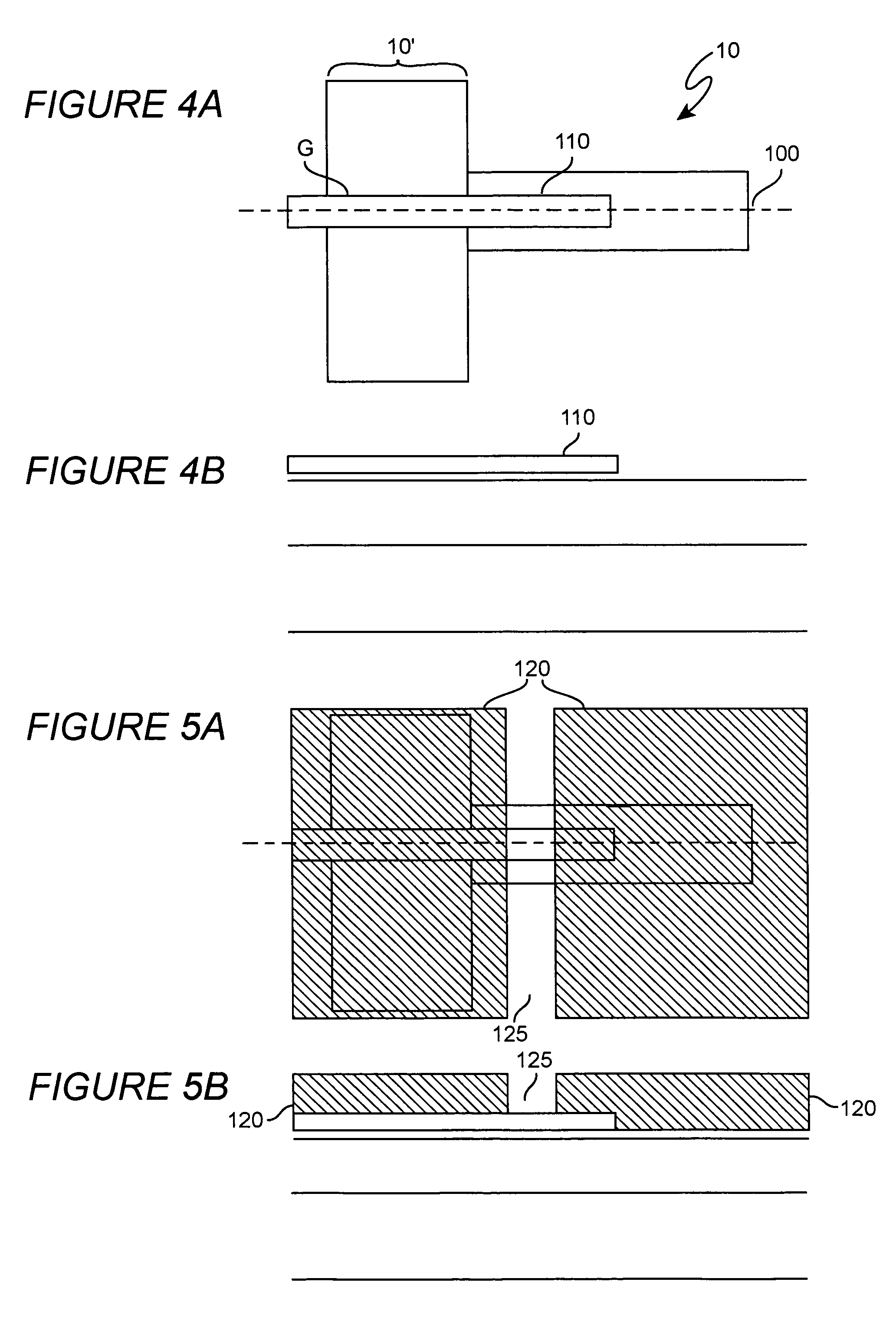

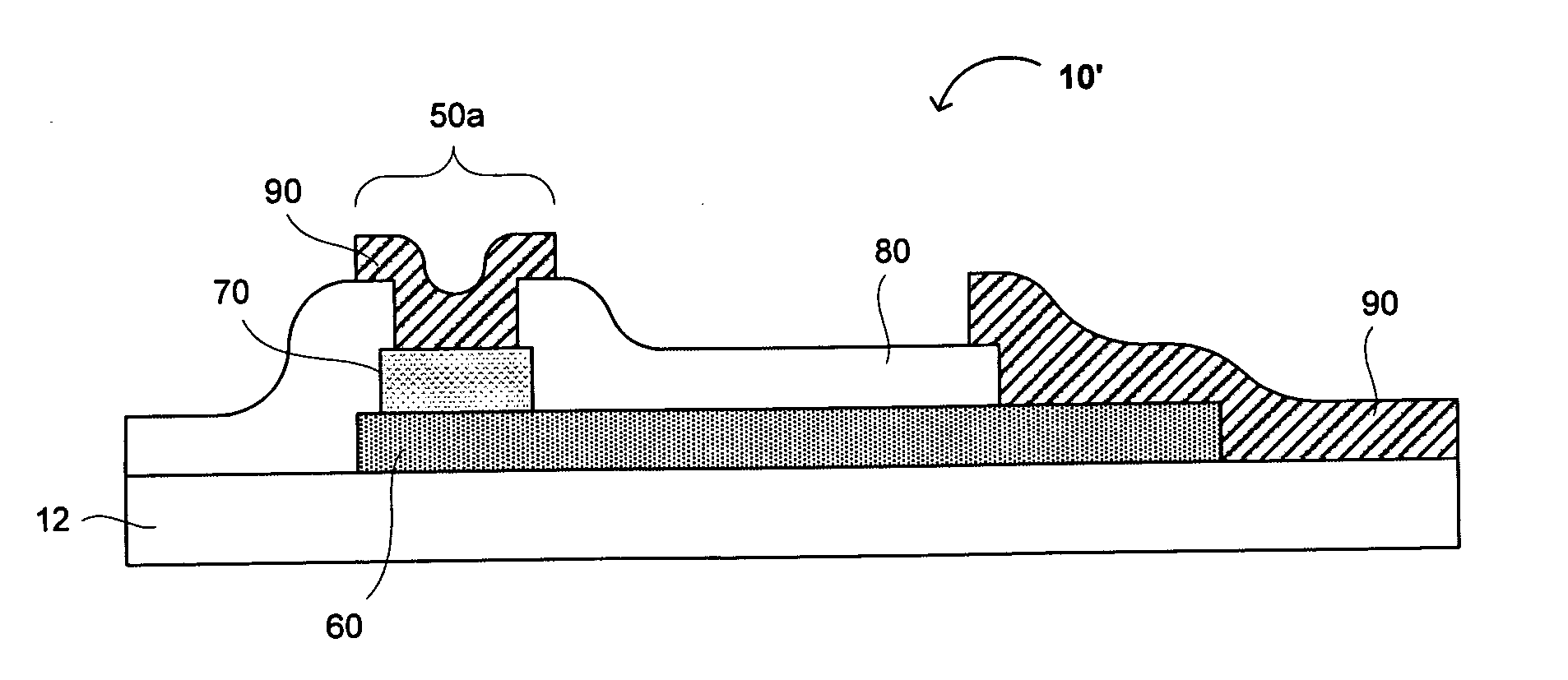

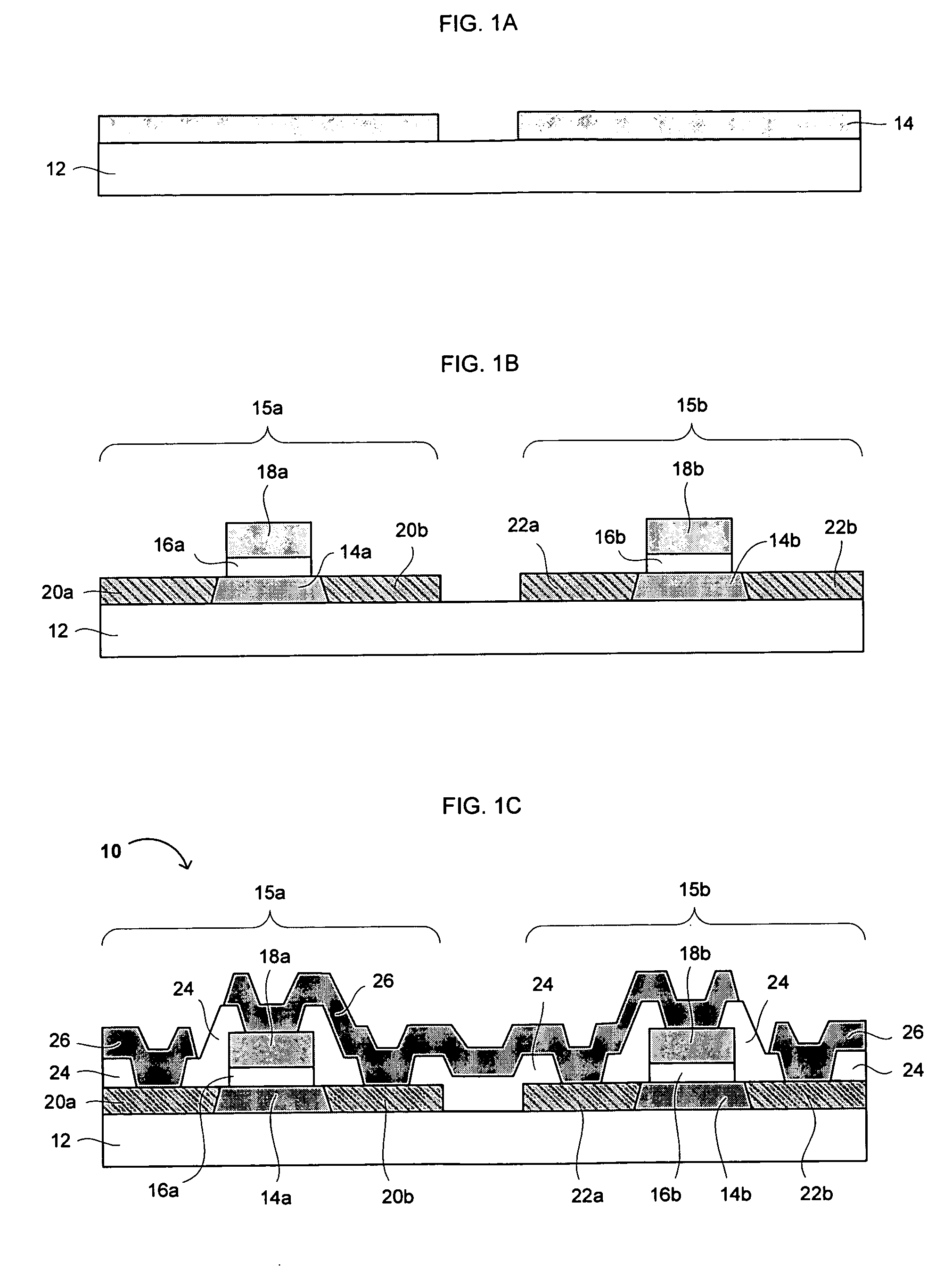

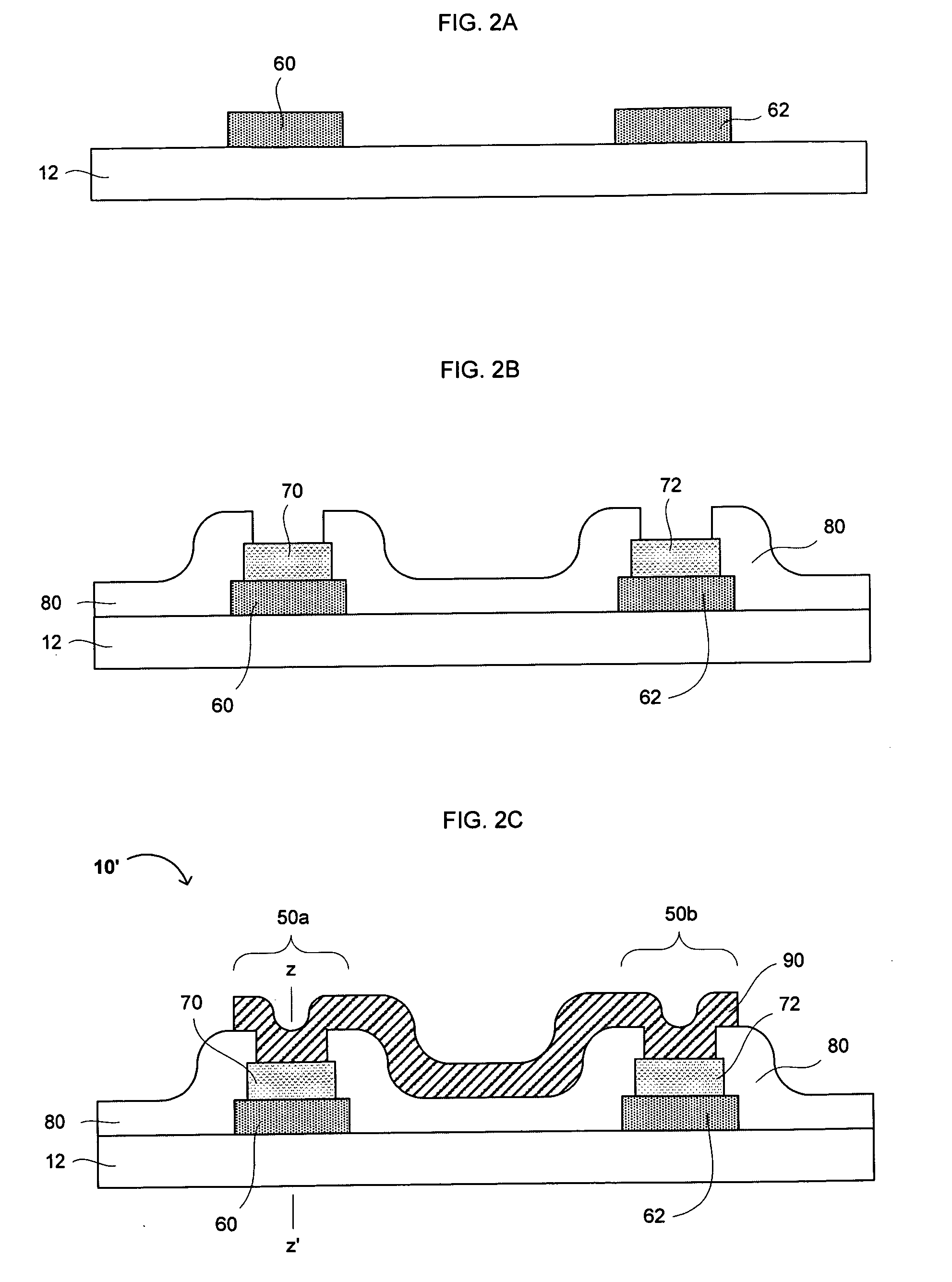

Process-variation tolerant diode, standard cells including the same, tags and sensors containing the same, and methods for manufacturing the same

ActiveUS20070128760A1Improve forward stabilityReadily apparentMaterial nanotechnologySolid-state devicesVoltage generatorComplementary pair

Process variation-tolerant diodes and diode-connected thin film transistors (TFTs), printed or patterned structures (e.g., circuitry) containing such diodes and TFTs, methods of making the same, and applications of the same for identification tags and sensors are disclosed. A patterned structure comprising a complementary pair of diodes or diode-connected TFTs in series can stabilize the threshold voltage (Vt) of a diode manufactured using printing or laser writing techniques. The present invention advantageously utilizes the separation between the Vt of an NMOS TFT (Vtn) and the Vt of a PMOS TFT (Vtp) to establish and / or improve stability of a forward voltage drop across a printed or laser-written diode. Further applications of the present invention relate to reference voltage generators, voltage clamp circuits, methods of controlling voltages on related or differential signal transmission lines, and RFID and EAS tags and sensors.

Owner:ENSURGE MICROPOWER ASA

Built in self test circuit for measuring total timing uncertainty in a digital data path

InactiveUS7400555B2Accurately determineAccurate recoveryDigital circuit testingElectromechanical unknown time interval measurementDigital dataProcessor register

A circuit for measuring timing uncertainty in a clocked digital path and in particular, the number of logic stages completed in any clock cycle. A local clock buffer receives a global clock and provides a complementary pair of local clocks. A first local (launch) clock is an input to a delay line, e.g., 3 clock cycles worth of series connected inverters. Delay line taps (inverter outputs) are inputs to a register that is clocked by the complementary clock pair to capture progression of the launch clock through the delay line and identify any variation (e.g., from jitter, VDD noise) in that progression. Global clock skew and across chip gate length variation can be measured by cross coupling launch clocks from a pair of such clock buffers and selectively passing the local and remote launch clocks to the respective delay lines.

Owner:GLOBALFOUNDRIES INC

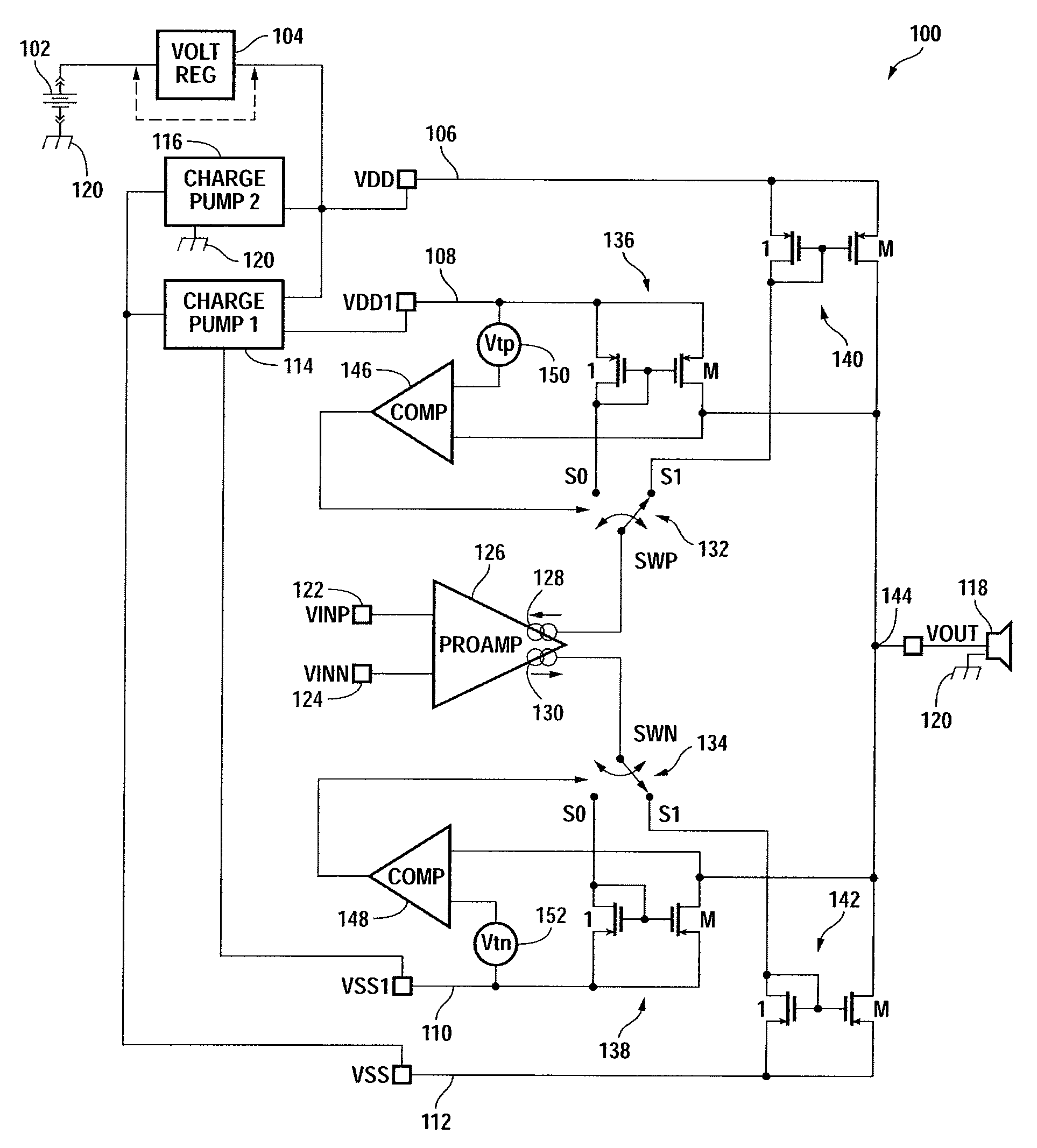

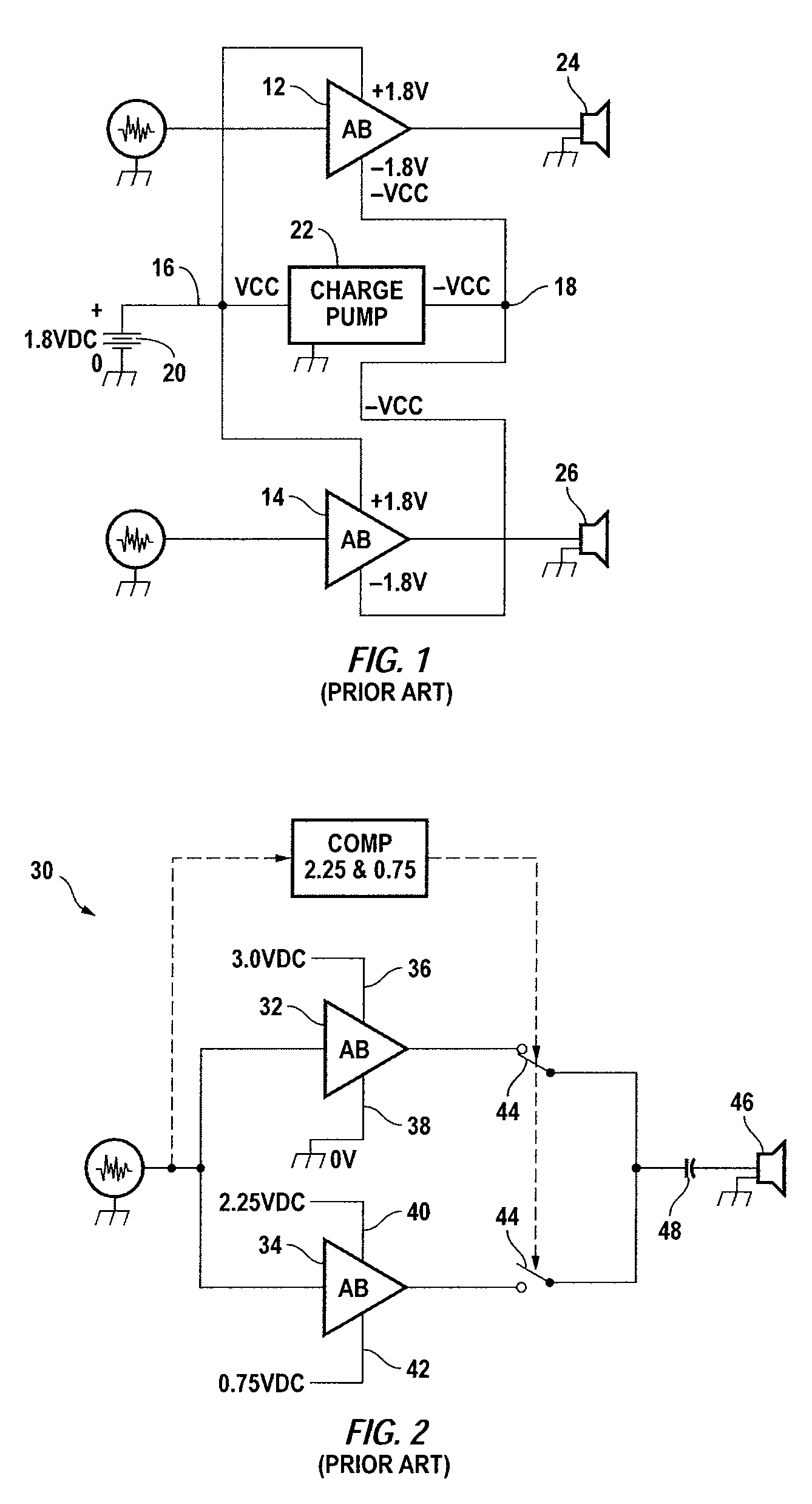

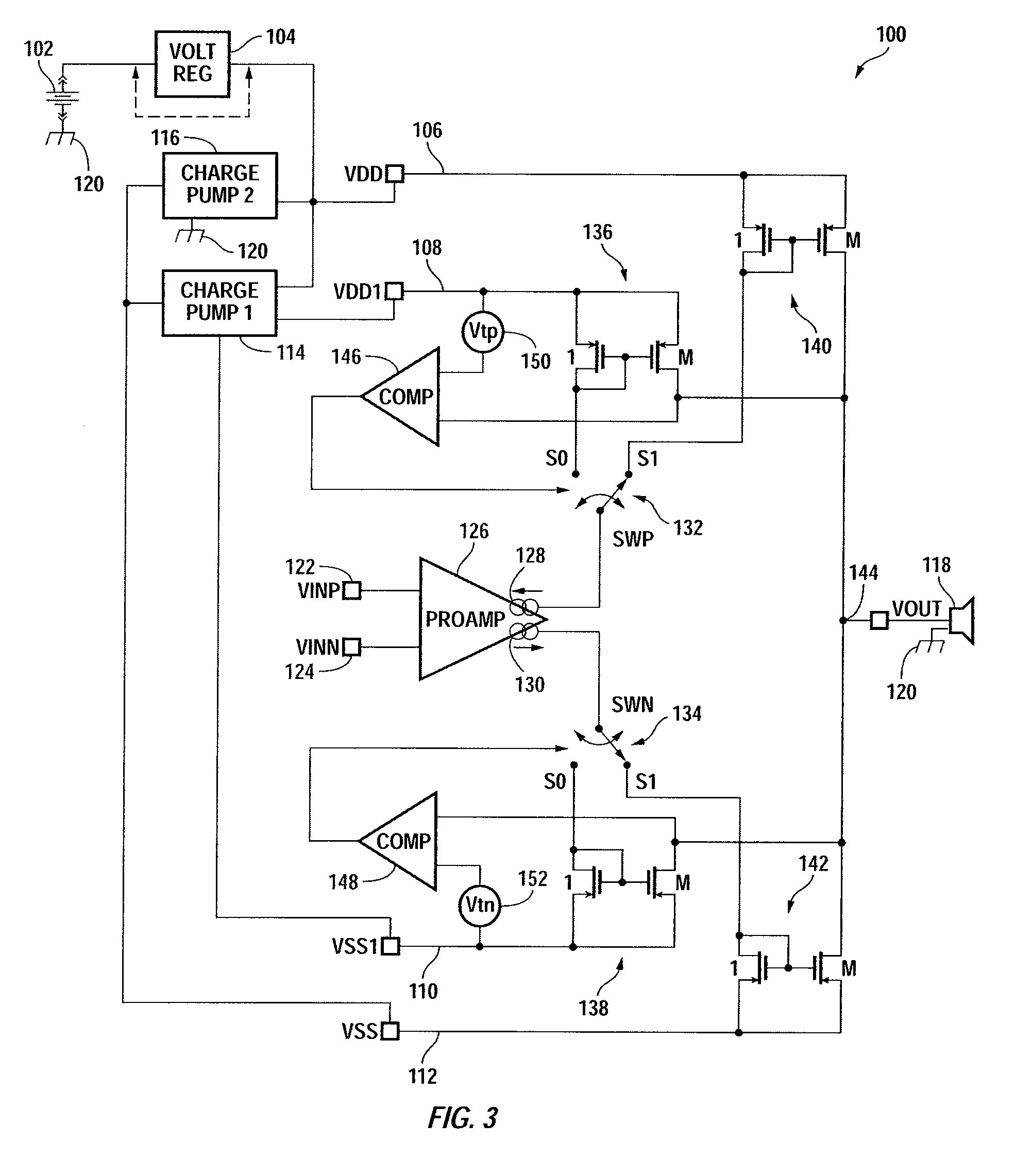

High efficiency audio amplifier

ActiveUS7733178B1Negative-feedback-circuit arrangementsPower amplifiersAudio power amplifierPortable power

According to the invention, an audio amplifier system for use with a single-ended portable power supply that is referenced to ground, such as a small battery, has a single-channel class G amplifier section, a multiple voltage output charge pump subsystem for supplying complementary pairs of power supply voltages at selected ratiometric levels to an amplifier section, a set of switches on the power supply rails and a power-measuring comparator for selecting which complementary pair of power supply voltages is provided to the amplifier section.

Owner:FAIRCHILD SEMICON CORP

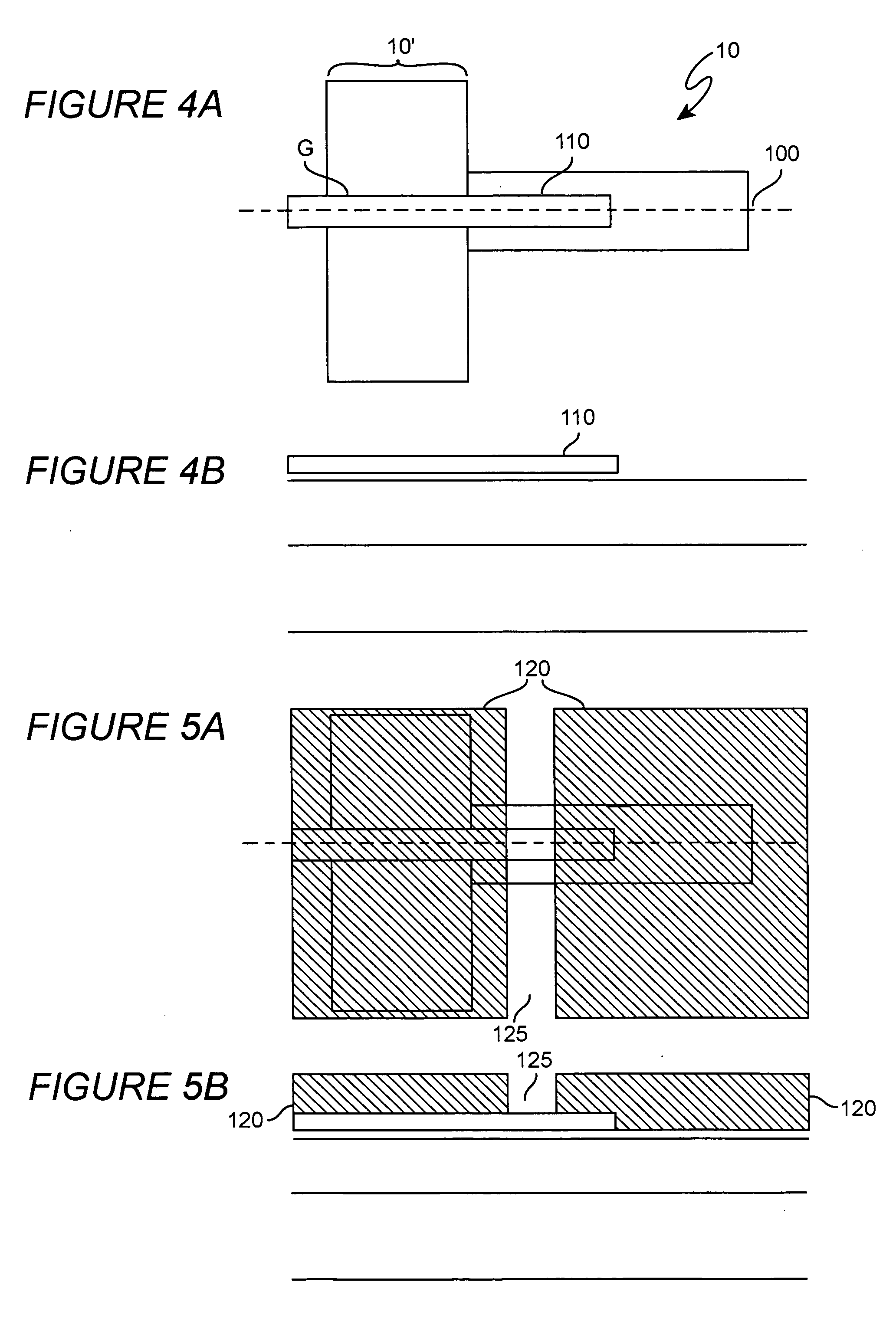

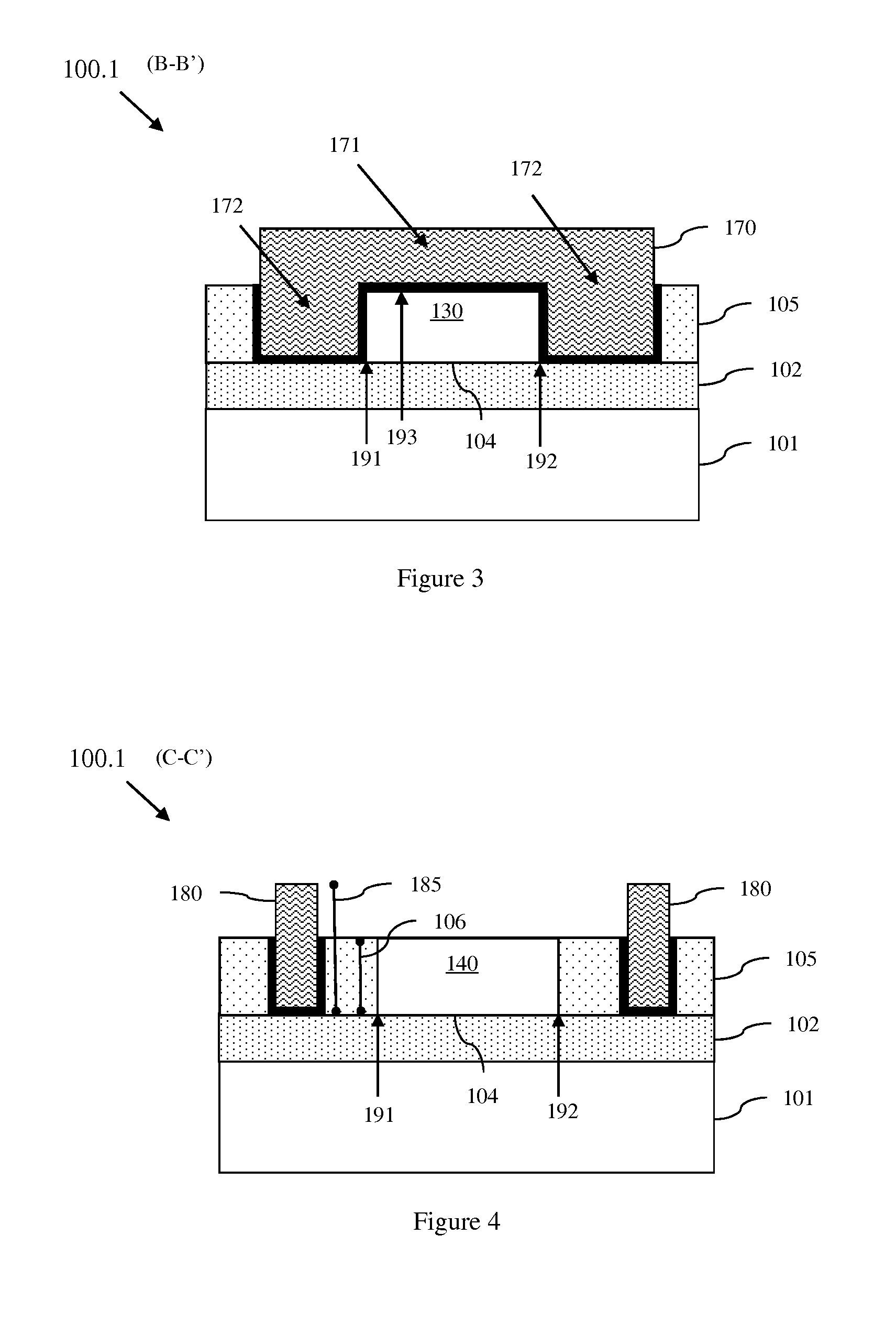

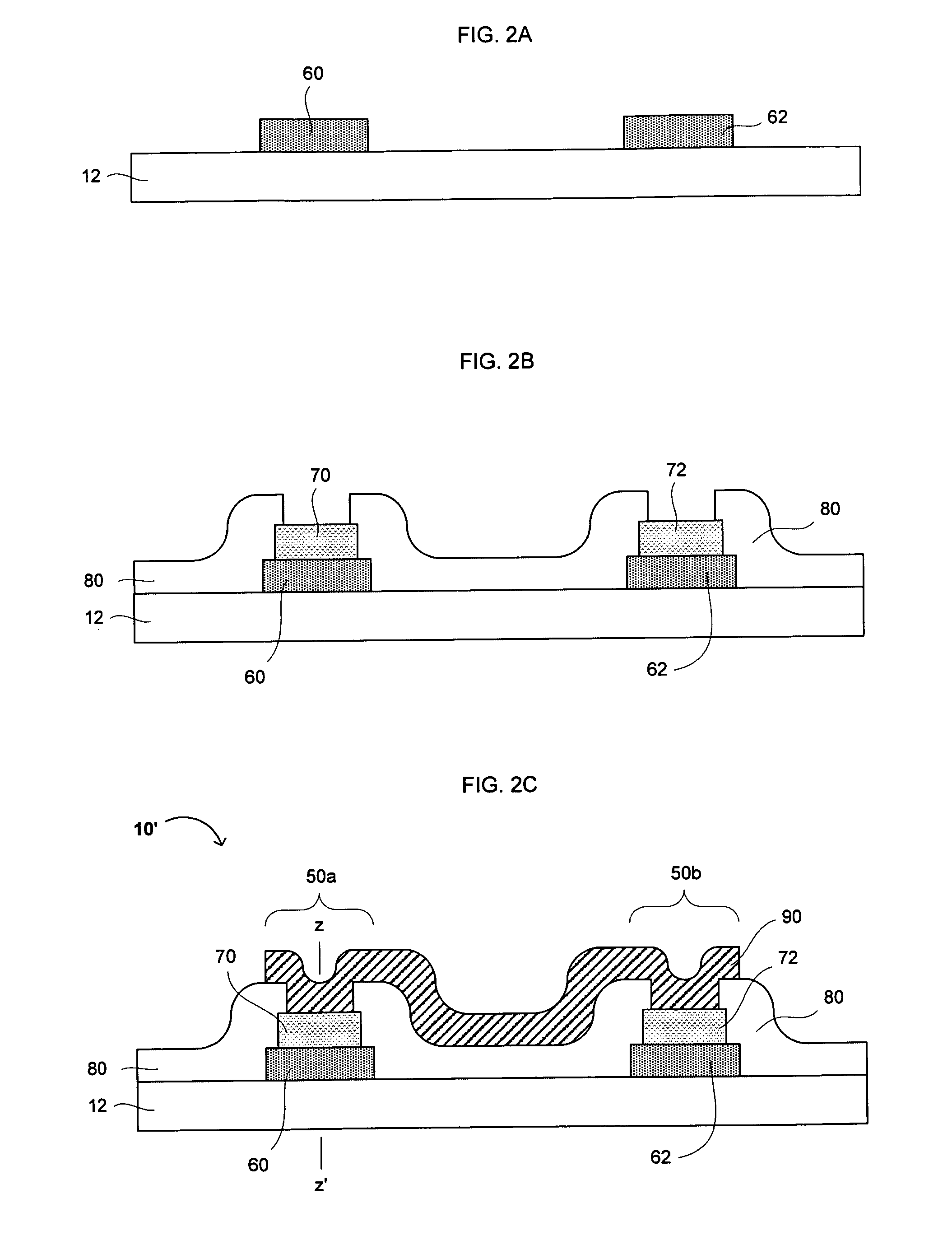

Via Structure Integrated in Electronic Substrate

ActiveUS20110139497A1Reducing electricalReducing magnetic fieldSemiconductor/solid-state device detailsSolid-state devicesComplementary pairOptoelectronics

A system of via structures disposed in a substrate. The system includes a first via structure that comprises an outer conductive layer, an inner insulating layer, and an inner conductive layer disposed in the substrate. The outer conductive layer separates the inner insulating layer and the substrate and the inner insulating layer separates the inner conductive layer and the outer conductive layer. A first signal of a first complementary pair passes through the inner conductive layer and a second signal of the first complementary pair passes through the outer conductive layer. In different embodiments, a method of forming a via structure in an electronic substrate is provided.

Owner:QUALCOMM INC

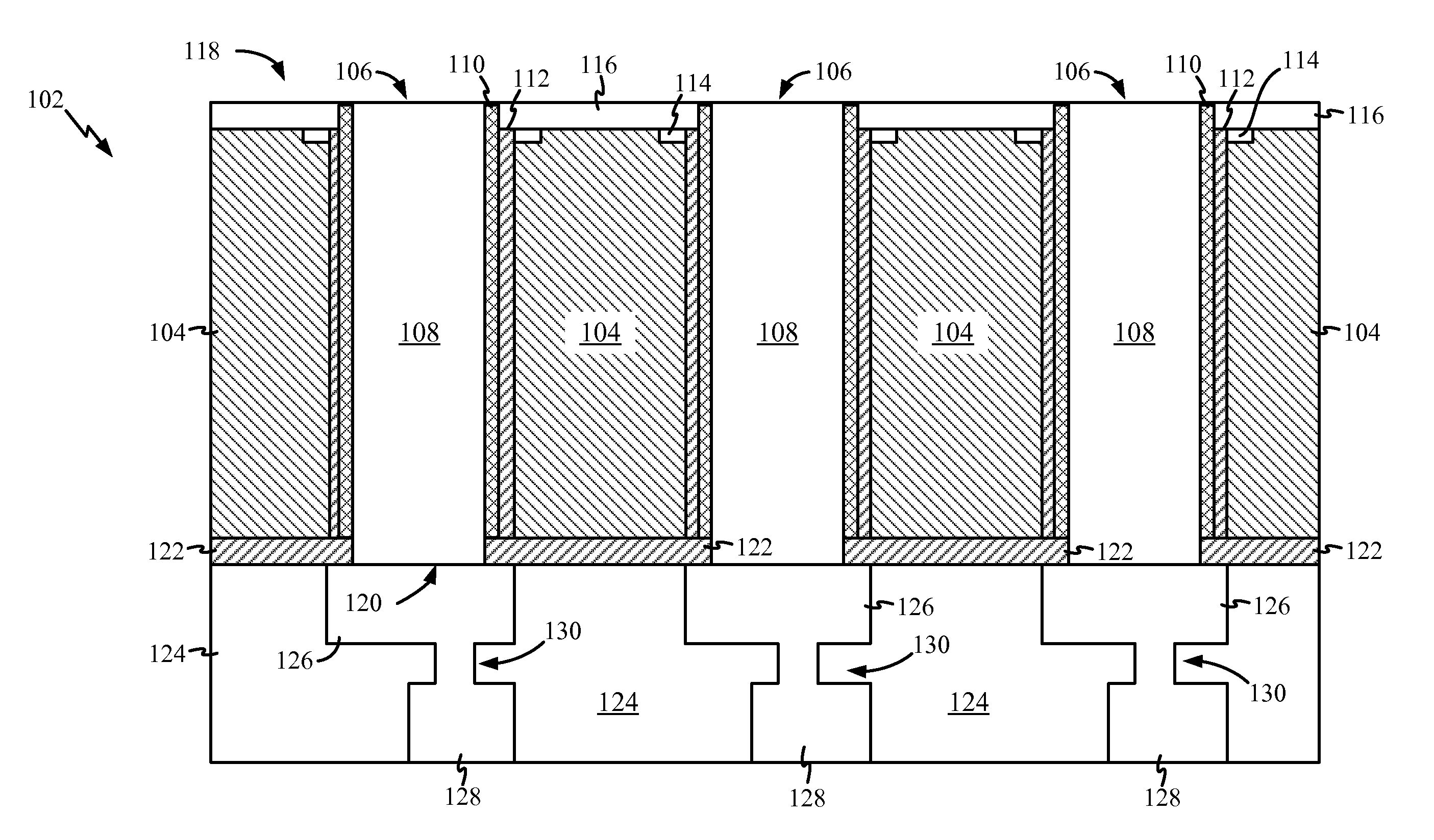

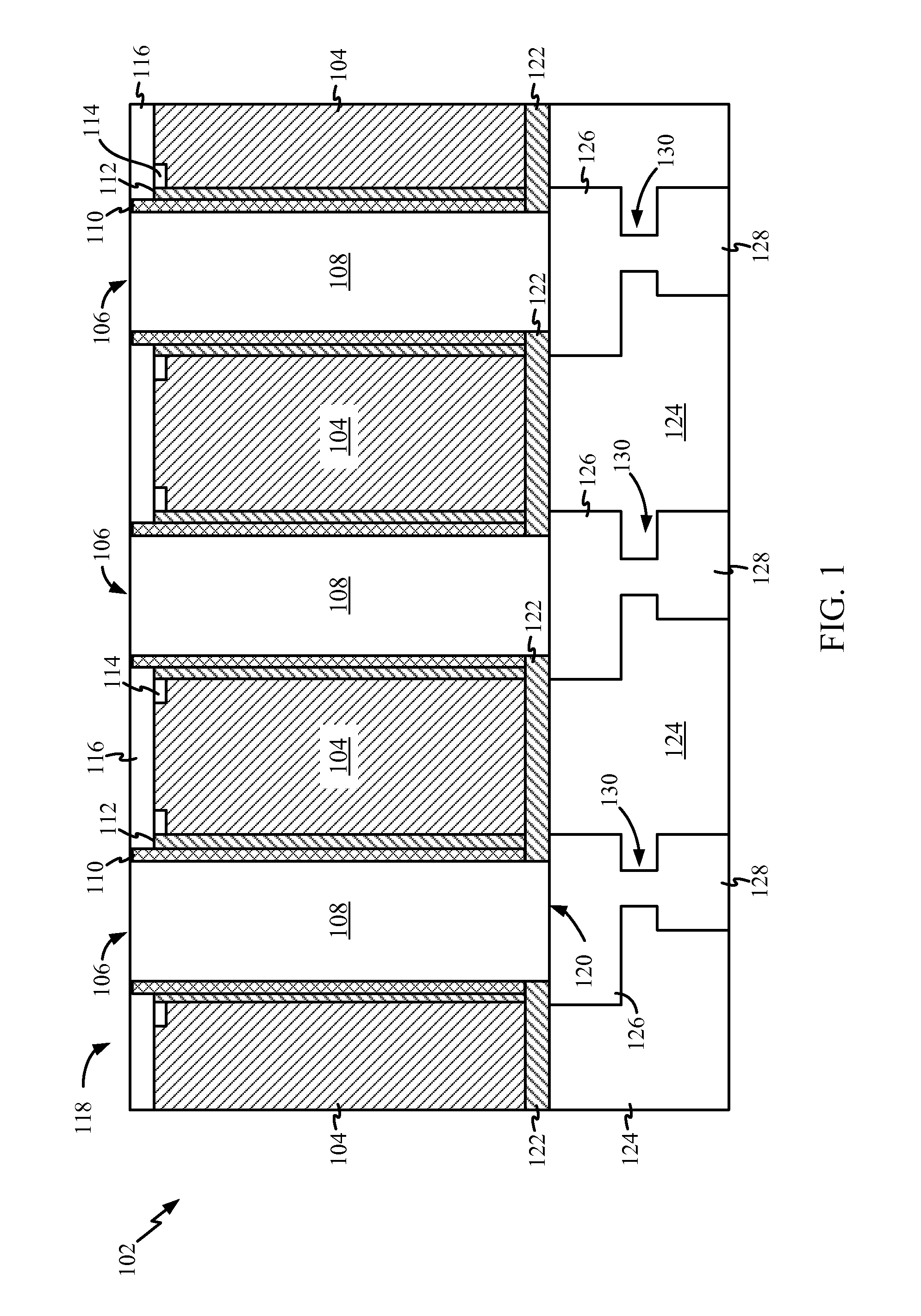

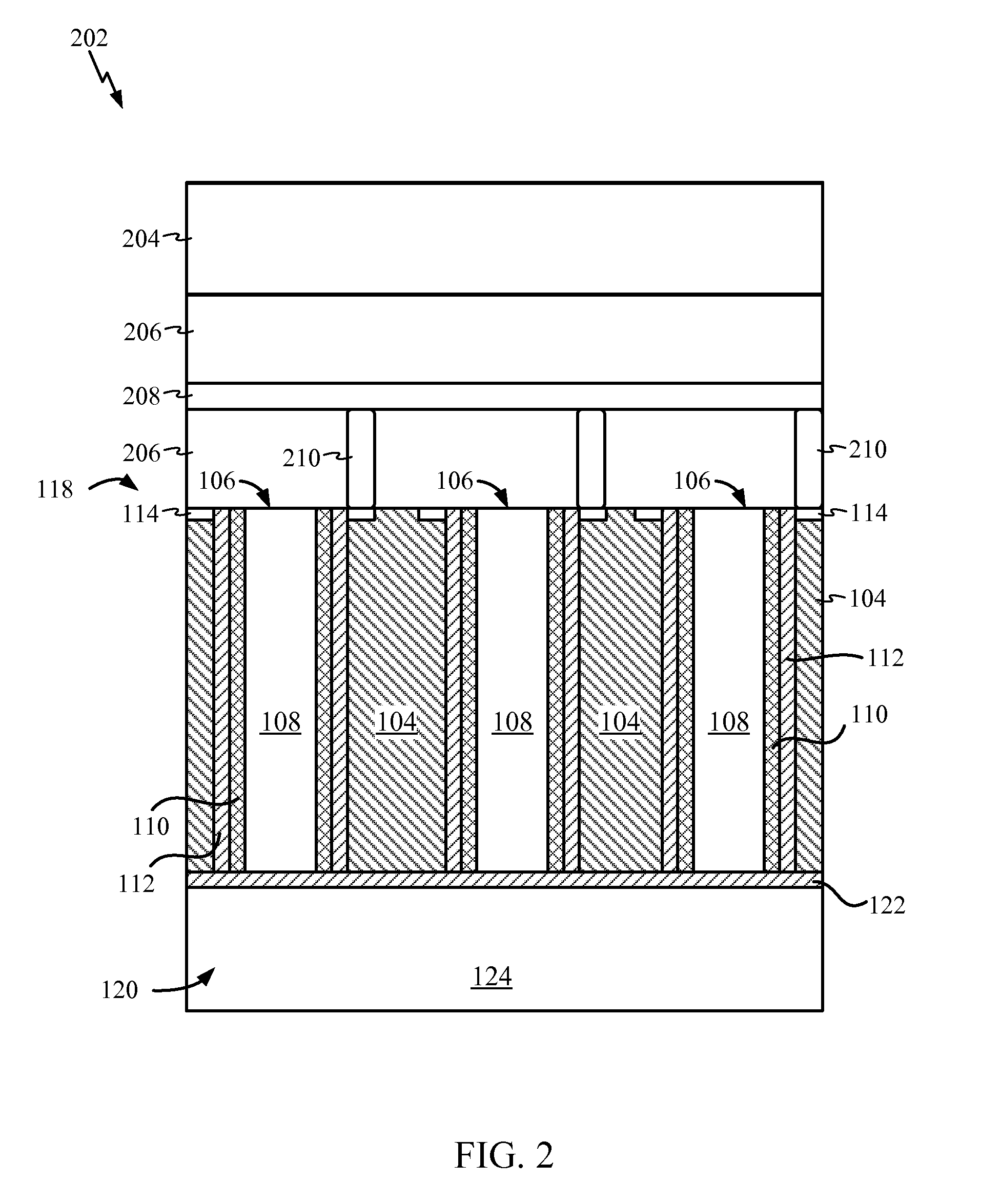

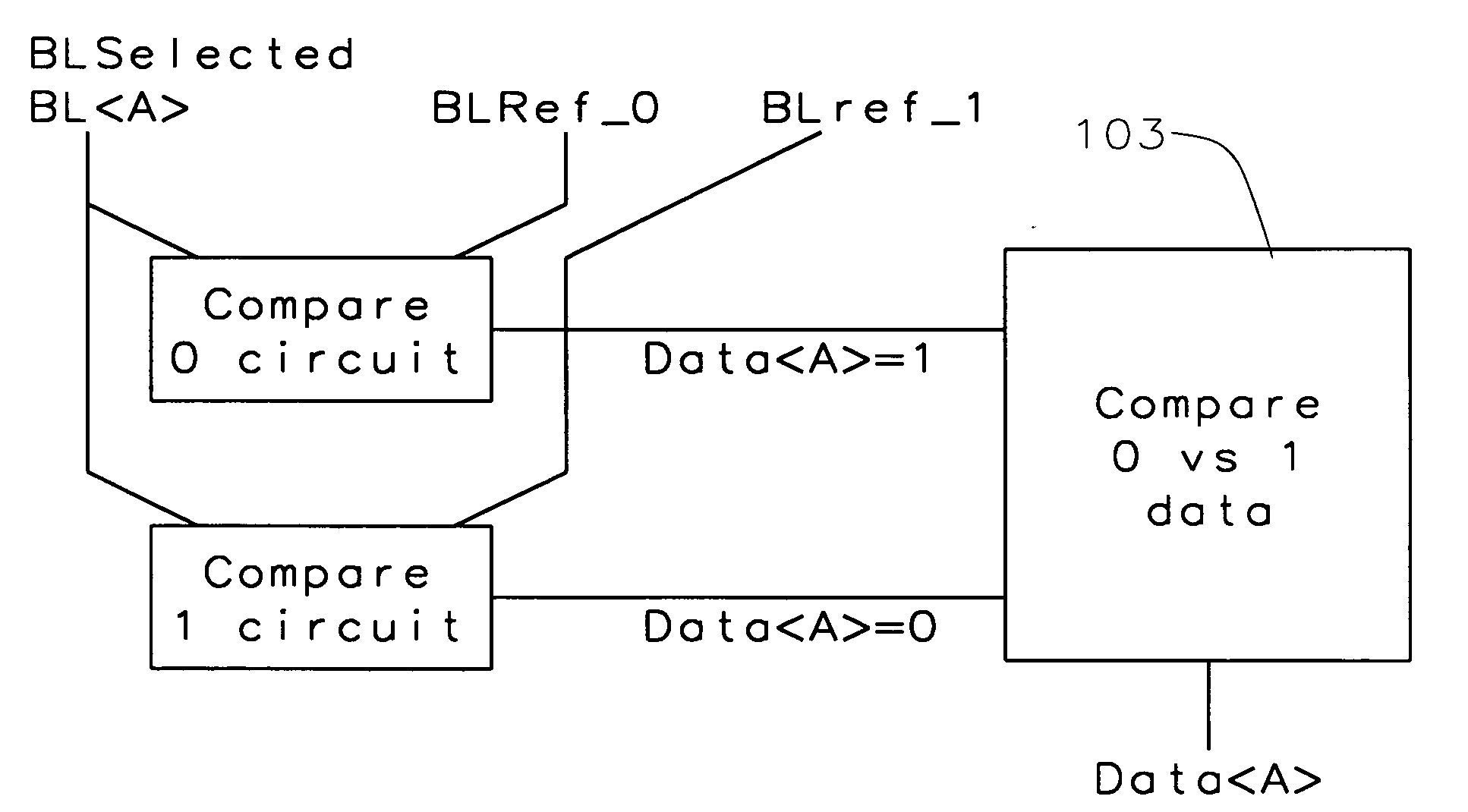

Complementary Reference method for high reliability trap-type non-volatile memory

ActiveUS20100046302A1Improve reliabilityHigh “cycling”Read-only memoriesDigital storageParallel computingComplementary pair

Methods of complementary pairing of memory cells are described. These methods include two physical memory cells in a complementary pair, a complementary pair of reference cells for each erase block, and a physical complementary pair storing multiple data bits.

Owner:HALO LSI INC

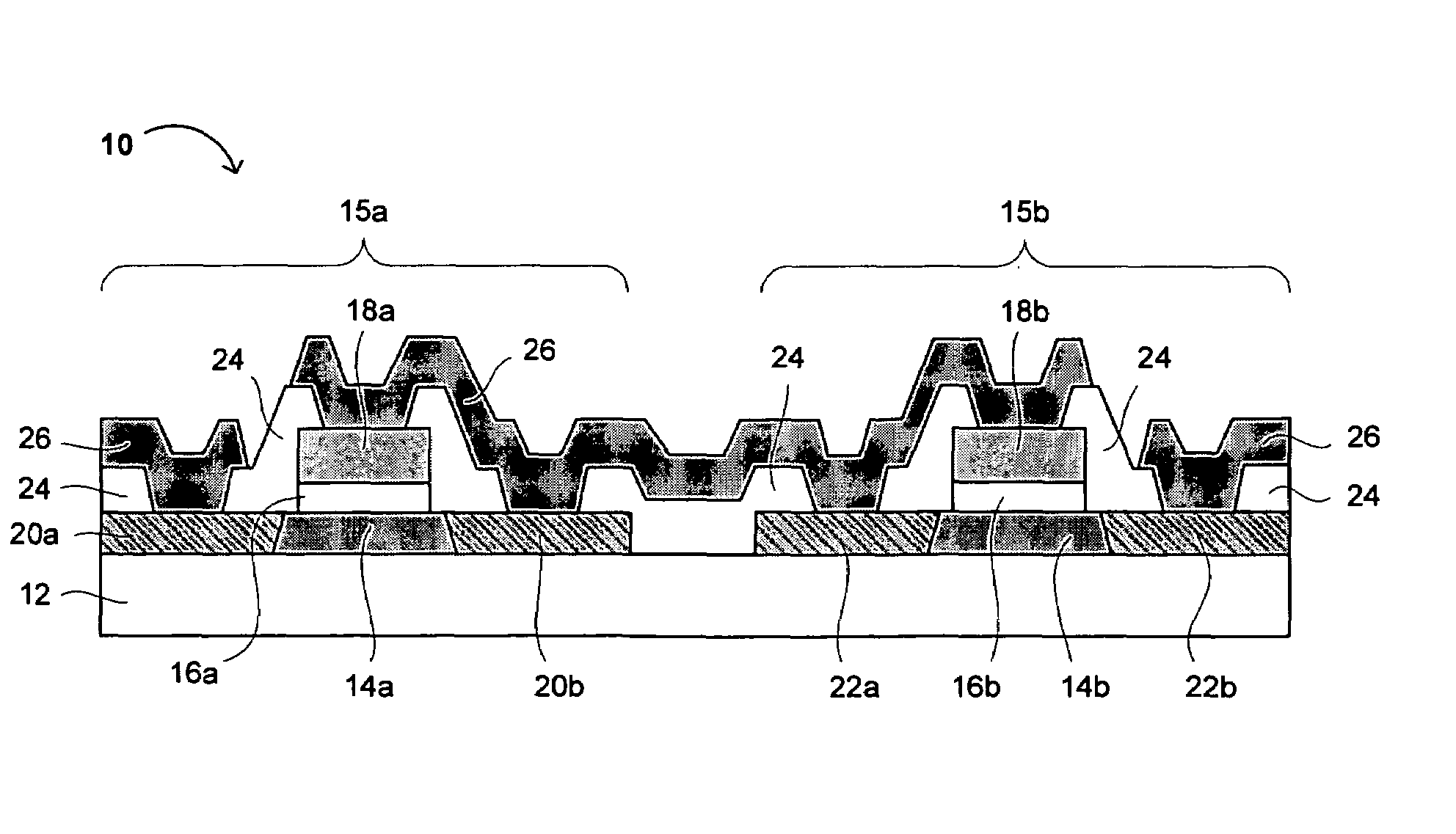

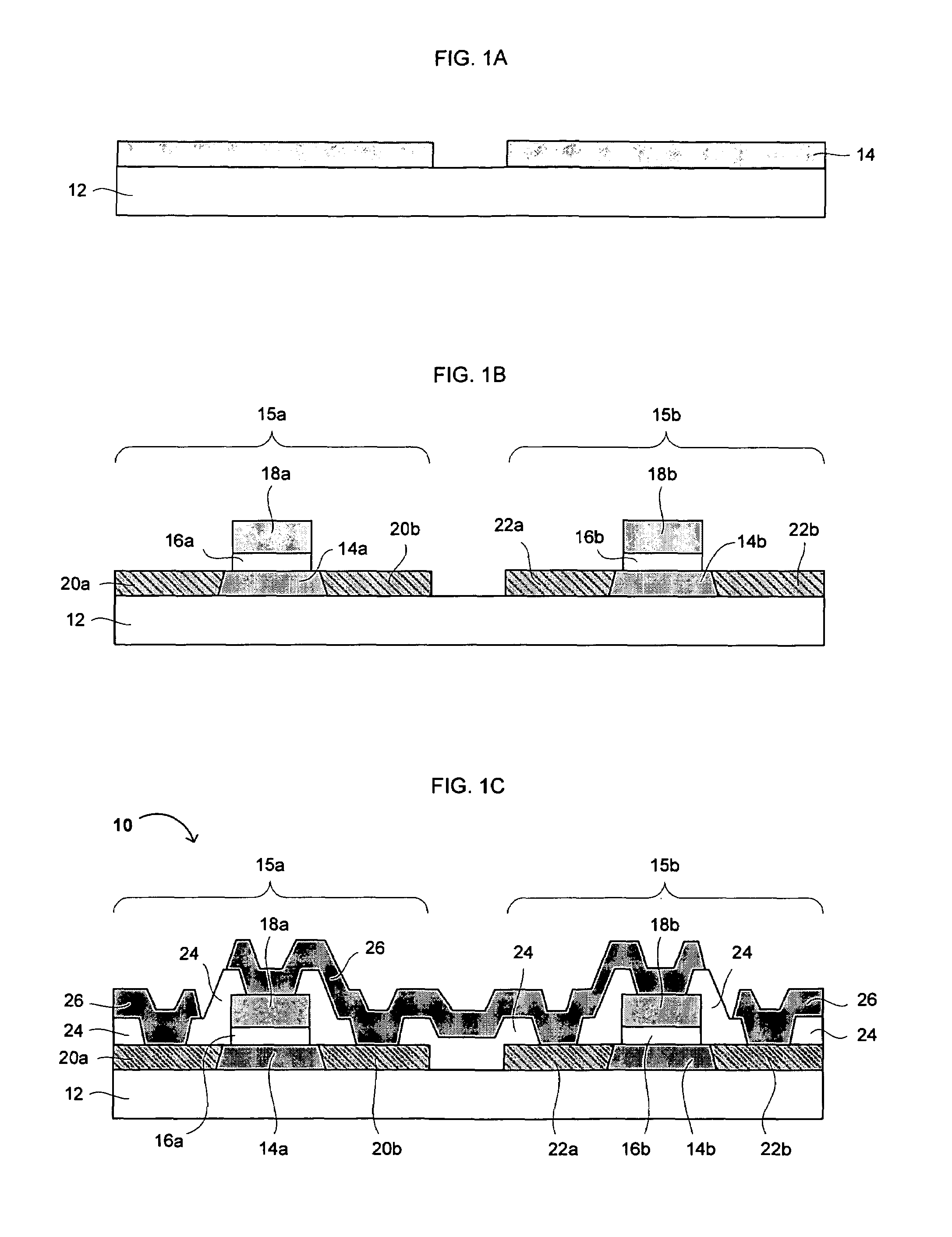

LATERAL EXTENDED DRAIN METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR (LEDMOSFET) HAVING A HIGH DRAIN-TO-BODY BREAKDOWN VOLTAGE (Vb), A METHOD OF FORMING AN LEDMOSFET, AND A SILICON-CONTROLLED RECTIFIER (SCR) INCORPORATING A COMPLEMENTARY PAIR OF LEDMOSFETS

InactiveUS20120168817A1Improve breakdown voltageTransistorSemiconductor/solid-state device manufacturingSilicon-controlled rectifierDopant

Disclosed are embodiments of a lateral, extended drain, metal oxide semiconductor, field effect transistor (LEDMOSFET) having a high drain-to-body breakdown voltage. Discrete conductive field (CF) plates are adjacent to opposing sides of the drain drift region, each having an angled sidewall such that the area between the drain drift region and the CF plate has a continuously increasing width along the length of the drain drift region from the channel region to the drain region. The CF plates can comprise polysilicon or metal structures or dopant implant regions within the same semiconductor body as the drain drift region. The areas between the CF plates and the drain drift region can comprise tapered dielectric regions or, alternatively, tapered depletion regions within the same semiconductor body as the drain drift region. Also disclosed are embodiments of a method for forming an LEDMOSFET and embodiments of a silicon-controlled rectifier (SCR) incorporating such LEDMOSFETs.

Owner:GLOBALFOUNDRIES INC

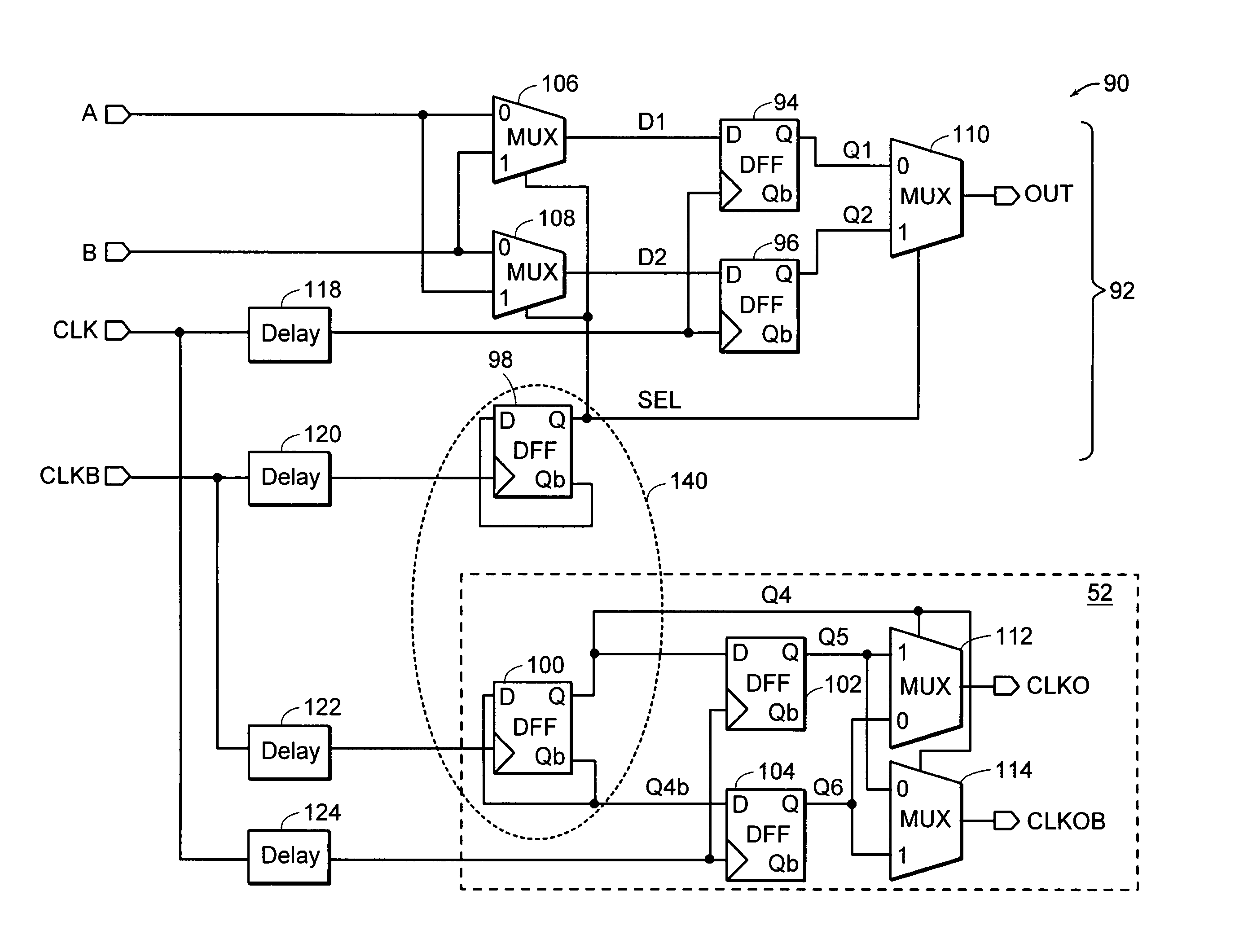

System and method for reducing skew in complementary signals that can be used to synchronously clock a double data rate output

Owner:MONTEREY RES LLC

Calibration of resistor ladder using difference measurement and parallel resistive correction

InactiveUS6628216B2Electric signal transmission systemsAnalogue-digital convertersDifferential measurementComplementary pair

Owner:INTERSIL INC

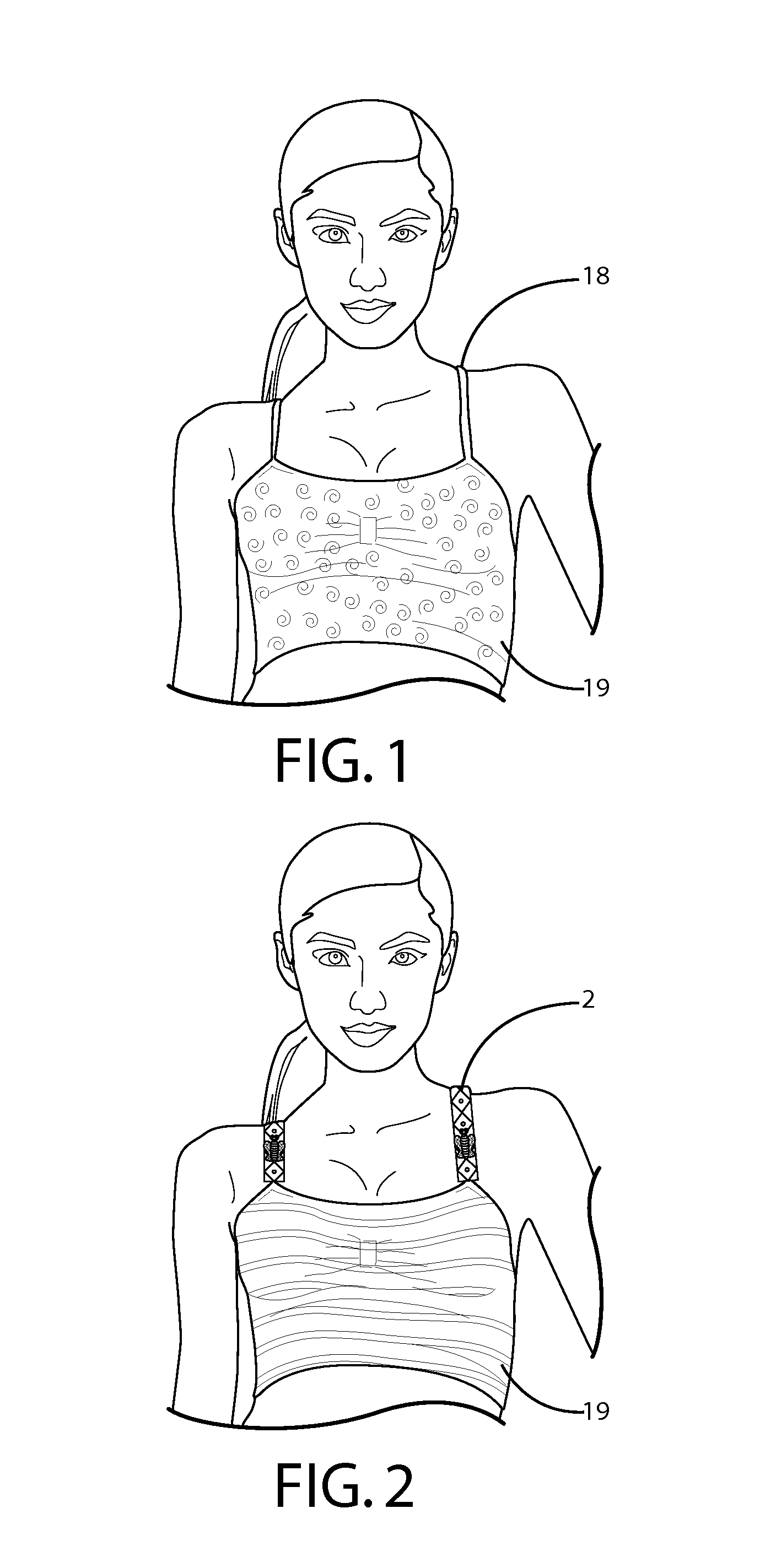

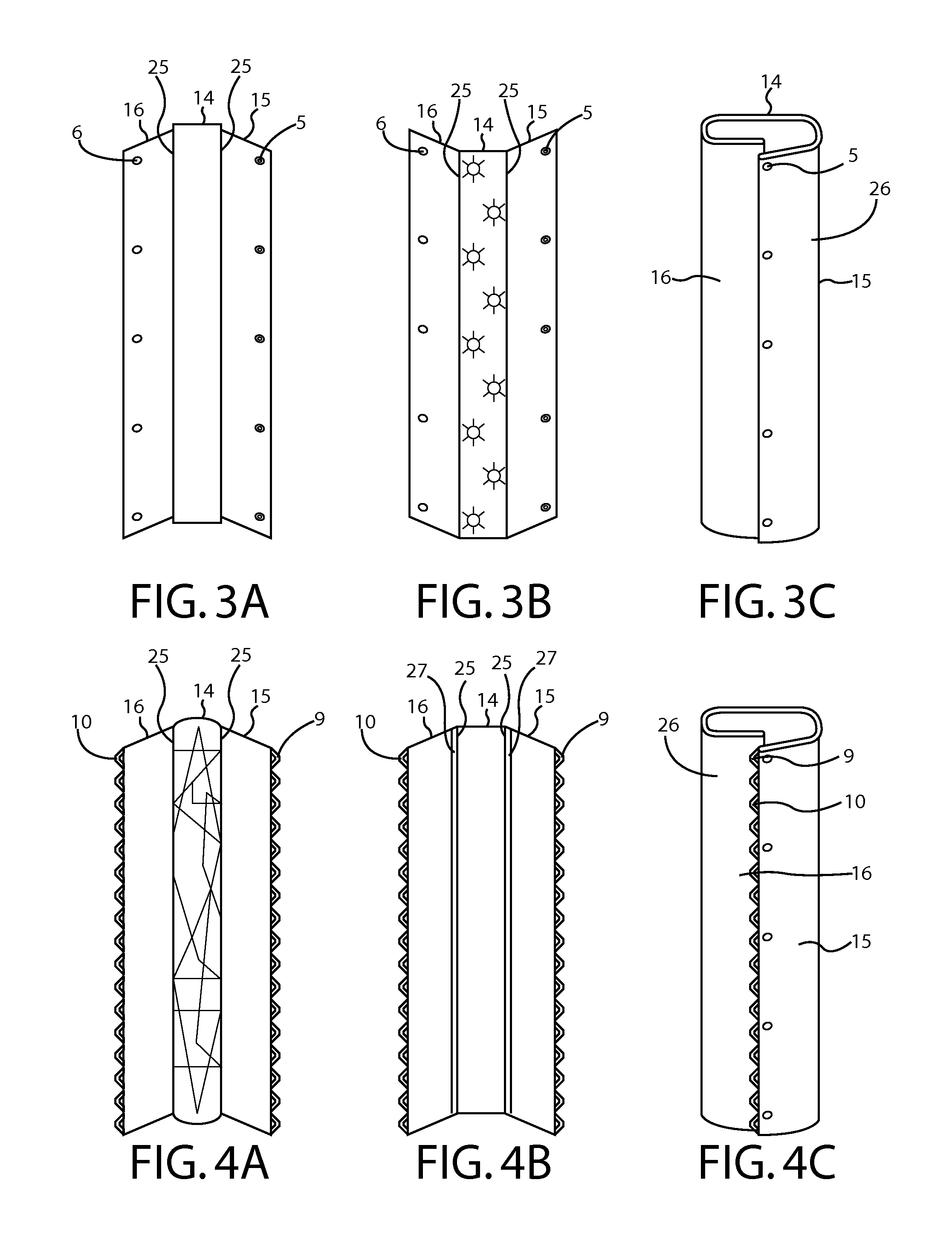

Bra strap covering device

Owner:PERTEH

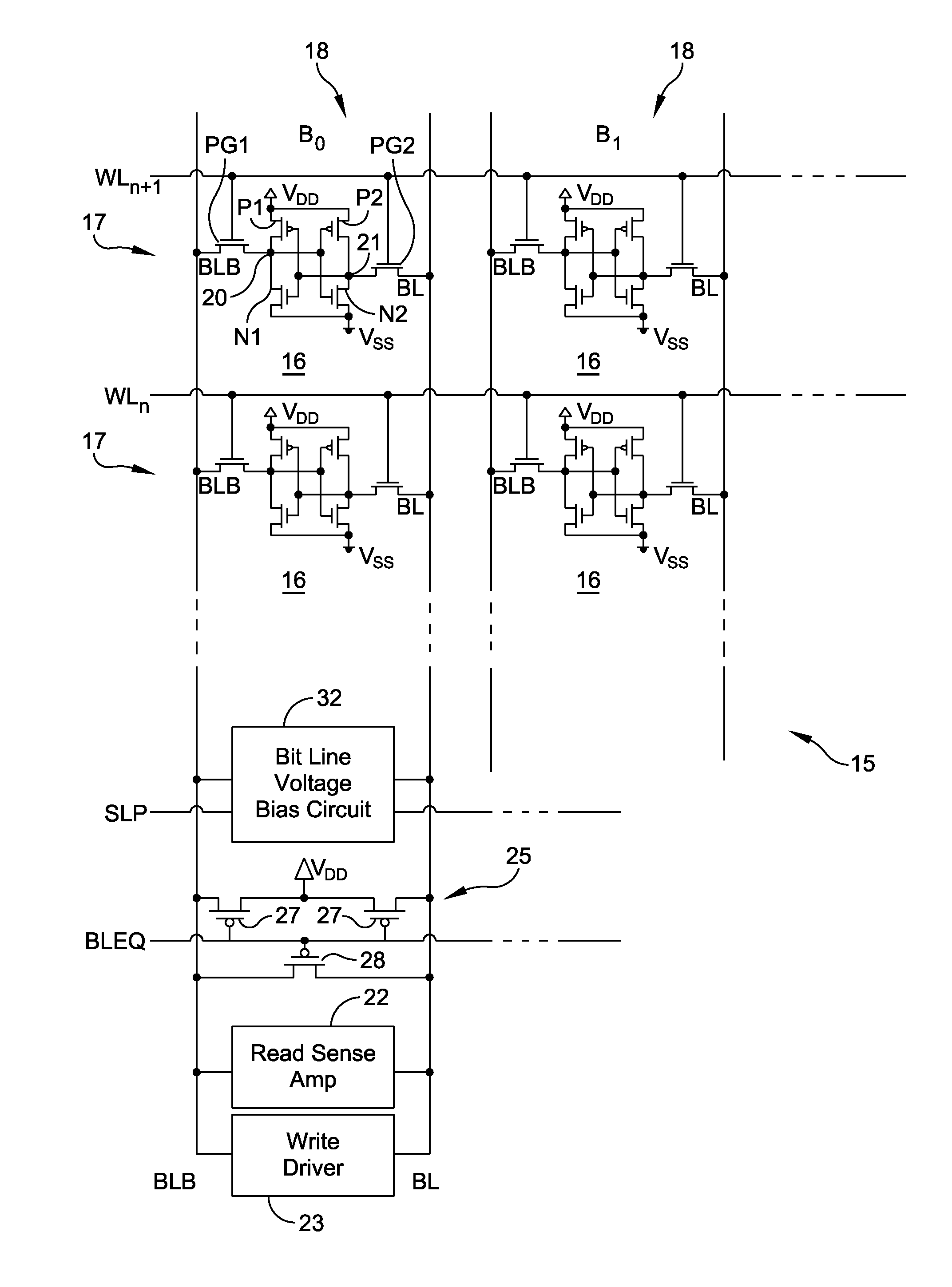

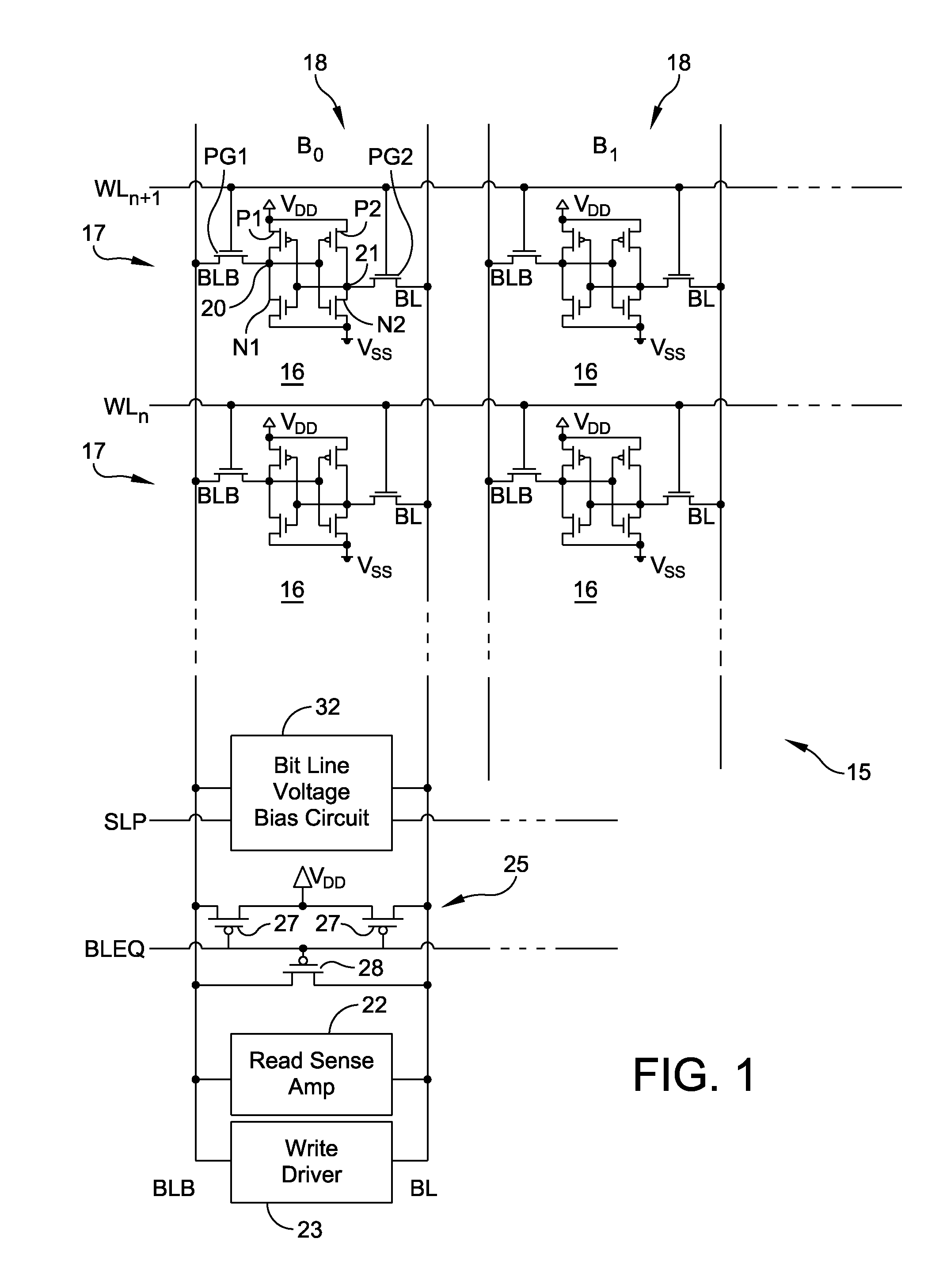

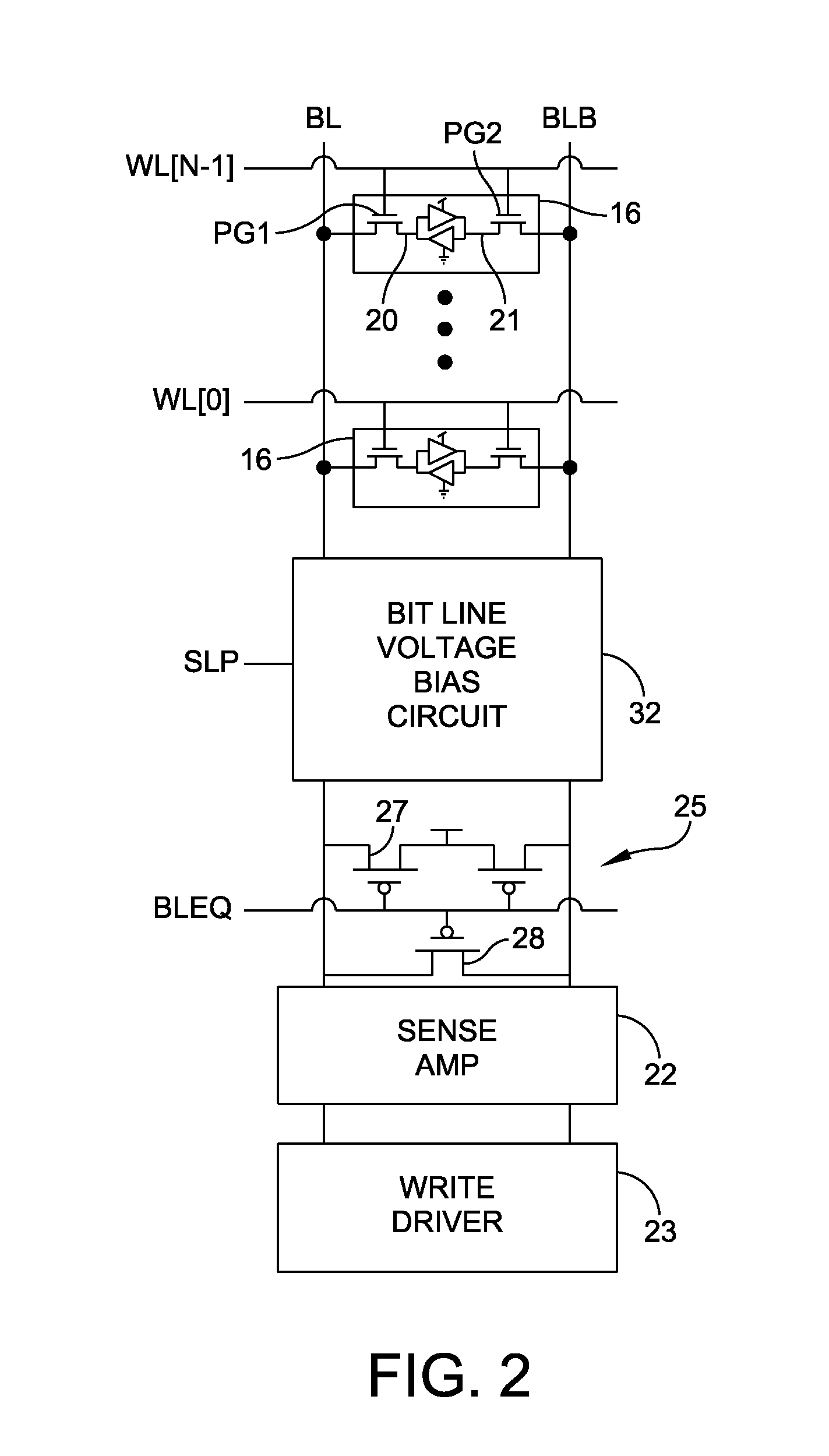

Bit line voltage bias for low power memory design

In a digital memory with an array of bit cells coupled to word lines and bit lines, each bit cell having cross coupled inverters isolated from bit lines by passing gate transistors until addressed, some or all of the bit cells are switchable between a sleep mode and a standby mode in response to a control signal. A bit line bias circuit controls the voltage at which the bit lines are caused to float when in the sleep mode. A pull-up transistor for each bit line BL or BLB in a complementary pair has a conductive channel coupled to a positive supply voltage and a gate coupled to the other bit line in the pair, BLB or BL, respectively. A connecting transistor also can be coupled between the bit lines of the complementary pair, bringing the floating bit lines to the supply voltage less a difference voltage ΔV.

Owner:TAIWAN SEMICON MFG CO LTD

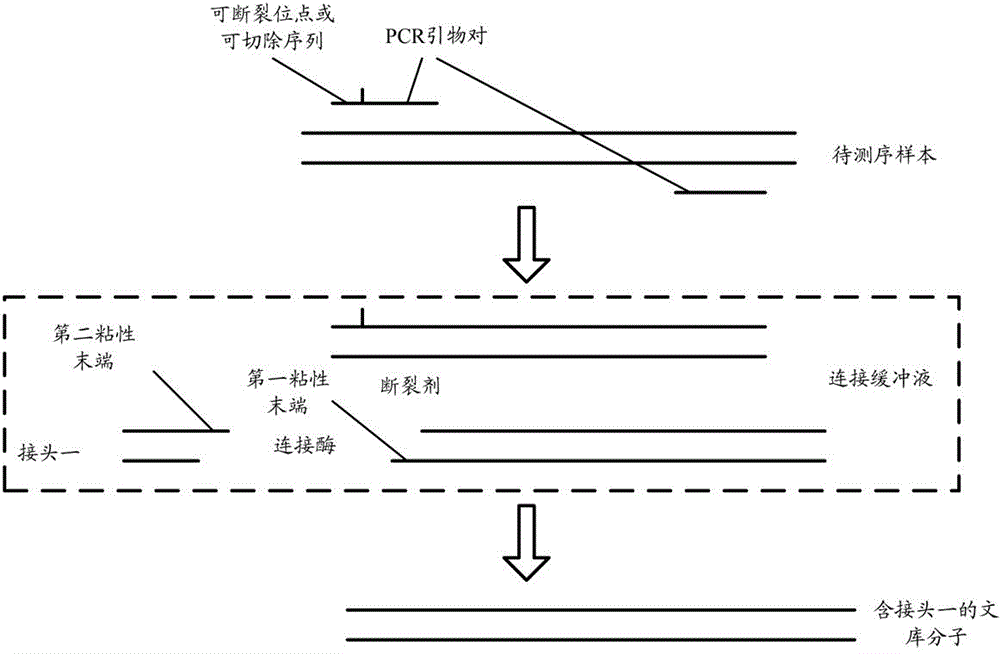

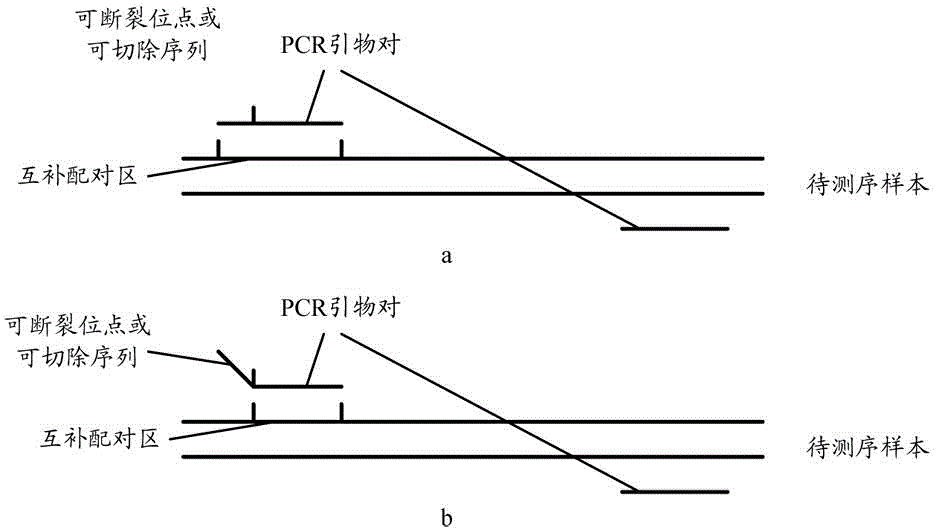

Rapid library building method

ActiveCN104480534ASimplify the experimental stepsImprove the efficiency of database constructionMicrobiological testing/measurementLibrary creationComplementary pairGenotyping

The invention relates to the fields of genetic engineering and molecular biology, and provides a rapid library building method, an SNP (single nucleotide polymorphism) genotyping method and a sequencing method. The rapid library building method includes the following steps: A. a sample to be sequenced goes through PCR (polymerase chain reaction) amplification, so as to obtain an amplified product; during the PCR amplification process, at least one PCR primer in a PCR primer pair for PCR amplification contains a breakable site or a cleavable sequence; B. the amplified product is added to a cleavage-ligation reaction system for cleavage and ligation, so as to obtain a library molecule containing a first linker; the cleavage-ligation reaction system comprises a ligase, a clastogen, the first linker and a ligation buffer solution; the clastogen is used for specific cleavage of the breakable site or the cleavable sequence in the amplified product, so as to form a first cohesive end; the first linker is a nucleic acid molecule, and contains a second cohesive end capable of completely complementary pairing with the first cohesive end. The invention simplifies experiment steps, and improves the library building efficiency.

Owner:SHENGZHEN CHINA GENE TECH COMPANY

Method of manufacturing complementary diodes

ActiveUS7528017B2Improve forward stabilityReadily apparentMaterial nanotechnologySolid-state devicesVoltage generatorDifferential signaling

Process variation-tolerant diodes and diode-connected thin film transistors (TFTs), printed or patterned structures (e.g., circuitry) containing such diodes and TFTs, methods of making the same, and applications of the same for identification tags and sensors are disclosed. A patterned structure comprising a complementary pair of diodes or diode-connected TFTs in series can stabilize the threshold voltage (Vt) of a diode manufactured using printing or laser writing techniques. The present invention advantageously utilizes the separation between the Vt of an NMOS TFT (Vtn) and the Vt of a PMOS TFT (Vtp) to establish and / or improve stability of a forward voltage drop across a printed or laser-written diode. Further applications of the present invention relate to reference voltage generators, voltage clamp circuits, methods of controlling voltages on related or differential signal transmission lines, and RFID and EAS tags and sensors.

Owner:ENSURGE MICROPOWER ASA

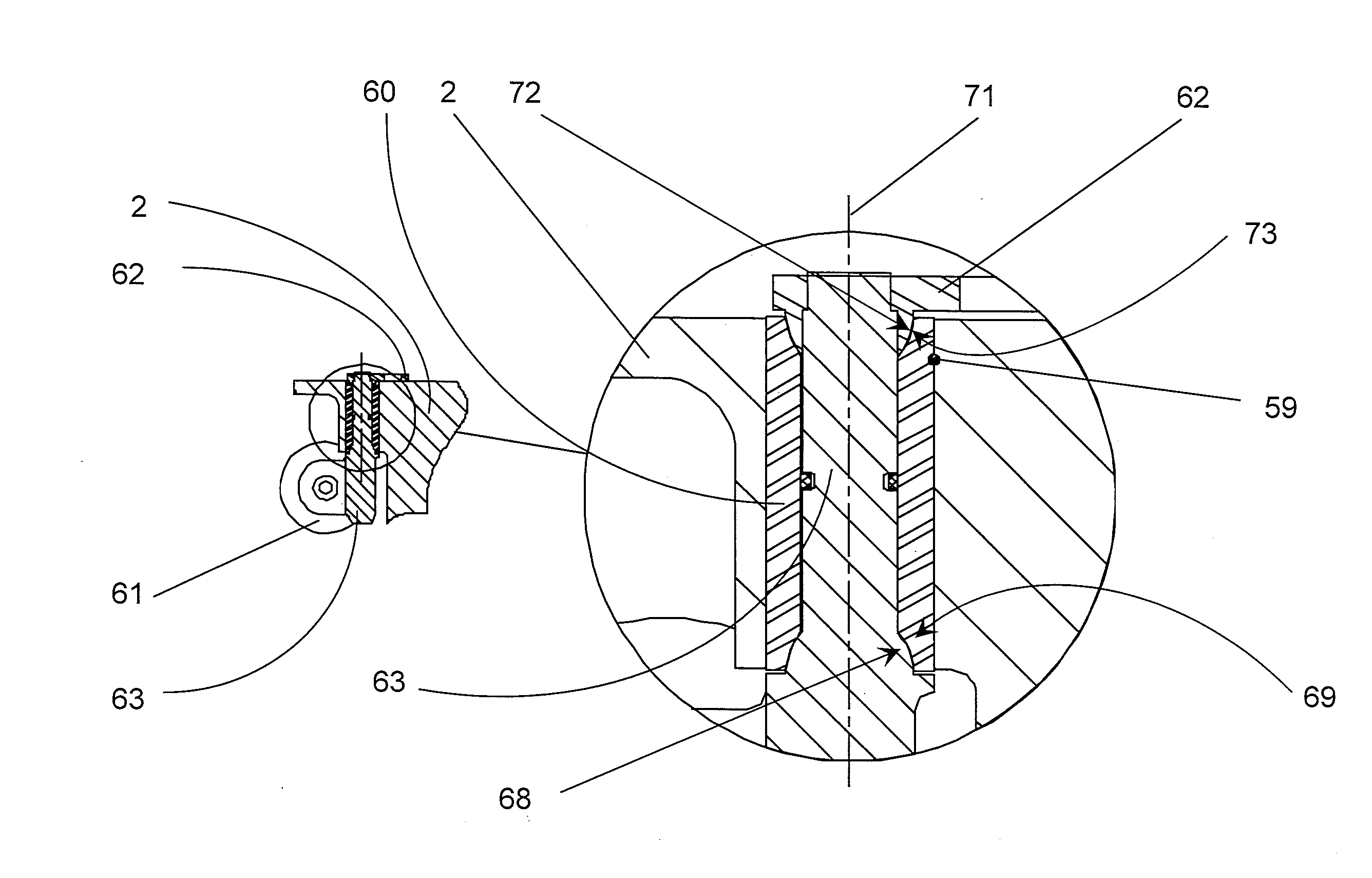

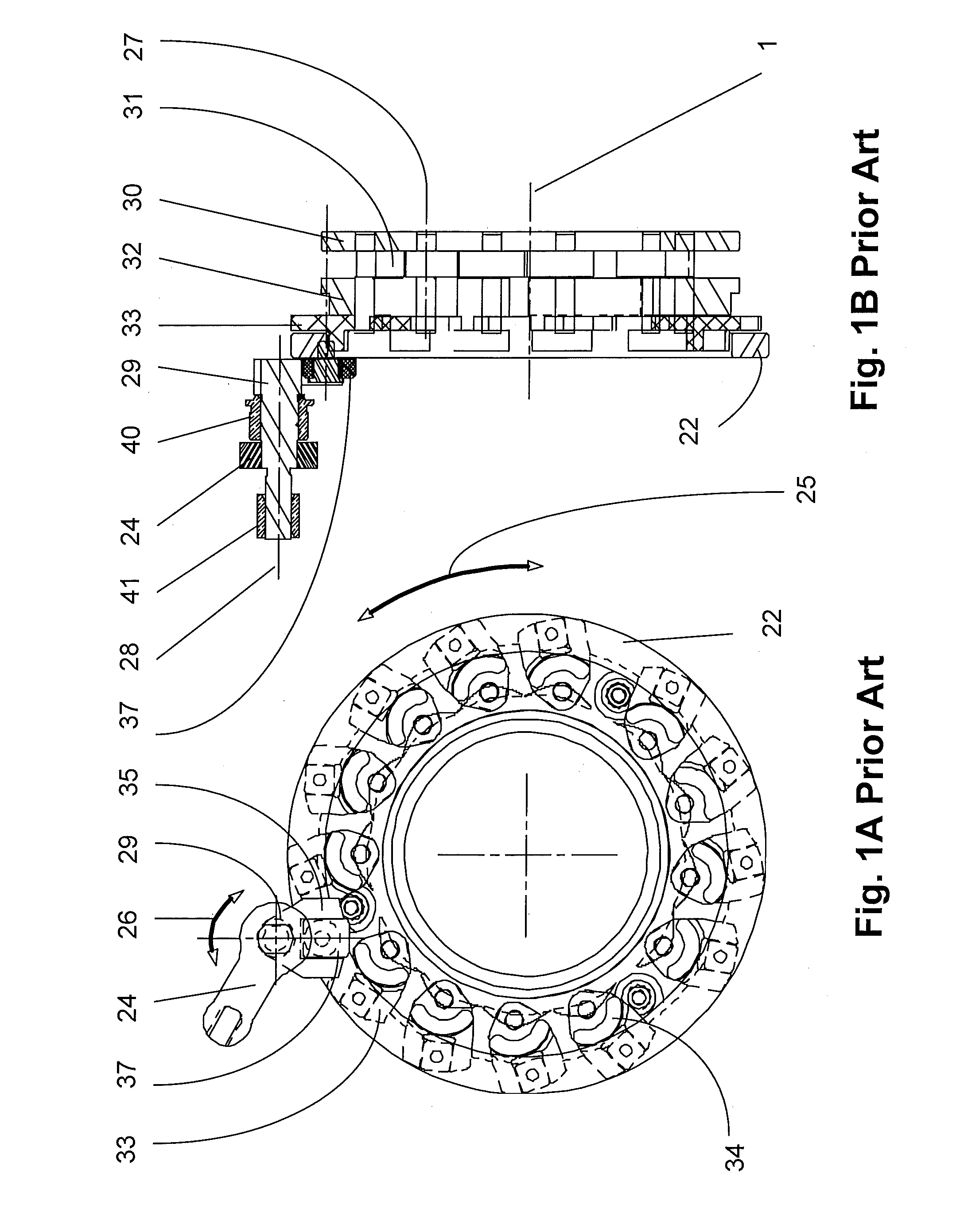

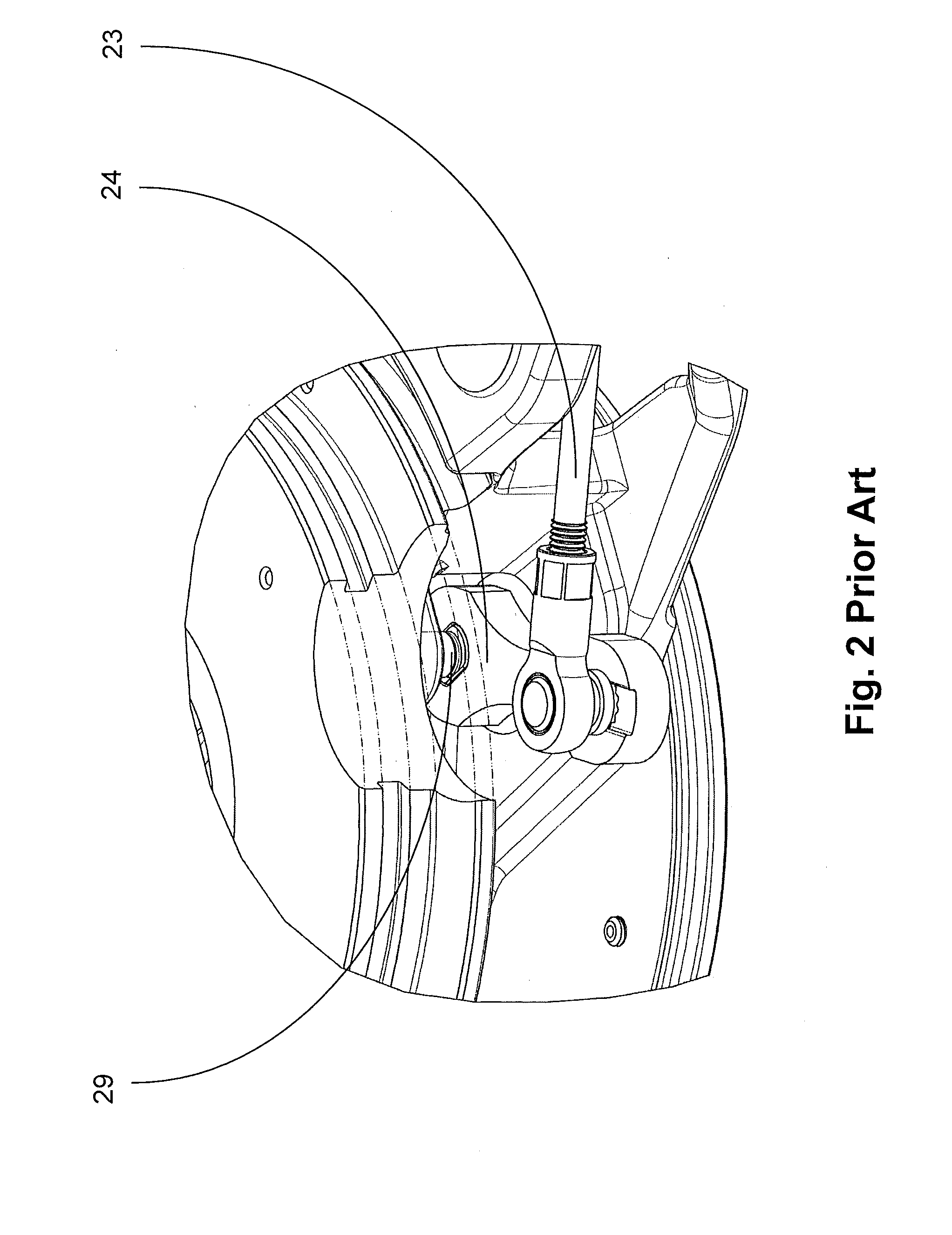

Control shaft seal

ActiveUS20130089411A1Improve sealingMaximizes retentionEngine sealsInternal combustion piston enginesTurbochargerComplementary pair

The propensity for gas leakage around a shaft, which connects volumes of differing pressures, in, e.g., a turbocharger is minimized in a simple cost-effective manner. The addition of a complementary pair of frusto-spherical, conical, or other profiles to the interface of the shaft and its bearing maintain concentricity of the shaft in its bore and thus improve the efficacy of existing sealing protocols.

Owner:BORGWARNER INC

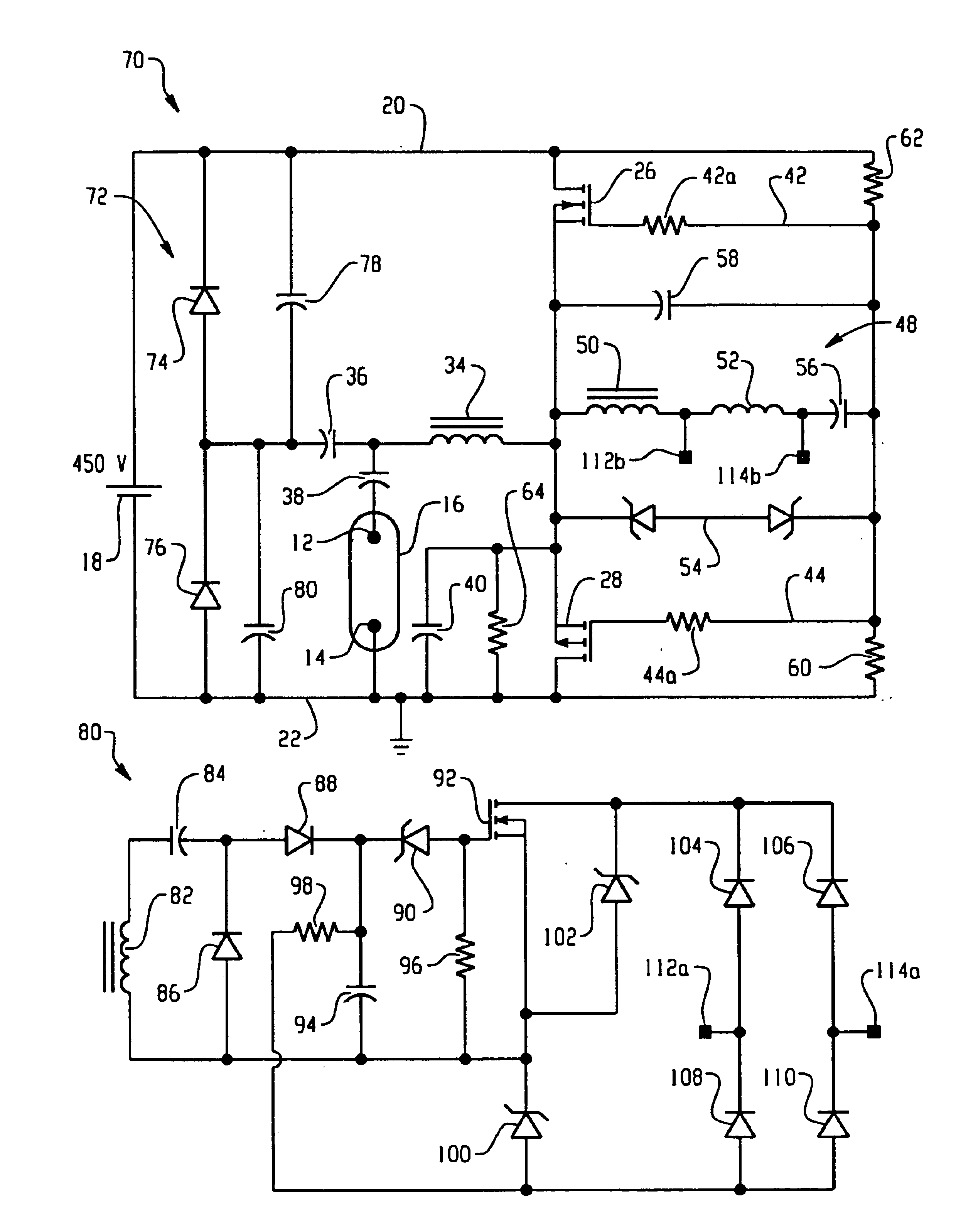

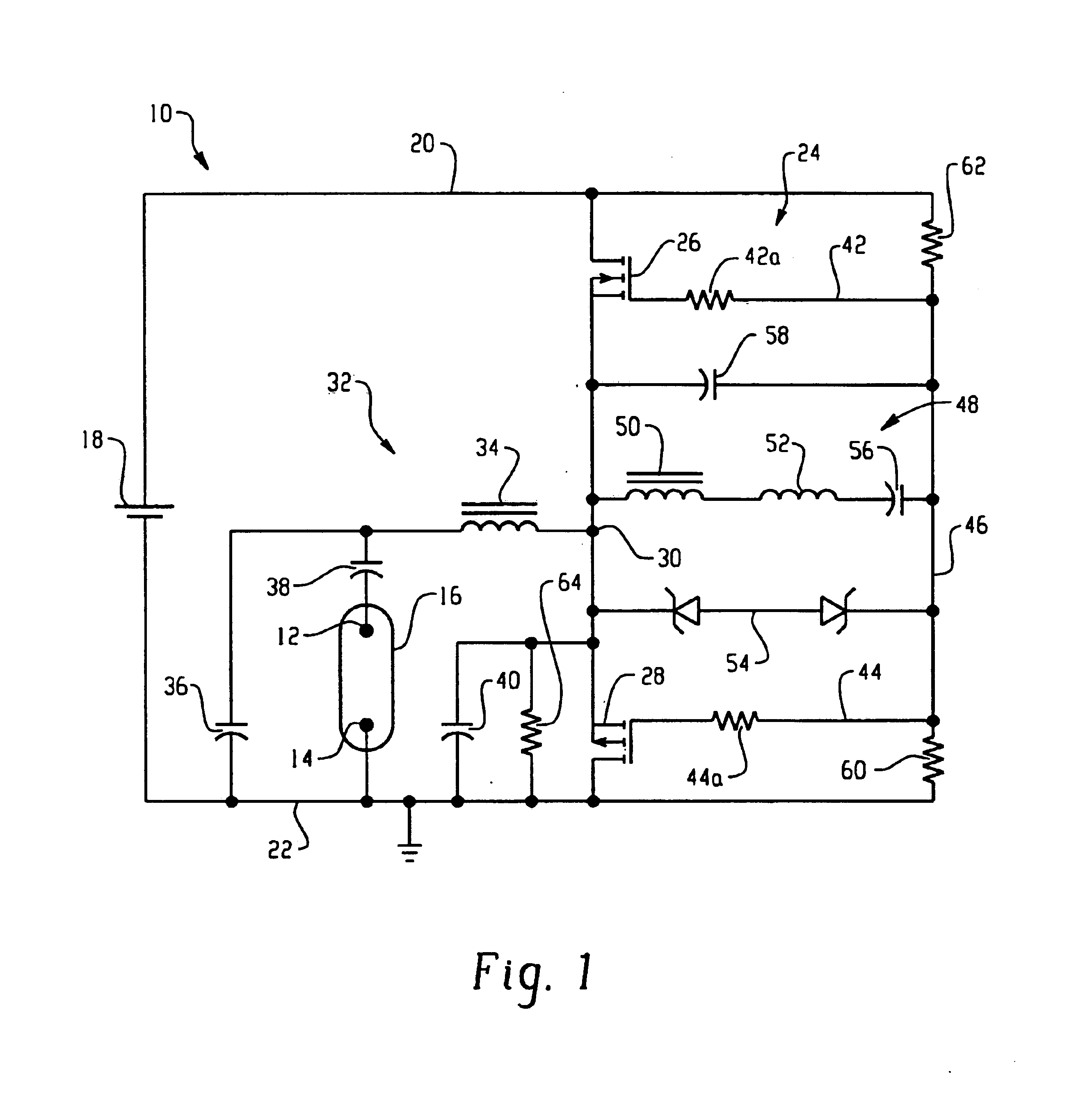

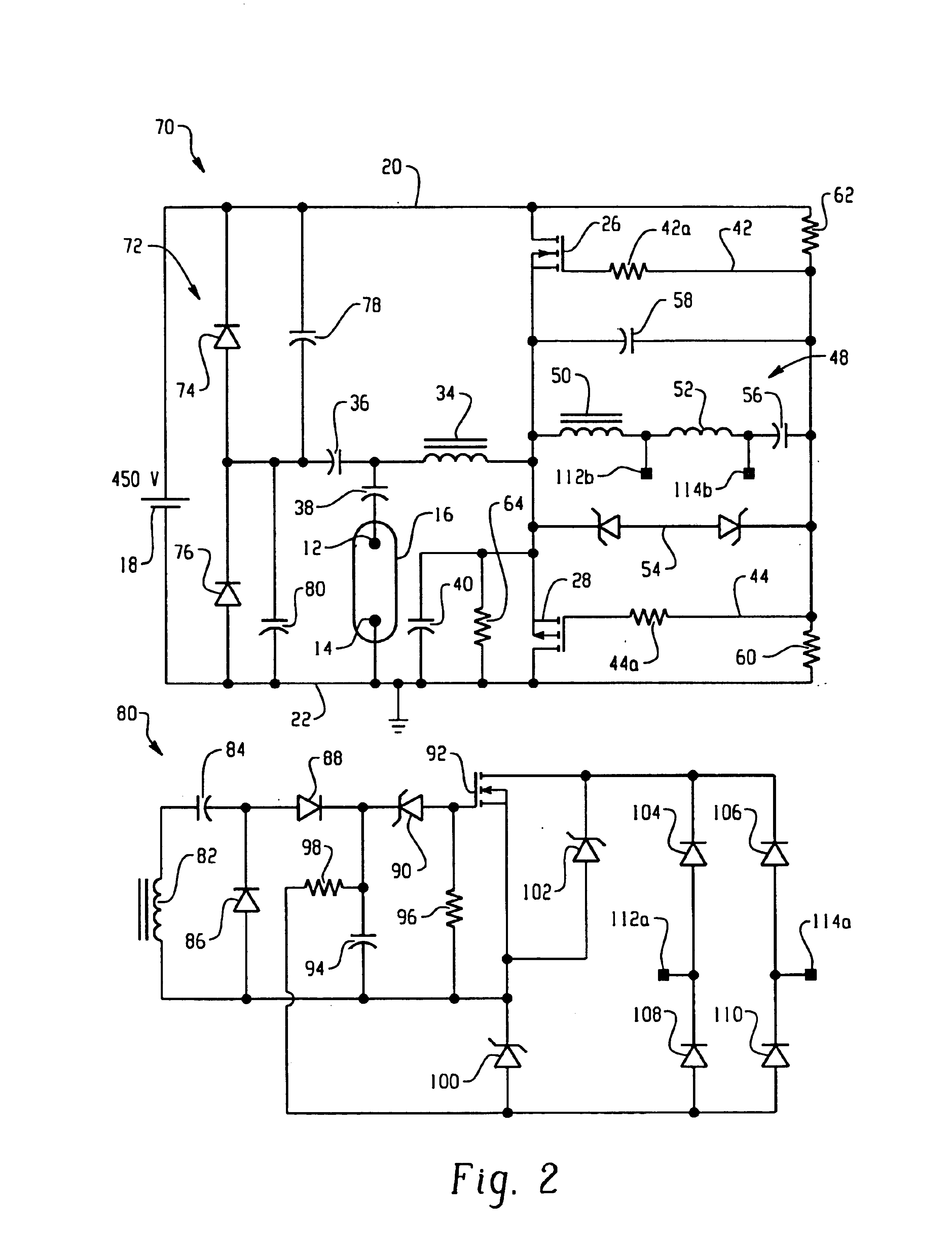

Continuous mode voltage fed inverter

InactiveUS6867553B2Electric light circuit arrangementElectric discharge lampsComplementary pairFeedback circuits

In accordance with one aspect of the present application, a continuous mode voltage fed inverter includes a resistor starting network configured to start a charging of the inverter. A resonant feedback circuit is configured to generate an oscillating signal following the starting of operation of the circuit by the resistor starting network. A complementary switching network has a pair of complementary common source connected switches configured to receive the oscillation signal generated by the resonant feedback circuit, wherein the oscillation signal determines a switching rate of the complementary pair of switches. A clamping circuit is configured to maintain an inverter current in an inductive mode, wherein the inductive current lags voltage across the pair of complementary common source connected switches. A fold-back circuit is connected, in one embodiment, to the complementary switching network to provide a two-level clamping action. A first-level clamps the output voltage sufficient to permit a starting of the lamp. A second level of the two-level clamping arrangement of the fold-back circuit clamps the output voltage to protect the inverter from overheating when a lamp is removed from the circuit.

Owner:GENERAL ELECTRIC CO

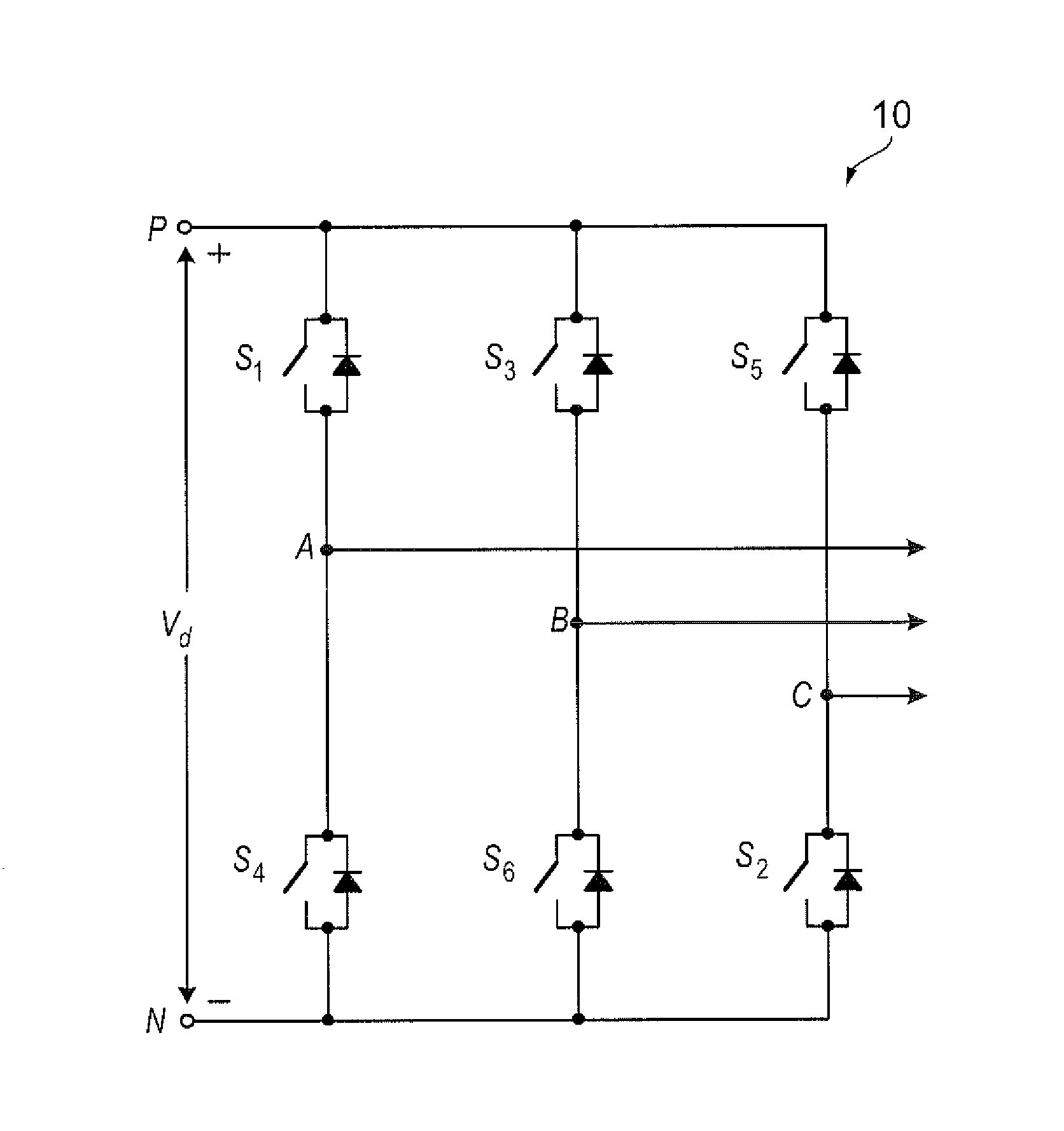

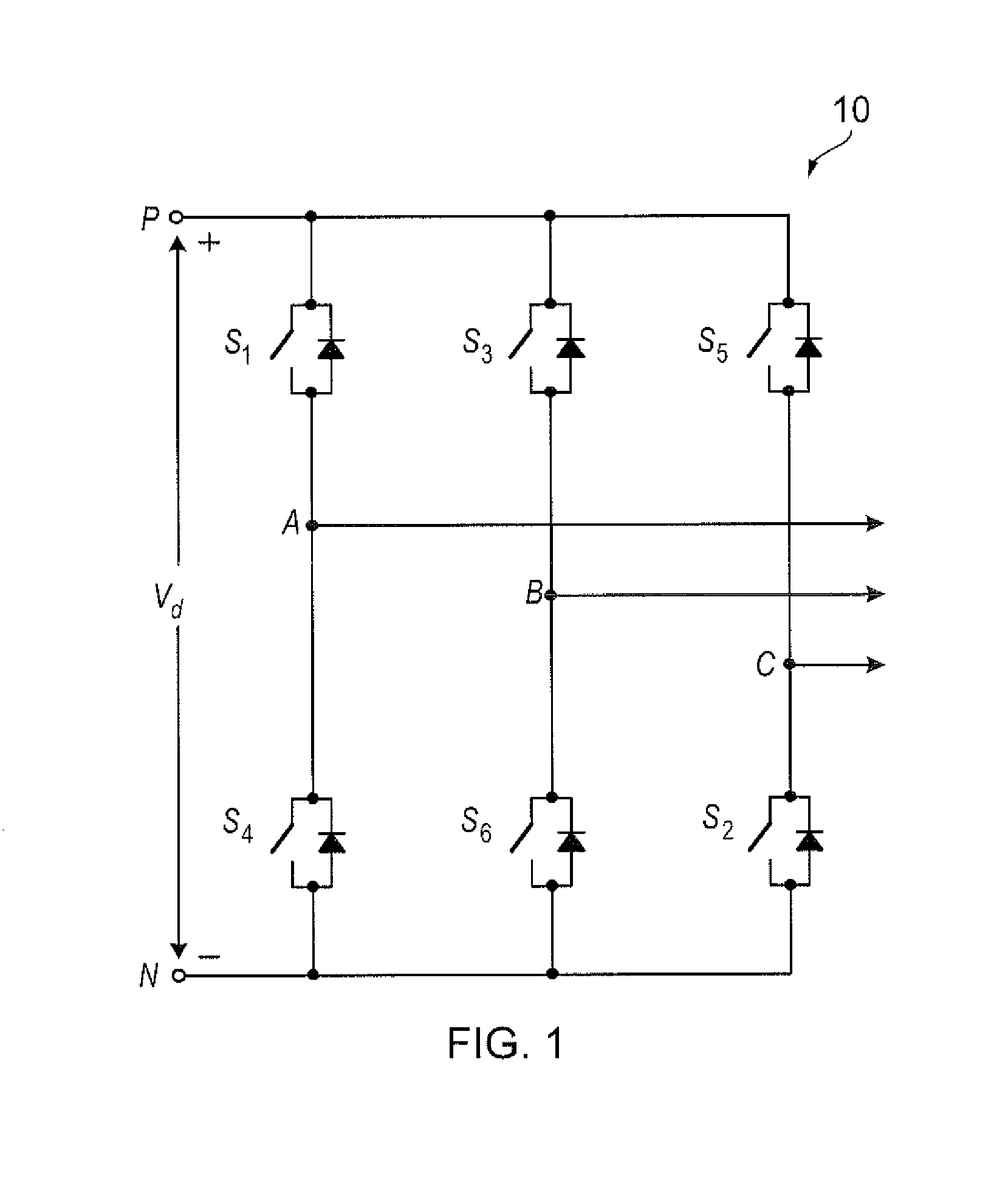

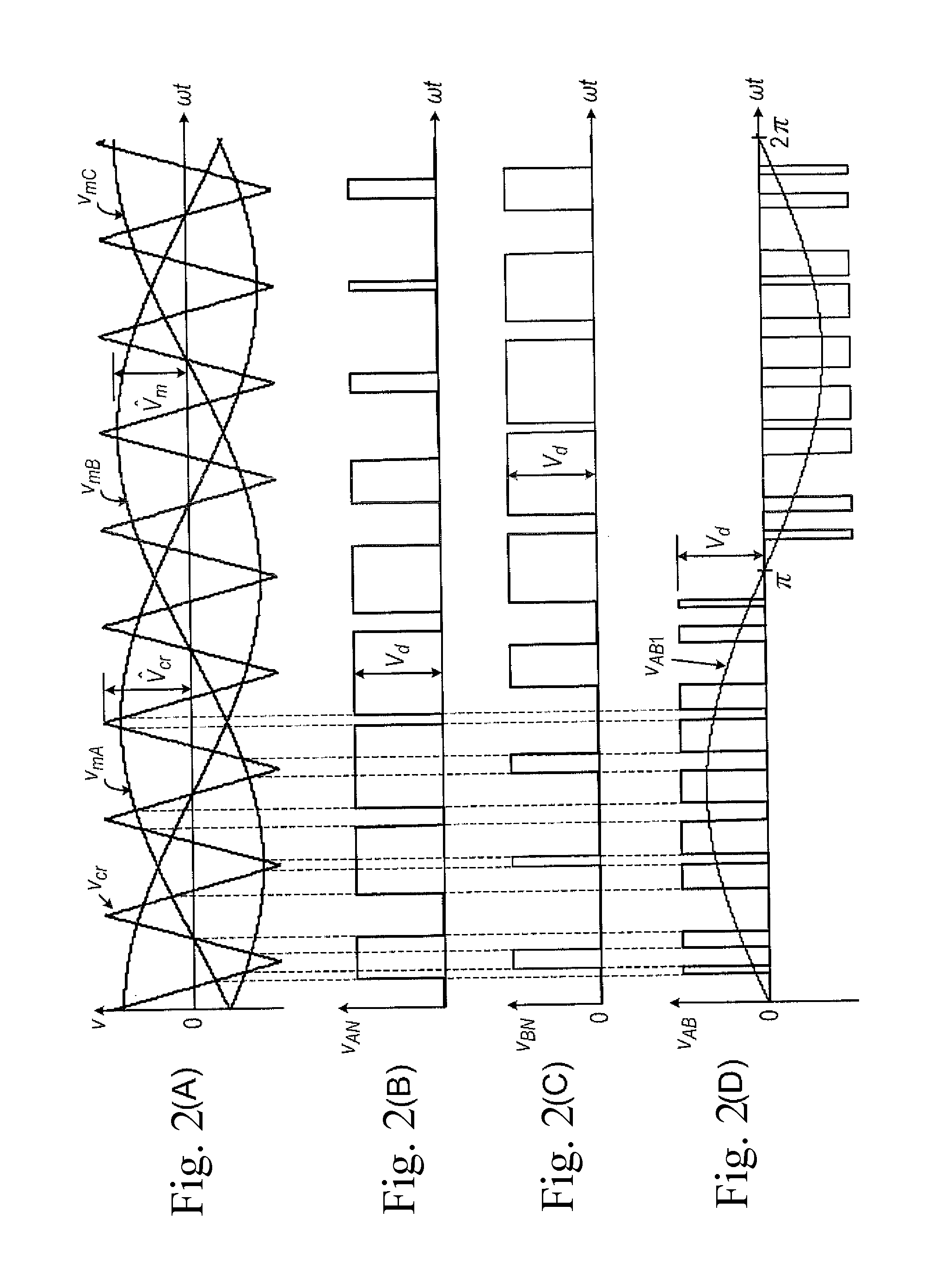

Inverter control method

InactiveUS20160315558A1Improve reliabilityImprove availabilityAc-dc conversionPower inverterPower flow

A method of controlling an inverter, in which the inverter includes a single-phase inverter arrangement comprising a complementary pair of power switches, comprises the steps of:controlling the complementary pair of power switches with a modulating signal to output an AC signal;judging which of the power switches in the complementary pair of power switches is at a higher temperature;determining the magnitude and sign of a DC offset signal to apply to the modulating signal to reduce the total current in the power switch judged to be at the higher temperature; andapplying the DC offset signal to the modulating signal.

Owner:ROLLS ROYCE PLC

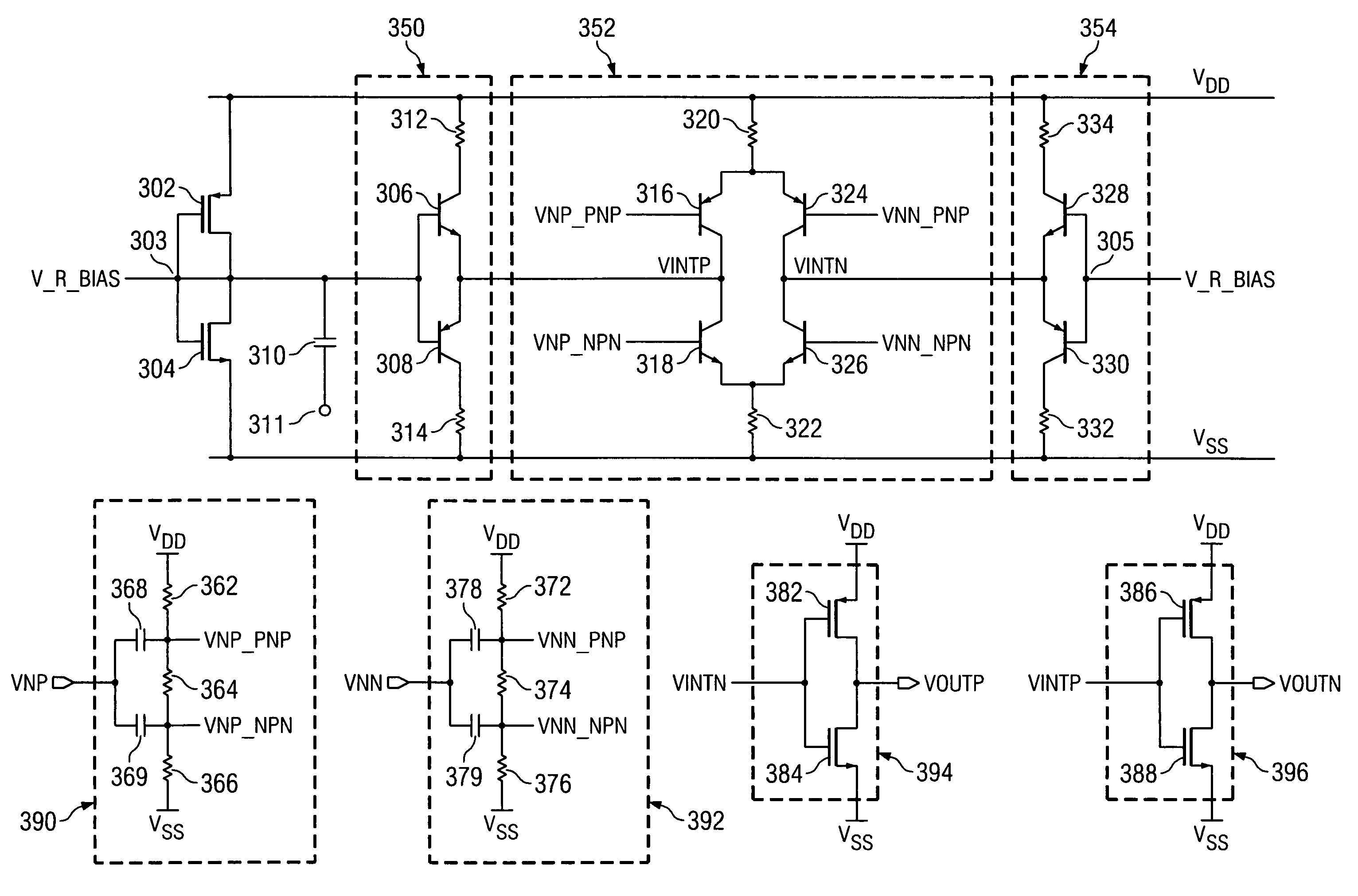

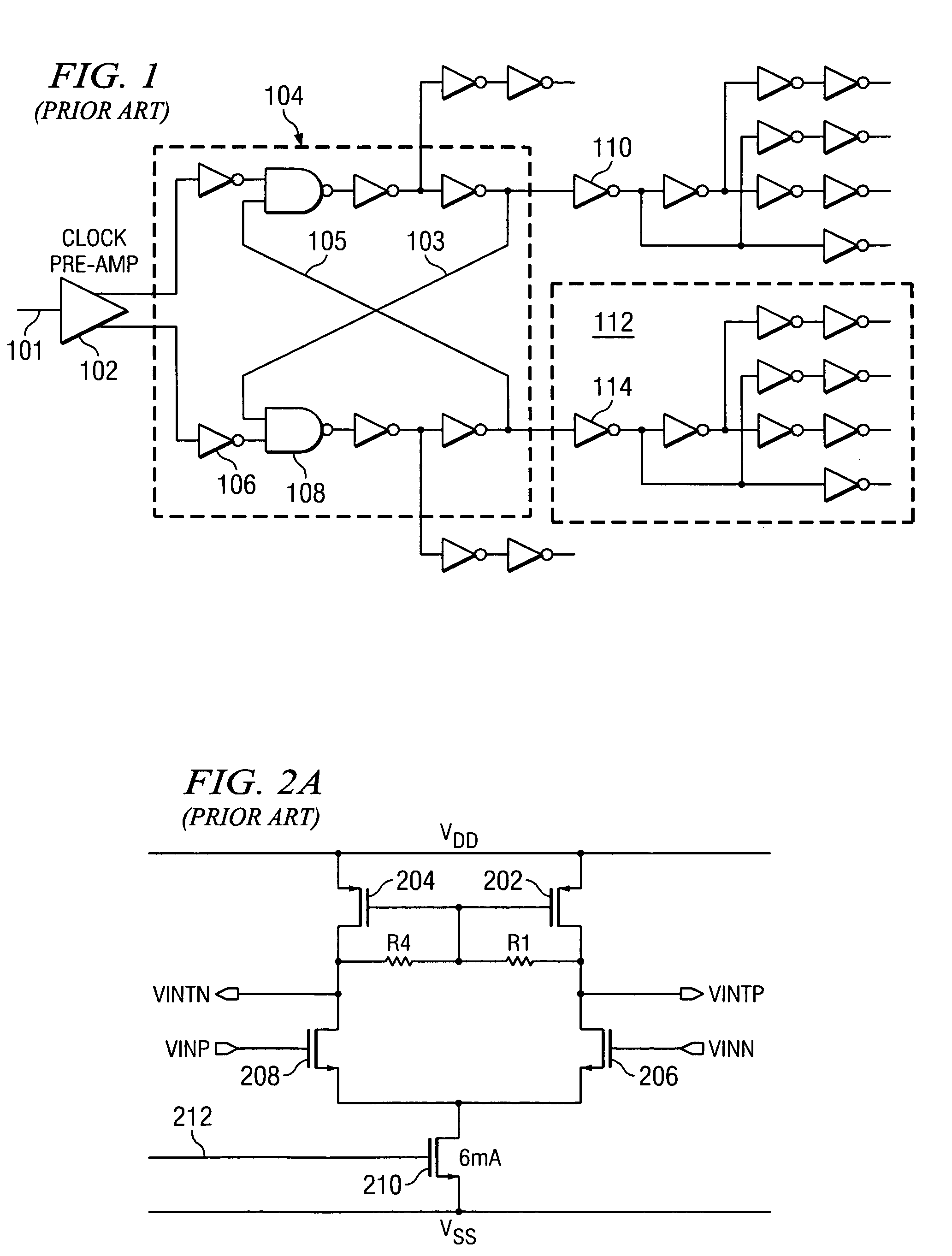

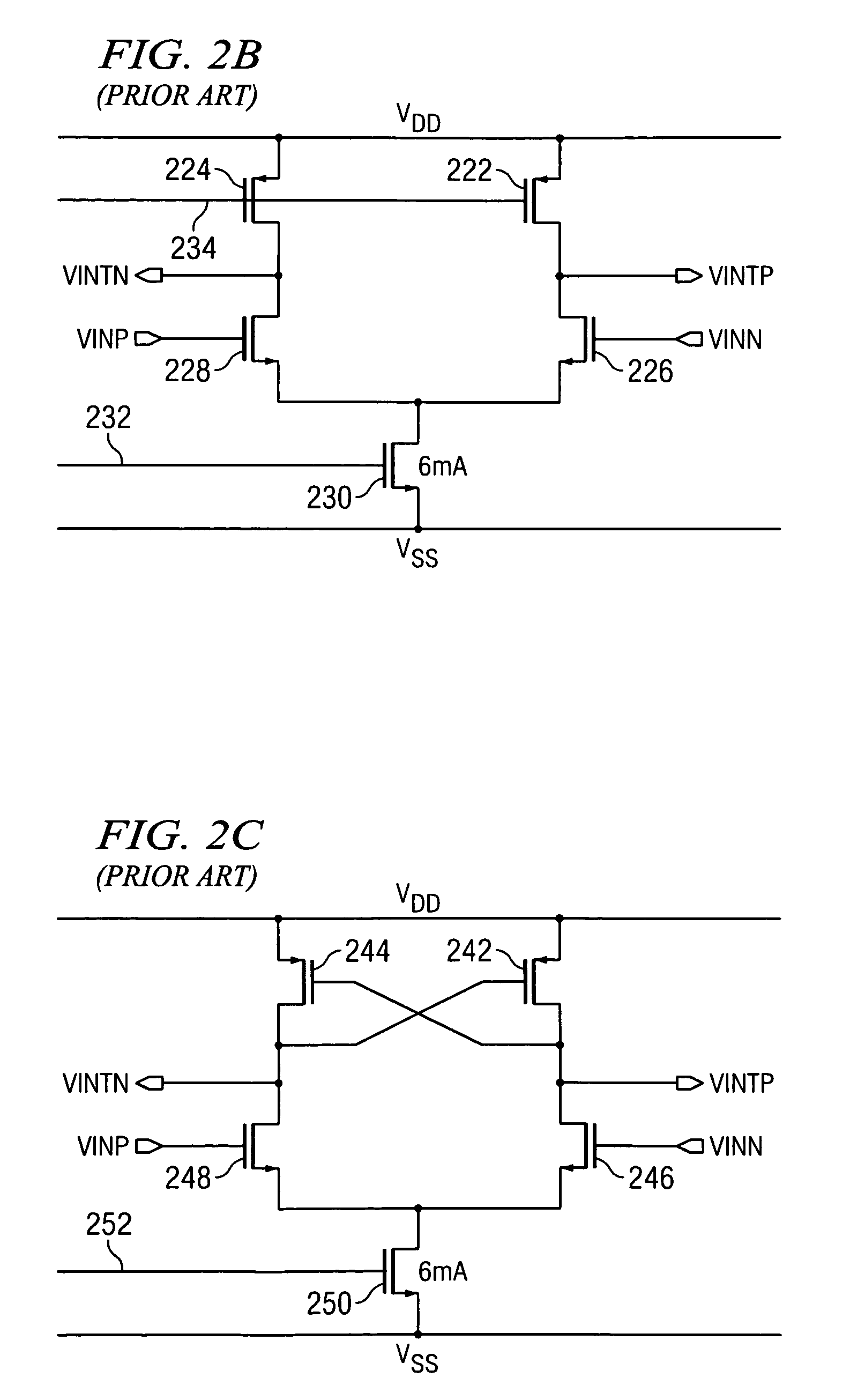

Method and apparatus for improved clock preamplifier with low jitter

ActiveUS7345528B2Avoid saturationControl swingAmplififers with field-effect devicesArbitary function generatorsMOSFETPower inverter

A clock signal preamplifier comprises complementary pairs of differentially coupled transistors, with an output signal coupled to an inverter further comprising a totem-pole arrangement of complementary MOSFET transistors. The input signal to the preamplifier is typically sinusoidal, and the output signal is rectangular. Preferably, the differentially coupled transistors are bipolar, and a pair of diode clamper circuits with bipolar transistors is preferably coupled to the complementary pairs of differentially coupled transistors. A reference voltage source is coupled to the control terminals of the clamper transistors. A reference voltage source, which preferably comprises a totem-pole arrangement of complementary MOSFET transistors with its output node is coupled to its input node, provides a reference voltage for the diode clamper circuits. Preferably, MOSFET transistors of the reference voltage source and MOSFET transistors of like kind of the inverter are configured to have substantially identical threshold voltages.

Owner:TEXAS INSTR INC

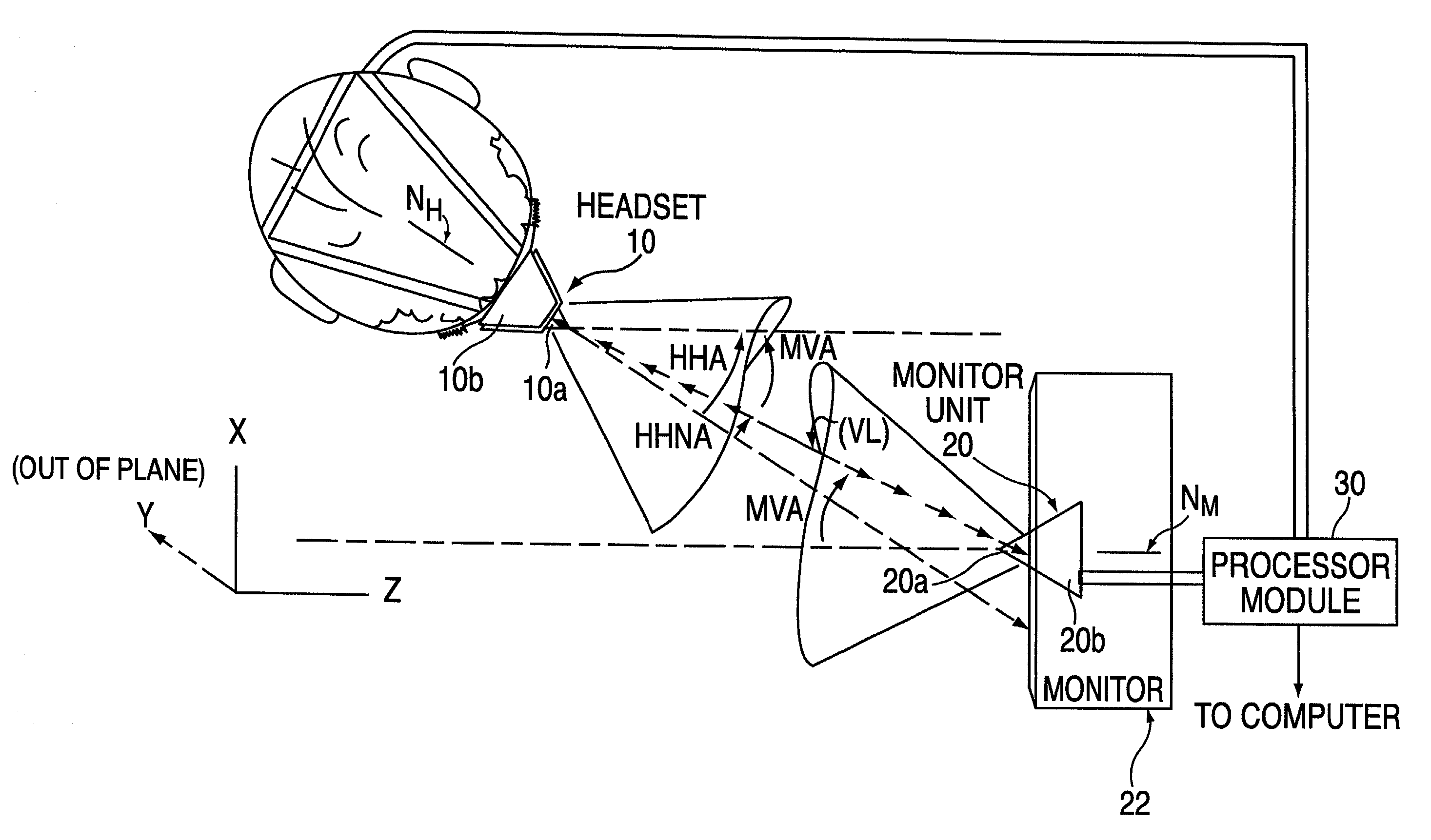

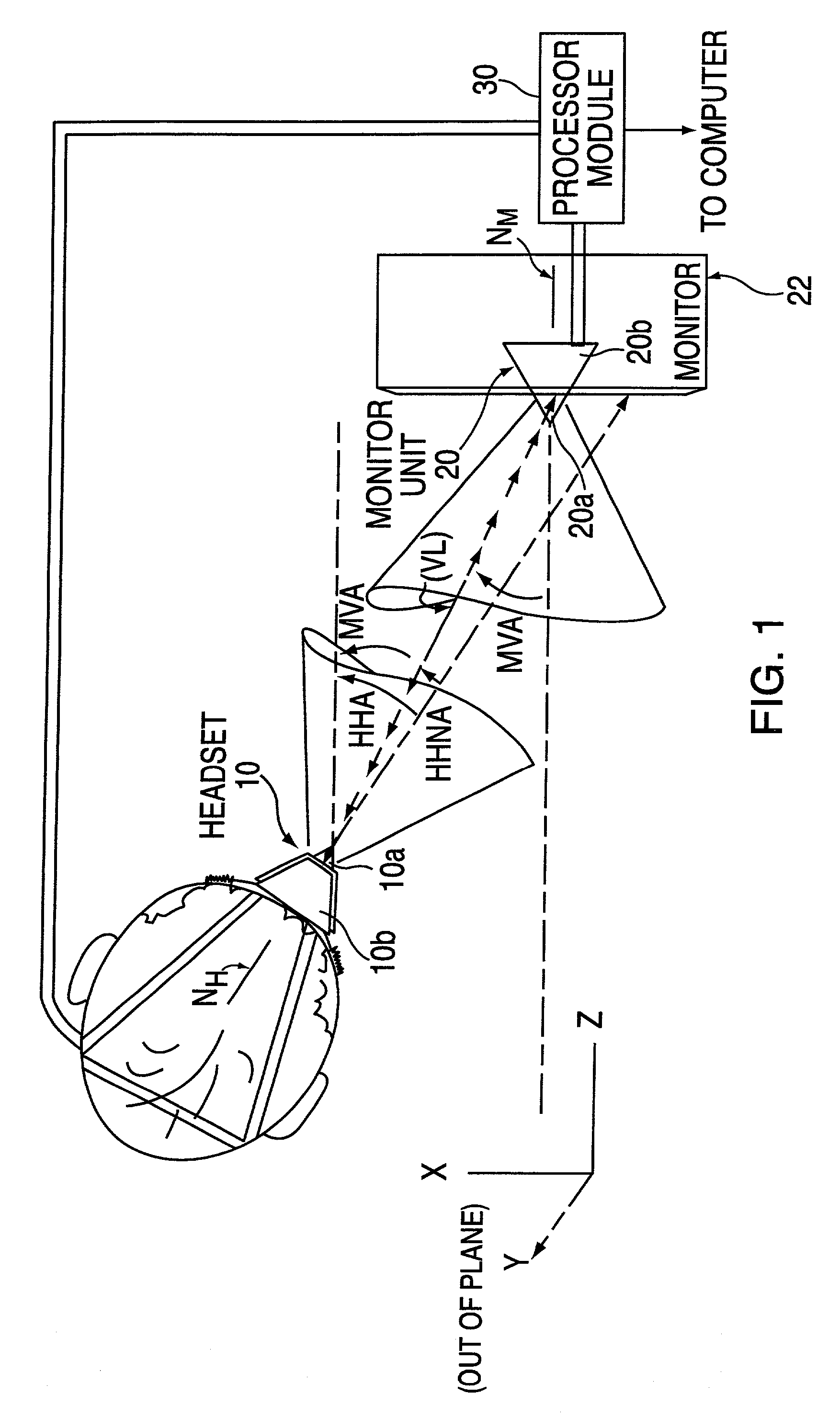

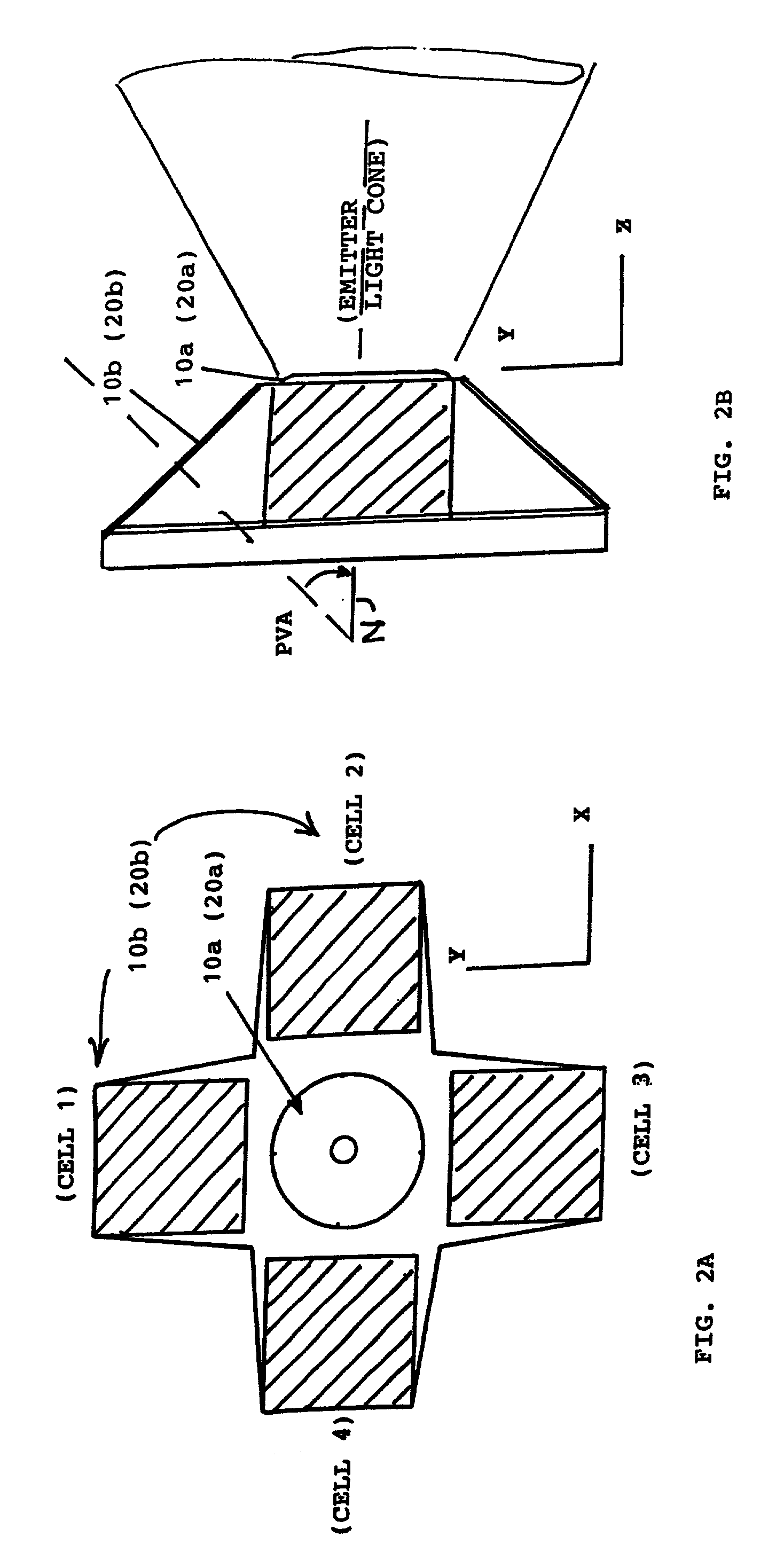

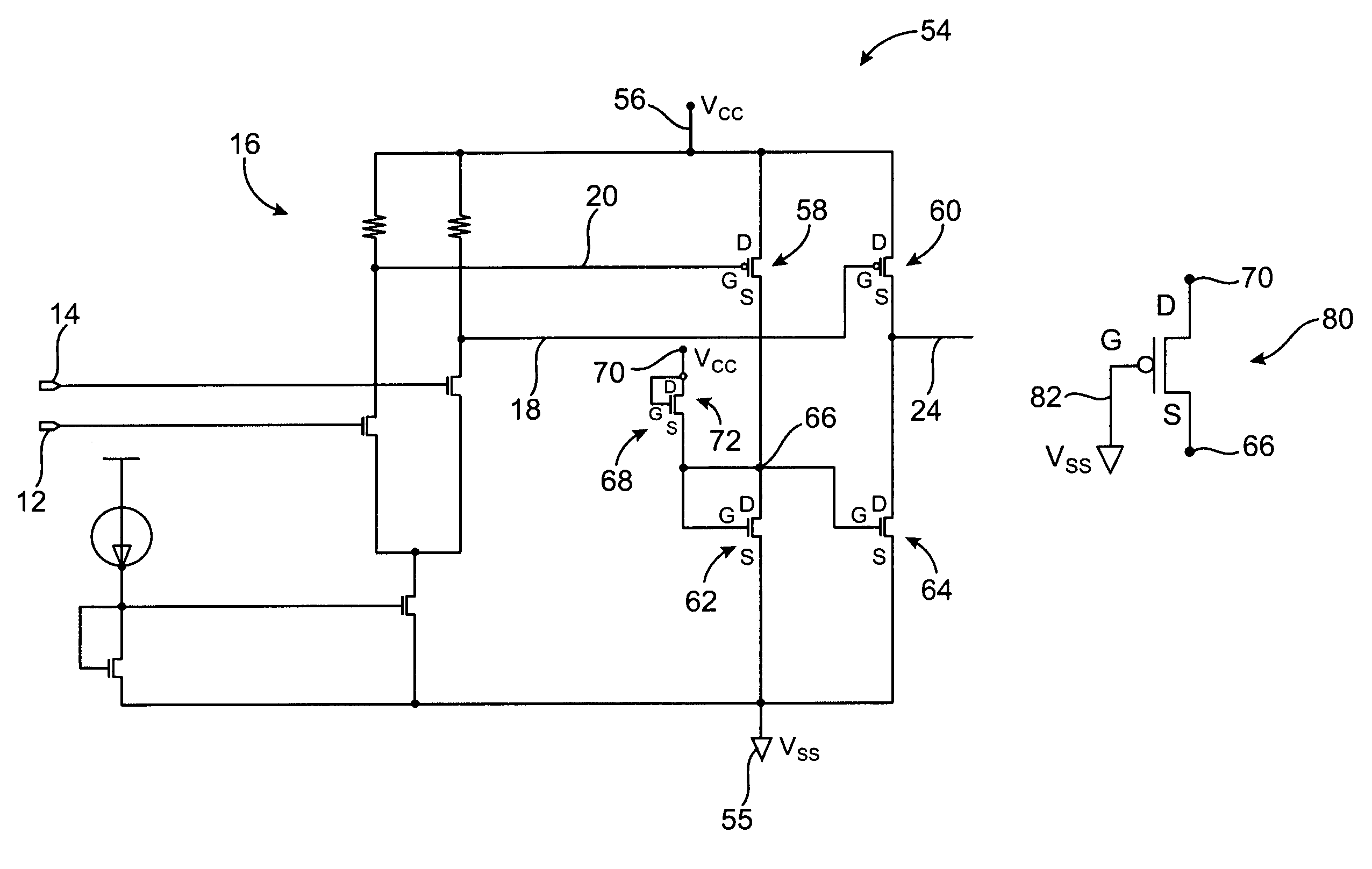

3D cursor or joystick device

InactiveUS7405726B2Easy to manufactureLow costInput/output for user-computer interactionCosmonautic condition simulationsAirplaneDetector cell

A 3D cursor or joystick device and control method employs a complementary pair of emitter / detector units, one worn on a part of a user's body (e.g., the head) and the other mounted in a stationary position on a display monitor facing the user. Each unit has an array of photovoltaic (PV) cells centered on a normal axis and an infrared diode for emitting a light beam on the normal axis. Each photodetectors array receives the infrared beam from the other unit and provides output signals representing the light intensities of the received beam on the PV cells. The PV cell response signals of the complementary units are used together to calculate the position and angular orientation of the user-worn unit relative to the stationary unit. The position and angle values are used by a software device driver installed on a computer to control 3D navigation functions of the associated application program on the computer. The system can be used for playing interctive 3D games, and also used for hands-free control in a wide range of other applications and environments, such as to control flight motions in a simulator or cockpit of an aircraft, or the command center of a naval vessel, spaceship, land vehicle, etc., for disabled persons to provide hands-free input to a computer, motorized wheelchair, prosthetic device, etc., and for controlling various functions in an industrial environment, such as guiding machine-assisted movement, or in CAD design, architectural, medical graphics, virtual reality, and other applications.

Owner:MAUI INNOVATIVE PERIPHERALS

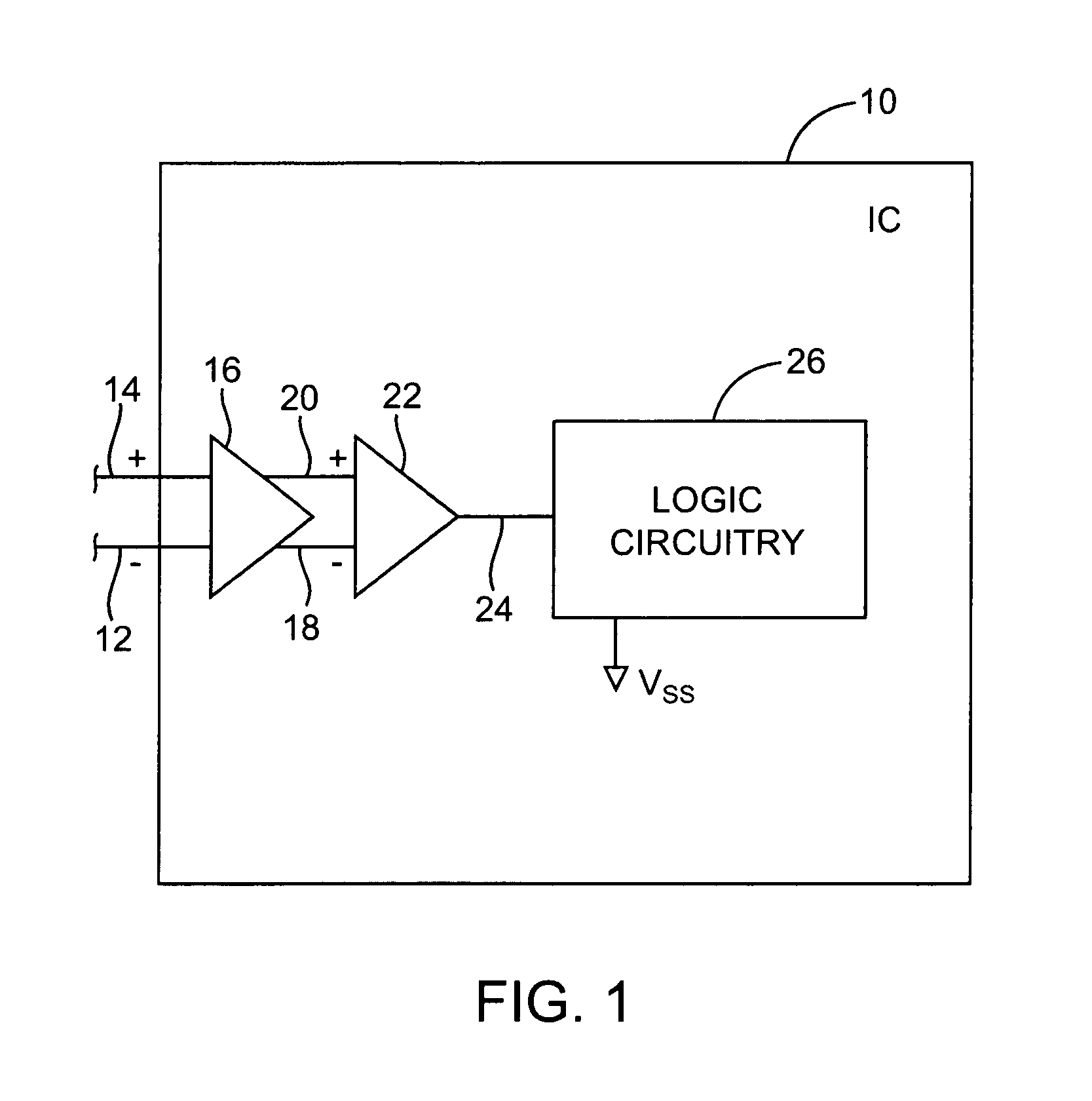

Low-jitter differential-to-single-ended data conversion circuits

InactiveUS7053671B1Stable voltageStable currentMultiple input and output pulse circuitsInstant pulse delivery arrangementsDigital dataTelecommunications link

Circuitry is provided for converting differential digital data to single-ended digital data. Differential data signals have complementary pairs of signals that are referenced to each other. Single-ended signals are referenced to ground. The circuitry can be used on an integrated circuit to convert incoming differential data from a high-speed communications link to single-ended data for processing by internal logic on the integrated circuit. The operation of the circuitry can be stabilized using load circuitry that reduces temperature effects and jitter in the single-ended data.

Owner:ALTERA CORP

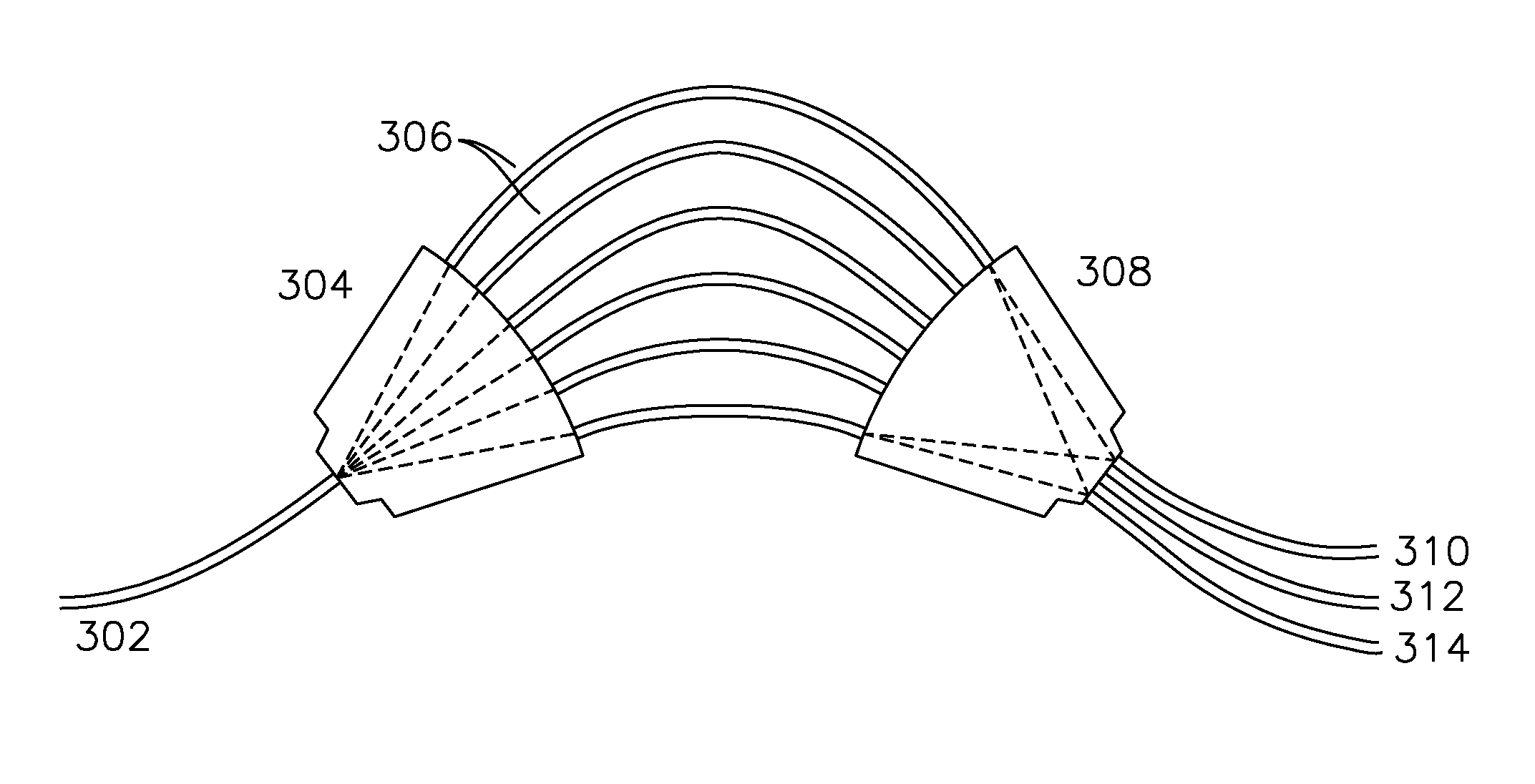

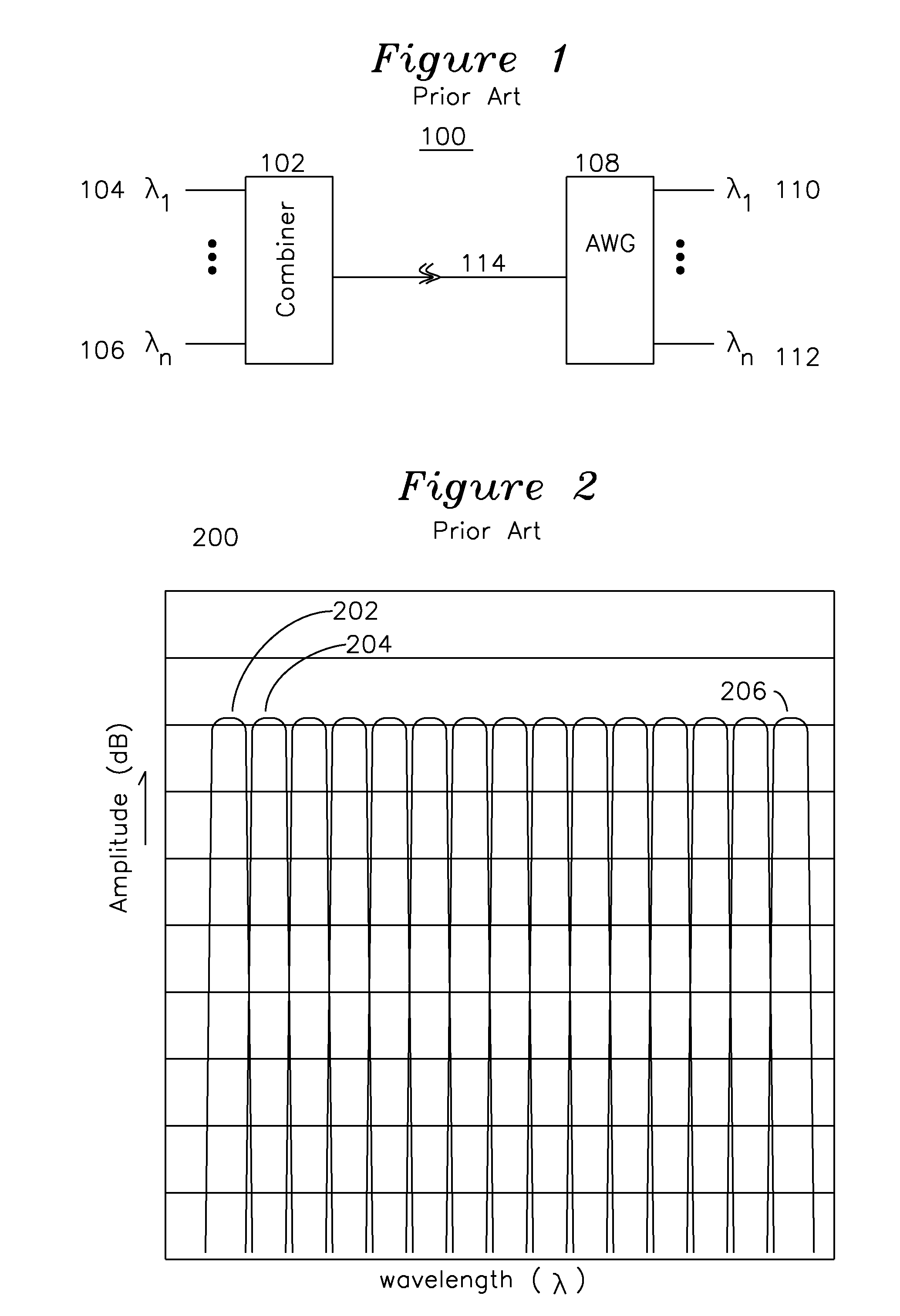

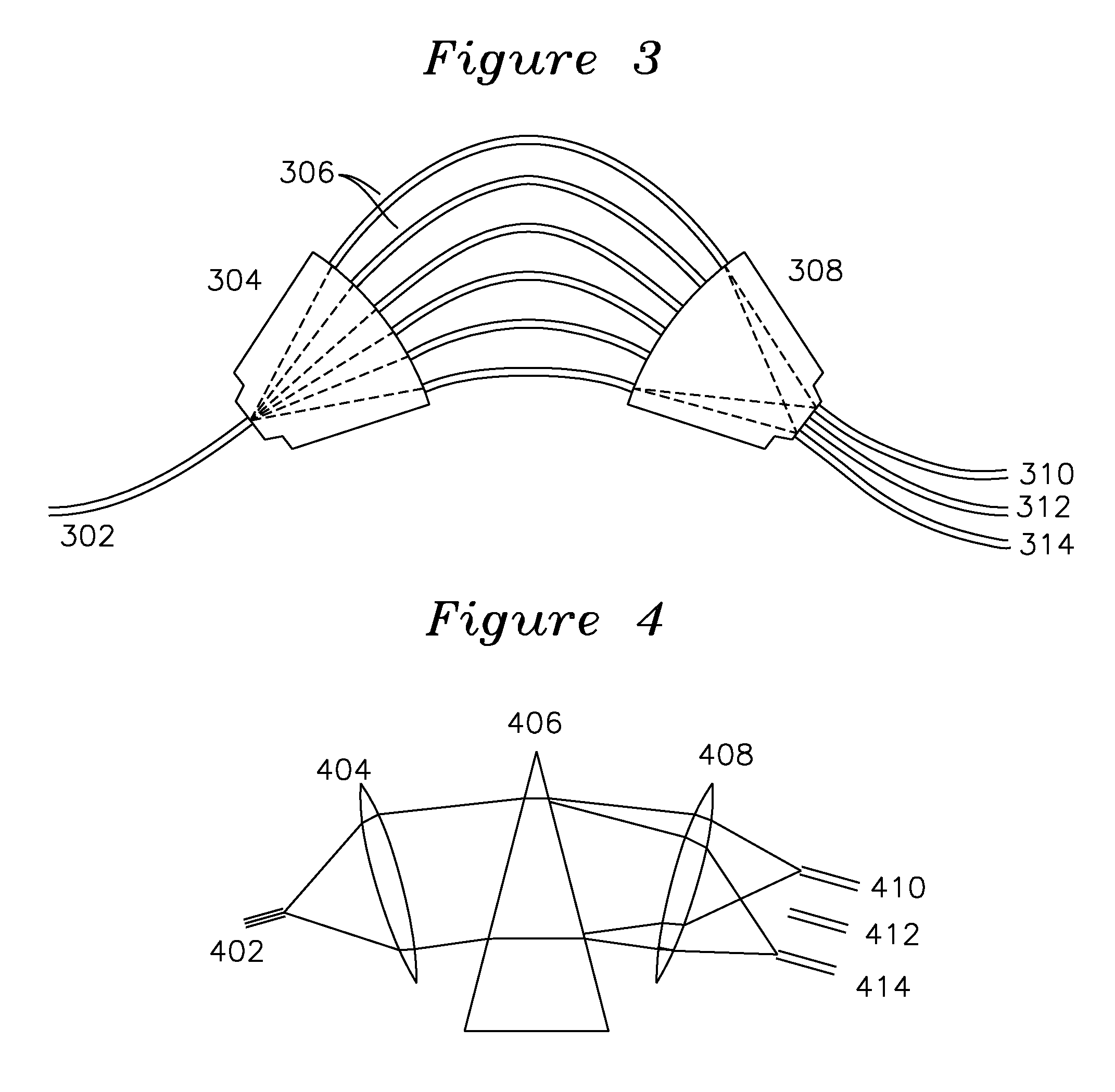

AWG filter for wavelength interrogator

A wavelength interrogator is coupled to a circulator which couples optical energy from a broadband source to an optical fiber having a plurality of sensors, each sensor reflecting optical energy at a unique wavelength and directing the reflected optical energy to an AWG. The AWG has a detector coupled to each output, and the reflected optical energy from each grating is coupled to the skirt edge response of the AWG such that the adjacent channel responses form a complementary pair response. The complementary pair response is used to convert an AWG skirt response to a wavelength.

Owner:INTELLIGENT FIBER OPTIC SYST

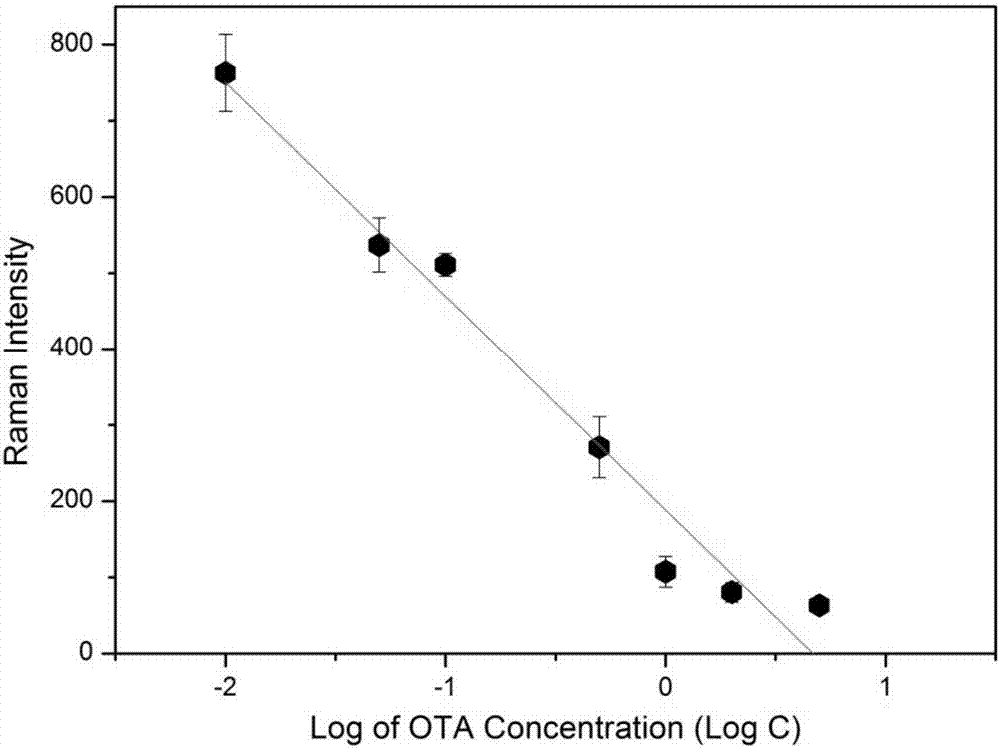

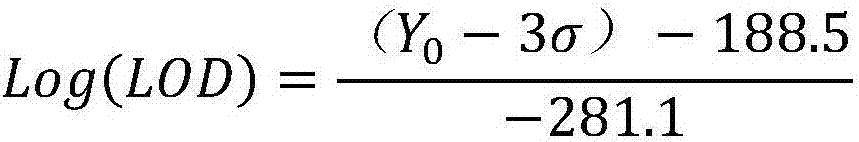

Construction method and application of SERS aptasensor based on nano-assembly structure

The invention discloses a construction method and application of SERS aptasensor based on nano-assembly structure. The method comprises the following steps: respectively modifying surfaces of gold nano-rod and gold nano-particle with two kinds of DNA complementary with an ochratoxin A aptamer segment part to form two nano-probes; then assembling an assembly nano-structure under complementary pairing connection of the two nano-probes and the DNA aptamer, and labeling a Raman beacon molecule on the assembly nano-structure; and adding a solution of a substance for detecting, and detecting the concentration of the assembly nano-structure by utilizing the fact that the SERS signal intensity of the assembly nano-structure is influenced by the substance for detecting. By adopting the method, reaction in a liquid environment is uniform, the detection has high sensitivity and high specificity, only one-step reaction is required, and the operation is simple.

Owner:ZHEJIANG UNIV