Patents

Literature

1446results about "Instant pulse delivery arrangements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

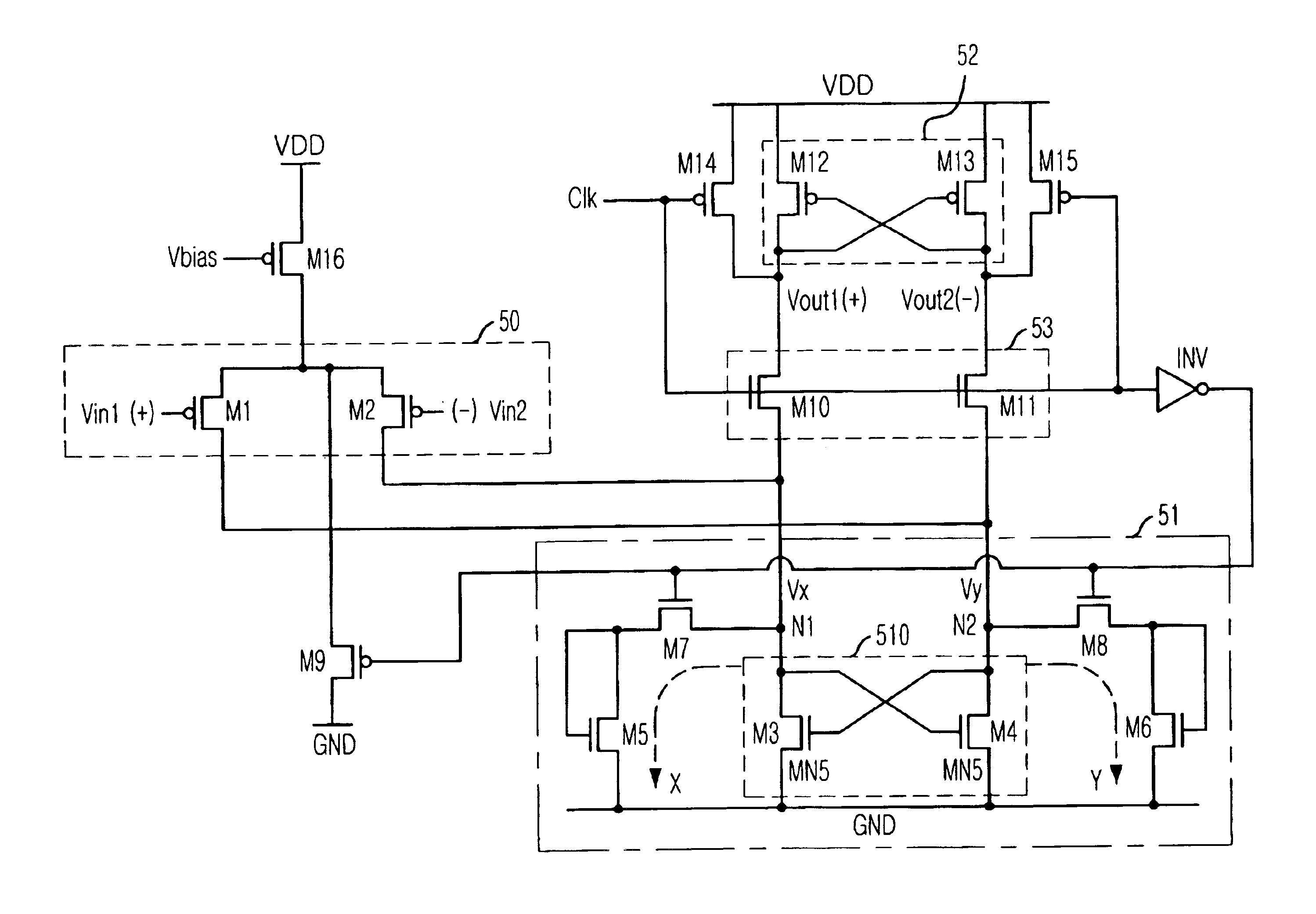

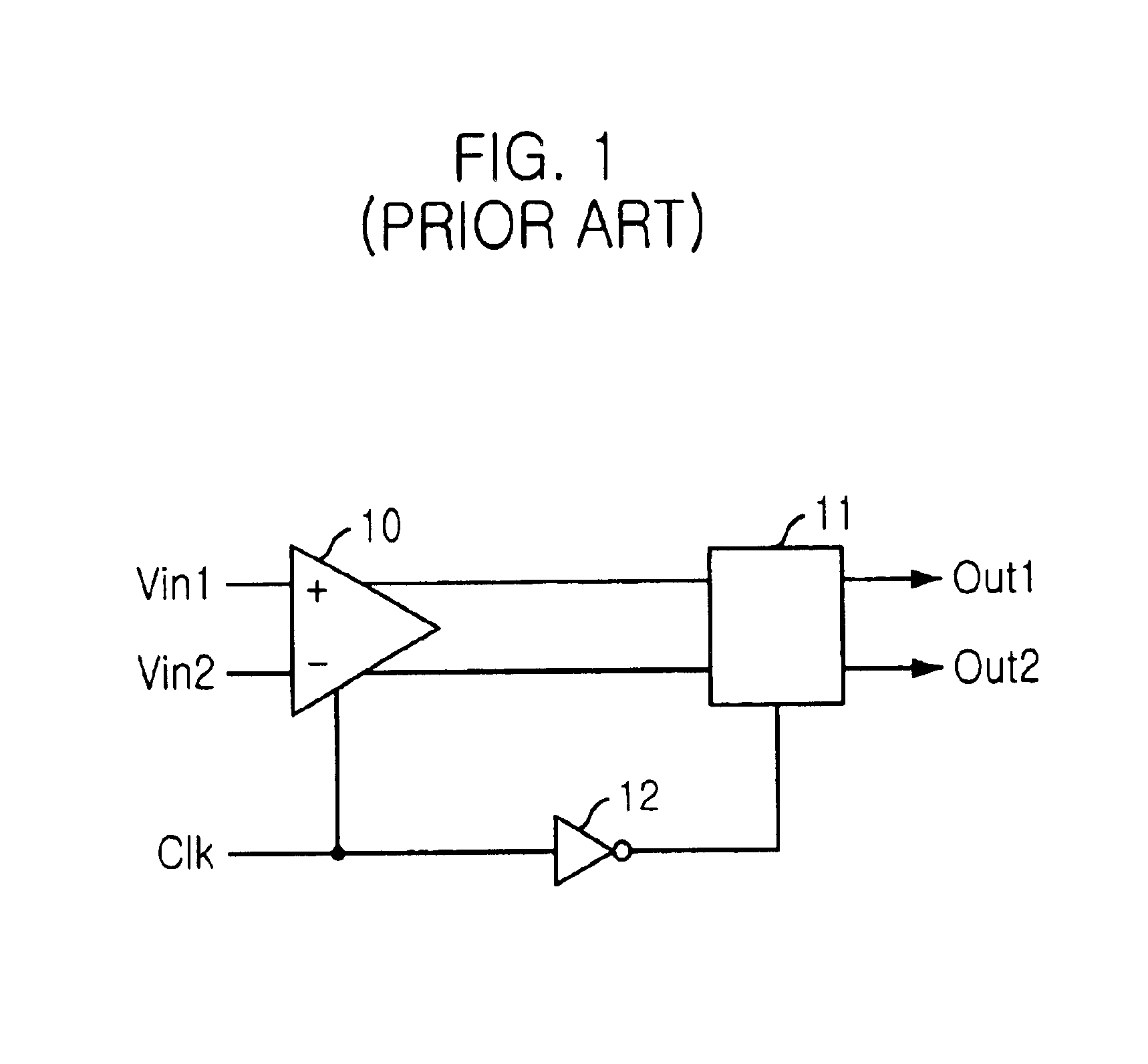

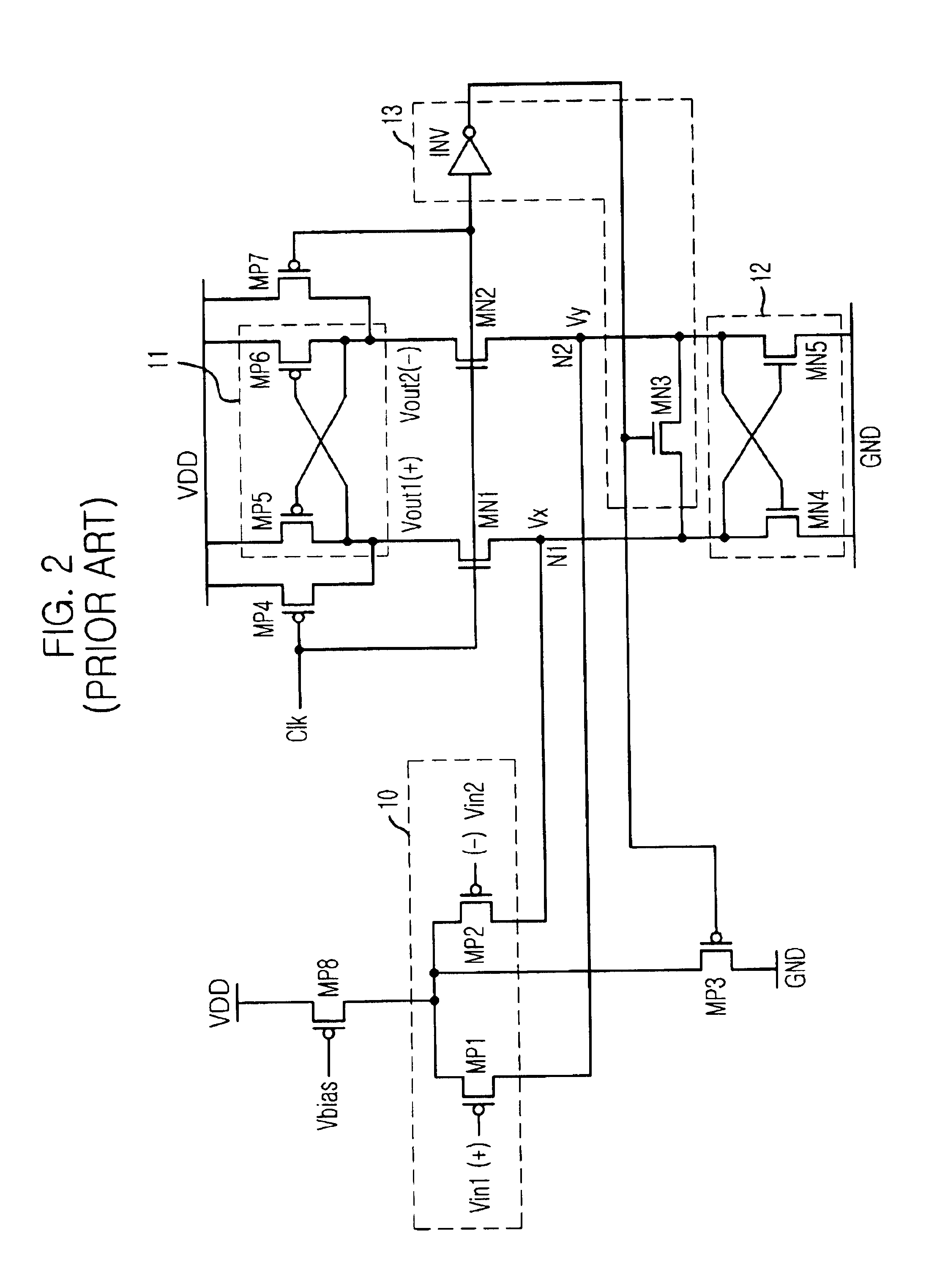

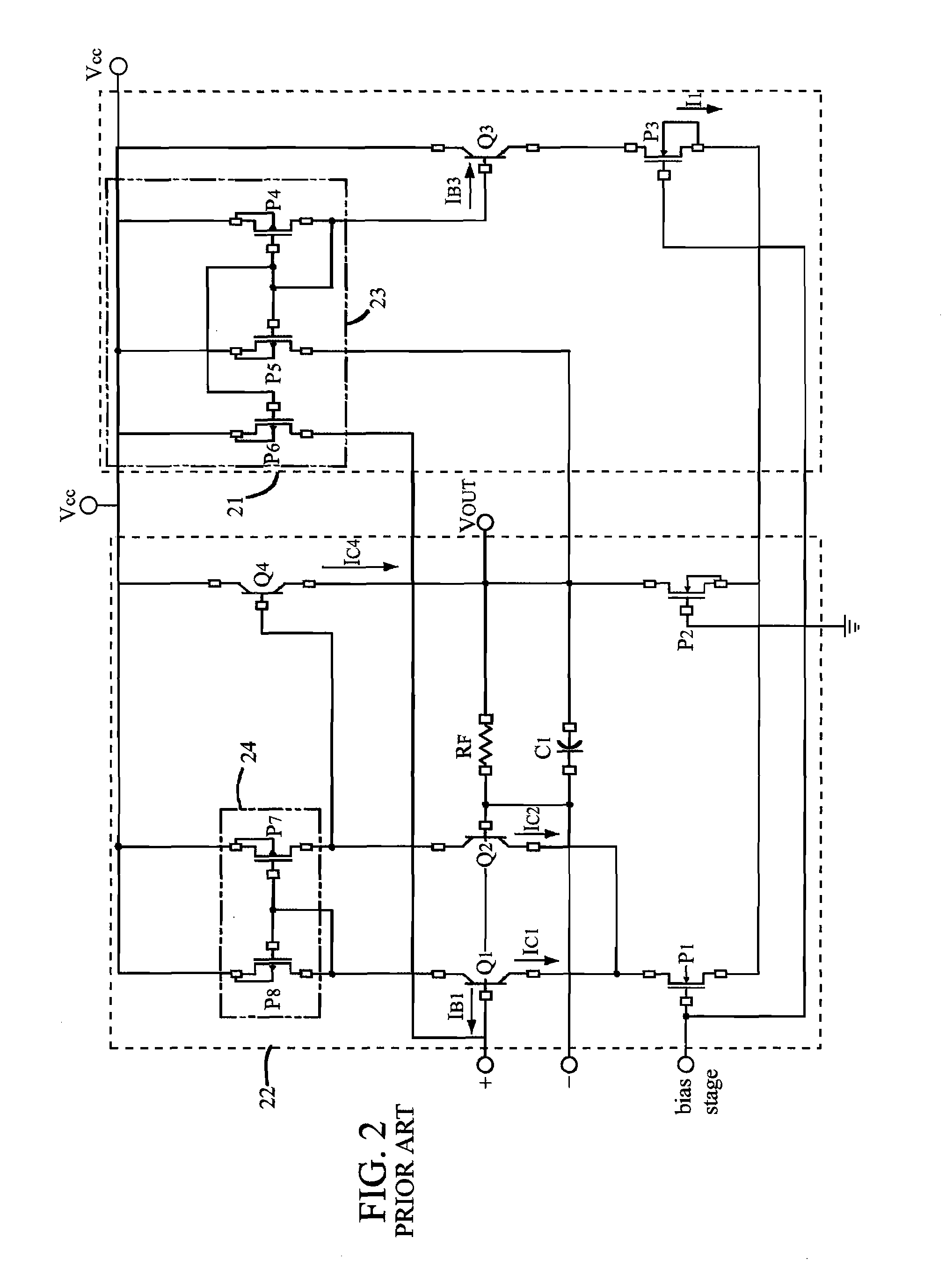

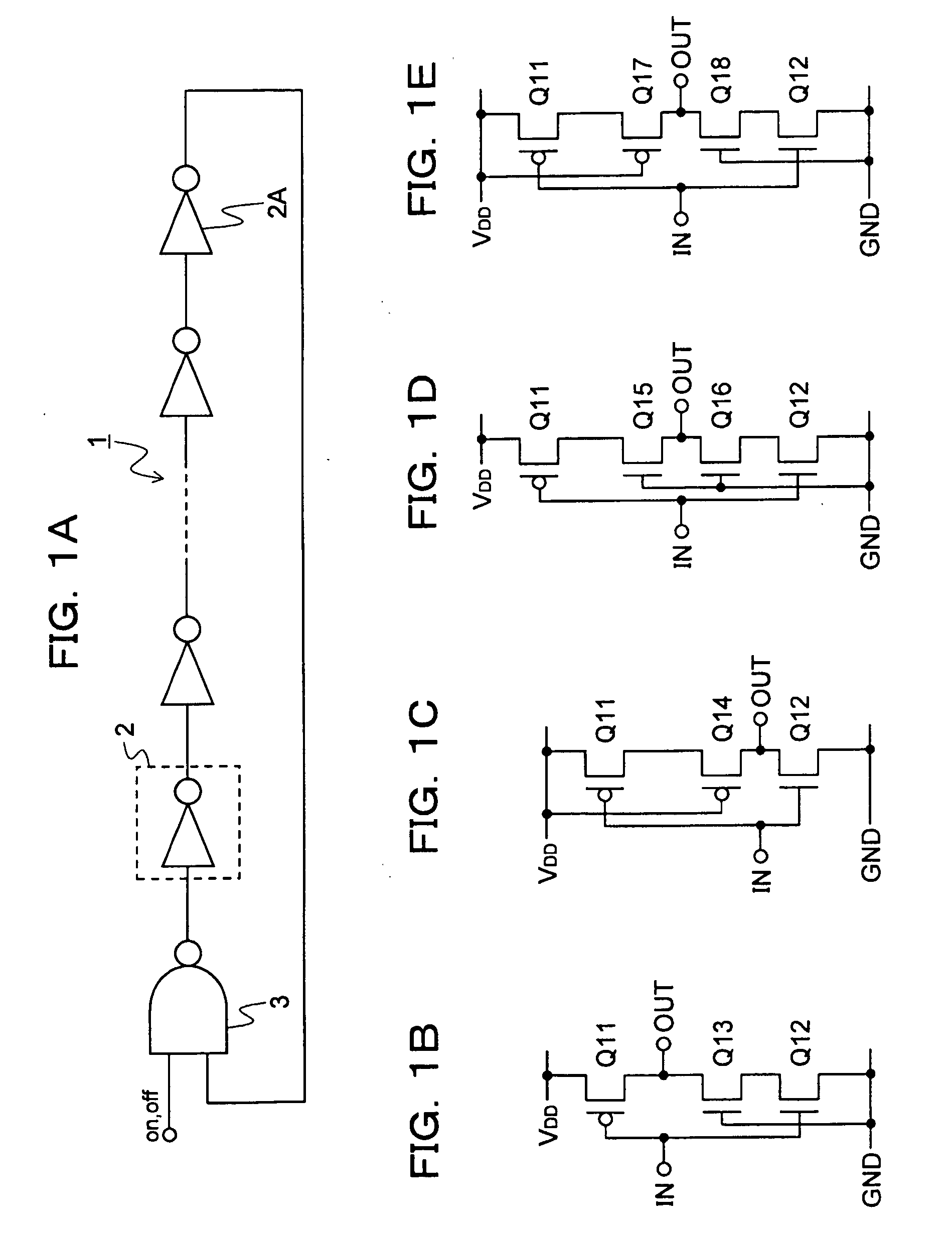

Comparison apparatus operated at a low voltage

InactiveUS6847234B2Inhibition of changes in propertiesGuaranteed uptimeElectric signal transmission systemsMultiple input and output pulse circuitsCmos comparatorLow voltage

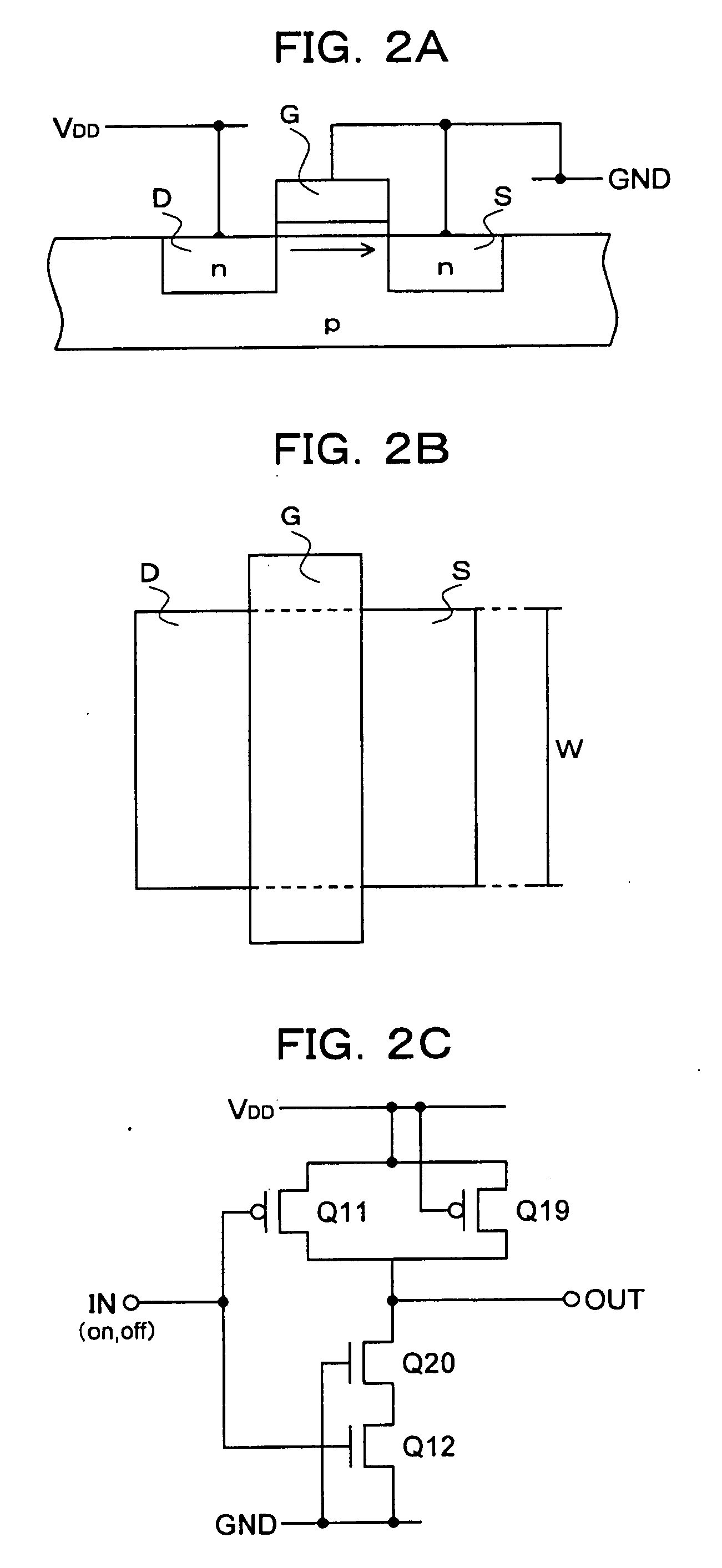

The present invention provide an CMOS comparator outputting one bit digital signal after comparing two analog input signals through alternately performing a track mode operation and latch mode operation decided by a clock signal having a constant period, including: a latching unit having the main / sub input terminal; a first switching transistor having the clock signal as a gate input and having one end coupled to main input terminal; a first load transistor diode-connected to the other end of the first switching transistor and a ground end; a second switching transistor having a gate receiving the clock signal as a gate input and one end coupled to the sub input terminal; and a second load transistor diode-connected to the second switching transistor and to the other end of the ground terminal.

Owner:KEY FOUNDRY CO LTD

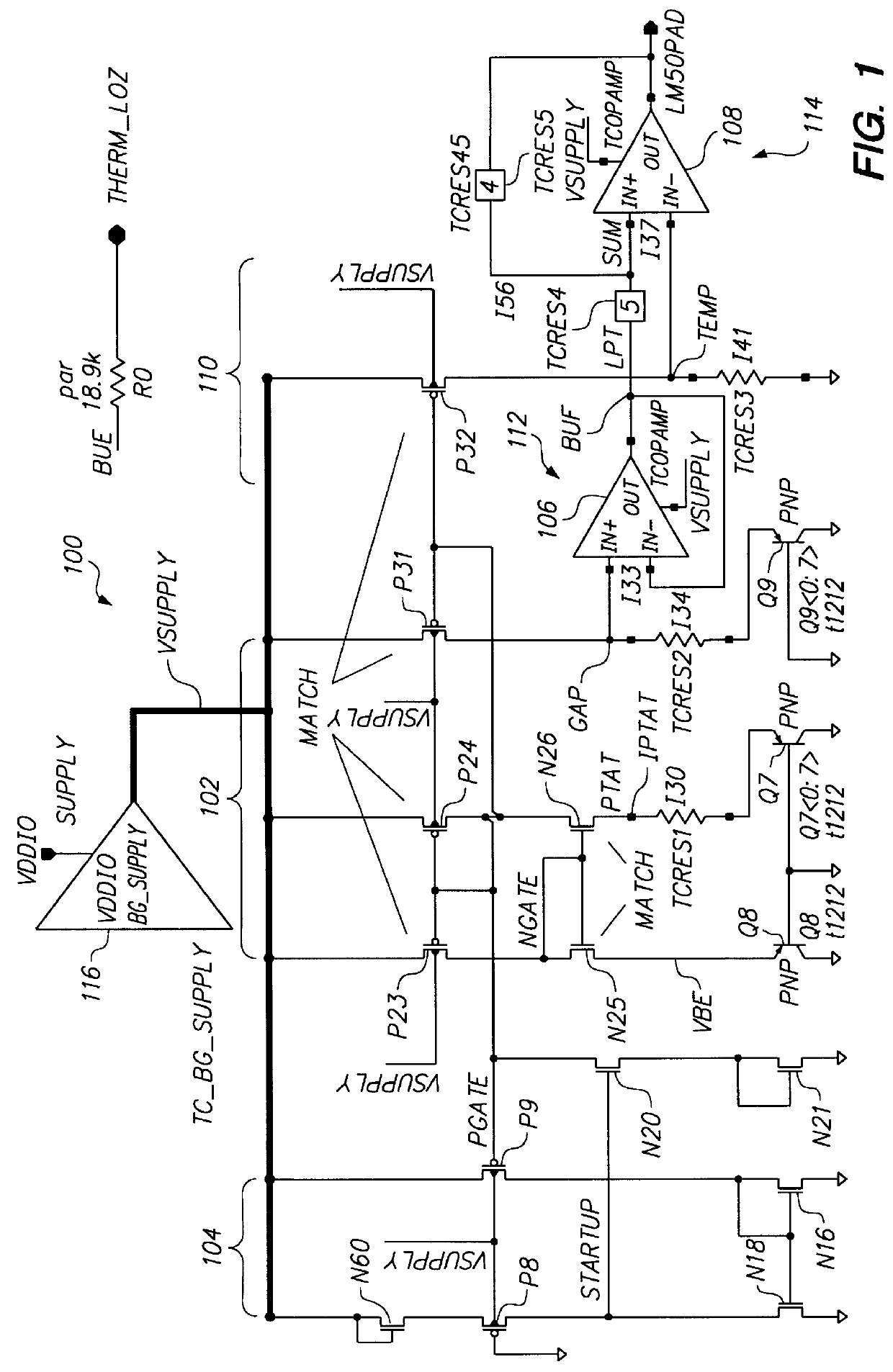

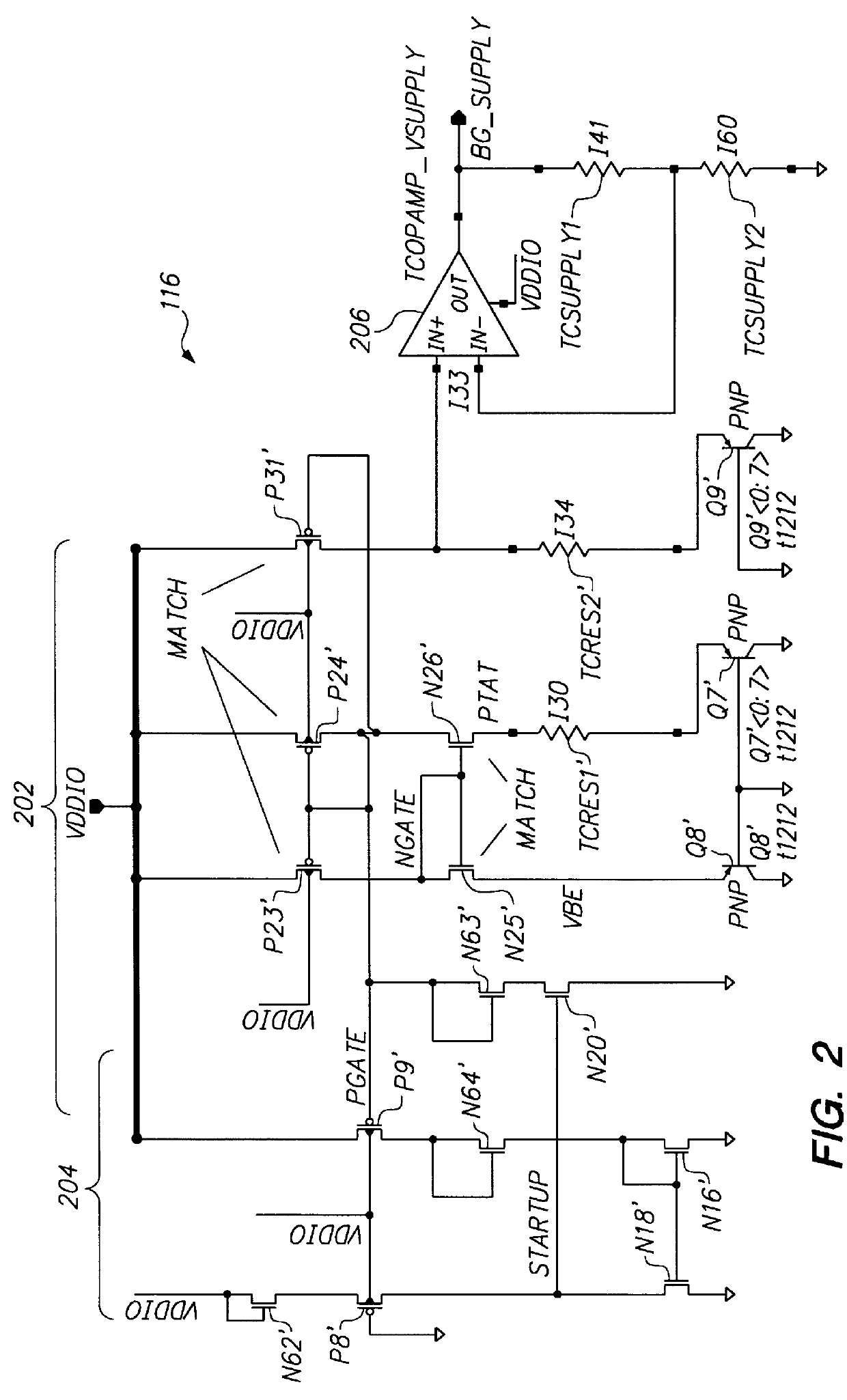

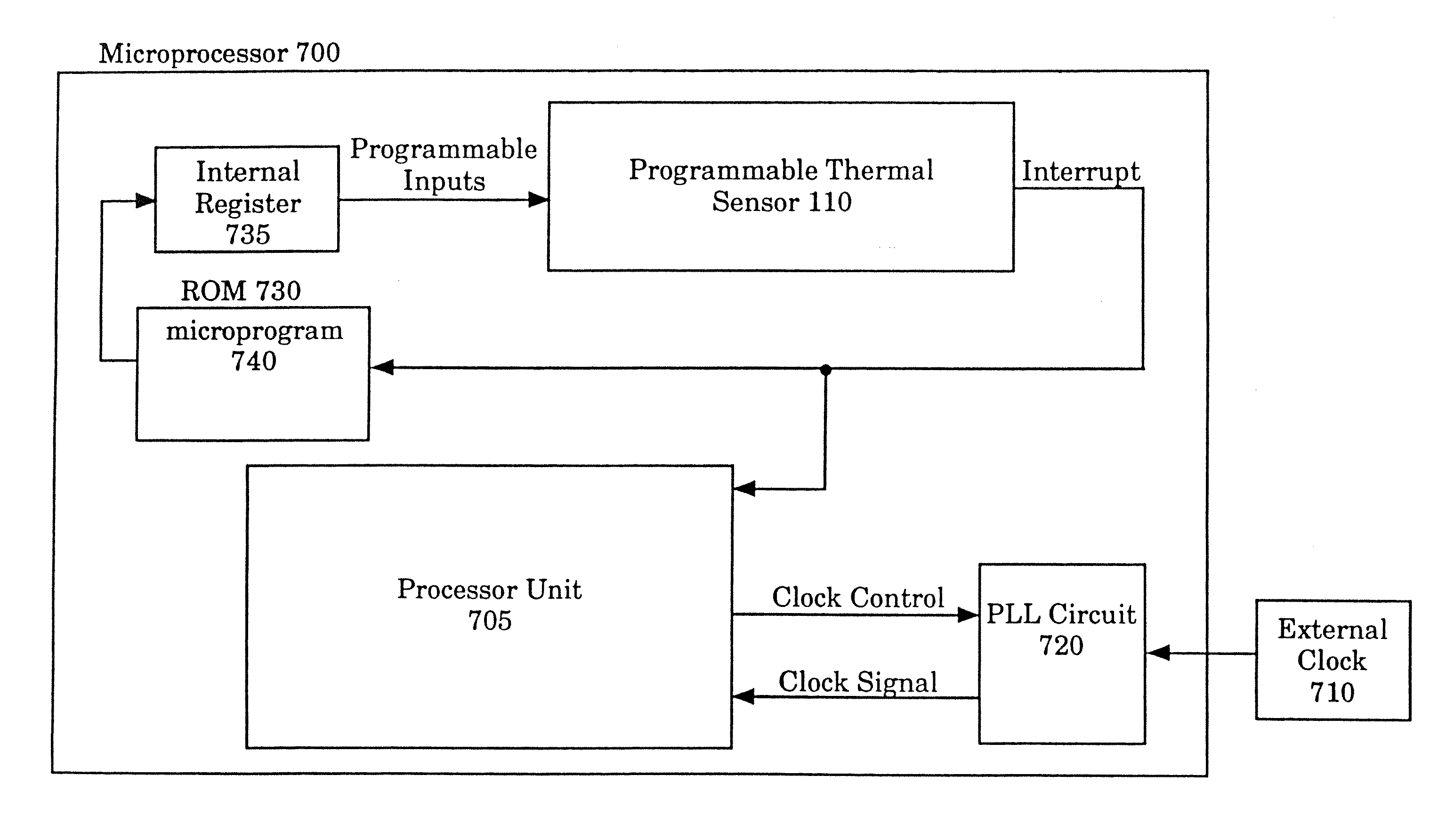

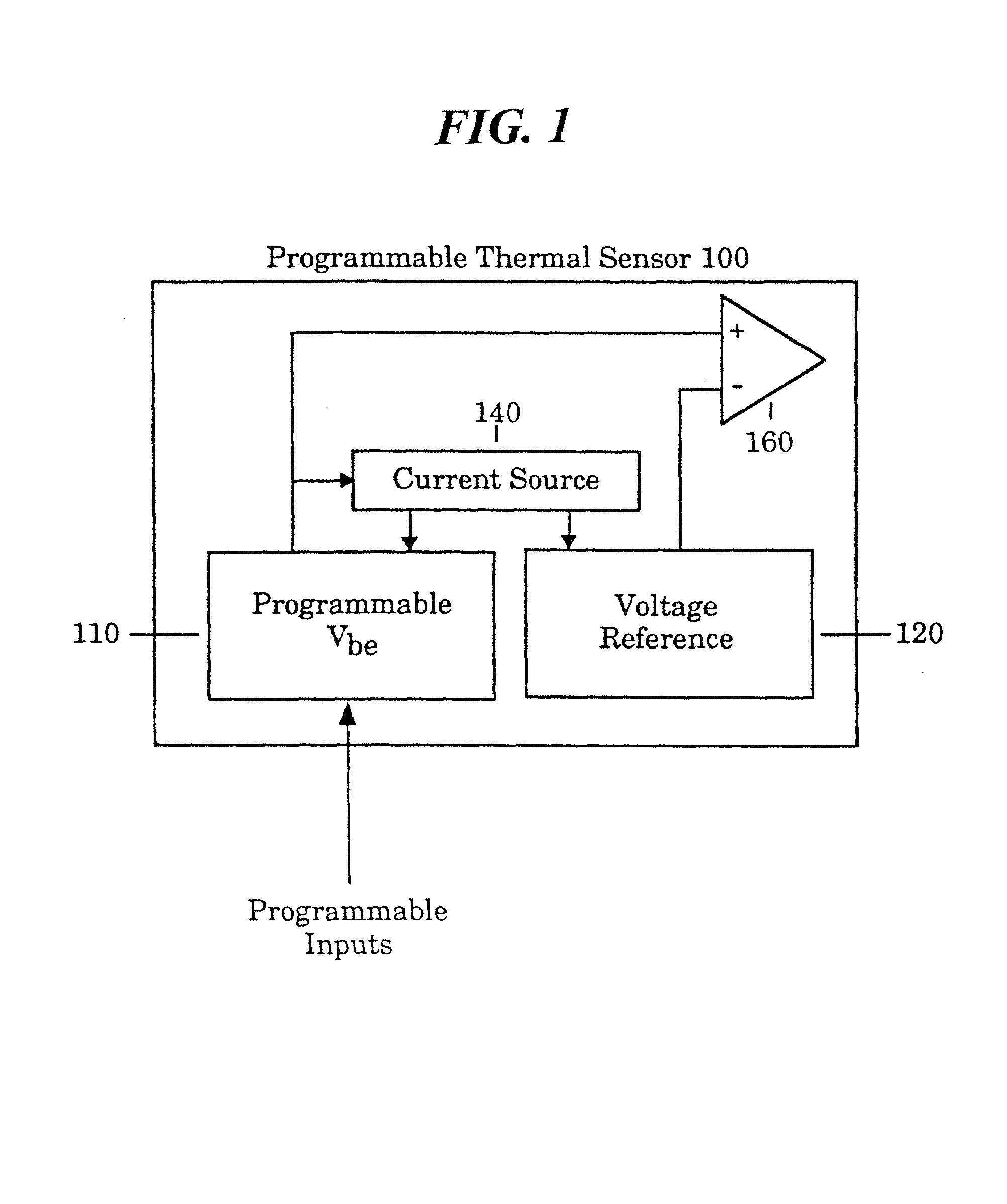

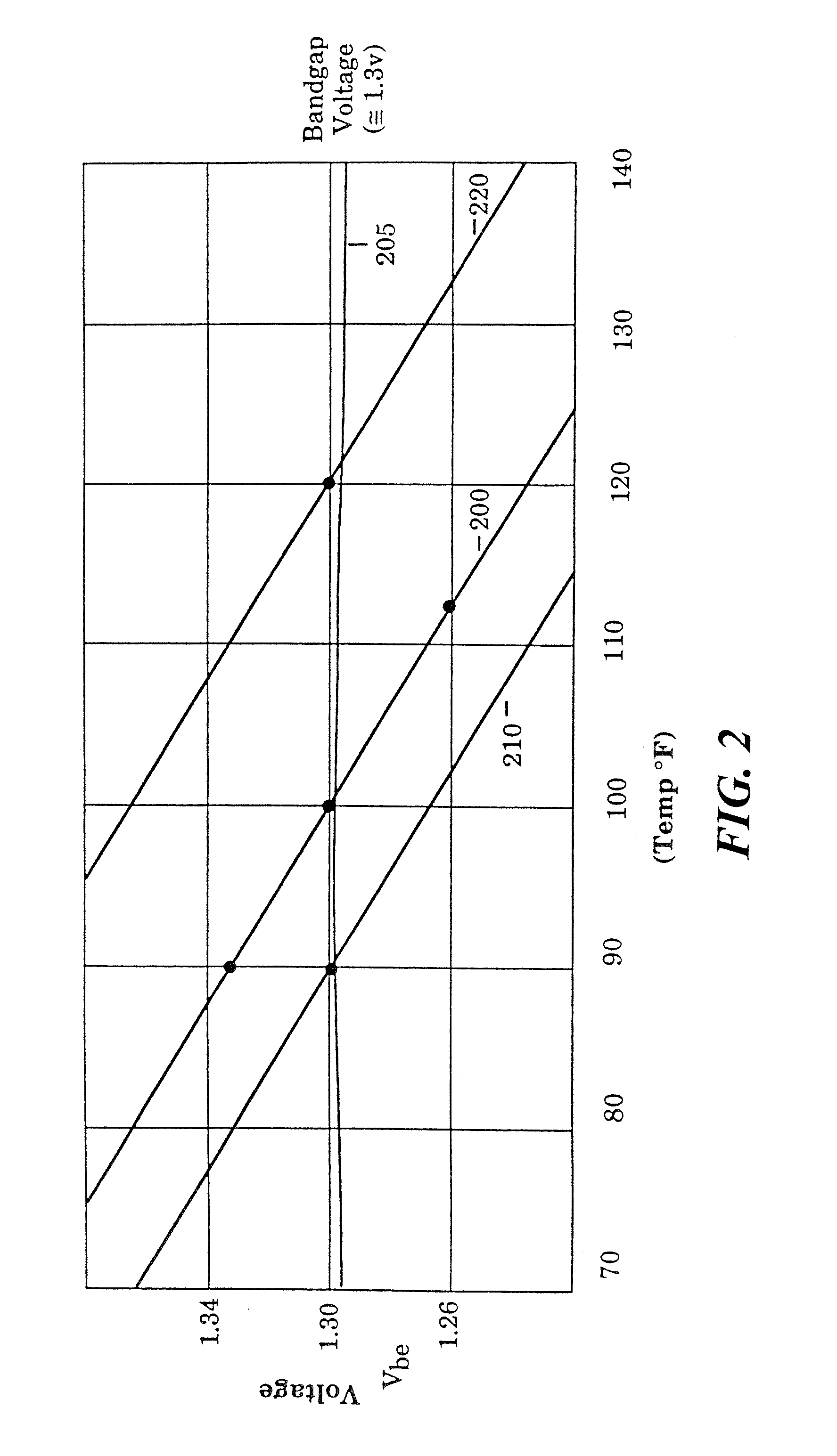

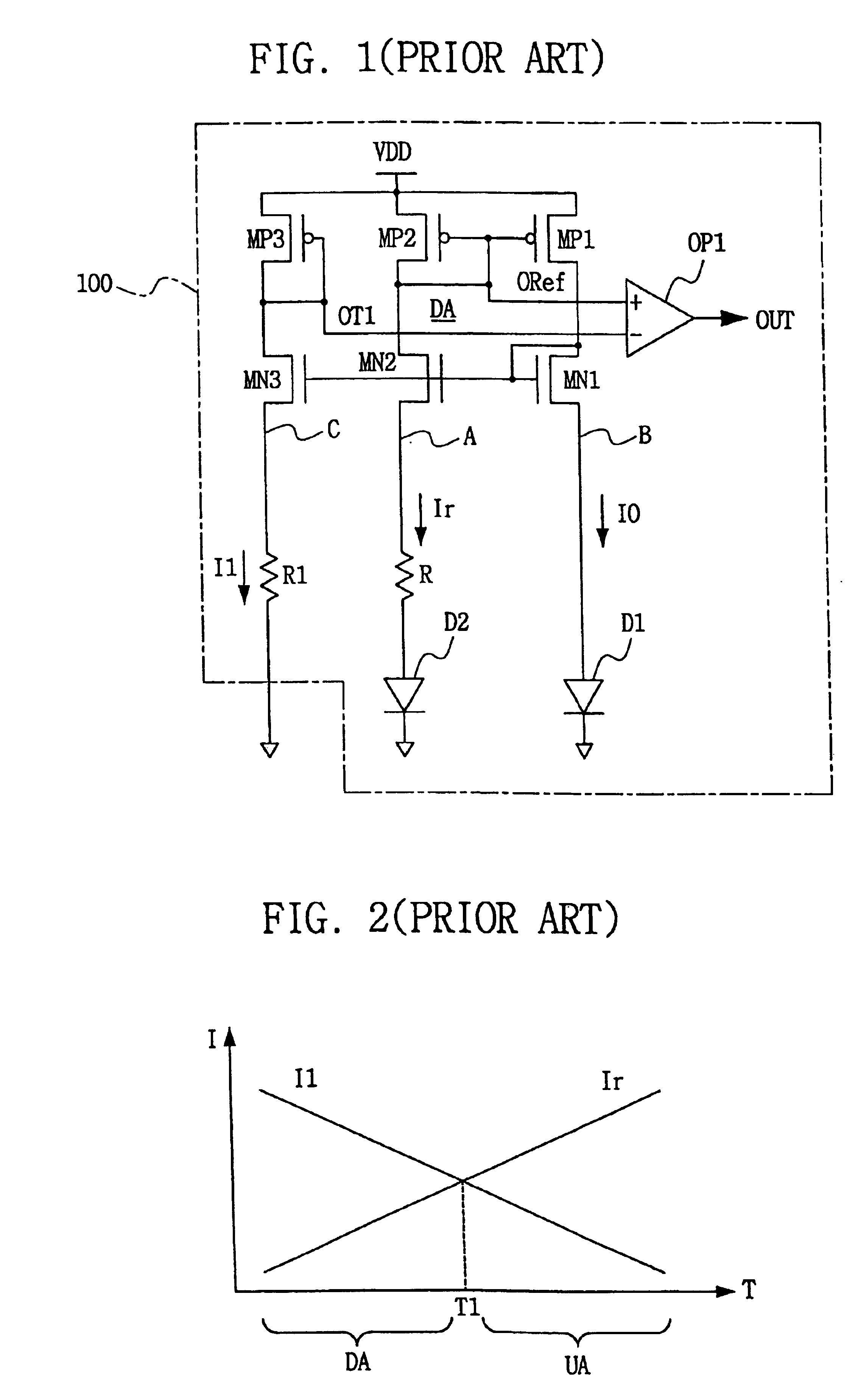

Power supply independent temperature sensor

InactiveUS6157244AMultiple input and output pulse circuitsInstant pulse delivery arrangementsAudio power amplifierEngineering

A temperature sensor is fabricated in an integrated circuit in combination with another device such as a microprocessor using a fabrication technology that is suitable for fabricating the device. Operation of the temperature sensor is based on the bandgap physics of semiconductors using a bandgap reference circuit and an amplifier that generate two measurement voltages, a voltage that is temperature-dependent and a voltage that is temperature-independent. The temperature sensor includes a bandgap power supply circuit that supplies a power supply voltage that is very stable to drive the temperature sensor so that the temperature sensor generates an output signal that is essentially independent of the power supply voltage.

Owner:GLOBALFOUNDRIES INC

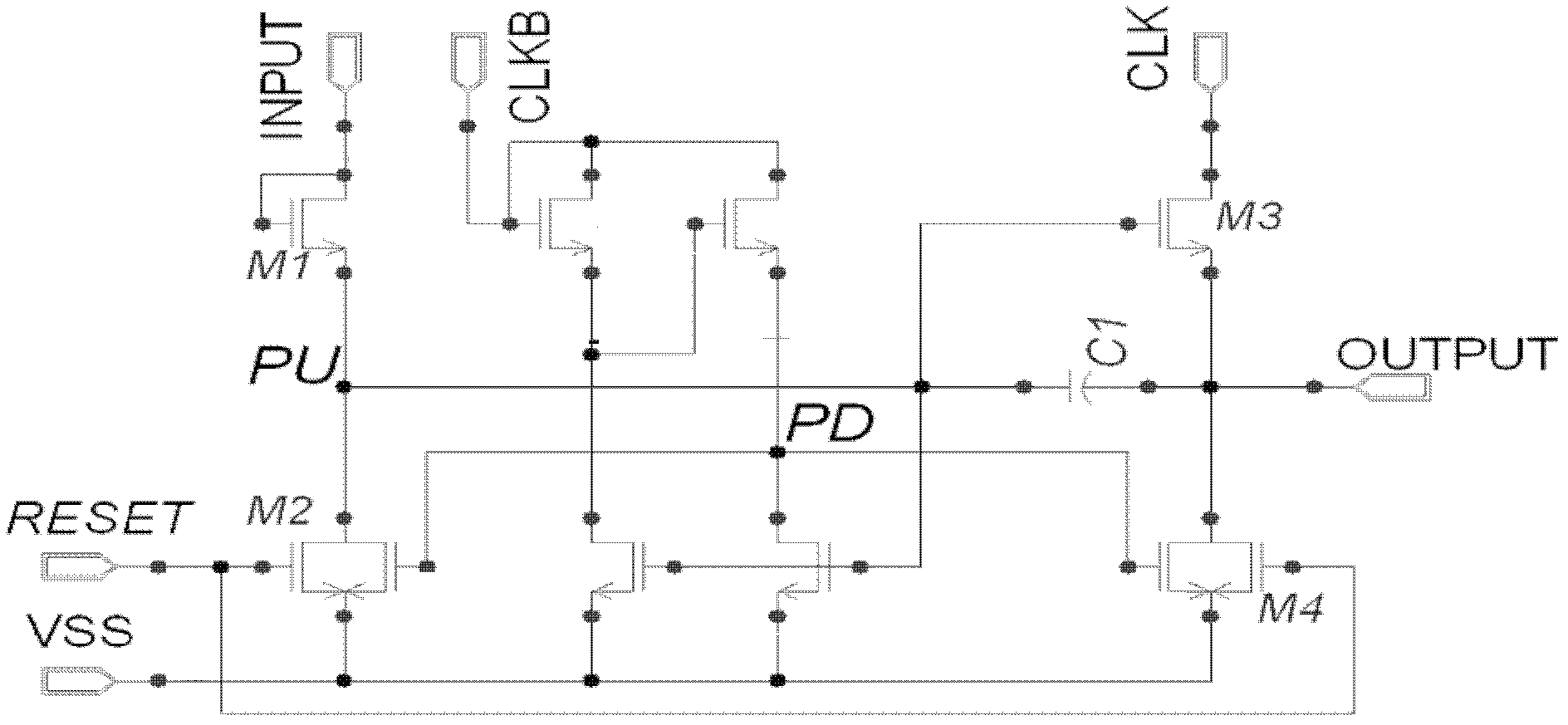

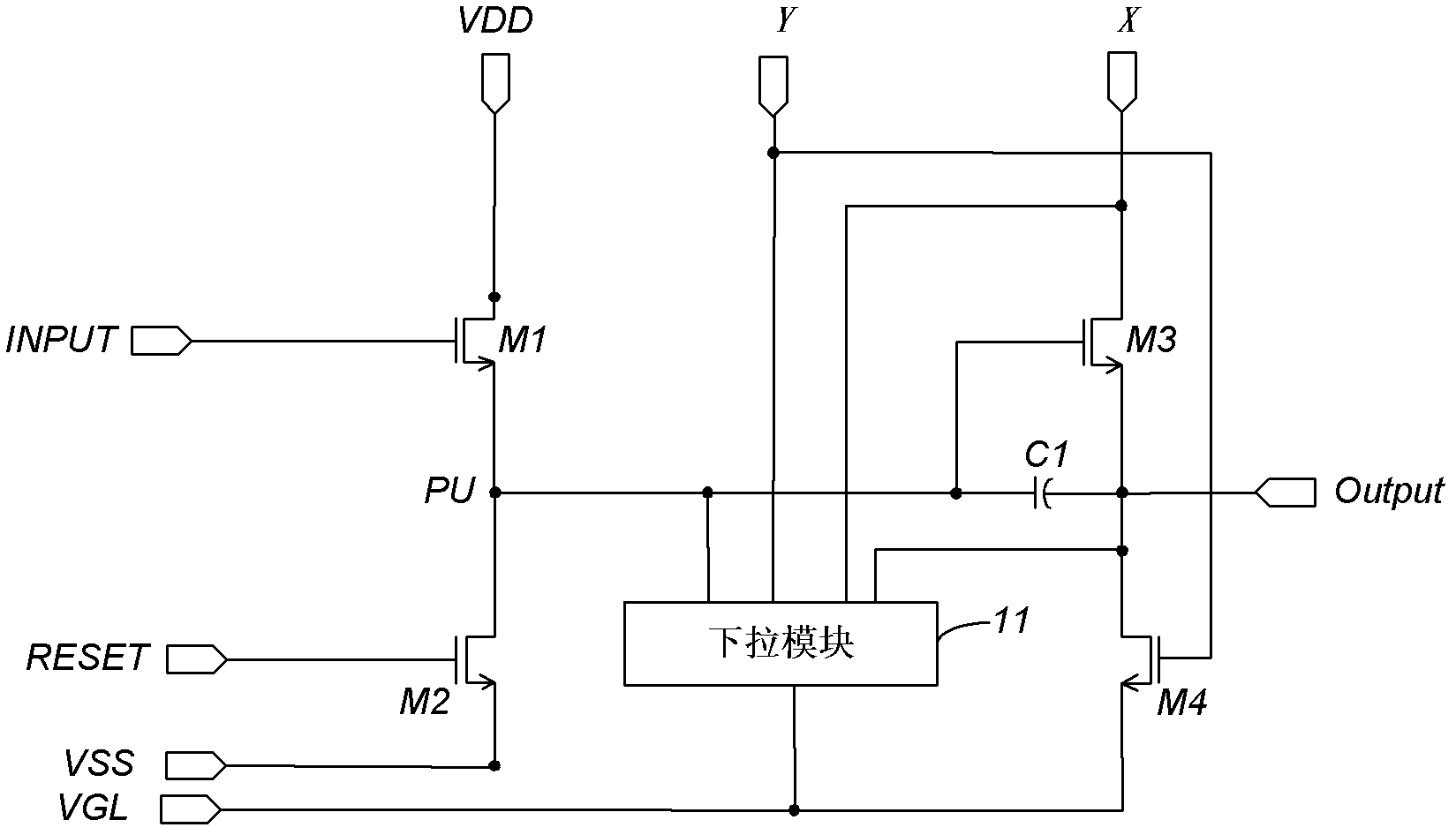

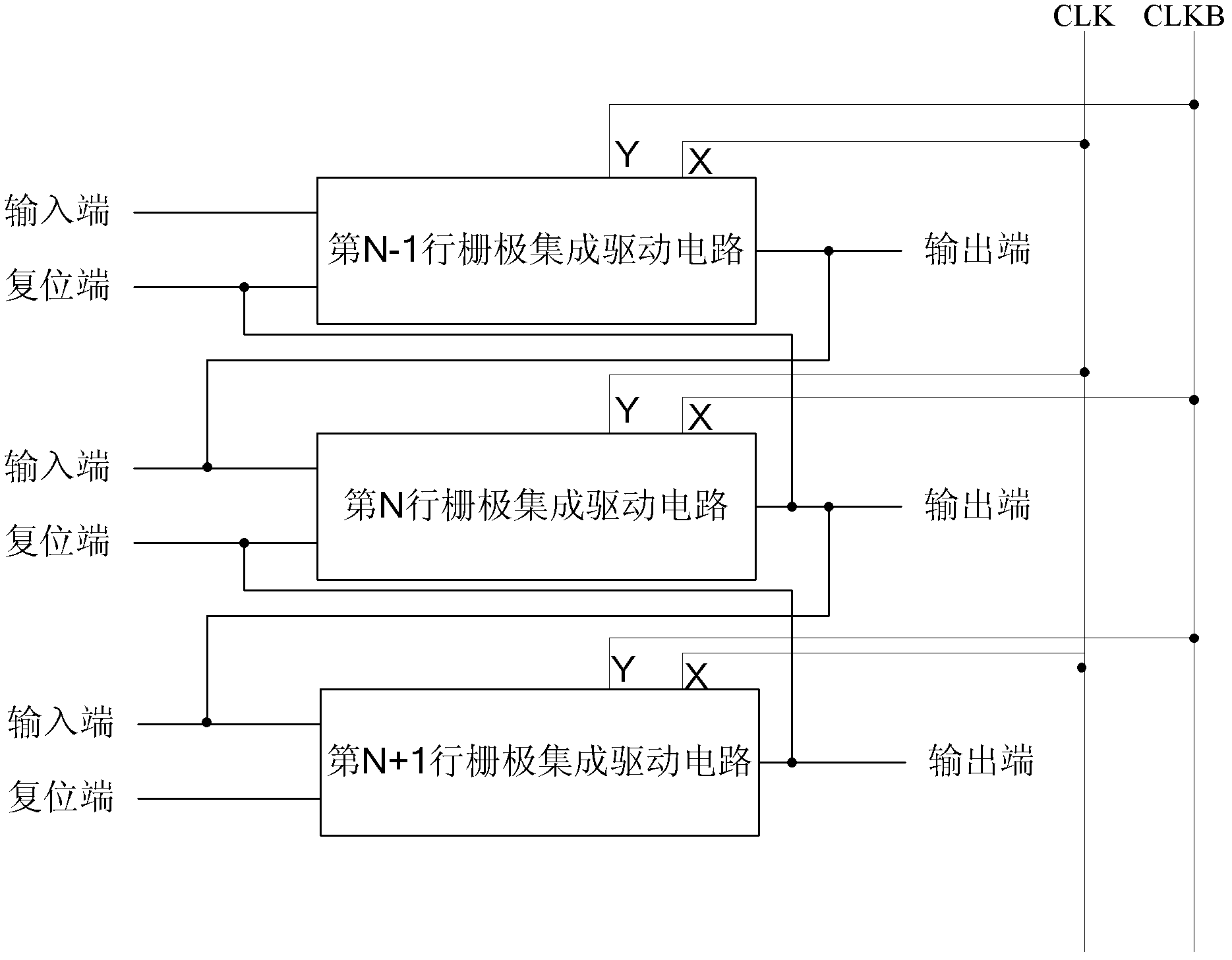

Circuit of gate drive on array, shift register and display screen

ActiveCN102629444AEnsure reliabilityGuarantee stabilityStatic indicating devicesInstant pulse delivery arrangementsCapacitanceDriver circuit

The embodiment of the invention relates to the liquid crystal display technology field, especially to a circuit of gate drive on array (GOA), a shift register and a display screen. The GOA circuit comprises a first thin film transistor (TFT), a second TFT, a third TFT, a fourth TFT, a capacitor and a drop-down module. The drop-down module, which is connected between a first clock signal input terminal, a second clock signal input terminal, a first node and an output terminal and is connected with a low level signal terminal, is used for maintaining the first node and the output terminal to be at a low level within non-working time of the GOA circuit of this row. According to the invention, functions of an input terminal and a reset terminal in the GOA circuit are designed to be symmetrical, so that the GOA circuit can realize bilateral scanning without changing charging and discharging characteristics of a node; and thus reliability and stability of the circuit are ensured.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

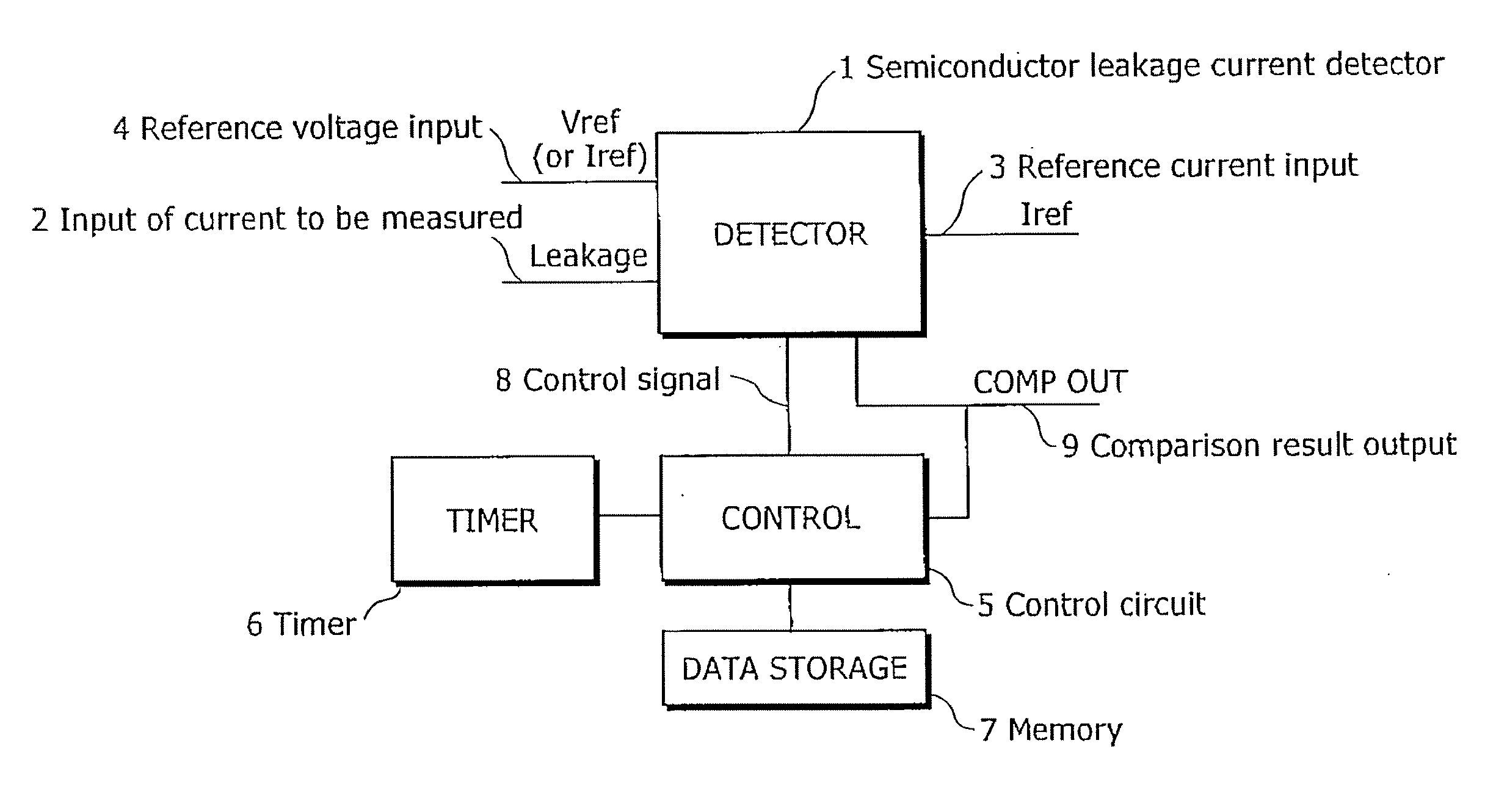

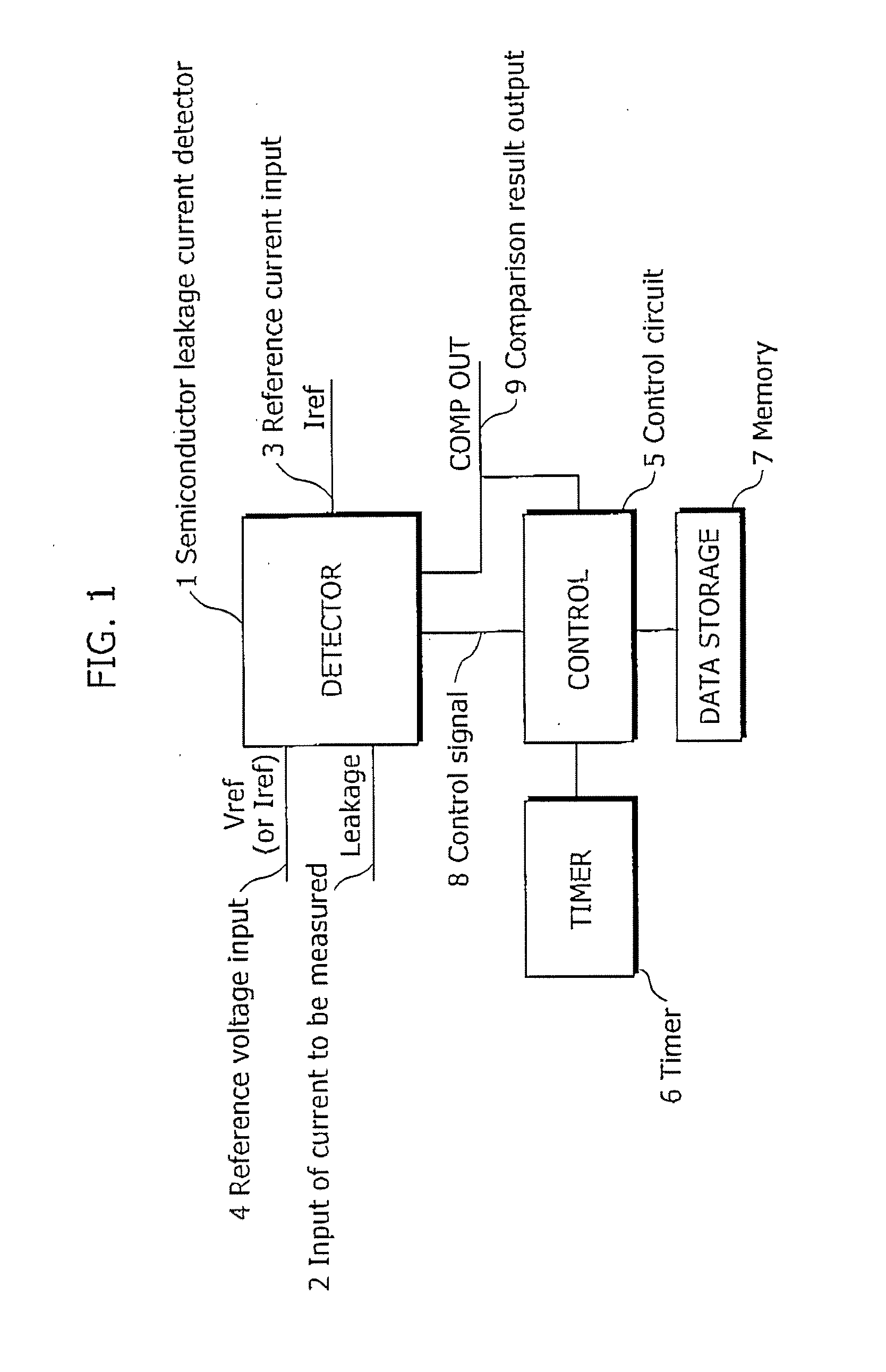

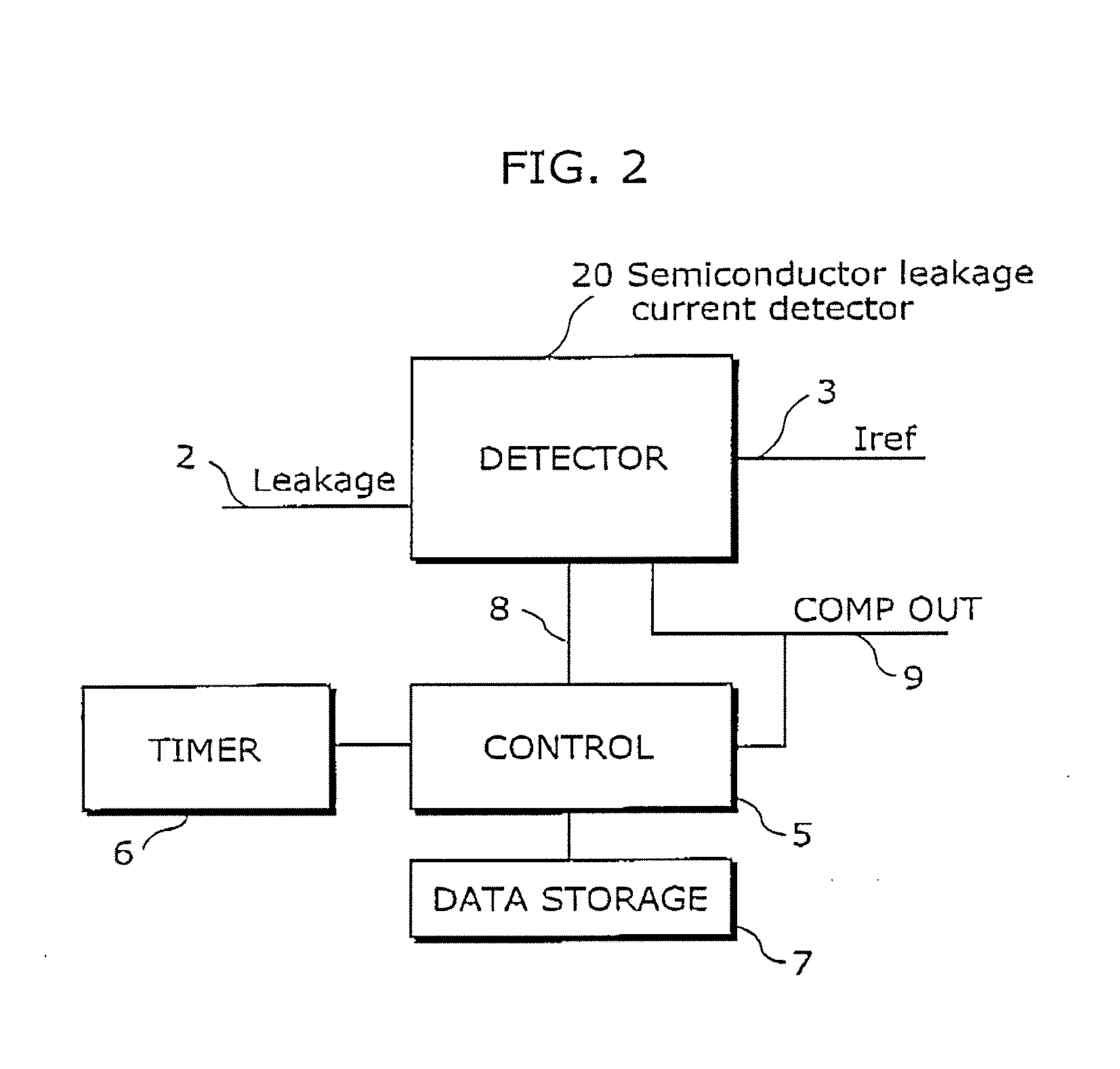

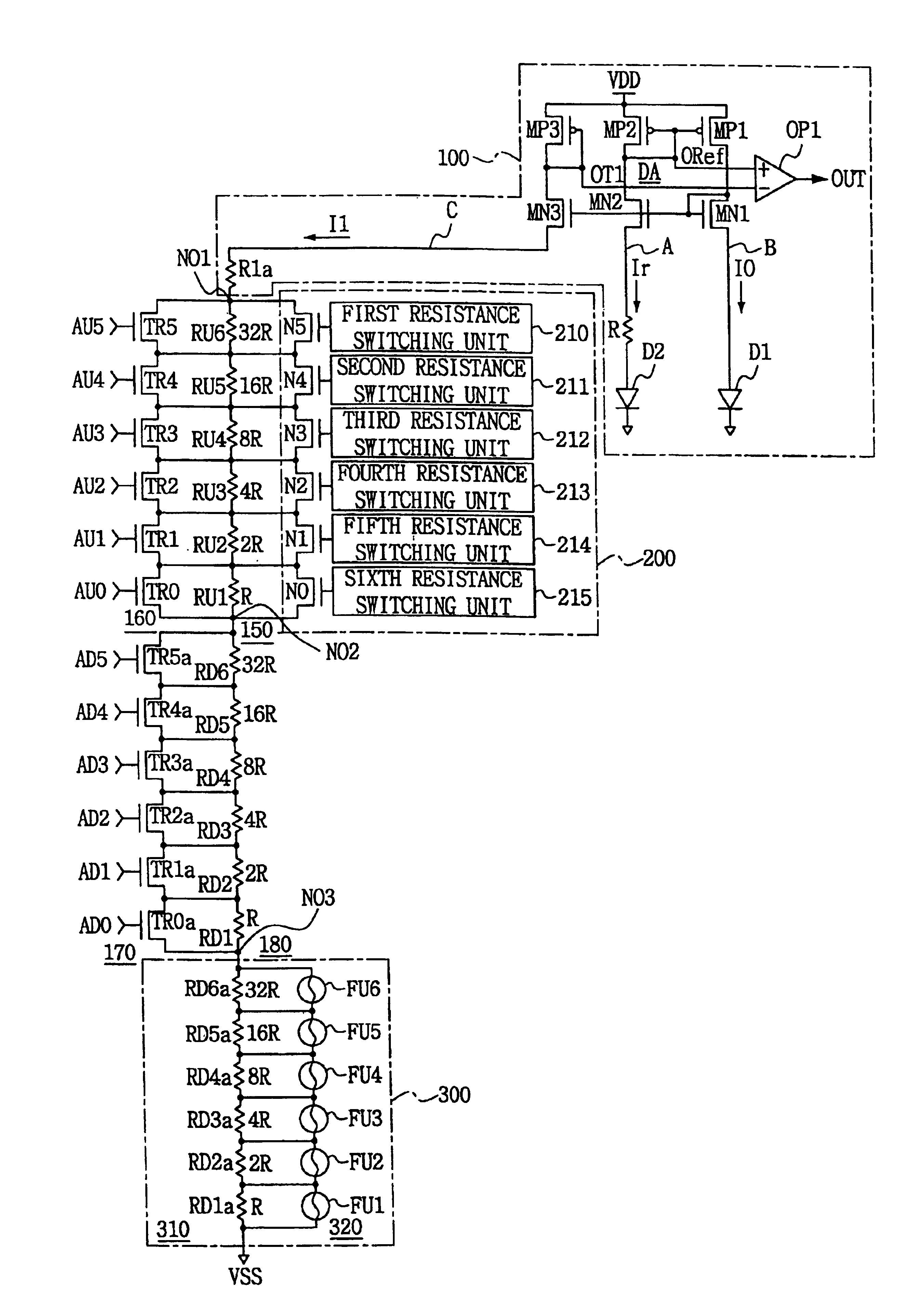

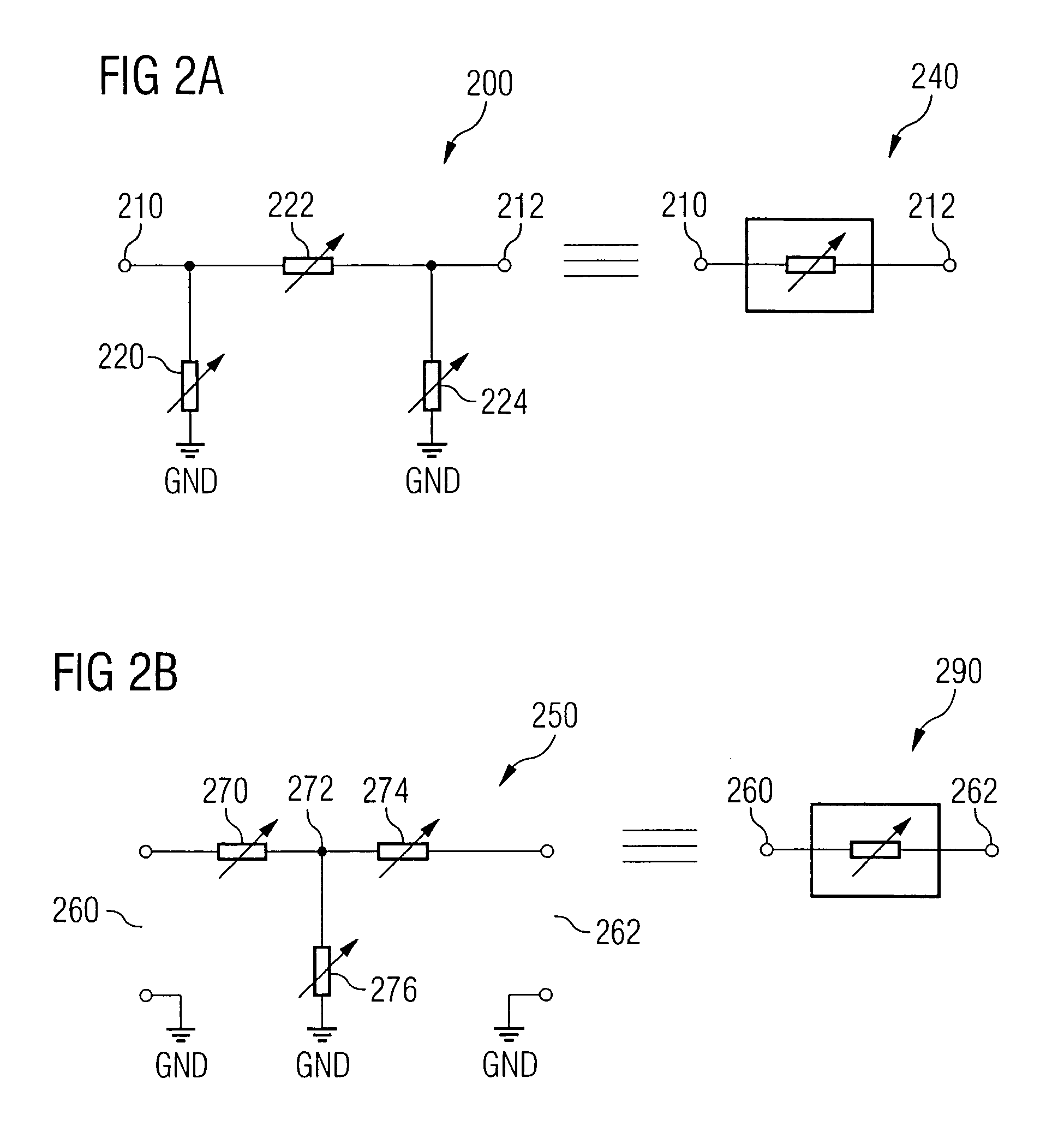

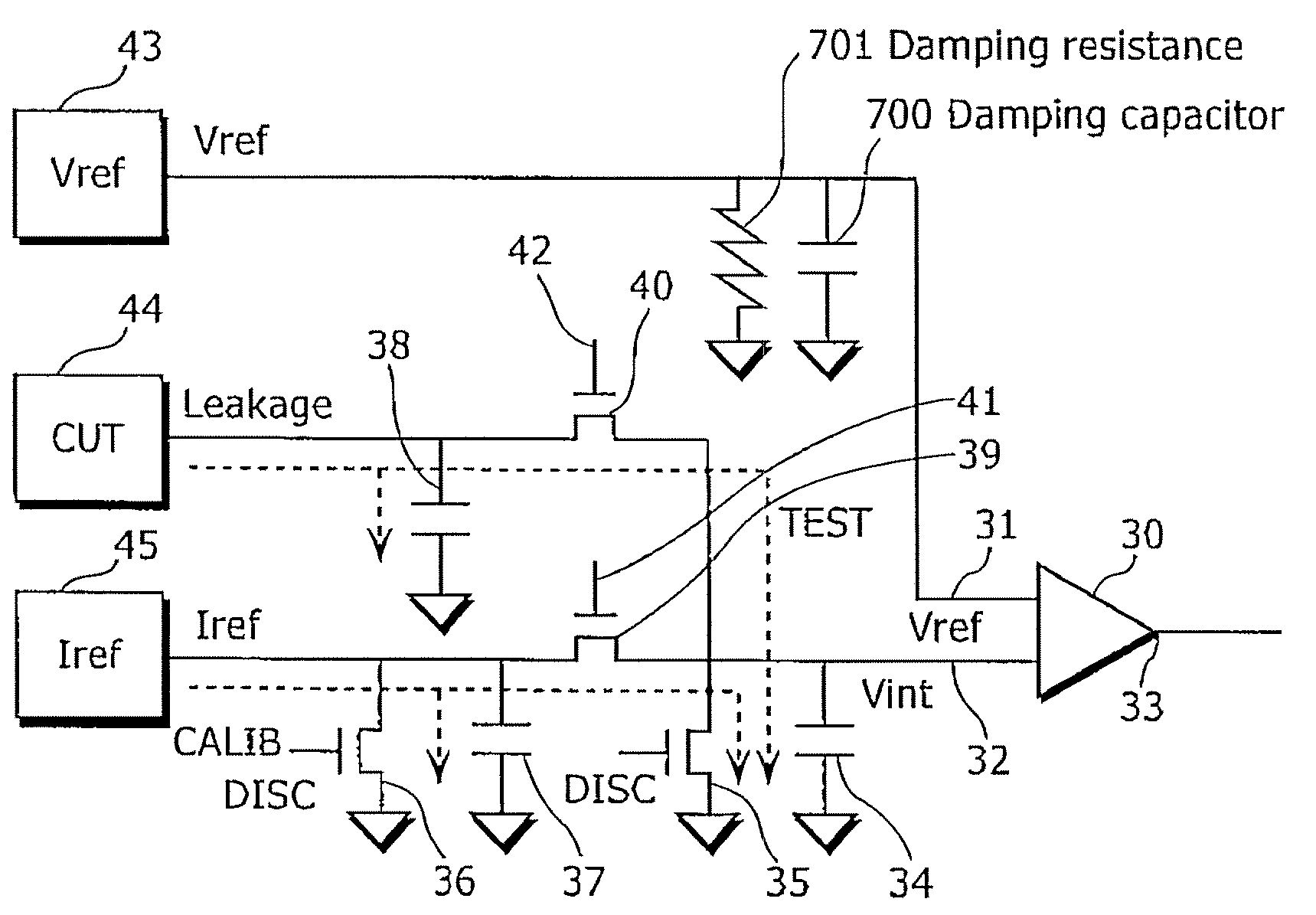

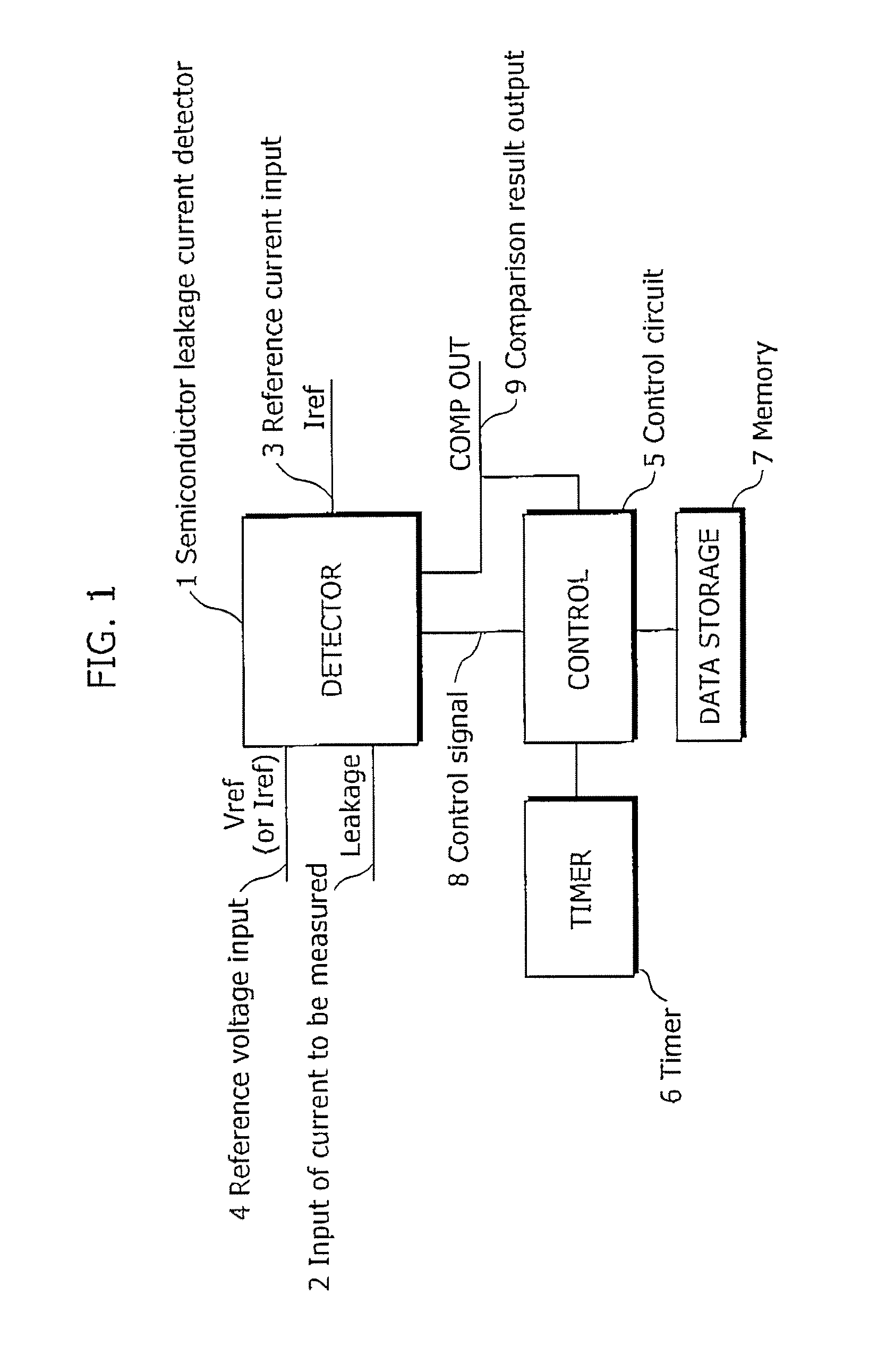

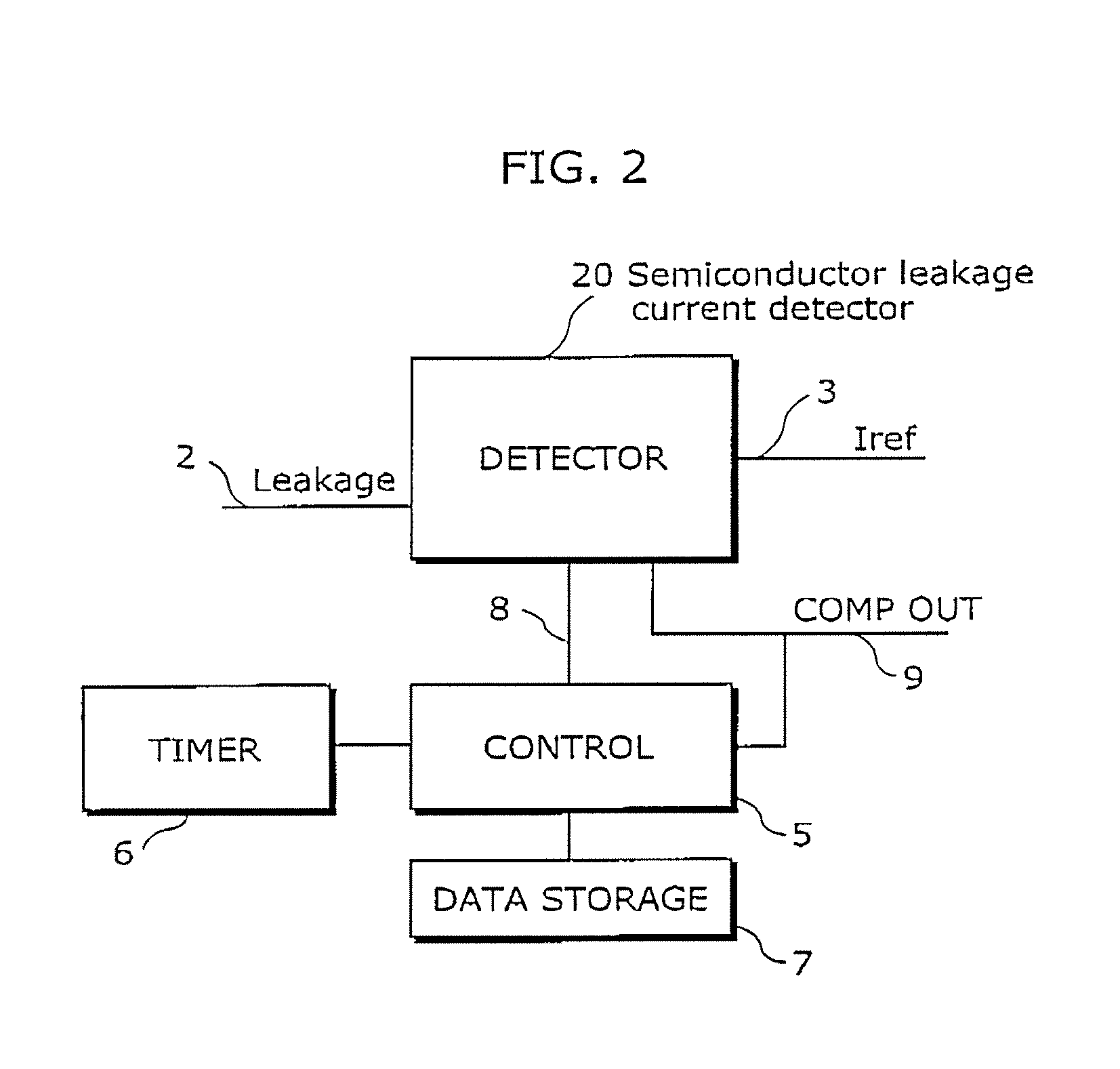

Semiconductor leakage current detector and leakage current measurement method, semiconductor leakage current detector with voltage trimming function and reference voltage trimming method, and semiconductor intergrated circuit thereof

ActiveUS20070145981A1Improve search speedReduce trimming timeMultiple input and output pulse circuitsDirection of current indicationCapacitanceReference current

A semiconductor leakage current detector of the present invention includes a first analog switch which causes a current to be measured to flow or to be cut off, a second analog switch which causes a reference current to flow or to be cut off, an integral capacitance element which is connected by the first analog switch and the second analog switch and is charged with the current to be measured or the reference current, a discharge unit which discharges the integral capacitor, and a comparison unit which compares the reference voltage with each of an integral voltage generated in the integral capacitor by a reference current after the discharge of the integral capacitor and an integral voltage generated in the integral capacitance element by the current to be measured after the discharge of the integral capacitor

Owner:III HLDG 12 LLC

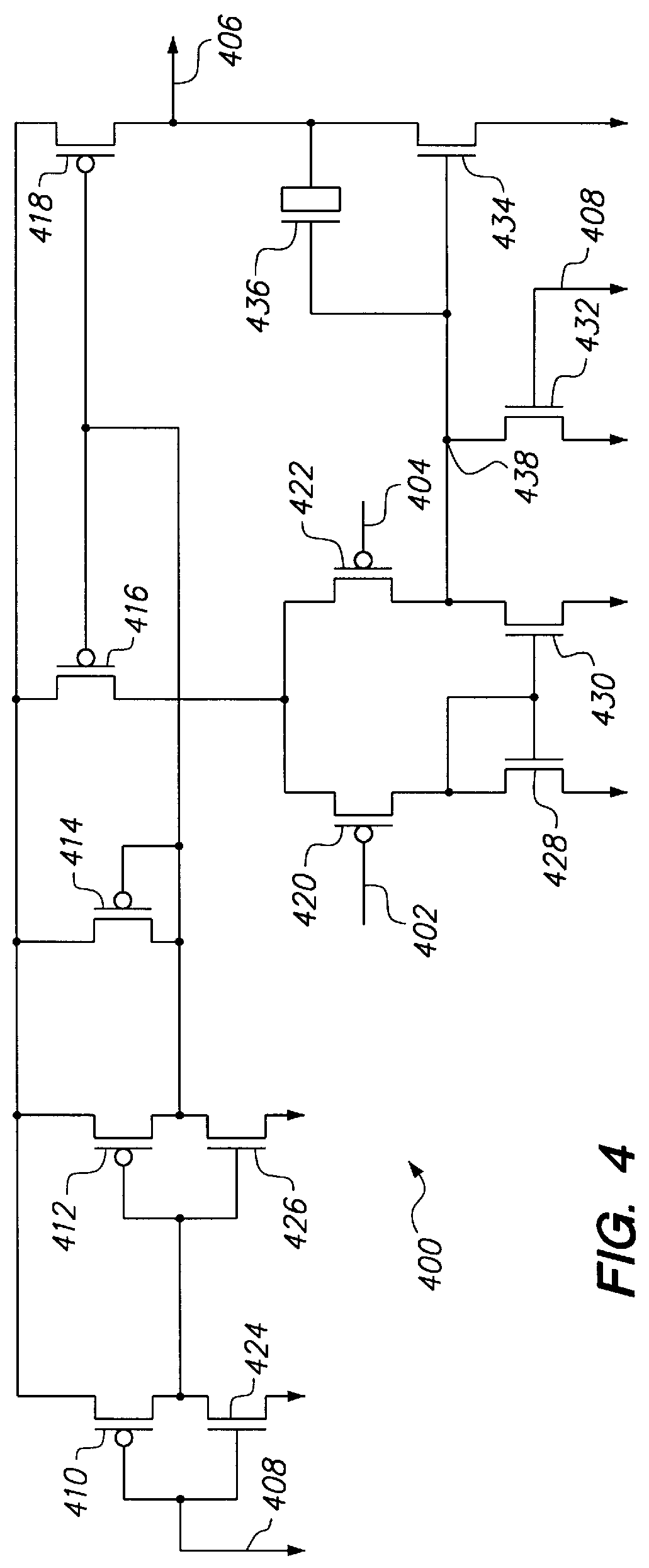

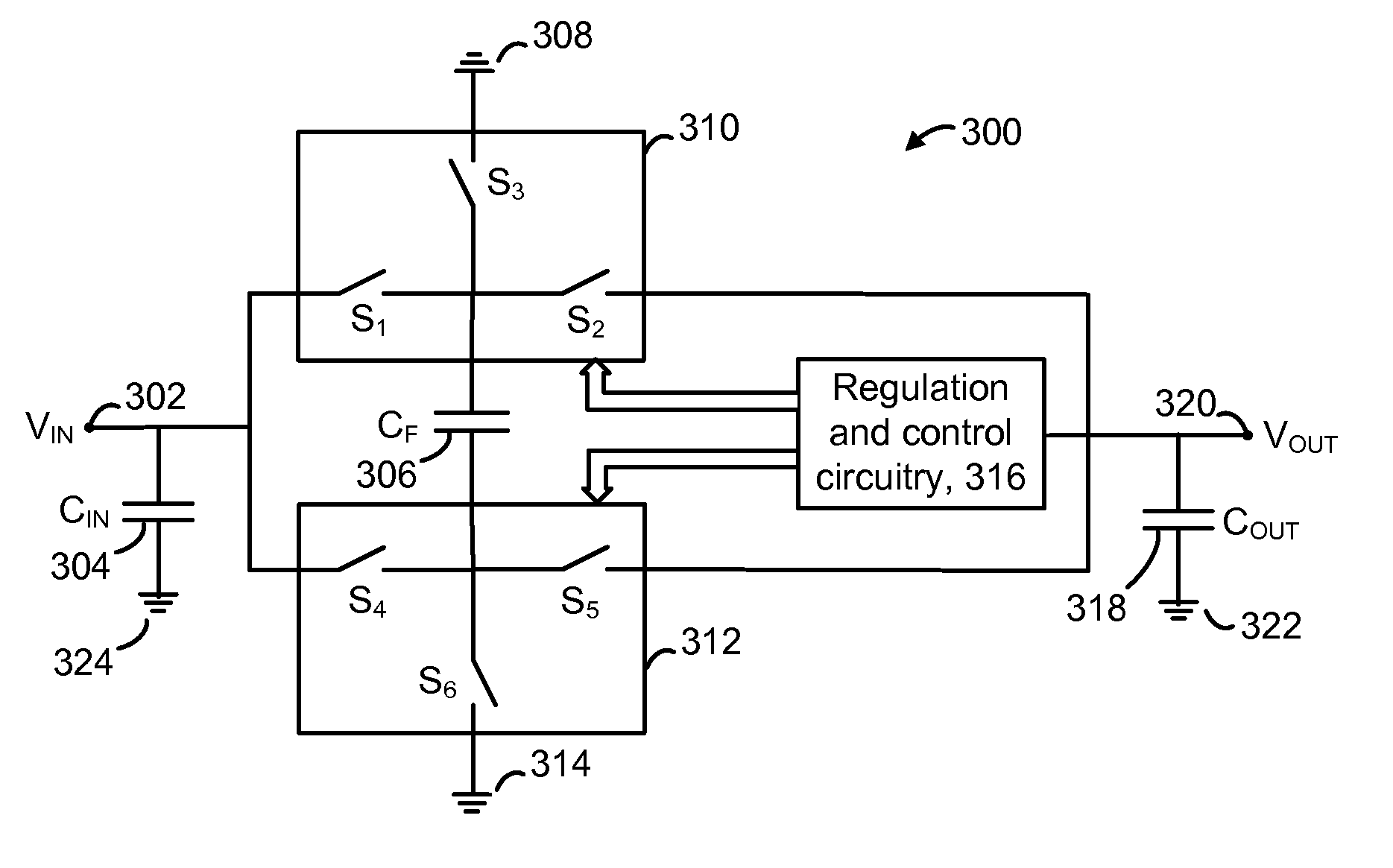

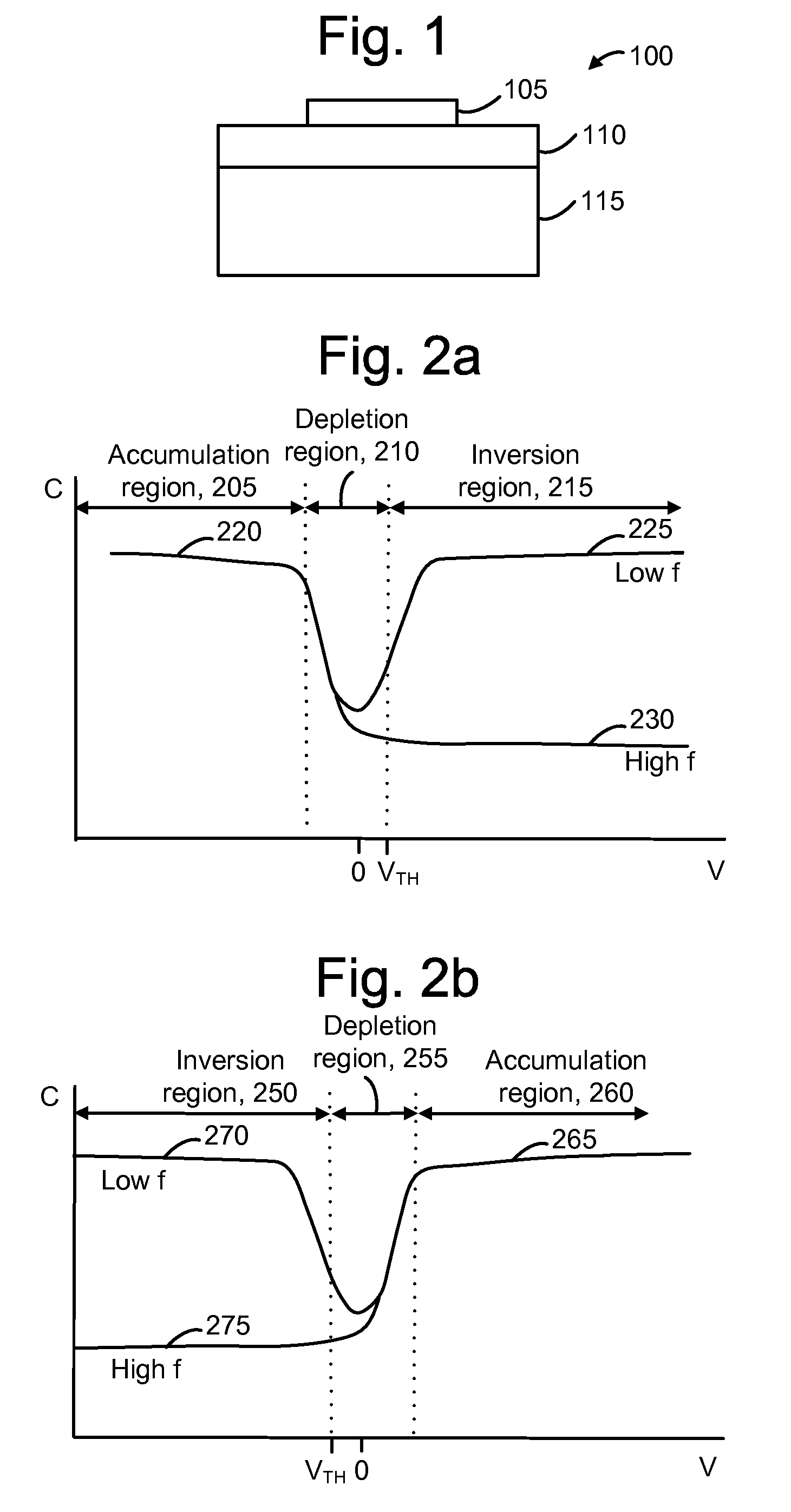

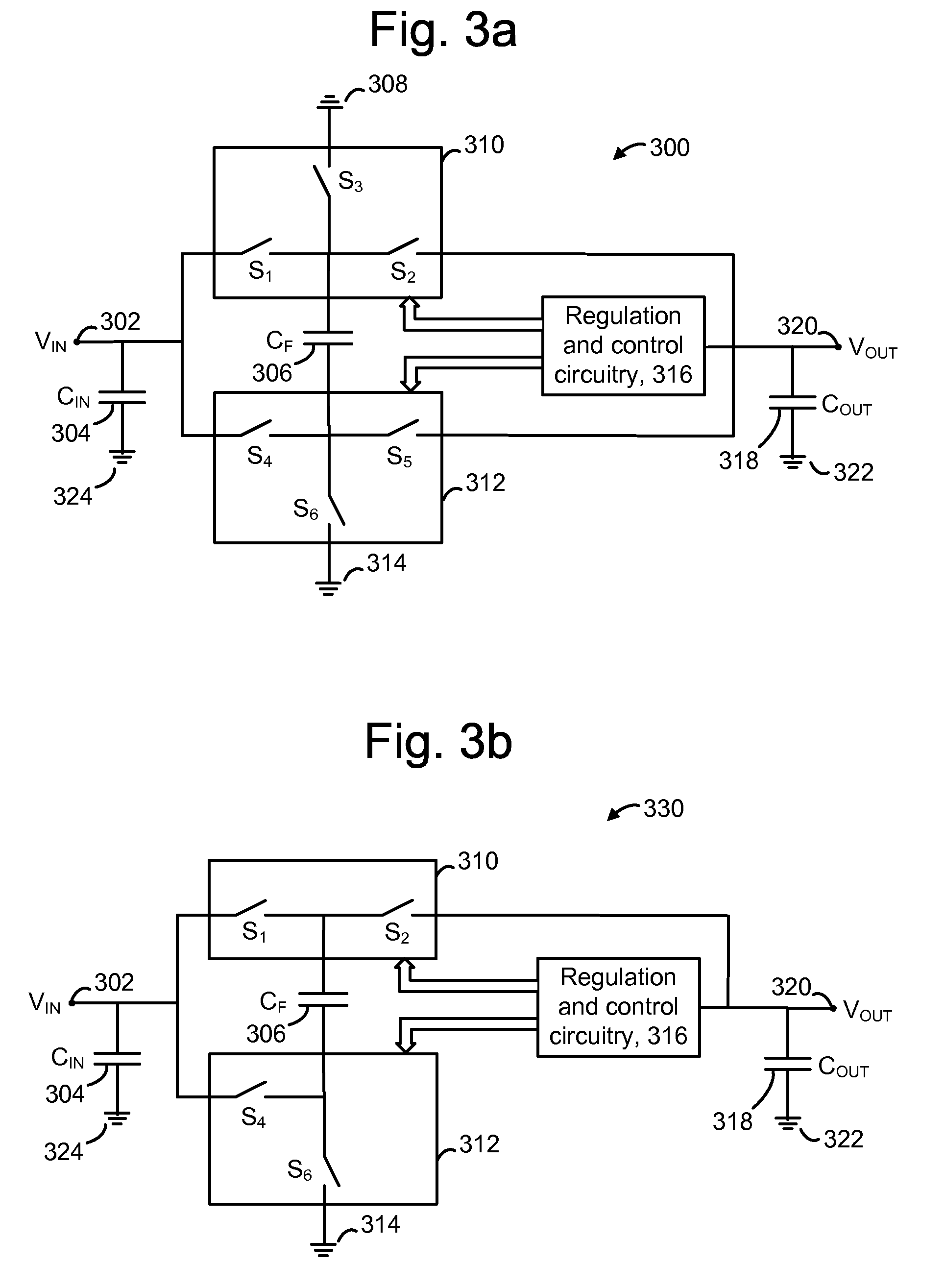

Charge coupled pump-efficient charge pump regulator with MOS capacitor

ActiveUS8040174B2Easy to operateCurrent/voltage measurementInstant pulse delivery arrangementsCapacitanceVoltage multiplier

A charge pump with a MOS-type capacitor, where the MOS-type capacitor is operated in an inversion region in which capacitance varies as a function of the frequency of the applied signal. The charge pump is switched to transfer charge from an input node to the capacitor and from the capacitor to an output node. During a transition interval, a relatively high frequency switching signal is used to lower the capacitance and increase efficiency. During a settling interval, a relatively low frequency switching signal is used, in which case the capacitance is higher, but similar to a level which would be seen if the capacitor was operated in an accumulation region. MOS capacitor dimensions and switching intervals are mutually optimized to provide high efficiency and required throughput. The charge pump may be configured as a voltage multiplier, divider, inverter or follower, for instance.

Owner:WESTERN DIGITAL ISRAEL LTD

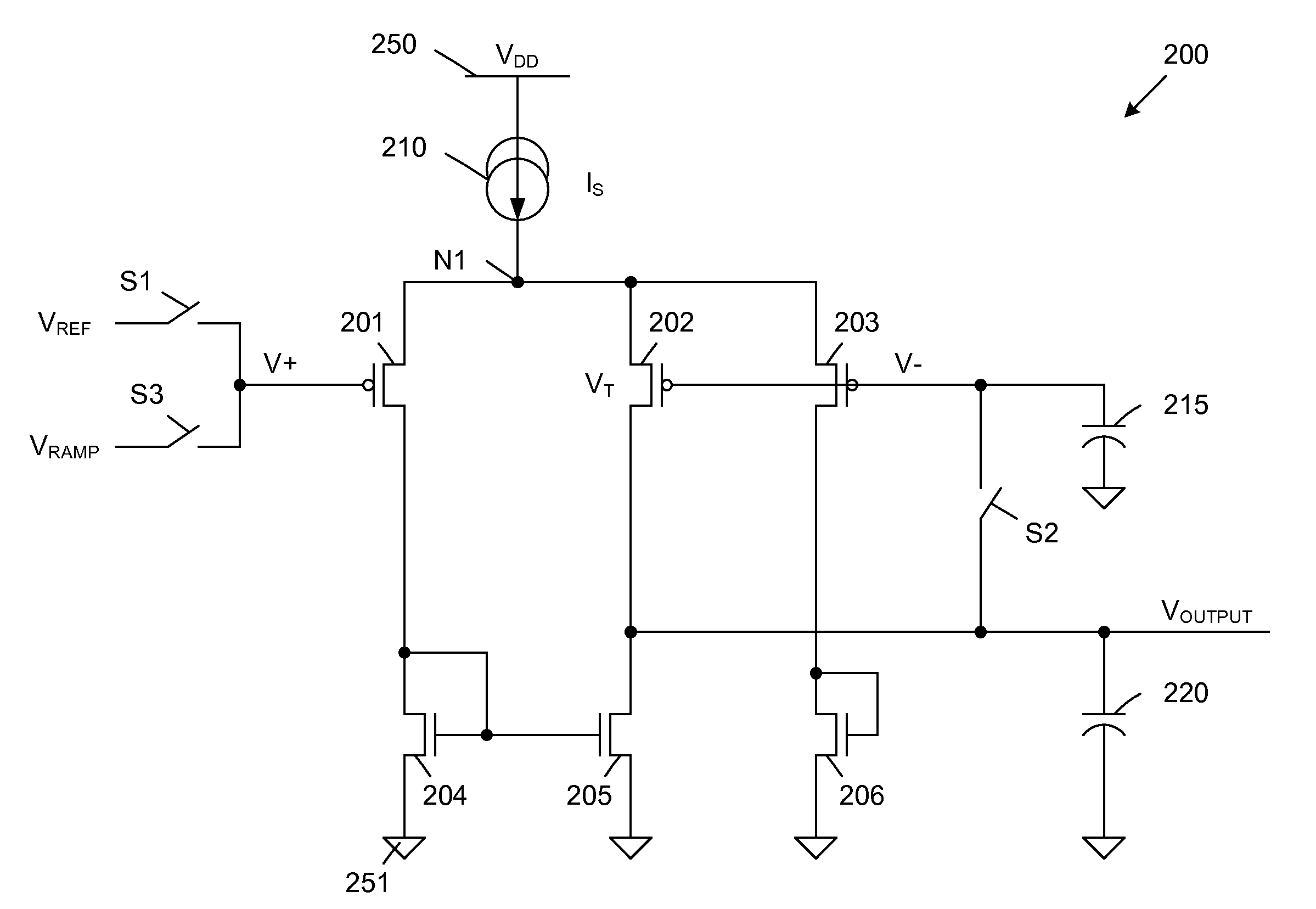

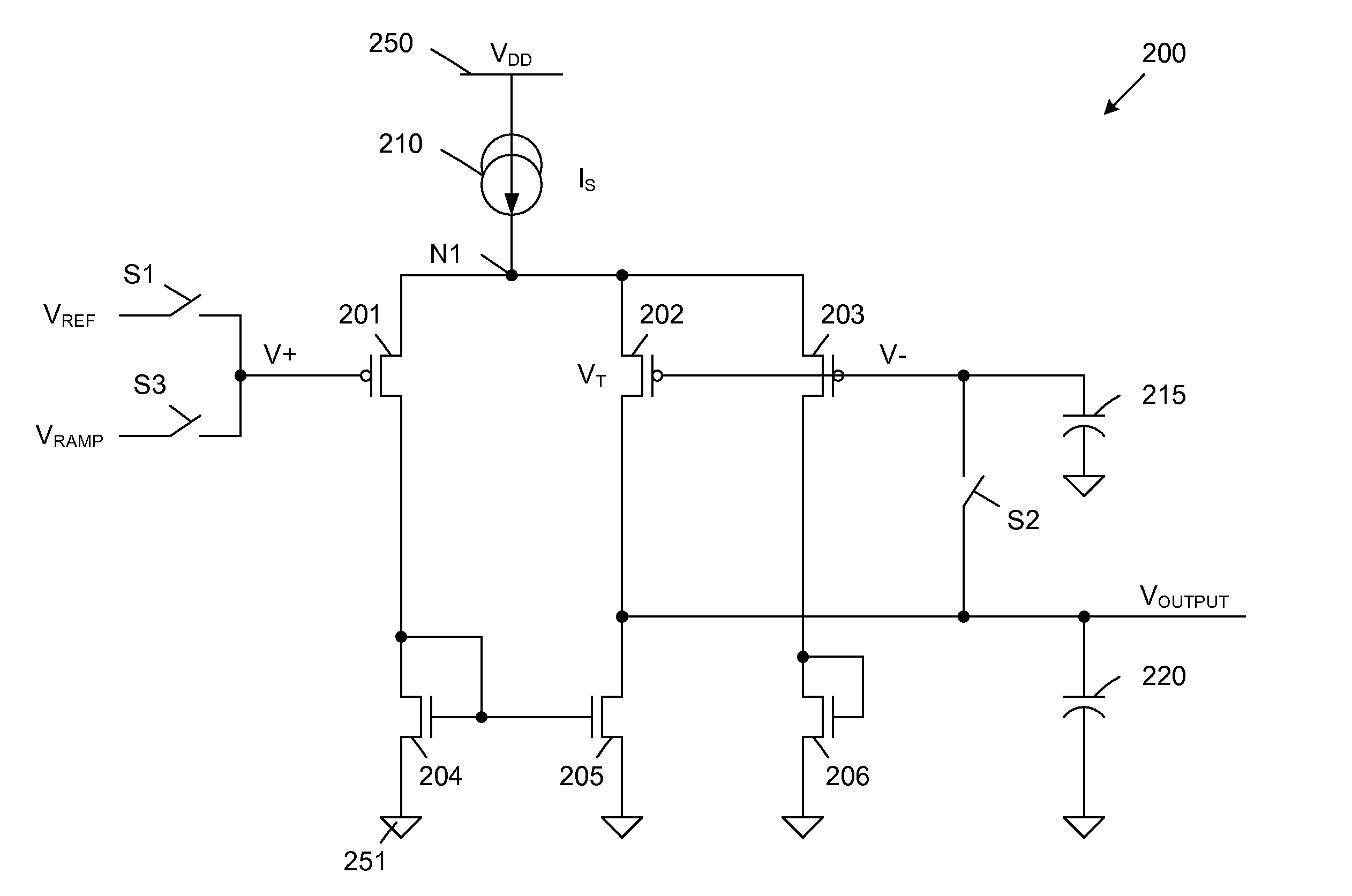

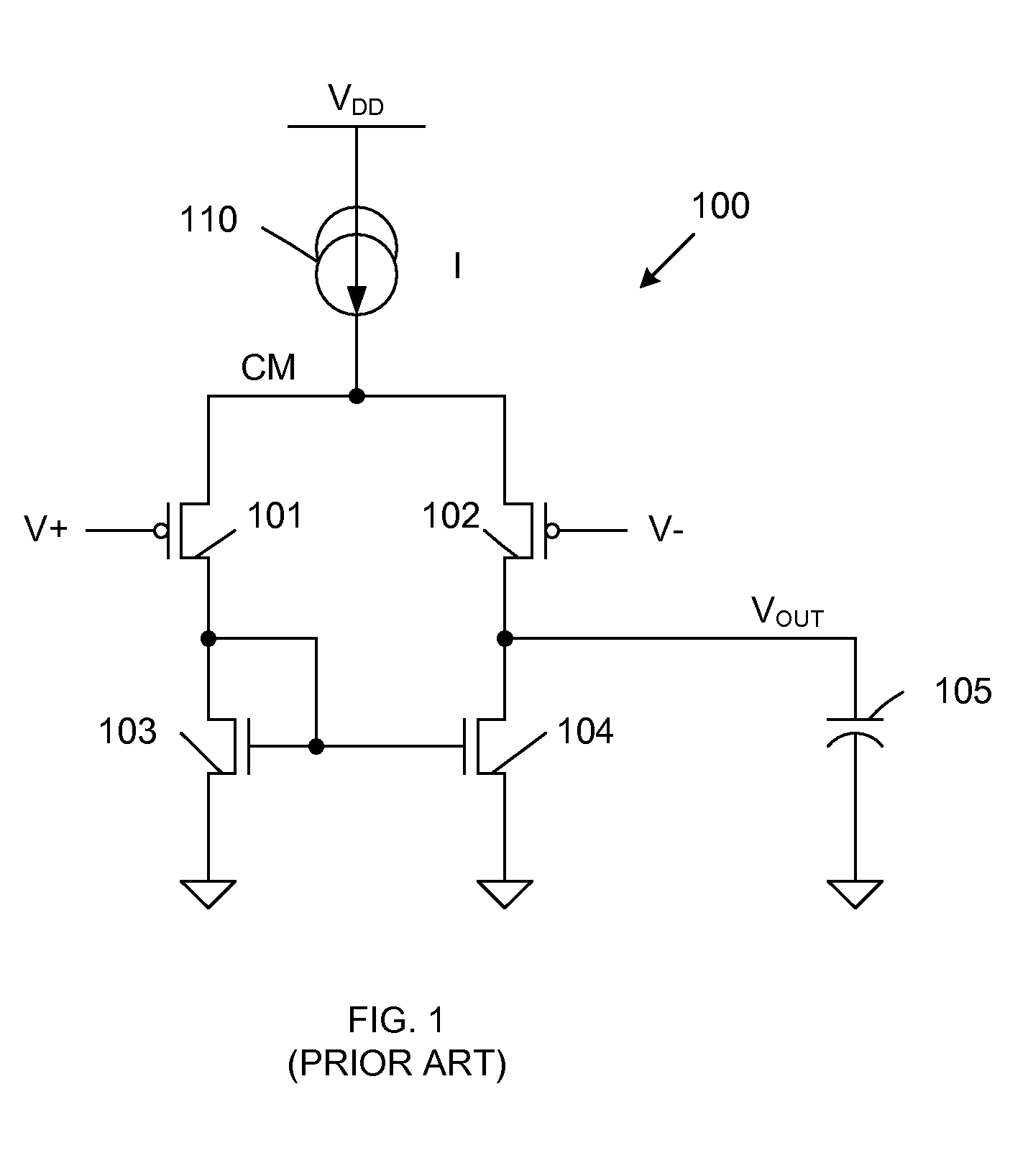

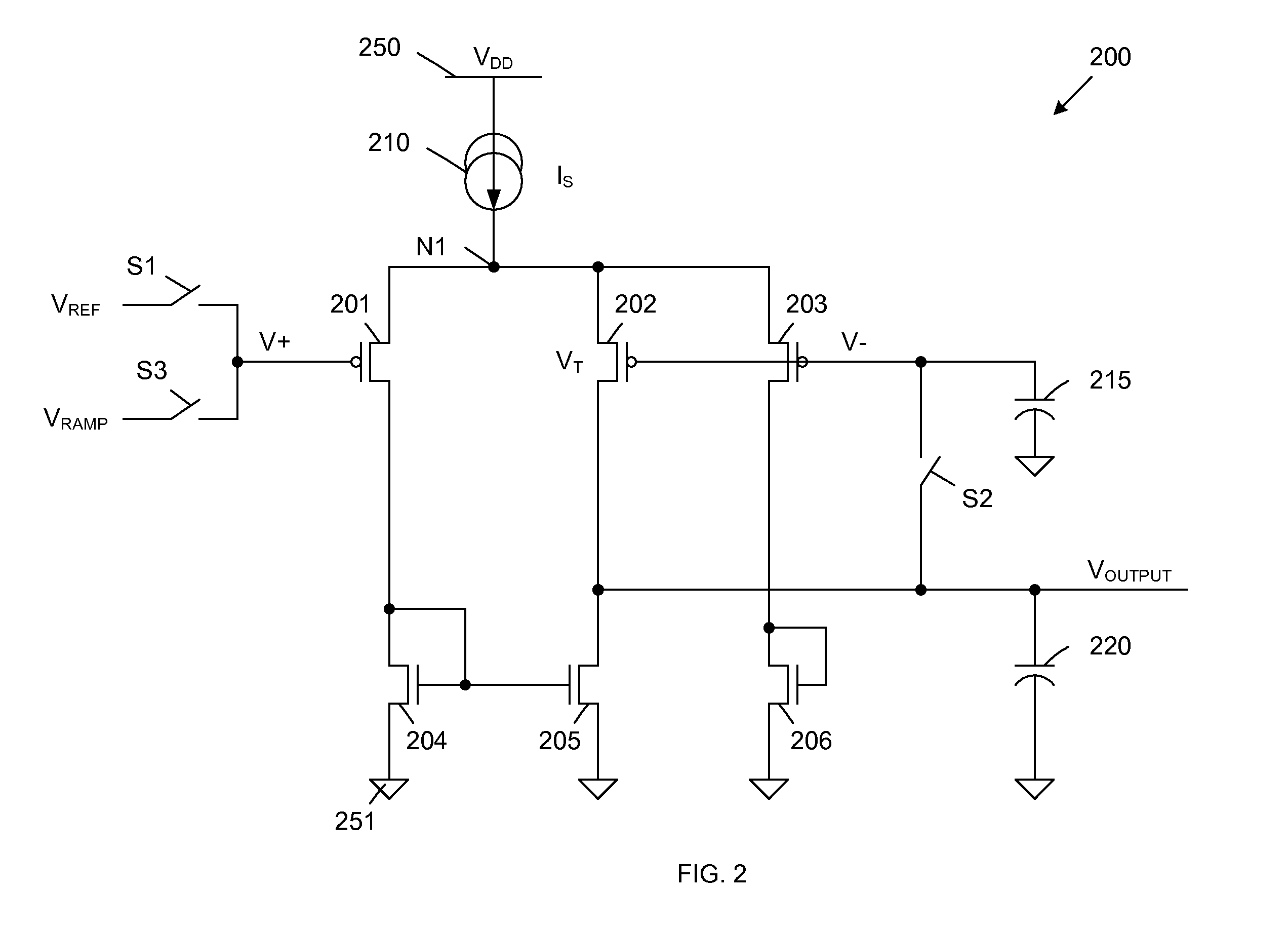

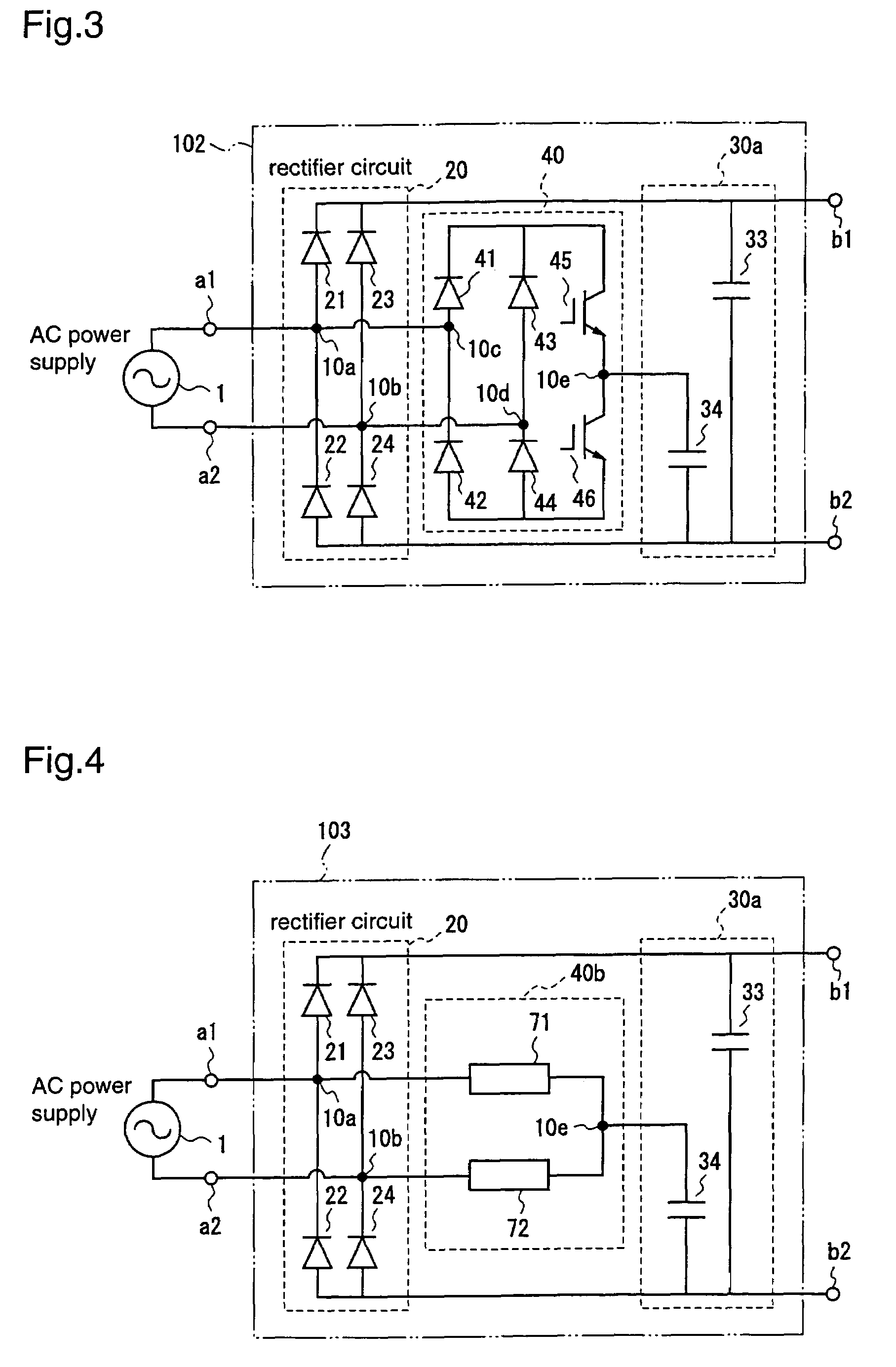

Comparator with low supply current spike and input offset cancellation

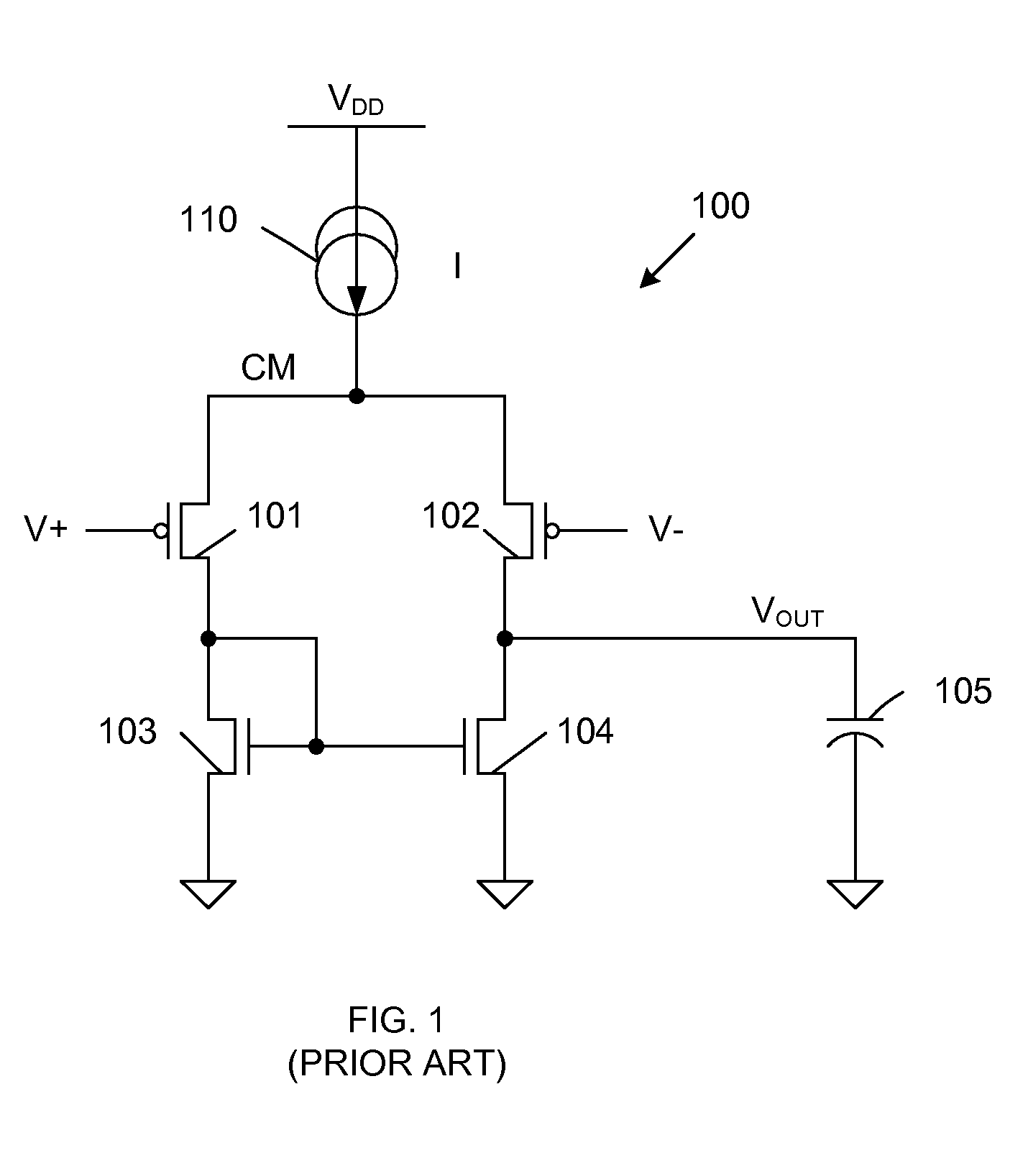

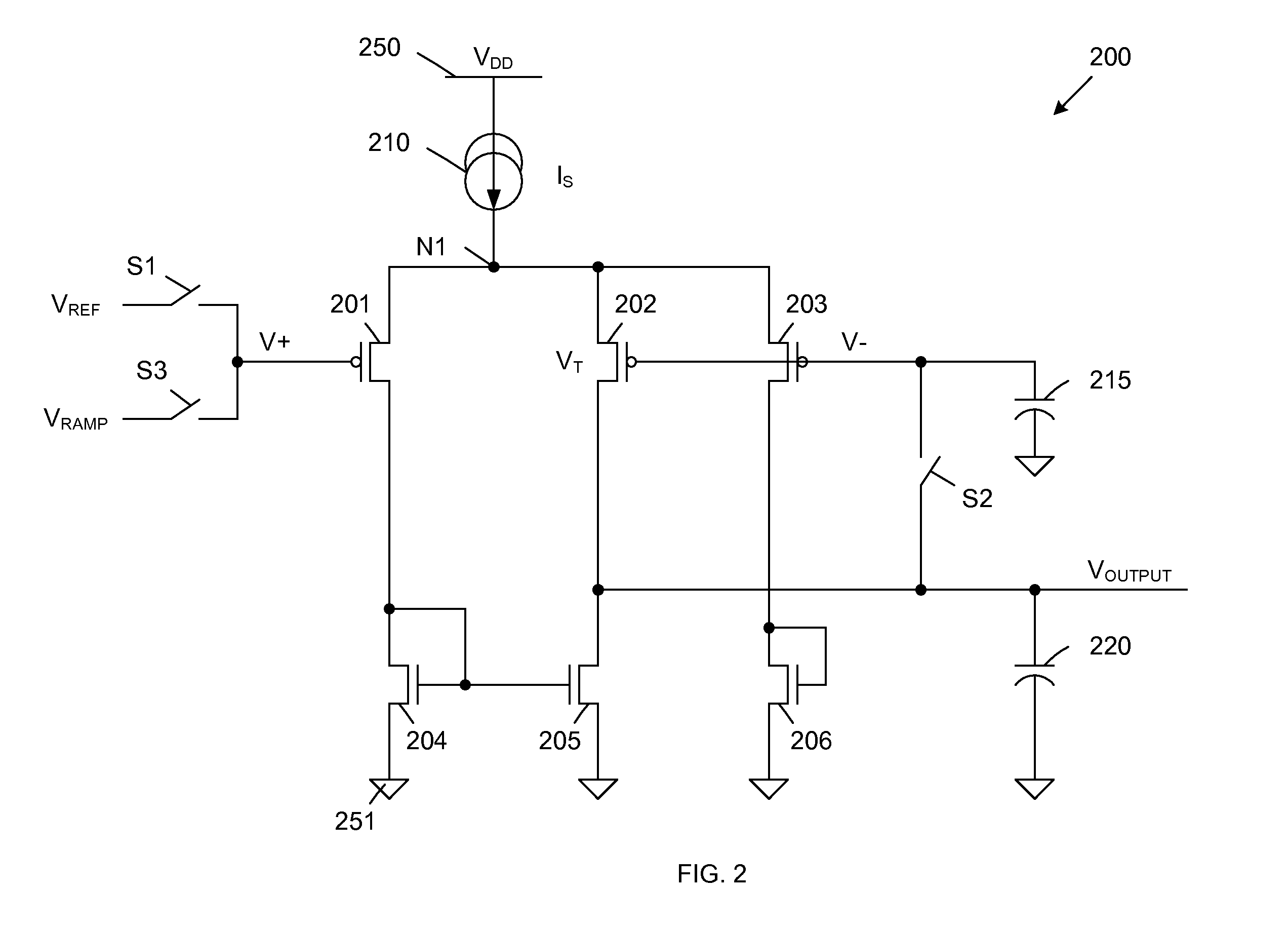

ActiveUS7609093B2Multiple input and output pulse circuitsInstant pulse delivery arrangementsOffset cancellationComparators circuits

A current control circuit is coupled in parallel with the current paths of a differential comparator circuit to ensure that a substantially constant current is drawn from a current source during all operating phases of a comparator. The current control circuit is biased by a reference voltage, which is also used to bias a V− input terminal of the differential comparator circuit. The reference voltage is stored by a sample capacitor, which is charged by applying the reference voltage to a V+ input terminal of the differential comparator circuit while coupling an output terminal of the differential comparator circuit to the sample capacitor in a unity feedback configuration.

Owner:TOWER SEMICONDUCTOR

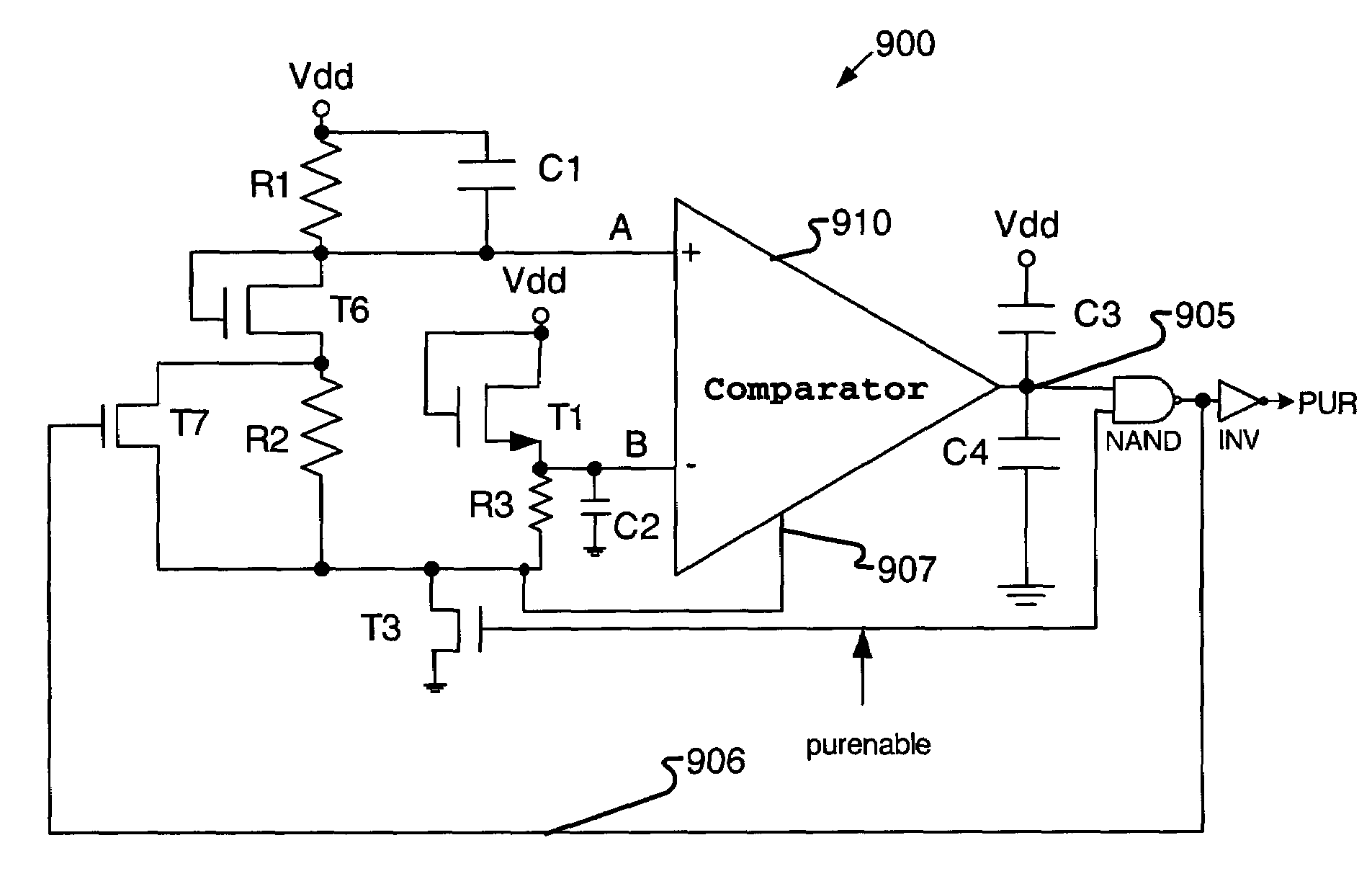

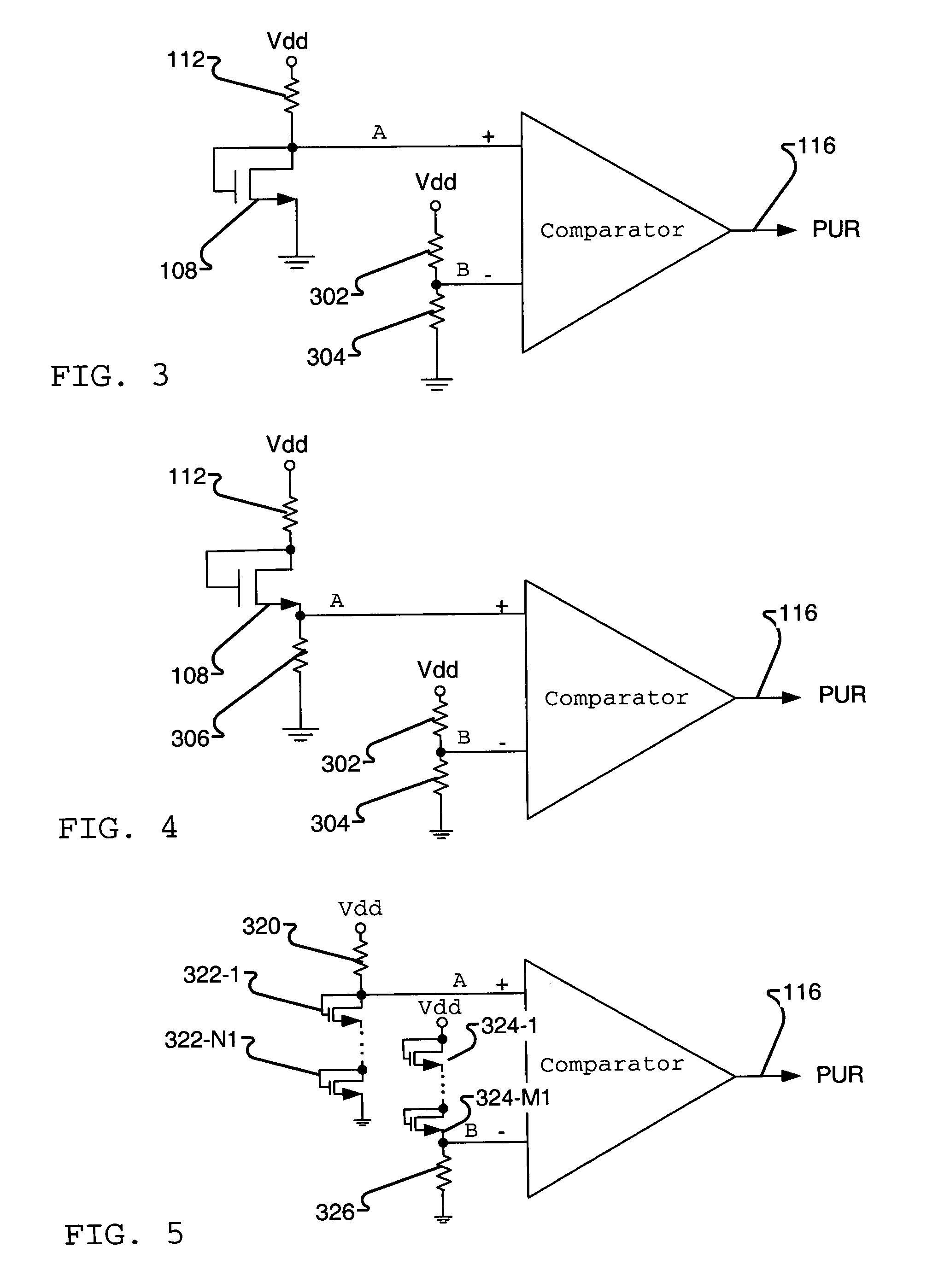

Voltage detector

InactiveUS7030668B1Pulse automatic controlInstant pulse delivery arrangementsDetector circuitsLow voltage

A voltage detector circuit such as a power up and / or brownout detector circuit (100) includes a comparator (102) having at least one of its inputs (104) coupled to a diode-connected transistor (108). The other input can include another diode-connected transistor (110) or a resistor divider (302). Optional compensation capacitors (118 and 120) can be added to the comparator output (116) to provide glitch compensation. Since comparator (102) only needs to output a high or low voltage level, the components that are used to build circuit (100) do not have to have very tight tolerances. Circuit (100) also can operate at very low voltages and consume low amounts of power.

Owner:XILINX INC

Comparator with low supplies current spike and input offset cancellation

ActiveUS20090033370A1Multiple input and output pulse circuitsInstant pulse delivery arrangementsOffset cancellationComparators circuits

A current control circuit is coupled in parallel with the current paths of a differential comparator circuit to ensure that a substantially constant current is drawn from a current source during all operating phases of a comparator. The current control circuit is biased by a reference voltage, which is also used to bias a V− input terminal of the differential comparator circuit. The reference voltage is stored by a sample capacitor, which is charged by applying the reference voltage to a V+ input terminal of the differential comparator circuit while coupling an output terminal of the differential comparator circuit to the sample capacitor in a unity feedback configuration.

Owner:TOWER SEMICONDUCTOR

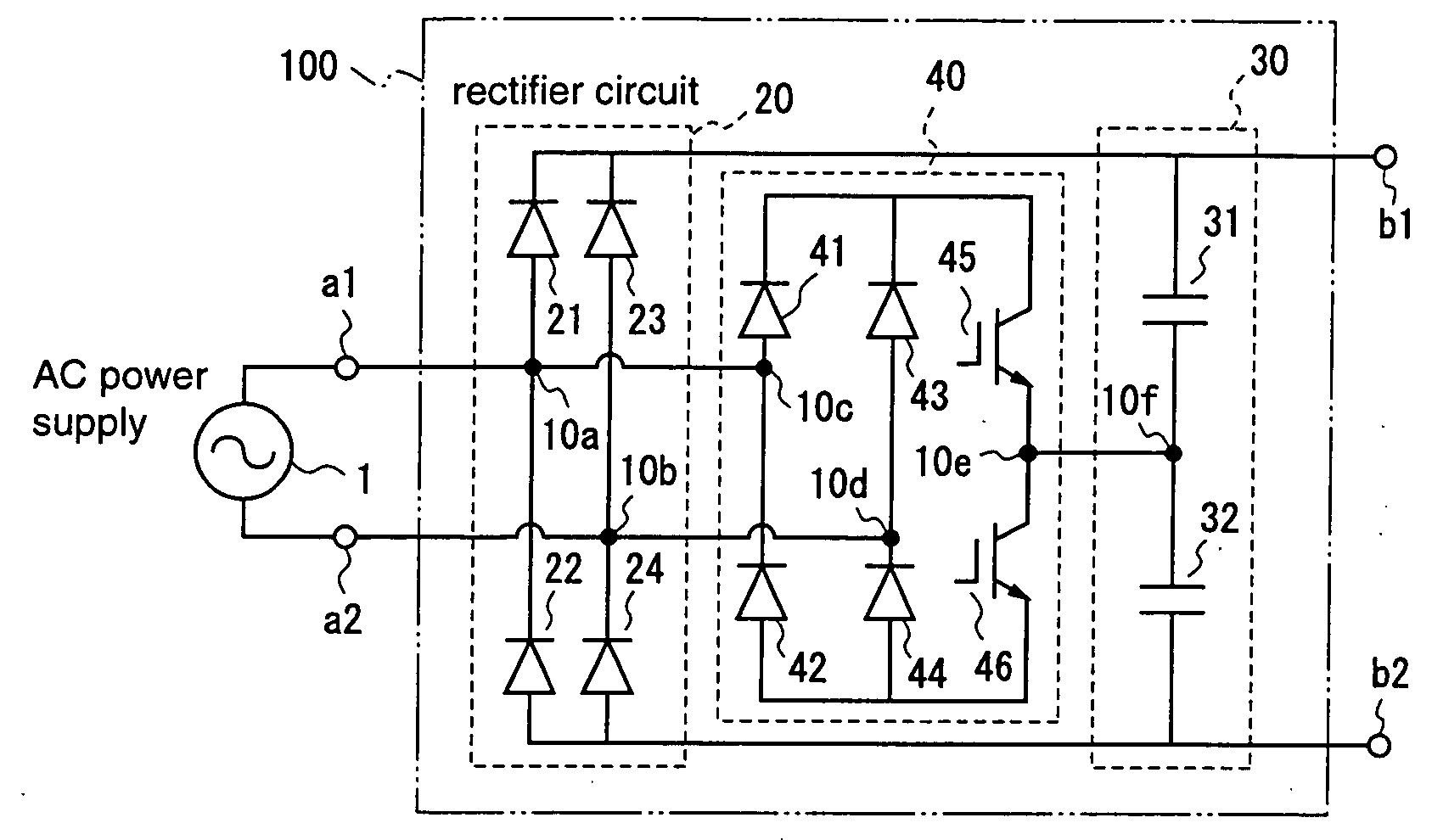

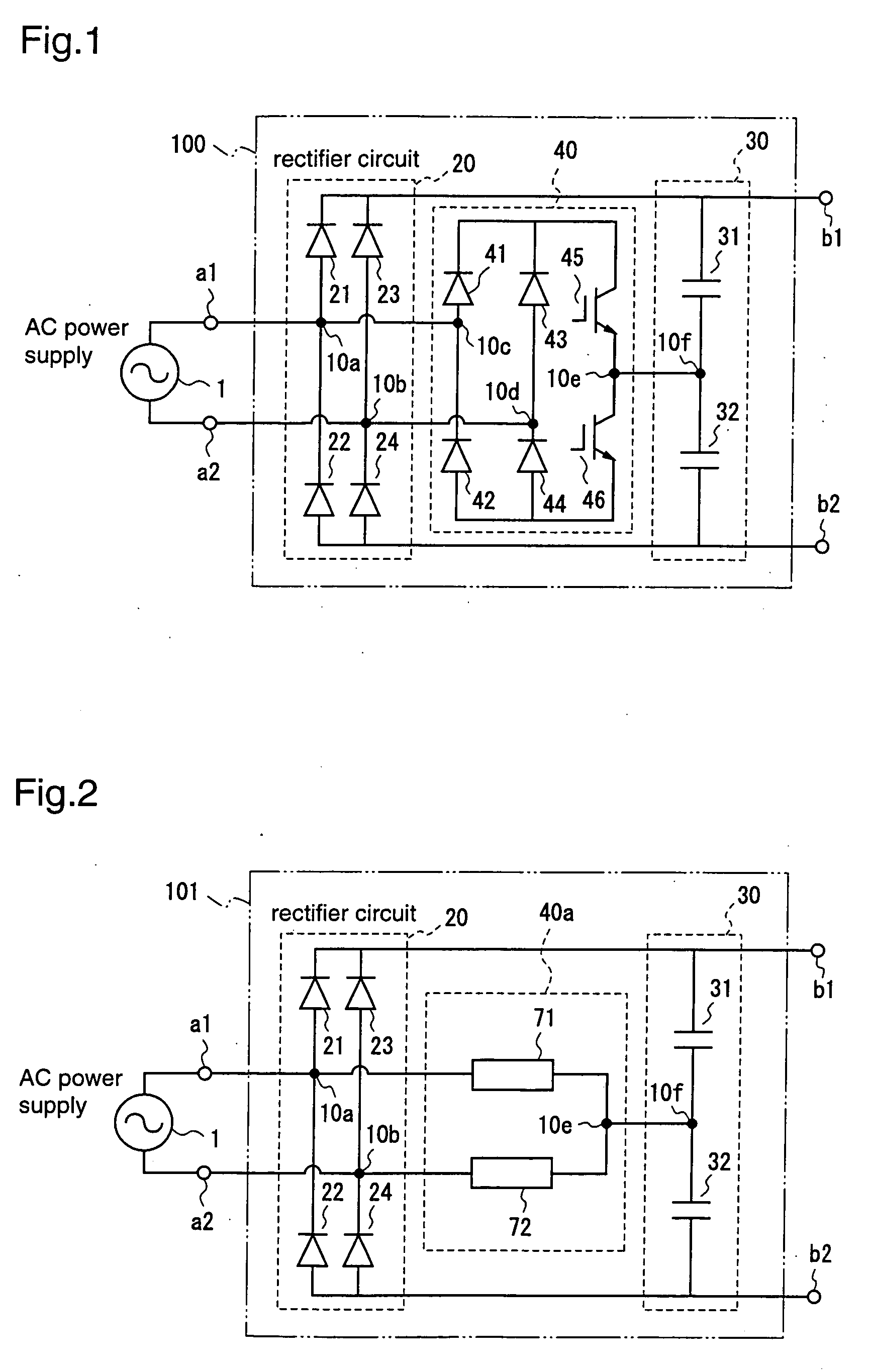

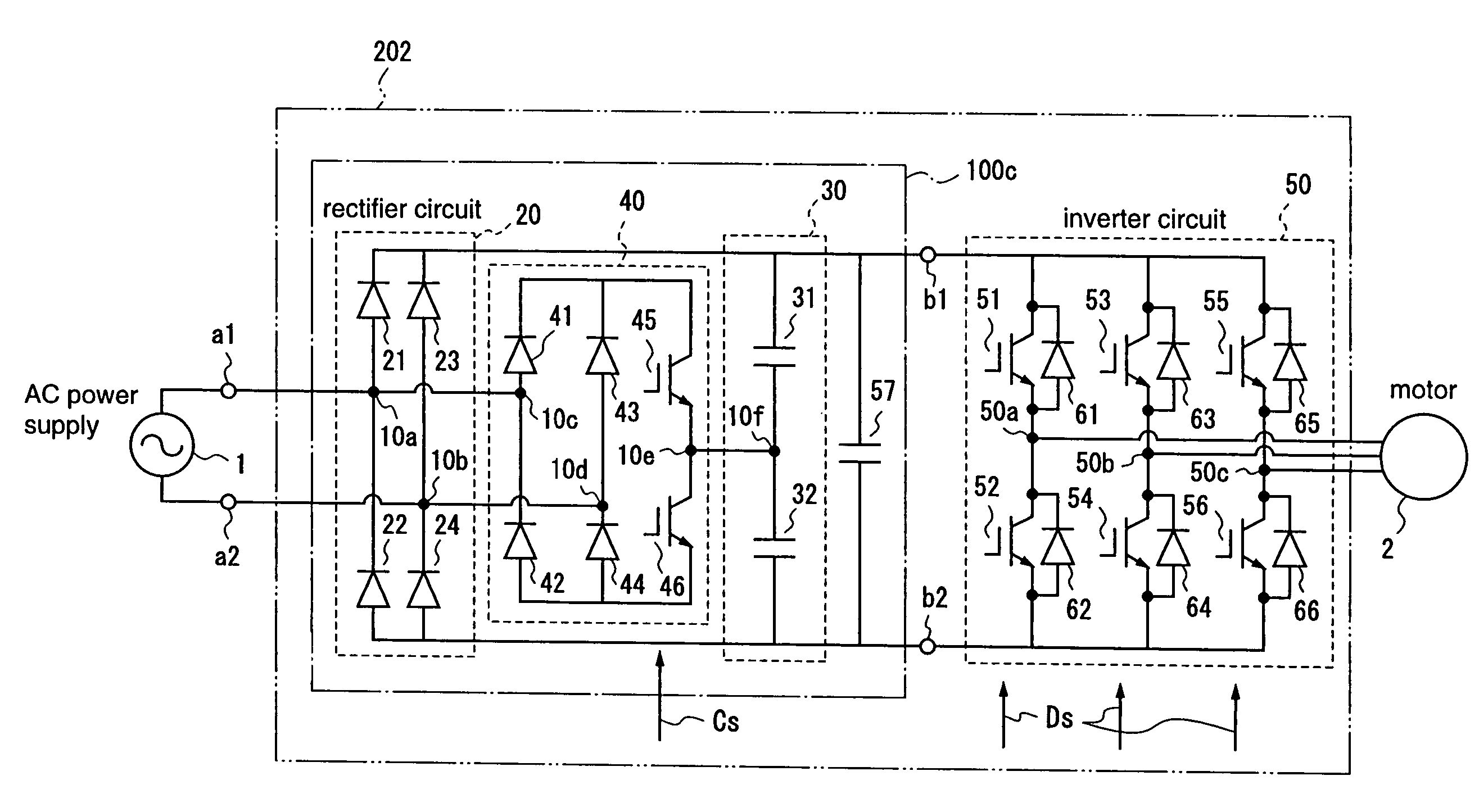

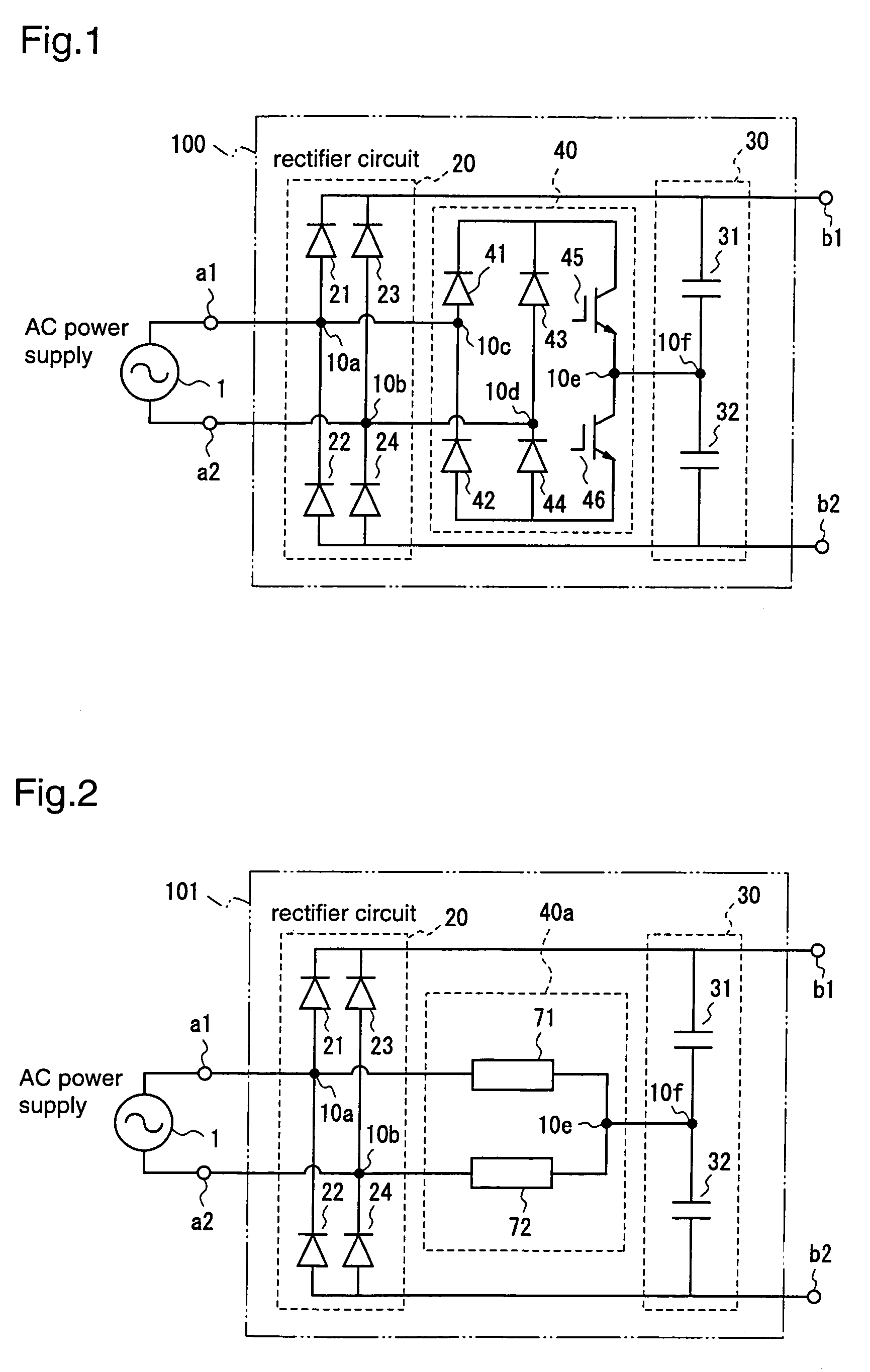

Converter circuit and motor driving apparatus

InactiveUS20050057210A1Reduce the capacitance of the capacitorLow costAc-dc conversion without reversalDC motor speed/torque controlMotor driveAC power

A converter circuit for converting an output voltage from an AC power supply is provided with a rectifier circuit for rectifying the output voltage of the AC power supply; first and second capacitors connected in series, for smoothing the output of the rectifier circuit; and a switch circuit for switching the connections between the respective capacitors and the AC power supply so that the output voltage of the AC power supply is applied to each of the respective capacitors at a cycle shorter than the cycle of the AC power supply.

Owner:PANASONIC CORP

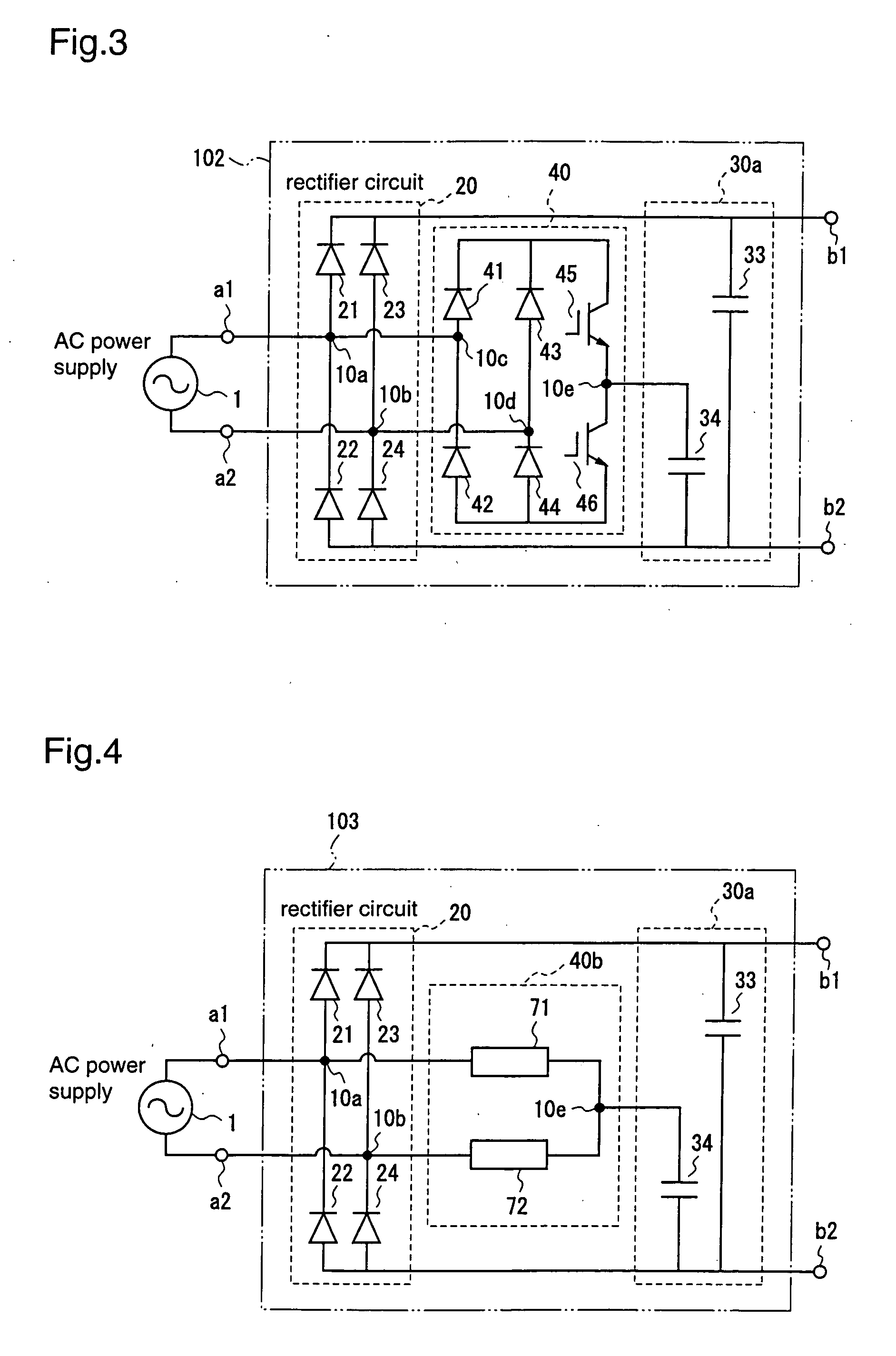

Delay compensation circuit

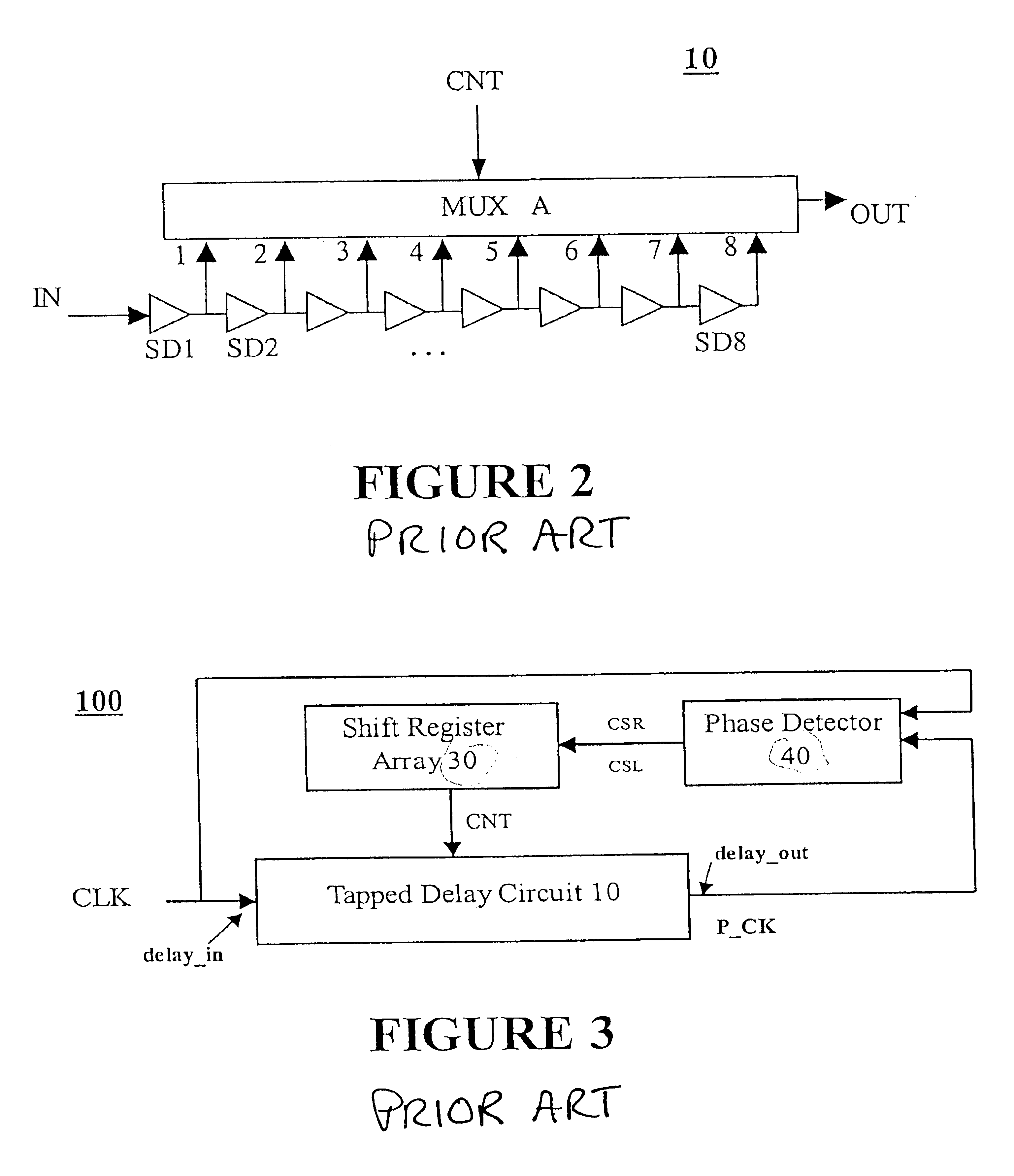

A delay compensation circuit that determines the effects of process, voltage, and temperature (PVT) conditions of a chip by measuring the effective delay time of delay components inside the chip. The delay compensation circuit includes a plurality of sampler modules, each of which receives a delayed clock signal from one of a series of delay cells within a tapped delay circuit. The delay compensation circuit generates an output value based on the total number of sampling modules that lock into a fixed input signal using the delayed clock signals. Since the delay time of each delay cell changes based on variations of PVT conditions, the output values generated by the delay compensation circuit are determinate of PVT conditions in the chip. These output values can be used to design components to compensate for variances in PVT conditions or to control a variable delay component based on detected PVT conditions.

Owner:ALCATEL-LUCENT USA INC +1

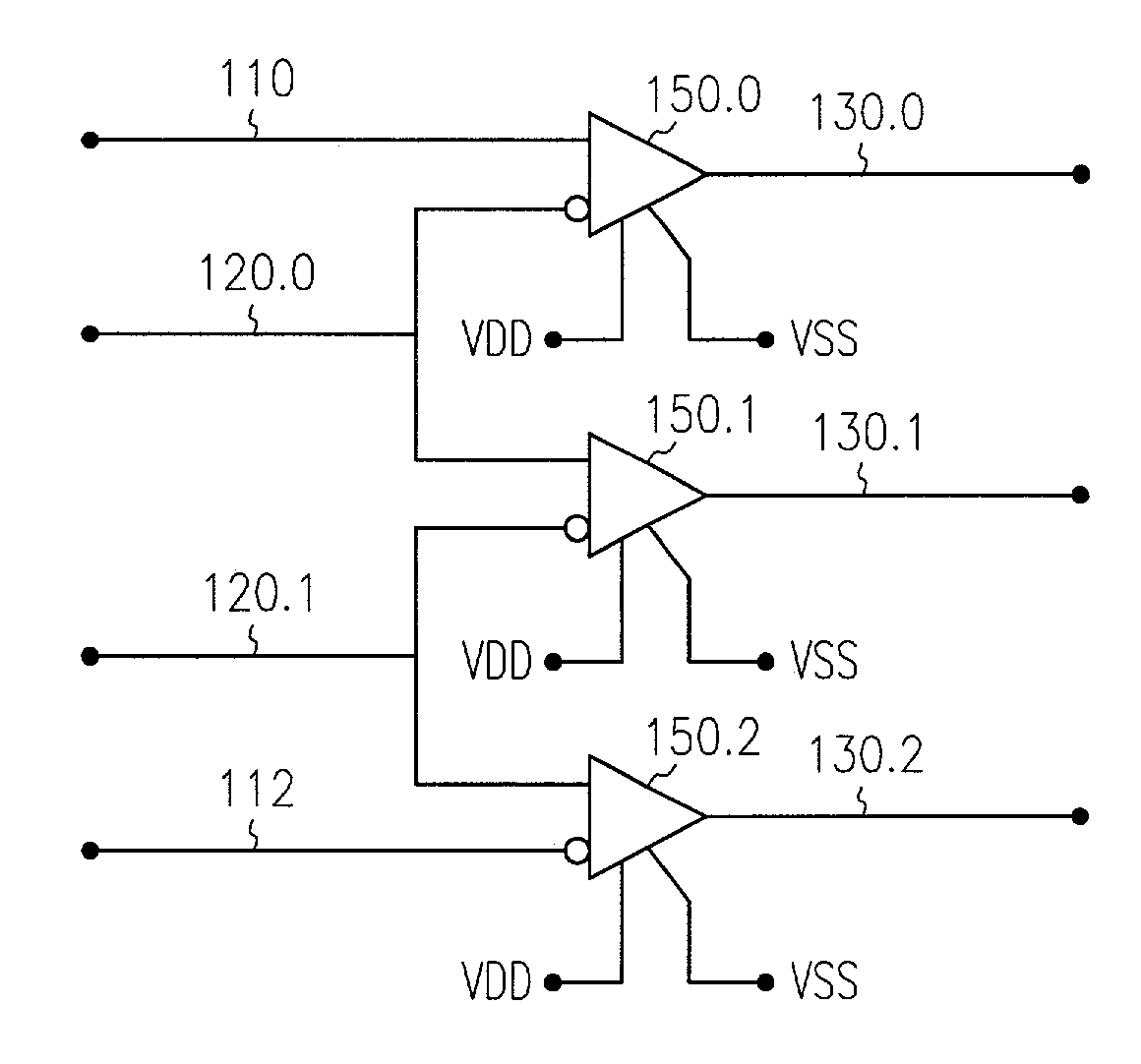

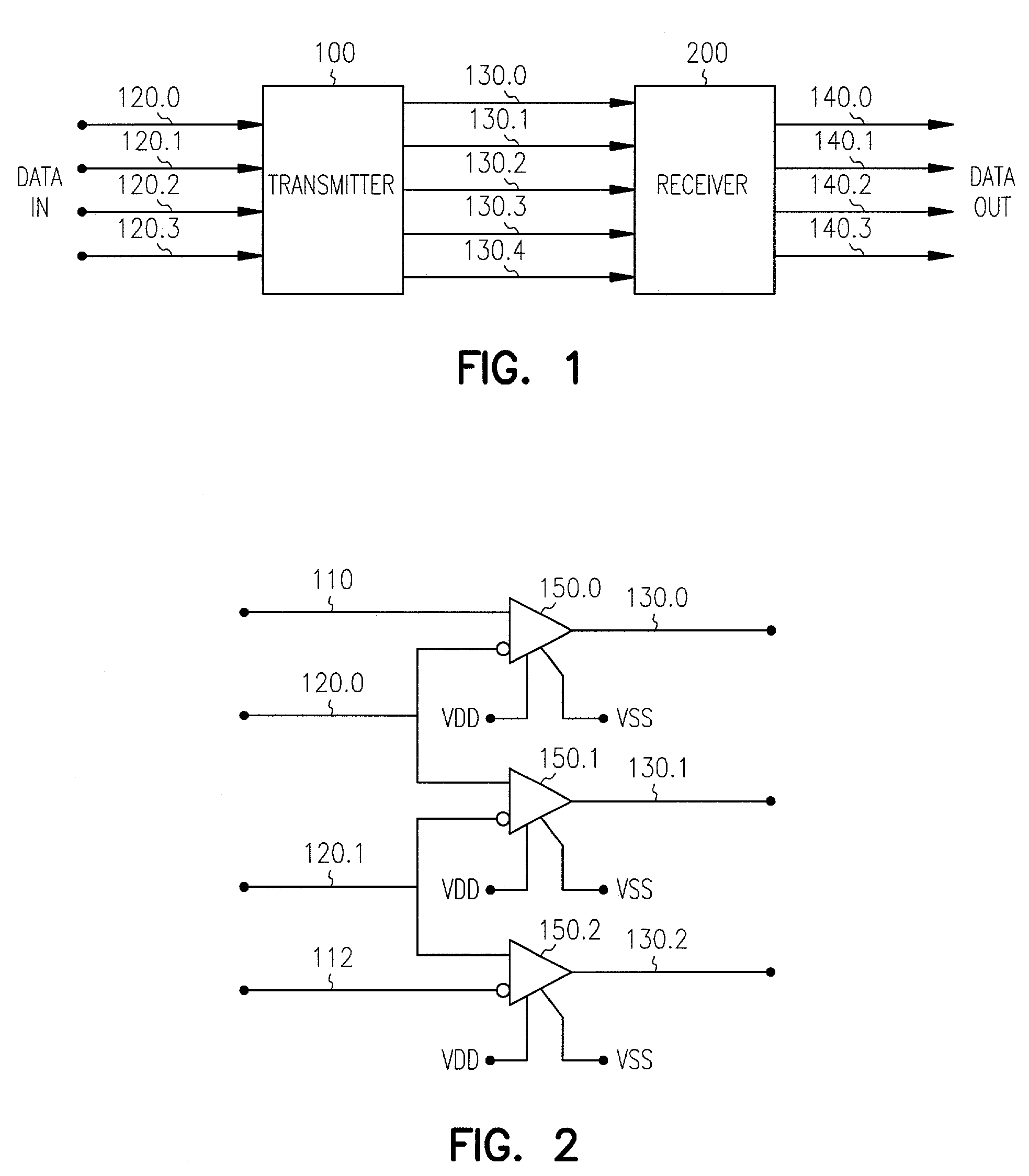

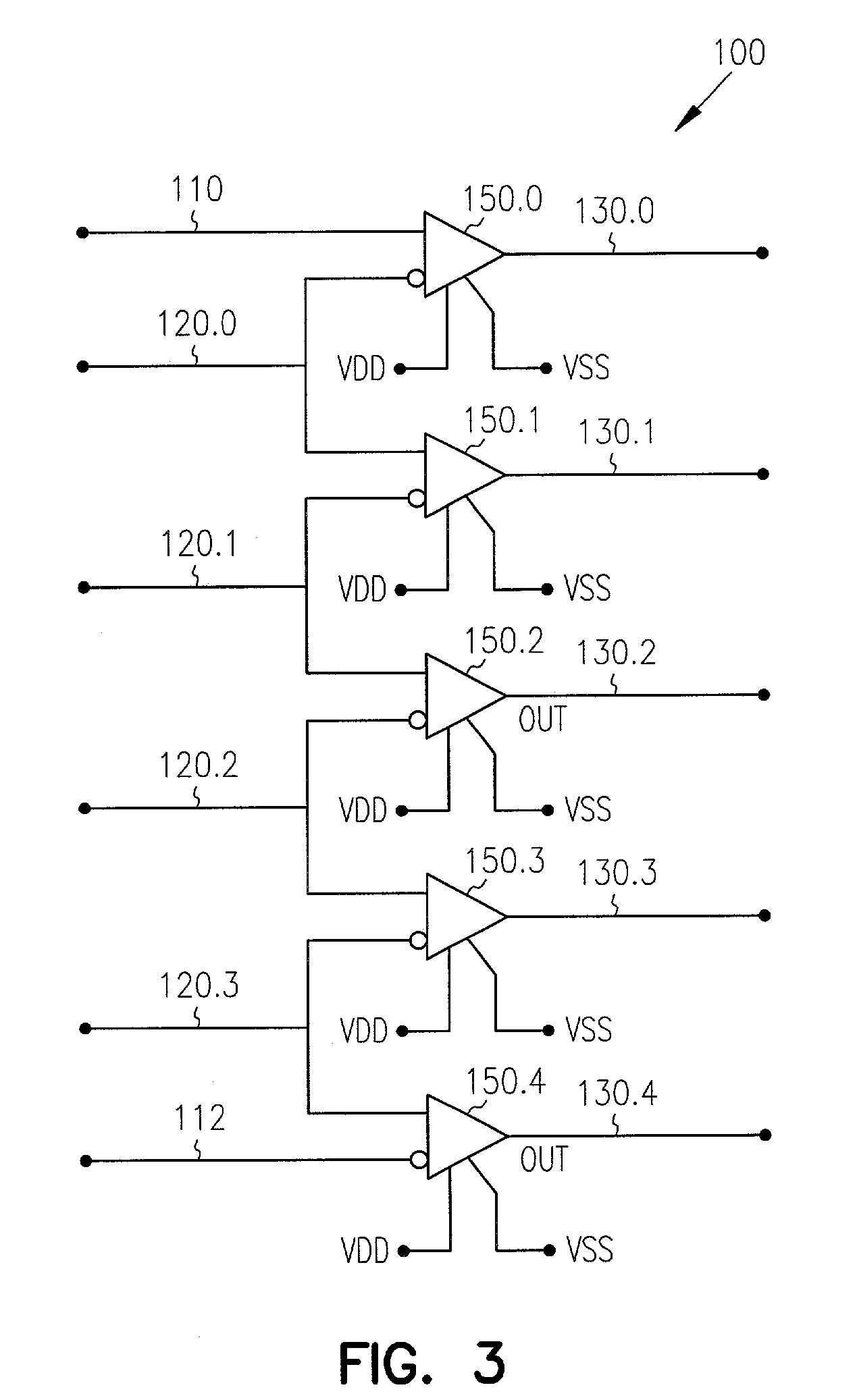

Spacial derivative bus encoder and decoder

InactiveUS7167523B2Reduce noiseReduce power consumptionMultiple input and output pulse circuitsChannel dividing arrangementsData signalBus encoding

A method and apparatus for providing efficient and accurate electronic data transmission of information on a data bus in the presence of noise. Data signals are received on a plurality of input lines by a spacial derivative encoder. The spacial derivative encoder encodes the signals and transmits them to a receiver having a spacial derivative decoder. The spacial derivative decoder then decodes the signals. Minimal overhead is required as for n input lines only n+1 lines are needed to transmit each of the encoded signals.

Owner:MORGAN STANLEY +1

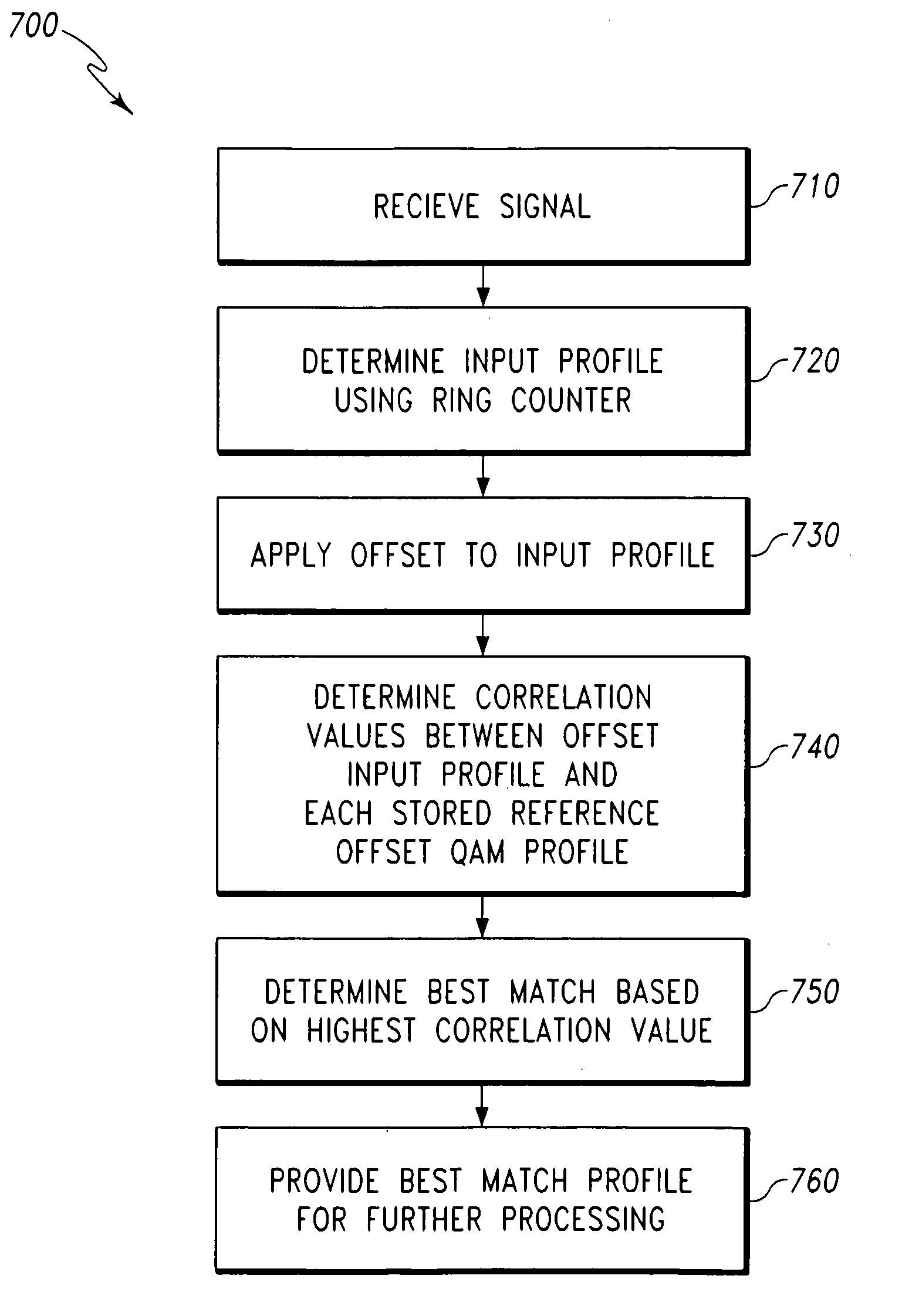

Apparatus and method for determination of signal format

InactiveUS20110074500A1Multiple input and output pulse circuitsMultiple modulation transmitter/receiver arrangementsRing counterSignal analyzer

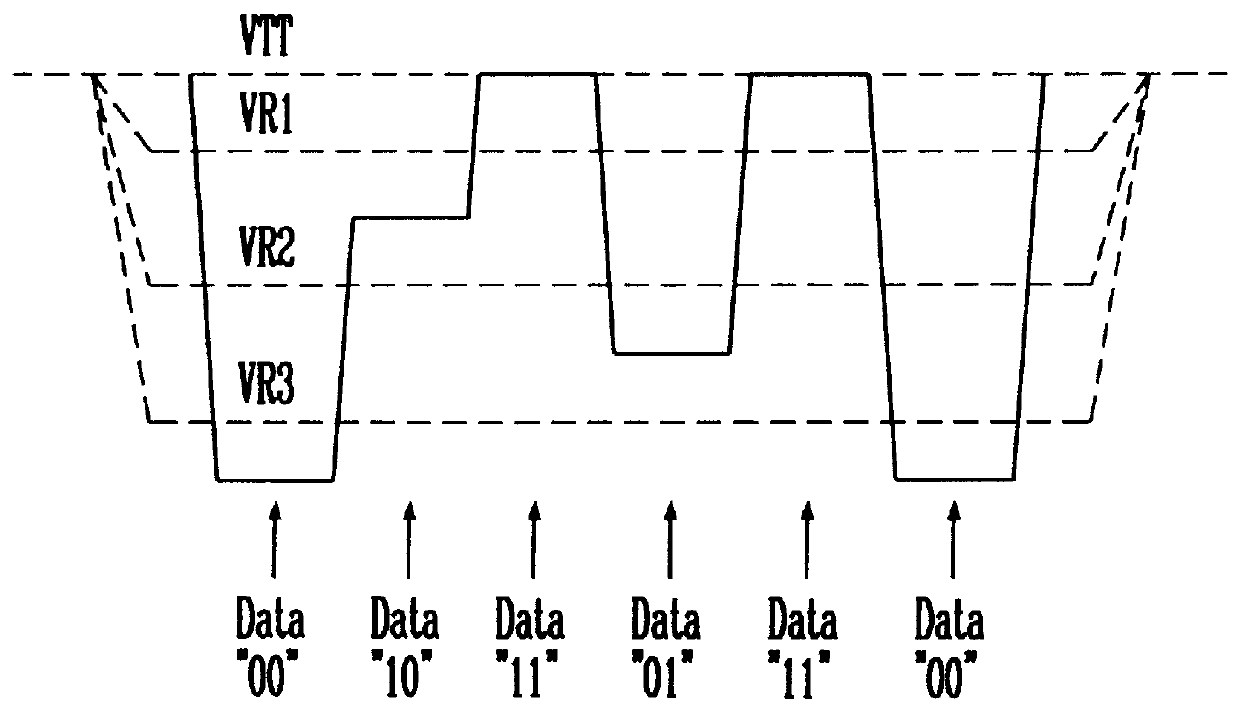

The determination of the signal modulation format for a channel is an important aspect of the operation of a signal receiver. A method (700) is described including the steps of receiving (710) a signal, comparing (720) a sample of the received signal to a first threshold value and a second threshold value, creating (720) a signal profile based on the comparison, and selecting (750) a modulation format for the received signal based on the signal profile. An apparatus (500) is also described including a ring counter (510) that receives a sample of an input signal, compares the sample to a first threshold value and a second threshold value, and creates a signal profile for the input signal, a signal profiler (550) that compares the signal profile for the input signal to at least two reference profiles, and a detector (560) that determines a modulation format for the input signal based on the comparison in the signal profiler (550).

Owner:MAGNOLIA LICENSING LLC

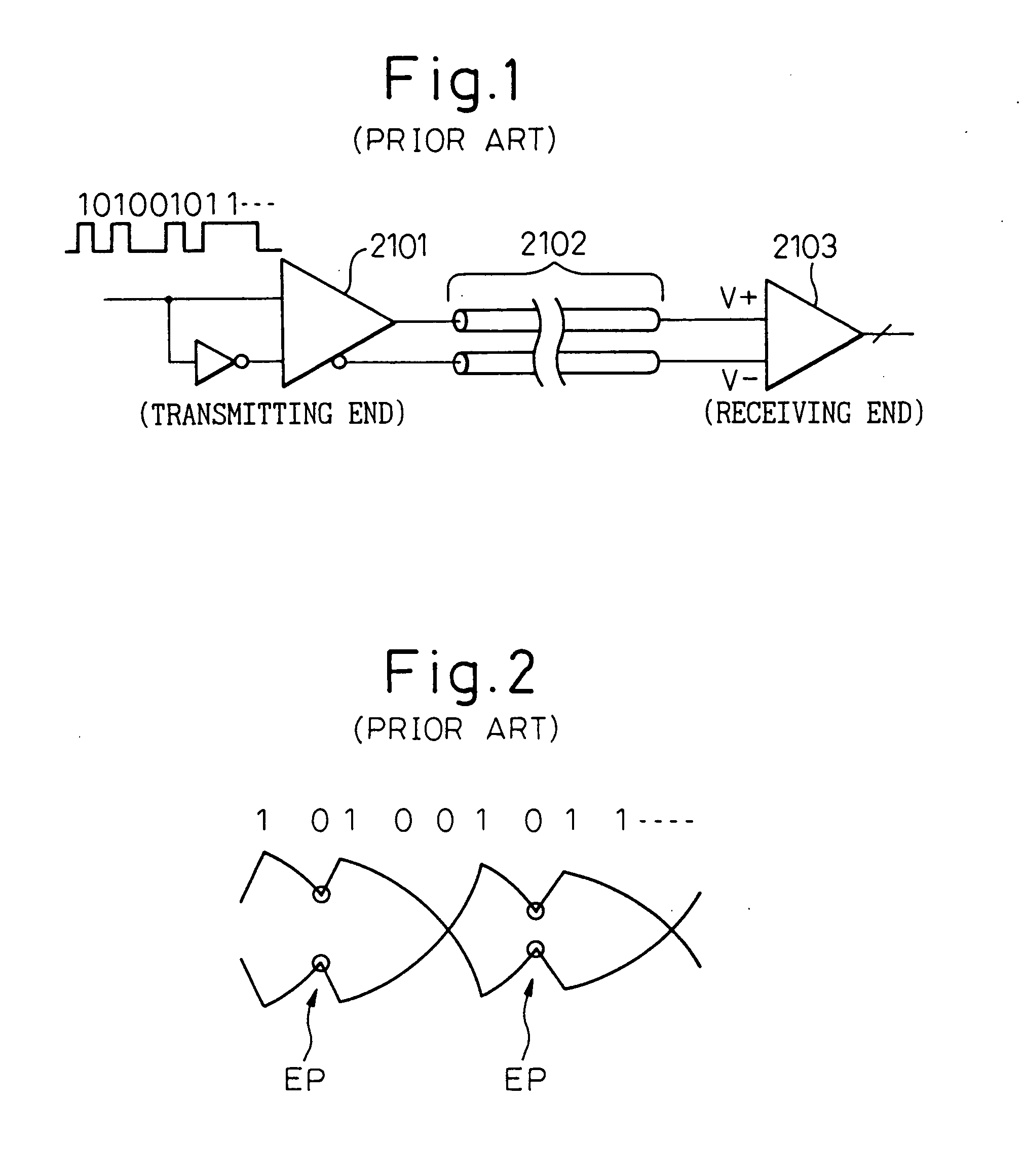

High speed interface apparatus

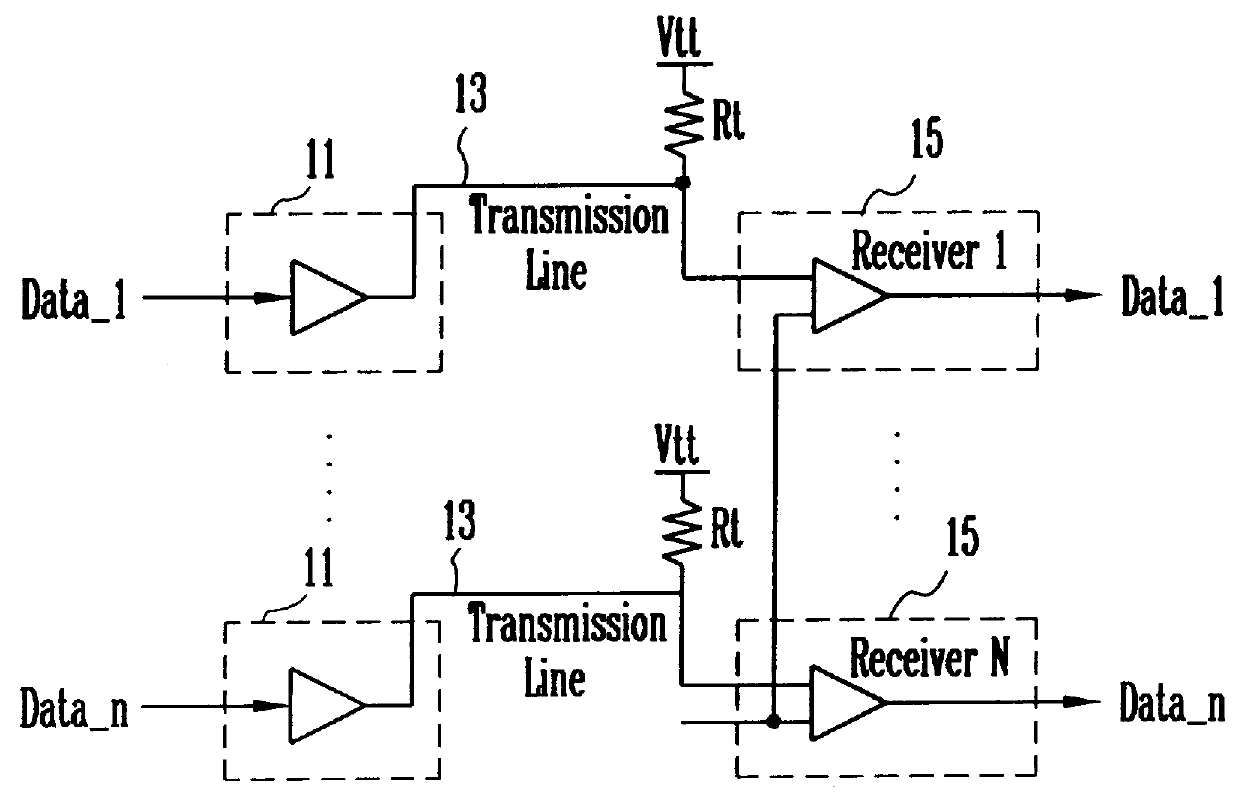

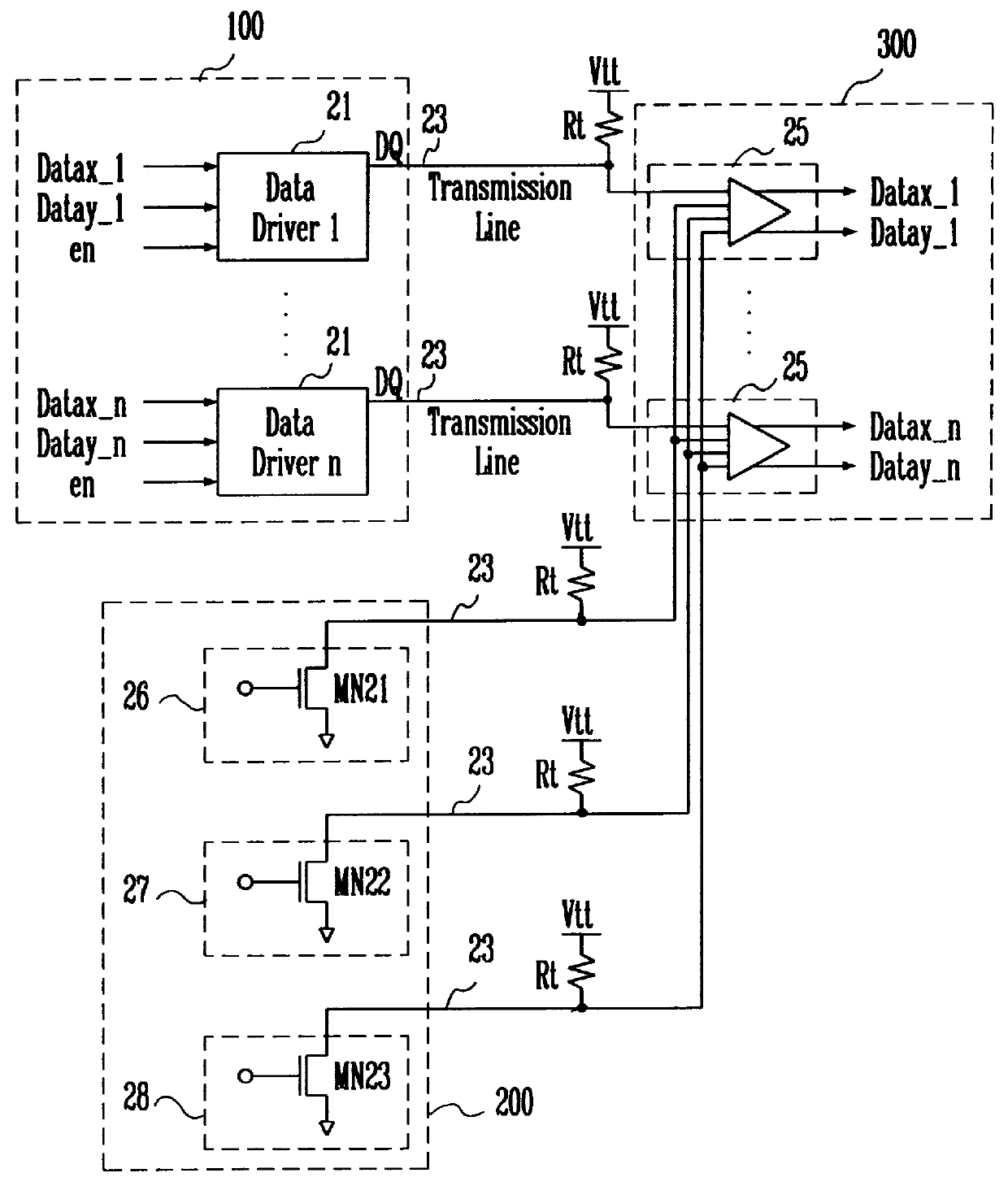

InactiveUS6140841AElectric signal transmission systemsElectric analogue storesThree levelData signal

The present invention discloses a much higher speed interface apparatus which comprises a data driving means for decoding two-bit data signals using them as inputs to output four-level data signals; a reference voltage generating means for generating three-level reference voltages to discriminate the voltage levels of the four-level data signals; and a receiver means for comparing the four-level data signals and the three-level reference voltage signals using them as inputs and for encoding the resulting signals to output two data signals.

Owner:HYUNDAI ELECTRONICS IND CO LTD

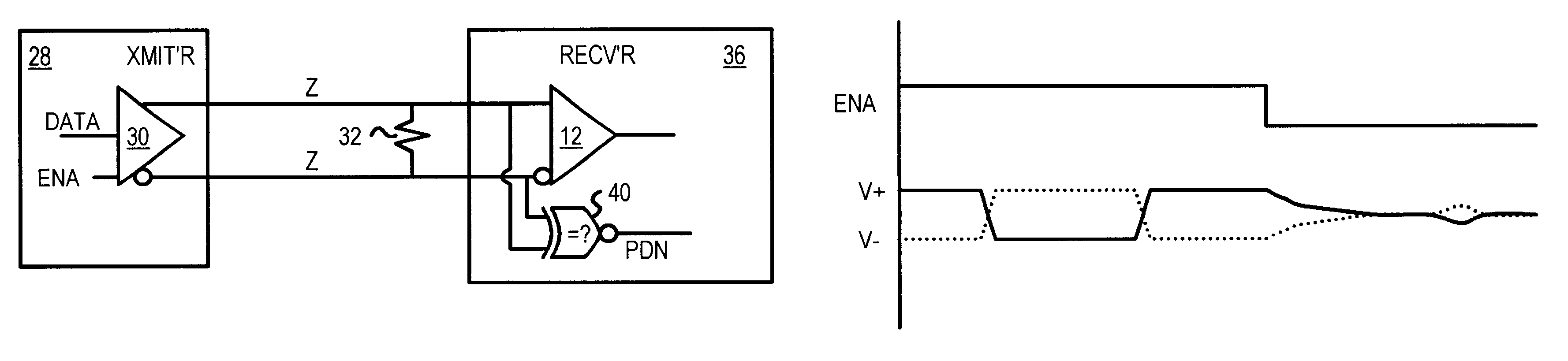

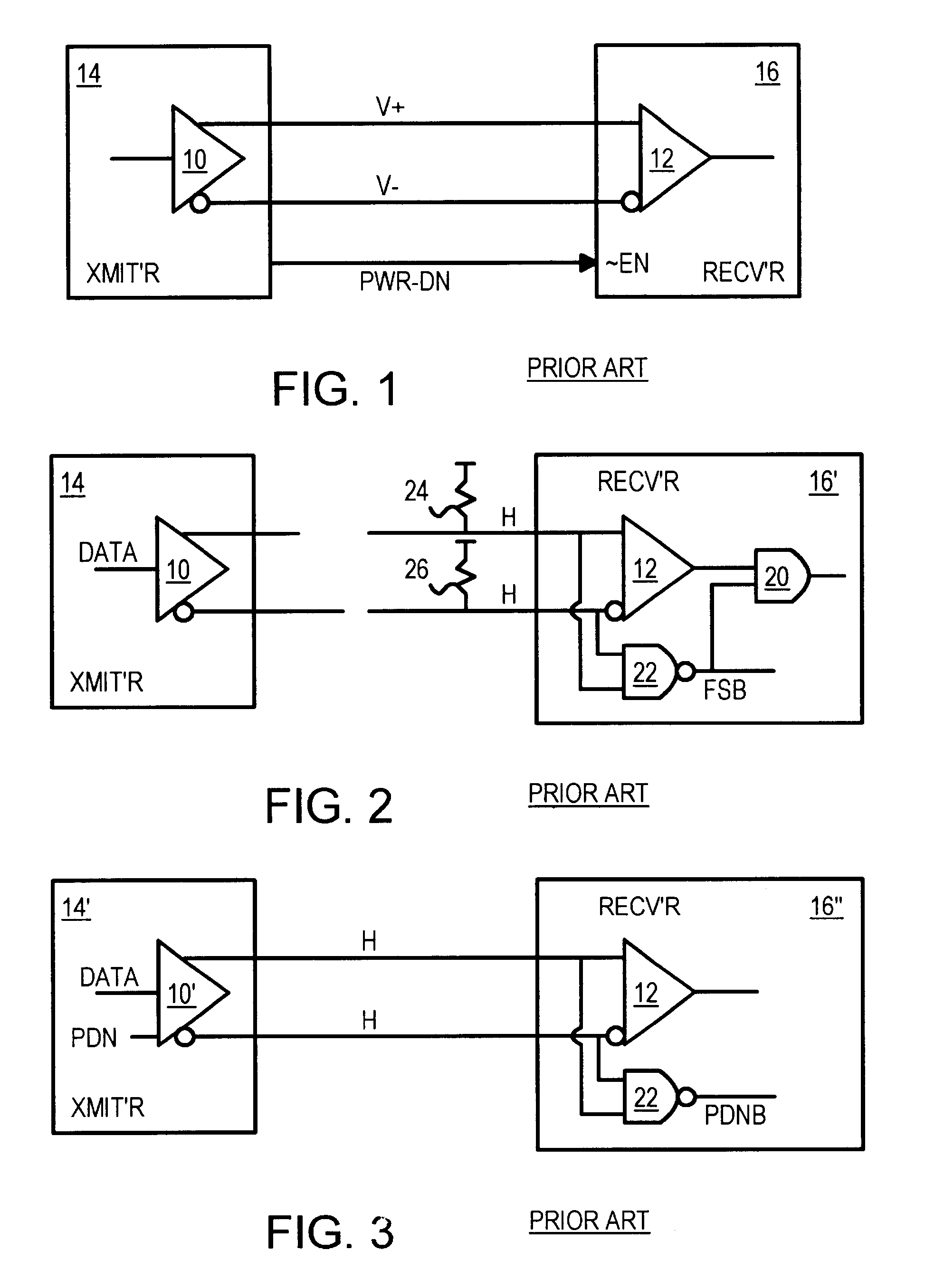

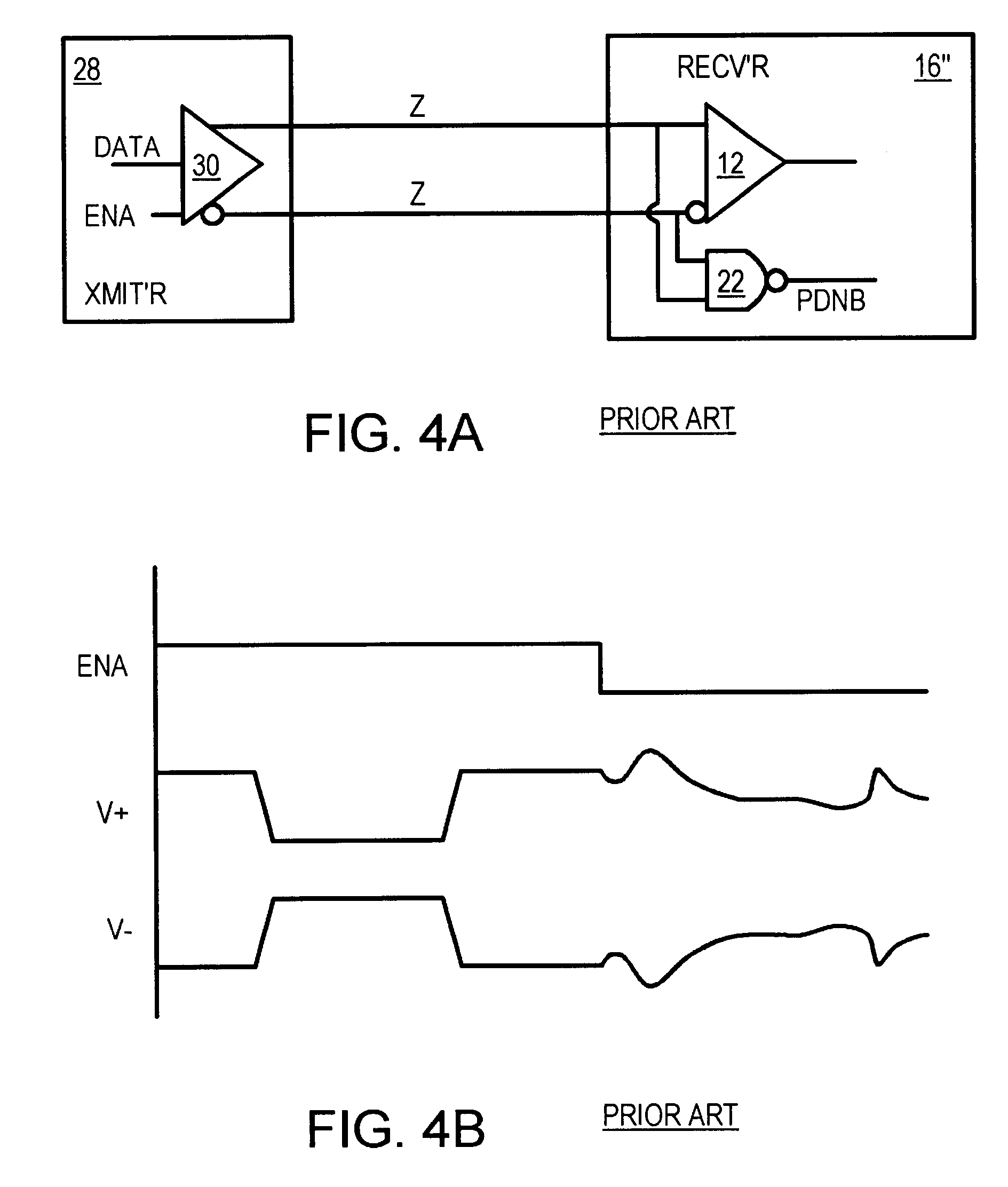

Power down mode signaled by differential transmitter's high-Z state detected by receiver sensing same voltage on differential lines

InactiveUS6593801B1Energy efficient ICTMultiple input and output pulse circuitsElectricityDifferential line

A power-down signal is encoded into a differential pair of lines between two chips. When the differential transmitter powers down, it enters a high-impedance state and floats the differential lines A shunt resistor between a pair of differential lines equalize the voltages on the differential lines so they float to a same voltage when a differential transmitter is disabled and enters a high-impedance state. The condition of equal voltages on the differential lines is detected by an equal-voltage detector that generates a power-down signal when the differential lines are at equal voltages for a period of time. The period of time can be greater than the cross-over time during normal switching to prevent false power-downs during normal switching. Standard differential drivers can signal power-down using the high-impedance state, which is detected by equal voltages on the differential lines. A sensitive dual-differential amplifier and a simpler detector are disclosed.

Owner:DIODES INC

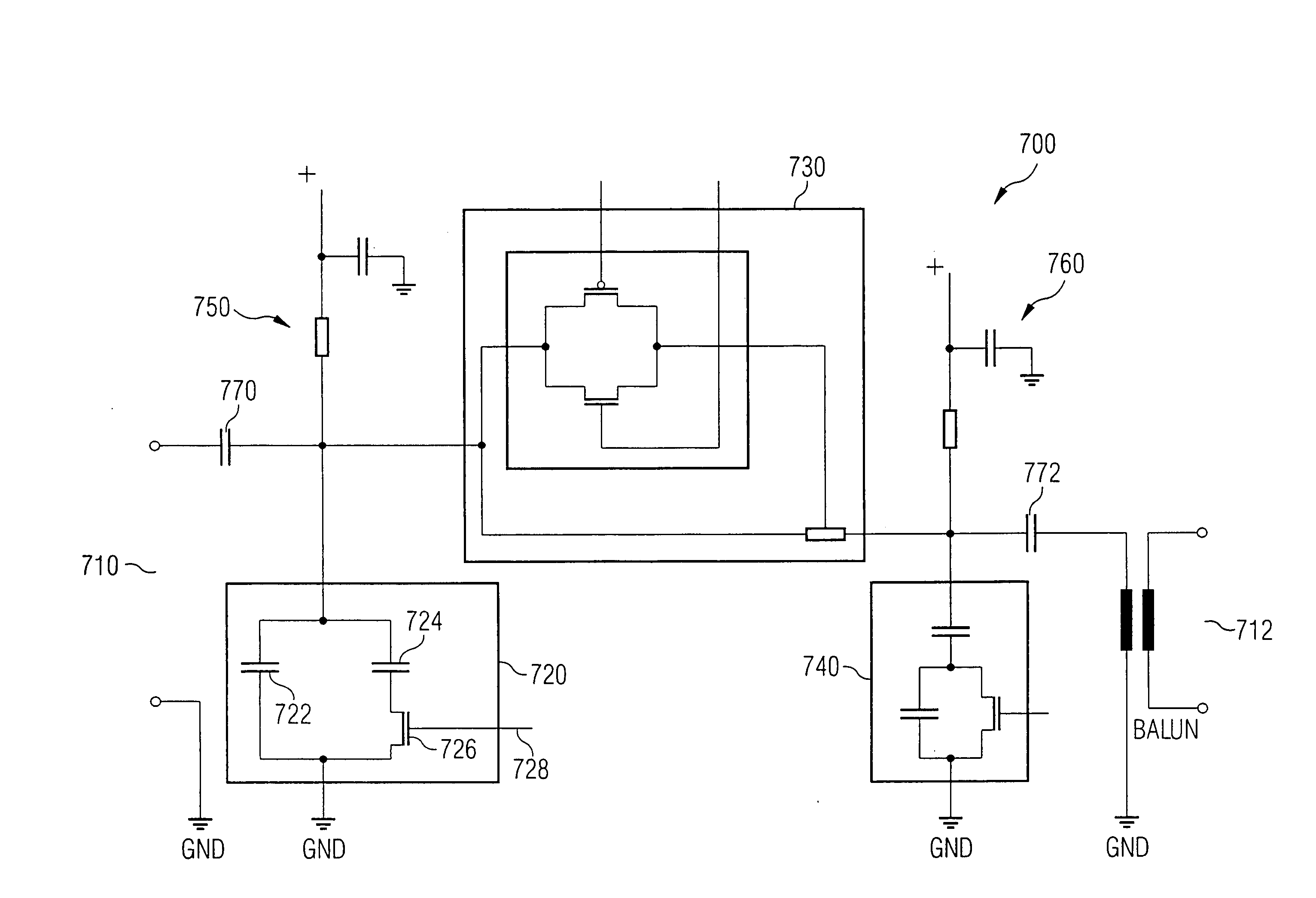

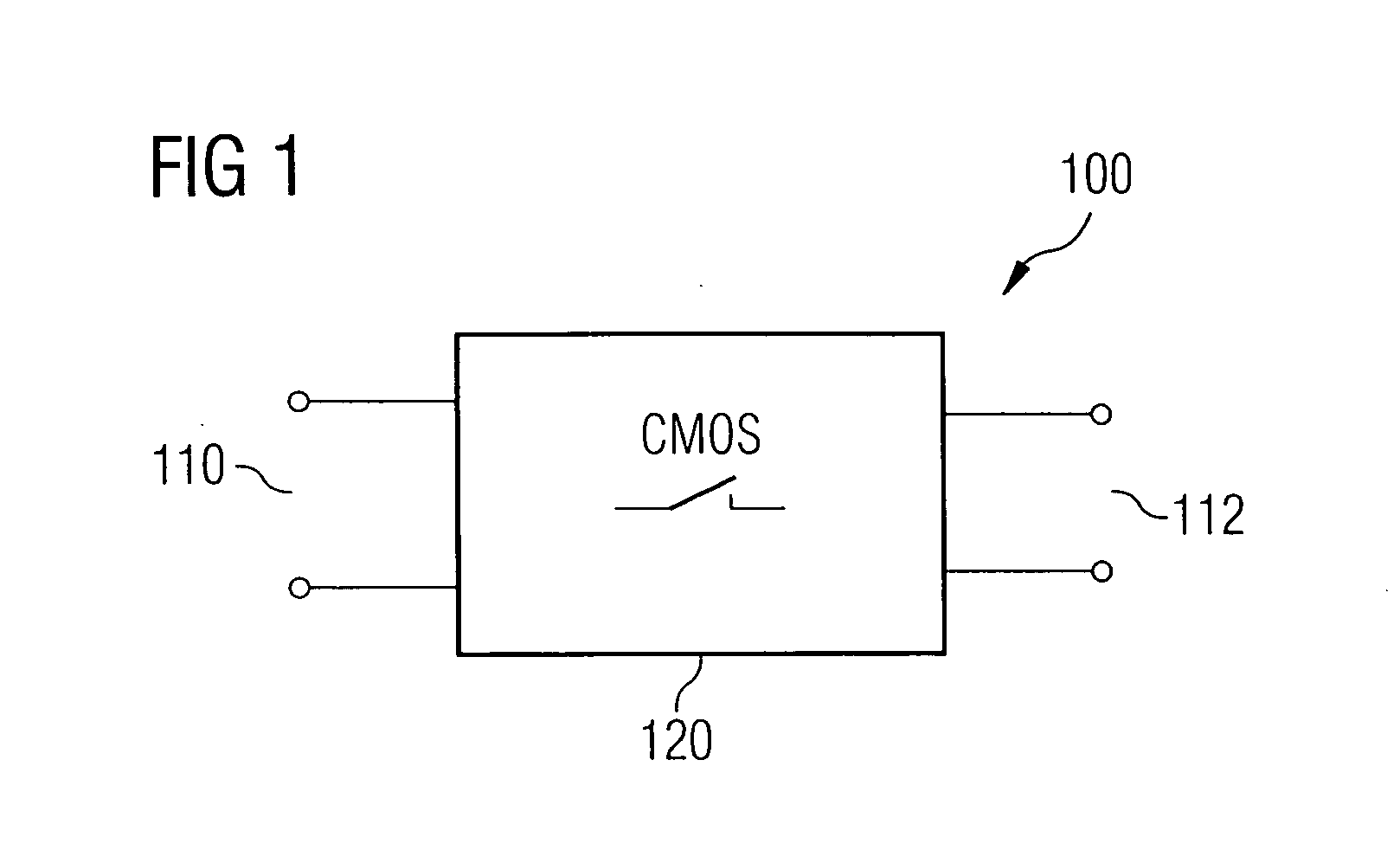

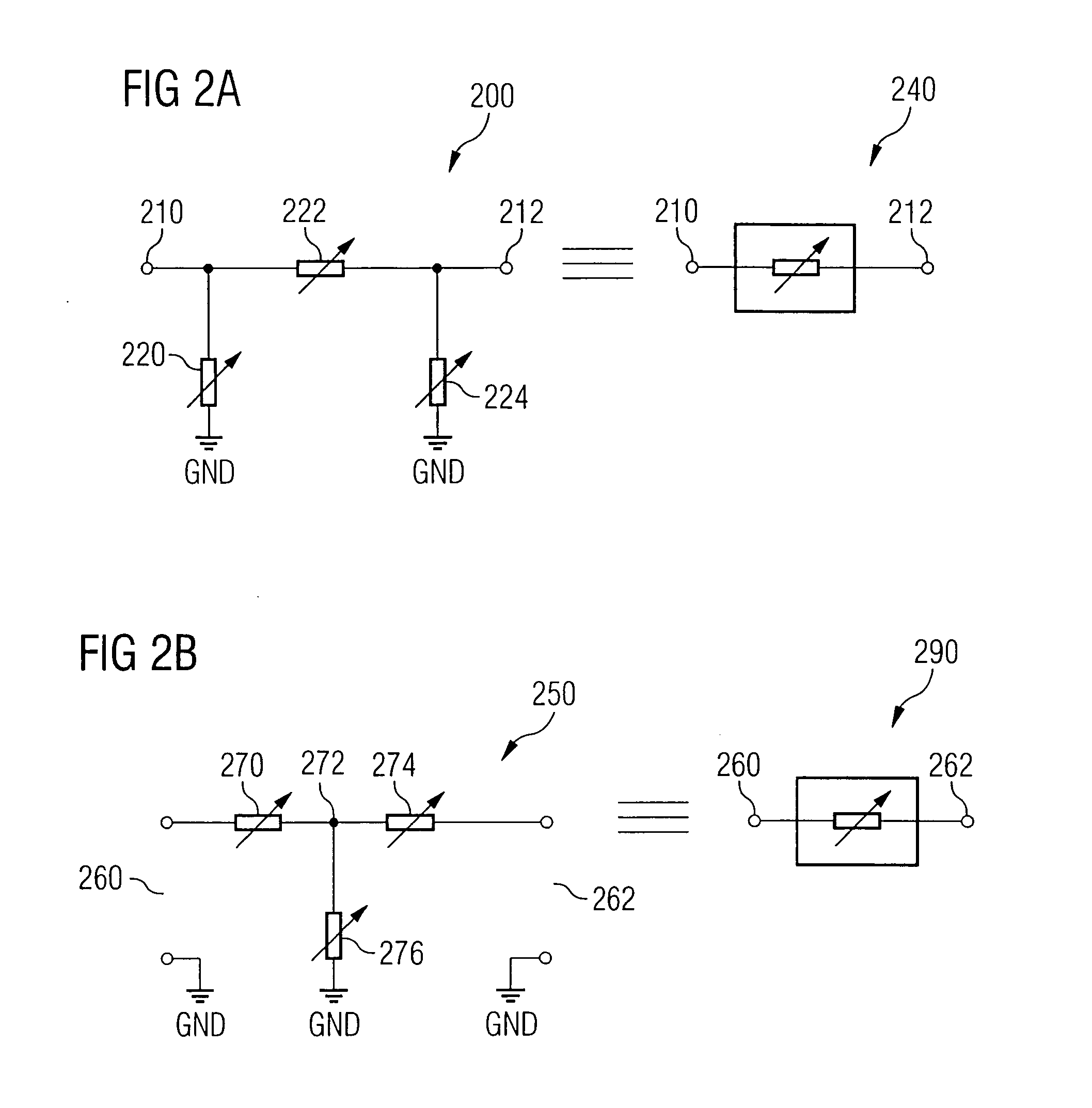

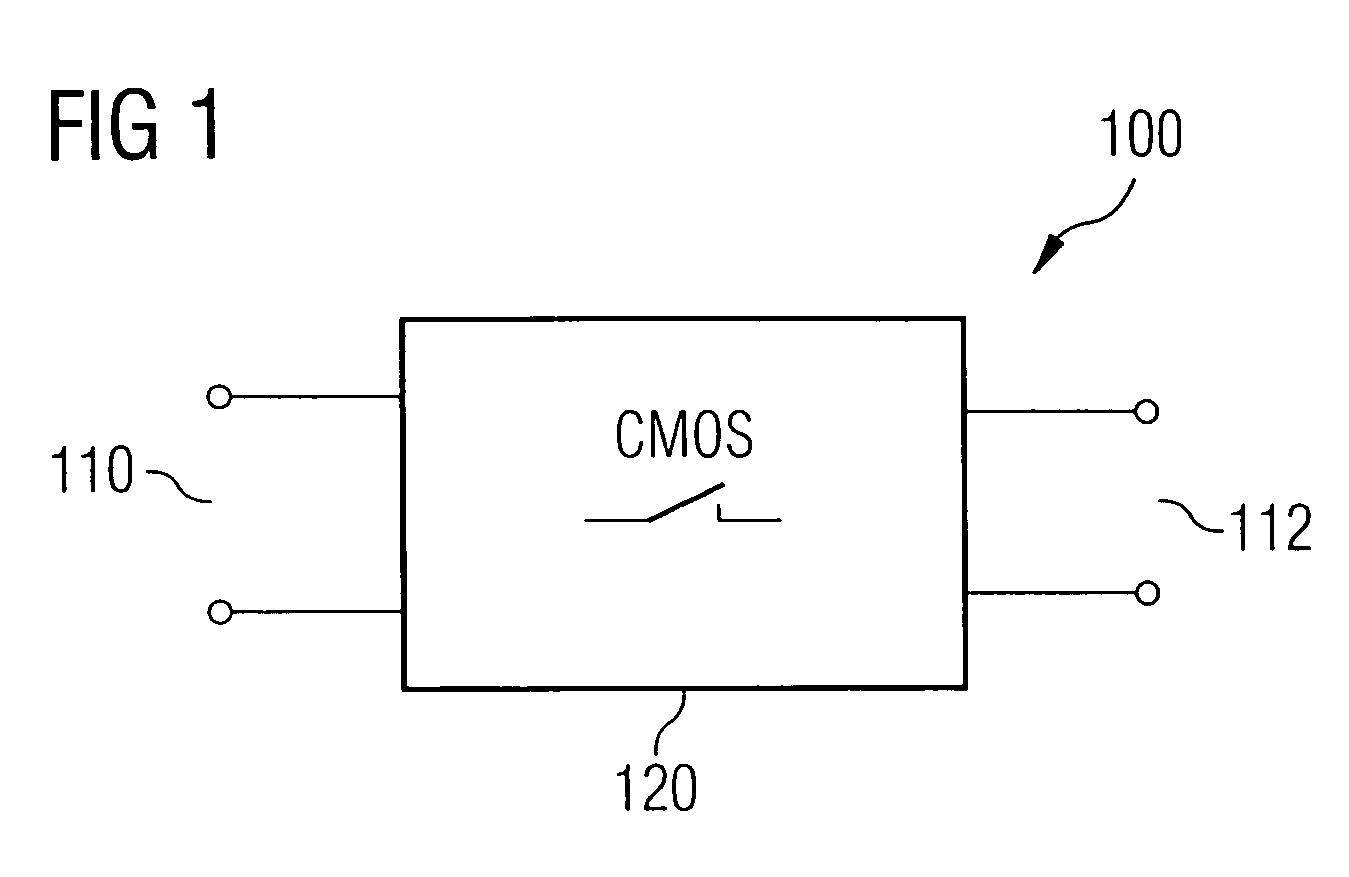

Matching network

InactiveUS20070155347A1Quick switchImproving Impedance MatchingMultiple-port networksResonant long antennasAudio power amplifierHigh frequency power

A matching network for matching an antenna to a transmitter or receiver comprises an input port for receiving high-frequency power, an output port and a switchable impedance transformation circuit, which is connected between the input port and the output port. The impedance transformation circuit comprises a CMOS switch in a high-frequency path, which has a first switching state and a second switching state. The impedance transformation circuit is implemented to match a first impedance applied to the output port to a first predetermined impedance in the first switching state, and to match a second impedance applied to the output port to a second predetermined impedance in the second switching state. The inventive matching network allows a particularly good utilization of power provided by a transmitting amplifier or an antenna.

Owner:INFINEON TECH AG

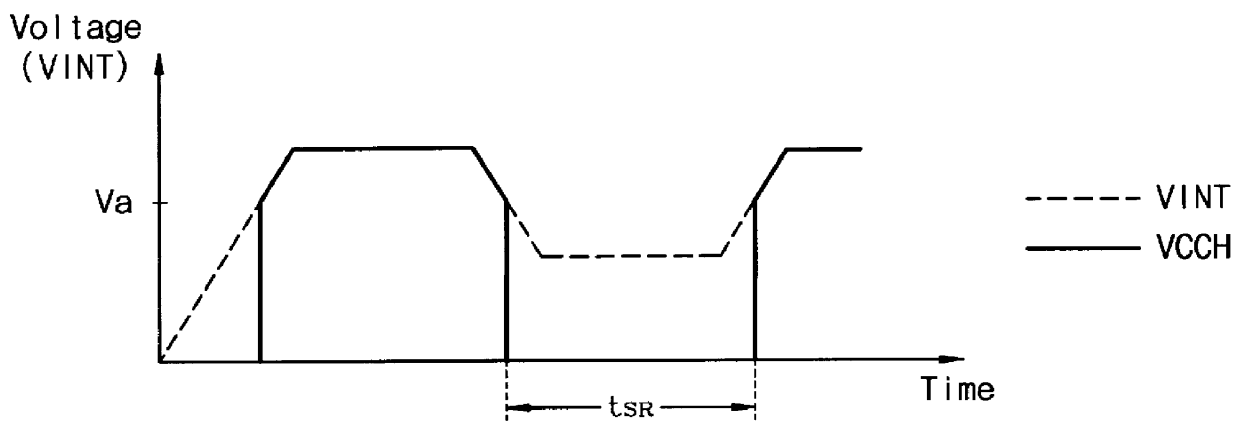

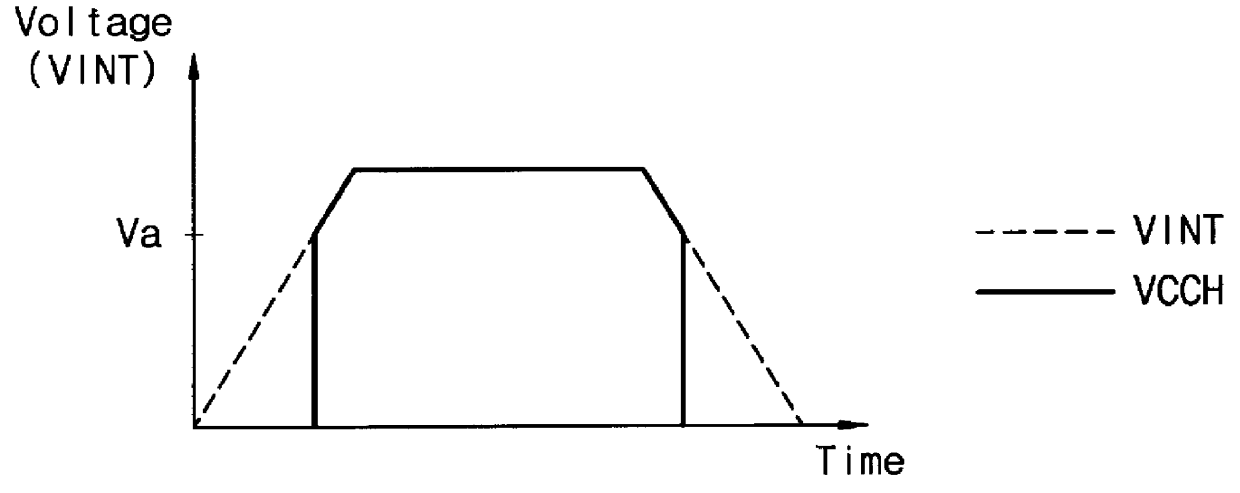

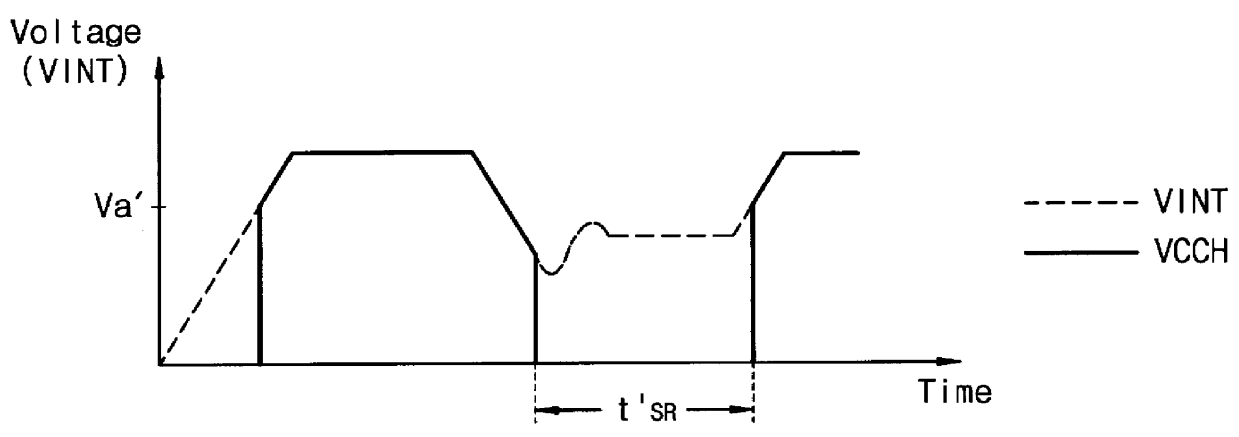

Power-up detection circuit of a semiconductor device

InactiveUS6104221AMultiple input and output pulse circuitsPulse automatic controlDevice materialEngineering

Disclosed is a power-up detection circuit of a semiconductor device which generates an output signal enabling an activation of the semiconductor device to be maintained only when an internal power voltage is more than a predetermined voltage level. In the power-up detection circuit, a level detection section is provided for detecting a level of the internal power voltage to generate a first level detection signal when the internal power voltage is less than the predetermined voltage level and to generate a second level detection signal when the internal power voltage is not less than the predetermined voltage level. And, an output driver is provided for enabling the internal circuits to be at inactive state in response to the first level detection signal, and generating the output signal having the same waveform as the internal power voltage in response to the second level detection signal.

Owner:SAMSUNG ELECTRONICS CO LTD

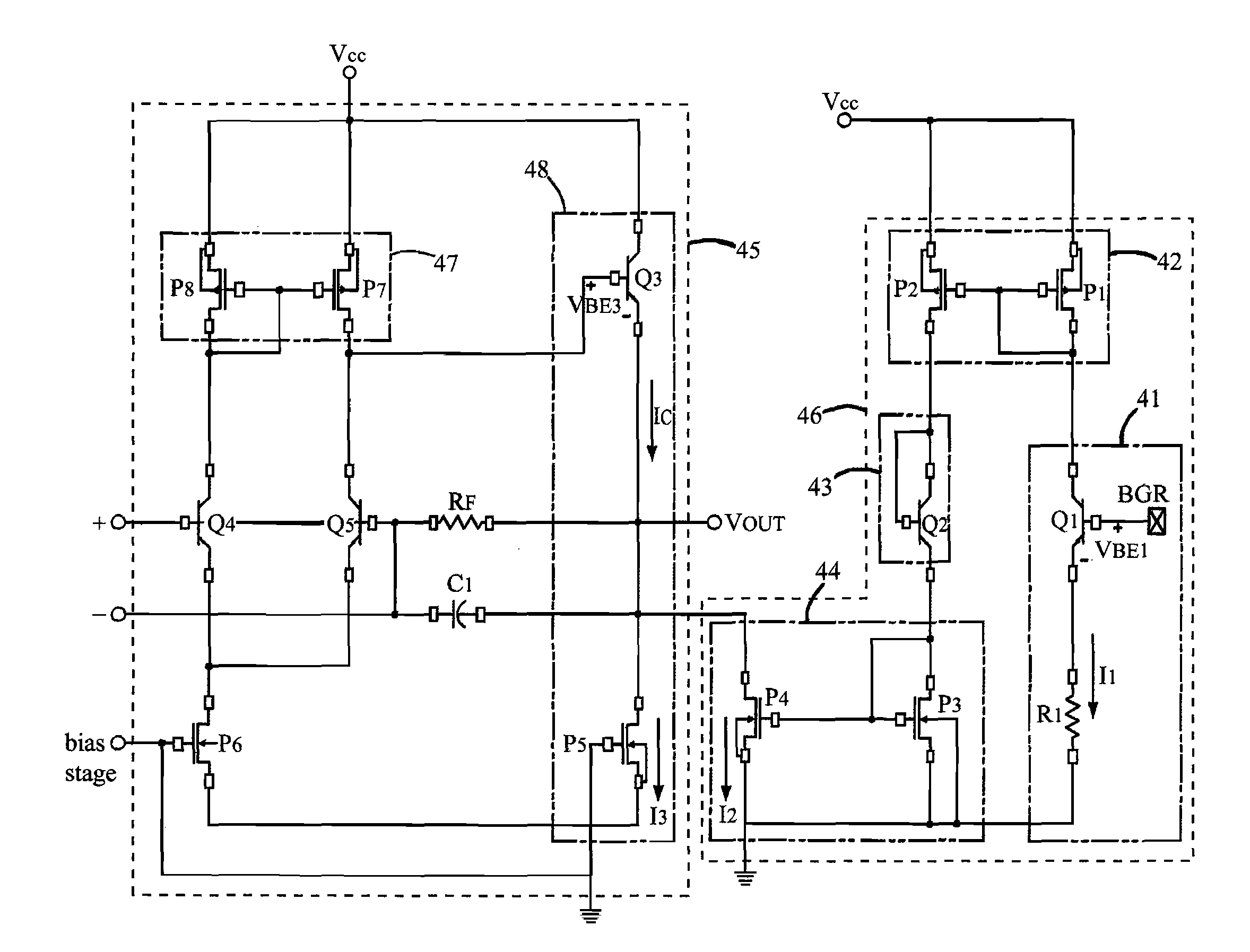

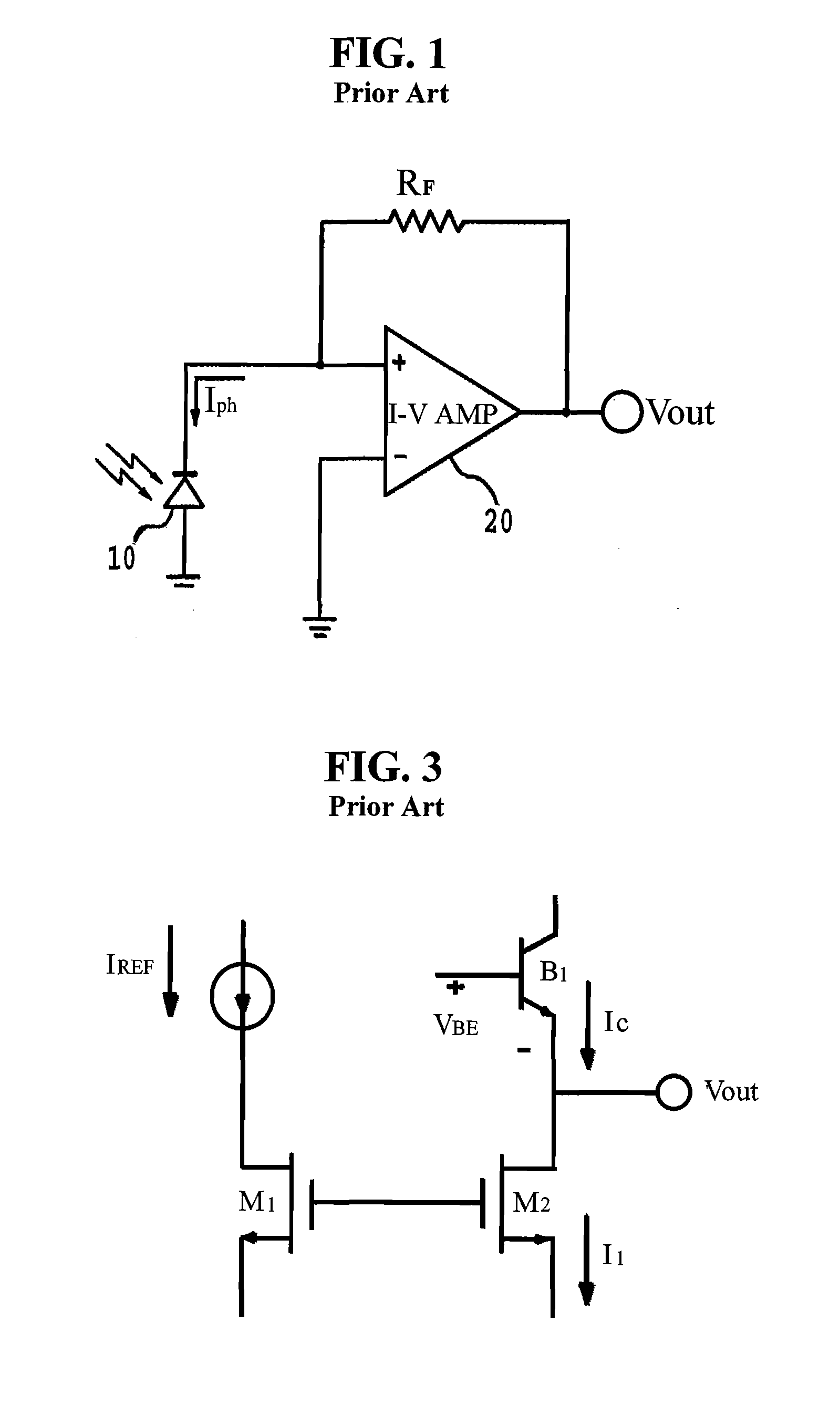

Circuit and method for compensating for offset voltage

InactiveUS7227389B2Variation in characteristicMultiple input and output pulse circuitsPulse automatic controlPhotovoltaic detectorsPhotodetector

A circuit for compensating for an offset voltage in a PhotoDetector Integrated Circuit (PDIC). The circuit includes a temperature detection unit, a current transfer unit and a current adjustment unit. The temperature detection unit generates a current that varies with variation in surrounding temperature. The current transfer unit transfers the generated current. The current adjustment unit adjusts the current transferred from the current transfer unit at a predetermined ratio and outputs the adjusted current.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

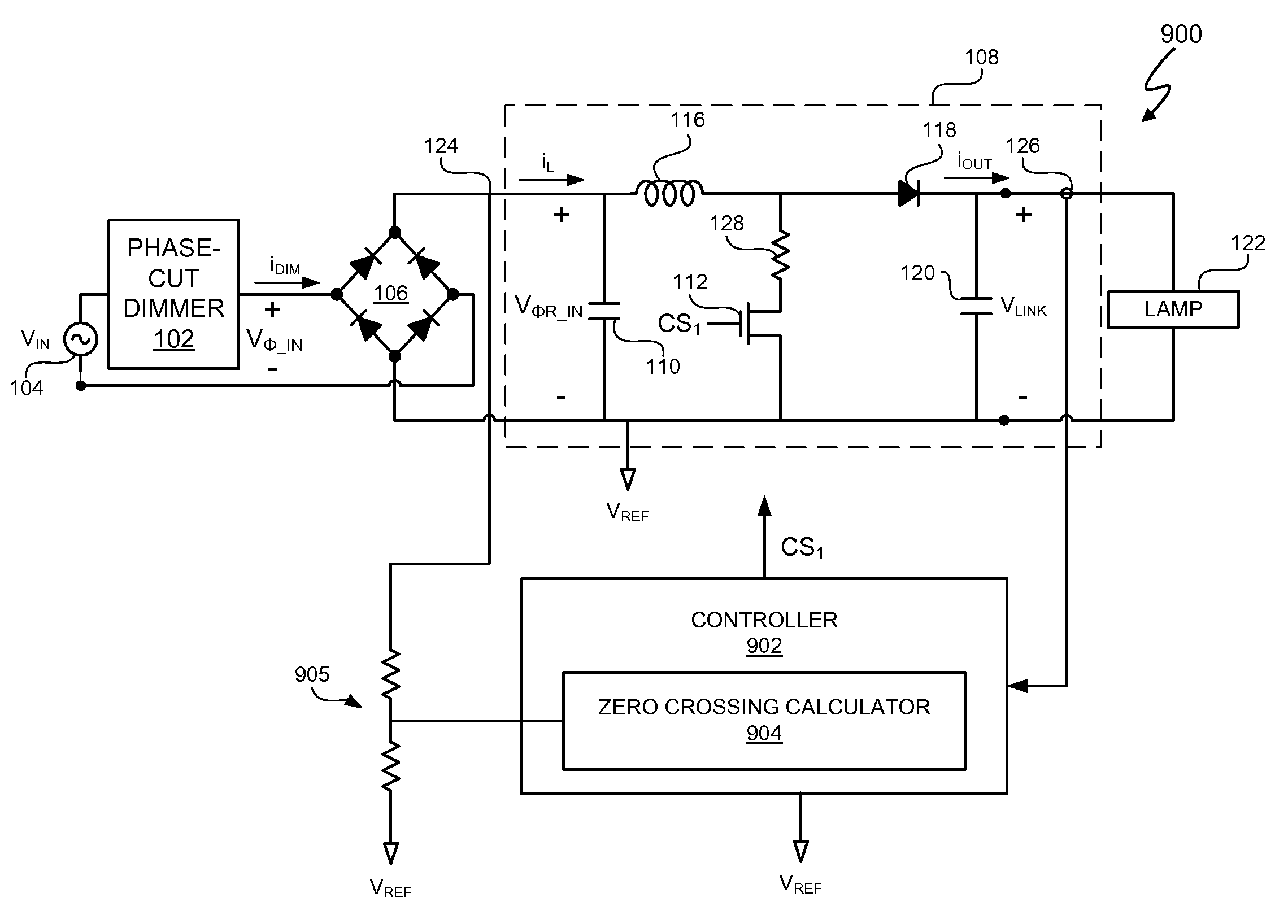

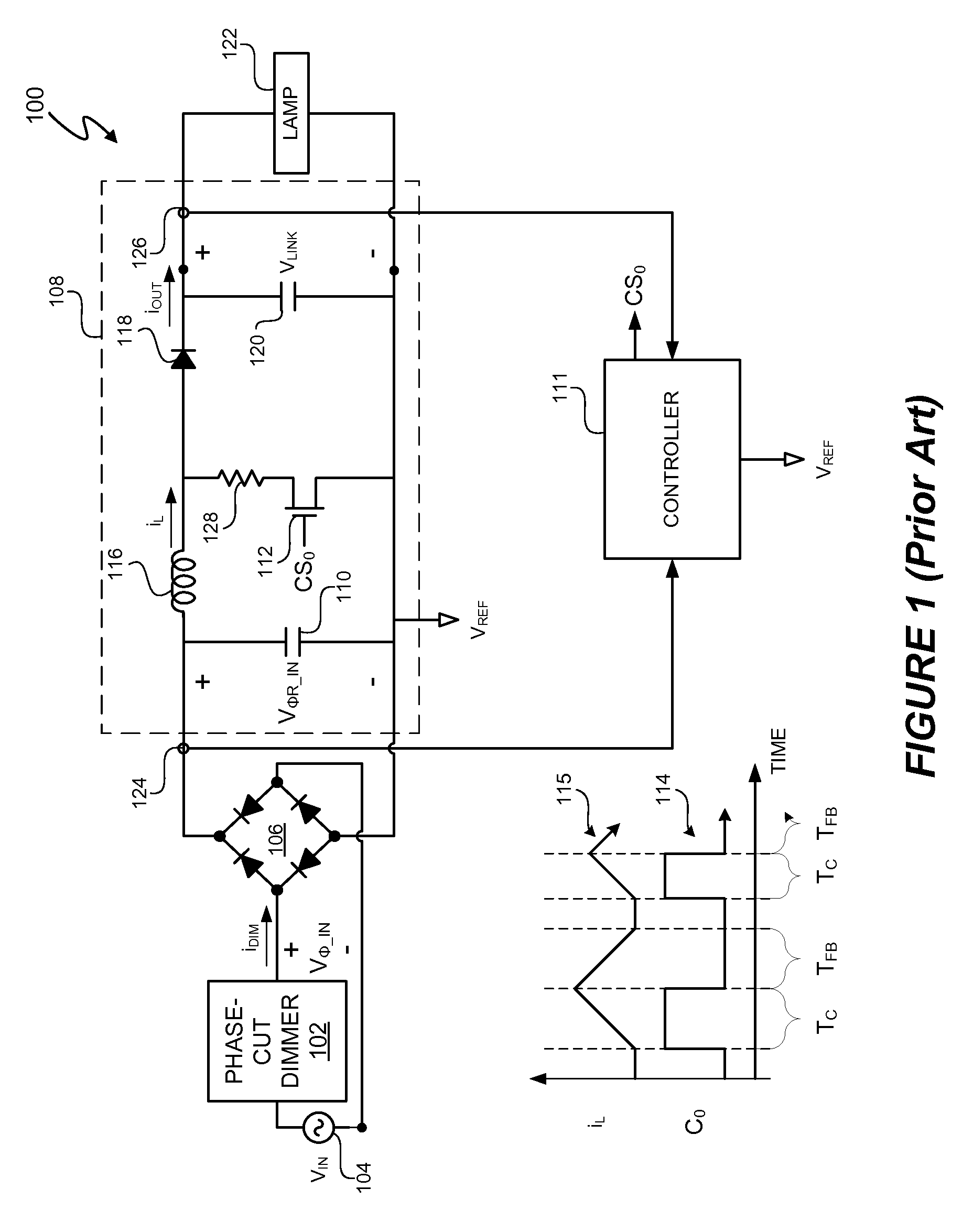

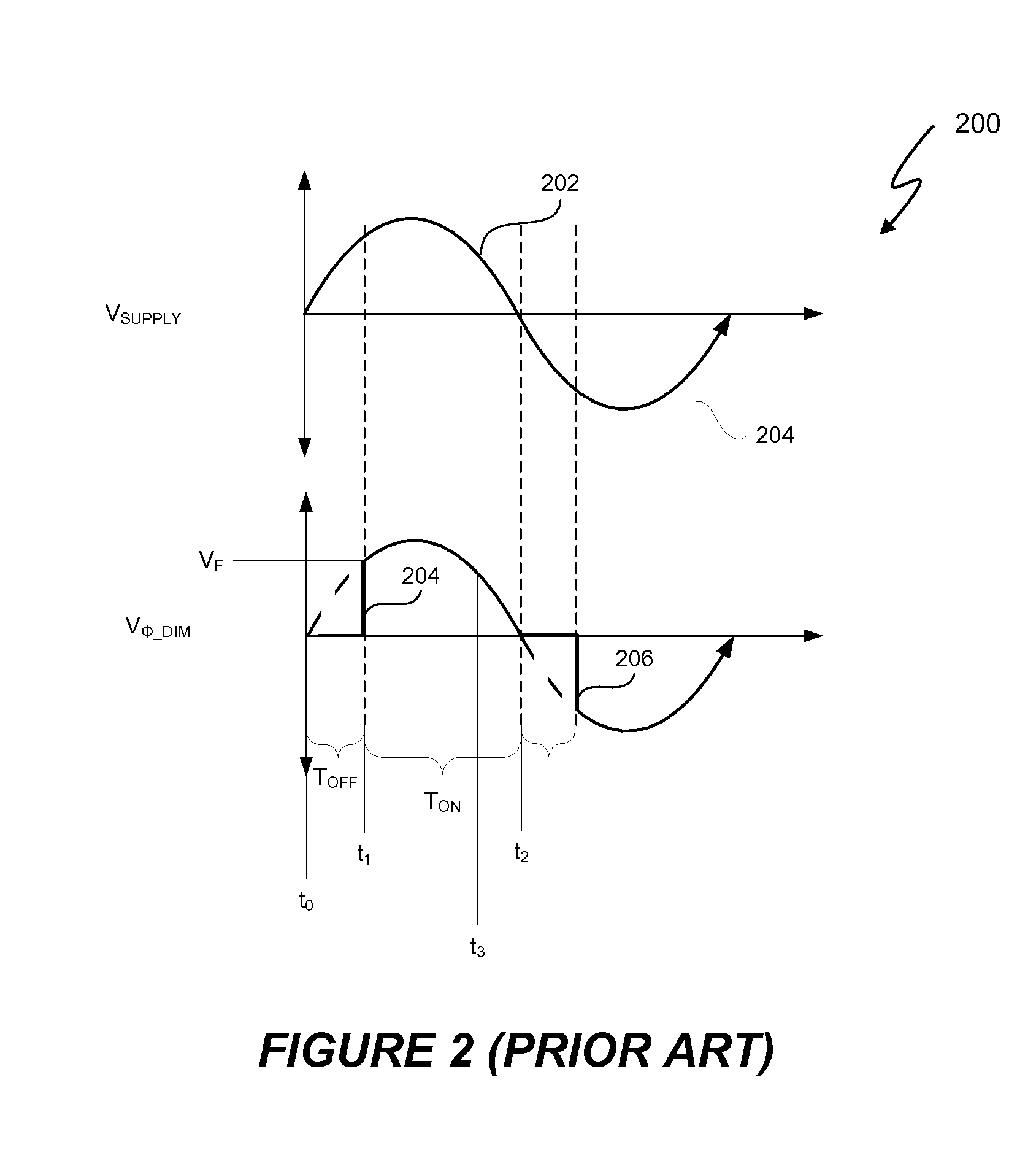

Switching power converter input voltage approximate zero crossing determination

ActiveUS8610365B2Multiple input and output pulse circuitsInstant pulse delivery arrangementsLeading edgeTransverter

In at least one embodiment, the controller senses a leading edge, phase cut AC input voltage value to a switching power converter during a cycle of the AC input voltage. The controller senses the voltage value at a time prior to a zero crossing of the AC input voltage and utilizes the voltage value to determine the approximate zero crossing. In at least one embodiment, by determining an approximate zero crossing of the AC input voltage, the controller is unaffected by any disturbances of the dimmer that could otherwise make detecting the zero crossing problematic. In at least one embodiment, the controller approximates the AC input voltage using a function that estimates a waveform of the AC input voltage and determines the approximate zero crossing of the AC input voltage from the approximation of the AC input voltage.

Owner:SIGNIFY HLDG BV

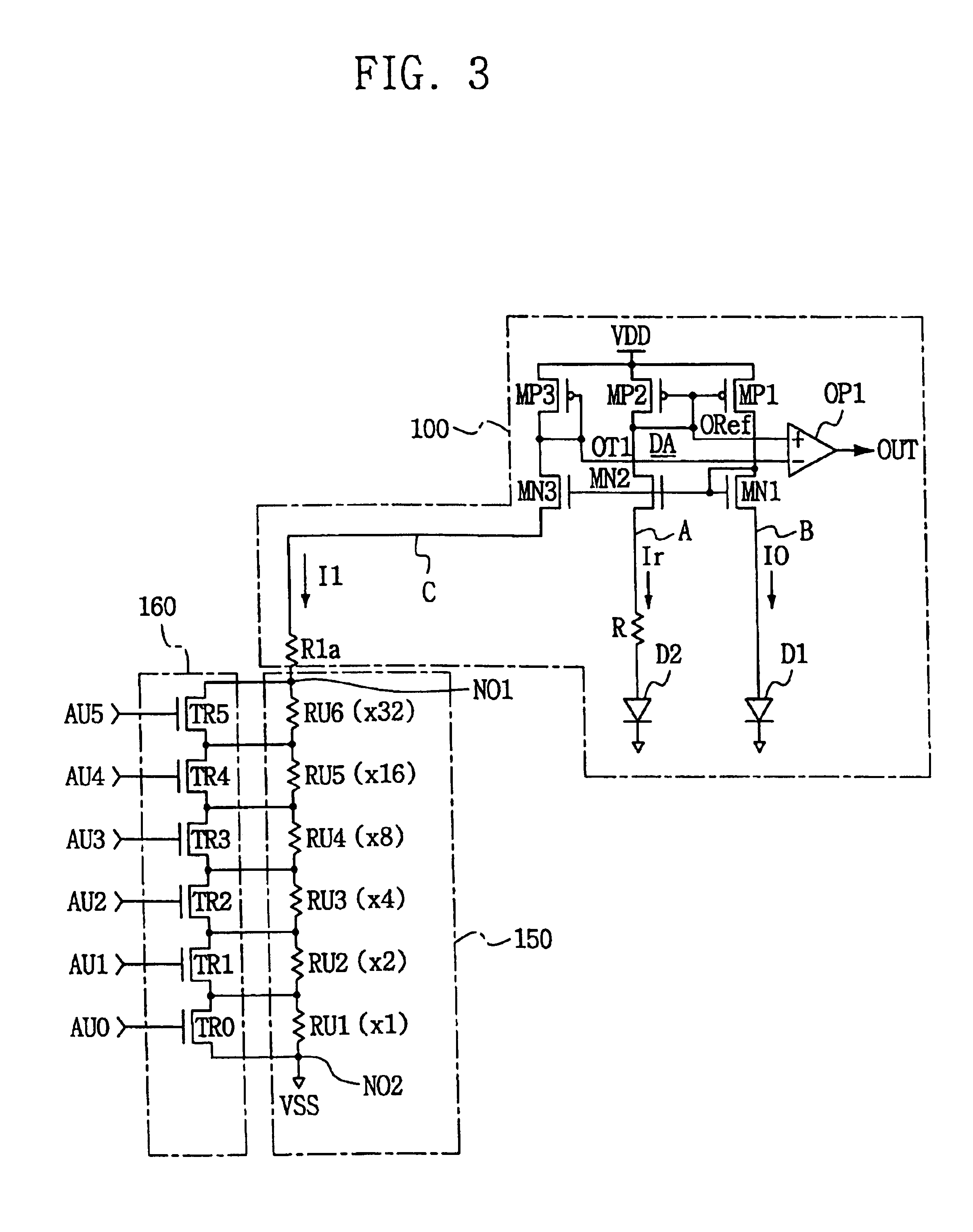

Temperature sensor and method for detecting trip temperature of a temperature sensor

InactiveUS6937087B2Multiple input and output pulse circuitsInstant pulse delivery arrangementsComparators circuitsTest sequence

A comparator circuit of a temperature sensor includes an output node and a variable current node. The output node is a first voltage at a given temperature when a current at the variable current node is less than a threshold current, and a different second voltage at the given temperature when the current at the variable current node is more than the threshold current. A variable resistance circuit includes at least n resistors of different resistive values connected in series between the variable current node of the comparator and a supply voltage, where n is an integer of 4 or more. A switching circuit is provided to selectively bypasses individual ones of the n resistors during a test sequence to determine a trip temperature of the sensor.

Owner:SAMSUNG ELECTRONICS CO LTD

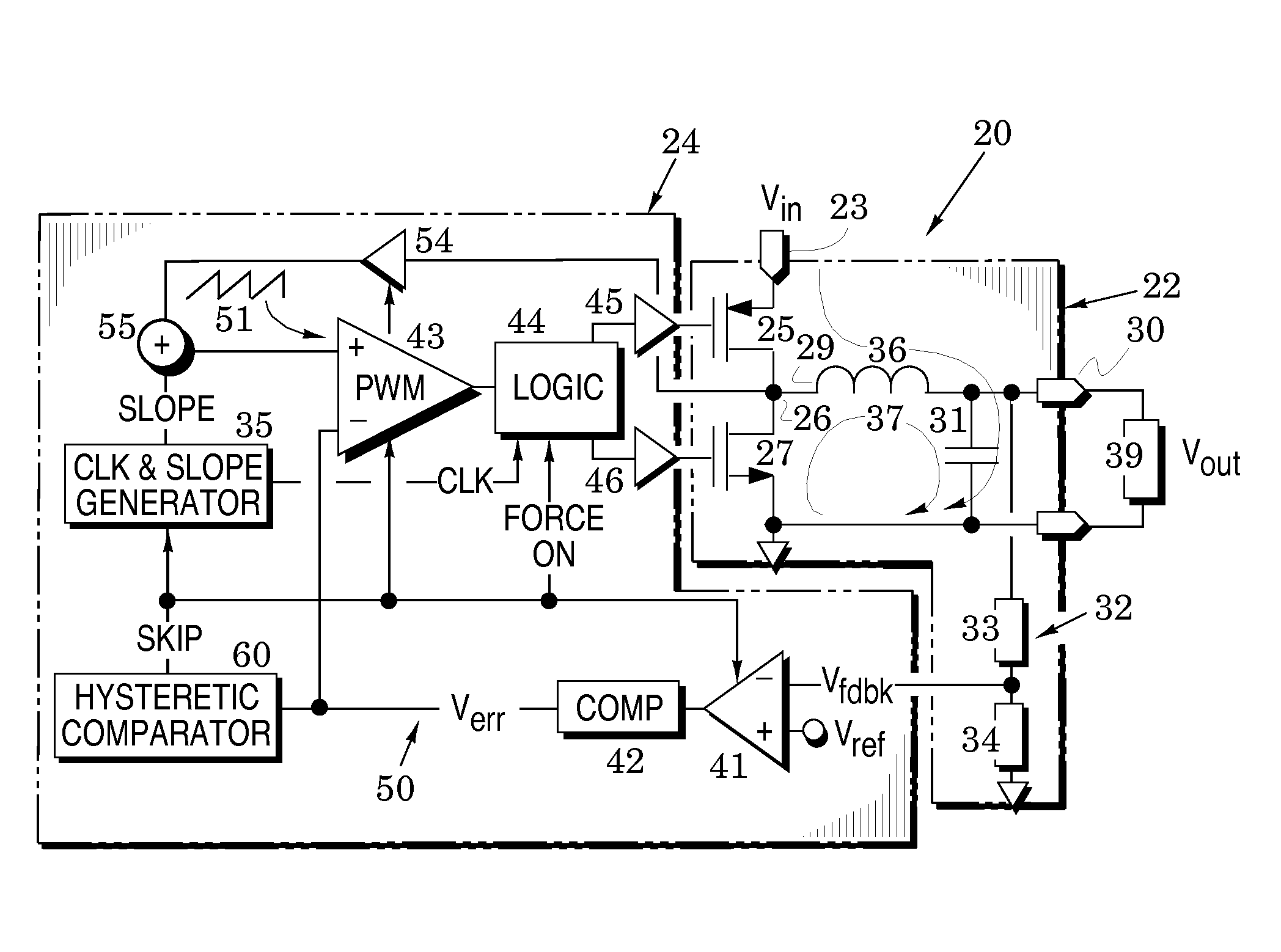

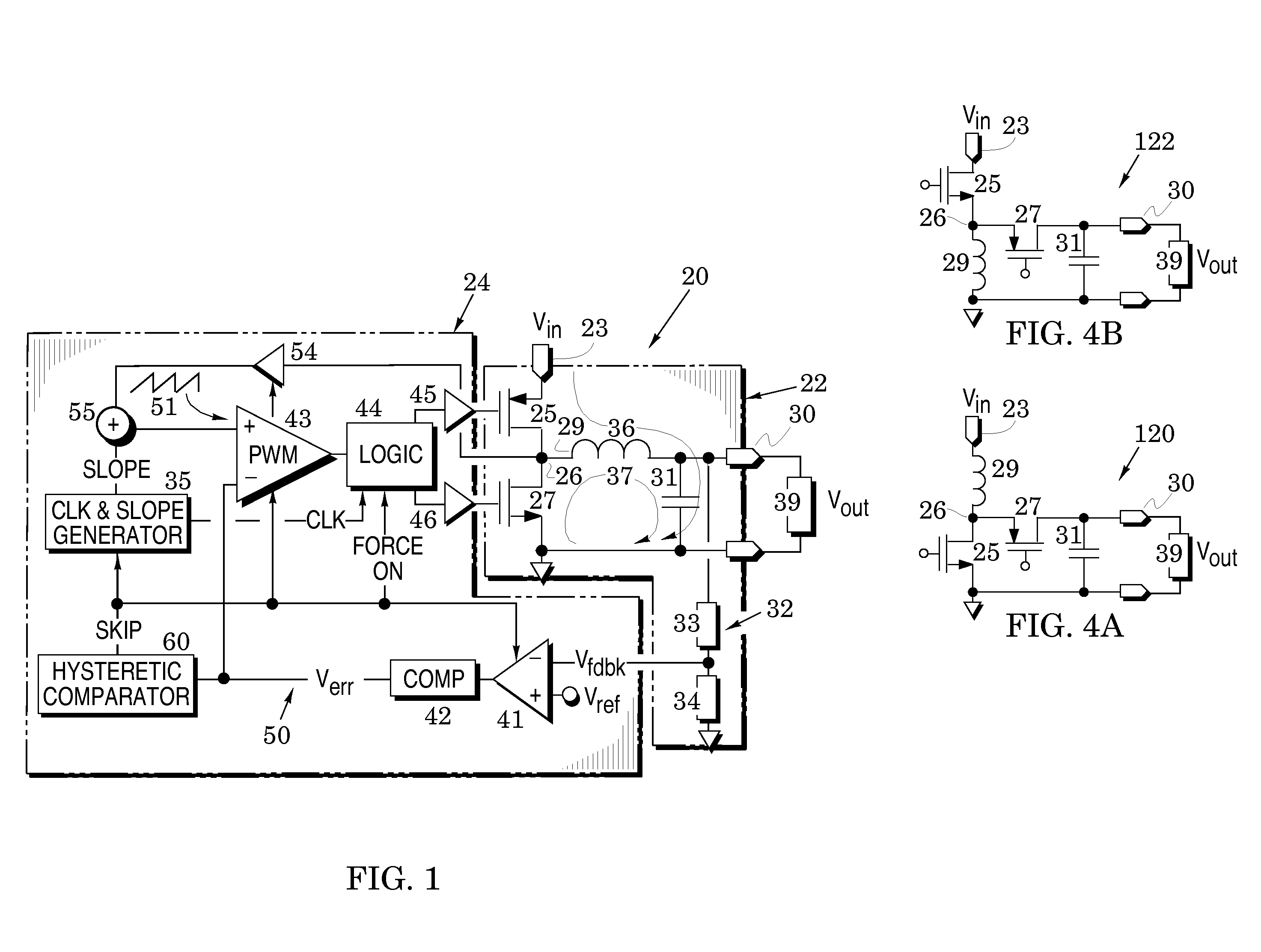

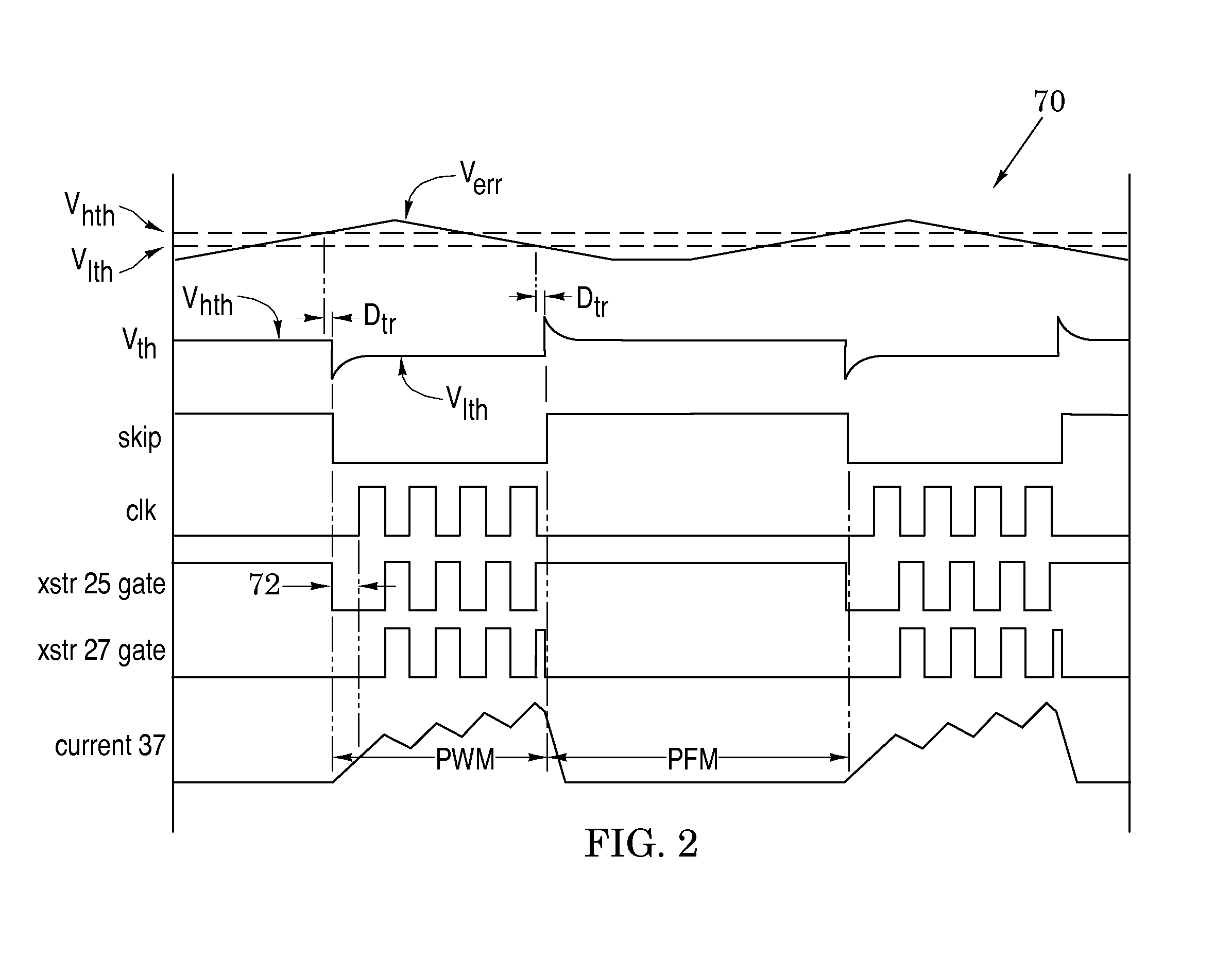

Switching voltage regulators with hysteretic control for enhanced mode-transition speed and stability

ActiveUS20120161728A1Multiple input and output pulse circuitsInstant pulse delivery arrangementsCurrent mode controlMode control

Switching voltage regulator embodiments are provided with hysteretic control to thereby switch between pulse-width modulation and pulse-frequency modulation operational modes. The switching is in response to different levels of an error voltage Verr in the feedback loop of voltage regulators. The hysteretic control is configured to provide a dc hysteretic response to changes in the error voltage Verr and also an ac hysteretic response to these changes. These two responses can be independently set to thereby enhance operational speed of the voltage regulators and also enhance immunity to transient noise signals that are generated by the mode switching. The voltage regulator embodiments facilitate instant return from the pulse-frequency modulation operational mode to the pulse-width modulation operational mode so that the stability of the feedback control of the regulator is enhanced. This feature is especially useful when the feedback loop is configured to include current-mode control as it minimizes the time duration in which the feedback loop operates in a voltage-mode control. The instant return insures that the feedback loop is immediately returned to the greater stability of the current-mode control.

Owner:ANALOG DEVICES INC

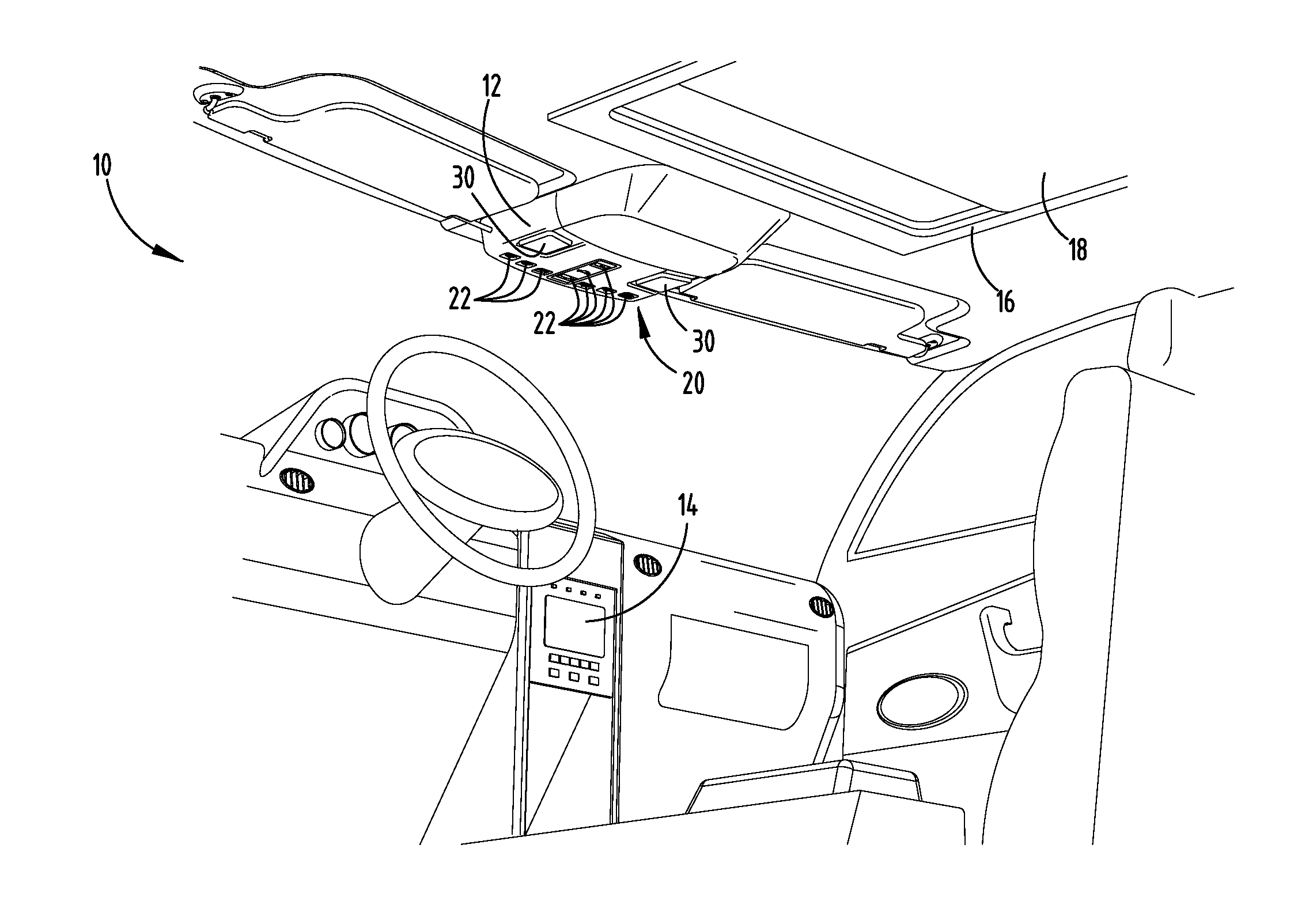

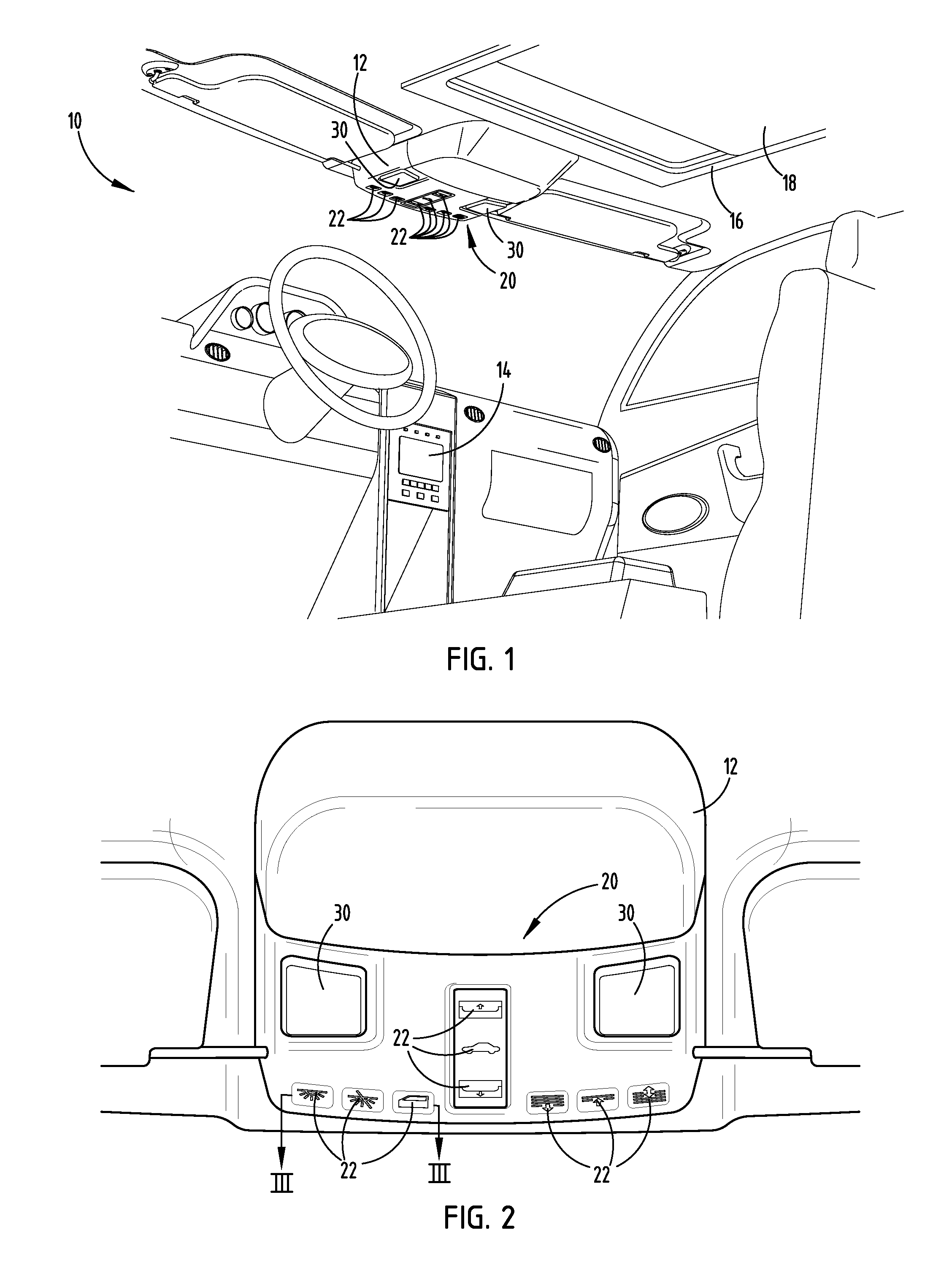

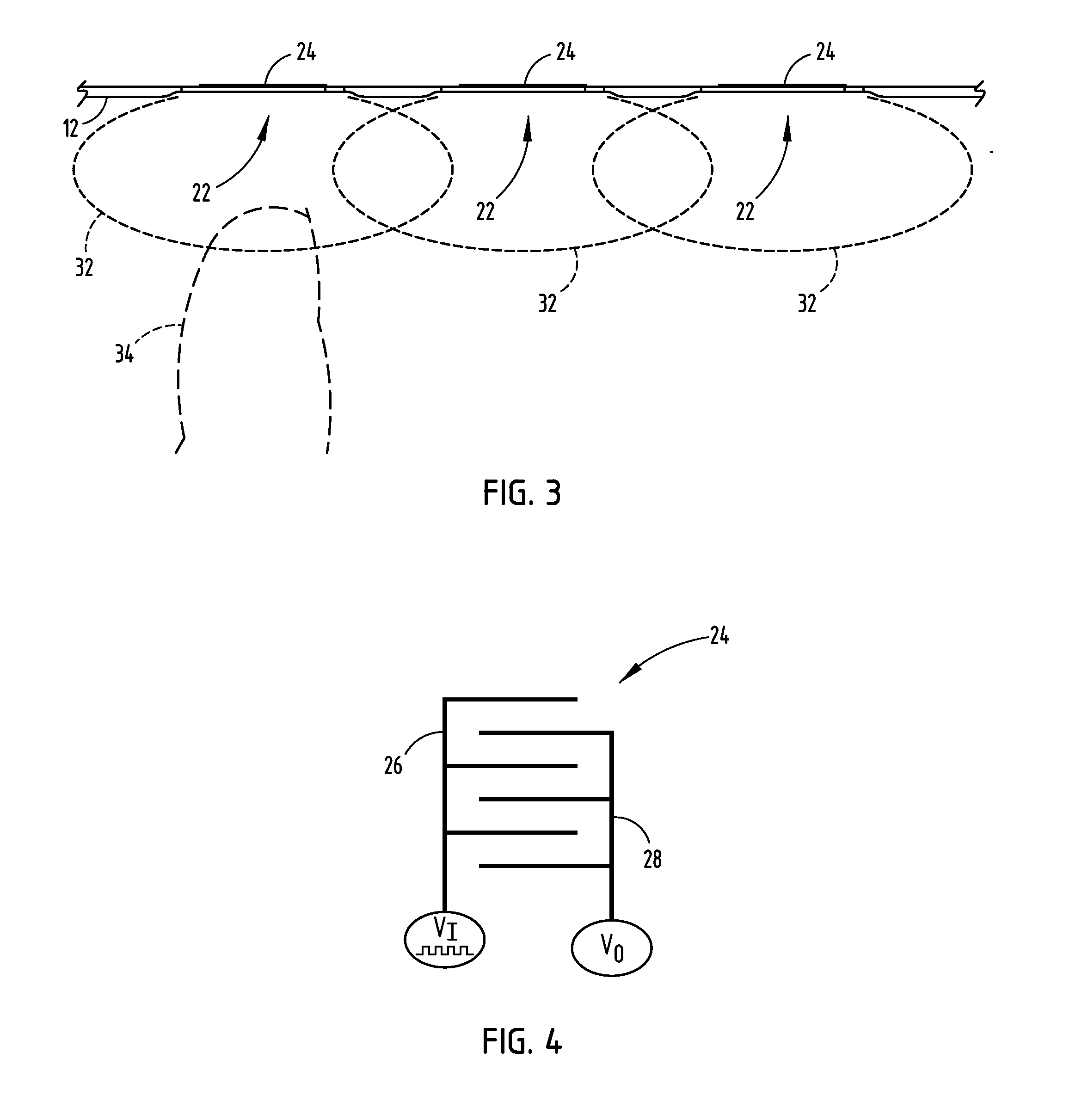

Proximity switch assembly and calibration method therefor

ActiveUS20130270899A1Boards/switchyards circuit arrangementsElectric devicesProximity sensorEngineering

A proximity switch assembly and method for detecting activation of a proximity switch assembly and calibrating the switch assembly. The assembly includes proximity switches each having a proximity sensor providing a sense activation field and control circuitry processing the activation field to sense activation. The control circuitry generates an activation output when a differential change in the signal exceeds a threshold and distinguishes an activation from an exploration of the plurality of switches. The control circuit further determines a rate of change and generates an output when the rate of change exceeds a threshold rate to enable activation of a switch and performs a calibration of the signals to reduce effects caused by changes in condensation.

Owner:FORD GLOBAL TECH LLC

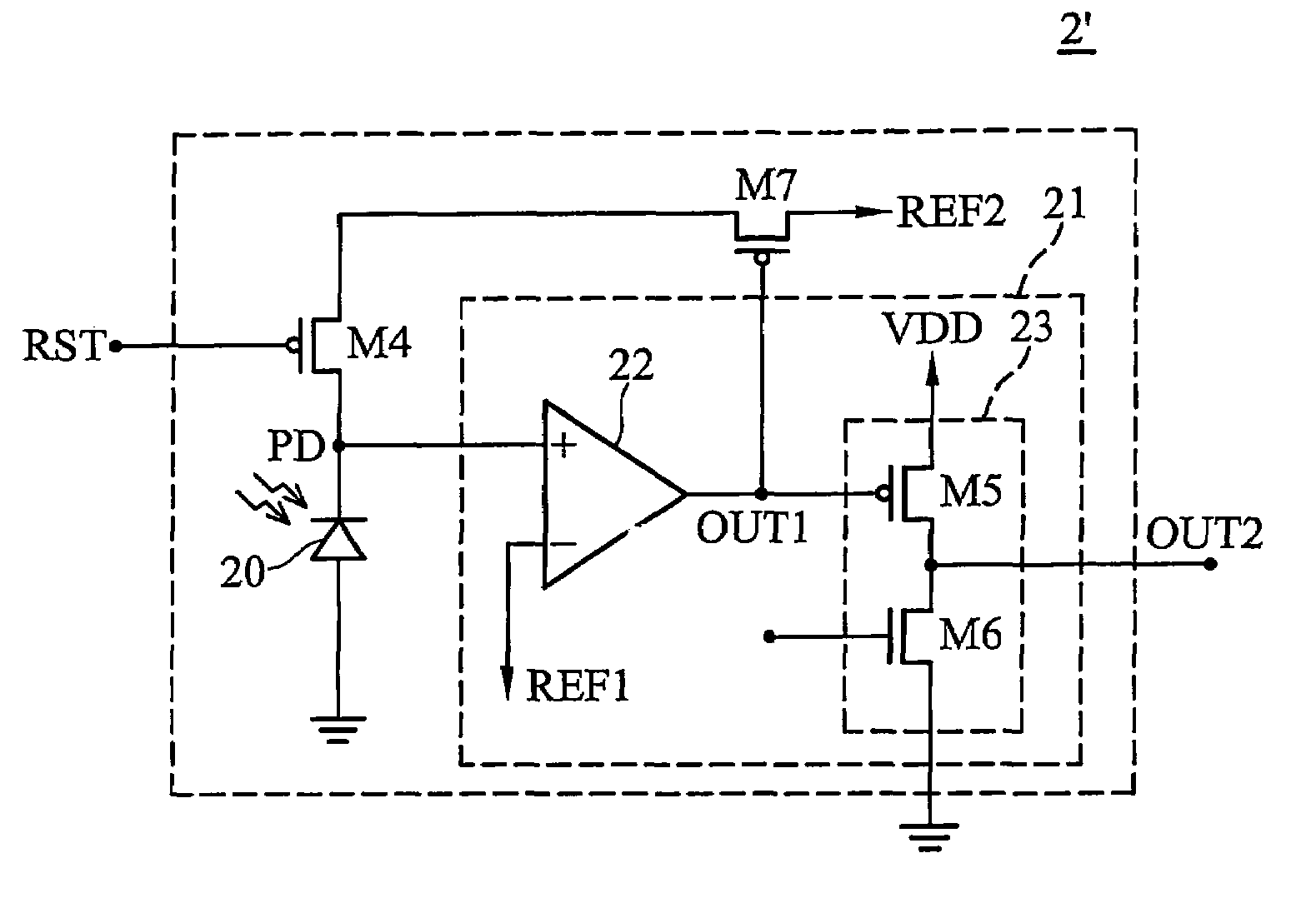

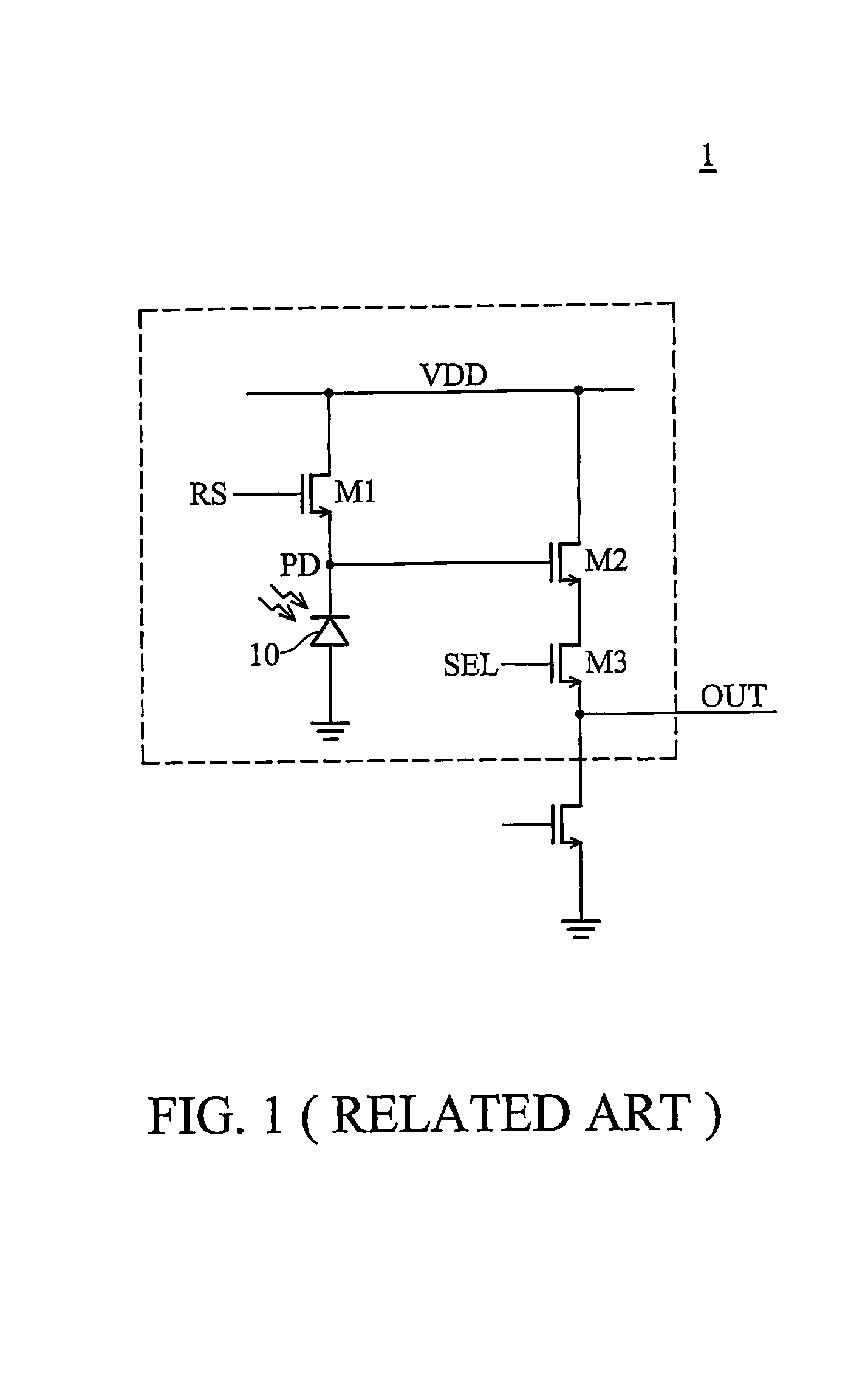

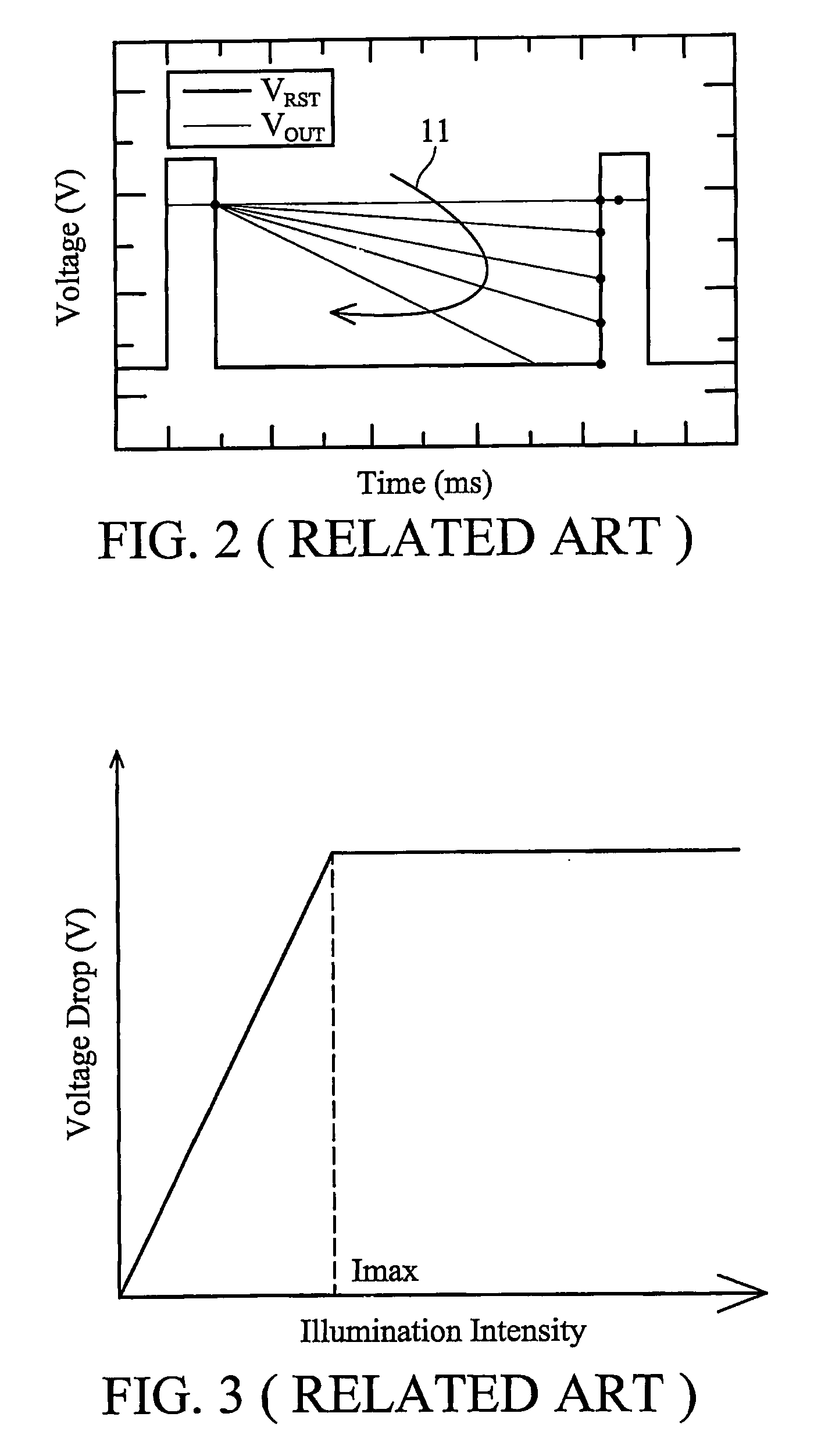

Digital pixel sensor with clock count output and operating method thereof

A digital pixel sensor, comprising a first switch coupled between a first voltage and a first node, turned on or off by a rest signal to provide a first voltage to the first node when turned on; a light sensing unit coupled to the first node generating a transformation current responsive to the intensity of an incident light source and thereby discharging the first node, and a decision device coupled with the first node and a reference signal to output an intensity reference signal corresponding to the intensity of the incident light source when the voltage at the first node is discharged to a level below that of the reference signal.

Owner:VIA TECH INC

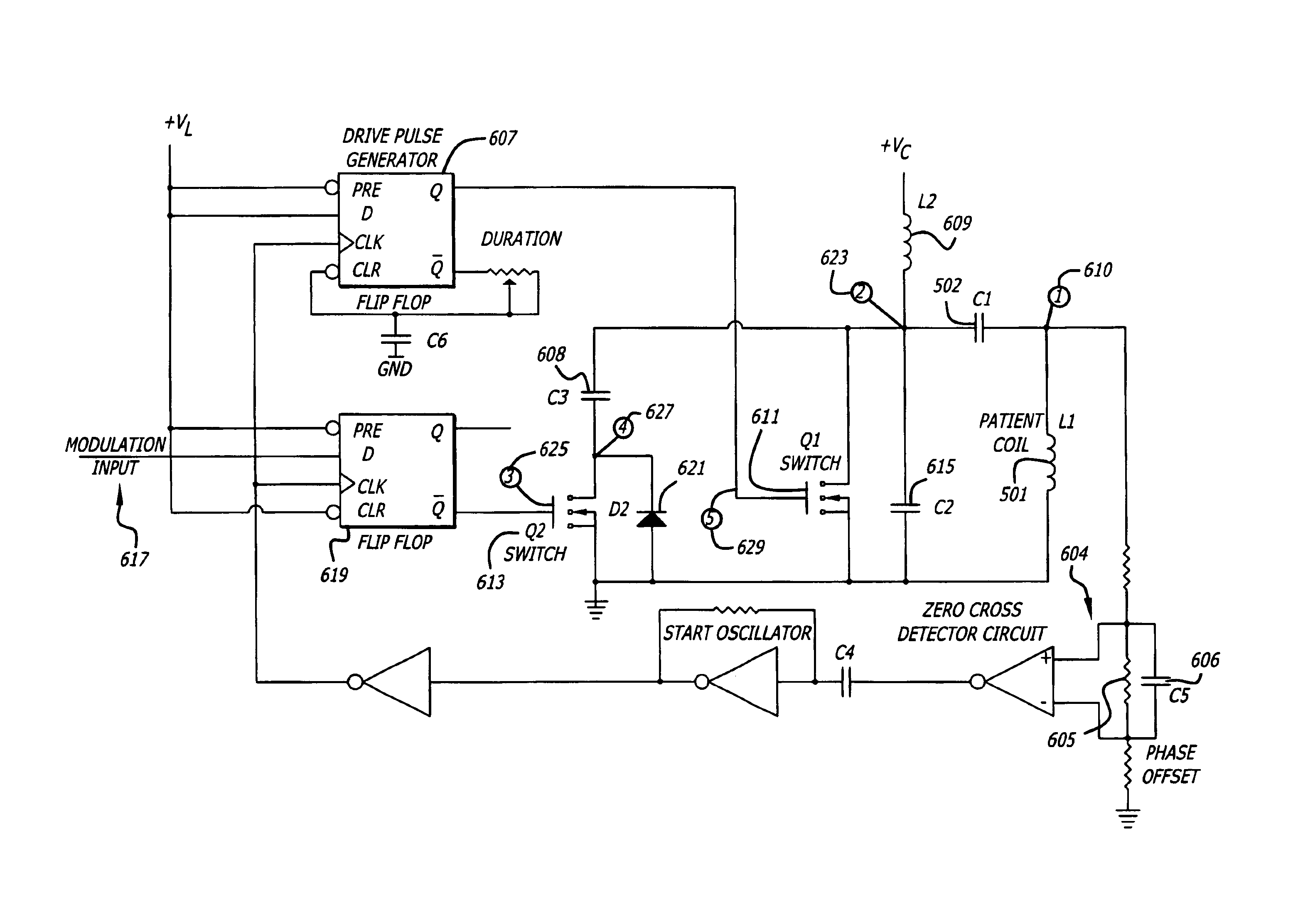

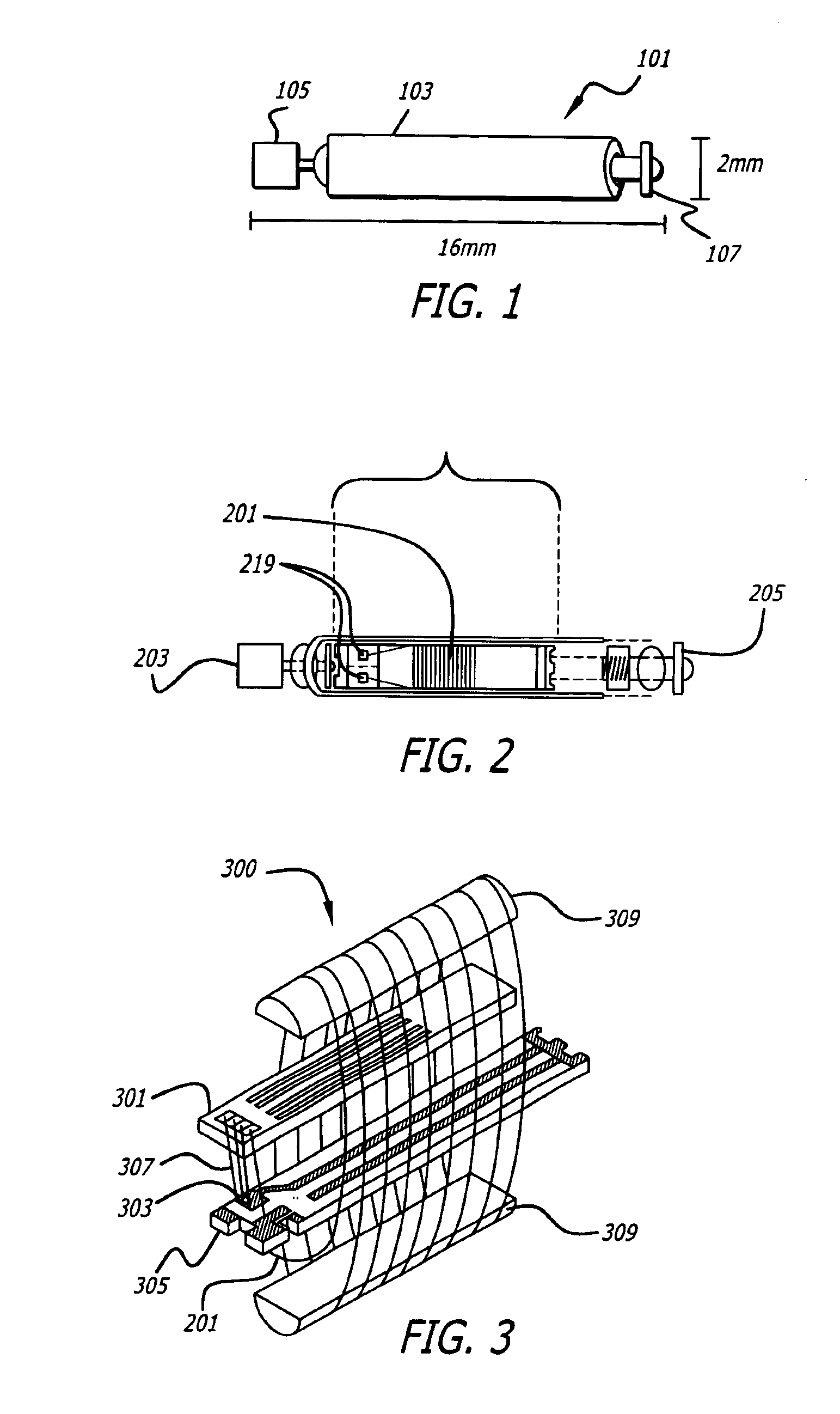

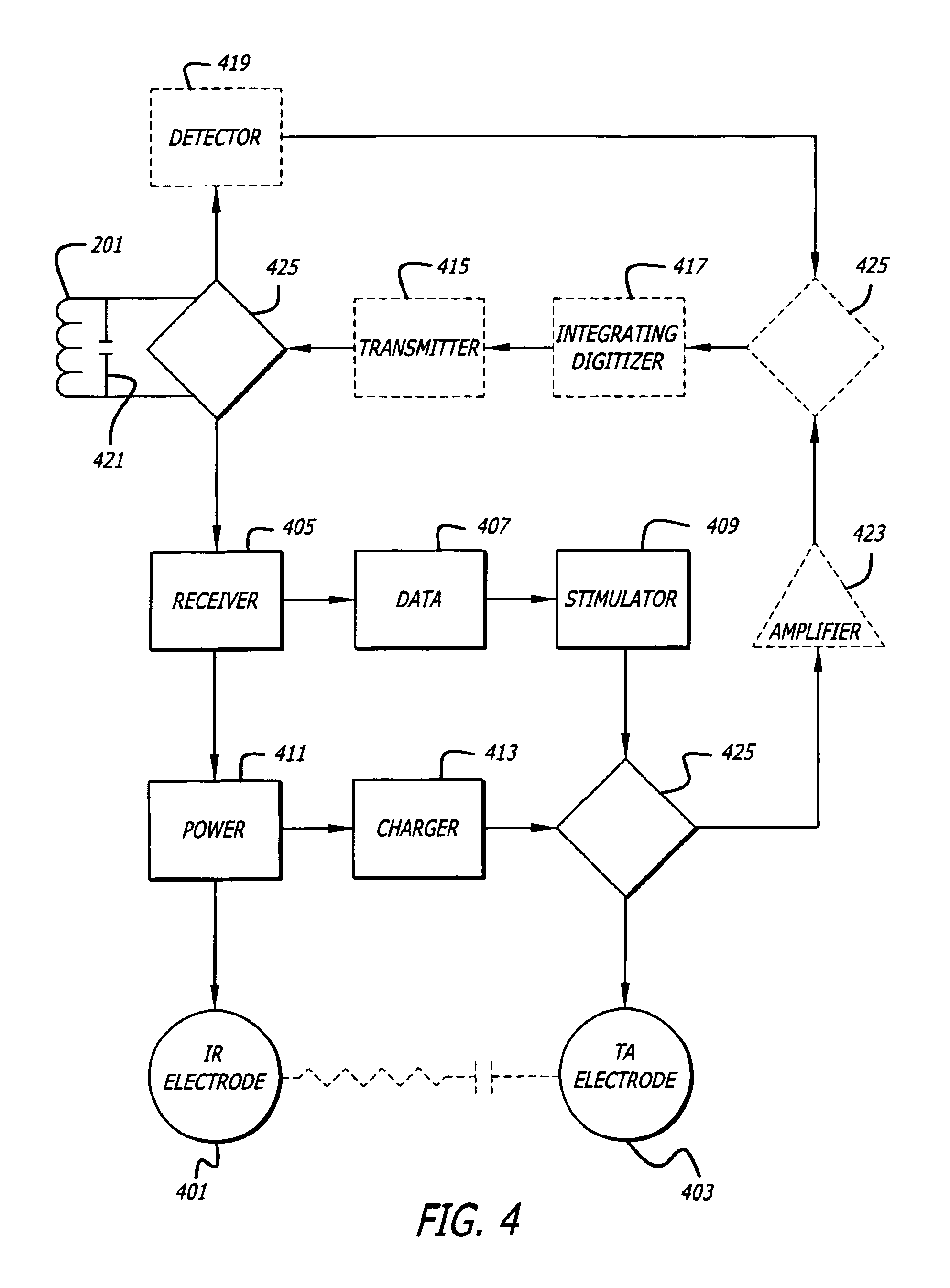

Switched reactance modulated E-class oscillator design

InactiveUS6864755B2Highly resonant operationRapid amplitude modulationMultiple input and output pulse circuitsElectrotherapyPropagation delayDetector circuits

A modulated Class E transmitter is disclosed. In one embodiment of the invention, the modulated Class E oscillator achieves high coil currents (˜1A) and voltages (˜500V) with low power components by precisely timed injection of current when the oscillating current in the inductor passes through zero. A detector circuit is used to trigger the current injection at the appropriate instant regardless of changes in the resonant frequency of the system. Its phase can be adjusted to compensate for propagation delays in the drive circuitry, while amplitude modulation is accomplished by switching in additional reactive conductance to increase the current injected into the tank circuit.

Owner:ALFRED E MANN INST FOR BIOMEDICAL ENG AT THE UNIV OF SOUTHERN CALIFORNIA

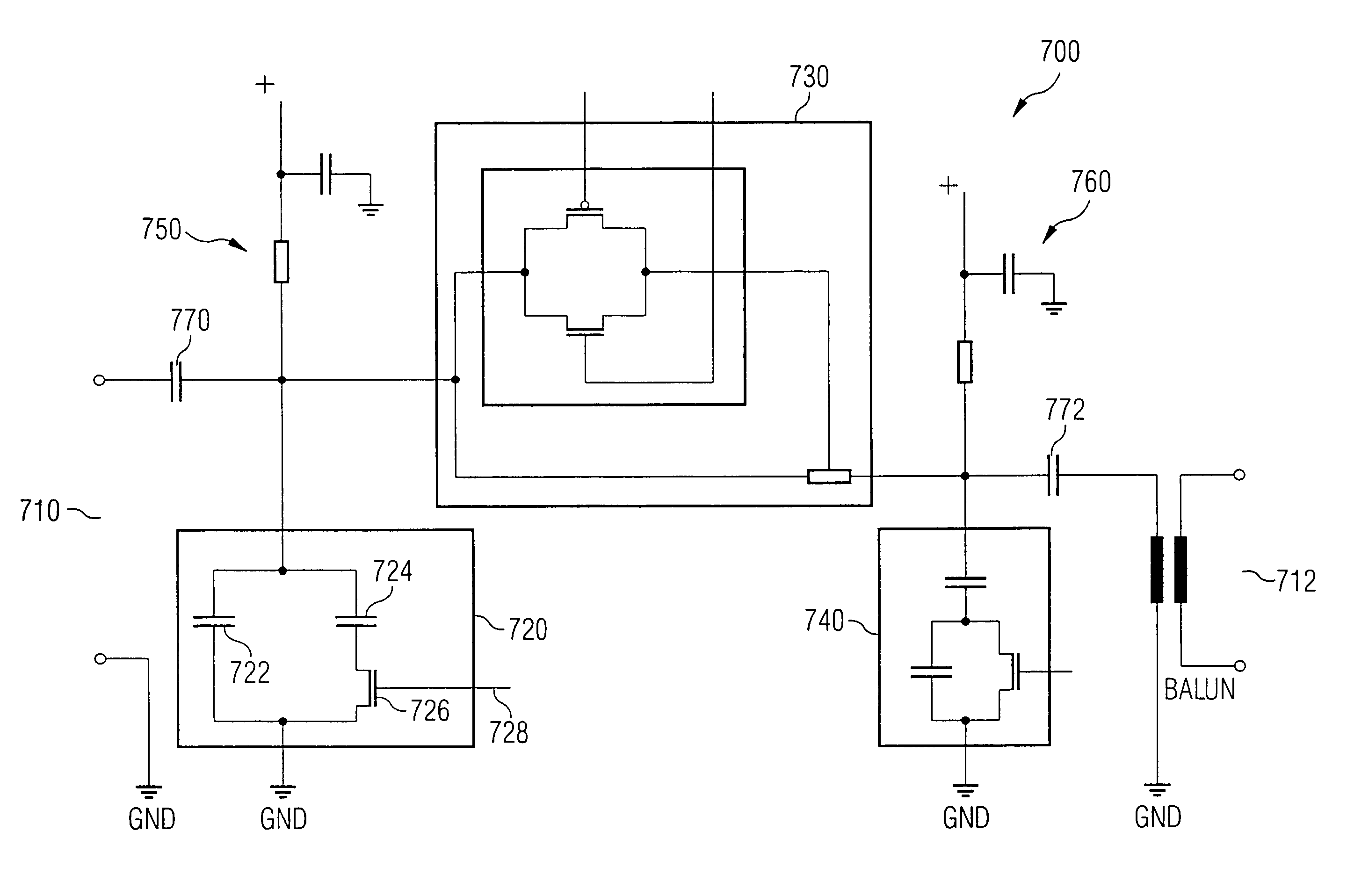

Matching network

InactiveUS7831219B2Easy to useMultiple-port networksMultiple input and output pulse circuitsHigh frequency powerAudio power amplifier

A matching network for matching an antenna to a transmitter or receiver comprises an input port for receiving high-frequency power, an output port and a switchable impedance transformation circuit, which is connected between the input port and the output port. The impedance transformation circuit comprises a CMOS switch in a high-frequency path, which has a first switching state and a second switching state. The impedance transformation circuit is implemented to match a first impedance applied to the output port to a first predetermined impedance in the first switching state, and to match a second impedance applied to the output port to a second predetermined impedance in the second switching state. The inventive matching network allows a particularly good utilization of power provided by a transmitting amplifier or an antenna.

Owner:INFINEON TECH AG

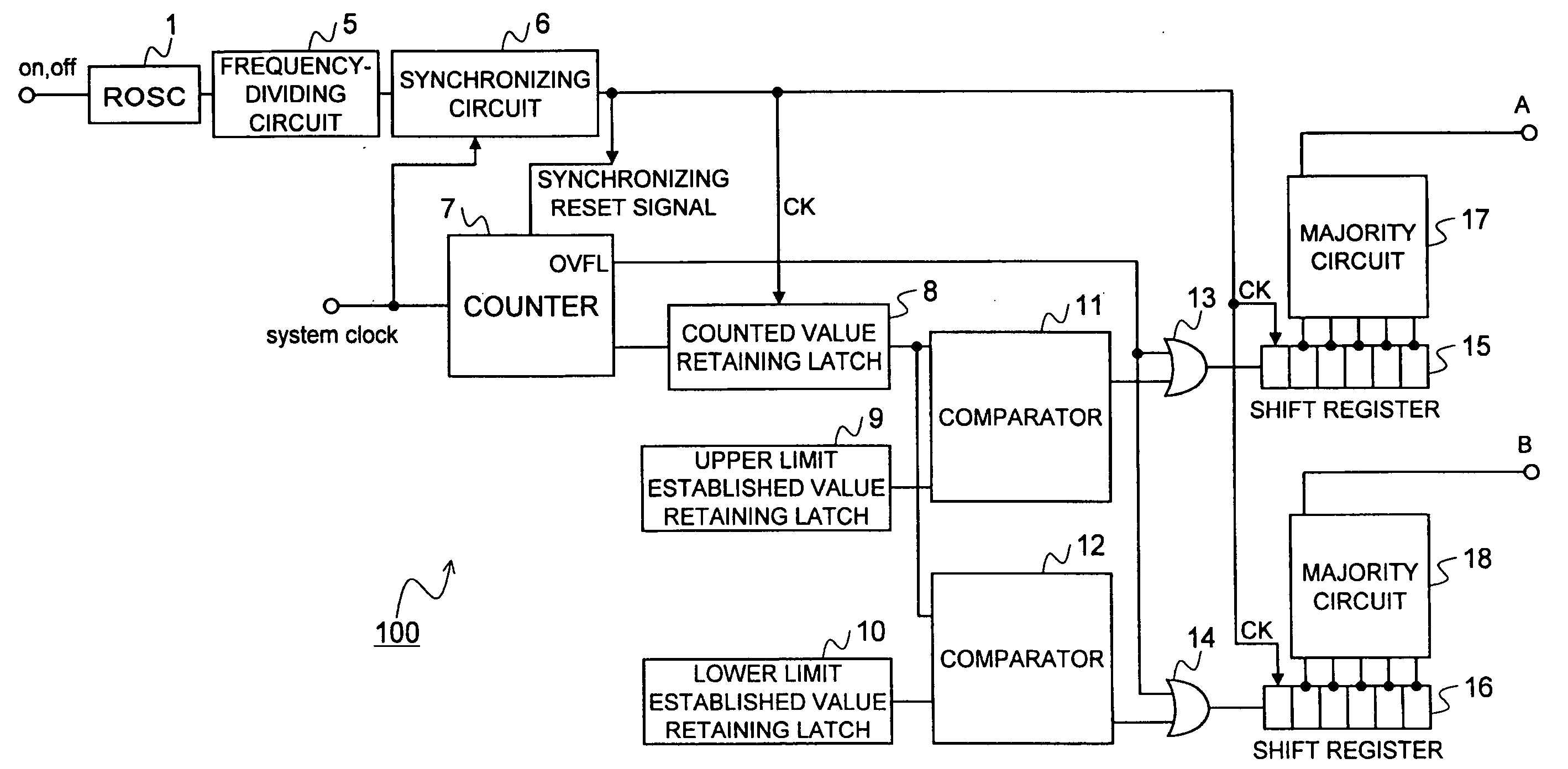

Ring oscillator for temperature sensor, temperature sensor circuit, and semiconductor device having the same

InactiveUS20090096495A1Substrate temperature can be accuratelyAccurate measurementPulse automatic controlThermometers using electric/magnetic elementsMOSFETPower semiconductor device

A ring oscillator includes an odd number of unit circuits connected in series each of which includes an inverter. Each of the unit circuits includes the inverter and a MOSFET. The MOSFET is an FET which is a temperature sensor, and uses a drain-source leakage current in a state that the FET is normally turned off.

Owner:FUJITSU LTD

Semiconductor leakage current detector and leakage current measurement method, semiconductor leakage current detector with voltage trimming function and reference voltage trimming method, and semiconductor integrated circuit thereof

ActiveUS7446549B2Shorten test timeLow costMultiple input and output pulse circuitsDirection of current indicationCapacitanceReference current

A semiconductor leakage current detector of the present invention includes a first analog switch which causes a current to be measured to flow or to be cut off, a second analog switch which causes a reference current to flow or to be cut off, an integral capacitance element which is connected by the first analog switch and the second analog switch and is charged with the current to be measured or the reference current, a discharge unit which discharges the integral capacitor, and a comparison unit which compares the reference voltage with each of an integral voltage generated in the integral capacitor by a reference current after the discharge of the integral capacitor and an integral voltage generated in the integral capacitance element by the current to be measured after the discharge of the integral capacitor.

Owner:III HLDG 12 LLC

Converter circuit and motor driving apparatus

InactiveUS7274579B2Reduce capacitanceLow costAC motor controlDC motor speed/torque controlMotor driveAC power

A converter circuit for converting an output voltage from an AC power supply includes a rectifier circuit for rectifying the output voltage of the AC power supply; first and second capacitors connected in series, for smoothing the output of the rectifier circuit; and a switch circuit for switching the connections between the respective capacitors and the AC power supply so that the output voltage of the AC power supply is applied to each of the respective capacitors at a cycle that is shorter than the cycle of the AC power supply.

Owner:PANASONIC CORP

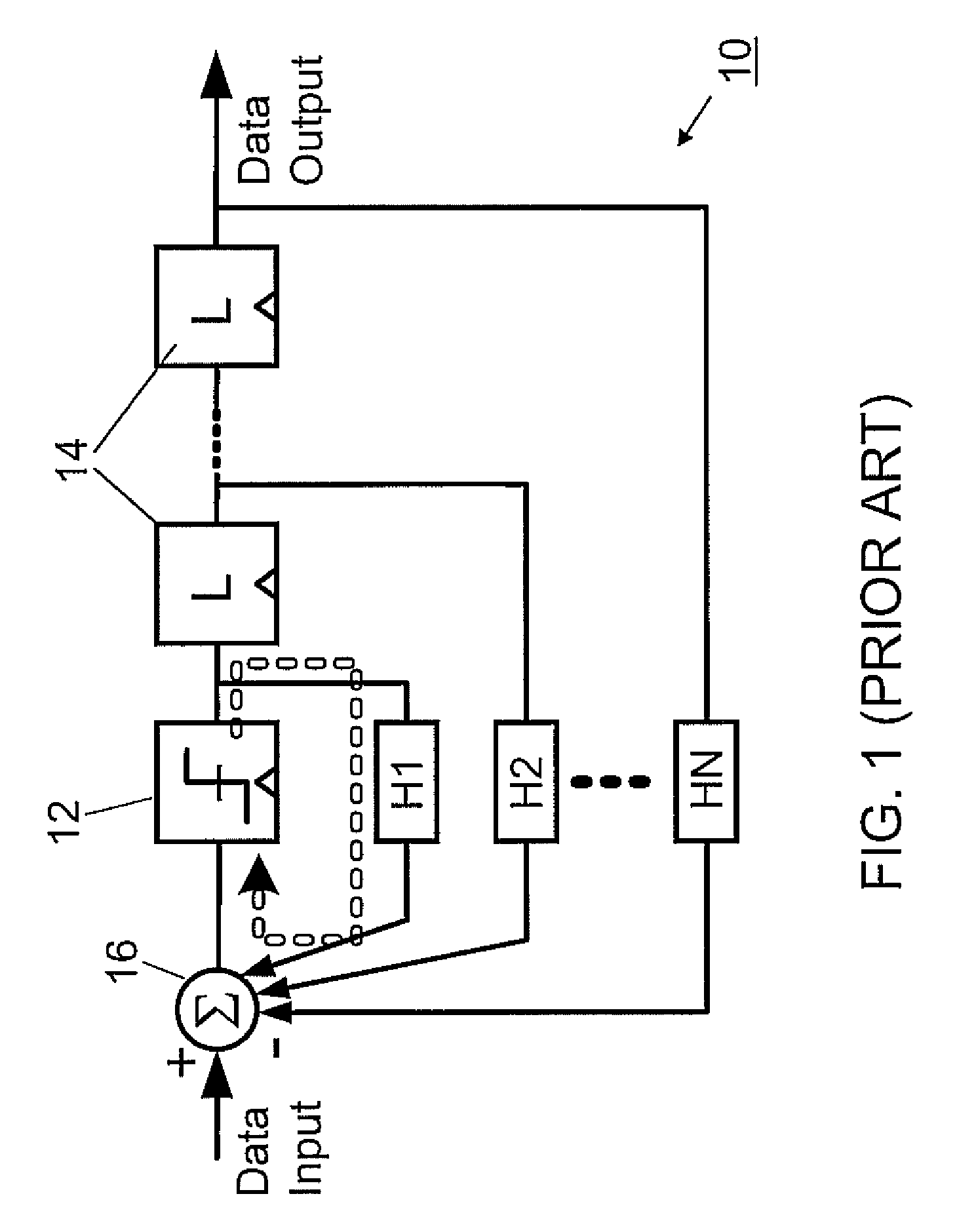

Receiver, transceiver circuit, signal transmission method, and signal transmission system

InactiveUS20050033902A1Optimize transmission/reception parametersImprove receiver sensitivityInstant pulse delivery arrangementsDc level restoring means or bias distort correctionDecision circuitTransceiver

A receiver has an offset application circuit for applying a known offset to an input signal, and a decision circuit for comparing the offset-applied input signal with a reference voltage. The level of the input signal is determined based on the known offset and on the result output from the decision circuit. With this configuration, a large common mode voltage can be eliminated in a circuit used for signal transmission.

Owner:FUJITSU LTD

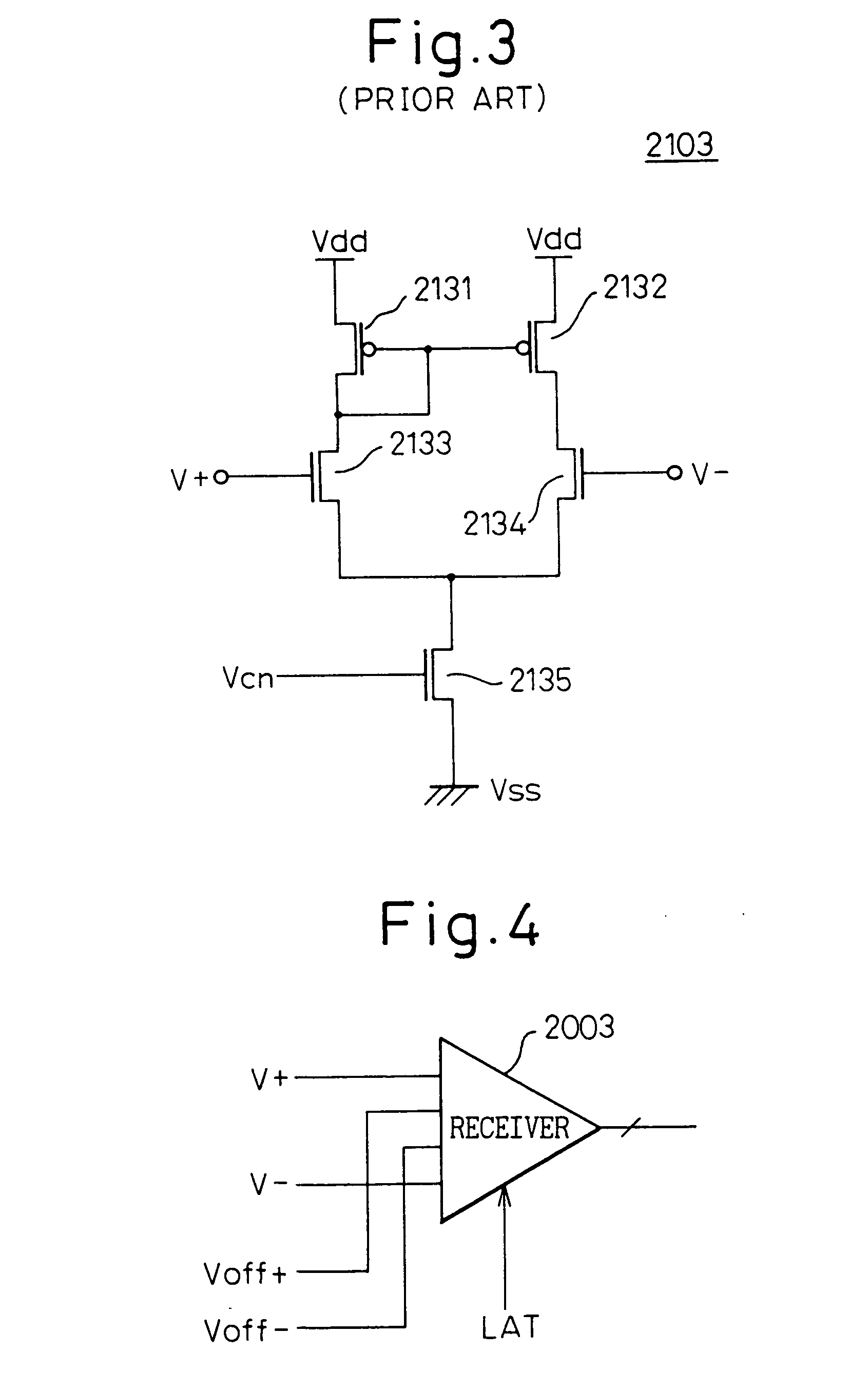

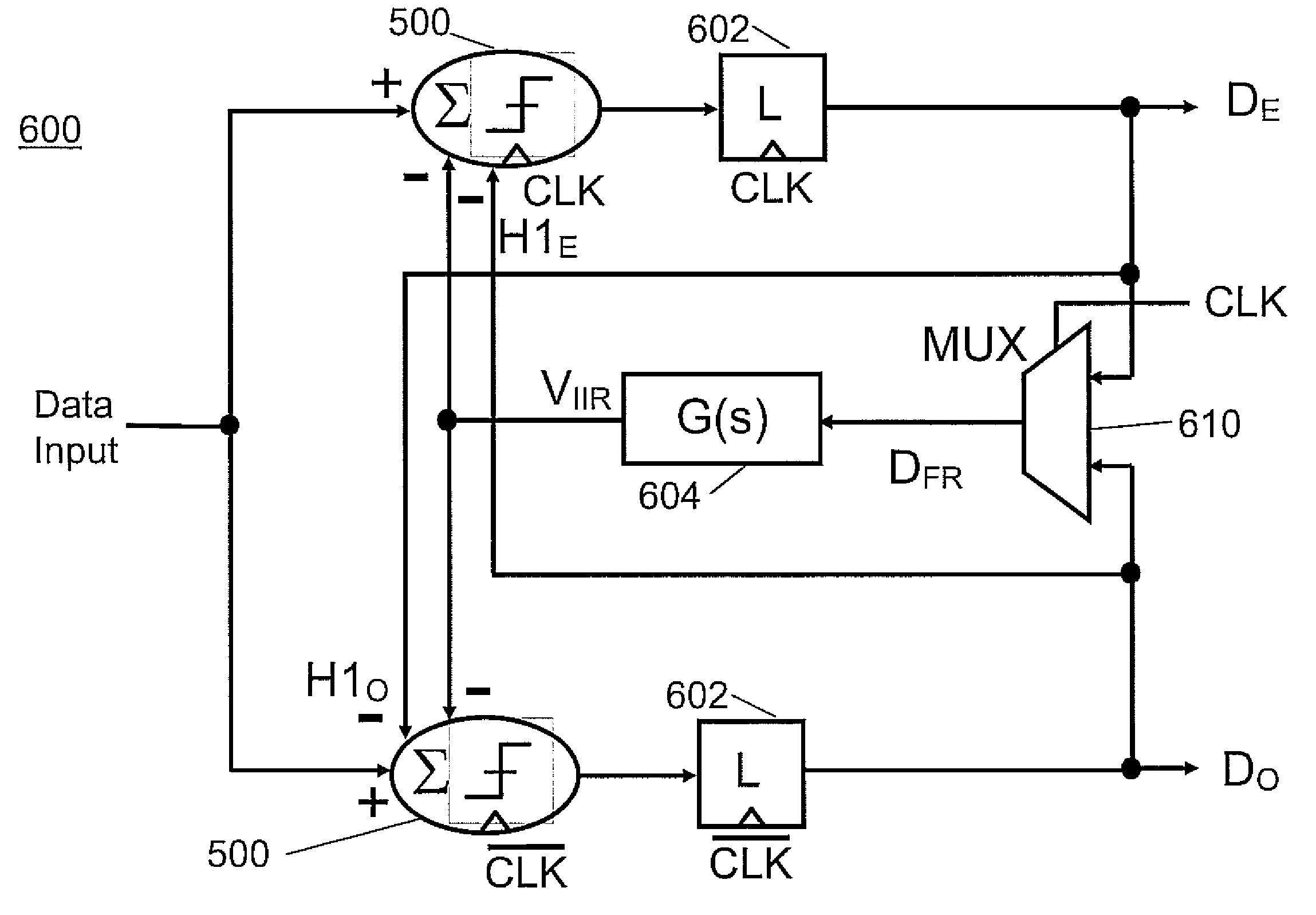

Circuits and methods for dfe with reduced area and power consumption

ActiveUS20100202506A1Increase speedHigh sensitivityMultiple-port networksFrequency/rate-modulated pulse demodulationMultiplexingMultiplexer

A 1 / n-rate decision feedback equalizer (DFE) and method include a plurality of branches. Each branch includes a summer circuit configured to add a feedback signal to a received input, and a latch configured to receive an output of the summer circuit in accordance with a clock signal. A feedback circuit includes a multiplexer configured to receive as input, an output of each branch, the multiplexer having a clocked select input and configured to multiplex the output of each branch to assemble a full rate bit sequence, and a filter configured to provide cancellation of intersymbol interference (ISI) from the received input to be provided to the summer circuit of each branch.

Owner:IBM CORP