Patents

Literature

5728results about How to "Shorten test time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System, method and apparatus for providing functions to applications on a digital electronic device

InactiveUS20100257539A1Enabling and simplifying application developmentShorten development timeService provisioningInterprogram communicationDiscrete functionsApplication software

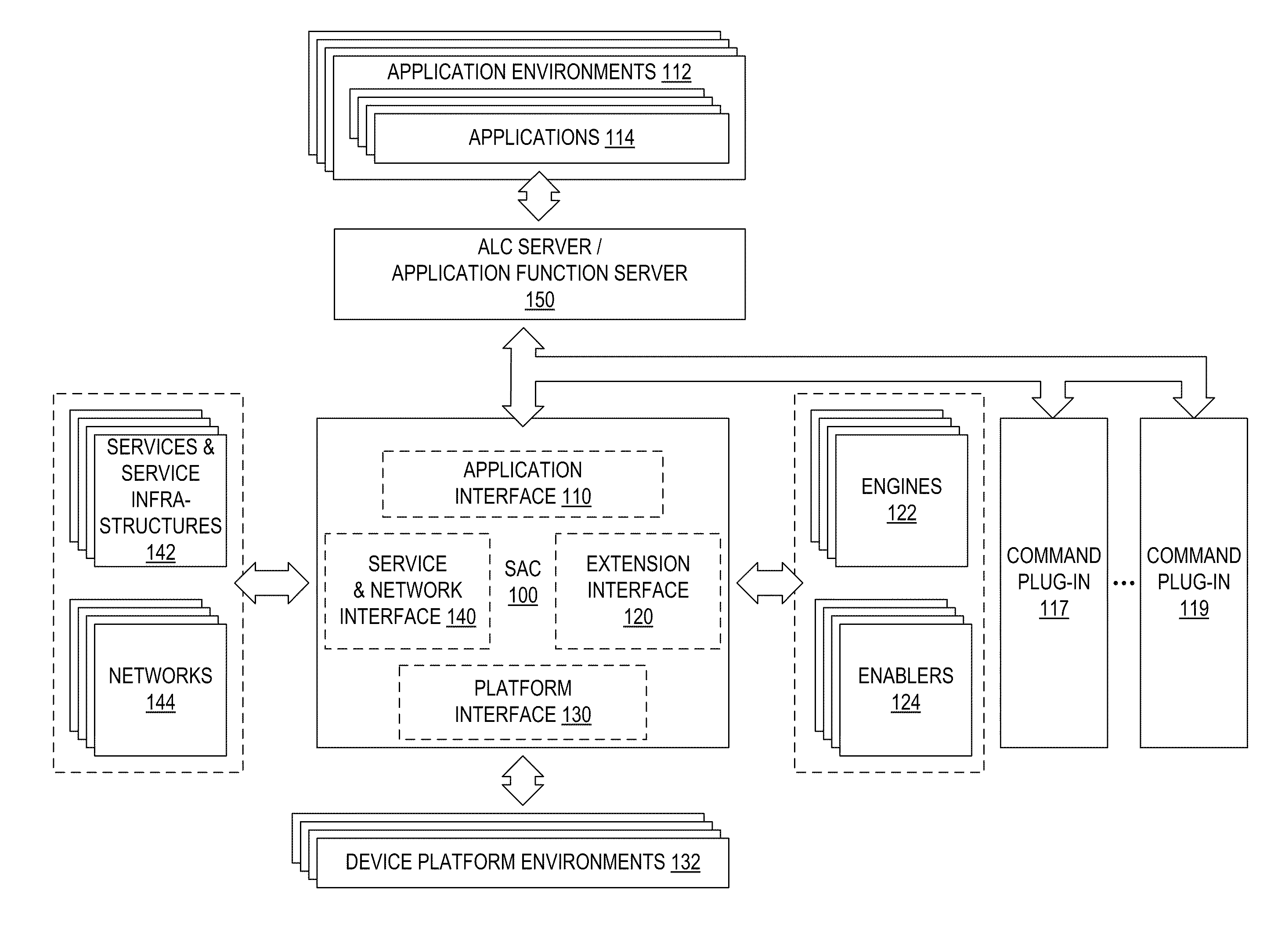

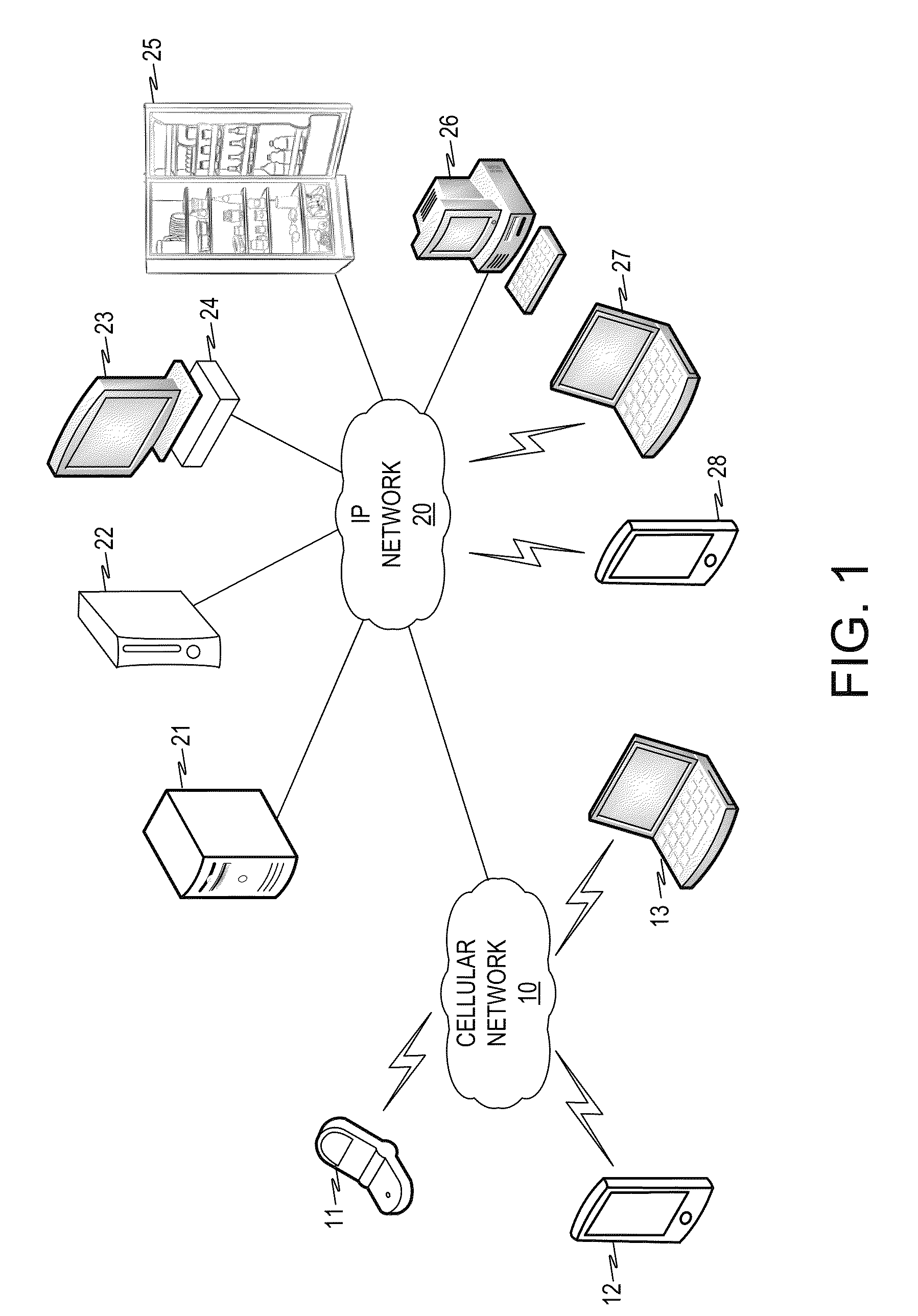

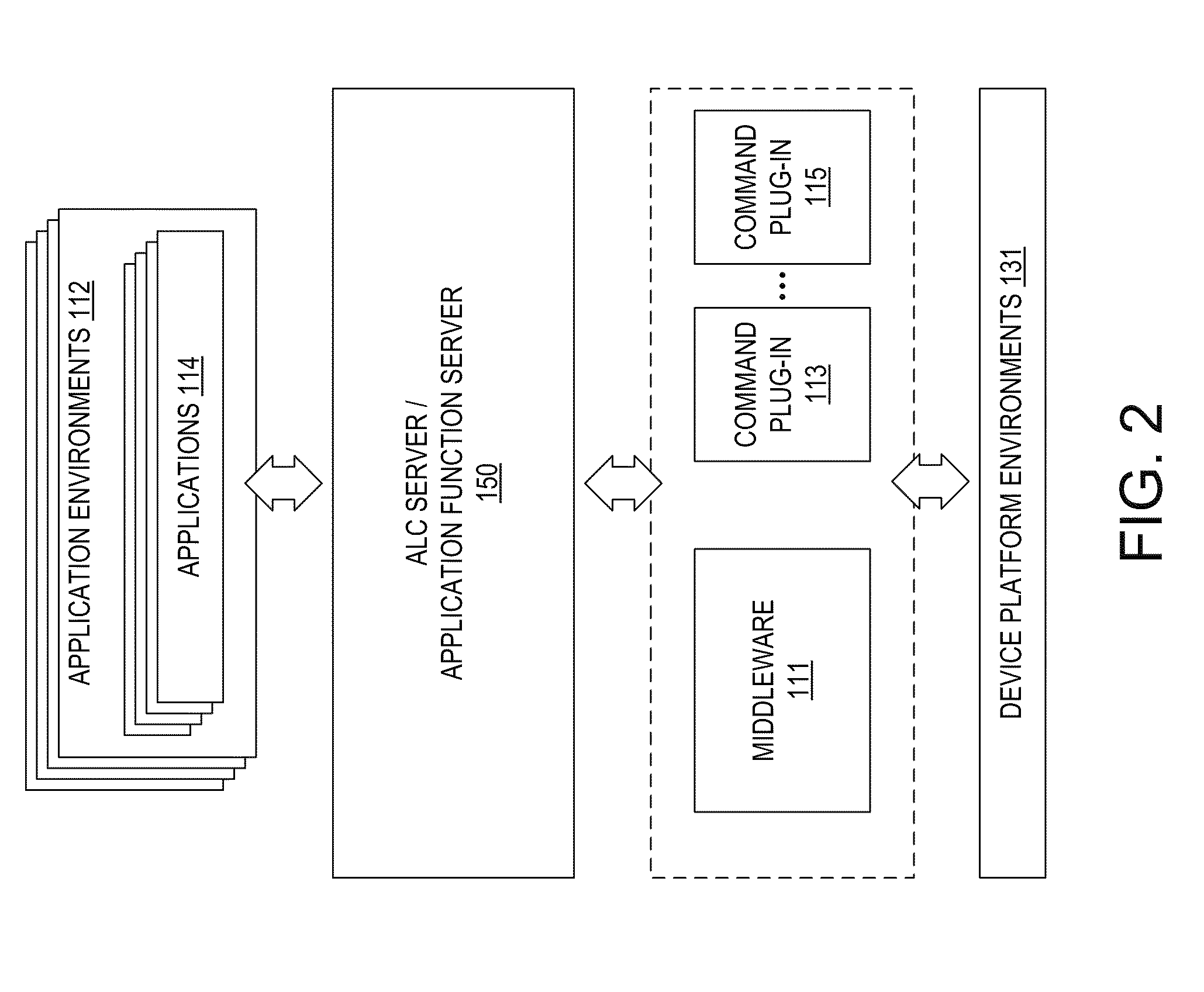

To greatly simplify the developer's task, an application function server or application logic controller (“ALC”) server runs on a digital electronic device with a common set of tools and methods to deliver high-value capabilities to applications developed in different application languages and running in various different application environments. The applications and the application function server have a local client-server relationship. The functions themselves are provided by various plug-ins. The interface of a plug-in illustratively is a discrete set of functions, common to the command plug-ins. The ALC Server accepts simplified commands directly from the applications, applies the appropriate policy, and interacts with the plug-ins to perform the requested functions on behalf of the applications. The result is that applications can use various capabilities without dealing with the complex methods, standards, and system interoperability required to make the technologies work, and technology additions and upgrades can be performed independently from the applications that use them.

Owner:ECRIO

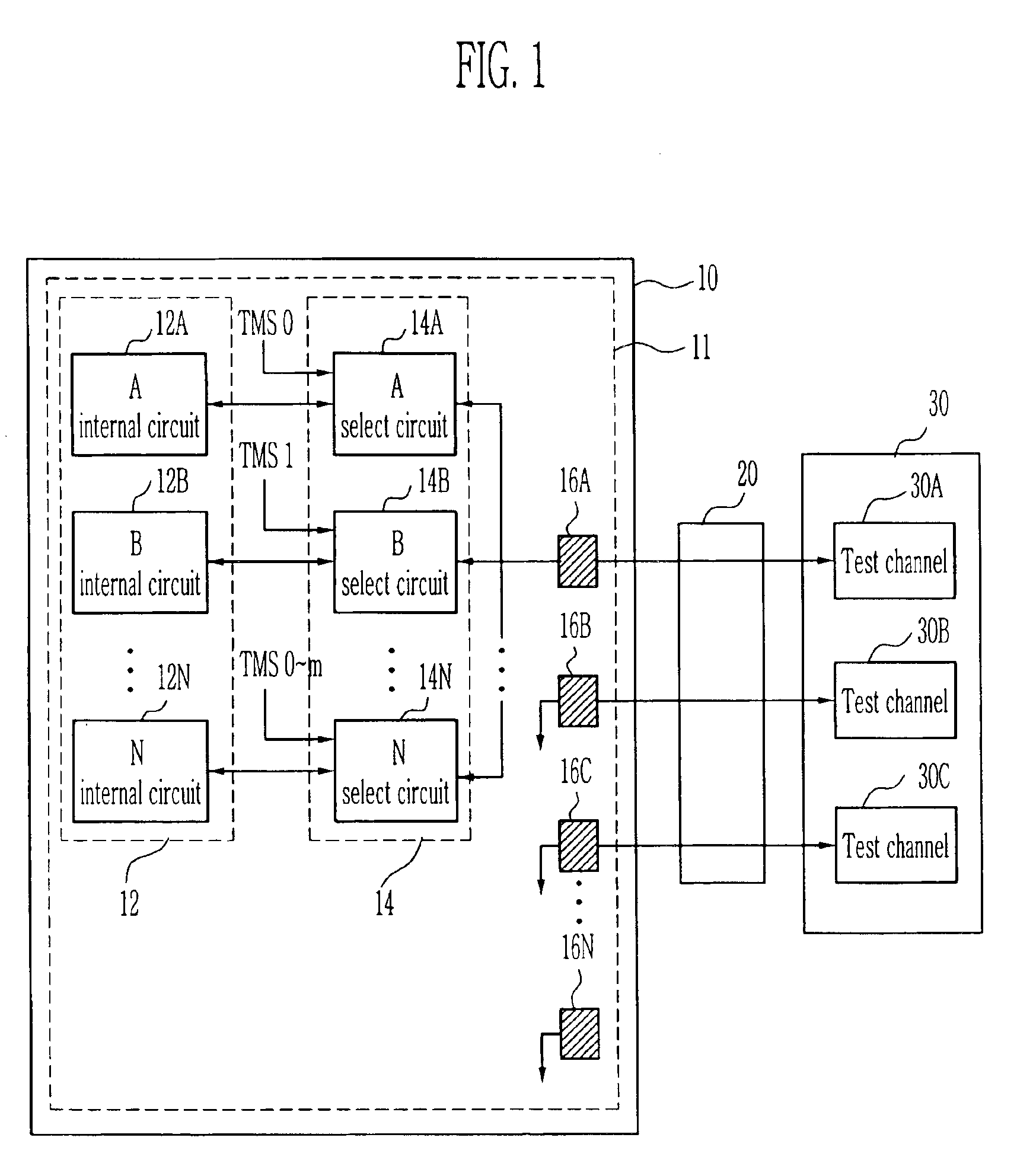

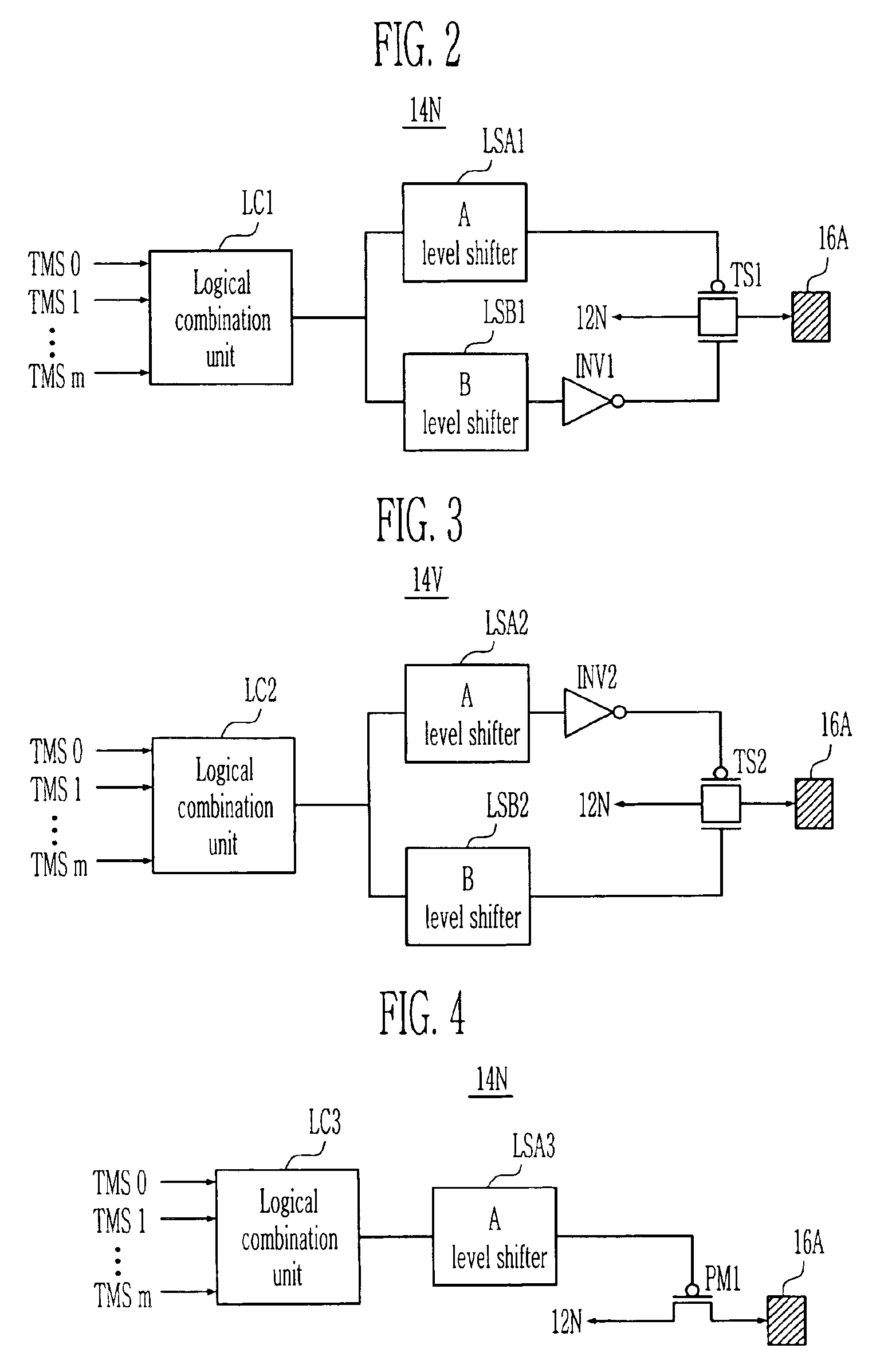

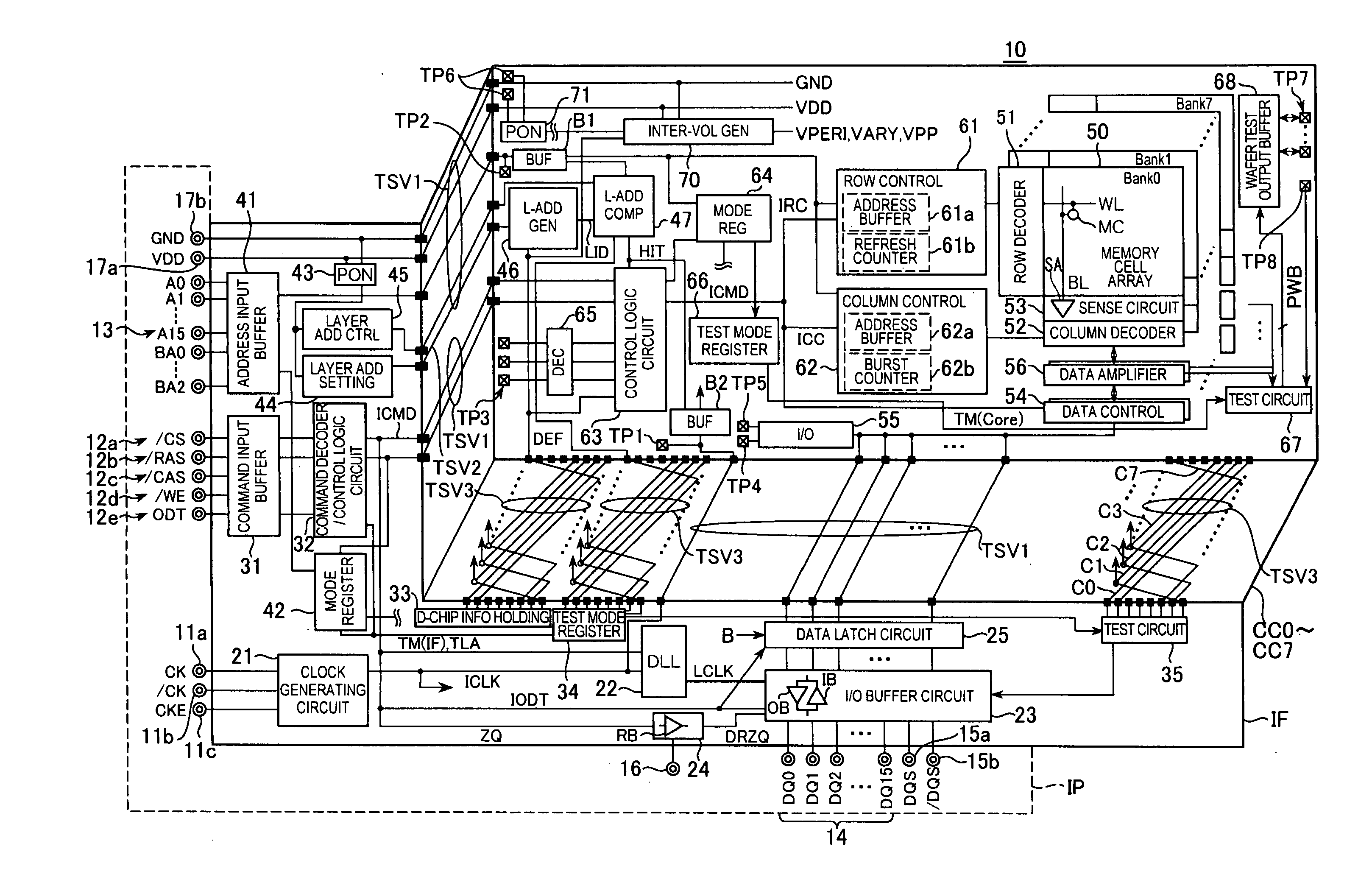

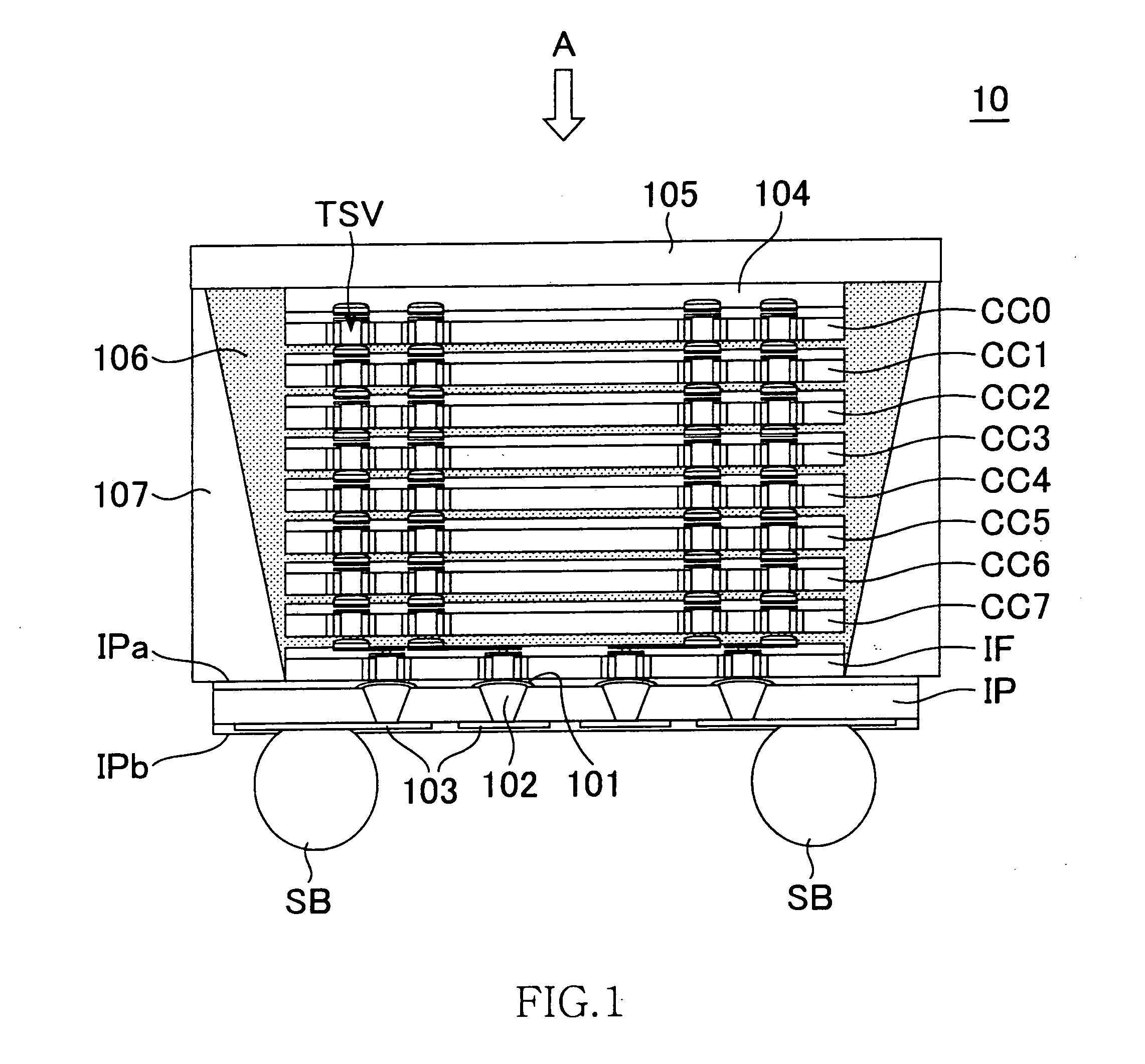

Semiconductor device for reducing the number of probing pad used during wafer test and method for testing the same

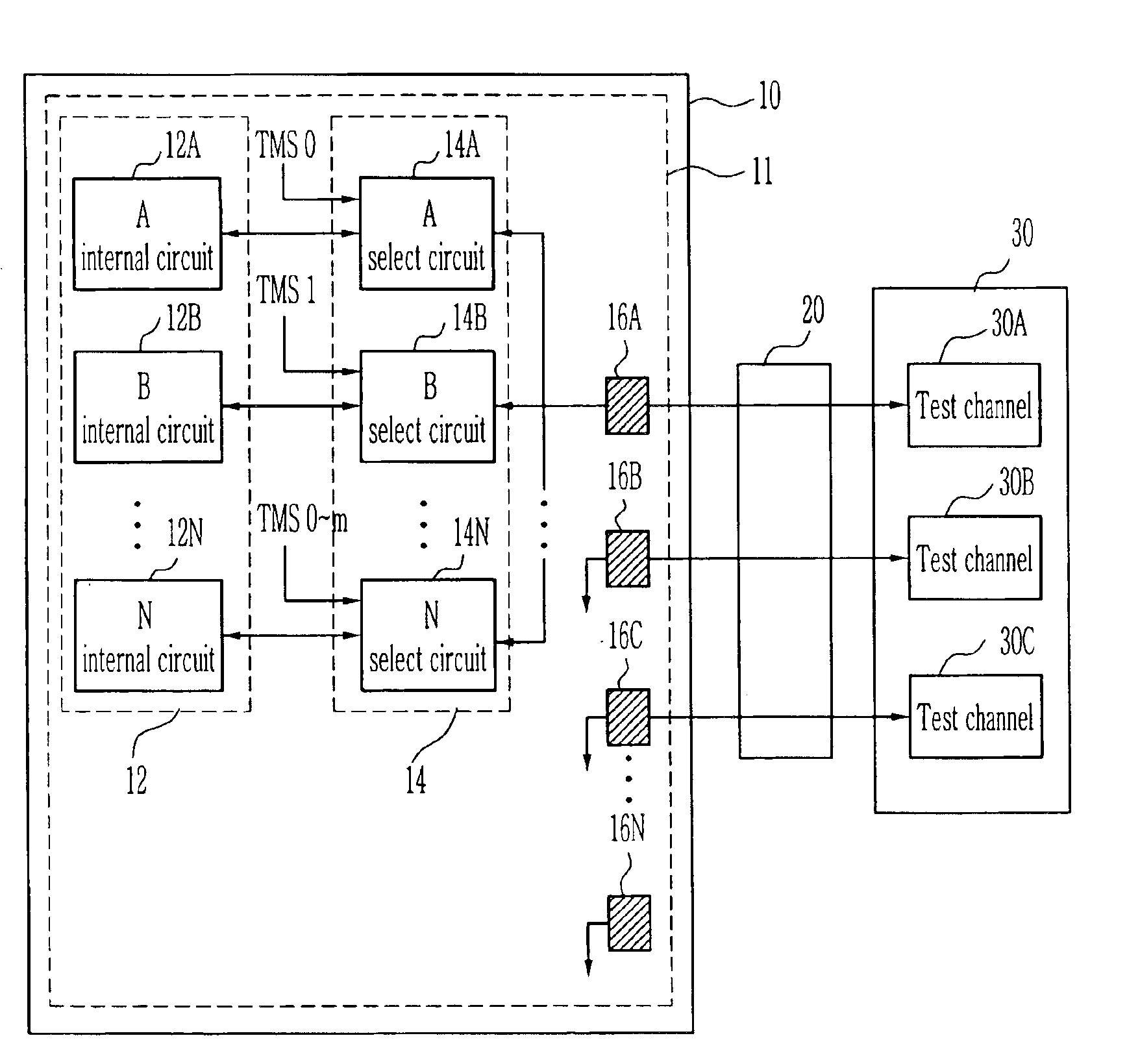

The present invention relates to a semiconductor device and a method for testing the same capable of reducing the number of probing pads used during wafer test. The semiconductor device includes a select circuit connected between a plurality of internal circuits to be tested and a single probing pad, for transmitting test signals inputted from the probing pads to any one of the plurality of the internal circuits according to a test mode signal generated in a wafer test mode. It is possible to reduce the number of the probing pads in the integrated circuit used for connection to a probe for contact of a probe card during wafer test. It is therefore possible to reduce test time.

Owner:SK HYNIX INC

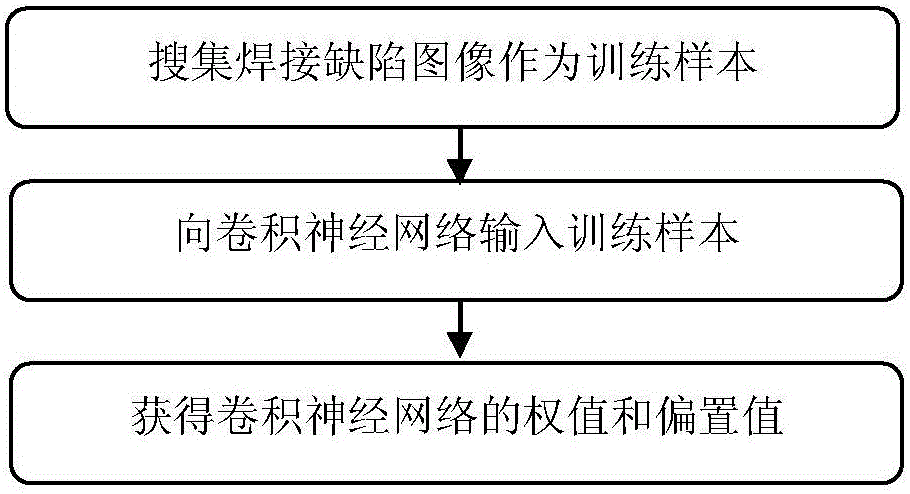

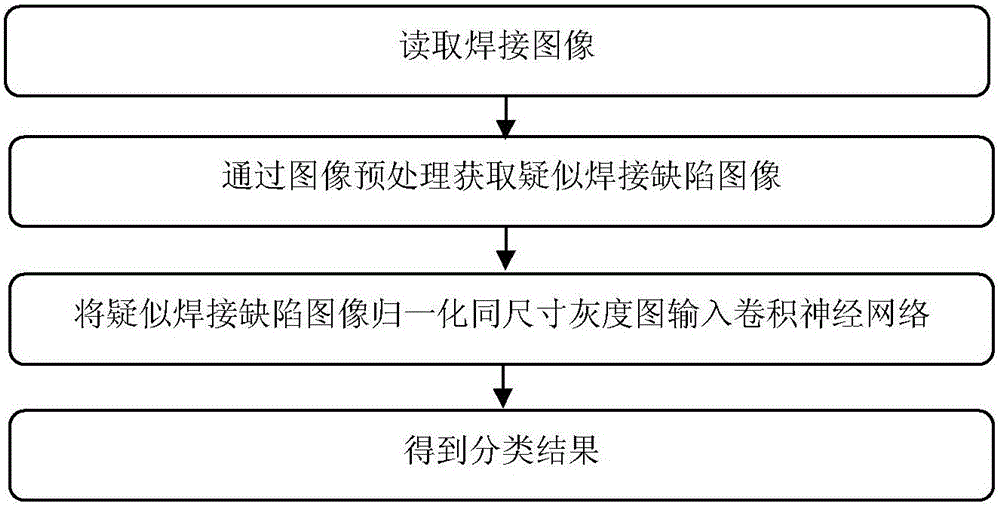

Welding visual detection method and device based on convolutional neural network

ActiveCN105891215AHigh precisionHigh speedOptically investigating flaws/contaminationTest phaseRegion of interest

A welding visual detection method based on a convolutional neural network includes the following steps that firstly, at the training stage, a training sample is input into the convolutional neural network, and the connection weight and offset value of the convolutional neural network are obtained; secondly, at the testing state, a welding picture is read in and preprocessed with the digital picture processing technology, and a region of interest is extracted and then subjected to picture size normalization processing to serve as input of the convolutional neural network. The invention further provides a welding visual detection device based on the convolutional neural network. The welding visual detection device based on the convolutional neural network comprises a crawling mechanism, a power transmission mechanism, visual detection equipment and a weld defect detection and analysis system. By means of the welding visual detection method and device based on the convolutional neural network, the automaton and intelligence level is improved, the detection precision is effectively improved, and the detection speed is effectively increased.

Owner:ZHEJIANG UNIV OF TECH

Wireless no-touch testing of integrated circuits

ActiveUS20050193294A1Immediate cost-reduction impactIncrease speedDigital circuit testingSemiconductor/solid-state device testing/measurementCircuit under testEngineering

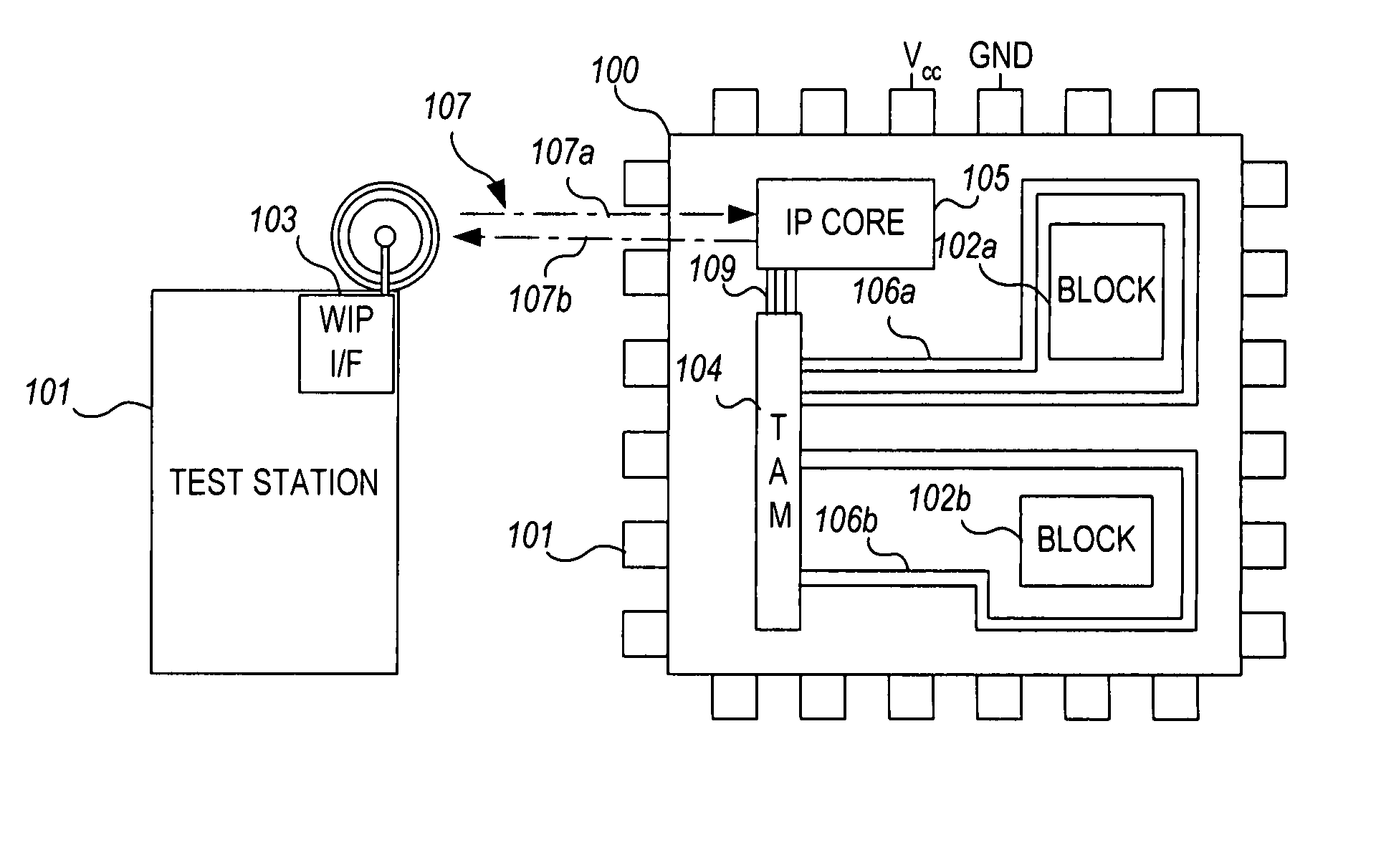

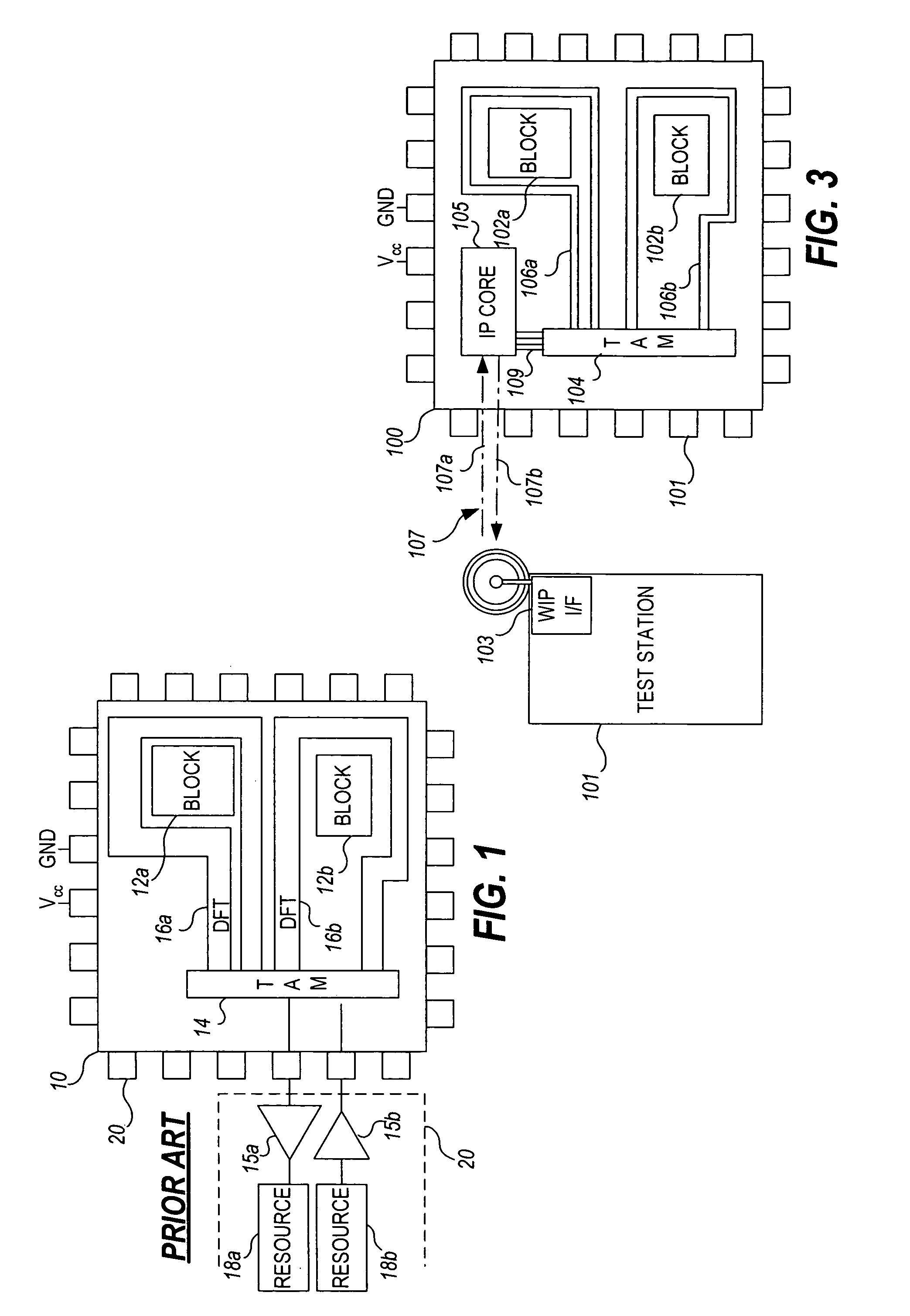

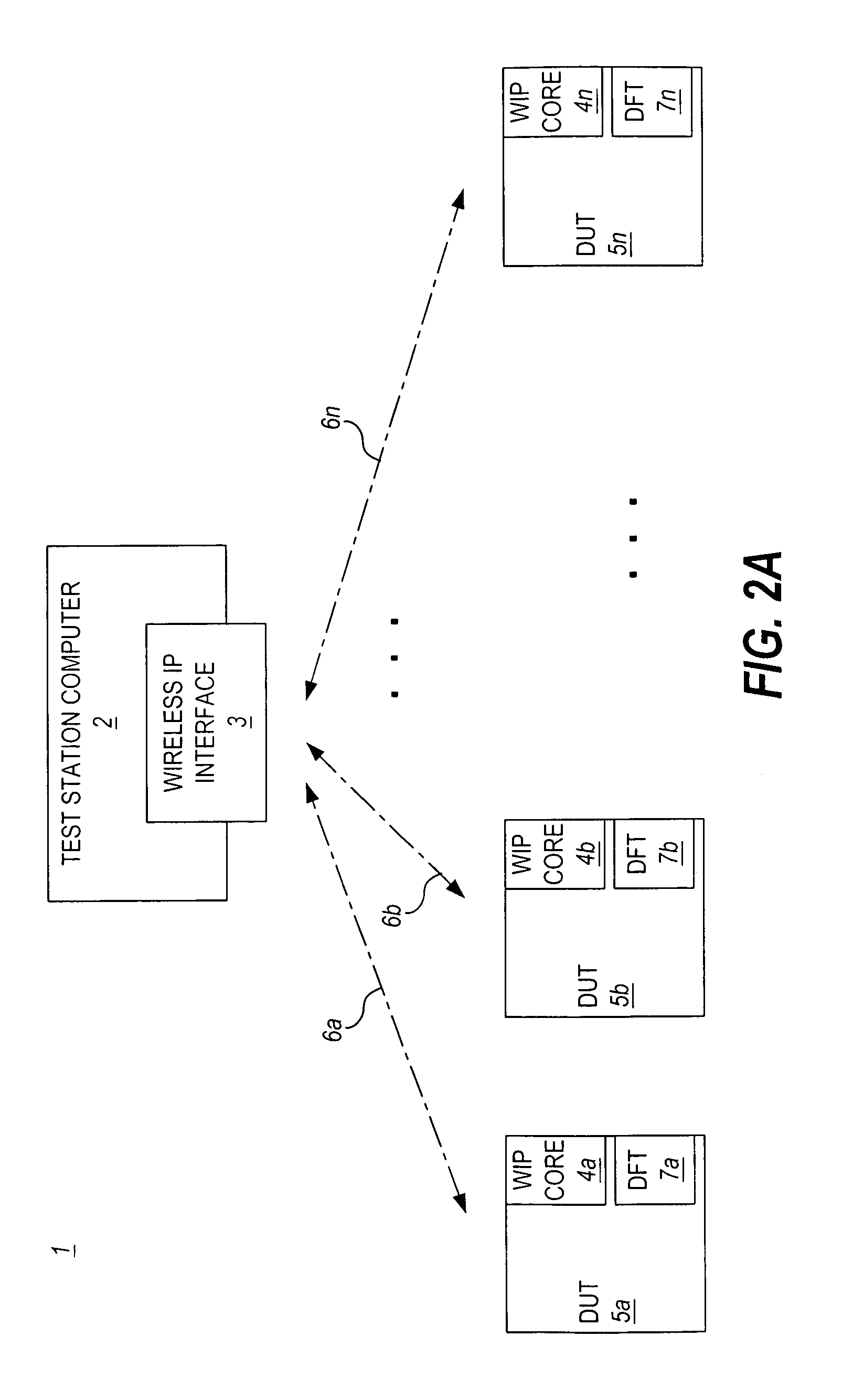

A wireless integrated circuit test method and system is presented. The invention allows testing of one or more integrated circuits configured with a wireless interface and a test access mechanism which controls input of test data received over a wireless connection from a test station to test structures which test functional blocks on the integrated circuit. Via the wireless connection, multiple integrated circuits or similarly equipped devices under test can be tested simultaneously. The invention also enables concurrent testing of independently testable functional blocks on any given integrated circuit under test.

Owner:ADVANTEST CORP

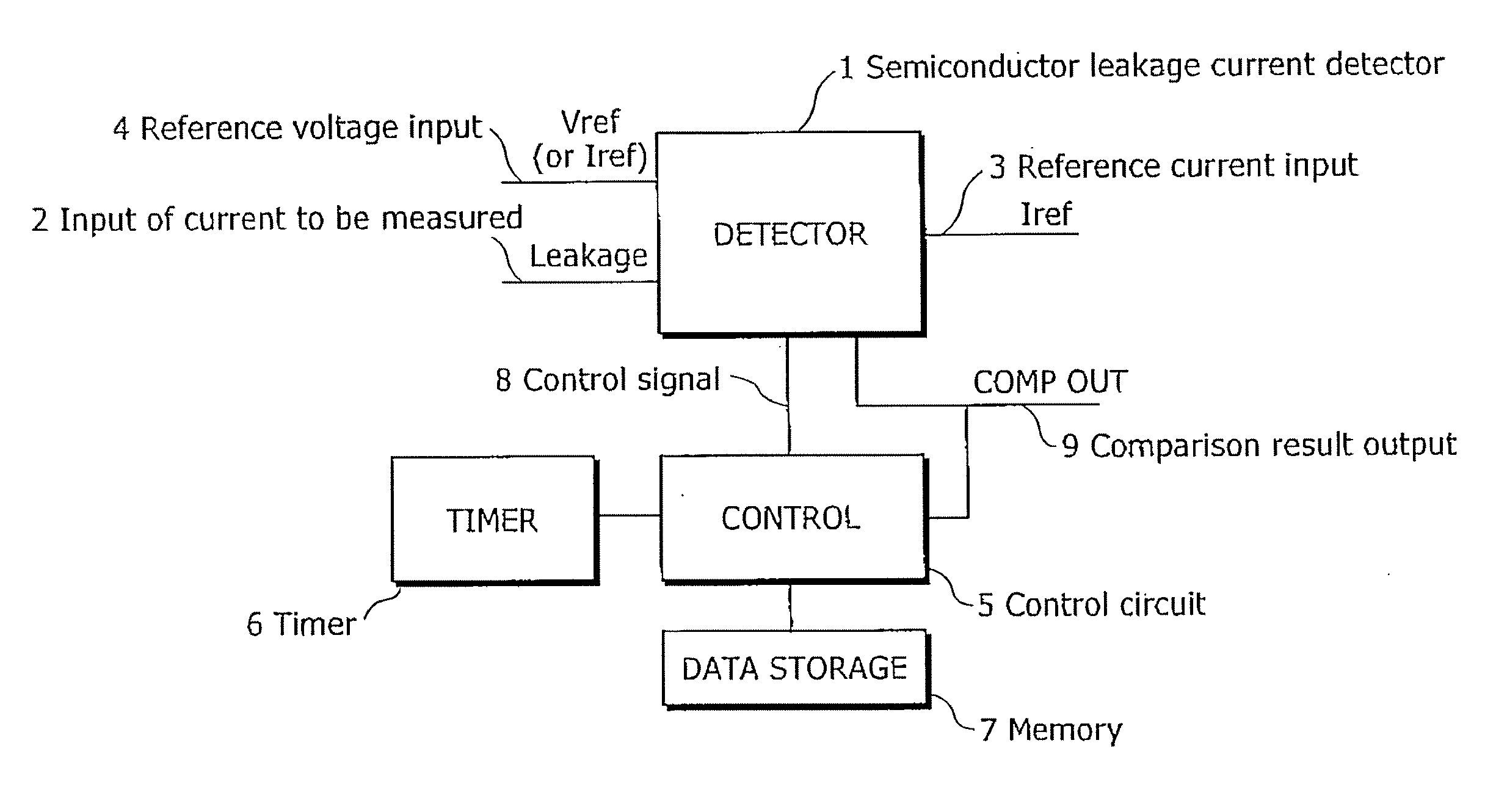

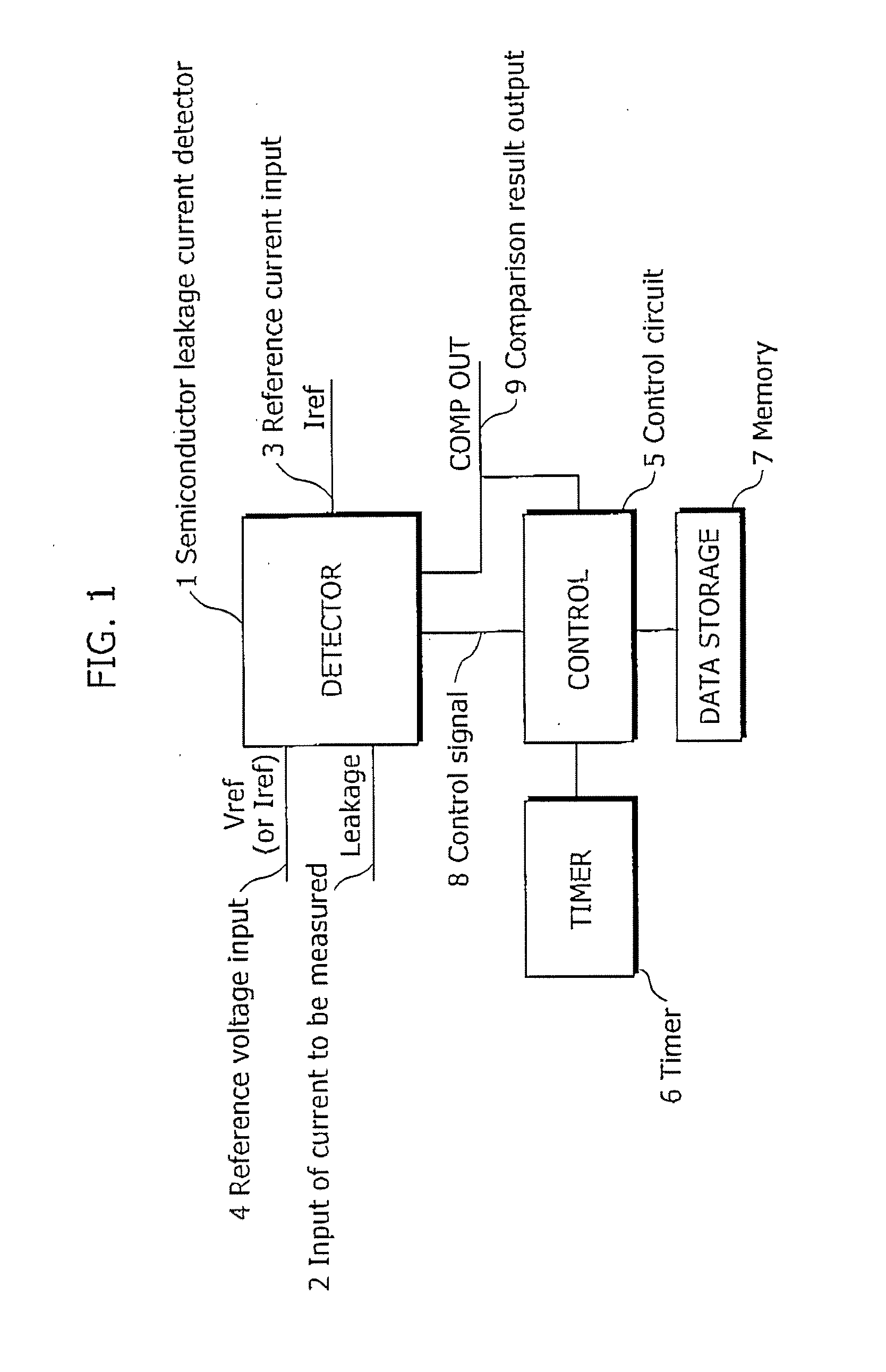

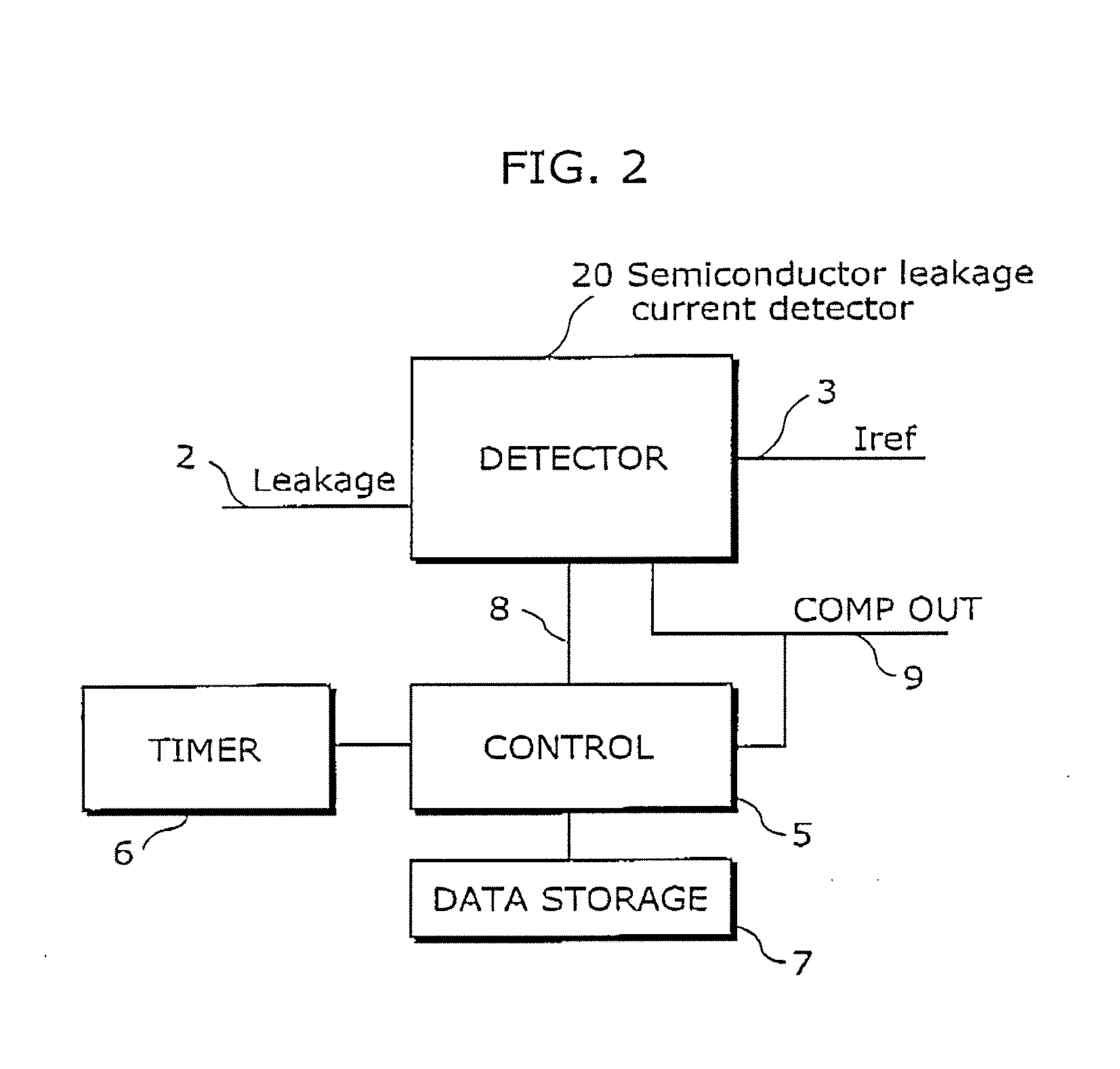

Semiconductor leakage current detector and leakage current measurement method, semiconductor leakage current detector with voltage trimming function and reference voltage trimming method, and semiconductor intergrated circuit thereof

ActiveUS20070145981A1Improve search speedReduce trimming timeMultiple input and output pulse circuitsDirection of current indicationCapacitanceReference current

A semiconductor leakage current detector of the present invention includes a first analog switch which causes a current to be measured to flow or to be cut off, a second analog switch which causes a reference current to flow or to be cut off, an integral capacitance element which is connected by the first analog switch and the second analog switch and is charged with the current to be measured or the reference current, a discharge unit which discharges the integral capacitor, and a comparison unit which compares the reference voltage with each of an integral voltage generated in the integral capacitor by a reference current after the discharge of the integral capacitor and an integral voltage generated in the integral capacitance element by the current to be measured after the discharge of the integral capacitor

Owner:III HLDG 12 LLC

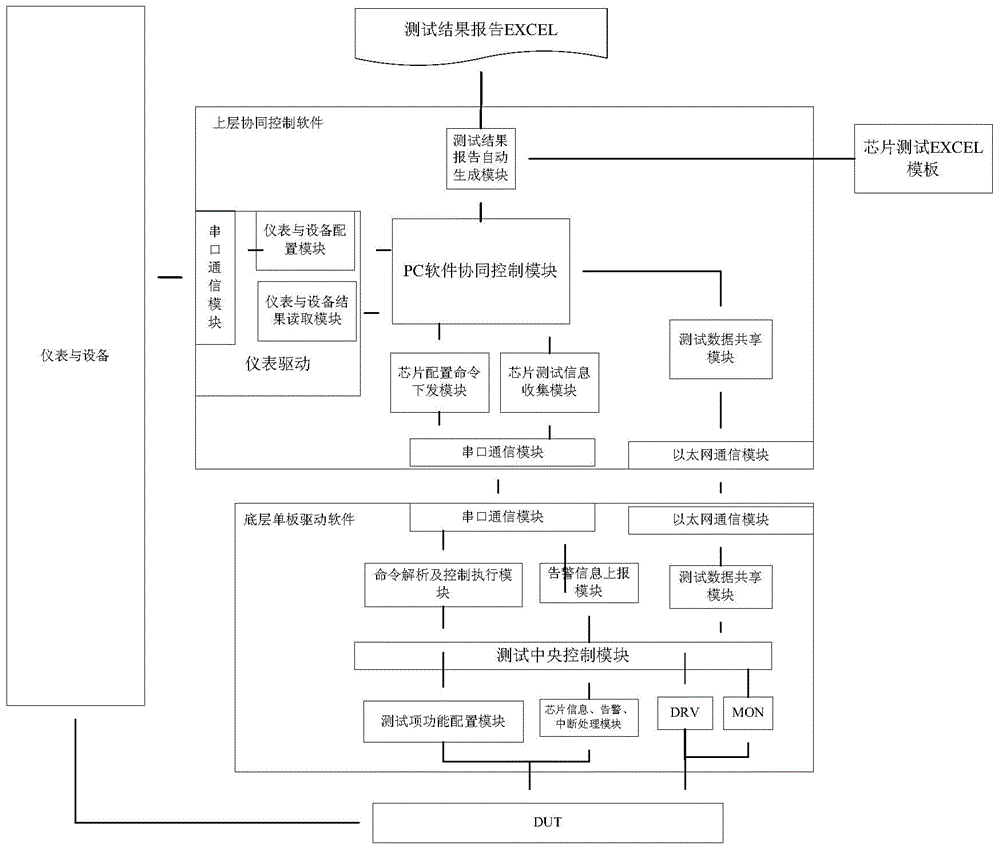

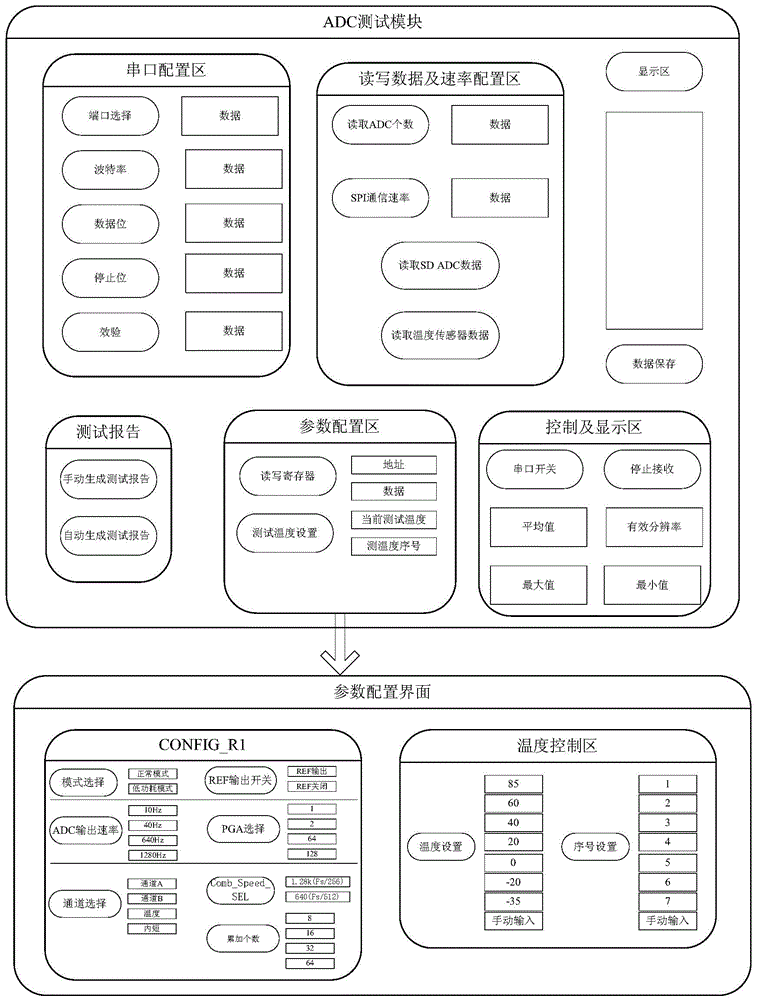

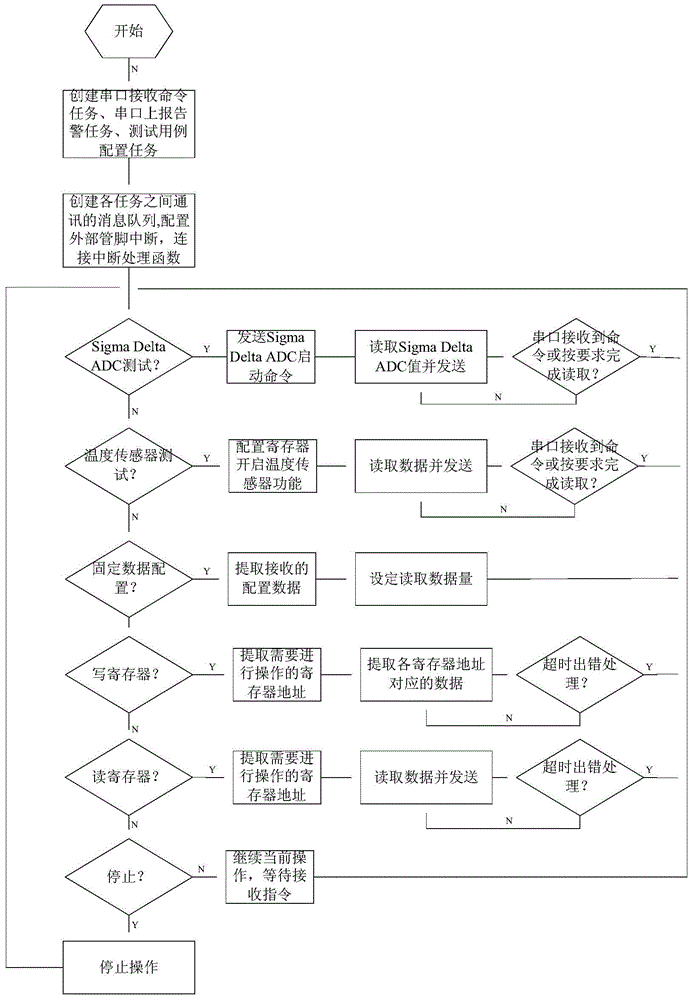

Automatic chip testing method

InactiveCN105004984AQuick testImplement automated testingElectronic circuit testingCommunication interfaceTest efficiency

The invention discloses a automatic chip testing method, which is characterized by comprising the steps that: the system is powered on, and initialization is completed; the configuration is carried out, a test thread needs to be started is determined according to chip types, and an instrument transceiving end is configured; a test command is generated, test items and test parameter setting in a chip integrated test case configuration file are read and analyzed, and a command frame is generated and transmitted to a single-board system through a communication interface; and the command is analyzed, and setting and testing steps are carried out. The automatic chip testing method can achieve the automatical test and data storage of chips, can be used for testing the chips quickly, is high in test efficiency, saves test time to a certain extent, can achieve the purposes of automatic configuration of a tested DUT chip, automatic configuration of instruments, automatic recovery of test results and automatic generation of test reports, automatic generation of test case reports and automatic switching of test cases through the development of an automatic chip testing platform.

Owner:CHIPSEA TECH SHENZHEN CO LTD

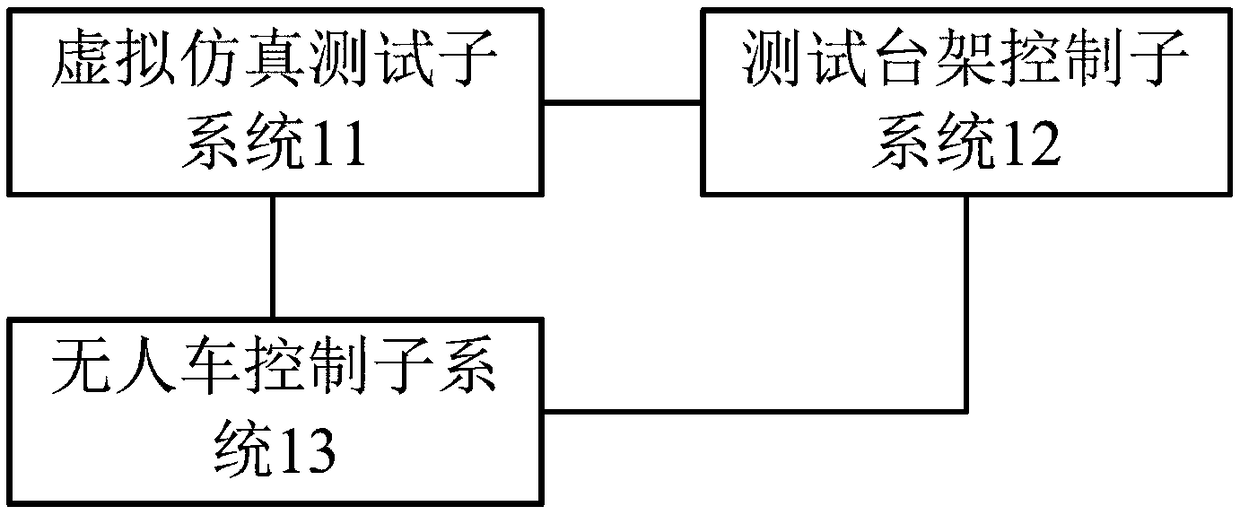

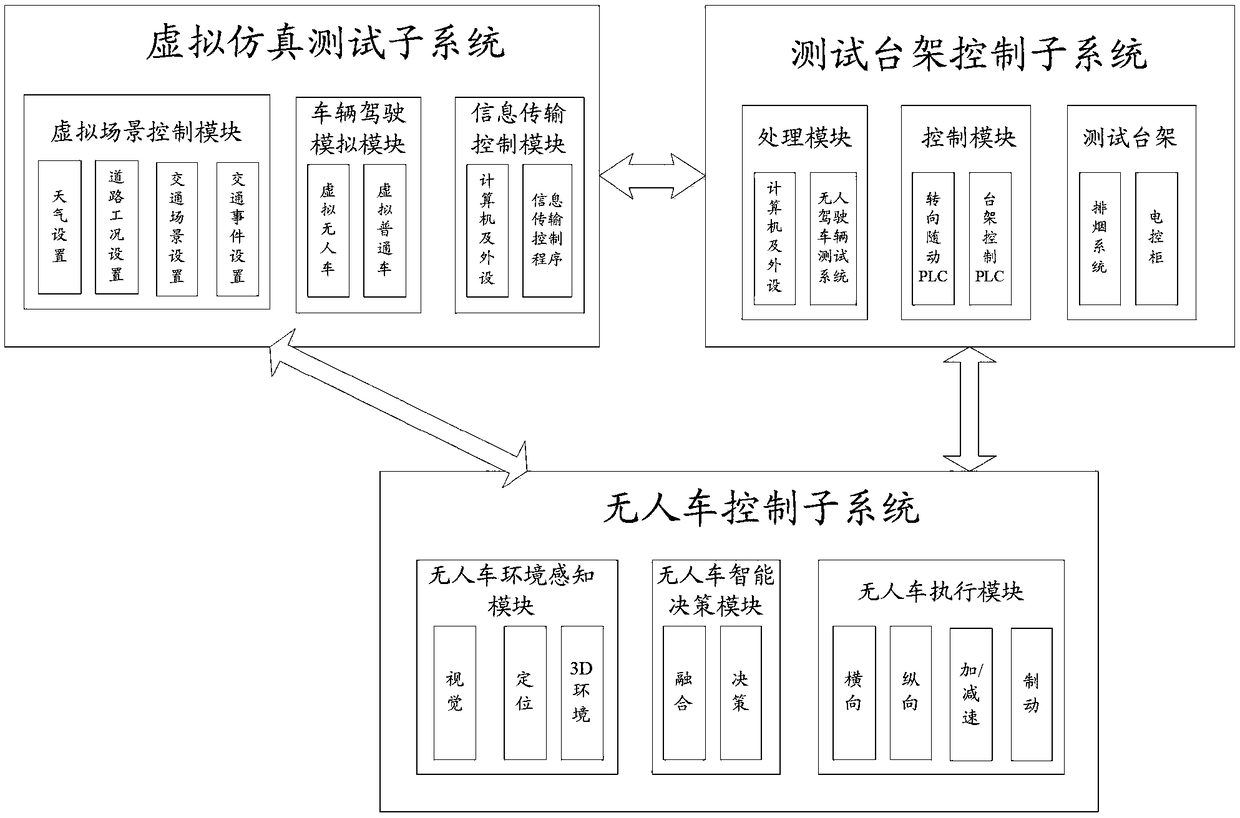

In-loop rapid simulation test system and method of unmanned vehicle

ActiveCN109100155AEnsure safetyGuaranteed reliabilityVehicle testingElectric testing/monitoringRoad surfaceHardware-in-the-loop simulation

The embodiment of the invention provides an in-loop rapid simulation test system of an unmanned vehicle. The system comprises: a virtual simulation test subsystem used for generating a virtual test scene and transmitting a pavement state control instruction to a test bench control subsystem; the test bench control subsystem used for simulating a pavement state, as well as estimating the driving performance of the unmanned vehicle according to driving parameters of the unmanned vehicle; and an unmanned vehicle control subsystem used for performing driving control on the unmanned vehicle according to the virtual test scene. The above system adopts the simulation test mode of combining the virtual reality technology with the hardware in-loop, so that a controllable, repeatable and effective in-loop rapid simulation test of the unmanned vehicle can be achieved indoors; and furthermore, all extreme or special road conditions are exhausted as much as possible, so that the safety and the reliability of the unmanned vehicle before start off can be fully guaranteed. The embodiment of the invention further provides an in-loop rapid simulation test method of the unmanned vehicle.

Owner:CHANGAN UNIV

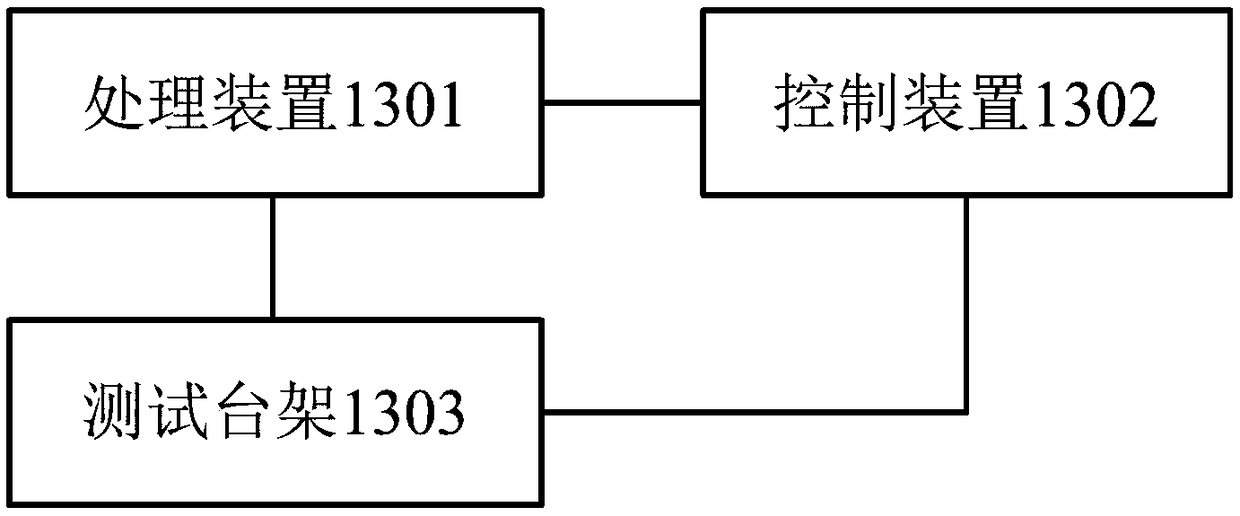

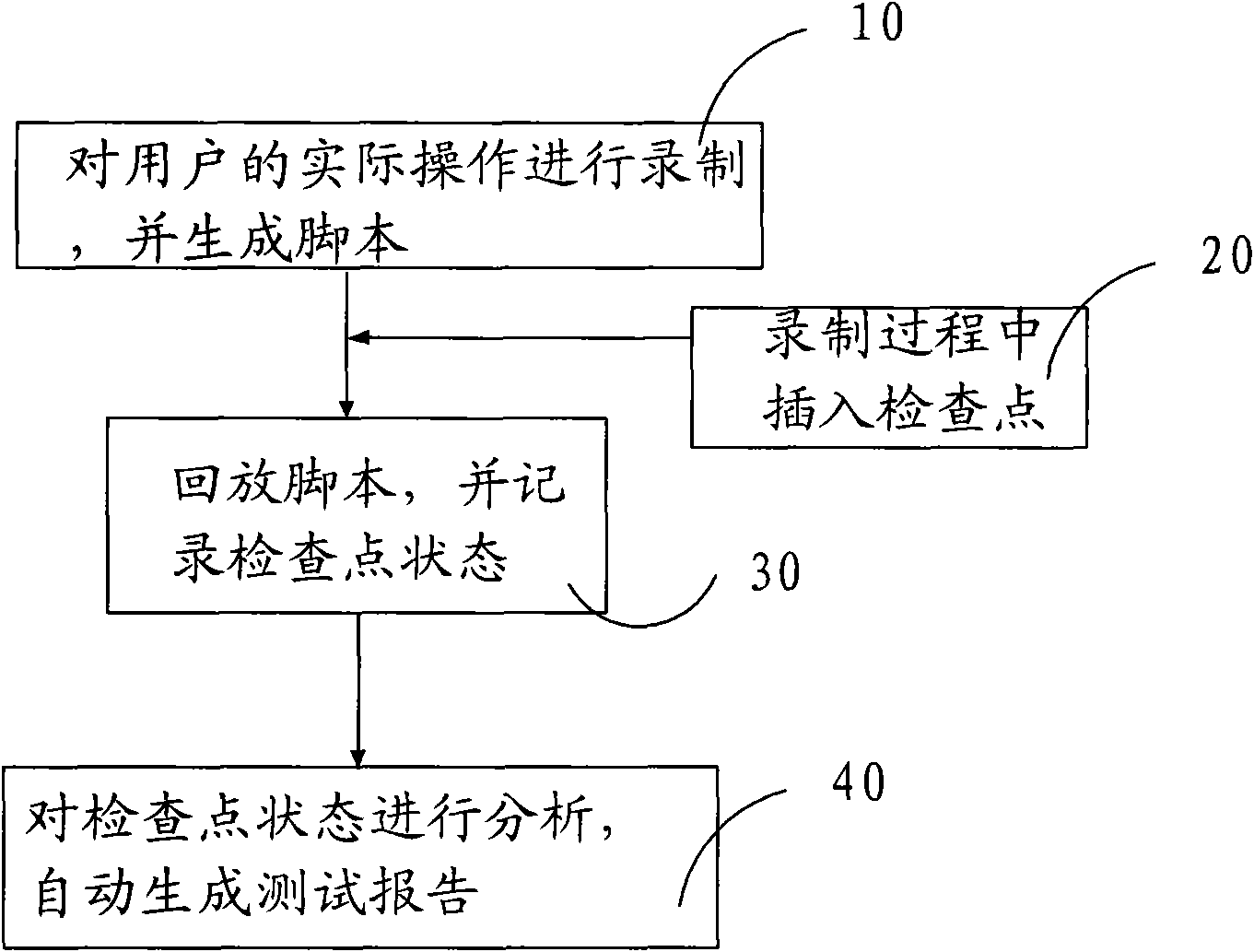

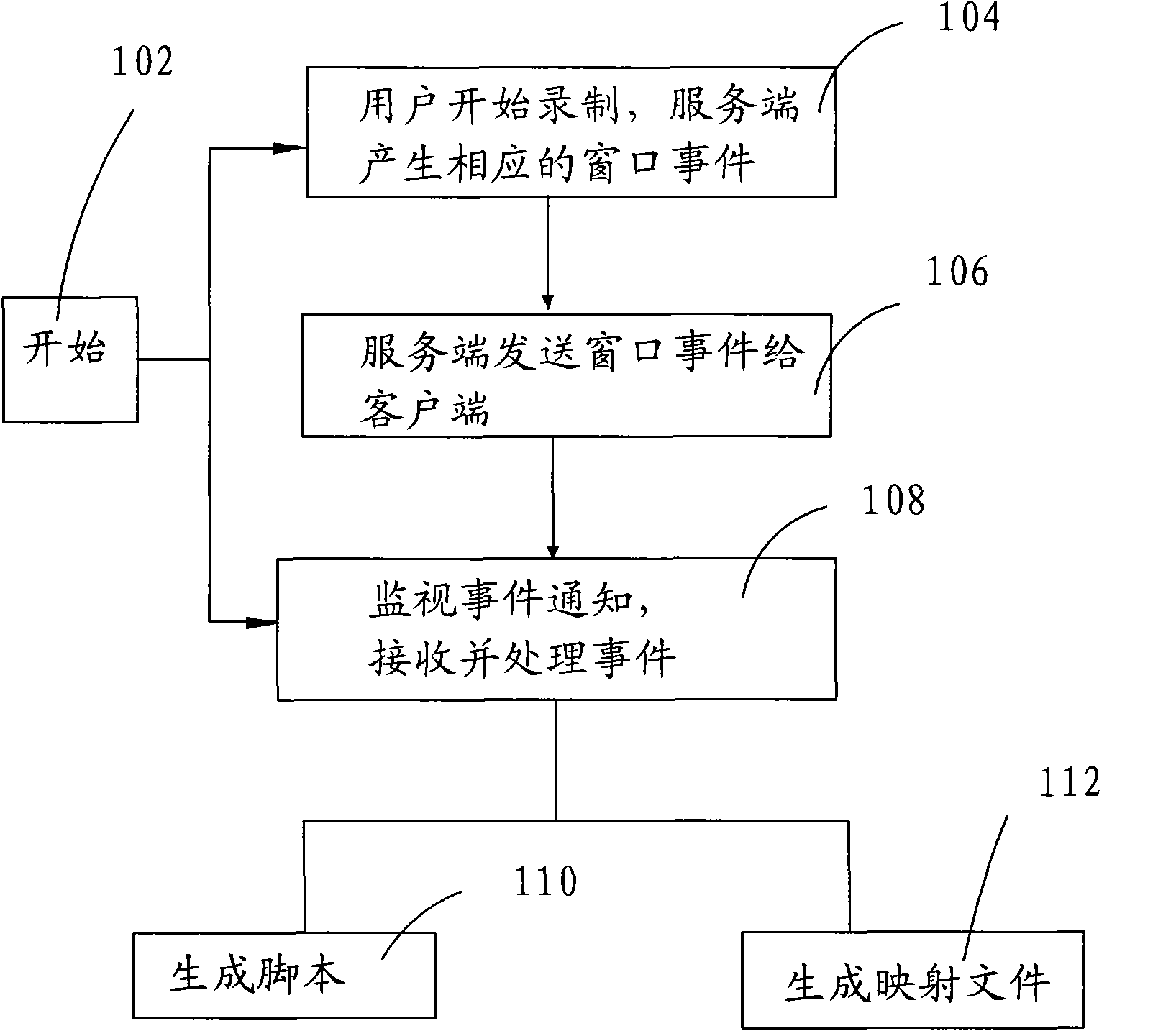

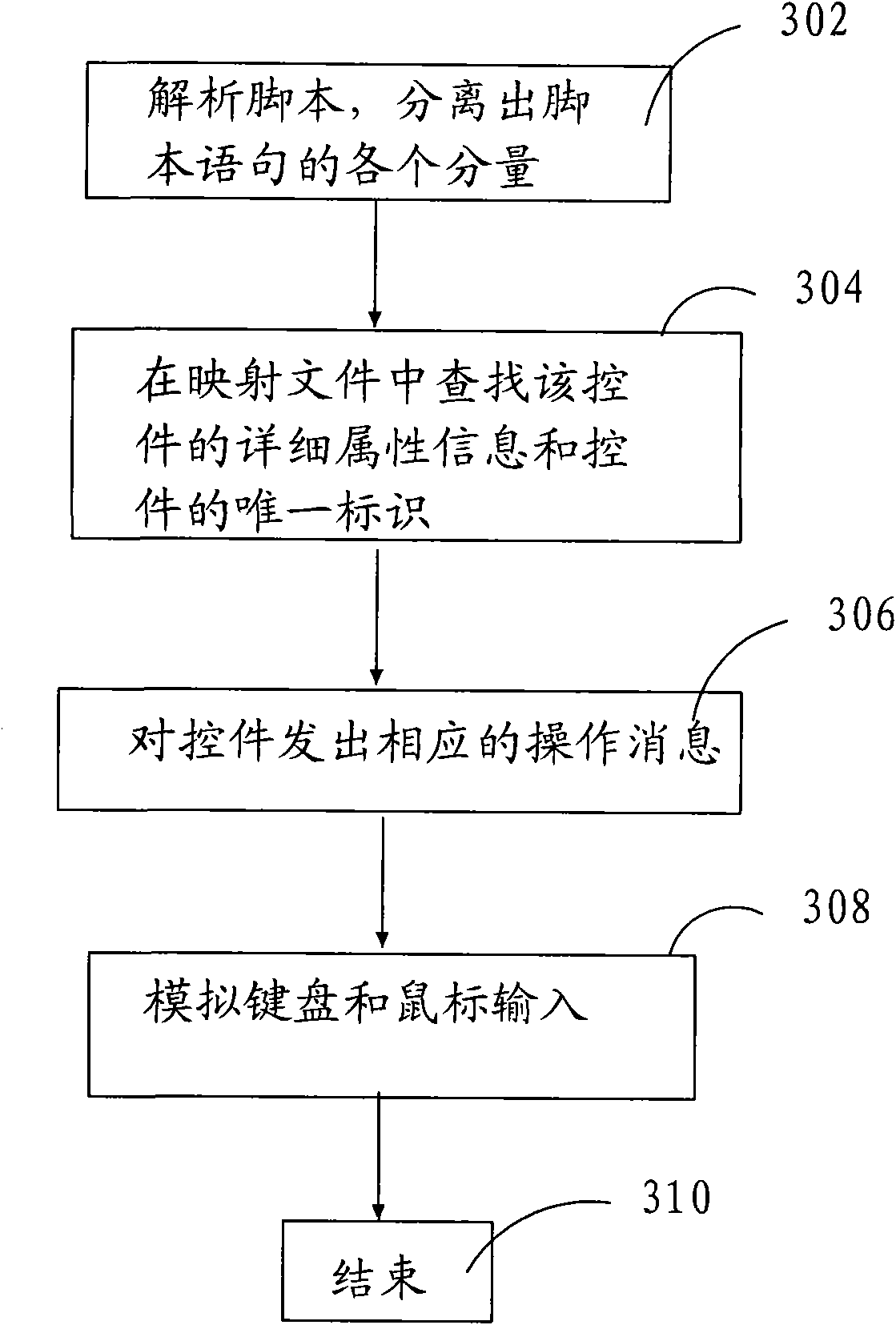

Method for automatically testing recording playback mode of terminal system

InactiveCN101620564ACheckpoints are reliableShorten test timeSoftware testing/debuggingCheck pointTerminal system

The invention relates to a method for automatically testing a recording playback mode of a terminal system, which comprises the following steps: 10, recording actual operation of a user, which comprises mouse operation and keyboard operation, and automatically generating a script which is easily understood by the user and can be edited manually; 20, in the recording process in the step 10, inserting a check point of which the state is required to be checked in an automatic test; 30, playing the script generated in the step 10 back, automatically executing the test, and recording the state of the check point; and 40, finishing the playback of the script, analyzing the recorded state of the check point, summarizing test results, and automatically generating a test report. The method has the advantages of being suitable for automatic functional tests of terminal embedded systems and non-embedded systems, supporting tests for functions of protocols such as ICA, RDP and the like, providing reliable check points for testing GUI functions, and saving testing time.

Owner:FUJIAN CENTM INFORMATION

Systems and methods for testing the performance of and simulating a wireless communication device

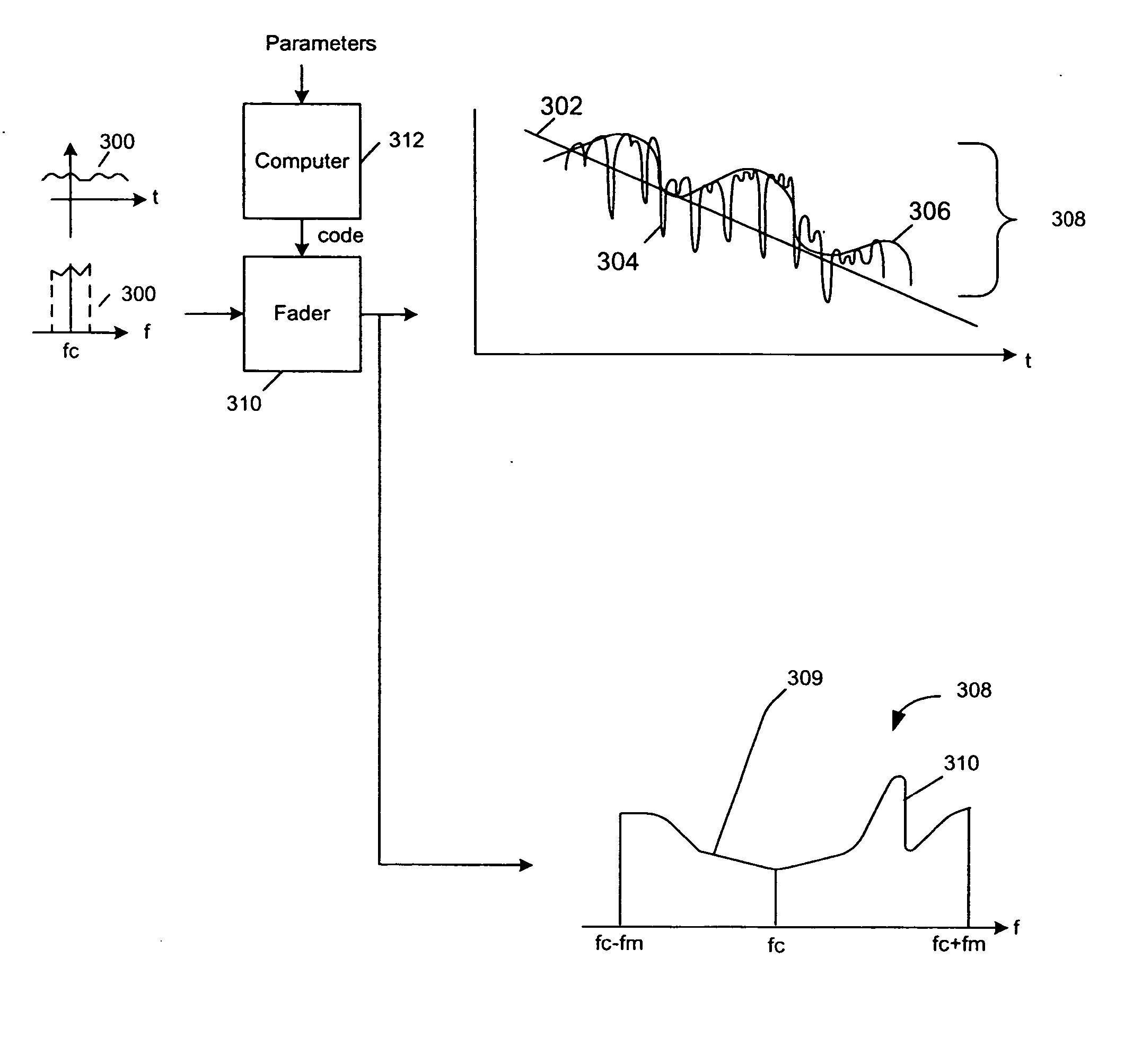

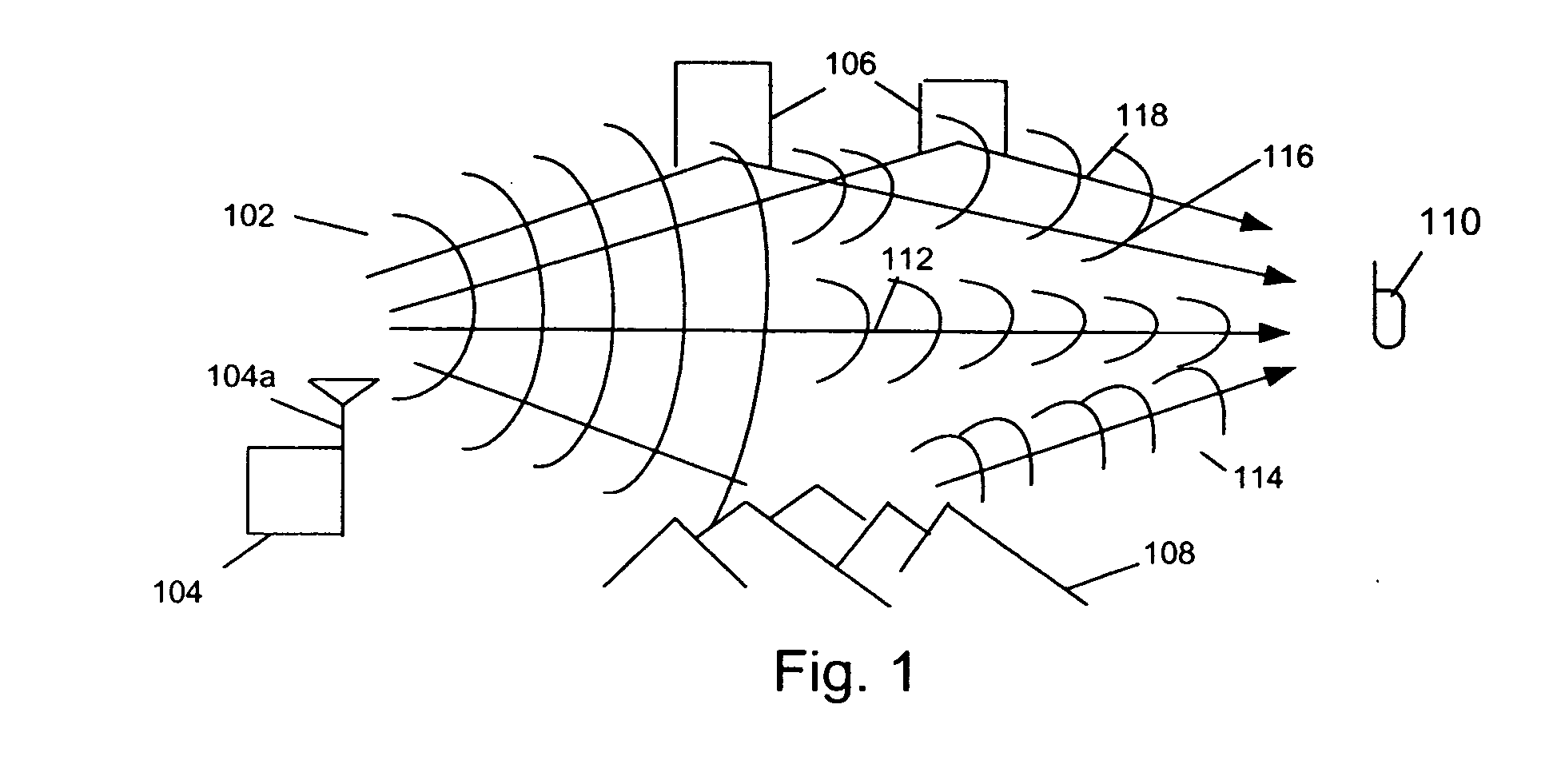

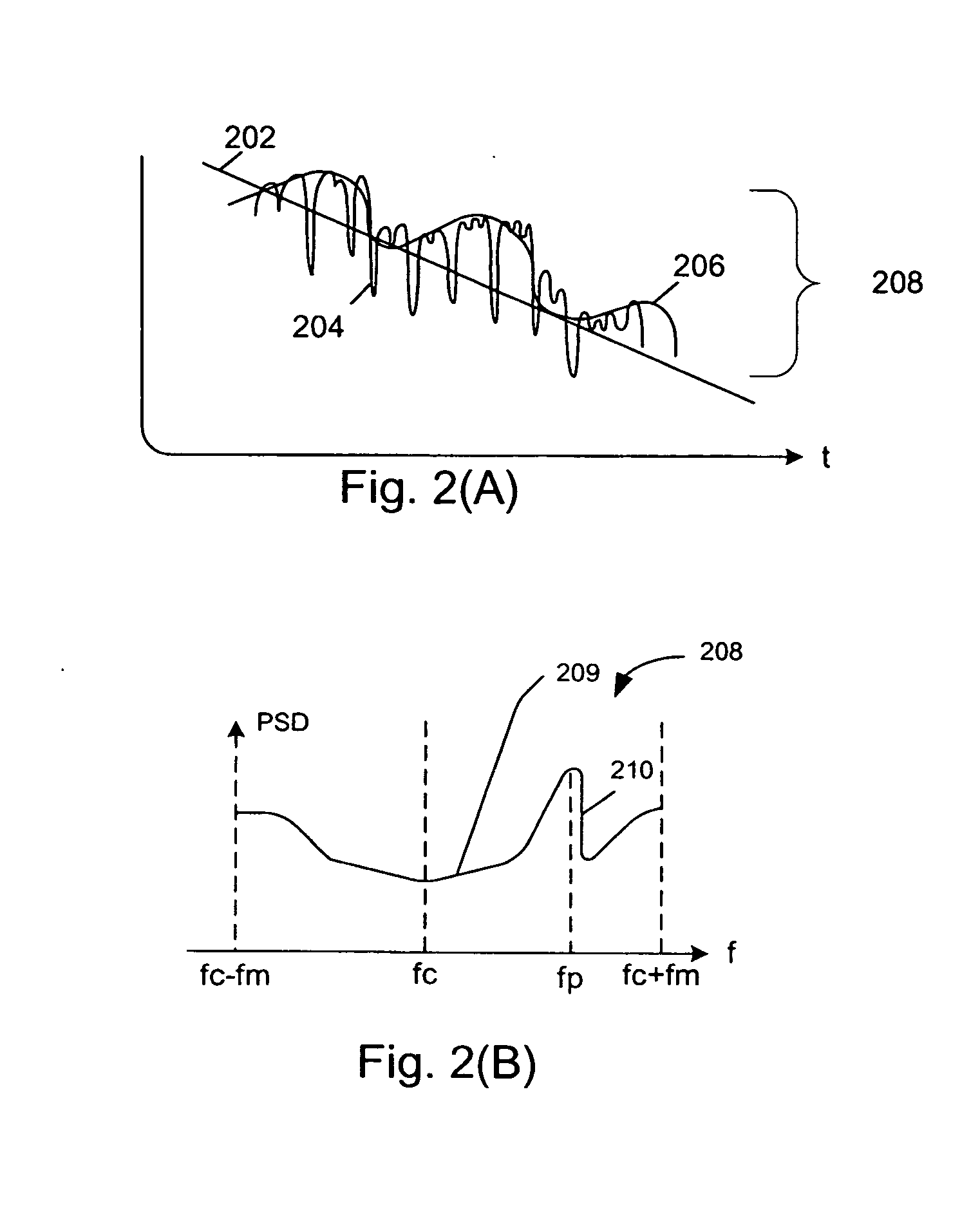

InactiveUS20070127559A1Exact reproductionMaintain optimum performancePolarisation/directional diversityTransmission monitoringControl signalData file

A system abstracts channel information from field data gathered in actual wireless communication system environments. The abstracted data is then transformed into control signals or programming codes that can be used to control channel simulators so as to recreate the field conditions, including path loss, slow fading, fast fading, path delay, fading power spectral density with and without line-of-sight (LOS), and different kind of handoff scenarios, such as soft, softer, intra-band hard, inter-band hard handoffs. The system thus can accurately simulate a realistic wireless communication link originated from multiple signal sources in different band channels and formed by multipath signal propagation. The simulated realistic wireless communication link can be condensed by selecting the most useful scenarios from its original field data files or modified by tuning its parameters as desired.

Owner:INTERDIGITAL PATENT HLDG INC

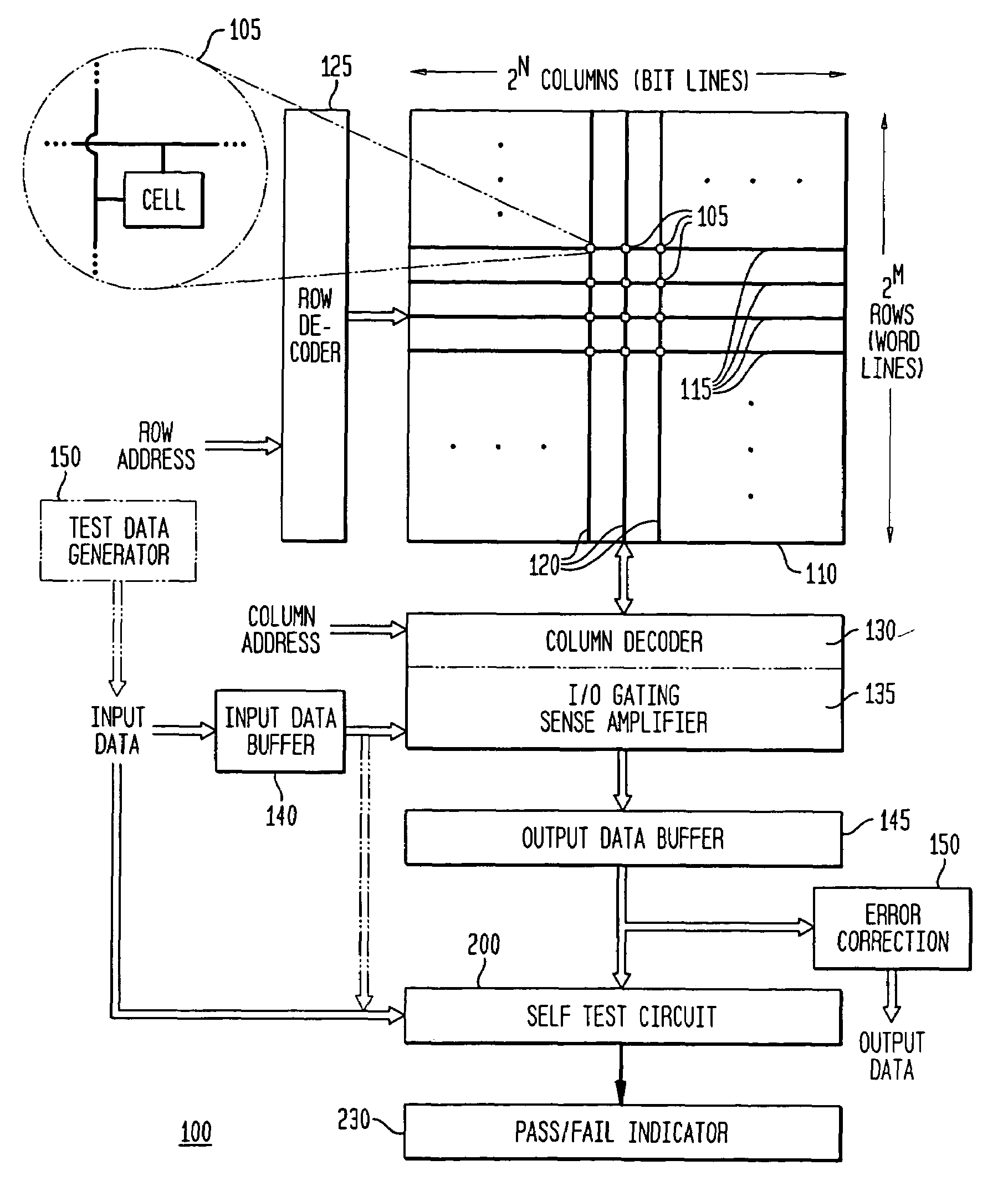

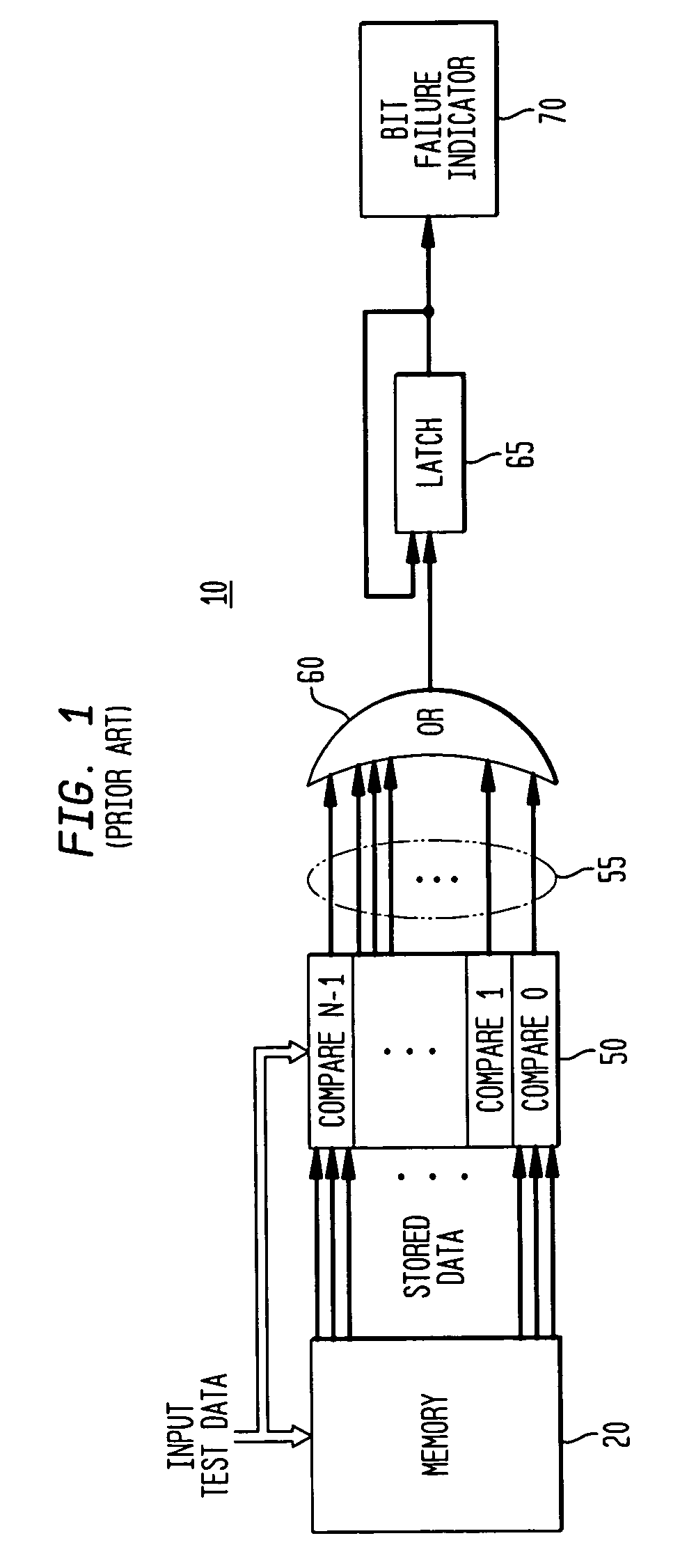

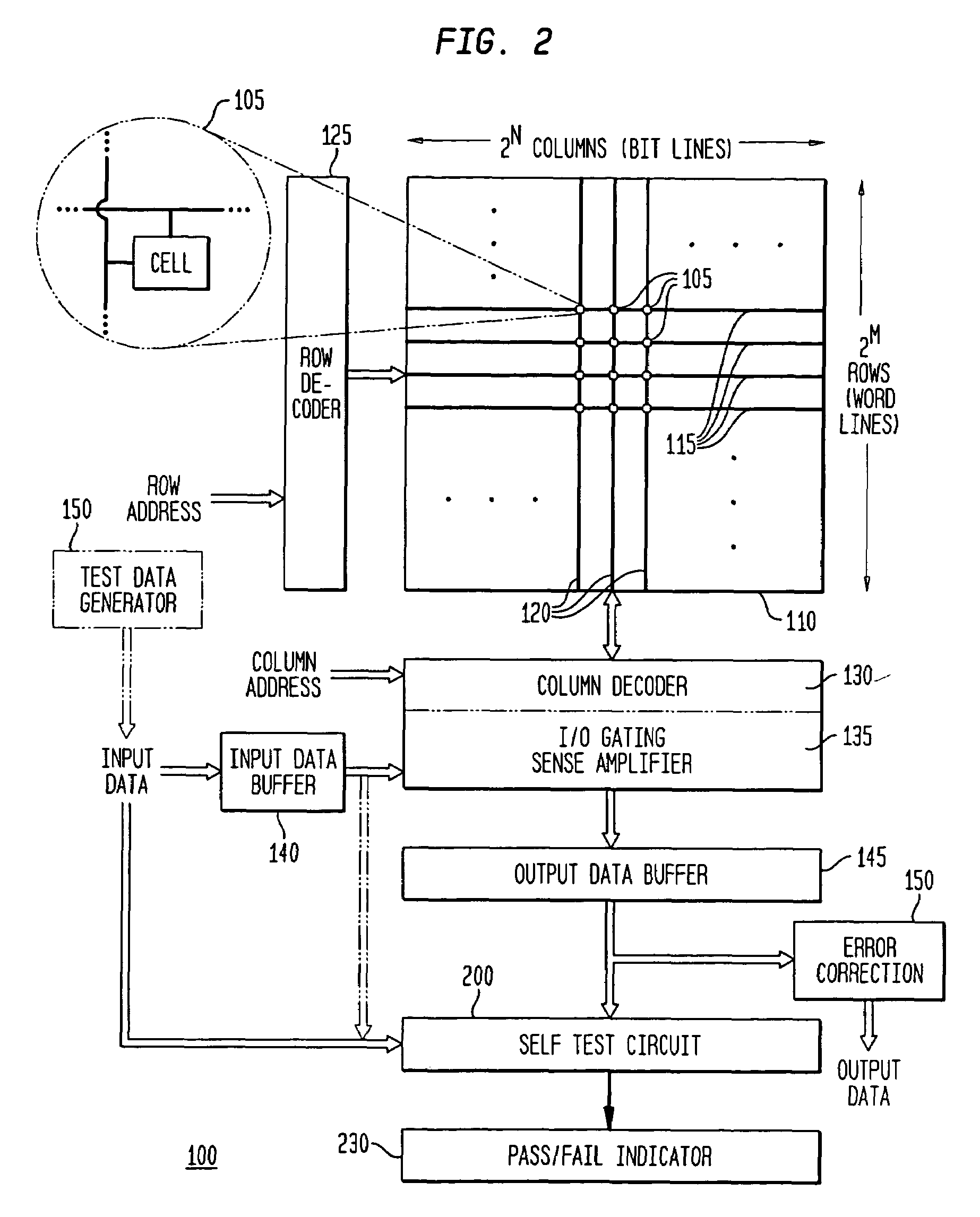

Built-in self test for memory arrays using error correction coding

InactiveUS7254763B2Increased and improved IC manufacturing yieldShorten test timeElectronic circuit testingError detection/correctionIntegratorControl circuit

A memory self-testing system, apparatus, and method are provided which allow for testing for a plurality of bit errors and passing memory arrays having an error level which is correctable using selected error correction coding. An exemplary system embodiment includes a memory array, a comparator, an integrator, and a test control circuit. The memory array is adapted to store input test data and output stored test data during a plurality of memory read and write test operations. The comparator compares the input test data and the stored test data for a plurality of bit positions, and provides a corresponding error signal when the stored test data is not identical to the input test data for each bit position of the plurality of bit positions. The integrator receives the corresponding error signal and maintains the corresponding error signal for each bit position during the plurality of test operations. The test control circuit provides a fail signal when a predetermined level of corresponding error signals have been provided for the plurality of bit positions.

Owner:AVAGO TECH INT SALES PTE LTD

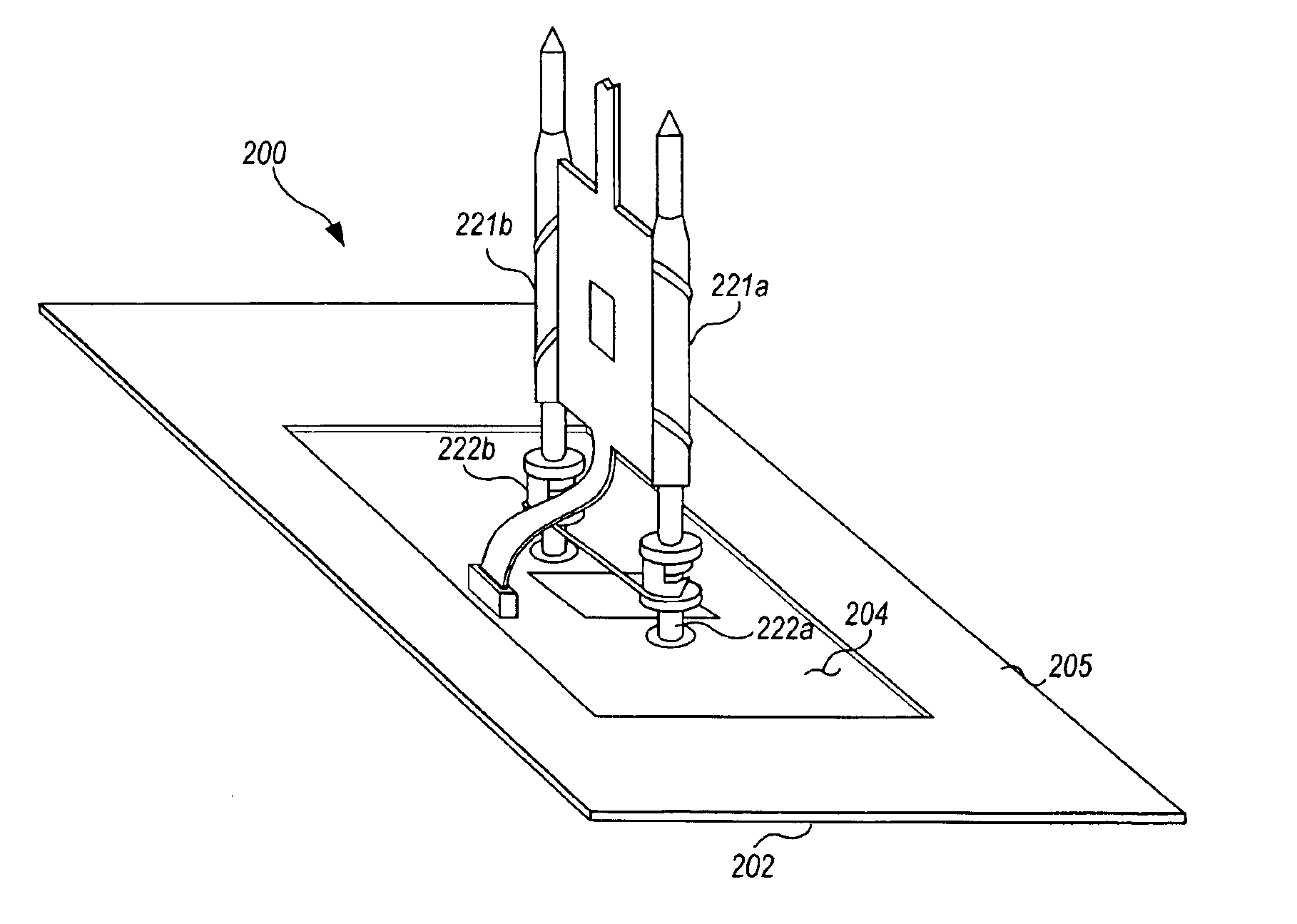

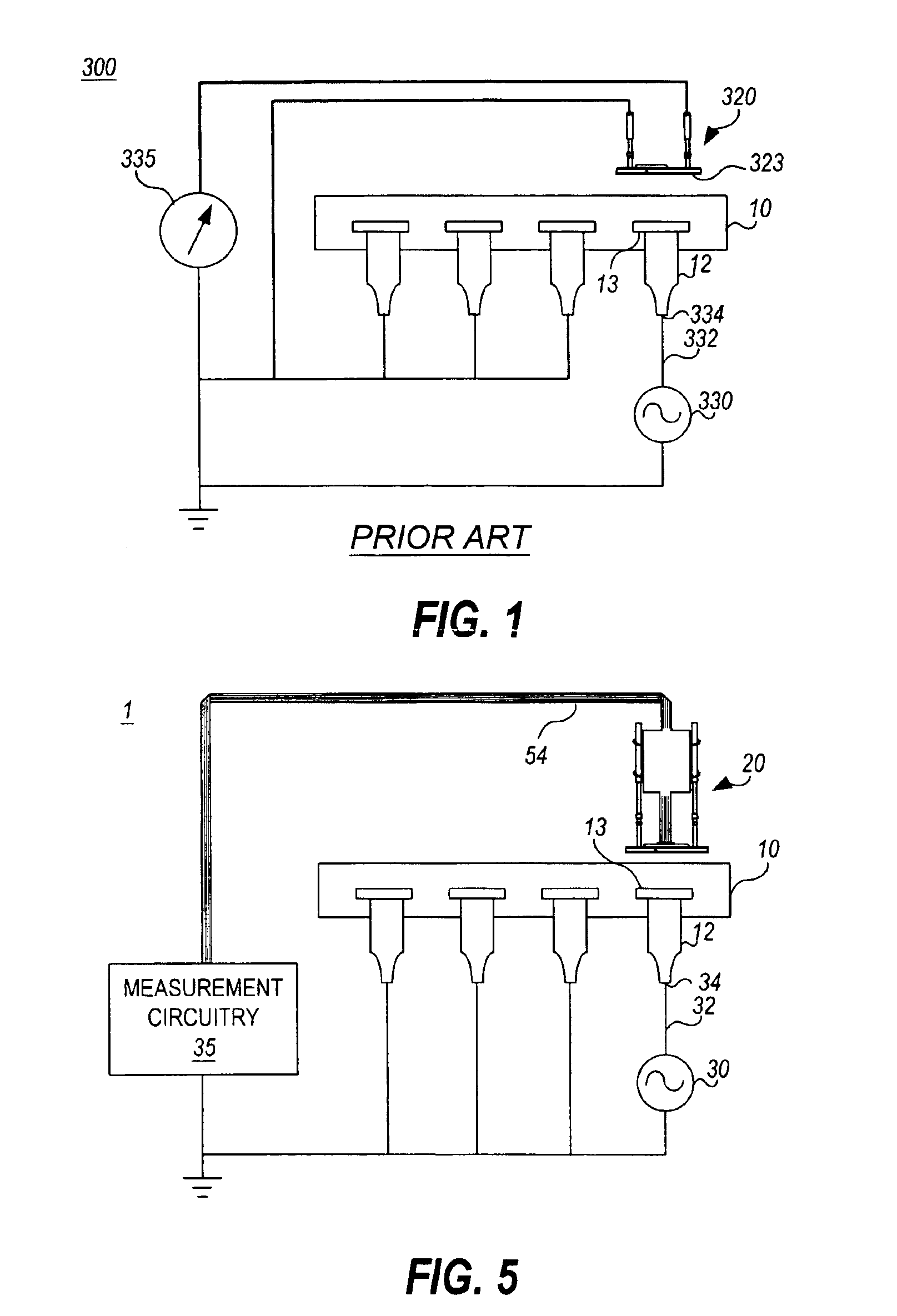

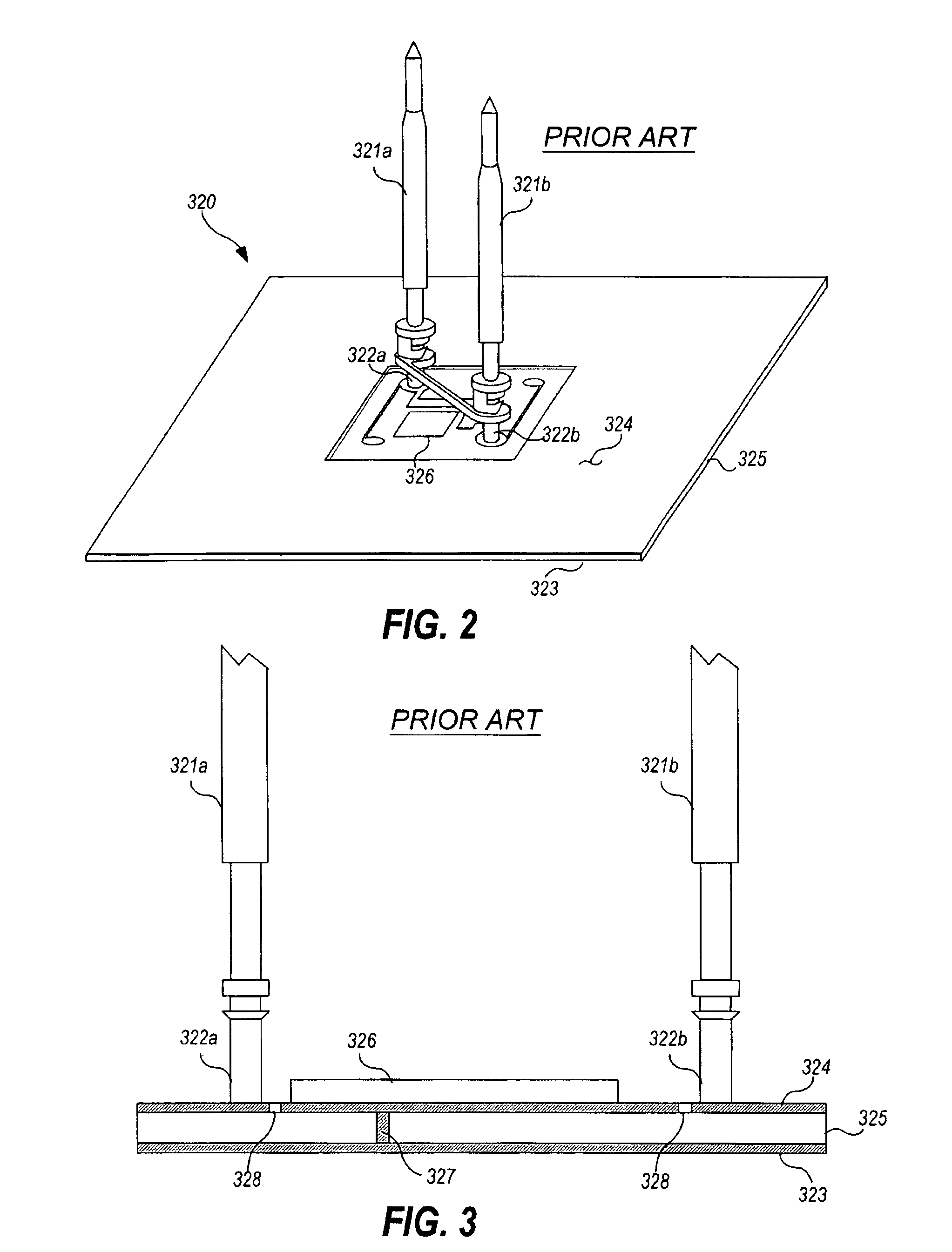

Capacitive probe assembly with flex circuit

InactiveUS6930494B2Reduce complexityReduce in quantityResistance/reactance/impedenceElectric connection testingAudio power amplifierFlexible circuits

A novel capacitive sensor assembly that utilizes a flex circuit for amplification of capacitively sensed signals and for separating the power, ground, and measurement signals is presented. The use of a flex circuit in the capacitive probe assembly allows implementation of multiple capacitive sensors for respectively capacitively coupling multiple signals from respective multiple test points of a circuit under test. The invention integrates the sensor plate, amplifier, and return wiring for each capacitive sensor all onto one flex circuit.

Owner:AGILENT TECH INC

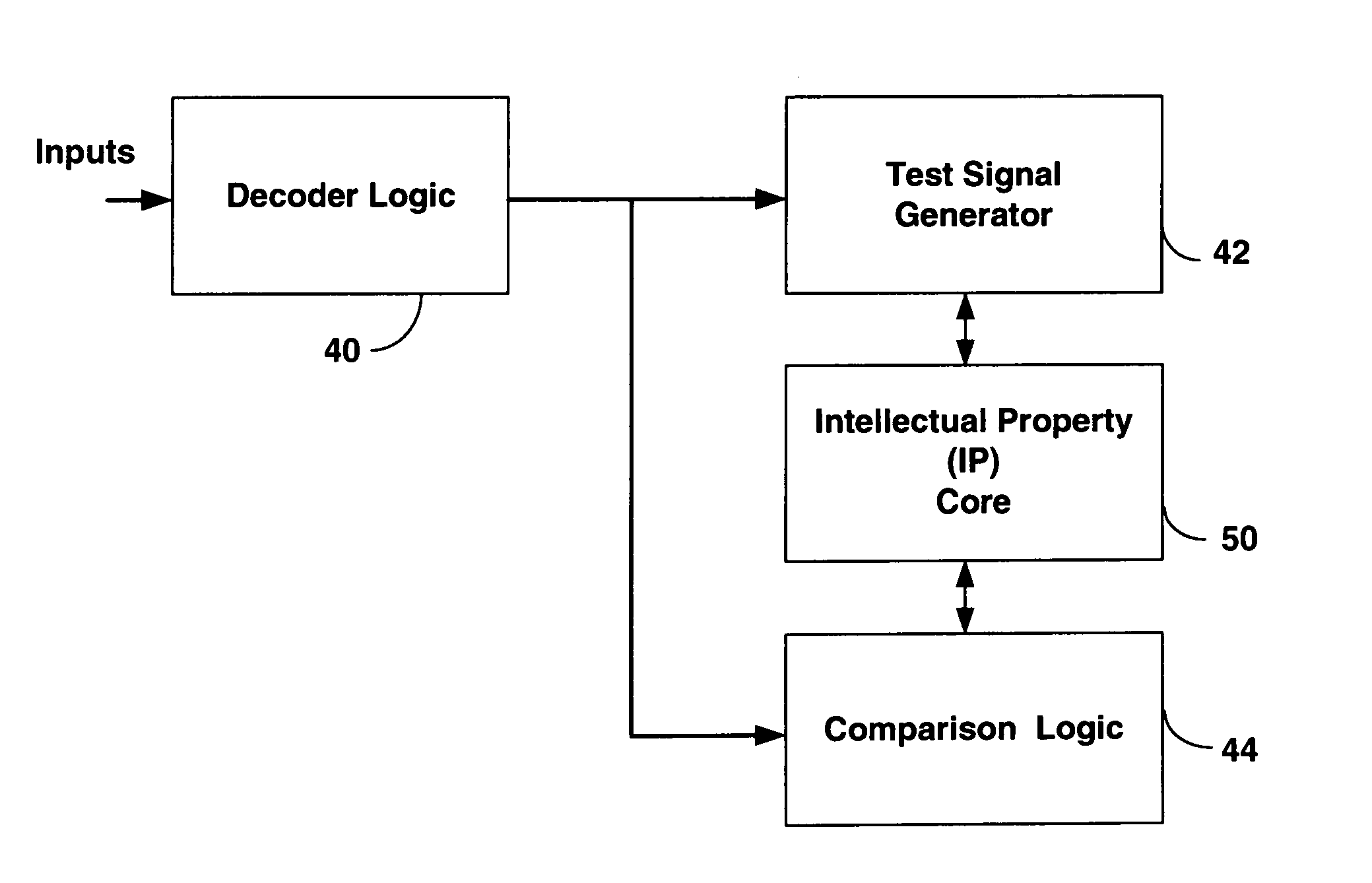

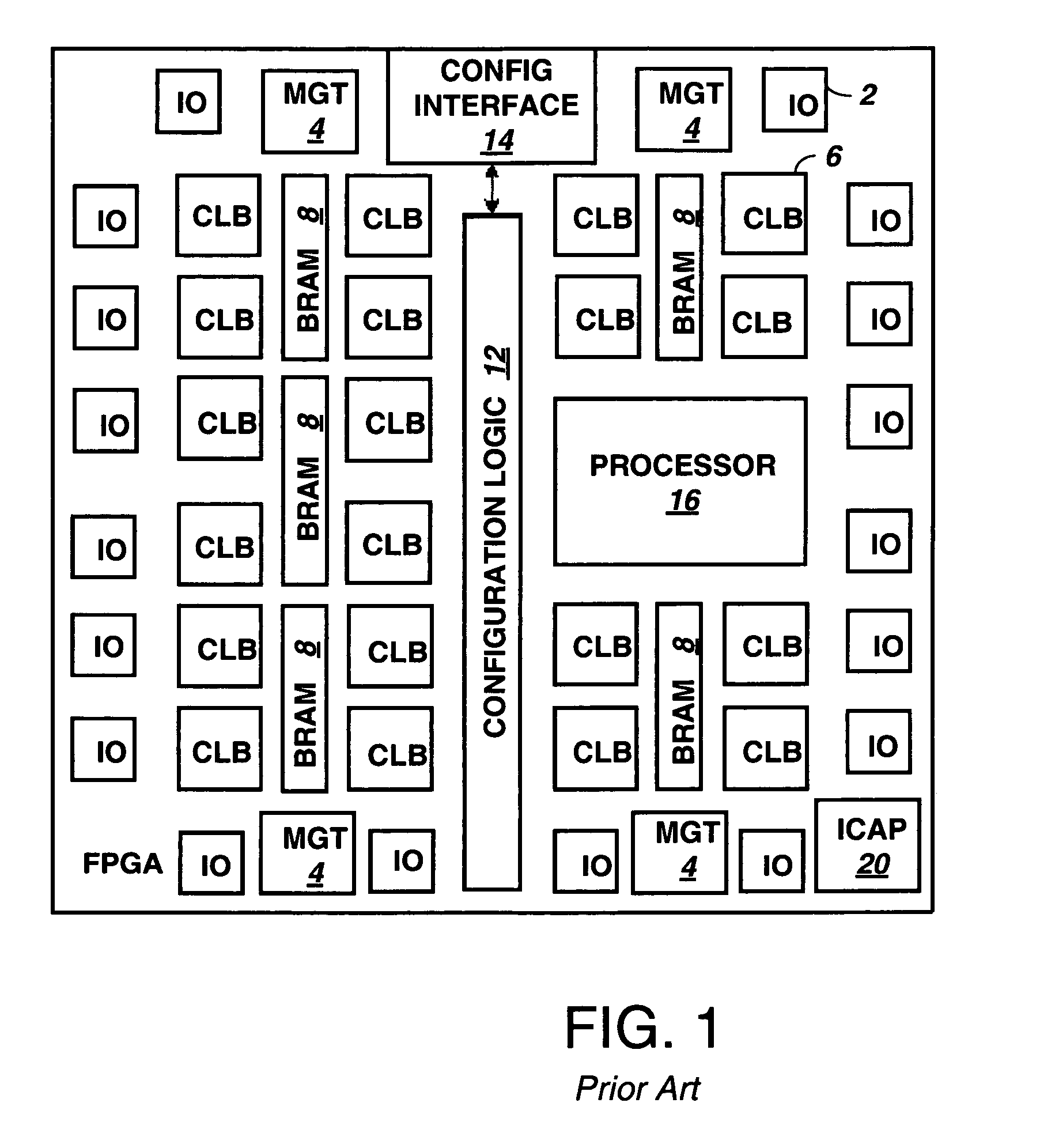

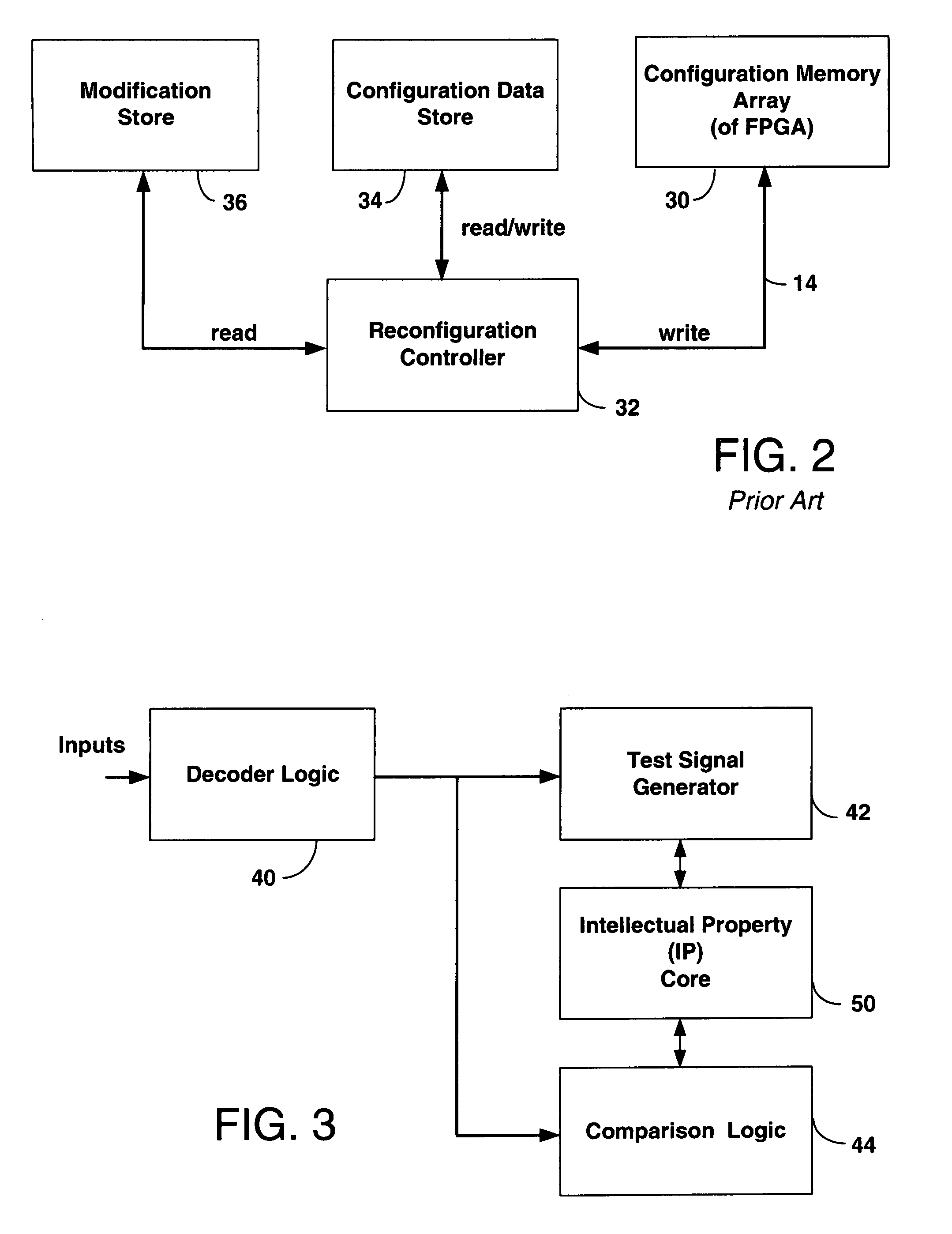

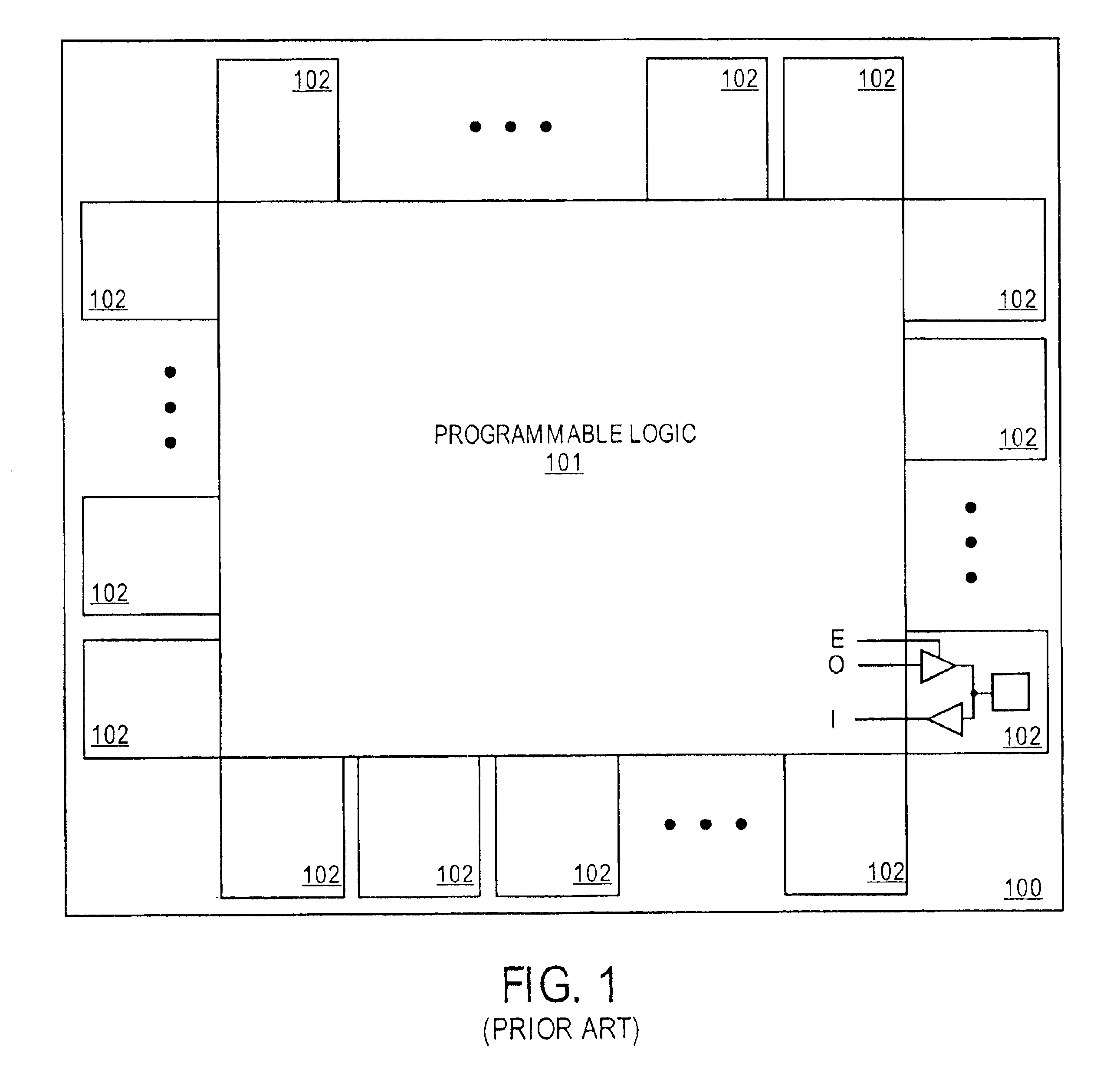

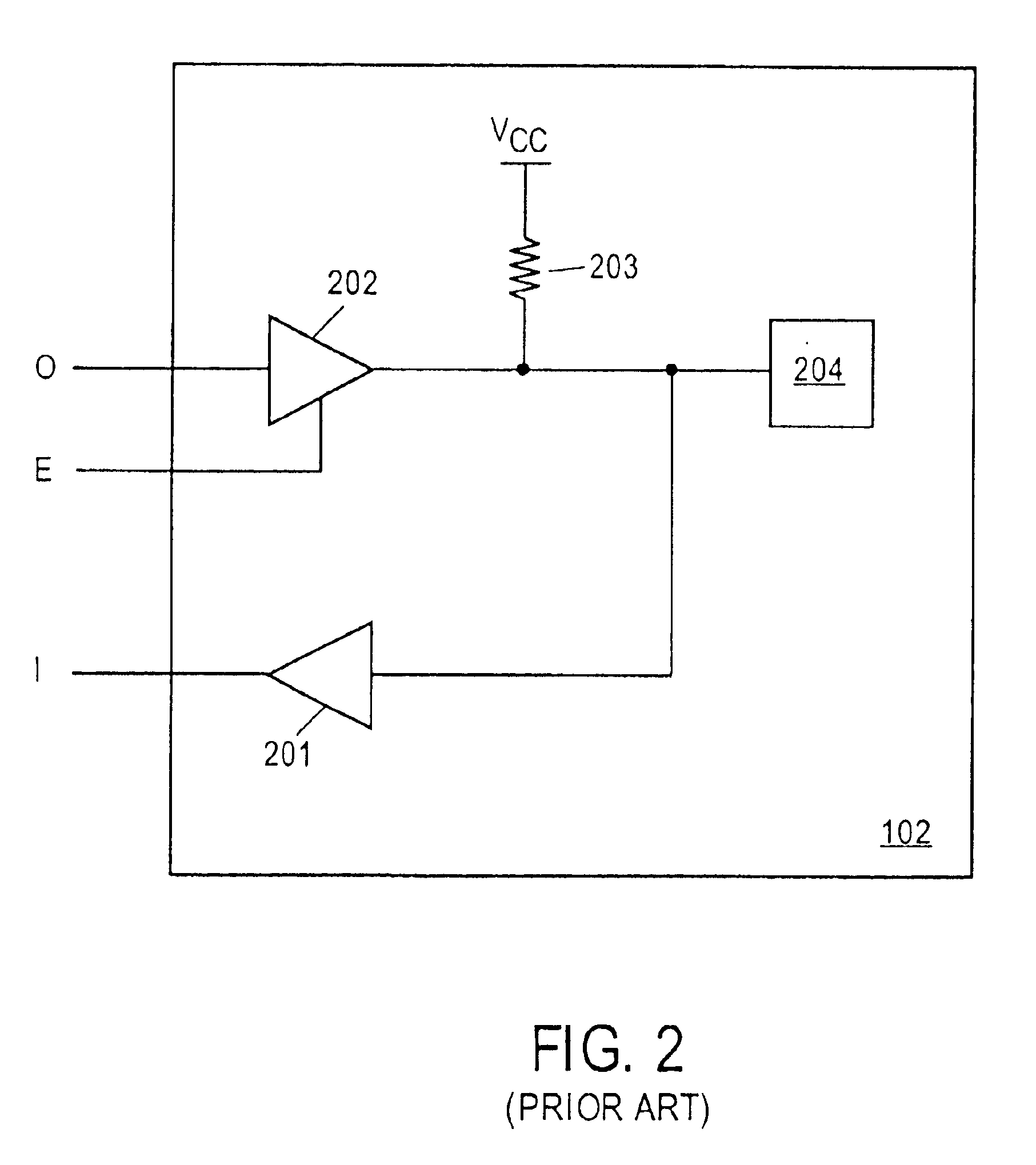

Built-in self test (BIST) technology for testing field programmable gate arrays (FPGAs) using partial reconfiguration

ActiveUS7302625B1Shorten test timeElectronic circuit testingCAD circuit designSignal generatorComputer science

A Built-in Self Test (BIST) system is provided in a Field Programmable Gate Array (FPGA) that can adjust test signal patterns provided for testing after partial reconfiguration of the FPGA. The BIST system includes a decoder that monitors I / O signals and provides an output indicating when I / O signals change indicating partial reconfiguration has occurred. The decoder output is provided to a BIST test signal generator providing signals to an IP core of the FPGA as well as a BIST comparator for monitoring test results to change test signals depending on the partial configuration mode.

Owner:XILINX INC

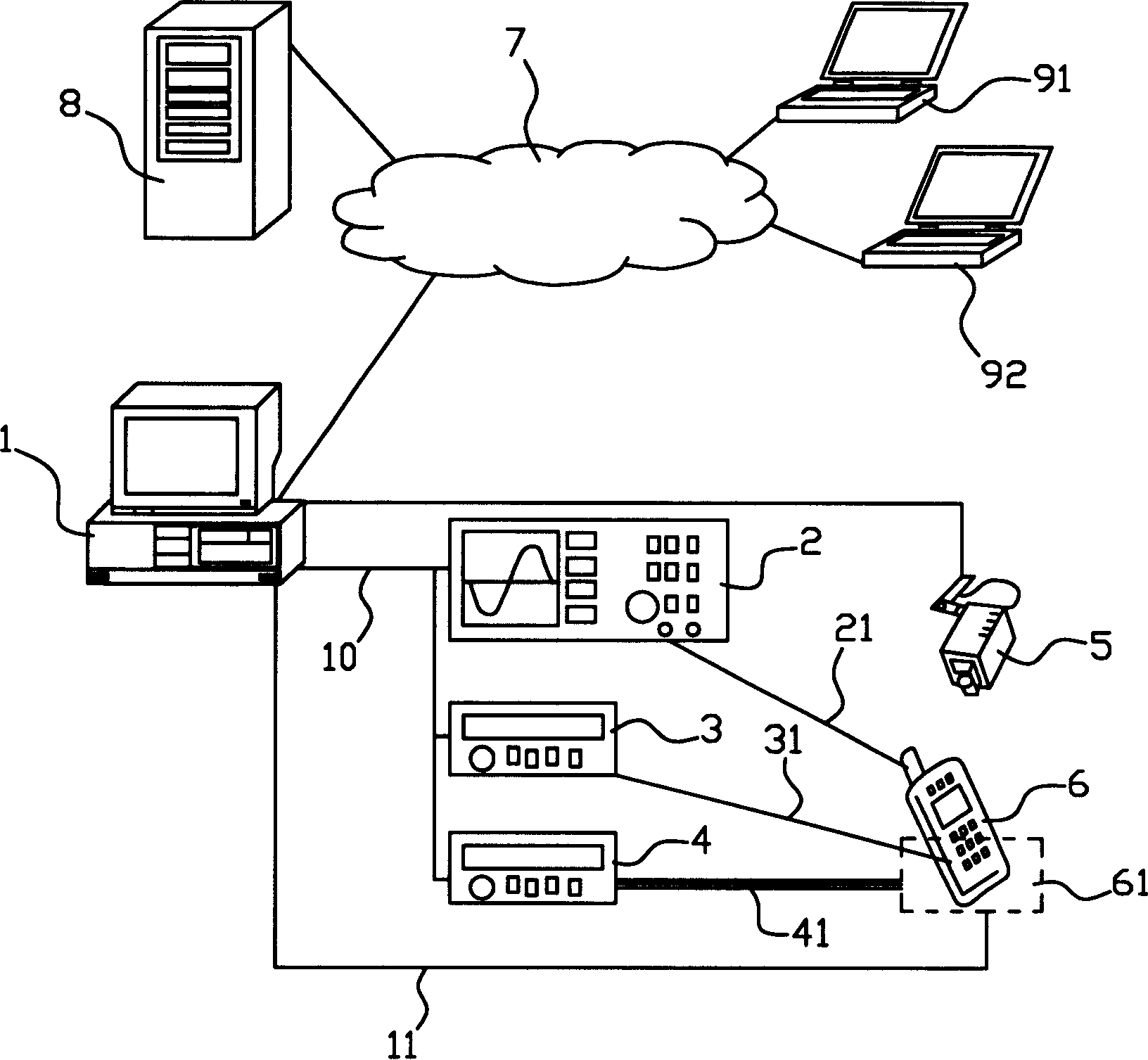

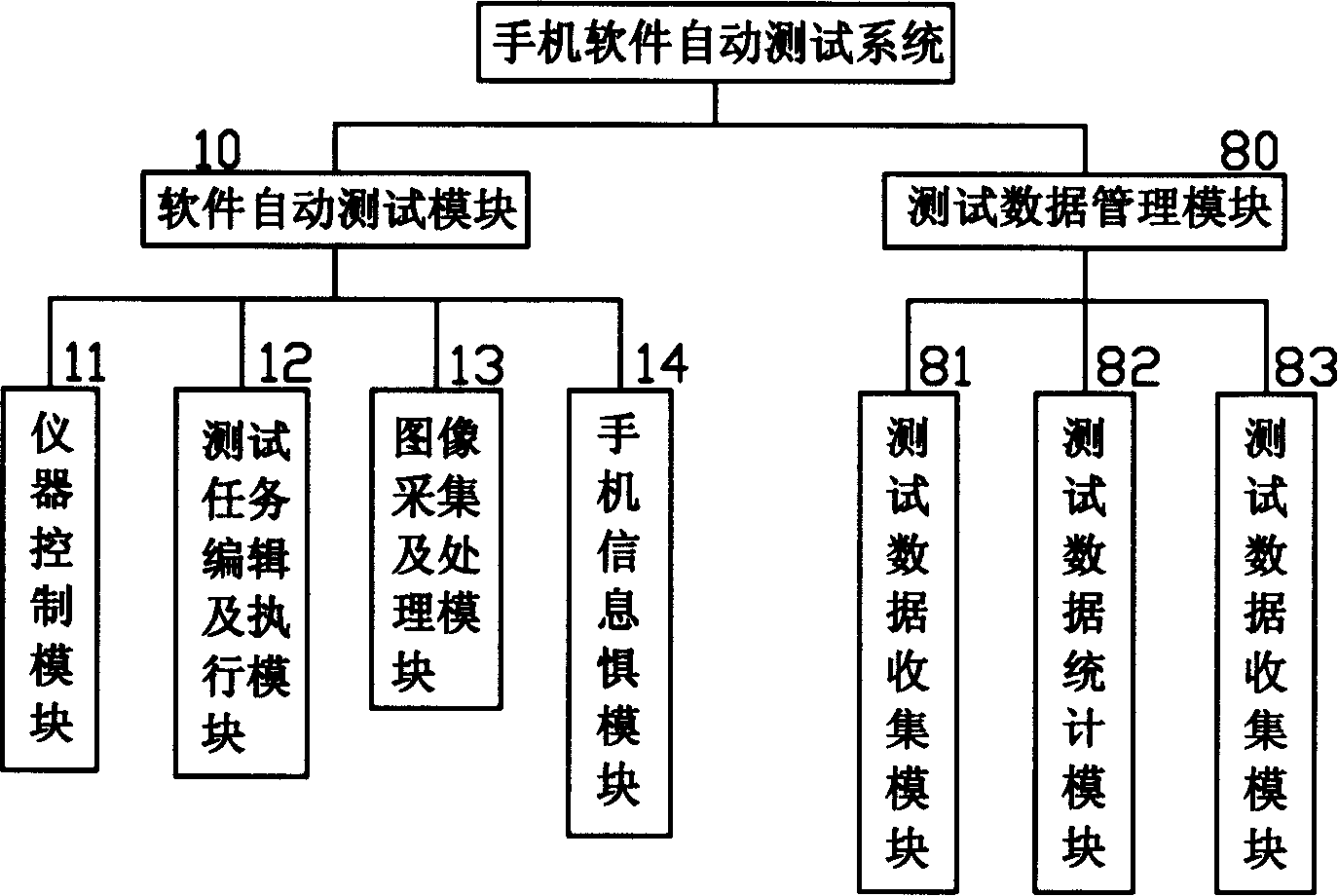

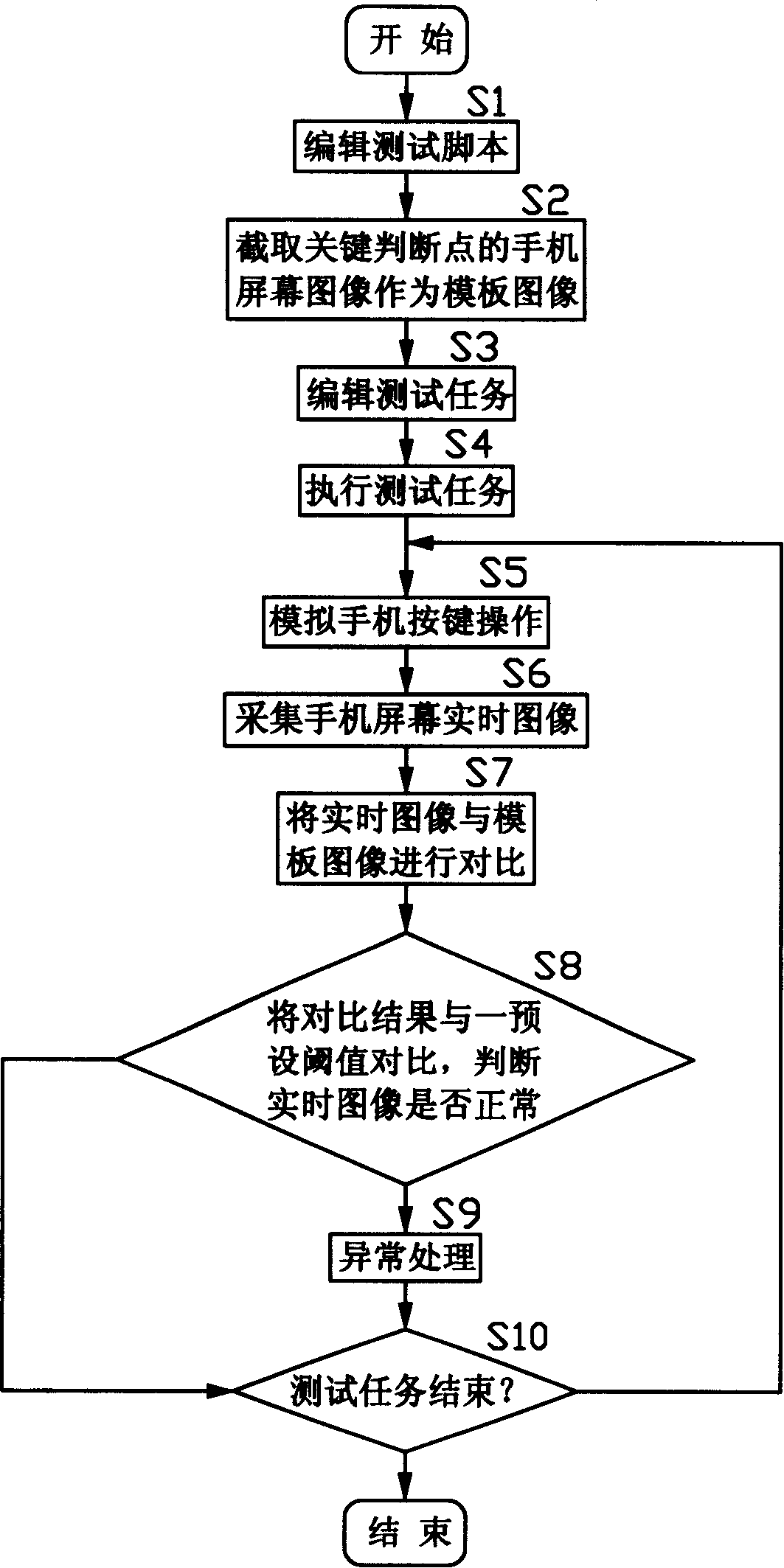

Automatic testing method and system for mobile phone software

InactiveCN101175285AShorten test timeIncrease coverageSoftware testing/debuggingSubstation equipmentTest efficiencyAutomatic test equipment

The present invention relates to the automatic test method and the system of mobile phone software. The method mainly includes five steps; firstly, the keystroke operation of a mobile phone is simulated by a program-controlled switching switch; secondly, communication between a base station and the mobile phone is simulated by a comprehensive mobile phone tester; thirdly, the images of the display screen of the mobile phone are real-timely collected by a camera; fourthly, according to a test task, an industrial control computer controls the unified operation of the program-controlled switching switch and the comprehensive mobile phone tester, collects information coming from the serial port of the mobile phone and the camera-collected real-time images of the display screen of the mobile phone and compares the collected real-time images with corresponding preset template images; fifthly, according to the information coming from the serial port of the mobile phone and the comparison result of the images, the industrial control computer judges the operation state of the mobile phone software. The present invention can accurately simulate the process in which a person operates a mobile phone, so the test result is more accurate. Moreover, the present invention can increase the test efficiency and ensure the comprehensive traversal of test cases.

Owner:LENOVO MOBILE COMM TECH

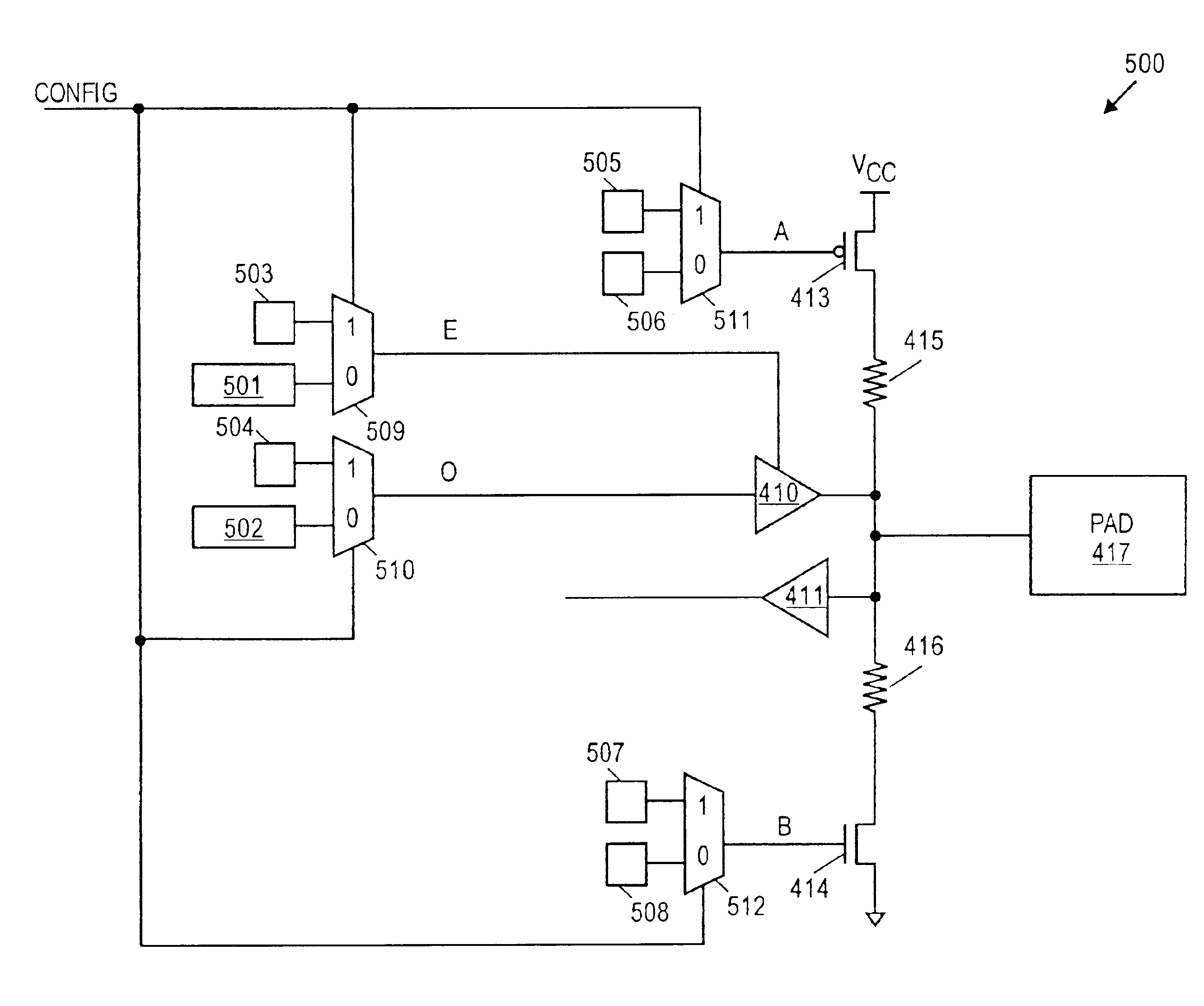

Input/output circuit with user programmable functions

InactiveUS6870397B1Increase flexibilityImprove performanceSolid-state devicesLogic circuits using elementary logic circuit componentsPropagation delayFir system

The I / O circuit of the present invention provides optimal flexibility and performance using a number of different structures and methods. The present invention provides a signal follower circuit for an input pad. In one embodiment, the output buffer is capable of injecting a constant onto a pad during reconfiguration of a configurable system logic circuit. The present invention also provides a circuit for generating a programmable data propagation delay, thereby guaranteeing zero hold time for an arbitrary input register. Zero hold time is accomplished by allowing the user to optimally characterize clock delay to a given input / output circuit. The present invention also provides fast switching between input pads, thereby minimizing data propagation delay between the input pads. Additionally, the present invention reduces time spent in production product test by facilitating the testing of multiple routes with one test configuration. A circuit expanding the number of data input channels available to system routing is provided. Lastly, a plurality of identical input / output block tiles (IOBTs) is disclosed, thereby enabling each I / O circuit to provide the same signals regardless of the IOBTs location in the I / O circuit.

Owner:XILINX INC

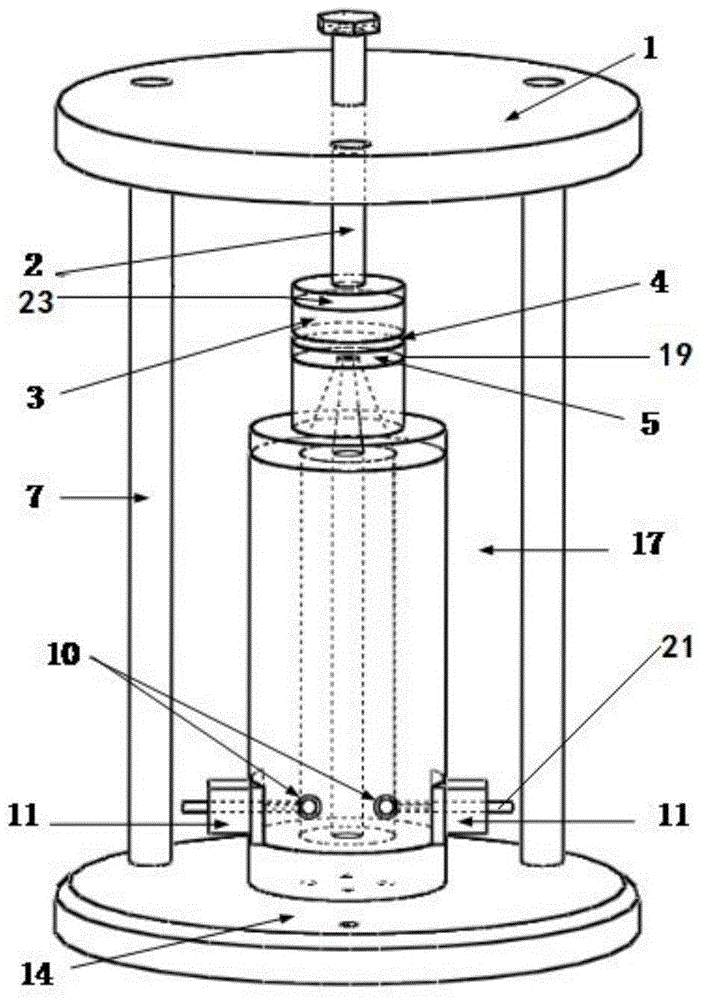

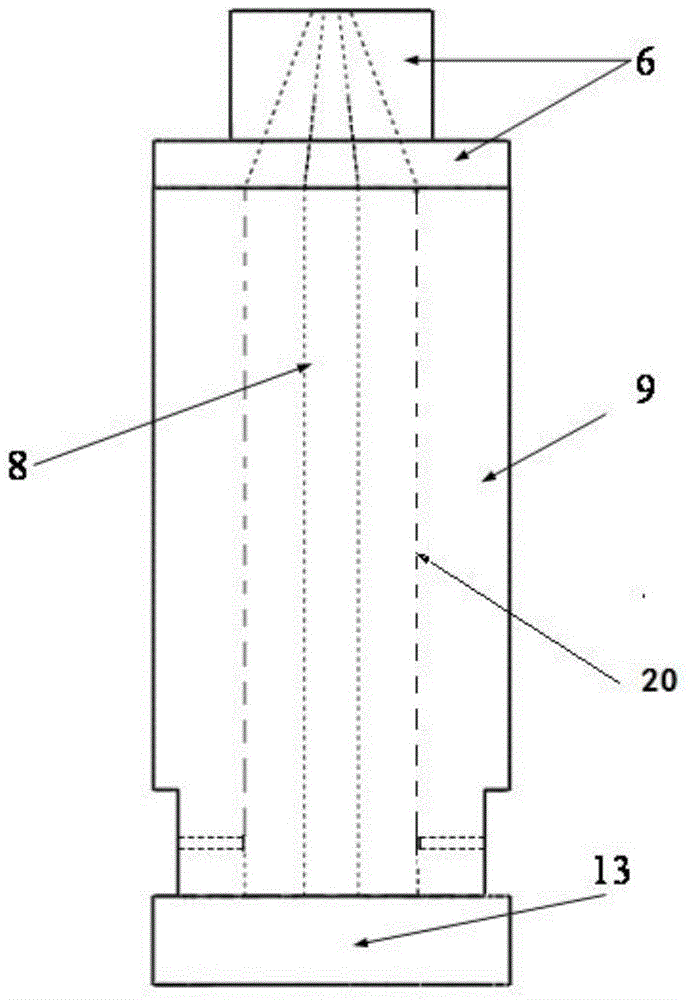

System and method for testing microwave complex permittivity of dielectric material

InactiveCN104407232ALower manufacturing requirementsShorten test timeResistance/reactance/impedenceElectricityResonant cavity

The invention provides a system and a method for testing microwave complex permittivity of a dielectric material. The system comprises a coaxial-open-type resonant cavity and a coupling quantity adjuster. The method includes the steps: a, recording resonant frequency f0 of the system without any sample loaded in a testing range and a quality factor Q0 of a corresponding frequency point; b, testing thickness d of a to-be-tested sample, and testing to acquire resonant frequency f1 of the system after the sample is loaded in the testing range and a Q1 of a corresponding loaded quality factor; c, utilizing a perturbation theory of the resonant cavity to extract complex permittivity of a to-be-tested material. By the system and the method, high-accuracy testing of the complex permittivity of the microwave dielectric material is realized, and troublesome precise calibration does not need to be performed on a network analyzer, so that testing time is reduced, and requirements, on sample manufacturing, of testing are lowered.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

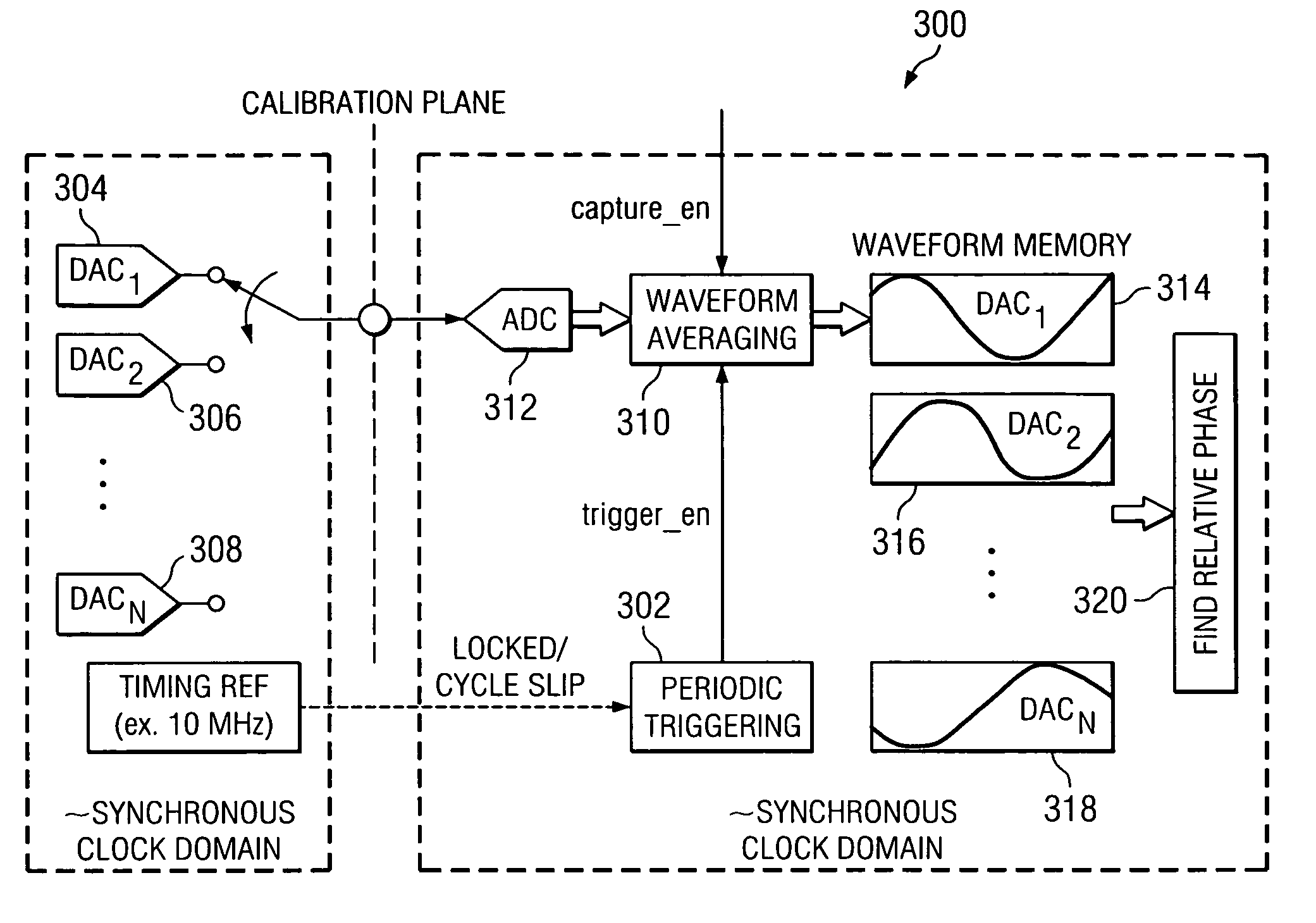

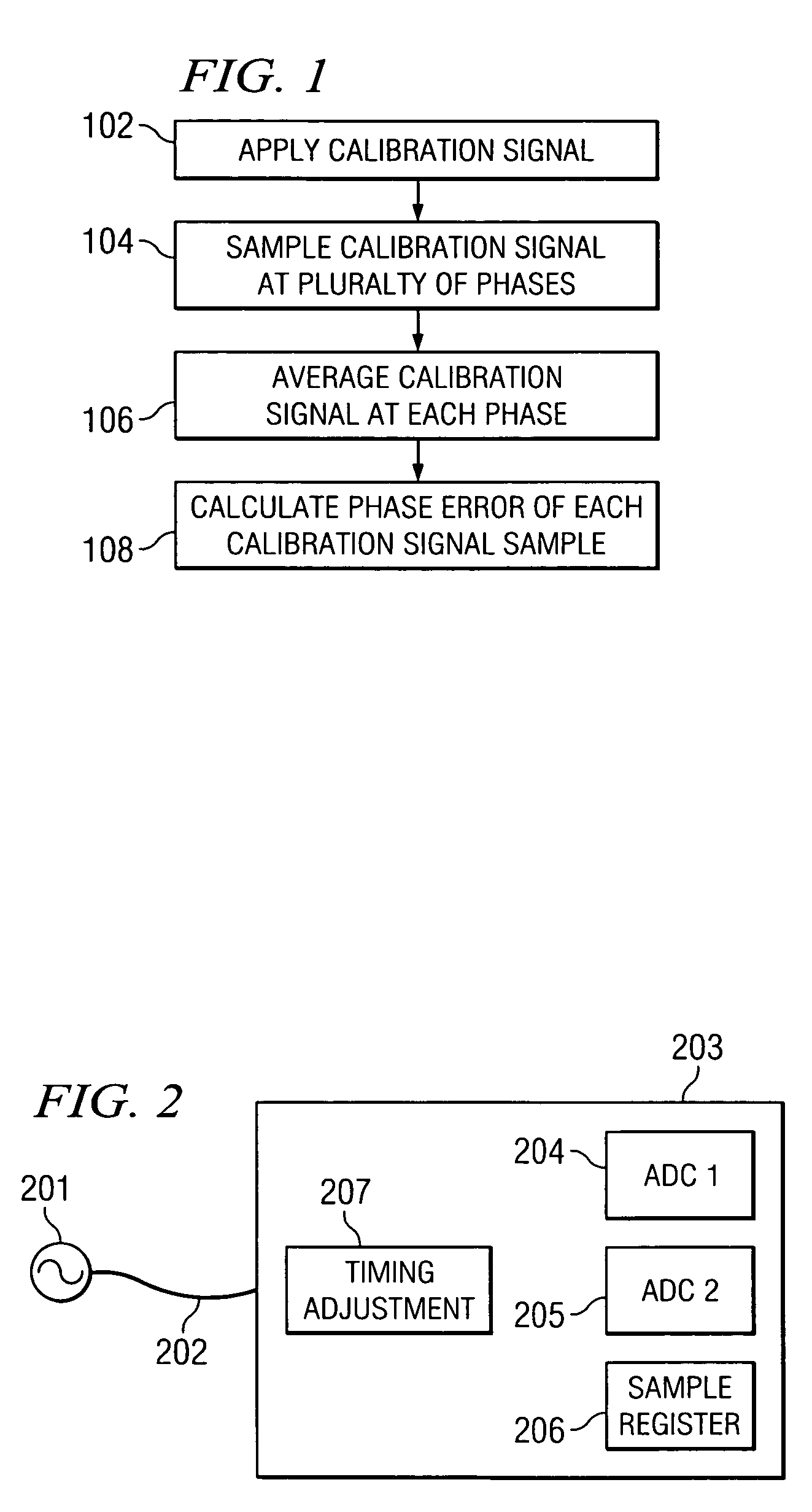

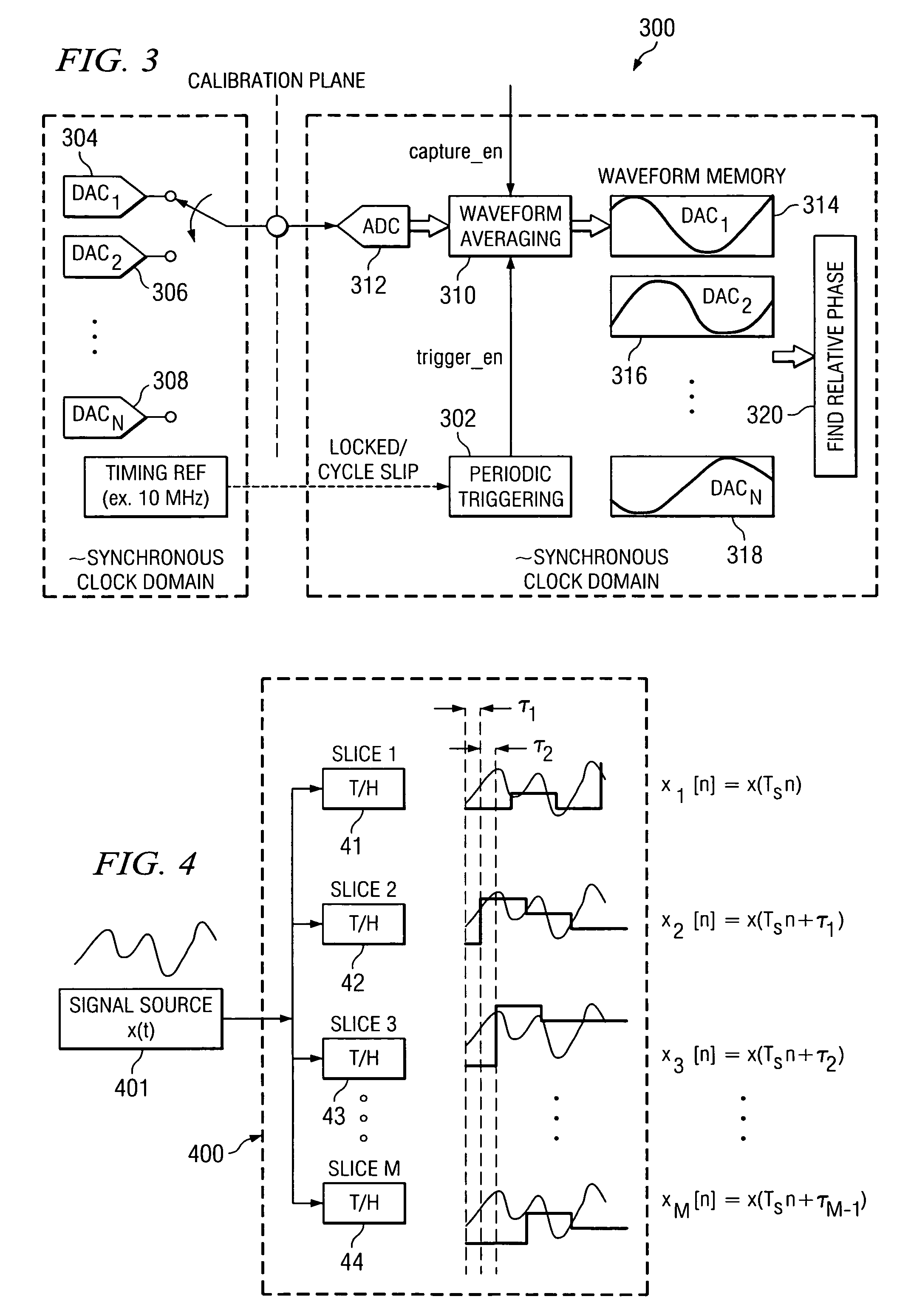

System and method for timing calibration of time-interleaved data converters

ActiveUS7148828B2Reduce supportShorten test timeElectric signal transmission systemsAnalogue/digital conversion calibration/testingFrequency spectrumTime interleaved

A method for calibrating time interleaved samplers comprising applying a calibration signal to a time-interleaved sampling device, wherein the signal is coherent with at least one sample clock on the device and is periodic and has a predetermined spectral content and frequency, sampling, by said time-interleaved sampling device, the calibration signal at a plurality of phases to form samples, averaging the formed samples, and calculating the phase error of each sample based on the average calibration signal sample.

Owner:KEYSIGHT TECH

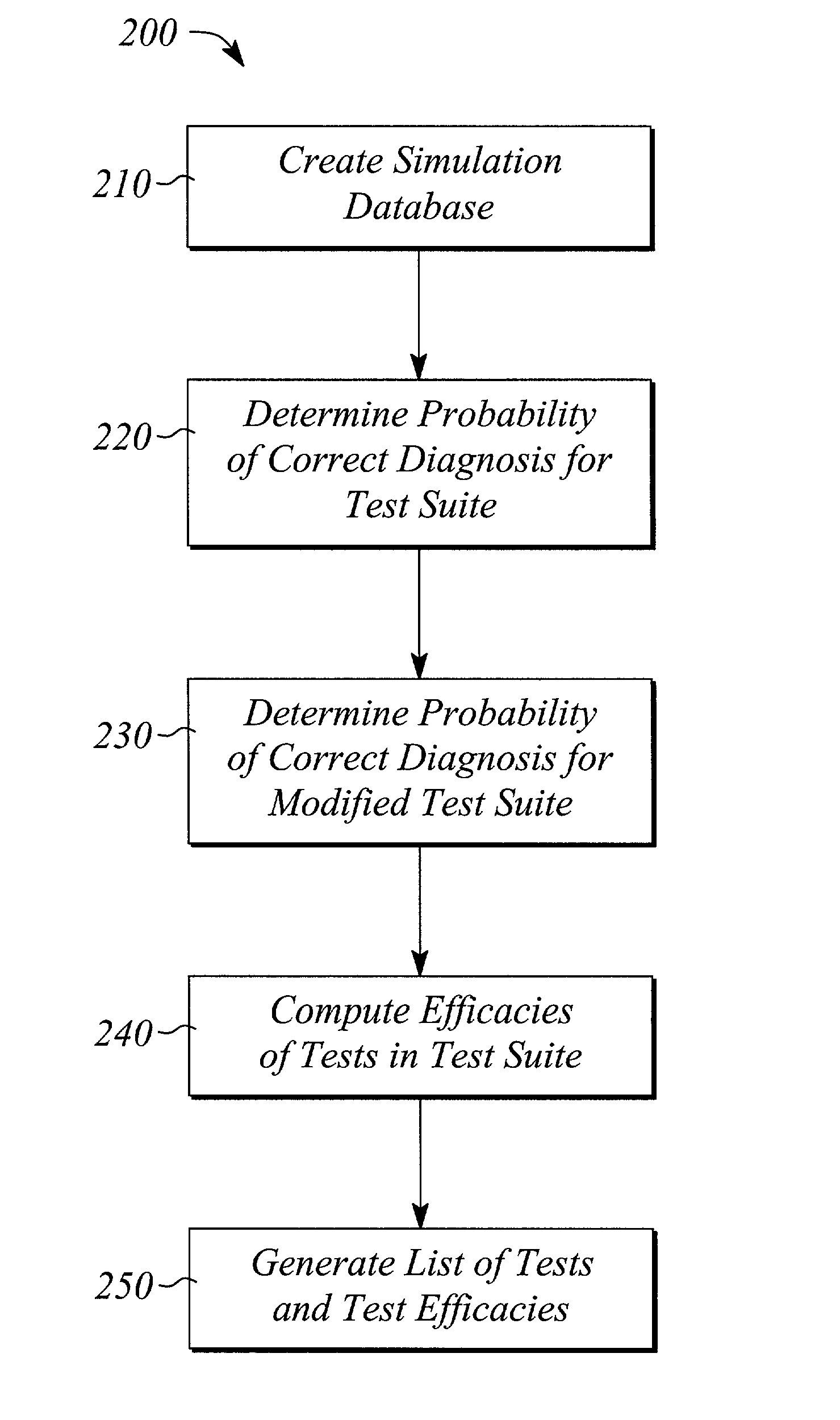

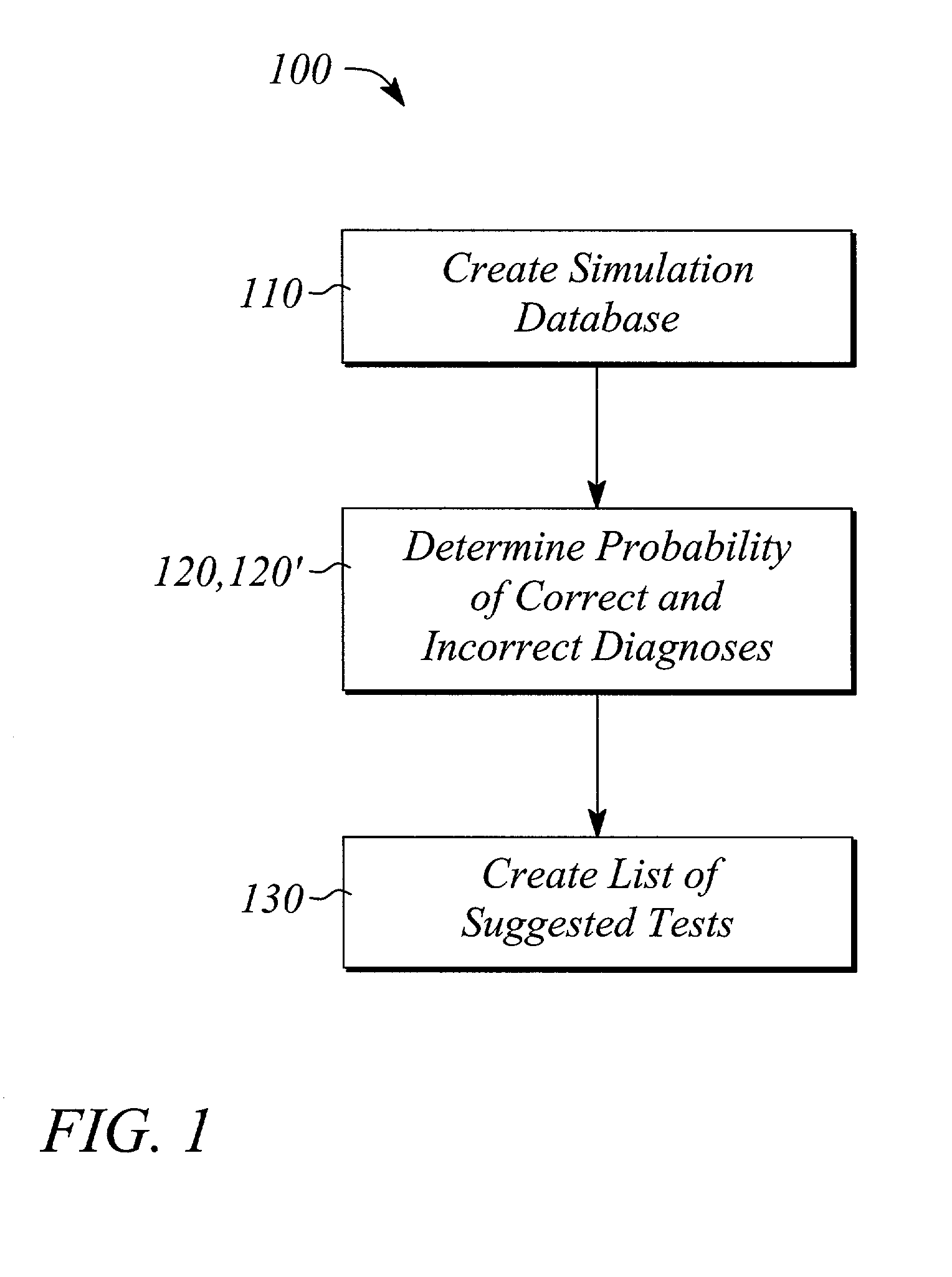

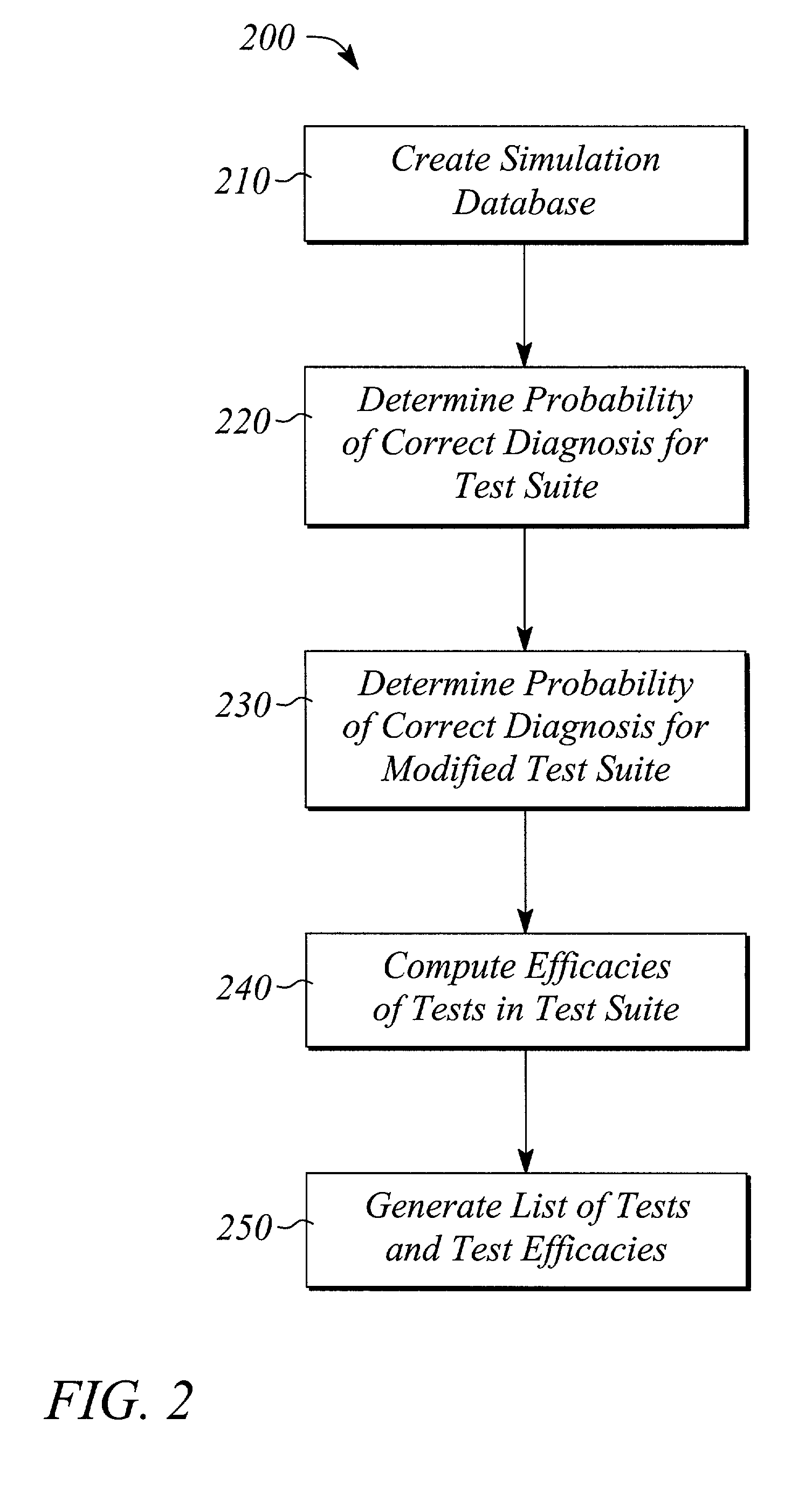

Revising a test suite using diagnostic efficacy evaluation

InactiveUS7139676B2Reduced effectivenessMinimally impacting effectivenessElectrical testingElectric testing/monitoringMedicineTest suite

A method and a system evaluate an efficacy of a test suite in a model-based diagnostic testing system to determine a revision of the test suite. The evaluation comprises suggesting a test to be added to the test suite based on probabilities of a correct diagnosis and an incorrect diagnosis. The evaluation either alternatively or further comprises identifying a test to be deleted from the test suite based on probabilities of a correct diagnosis for the test suite and for a modified test suite that does not include a test. An efficacy value of each test in the test suite is computed. The system has a computer program comprising instructions that implement an evaluation of diagnostic efficacy of the test suite. The system either is a stand-alone system or is incorporated into the testing system.

Owner:AGILENT TECH INC

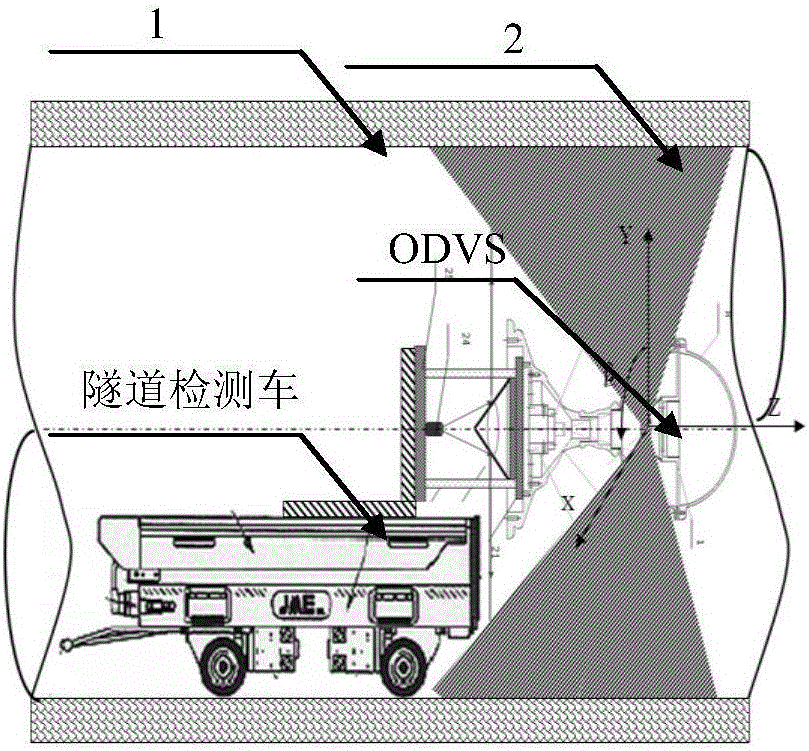

Panoramic image CNN based tunnel disease automatic identification device

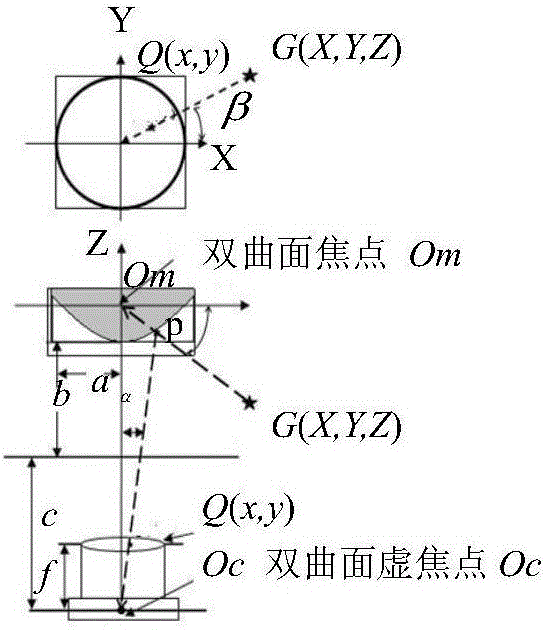

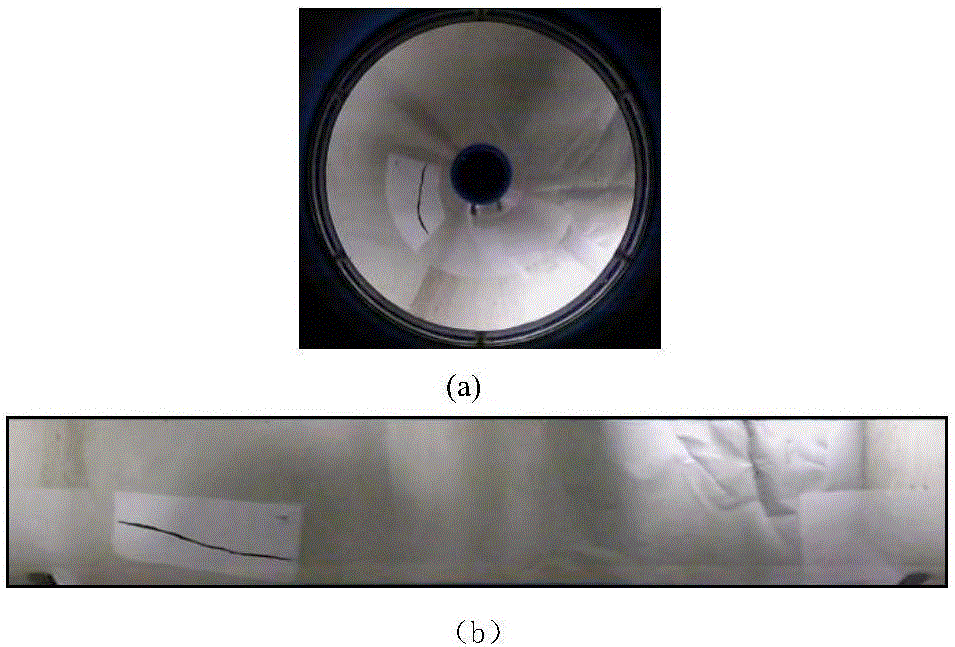

InactiveCN106841216ASolve complexityResolve promotional conflictsOptically investigating flaws/contaminationIdentification deviceComputer vision

The invention discloses a panoramic image CNN based tunnel disease automatic identification device. According to the device, firstly, a panoramic image of a tunnel inner wall is quickly acquired with a panoramic vision sensor; then the panoramic image is processed mainly by panorama unrolling, image preprocessing, binarization processing and the like to extract suspected disease region; and finally, the disease is subjected to automatic detection and classification identification by adopting a convolutional neural network. According to the scheme, the structure of the detection device in extracting a tunnel inner wall panoramic image is greatly simplified, and various tunnel disease characteristics can be automatically extracted, detected and identified by the end-to-end convolutional neural network, and an effective technical support is provided to tunnel maintenance and completion acceptance.

Owner:ZHEJIANG UNIV OF TECH

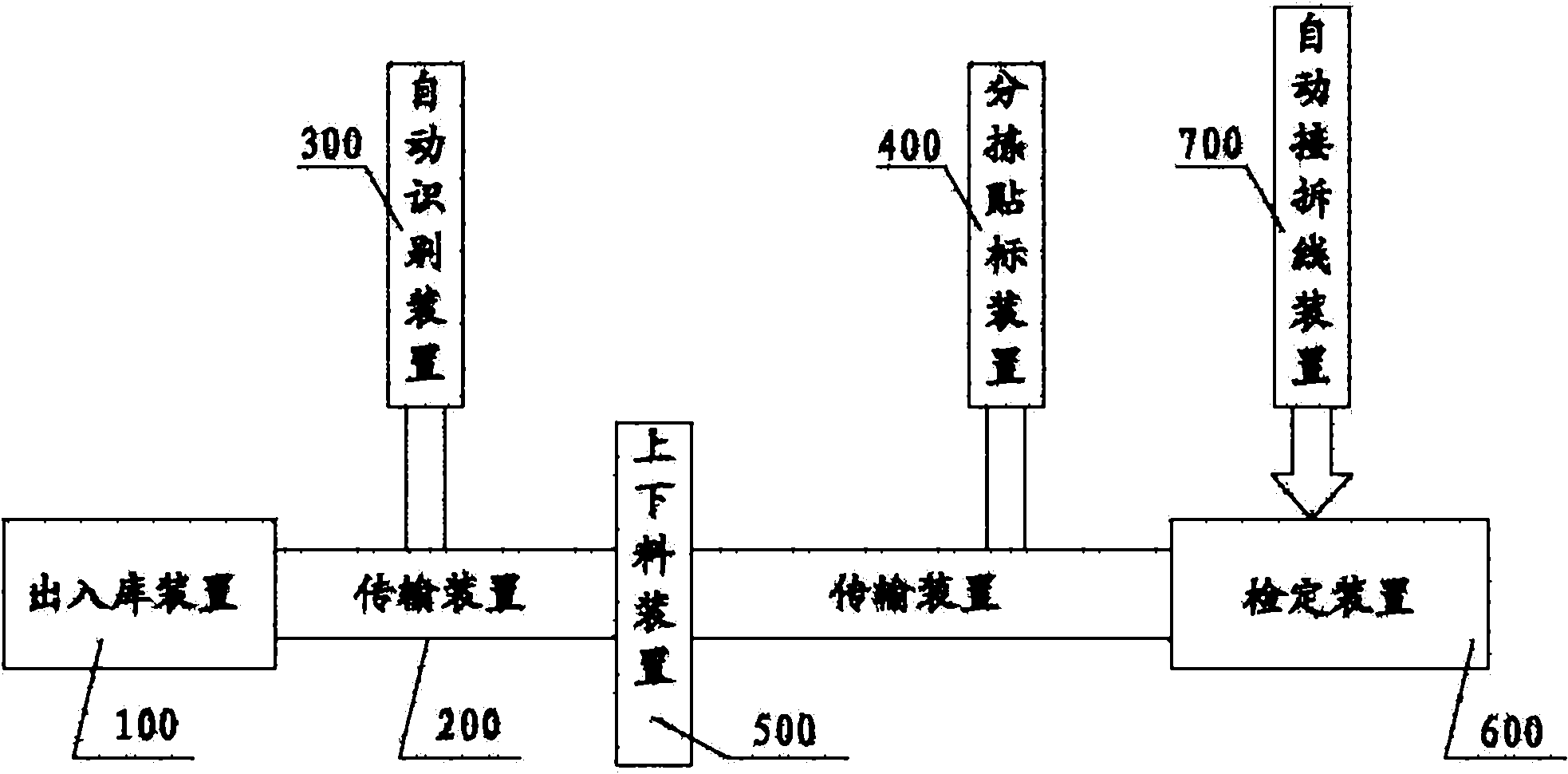

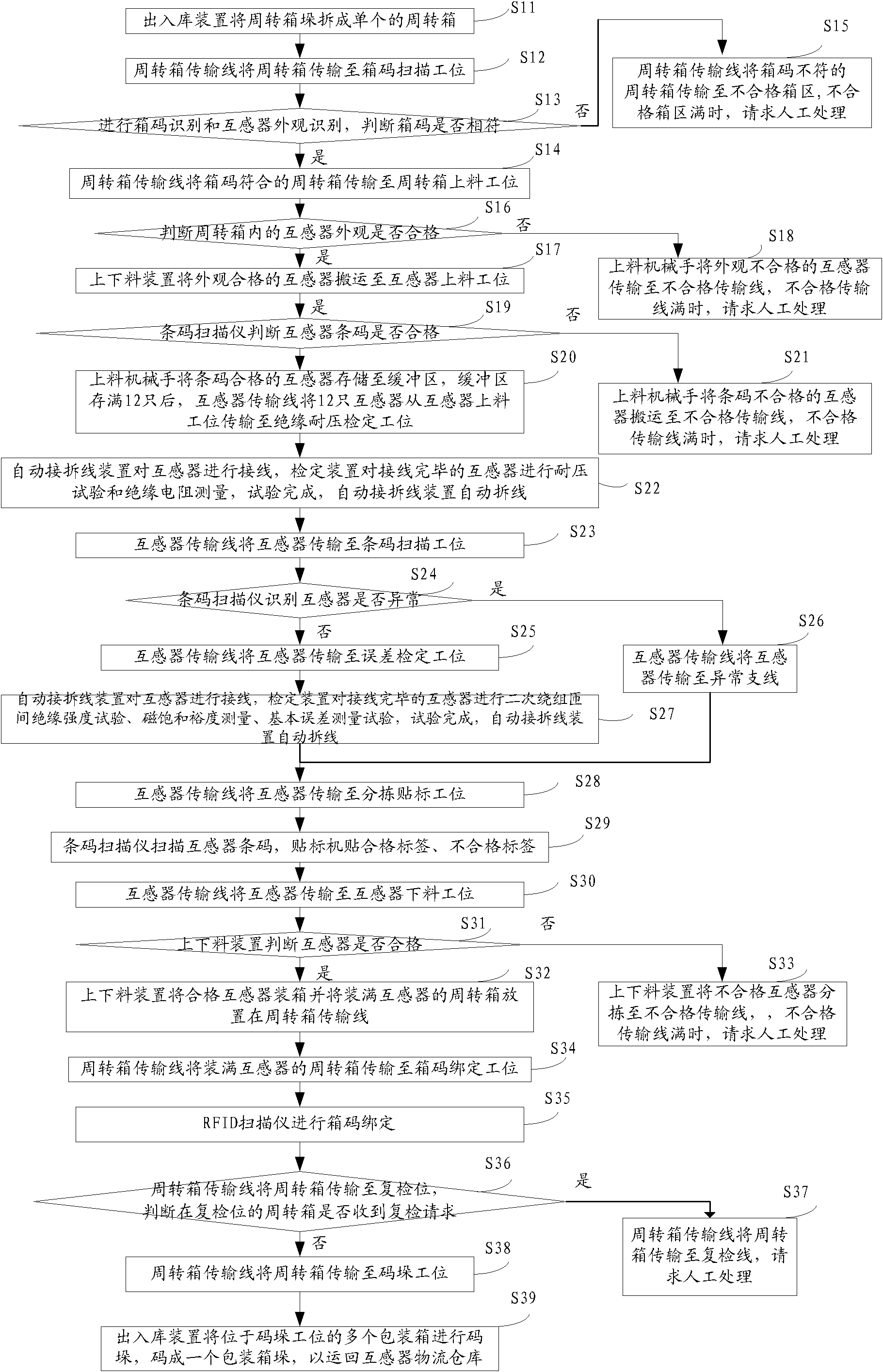

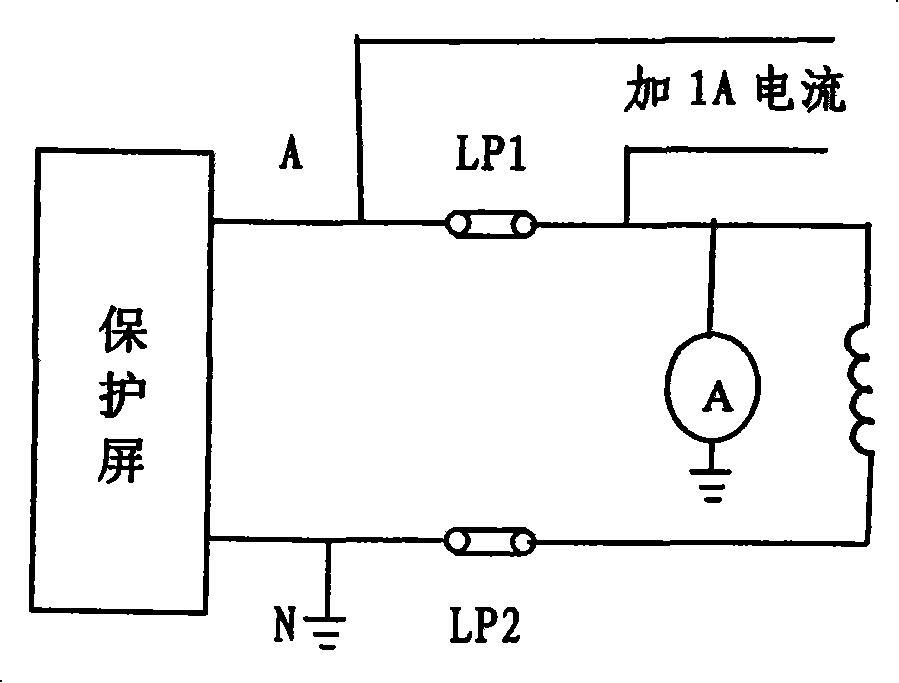

Automatic calibration line and method for intelligent type low-tension current transformers

ActiveCN102135607AImprove test efficiencyReduce human errorElectrical measurementsEngineeringIdentification device

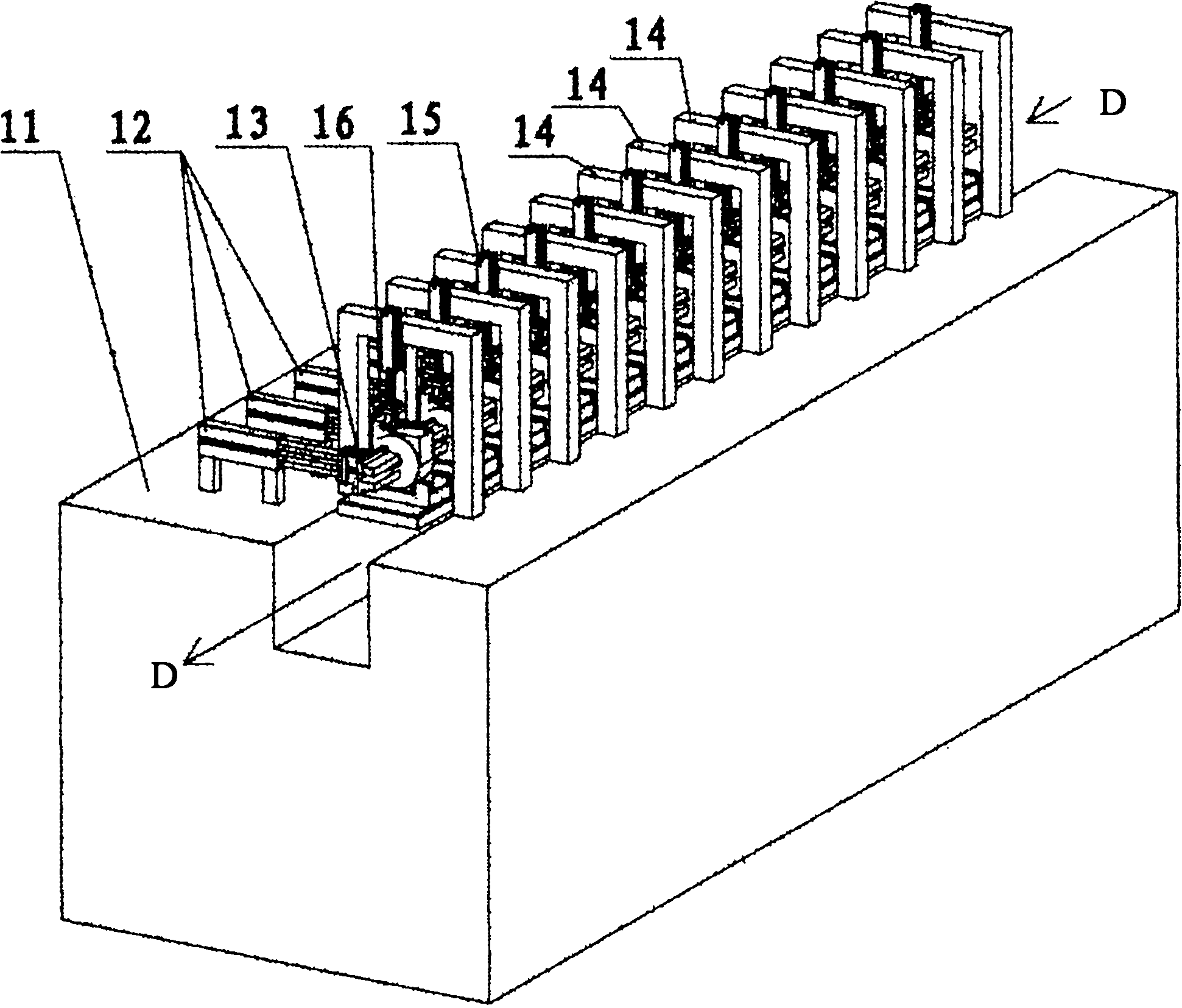

The invention discloses an automatic calibration line for intelligent type low-tension current transformers, comprising a warehouse in-out device, a loading and unloading device, an automatic identification device, a transmission device, an automatic line connecting and disconnecting device, a calibration device and a sorting and labeling device, wherein the warehouse in-out device realizes the automatic warehouse in-out of the intelligent type low-tension current transformers; the material loading and unloading device realizes the automatic loading and unloading of the intelligent type low-tension current transformers; the automatic identification device realizes the automatic identification of the intelligent type low-tension current transformers; the transmission device realizes the automatic transmission of the intelligent type low-tension current transformers; the automatic line connecting and disconnecting device realizes the automatic line connection of the intelligent type low-tension current transformers for the calibration by the calibration device and also realizes the automatic line disconnection of the intelligent type low-tension current transformers; and the sortingand labeling device realizes the automatic sorting of the intelligent type low-tension current transformers. The automatic calibration line is free from manually carrying out the warehouse in-out, the transmission, the identification, the sorting, the loading and unloading and the line connection and disconnection on the intelligent type low-tension current transformer when calibrating the intelligent type low-tension current transformer, and has the advantages of no personal error, high calibration efficiency, good automation degree and capability of automatically measuring multiple transformers. The invention also discloses an automatic calibration method of the intelligent type low-tension current transformer.

Owner:WUHAN NARI LIABILITY OF STATE GRID ELECTRIC POWER RES INST +2

Wireless no-touch testing of integrated circuits

ActiveUS7181663B2Count is minimizedShorten test timeDigital circuit testingSemiconductor/solid-state device testing/measurementEngineeringWireless connectivity

A wireless integrated circuit test method and system is presented. The invention allows testing of one or more integrated circuits configured with a wireless interface and a test access mechanism which controls input of test data received over a wireless connection from a test station to test structures which test functional blocks on the integrated circuit. Via the wireless connection, multiple integrated circuits or similarly equipped devices under test can be tested simultaneously. The invention also enables concurrent testing of independently testable functional blocks on any given integrated circuit under test.

Owner:ADVANTEST CORP

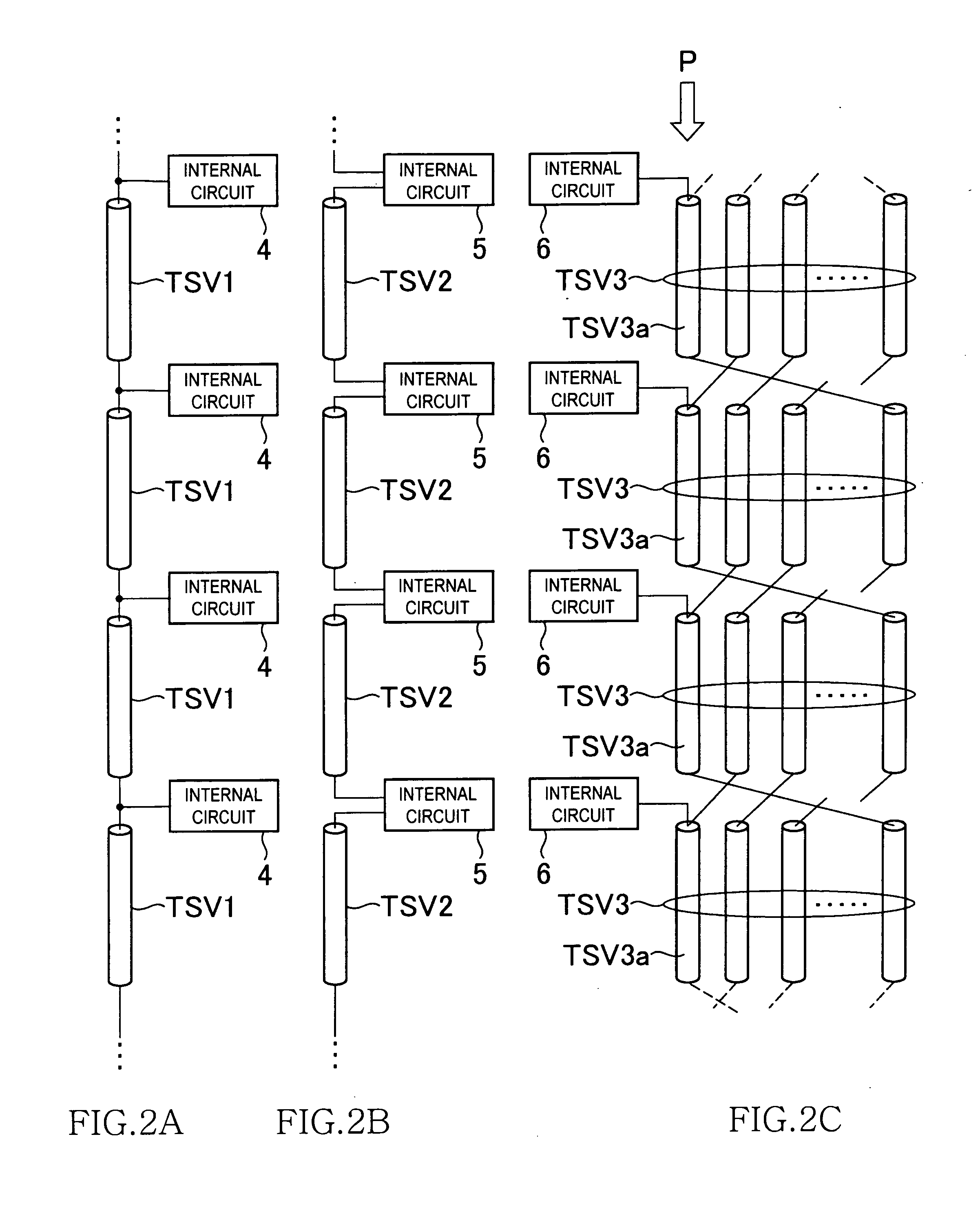

Semiconductor device and test method thereof

ActiveUS20120092943A1Reduce in quantityShorten the timeSolid-state devicesRead-only memoriesSemiconductorElectrical current

plurality of core chips to which chip identification information different from each other is allocated and an interface chip are layered, the plurality of core chips are commonly connected to the interface chip through a first current path including at least a through silicon via, the interface chip serially supplies an enable signal to the plurality of core chips through the first current path, and the plurality of core chips are activated based on a logic level of a bit corresponding to the chip identification information among a plurality of bits configuring the enable signal. The present invention can reduce the number of through silicon vias required to supply an enable signal.

Owner:LONGITUDE LICENSING LTD

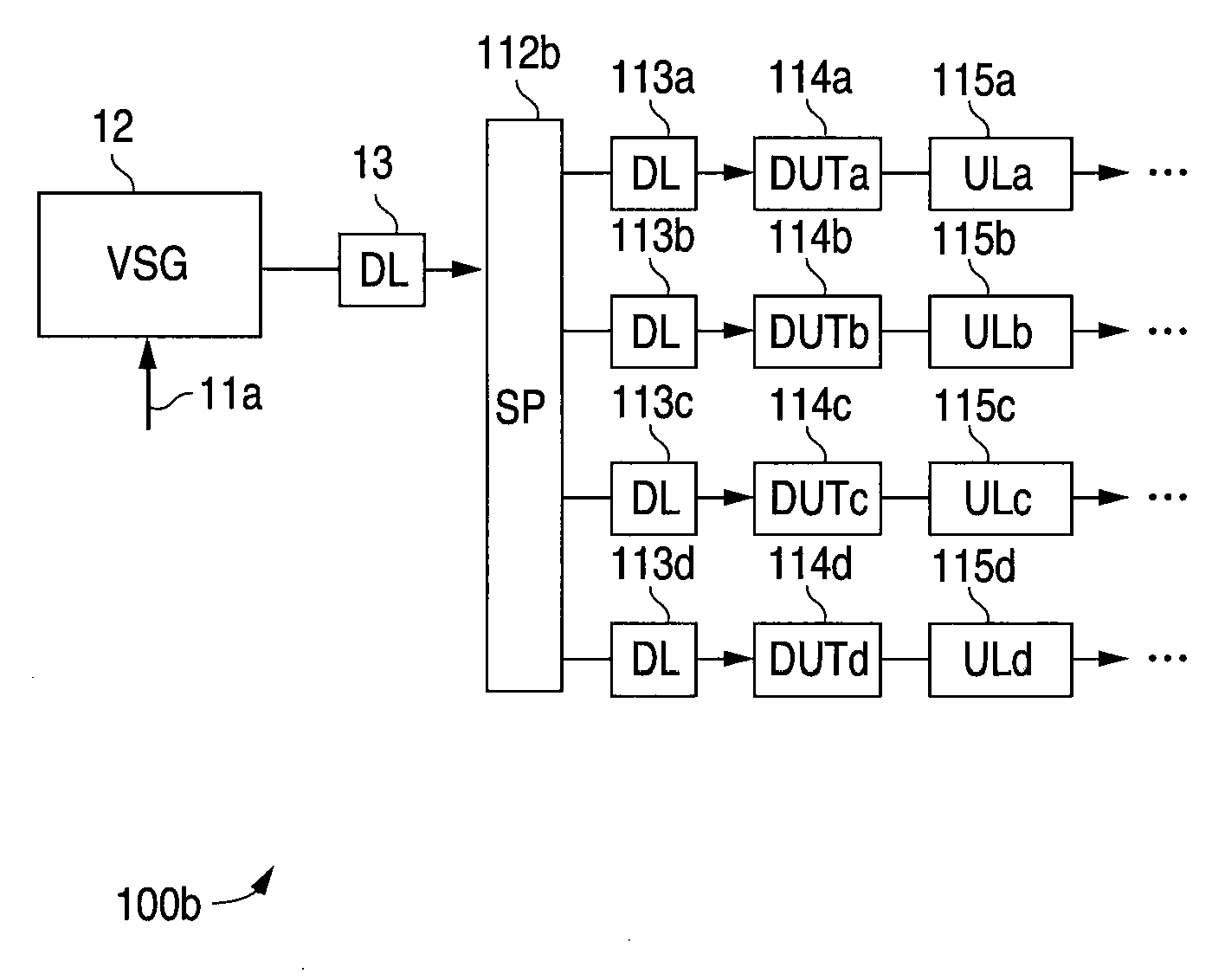

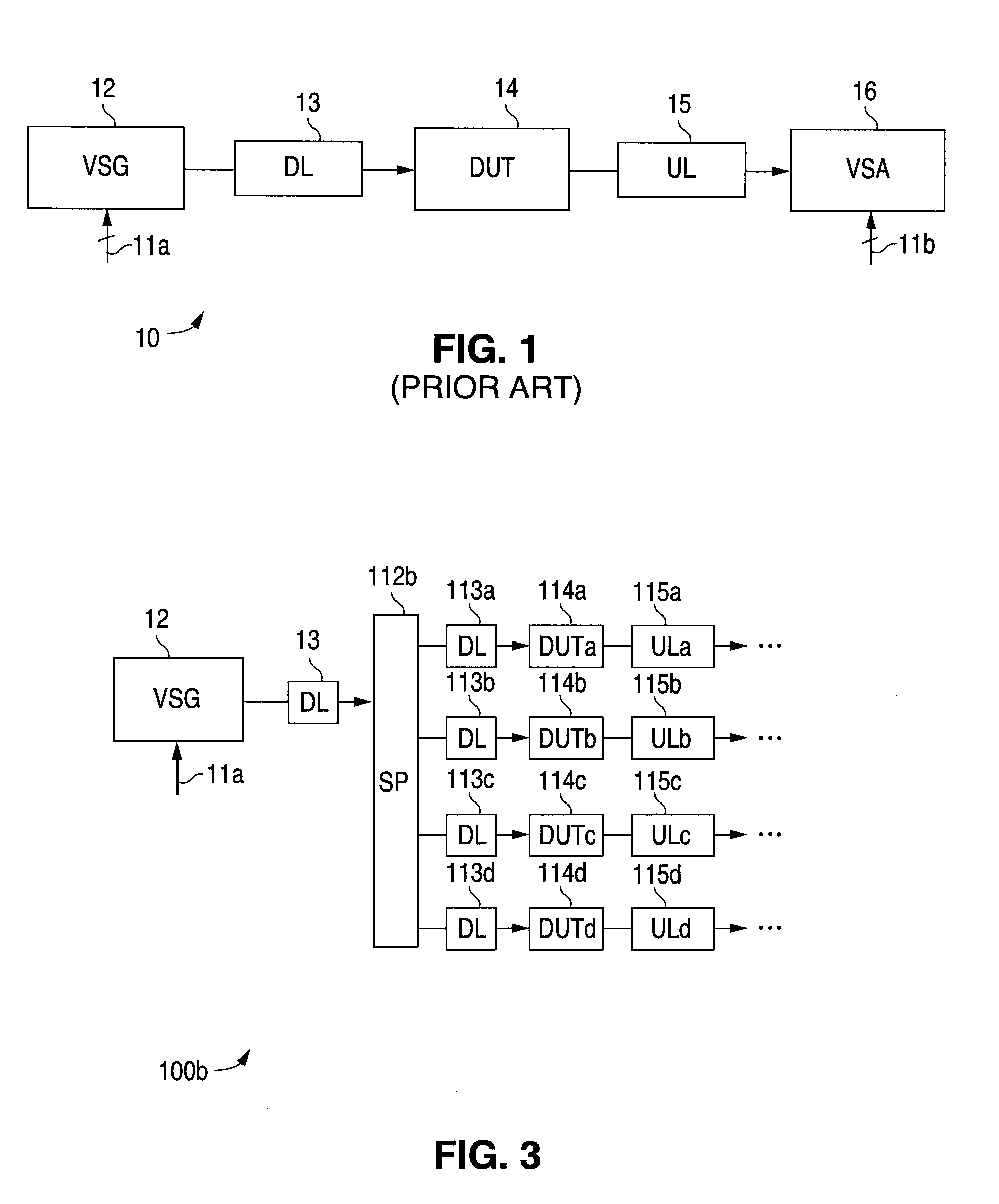

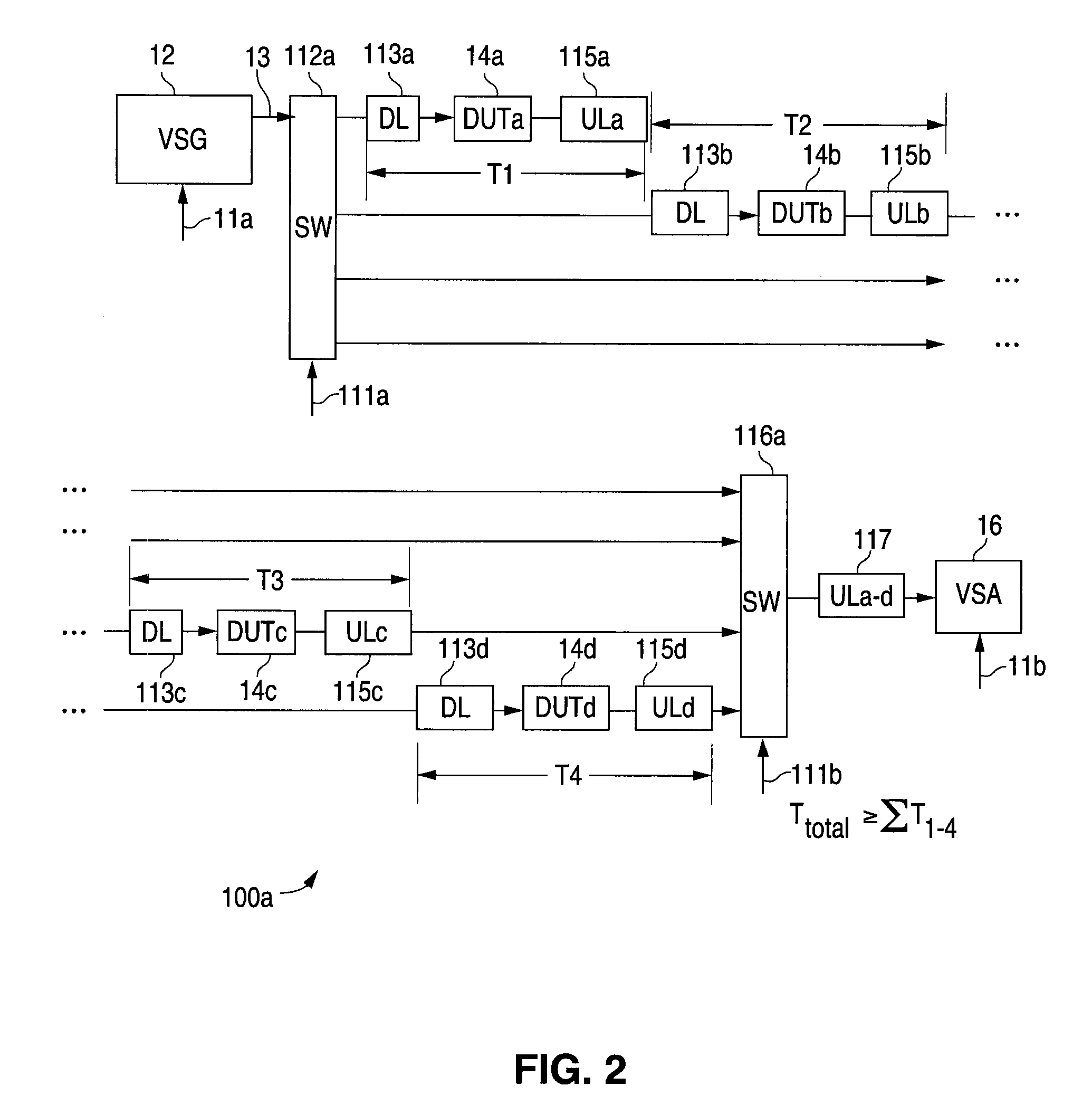

Method and system for testing multiple data packet transceivers together during a predetermined time interval

InactiveUS20110069624A1Shorten test timeError preventionTransmission systemsTransceiverSignal parameter

A method and system for testing multiple data packet transceivers together during a predetermined time interval. A sequence of downlink data packets are generated and distributed as corresponding sequences of downlink data packets for reception by multiple data packet transceivers each one of which is responsive during at least a respective portion of a predetermined time interval to a respective one of the corresponding sequences of downlink data packets by transmitting a respective one of multiple corresponding sequences of uplink data packets. At least a portion of each of the corresponding sequences of uplink data packets are combined to provide a sequence of test data packets of which at least one signal parameter is measured.

Owner:LITEPOINT

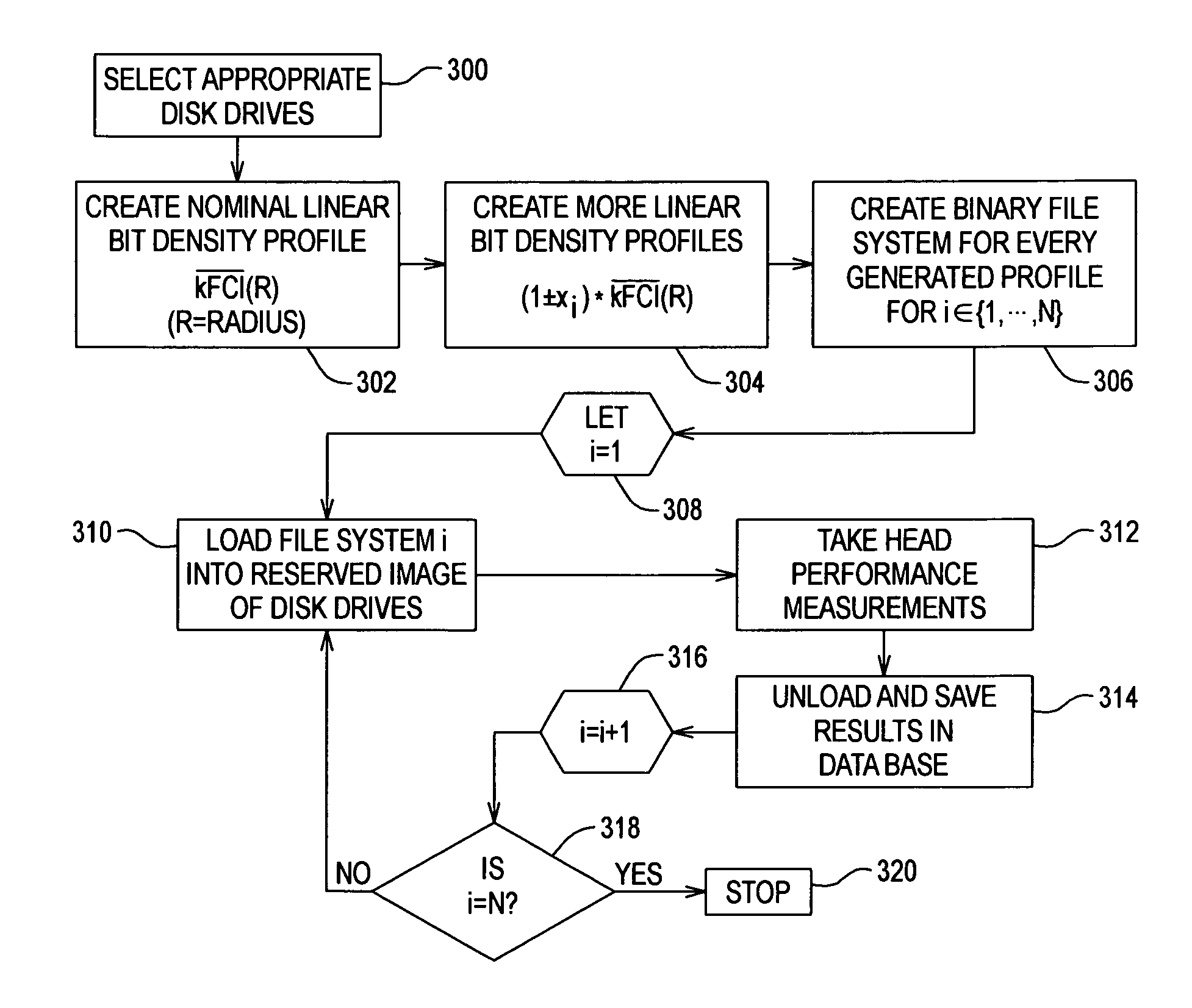

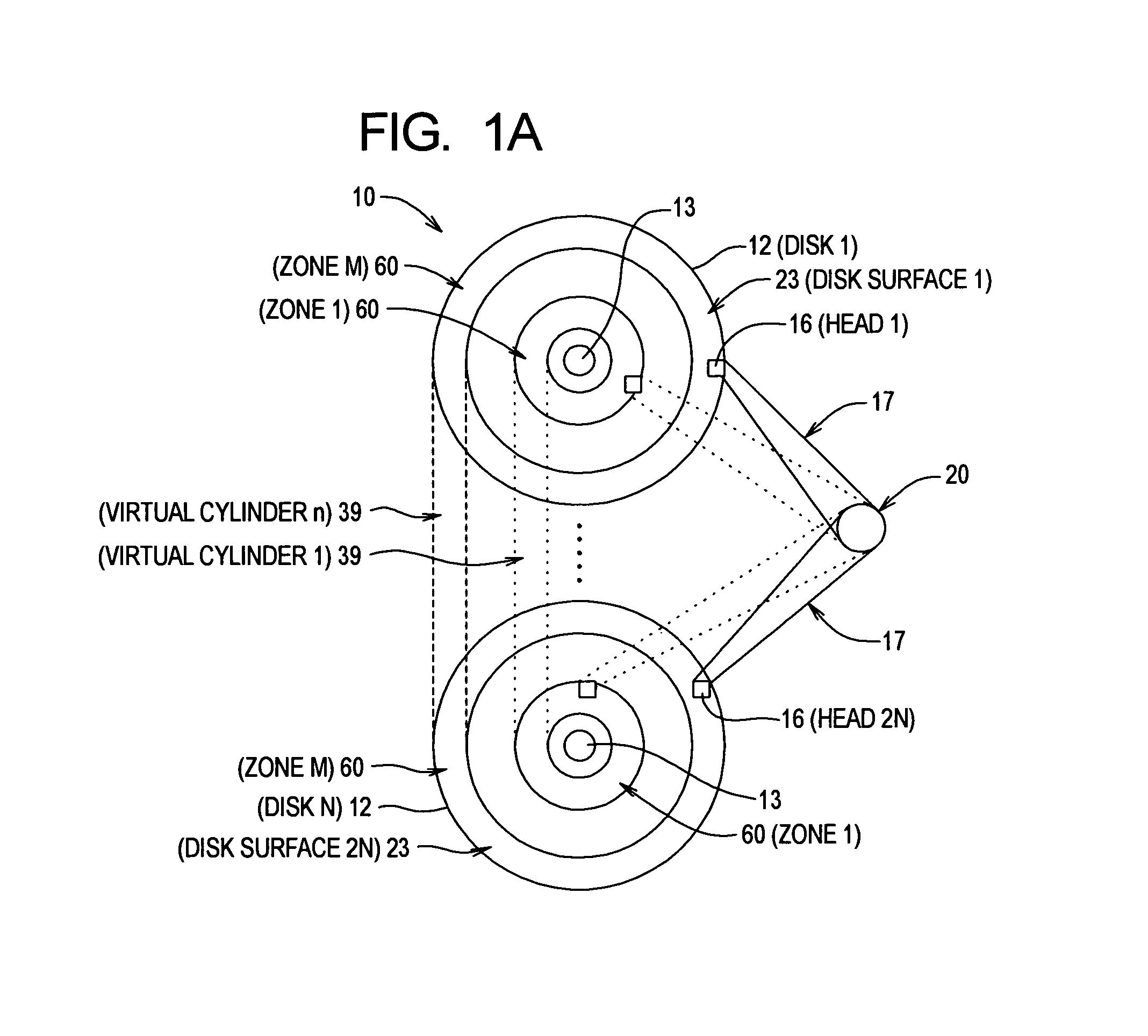

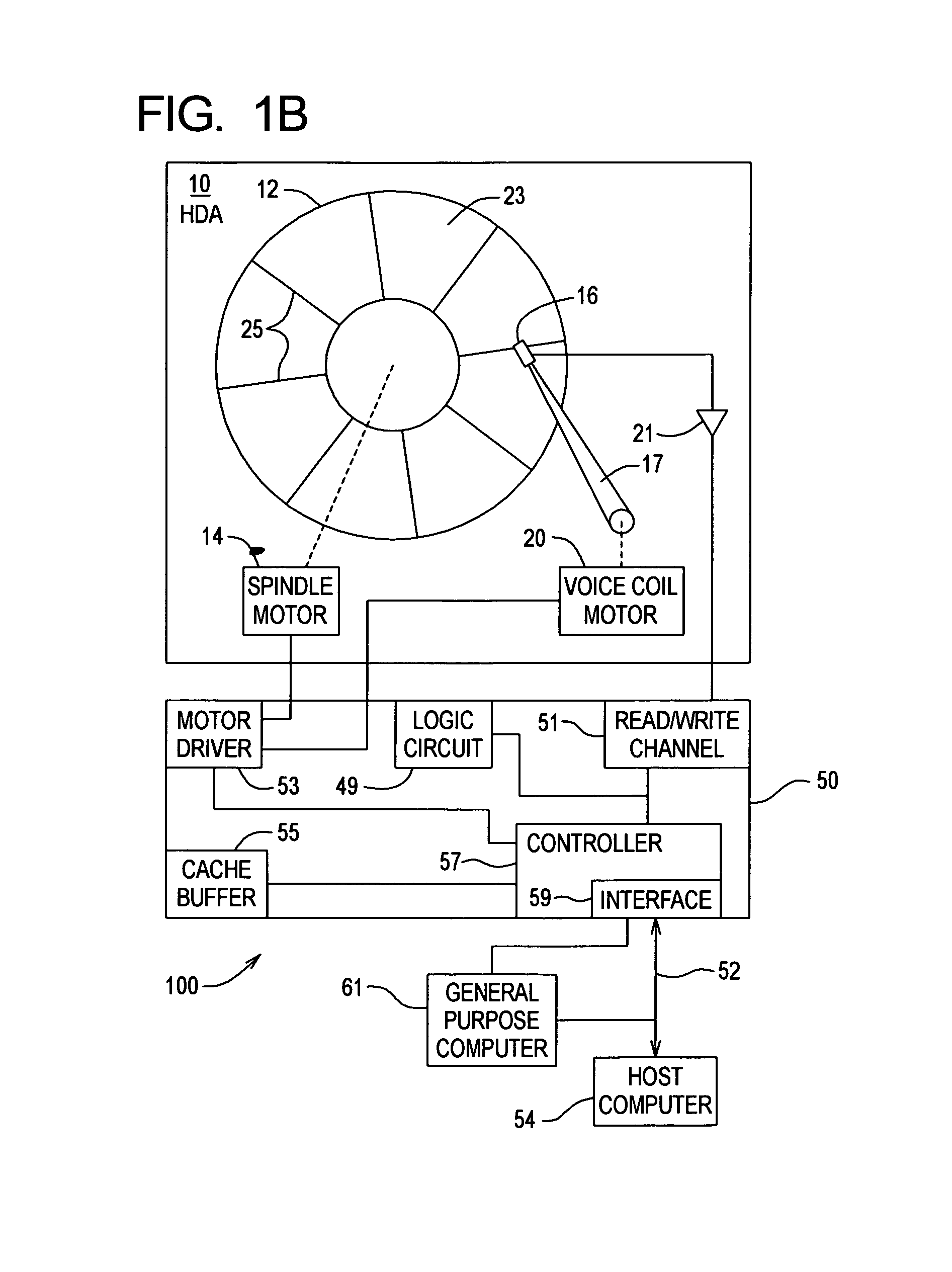

Per zone variable BPI for improving storage device capacity and yield

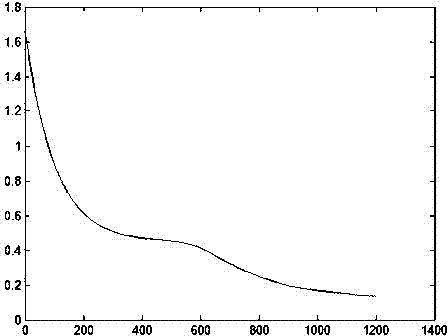

InactiveUS7012771B1Increase storage capacityHigh yieldRecord information storageCarrier monitoringDensity distributionTransducer

A method of defining such a storage format in multiple data storage devices, each data storage device having a plurality of storage media and a plurality of corresponding data transducer heads, each transducer head for recording on and playback of information from a corresponding storage medium in at least one zone, wherein each zone includes a plurality of concentric tracks for recording on and playback of information. The method includes the steps of: selecting a plurality of said data storage devices; for each selected data storage device, measuring a record / playback performance capability of each head at one or more read / write frequencies per zone; based on said performance capability measurements, generating storage density distributions corresponding to at least a number of the heads in said selected data storage devices; selecting a group of read / write frequencies for said multiple data storage devices, two or more frequencies for each zone, based on said storage density distributions; and assigning one of said read / write frequencies to each head based on performance capability of that head.

Owner:MAXTOR

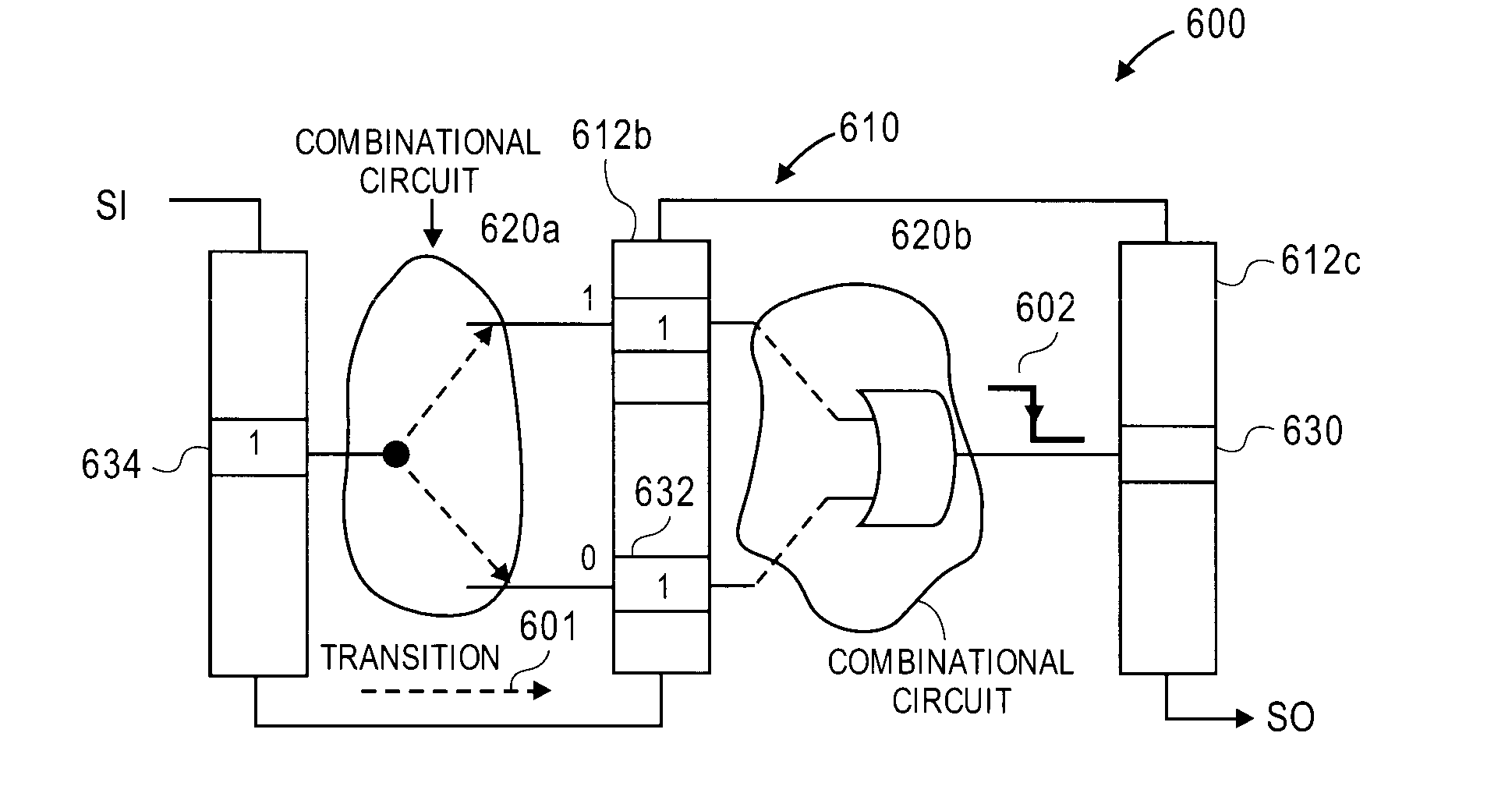

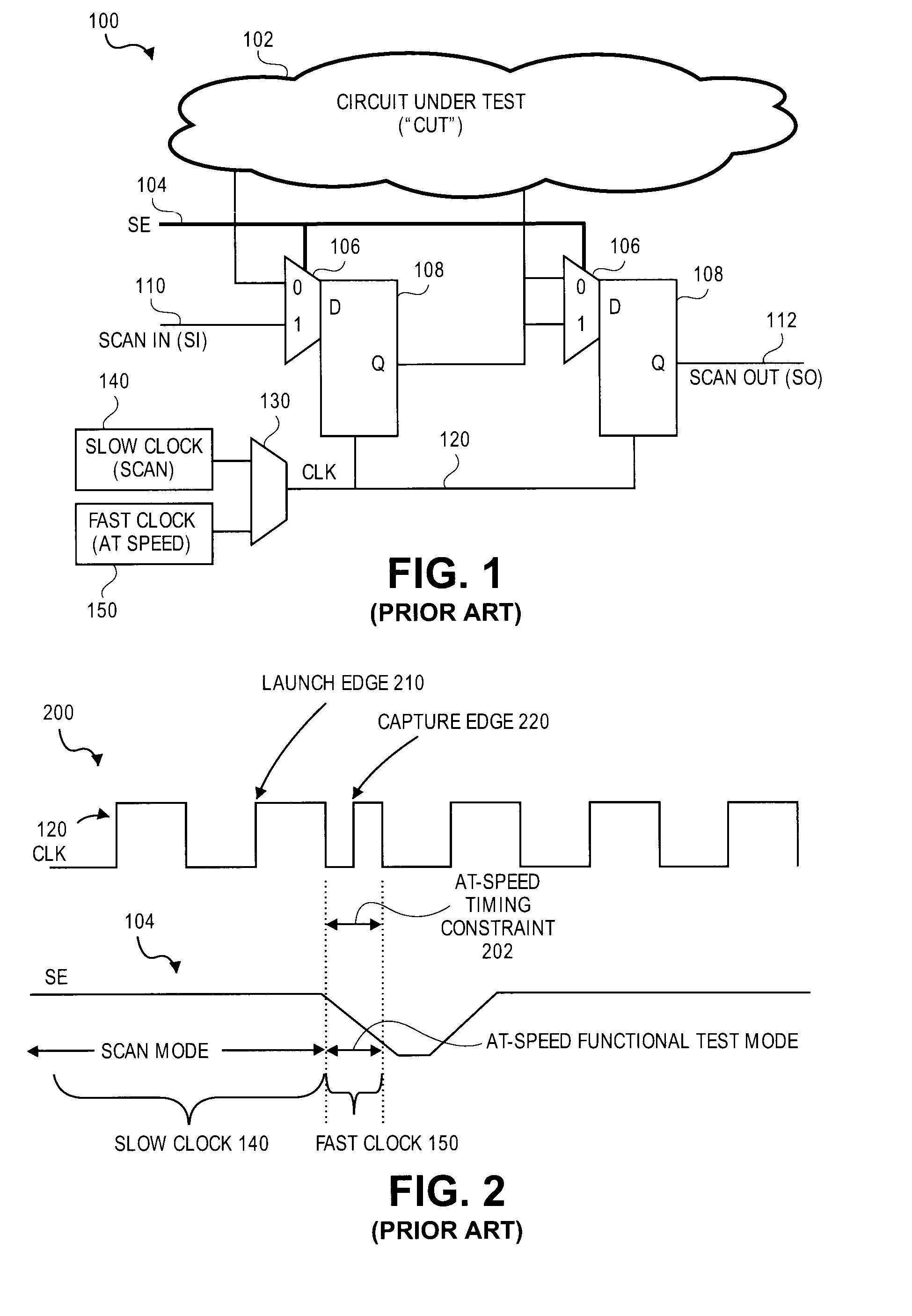

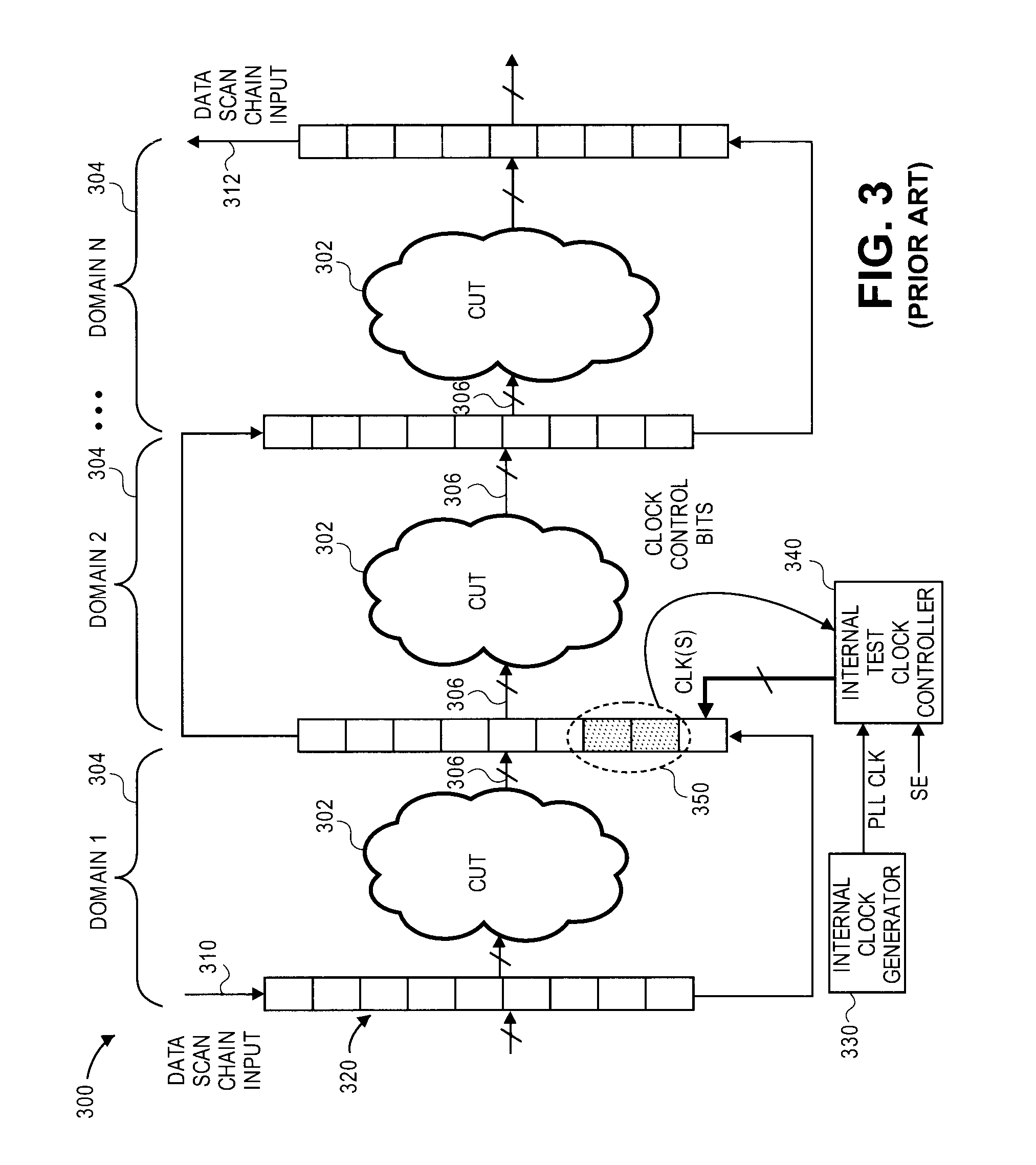

Test clock control structures to generate configurable test clocks for scan-based testing of electronic circuits using programmable test clock controllers

ActiveUS20080010573A1Reduce the number of timesLow costElectronic circuit testingFunctional testingControl layerProgrammable logic controller

Systems, structures and methods for generating a test clock for scan chains to implement scan-based testing of electronic circuits are disclosed. In one embodiment, a test clock control structure includes a programmable test clock controller. The programmable test clock controller includes a test clock generator for generating a configurable test clock. It also includes a scan layer interface to drive a scan chain portion with the configurable test clock, and a control layer interface configured to access control information for controlling the scan chain portion. In another embodiment, a method effectuates scan-based testing of circuits. The method includes performing at least one intra-domain test and performing at least one inter-domain test using implementing dynamic fault detection test patterns, which can include last-shift-launch test patterns and broadside test patterns.

Owner:LATTICE SEMICON CORP

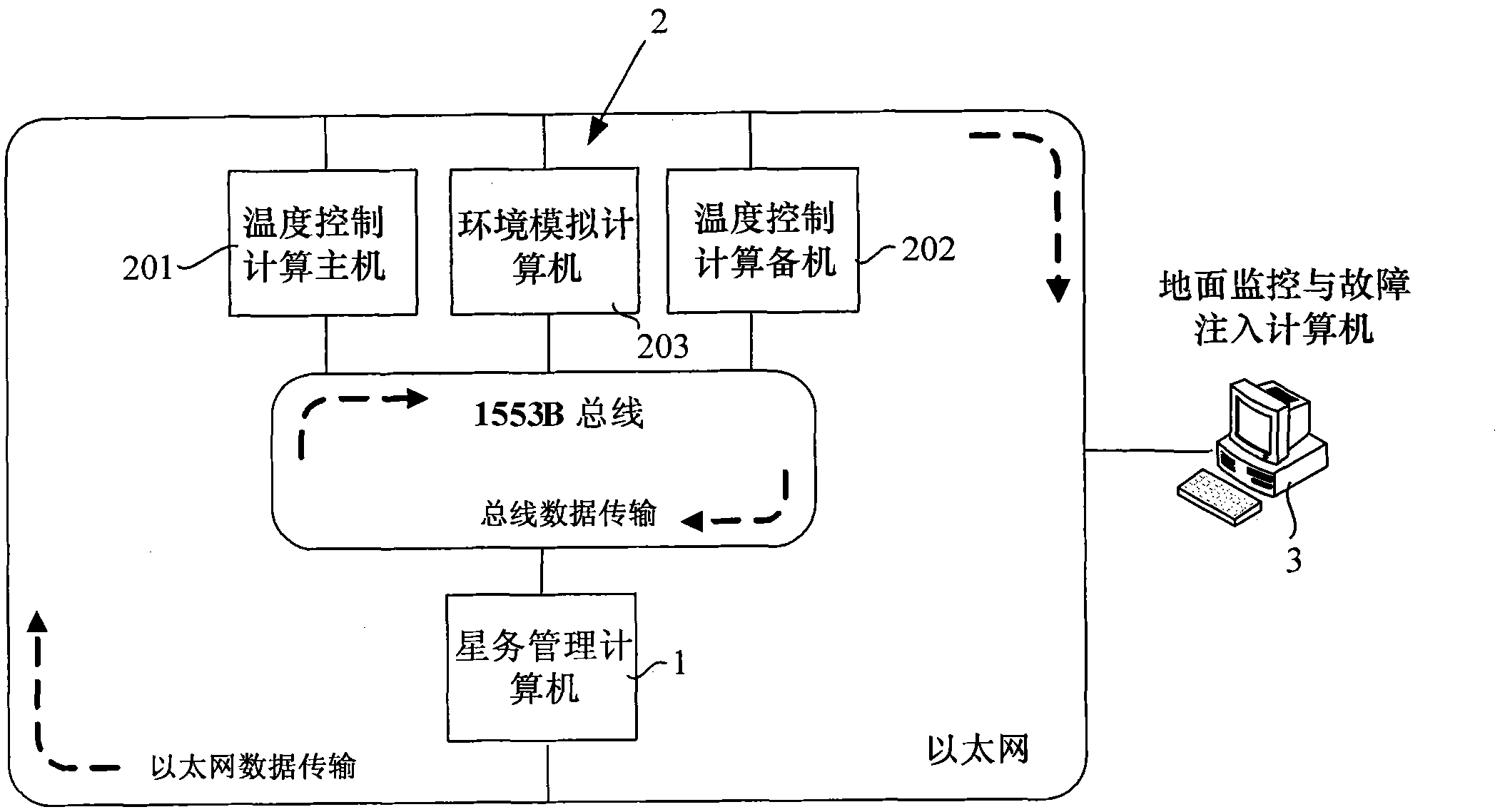

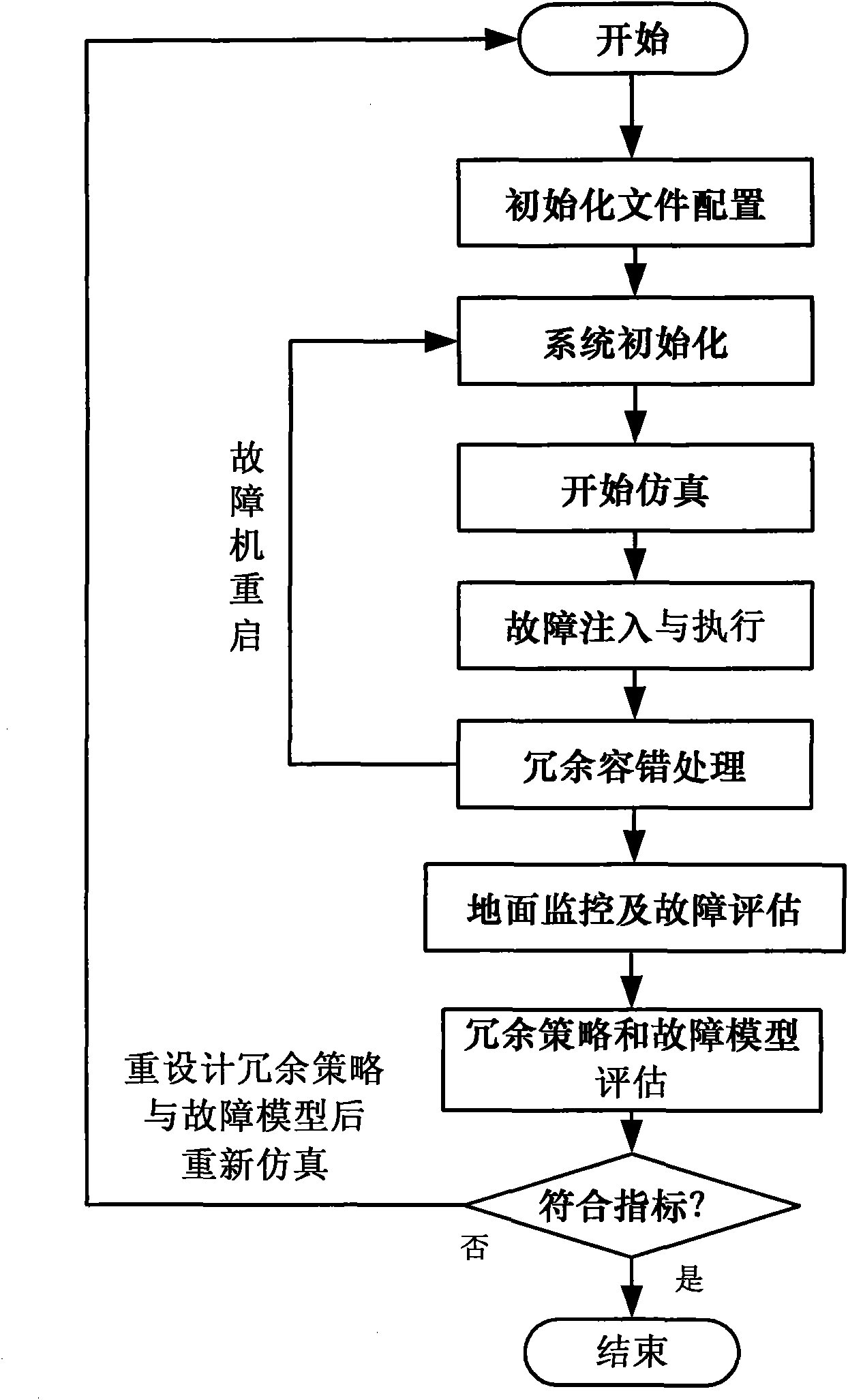

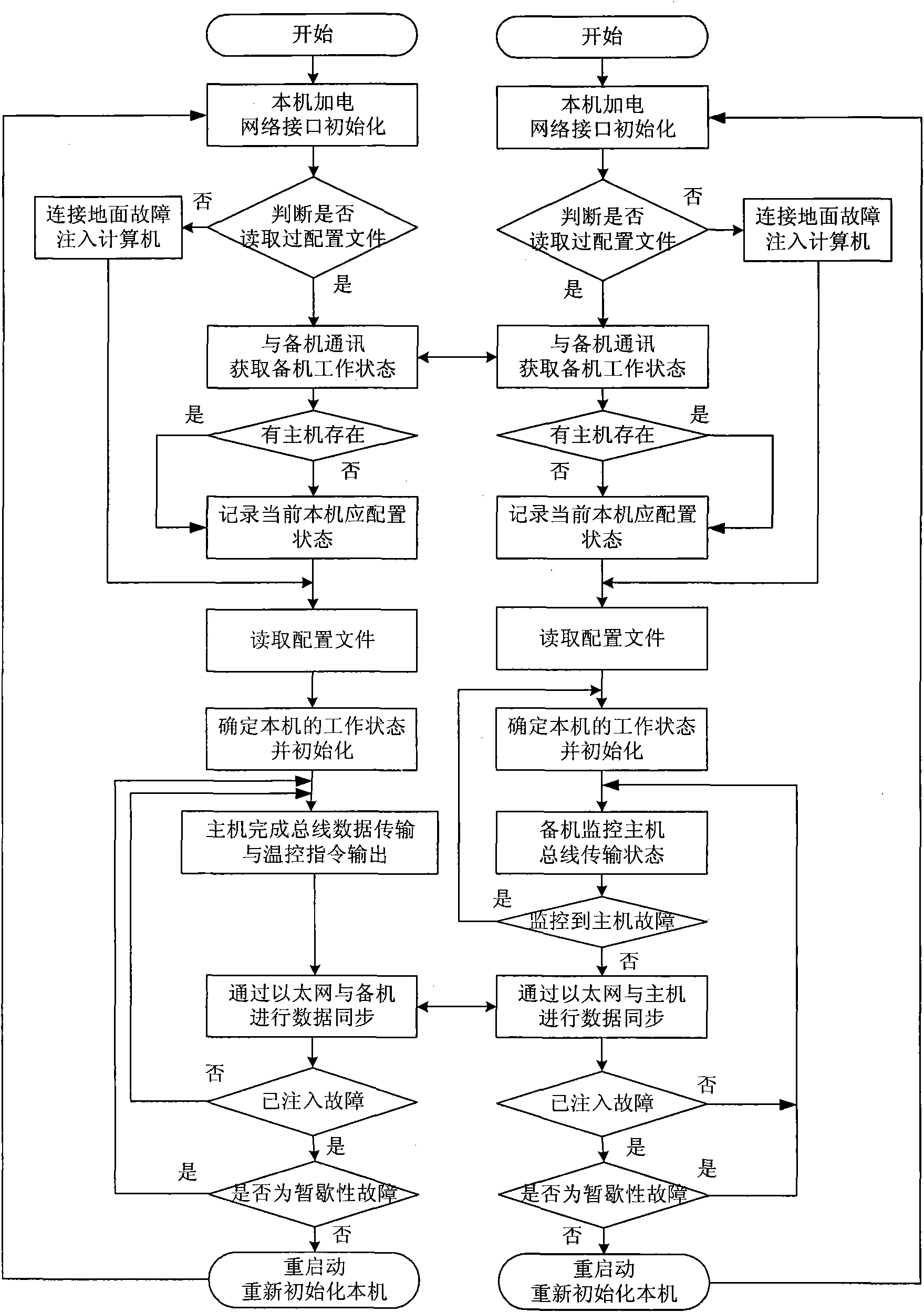

Embedded satellite-borne fault-tolerant temperature control system and verification method thereof

InactiveCN101819445AIn line with the development trendWith real development prospectsTemperatue controlError detection/correctionFault toleranceTemperature control

The invention discloses an embedded satellite-borne fault-tolerant temperature control system and a verification method thereof. The system comprises a satellite management computer, an on-satellite temperature control system and a ground monitoring and fault injection computer; the on-satellite temperature control system comprises a temperature control calculation host machine, a temperature control calculation standby machine and an environmental simulation computer; and the temperature control calculation host machine and the temperature control calculation standby machine are temperature control computers. The verification method comprises the following steps of: 1, initializing a file allocation; 2, initializing the system; 3, beginning simulation; 4, injecting and executing a fault; 5, processing redundant fault tolerance; 6, monitoring the ground and evaluating the fault; and 7, evaluating a fault model and a redundancy strategy of the temperature control system. The fault injection and the verification process of the whole running stage of the real satellite-borne temperature control system are completely realized; and the method is simple, convenient and reliable, and greatly reduces the test time and expense for the practical system.

Owner:BEIHANG UNIV

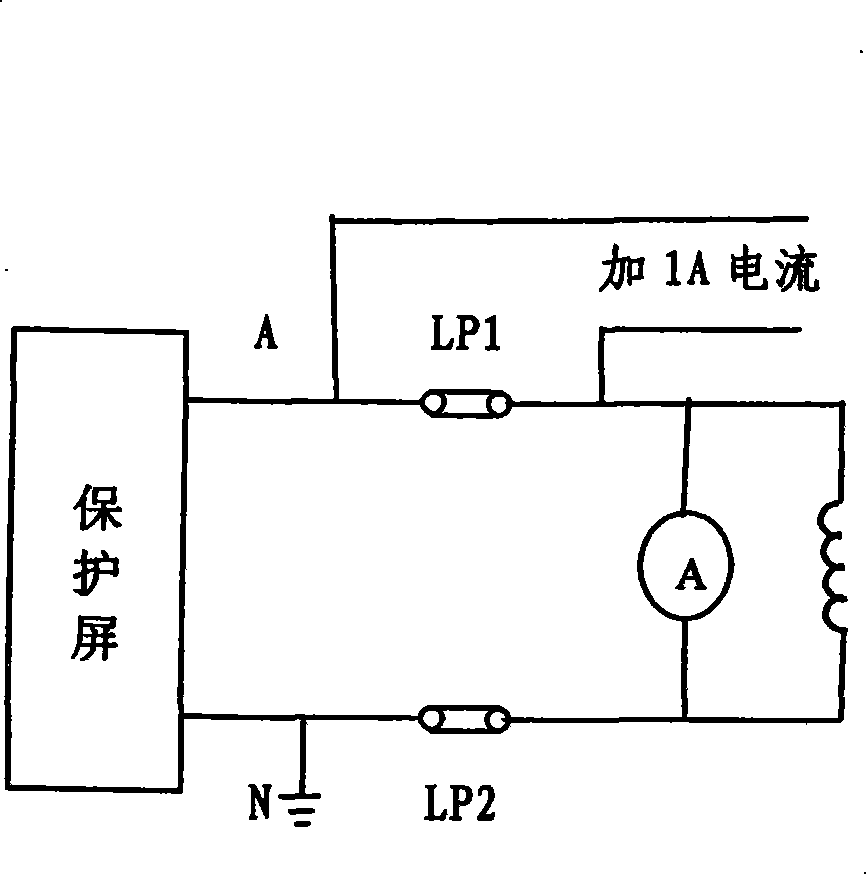

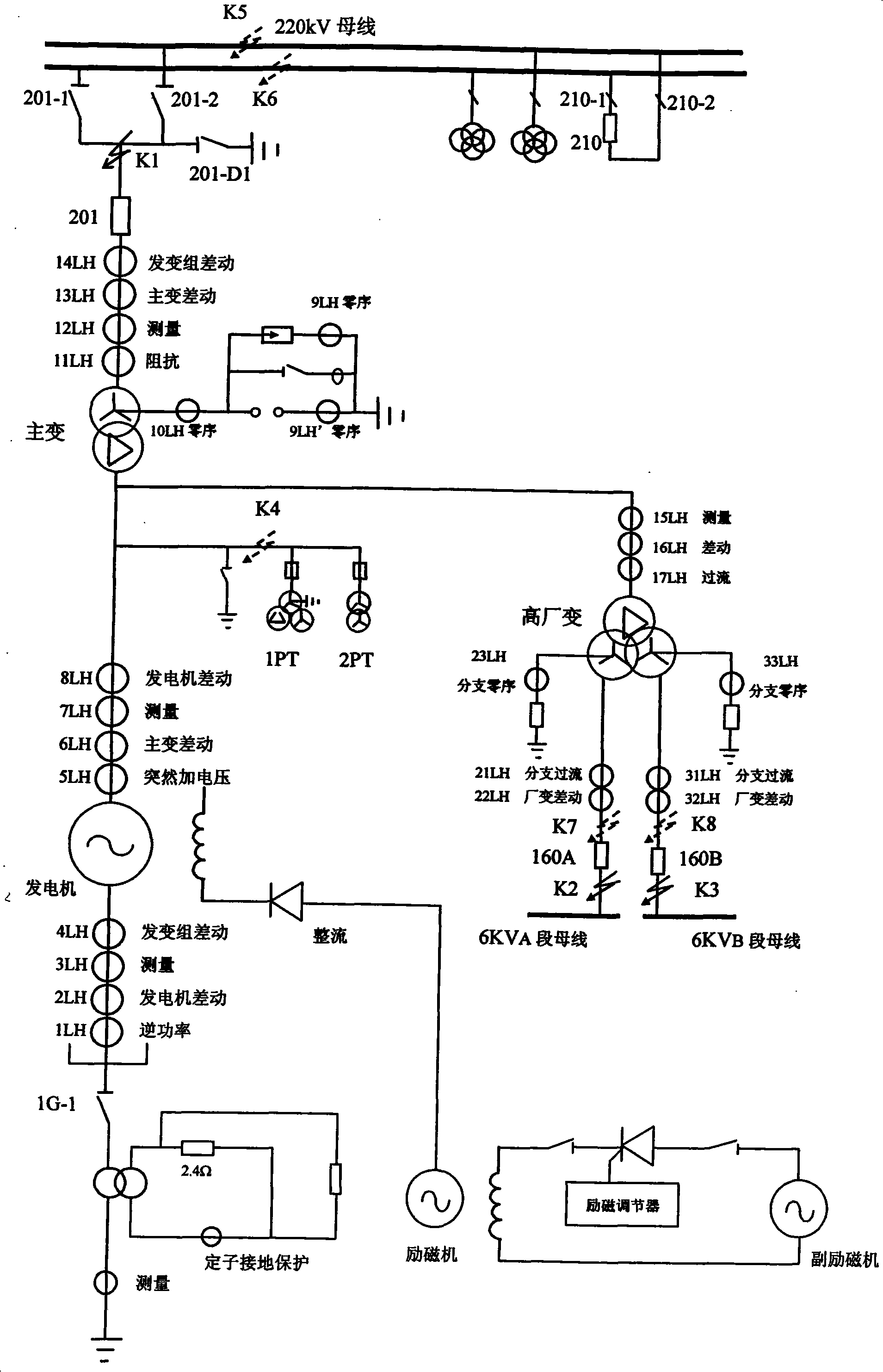

Method for testing electric secondary AC loop

ActiveCN101251569AGuaranteed correctnessCorrect circuitEmergency protective circuit arrangementsFault locationBogieLow voltage

The invention relates to an electric secondary AC circuit detection method which comprises the following steps: before a power plant machine set is started, a low-voltage short-circuit point or a short-circuit bogie is input; three-phase 380 V voltage is added at the high-voltage side of a booster station to form a circuit by means of the impedance of a transformer and a generator; current amplitude and phase are measured through a current detecting apparatus to check polarity and transformation ratio in advance; all current protective directions such as generator differential motion are measured. When a neutral point is not connected, a short-circuit point is made at a high plant transformer low-voltage side, and the three-phase 380 V voltage is added at the neutral point of the generator, thereby realizing overall checkup of a generator AC circuit; then, the three-phase 380 V voltage is converted into one-phase voltage or two-phase voltage to carry out overall checkup of a zero sequence circuit. The detection method can check all CT and PT circuits of a generation-transformer group before power transmission; moreover, all protection directions of the generation-transformer group are checked in advance, thereby saving time and fuel oil along with economical efficiency, environmental protection and safety. The electric secondary AC circuit detection method can check secondary circuits such as the transformer and the bus differential protection of a transformer substation.

Owner:ELECTRIC POWER RESEARCH INSTITUTE OF STATE GRID SHANDONG ELECTRIC POWER COMPANY +1

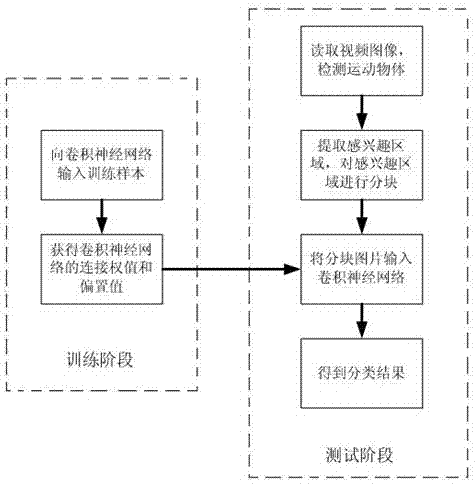

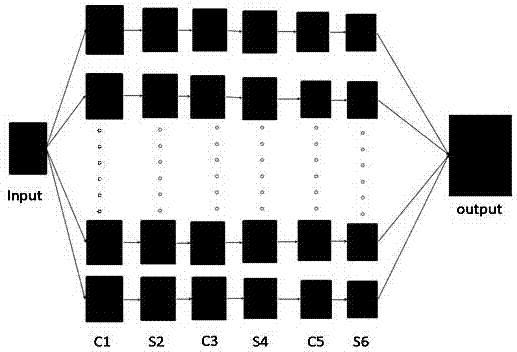

Face detection method based on convolutional neural network

InactiveCN104504362AReduce in quantityReduce complexityCharacter and pattern recognitionNeural learning methodsFace detectionTest phase

The invention discloses a face detection method based on a convolutional neural network. The face detection method comprises a training stage and a testing stage, wherein the training stage comprises the following steps: inputting a training sample into the convolutional neural network, and obtaining a connection weight and an offset value of the convolutional neural network. The testing stage comprises the following steps: reading a video image; when a moving object is detected, extracting an interested area, moving for one pixel each time by utilizing a block with a n*n pixel size, and carrying out partitioning processing to the interested area to obtain a plurality of pictures; zooming the partitioned pictures to a size which is the same with the size of the training sample; and inputting the pictures into the convolutional neural network which finishes training for classification, wherein n is greater than or equal to 50 and less than or equal to 70. The convolutional neural network is used as a classifier, so that detection precision and speed can be improved.

Owner:NANJING AIKELESI NETWORK TECH CO LTD

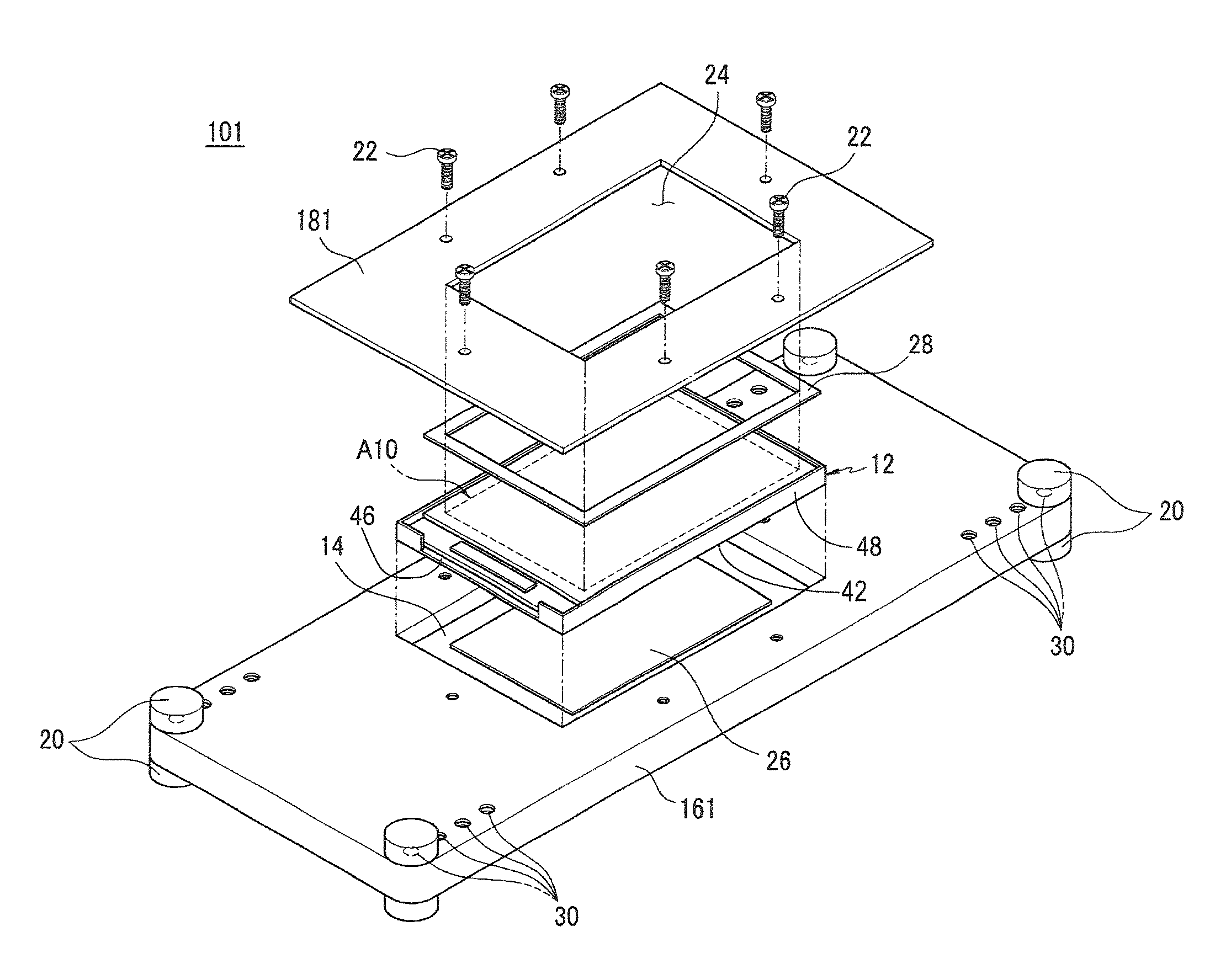

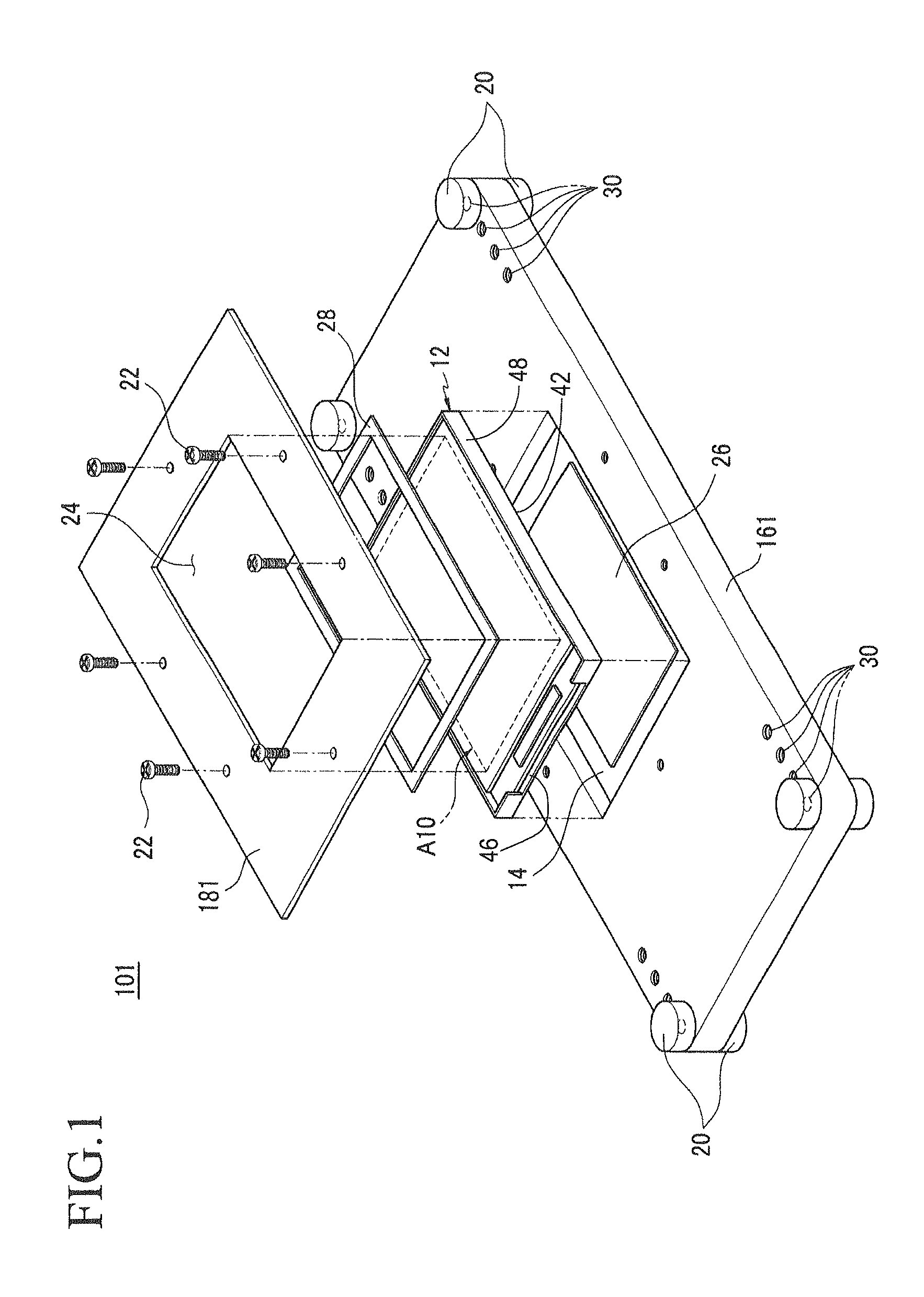

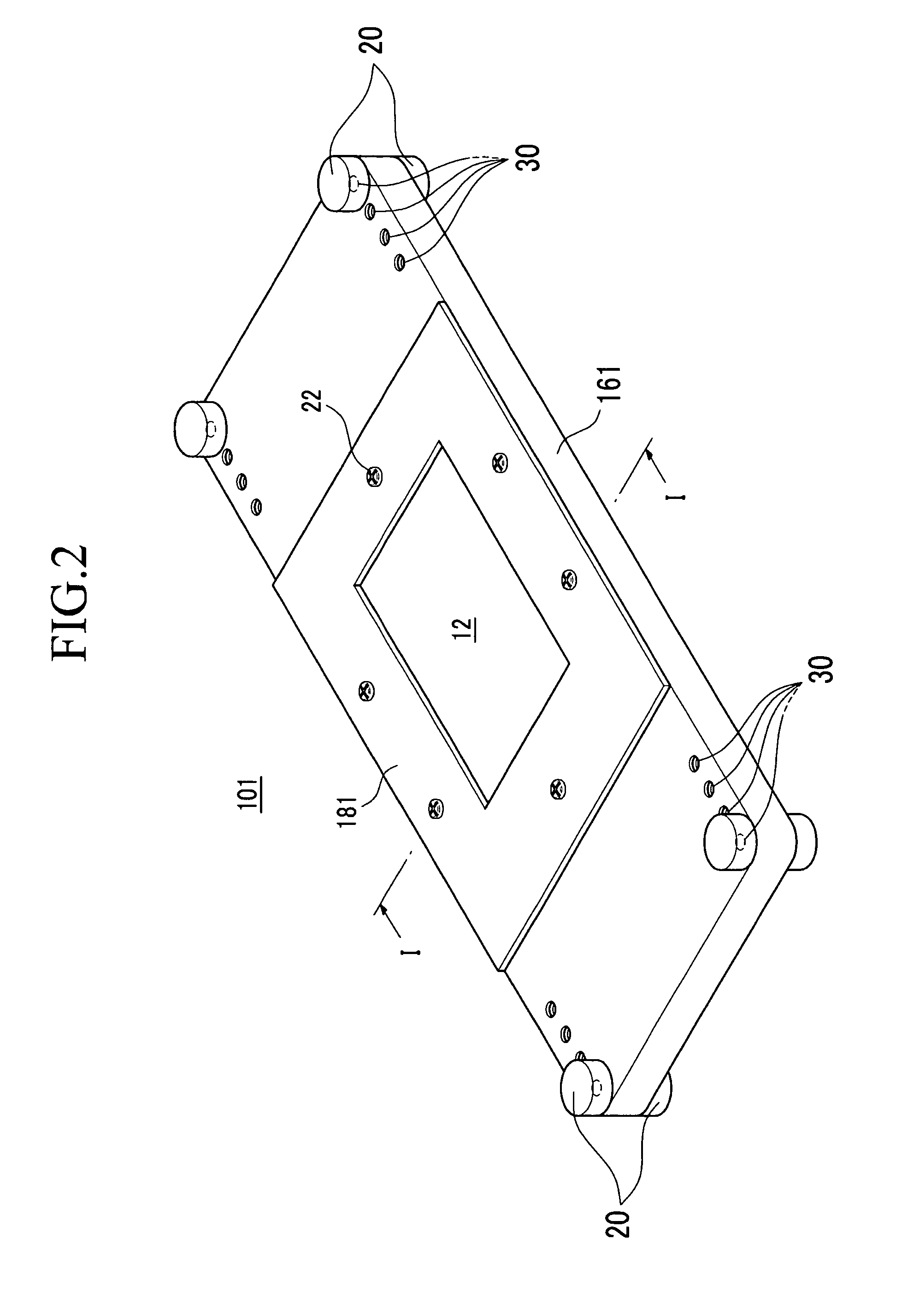

Jig frame for drop test of flat panel display device

InactiveUS7966861B2Efficient identificationShorten test timeAcceleration measurementNon-linear opticsDisplay deviceEngineering

A jig frame for a drop test of a flat panel display, which is designed to allow a tester to effectively identify if the flat panel display is damaged and to easily adjust its weight and degree of deformation is provided. The jig frame for a drop test of a flat panel display includes a base plate having a groove for receiving the flat panel display and a cover plate fixing the flat panel display by covering the flat panel display and being coupled to the base plate. The cover plate is formed of transparent material so that the flat panel display installed in the jig frame is visible to outside of the cover plate.

Owner:SAMSUNG DISPLAY CO LTD

Paraffin section method for fern gametophytes

InactiveCN102607907AAvoid poor resultsGood slice methodPreparing sample for investigationParaffin waxMicroscopic exam

The invention discloses a paraffin section method for fern gametophytes, which comprises the steps of material selection and fixation, washing, coloration and bluing, dehydration and hyalinizing, waxing and embedding, sectioning, patching, dewaxing and mounting, as well as microscopic examination and photographing, wherein improved FAA (formalin, acetic acid and alcohol) stationary liquid is adopted in the fixation, and the stationary liquid consists of formalin, acetic acid and 30% alcohol (formalin:acetic acid:30% alcohol = 1:1:18). The method is adopted, so that the disadvantage of much youngness of the fern gametophytes can be effectively overcome; the fixation can be well performed for cell divisions at all stages; from a paraffin section in a later stage, a plurality of mitotic sections can be observed, so that a whole development process can be reflected detailedly; therefore, the method has high development and application values.

Owner:NORTHEAST AGRICULTURAL UNIVERSITY

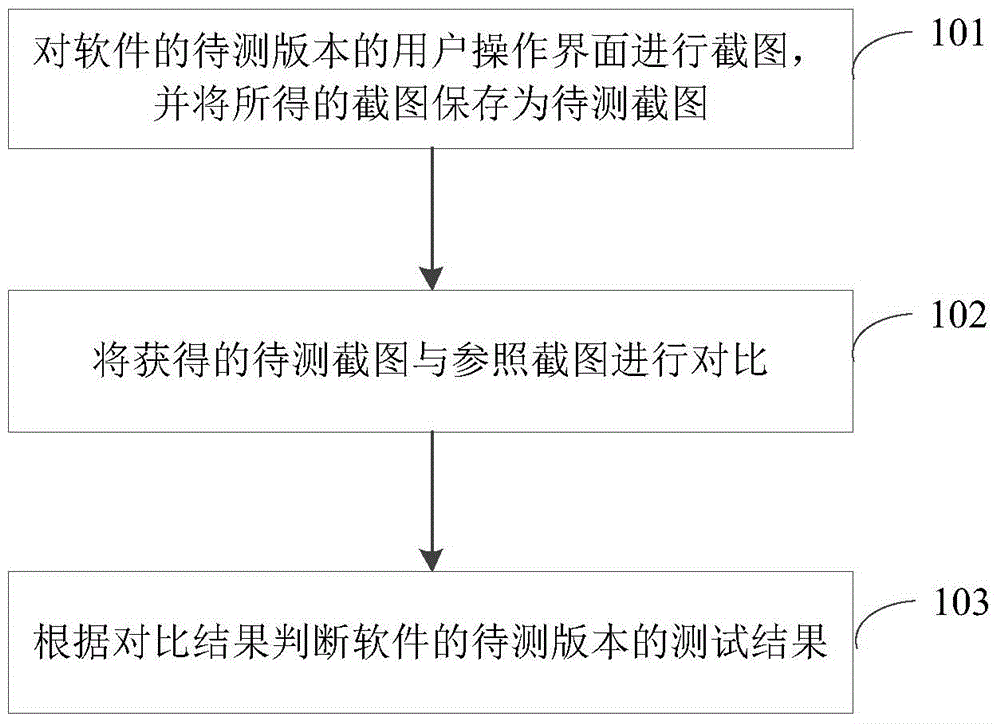

Automatic software testing method and apparatus

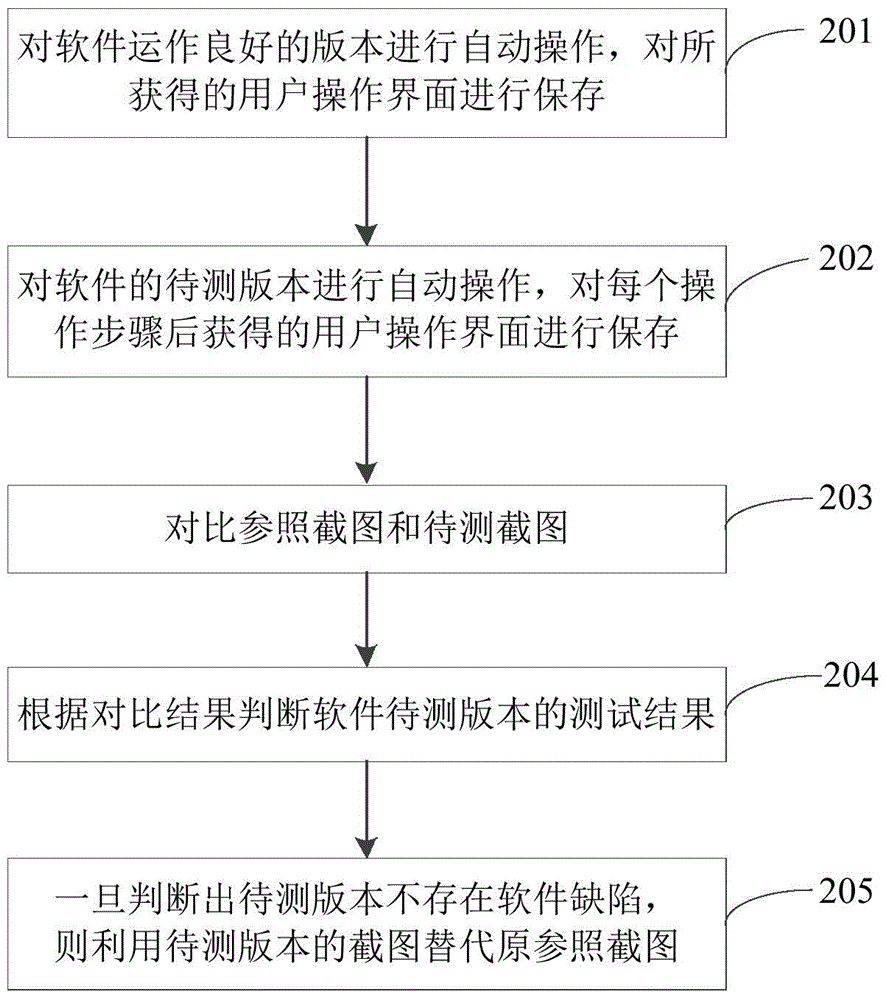

InactiveCN104978270ASimplify writingReduce the amount of codeSoftware testing/debuggingSoftware engineeringAutomatic testing

The embodiment of the present invention provides an automatic software testing method and apparatus. The automatic software testing method comprises: carrying out screen shooting on a user operation interface of a version to be tested of software and storing an obtained screenshot as a screenshot to be tested; comparing the obtained screenshot to be tested with a reference screenshot; and according to a comparison result, judging a testing result of the version to be tested of the software. According to the embodiment of the present invention, automatic testing efficiency and accuracy can be higher.

Owner:SHANGHAI CHULE (COOTEK) INFORMATION TECH CO LTD