Patents

Literature

1701 results about "Through-silicon via" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

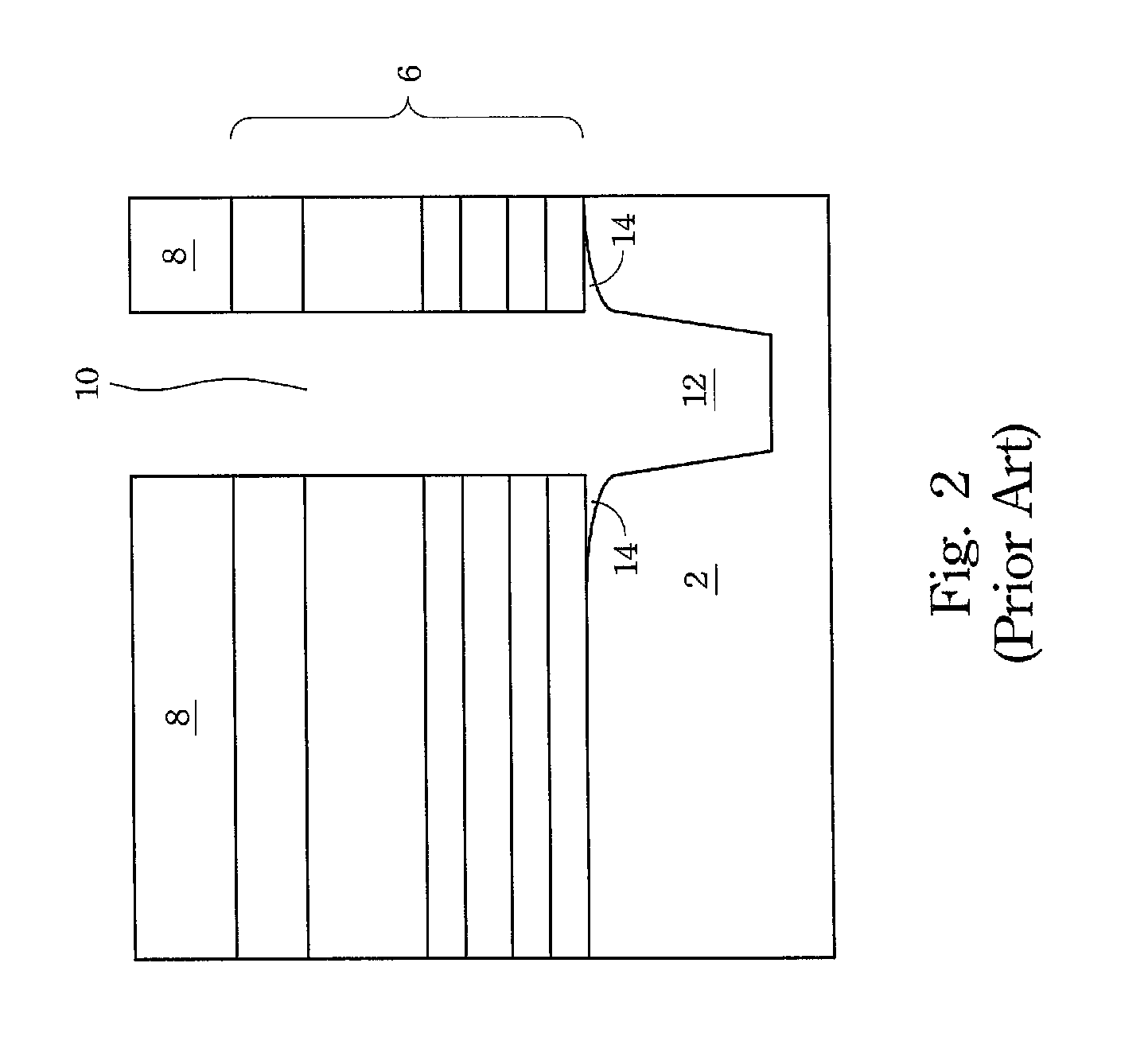

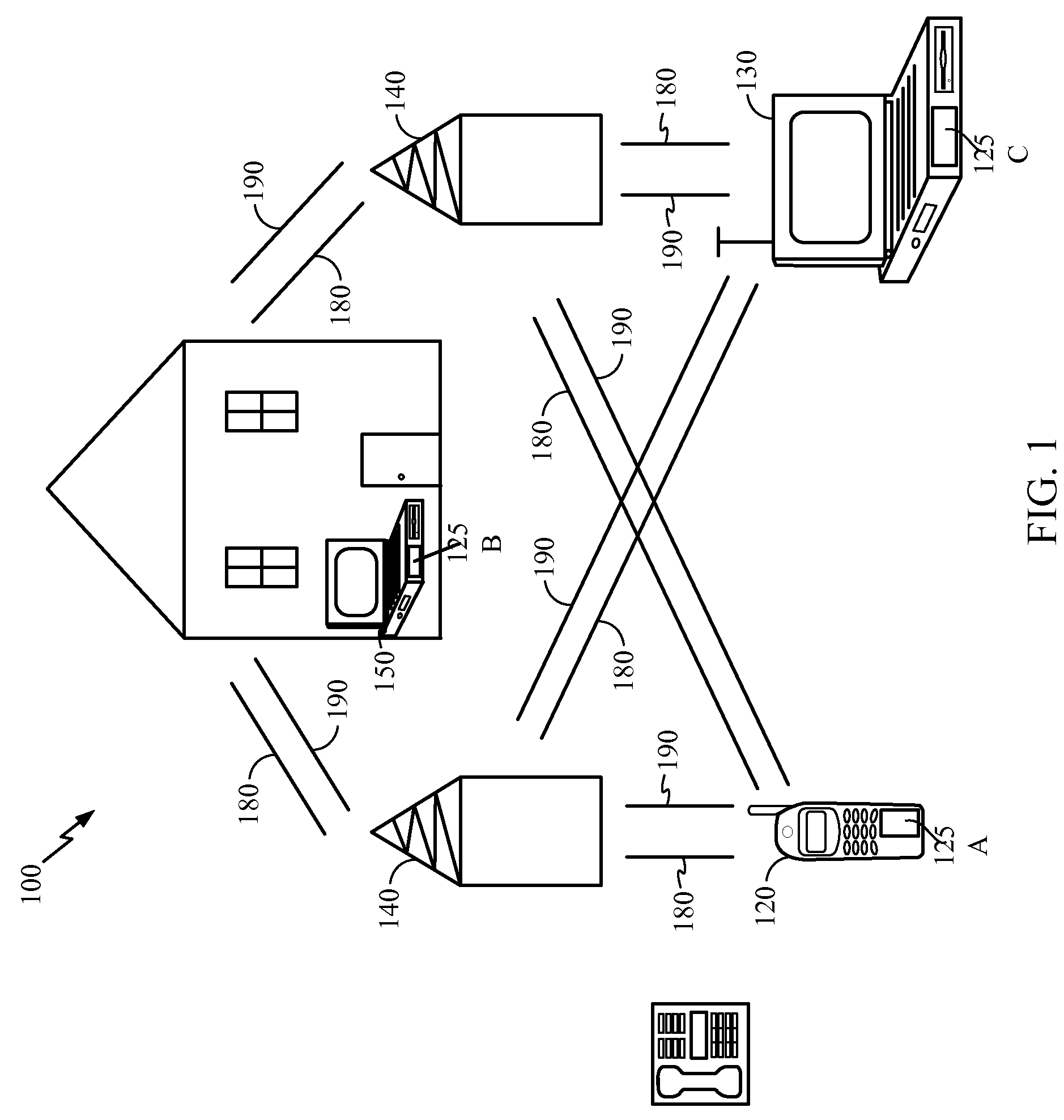

In electronic engineering, a through-silicon via (TSV) or through-chip via is a vertical electrical connection (via) that passes completely through a silicon wafer or die. TSVs are high performance interconnect techniques used as an alternative to wire-bond and flip chips to create 3D packages and 3D integrated circuits. Compared to alternatives such as package-on-package, the interconnect and device density is substantially higher, and the length of the connections becomes shorter.

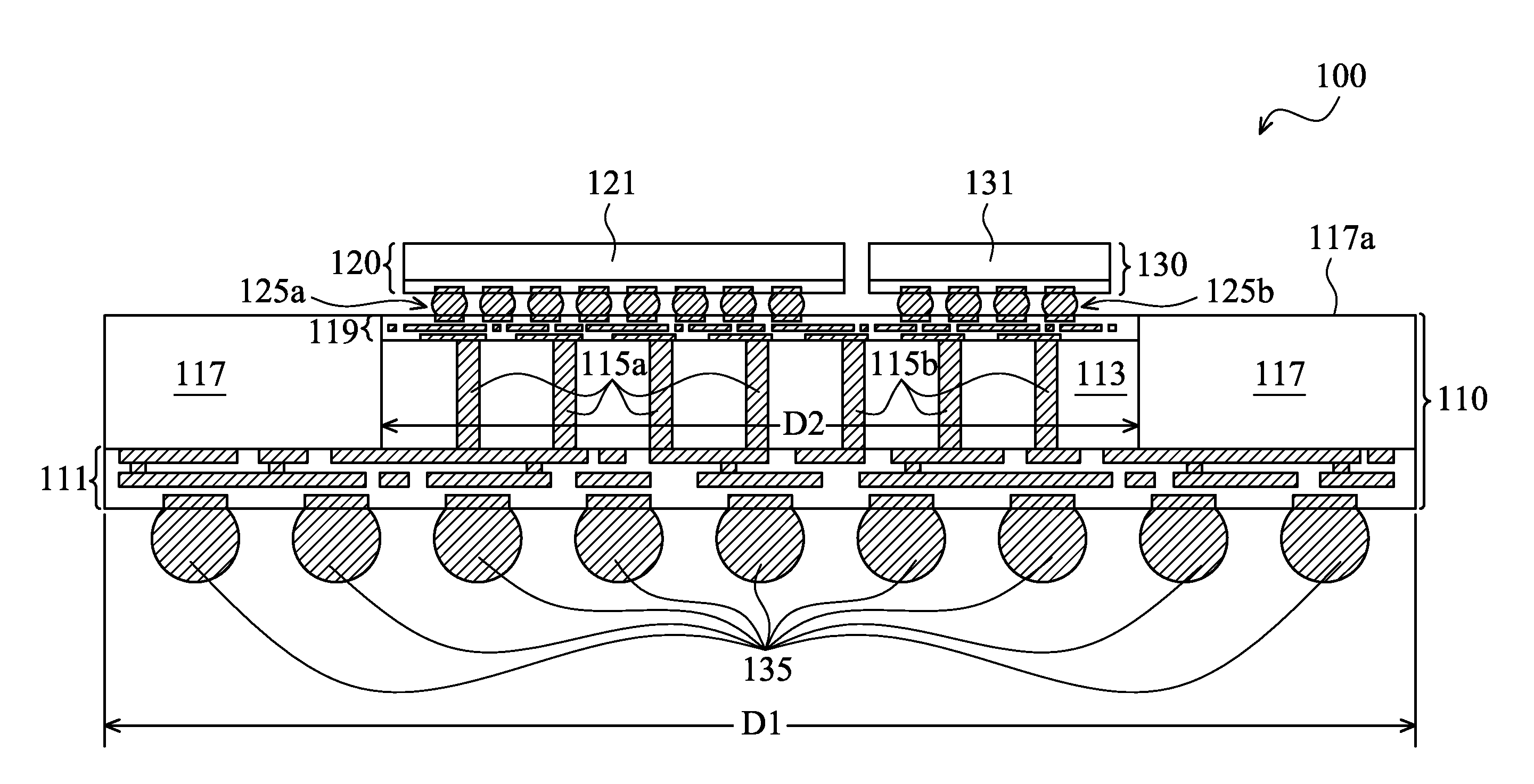

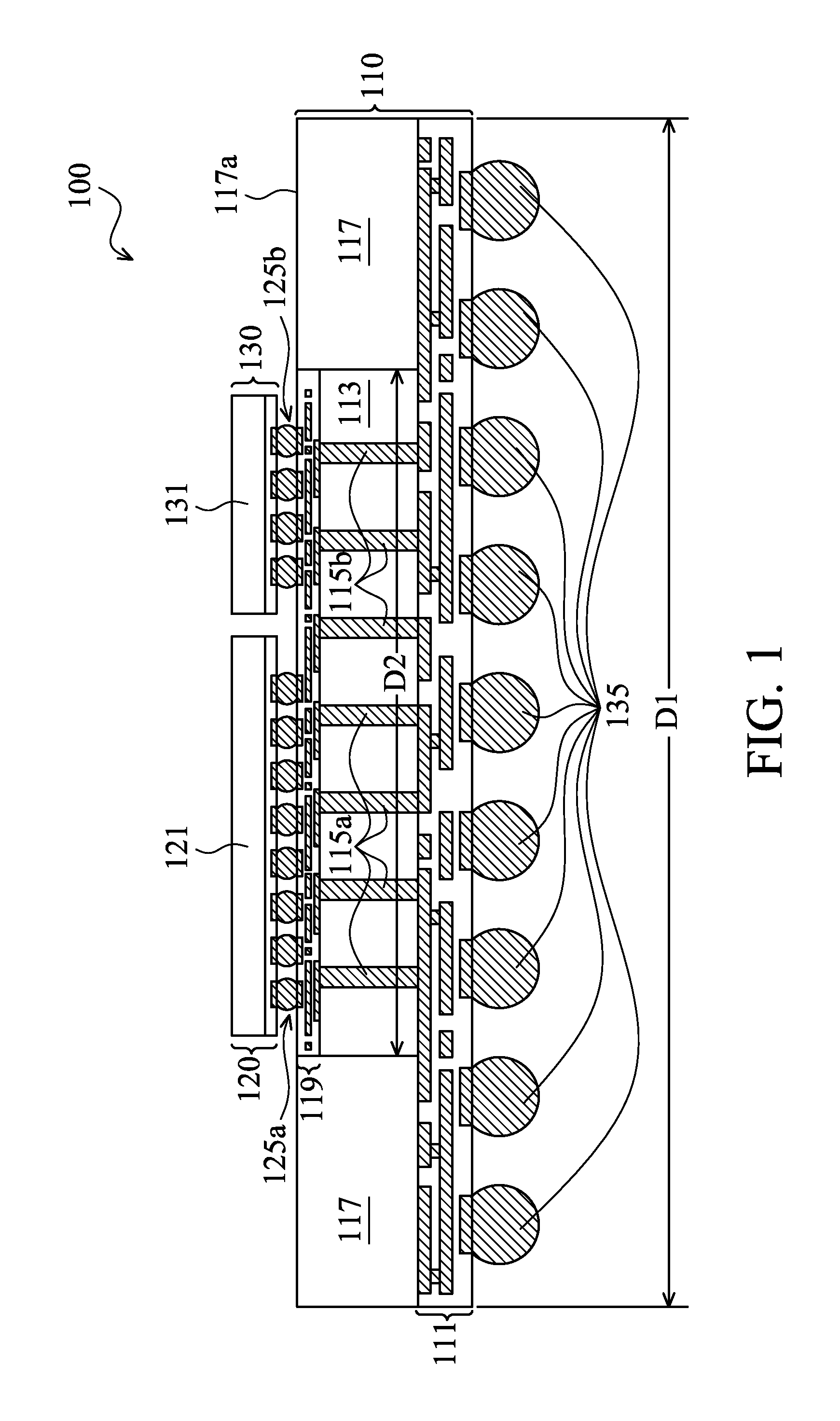

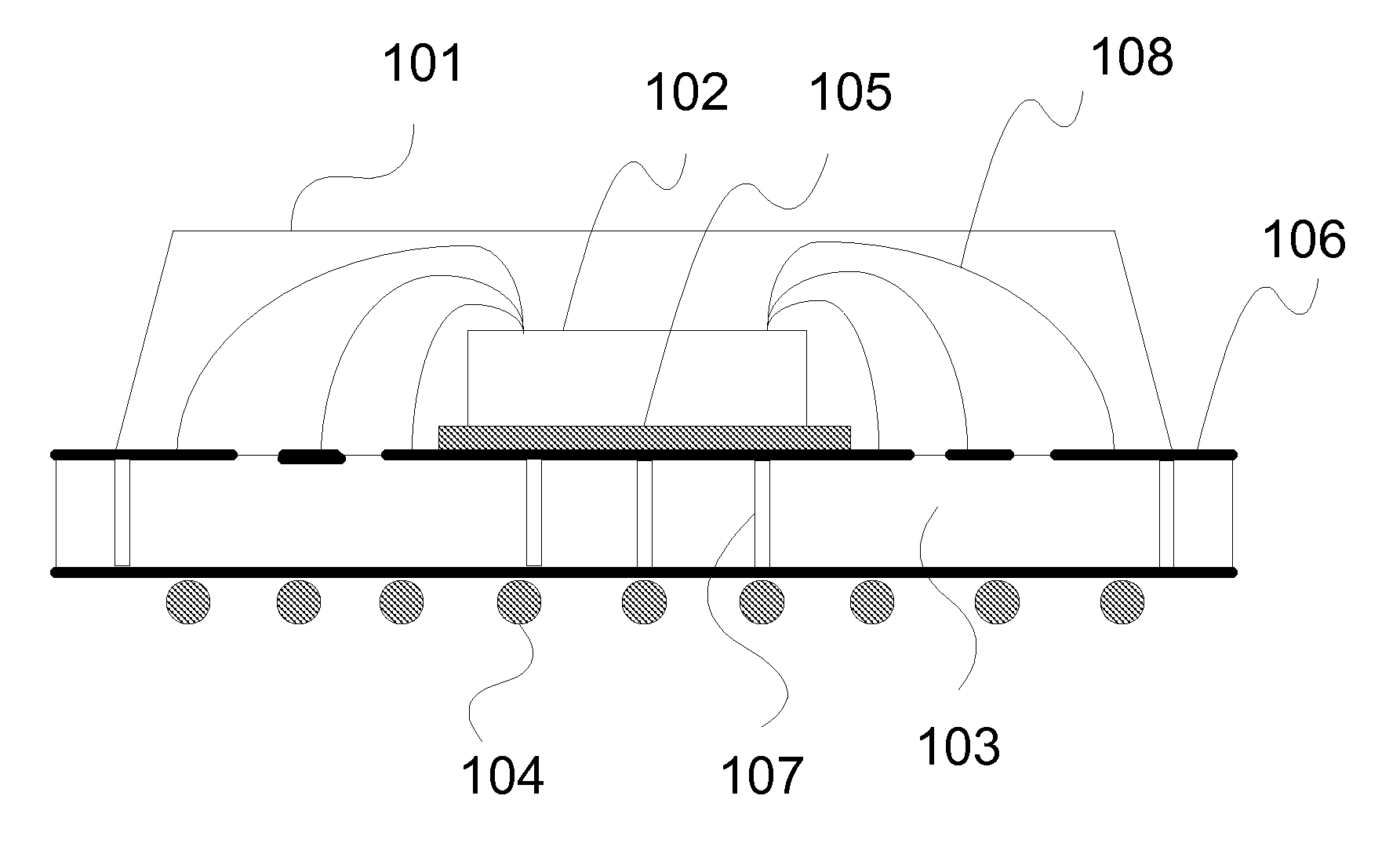

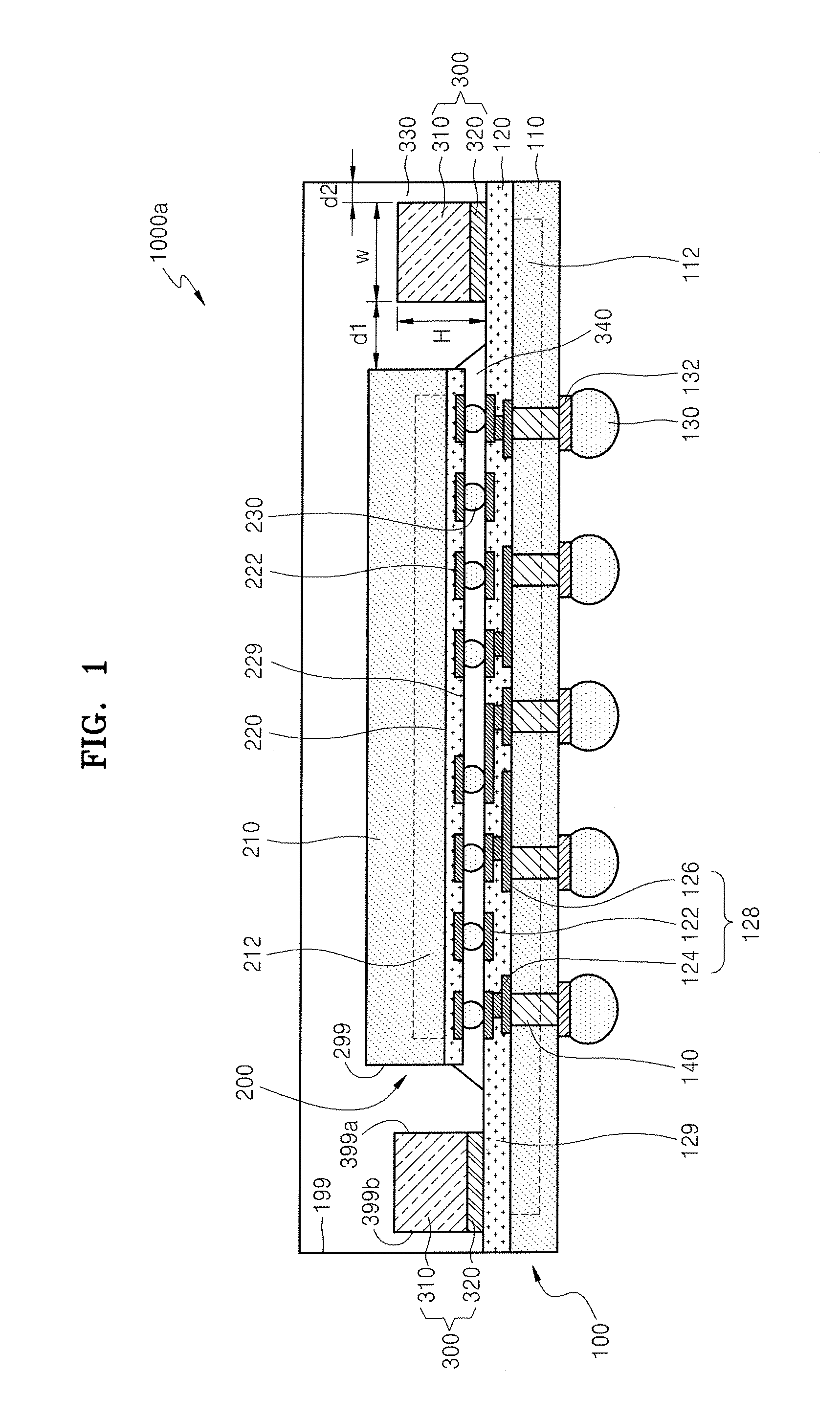

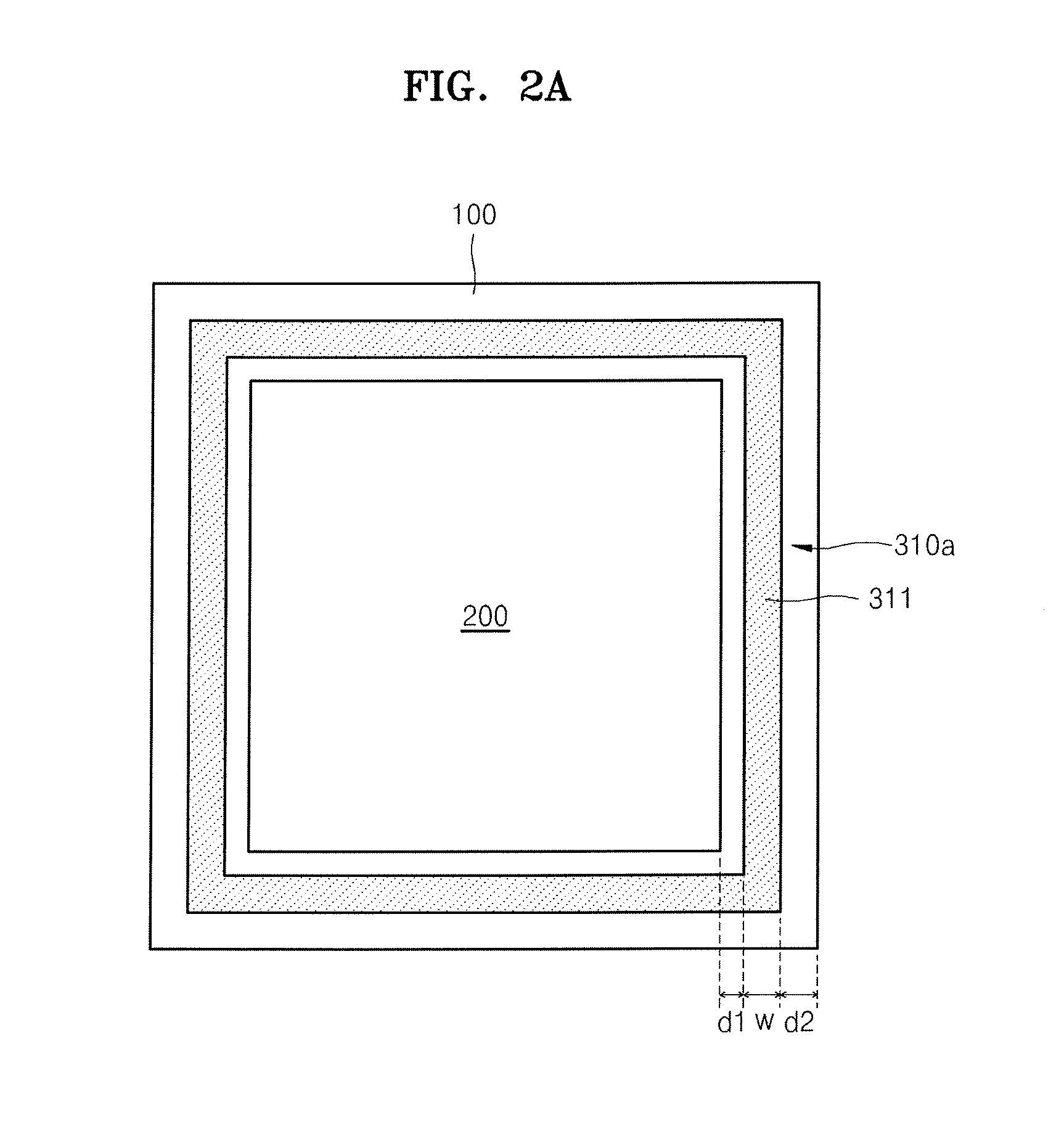

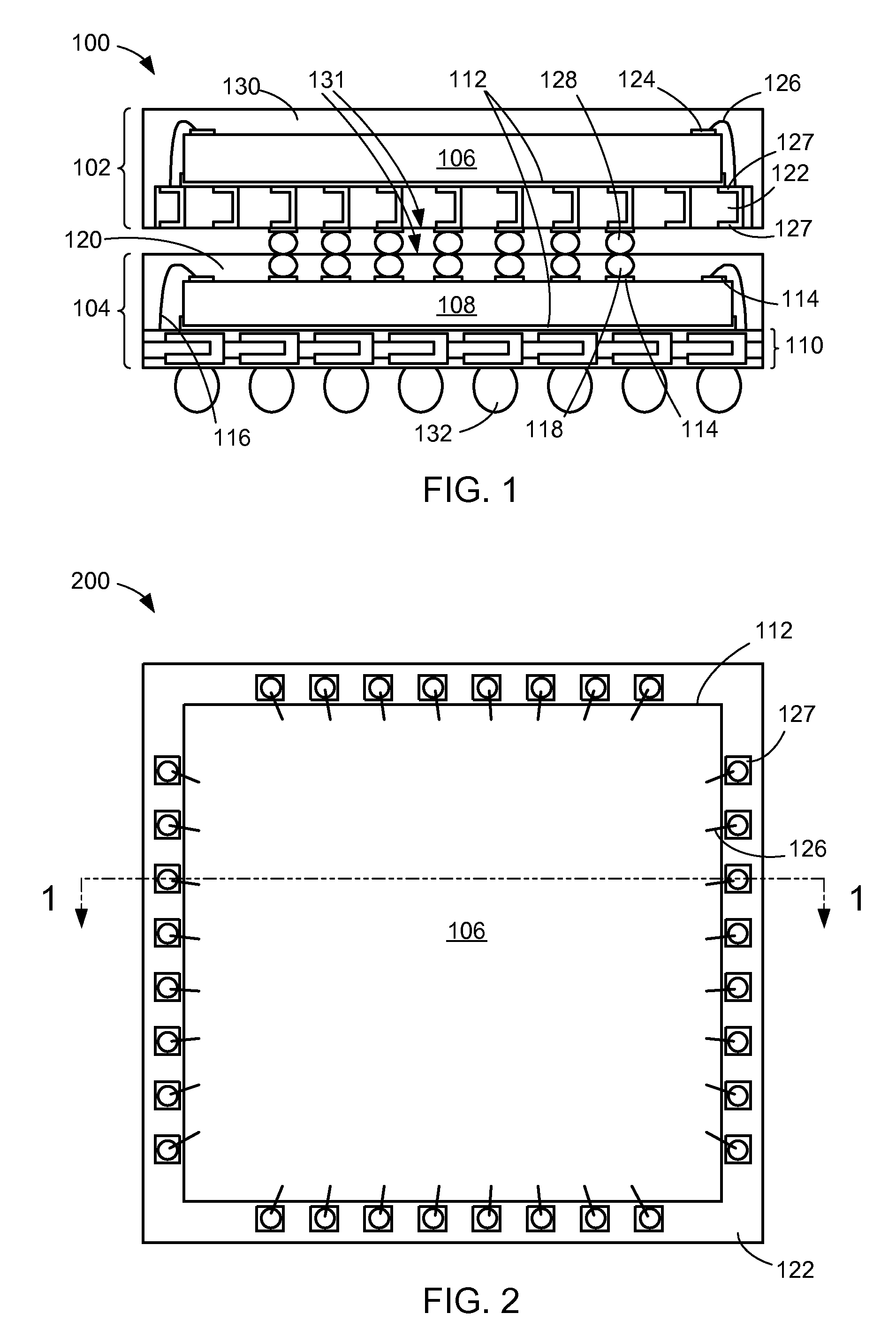

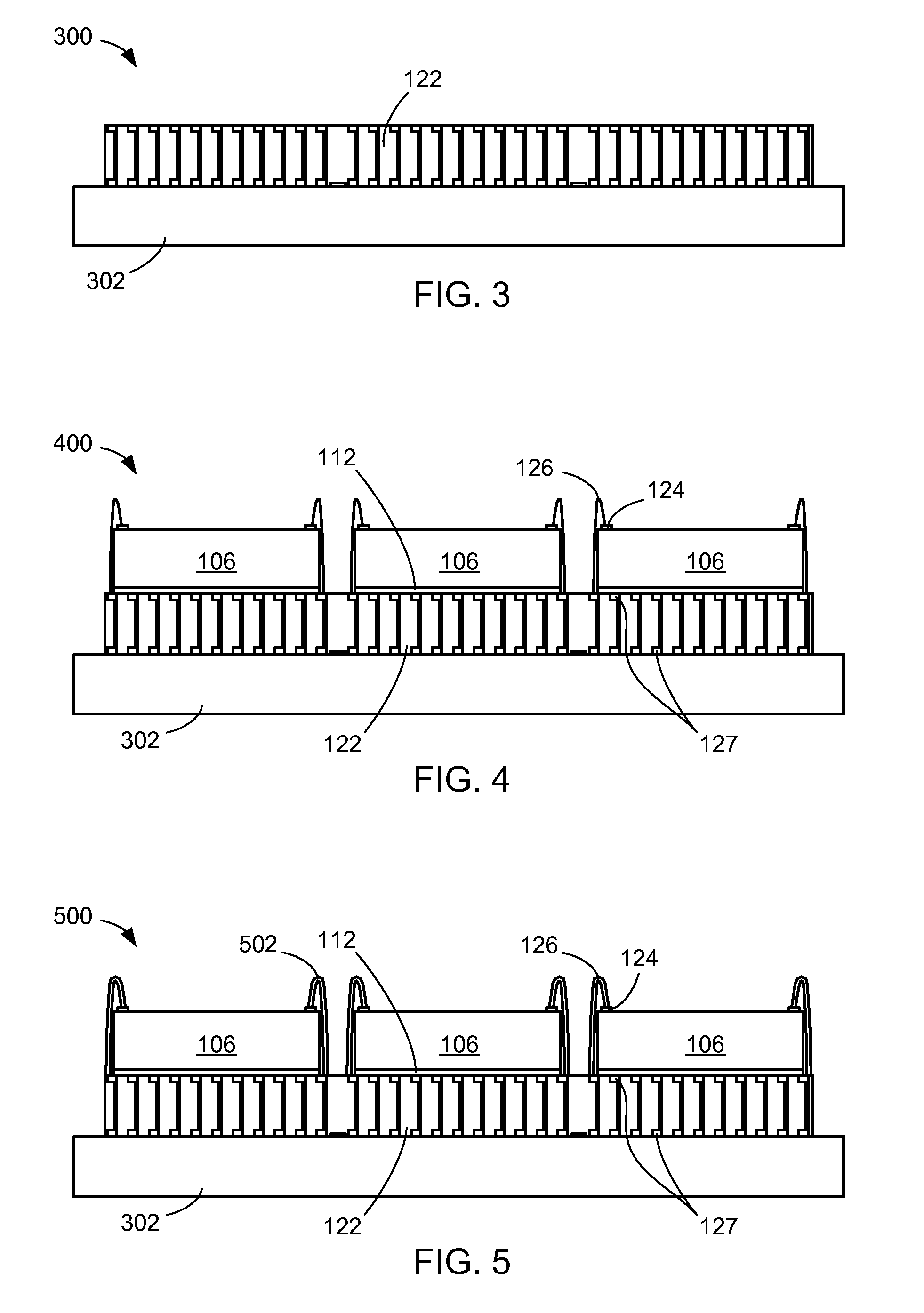

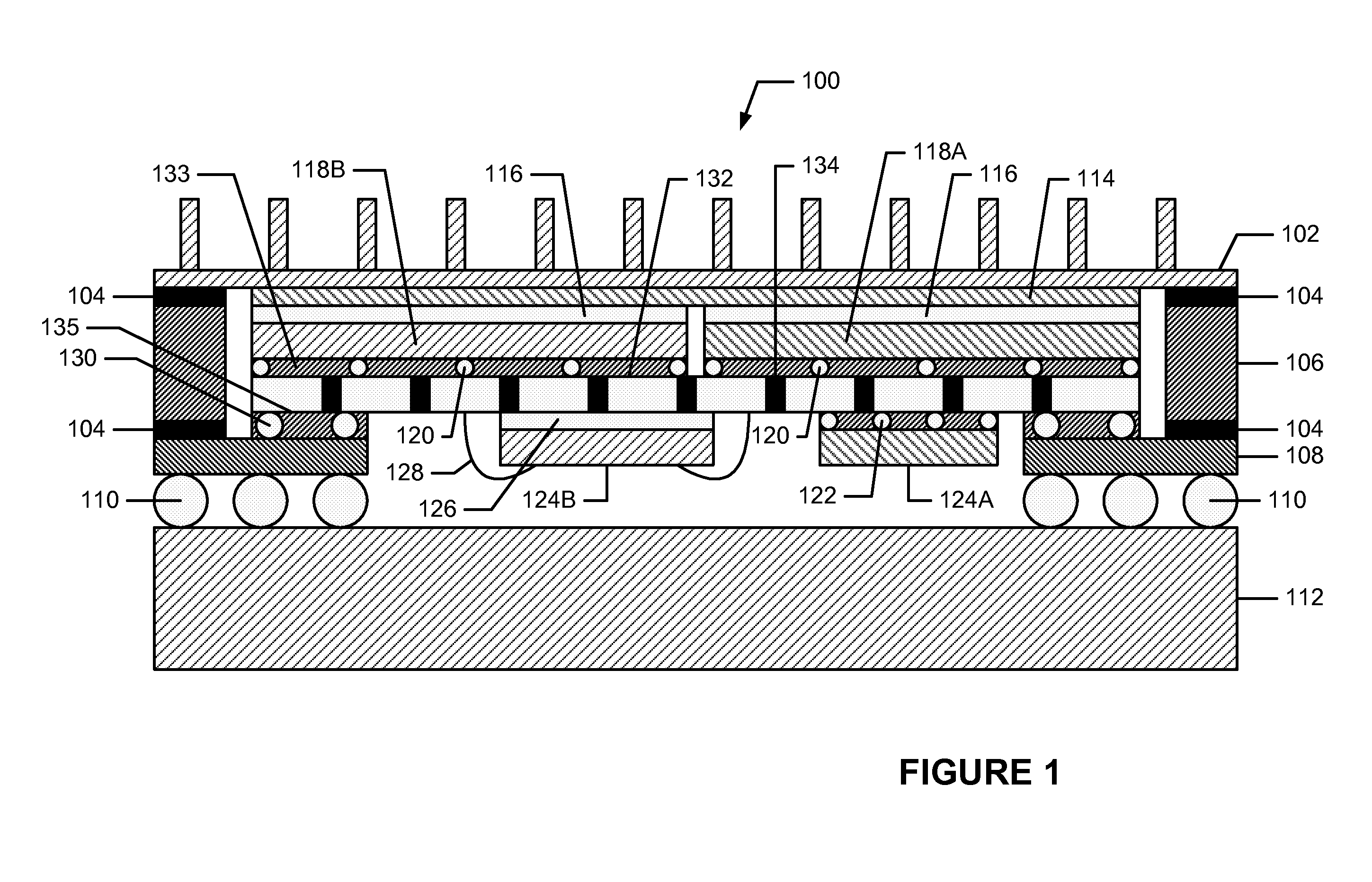

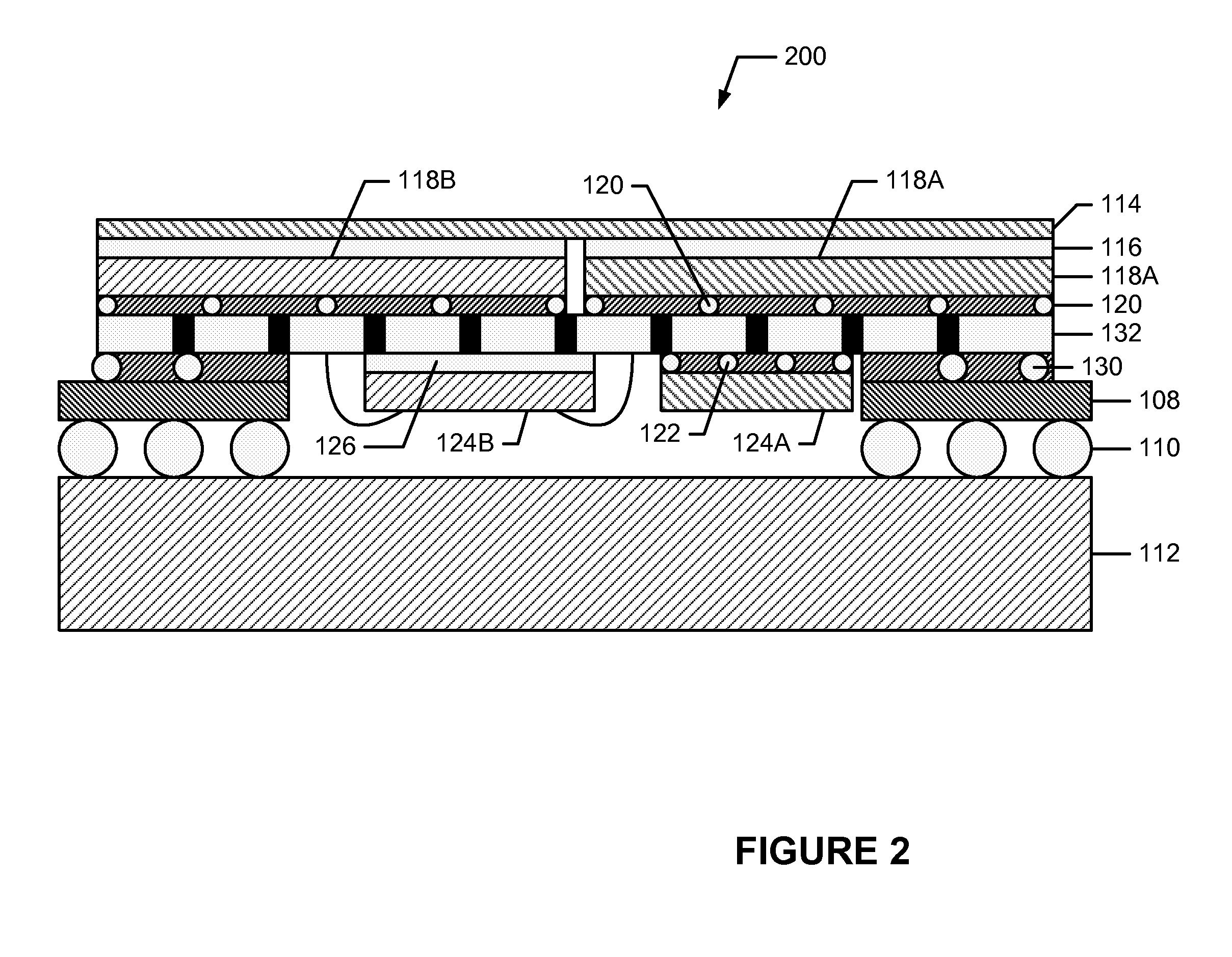

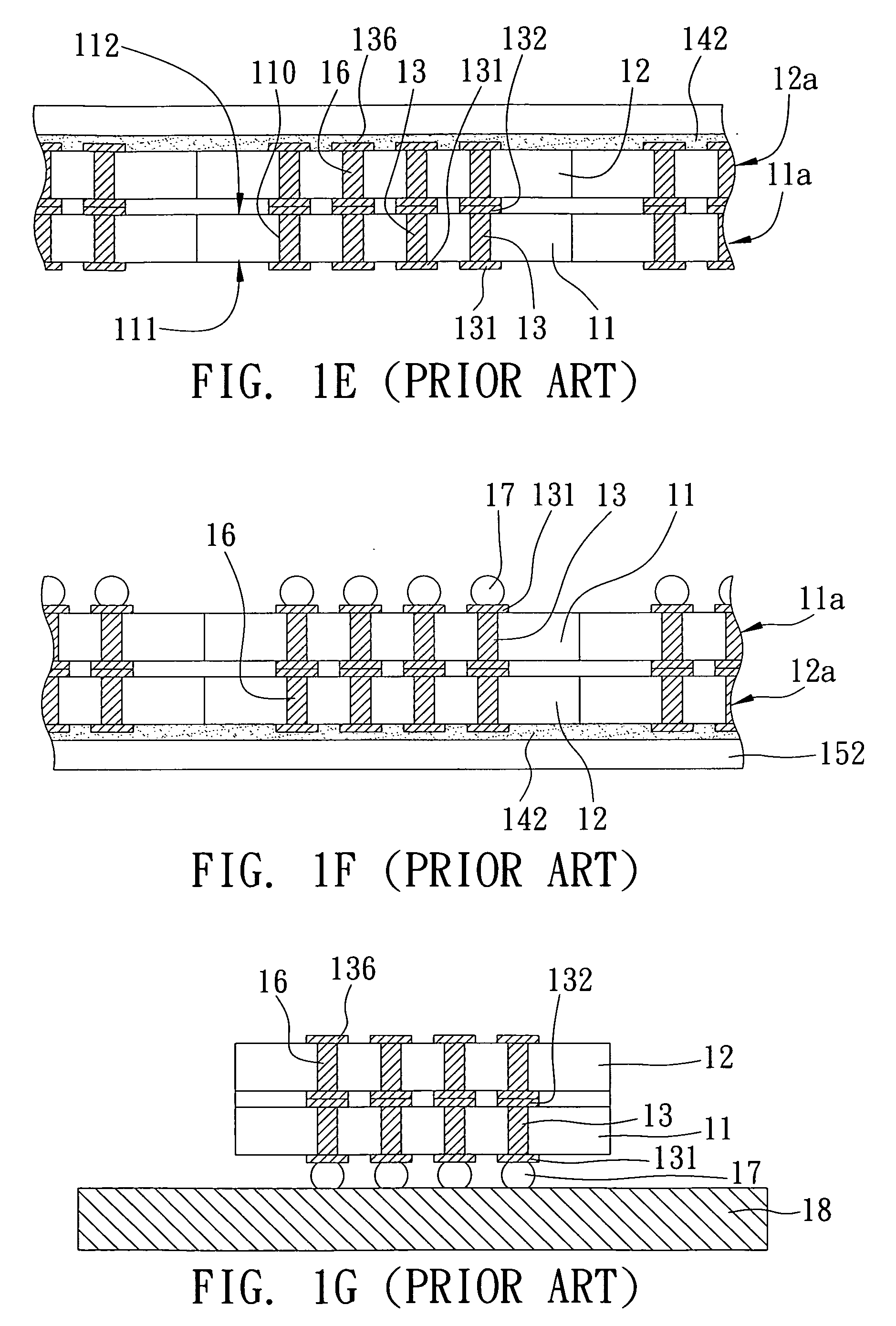

Package systems having interposers

A package system includes an integrated circuit disposed over an interposer. The interposer includes a first interconnect structure. A first substrate is disposed over the first interconnect structure. The first substrate includes at least one first through silicon via (TSV) structure therein. A molding compound material is disposed over the first interconnect structure and around the first substrate. The integrated circuit is electrically coupled with the at least one first TSV structure.

Owner:TAIWAN SEMICON MFG CO LTD

Package systems having interposers

ActiveUS20110291288A1Semiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A package system includes an integrated circuit disposed over an interposer. The interposer includes a first interconnect structure. A first substrate is disposed over the first interconnect structure. The first substrate includes at least one first through silicon via (TSV) structure therein. A molding compound material is disposed over the first interconnect structure and around the first substrate. The integrated circuit is electrically coupled with the at least one first TSV structure.

Owner:TAIWAN SEMICON MFG CO LTD

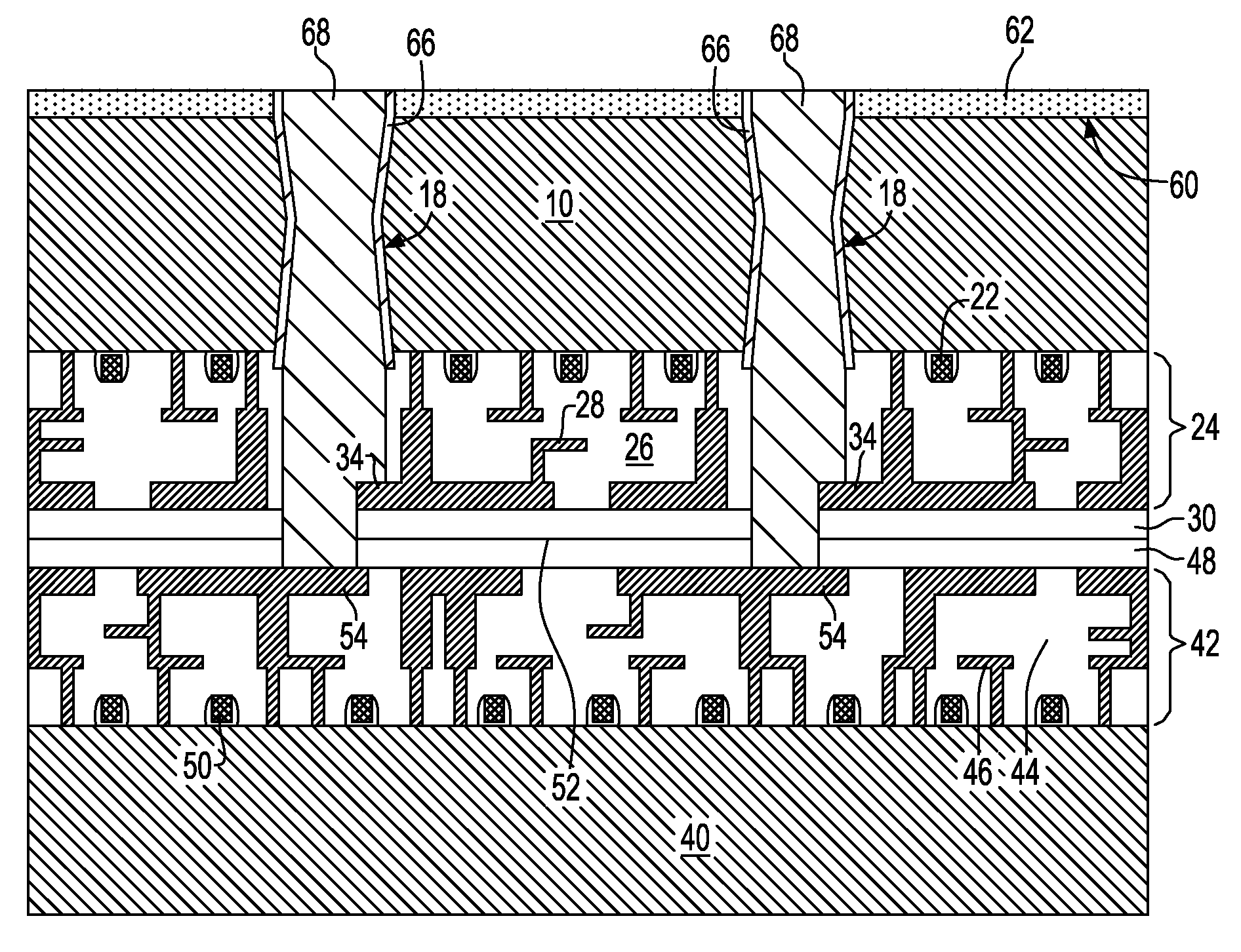

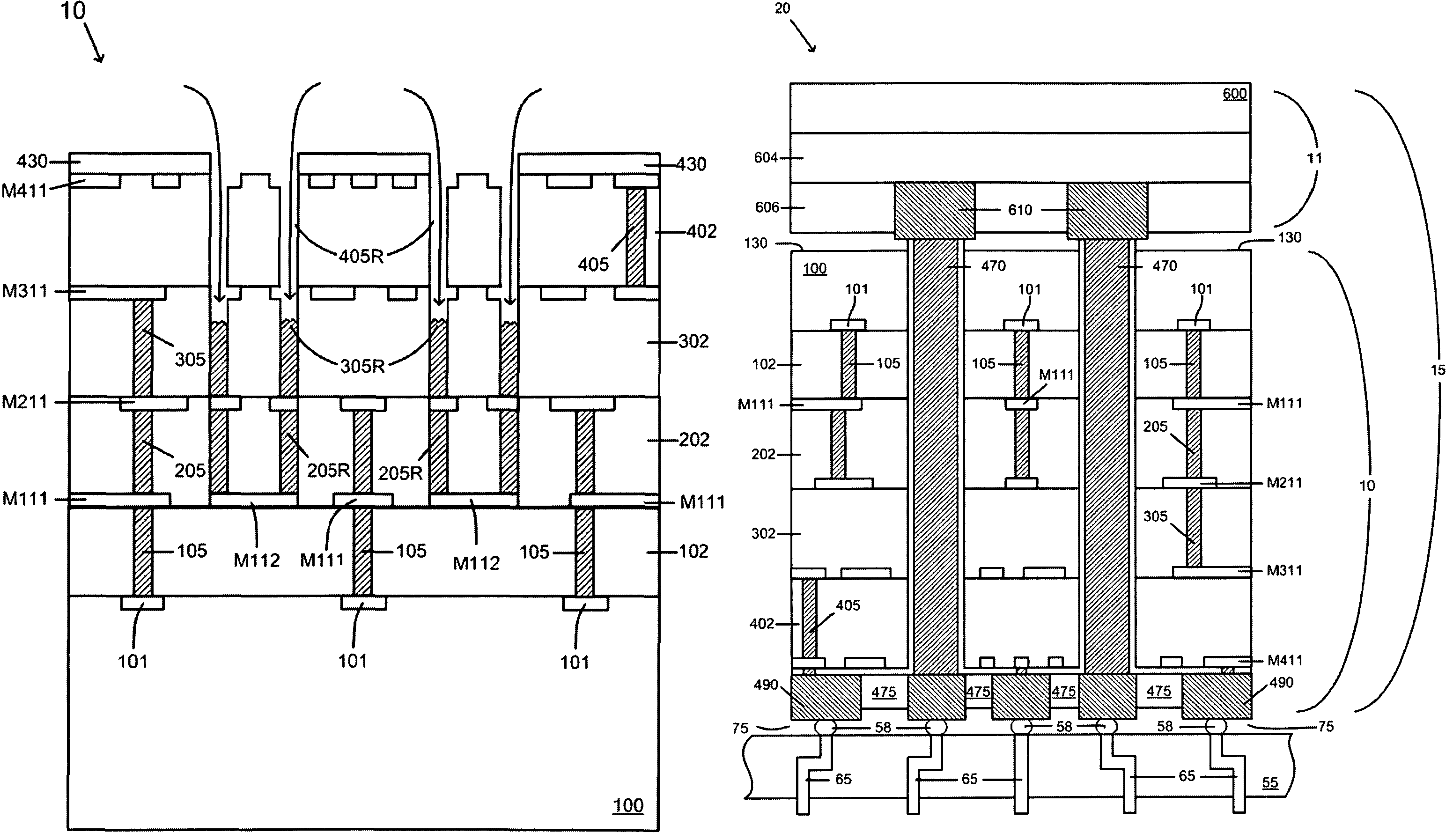

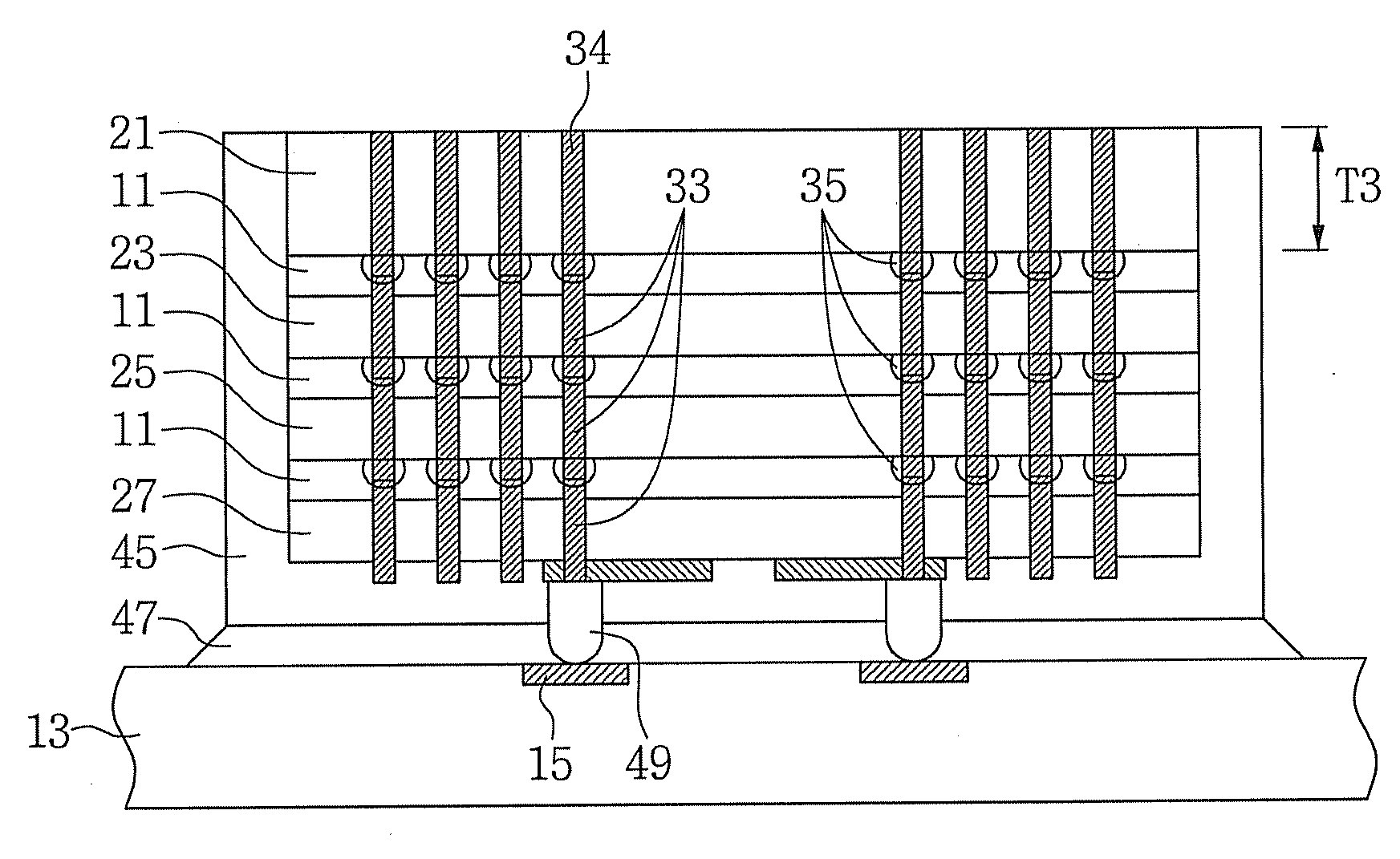

Method of making 3D integrated circuits and structures formed thereby

ActiveUS20100193964A1Semiconductor/solid-state device detailsSolid-state devices3d integrated circuitEngineering

A method and structure of connecting at least two integrated circuits in a 3D arrangement by a through silicon via which simultaneously connects a connection pad in a first integrated circuit and a connection pad in a second integrated circuit.

Owner:GLOBALFOUNDRIES US INC

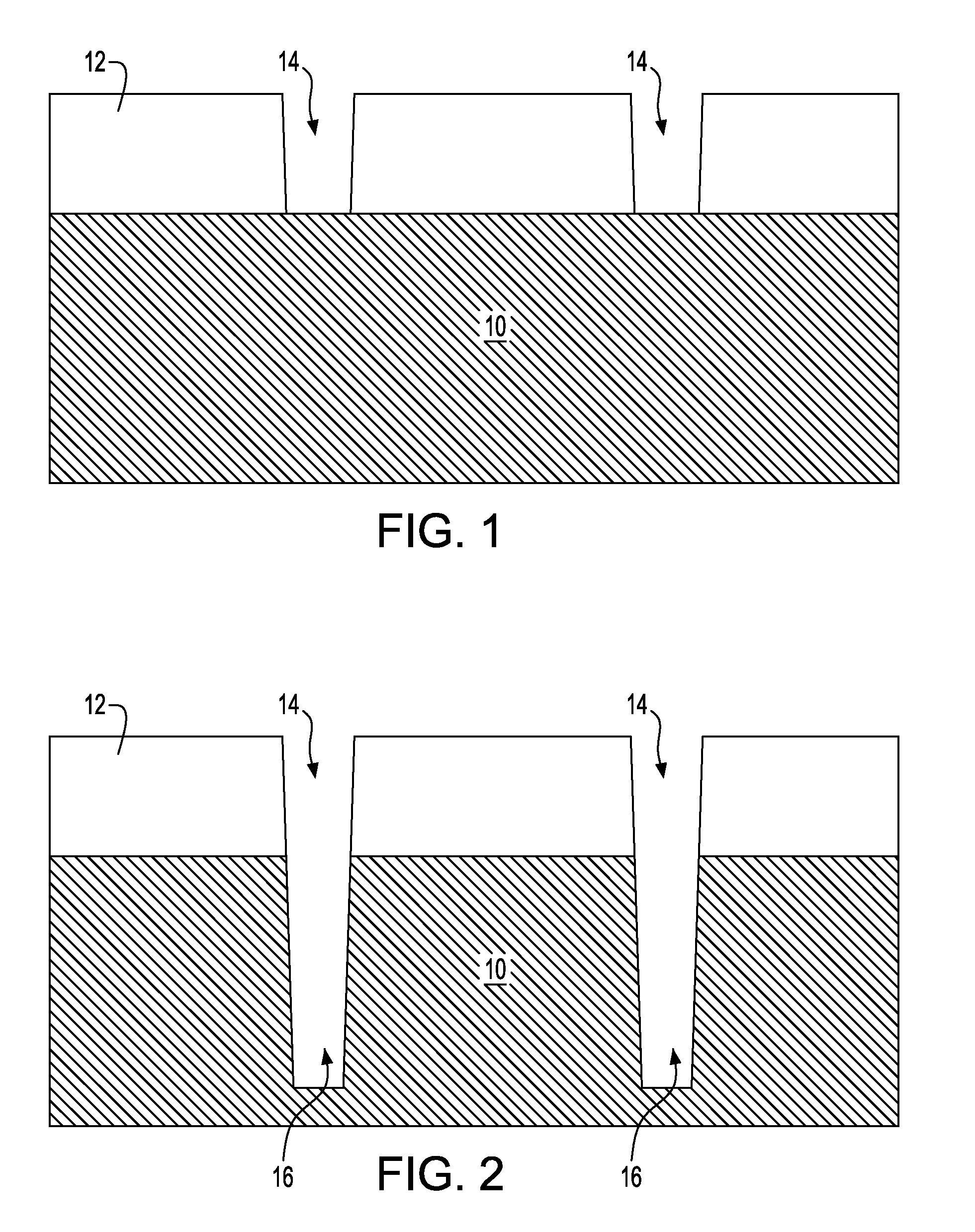

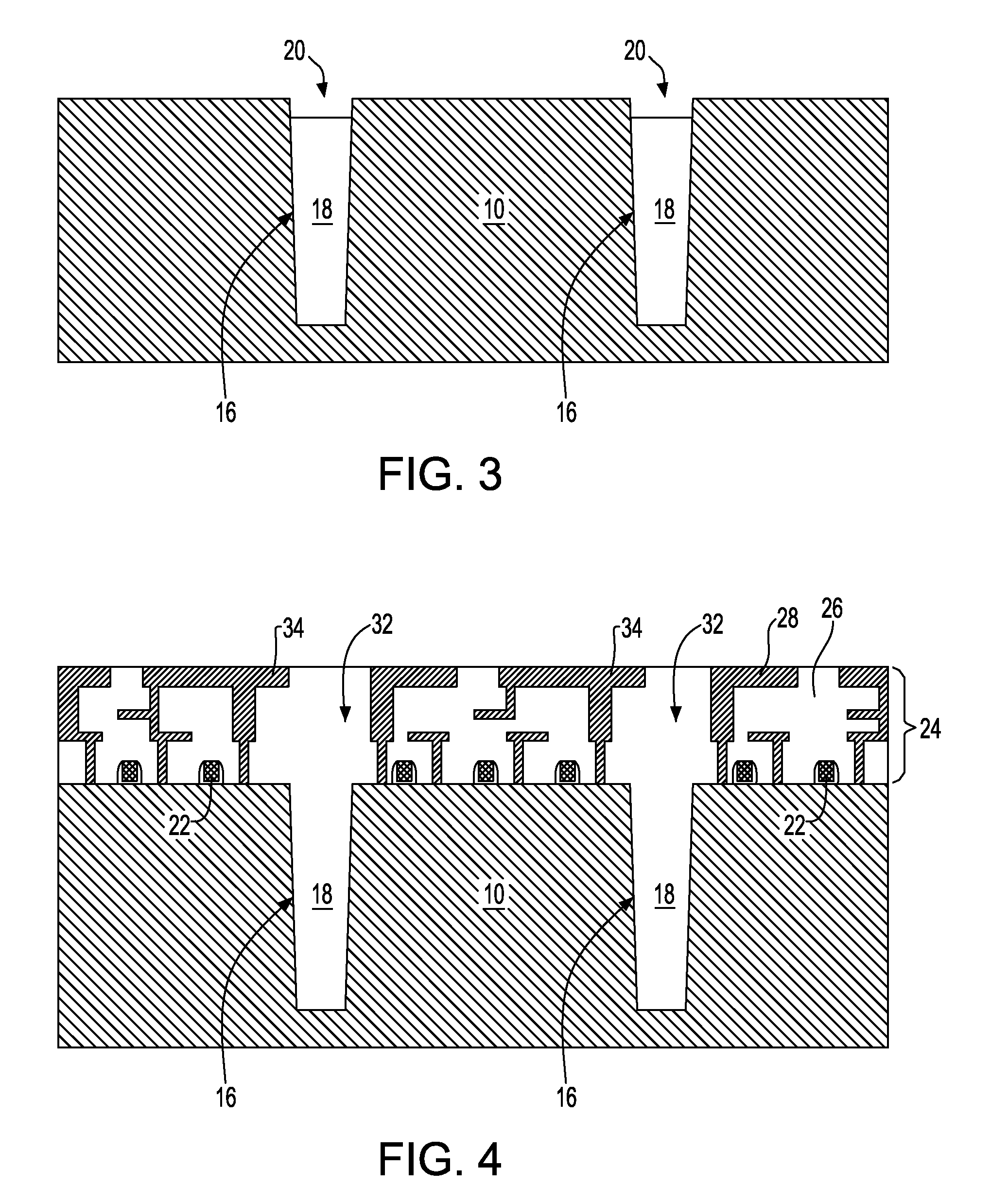

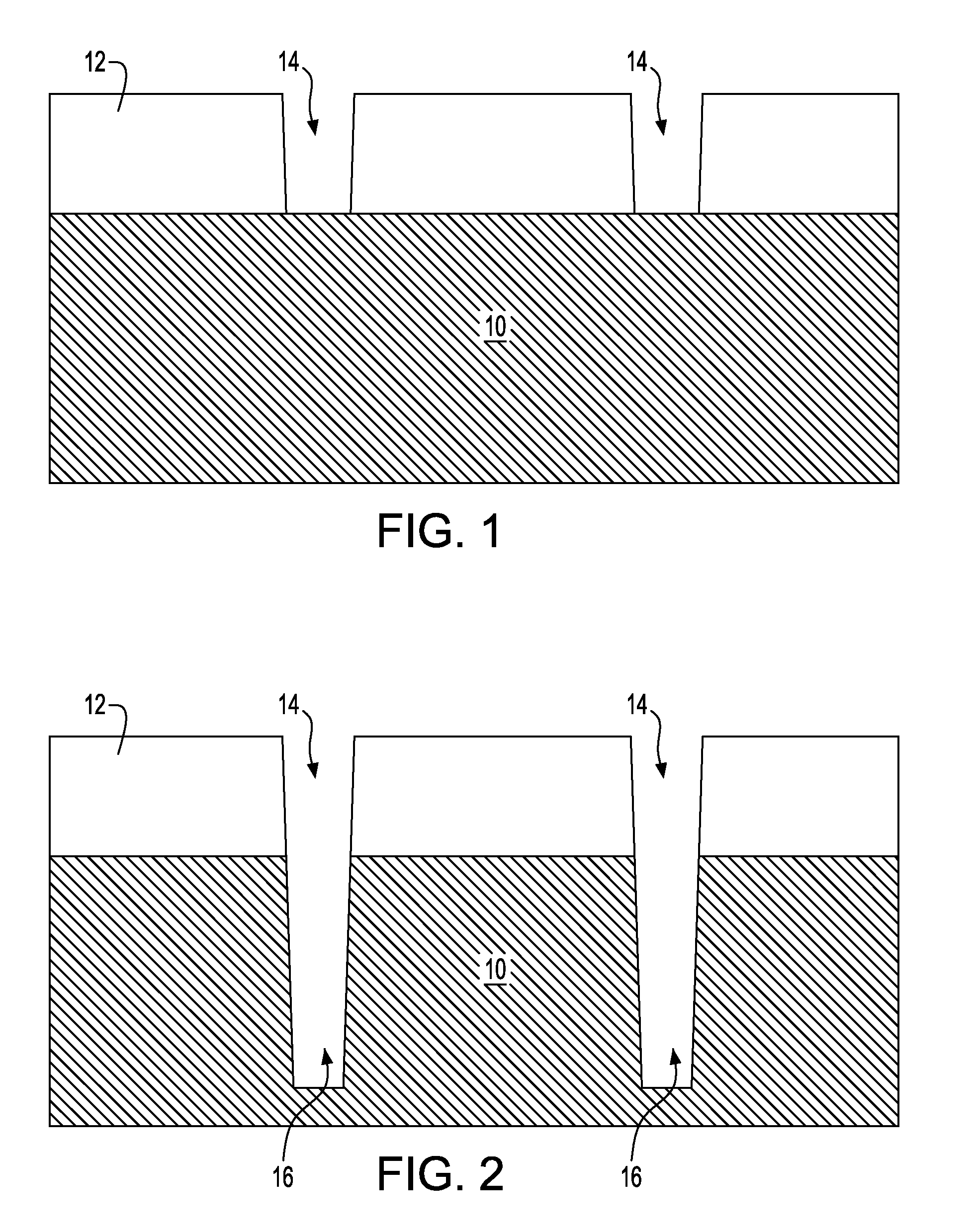

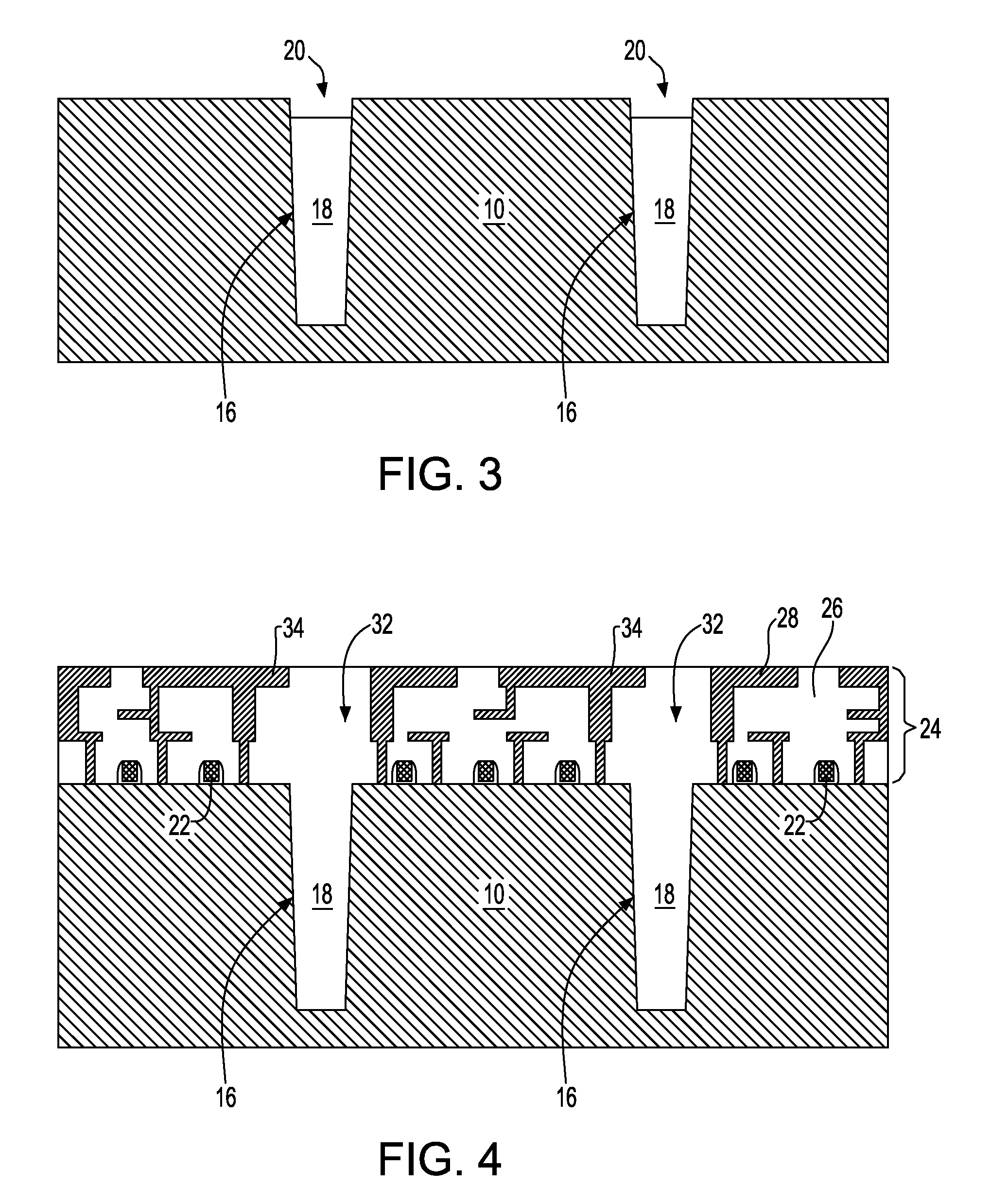

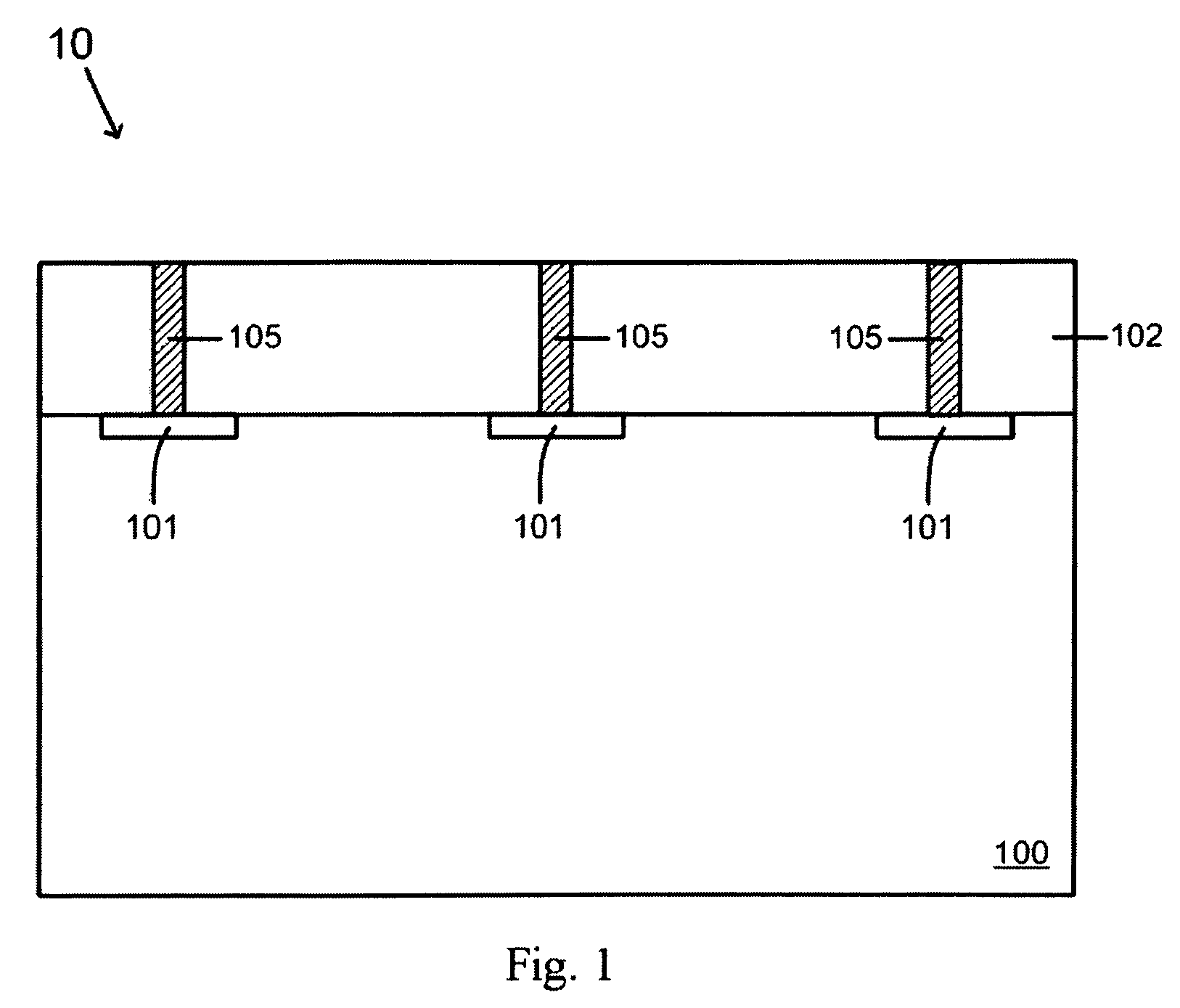

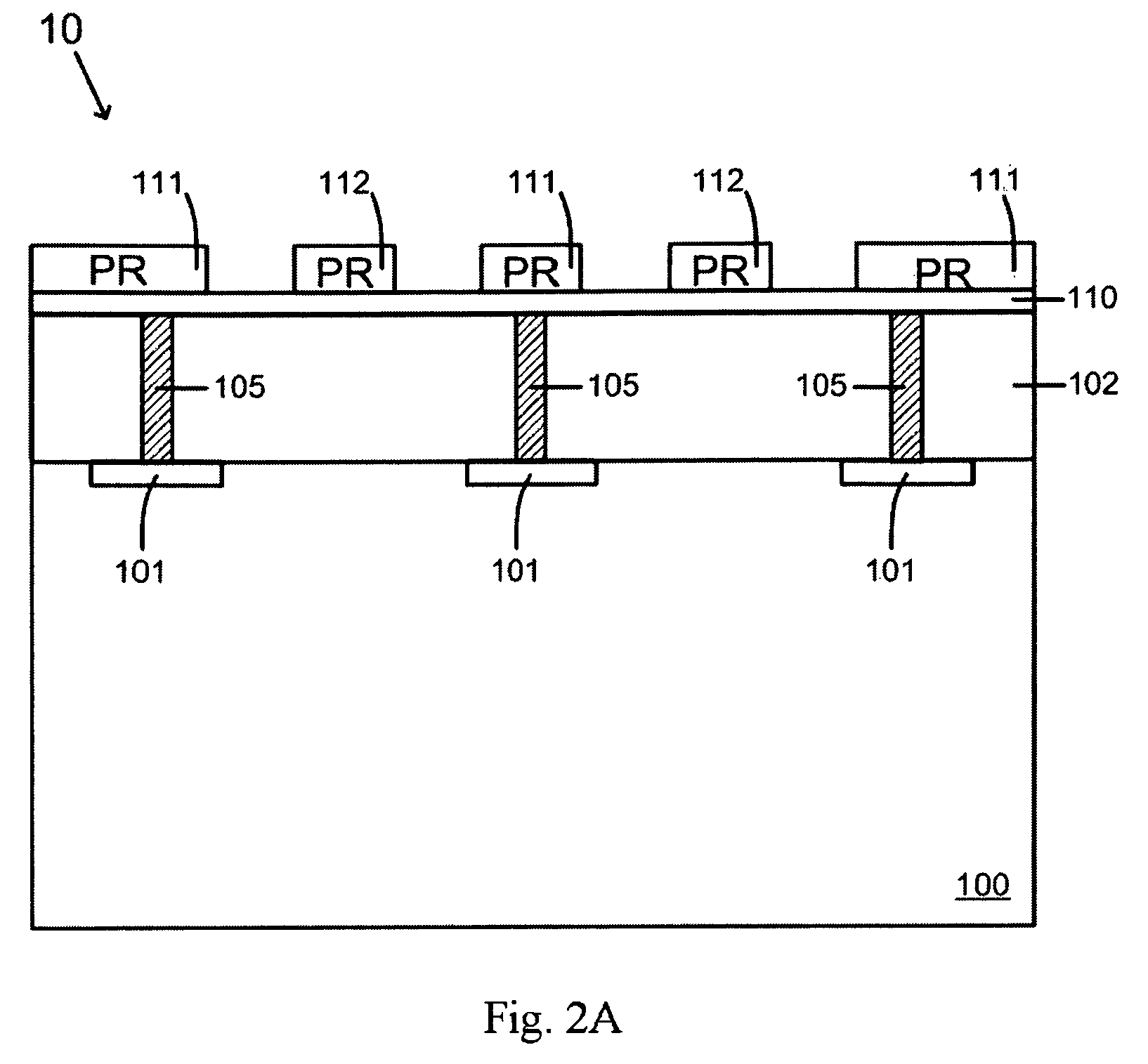

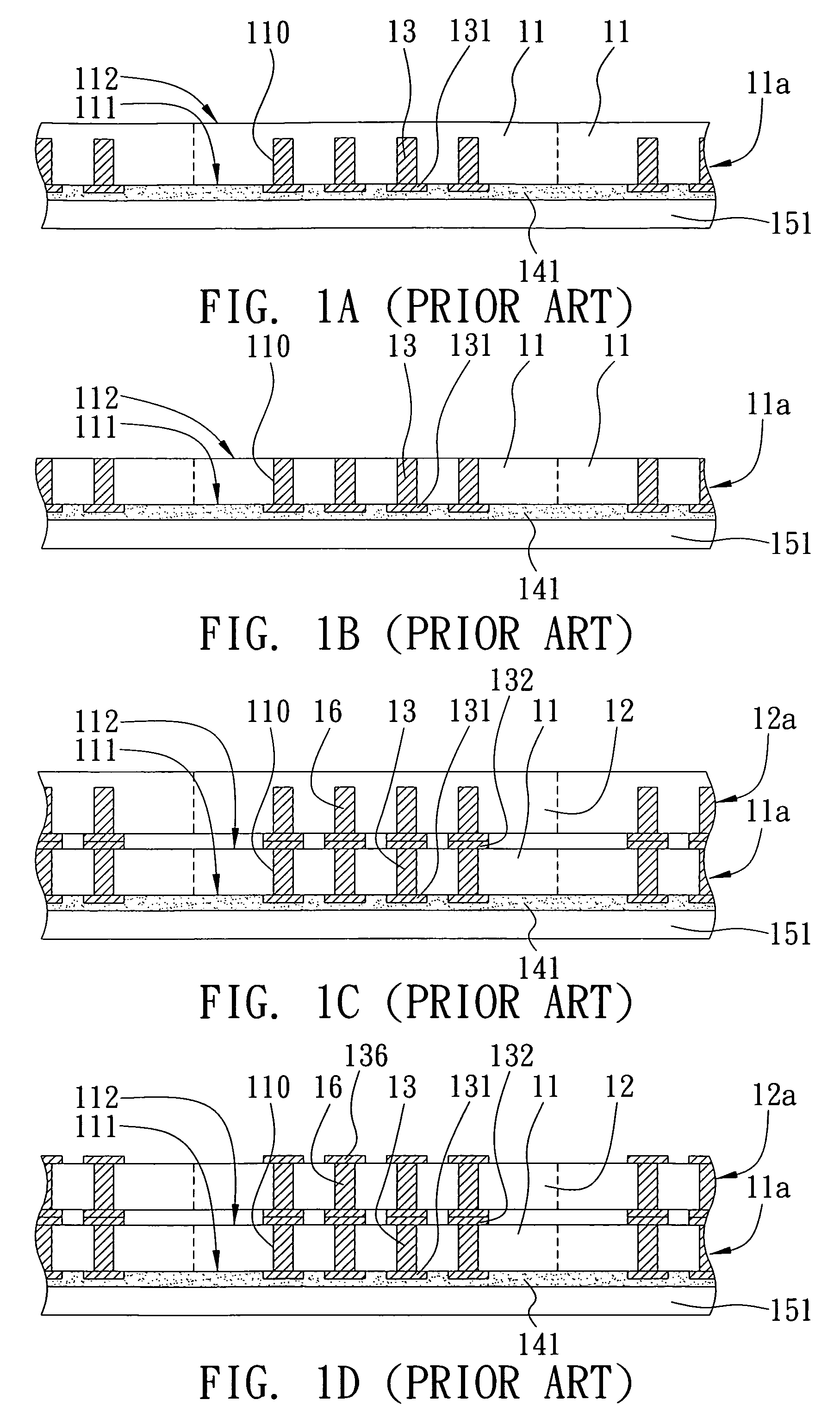

Small Area, Robust Silicon Via Structure and Process

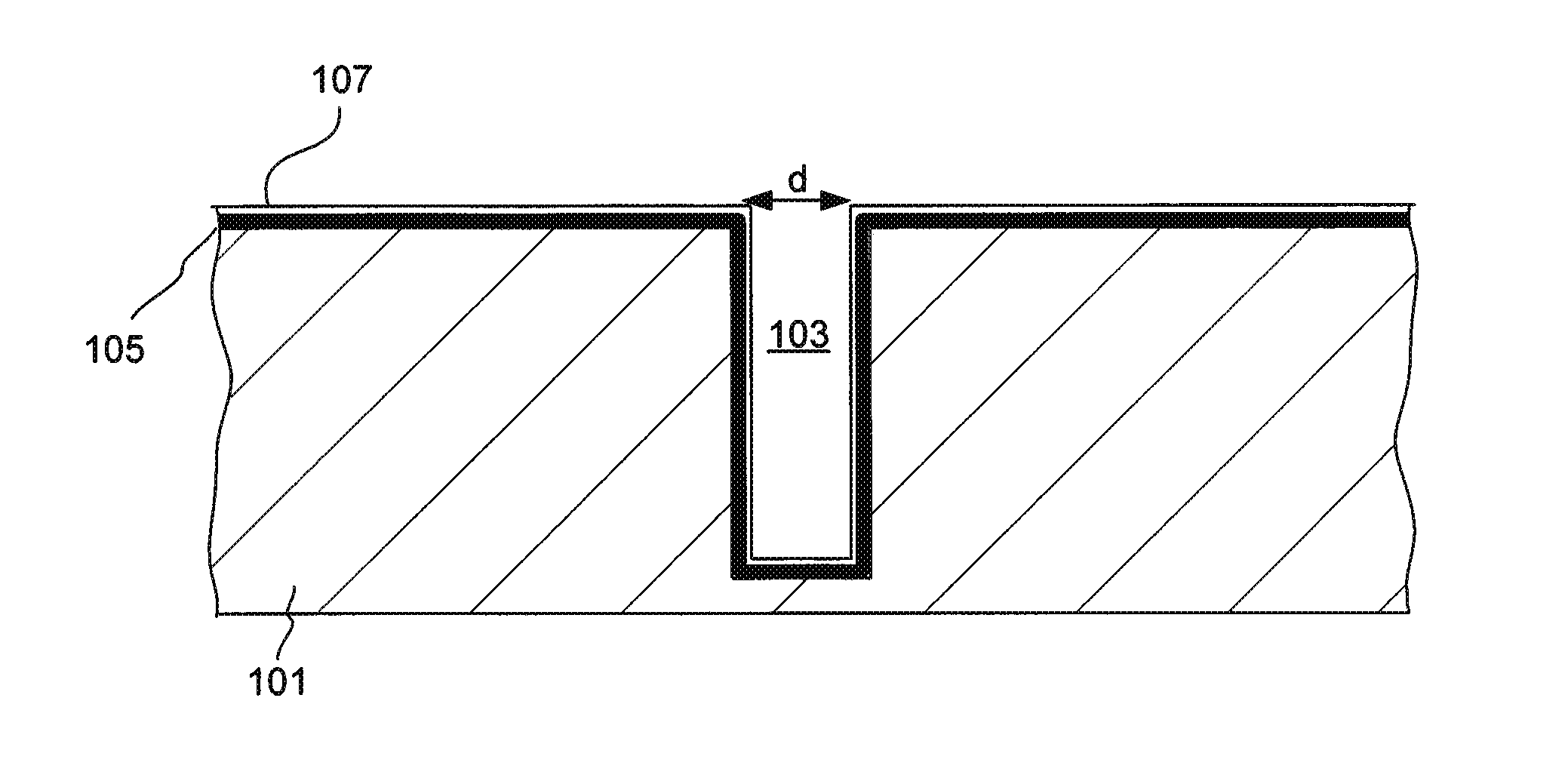

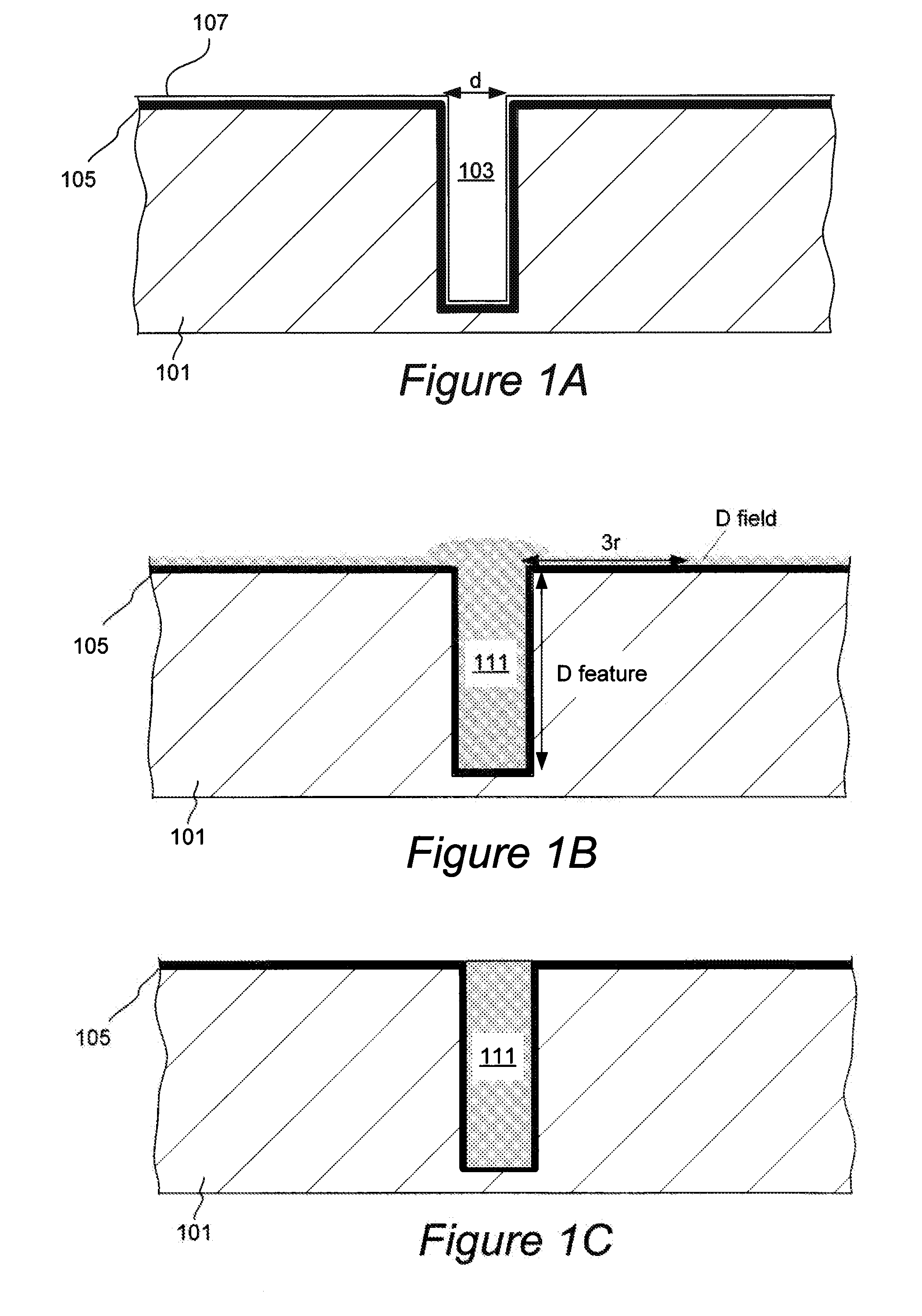

ActiveUS20090032951A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor structureMaterials science

A semiconductor structure includes: at least one silicon surface wherein the surface can be a substrate, wafer or other device. The structure further includes at least one electronic circuit formed on each side of the at least one surface; and at least one conductive high aspect ratio through silicon via running through the at least one surface. Each through silicon via is fabricated from at least one etch step and includes: at least one thermal oxide dielectric for coating at least some of a sidewall of the through silicon via for a later etch stop in fabrication of the through silicon via.

Owner:GLOBALFOUNDRIES US INC

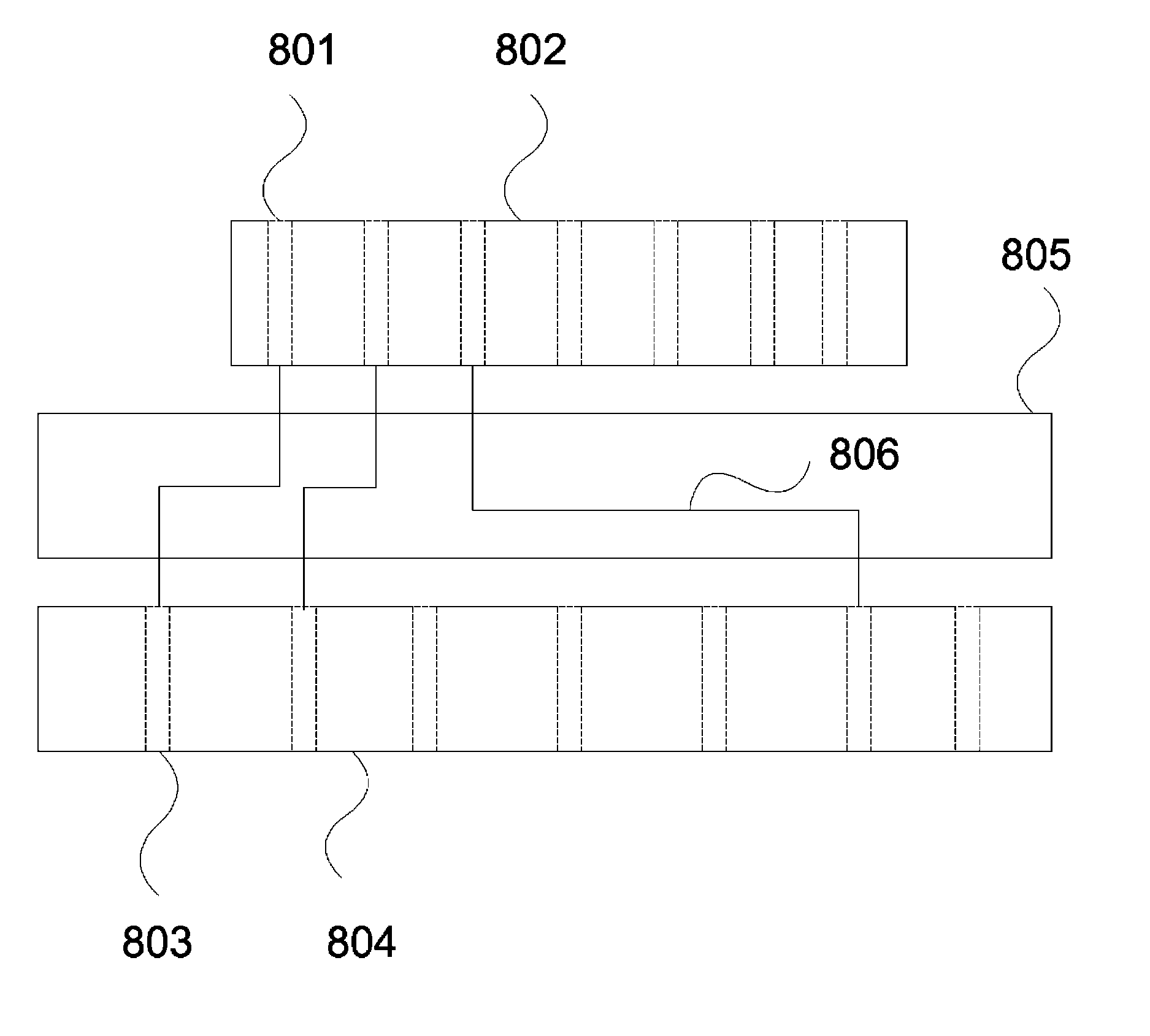

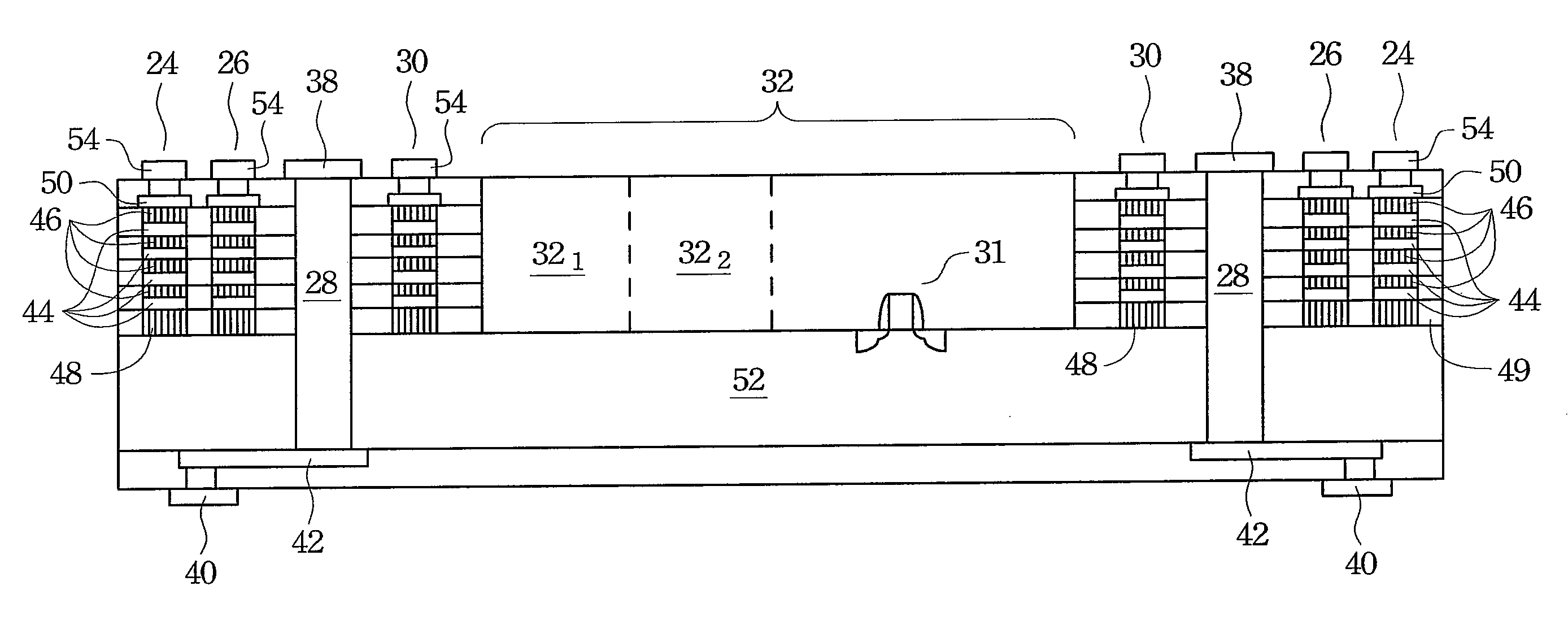

Stacking Integrated Circuits containing Serializer and Deserializer Blocks using Through Silicon Via

ActiveUS20100058580A1Reduce and eliminate inductanceReduce and eliminate and capacitancePrinted circuit assemblingSemiconductor/solid-state device detailsThrough-silicon viaIntegrated circuit

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

Method of making 3D integrated circuits

ActiveUS8158515B2Semiconductor/solid-state device detailsSolid-state devices3d integrated circuitEngineering

A method and structure of connecting at least two integrated circuits in a 3D arrangement by a through silicon via which simultaneously connects a connection pad in a first integrated circuit and a connection pad in a second integrated circuit.

Owner:GLOBALFOUNDRIES US INC

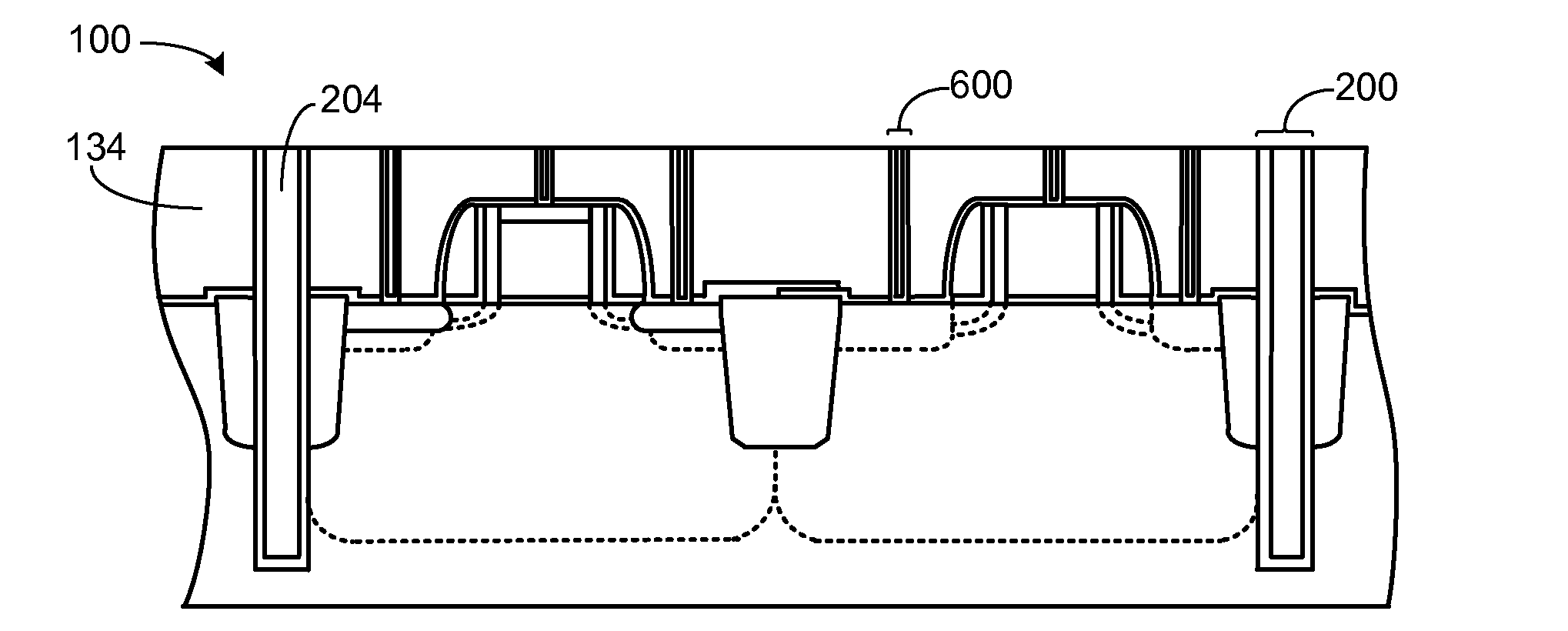

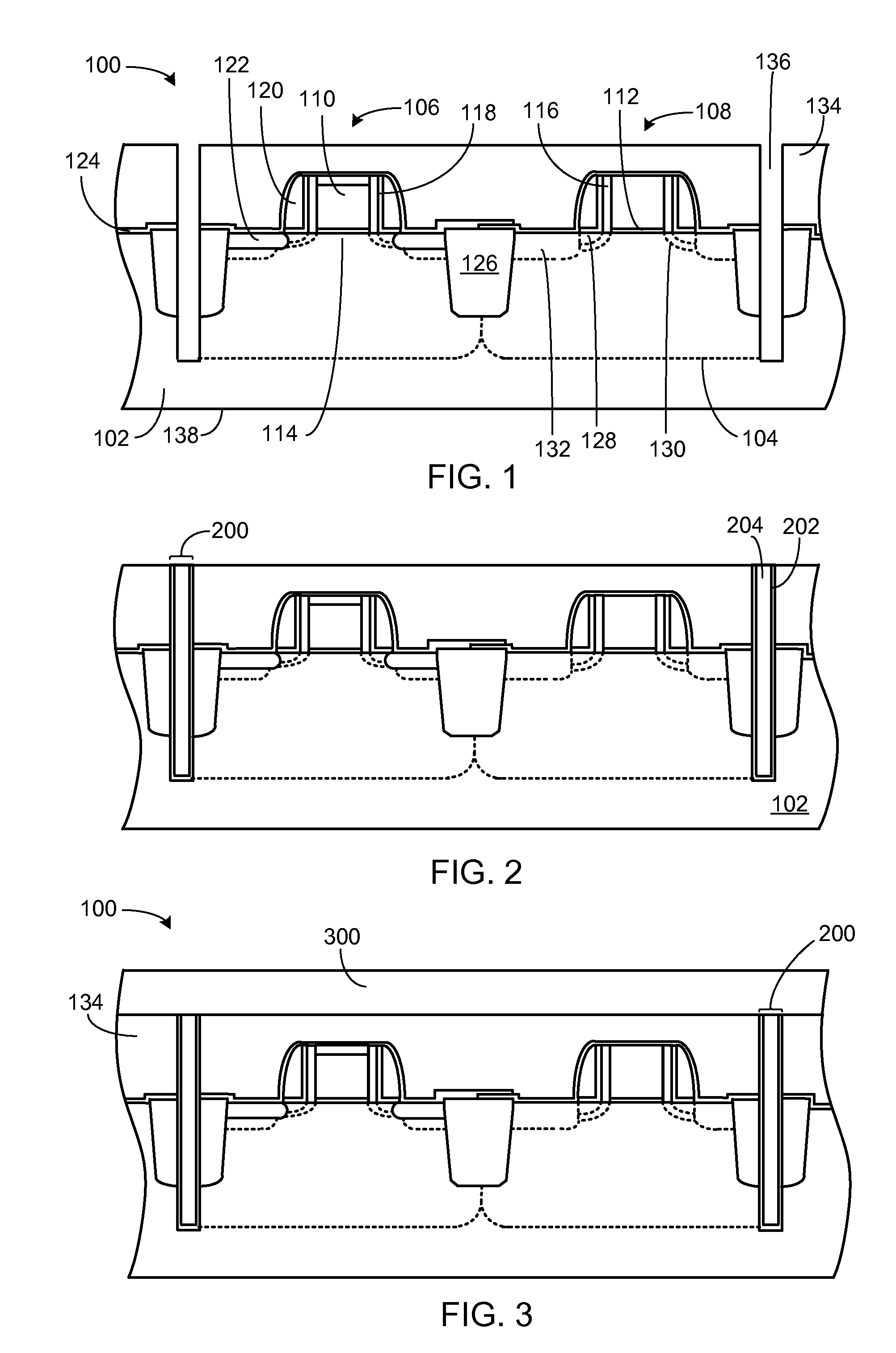

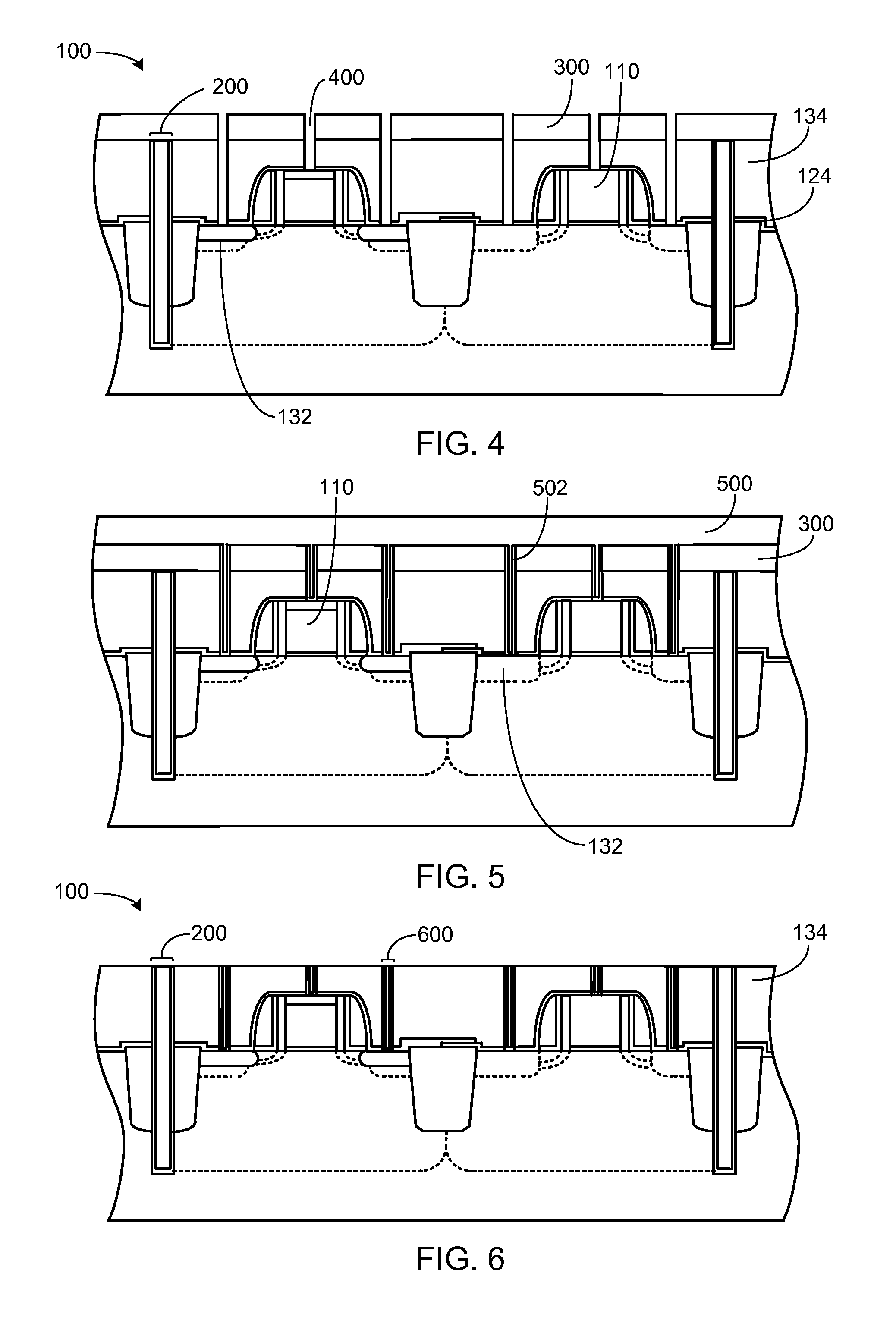

Through-Silicon Via Sidewall Isolation Structure

InactiveUS20100187694A1Semiconductor/solid-state device detailsSolid-state devicesConductive materialsDielectric layer

A system and method for an improved through-silicon via isolation structure is provided. An embodiment comprises a semiconductor device having a substrate with electrical circuitry formed thereon. One or more dielectric layers are formed over the substrate, and an opening is etched into the structure extending from a surface of the one or more dielectric layers through the one or more dielectric layers into the substrate; the opening having sidewalls. A low-K dielectric layer is formed over the sidewalls of the opening. The opening is filled with a conductive material and / or a barrier layer creating a through-silicon via that is isolated from the surrounding substrate by the low-K dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor package with through silicon via and related method of fabrication

InactiveUS20080284041A1Improved electrical interconnectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

In a semiconductor package, an electrode has a first part extending through a semiconductor substrate and a second part extending from the first part through a compositional layer to reach a conductive pad.

Owner:SAMSUNG ELECTRONICS CO LTD

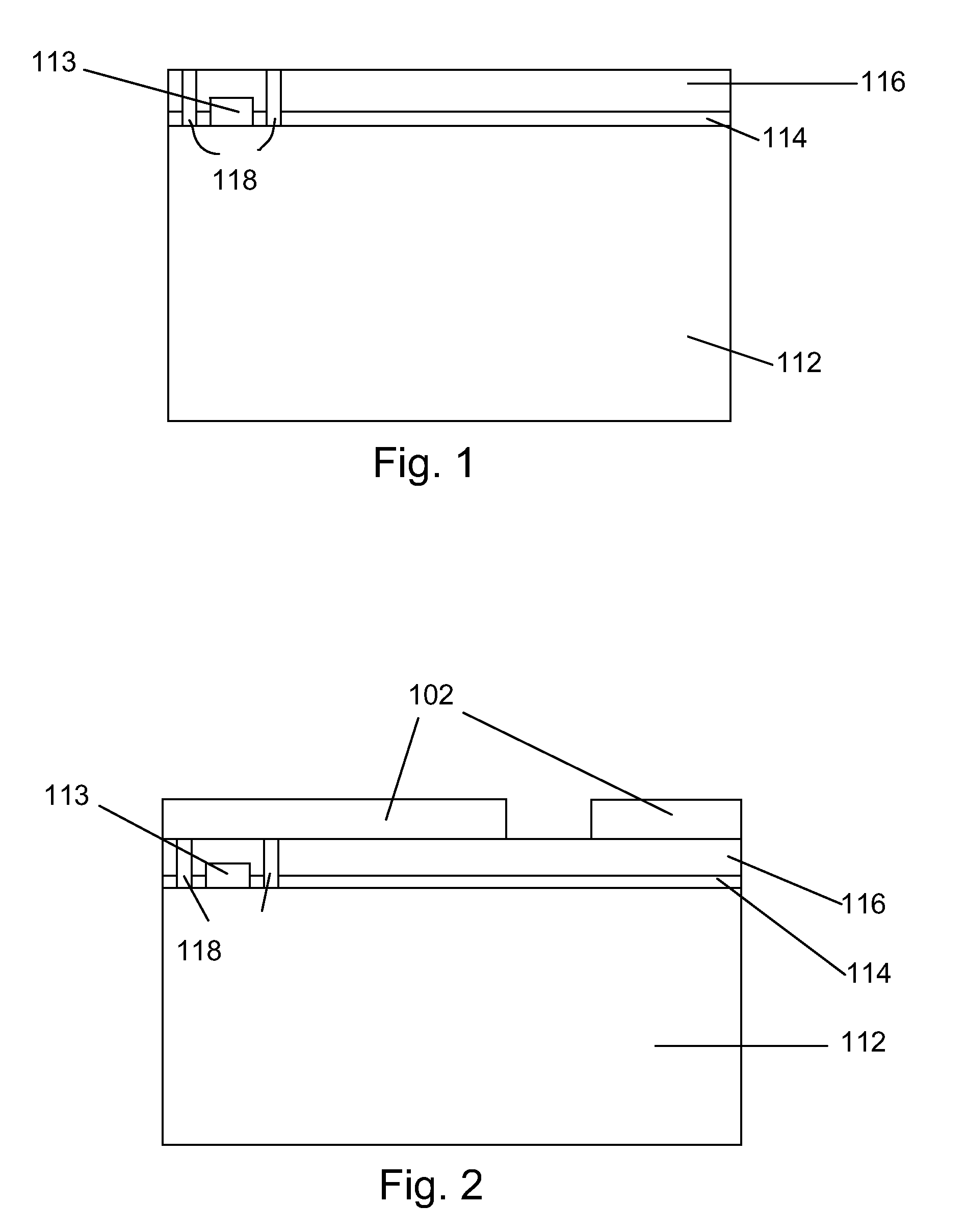

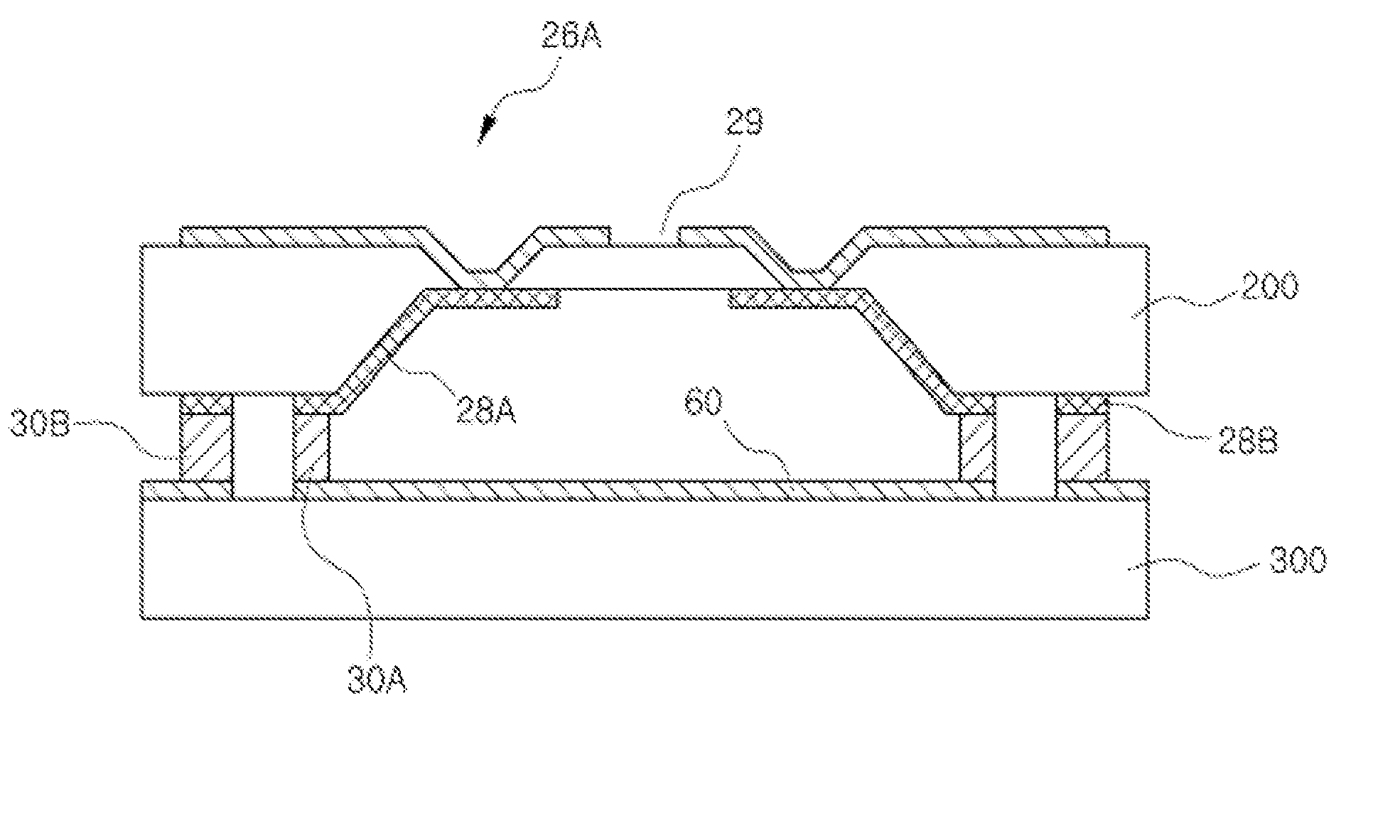

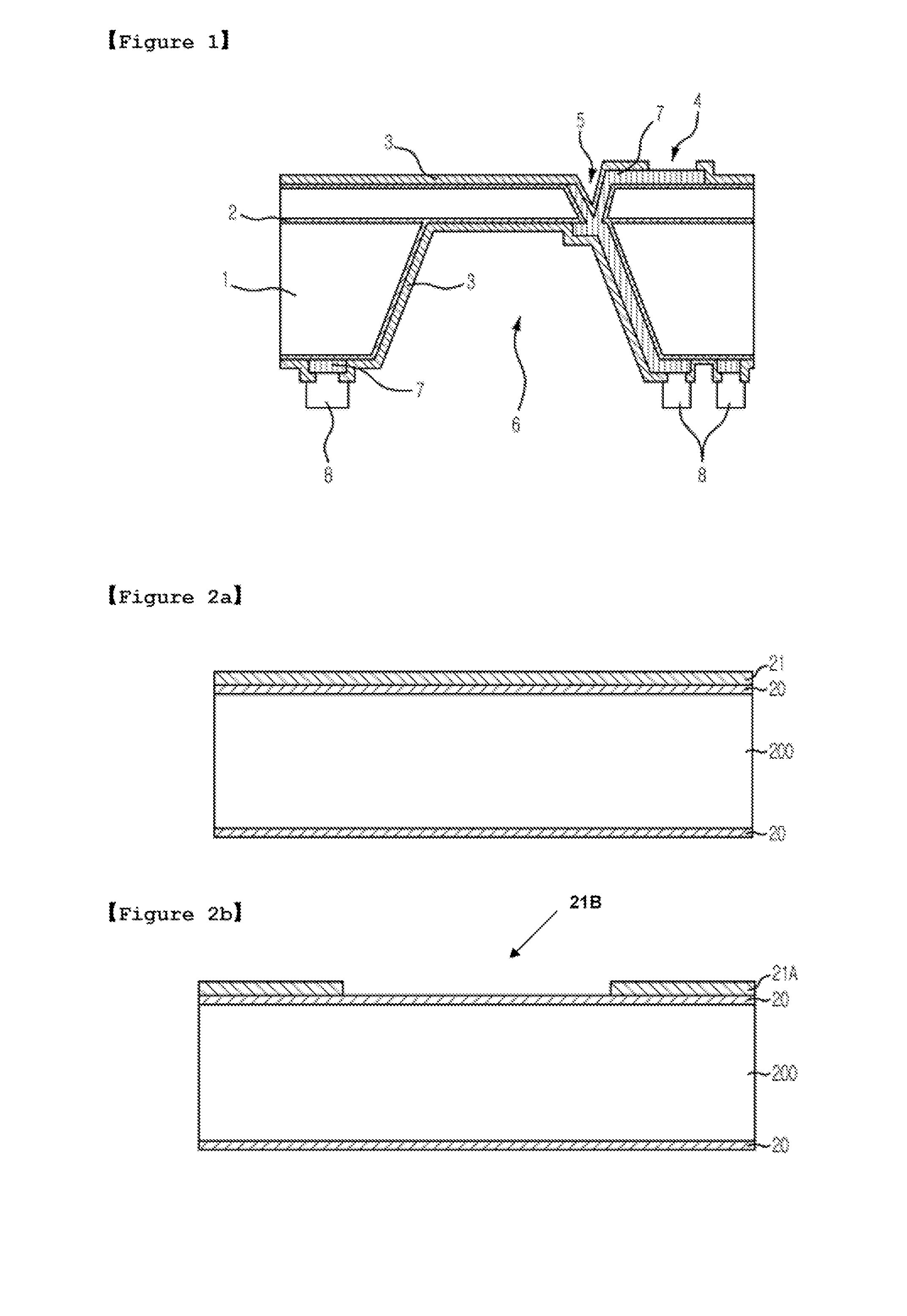

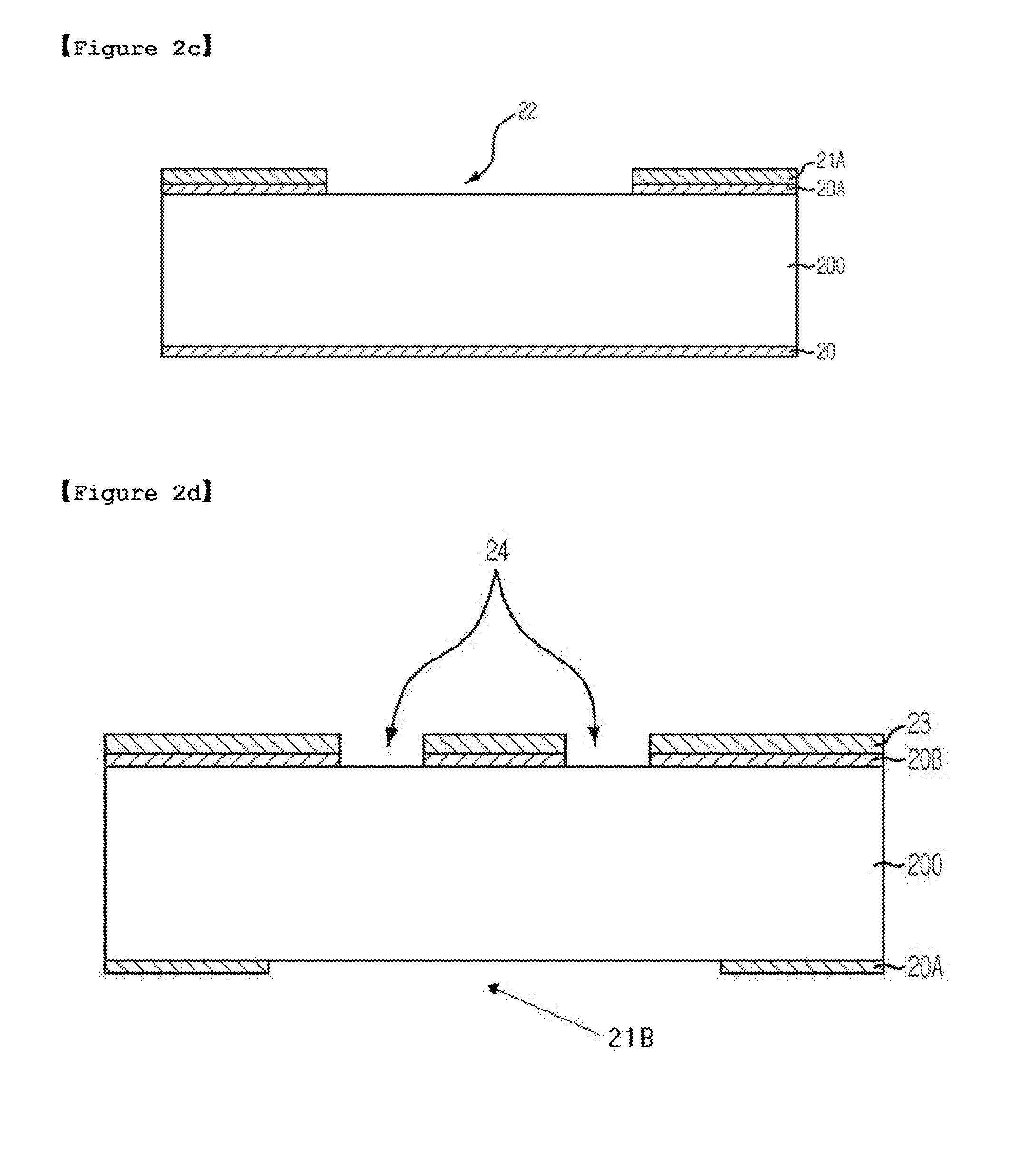

Cap Wafer for Wafer Bonded Packaging and Method for Manufacturing the Same

InactiveUS20080081398A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

The present invention relates to semiconductor device manufacturing techniques, and specifically to a field of device packaging techniques at wafer level. More specifically, it relates to a cap wafer for wafer bonding application that is bonded to top part of a device wafer. The method of the present invention excludes the use of deep reactive ion etching of silicon to form a through silicon via. The present invention provides a method for the preparation of cap wafer for wafer bonding application with a simple process of through silicon via interconnection and a wafer level packaging method using the same.

Owner:PHOCO

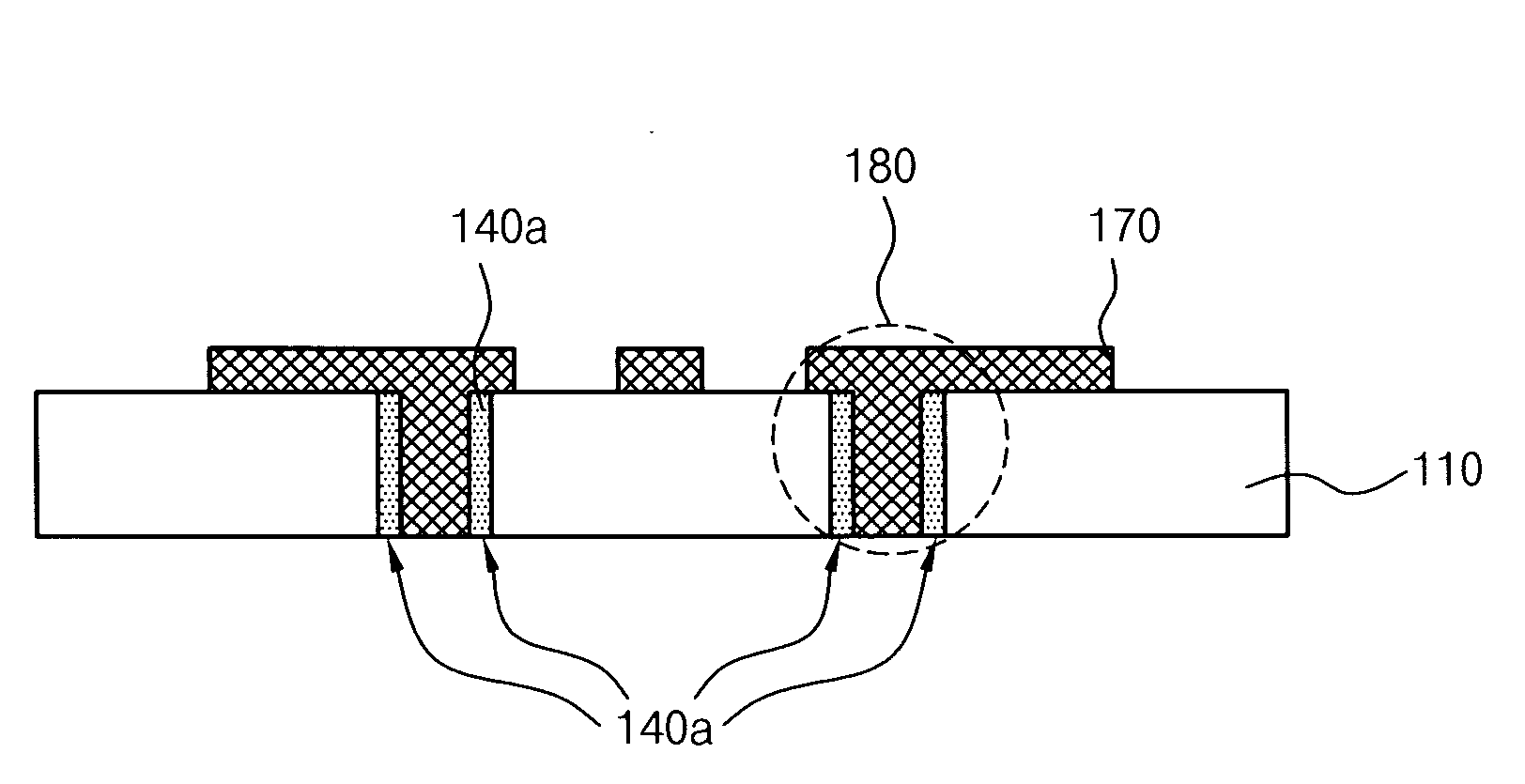

Stack package and semiconductor package including the same

ActiveUS20120018871A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A stack package usable in a three-dimensional (3D) system-in-package (SIP) includes a first semiconductor chip, a second semiconductor chip, and a supporter. The first semiconductor chip includes a through silicon via (TSV), and the second semiconductor chip is stacked on the first semiconductor chip and is electrically connected to the first semiconductor chip through the TSV of the first semiconductor chip. The supporter is attached onto the first semiconductor chip so as to be spaced apart from an edge of the second semiconductor chip.

Owner:SAMSUNG ELECTRONICS CO LTD

Stacking integrated circuits containing serializer and deserializer blocks using through silicon via

ActiveUS8014166B2Efficiently routedReduce and eliminate and capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

Method of forming through-silicon vias

ActiveUS7825024B2Semiconductor/solid-state device detailsSolid-state devicesConductive materialsDielectric layer

A method of forming a semiconductor device having a through-silicon via (TSV) is provided. A semiconductor device is provided having a first dielectric layer formed thereon. One or more dielectric layers are formed over the first dielectric layer, such that each of the dielectric layers have a stacking structure, wherein the stacking structures in the one or more dielectric layers are vertically aligned. The stacking structures may be, for example, metal rings. The stacking structures are then removed to form a first recess. A second recess is formed by extending the first recess into the substrate. The second recess is filled with a conductive material to form the TSV.

Owner:TAIWAN SEMICON MFG CO LTD

Integrated circuit system with through silicon via and method of manufacture thereof

ActiveUS20100297844A1Semiconductor/solid-state device detailsSolid-state devicesInsulation layerEngineering

A method of manufacture of an integrated circuit system includes: providing a substrate including an active device; forming a through-silicon-via into the substrate; forming an insulation layer over the through-silicon-via to protect the through-silicon-via; forming a contact to the active device after forming the insulation layer; and removing the insulation layer.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

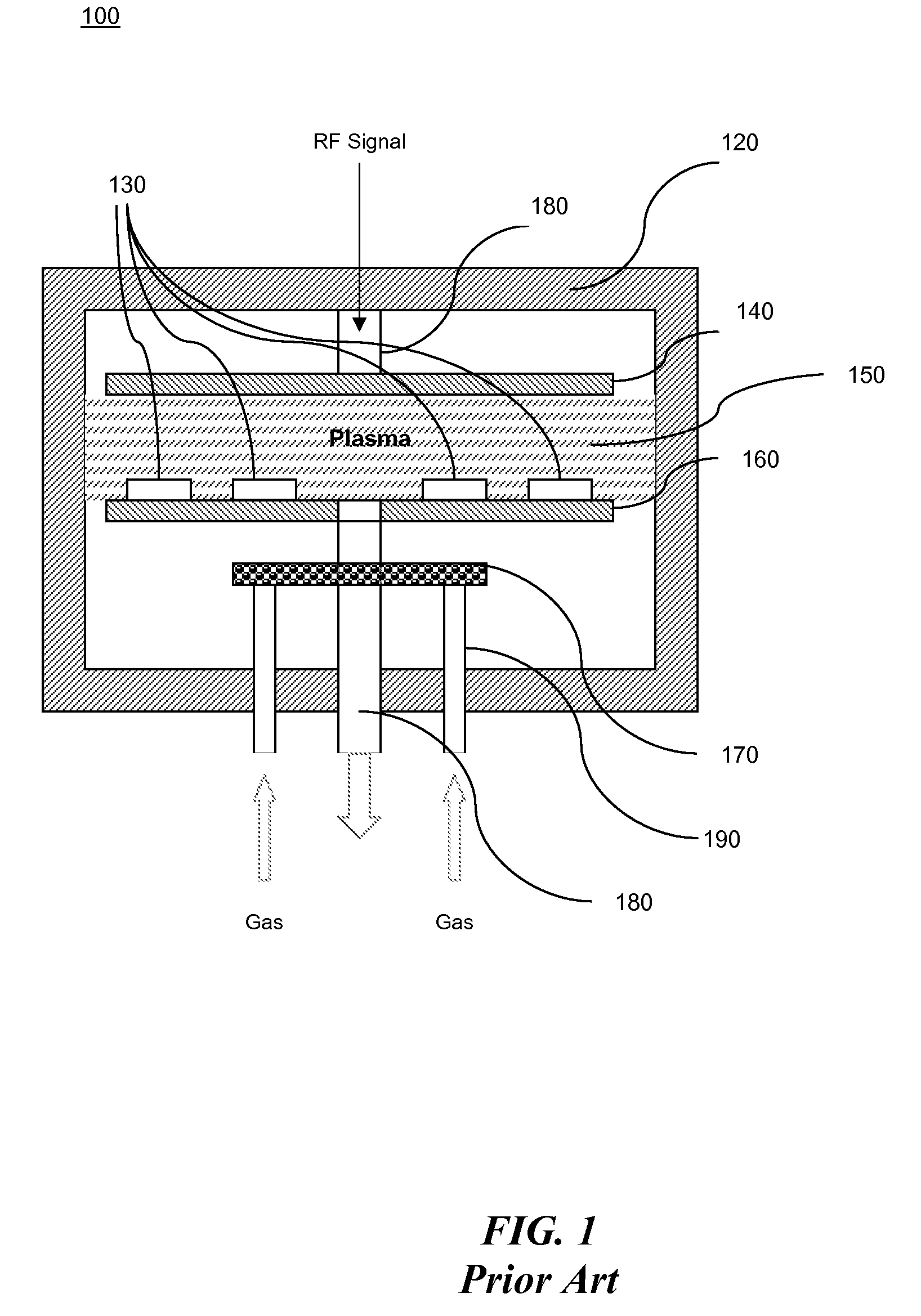

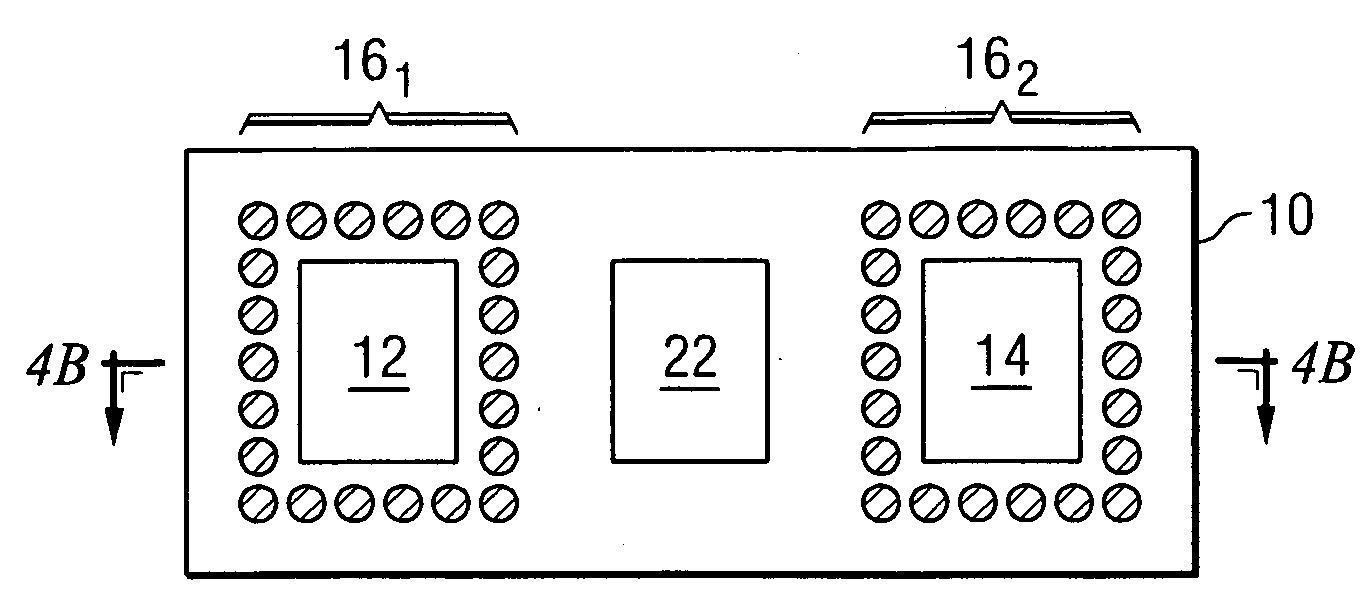

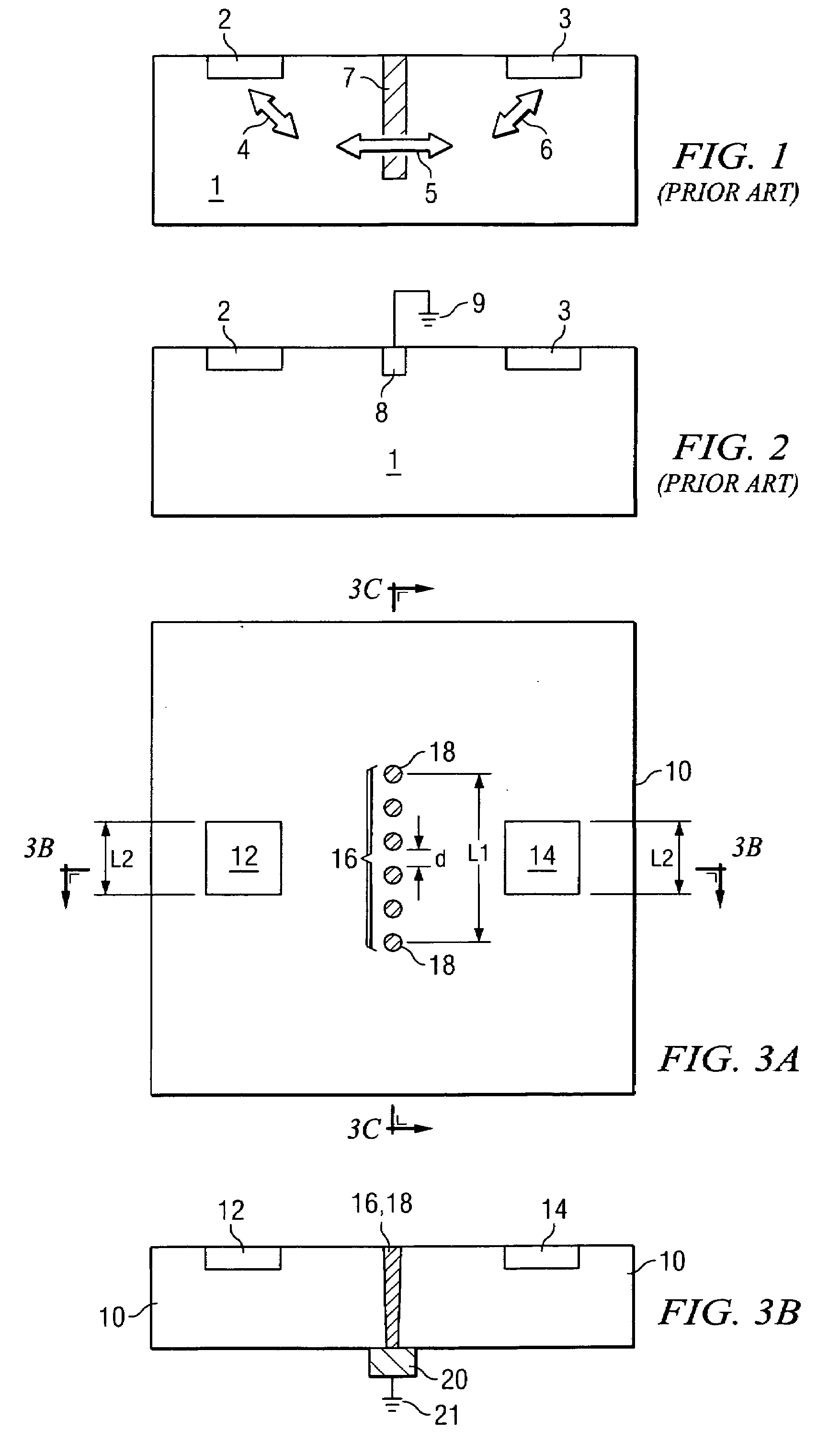

Electromagnetic shielding using through-silicon vias

ActiveUS20080073747A1Good electromagnetic isolationImprove isolationSemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceDirect path

An isolation structure for electromagnetic interference includes a semiconductor substrate, a first integrated circuit in the semiconductor substrate, a second integrated circuit in the semiconductor substrate, and an isolation structure in a direct path between the first and the second integrated circuits, wherein the isolation structure comprises a through-silicon via.

Owner:TAIWAN SEMICON MFG CO LTD

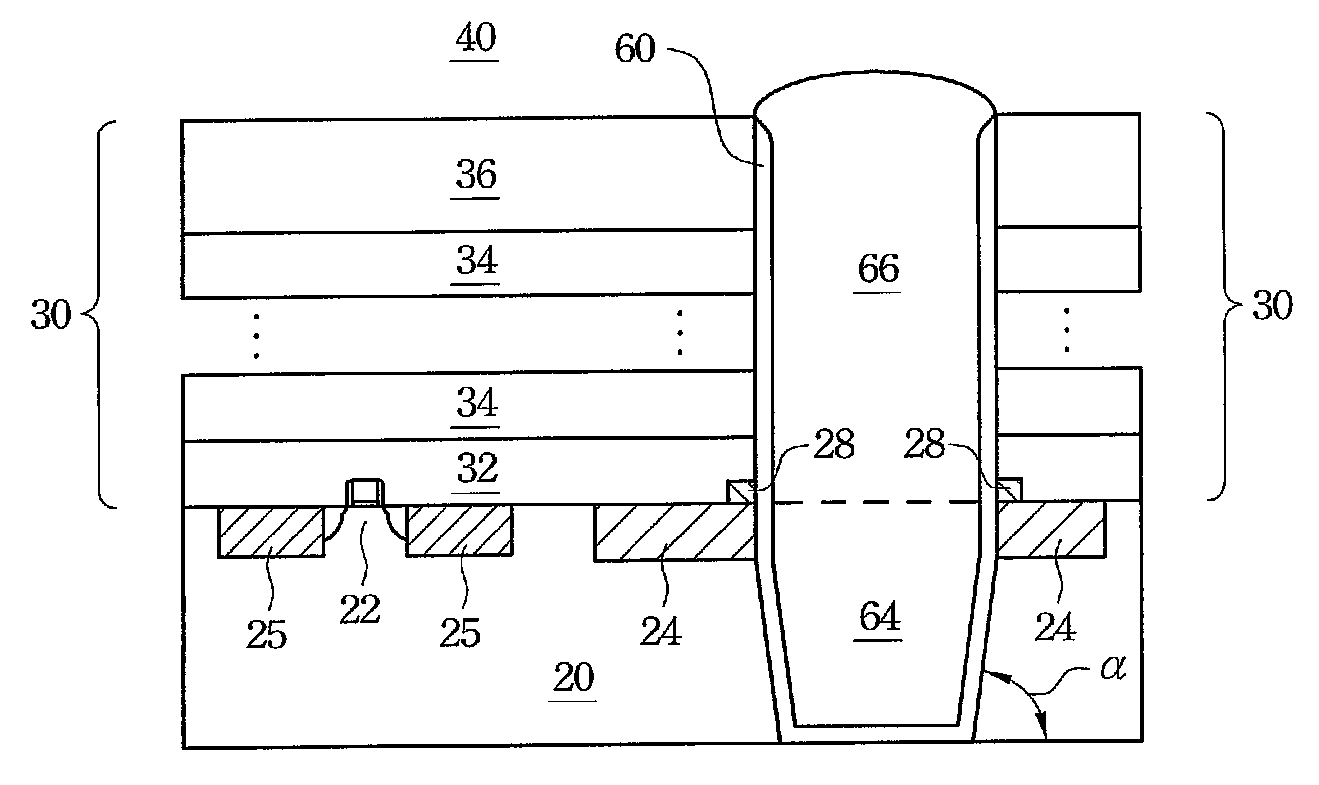

Tapered through-silicon via structure

ActiveUS7564115B2Expand coverageReduce undercuttingSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

An integrated circuit structure includes a substrate; a through-silicon via (TSV) in the substrate, the TSV being tapered; a hard mask region extending from a top surface of the substrate into the substrate, wherein the hard mask encircles a top portion of the TSV; dielectric layers over the substrate; and a metal post extending from a top surface of the dielectric layers to the TSV, wherein the metal post comprises same materials as the TSV.

Owner:TAIWAN SEMICON MFG CO LTD

Through-silicon via and method for forming the same

InactiveUS20080079121A1Low costSecure characteristicSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor chip

A method for forming a through-silicon via includes the steps of defining a groove in each chip of a wafer which has a plurality of semiconductor chips; applying liquid polymer on the wafer to fill the groove; forming an insulation layer on a sidewall of the groove through patterning the polymer; forming a metal layer to fill the groove which is formed with the insulation layer on the sidewall thereof; and back-grinding a backside of the wafer to expose the metal layer filled in the groove.

Owner:SK HYNIX INC

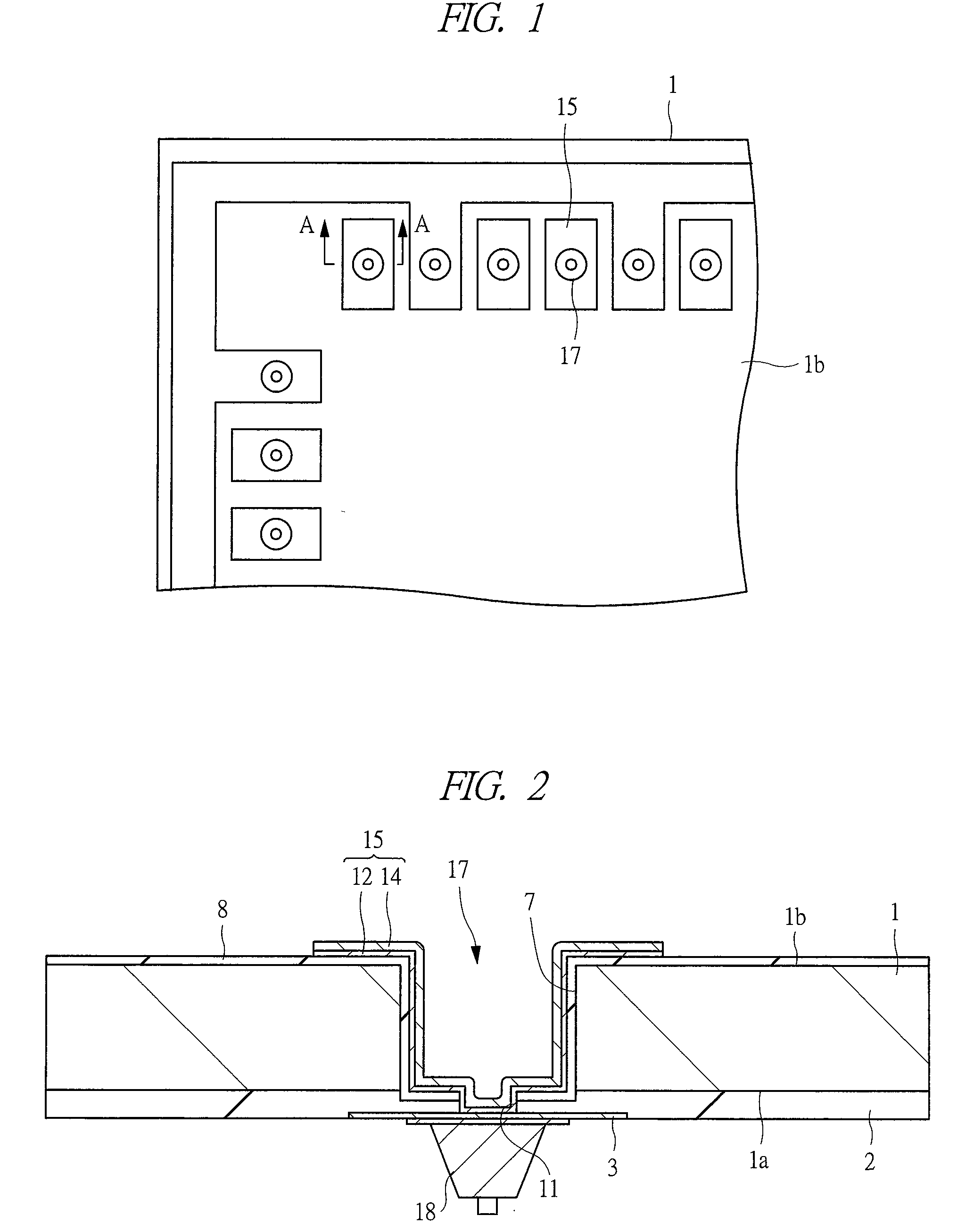

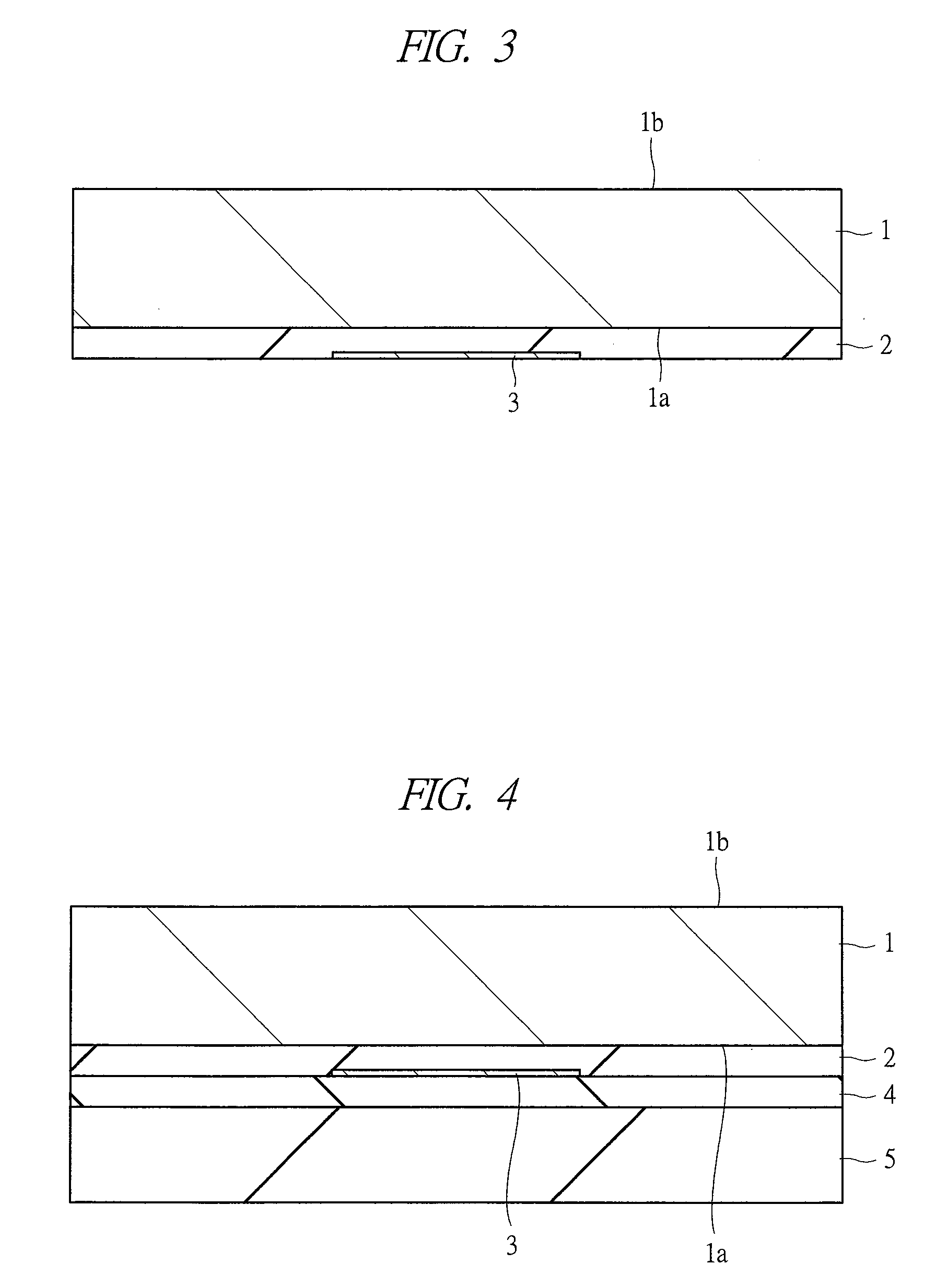

Manufacturing process and structure of through silicon via

InactiveUS20090014843A1Improve manufacturing yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductorThrough-silicon via

A through silicon via reaching a pad from a second surface of a semiconductor substrate is formed. A penetration space in the through silicon via is formed of a first hole and a second hole with a diameter smaller than that of the first hole. The first hole is formed from the second surface of the semiconductor substrate to the middle of the interlayer insulating film. Further, the second hole reaching the pad from the bottom of the first hole is formed. Then, the interlayer insulating film formed on the first surface of the semiconductor substrate has a step shape reflecting a step difference between the bottom surface of the first hole and the first surface of the semiconductor substrate. More specifically, the thickness of the interlayer insulating film between the bottom surface of the first hole and the pad is smaller than that in other portions.

Owner:RENESAS ELECTRONICS CORP

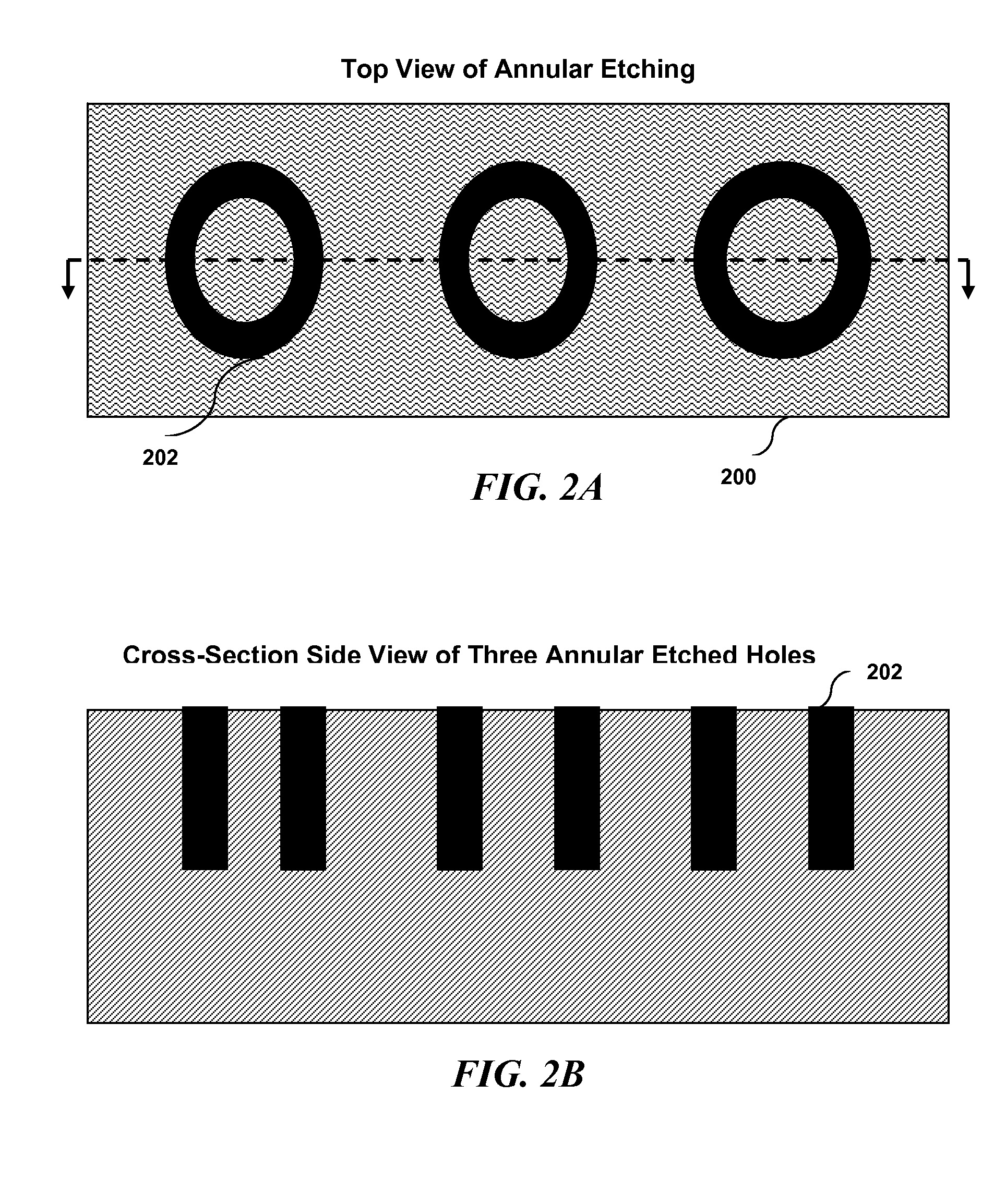

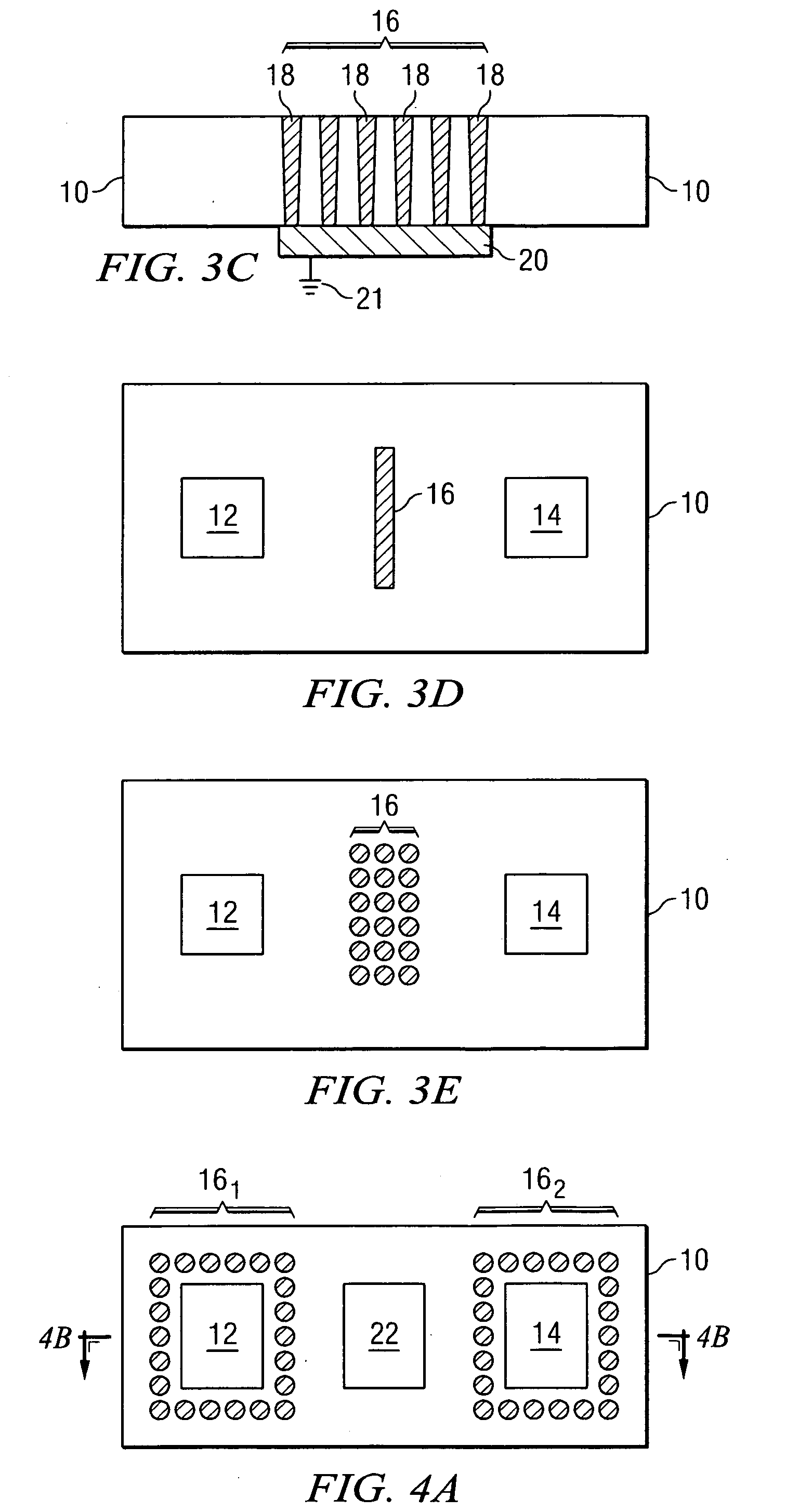

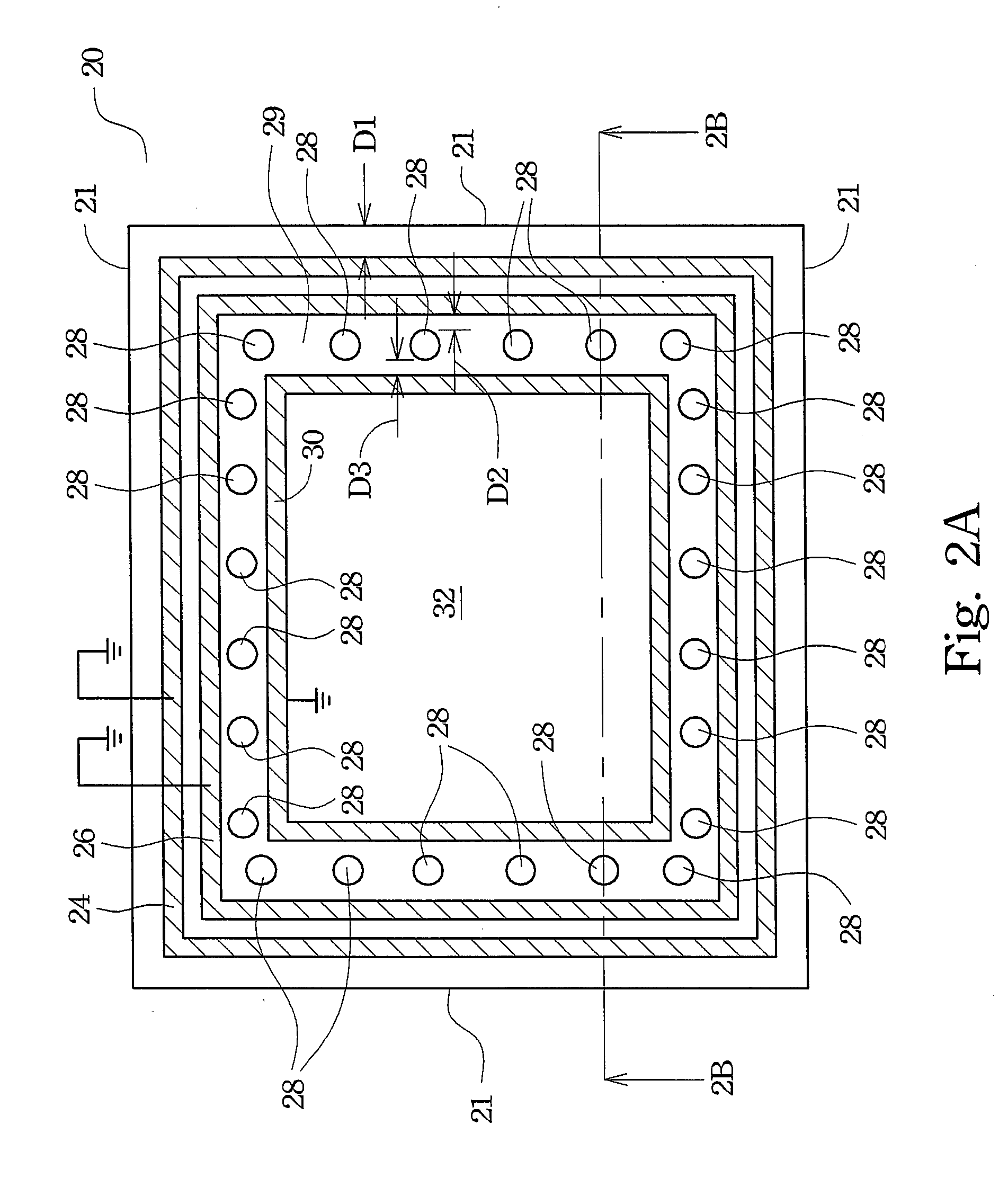

Structures for Preventing Cross-talk Between Through-Silicon Vias and Integrated Circuits

ActiveUS20090134500A1Reduce crosstalkSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipThrough-silicon via

A semiconductor chip includes a through-silicon via (TSV), a device region, and a cross-talk prevention ring encircling one of the device region and the TSV. The TSV is isolated from substantially all device regions comprising active devices by the cross-talk prevention ring.

Owner:TAIWAN SEMICON MFG CO LTD

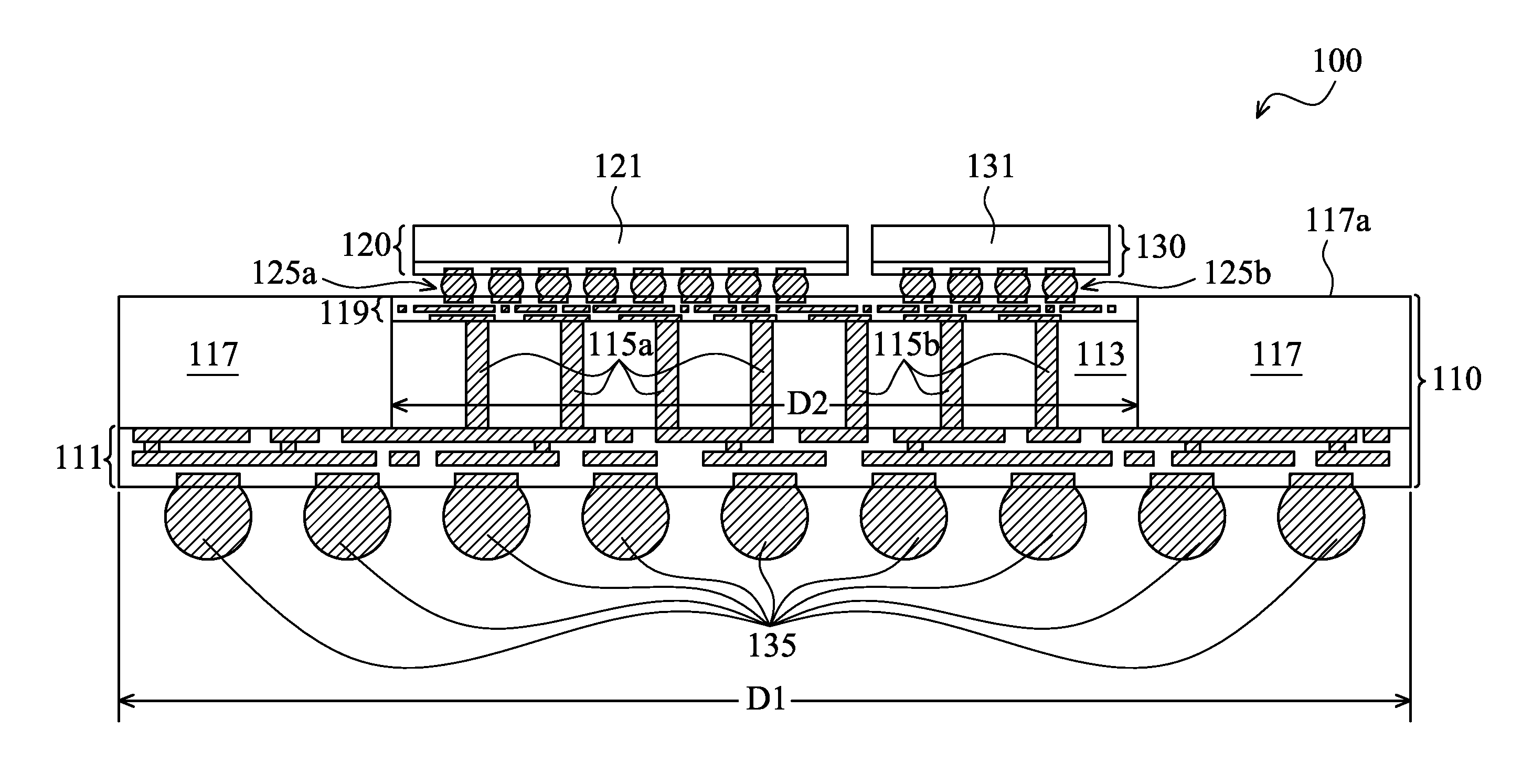

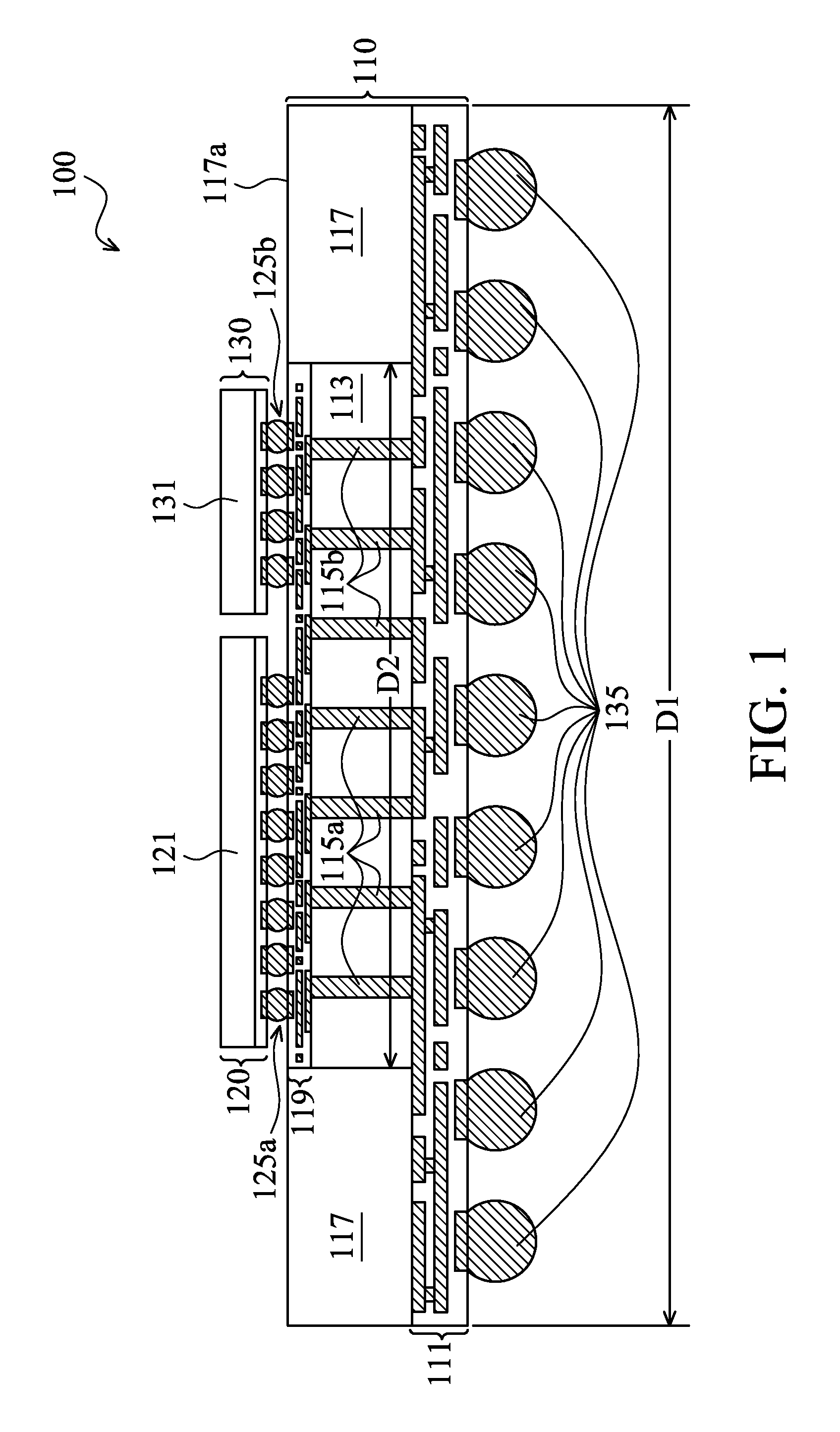

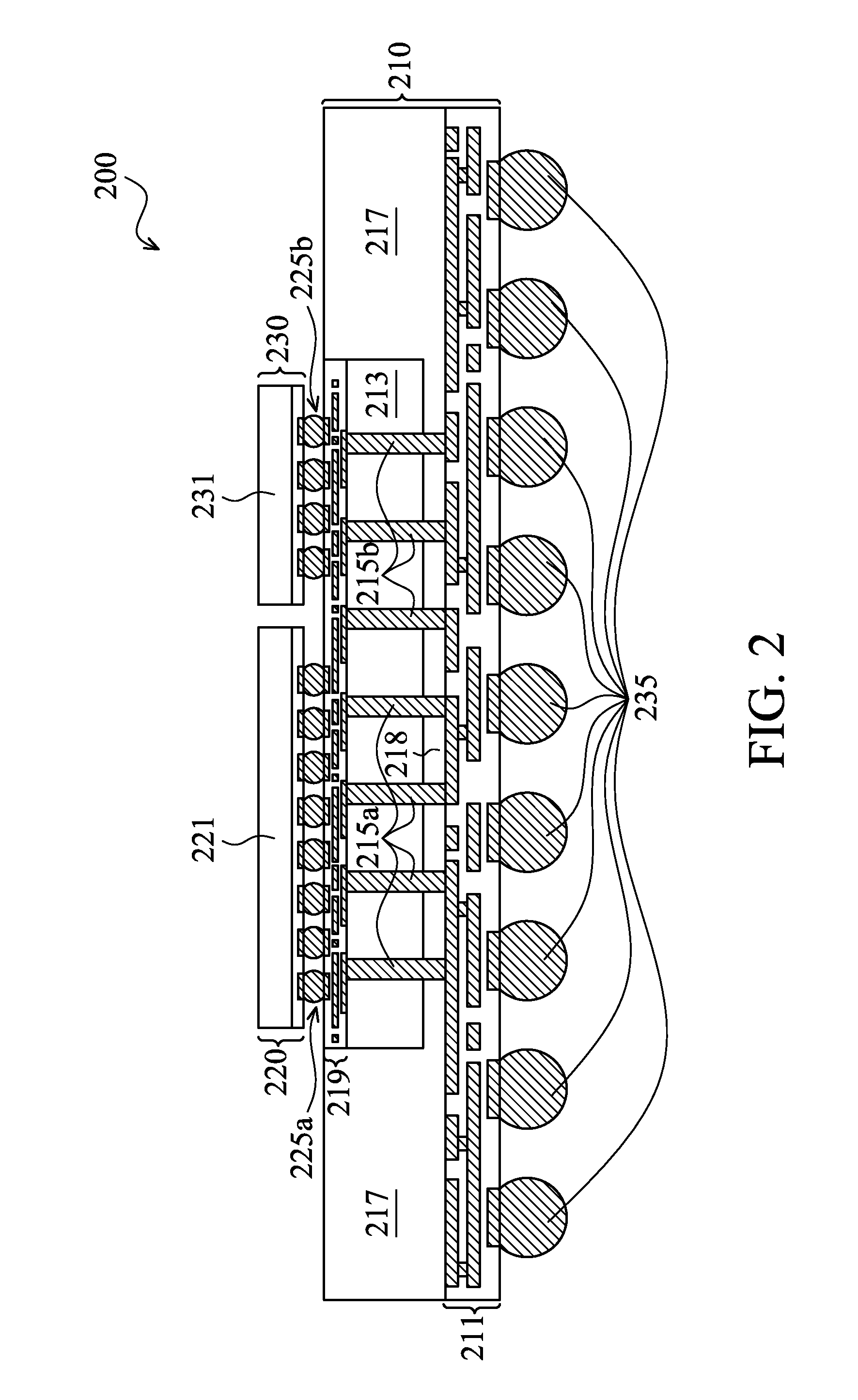

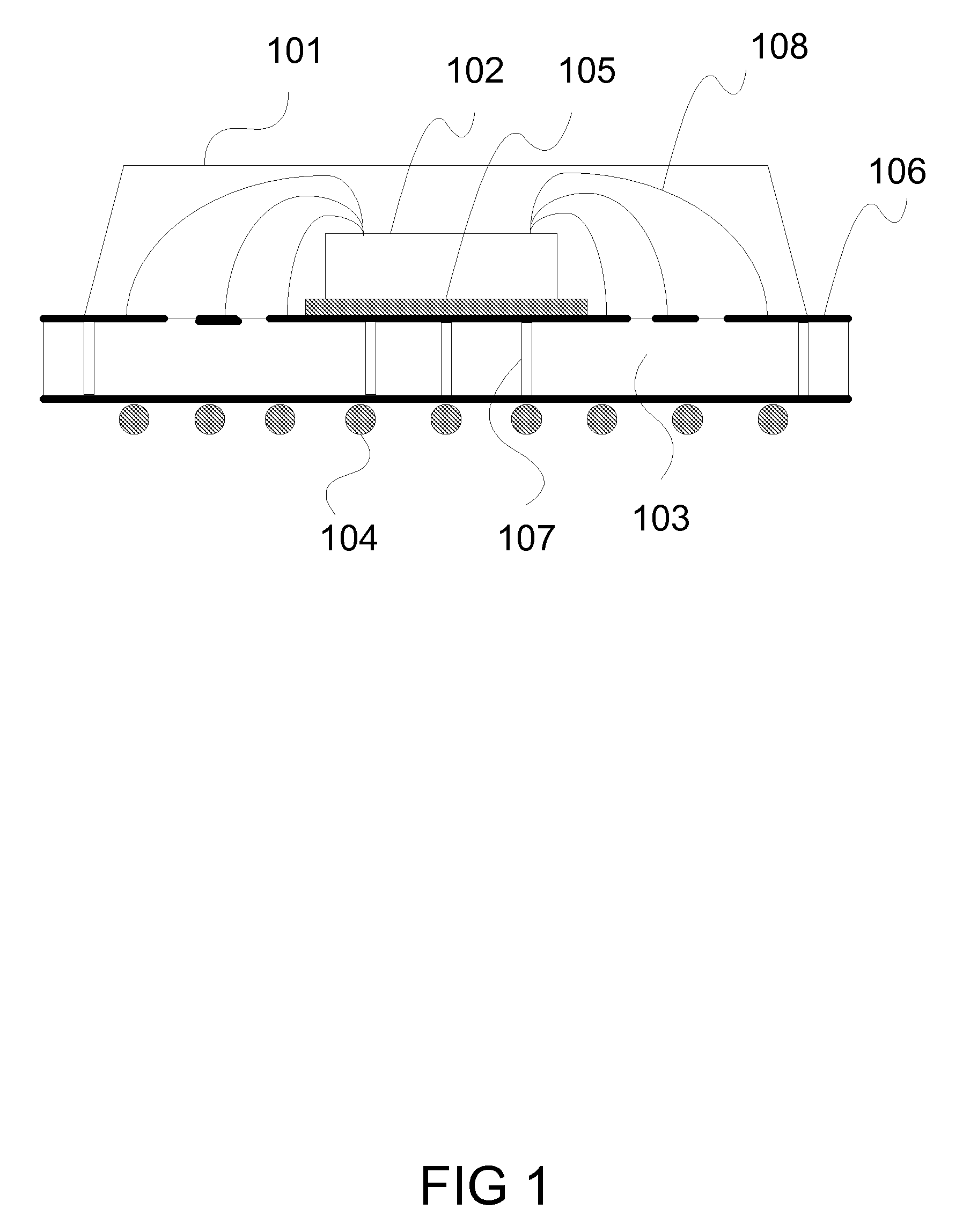

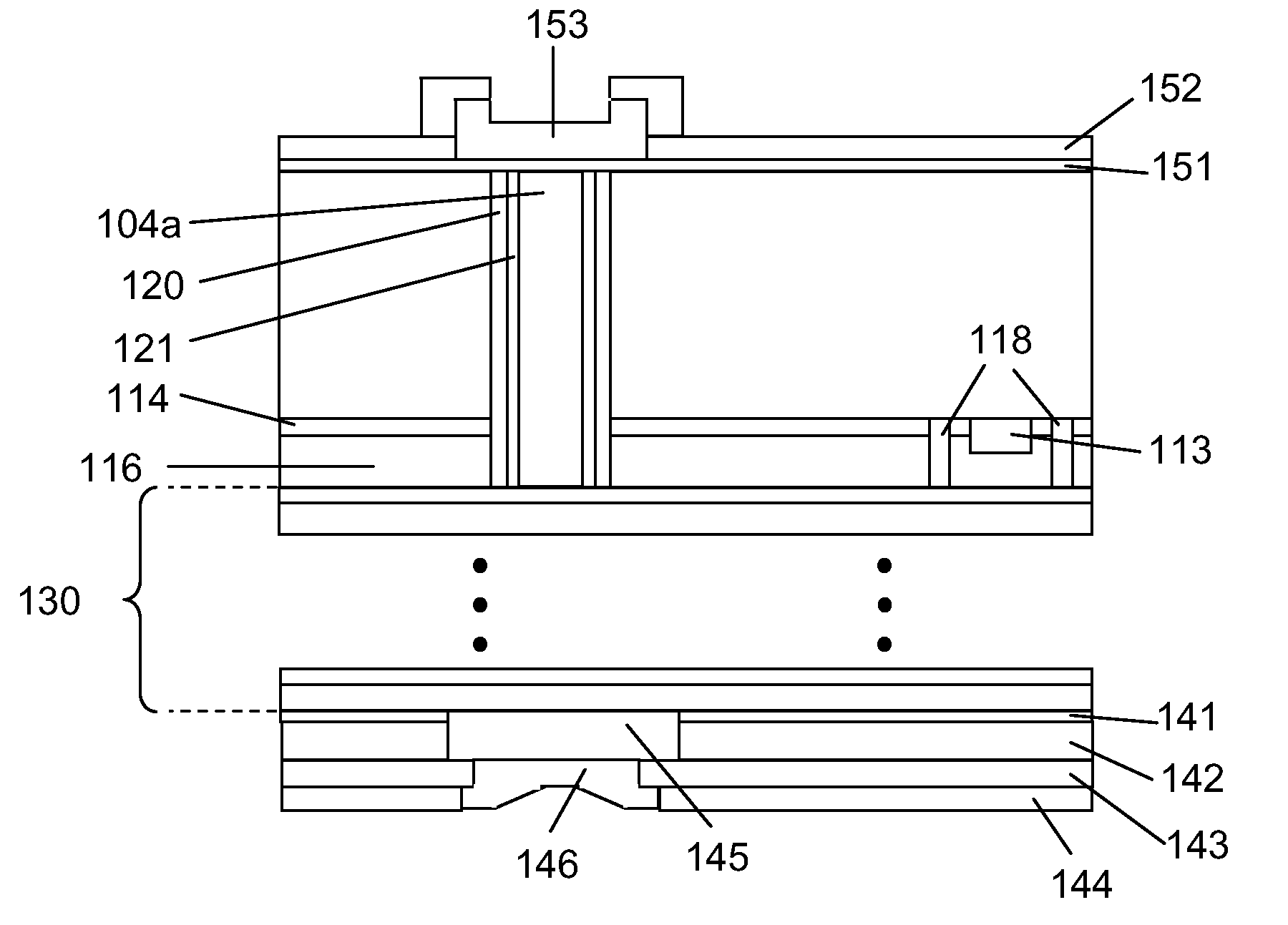

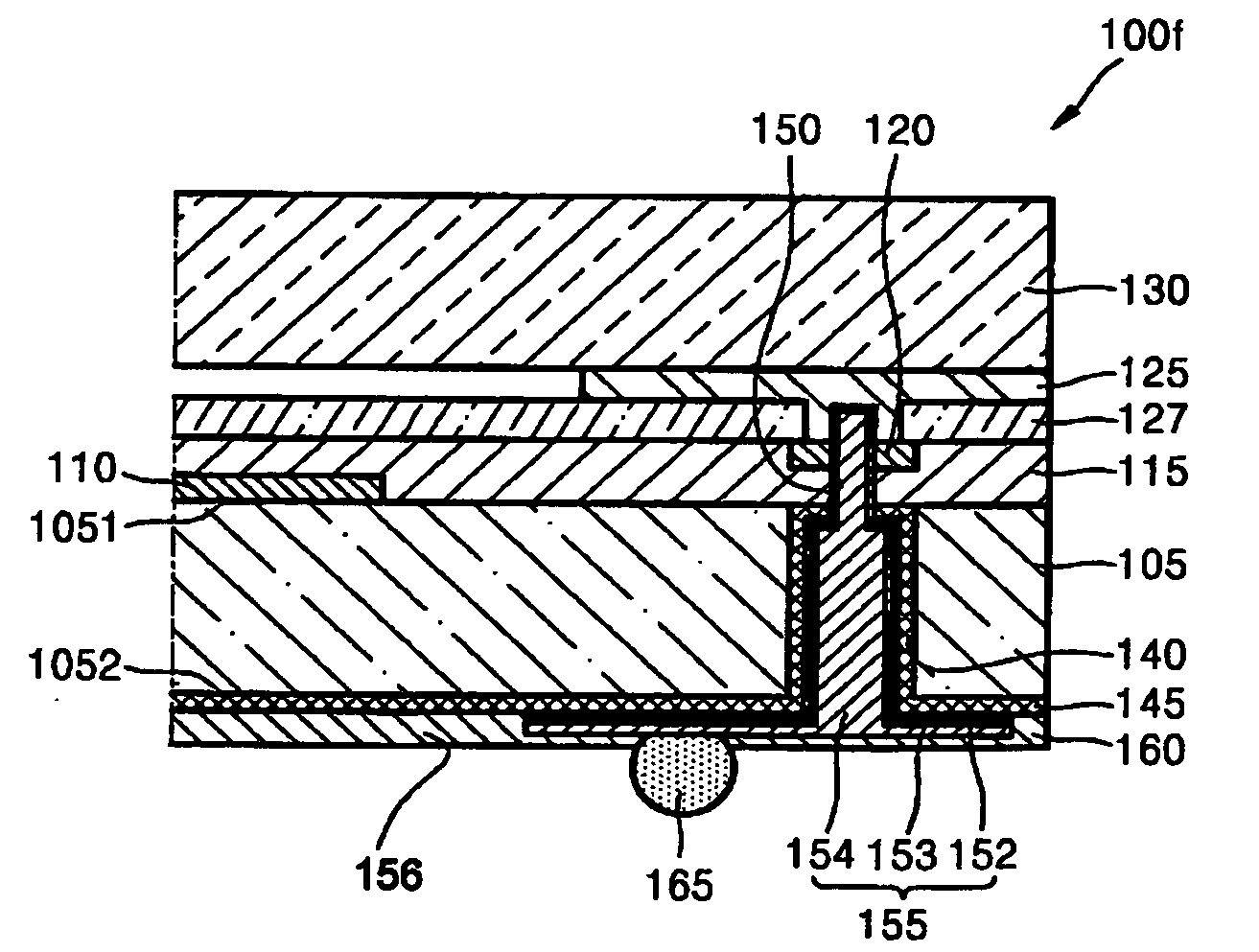

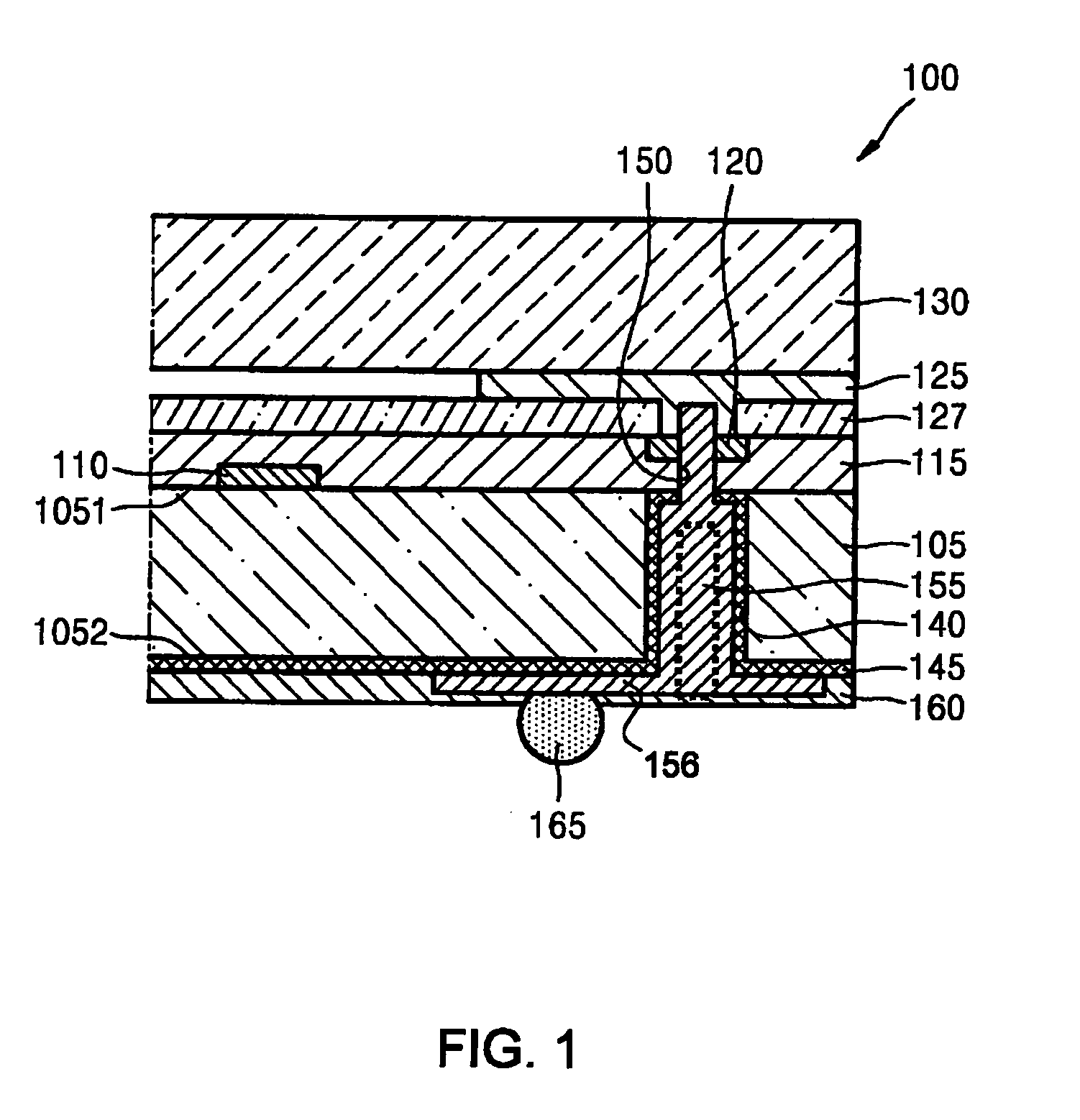

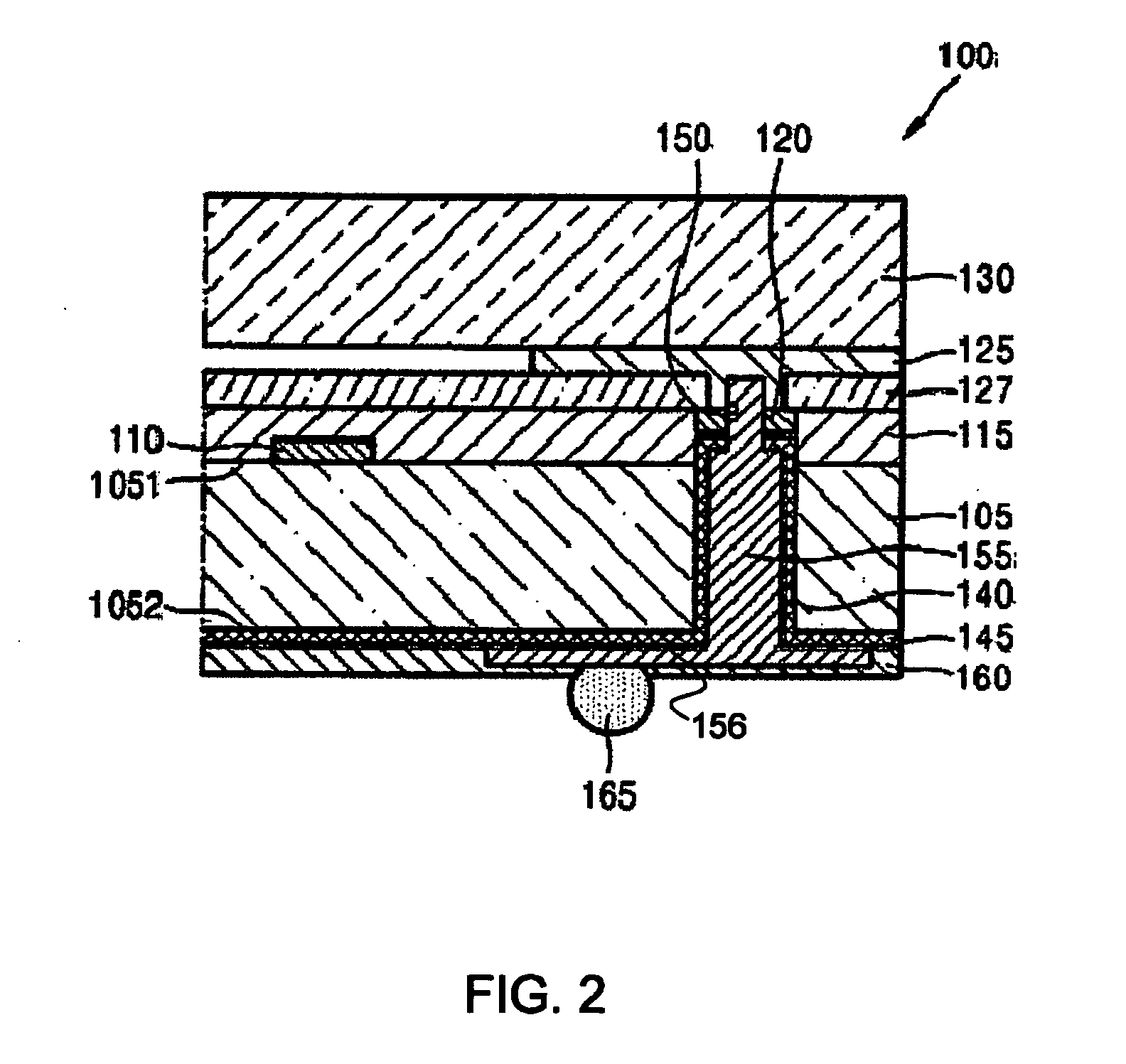

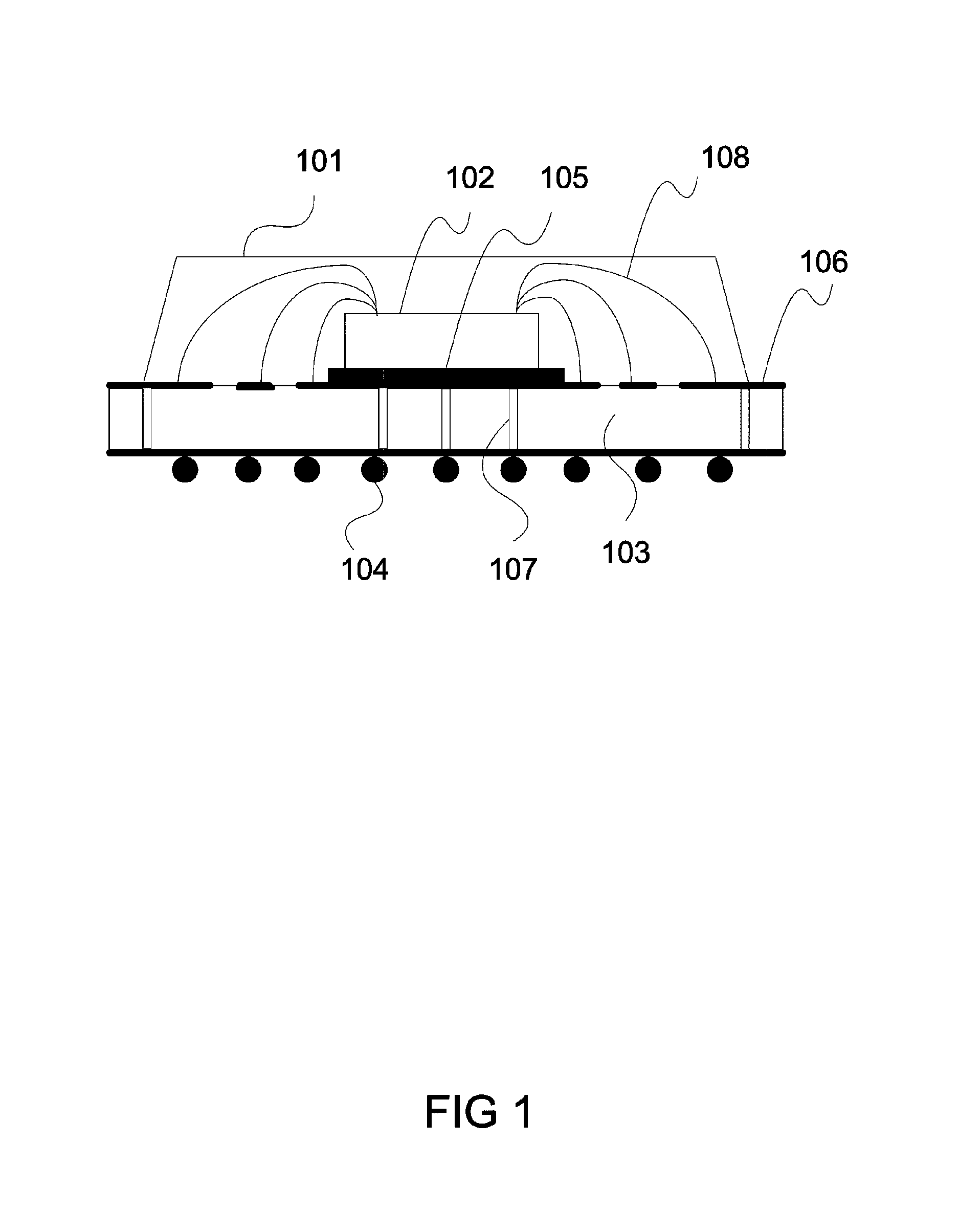

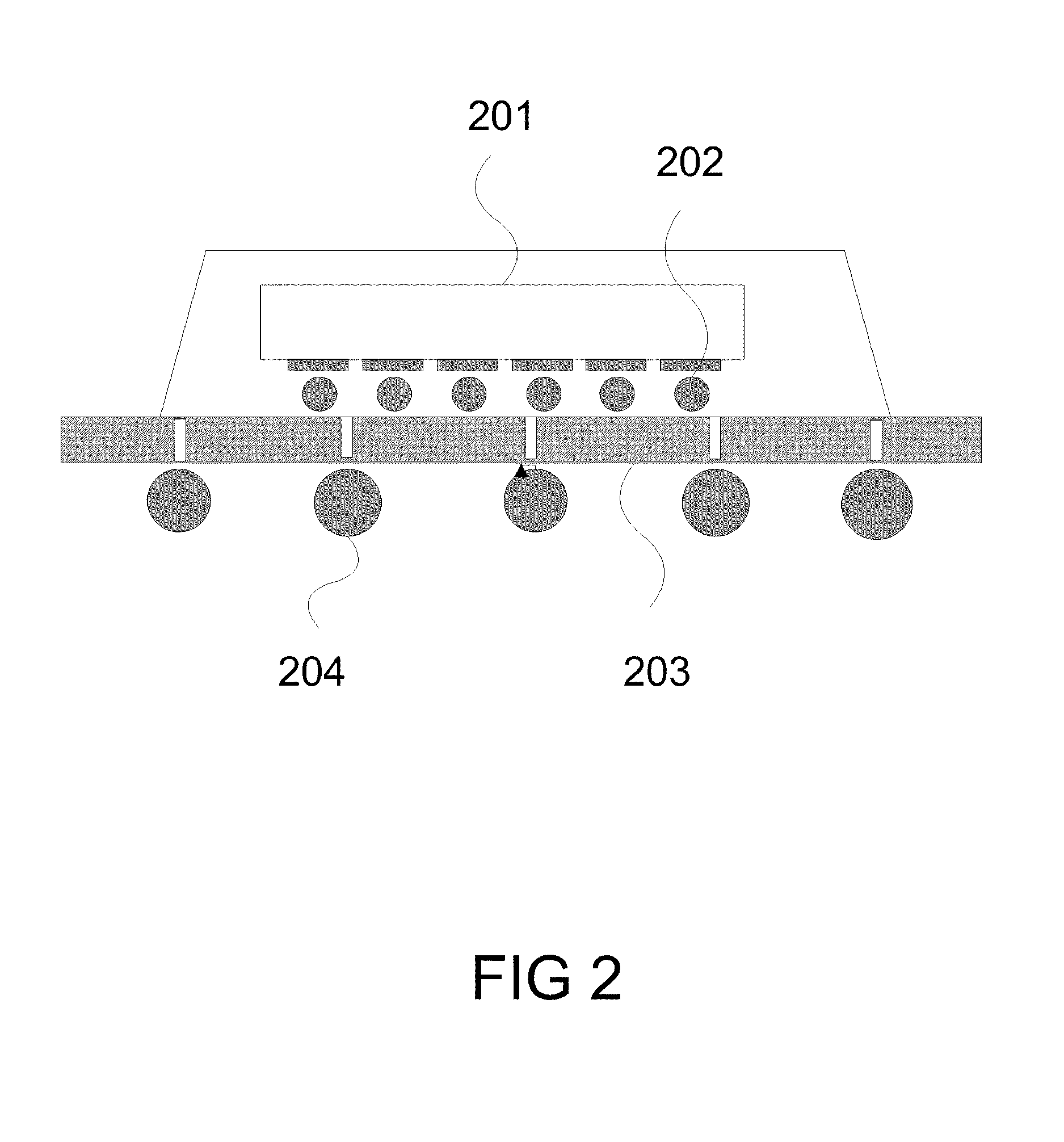

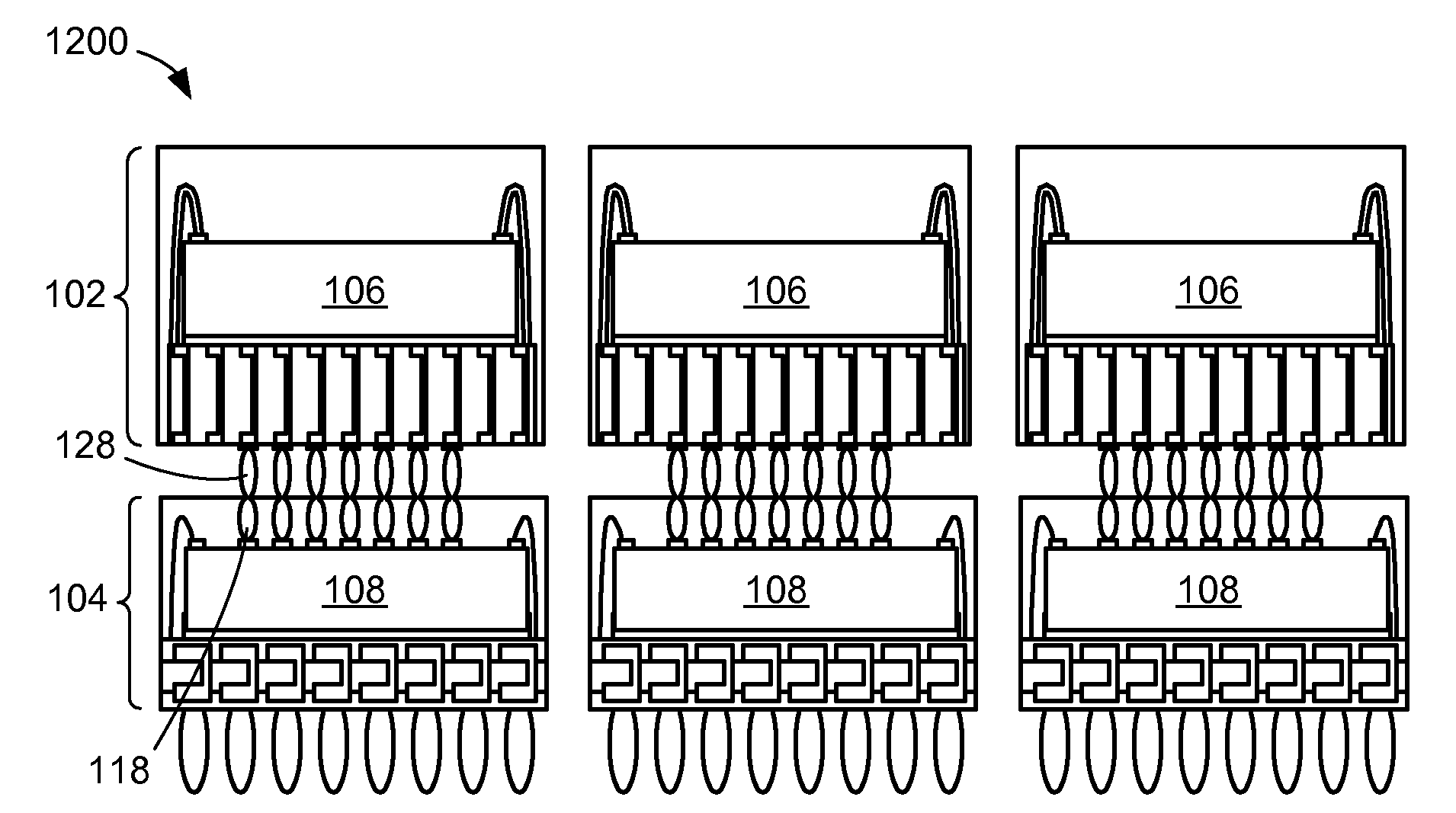

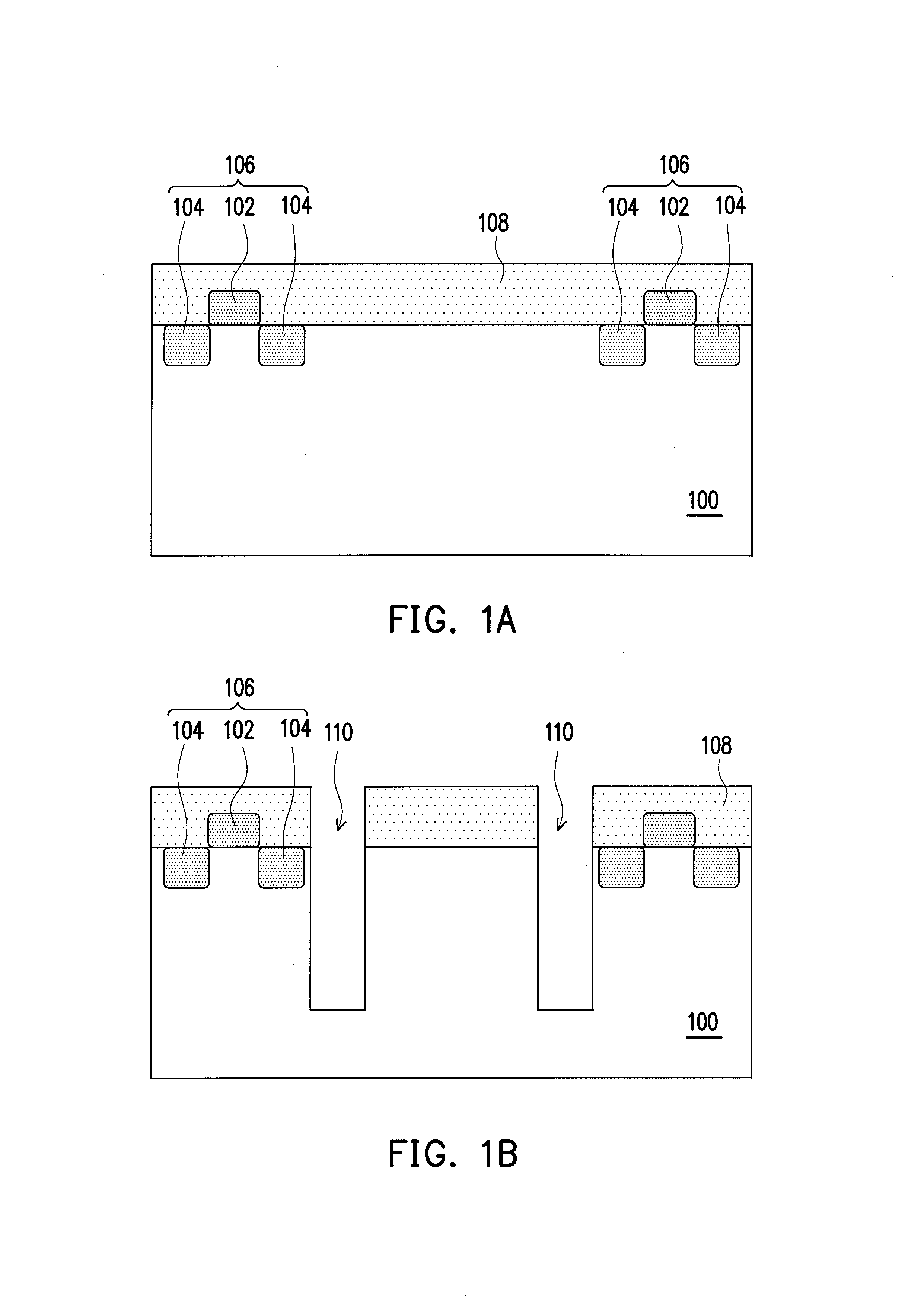

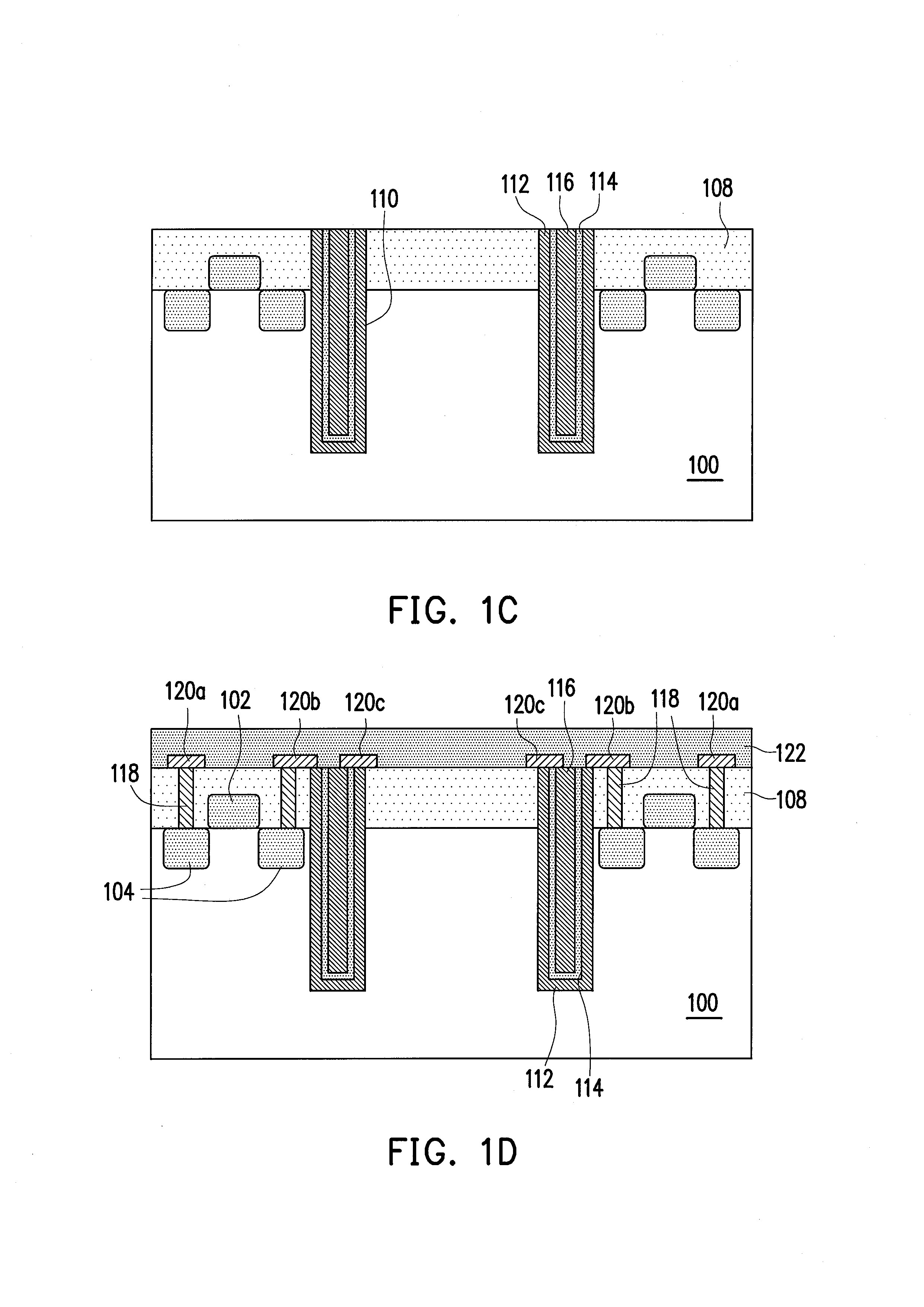

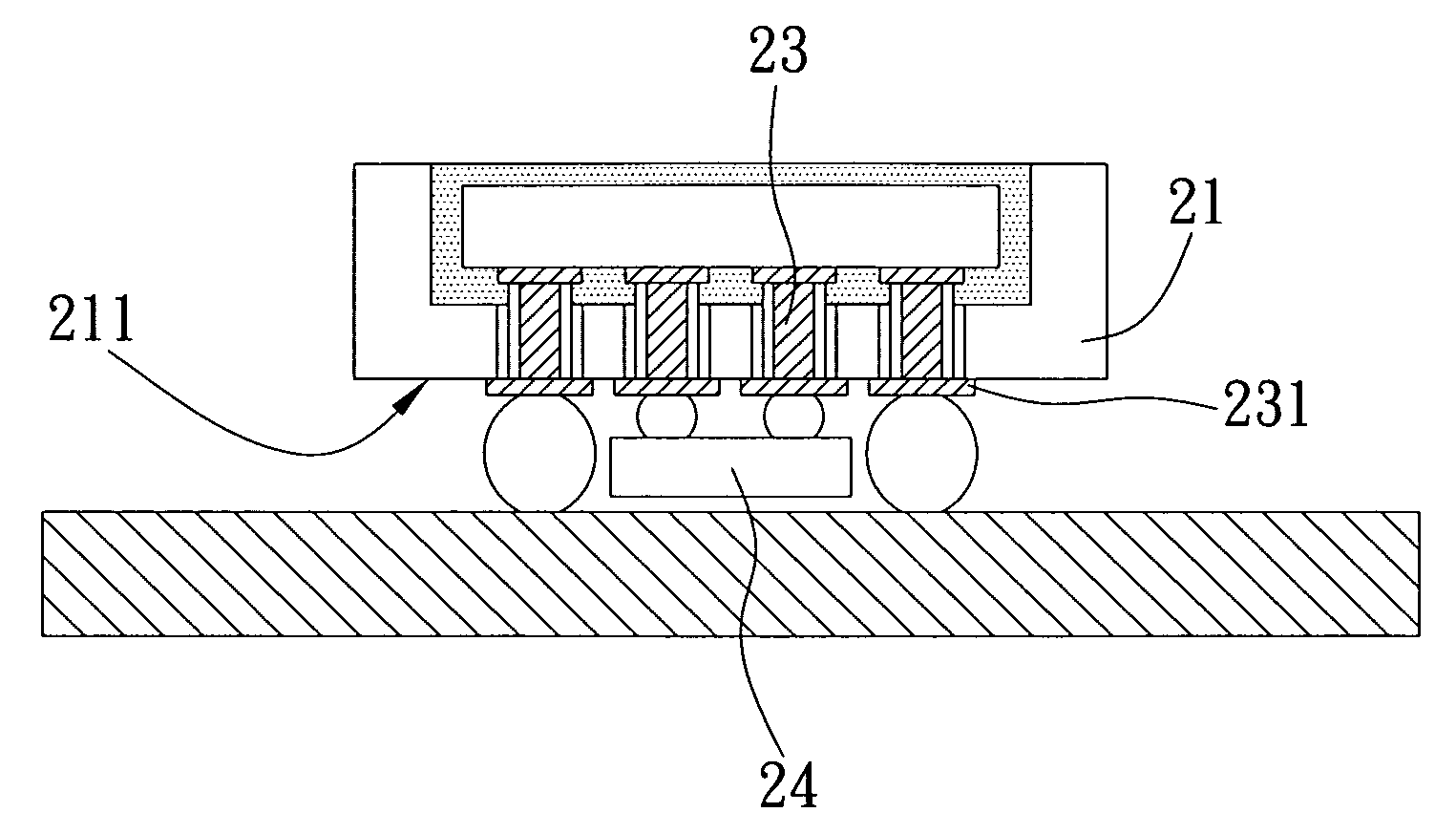

Semiconductor package system with through silicon via interposer

ActiveUS20100078789A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageInterposer

A semiconductor package system includes: providing a top package, a through silicon via interposer embedded in the top package; providing a bottom package having a bottom semiconductor die with a top connection adjacent the center active face thereof, a substrate interposer being embedded in the bottom package, the bottom semiconductor die being attached to the substrate interposer; and attaching the top package to the bottom package, the top package having the through silicon via interposer having a via connected to the top connection.

Owner:STATS CHIPPAC LTD

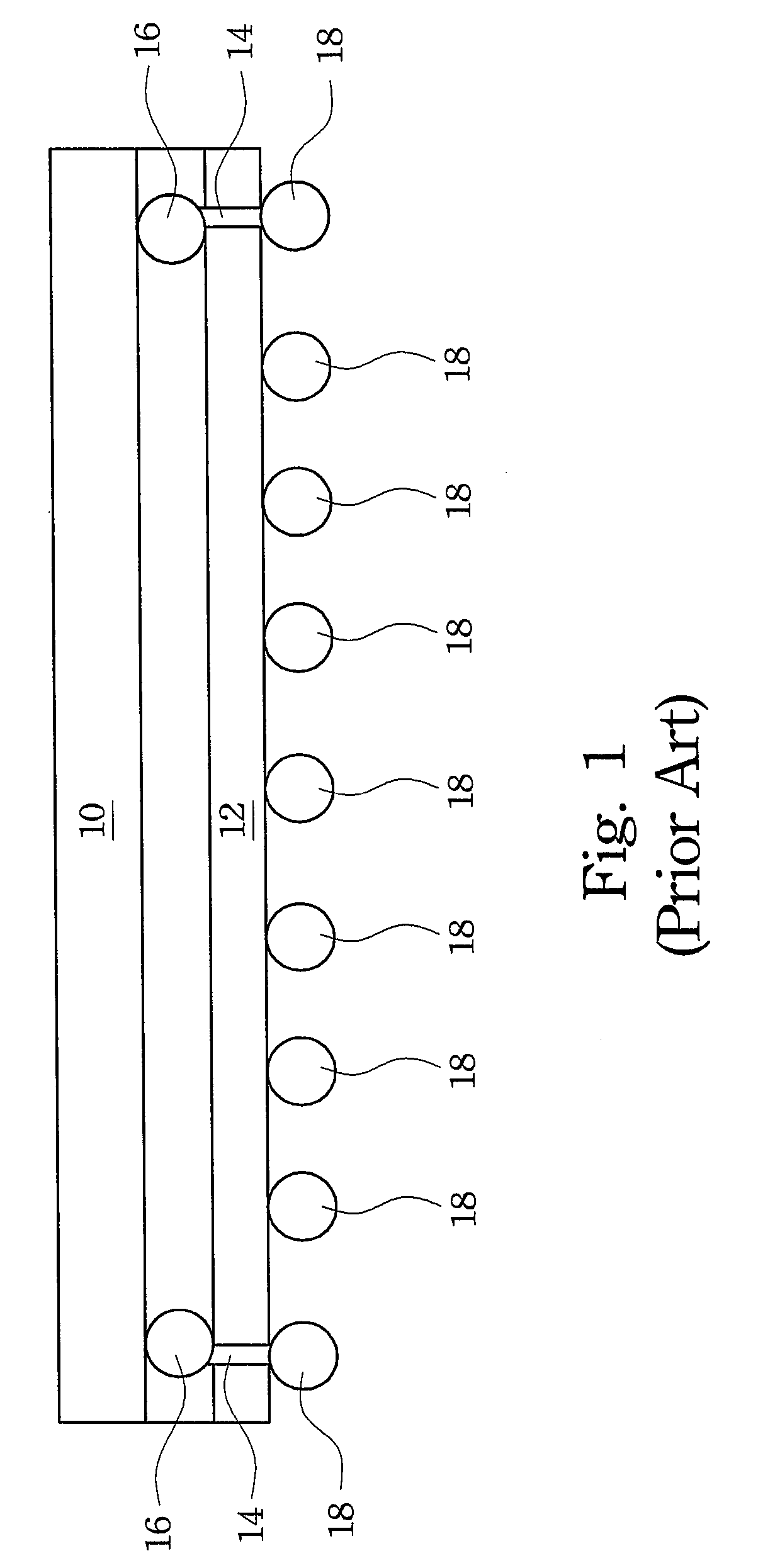

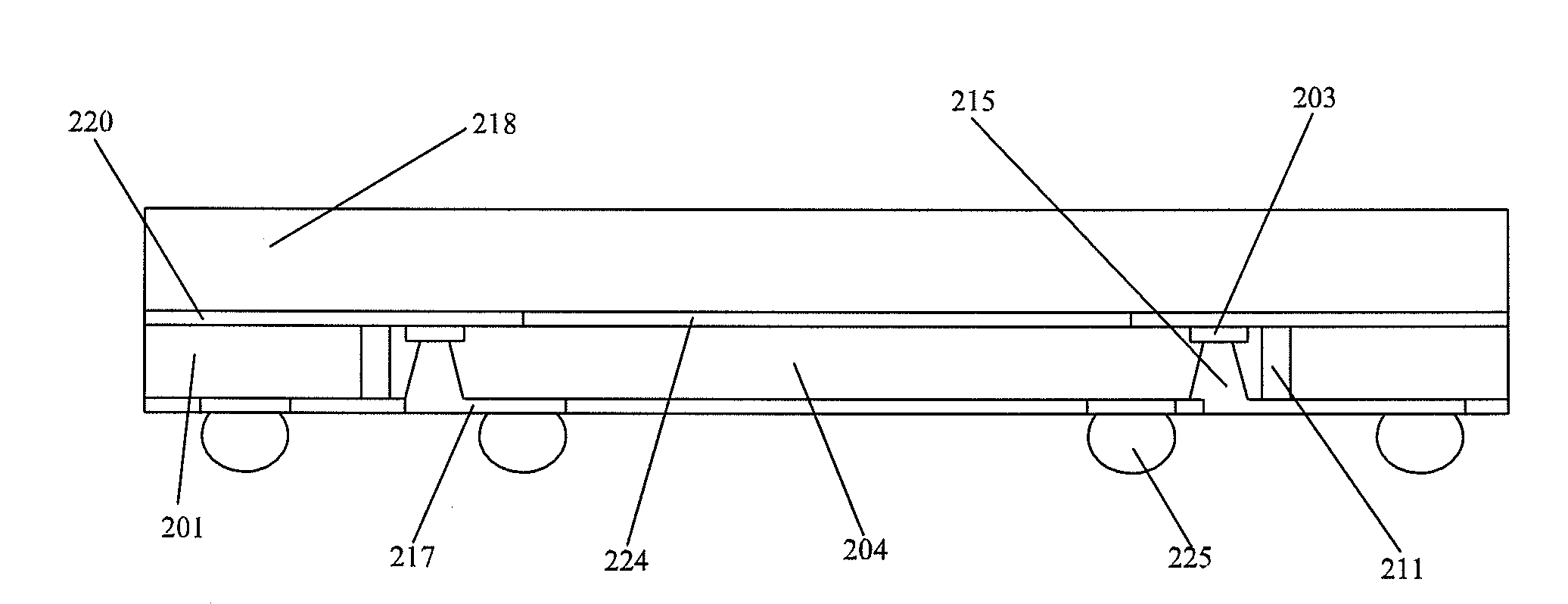

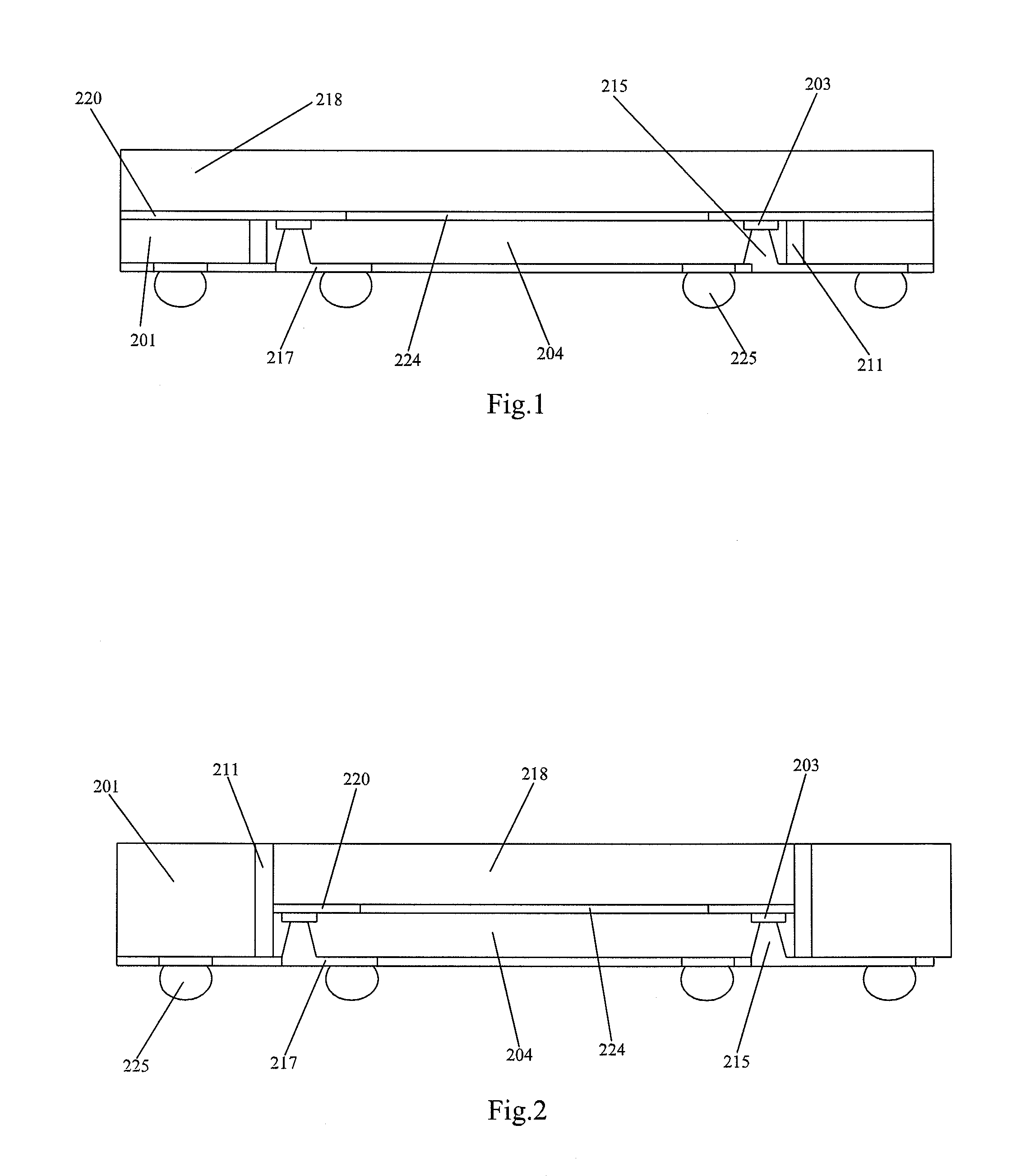

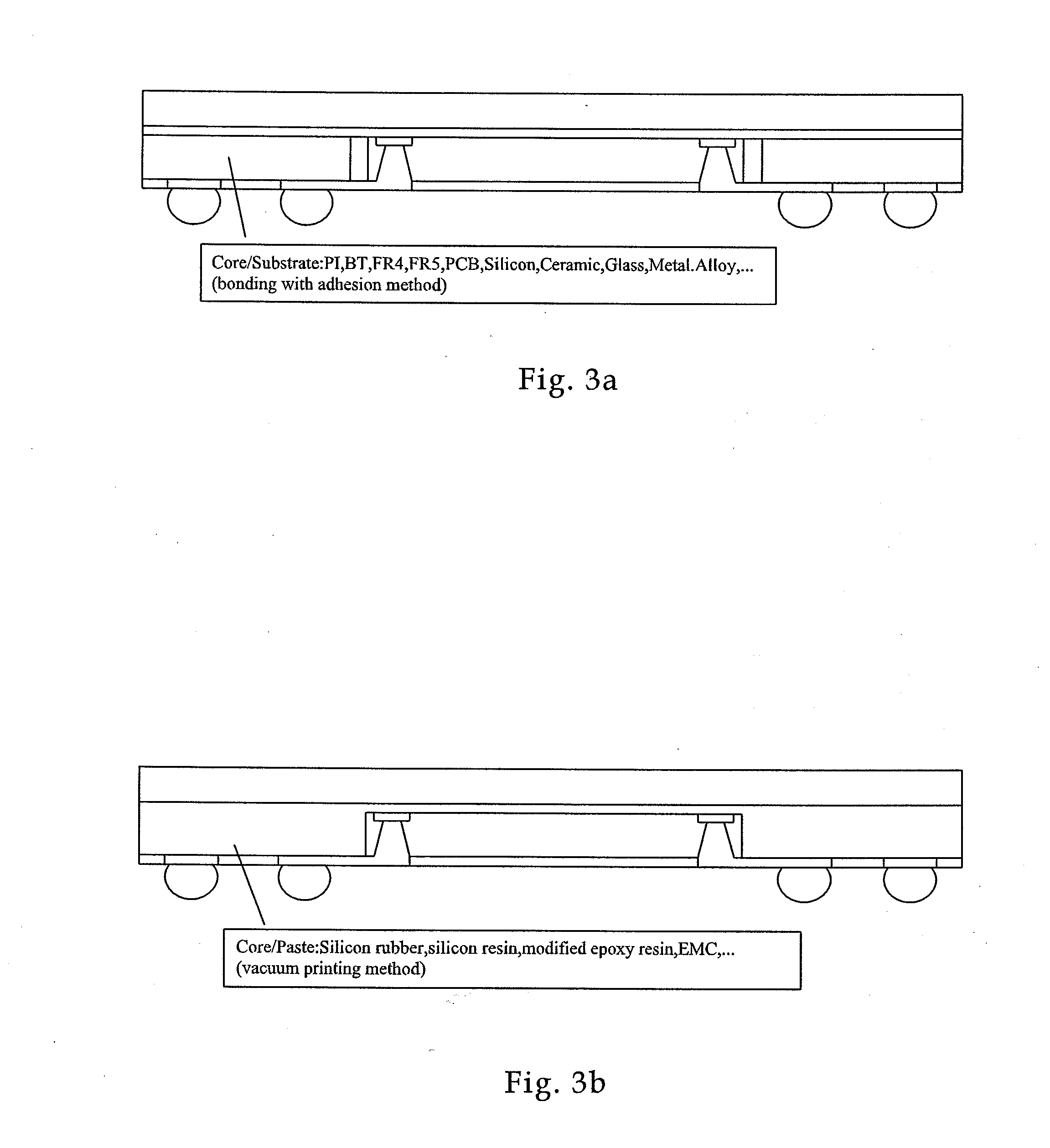

Inter-connecting structure for semiconductor device package and method of the same

InactiveUS20090166873A1Low costImprove performanceSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor package

The interconnecting structure for a semiconductor die includes a die having bonding pads on an active surface; a core attached the side wall (edge) of the die by adhesion material; an isolating base adhered on the active surface of the die by adhesion glue; a through silicon via (TSV) open from the back side of the die to expose the bonding pads; a build up layer coupled between the bonding pads to terminal metal pads by the through silicon via; solder balls melted on terminal pads, wherein the terminal pads located on the core and / or the die.

Owner:ADVANCED CHIP ENG TECH

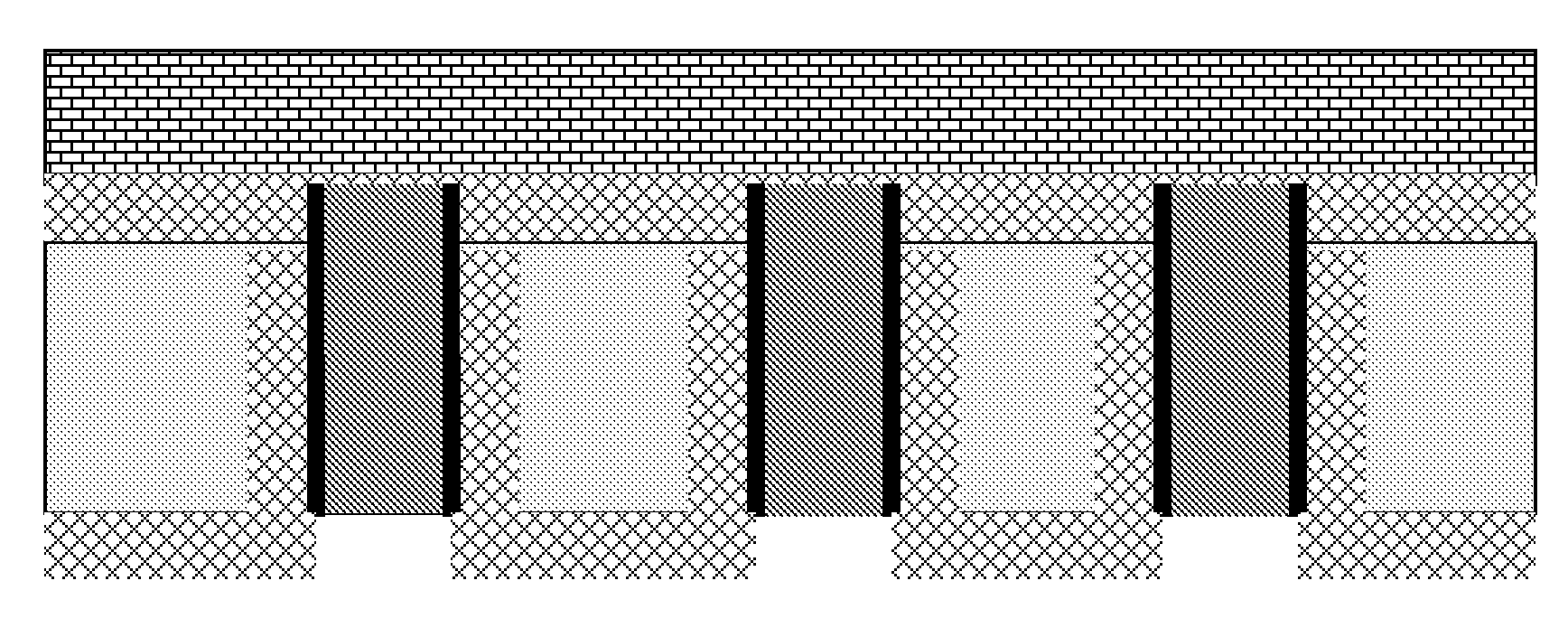

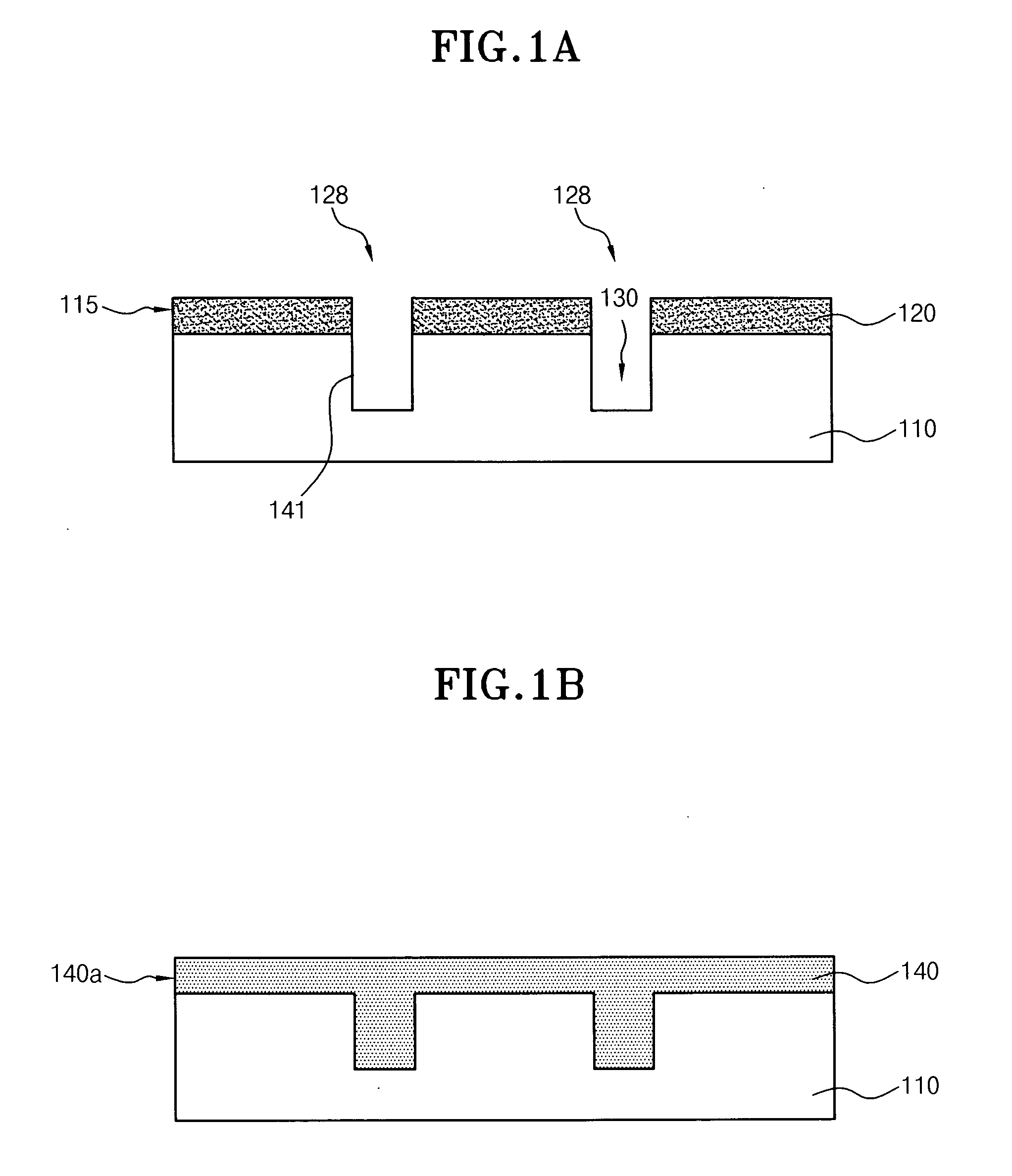

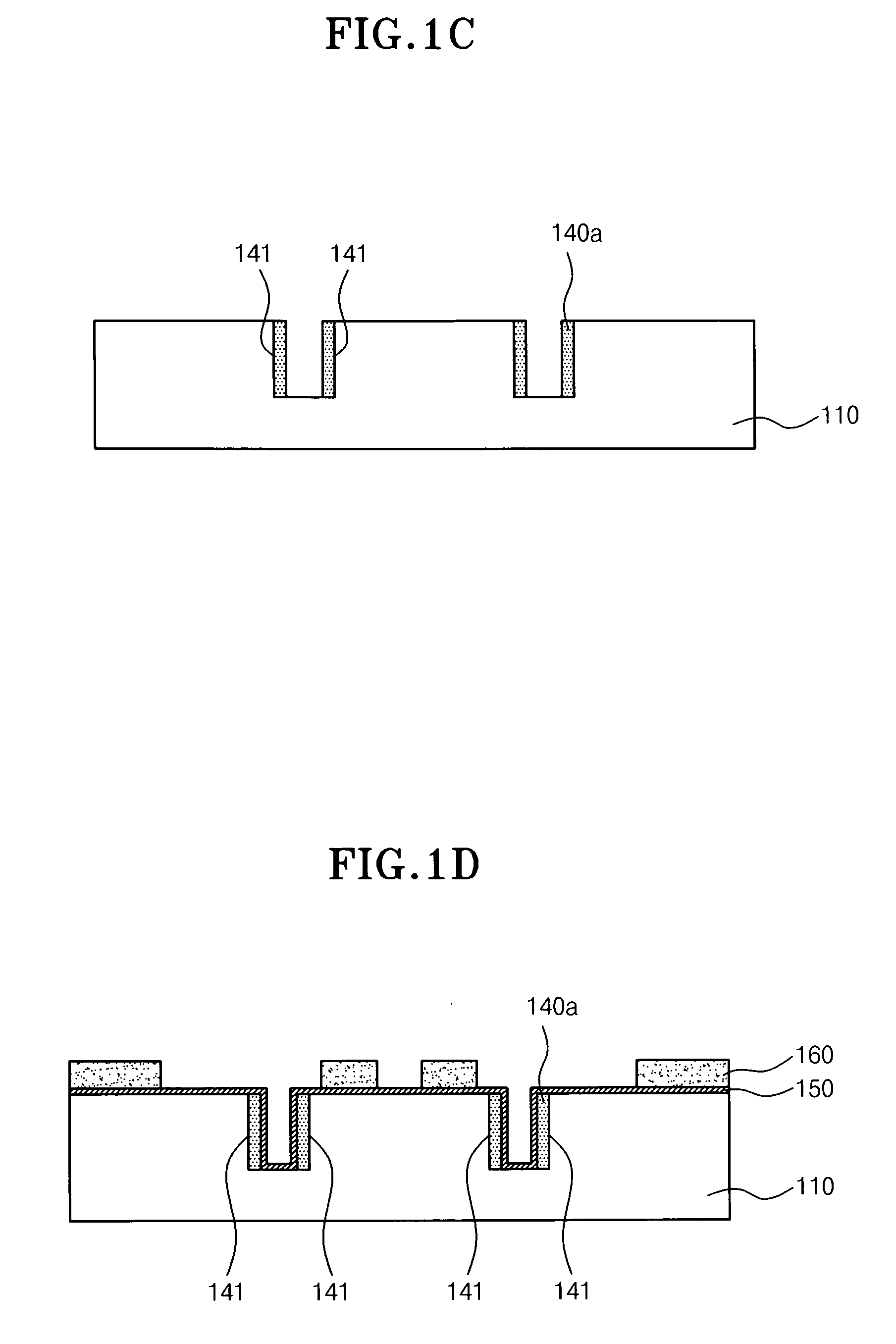

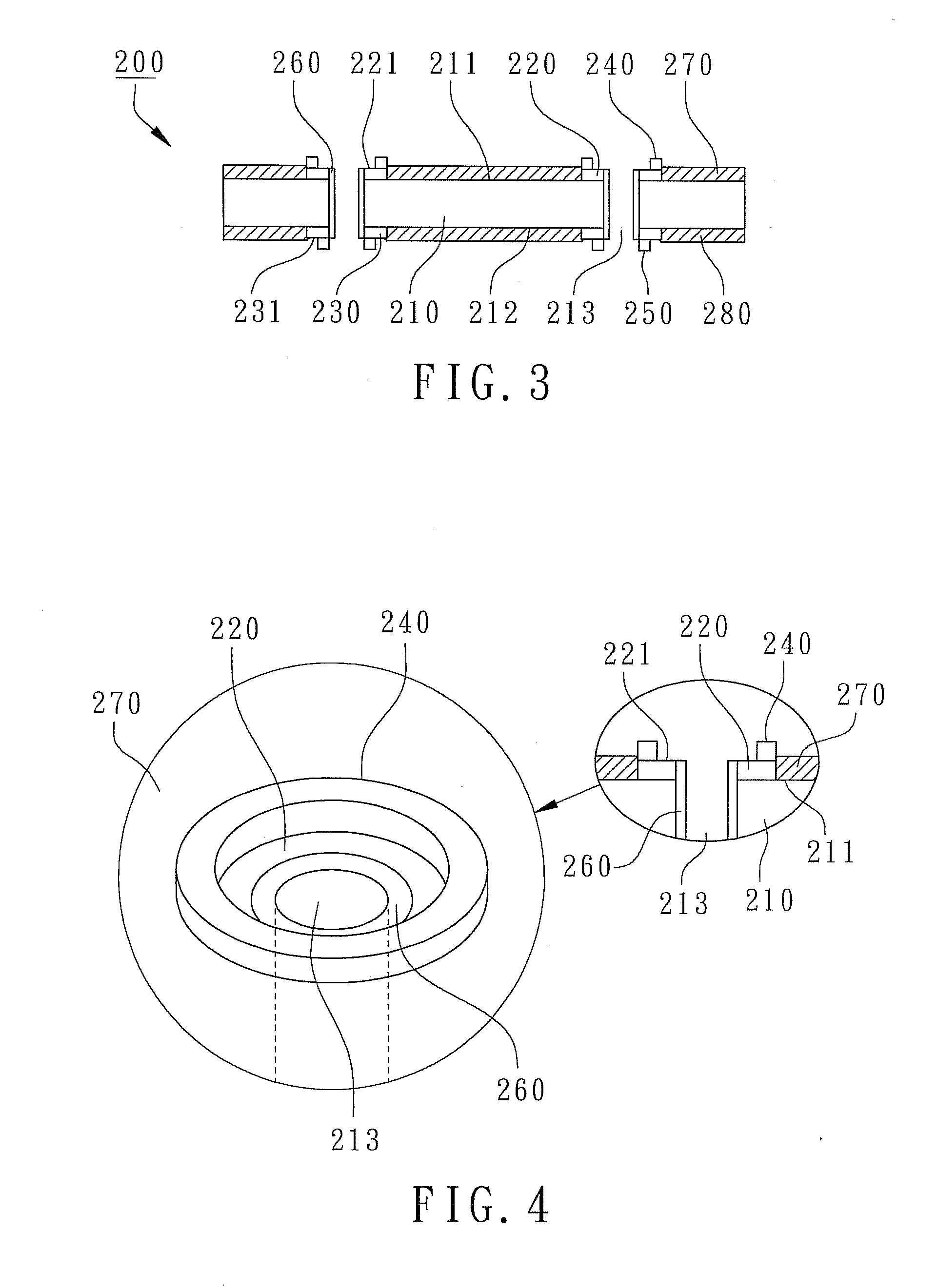

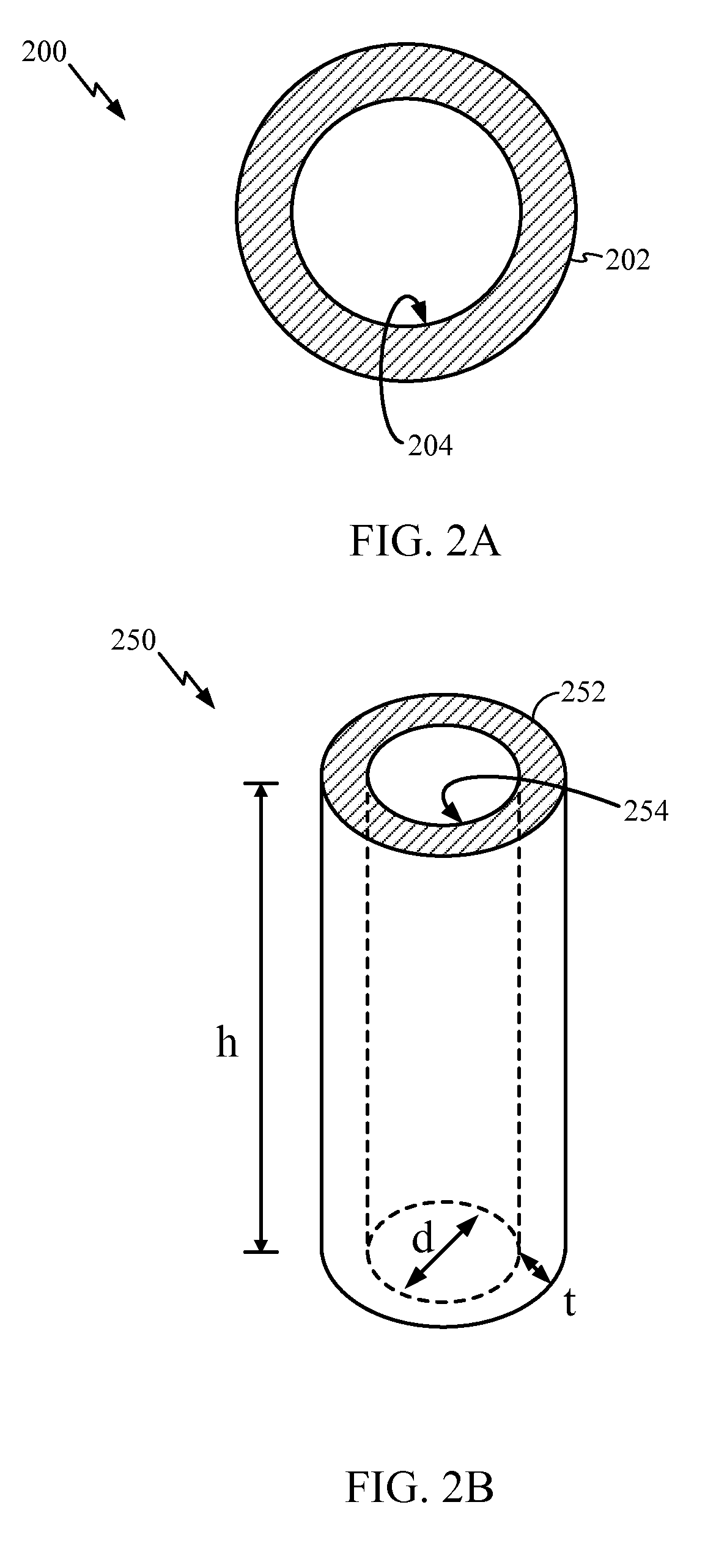

Method of manufacturing through-silicon-via and through-silicon-via structure

A method of manufacturing through-silicon-via (TSV) and a TSV structure are provided. The TSV structure includes a silicon substrate, an annular capacitor, a conductive through-via, a layer of low-k material, and a bump. The annular capacitor is within the silicon substrate and constituted of a first conductive layer, a capacitor dielectric layer, and a second conductive layer from the inside to the outside. The conductive through-via is disposed in the silicon substrate surrounded by the annular capacitor, and the layer of low-k material is between the annular capacitor and the conductive through-via. The bump is in touch with the conductive through-via for bonding other chip.

Owner:IND TECH RES INST

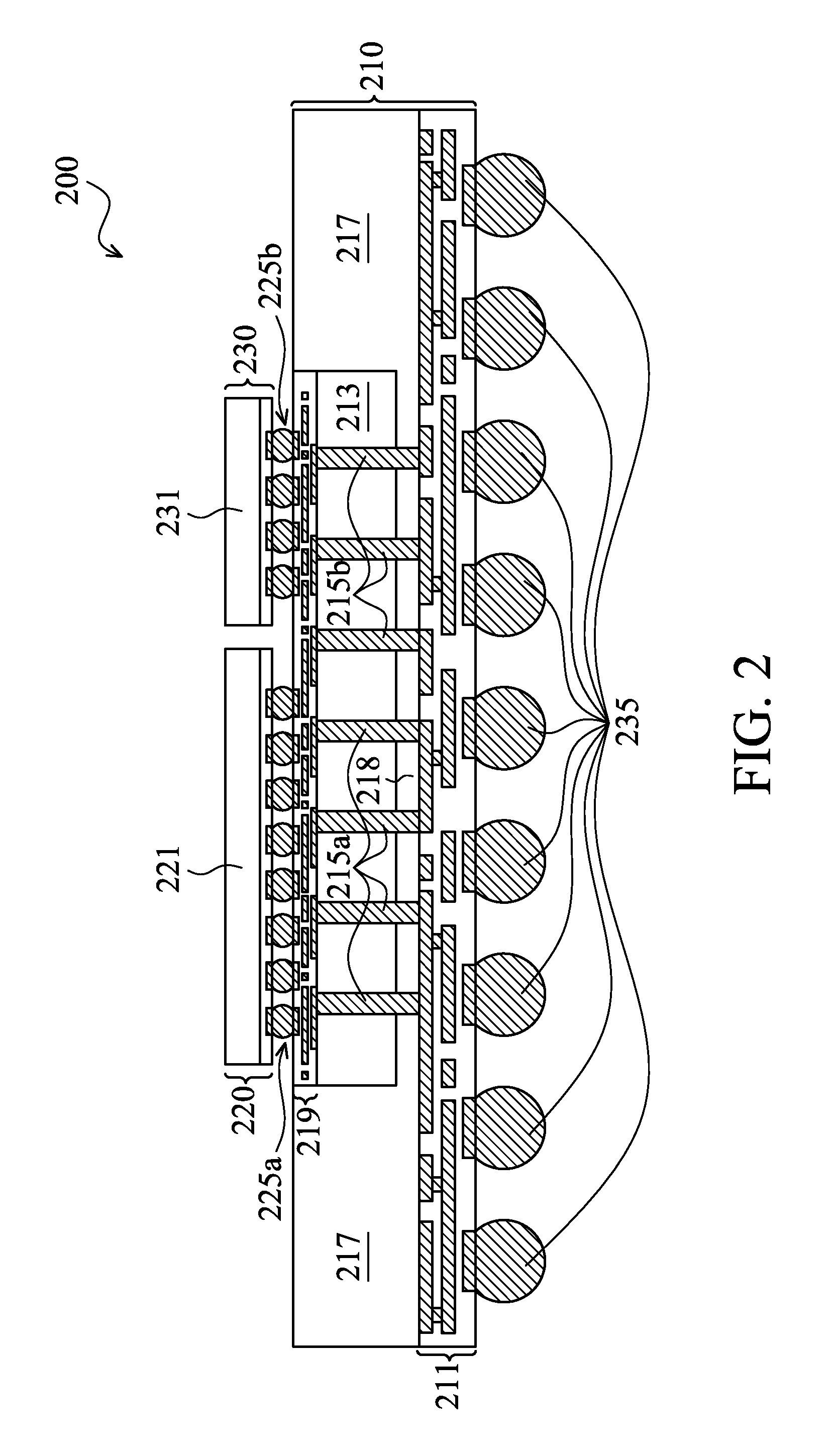

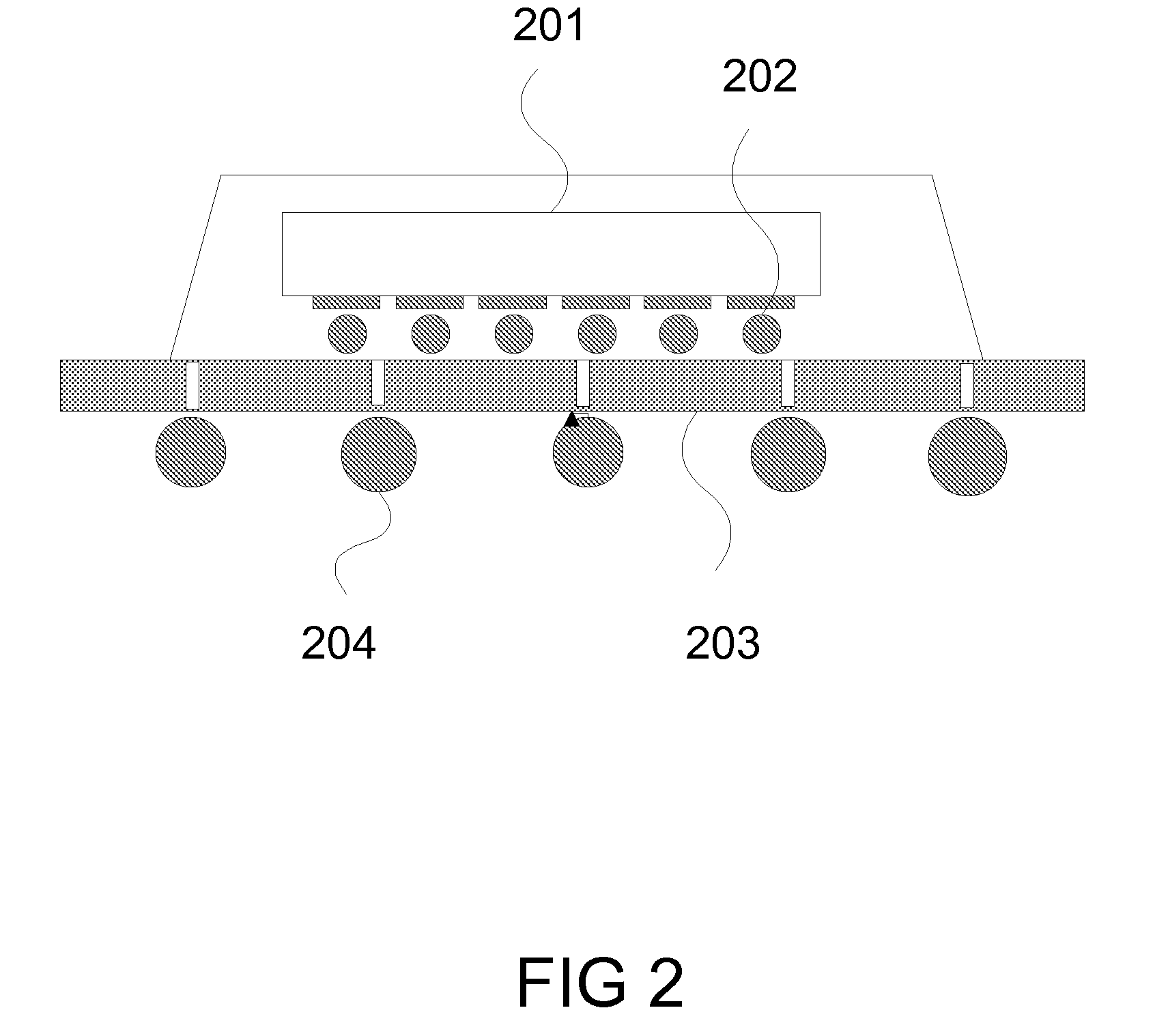

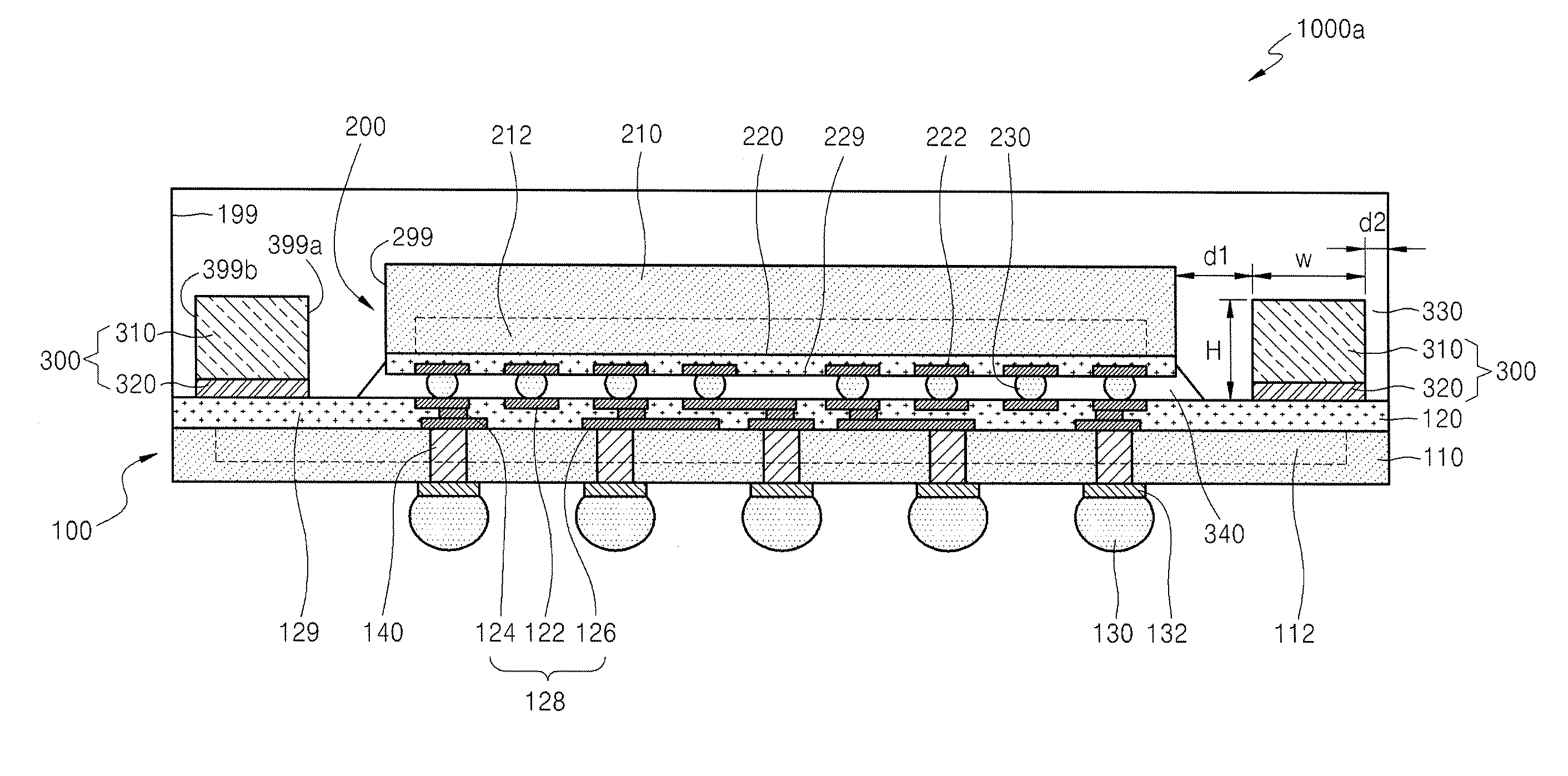

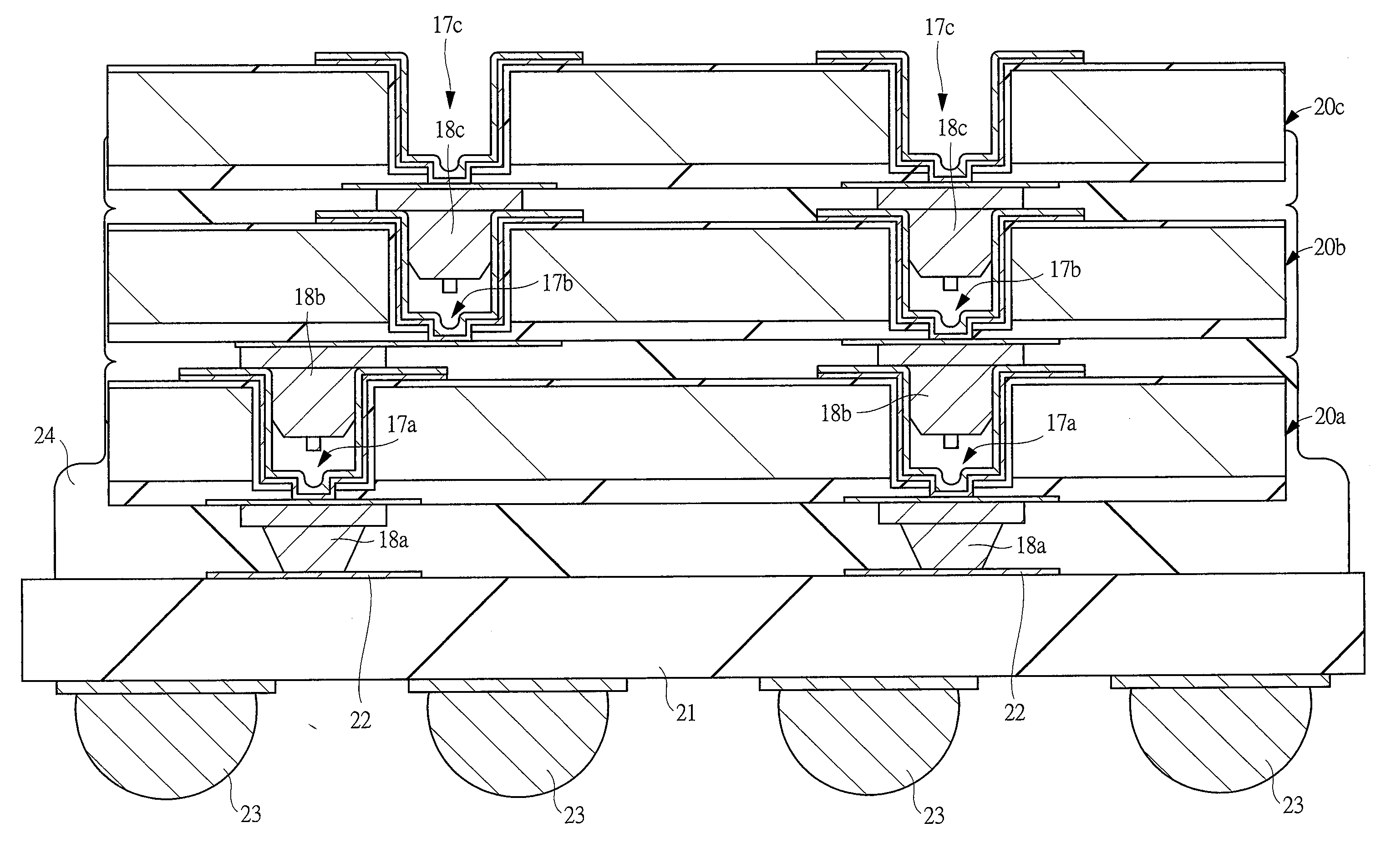

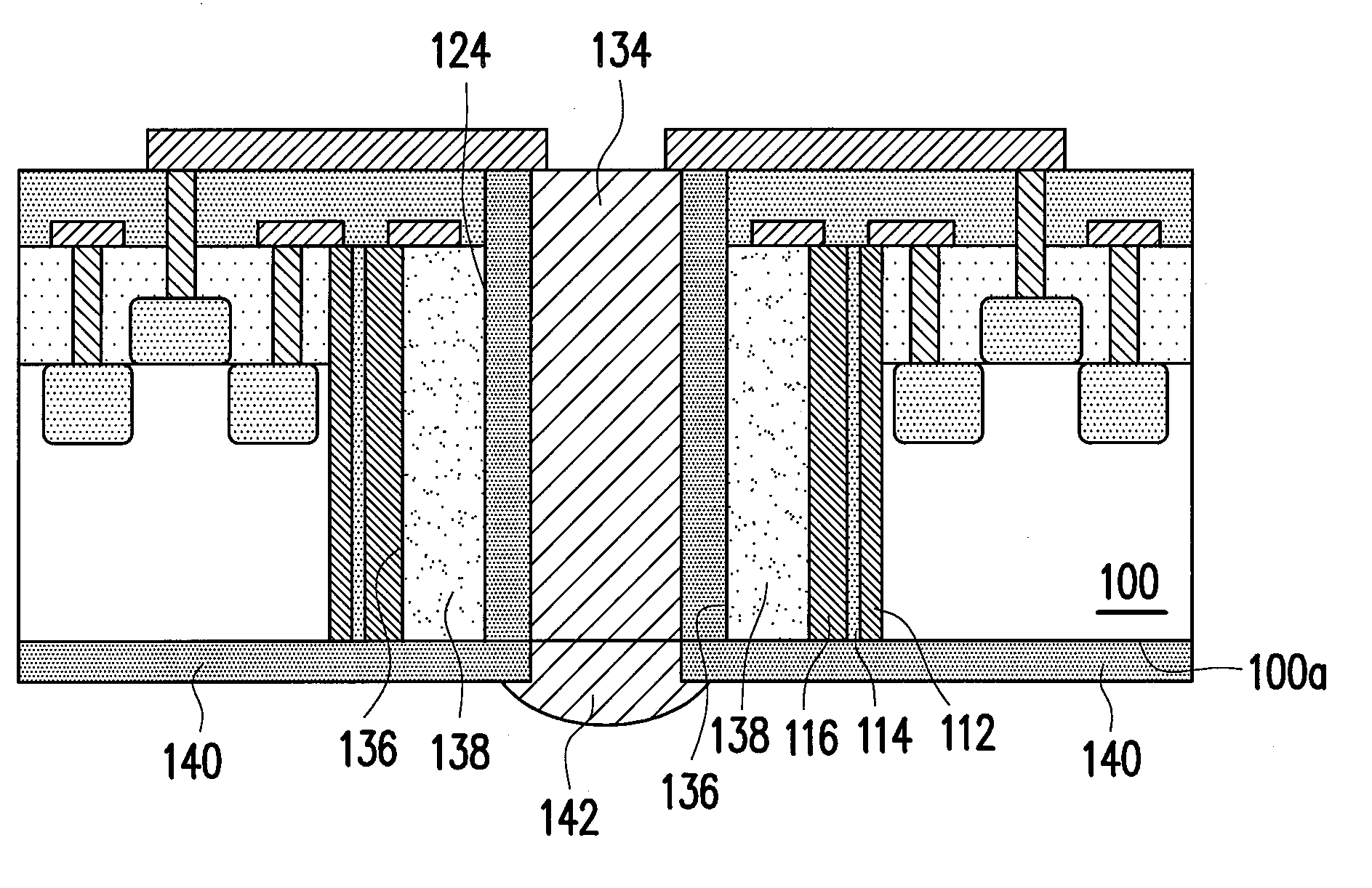

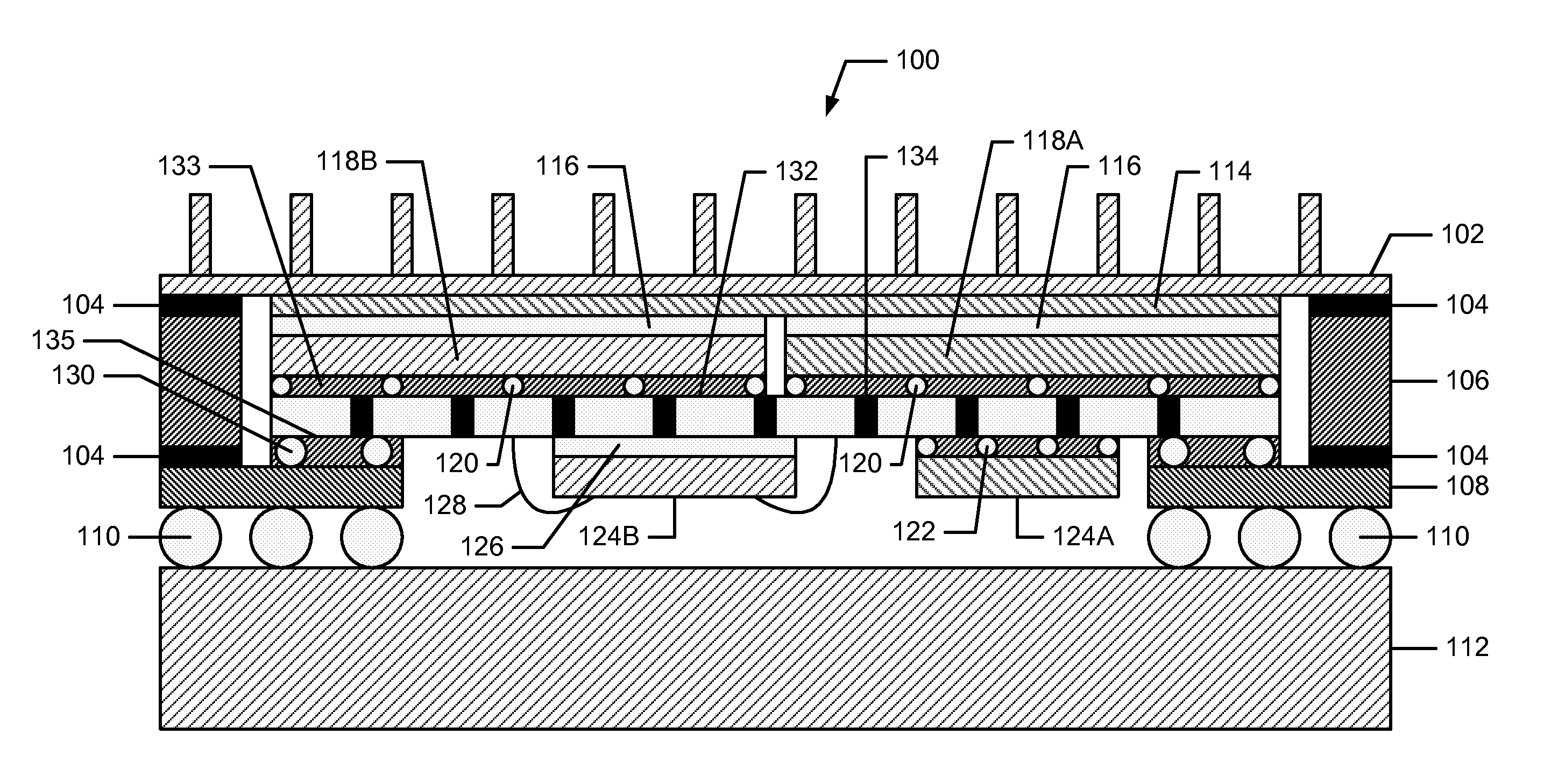

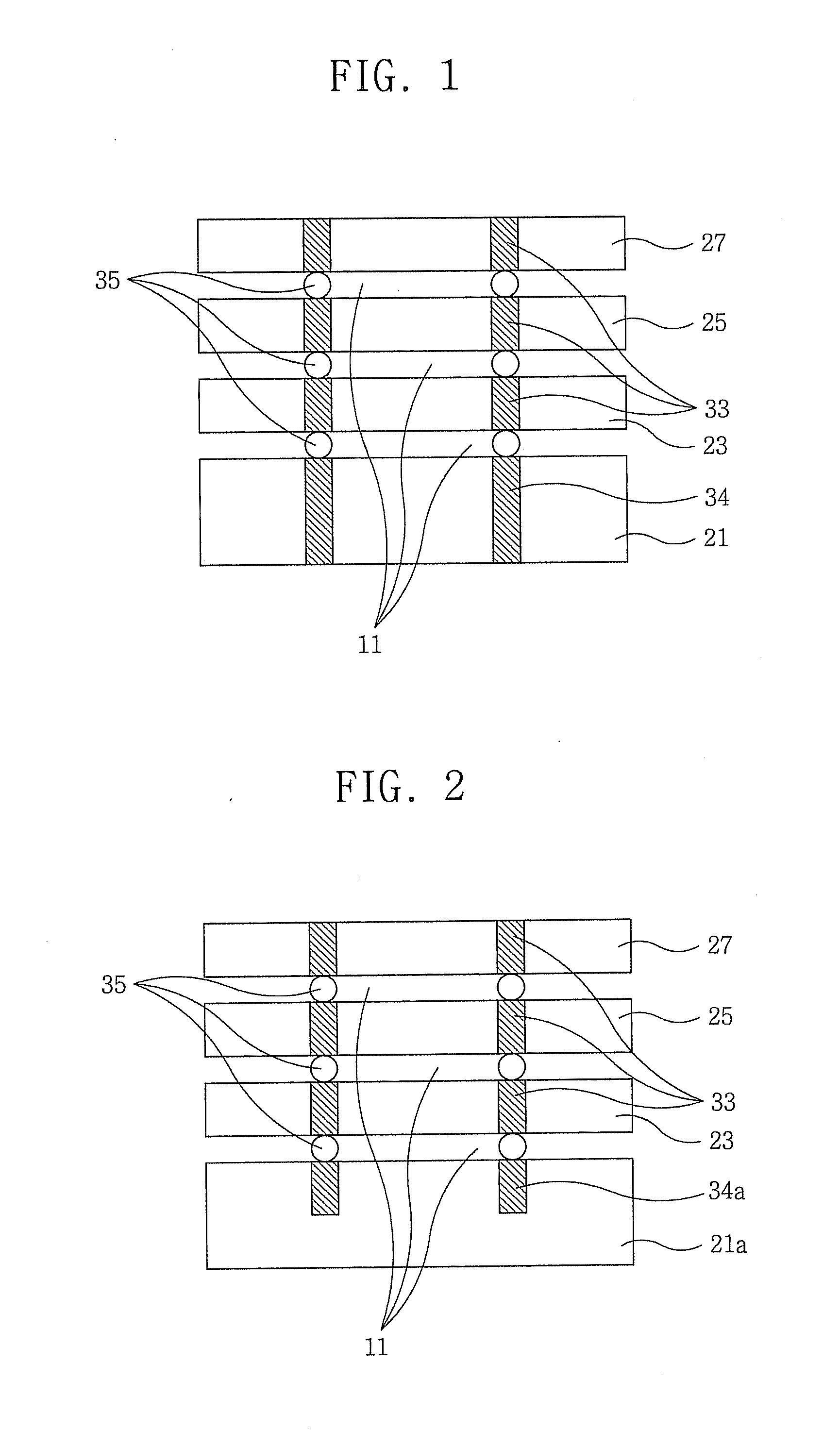

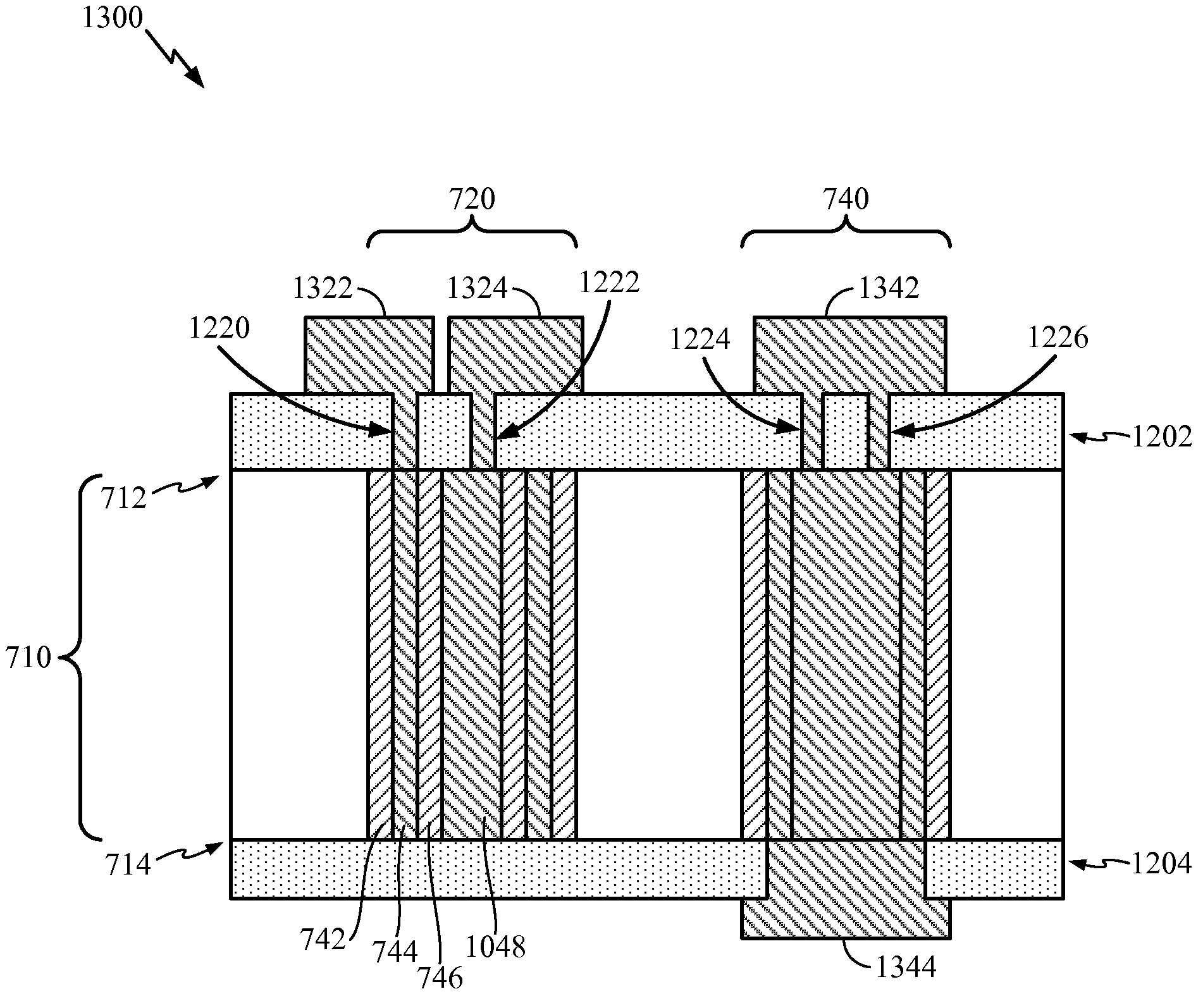

Apparatus having thermal-enhanced and cost-effective 3D IC integration structure with through silicon via interposers

ActiveUS20100213600A1Improved thermal managementImprove thermal performanceSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerInterposer

An apparatus having a three-dimensional integrated circuit structure is described herein. The apparatus include an interposer for carrying a plurality of high and low-power chips. The high-power chips are attached and connected to one side of the interposer, while the low-power chips are attached and connected to the other side of the interposer. In generally, the high-power chips produce more heat than does the low-power chip during their operations. The interposer further include through silicon vias and redistribution layers for connecting the chips on both surfaces. In addition, the interposer assembly is attached and connected to a substrate layer, which is in turn attached and connected to a printed circuit board. In order to provide improve thermal management, the interposer surface carrying the high-power chips are oriented away from the circuit board. A heat spreader is attached to the back sides of the high-power chips for dissipating the heat.

Owner:THE HONG KONG UNIV OF SCI & TECH

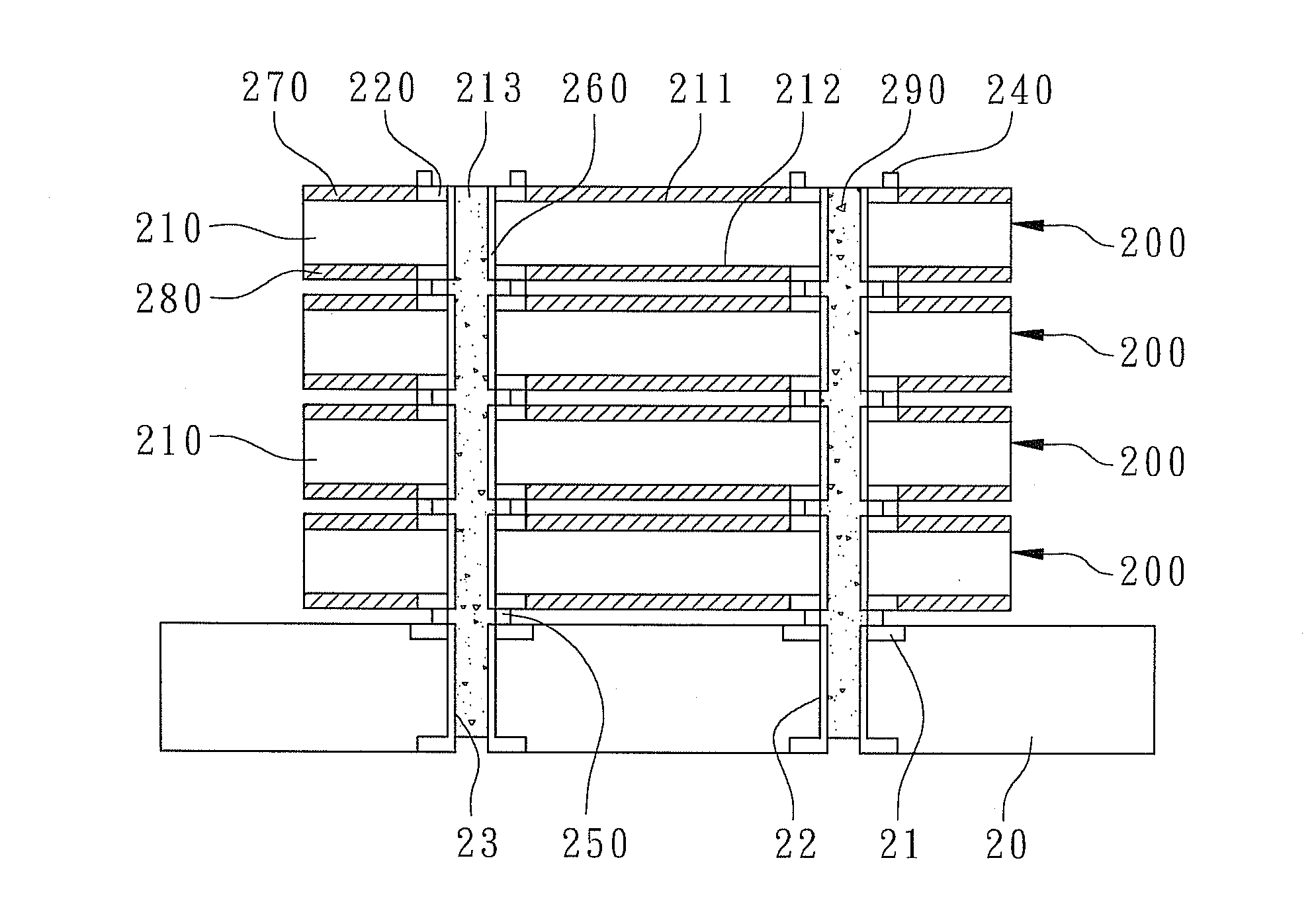

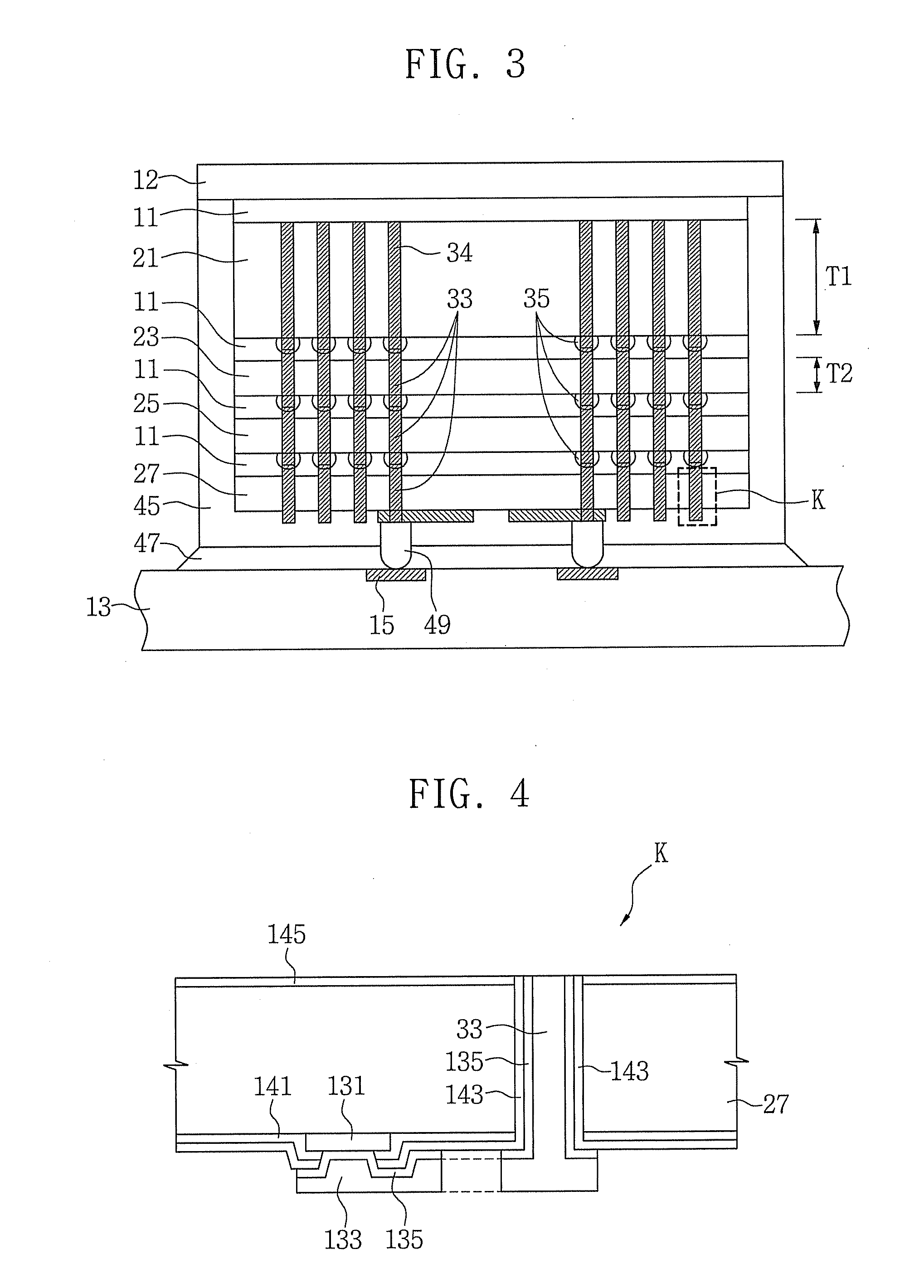

Semiconductor chip having TSV (through silicon via) and stacked assembly including the chips

InactiveUS20090267194A1Precise alignmentReduce the overall heightSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip having through silicon vias (TSV) and a stacked assembly including the chip are revealed. The chip has a plurality of first and second bonding pads disposed on two opposing surfaces of a semiconductor substrate respectively. Through hole vertically penetrate through the semiconductor substrate and the first and second bonding pads. By forming first extruded ring, the first bonding pad has a first contact surface located between the first extruded ring and the through hole. By forming second extruded ring, the second bonding pad has a second contact surface located outside and adjacent to the second extruded rings to encircle the second extruded ring. The second extruded ring has a proper dimension to fit in the first extruded ring. Accordingly, a plurality of semiconductor chip can be stacked each other with accurate alignment without shifting to effectively reduce the stacked assembly height, moreover, chip stacking processes are accomplished by vertically stacking a plurality of chips first then filling conductive material into the through holes without electrical short between the adjacent bonding pads due to overflow of conductive material to meet the fine-pitch requirements of TSV. The process flow for the stacked assembly is simplified with higher production yields.

Owner:POWERTECH TECHNOLOGY

Stacked Semiconductor Device And Method Of Fabricating The Same

InactiveUS20120038045A1Easily emit heatDecrease fault rate of reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A stacked semiconductor device may have a plurality of chips stacked in three-dimension. The stacked semiconductor device may include a first semiconductor chip and at least one second semiconductor chip. The first semiconductor chip may include a plurality of first through silicon vias (TSVs). The at least one second semiconductor chip may include a plurality of second TSVs. The at least one second semiconductor chip may be stacked above the first semiconductor chip and may be thinner than the first semiconductor chip. Therefore, the stacked semiconductor device may have an improved reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

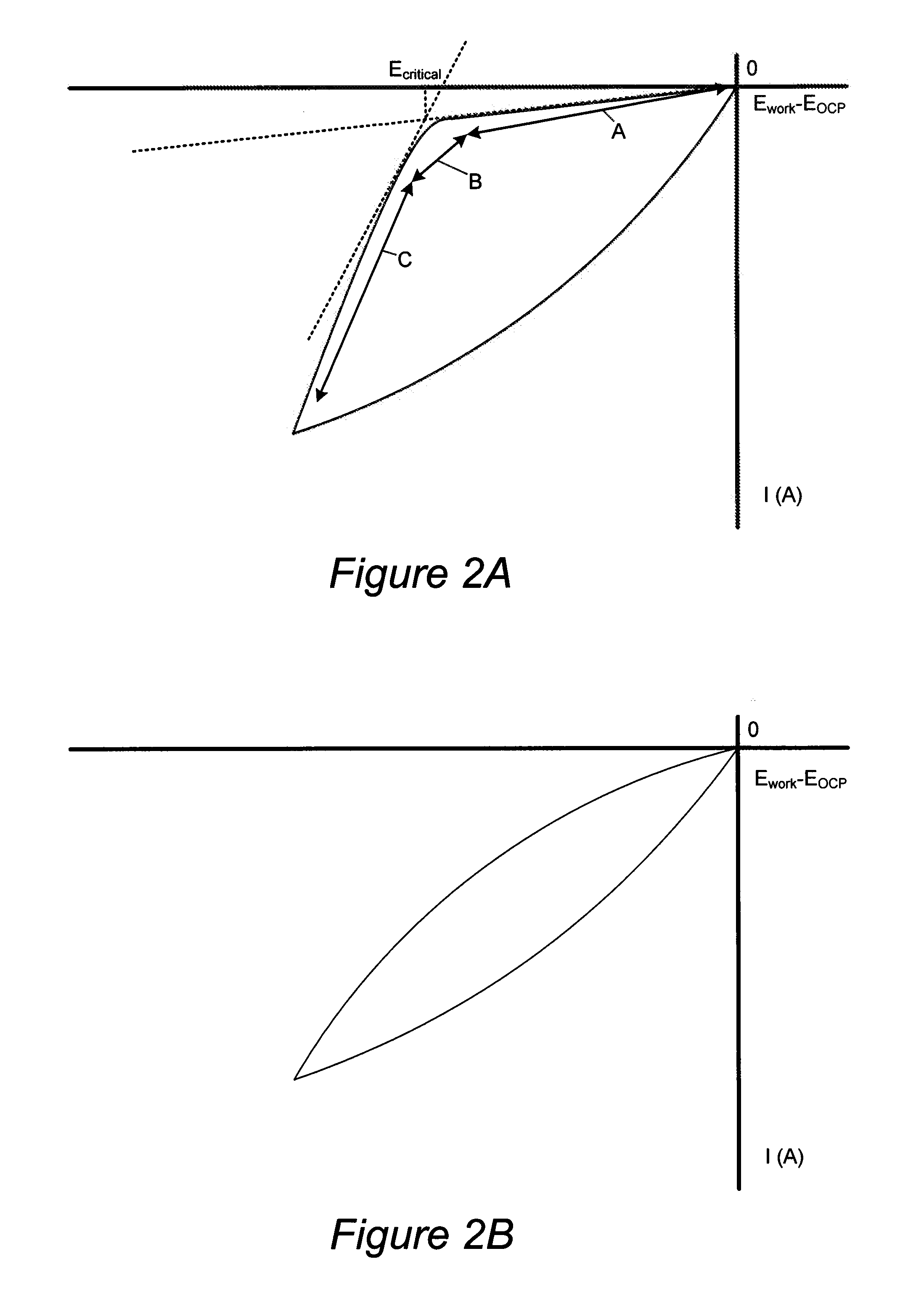

Through silicon via filling using an electrolyte with a dual state inhibitor

ActiveUS20110284386A1Faster rateLittle and depositionCellsMachining electric circuitsElectricityElectroplating

A method for electrofilling large, high aspect ratio recessed features with copper without depositing substantial amounts of copper in the field region is provided. The method allows completely filling recessed features having aspect ratios of at least about 5:1 such as at least about 10:1, and widths of at least about 1 μm in a substantially void-free manner without depositing more than 5% of copper in the field region (relative to the thickness deposited in the recessed feature). The method involves contacting the substrate having one or more large, high aspect ratio recessed features (such as a TSVs) with an electrolyte comprising copper ions and an organic dual state inhibitor (DSI) configured for inhibiting copper deposition in the field region, and electrodepositing copper under potential-controlled conditions, where the potential is controlled not exceed the critical potential of the DSI.

Owner:NOVELLUS SYSTEMS

Through Silicon Via With Embedded Decoupling Capacitor

ActiveUS20100308435A1Semiconductor/solid-state device detailsSolid-state devicesDielectricEngineering

A semiconductor die, having a substrate, includes a through silicon via. The through silicon via includes a decoupling capacitor having a first co-axial conductor, a second co-axial conductor, and a co-axial dielectric separating the first co-axial conductor from the second co-axial conductor. The decoupling capacitor is configured to provide local charge storage for components on the semiconductor die.

Owner:QUALCOMM INC

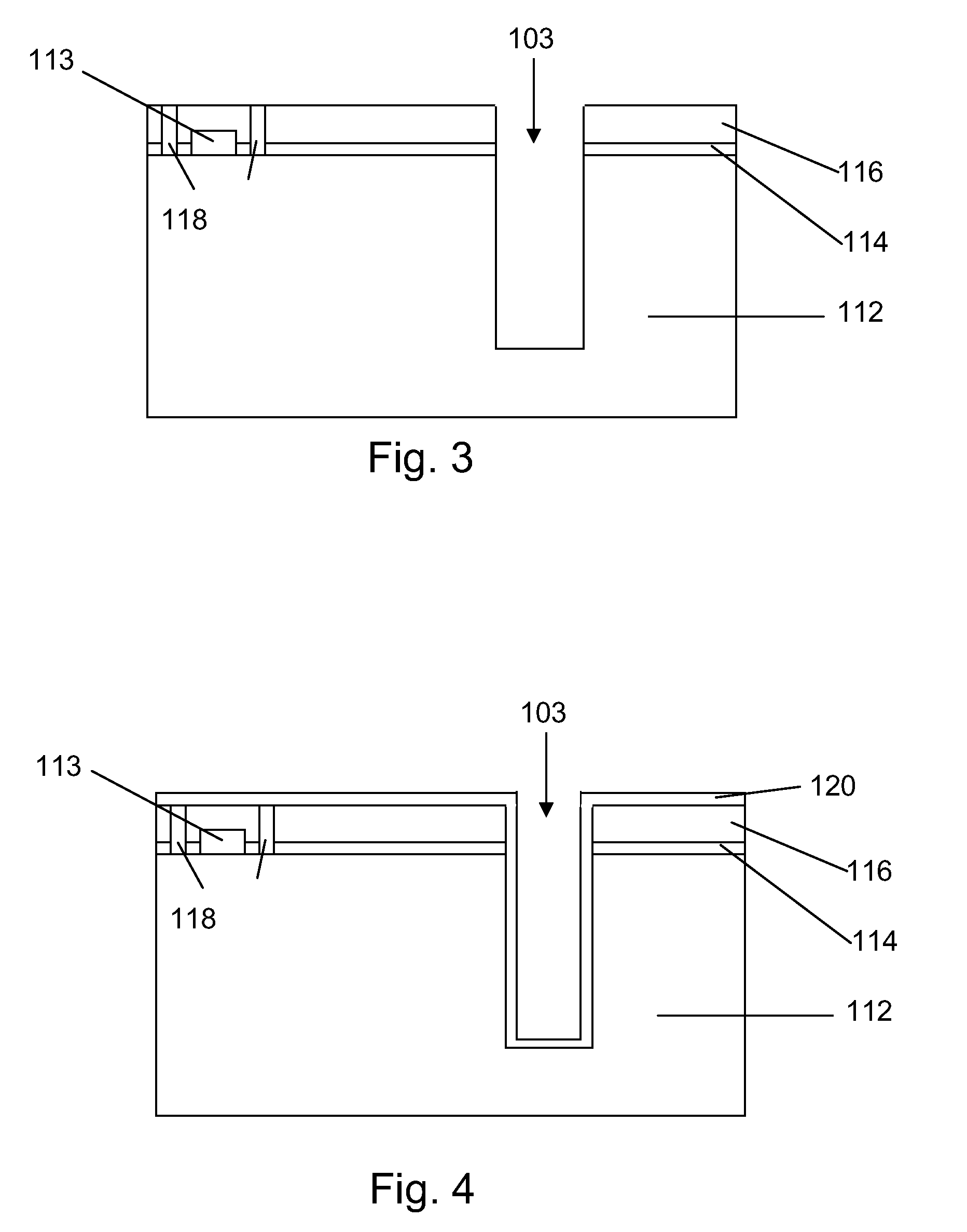

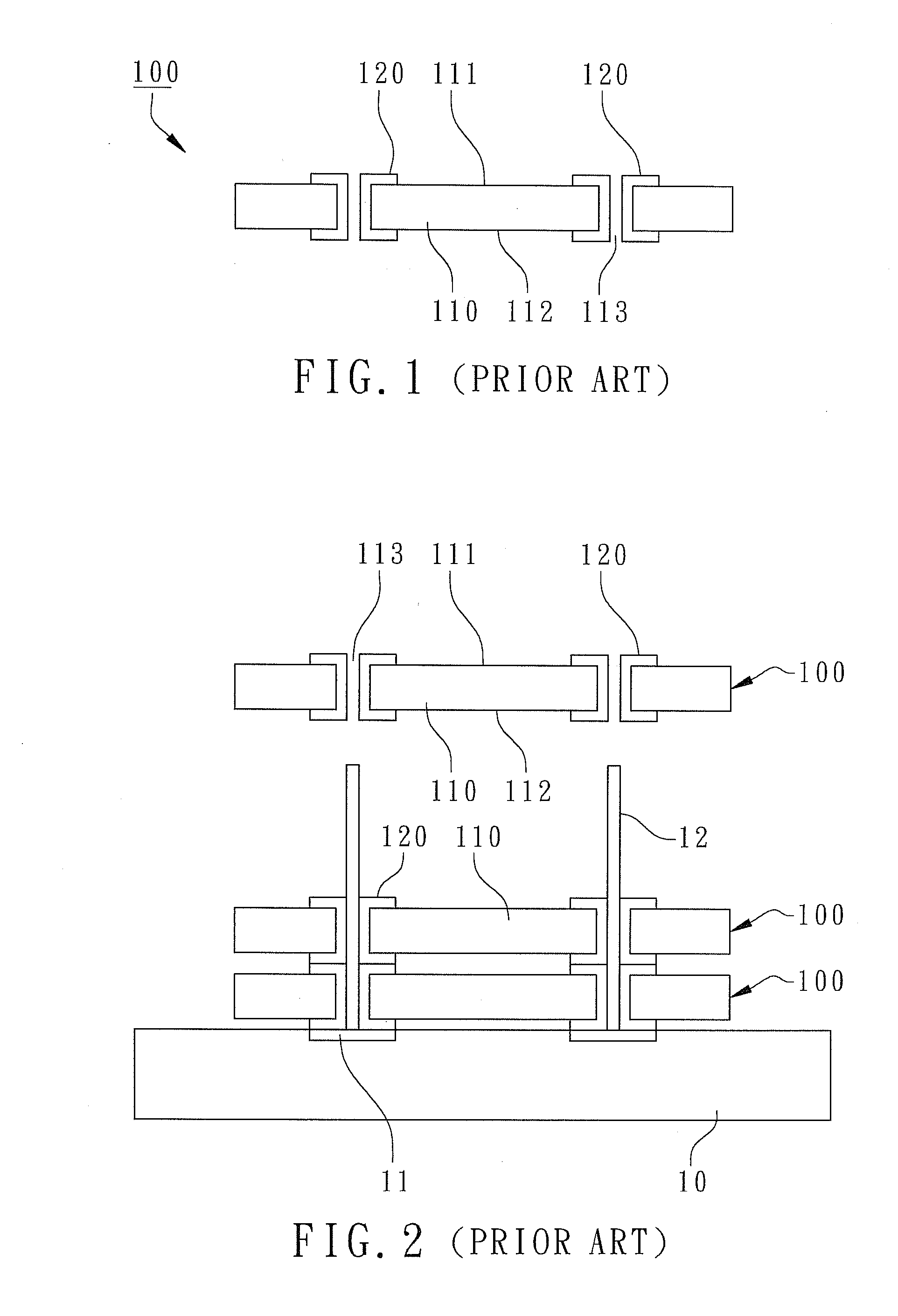

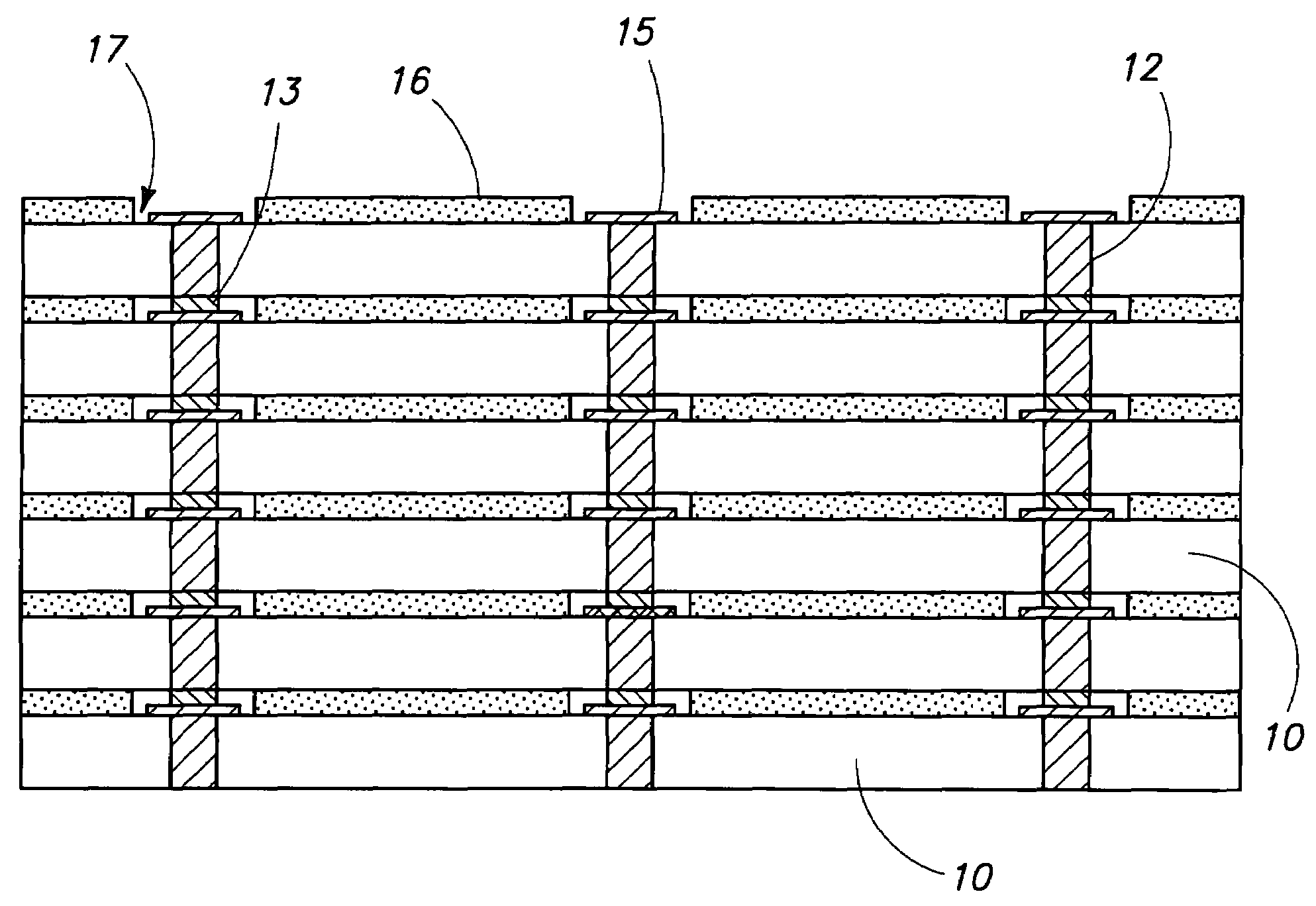

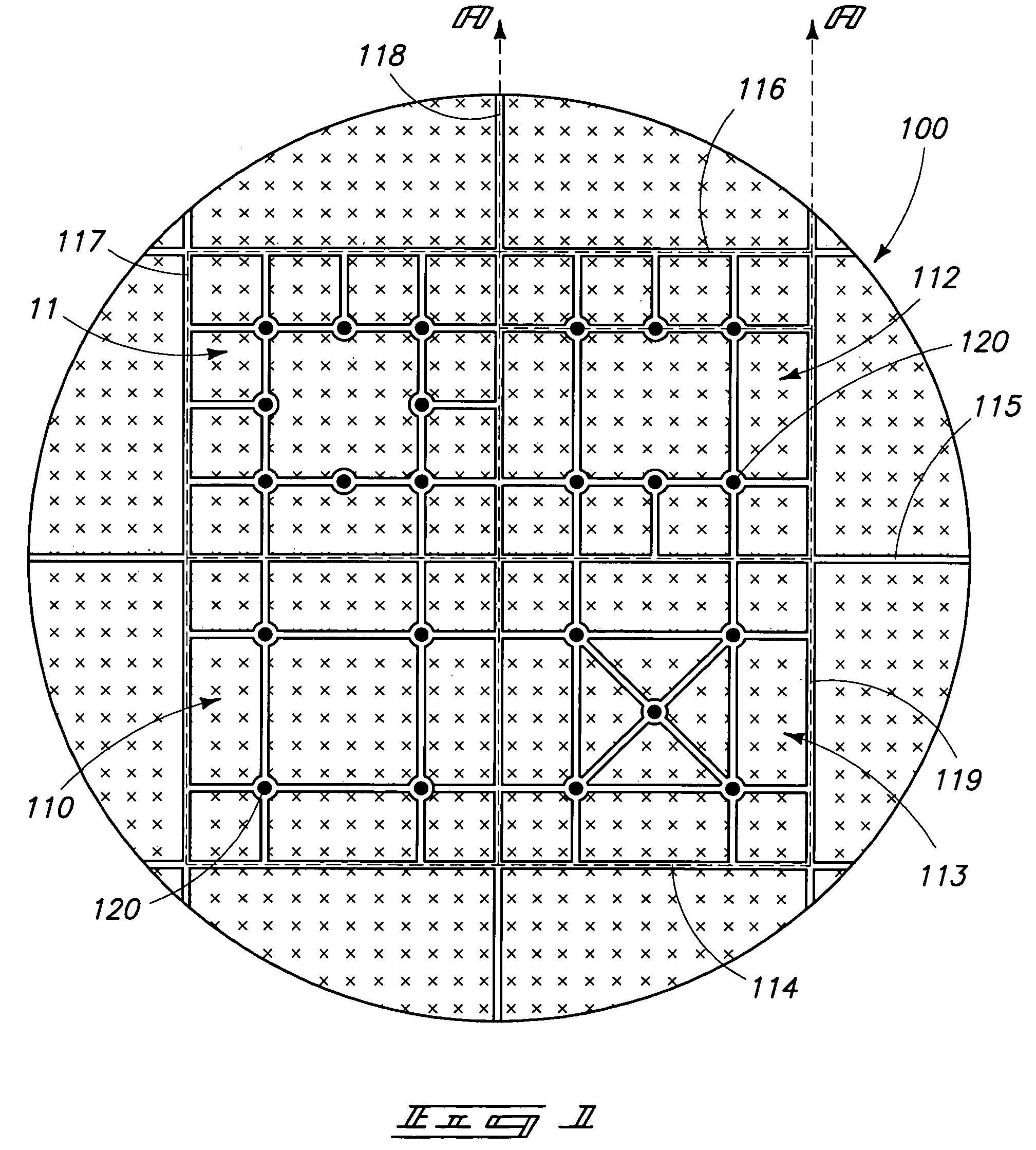

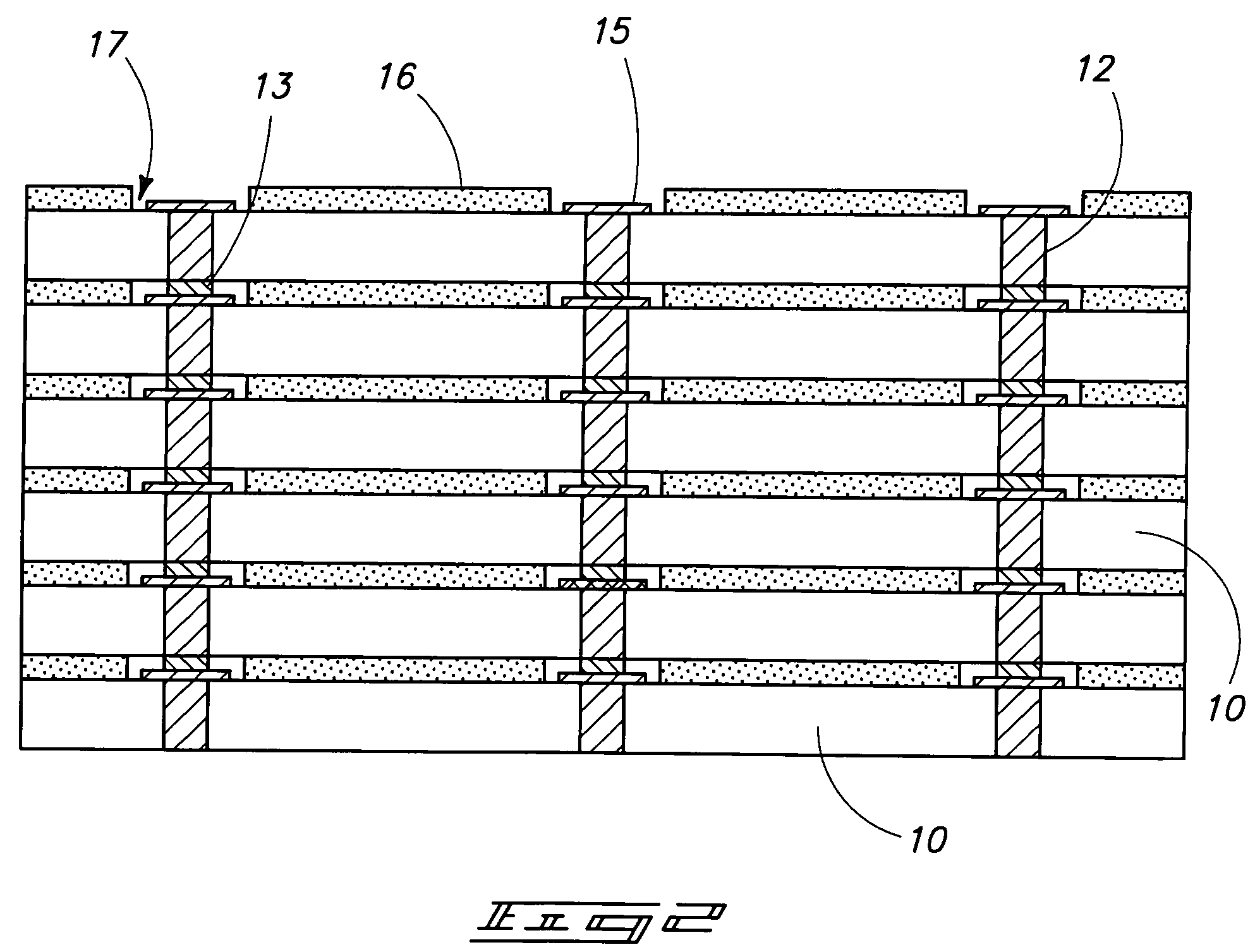

Multi-chip stack structure having through silicon via and method for fabrication the same

InactiveUS20090032928A1Simplify the manufacturing processReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesChip stackingContamination

The invention discloses a multi-chip stack structure having through silicon via and a method for fabricating the same. The method includes: providing a wafer having a plurality of first chips; forming a plurality of holes on a first surface of each of the first chips and forming metal posts and solder pads corresponding to the holes so as to form a through silicon via (TSV) structure; forming at least one groove on a second surface of each of the first chips to expose the metal posts of the TSV structure so as to allow at least one second chip to be stacked on the first chip, received in the groove and electrically connected to the metal posts exposed from the groove; filling the groove with an insulating material for encapsulating the second chip; mounting conductive elements on the solder pads of the first surface of each of the first chips and singulating the wafer; and mounting and electrically connecting the stacked first and second chips to a chip carrier via the conductive elements. The wafer, which is not totally thinned but includes a plurality of first chips, severs a carrying purpose during the fabrication process and thereby solves problems, namely a complicated process, high cost, and adhesive layer contamination, facing the prior art that entails repeated use of a carrier board and an adhesive layer for vertically stacking a plurality of chips and mounting the stacked chips on a chip carrier.

Owner:SILICONWARE PRECISION IND CO LTD

Bonding method for through-silicon-via based 3D wafer stacking

ActiveUS7683459B2Semiconductor/solid-state device detailsSolid-state devicesOutgassingWafer stacking

There is described a hybrid bonding method for through-silicon-via based wafer stacking. Patterned adhesive layers are provided to join together adjacent wafers in the stack, while solder bonding is used to electrically connect the vias. The adhesive layers are patterned to enable outgassing and to provide stress relief.

Owner:HONG KONG APPLIED SCI & TECH RES INST

Stacked-chip device

InactiveUS20100052111A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductorThrough-silicon via

A stacked chip device includes a first chip having a first function, and a second chip having a second function which is different from the first function, which is stacked on the first chip. The first chip is a through-silicon-via chip which is comprised of a first semiconductor substrate having first and second surfaces, a first semiconductor integrated circuit which is provided on the first surface of the first semiconductor substrate, a first conductive layer connecting to the first semiconductor integrated circuit, which goes through the first surface of the first semiconductor substrate to the second surface of the first semiconductor substrate, and a second conductive layer not connecting to the first semiconductor integrated circuit, which goes through the first surface of the first semiconductor substrate to the second surface of the first semiconductor substrate. The first and second conductive layers have the same shape and the same structure.

Owner:KK TOSHIBA

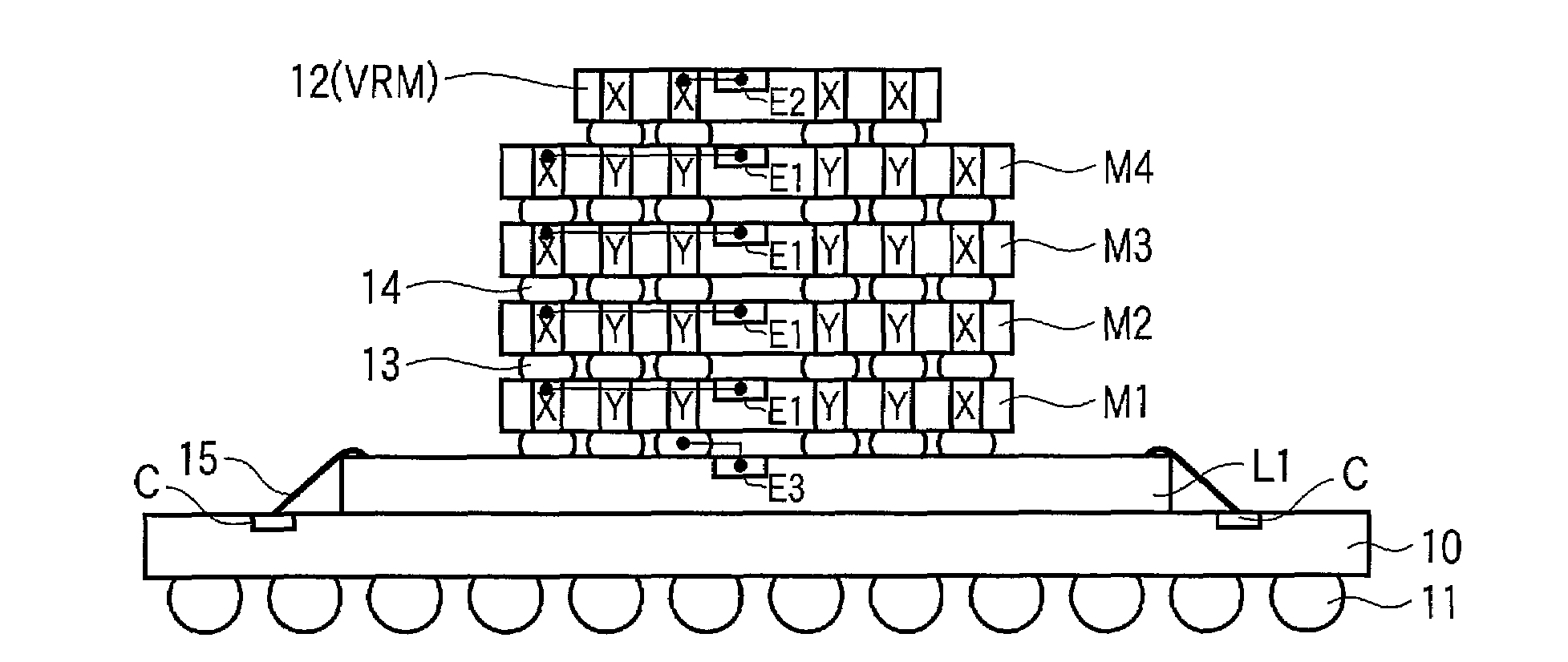

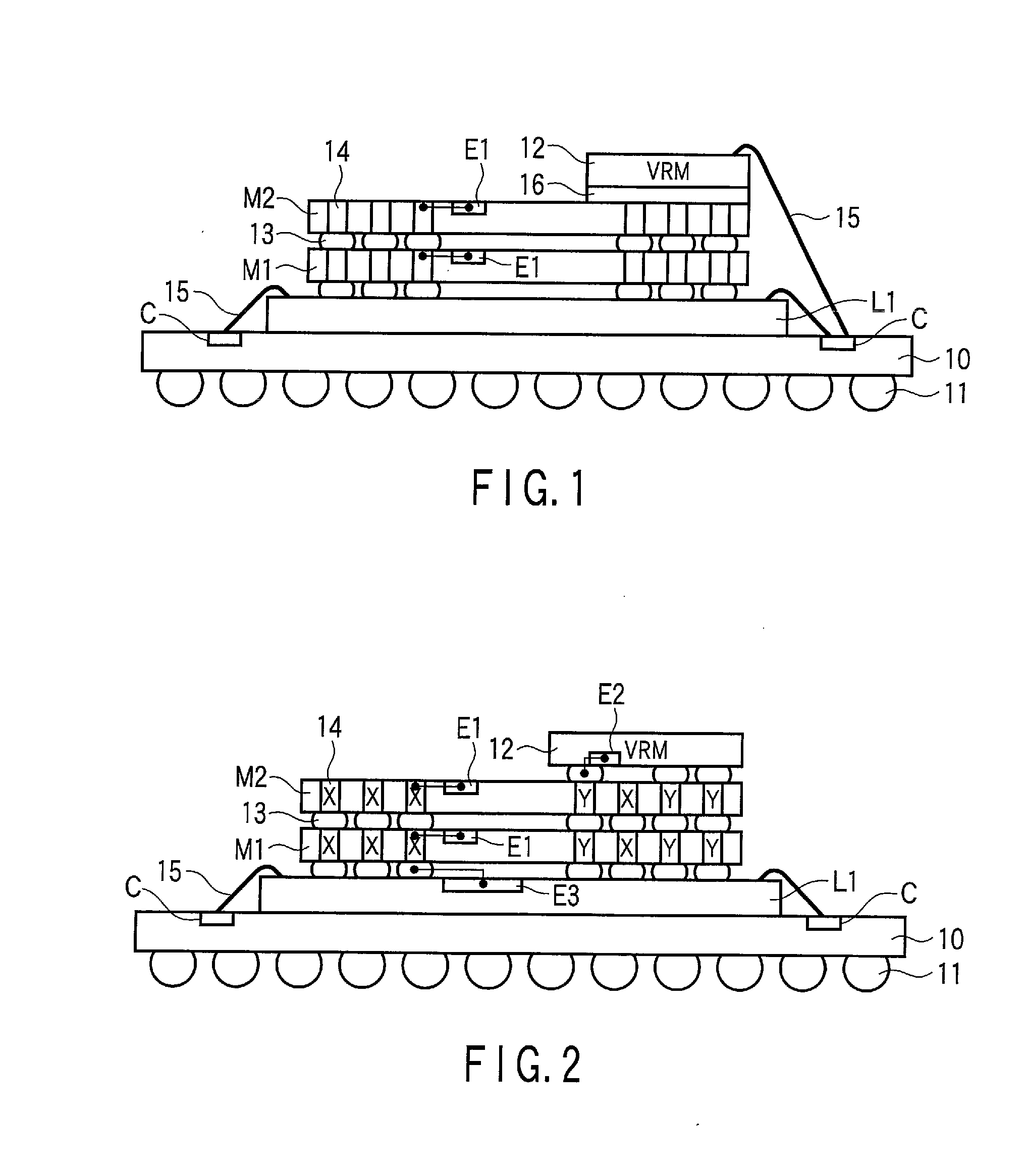

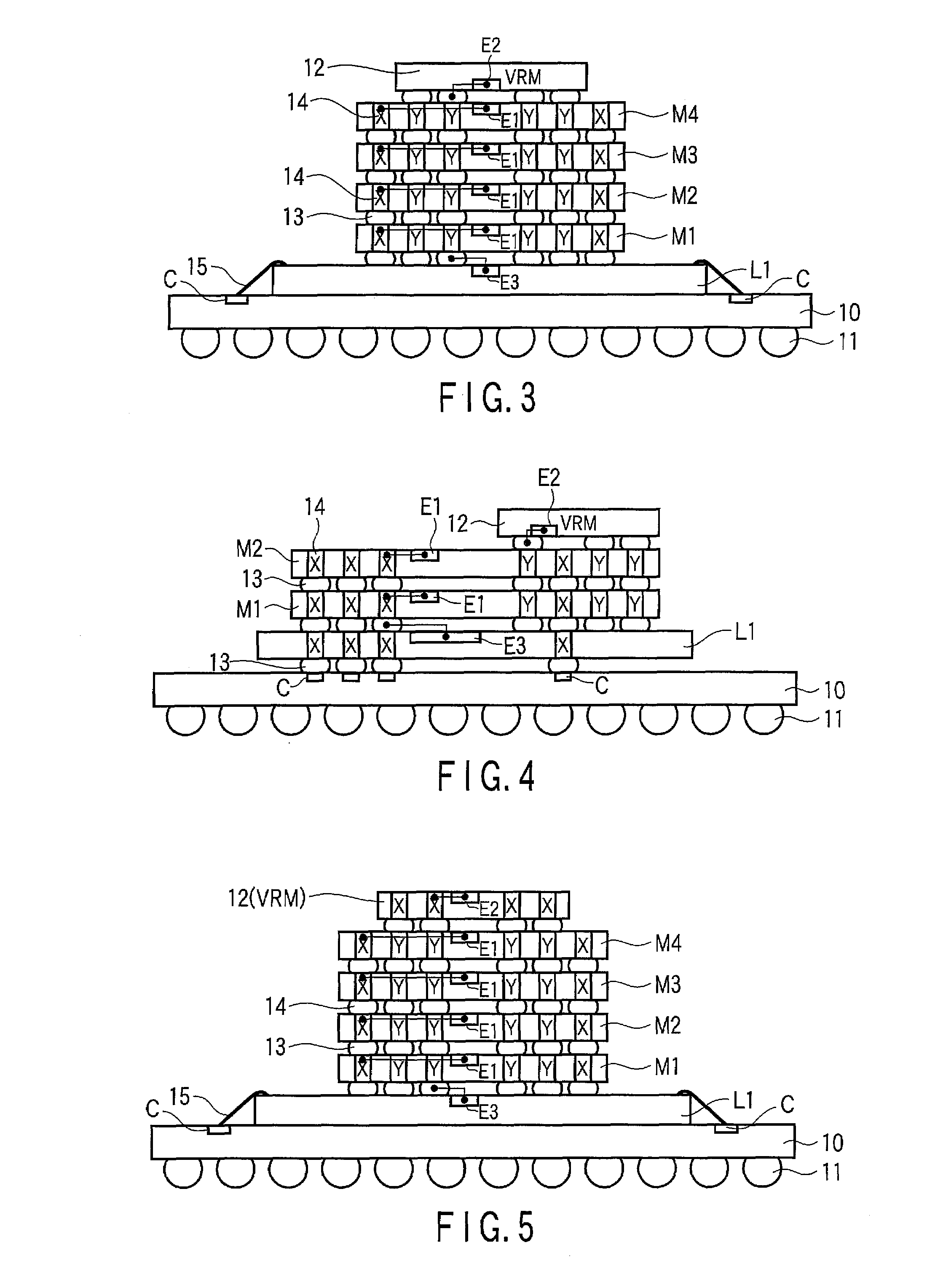

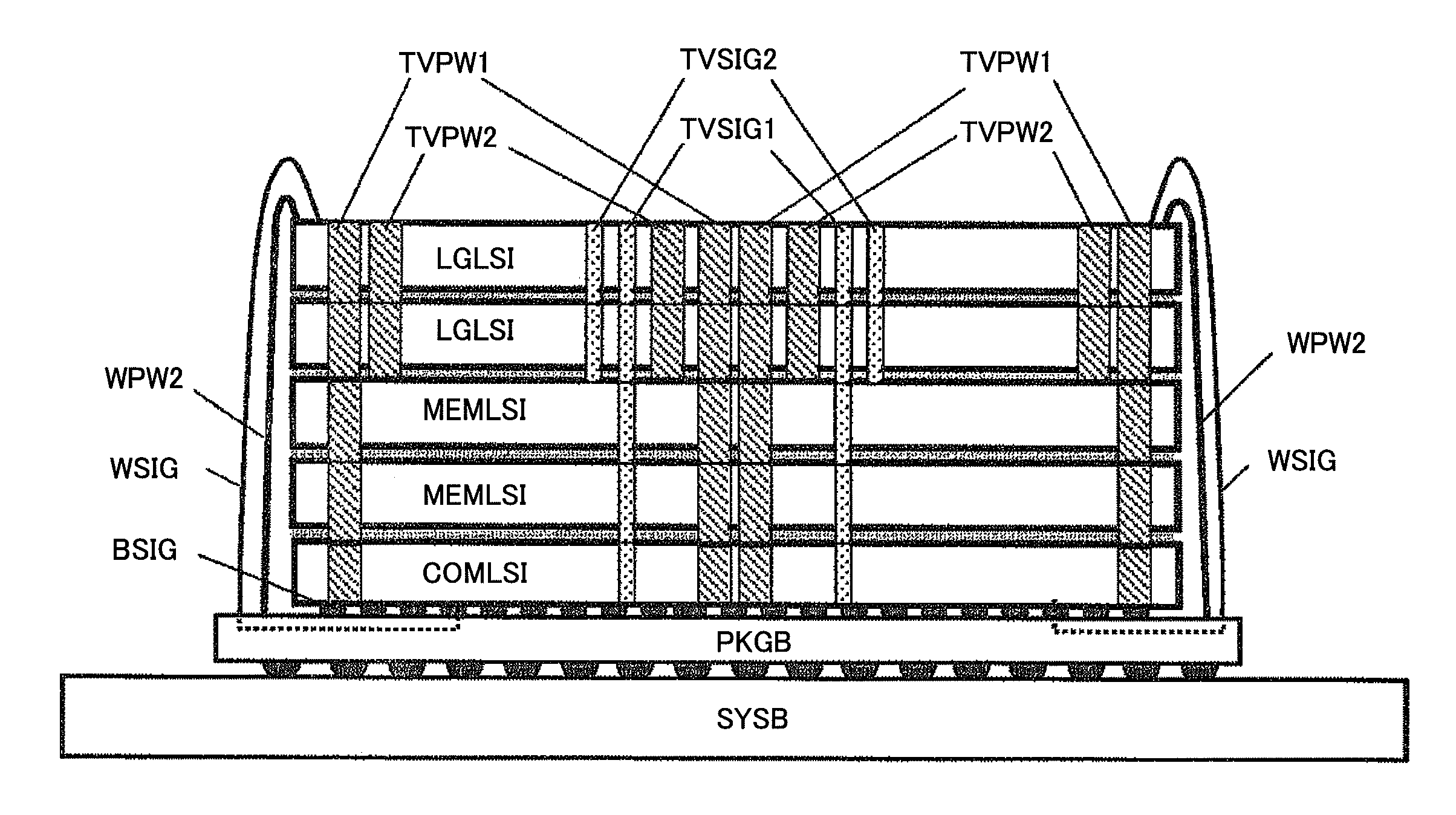

Semiconductor device

InactiveUS20100008058A1Perform communicationImprove system performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor package

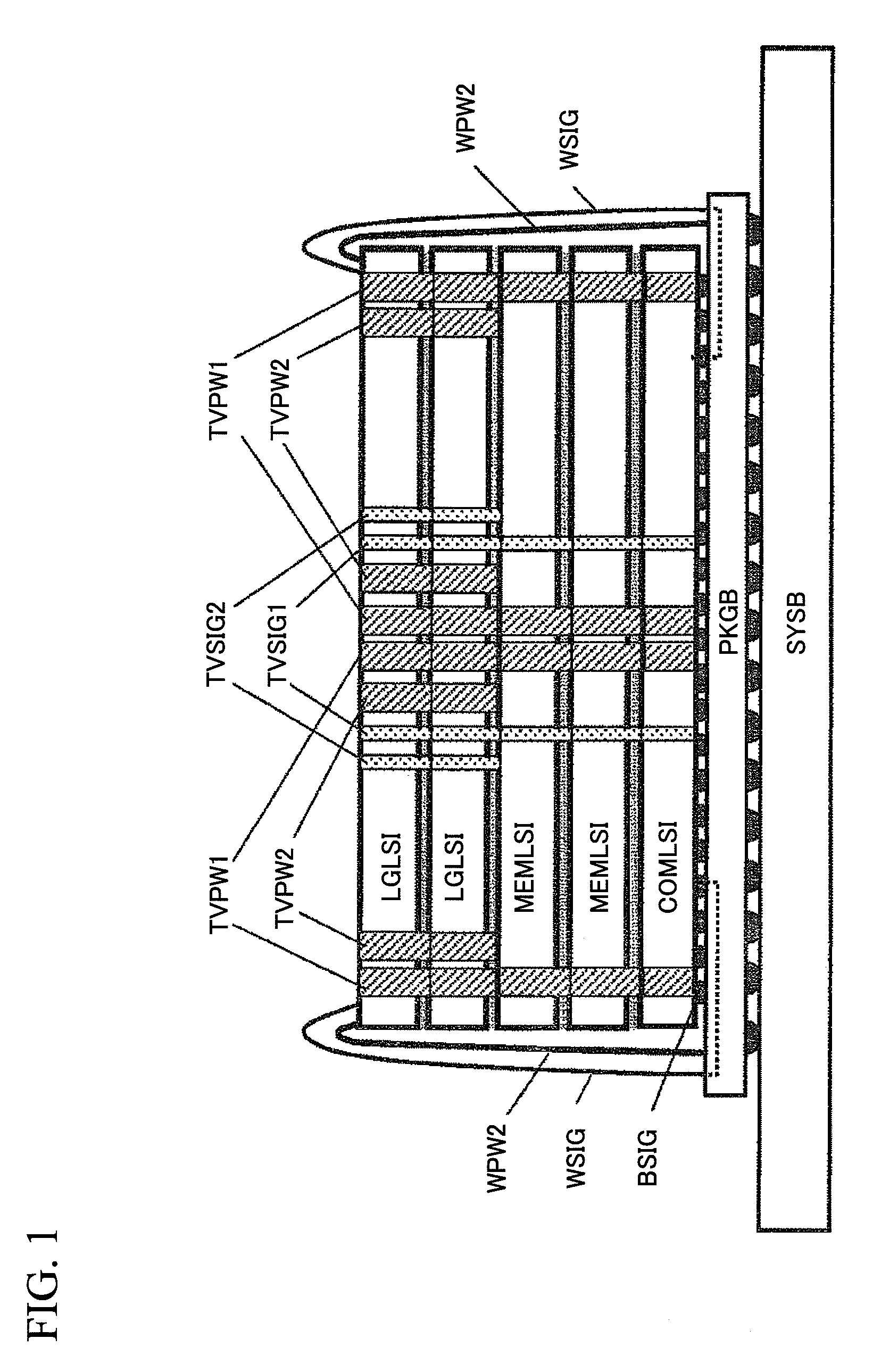

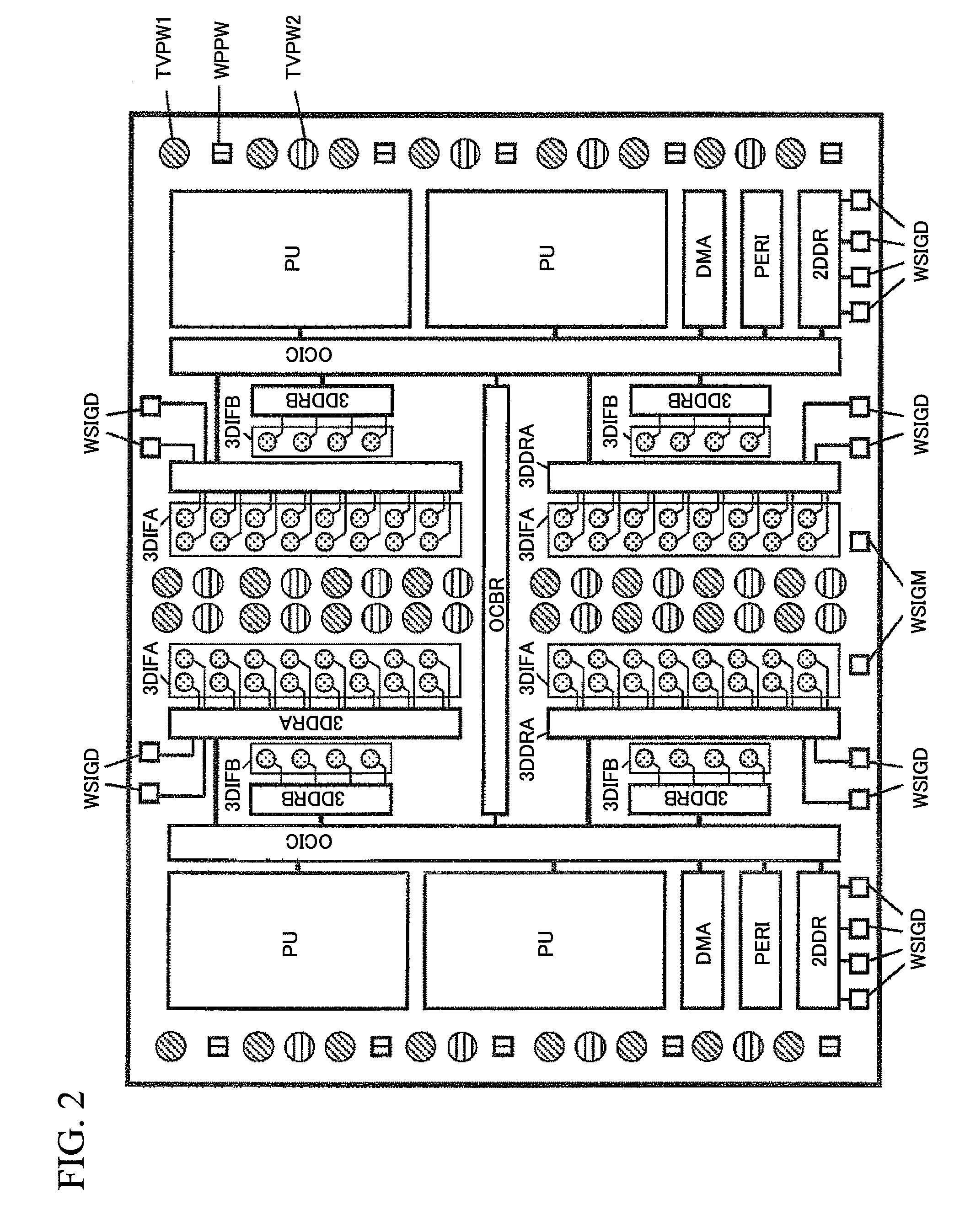

Traffic between logic LSIs and memory is increasing year by year and there is demand for increase of capacity of communication between them and reduction of power consumption in the communication. Communication distances between LSIs can be reduced by stacking the LSIs. However, in a simple stack of logic LSIs and memory LSIs, it is difficult to ensure heat dissipation to cope with increasing heat densities and ensure transmission characteristics for fast communication with the outside of the stacked package. Also required is a connection topology that improves the performance of communication among the stacked LSIs while ensuring the versatility of the LSIs. An external-communication LSI, a memory LSI, and a logic LSI are stacked in this order in a semiconductor package and are interconnected by through silicon vias. Output terminals of multiple stacked LSIs are connected to an input terminal of a through silicon via of the stacked memory LSI and input terminals of multiple stacked LSIs are connected to an output terminal of a through silicon via of the stacked memory LSI, thereby directly connecting both of the external-communication LSI and the logic LSI to a wiring line of the memory LSI.

Owner:HITACHI LTD