Patents

Literature

228 results about "Deep reactive-ion etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

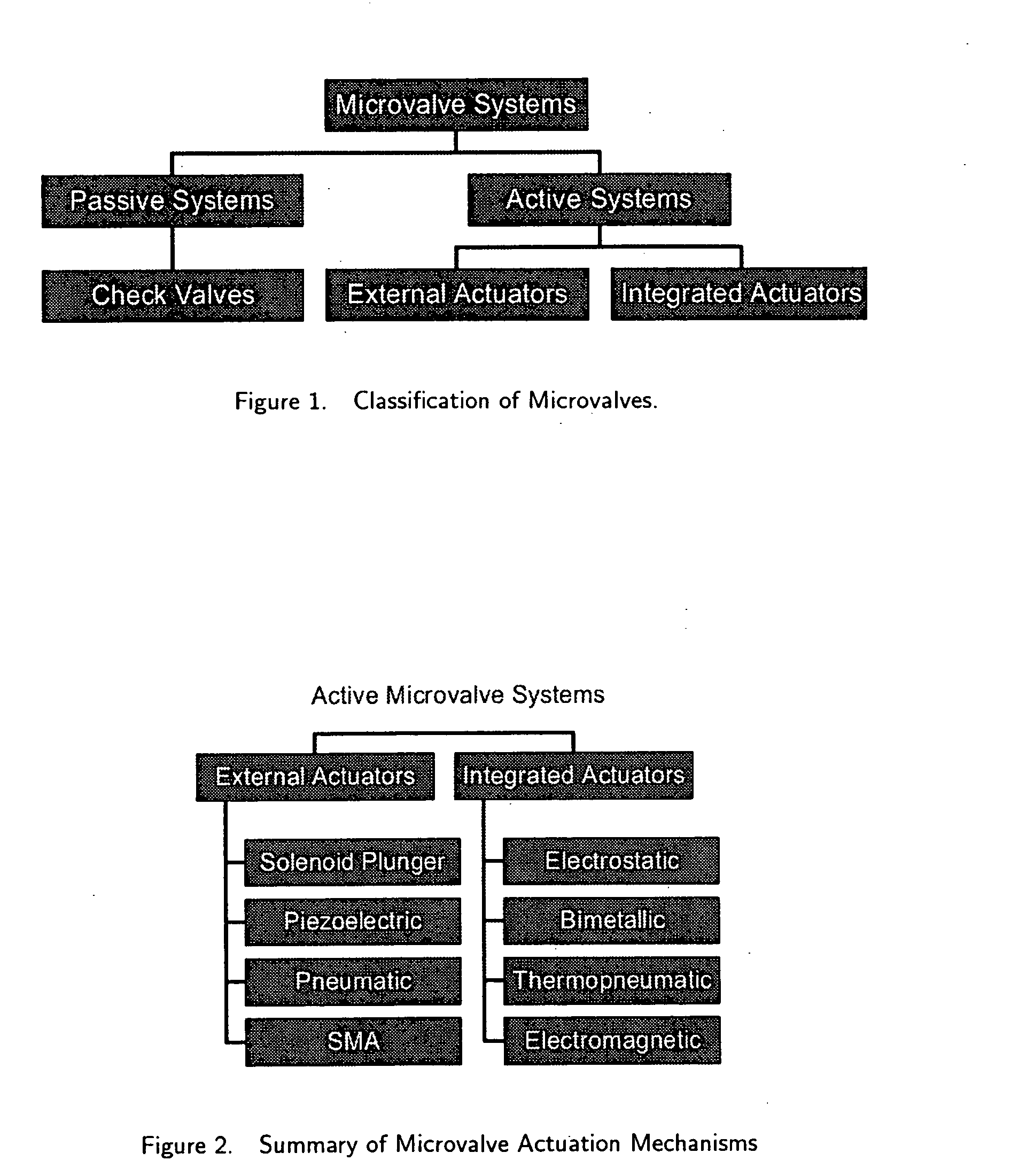

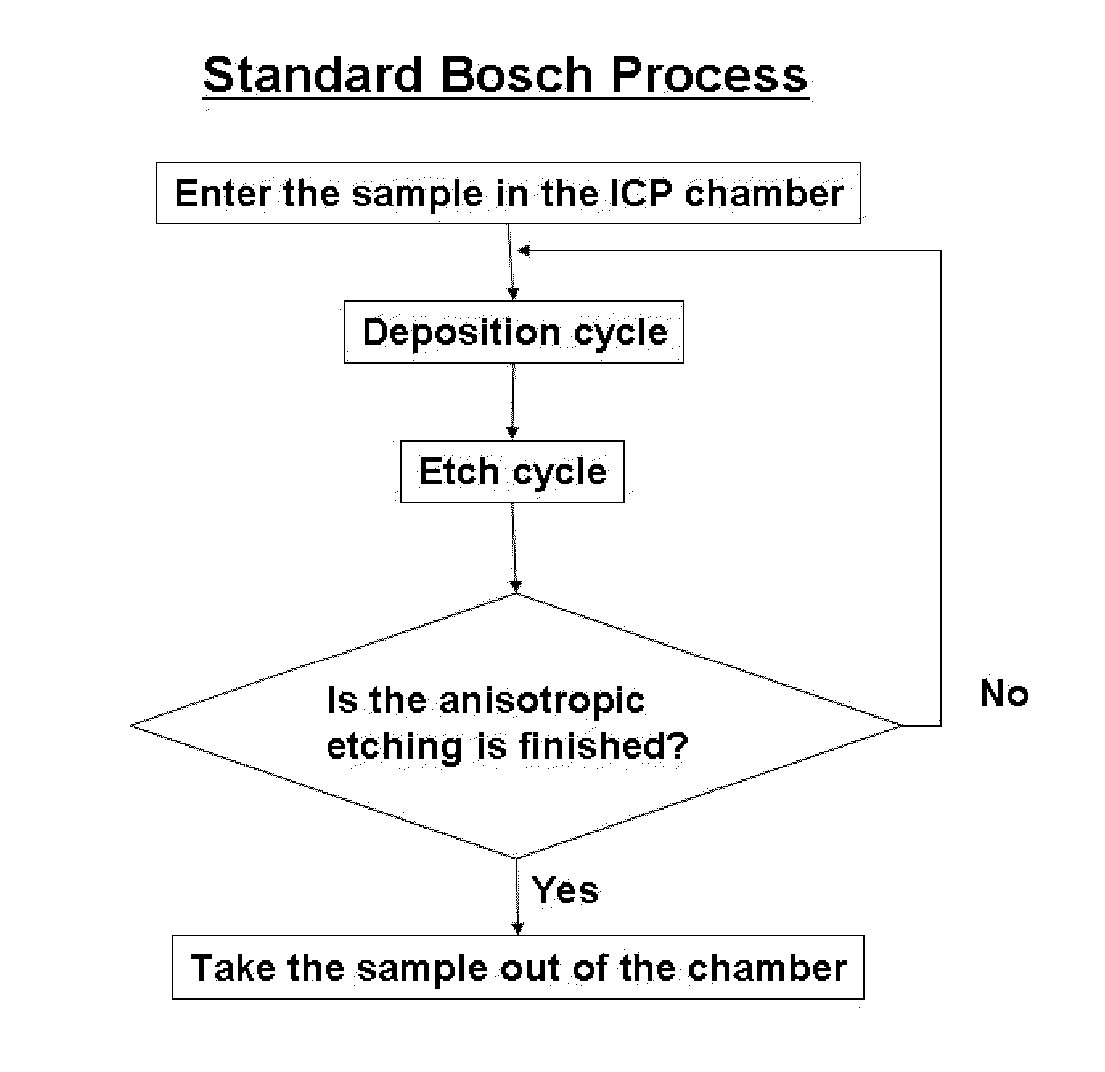

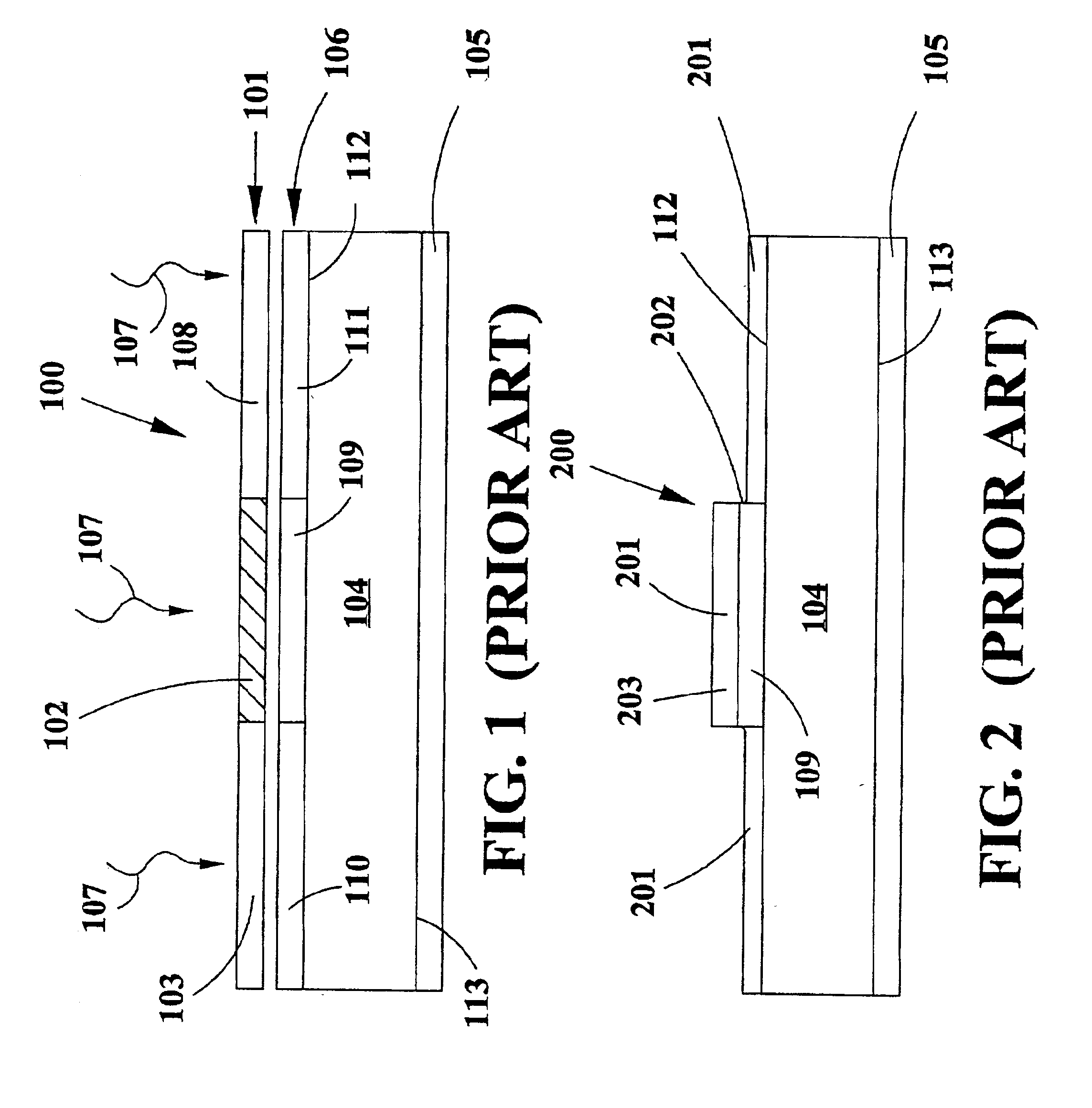

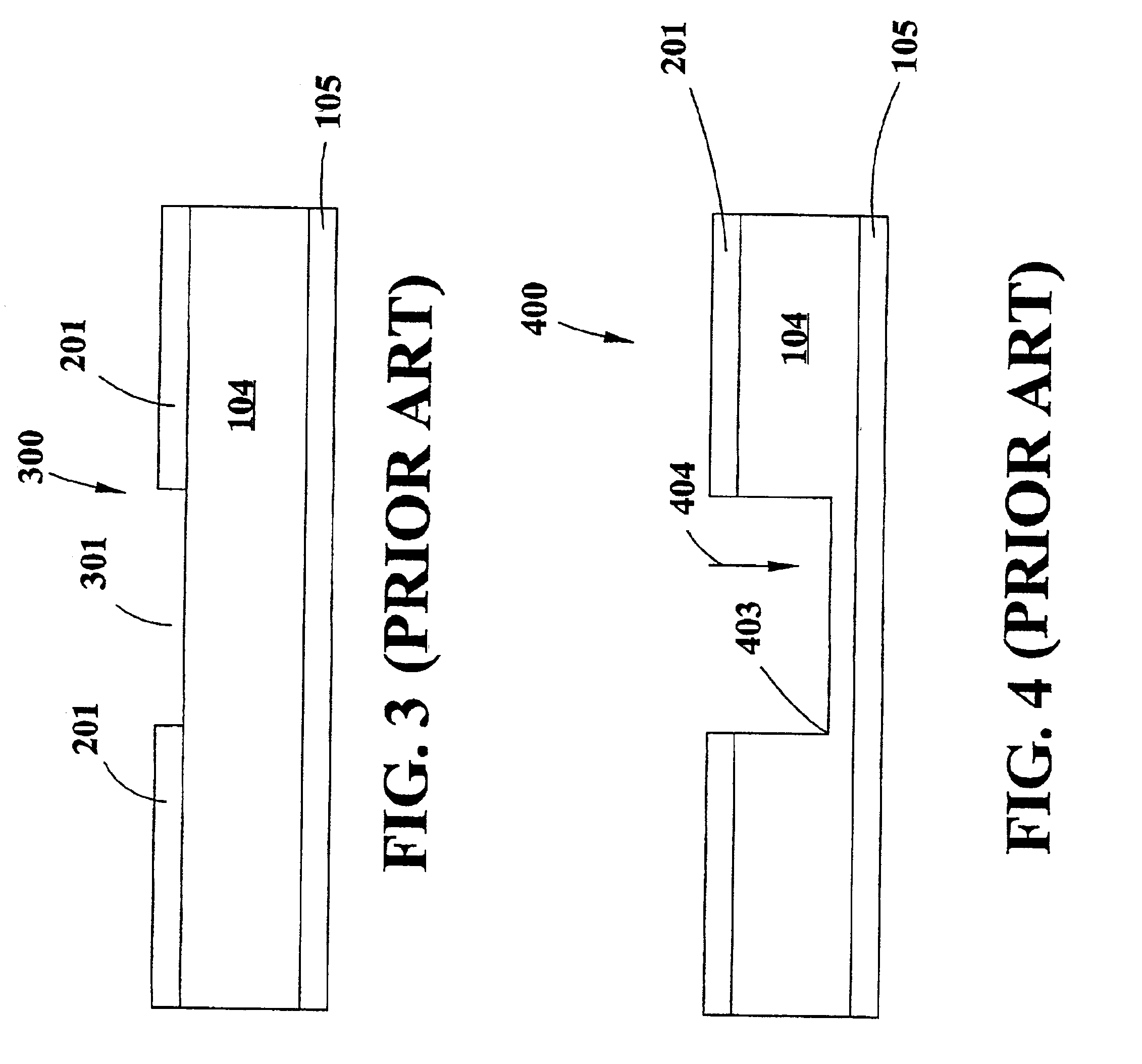

Deep reactive-ion etching (DRIE) is a highly anisotropic etch process used to create deep penetration, steep-sided holes and trenches in wafers/substrates, typically with high aspect ratios. It was developed for microelectromechanical systems (MEMS), which require these features, but is also used to excavate trenches for high-density capacitors for DRAM and more recently for creating through silicon vias (TSVs) in advanced 3D wafer level packaging technology.

Cap Wafer for Wafer Bonded Packaging and Method for Manufacturing the Same

InactiveUS20080081398A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

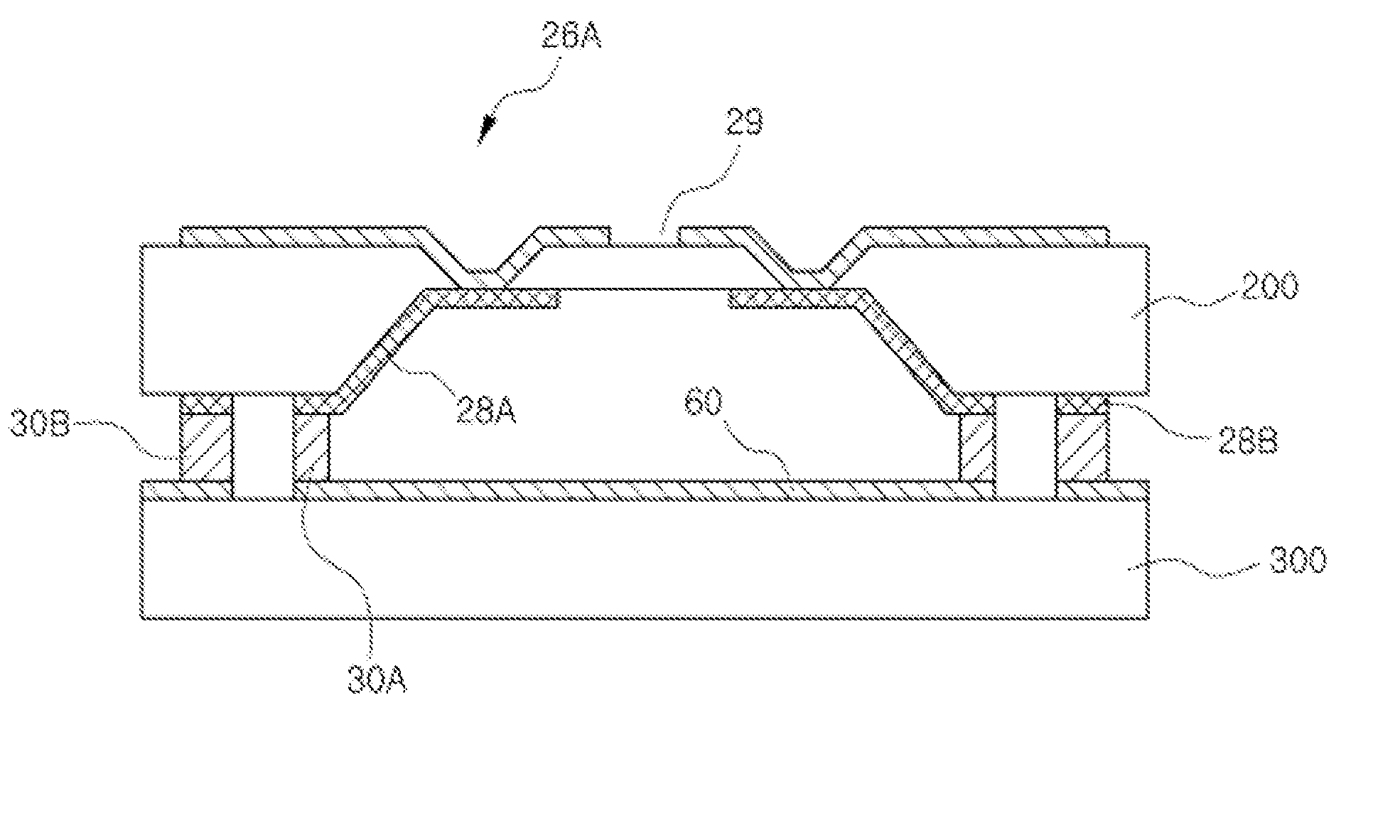

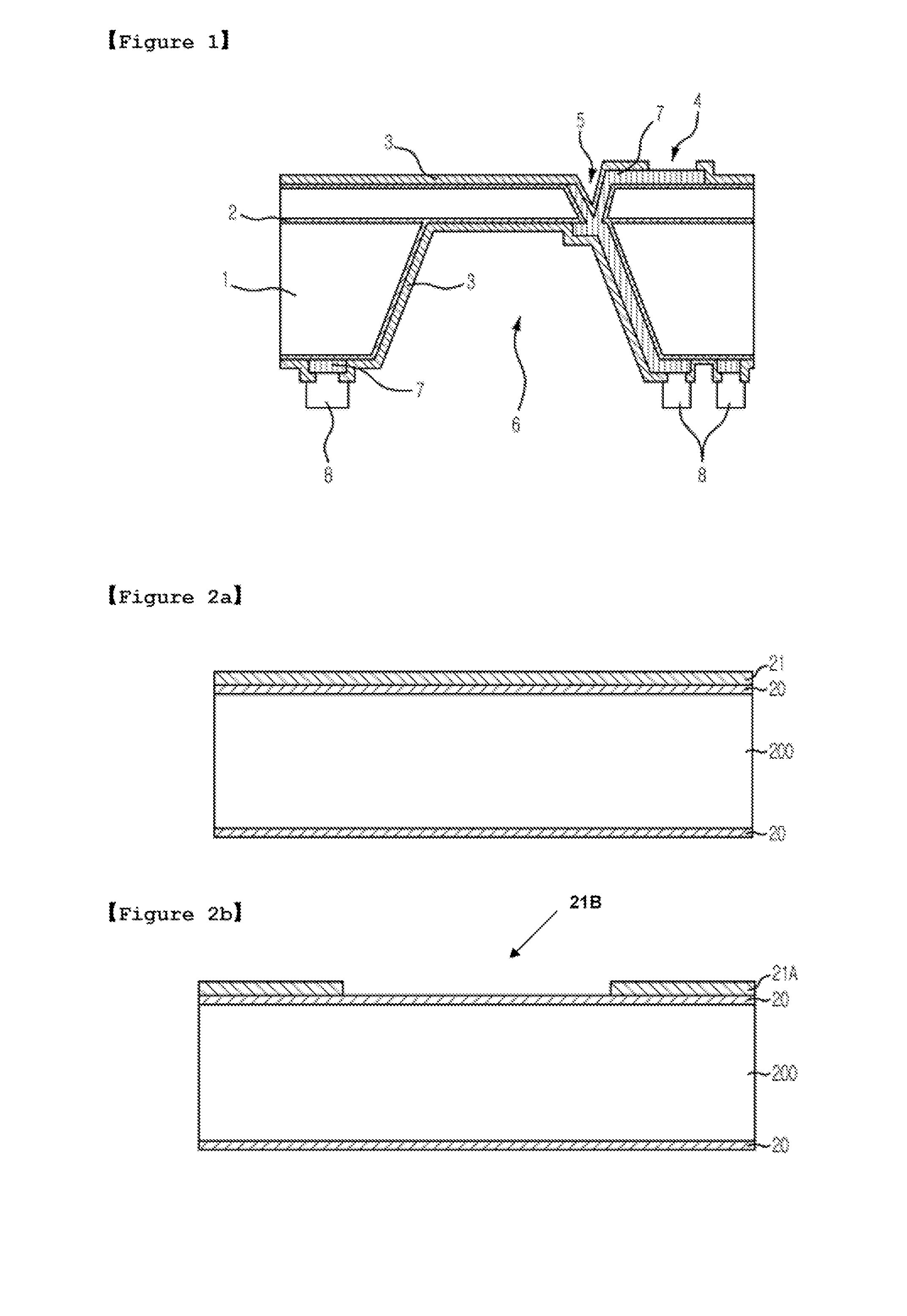

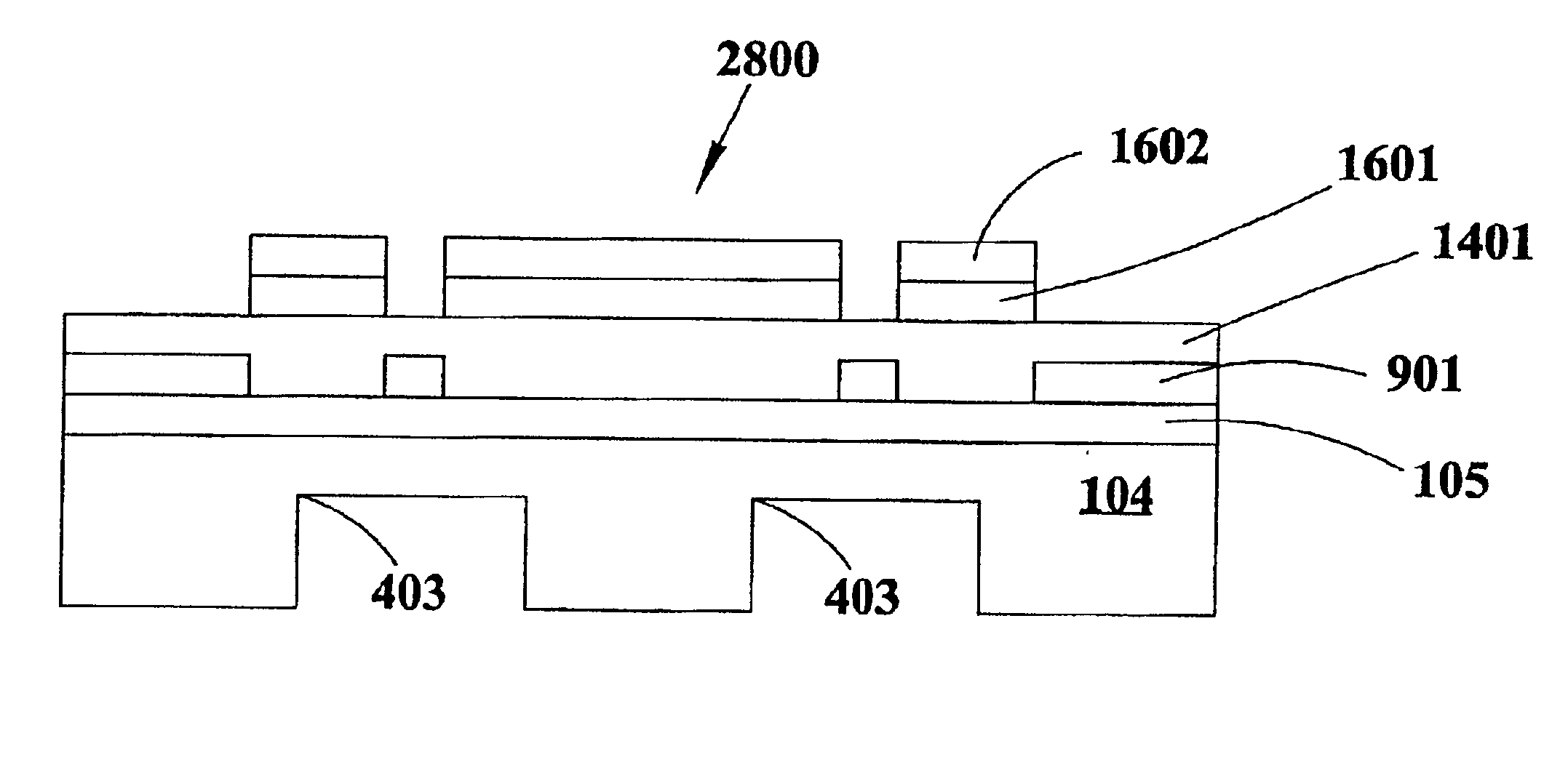

The present invention relates to semiconductor device manufacturing techniques, and specifically to a field of device packaging techniques at wafer level. More specifically, it relates to a cap wafer for wafer bonding application that is bonded to top part of a device wafer. The method of the present invention excludes the use of deep reactive ion etching of silicon to form a through silicon via. The present invention provides a method for the preparation of cap wafer for wafer bonding application with a simple process of through silicon via interconnection and a wafer level packaging method using the same.

Owner:PHOCO

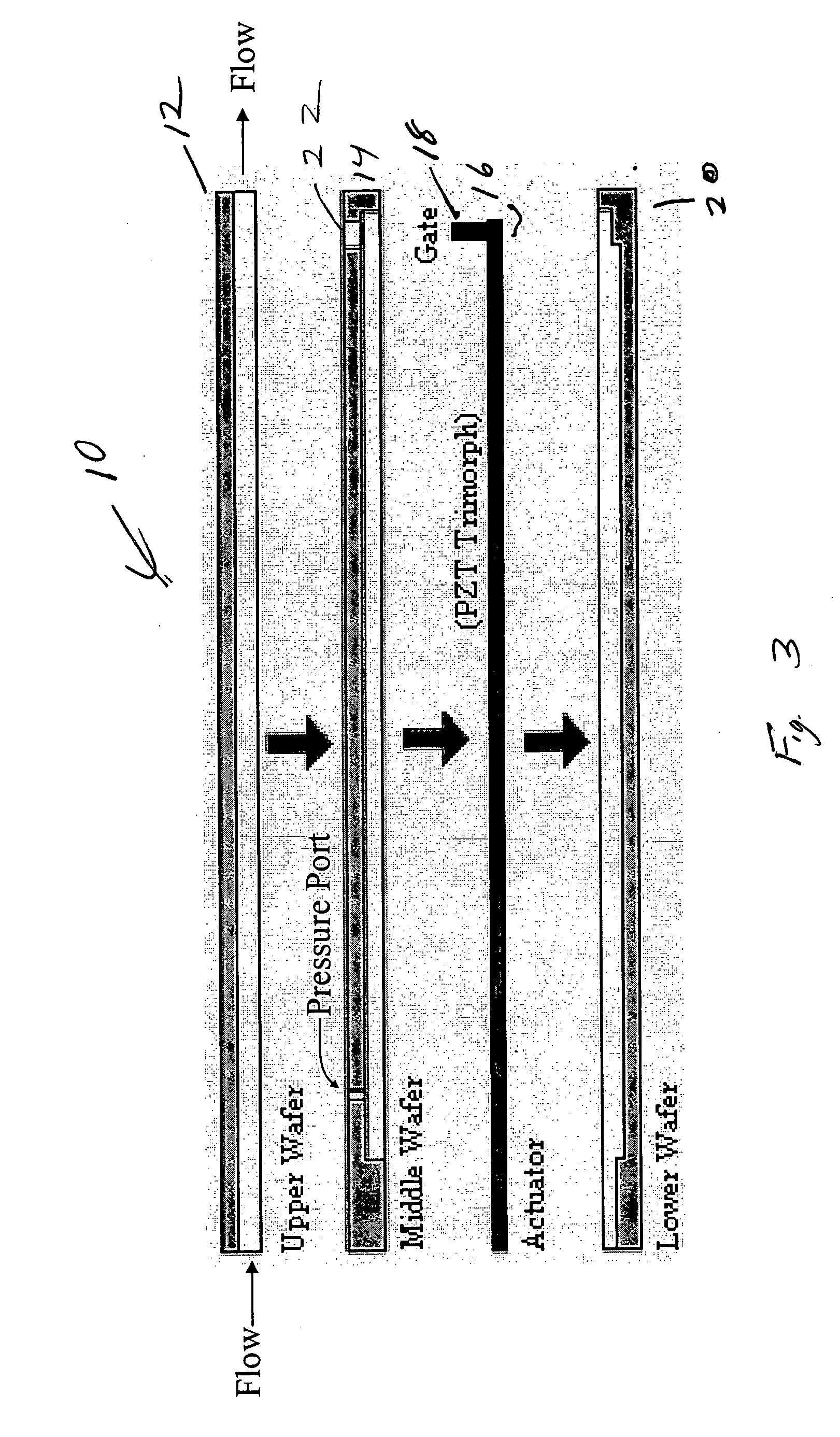

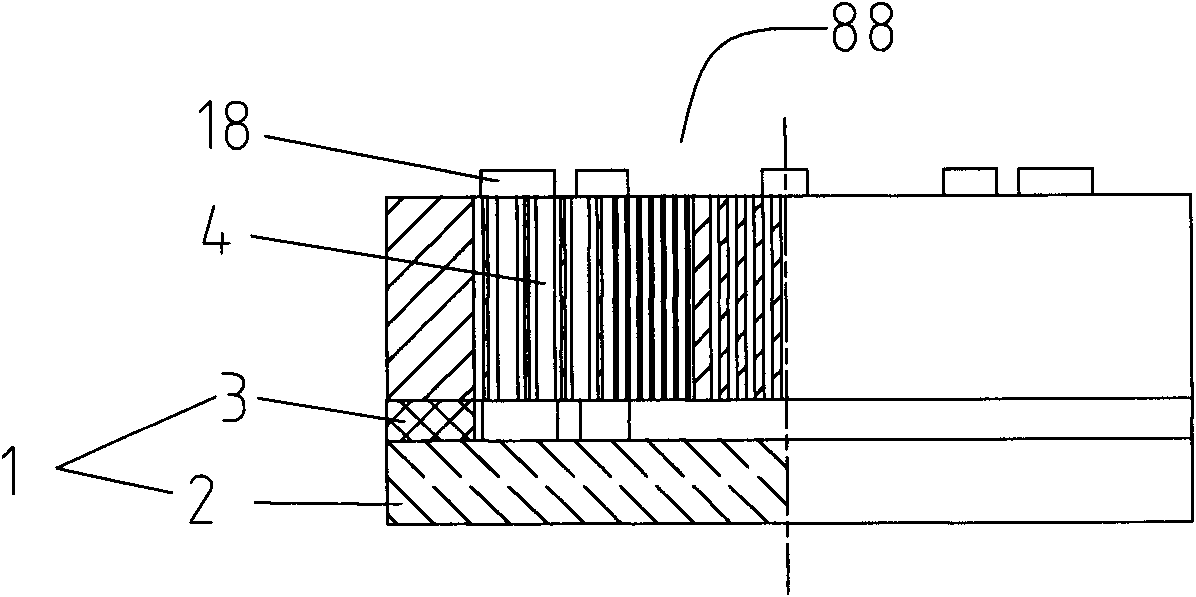

Piezoelectric axial flow microvalve

InactiveUS20040137300A1Operating means/releasing devices for valvesFinal product manufactureEpoxyPhotonics

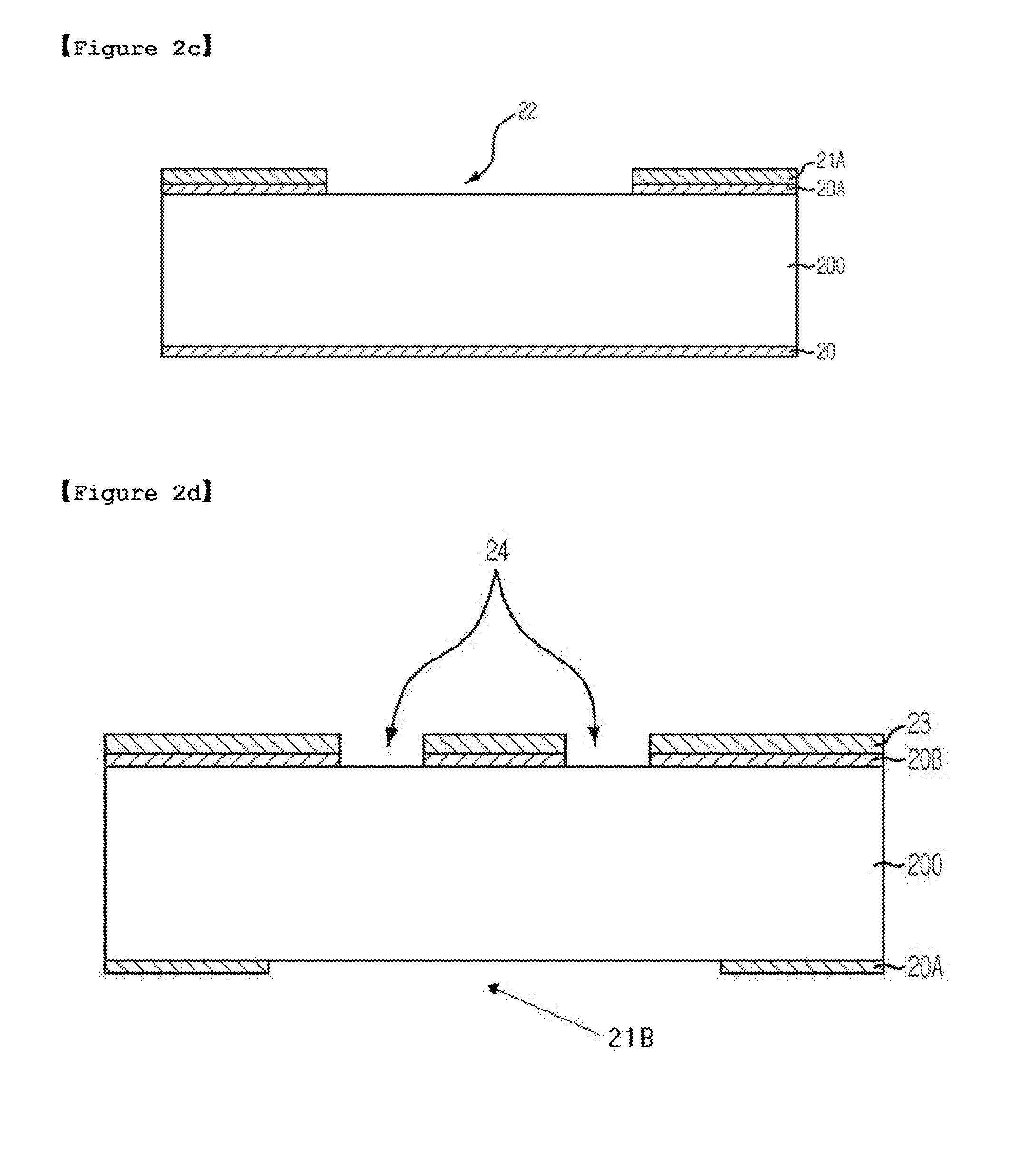

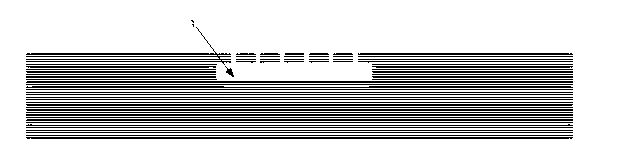

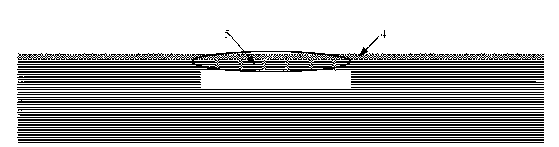

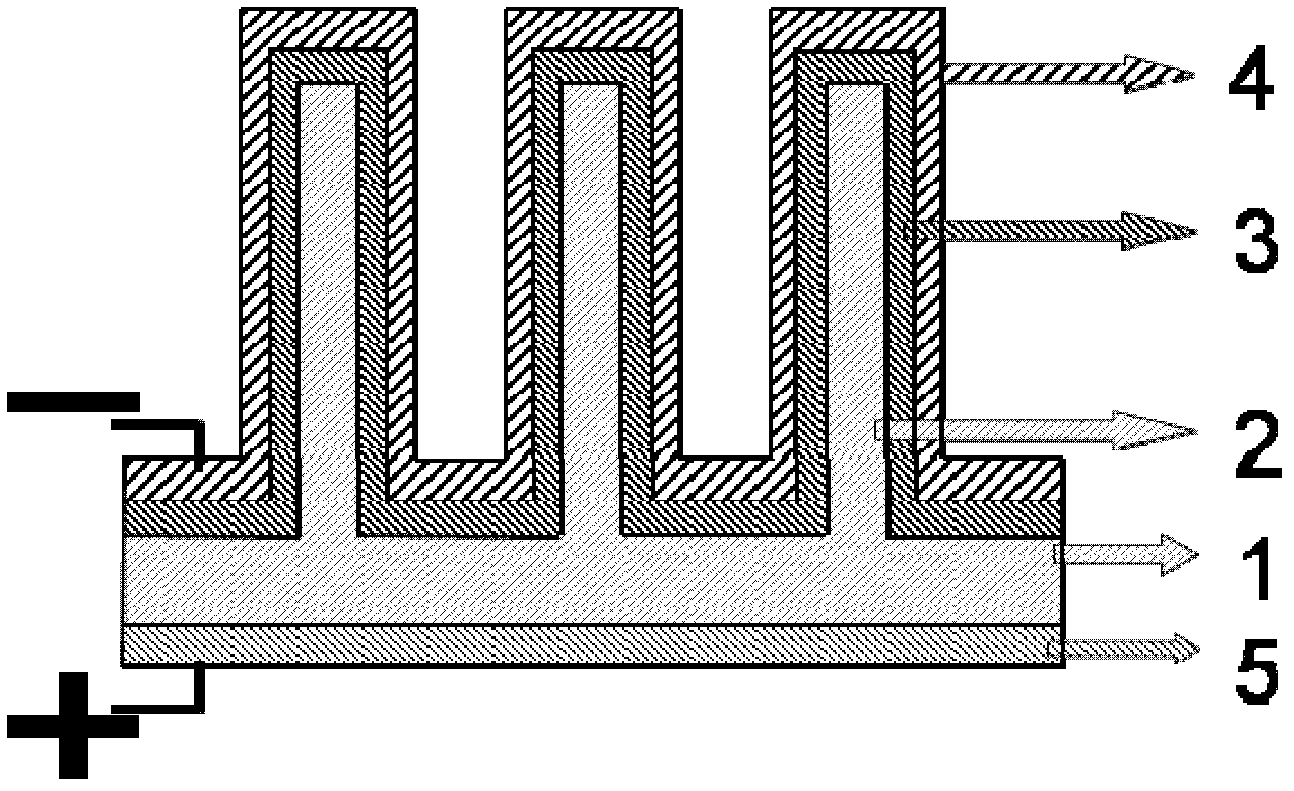

This paper presents the fabrication and preliminary testing of a novel piezoelectric microvalve. Fabrication has three steps, which are the actuator fabrication, valve body fabrication and assembly of the microvalve. Fabricating an actuator involves cutting piezoelectric and brass beams, gluing the brass and piezoceramic beams into a trimorph sandwich structure, and curing them under pressure at elevated temperatures. Actuators are then wired either by using conductive epoxy or soldering. Valve body parts are constructed from single crystal silicon substrates using deep reactive ion etching (DRIE). DRIE is a subtractive process, whereby a mask is created on the surface of the stock, which will shield the parts that are not to be machined. Refinements in the actuator manufacturing process are made to increase the quality and decrease the fabrication time. Using a photonic probe, tip deflections of the actuators have been tested at various temperature and voltage levels. Currently, the valves are being assembled. Once assembled, multiple microvalves will undergo cold flow testing with air followed by extensive flow extensive flow testing at elevated temperatures with humidified hydrogen.

Owner:THE UNITED STATES AS REPRESENTED BY THE DEPARTMENT OF ENERGY

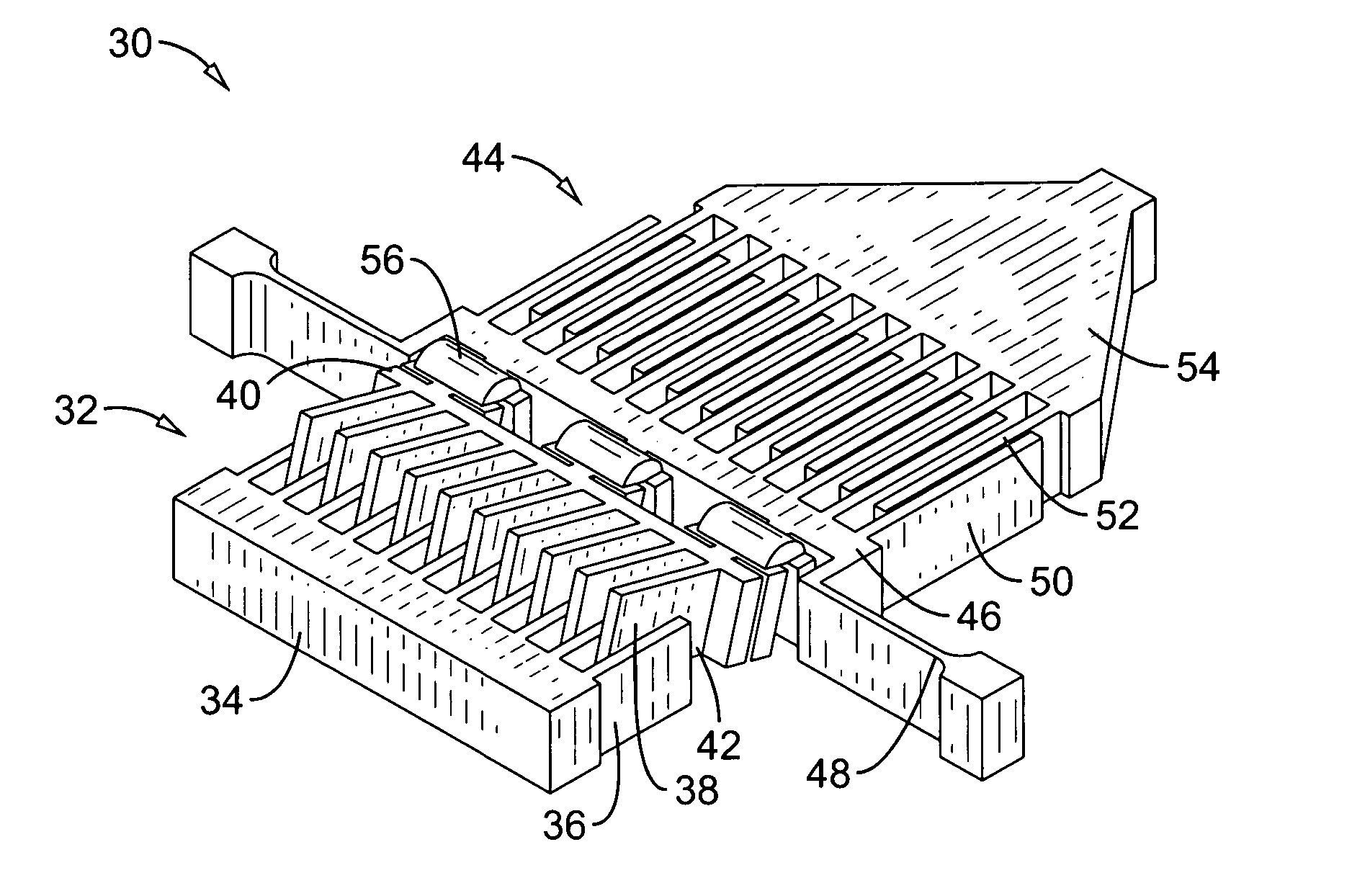

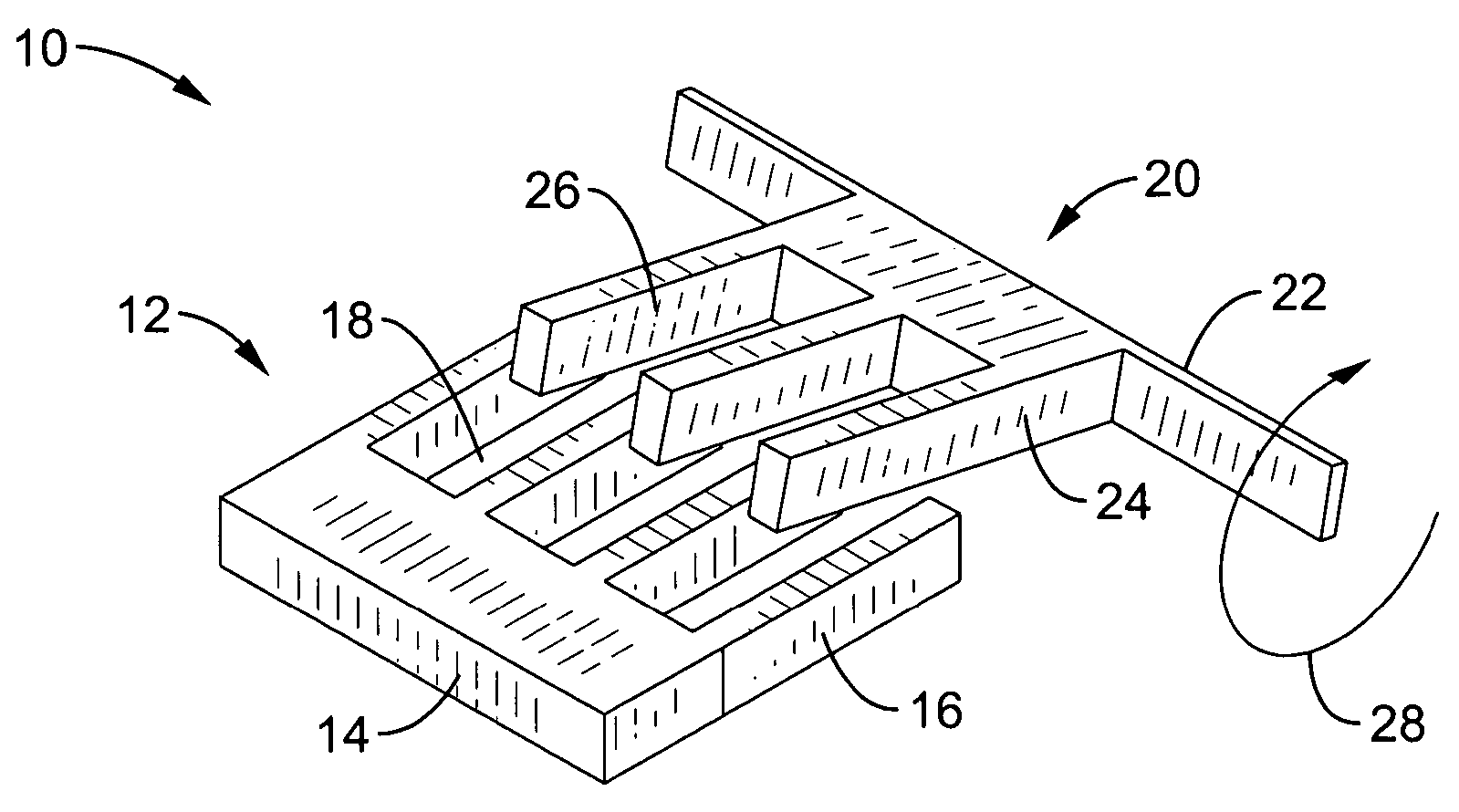

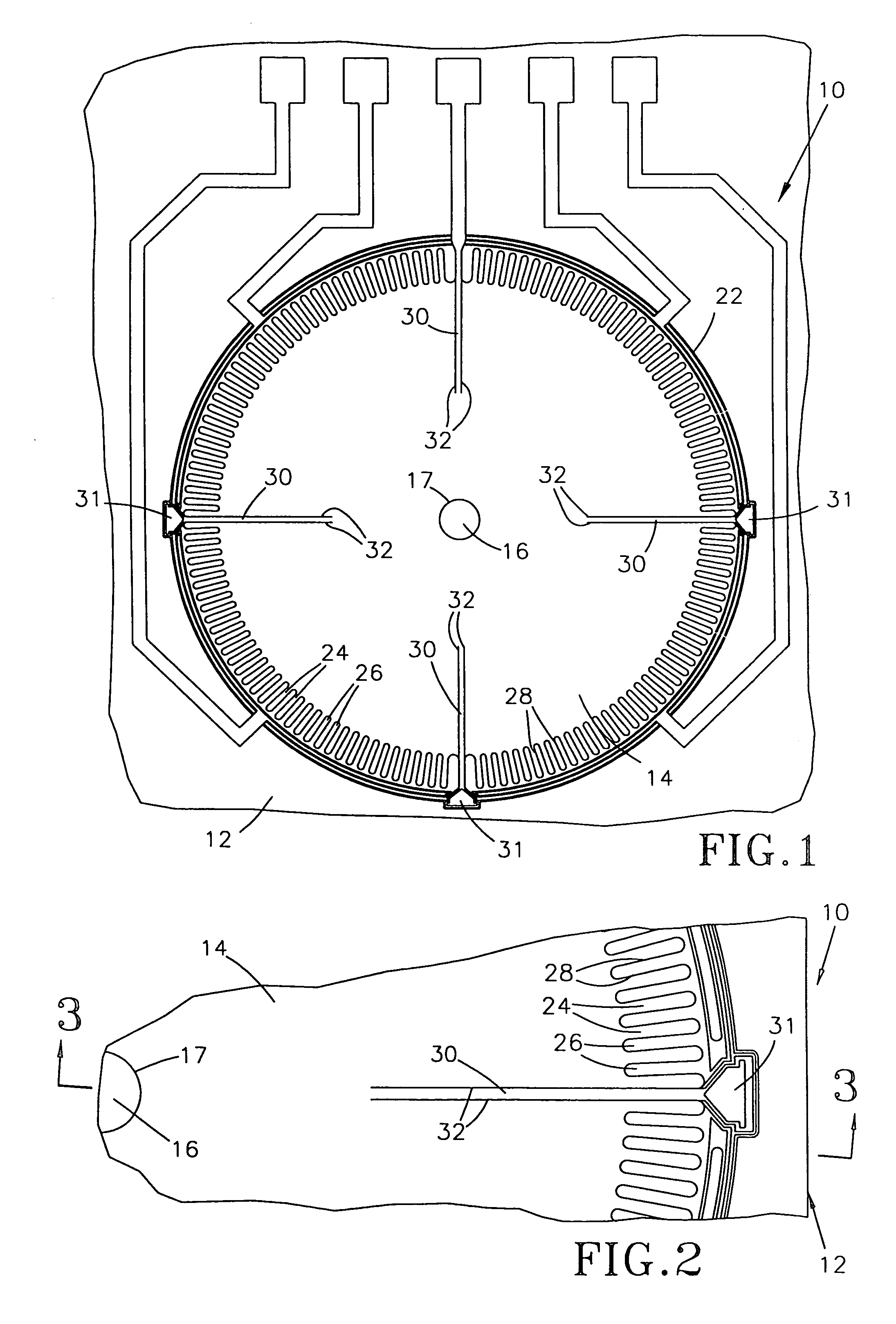

MEMS tunable capacitor based on angular vertical comb drives

InactiveUS7085122B2Appreciates the drawbacks inherent in lateral drive MEMS capacitorsIncrease tuning rangeMultiple-port networksMechanically variable capacitor detailsCapacitanceComb finger

A MEMS tunable capacitor with angular vertical comb-drive (AVC) actuators is described where high capacitances and a wide continuous tuning range is achieved in a compact space. The comb fingers rotate through a small vertical angle which allows a wider tuning range than in conventional lateral comb drive devices. Fabrication of the device is straightforward, and involves a single deep reactive ion etching step followed by release and out-of-plane assembly of the angular combs.

Owner:RGT UNIV OF CALIFORNIA

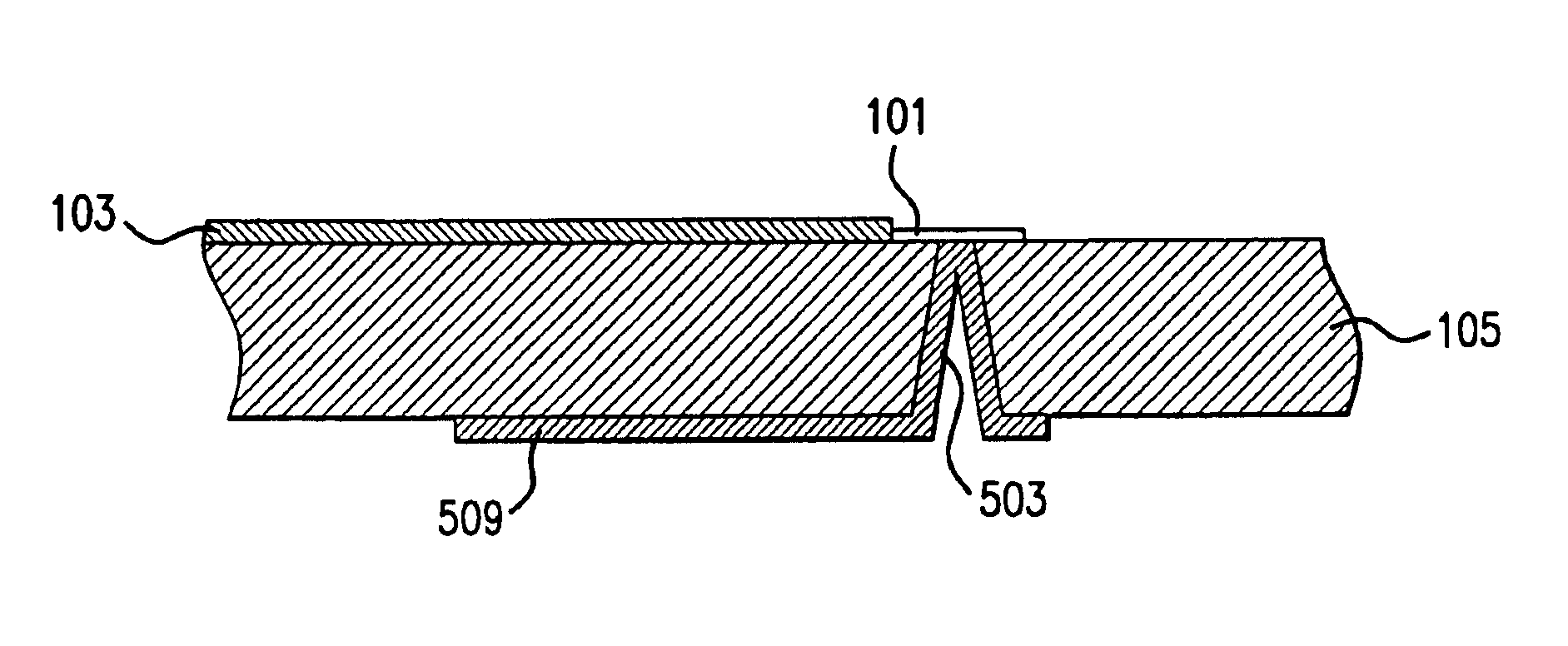

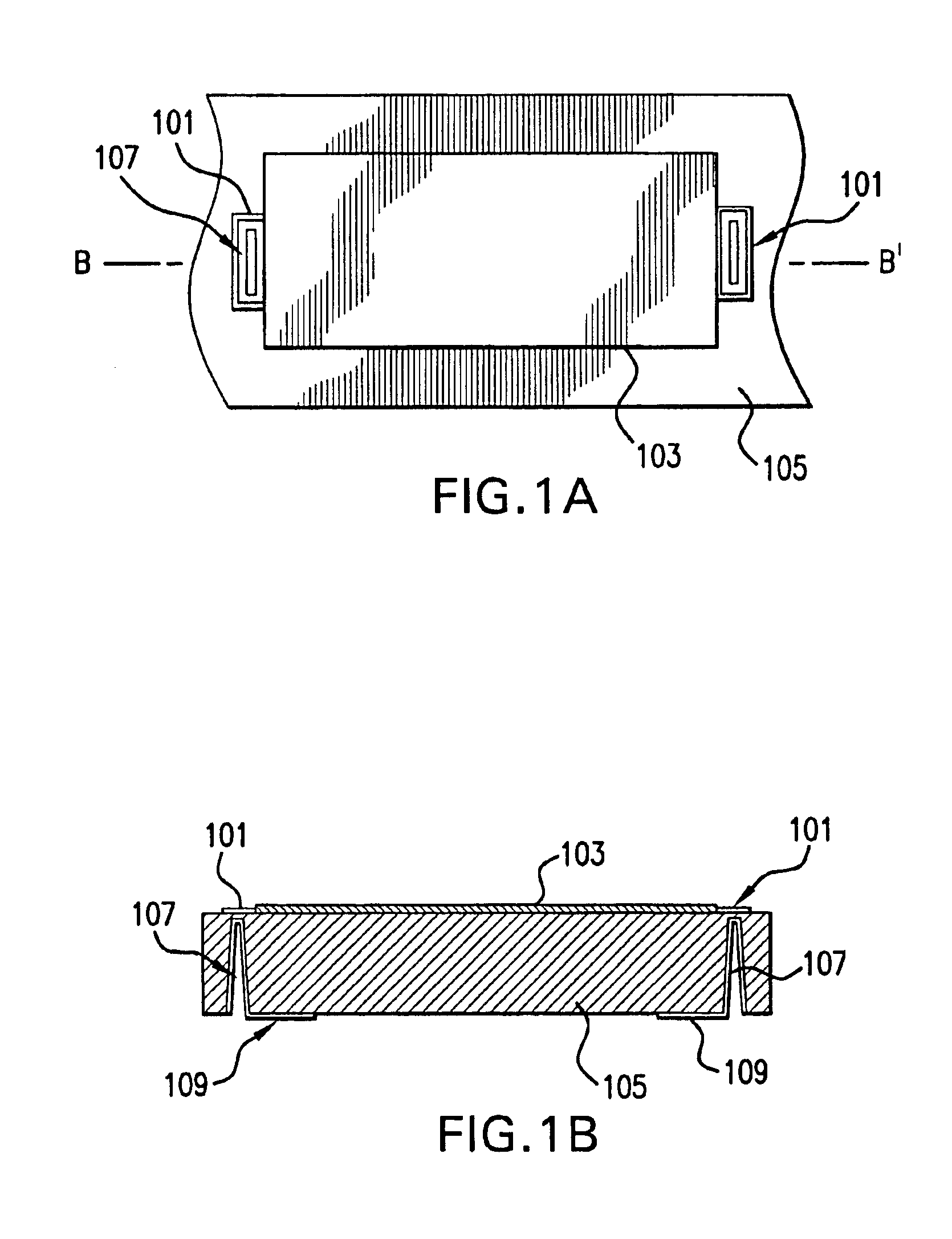

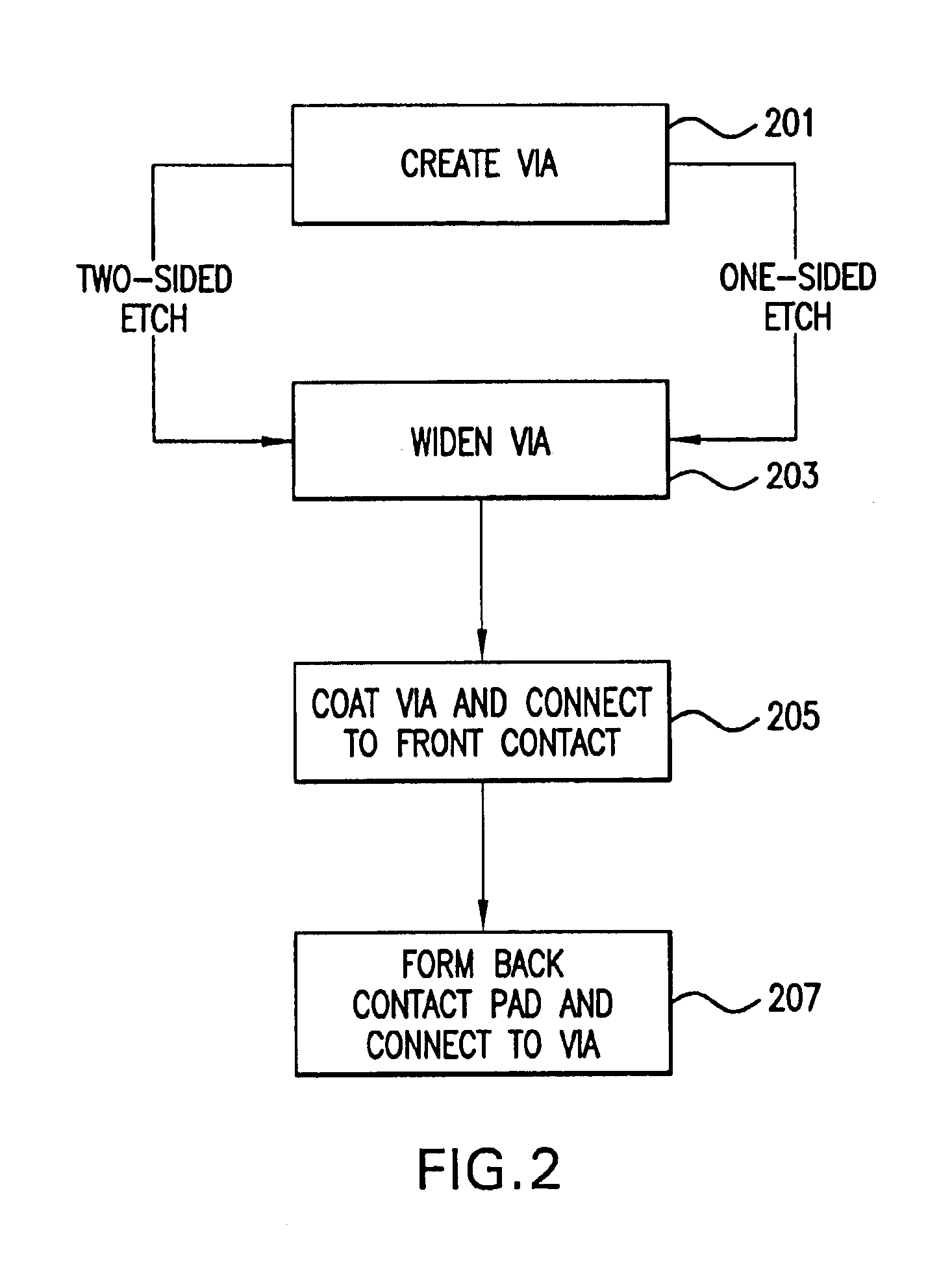

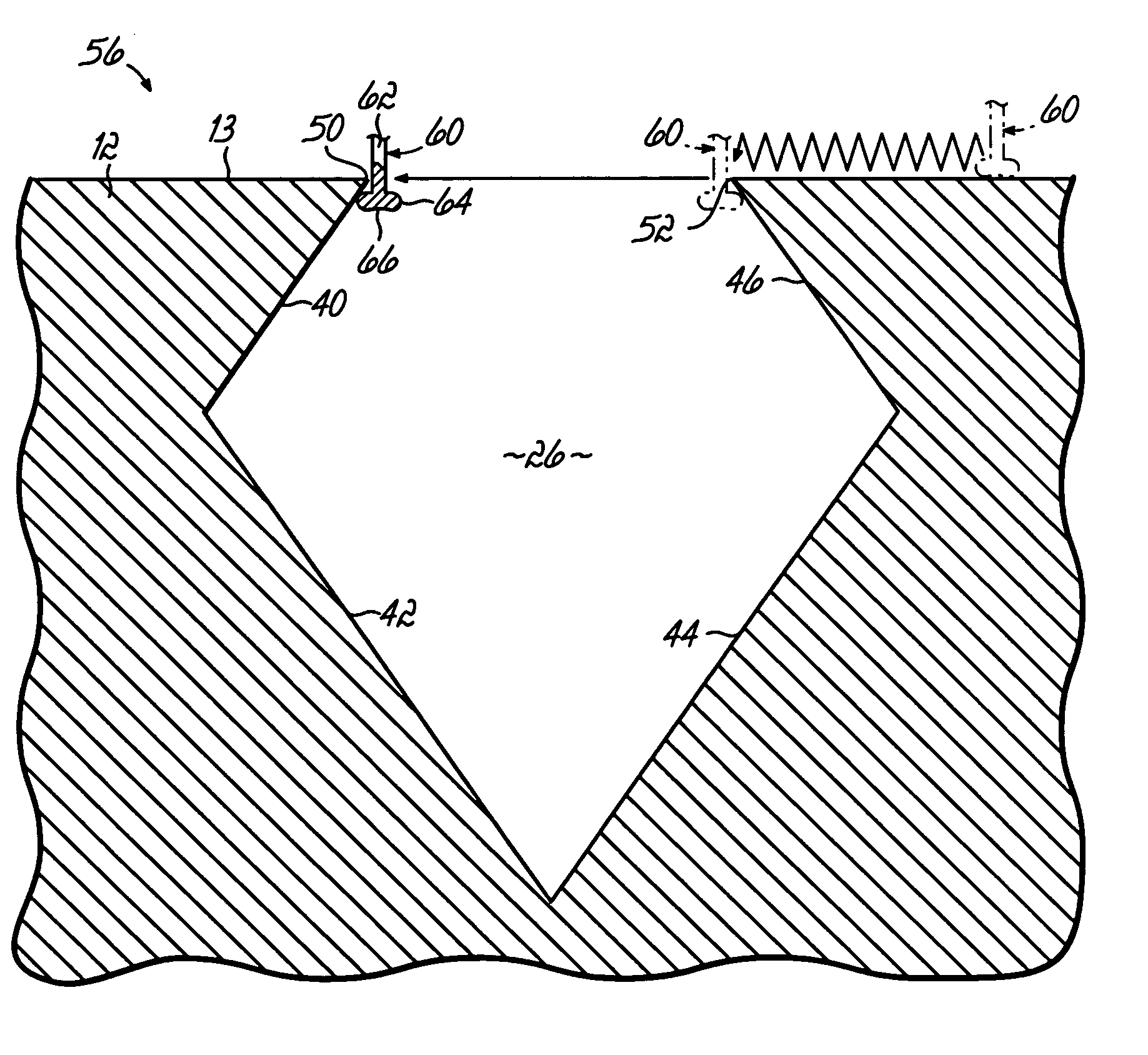

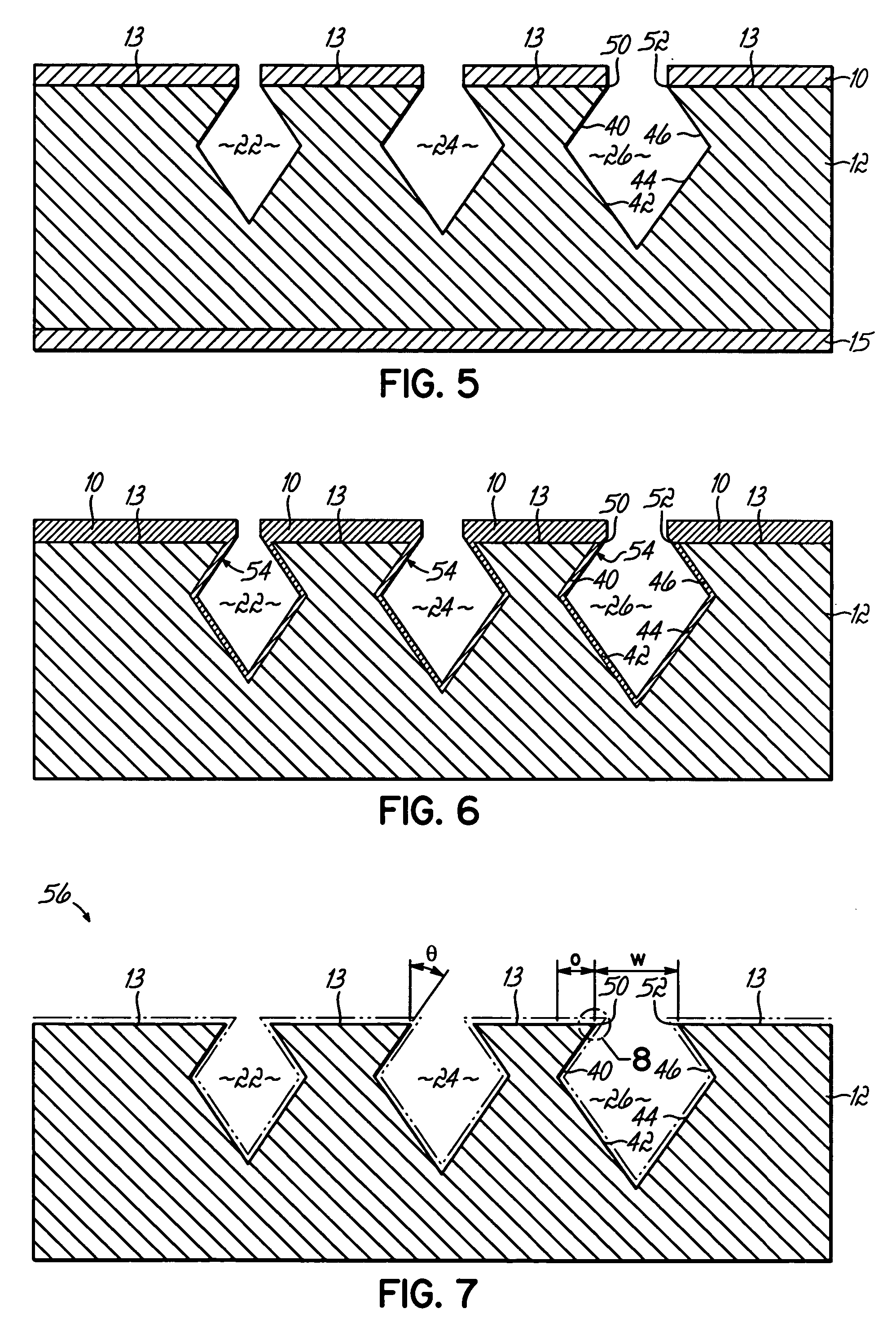

Sloped via contacts

InactiveUS6903012B2Reduce signal lossReduce chip areaSemiconductor/solid-state device detailsSolid-state devicesSputteringEngineering

A sloped via contact is used to connect a contact on the front side of a wafer to a contact on the back side of the wafer. The walls of a small (less than 50-80 microns wide) via have typically been difficult to coat with metal. The present invention forms a small via with sloped walls, allowing easy access to the inside walls of the via for metal sputtering or plating. The small via can be formed using a dry etch process such as the well-known deep reactive ion etching (DRIE) process. Using any isotropic plasma etch process, the walls of the via are further etched from the wafer backside to create sloped walls in the via. The via is then coated with metal to make it conductive.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

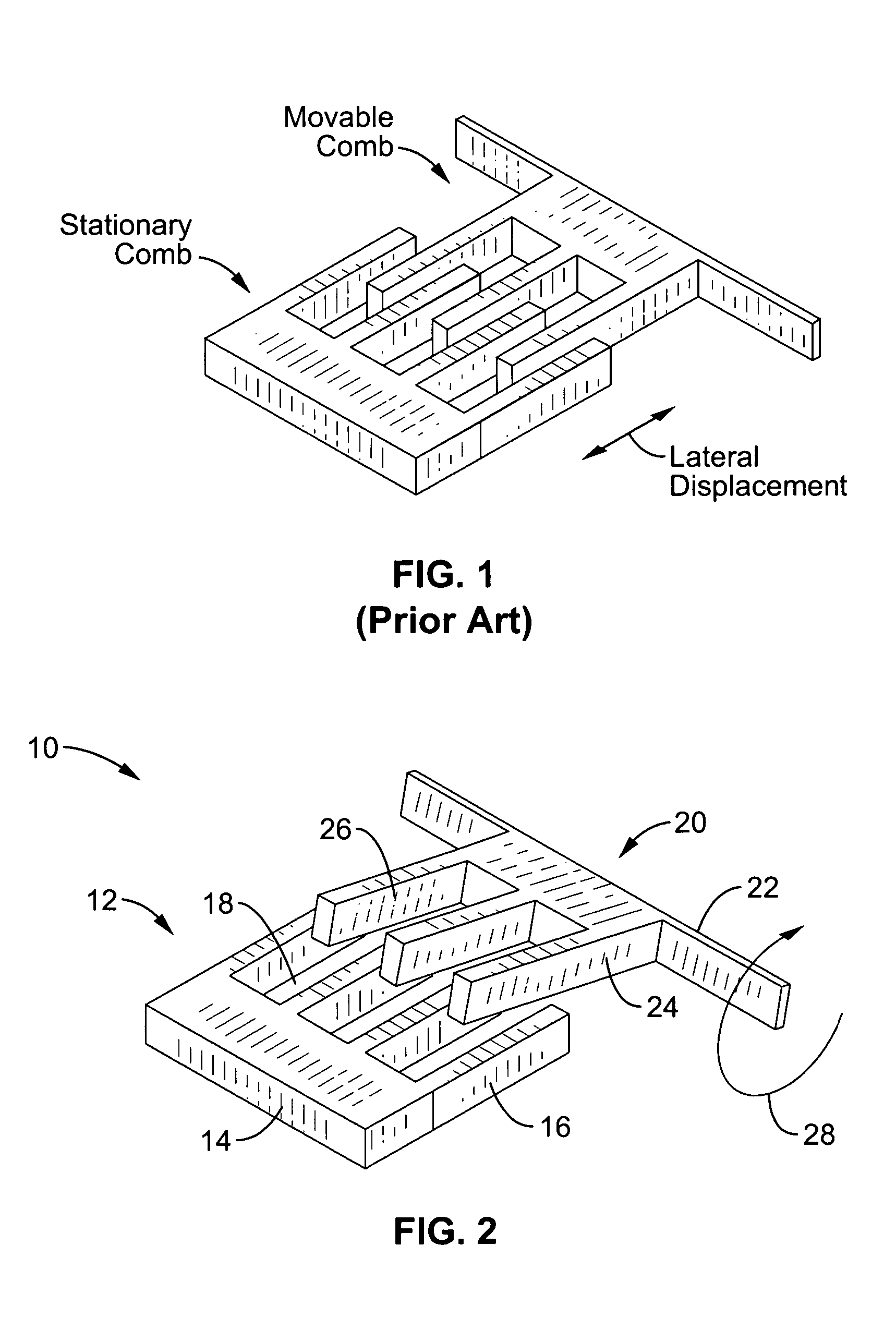

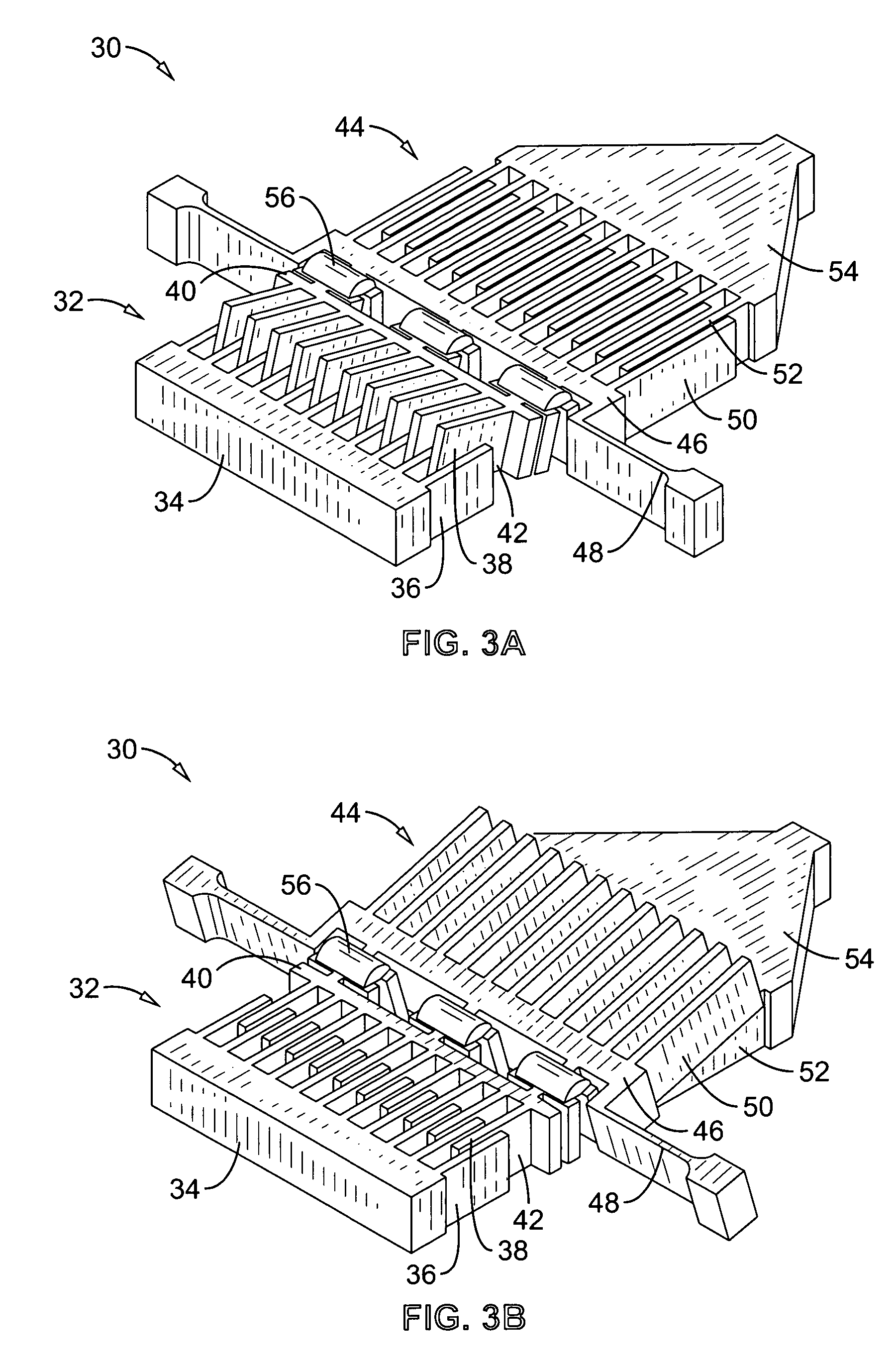

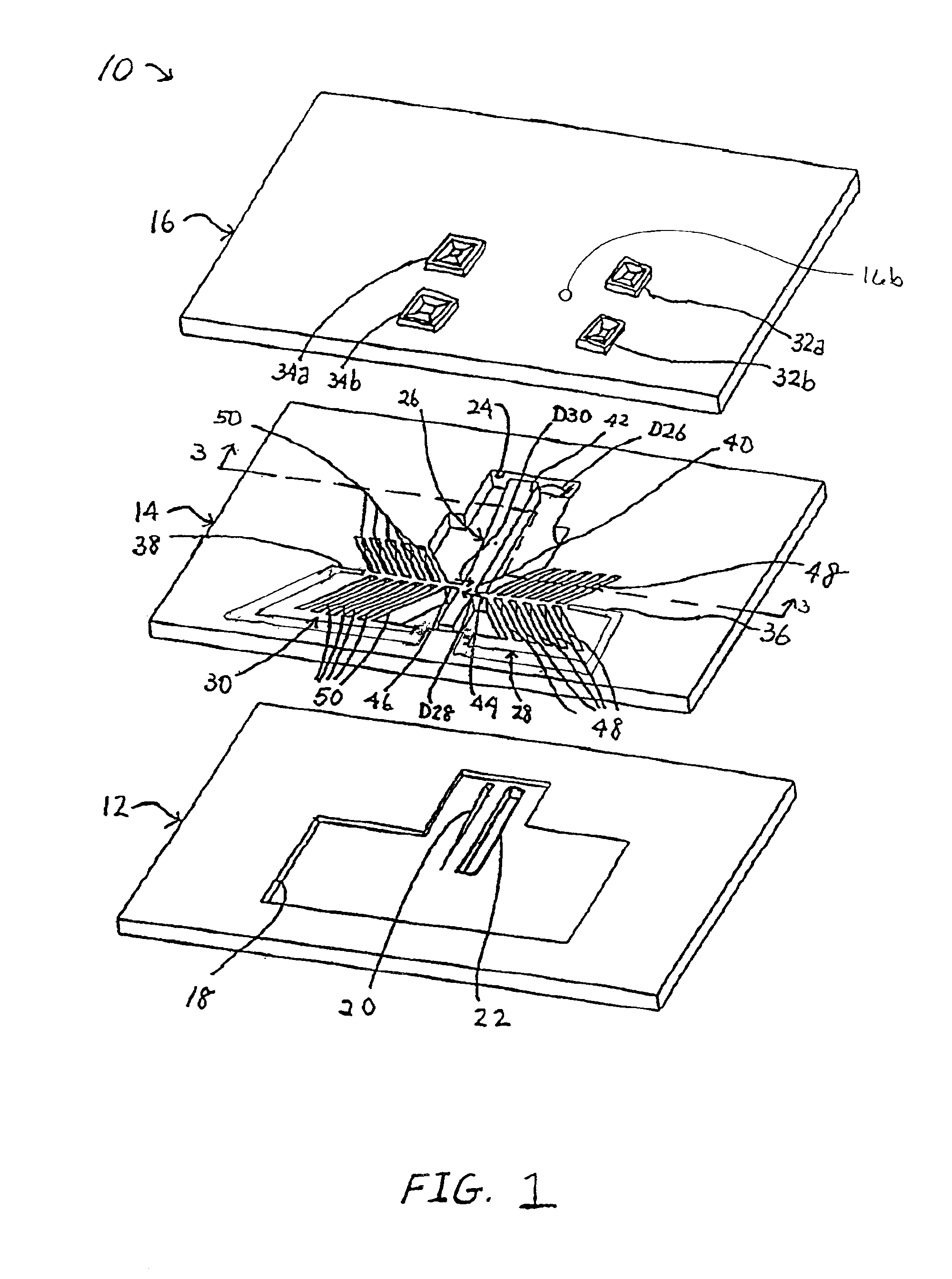

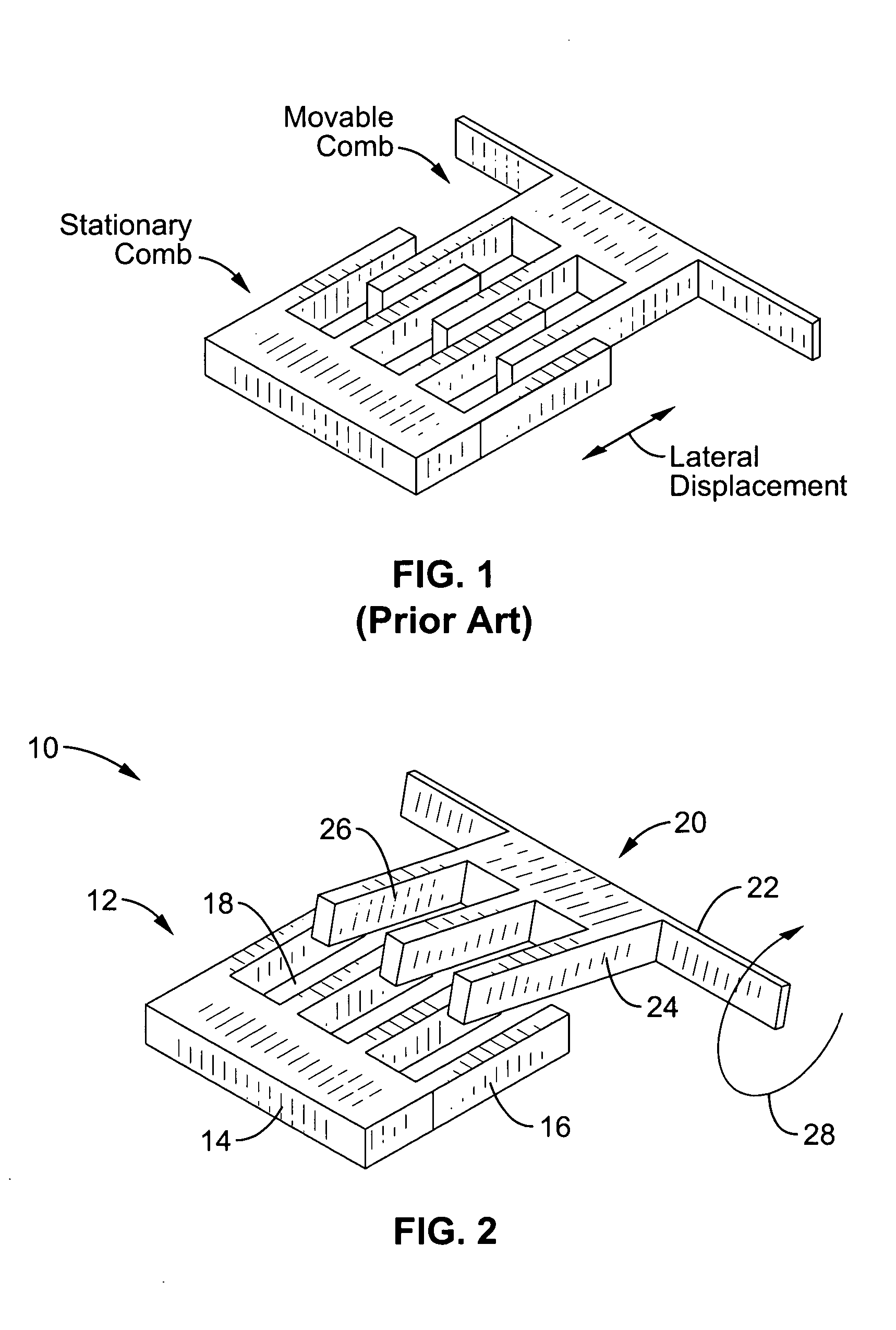

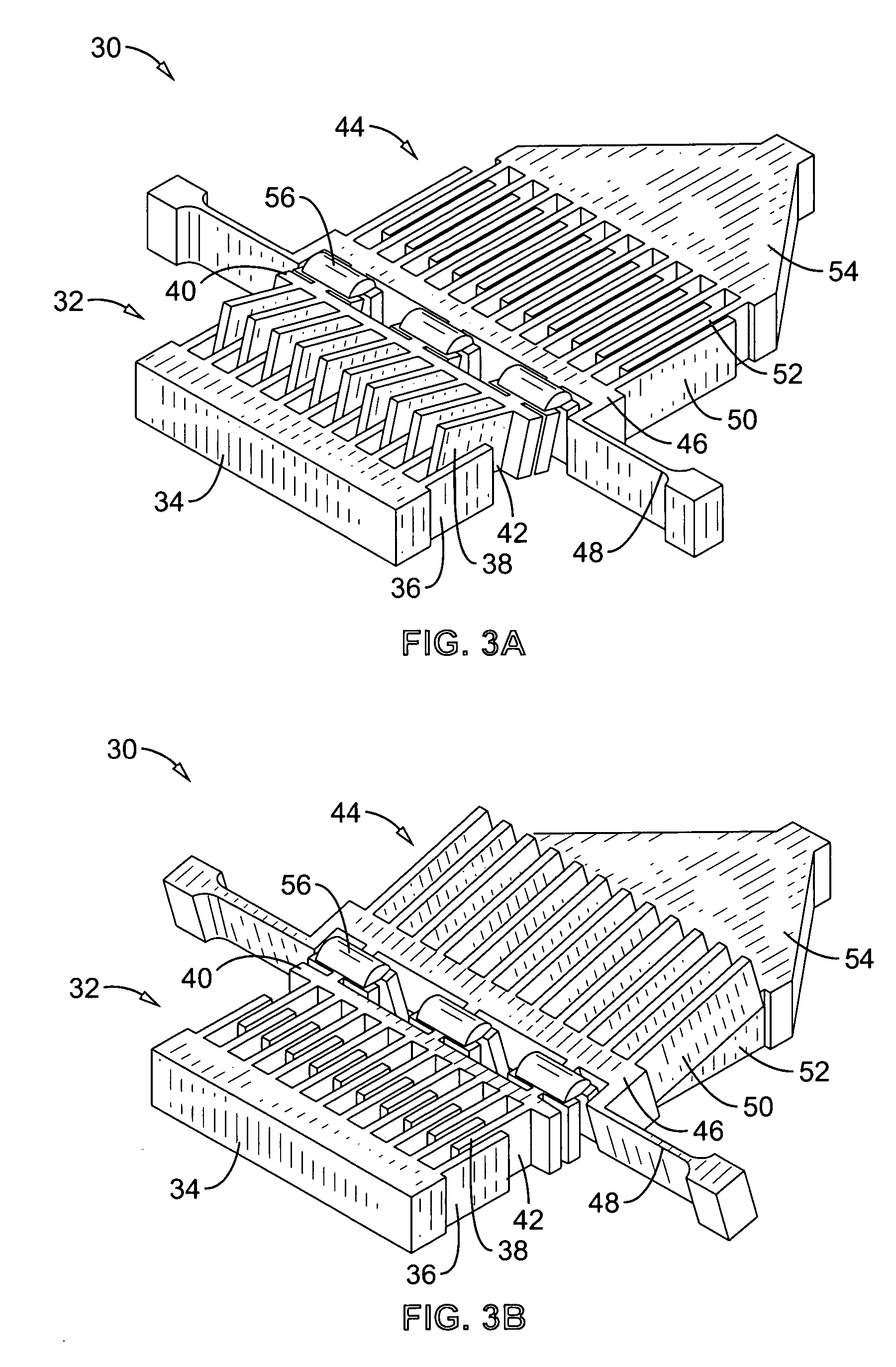

Method and apparatus for micro electro-mechanical systems and their manufacture

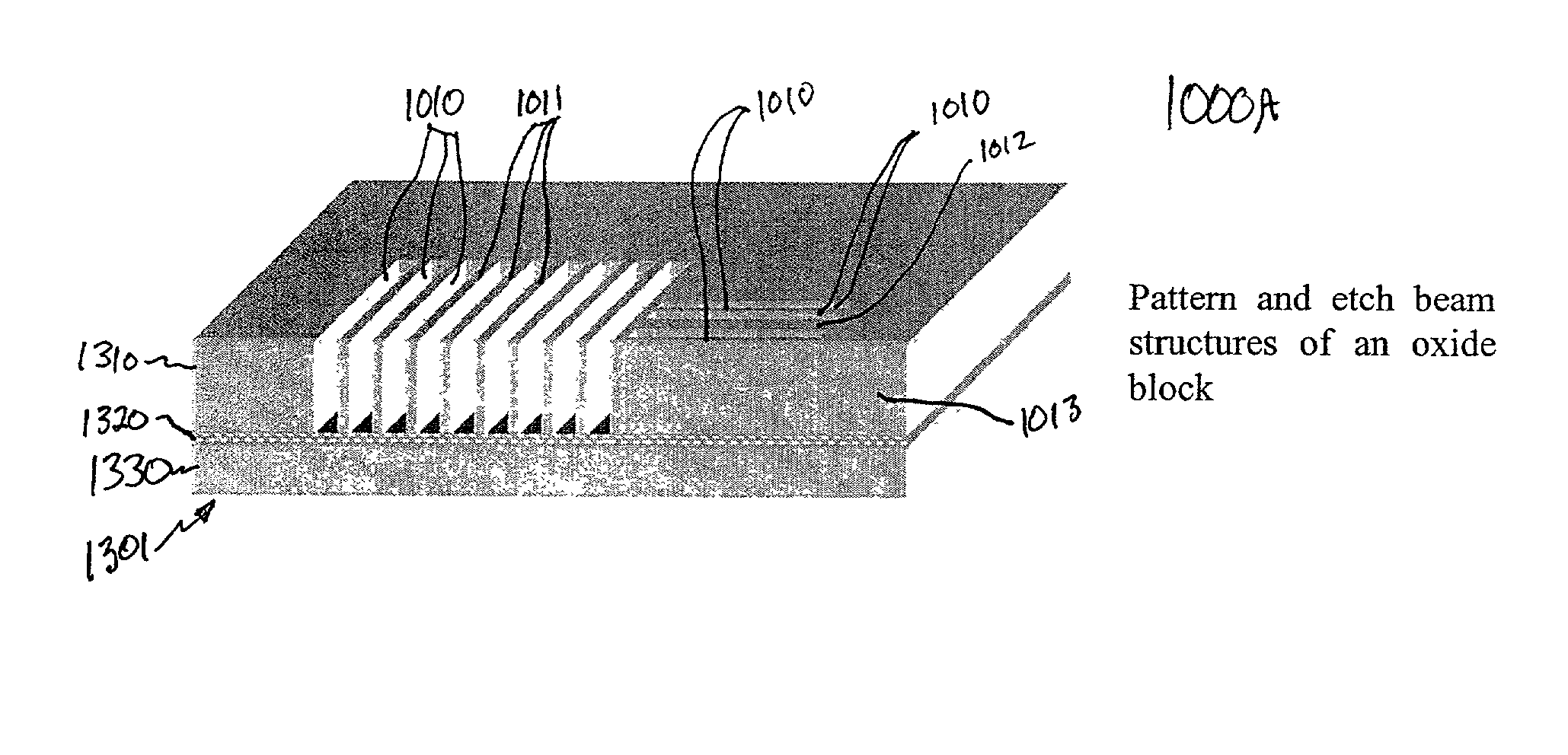

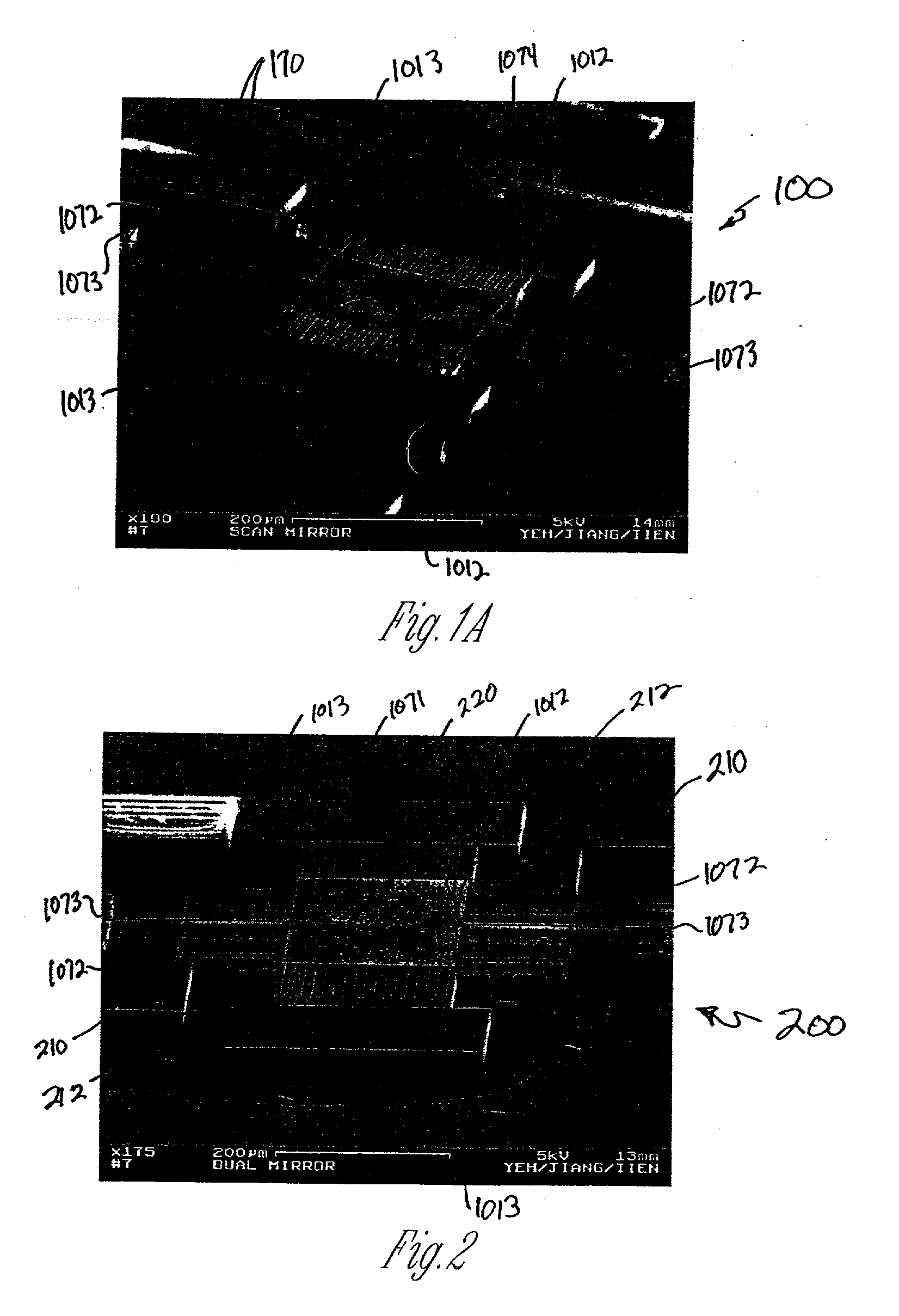

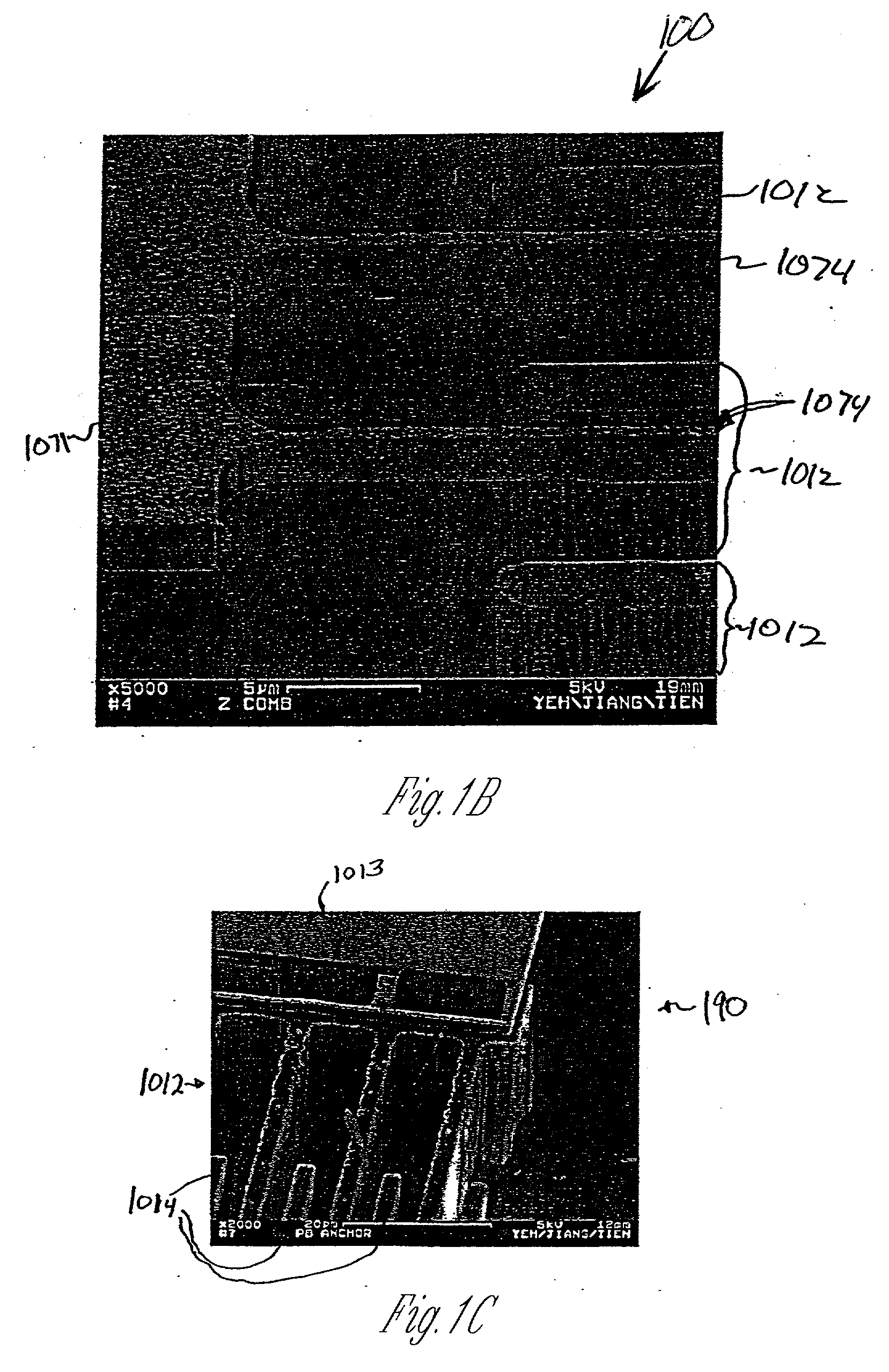

InactiveUS20020127760A1Less driving voltageSemiconductor electrostatic transducersSemiconductor/solid-state device manufacturingOut of plane motionActuator

The present invention provides a fabrication process that integrates high-aspect-ratio silicon structures with polysilicon surface micromachined structures. In some embodiments the process includes forming an oxide block by etching a plurality of trenches to leave a plurality of vertical-walled silicon structures standing on the substrate, thermally and substantially completely oxidizing the vertical-walled silicon structures, and substantially filling spaces between the oxidized vertical-walled silicon structures with an oxide of silicon to form the oxide block. The process retains not only the high-aspect-ratio silicon structures possible with deep reactive ion etching (DRIE) but also the design flexibility of polysilicon surface micromachining. Using this process, polysilicon platforms have been fabricated, which are actuated by high-aspect-ratio combdrives for many applications such as x-y-z stages and scanning devices. The actuators include an asymmetric combdrive that actuates in torsional / out-of-plane motions, and a high-aspect-ratio combdrive that drives in translational motion.

Owner:CORNELL RES FOUNDATION INC

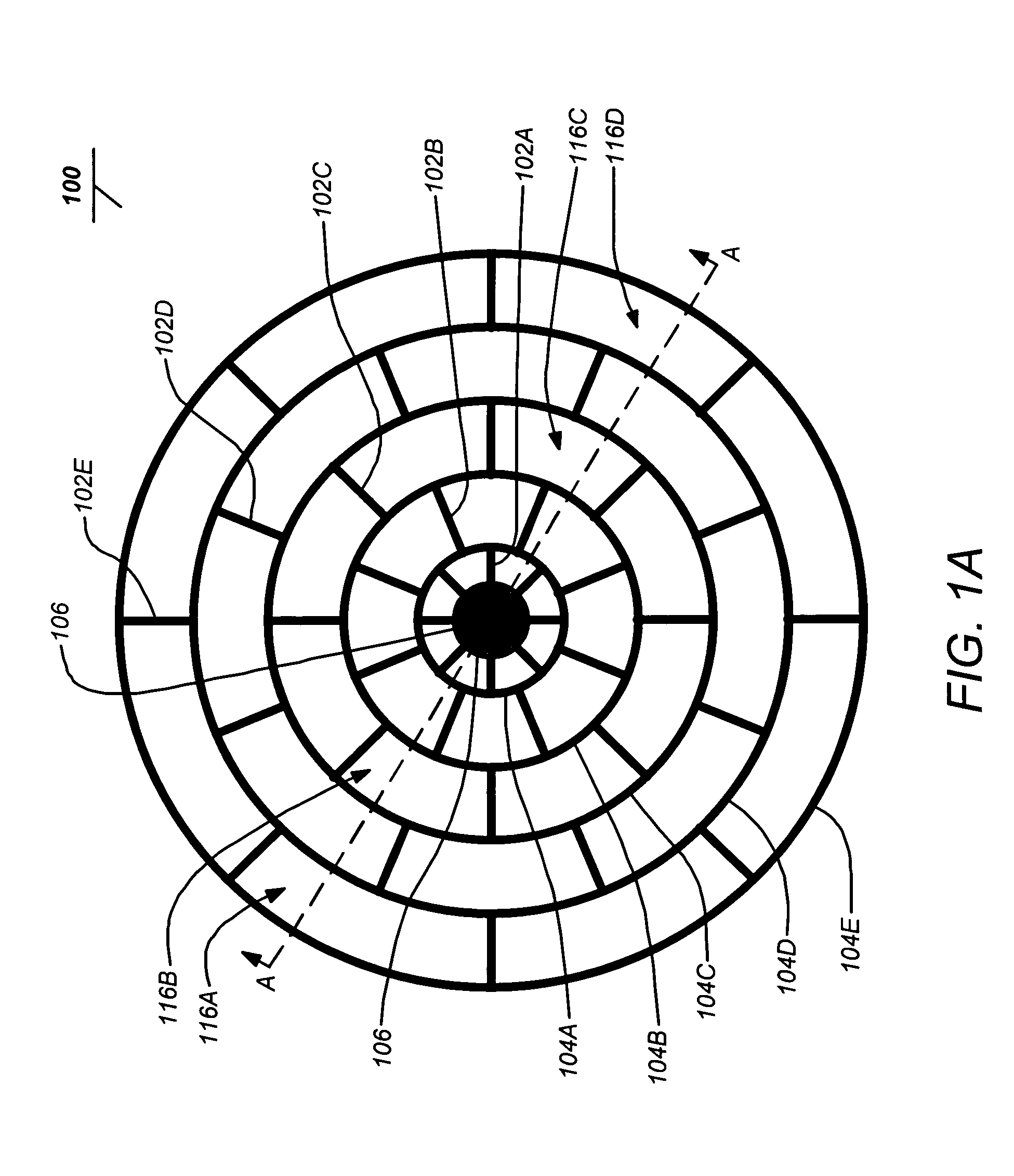

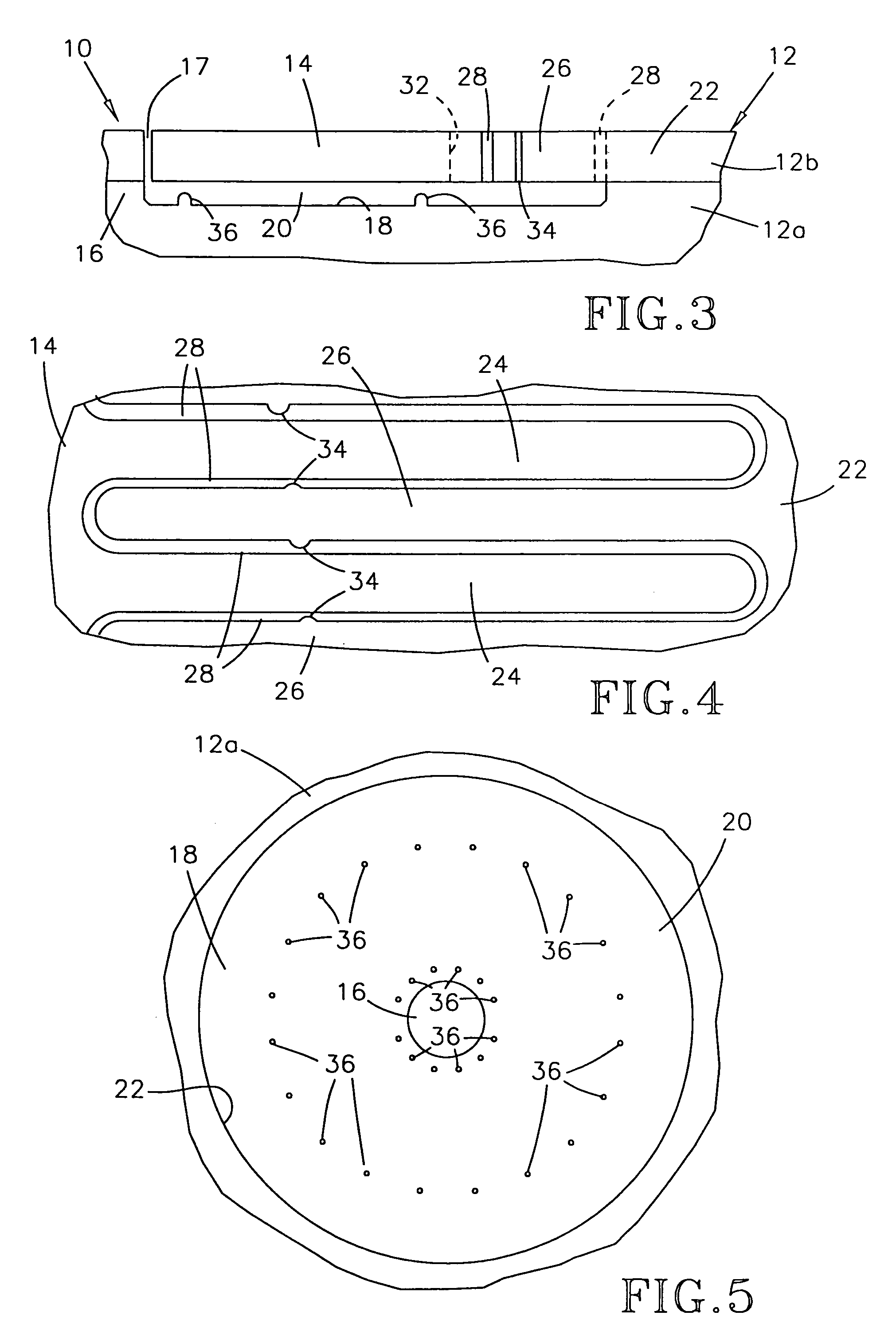

Proportional micromechanical valve

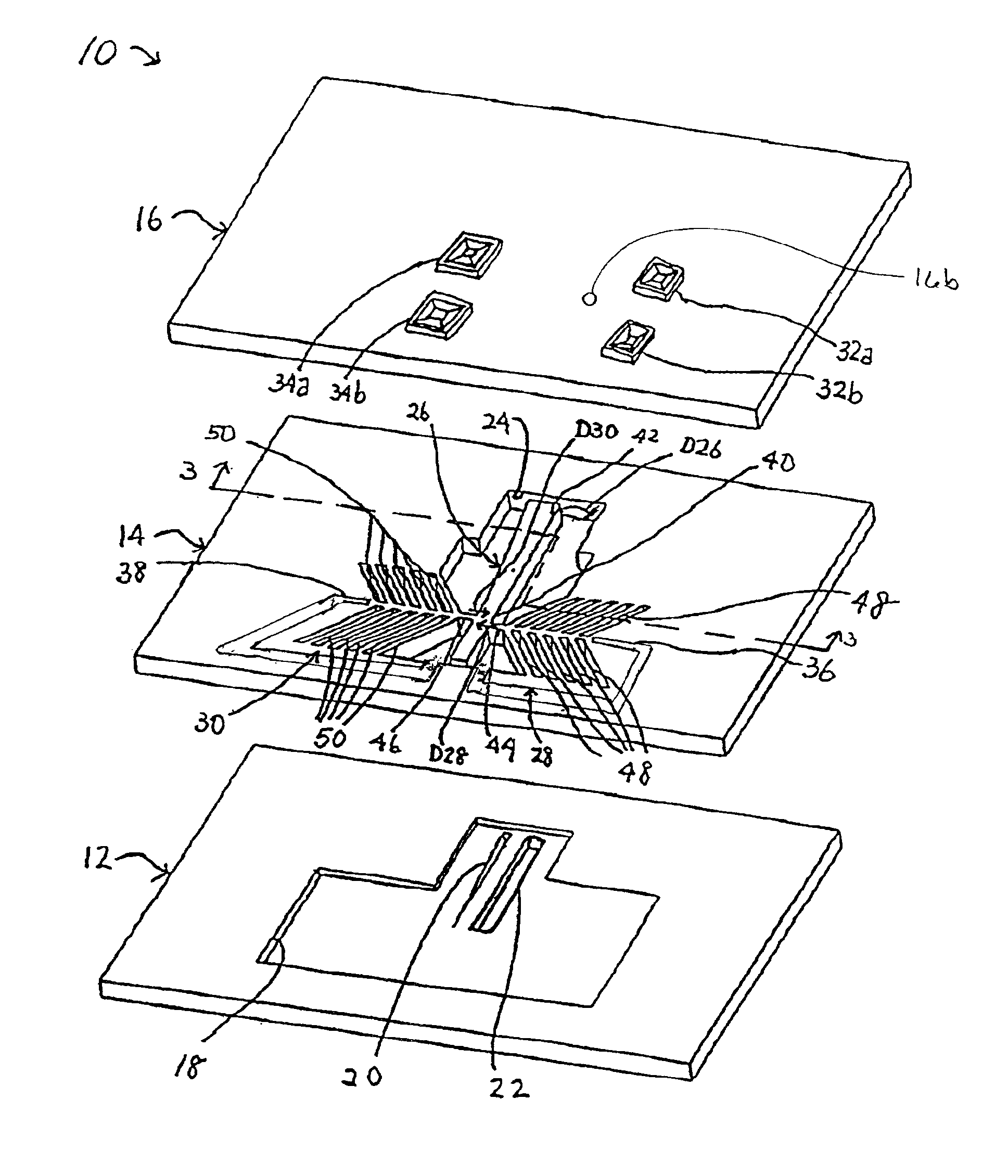

InactiveUS7011378B2Easy to manufactureWithout hysteresisOperating means/releasing devices for valvesCircuit elementsEngineeringActuator

The present invention provides a proportional microvalve having a first, second and third layer, and having high aspect ratio geometries. The first layer defines a cavity with inlet and outlet ports. The second layer, doped to have a low resistivity and bonded between the first and third layers, defines a cavity having a flow area to permit fluid flow between the inlet and outlet ports. The second layer further defines an actuatable displaceable member, and one or more thermal actuators for actuating the displaceable member to a position between and including an open and a closed position to permit or occlude fluid flow. The third layer provides one wall of the cavity and provides electrical contacts for electrically heating the thermally expandable actuators. The thermal actuators and the displaceable member have high aspect ratios and are formed by deep reactive ion etching such that they are displaceable in the plane of the second layer while being very stiff out of the plane. Thus, both actuation and displacement of the displaceable member are in the plane of the layer.

Owner:AMPHENOL THERMOMETRICS +1

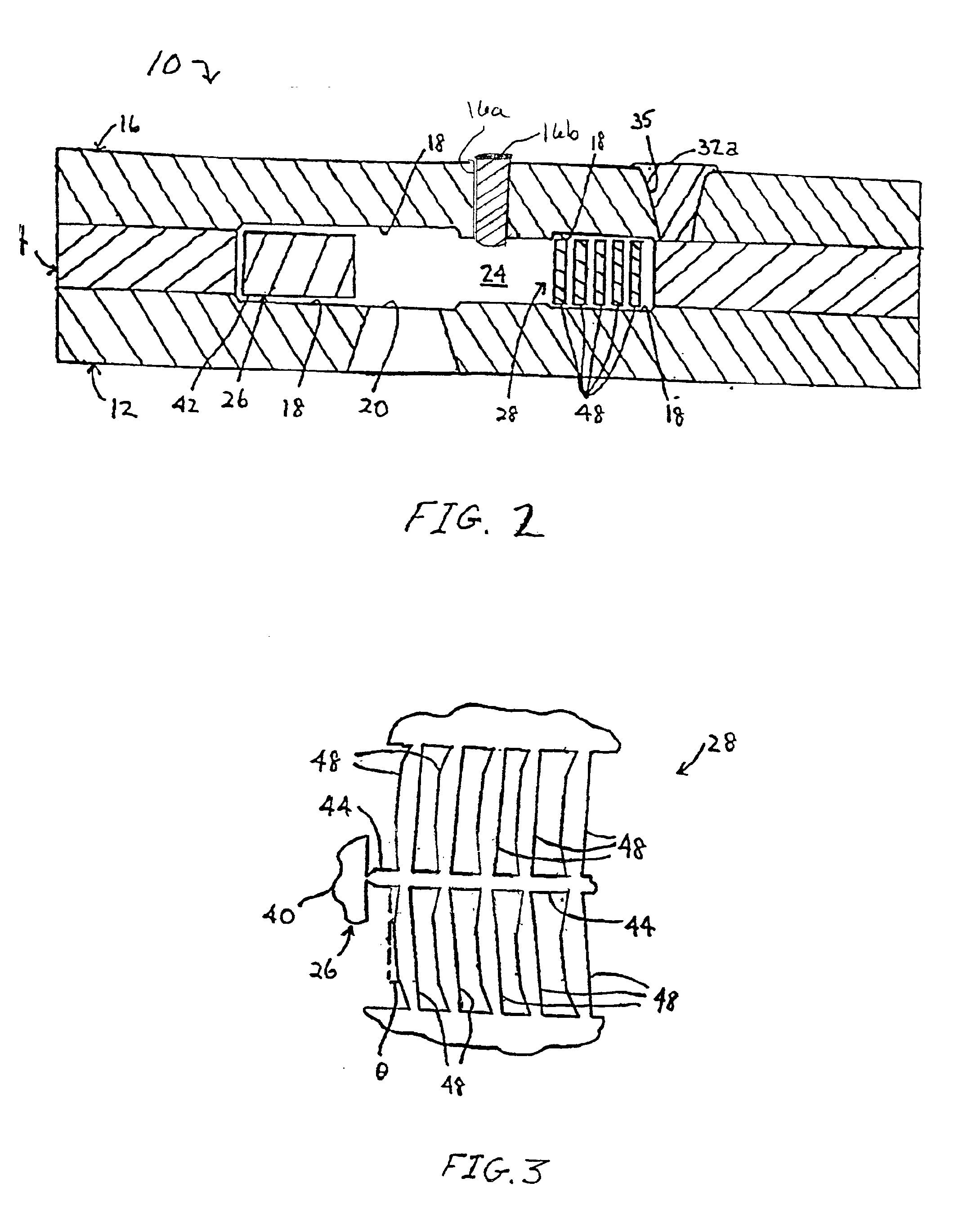

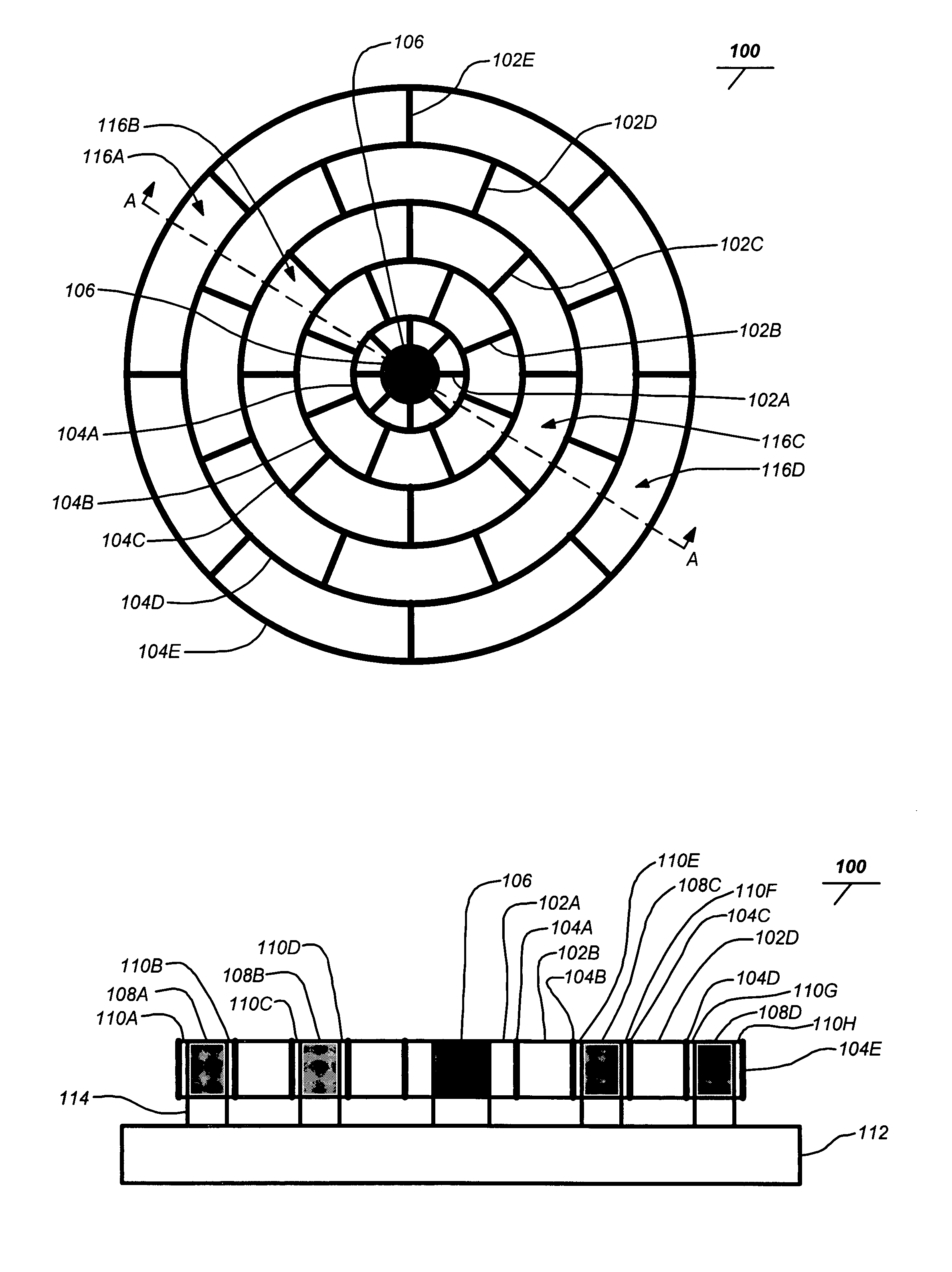

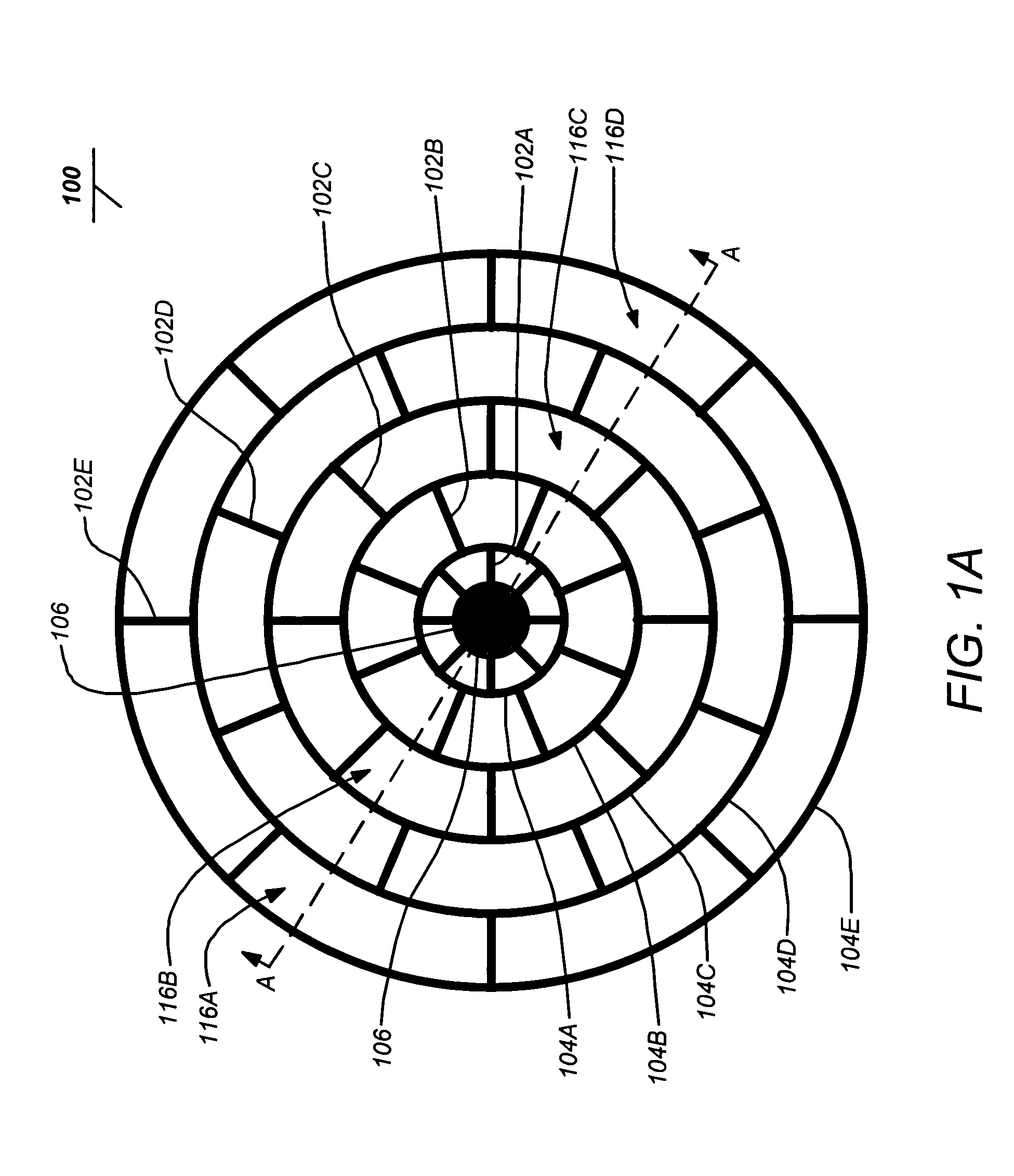

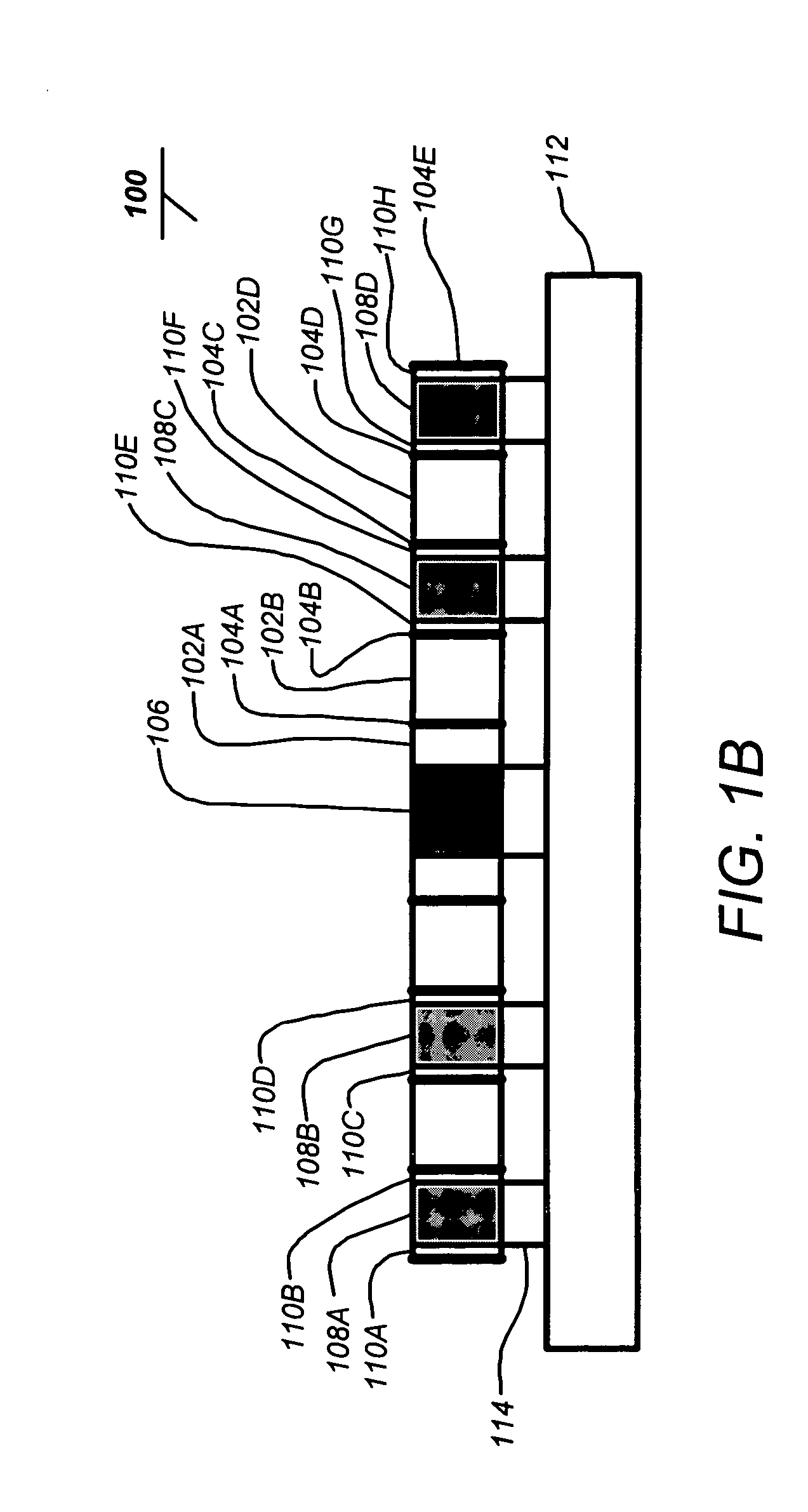

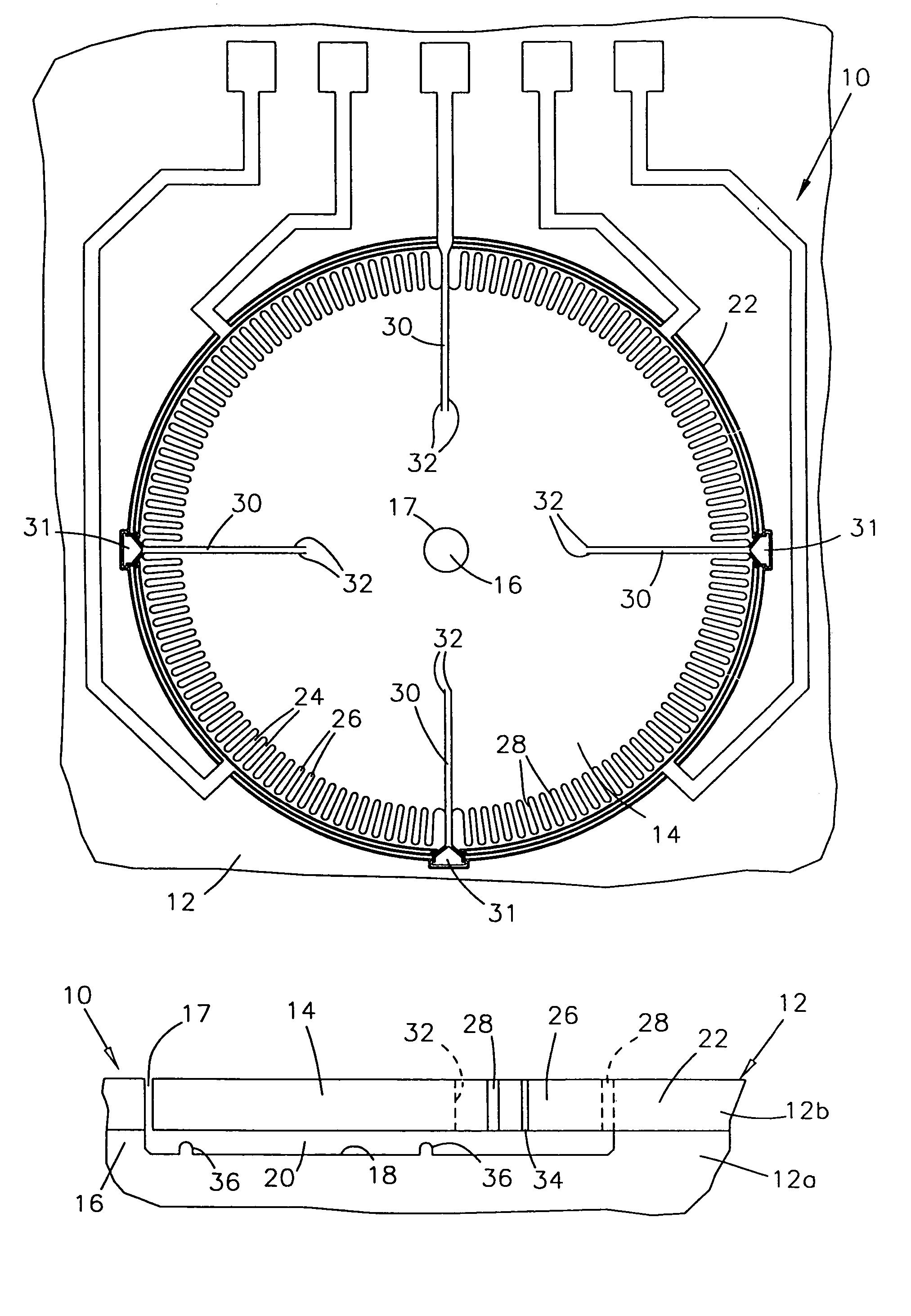

Isolated planar mesogyroscope

InactiveUS7168318B2Acceleration measurement using interia forcesSpeed measurement using gyroscopic effectsIn planeThermal expansion

Owner:CALIFORNIA INST OF TECH +1

MEMS tunable capacitor based on angular vertical comb drives

InactiveUS20050013087A1Increase tuning rangeAppreciates the drawbacks inherent in lateral drive MEMS capacitorsMultiple-port networksMechanically variable capacitor detailsCapacitanceComb finger

A MEMS tunable capacitor with angular vertical comb-drive (AVC) actuators is described where high capacitances and a wide continuous tuning range is achieved in a compact space. The comb fingers rotate through a small vertical angle which allows a wider tuning range than in conventional lateral comb drive devices. Fabrication of the device is straightforward, and involves a single deep reactive ion etching step followed by release and out-of-plane assembly of the angular combs.

Owner:RGT UNIV OF CALIFORNIA

Isolated planar mesogyroscope

ActiveUS20050172714A1Reduce frequencyEffect of errorAcceleration measurement using interia forcesSpeed measurement using gyroscopic effectsIn planeThermal expansion

An inertial sensor includes a mesoscaled disc resonator comprised of micro-machined substantially thermally non-conductive wafer with low coefficient of thermal expansion for sensing substantially in-plane vibration, a rigid support coupled to the resonator at a central mounting point of the resonator, at least one excitation electrode within an interior of the resonator to excite internal in-plane vibration of the resonator, and at least one sensing electrode within the interior of the resonator for sensing the internal in-plane vibration of the resonator. The inertial sensor is fabricated by etching a baseplate, bonding the substantially thermally non-conductive wafer to the etched baseplate, through-etching the wafer using deep reactive ion etching to form the resonator, depositing a thin conductive film on the through-etched wafer. The substantially thermally non-conductive wafer may comprise a silicon dioxide glass wafer, which is a silica glass wafer or a borosilicate glass wafer, or a silicon-germanium wafer.

Owner:CALIFORNIA INST OF TECH +1

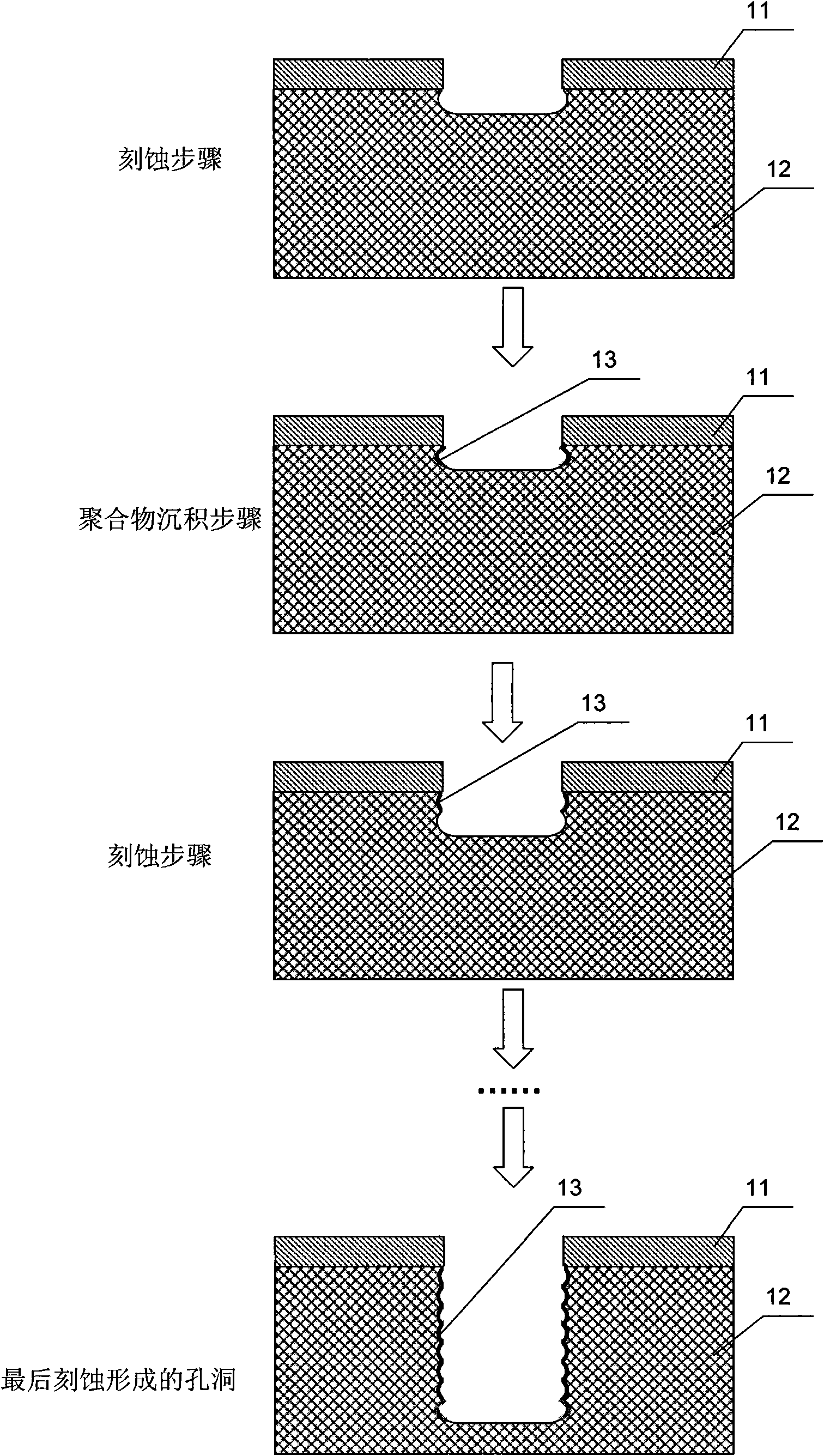

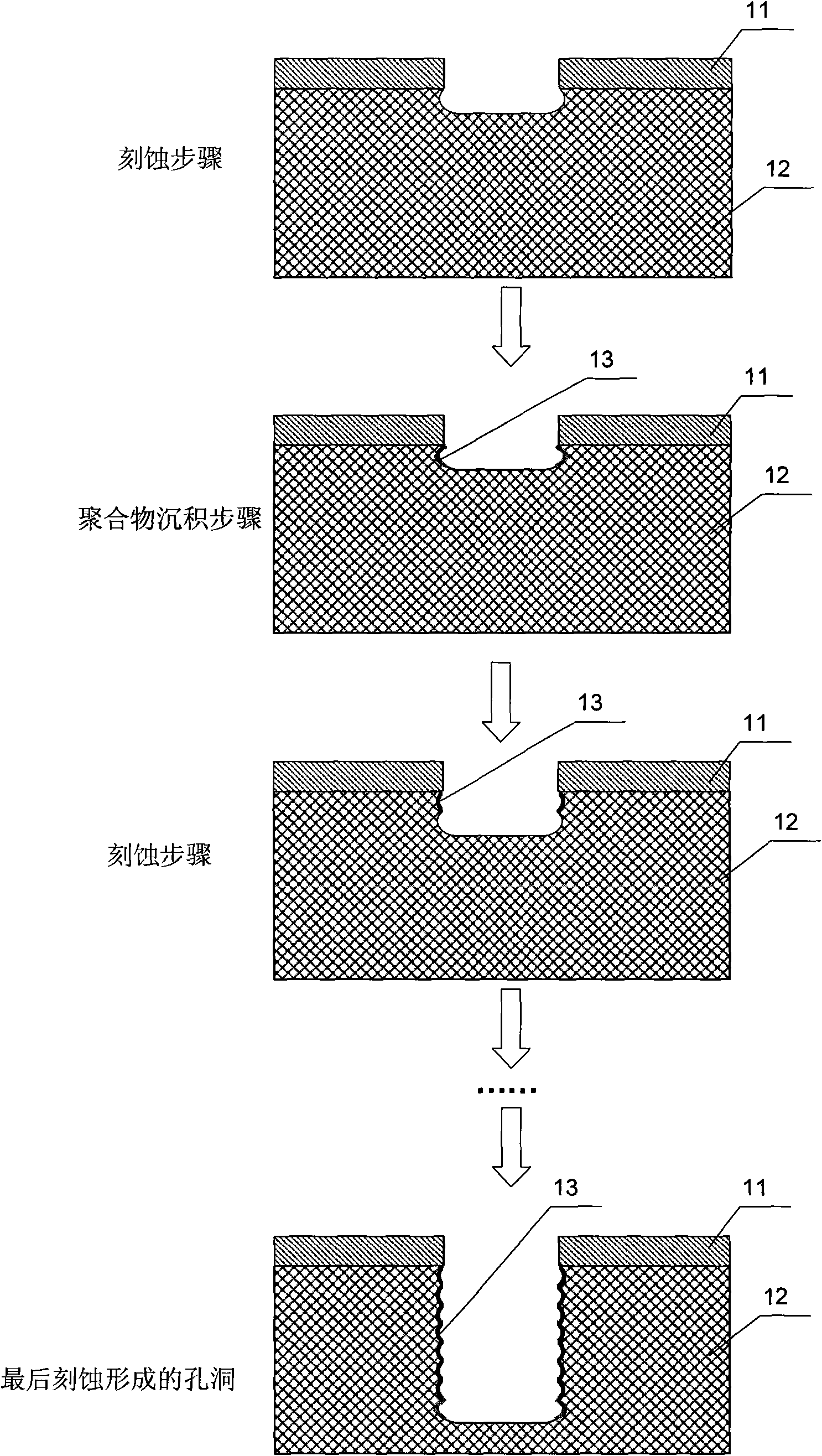

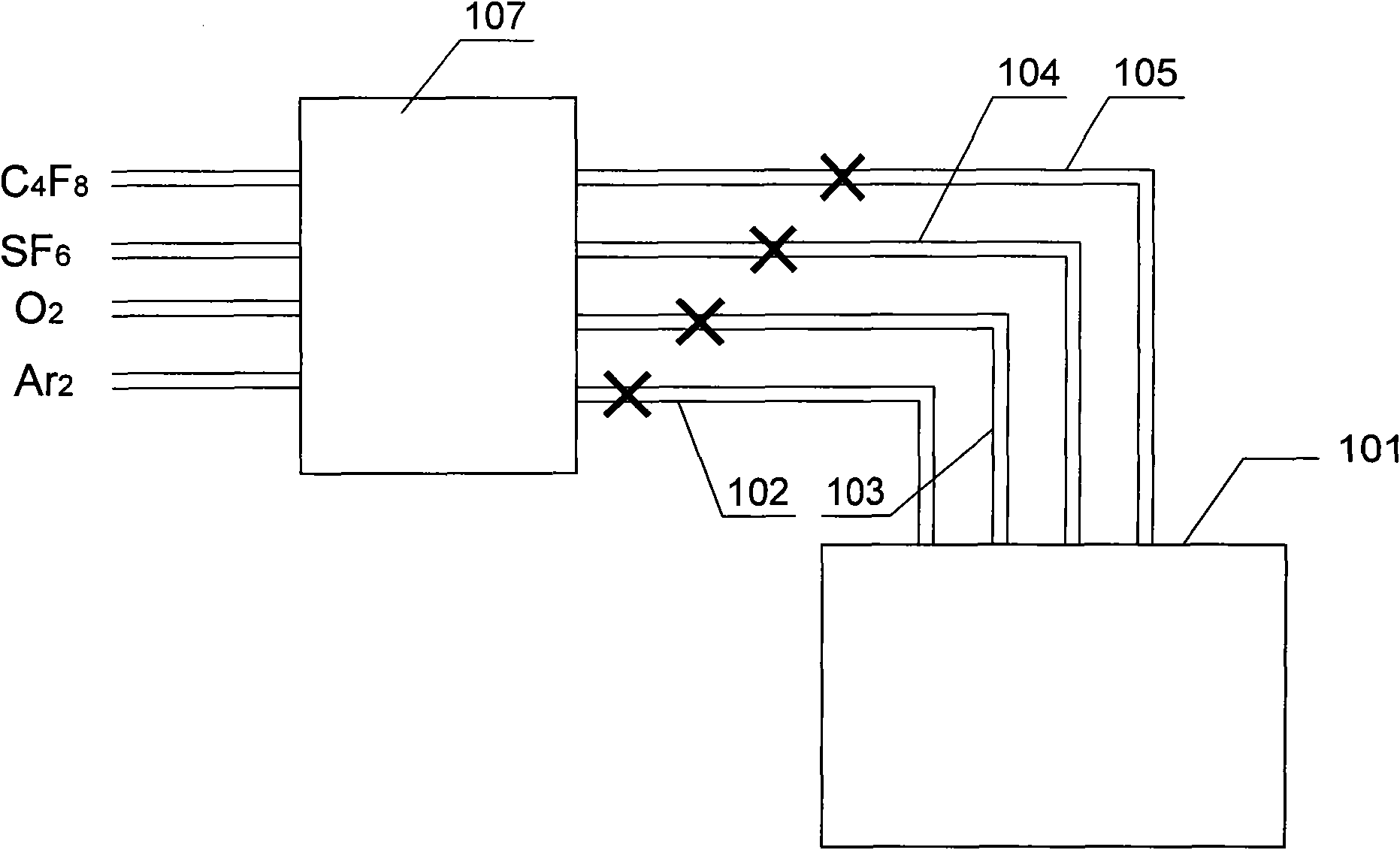

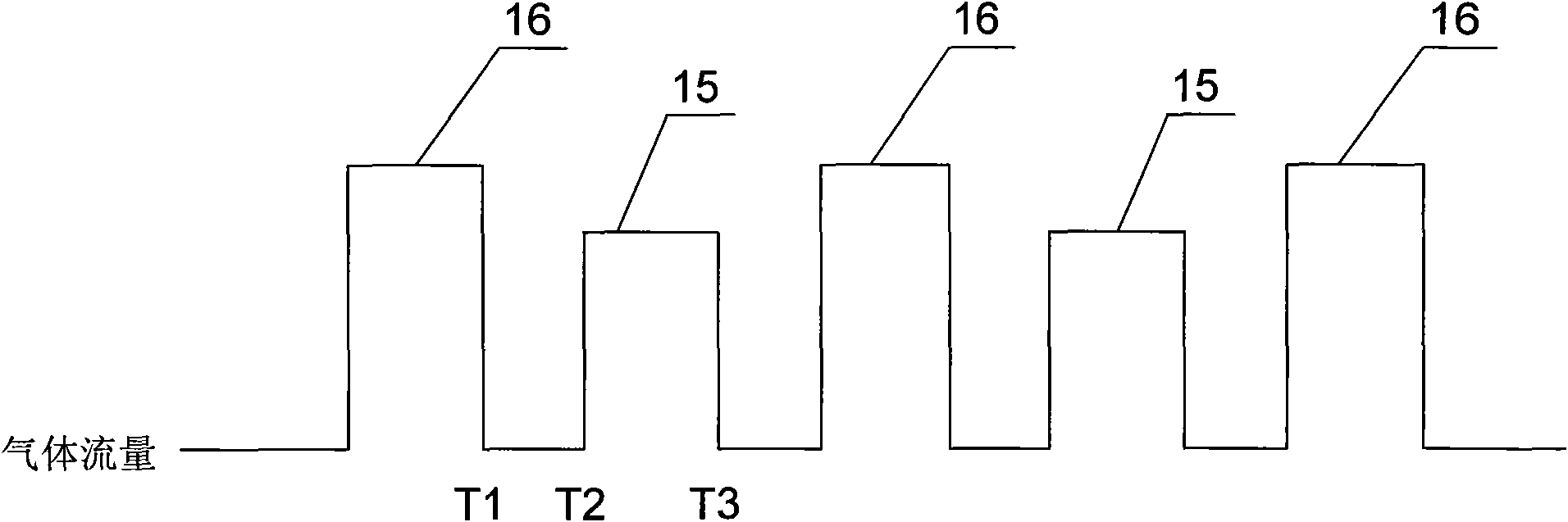

Deep reactive ion etching method and gas flow control device thereof

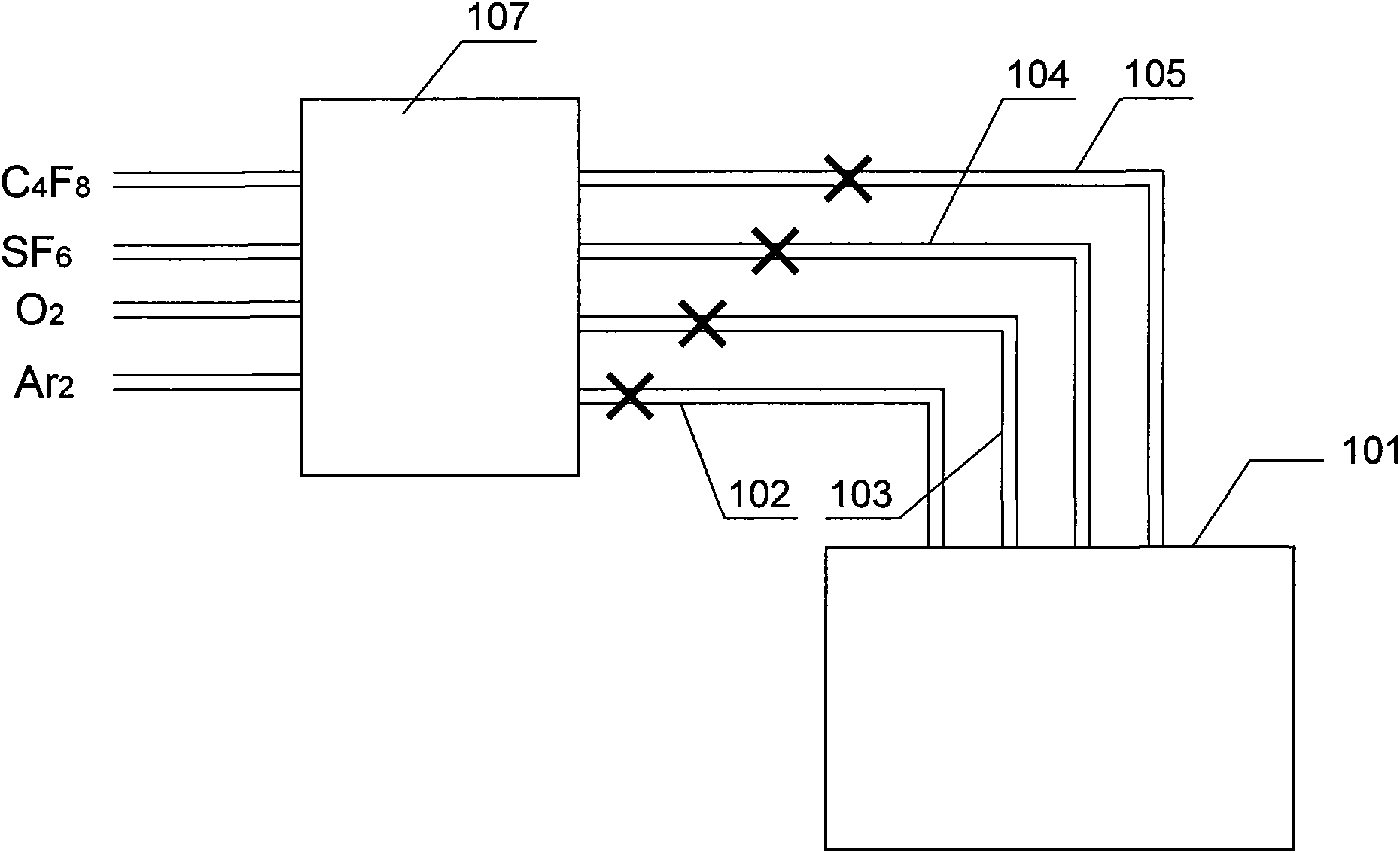

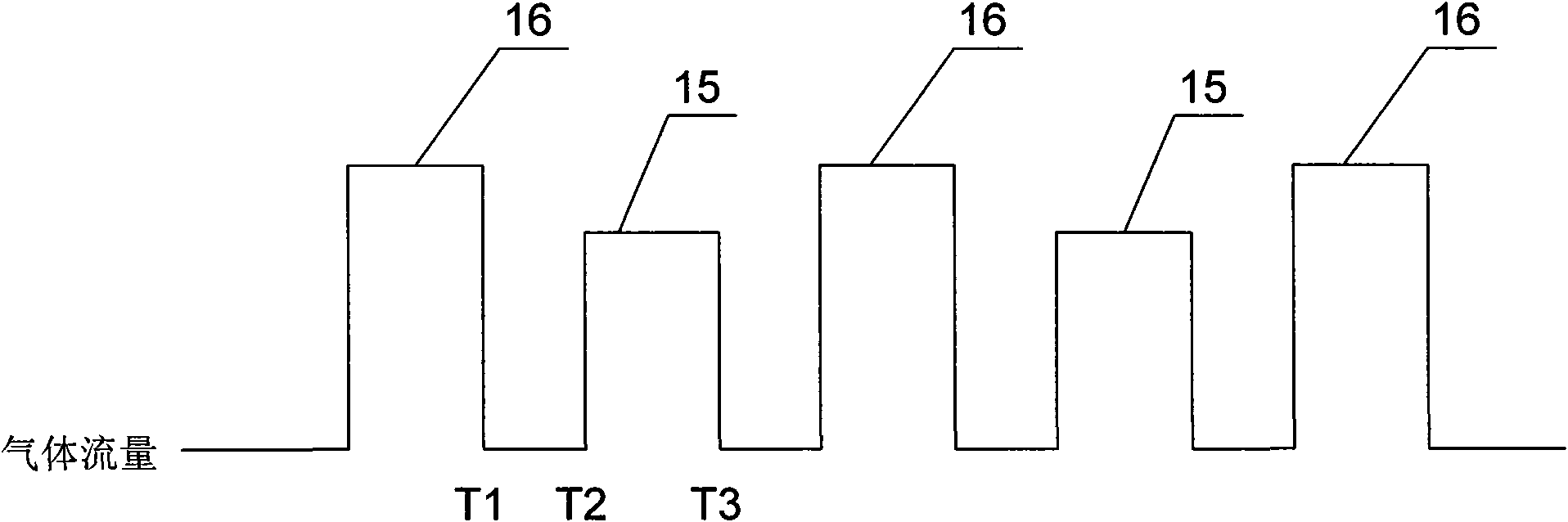

InactiveCN101958244AImprove smoothnessReduce the overall heightSemiconductor/solid-state device manufacturingFlow controlReactive gasShielding gas

The invention discloses a deep reactive ion etching method, which belongs to the technical field of semiconductor manufacturing. The method comprises a plurality of cyclically-performed etching cycles, and each etching cycle comprises an etching step and a polymer deposition step, wherein etching reactive gases are supplied for the etching step, sidewall protective gases are supplied for the polymer deposition step, and in the process of transforming the etching step to the polymer deposition step, the supply times of the etching reactive gas and the sidewall protective gas are overlapped. The invention has the following advantages that: sidewalls of a deep through hole etched by using the deep reactive ion etching method of the invention is good in smoothness; and the etching efficiency is high.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

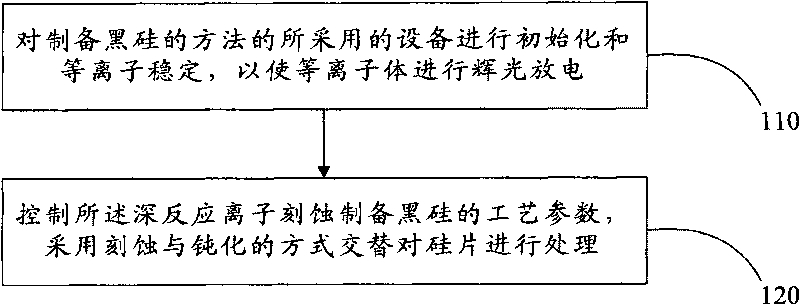

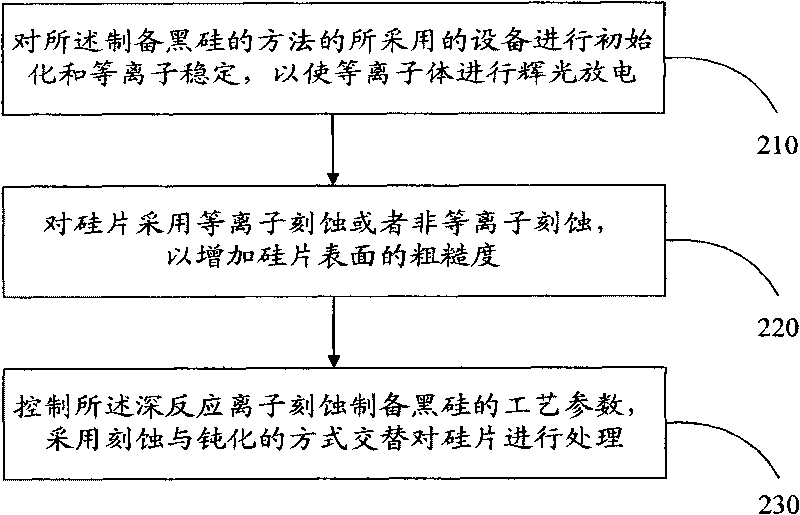

Maskless method for preparing black silicon by deep reactive ion etching

ActiveCN101734611AImprove efficiencyWon't breakNanostructure manufactureDecorative surface effectsNanostructureLarge range

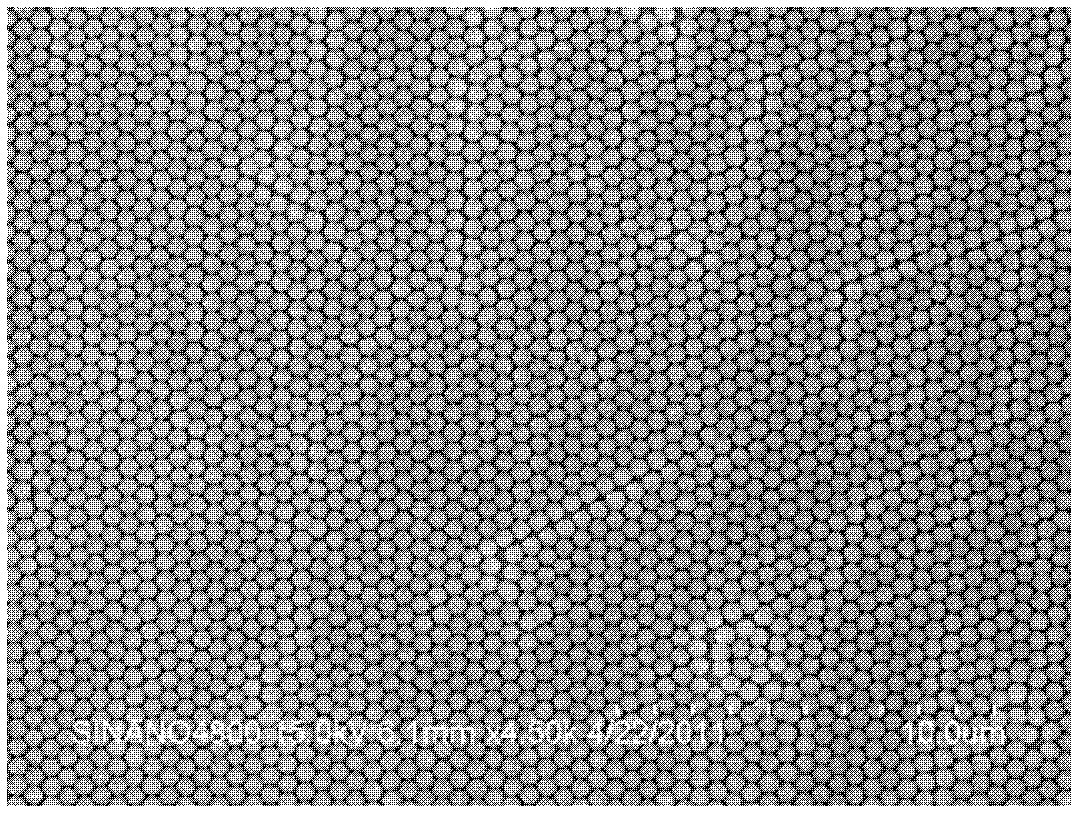

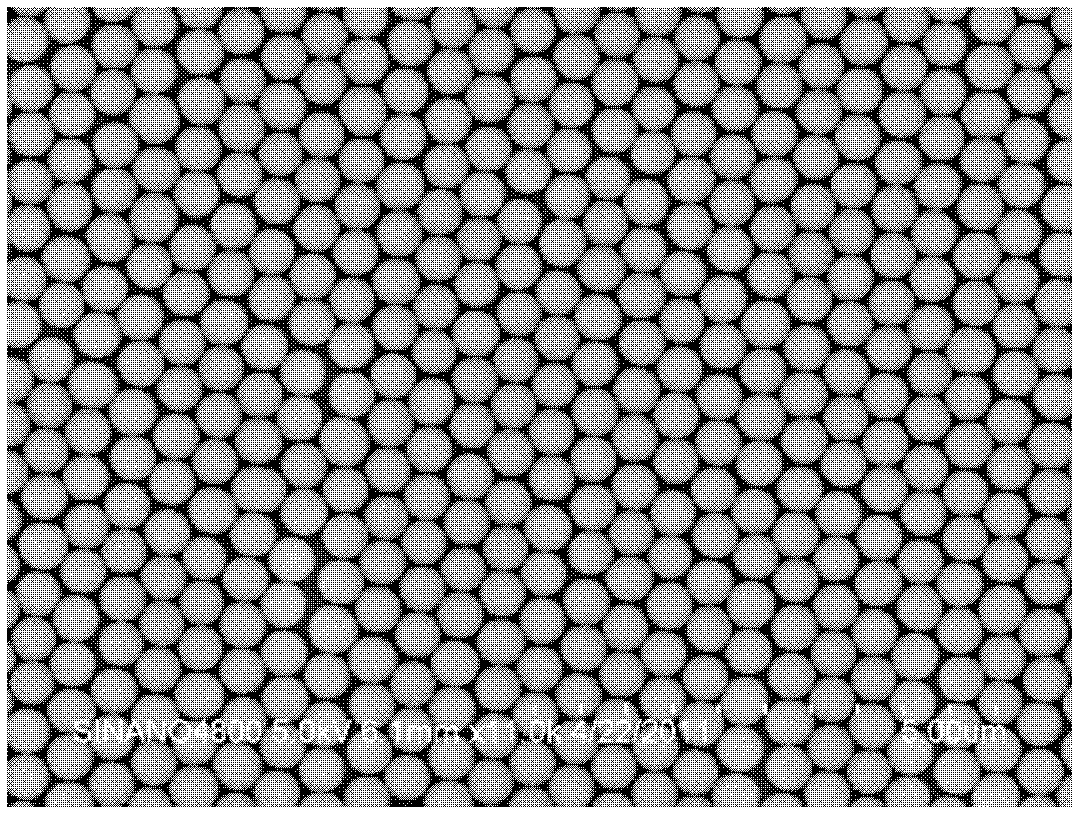

The invention discloses a maskless method for preparing black silicon by deep reactive ion etching, which comprises the following steps: performing initialization and plasma stability on equipment adopted by the method for preparing the black silicon so as to make plasma perform glow discharge; and controlling technological parameters for preparing the black silicon by deep reactive ion etching, and adopting etching and passivating modes to alternately process a silicon chip, wherein the parameters comprise plasma gas flow, panel etching power, panel passivating power, coil power, and etching and passivating cycle and temperature. The maskless method directly performs plasma processing on the surface of the silicon chip, and can generate large-range high-intensity nanostructures on the surface of the silicon chip in case of no nano mask by adjusting and selecting proper etching technological parameters. Meanwhile, the method for preparing the black silicon has high efficiency and low cost, and can be integrated with other micro-fabrication technology.

Owner:PEKING UNIV

Etching radical controlled gas chopped deep reactive ion etching

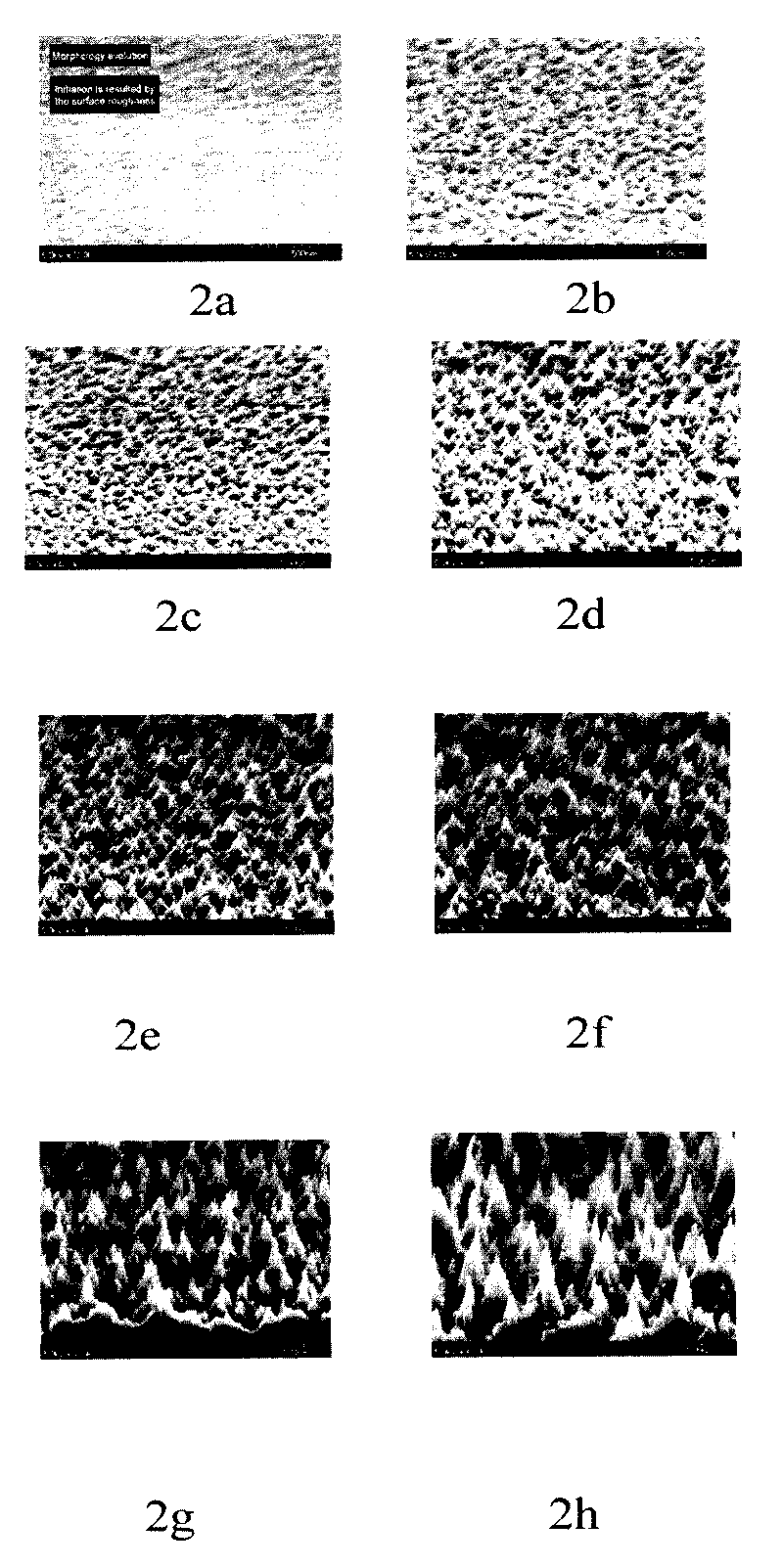

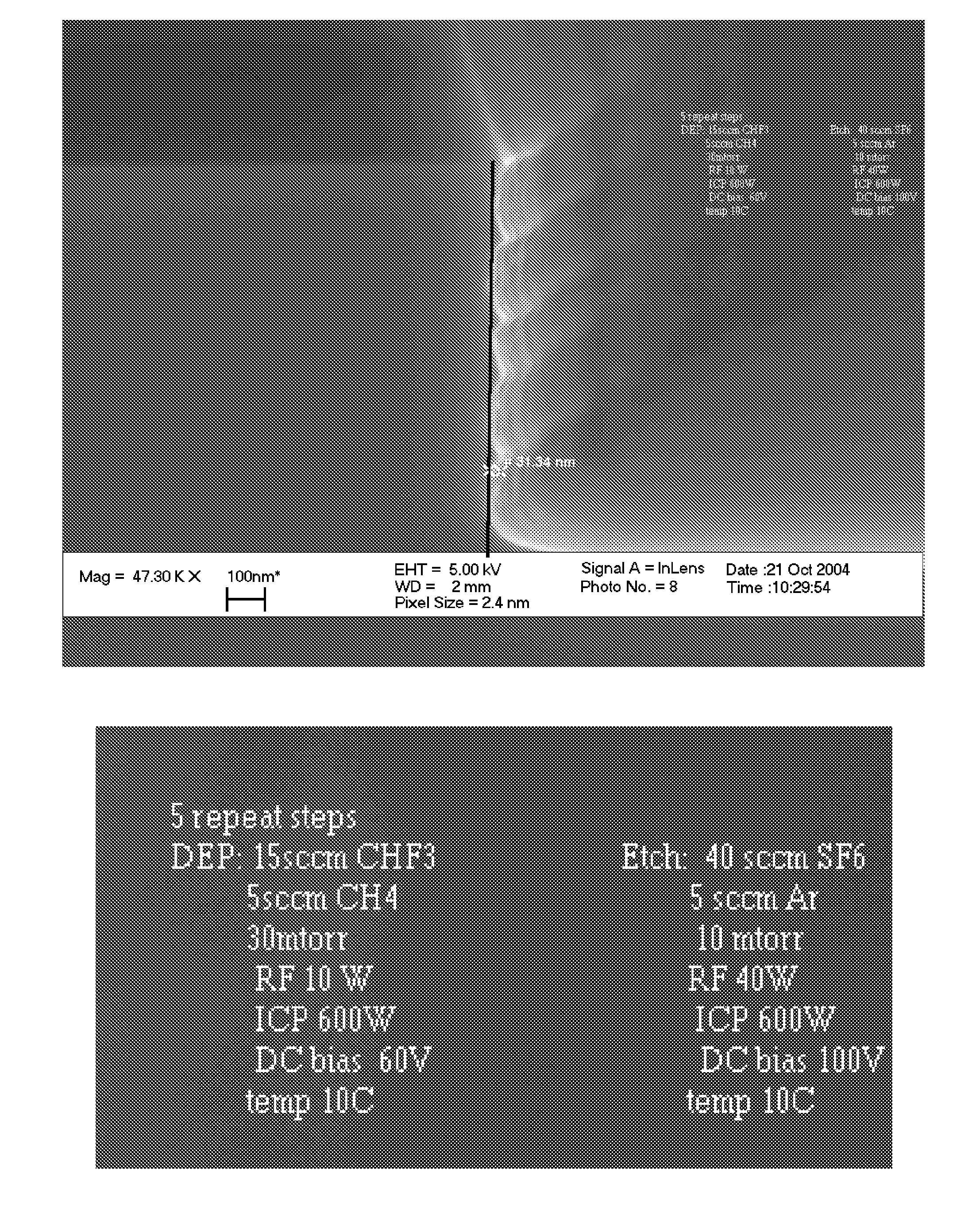

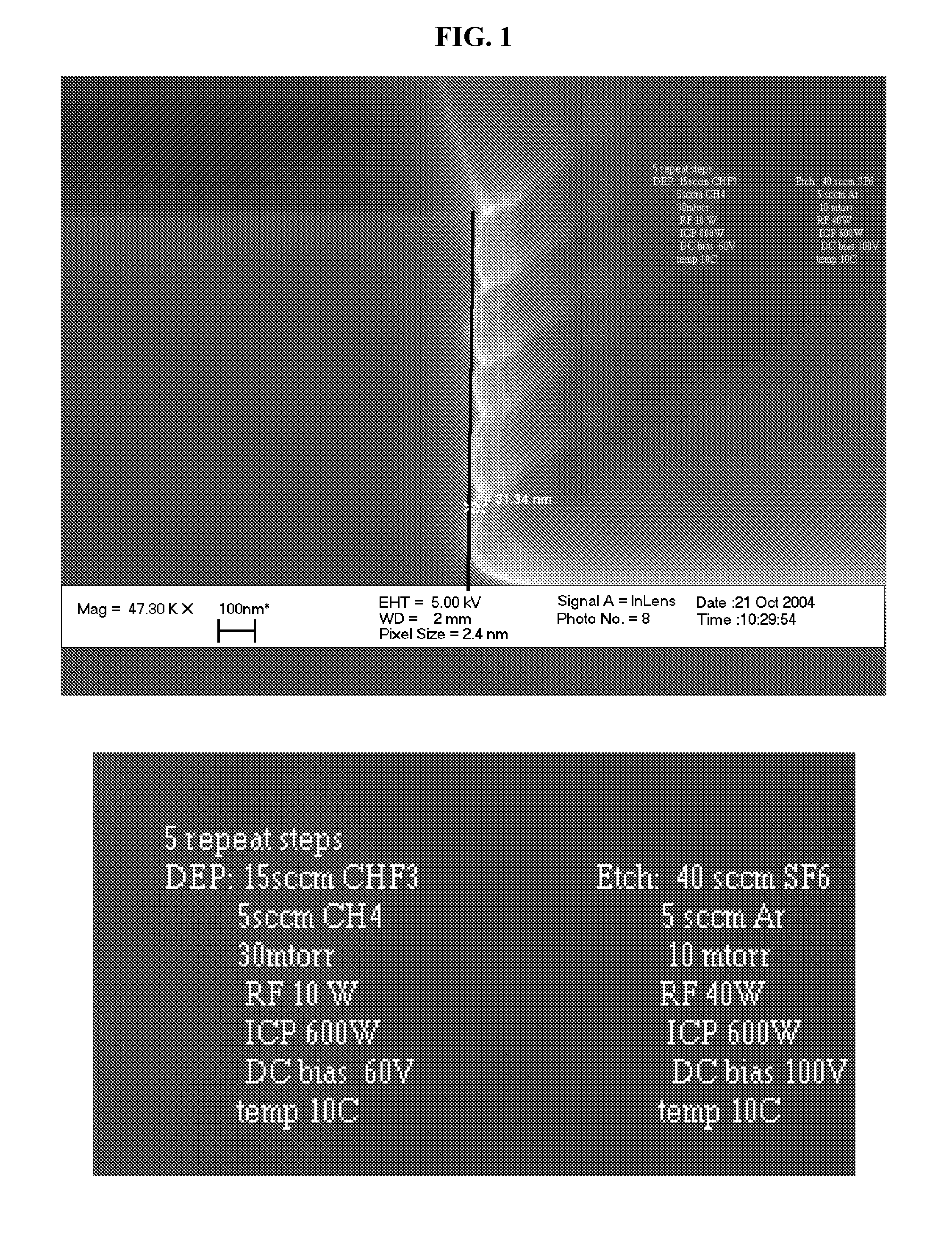

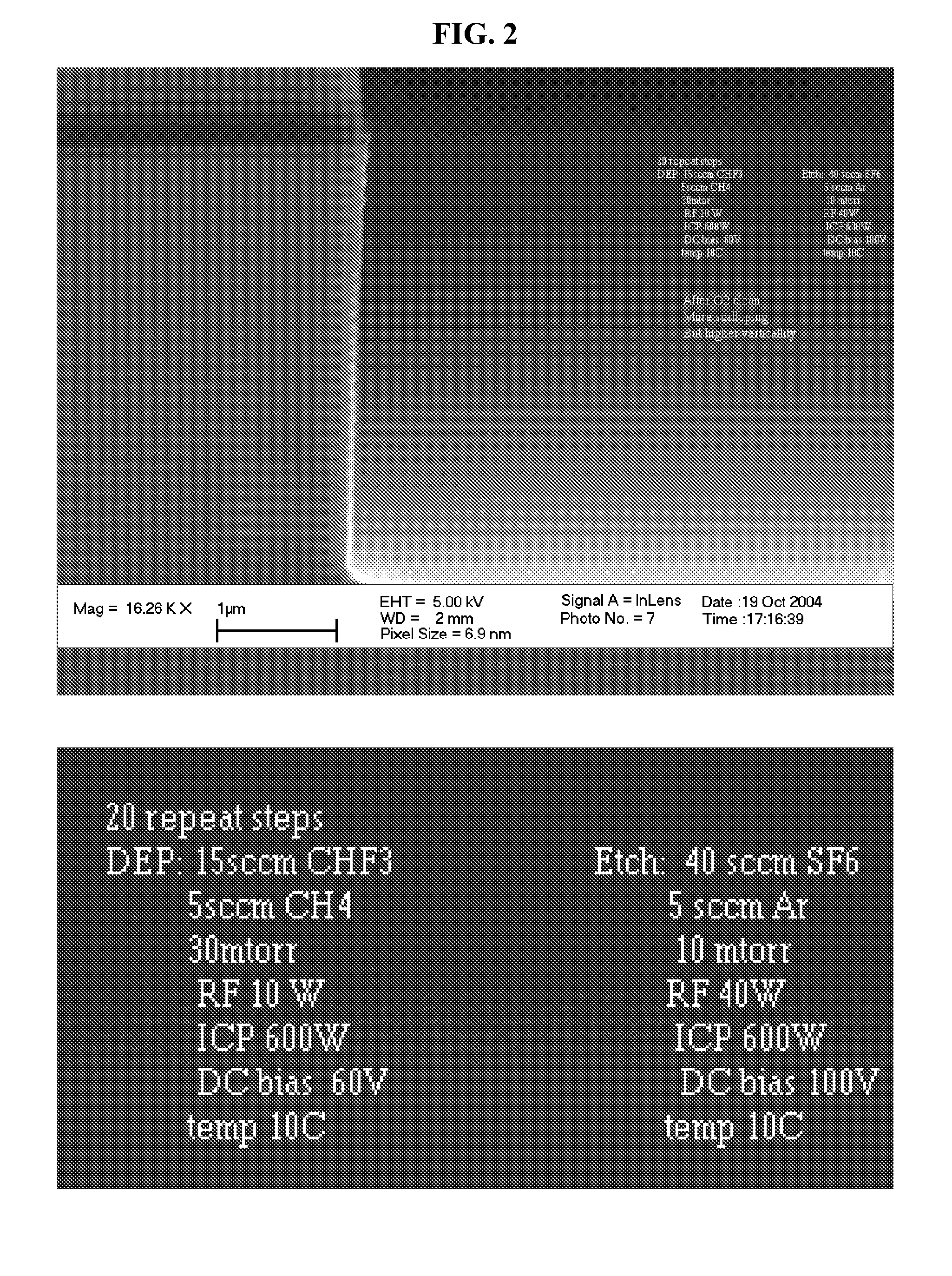

ActiveUS20070015371A1Decorative surface effectsSemiconductor/solid-state device manufacturingInductively coupled plasmaChemical measurement

A method for silicon micromachining techniques based on high aspect ratio reactive ion etching with gas chopping has been developed capable of producing essentially scallop-free, smooth, sidewall surfaces. The method uses precisely controlled, alternated (or chopped) gas flow of the etching and deposition gas precursors to produce a controllable sidewall passivation capable of high anisotropy. The dynamic control of sidewall passivation is achieved by carefully controlling fluorine radical presence with moderator gasses, such as CH4 and controlling the passivation rate and stoichiometry using a CF2 source. In this manner, sidewall polymer deposition thicknesses are very well controlled, reducing sidewall ripples to very small levels. By combining inductively coupled plasmas with controlled fluorocarbon chemistry, good control of vertical structures with very low sidewall roughness may be produced. Results show silicon features with an aspect ratio of 20:1 for 10 nm features with applicability to nano-applications in the sub-50 nm regime. By comparison, previous traditional gas chopping techniques have produced rippled or scalloped sidewalls in a range of 50 to 100 nm roughness.

Owner:RGT UNIV OF CALIFORNIA

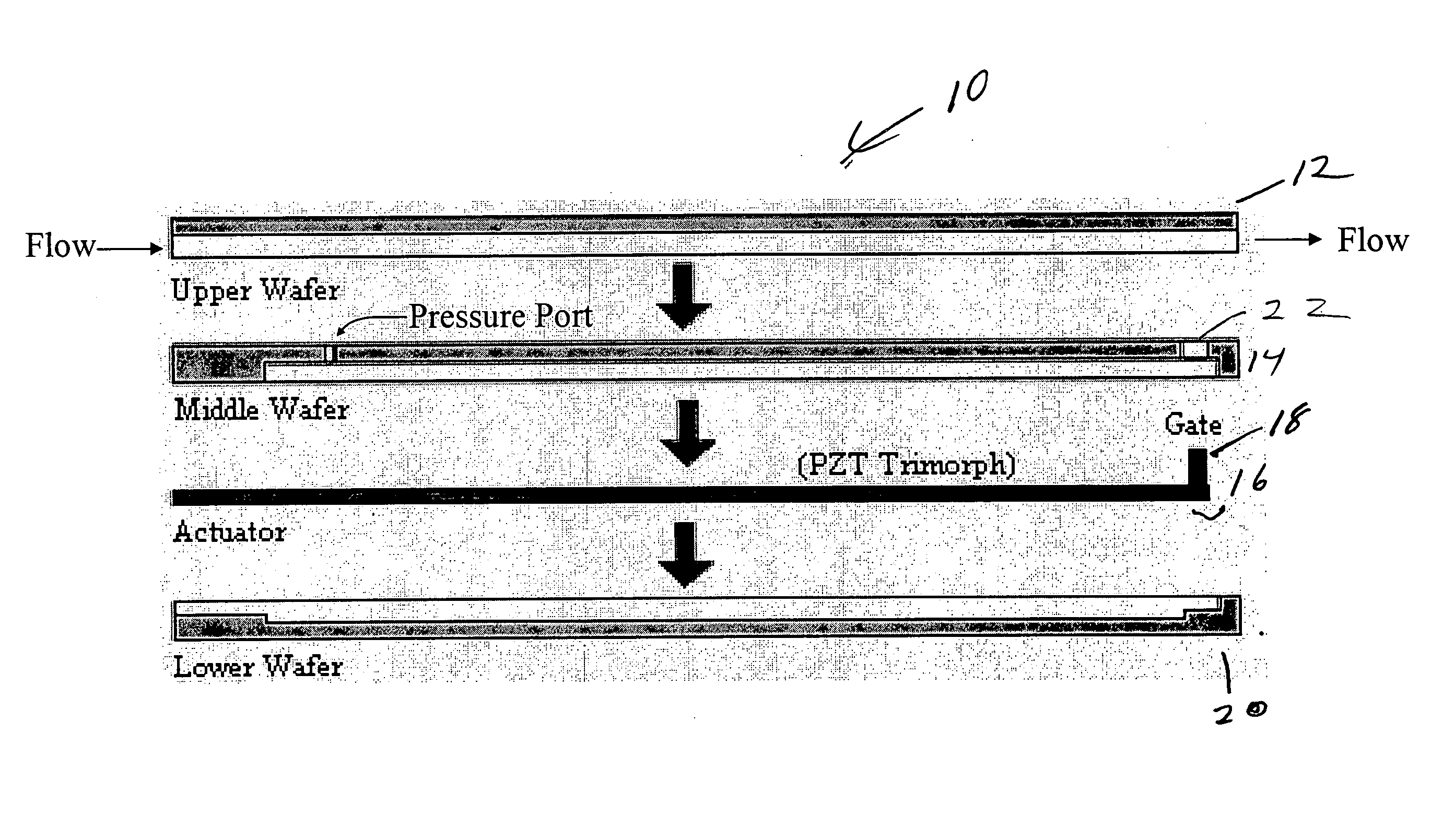

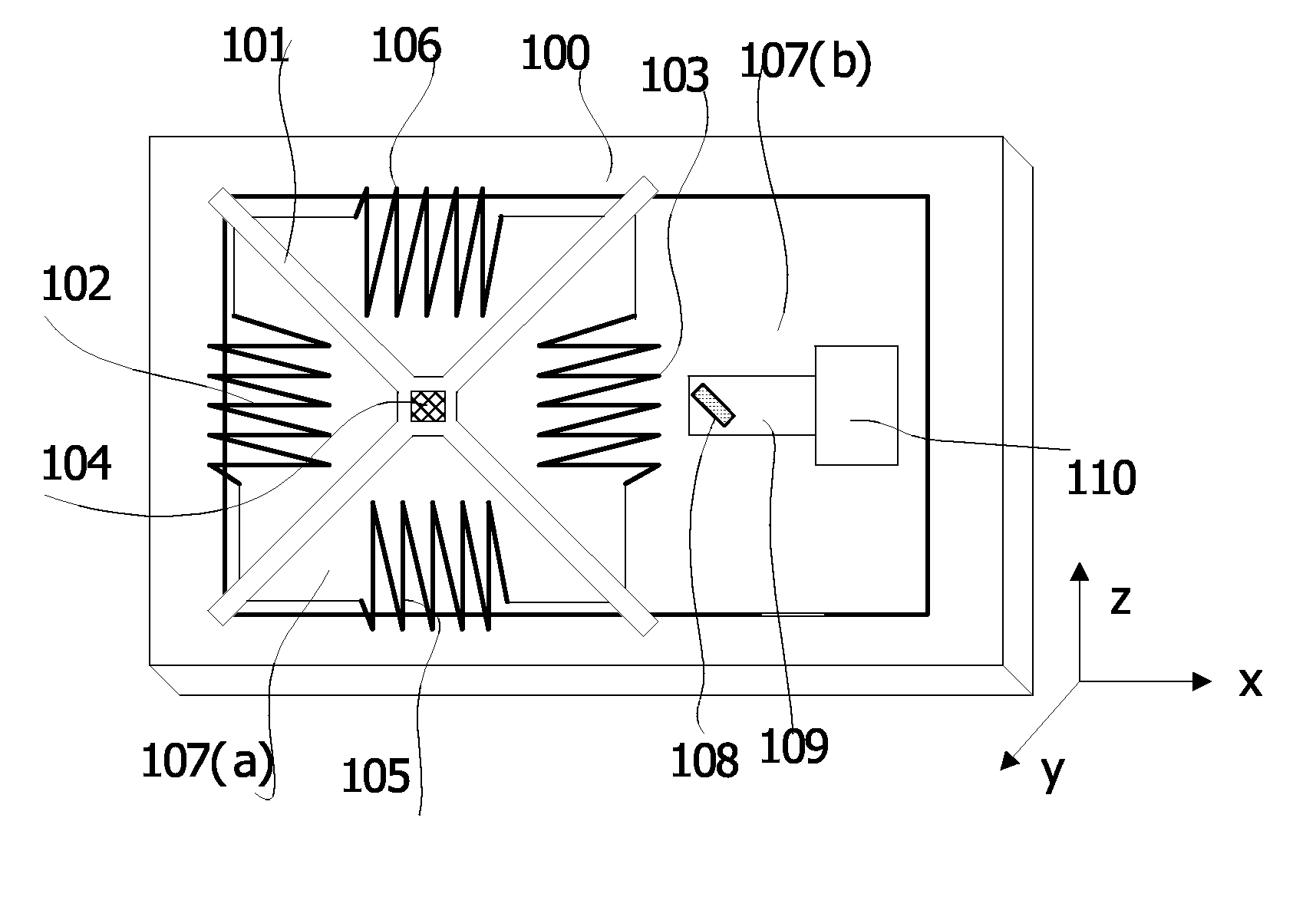

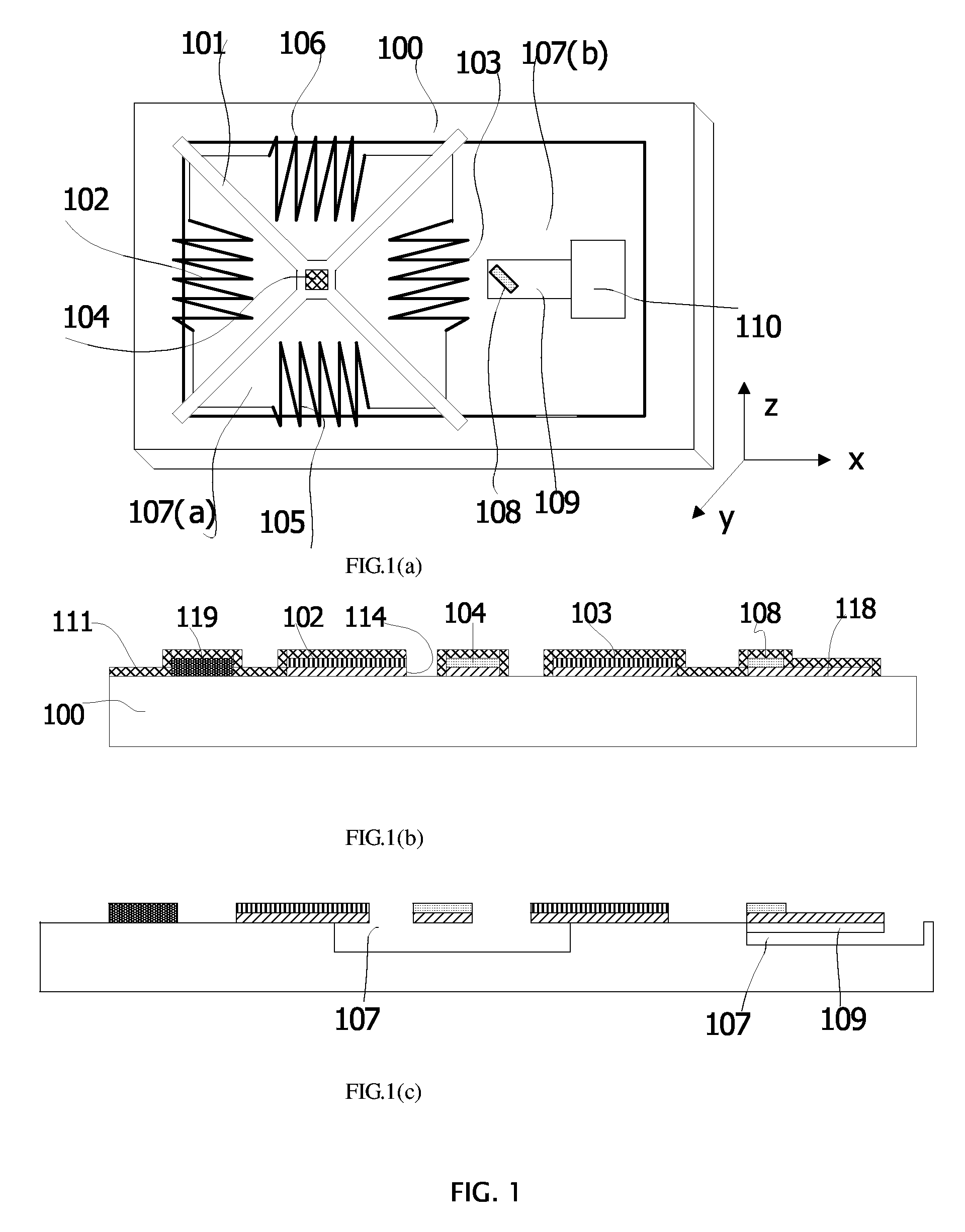

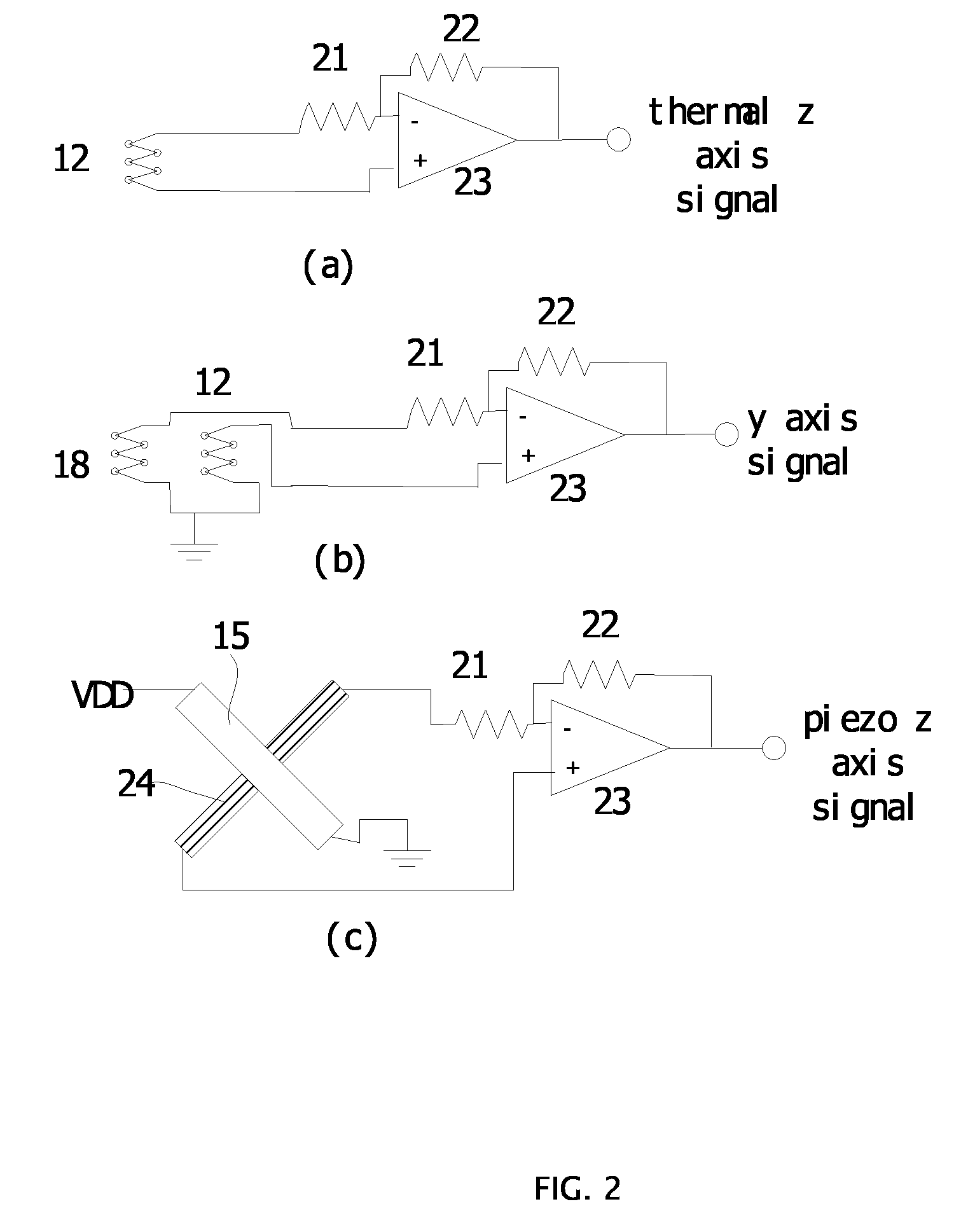

Ultra-small Profile, Low Cost Chip Scale Accelerometers of Two and Three Axes Based on Wafer Level Packaging

Several micro-machined, ultra-profile two-axis and three-axis accelerometers are fabricated by CMOS-compatible process, which makes them suitable for volume production. The x, y axis signal is based on natural thermal convection, and z-axis signal may be based on thermal convention or piezoresistive in nature. The bulk MEMS (Micro-Electro-Mechanical-Systems) process is based on Deep Reactive Ion Etching (DRIE). After the front-end fabrication process, the accelerometers are packaged at wafer level by glass frit and / or anodic bonding, which lowers the device cost.

Owner:WUHAN FINEMEMS

Deep reactive ion etching

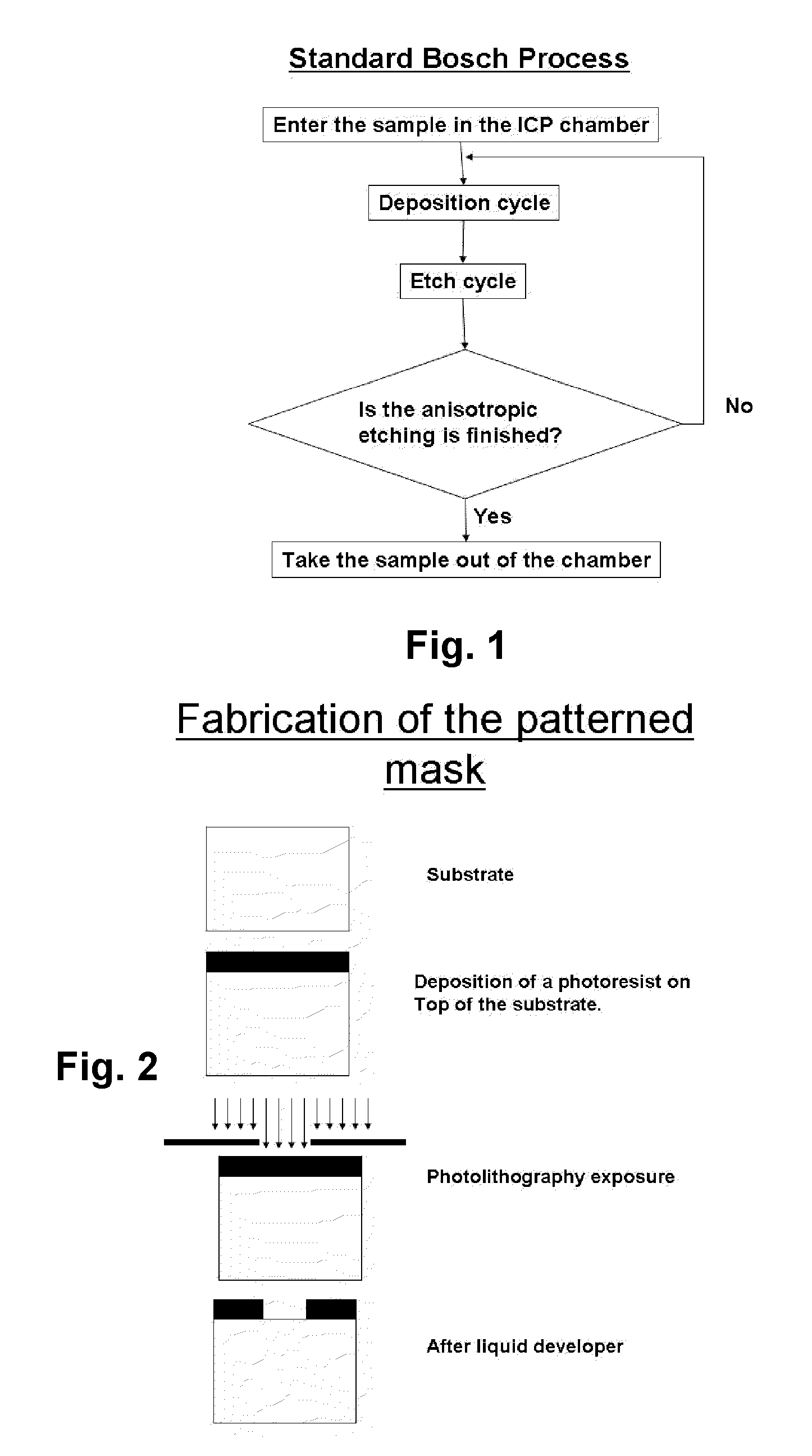

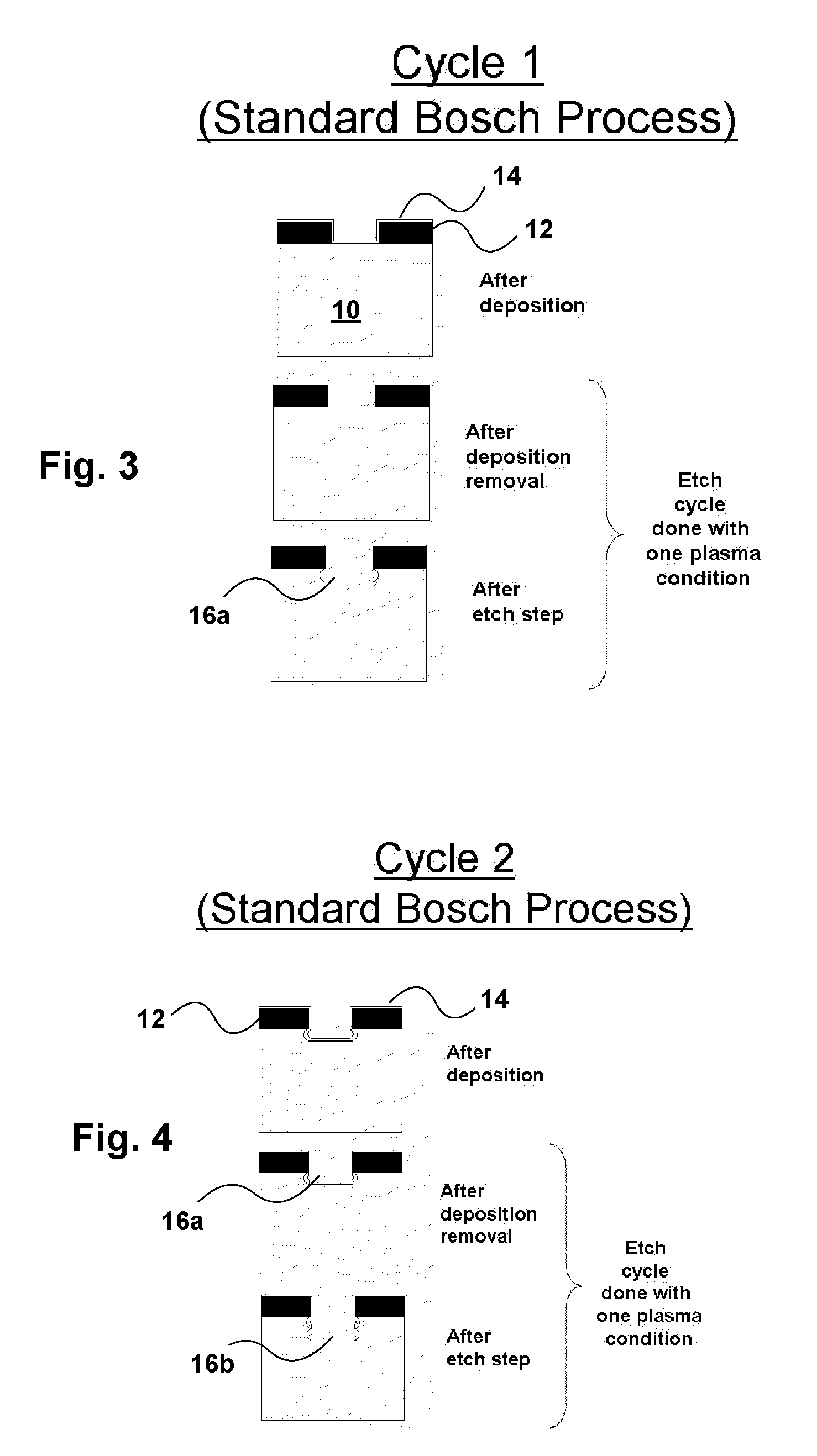

InactiveUS20090242512A1Reduce roughnessIncrease pressureDecorative surface effectsSemiconductor/solid-state device manufacturingSurface roughnessInductively coupled plasma

In a method of performing an anisotropic etch on a substrate in an inductively coupled plasma etch chamber, at least three cycles of a procedure consisting essentially of the four following steps are performed:a. depositing a protective polymer on a patterned substrate;b. performing a first low pressure etch to partially remove the deposited protective polymer at a pressure less than 40 mTorr;c. performing a high pressure etch at a pressure between between 40 mT and 1000 mT to form a portion of a trench in the substrate; andd. performing a second low pressure etch at a pressure less than 40 MTorr to reduce surface roughness.This method permits the fabrication of deep trenches with reduced surface roughness.

Owner:DALSA SEMICON INC

High, depth and width three-dimensional uprightness interconnect and realization method of three-dimensional integrate circuit

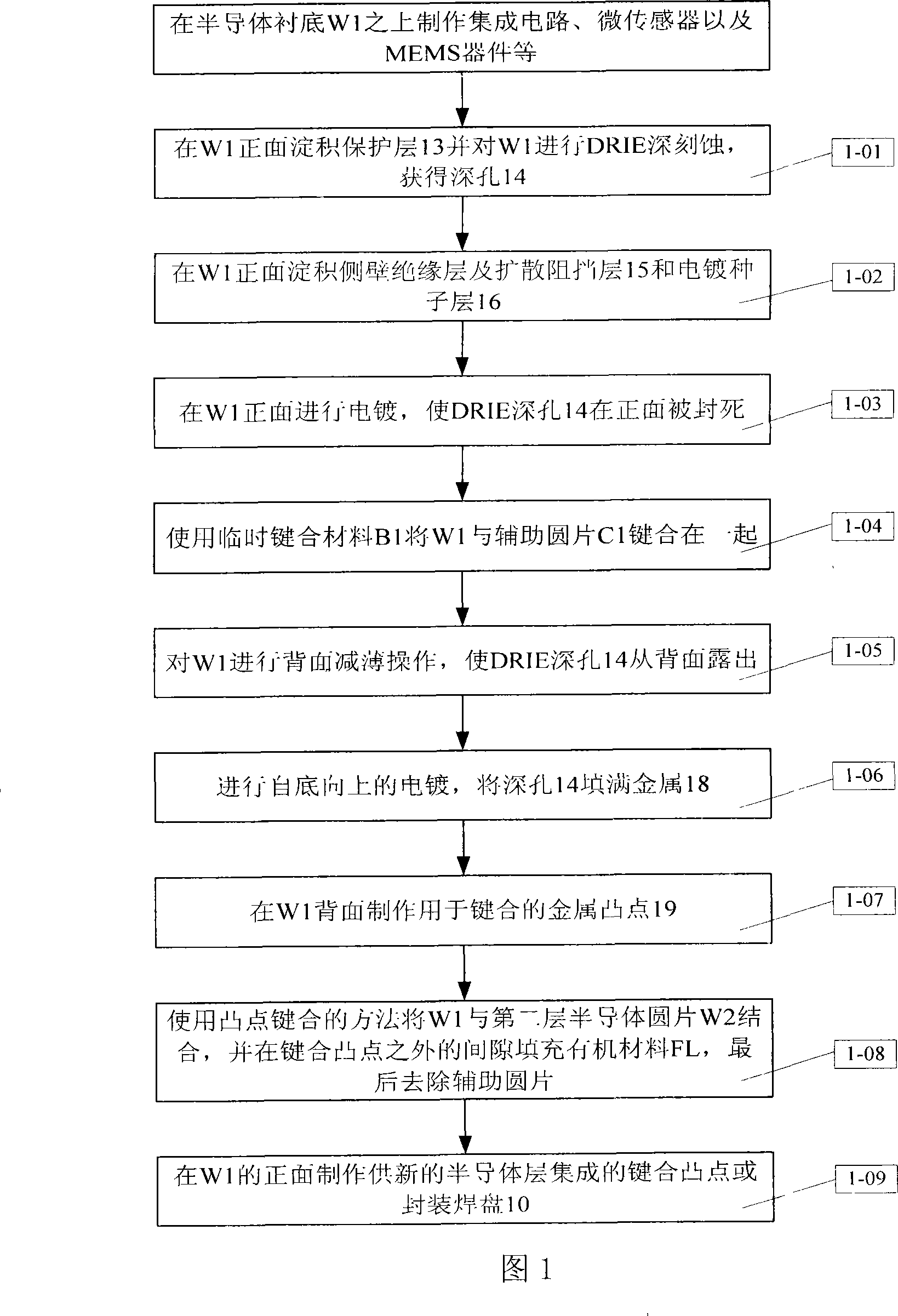

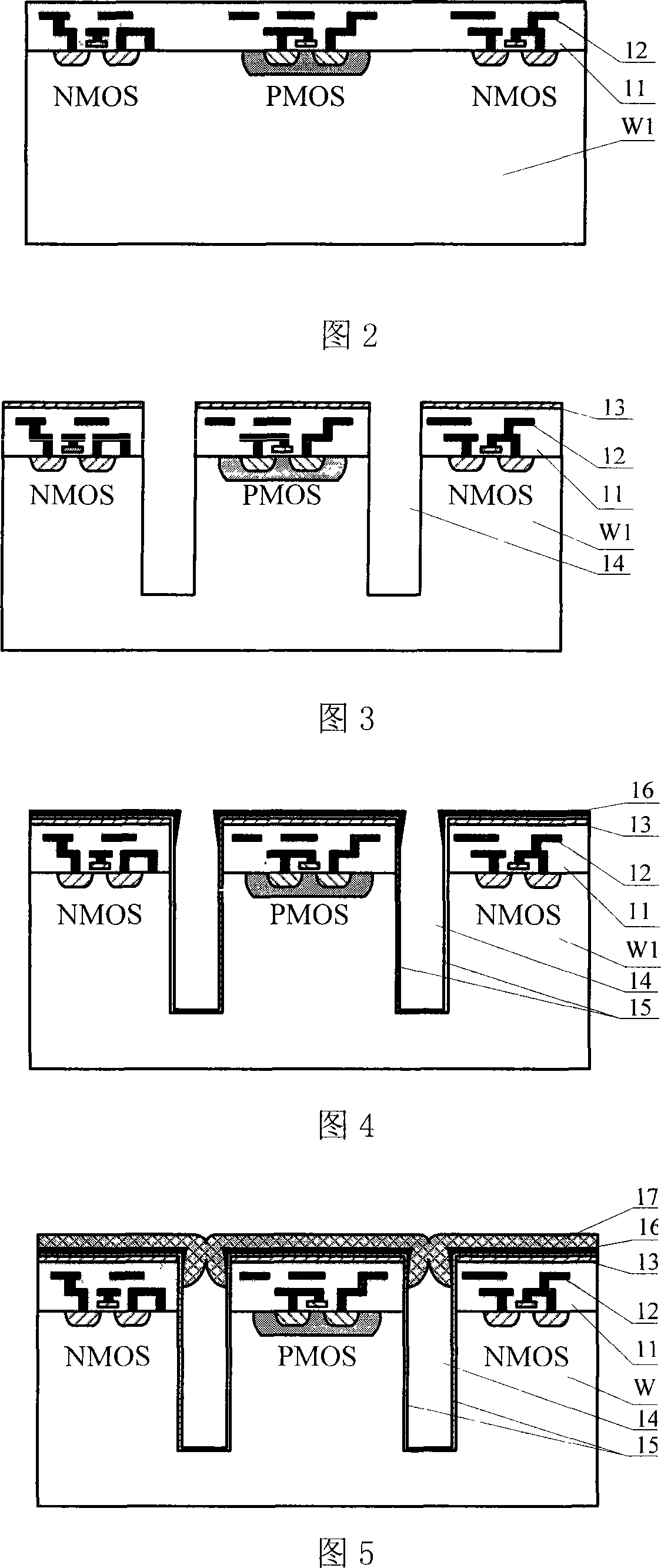

InactiveCN101179037AAvoid lateral undercuttingEliminate dependenciesSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerManufacturing technology

The invention discloses a method for implementing a high aspect ratio three-dimensional vertical interconnection and a three-dimensional integrated circuit, which belongs to fields of semiconductor manufacture technology and micro-sensor manufacture technology. The method includes the following steps: carrying out a deep reactive ion etching at the front side of a semiconductor wafer with a prepared plant integrated circuit or a prepared micro-sensor, and gaining deep pores; precipitating a insulation layer, a diffusion barrier and a plating seed layer at the front side; temporarily bonding the semiconductor wafer plating face and an assistant wafer, thinning the back of the semiconductor wafer in such a manner that DRIE deep pores are exposed from the back; precipitating the insulation layer, the diffusion barrier and the plating seed layer at the back side; carrying out the plating upwards from the bottom and filling the DRIE deep pores to form the high aspect ratio three-dimensional vertical interconnection; removing the assistant wafer and implementing the vertical integration of two layers of wafers; and repeating the steps above and implementing the three-dimensional integrated circuit with more layers. The invention reduces difficulty of the process for filling the high aspect ratio through-hole, simplifies the manufacturing process, and ensures the yield.

Owner:TSINGHUA UNIV

Process for processing surface plasmon polariton coupled nano array based on scallop effect

ActiveCN104495742AOptimized Design Coupling StructureConvenient researchDecorative surface effectsChemical vapor deposition coatingDiffraction effectNano structuring

The invention discloses a method for preparing a surface plasmon polariton coupled nano array. The method comprises the following steps: performing deep reactive ion etching on a substrate by adopting a nano-scale etching mask which is manufactured by electron beam exposure, and then performing metallic membrane plating to obtain a three-dimensional 'metal nano structure array-nano space layer-metallic film' structure. The metallic nano structure generates local electromagnetic field resonance of photon and free electron to generate a very strong local surface plasmon polariton, and a diffraction effect provides wave vector compensation to excite a propagating type surface plasmon polariton of the metallic film so as to form local surface plasmon polariton-propagating type surface plasmon polariton coupling, so that light is restrained in a nano scale to initiate very strong surface local near field enhancement between a metal and a medium interface. The structure manufactured by the process disclosed by the invention can promote new mechanism exploration of the surface plasmon polariton, and has important application prospects in the fields of metamaterials, ultrahigh-sensitivity optical biosensing and the like.

Owner:PEKING UNIV

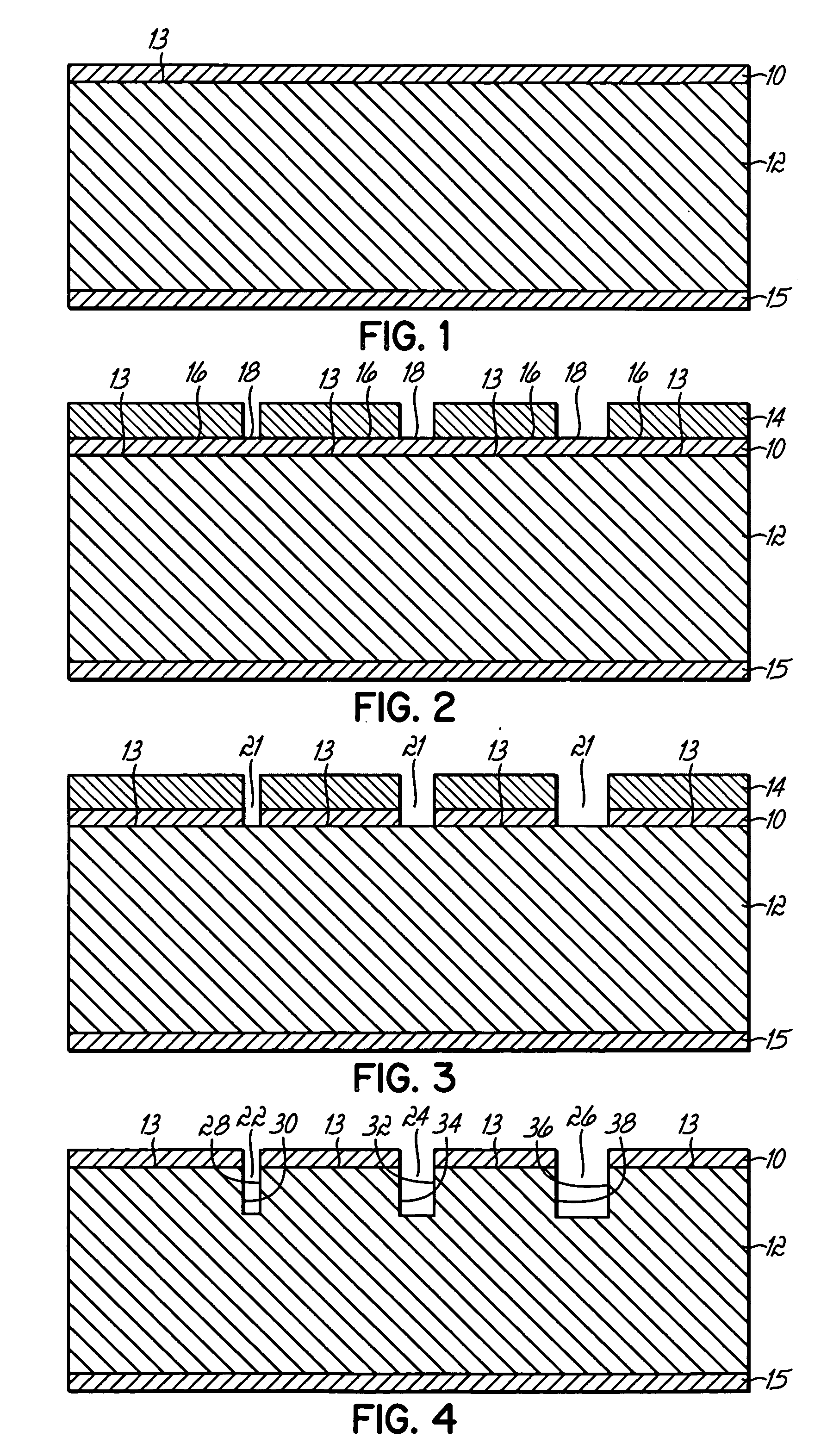

Deep reactive ion etching process and microelectromechanical devices formed thereby

InactiveUS7077007B2Uniform widthConstant gap widthAcceleration measurement using interia forcesDecorative surface effectsDevice formEngineering

A process for forming a microelectromechanical system (MEMS) device by a deep reactive ion etching (DRIE) process during which a substrate overlying a cavity is etched to form trenches that breach the cavity to delineate suspended structures. A first general feature of the process is to define suspended structures with a DRIE process, such that the dimensions desired for the suspended structures are obtained. A second general feature is the proper location of specialized features, such as stiction bumps, vulnerable to erosion caused by the DRIE process. Yet another general feature is to control the environment surrounding suspended structures delineated by DRIE in order to obtain their desired dimensions. A significant problem identified and solved by the invention is the propensity for the DRIE process to etch certain suspended features at different rates. In addition to etching wider trenches more rapidly than narrower trenches, the DRIE process erodes suspended structures more rapidly at greater distances from anchor sites of the substrate being etched. At the masking level, the greater propensity for backside and lateral erosion of certain structures away from substrate anchor sites is exploited so that, at the completion of the etch process, suspended structures have acquired their respective desired widths.

Owner:GOOGLE LLC

Deep reactive ion etching method and gas-flow control device thereof

ActiveCN101988196AReduce the overall heightImprove smoothnessSemiconductor/solid-state device manufacturingProcess conditionsSemiconductor

A deep reactive ion etching method belongs to the technical field of manufacturing of semiconductors. The method comprises an etching step and a polymer-depositing step which are alternately performed, wherein the conversion between a first process condition employed by the etching step and a second process condition employed by the polymer-depositing step is realized by a gradually changed conversion method. The side wall of a deep through hole etched by the deep reactive ion etching method has good smoothness; and the etching efficiency of the method is high.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

Methods of fabricating structures for characterizing tip shape of scanning probe microscope probes and structures fabricated thereby

InactiveUS20050252282A1NanotechnologyScanning probe techniquesScanning probe microscopyAnisotropic etching

A characterizer for determining the shape of a probe tip for an atomic force microscope and methods of fabricating and using the characterizer. The characterizer includes a micromachined crystalline structure with opposed edges separated by a width suitable for characterizing a dimension of the probe tip. At least one of the opposed edges overhangs an undercut region of the micromachined crystalline structure by an overhang distance that is greater than one third of the width. The probe tip is scanned across the edges of the characterizer for shape determination. The characterizer is formed by serially deep reactive ion etching and anisotropic etching (100) single crystal silicon. The opposed edges may be oxidation sharpened for use in profiling a bottom surface of the probe tip.

Owner:BRUKER NANO INC

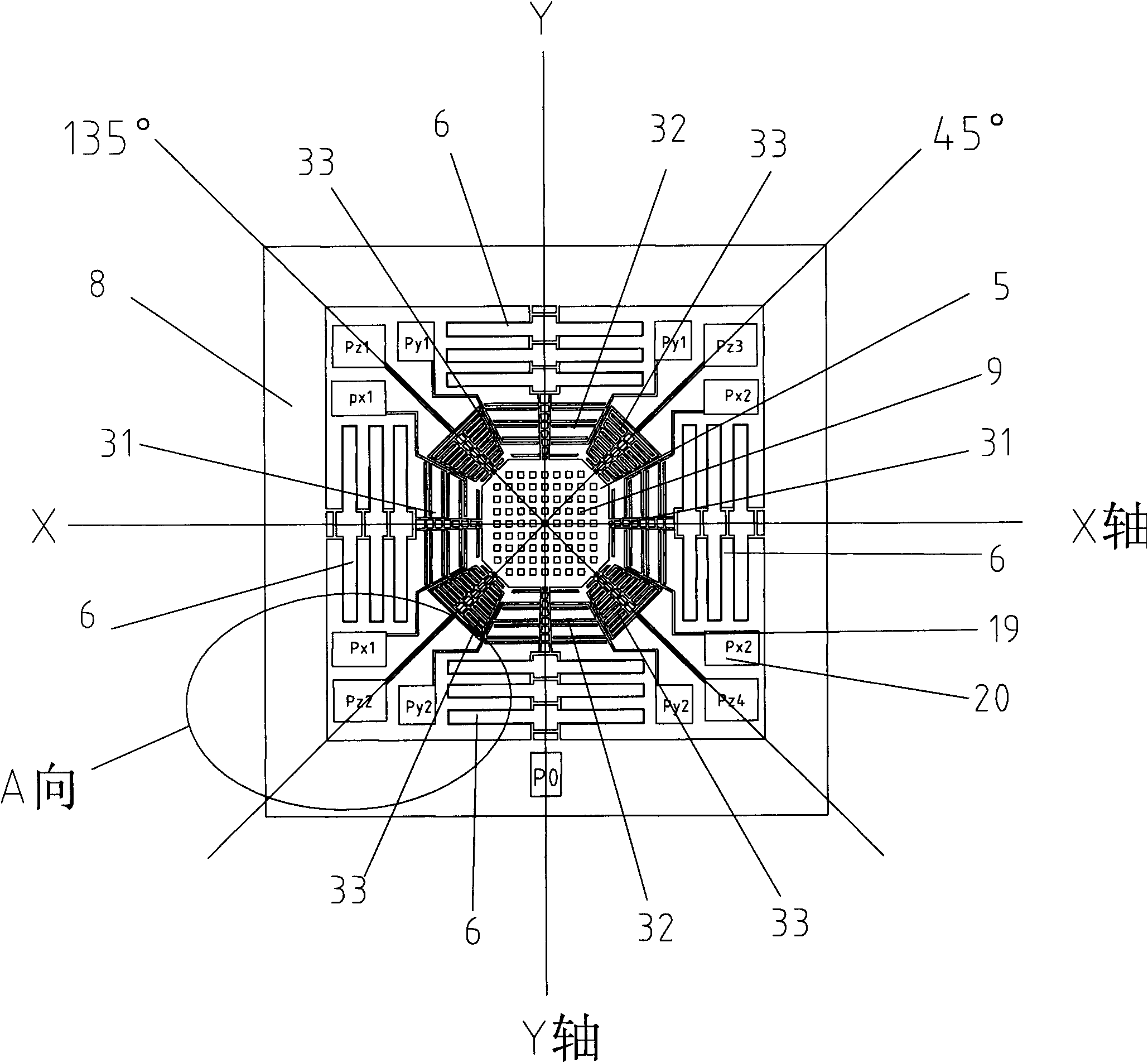

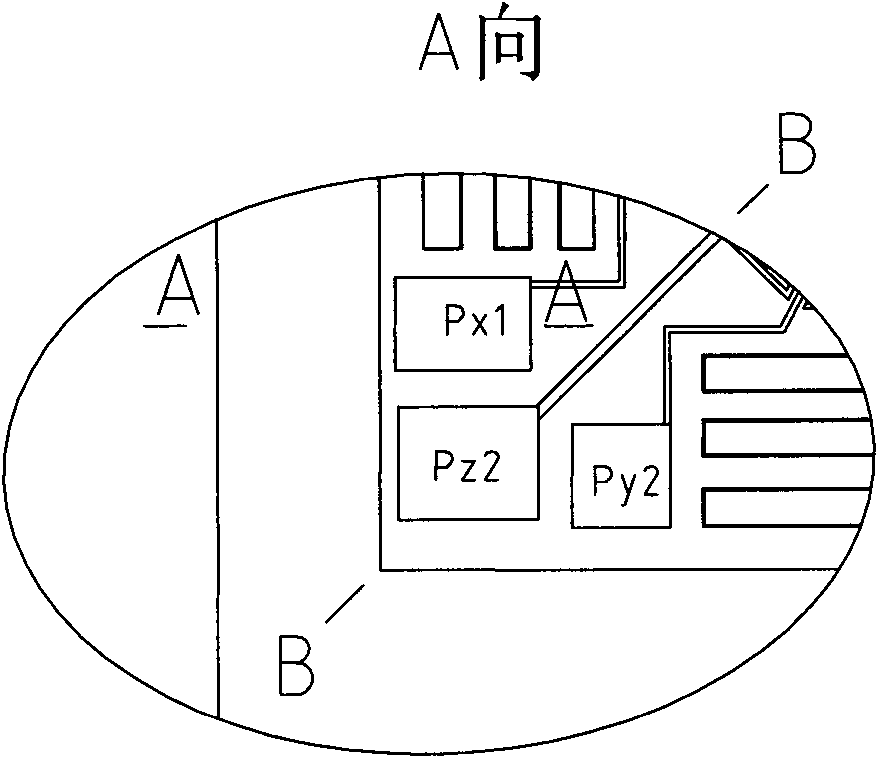

Capacitive single-mass block full comb electrode sensor for triaxial acceleration and manufacturing method thereof

ActiveCN102384984ALarge displacementQuality improvementAcceleration measurement using interia forcesDecorative surface effectsClassical mechanicsCapacitive sensing

The invention discloses a capacitive single-mass block full comb electrode sensor for triaxial acceleration and a manufacturing method thereof, wherein the acceleration sensor uses single-mass block design, and x, y and z axis all use comb structures on the x y planes as induction acceleration electrodes. An inducing mechanism, which is produced by performing deep reactive ion etching on severelydoped monocrystalline silicon, is composed of a mass block, a spring mechanism and a comb structure. The spring mechanism comprises four groups of U-shaped springs and beam structures, which are symmetrically distributed; two groups of x axis comb mechanisms are symmetrically distributed in the x y plane along the x axis, taking the mass block as the centre; two groups of y axis comb mechanisms are symmetrically distributed in the x y plane along the y axis, taking the mass block as the centre; four groups of z comb mechanisms are symmetrically distributed in the x y plane along the 45 degrees and the 135 degrees lines taking the mass block as the centre. Triaxial acceleration measuring signal outputs do not interfere with each other. The invention achieves triaxial acceleration measurement with a single mass block and a full comb structure electrode.

Owner:孙博华

Multi-functional micro electromechanical devices and method of bulk manufacturing same

InactiveUS6706549B1Avoid destructionDoubling the fabrication cost for makingAcceleration measurement using interia forcesDecorative surface effectsResistPhosphoric acid

A method of bulk manufacturing SiC sensors is disclosed and claimed. Materials other than SiC may be used as the substrate material. Sensors requiring that the SiC substrate be pierced are also disclosed and claimed. A process flow reversal is employed whereby the metallization is applied first before the recesses are etched into or through the wafer. Aluminum is deposited on the entire planar surface of the metallization. Photoresist is spun onto the substantially planar surface of the Aluminum which is subsequently masked (and developed and removed). Unwanted Aluminum is etched with aqueous TMAH and subsequently the metallization is dry etched. Photoresist is spun onto the still substantially planar surface of Aluminum and oxide and then masked (and developed and removed) leaving the unimidized photoresist behind. Next, ITO is applied over the still substantially planar surface of Aluminum, oxide and unimidized photoresist. Unimidized and exposed photoresist and ITO directly above it are removed with Acetone. Next, deep reactive ion etching attacks exposed oxide not protected by ITO. Finally, hot phosphoric acid removes the Al and ITO enabling wires to connect with the metallization. The back side of the SiC wafer may be also be etched.

Owner:NASA

Preparation method of capacitive barometric sensor of micro-electronic-mechanical system

InactiveCN103011057ARealize batchAchieve mass productionDecorative surface effectsChemical vapor deposition coatingCapacitancePhosphonium

The invention discloses a preparation method of a capacitive barometric sensor of a micro-electronic-mechanical system. The method comprises the following steps of: step 1), anisotropic deep reactive ion etching at the upper part of an N-type silicon substrate to form silicon corrosion holes; step 2), isotropic deep reactive ion etching on the silicon substrate to form a cavity; step 3), epitaxial growth of a monocrystalline silicon layer above the silicon substrate to form an epitaxy monocrystalline silicon layer; step 4), injection of phosphonium ions to form a phosphonium ion heavily doped diffusion area; step 5) chemical vapor deposition of an oxide layer and patterning; step 6), sputtering of a metal layer and patterning above the oxide layer; step 7), chemical vapor deposition of a passivation layer and patterning above the metal layer; and step 8), removal of part of the oxide layer by using a slow-release hydrofluoric corrosive liquid, to obtain a capacitance clearance cavity between a lower capacitance pole plate and an upper capacitance pole plate, thus forming the capacitive barometric sensor. The preparation method is compatible with the CMOS (Complementary Metal-Oxide-Semiconductor Transistor) standard process, and can be used for large scale production of the capacitive barometric sensor.

Owner:SOUTHEAST UNIV

Manufacturing process for realizing through silicon via packaging by adopting BCB (Benzocyclobutene) supplementary bonding

InactiveCN101834159AQuality improvementThe overall thickness is thinSemiconductor/solid-state device manufacturingSputteringOptoelectronics

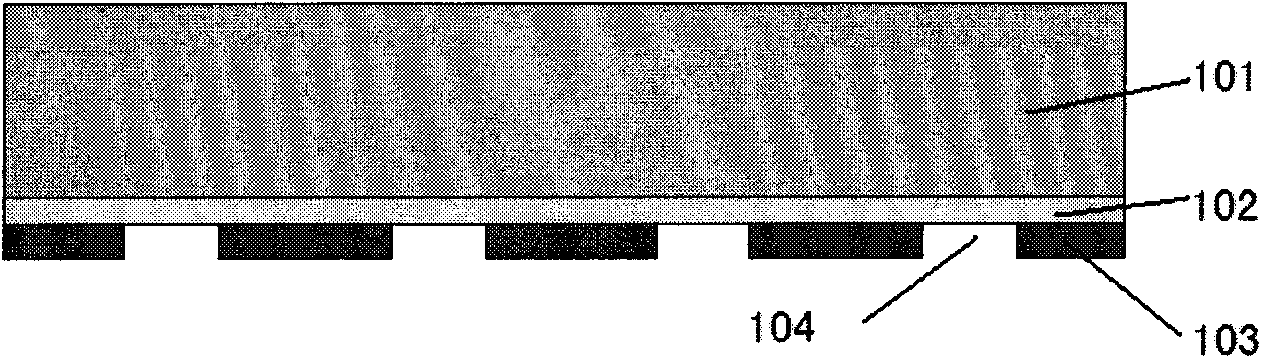

The invention relates to a manufacturing process for realizing through silicon via packaging by adopting BCB (Benzocyclobutene) supplementary bonding. The manufacturing process is characterized being a method for manufacturing the TSV (Through Silicon Via) packaging after a wafer is thinned under the assistance of a support wafer which is bonded at low temperature by utilizing organic matter BCB. The manufacturing process of the TSV packaging comprises the following steps of: sputtering a metal layer on the naked support wafer, coating a layer of BCB and then carrying out photoetching; carrying out DRIE (Deep Reactive Ion Etching) on the front face of the TSV wafer to form a TSV array; aligning one side of the support wafer with the BCB with the front face of the TSV wafer and then carrying out BCB low-temperature bonding in a bonding machine; and manufacturing TSV subsequent process after the TSV wafer is thinned. The TSV packaging manufacturing process has higher reliability, and the adopted device and the adopted process are both a conventional process and a device in the semiconductor machining.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method for Producing Porous Microneedles and their Use

InactiveUS20090200262A1Easily controllableEasily manageablePaper/cardboard articlesDecorative surface effectsSiliconDeep reactive-ion etching

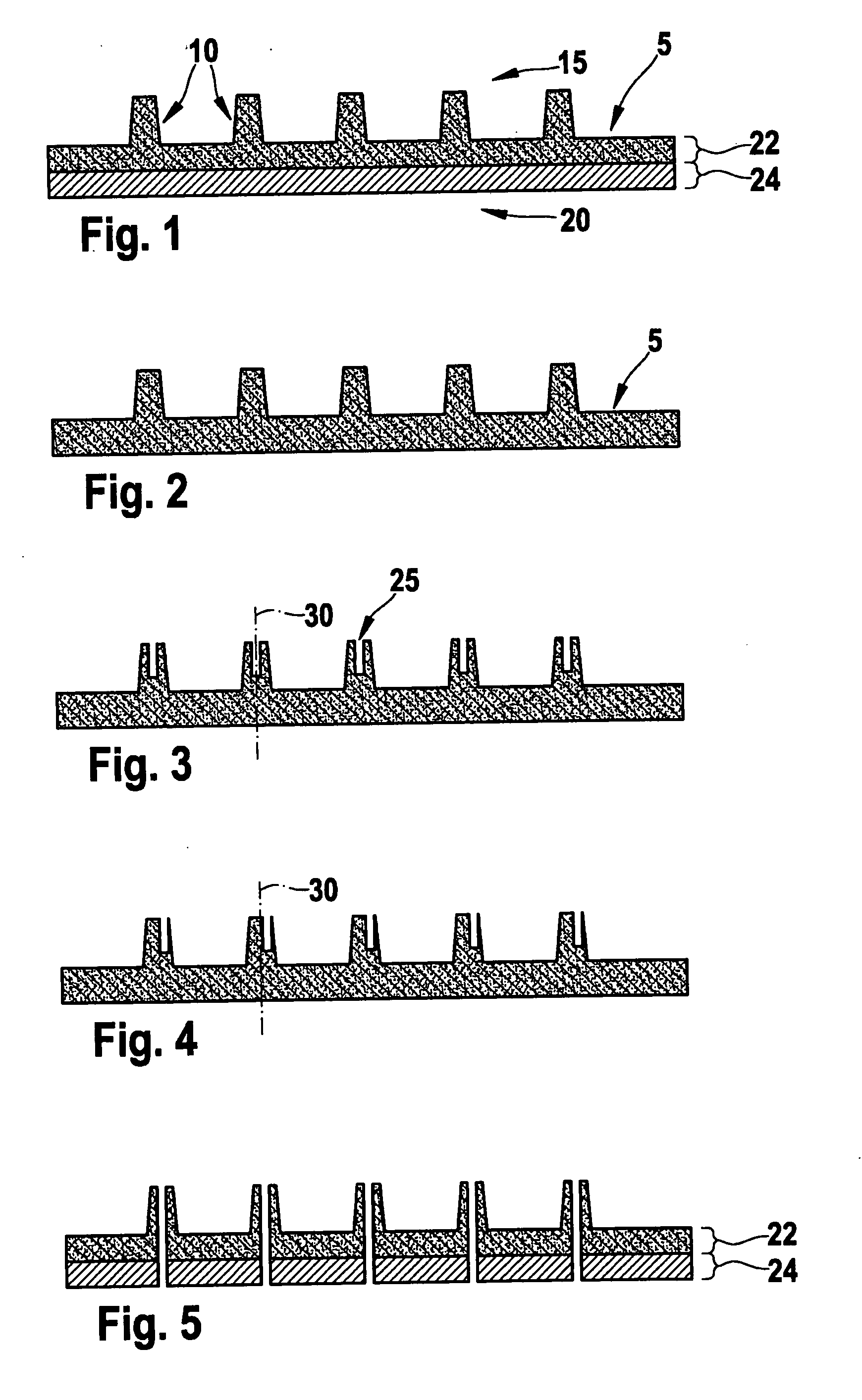

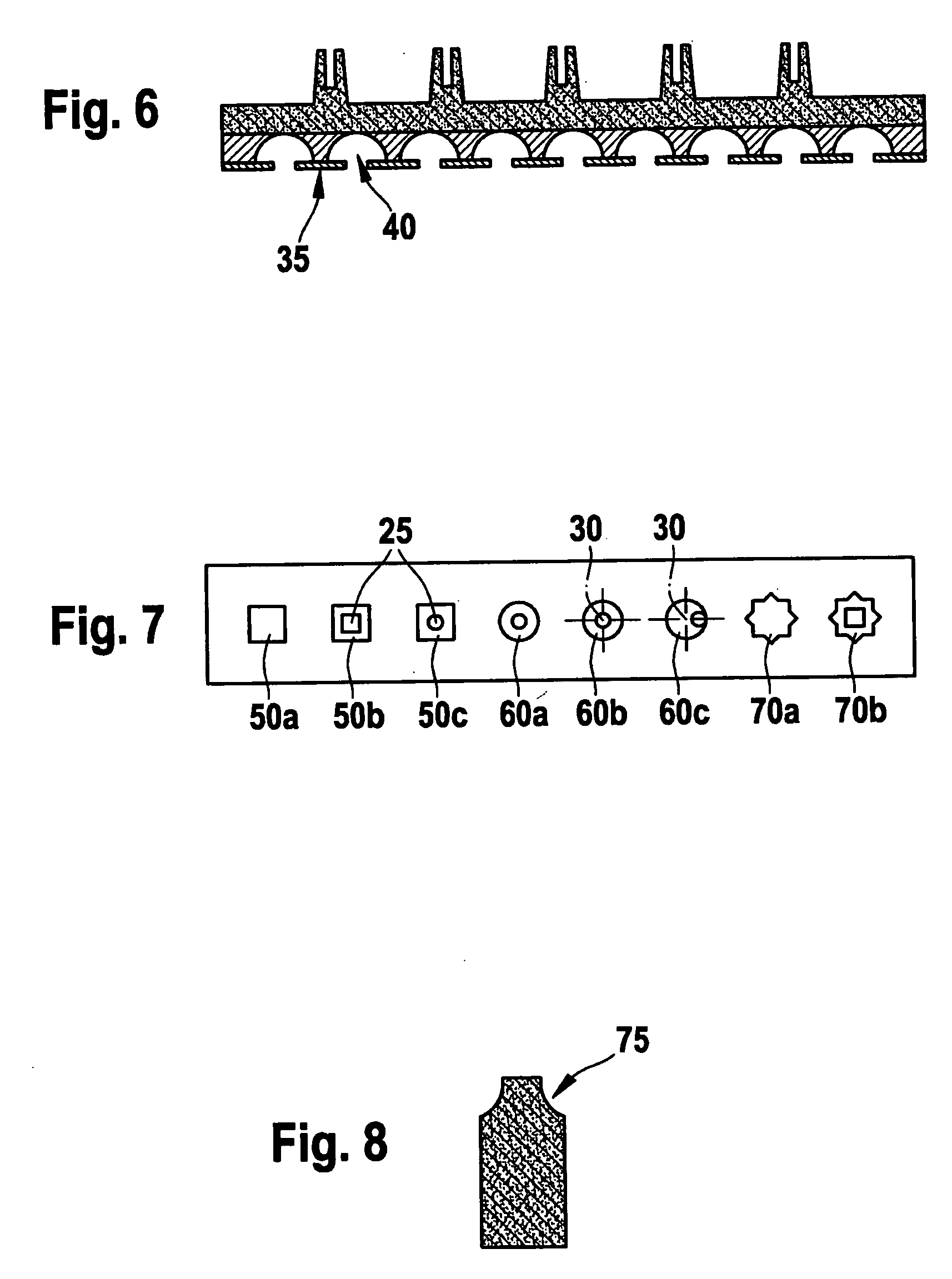

A method for producing porous microneedles (10) situated in an array on a silicon substrate includes: providing a silicon substrate, applying a first etching mask, patterning microneedles using a DRIE process (“deep reactive ion etching”), removing the first etching mask, at least partially porosifying the Si substrate, the porosification beginning on the front side of the Si substrate and a porous reservoir being formed.

Owner:ROBERT BOSCH GMBH

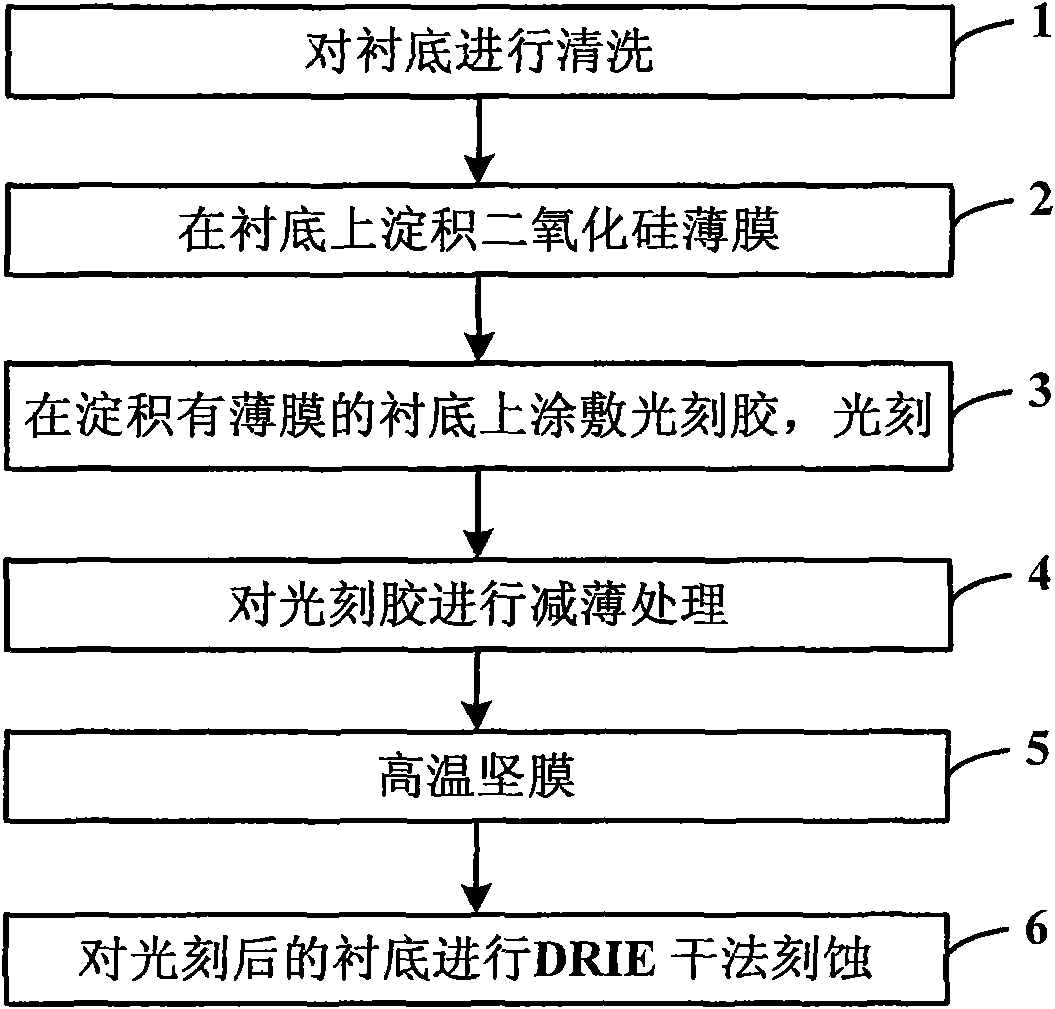

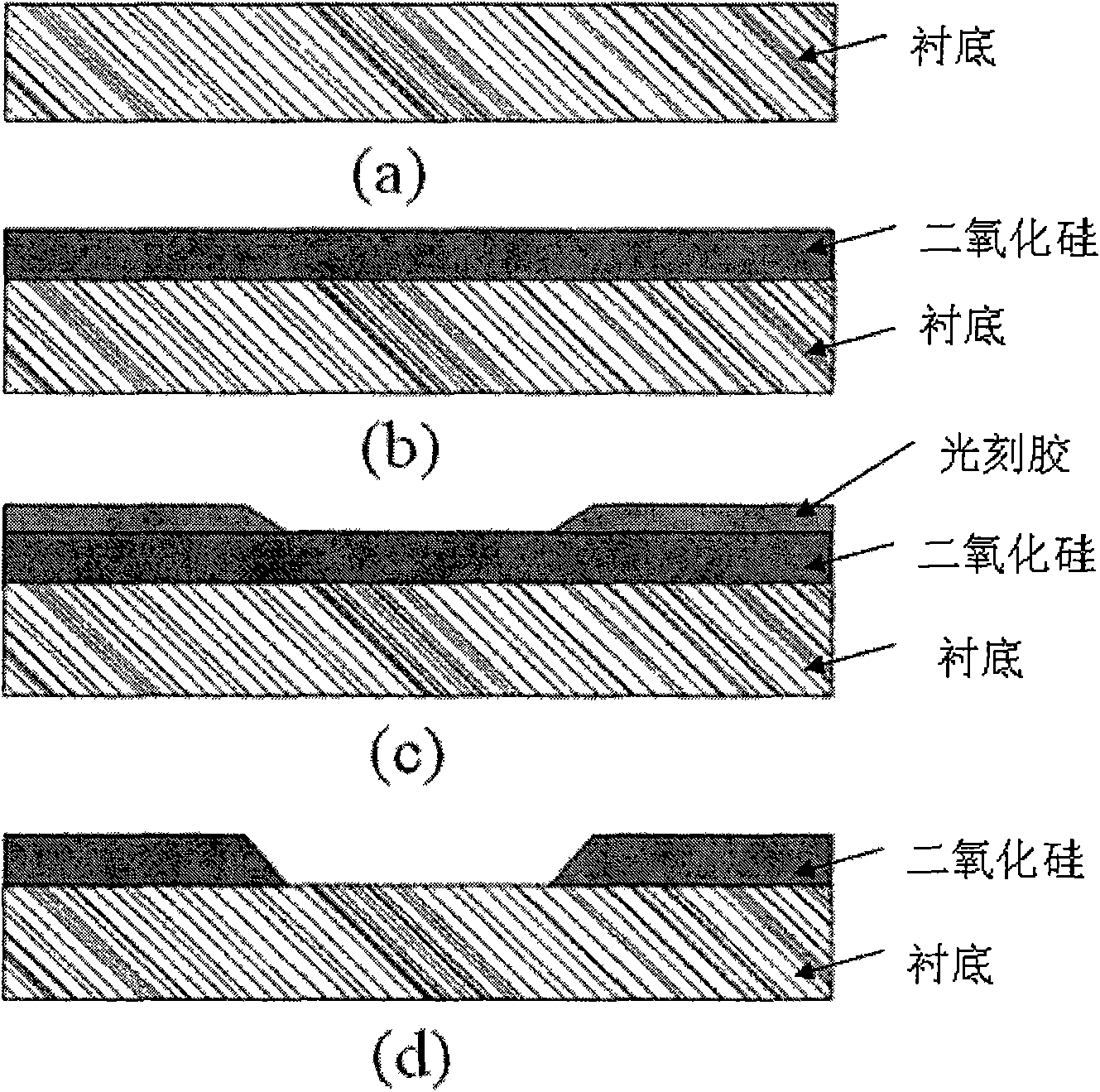

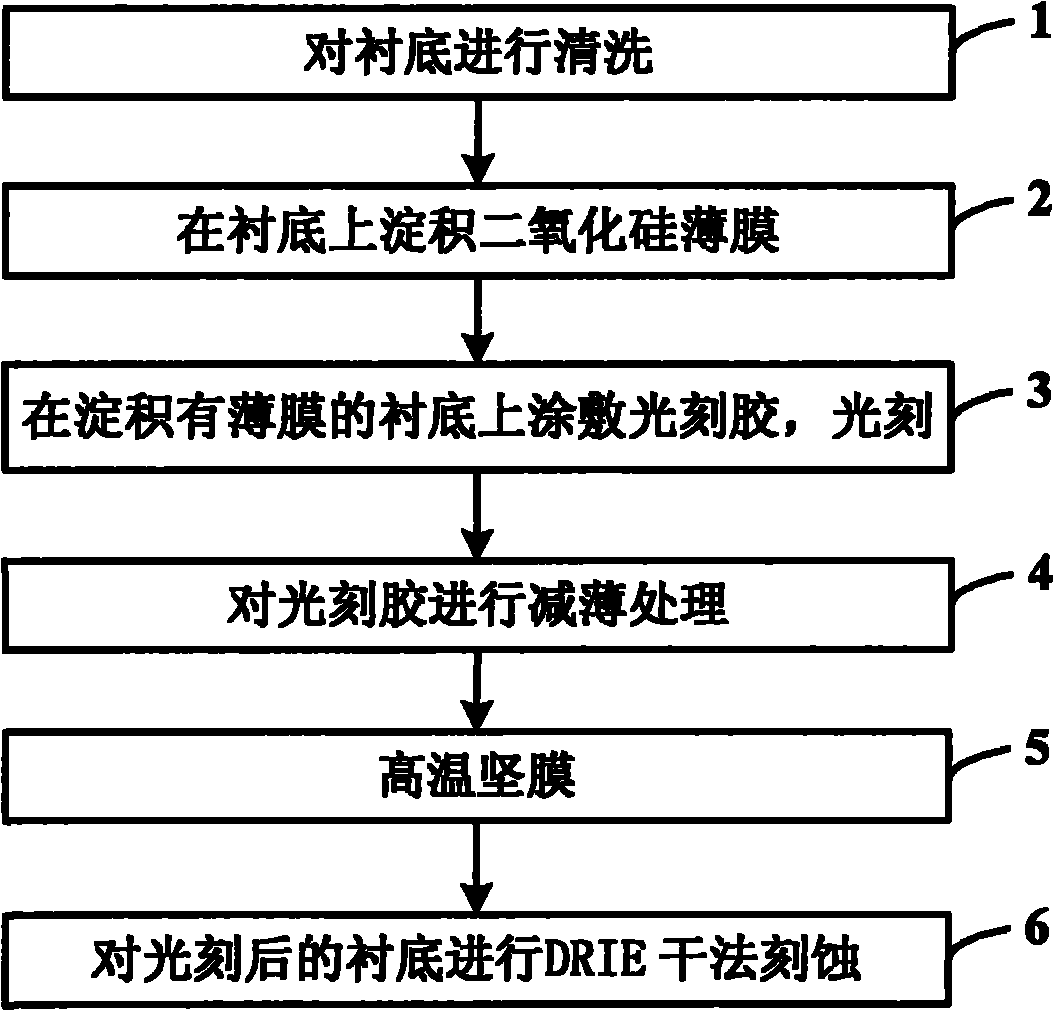

Method for manufacturing sloped sidewall silicon dioxide structure by adopting photoetching and dry etching

InactiveCN101863447AThe method is simple and fastUniversalDecorative surface effectsChemical vapor deposition coatingSilicon dioxidePhotoresist

The invention discloses a method for manufacturing a sloped sidewall silicon dioxide structure by adopting photoetching and dry etching. The method comprises the following steps of: (1) cleaning a substrate; (2) depositing a silicon dioxide thin film on the substrate; (3) coating photoresist on the substrate with the deposited thin film and photoetching; (4) thinning the photoresist; (5) hardening the film at high temperature; and (6) carrying out DRIE (Deep Reactive Ion Etching) dry etching on the photoetched substrate. A sloped silicon dioxide sidewall appearance can be obtained by photoetching and etching only once, and the method is simple and quick and has strong universality.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

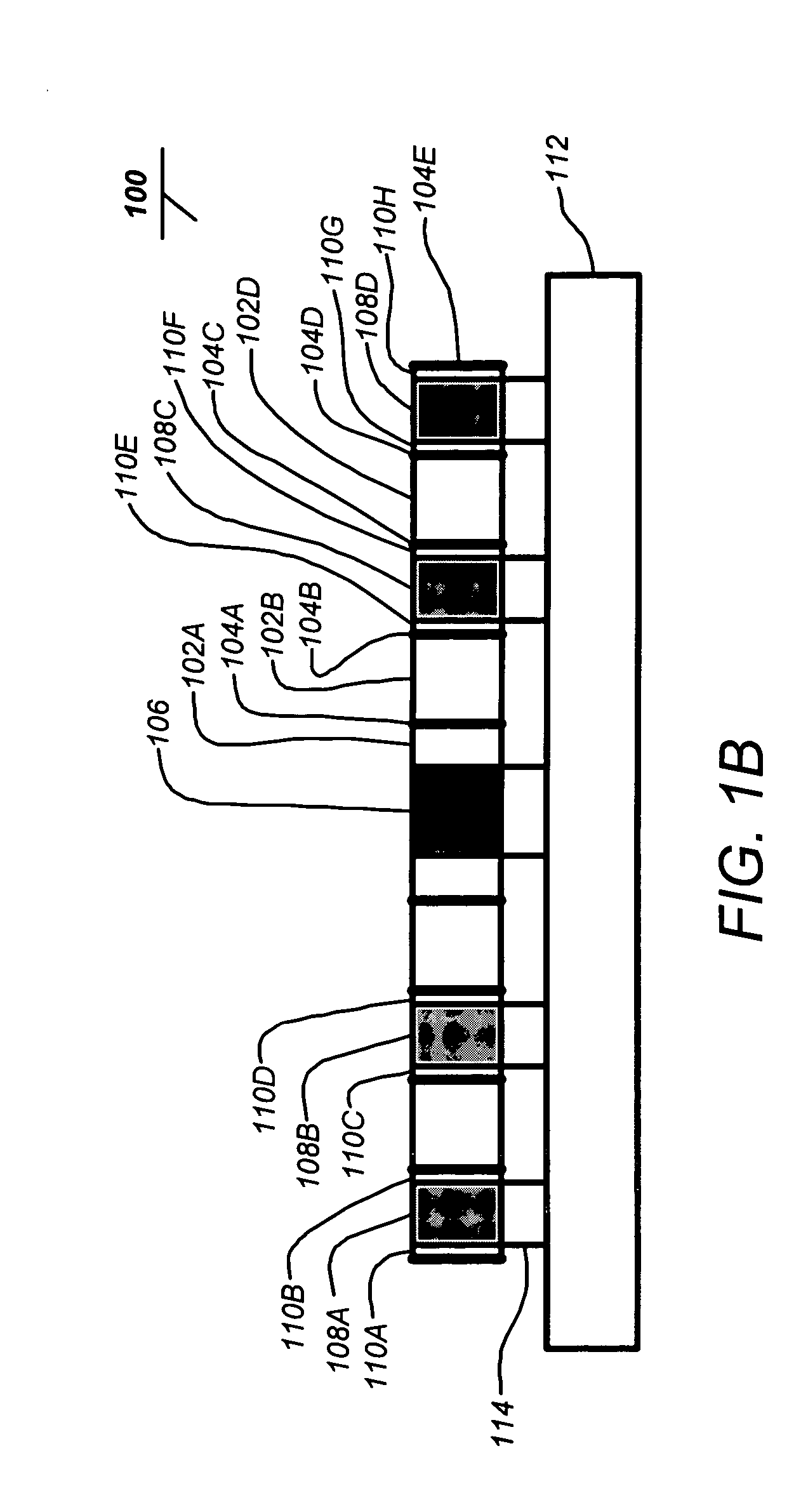

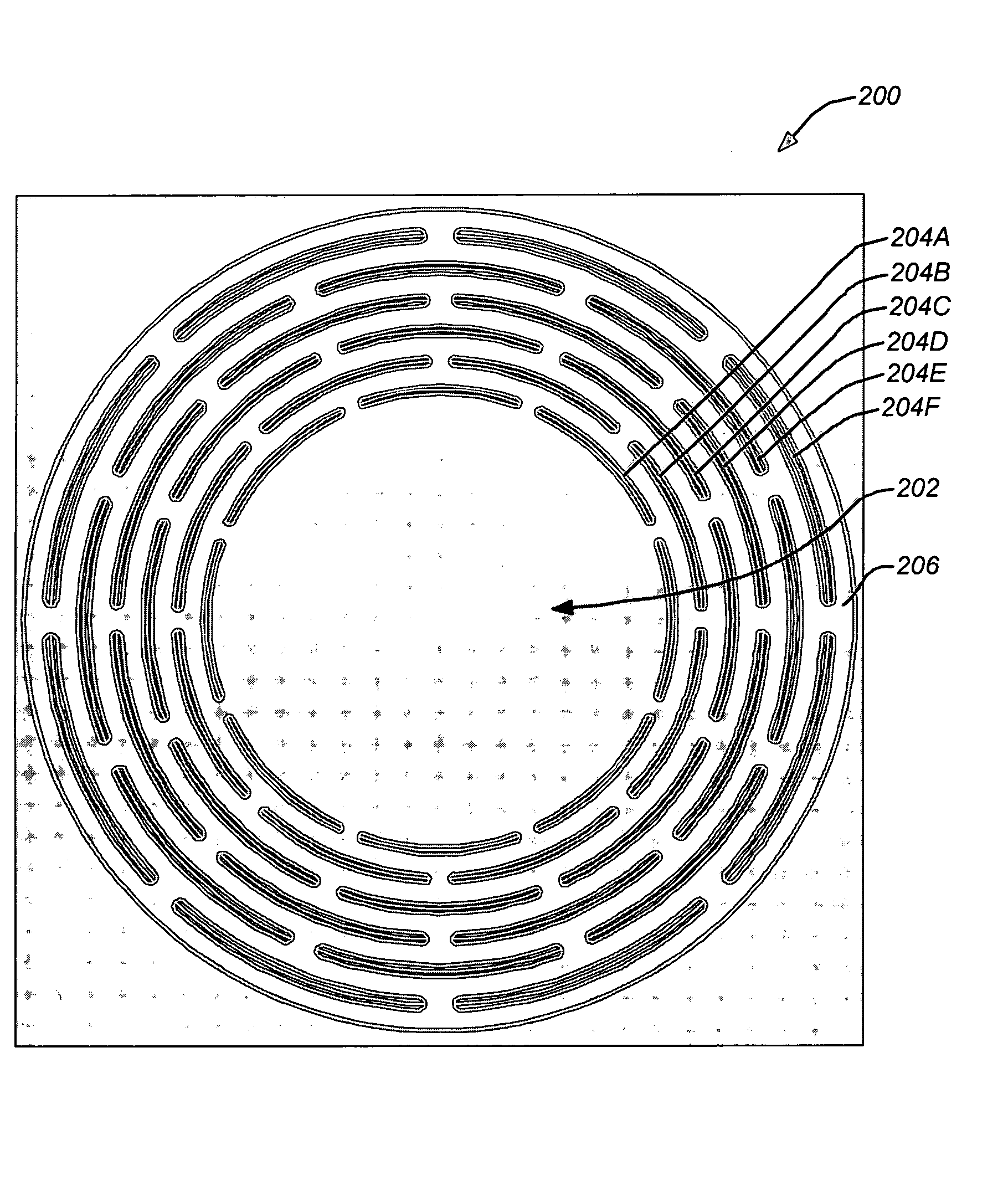

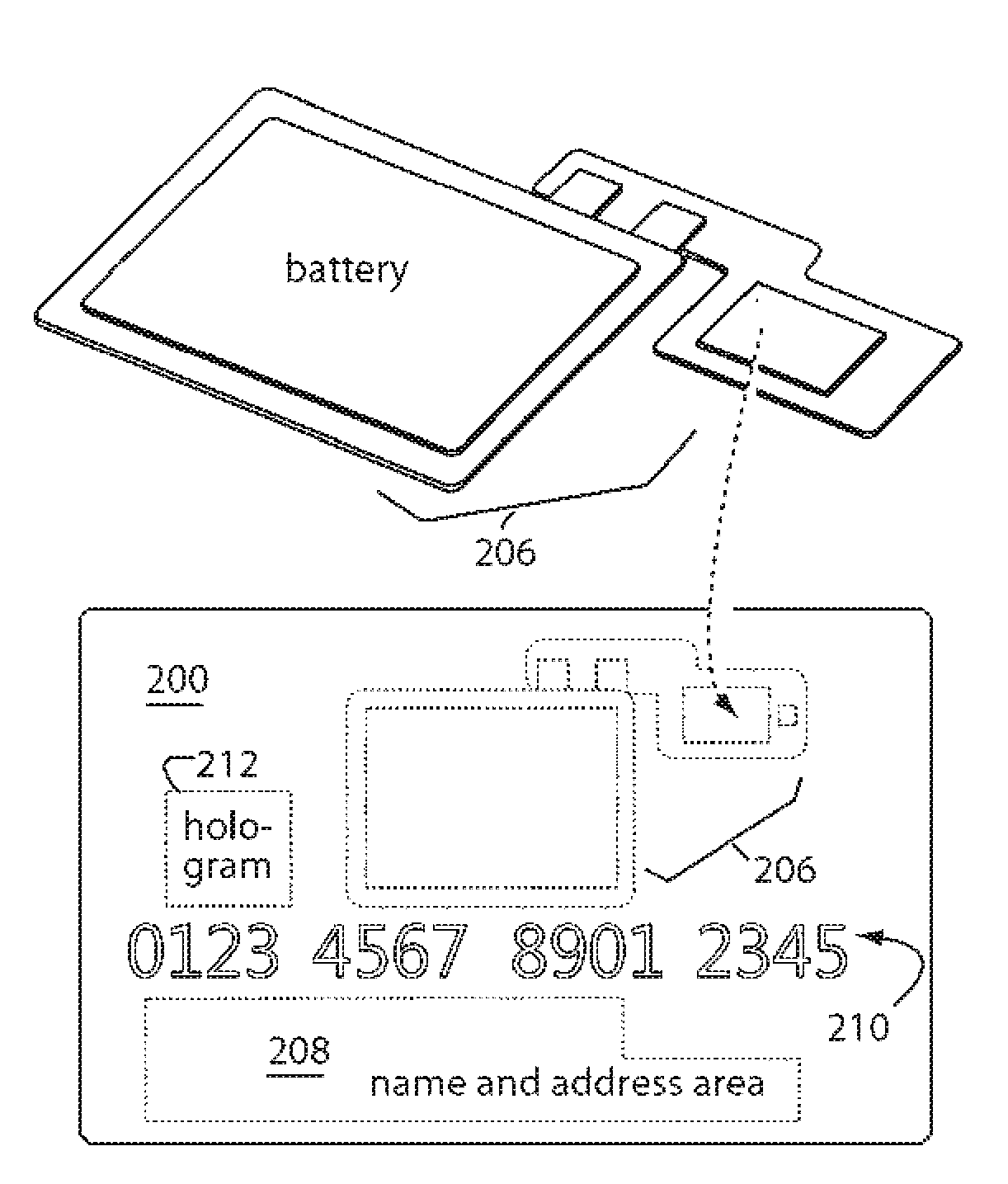

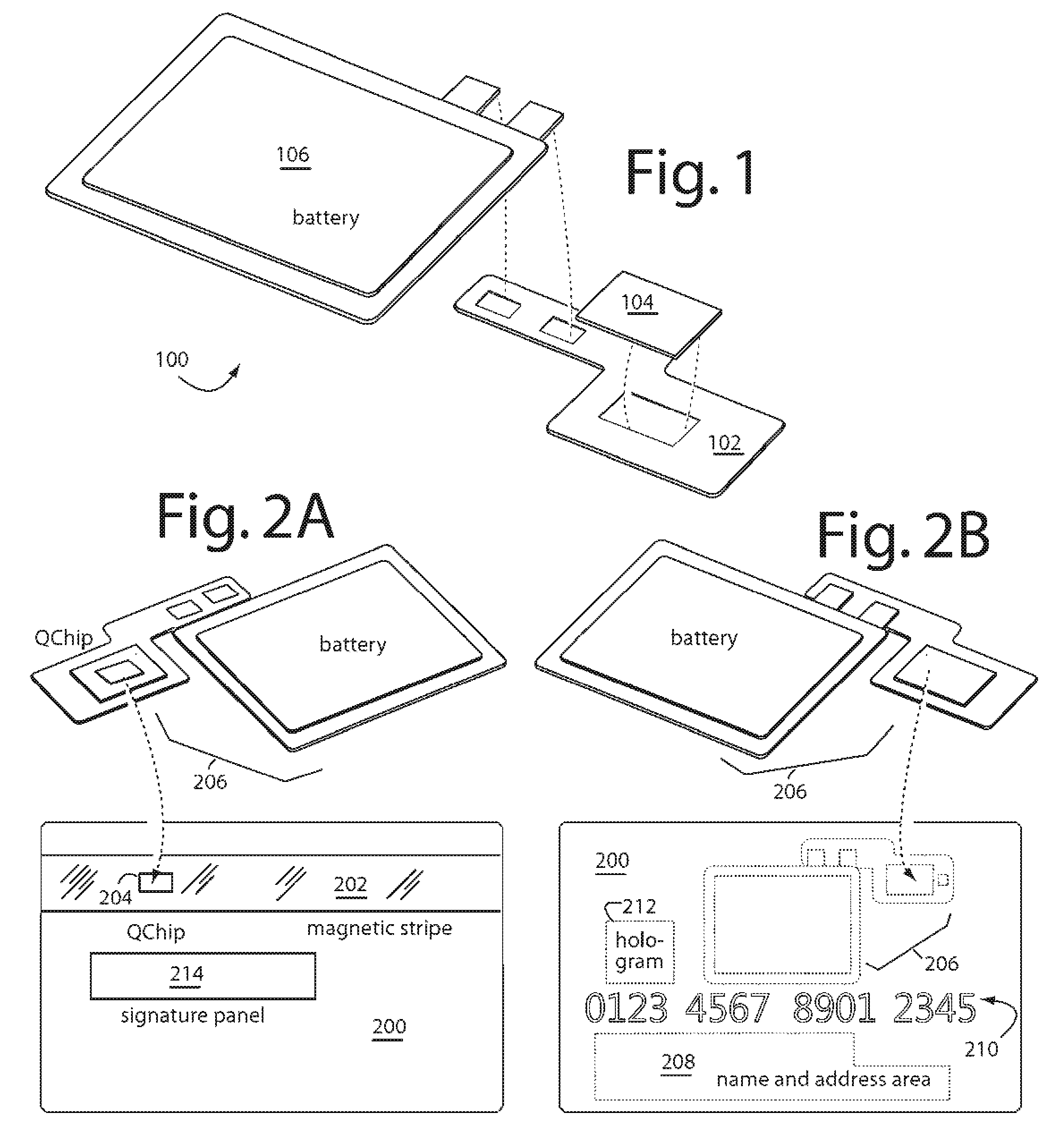

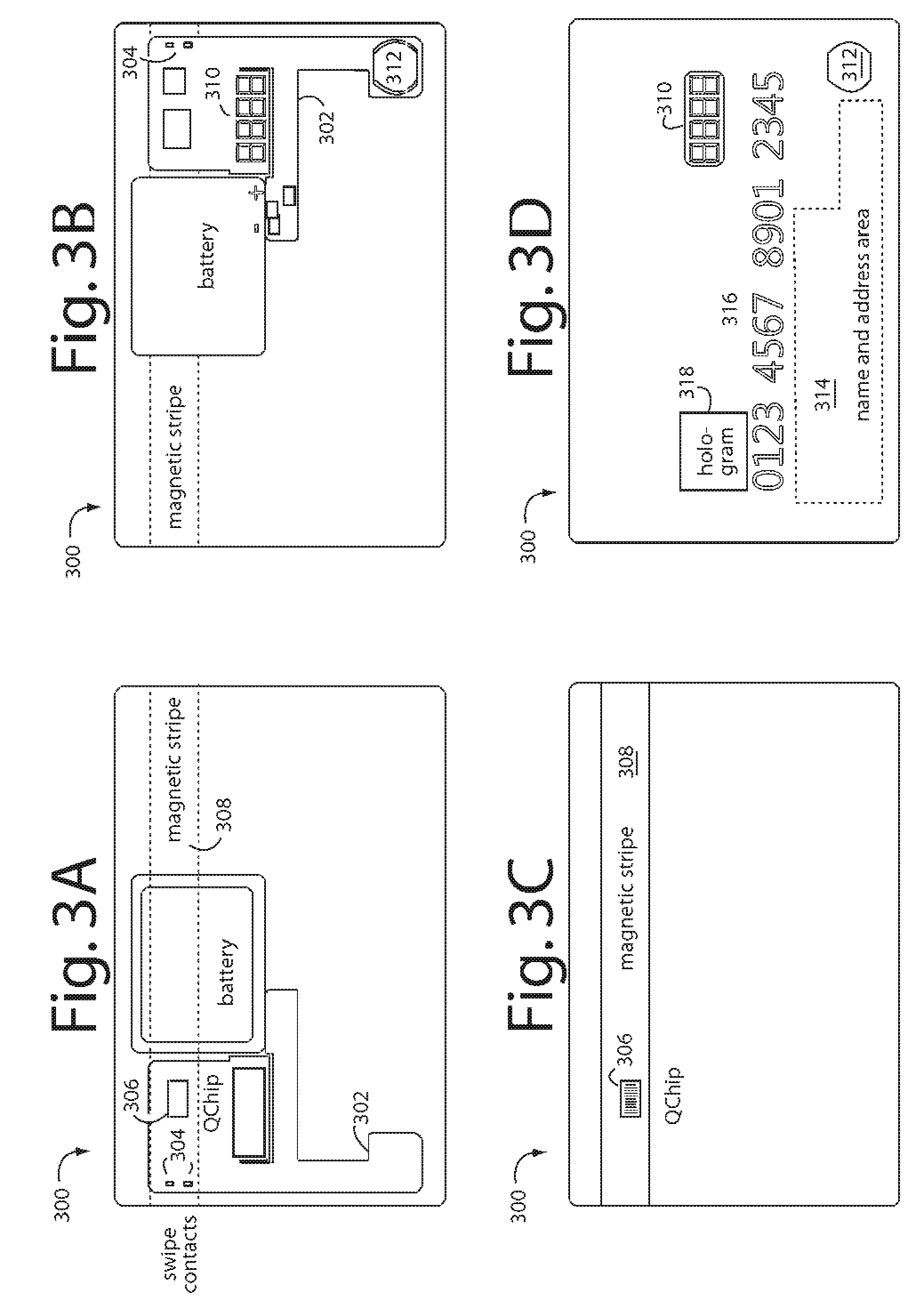

Electronic payment card manufacturing process

InactiveUS20110062239A1Semiconductor/solid-state device detailsSolid-state devicesPersonalizationCoil array

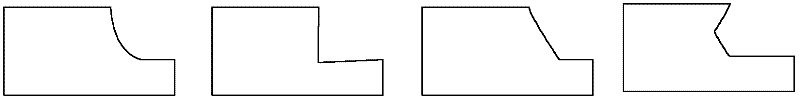

A payment card manufacturing process for a magnetic device (QChip) with a bit coil array to individually write several dynamic magnetic data bits into the magnetic material. The magnetic device fits inside the payment card's magnetic strip and contributes to the data recorded statically in the magnetic stripe. The magnetic device edges physically nearest the leading and trailing dynamic magnetic data bits are trimmed very closely and precisely by scoring the tops with deep reactive ion etching to produce deep trenches, and then back-grinding up from underneath to the trench bottoms. The magnetic device is inserted into a high precision die or laser cut opening in the magnetic stripe in each payment card. The locations of the static magnetic bits in the magnetic stripe are precisely recorded maintaining continuous signal integrity and integration during card personalization after electronically sensing the X,Y locations of the magnetic device's dynamic magnetic data bits.

Owner:LAU RACHEL +2

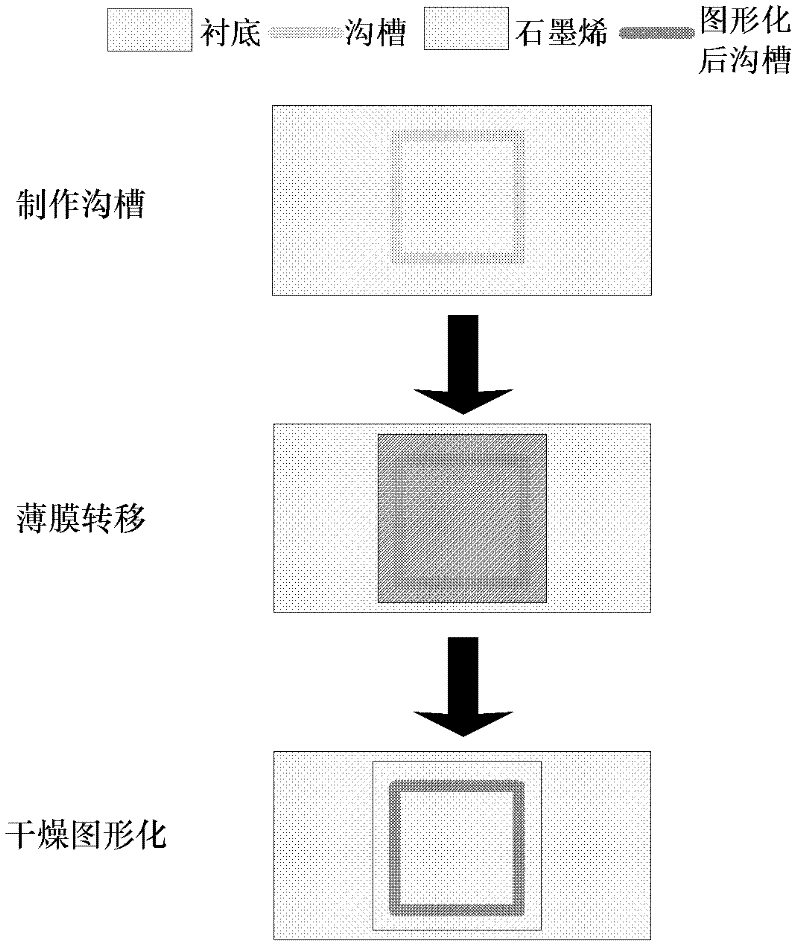

Graphene graphing methods

ActiveCN102263013AAccurate locationLocation pinpointingSemiconductor/solid-state device manufacturingCvd graphenePollution

The invention discloses a method for graphic modeling of graphene by using grooves which are formed on a substrate, comprising the following steps: manufacturing a graph structure taking the grooves as boundaries on the substrate by using a DRIE (deep reactive ion etching) technology, a micro cutting technology or a wet etching technology in a micromachining technology; transferring a supportlesslarge-area graphene film to the graphic modeling substrate with the grooves from a solution; and drying the substrate and the graphene, and breaking the graphene in a groove area by using the surfacetension of the solution so as to obtain the required graphic modeling graphene. By the method, the position of the graphic modeling graphene can be accurately determined on the substrate in no need of carrying out photoetching on the graphene, thus preventing the crystal lattice quality of the graphene from being damaged and solving the problems that the cost is high, the positioning is difficultand the pollution occurs easily in the former graphene graphical modeling process.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

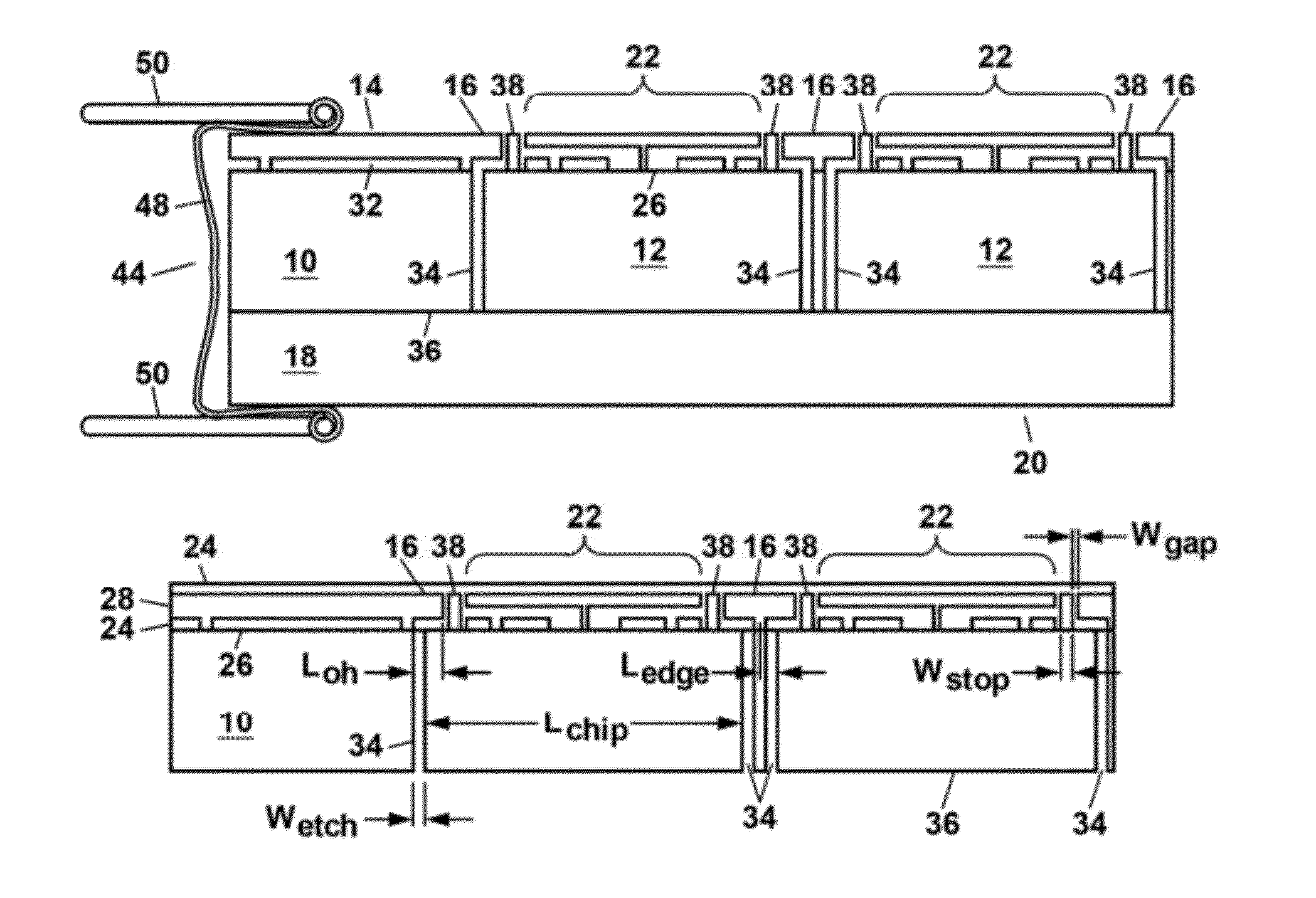

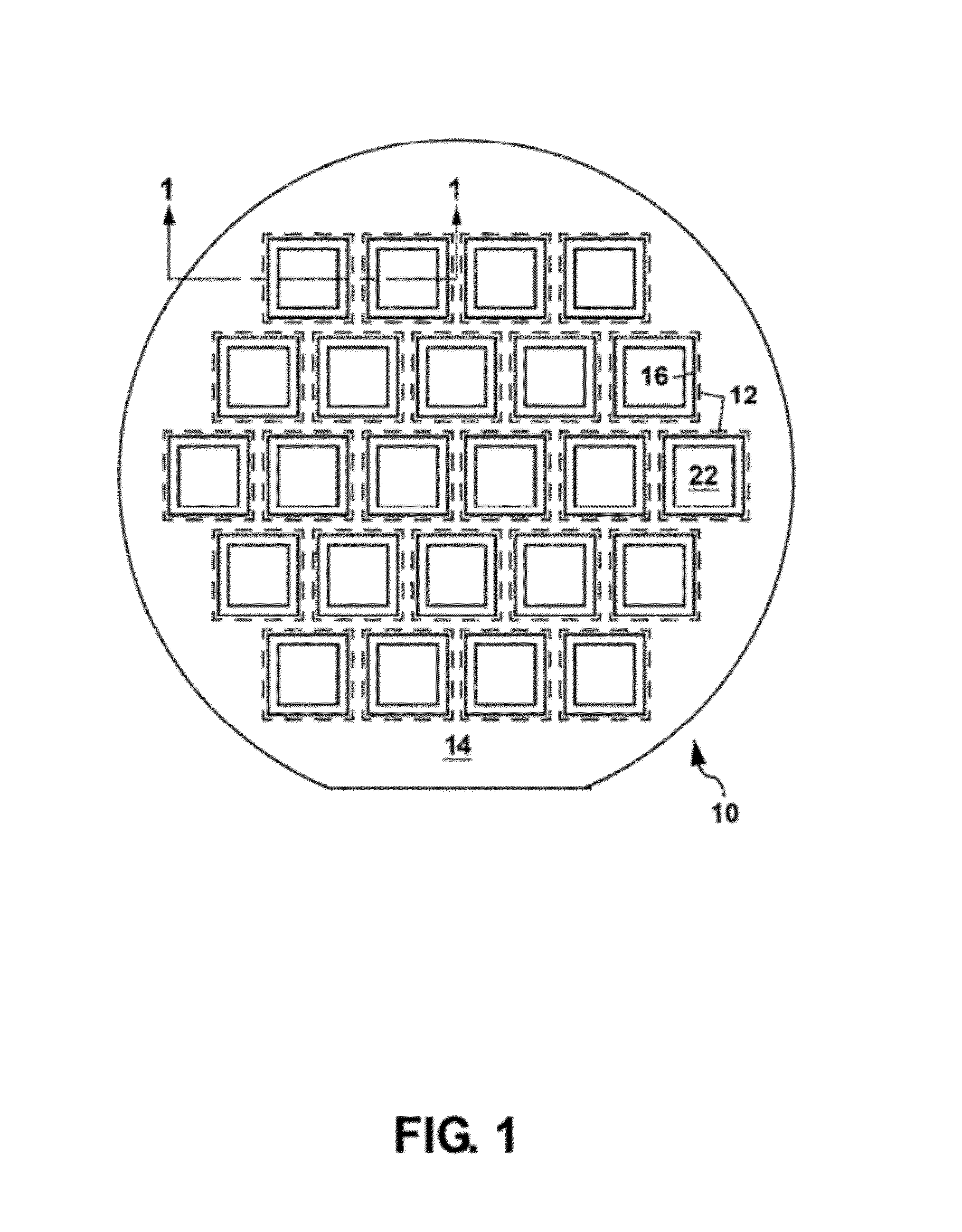

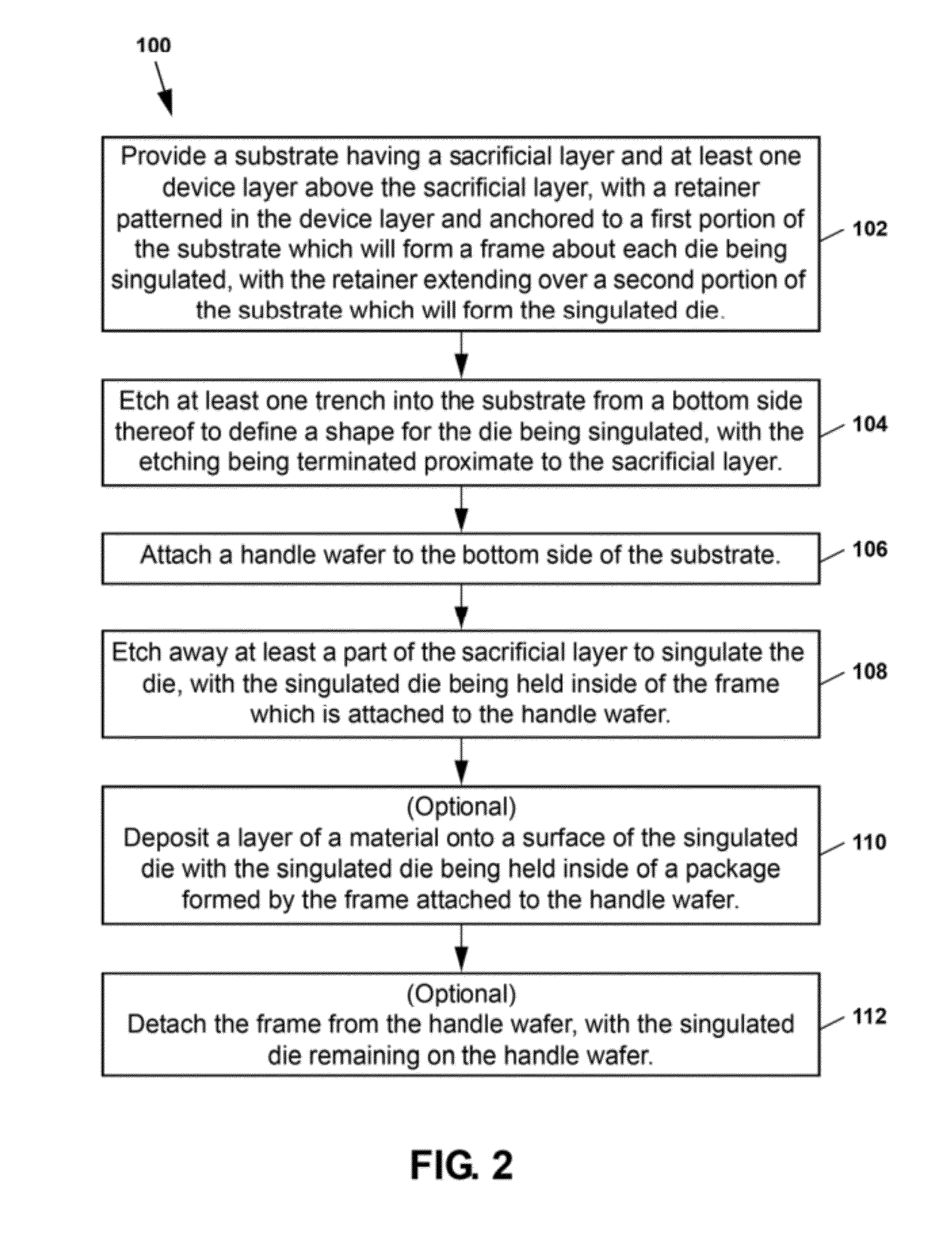

Die singulation method and package formed thereby

ActiveUS8236611B1Restrict movementSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

A method is disclosed for singulating die from a substrate having a sacrificial layer and one or more device layers, with a retainer being formed in the device layer(s) and anchored to the substrate. Deep Reactive Ion Etching (DRIE) etching of a trench through the substrate from the bottom side defines a shape for each die. A handle wafer is then attached to the bottom side of the substrate, and the sacrificial layer is etched to singulate the die and to form a frame from the retainer and the substrate. The frame and handle wafer, which retain the singulated die in place, can be attached together with a clamp or a clip and to form a package for the singulated die. One or more stops can be formed from the device layer(s) to limit a sliding motion of the singulated die.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

Silicon-based light-emitting device and preparation method thereof

InactiveCN102280545AImprove injection efficiencyImprove light extraction efficiencySemiconductor devicesNano siliconNanopillar

The invention discloses a silicon-based light-emitting device and a preparation method thereof. The device includes a silicon substrate, the front of the substrate is etched to form a nano-column photonic crystal array, and a film layer containing a silicon nanocrystal quantum dot structure is conformally deposited on the array, and the film layer is covered with a transparent conformal electrode. Ohmic contact electrodes are deposited on the bottom and back; the method is as follows: using microsphere mask etching technology on the front of the substrate to obtain a silicon nanocolumn photonic crystal array through deep reactive ion etching, and then co-existing on the silicon nanocolumn photonic crystal array. Formally grow a thin film layer containing a nano-silicon quantum dot structure and a transparent conformal electrode, and deposit an ohmic contact electrode on the back of the substrate to obtain the target product. The silicon-based light-emitting device of the present invention adopts photonic crystal nano-column array and silicon nano-crystal quantum dot structure at the same time, which effectively improves the light extraction efficiency and carrier injection efficiency, thereby improving the luminous intensity and light emission efficiency of the device, and the device structure is simple, The process is simple and the cost is low.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

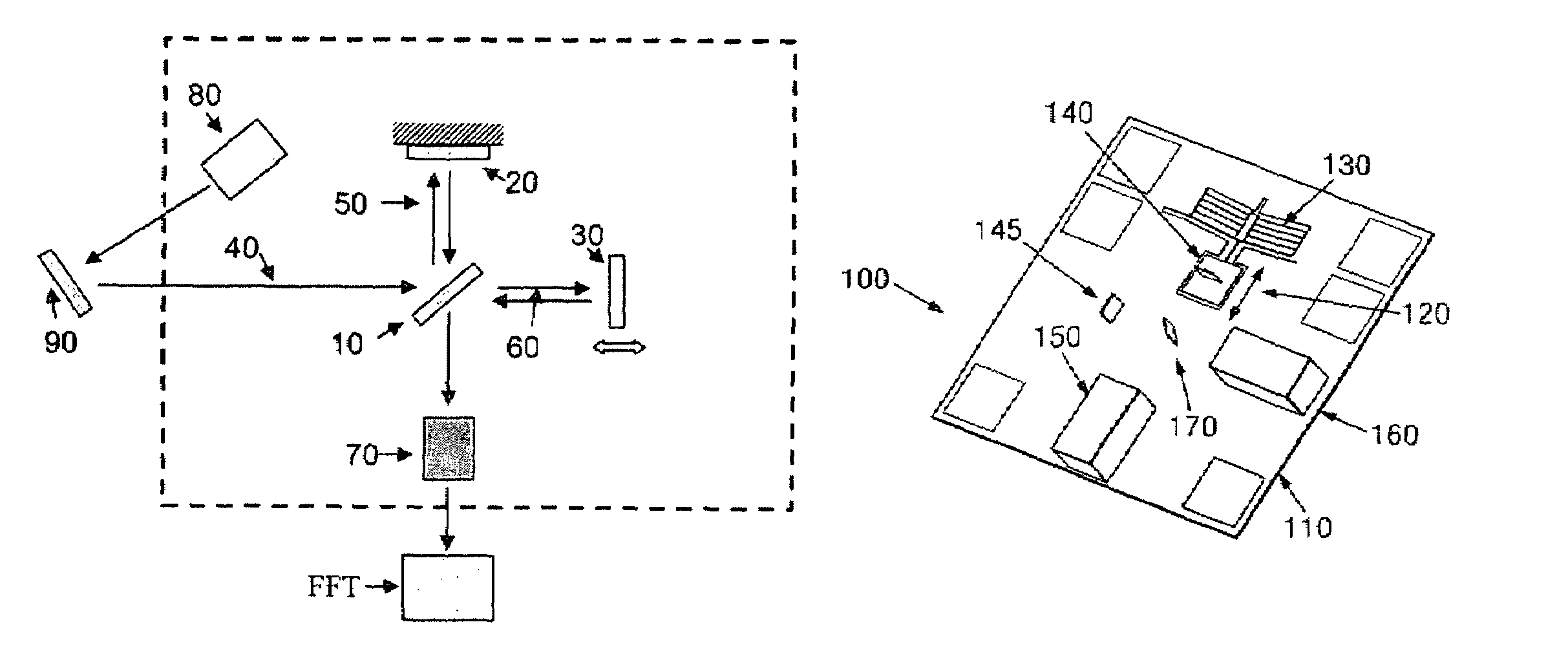

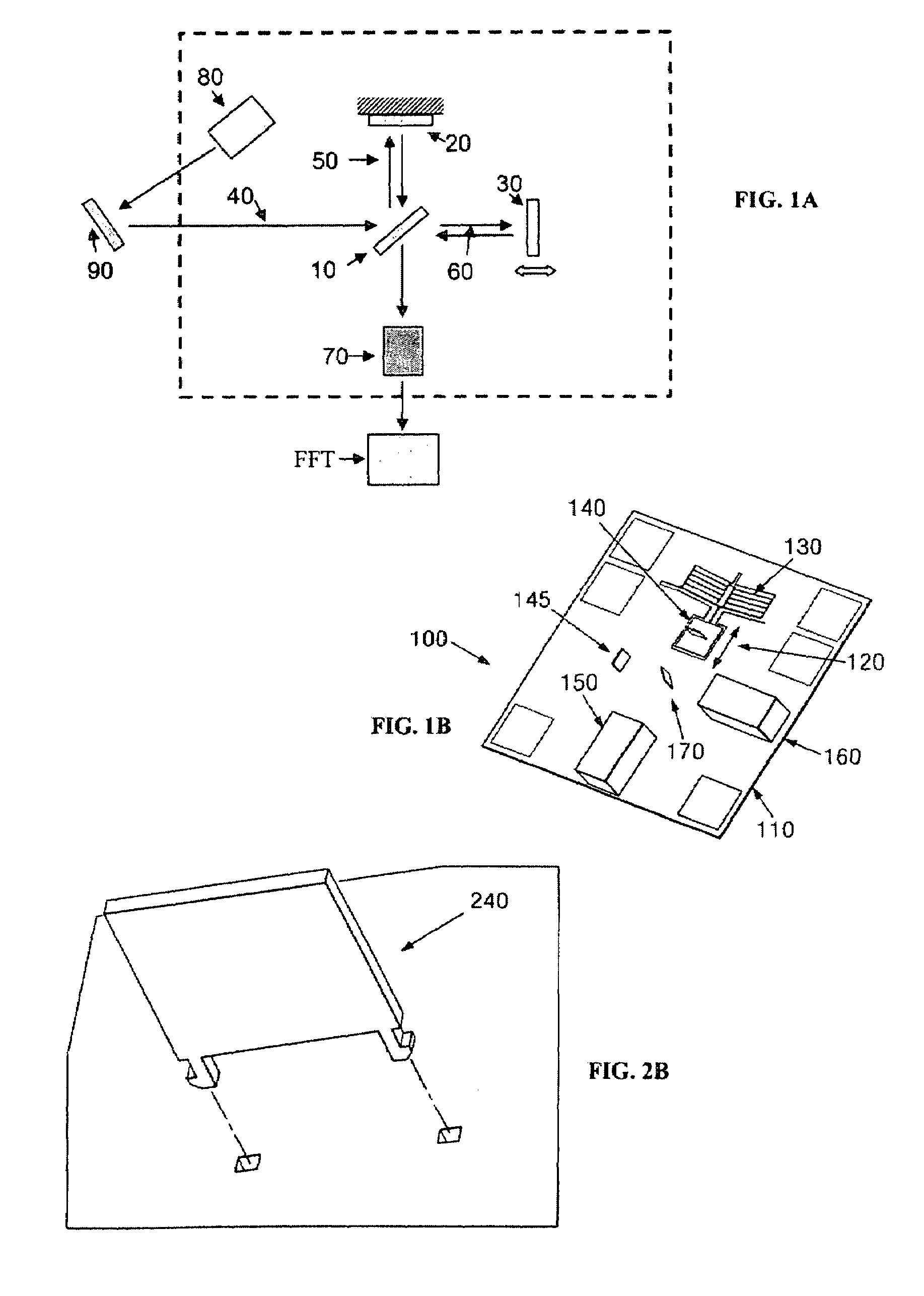

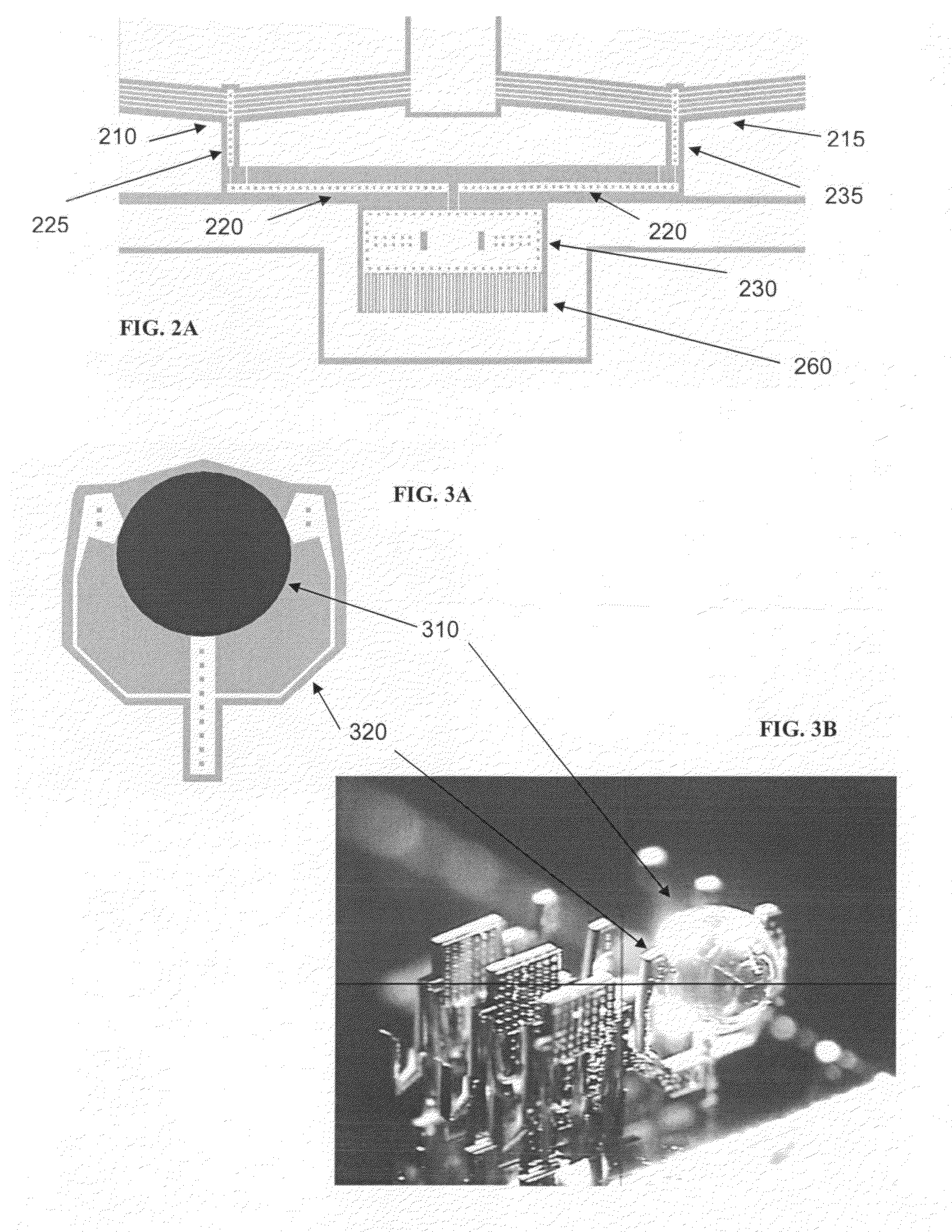

Devices in miniature for interferometric use and fabrication thereof

A device in miniature and fabrication of such a device for interferometric use is described, the device including a substrate with at least one deep reactive ion etching structure on at least one surface of the substrate forming an optical bench. The optical bench preferably comprises a moving stage, an actuator, one or more connector sockets and one or more optical components.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST