Patents

Literature

7962 results about "Single crystal silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

About Silicon Single Crystal. Single Crystal Silicon for solar energy applications includes p-type and n-type silicon. Silicon-based photovoltaic cells (PV Cells) for solar energy are fabricated from a positively charged or p-type silicon layer underneath a negatively charged or n-type silicon layer.

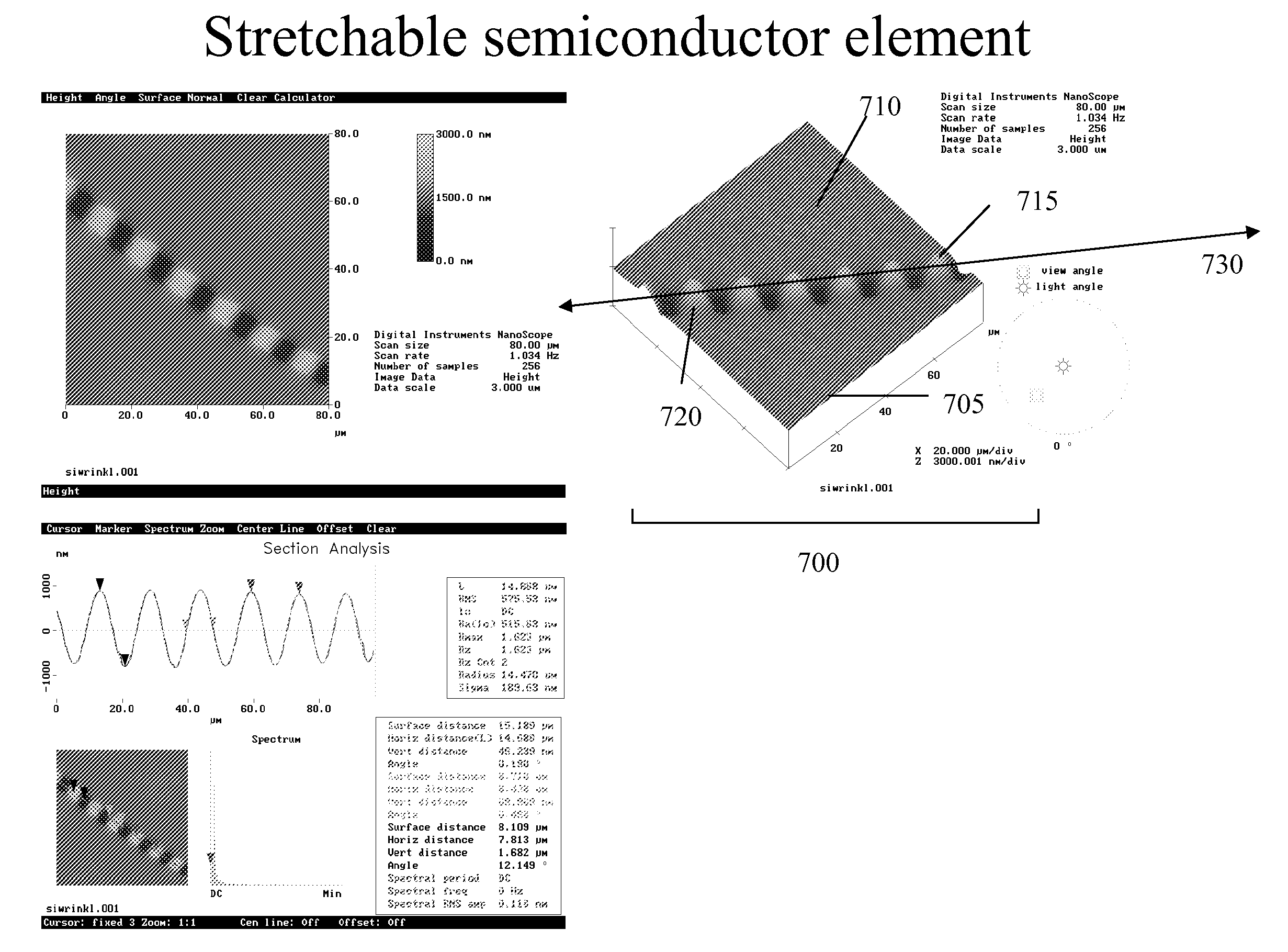

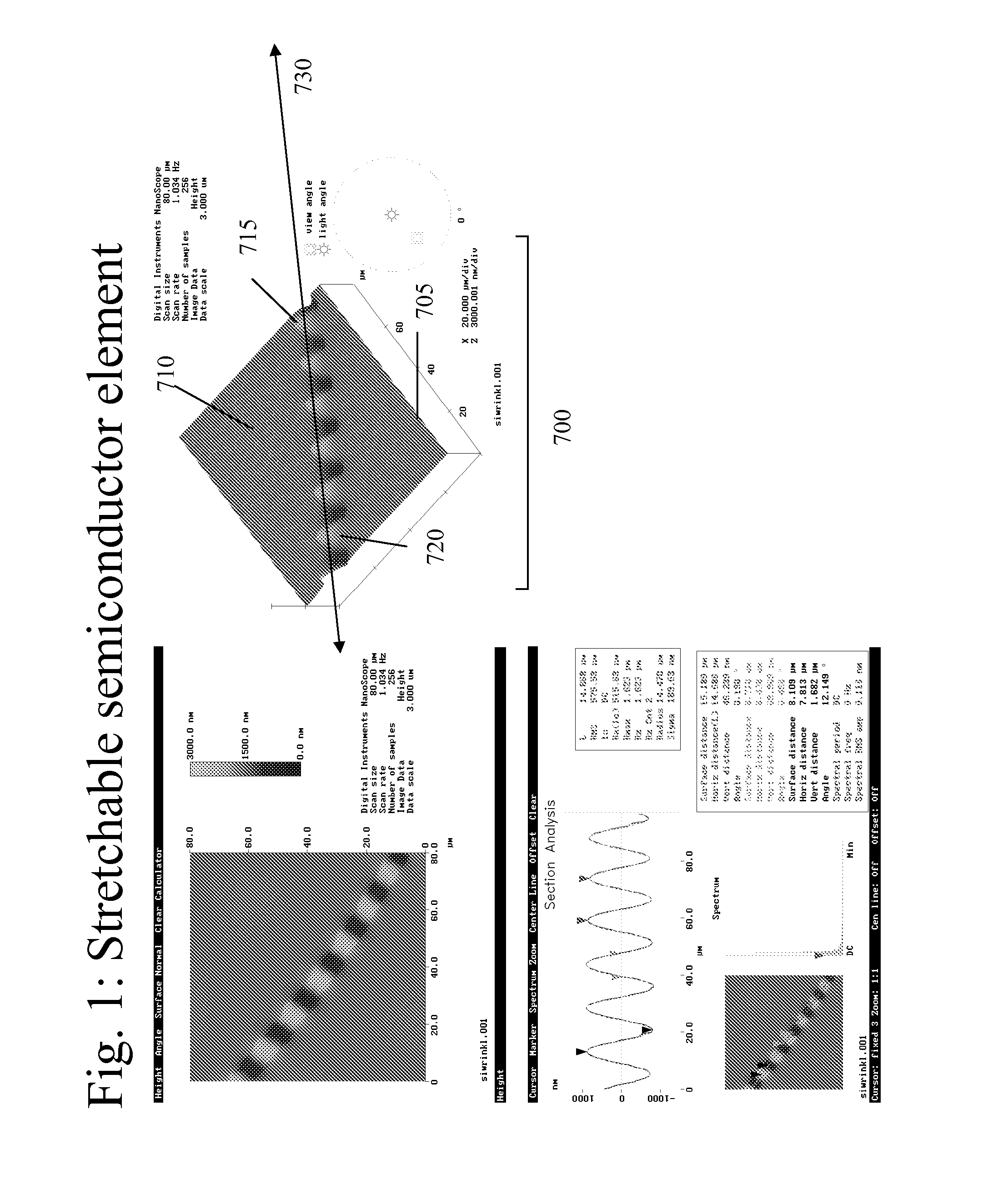

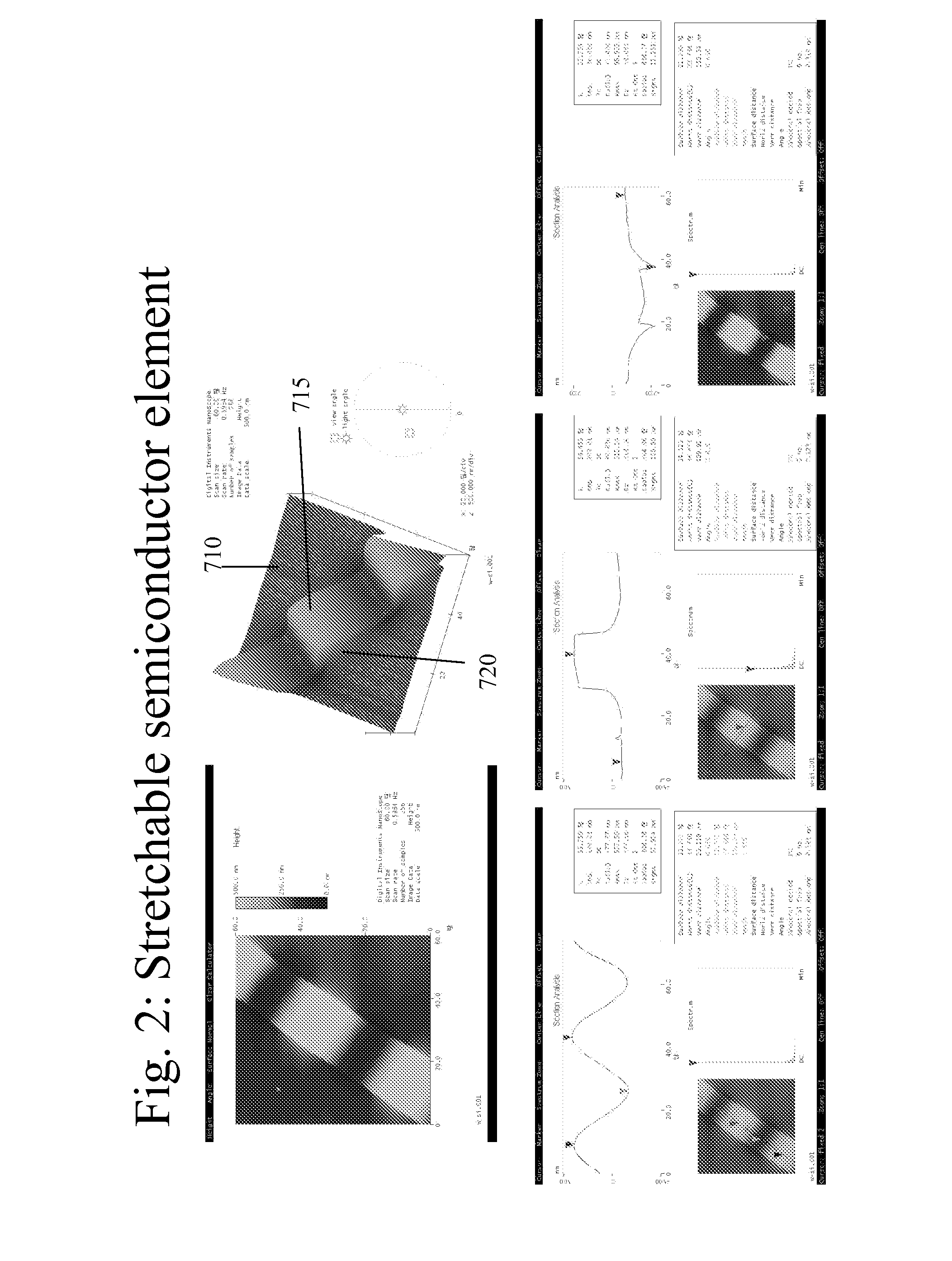

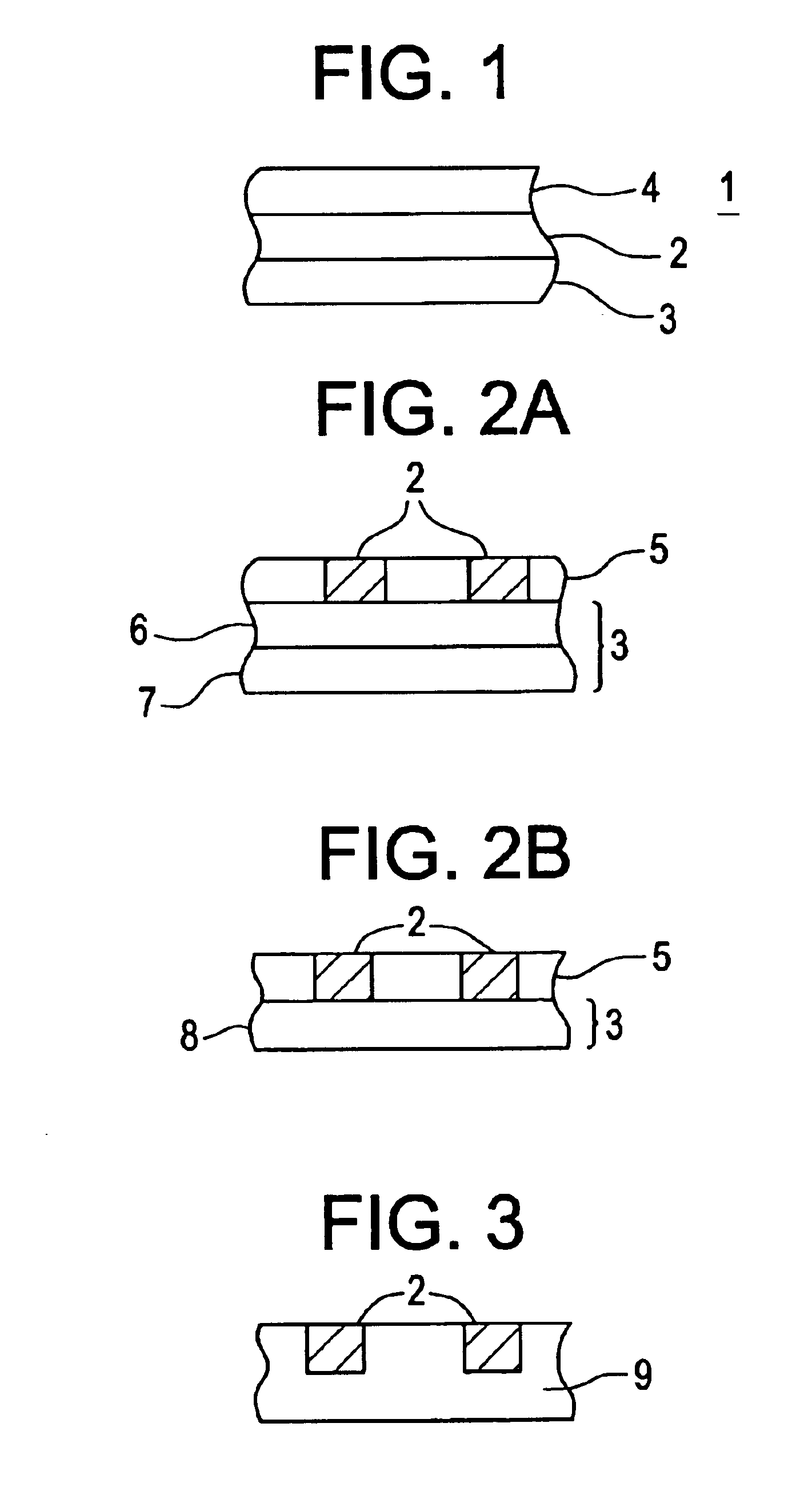

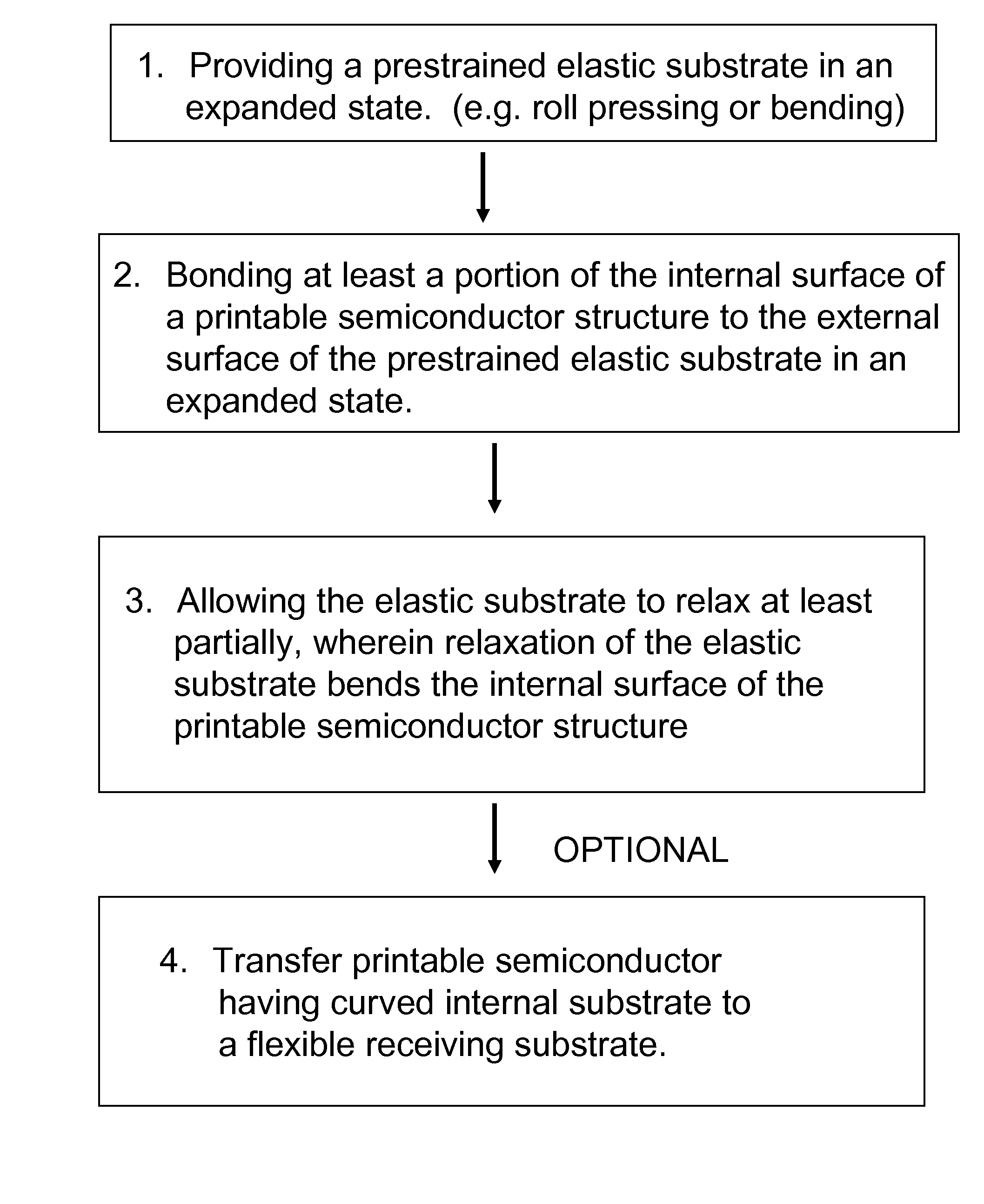

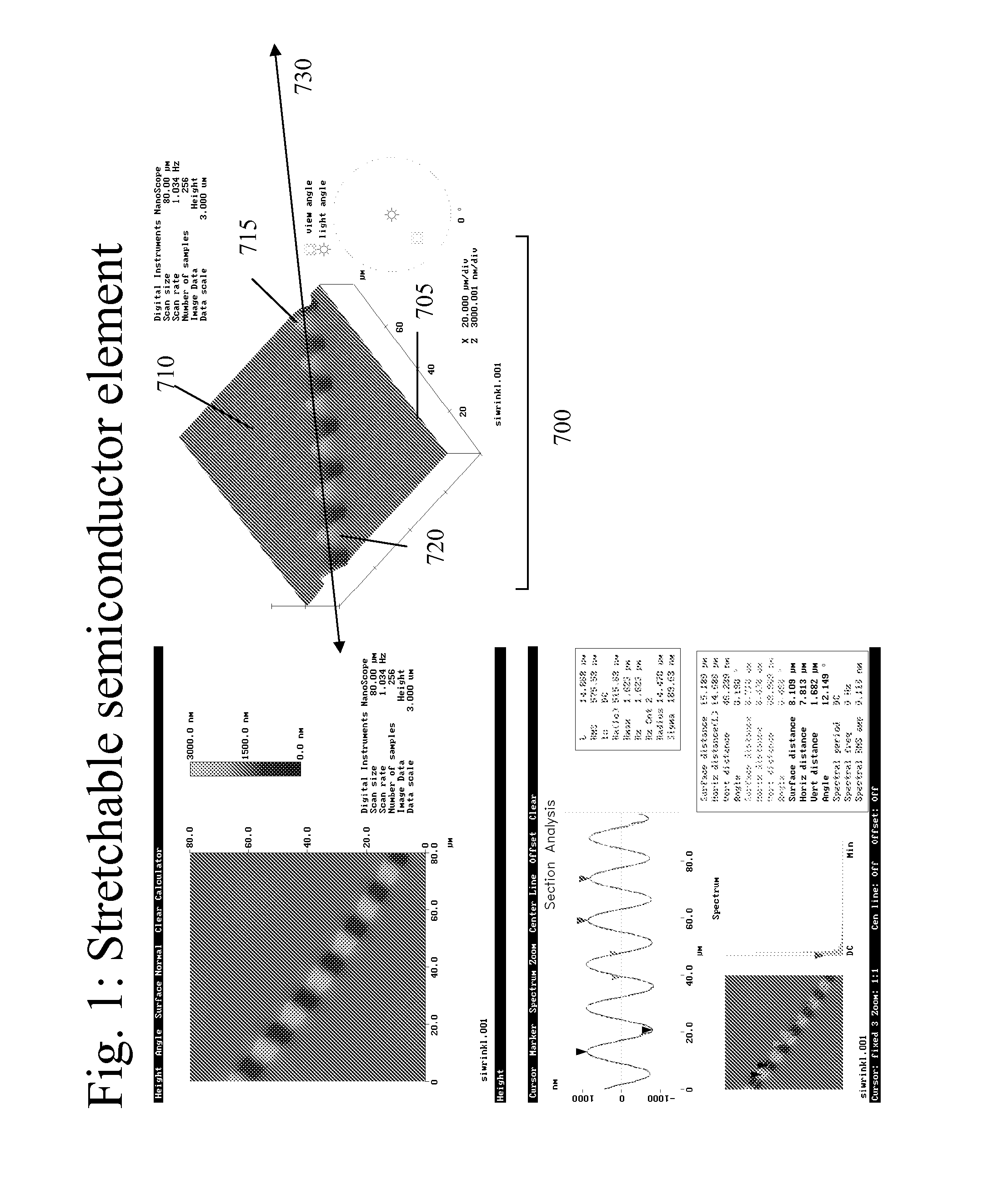

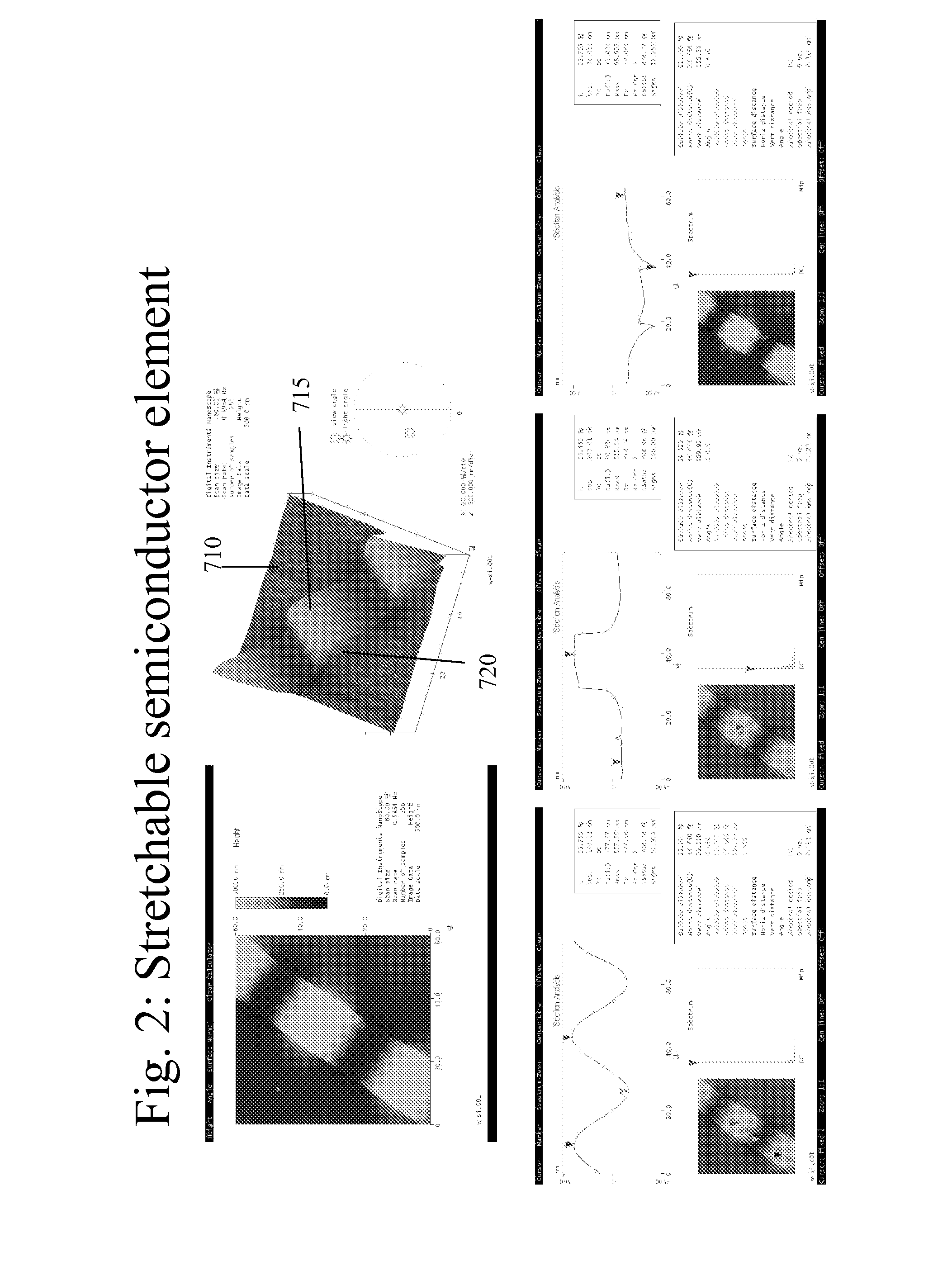

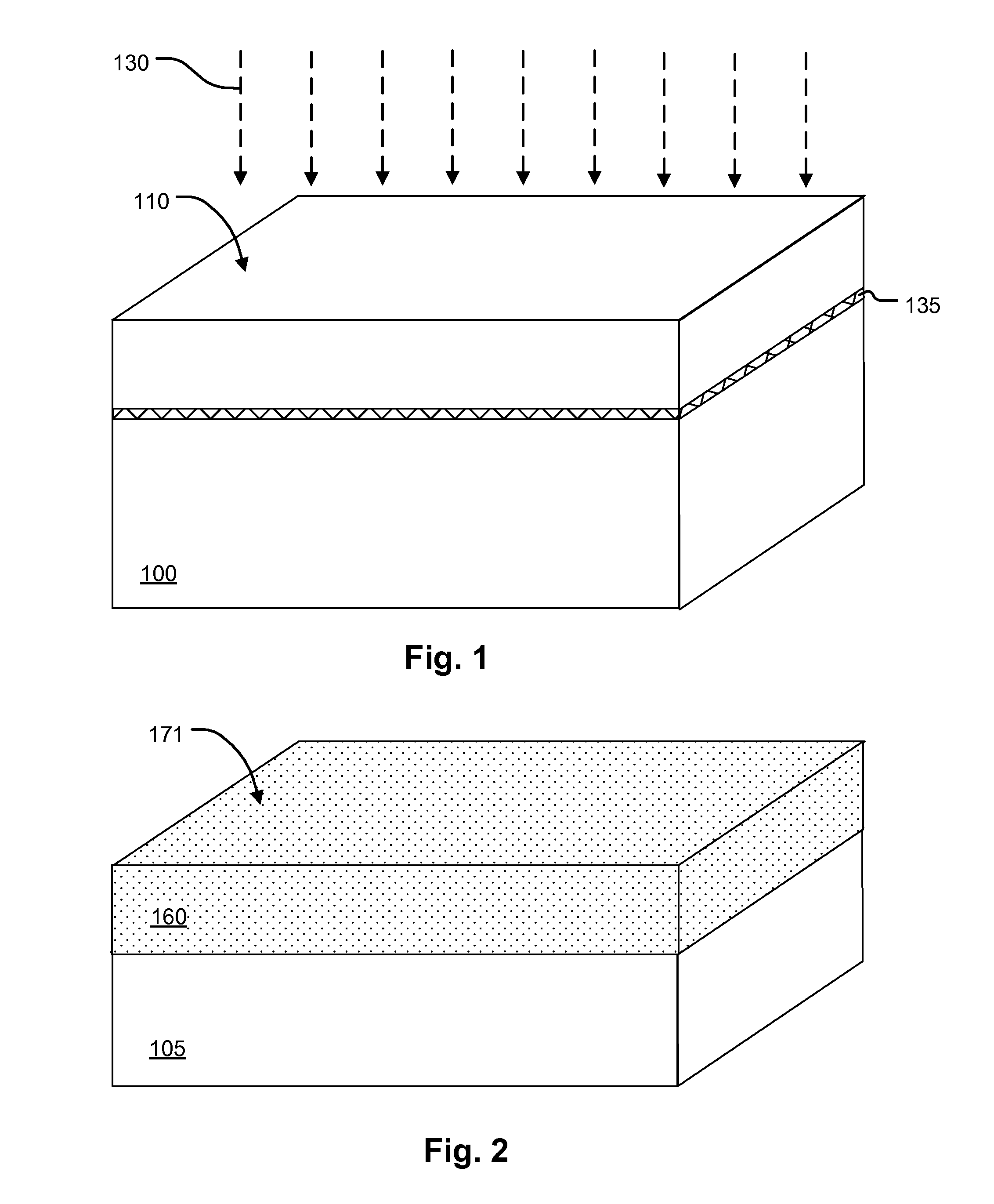

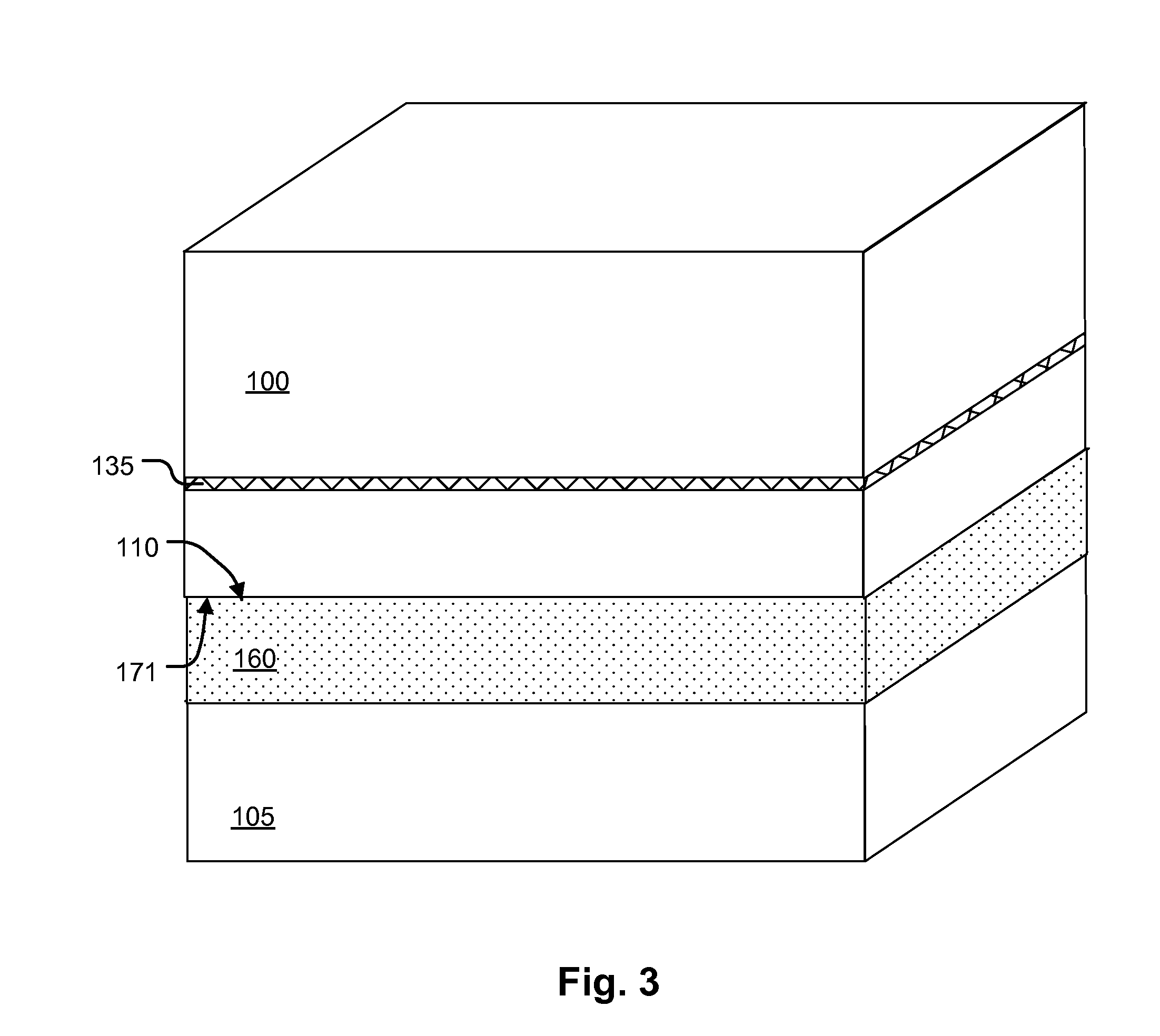

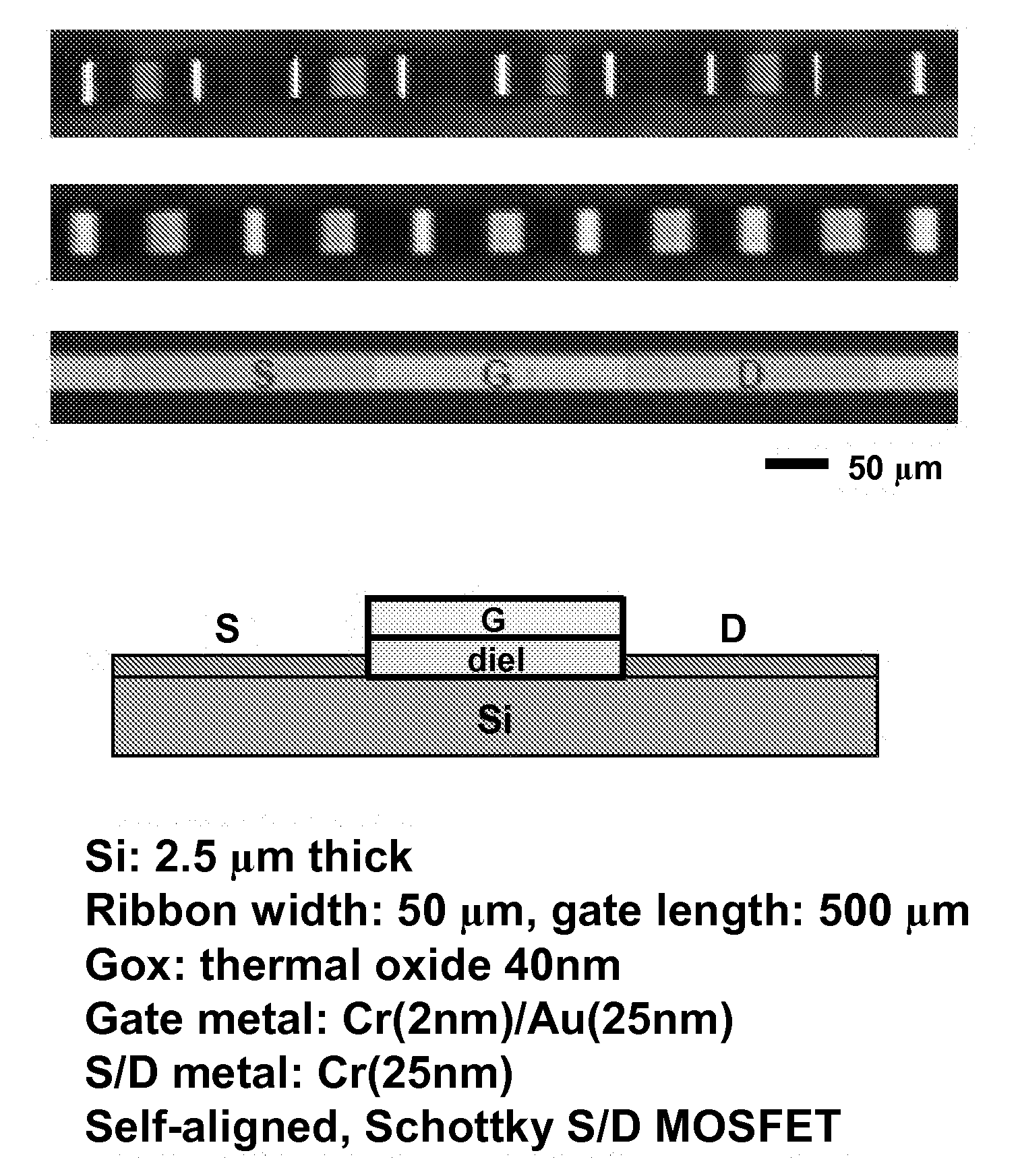

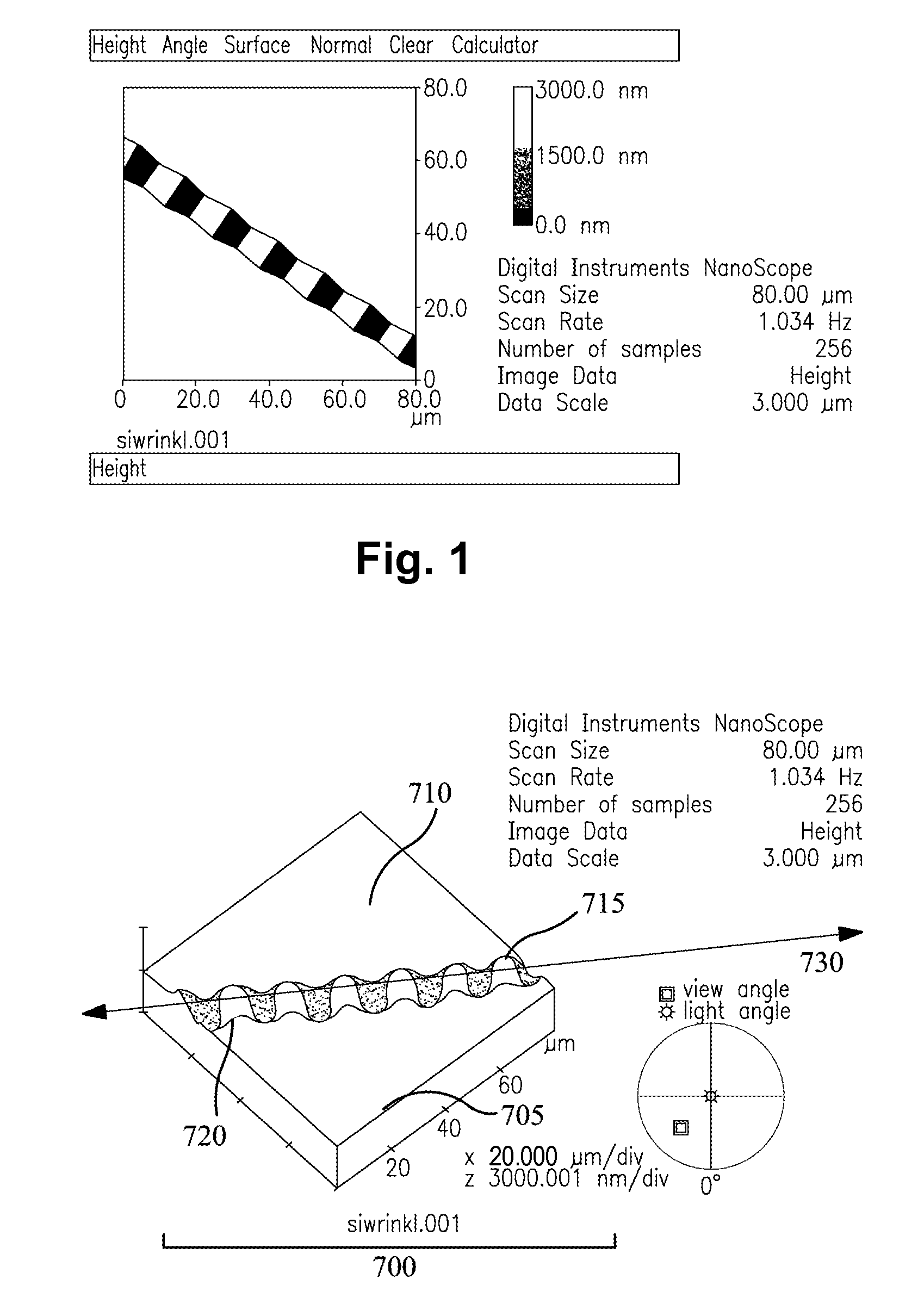

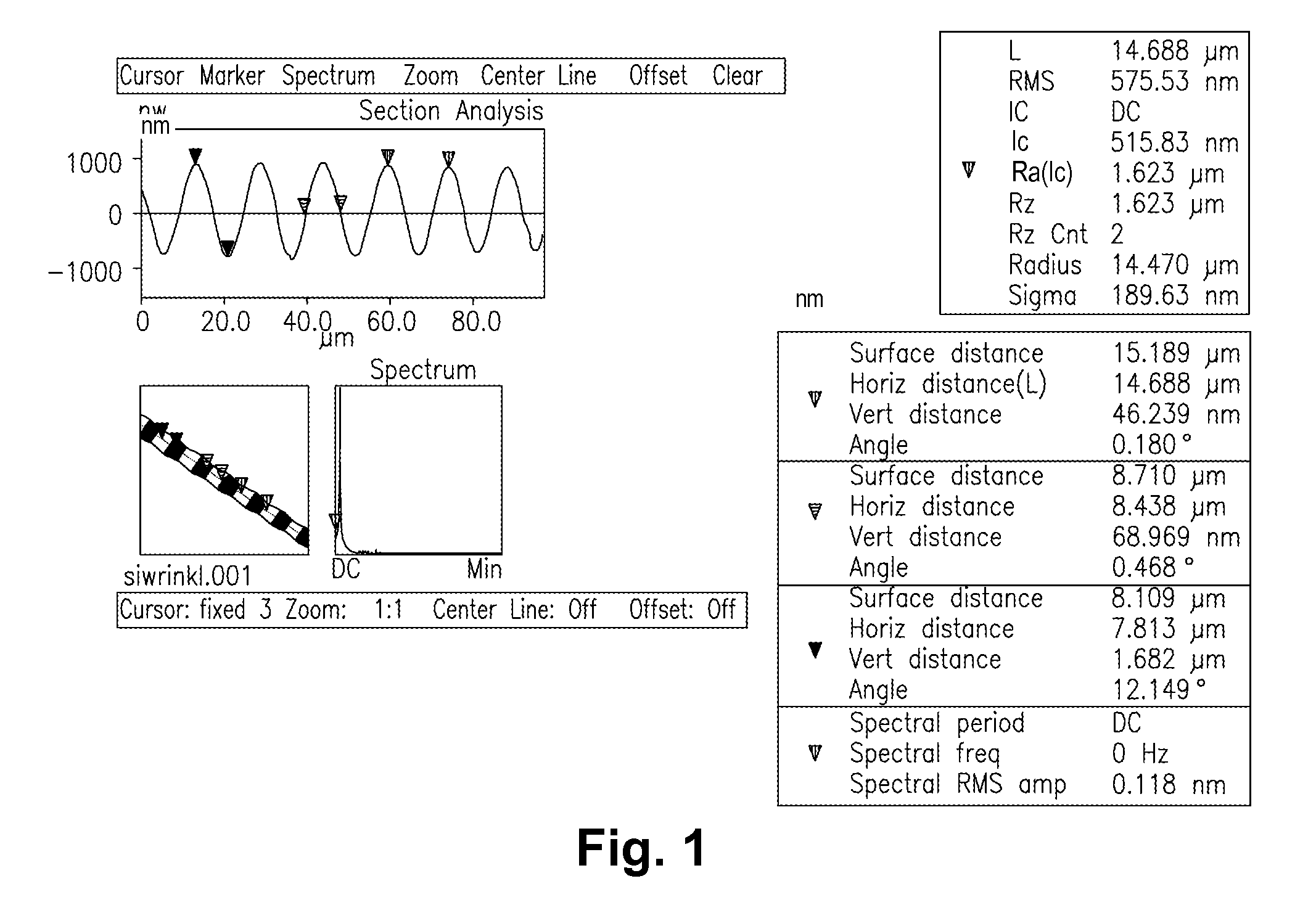

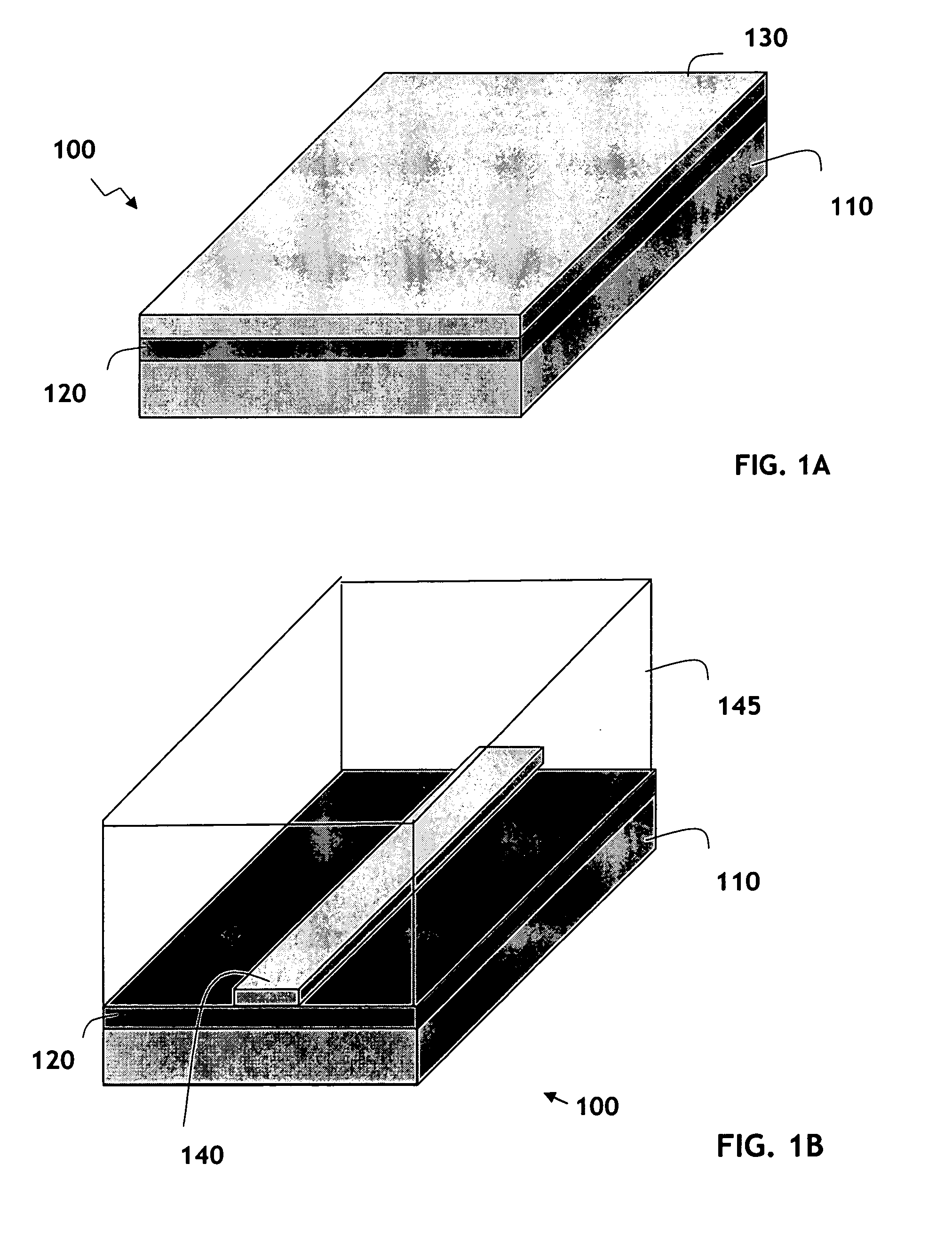

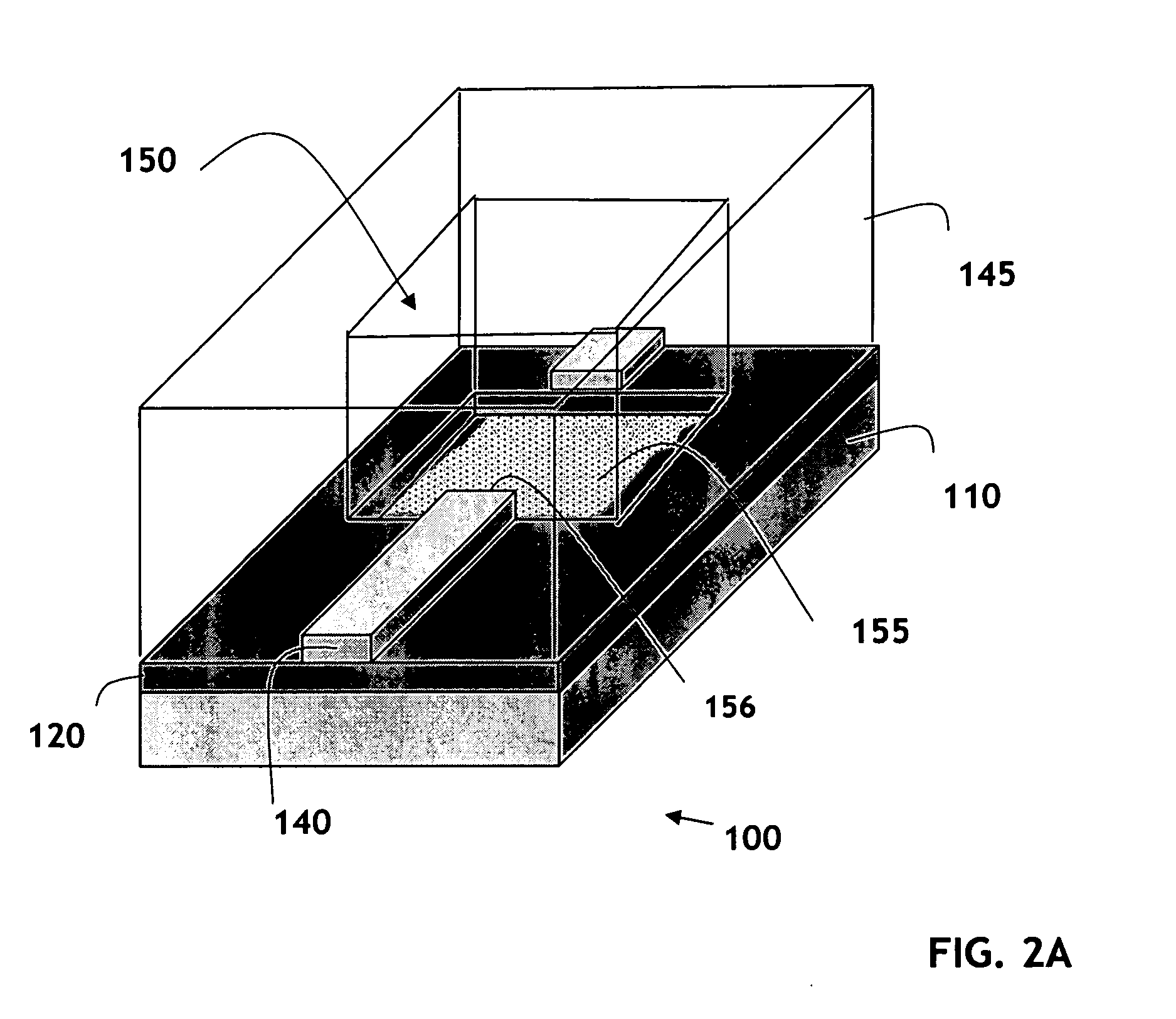

Stretchable form of single crystal silicon for high performance electronics on rubber substrates

ActiveUS7521292B2Large elongationSignificant flexingTransistorCircuit bendability/stretchabilityEngineeringFlexible electronics

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

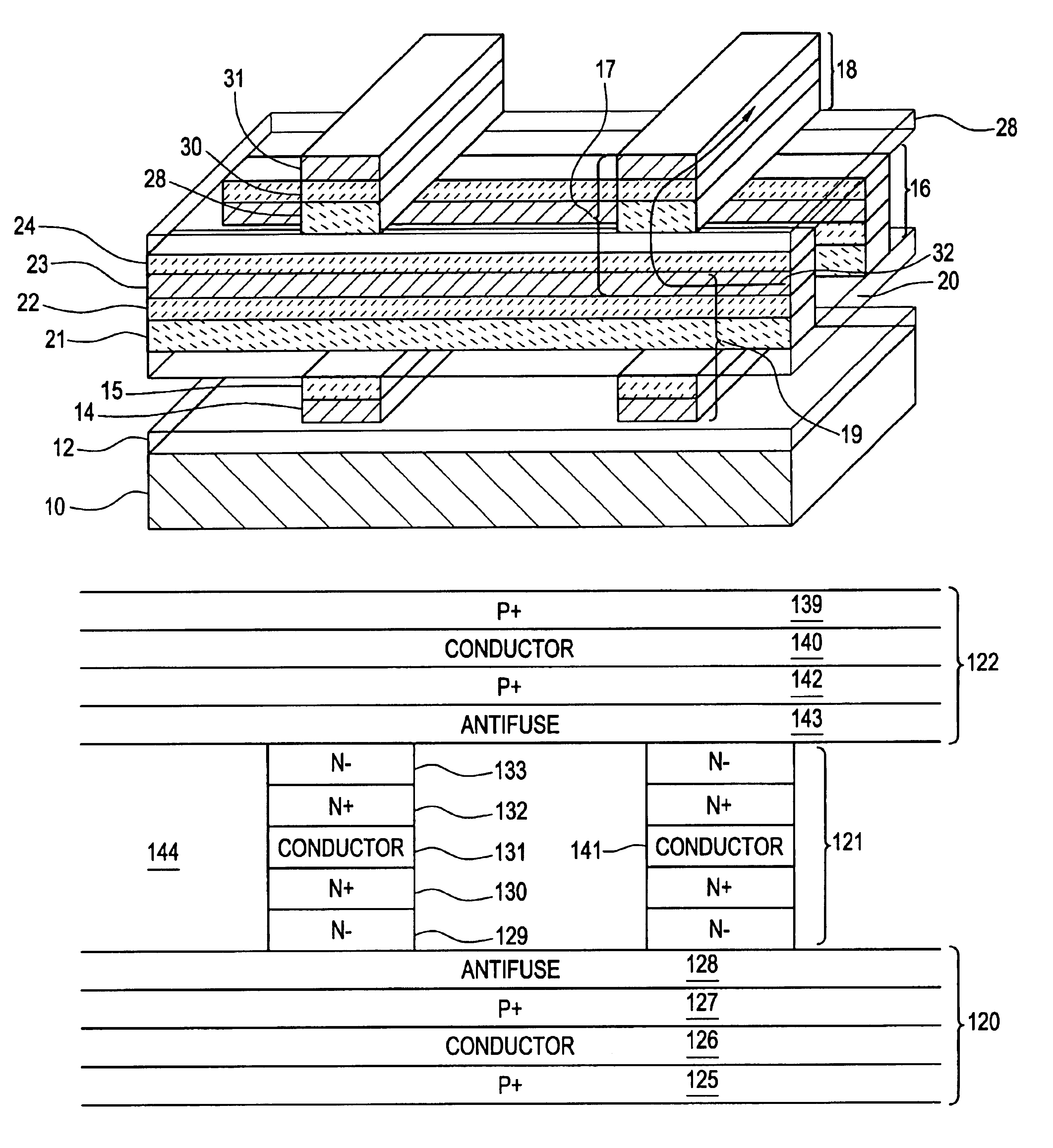

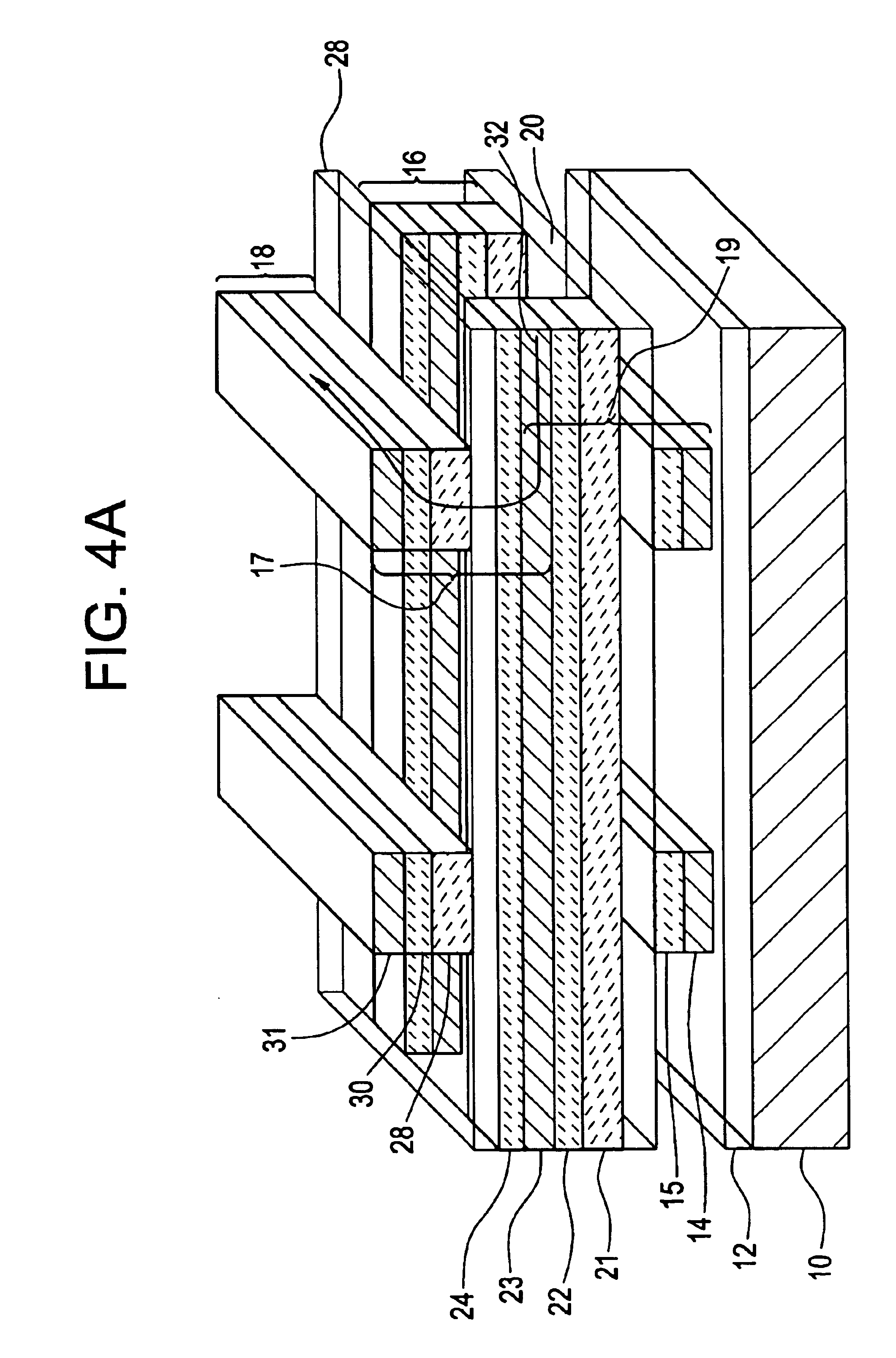

Nonvolatile memory on SOI and compound semiconductor substrates and method of fabrication

A nonvolatile memory array is provided. The array includes an array of nonvolatile memory devices, at least one driver circuit, and a substrate. The at least one driver circuit is not located in a bulk monocrystalline silicon substrate. The at least one driver circuit may be located in a silicon on insulator substrate or in a compound semiconductor substrate.

Owner:SANDISK TECH LLC

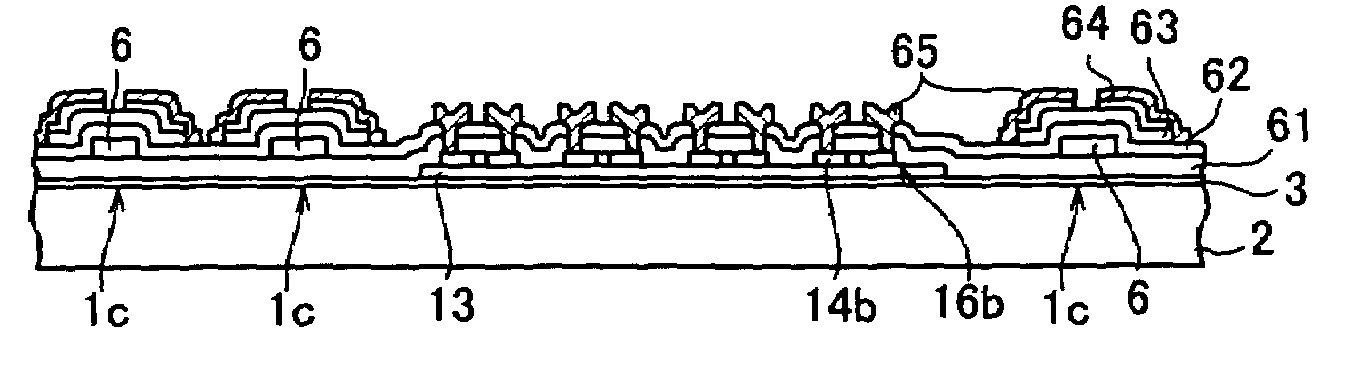

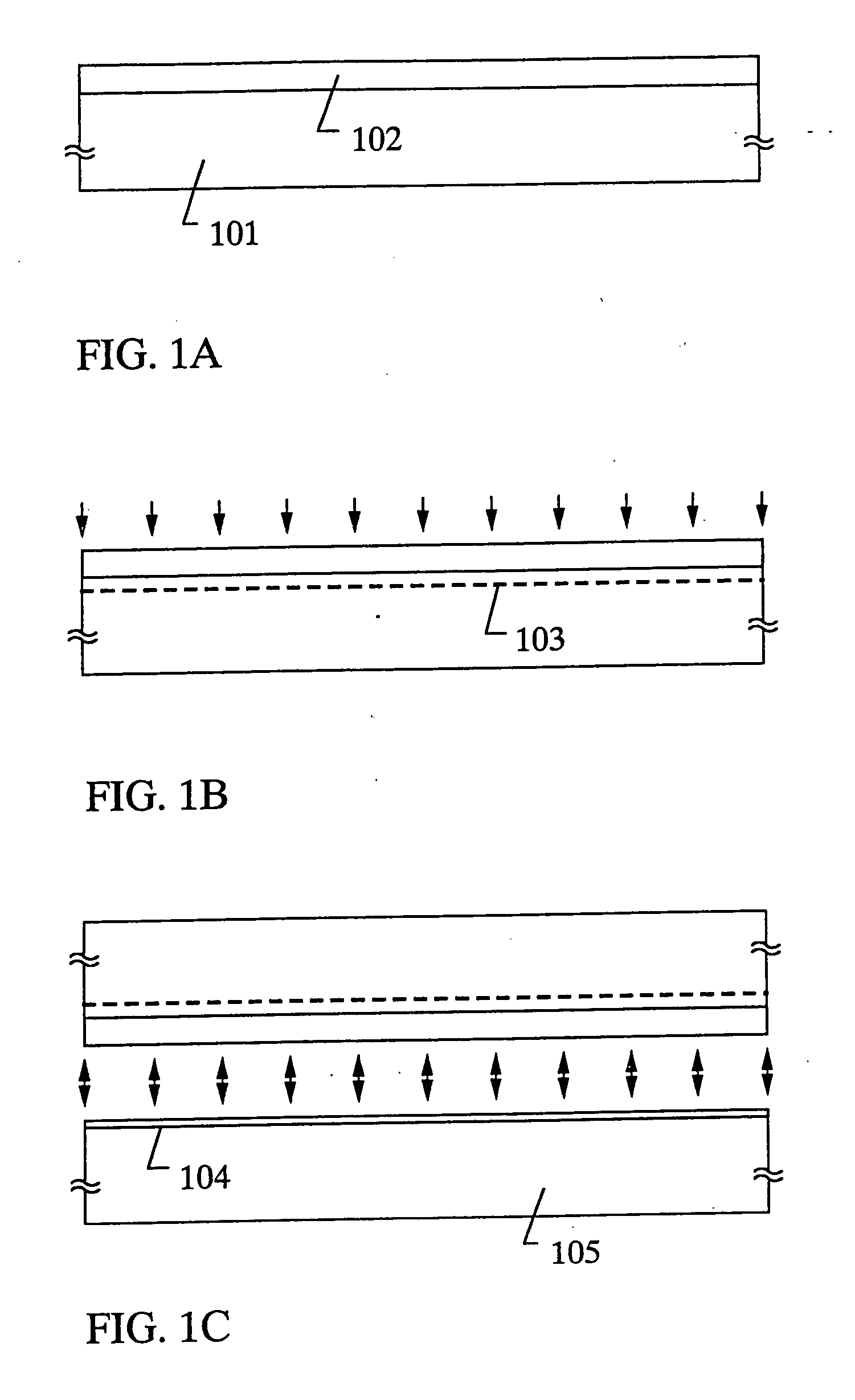

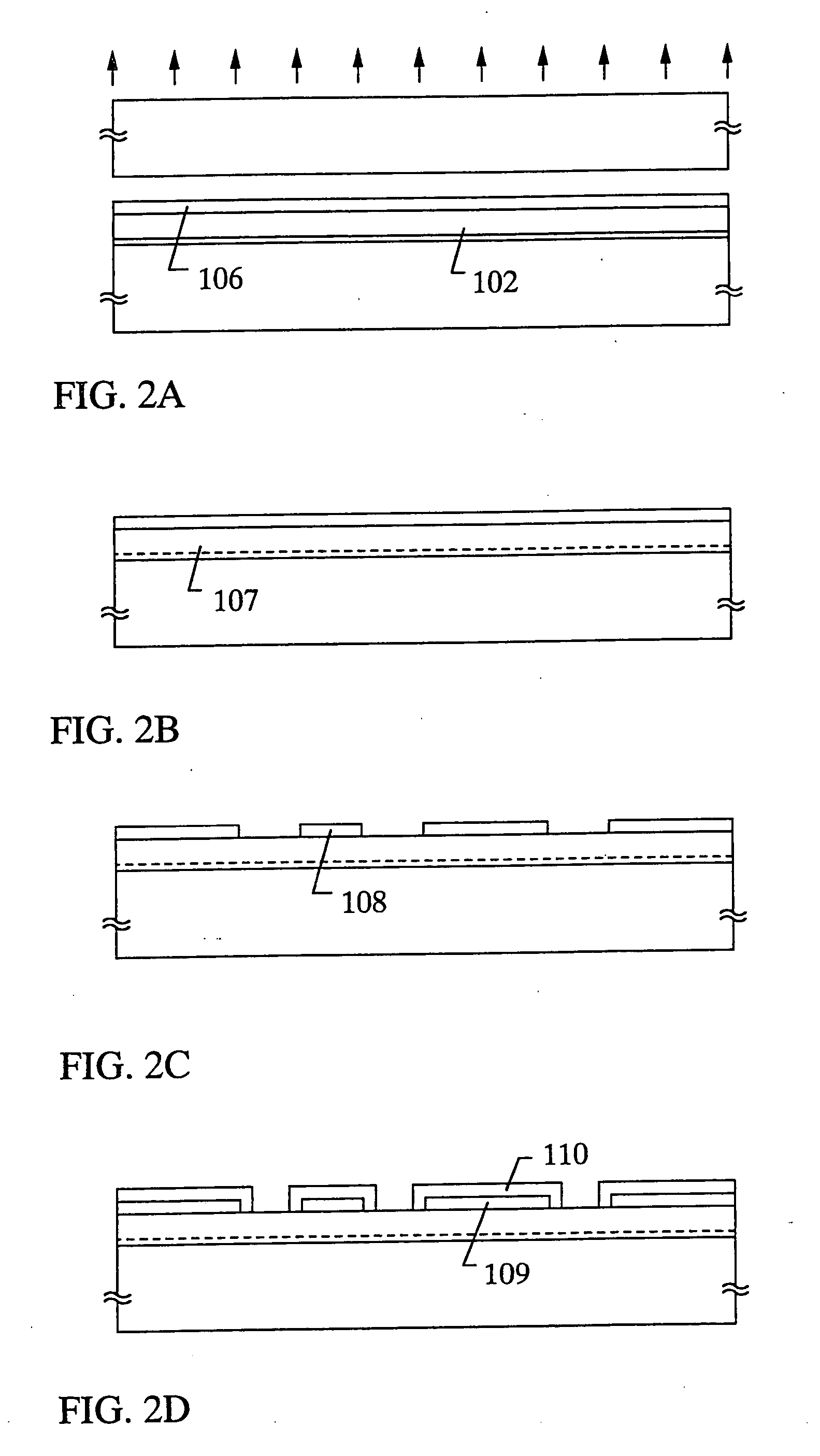

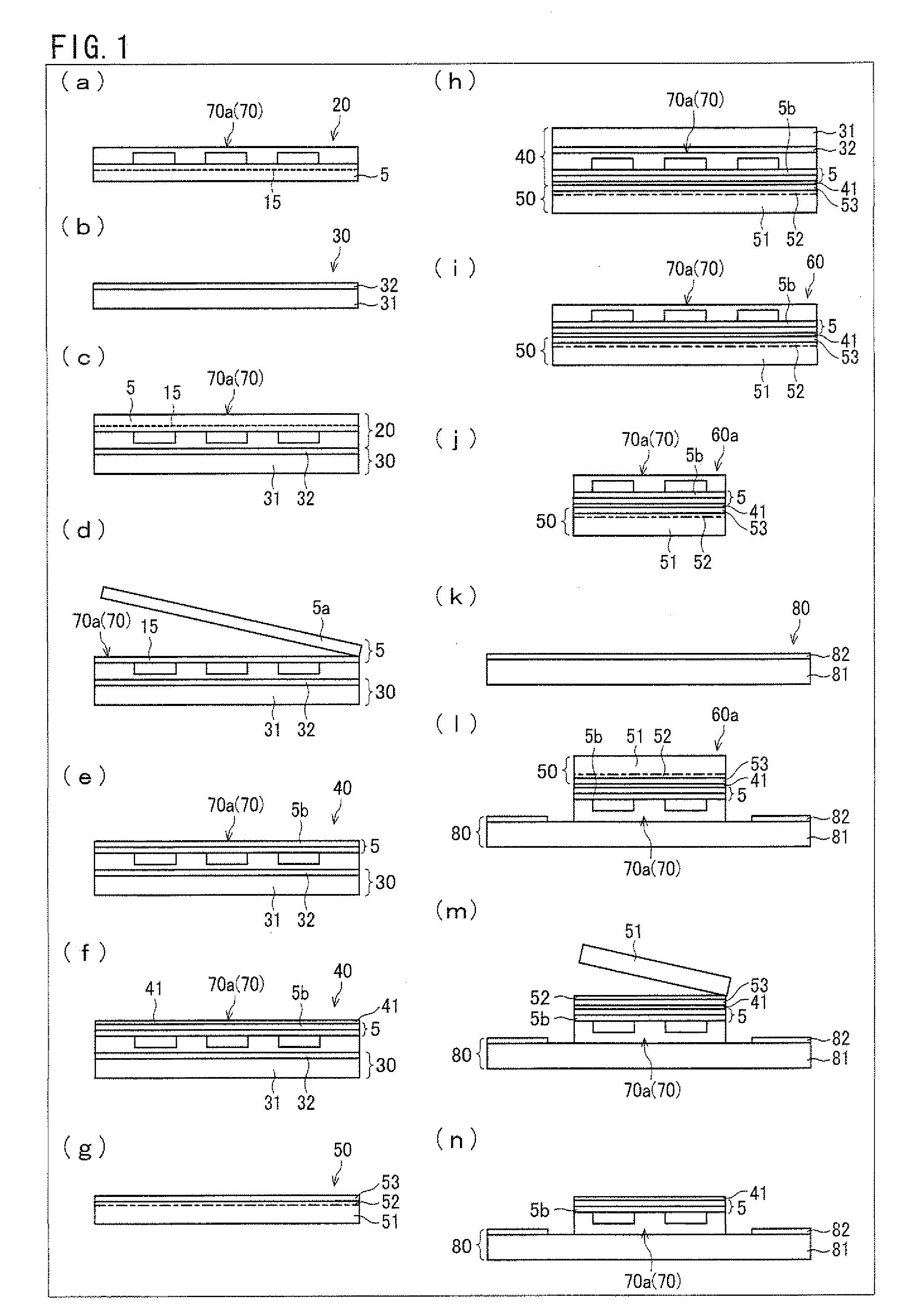

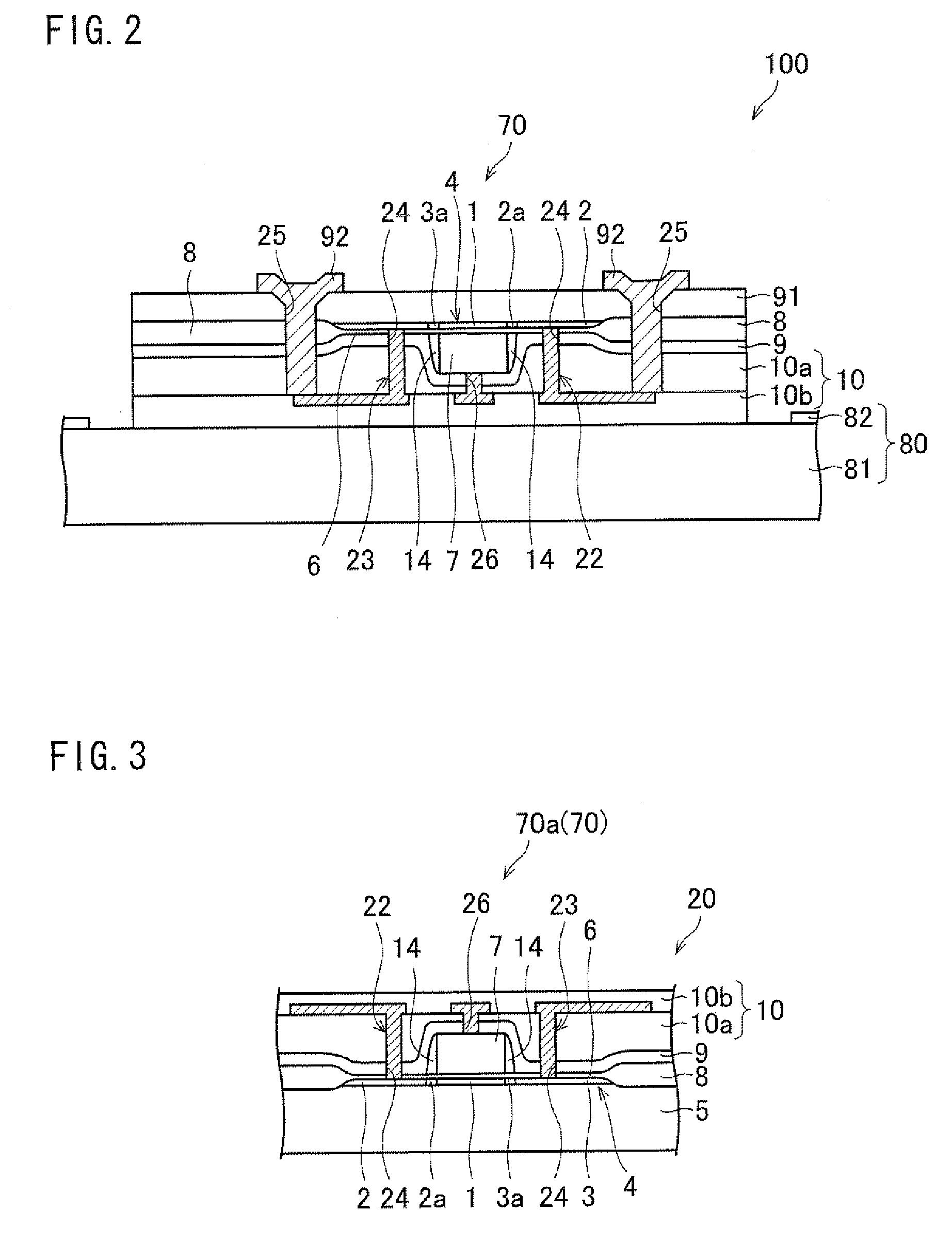

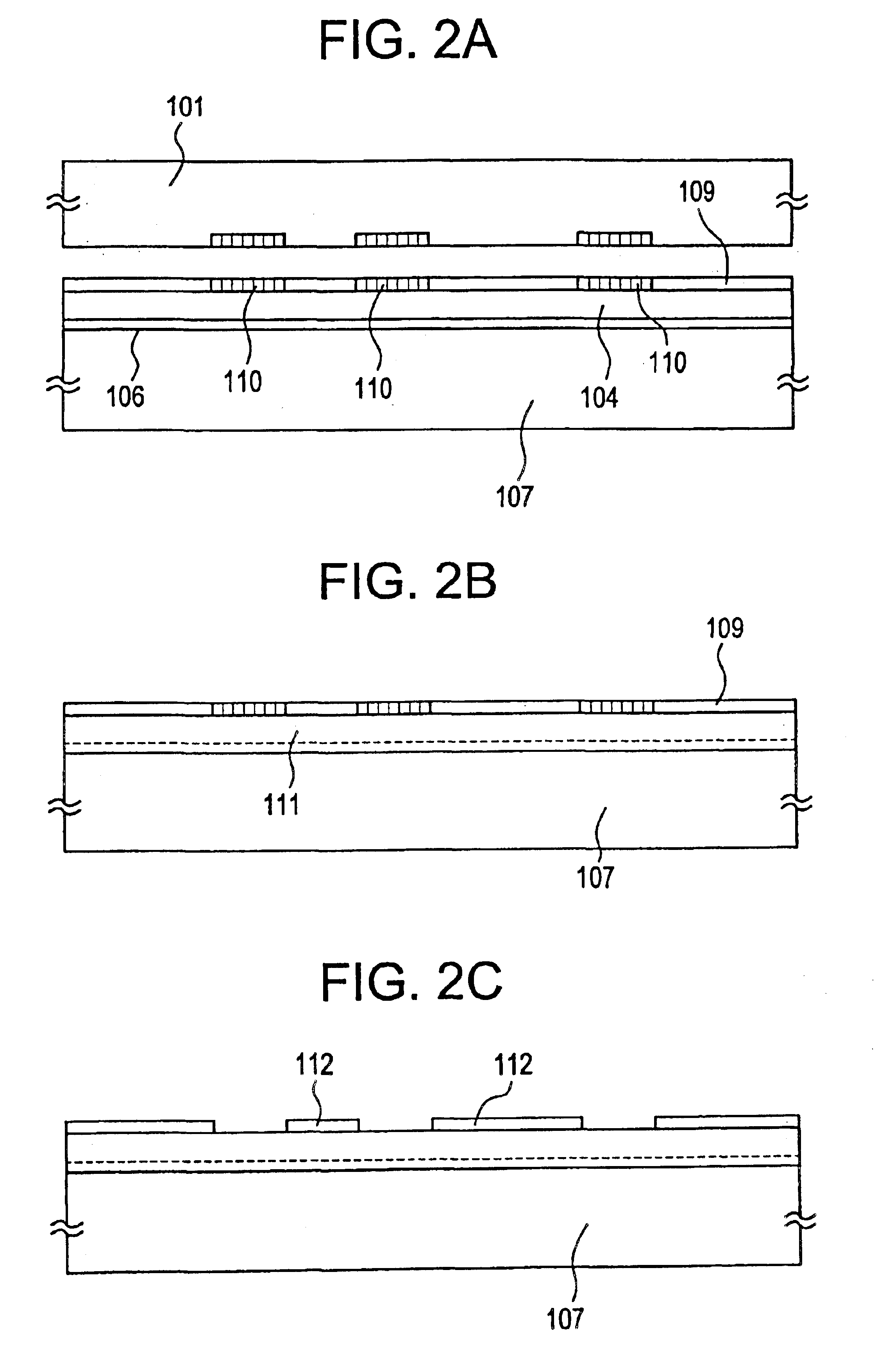

Single-crystal silicon substrate, SOI substrate, semiconductor device, display device, and manufacturing method of semiconductor device

InactiveUS7508034B2Well formedHigh bonding strengthTransistorSolid-state devicesDisplay deviceSoi substrate

A semiconductor device of the present invention is arranged in such a manner that a MOS non-single-crystal silicon thin-film transistor including a non-single-crystal silicon thin film made of polycrystalline silicon, a MOS single-crystal silicon thin-film transistor including a single-crystal silicon thin film, and a metal wiring are provided on an insulating substrate. With this arrangement, (i) a semiconductor device in which a non-single-crystal silicon thin film and a single-crystal silicon thin-film device are formed and high-performance systems are integrated, (ii) a method of manufacturing the semiconductor device, and (iii) a single-crystal silicon substrate for forming the single-crystal silicon thin-film device of the semiconductor device are obtained.

Owner:SHARP KK

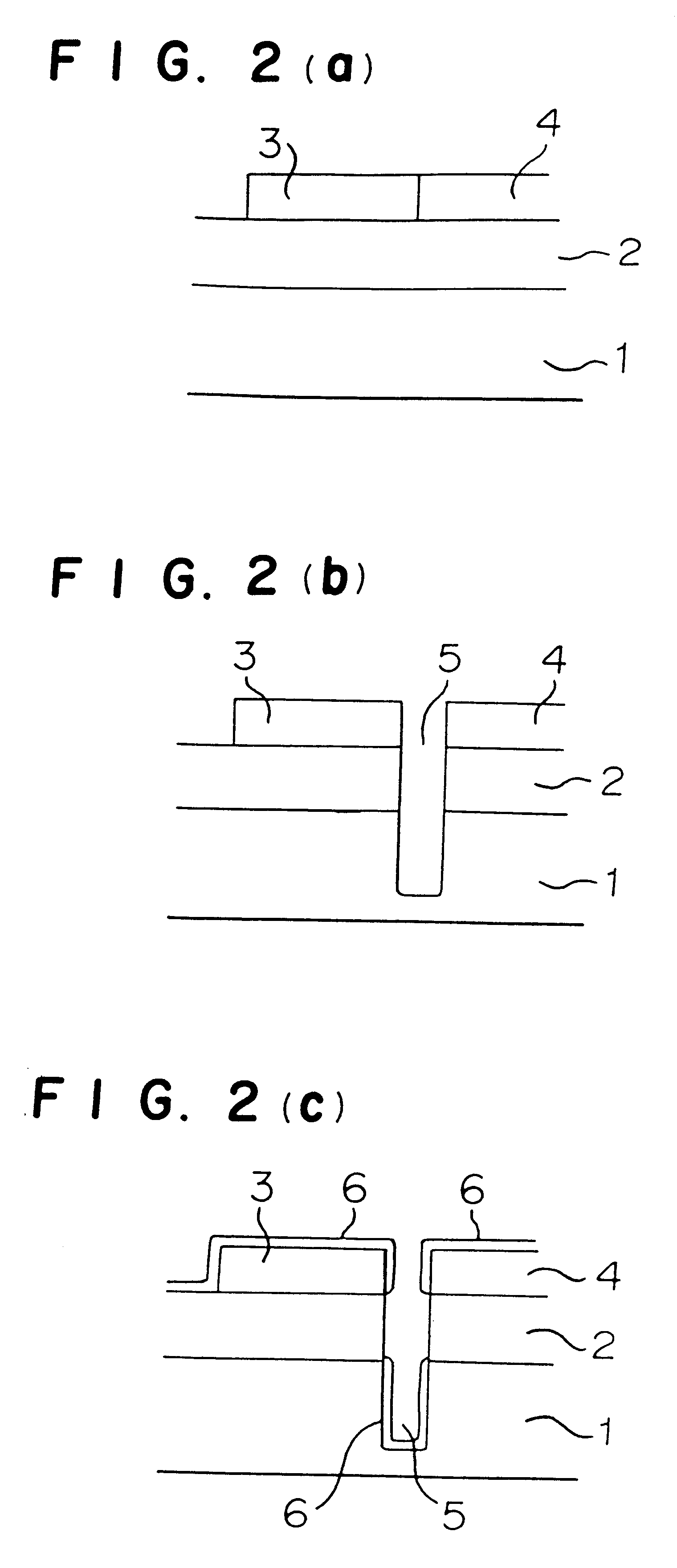

Method of manufacturing a semiconductor device

InactiveUS7199024B2Relaxation stressGuaranteed uptimeTransistorSolid-state devicesSmart CutSemiconductor

There is provided a method of removing trap levels and defects, which are caused by stress, from a single crystal silicon thin film formed by an SOI technique. First, a single crystal silicon film is formed by using a typical bonding SOI technique such as Smart-Cut or ELTRAN. Next, the single crystal silicon thin film is patterned to form an island-like silicon layer, and then, a thermal oxidation treatment is carried out in an oxidizing atmosphere containing a halogen element, so that an island-like silicon layer in which the trap levels and the defects are removed is obtained.

Owner:SEMICON ENERGY LAB CO LTD

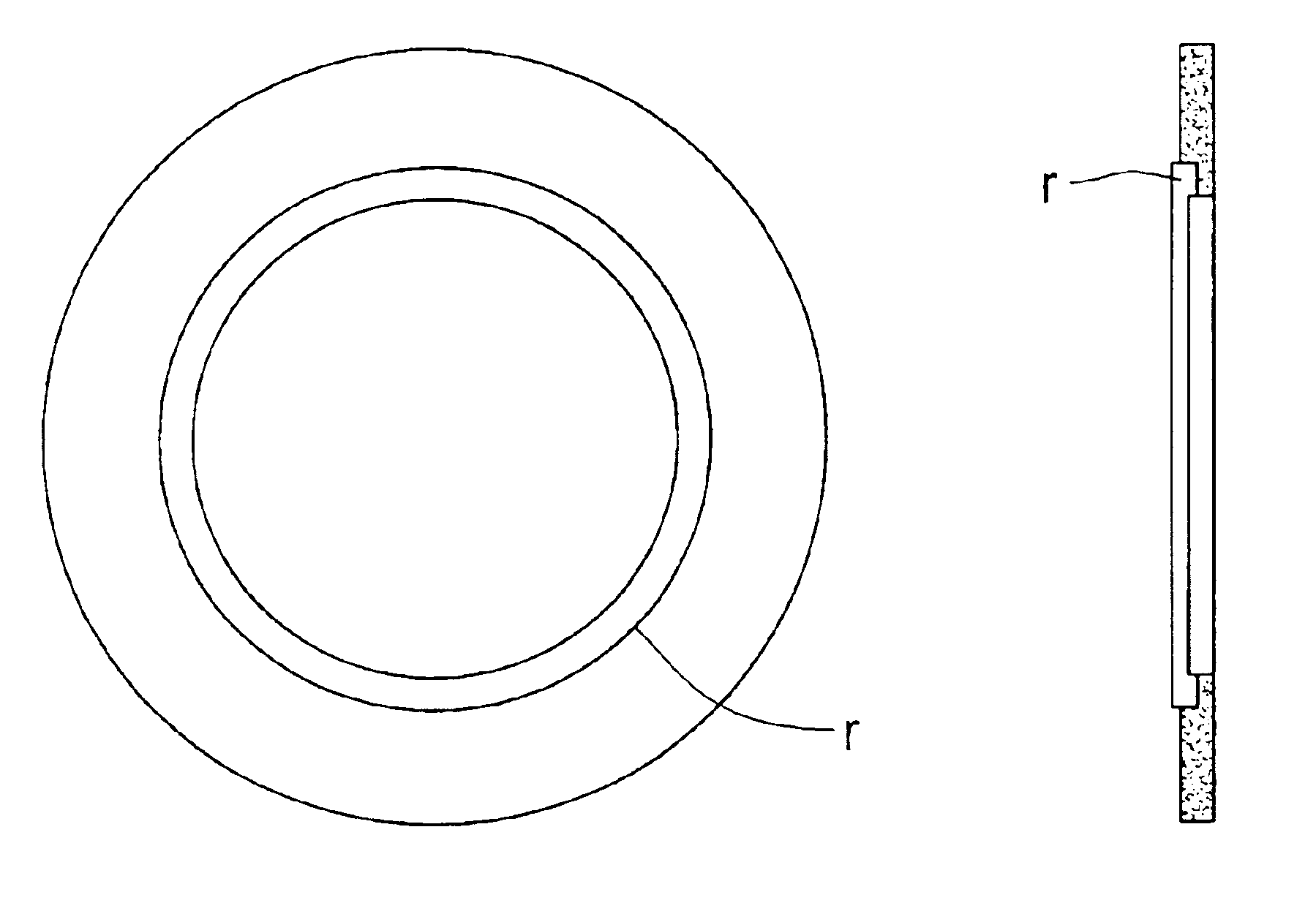

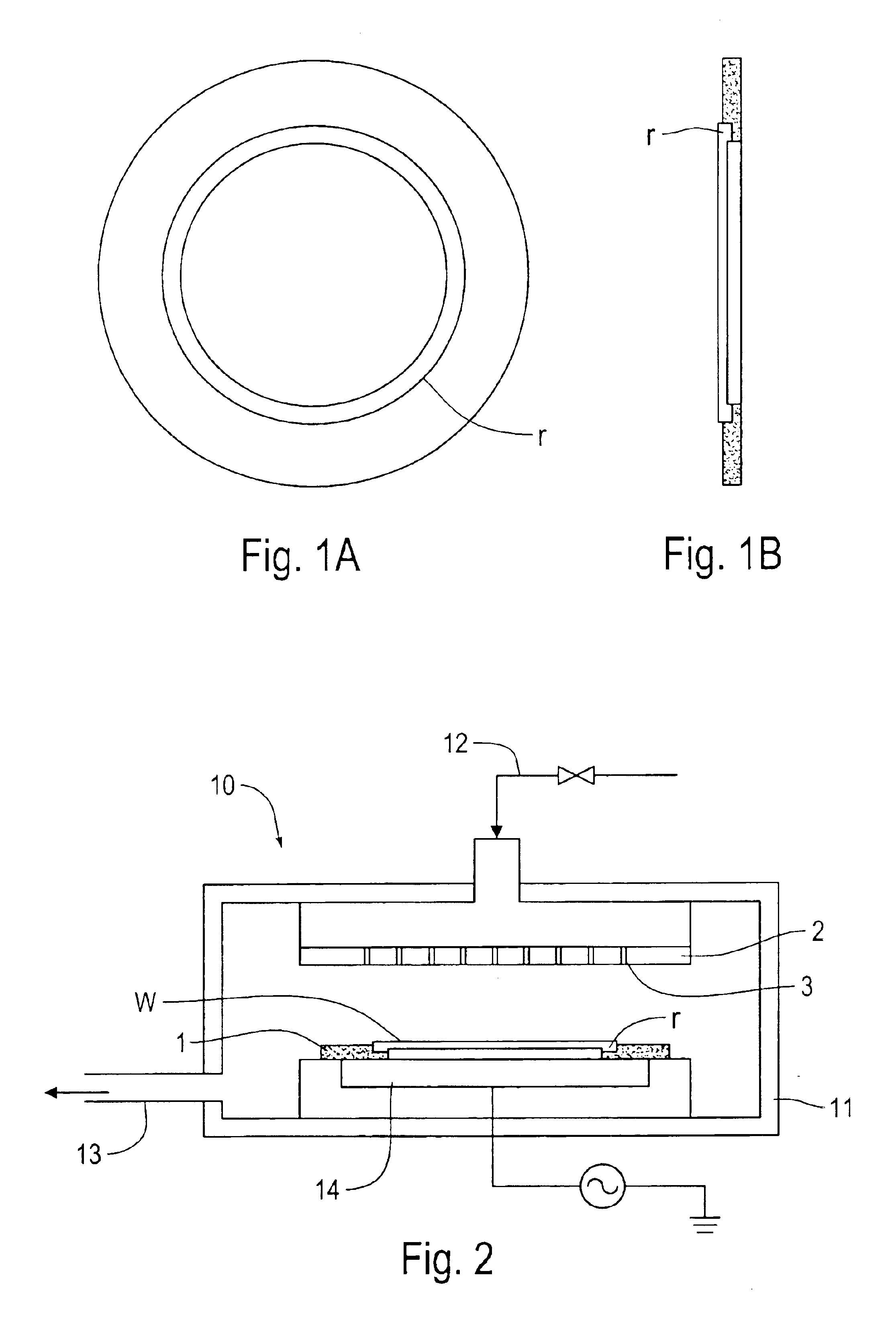

Silicon focus ring and method for producing the same

InactiveUS6815352B1Reduce Particle GenerationAvoid roughnessPolycrystalline material growthElectric discharge tubesCzochralski methodSingle crystal

There is disclosed a silicon focus ring consisting of silicon single crystal used as a silicon focus ring in a plasma apparatus, wherein concentration of interstitial oxygen contained in the silicon focus ring is not less than 5x10<17 >atoms / cm<3 >and not more than 1.5x10<18 >atoms / cm<3>, and a producing method for a silicon focus ring used for a plasma apparatus, wherein a single crystal silicon wherein concentration of interstitial oxygen contained in the silicon focus ring is not less than 5x10<17 >atoms / cm<3 >and not more than 1.5x10<18 >atoms / cm<3 >is grown by a Czochralski method, the single crystal silicon is processed in a circle, and a silicon focus ring is produced. There can be provided a silicon focus ring, which can prevent disadvantage due to impurities such as heavy metal.

Owner:SHIN ETSU CHEM IND CO LTD

A Stretchable Form of Single Crystal Silicon for High Performance Electronics on Rubber Substrates

ActiveUS20060286785A1Large elongationSignificant flexingTransistorCircuit bendability/stretchabilityEngineeringFlexible electronics

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

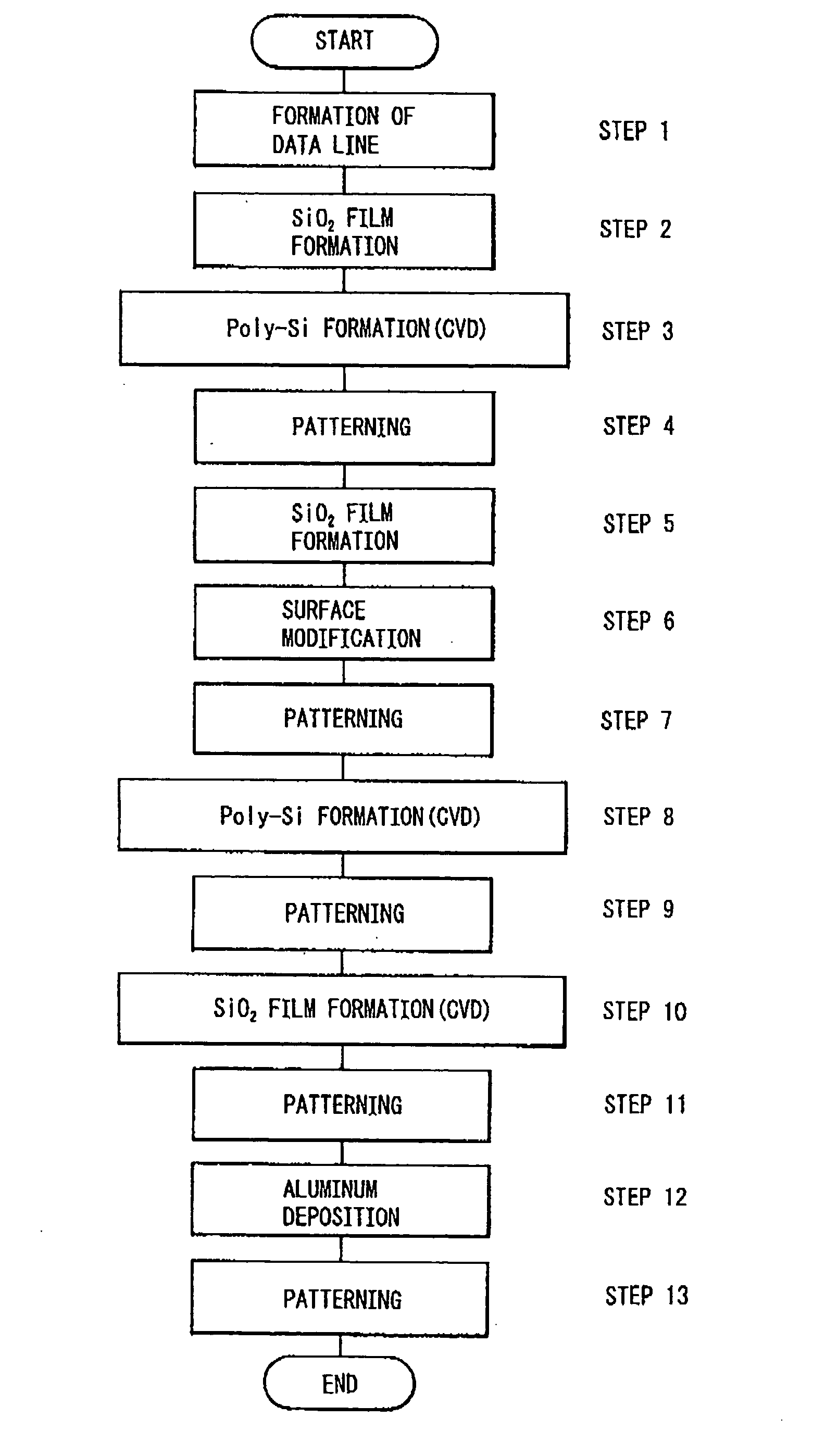

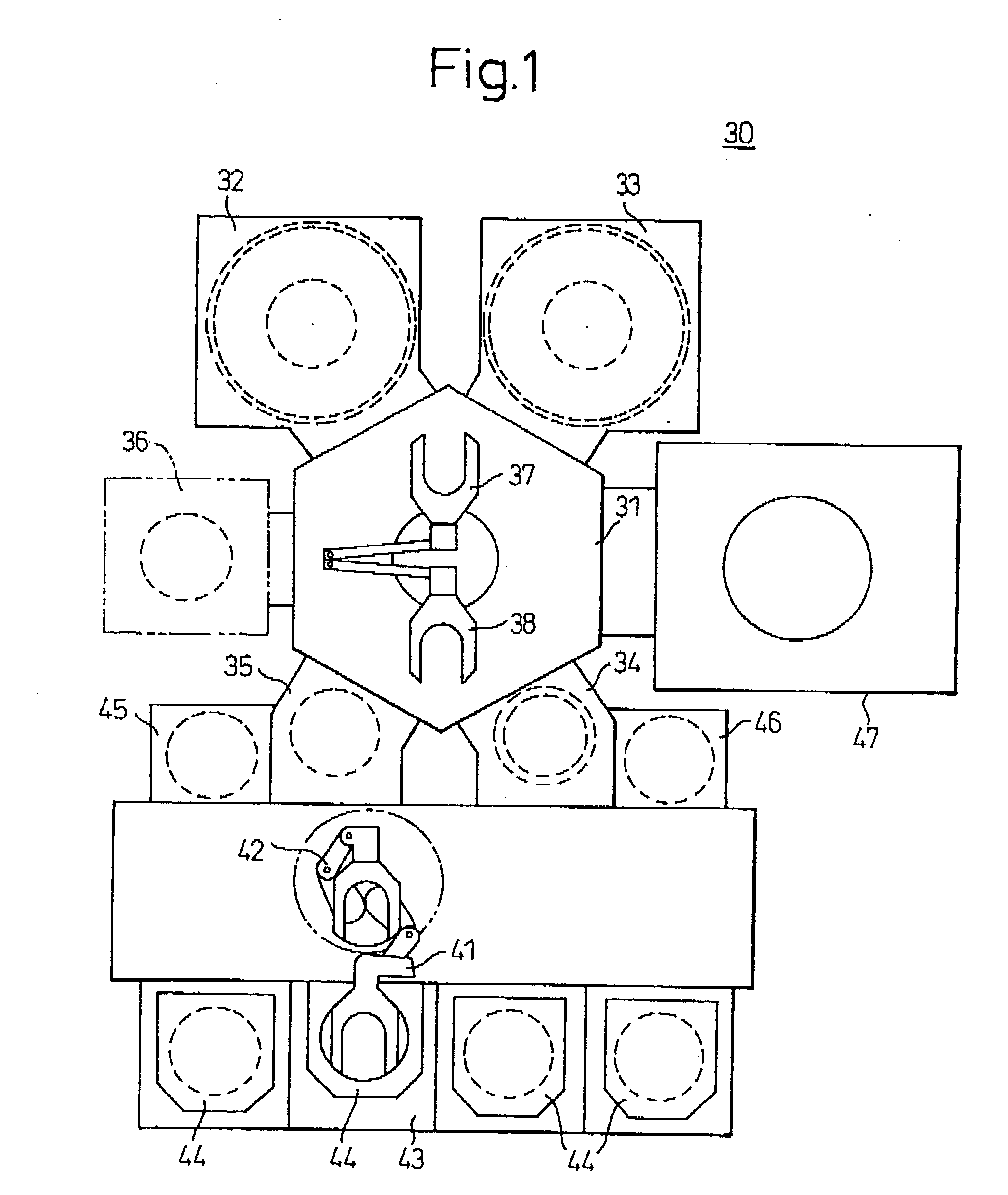

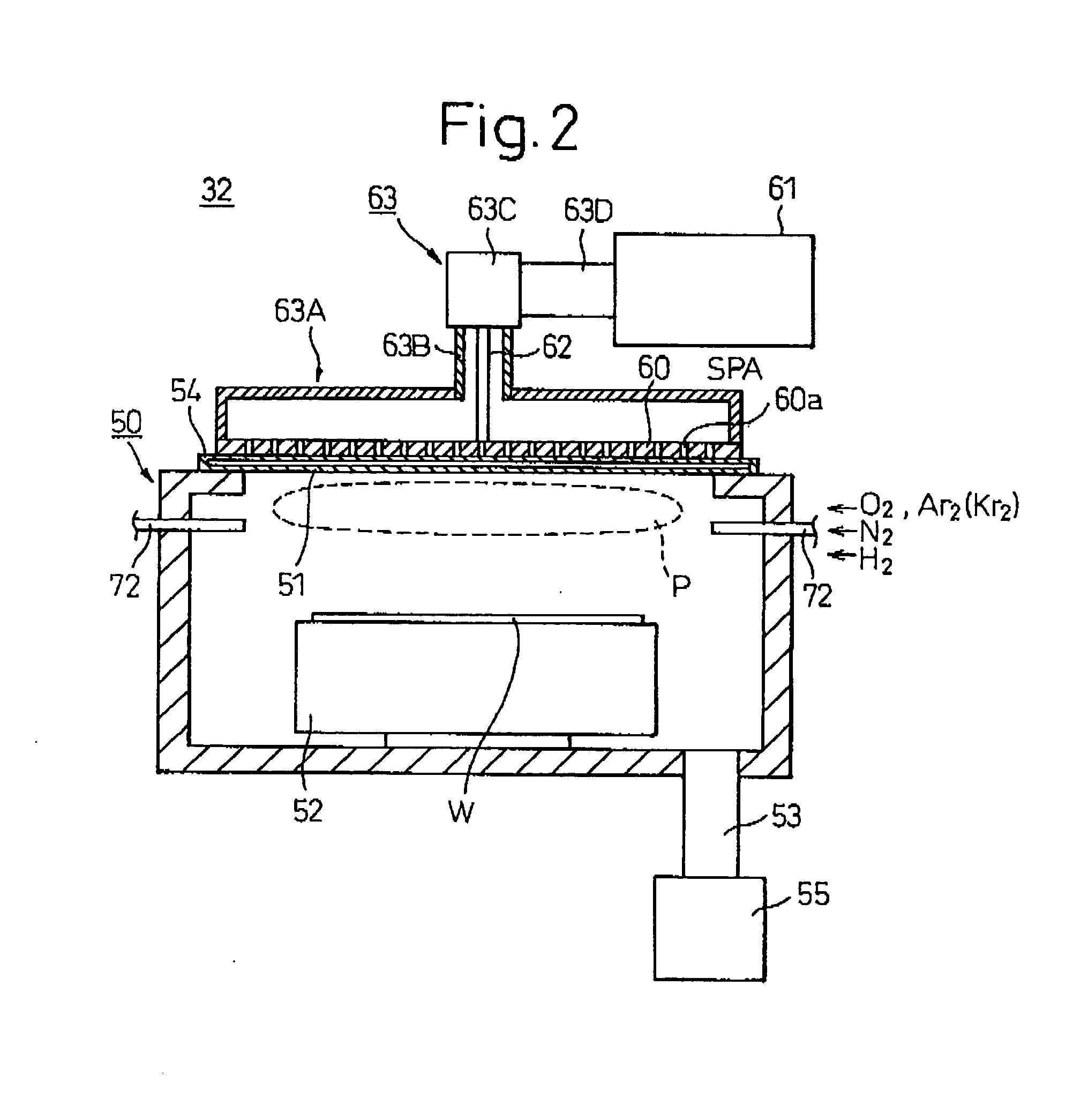

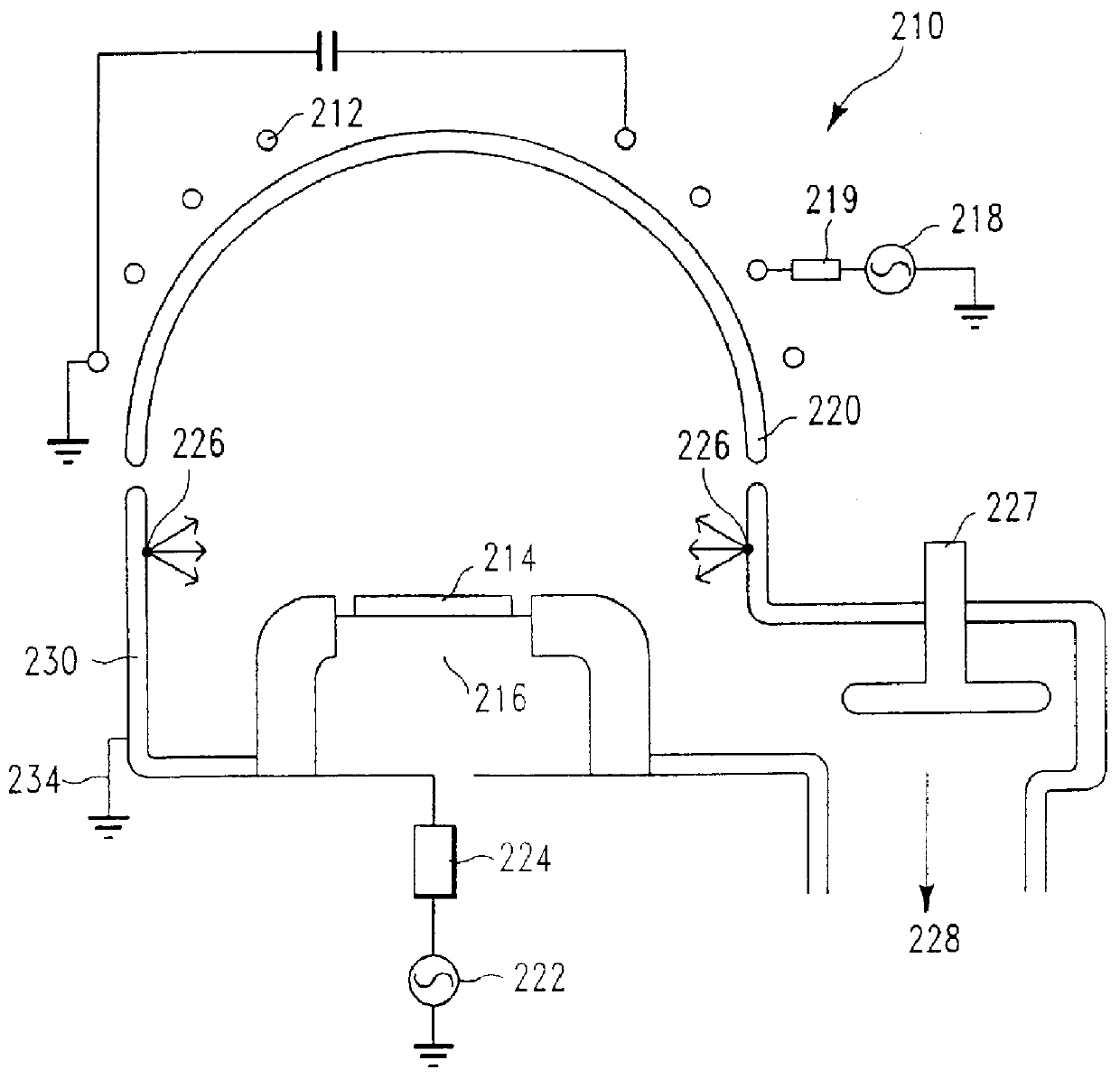

Method of producing electronic device material

InactiveUS20040048452A1High densityLow electron temperatureElectric discharge tubesSemiconductor/solid-state device manufacturingDevice materialEngineering

A process for producing an electronic device material of a high quality MOS-type semiconductor comprising an insulating layer and a semiconductor layer excellent in the electrical characteristic. The process includes: a step of CVD-treating a substrate to be processed comprising single-crystal silicon as a main component, to thereby form an insulating layer; and a step of exposing the substrate to be processed to a plasma which has been generated from a process gas on the basis of microwave irradiation via a plane antenna member having a plurality of slots, to thereby modify the insulating film by using the thus generated plasma.

Owner:TOKYO ELECTRON LTD

Method of manufacturing a semiconductor device

InactiveUS20070173000A1Improve business performanceImprove performanceTransistorSolid-state devicesDevice materialSmart Cut

There is provided a method of removing trap levels and defects, which are caused by stress, from a single crystal silicon thin film formed by an SOI technique. First, a single crystal silicon film is formed by using a typical bonding SOI technique such as Smart-Cut or ELTRAN. Next, the single crystal silicon thin film is patterned to form an island-like silicon layer, and then, a thermal oxidation treatment is carried out in an oxidizing atmosphere containing a halogen element, so that an island-like silicon layer in which the trap levels and the defects are removed is obtained.

Owner:SEMICON ENERGY LAB CO LTD

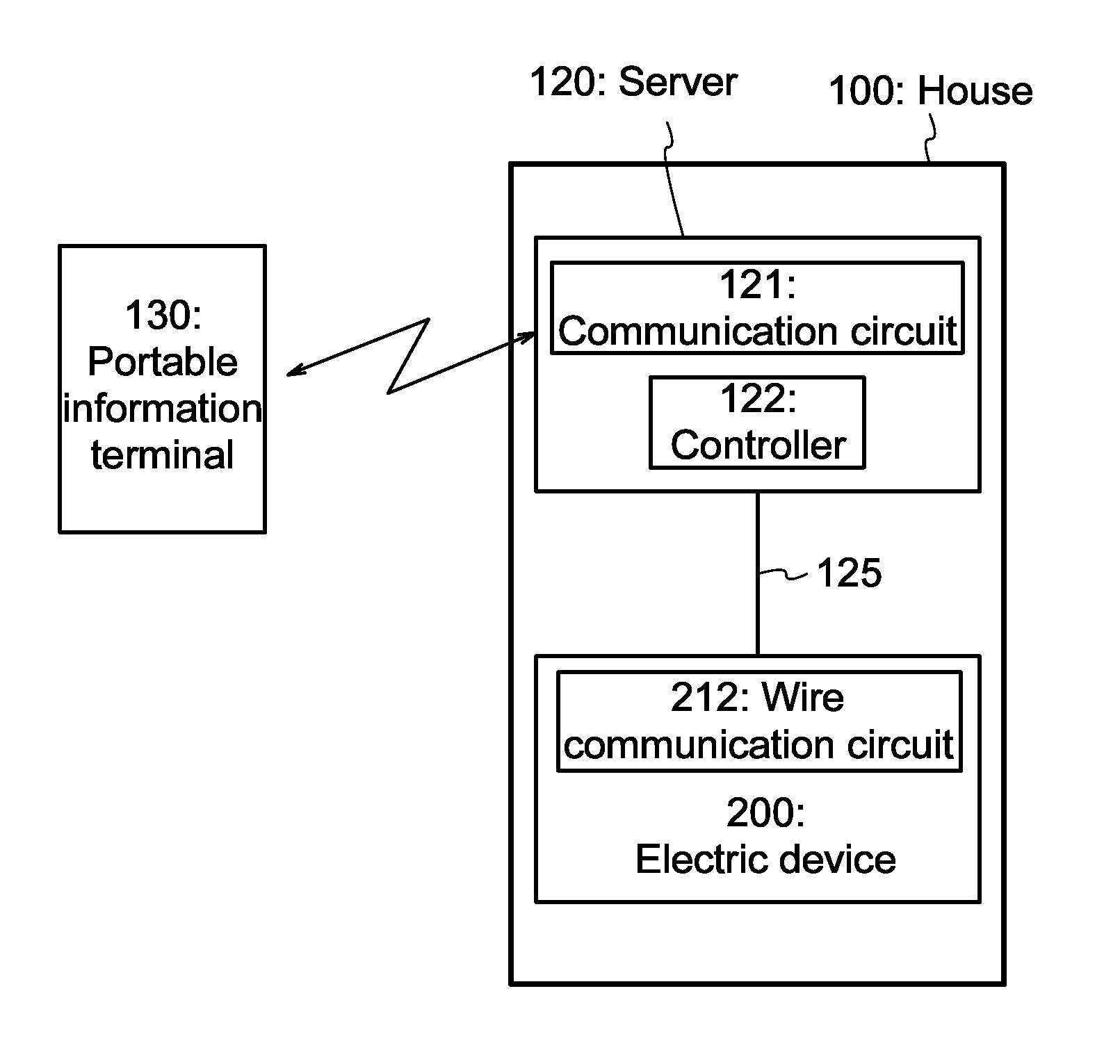

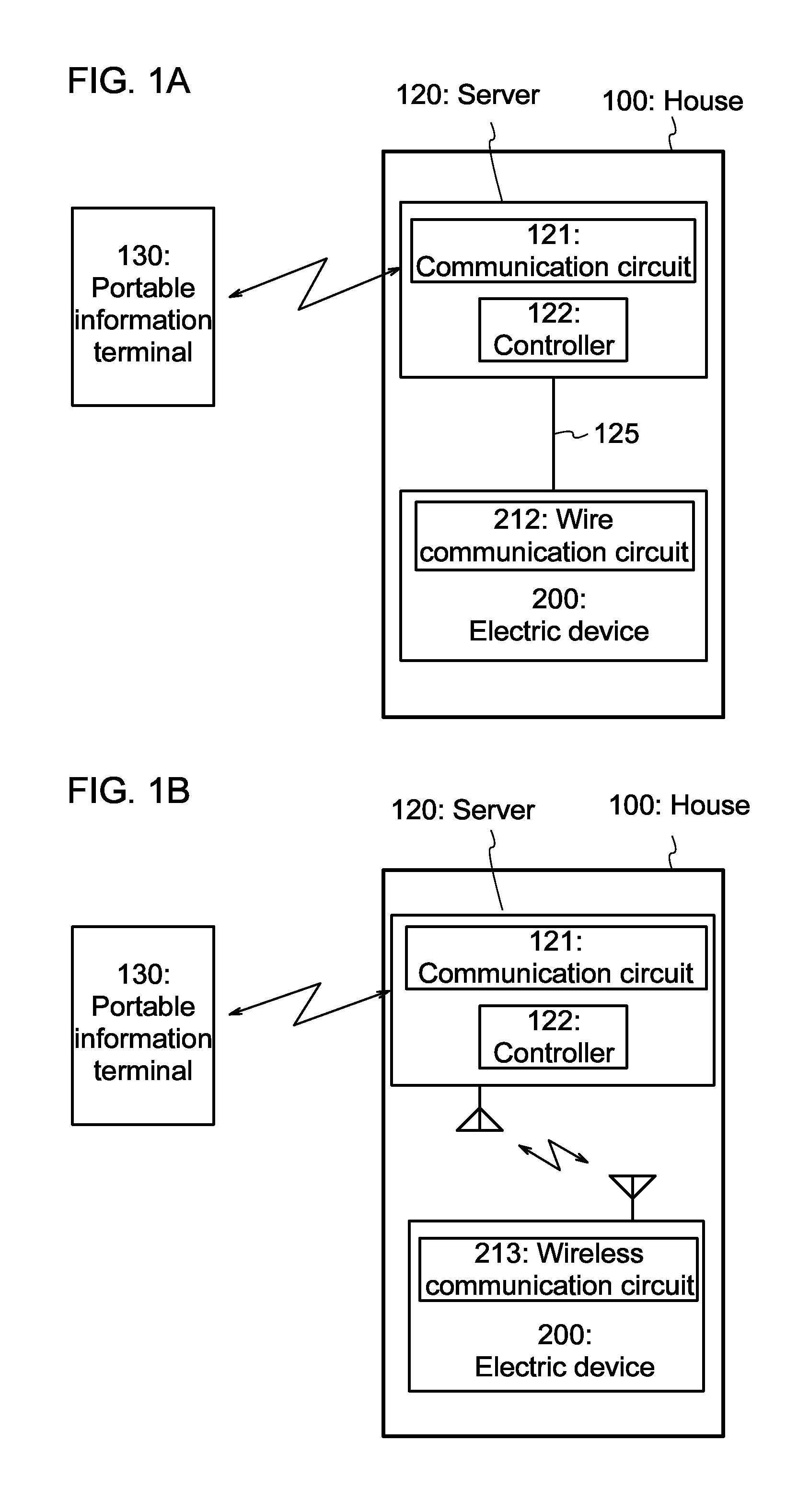

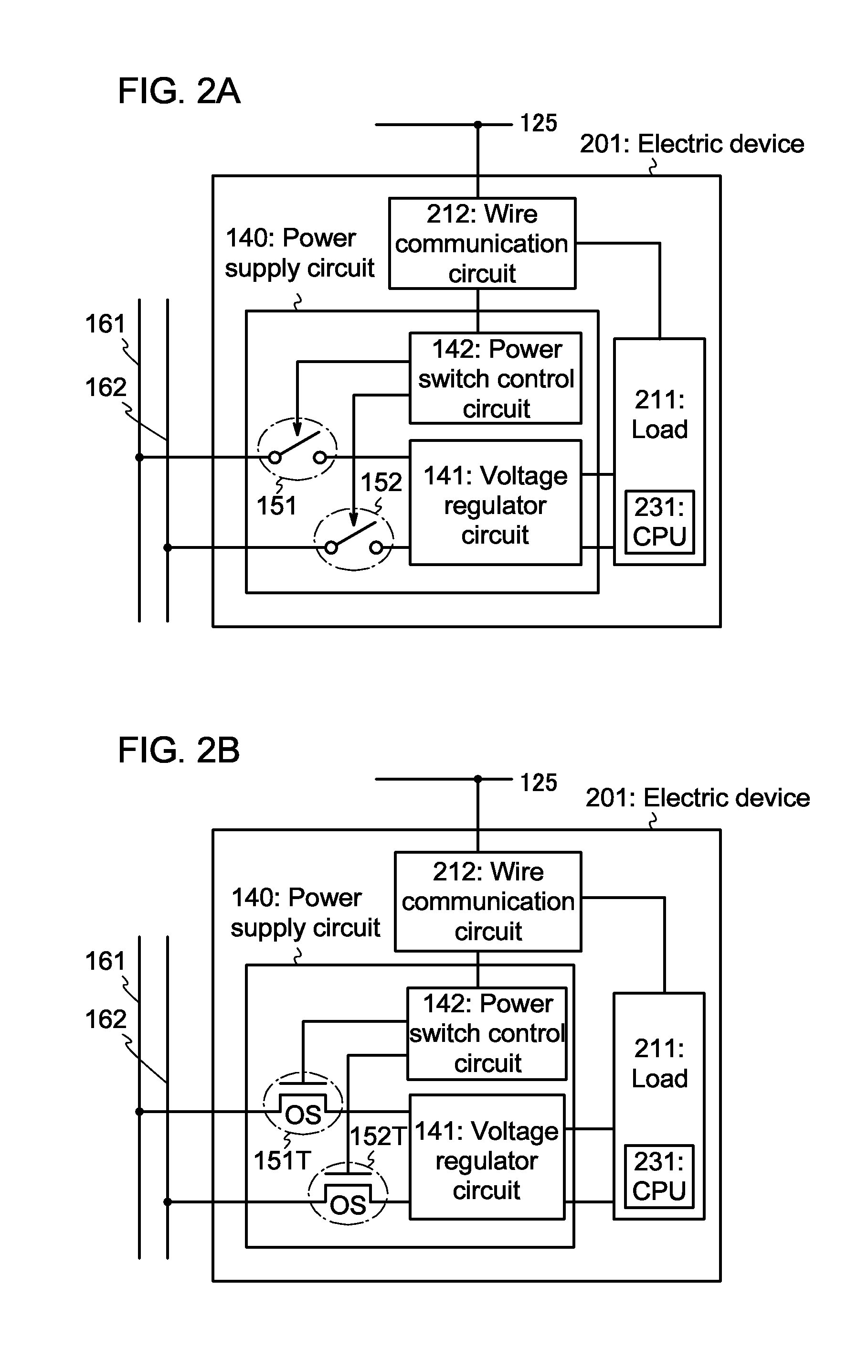

Remote control system

ActiveUS20140009270A1Total current dropReduce power consumptionTransistorElectric signal transmission systemsRemote controlComputer terminal

Provided is a remote control system with which leakage current flowing in a switch can be reduced so that power consumption can be reduced. The remote control system includes a portable information terminal, a server, and an electric device. The on / off of the switch included in the electric device is controlled using information transmitted from the portable information terminal to the server. The switch includes a transistor formed using a semiconductor whose band gap is larger than that of single crystal silicon in a channel formation region.

Owner:SEMICON ENERGY LAB CO LTD

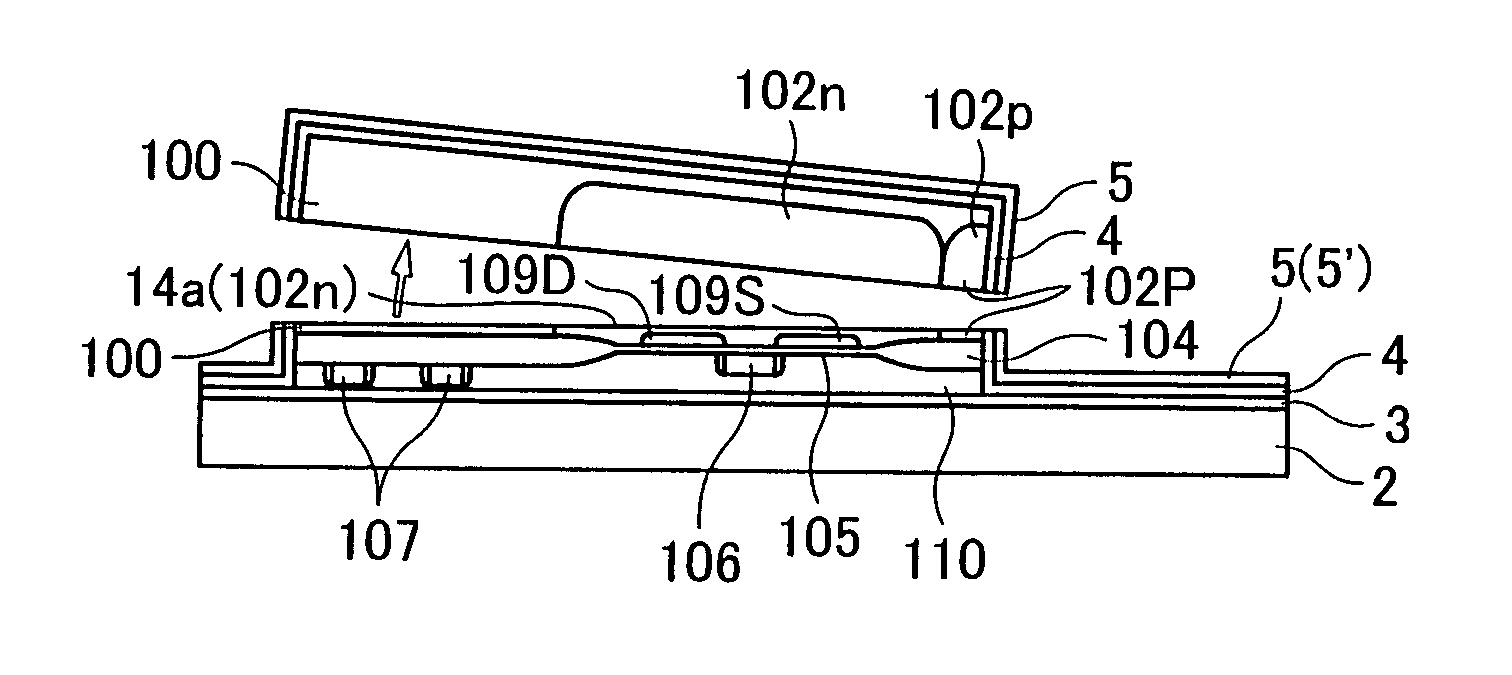

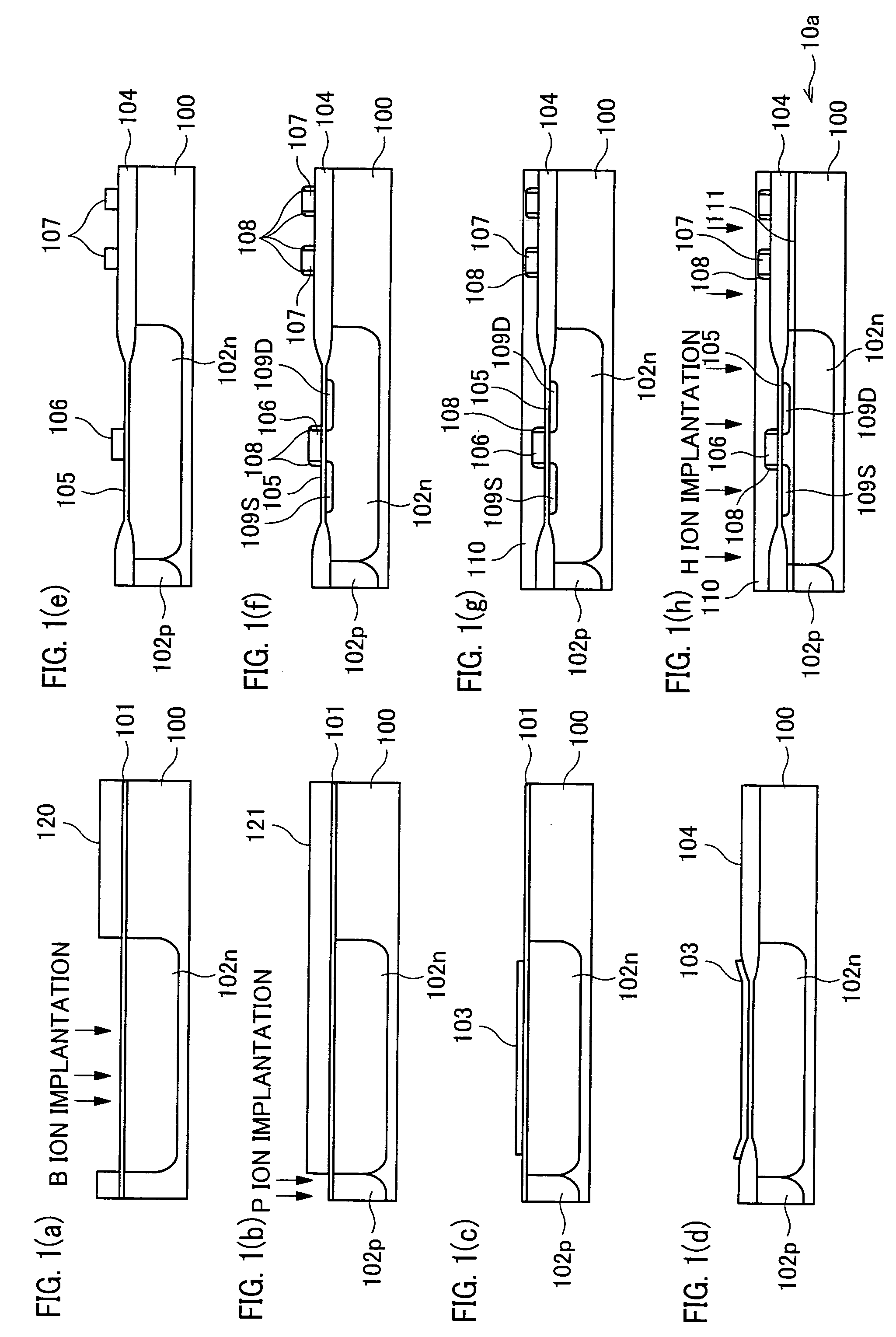

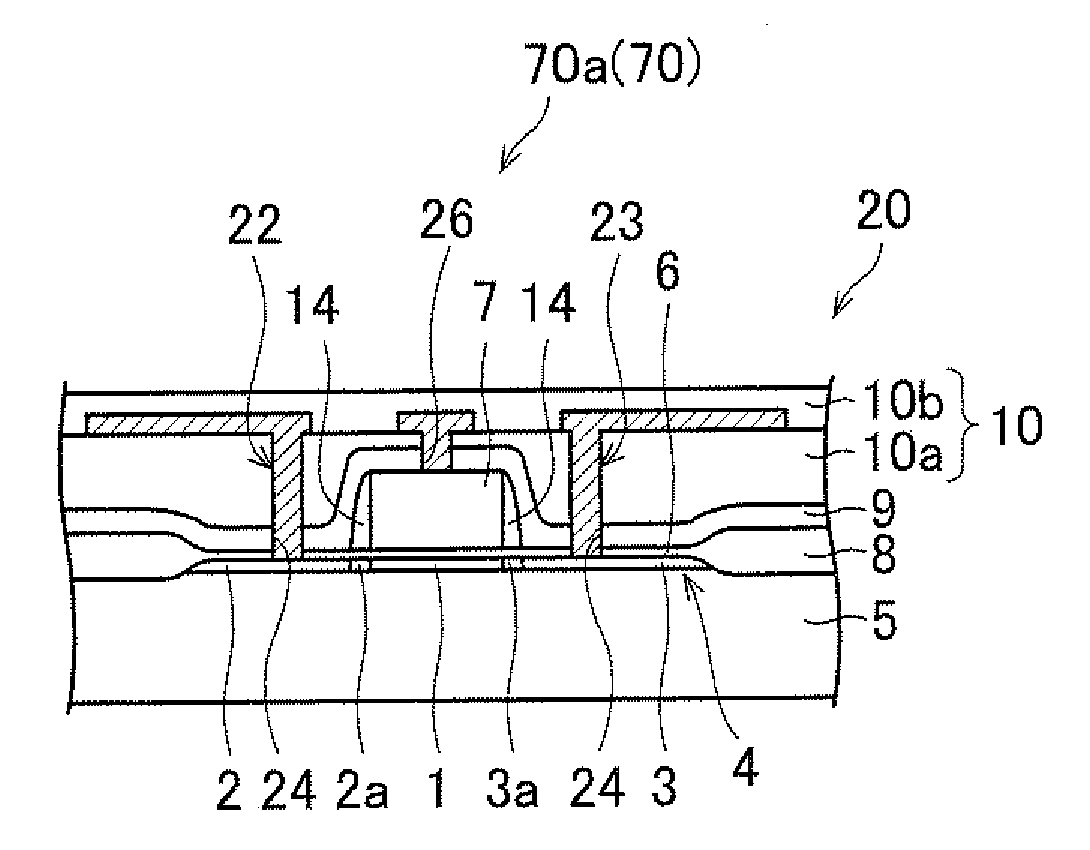

Semiconductor device and fabrication method for the same

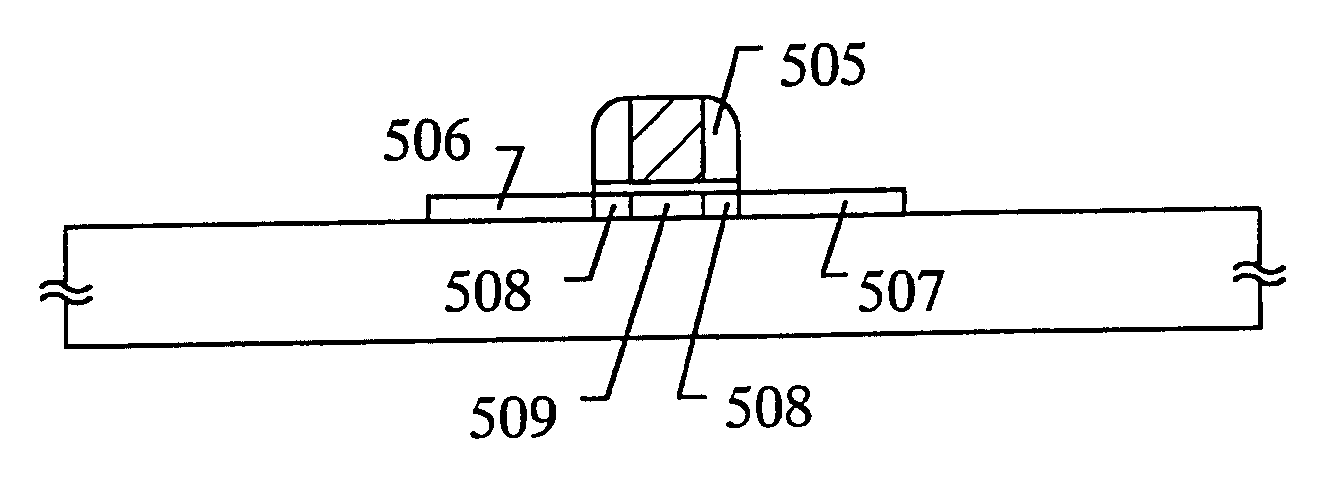

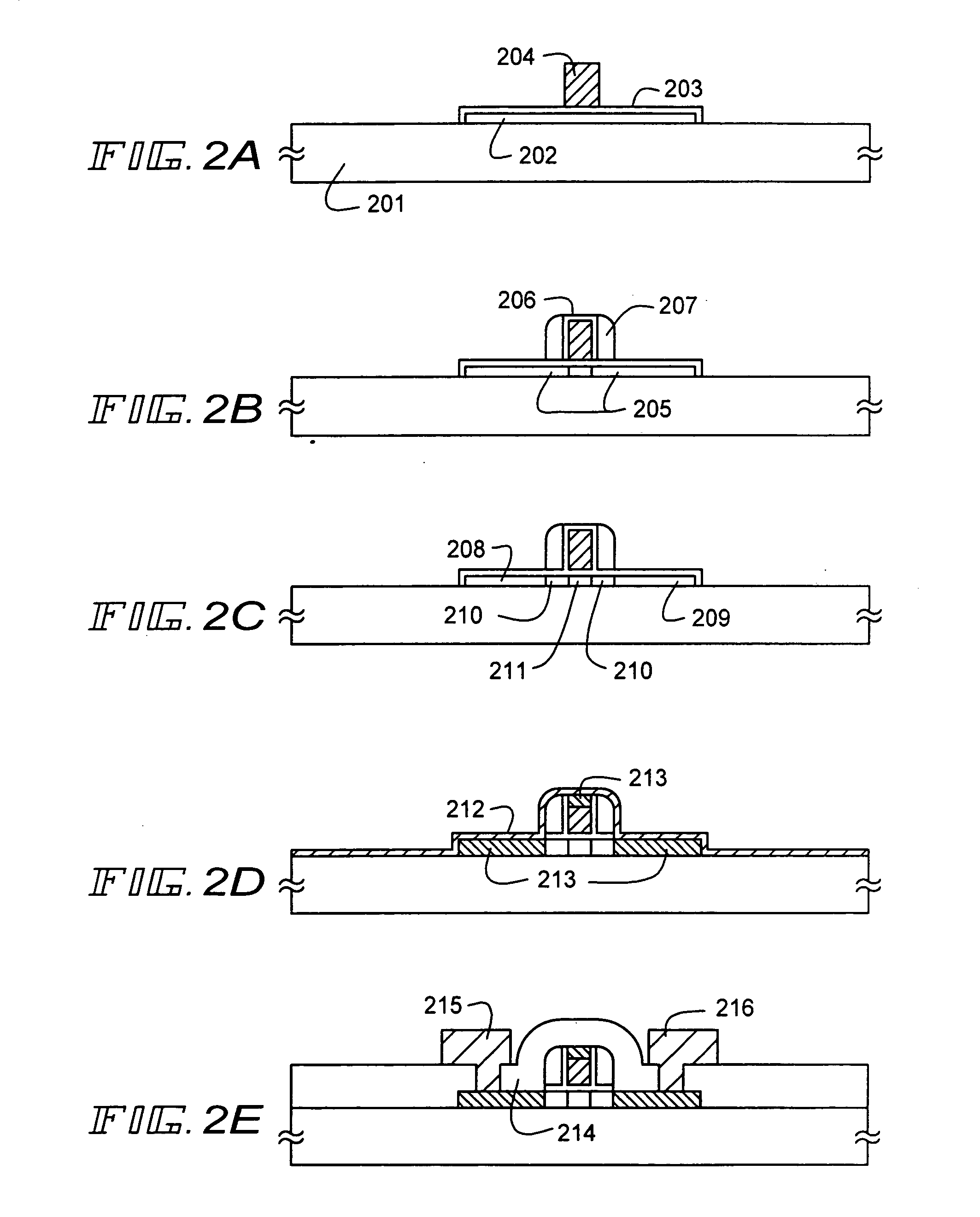

InactiveUS7205204B2Secure performanceImprove reliabilityTransistorSemiconductor/solid-state device detailsLOCOSSingle crystal

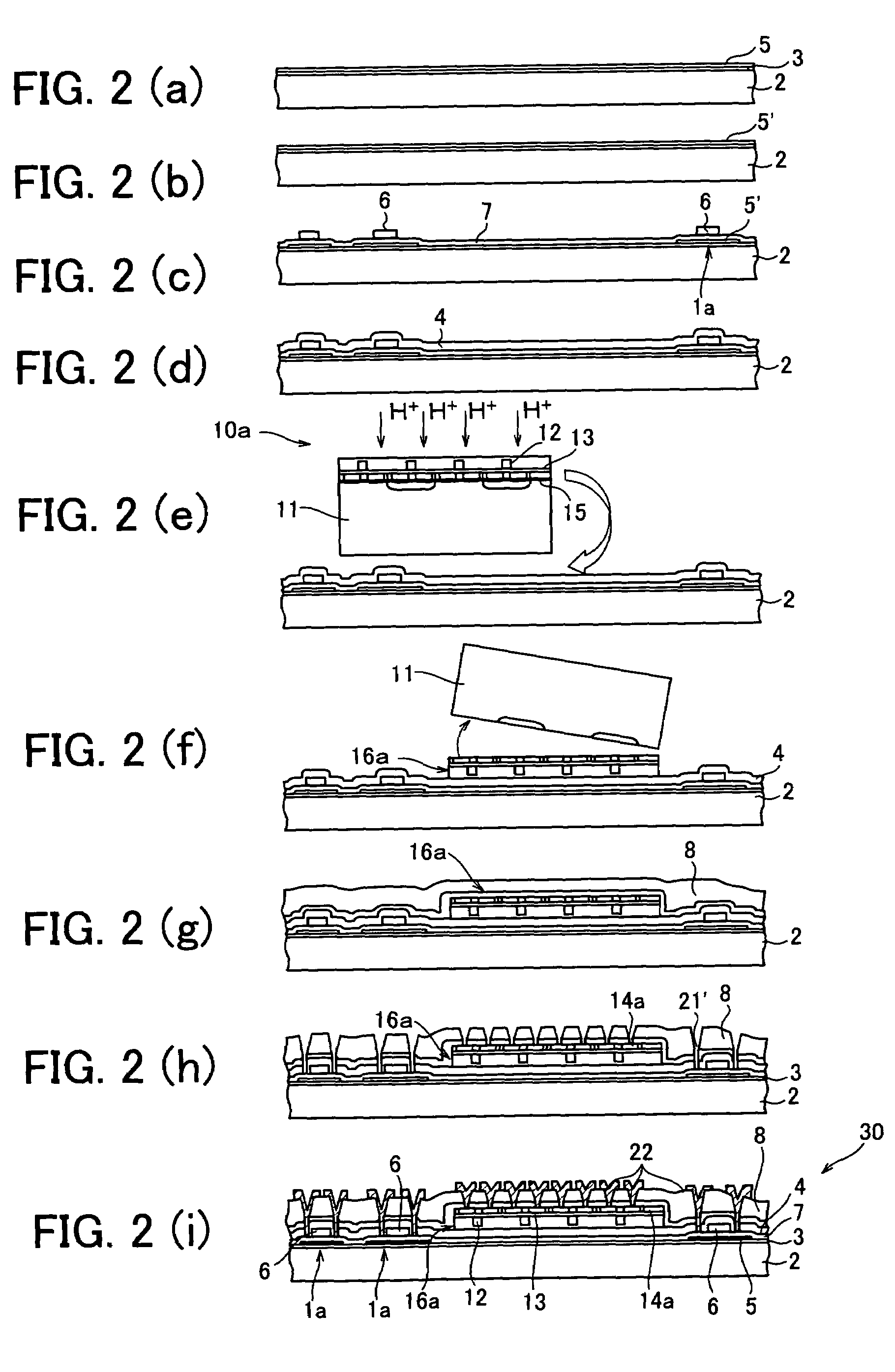

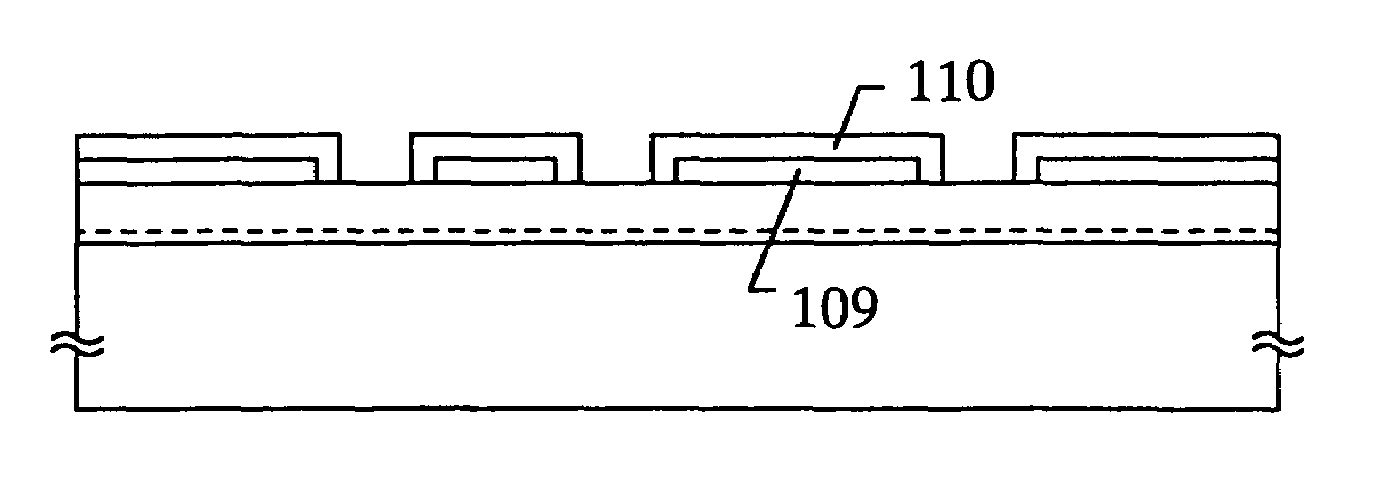

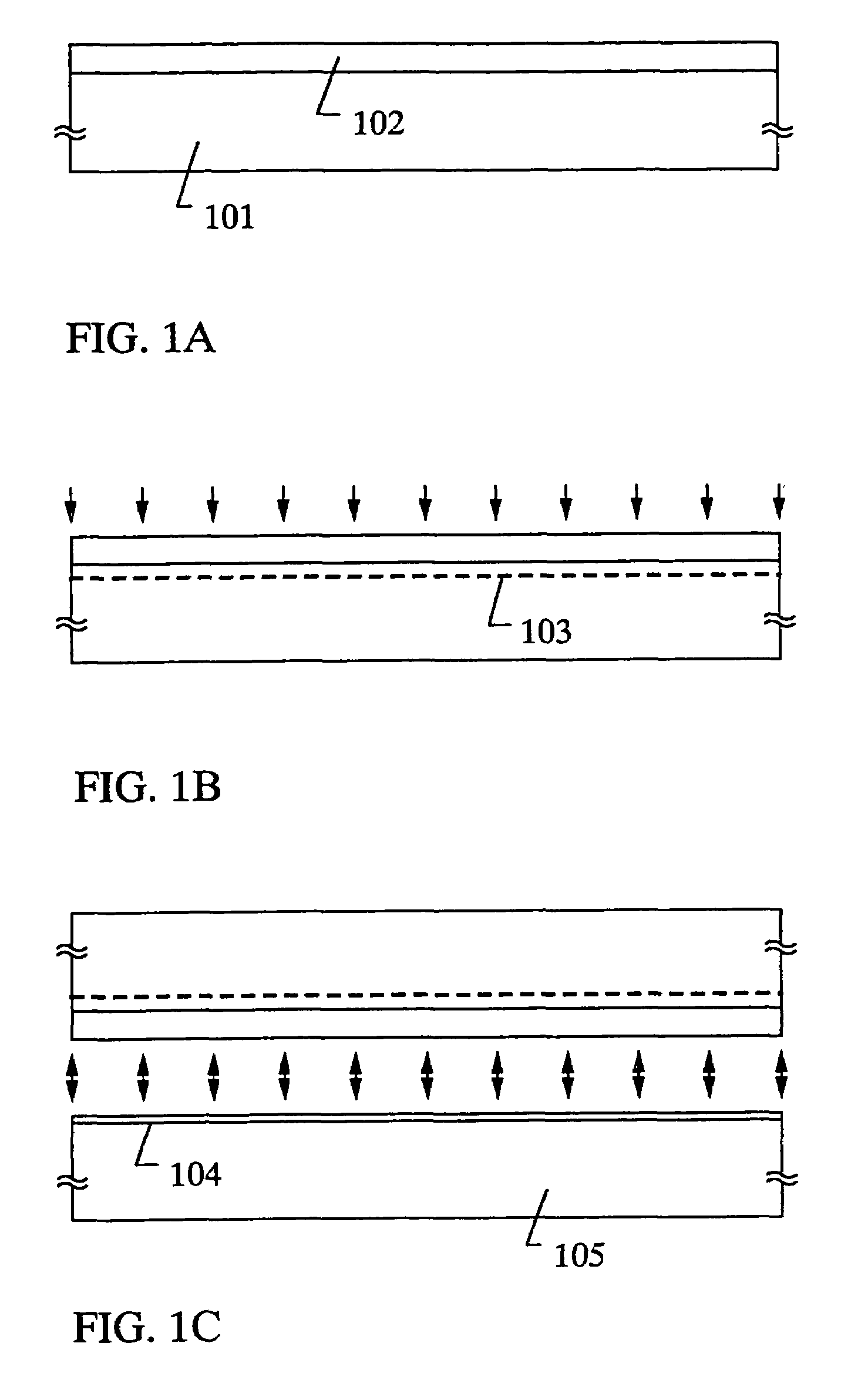

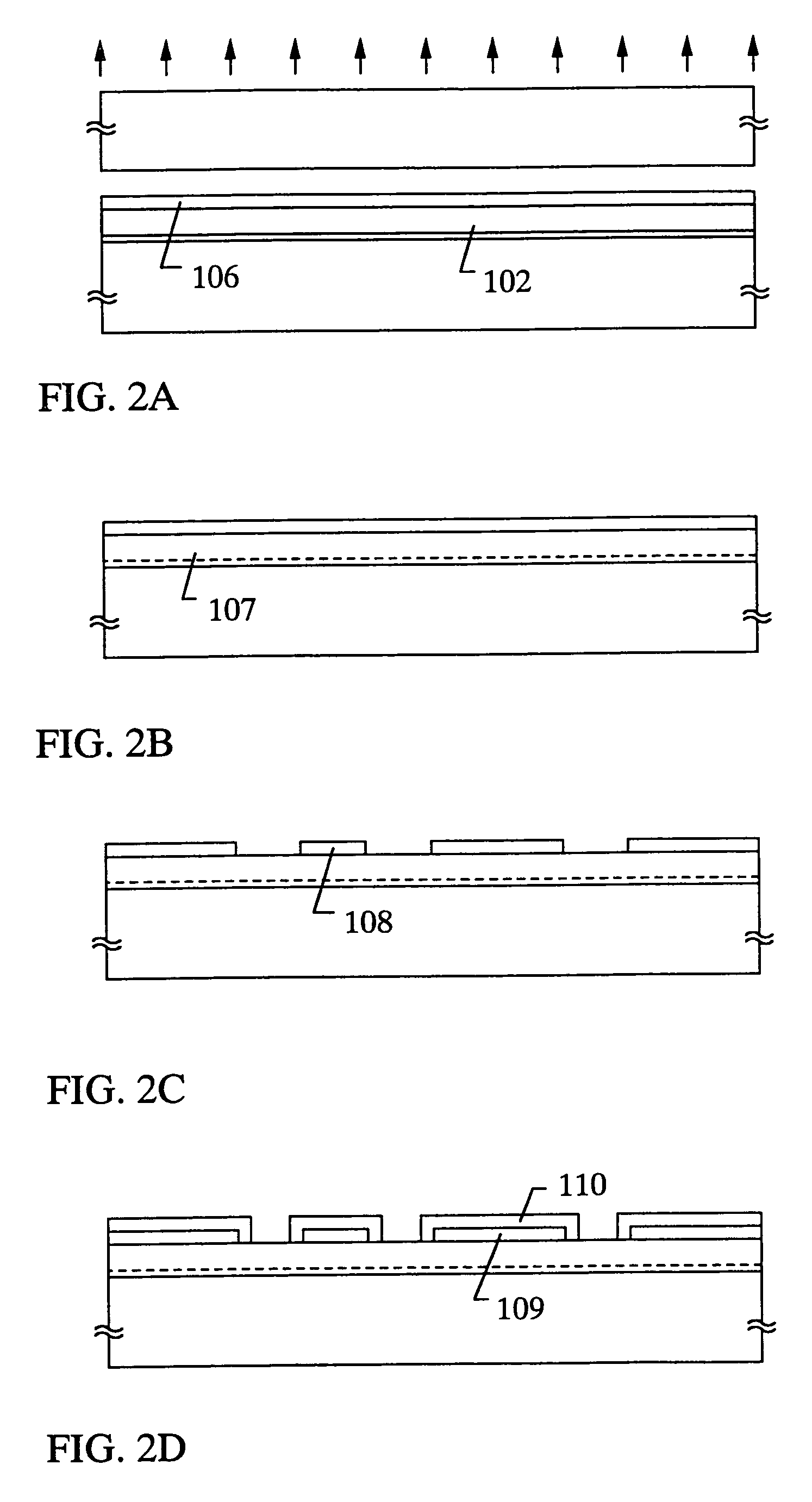

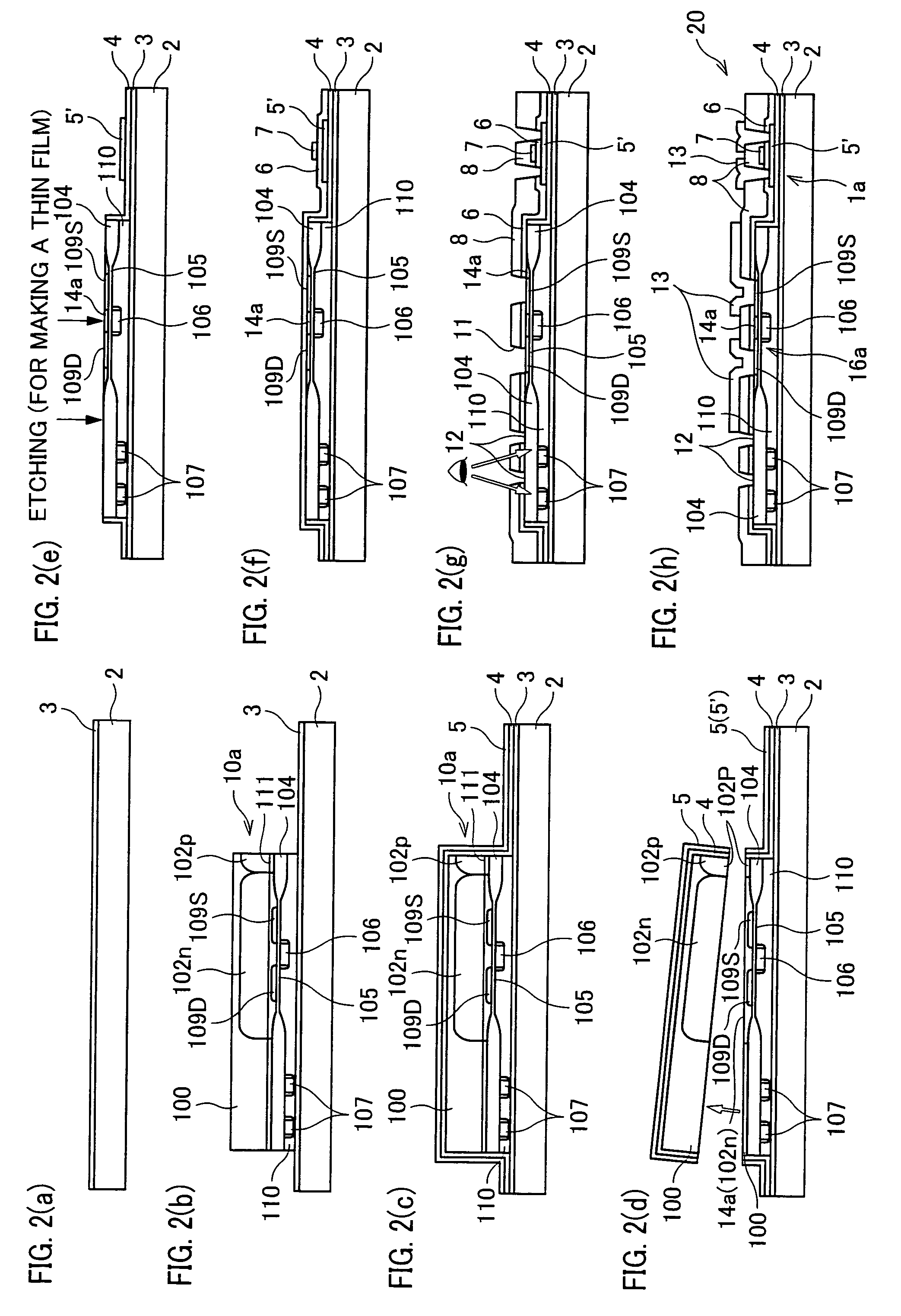

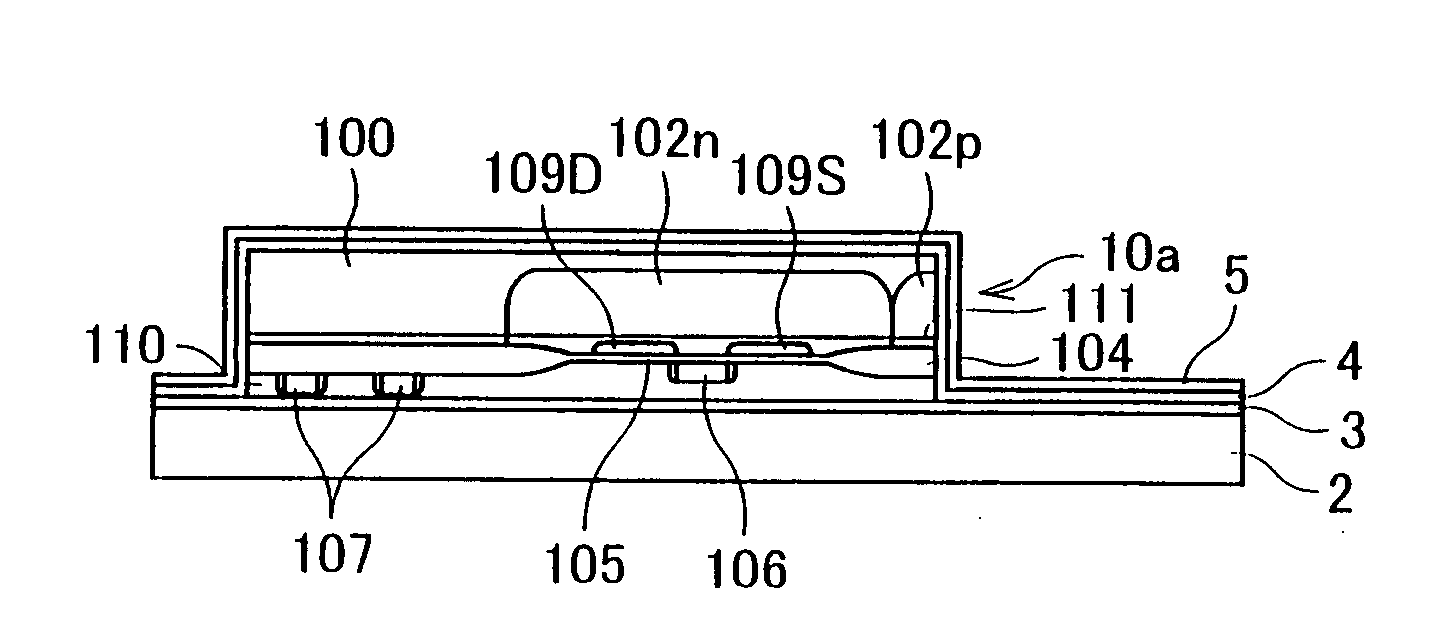

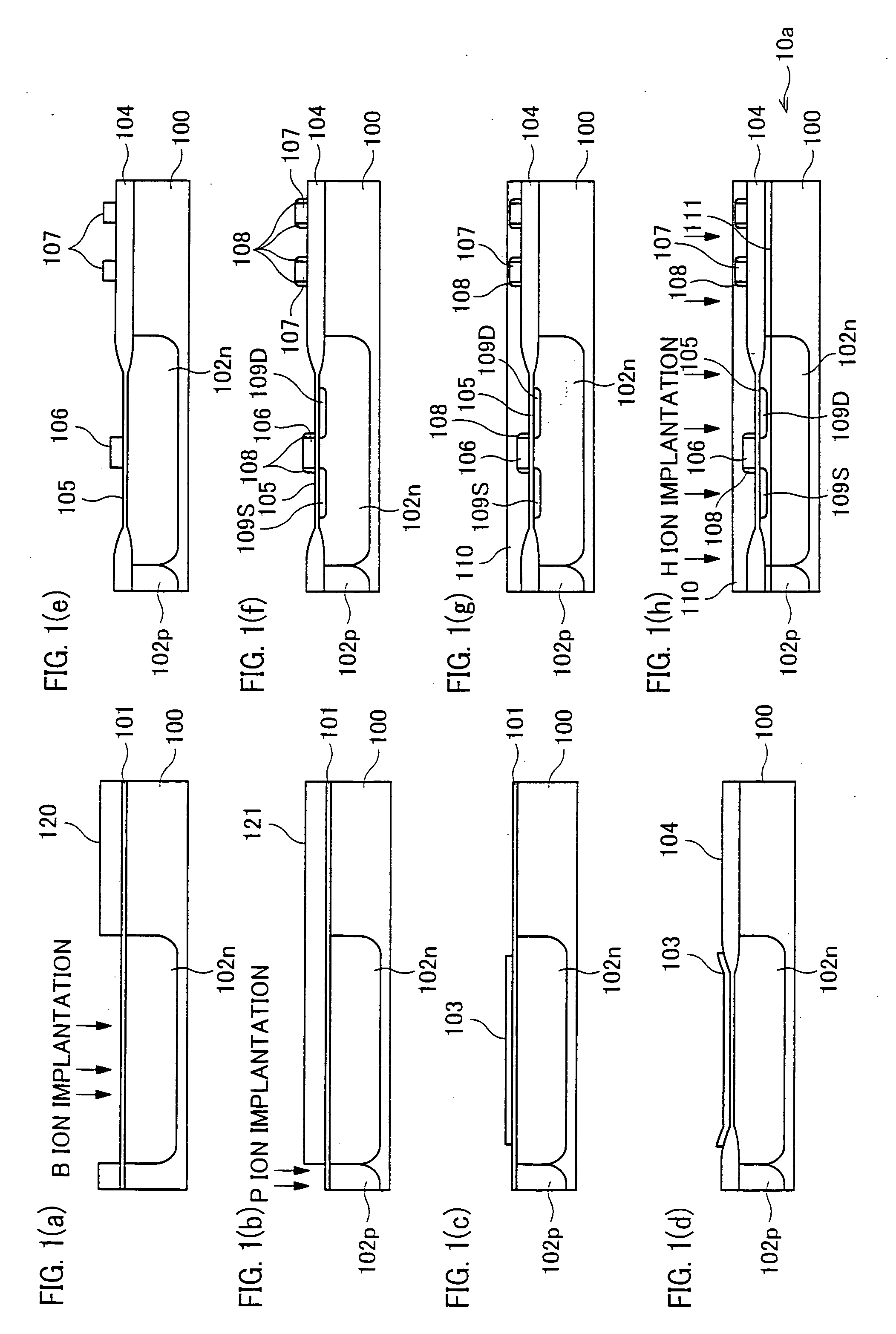

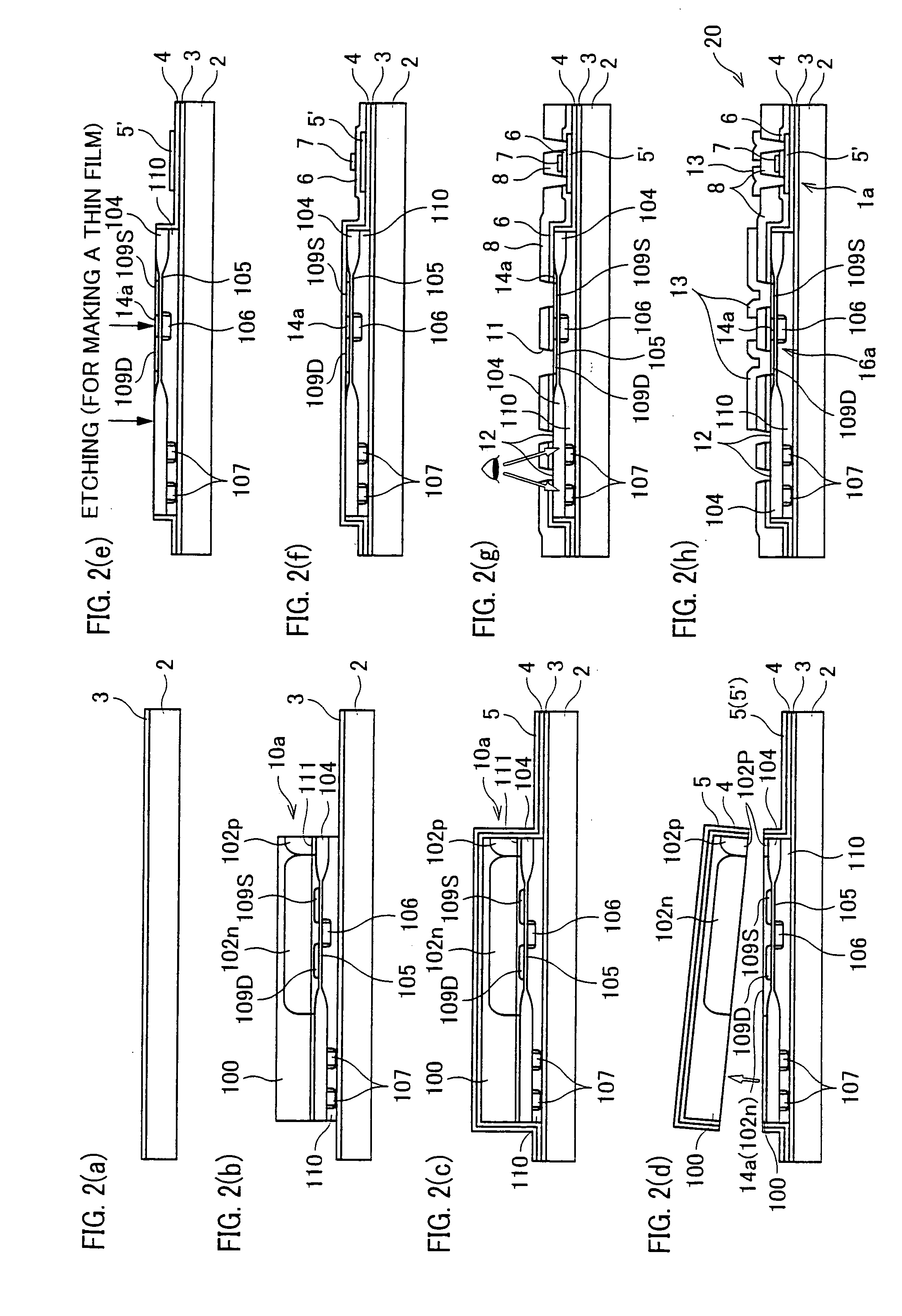

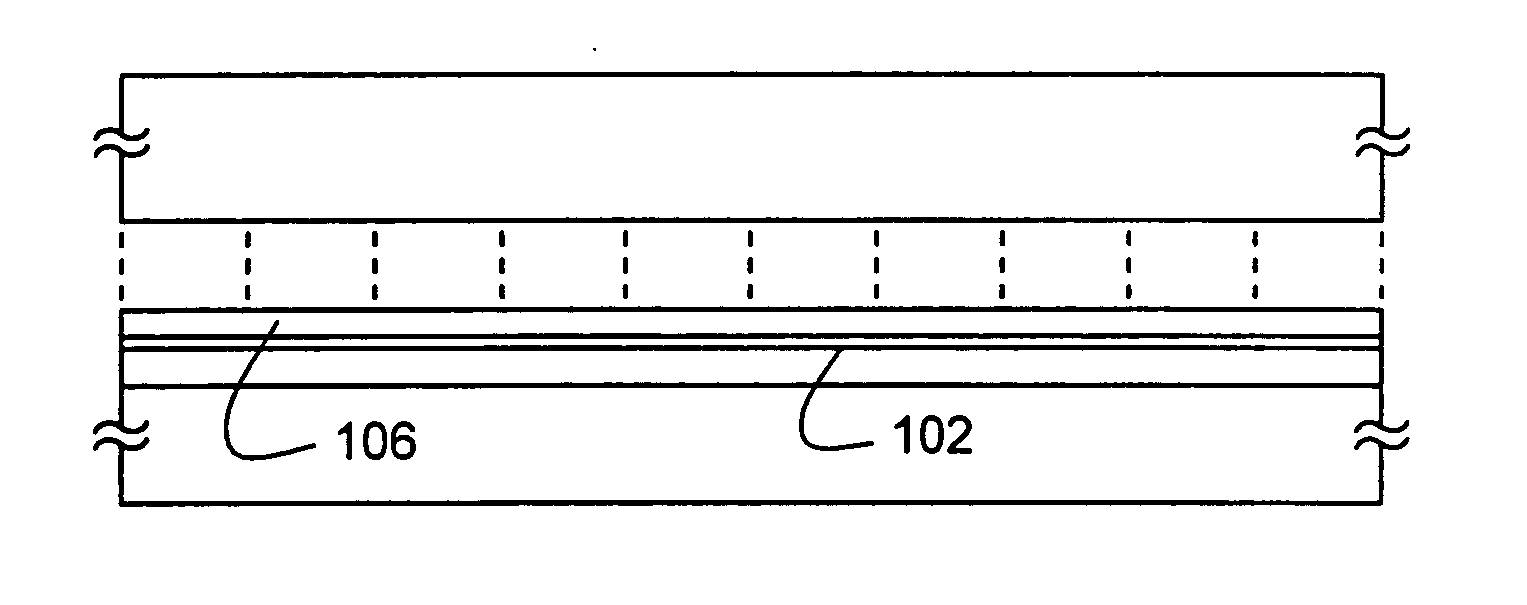

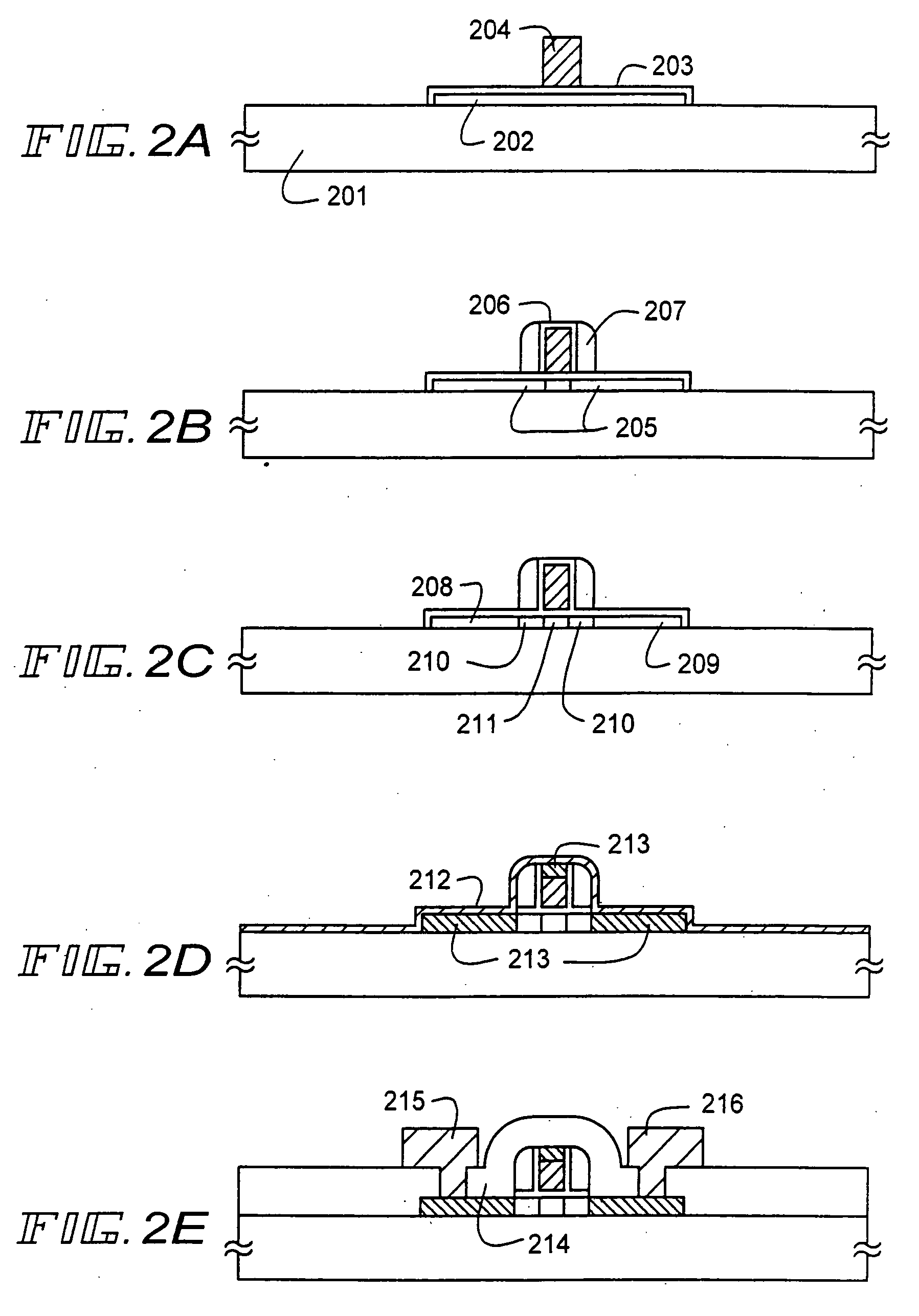

In a semiconductor device including a monocrystalline thin film transistor 16a that has been formed on a monocrystalline Si wafer 100 and then is transferred to a insulating substrate 2, LOCOS oxidization is performed with respect to the element-isolation region of the monocrystalline Si wafer 100 so as to create a field oxide film (SiO2 film) 104, and a marker 107 is formed on the field oxide film 104. With this structure, alignment of components may be performed based on a gate electrode 106 upon or after the transfer step.

Owner:SHARP KK

Semiconductor device and fabrication method for the same

InactiveUS20070108523A1Secure performanceImprove reliabilityTransistorSemiconductor/solid-state device detailsDevice materialLOCOS

In a semiconductor device including a monocrystalline thin film transistor 16a that has been formed on a monocrystalline Si wafer 100 and then is transferred to a insulating substrate 2, LOCOS oxidization is performed with respect to the element-isolation region of the monocrystalline Si wafer 100 so as to create a field oxide film (SiO2 film) 104, and a marker 107 is formed on the field oxide film 104. With this structure, alignment of components may be performed based on a gate electrode 106 upon or after the transfer step.

Owner:SHARP KK

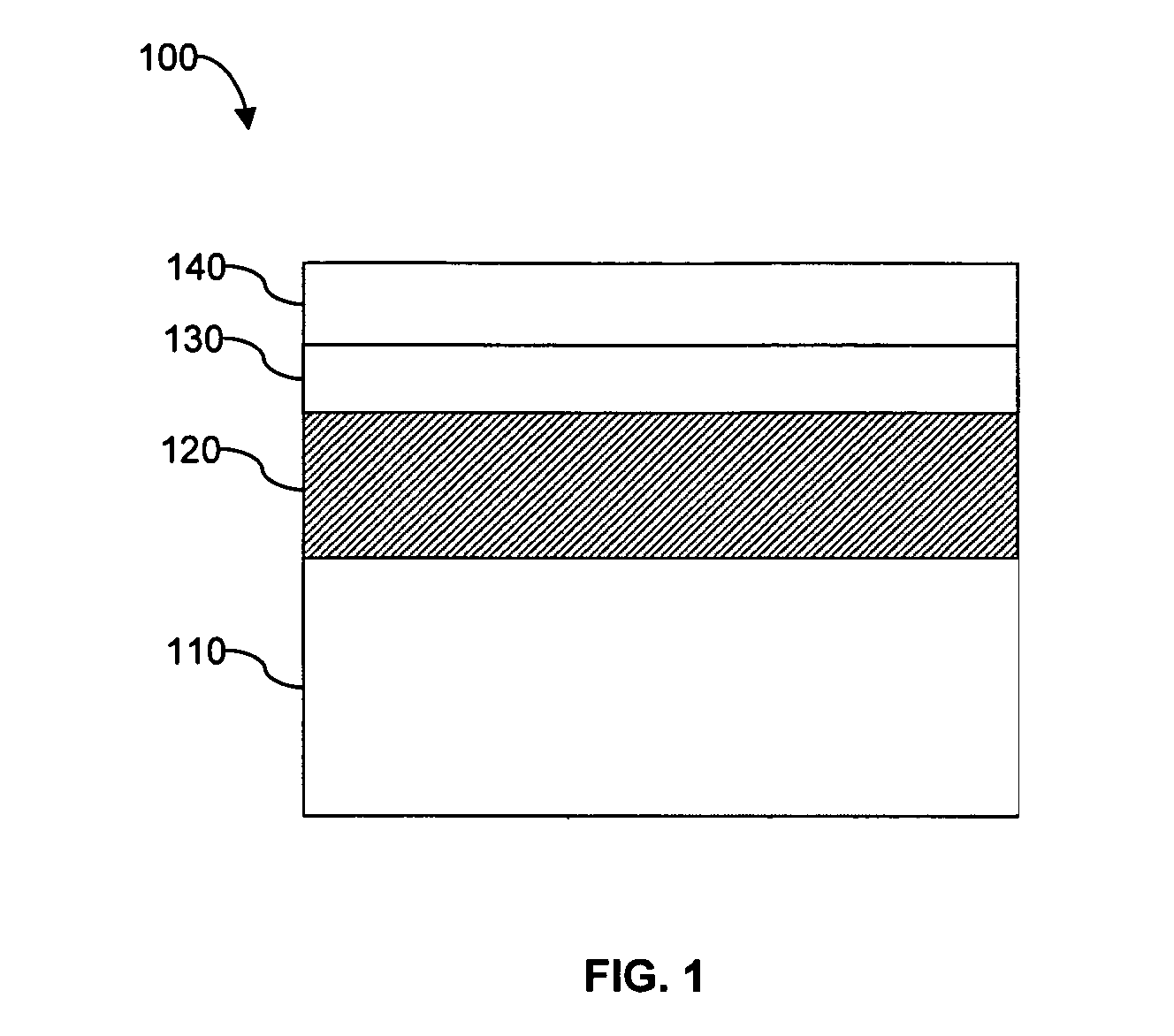

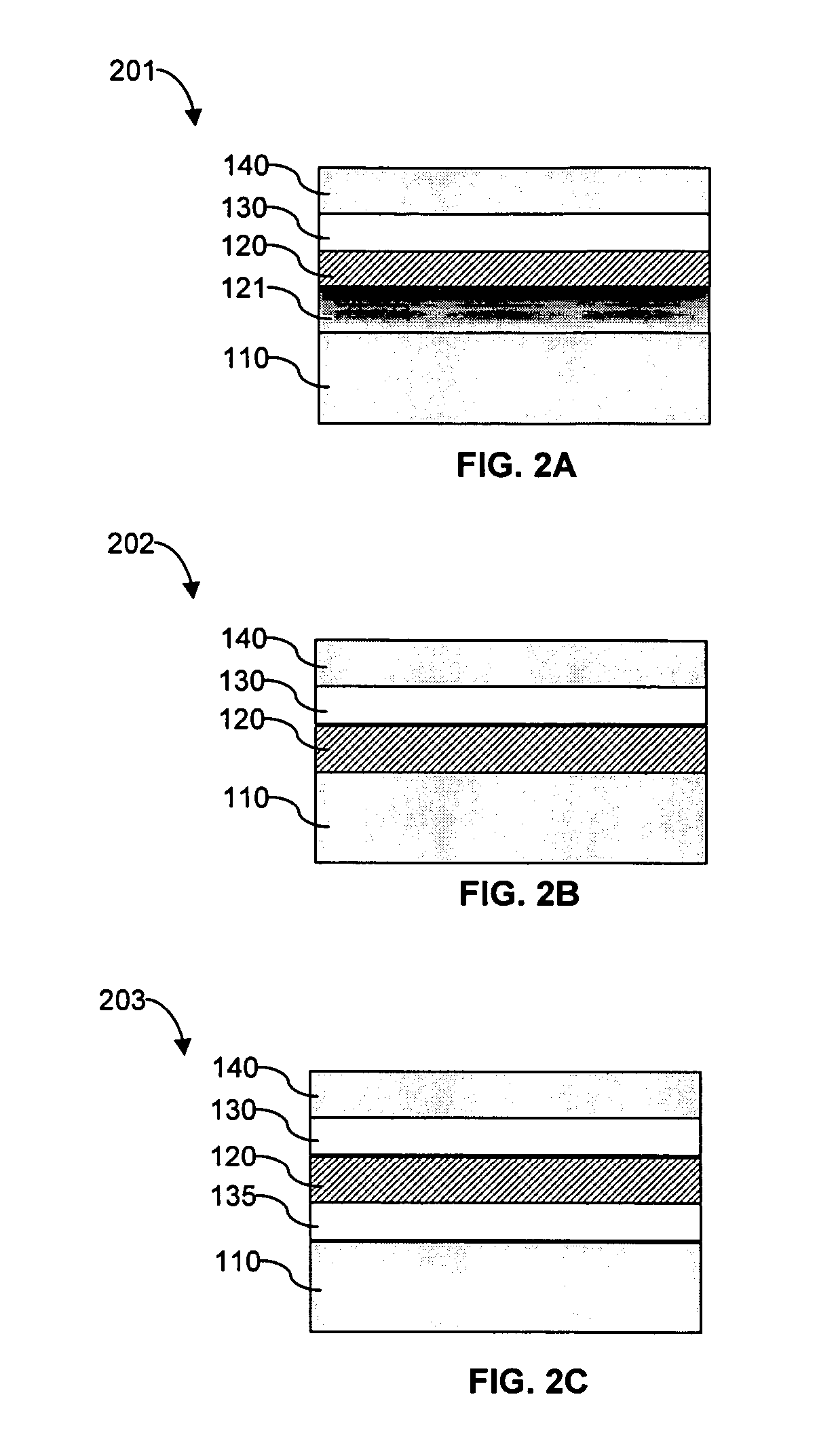

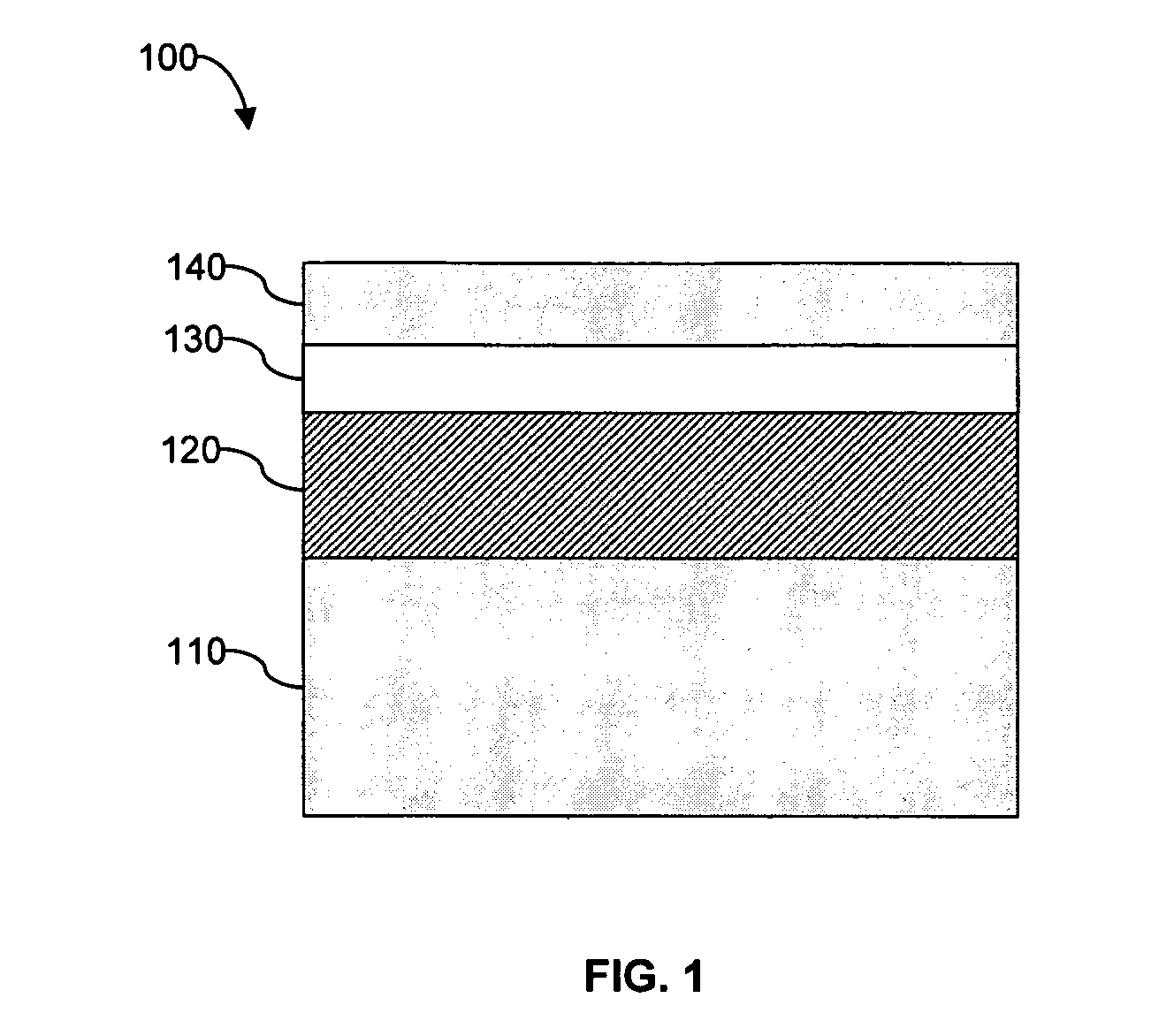

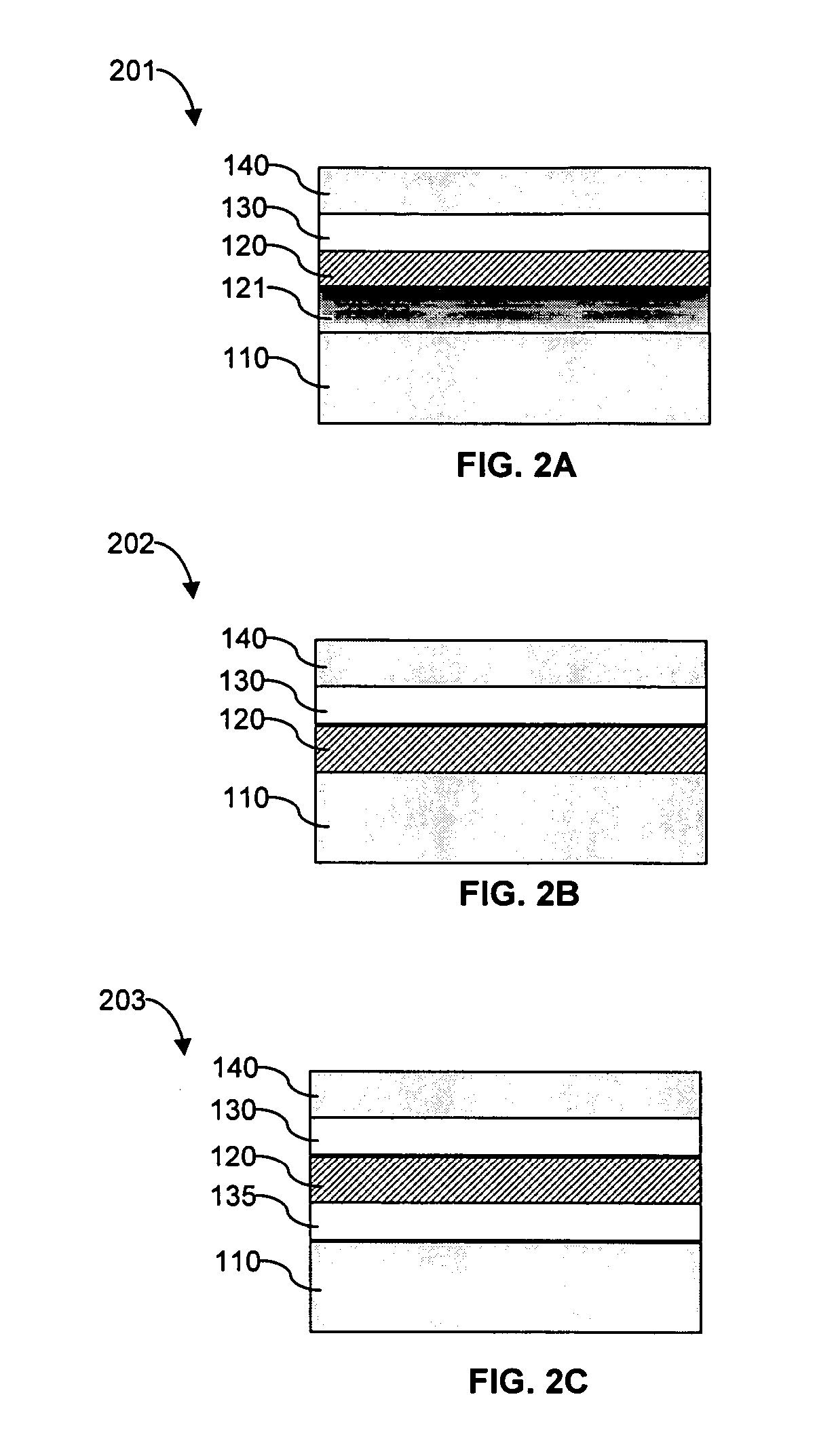

Monolithically integrated light emitting devices

ActiveUS7535089B2Layered productsSemiconductor/solid-state device detailsSingle crystalLattice constant

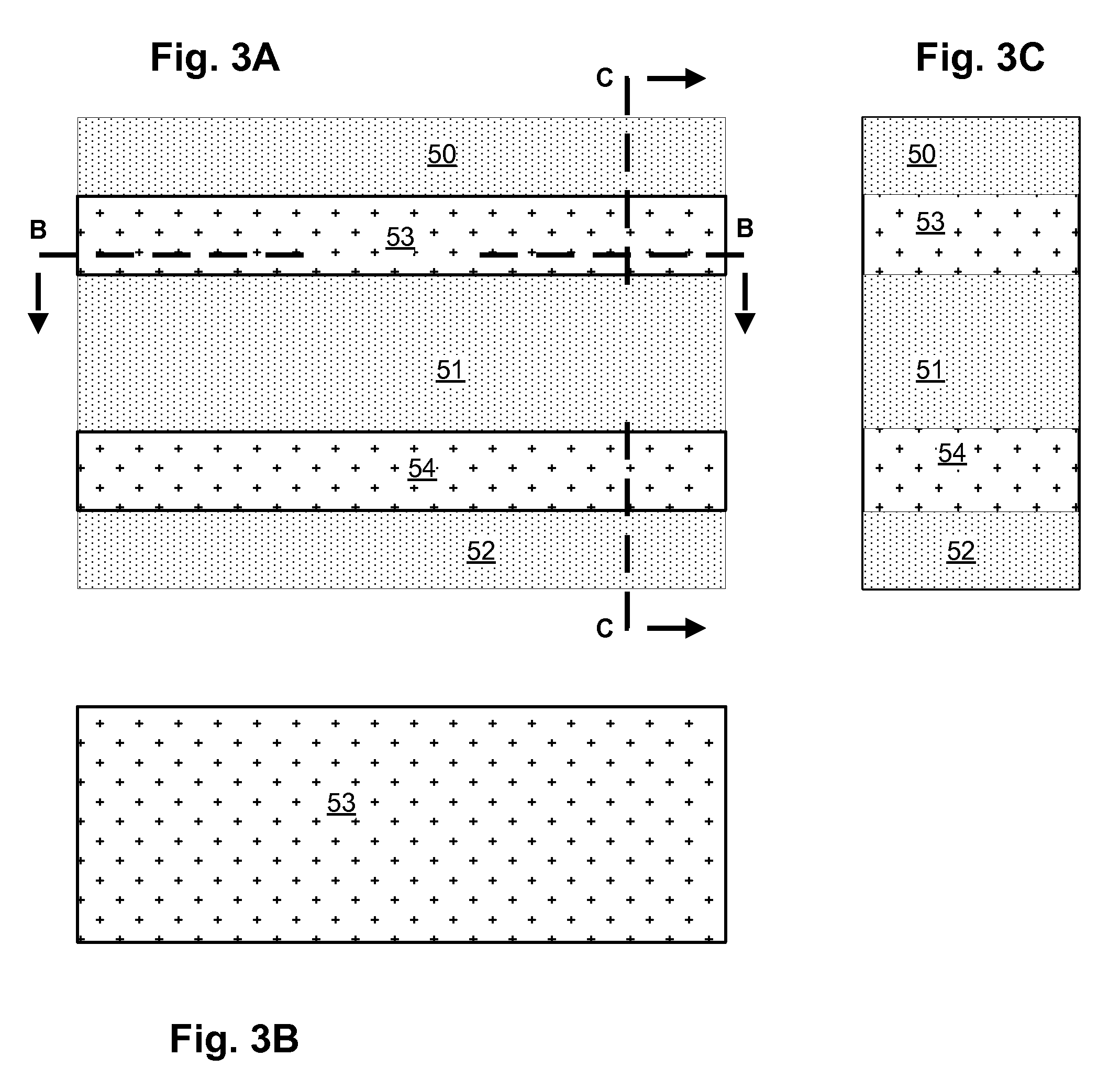

Methods and structures for monolithically integrating monocrystalline silicon and monocrystalline non-silicon materials and devices are provided. In one structure, a monolithically integrated semiconductor device structure comprises a silicon substrate and a first monocrystalline semiconductor layer disposed over the silicon substrate, wherein the first monocrystalline semiconductor layer has a lattice constant different from a lattice constant of relaxed silicon. The structure further includes an insulating layer disposed over the first monocrystalline semiconductor layer in a first region and a monocrystalline silicon layer disposed over the insulating layer in the first region. The structure includes at least one silicon-based electronic device including an element including at least a portion of the monocrystalline silicon layer. The structure also includes a second monocrystalline semiconductor layer disposed over at least a portion of the first monocrystalline semiconductor layer in a second region and absent from the first region, wherein the second monocrystalline semiconductor layer has a lattice constant different from the lattice constant of relaxed silicon. The structure includes at least one III-V light-emitting device including an active region including at least a portion of the second monocrystalline semiconductor layer.

Owner:MASSACHUSETTS INST OF TECH

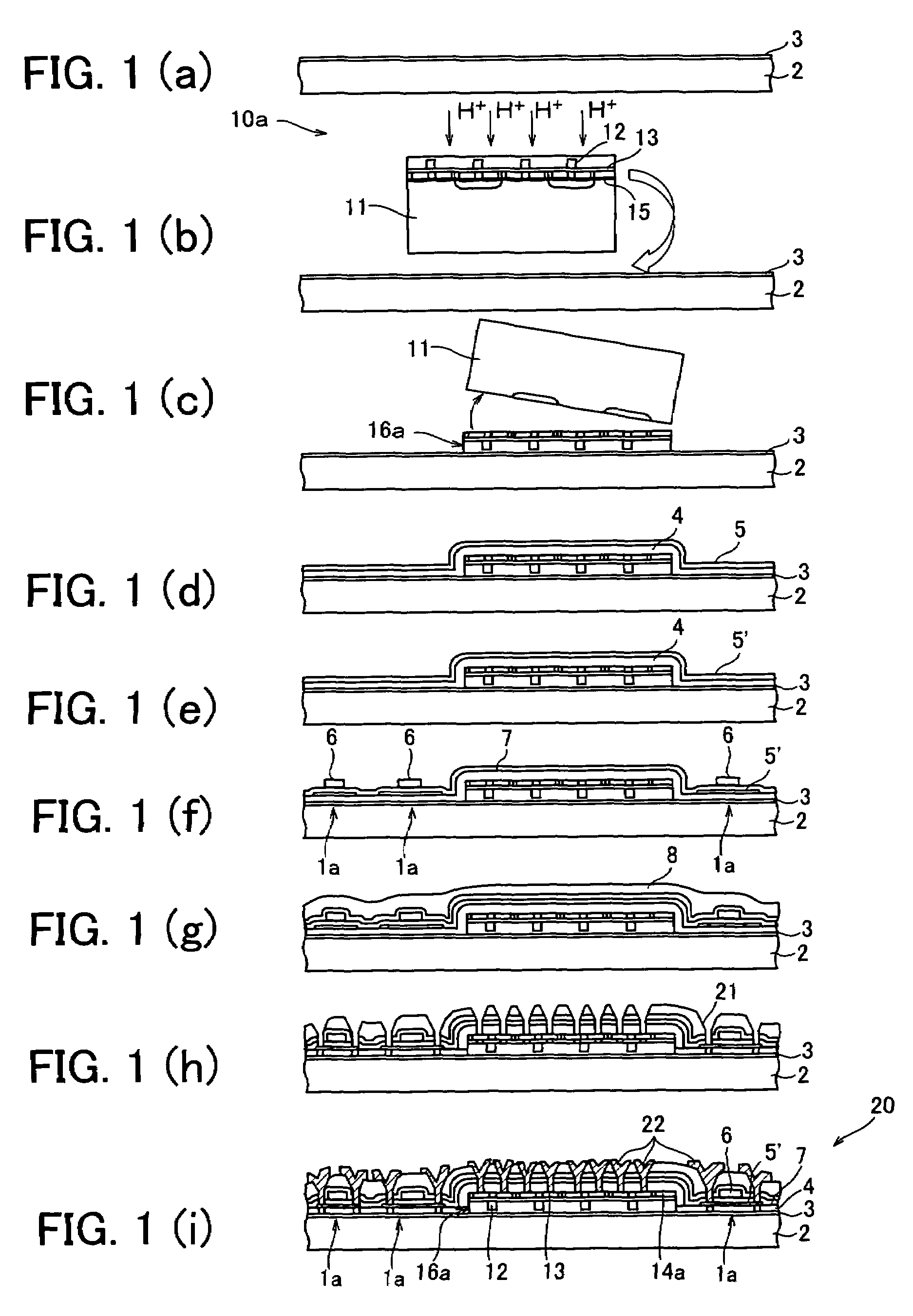

Method for Transferring Semiconductor Element, Method for Manufacturing Semiconductor Device, and Semiconductor Device

ActiveUS20090001504A1Improve bonding strengthLow pour pointSolid-state devicesSemiconductor/solid-state device manufacturingTransistor channelMonocrystalline silicon

A transistor formed on a monocrystalline Si wafer is temporarily transferred onto a first temporary supporting substrate. The first temporarily supporting substrate is heat-treated at high heat so as to repair crystal defects generated in a transistor channel of the monocrystalline Si wafer when transferring the transistor. The transistor is then made into a chip and transferred onto a TFT substrate. In order to transfer the transistor which has been once separated from the monocrystalline Si wafer, a different method from a stripping method utilizing ion doping is employed.

Owner:SHARP KK

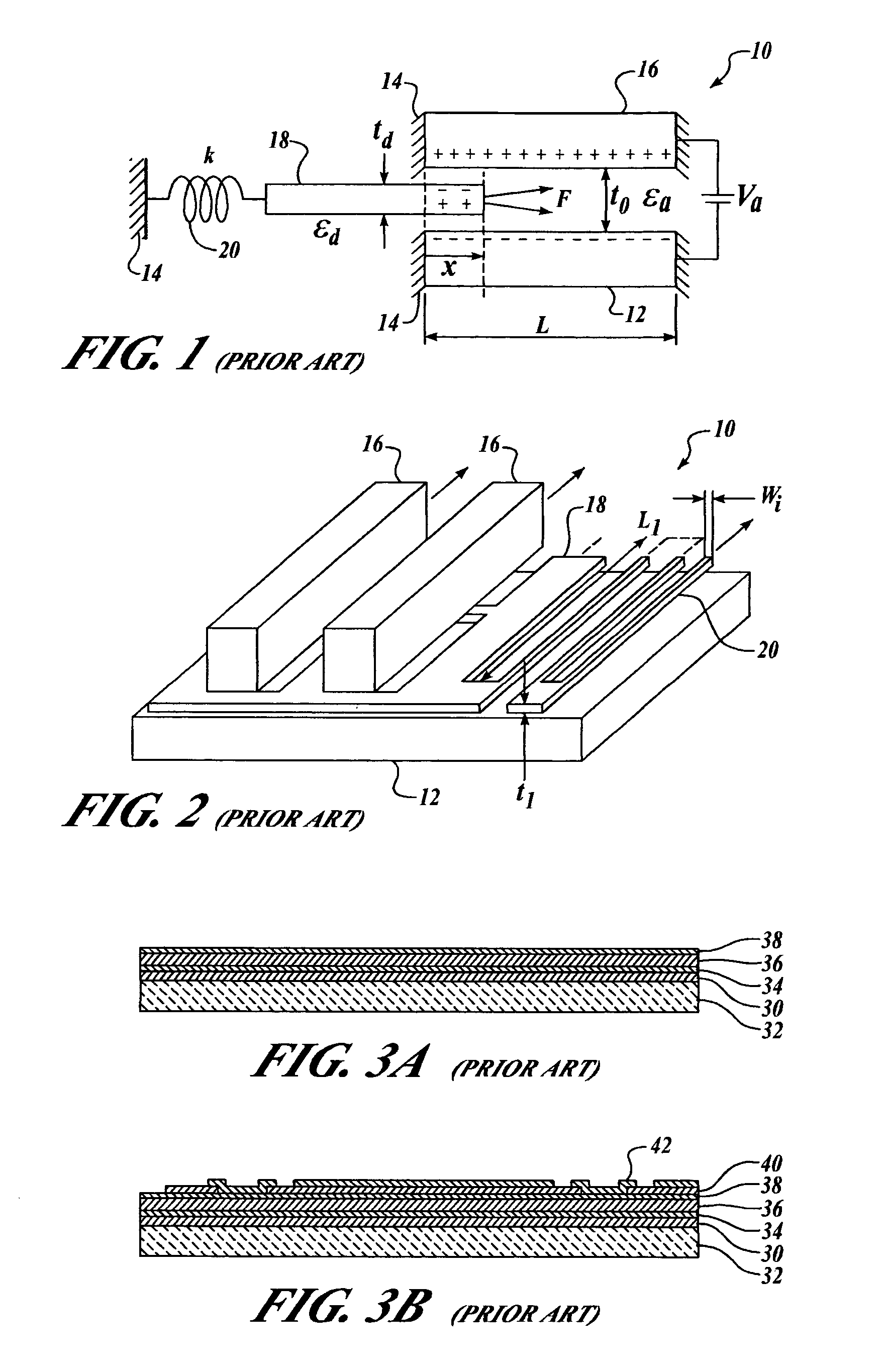

Method of manufacturing vibrating micromechanical structures

A method for fabrication of single crystal silicon micromechanical resonators using a two-wafer process, including either a Silicon-on-insulator (SOI) or insulating base and resonator wafers, wherein resonator anchors, a capacitive air gap, isolation trenches, and alignment marks are micromachined in an active layer of the base wafer; the active layer of the resonator wafer is bonded directly to the active layer of the base wafer; the handle and dielectric layers of the resonator wafer are removed; viewing windows are opened in the active layer of the resonator wafer; masking the single crystal silicon semiconductor material active layer of the resonator wafer with photoresist material; a single crystal silicon resonator is machined in the active layer of the resonator wafer using silicon dry etch micromachining technology; and the photoresist material is subsequently dry stripped.

Owner:HONEYWELL INT INC

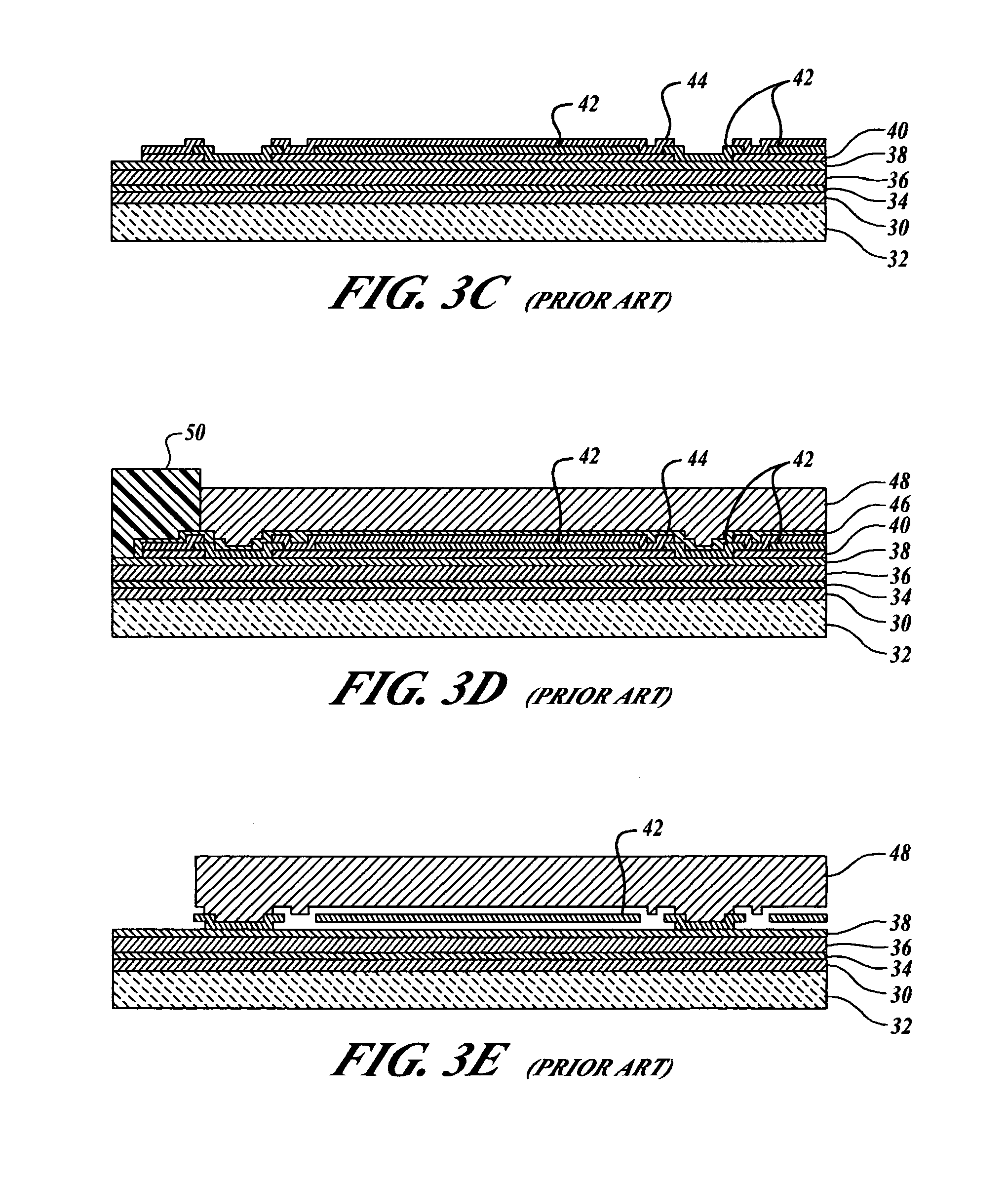

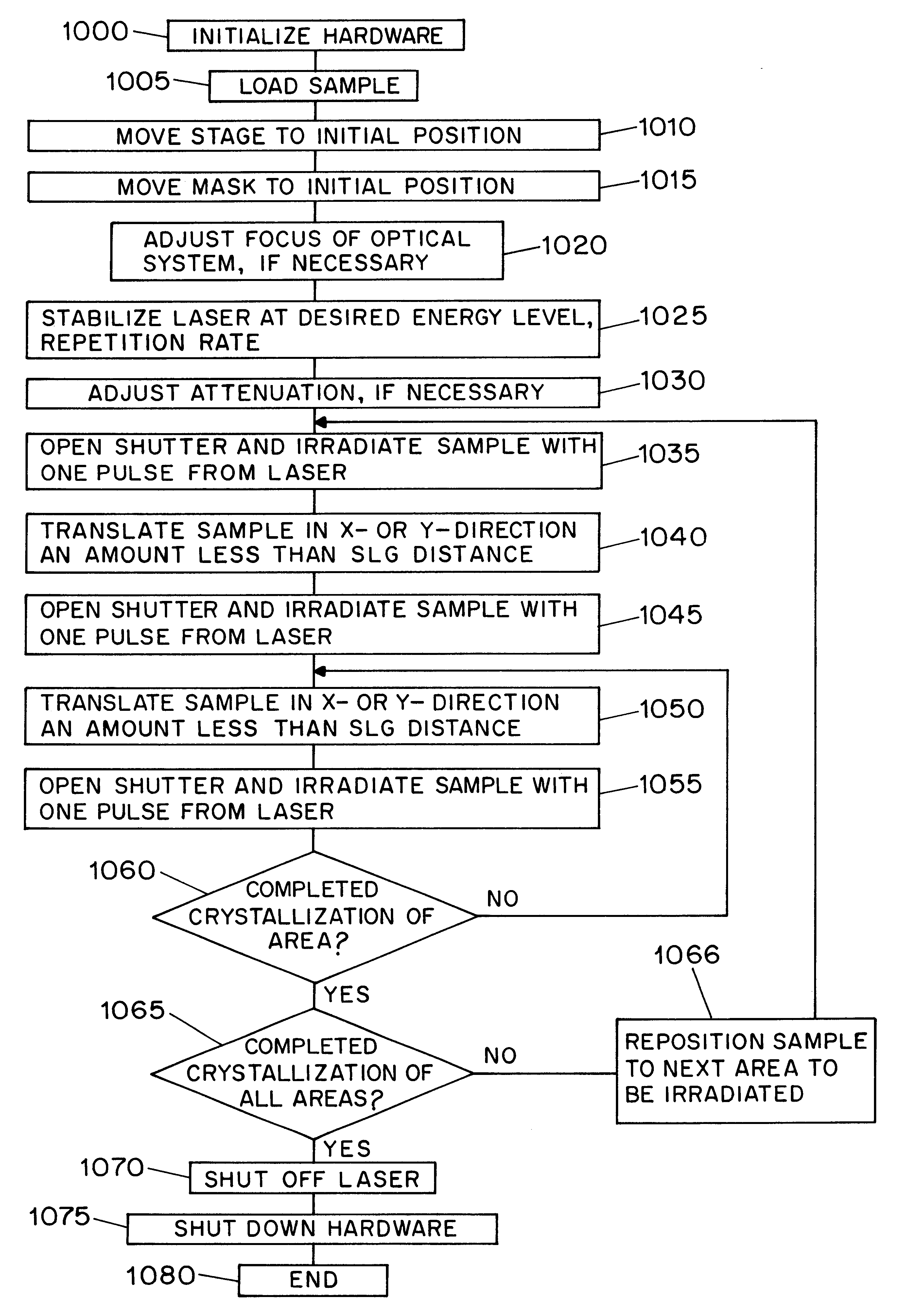

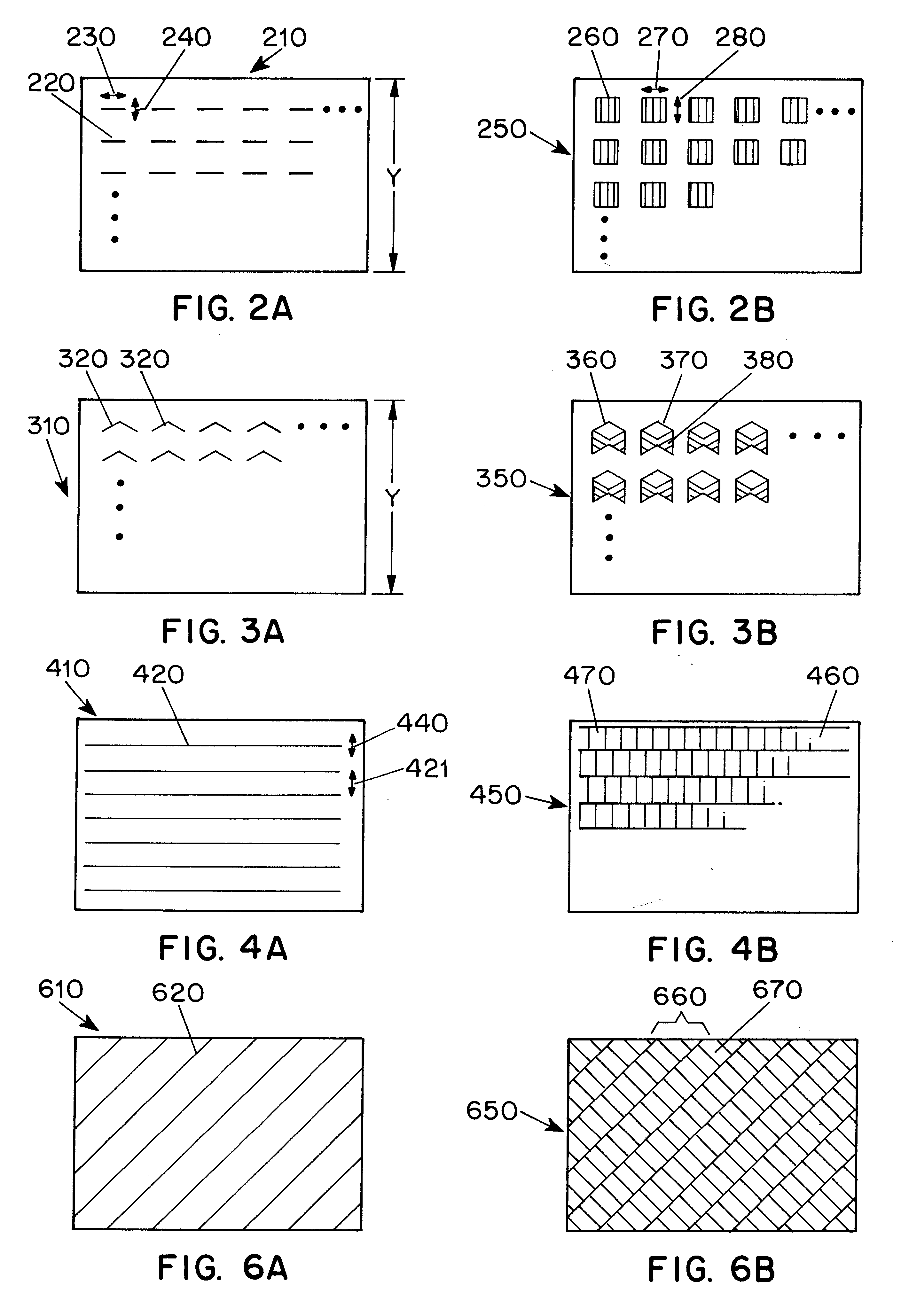

Methods for producing uniform large-grained and grain boundary location manipulated polycrystalline thin film semiconductors using sequential lateral solidification

Methods for processing an amorphous silicon thin film sample into a polycrystalline silicon thin film are disclosed. In one preferred arrangement, a method includes the steps of generating a sequence of excimer laser pulses, controllably modulating each excimer laser pulse in the sequence to a predetermined fluence, homoginizing each modulated laser pulse in the sequence in a predetermined plane, masking portions of each homogenized fluence controlled laser pulse in the sequence with a two dimensional pattern of slits to generate a sequence of fluence controlled pulses of line patterned beamlets, each slit in the pattern of slits being sufficiently narrow to prevent inducement of significant nucleation in region of a silicon thin film sample irradiated by a beam let corresponding to the slit, irradiating an amorphous silicon thin film sample with the sequence of fluence controlled slit patterned beamlets to effect melting of portions thereof corresponding to each fluence controlled patterned beamlet pulse in the sequence of pulses of patterned beamlets, and controllably sequentially translating a relative position of the sample with respect to each of the fluence controlled pulse of slit patterned beamlets to thereby process the amorphous silicon thin film sample into a single or polycrystalline silicon thin film.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

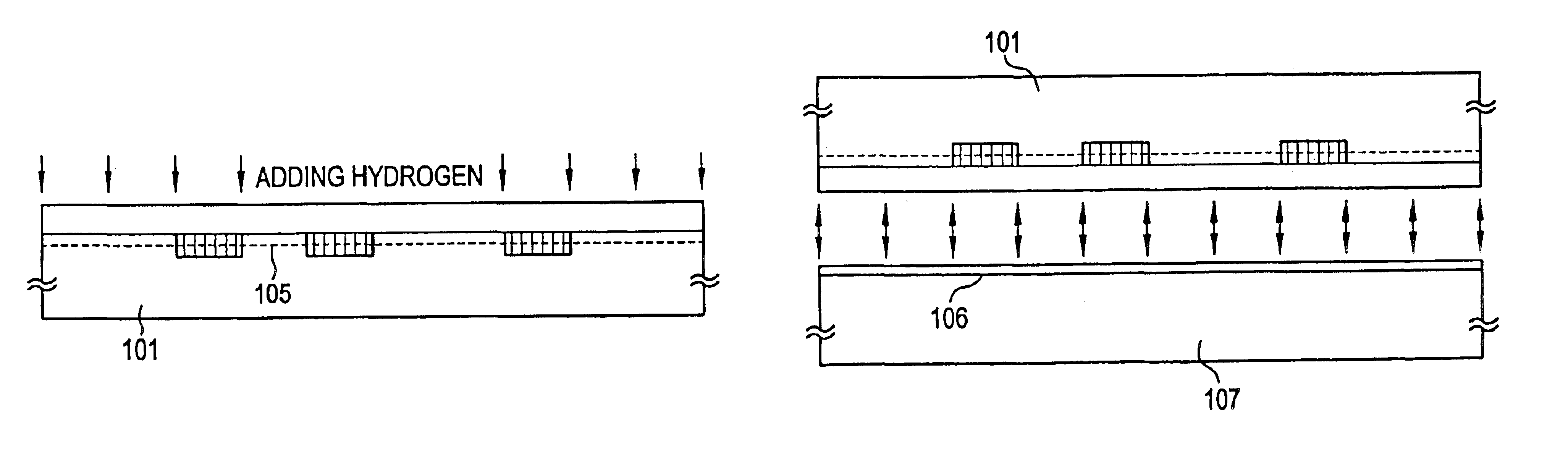

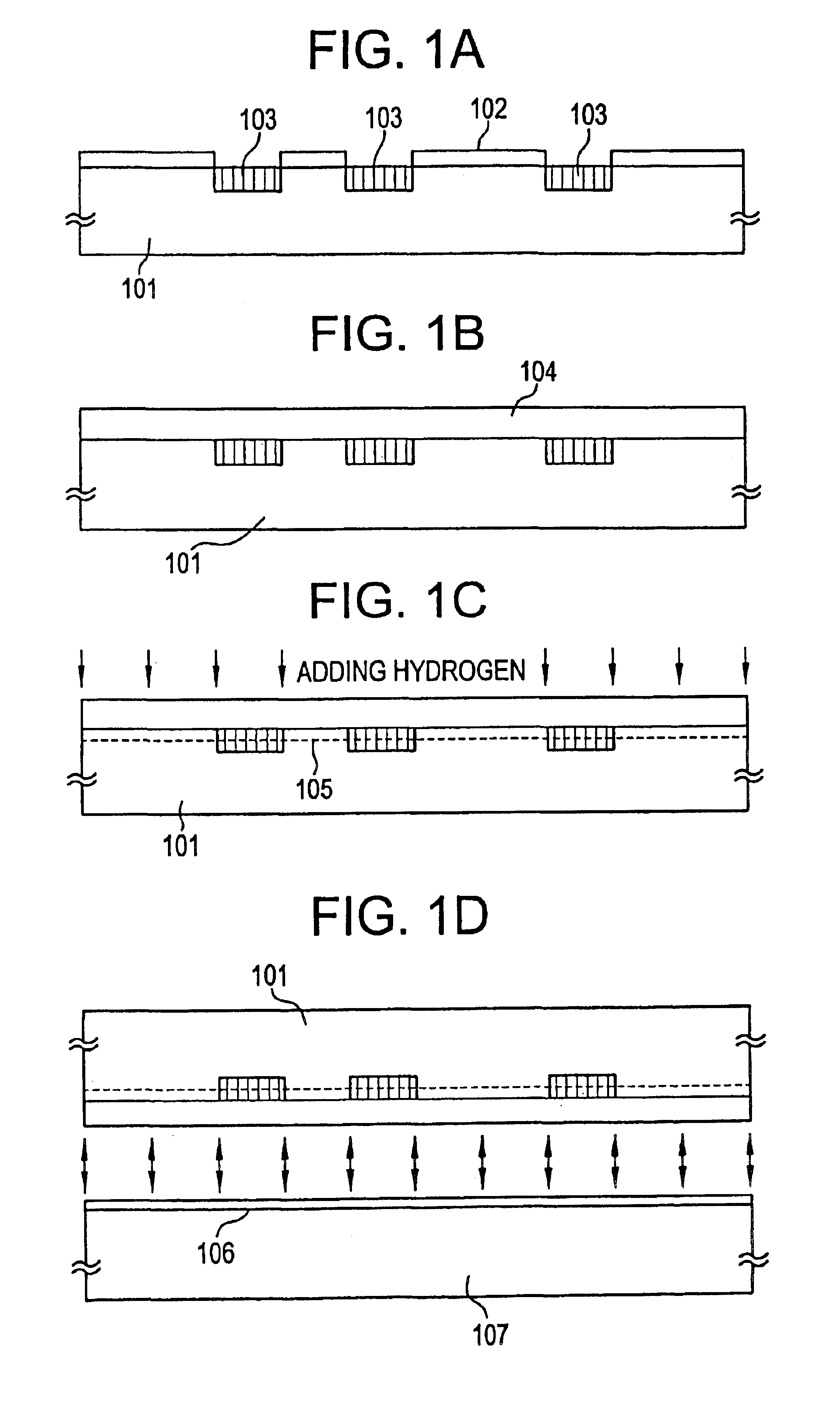

Process for production of SOI substrate and process for production of semiconductor device

A process for producing an adhered SOI substrate without causing cracking and peeling of a single-crystal silicon thin film. The process consists of selectively forming a porous silicon layer in a single-crystal semiconductor substrate, adding hydrogen into the single-crystal semiconductor substrate to form a hydrogen-added layer, adhering the single-crystal semiconductor substrate to a supporting substrate, separating the single-crystal semiconductor substrate at the hydrogen-added layer by thermal annealing, performing thermal annealing again to stabilize the adhering interface, and selectively removing the porous silicon layer to give single-crystal silicon layer divided into islands.

Owner:SEMICON ENERGY LAB CO LTD

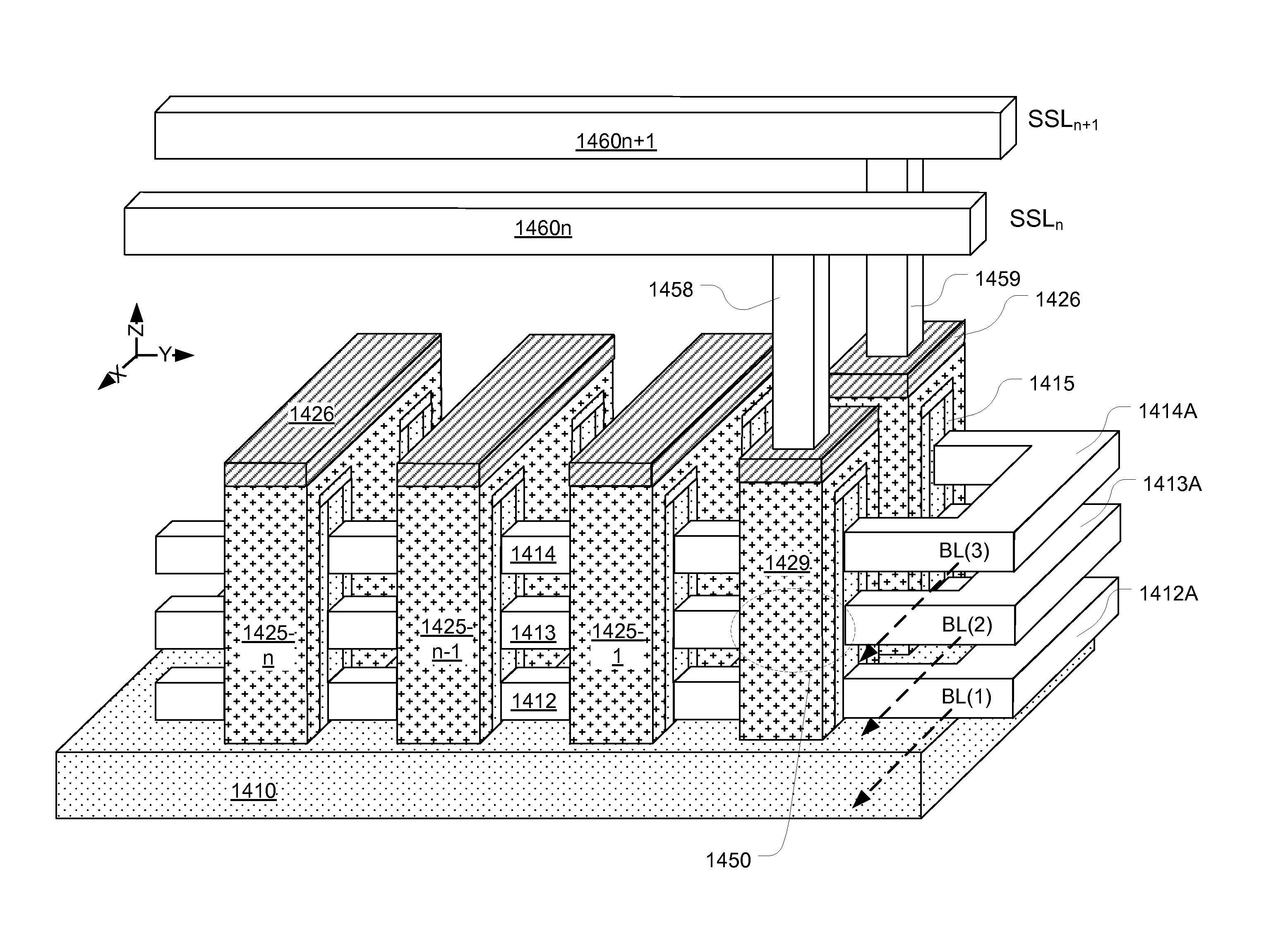

Multi-Layer Single Crystal 3D Stackable Memory

ActiveUS20120181654A1Solid-state devicesSemiconductor/solid-state device manufacturingSingle crystalOptoelectronics

Technology is described herein for manufacturing a three-dimensional 3D stacked memory structure having multiple layers of single crystal silicon or other semiconductor. The multiple layers of single crystal semiconductor are suitable for implementing multiple levels of high performance memory cells.

Owner:MACRONIX INT CO LTD

Stretchable Form of Single Crystal Silicon for High Performance Electronics on Rubber Substrates

ActiveUS20100059863A1Large elongationSignificant flexingTransistorCircuit bendability/stretchabilityFlexible electronicsSemiconductor

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

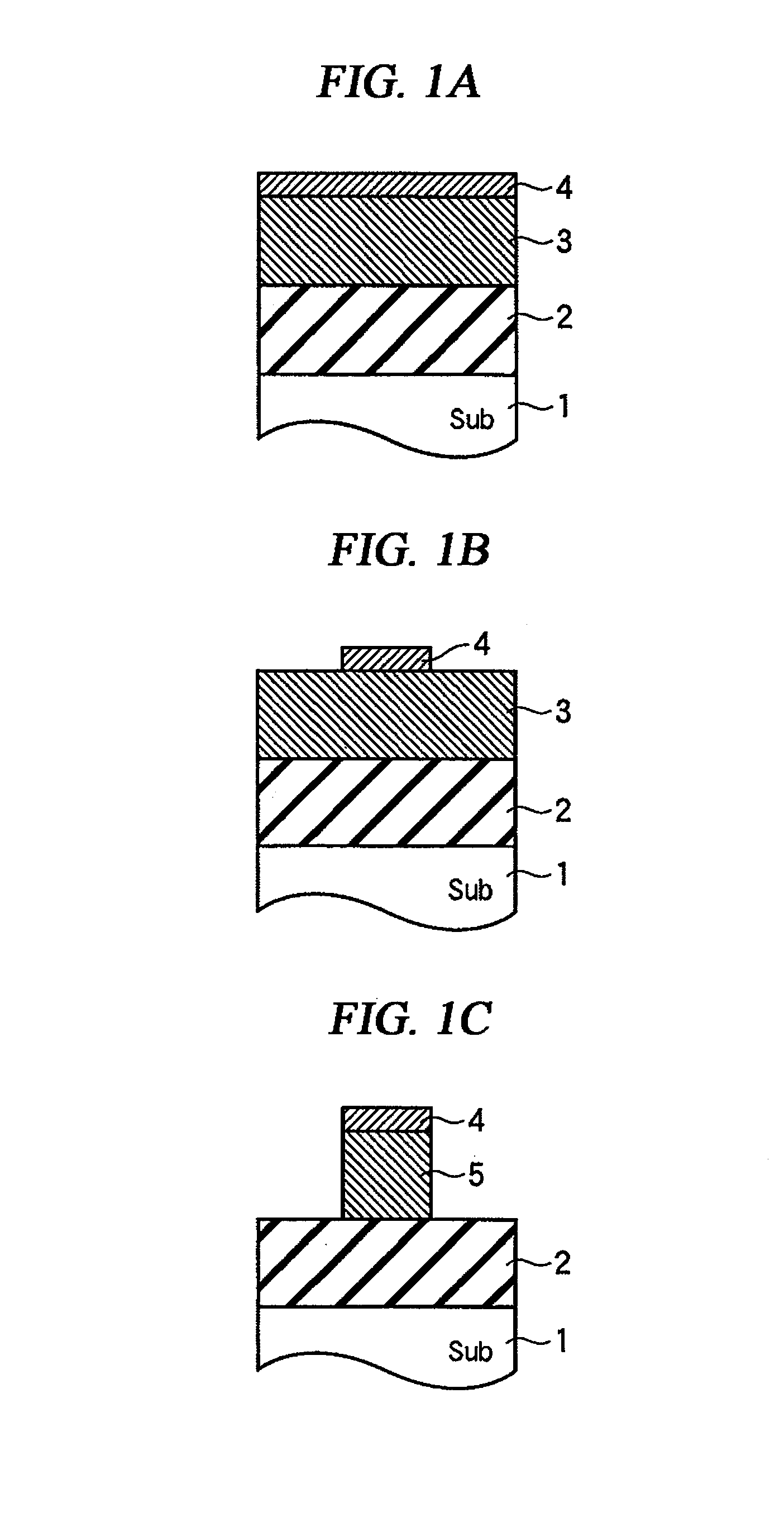

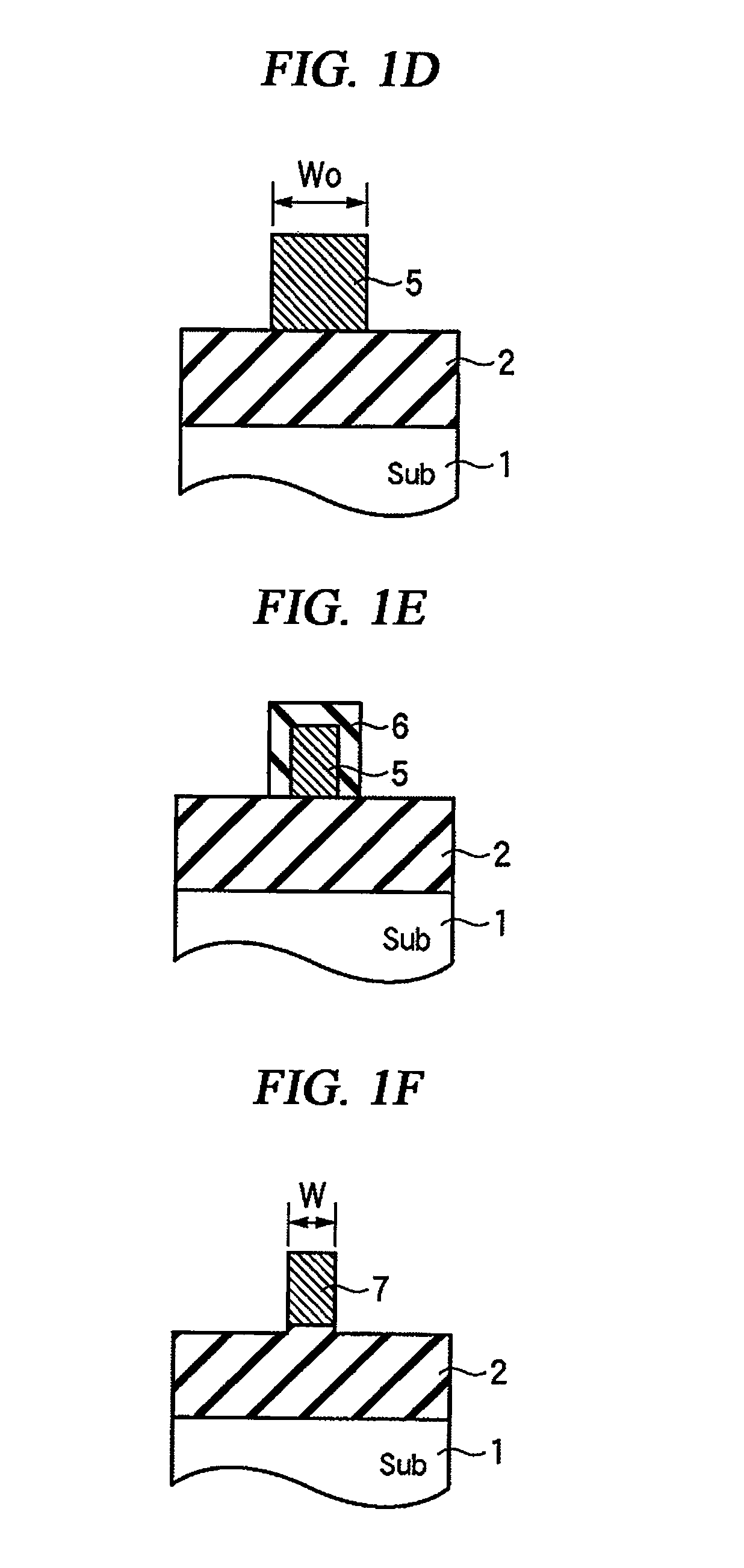

Manufacturing method of fin-type field effect transistor

InactiveUS20080171407A1Inhibition formationIncrease etch rateSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

A method for manufacturing a fin-type field effect transistor simply and securely by using a SOI (Silicon On Insulator) wafer, capable of suppressing an undercut formation, is disclosed. The method includes forming a fin-shaped protrusion by selectively dry-etching a single crystalline silicon layer until an underlying buried oxide layer is exposed; forming a sacrificial oxide film by oxidizing a surface of the protrusion including a damage inflicted thereon; and forming a fin having a clean surface by removing the sacrificial oxide film by etching, wherein an etching rate r1 of the sacrificial oxide film is higher than an etching rate r2 of the buried oxide layer during the etching.

Owner:TOKYO ELECTRON LTD

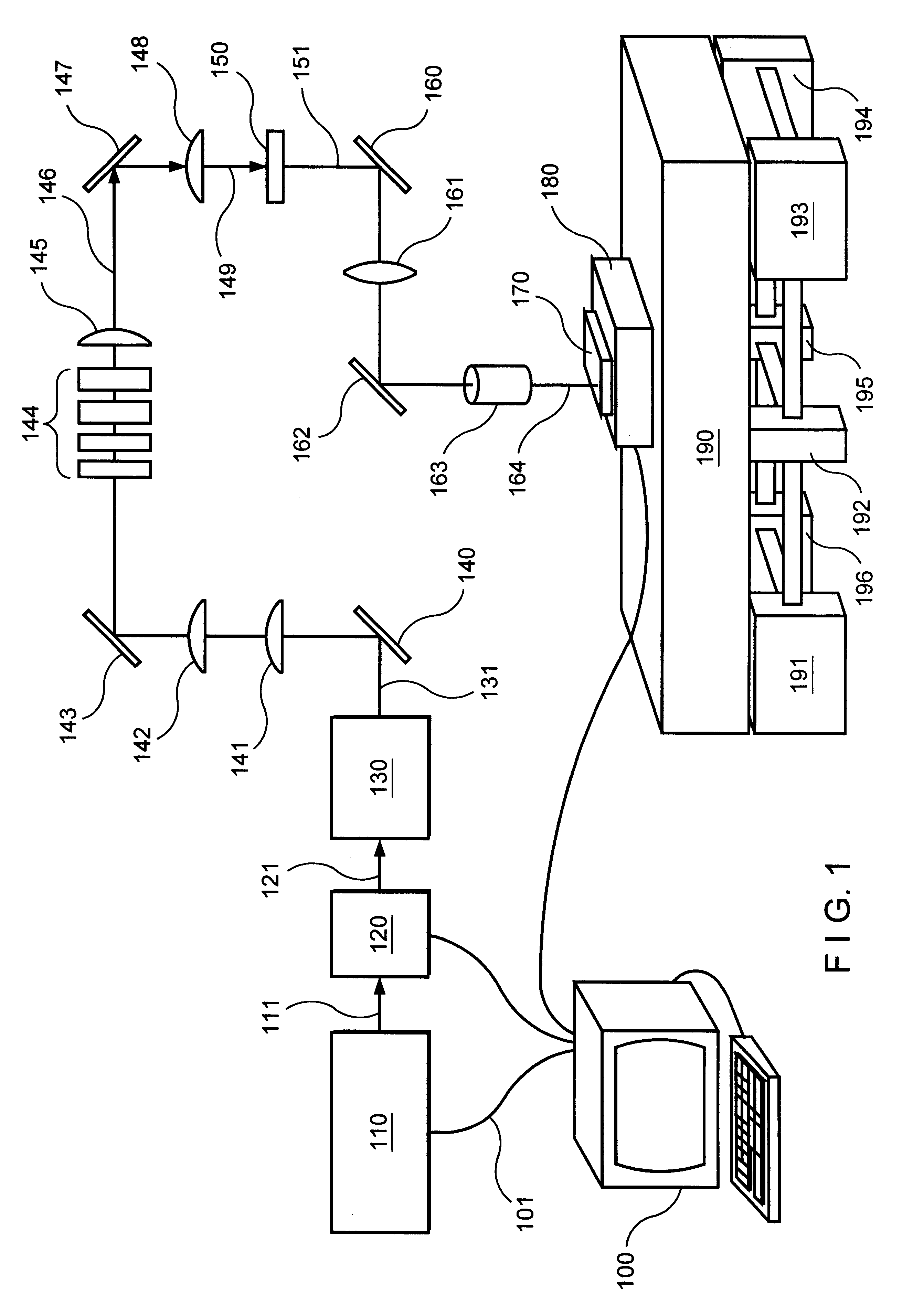

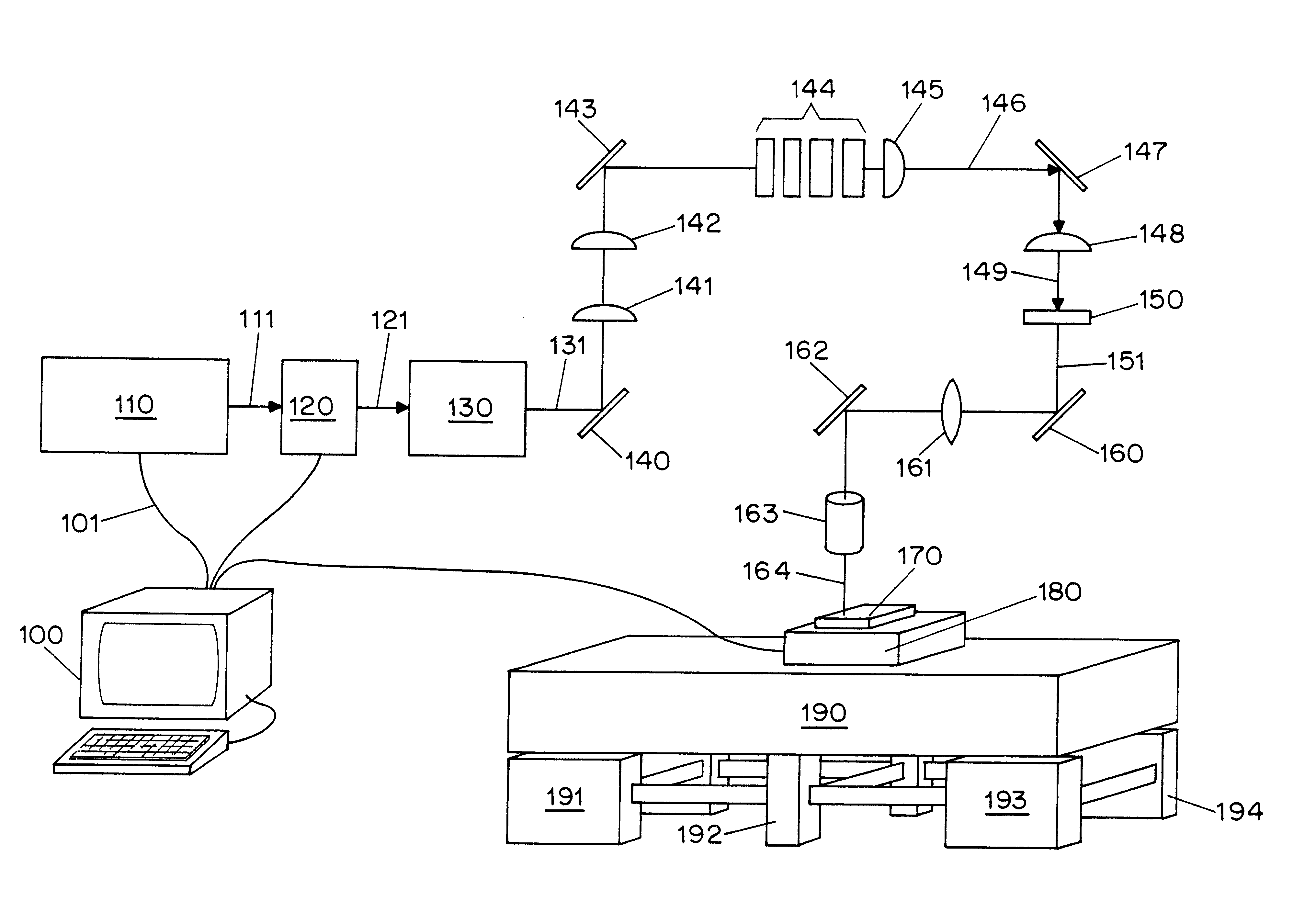

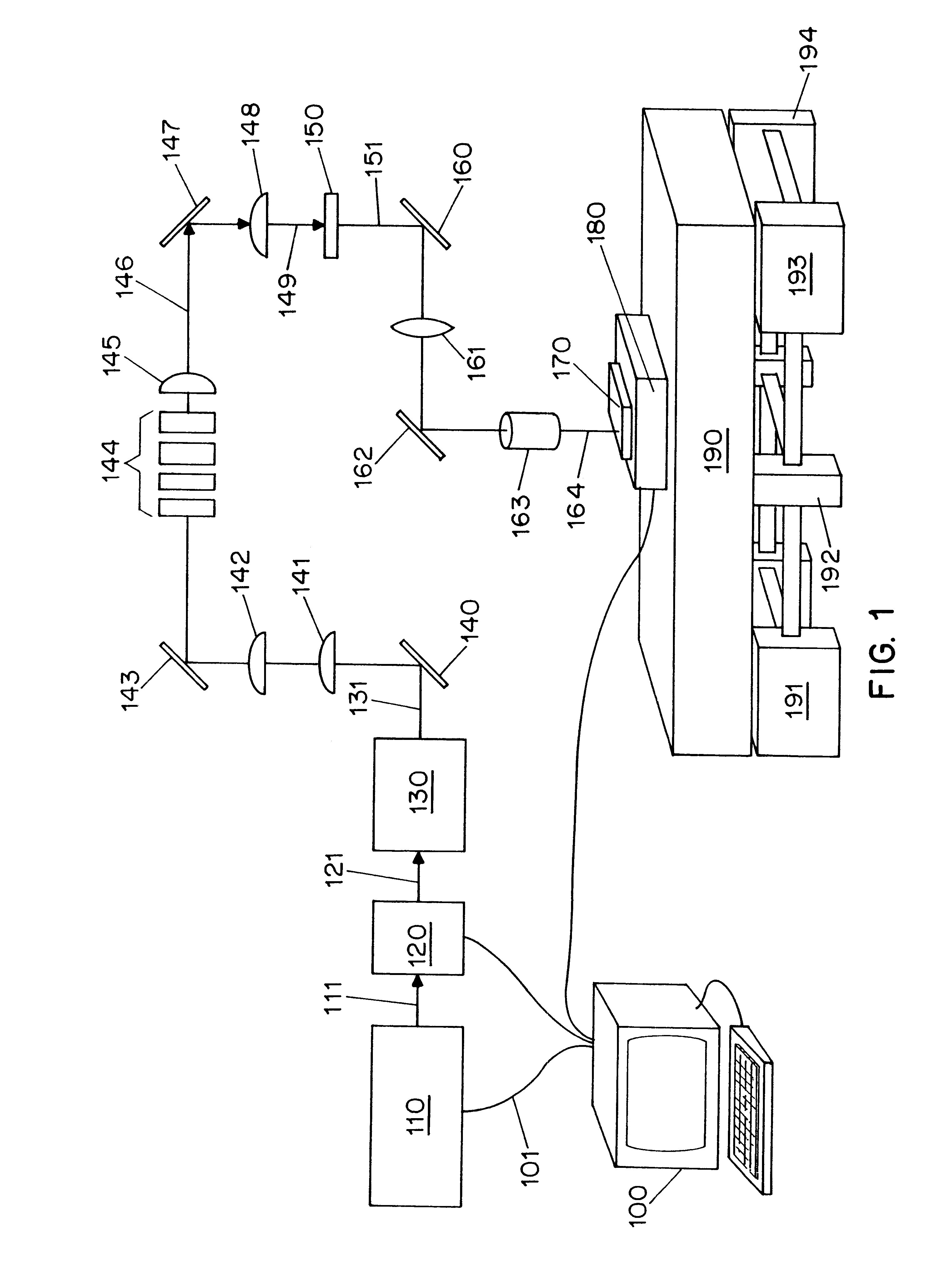

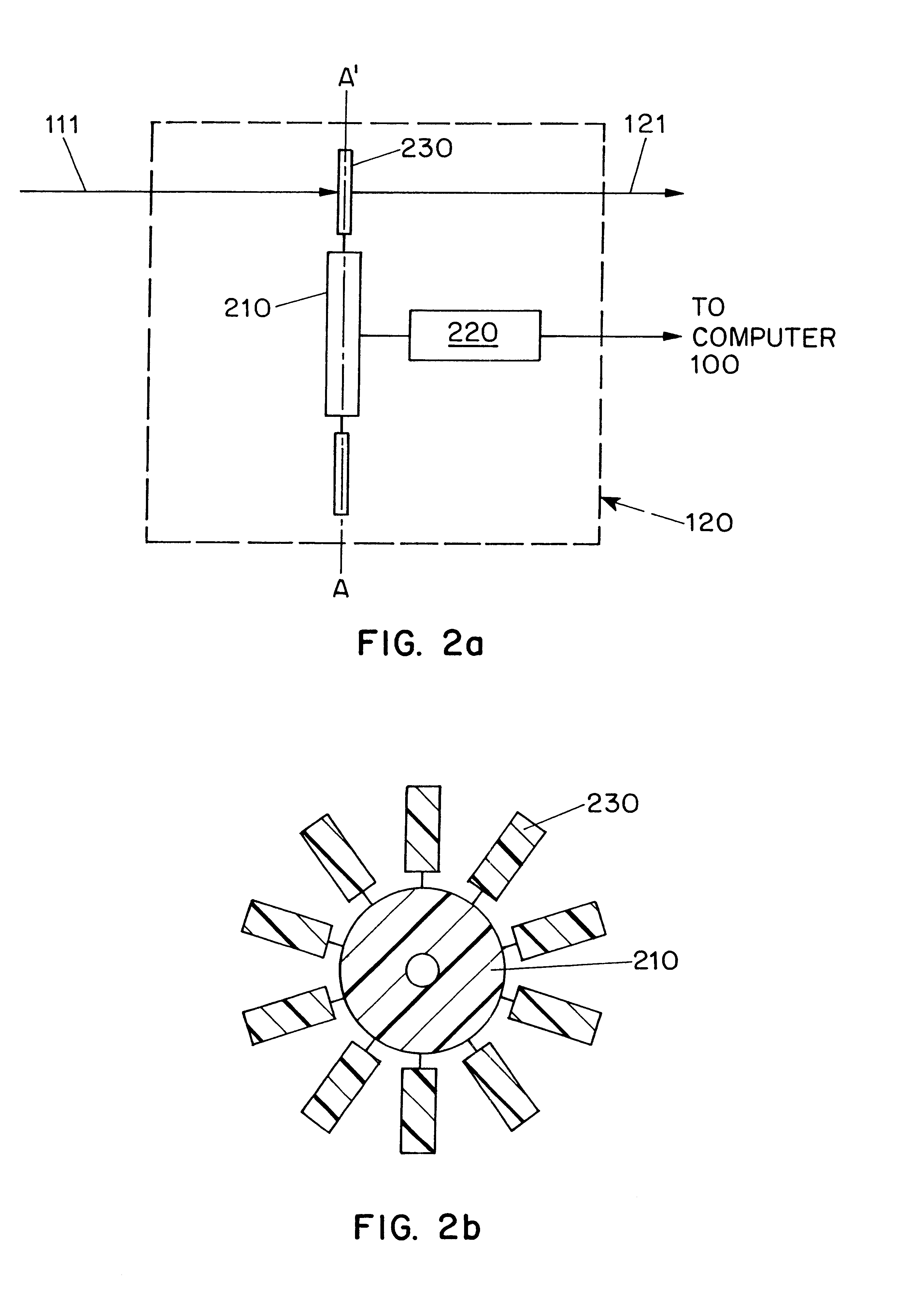

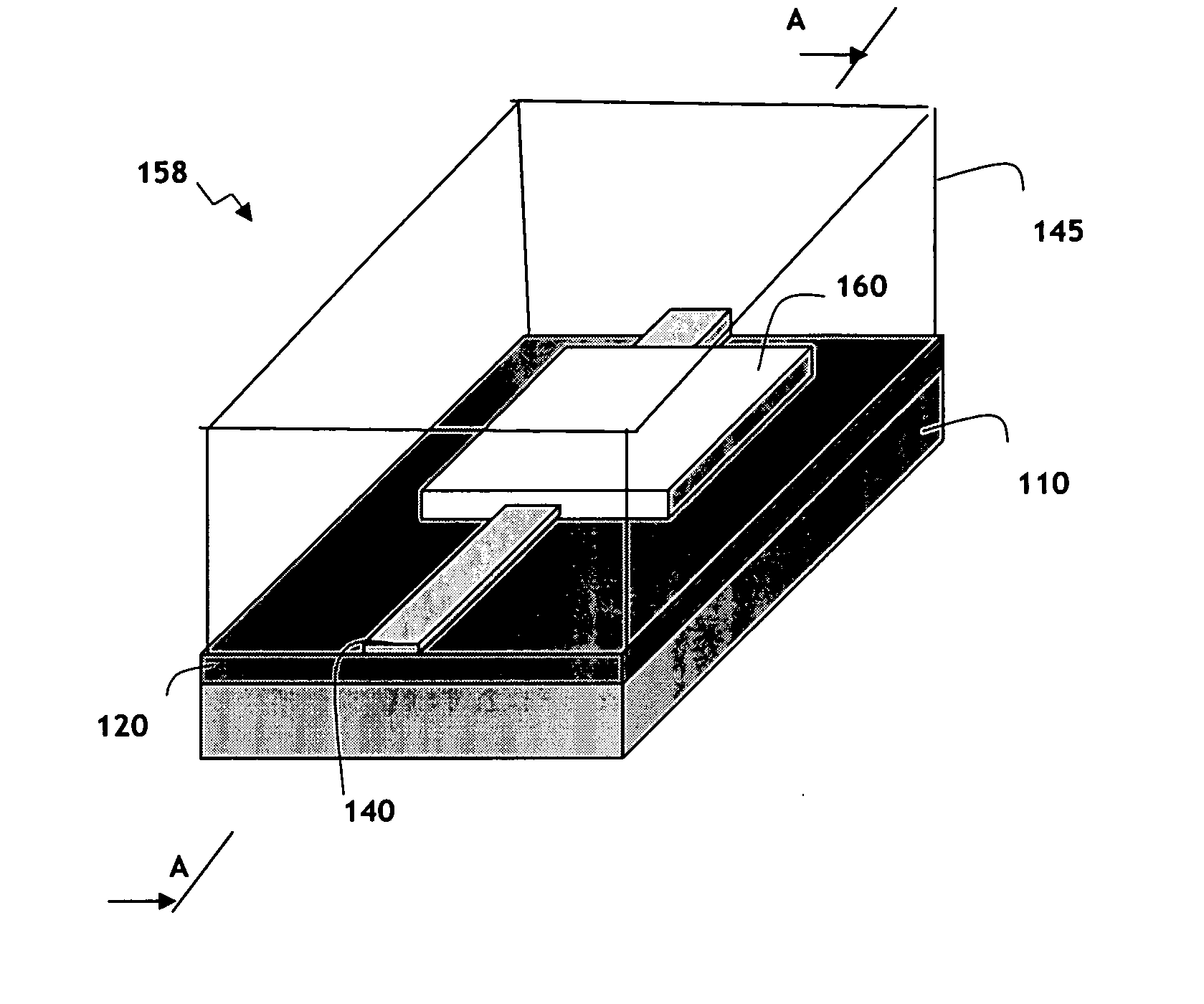

Systems and methods using sequential lateral solidification for producing single or polycrystalline silicon thin films at low temperatures

System and methods for processing an amorphous silicon thin film sample into a single or polycrystalline silicon thin film are disclosed. The system includes an excimer laser for generating a plurality of excimer laser pulses of a predetermined fluence, an energy density modulator for controllably modulating fluence of the excimer laser pulses, a beam homoginizer for homoginizing modulated laser pulses in a predetermined plane, a mask for masking portions of the homoginized modulated laser pulses into patterned beamlets, a sample stage for receivingthe patterned beamlets to effect melting of portions of any amorphous silicon thin film sample placed thereon corresponding to the beamlets, translating means for controllably translating a relative position of the sample stage with respect to a position of the mask and a computer for controlling the controllable fluence modulation of the excimer laser pulses and the controllable relative positions of the sample stage and mask, and for coordinating excimer pulse generation and fluence modulation with the relative positions of the sample stage and mask, to thereby process amorphous silicon thin film sample into a single or polycrystalline silicon thin film by sequential translation of the sample stage relative to the mask and irradiation of the sample by patterned beamlets of varying fluence at corresponding sequential locations thereon.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

Laterally-integrated waveguide photodetector apparatus and related coupling methods

InactiveUS20070104441A1Increase data rateCoupling light guidesOptical waveguide light guideCMOSPhotovoltaic detectors

High-speed optoelectronic devices having a waveguide densely integrated with and efficiently coupled to a photodetector are fabricated utilizing methods generally compatible with CMOS processing techniques. In various implementations, the waveguide consists essentially of single-crystal silicon and the photodetector contains, or consists essentially of, epitaxially grown germanium or a silicon-germanium alloy having a germanium concentration exceeding about 90%.

Owner:MASSACHUSETTS INST OF TECH

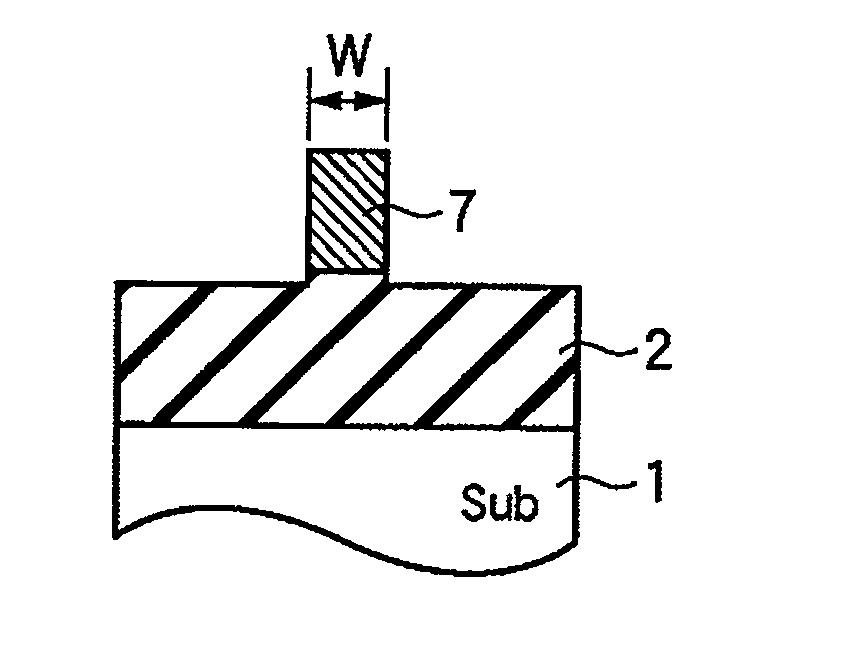

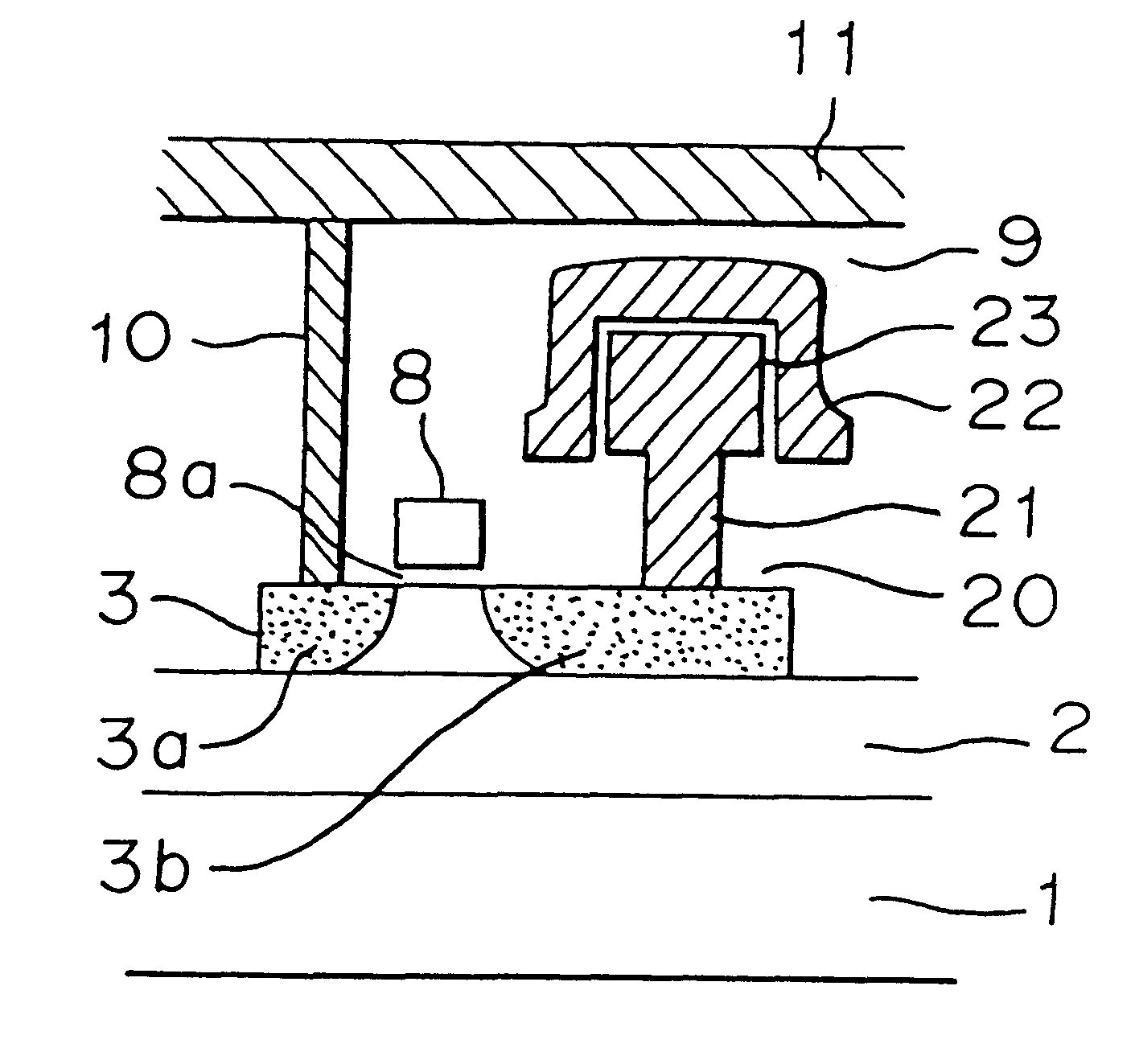

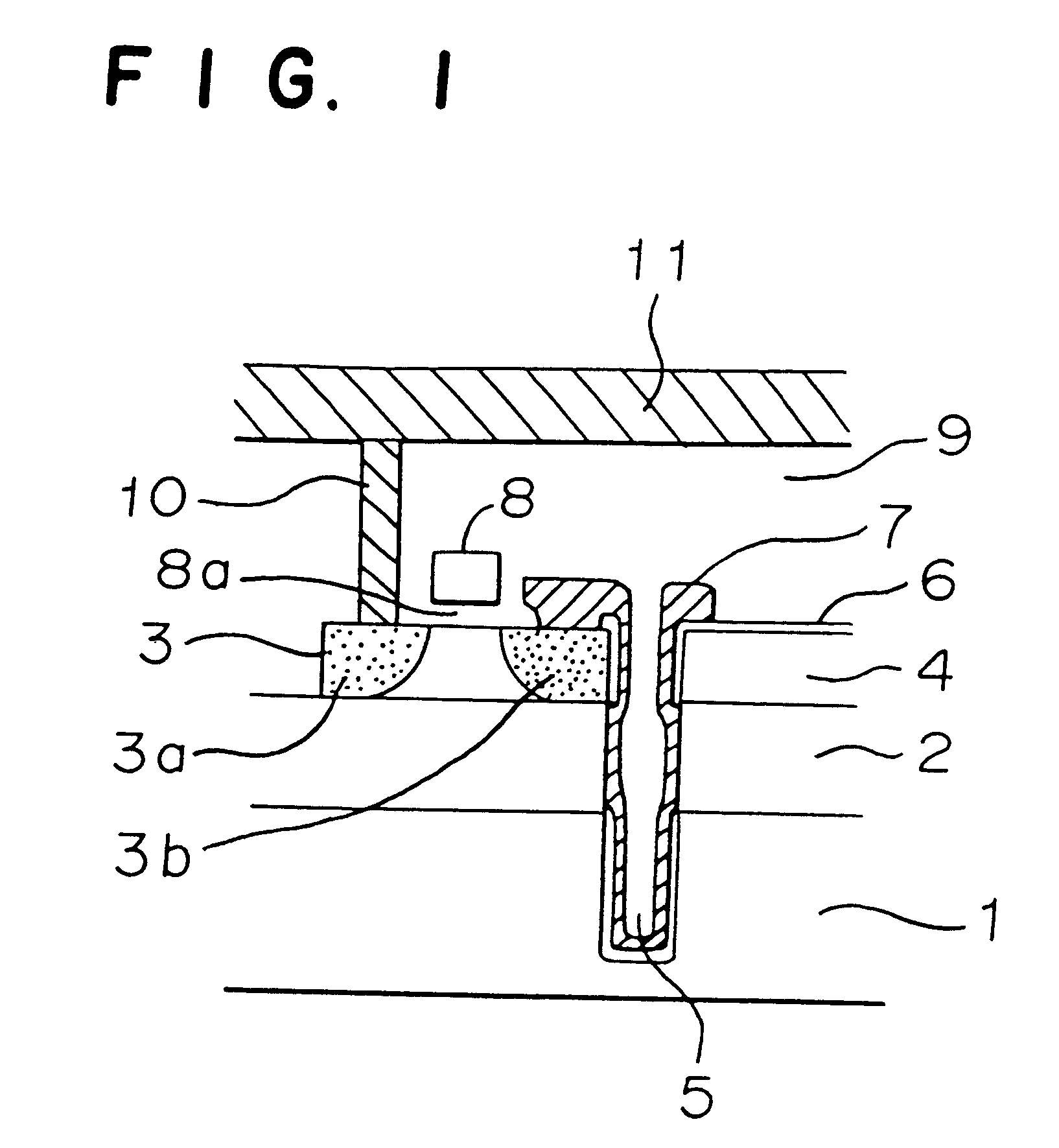

Method of manufacturing a semiconductor memory device

A method of manufacturing a semiconductor memory device comprising: a step of forming a storage node in which a conductive layer 7 to be the storage node is formed in the vicinity of single crystalline silicon 3 formed on an insulator 2, a gettering step for conducting heat treatment to the single crystalline silicon 3 after the step of forming the storage node and gettering contaminants contained in the single crystalline silicon 3 by the conductive layer 7 connected to the single crystalline silicon, and a step of forming a gate oxide film 8a on the single crystalline silicon 3 after the step of gettering is provided to thereby obtain a sufficient gettering effect even though the width of an element and / or the thickness of the element is reduced in accordance with microminiaturization of the element.

Owner:MITSUBISHI ELECTRIC CORP

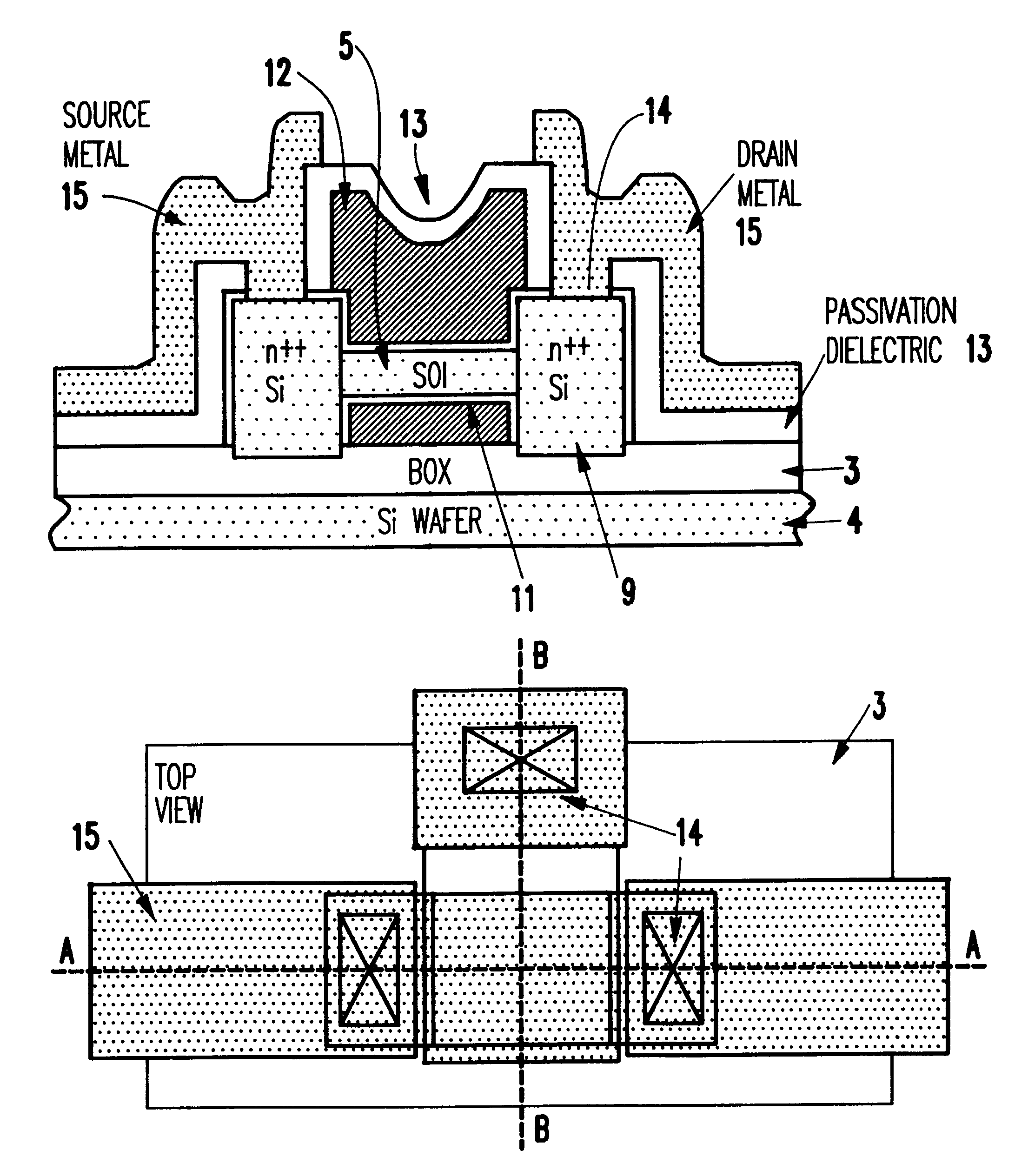

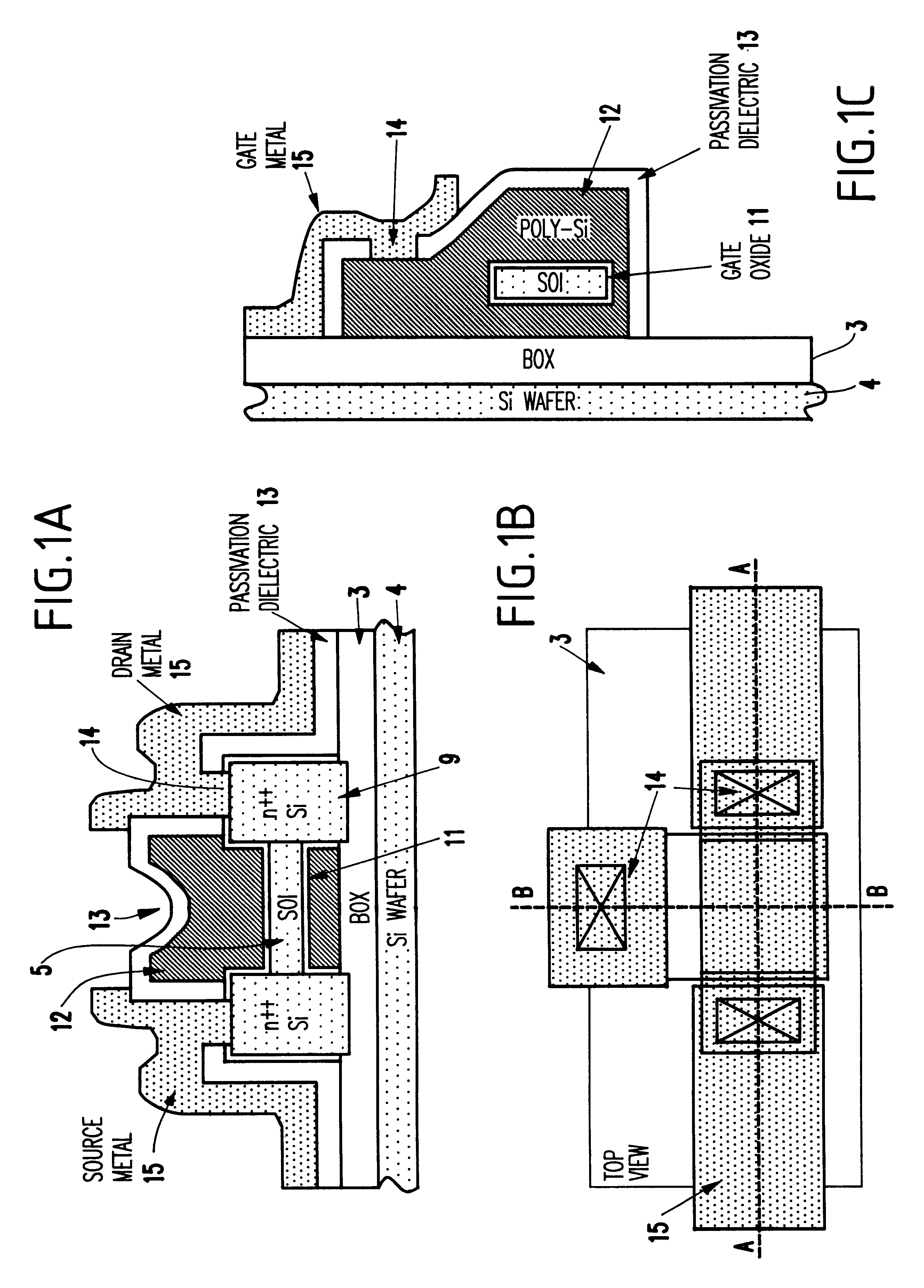

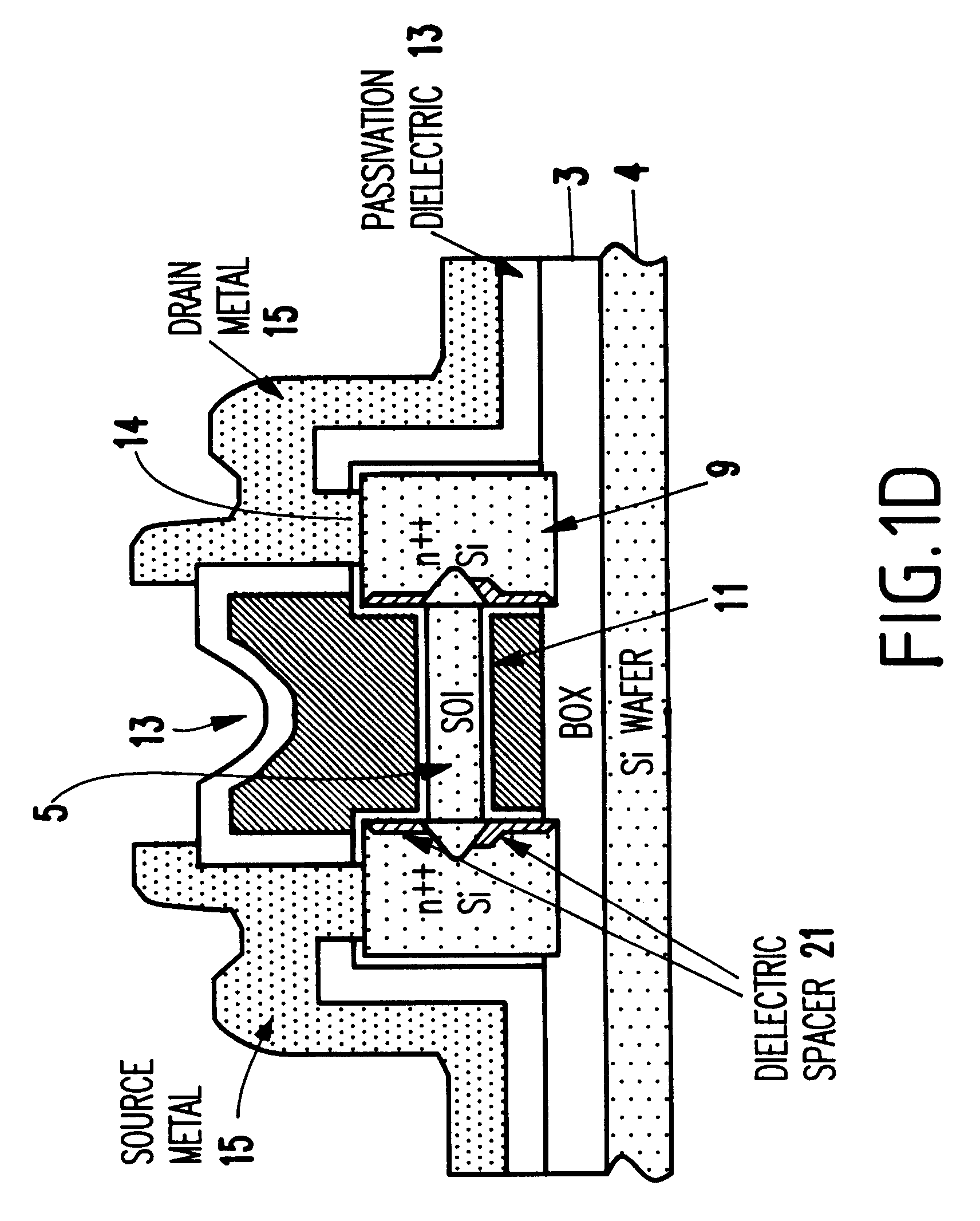

Self-aligned double-gate MOSFET by selective epitaxy and silicon wafer bonding techniques

InactiveUS6365465B1Controlled diffusionReduce diffuseTransistorSemiconductor/solid-state device manufacturingElectrical conductorEngineering

A structure and a method of manufacturing a double-gate metal oxide semiconductor transistor includes forming a laminated structure having a single crystal silicon channel layer and insulating oxide and nitride layers on each side of the single crystal silicon channel, forming openings in the laminated structure, forming drain and source regions in the openings, doping the drain and source regions, forming a mask over the laminated structure, removing portions of the laminated structure not protected by the mask, removing the mask and the insulating oxide and nitride layers to leave the single crystal silicon channel layer suspended from the drain and source regions, forming an oxide layer to cover the drain and source regions and the channel layer, and forming a double-gate conductor over the oxide layer such that the double-gate conductor includes a first conductor on a first side of the single crystal silicon channel layer and a second conductor on a second side of the single crystal silicon channel layer.

Owner:IBM CORP

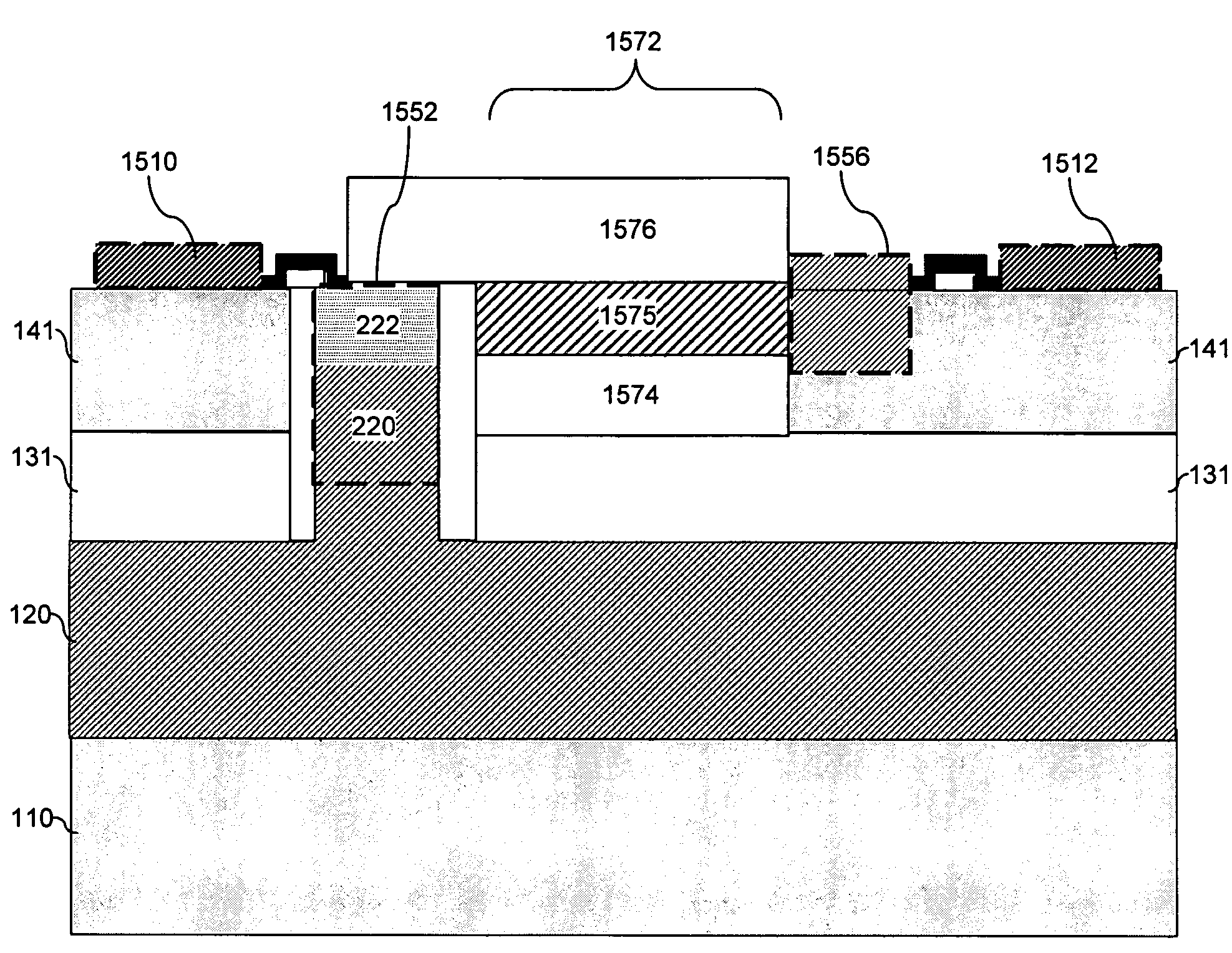

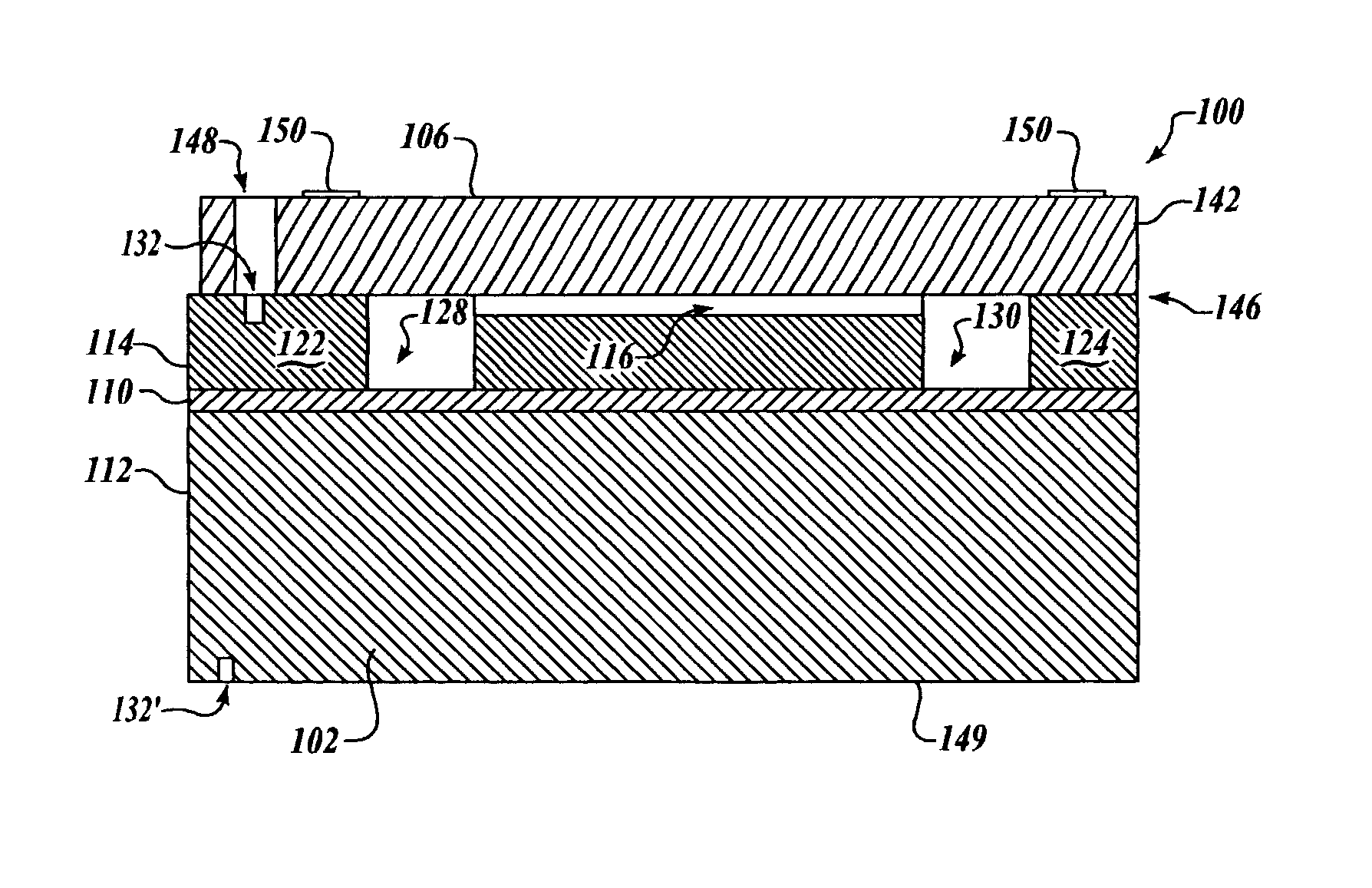

Integrated circuit memory with single crystal silicon on silicide driver and manufacturing method

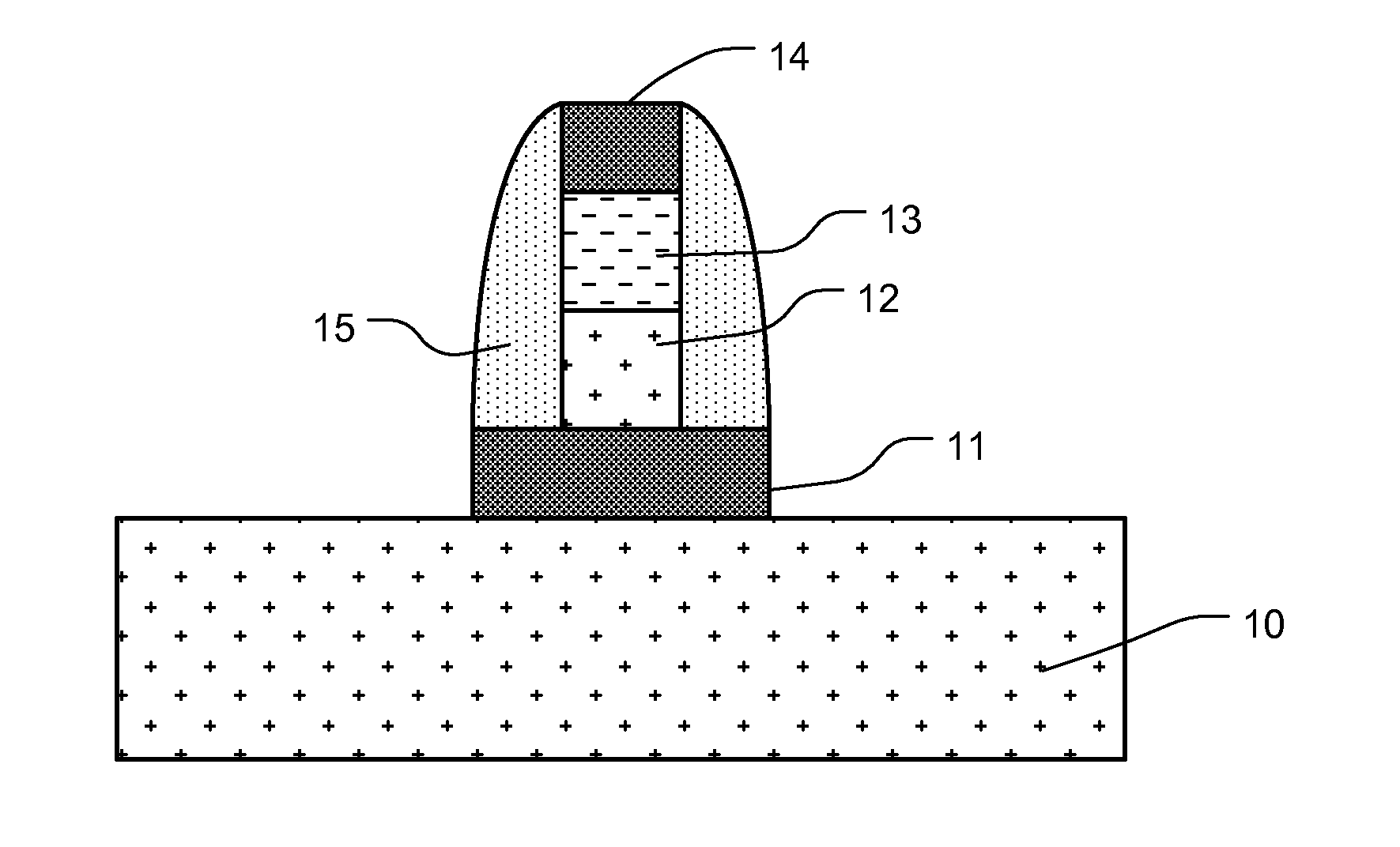

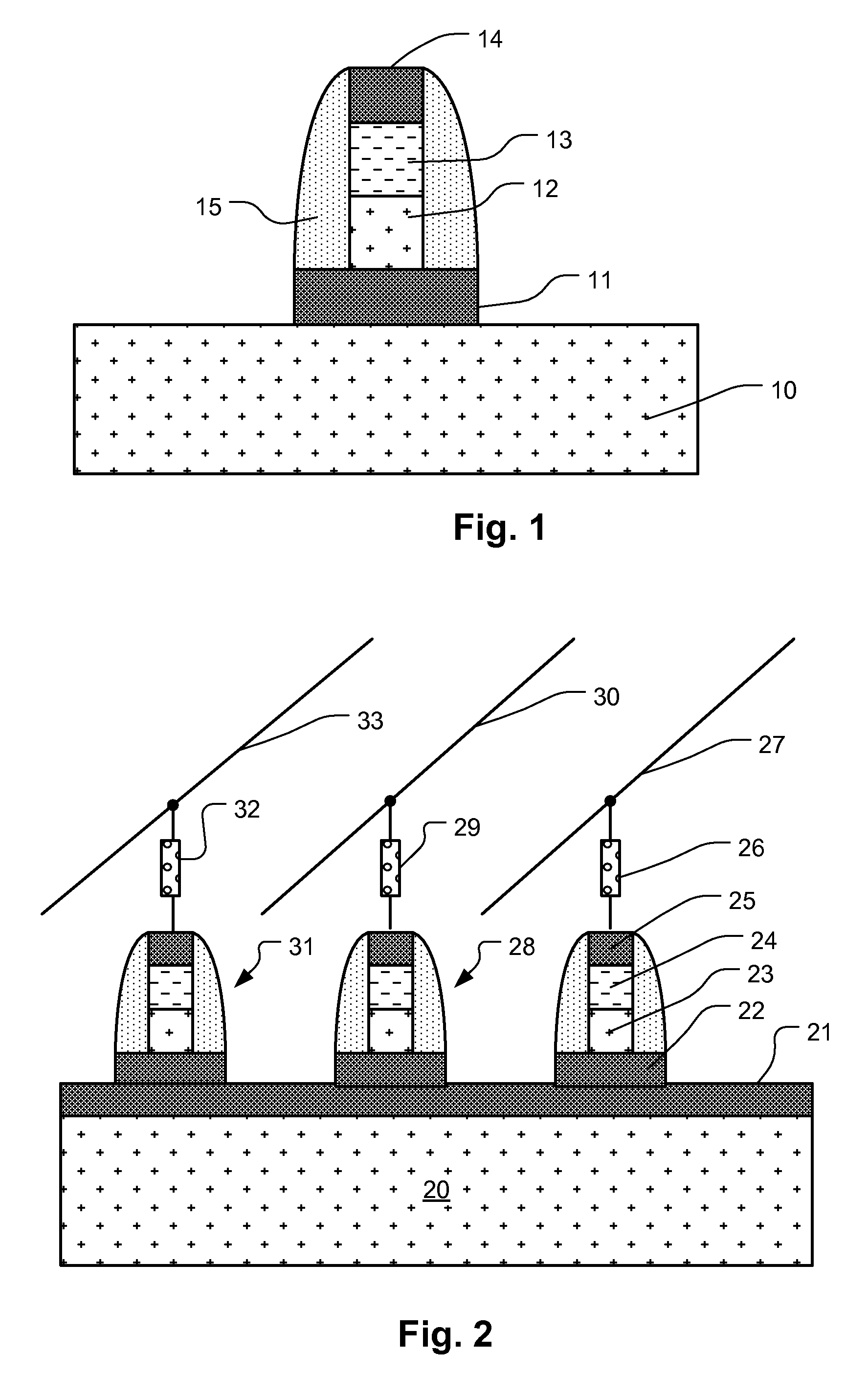

ActiveUS20100171086A1Excellent ElectricalExcellent structural characteristicSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitMonocrystalline silicon

A memory device includes a diode driver and a data storage element, such as an element comprising phase change memory material, and in which the diode driver comprises a silicide element on a silicon substrate with a single crystal silicon node on the silicide element. The silicide element separates the single crystal silicon node from the underlying silicon substrate, preventing the flow of carriers from the single crystal silicon node into the substrate, and is capable of acting as a conductive element for interconnecting devices on the device. The single crystal silicon node acts as one terminal of a diode, and a second semiconductor node is formed on top of it, acting as the other terminal of the diode.

Owner:MACRONIX INT CO LTD

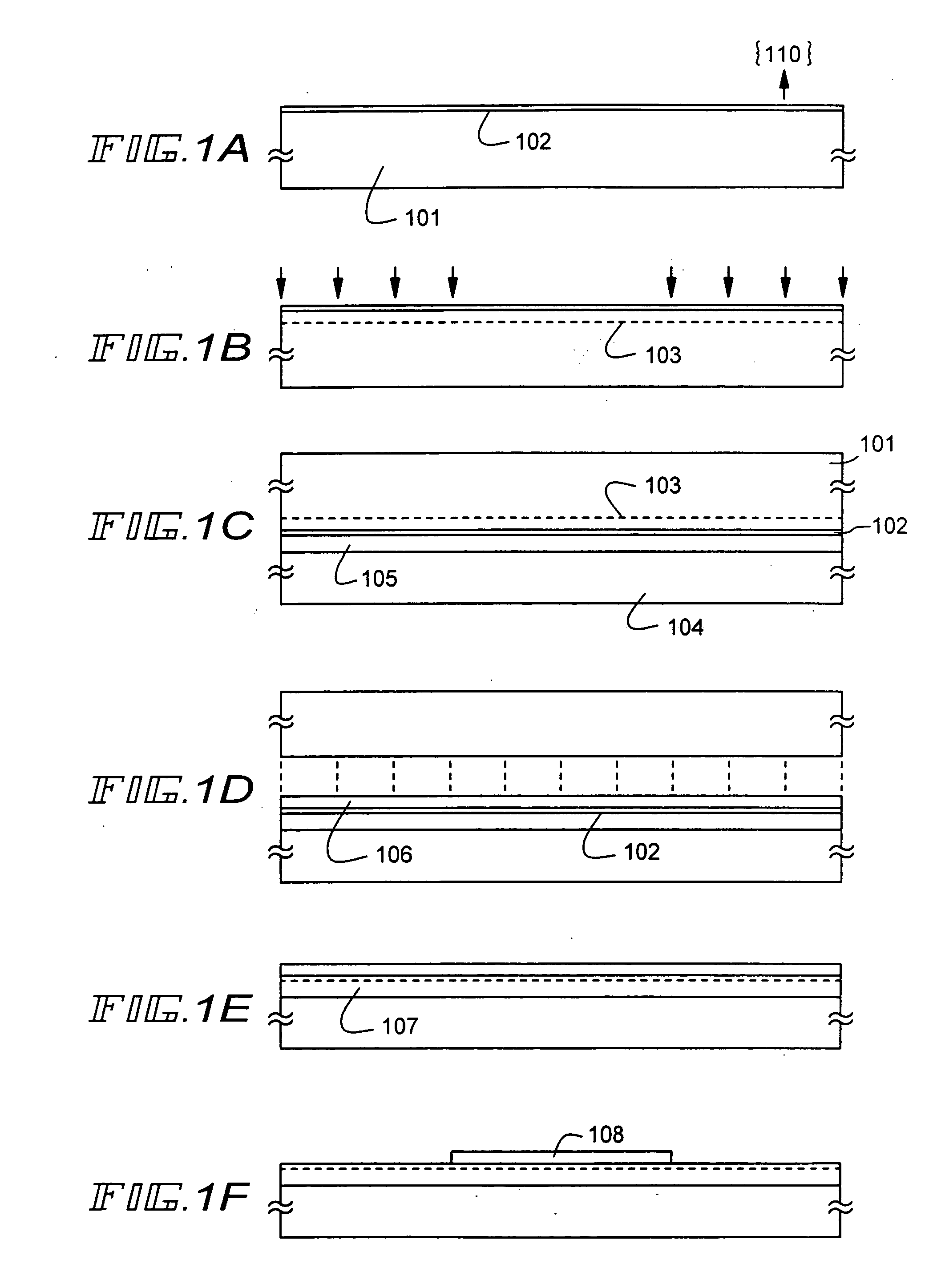

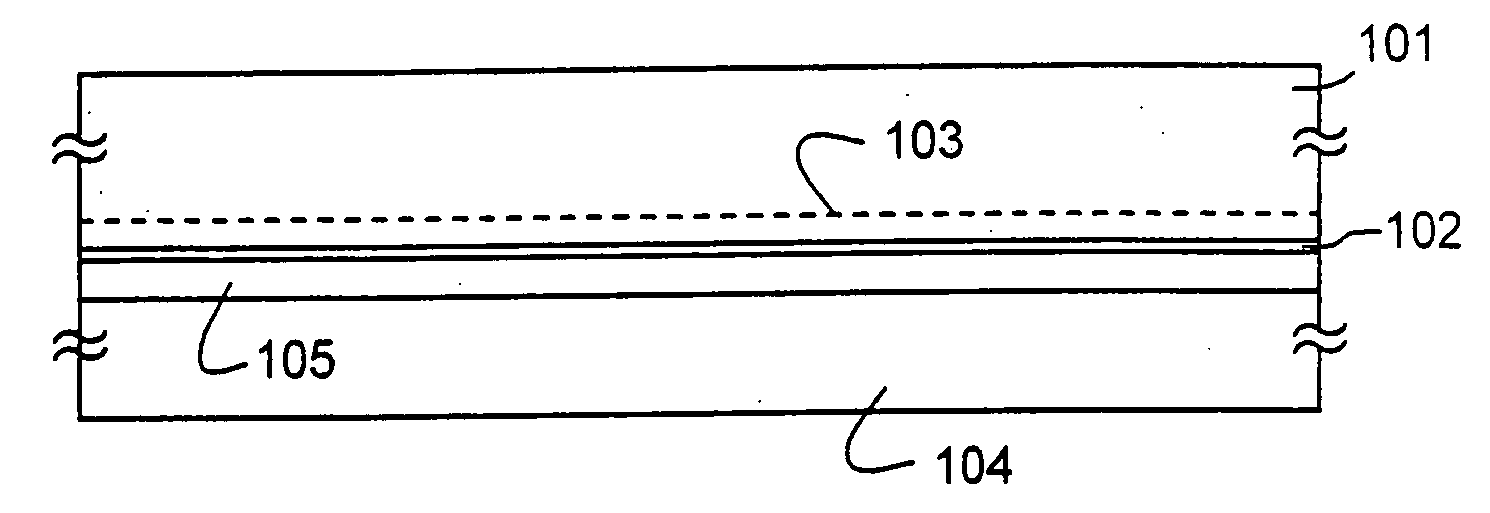

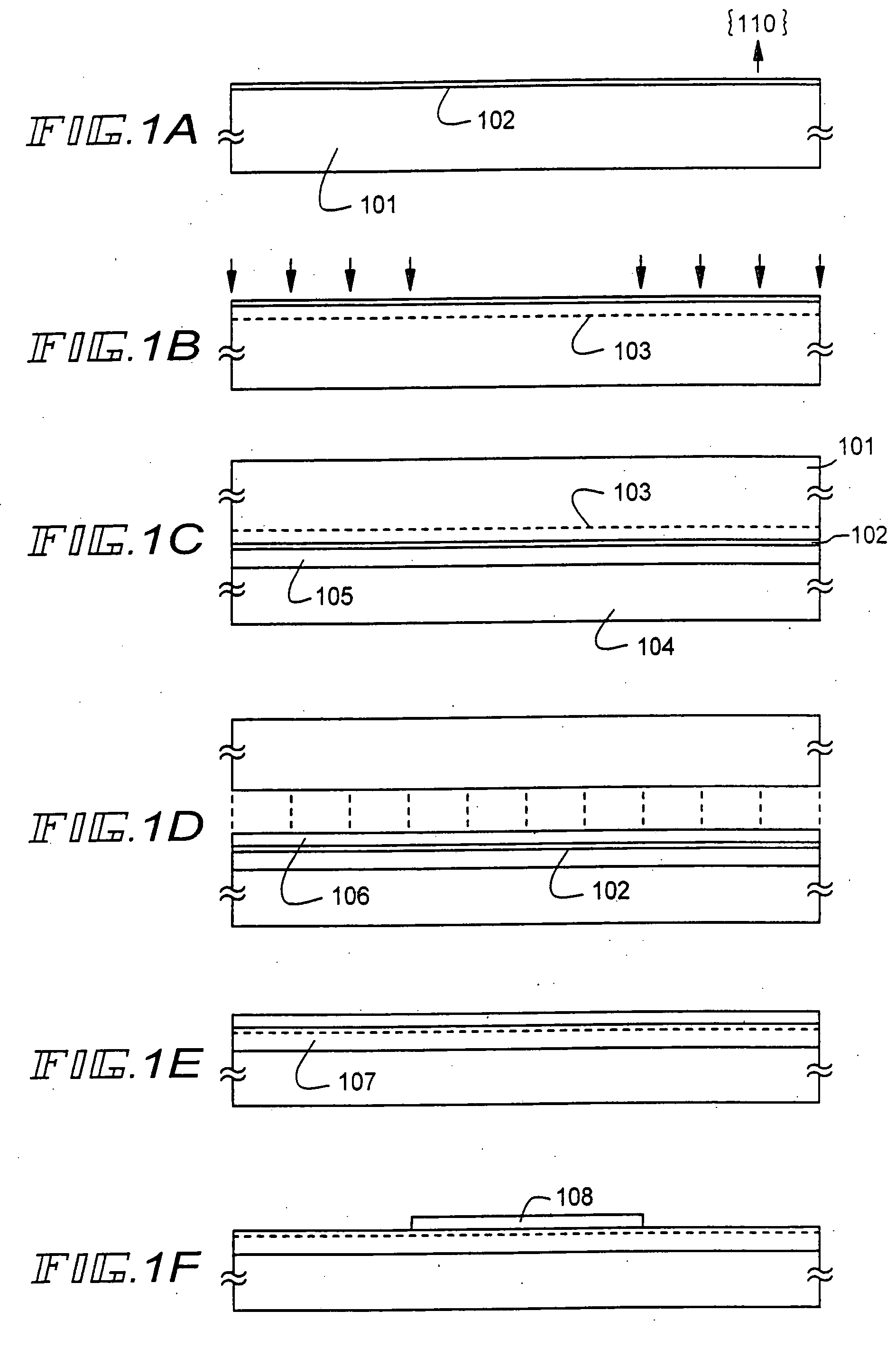

Method of fabricating a semiconductor device

A semiconductor device with high reliability is provided using an SOI substrate. When the SOI substrate is fabricated by using a technique typified by SIMOX, ELTRAN, or Smart-Cut, a single crystal semiconductor substrate having a main surface (crystal face) of a {110} plane is used. In such an SOI substrate, adhesion between a buried insulating layer as an under layer and a single crystal silicon layer is high, and it becomes possible to realize a semiconductor device with high reliability.

Owner:SEMICON ENERGY LAB CO LTD

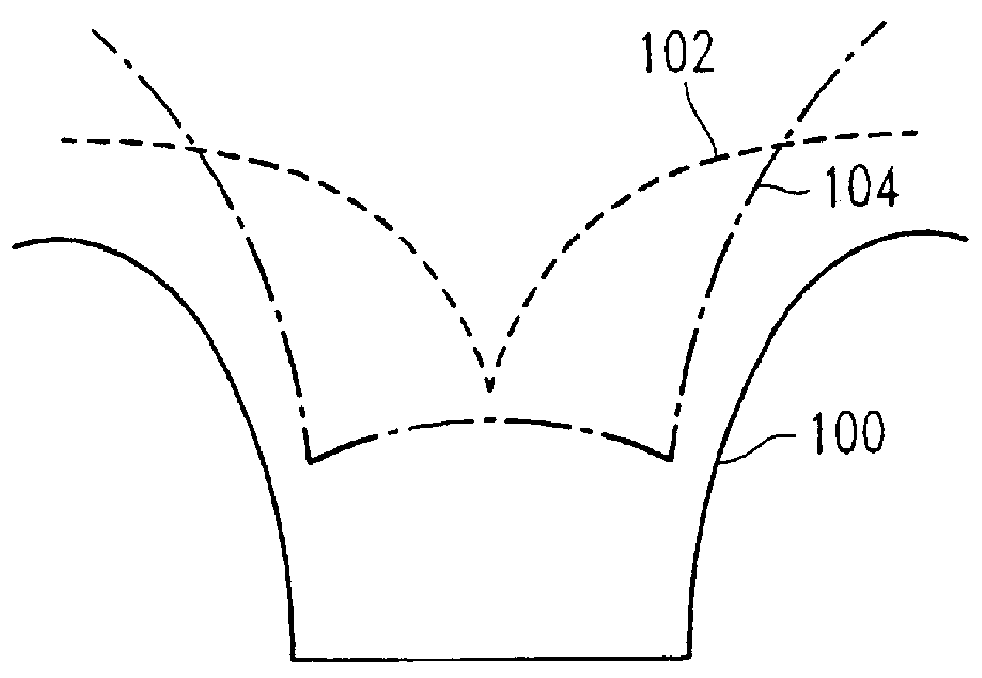

Process for control of the shape of the etch front in the etching of polysilicon

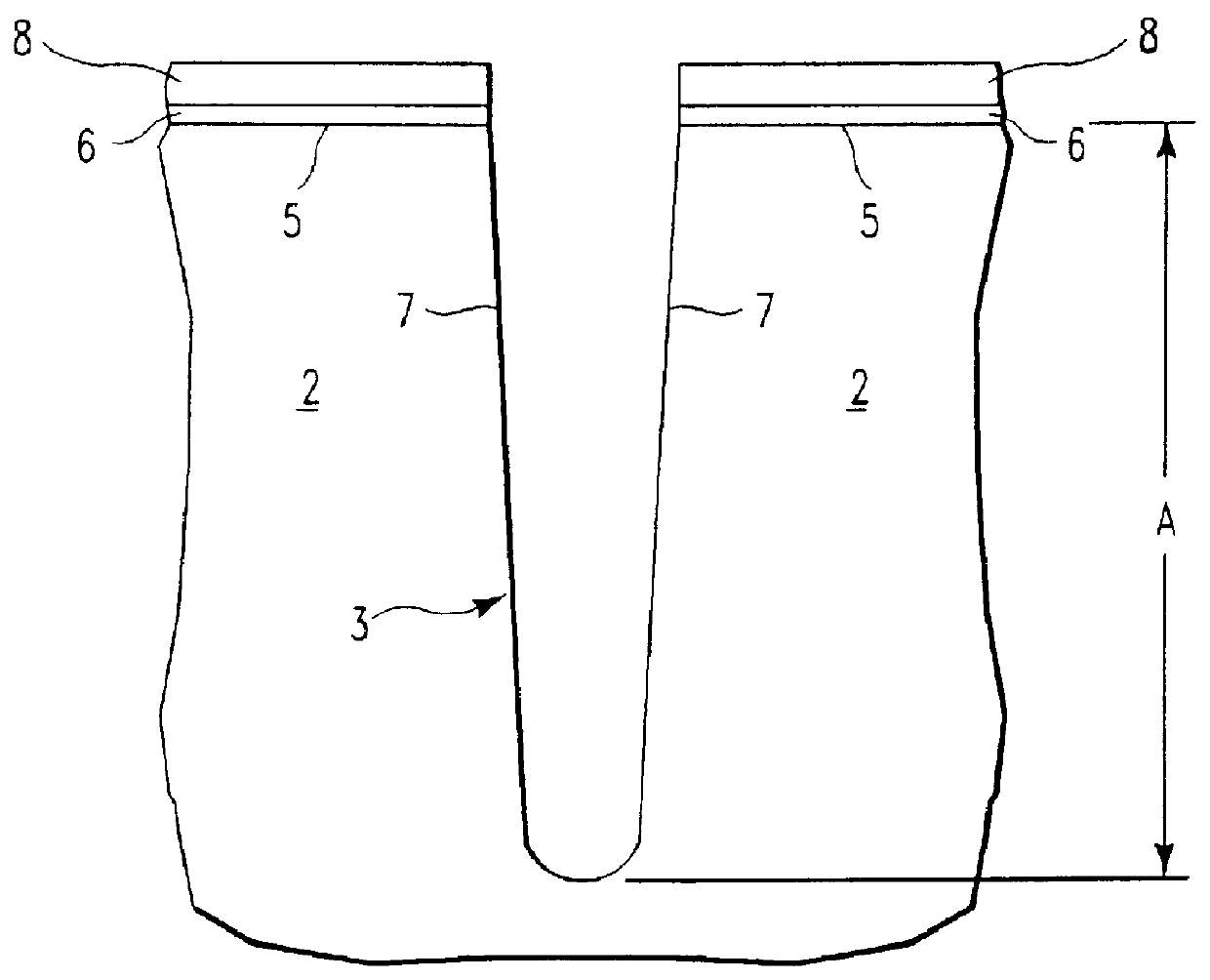

The present disclosure pertains to our discovery that the use of a particular combination of etchant gases results in the formation of a substantially flat etch front for polysilicon etching applications. In general, the process of the invention is useful for controlling the shape of the etch front during the etchback of polysilicon. Typically, the process comprises isotropically etching the polysilicon using a plasma produced from a plasma source gas comprising a particular combination of reactive species which selectively etch polysilicon. The plasma source gas comprises from about 80% to about 95% by volume of a fluorine-comprising gas, and from about 5% to about 20% by volume of an additive gas selected from a group consisting of a bromine-comprising gas, a chlorine-comprising gas, an iodine-comprising gas, or a combination thereof. One preferred mixture is SF6, Cl2 and HBr. A preferred method of the invention, used to perform recess etchback of a polysilicon-filled trench in a substrate, comprises the following steps: a) providing a trench 3 formed in a semiconductor structure, wherein the structure includes a substrate 2, at least one gate dielectric layer 6 overlying a surface of the substrate, and at least one etch barrier layer 8 overlying the gate dielectric layer; b) forming a conformal dielectric film 10 overlying the etch barrier layer and the sidewall and bottom of the trench; c) filling the trench with a layer of polysilicon 12 which overlies the conformal dielectric film; and d) isotropically etching the polysilicon back to a predetermined depth within the trench using a plasma produced from the invention plasma source gas. Also disclosed herein is a method of forming a trench capacitor in a single-crystal silicon substrate, the trench capacitor including a dielectric collar and a buried strap.

Owner:APPLIED MATERIALS INC

Method of fabricating a semiconductor device

A semiconductor device with high reliability is provided using an SOI substrate. When the SOI substrate is fabricated by using a technique typified by SIMOX, ELTRAN, or Smart-Cut, a single crystal semiconductor substrate having a main surface (crystal face) of a {110} plane is used. In such an SOI substrate, adhesion between a buried insulating layer as an under layer and a single crystal silicon layer is high, and it becomes possible to realize a semiconductor device with high reliability.

Owner:SEMICON ENERGY LAB CO LTD

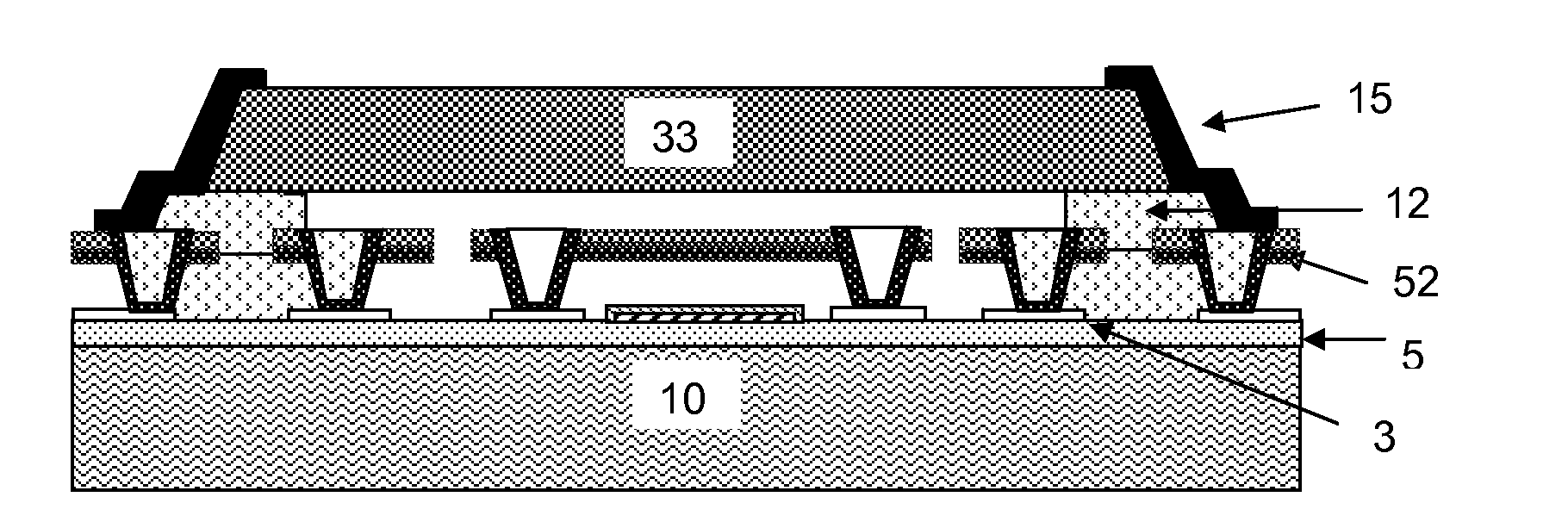

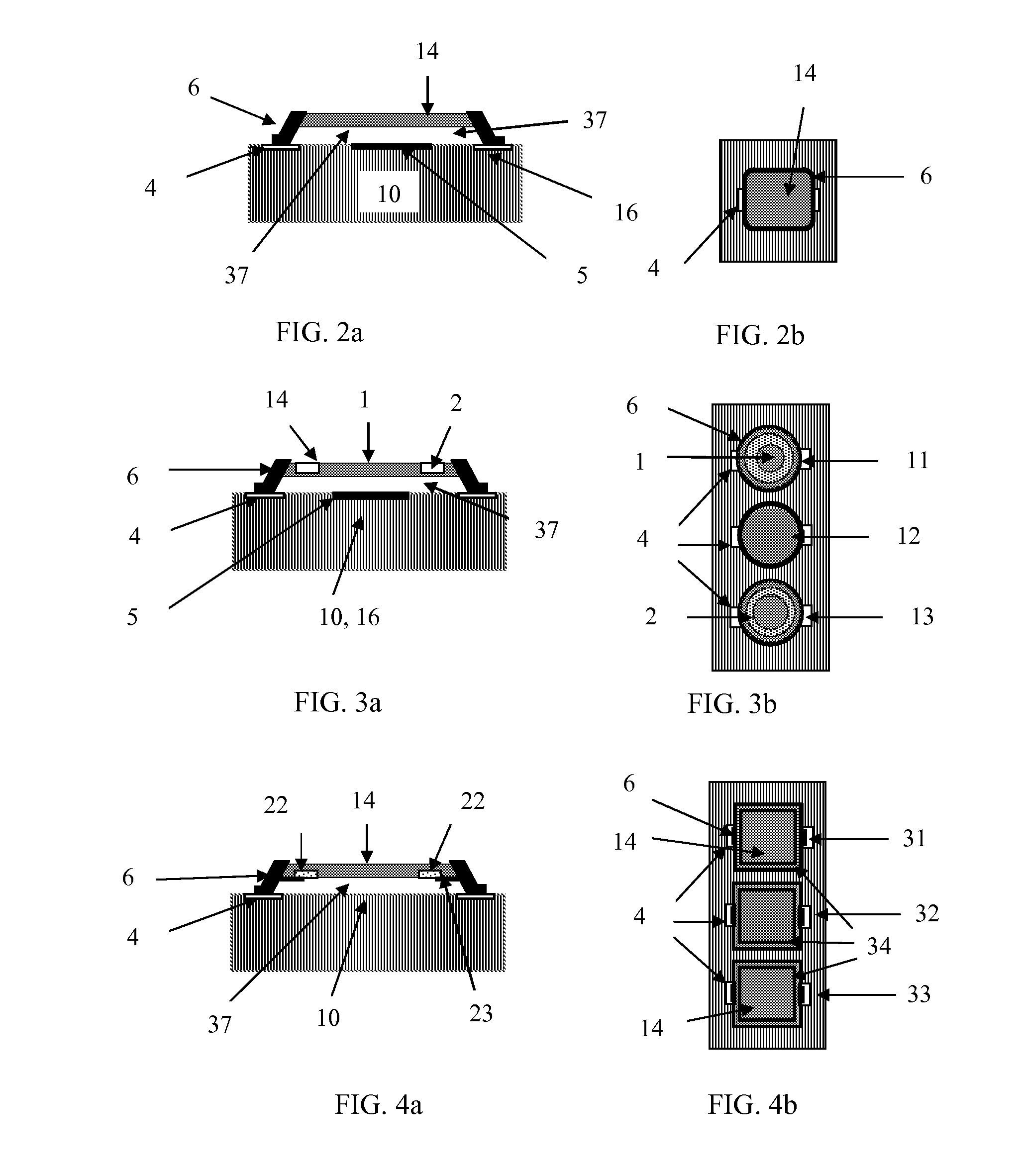

System and method of fabricating micro cavities

InactiveUS20080308920A1Decorative surface effectsSemiconductor/solid-state device detailsEpoxyMicroelectromechanical systems

A system and method for manufacturing micro cavity packaging enclosure at the wafer level using MEMS (MicroElectroMechanical Systems) process, wherein micro cavities are formed from epoxy-bonded single-crystalline silicon wafer as its cap, epoxy and deposited metal or insulator as at least part of its sidewall, on substrate wafers.

Owner:WAN CHANG FENG

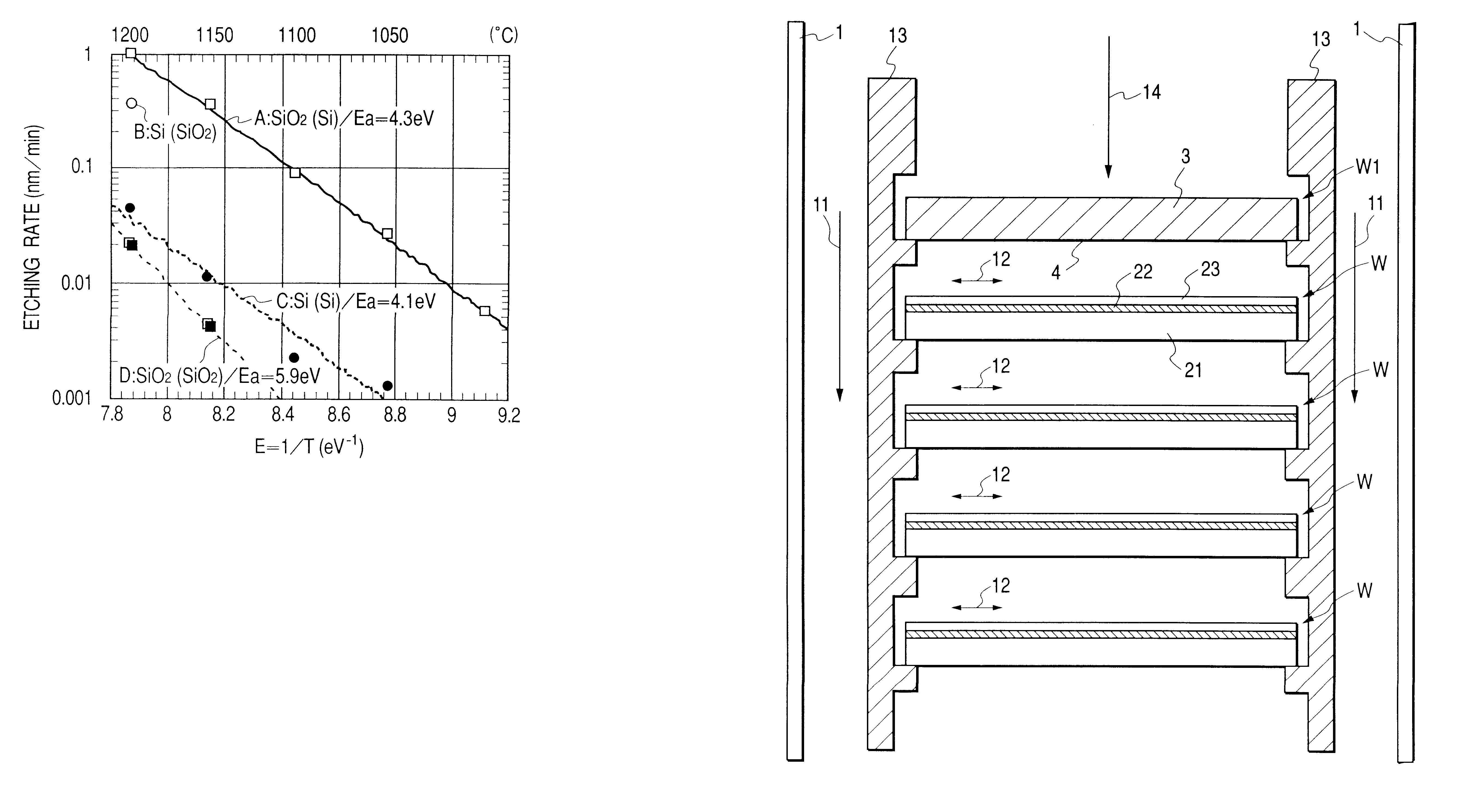

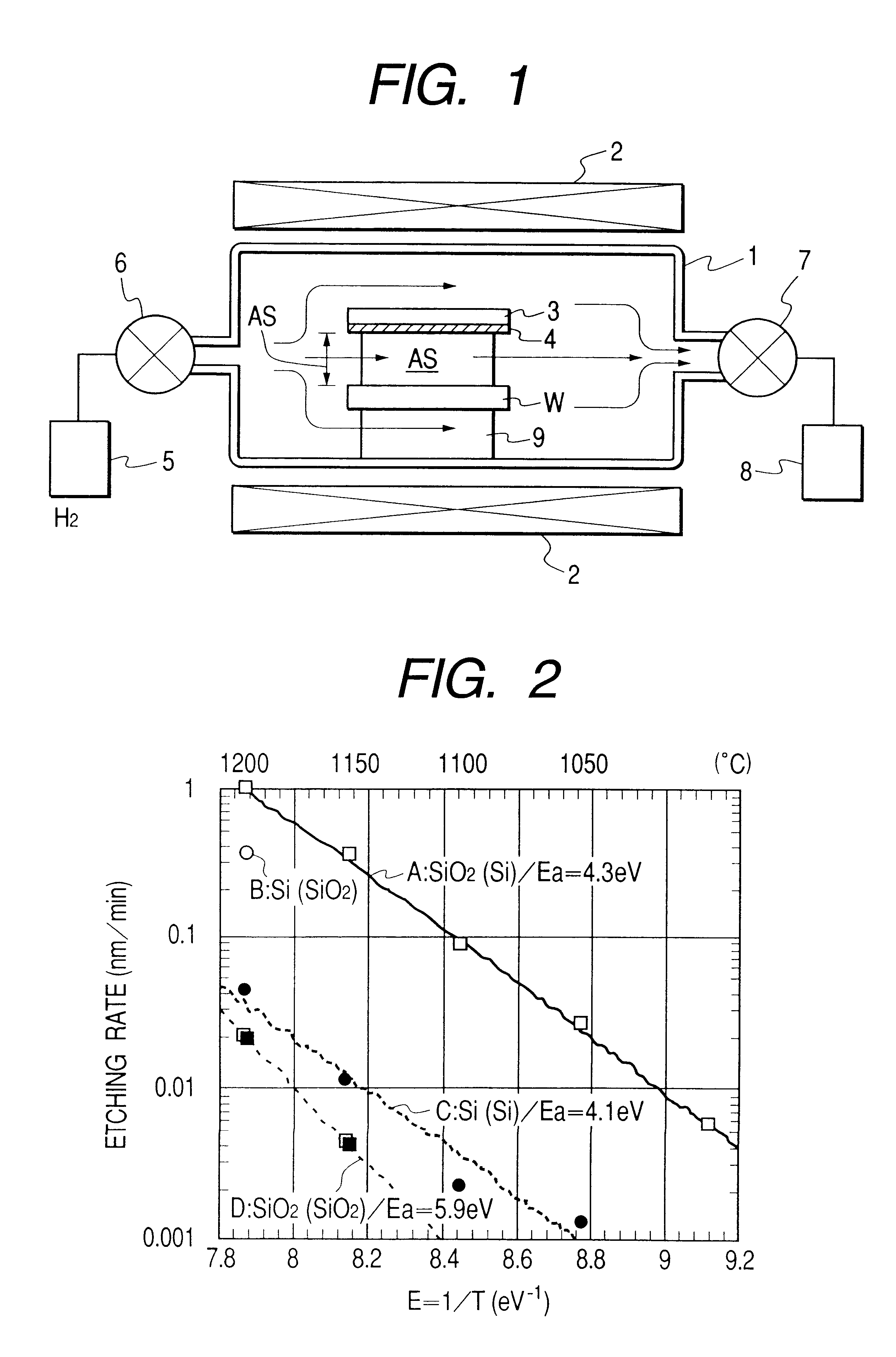

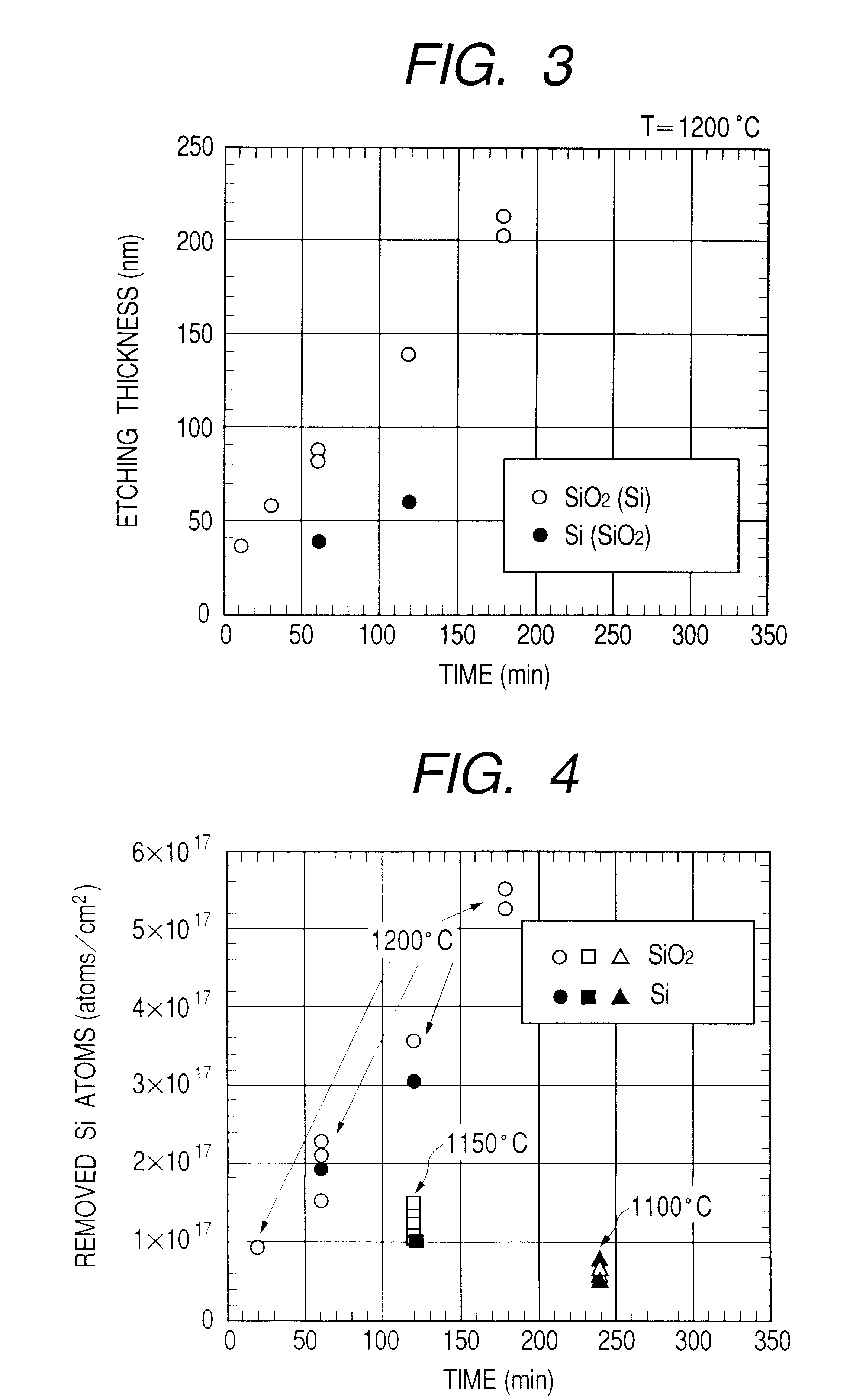

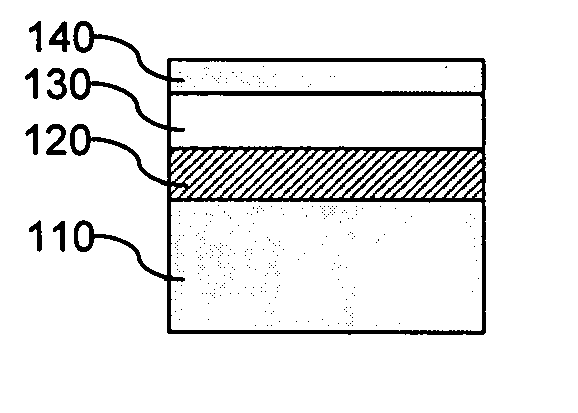

Method and apparatus for heat-treating an SOI substrate and method of preparing an SOI substrate by using the same

InactiveUS6171982B1Reduce the presence of impuritiesMaintain consistencyMuffle furnacesSolid-state devicesWaferingHydrogen

An SOI substrate having on the surface thereof a single crystal silicon film formed on an insulator is heat-treated in a hydrogen-containing reducing atmosphere in order to smooth the surface and reduce the boron concentration without damaging the film thickness uniformity in a single wafer and among different wafers. The method is characterized in that the single crystal silicon film is arranged opposite to a member of non-oxidized silicon for heat treatment.

Owner:CANON KK

Monolithically integrated light emitting devices

ActiveUS20070105256A1Layered productsSemiconductor/solid-state device detailsDevice materialSingle crystal

Methods and structures for monolithically integrating monocrystalline silicon and monocrystalline non-silicon materials and devices are provided. In one structure, a monolithically integrated semiconductor device structure comprises a silicon substrate and a first monocrystalline semiconductor layer disposed over the silicon substrate, wherein the first monocrystalline semiconductor layer has a lattice constant different from a lattice constant of relaxed silicon. The structure further includes an insulating layer disposed over the first monocrystalline semiconductor layer in a first region and a monocrystalline silicon layer disposed over the insulating layer in the first region. The structure includes at least one silicon-based electronic device including an element including at least a portion of the monocrystalline silicon layer. The structure also includes a second monocrystalline semiconductor layer disposed over at least a portion of the first monocrystalline semiconductor layer in a second region and absent from the first region, wherein the second monocrystalline semiconductor layer has a lattice constant different from the lattice constant of relaxed silicon. The structure includes at least one III-V light-emitting device including an active region including at least a portion of the second monocrystalline semiconductor layer.

Owner:MASSACHUSETTS INST OF TECH