Patents

Literature

6916results about How to "Total current drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Amorphous Oxide And Thin Film Transistor

InactiveUS20070194379A1High ionicityGeneration of oxygen defects is less frequentTransistorVacuum evaporation coatingCharge carrierElectron

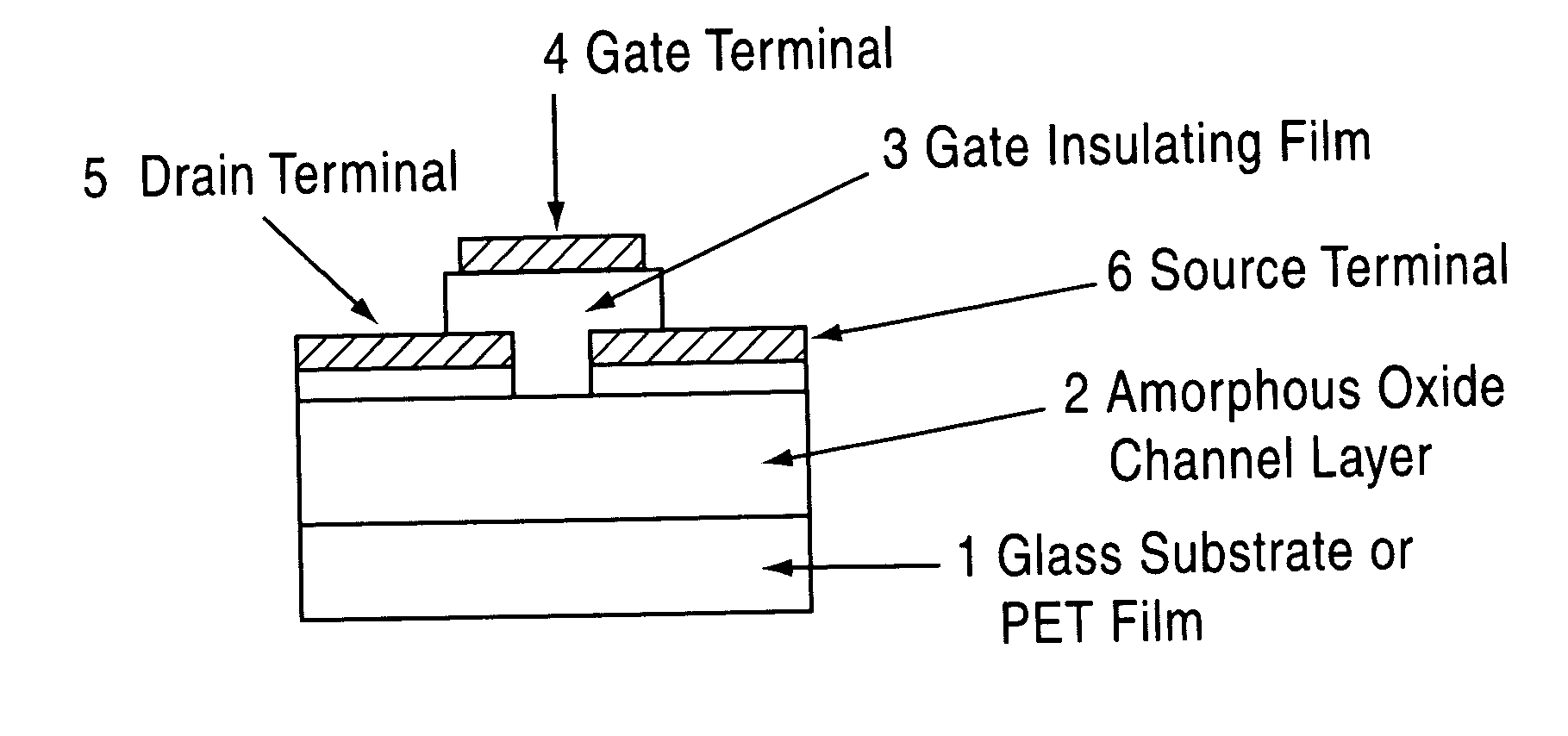

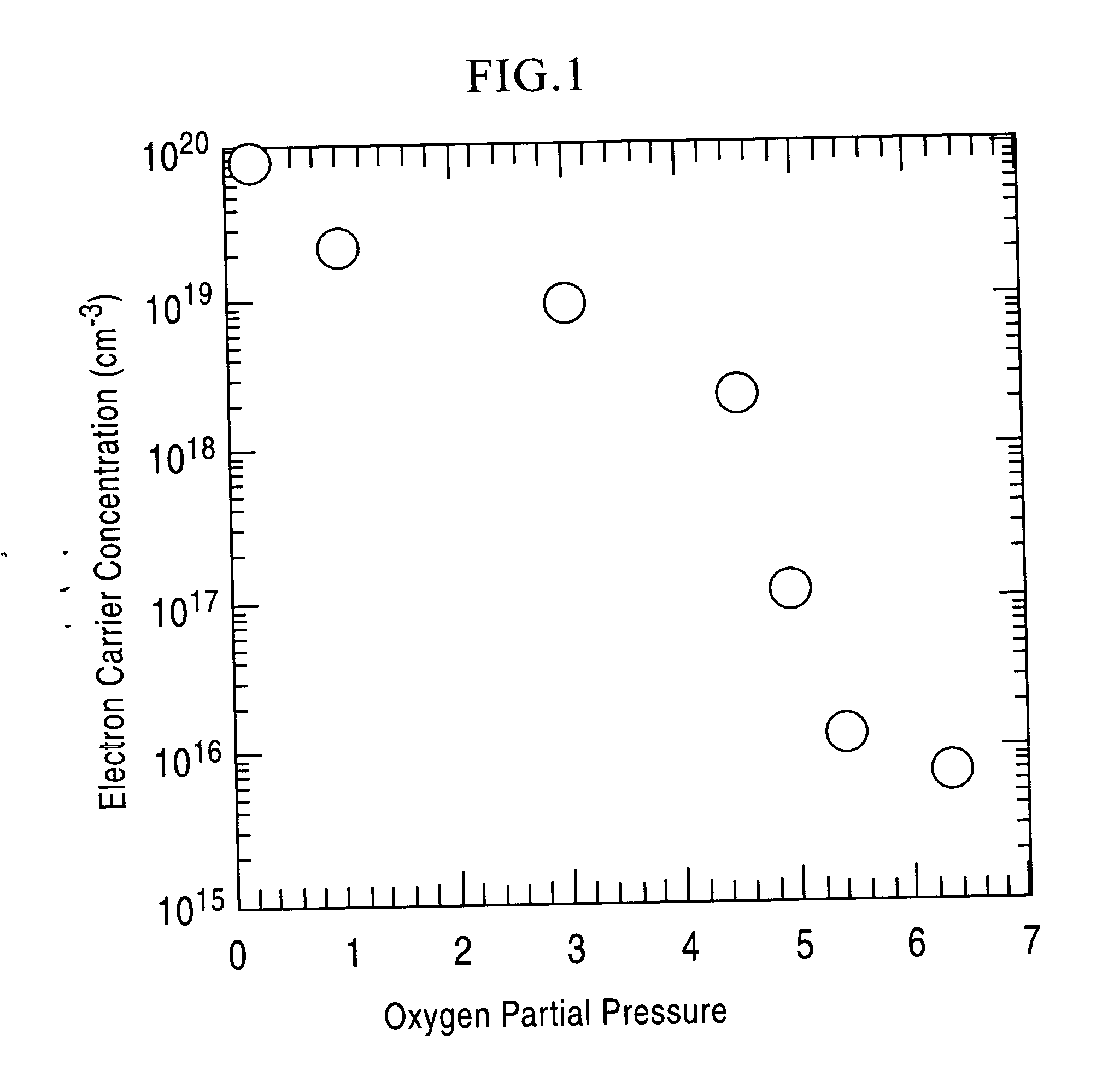

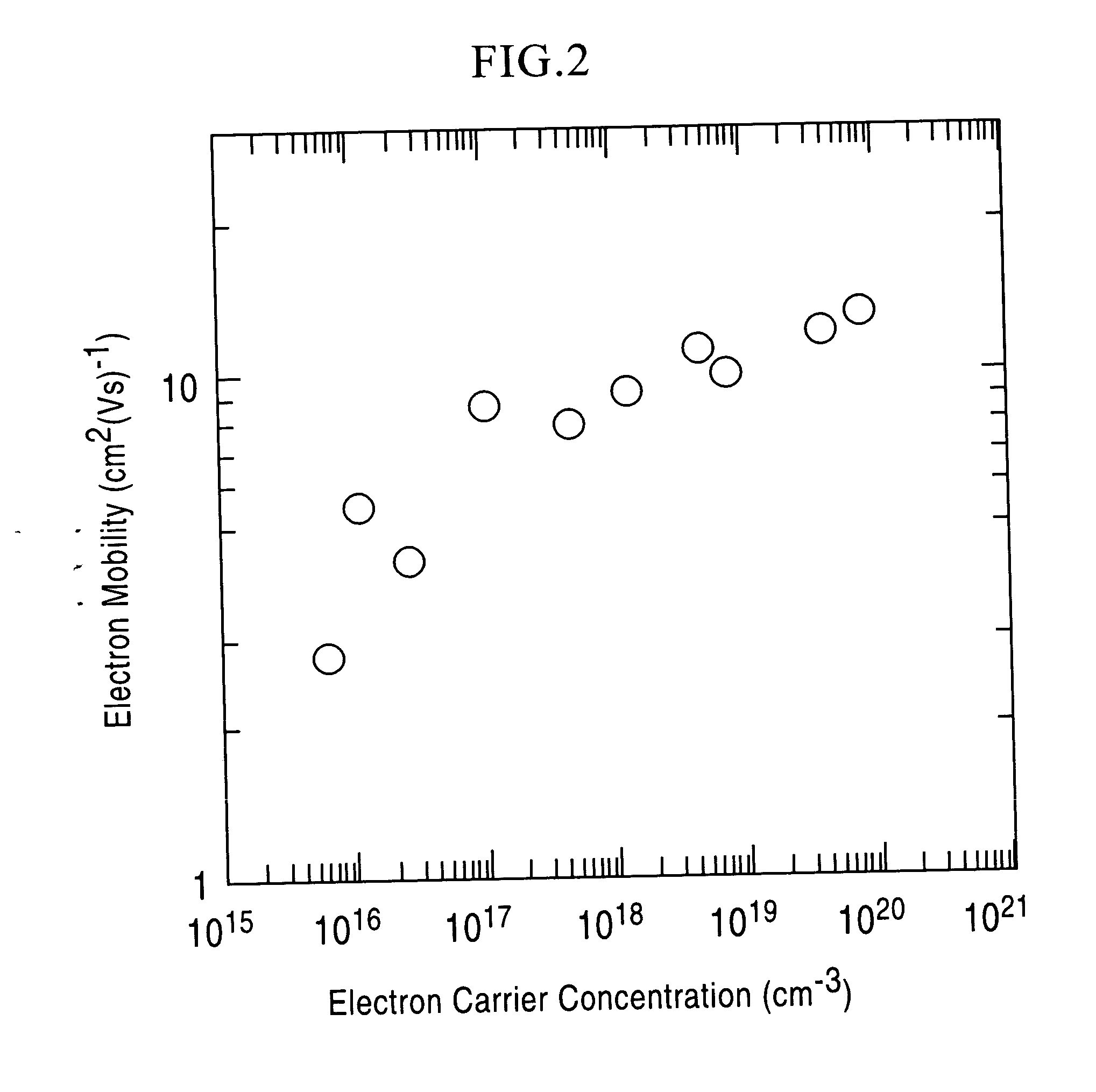

The present invention relates to an amorphous oxide and a thin film transistor using the amorphous oxide. In particular, the present invention provides an amorphous oxide having an electron carrier concentration less than 1018 / cm3, and a thin film transistor using such an amorphous oxide. In a thin film transistor having a source electrode 6, a drain electrode 5, a gate electrode 4, a gate insulating film 3, and a channel layer 2, an amorphous oxide having an electron carrier concentration less than 1018 / cm3 is used in the channel layer 2.

Owner:JAPAN SCI & TECH CORP

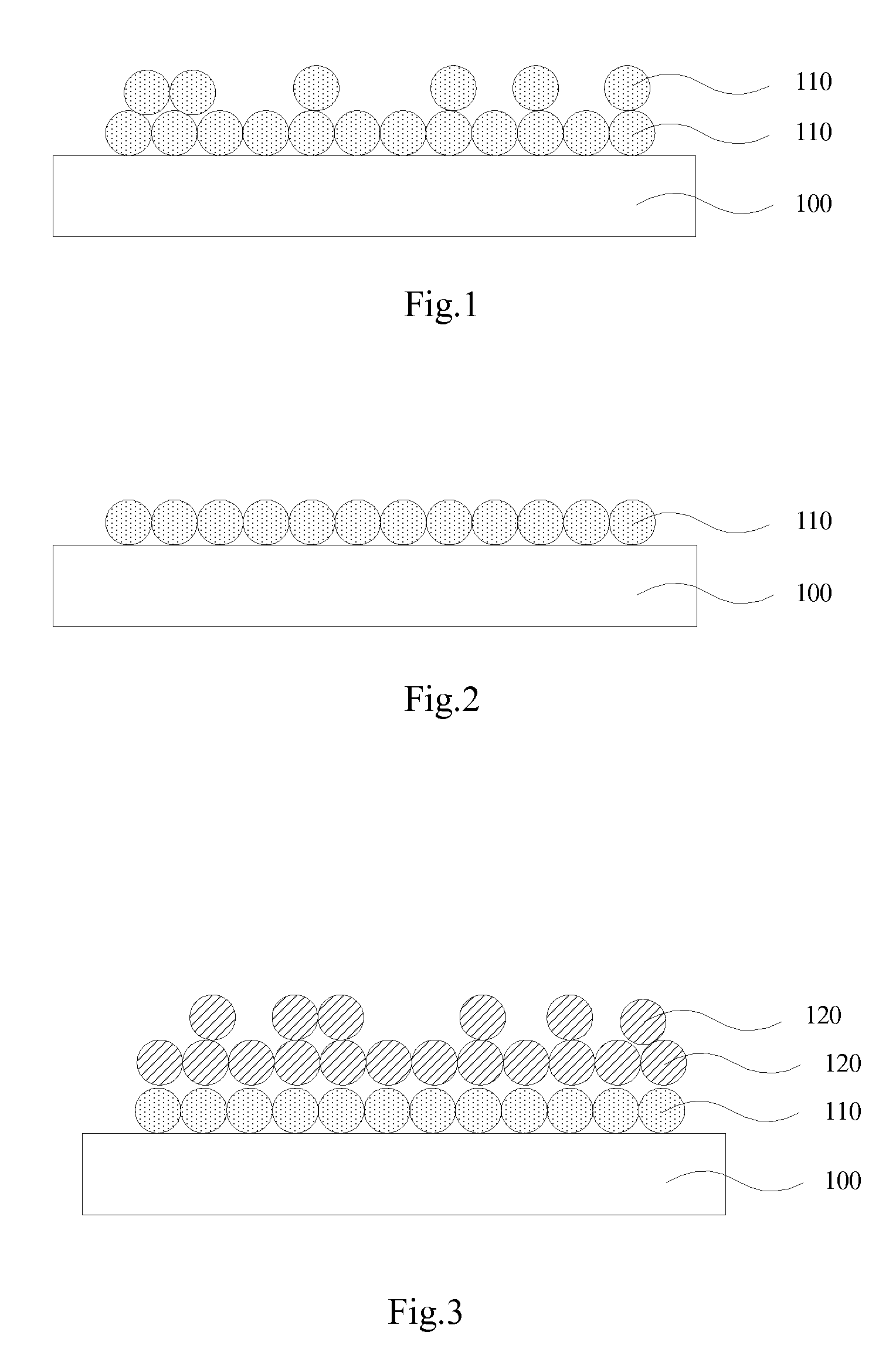

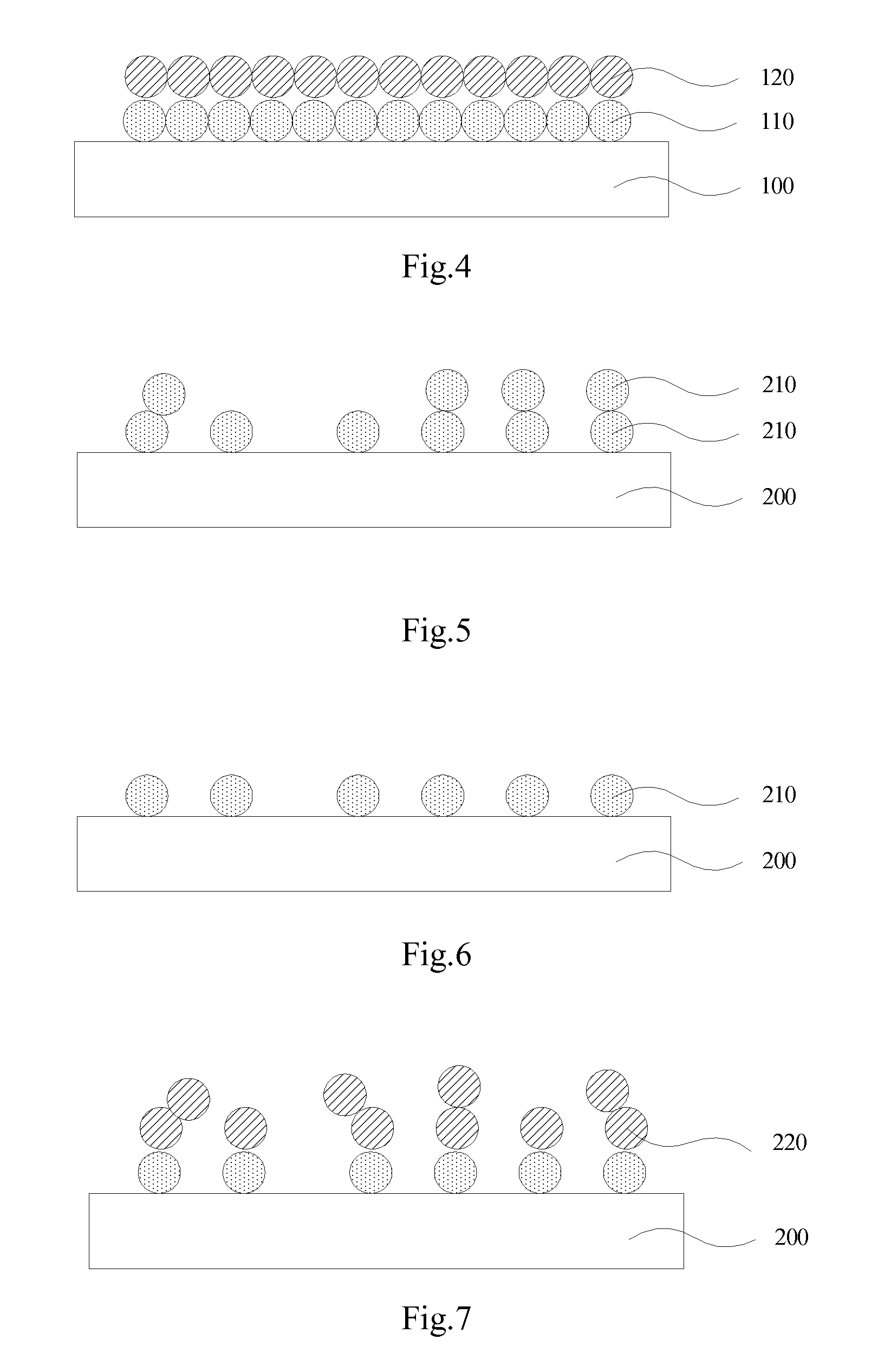

Atomic Layer Deposition Method and Semiconductor Device Formed by the Same

ActiveUS20080315292A1Improve storage capability capabilityImprove capability memory isolation capabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingAtomic layer depositionDielectric layer

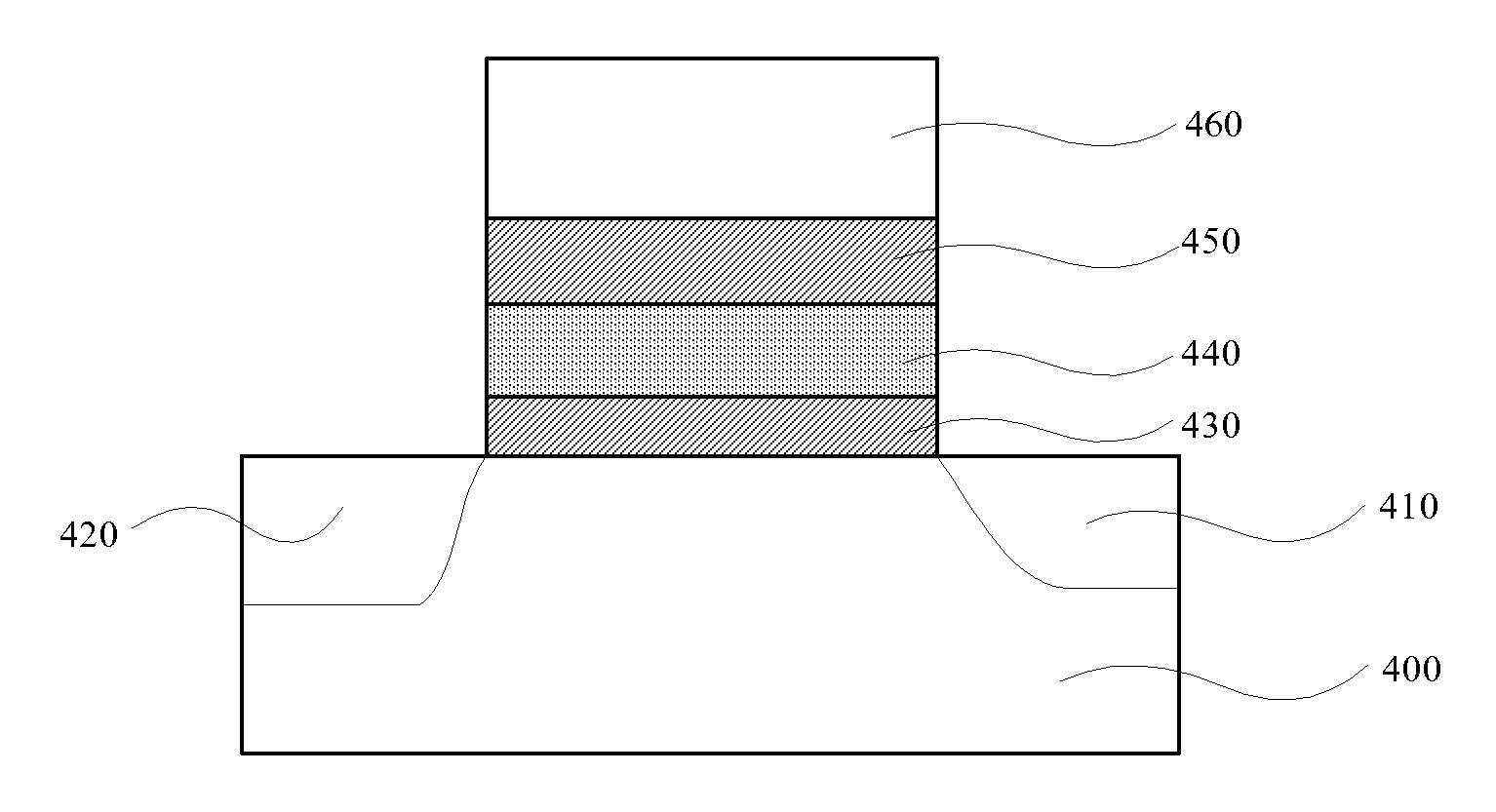

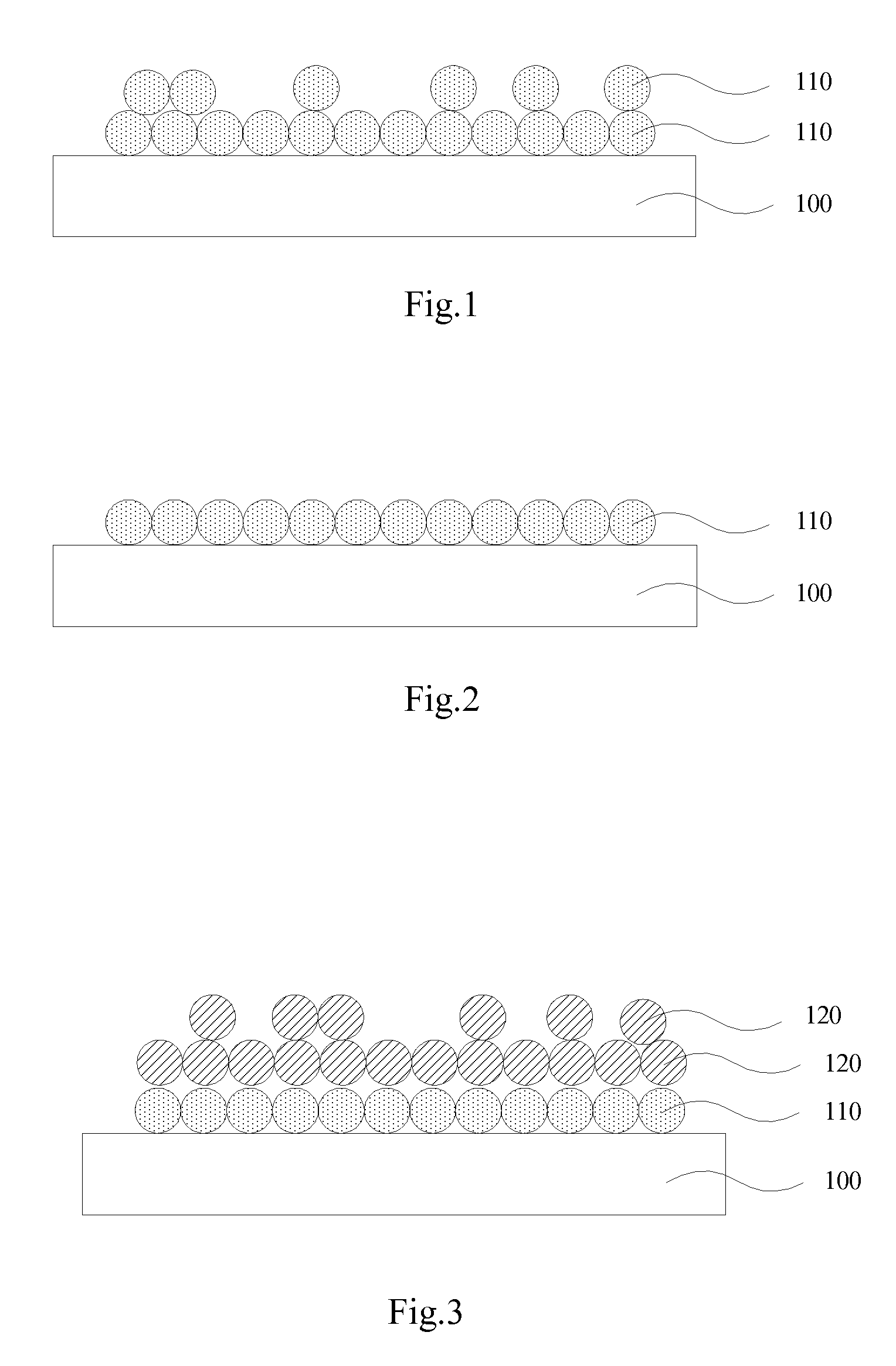

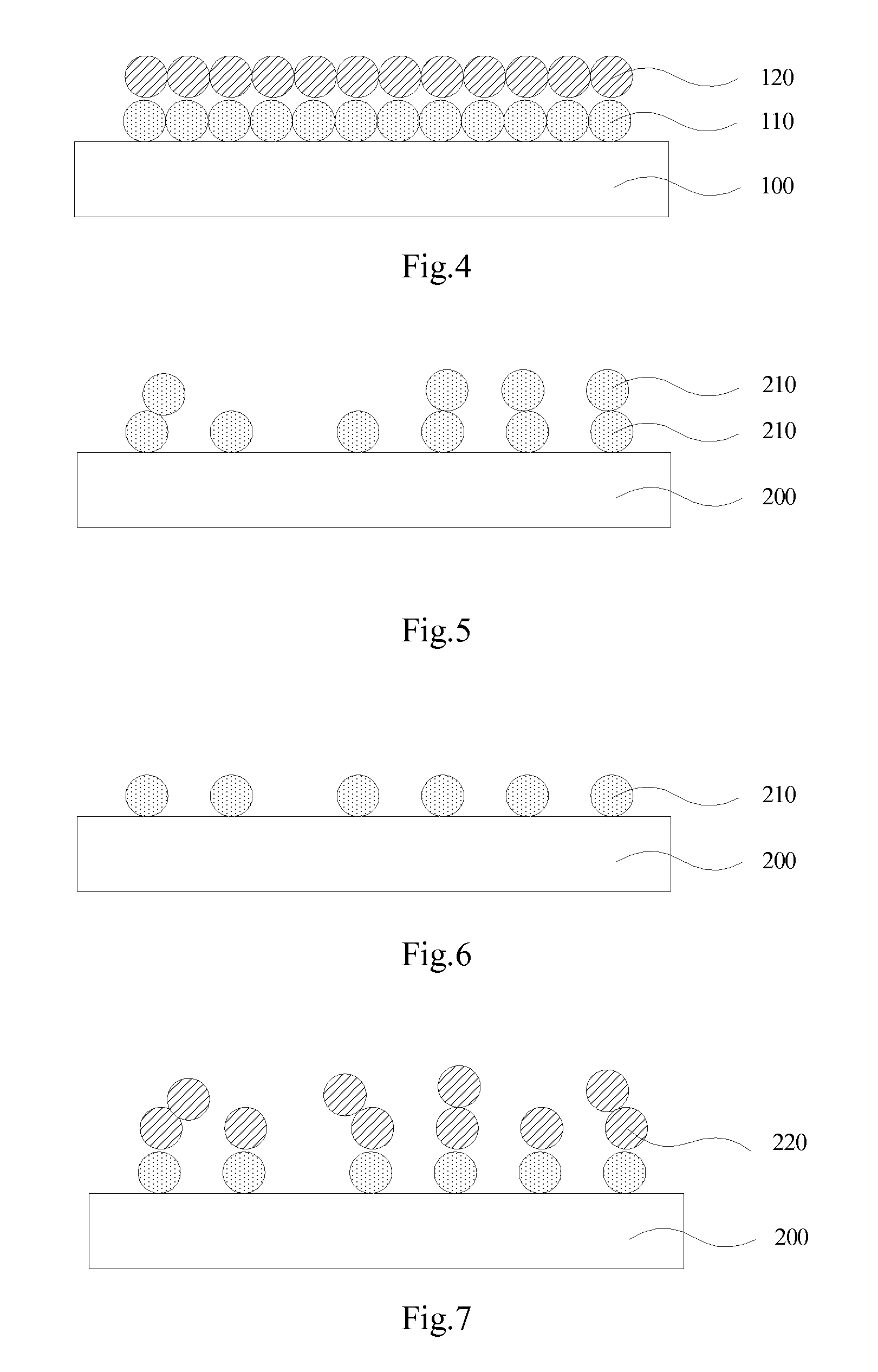

There is provided a method of manufacturing a semiconductor device, including the following steps: flowing a first precursor gas to the semiconductor substrate within a ALD chamber to form a first discrete monolayer on the semiconductor substrate; flowing an inert purge gas to the semiconductor substrate within the ALD chamber; flowing a second precursor gas to the ALD chamber to react with the first precursor gas which has formed the first monolayer, thereby forming a first discrete compound monolayer; and flowing an inert purge gas; forming a first dielectric layer to cover the discrete compound monolayer; forming a second third monolayer above first dielectric layer; and forming a second discrete compound monolayer; and forming a second dielectric layer to cover the second discrete compound monolayer above the first dielectric layer. There is also provided a semiconductor device formed by the ALD method.

Owner:SEMICON MFG INT (SHANGHAI) CORP

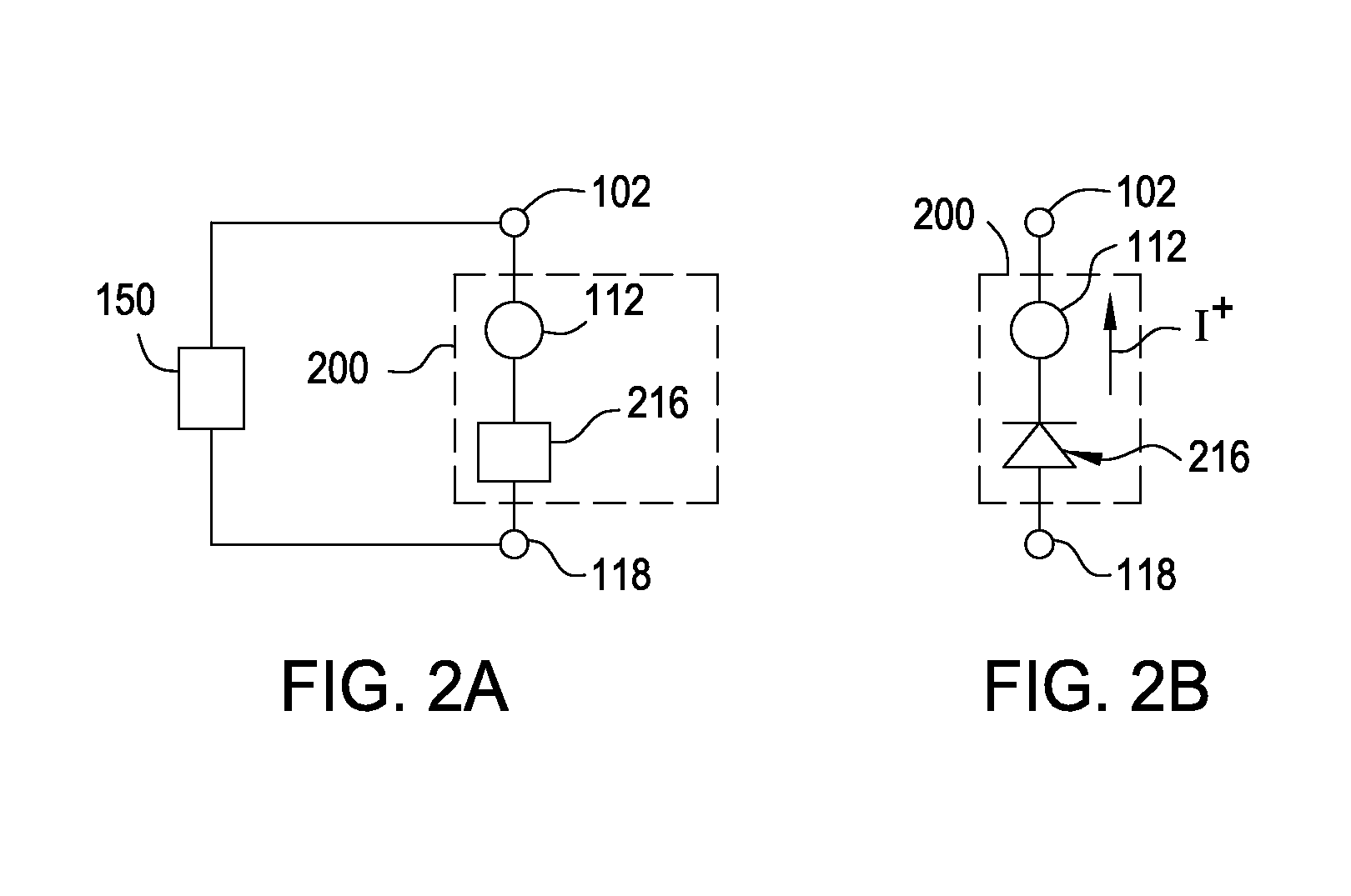

Nonvolatile memory device using a varistor as a current limiter element

ActiveUS20130214232A1Reduce voltageTotal current dropSolid-state devicesSemiconductor/solid-state device manufacturingSoftware engineeringMusic player

Embodiments of the invention include a method of forming a nonvolatile memory device that contains a resistive switching memory element that has improved device switching performance and lifetime, due to the addition of a current limiting component disposed therein. The electrical properties of the current limiting component are configured to lower the current flow through the variable resistance layer during the logic state programming steps by adding a fixed series resistance in the resistive switching memory element of the nonvolatile memory device. In some embodiments, the current limiting component comprises a varistor that is a current limiting material disposed within a resistive switching memory element in a nonvolatile resistive switching memory device. Typically, resistive switching memory elements may be formed as part of a high-capacity nonvolatile memory integrated circuit, which can be used in various electronic devices, such as digital cameras, mobile telephones, handheld computers, and music players.

Owner:KK TOSHIBA +1

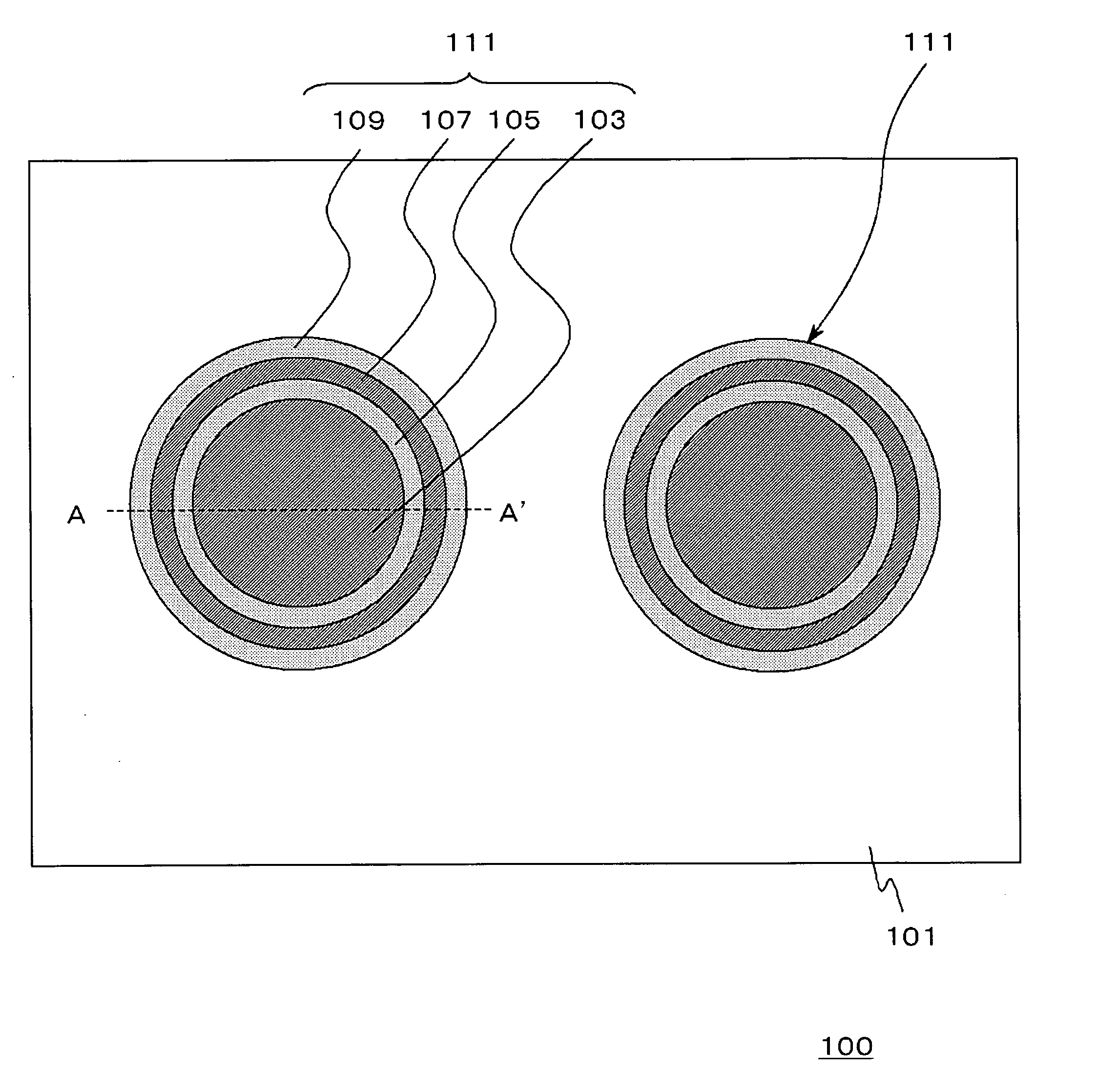

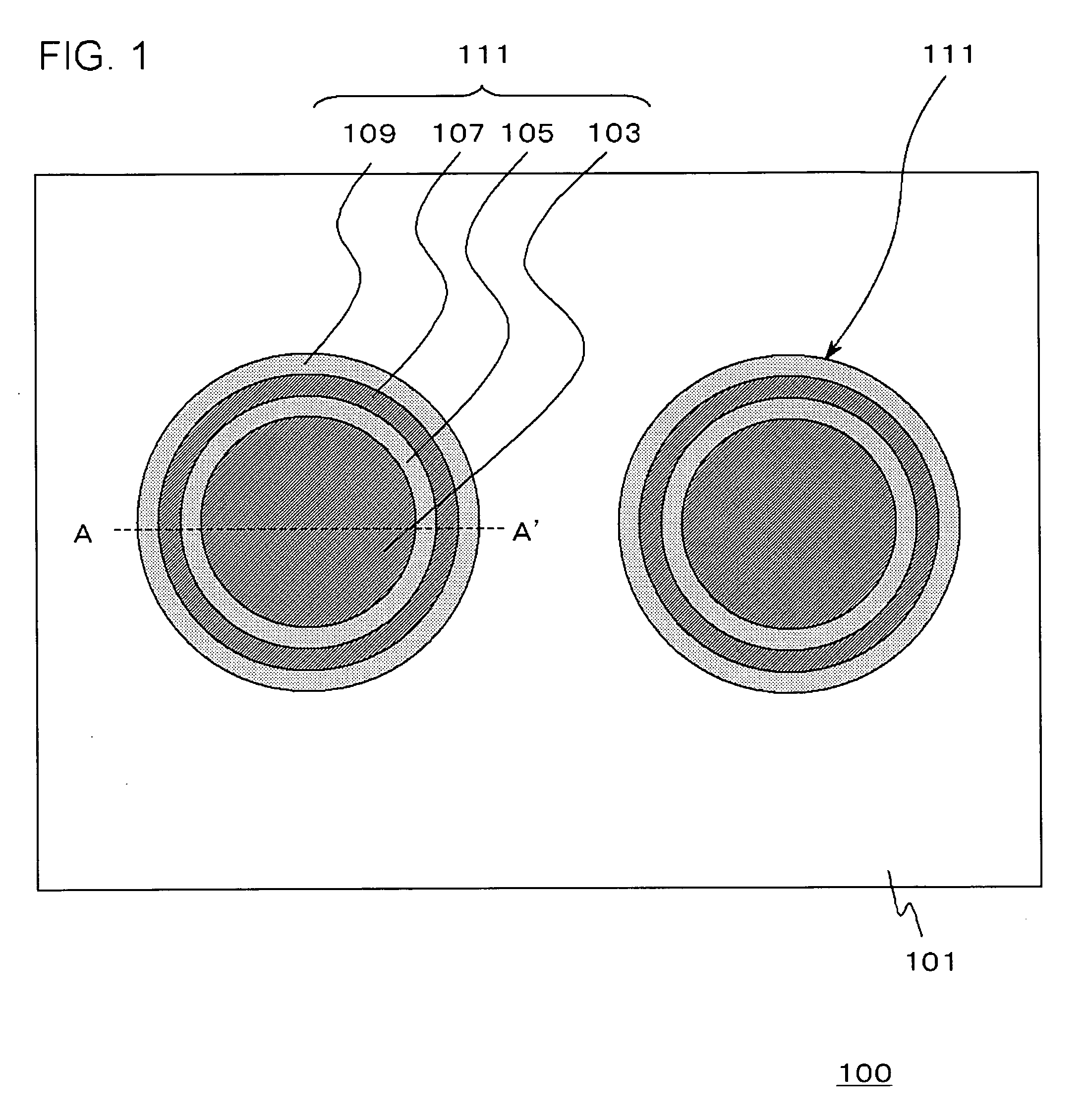

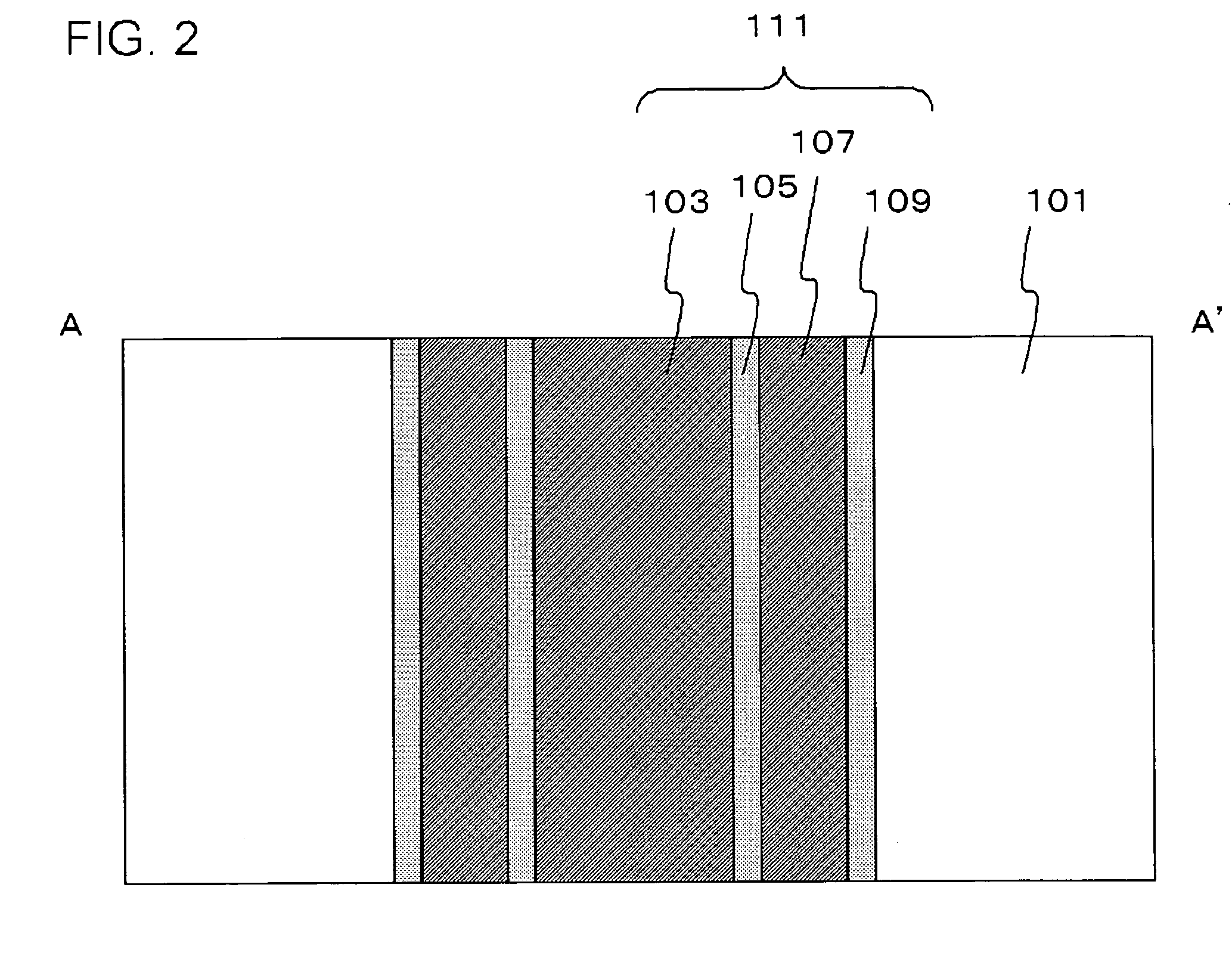

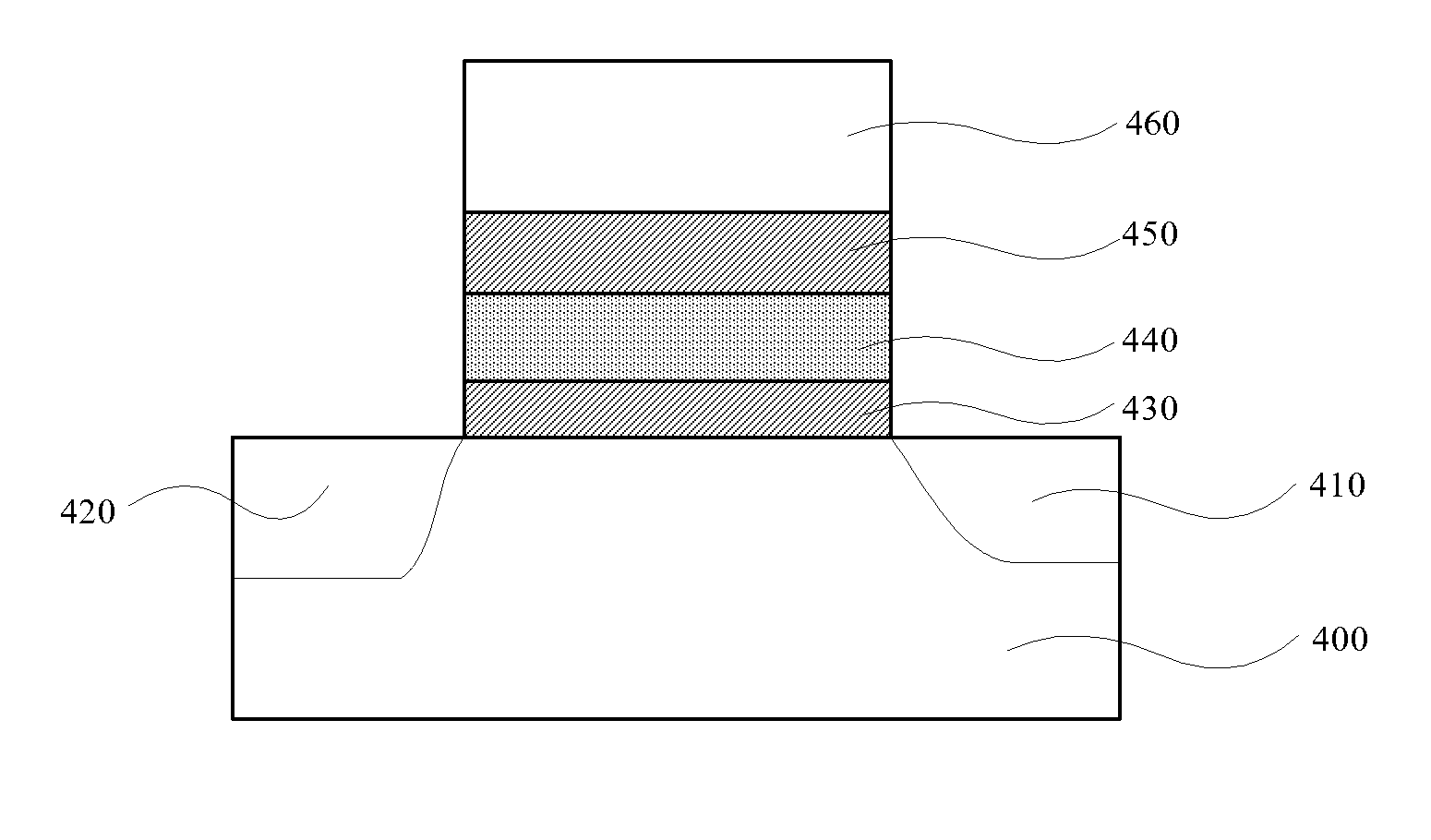

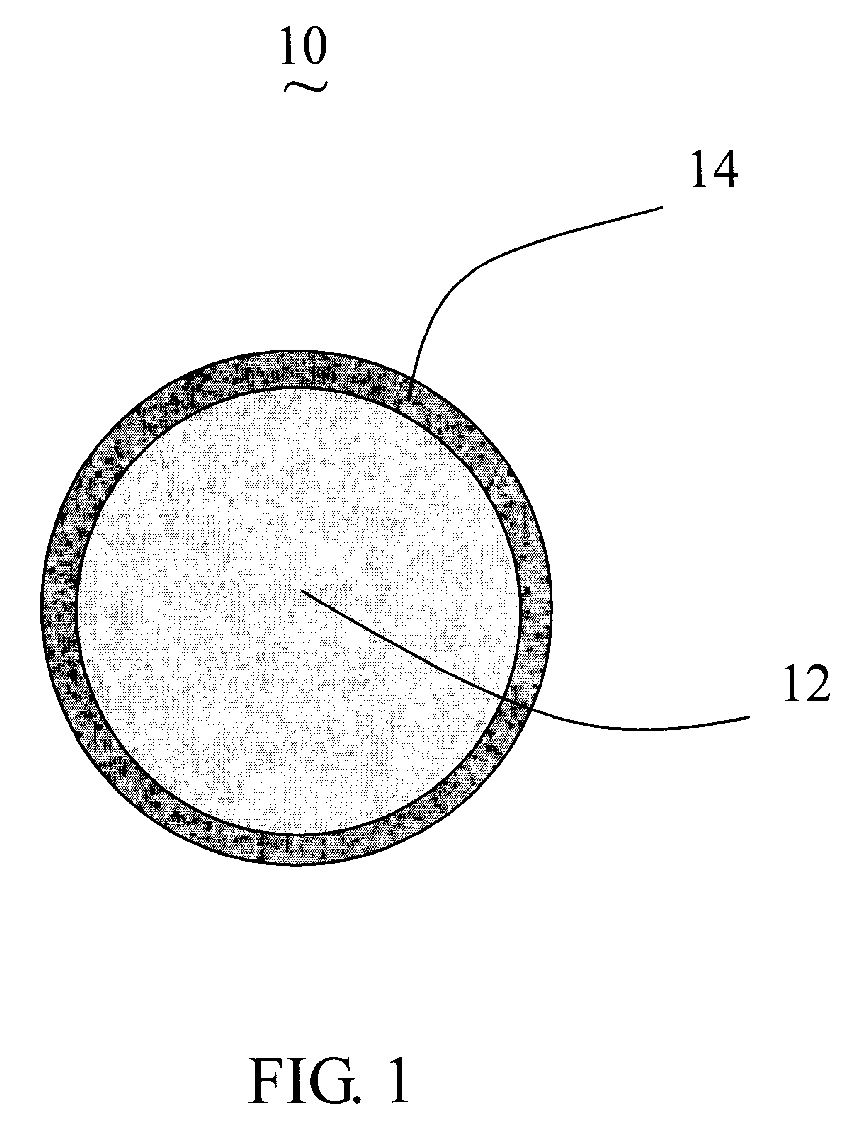

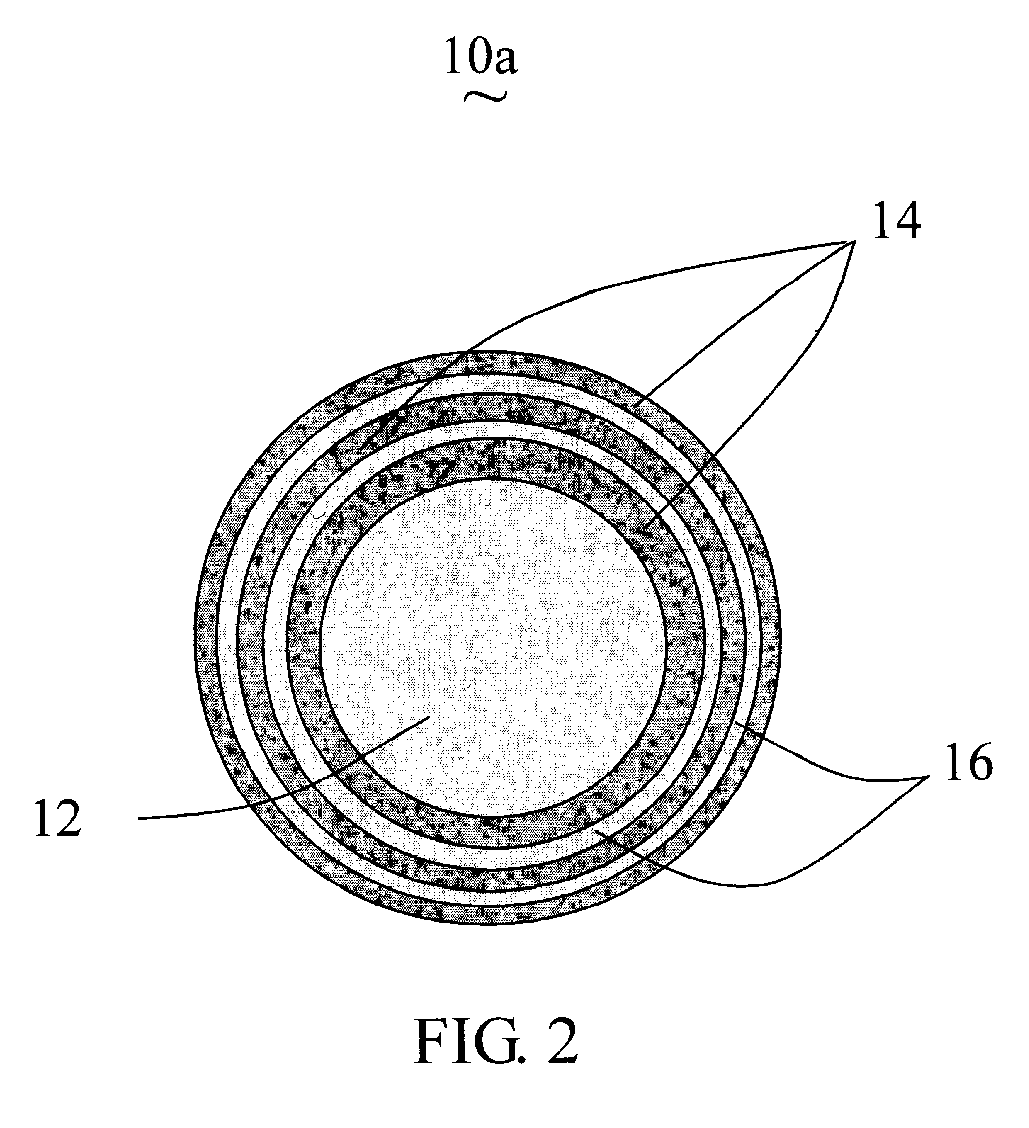

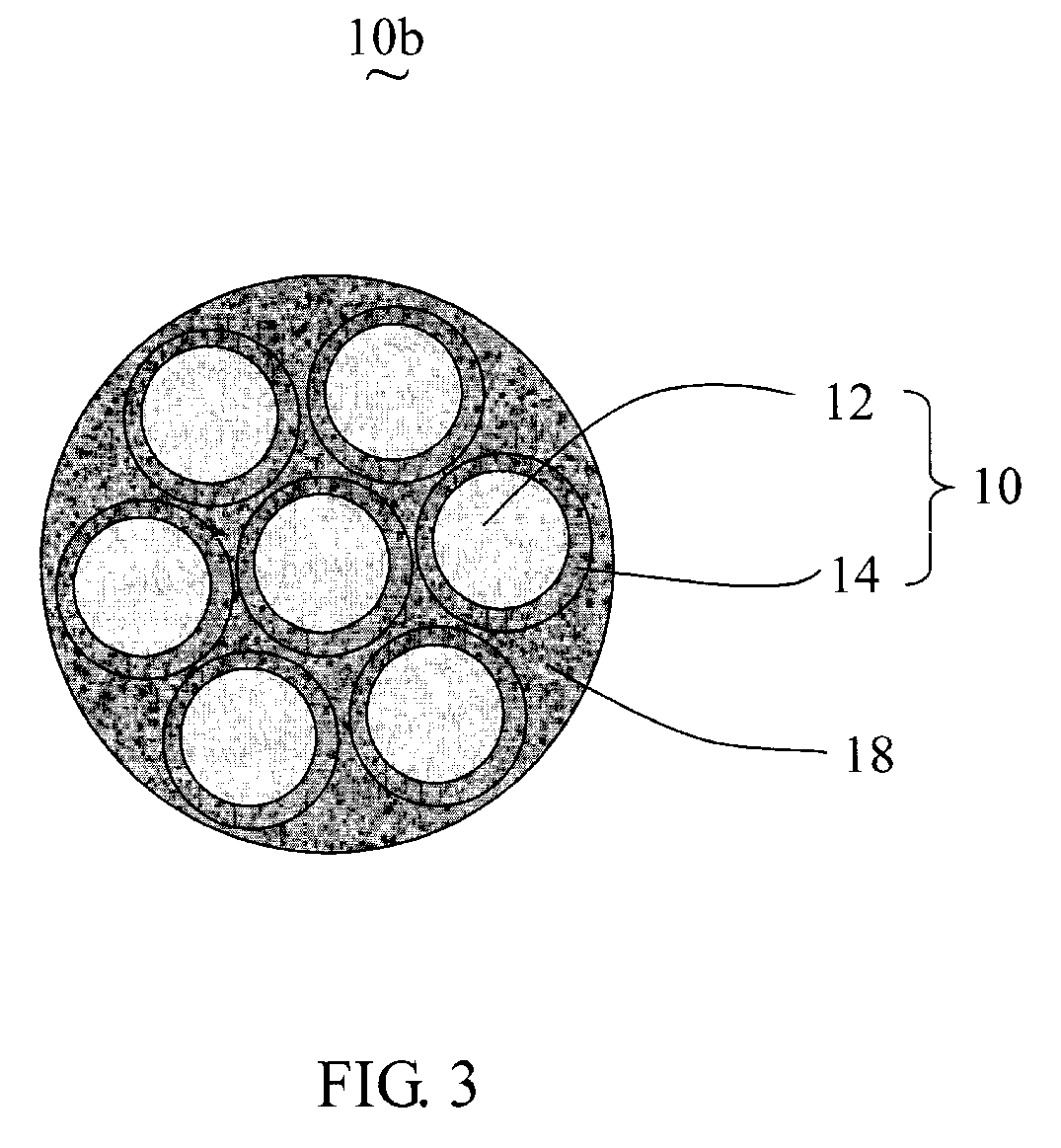

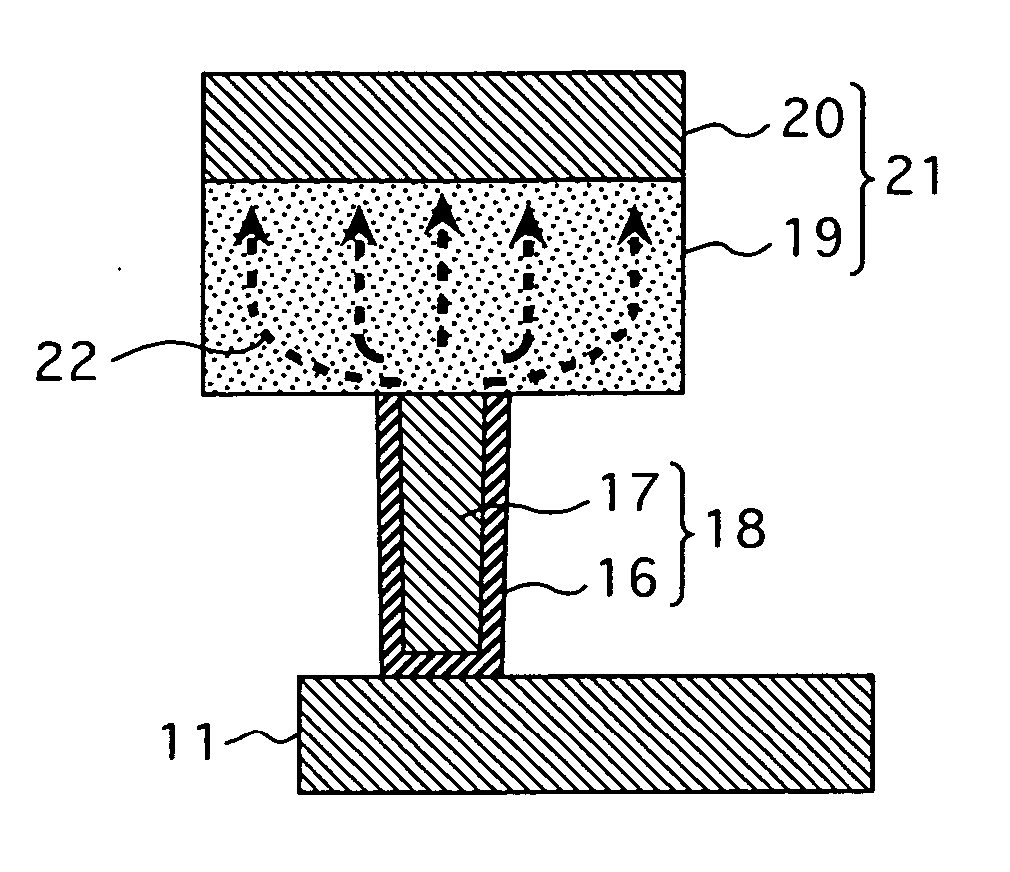

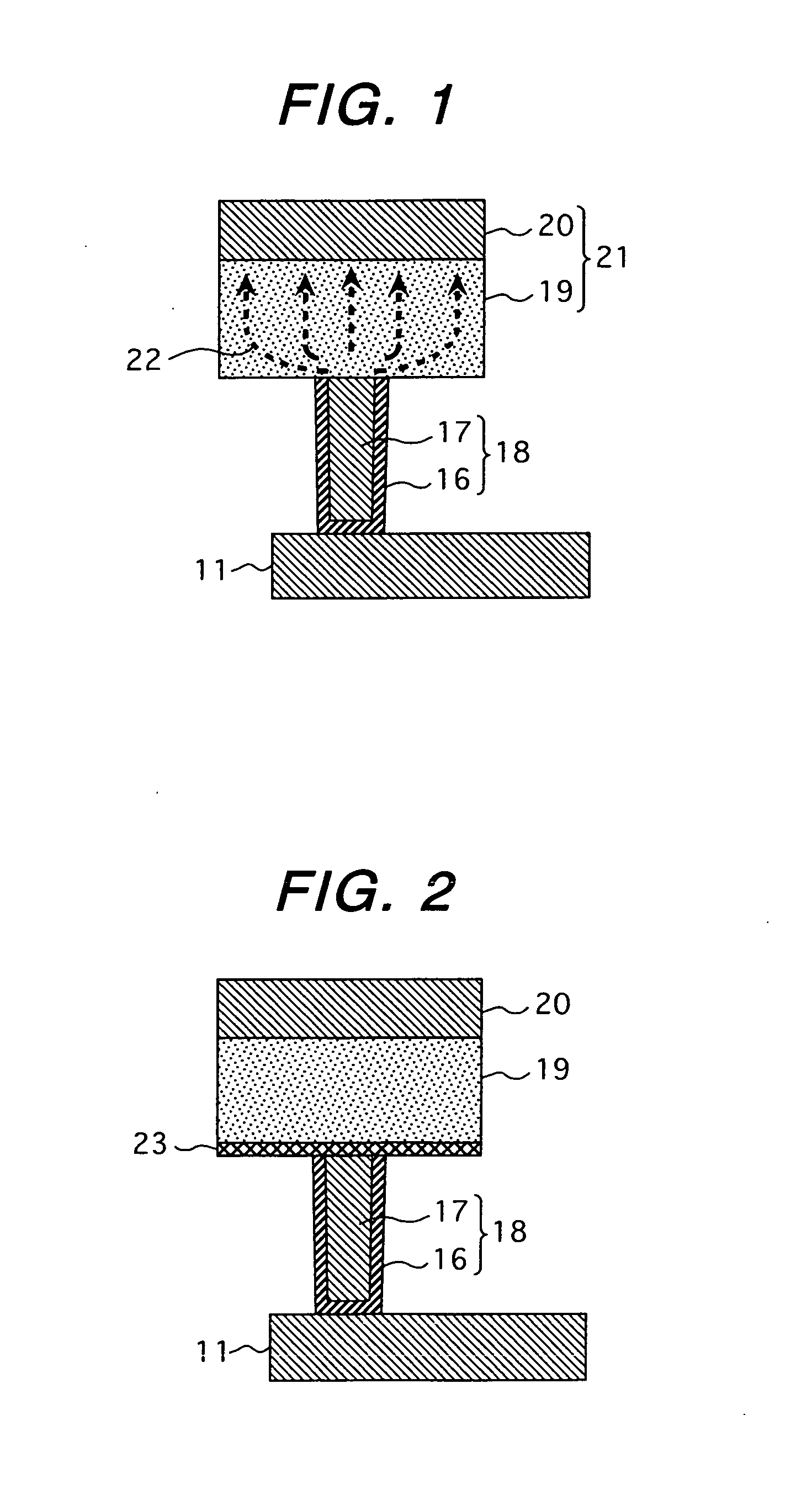

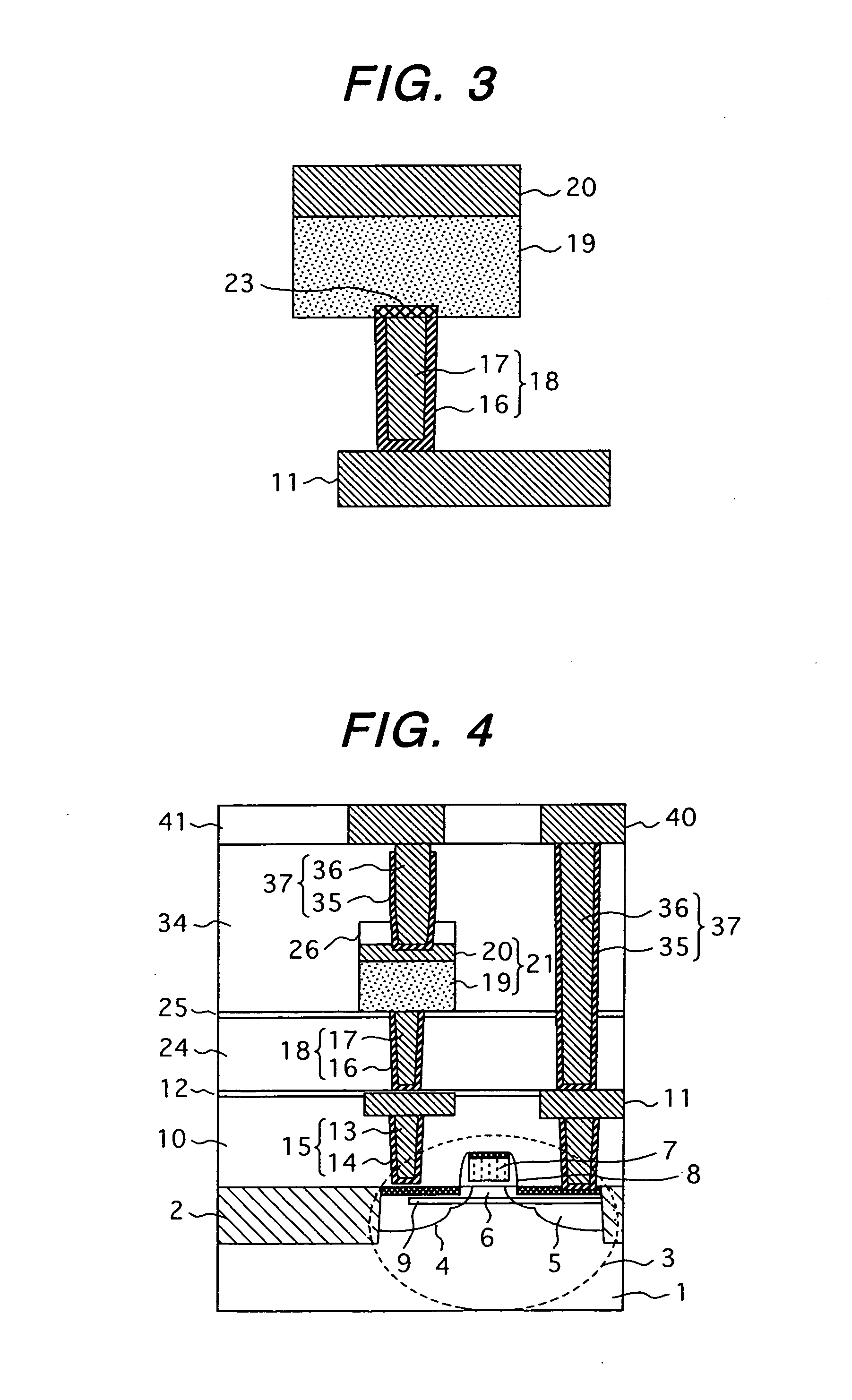

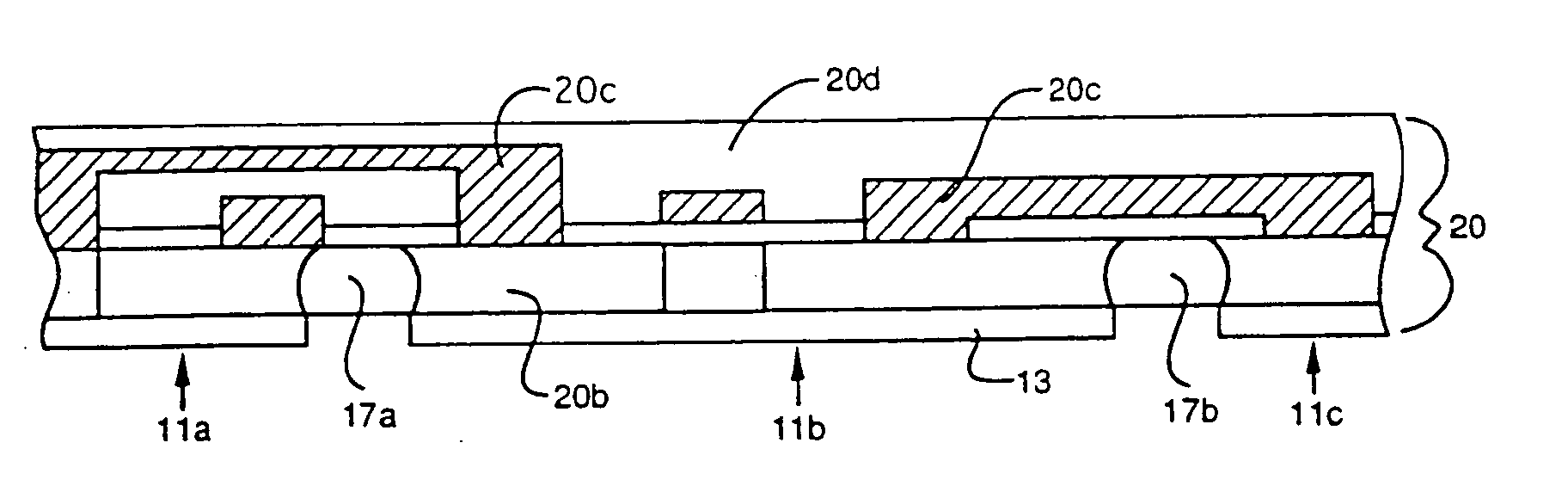

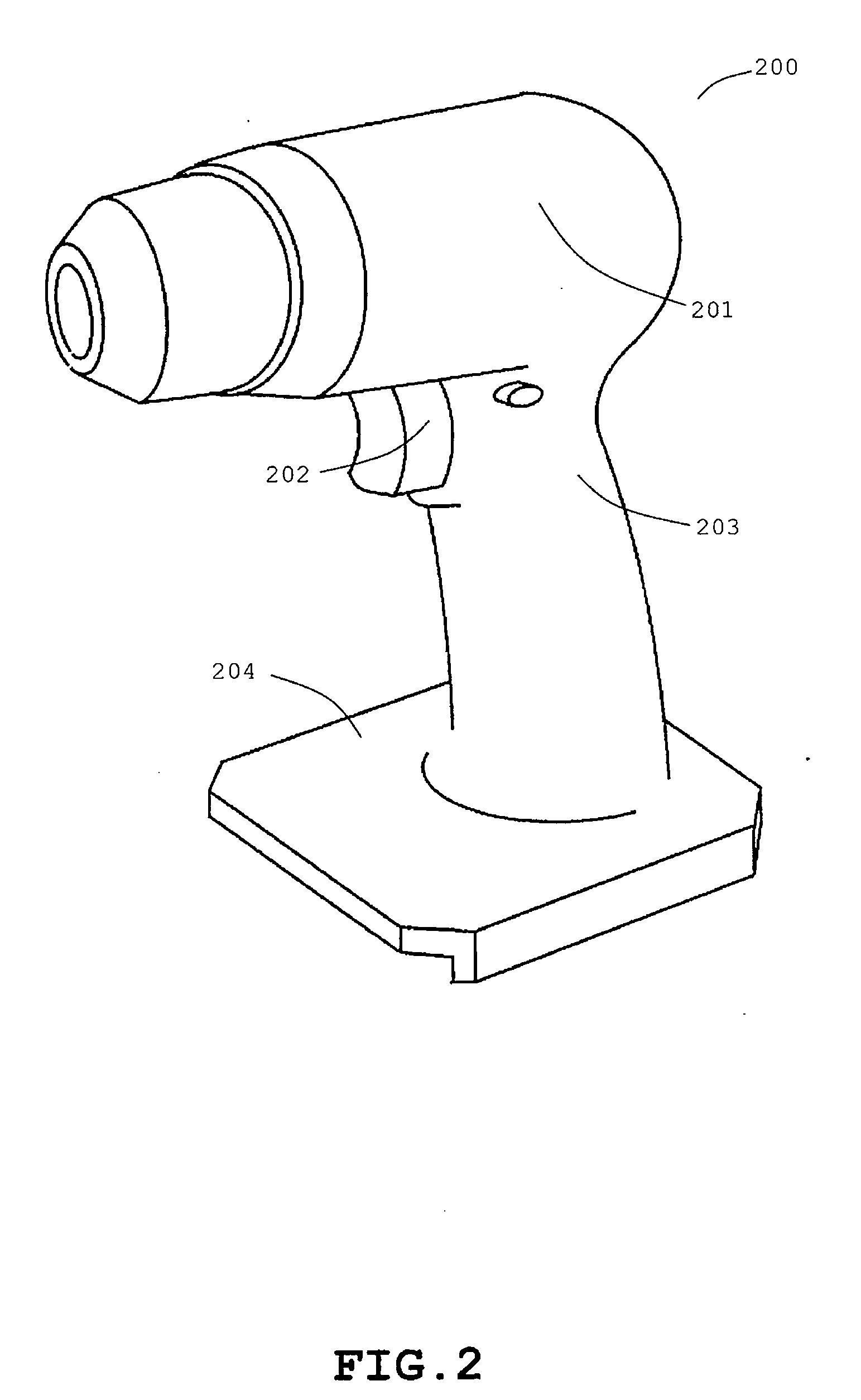

Semiconductor device and method for manufacturing the same

ActiveUS20060001174A1Stable productionSimple processSemiconductor/solid-state device detailsSolid-state devicesSecondary layerEngineering

A semiconductor device 100 is provided with a multiplex through plug 111 that fills an opening extending through the silicon substrate 101. The multiplex through plugs 111 comprises a column-shaped and solid first through electrode 103, a first insulating film 105 that covers the cylindrical face of the first through electrode 103, a second through electrode 107 that covers the cylindrical face of the first insulating film 105 and a second insulating film 109 that covers the cylindrical face of the second through electrode 107, and these have a common central axis. The upper cross sections of the first insulating film 105, the second through electrode 107 and the second insulating film 109 are annular-shaped.

Owner:TESSERA ADVANCED TECH

Atomic layer deposition method and semiconductor device formed by the same

ActiveUS8158512B2Improve abilitiesTotal current dropSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectric layerAtomic layer deposition

There is provided a method of manufacturing a semiconductor device, including the following steps: flowing a first precursor gas to the semiconductor substrate within a ALD chamber to form a first discrete monolayer on the semiconductor substrate; flowing an inert purge gas to the semiconductor substrate within the ALD chamber; flowing a second precursor gas to the ALD chamber to react with the first precursor gas which has formed the first monolayer, thereby forming a first discrete compound monolayer; and flowing an inert purge gas; forming a first dielectric layer to cover the discrete compound monolayer; forming a second third monolayer above first dielectric layer; and forming a second discrete compound monolayer; and forming a second dielectric layer to cover the second discrete compound monolayer above the first dielectric layer. There is also provided a semiconductor device formed by the ALD method.

Owner:SEMICON MFG INT (SHANGHAI) CORP

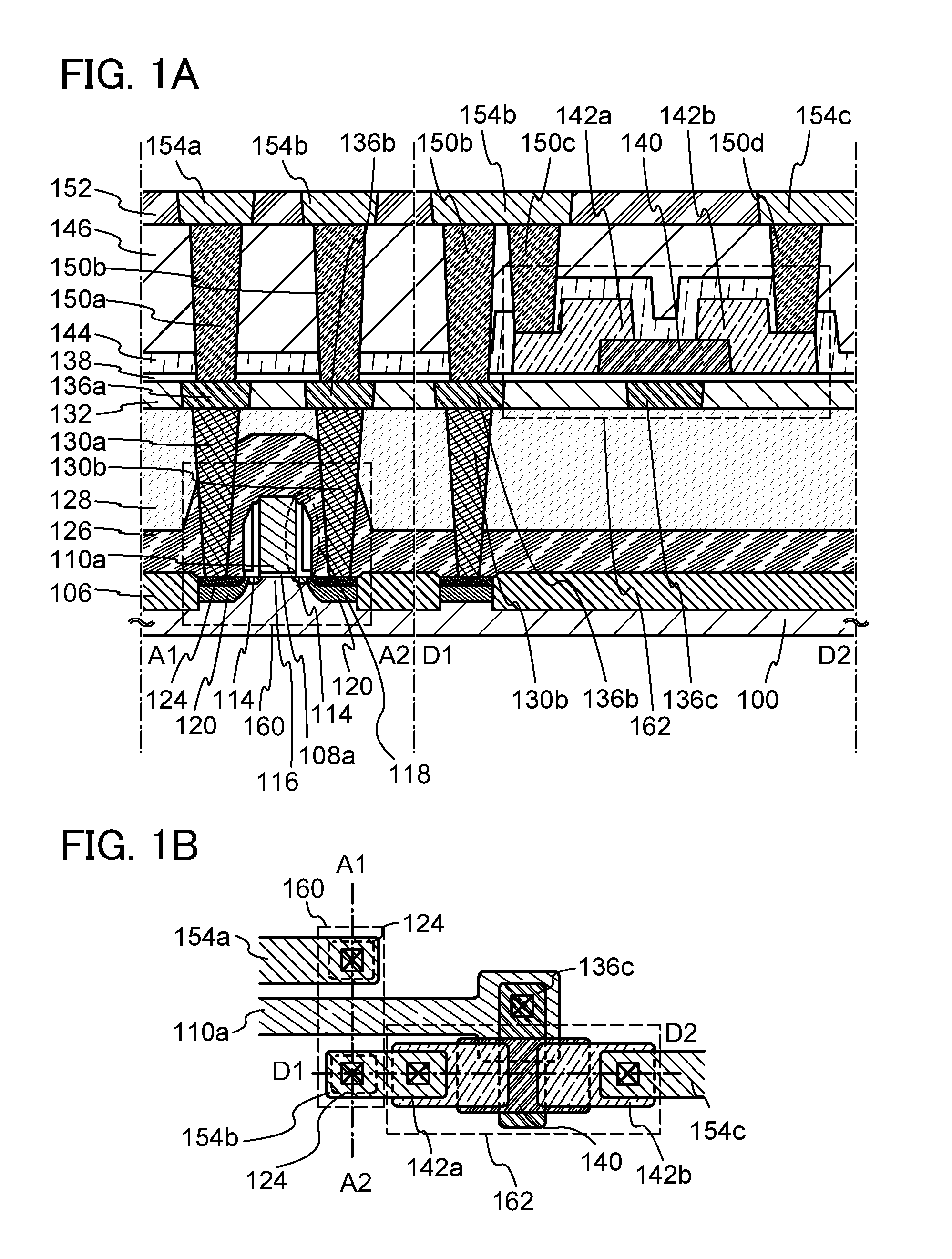

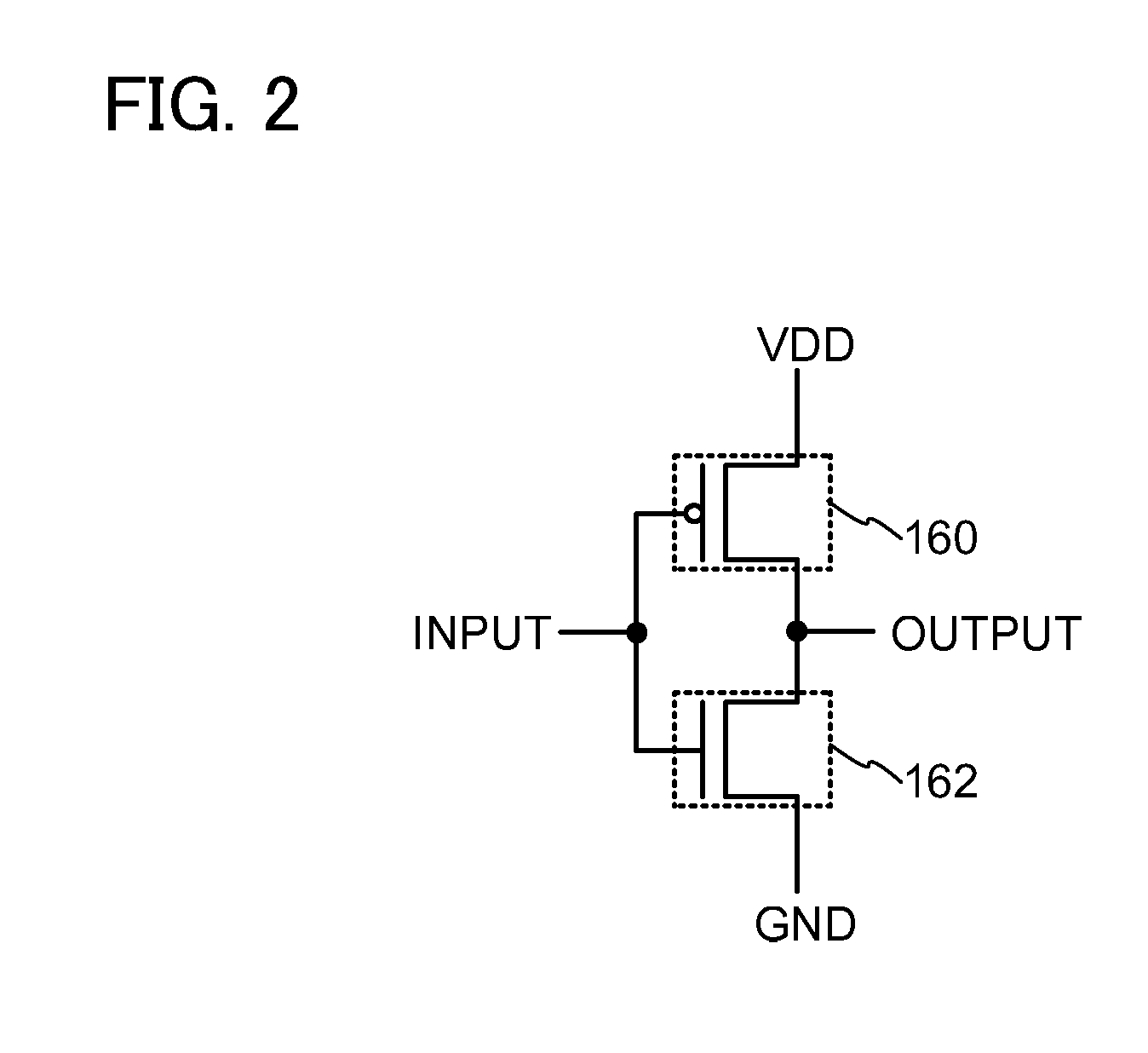

Semiconductor device

InactiveUS20110089417A1Excellent switching characteristicExcellent semiconductor device can be madeSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorOxide

An objet of the present invention is to provide a semiconductor device with a new structure. Disclosed is a semiconductor device including a first transistor which includes a channel formation region on a substrate containing a semiconductor material, impurity regions formed with the channel formation region interposed therebetween, a first gate insulating layer over the channel formation region, a first gate electrode over the first gate insulating layer, and a first source electrode and a first drain electrode which are electrically connected to the impurity region; and a second transistor which includes a second gate electrode over the substrate containing a semiconductor material, a second gate insulating layer over the second gate electrode, an oxide semiconductor layer over the second gate insulating layer, and a second source electrode and a second drain electrode which are electrically connected to the oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

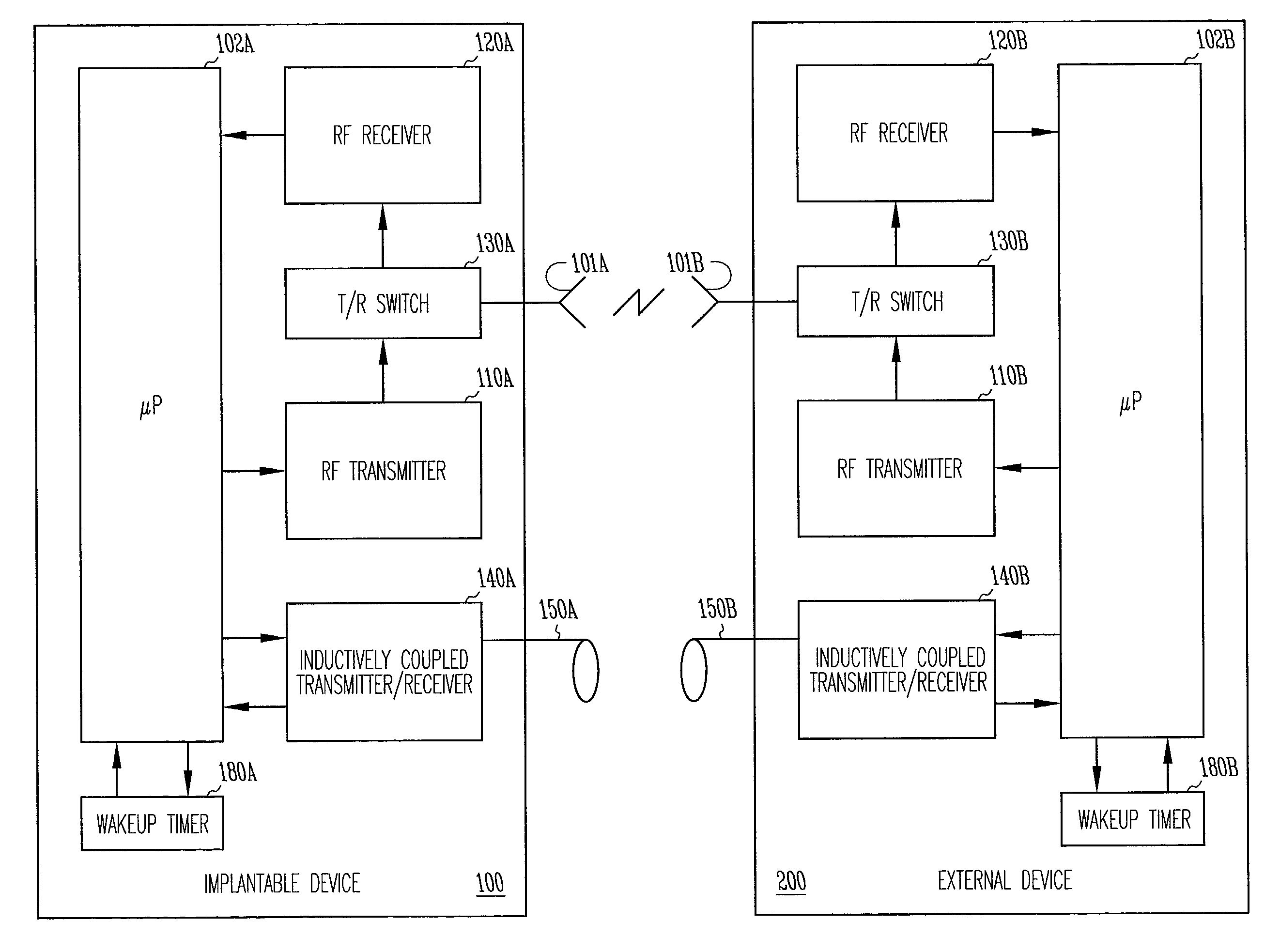

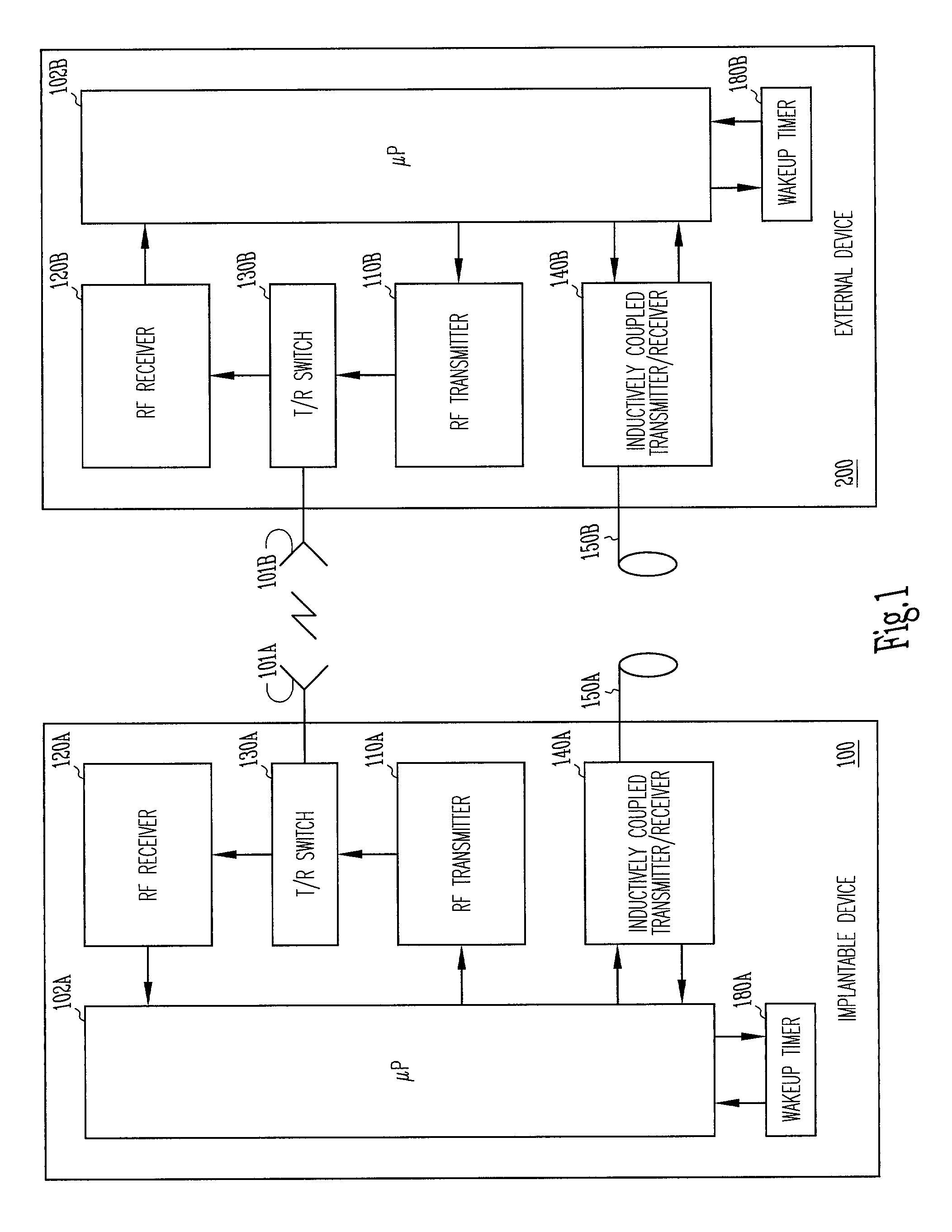

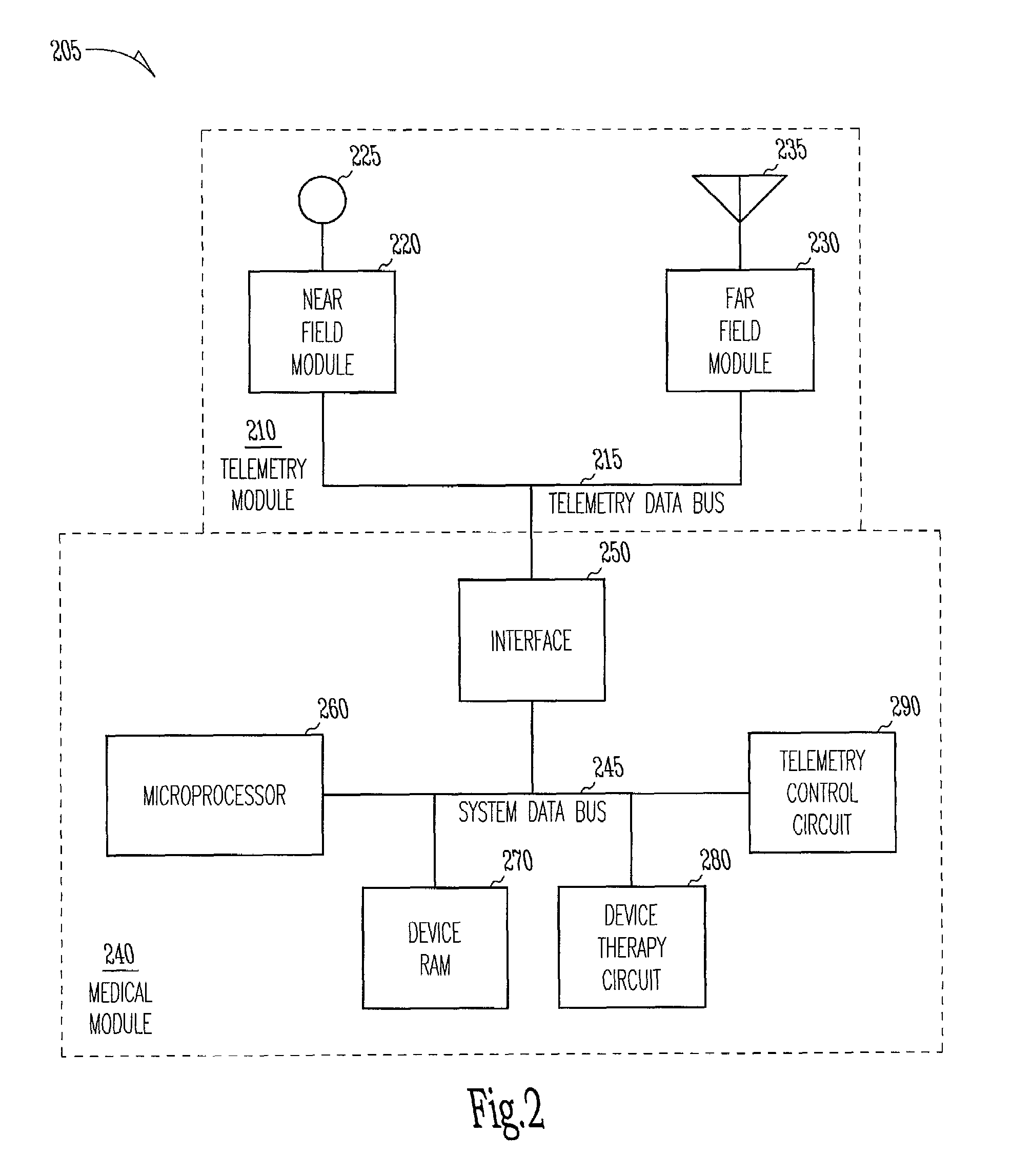

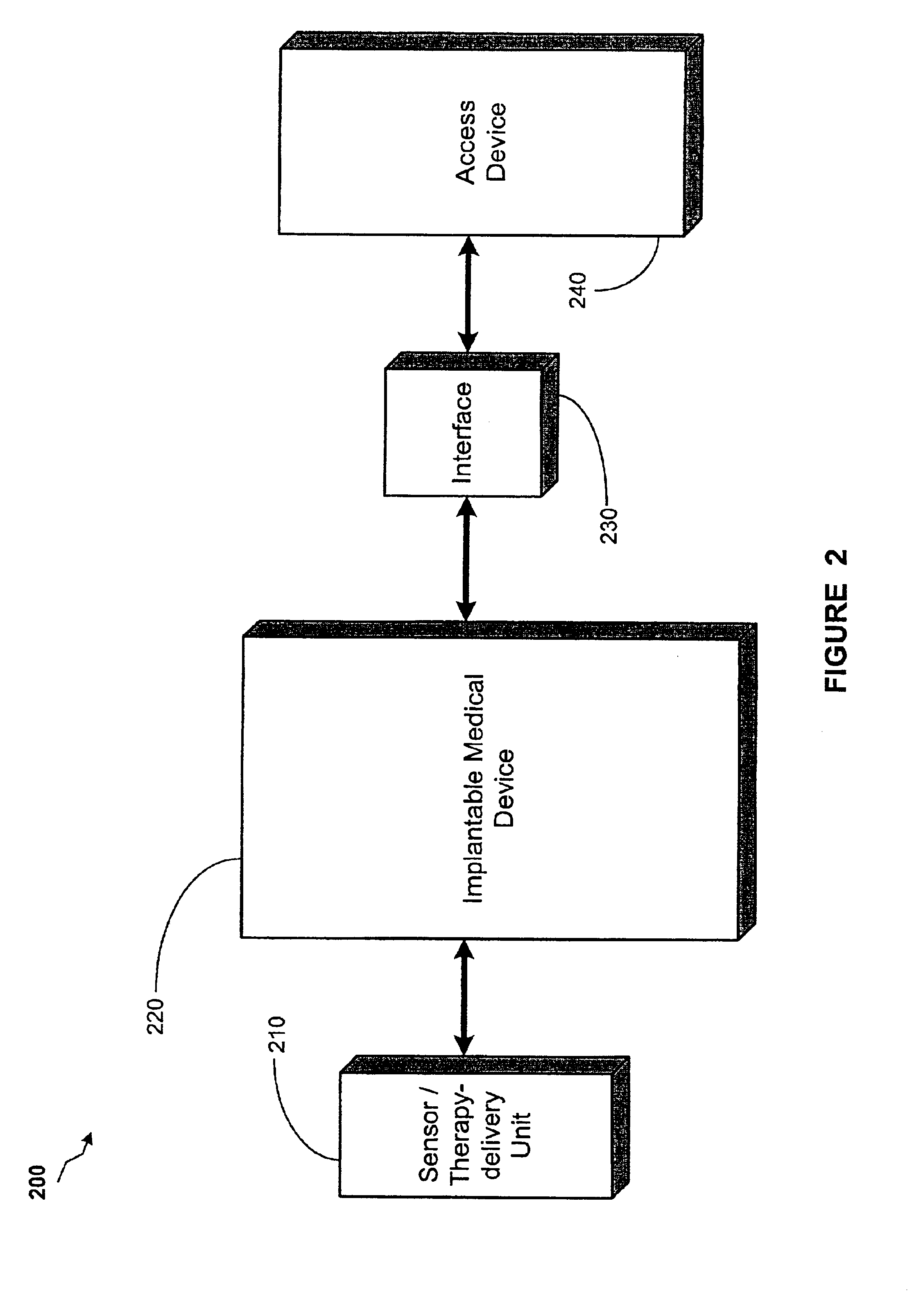

Telemetry duty cycle management system for an implantable medical device

InactiveUS6993393B2Reduce power consumptionTotal current dropHeart defibrillatorsRadio frequencyTelecommunications link

A telemetry system enabling radio frequency (RF) communications between an implantable medical device and an external device, or programmer, in which the RF circuitry is normally maintained in a powered down state in order to conserve power. At synchronized wakeup intervals, one of the devices designated as a master device powers up its RF transmitter to request a communications session, and the other device designated as a slave device powers up its RF transmitter to listen for the request. Telemetry is conducted using a far field or near field communication link.

Owner:CARDIAC PACEMAKERS INC

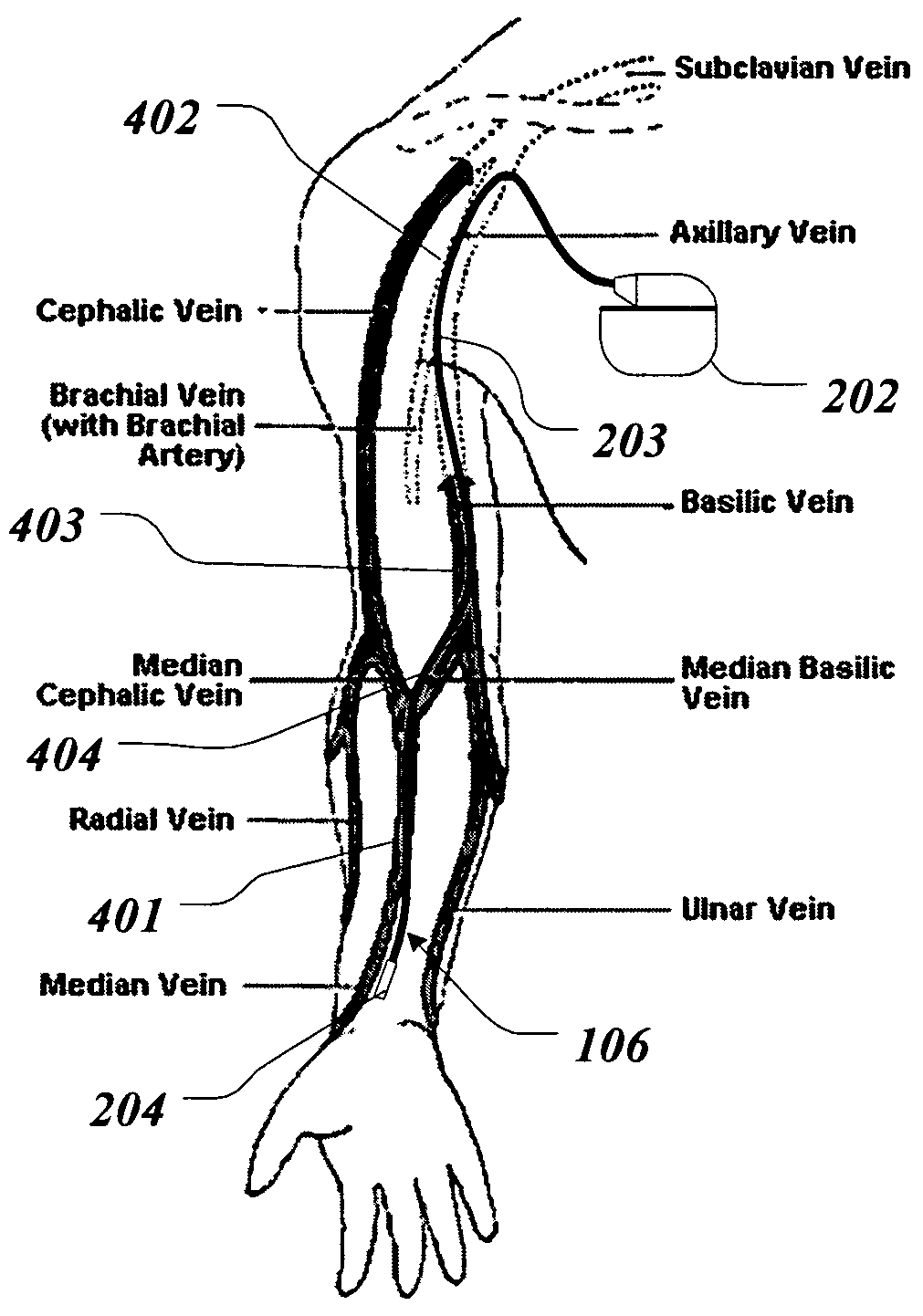

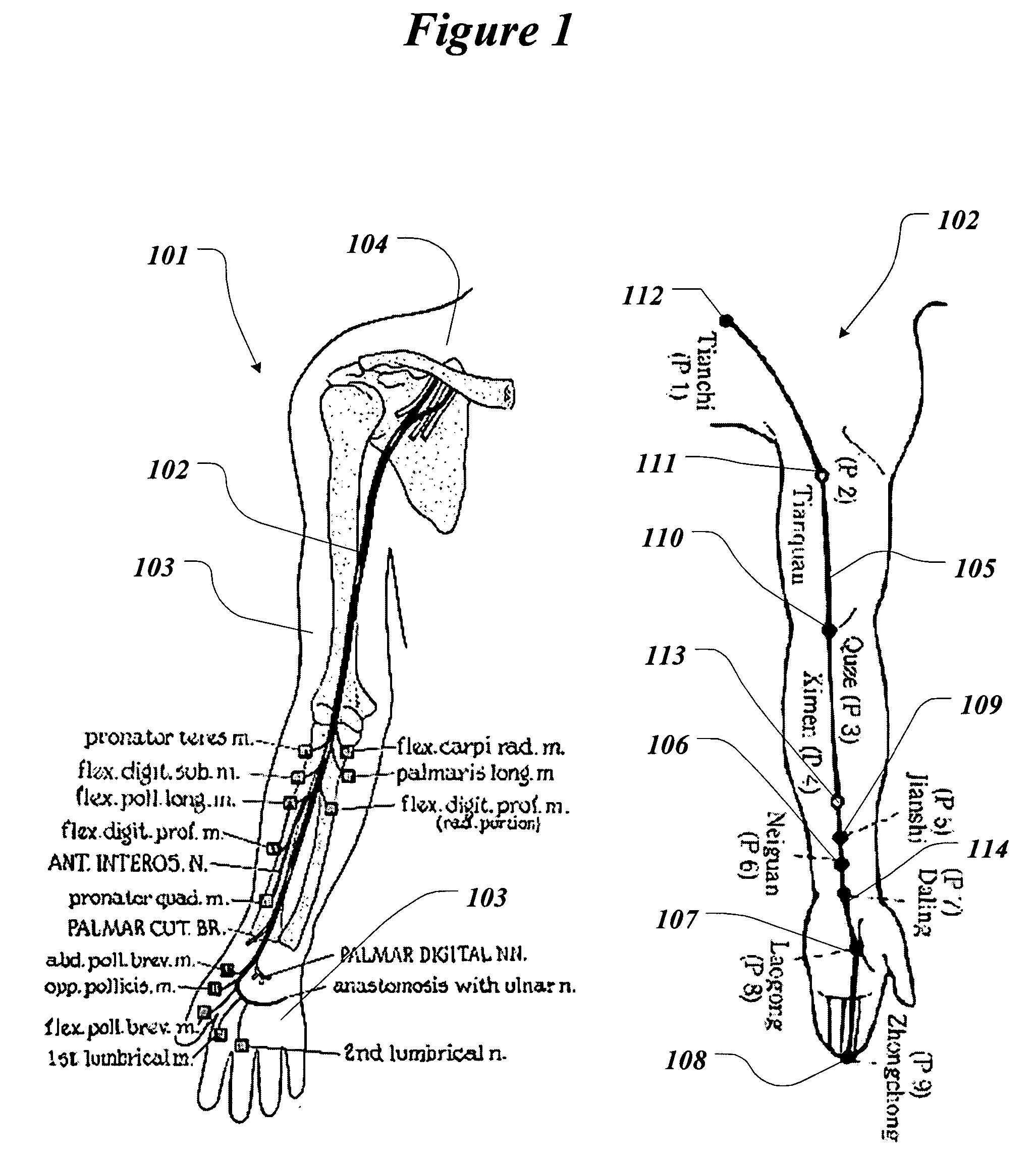

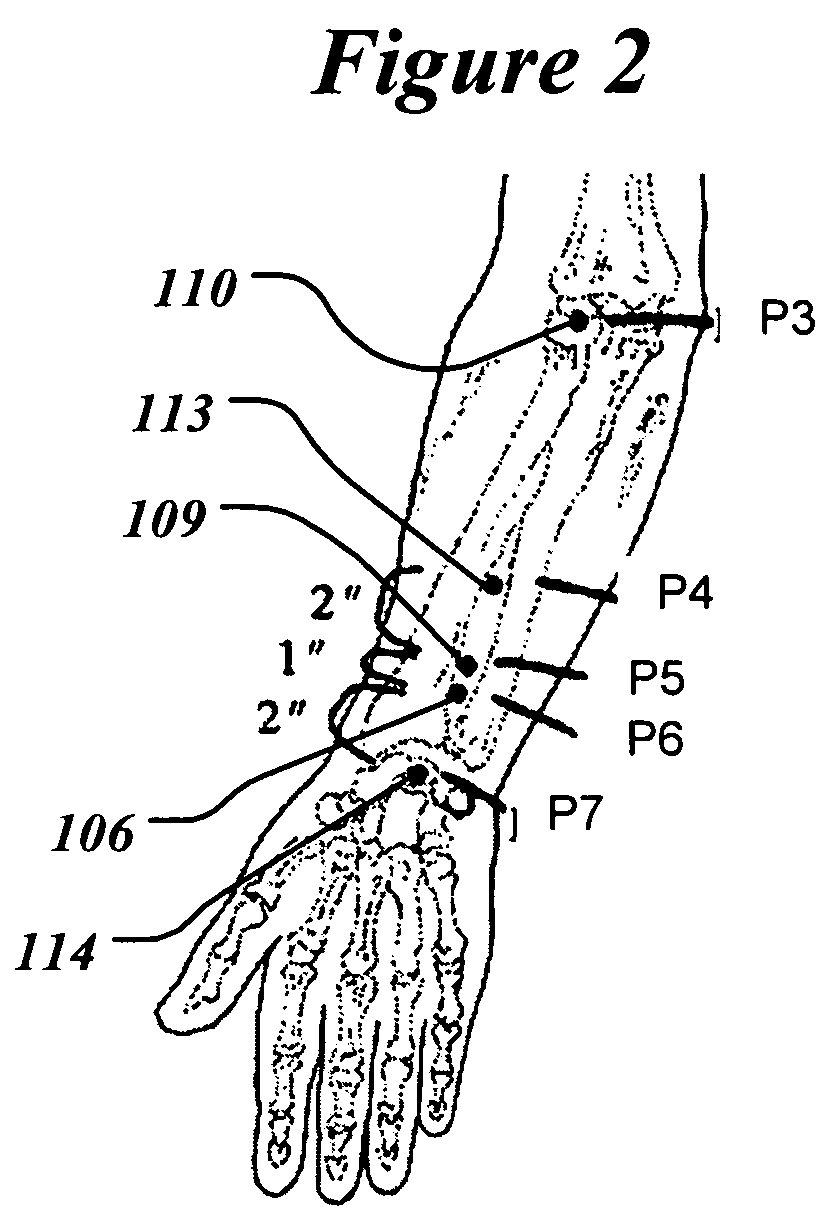

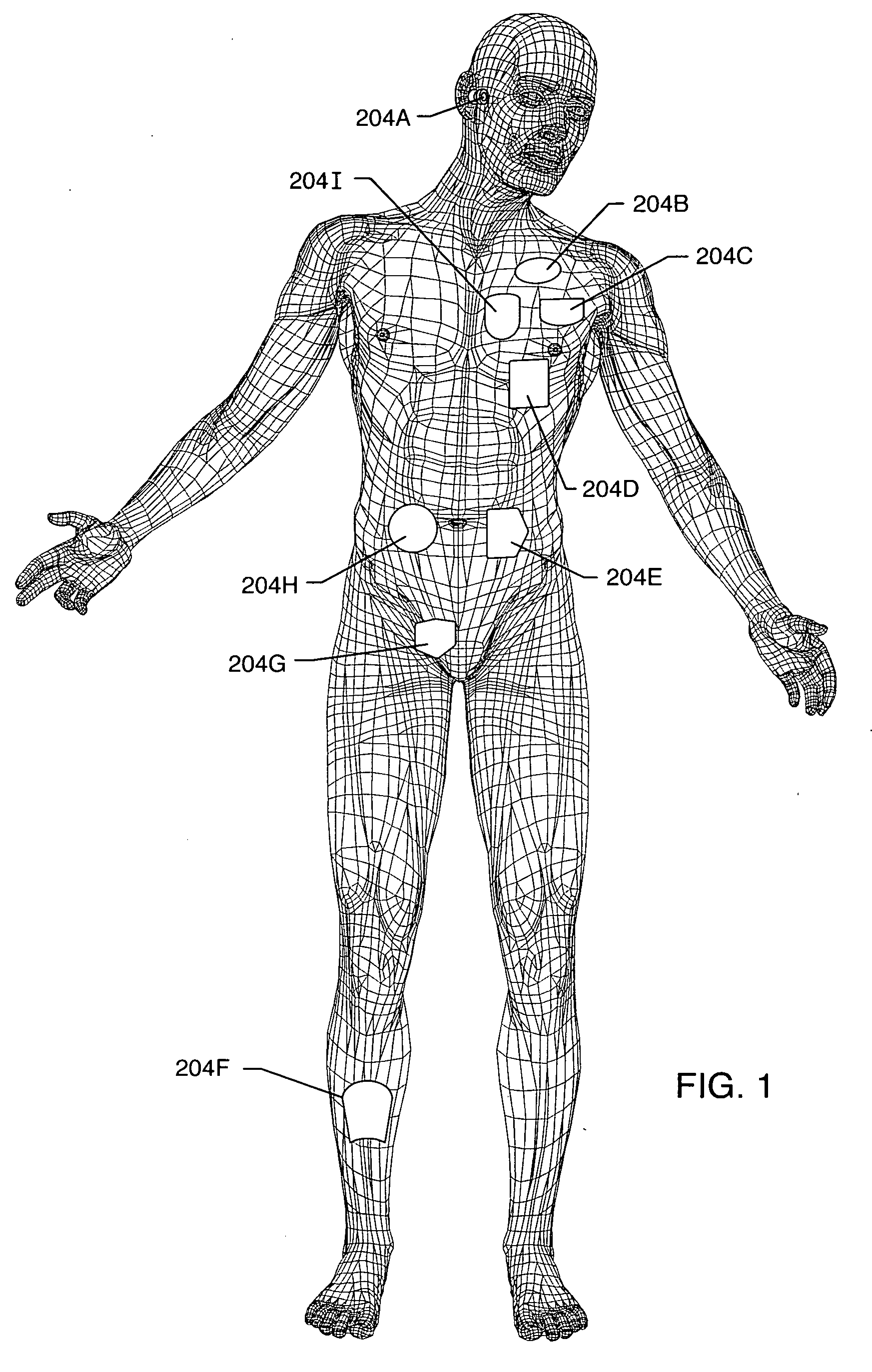

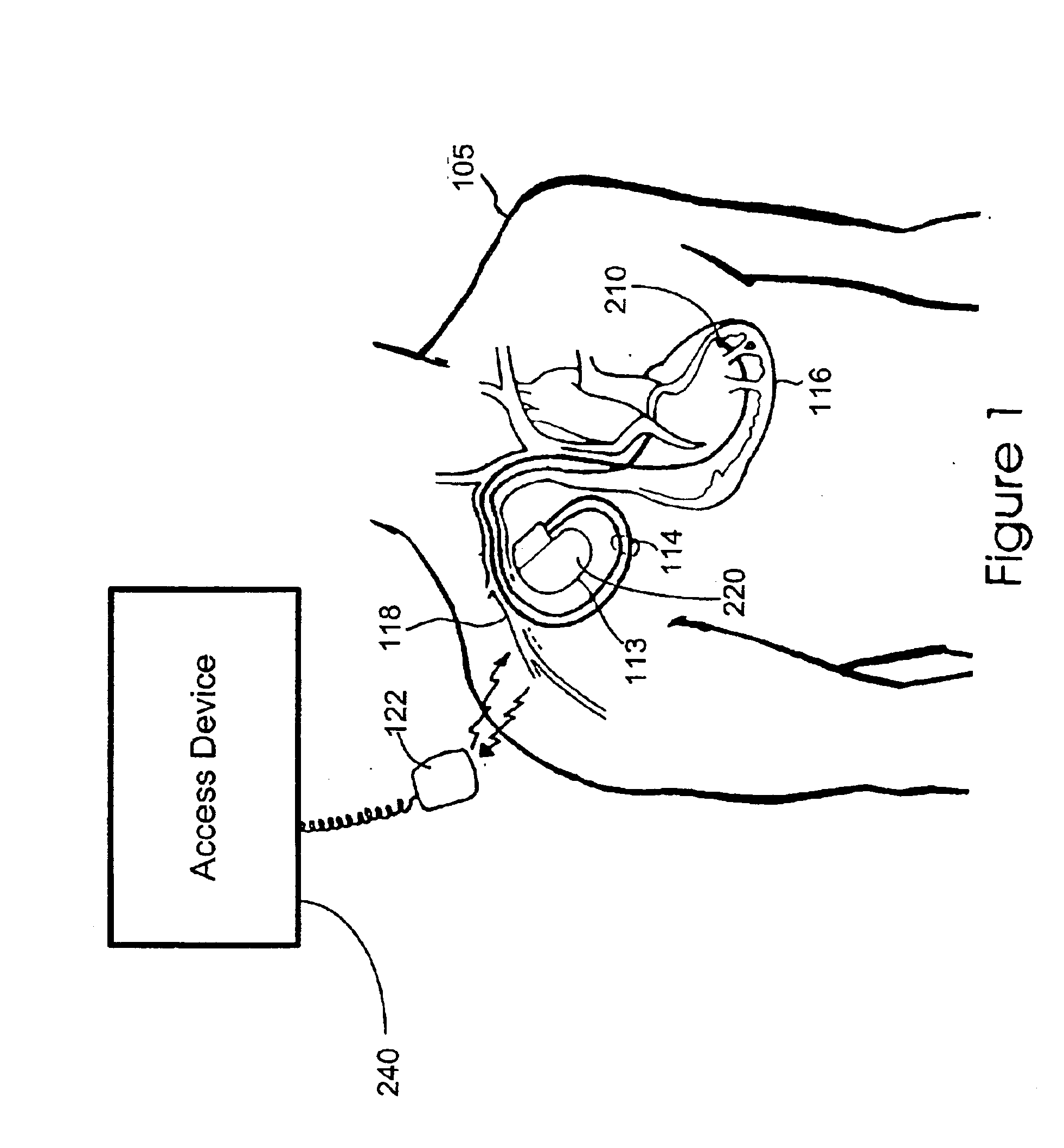

Implantable device and method for treatment of hypertension

ActiveUS7373204B2Improve dysfunctionIncrease probabilityElectrotherapySurgeryPower flowImplanted device

A method and apparatus for treatment of hypertension with electrostimulation of peripheral nerves. Treatment is performed by periodically stimulating a nerve such as a median nerve. Apparatus for stimulation is permanently implanted in the body. The nerve is stimulated by electric current applied to electrodes that are placed near the target nerve or the muscle innervated by the target nerve.

Owner:LIFESTIM

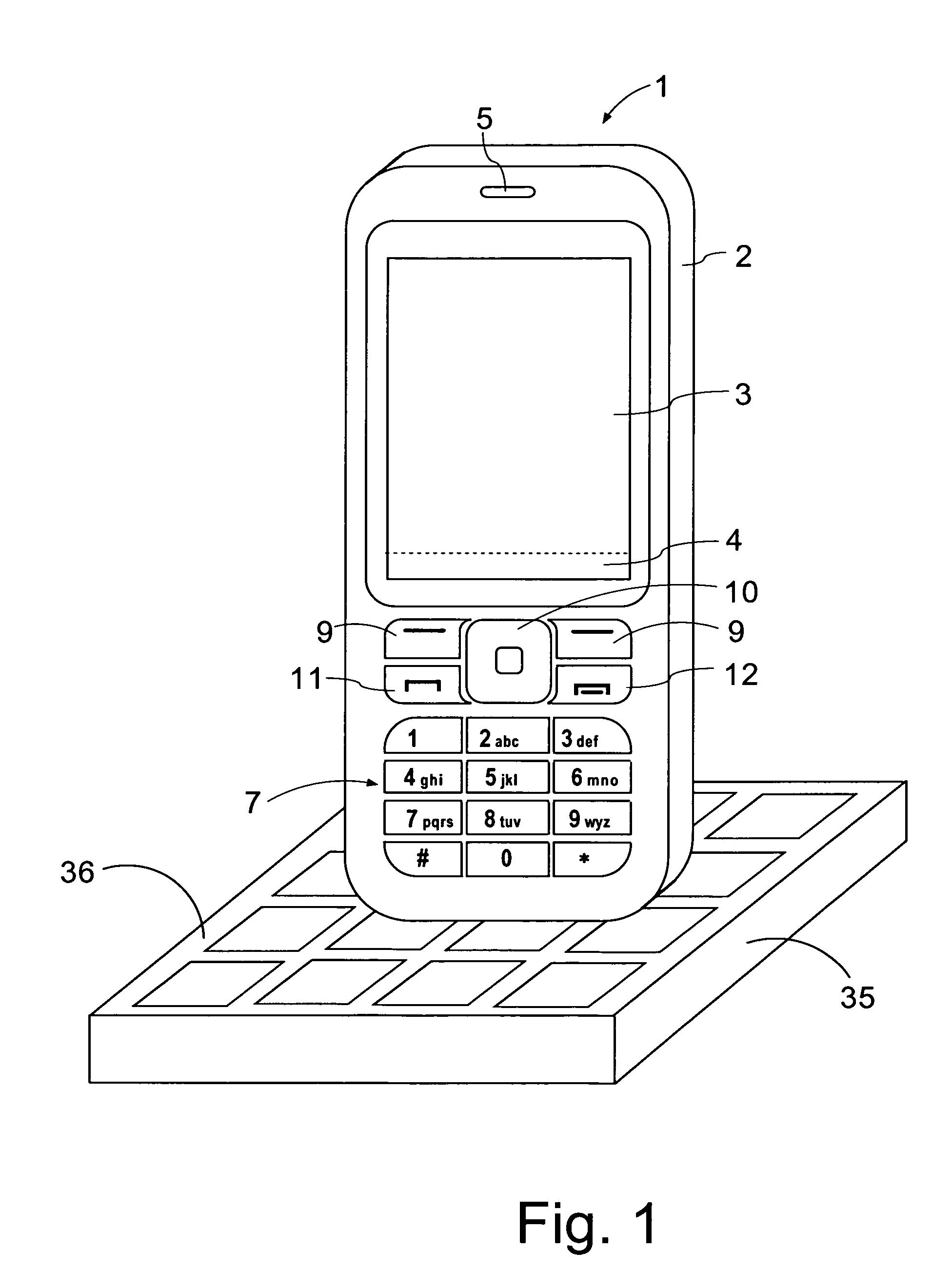

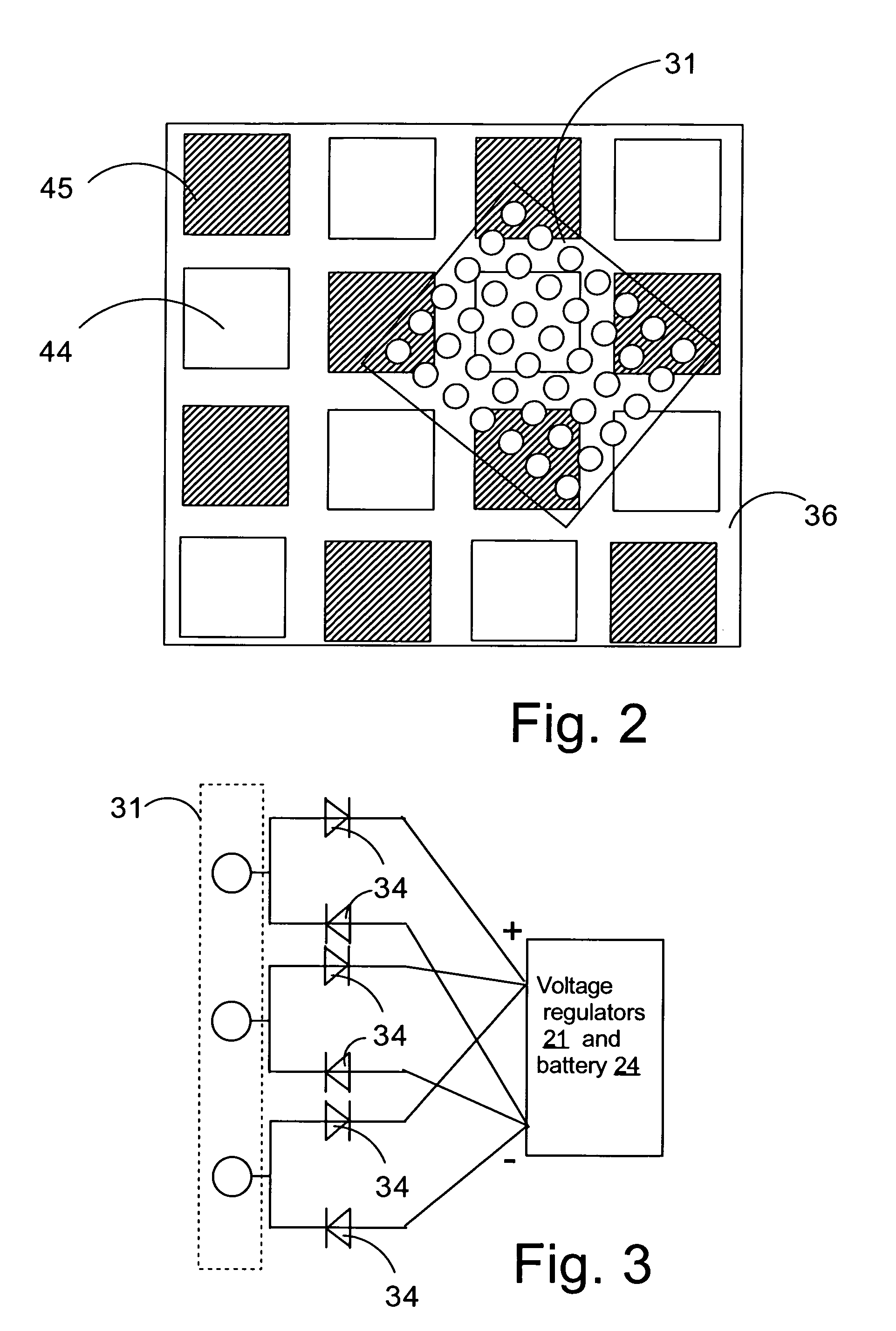

Wireless Galvanic Charging Device,Method of Operation Thereof and Mobile Electric Device to be Charged

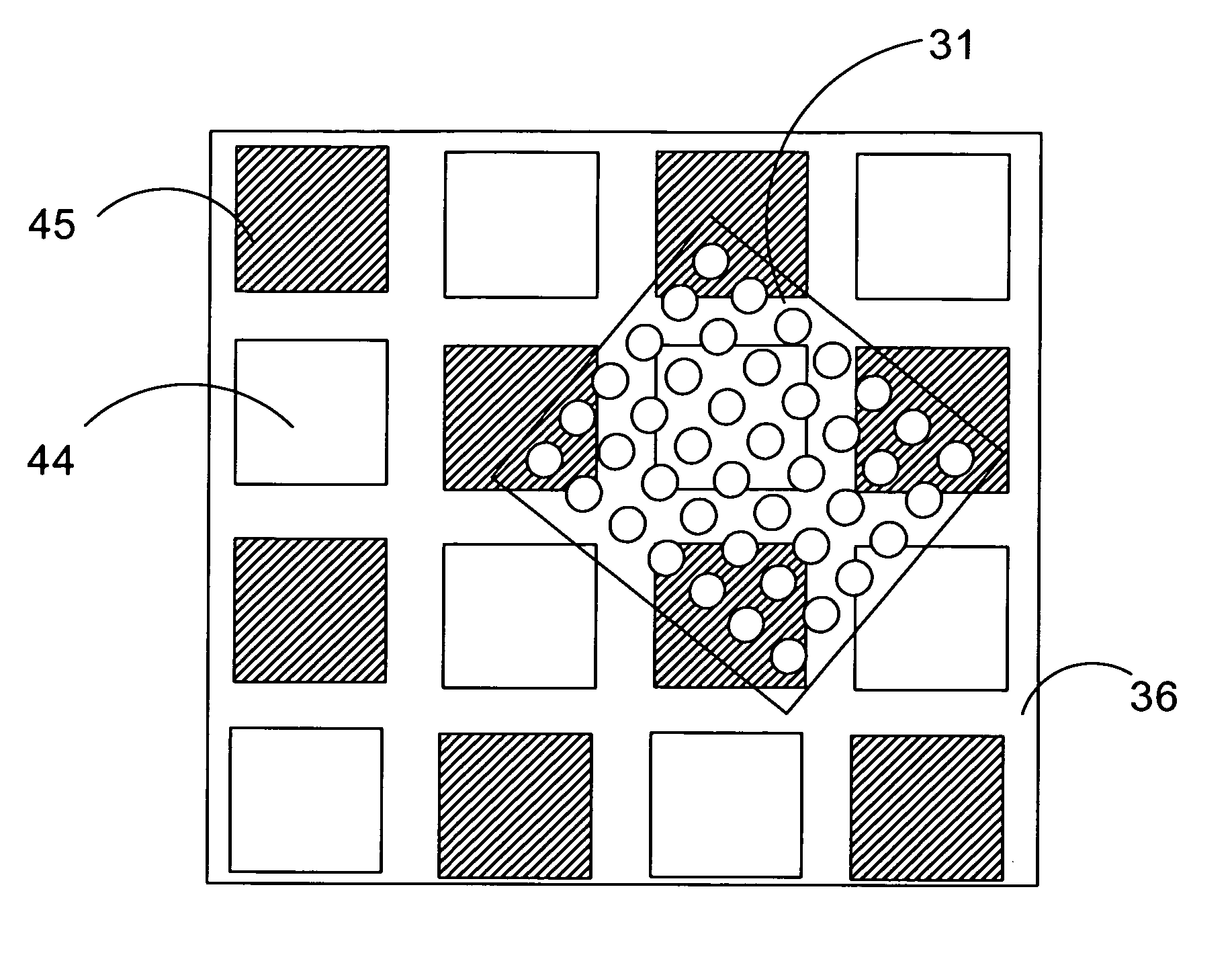

InactiveUS20110133691A1Avoid consumptionReduce energy consumptionElectric powerExchanging data chargerPower flowElectrical battery

A wireless charging device (35) for charging a battery of a mobile electronic device (1). The charging device (35) includes a wireless receiver (39) and a plurality of electrodes (44, 45) that are connected to a power source. The power source is controlled by a controller (40) that is coupled to the wireless receiver (39). Whilst the wireless receiver (39) receives a wireless signal that is associated with a compatible mobile device (1) the controller (40) instructs the power source to power the electrodes (44, 45). Alternatively, the wireless signal can be indicative of the need of the mobile device (1) to be charged and the controller (40) will only power the electrodes (44, 45) if a signal indicating that the mobile device (1) needs to be charged is received. A mobile battery operated device (1) that sends an indicating signal when the battery of the device needs to be charged.

Owner:NOKIA CORP

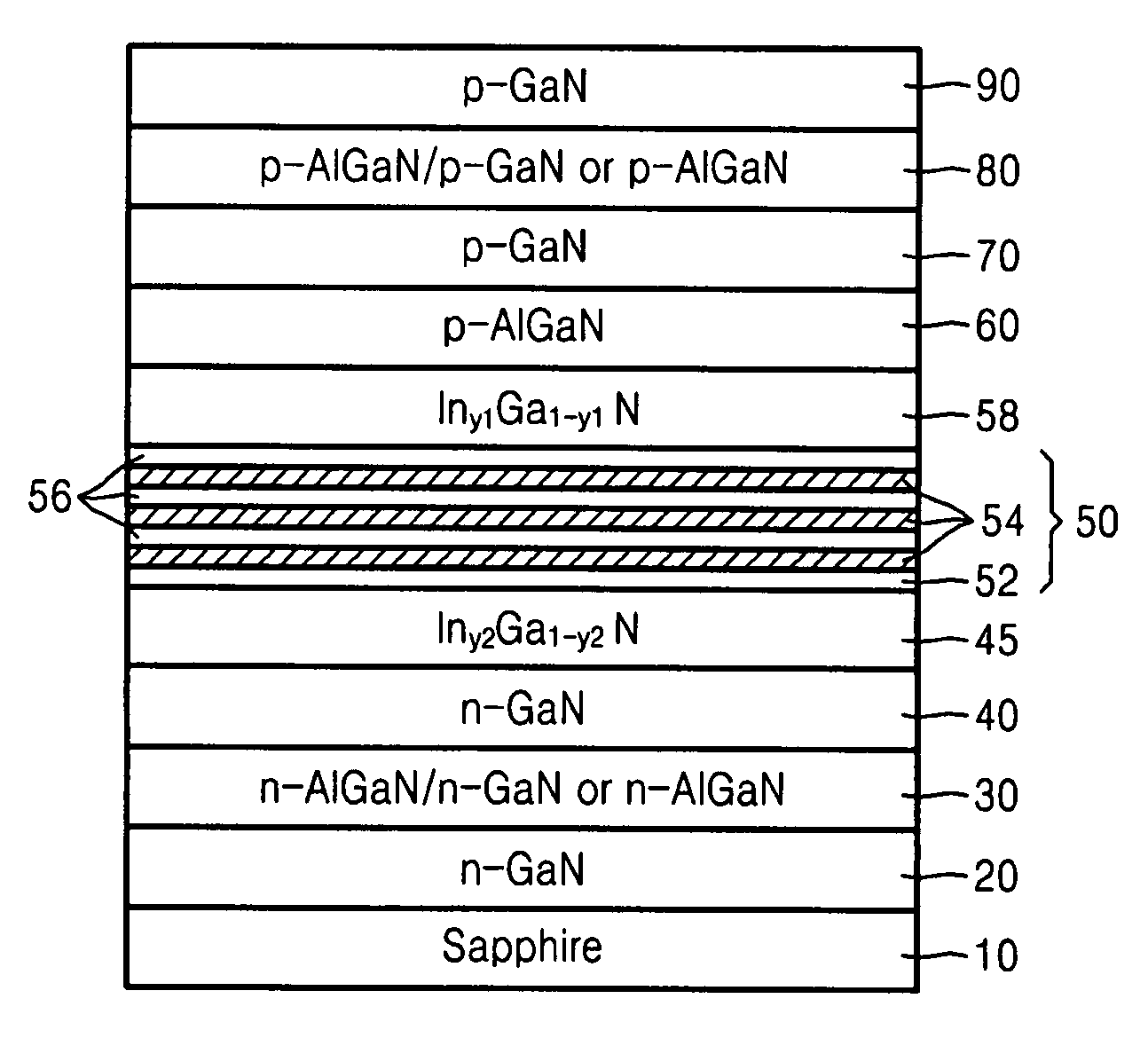

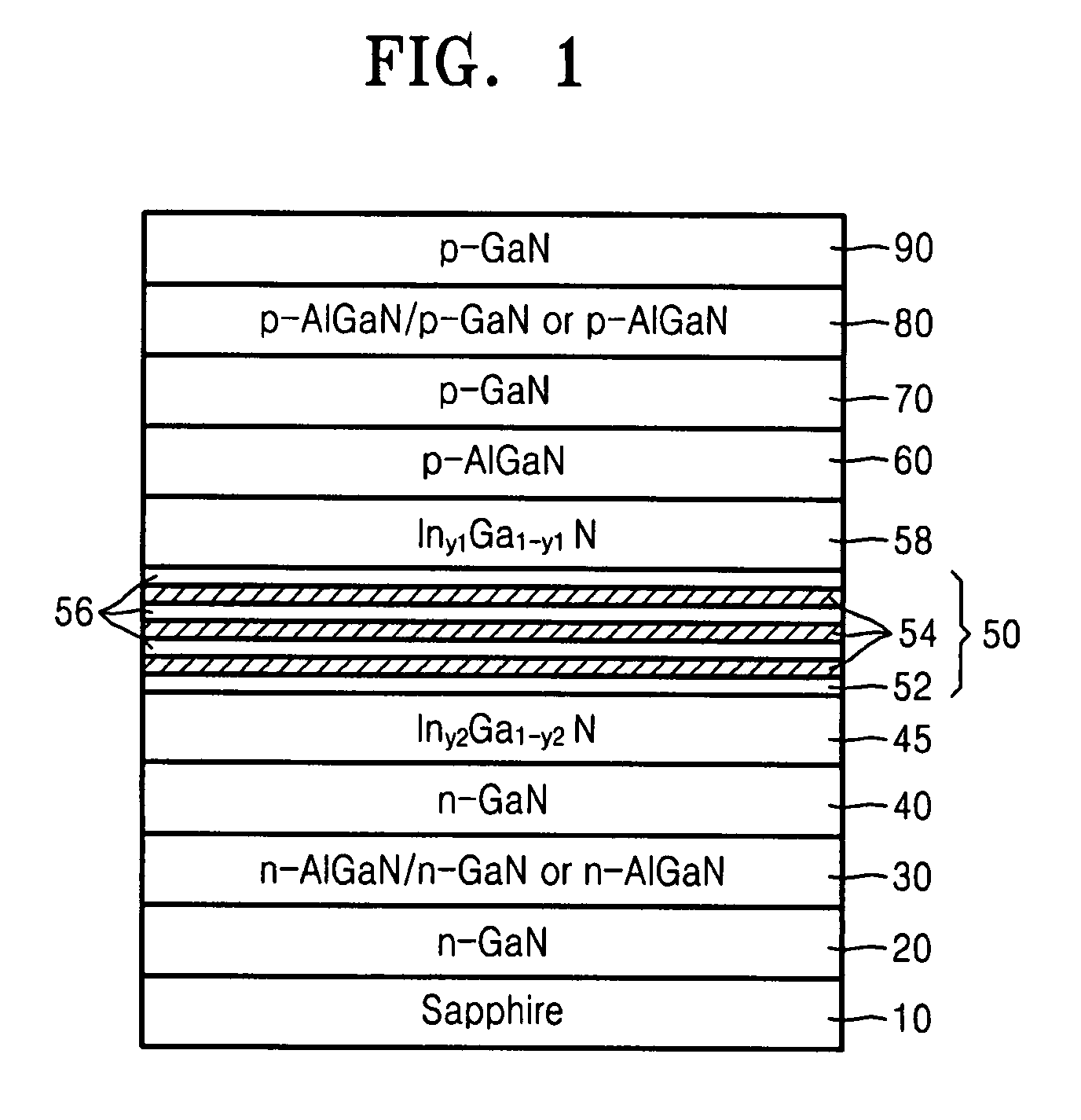

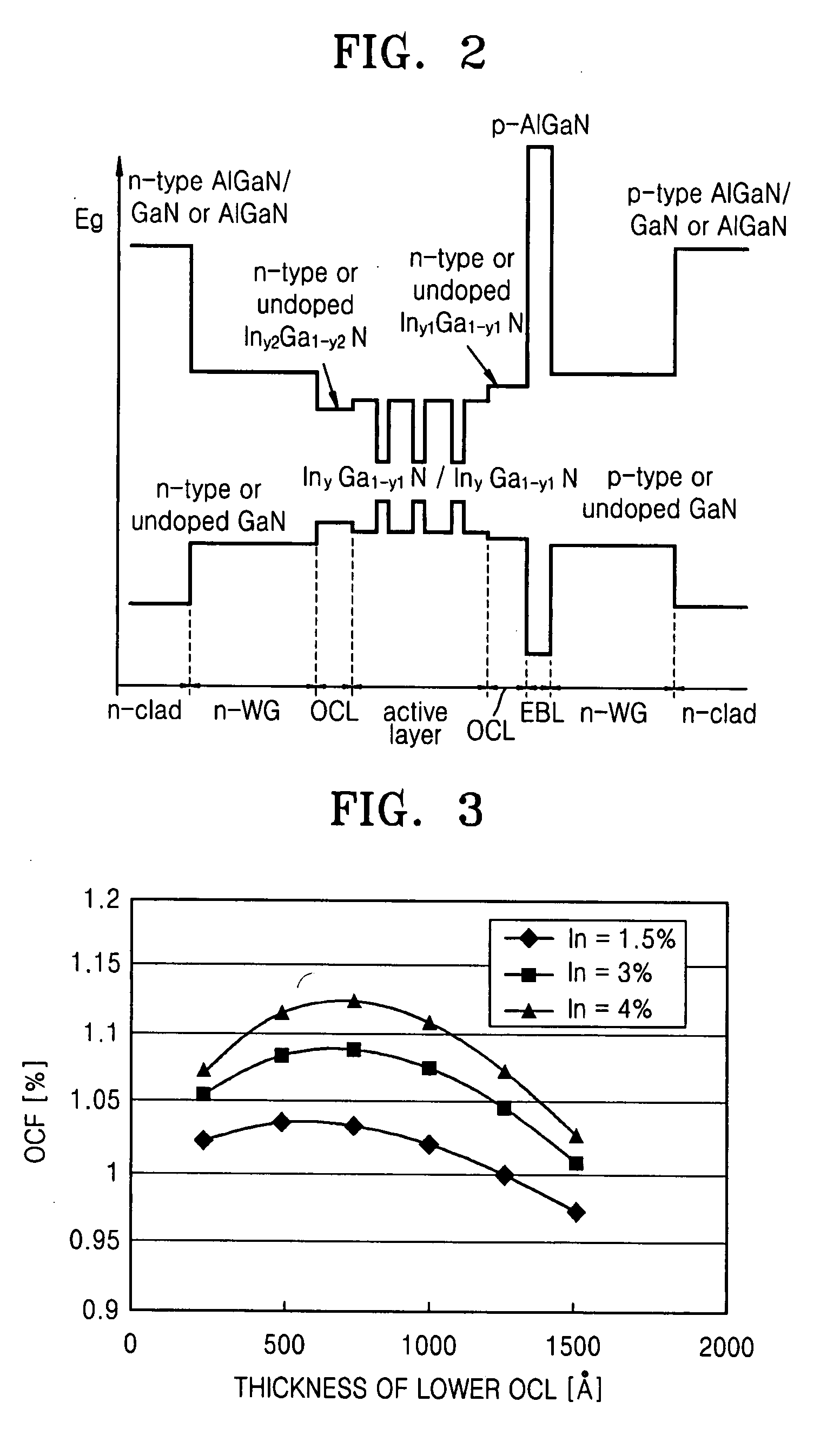

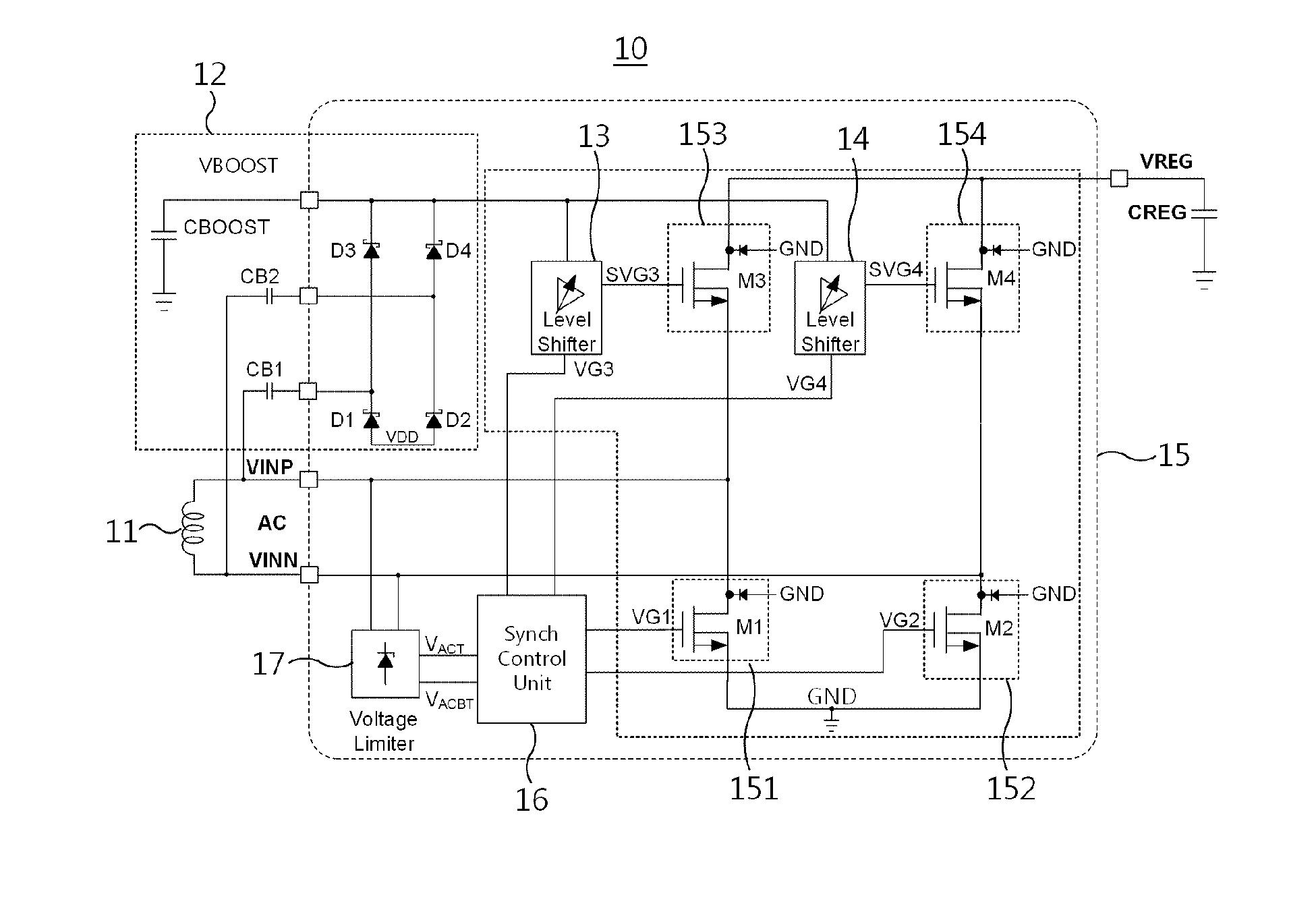

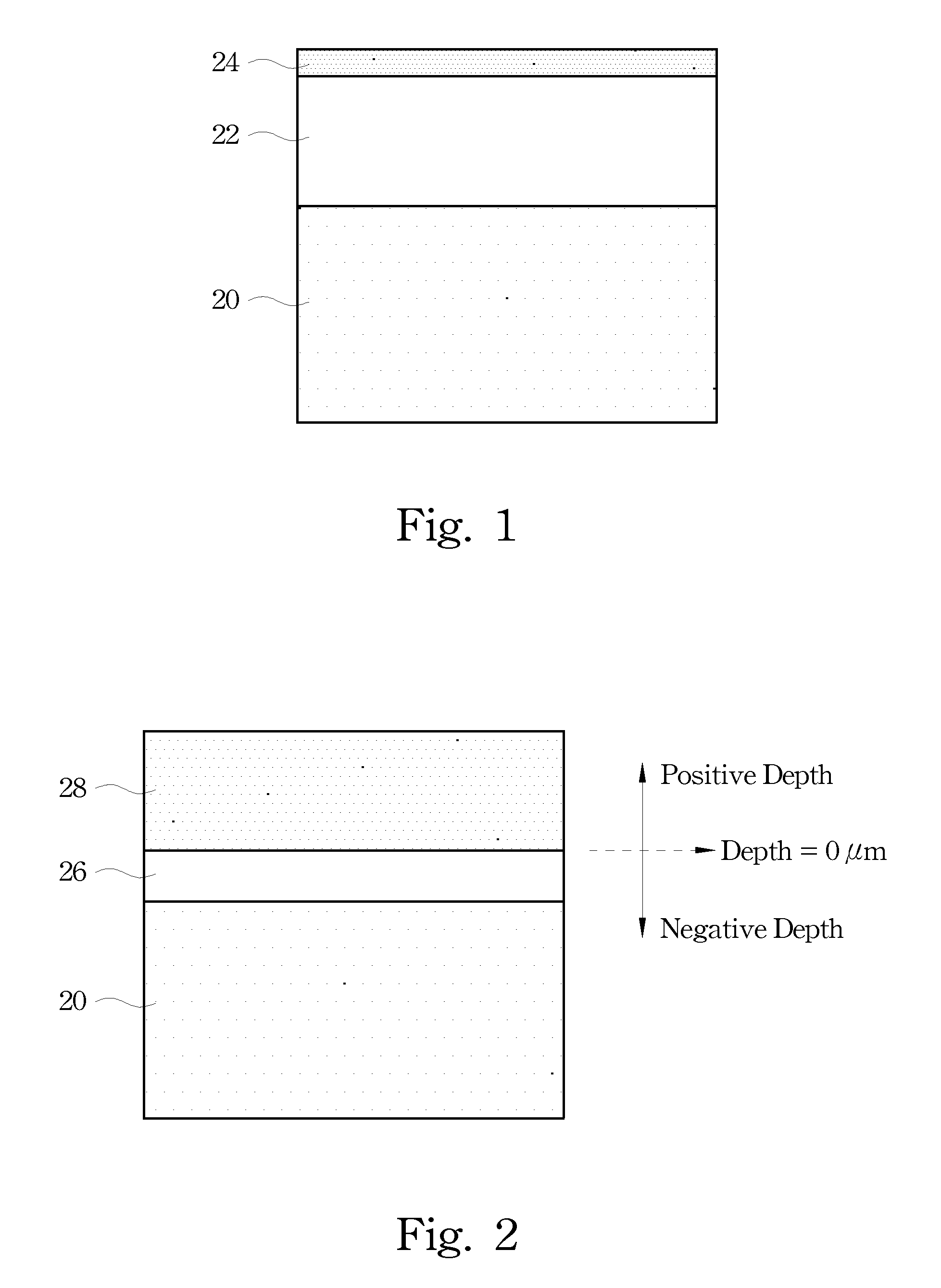

Semiconductor optoelectronic device and method of fabricating the same

ActiveUS20080095492A1Reducing internal lossImprove internal quantum efficiencyNanoopticsSemiconductor lasersQuantum wellOpto electronic

Provided is a semiconductor opto-electronic device that may comprise an active layer including a quantum well and a barrier layer on a substrate, upper and lower waveguide layers on and underneath the active layer, respectively, and upper and lower clad layers on and underneath the upper and lower waveguide layers, respectively. The semiconductor opto-electronic device may further comprise an upper optical confinement layer (OCL) between the active layer and the upper waveguide layer and having an energy gap smaller than the energy gap of the upper waveguide layer and equal to or larger than the energy gap of the barrier layer, and a lower OCL between the active layer and the lower waveguide layer and having an energy gap smaller than the energy gap of the lower waveguide layer and equal to or smaller than the energy gap of the barrier layer. Also provided is a method of fabricating the semiconductor opto-electronic device.

Owner:SAMSUNG ELECTRONICS CO LTD

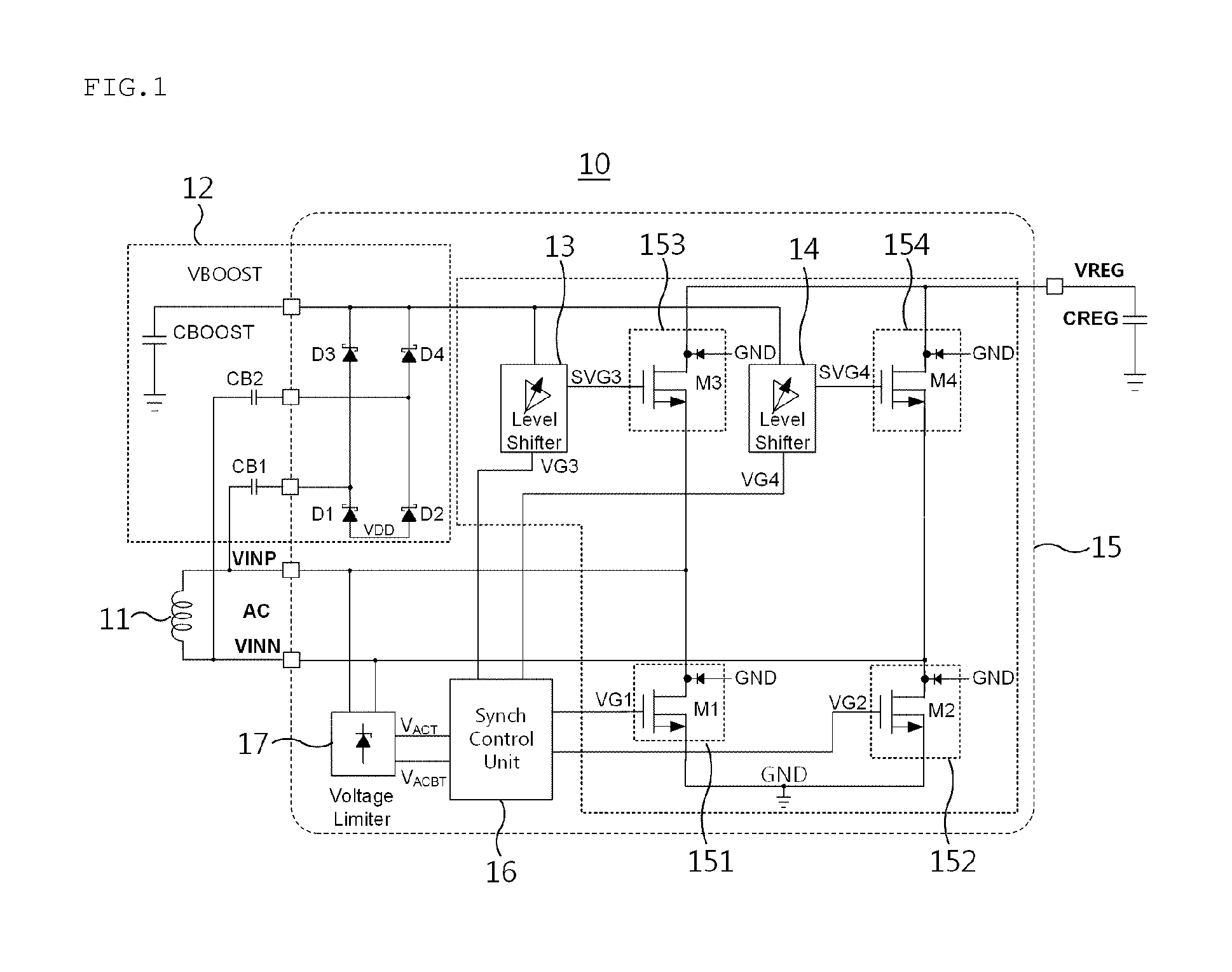

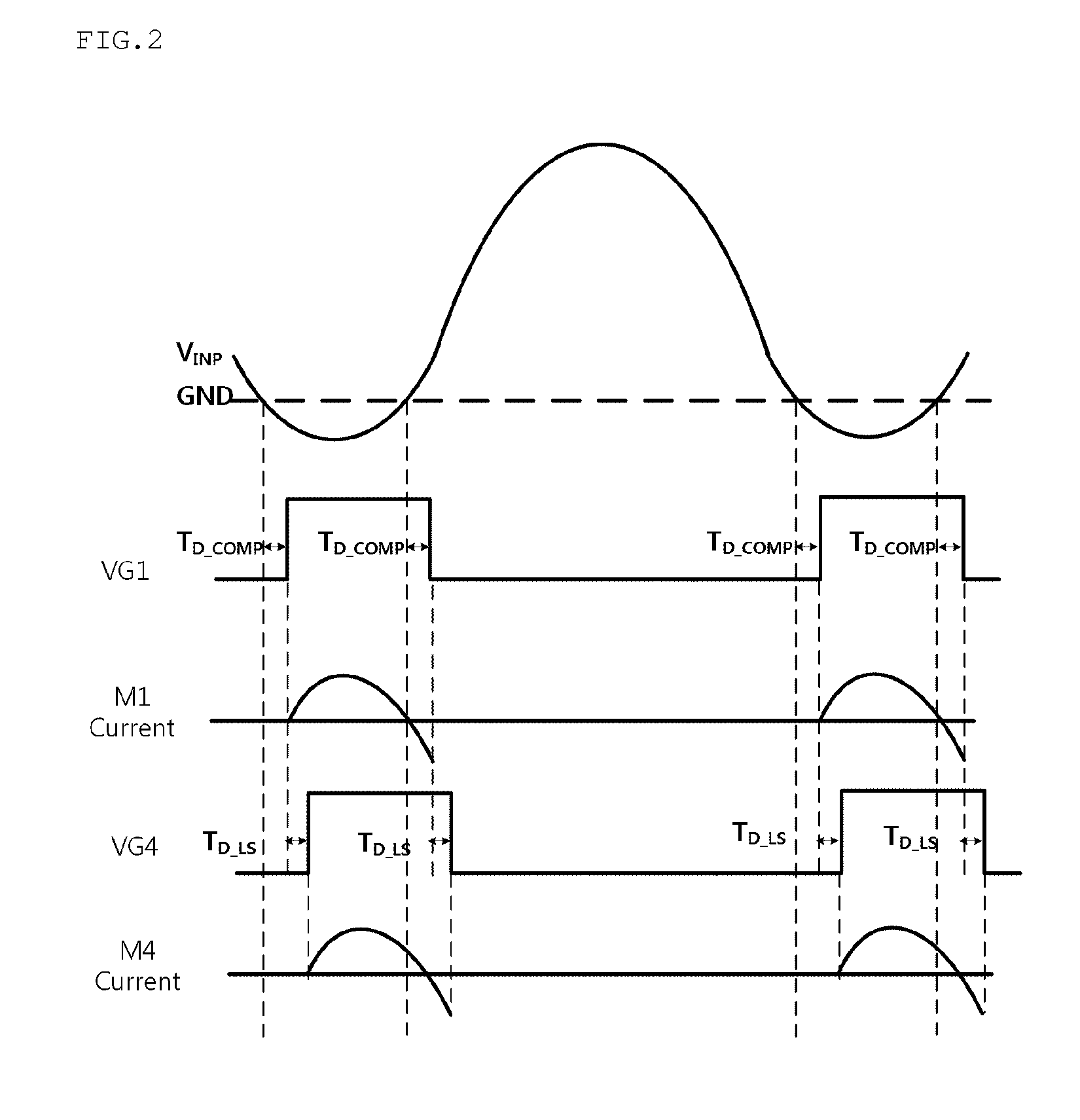

Active rectifier and wireless power receiving apparatus using the same that can reduce reverse current leakage

ActiveUS20150263534A1Total current dropAc-dc conversion without reversalTransformersReverse currentDelayed time

An active rectifier and a wireless power reception apparatus using the same are disclosed herein. The active rectifier includes first and fourth switches, second and third switches, and a synchronization control unit. The first and fourth switches are turned on while the voltage of an alternating current (AC) input is negative, and apply the current of the AC input to a rectifying capacitor. The second and third switches are turned on while a voltage of the AC input is positive, and apply the current of the AC input to the rectifying capacitor. The synchronization control unit compensates for the delay time of the comparator for detecting zero-crossing of the AC input so as to switch the first to fourth switches.

Owner:SKAI CHIPS

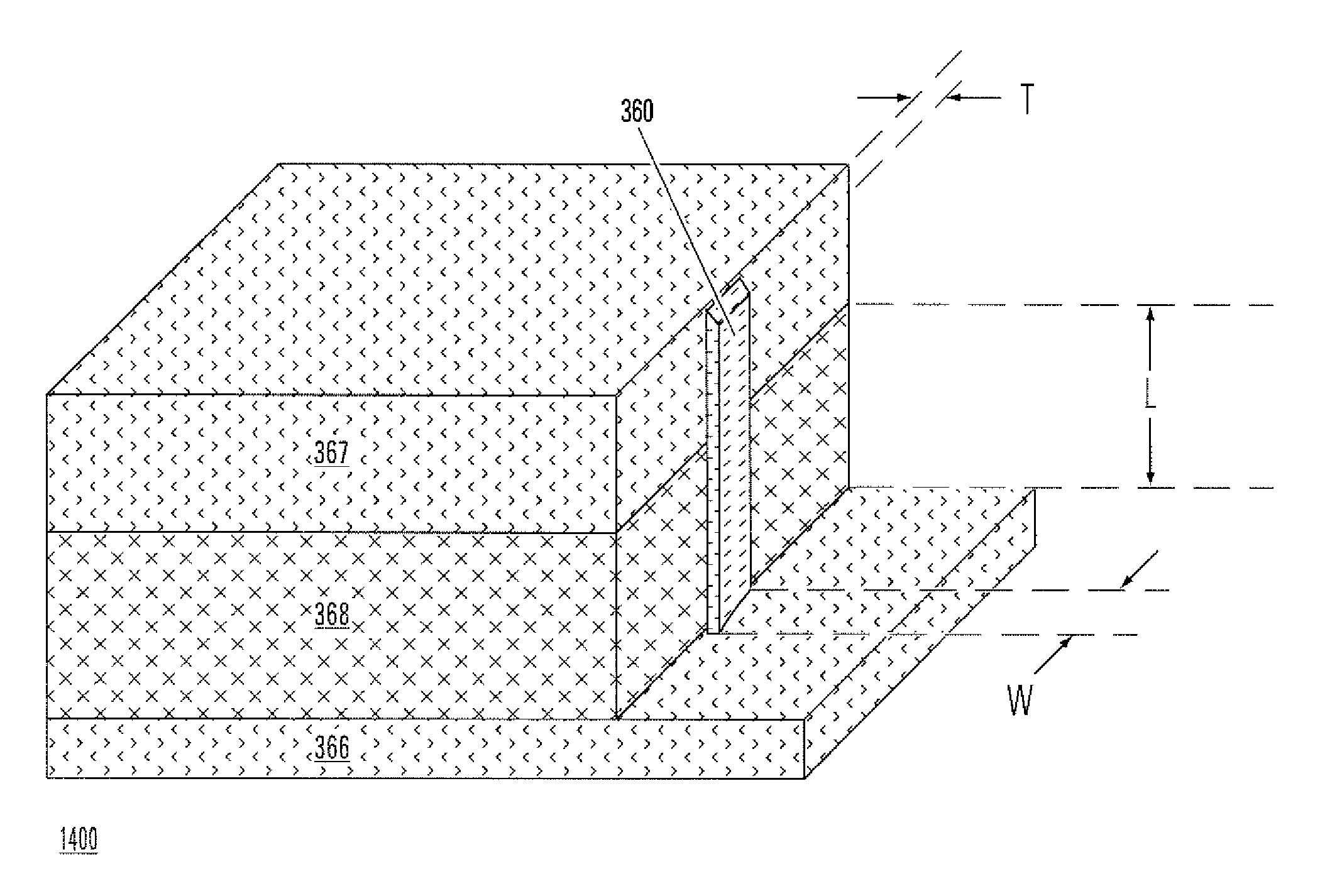

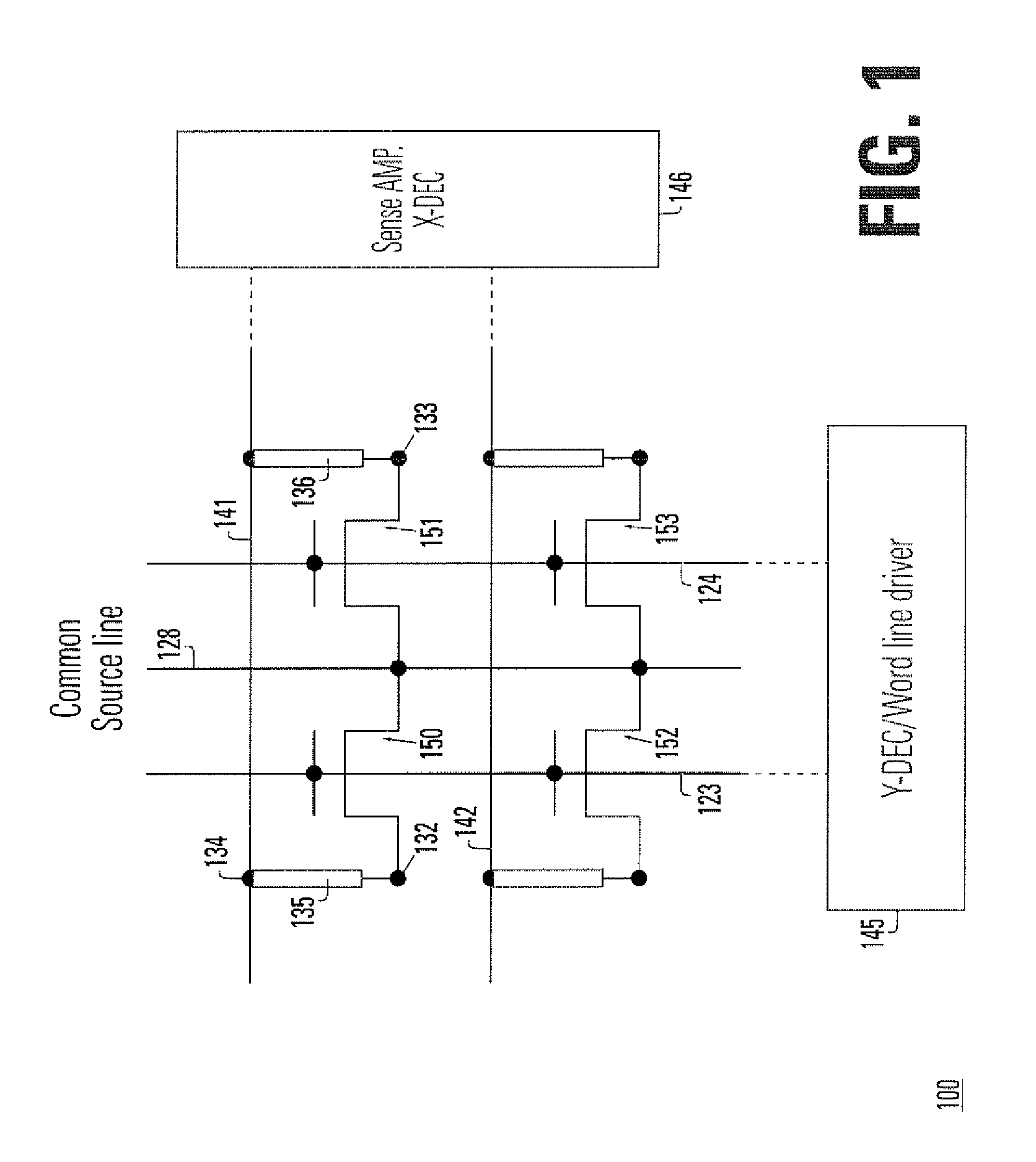

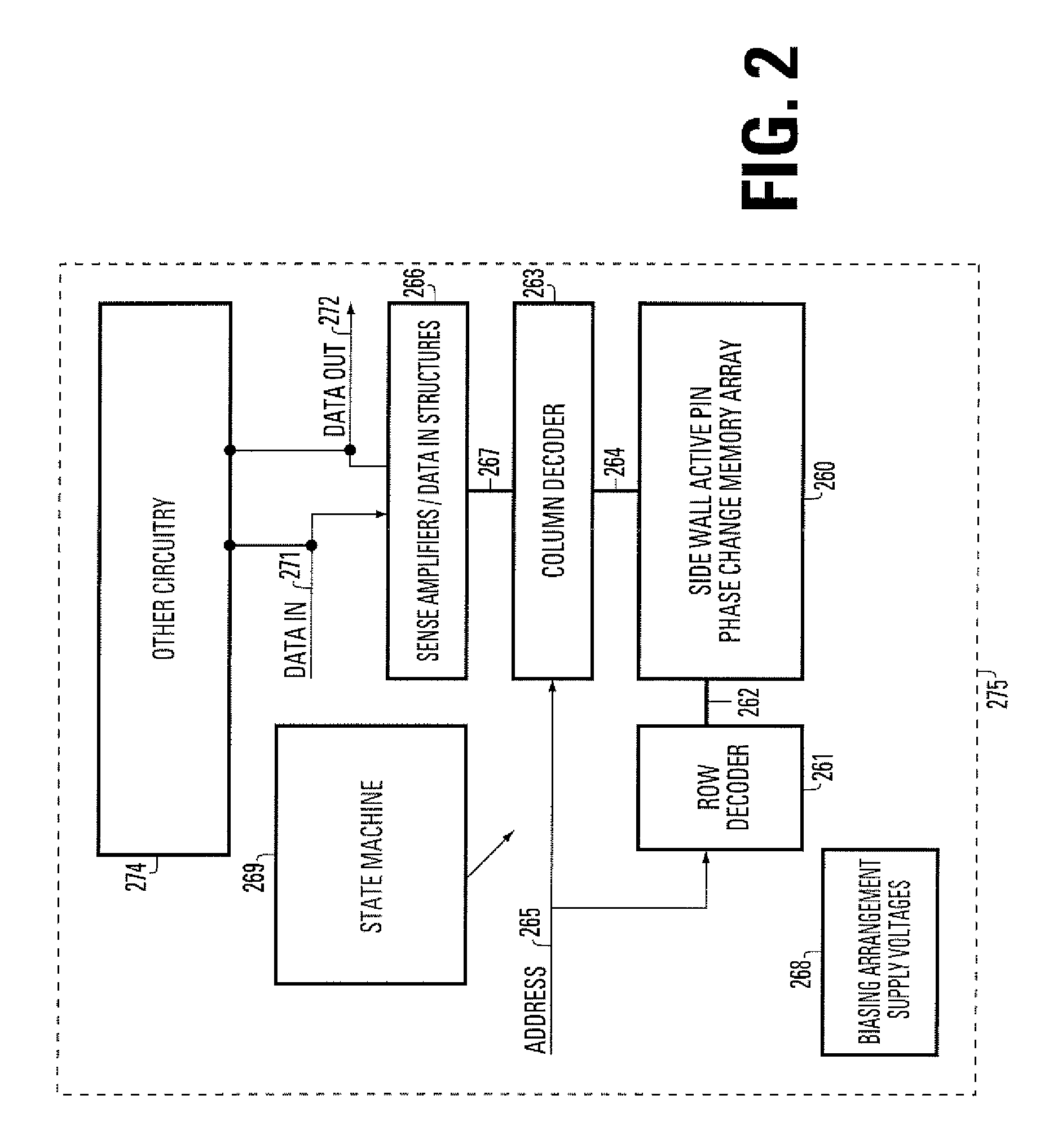

Vertical Side Wall Active Pin Structures in a Phase Change Memory and Manufacturing Methods

ActiveUS20070176261A1Reduce electrical currentLow resistivitySolid-state devicesSemiconductor devicesEngineeringPhase-change material

A programmable resistor memory, such as a phase change memory, with a memory element comprising narrow vertical side wall active pins is described. The side wall active pins comprise a programmable resistive material, such as a phase change material. In a first aspect of the invention, a method of forming a memory cell is described which comprises forming a stack comprising a first electrode having a principal surface with a perimeter, an insulating layer overlying a portion of the principal surface of the first electrode, and a second electrode vertically separated from the first electrode and overlying the insulating layer. Side walls on the insulating layer and on the second electrode are positioned over the principle surface of the first electrode with a lateral offset from the perimeter of the first electrode.

Owner:MACRONIX INT CO LTD

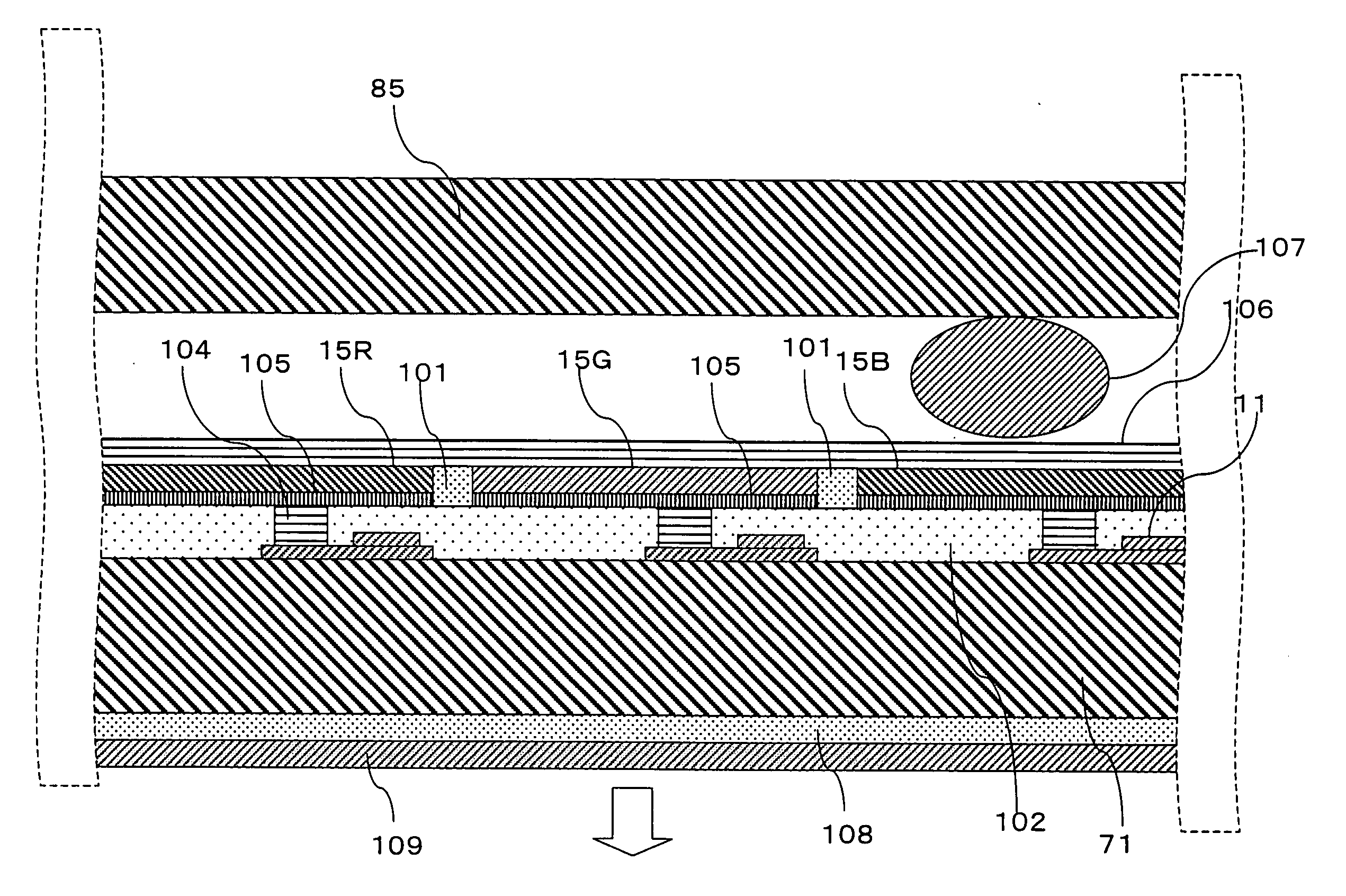

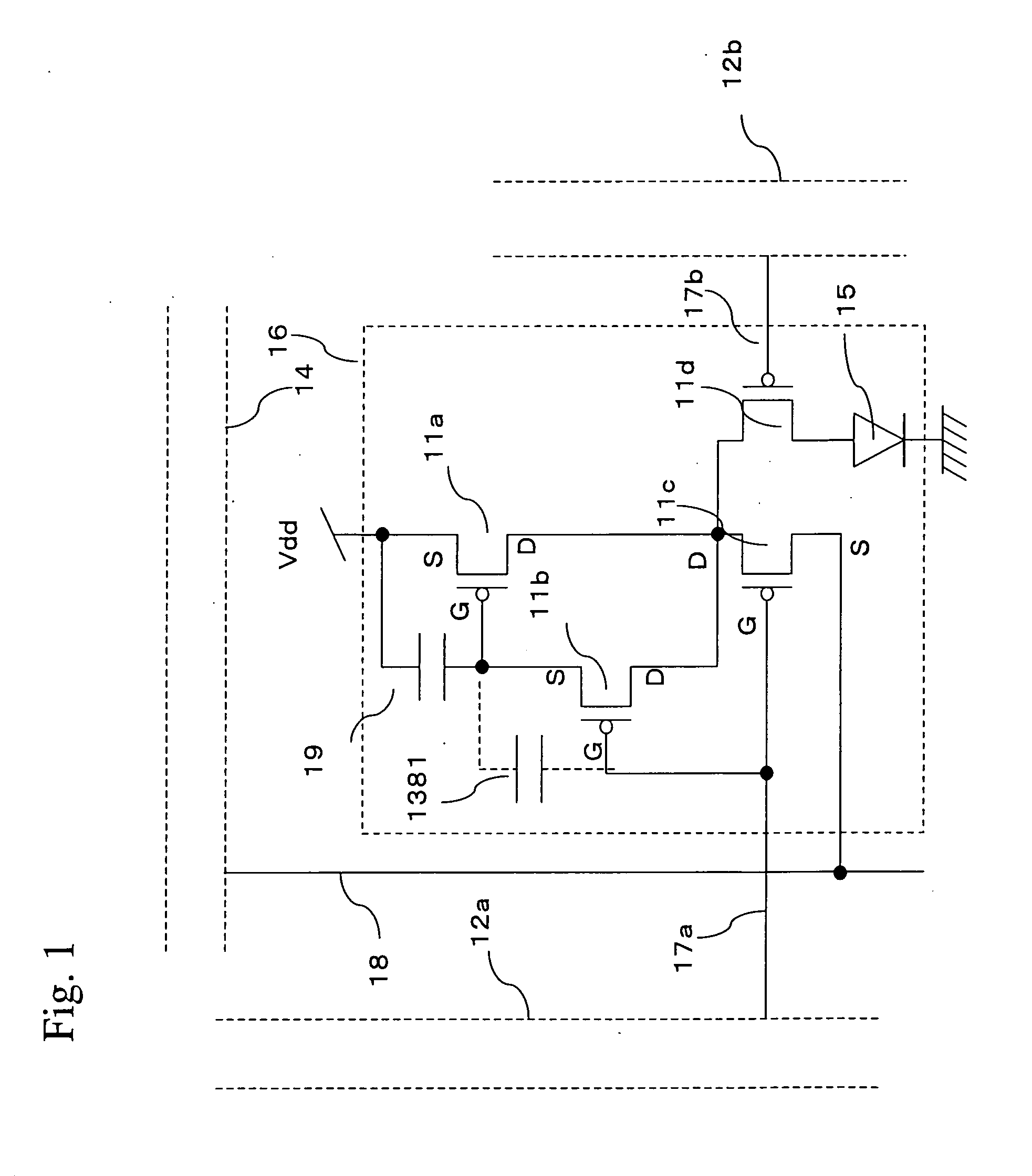

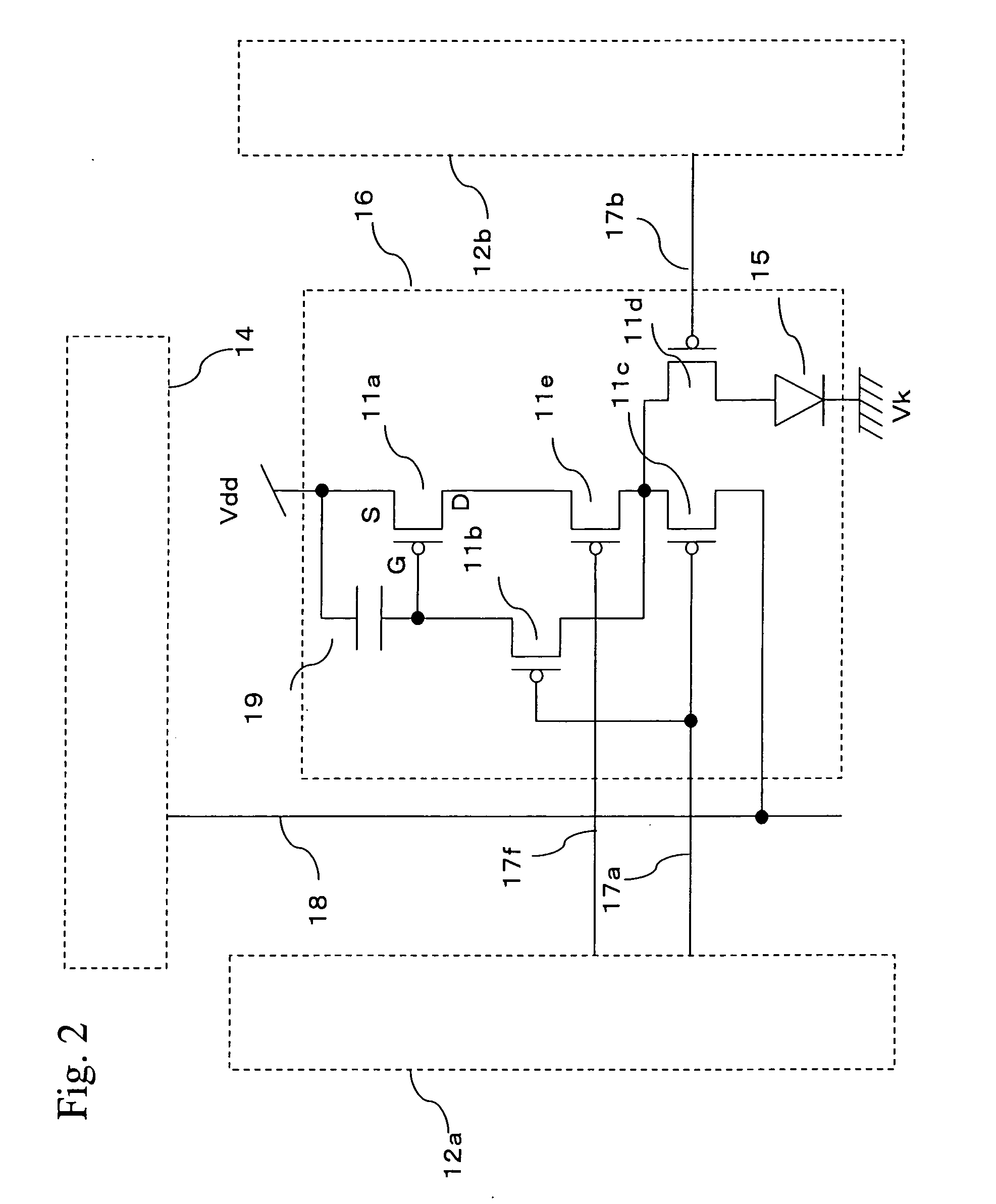

Drive method of el display panel

ActiveUS20050168491A1Show unityUniform screen displayElectroluminescent light sourcesSolid-state devicesDriver circuitParasitic capacitance

In order to charge and discharge parasitic capacitance of a source signal line sufficiently and program a predetermined current value into a pixel transistor, it is necessary to output a relatively large current from the source driver circuit. However, if such a large current is passed through the source signal line, the value of this current is programmed into the pixel, causing a larger than desired current to flow through an EL element 15. For example, if a 10 times larger current is used for programming, a 10 times larger current flows through the EL element 15, and thus the EL element 15 illuminates 10 times more brightly. To obtain predetermined emission brightness, the time during which the current flows through the EL element can be reduced to 1 / 10 of one frame (1 F). This way, the parasitic capacitance of the source signal line can be charged and discharged sufficiently and the predetermined emission brightness can be obtained.

Owner:JAPAN DISPLAY CENT INC

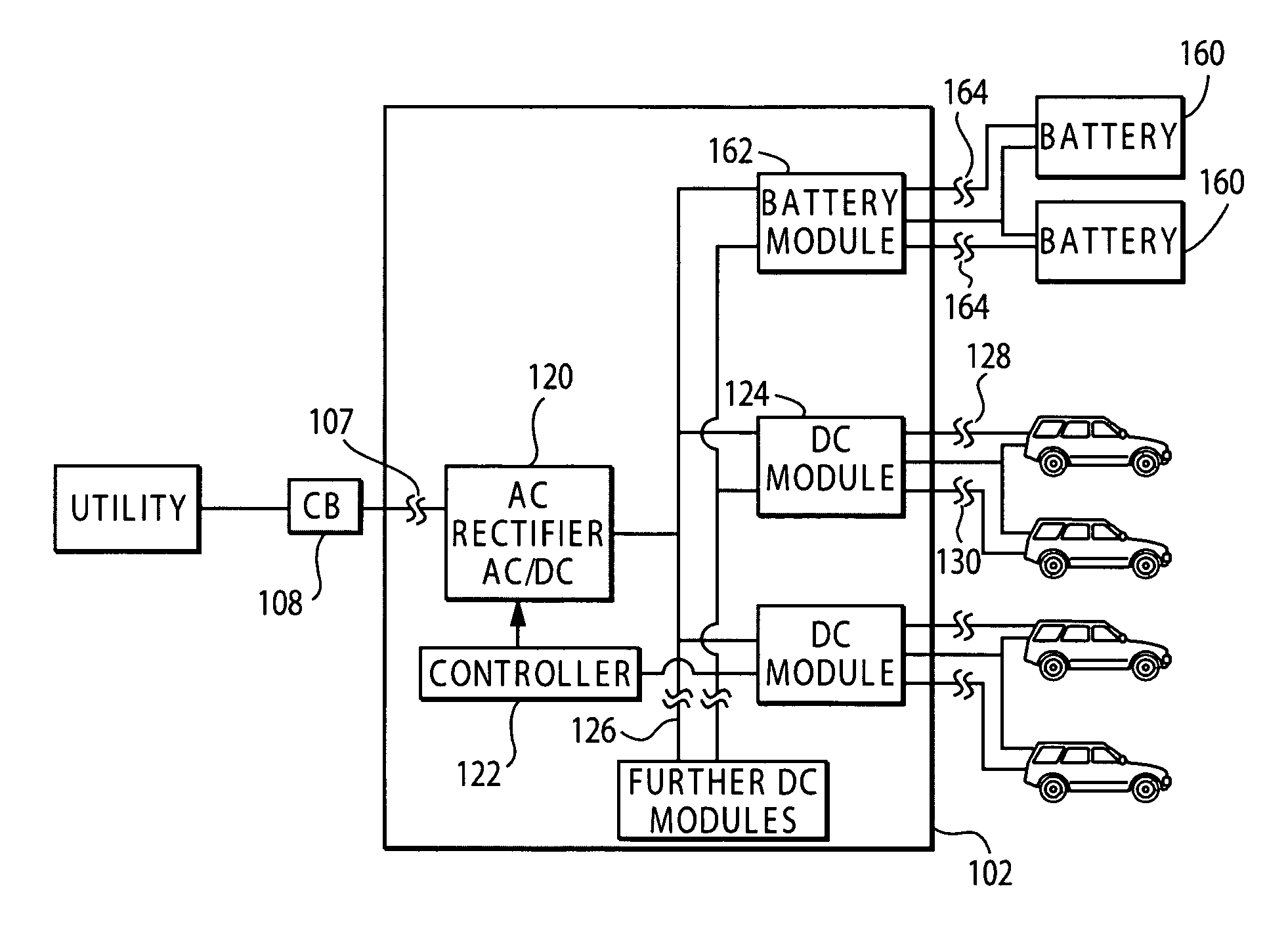

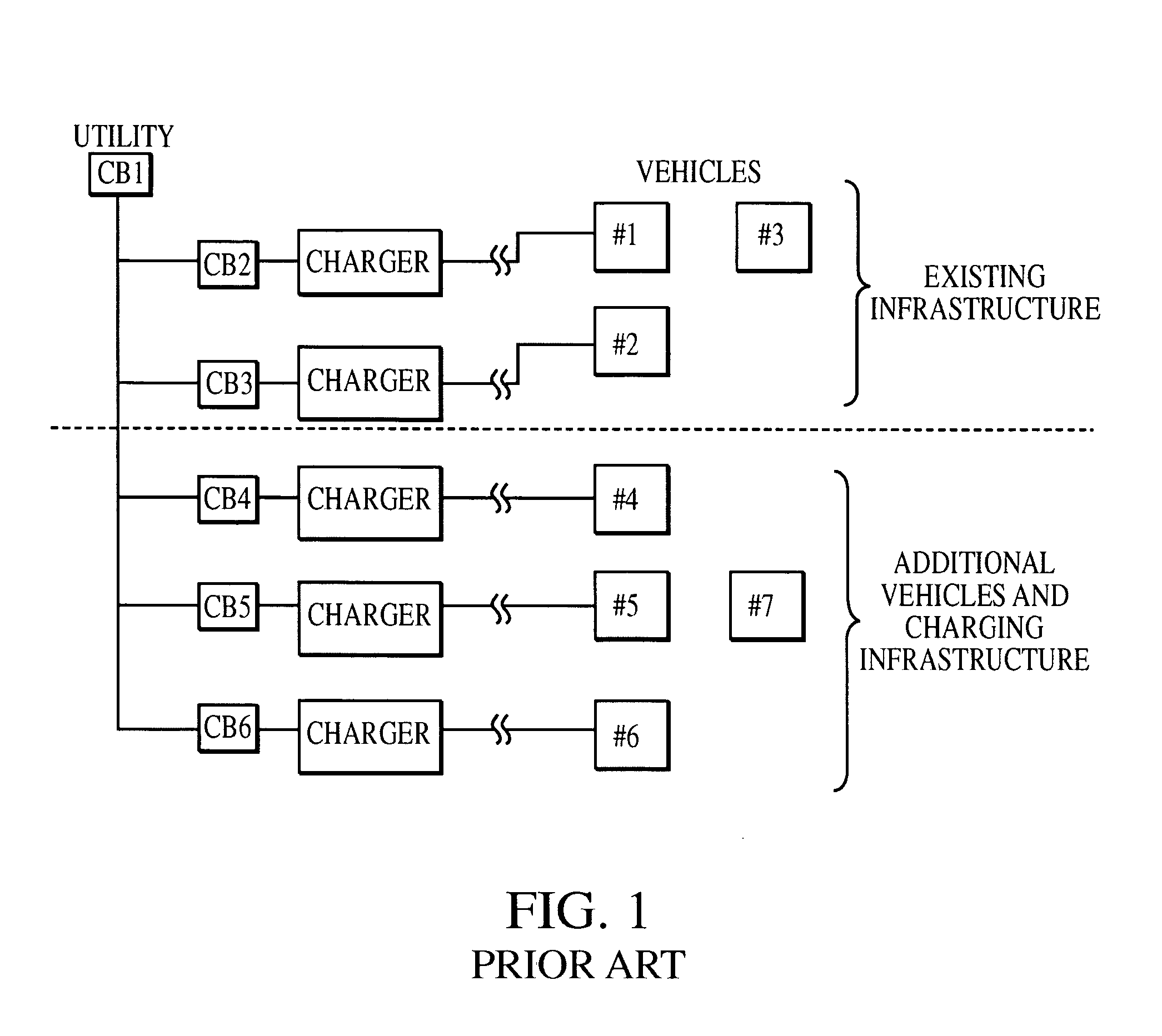

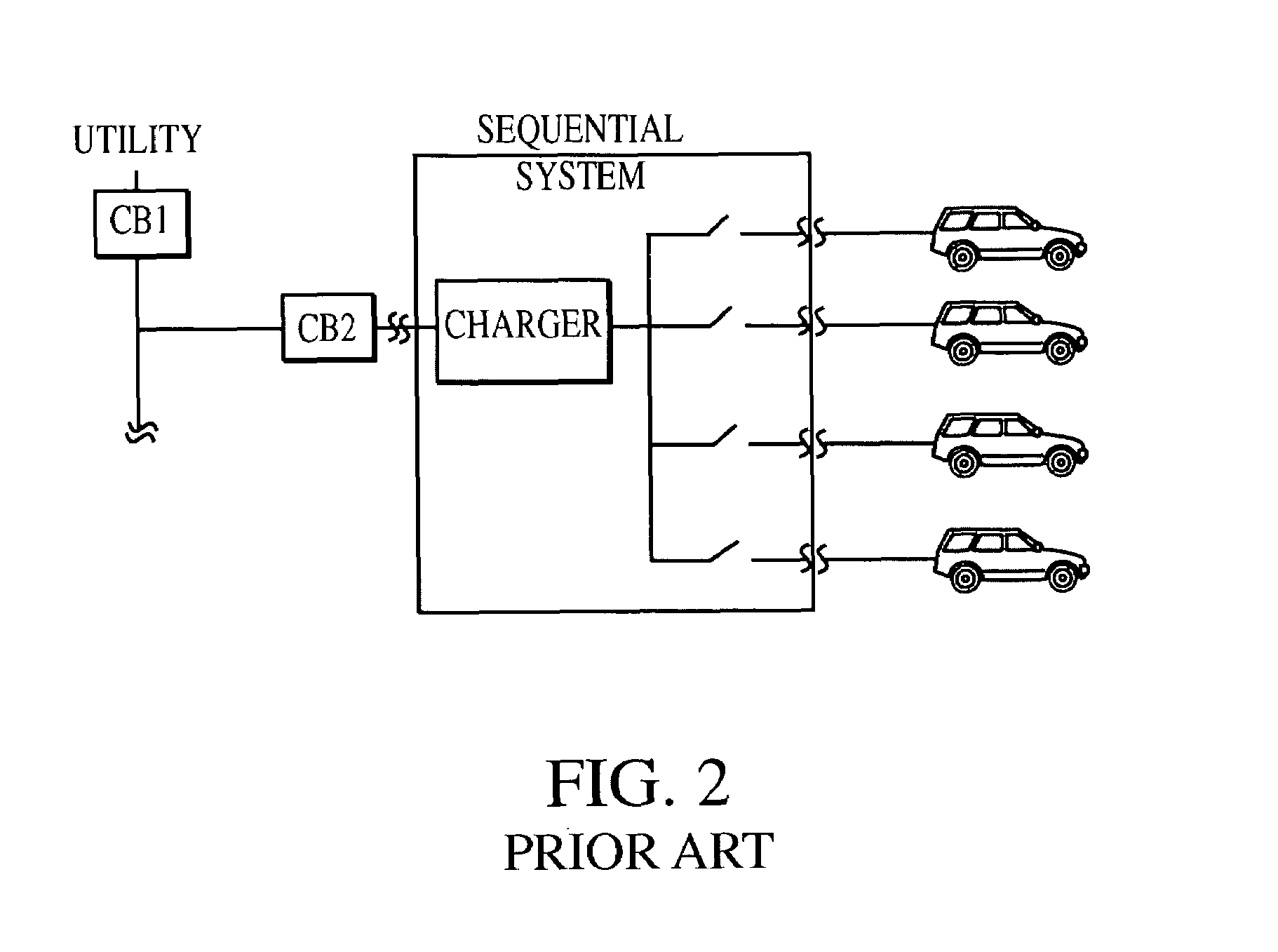

Battery charging system and method

InactiveUS7256516B2Meet system requirementsMeet power requirementsLoad balancing in dc networkDc source parallel operationEngineeringAC power

A charging system for simultaneously charging the batteries of a plurality of battery powered vehicles. The charging includes one or more DC-DC power converters having one or more charging ports configured to plug into the batteries. The DC-DC power converters are each configured to selectively connect to more than one charging port to selectively provide for higher port power levels. The DC-DC power converters connect to an AC rectifier through a DC bus. The AC rectifier connects to an AC power source having a limited power rating. The AC charging system also has a controller that controls the operation of the DC-DC power converters such that the total power draw on the AC rectifier does not exceed the power rating. The system is further configured such that the DC-DC power converters can drain selected batteries to obtain power for charging other batteries, thus allowing for batteries to be cycled.

Owner:WEBASTO CHARGING SYST INC

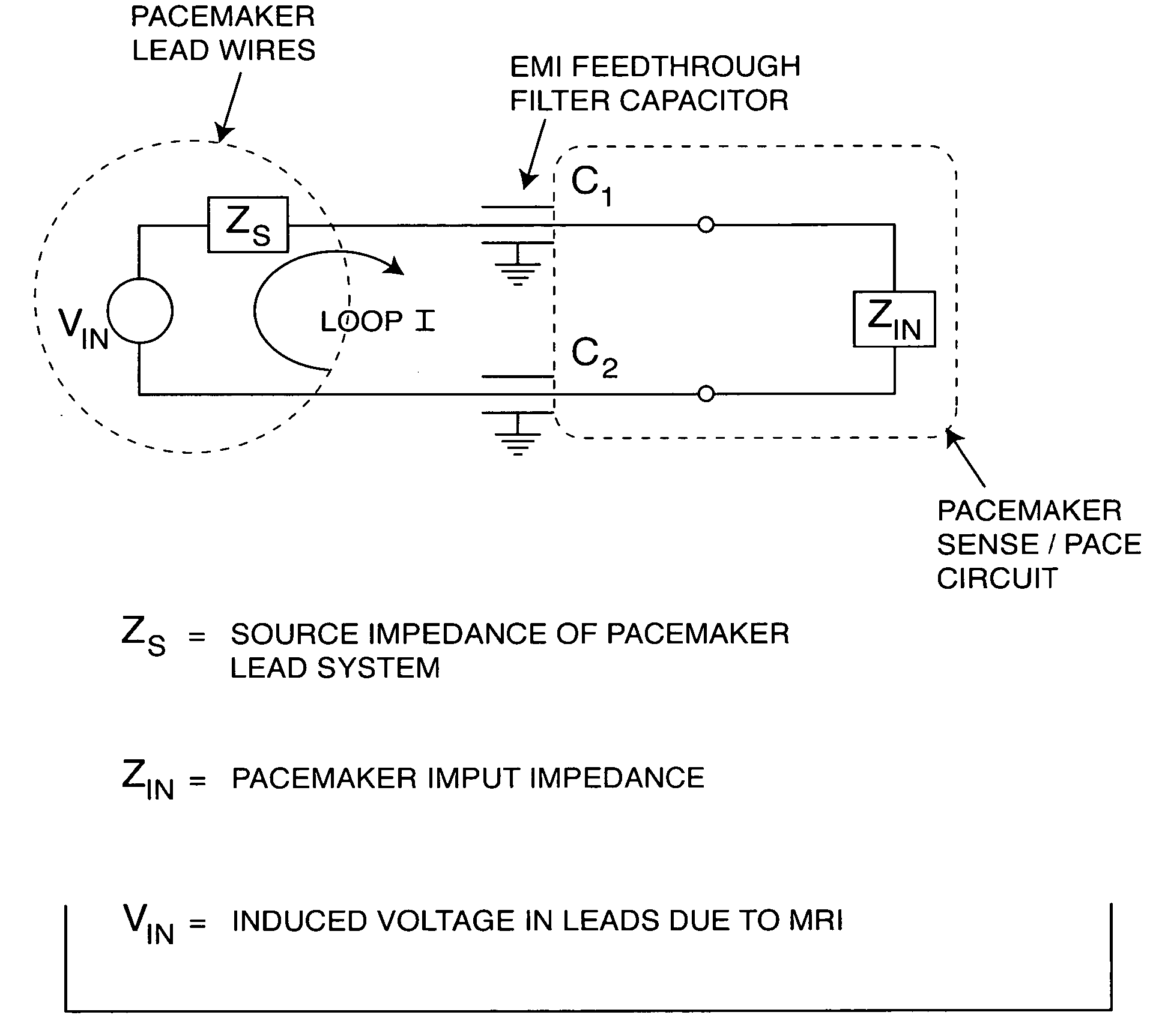

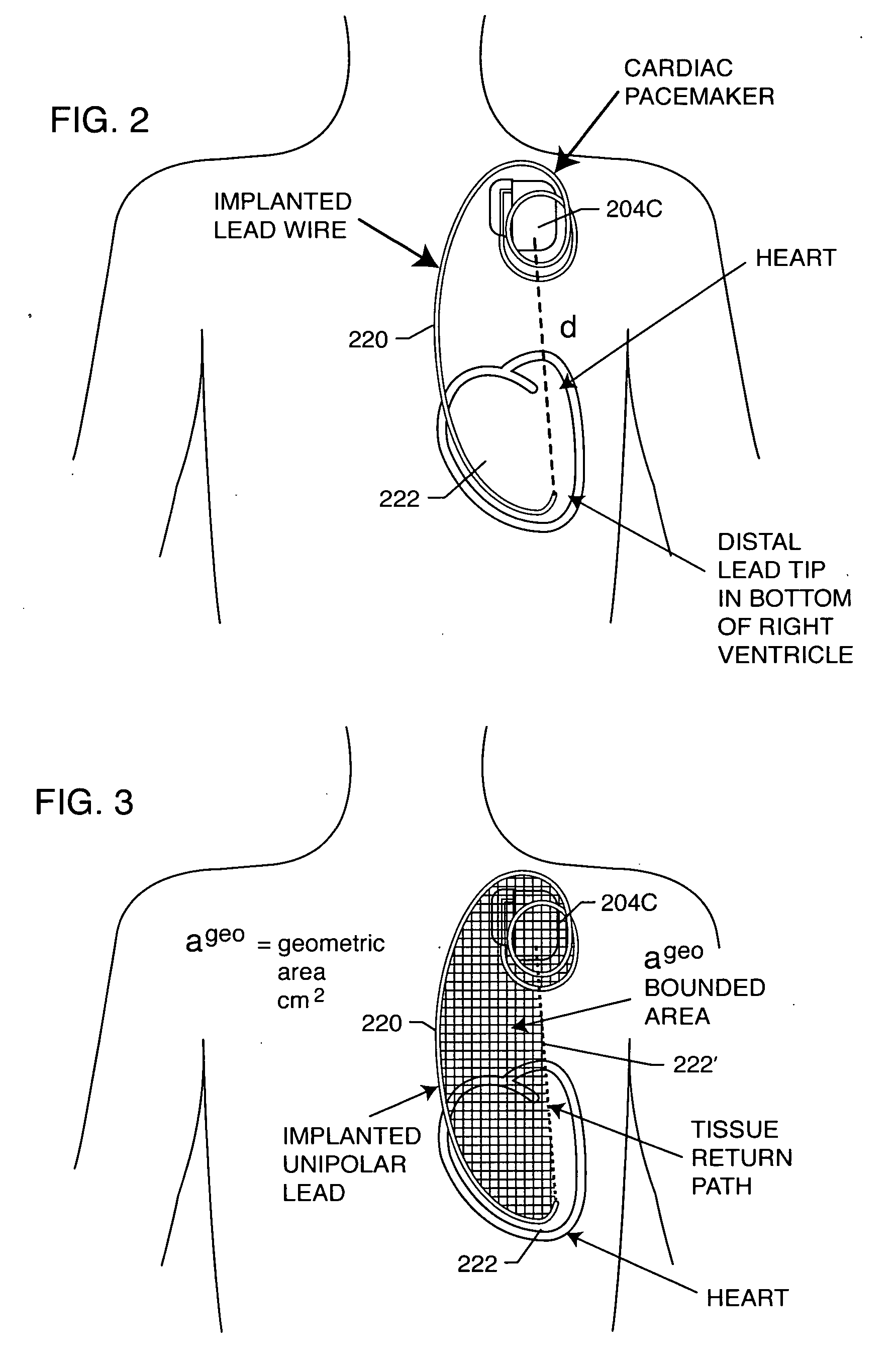

Apparatus and process for reducing the susceptability of active implantable medical devices to medical procedures such as magnetic resonance imaging

InactiveUS20050197677A1Improving impedanceReducing magnetic flux core saturationAnti-noise capacitorsElectrotherapyPhase cancellationElectromagnetic field

A feedthrough terminal assembly for an active implantable medical device (AIMD) includes a plurality of leadwires extending from electronic circuitry of the AIMD, and a lossy ferrite inductor through which the leadwires extend in non-conductive relation for increasing the impedance of the leadwires at selected RF frequencies and reducing magnetic flux core saturation of the lossy ferrite inductor through phase cancellation of signals carried by the leadwires. A process is also provided for filtering electromagnetic interference (EMI) in an implanted leadwire extending from an AIMD into body fluids or tissue, wherein the leadwire is subjected to occasional high-power electromagnetic fields such as those produced by medical diagnostic equipment including magnetic resonance imaging.

Owner:GREATBATCH SIERRA INC

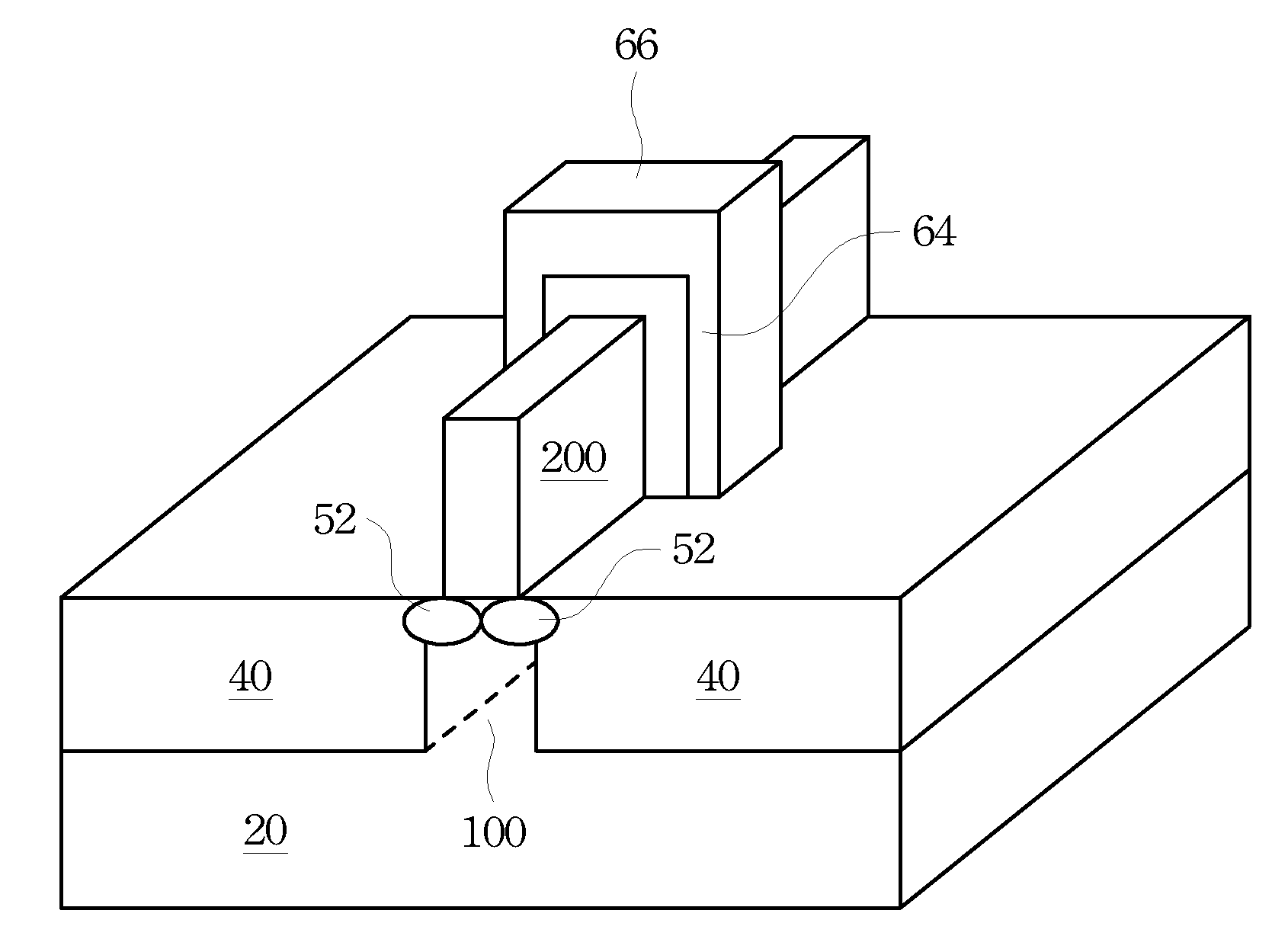

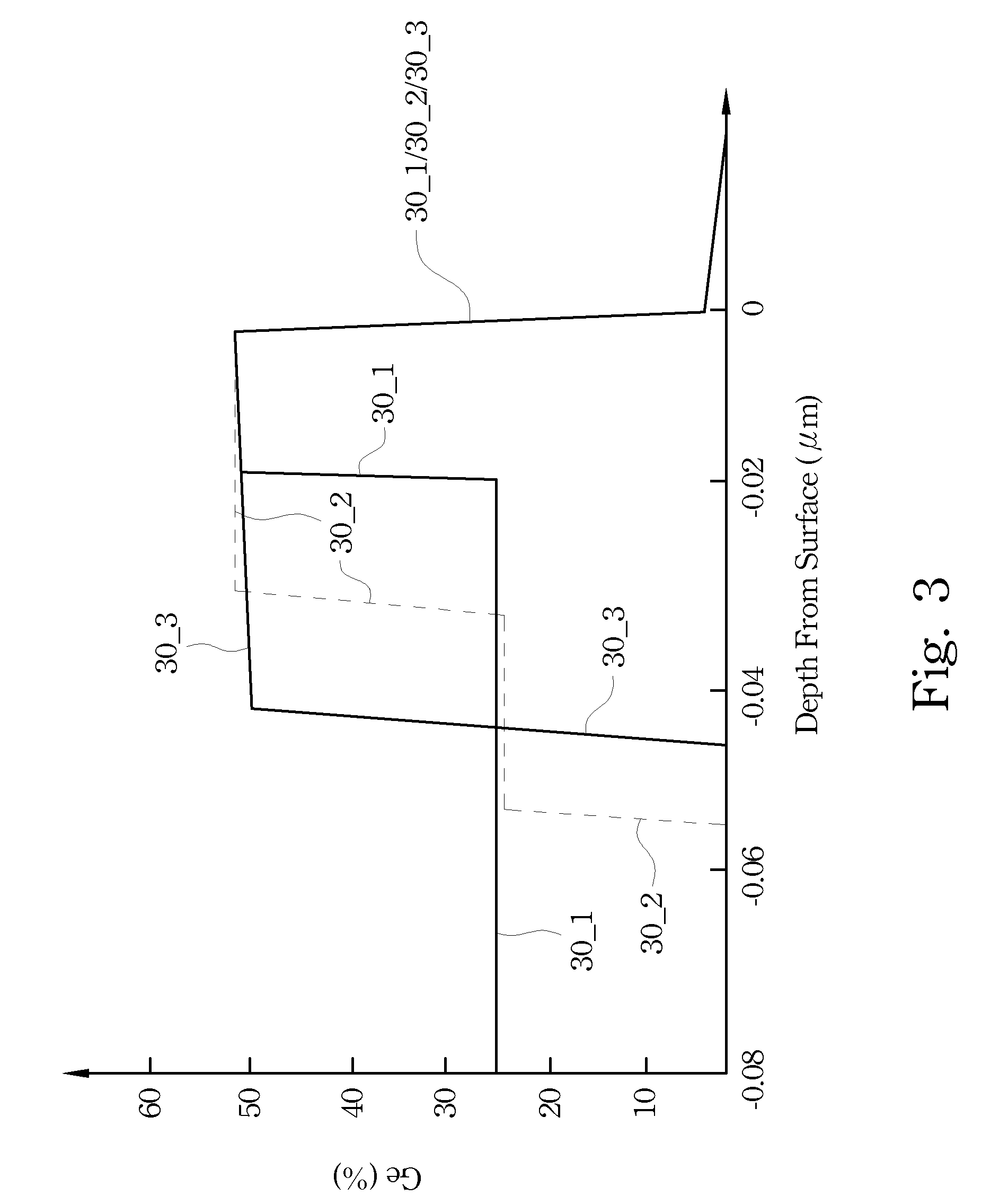

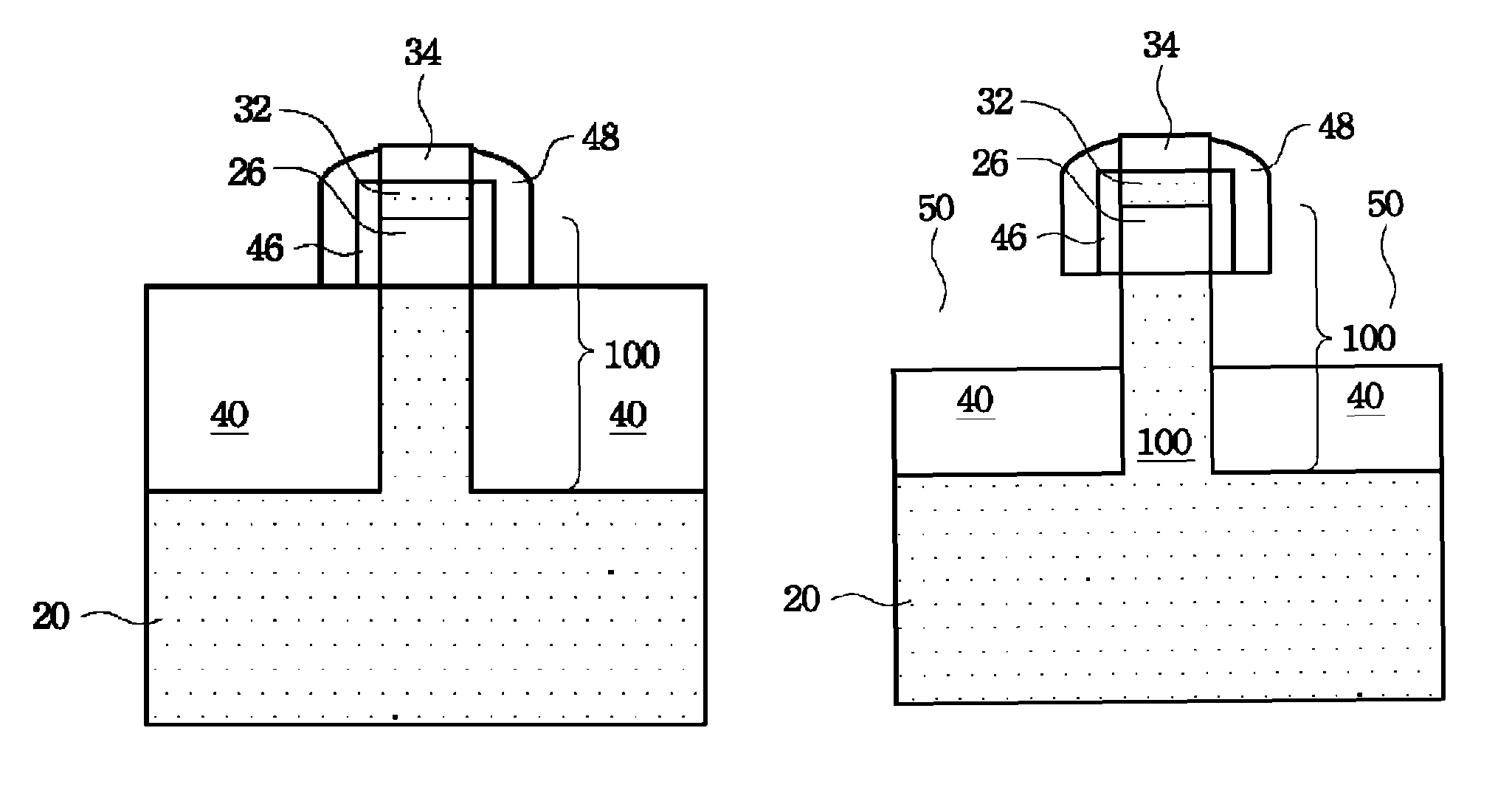

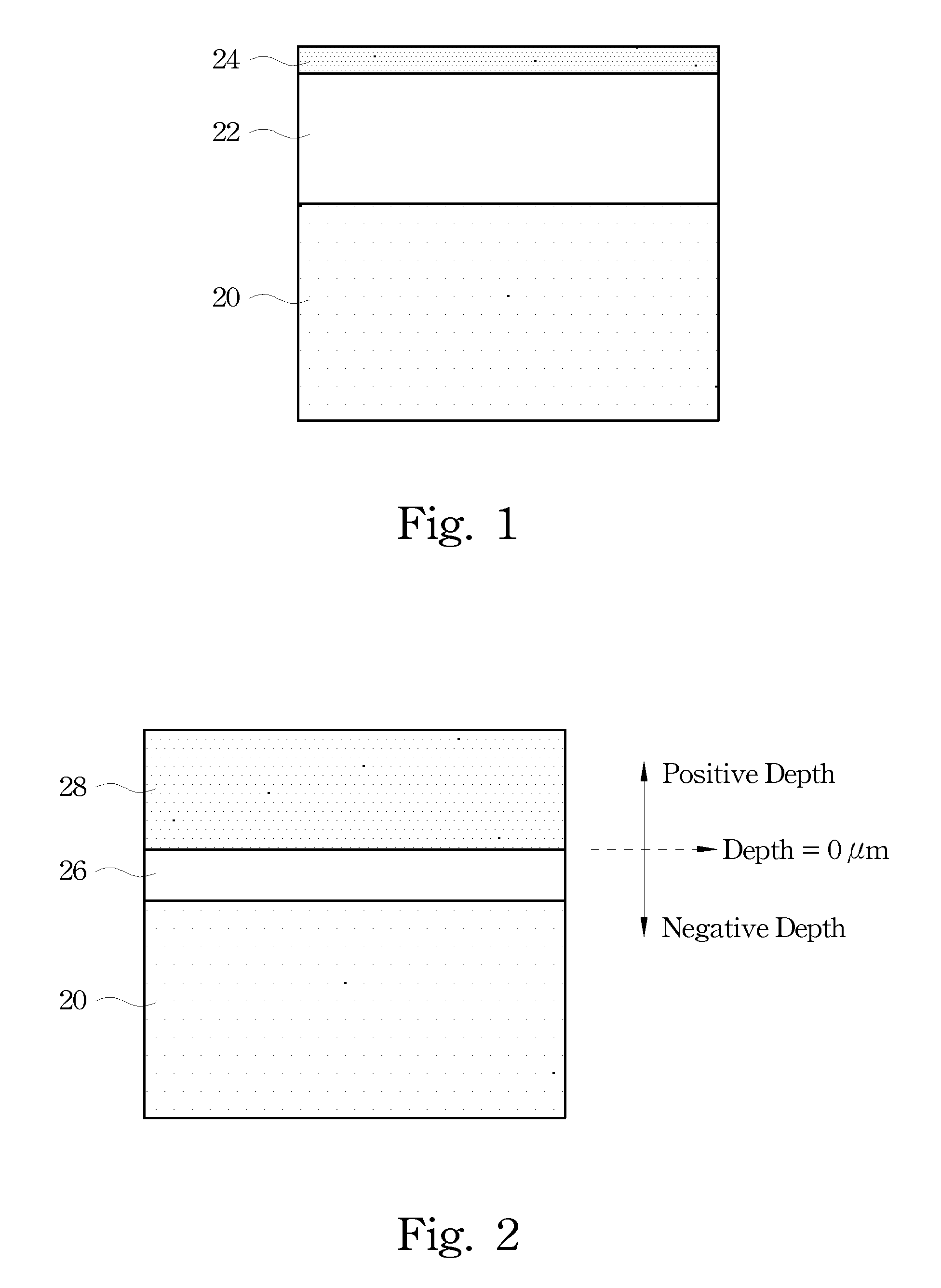

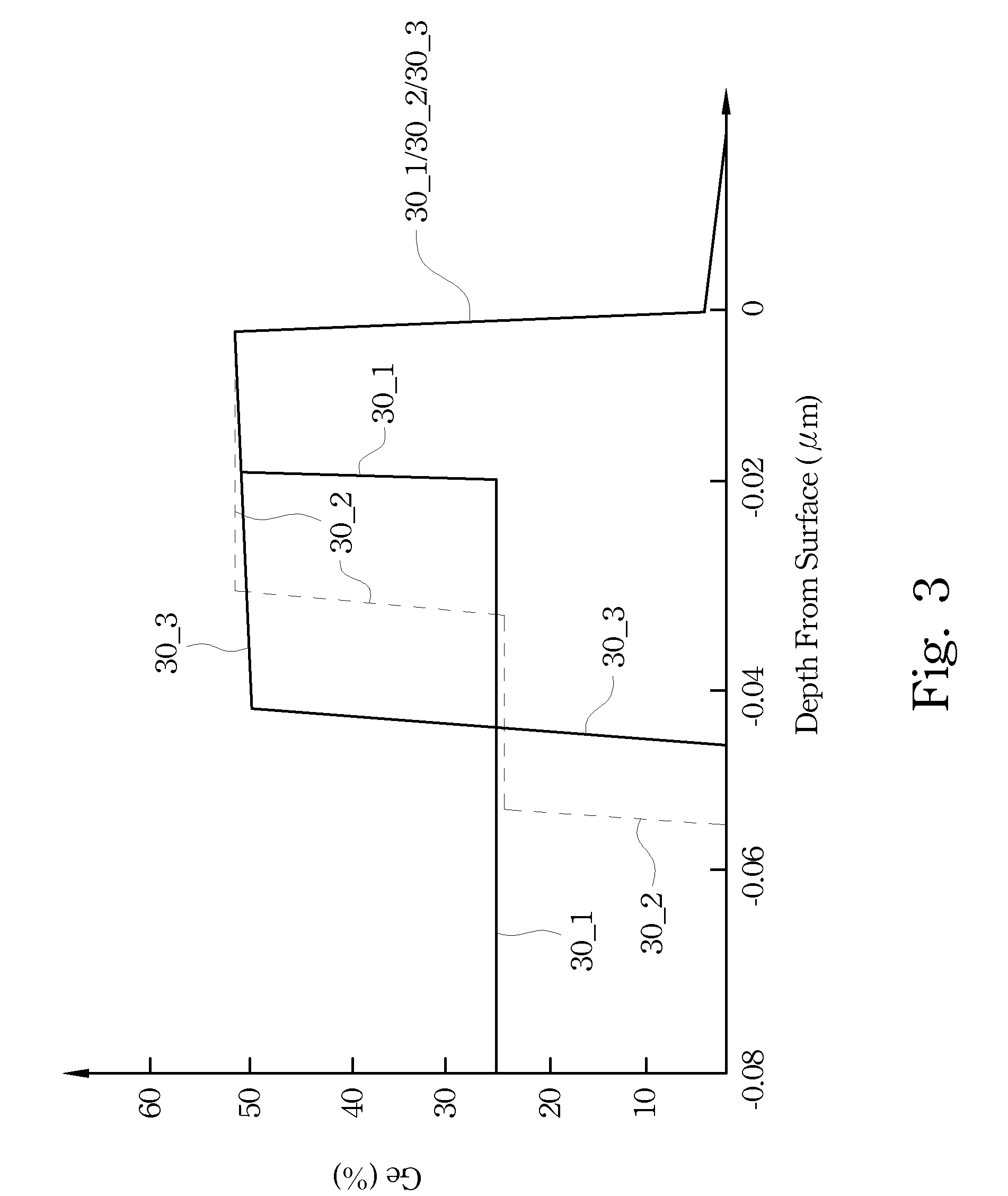

Germanium FinFETs Having Dielectric Punch-Through Stoppers

ActiveUS20100144121A1Total current dropHigh carrier mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesComposite substrateSemiconductor structure

A method of forming a semiconductor structure includes providing a composite substrate, which includes a bulk silicon substrate and a silicon germanium (SiGe) layer over and adjoining the bulk silicon substrate. A first condensation is performed to the SiGe layer to form a condensed SiGe layer, so that the condensed SiGe layer has a substantially uniform germanium concentration. The condensed SiGe layer and a top portion of the bulk silicon substrate are etched to form a composite fin including a silicon fin and a condensed SiGe fin over the silicon fine. The method further includes oxidizing a portion of the silicon fin; and performing a second condensation to the condensed SiGe fin.

Owner:TAIWAN SEMICON MFG CO LTD

Germanium FinFETs having dielectric punch-through stoppers

InactiveUS8048723B2High carrier mobilityTotal current dropSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureComposite substrate

A method of forming a semiconductor structure includes providing a composite substrate, which includes a bulk silicon substrate and a silicon germanium (SiGe) layer over and adjoining the bulk silicon substrate. A first condensation is performed to the SiGe layer to form a condensed SiGe layer, so that the condensed SiGe layer has a substantially uniform germanium concentration. The condensed SiGe layer and a top portion of the bulk silicon substrate are etched to form a composite fin including a silicon fin and a condensed SiGe fin over the silicon fine. The method further includes oxidizing a portion of the silicon fin; and performing a second condensation to the condensed SiGe fin.

Owner:TAIWAN SEMICON MFG CO LTD

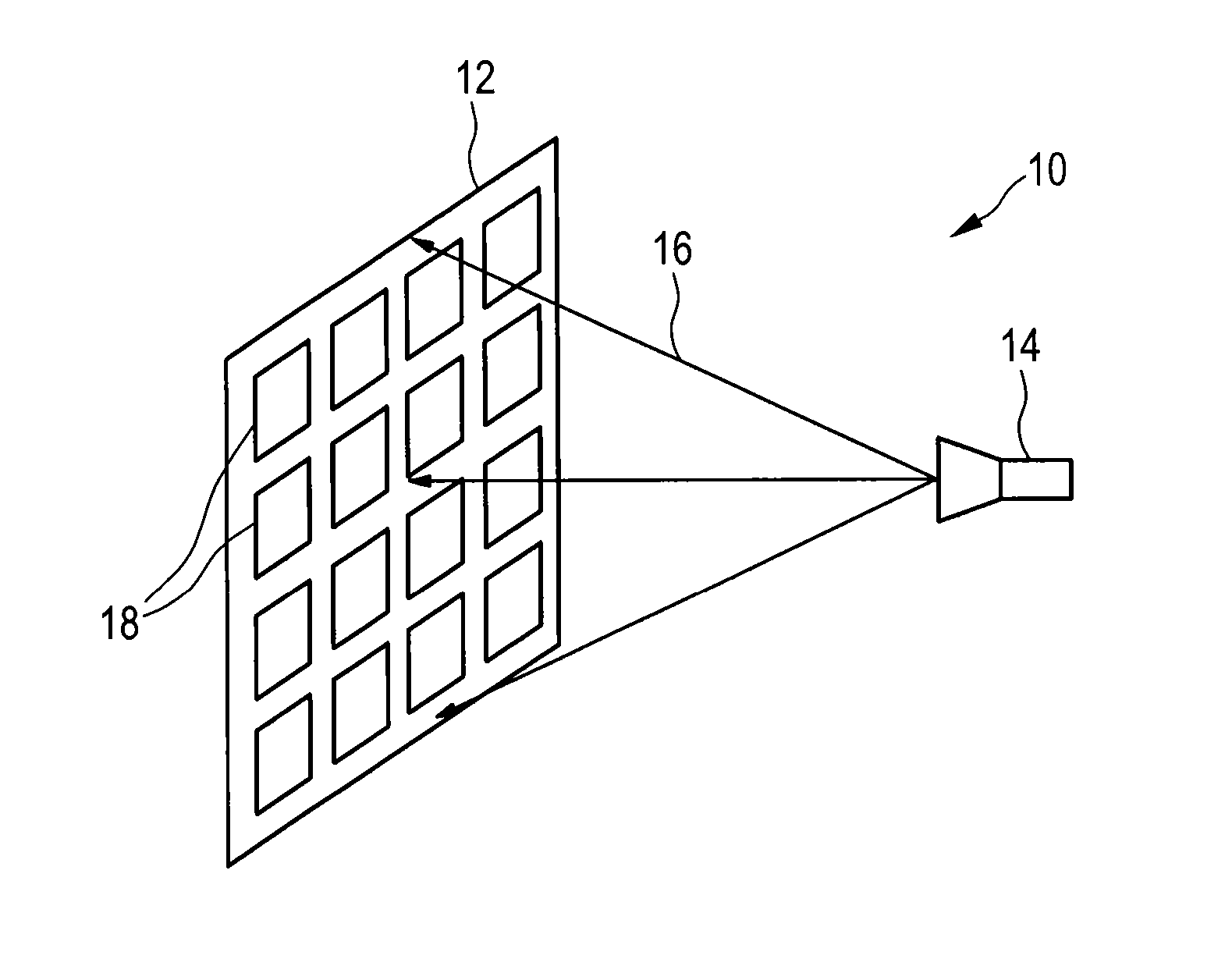

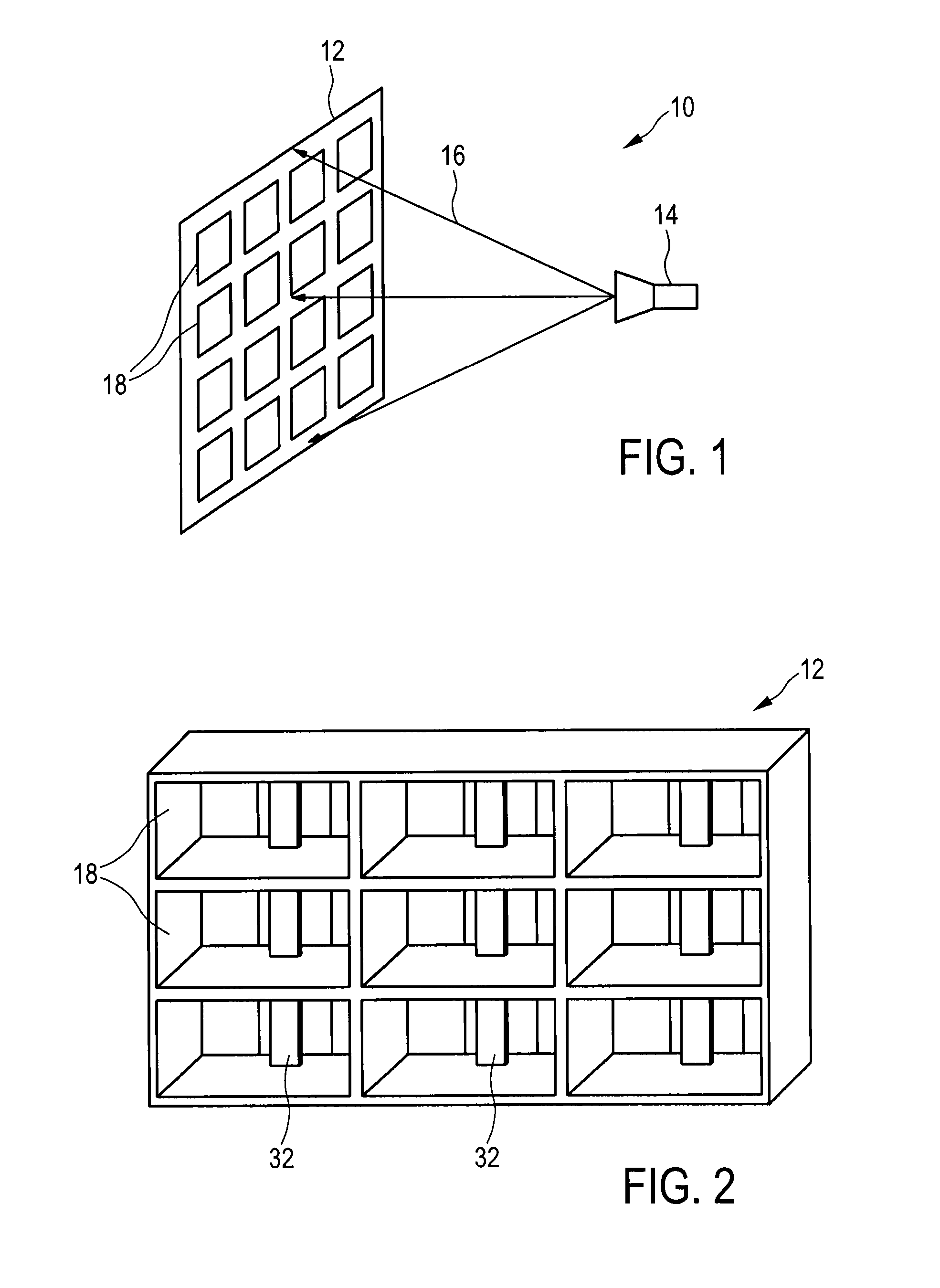

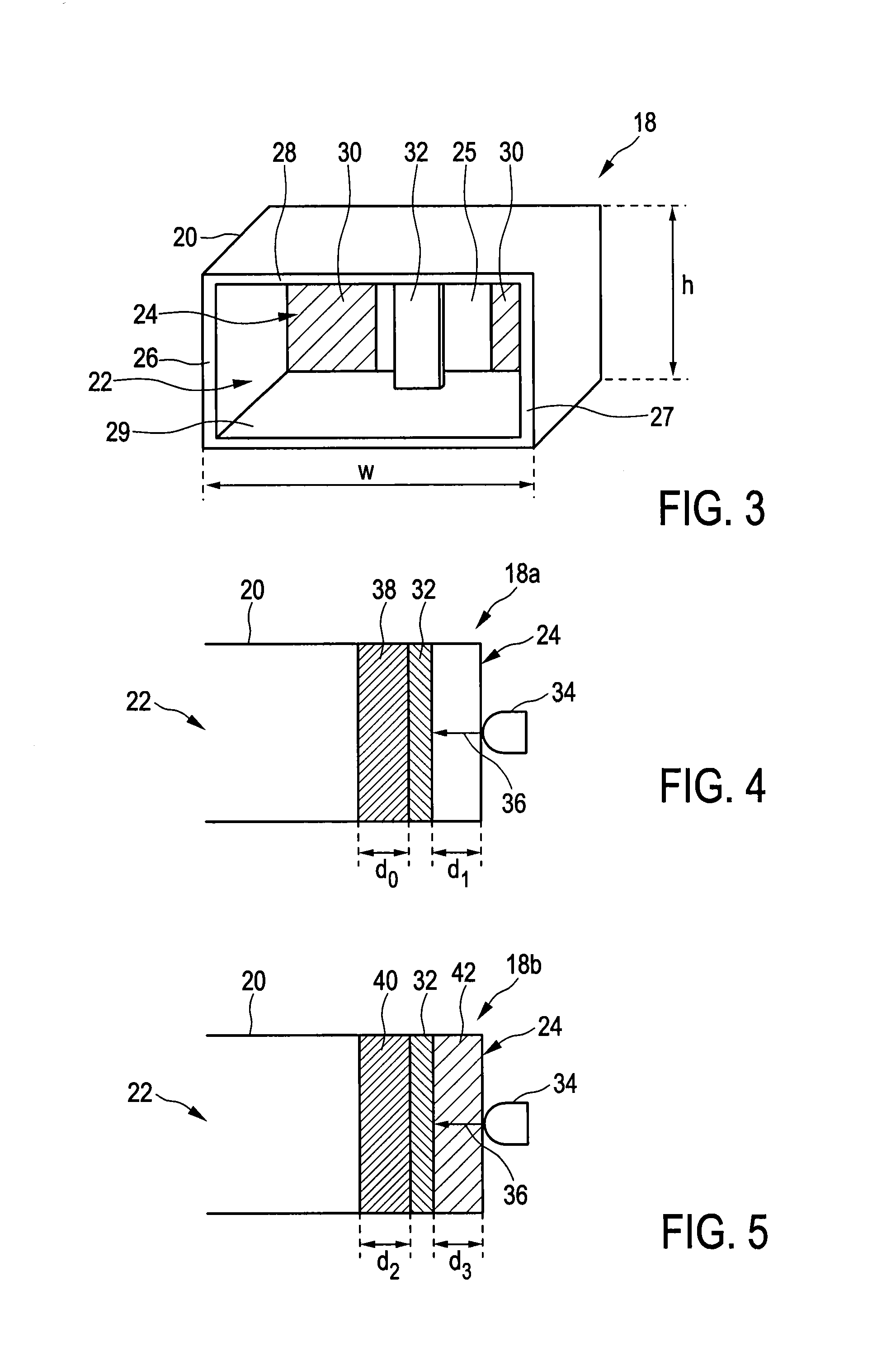

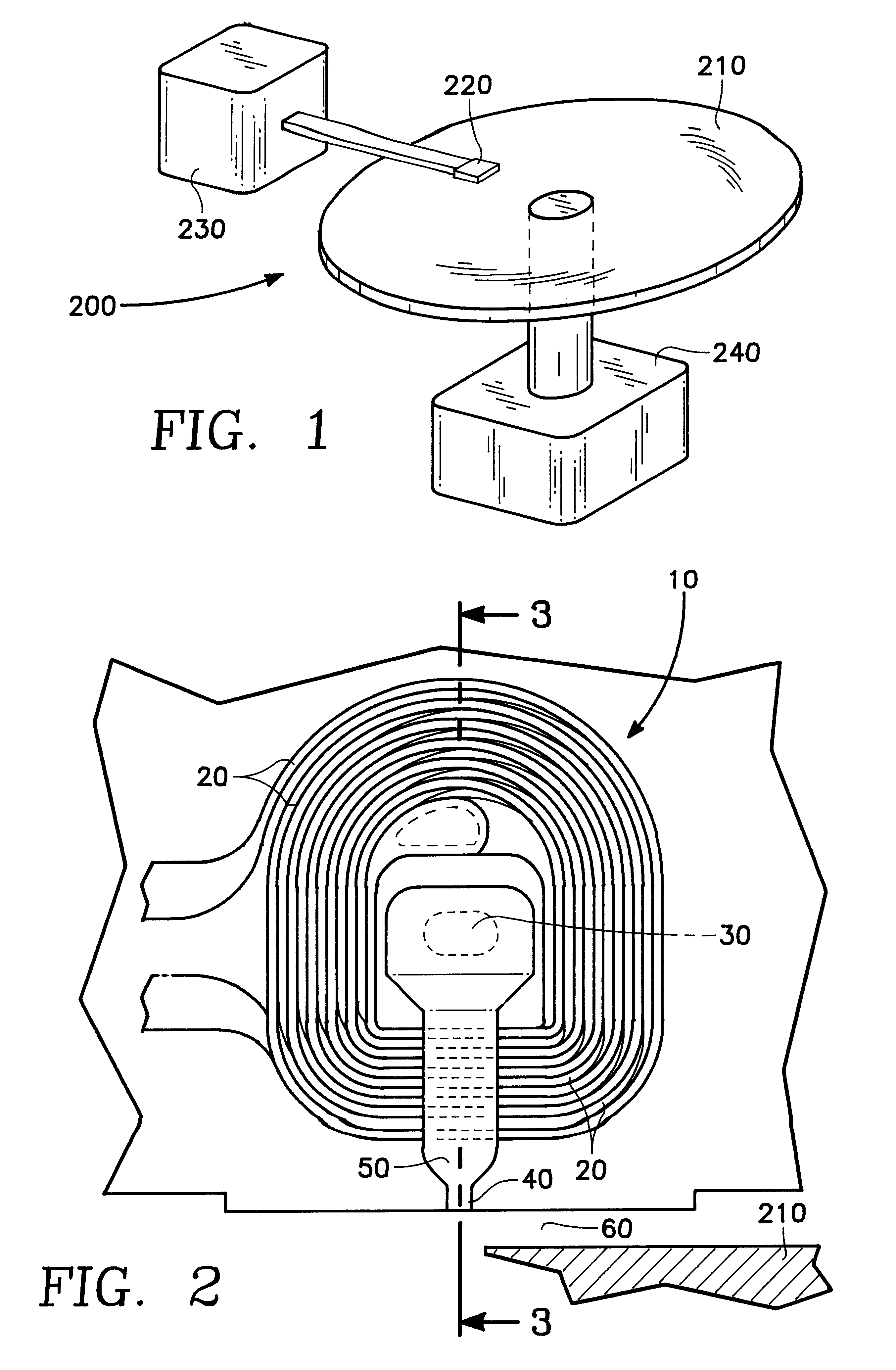

Dual-polarized optically controlled microwave antenna

An optically controlled microwave antenna that reduces the optical power consumed by the antenna and to enable polarimetric detection an optically controlled microwave antenna comprises an antenna array and a feed for illuminating said antenna array with and / or receiving microwave radiation. The antenna array comprises a plurality of antenna elements each including a waveguide, two optically controllable semiconductor elements arranged within the waveguide in front of the light transmissive portion of the second end portion, a controllable light source arranged at or close to the light transmissive portion of the second end portion for projecting a controlled light beam onto said semiconductor element for controlling its material properties, and a septum arranged within the waveguide in front of the light transmissive portion of the second end portion and separating said waveguide into two waveguide portions.

Owner:SONY CORP

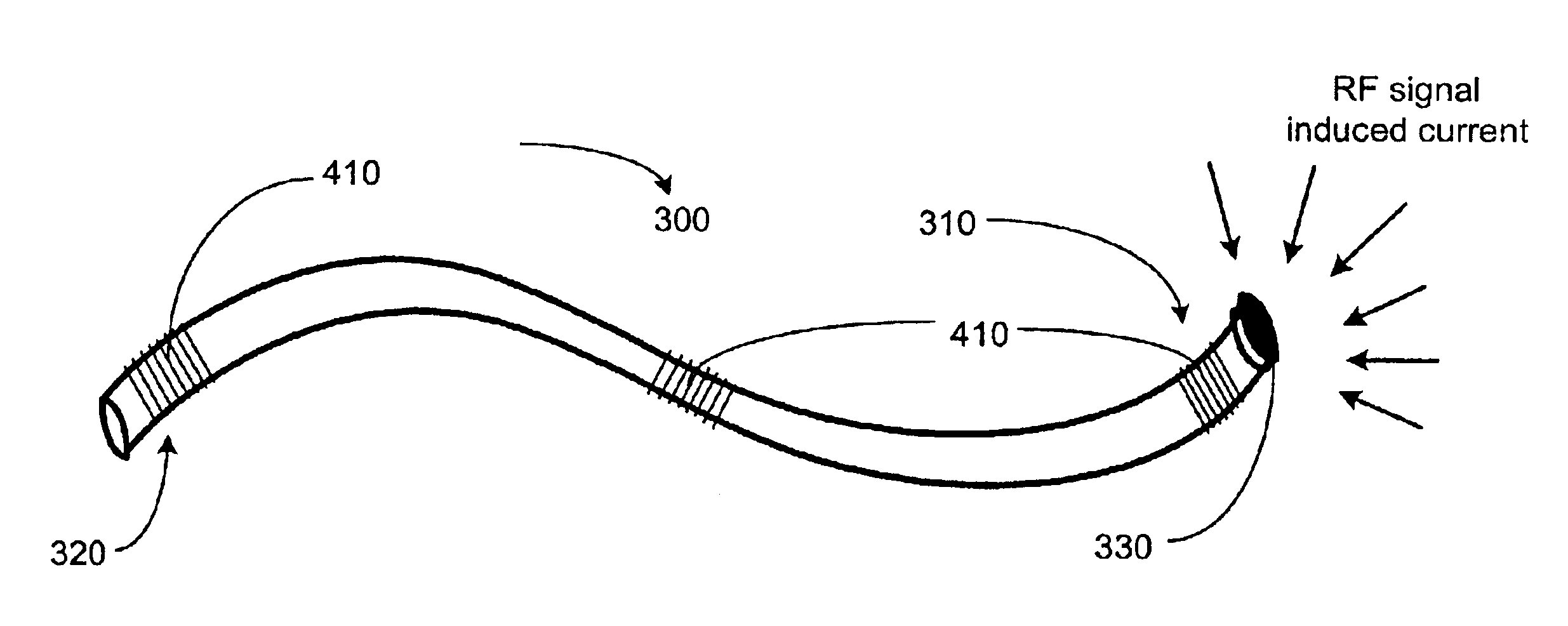

Conditioning of coupled electromagnetic signals on a lead

InactiveUS7013180B2Reducing coupled currentTotal current dropTransvascular endocardial electrodesSurgeryElectromagnetic shieldingEngineering

Owner:MEDTRONIC INC

Ferromagnetic powder for dust core

InactiveUS7498080B2Increase resistanceTotal current dropLiquid surface applicatorsInductances/transformers/magnets manufactureElectrical resistance and conductanceEddy current

Owner:HON HAI PRECISION IND CO LTD

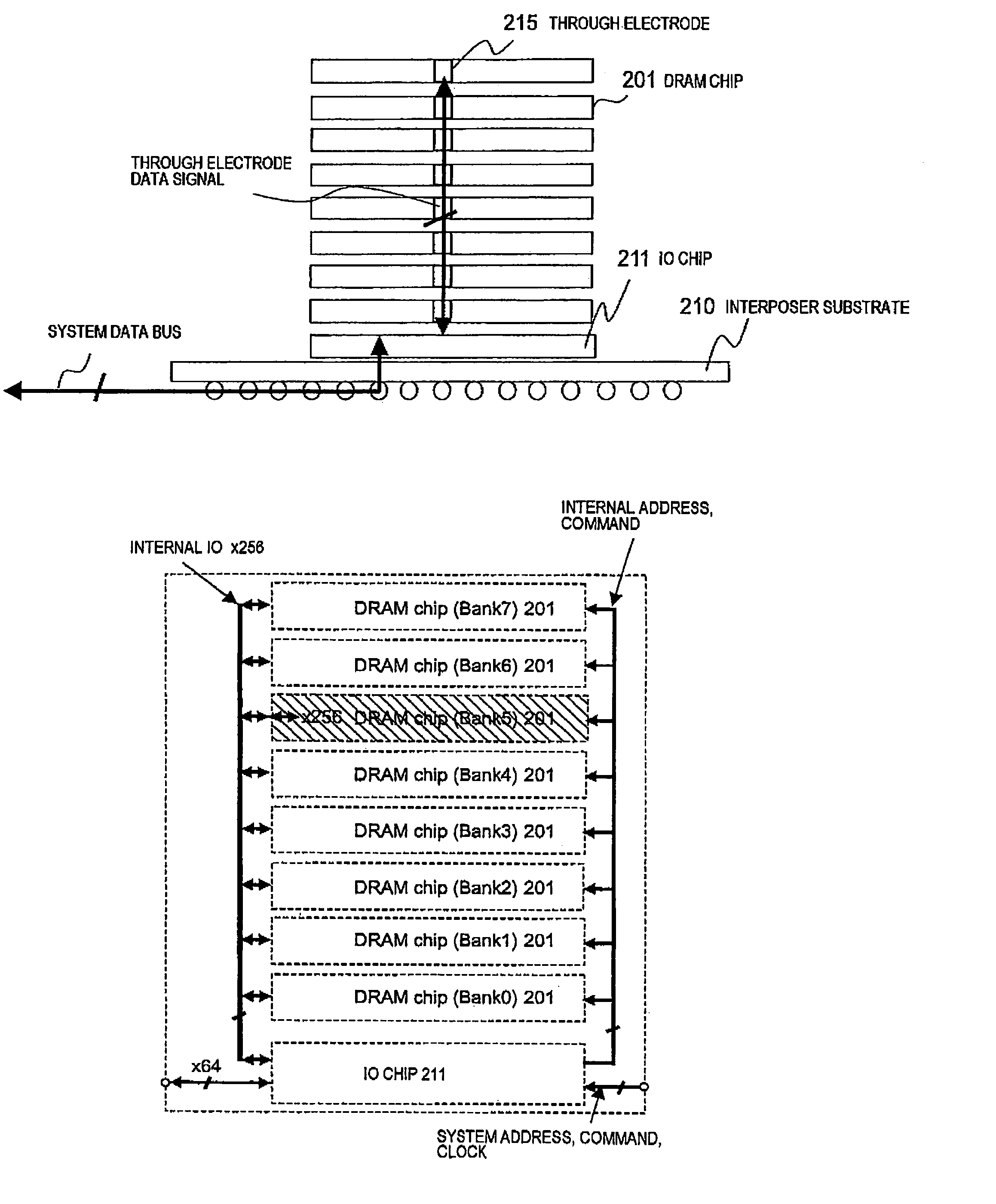

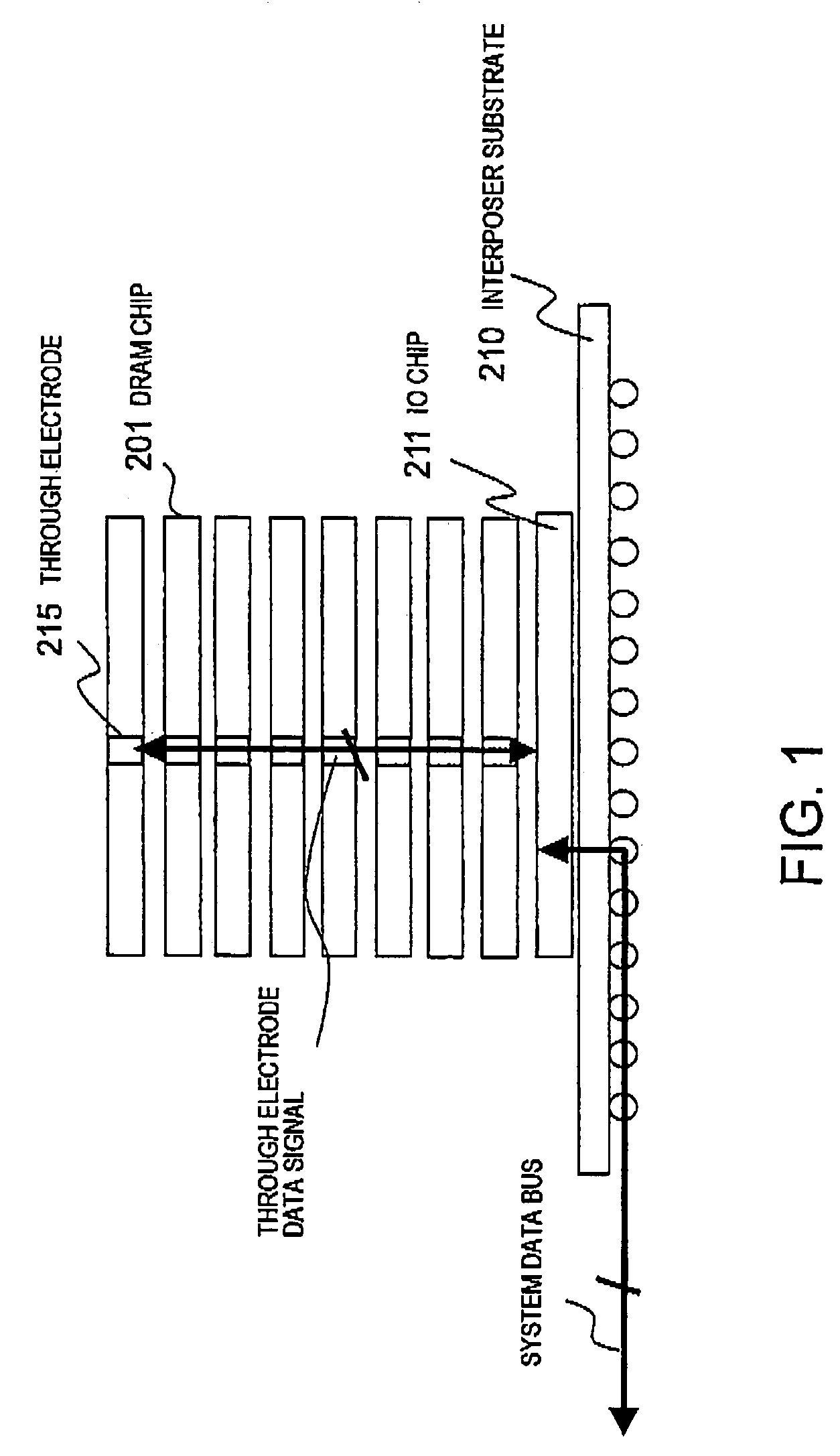

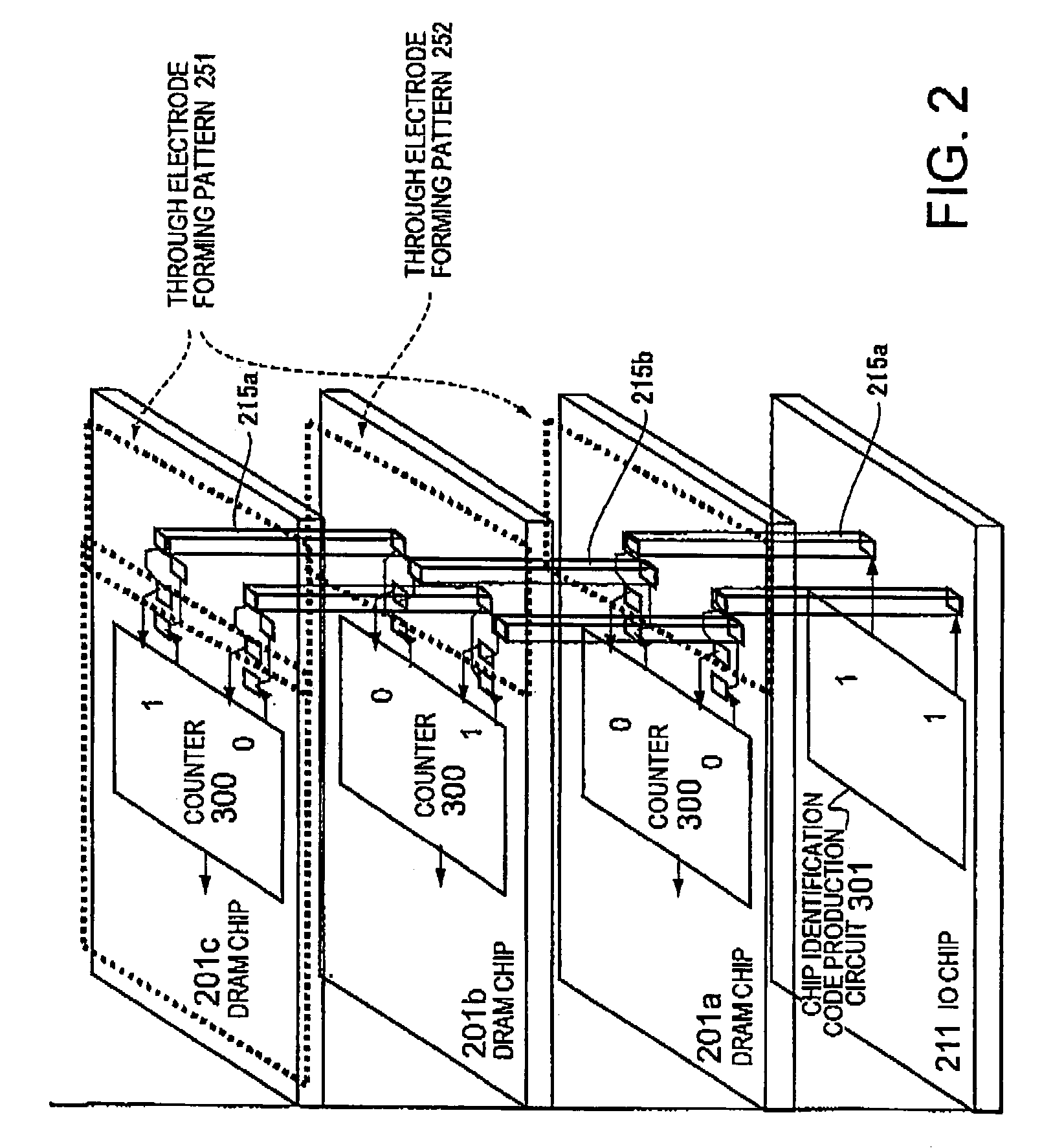

Memory module and memory system

ActiveUS7123497B2Increase chanceVarious problemDomestic stoves or rangesLighting and heating apparatusData signalComputer module

In a memory module including a plurality of DRAM chips which transmit / receive a system data signal with a predetermined data width and at a transfer rate and which transmit / receive an internal data signal having a larger data width and a lower transfer rate as compared with the system data signal, it has become clear that there is a restriction on the transfer rate of the system data signal and that speeding-up cannot be expected. A current consumption in a plurality of DRAMs constituting the memory module is large, and this is also a factor for hindering the speeding-up. There is obtained a memory module in which a plurality of DRAM chips are stacked on an IO chip and in which each DRAM chip is connected to the IO chip by a through electrode and which comprises a constitution for mutually converting the system data signal and the internal data signal in each DRAM chip by the IO chip. In this constitution, a wiring between the DRAM chips can be shortened, and DLL having a large current consumption may be disposed only on the IO chip.

Owner:LONGITUDE LICENSING LTD

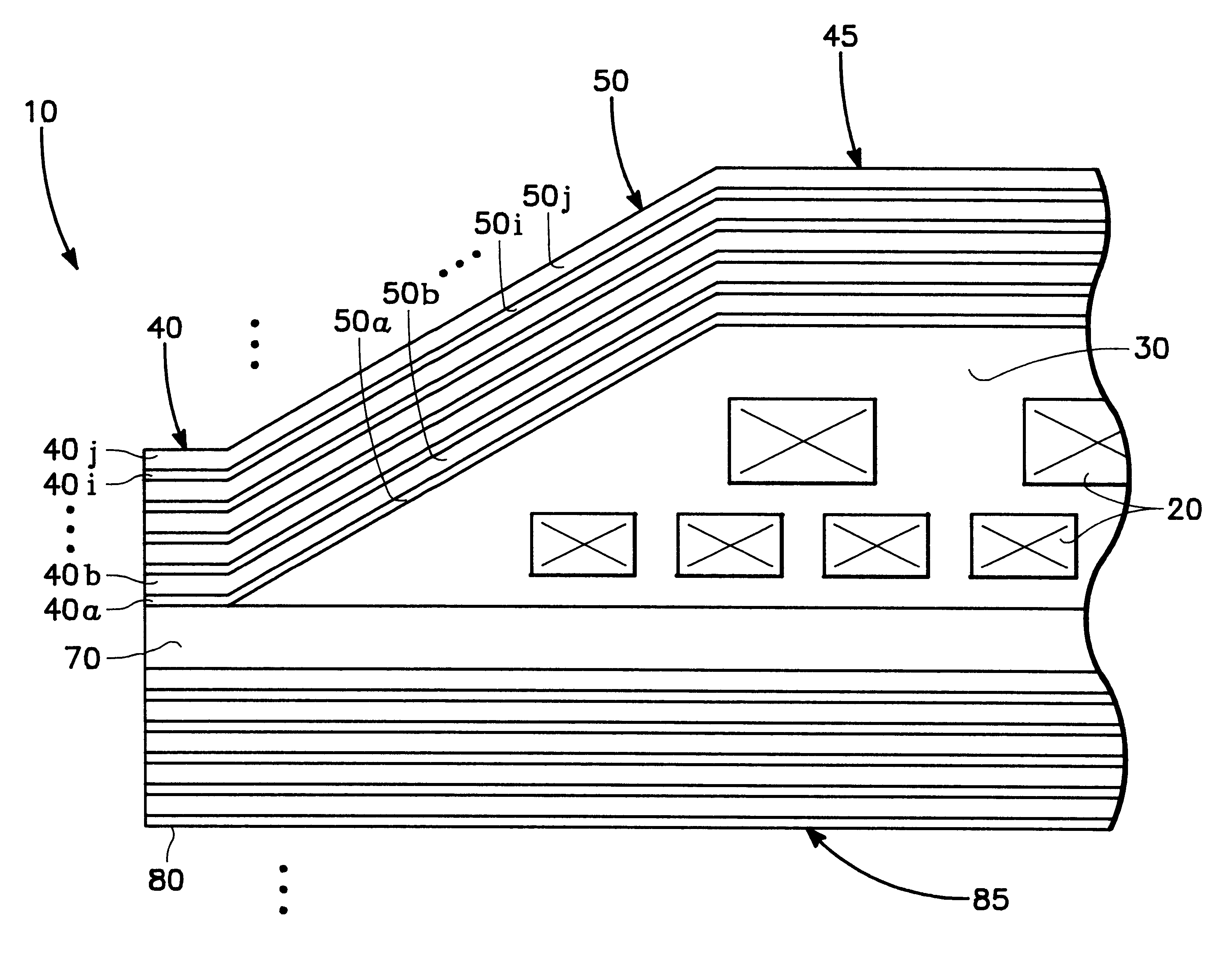

LED with series-connected monolithically integrated mesas

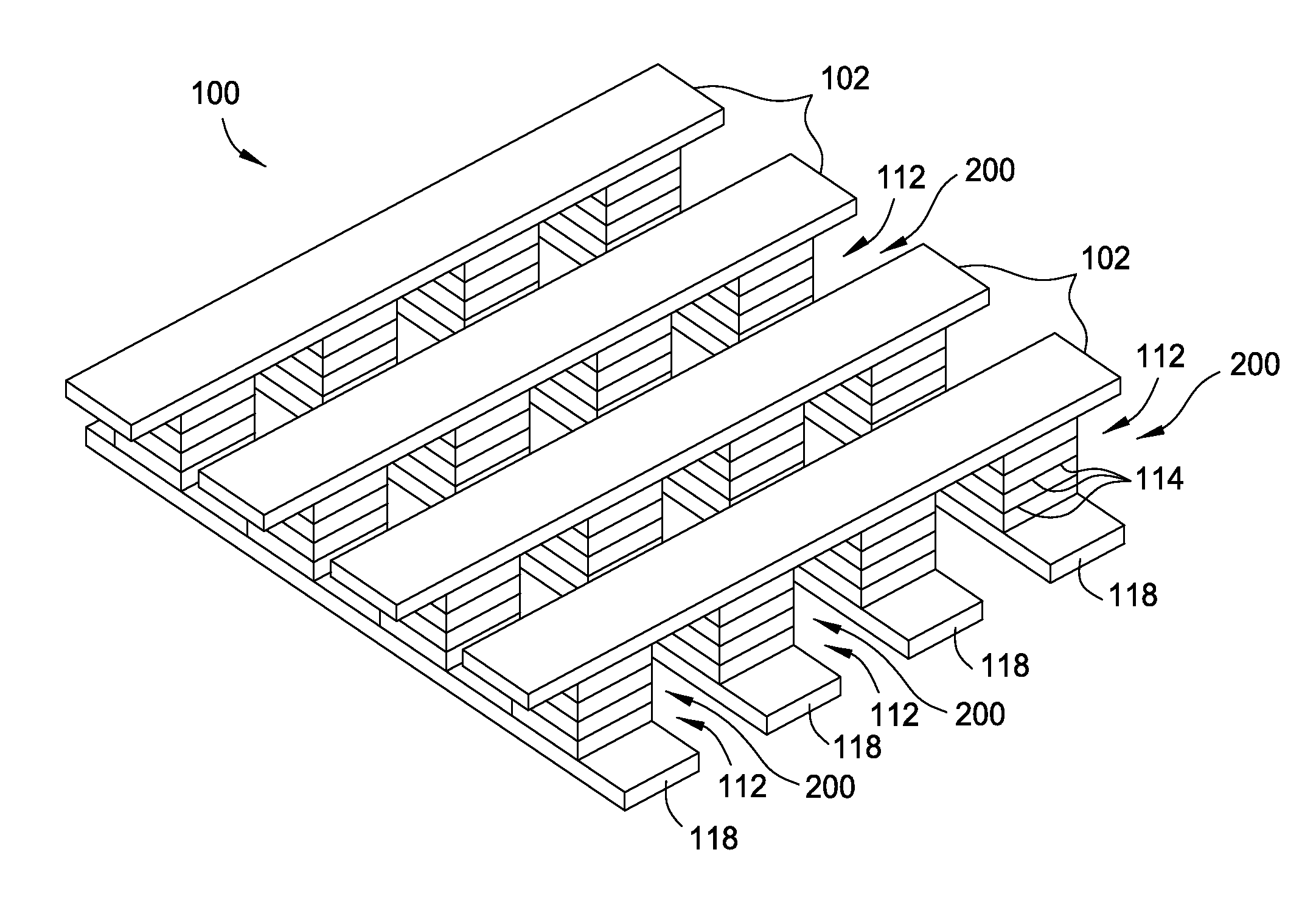

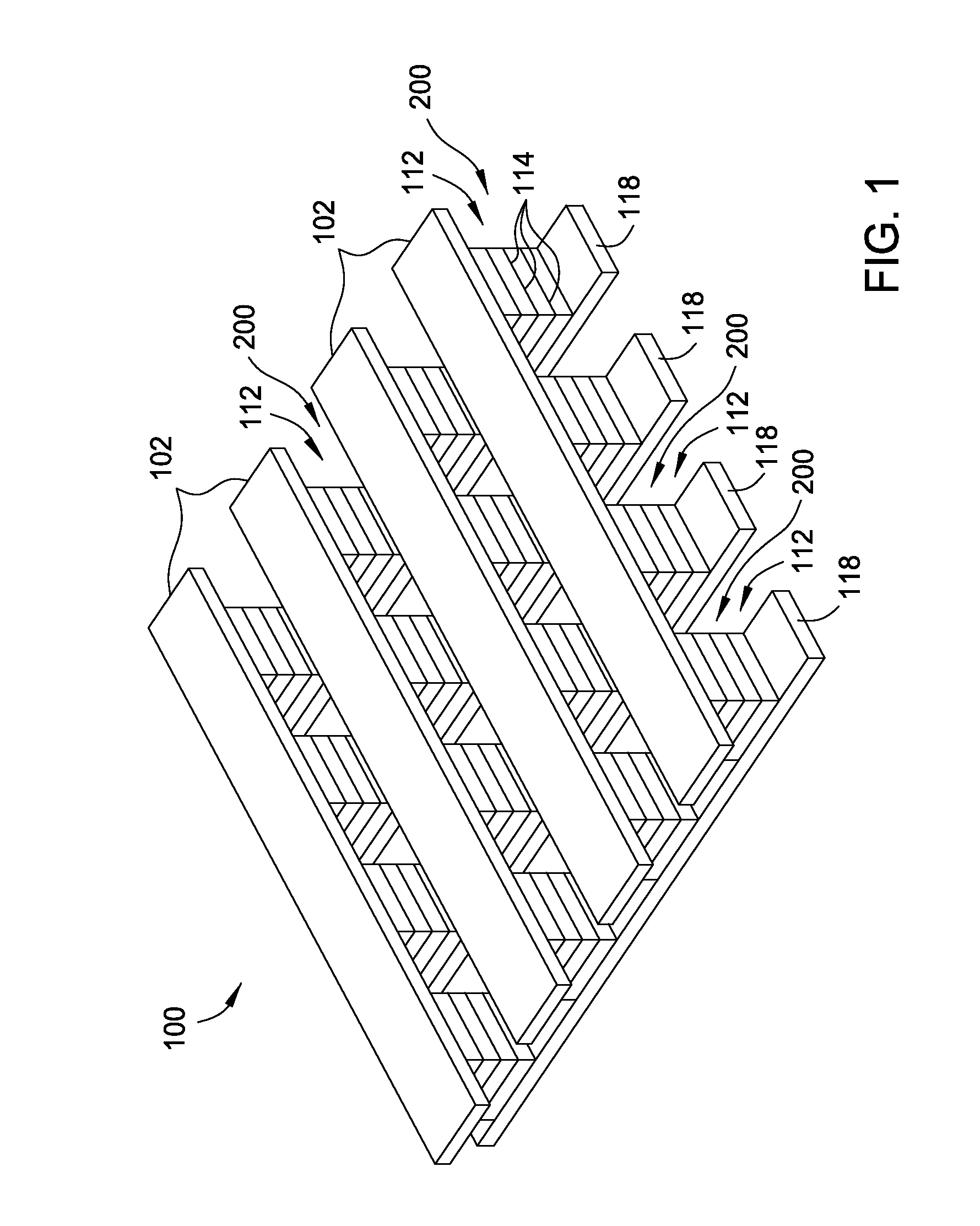

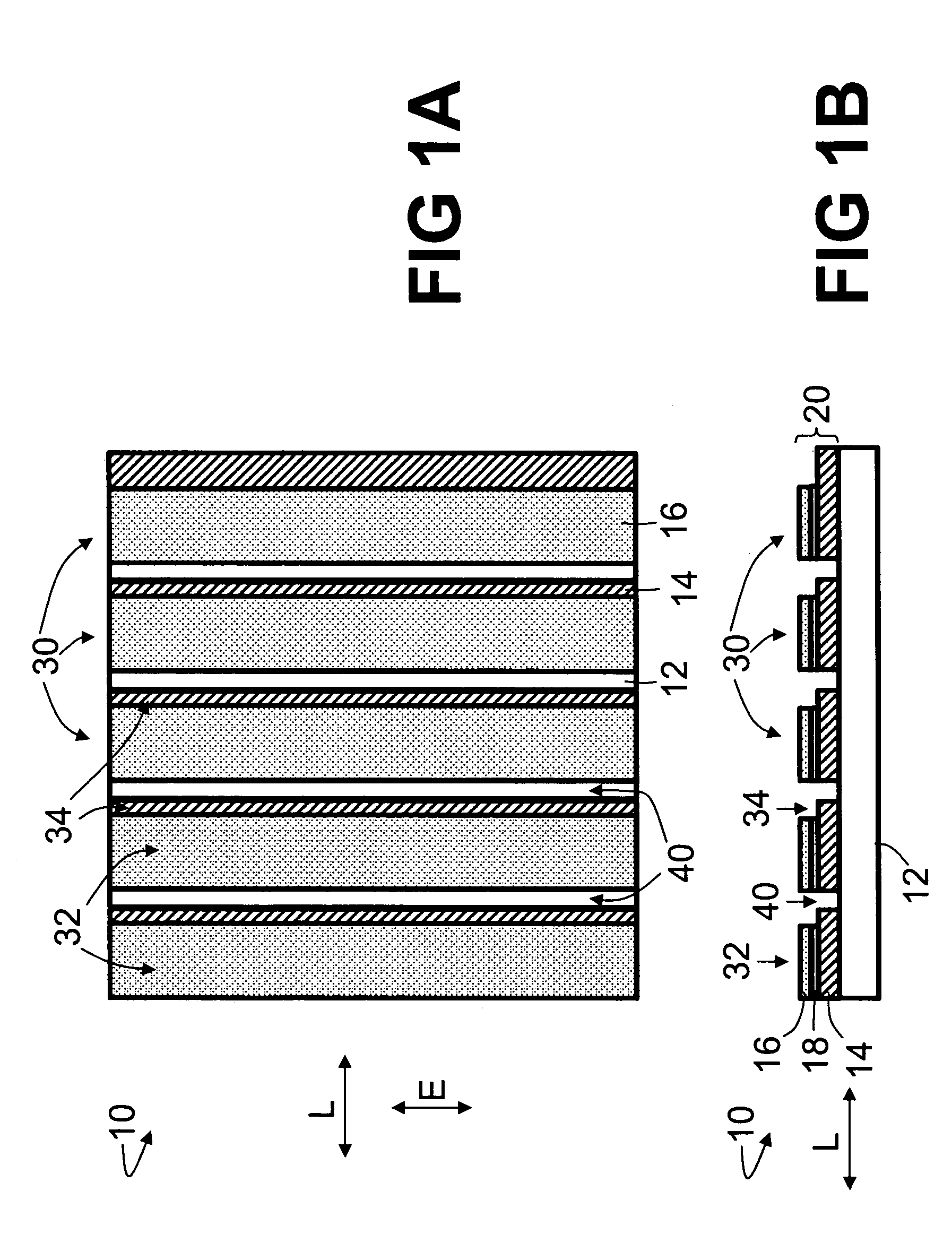

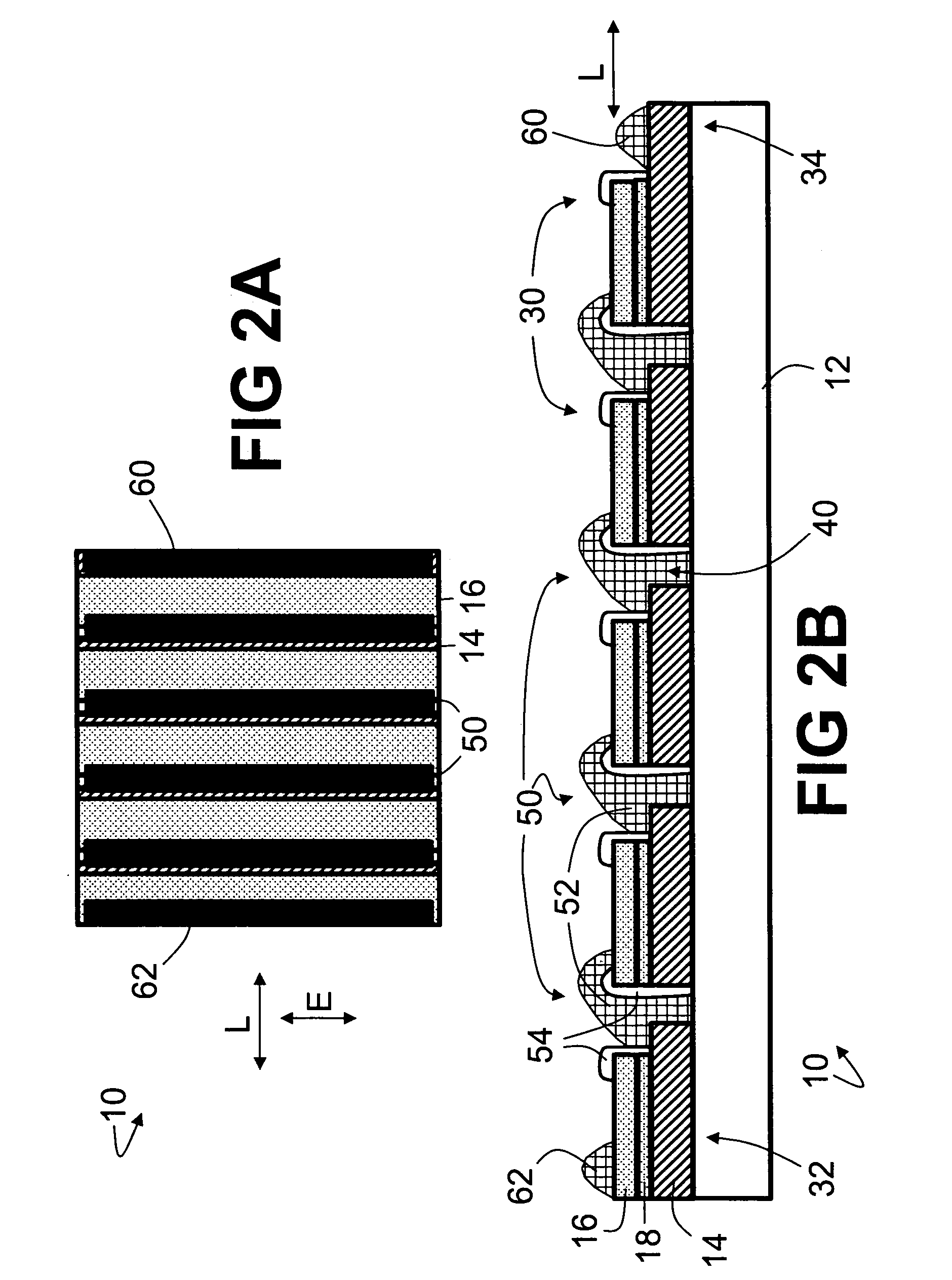

ActiveUS7285801B2Improve uniformityReduces hotspotSolid-state devicesSemiconductor/solid-state device manufacturingInterconnectionLight-emitting diode

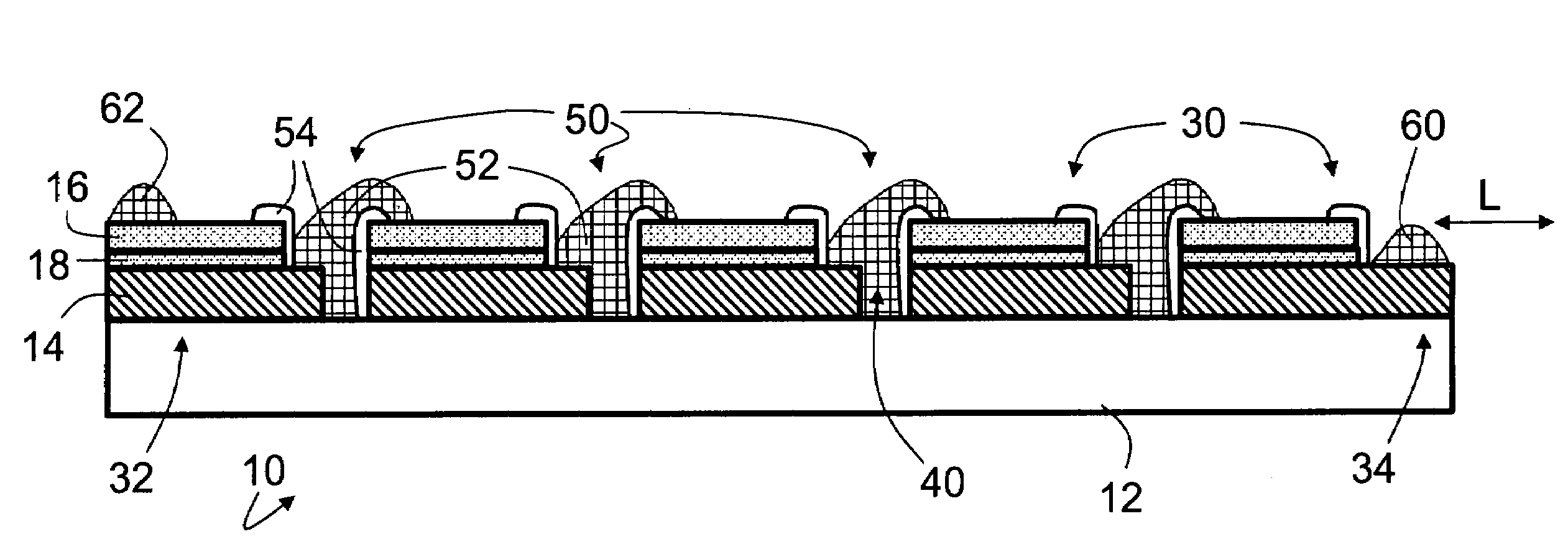

A light emitting semiconductor device die (10, 110, 210, 310) includes an electrically insulating substrate (12, 112). First and second spatially separated electrodes (60, 62, 260, 262, 360, 362) are disposed on the electrically insulating substrate. The first and second electrodes define an electrical current flow direction directed from the first electrode to the second electrode. A plurality of light emitting diode mesas (30, 130, 130′, 230, 330) are disposed on the substrate between the first and second spatially separated electrodes. Electrical series interconnections (50, 150, 250, 350) are disposed on the substrate between neighboring light emitting diode mesas. Each series interconnection carries electrical current flow between the neighboring mesas in the electrical current flow direction.

Owner:GE LIGHTING SOLUTIONS LLC

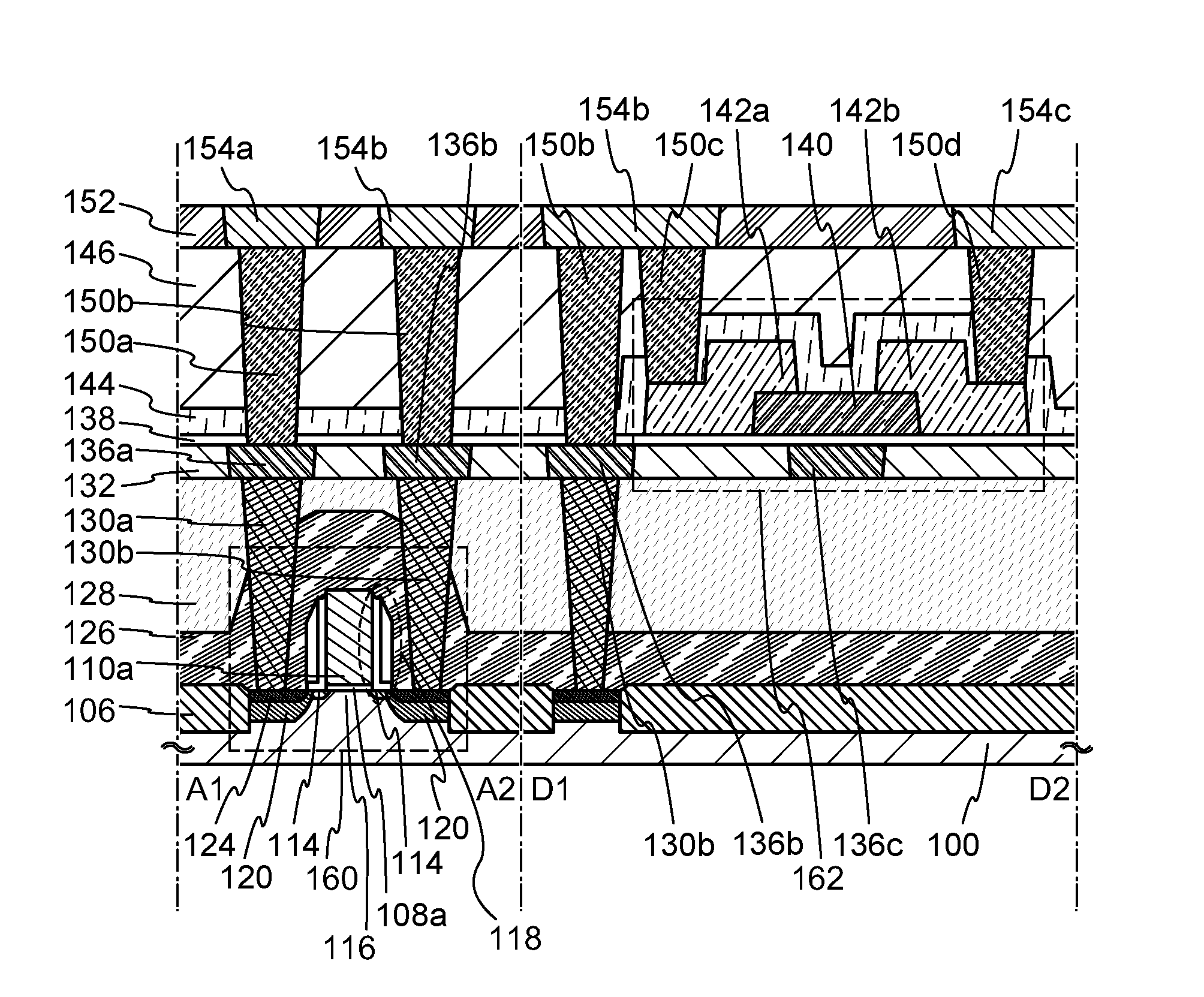

Semiconductor integrated circuit device and method of manufacturing the same

ActiveUS20060113520A1Extend kindReduce power consumptionSolid-state devicesBulk negative resistance effect devicesIntegrated circuitOxide

Disclosed herein is a phase change memory semiconductor integrated circuit device using a chalcogenide film that solves a problem that the operation temperature capable of ensuring long time memory retention is low due to low phase change temperature is and, at the same time, a problem that power consumption of the device is high since a large current requires to rewrite memory information due to low resistance. A portion of constituent elements for a chalcogenide comprises nitride, oxide or carbide which are formed to the boundary between the chalcogenide film and a metal plug as an underlying electrode and to the grain boundary of chalcogenide crystals thereby increasing the phase change temperature and high Joule heat can be generated even by a small current by increasing the resistance of the film.

Owner:RENESAS ELECTRONICS CORP

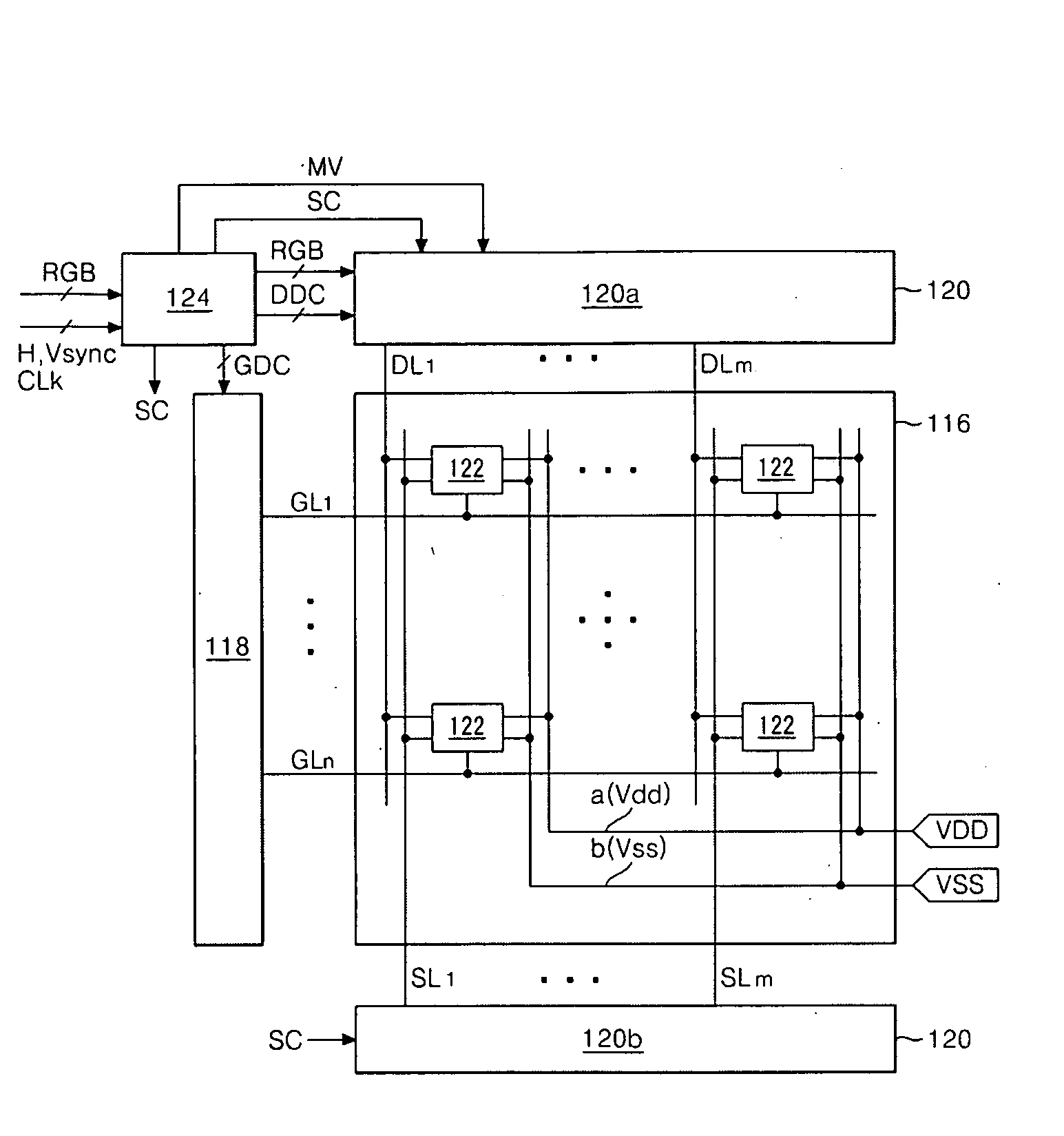

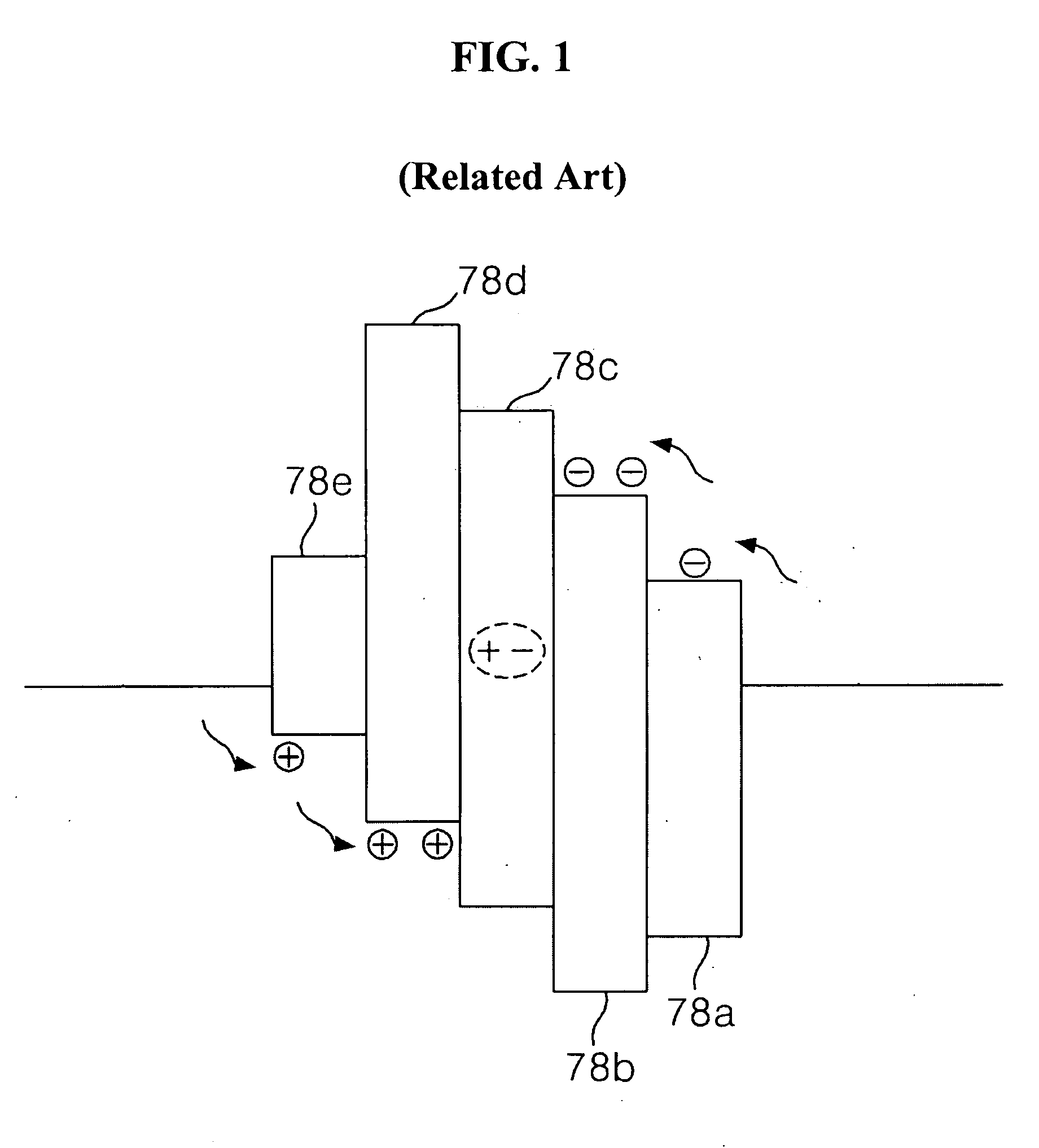

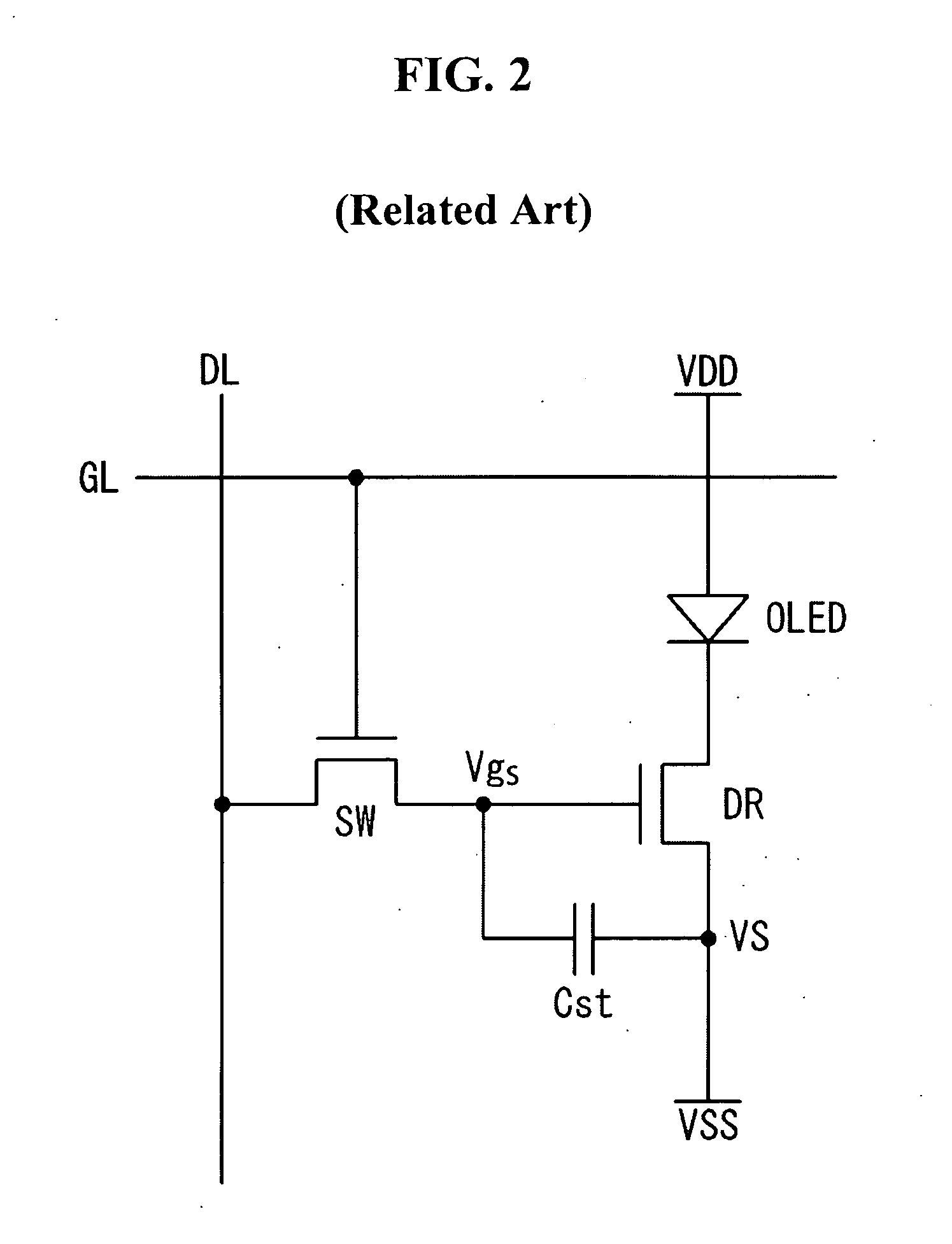

Organic light emitting diode display and method of driving the same

ActiveUS20090213046A1Increase qualityMinimize deterioration of threshold voltageElectrical apparatusStatic indicating devicesData linesVoltage source

An organic light emitting diode display includes a data line, a gate line that crosses the data line to receive a scan pulse, a high potential driving voltage source to generate a high potential driving voltage, a low potential driving voltage source to generate a low potential driving voltage, a light emitting element to emit light due to a current flowing between the high potential driving voltage source and the low potential driving voltage source, a drive element connected between the high potential driving voltage source and the light emitting element to control a current flowing in the light emitting element depending on a voltage between a gate electrode and a source electrode of the drive element, and a driving current stabilization circuit to apply a first voltage to the gate electrode of the drive element to turn on the drive element and to sink a reference current through the drive element to set a source voltage of the drive element at a sensing voltage and to modify the voltage between the gate and source electrodes of the drive element to scale a current to be applied to the light emitting element from the reference current.

Owner:LG DISPLAY CO LTD

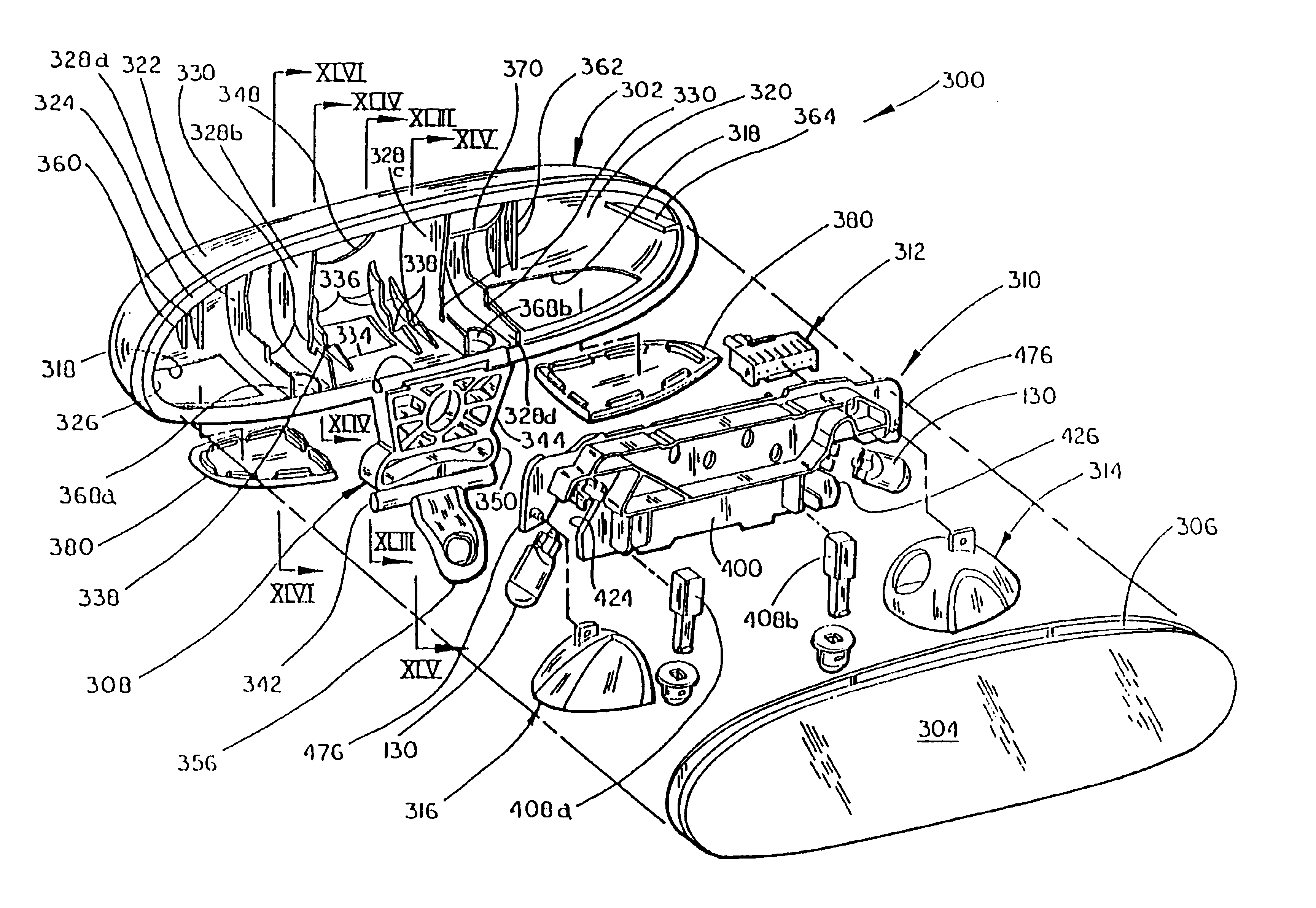

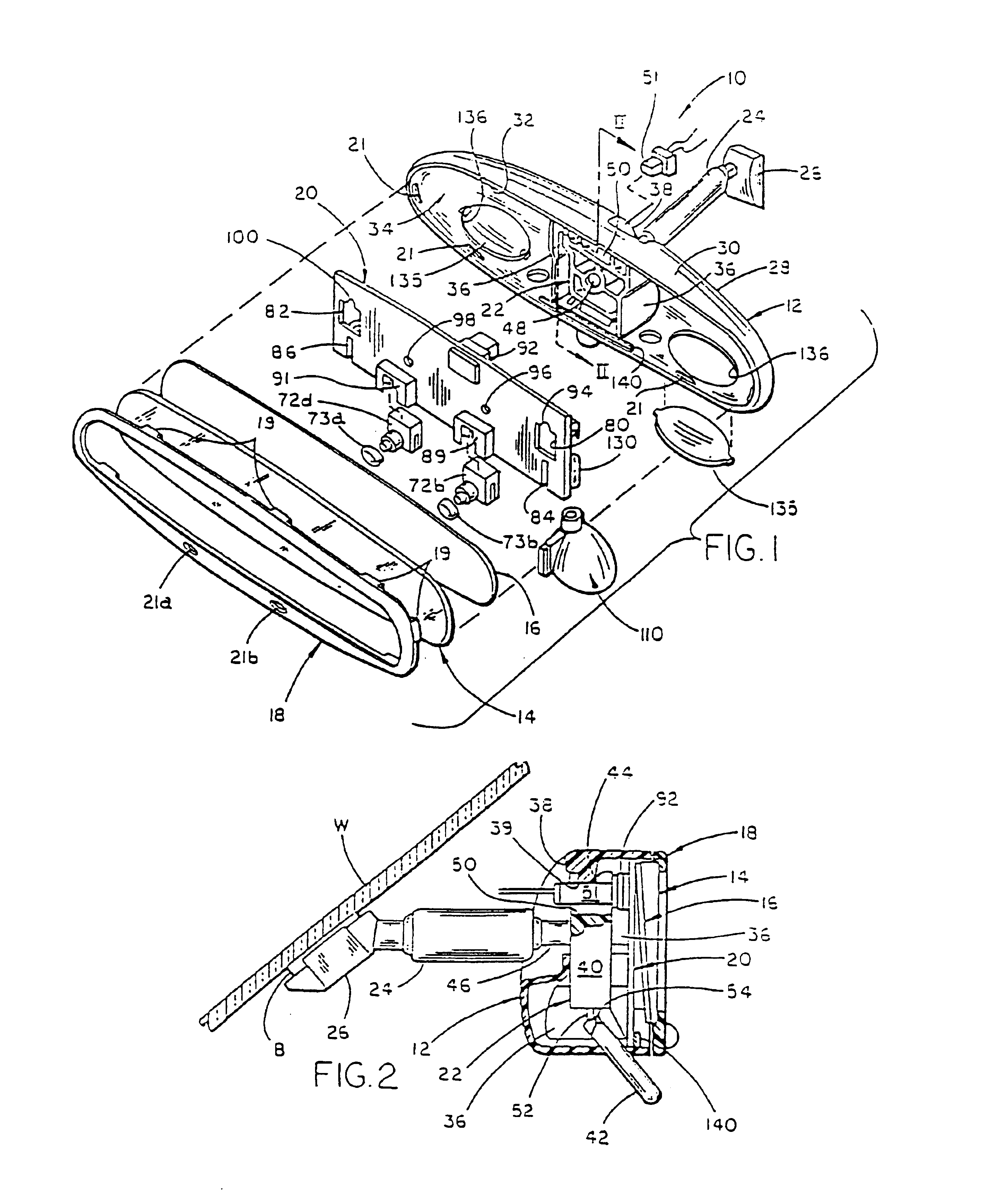

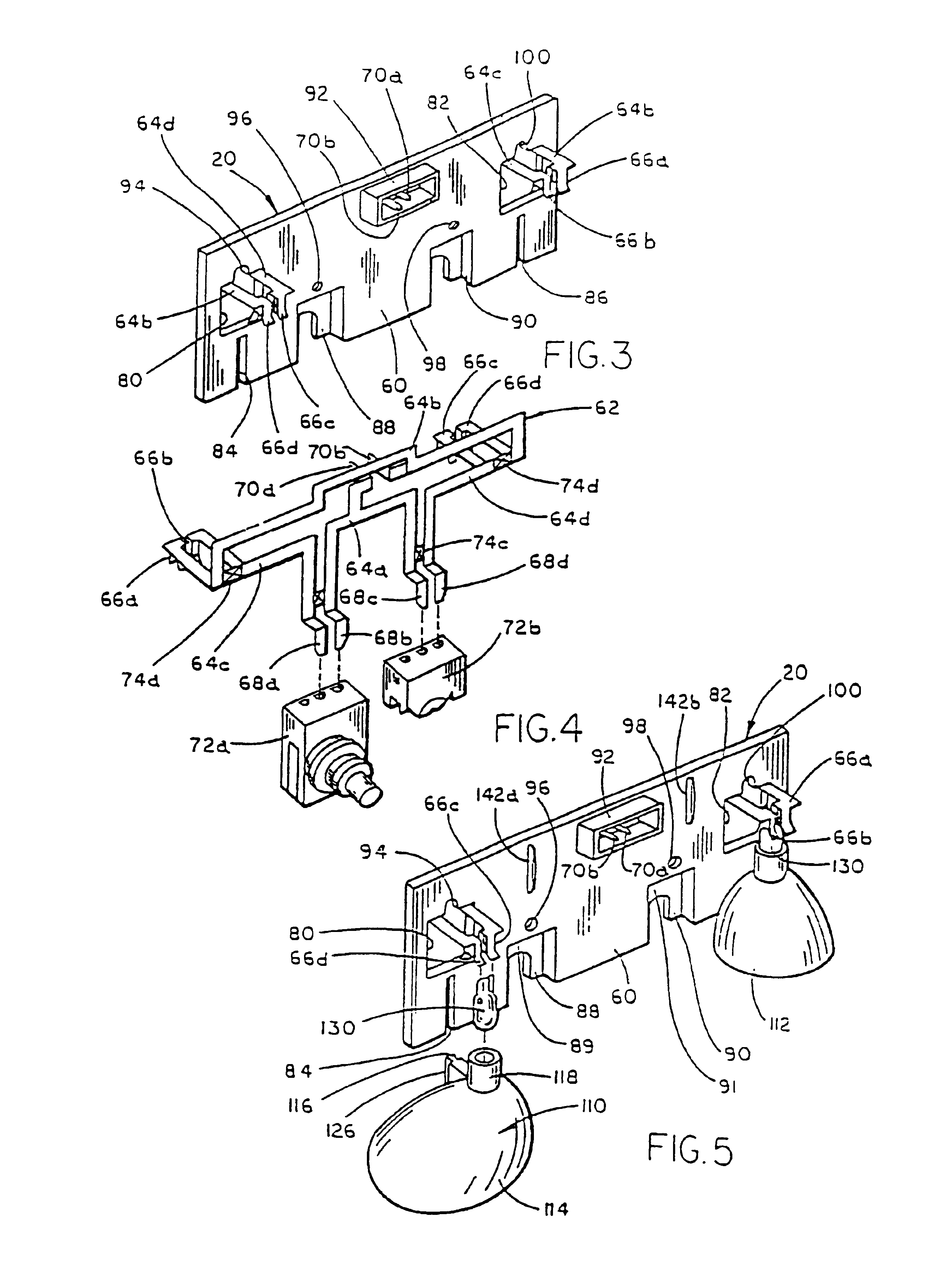

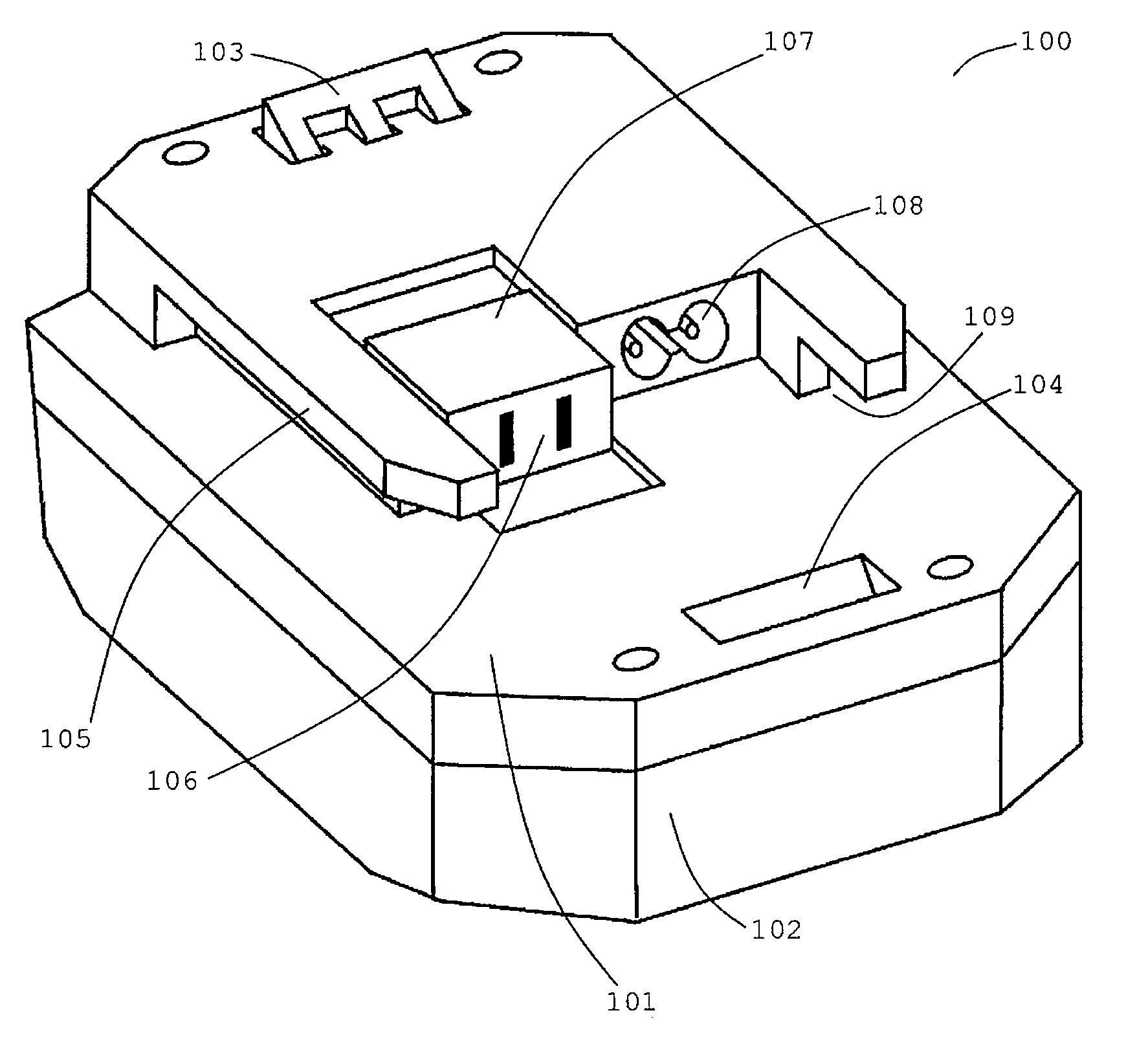

Modular rearview mirror assembly

InactiveUS6877888B2Increased durabilityImprove reliabilityLighting elementsClosed circuit television systemsPolymer resinElectrical devices

An interior rearview mirror assembly for vehicles incorporates a reflective mirror element for viewing by a user of the mirror assembly, a lip formed from moldable polymeric resin selected to expand sufficiently when heated to allow snap in insertion of the reflective mirror element while the lip is warm and flexable, a carrier located to the rear of the reflective element such that the carrier is closer to a windshield of the vehicle than the mirror element when the mirror element is mounted in the vehicle, at least one electrical accessory, and an electrical connector adapted to receive a connector from the vehicle electrical system with the electrical accessory connected to the electrical connector. Preferably, the electrical accessory is supported by the carrier and is selected from a variety of electrical devices, lamps, lights, sensors and the like.

Owner:DONNELLY CORP

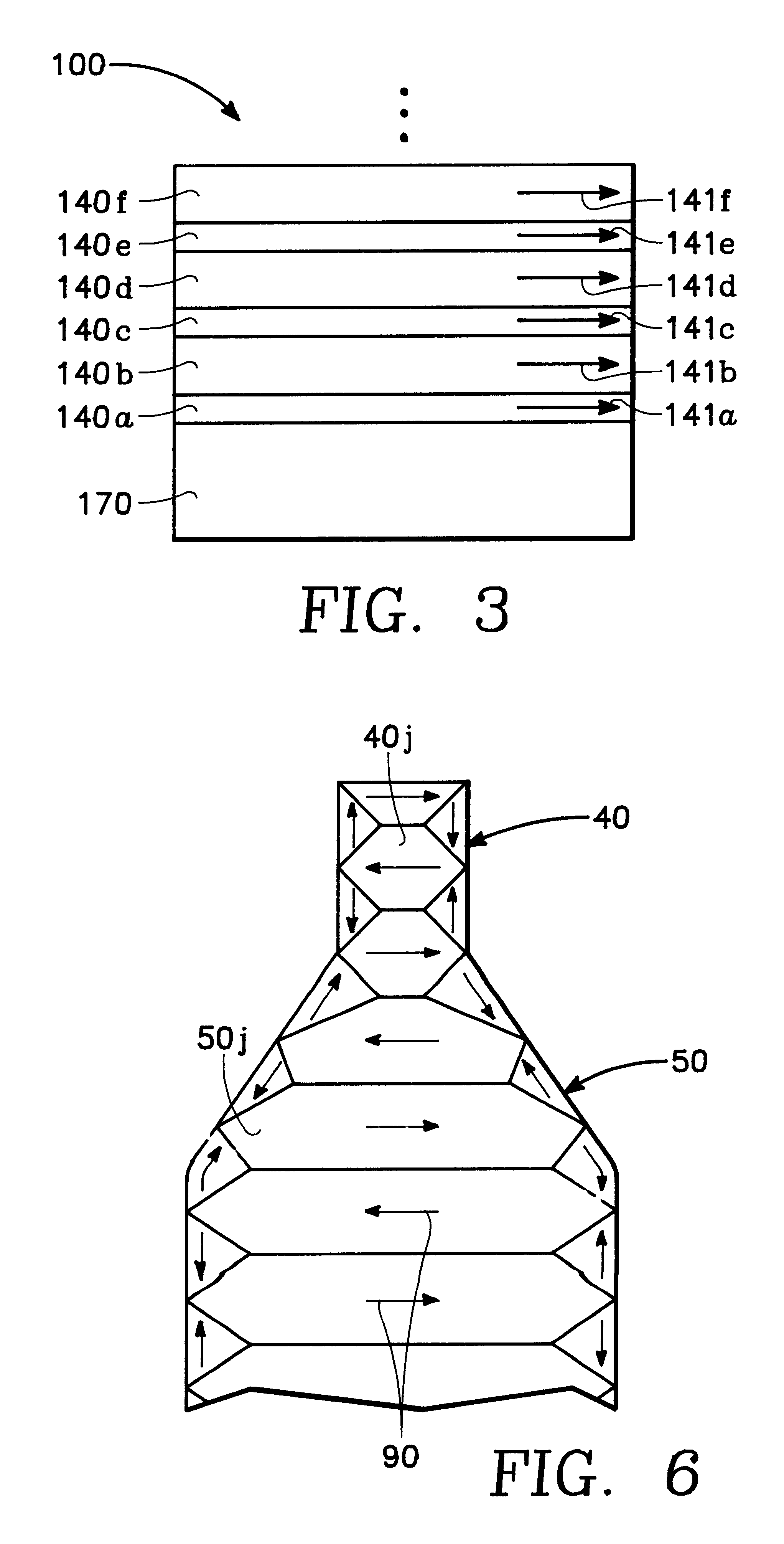

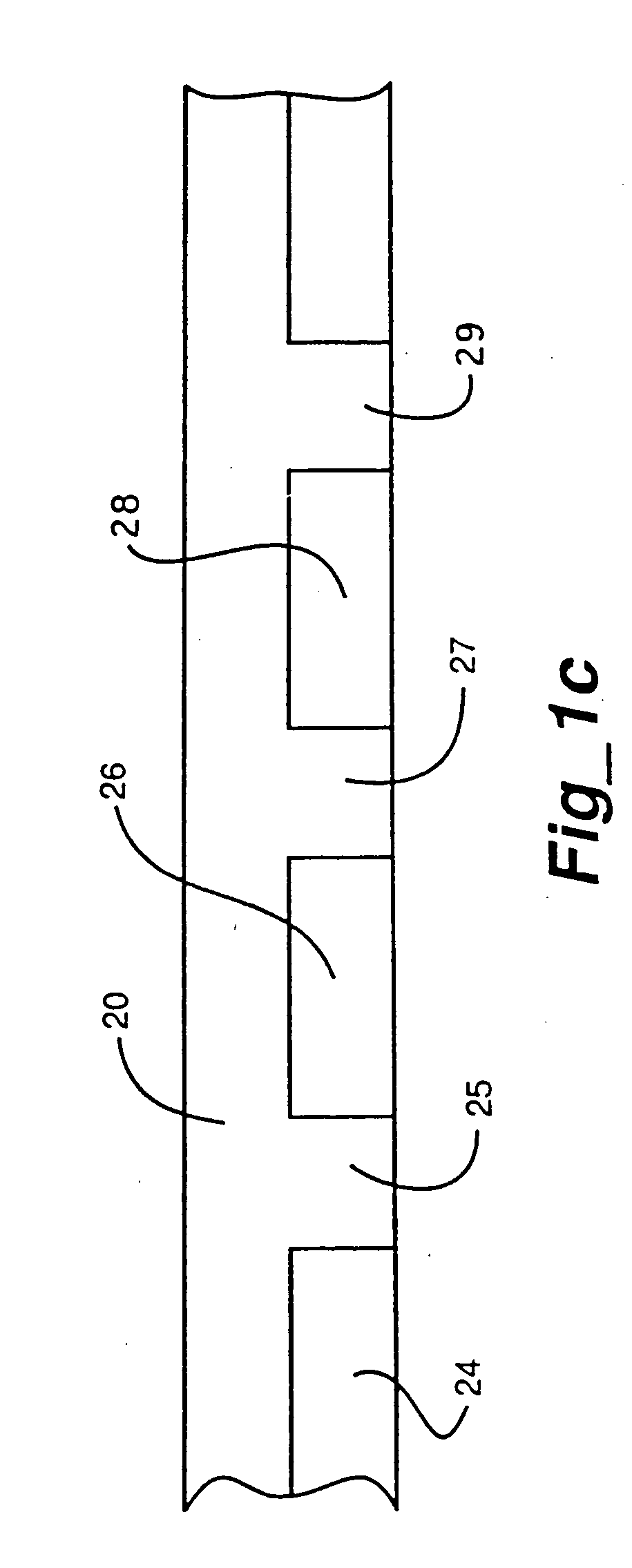

Thin film write head with improved laminated flux carrying structure and method of fabrication

InactiveUS6233116B1High resistivityExcellent soft magnetic propertiesConstruction of head windingsHeads using thin filmsLower poleHigh resistivity

The present invention provides a thin film write head having an improved laminated flux carrying structure and method of fabrication. The preferred embodiment provides laminated layers of: high moment magnetic material, and easily aligned high resistivity magnetic material. In the preferred embodiment, the easily aligned laminating layer induces uniaxial anisotropy, by exchange coupling, to improve uniaxial anisotropy in the high moment material. This allows deposition induced uniaxial anisotropy by DC magnetron sputtering and also provides improved post deposition annealing, if desired. It is preferred to laminate FeXN, such as FeRhN, or other crystalline structure material, with an amorphous alloy material, preferably Co based, such as CoZrCr. In the preferred embodiment, upper and lower pole structures may both be laminated as discussed above. Such laminated structures have higher Bs than structures with insulative laminates, and yokes and pole tips and may be integrally formed, if desired, because flux may travel along or across the laminating layers. The preferred embodiment of the present invention improves soft magnetic properties, reduces eddy currents, improves hard axis alignment while not deleteriously affecting the coercivity, permeability, and magnetostriction of the structure, thus allowing for improved high frequency operation.

Owner:WESTERN DIGITAL TECH INC +1

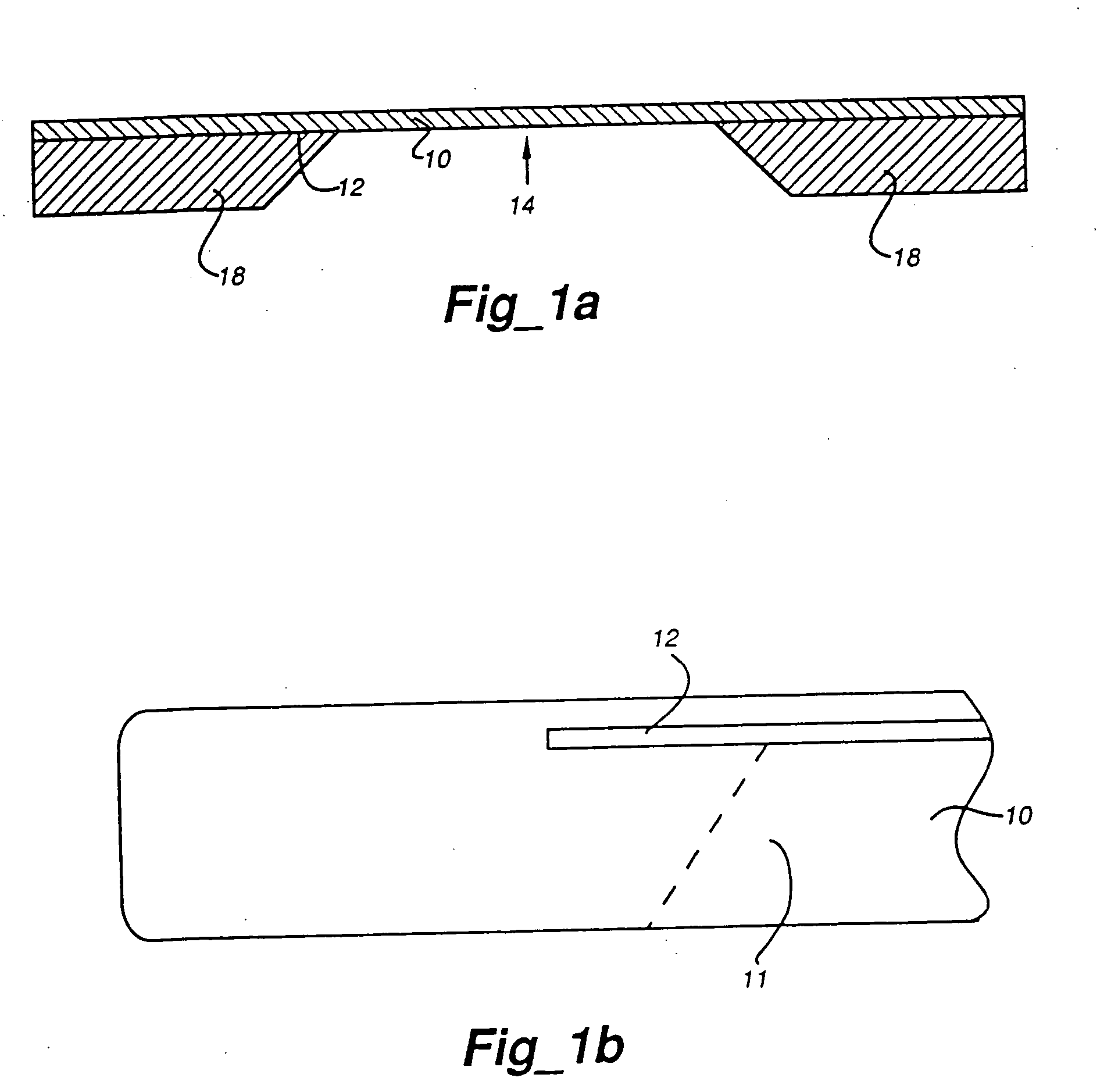

Methods for maskless lithography

InactiveUS20050130351A1Reduce processing costsLow processingSemiconductor/solid-state device detailsSolid-state devicesFlat panel displayPhysics

General purpose methods for the fabrication of integrated circuits from flexible membranes formed of very thin low stress dielectric materials, such as silicon dioxide or silicon nitride, and semiconductor layers. Semiconductor devices are formed in a semiconductor layer of the membrane. The semiconductor membrane layer is initially formed from a substrate of standard thickness, and all but a thin surface layer of the substrate is then etched or polished away. In another version, the flexible membrane is used as support and electrical interconnect for conventional integrated circuit die bonded thereto, with the interconnect formed in multiple layers in the membrane. Multiple die can be connected to one such membrane, which is then packaged as a multi-chip module. Other applications are based on (circuit) membrane processing for bipolar and MOSFET transistor fabrication, low impedance conductor interconnecting fabrication, flat panel displays, maskless (direct write) lithography, and 3D IC fabrication.

Owner:TAIWAN SEMICON MFG CO LTD

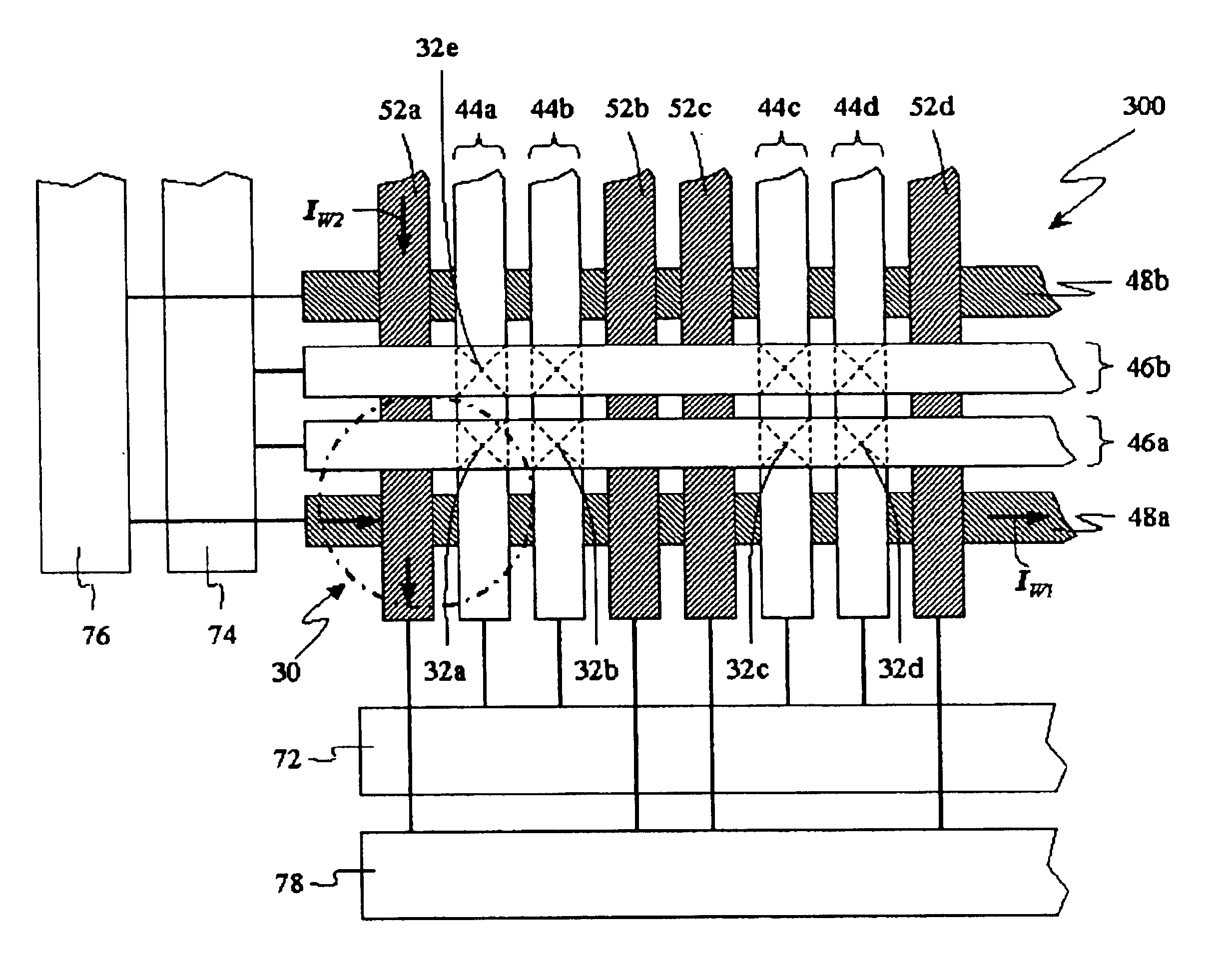

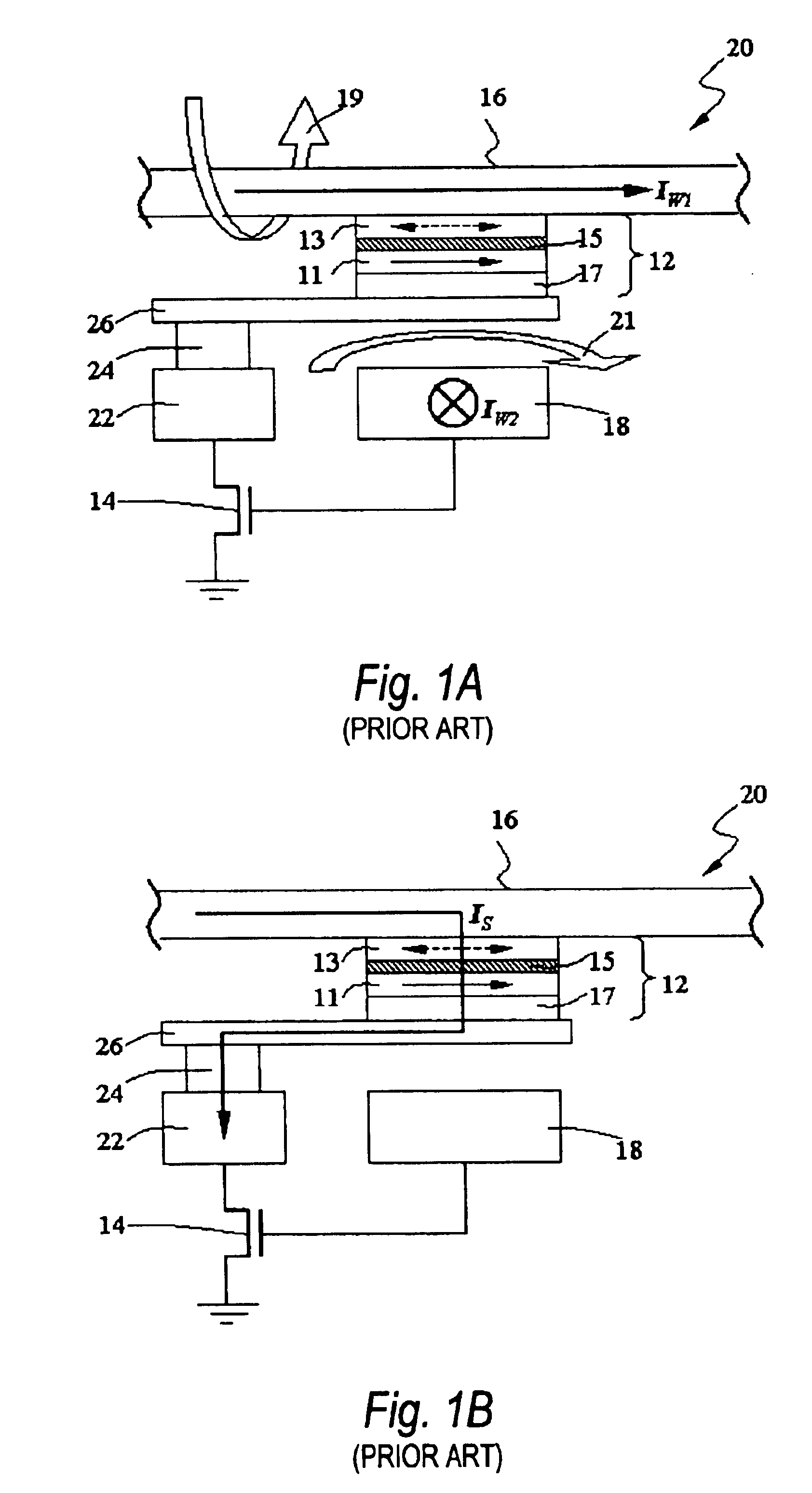

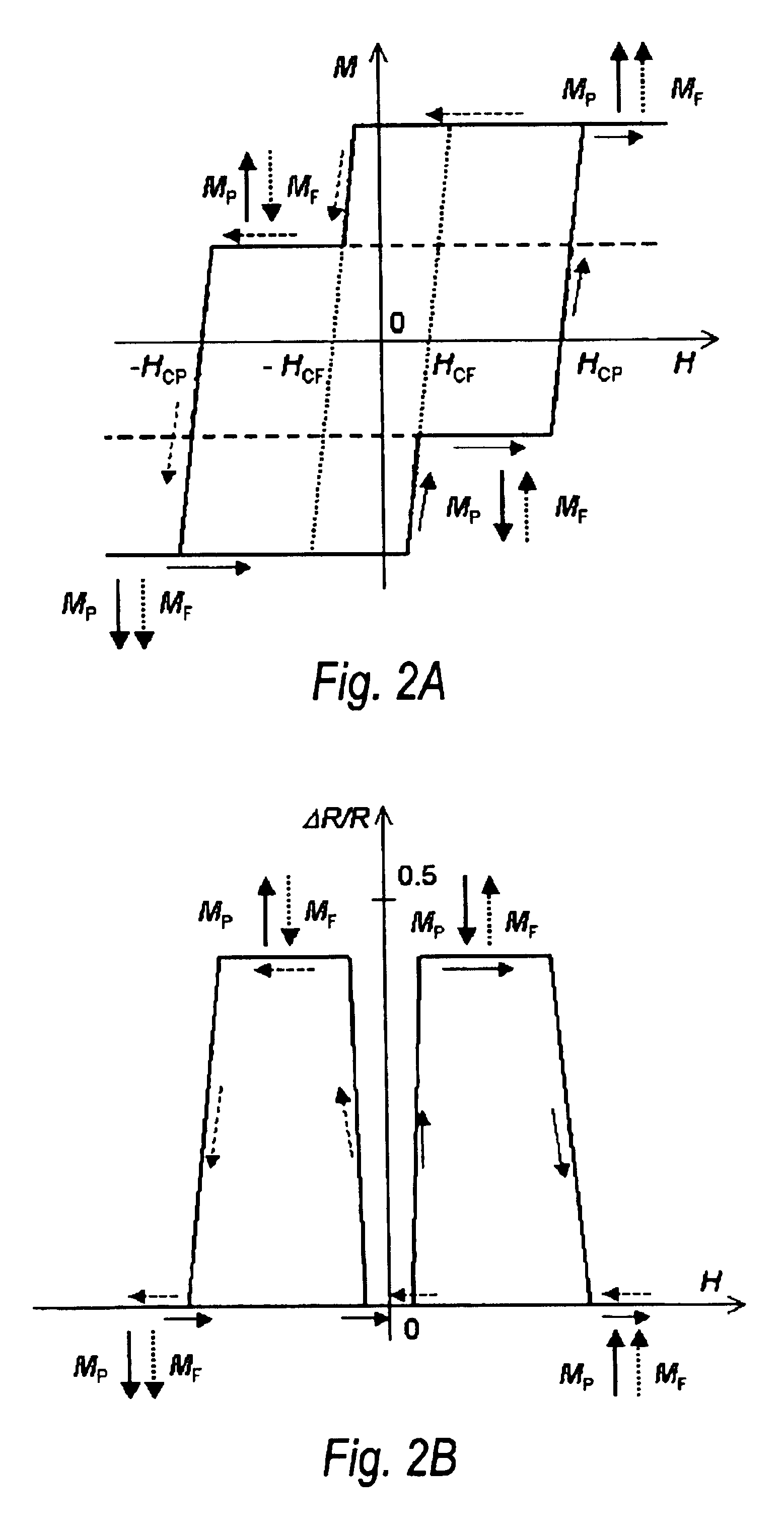

Magnetic tunnel junction memory device

InactiveUS6845038B1Improve permeabilityLow resistivityDigital storageBit linePerpendicular magnetization

A memory cell for magnetic random access memory devices based on a magnetic tunnel junction (MTJ) memory element with a perpendicular orientation of magnetization in pinned and free magnetic layers, and a tunnel barrier layer sandwiched between the pinned and free layers. The memory cell can include the MTJ memory element, a magnetic flux guide in series with selection devices, such as a bit line, a word line, and a transistor. The magnetic flux guide can have two electrically conductive magnetic portions with the MTJ memory element positioned between the magnetic portions. The MTJ memory element is magnetically isolated from the magnetic flux guide by thin non-magnetic conductive spacers. The MTJ memory element is arranged in a vertical space between the intersecting bit and word lines at their intersection region. The memory cell also includes write and excitation lines. The write line is parallel to the bit line and the excitation line is parallel to the word line. The write and excitation lines also intersect each other and define a corner. The MTJ memory element is positioned in the corner of the intercepting write and excitation lines.

Owner:SHUKH ALLA MIKHAILOVNA

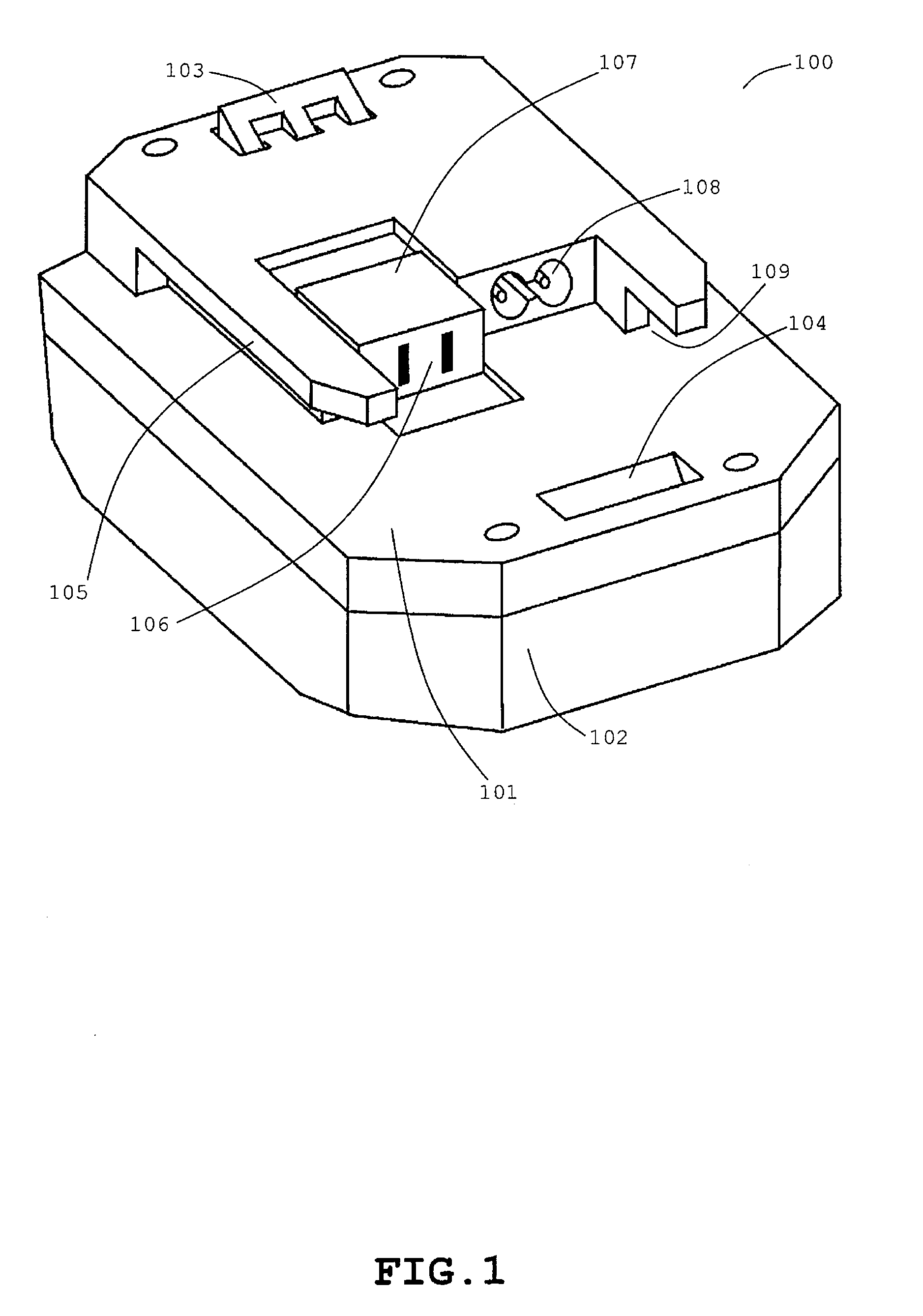

Battery pack

InactiveUS20100181966A1Consumption of MINsImprove power supply efficiencyCircuit monitoring/indicationIndicating/monitoring circuitsPower toolElectrical battery

A cordless power tool system is provided which is driven by using a battery pack as a power source, and which has work performance equivalent to an AC power tool is driven by using a commercial power source as a power source. The cordless power tool system is configured to include: a battery pack in which DC voltage of battery modules is converted into AC voltage, to thereby output the AC voltage having a level which is comparable to that of the commercial power source; a cordless power tool which is driven by using the battery pack as a power source; an electrical cord adapter which allows power supply from the commercial power source to the battery pack for charging the battery pack; and an electrical cord adapter which allows power supply from the commercial power source to the cordless power tool for driving the cordless power tool.

Owner:SAKAKIBARA KAZUYUKI

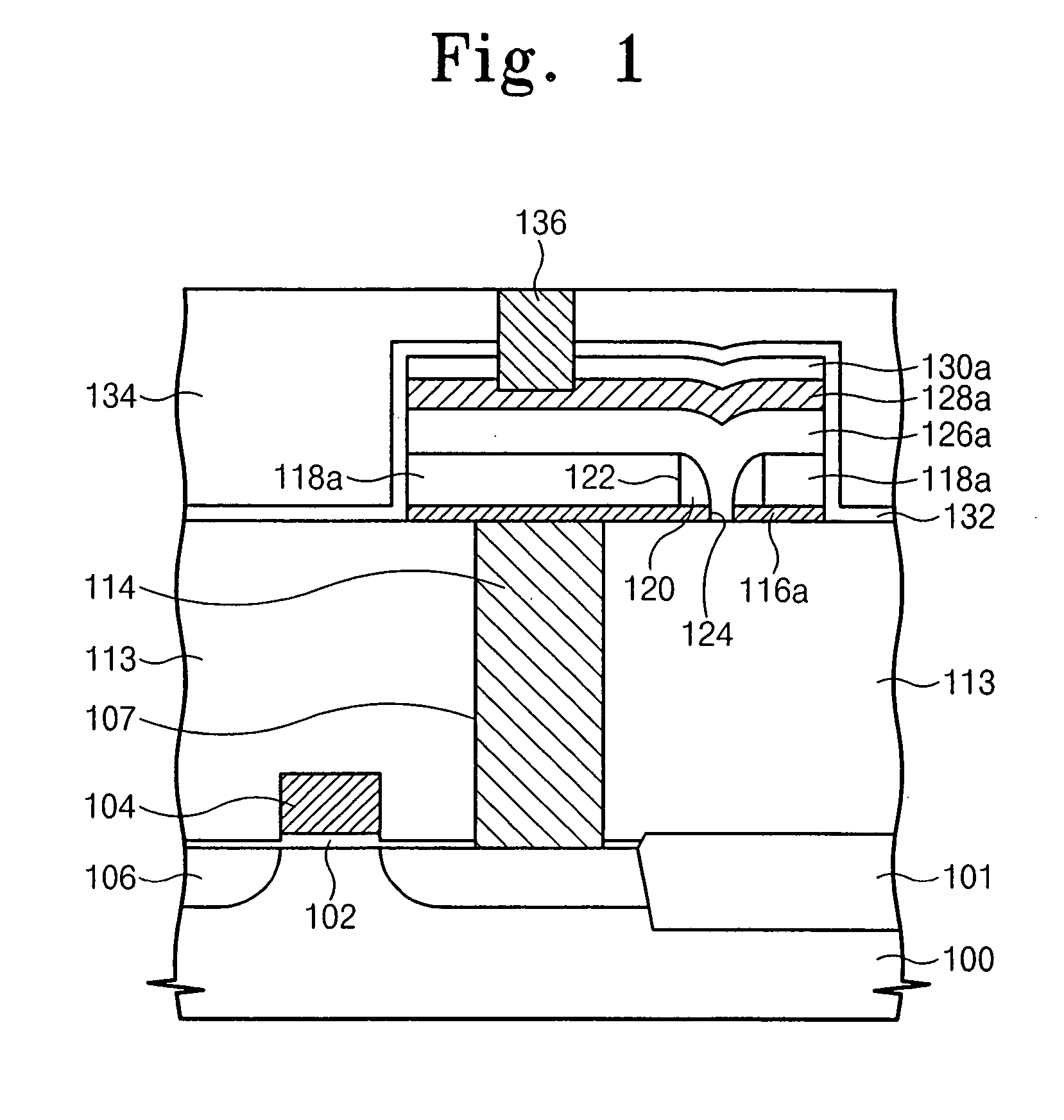

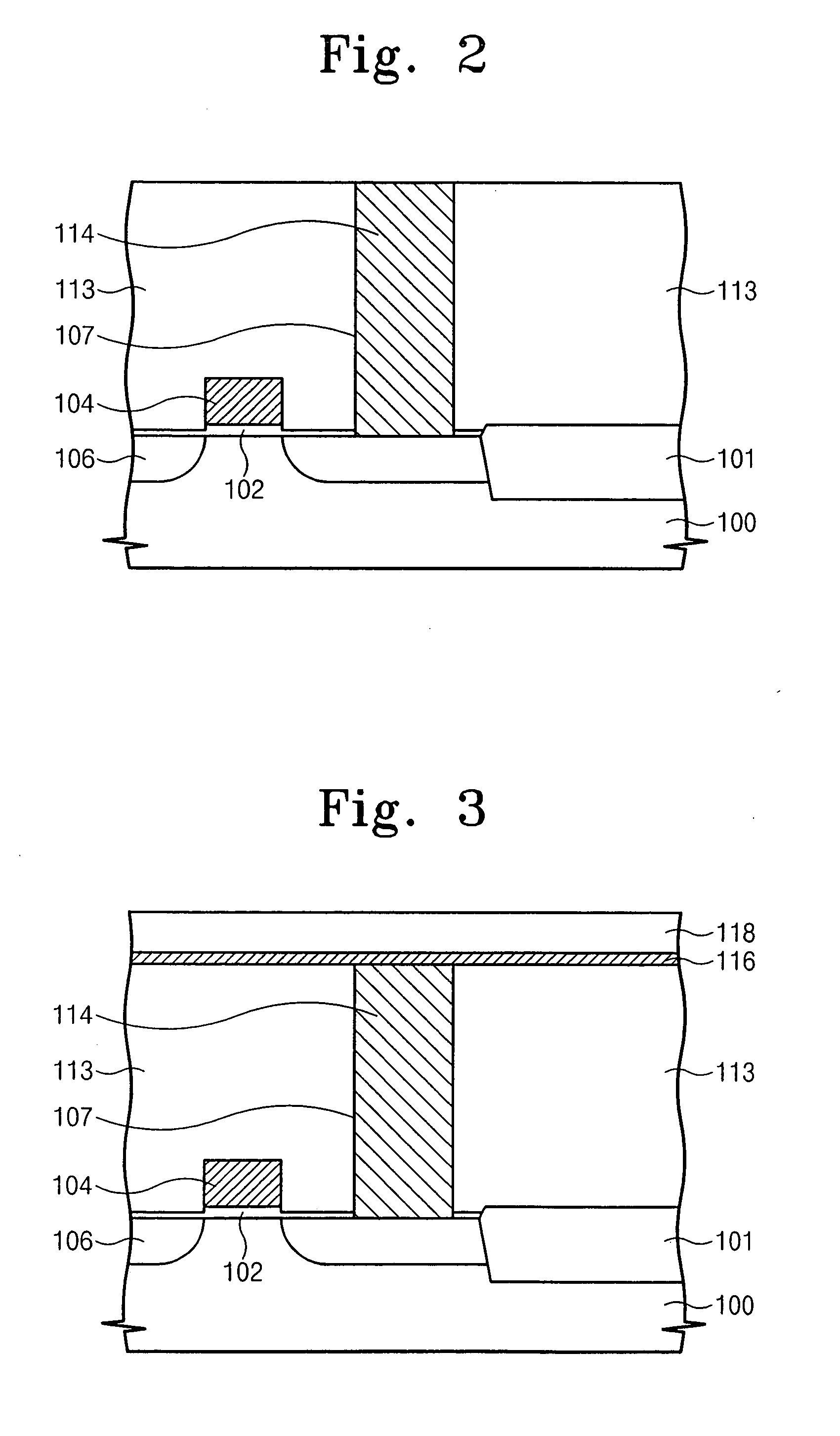

Phase changeable memory device and method of formation thereof

ActiveUS20060110888A1Total current dropSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryPhysics

In a phase changeable memory device and a method of formation thereof, the phase changeable memory device comprises: a lower electrode pattern on an interlayer insulating layer; an insulating pattern located on the lower electrode pattern; a phase changeable pattern penetrating the insulating pattern and the lower electrode pattern to contact the lower electrode pattern and the interlayer insulating layer; and an upper electrode on the phase changeable pattern.

Owner:SAMSUNG ELECTRONICS CO LTD