Patents

Literature

990 results about "Tunnel barrier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

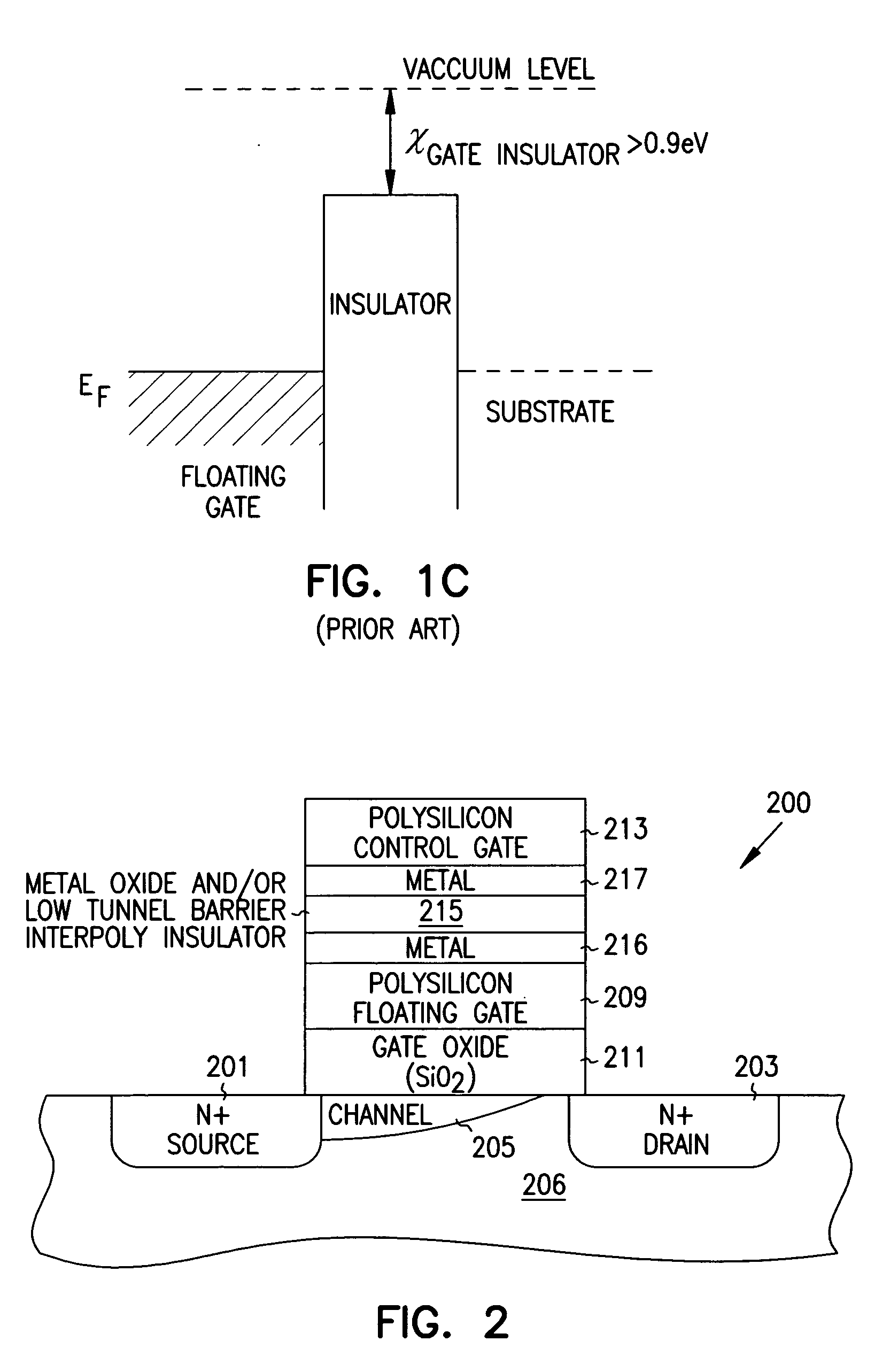

Barrier tunneling happens when, let say, an electron tunnels through a region when it has lower energy compared to the energy of the region (potential barrier).

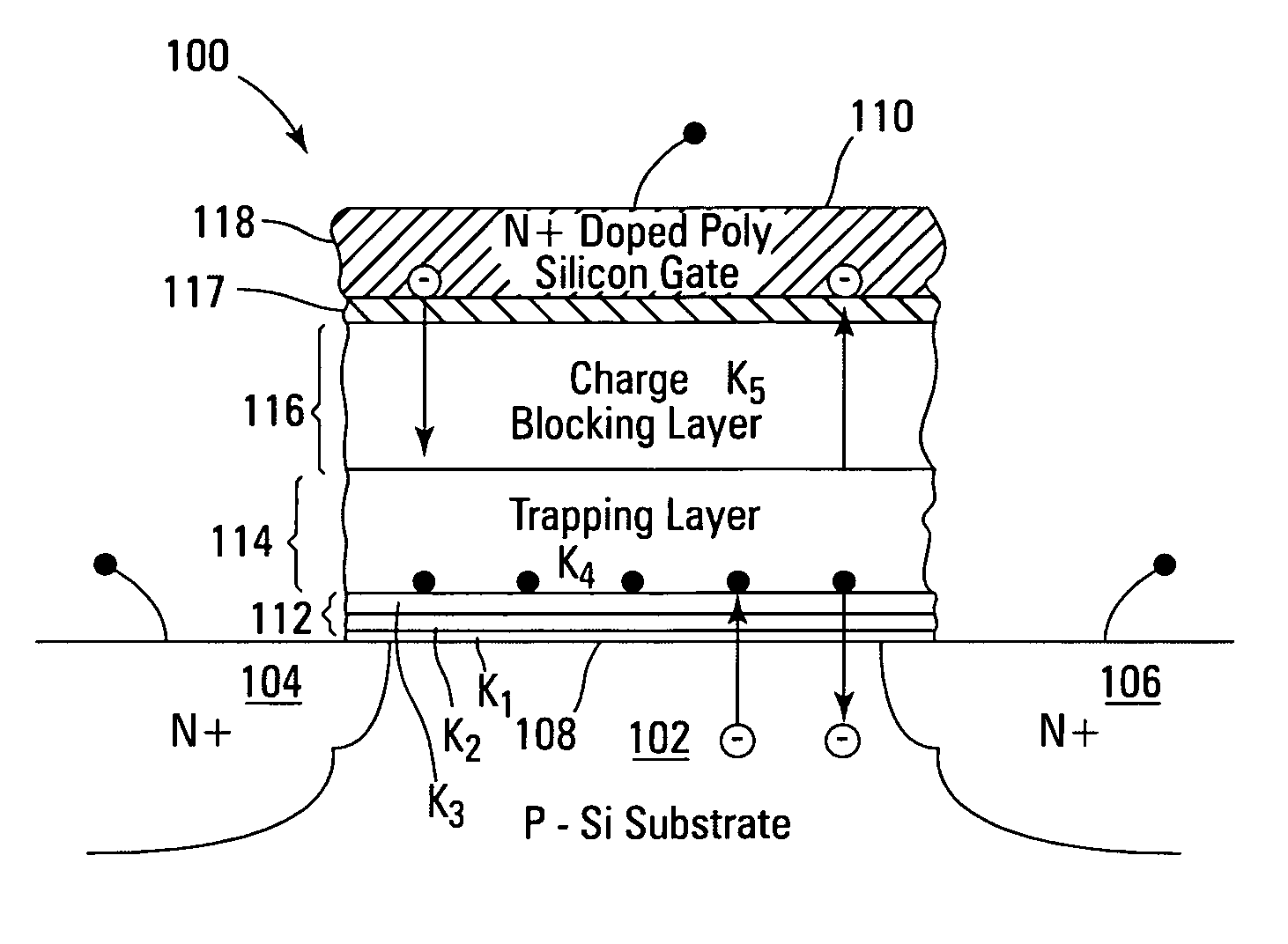

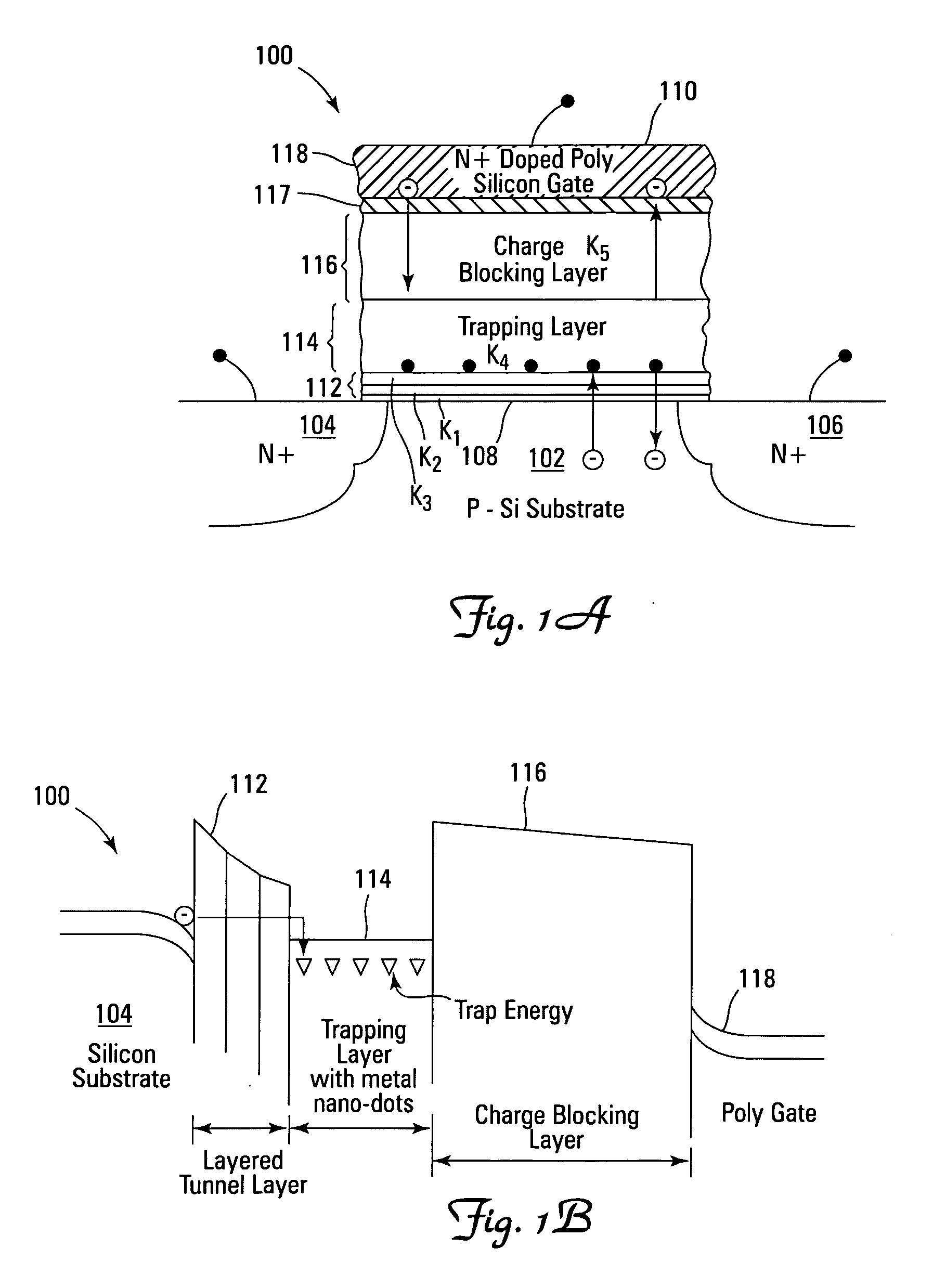

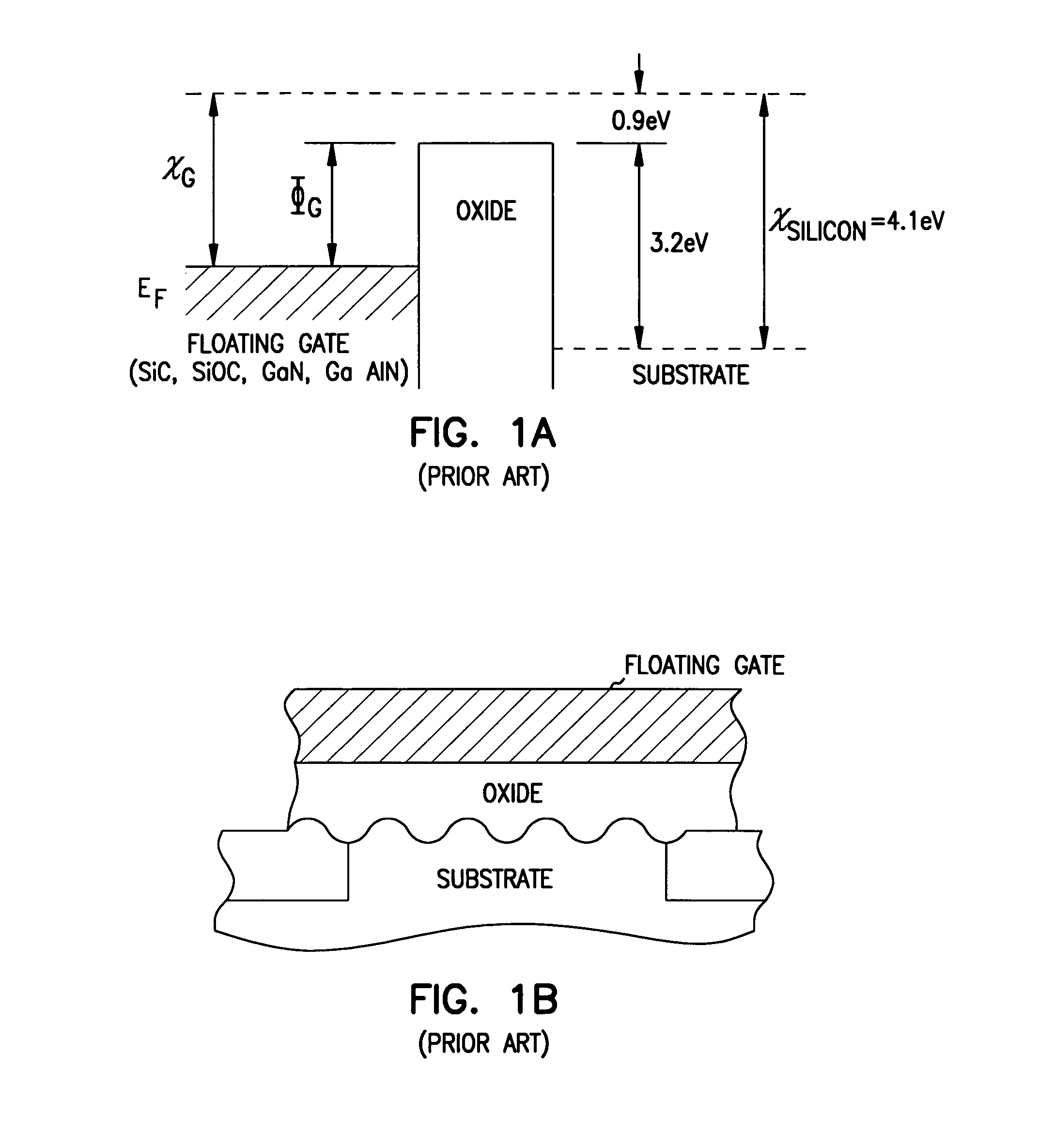

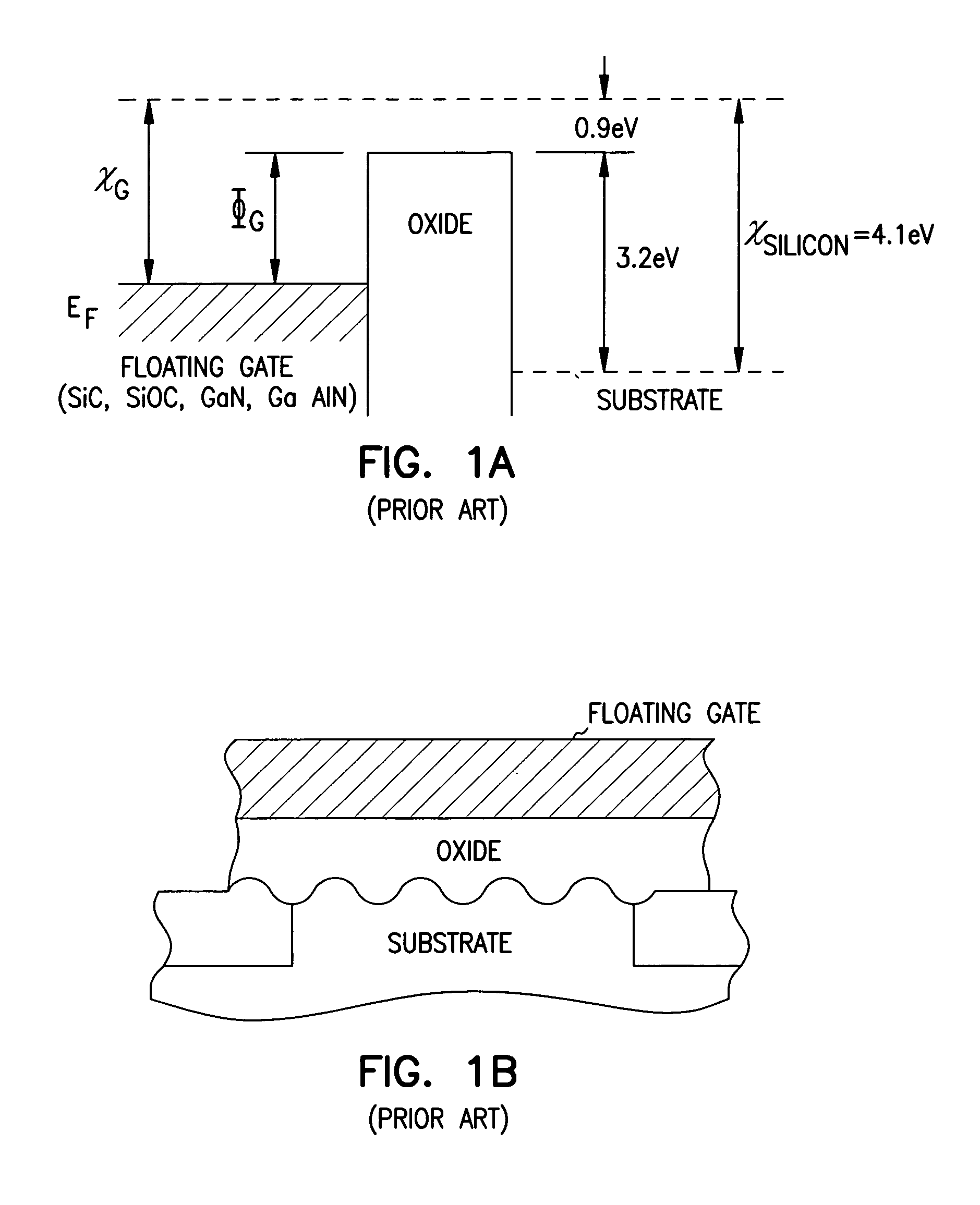

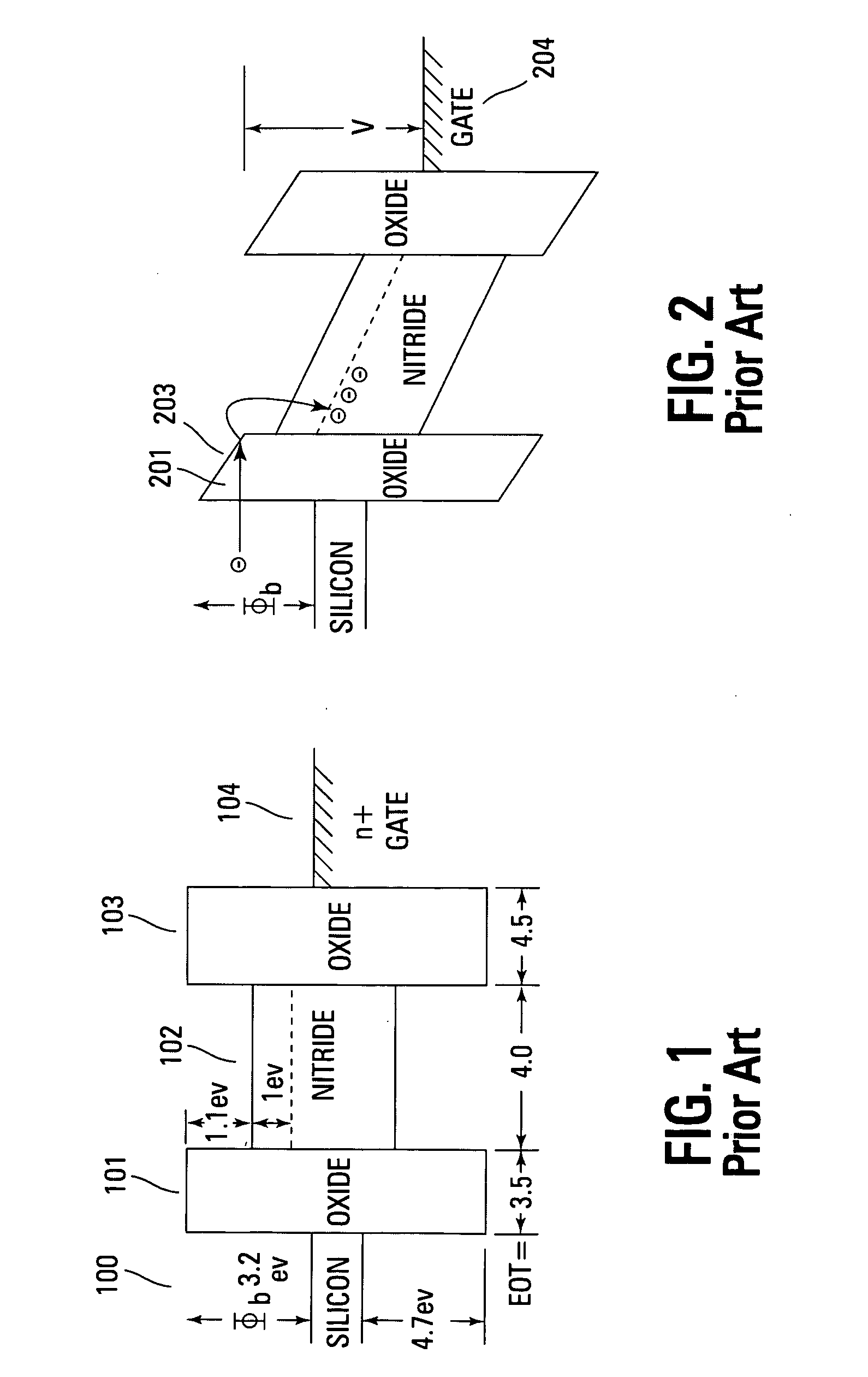

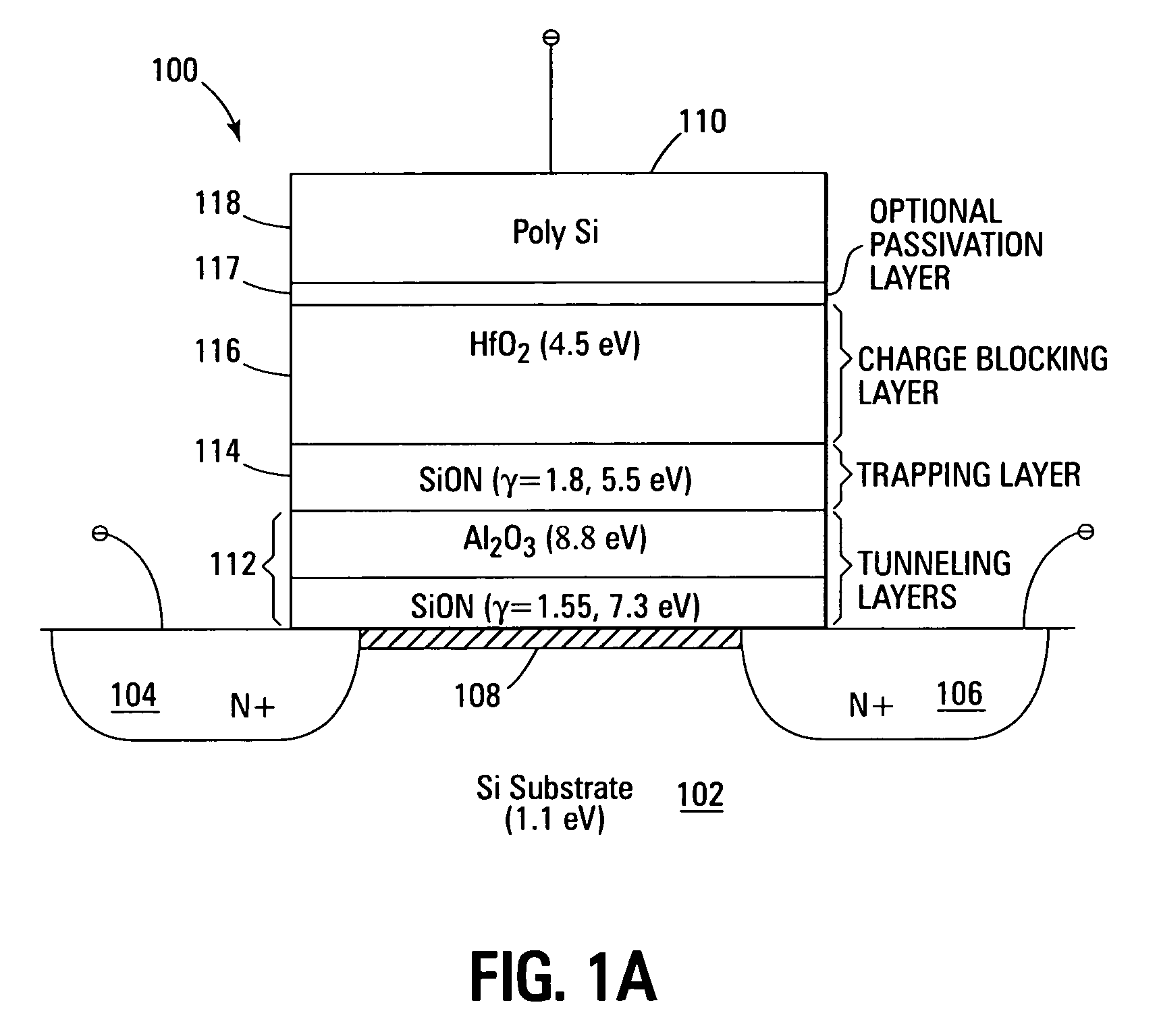

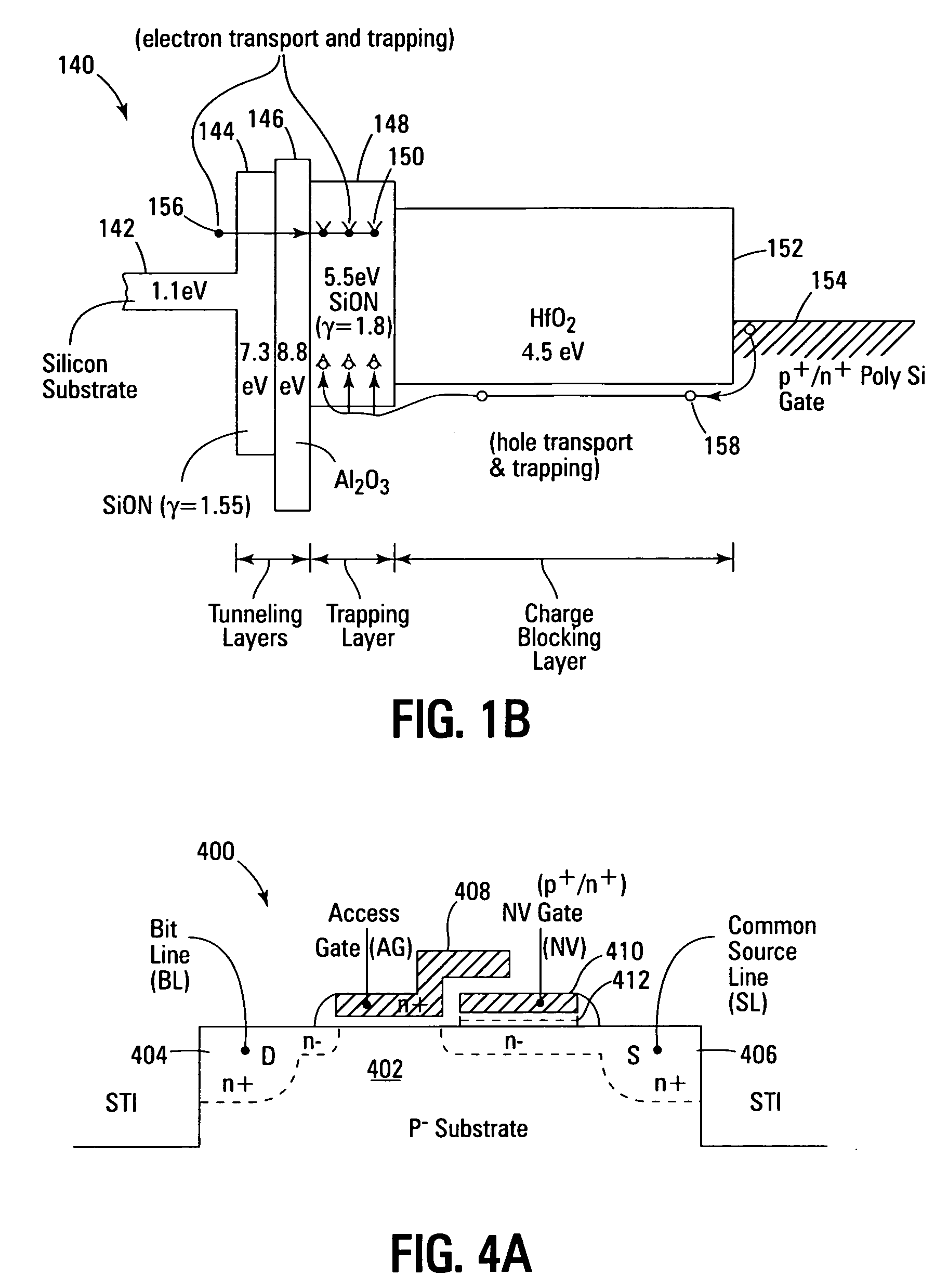

Novel low power non-volatile memory and gate stack

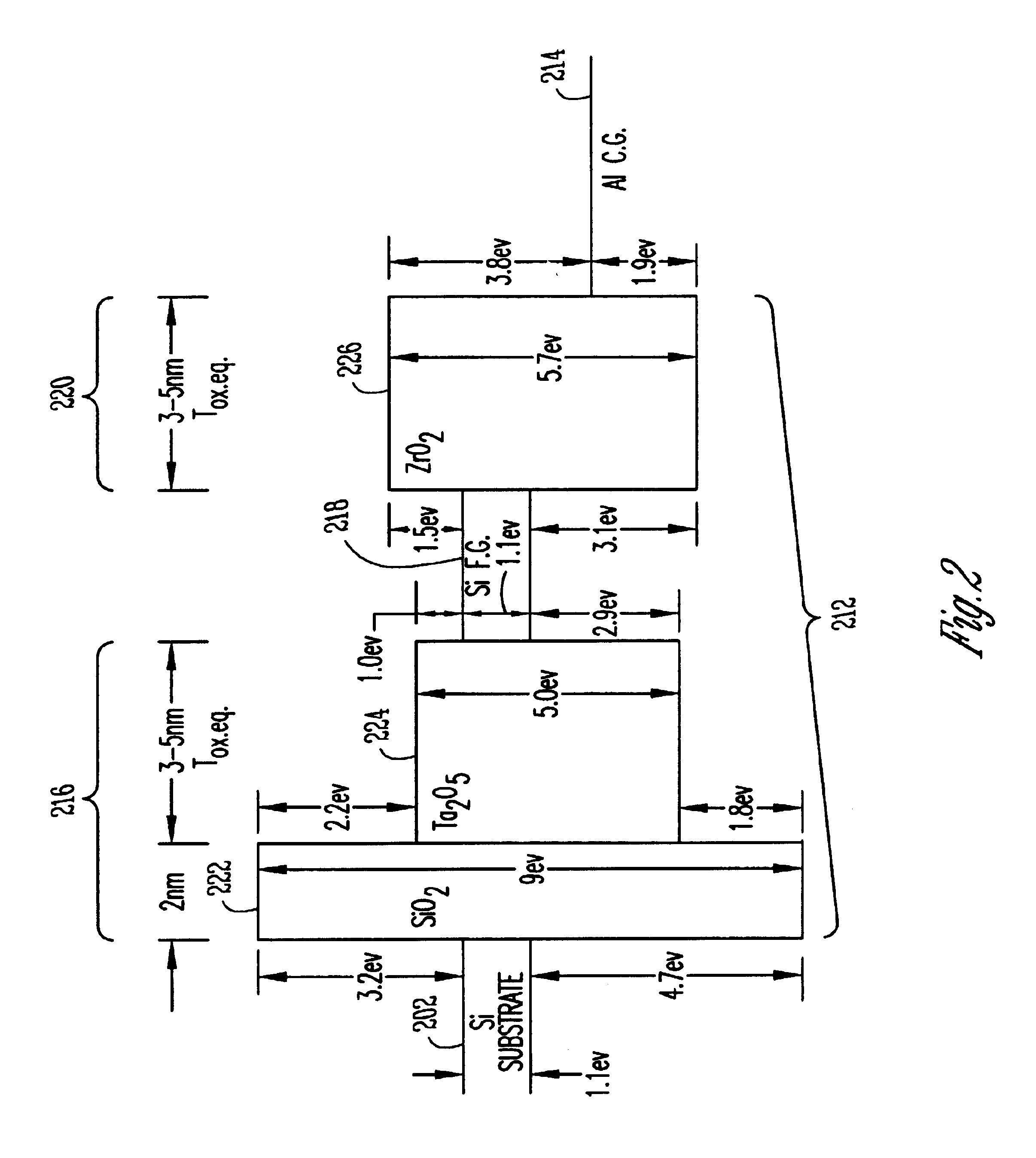

ActiveUS20060261401A1High charge blocking barrierExcellent charge retentionTransistorNanoinformaticsCharge retentionLow voltage

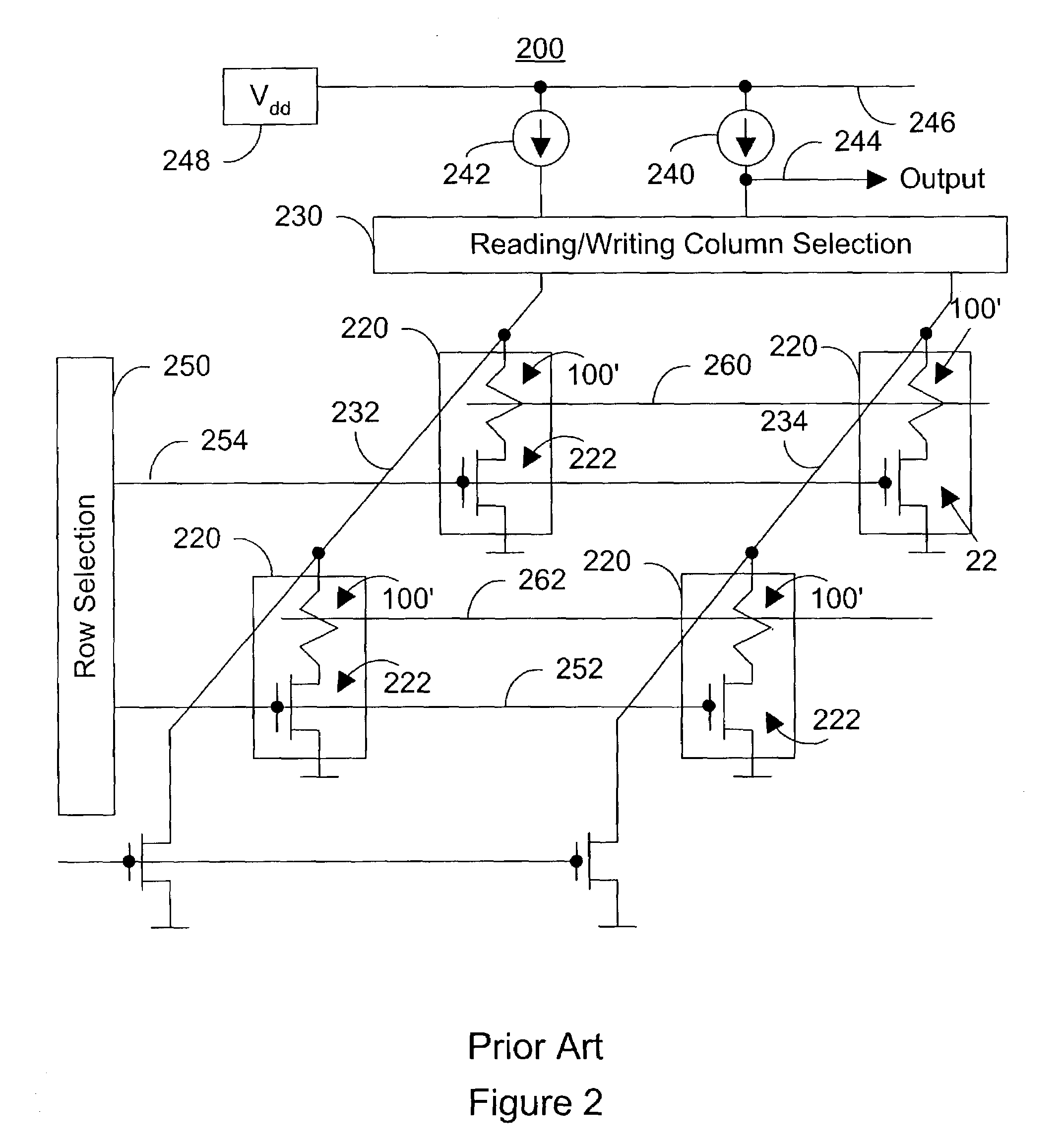

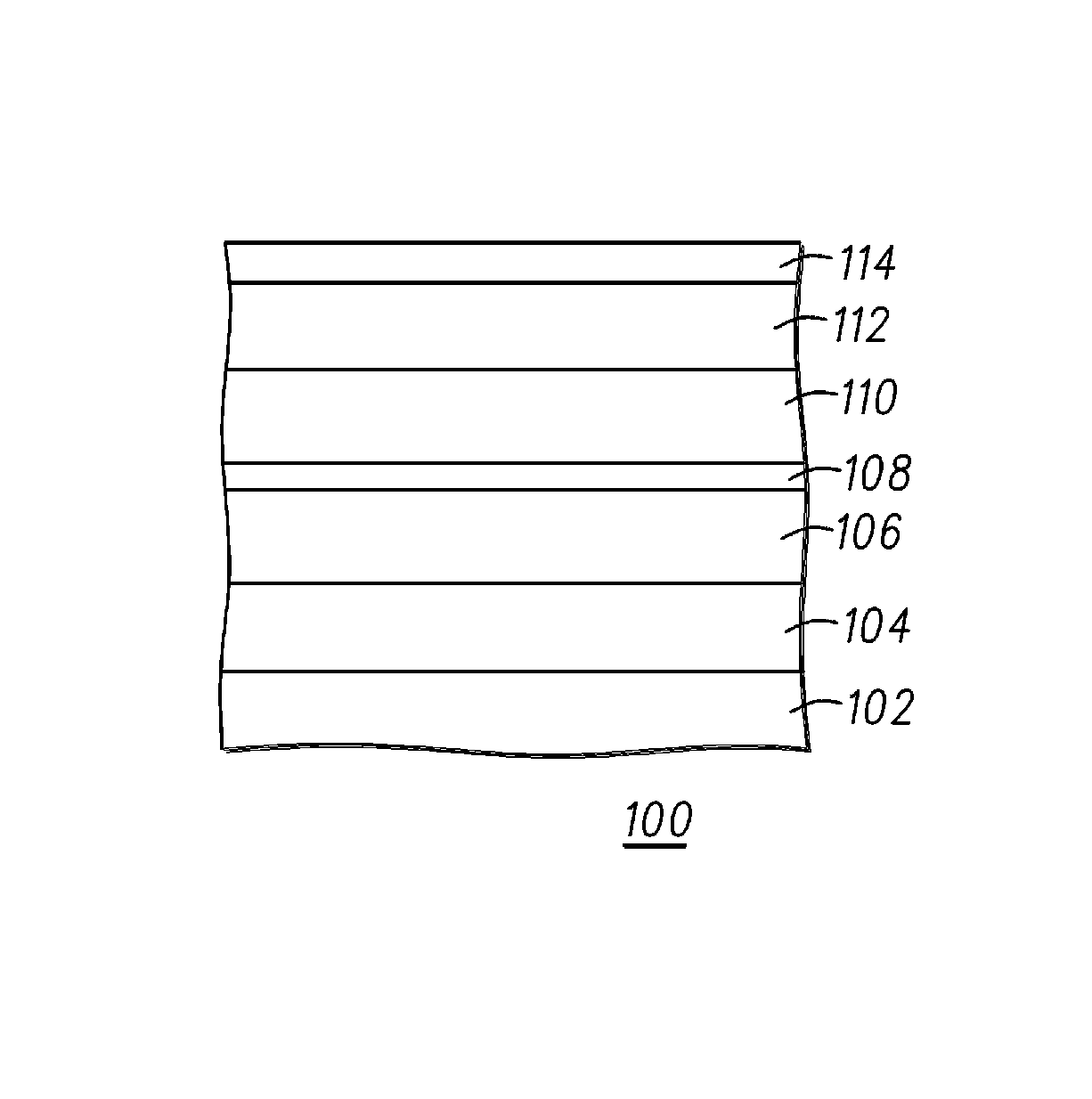

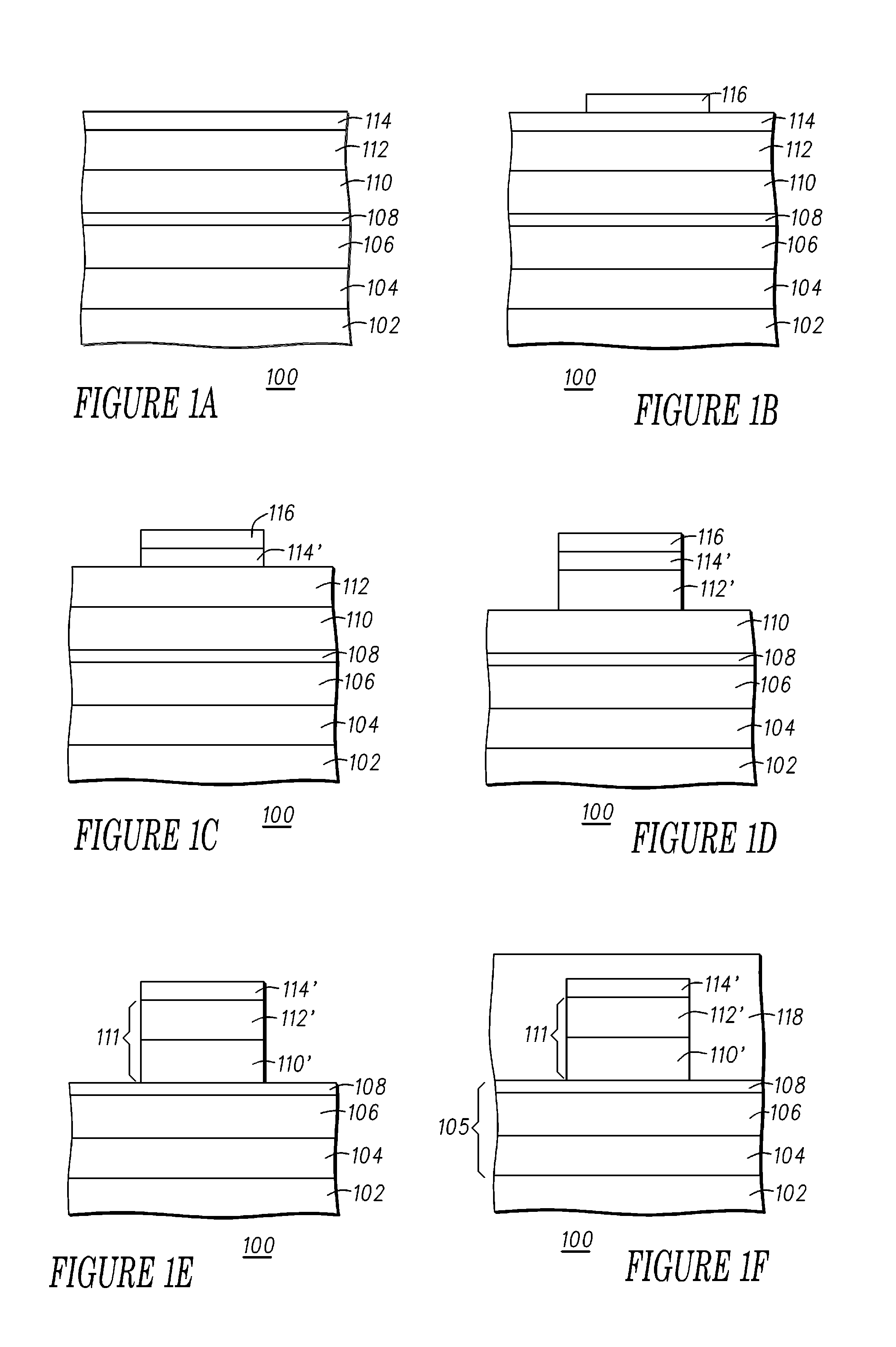

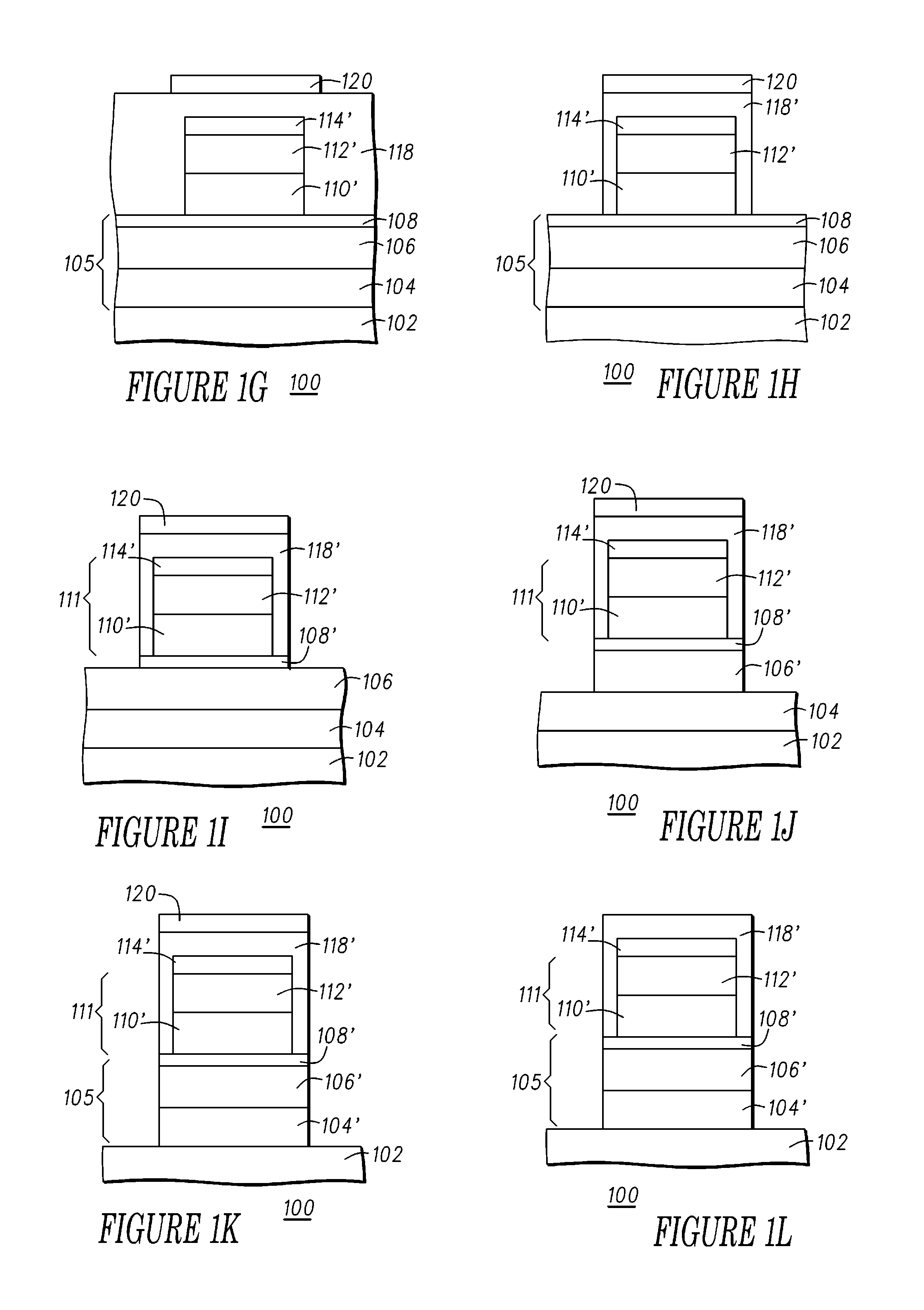

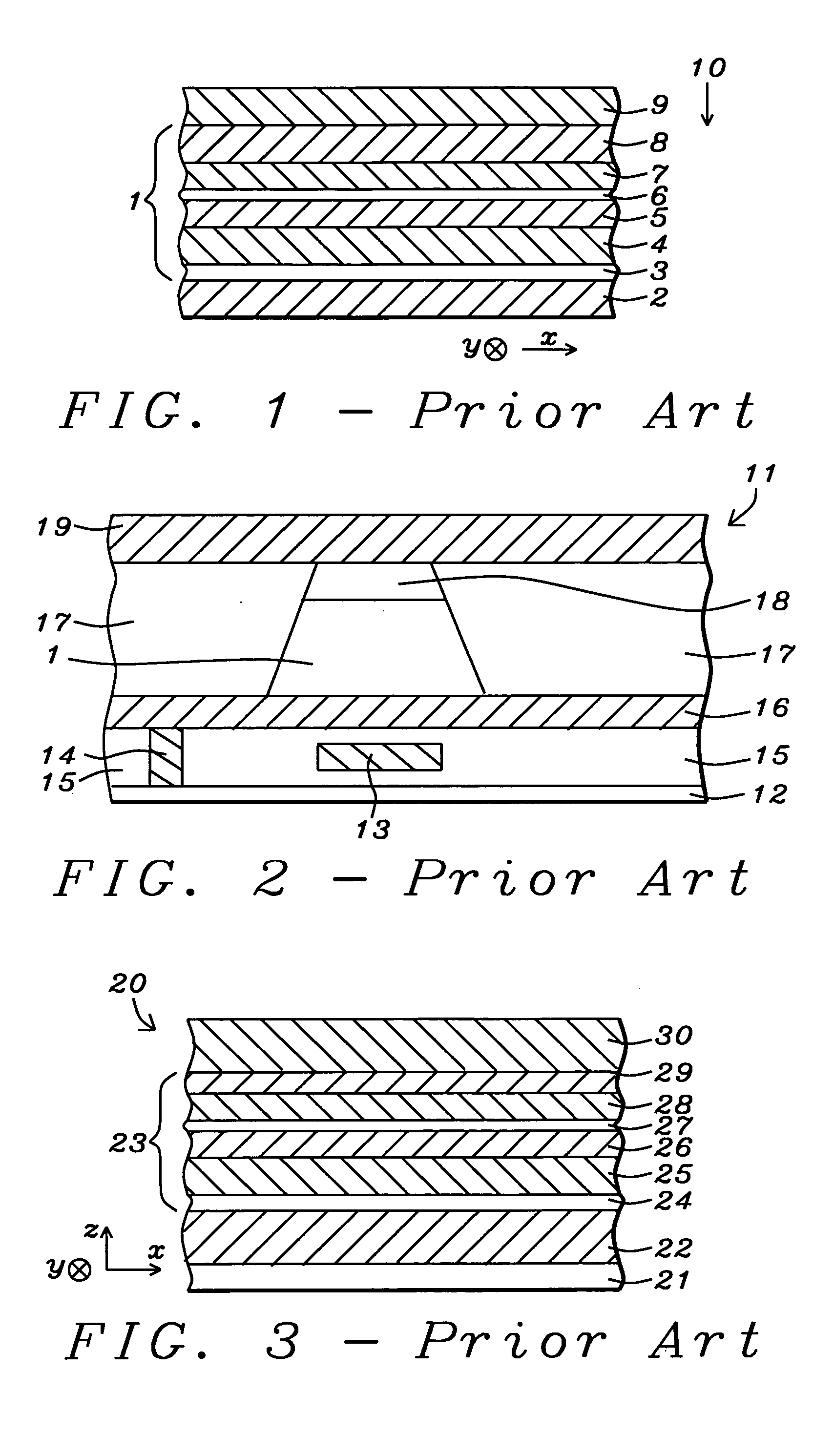

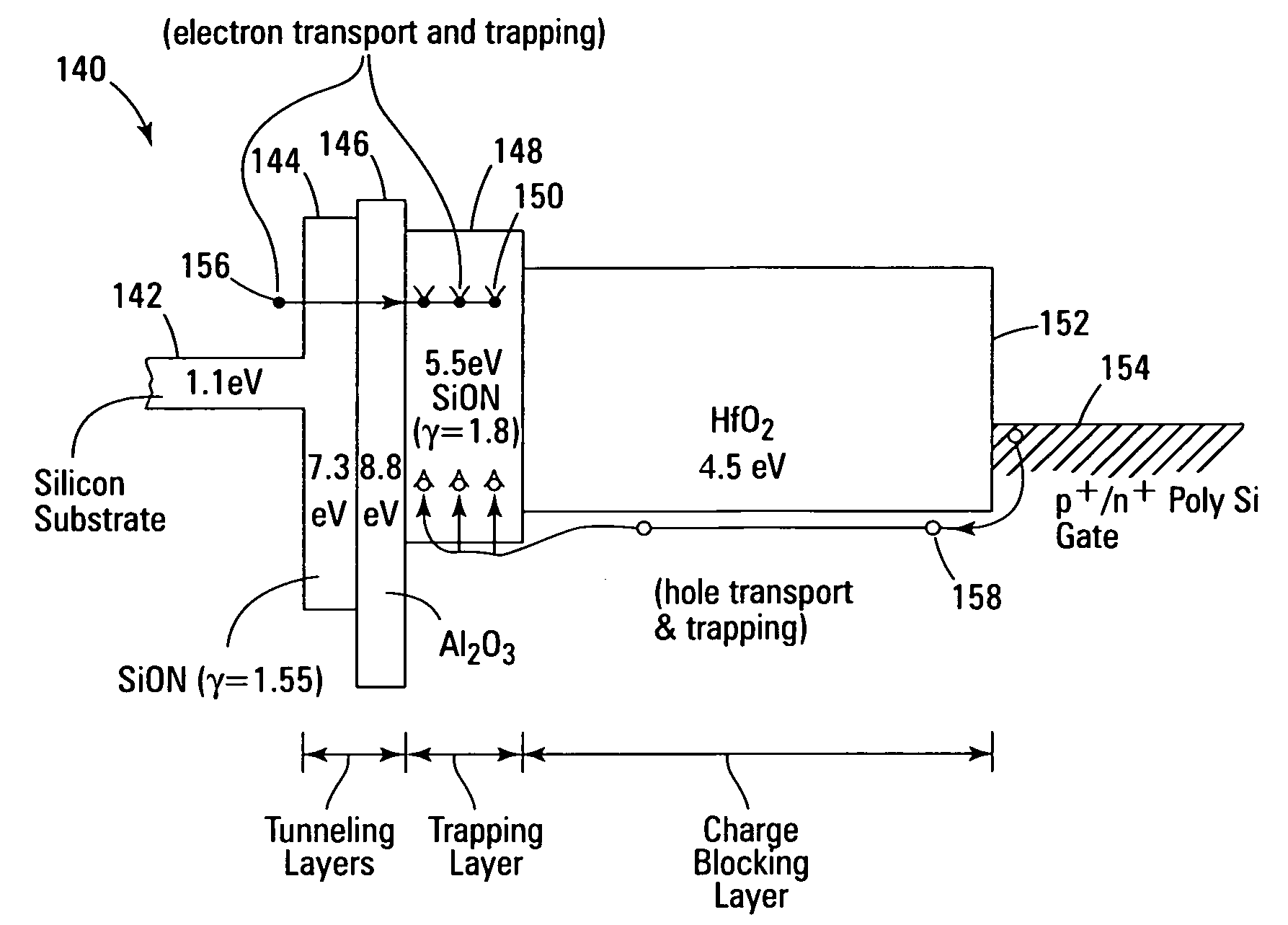

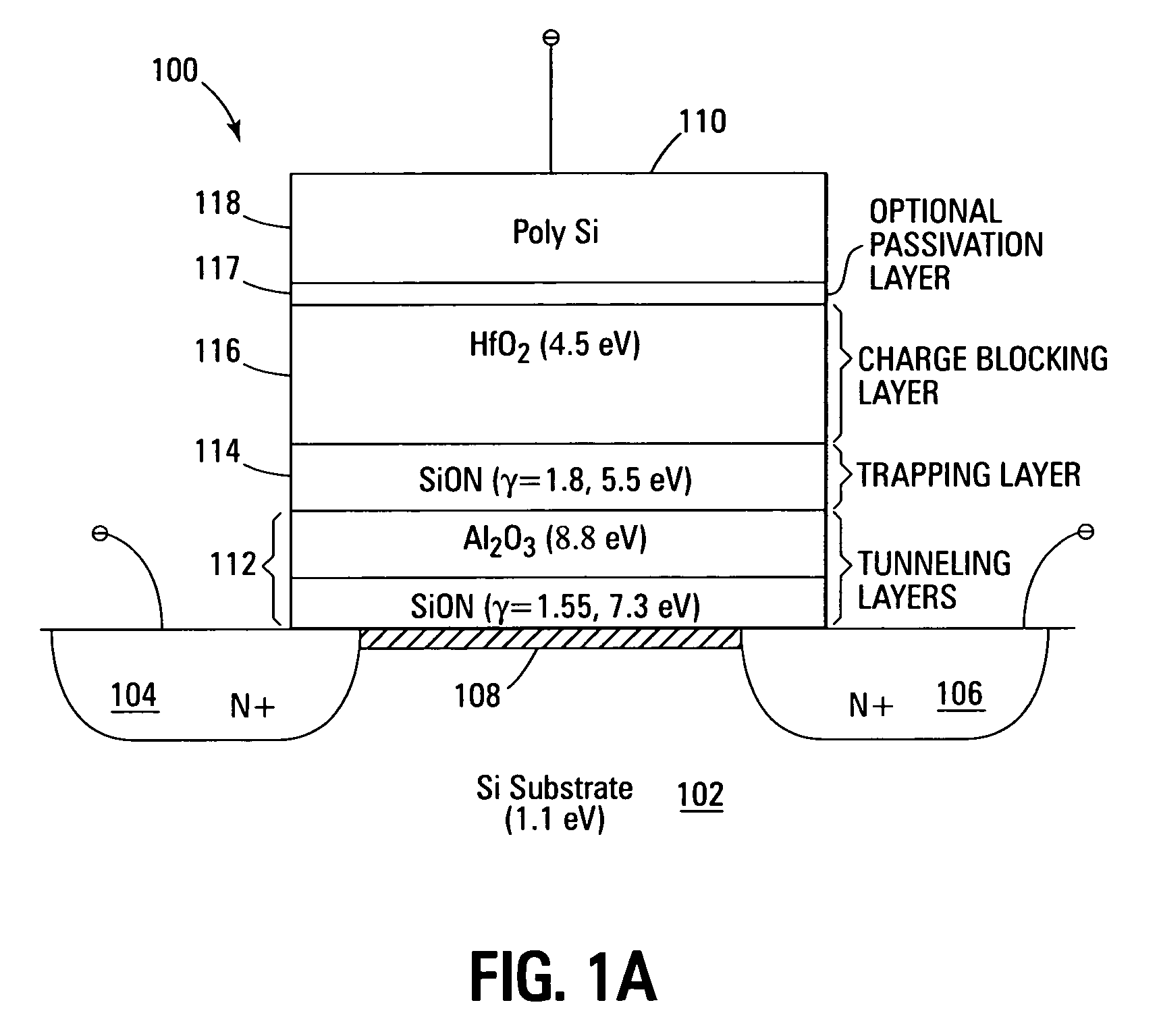

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

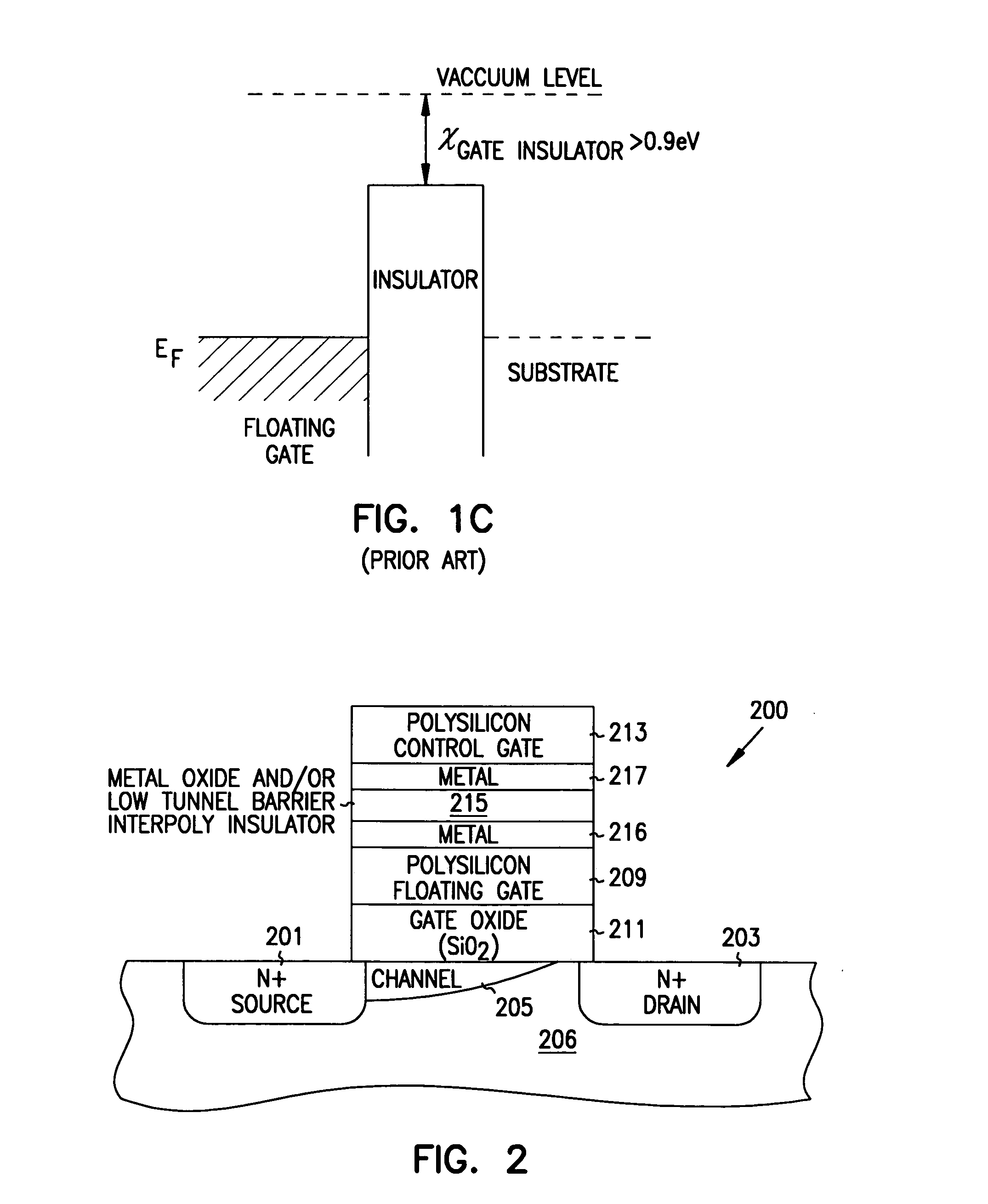

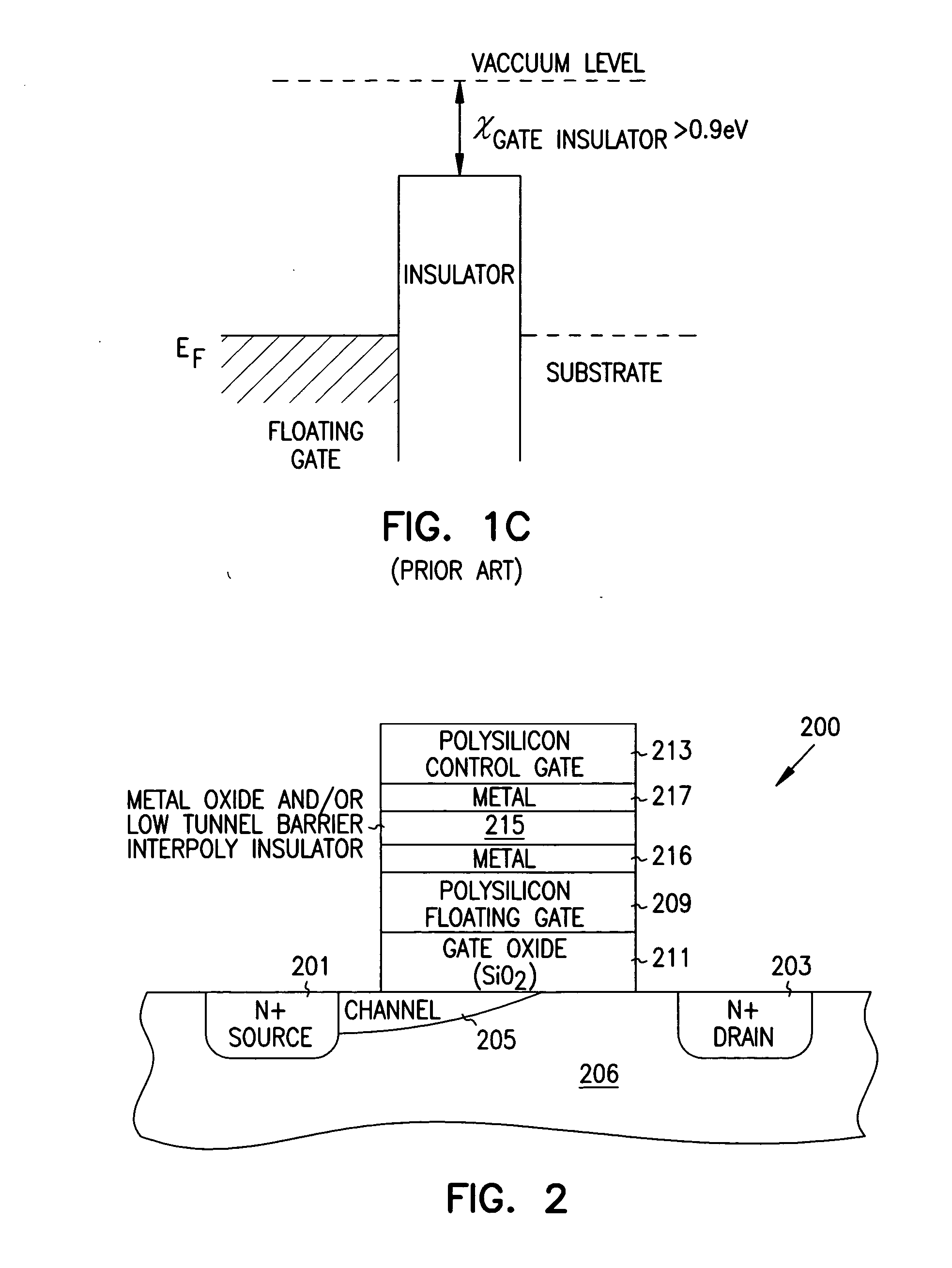

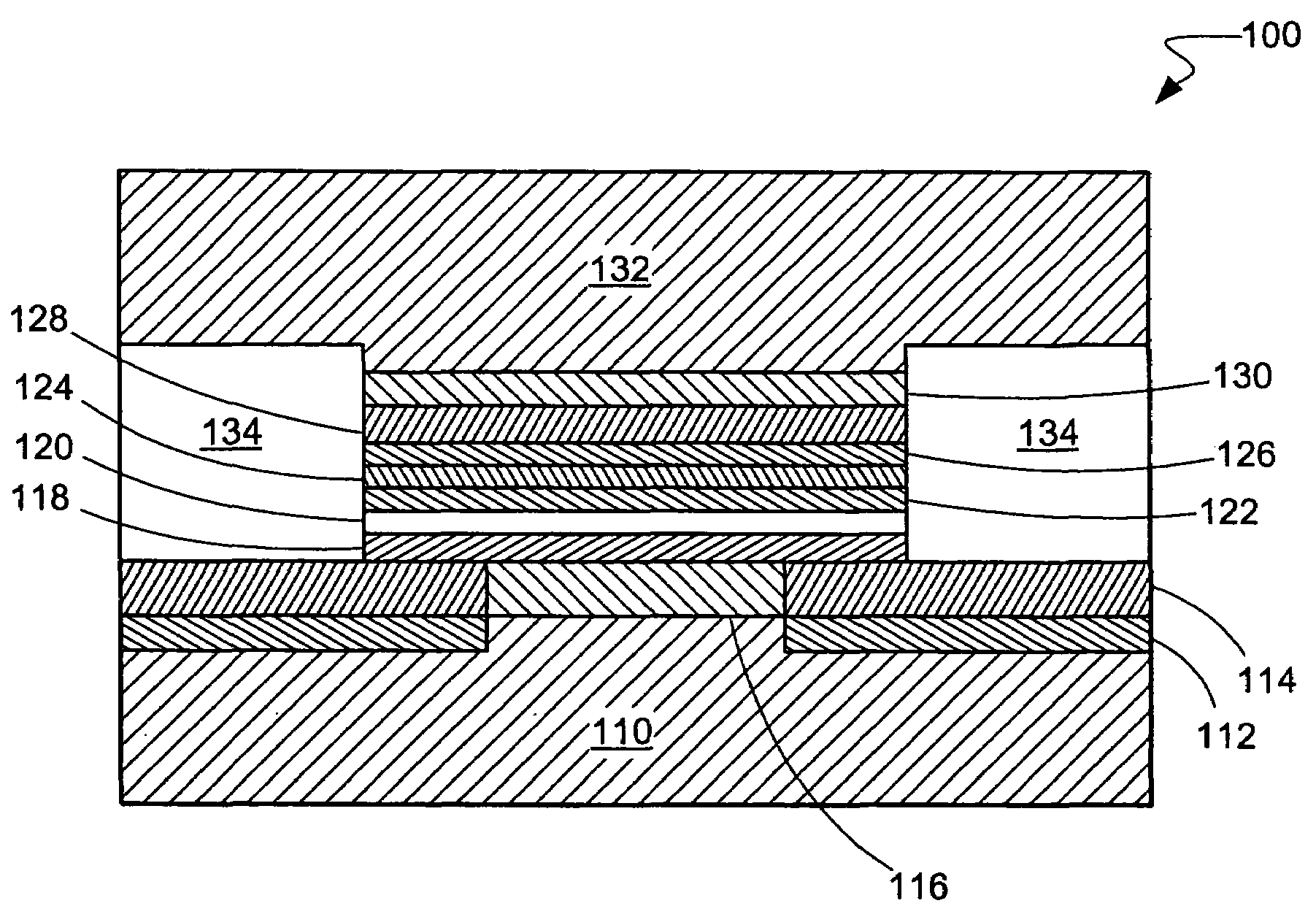

Atomic layer deposition of metal oxide and/or low asymmetrical tunnel barrier interpoly insulators

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator formed by atomic layer deposition. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3.

Owner:MICRON TECH INC

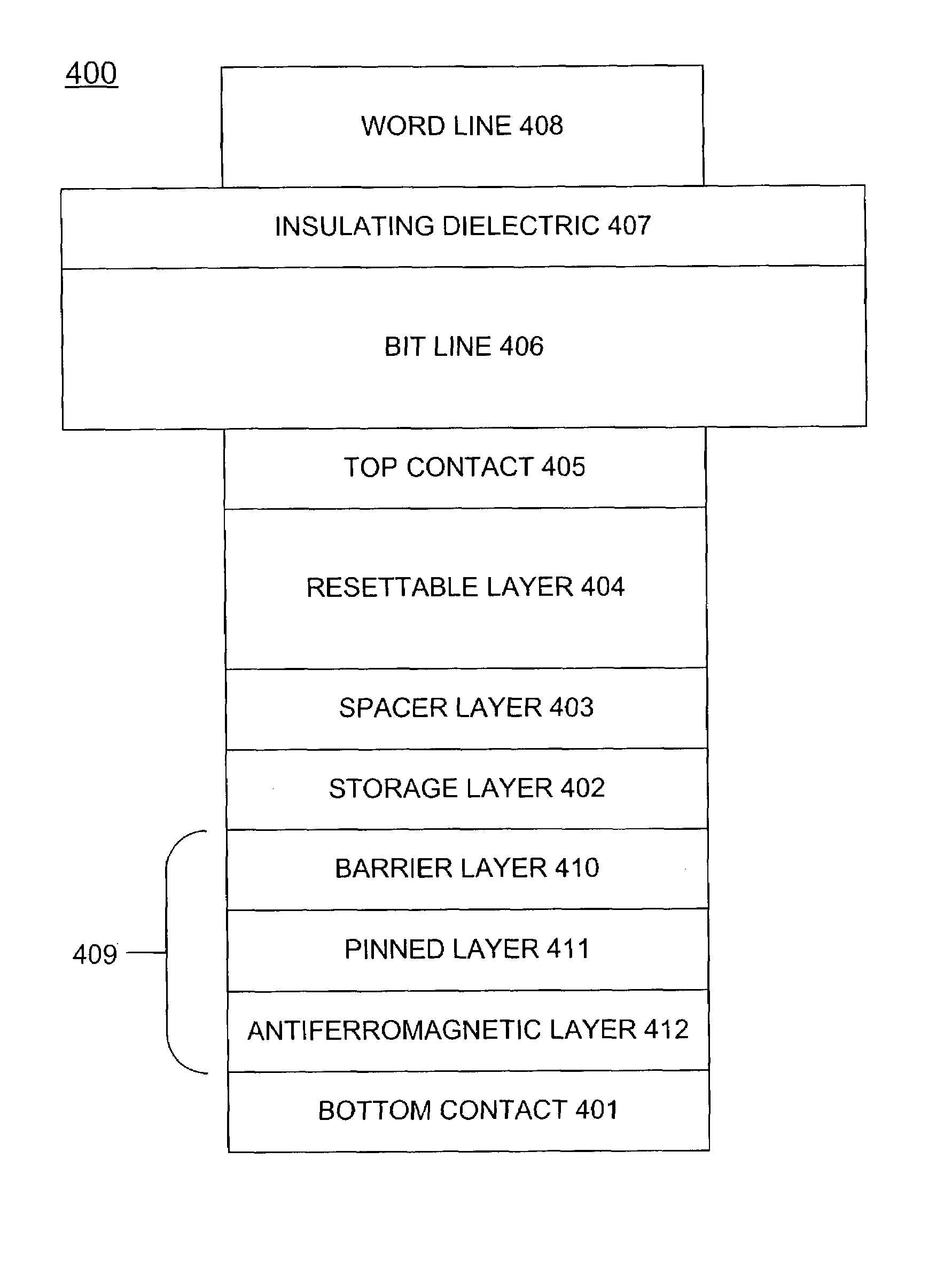

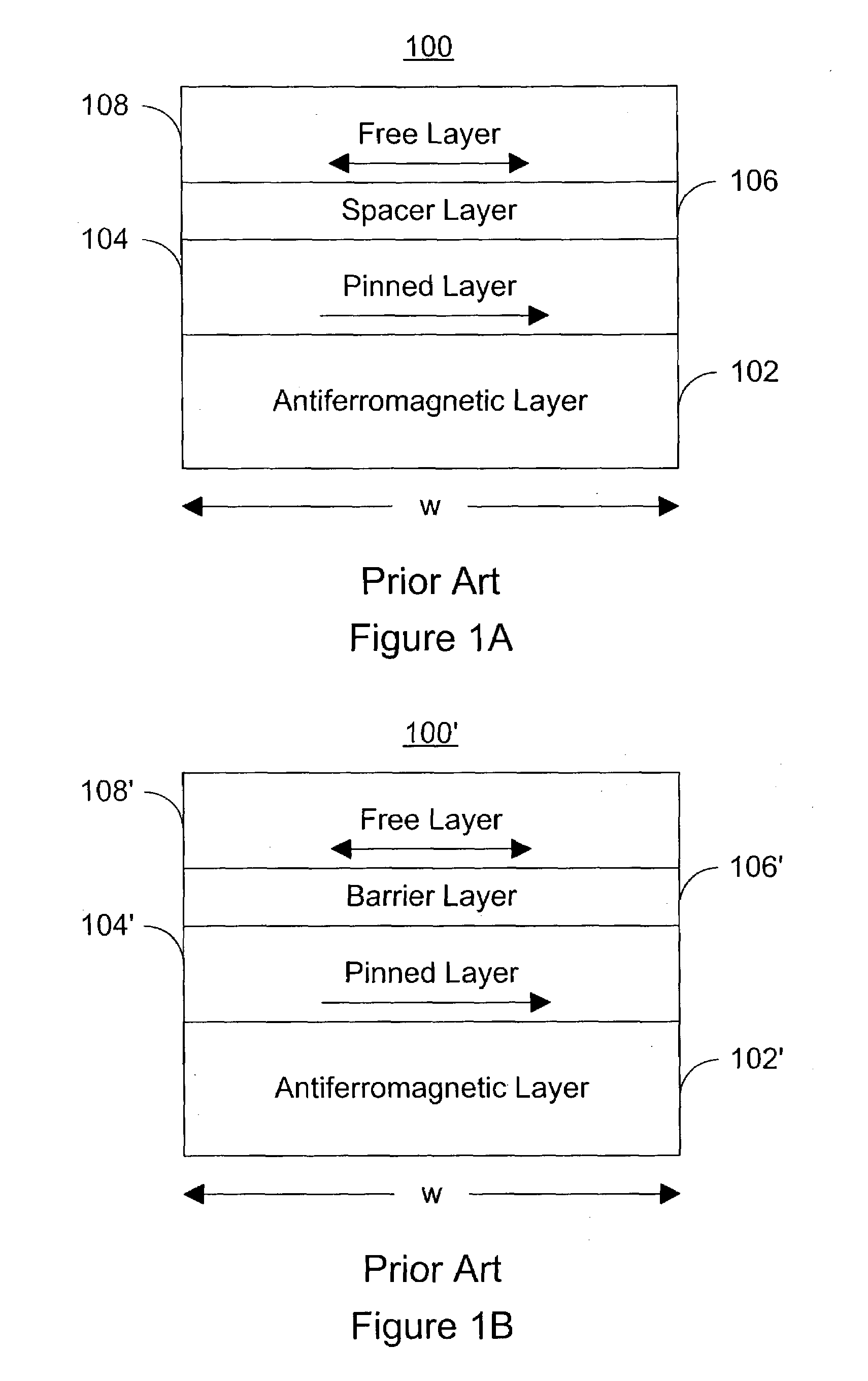

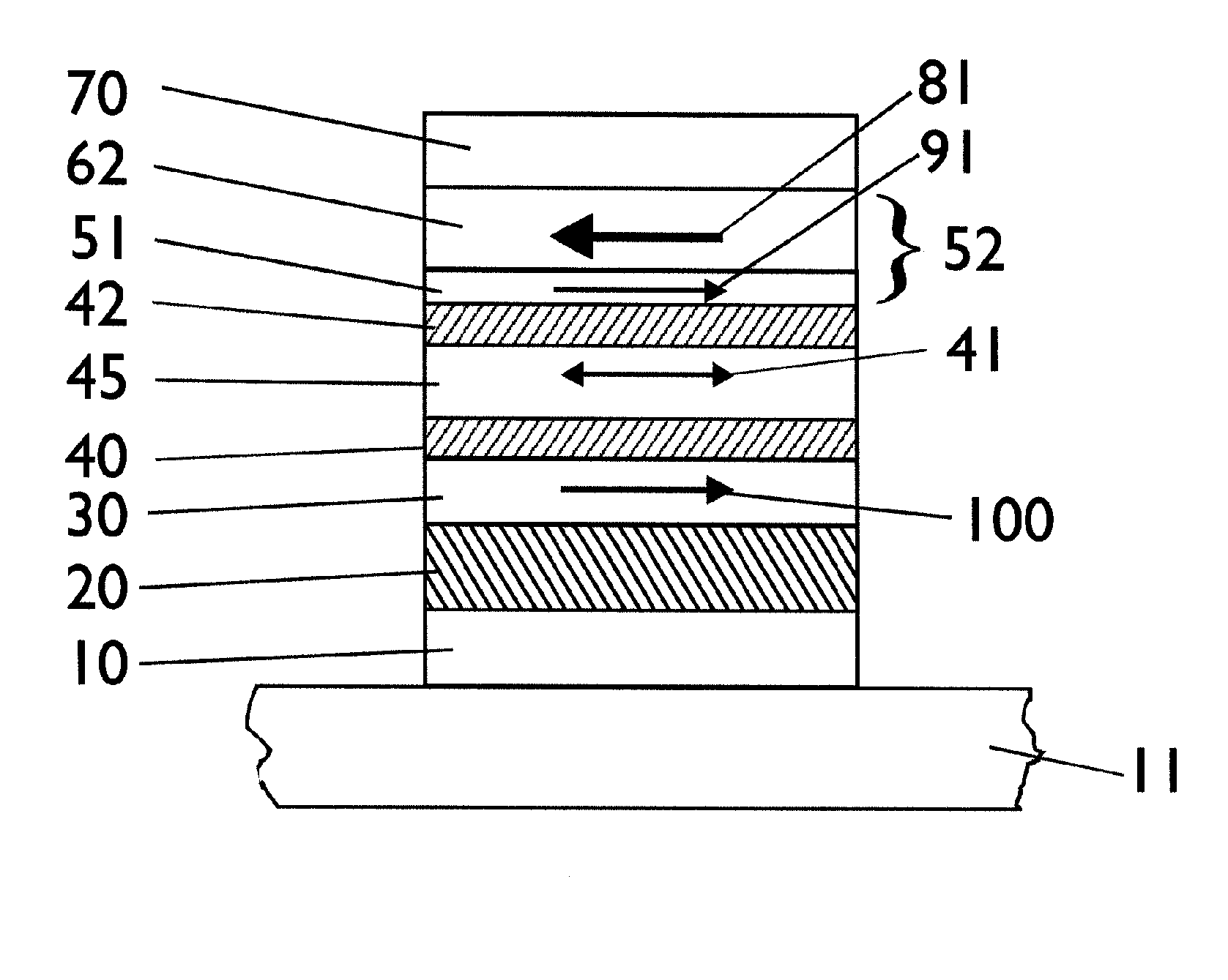

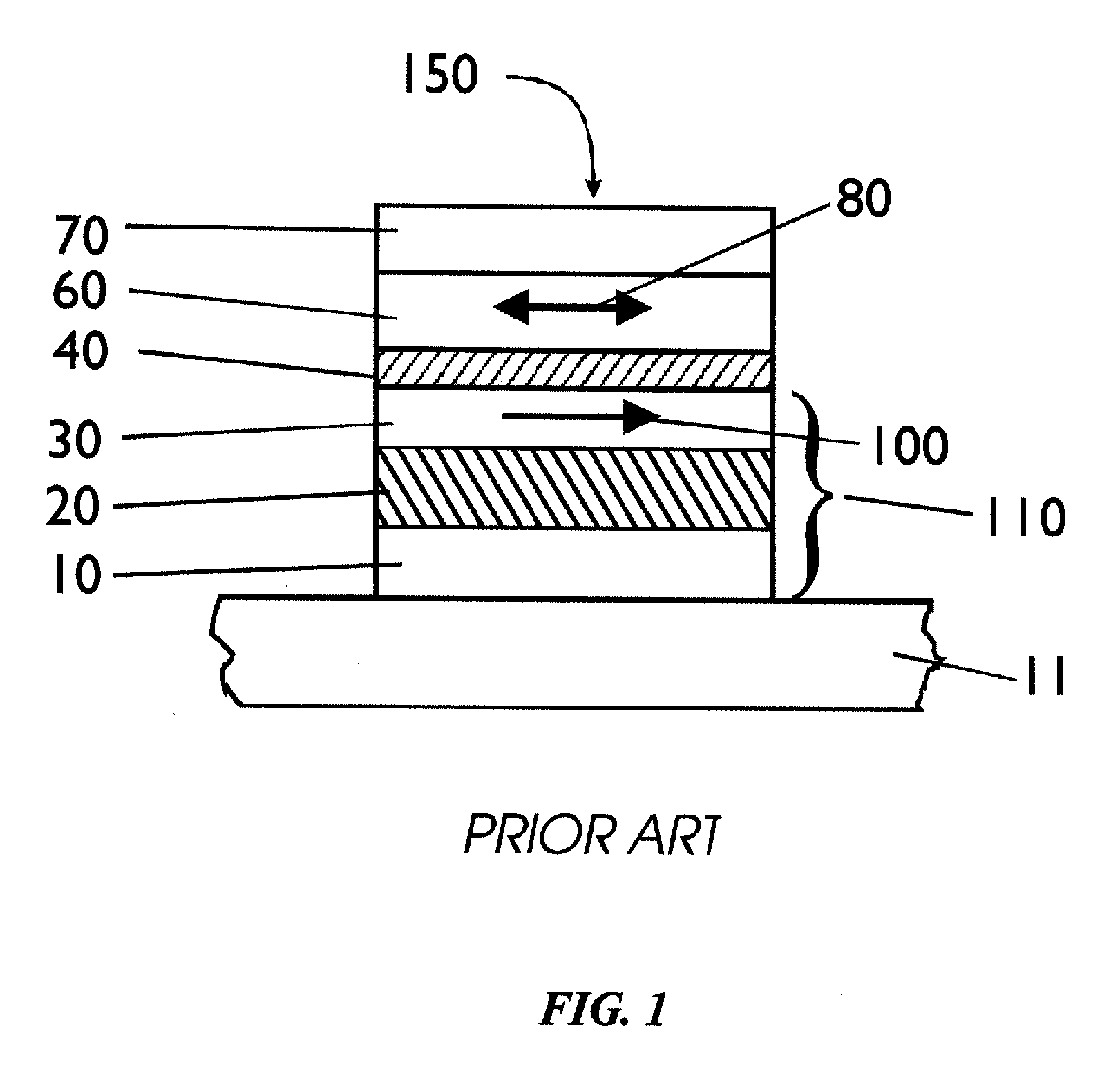

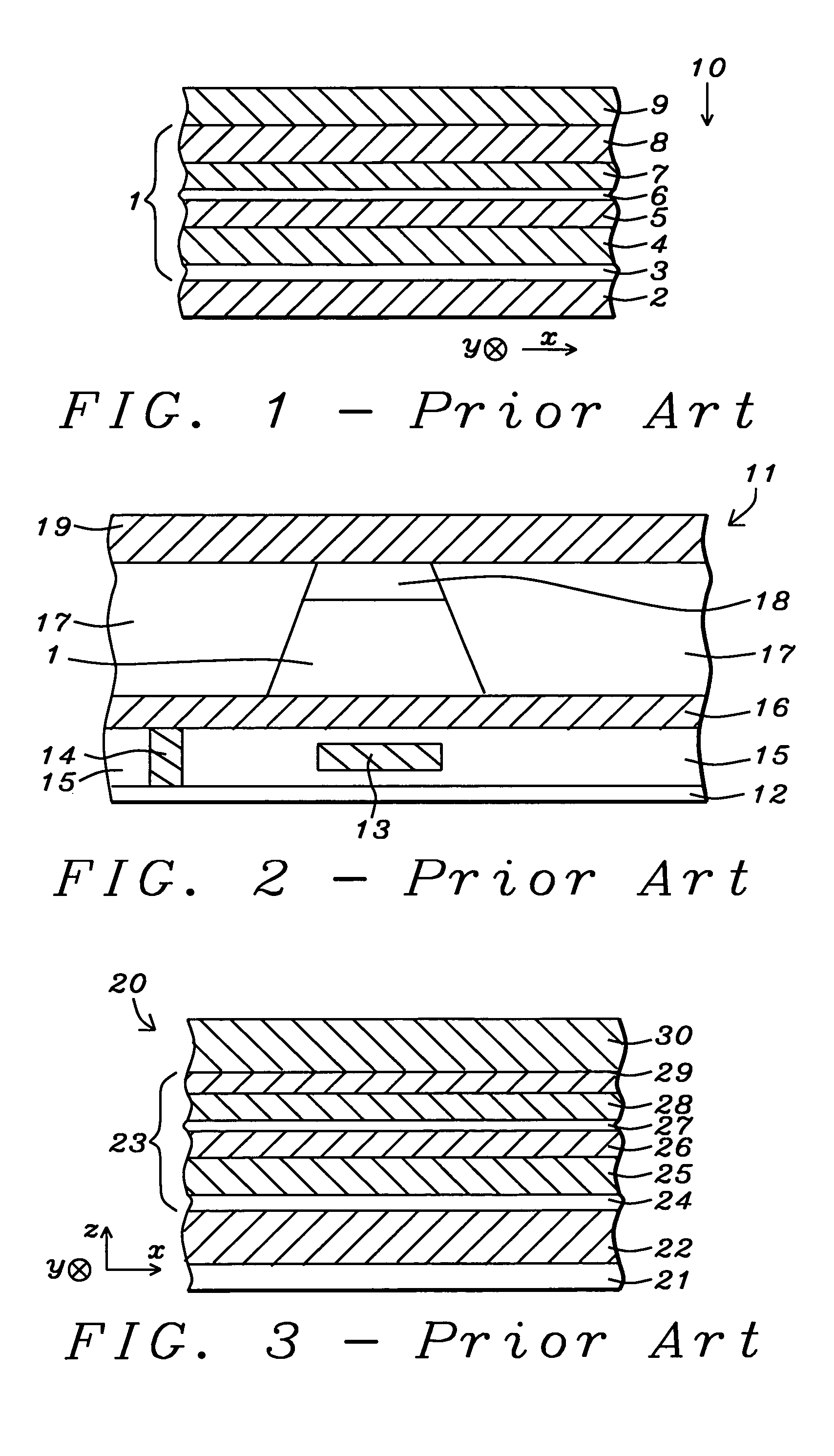

Spin-transfer multilayer stack containing magnetic layers with resettable magnetization

InactiveUS7190611B2Minimizing densityReduce process complexityGalvano-magnetic devicesSolid-state devicesHigh densitySpin transfer

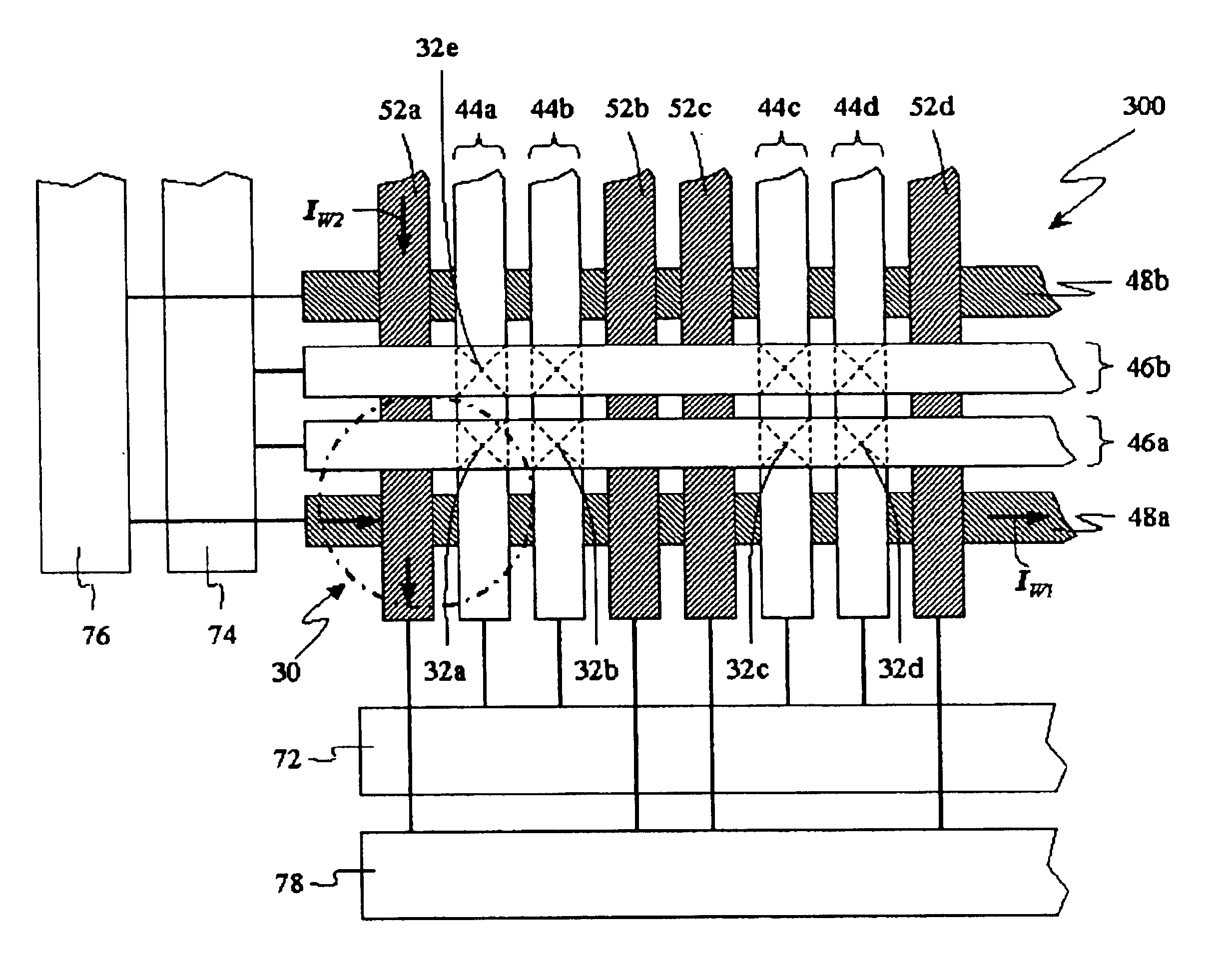

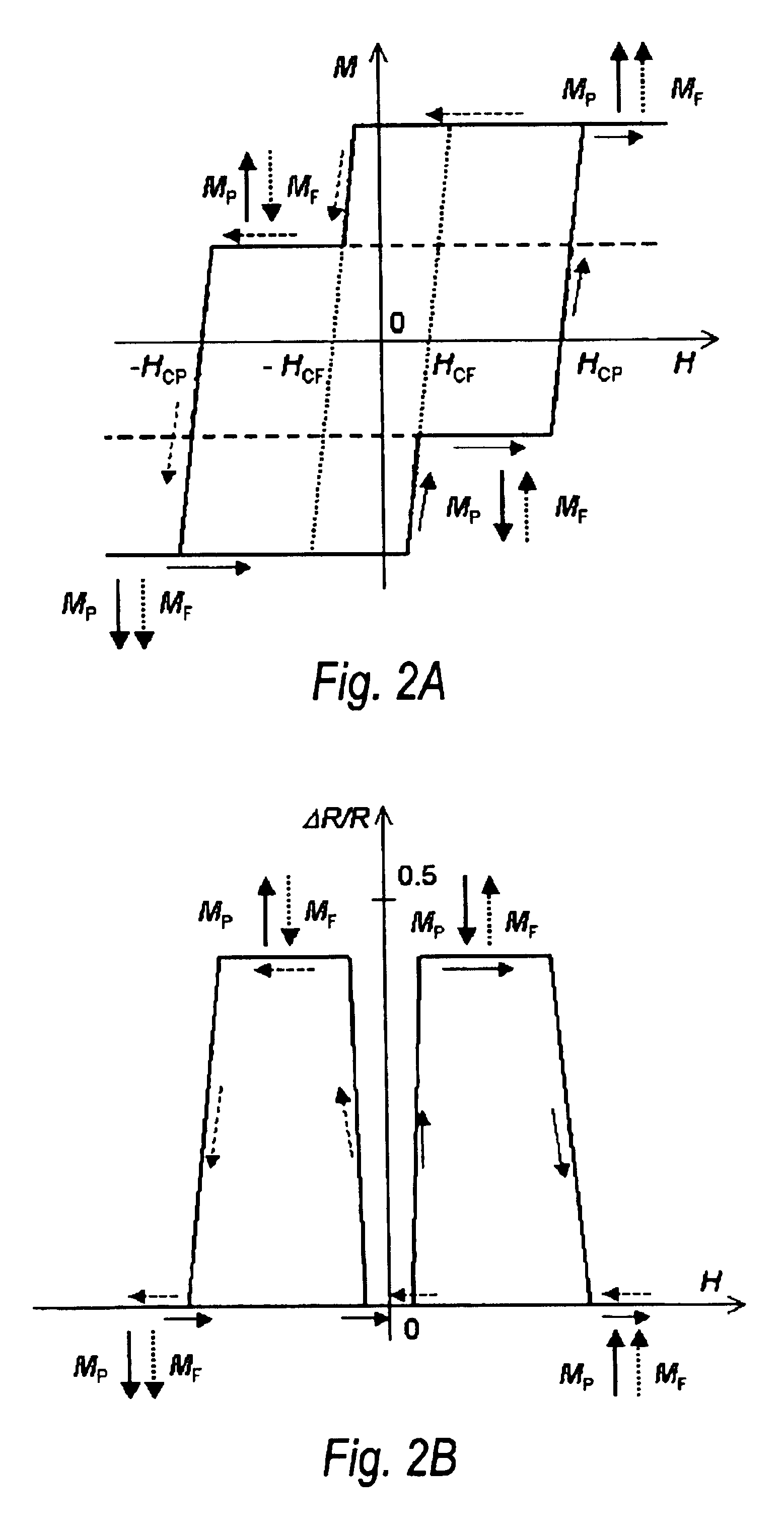

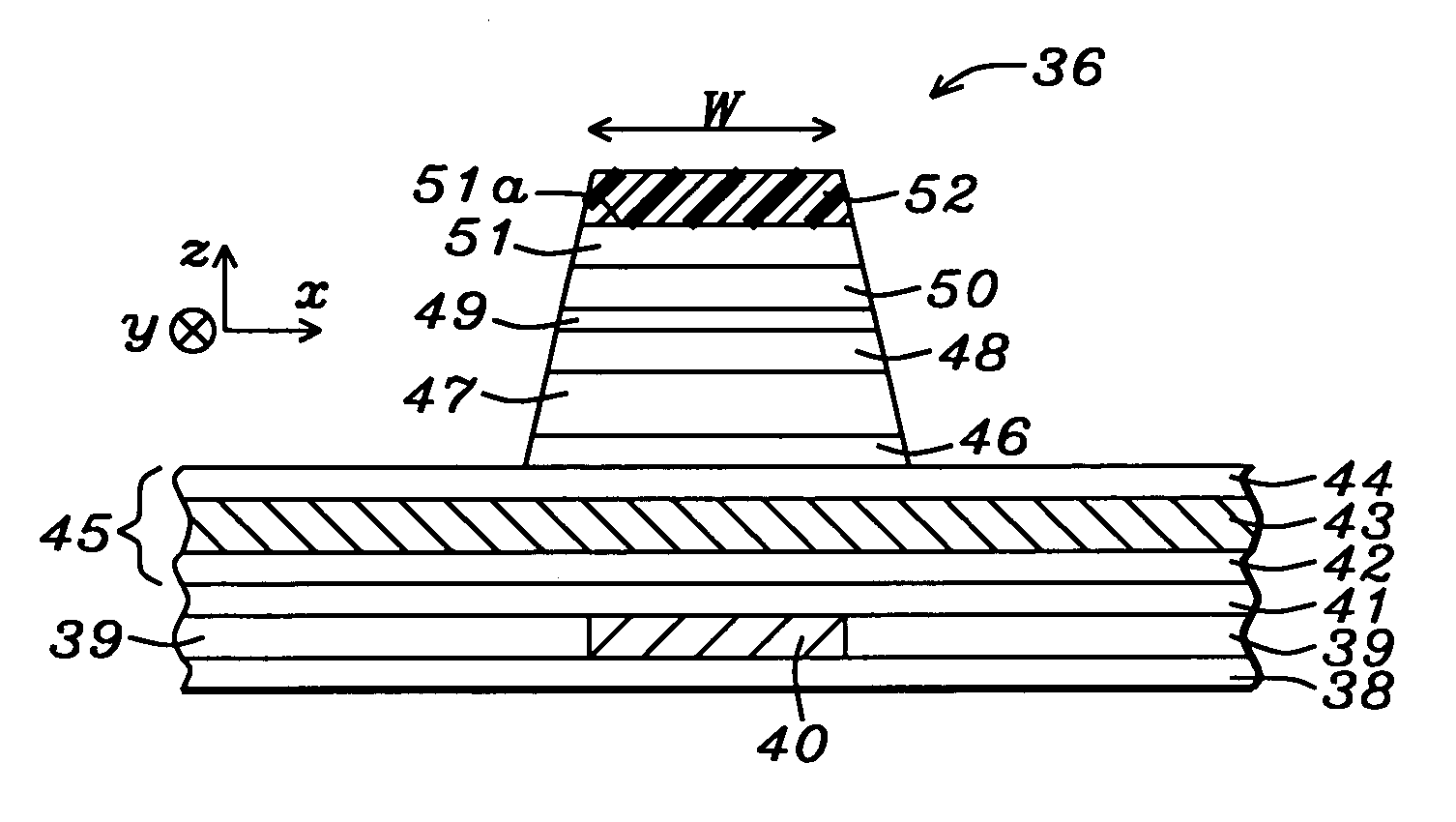

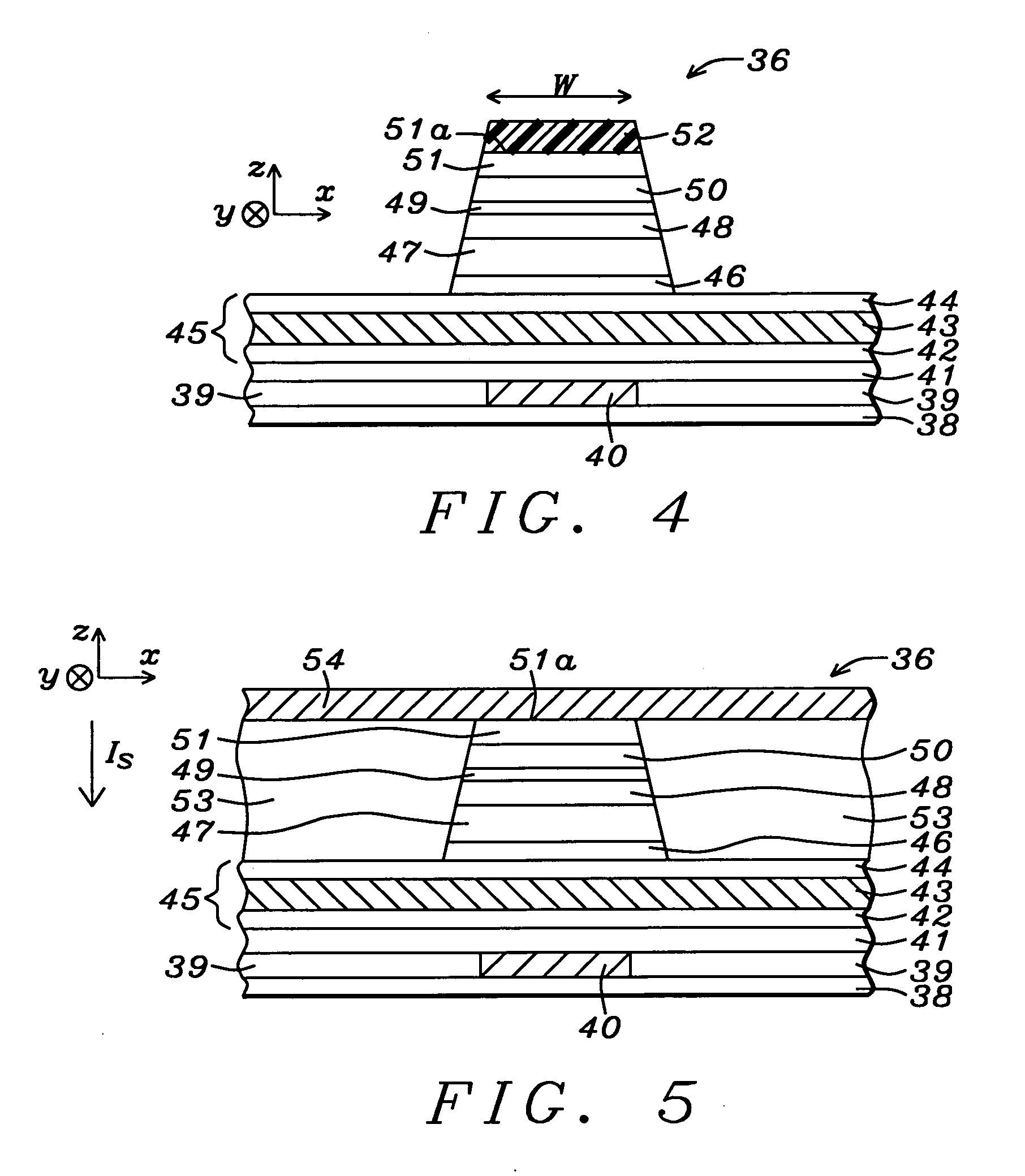

A magnetic element for a high-density memory array includes a resettable layer and a storage layer. The resettable layer has a magnetization that is set in a selected direction by at least one externally generated magnetic field. The storage layer has at least one magnetic easy axis and a magnetization that changes direction based on the spin-transfer effect when a write current passes through the magnetic element. An alternative embodiment of the magnetic element includes an additional multilayer structure formed from a tunneling barrier layer, a pinned magnetic layer and an antiferromagnetic layer that pins the magnetization of the pinned layer in a predetermined direction. Another alternative embodiment of the magnetic element includes an additional multilayer structure that is formed from a tunneling barrier layer and a second resettable layer having a magnetic moment that is different from the magnetic moment of the resettable layer of the basic embodiment.

Owner:SAMSUNG SEMICON

Method of manufacturing a magnetoresistive-based device

ActiveUS8747680B1Decorative surface effectsSemiconductor/solid-state device manufacturingMagnetic reluctanceHard mask

A method of manufacturing a magnetoresistive-based device having magnetic material layers formed between a first electrically conductive layer and a second electrically conductive layer, the magnetic materials layers including a tunnel barrier layer formed between a first magnetic materials layer and a second magnetic materials layer, including removing the first electrically conductive layer and the first magnetic materials layer unprotected by a first hard mask, to form a first electrode and a first magnetic materials, respectively; and removing the tunnel barrier layer, second magnetic materials layer, and second electrically conductive layer unprotected by the second hard mask to form a tunnel barrier, second magnetic materials, and a second electrode.

Owner:EVERSPIN TECHNOLOGIES

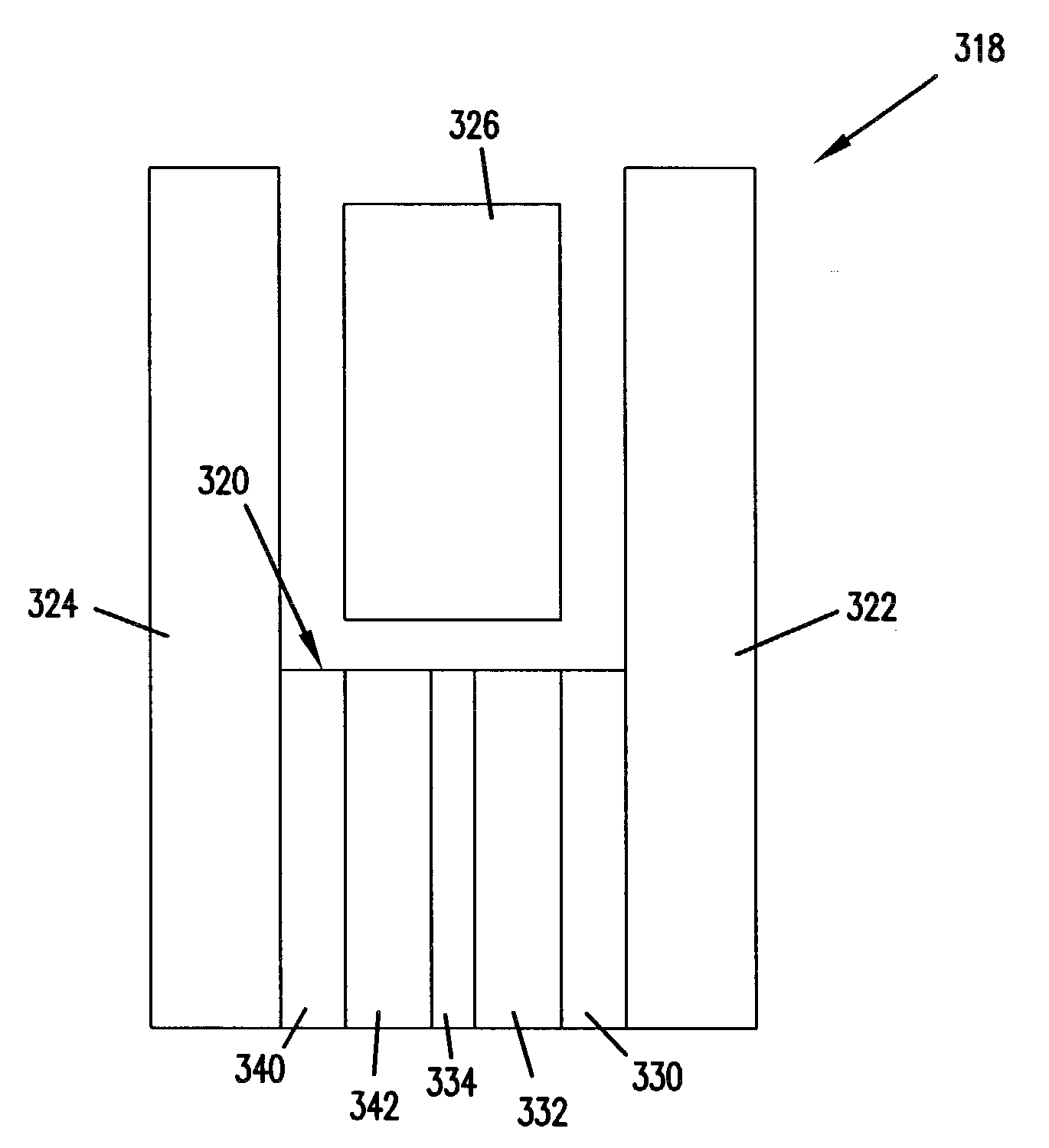

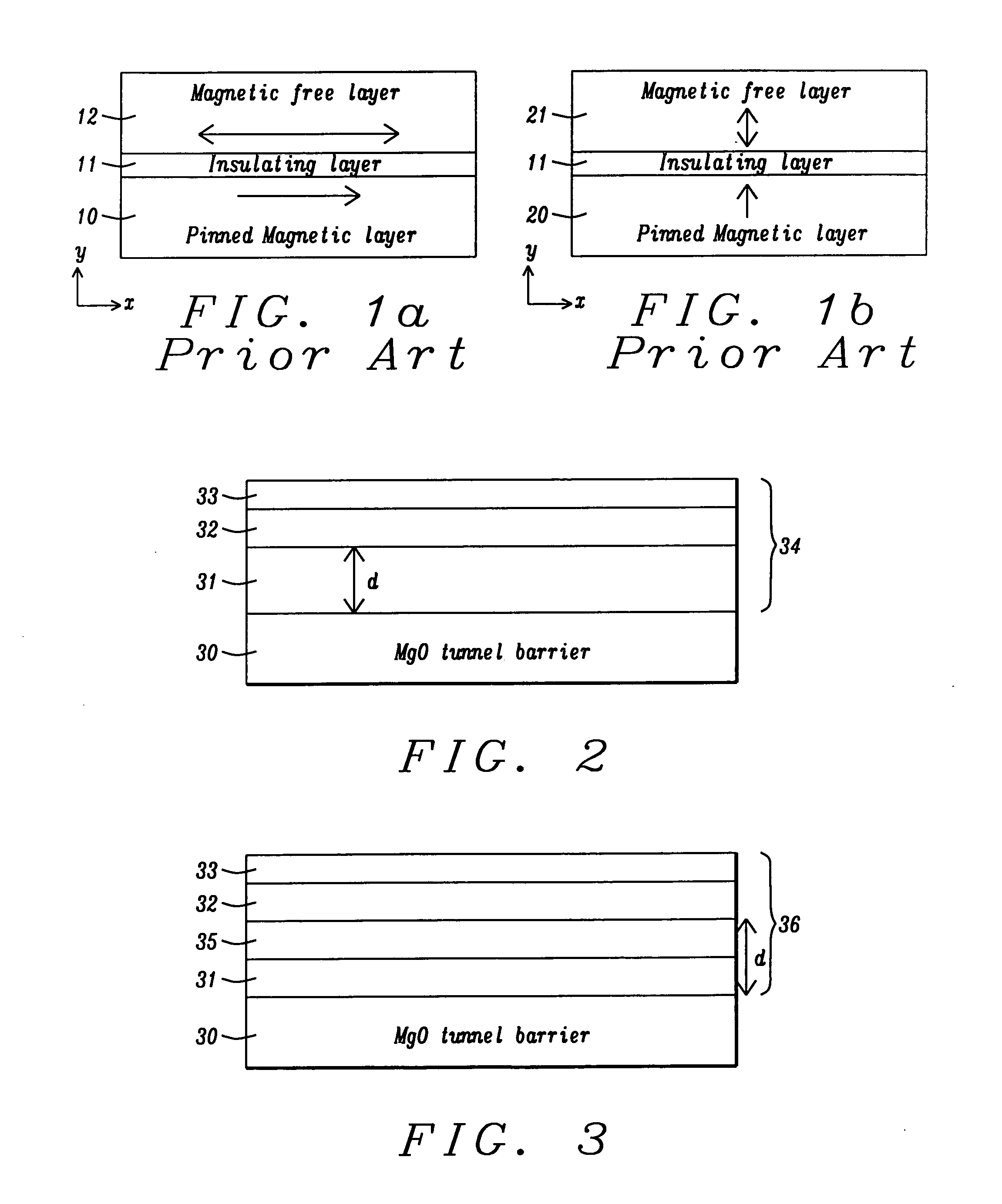

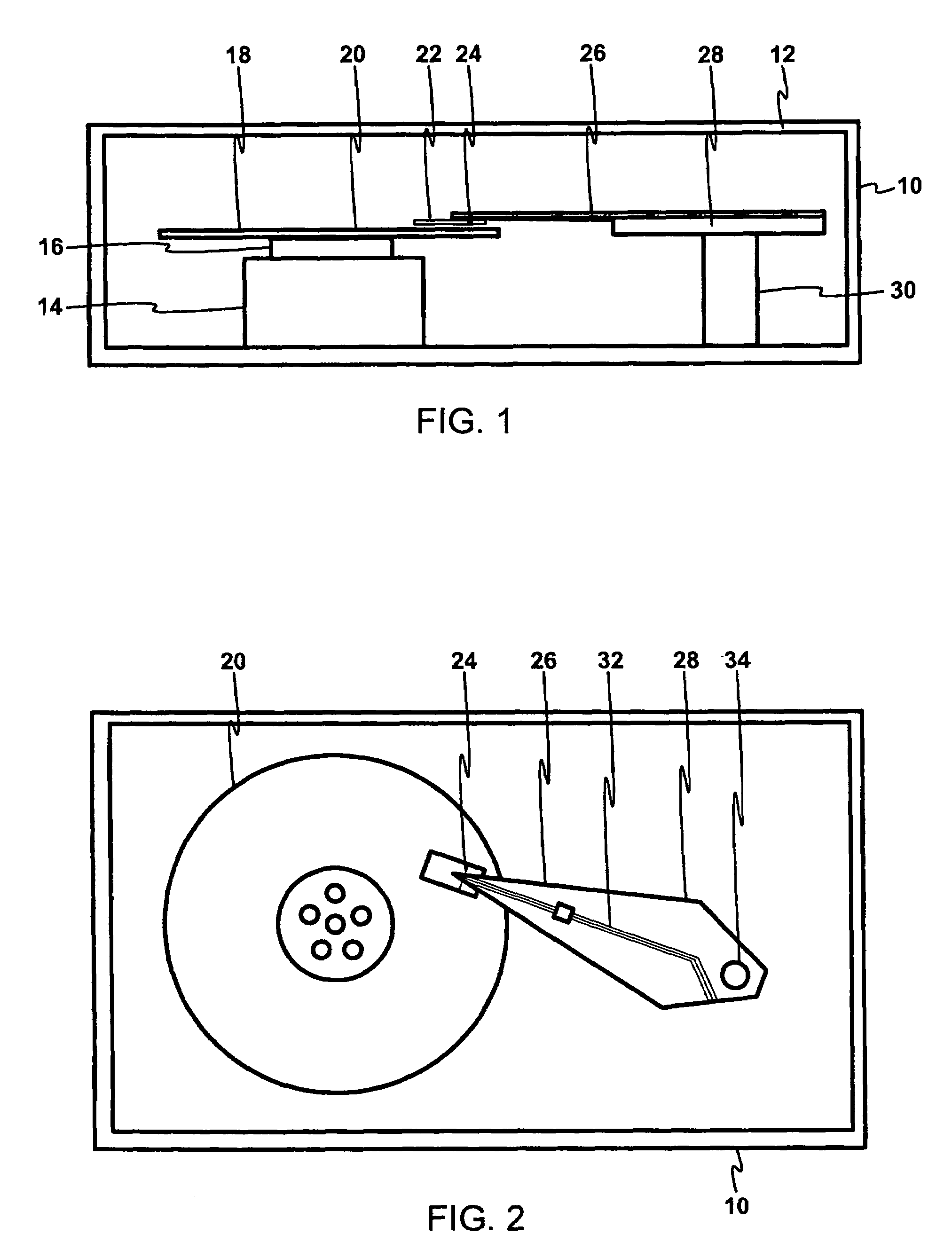

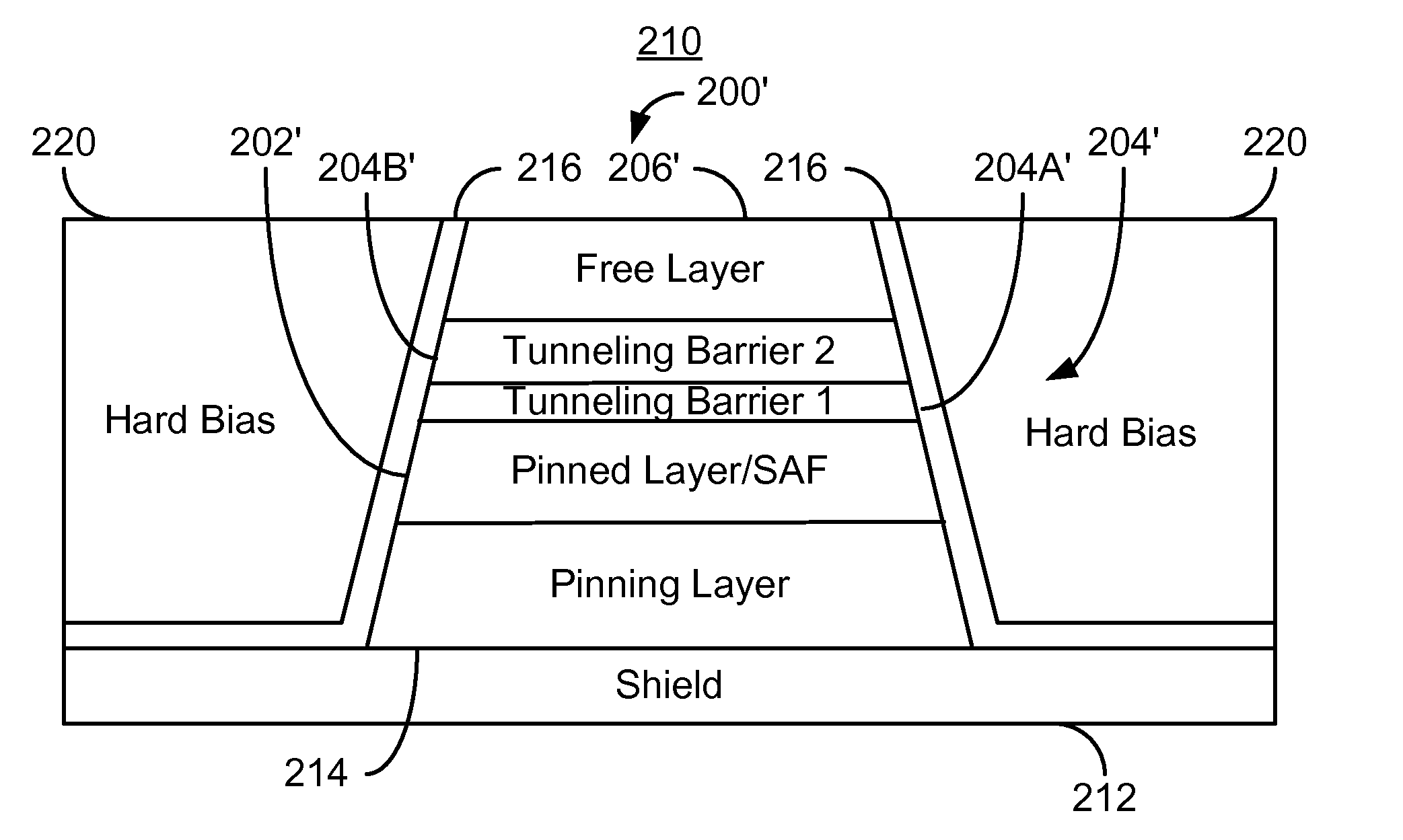

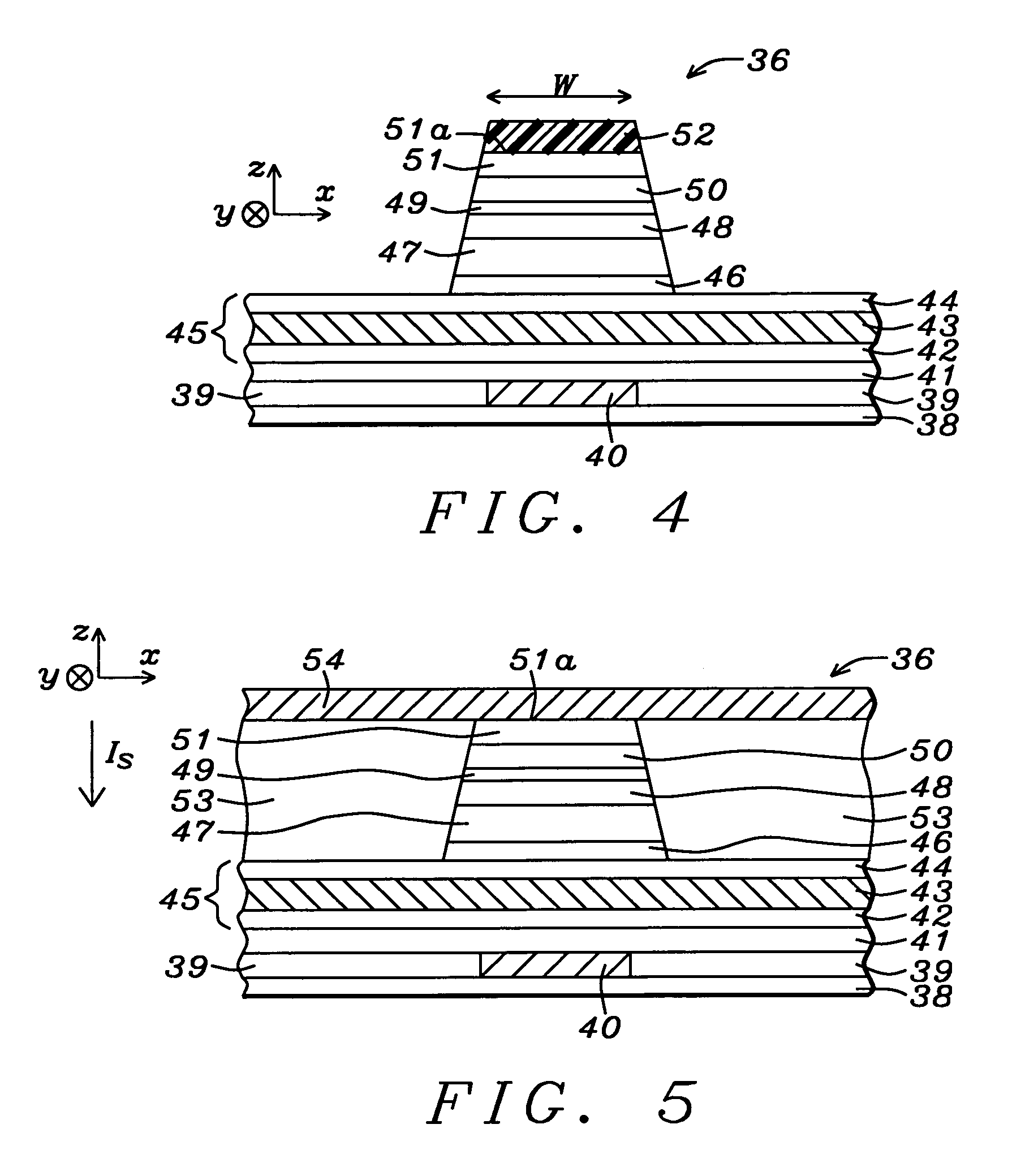

Structure to achieve sensitivity and linear density in tunneling GMR heads using orthogonal magnetic alignments

ActiveUS7035062B1Increase linear densityHigh sensitivityNanomagnetismNanoinformaticsMagnetic reluctanceMagnetization

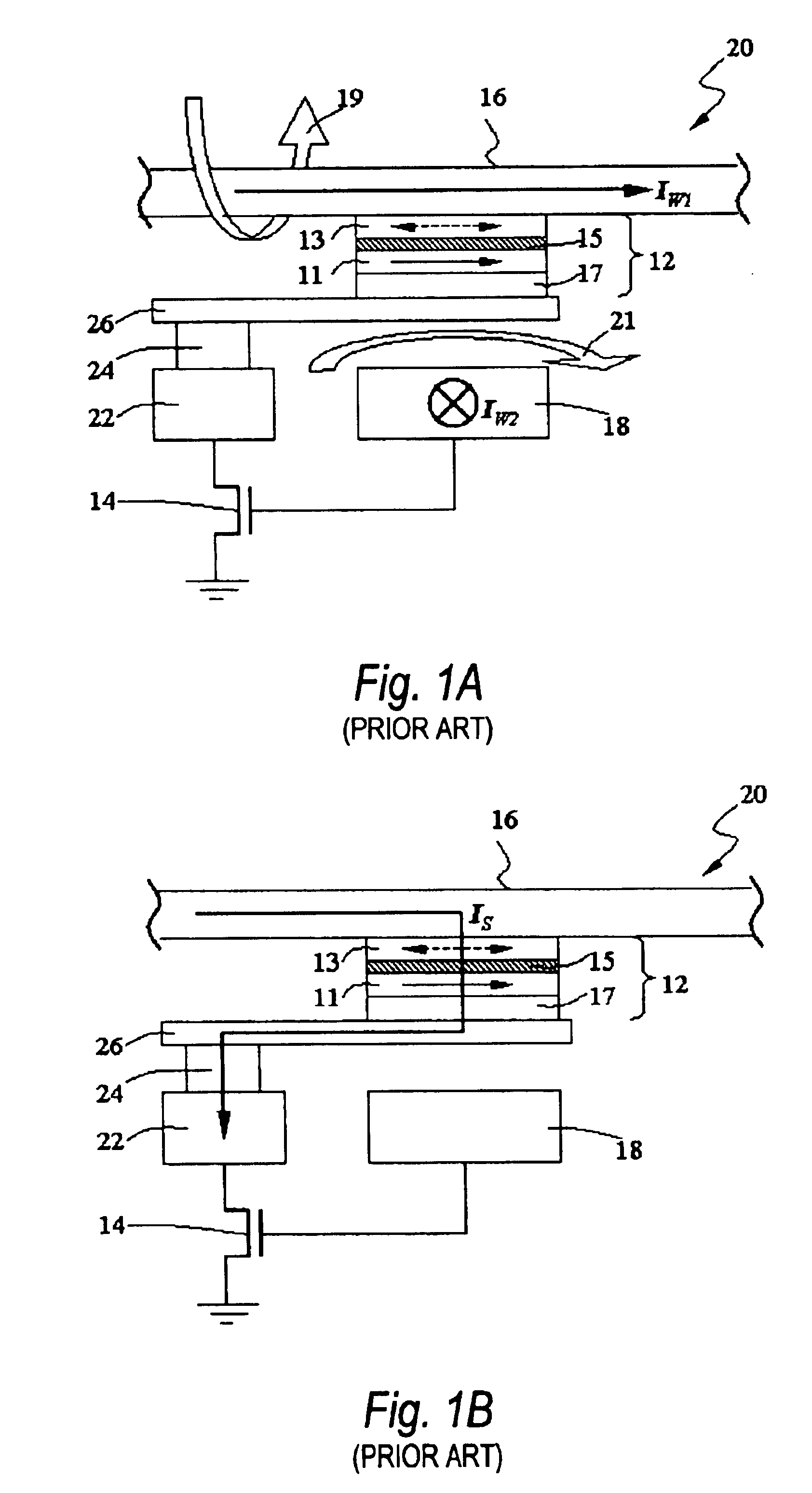

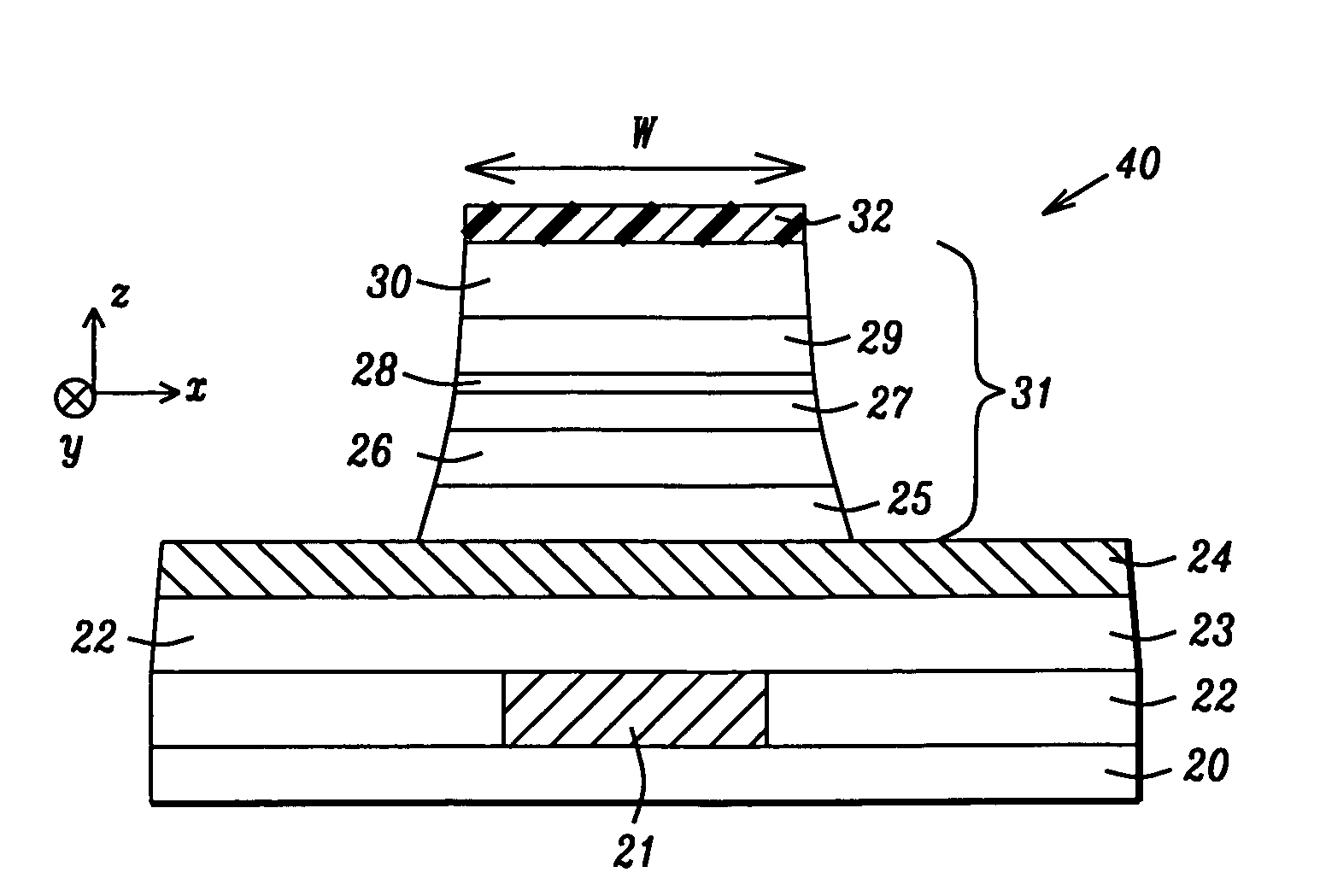

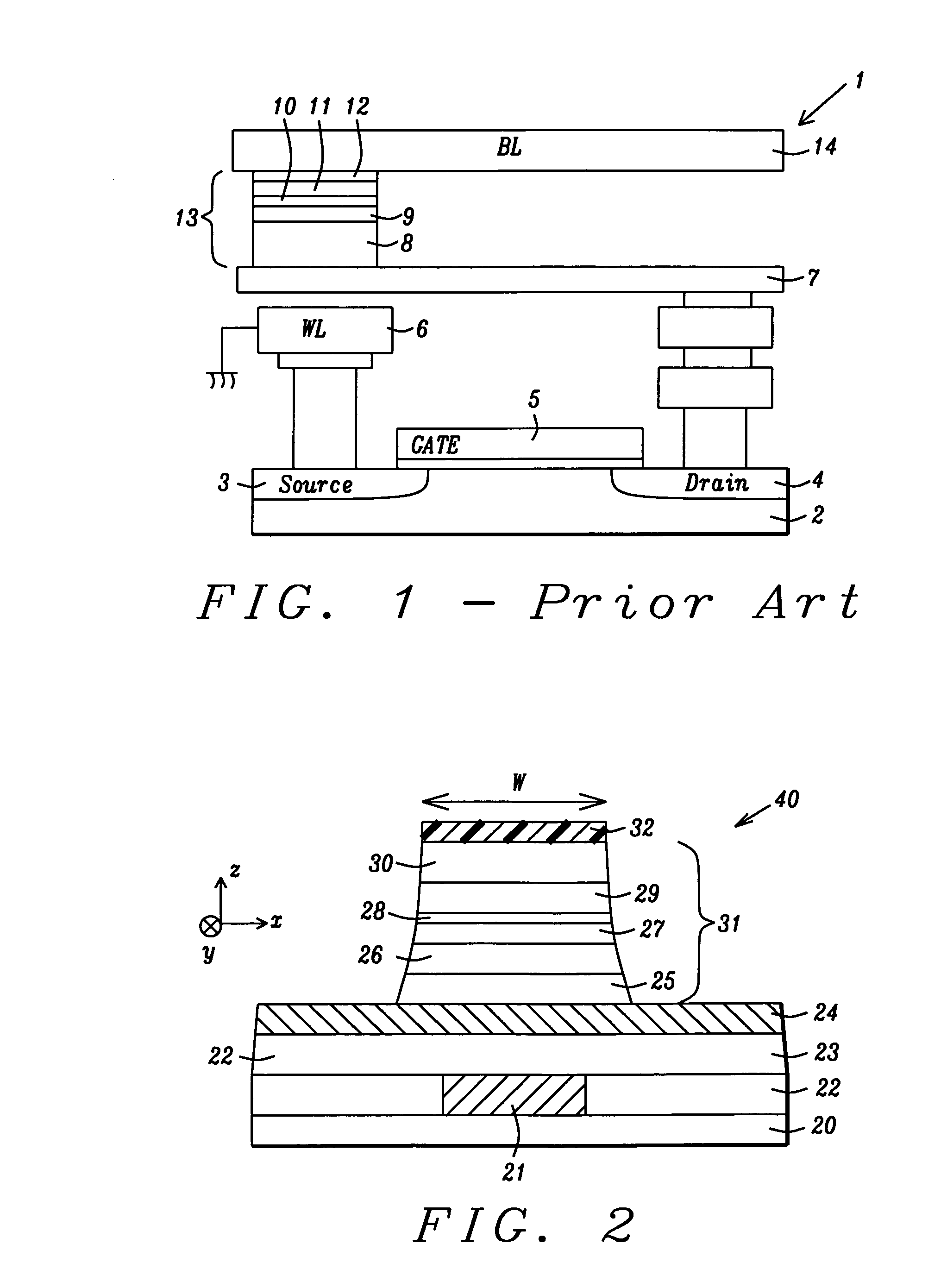

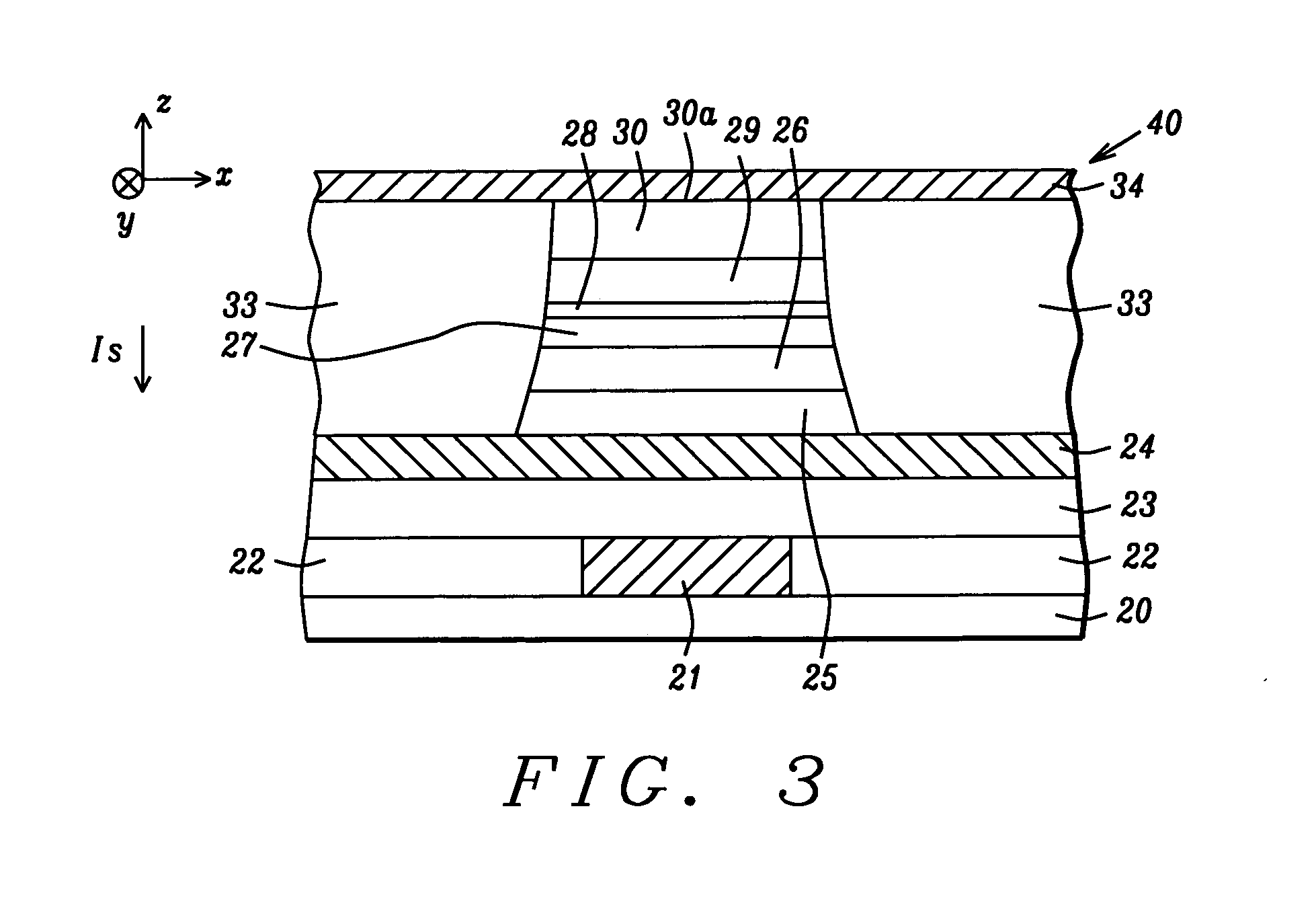

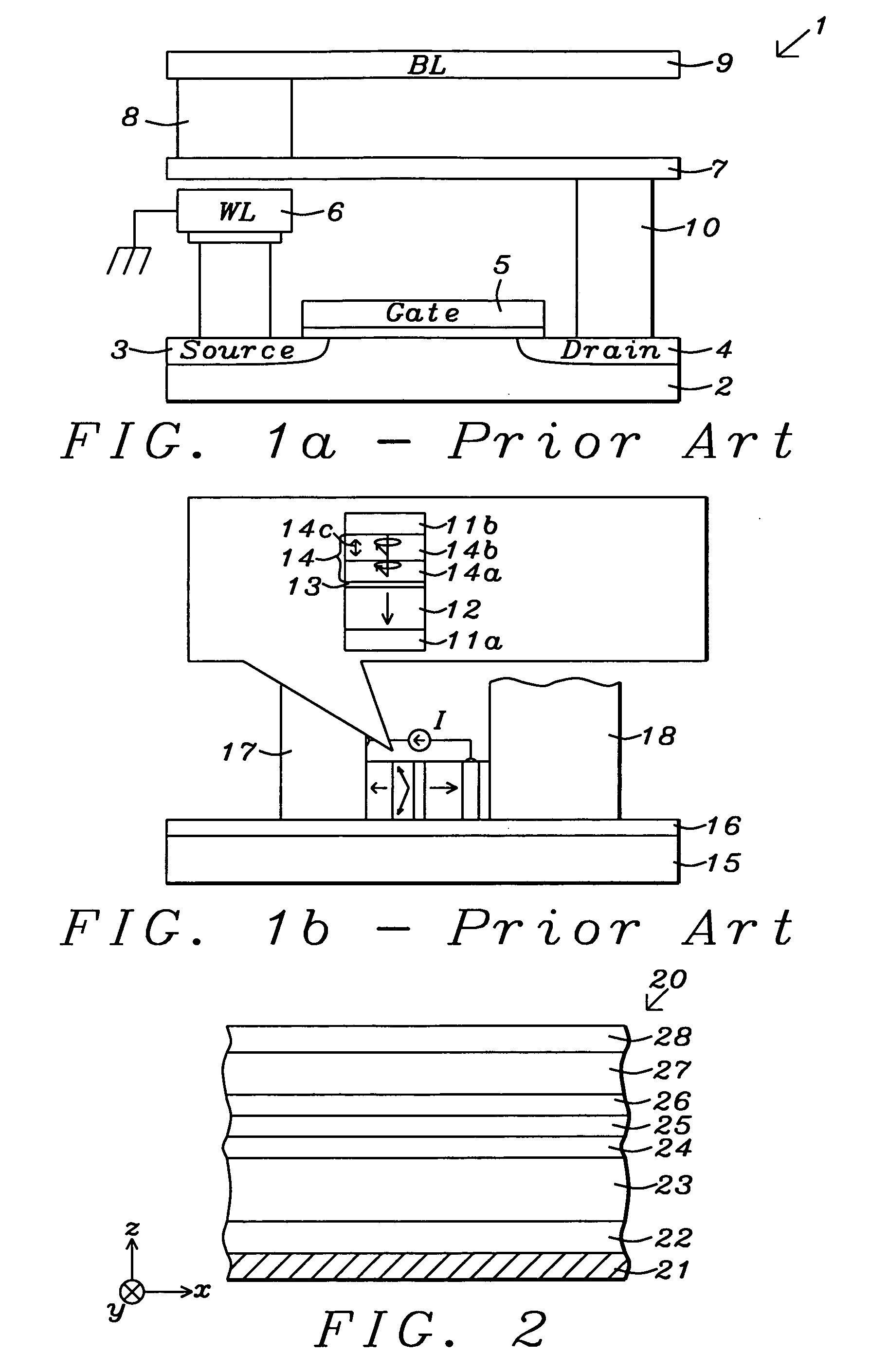

The present invention provides a tunneling magneto-resistive read sensor structure that improves sensitivity and linear density of the sensor structure. The sensor includes first and second electrodes and a stack positioned between the electrodes. The stack includes first and second free layers with magnetization orientations that are biased relative to each other. A tunneling barrier (insulating layer) or non-magnetic metal spacer is positioned between the first and second free layers. A sense current is passed between the first and second free layers of the stack. The amount of current passing through the first and second free layer changes based upon the orientation of the first and second free layers relative to each other.

Owner:SEAGATE TECH LLC

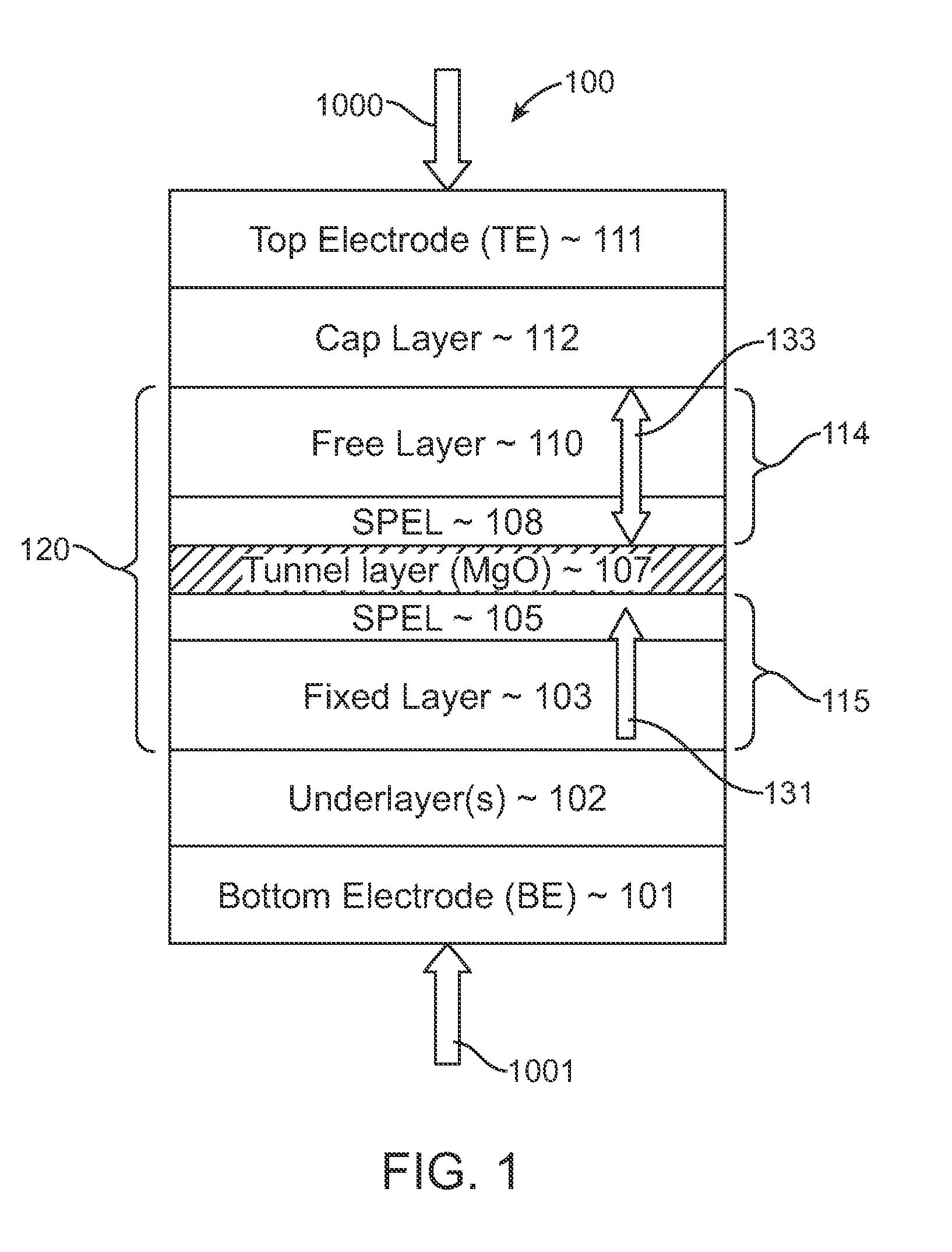

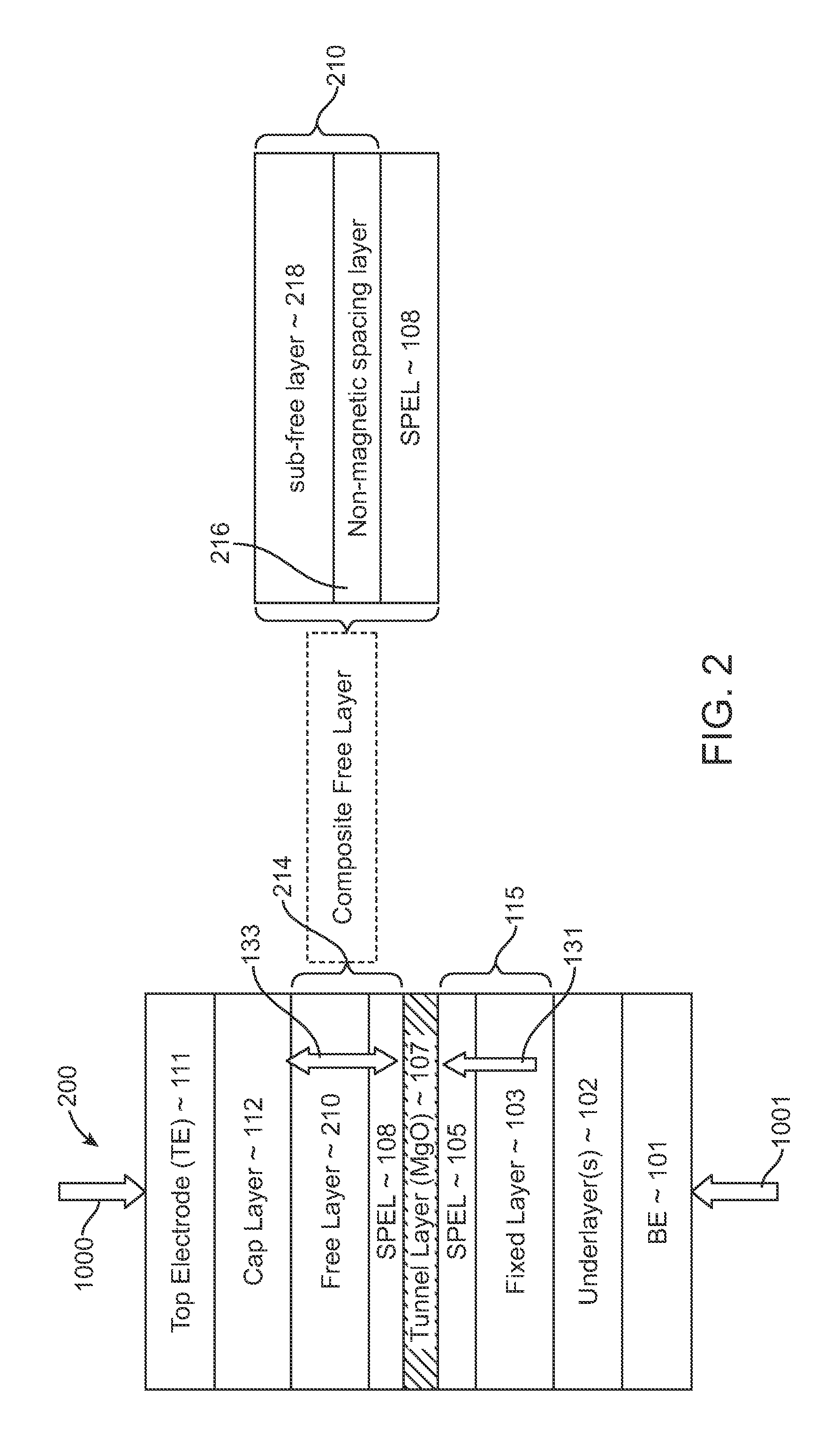

Spin-transfer torque magnetic random access memory having magnetic tunnel junction with perpendicular magnetic anisotropy

A spin-torque transfer memory random access memory (STTMRAM) element includes a fixed layer formed on top of a substrate and a a tunnel layer formed upon the fixed layer and a composite free layer formed upon the tunnel barrier layer and made of an iron platinum alloy with at least one of X or Y material, X being from a group consisting of: boron (B), phosphorous (P), carbon (C), and nitride (N) and Y being from a group consisting of: tantalum (Ta), titanium (Ti), niobium (Nb), zirconium (Zr), tungsten (W), silicon (Si), copper (Cu), silver (Ag), aluminum (Al), chromium (Cr), tin (Sn), lead (Pb), antimony (Sb), hafnium (Hf) and bismuth (Bi), molybdenum (Mo) or rhodium (Ru), the magnetization direction of each of the composite free layer and fixed layer being substantially perpendicular to the plane of the substrate.

Owner:AVALANCHE TECH

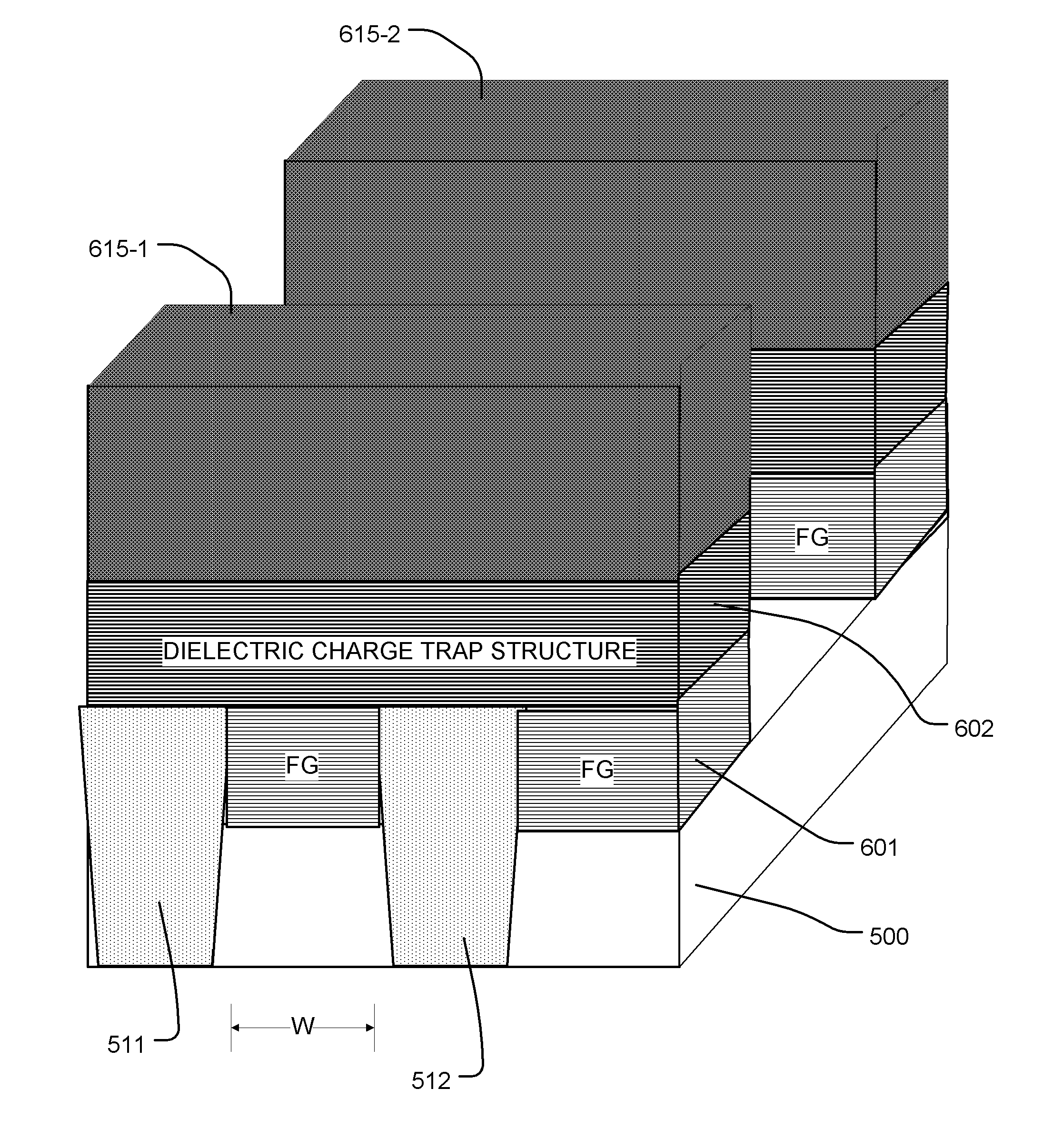

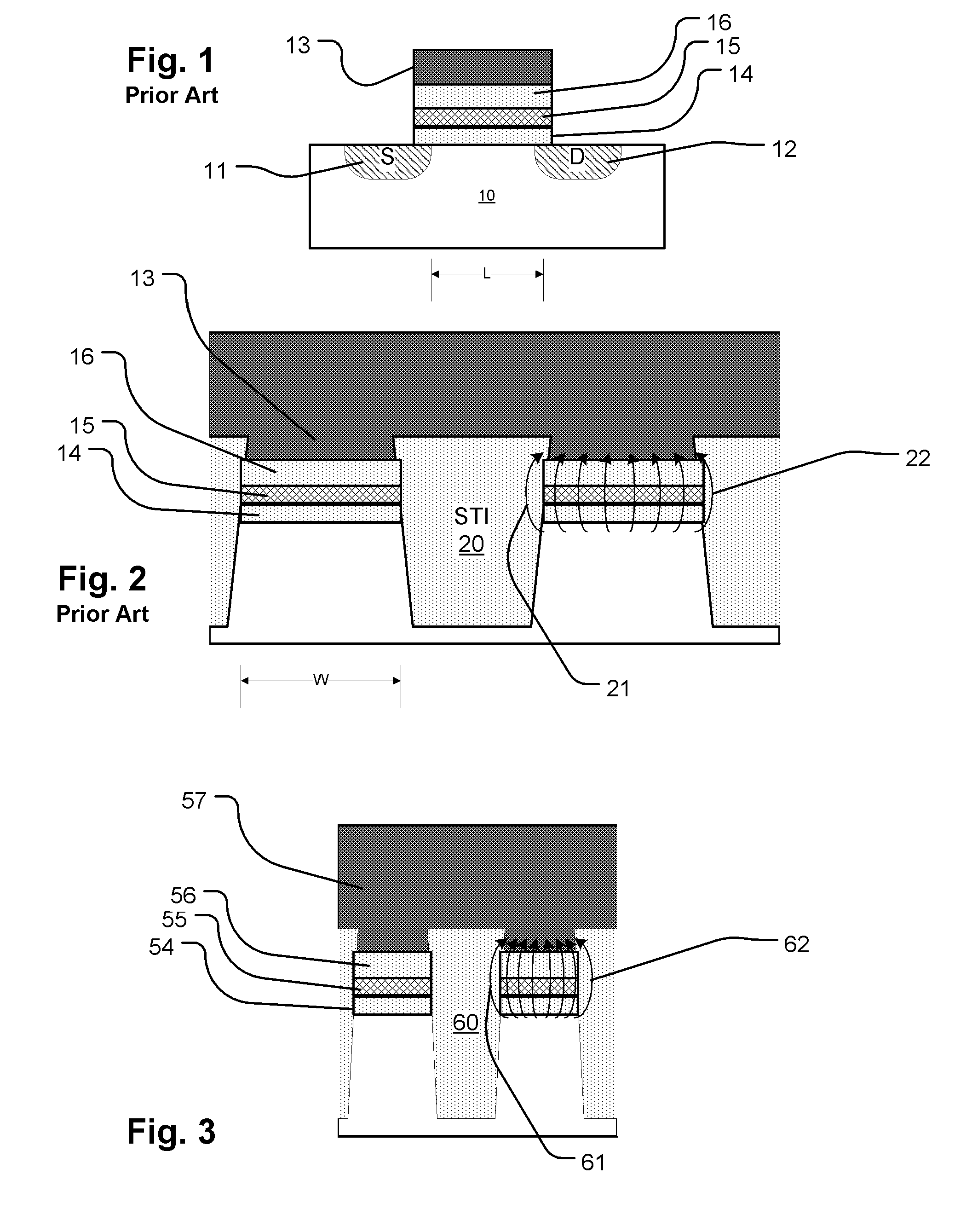

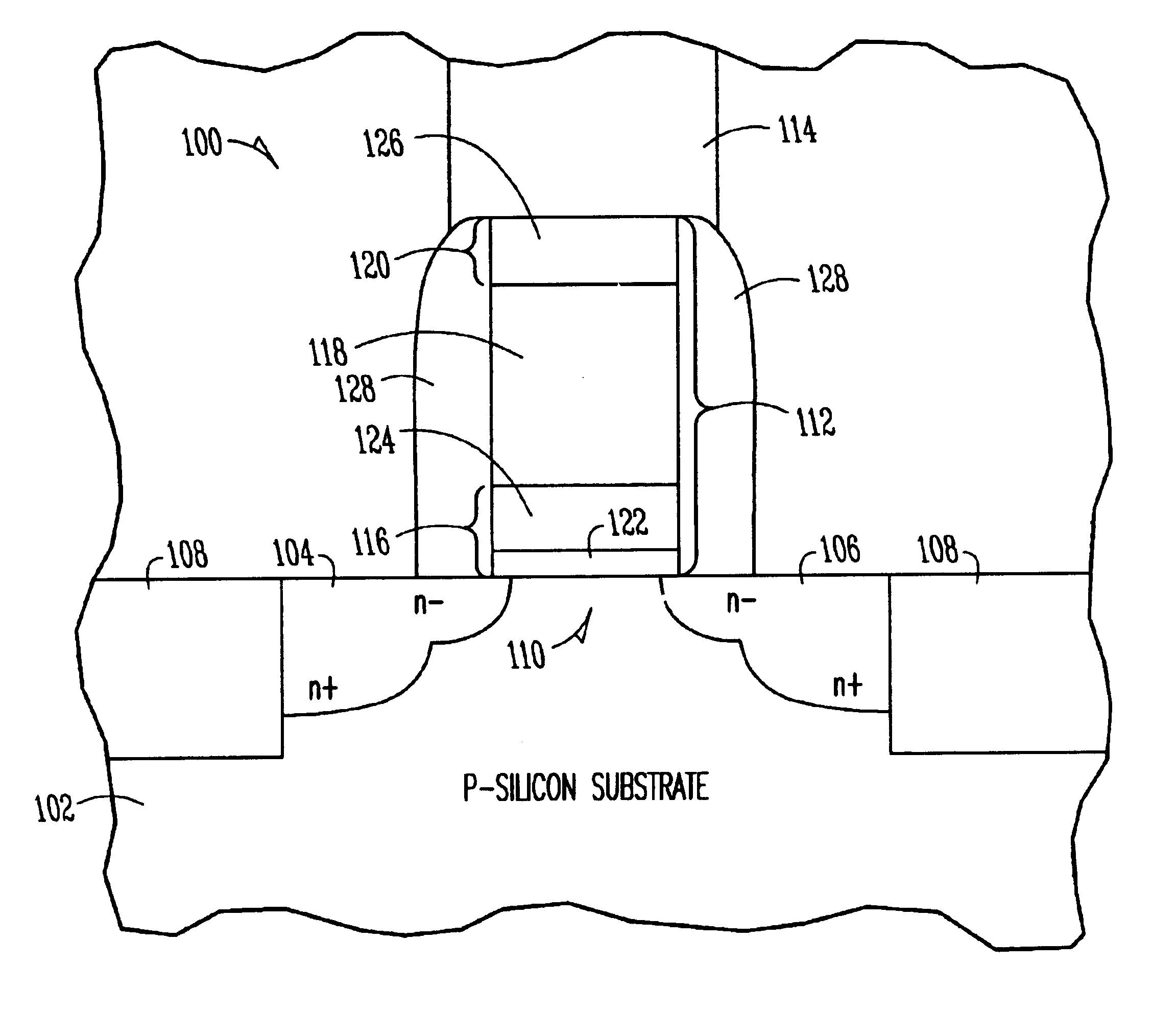

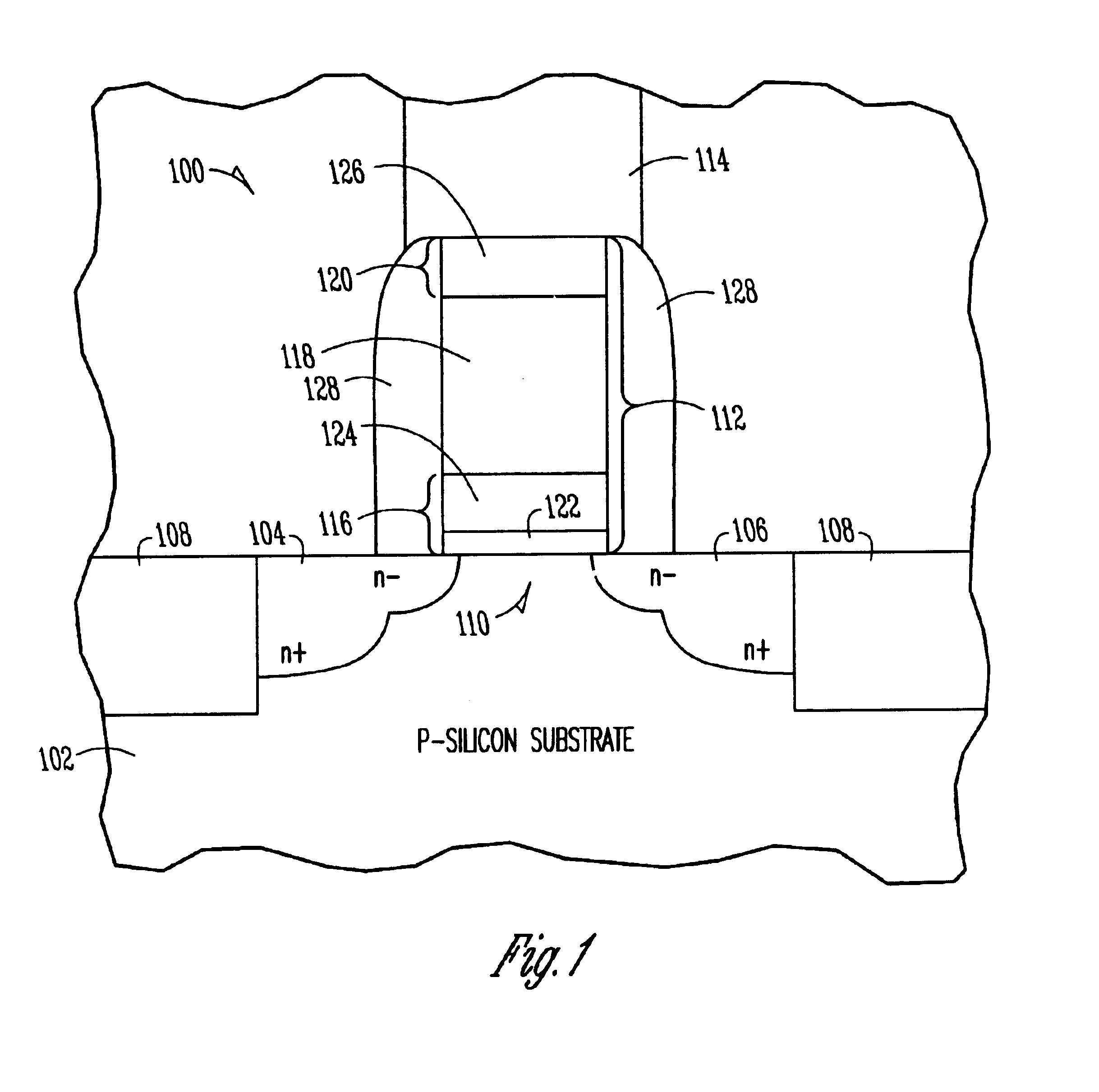

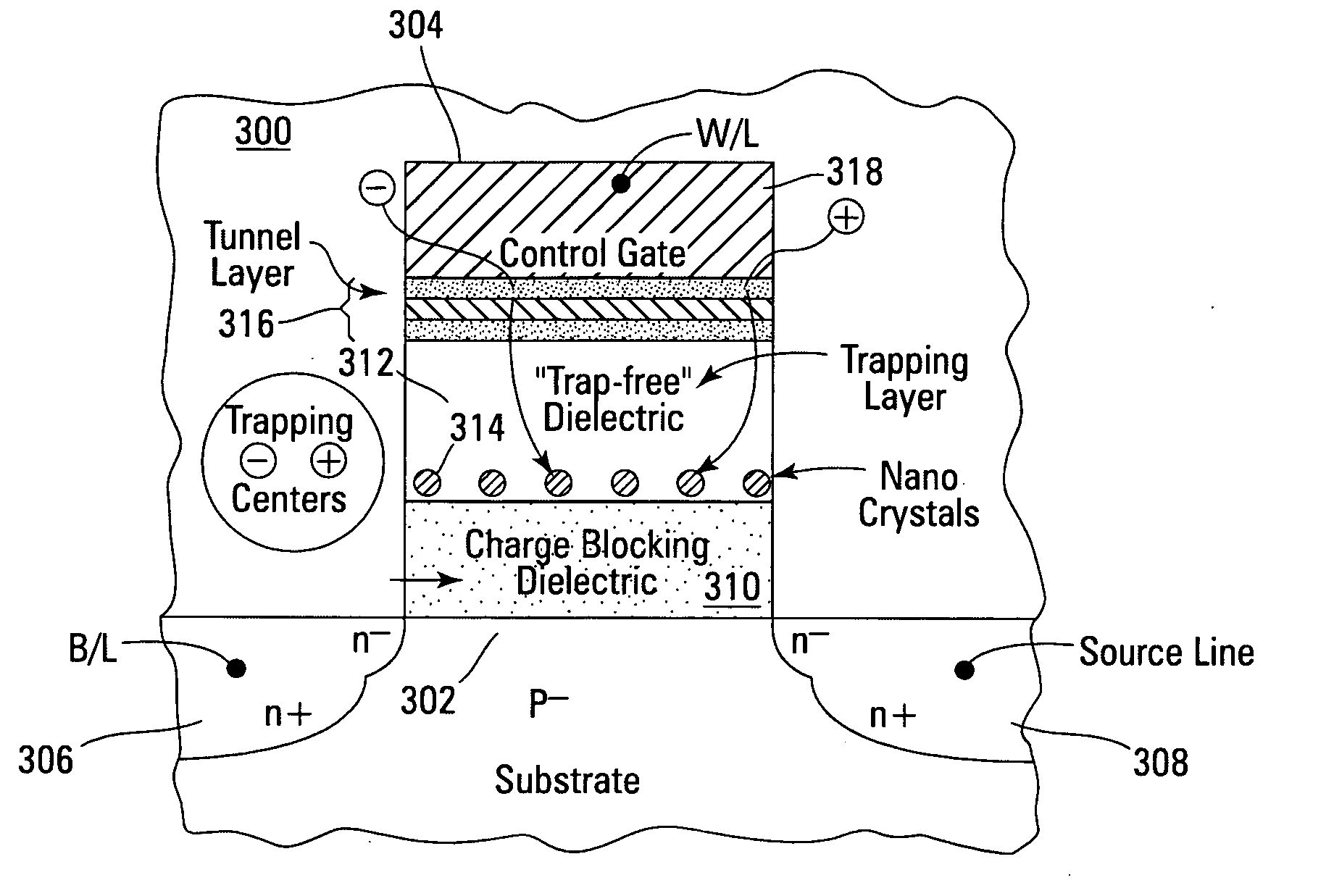

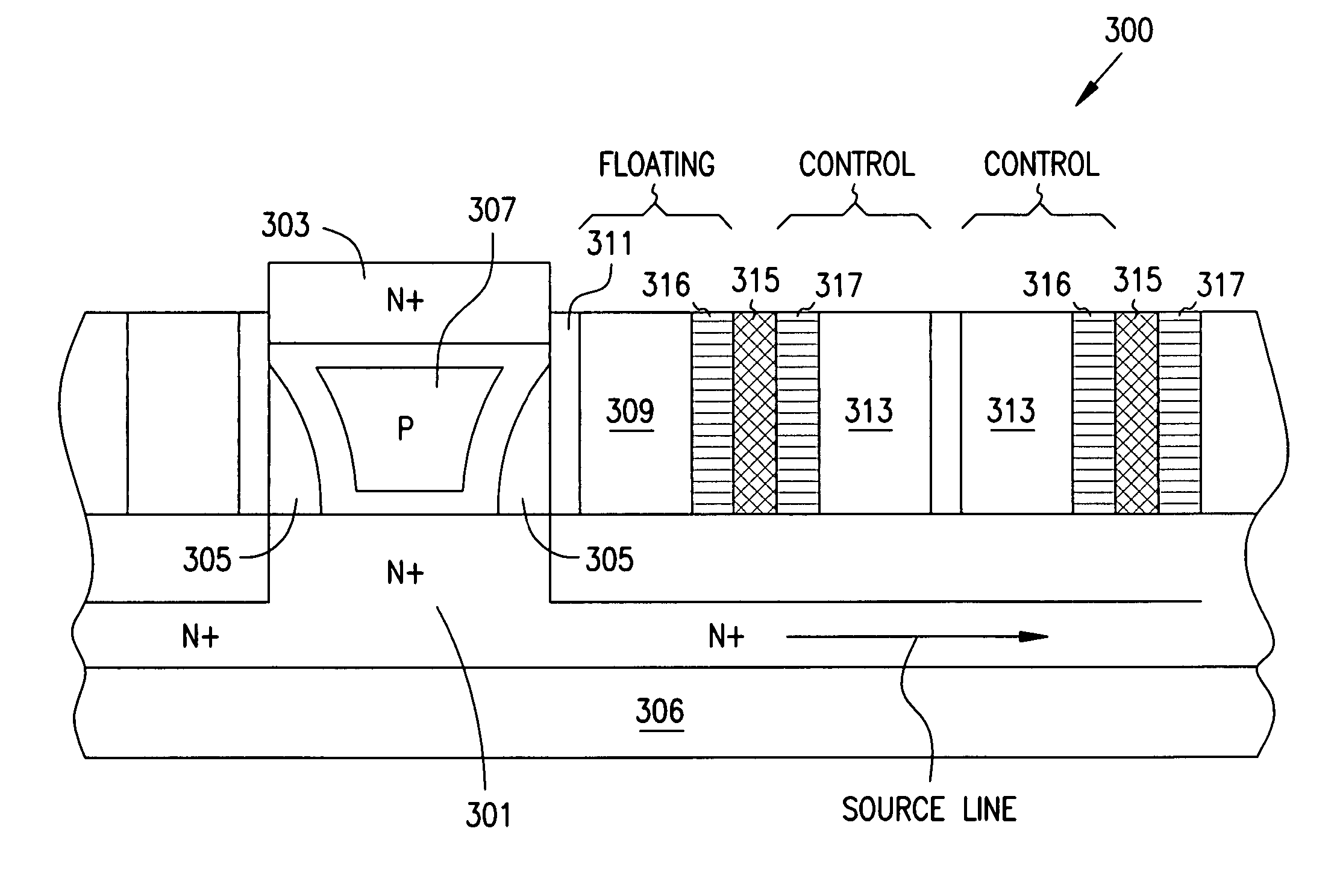

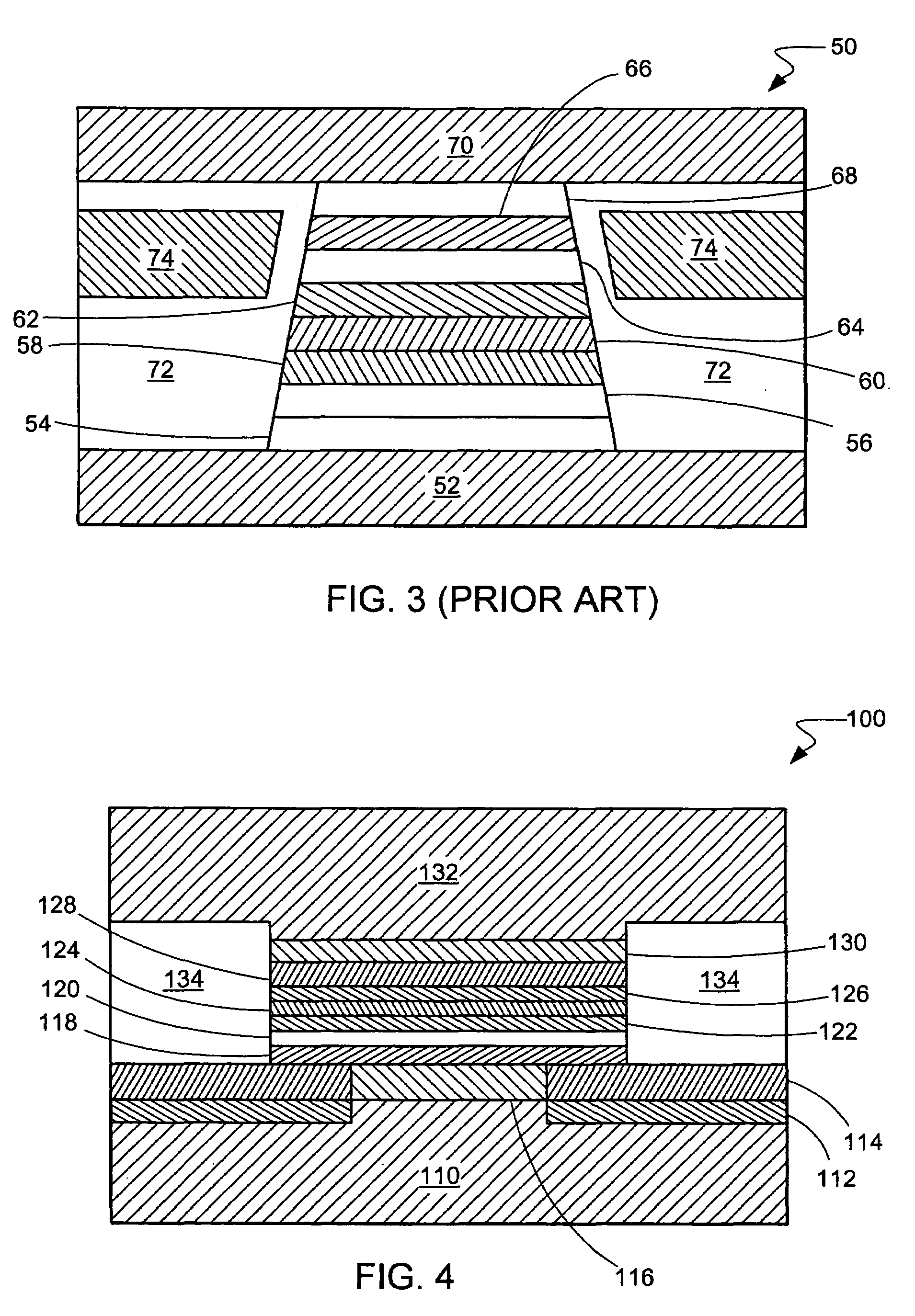

Floating gate memory device with interpoly charge trapping structure

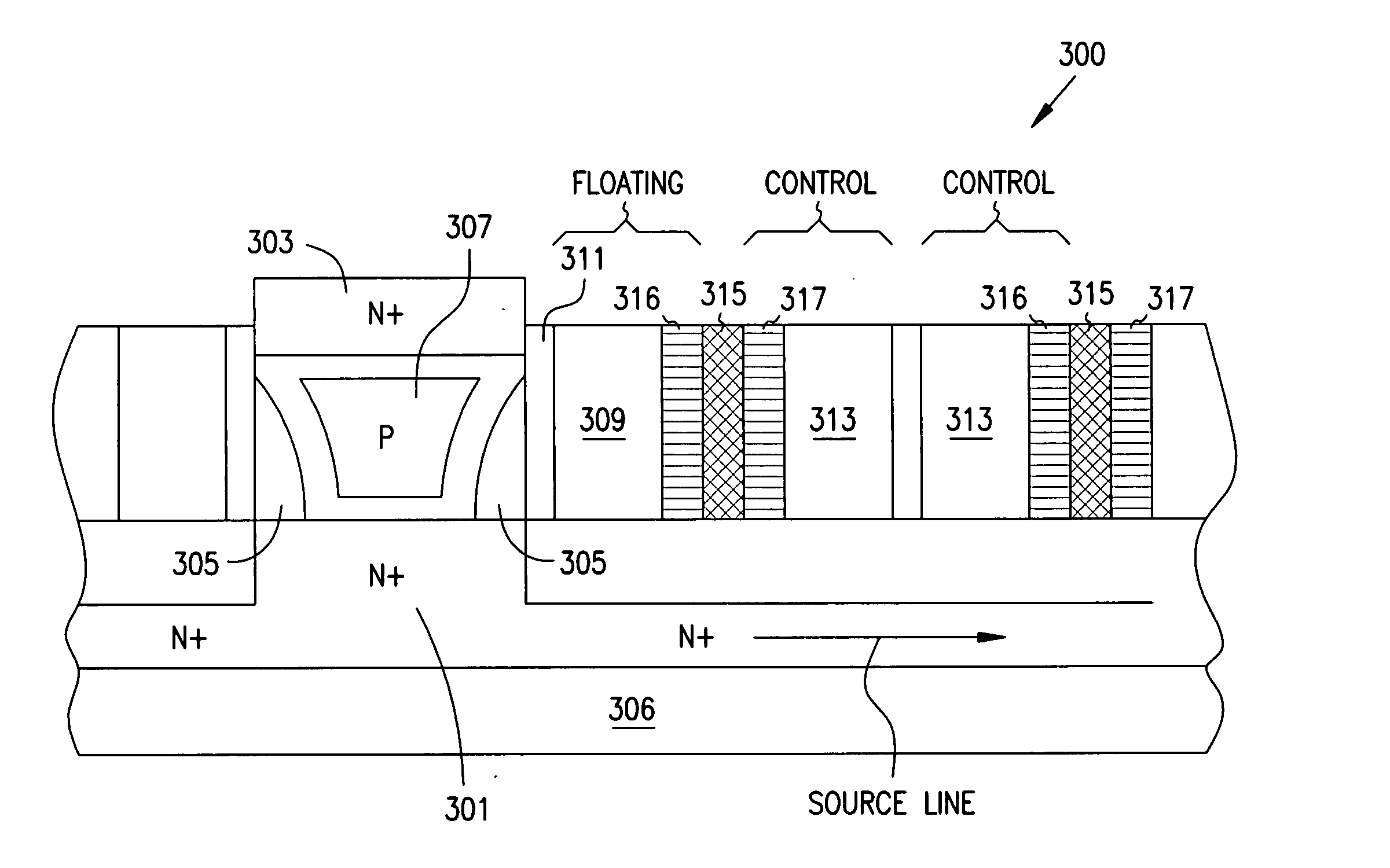

ActiveUS20090262583A1Constant threshold voltageReduce distractionsTransistorSolid-state devicesElectrical conductorTrapping

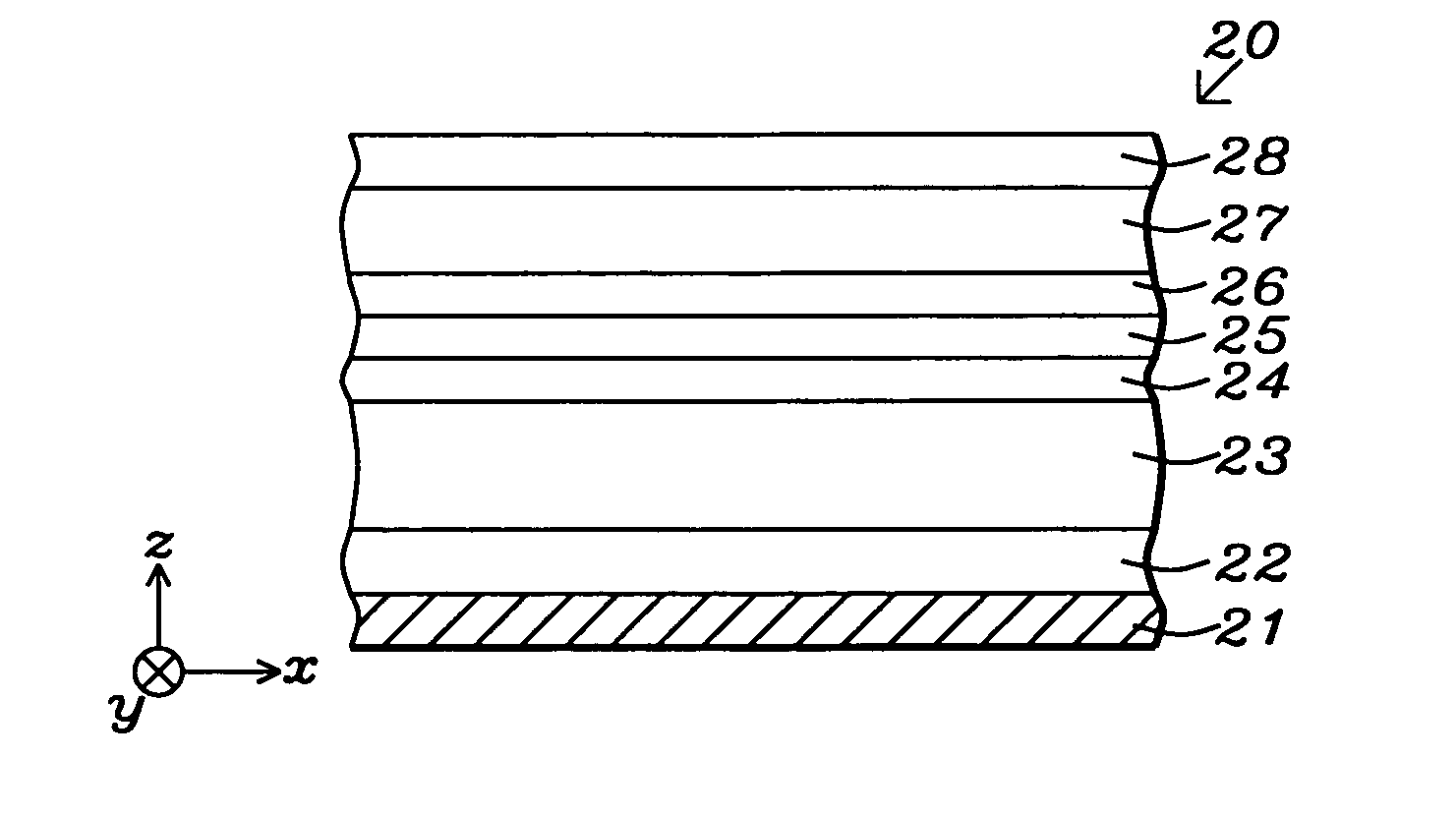

A charge trapping floating gate is described with asymmetric tunneling barriers. The memory cell includes a source region and a drain region separated by a channel region. A first tunneling barrier structure is disposed above the channel region. A floating gate is disposed above the first tunneling barrier structure covering the channel region. A second tunneling barrier is disposed above the floating gate. A dielectric charge trapping structure disposed above the second tunneling barrier and a blocking dielectric structure is disposed above the charge trapping structure. A top conductive layer disposed above the top dielectric structure acts as a gate. The second tunneling barrier is a more efficient conductor of tunneling current, under bias conditions applied for programming and erasing the memory cell, than the first tunneling barrier structure.

Owner:MACRONIX INT CO LTD

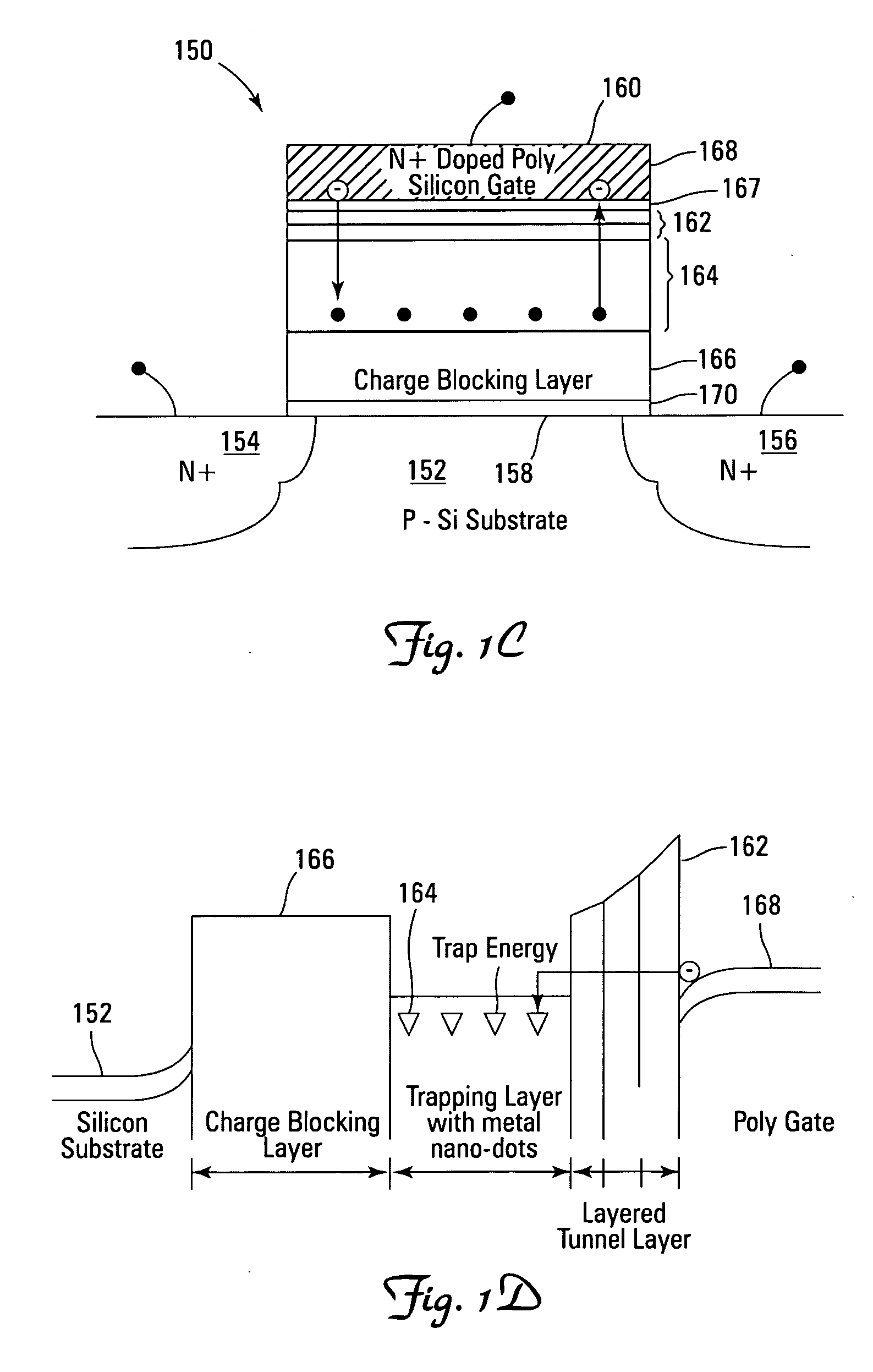

High density NAND non-volatile memory device

ActiveUS20070012988A1Efficient eraseReduce harmSolid-state devicesRead-only memoriesCharge retentionLow voltage

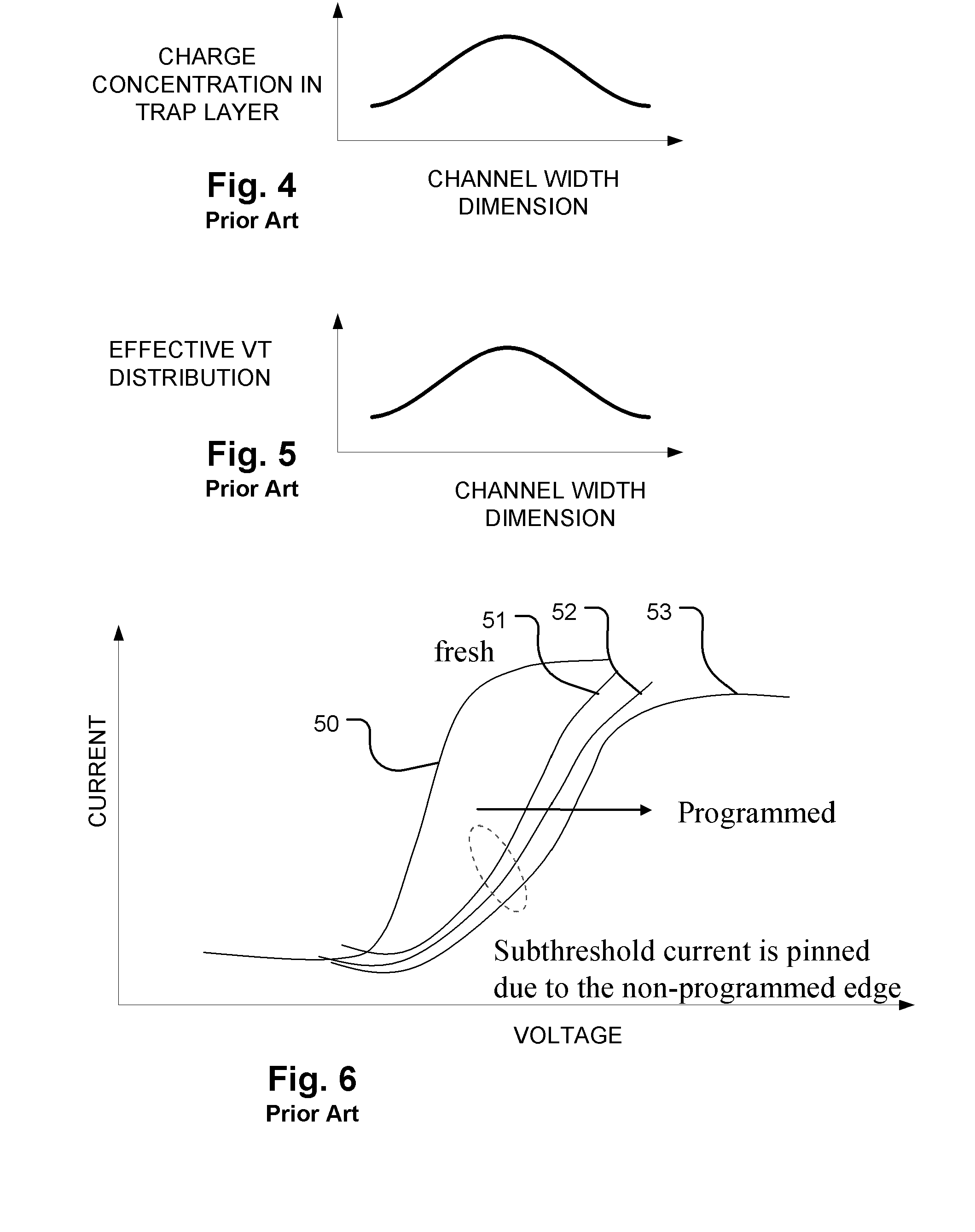

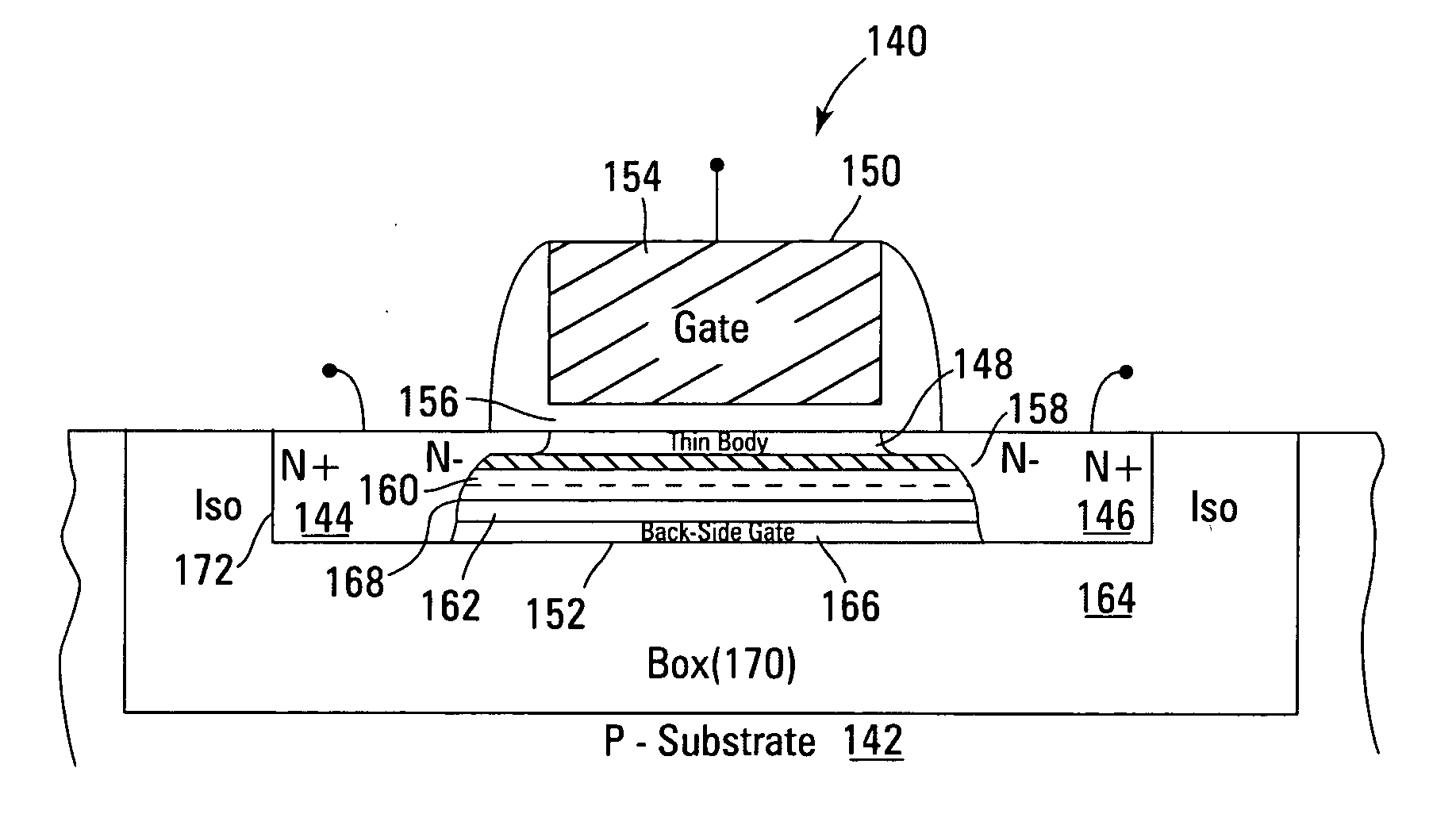

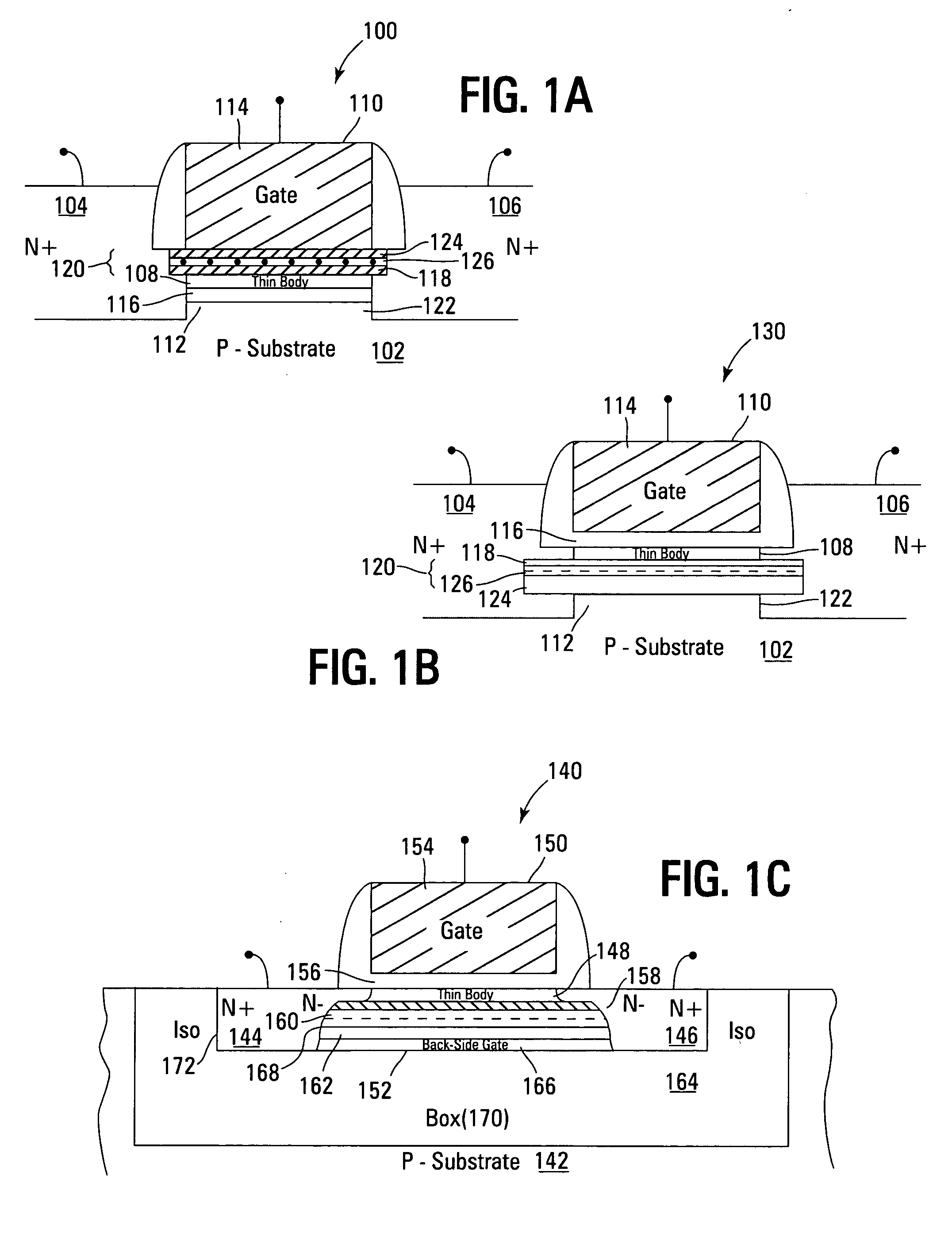

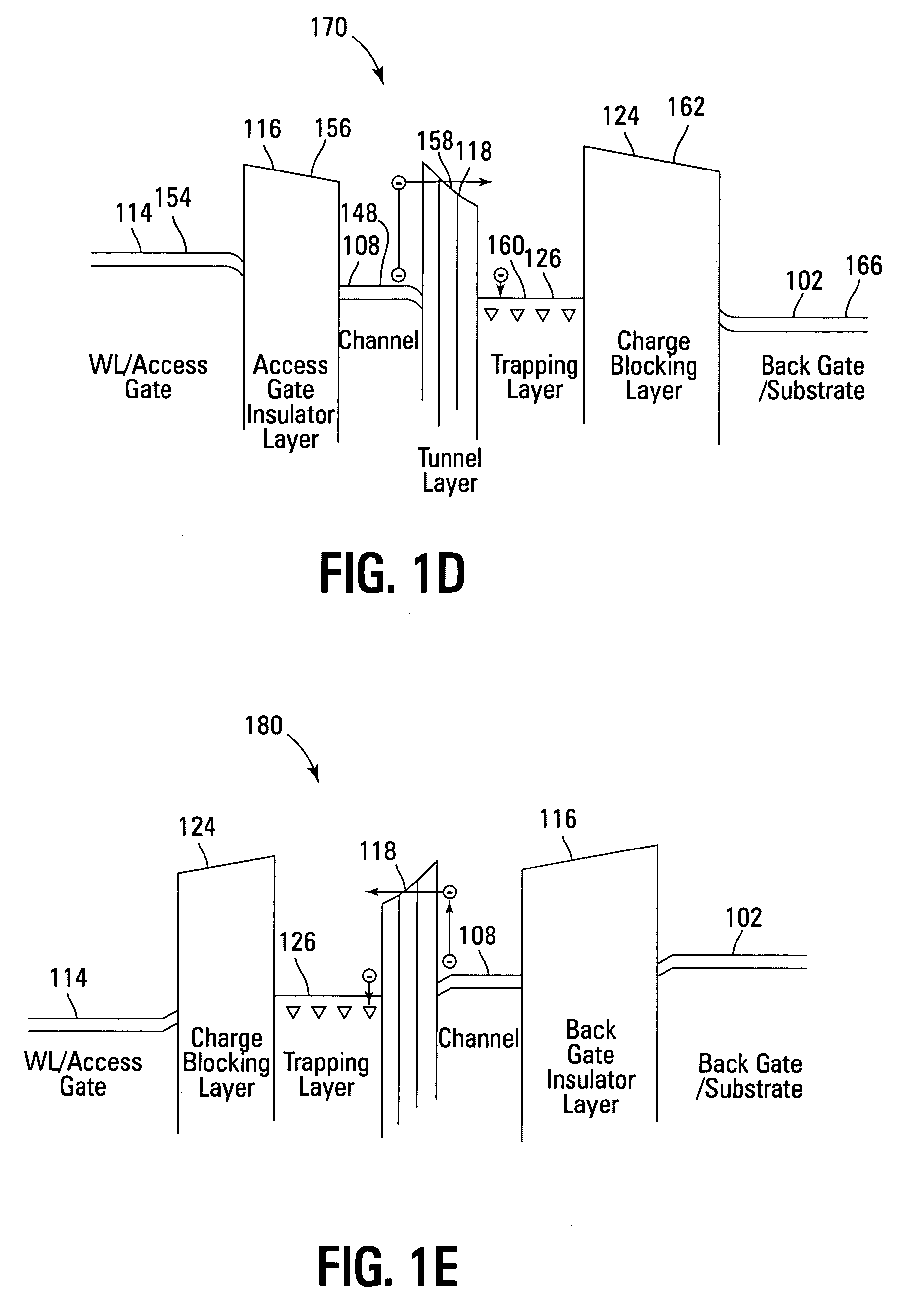

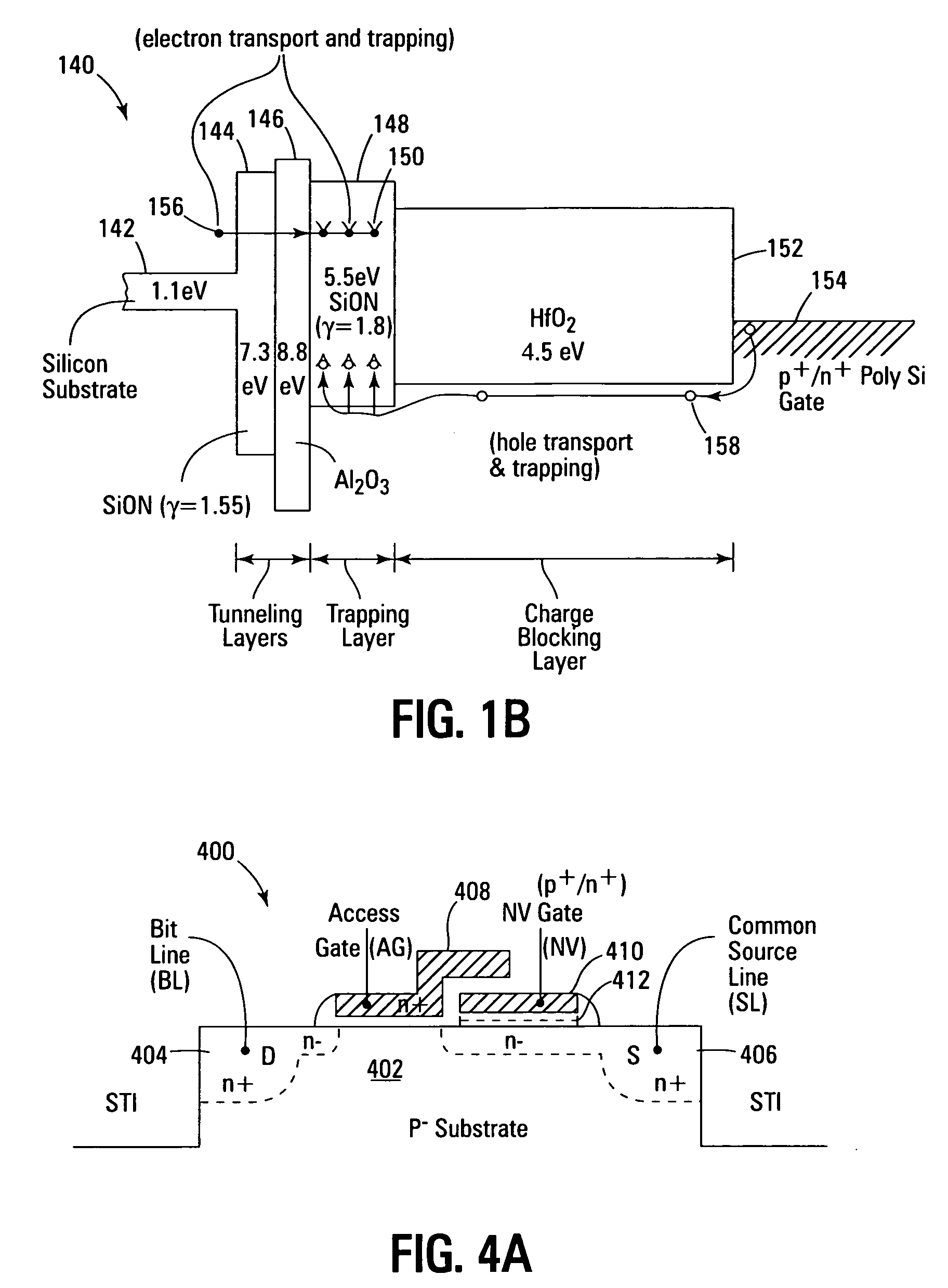

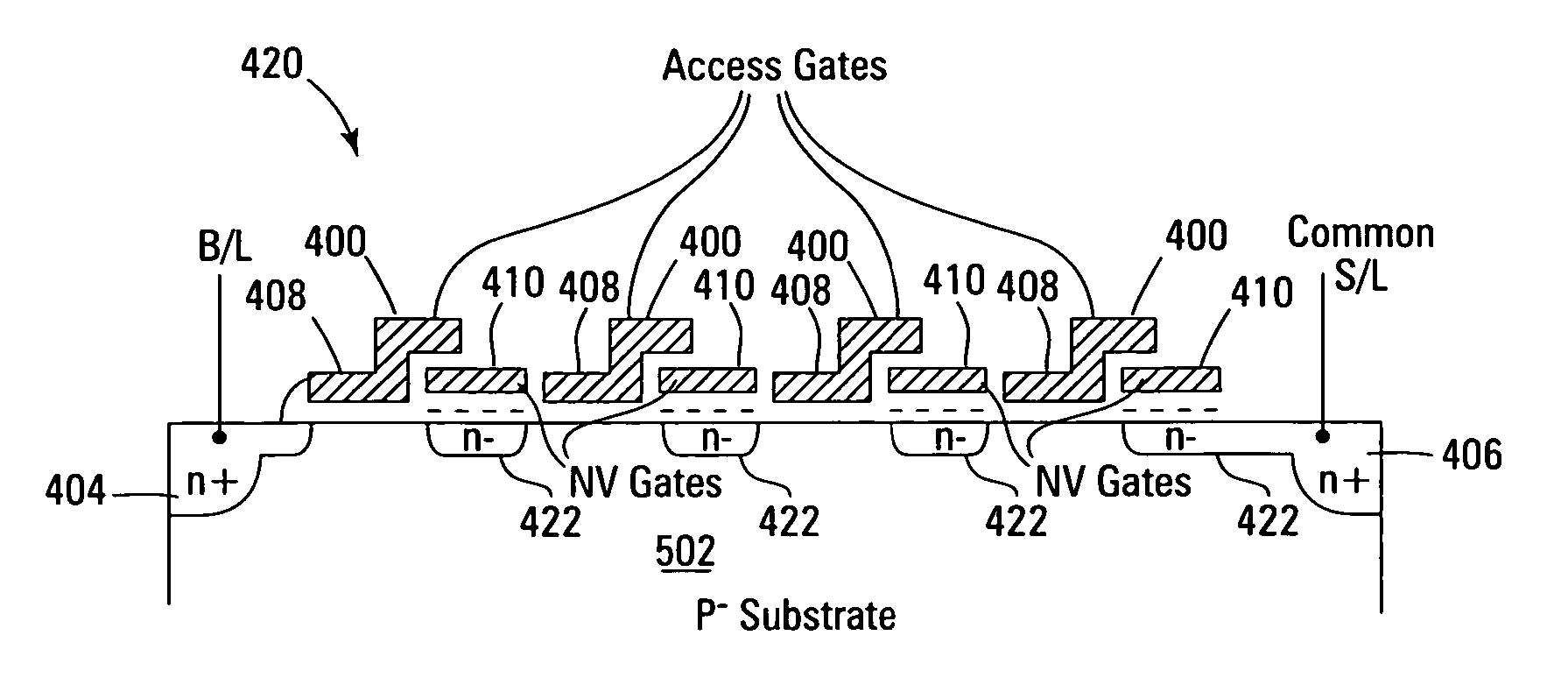

Non-volatile memory devices and arrays are described that utilize dual gate (or back-side gate) non-volatile memory cells with band engineered gate-stacks that are placed above or below the channel region in front-side or back-side charge trapping gate-stack configurations in NAND memory array architectures. The band-gap engineered gate-stacks with asymmetric or direct tunnel barriers of the floating node memory cells of embodiments of the present invention allow for low voltage tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The memory cell architecture also allows for improved high density memory devices or arrays with the utilization of reduced feature word lines and vertical select gates.

Owner:MICRON TECH INC

Magnetic tunnel junction memory device

InactiveUS6845038B1Improve permeabilityLow resistivityDigital storageBit linePerpendicular magnetization

A memory cell for magnetic random access memory devices based on a magnetic tunnel junction (MTJ) memory element with a perpendicular orientation of magnetization in pinned and free magnetic layers, and a tunnel barrier layer sandwiched between the pinned and free layers. The memory cell can include the MTJ memory element, a magnetic flux guide in series with selection devices, such as a bit line, a word line, and a transistor. The magnetic flux guide can have two electrically conductive magnetic portions with the MTJ memory element positioned between the magnetic portions. The MTJ memory element is magnetically isolated from the magnetic flux guide by thin non-magnetic conductive spacers. The MTJ memory element is arranged in a vertical space between the intersecting bit and word lines at their intersection region. The memory cell also includes write and excitation lines. The write line is parallel to the bit line and the excitation line is parallel to the word line. The write and excitation lines also intersect each other and define a corner. The MTJ memory element is positioned in the corner of the intercepting write and excitation lines.

Owner:SHUKH ALLA MIKHAILOVNA

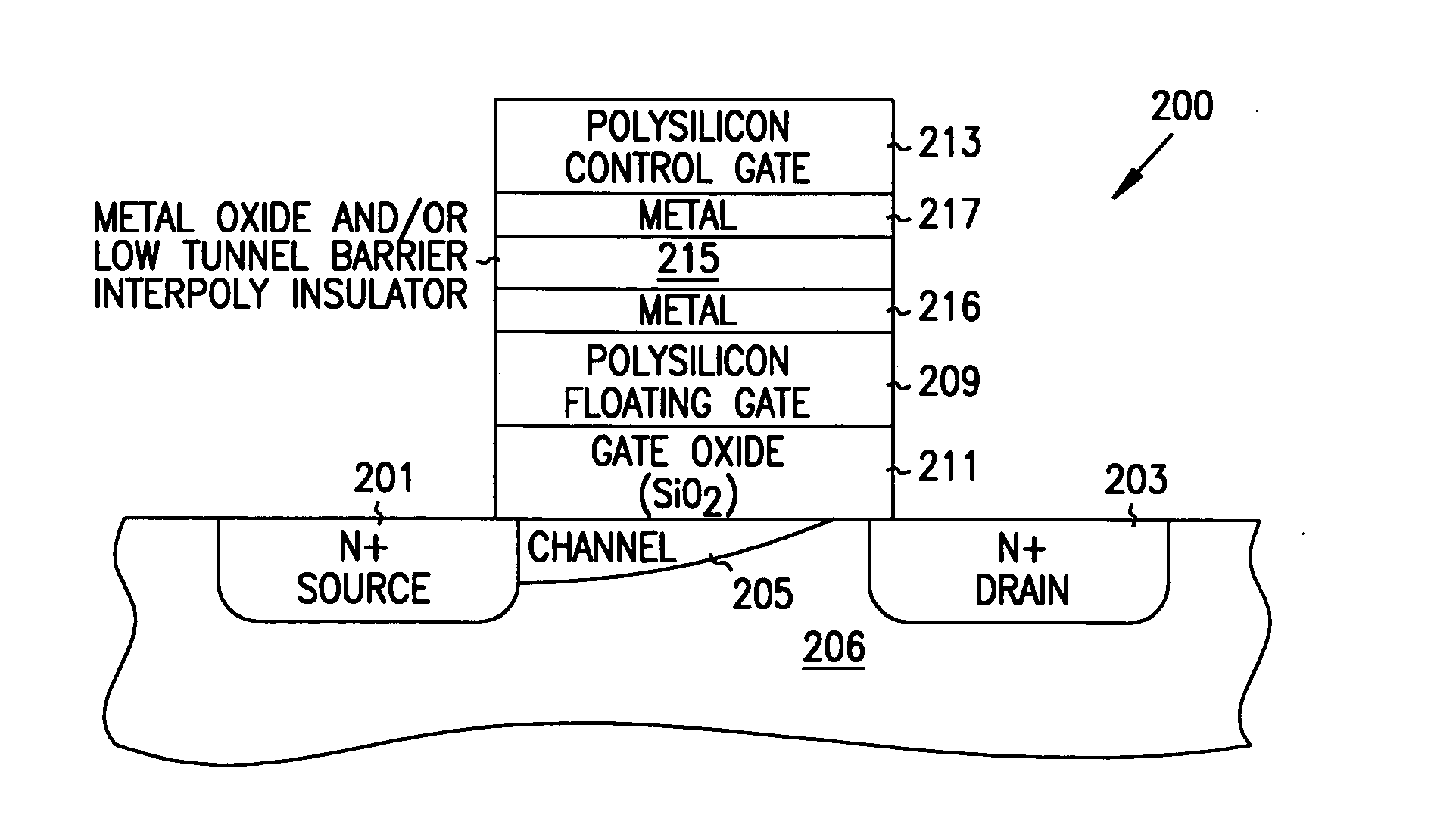

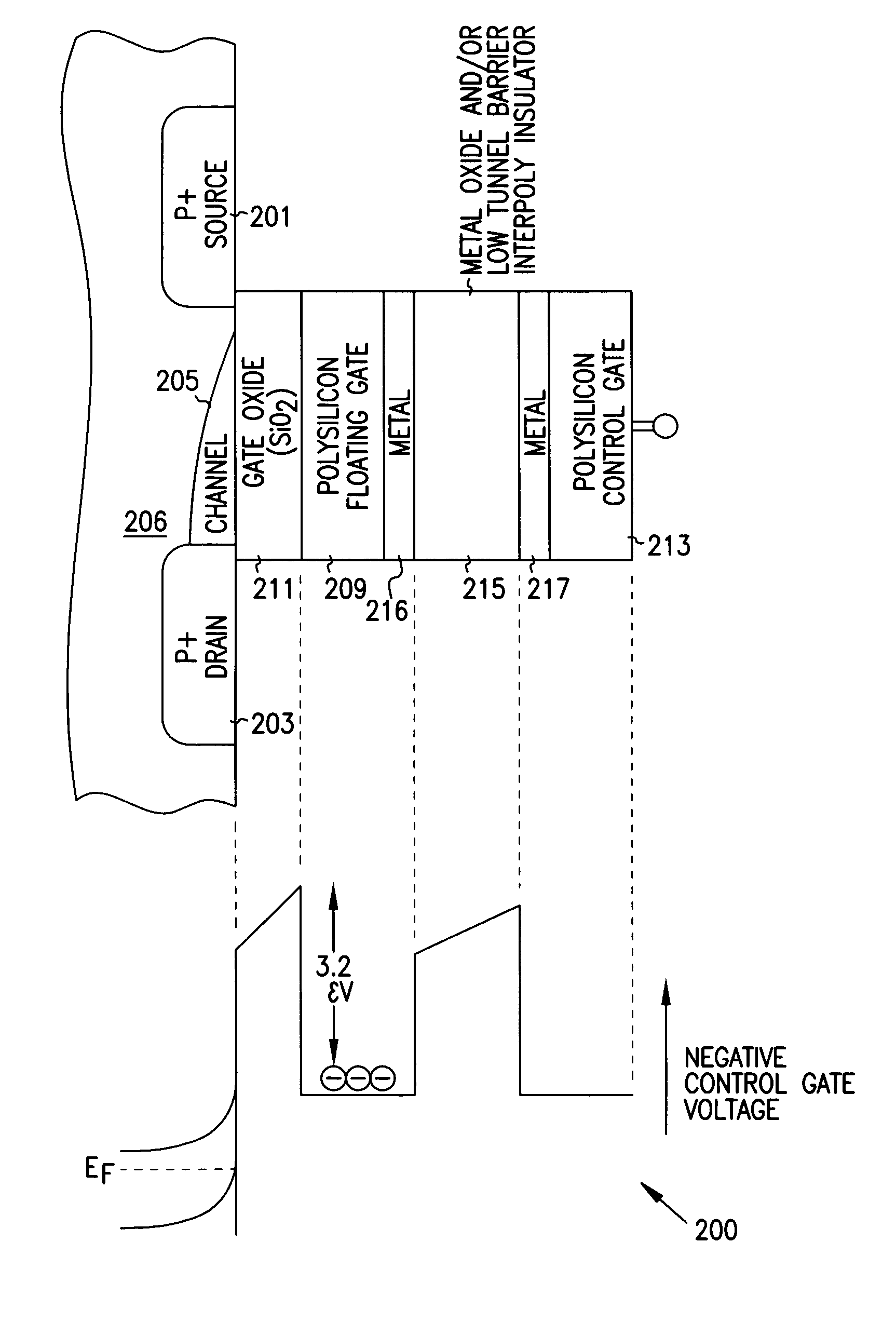

Flash memory with low tunnel barrier interpoly insulators

Structures and methods for Flash memory with low tunnel barrier intergate insulators are provided. The non-volatile memory includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, and Nb2O5. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Asymmetric band-gap engineered nonvolatile memory device

Owner:MICRON TECH INC

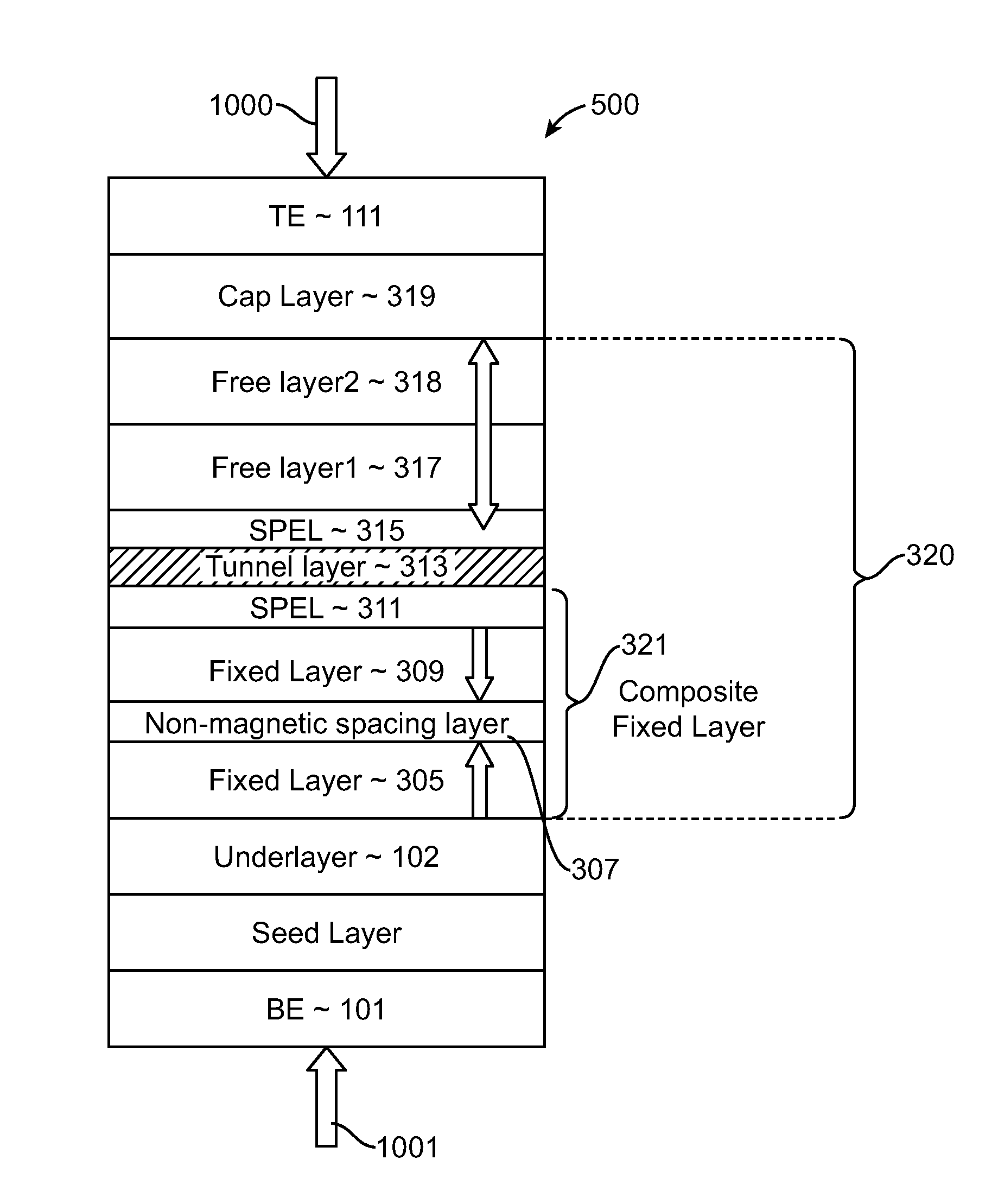

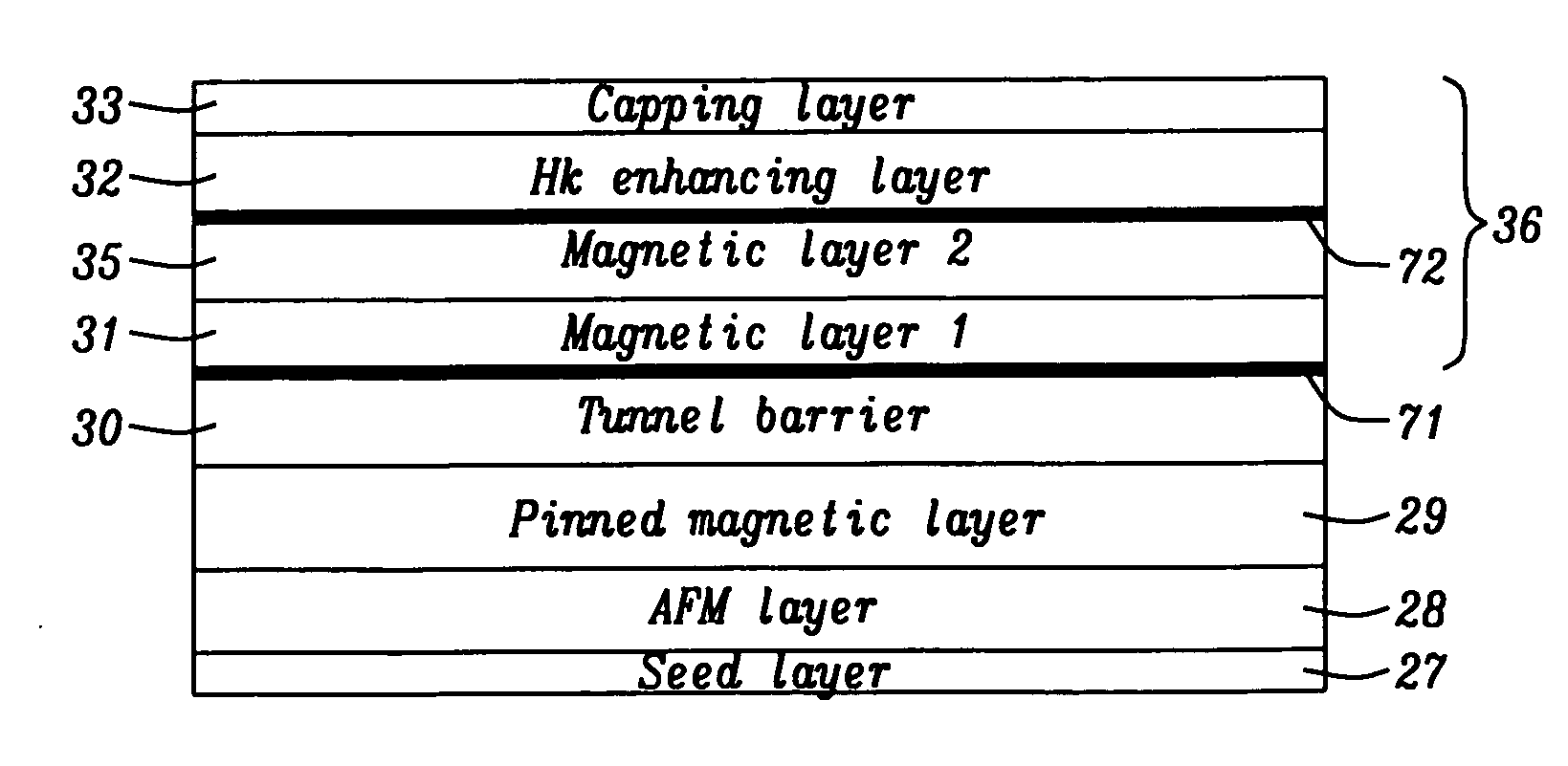

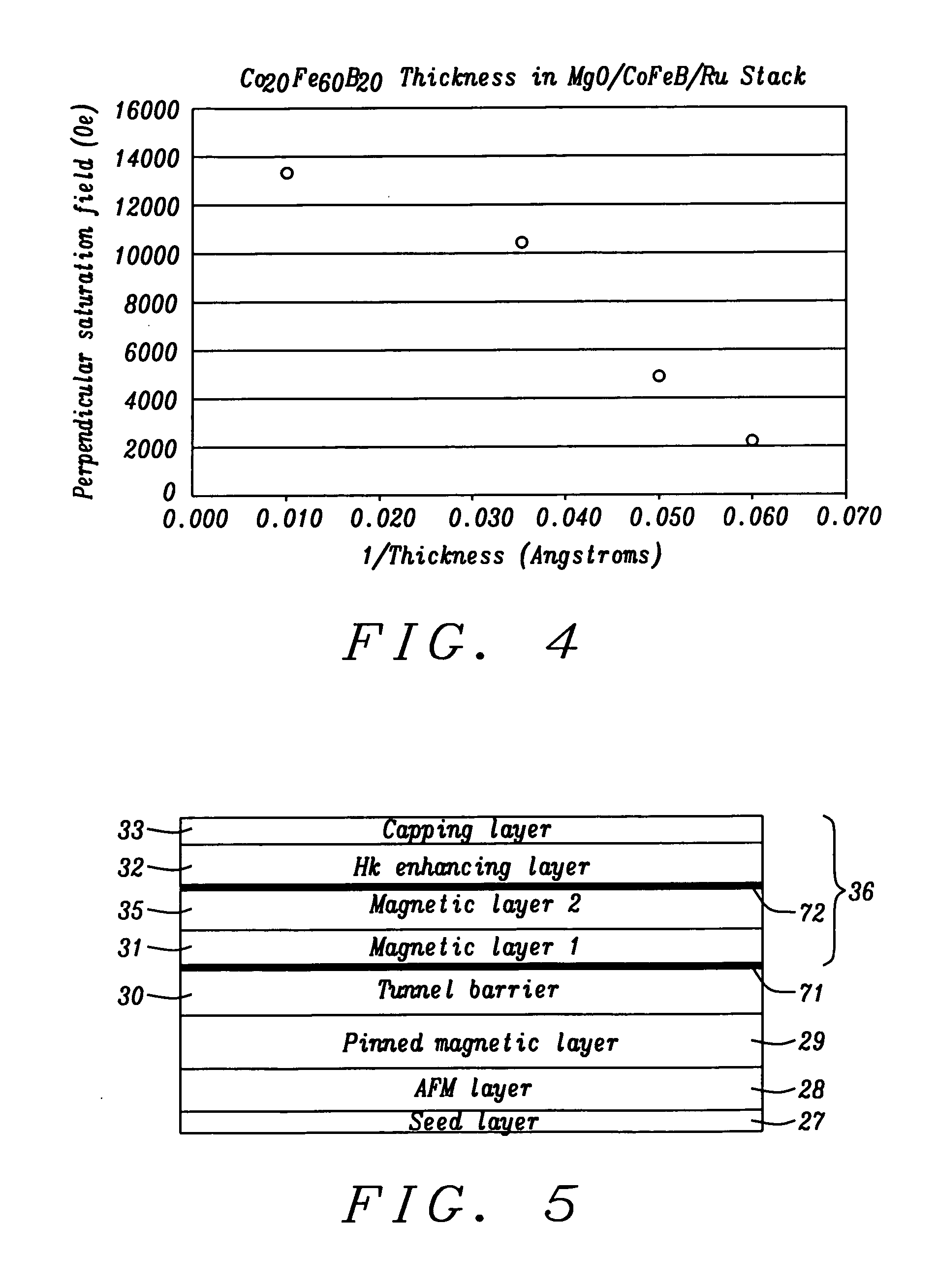

Magnetic element with improved out-of-plane anisotropy for spintronic applications

ActiveUS20120205758A1Without degrading thermal stability and MR ratioEnhanced interfacial perpendicular anisotropyMagnetic-field-controlled resistorsGalvano-magnetic material selectionPerpendicular anisotropyAlloy

A magnetic element is disclosed wherein first and second interfaces of a free layer with a Hk enhancing layer and tunnel barrier, respectively, produce enhanced surface perpendicular anisotropy to lower switching current or increase thermal stability in a magnetic tunnel junction (MTJ). In a MTJ with a bottom spin valve configuration where the Hk enhancing layer is an oxide, the capping layer contacting the Hk enhancing layer is selected to have a free energy of oxide formation substantially greater than that of the oxide. The free layer may be a single layer or composite comprised of an Fe rich alloy such as Co20Fe60B20. With a thin free layer, the interfacial perpendicular anisotropy may dominate the shape anisotropy to generate a magnetization perpendicular to the planes of the layers. The magnetic element may be part of a spintronic device or serve as a propagation medium in a domain wall motion device.

Owner:TAIWAN SEMICON MFG CO LTD

Novel magnetic tunnel junction (MTJ) to reduce spin transfer magnetization switching current

ActiveUS20080179699A1Reduce magnetic “ dead layer ”Magnetic-field-controlled resistorsSolid-state devicesLayer interfaceSpins

Owner:TAIWAN SEMICON MFG CO LTD

Novel capping structure for enhancing dR/R of the MTJ device

InactiveUS20050276099A1Well controlled magnetizationWell controlled switching characteristicNanomagnetismNanoinformaticsElectrical conductorOxygen

Owner:HEADWAY TECH INC +1

MTJ incorporating CoFe/Ni multilayer film with perpendicular magnetic anisotropy for MRAM application

ActiveUS20110096443A1Minimize impinging ion energyMaximize PMA propertyMagnetic measurementsVacuum evaporation coatingSpin transferSpin valve

A MTJ for a spintronic device is disclosed and includes a thin composite seed layer made of at least Ta and a metal layer having fcc(111) or hcp(001) texture as in Ta / Ti / Cu to enhance perpendicular magnetic anisotropy (PMA) in an overlying laminated layer with a (CoFe / Ni)X, (Co / NiFe)X, (Co / NiCo)X, (CoFe / NiFe)X, or (CoFe / NiCo)X composition where x is from 5 to 30. In one embodiment, a CPP-TMR spin valve has one or both of a laminated free layer and laminated reference layer with the aforementioned compositions. The MTJ includes an interfacial layer made of CoFeB, CoFeB / CoFe, or CoFe / CoFeB between each laminated structure and the tunnel barrier. The laminated layers are deposited by a low power and high Ar pressure process to avoid damaging interfaces between adjoining layers. Annealing occurs at 220° C. to 400° C. A laminated layer with high PMA may also be included in one or more layers of a spin transfer oscillator.

Owner:TAIWAN SEMICON MFG CO LTD

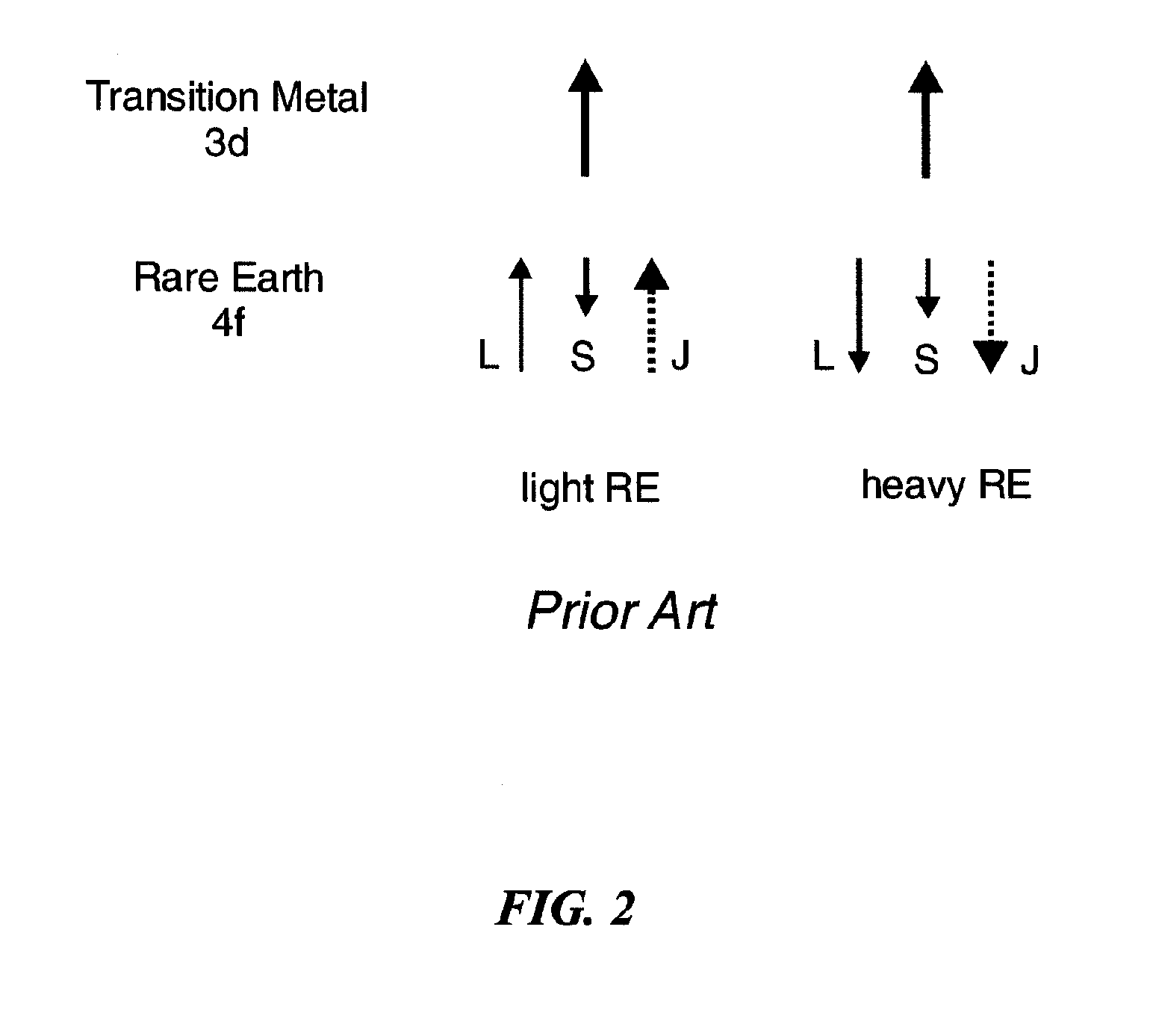

Spin-polarization devices using rare earth-transition metal alloys

ActiveUS7230265B2Magnetic-field-controlled resistorsGalvano-magnetic material selectionRare-earth elementMetal alloy

A tunnel barrier in proximity with a layer of a rare earth element-transition metal (RE—TM) alloy forms a device that passes negatively spin-polarized current. The rare earth element includes at least one element selected from the group consisting of Gd, Tb, Dy, Ho, Er, Tm, and Yb. The RE and TM have respective sub-network moments such that the absolute magnitude of the RE sub-network moment is greater than the absolute magnitude of the TM sub-network moment. An additional layer of magnetic material may be used in combination with the tunnel barrier and the RE—TM alloy layer to form a magnetic tunnel junction. Still other layers of tunnel barrier and magnetic material may be used in combination with the foregoing to form a flux-closed double tunnel junction device.

Owner:IBM CORP

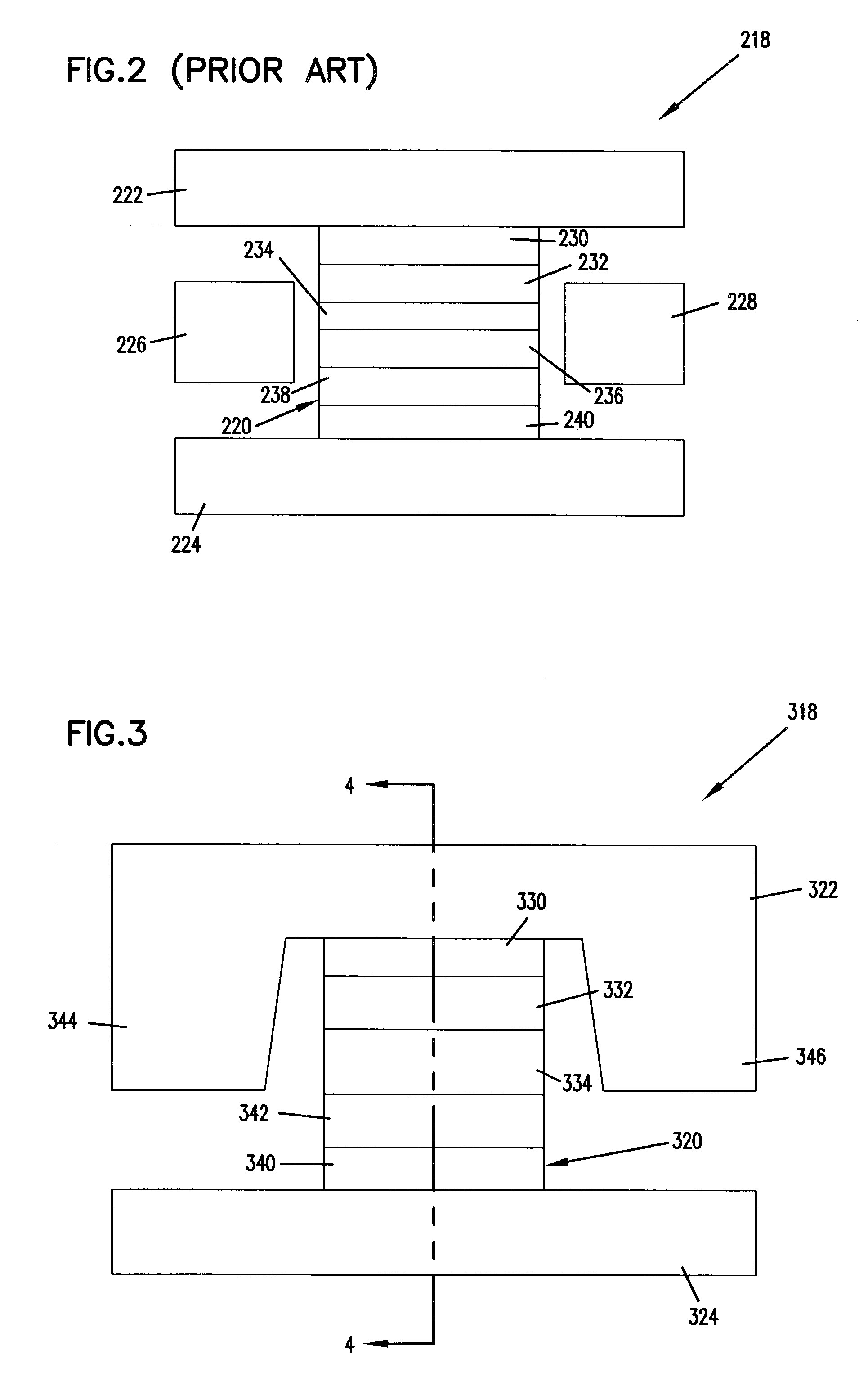

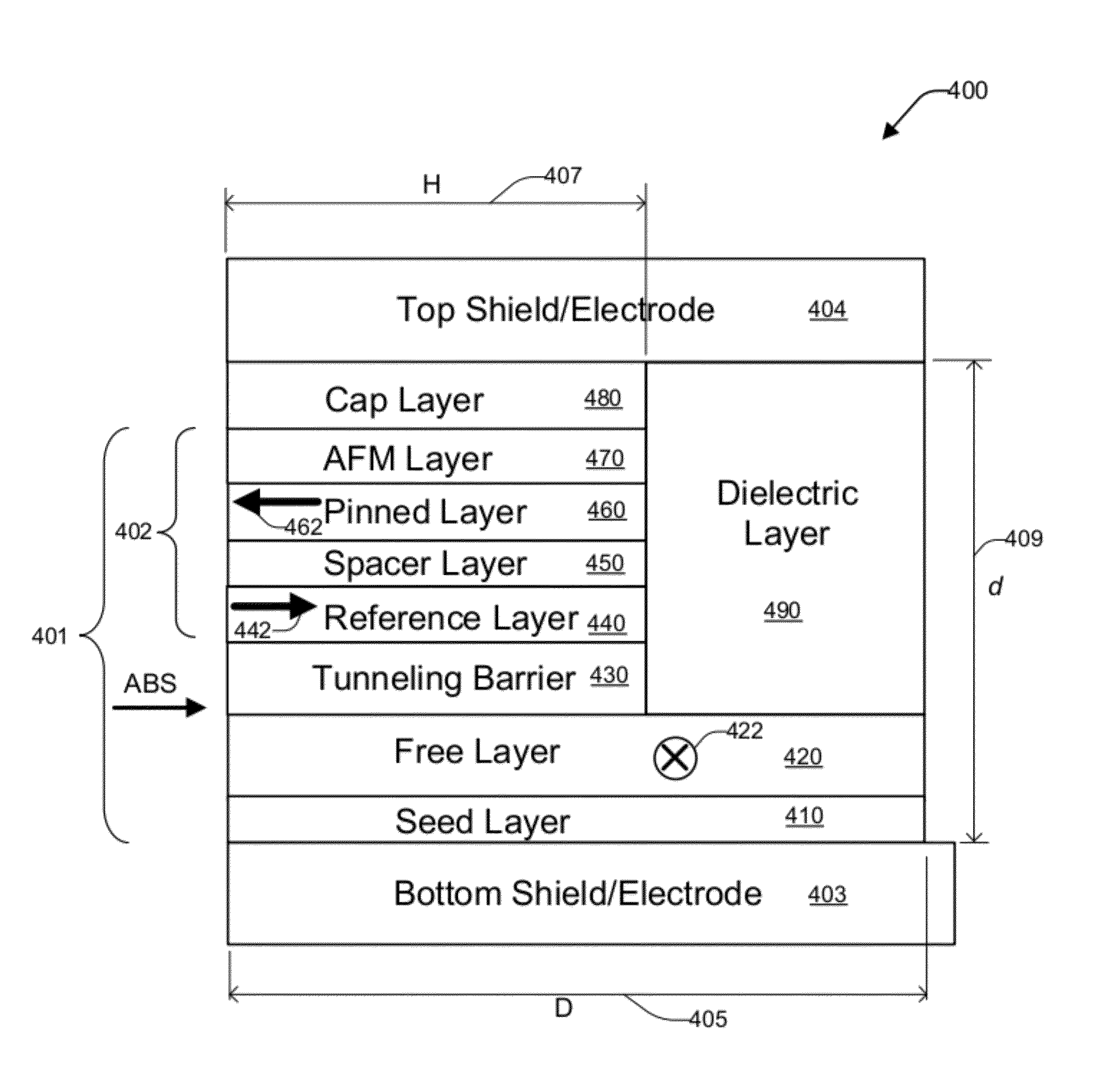

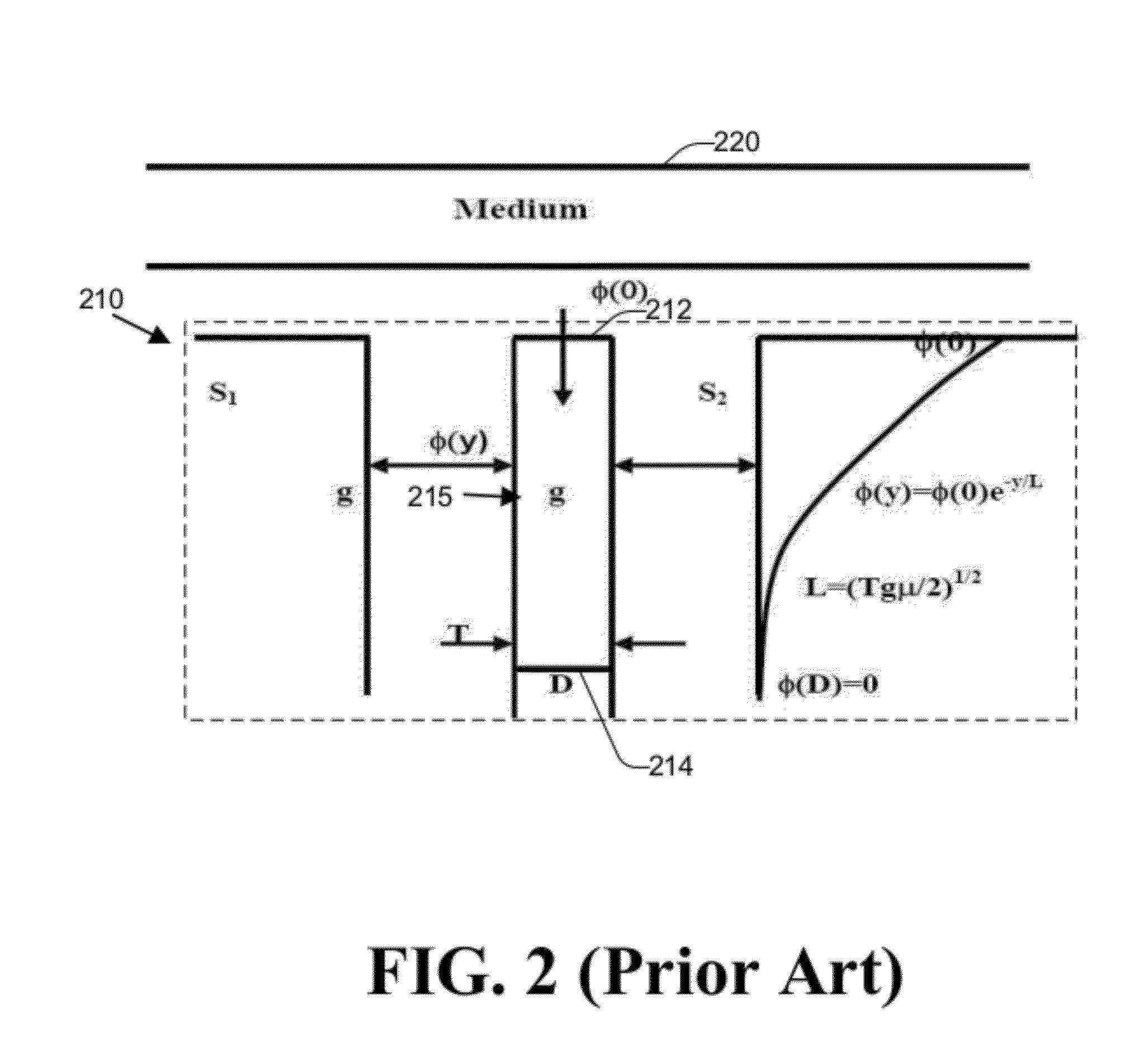

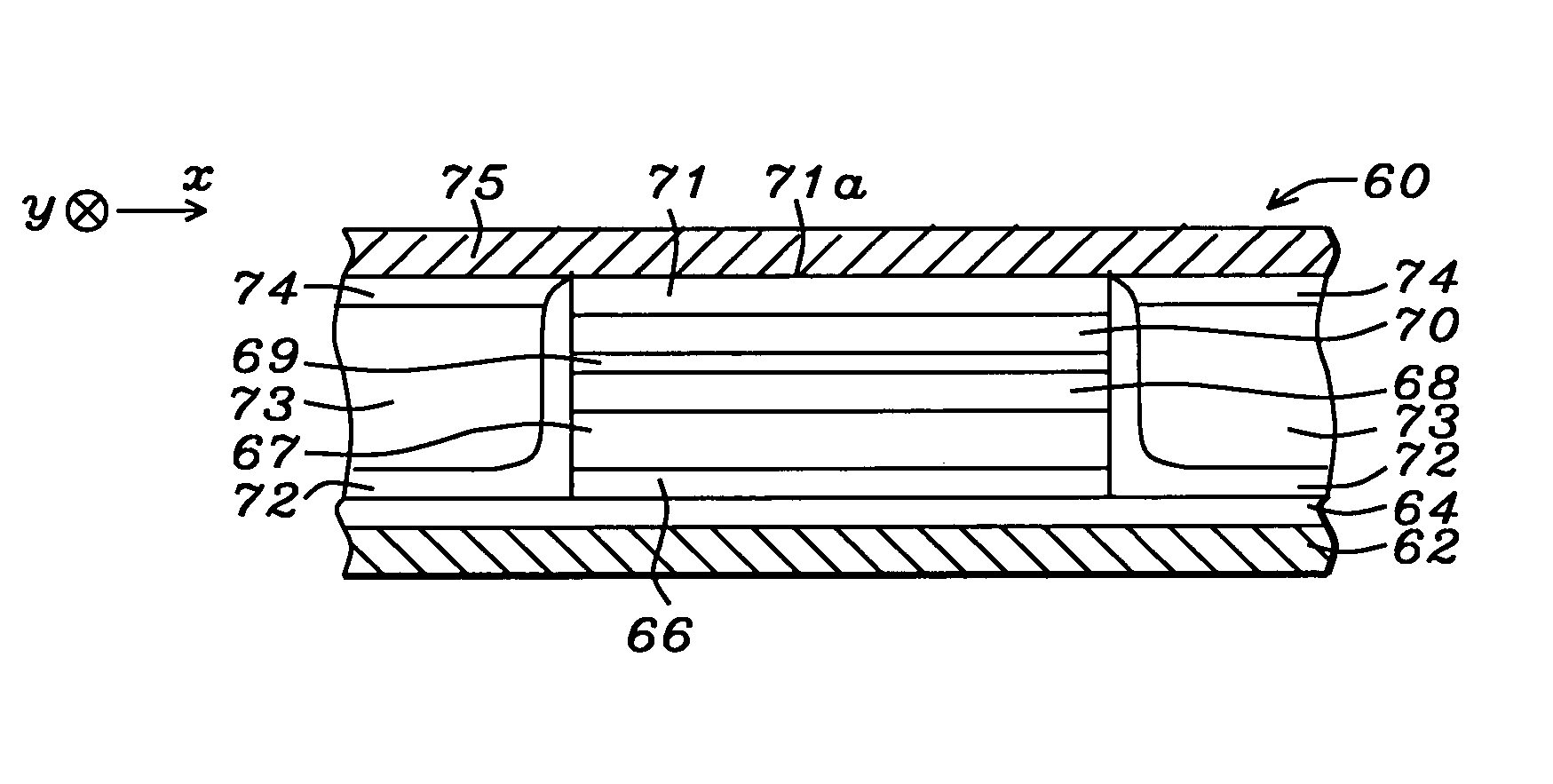

TMR read head structures with differential stripe heights

InactiveUS8194366B1Magnetic measurementsMagnetic-field-controlled resistorsMagnetic layerElectrical and Electronics engineering

A tunneling magnetoresistance (TMR) read head and a method of producing the same are disclosed. A free layer having a free layer stripe height is provided, the free layer having a first side and a second side. A tunneling barrier layer is formed adjacent to the first side of the free layer, the tunneling barrier layer having a first side and a second side, the second side of the tunneling barrier layer facing the first side of the free layer. A pinned stack is formed adjacent to the first side of the tunneling barrier layer. The pinned stack comprises at least one magnetic layer having a current path stripe height that is less than the free layer stripe height.

Owner:WESTERN DIGITAL TECH INC

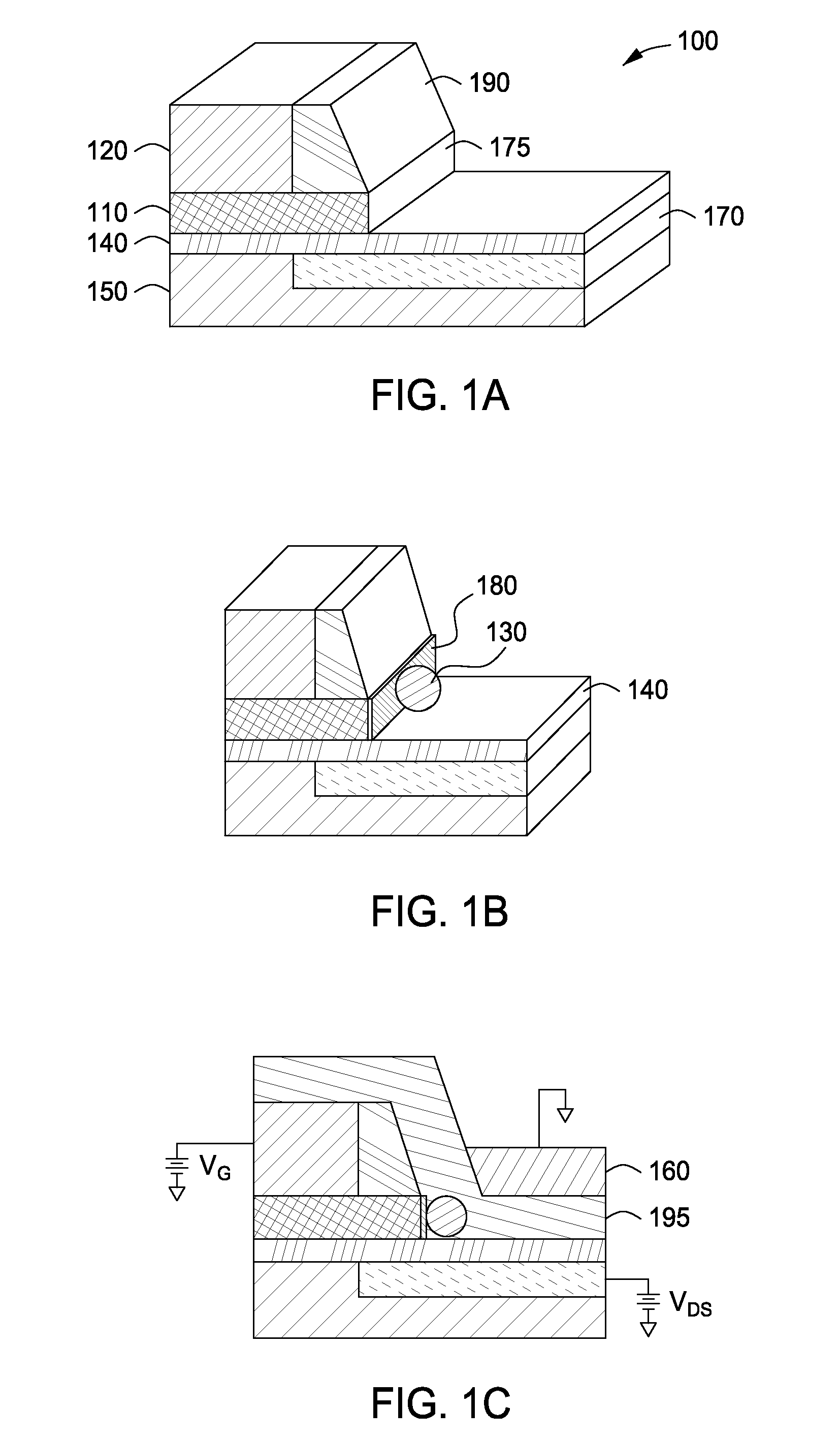

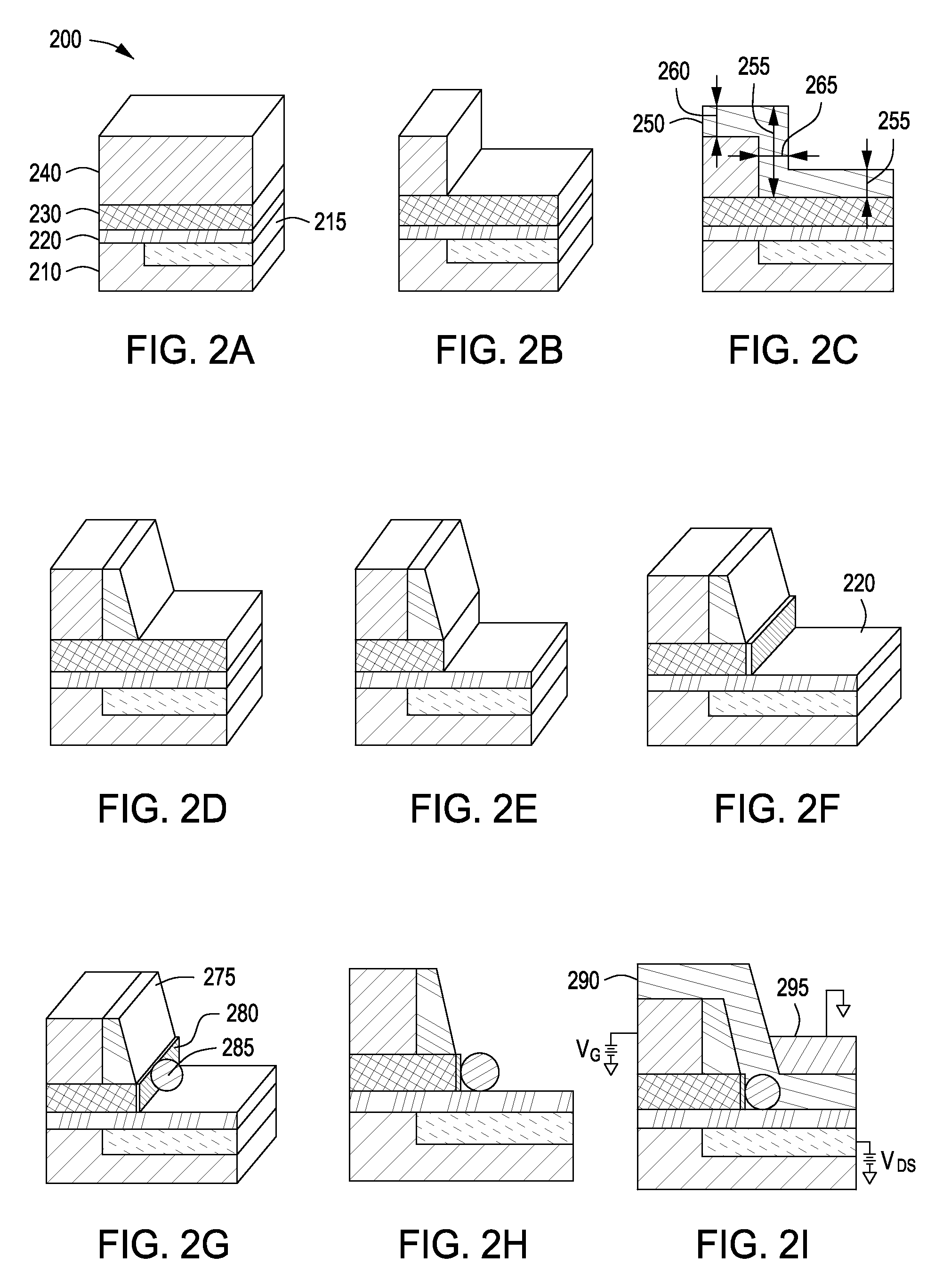

Positioning of nanoparticles and fabrication of single electron devices

InactiveUS7465953B1NanoinformaticsMaterial analysis by electric/magnetic meansSingle electronDevice form

The present invention includes single electron structures and devices comprising a substrate having an upper surface, one or more dielectric layers formed on the upper surface of the substrate and having at least one exposed portion, at least one monolayer of self-assembling molecules attracted to and in contact with the at least one exposed portion of only one of the one or more dielectric layers, one or more nanoparticles attracted to and in contact with the at least one monolayer, and at least one tunneling barrier in contact with the one or more nanoparticles. Typically, the single electron structure or device formed therefrom further comprise a drain, a gate and a source to provide single electron behavior, wherein there is a defined gap between source and drain and the one or more nanoparticles is positioned between the source and drain.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

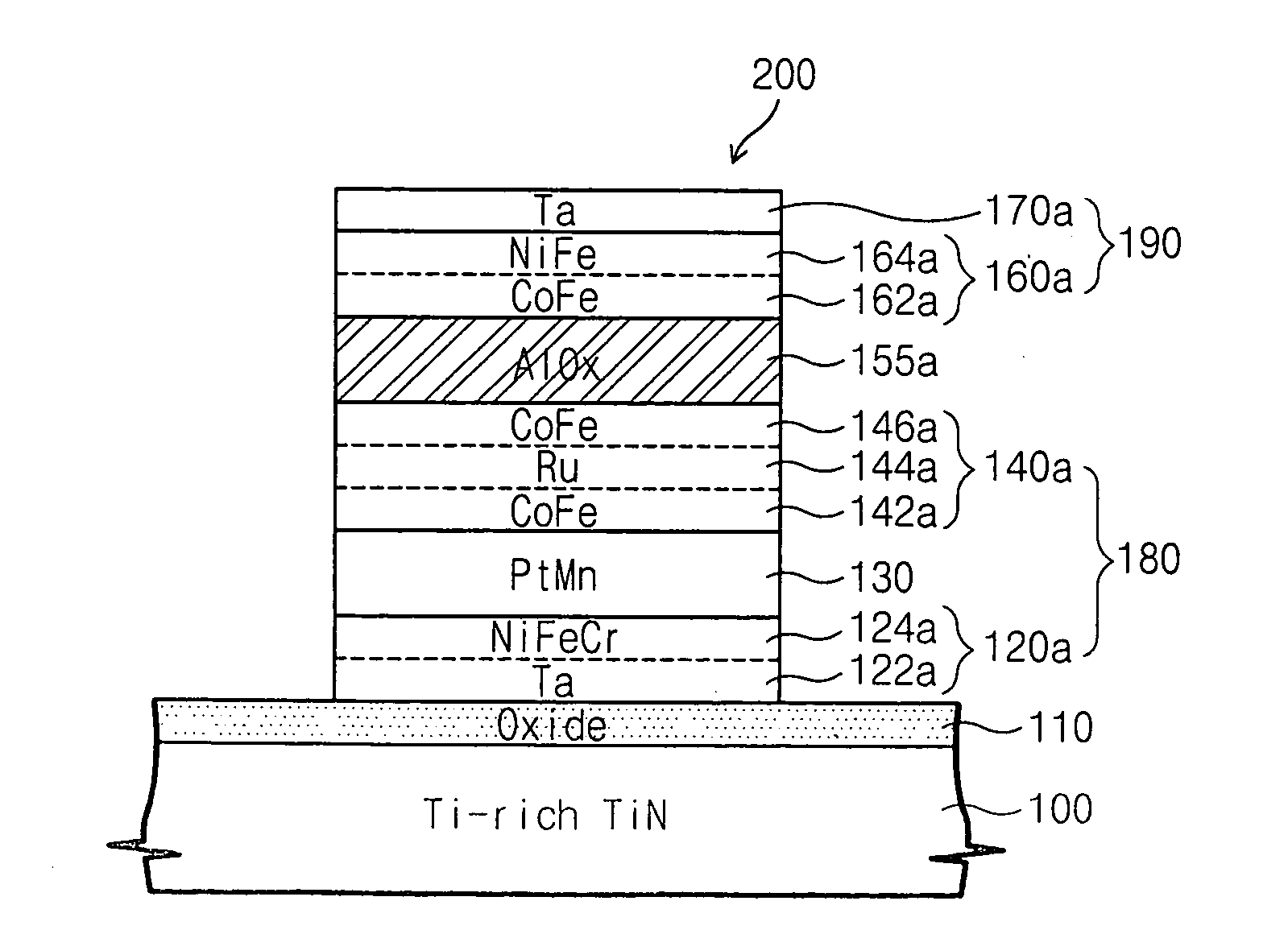

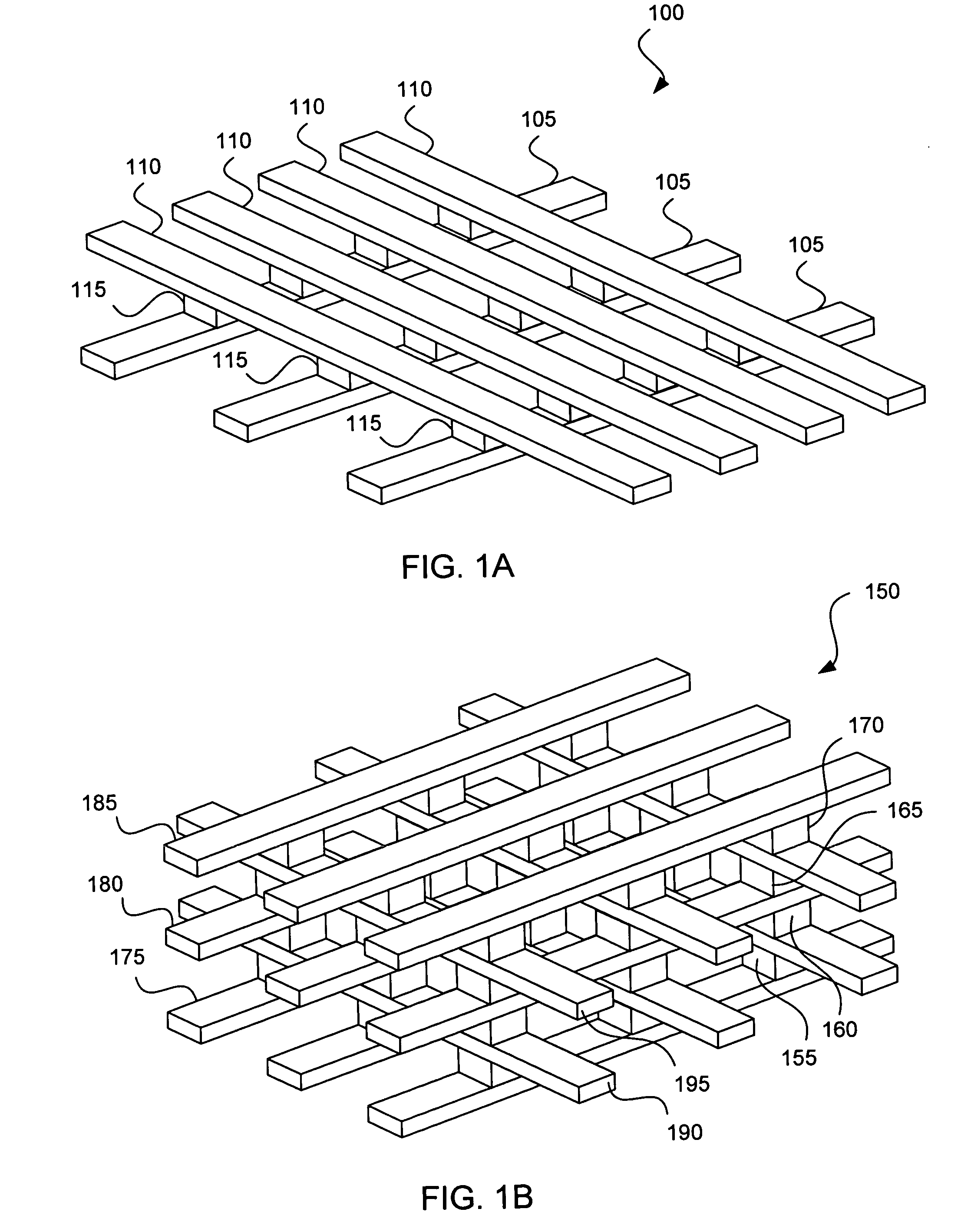

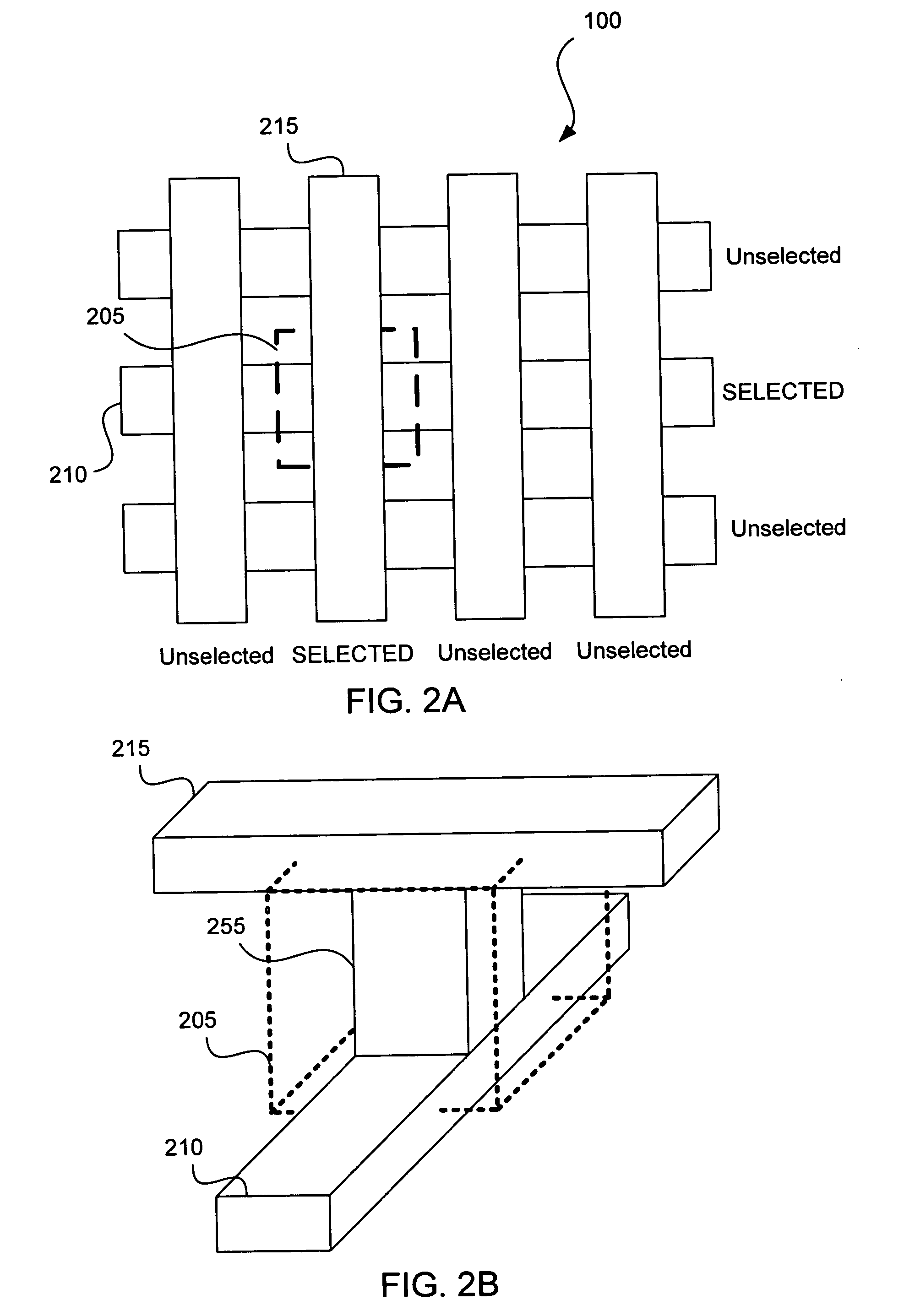

Magnetic random access memory devices having titanium-rich lower electrodes with oxide layer and oriented tunneling barrier, and methods for forming the same

ActiveUS20050006682A1Addressing Insufficient ControlLow polishing rateNanostructure applicationNanomagnetismRandom access memoryTitanium

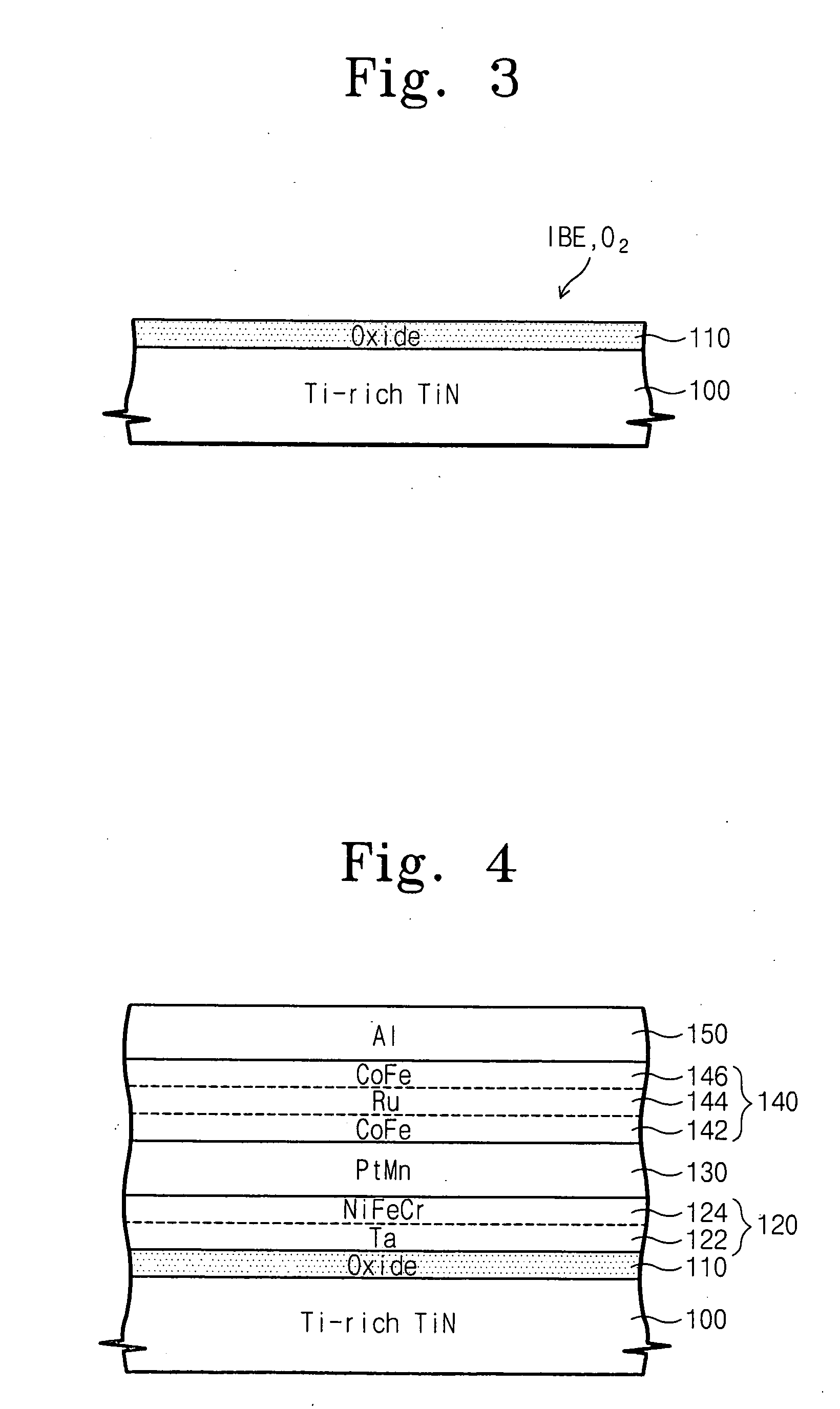

Magnetic Random Access Memory (MRAM) devices include a lower electrode and a magnetic tunnel junction on the lower electrode. The magnetic tunnel junction includes a seed layer and a tunneling barrier that is oriented in a same direction as the most closely packed plane direction of the seed layer. An oxide layer may be provided between the lower electrode and the magnetic tunnel junction. The lower electrode may be a titanium-rich TiN layer having more than 50 atomic percent titanium content. Analogous fabrication methods are also described.

Owner:SAMSUNG ELECTRONICS CO LTD

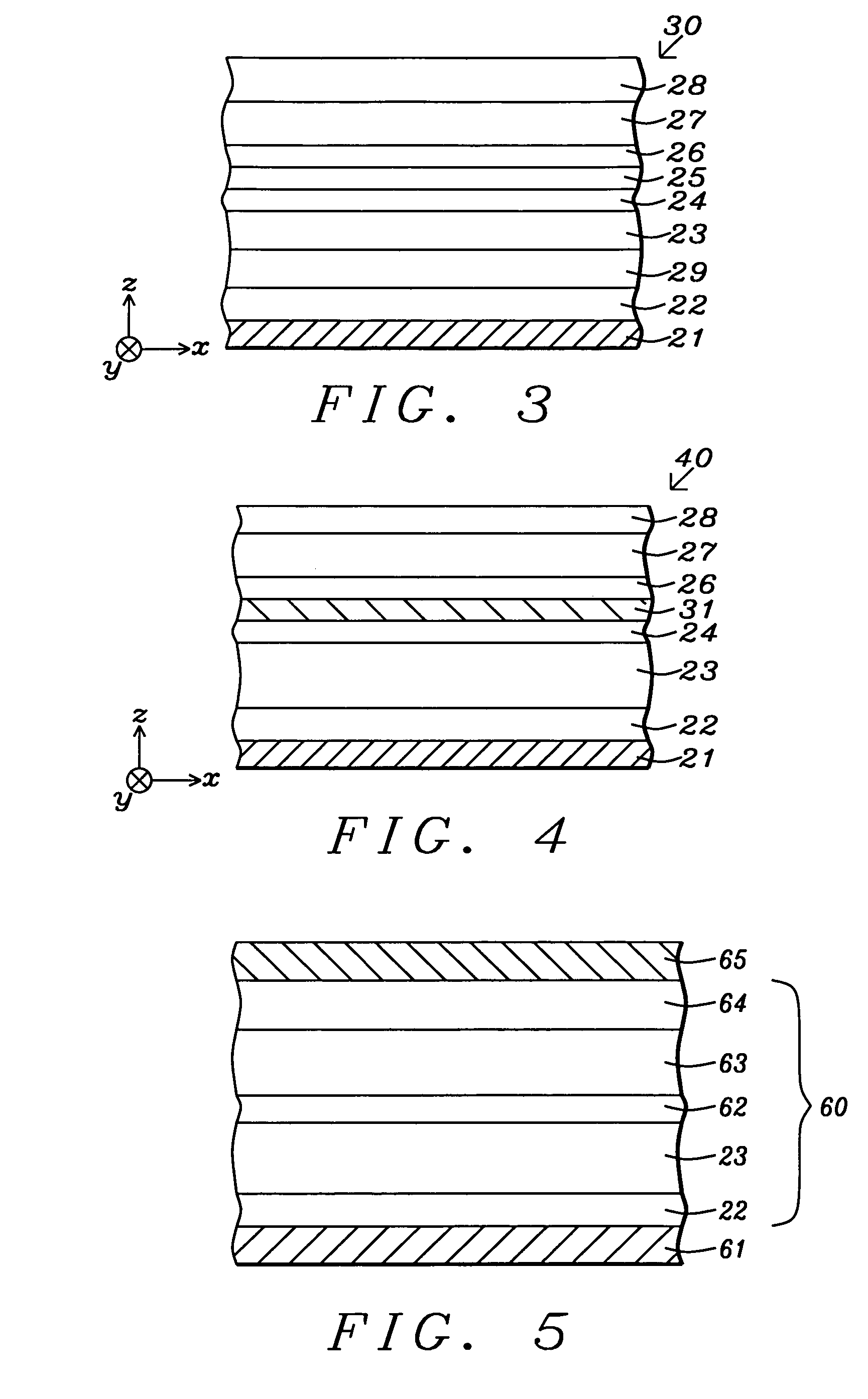

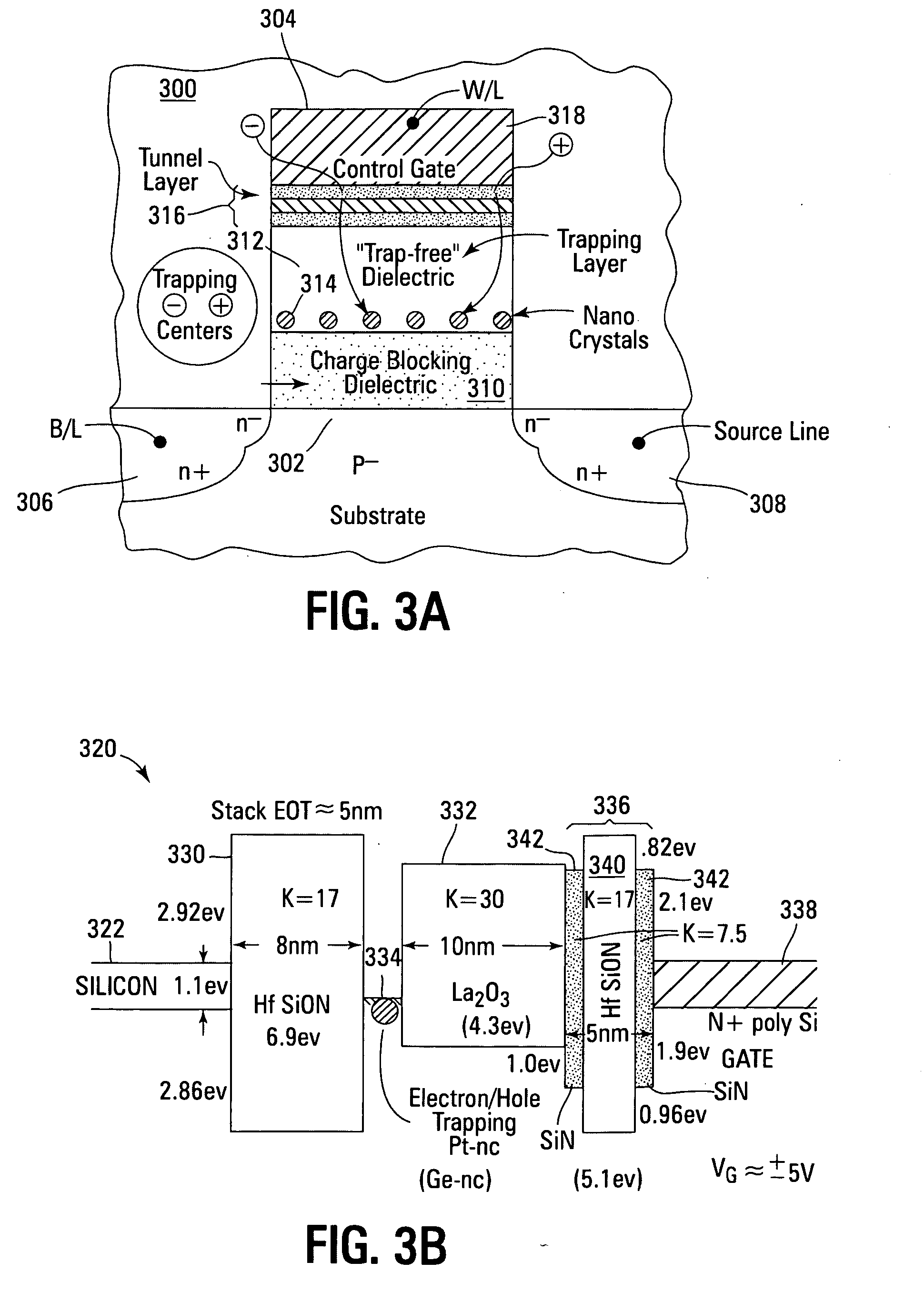

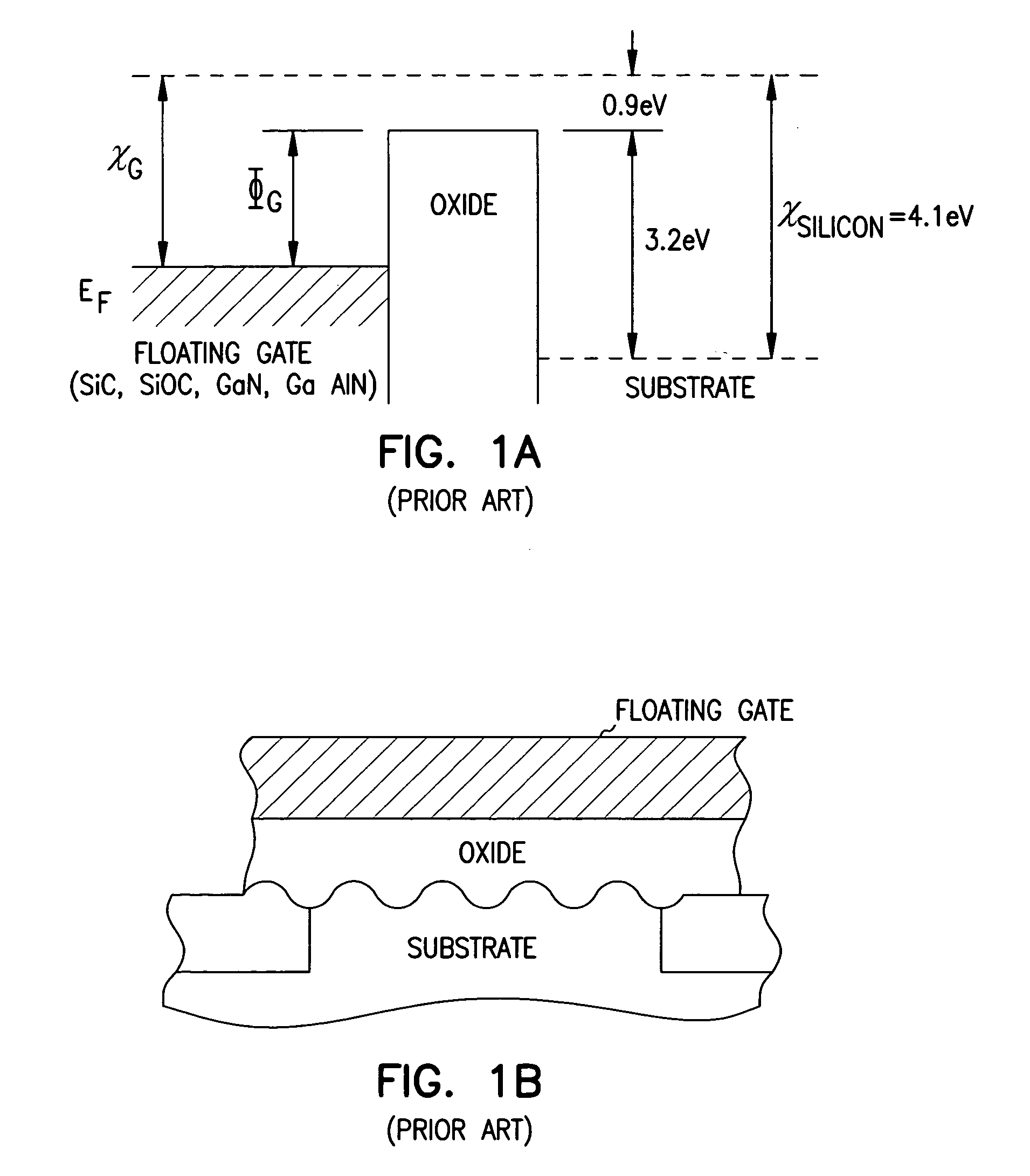

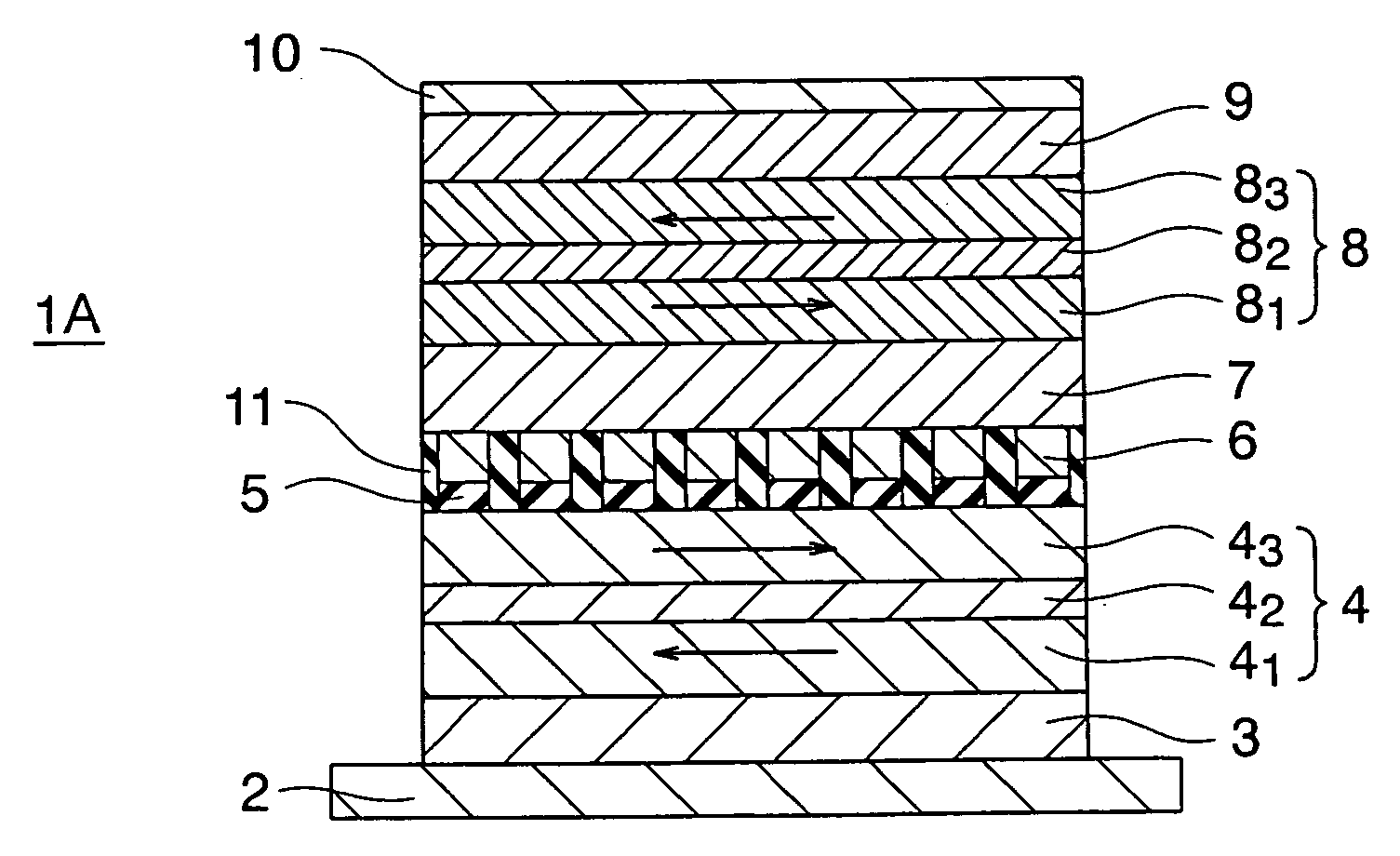

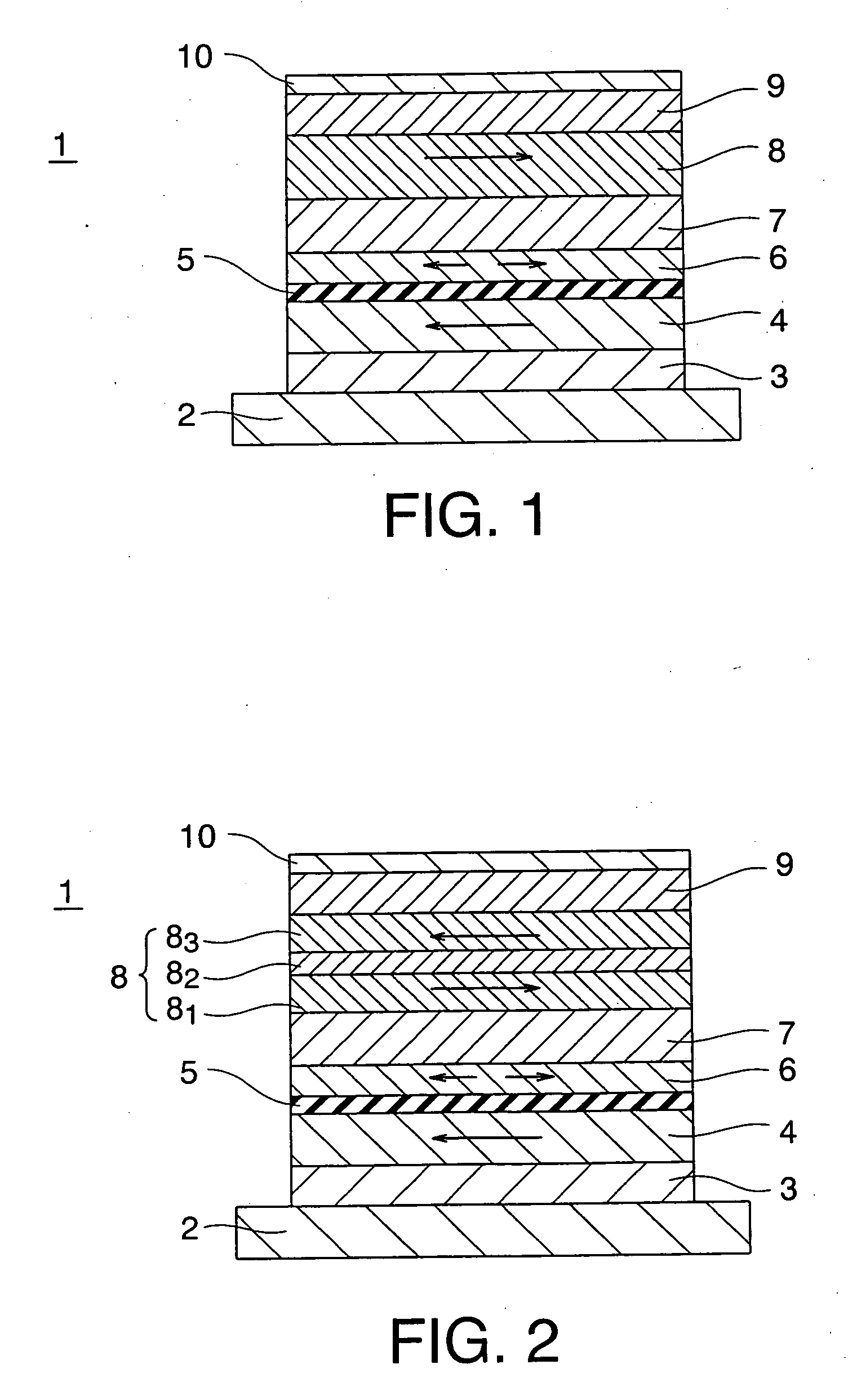

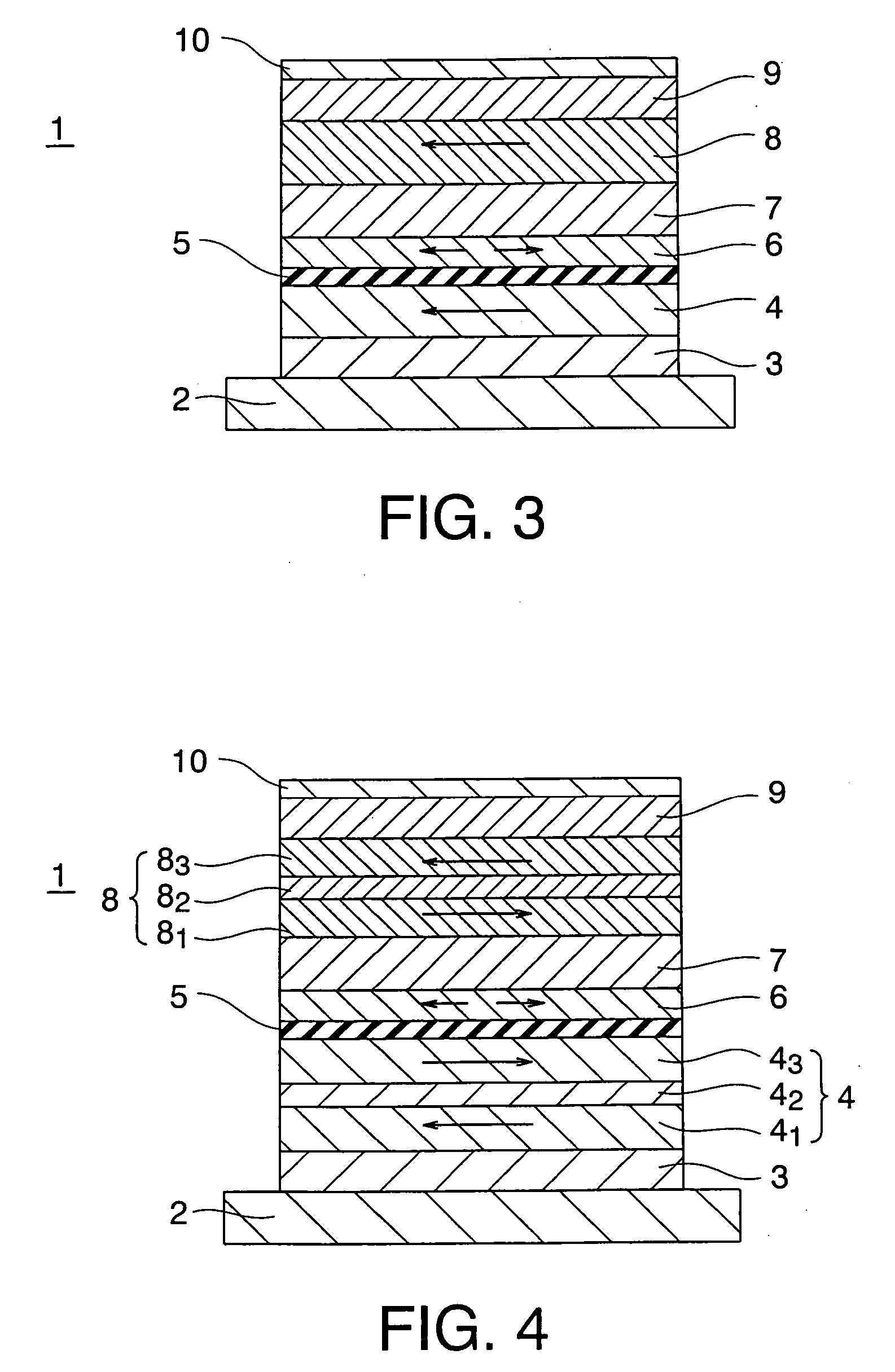

Band-engineered multi-gated non-volatile memory device with enhanced attributes

ActiveUS7279740B2Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC

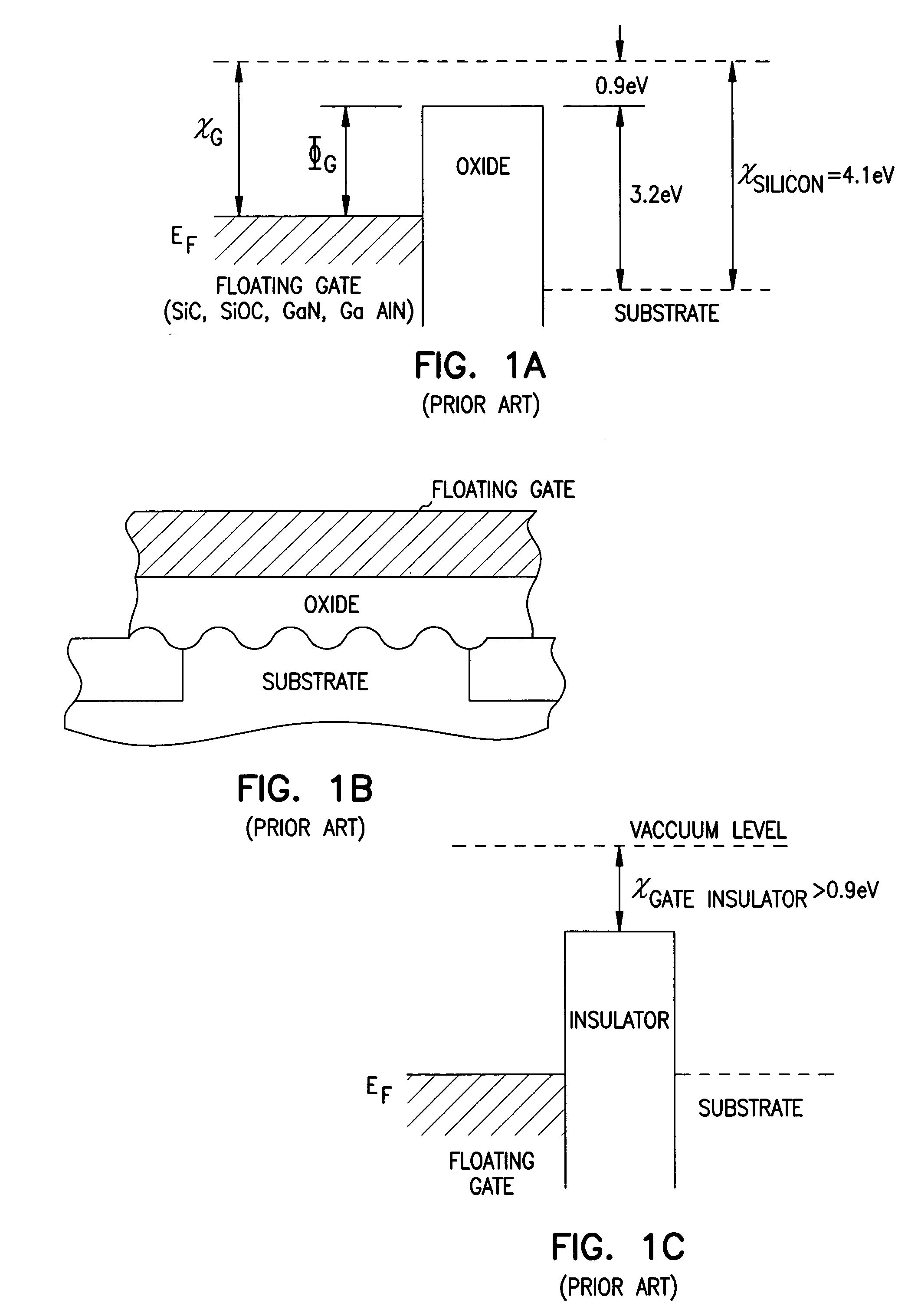

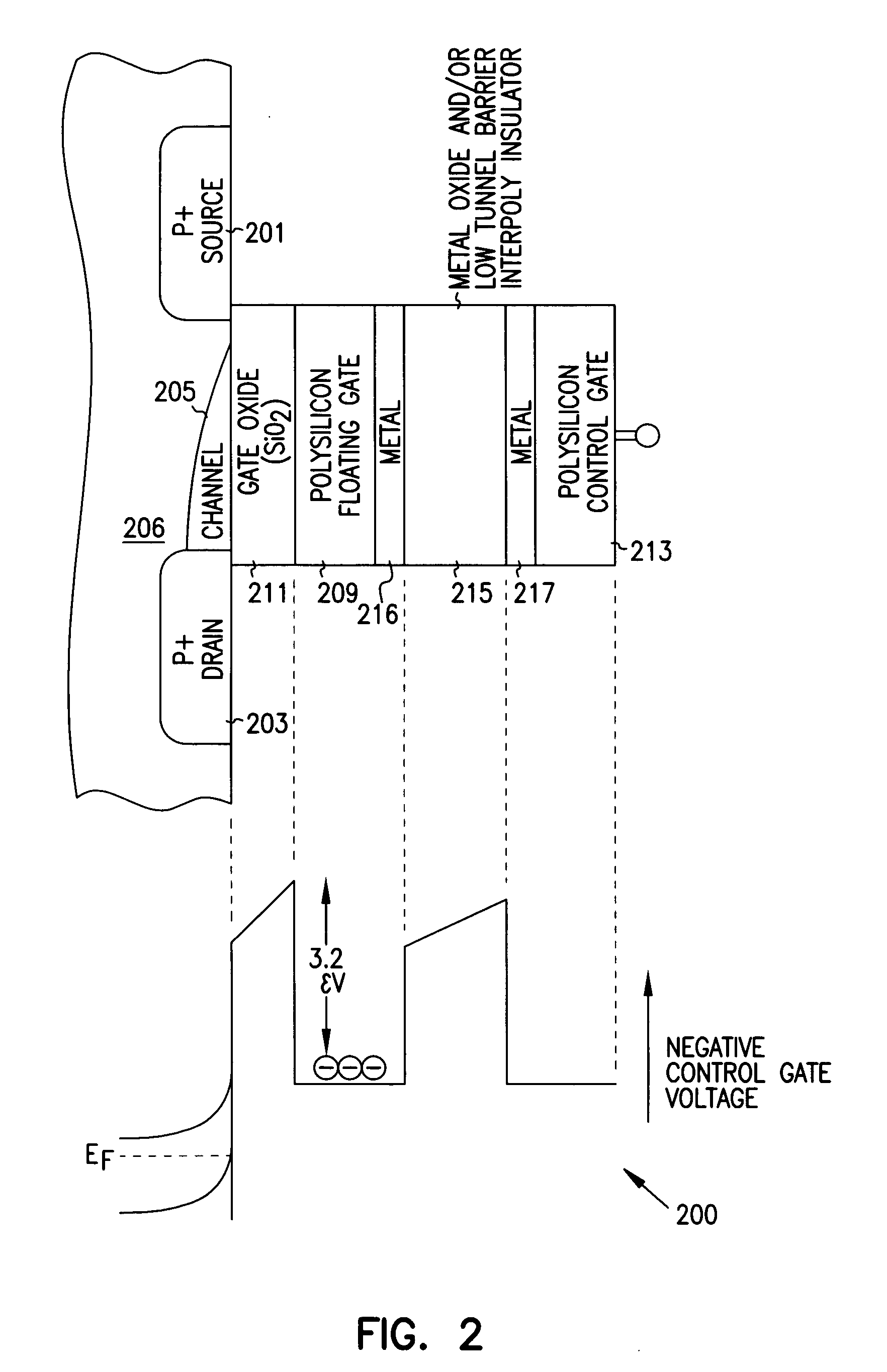

Programmable array logic or memory with p-channel devices and asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory with p-channel devices and asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include p-channel non-volatile memory which has a first source / drain region and a second source / drain region separated by a p-type channel region in an n-type substrate. A floating gate opposing the p-type channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

Programmable array logic or memory devices with asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

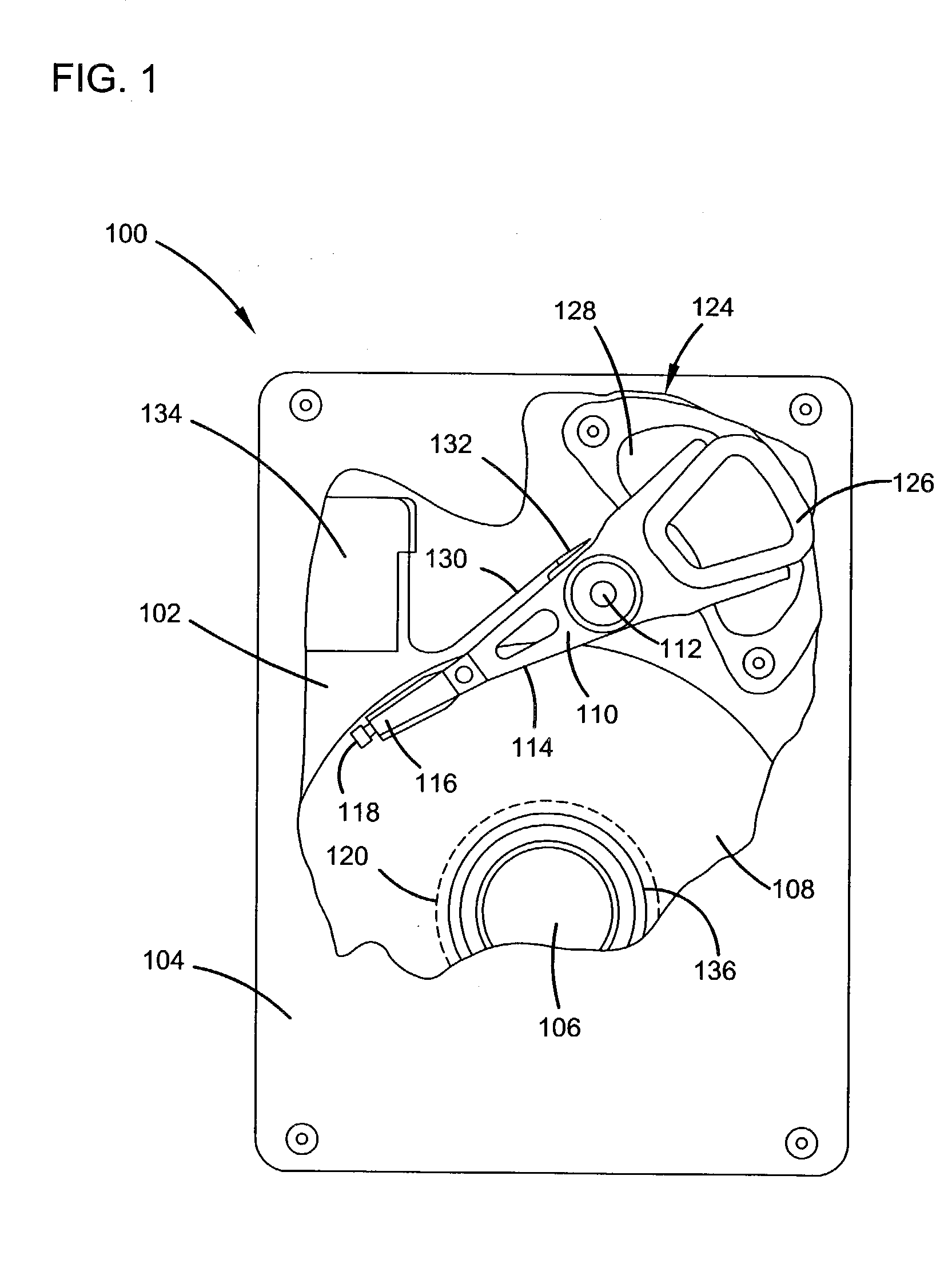

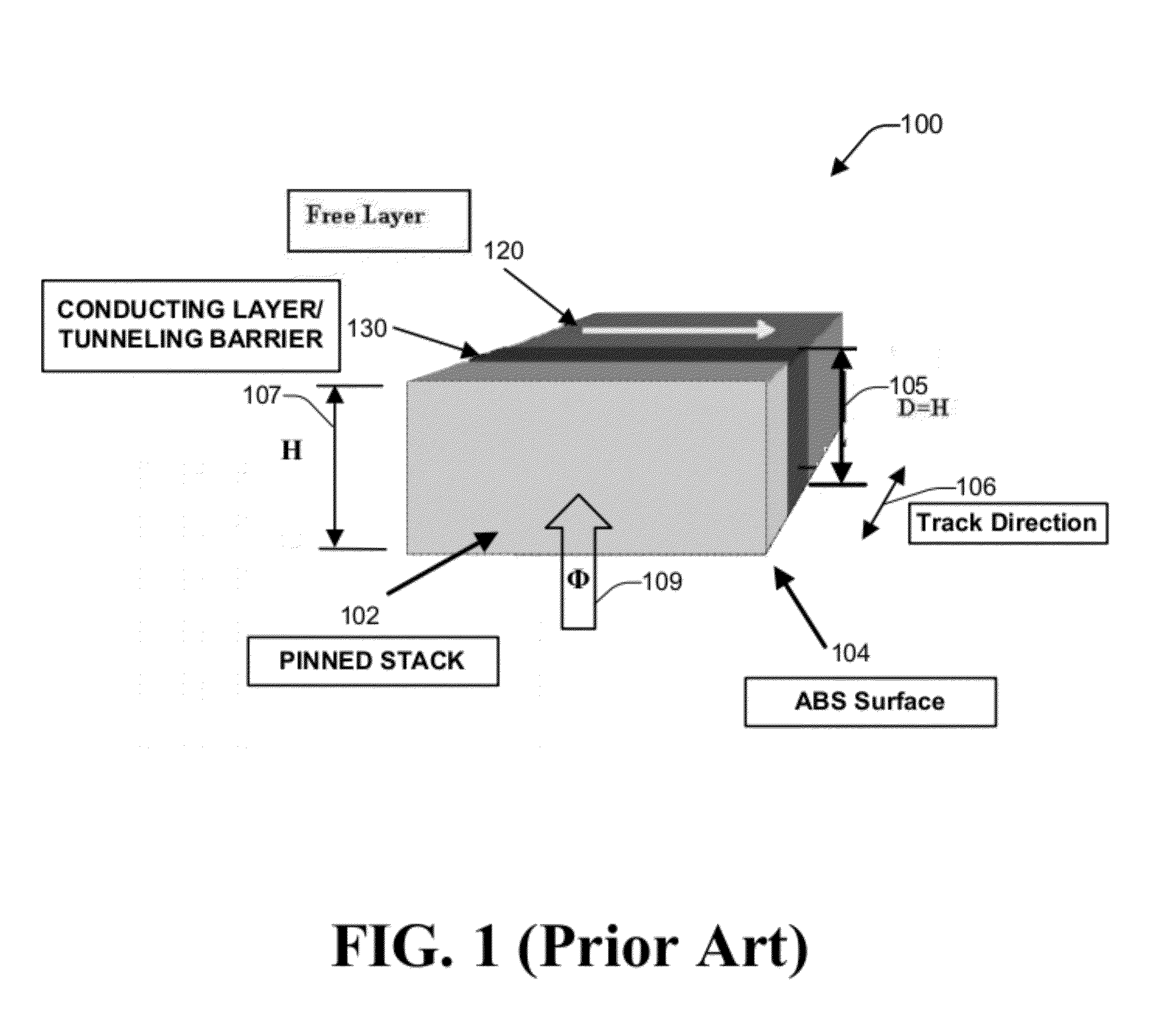

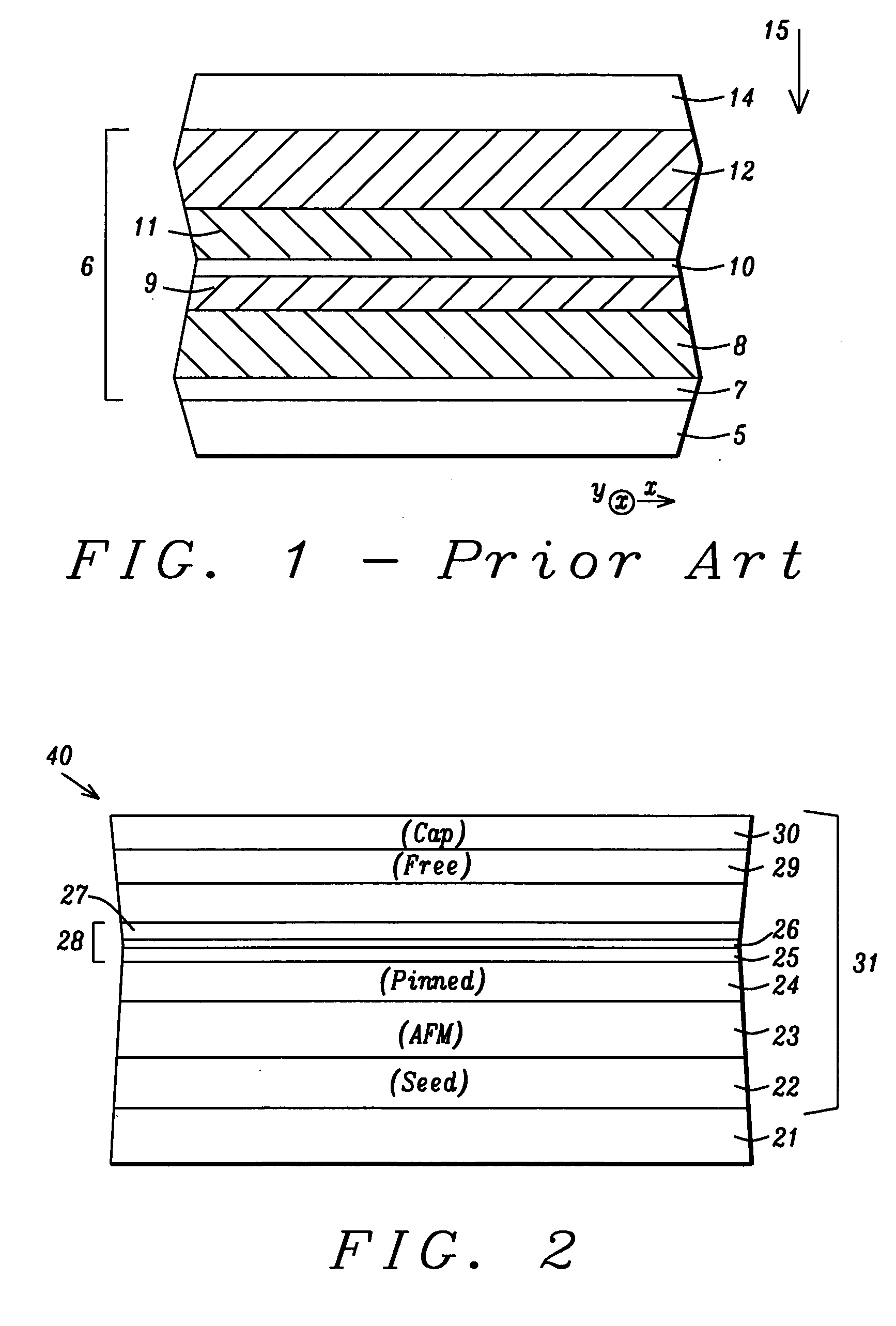

Spin-dependent tunneling read/write sensor for hard disk drives

A hard biased spin-dependent tunneling sensor and manufacturing method therefor is provided having a substrate with a first lead formed thereon. A hard magnet is formed over the first lead and a free layer is formed over the hard magnet. A tunneling barrier layer with a first pinned layer formed thereon is formed over the free layer. A nonmagnetic coupling layer with a second pinned layer formed thereon is formed over the first pinned layer. A pinning layer is formed over the second pinned layer and a second lead is formed over the pinning layer.

Owner:WESTERN DIGITAL TECH INC

Band-engineered multi-gated non-volatile memory device with enhanced attributes

ActiveUS20060258090A1Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC

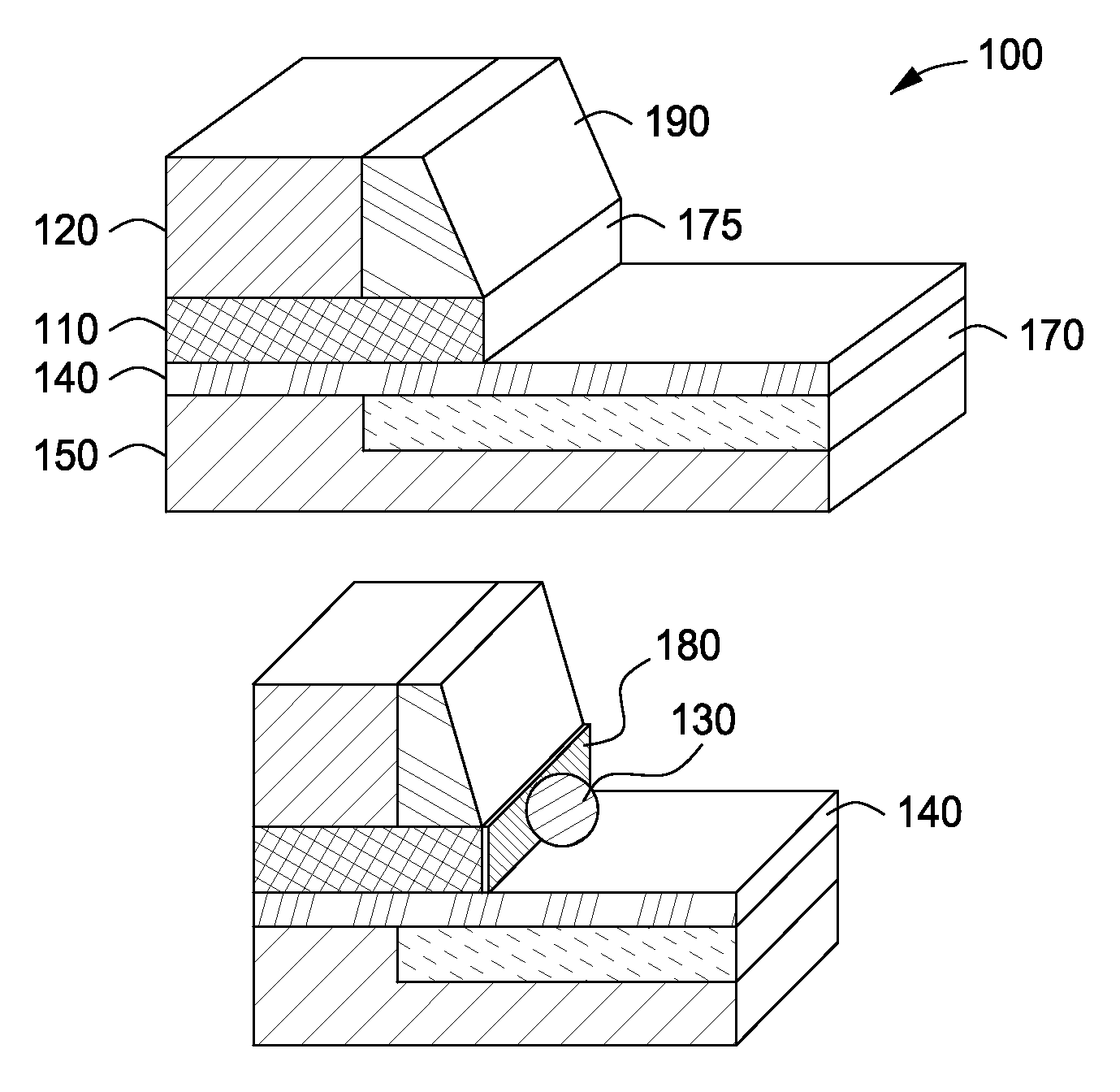

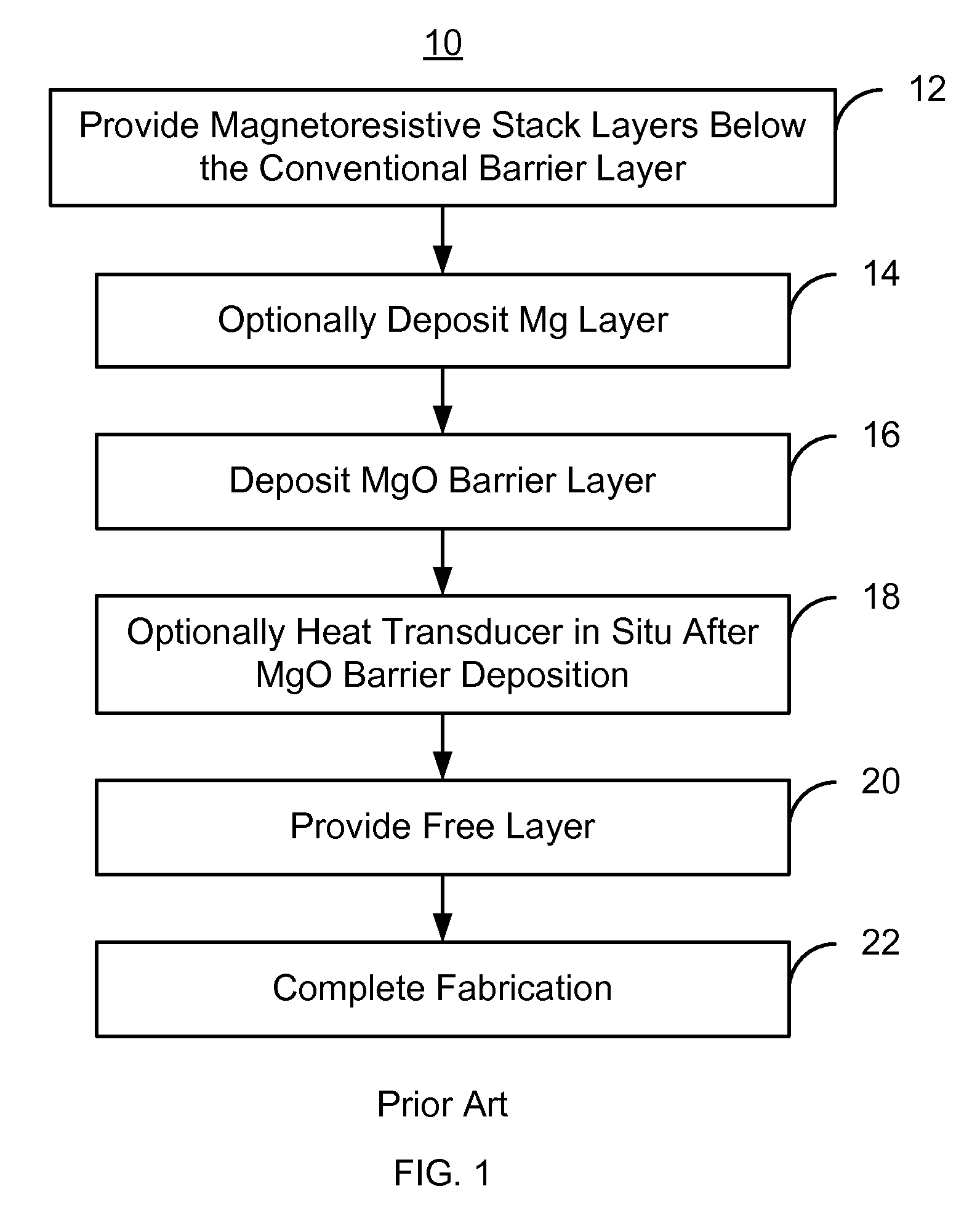

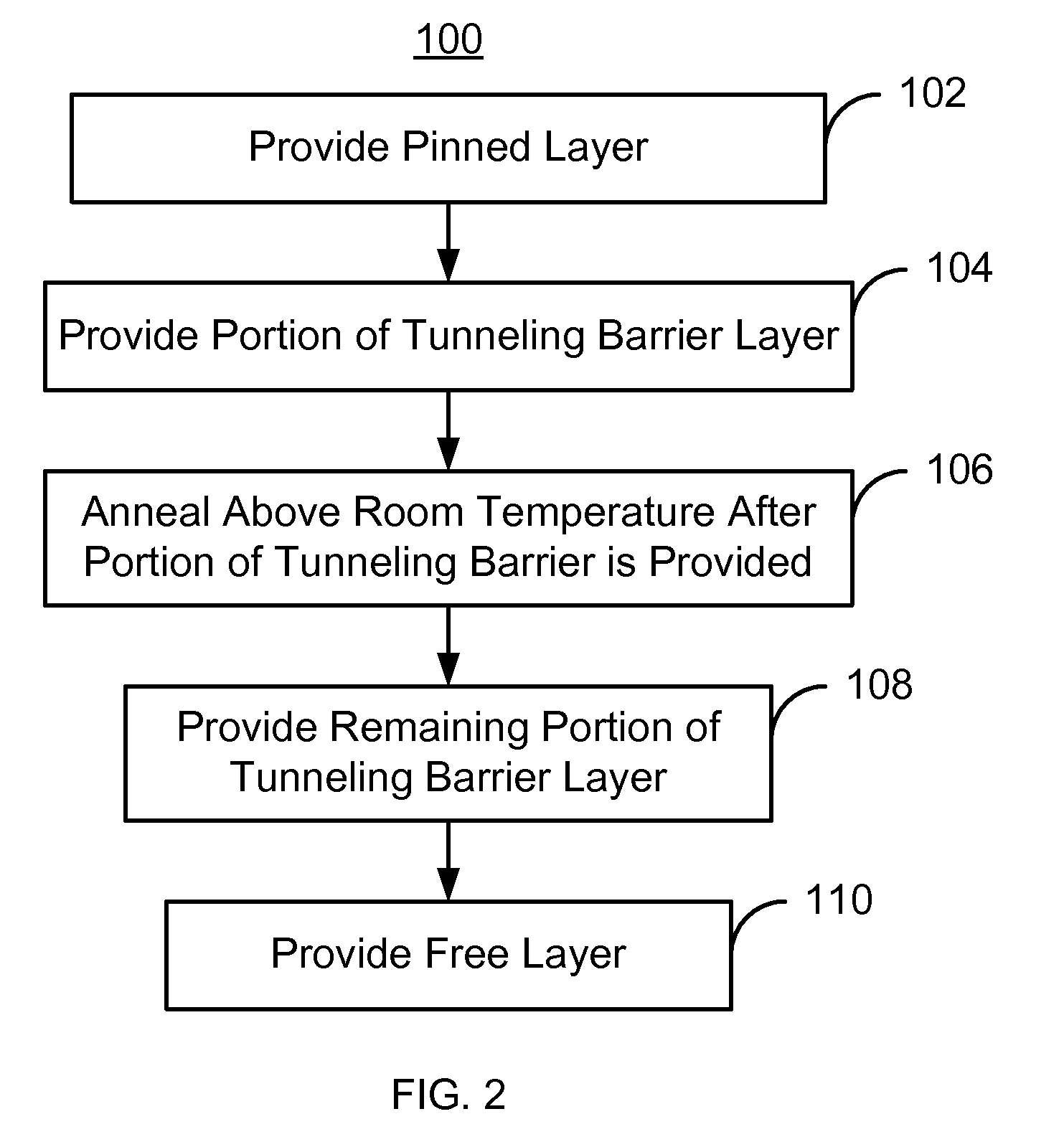

Method for providing a magnetic recording transducer

Owner:WESTERN DIGITAL TECH INC

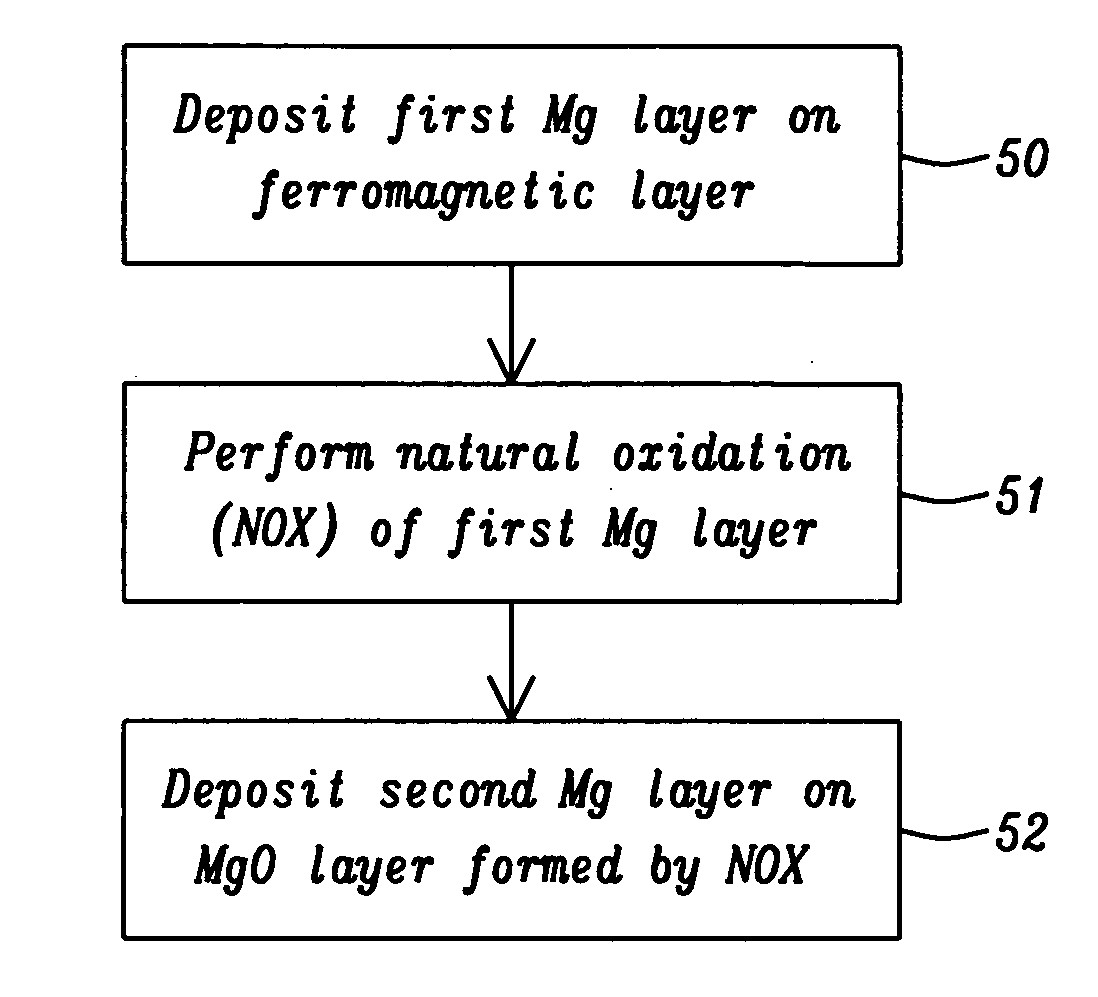

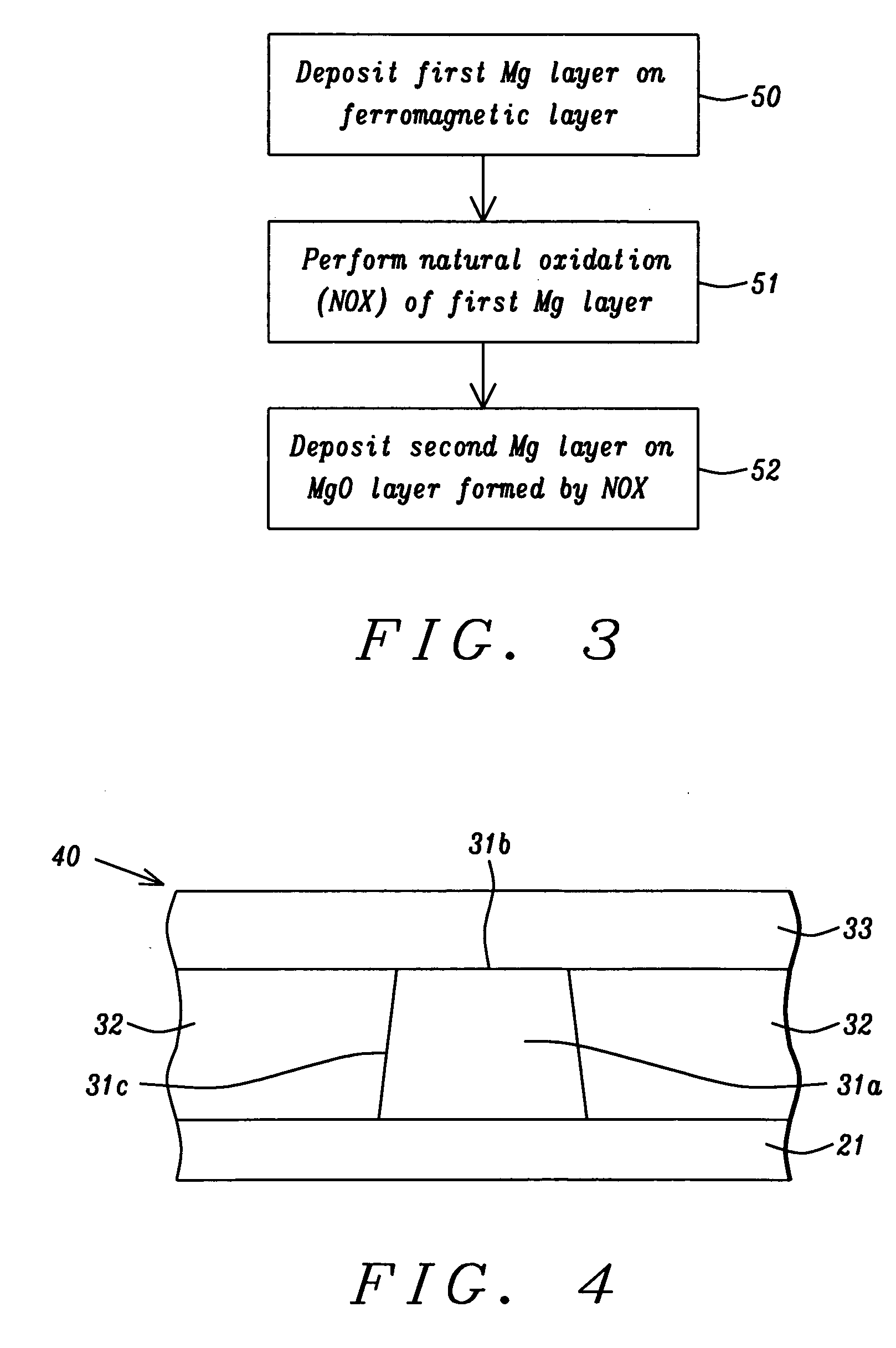

Low resistance tunneling magnetoresistive sensor with natural oxidized double MgO barrier

ActiveUS20070111332A1Improve uniformityHigh MR ratioNanomagnetismMagnetic measurementsSpin valveMaterials science

A high performance TMR sensor is fabricated by incorporating a tunnel barrier having a Mg / MgO / Mg configuration. The 4 to 14 Angstroms thick lower Mg layer and 2 to 8 Angstroms thick upper Mg layer are deposited by a DC sputtering method while the MgO layer is formed by a NOX process involving oxygen pressure from 0.1 mTorr to 1 Torr for 15 to 300 seconds. NOX time and pressure may be varied to achieve a MR ratio of at least 34% and a RA value of 2.1 ohm-um2. The NOX process provides a more uniform MgO layer than sputtering methods. The second Mg layer is employed to prevent oxidation of an adjacent ferromagnetic layer. In a bottom spin valve configuration, a Ta / Ru seed layer, IrMn AFM layer, CoFe / Ru / CoFeB pinned layer, Mg / MgO / Mg barrier, CoFe / NiFe free layer, and a cap layer are sequentially formed on a bottom shield in a read head.

Owner:HEADWAY TECH INC

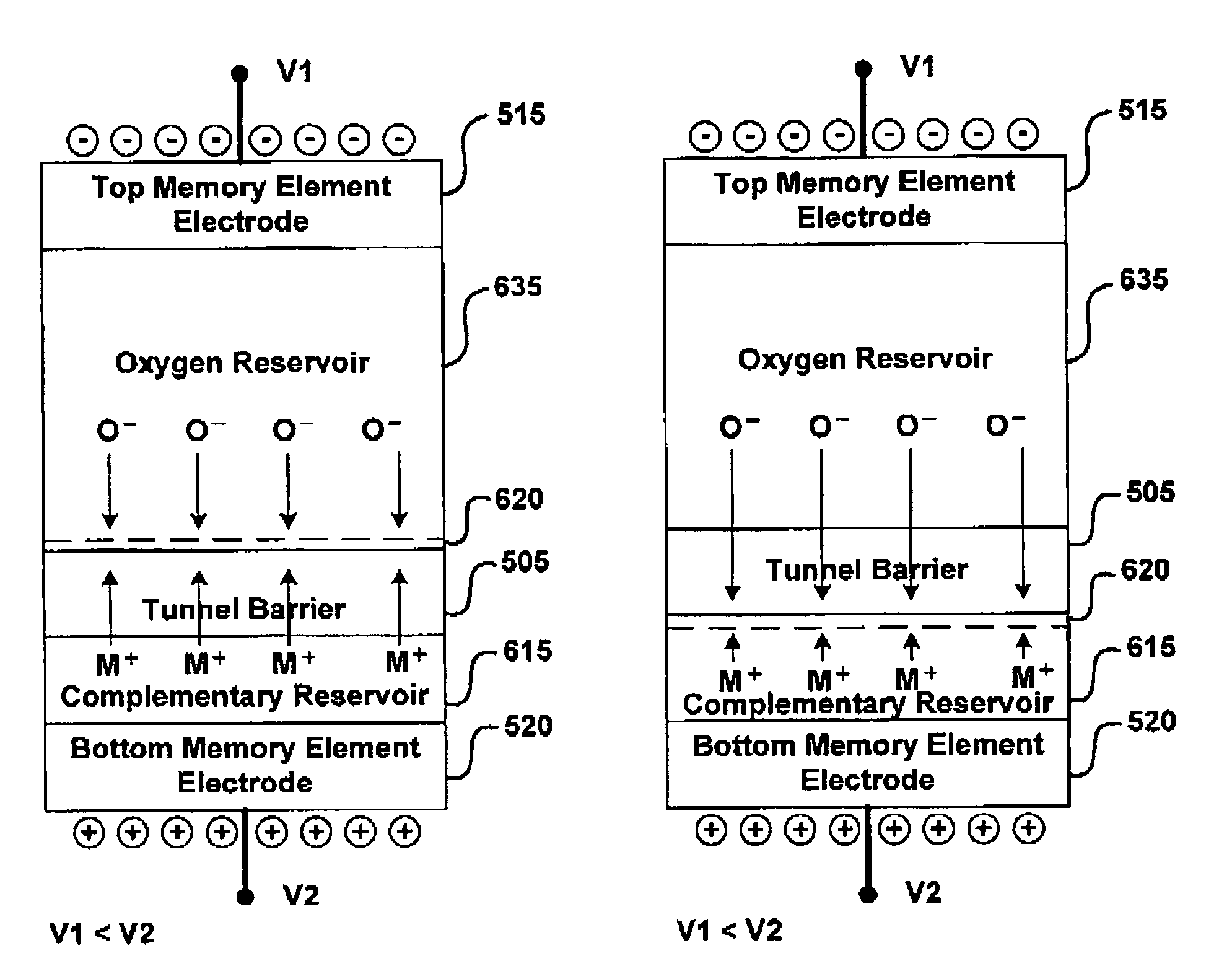

Memory using variable tunnel barrier widths

A memory using a tunnel barrier is disclosed. A memory element includes a tunneling barrier and two conductive materials. The conductive material typically has mobile ions that either move towards or away from the tunneling barrier in response to a voltage across the memory element. A low conductivity region is irreversibly formed for one time programmable memory. The tunneling barrier can be formed by mobile ions combining with complementary ions. The low conductivity region increases the effective width of the tunnel barrier, making electrons tunnel a greater distance, which reduces the memory element's conductivity. By varying conductivity, multiple states can be created in the memory cell.

Owner:HEFEI RELIANCE MEMORY LTD

Magneto-resistance effect element and magnetic memory

InactiveUS20060227465A1Lower average currentNanomagnetismMagnetic-field-controlled resistorsMagnetizationMagnetic memory

It is possible to reduce a current required for spin injection writing. A magneto-resistance effect element includes: a first magnetization pinned layer; a magnetization free layer; a tunnel barrier layer; a second magnetization pinned layer whose direction of magnetization is pinned to be substantially anti-parallel to the direction of magnetization of the first magnetization pinned layer, and; a non-magnetic layer. When the second magnetization pinned layer is made of ferromagnetic material including Co, material for the non-magnetic layer is metal including at least one element selected from the group consisting of Zr, Hf, Rh, Ag, and Au; when the second magnetization pinned layer is made of ferromagnetic material including Fe, material for the non-magnetic layer is metal including at least one element selected from the group consisting of Rh, Pt, Ir, Al, Ag, and Au; and when the second magnetization pinned layer is made of ferromagnetic material including Ni, material for the non-magnetic layer is metal including at least one element selected from the group consisting of Zr, Hf, Au, and Ag.

Owner:KK TOSHIBA

Capping structure for enhancing dR/R of the MTJ device

An MTJ in an MRAM array or in a TMR read head is comprised of a capping layer with a lower inter-diffusion barrier layer, an intermediate oxygen gettering layer, and an upper metal layer that contacts a top conductor. The composite capping layer is especially useful with a moderate spin polarization free layer such as a NiFe layer with a Fe content of about 17.5 to 20 atomic %. The capping layer preferably has a Ru / Ta / Ru configuration in which the lower Ru layer is about 10 to 30 Angstroms thick and the Ta layer is about 30 Angstroms thick. As a result, a high dR / R of about 40% is achieved with low magnetostriction less than about 1.0 E−6 in an MTJ in an MRAM array. Best results are obtained with an AlOx tunnel barrier layer formed by an in-situ ROX process on an 8 to 10 Angstrom thick Al layer.

Owner:HEADWAY TECH INC +1