Patents

Literature

8175 results about "Random access" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, random access (more precisely and more generally called direct access) is the ability to access an arbitrary element of a sequence in equal time or any datum from a population of addressable elements roughly as easily and efficiently as any other, no matter how many elements may be in the set. It is typically contrasted to sequential access.

Data processing system and method

InactiveUS6215898B1Reduce overheadHigh sensitivityImage enhancementImage analysisStatic random-access memoryHigh memory

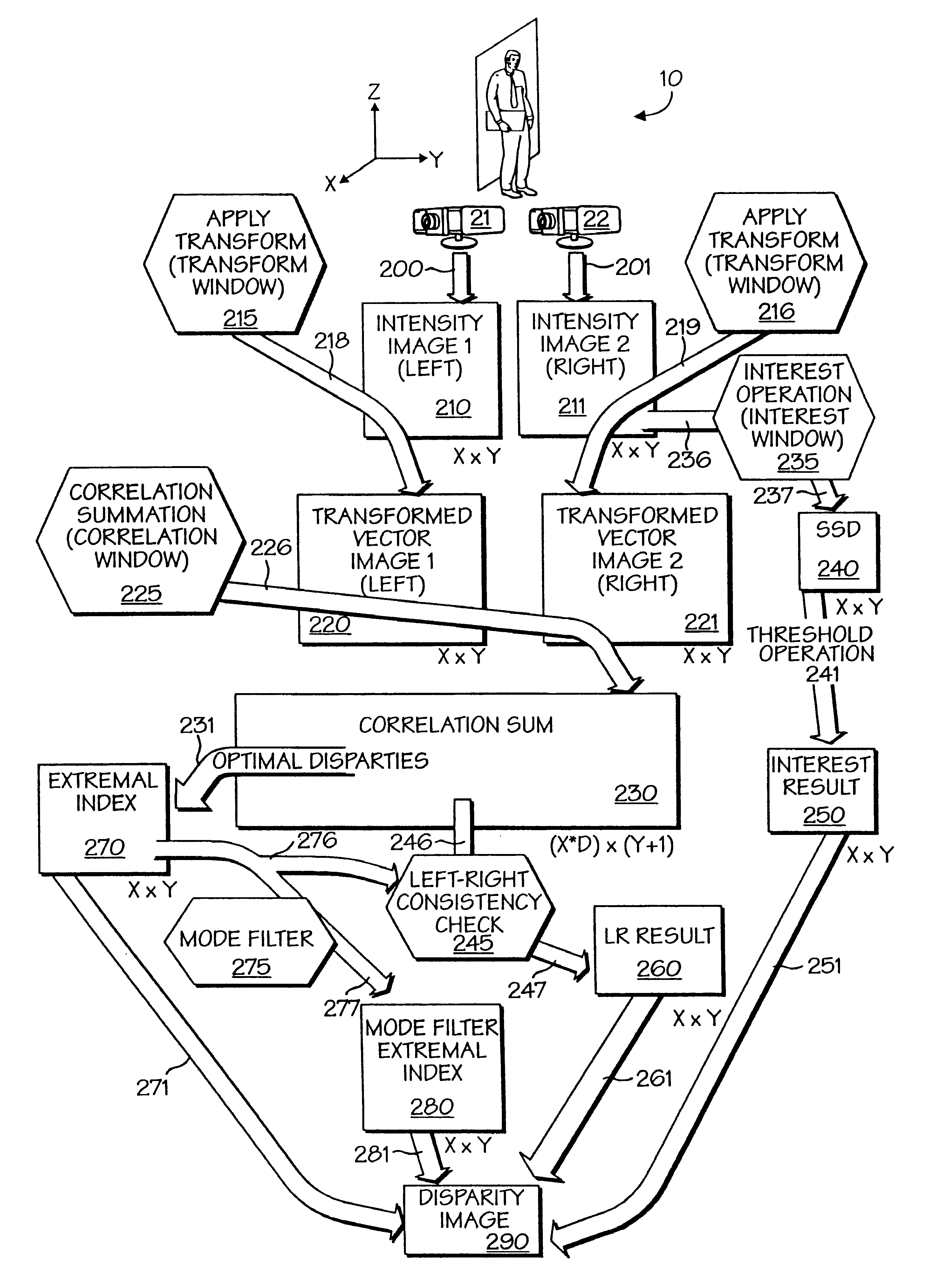

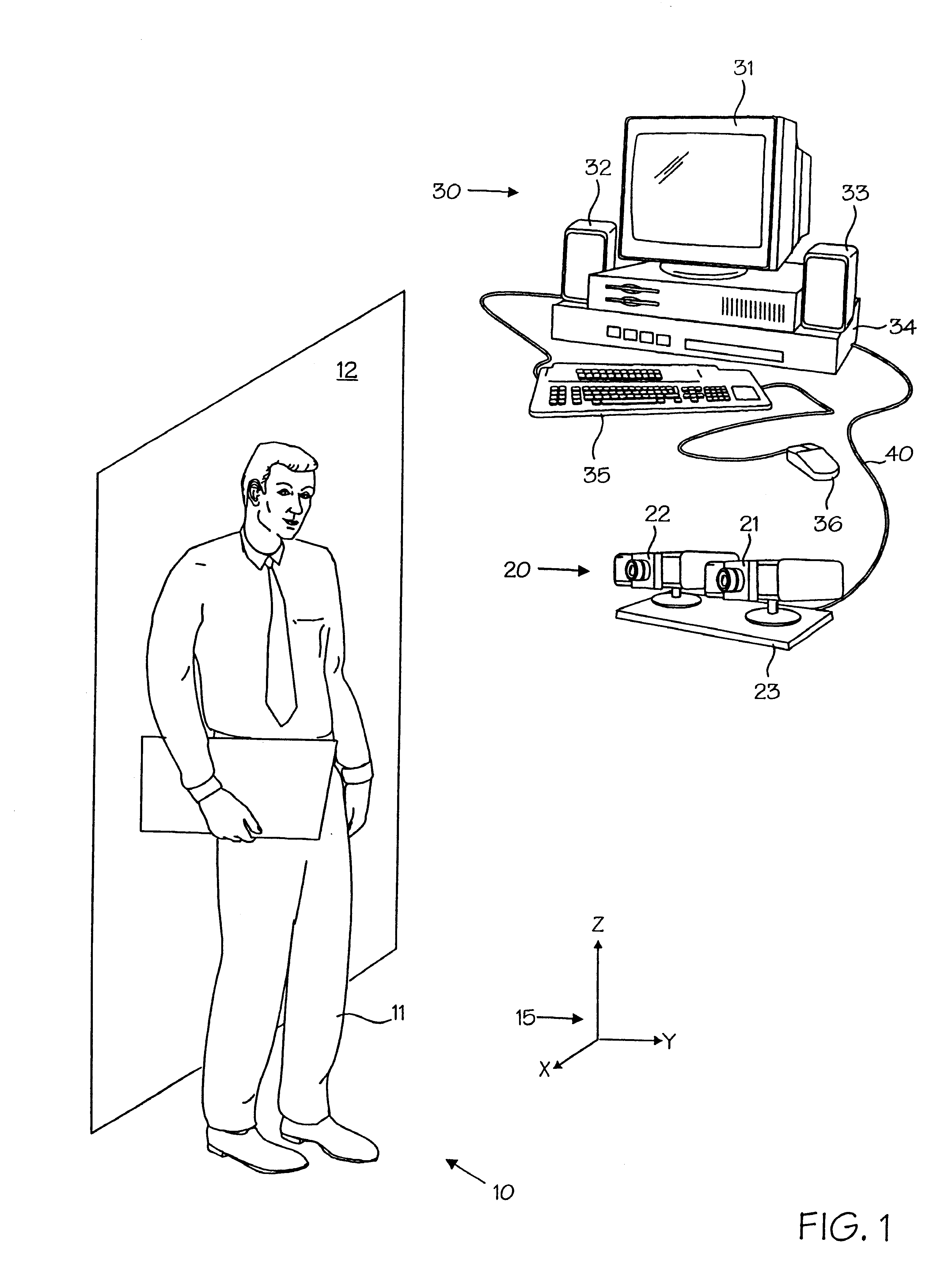

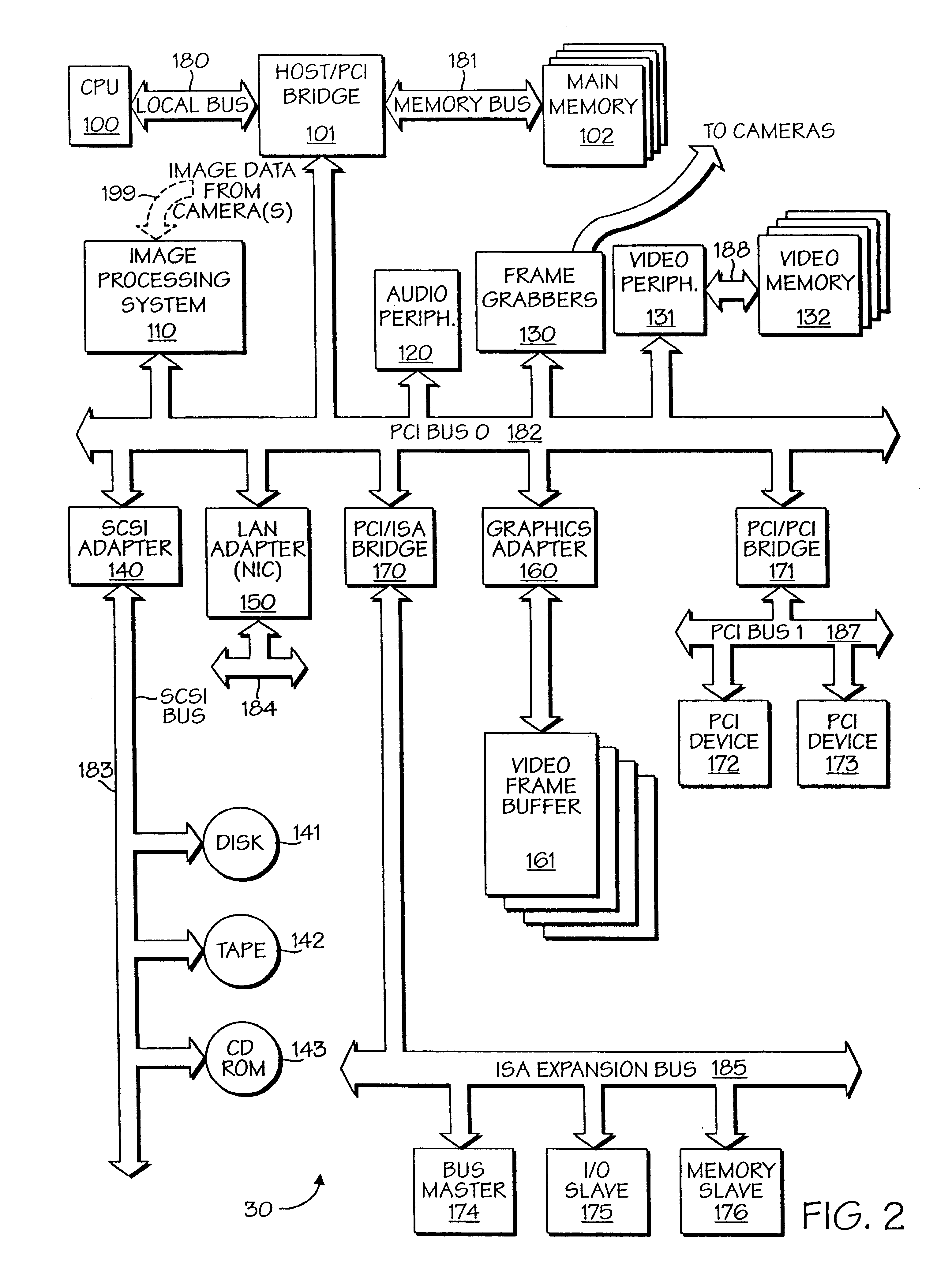

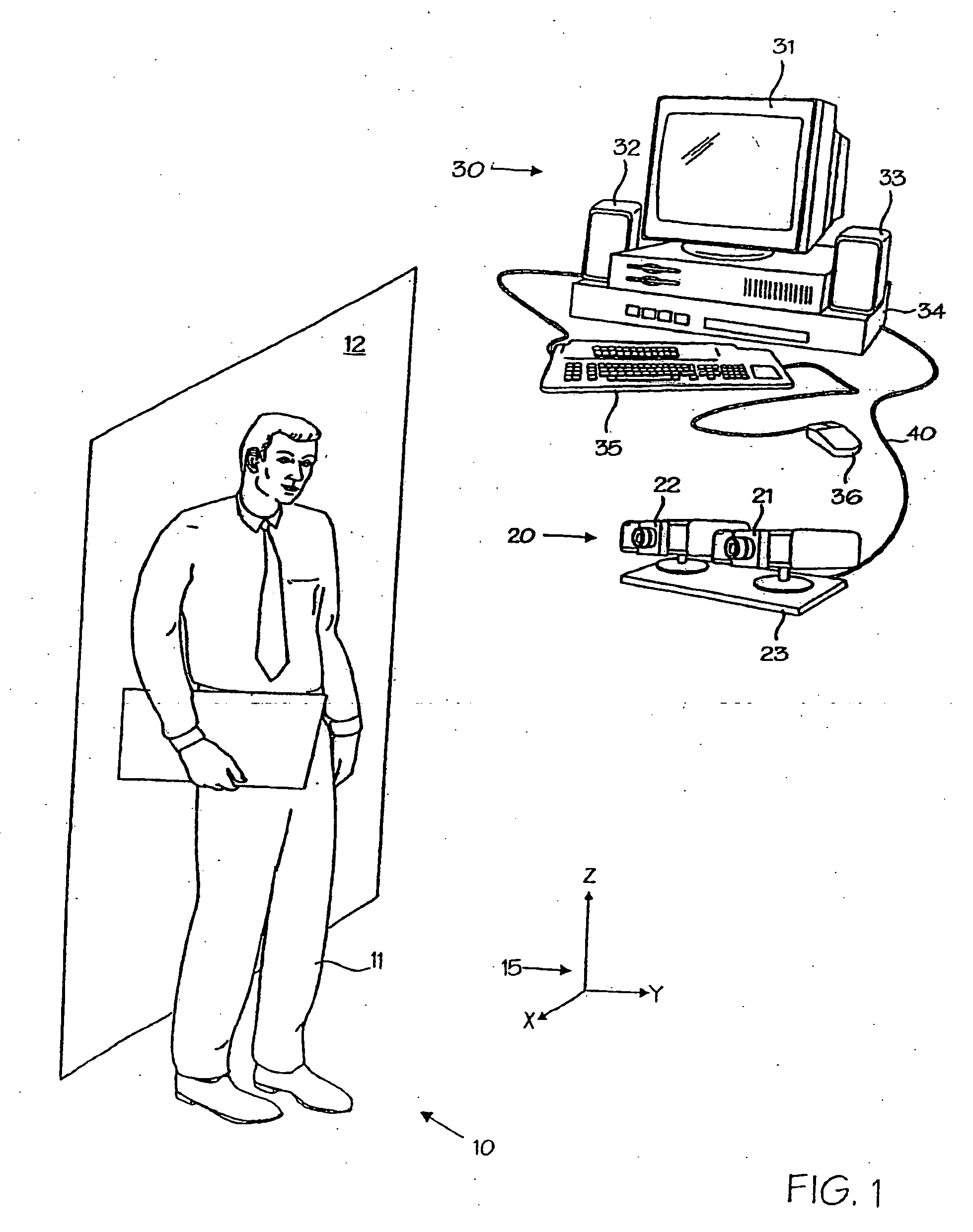

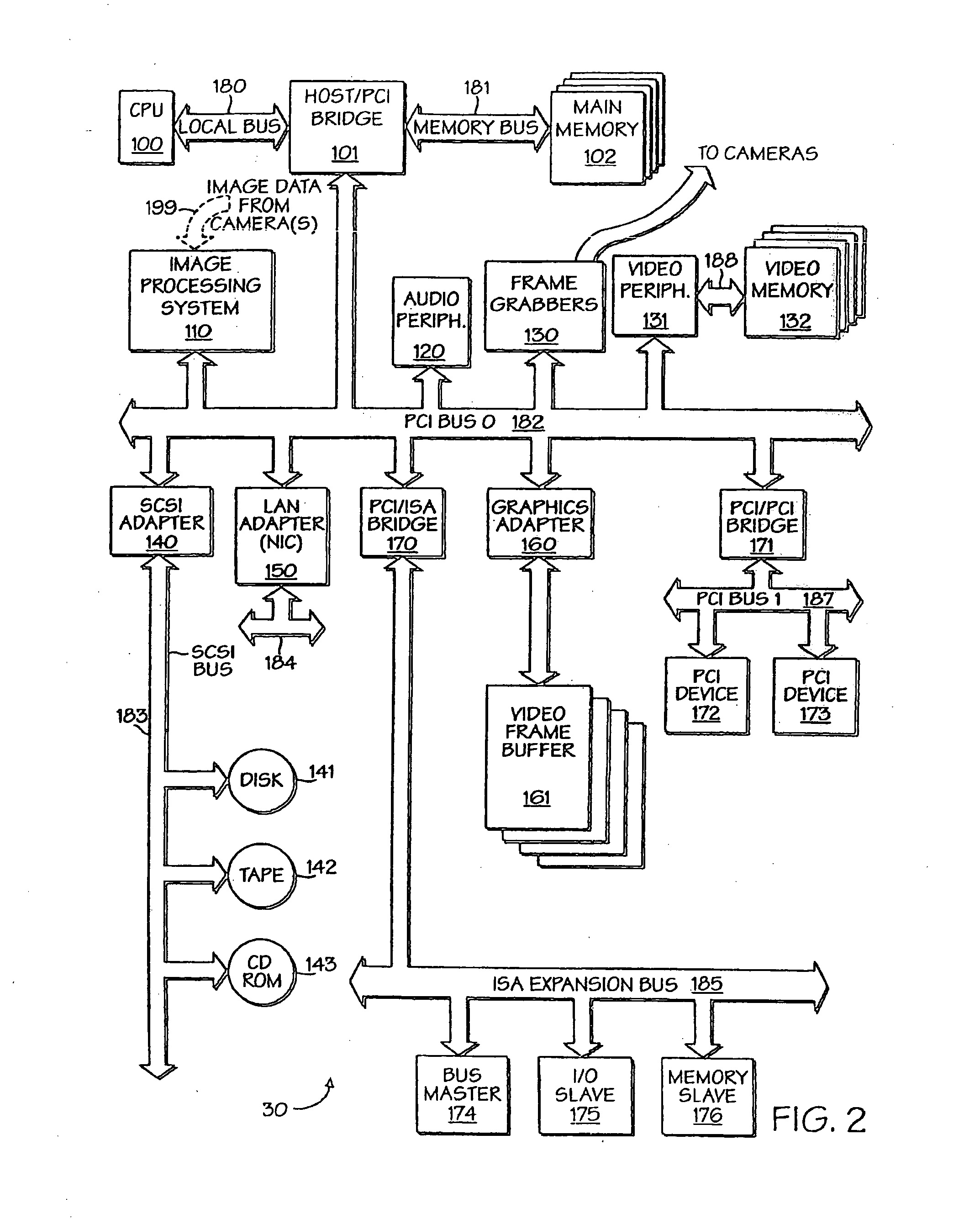

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

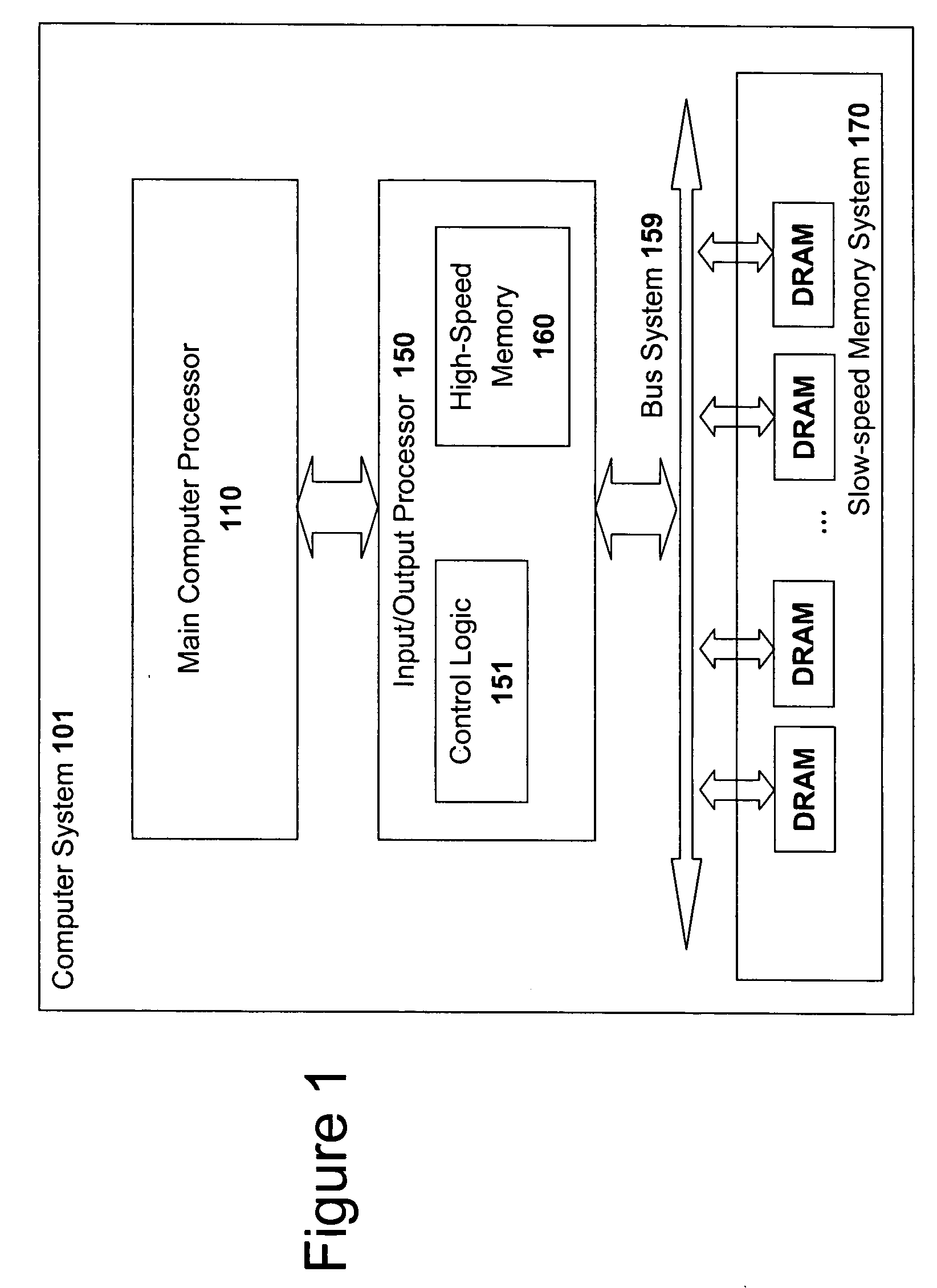

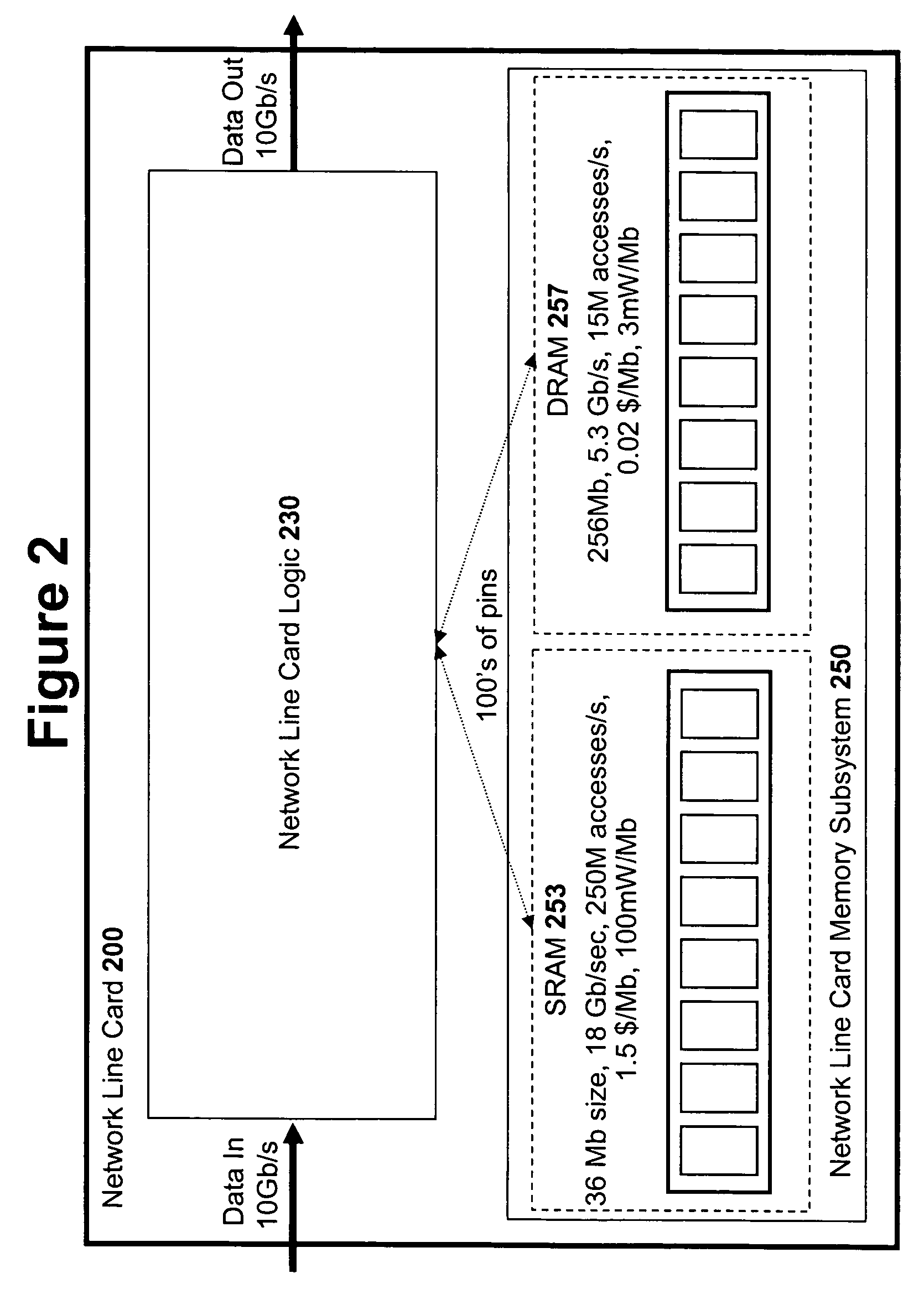

High speed memory control and I/O processor system

ActiveUS20050240745A1Easy to handleSimplify memory access taskMemory architecture accessing/allocationMemory adressing/allocation/relocationHigh speed memoryTailored approach

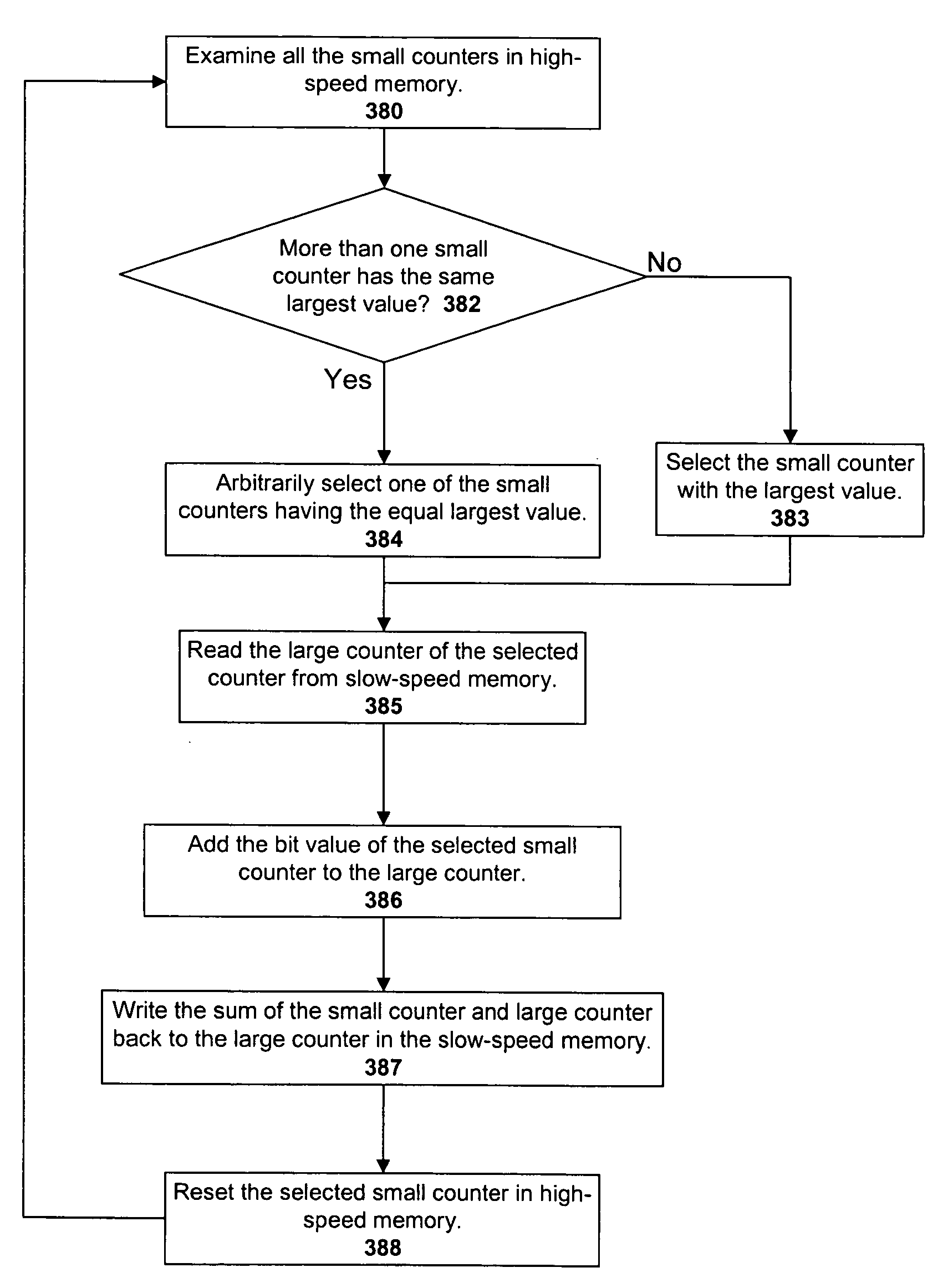

An input / output processor for speeding the input / output and memory access operations for a processor is presented. The key idea of an input / output processor is to functionally divide input / output and memory access operations tasks into a compute intensive part that is handled by the processor and an I / O or memory intensive part that is then handled by the input / output processor. An input / output processor is designed by analyzing common input / output and memory access patterns and implementing methods tailored to efficiently handle those commonly occurring patterns. One technique that an input / output processor may use is to divide memory tasks into high frequency or high-availability components and low frequency or low-availability components. After dividing a memory task in such a manner, the input / output processor then uses high-speed memory (such as SRAM) to store the high frequency and high-availability components and a slower-speed memory (such as commodity DRAM) to store the low frequency and low-availability components. Another technique used by the input / output processor is to allocate memory in such a manner that all memory bank conflicts are eliminated. By eliminating any possible memory bank conflicts, the maximum random access performance of DRAM memory technology can be achieved.

Owner:CISCO TECH INC

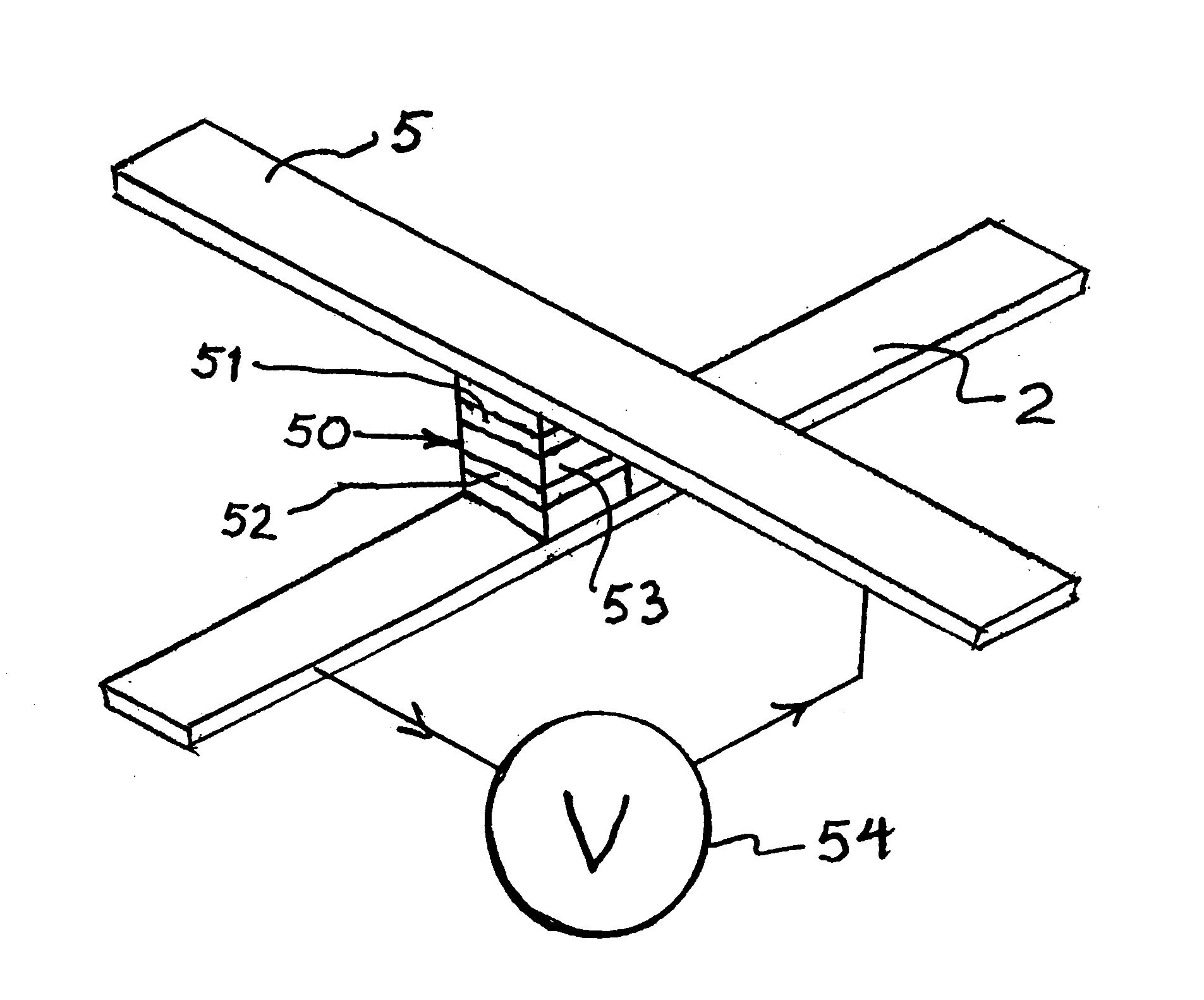

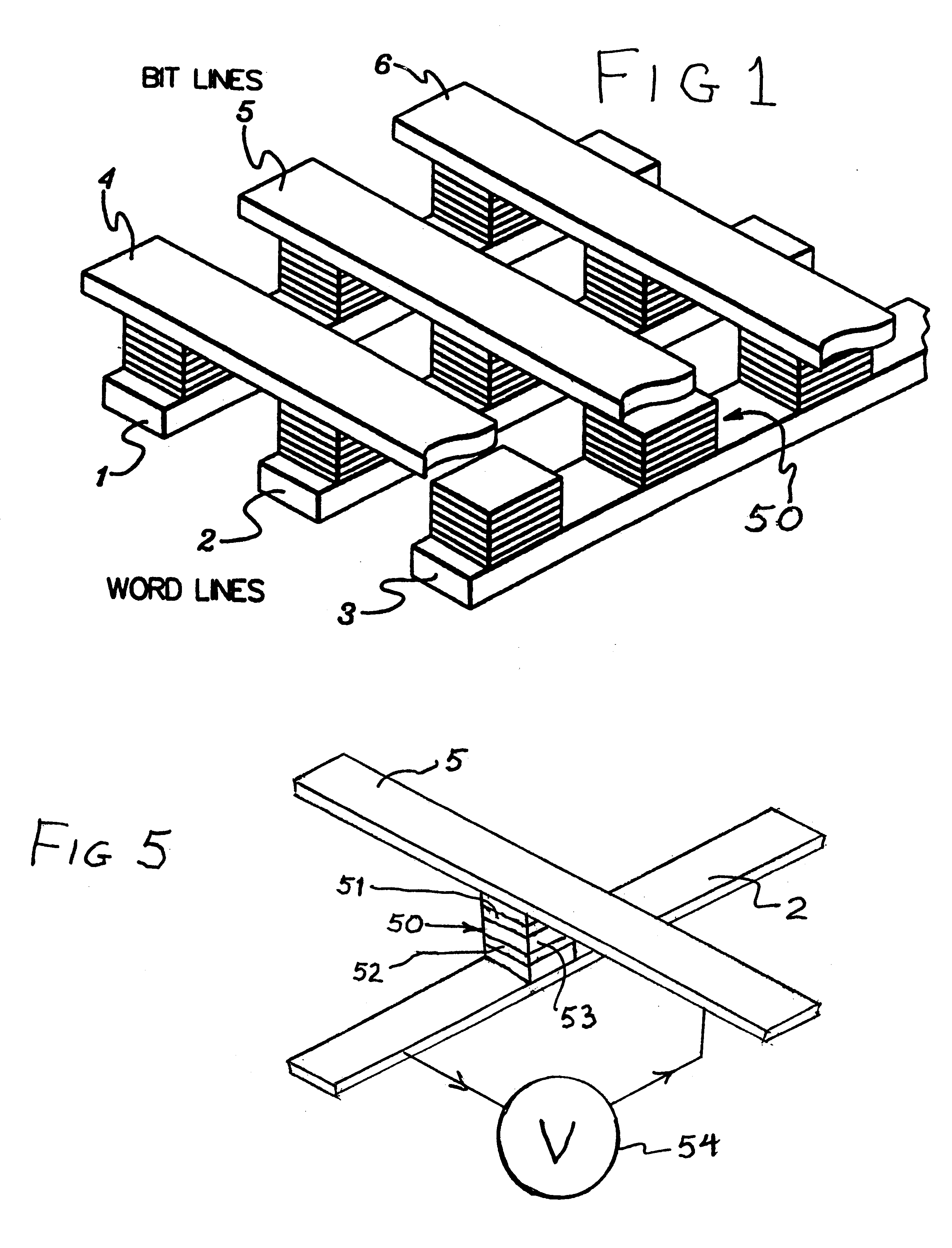

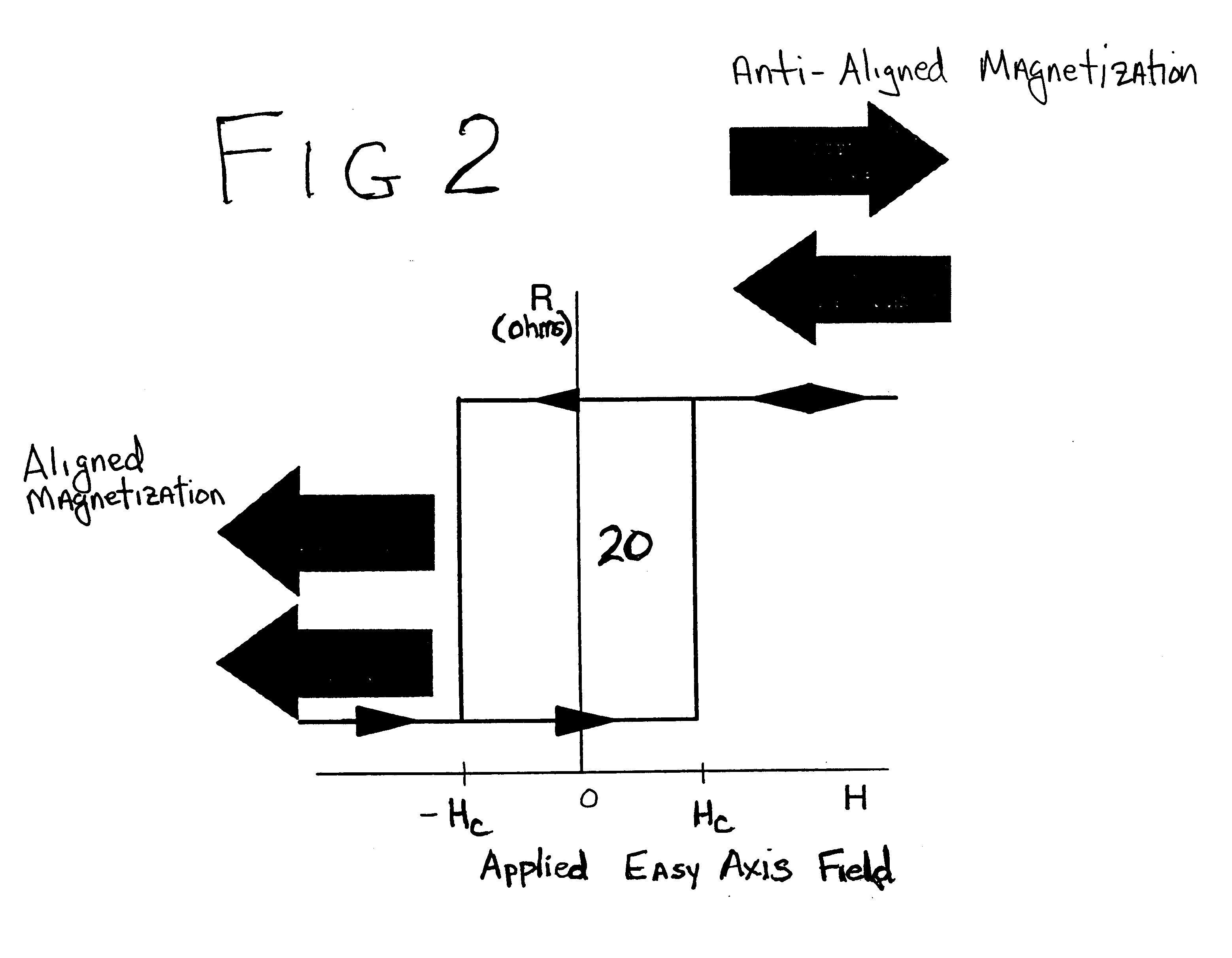

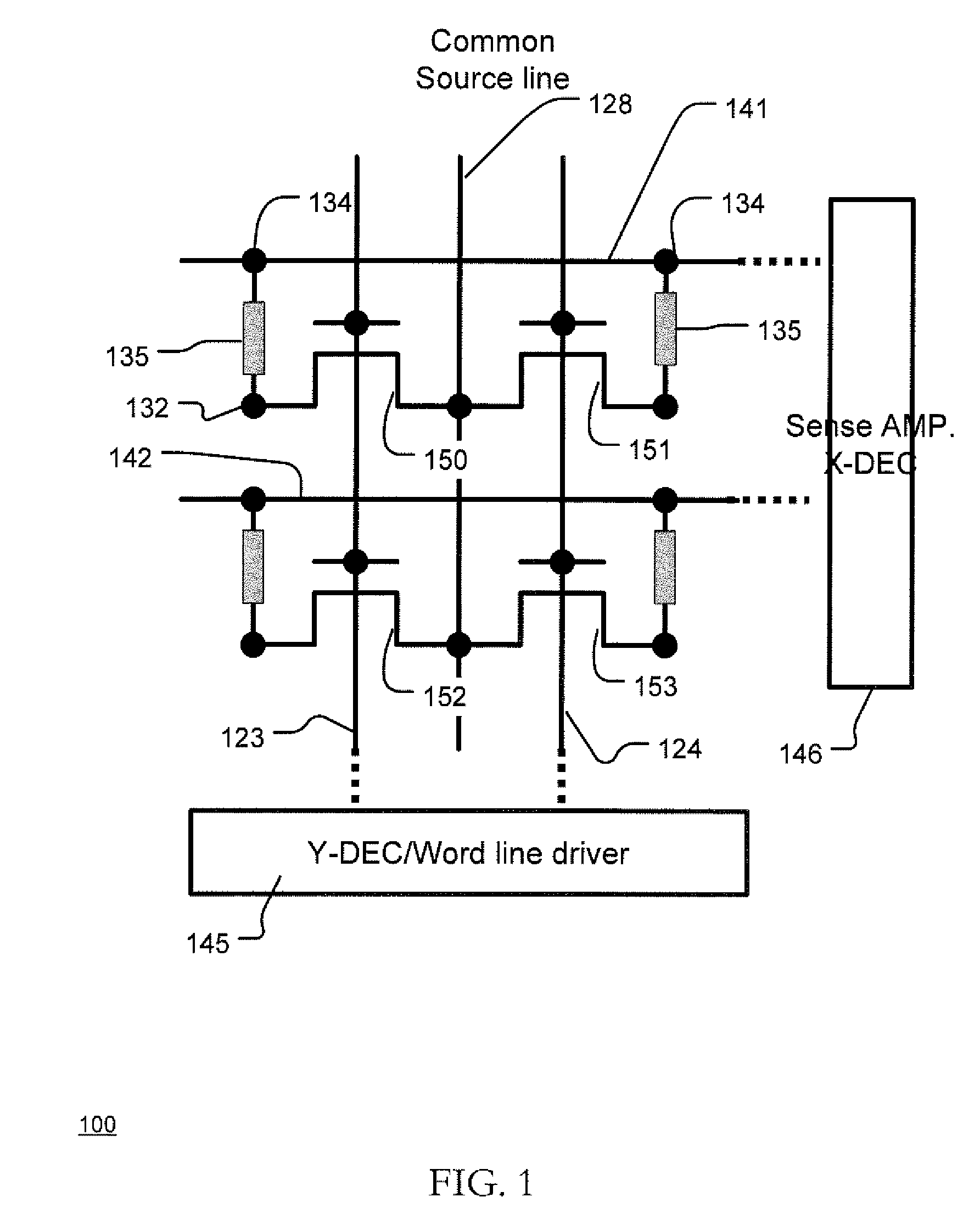

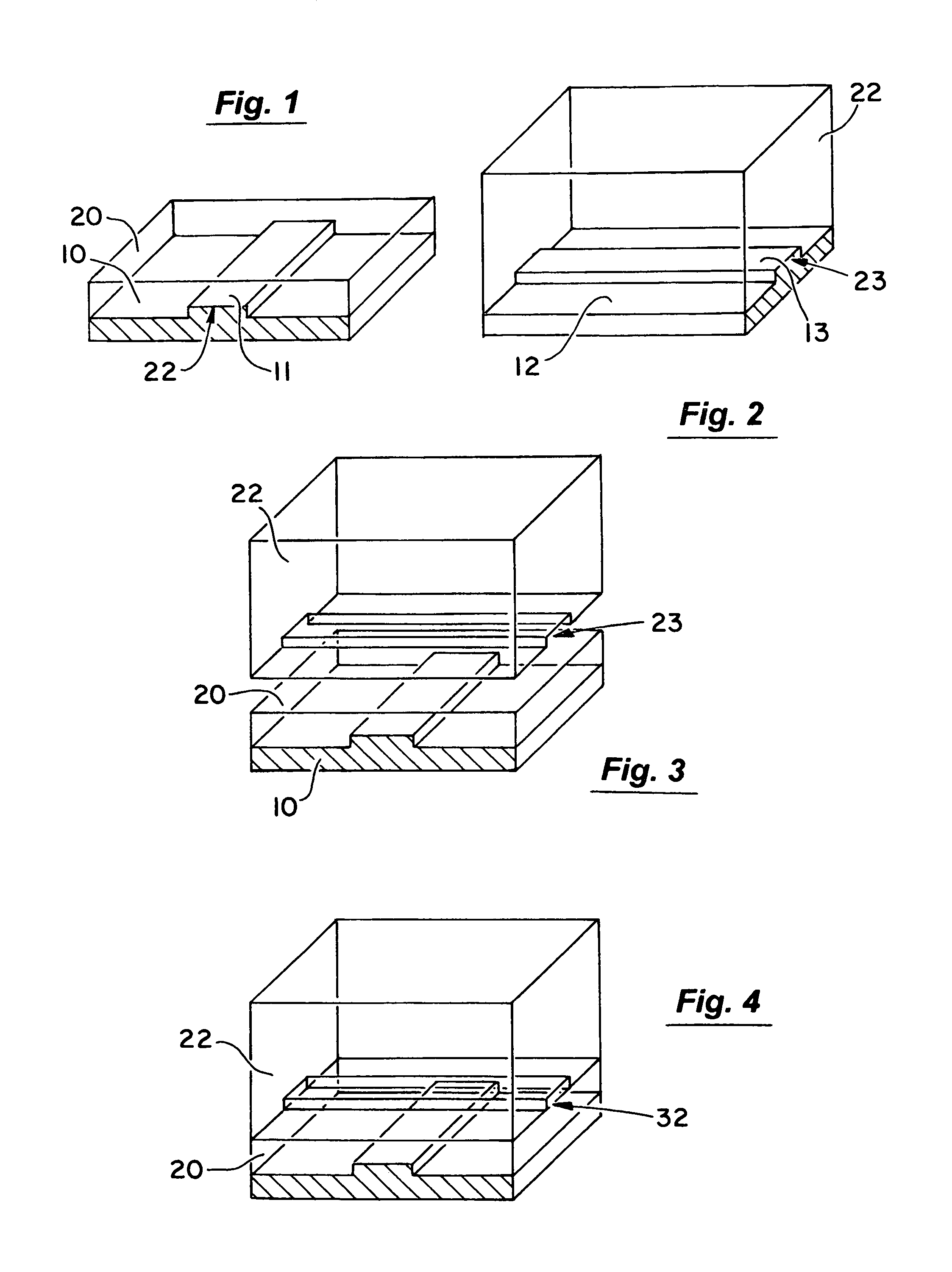

Thermally-assisted magnetic random access memory (MRAM)

It is important to ensure good selectivity of a single magnetic tunnel junction storage cell within a memory array without affecting nearby storage cells. For this purpose, this memory array of storage cells preferably comprises a) an array of electrically conducting bit lines and electrically conducting word lines which form intersections therebetween, b) a storage cell disposed at each of said intersections, each storage cell comprising at least one reversible magnetic region or layer characterized by a magnetization state which can be reversed by applying thereto a selected external magnetic field, said reversible magnetic layer comprising a material whose magnetization state is more easily reversed upon a change in the temperature thereof, and c) a temperature change generator for changing the temperature of said reversible magnetic layer of only a selected one of said array of storage cells at any moment. To select a cell, it is preferable to select a cell by using a brief pulse of tunnelling current between the intersecting bit and word lines at that cell in order to provide sufficient Joule heating to facilitate a change in the magnetization state of its reversible magnetic layer, which preferably comprises a ferrimagnetic material.

Owner:IBM CORP

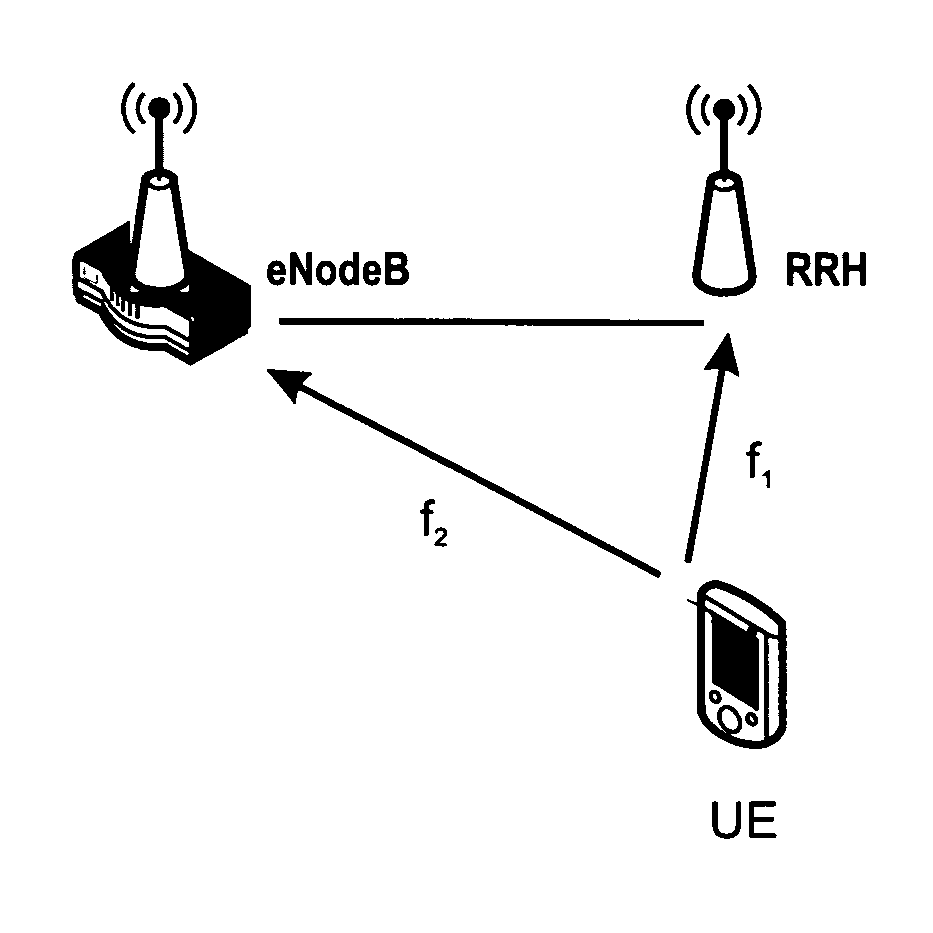

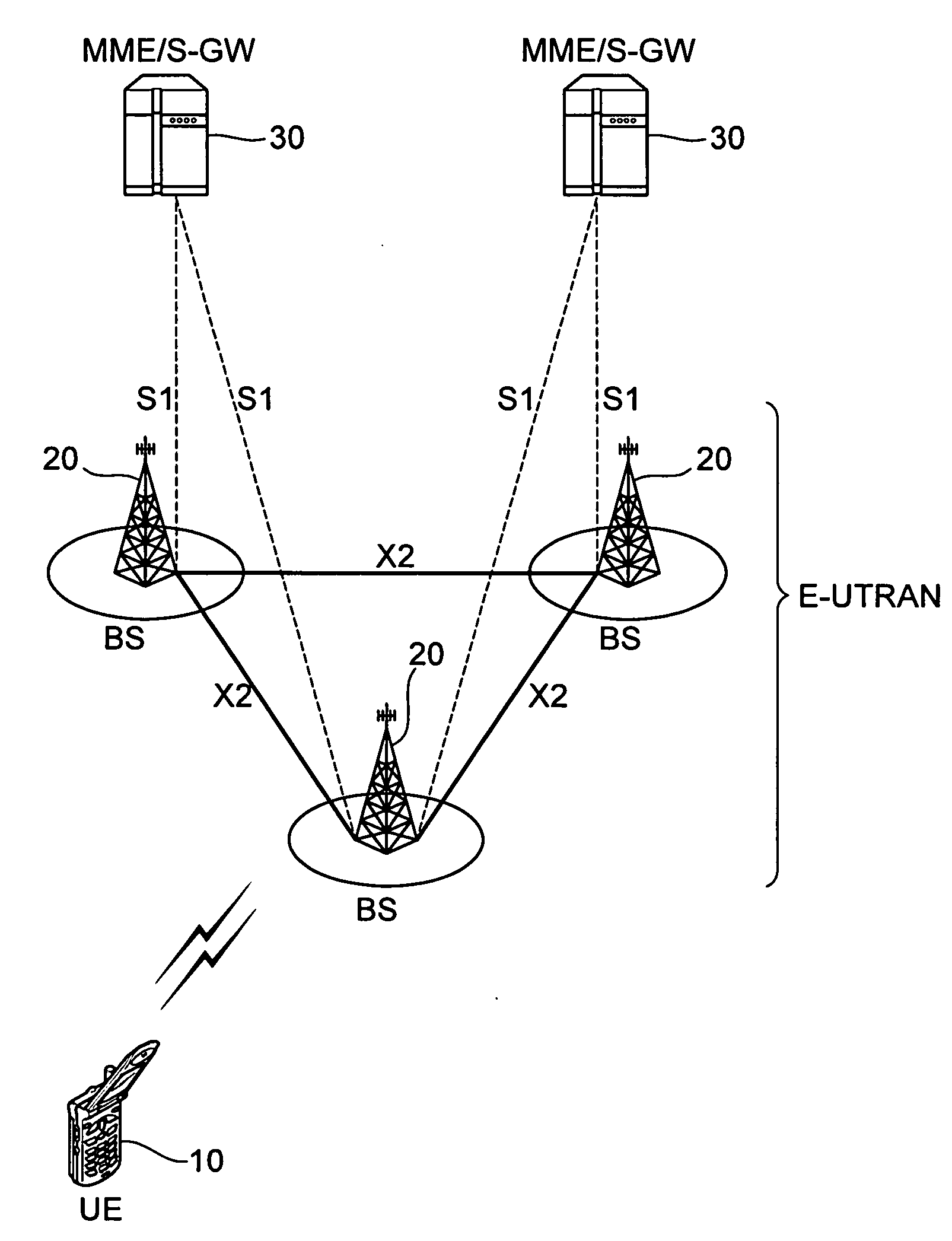

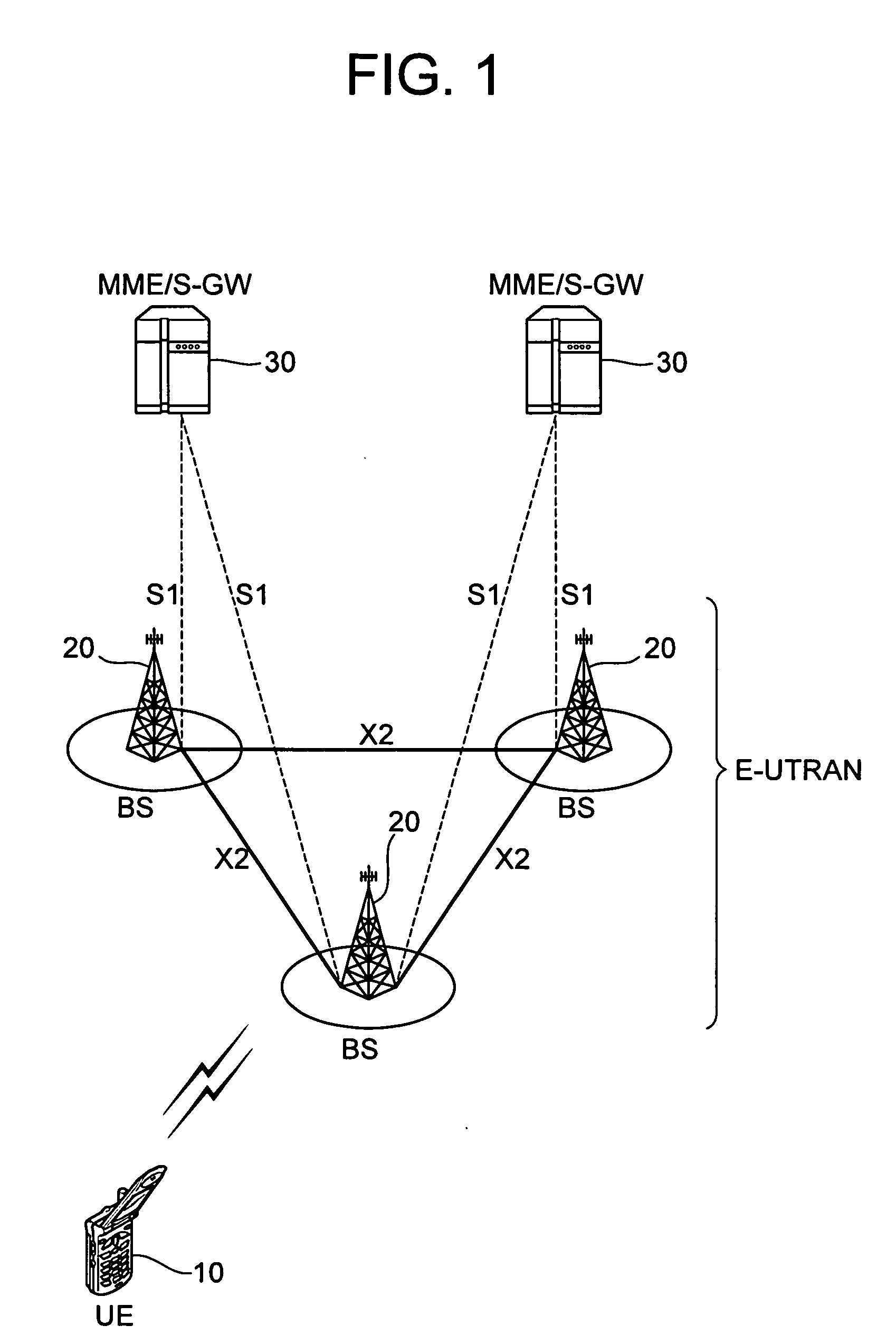

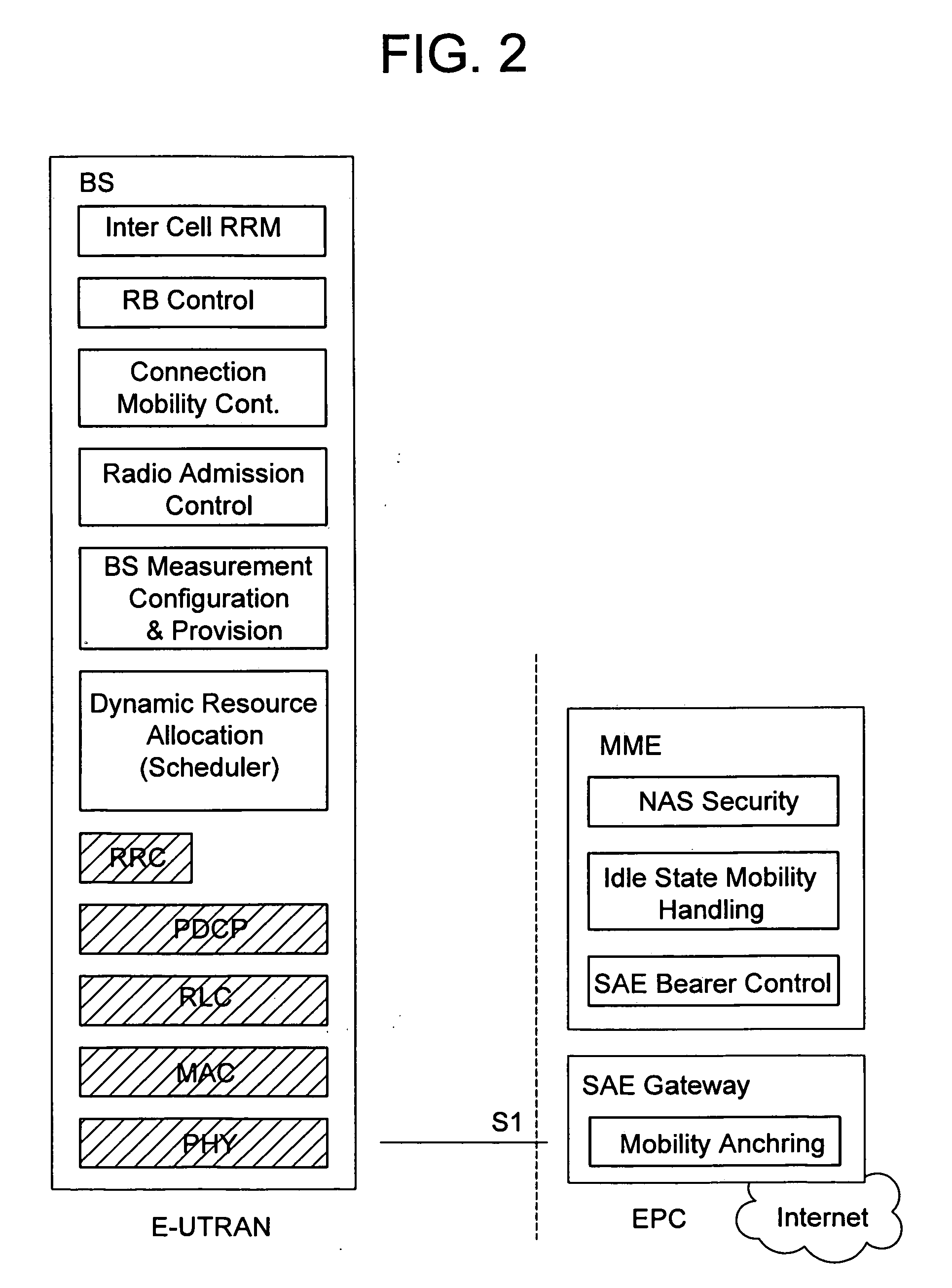

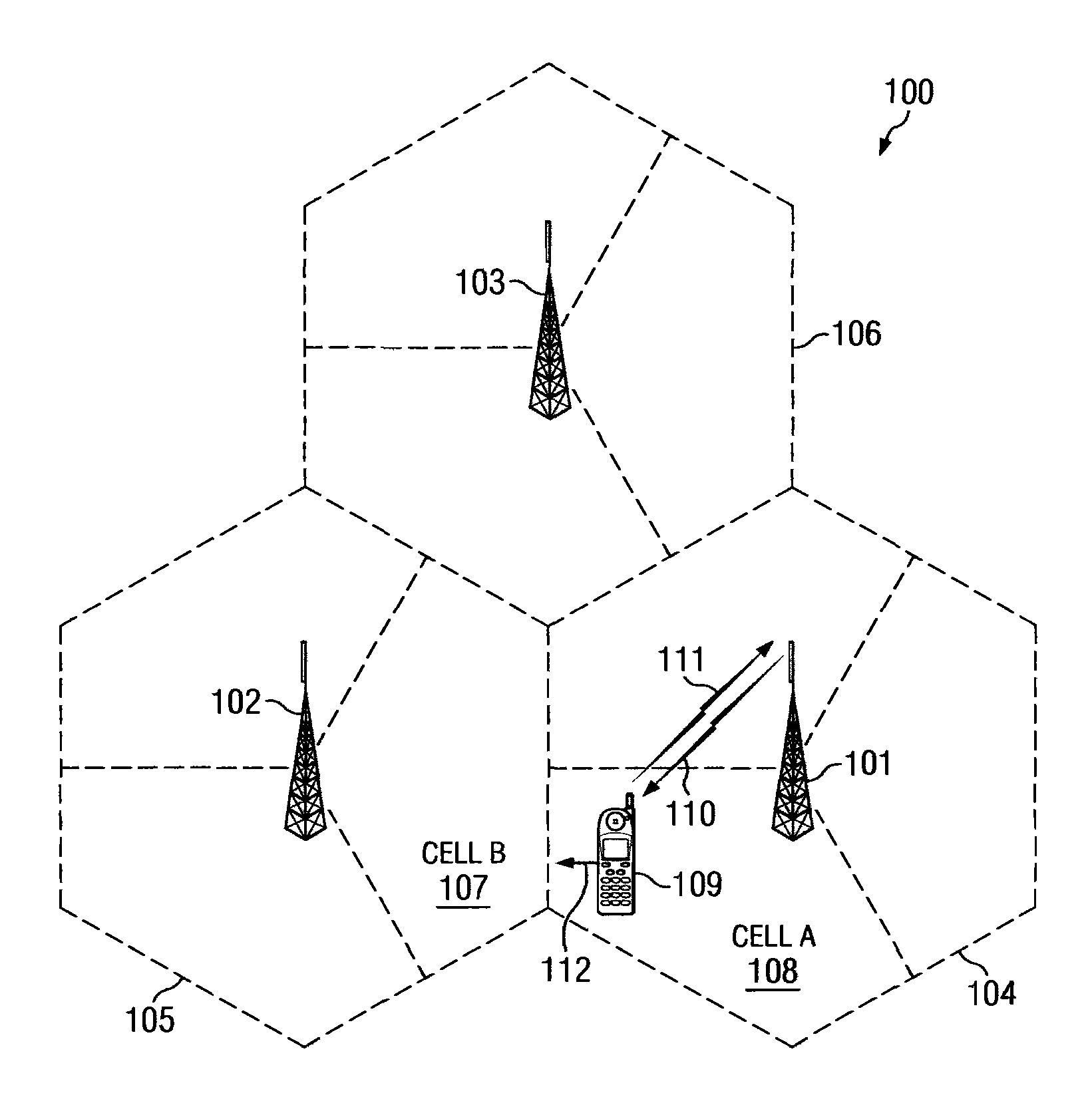

Transmit power control for physical random access channels

ActiveUS20130058315A1Increase the likelihood of successAvoid low successPower managementSynchronisation arrangementUplink transmissionTransmitted power

The invention relates to methods for adjusting the transmit power utilized by a mobile terminal for uplink transmissions, and to methods for adjusting the transmit power used by a mobile terminal for one or more RACH procedures. The invention is also providing apparatus and system for performing these methods, and computer readable media the instructions of which cause the apparatus and system to perform the methods described herein. In order to allow for adjusting the transmit power of uplink transmissions on uplink component carriers, the invention suggests introducing a power scaling for uplink PRACH transmissions performing RACH procedures on an uplink component carrier. The power scaling is proposed on the basis of a prioritization among multiple uplink transmissions or on the basis of the uplink component carriers on which RACH procedures are performed.

Owner:SUN PATENT TRUST

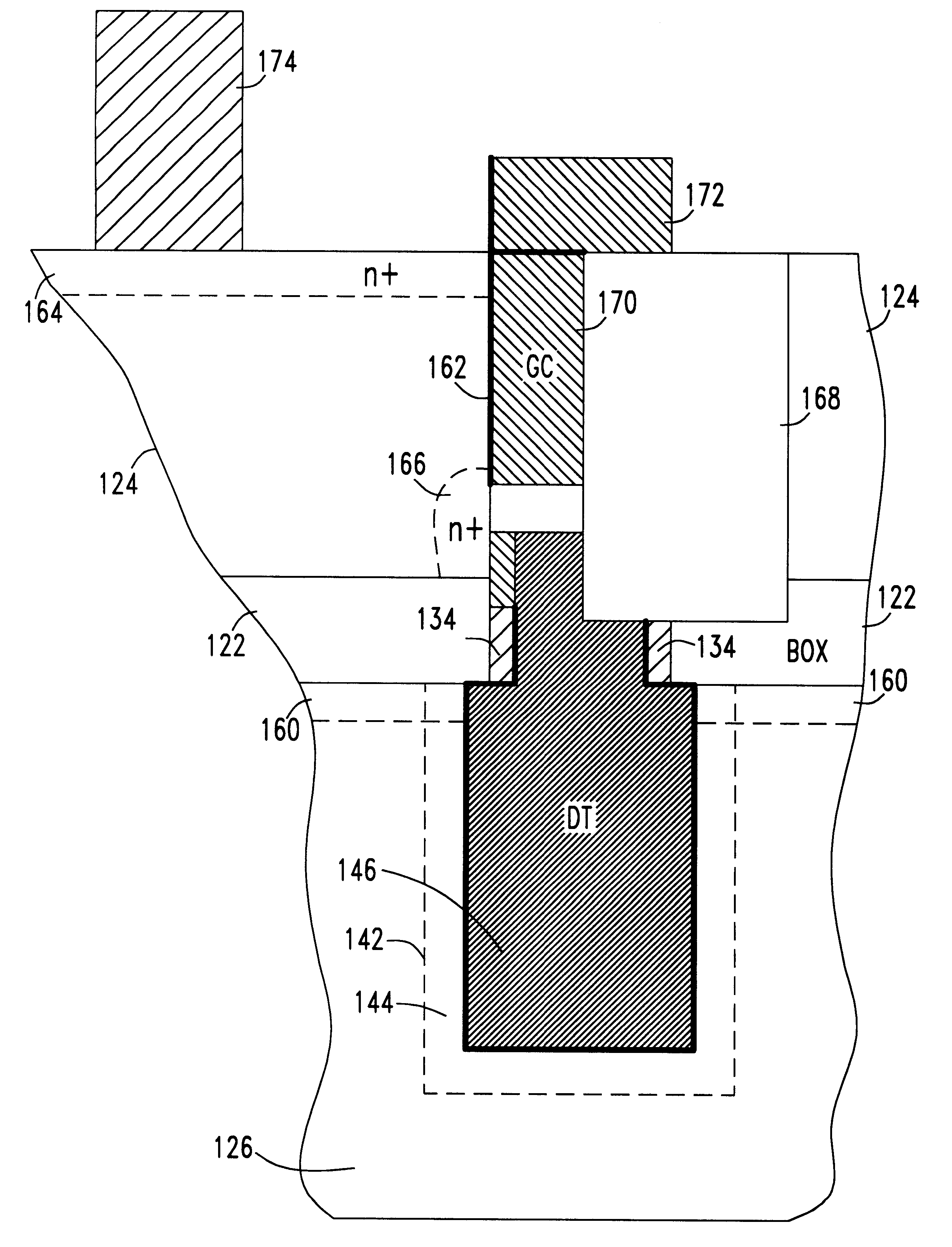

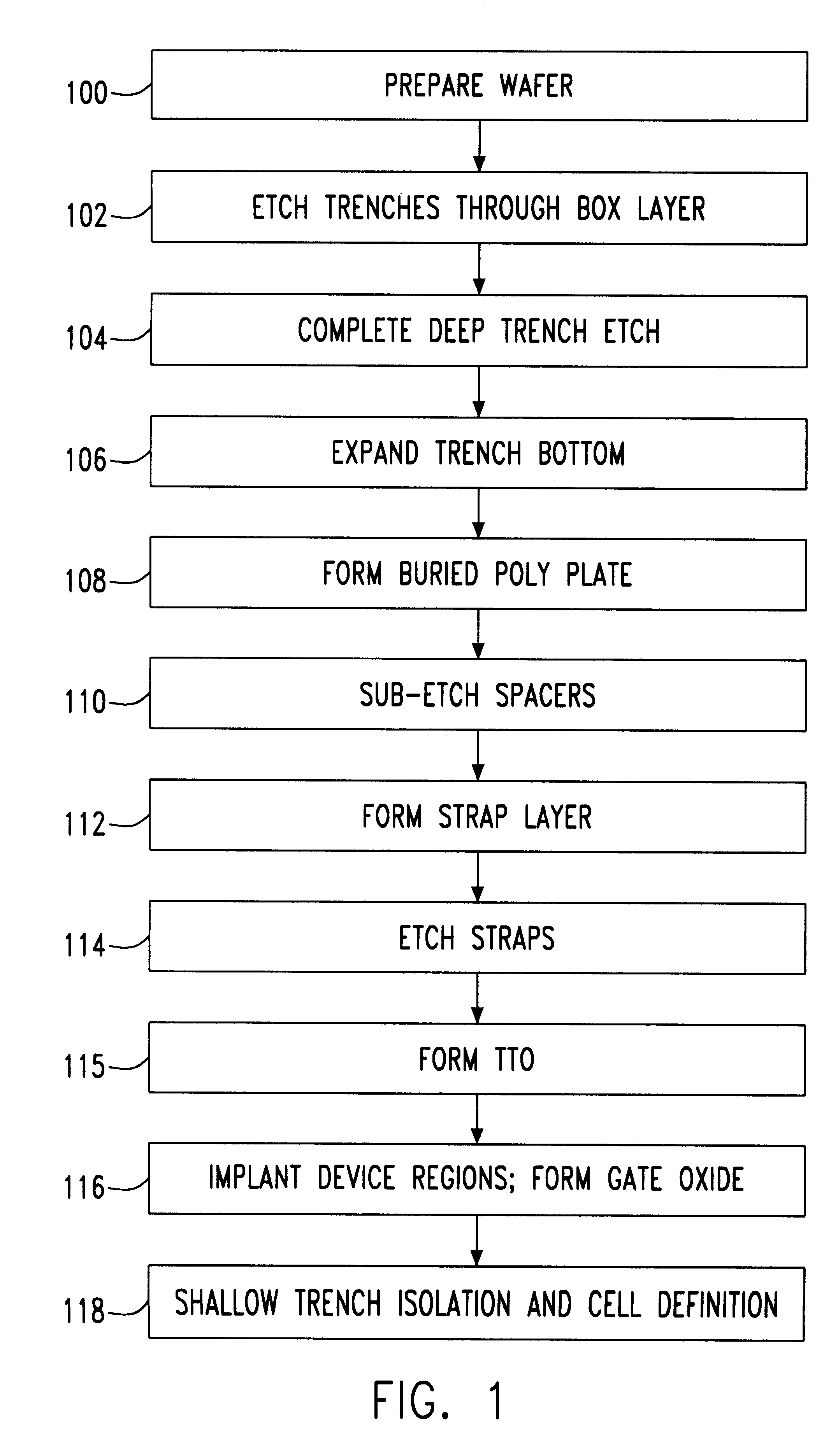

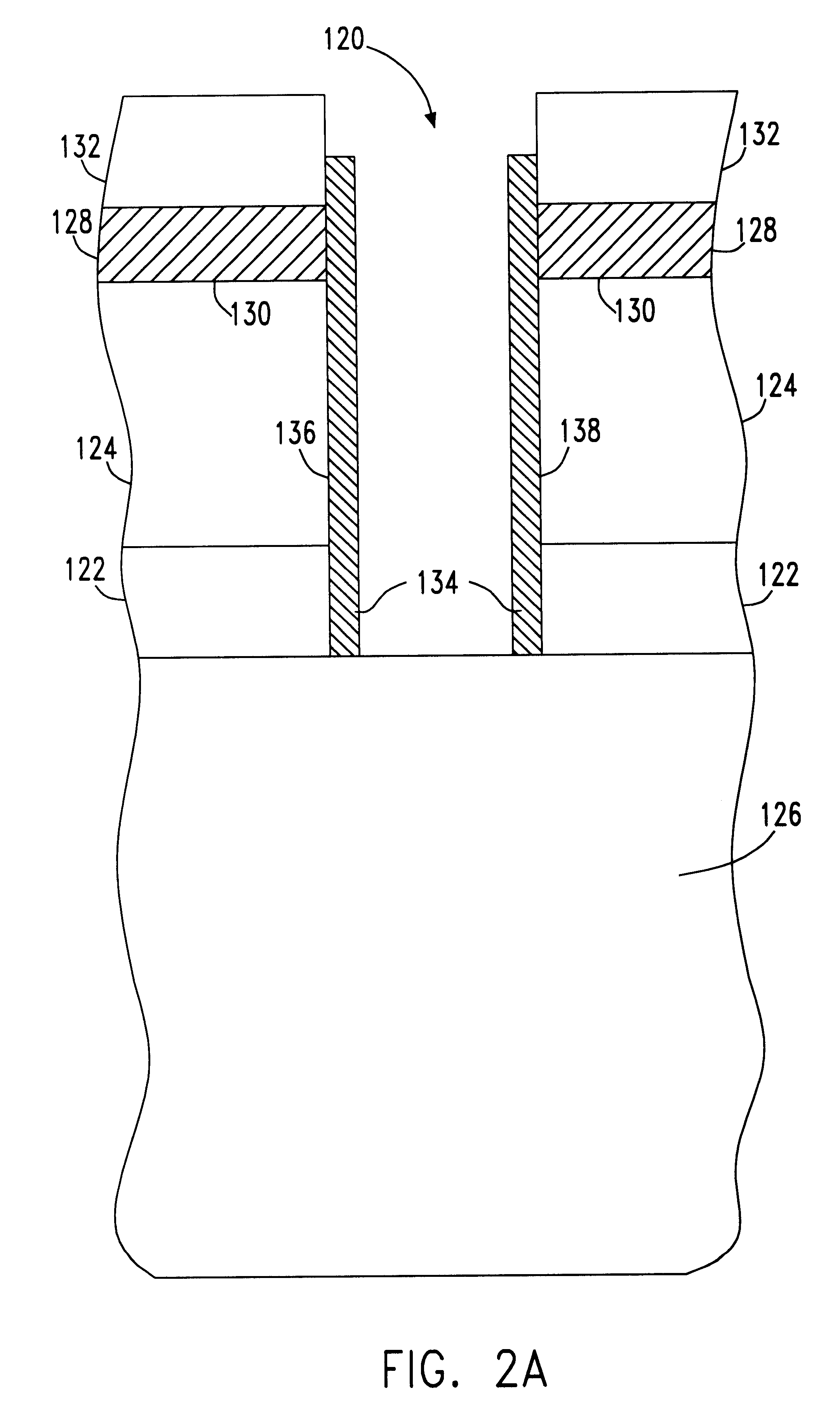

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

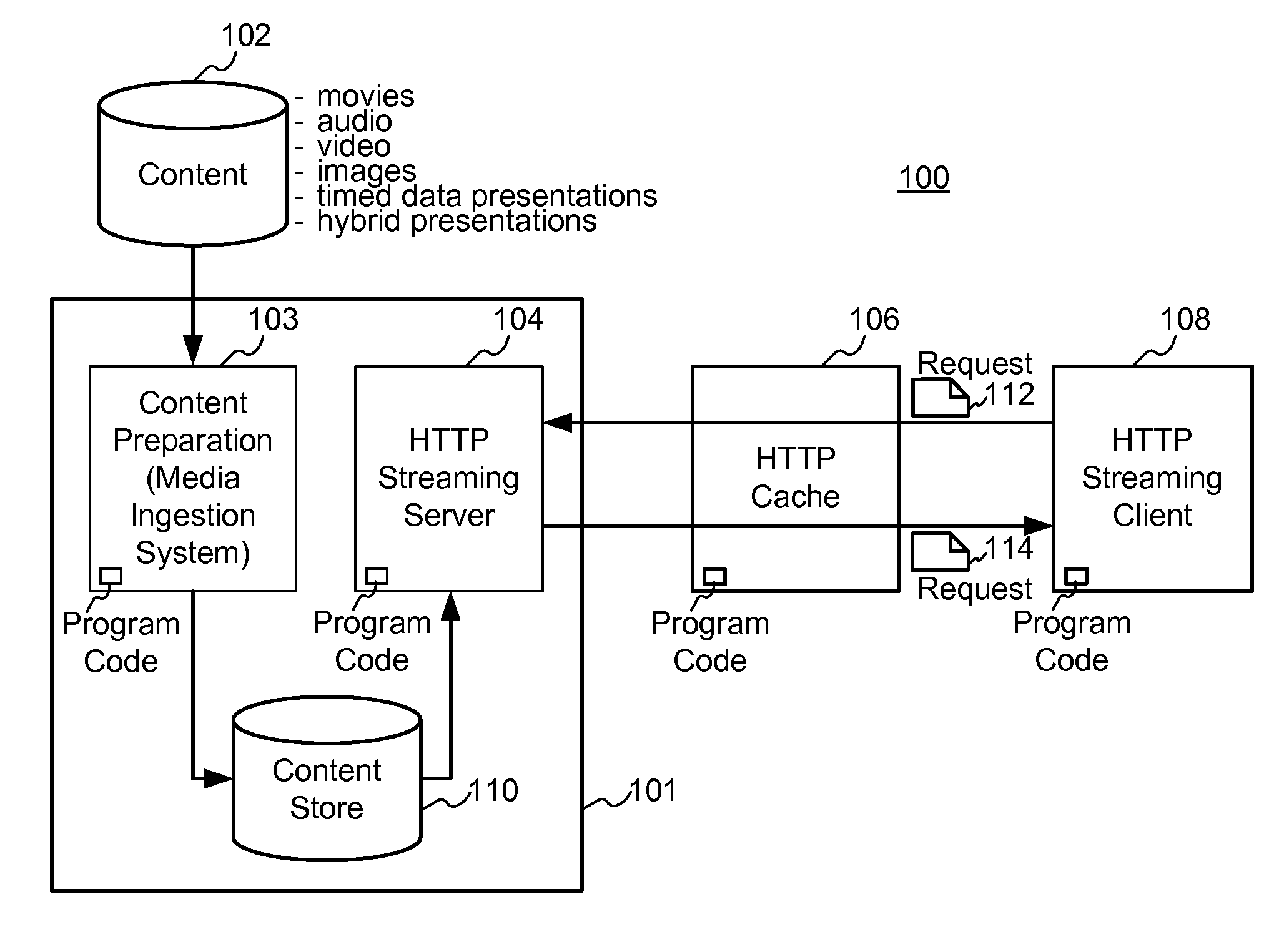

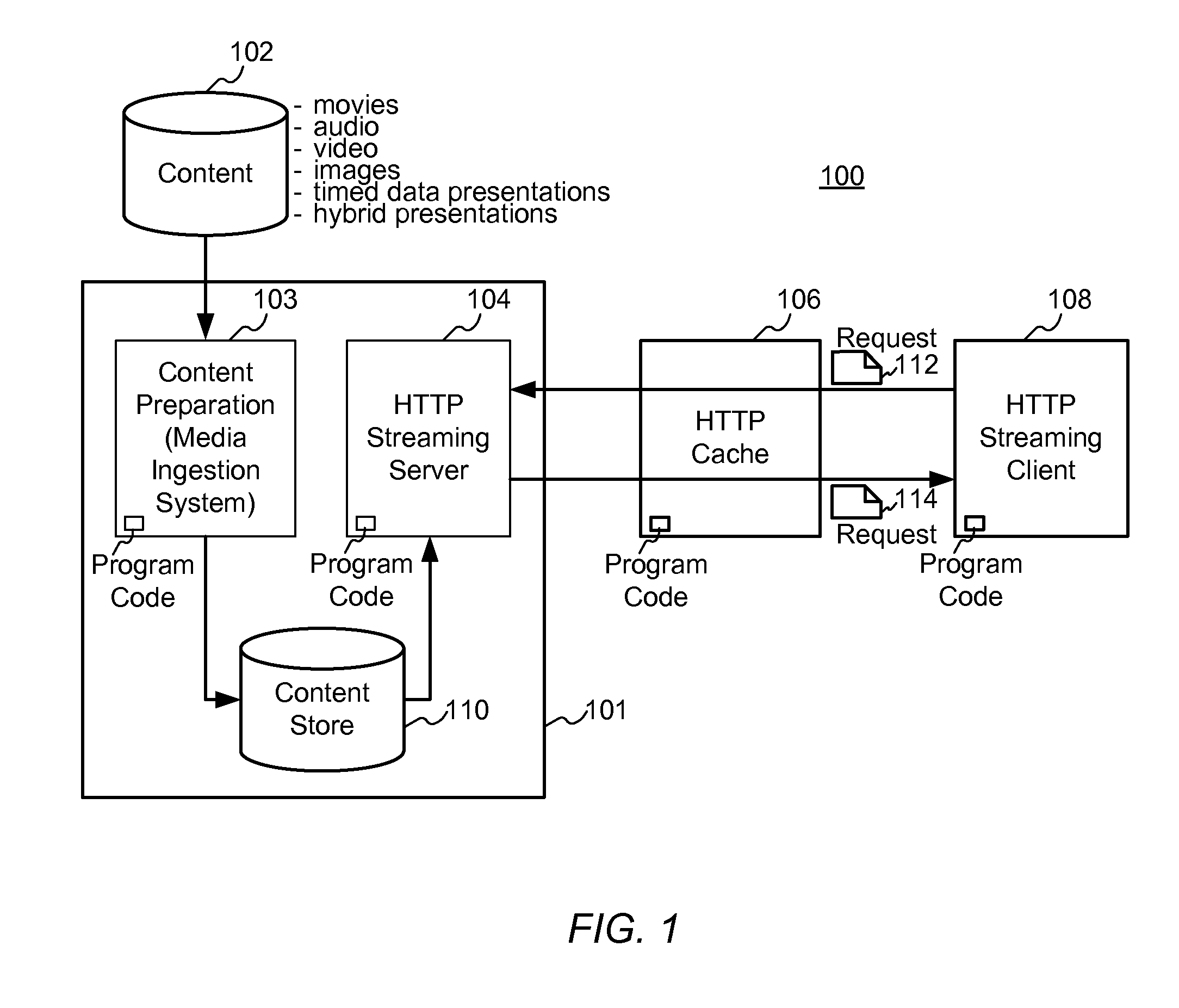

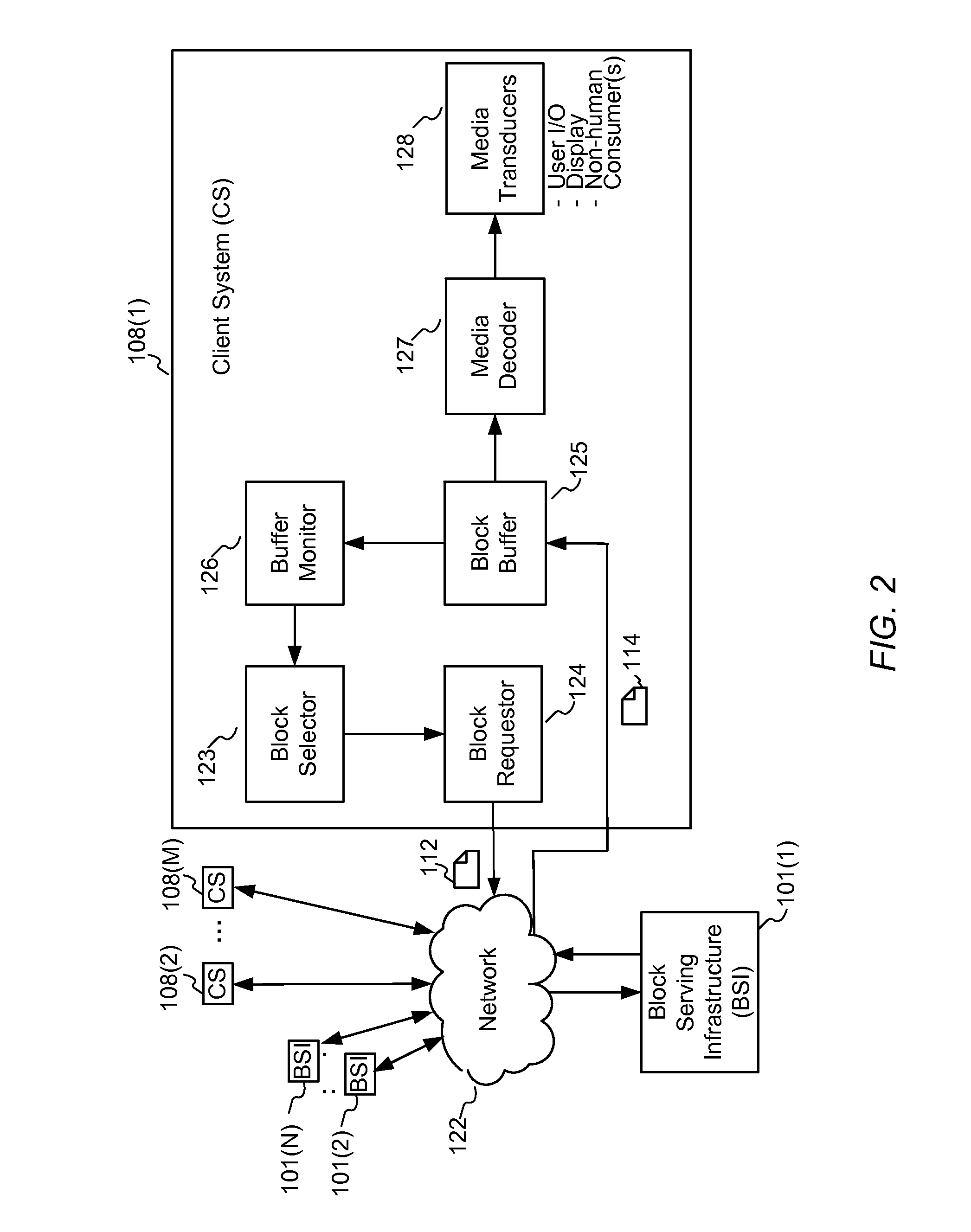

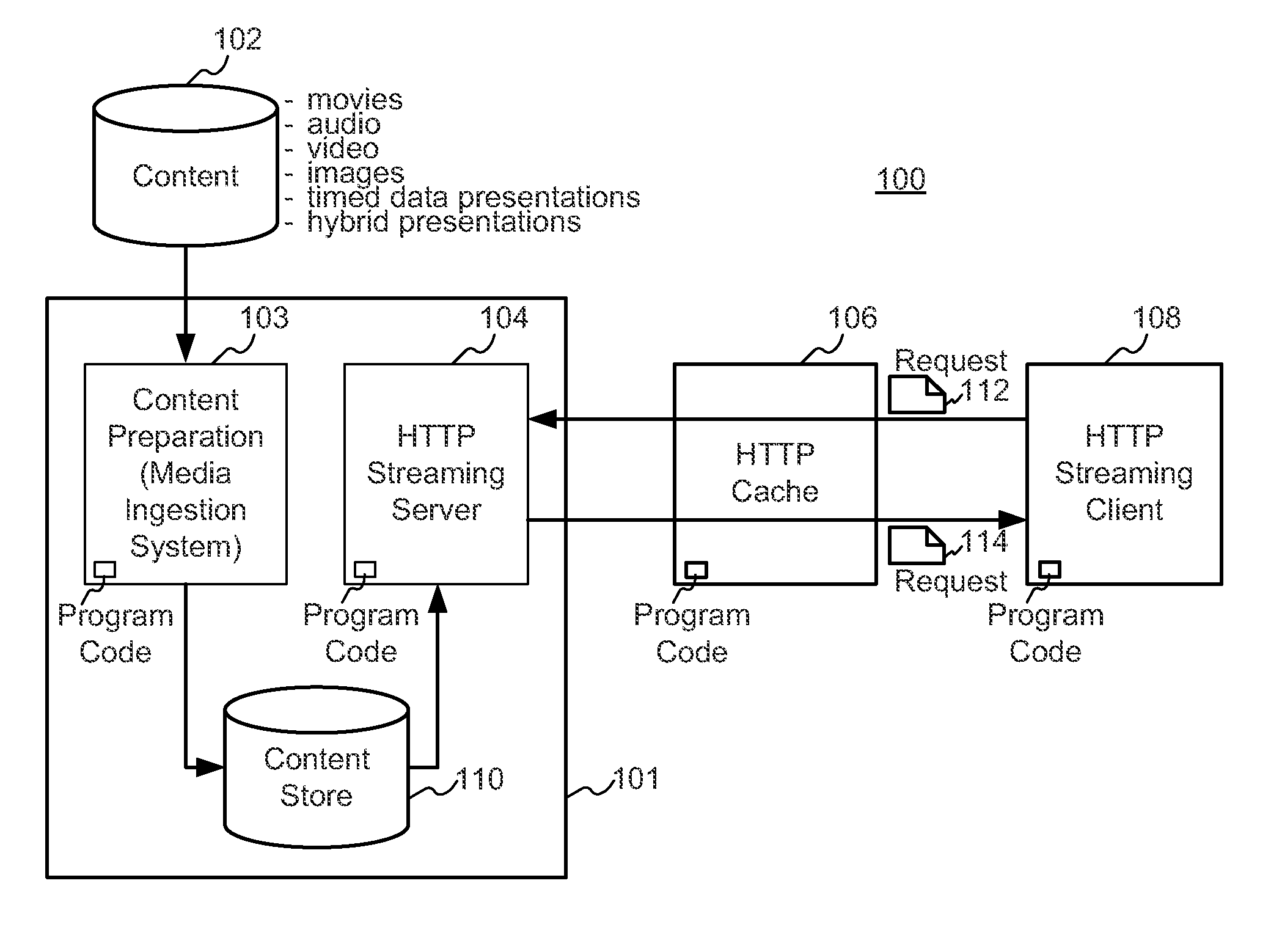

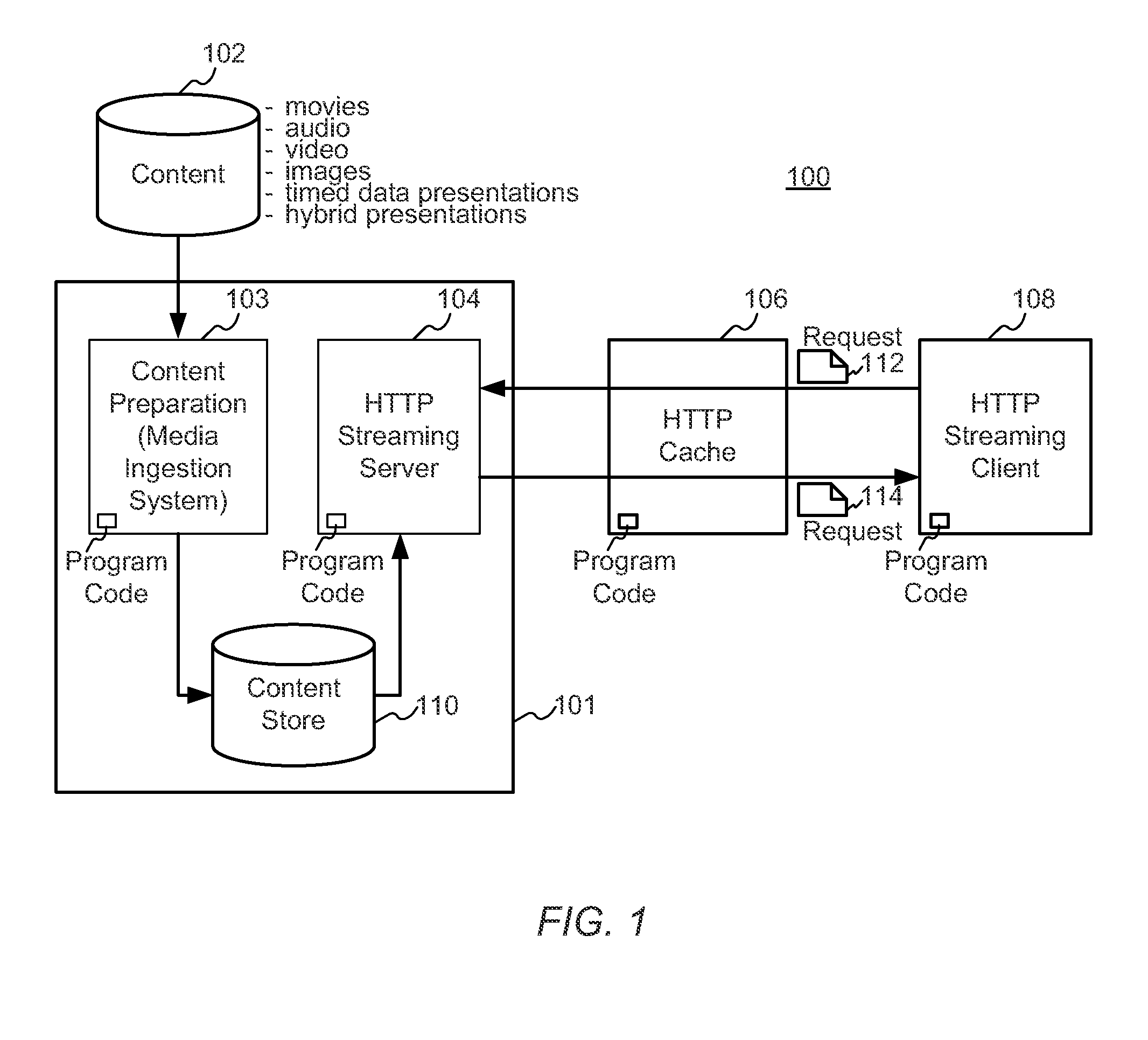

Enhanced block-request streaming system for handling low-latency streaming

ActiveUS20130007223A1Improve bandwidth efficiencyImprove user experienceMultiple digital computer combinationsTransmissionTransport systemLatency (engineering)

A block-request streaming system provides for low-latency streaming of a media presentation. A plurality of media segments are generated according to an encoding protocol. Each media segment includes a random access point. A plurality of media fragments are encoded according to the same protocol. The media segments are aggregated from a plurality of media fragments.

Owner:QUALCOMM INC

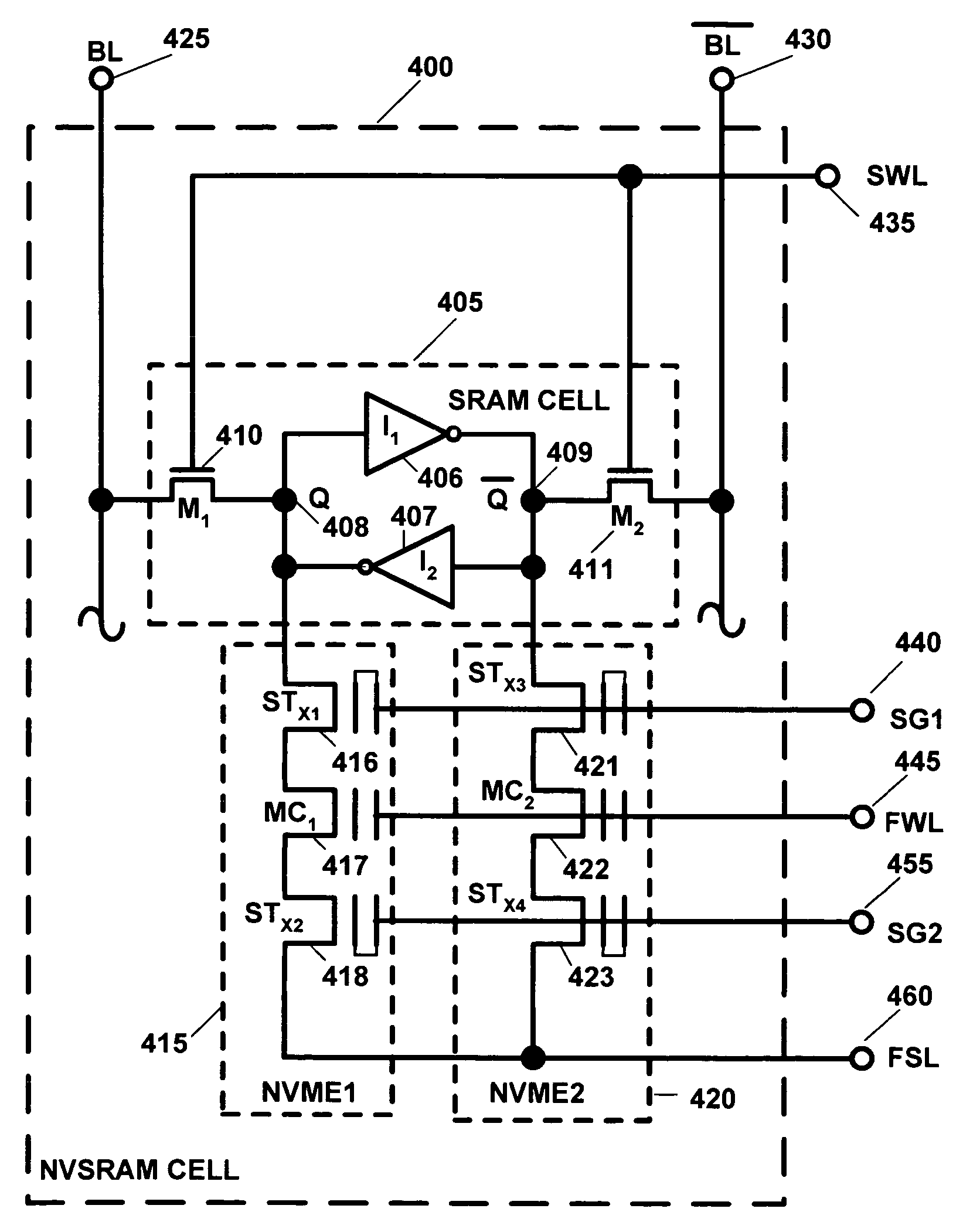

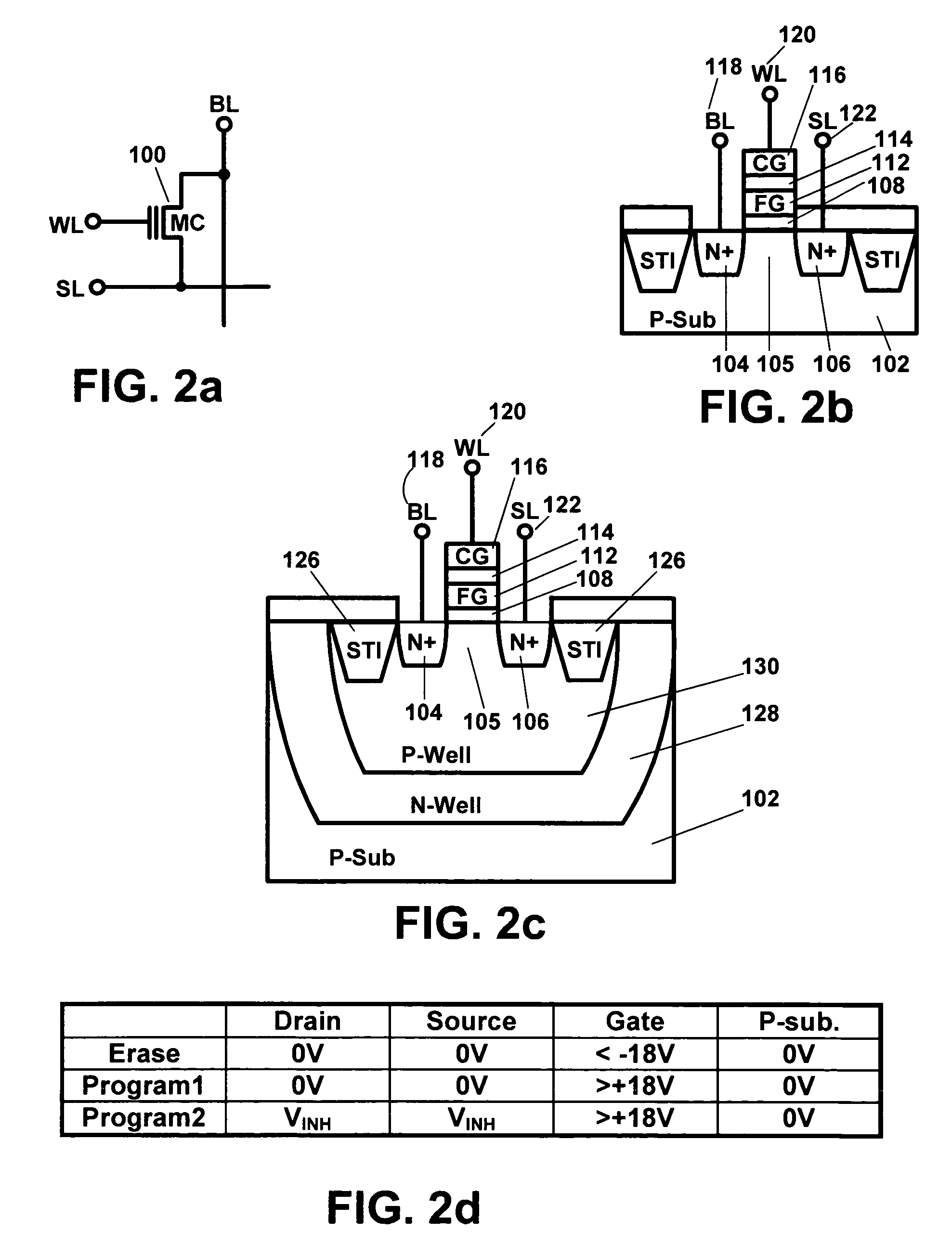

NVRAM memory cell architecture that integrates conventional SRAM and flash cells

A nonvolatile SRAM array has an array of integrated nonvolatile SRAM circuits arranged in rows and columns on a substrate. Each of the integrated nonvolatile SRAM circuits includes an SRAM cell, a first and second nonvolatile memory element. The SRAM cell has a latched memory element in communication first and second nonvolatile memory elements to receive and permanently retain the digital signal from the latched memory element. A power detection circuit detects a power interruption and a power initiation and communicates the detection of the power interruption and power initiation to the plurality of integrated nonvolatile SRAM circuits. The SRAM cell, upon detection of the power interruption, transmits the digital signal to the first and second nonvolatile memory elements. The SRAM cell of each of the nonvolatile static random access memories upon detection of the power initiation, receives the digital signal from the first and second nonvolatile memory elements.

Owner:ABEDNEJA ASSETAB L L C

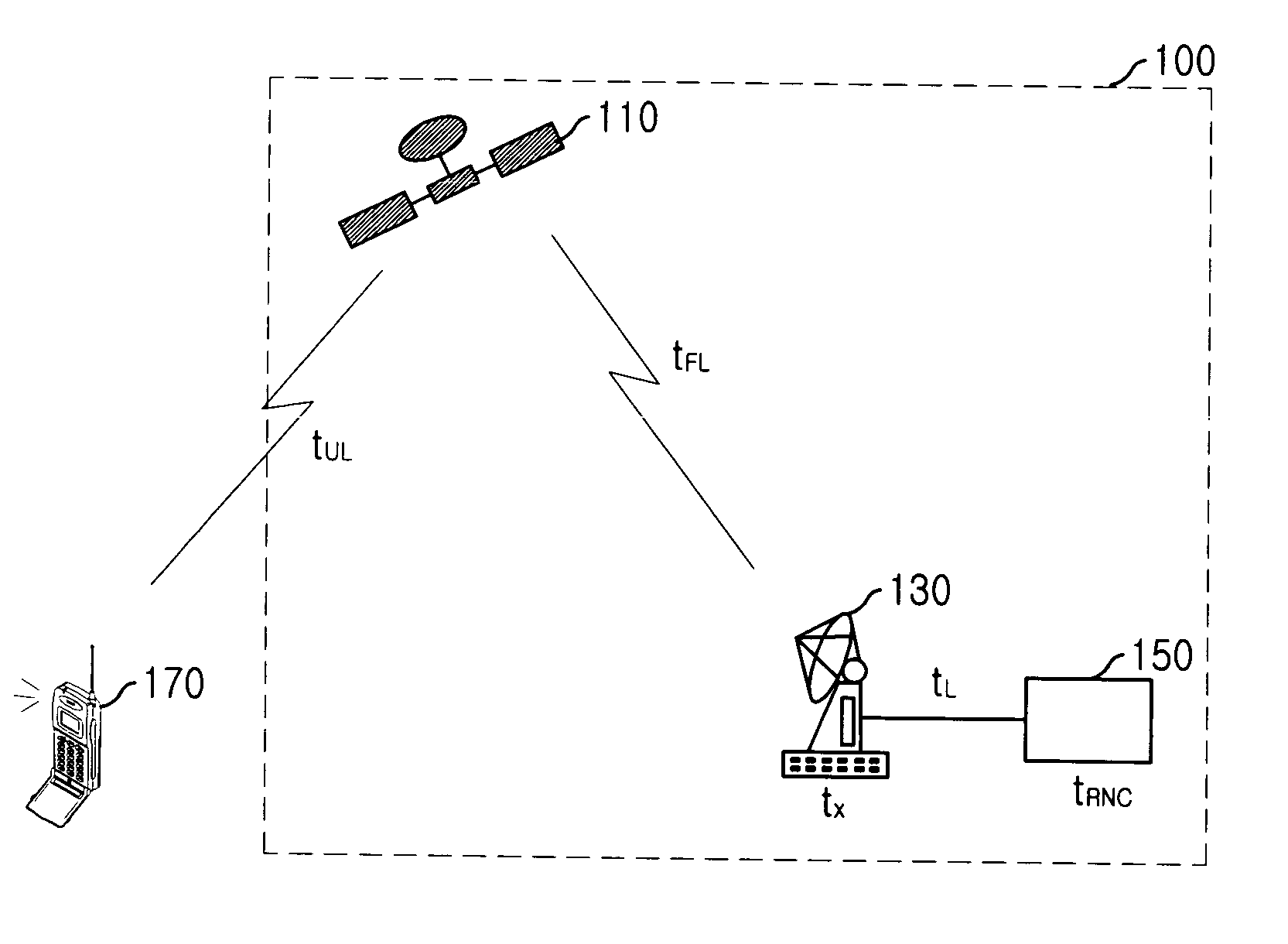

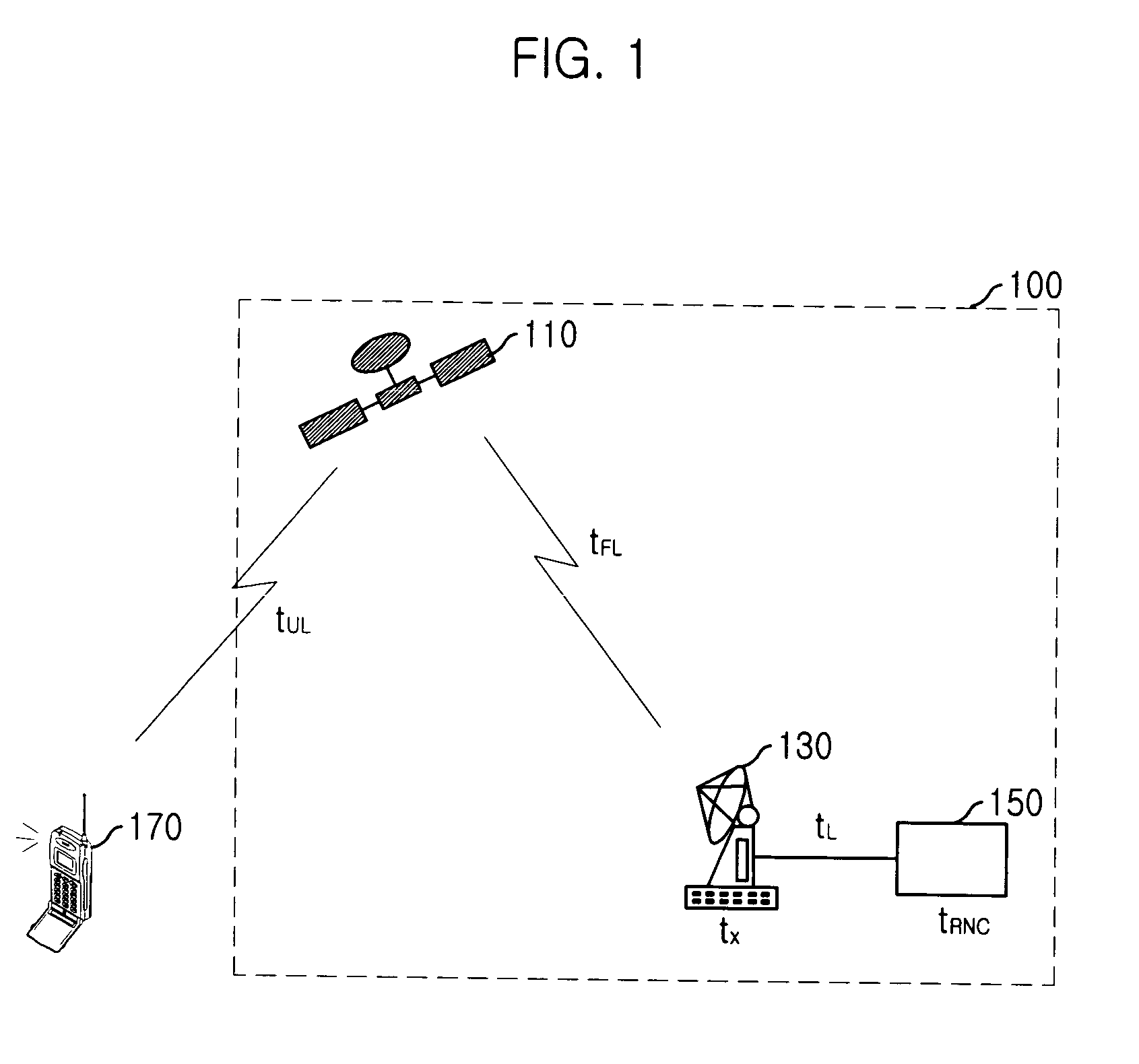

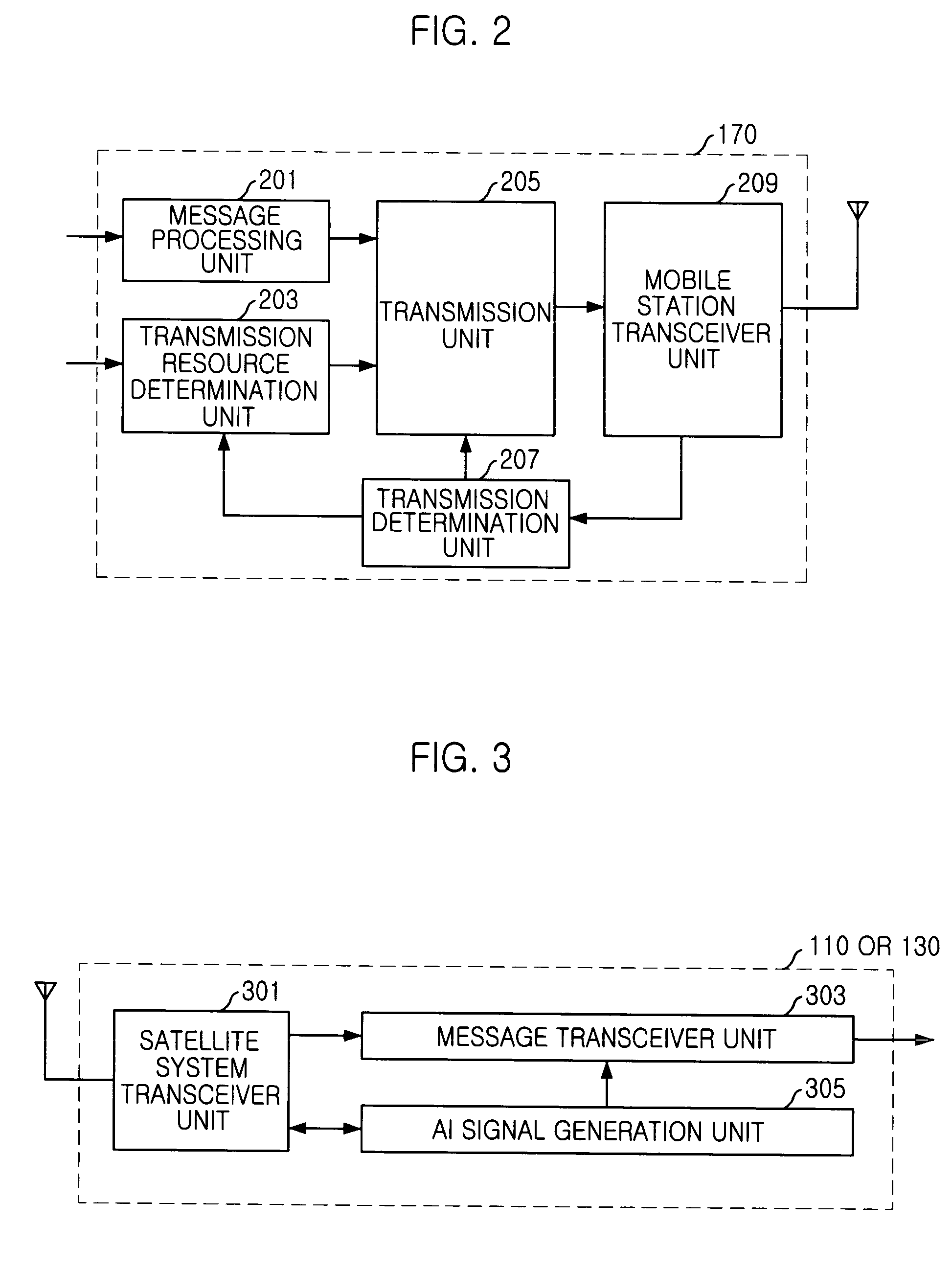

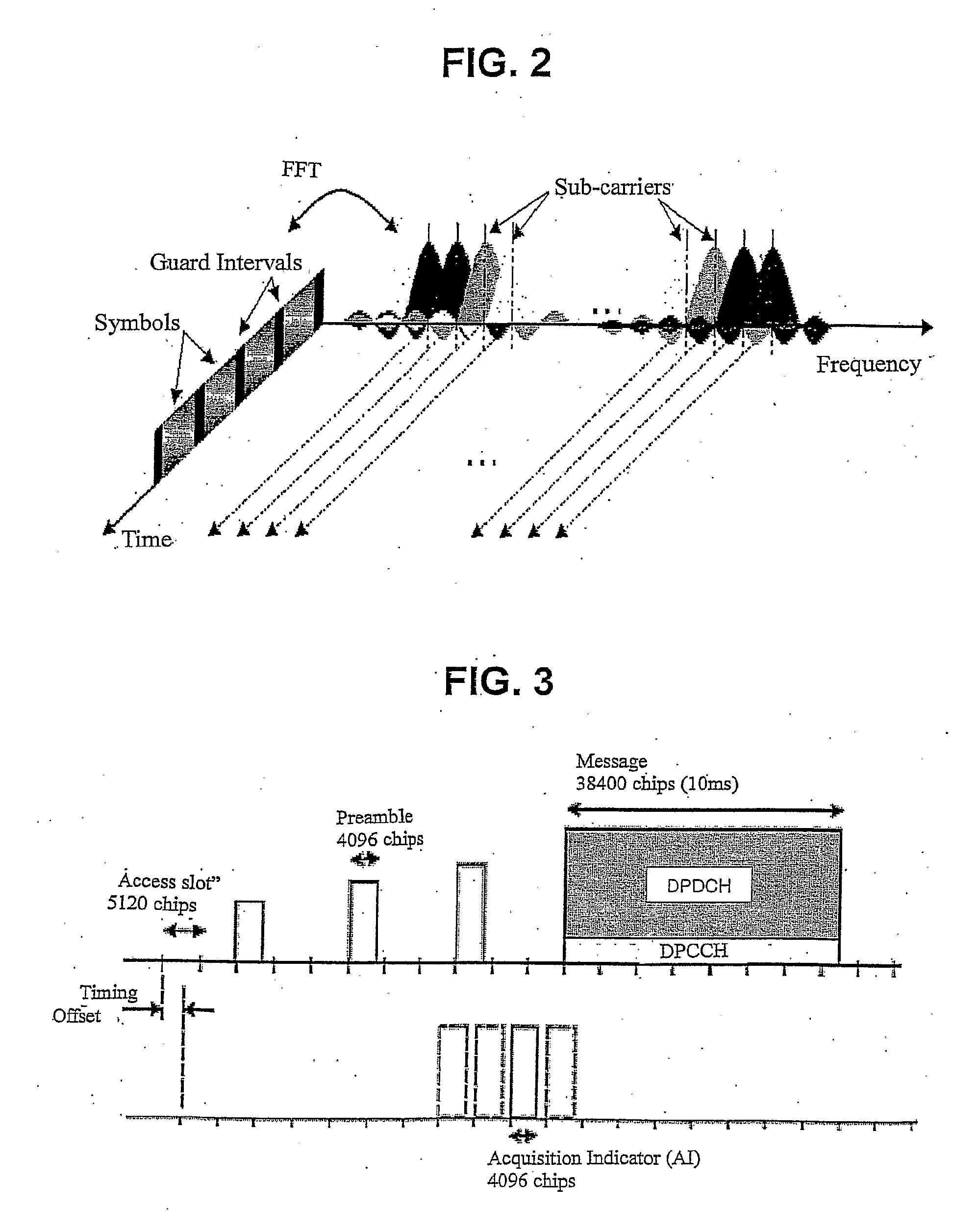

Random access channal access apparatus for mobile satellite communication system and method therefor

ActiveUS20040014452A1Reduce transmission delay timeIncrease probabilityTransmission control/equalisingNetwork topologiesTelecommunicationsRandom-access channel

The present invention relates to Random Access Channel (RACH) access apparatus for mobile satellite communication system and method therefor. The method for accessing random access channel (RACH) on satellite system, random access channel (RACH) carrying message from a plurality of mobile stations to the satellite system, the method includes the steps of: receiving preamble and the message, the message successively transmitted with the preamble from the plurality of mobile stations; and transmitting acquisition response signal corresponding to the preamble or the message to the plurality of mobile stations. Accordingly, success of packet reception of satellite system is improved and transmission delay is reduced.

Owner:ELECTRONICS & TELECOMM RES INST

Method of performing random access procedure in wireless communication system

ActiveUS20090186613A1Reliable data transmissionSynchronisation arrangementTransmission path divisionCommunications systemResource allocation

A method includes transmitting a random access preamble, receiving a random access response as a response of the random access preamble, wherein the random access response comprises an uplink resource assignment and a request for transmission of a Channel Quality Indicator (CQI), and transmitting the CQI in the uplink resource assignment.

Owner:LG ELECTRONICS INC

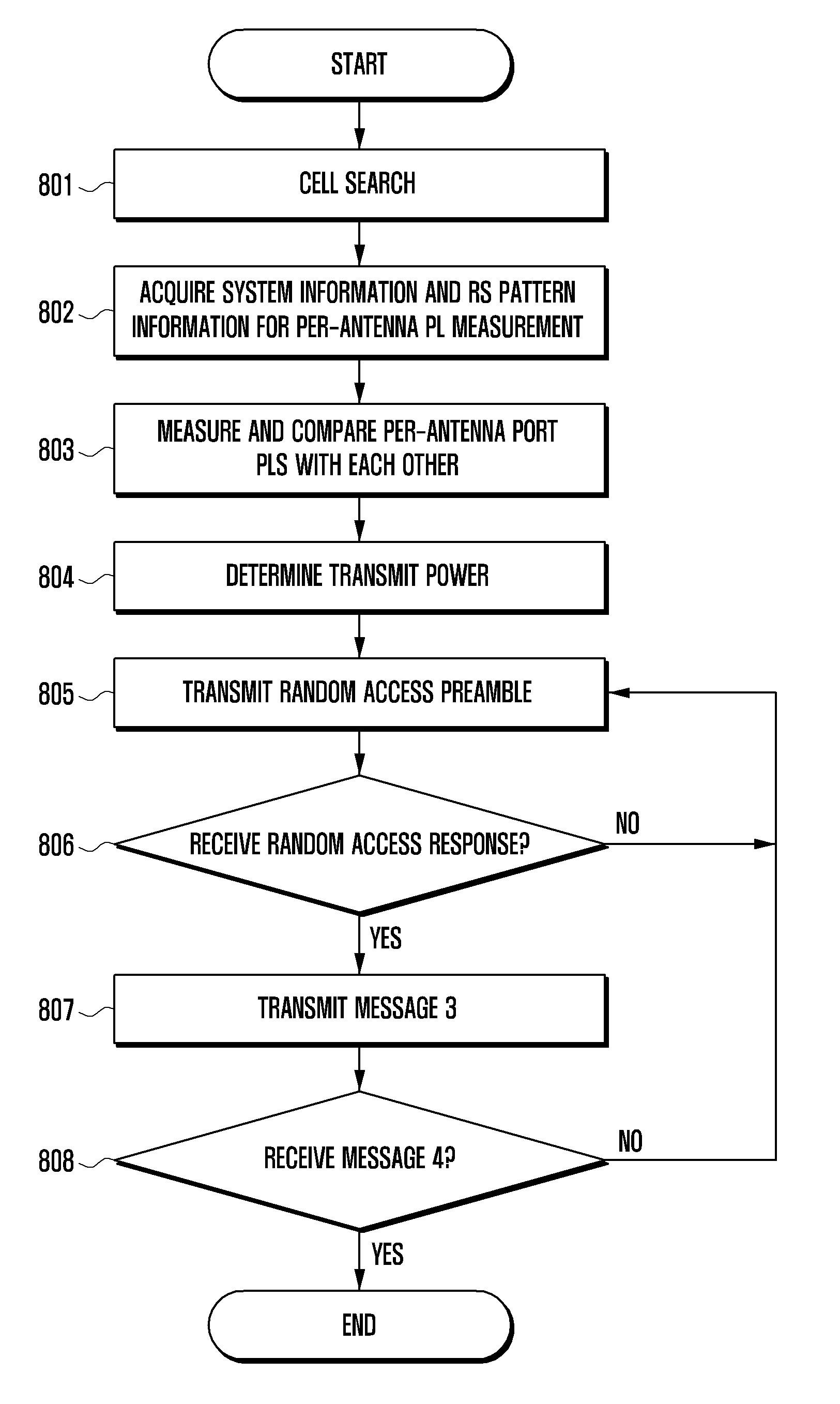

User equipment and power control method for random access

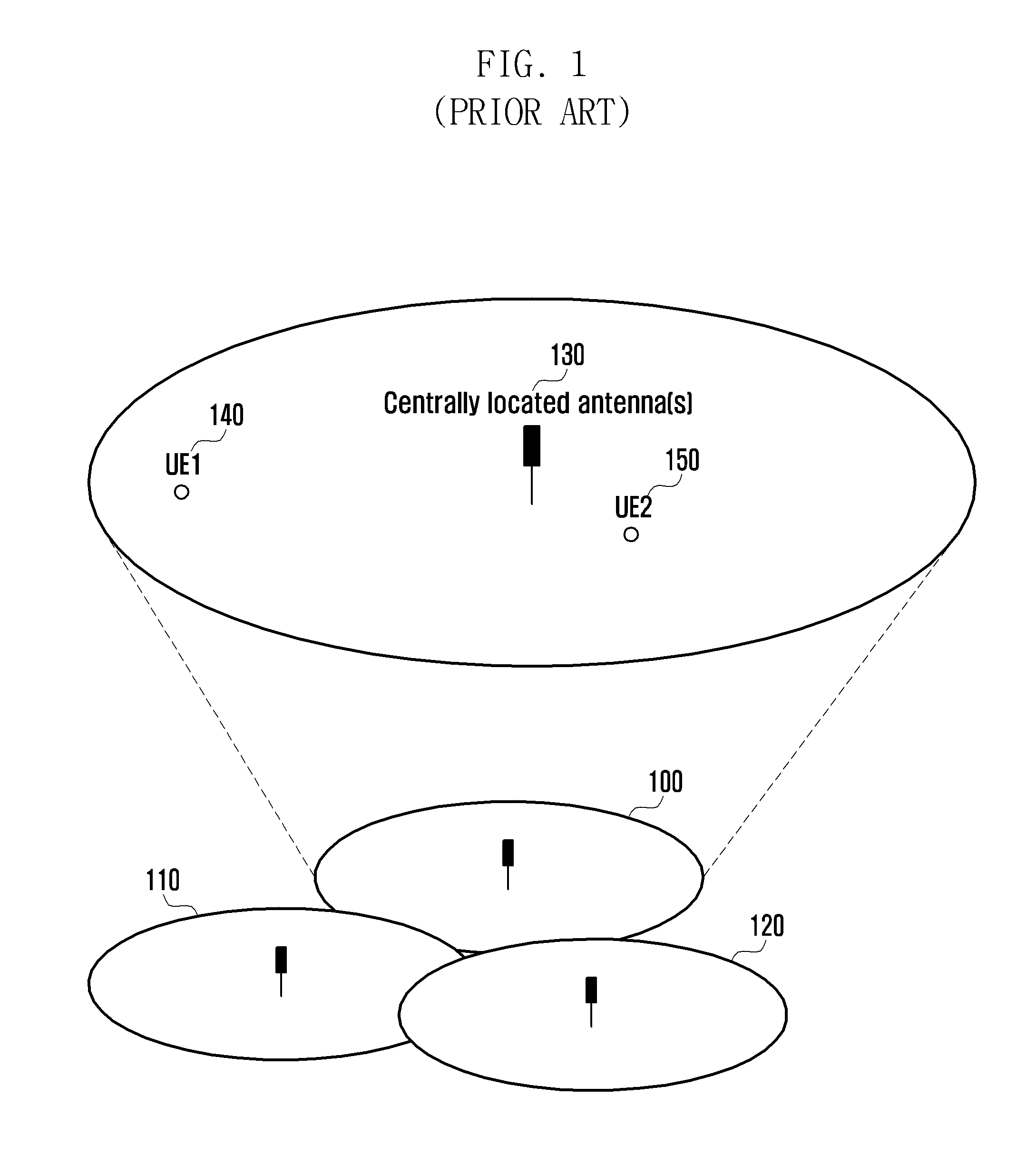

An improved power control method and apparatus of a mobile terminal is provided for facilitating random access procedure in a mobile communication system based on a distributed antenna system. A method includes receiving, by the terminal, system information from a base station, the system information including transmit power information for transmitting a random access preamble; calculating a transmit power using the transmit power information; and transmitting the random access preamble using with the calculated transmit power.

Owner:SAMSUNG ELECTRONICS CO LTD

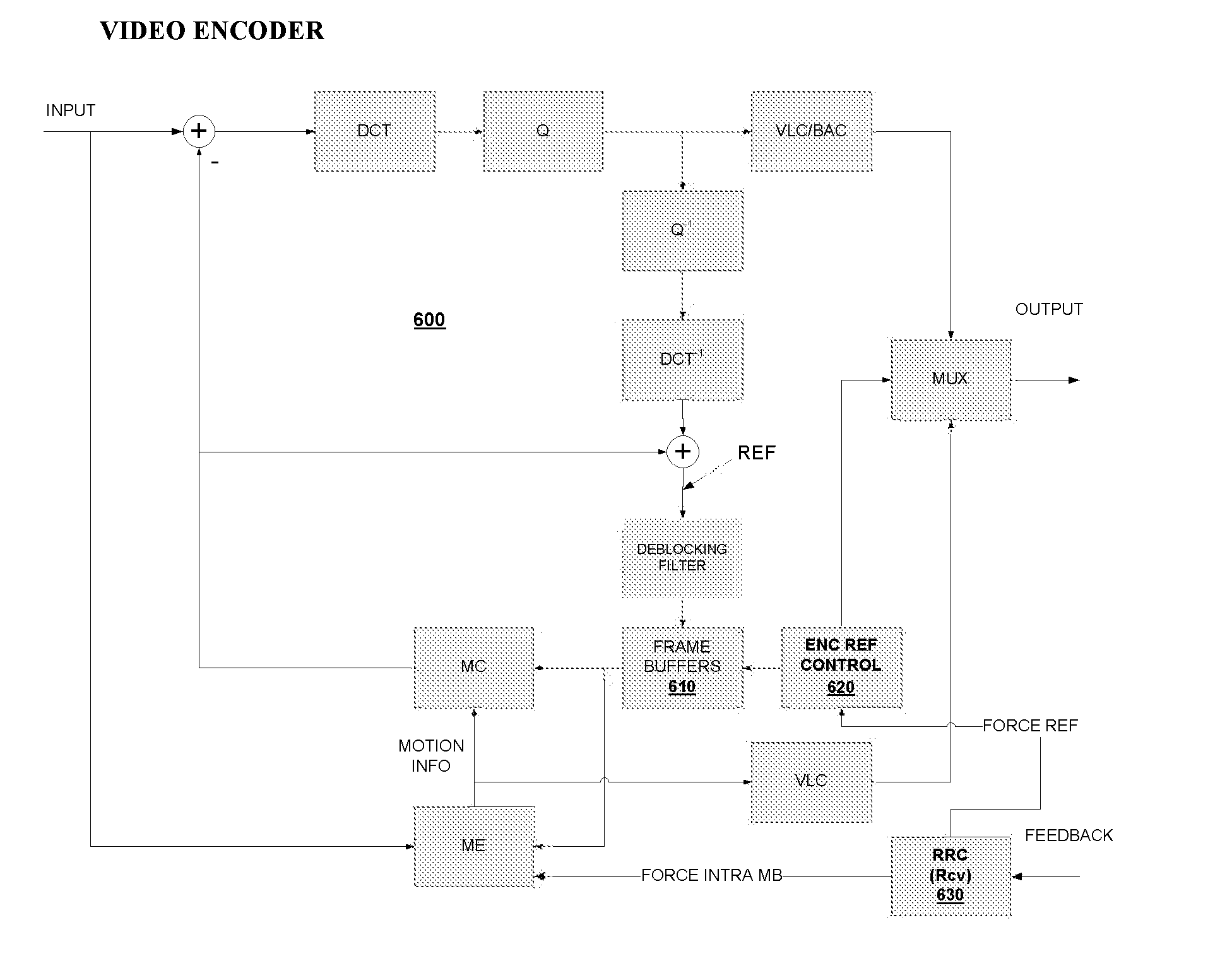

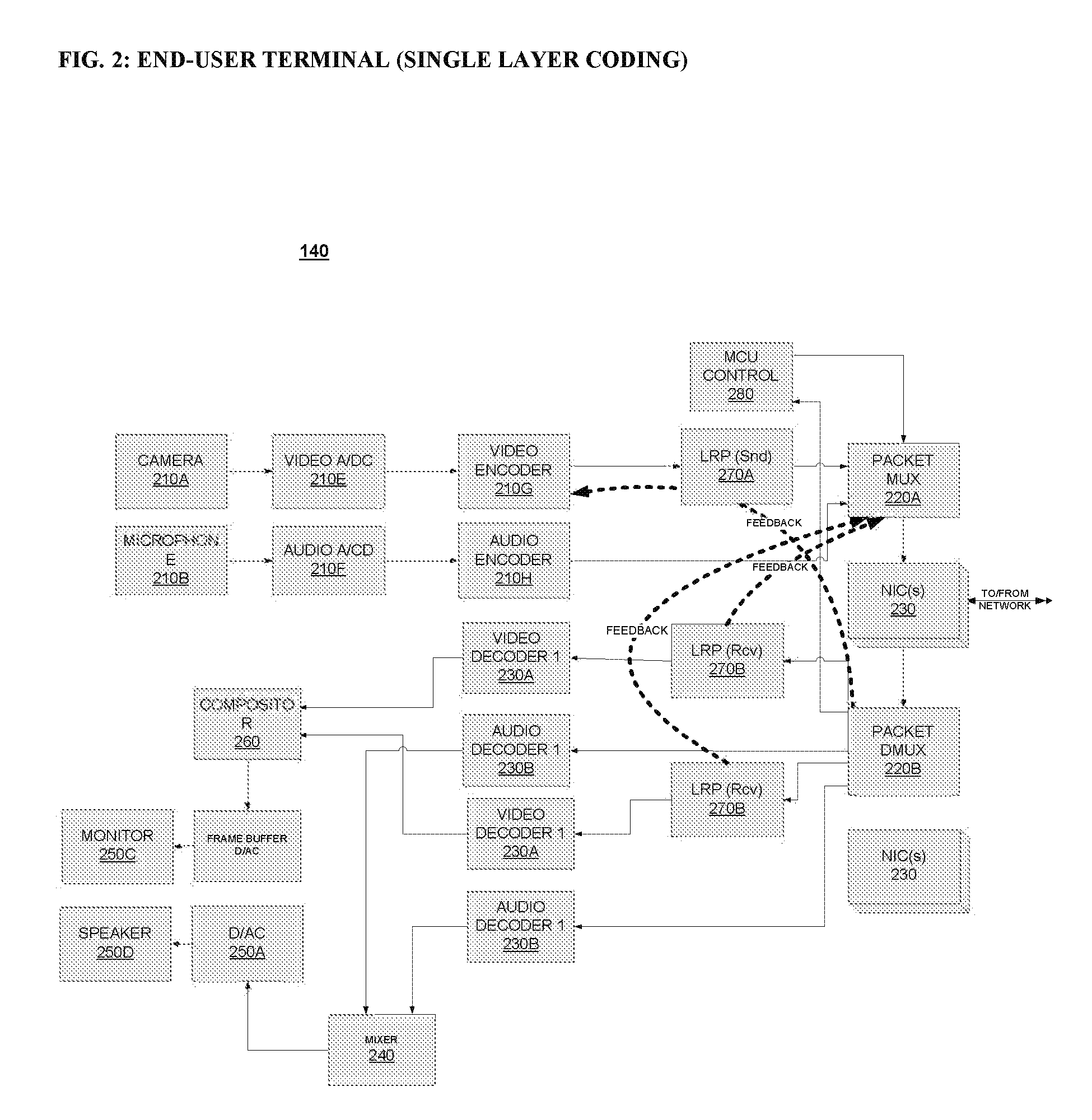

Systems and methods for error resilience and random access in video communication systems

ActiveUS20070206673A1Improve fault toleranceColor television with pulse code modulationError preventionComputer hardwareCommunications system

Systems and methods for error resilient transmission and for random access in video communication systems are provided. The video communication systems are based on single-layer, scalable video, or simulcast video coding with temporal scalability, which may be used in video communication systems. A set of video frames or pictures in a video signal transmission is designated for reliable or guaranteed delivery to receivers using secure or high reliability links, or by retransmission techniques. The reliably-delivered video frames are used as reference pictures for resynchronization of receivers with the transmitted video signal after error incidence and for random access.

Owner:VIDYO

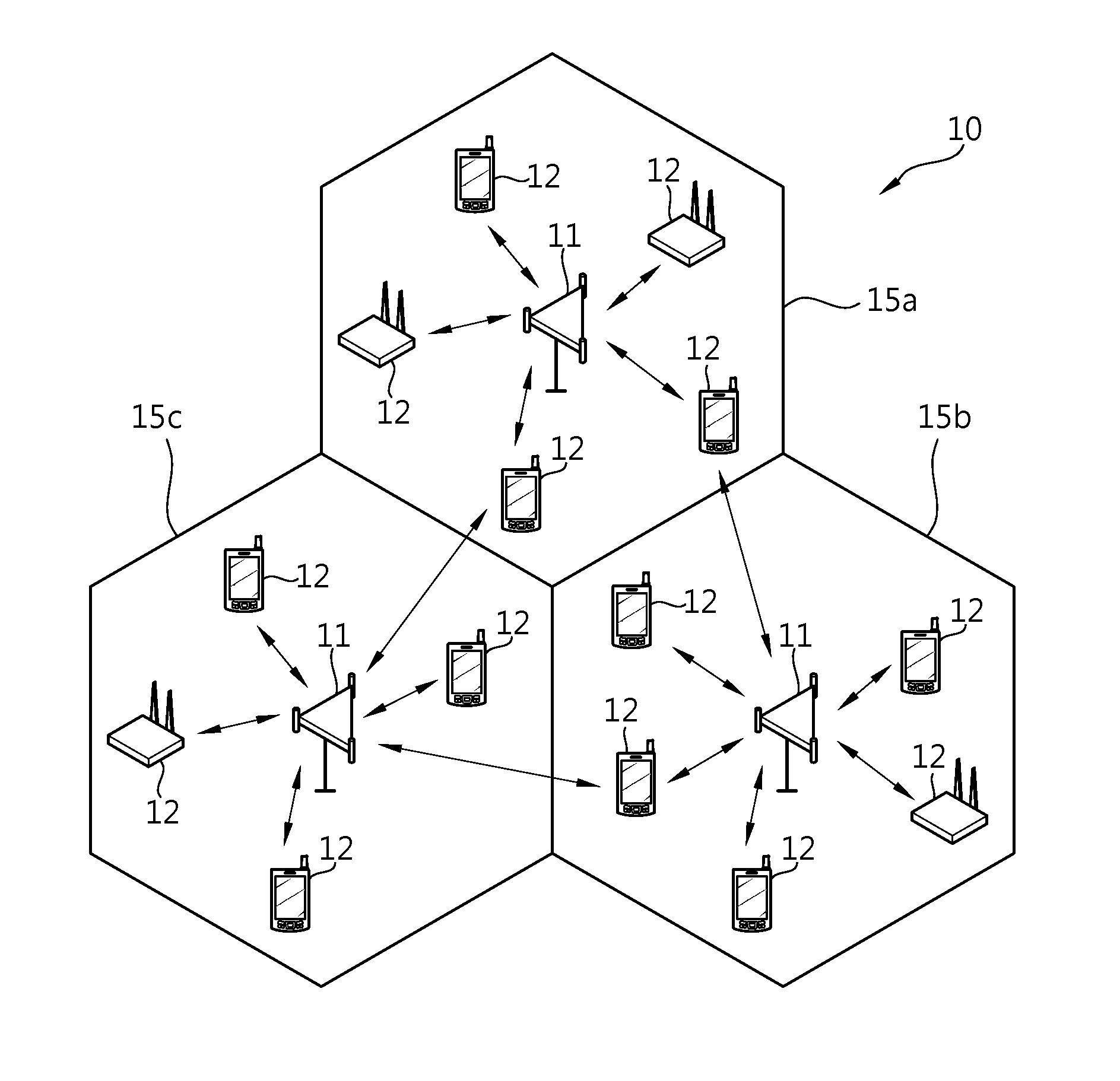

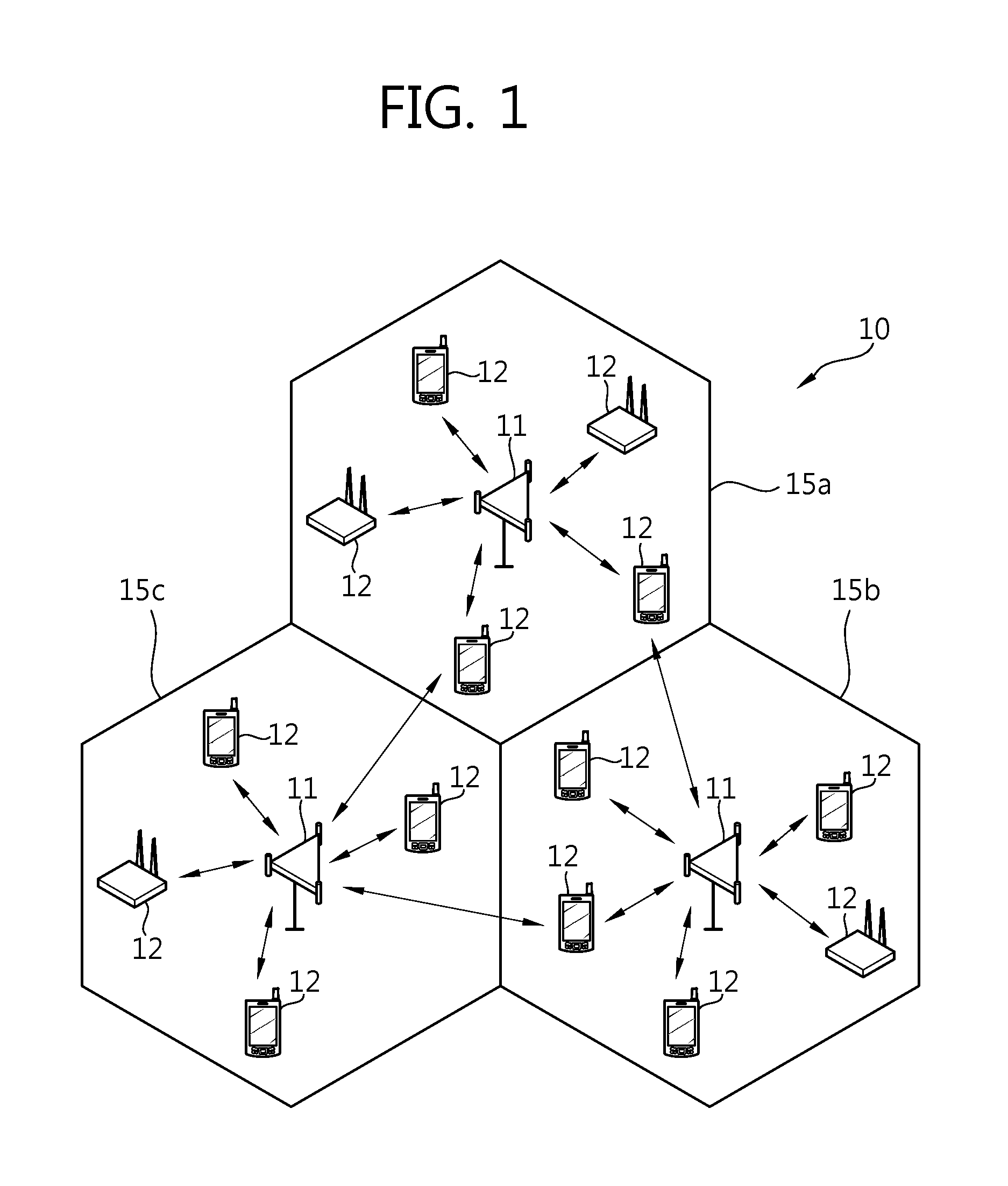

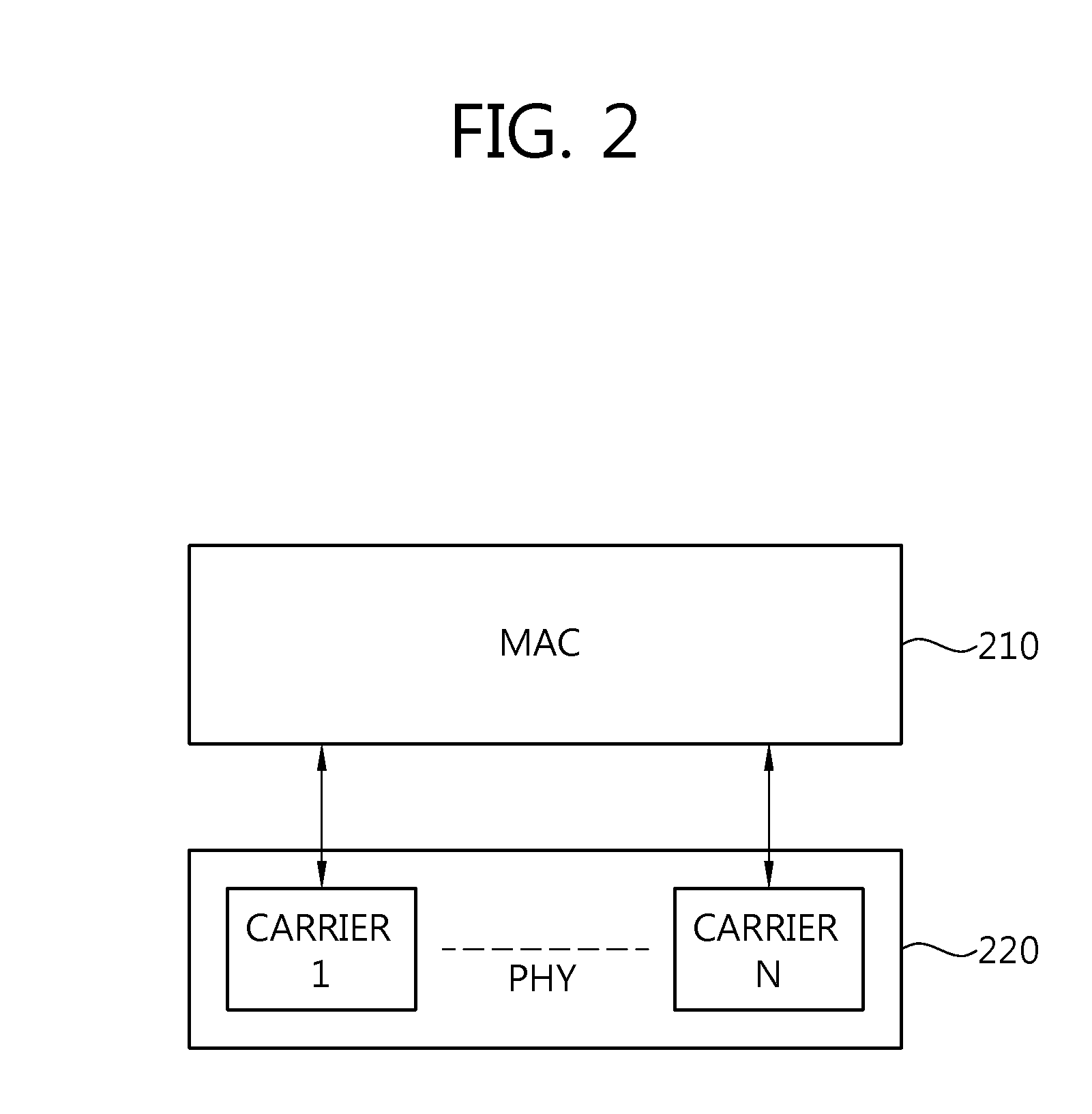

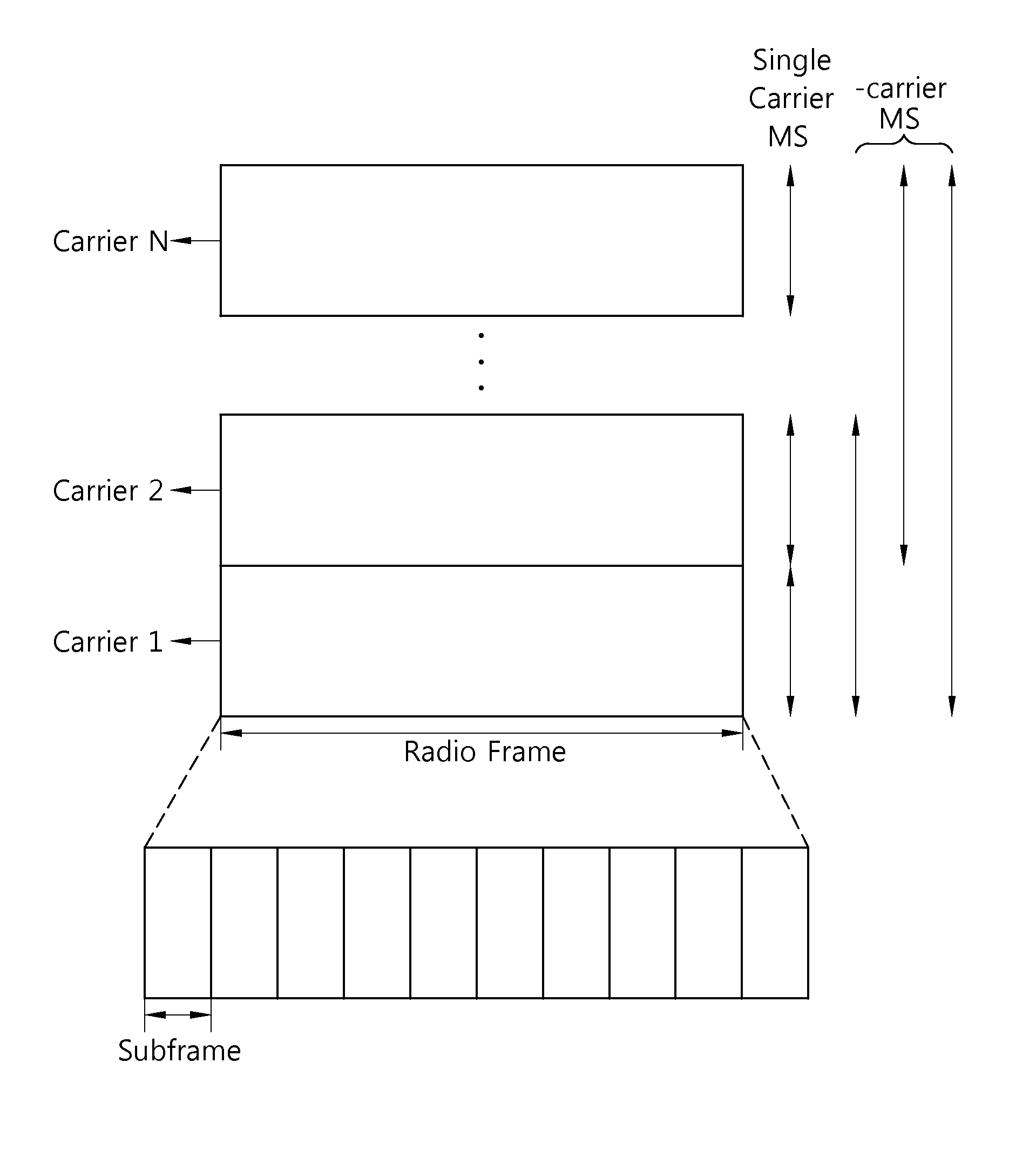

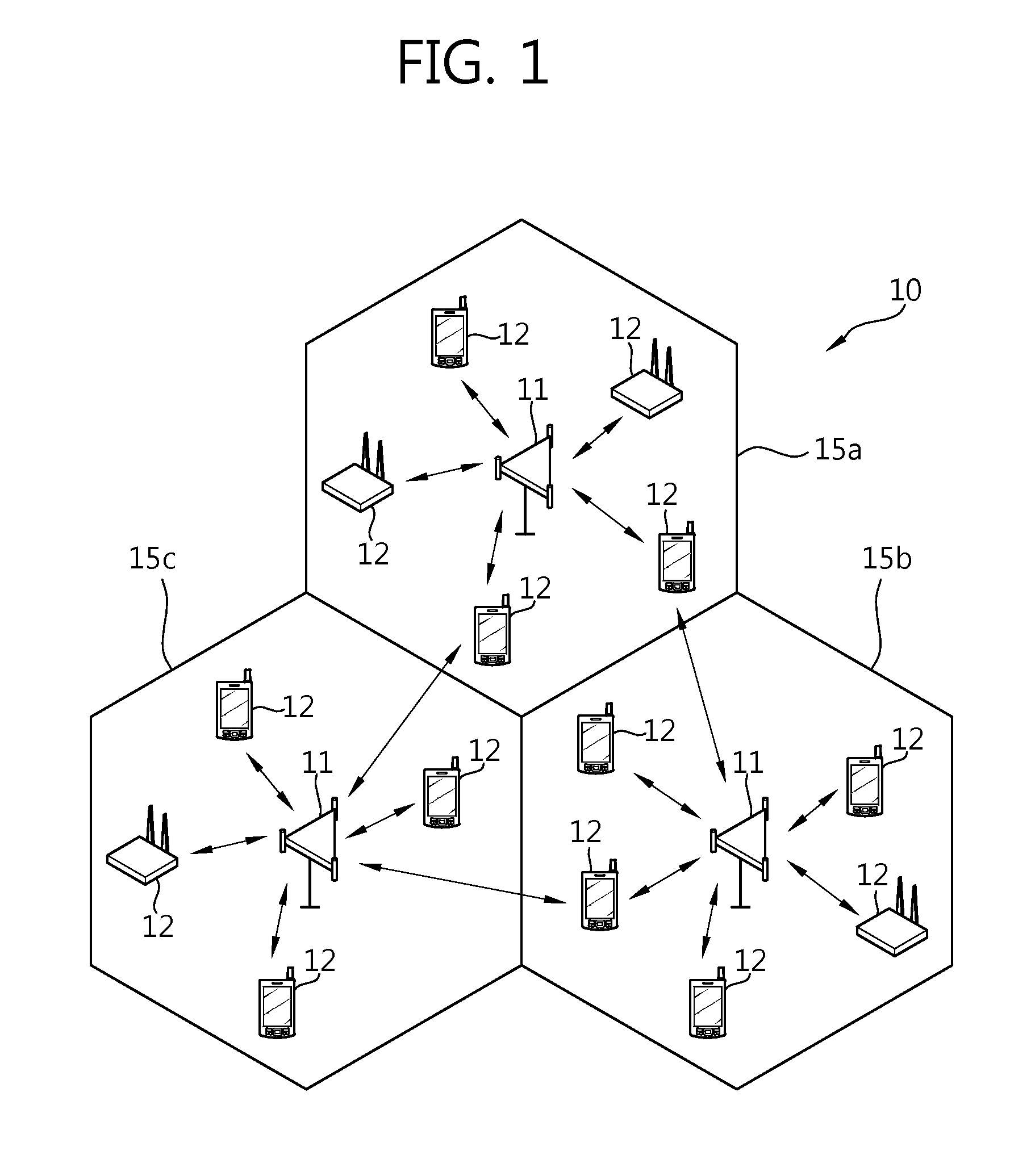

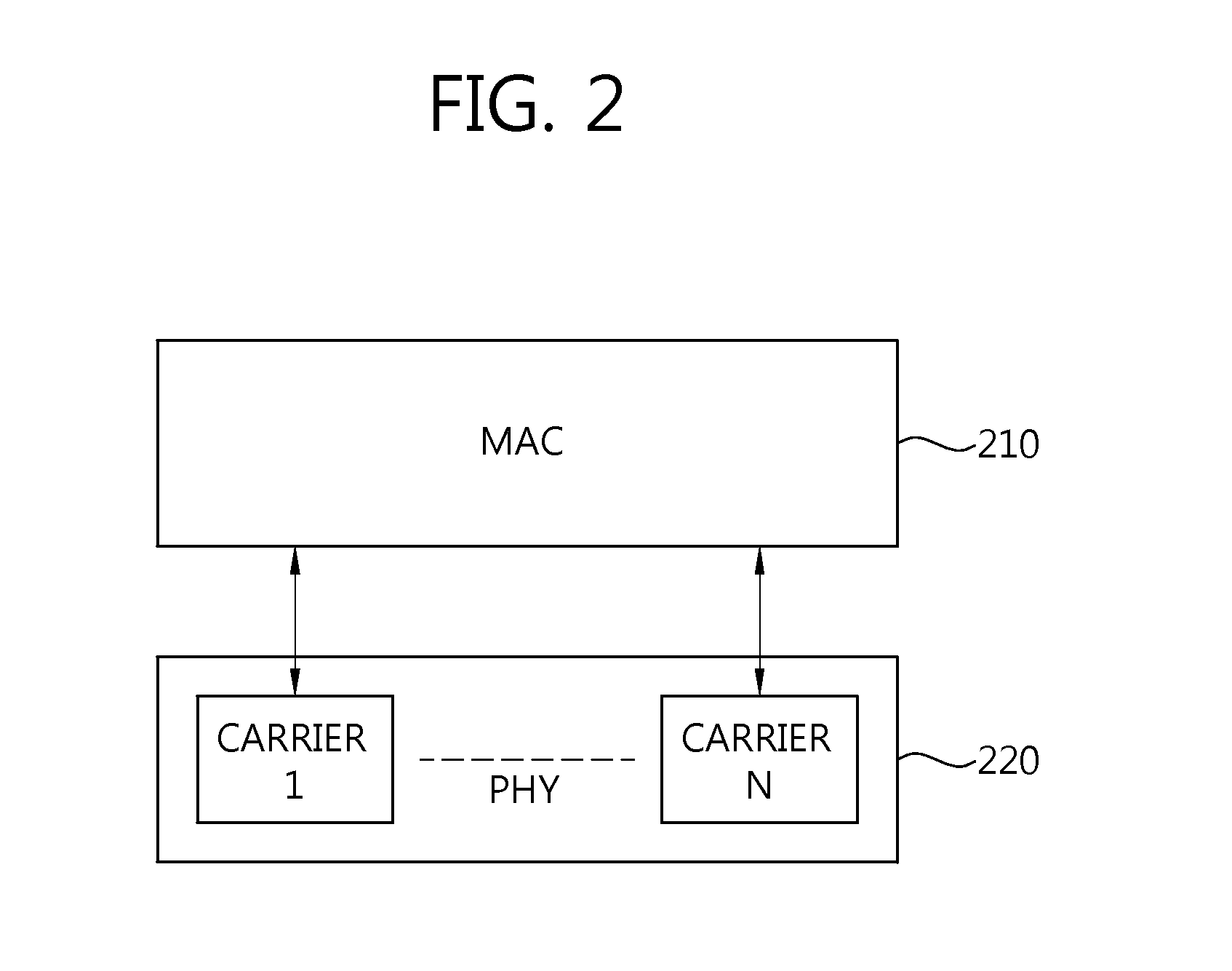

Apparatus and method for performing random access in multi-carrier system

InactiveUS20110249641A1Synchronisation arrangementModulated-carrier systemsResponse generationCarrier signal

A method for performing a random access in a multi-carrier system includes transmitting a random access preamble on an uplink component carrier to a base station, and receiving a random access response on a first downlink component carrier. The random access response includes information regarding a second downlink component carrier used to transmit a contention resolution message indicating that a random access collision with other mobile stations are resolved. A base station to perform the method includes a preamble reception unit to receive the random access preamble, a response generation unit to generate the random access response, and a response transmission unit to transmit the random access response. A mobile station to perform the method includes a preamble transmission unit, a response reception unit, a carrier configuration unit, and a message reception unit.

Owner:PANTECH CO LTD

Enhanced block-request streaming system using signaling or block creation

ActiveUS20110238789A1Improve bandwidth efficiencyImprove user experiencePulse modulation television signal transmissionMultiple digital computer combinationsTransport systemPoint placement

A block-request streaming system provides for improvements in the user experience and bandwidth efficiency of such systems, typically using an ingestion system that generates data in a form to be served by a conventional file server (HTTP, FTP, or the like), wherein the ingestion system intakes content and prepares it as files or data elements to be served by the file server. The system might include controlling the sequence, timing and construction of block requests, time based indexing, variable block sizing, optimal block partitioning, control of random access point placement, including across multiple presentation versions, dynamically updating presentation data, and / or efficiently presenting live content and time shifting.

Owner:QUALCOMM INC

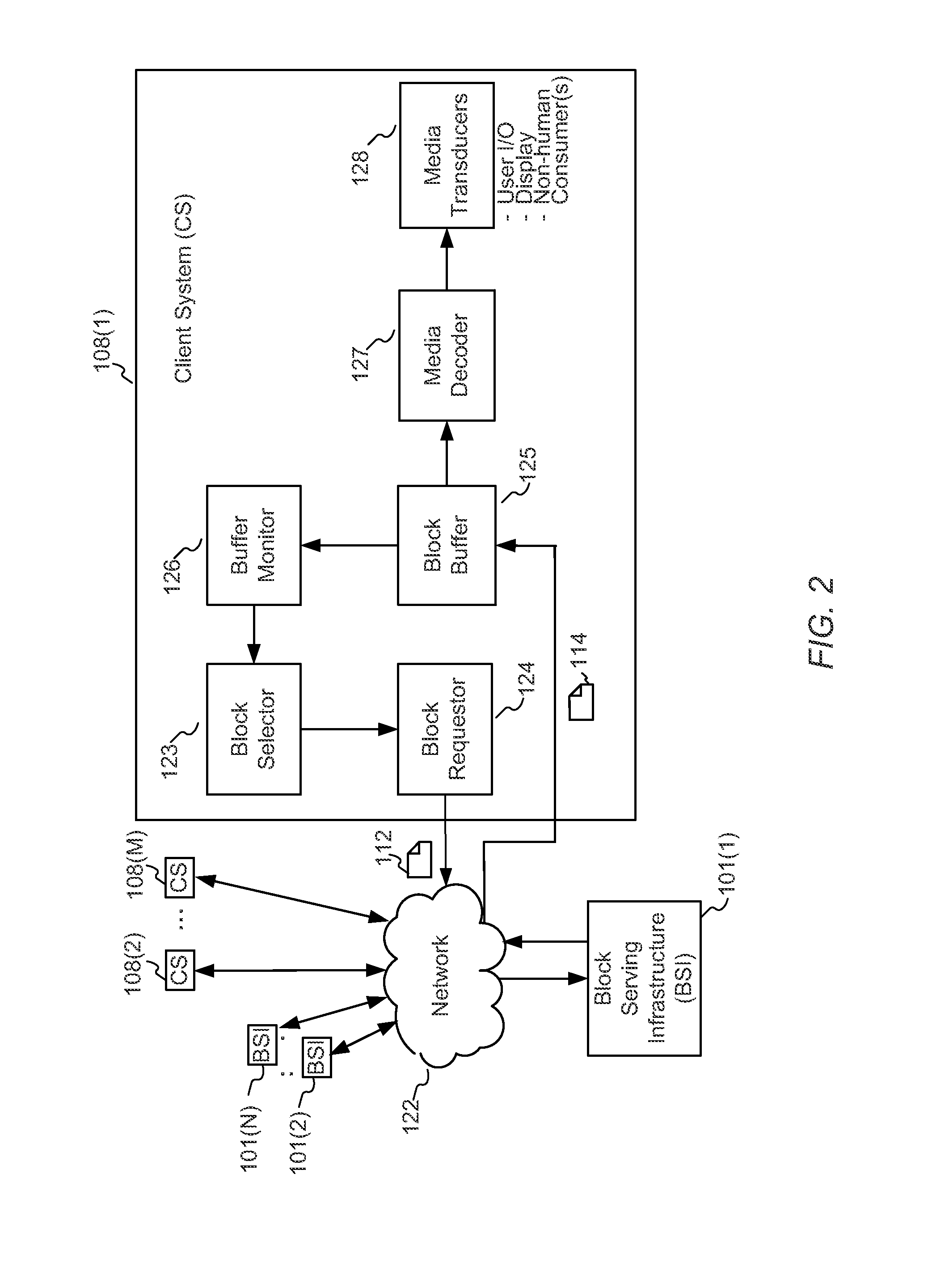

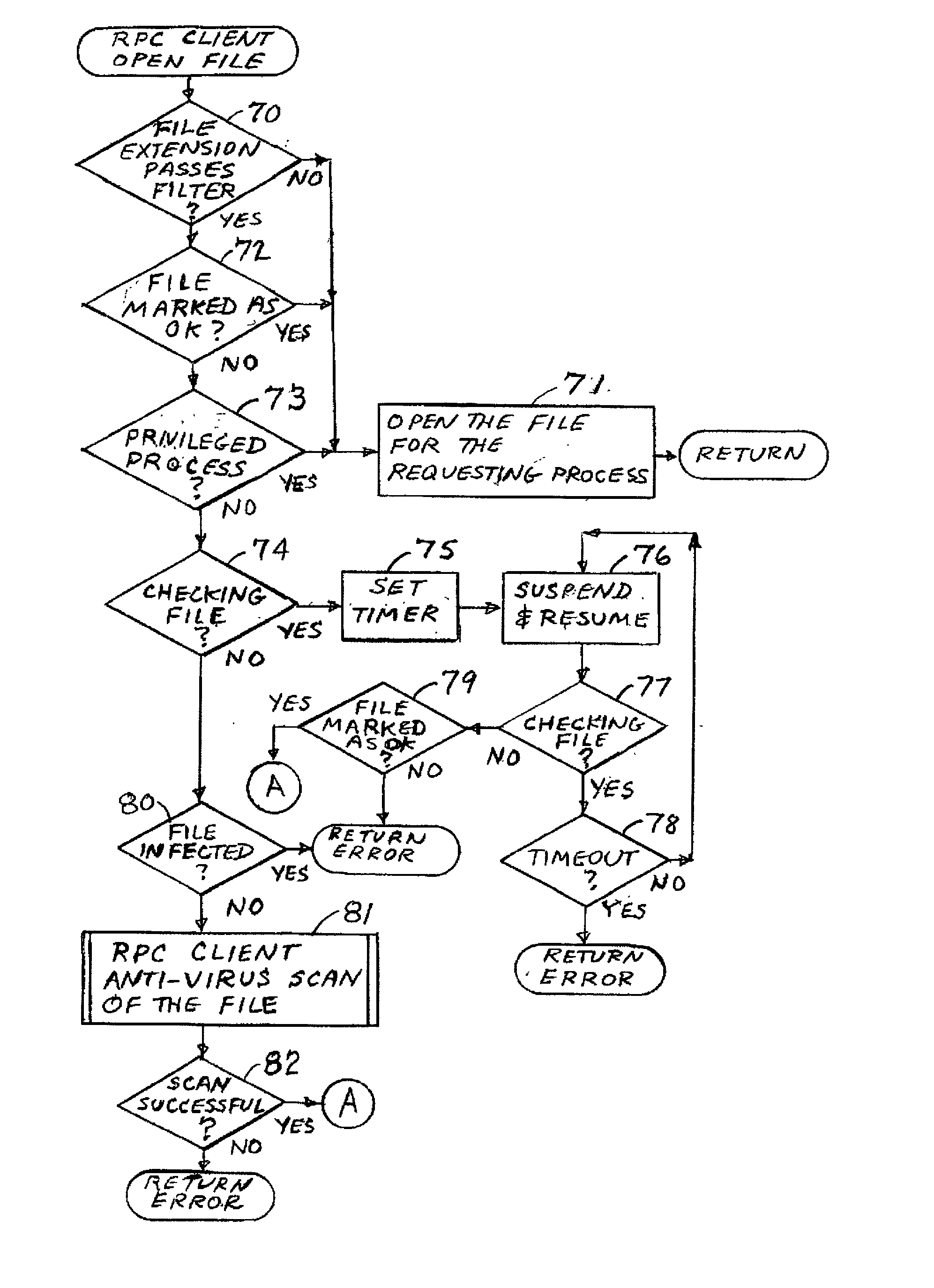

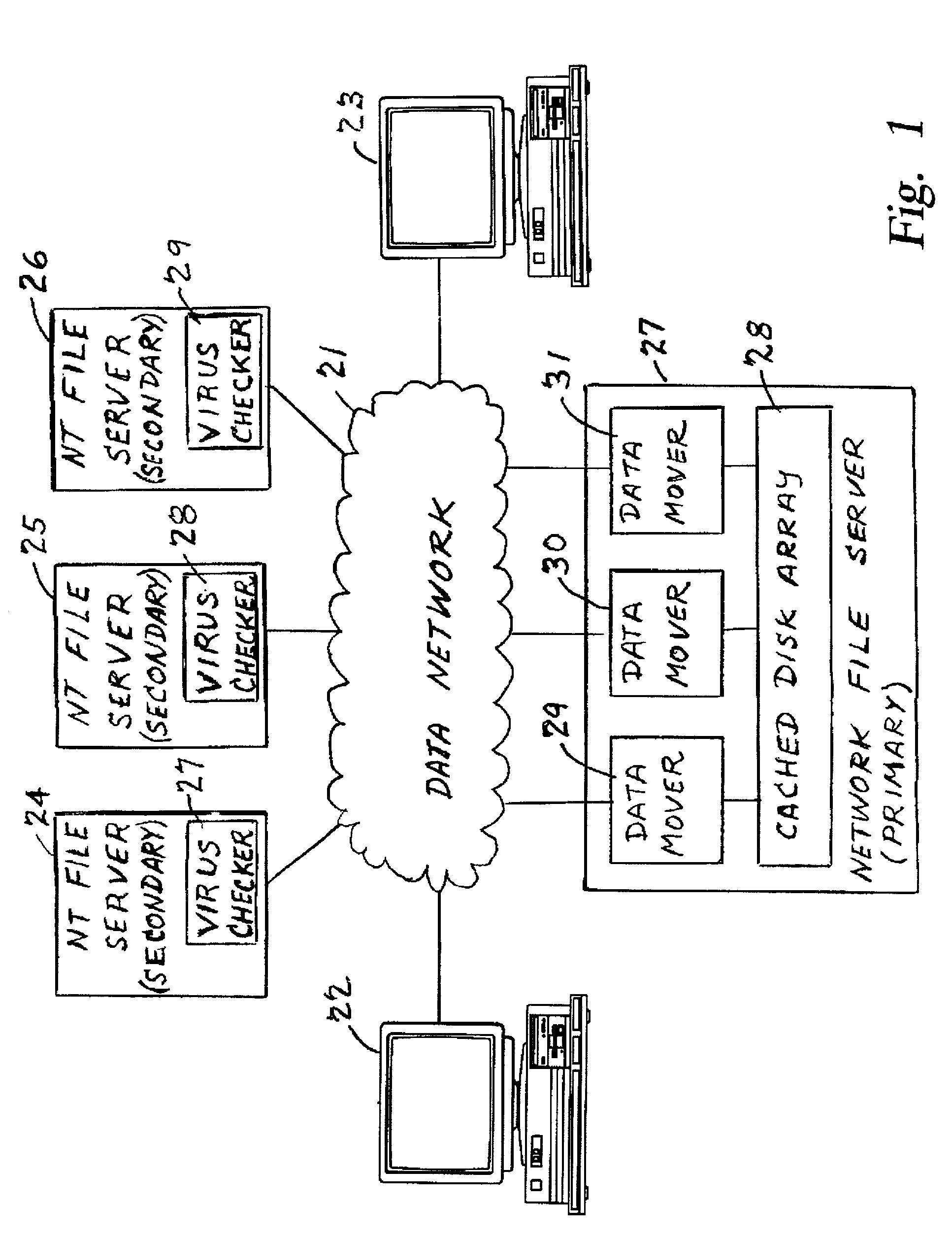

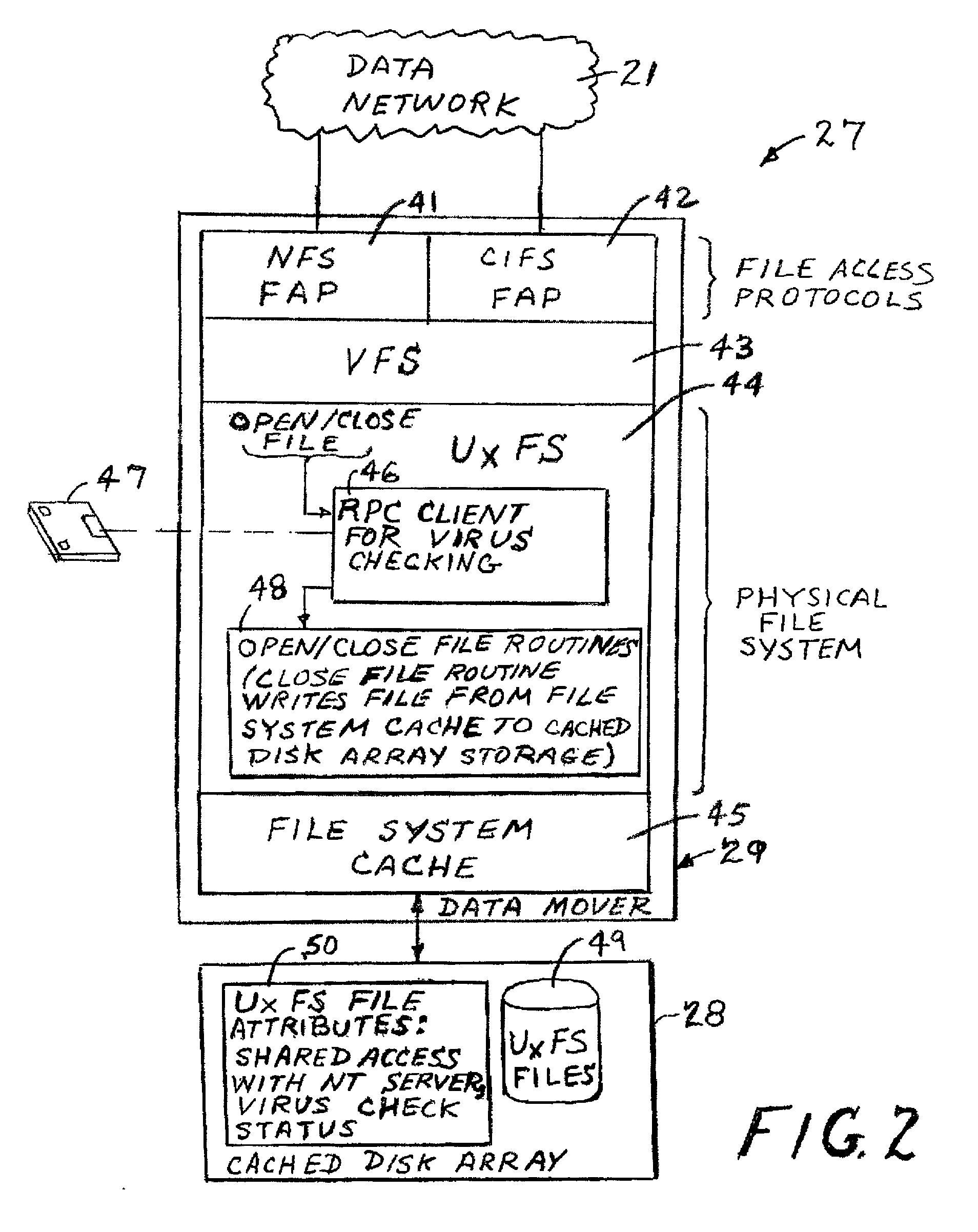

Using a virus checker in one file server to check for viruses in another file server

ActiveUS20020129277A1Memory loss protectionUnauthorized memory use protectionAnti virusRandom access memory

When a network client accesses a file in a network file server, the network file server invokes a conventional virus checker program in an NT file server to transfer pertinent file data from the network file server to random access memory in the NT file server to perform an anti-virus scan. Users may interact with the virus checker program in the usual fashion, to select file types to check, and actions to perform when a virus is detected. This method eliminates the need for porting the virus checker program to the network file server, and avoids maintenance problems when the virus checker program is updated or upgraded. Moreover, a kernel mode driver in the NT file server may provide an indirect interface to the virus checker program for initiating an anti-virus scan. Therefore, the driver supports a wide variety of virus checker programs and ensures continued operation when the virus checker program is upgraded.

Owner:EMC IP HLDG CO LLC

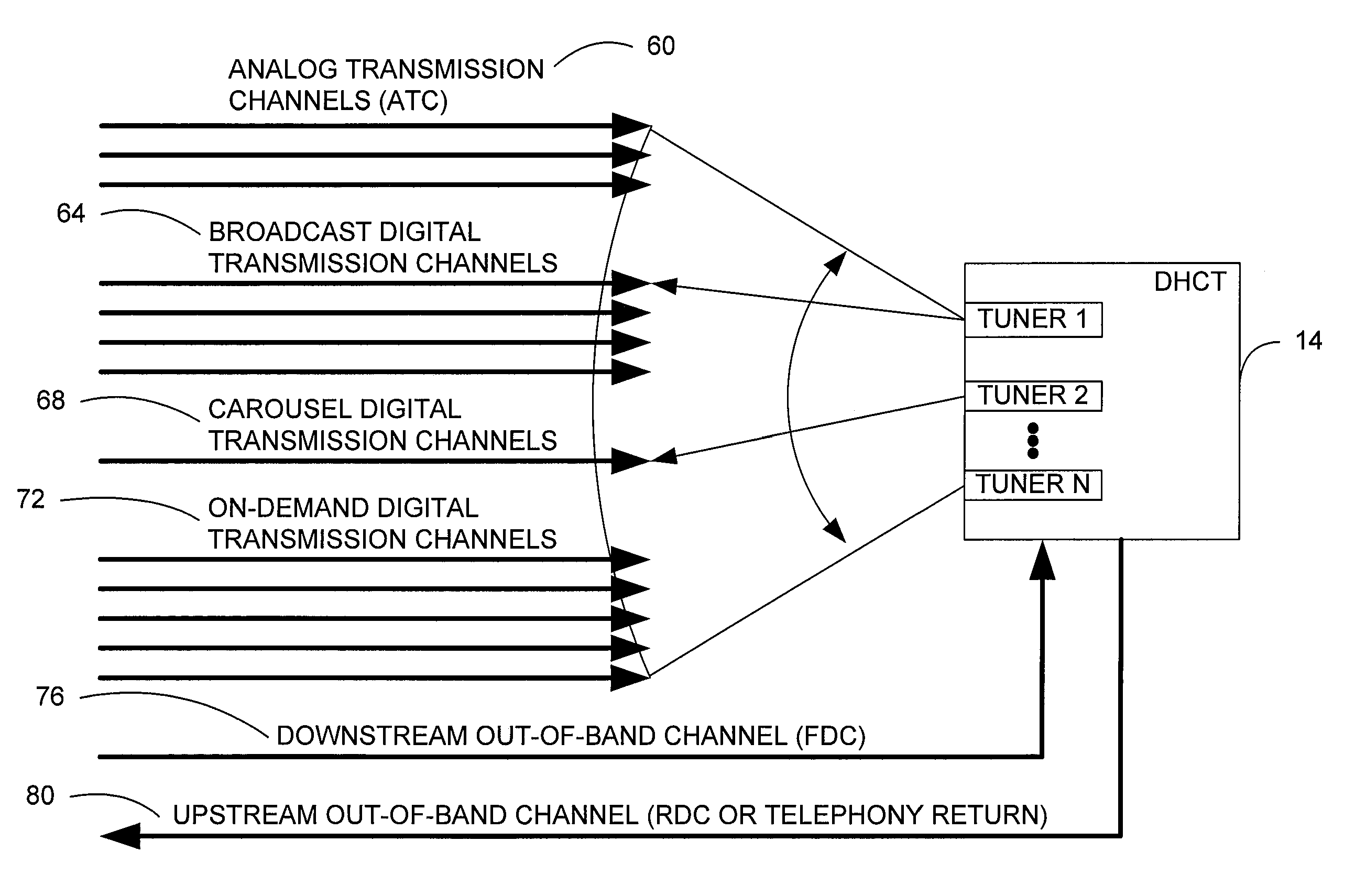

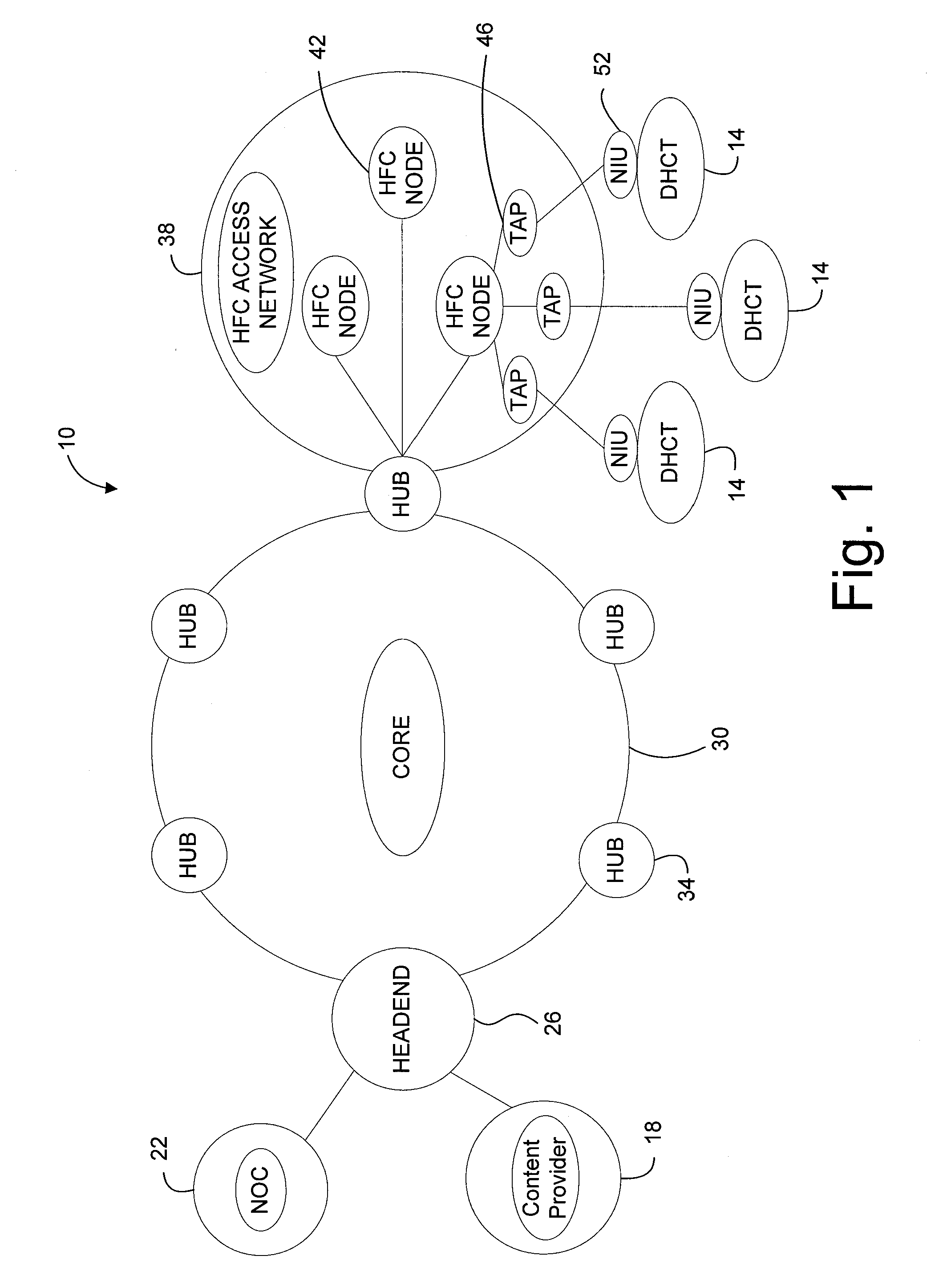

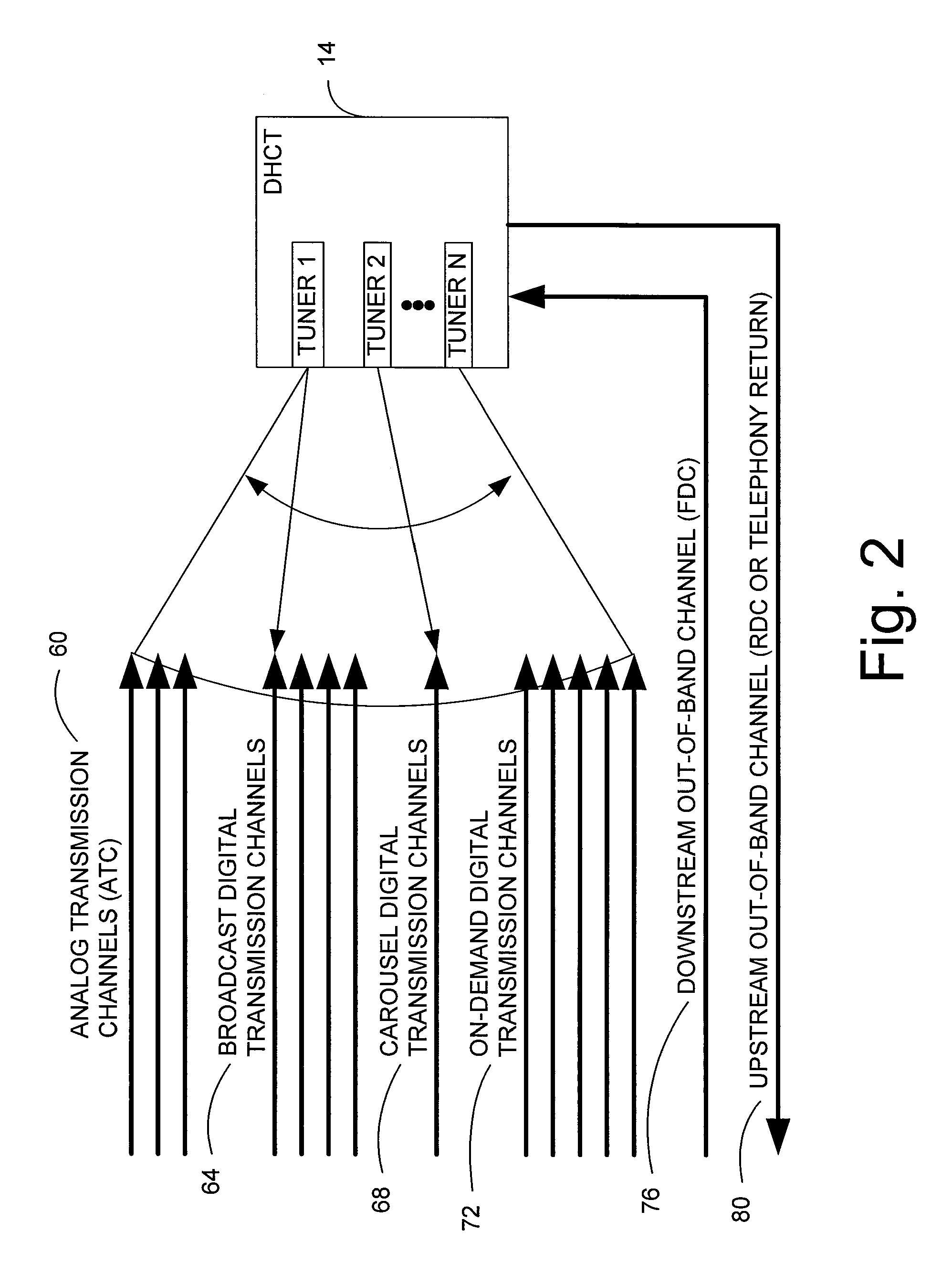

Systems and methods for adaptive pricing in a digital broadband delivery system

InactiveUS7340759B1Influence viewing patternEasy to useAnalogue secracy/subscription systemsSelective content distributionSelf adaptiveComputer science

Methods and systems are provided for dynamically pricing viewing options in a digital broadband communication network by receiving bandwidth allocation information from a bandwidth allocation manager and dynamically assigning a price criterion to each of a group of viewing options based at least in part on the bandwidth allocation information. The group of viewing options may, for example, comprise a reservation option, a normal-play option, a random access option, an on-demand random access option, and an adjust preference option. In addition, the method may optionally comprise receiving a subscriber request related to at least one viewing option selected from the group of viewing options and transmitting a price criterion for the viewing option to the subscriber in response to the subscriber request. The subscriber request may comprise, for example, a request for a price criterion for a viewing option, a request for viewing a program according to a viewing option, and / or a request for a list of available viewing options. In addition, the price criterion may be based, in part, on subscriber profile data.

Owner:CISCO TECH INC

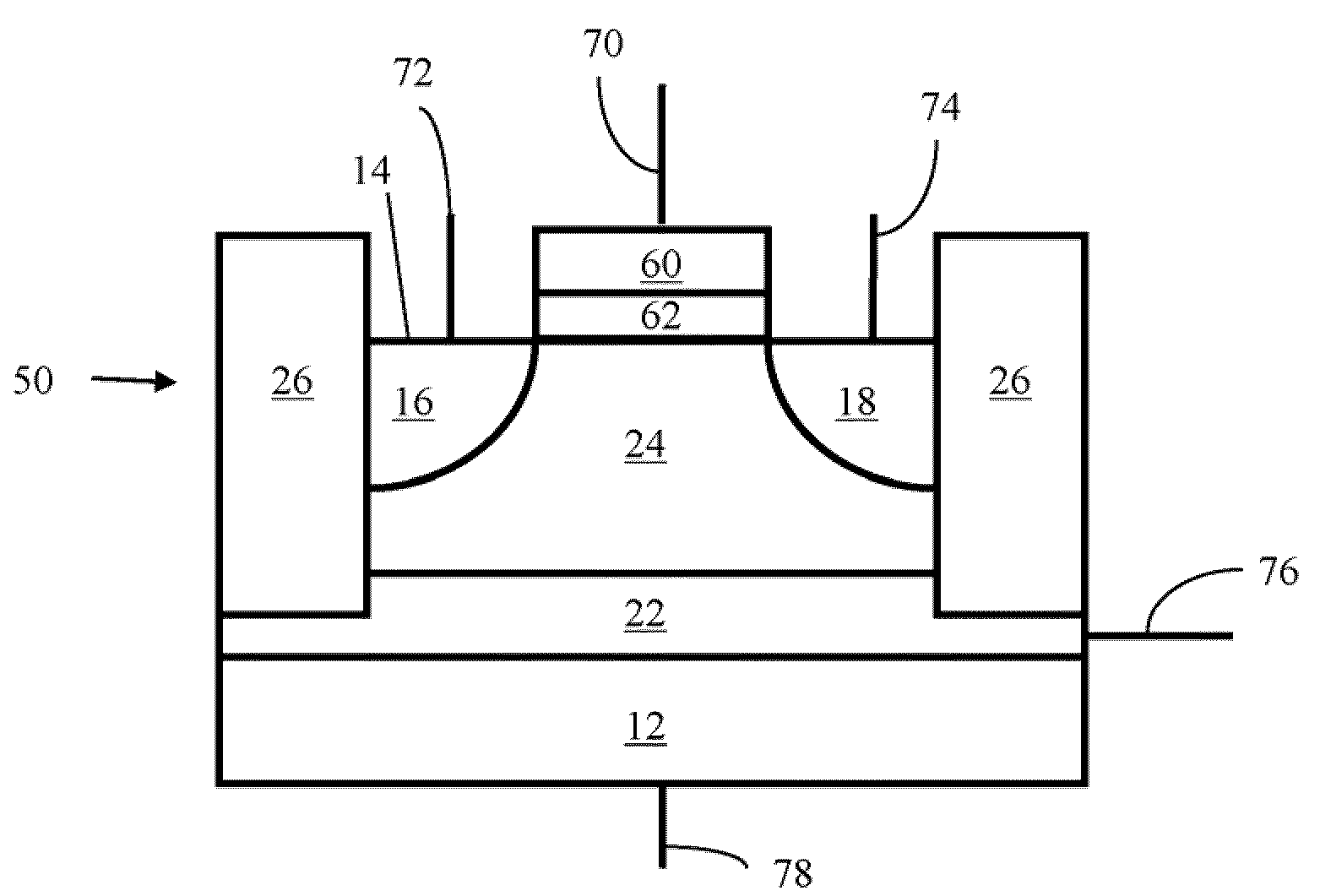

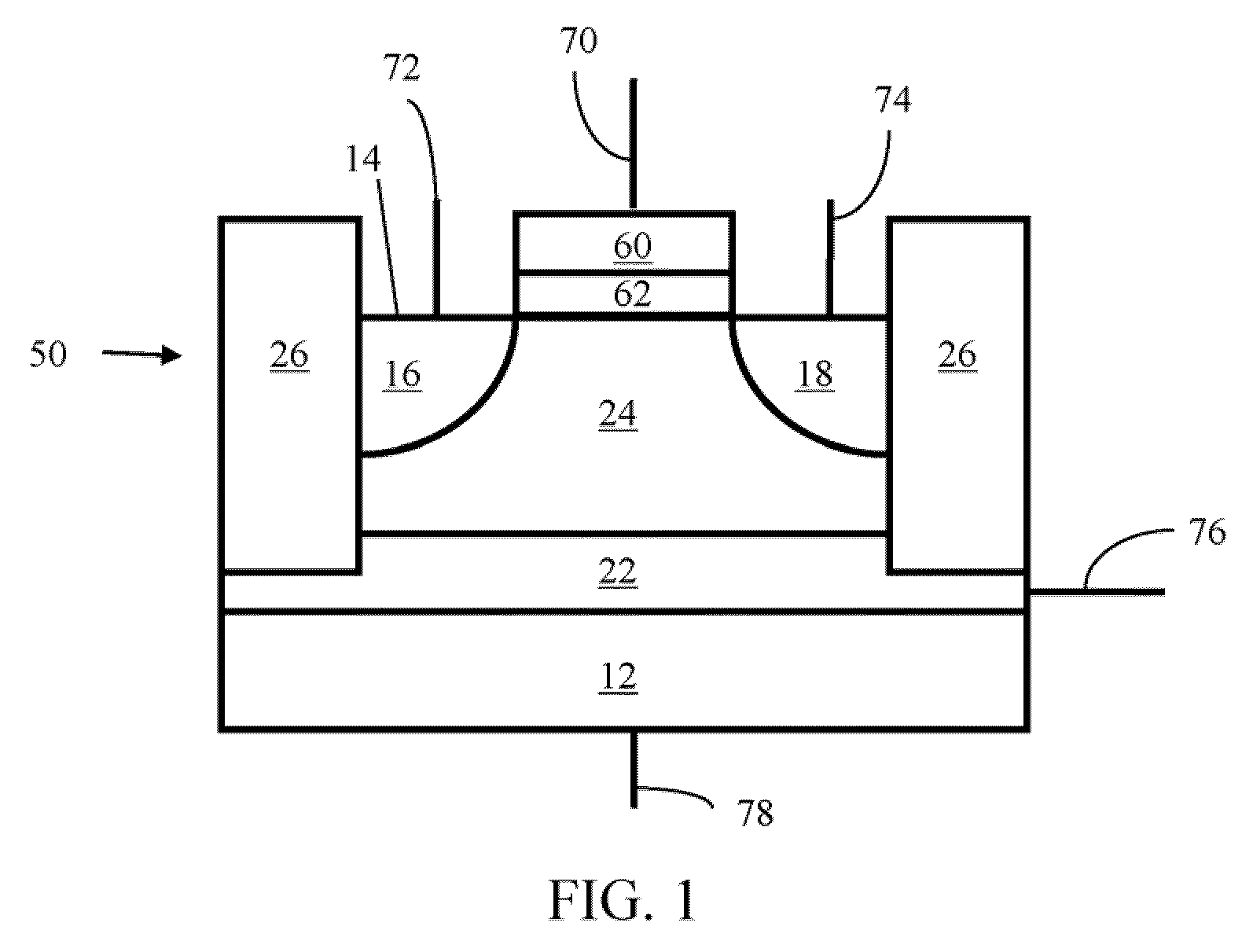

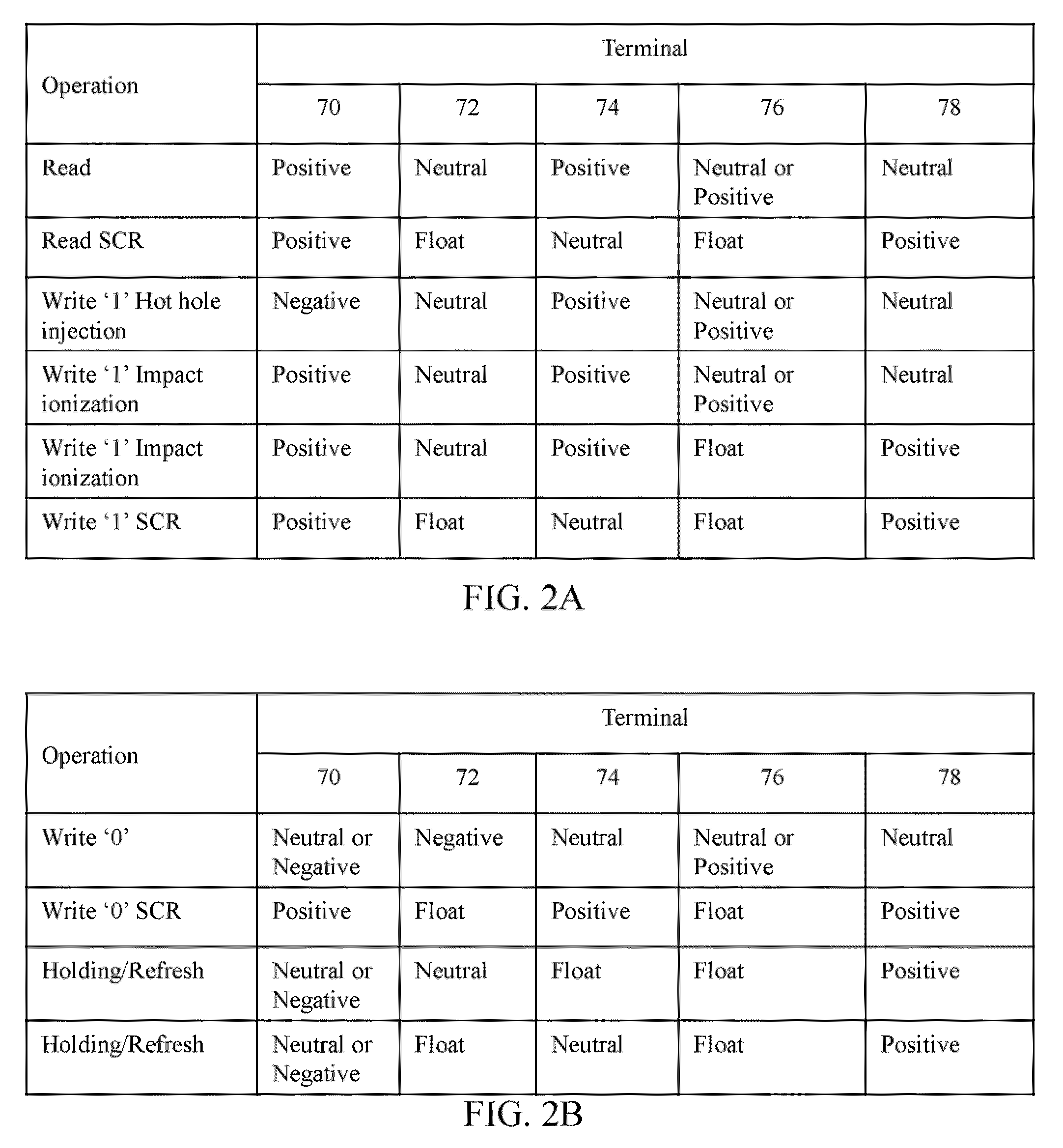

Method of operating semiconductor memory device with floating body transistor using silicon controlled rectifier principle

Methods of operating semiconductor memory devices with floating body transistors, using a silicon controlled rectifier principle are provided, as are semiconductor memory devices for performing such operations. A method of maintaining the data state of a semiconductor dynamic random access memory cell is provided, wherein the memory cell comprises a substrate being made of a material having a first conductivity type selected from p-type conductivity type and n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type; a second region having the second conductivity type, the second region being spaced apart from the first region; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; and a gate positioned between the first and second regions and adjacent the body region. The memory cell is configured to store a first data state which corresponds to a first charge in the body region in a first configuration, and a second data state which corresponds to a second charge in the body region in a second configuration. The method includes: providing the memory cell storing one of the first and second data states; and applying a positive voltage to a substrate terminal connected to the substrate beneath the buried layer, wherein when the body region is in the first state, the body region turns on a silicon controlled rectifier device of the cell and current flows through the device to maintain configuration of the memory cell in the first memory state, and wherein when the memory cell is in the second state, the body region does not turn on the silicon controlled rectifier device, current does not flow, and a blocking operation results, causing the body to maintain the second memory state.

Owner:ZENO SEMICON

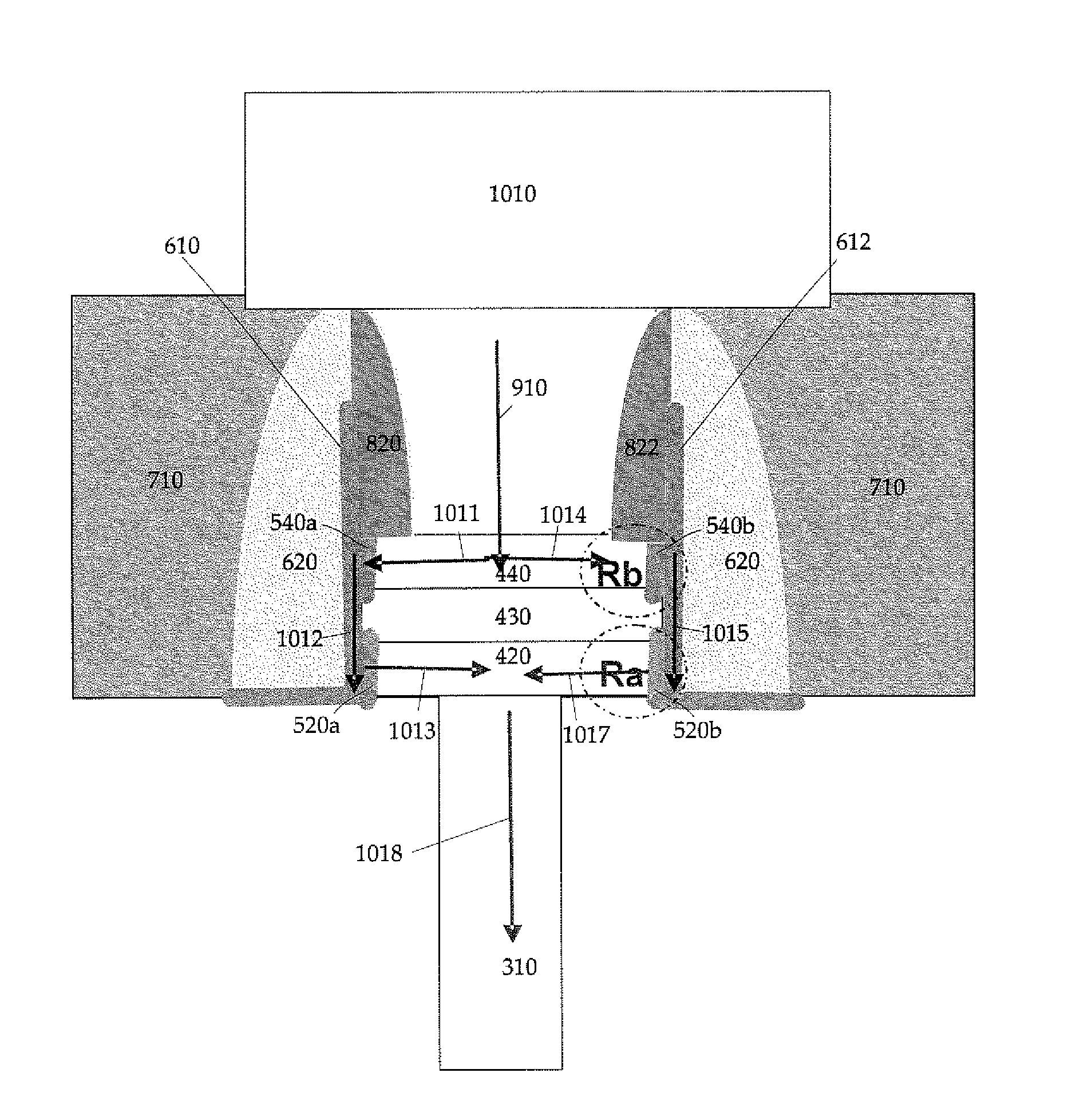

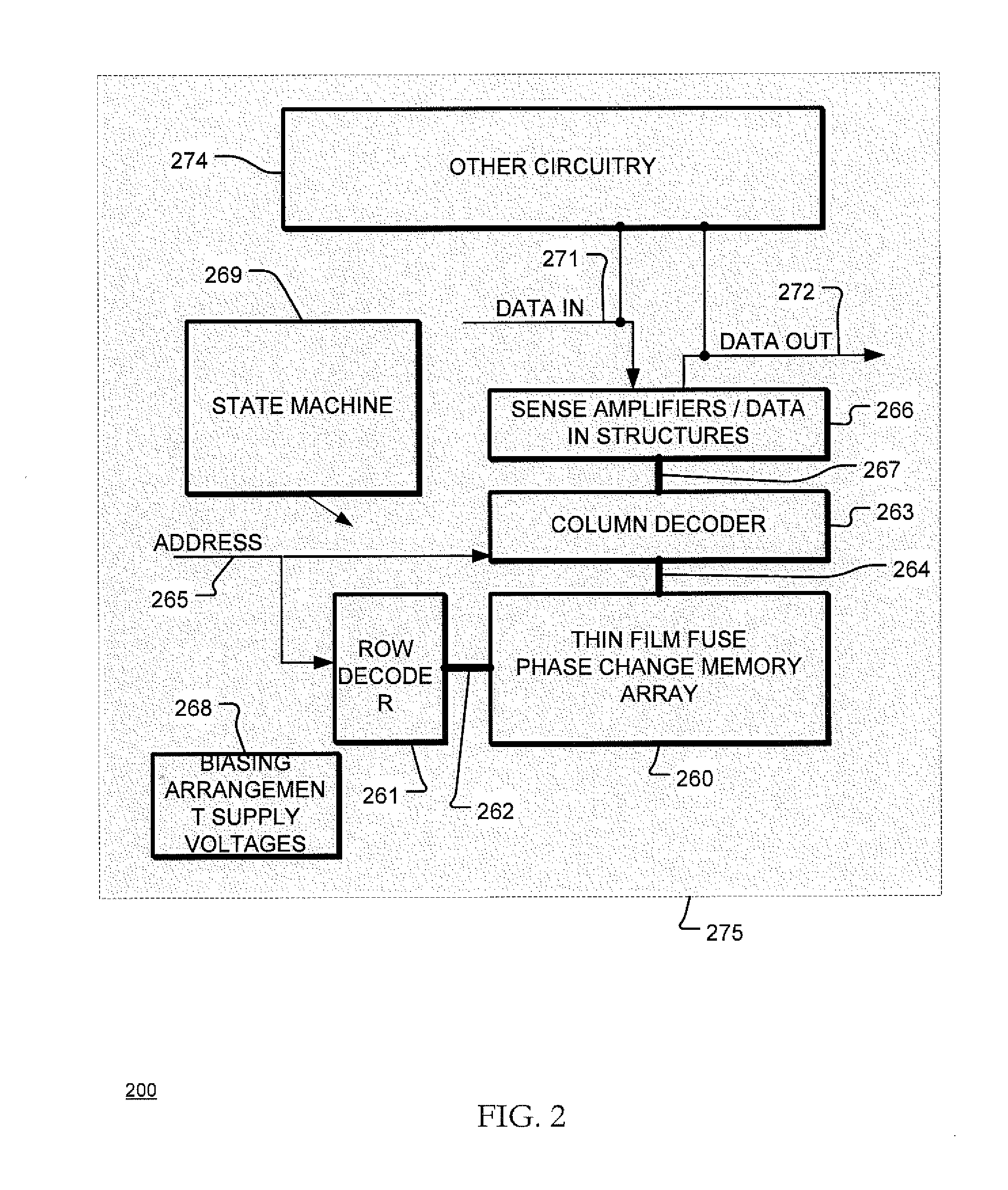

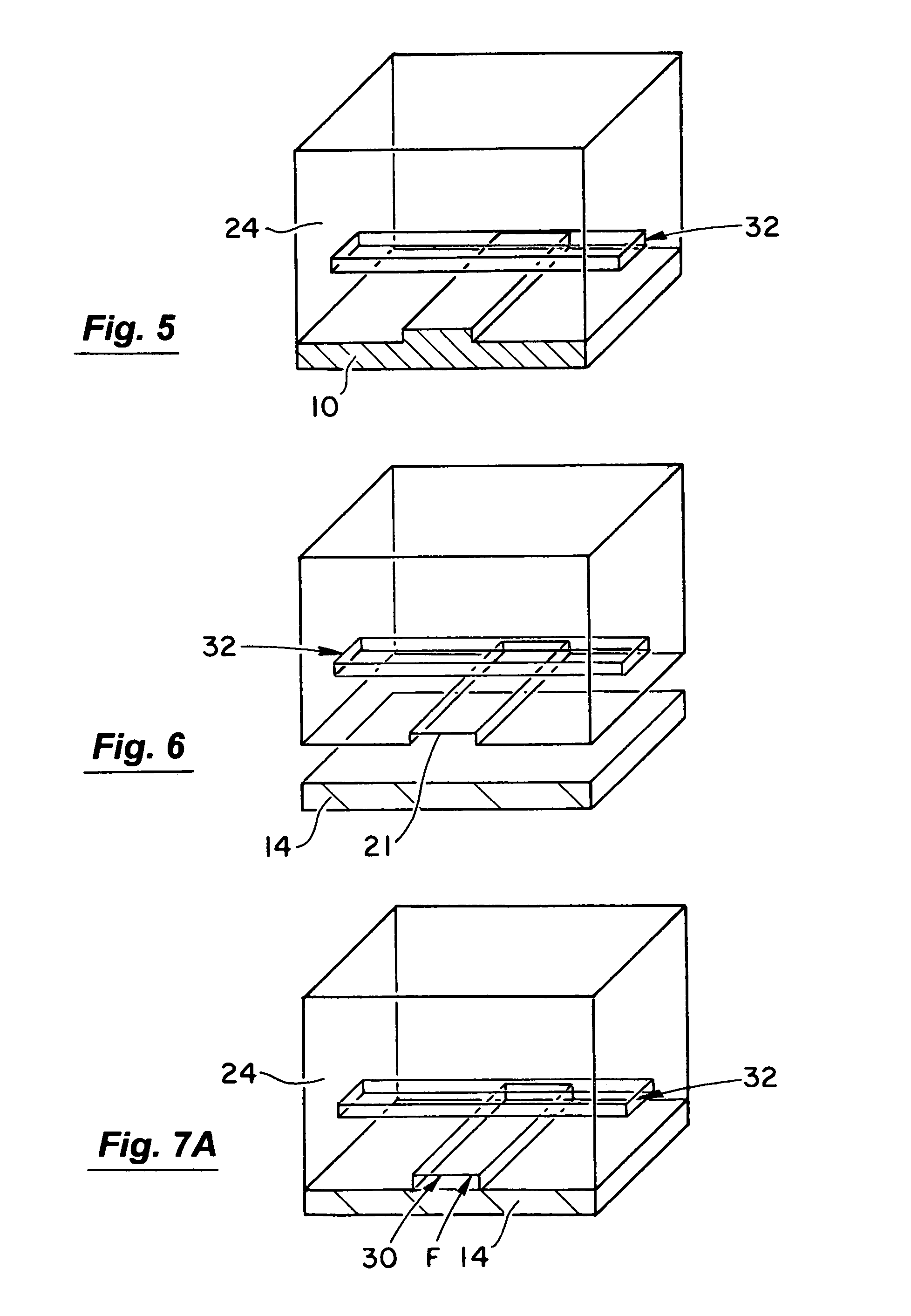

Multi-level cell resistance random access memory with metal oxides

ActiveUS7697316B2High densityElectrical apparatusElectric analogue storesRandom access memoryElectrical battery

A bistable resistance random access memory comprises a plurality of programmable resistance random access memory cells where each programmable resistance random access memory cell includes multiple memory members for performing multiple bits for each memory cell. The bistable RRAM includes a first resistance random access member connected to a second resistance random access member through interconnect metal liners and metal oxide strips. The first resistance random access member has a first resistance value Ra, which is determined from the thickness of the first resistance random access member based on the deposition of the first resistance random access member. The second resistance random access member has a second resistance value Rb, which is determined from the thickness of the second resistance random access member based on the deposition of the second resistance random access member.

Owner:MACRONIX INT CO LTD

Random Access Design for High Doppler in Wireless Networks

UE-initiated accesses within a cellular network are optimized to account for Doppler shift. A user equipment (UE) receives information that designates a particular access slot as high-speed and designates another access slot as low-speed within a given cell. The UE determines its relative speed to a serving base station (NodeB) within the cell. The UE selects either a baseline structure or an alternate structure if the relative speed is less than a threshold value or only an alternate structure if the relative speed exceeds the threshold value. The UE transmits a signal to the NodeB using the selected structure, such that the baseline structure is transmitted only in the designated low-speed access slot and that the alternate structure is transmitted only in the designated high-speed request slot.

Owner:TEXAS INSTR INC

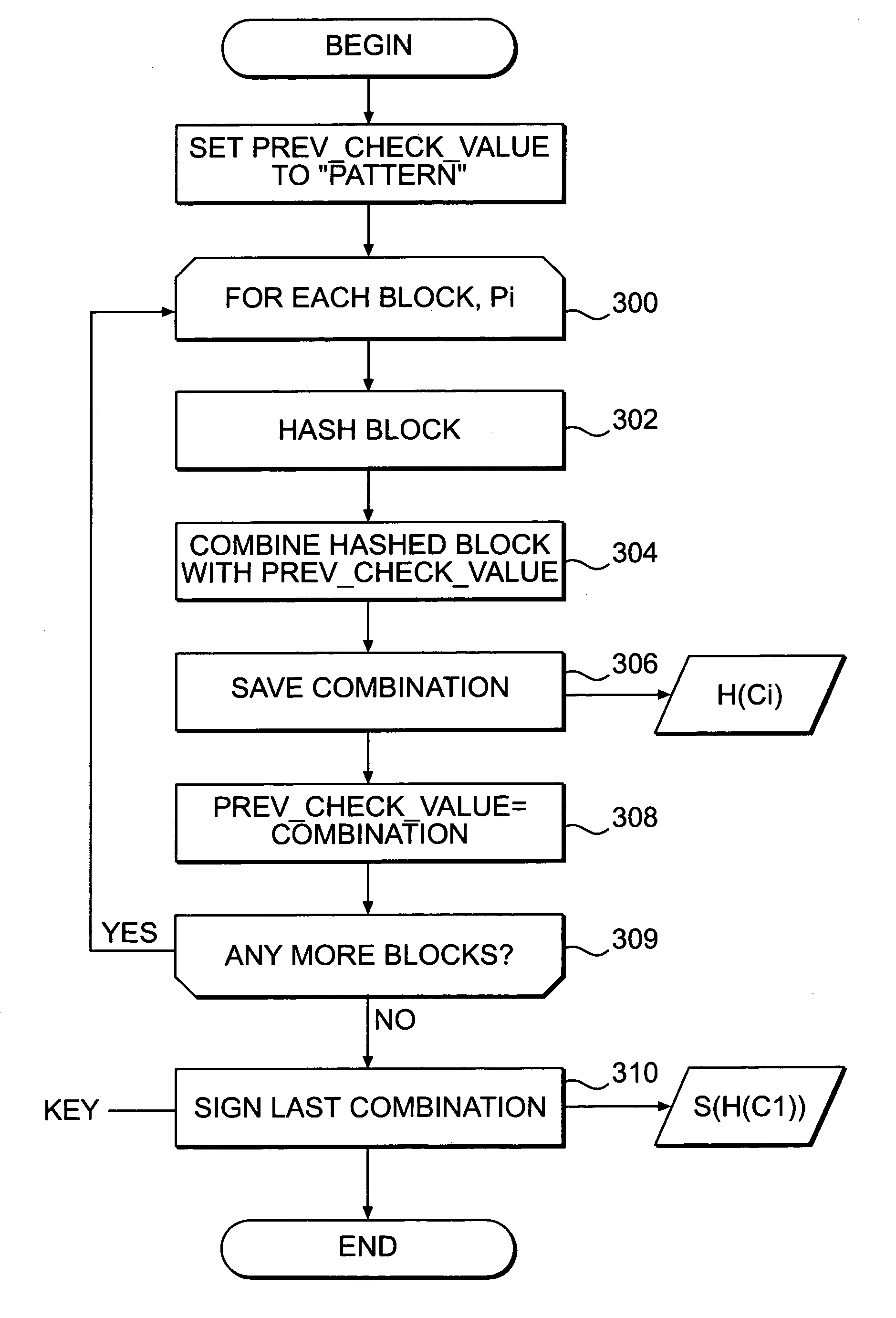

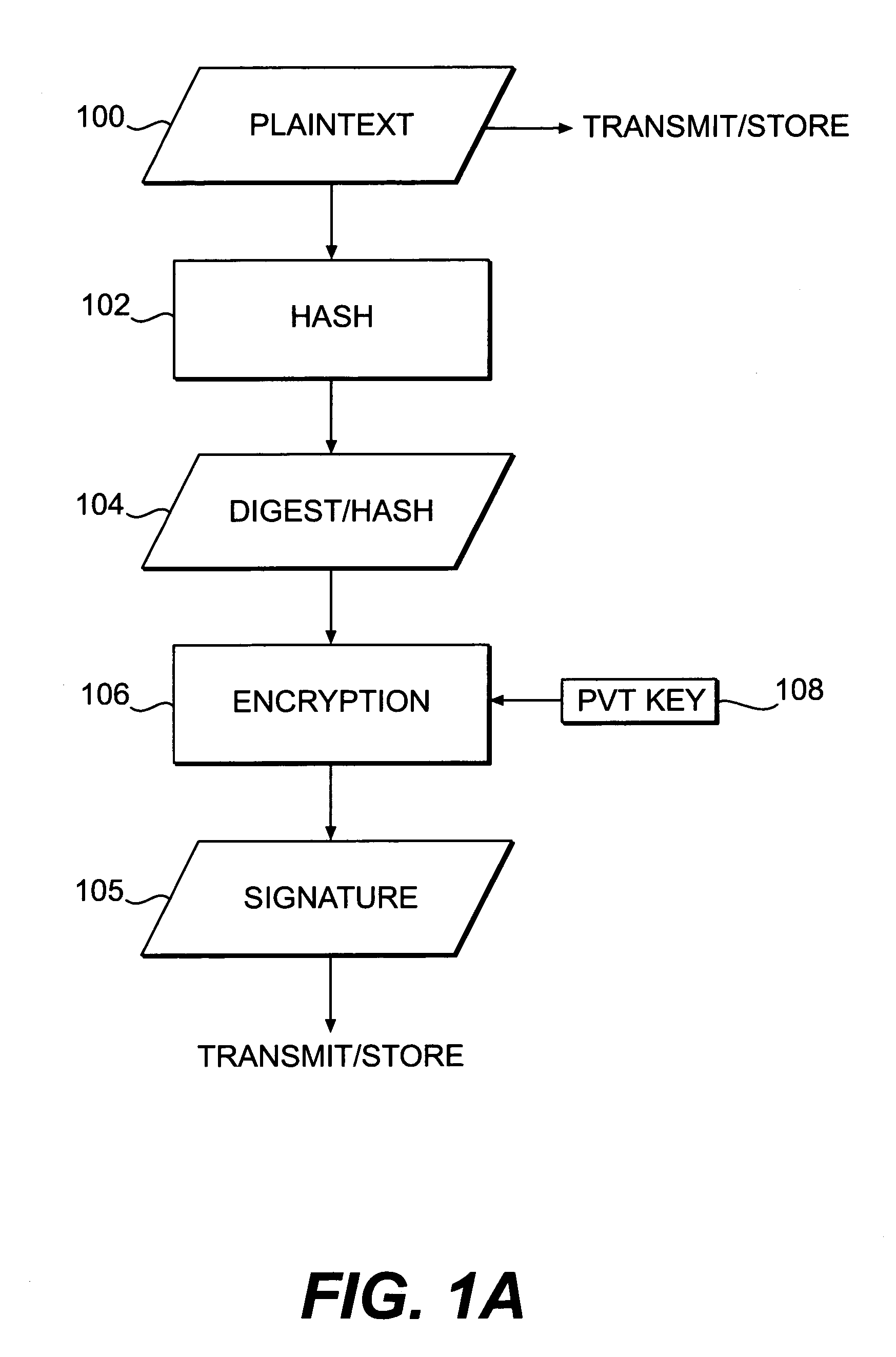

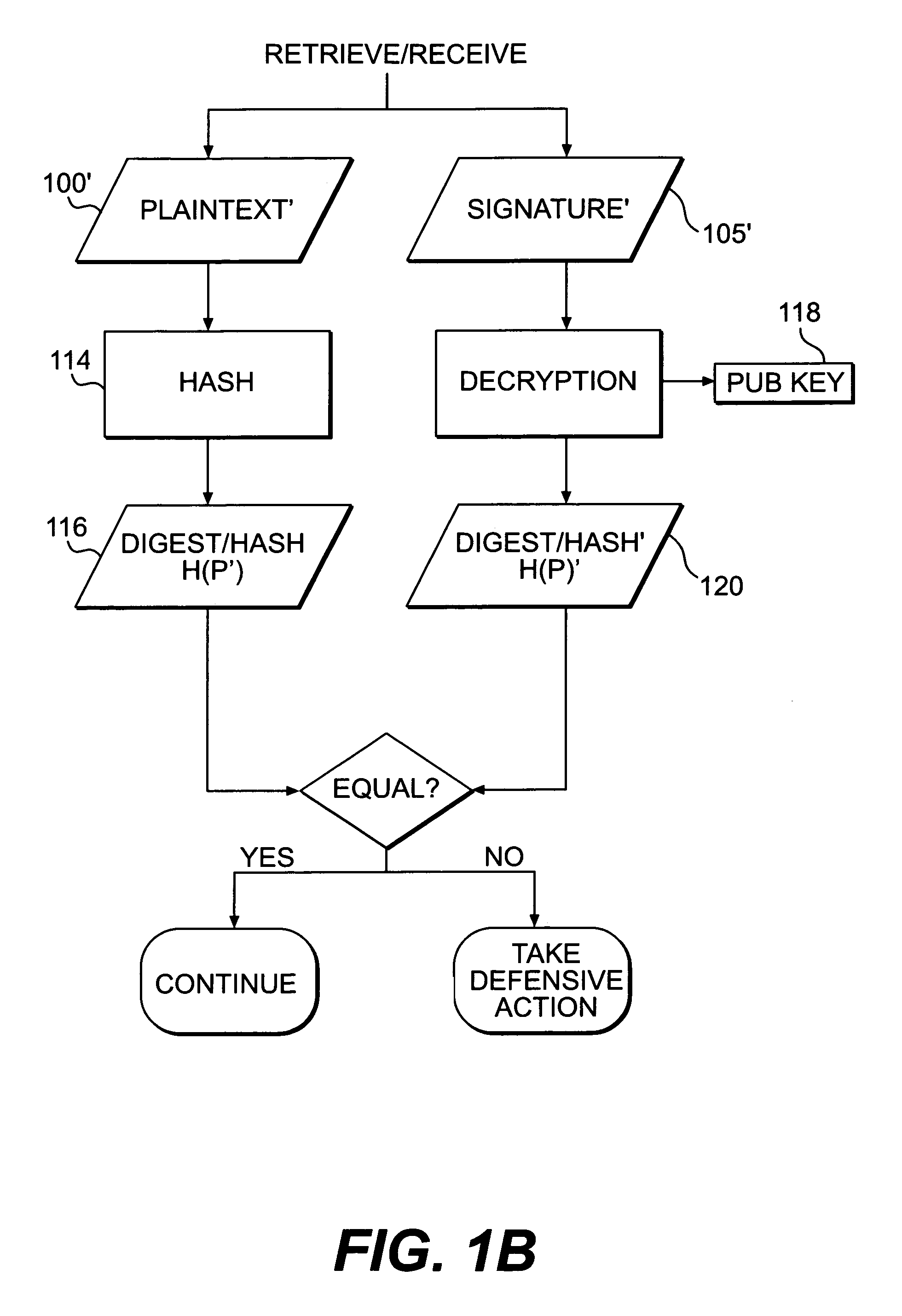

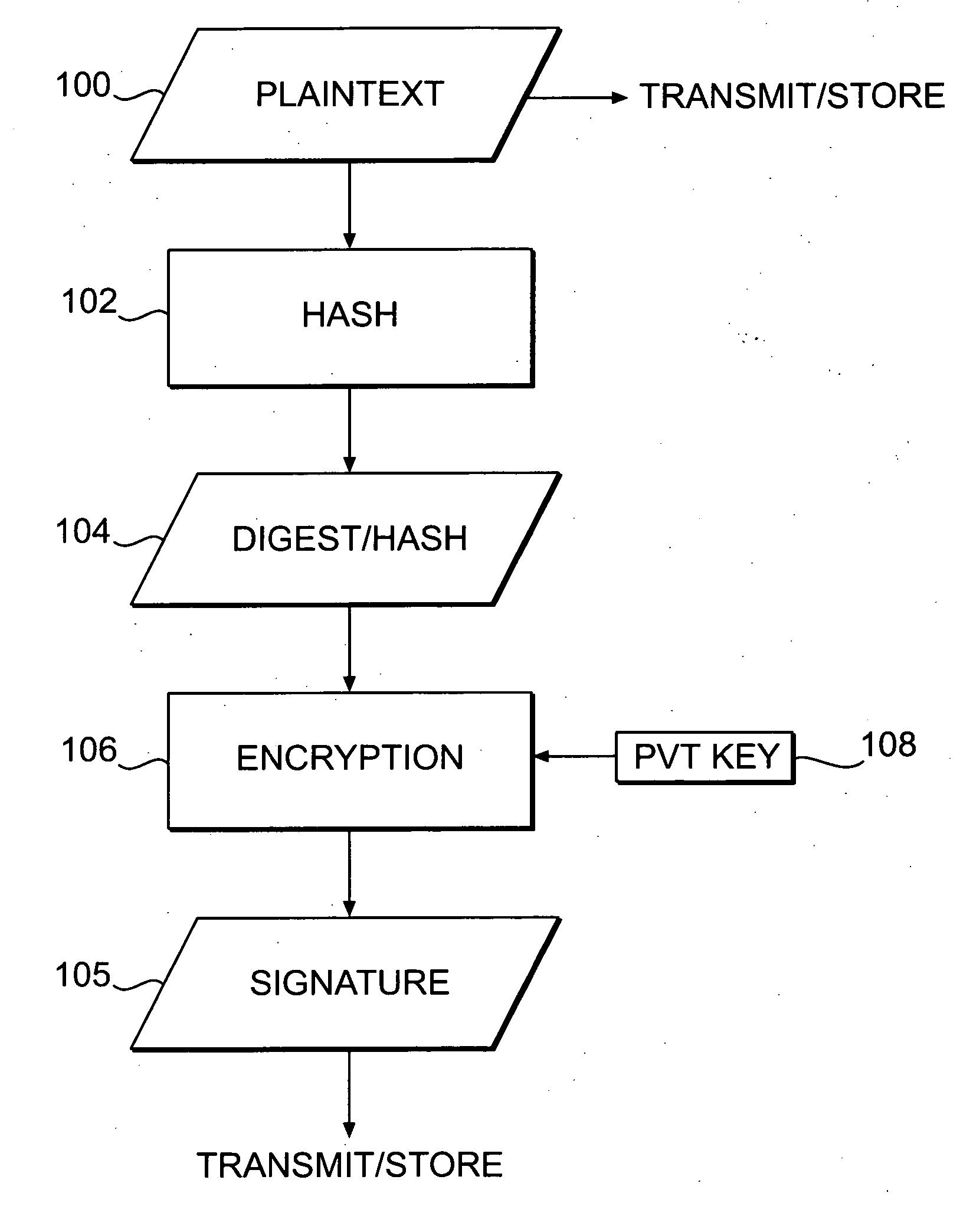

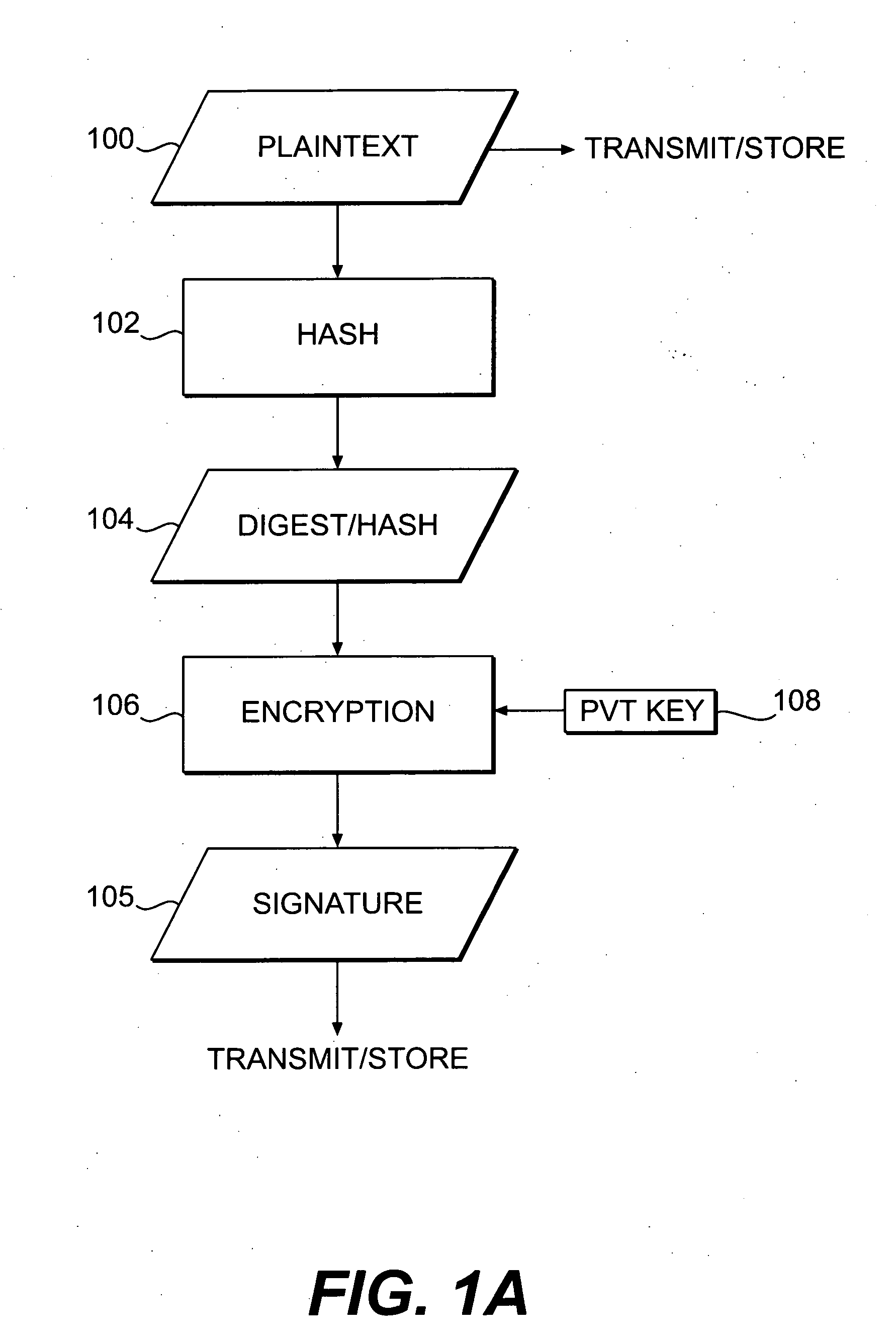

Systems and methods for authenticating and protecting the integrity of data streams and other data

InactiveUS6959384B1Authentication is convenientDetecting errorUser identity/authority verificationDigital data protectionError checkFault tolerance

Systems and methods are disclosed for enabling a recipient of a cryptographically-signed electronic communication to verify the authenticity of the communication on-the-fly using a signed chain of check values, the chain being constructed from the original content of the communication, and each check value in the chain being at least partially dependent on the signed root of the chain and a portion of the communication. Fault tolerance can be provided by including error-check values in the communication that enable a decoding device to maintain the chain's security in the face of communication errors. In one embodiment, systems and methods are provided for enabling secure quasi-random access to a content file by constructing a hierarchy of hash values from the file, the hierarchy deriving its security in a manner similar to that used by the above-described chain. The hierarchy culminates with a signed hash that can be used to verify the integrity of other hash values in the hierarchy, and these other hash values can, in turn, be used to efficiently verify the authenticity of arbitrary portions of the content file.

Owner:INTERTRUST TECH CORP

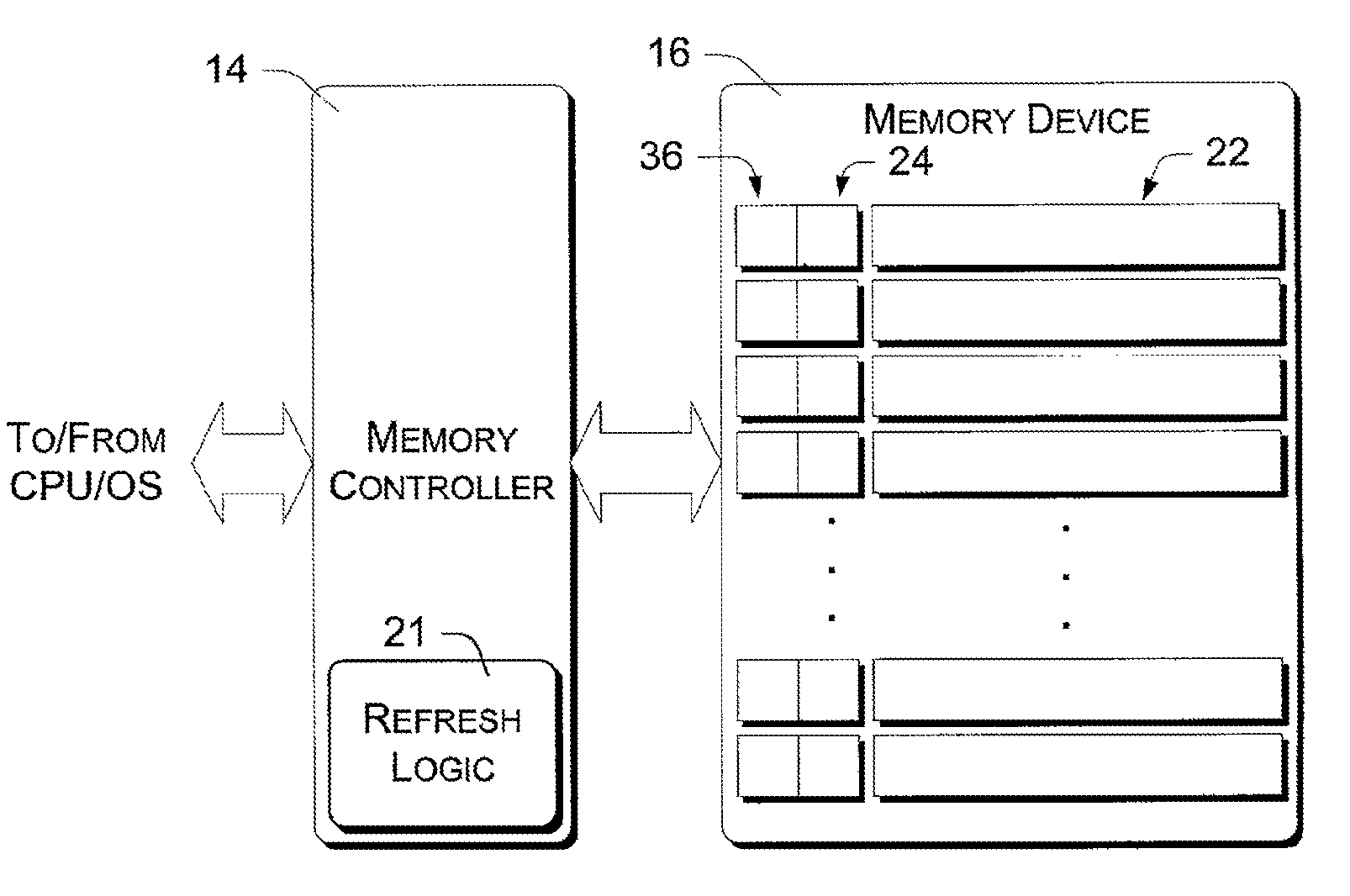

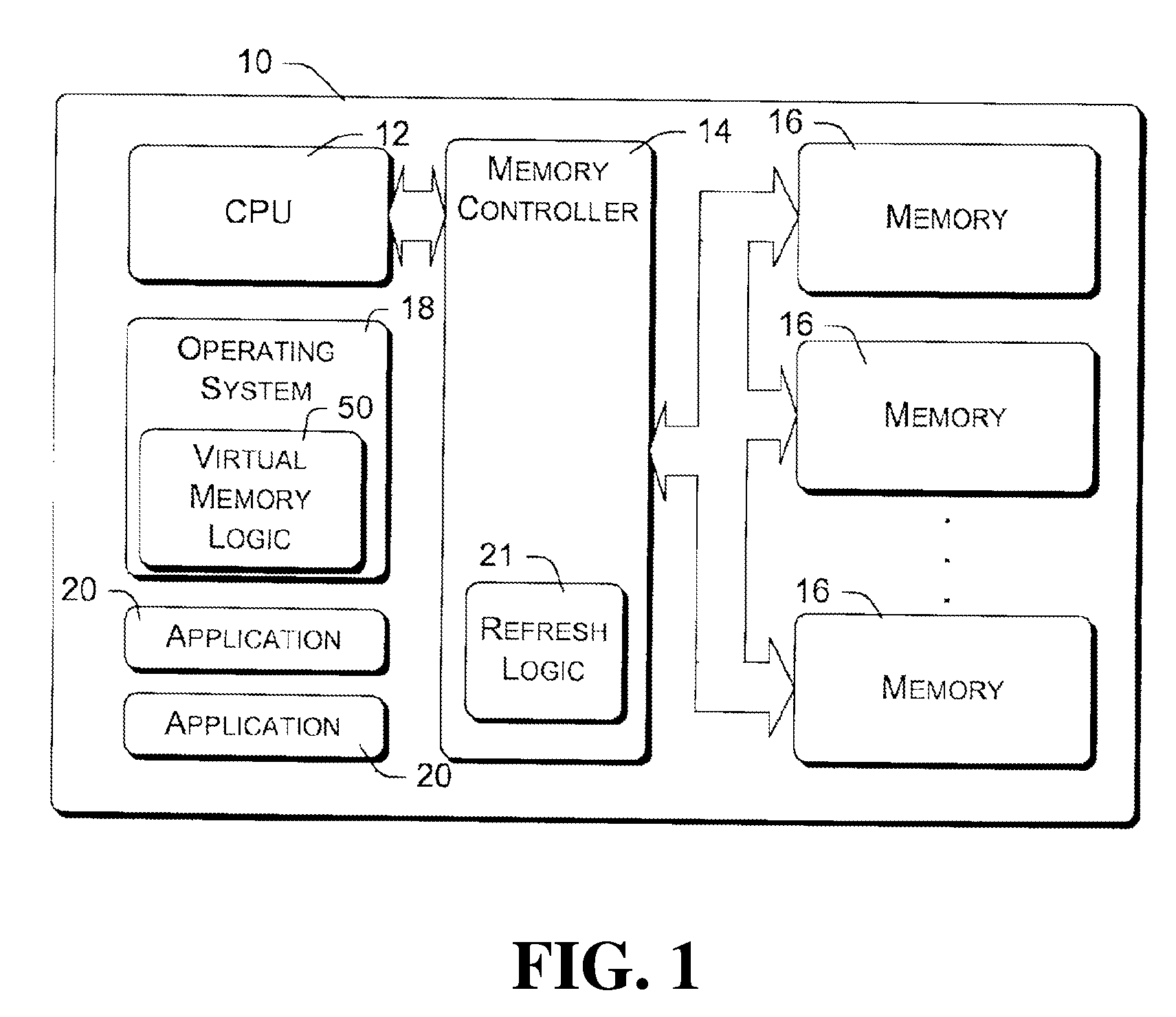

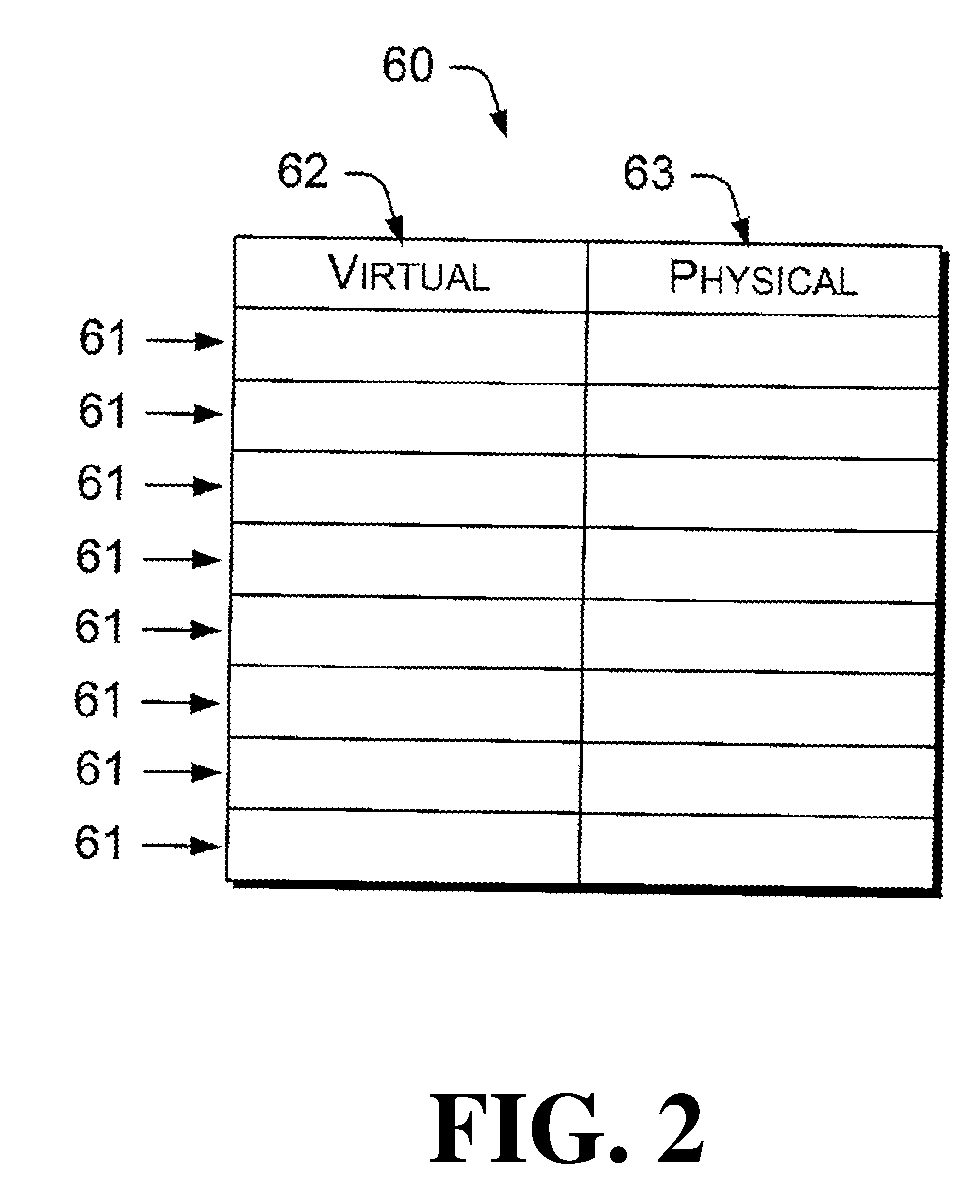

Redistribution of memory to reduce computer system power consumption

InactiveUS20070106860A1Limited amount of powerLowering thermal profileEnergy efficient ICTVolume/mass flow measurementDIMMPower mode

A method, apparatus and system are disclosed for redistributing memory allocation to portions of dynamic random access memory (DRAM) and dual in-line memory module (DIMM) devices that are underutilized, in order to balance memory usage more evenly amongst active devices so as to limit the amount of power and the thermal load consumed by an individual memory component. The disclosed method, apparatus and system are capable of identifying and tracking memory usage to minimize power consumption in a way that lessens the detrimental effects of “throttling” or reduced power modes for memory devices.

Owner:LENOVO GLOBAL TECH INT LTD

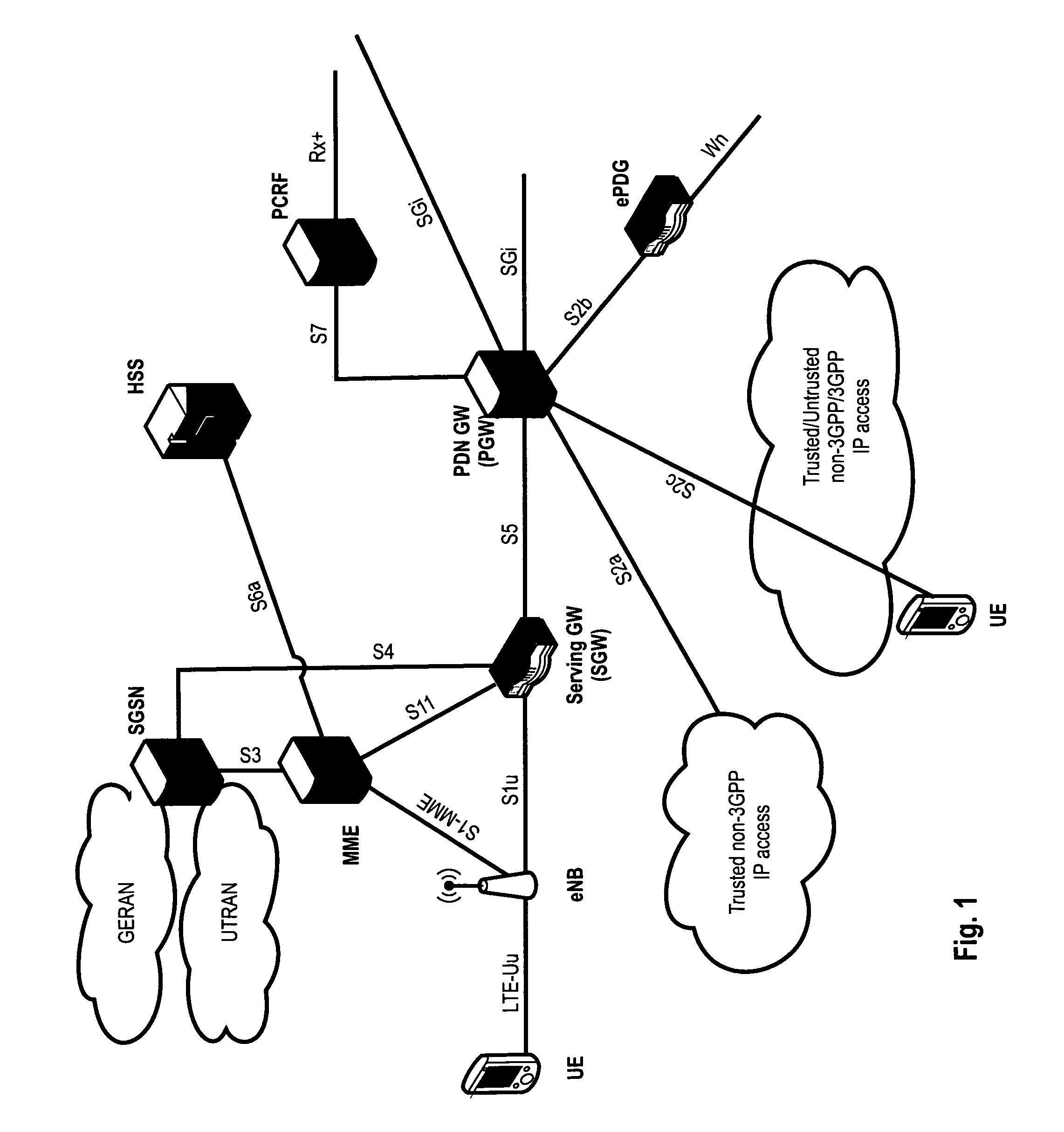

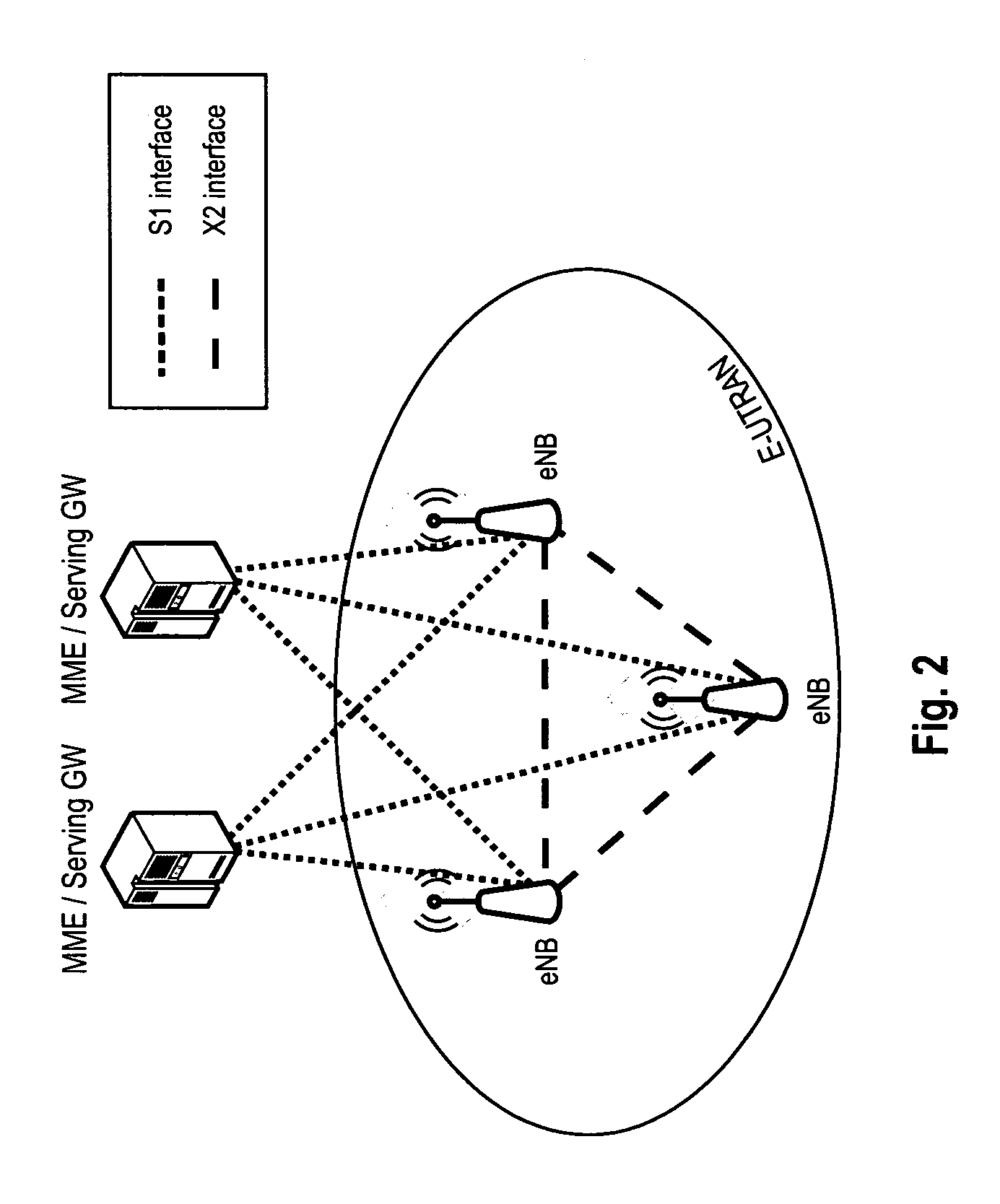

Apparatus and method for performing uplink synchronization in wireless communication system

ActiveUS20120300752A1Reduce overheadSynchronisation arrangementNetwork traffic/resource managementCommunications systemMobile station

This specification relates to an apparatus and method for performing random access in a wireless communication system. This specification discloses a mobile station, including a reception unit for receiving TAG configuration information on which at least one serving cell configured in the mobile station is classified as a Timing Alignment Group (TAG) from a base station and a transmission unit for transmitting a random access preamble to the base station on one representative serving cell within the TAG. In accordance with this specification, a procedure of obtaining a TAV for a serving cell in order to secure and maintain uplink timing synchronization becomes clear, the time taken to obtain uplink synchronization for a serving cell may be reduced, and overhead due to excessive random access attempts may be reduced by obtaining a TAV for a plurality of serving cells through one random access procedure.

Owner:APPLE INC

Systems and methods for authenticating and protecting the integrity of data streams and other data

InactiveUS20050235154A1Authentication is convenientDetecting errorUser identity/authority verificationDigital data protectionError checkFault tolerance

Systems and methods are disclosed for enabling a recipient of a cryptographically-signed electronic communication to verify the authenticity of the communication on-the-fly using a signed chain of check values, the chain being constructed from the original content of the communication, and each check value in the chain being at least partially dependent on the signed root of the chain and a portion of the communication. Fault tolerance can be provided by including error-check values in the communication that enable a decoding device to maintain the chain's security in the face of communication errors. In one embodiment, systems and methods are provided for enabling secure quasi-random access to a content file by constructing a hierarchy of hash values from the file, the hierarchy deriving its security in a manner similar to that used by the above-described chain. The hierarchy culminates with a signed hash that can be used to verify the integrity of other hash values in the hierarchy, and these other hash values can, in turn, be used to efficiently verify the authenticity of arbitrary portions of the content file.

Owner:INTERTRUST TECH CORP

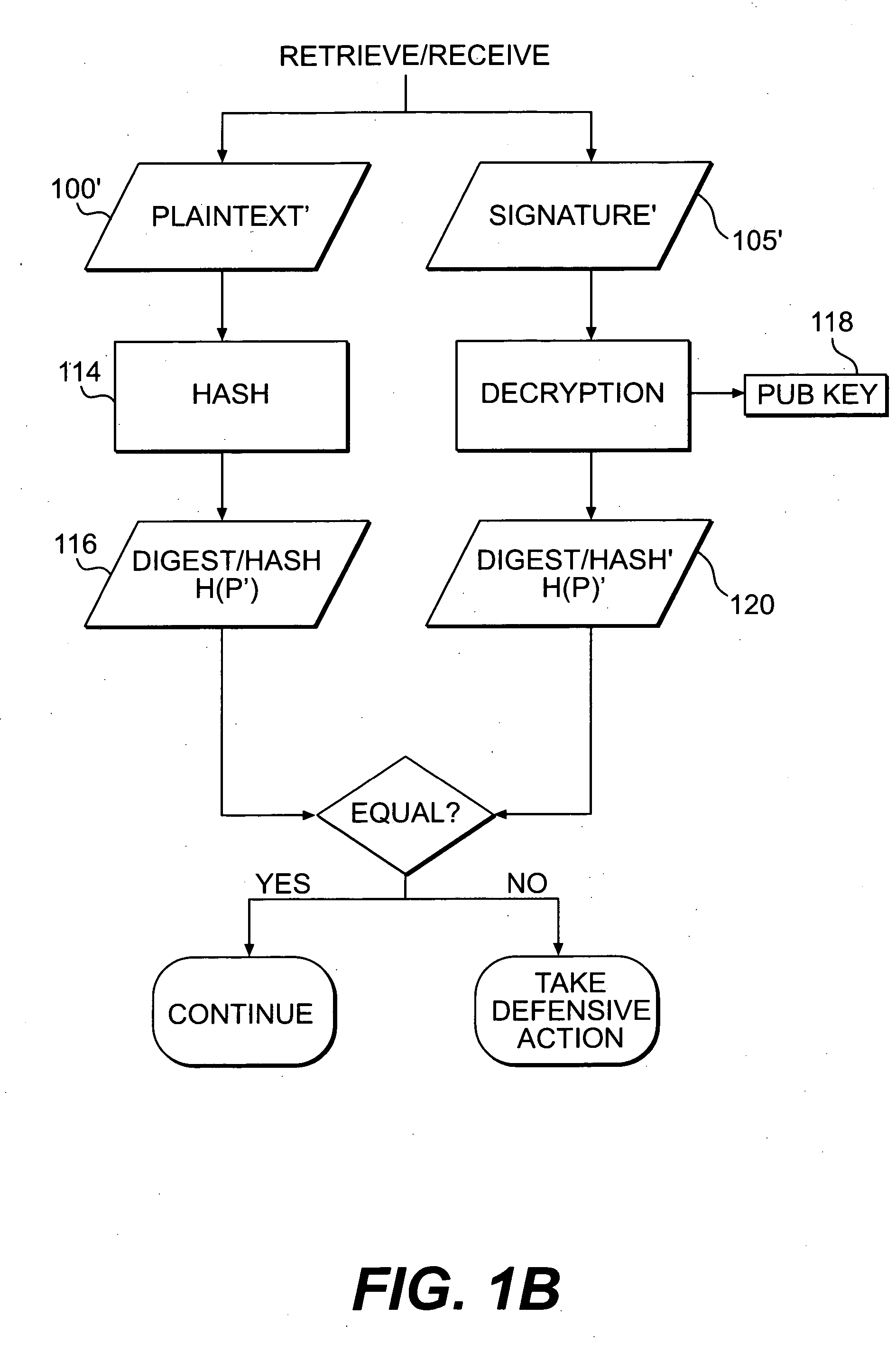

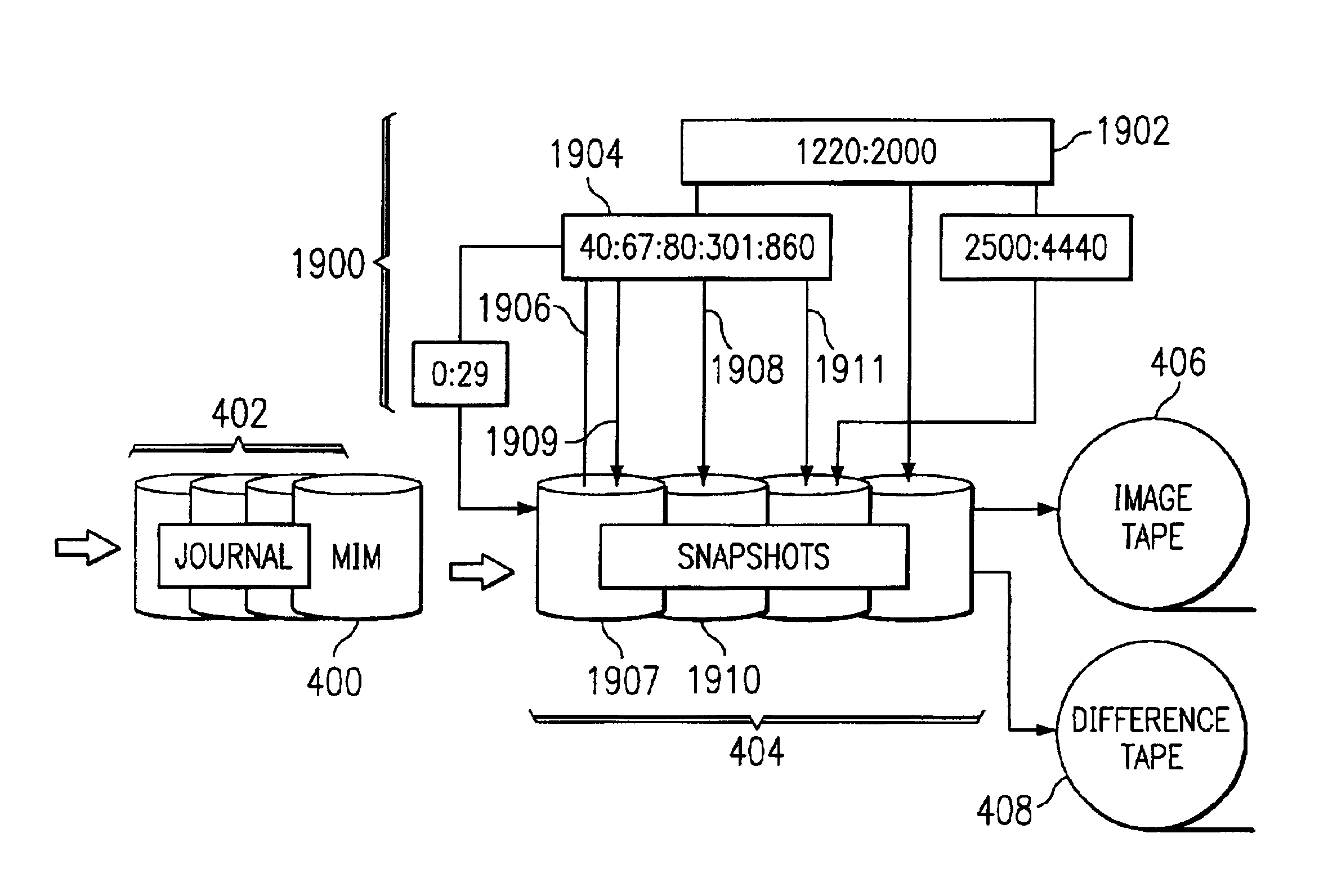

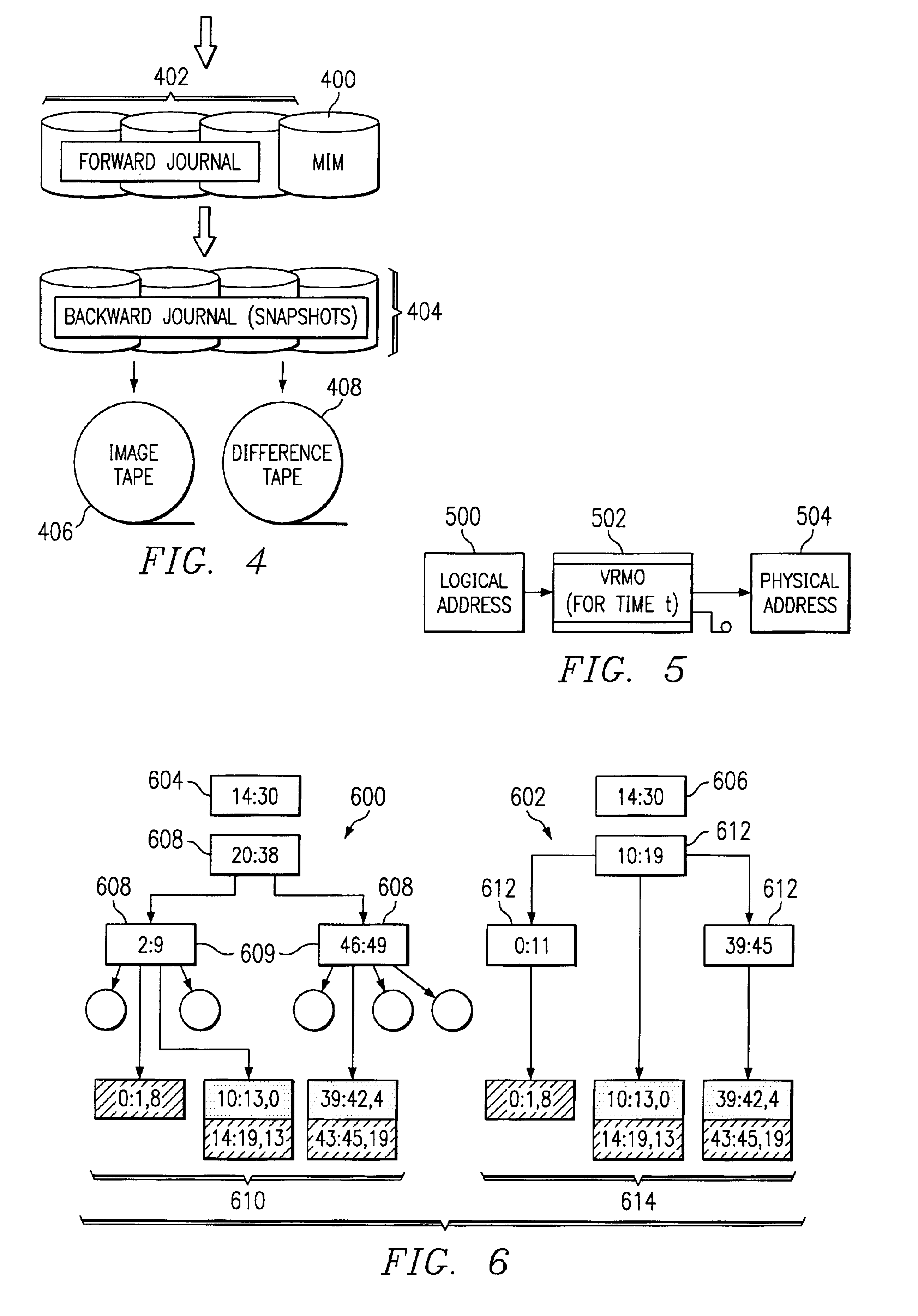

Data management appliance

ActiveUS6898688B2Quick and random-access recovery of dataError preventionError detection/correctionAssistive technologyData management

The present invention is directed toward a data management appliance and ancillary technologies for replicating data written to a primary storage system. The data management appliance is a random-access storage system that at the logical block level replicates the contents of a primary storage system over time.

Owner:ORACLE INT CORP

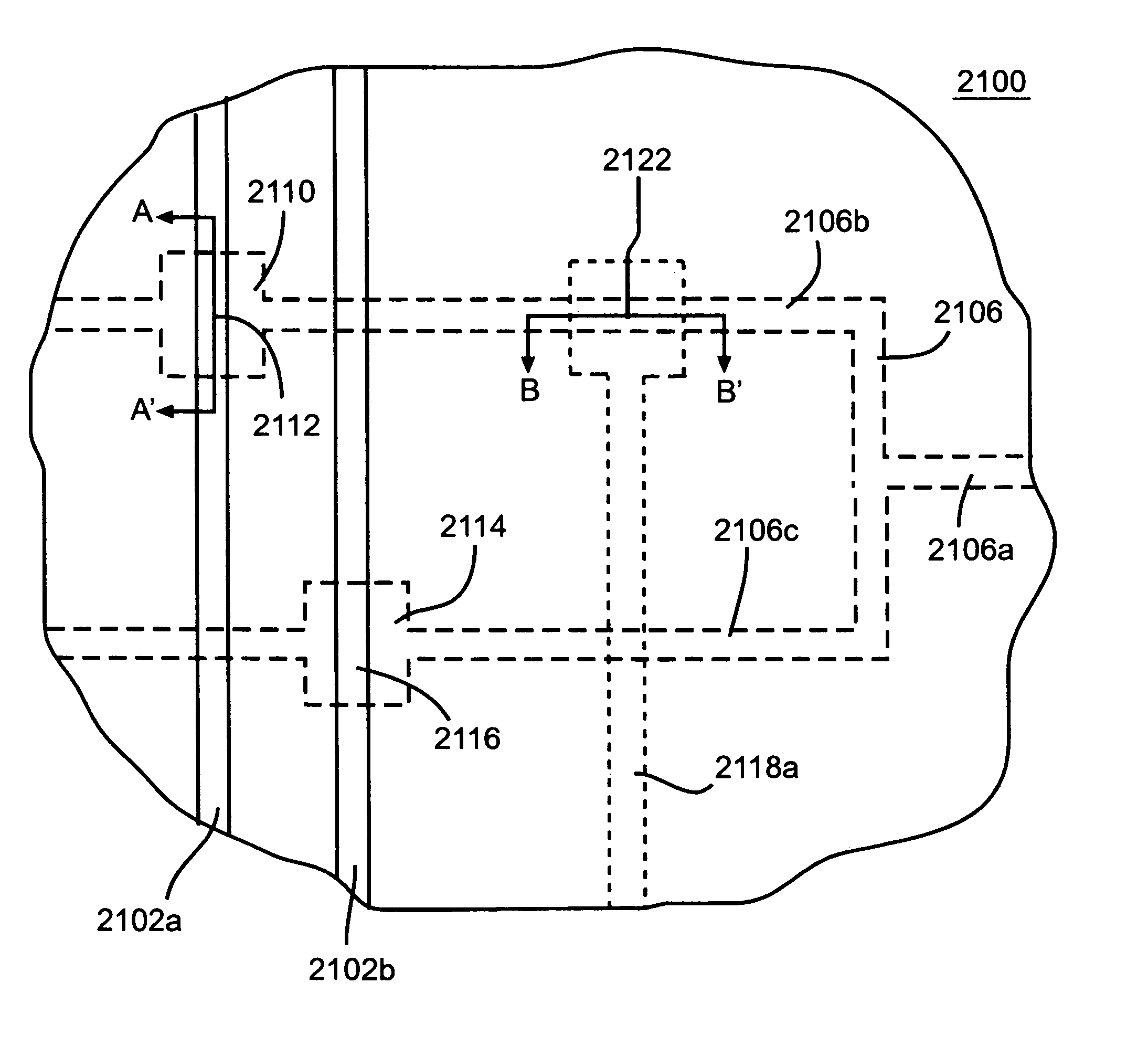

Microfluidic large scale integration

ActiveUS7143785B2Easy to handleDiaphragm valvesOperating means/releasing devices for valvesHigh densityRandom access memory

High-density microfluidic chips contain plumbing networks with thousands of micromechanical valves and hundreds of individually addressable chambers. These fluidic devices are analogous to electronic integrated circuits fabricated using large scale integration (LSI). A component of these networks is the fluidic multiplexor, which is a combinatorial array of binary valve patterns that exponentially increases the processing power of a network by allowing complex fluid manipulations with a minimal number of inputs. These integrated microfluidic networks can be used to construct a variety of highly complex microfluidic devices, for example the microfluidic analog of a comparator array, and a microfluidic memory storage device resembling electronic random access memories.

Owner:MOTOROLA INC +1

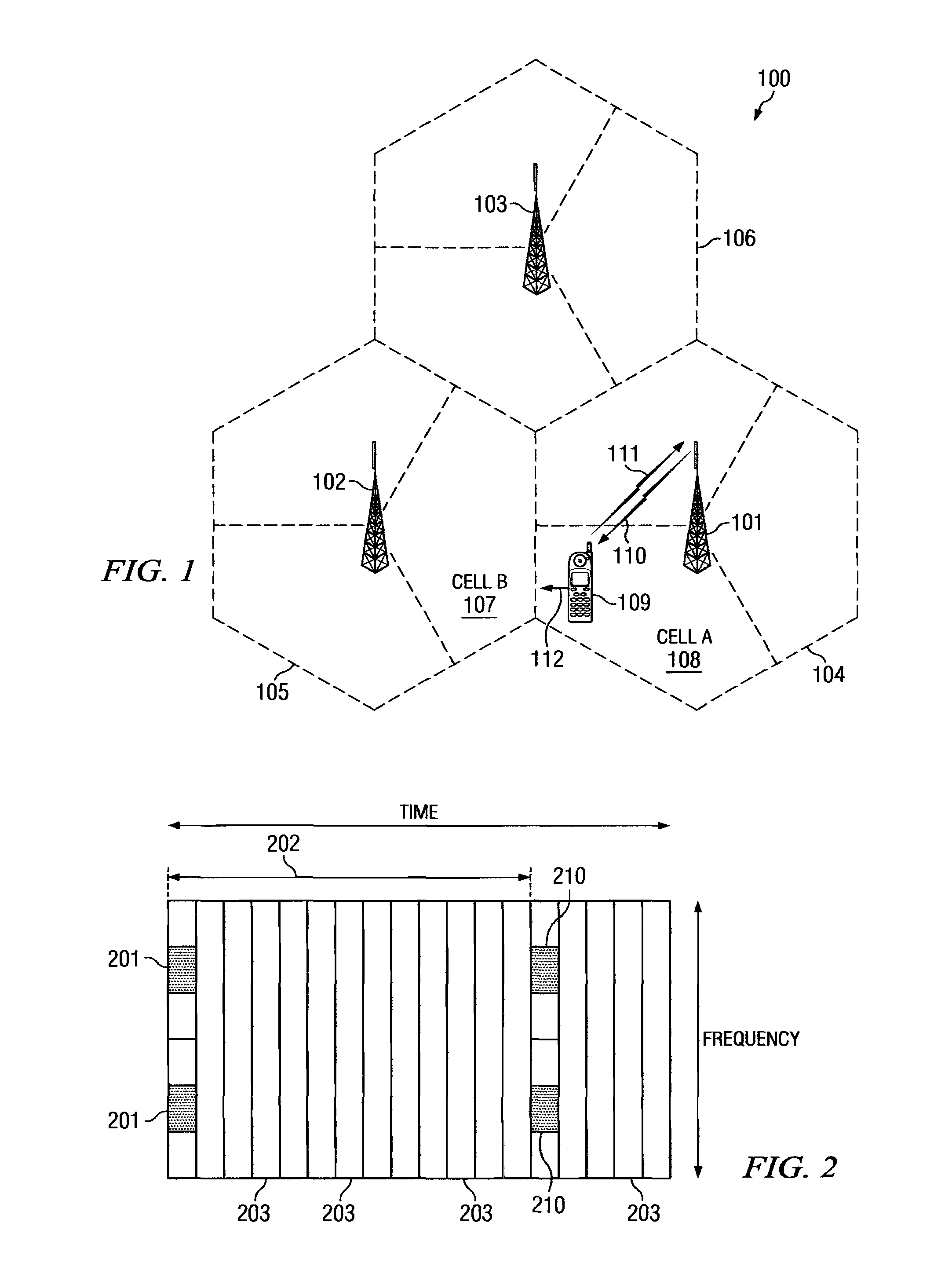

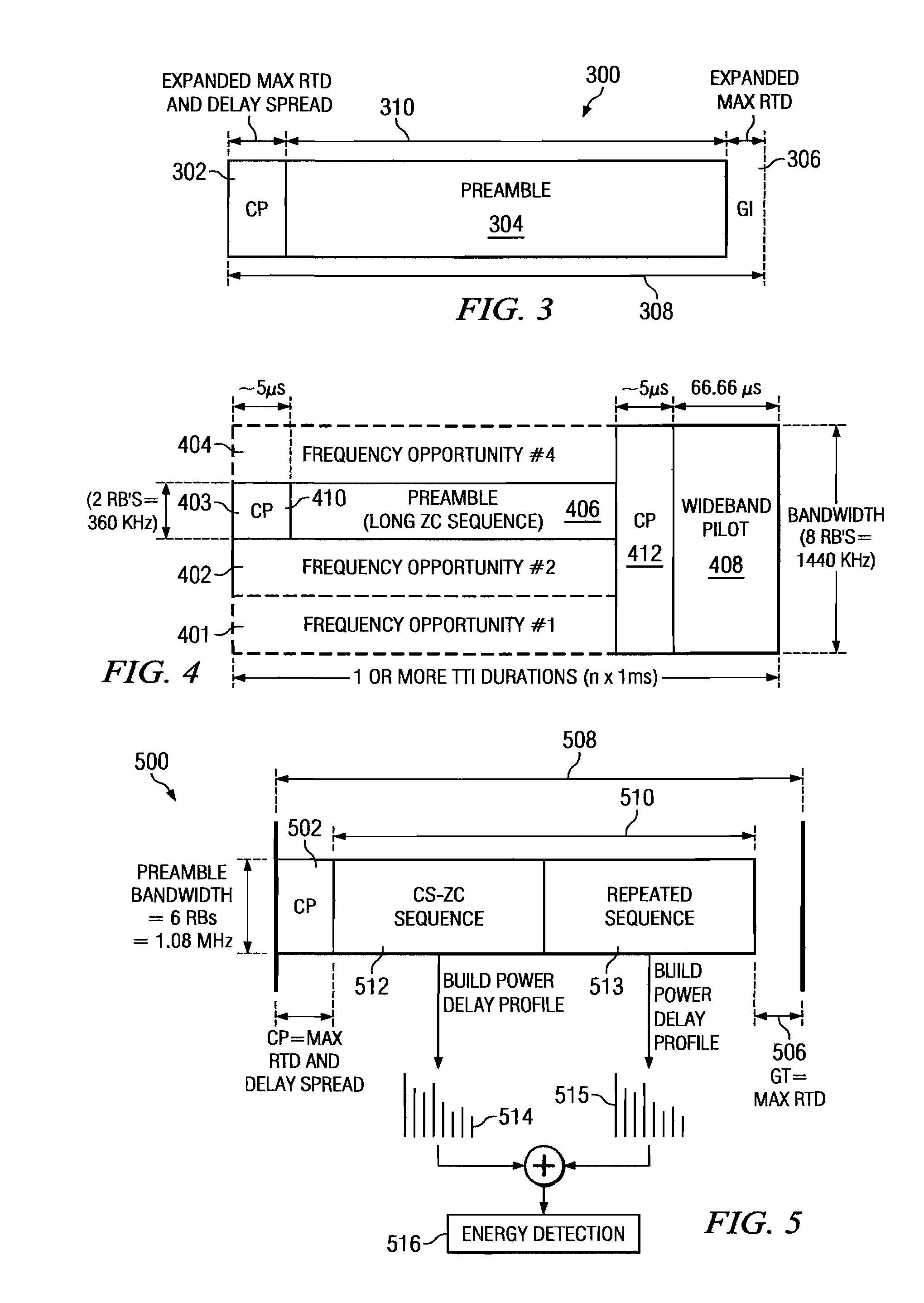

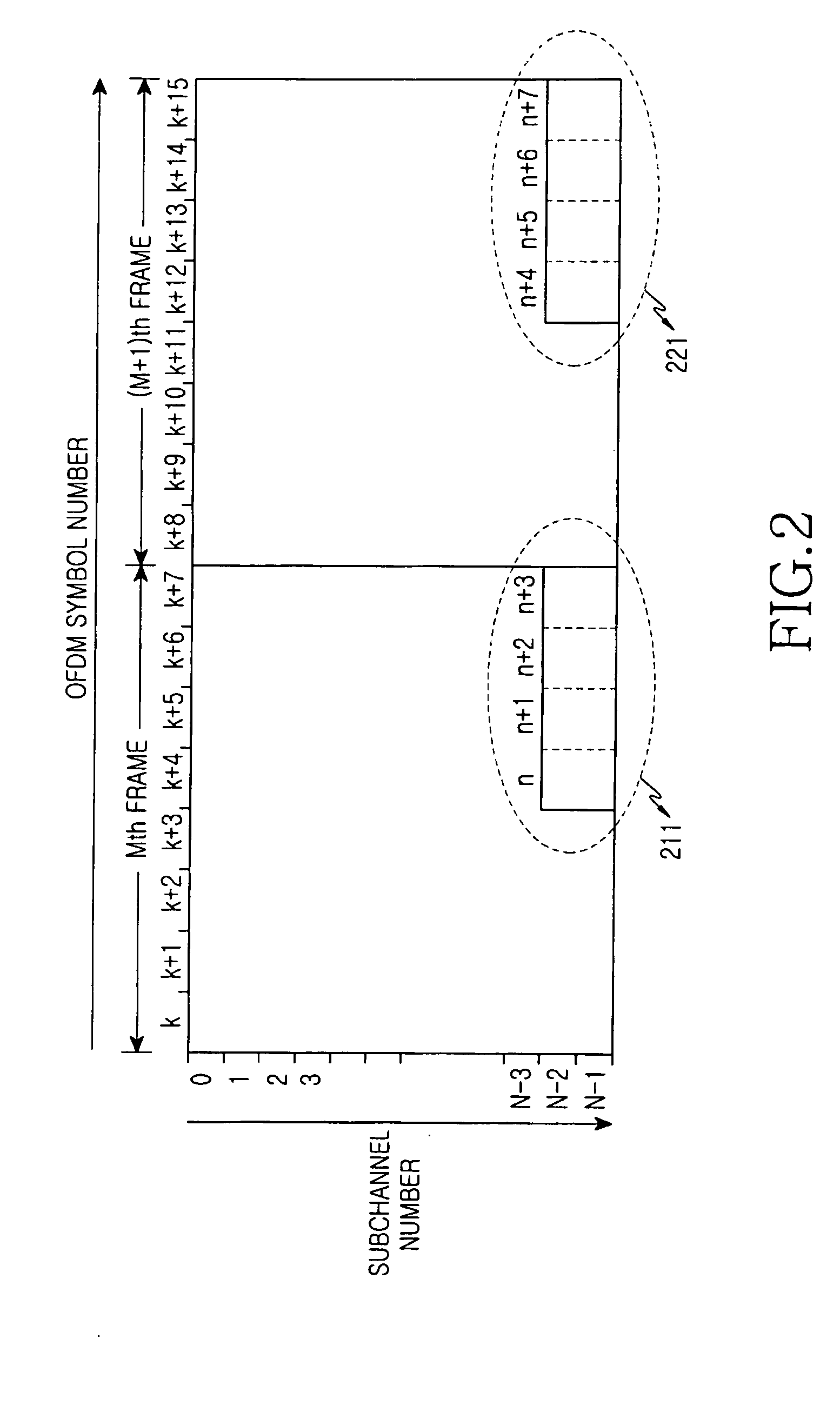

Random Access Channel Hopping for Frequency Division Multiplexing Access Systems

ActiveUS20080267126A1Frequency-division multiplex detailsCode division multiplexTelecommunicationsFrequency-division multiplexing

A method of coordinating resources for repetition of random access bursts performed by a mobile terminal, the method comprising: determining groups of access slots based on parameters from a network, wherein each access slot is defined by any combination of frequency, time and code, and the access slots are organized according to a frequency pattern; transmitting an access burst on an access slot from a chosen group of access slots; and re-transmitting the access burst on the next access slot from the chosen group of access slots.

Owner:LG ELECTRONICS INC

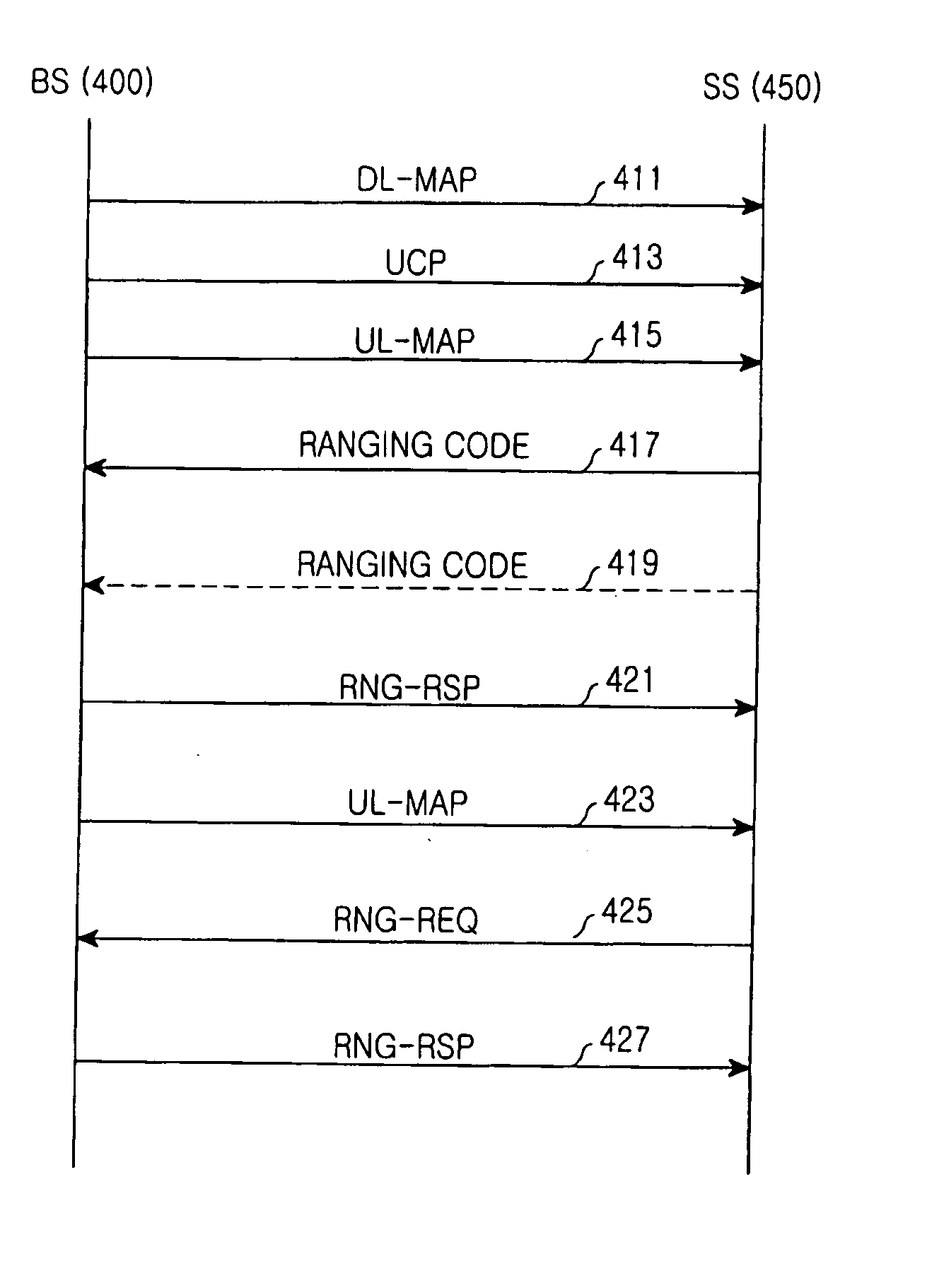

Ranging method in a mobile communication system using orthogonal frequency division multiple access

InactiveUS20050058058A1Minimizing access delayPreventing ranging code collisionData switching by path configurationOrthogonal multiplexControl communicationsNull state

Disclosed is a method for controlling an operational state of at least one subscriber stations in an OFDM / OFDMA communication system having ranging slots and ranging codes to be used for rangings. The subscriber station performing in a Null state, an initial ranging if an initial ranging request occurs, and transitioning from the Null state to an Idle state if the initial ranging is successful; transitioning to an Access state if a bandwidth request ranging request occurs in the Idle state, and performing in the Access state the bandwidth request ranging based on a random access technique; transitioning from the Access state to a Busy state if the random access-based bandwidth request ranging is successful, performing the bandwidth request ranging based on a scheduled access technique if the bandwidth request ranging request occurs in the Busy state, and transmitting data if the scheduled access-based bandwidth request ranging is successful; and transitioning to a Hold state if the data transmission is ended in the Busy state, and performing the scheduled access-based bandwidth request ranging if the bandwidth request ranging request occurs in the Hold state.

Owner:SAMSUNG ELECTRONICS CO LTD

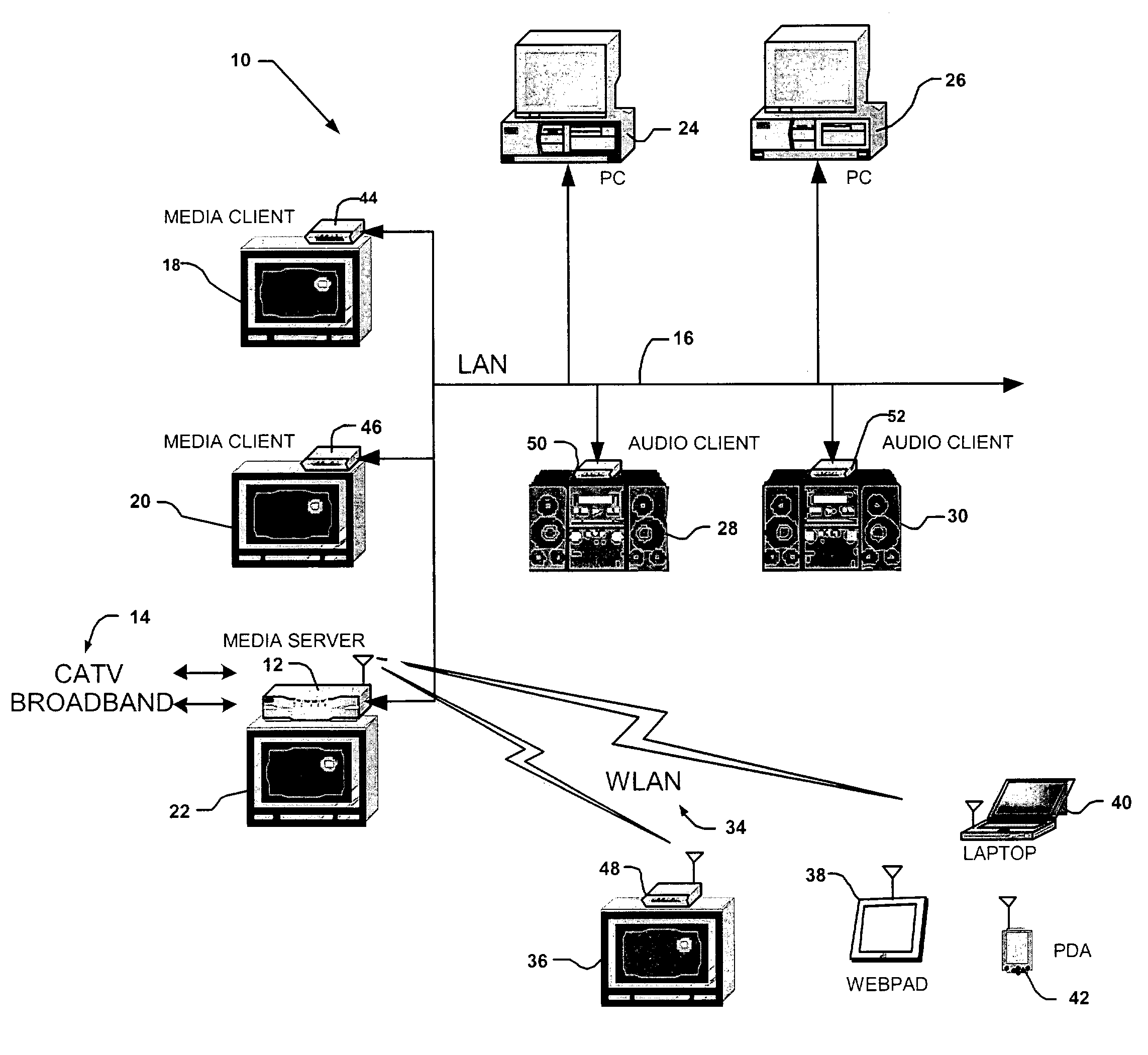

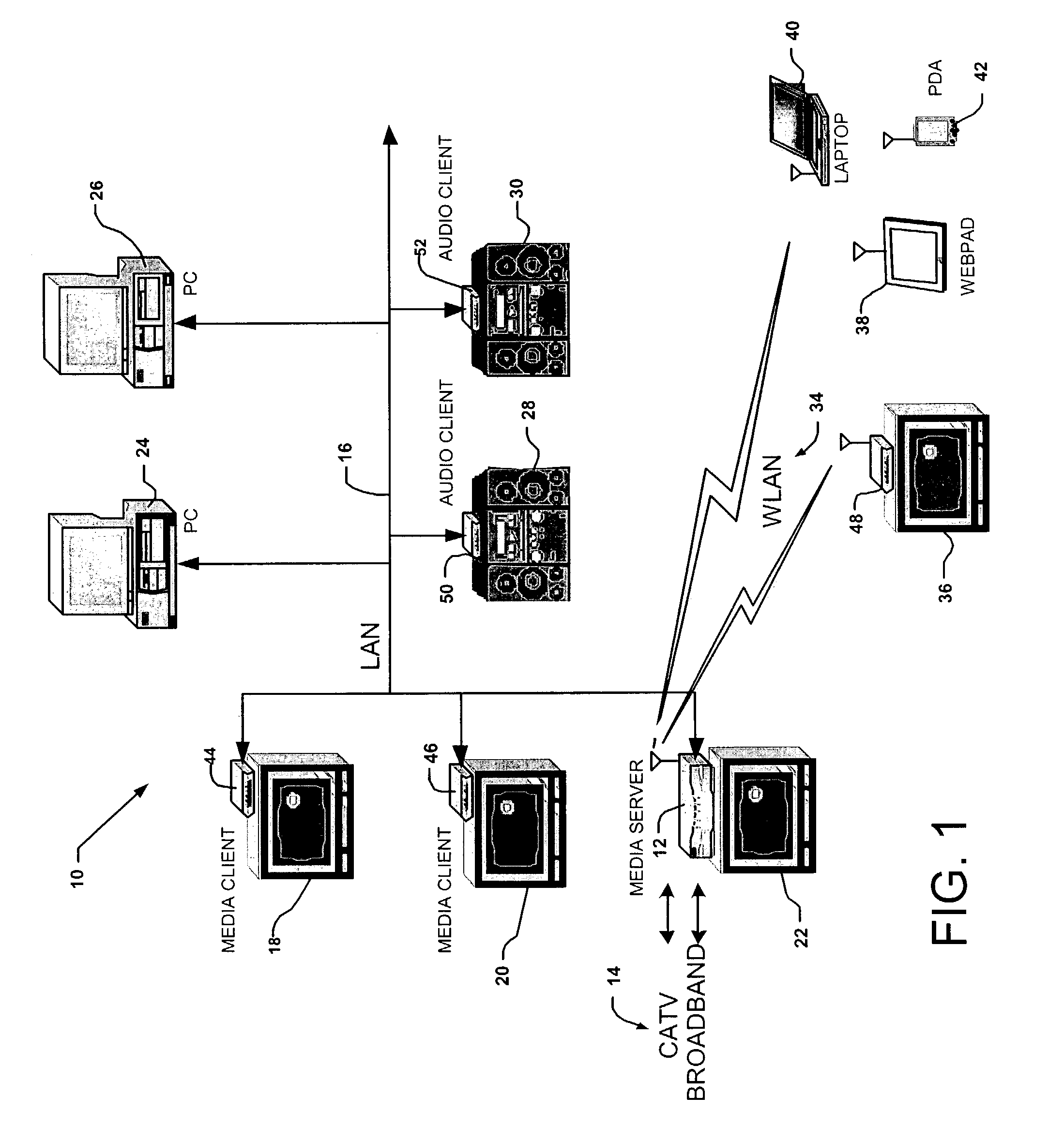

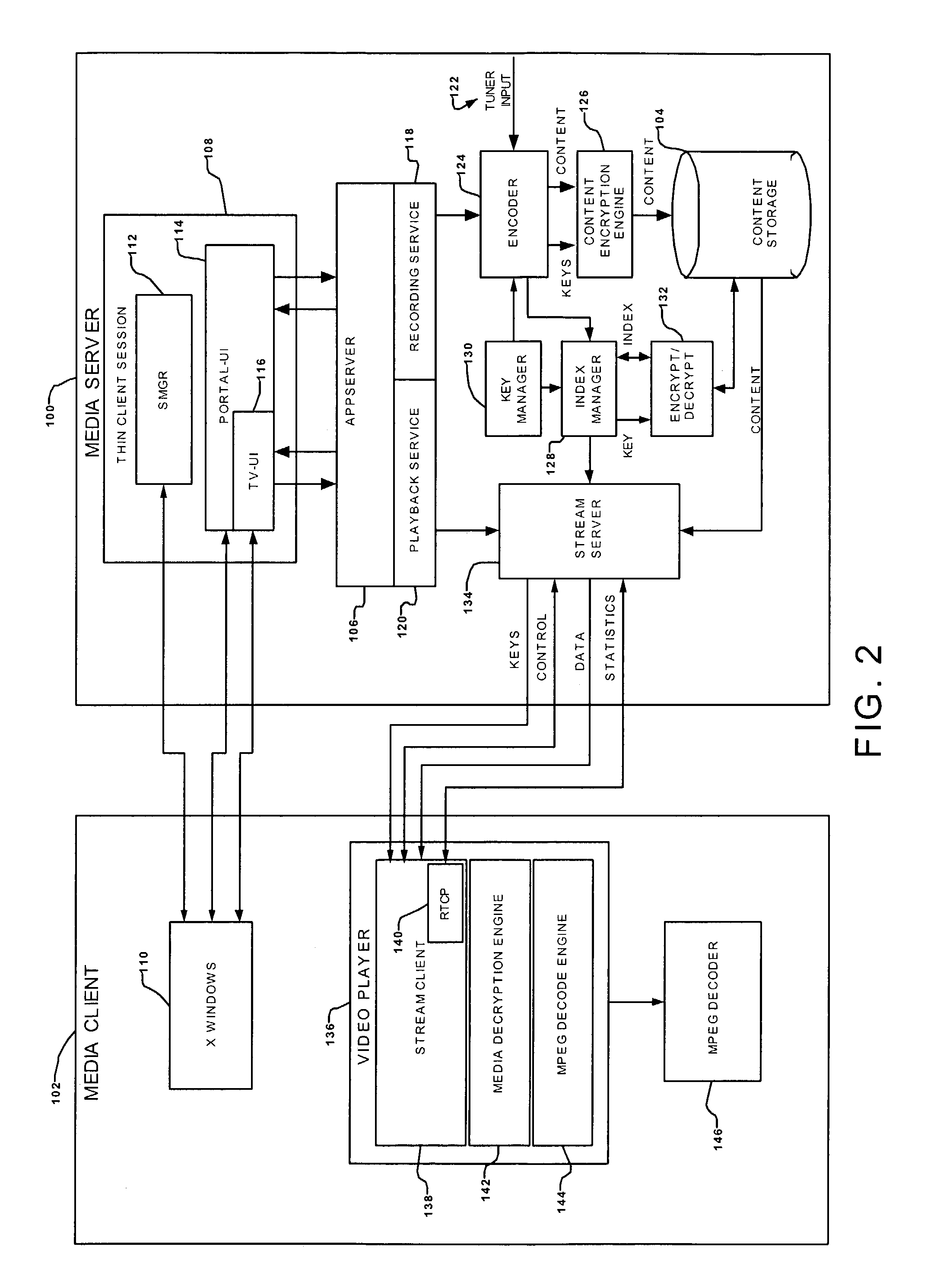

Networked digital video recording system with copy protection and random access playback

ActiveUS7231516B1Effective positioningHigh rateTelevision system detailsData resettingDigital videoDigital recording

In a multimedia recording and playback network for receiving from a content server a service package of multimedia content, the network including a media server in communication with the content server, a method of securely transmitting a master encryption key from the content server to the media server, including the steps downloading a service package certificate from the content server to the media server, authenticating, in the media server, the received service package certificate, the content server providing to the media server a key server certificate, a public key of the content server, and a client certificate request, the media server authenticating the key server certificate, providing to the content server, upon authentication of the key server certificate by the media server, a client certificate including a challenge signature, and a public key of the media server, the content server authenticating the client certificate including the challenge signature received from the media server, the media server requesting the master encryption key from the content server, and the content server responding by transmitting the master encryption key to media server.

Owner:GOOGLE TECH HLDG LLC

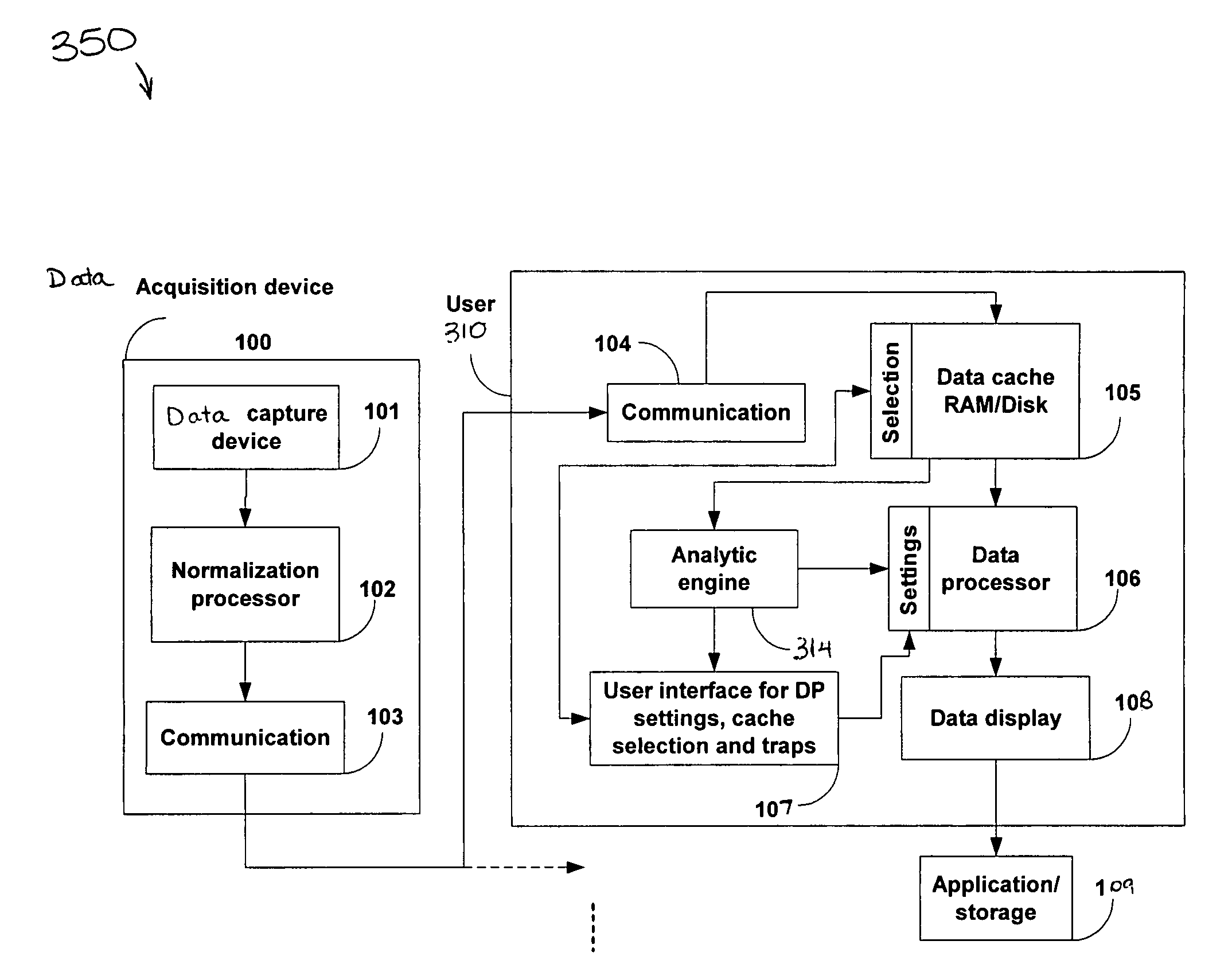

Dynamic object-driven database manipulation and mapping system having a simple global interface and an optional multiple user need only caching system with disable and notify features

The present invention provides enhanced database access and performance when correlating or translating one database to another database or to an object programming application. The system and method of enhanced database access and performance of the invention provides a simplified high-level wrapper interface for global coordination of multiple software components and ease of use. Performance is also enhanced by utilizing an optional enhanced multiple user data caching system. The multiple user caching system of the invention provides a process of obtaining data from a data source, creating accessible data in the random access memory of at least one computer system the first time such data is read by a user wherein the data source corresponding to the cache is accessible to at least two users. Thus, the present invention is directed to dynamic mapping of databases to selected objects and a system and method for providing a multiple user caching system in such an environment or system.

Owner:THOUGHT

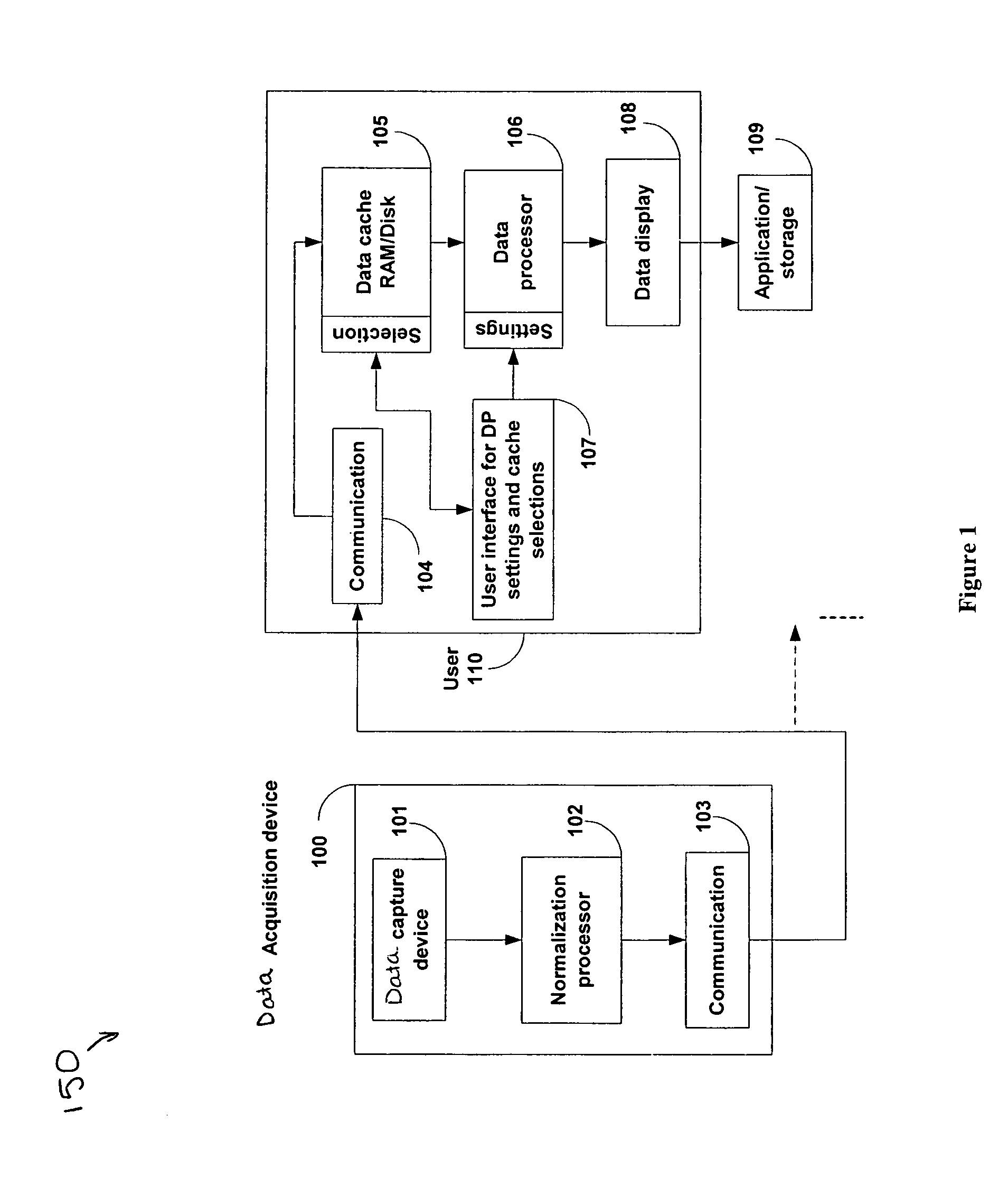

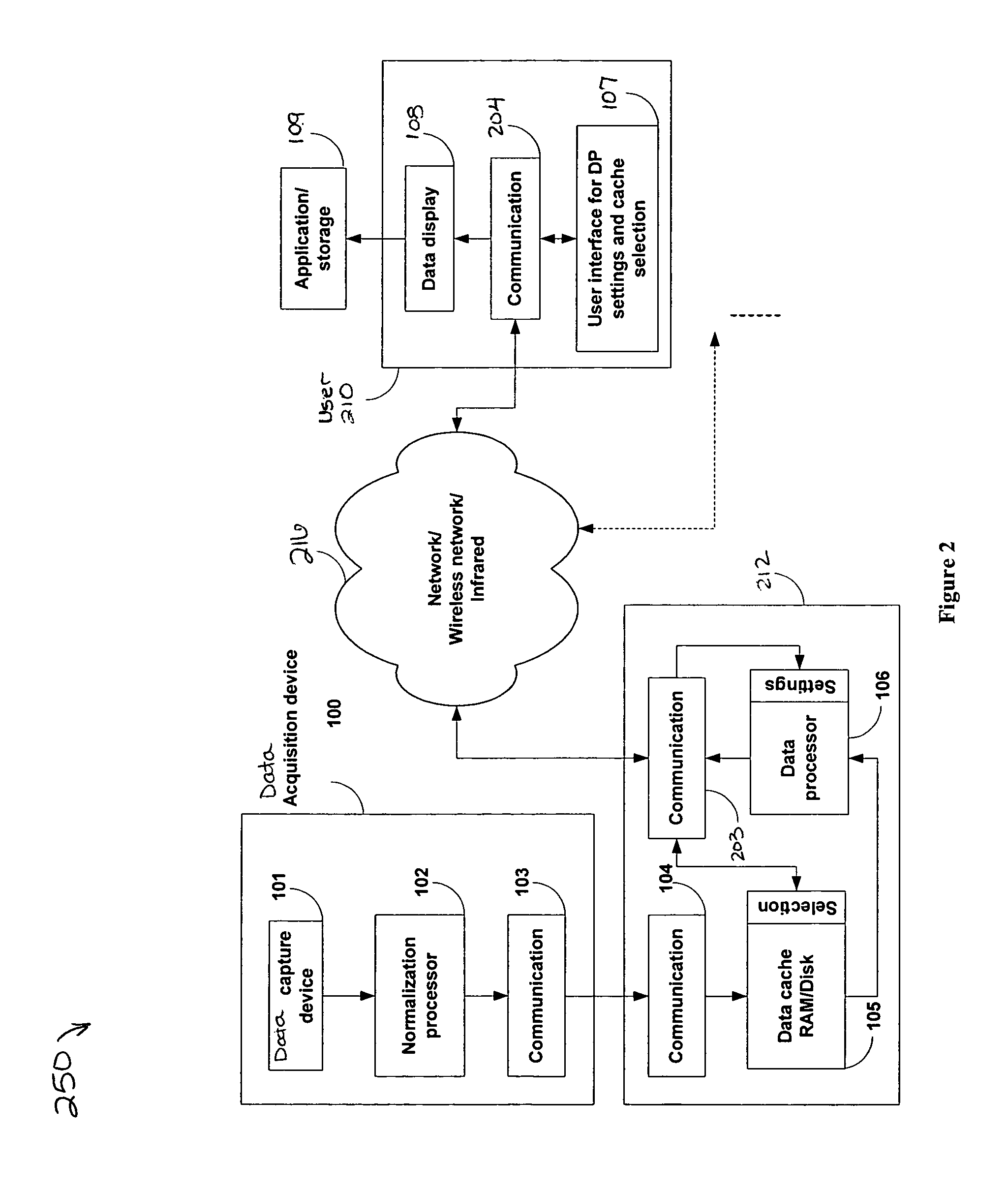

Systems and methods of accessing random access cache for rescanning

ActiveUS7545529B2Data augmentationAdvantages with regard to speedDigitally marking record carriersDigital computer detailsDigital dataNon real time

An efficient method and system to enhance digital acquisition devices for analog data is presented. The enhancements offered by the method and system are available to the user in local as well as in remote deployments yielding efficiency gains for a large variety of business processes. The quality enhancements of the acquired digital data are achieved efficiently by employing virtual reacquisition. The method of virtual reacquisition renders unnecessary the physical reacquisition of the analog data in case the digital data obtained by the acquisition device are of insufficient quality. The method and system allows multiple users to access the same acquisition device for analog data. In some embodiments, one or more users can virtually reacquire data provided by multiple analog or digital sources. The acquired raw data can be processed by each user according to his personal preferences and / or requirements. The preferred processing settings and attributes are determined interactively in real time as well as non real time, automatically and a combination thereof.

Owner:KOFAX

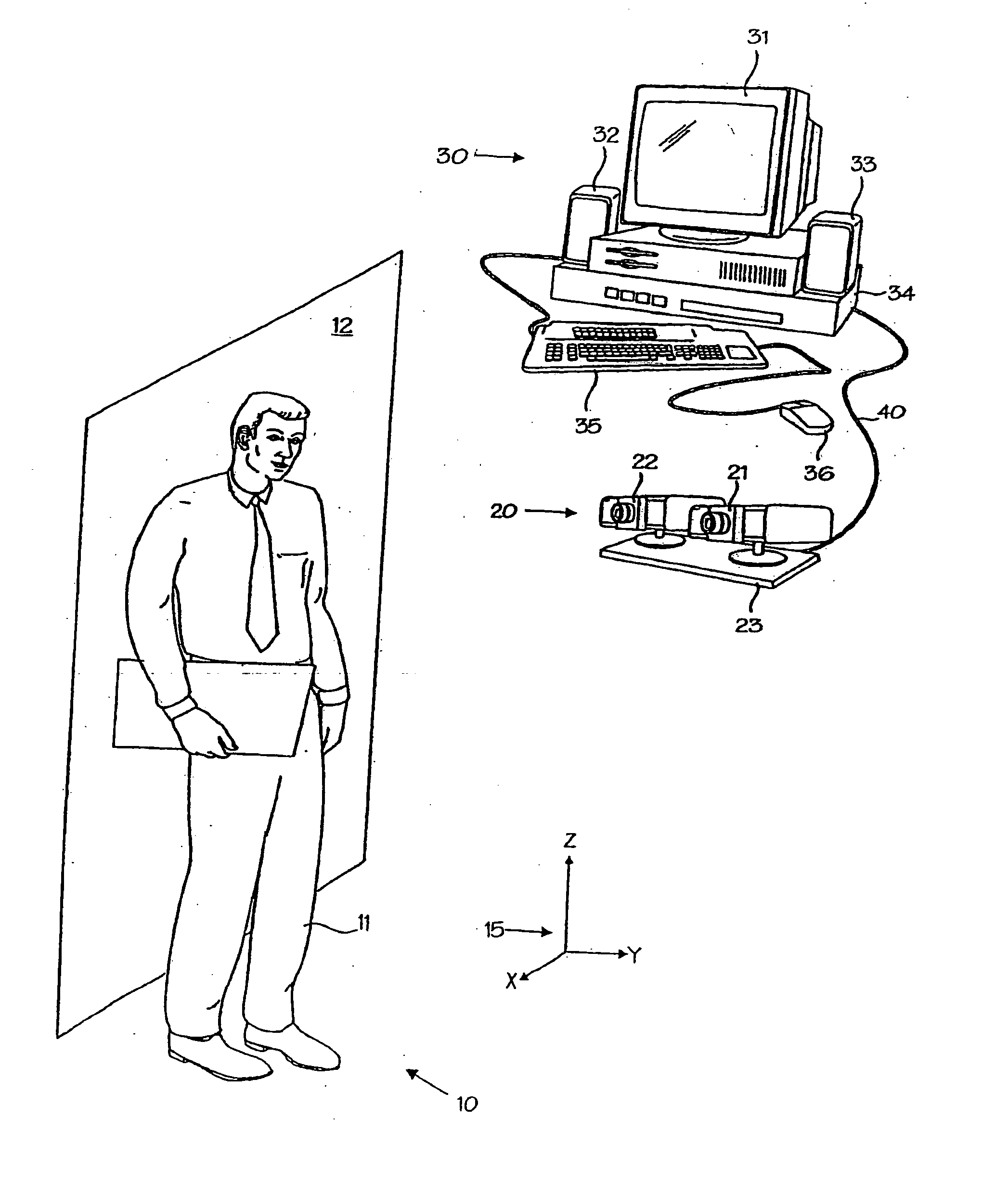

Data processing system and method

InactiveUS20060013473A1Eliminate informationImage enhancementImage analysisStatic random-access memoryHigh memory

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP