Patents

Literature

4373 results about "Bus interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

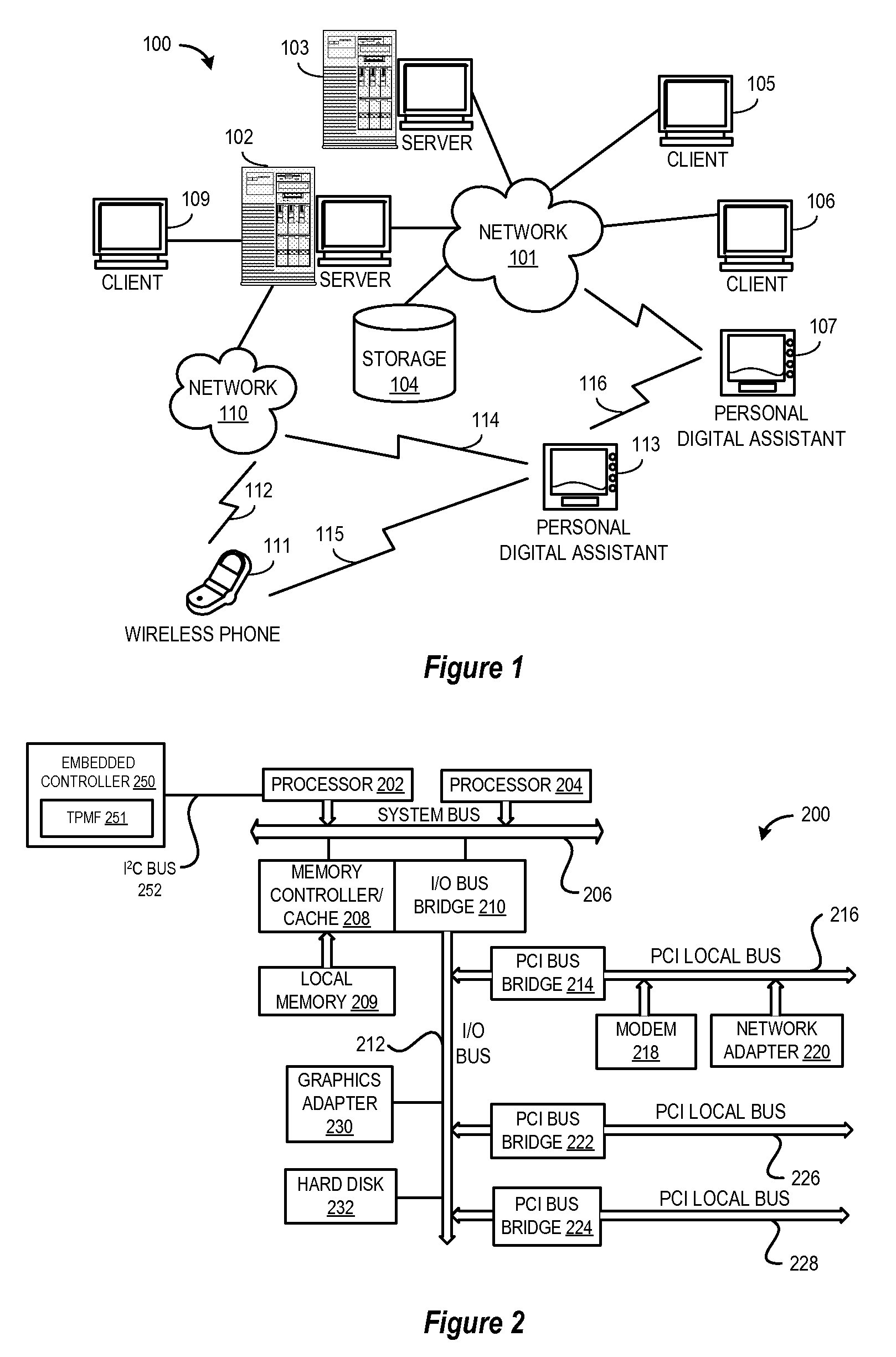

Data processing system and method

InactiveUS6215898B1Reduce overheadHigh sensitivityImage enhancementImage analysisStatic random-access memoryHigh memory

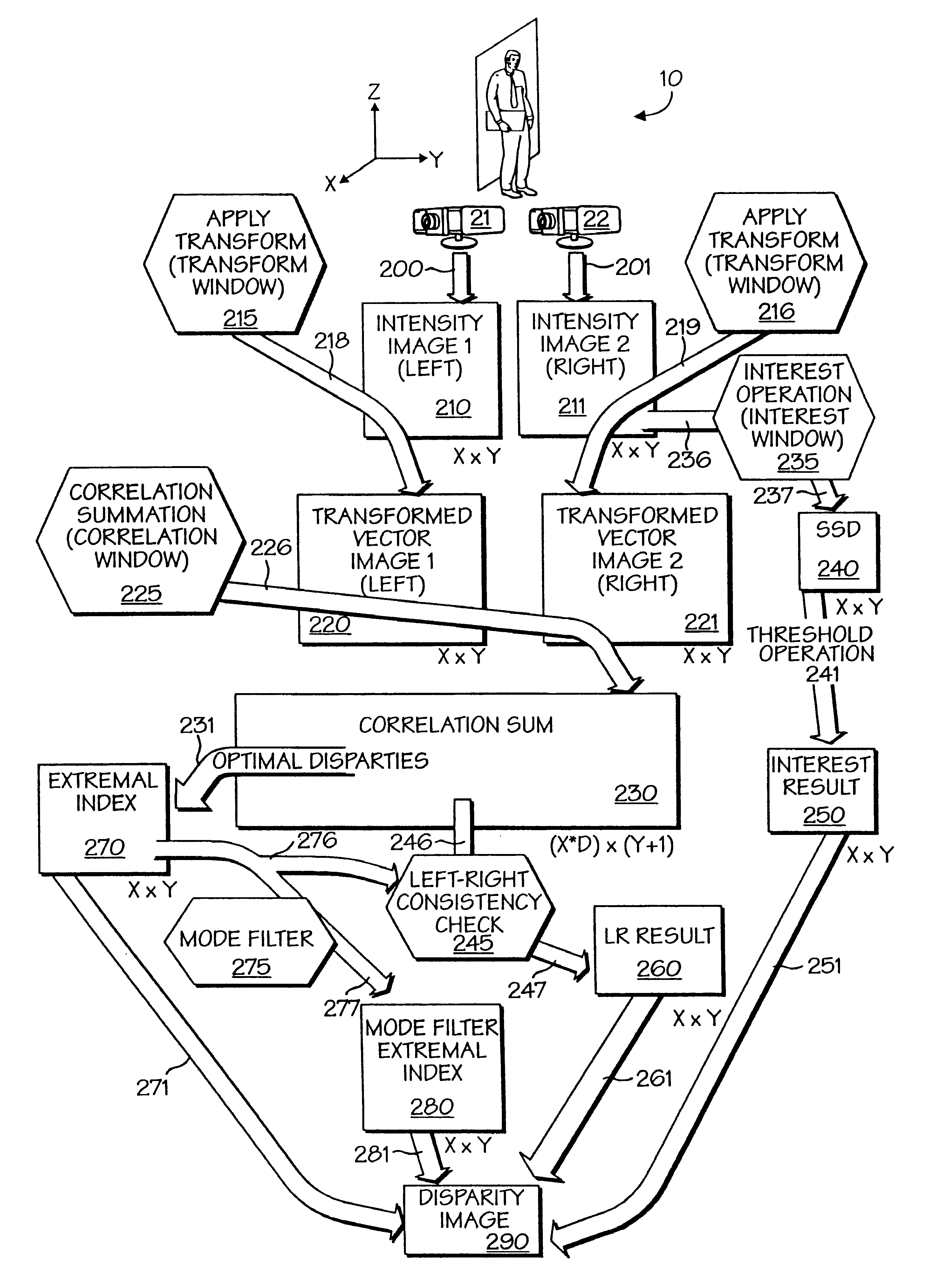

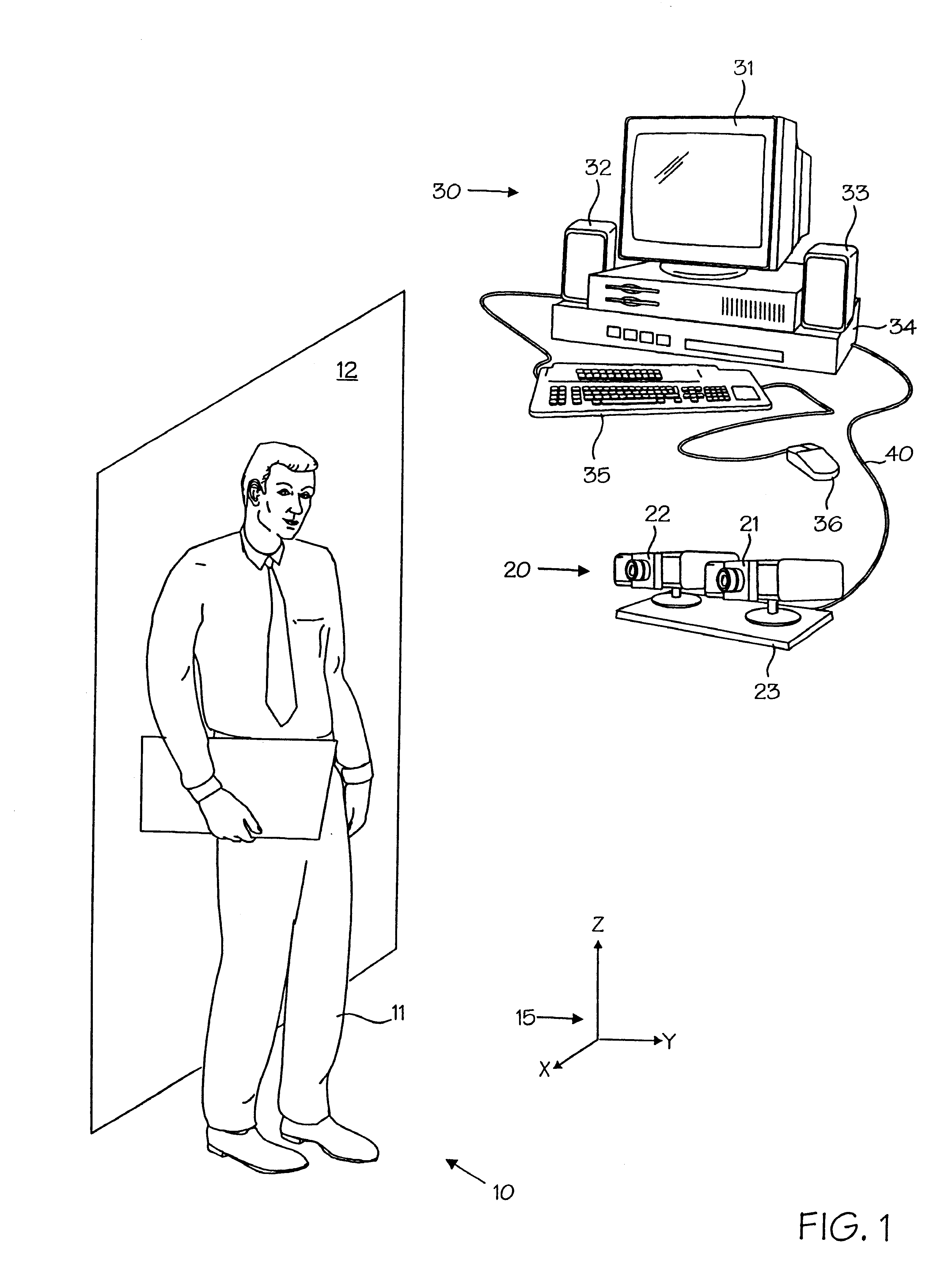

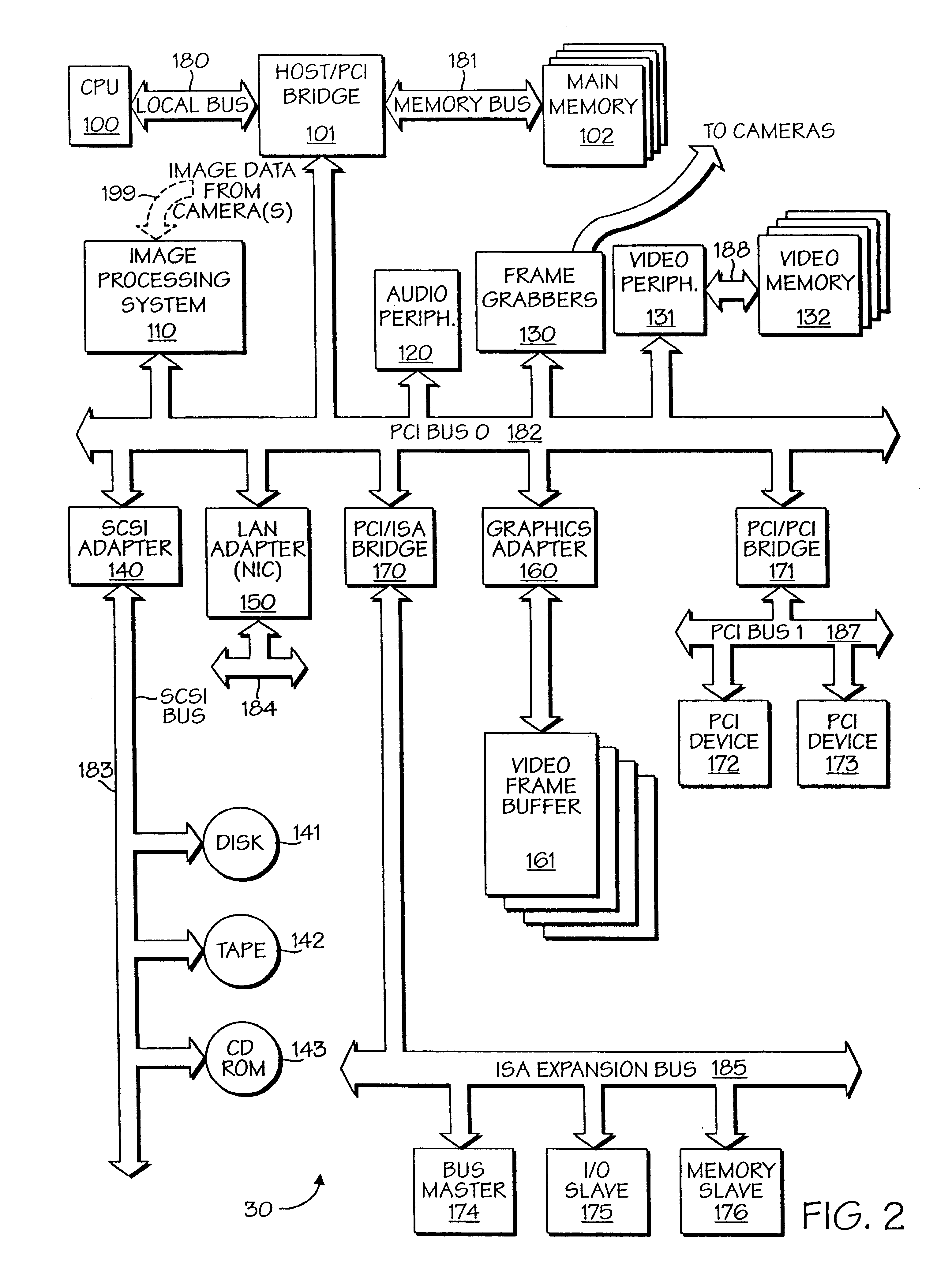

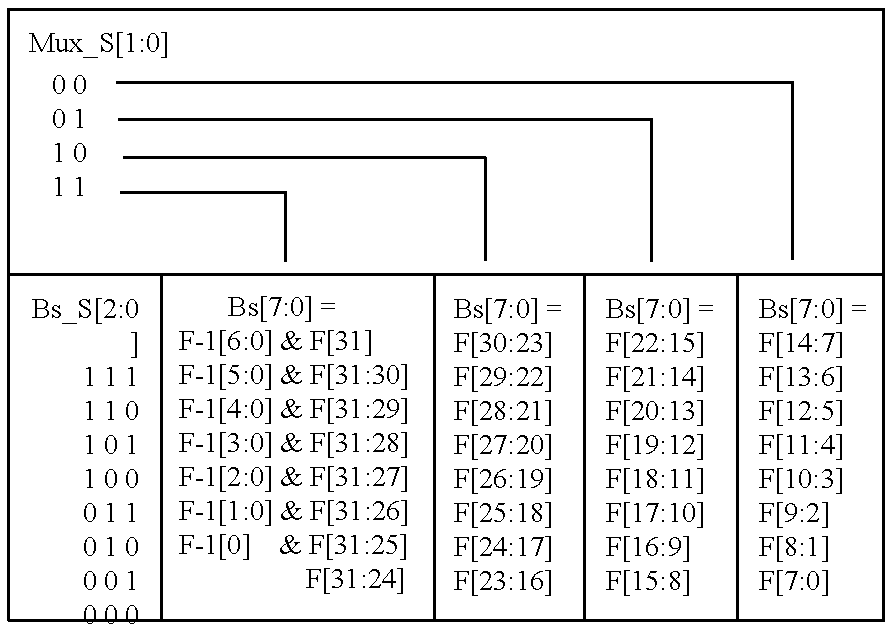

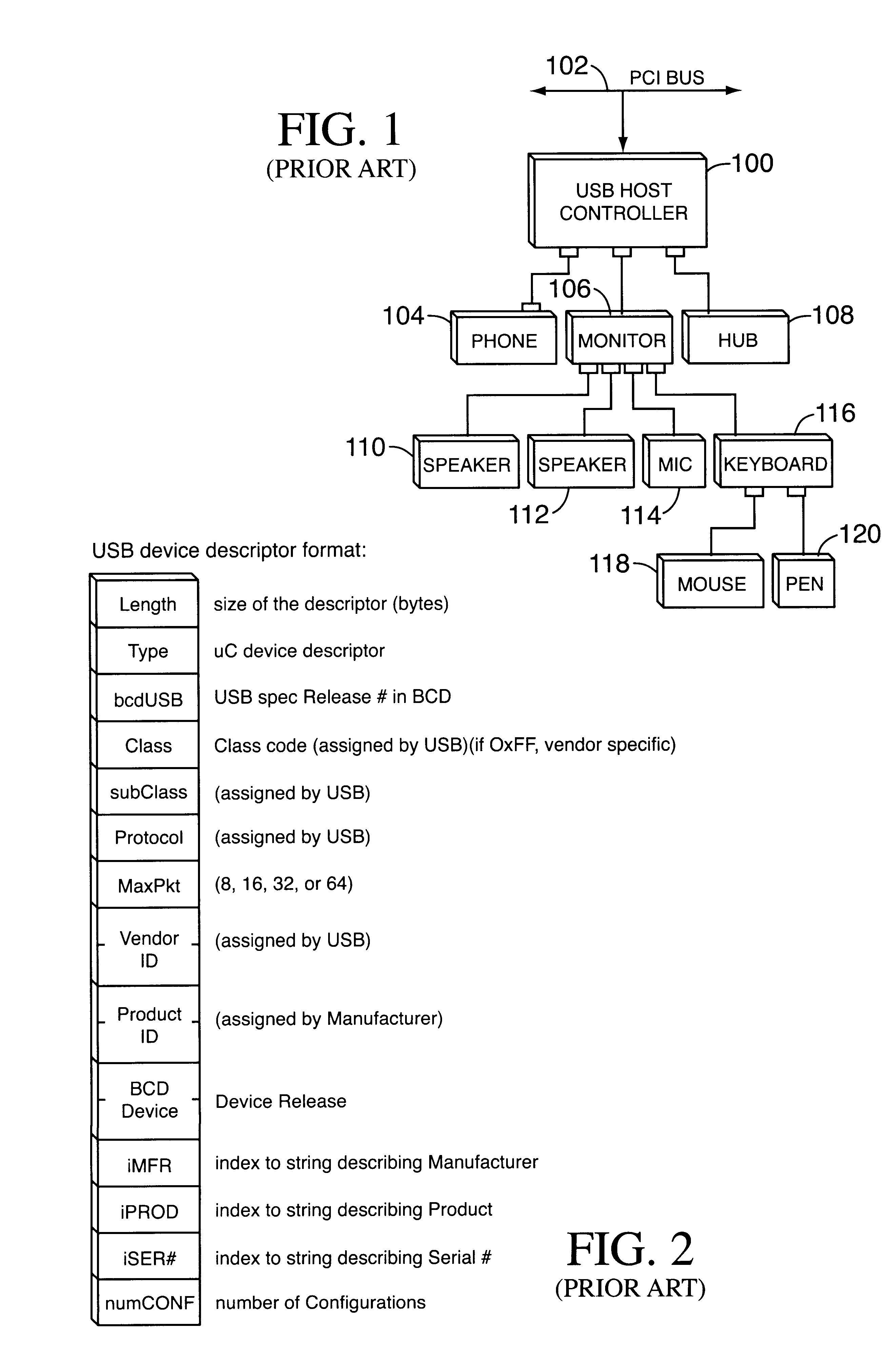

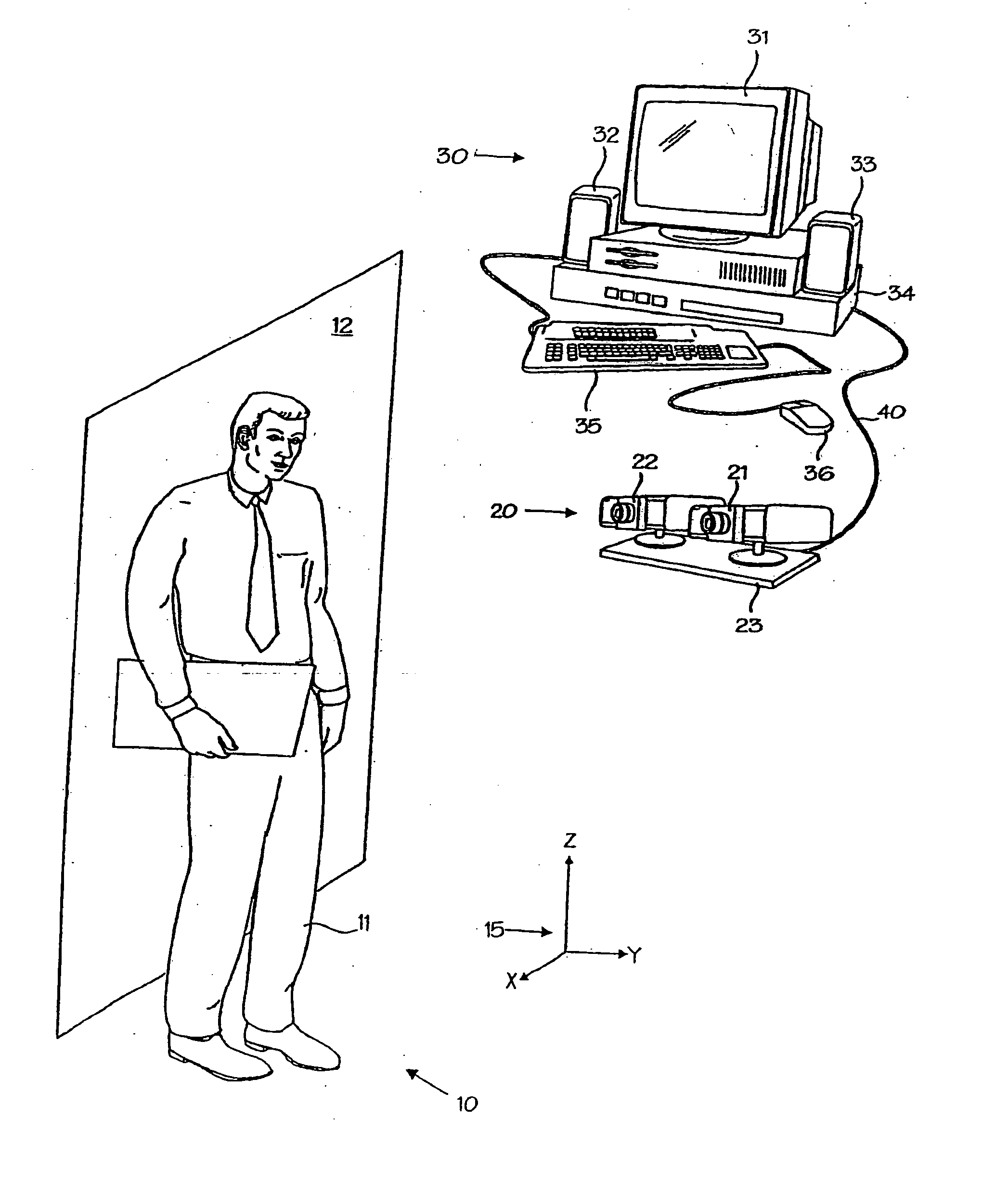

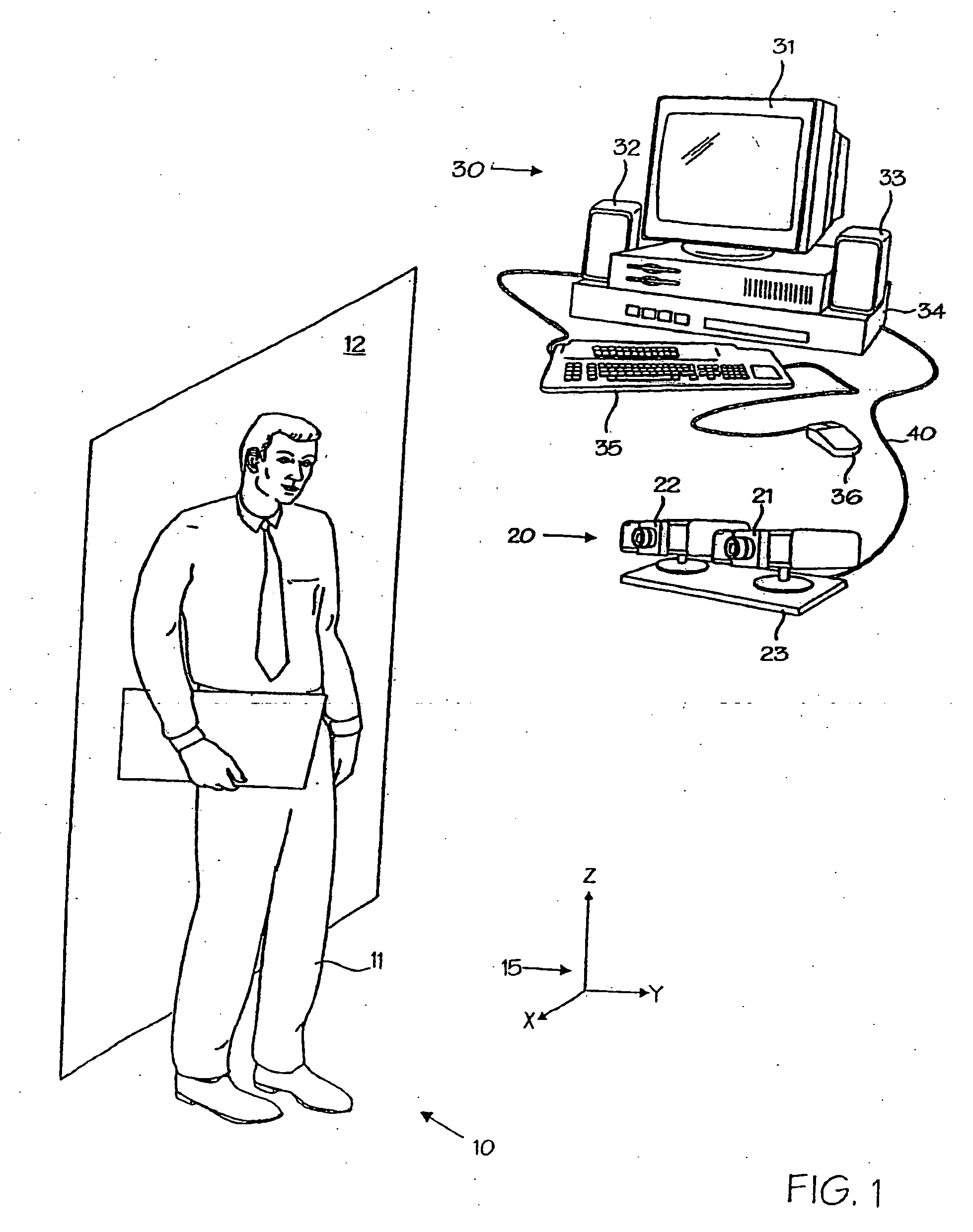

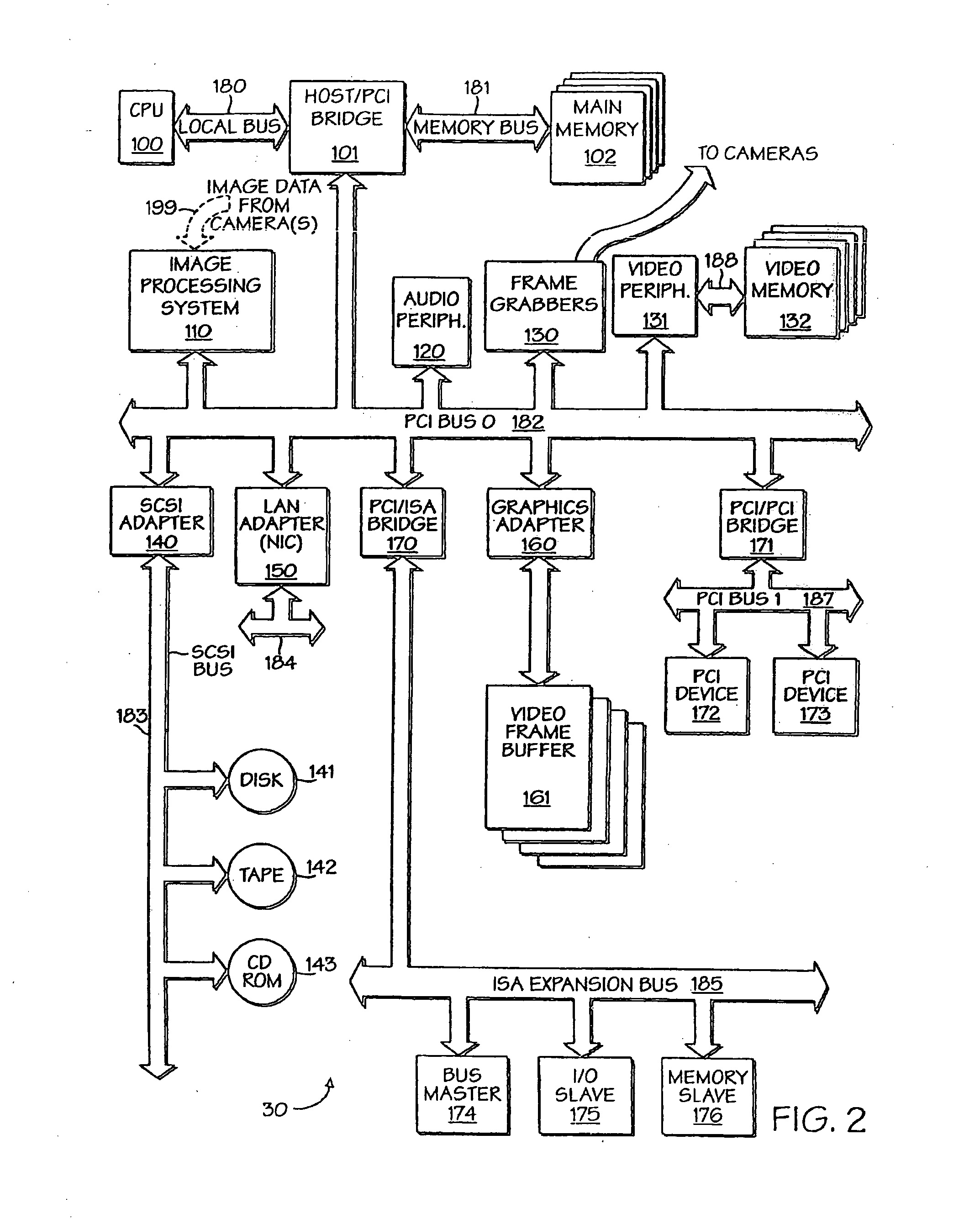

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

Audio and video decoder circuit and system

InactiveUS6369855B1Accelerates memory block moveAvoid confictTelevision system detailsPulse modulation television signal transmissionCoprocessorNetwork packet

An improved audio-visual circuit is provided that includes a transport packet parsing circuit for receiving a transport data packet stream, a CPU circuit for initializing said integrated circuit and for processing portions of said data packet stream, a ROM circuit for storing data, a RAM circuit for storing data, an audio decoder circuit for decoding audio portions of said data packet stream, a video decoder circuit for decoding video portions of said data packet stream, an NTSC / PAL encoding circuit for encoding video portions of said data packet stream, an OSD coprocessor circuit for processing OSD portions of said data packets, a traffic controller circuit moving portions of said data packet stream between portions of said integrated circuit, an extension bus interface circuit, a P1394 interface circuit, a communication coprocessors circuit, an address bus connected to said circuits, and a data bus connected to said circuits.

Owner:TEXAS INSTR INC

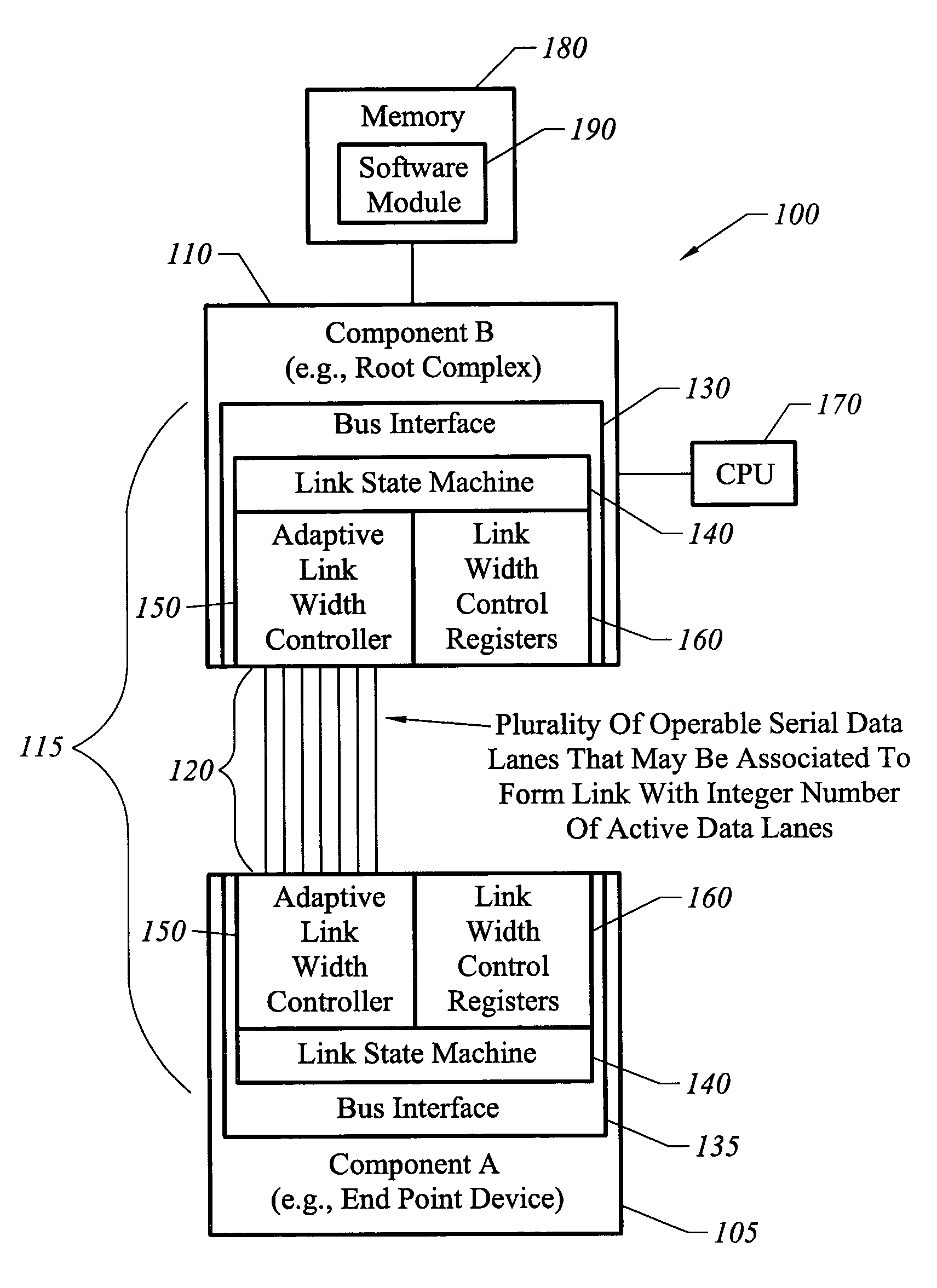

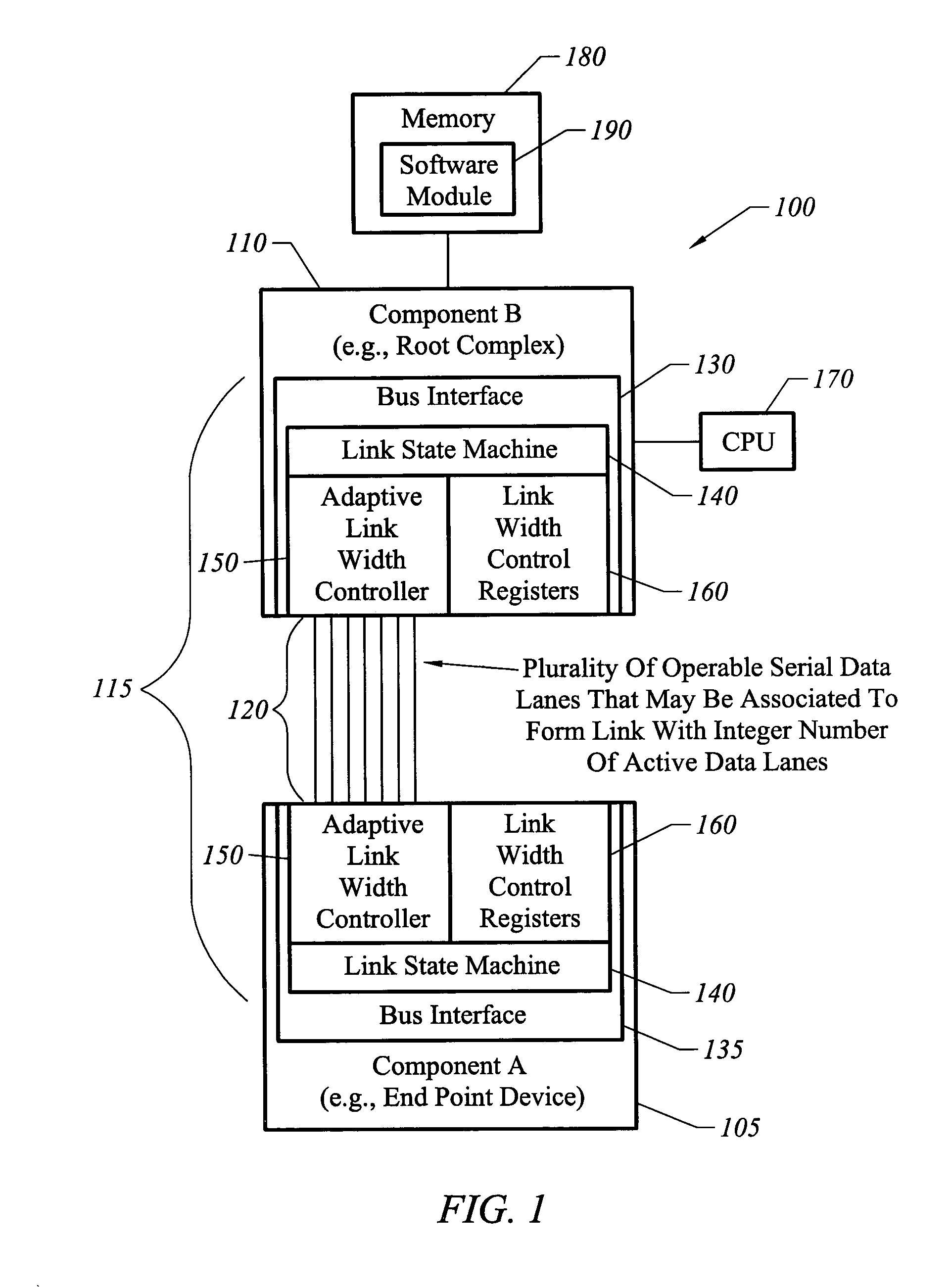

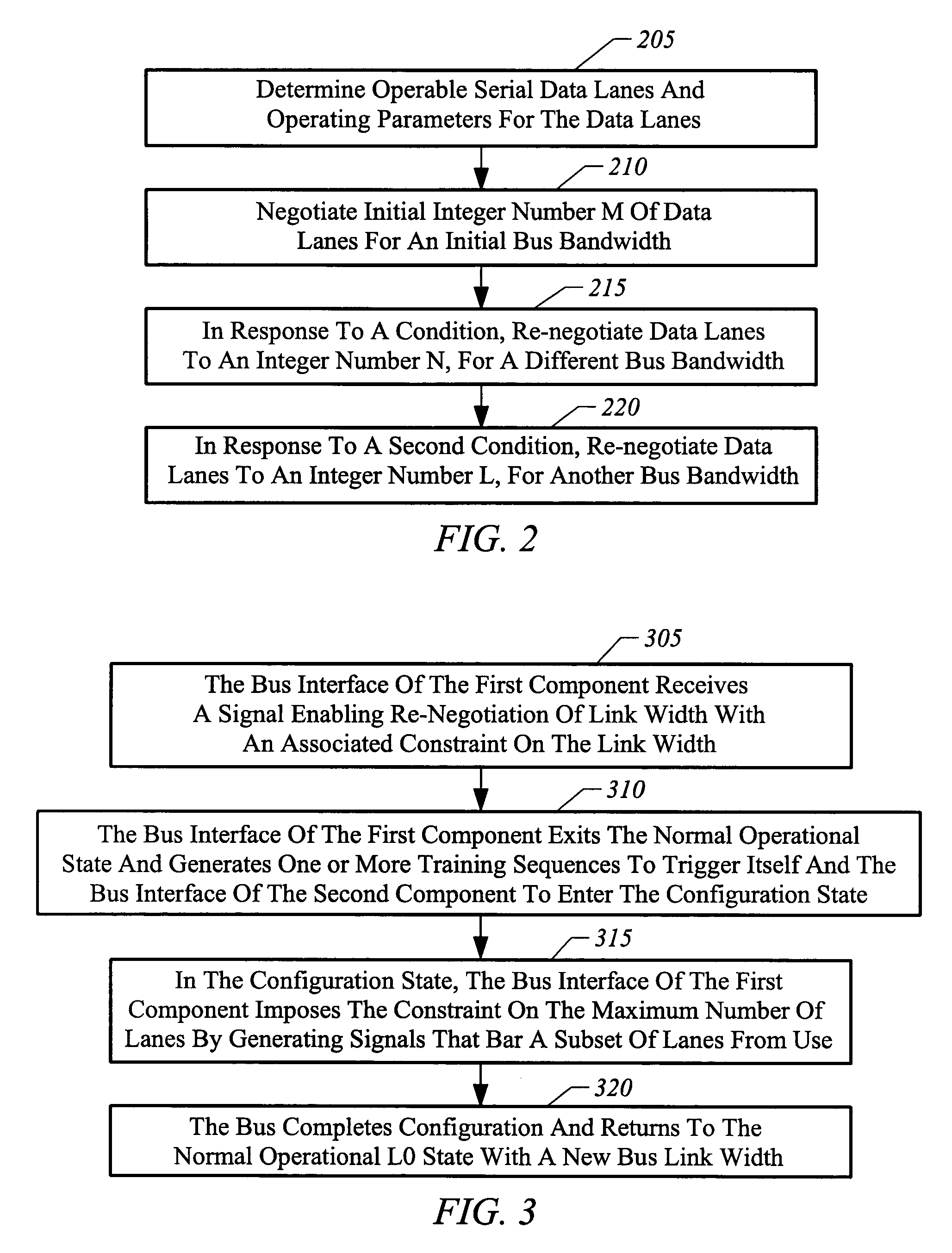

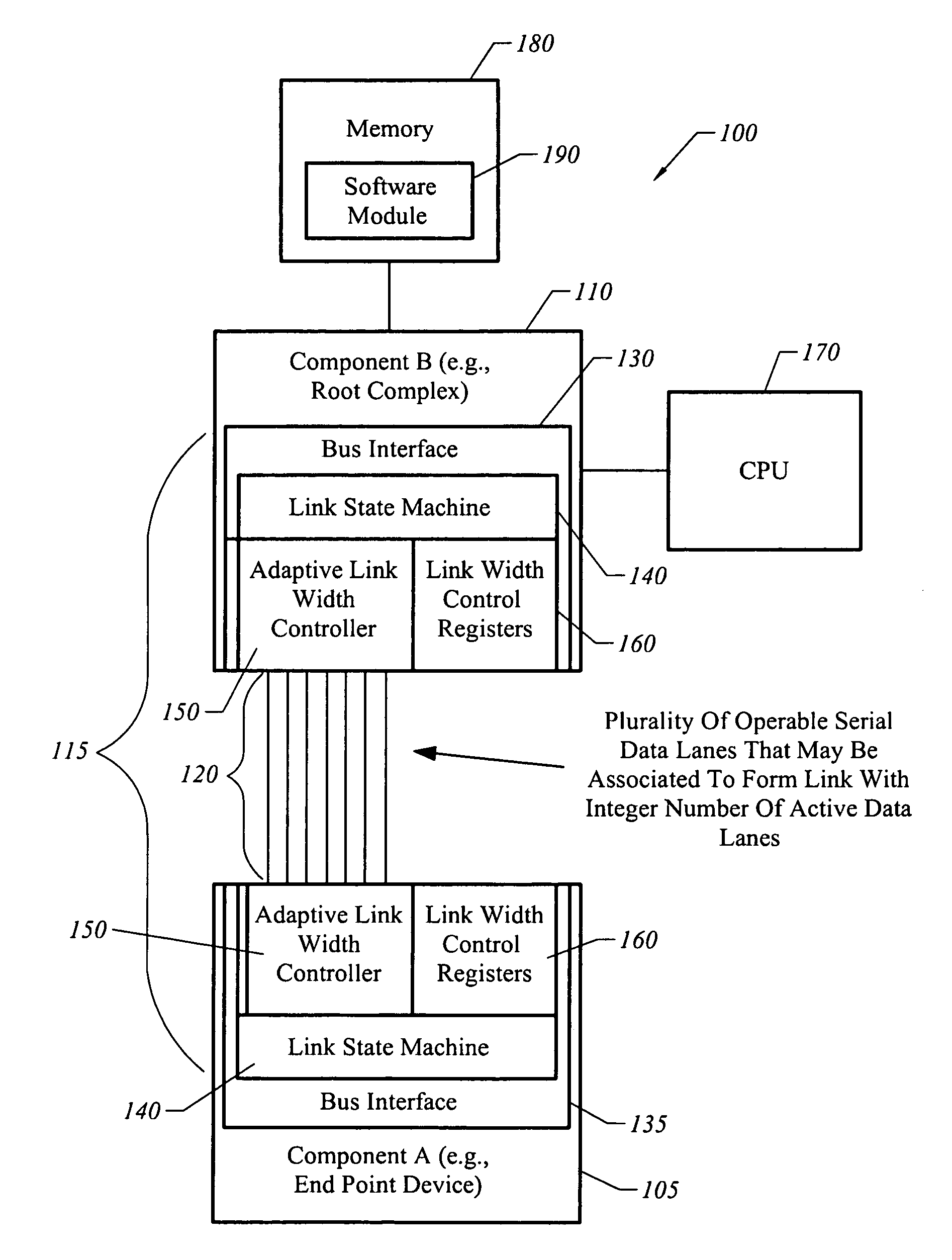

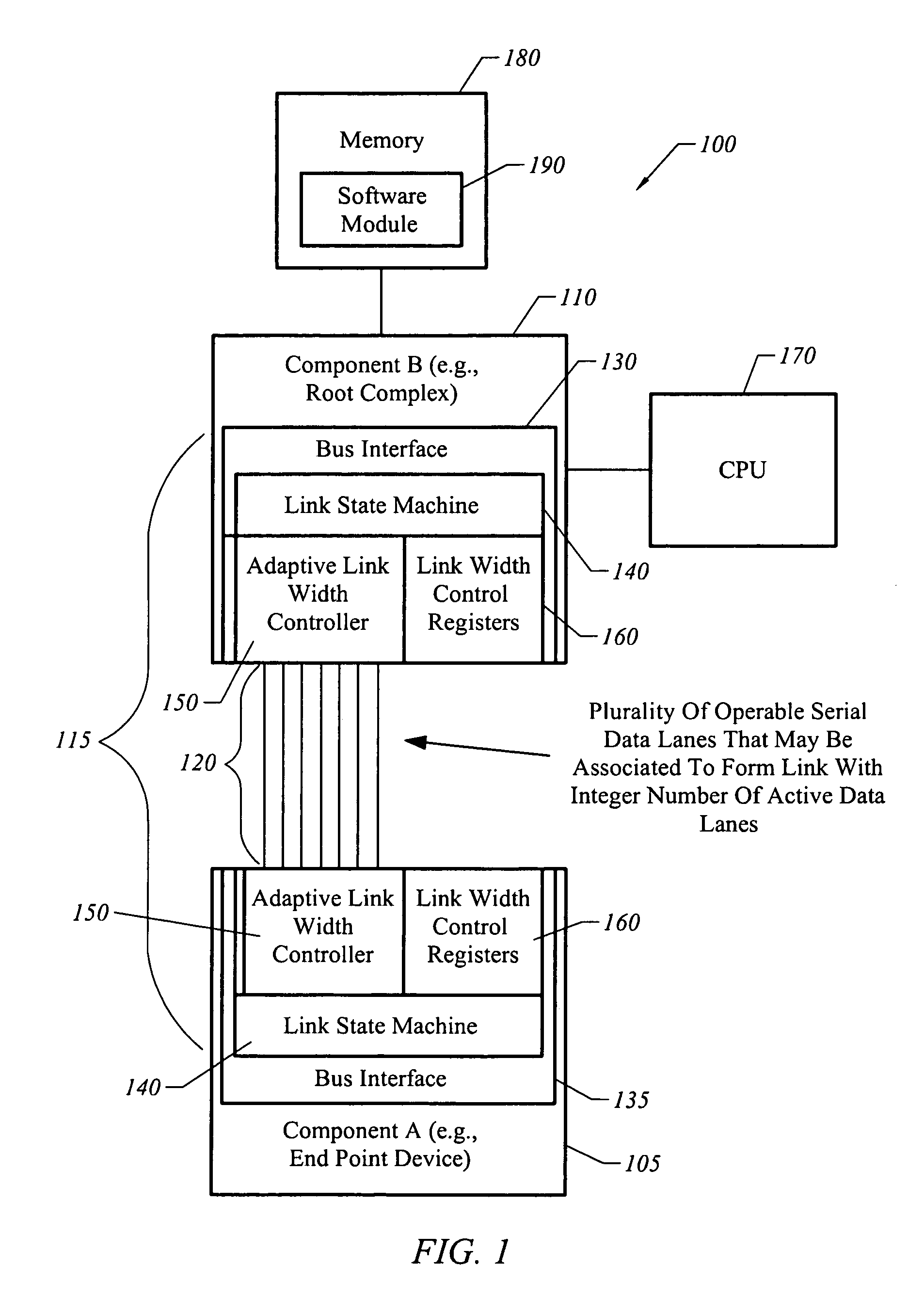

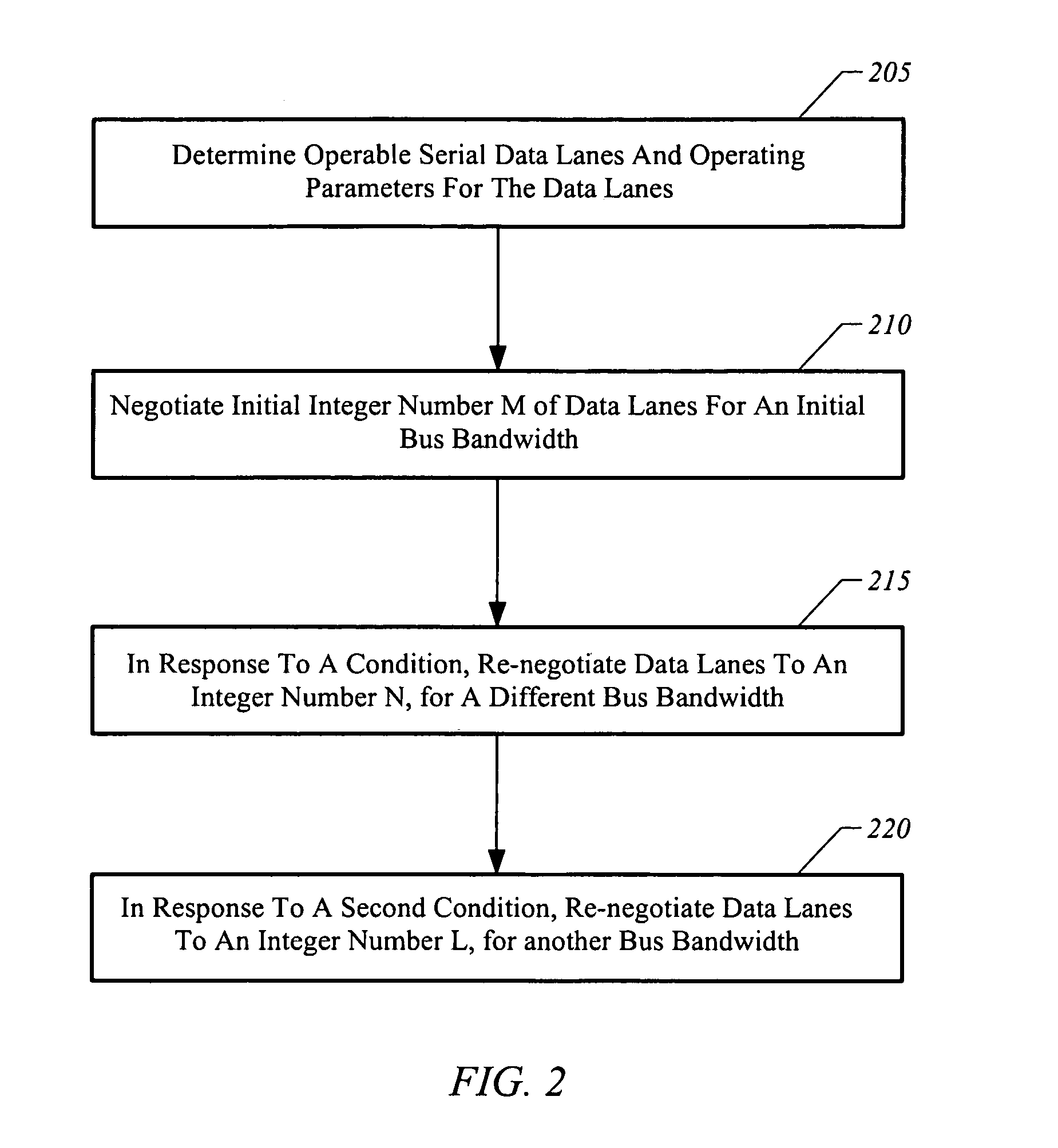

Apparatus, system, and method for bus link width optimization

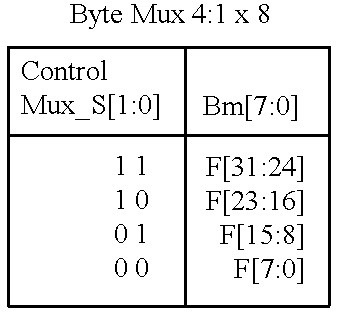

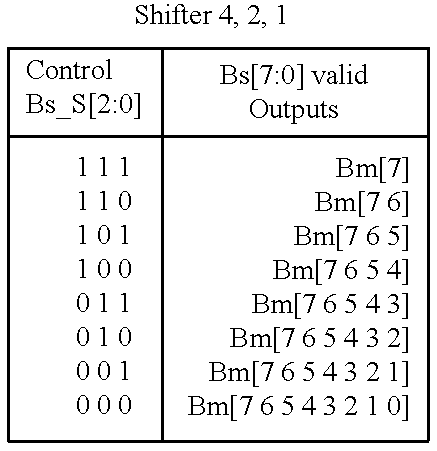

ActiveUS7136953B1High bandwidthReducing bus power requirementEnergy efficient ICTStatic indicating devicesBus interfaceBandwidth requirement

Owner:NVIDIA CORP

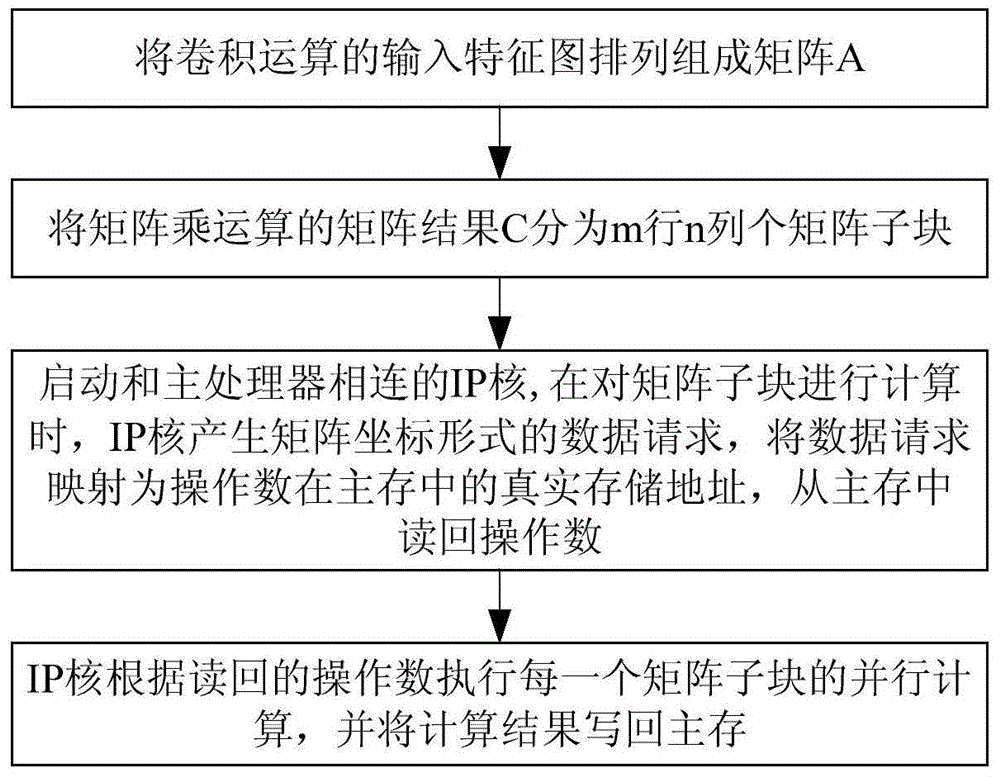

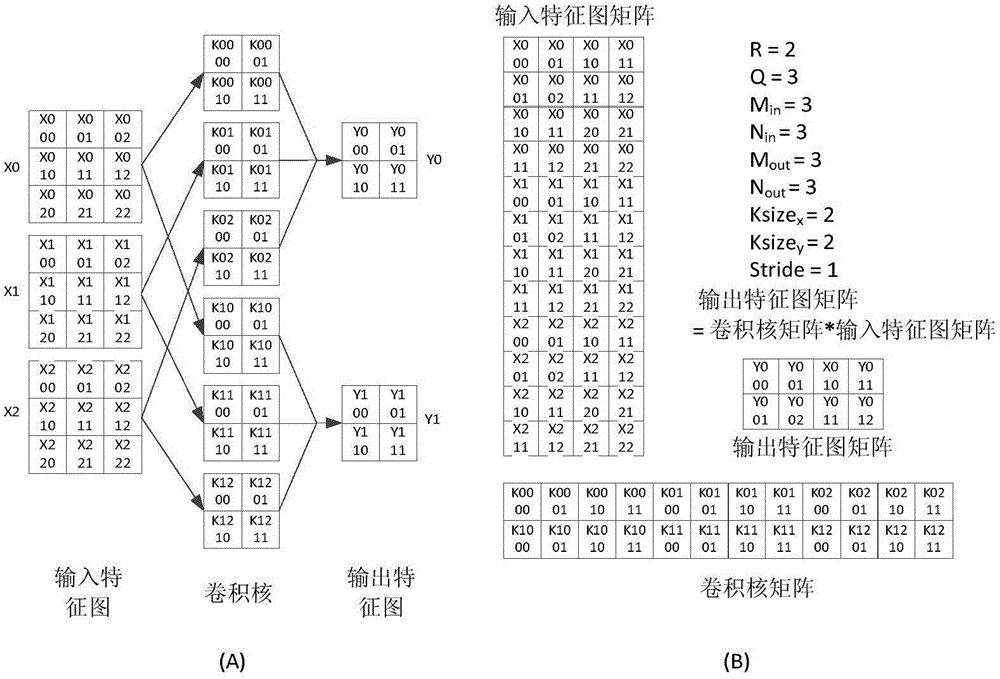

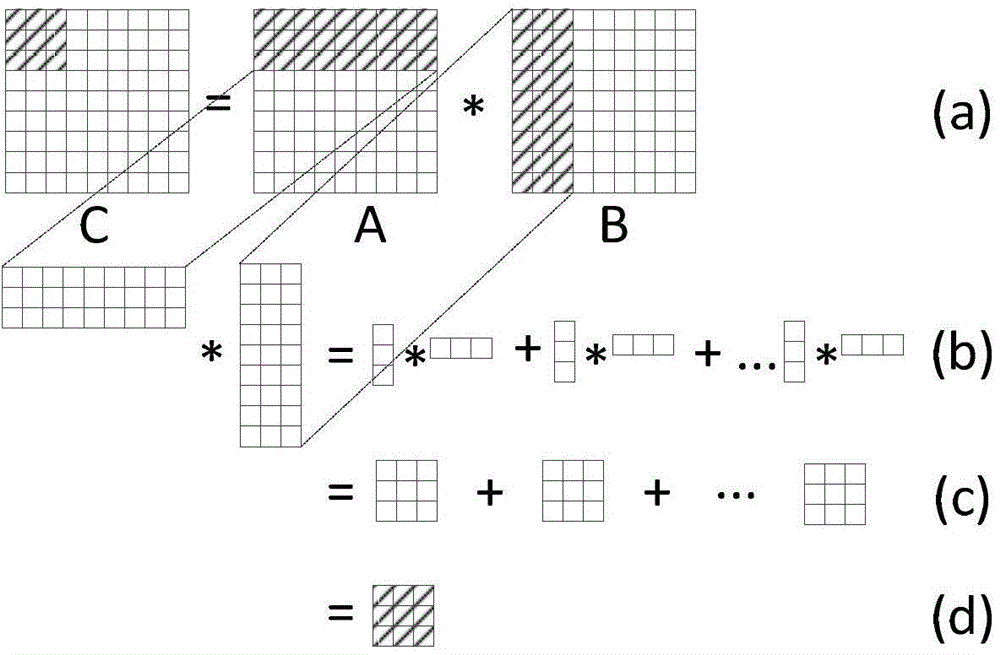

Method for accelerating convolution neutral network hardware and AXI bus IP core thereof

ActiveCN104915322AImprove adaptabilityIncrease flexibilityResource allocationMultiple digital computer combinationsChain structureMatrix multiplier

The invention discloses a method for accelerating convolution neutral network hardware and an AXI bus IP core thereof. The method comprises the first step of performing operation and converting a convolution layer into matrix multiplication of a matrix A with m lines and K columns and a matrix B with K lines and n columns; the second step of dividing the matrix result into matrix subblocks with m lines and n columns; the third step of starting a matrix multiplier to prefetch the operation number of the matrix subblocks; and the fourth step of causing the matrix multiplier to execute the calculation of the matrix subblocks and writing the result back to a main memory. The IP core comprises an AXI bus interface module, a prefetching unit, a flow mapper and a matrix multiplier. The matrix multiplier comprises a chain type DMA and a processing unit array, the processing unit array is composed of a plurality of processing units through chain structure arrangement, and the processing unit of a chain head is connected with the chain type DMA. The method can support various convolution neutral network structures and has the advantages of high calculation efficiency and performance, less requirements for on-chip storage resources and off-chip storage bandwidth, small in communication overhead, convenience in unit component upgrading and improvement and good universality.

Owner:NAT UNIV OF DEFENSE TECH

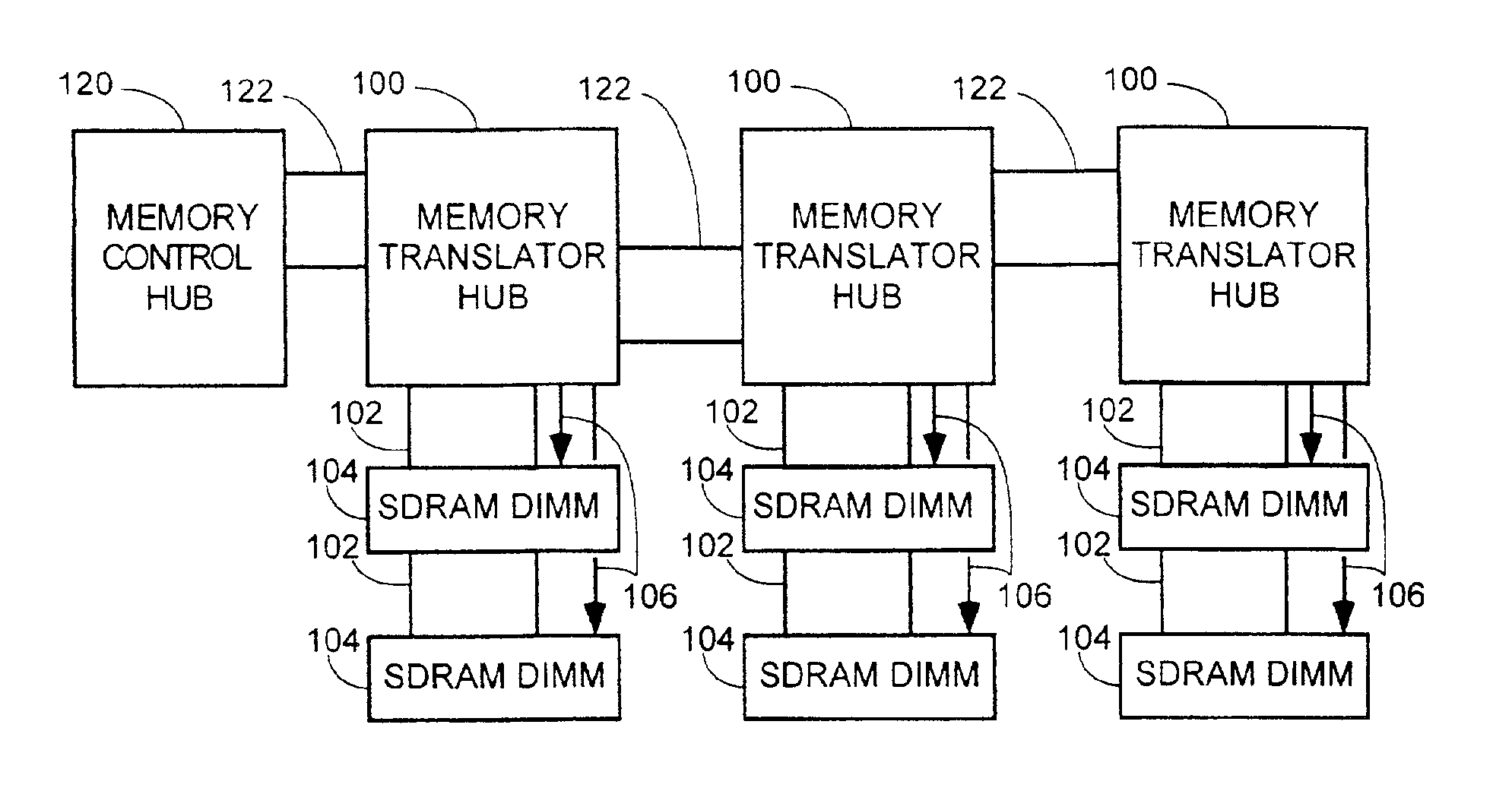

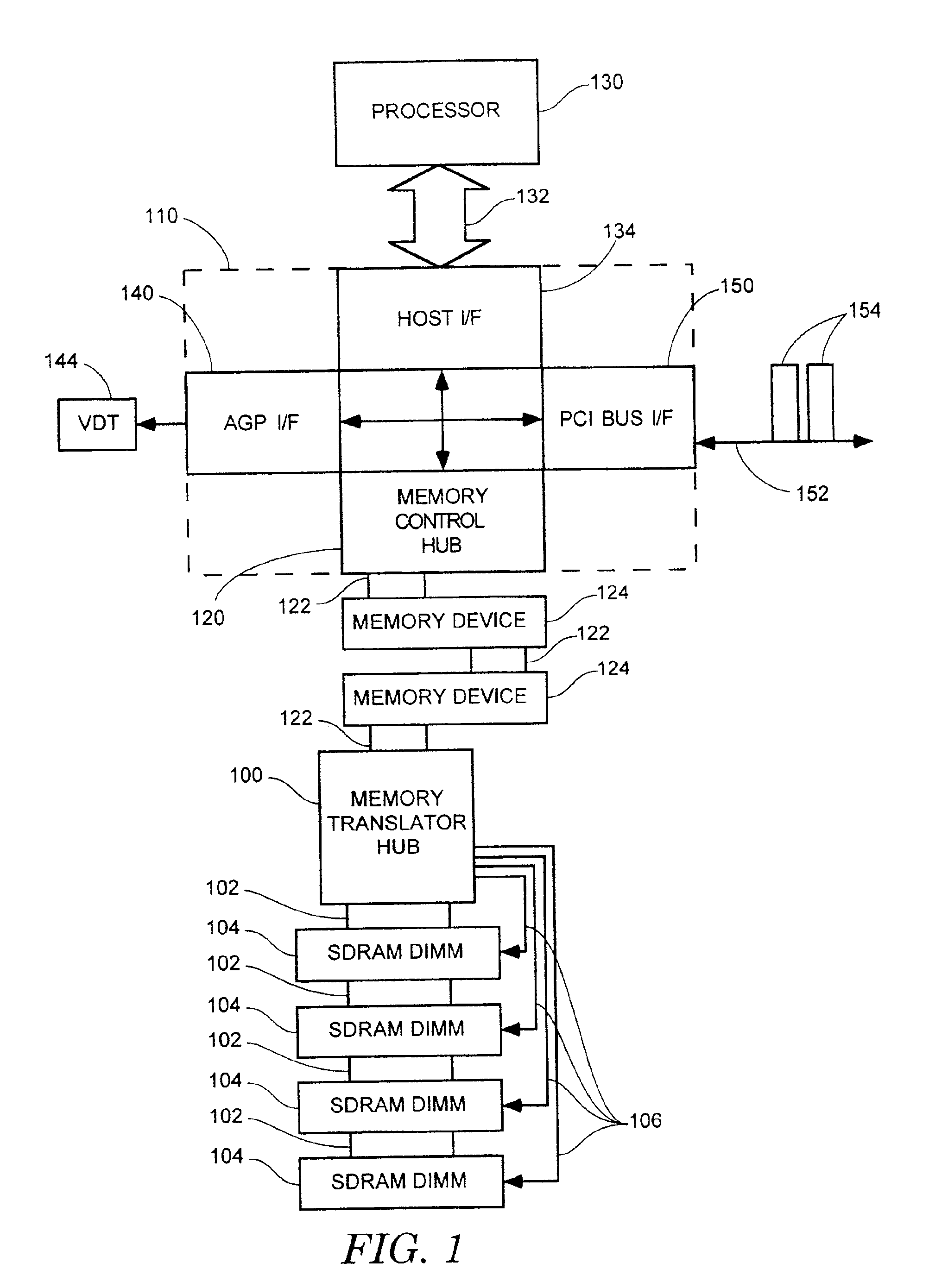

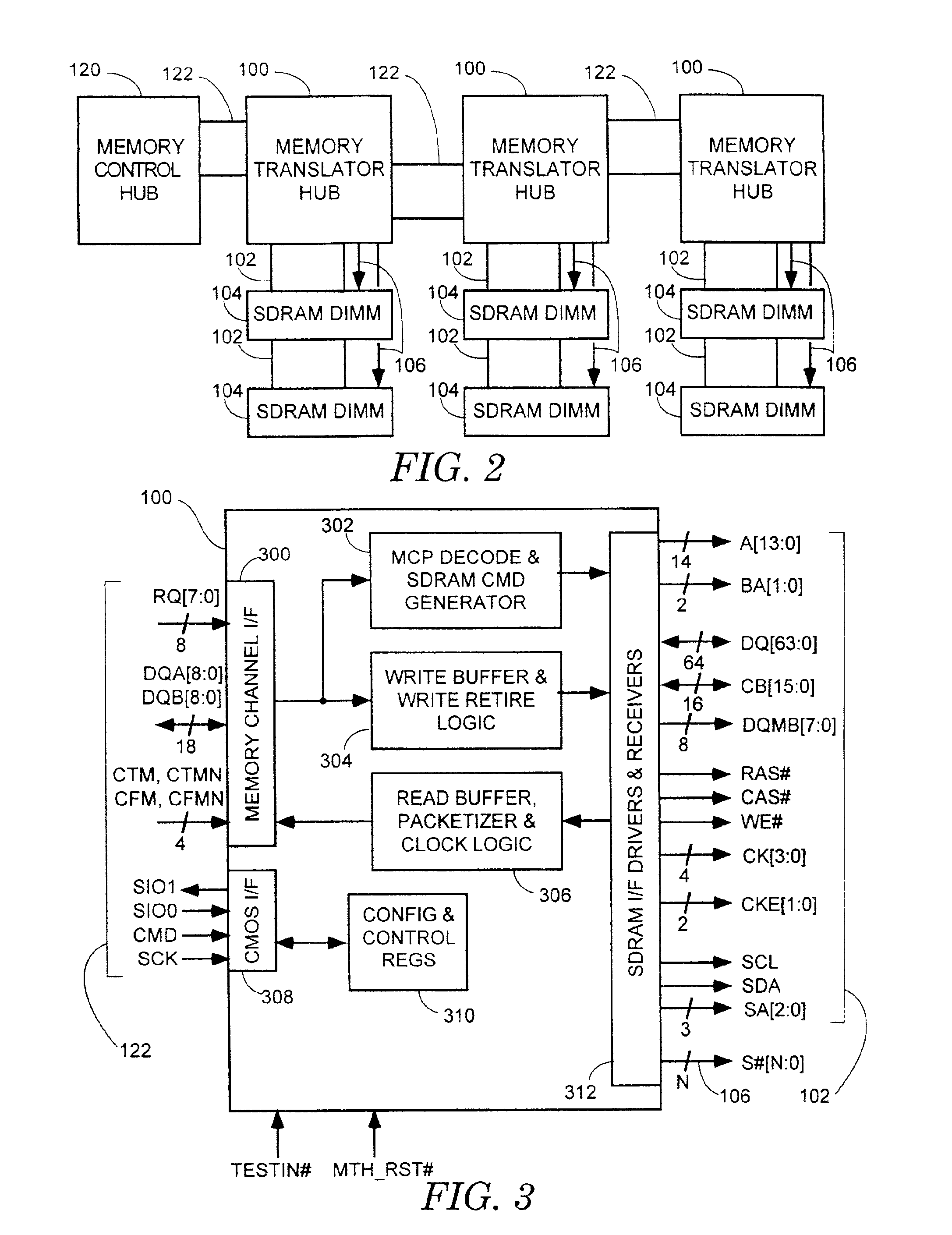

Method and apparatus for supporting SDRAM memory

A memory translation hub comprising a memory channel interface, a memory bus interface, and a command generator coupled to the memory channel interface and to the memory bus interface. The memory channel interface receives a memory control packet from a memory channel. The memory bus interface provides a memory bus. The command generator causes the memory bus interface to provide memory control signals on the memory bus responsive to the memory control packet.

Owner:INTEL CORP

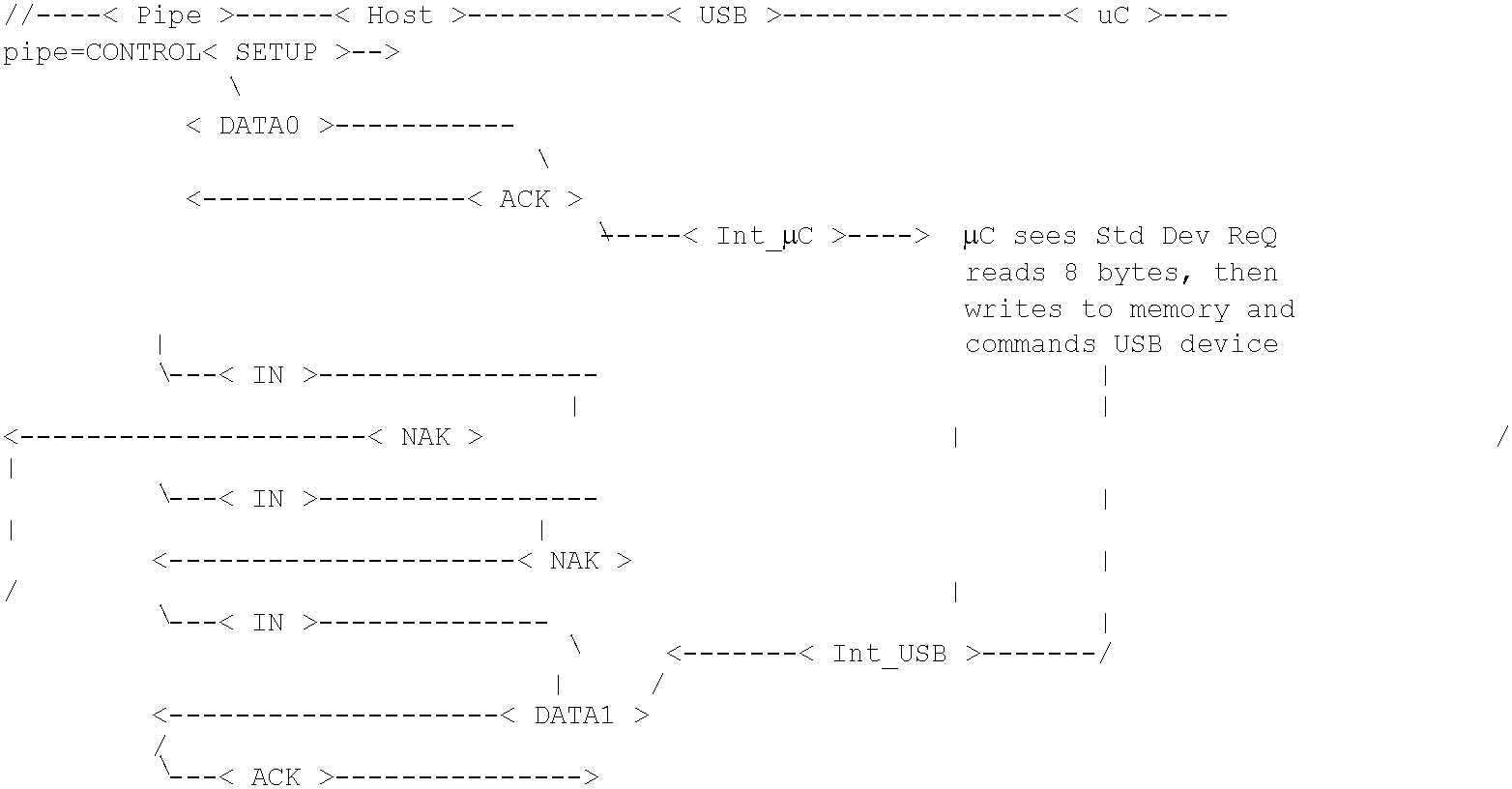

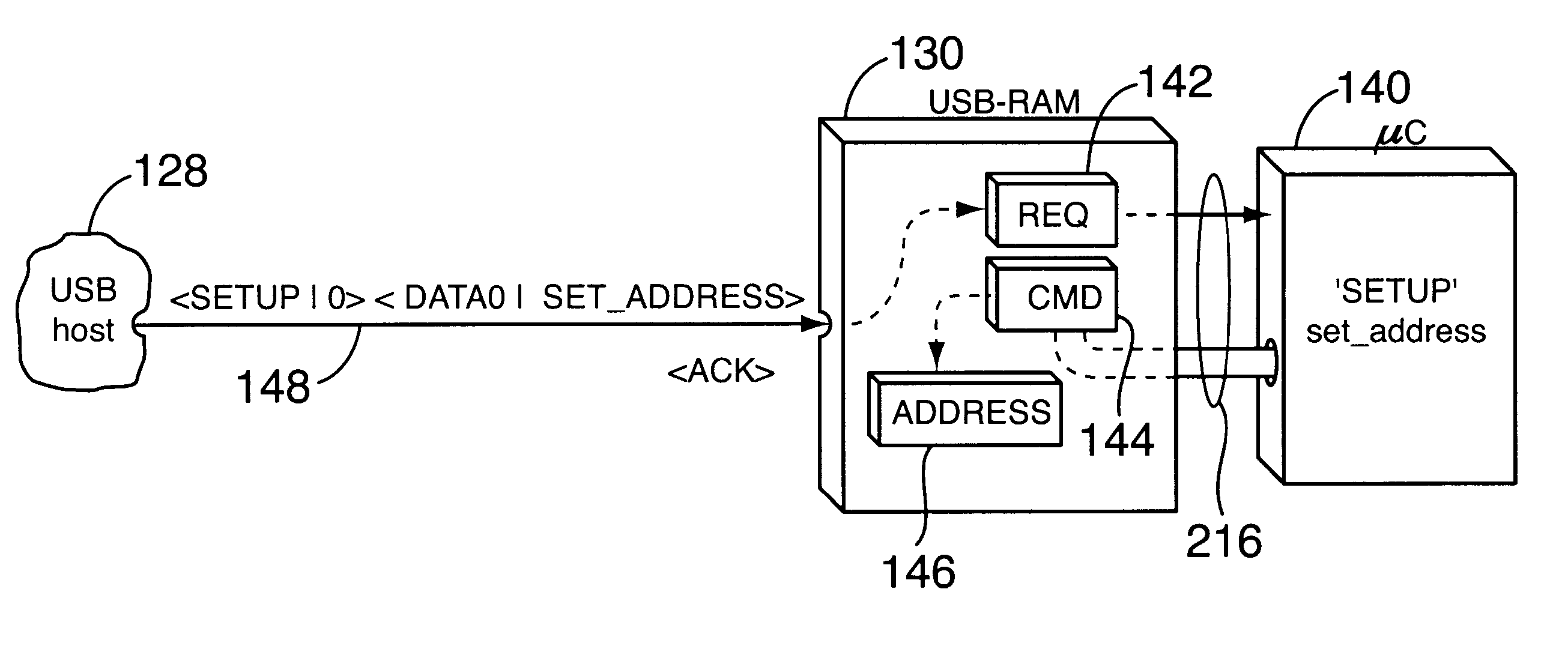

Universal serial bus (USB) RAM architecture for use with microcomputers via an interface optimized for integrated services device network (ISDN)

InactiveUS6219736B1Special service provision for substationHybrid switching systemsMicrocomputerMicrocontroller

A RAM-based interrupt-driven interface device is disclosed for establishing a communication link between a universal serial bus (USB) host and a microcontroller device for providing a control function, the interface device being operative to receive digital information in the form of command, data and control packets from the host and to process the packets and communicate the processed digital information to the microcontroller device, and in response thereto, the microcontroller device being operative to communicate digital information to the interface device for processing and transfer thereof to the host. The interface device includes means for receiving a command generated by the host through a USB bus, means for storing the host-generated command and for generating an interface device interrupt signal upon storage of said host-generated command for use by the microcontroller device in responding to the host-generated command, a microcontroller bus for transferring microcontroller information and the interface device interrupt signal between the interface device and the microcontroller device. The interface device further includes means for receiving a microcontroller command from the microcontroller device in response to said interface device interrupt signal and means for storing the microcontroller command and it is operative to generate a microcontroller device interrupt signal upon storage of the microcontroller command for use by the interface device in developing an address for identification of the interface device to the host during subsequent communications therebetween, wherein during communication between the host and the interface device, the interface device-developed address is used by the interface device to identify host-provided information in the form of packets, and upon processing of the host-provided information, to provide the microcontroller device with the necessary information to allow it to respond to the host thereby allowing a generic microcontroller device to be flexibly interfaced with a USB, host for communication therebetween.

Owner:SK HYNIX INC

Data processing system and method

InactiveUS20060013473A1Eliminate informationImage enhancementImage analysisStatic random-access memoryHigh memory

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

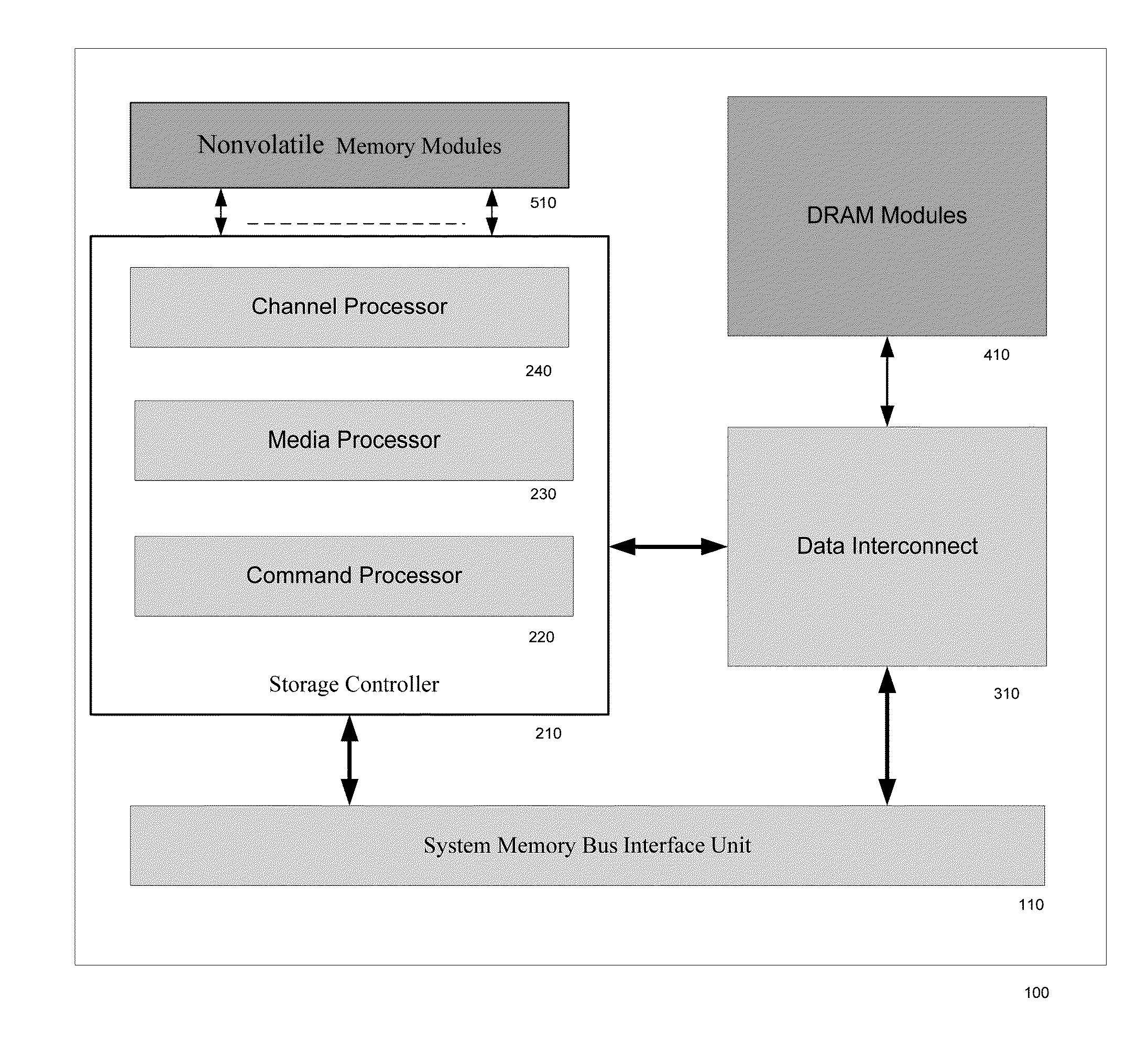

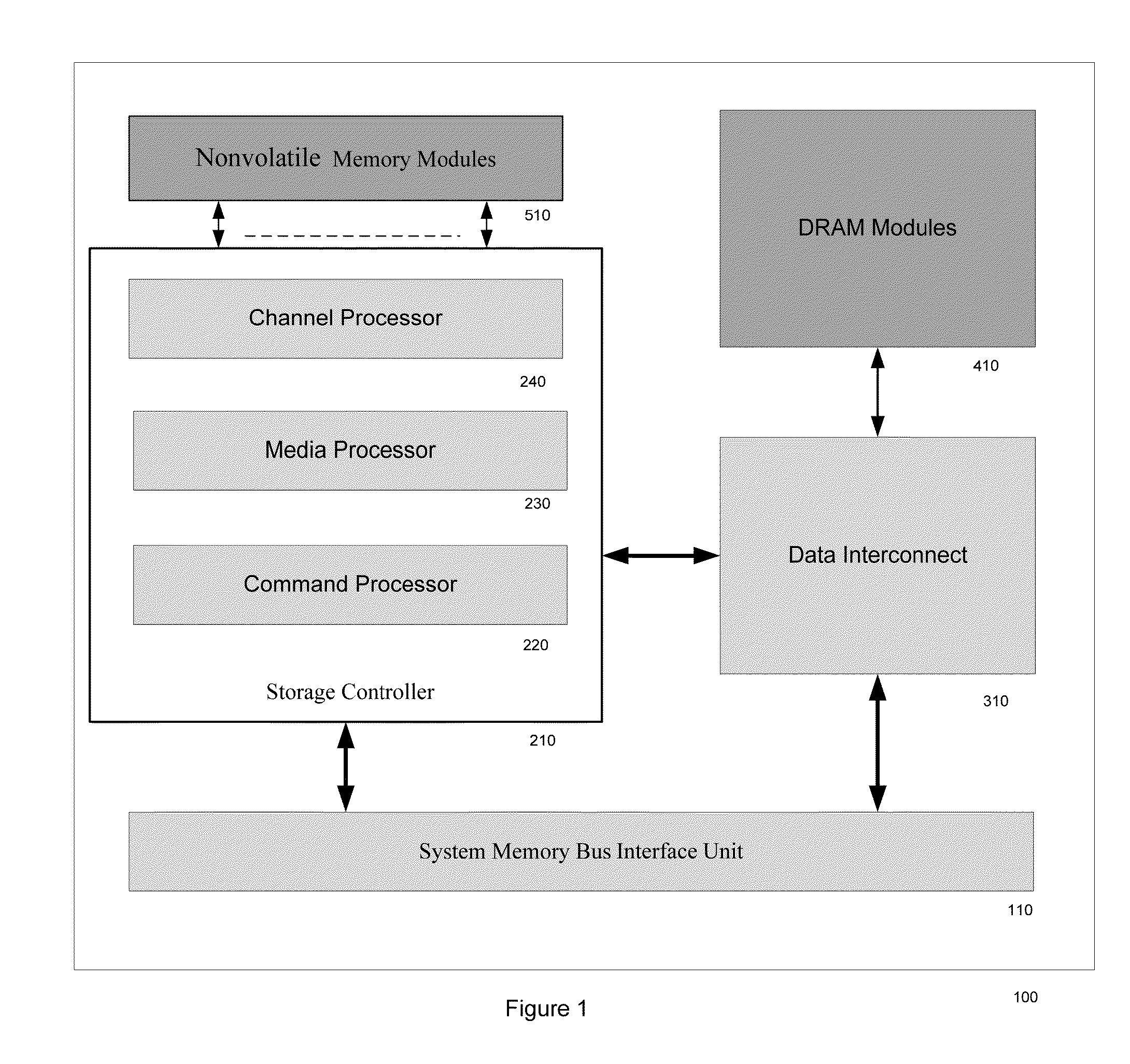

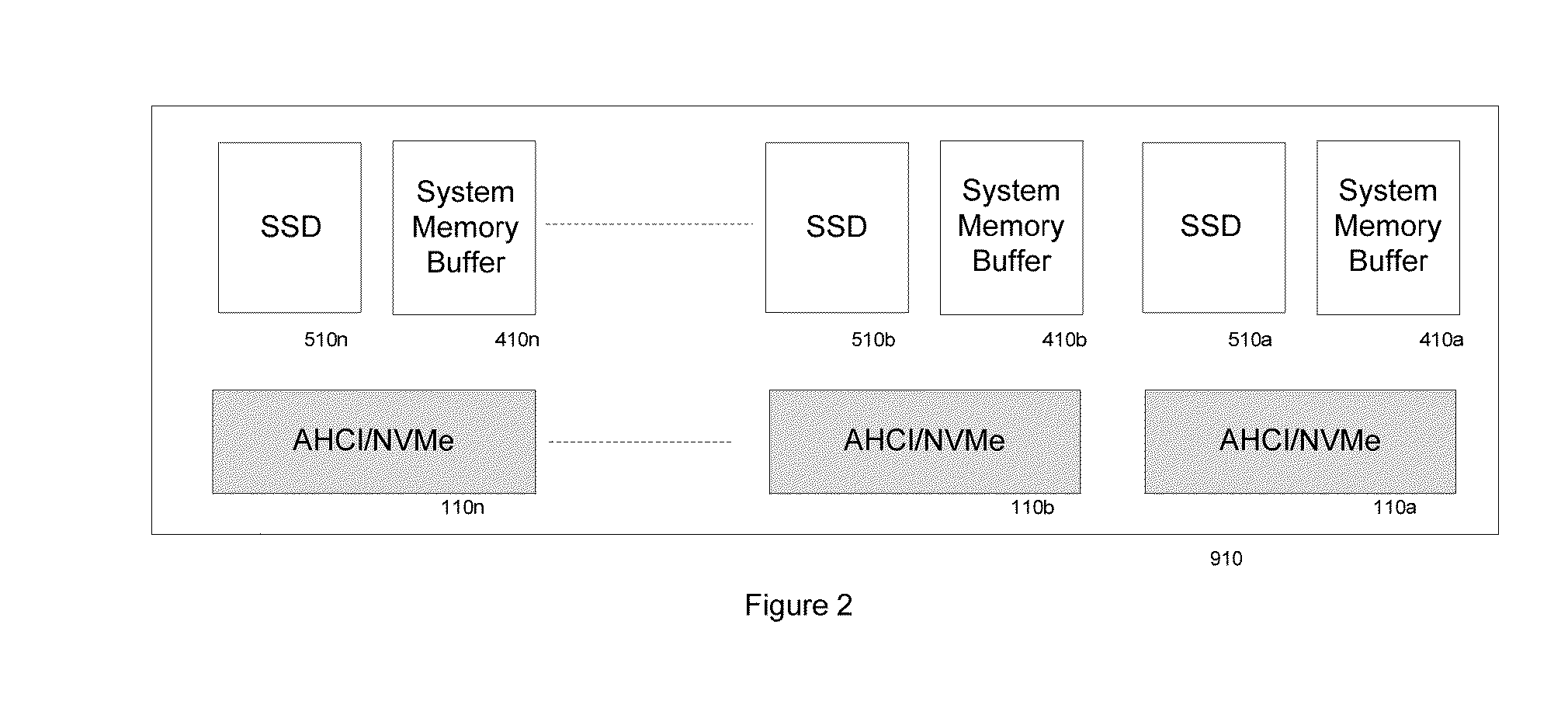

METHOD OF DIRECT CONNECTING AHCI OR NVMe BASED SSD SYSTEM TO COMPUTER SYSTEM MEMORY BUS

A SSD system directly connected to the system memory bus includes at least one system memory bus interface unit, one storage controller with associated data buffer / cache, one data interconnect unit, one nonvolatile memory (NVM) module, and flexible association between storage commands and the NVM module. A logical device interface, the Advanced Host Controller Interface (AHCI) or NVM Express (NVMe), is used for the SSD system programming. The SSD system appears to the computer system physically as a dual-inline-memory module (DIMM) attached to the system memory controller, and logically as an AHCI device or an NVMe device. The SSD system may sit in a DIMM socket and scaling with the number of DIMM sockets available to the SSD applications. The invention moves the SSD system from I / O domain to the system memory domain.

Owner:HUANG MING +1

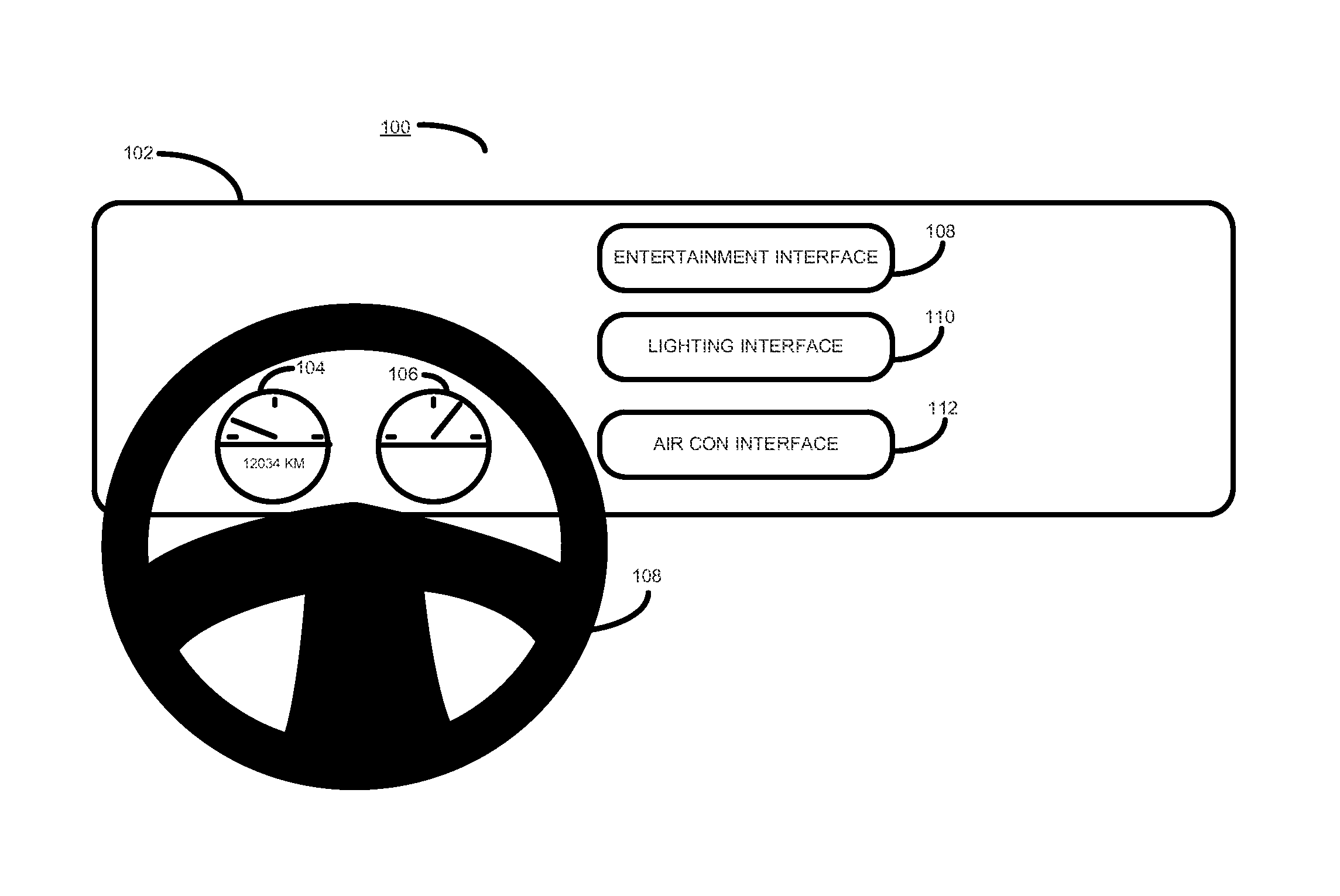

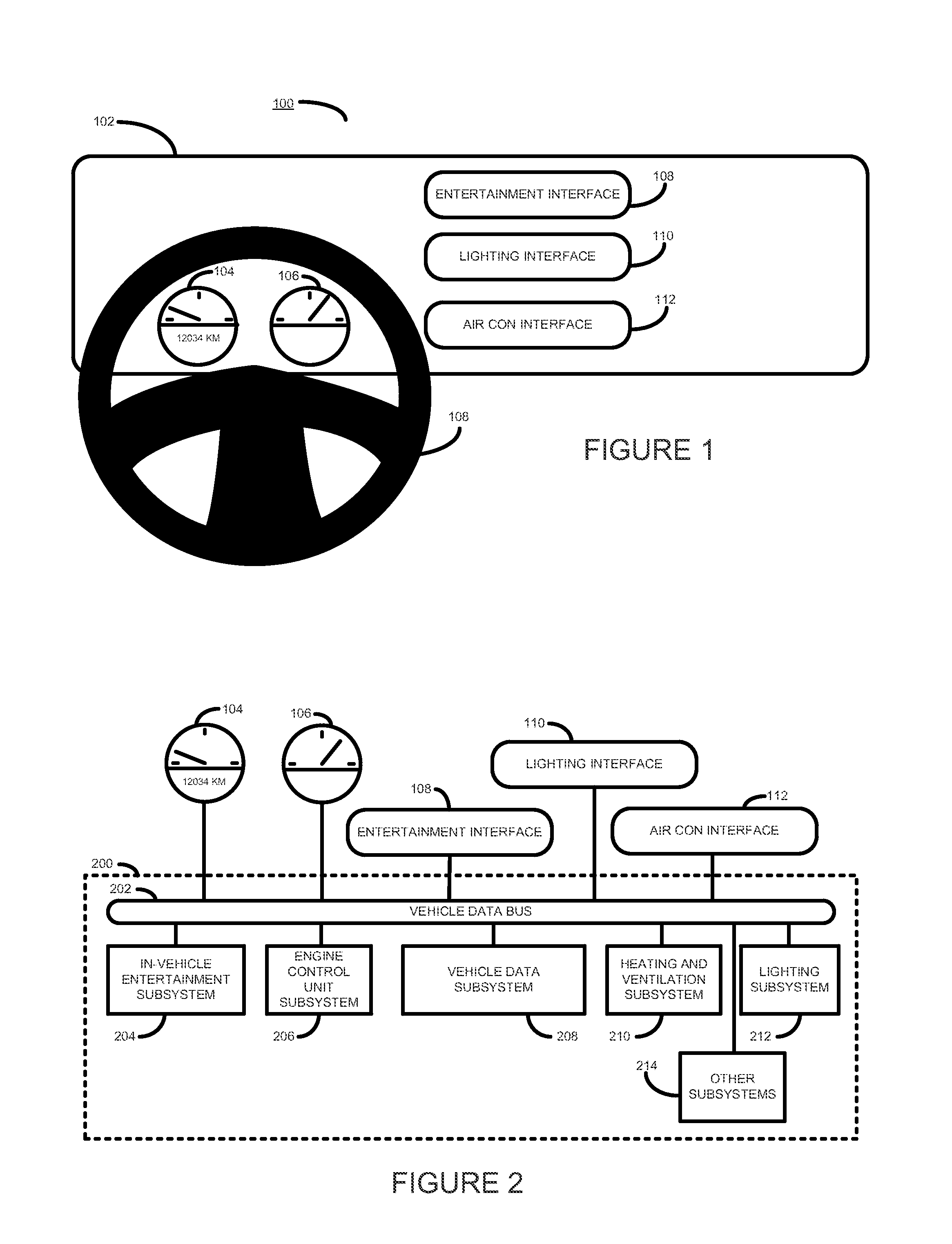

Dashboard display method and apparatus

ActiveUS20130207794A1Dashboard fitting arrangementsInstrument arrangements/adaptationsDashboardDisplay device

According to one example of the present invention, there is provided apparatus for displaying a dashboard display in a vehicle. The apparatus comprises a vehicle data bus interface for communicating with vehicle subsystems of a vehicle management system, a rules store for storing a set of dashboard display rules, and a dashboard display module. The dashboard display module is arranged to obtain a dashboard display definition, to determine whether the dashboard display definition is in compliance with the dashboard display rules; to obtain, where it is so determined, data from one or more of the vehicle subsystems in accordance with the dashboard display definition, and to display the obtained data in accordance with the dashboard display definition.

Owner:ENT SERVICES DEV CORP LP

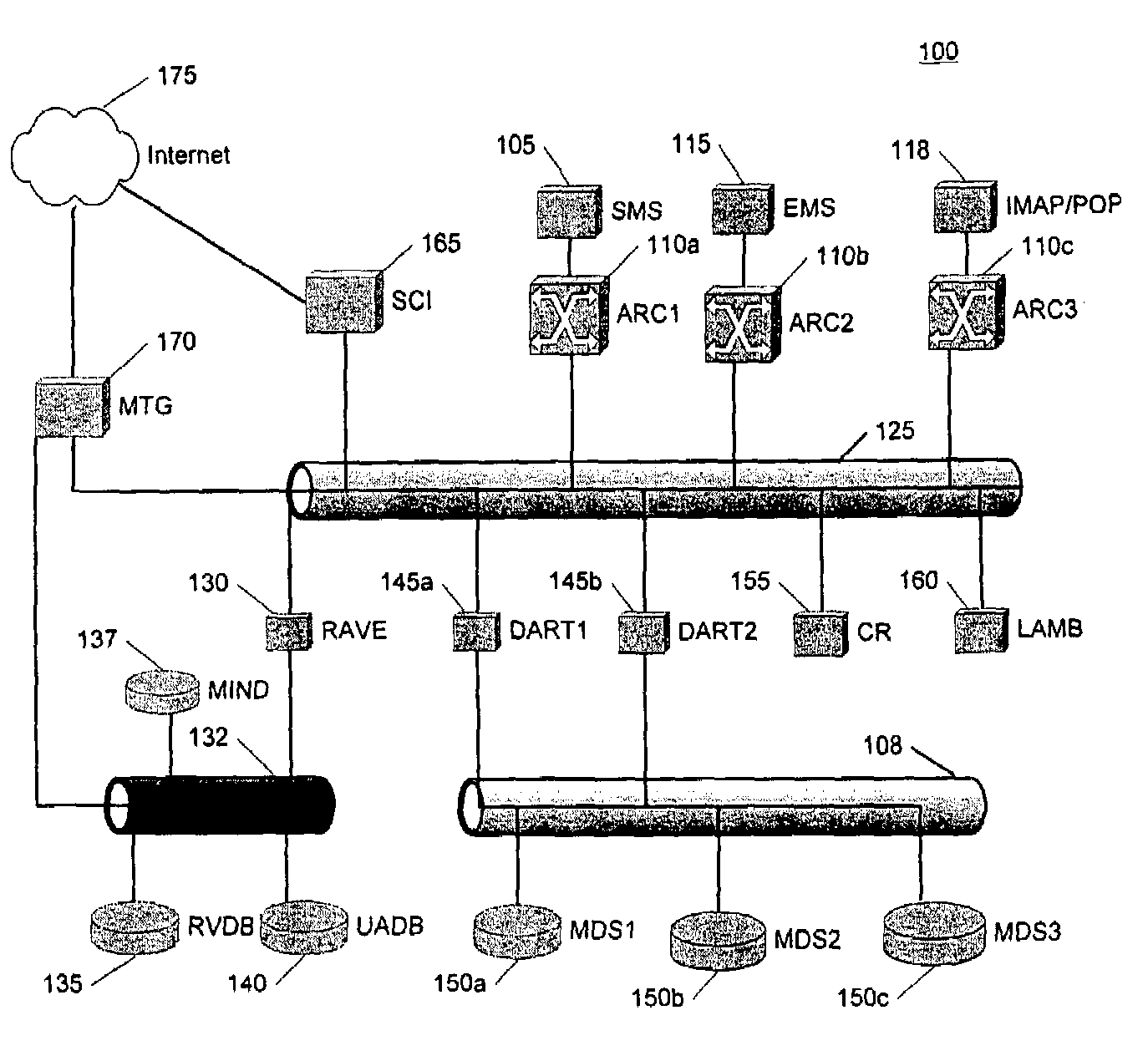

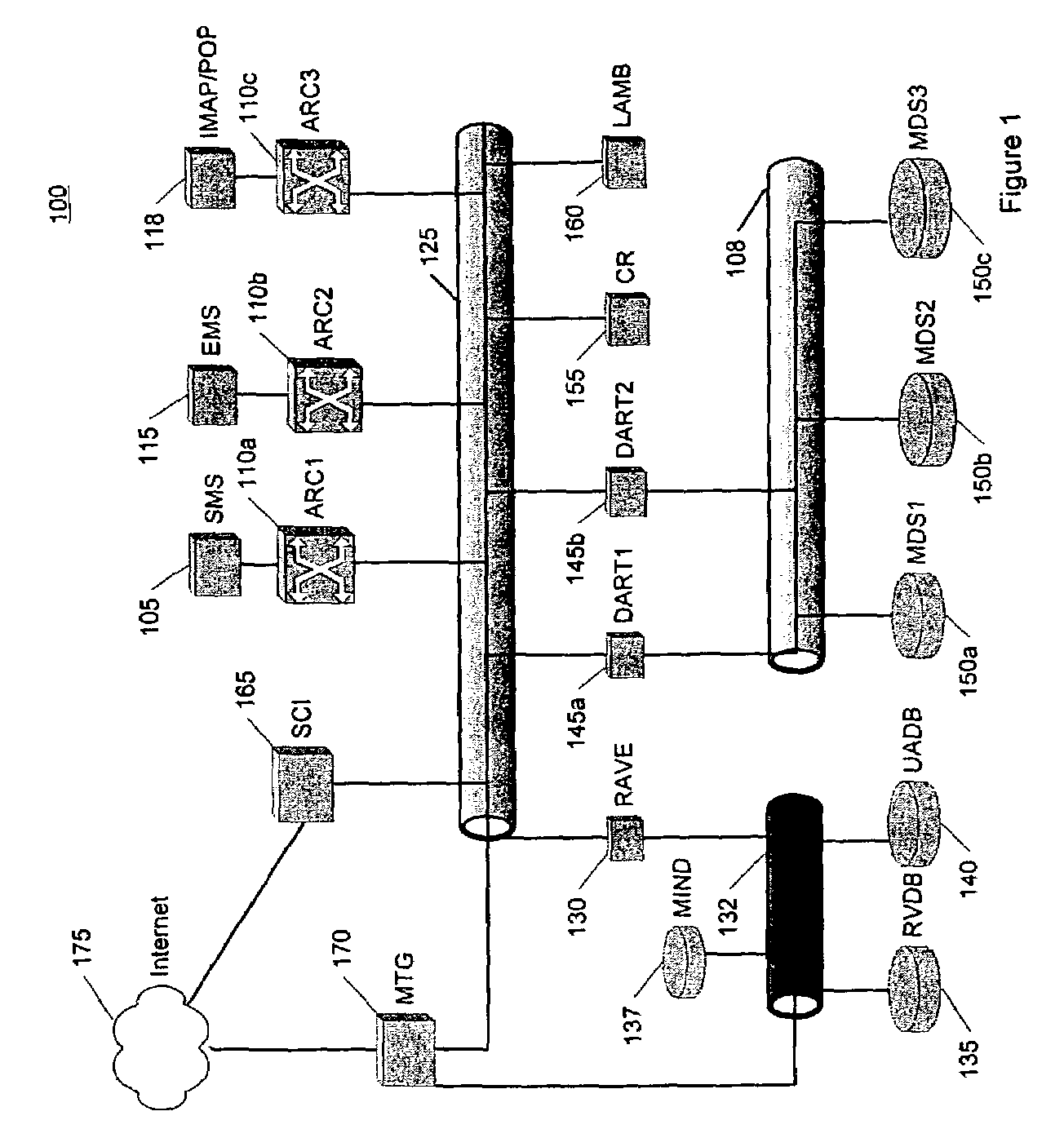

System for translation and communication of messaging protocols into a common protocol

InactiveUS7617328B2Information formatMultiple digital computer combinationsBus interfaceMessage passing

An adapter for passing messages in a telecommunications infrastructure from a first device to a second device. The adapter comprises a messaging interface, a processor, and a bus interface. The messaging interface is in communication with the first device and is operable to receive a received message in a first messaging format from the first device. The processor is coupled to the messaging interface and is operable to receive the received message from the messaging interface and translate the received message into a common message in a common format. The bus interface is coupled to the processor and is operable to receive the common message from the processor and transmit the common message to the second device through a bus.

Owner:AT&T MOBILITY II LLC

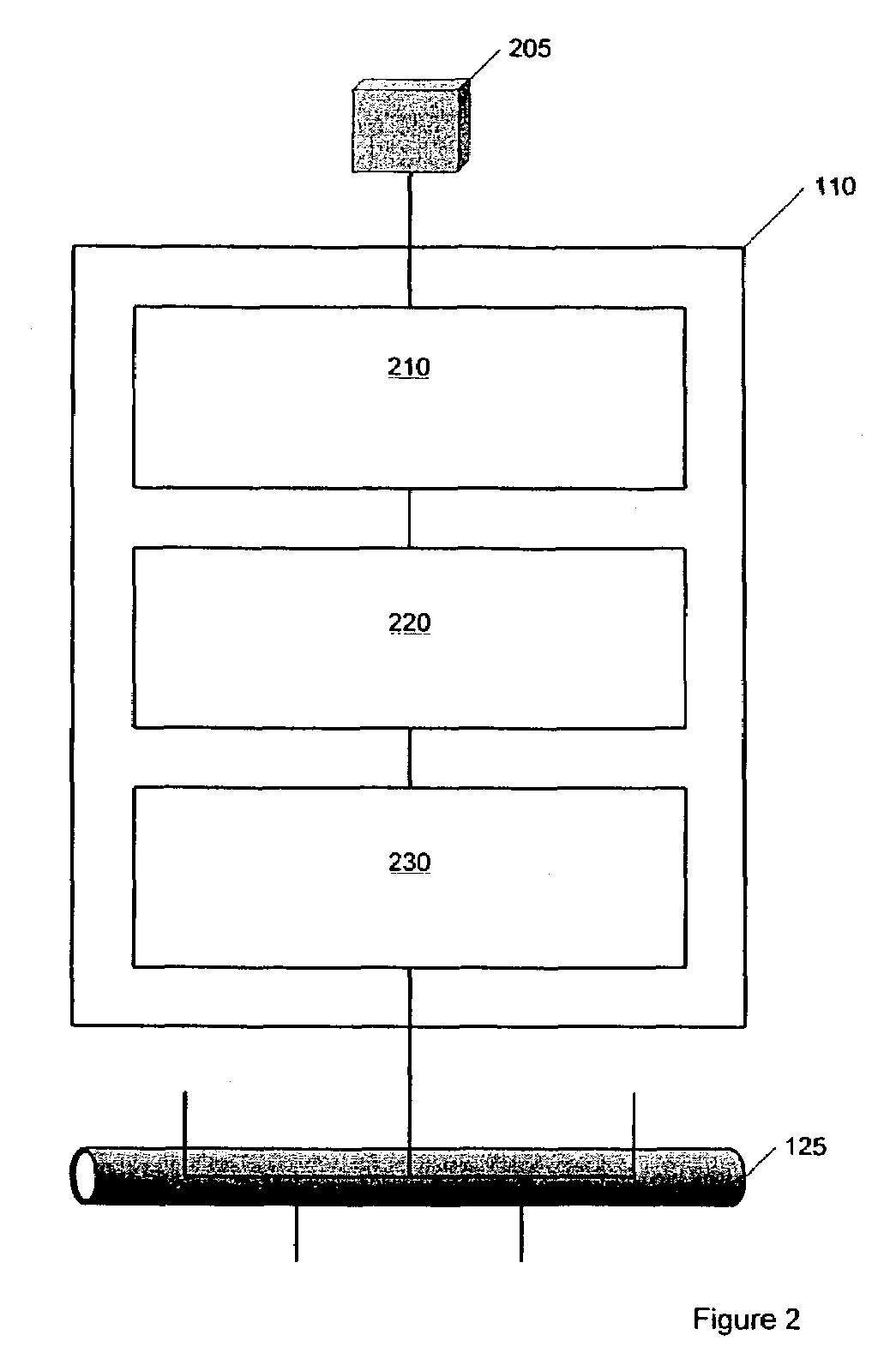

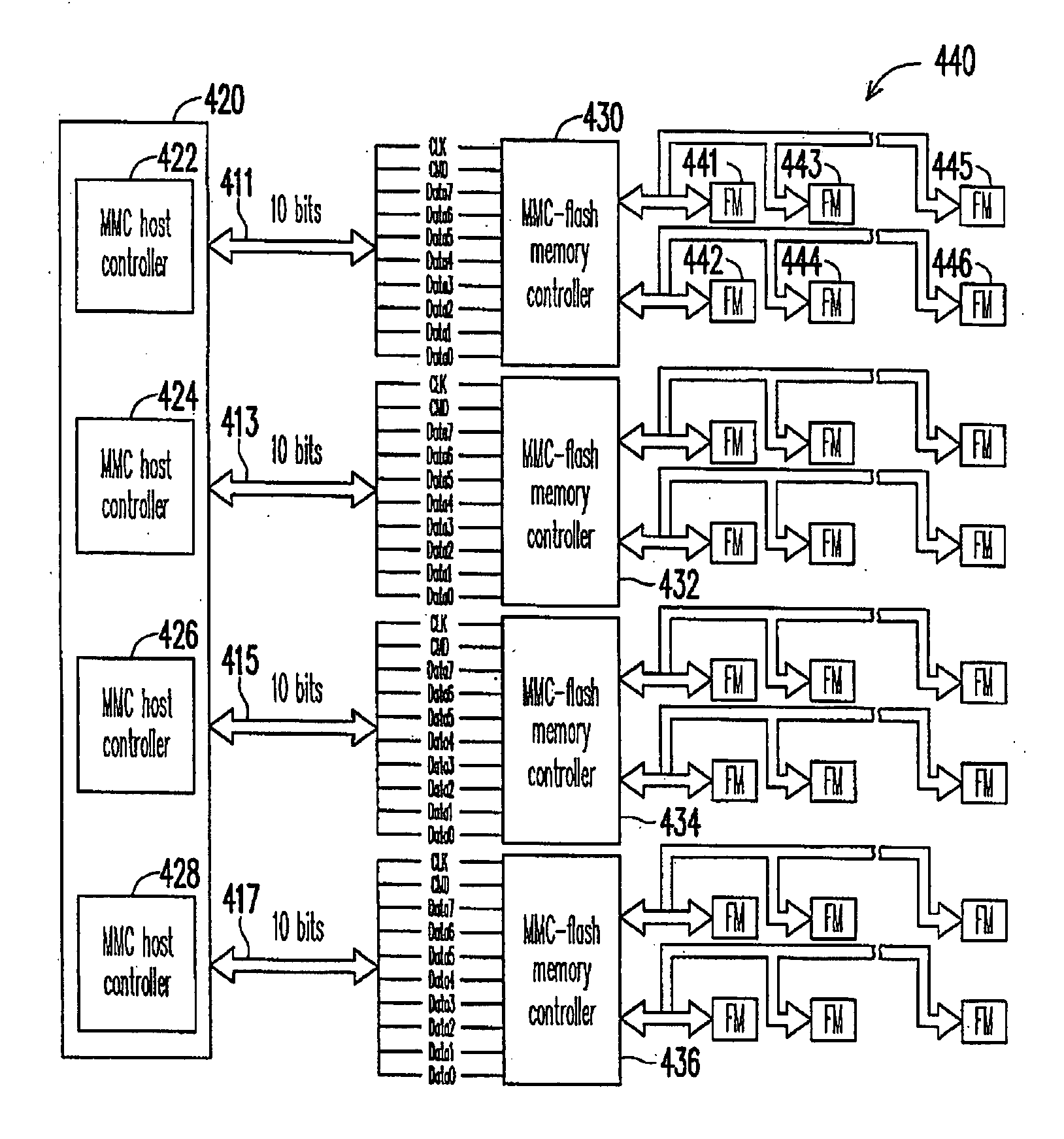

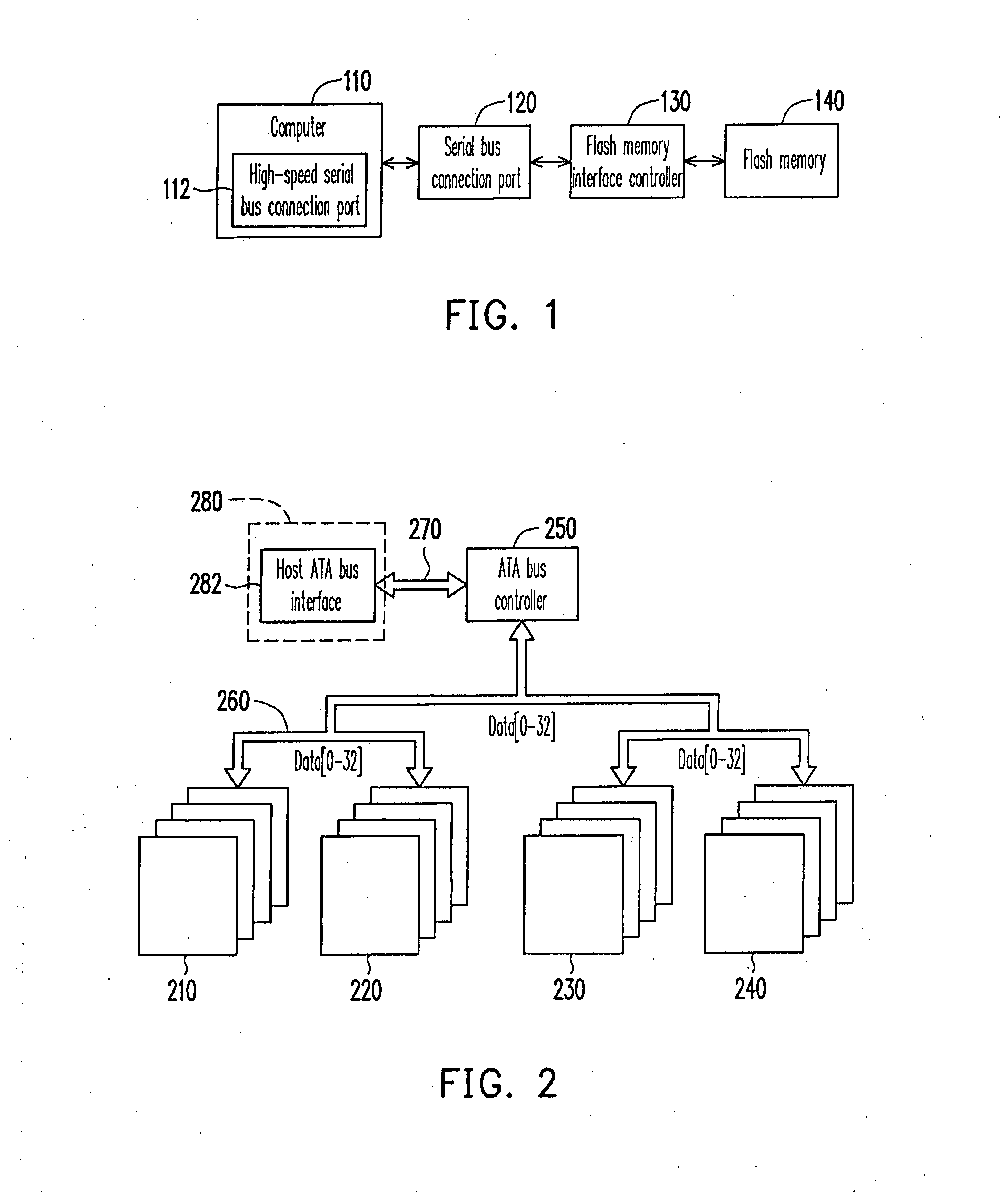

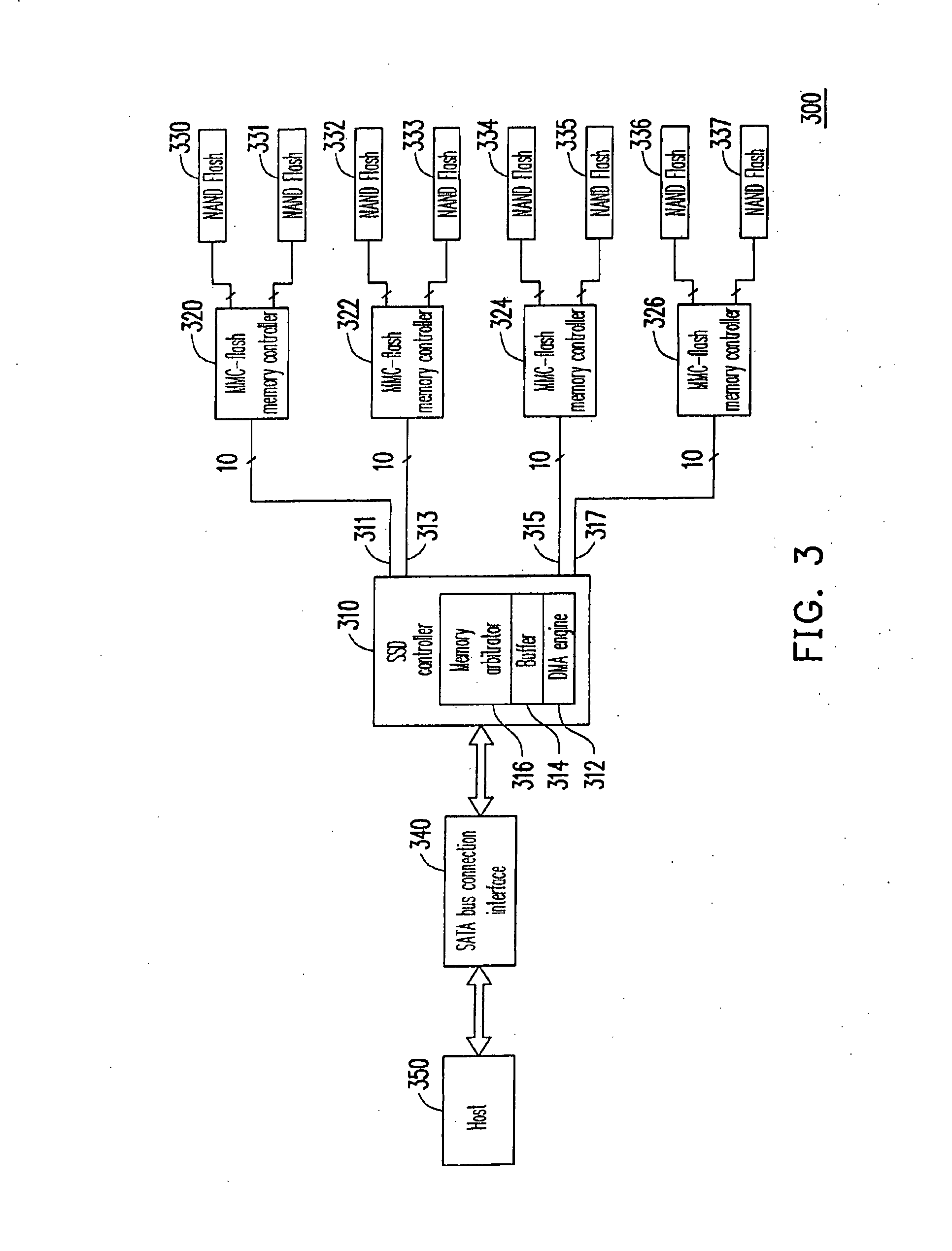

Solid state disk storage system with parallel accesssing architecture and solid state disck controller

InactiveUS20090083476A1Memory systemsInput/output processes for data processingBus interfaceSolid-state

A solid state disk (SSD) storage system with a parallel accessing architecture, including a SSD controller and a plurality of transmission interfaces of a predetermined bit number and bandwidth, and a solid state disk controller thereof are provided. The SD controller forms channels for transmitting control signals and data with one or more flash memories through each of the transmission interfaces. That is, independent transmission channels are constituted between the SSD controller, the transmission interfaces with multiple bits, and the flash memories. In one embodiment, the transmission interfaces are compatible with MMC 4.0 protocol or higher. Moreover, a host controls and accesses the flash memories through a SATA bus interface and the SSD controller, and uses a direct memory access (DMA) engine with a bidirectional connection port in the SSD controller to transmit data.

Owner:PHISON ELECTRONICS

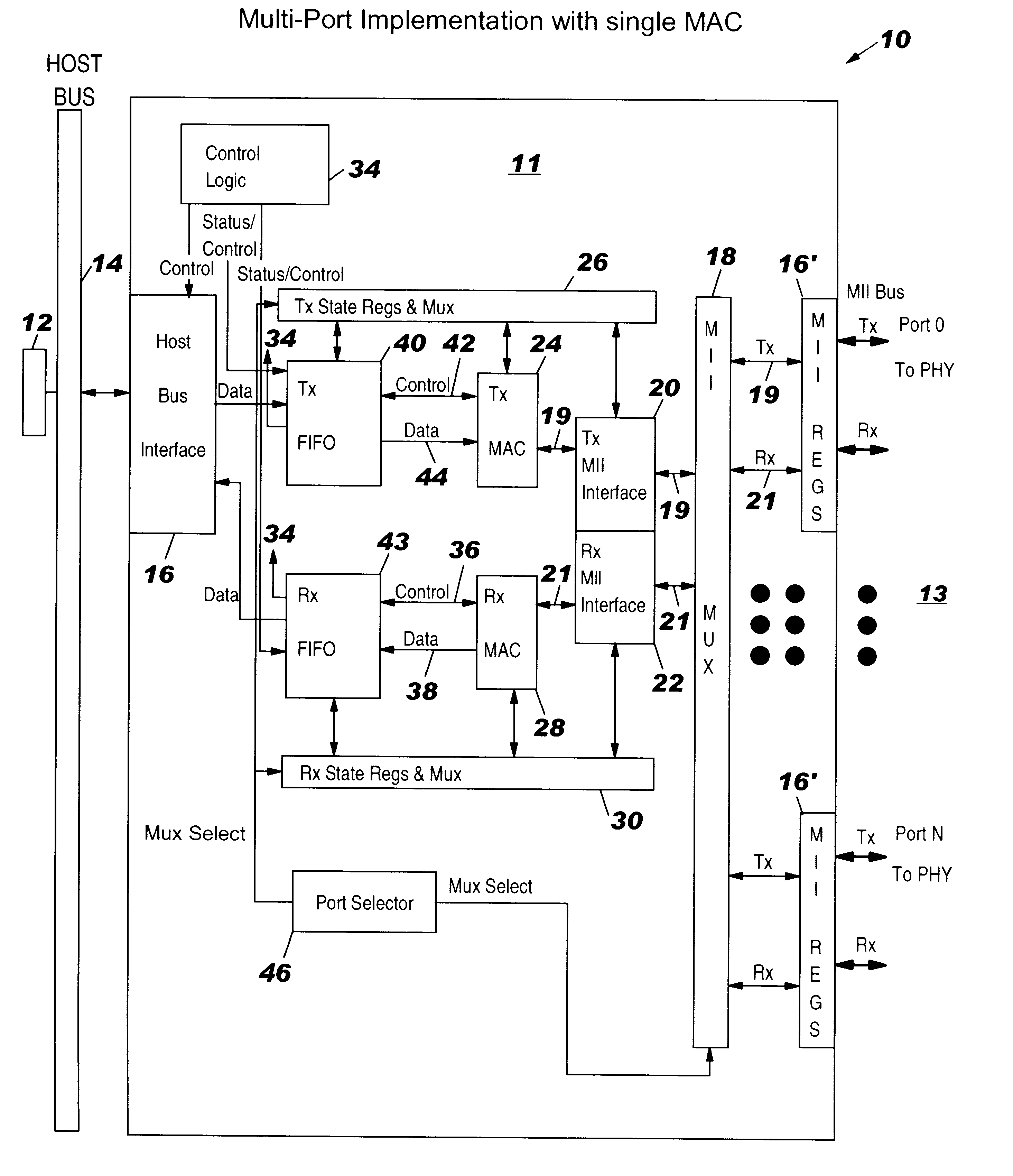

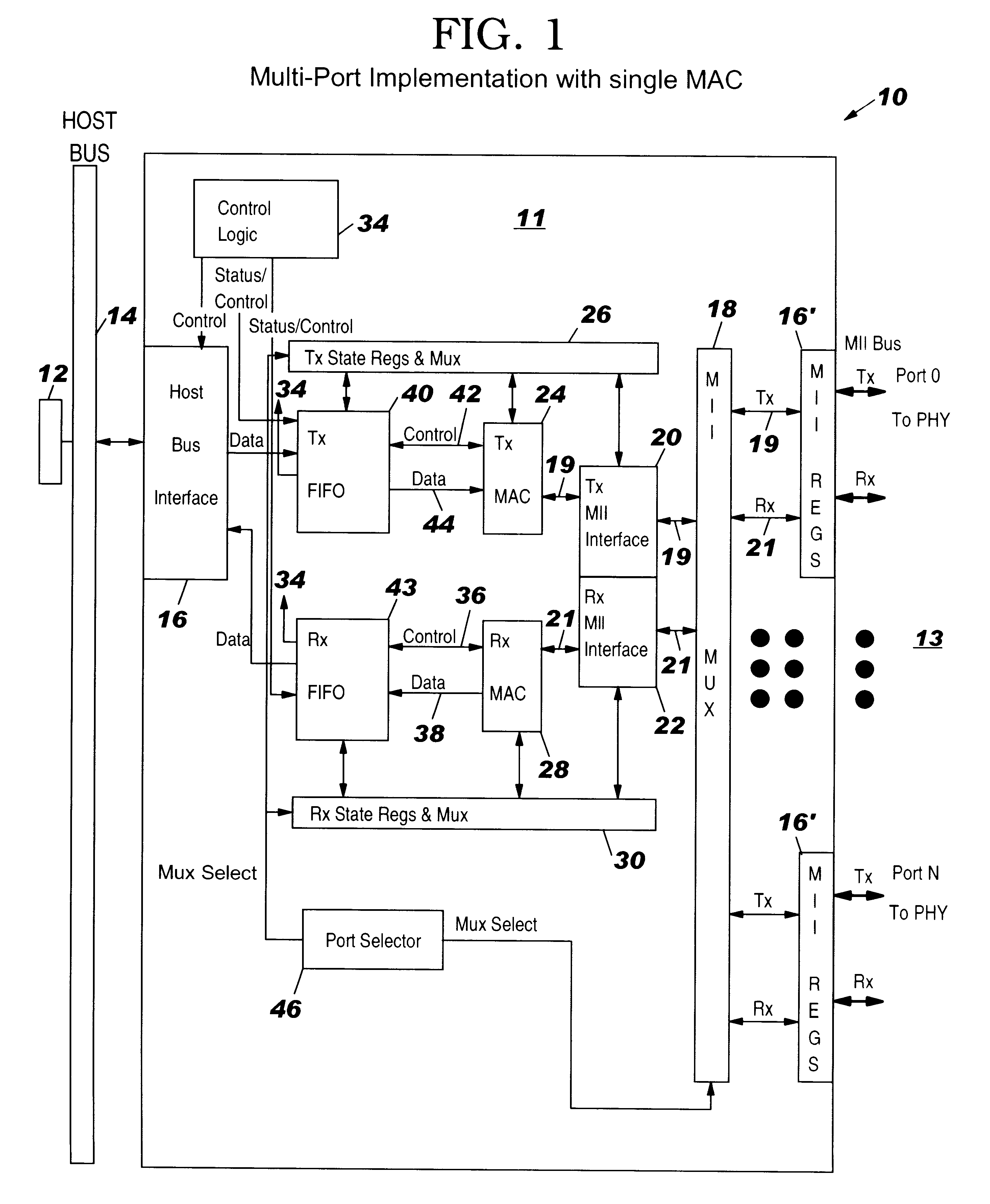

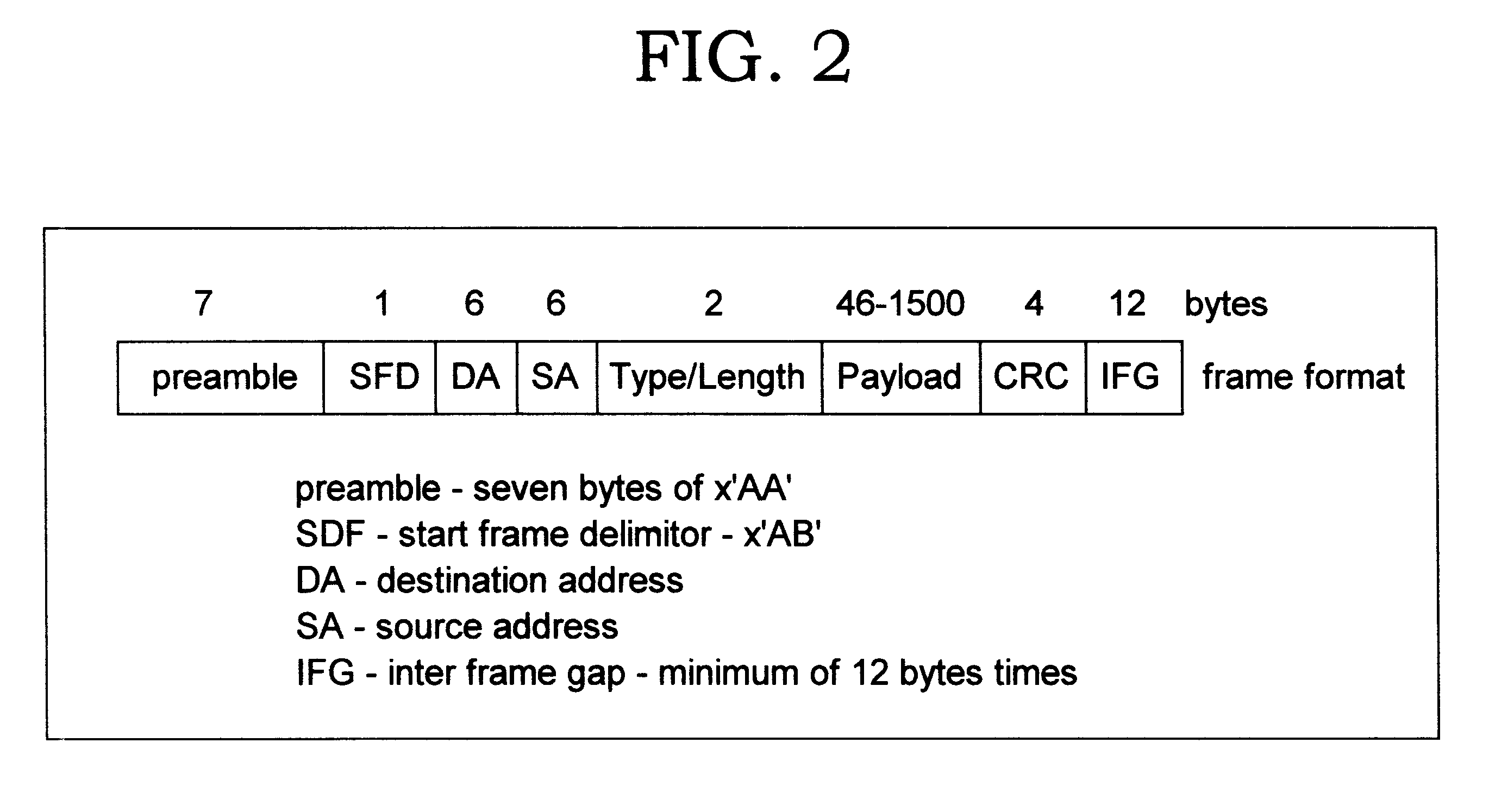

Architecture for a multi-port adapter with a single media access control (MAC)

InactiveUS6373848B1Data switching by path configurationStore-and-forward switching systemsBus interfaceMulti port

A multi-port adapter having a single MAC chip has reduced logic circuits for transferring data between a host system and a TDM communication system. The MAC chip includes a transmit MAC and a receive MAC, each coupled at one end to a port multiplexer through an interface and at the other end to respective storage registers. The port multiplexer is coupled to the Physical Layer of each port. Transmit and receive state registers track the state of each port in the transfer of data in the transmit and receive directions. The storage registers are coupled through a host bus interface to a host bus and to the host system. Control logic is coupled to the storage register to control the transfer of data between the system and the storage registers. A port selector coupled between the multiplexer and the transmit and receive state registers selects ports for transfer of data in succession. On each chip clock cycle, the port selector selects a state machine register to determine the state of the MACs for processing the data and a section of the FIFO's to write or read data for the selected port. At the end of the cycle, the state registers are set and stay set until selected again. The process repeats for each port in a cyclic manner. Once data is accumulated in the receive storage register, control logic reads the data of the host bus. Once space is available in the transmit storage register, the control logic writes data from the host system to the transmit storage register.

Owner:IBM CORP

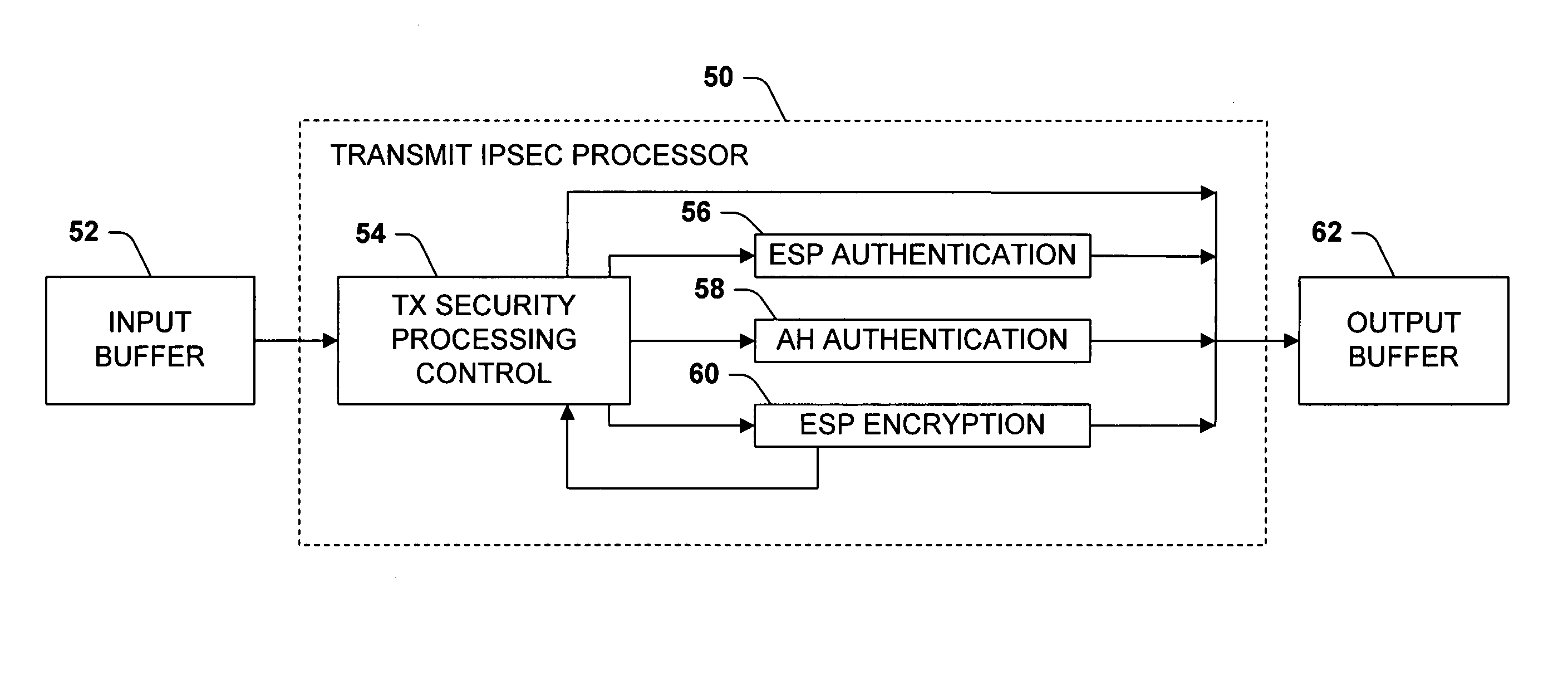

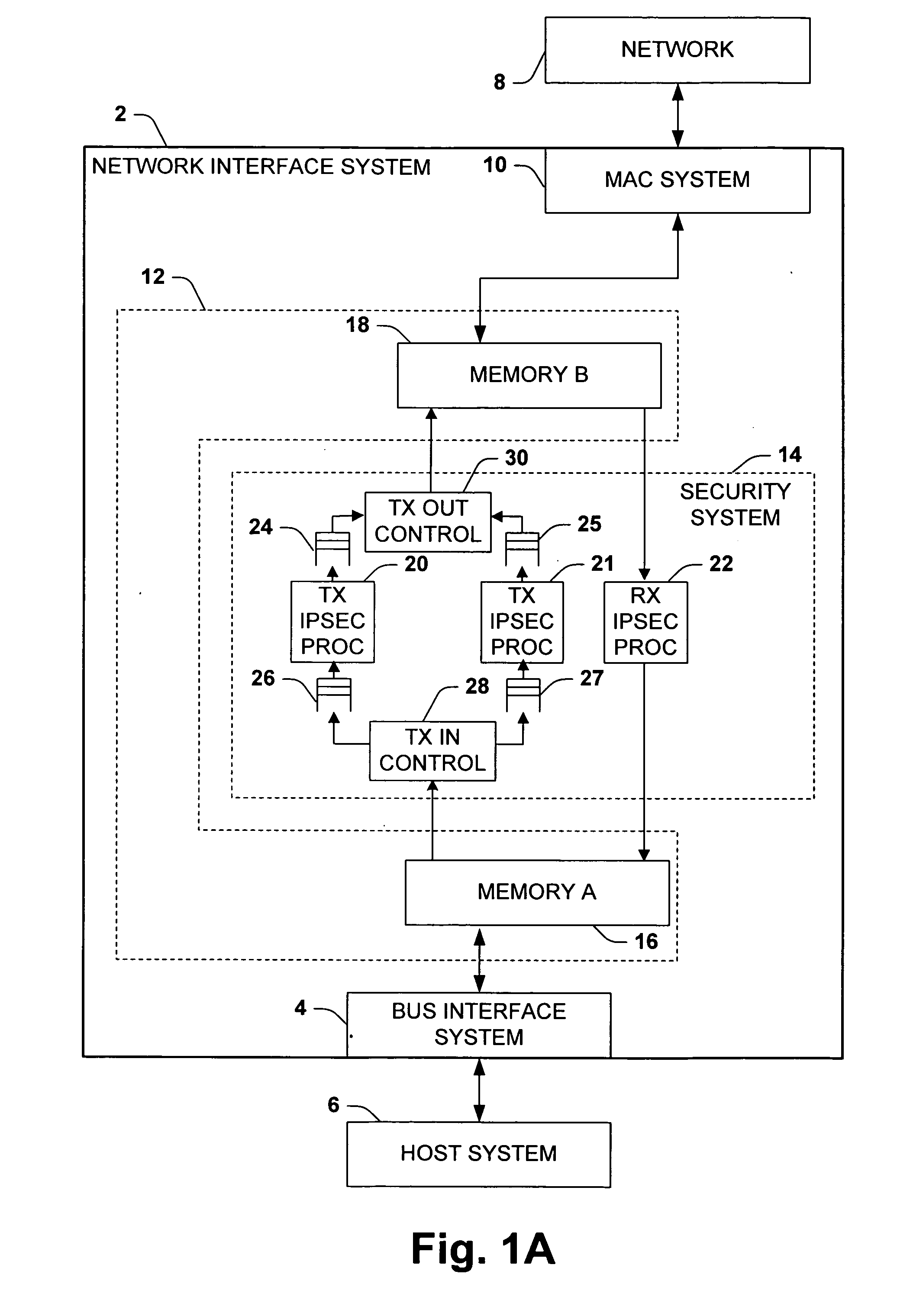

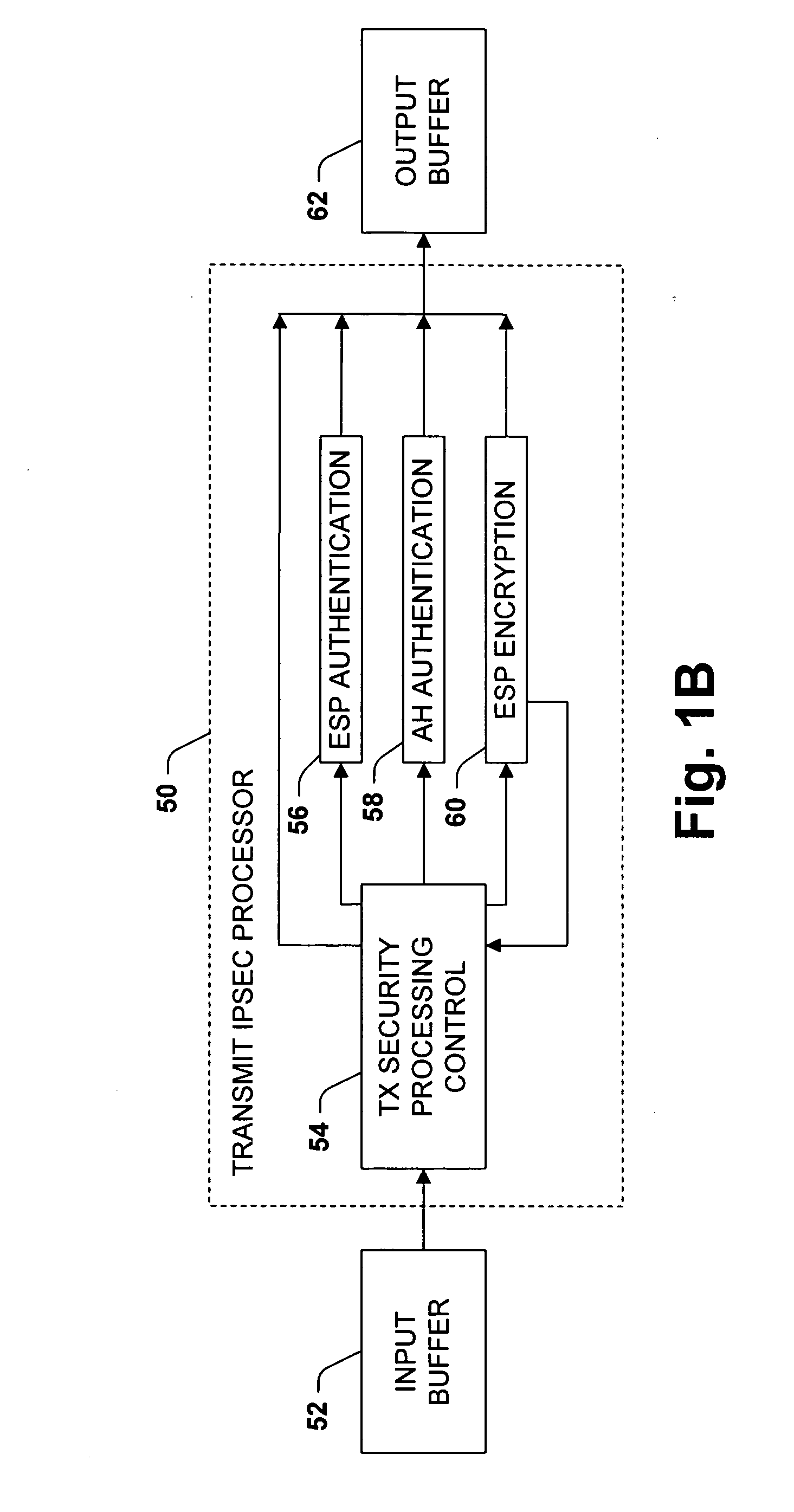

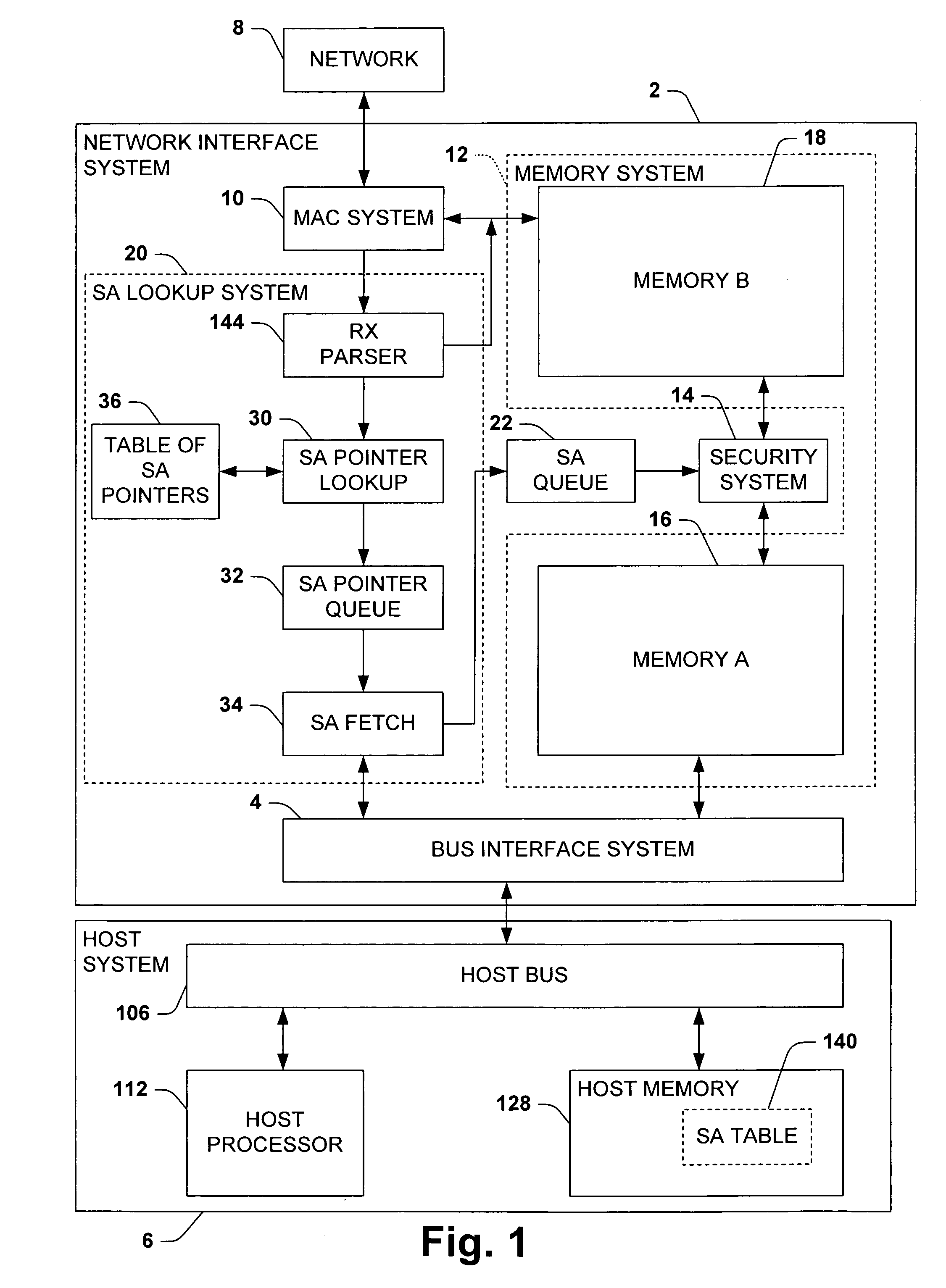

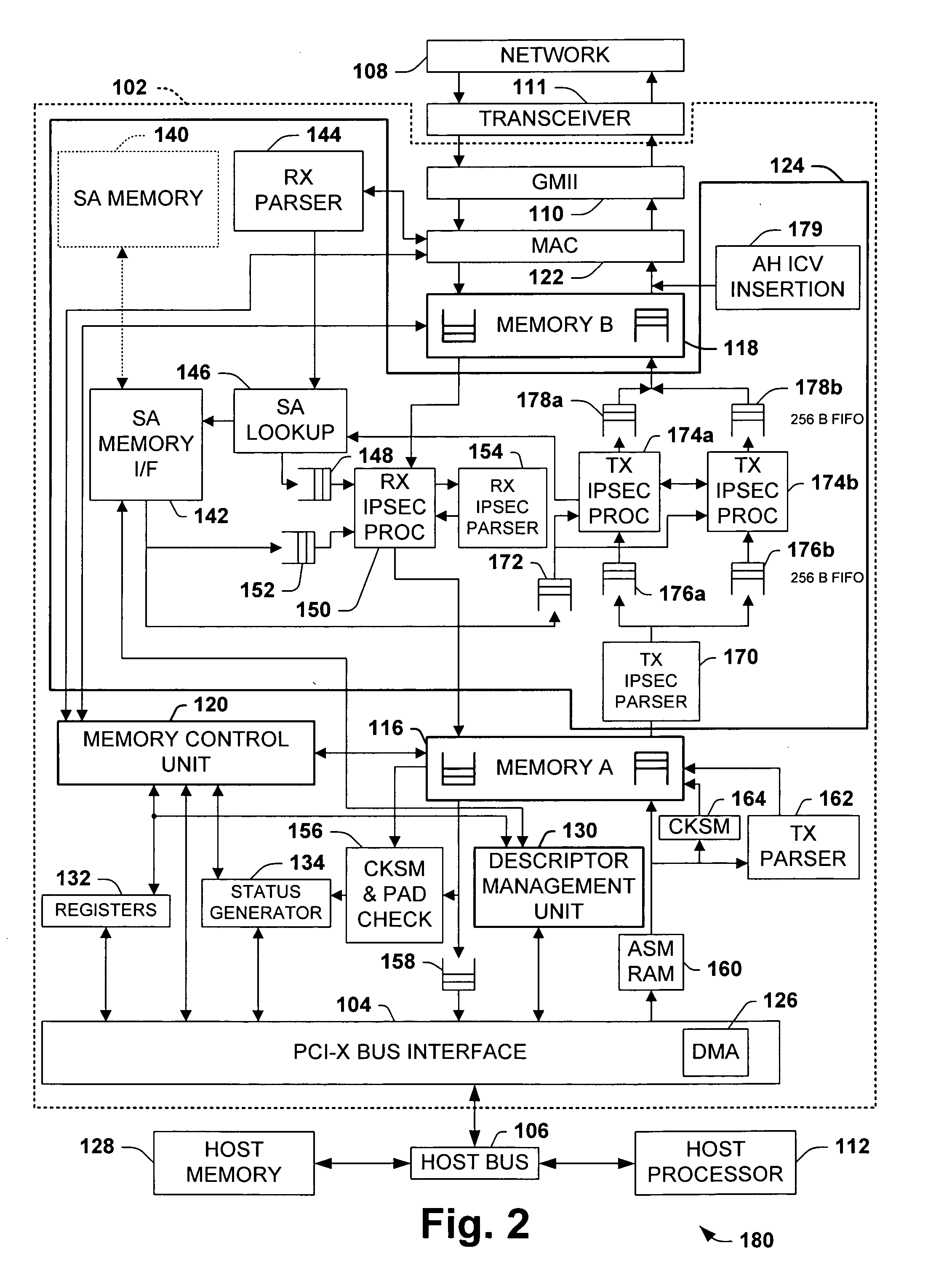

Two parallel engines for high speed transmit IPSEC processing

ActiveUS20050198531A1Avoid spreadingEliminates a potential bottleneckDigital data processing detailsUnauthorized memory use protectionControl systemIPsec

The invention relates to a network interface system for interfacing a host system with a network. The network interface system includes a bus interface system, a media access control system, and a security system. The network interface offloads IPsec processing from the host processor. According to the invention, the security system includes two processors for encrypting and authenticating the outgoing data. Outgoing data packets are sent alternately to one or the other processor, whereby transmission processing can be accelerated relative to receive processing.

Owner:ADVANCED MICRO DEVICES INC

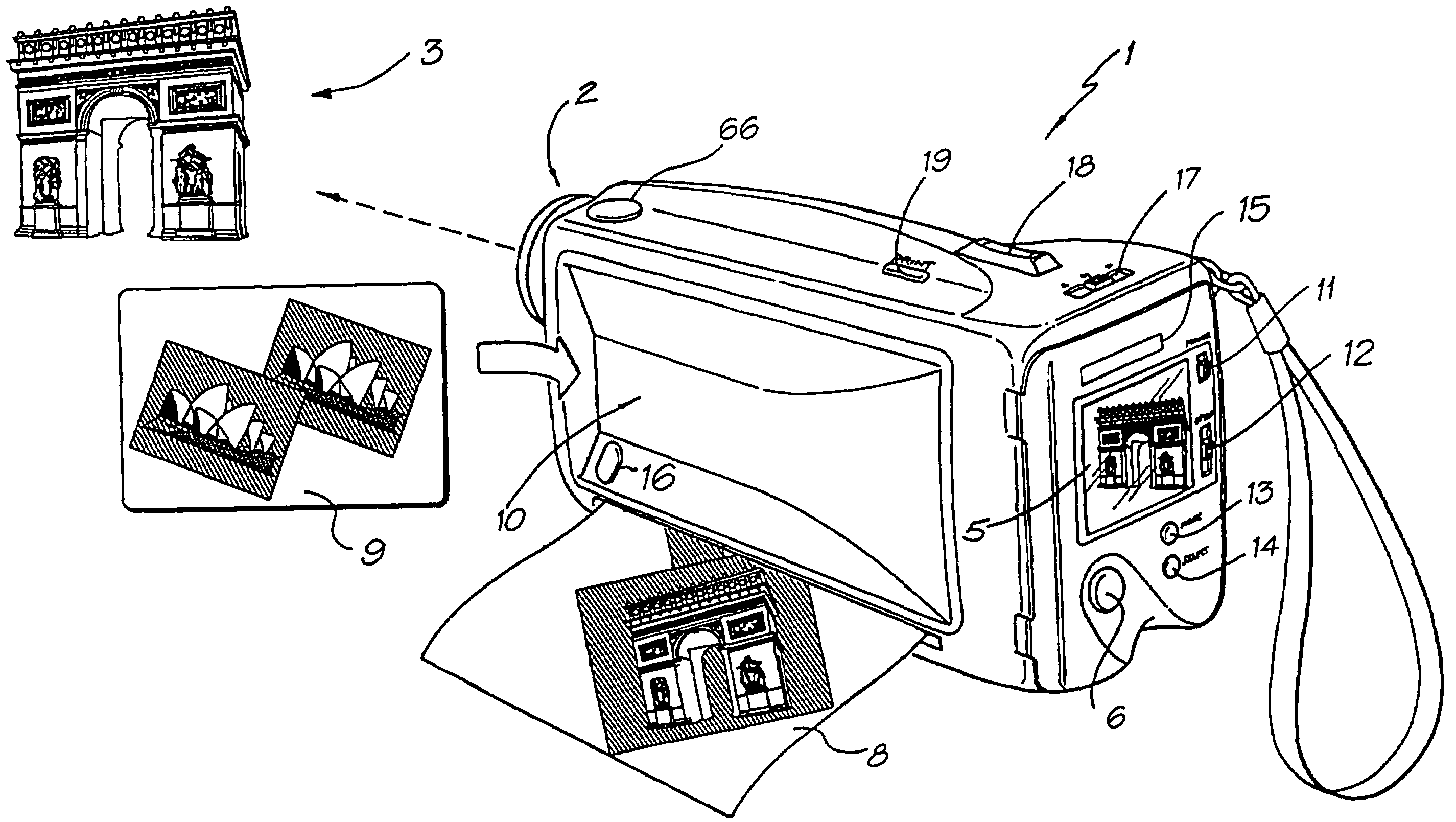

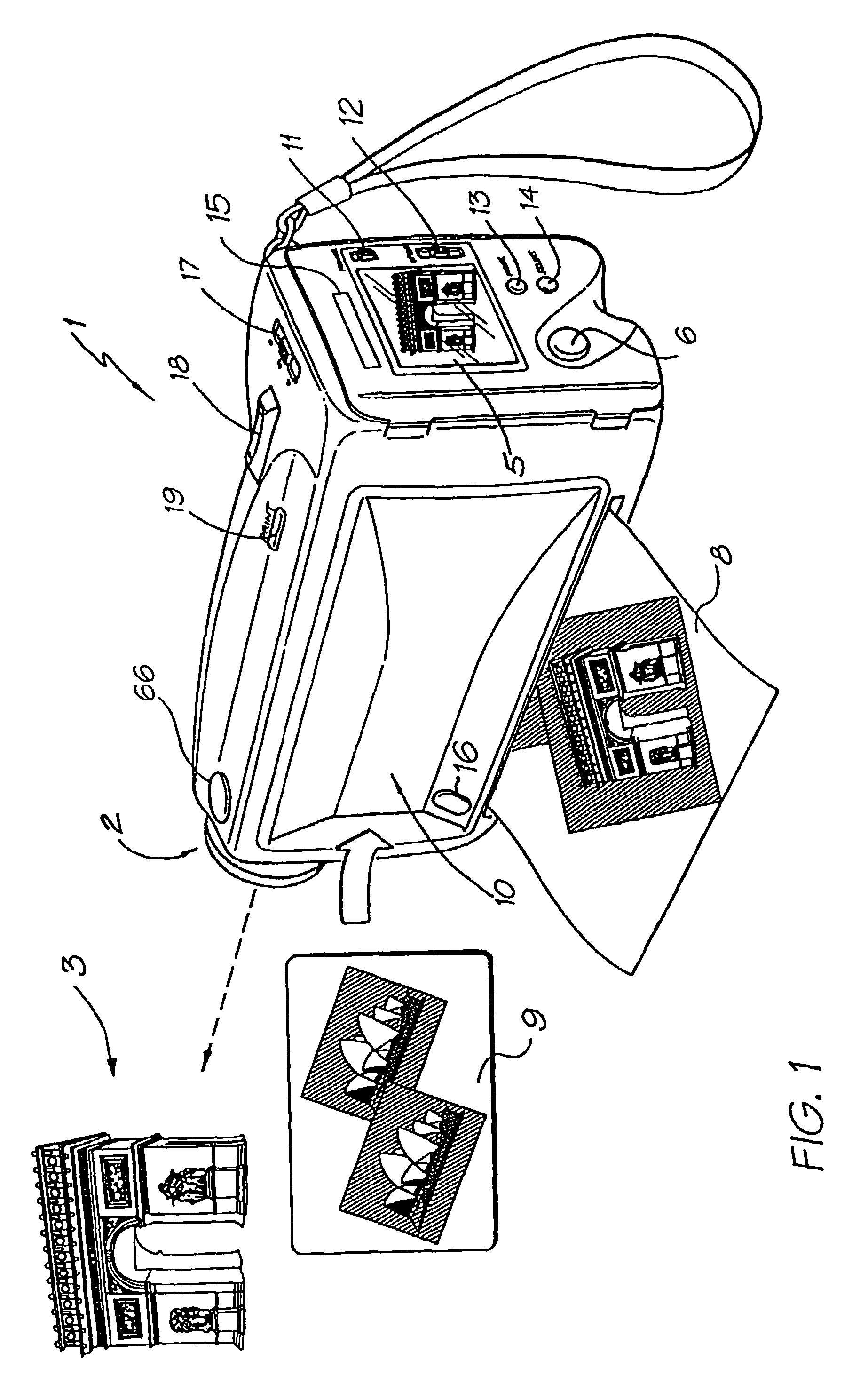

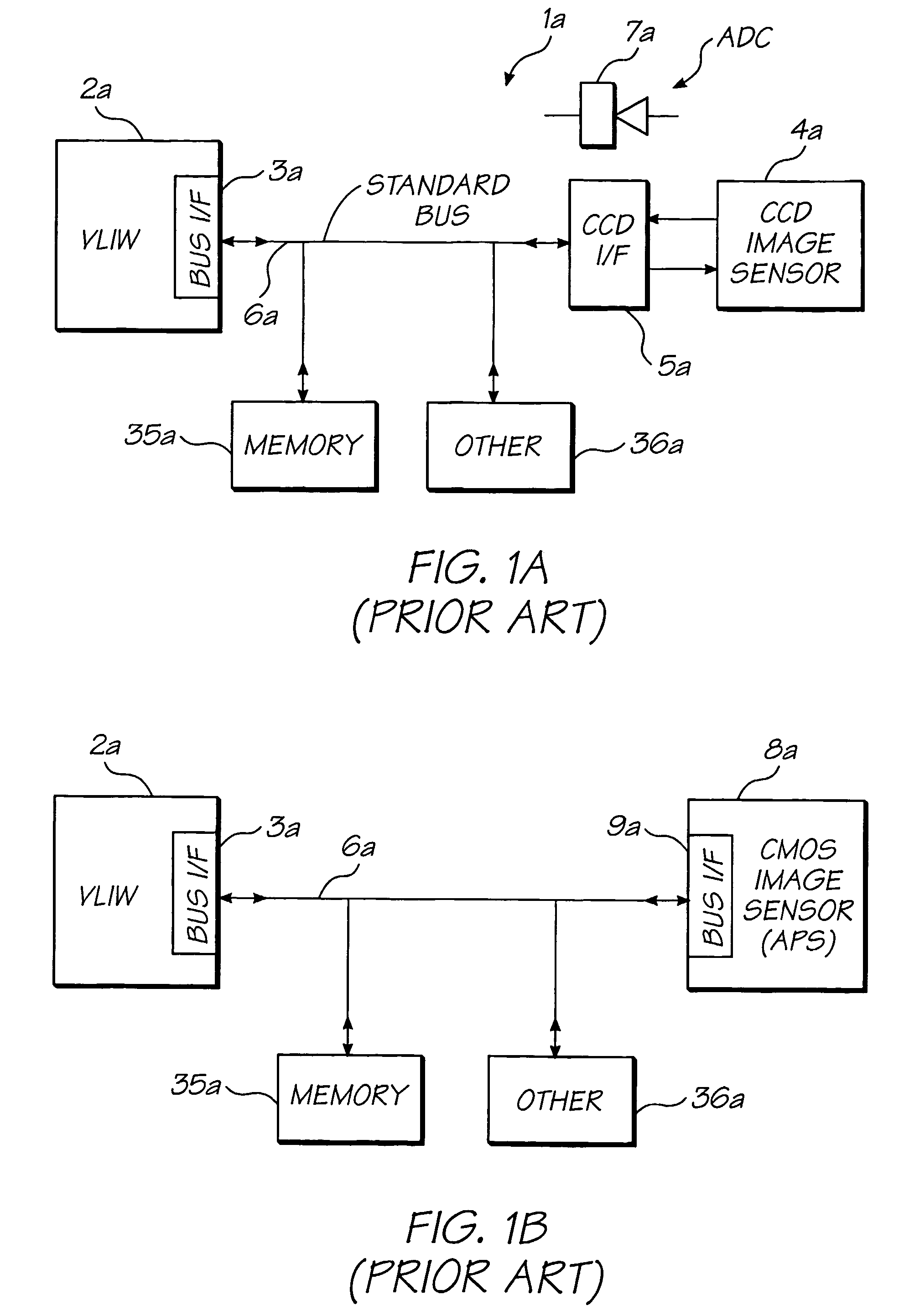

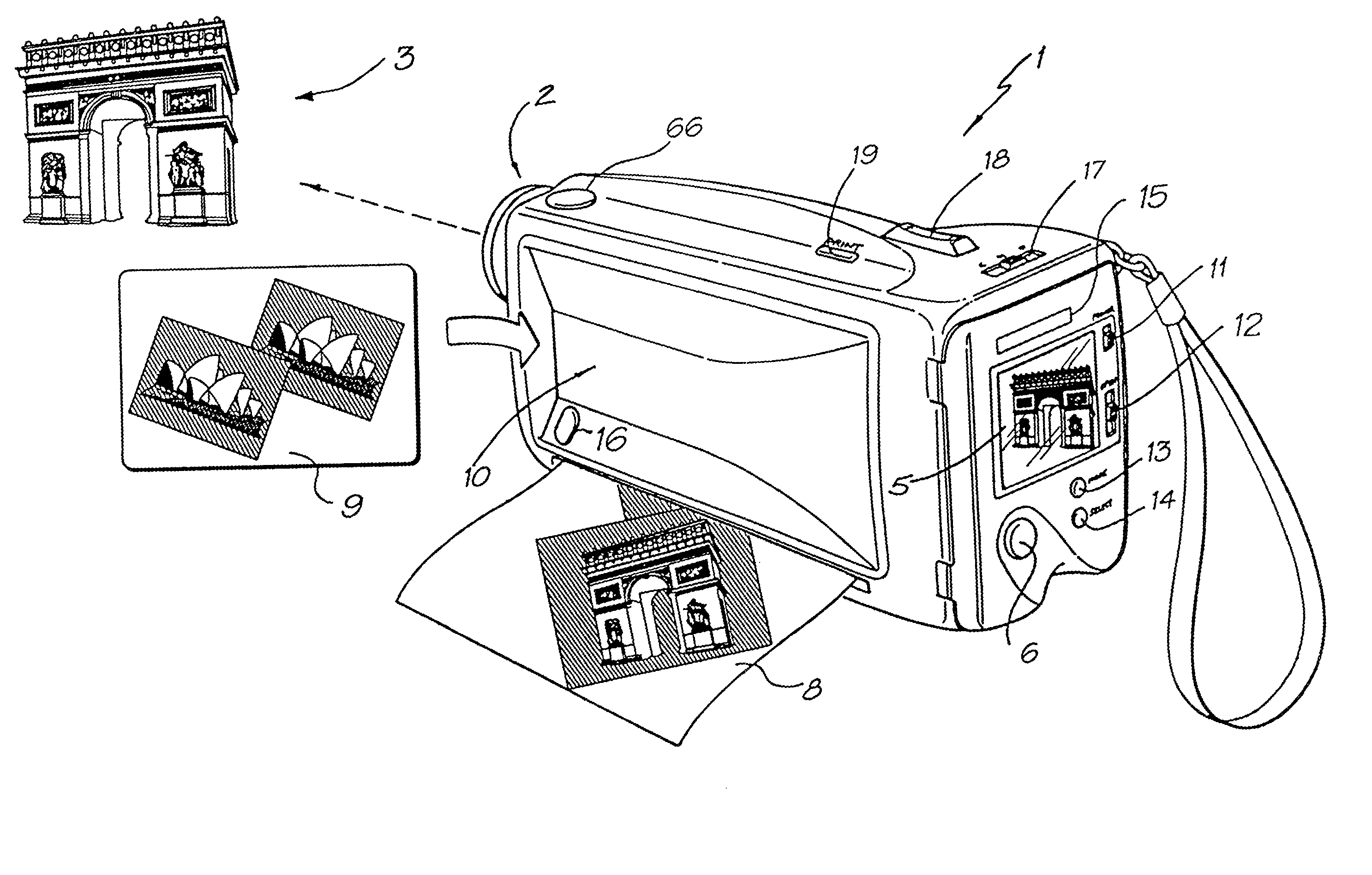

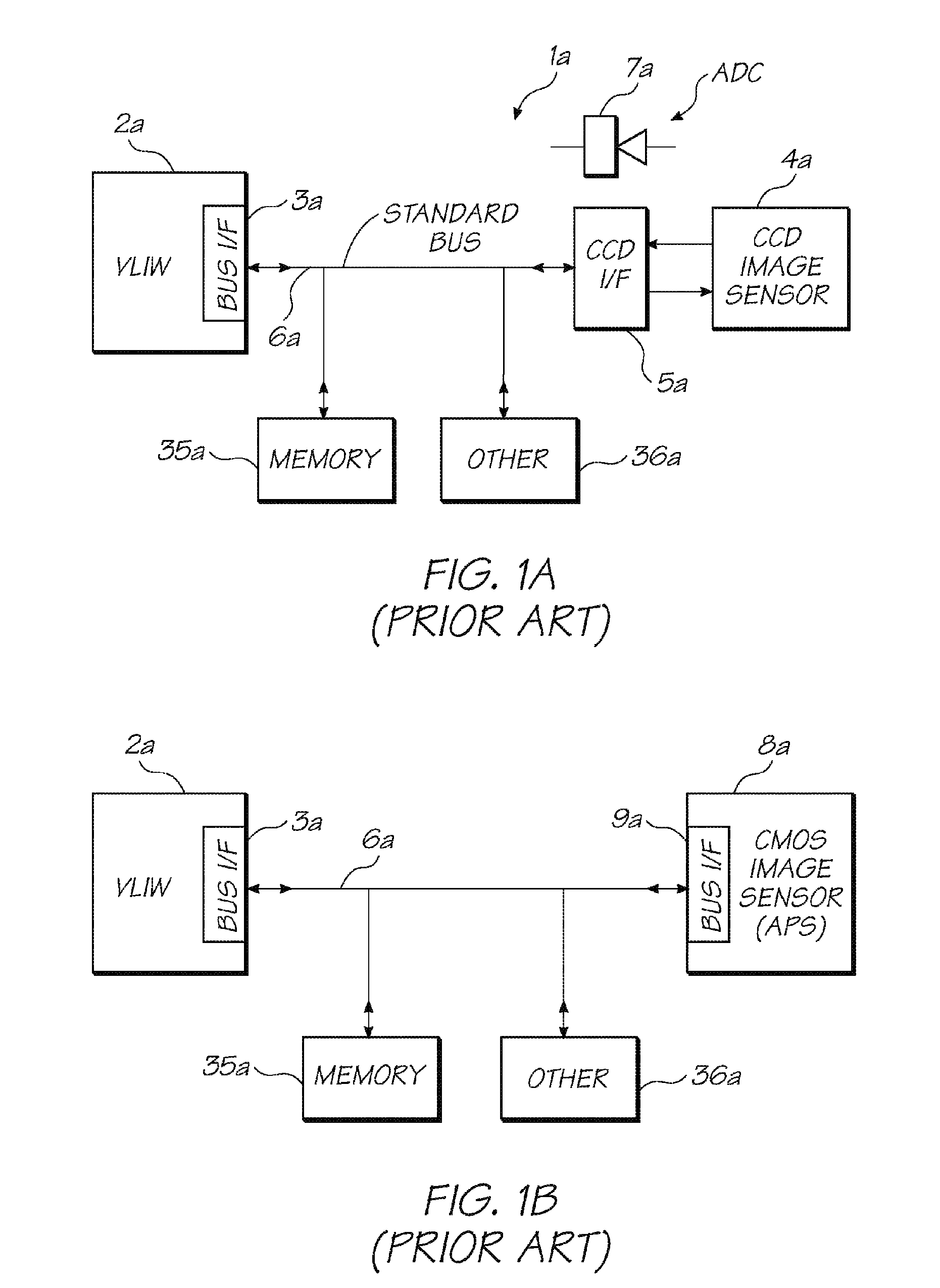

Image sensing apparatus including a microcontroller

InactiveUS7443434B2Digitally marking record carriersTelevision system scanning detailsMicrocontrollerBus interface

An image sensing and processing apparatus includes an image sensor that is capable of generating signals carrying data relating to an image sensed by the image sensor. The apparatus includes a microcontroller. The microcontroller includes a wafer substrate. VLIW processor circuitry is positioned on the wafer substrate. Image sensor interface circuitry is positioned on the wafer substrate and is connected between the VLIW processor circuitry and the image sensor. The image sensor interface circuitry is configured to facilitate communication between the VLIW processor circuitry and the image sensor. Bus interface circuitry that is discrete from the image sensor interface circuitry is connected to the VLIW processor circuitry so that the VLIW processor circuitry can communicate with devices other than the image sensor via a bus.

Owner:GOOGLE LLC

Apparatus, system, and method for bus link width optimization of a graphics system

InactiveUS7426597B1High bandwidthReduce bandwidth requirementsEnergy efficient ICTEnergy efficient computingGraphicsGraphic system

Owner:NVIDIA CORP

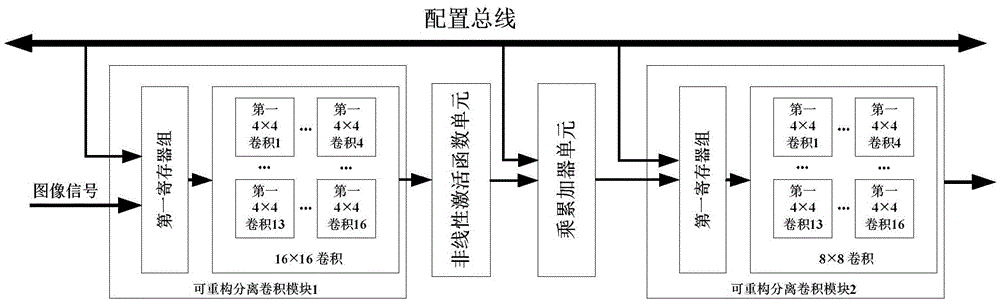

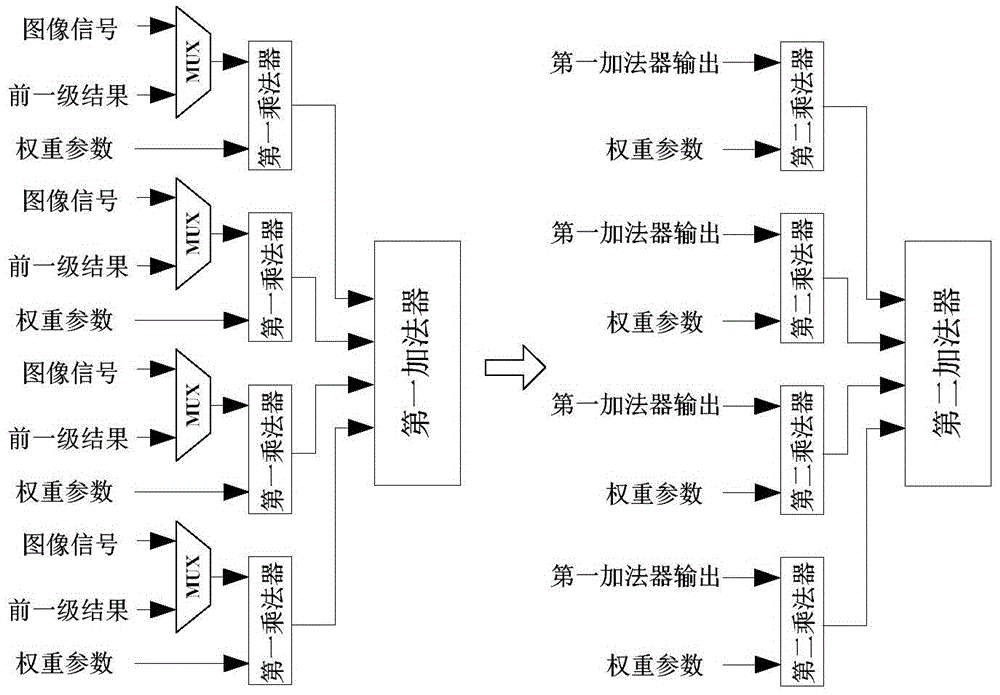

Convolution network arithmetic unit, reconfigurable convolution neural network processor and image de-noising method of reconfigurable convolution neural network processor

ActiveCN105681628AReduce consumptionReduce the number of convolutionsTelevision system detailsColor signal processing circuitsComputer architectureResource consumption

The invention discloses a convolution network arithmetic unit, a reconfigurable convolution neural network processor and an image de-noising method of the reconfigurable convolution neural network processor. The reconfigurable convolution neural network processor comprises a bus interface, a preprocessing unit, a reconfigurable hardware controller, an SRAM, an SRAM control module, an input caching module, an output caching module, a memory, a data memory controller and the convolution network arithmetic unit. The processor is featured by few resources and rapid speed and can be applicable to common convolution neural network architecture. According to the unit, the processor and the method provided by the invention, convolution neural networks can be realized; the processing speed is rapid; transplanting is liable to be carried out; the resource consumption is little; an image or a video polluted by raindrops and dusts can be recovered; and raindrop and dust removing operations can be taken as preprocessing operations for providing help in follow-up image identification or classification.

Owner:XI AN JIAOTONG UNIV

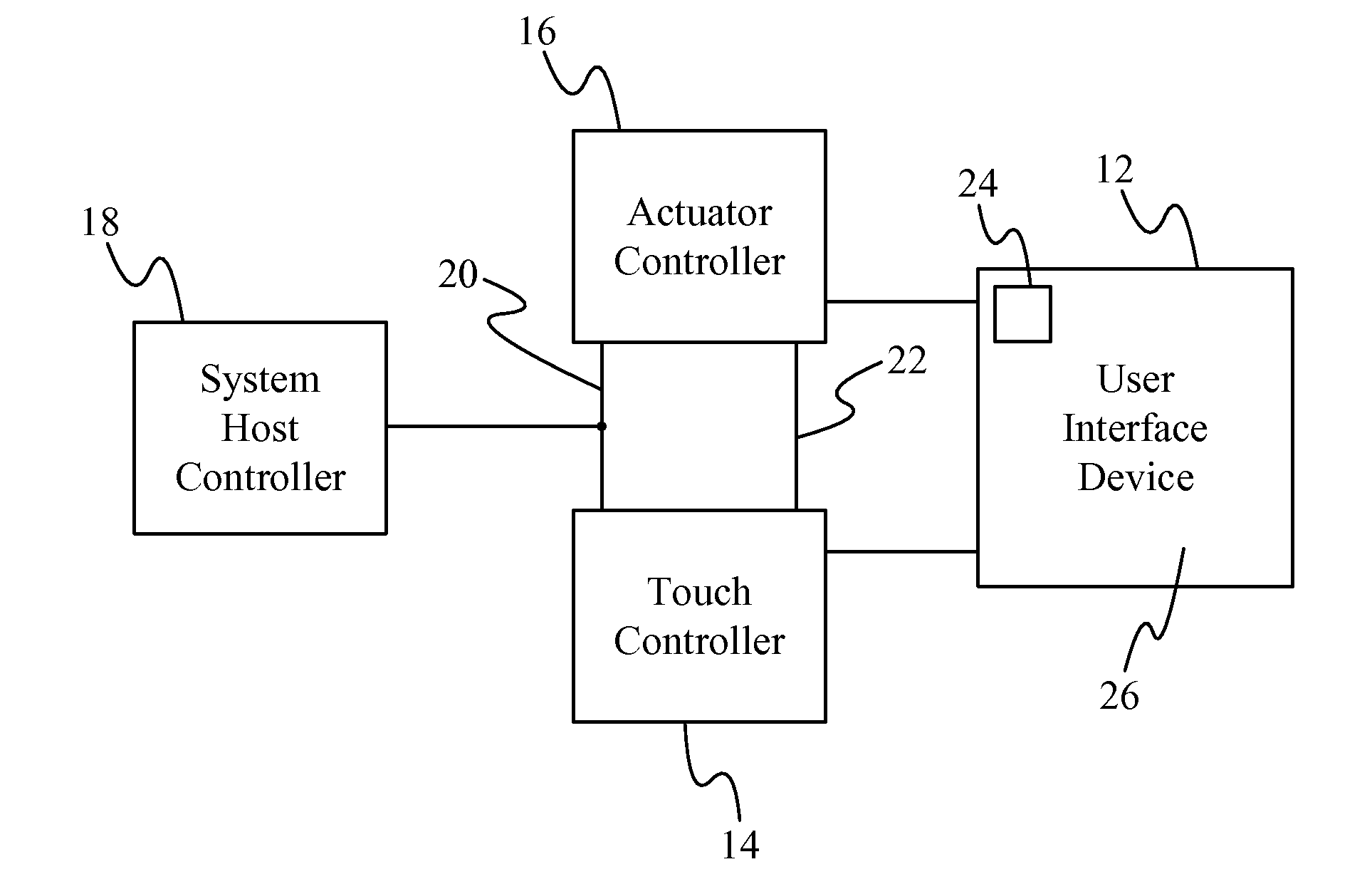

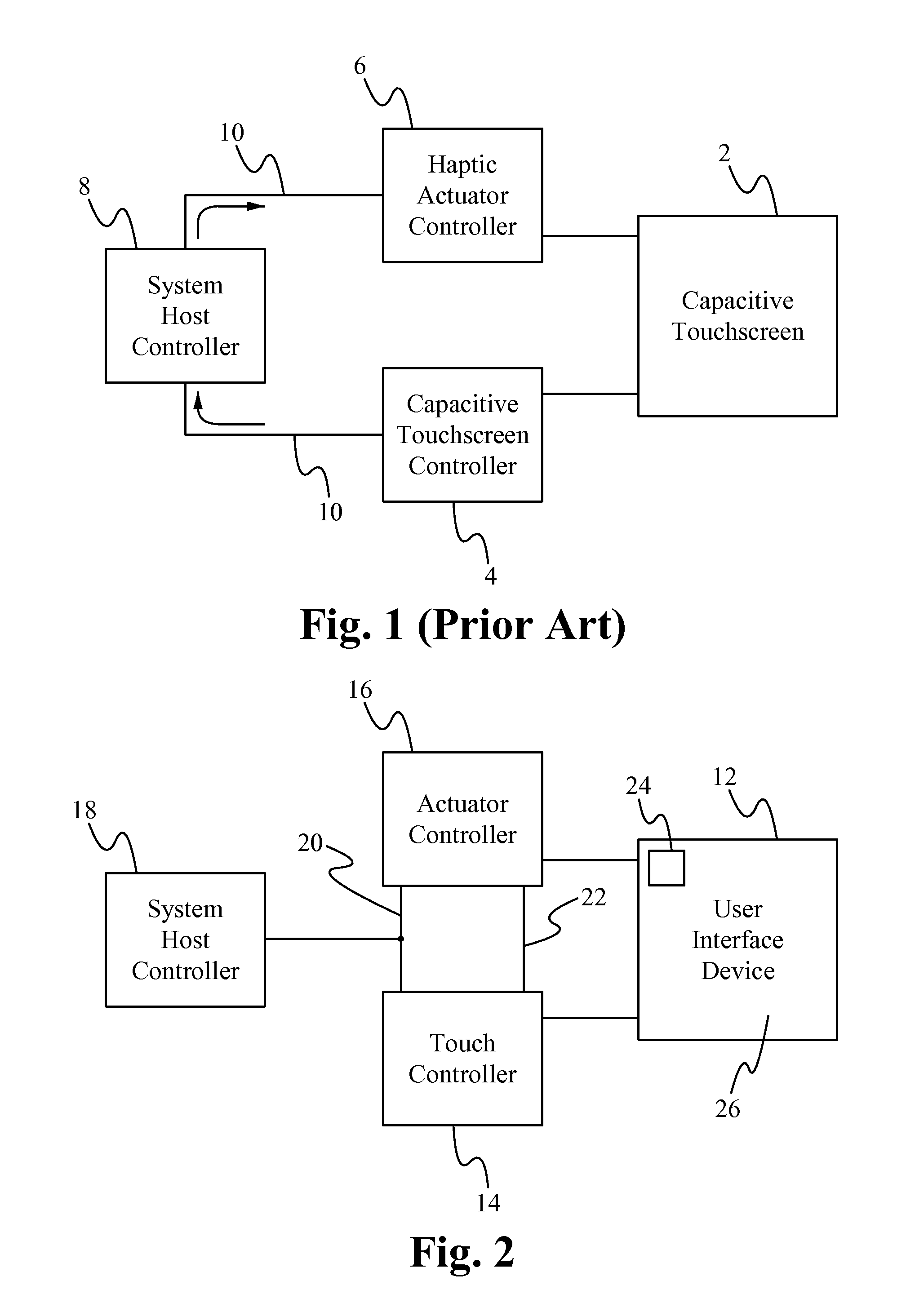

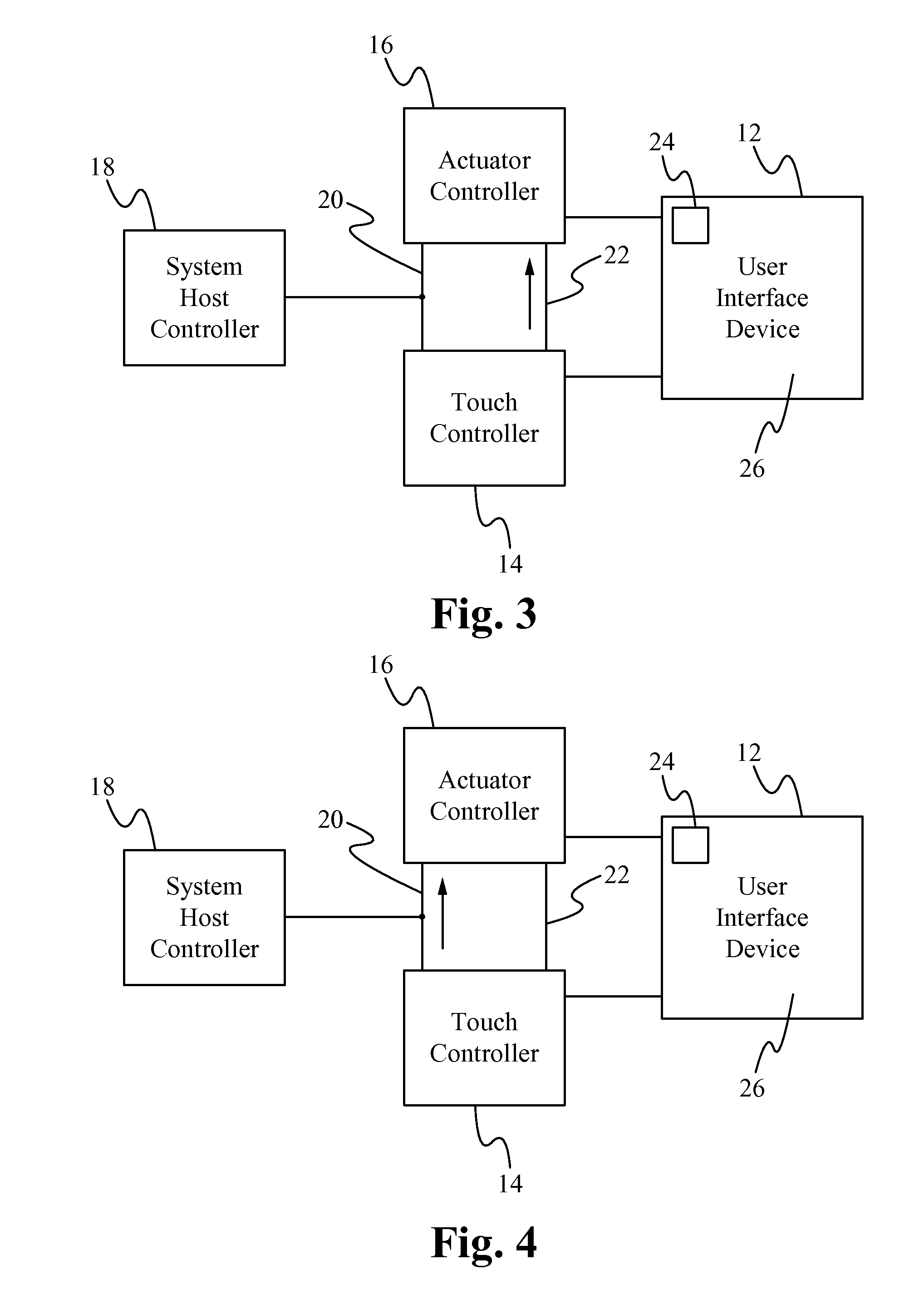

System integration of tactile feedback and touchscreen controller for near-zero latency haptics playout

Owner:MAXIM INTEGRATED PROD INC

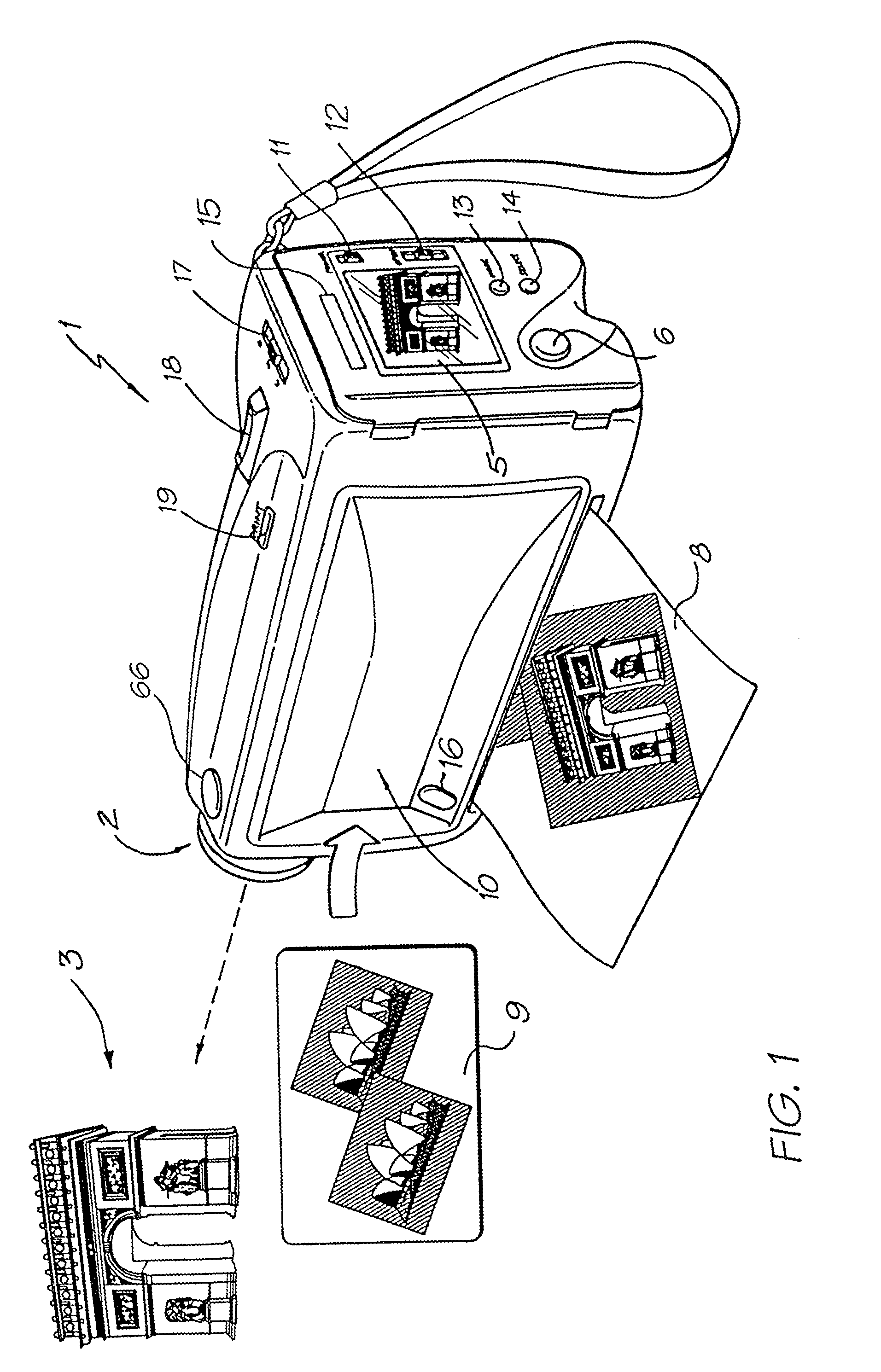

VLIW image processor

A microcontroller for an image sensing and processing apparatus is provided. The microcontroller has VLIW processor circuitry, image sensor interface circuitry connected between the VLIW processor circuitry and the image sensor, bus interface circuitry connected between the VLIW processor circuitry and a bus connectable with devices other than the image sensor, and buffer memory and queuing circuitry intermediate the image sensor and bus interface circuitry and the VLIW processor to control delivery of information to the VLIW processor.

Owner:GOOGLE LLC

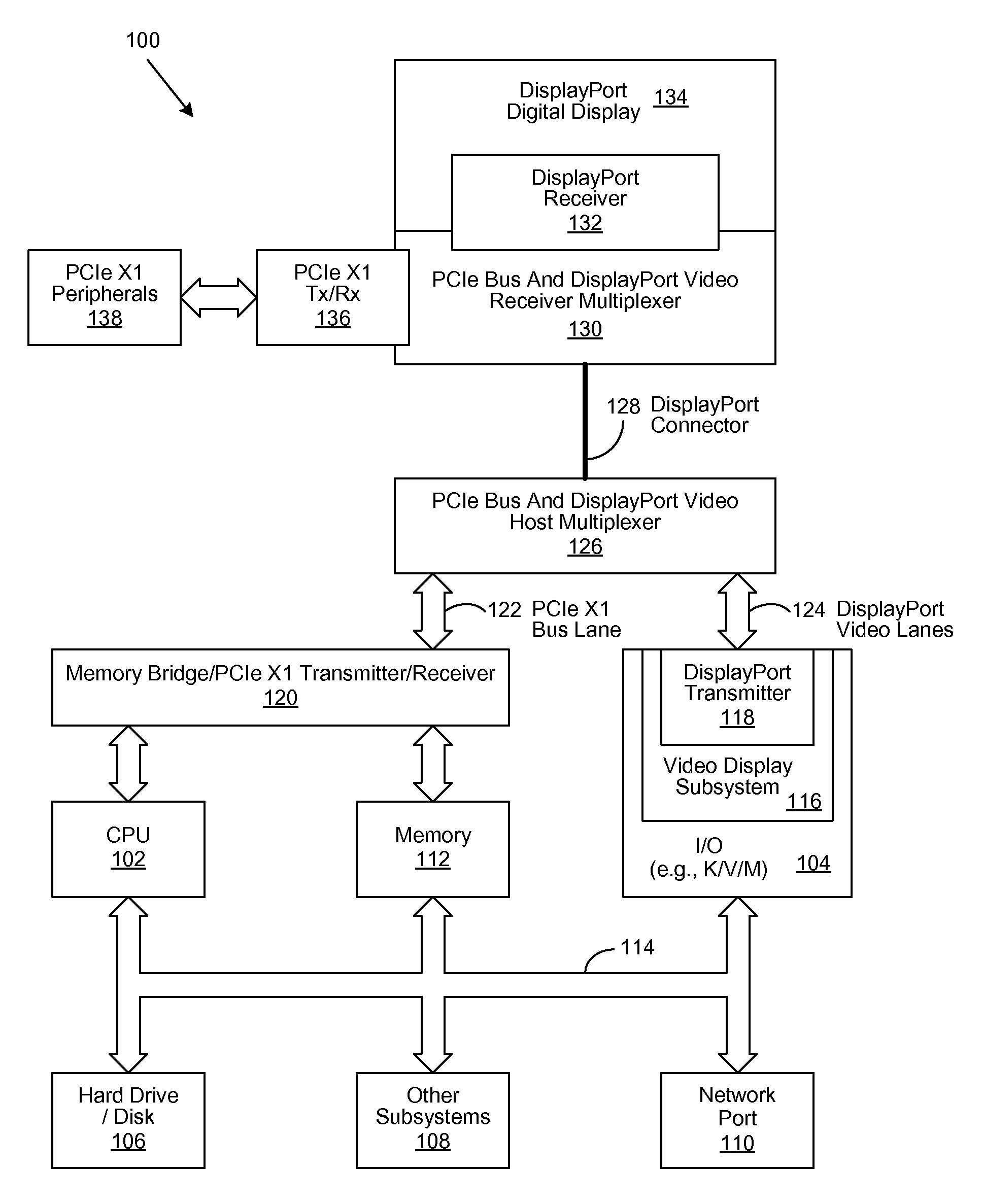

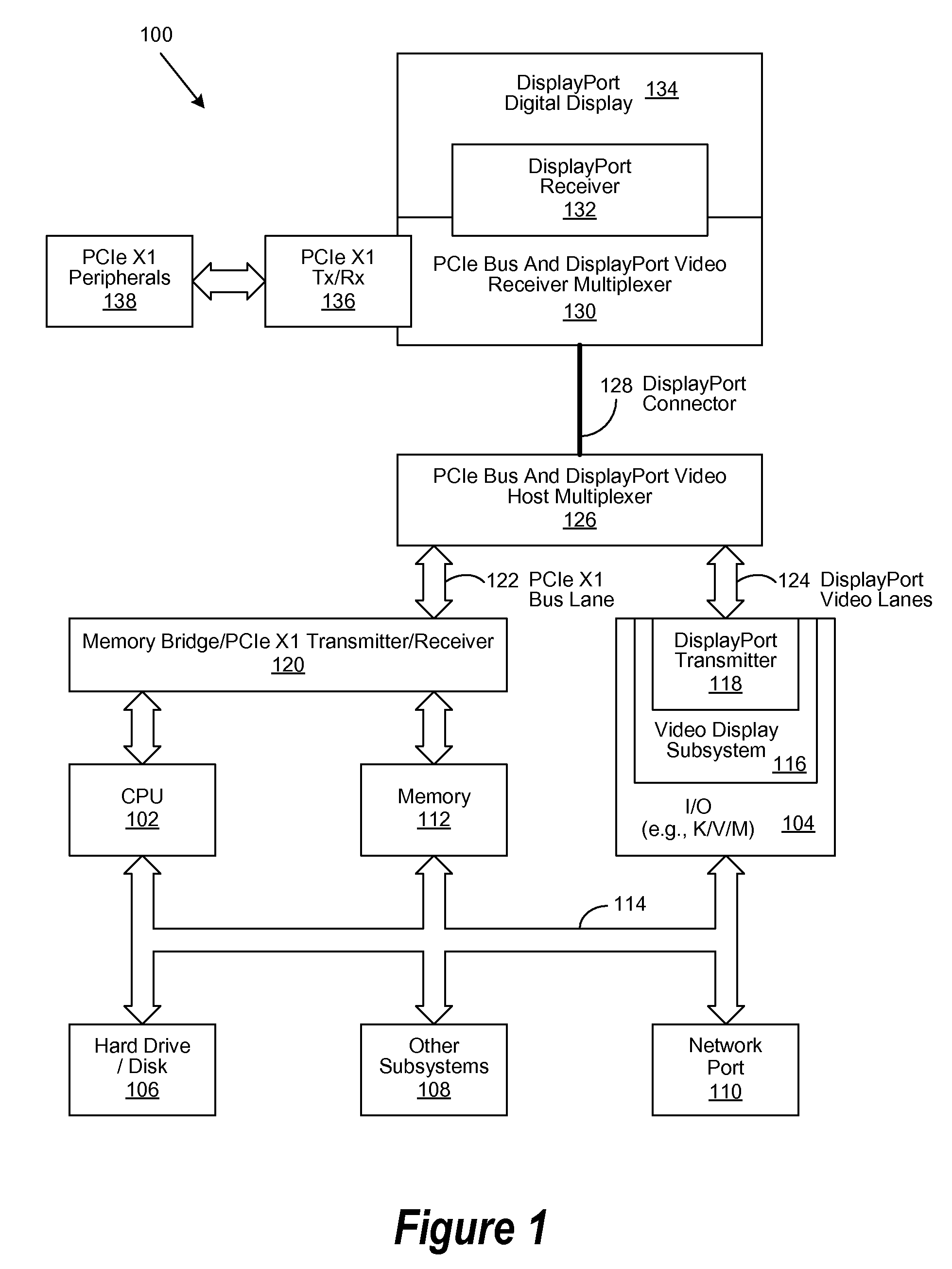

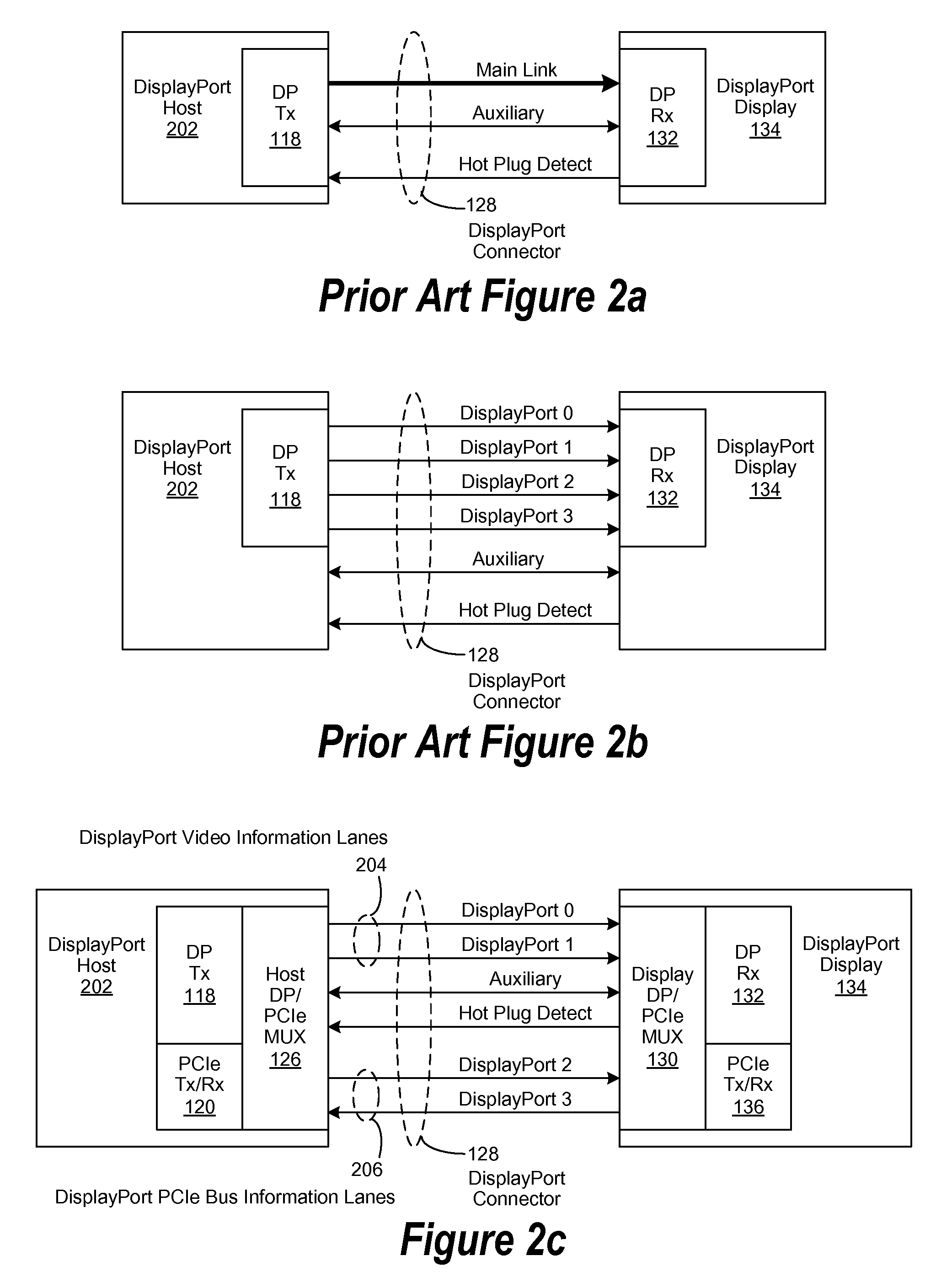

System and method for providing PCIe over displayport

An apparatus and method is disclosed for providing an extensible information handling system (IHS) bus implemented on predetermined channels of a digital video interface. IHS video signal information is multiplexed with IHS bus information by a host multiplexer for transmission across a digital video connector. The multiplexed IHS video signal and IHS bus information is received by a display multiplexer, where it is demultiplexed. Demultiplexed IHS video signal information is received by a video interface receiver, where it is used to generate an image on a digital display. Demultiplexed IHS bus information is received by a host bus interface transmitter / receiver, where it is used to support peripheral devices attached to the digital display.

Owner:DELL PROD LP

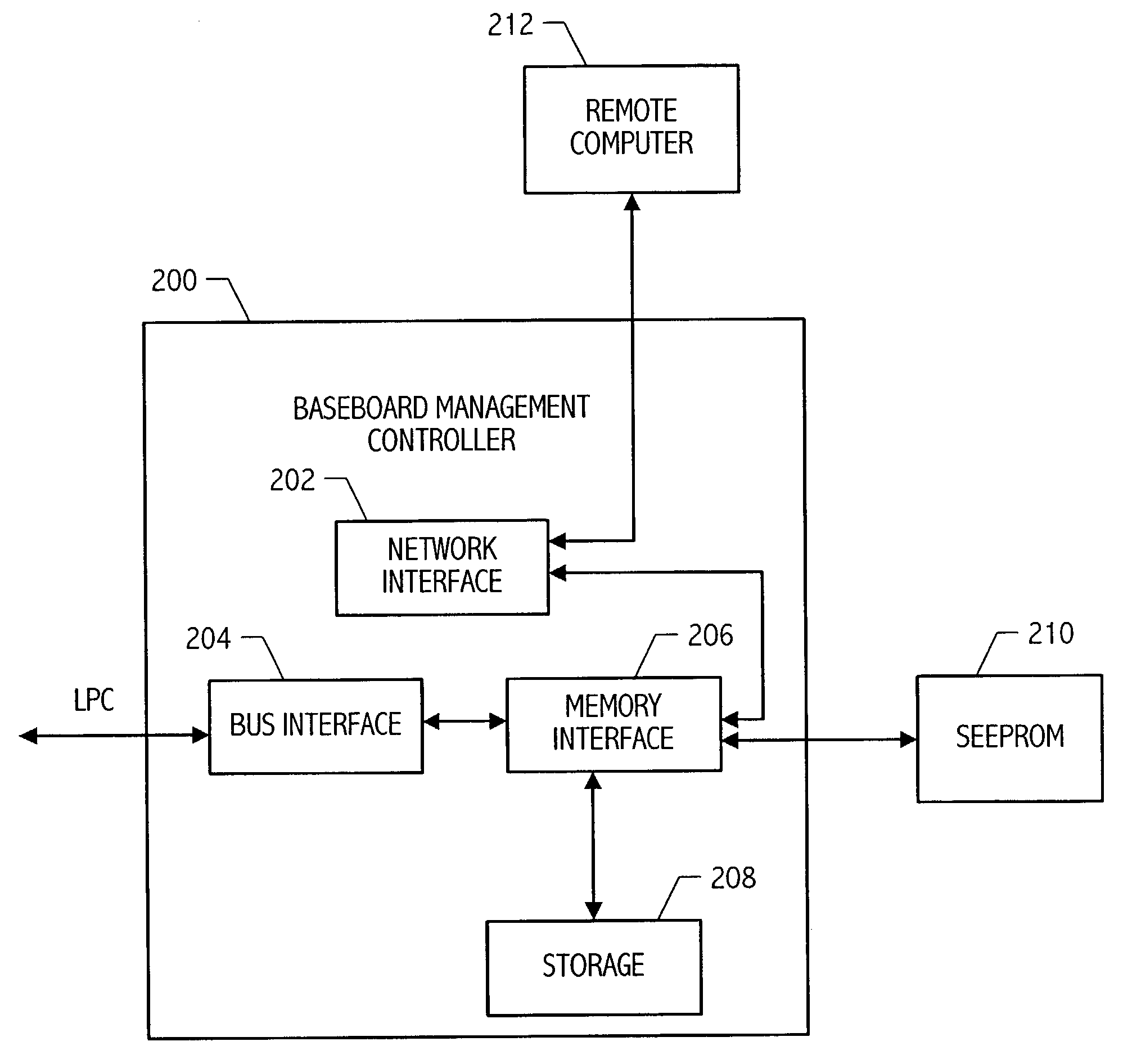

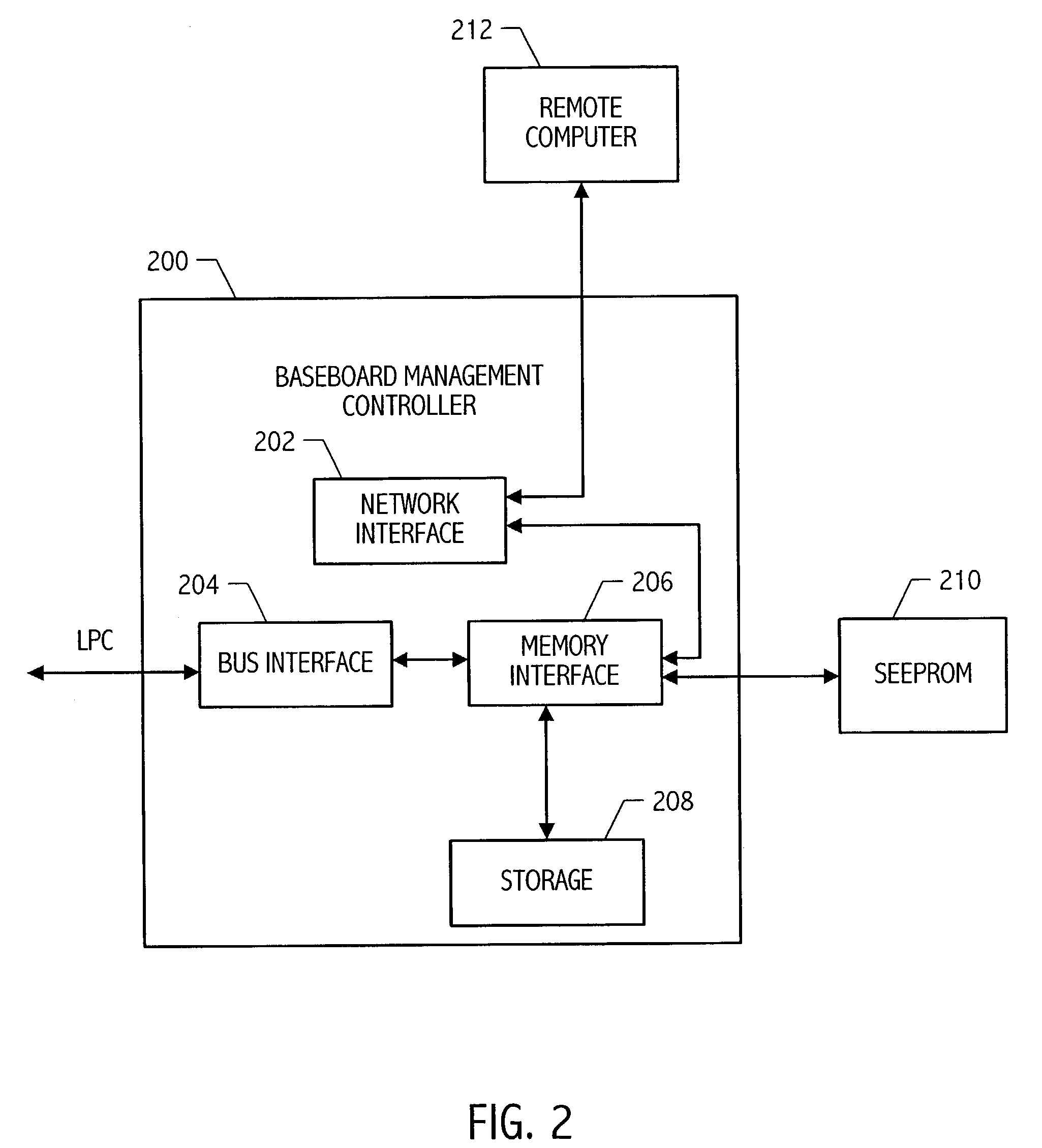

BMC-hosted boot ROM interface

A baseboard management controller (BMC) integrated circuit hosts a BIOS ROM interface. The BMC includes a bus interface responsive to an access to an address range associated with host operations, e.g., an address range associated with BIOS. The BMC includes an interface coupled to communicate with a remote computer for receiving BIOS updates and / or a BIOS patches from the remote computer. Multiple computers may each include a BMC-hosted BIOS ROM interface and may be coupled to a remote computer for communicating BIOS information between the BMCs and the remote computer.

Owner:GLOBALFOUNDRIES US INC

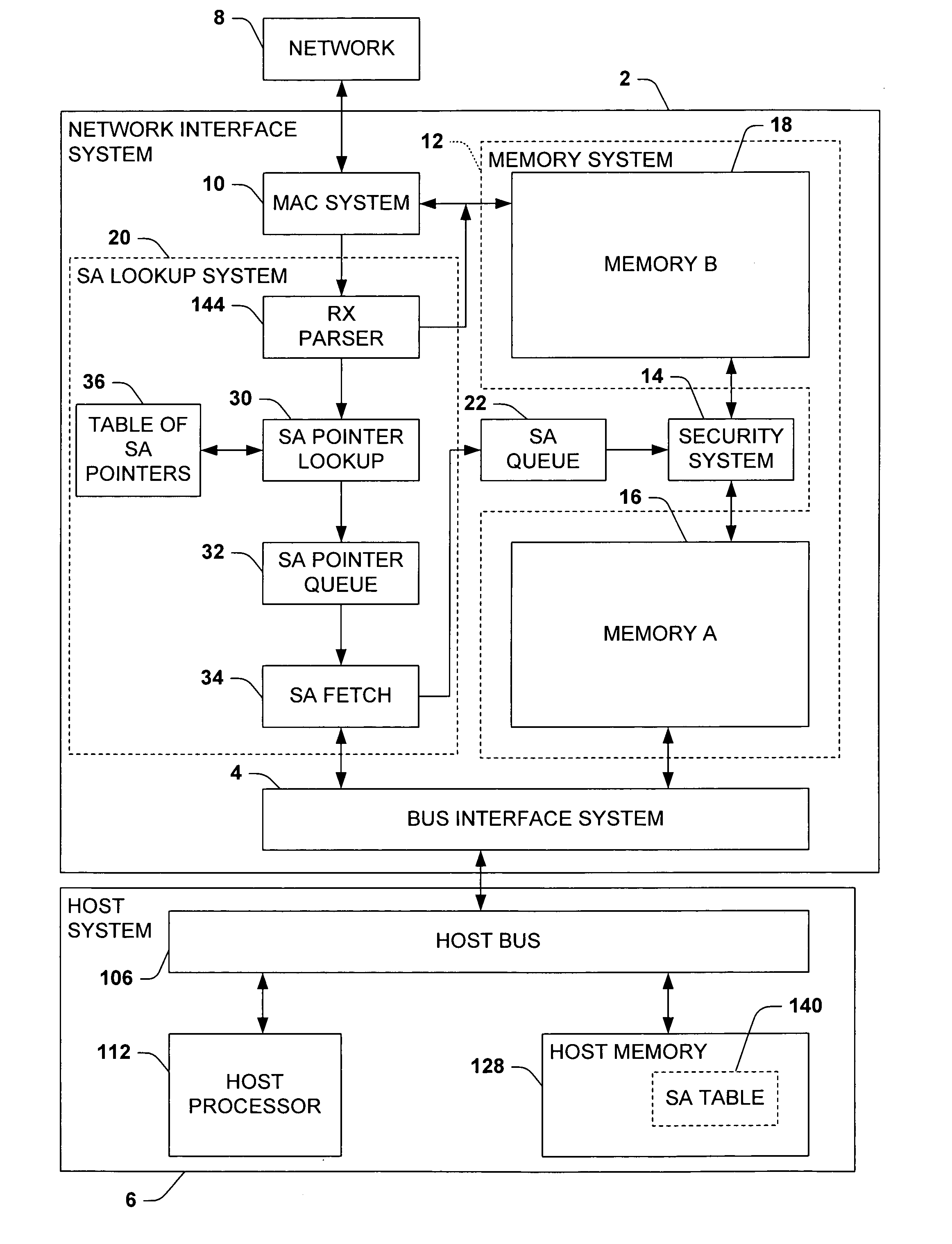

Network interface with security association data prefetch for high speed offloaded security processing

ActiveUS20050256975A1Facilitates high speed security processingTo overcome the large delayMultiple digital computer combinationsData switching networksExternal storageSecurity association

One aspect of the invention relates to a network interface system for interfacing a host system with a network. The network interface system includes a bus interface system, a media access control system, and a security system. The security system selectively perform security processing on data incoming from the network based on security associations stored in a memory external to the network interface system, typically a host system memory. The security association for any given frame, when available, is fetched from the external memory after the frame begins to arrive in the network interface system based in part on information contained in the frame. Preferably, the fetch begins before the frame is fully received and the security association is queued whereby security processing can begin without having to wait for the security association to be fetched.

Owner:MEDIATEK INC

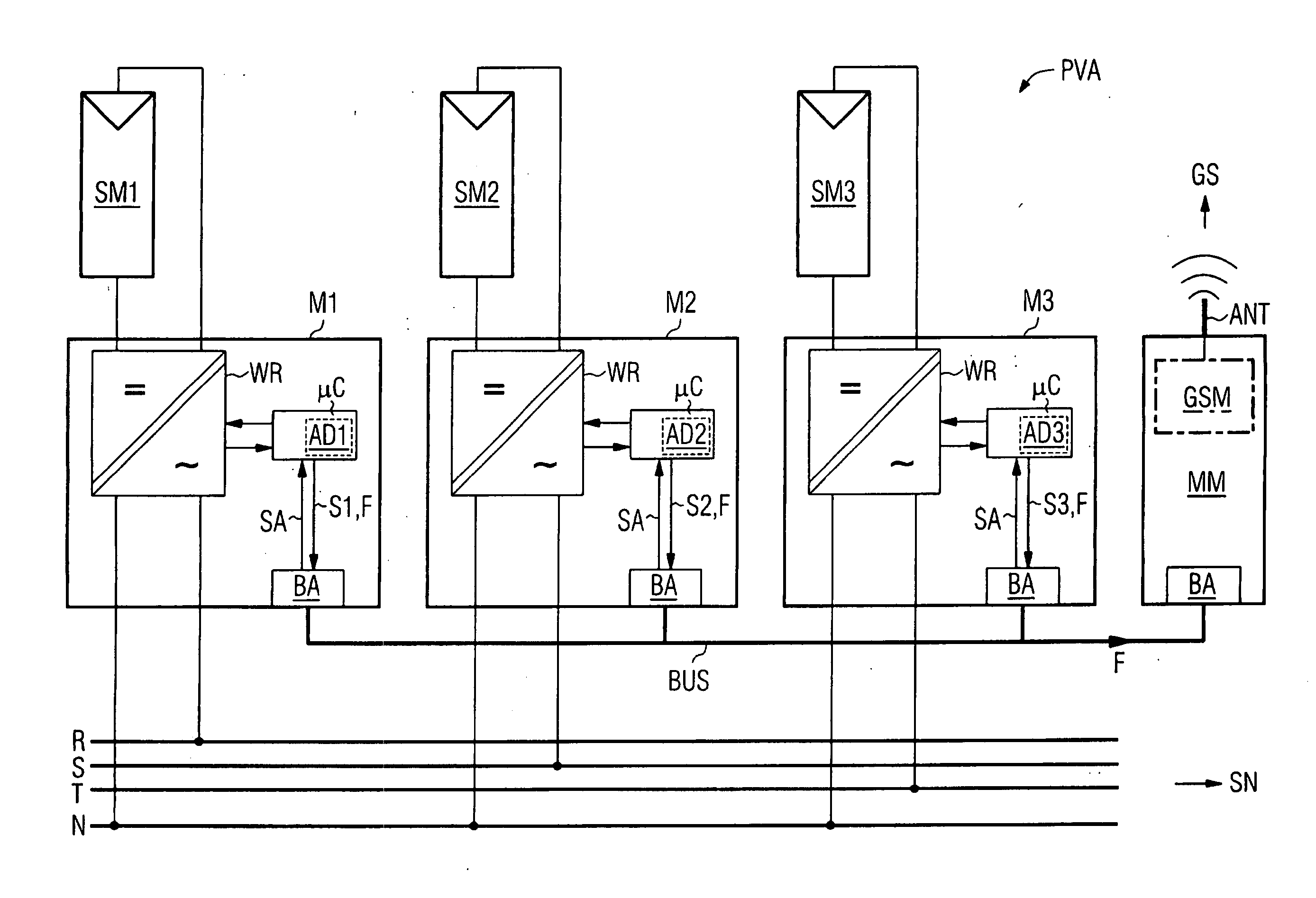

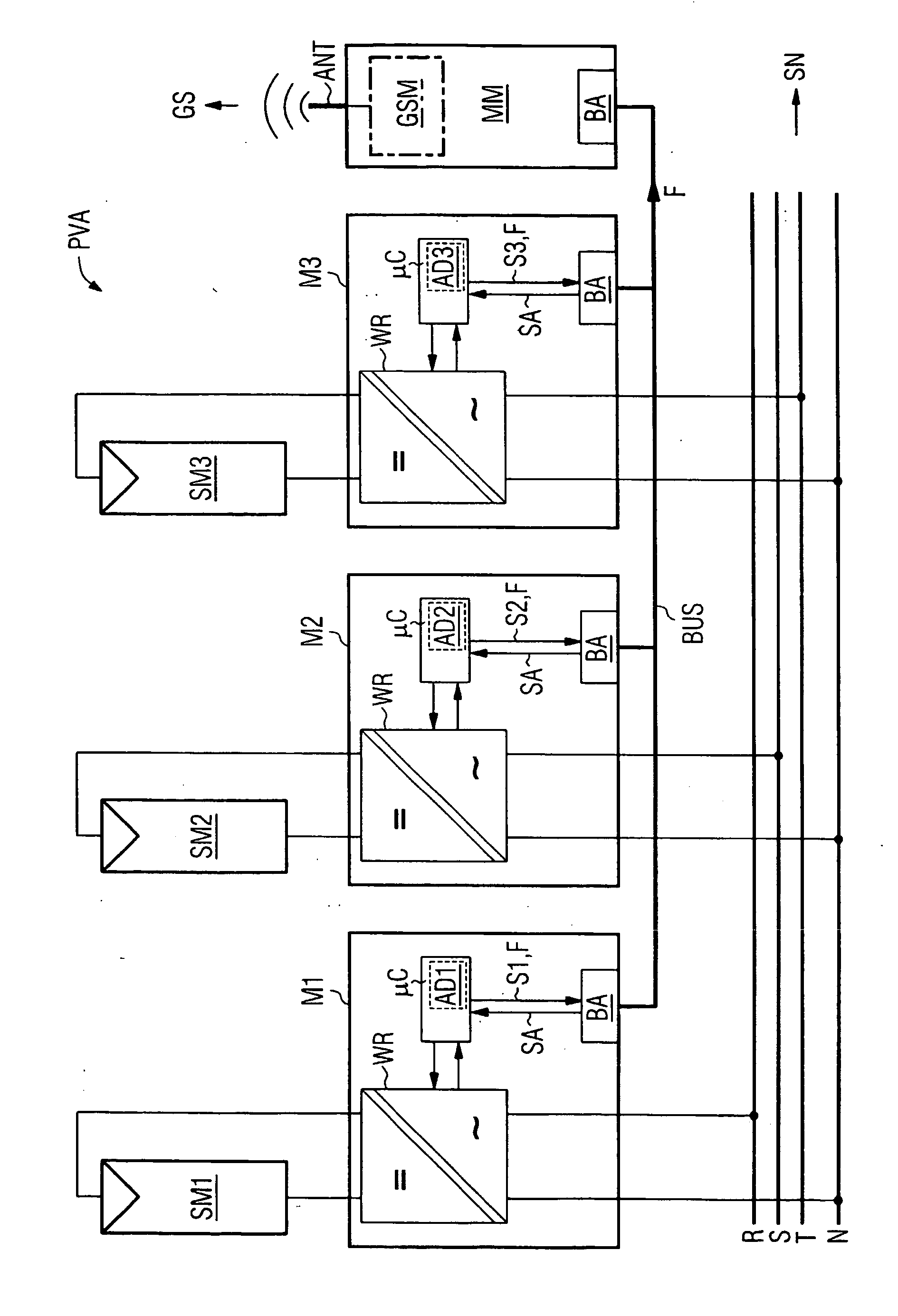

Solar Inverter and Photovoltaic Installation Comprising Several Solar Inverters

InactiveUS20070252716A1Compact implementationBatteries circuit arrangementsSingle network parallel feeding arrangementsElectric power systemComputer module

In one aspect, a solar inverter which can be connected to at least one photovoltaic generator at the input end and to a power system at the output end is provided. The solar inverter includes an inverter module, an electronic control unit at least for diagnosing an inverter module, and a bus interface for technically connecting the electronic control unit to a communication bus. The electronic control unit cyclically outputs a piece of status information of the solar inverter on the communication bus, and outputs an error message on the communication bus, cyclically reads status information of other solar inverters that are connected to the communication bus, and outputs an error message on the communication bus in case at least one expected additional piece of status information fails to be output. Whereby, the need for a separate monitoring unit is eliminated.

Owner:SIEMENS AG

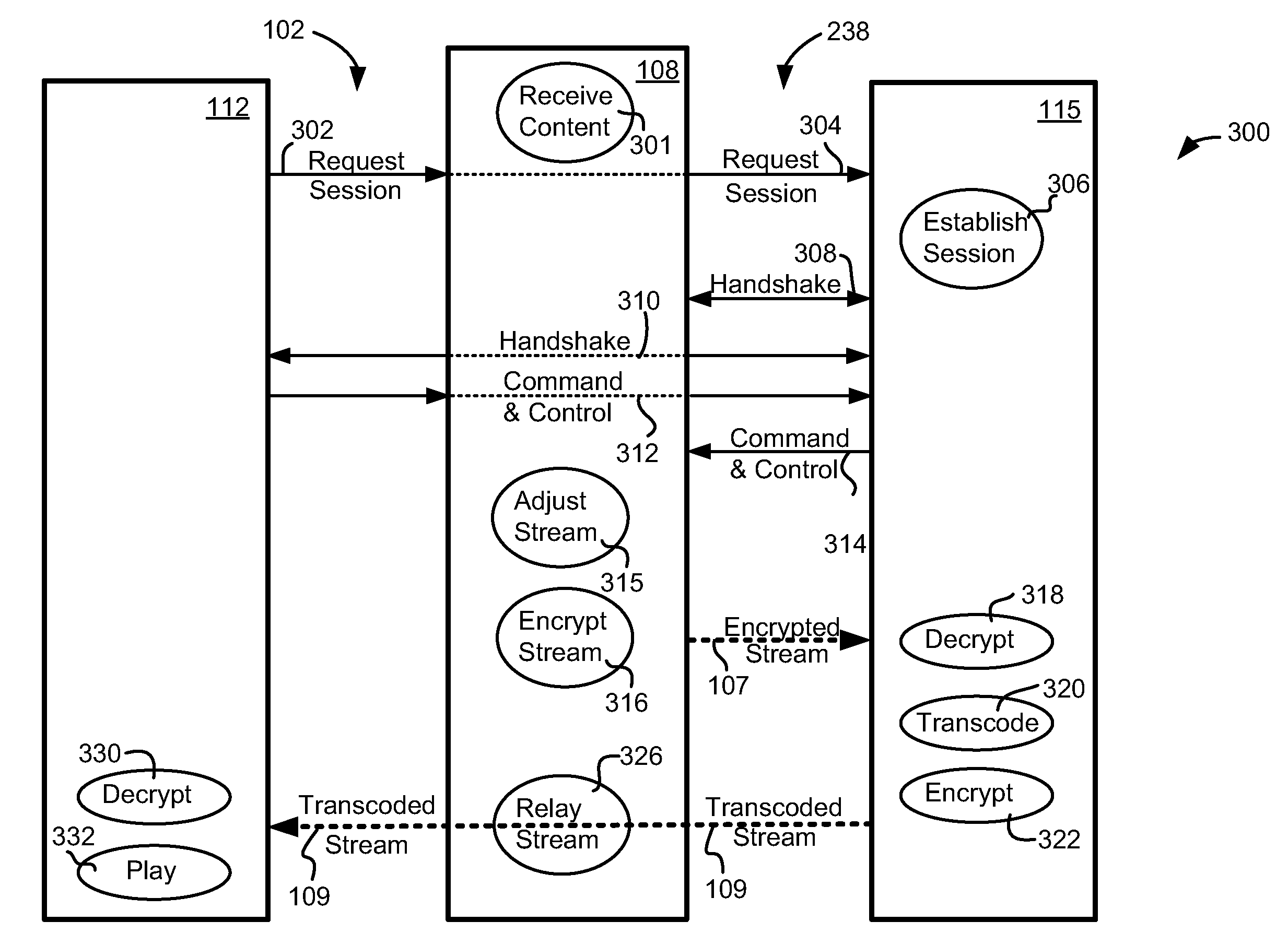

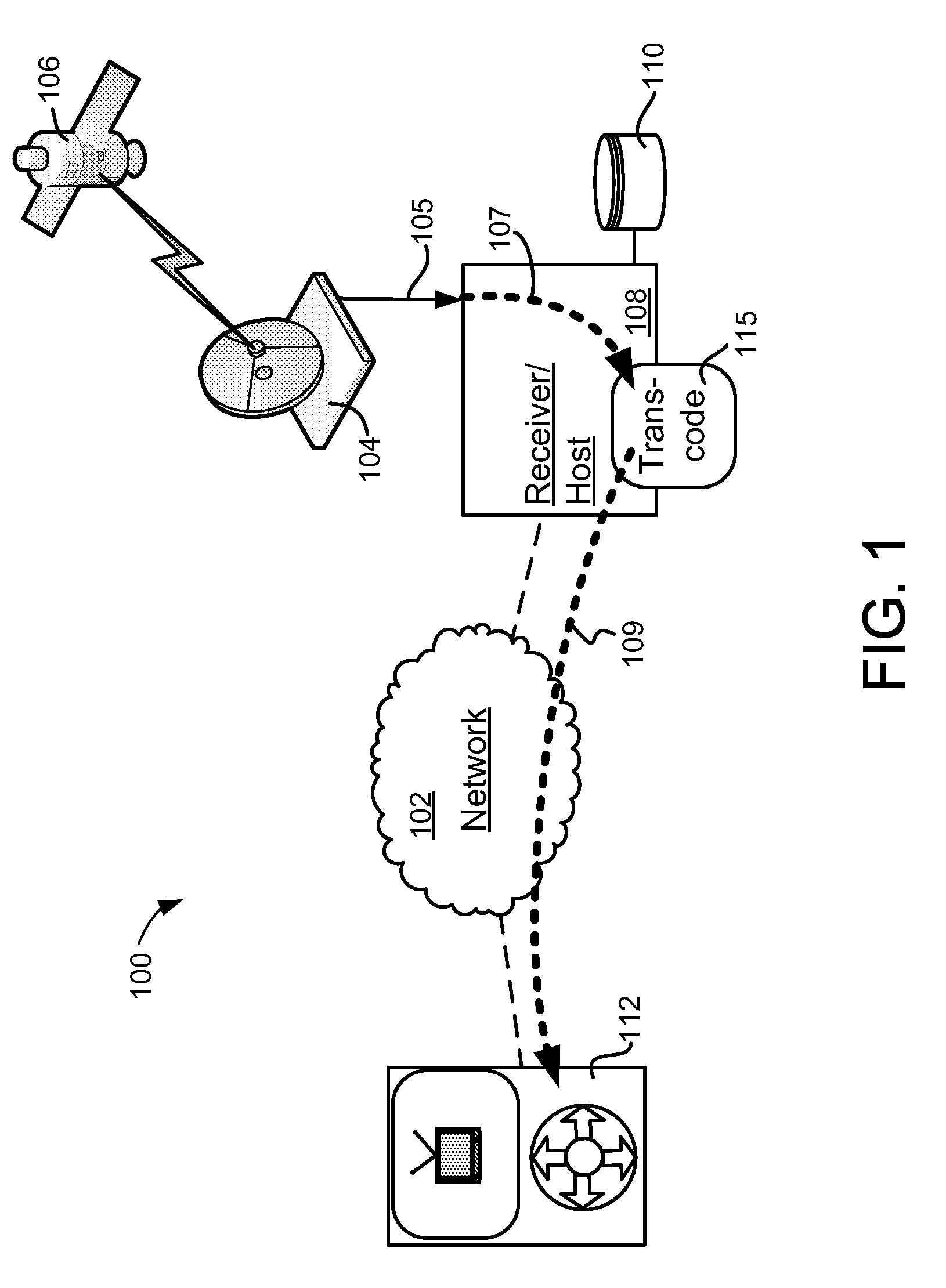

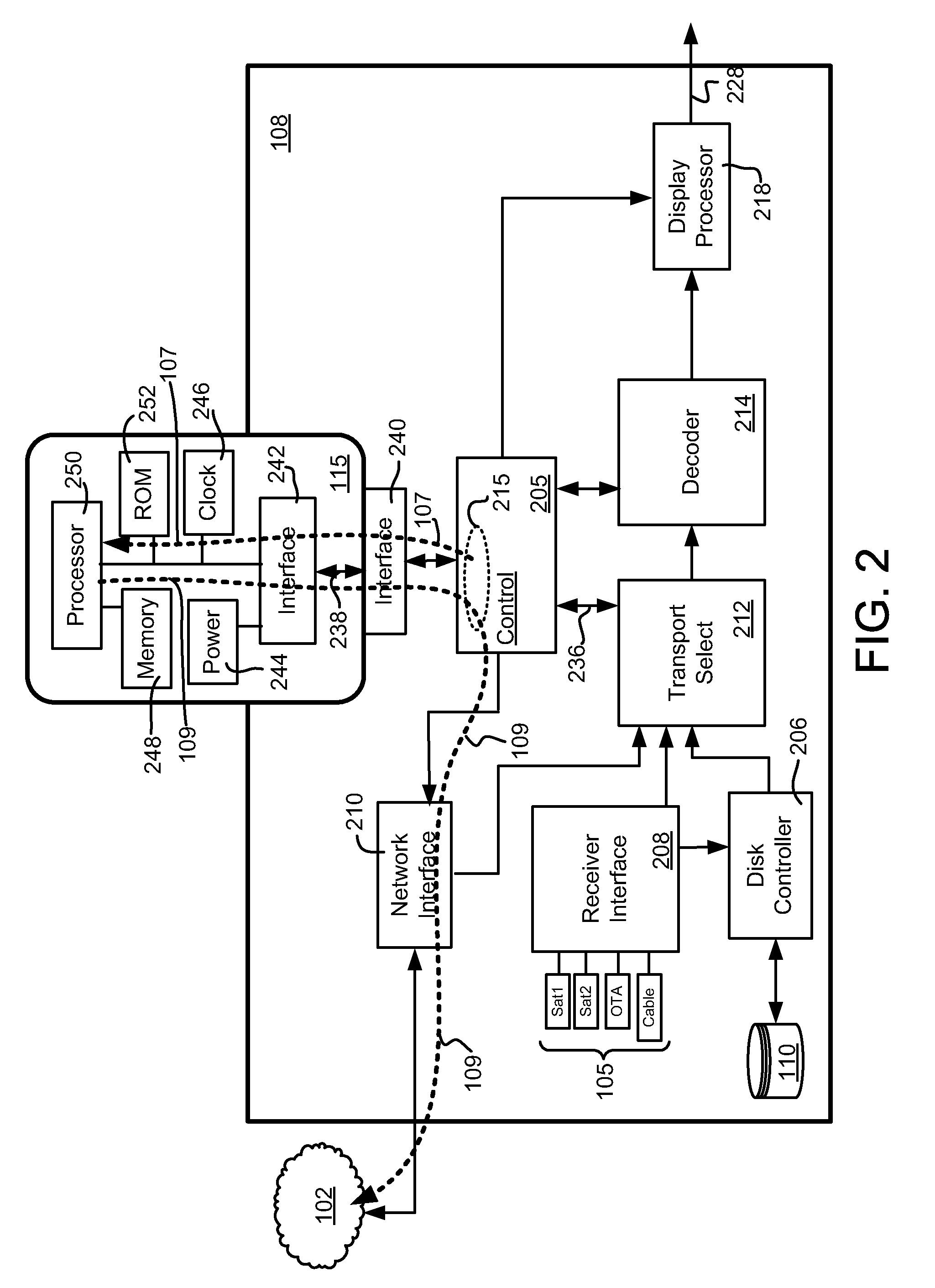

Systems and methods for transcoding and place shifting media content

ActiveUS20110055864A1Enhanced transcodingImprove abilitiesMultiple keys/algorithms usageData stream serial/continuous modificationDigital videoVideo player

A set-top box (STB), digital video recorder (DVR), video player or other host device receives and interacts with a transcode module to provide enhanced transcoding capabilities that may be useful in placeshifting or other applications. The transcode module includes a host interface that couples to and communicates with the host device. The transcode module also includes a processor that receives an encrypted media stream from the host device via the bus interface, decrypts the encrypted media stream, transcodes the encrypted media stream to a different format, re-encrypts the transcoded stream, and provides the re-encrypted media stream to the host device via the host interface. The transcoded media content may be placeshifted to a remote player, stored at the host, or used for any other purpose.

Owner:SLING MEDIA LLC

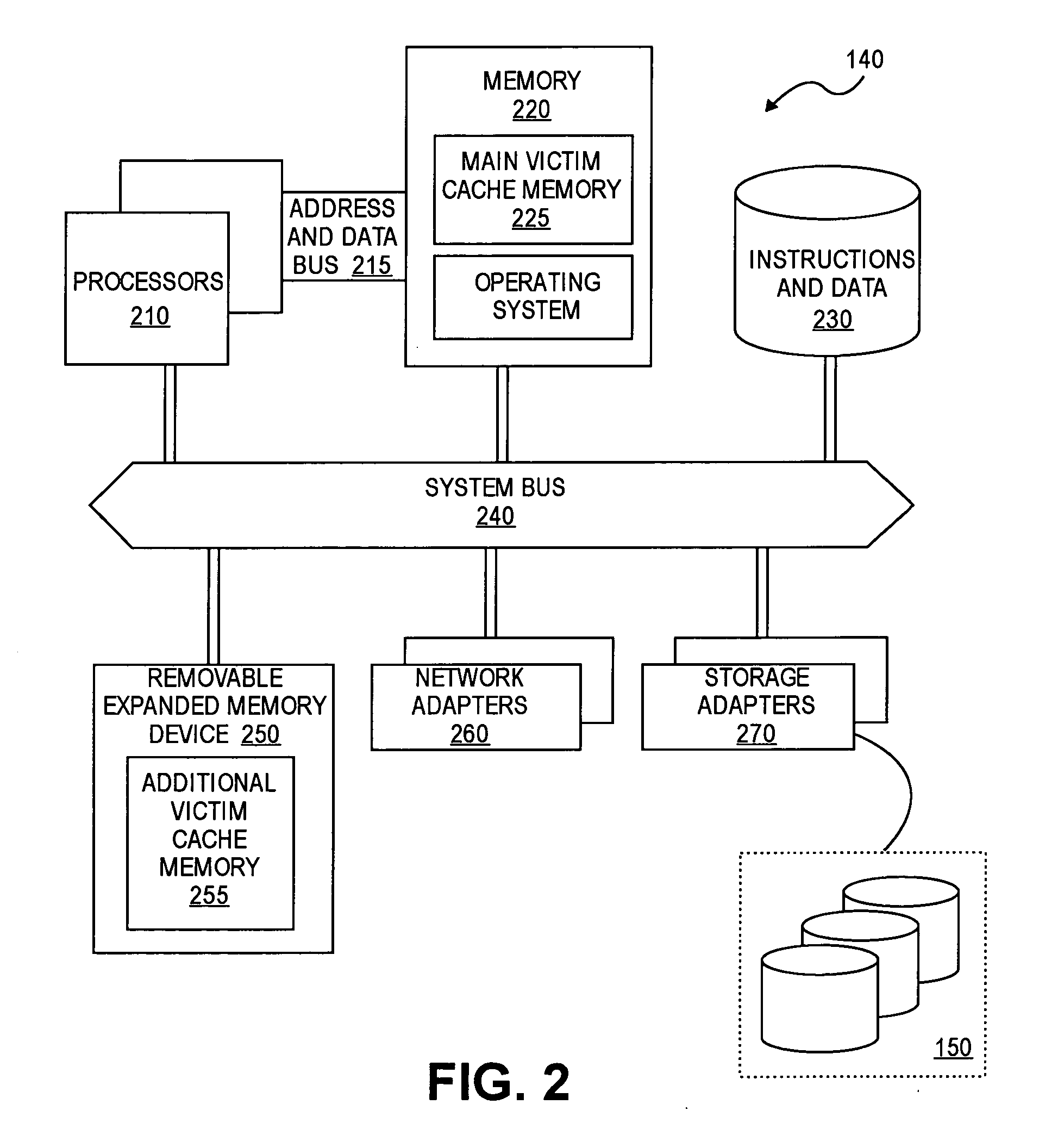

Memory scrubbing of expanded memory

Embodiments of the invention include a memory device, such as a removable expanded memory card, having a host bus interface that allows a host to access a memory of the device. The memory device also includes memory scrubbing circuitry to read data stored at addresses in the memory and to identify single-bit errors and multiple-bit errors in the data read from the memory.

Owner:NETWORK APPLIANCE INC

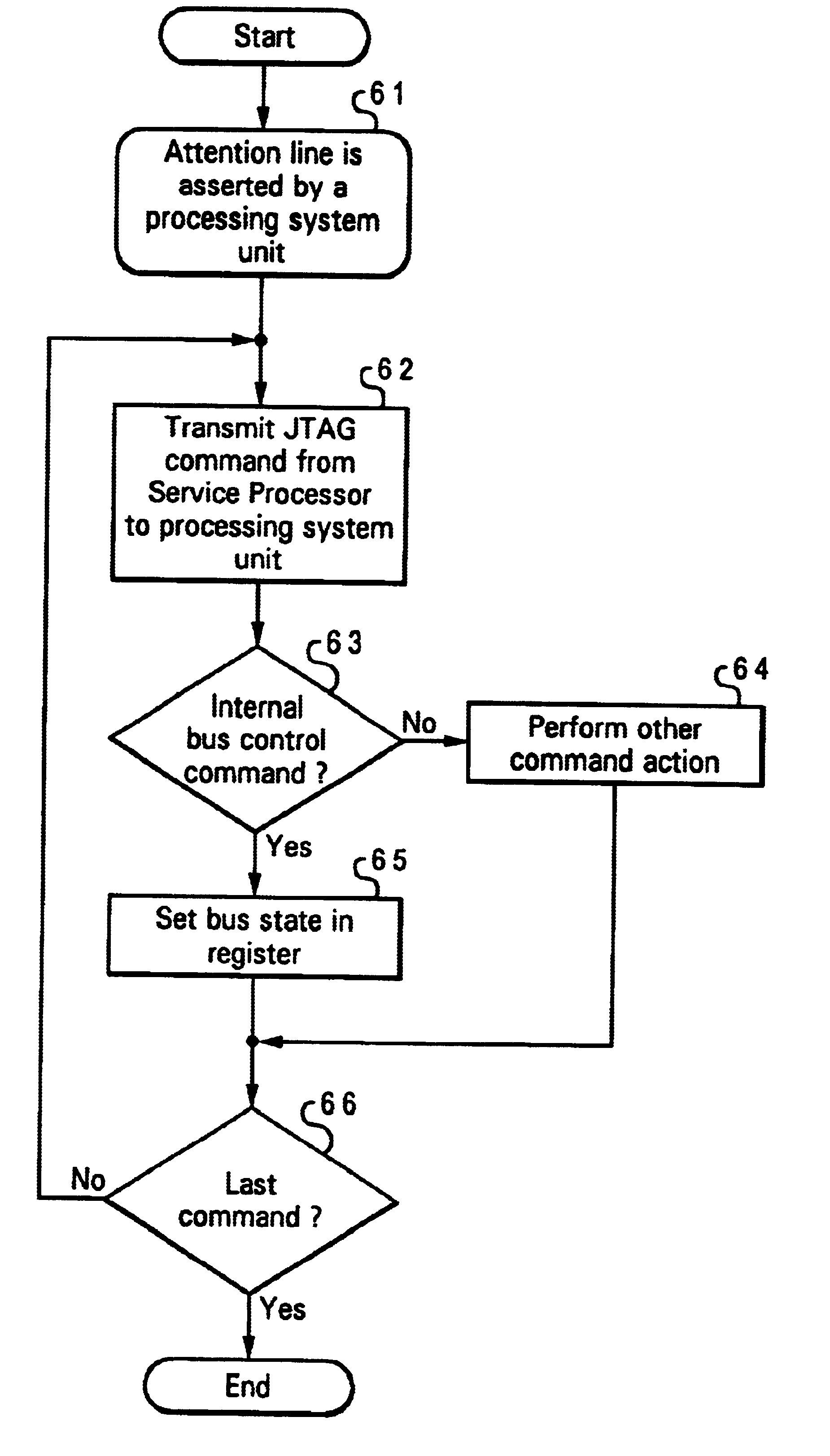

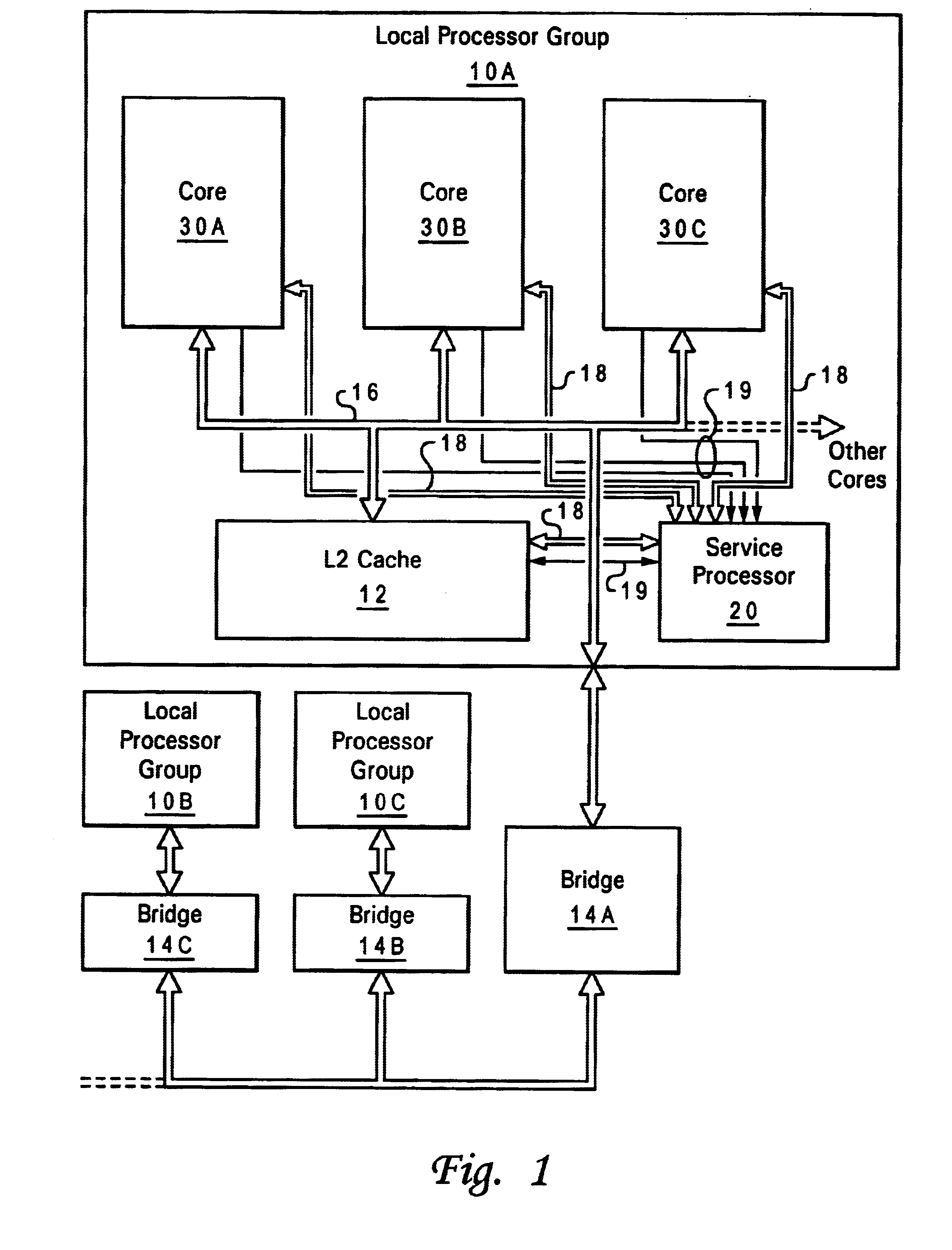

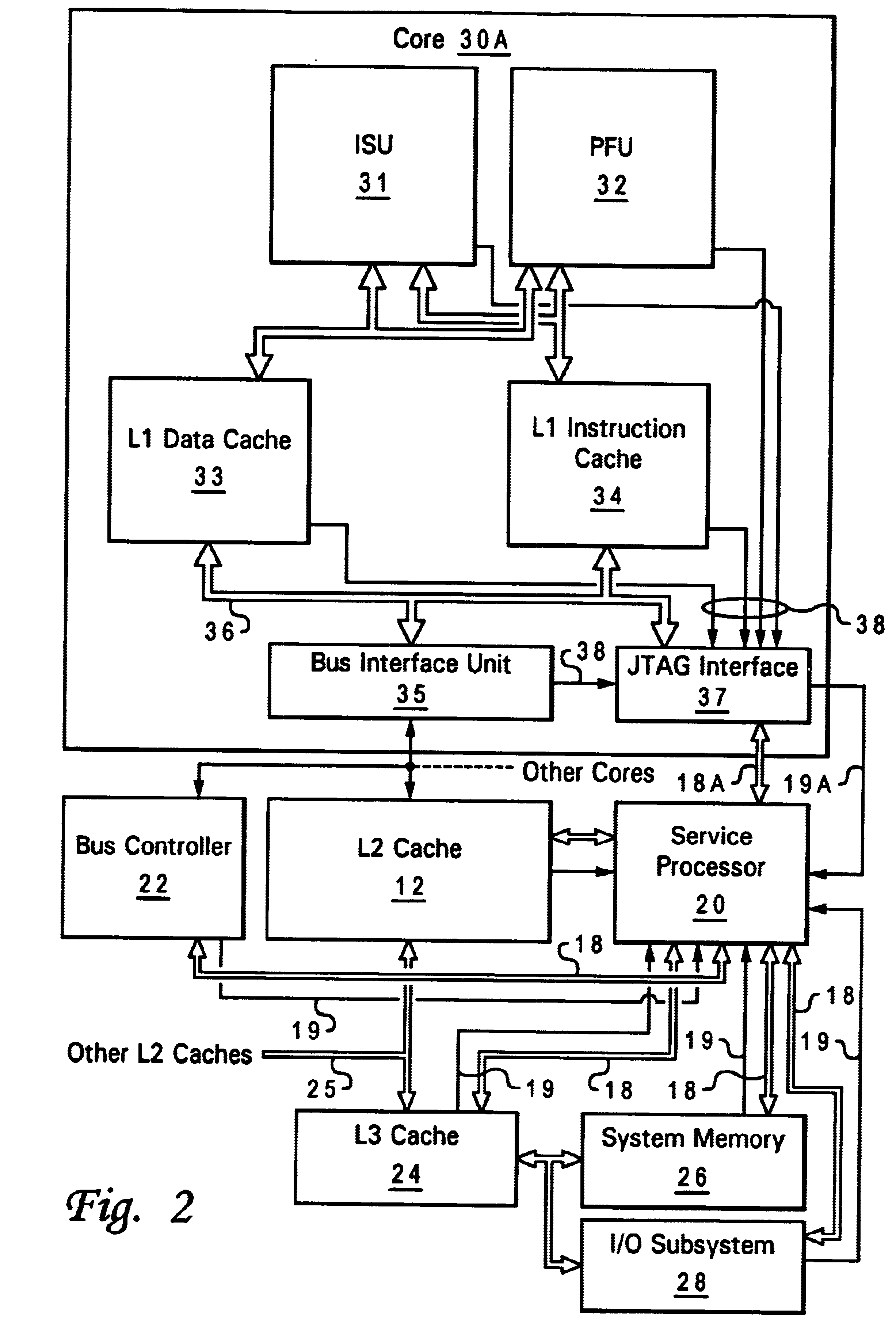

Method and apparatus for servicing a processing system through a test port

InactiveUS6629268B1Error detection/correctionMemory systemsProcessor registerJoint Test Action Group

A method and apparatus for servicing a processing system through a test port allow initialization and fault recovery capability including the ability to coherently access cache memory while the processing system is operating. A JTAG standard interface is used to access registers in a main processing component and has the additional capability to generate internal bus transactions to access registers, cache and memory both within the main processor, and externally by causing a bus interface in the main processor to generate external bus transactions. The service processor can coherently access cache by this mechanism, allowing fault tolerant recovery from operations in which the cache must be coherently flushed in order to maintain proper system operation.

Owner:GOOGLE LLC

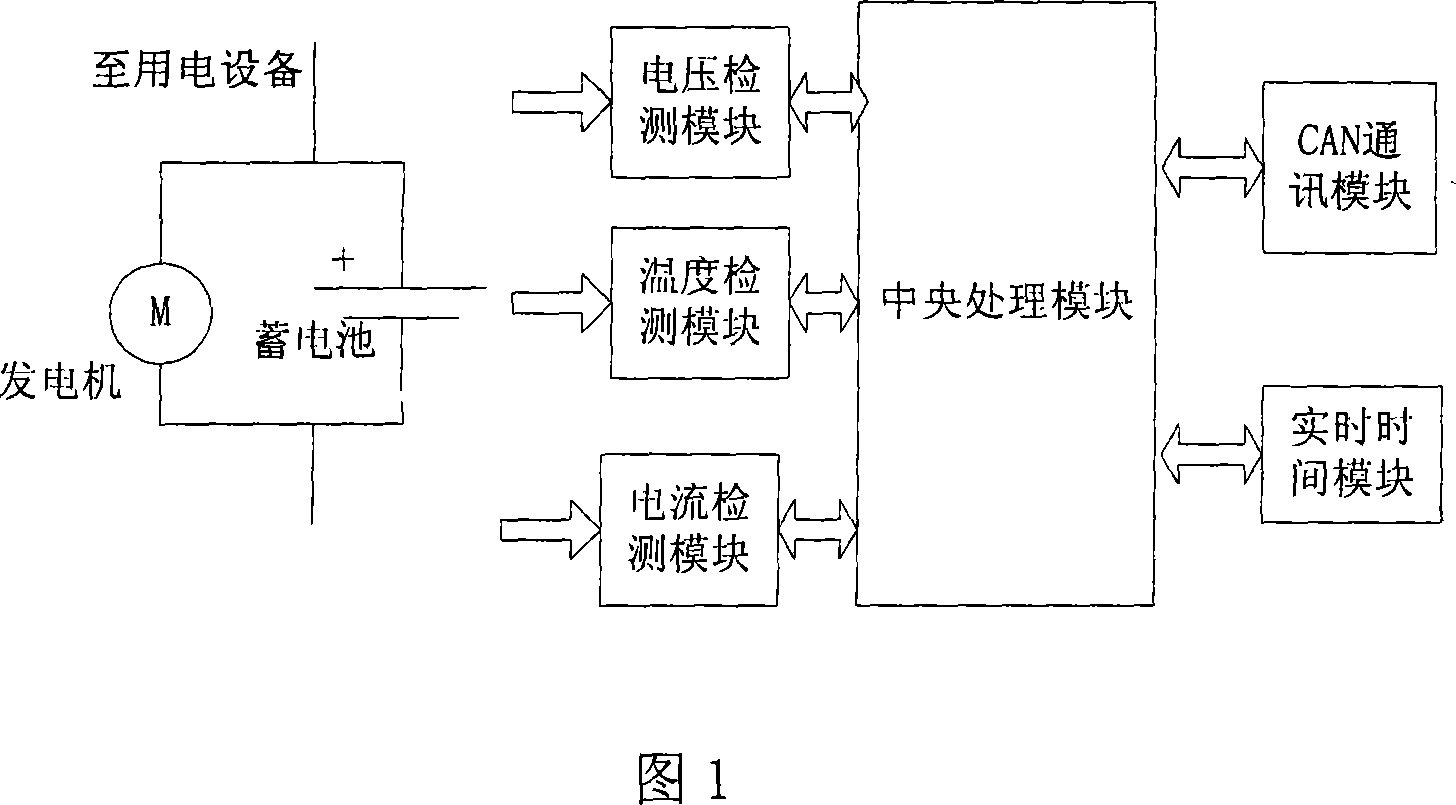

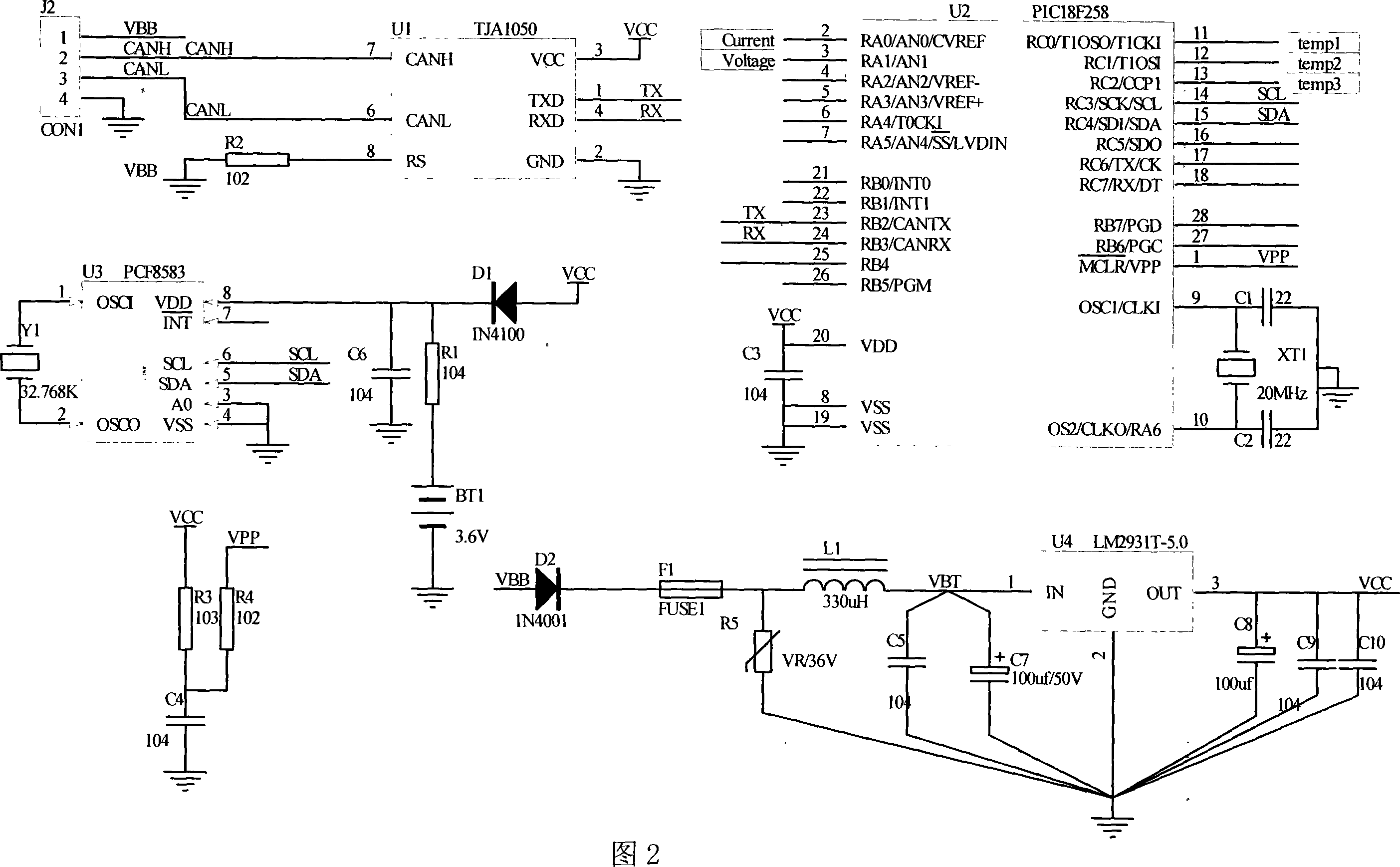

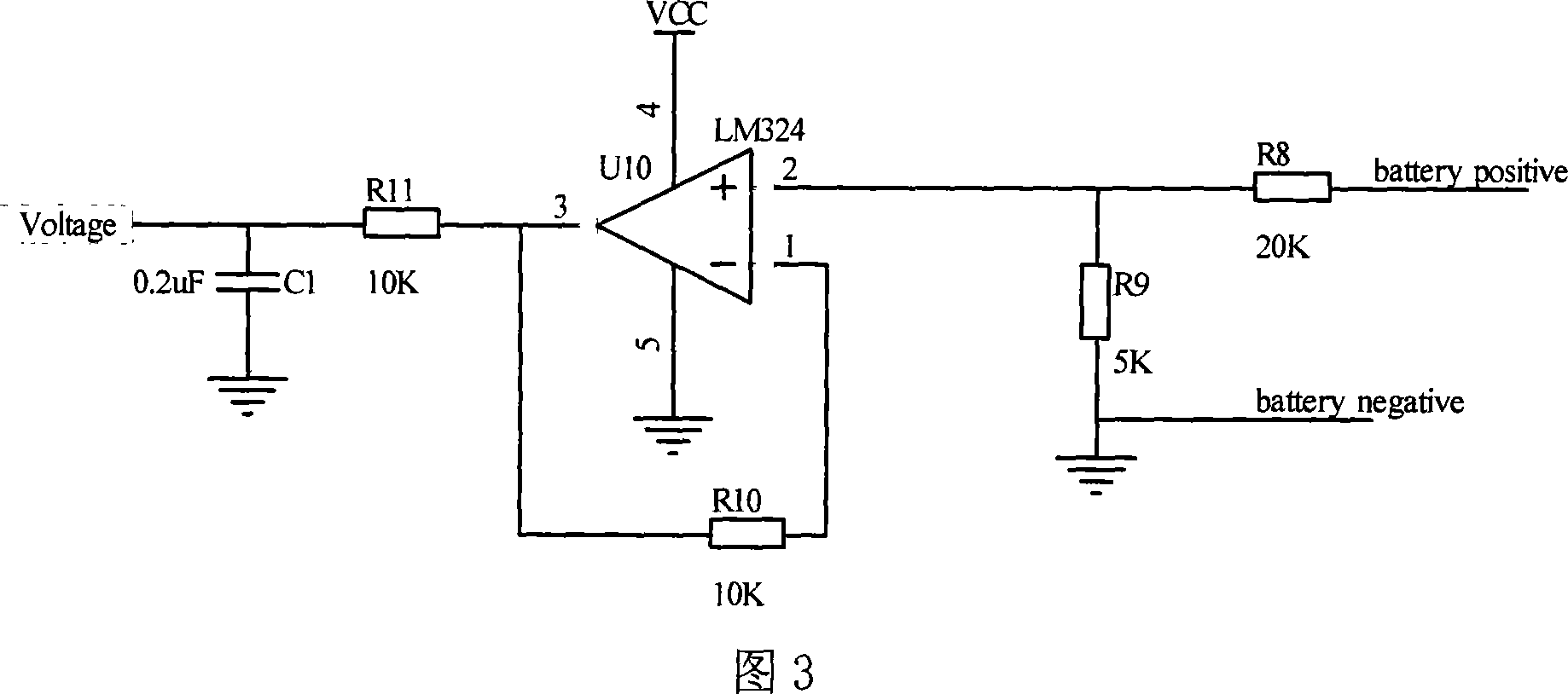

Vehicle mounted battery monitor system

The invention relates to a vehicle battery monitoring system, comprising central processing module, current detecting module, temperature detecting module, voltage detecting module and real-time time module. The voltage collecting module and the temperature collecting module are connected to the AD inputting port of central processing module SCM directly. Digital signals outputted by the temperature collecting module are connected and communicated with I0 ports of central processing module SCM. The outputting end of real-time time module is communicated with other components by I2C bus and it is connected with the I2C bus interface of SCM. The CAN communication module is connected with the CAN interface of SCM directly. The central processing module measures battery temperature, battery voltage and battery current. It integrates charging and discharging electric quantity and estimates residual capability of battery. When the residual capability of battery is lower than the threshold value, the central processing module emits alarm information and hints that auto owner closes air conditioner, DVD, and vehicle refrigerator so on so that the capability of battery maintains certain amount.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

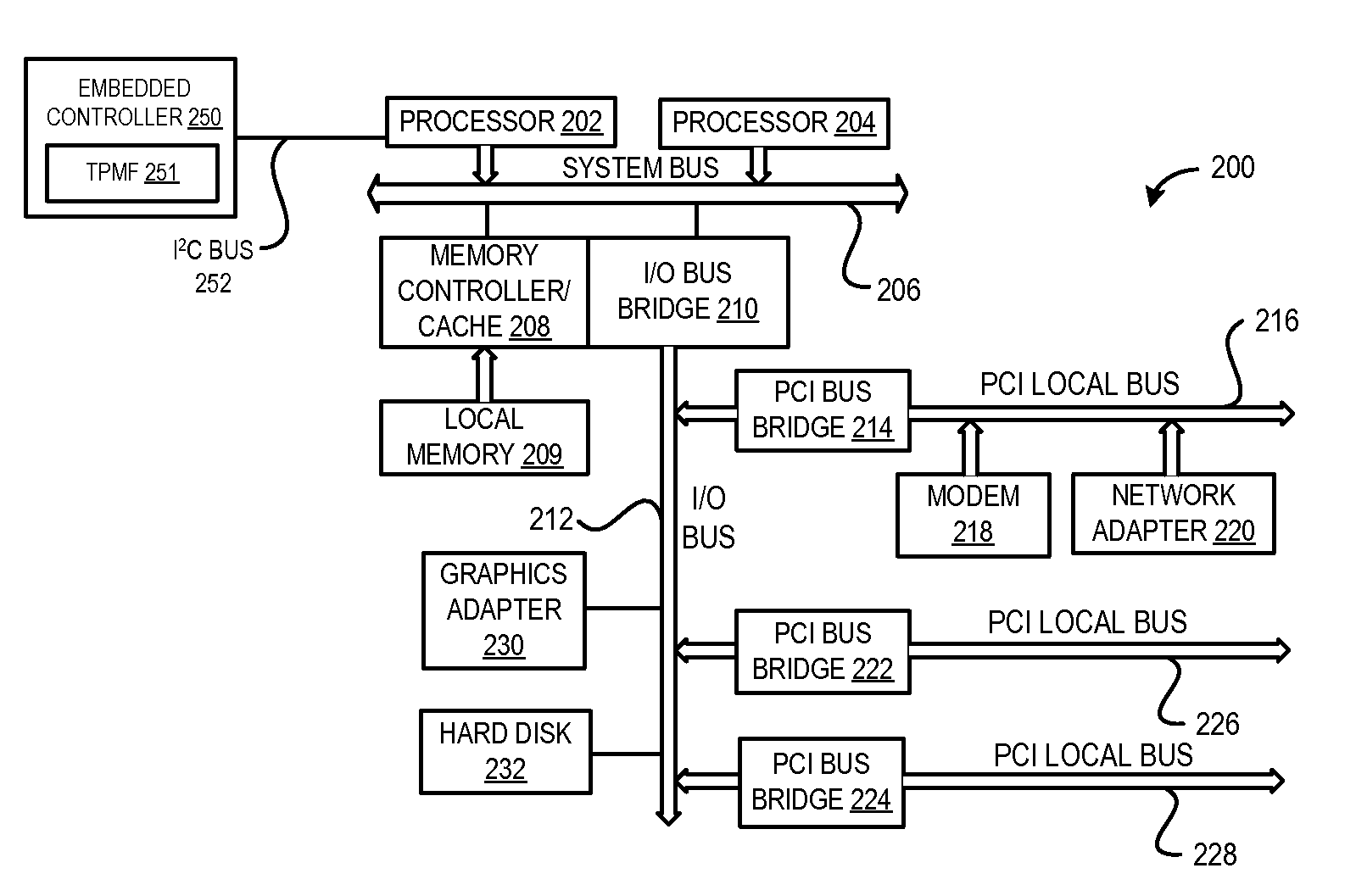

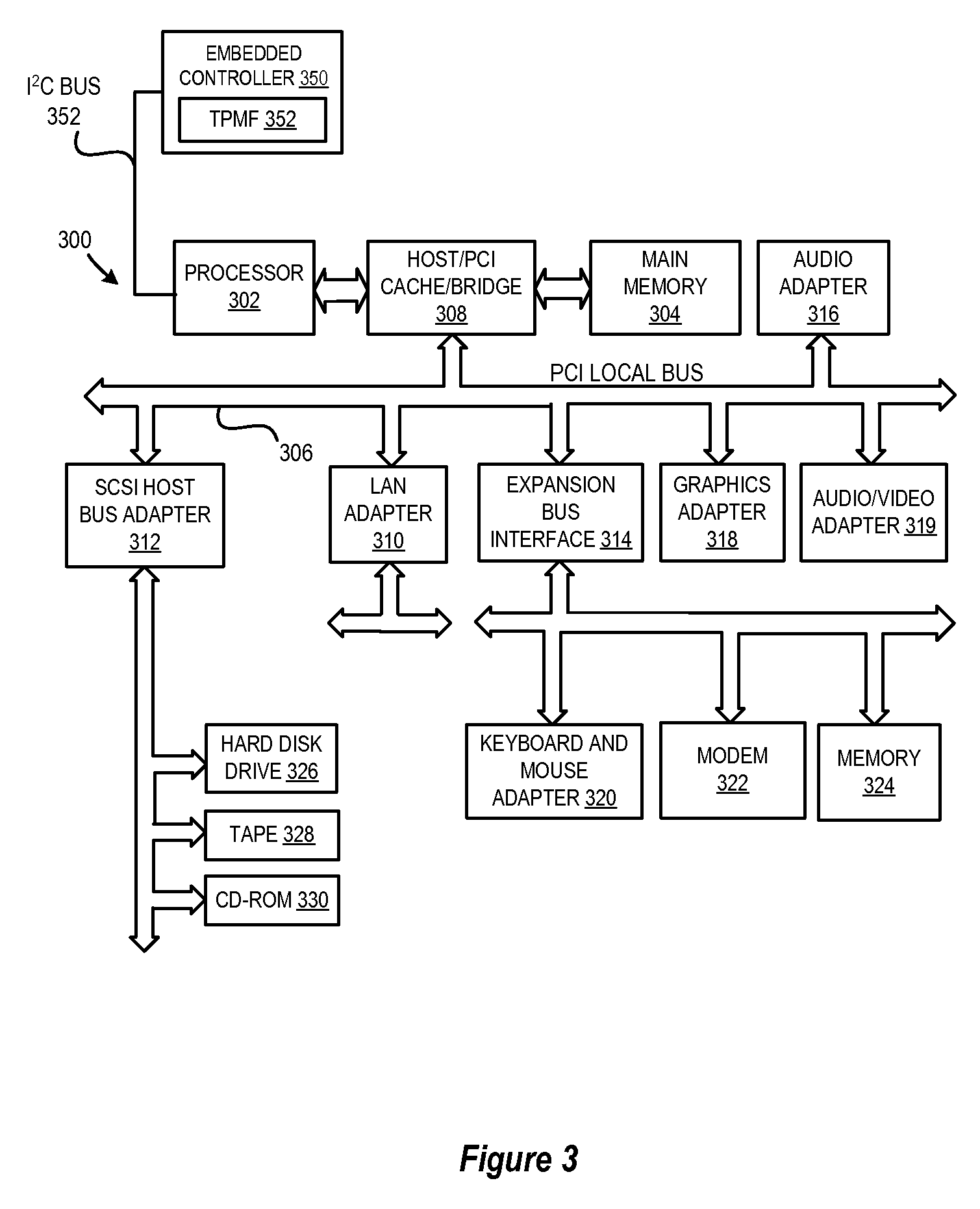

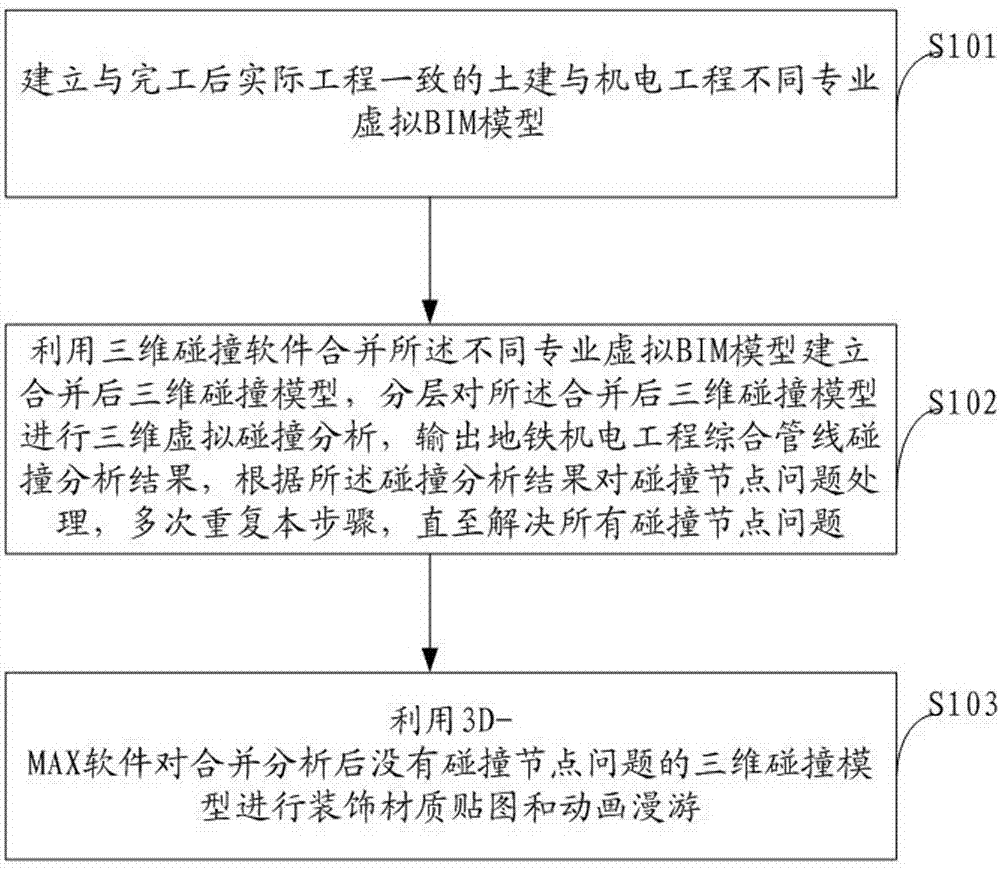

I2C bus interface and protocol for thermal and power management support

A method, apparatus and computer instructions are provided for controlling communications between controller devices over an I2C bus hardware interface and a separate communication line, such as a GPIO line. With thermal / power management firmware installed on a system controller device, communications between the system controller device and a real time embedded controller device are sent using a predefined protocol whereby the system controller generates commands to the embedded controller by first performing an I2C write with a command packet, followed immediately thereafter by an I2C read to get the return packet. The embedded controller processes the command and returns the response to the I2C read. In addition, the embedded controller is able to make the system controller aware that it has a communication request by interrupting the system controller by asserting the separate communication line, in response to which the system controller issues a status request command to the embedded controller.

Owner:IBM CORP

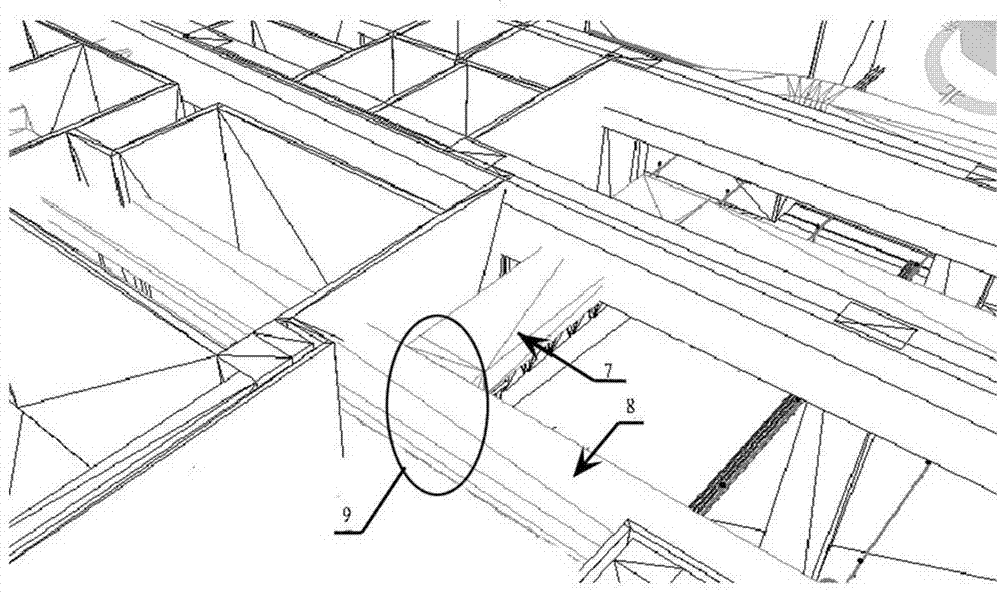

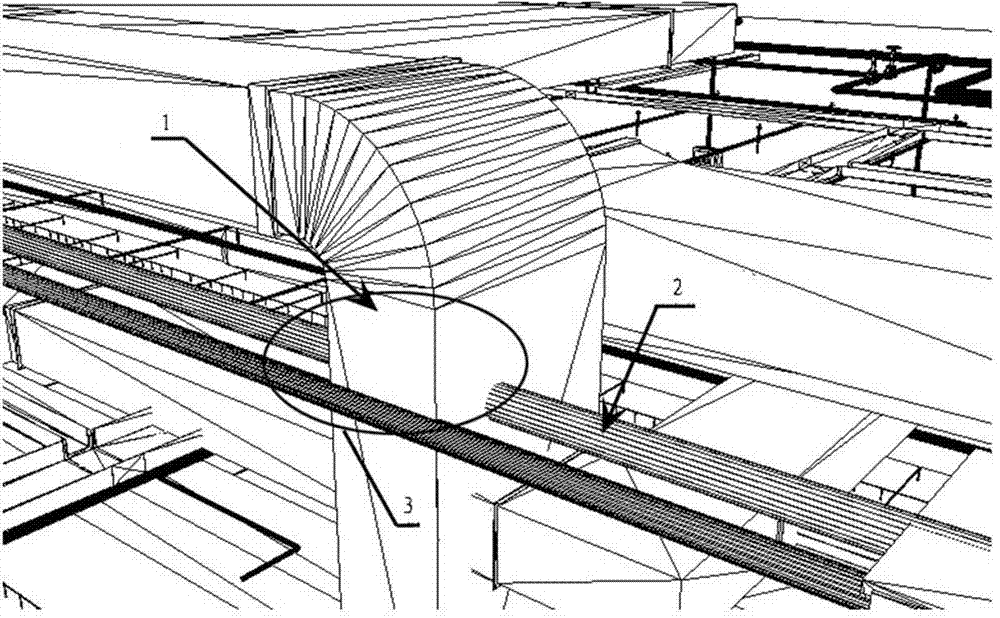

Complex pipeline collision optimization method of subway electromechanical engineering

ActiveCN103093061AOvercome the shortcomings of error-prone, omission and bump-to-missSolving technical issues with cross collisionsSpecial data processing applicationsNODALCollision analysis

The invention belongs to the technical field of electromechanical device installation and discloses a complex pipeline collision optimization method of subway electromechanical engineering. According to the method, three-dimensional bus interface module (BIM) software is used for establishing different professional virtual BIM models which are consistent with completed engineering and then output to three-dimensional collision software for establishment of a combined three-dimensional collision model for collision analysis, collision nodes are then processed and optimized, and then decorative texture mapping and animation roaming are carried out on the combined, analysed and processed three-dimensional collision model without the collision node problem through 3D - MAX software, and therefore collision optimization of complex pipelines of the subway electromechanical engineering is achieved. According to the complex pipeline collision optimization method of the subway electromechanical engineering, the BIM technology is utilized to solve the problem that collision of various complex pipelines causes construction ceasing during electromechanical installation, reasonable planning and utilization of electromechanical pipeline equipment and the like are achieved by means of the optimized design, construction waste is reduced, construction time is shortened, working efficiency at site is improved greatly, and initial investment of a proprietor is reduced.

Owner:ELECTRIFICATION ENG CO LTD OF CHINA RAILWAY 22TH BUREAU GRP +1

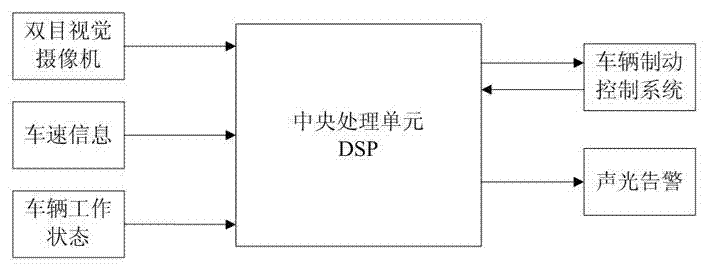

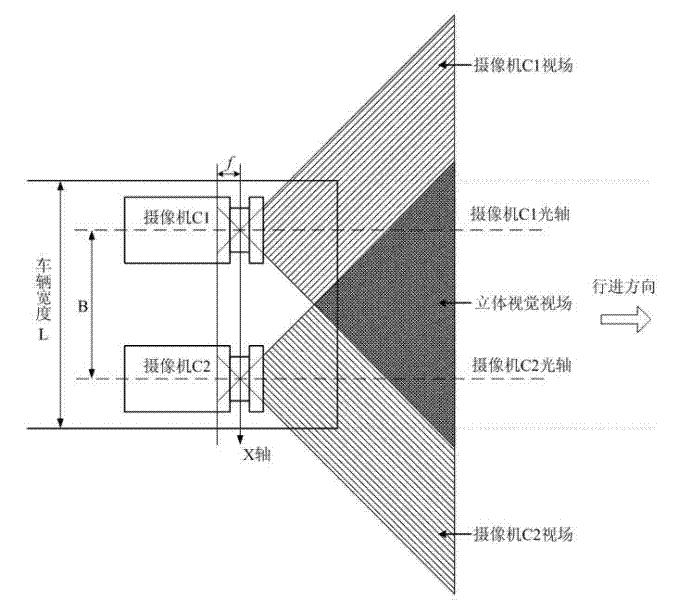

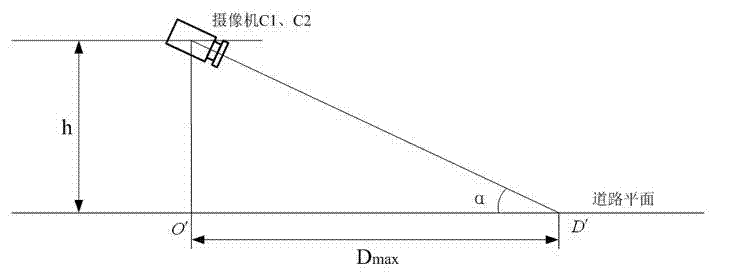

Stereoscopic vision based emergency treatment device and method for running vehicles

ActiveCN102390370AReduce speedAcoustic signal devicesAutomatic initiationsDriver/operatorVision based

The invention relates to a stereoscopic vision based emergency treatment device and method for running vehicles, wherein the device comprises a binocular-vision image pick-up unit, an on-board bus interface, a central processing unit, a vehicle braking control system and an acousto-optic alarm circuit. The binocular-vision image pick-up unit is used for capturing an image of a road in front of a vehicle; the DSP (digital signal processor) based central processing unit is adopted for carrying out real-time quick calculation on a visual image so as to obtain a three-dimensional road scene, and compares the obtained three-dimensional road scene with a safe driving road model set up by a system so as to judge whether obstacles or dangers exist in the traveling direction of the vehicle; when adanger is found, the vehicle braking control system is started so as to reduce the speed of the vehicle and send an acousto-optic alarm to a driver; meanwhile, the central processing unit is connected with a vehicle sensor by an inter-vehicle bus so as to detect the state of the vehicle, and when the vehicle has mechanical or circuit faults, a braking system is started so as to reduce the speed of the vehicle and send an acousto-optic alarm. The device disclosed by the invention can be arranged on ordinary motor vehicles so as to avoid the occurrence of accidents or reduce the accident loss, thereby improving the driving safety performance.

Owner:HOHAI UNIV

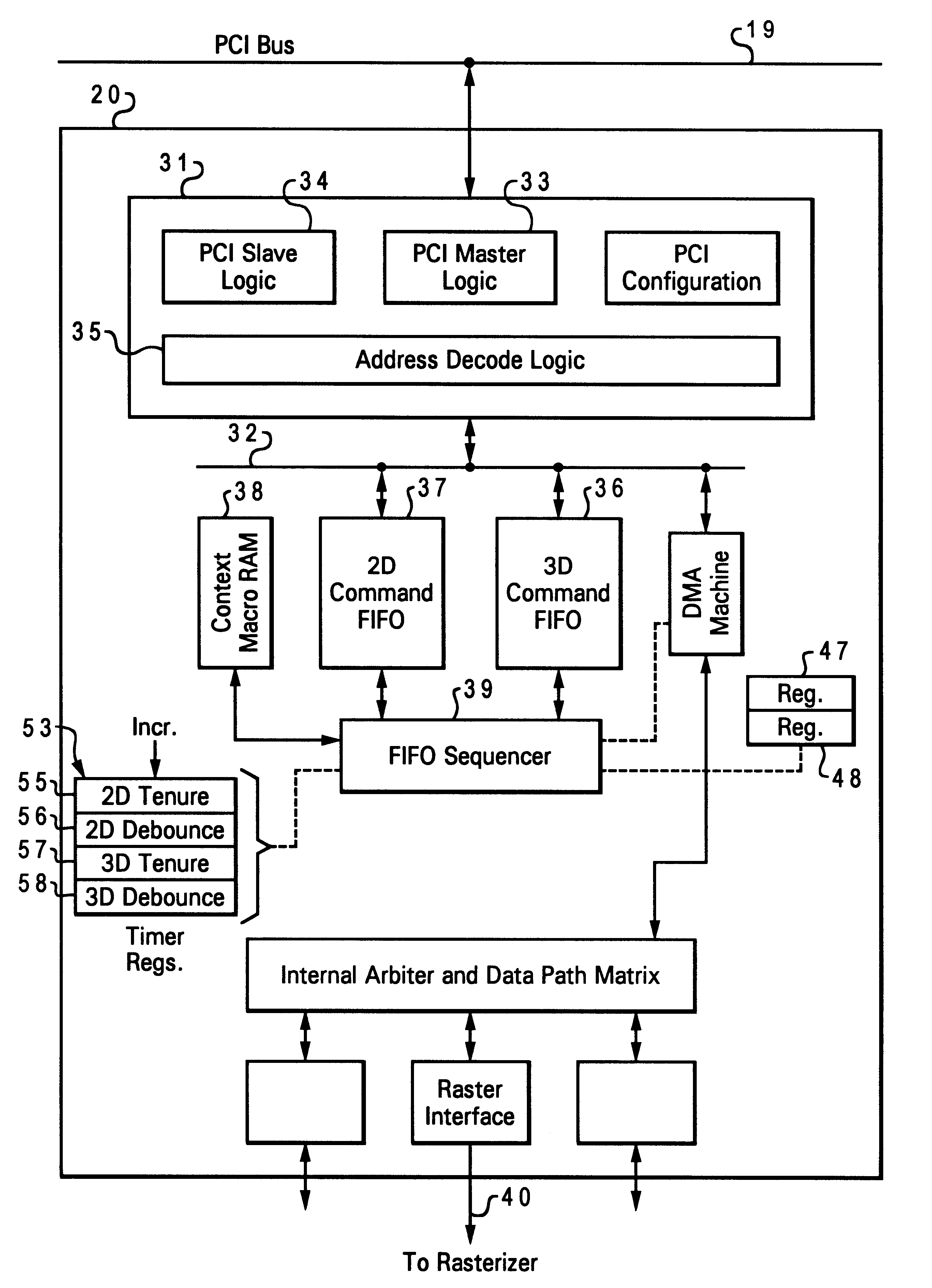

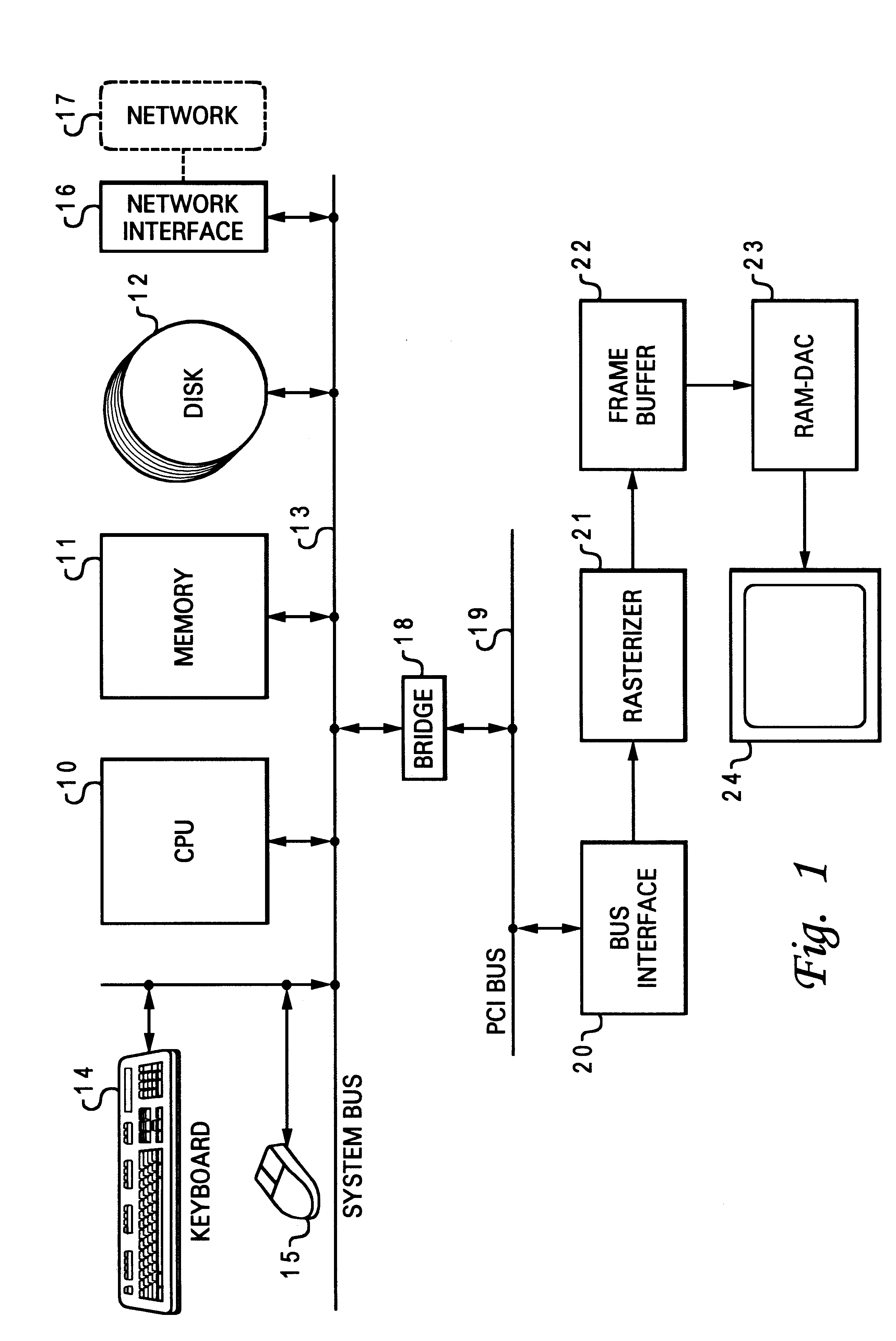

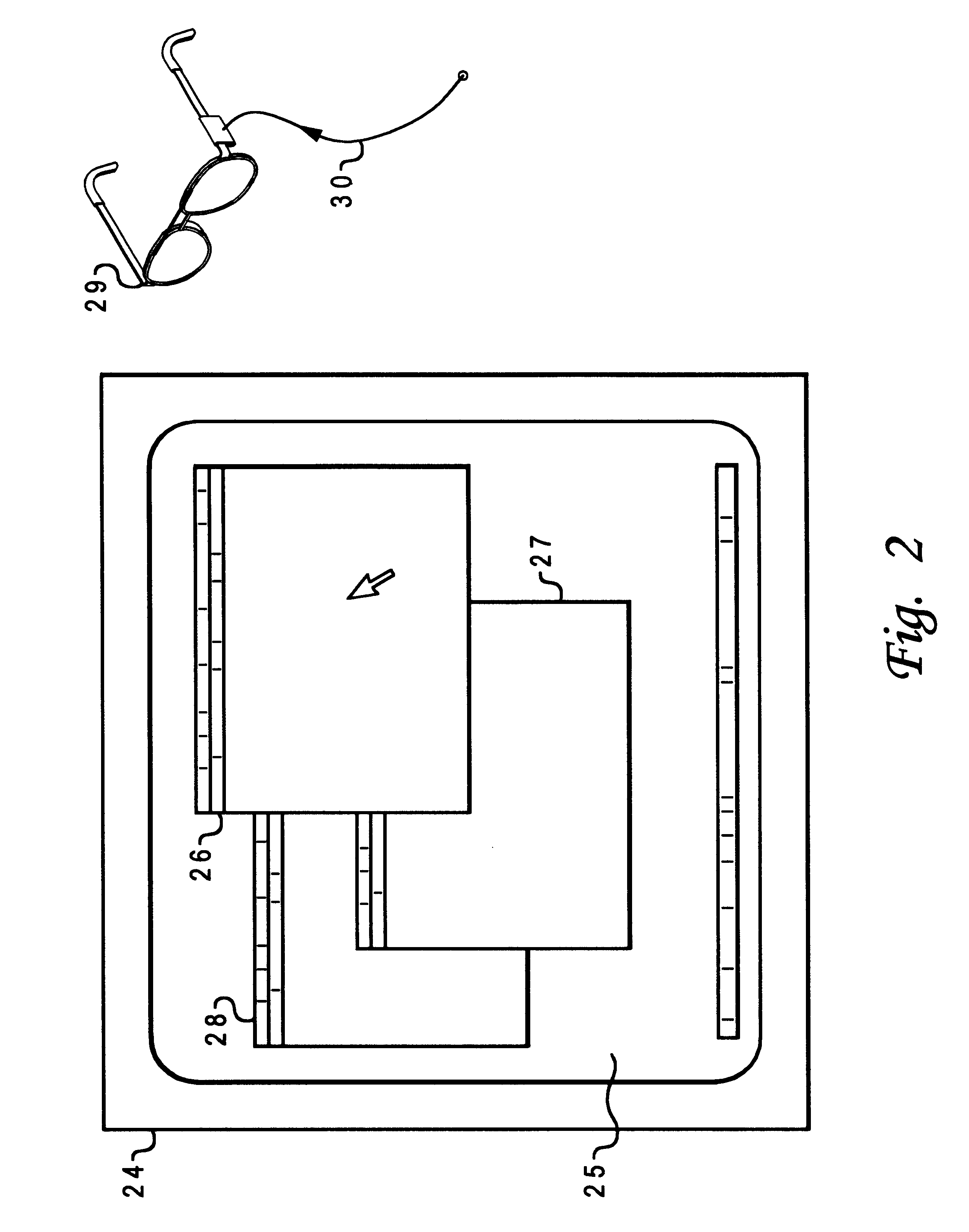

Computer graphics system with dual FIFO interface

InactiveUS6252600B1Minimum delayEasy to useImage memory managementCathode-ray tube indicatorsGraphic systemComputerized system

A computer system has a graphics subsystem employing a rasterizer and a frame buffer, with a digital-to-analog converter for producing drive signals to a video display. A bus interface acts as a gateway between a PCI bus and the graphics subsystem; this interface manages commands and DMAs passing between the host processor and various parts of the graphics subsystem. Within the interface, two command FIFOs are employed, one for storing commands / data sent from the host for 2D display (window management) and another for 3D applications. Using two command FIFOs eliminates the need for host semaphore, FIFO draining, and the latency associated with these operations. Timers are provided in the interface, associated with the two command FIFOs, to manage and regulate the frequency with which the system automatically switches between 2D and 3D FIFO processing. Host intervention is minimized by use of a context macro store for holding locally the sequences for context save and context restore which are used repeatedly.

Owner:IBM CORP