Patents

Literature

4682 results about "Memory control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

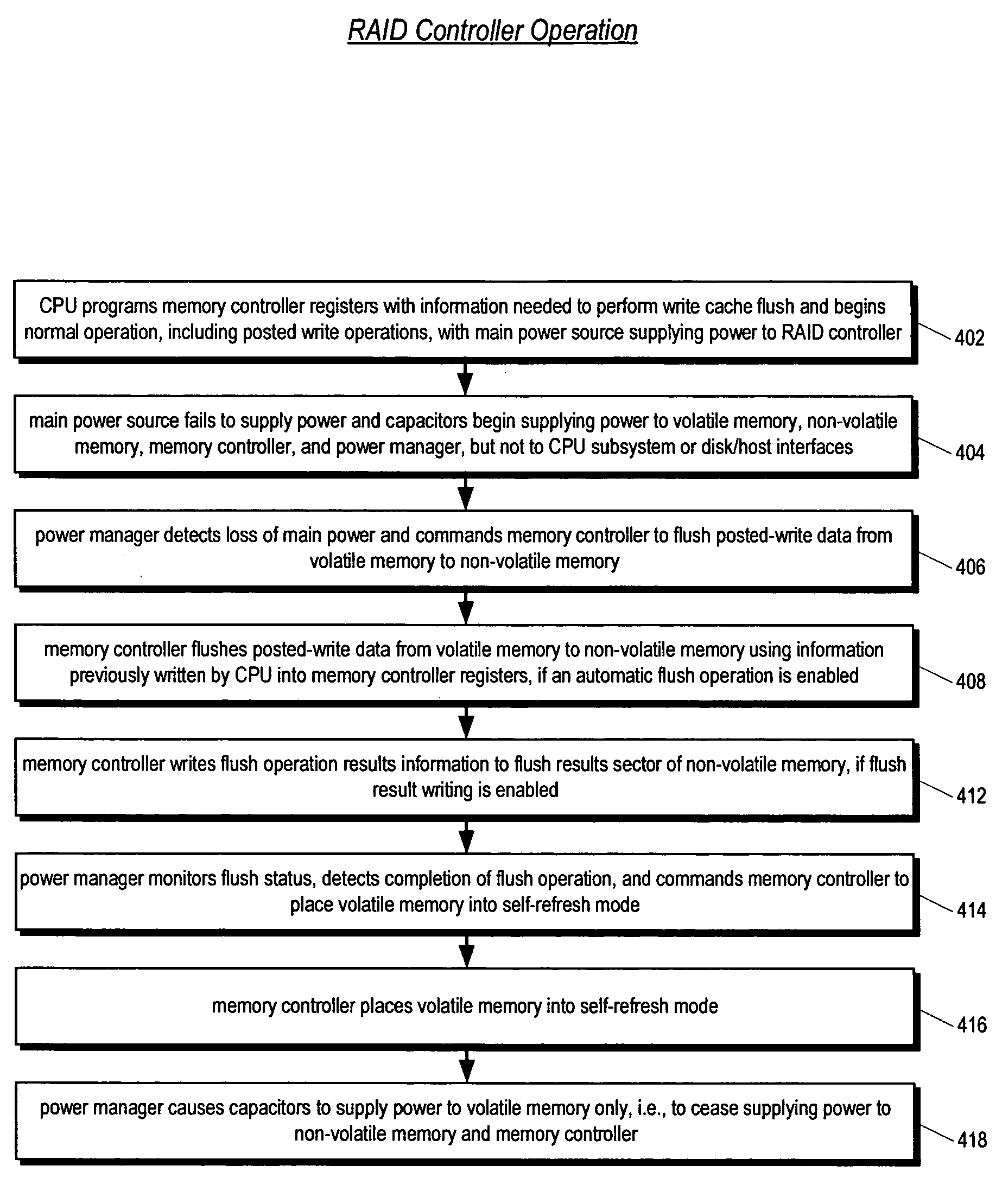

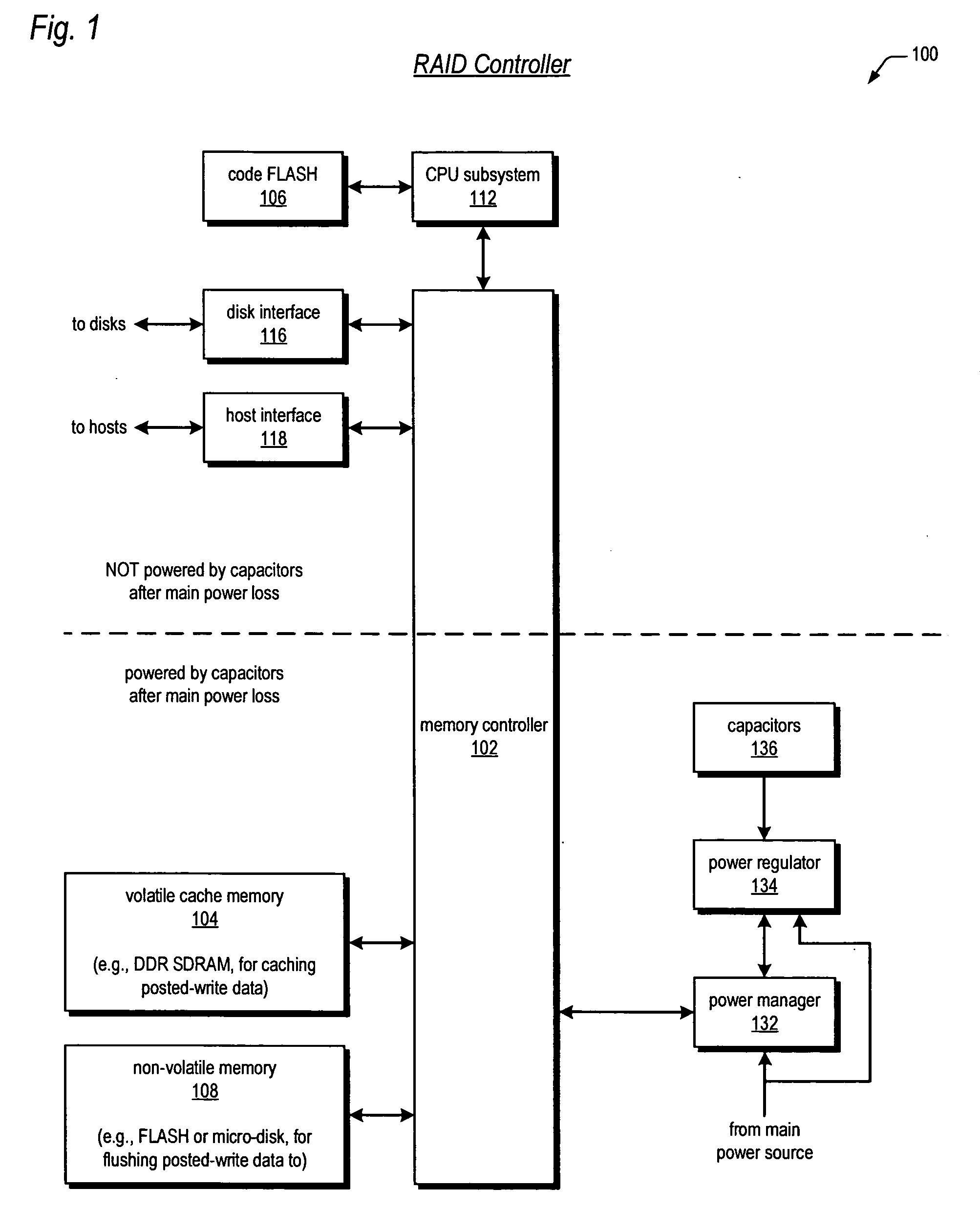

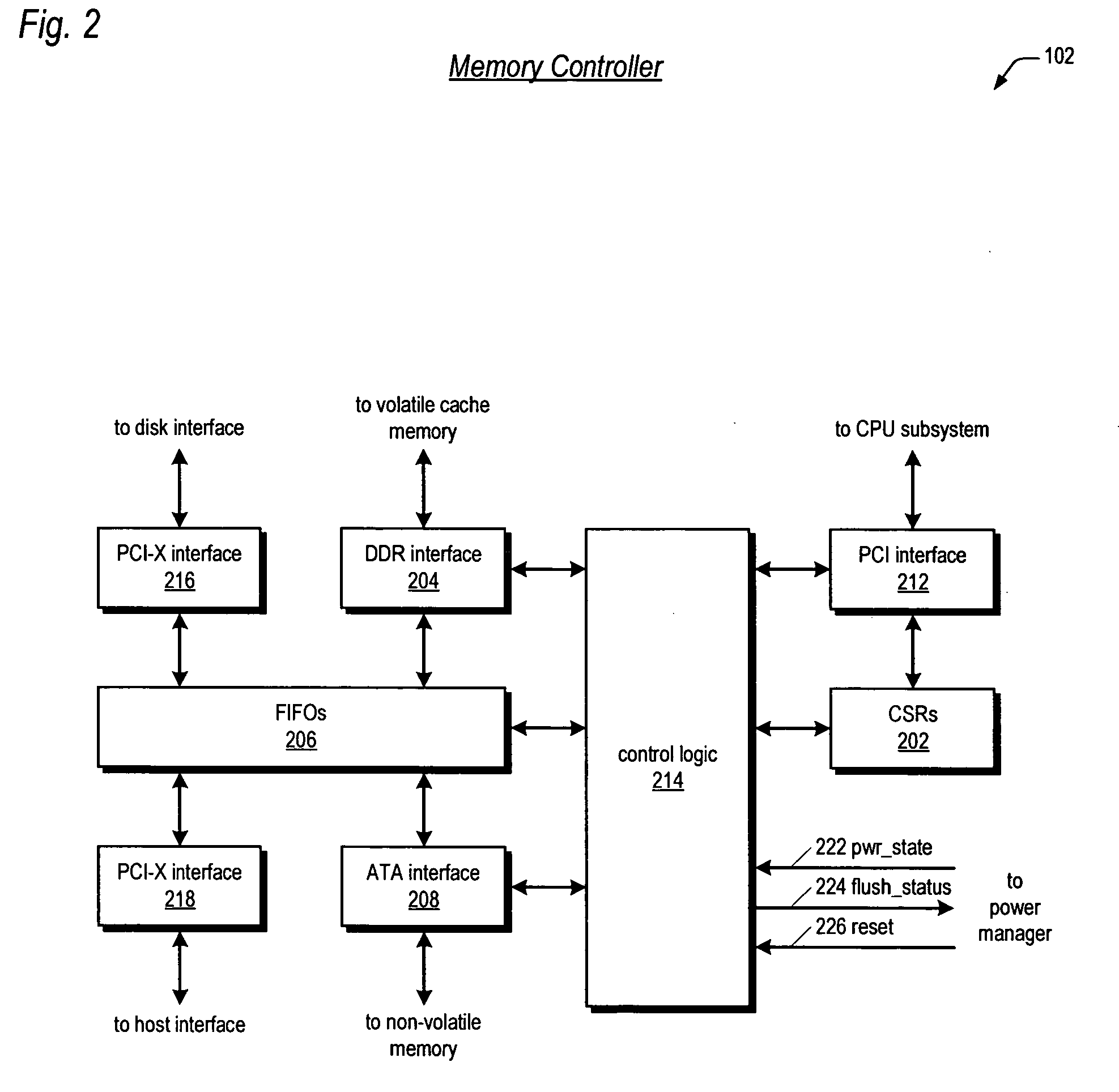

Raid controller using capacitor energy source to flush volatile cache data to non-volatile memory during main power outage

InactiveUS20060015683A1Reduces amount of energy storage capacity requirementLess expensiveEnergy efficient ICTMemory loss protectionRAIDStored energy

A write-caching RAID controller is disclosed. The controller includes a CPU that manages transfers of posted-write data from host computers to a volatile memory and transfers of the posted-write data from the volatile memory to storage devices when a main power source is supplying power to the RAID controller. A memory controller flushes the posted-write data from the volatile memory to the non-volatile memory when main power fails, during which time capacitors provide power to the memory controller, volatile memory, and non-volatile memory, but not to the CPU, in order to reduce the energy storage requirements of the capacitors. During main power provision, the CPU programs the memory controller with information needed to perform the flush operation, such as the location and size of the posted-write data in the volatile memory and various flush operation characteristics.

Owner:DOT HILL SYST

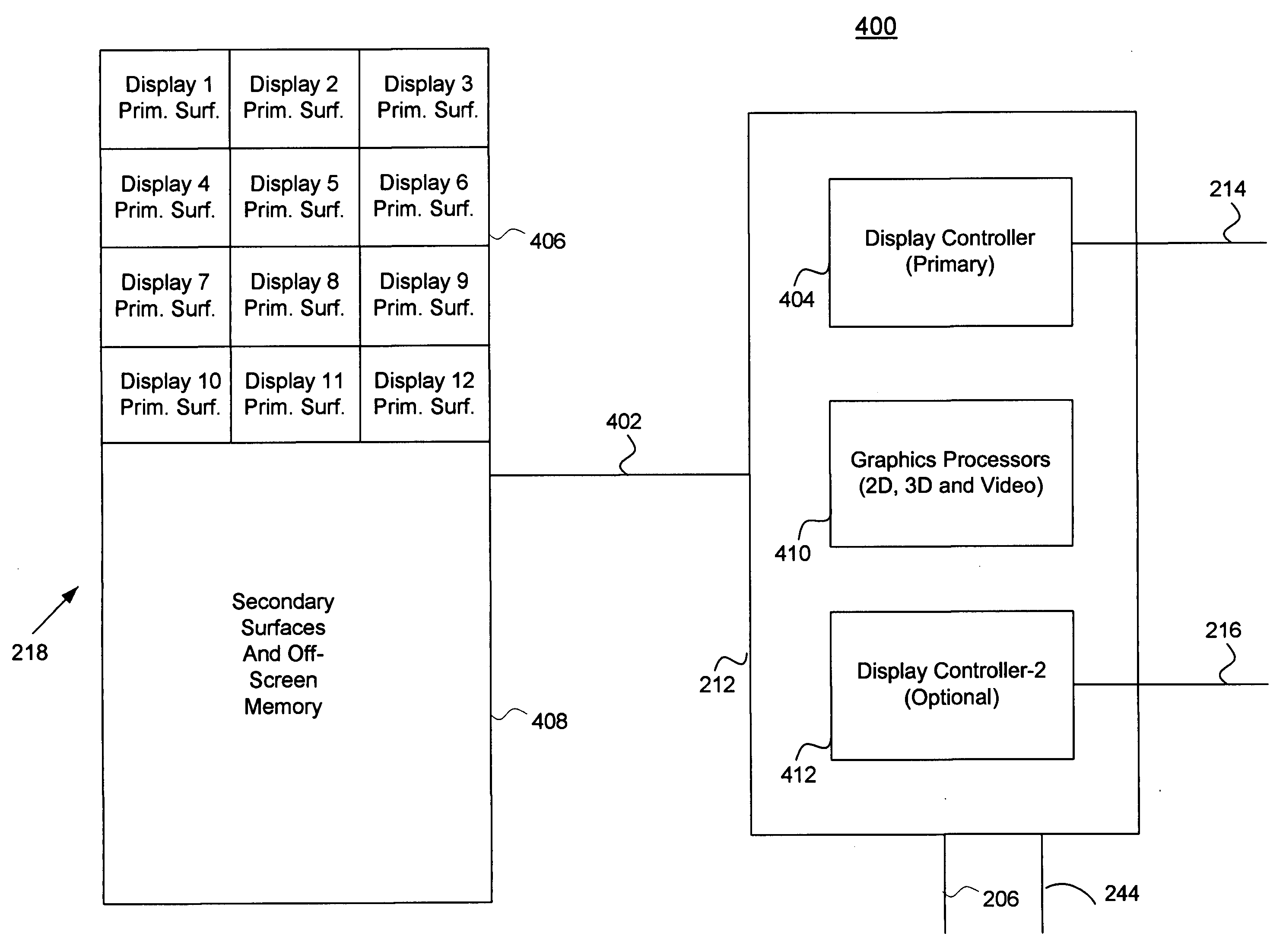

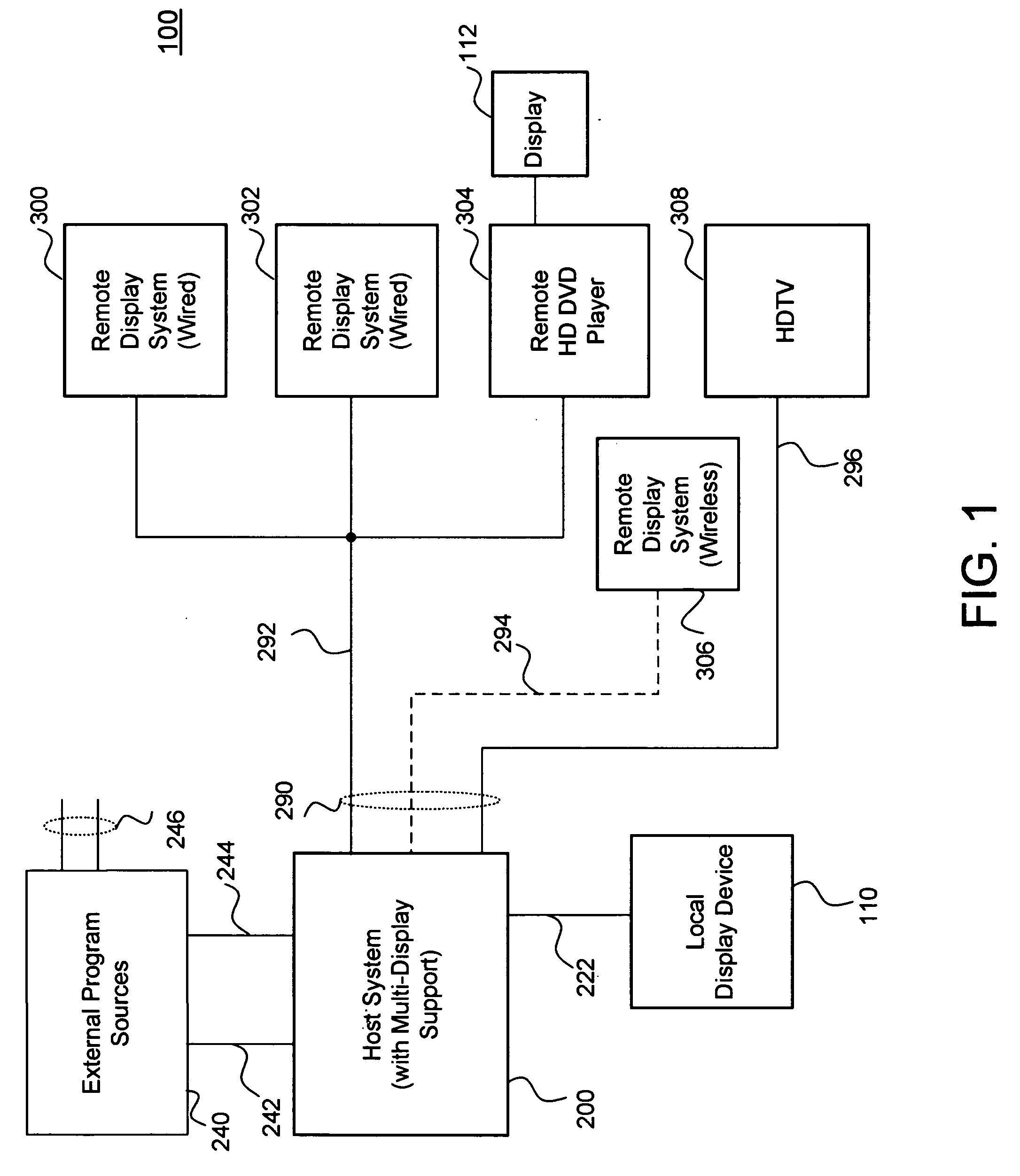

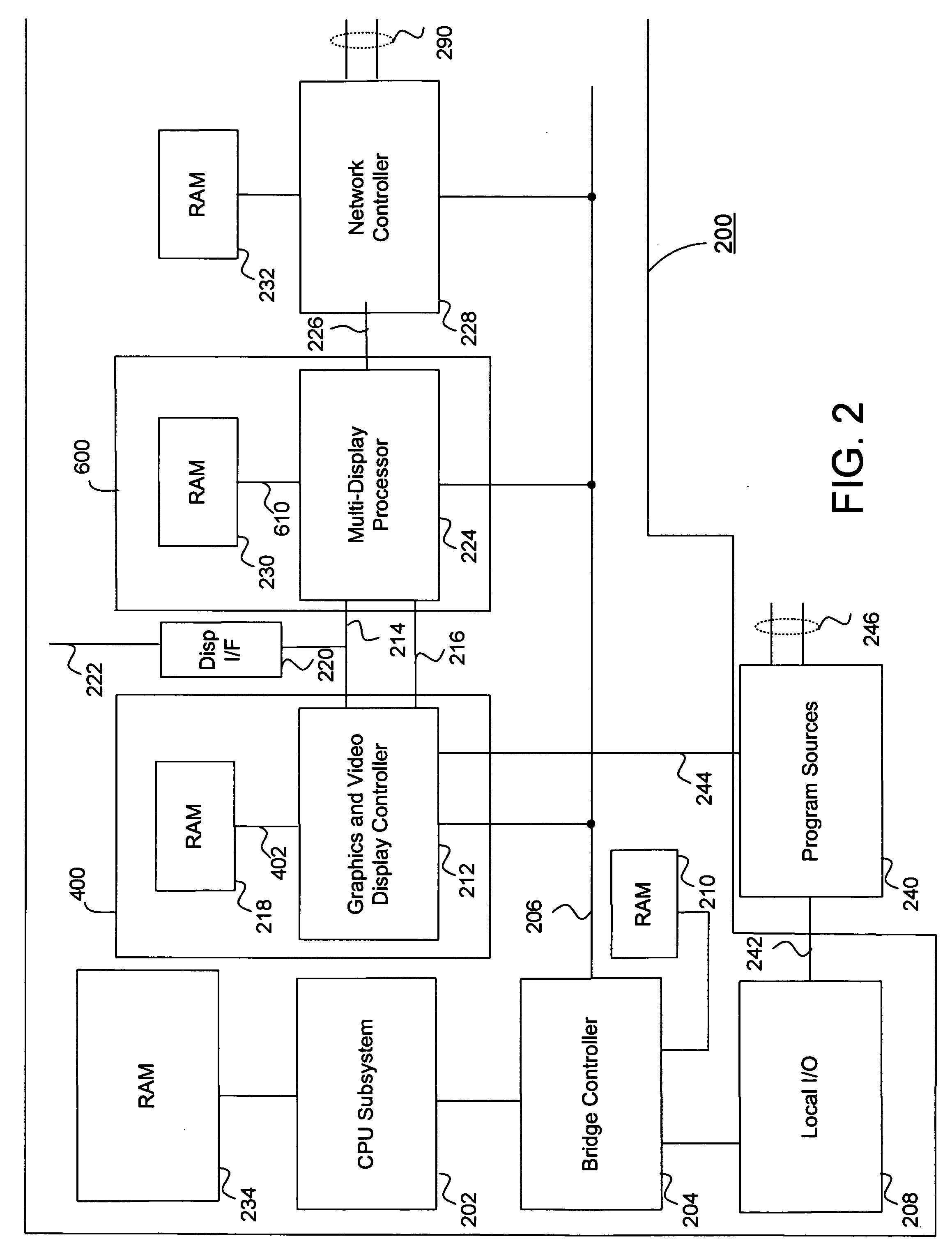

Multiple remote display system

InactiveUS20060282855A1Lower latencyGood frame rateTelevision system detailsColor television detailsGraphicsInternet traffic

A multi-display system includes a host system that supports both graphics and video based frames for multiple remote displays, multiple users or a combination of the two. For each display and for each frame, a multi-display processor responsively manages each necessary aspect of the remote display frame. The necessary portions of the remote display frame are further processed, encoded and where necessary, transmitted over a network to the remote display for each user. In some embodiments, the host system manages a remote desktop protocol and can still transmit encoded video or encoded frame information where the encoded video may be generated within the host system or provided from an external program source. Embodiments integrate the multi-display processor with either the video decoder unit, graphics processing unit, network controller, main memory controller, or any combination thereof The encoding process is optimized for network traffic and attention is paid to assure that all users have low latency interactive capabilities.

Owner:III HLDG 1

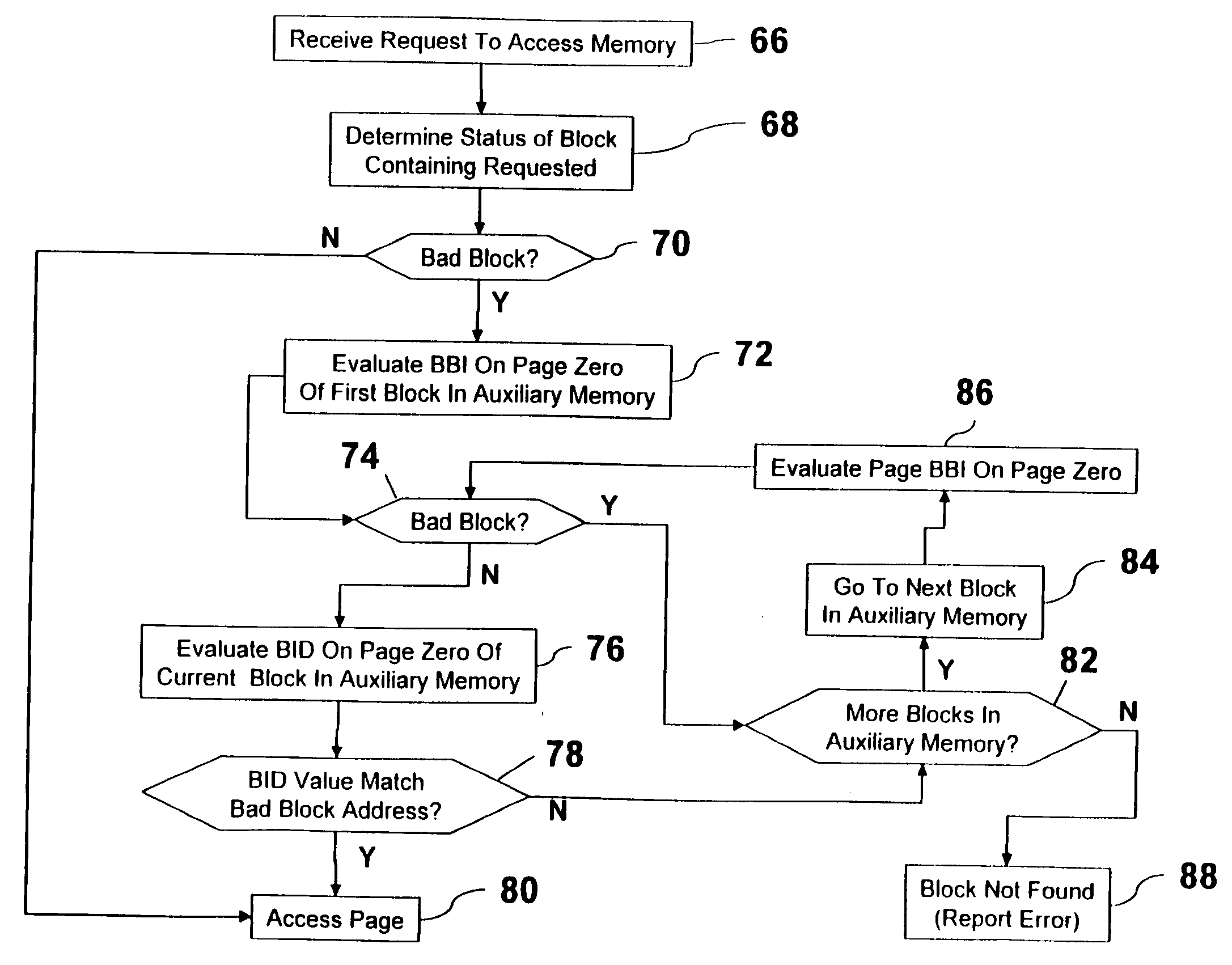

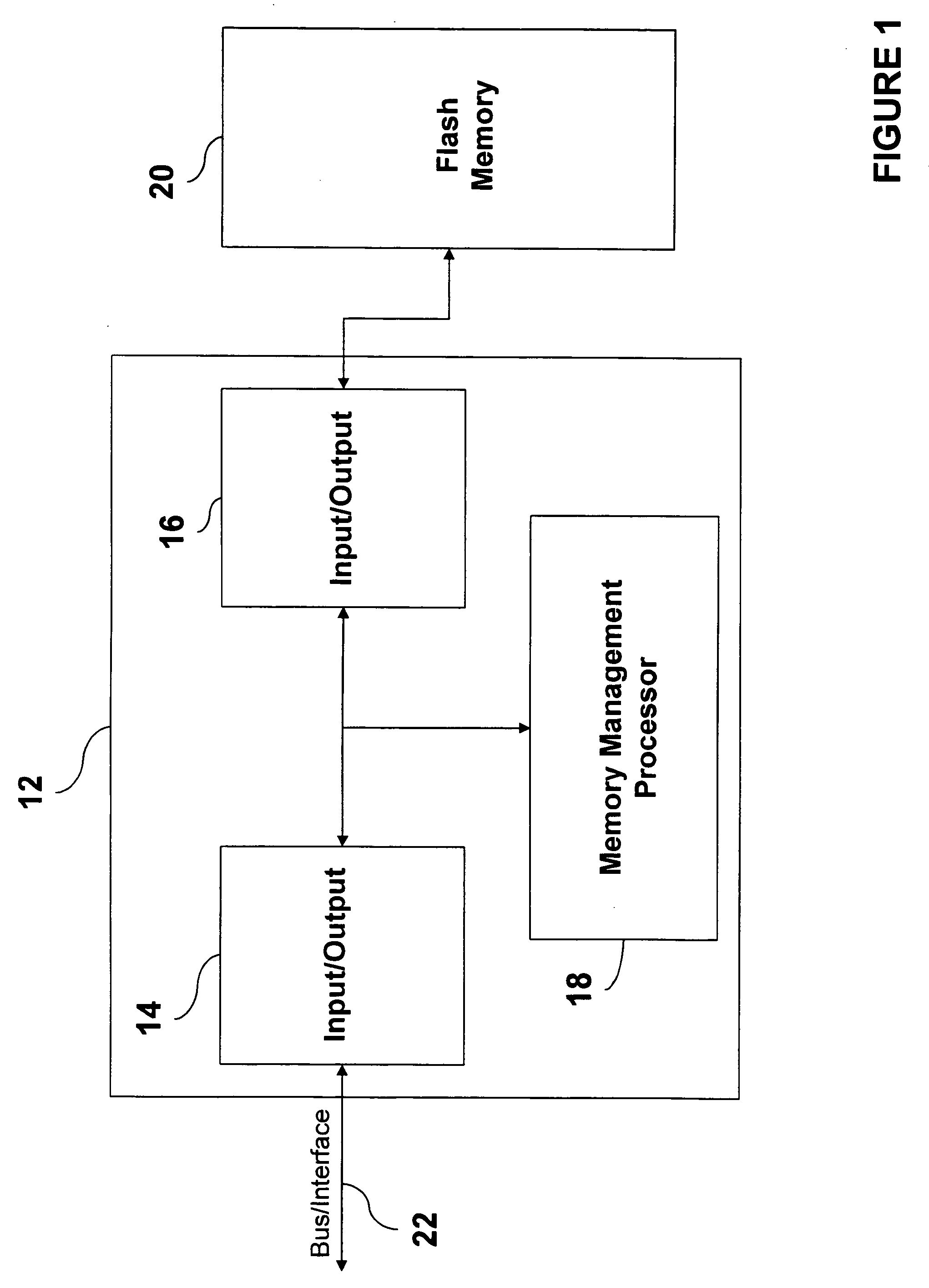

NAND flash memory management

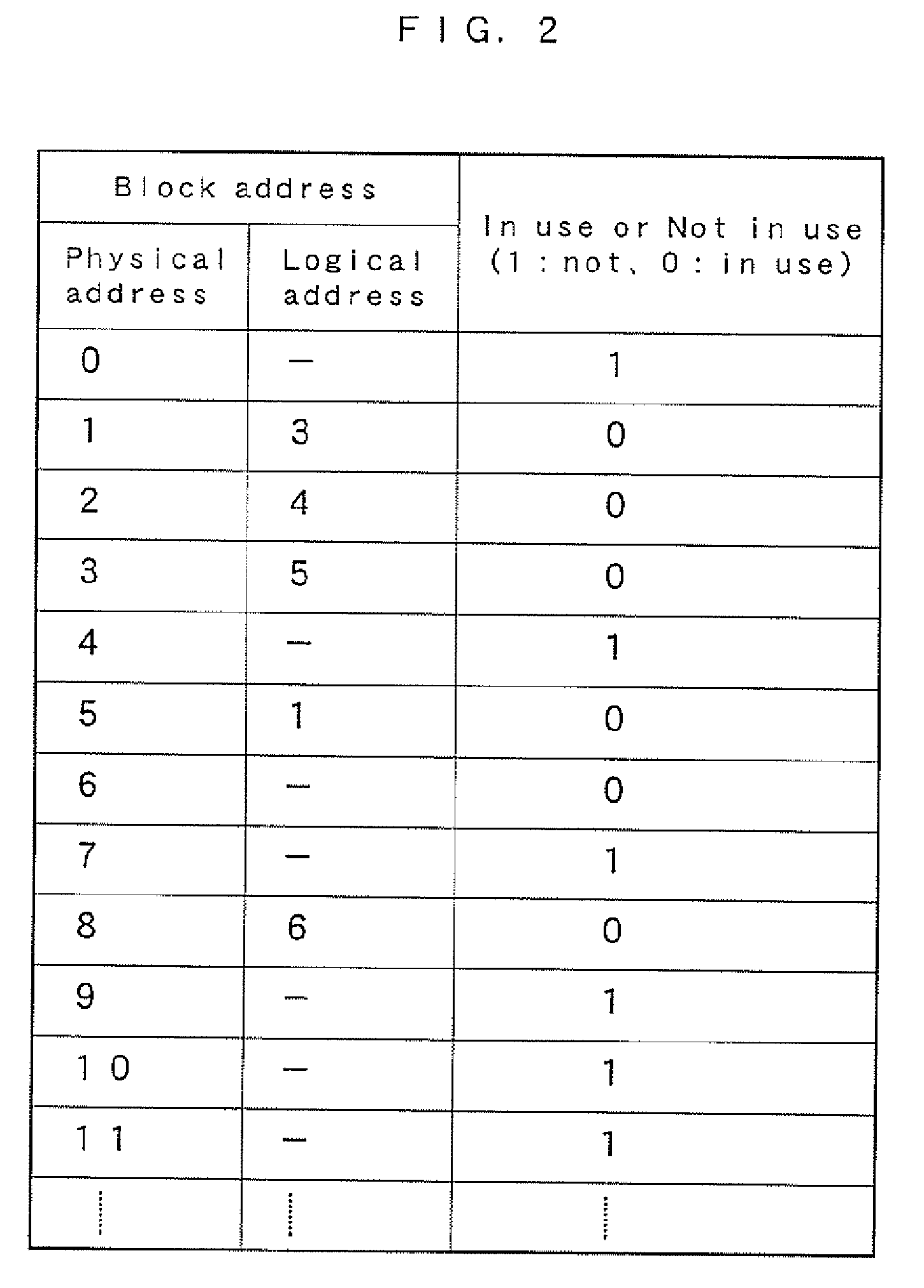

A memory controller is utilized to overcome NAND flash memory's propensity for comprising bad blocks of memory. The memory controller utilizes minimal hardware and is essentially transparent to a device requesting access to the NAND memory. A NAND flash memory device is configured to comprise a set of main blocks of memory and a set of auxiliary blocks of memory. Each block is divided into pages of memory and each page includes metadata. The metadata includes a block status indicator, indicating whether a block is good or bad. When receiving a request to access a page in the NAND flash memory, if the block in which the page resides is good, that block is accessed. If the block is bad, auxiliary memory is searched until a block containing the address of the bad block in its metadata is found. The found block is accessed in lieu of the bad block.

Owner:MICROSOFT TECH LICENSING LLC

Management of non-volatile memory systems having large erase blocks

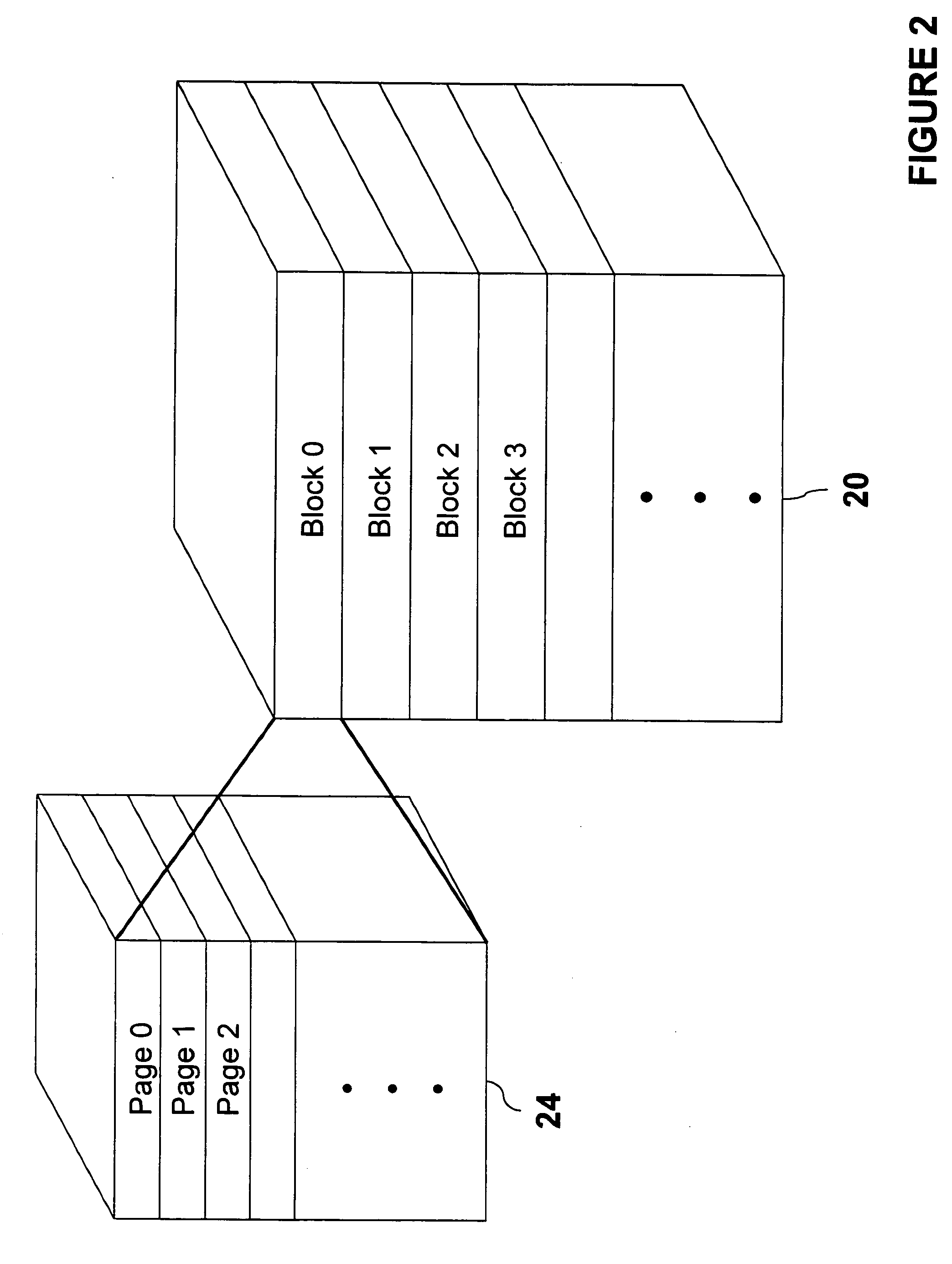

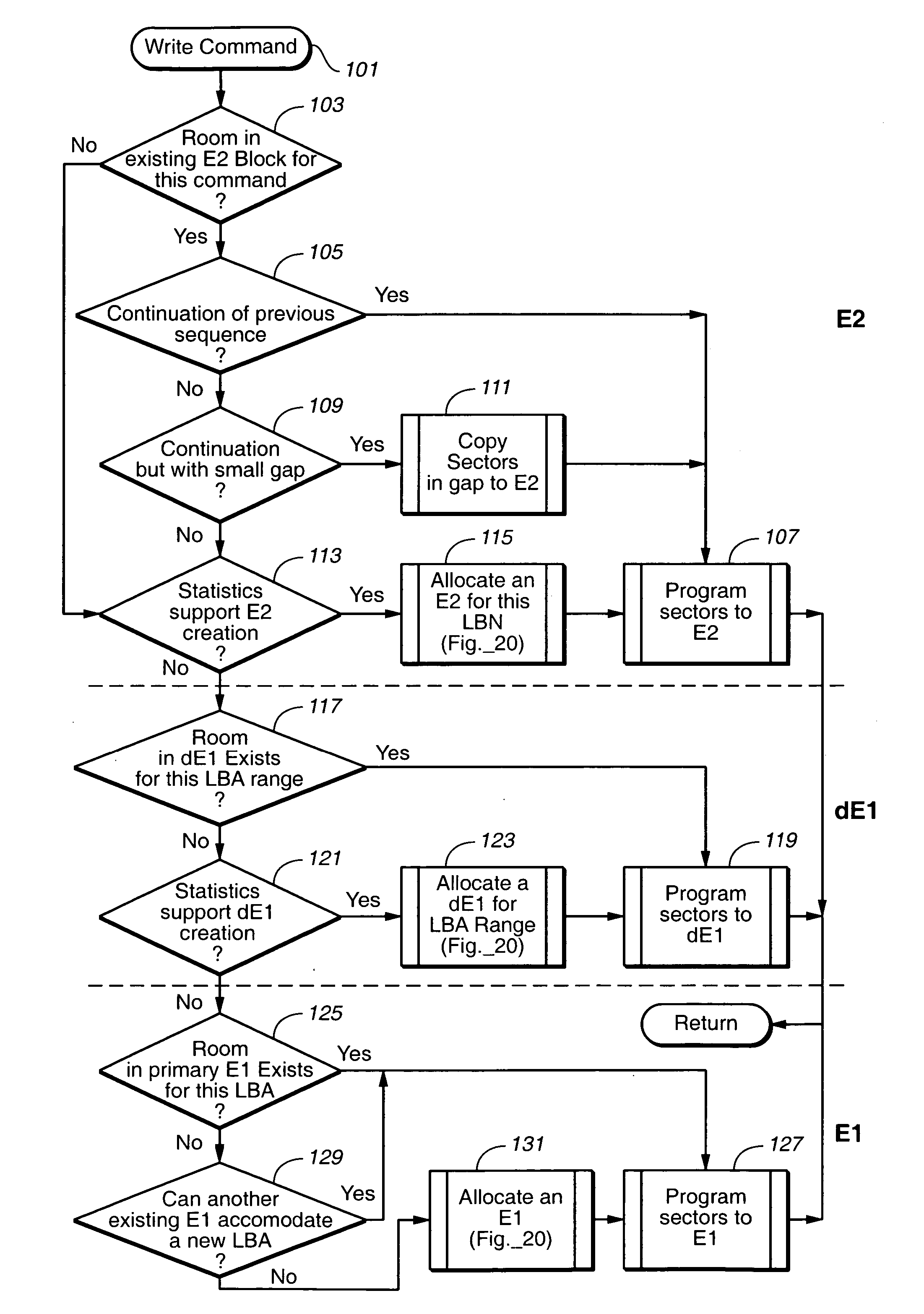

ActiveUS20050144358A1Reduce amountImprove system performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationOriginal dataTerm memory

A non-volatile memory system of a type having blocks of memory cells erased together and which are programmable from an erased state in units of a large number of pages per block. If the data of only a few pages of a block are to be updated, the updated pages are written into another block provided for this purpose. Updated pages from multiple blocks are programmed into this other block in an order that does not necessarily correspond with their original address offsets. The valid original and updated data are then combined at a later time, when doing so does not impact on the performance of the memory. If the data of a large number of pages of a block are to be updated, however, the updated pages are written into an unused erased block and the unchanged pages are also written to the same unused block. By handling the updating of a few pages differently, memory performance is improved when small updates are being made. The memory controller can dynamically create and operate these other blocks in response to usage by the host of the memory system.

Owner:SANDISK TECH LLC

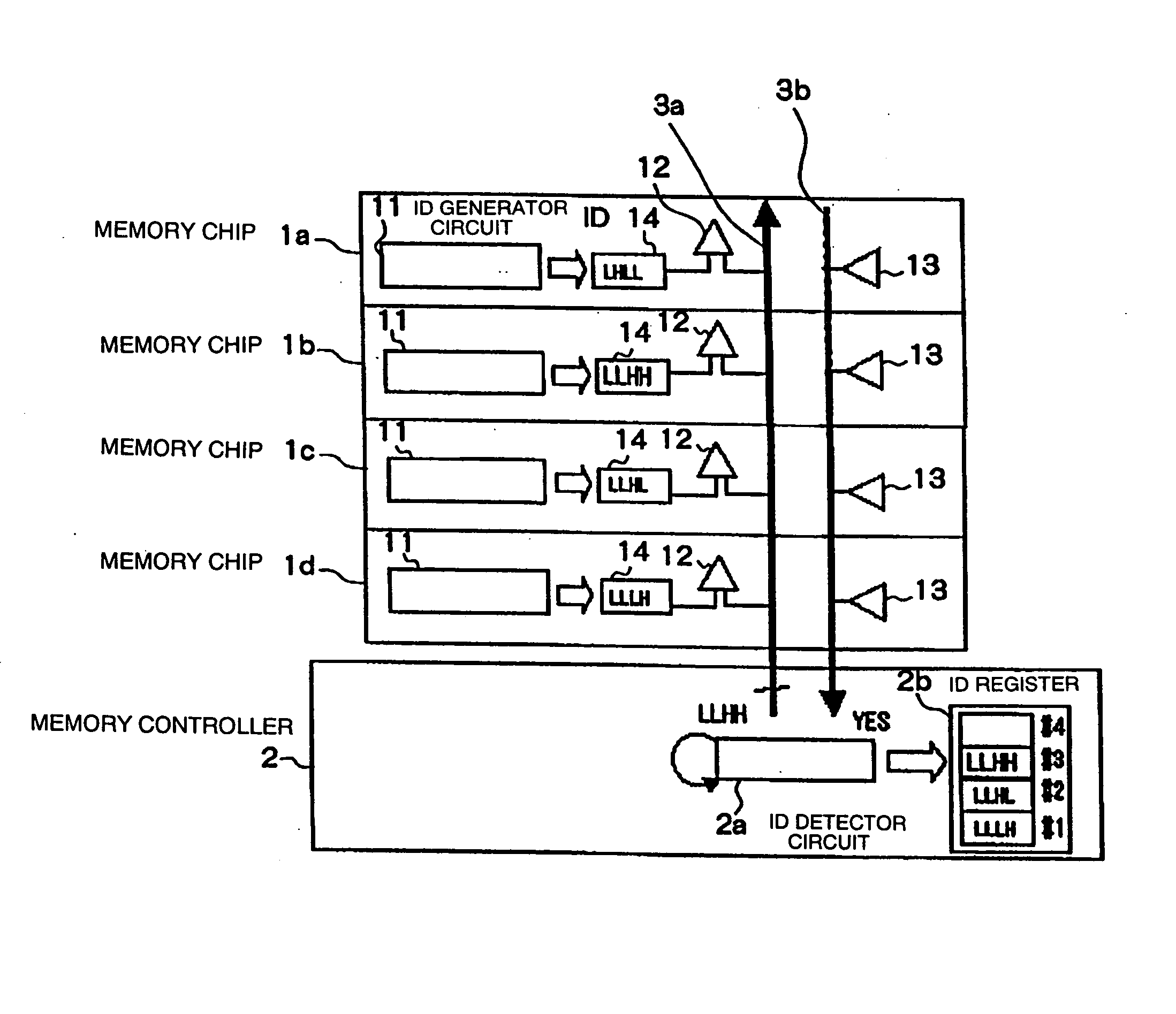

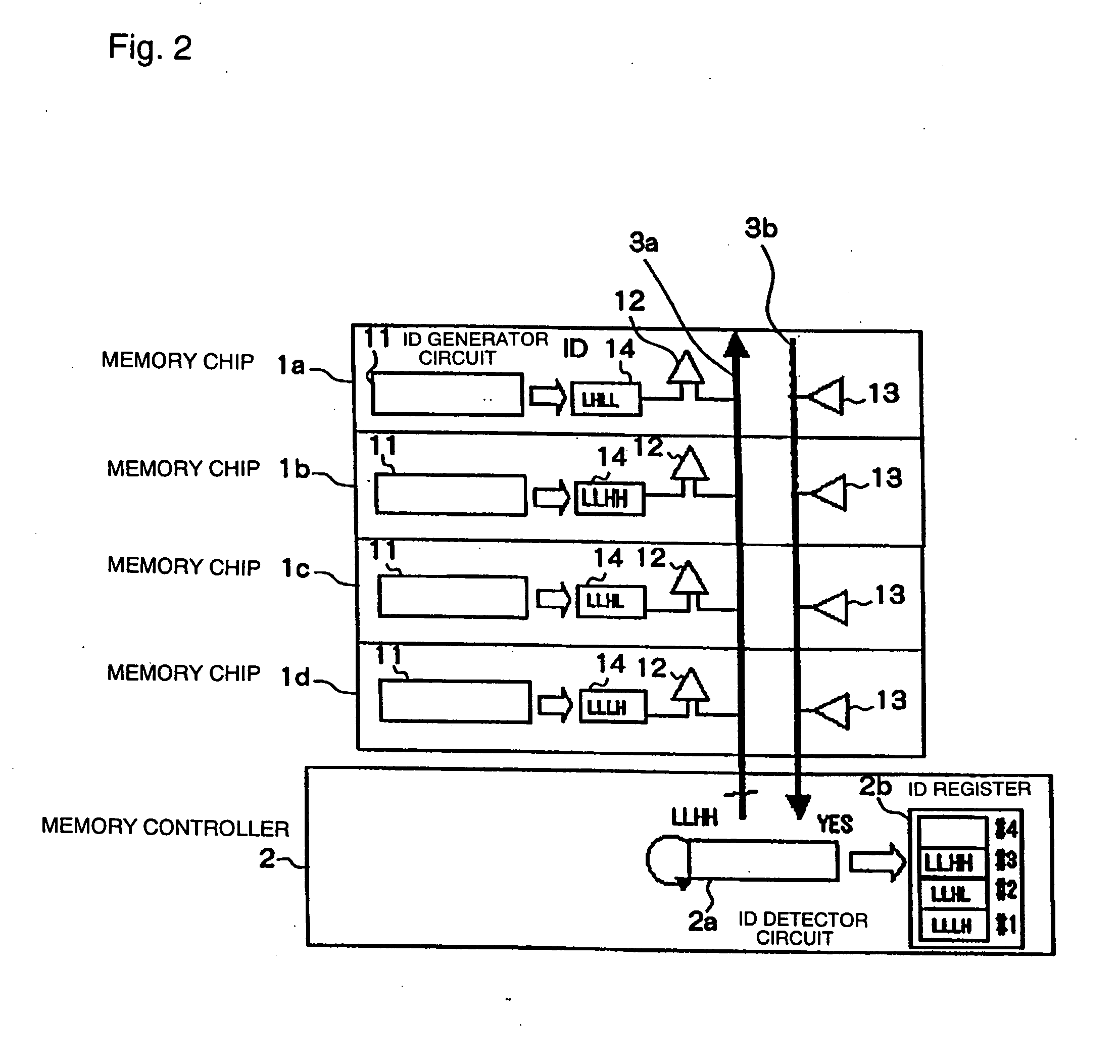

Stacked semiconductor device and semiconductor chip control method

InactiveUS20050082664A1Semiconductor/solid-state device detailsSolid-state devicesMemory chipDetector circuits

Each of stacked memory chips has an ID generator circuit for generating identification information in accordance with its manufacturing process. Since the memory chip manufacturing process implies process variations, the IDs generated by the respective ID generator circuits are different from one another even though the ID generator circuits are identical in design. A memory controller instructs an ID detector circuit to detect the IDs of the respective memory chips, and individually controls the respective memory chips based on the detected IDs.

Owner:ELPIDA MEMORY INC

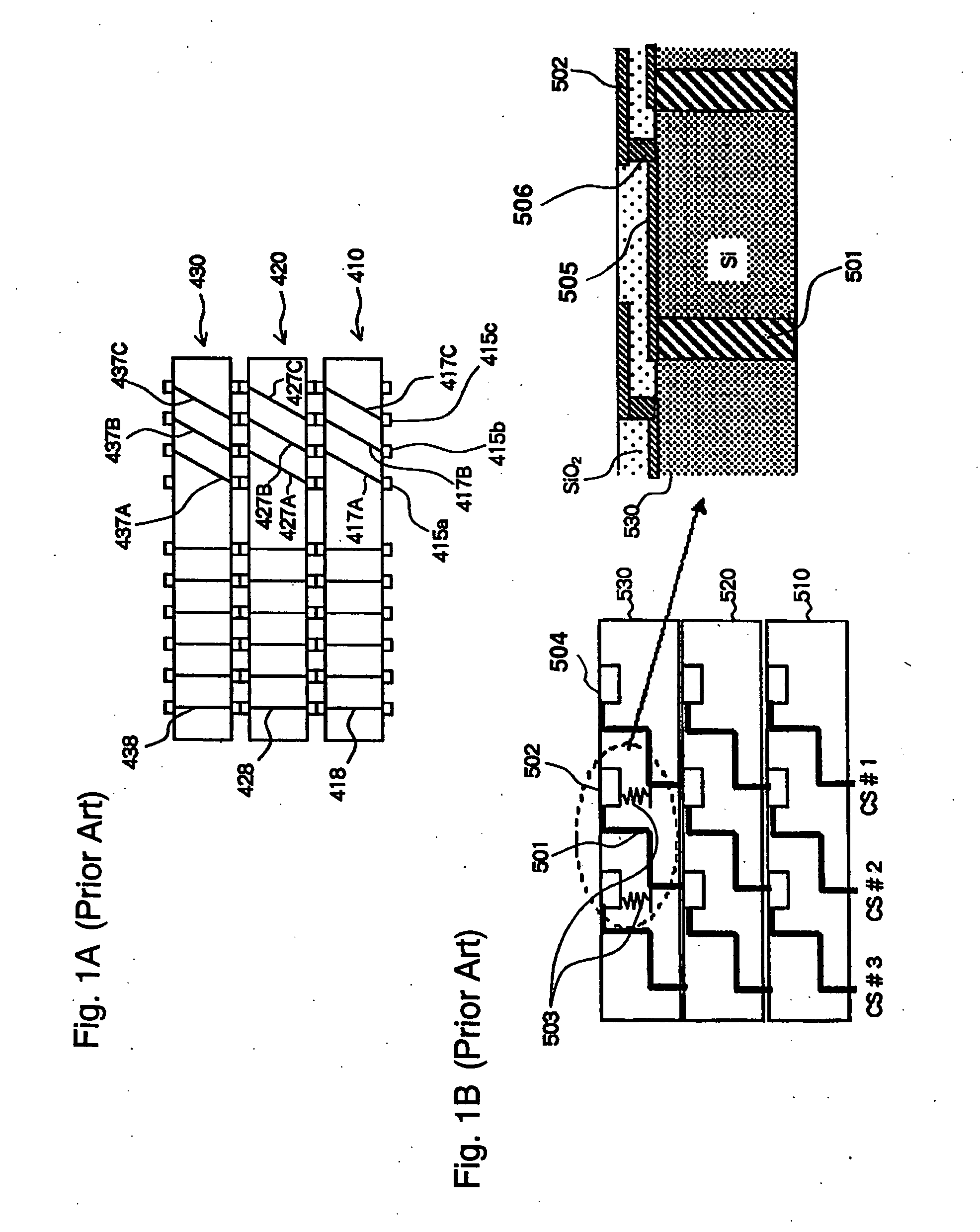

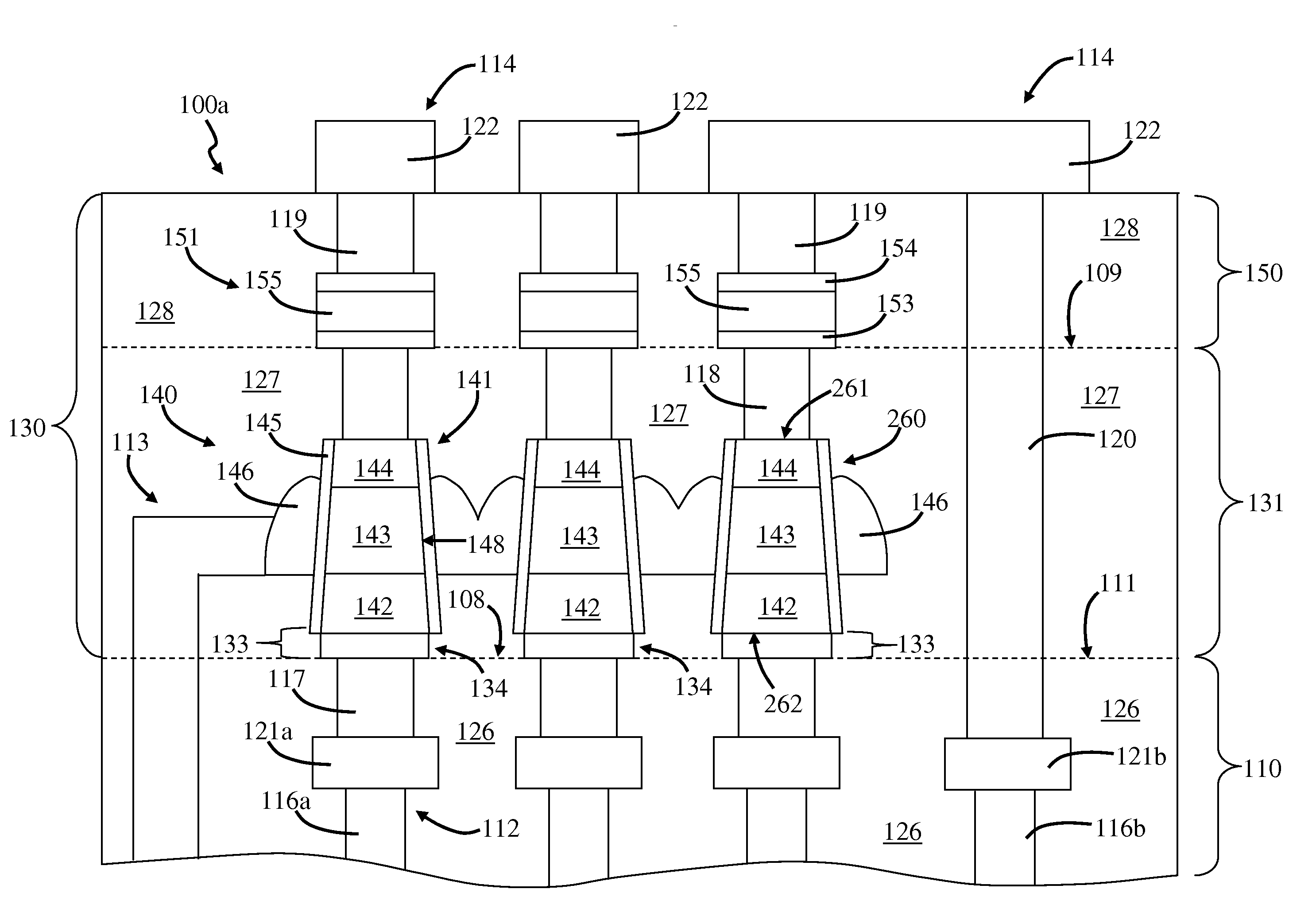

Information storage system which includes a bonded semiconductor structure

An information storage system includes a bonded semiconductor structure having a memory circuit region carried by an interconnect region. The memory circuit region includes a memory control device region having a vertically oriented memory control device. The memory circuit region includes a memory device region in communication with the memory control device region. The memory device region includes a memory device whose operation is controlled by the vertically oriented memory control device.

Owner:BESANG

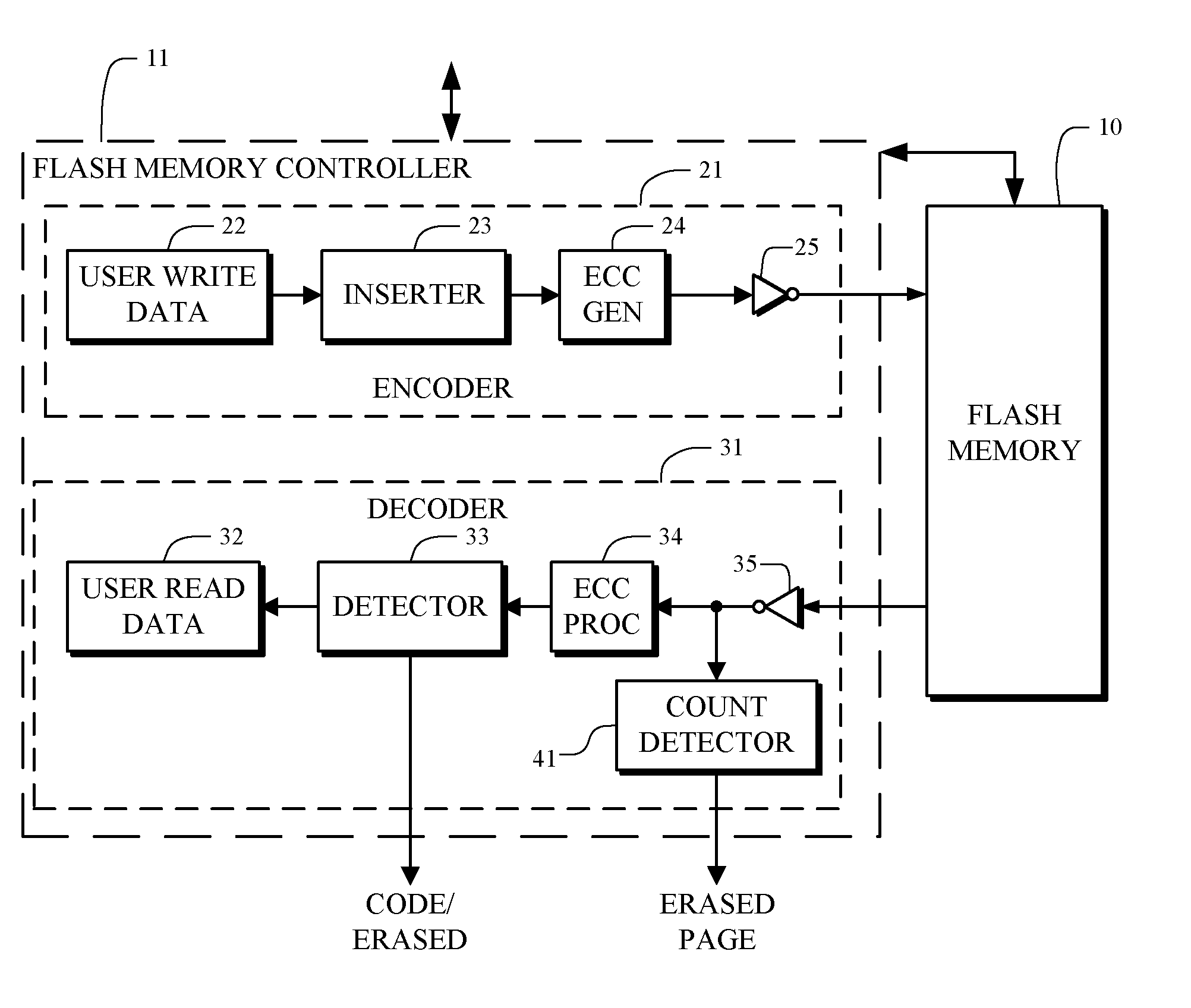

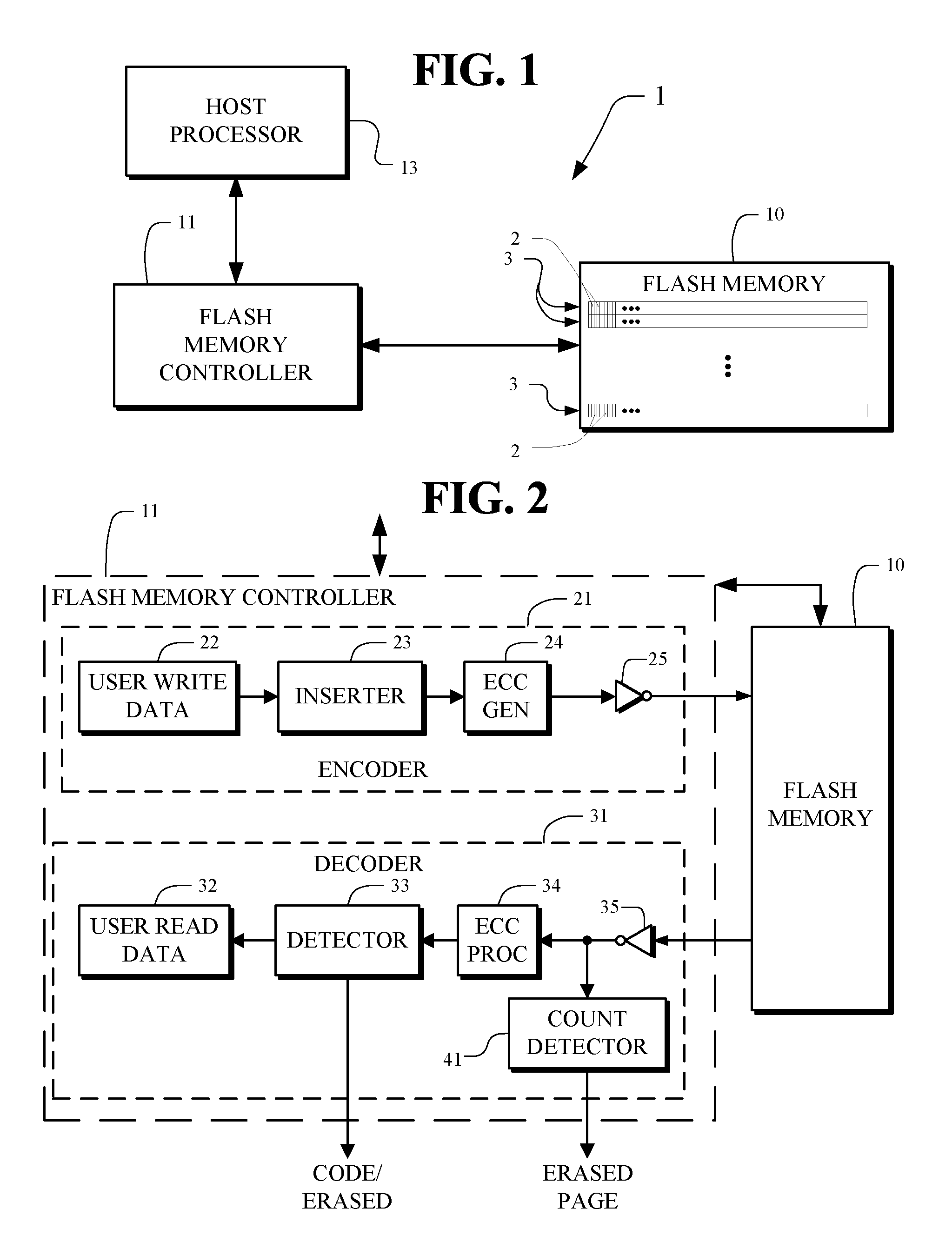

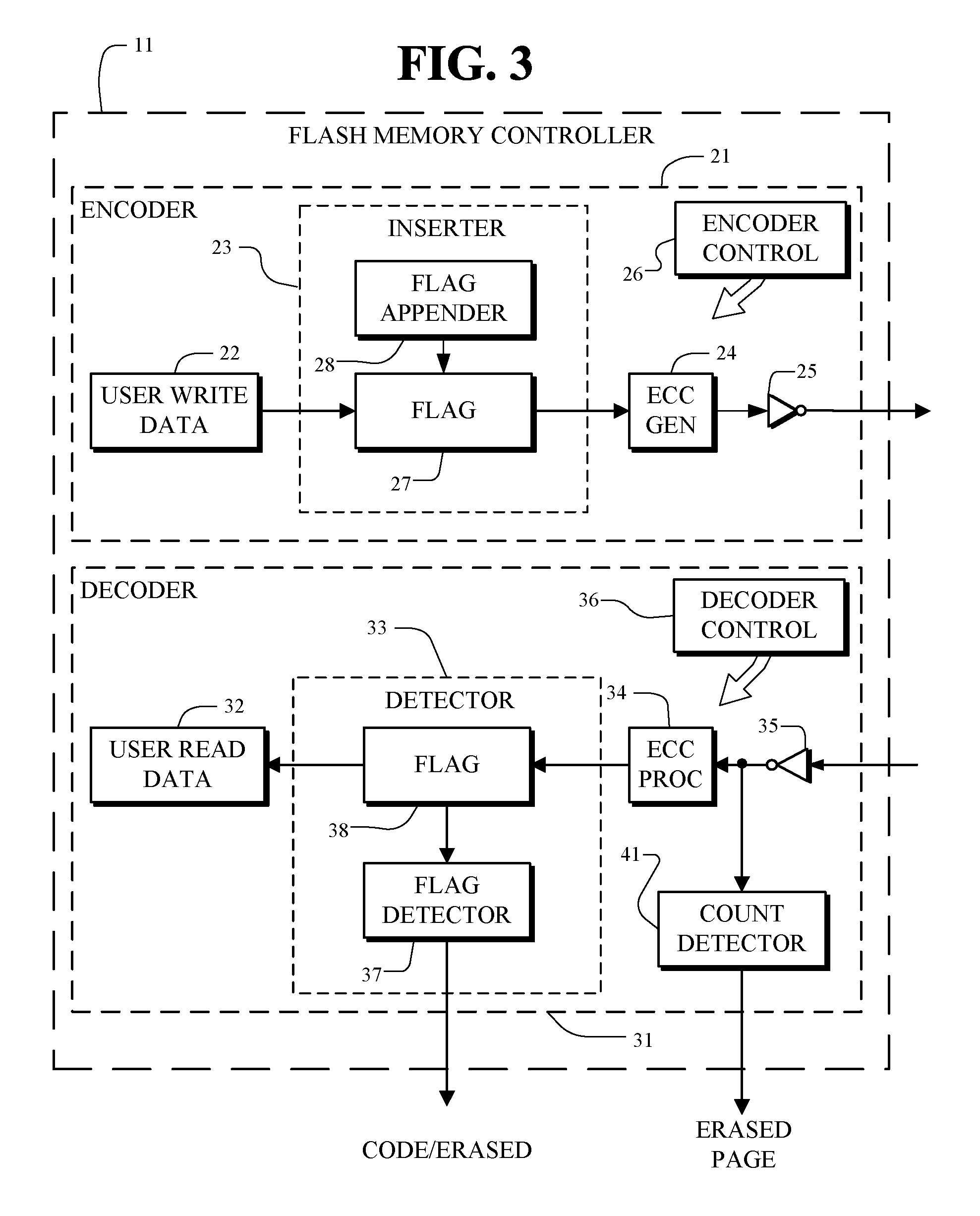

Erased page detection

A memory device and method, such as a flash memory device and method, includes a memory having a plurality of nonvolatile memory cells for storing stored values of user data. The memory device and method includes a memory controller for controlling the memory. The memory controller includes an encoder for encoding user write data for storage of code values as the stored values in the memory. The encoder includes an inserter for insertion of an indicator as part of the stored values for use in determining when the stored values are or are not in an erased state. The memory controller includes a decoder for reading the stored values from the memory to form user read data values when the stored values are not in the erased state.

Owner:MARVELL ASIA PTE LTD

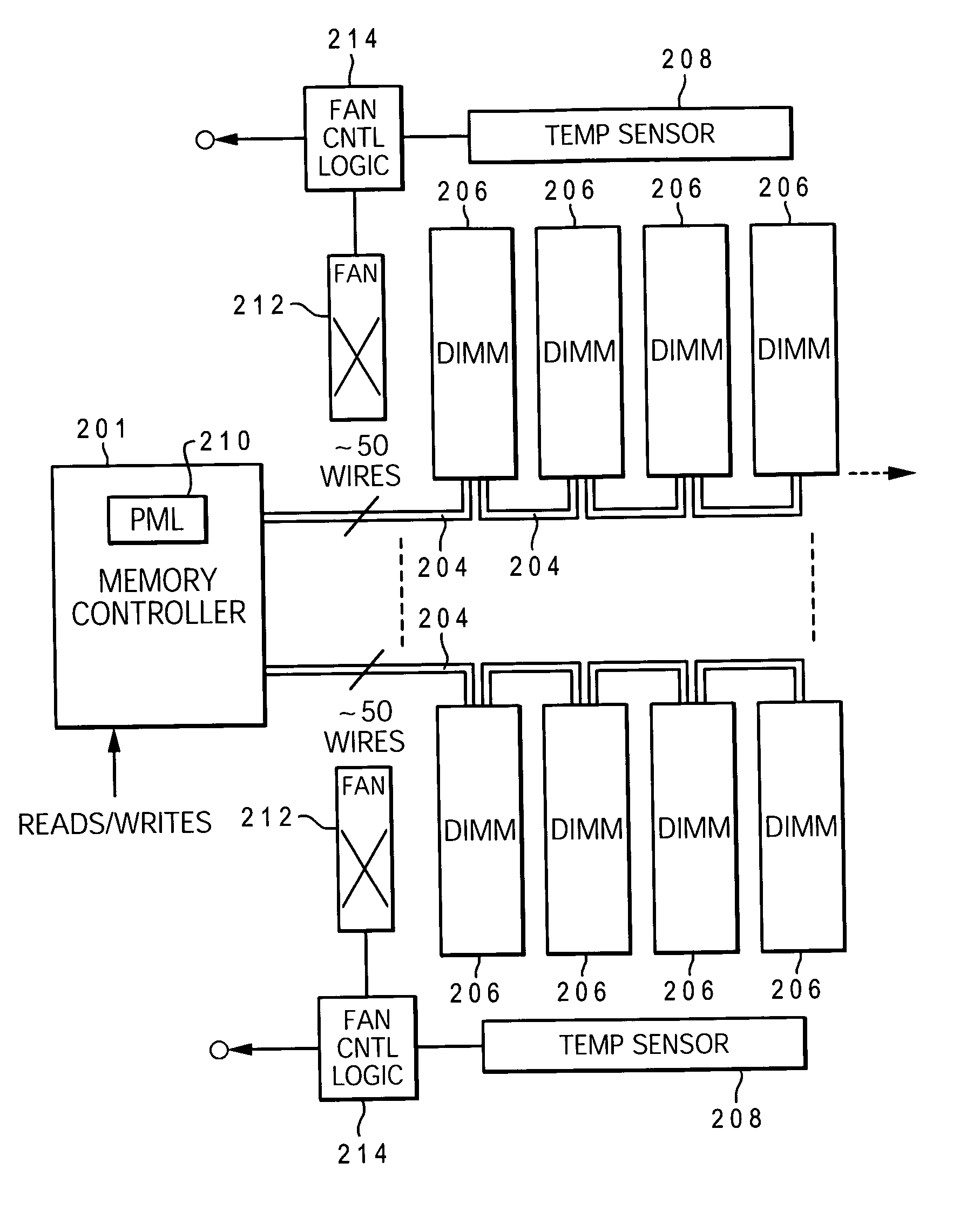

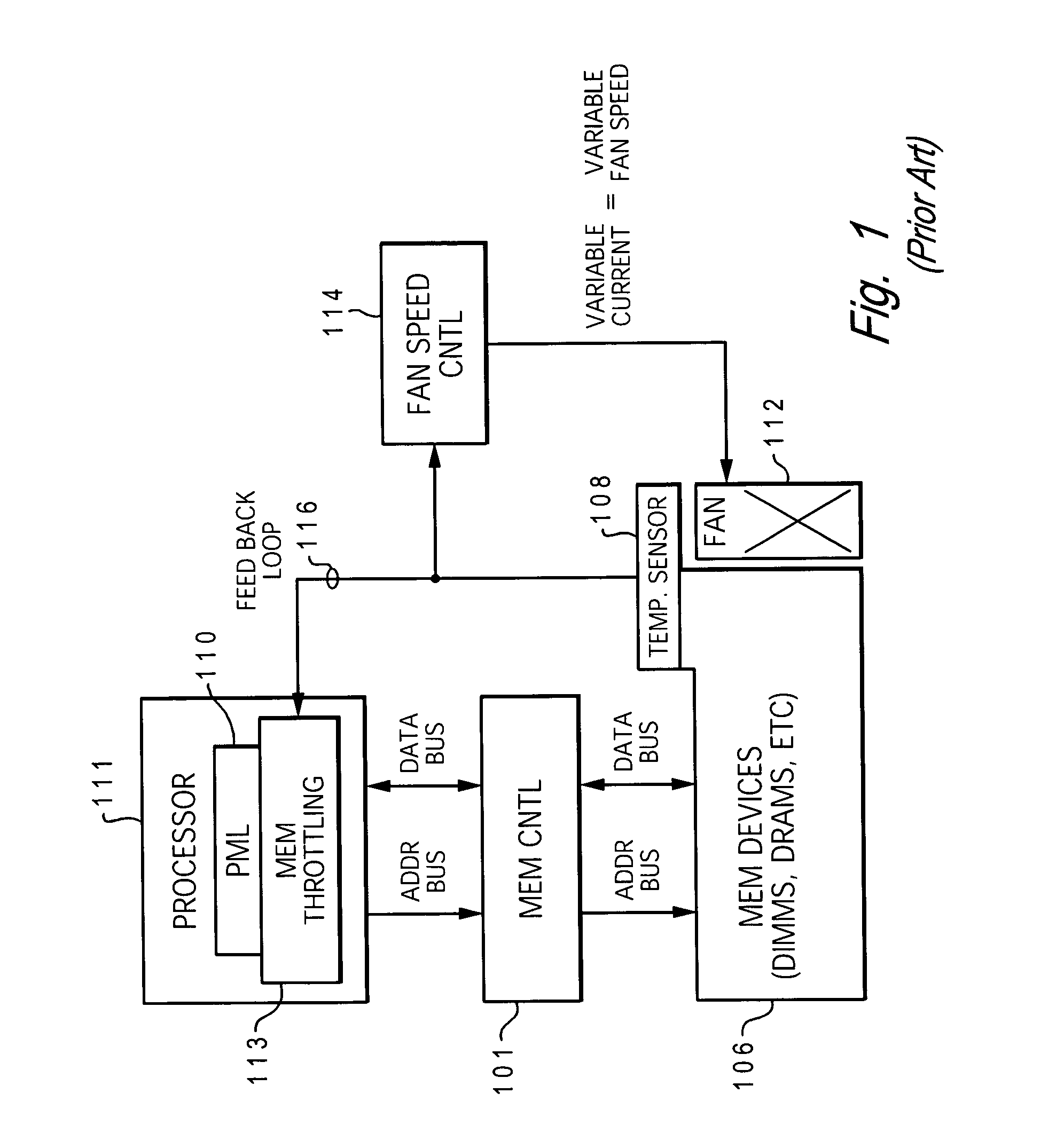

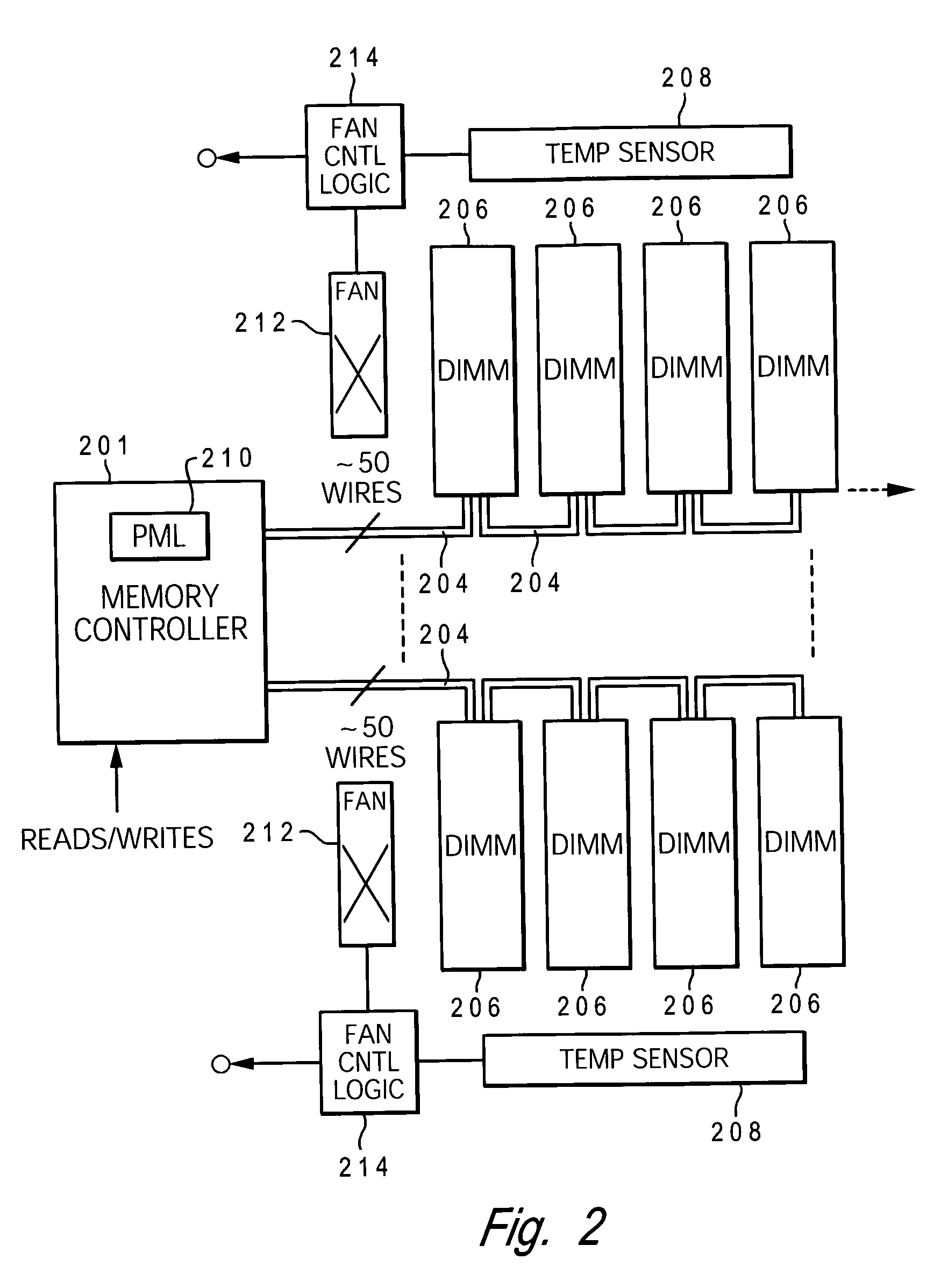

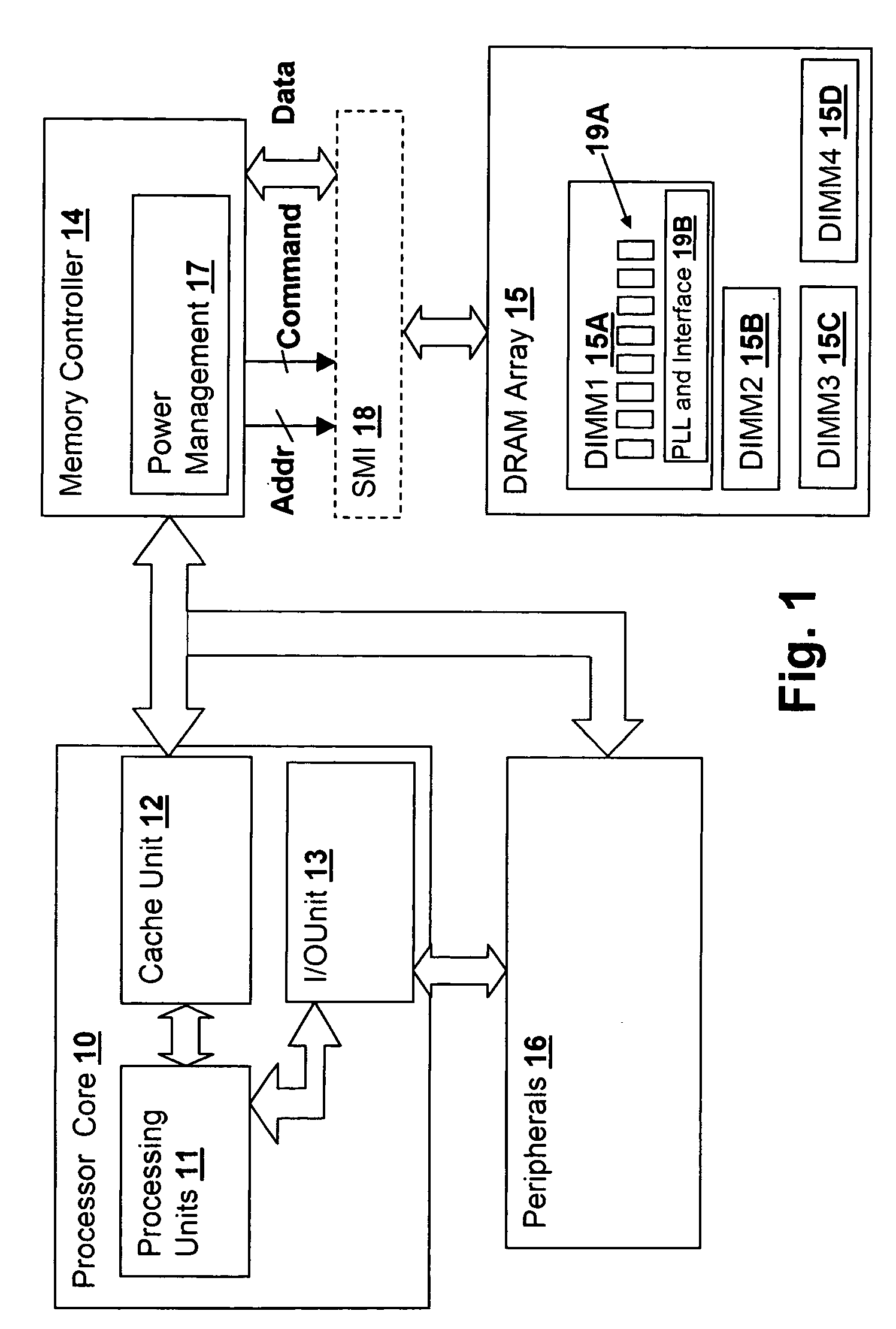

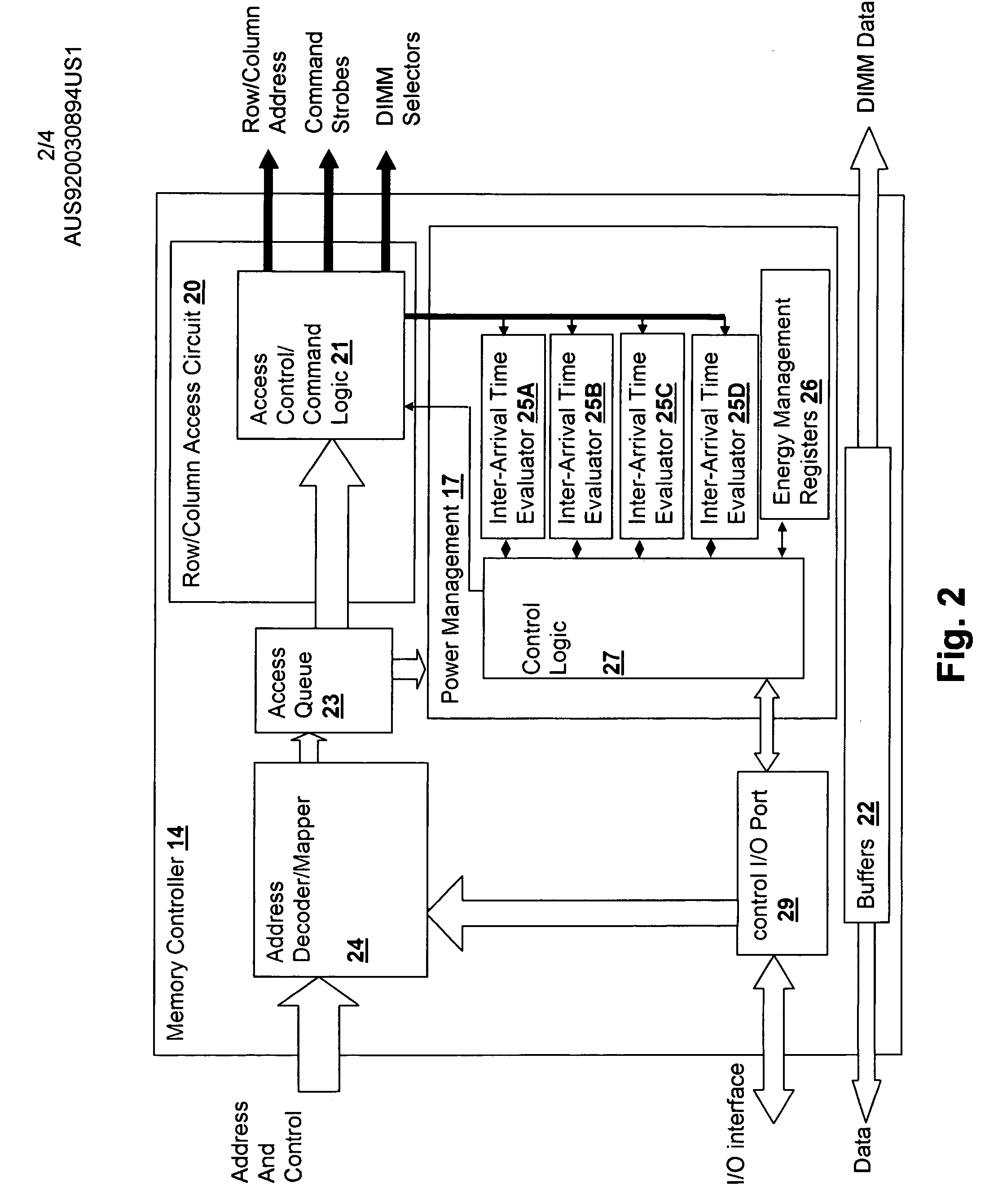

Dynamic power management via DIMM read operation limiter

InactiveUS20060179334A1Little or no usePower usageEnergy efficient ICTVolume/mass flow measurementDIMMDynamic power management

A method and system for enabling directed temperature / power management at the DIMM-level and / or DRAM-level utilizing intelligent scheduling of memory access operations received at the memory controller. Hot spots within the memory subsystem, caused by operating the DIMMs / DRAMs above predetermined / preset threshold power / temperature values for operating a DIMM and / or a DRAM, are avoided / controlled by logic within the memory controller. The memory controller logic throttles the number / frequency at which commands (read / write operations) are issued to the specific DIMM / DRAM based on feedback data received from the specific DIMM / DRAM reaching the preset threshold power usage value.

Owner:IBM CORP

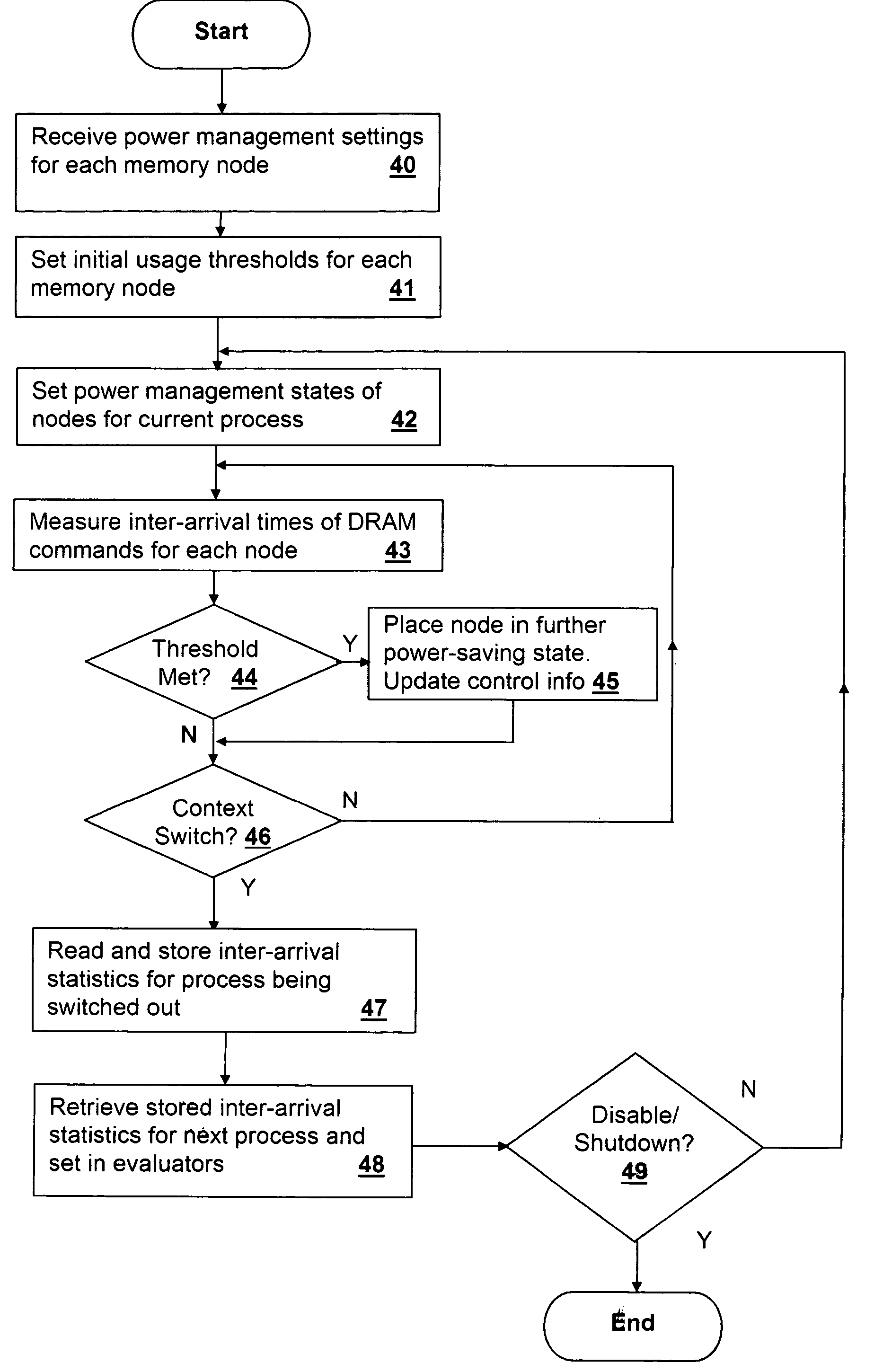

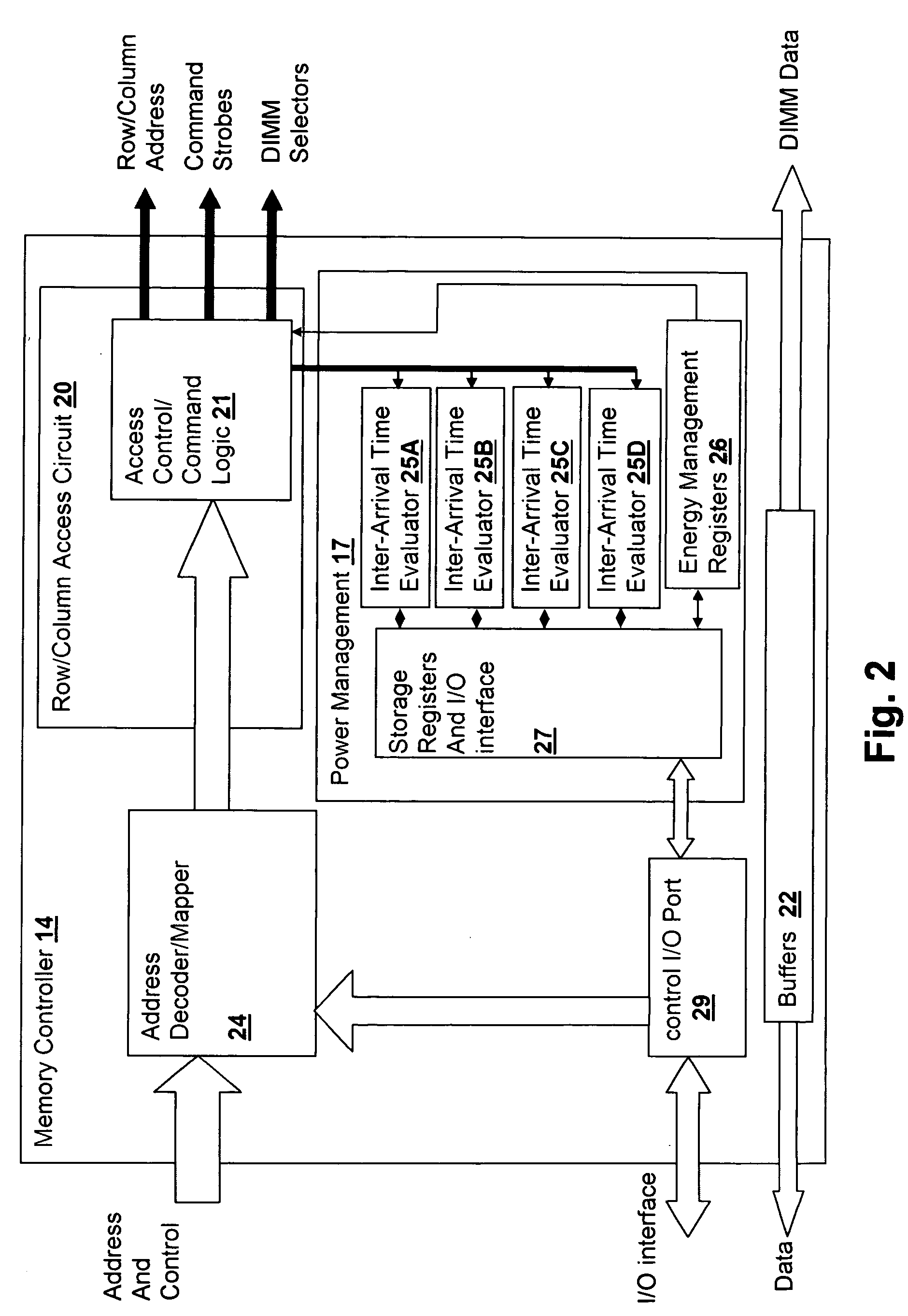

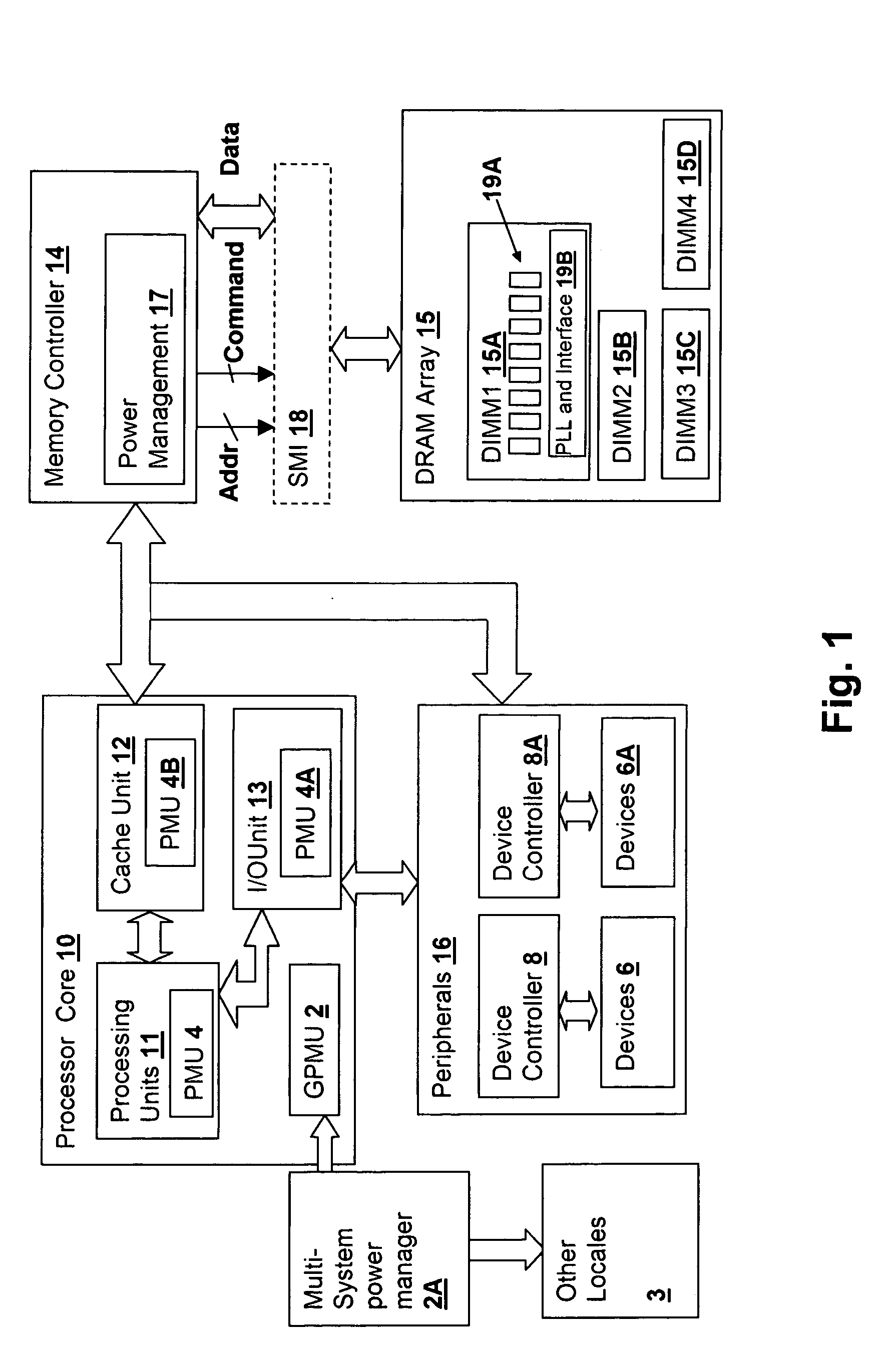

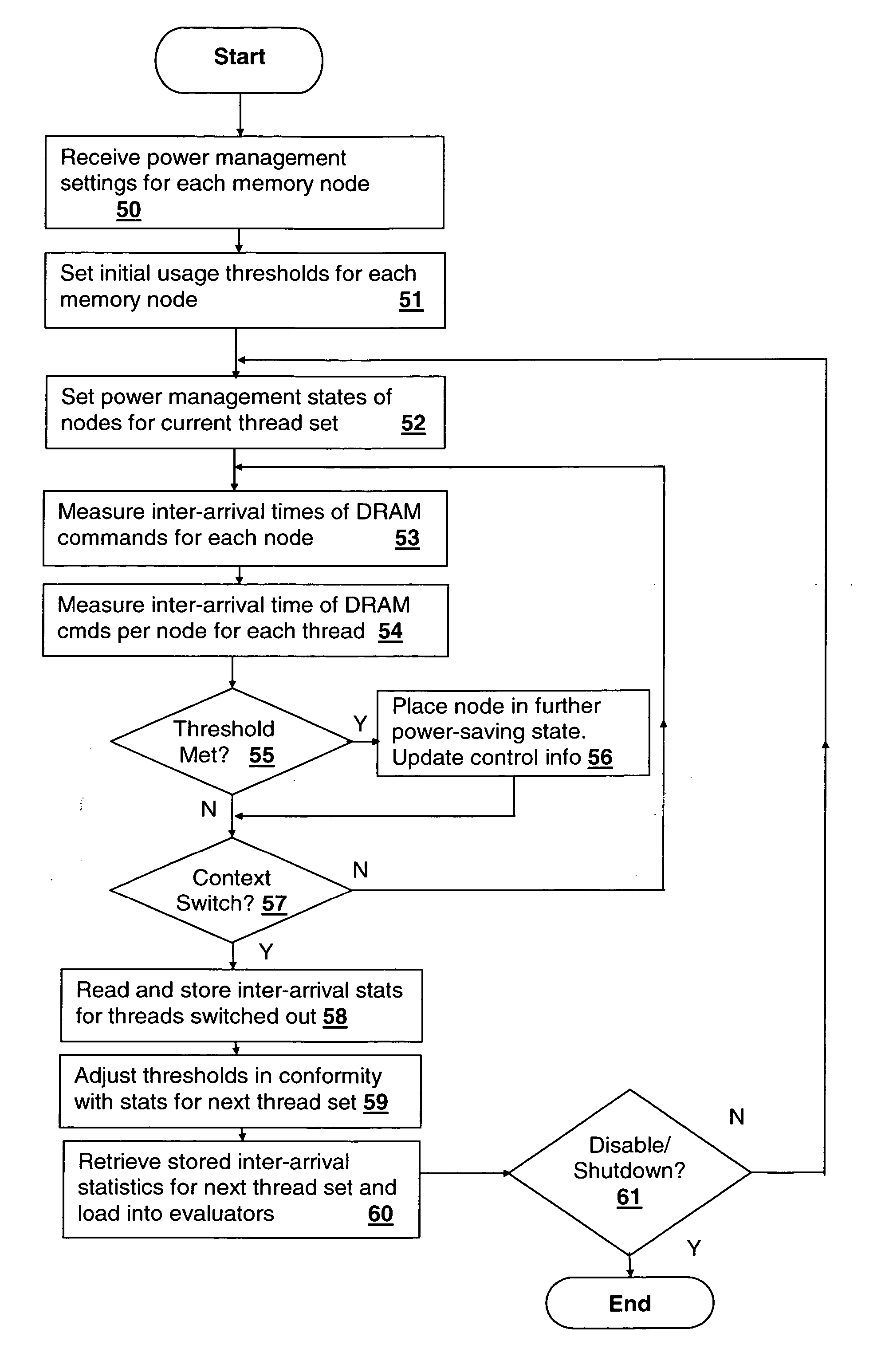

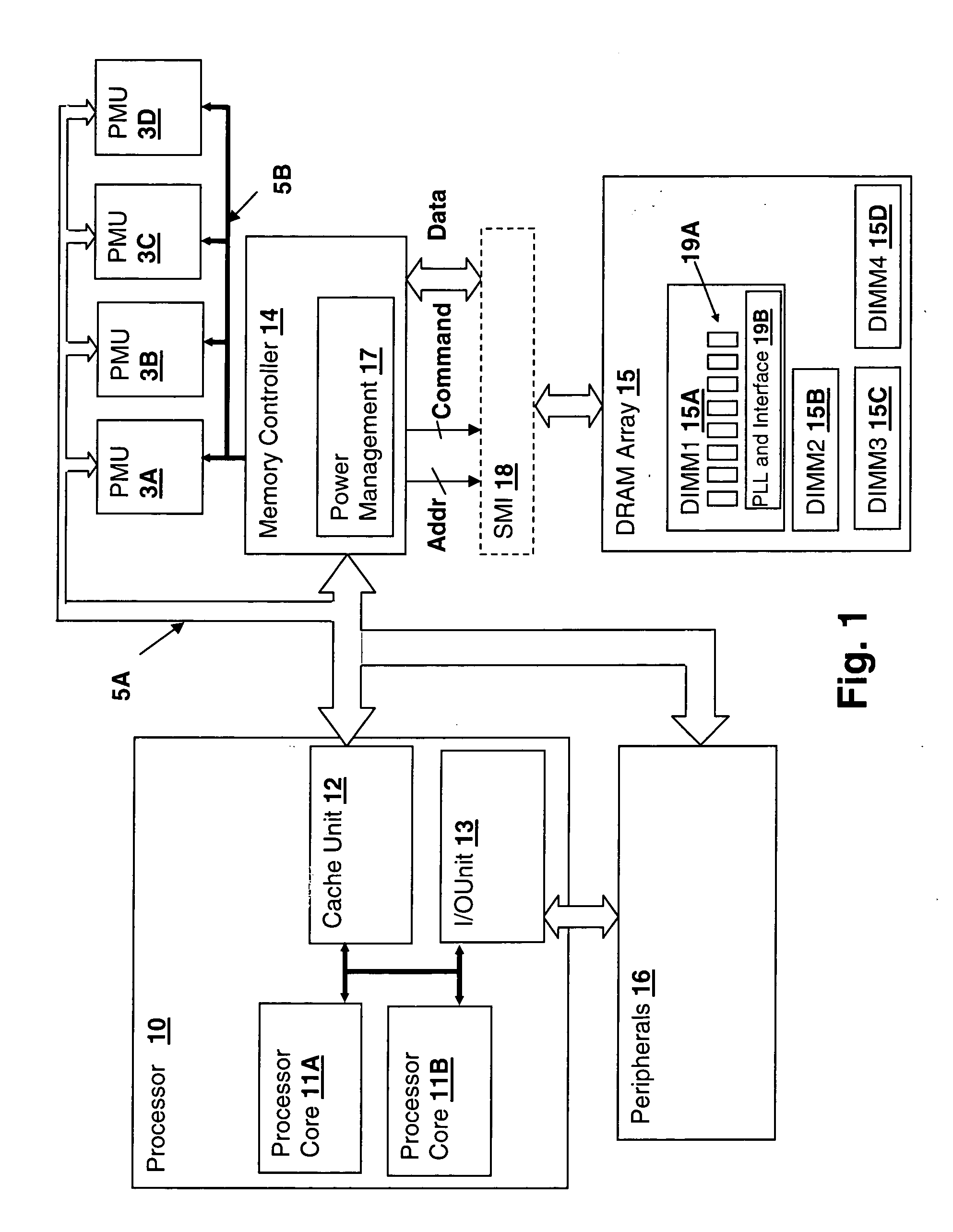

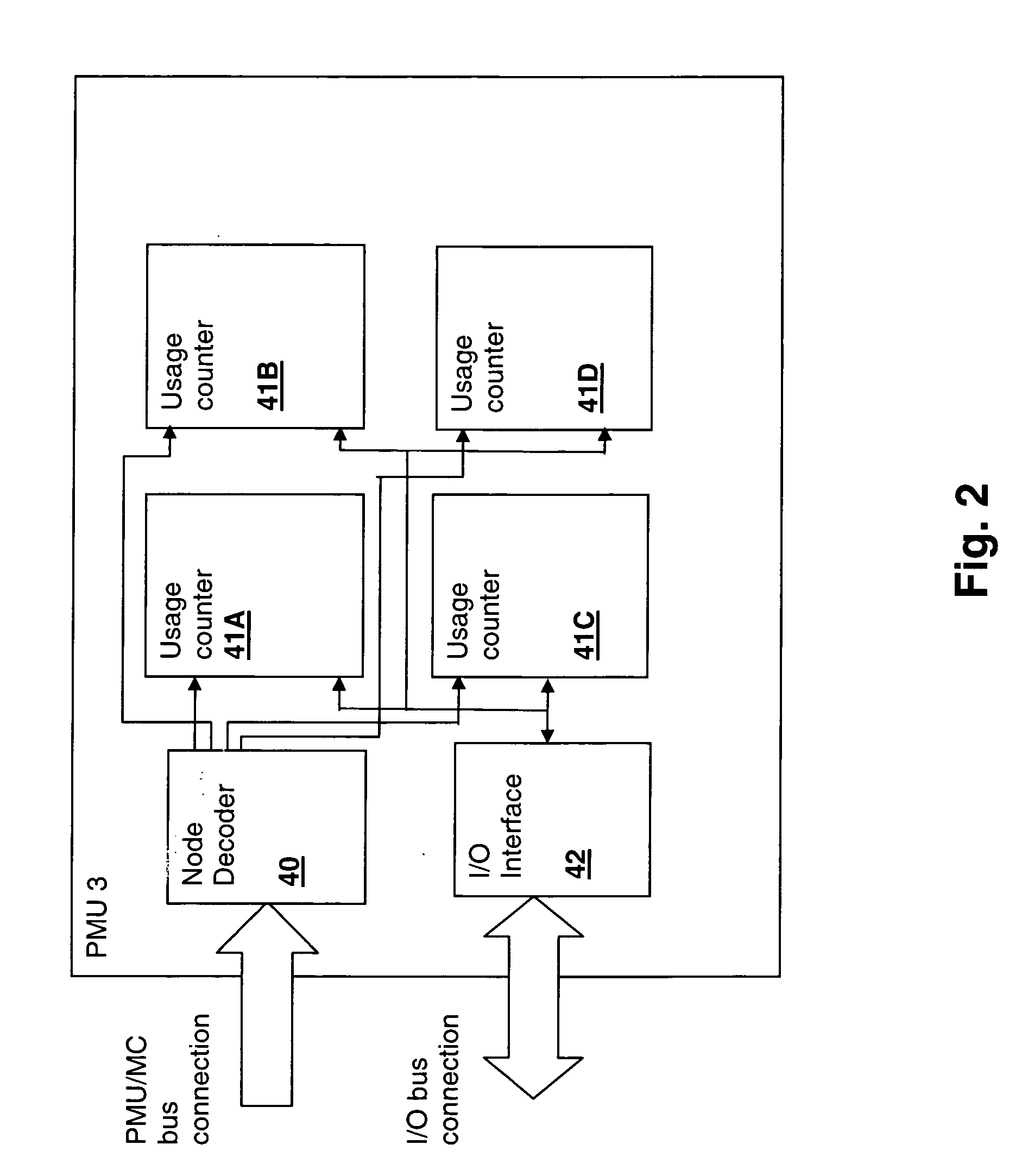

Method and system for power management including device controller-based device use evaluation and power-state control

InactiveUS20050125702A1Lower latencyReduce power consumptionEnergy efficient ICTVolume/mass flow measurementOperational systemDevice Usage

A method and system for power management including device controller-based device use evaluation and power-state control provides improved performance in a power-managed processing system. Per-device usage information is measured and evaluated during process execution and is retrieved from the device controller upon a context switch, so that upon reactivation of the process, the previous usage evaluation state can be restored. The device controller can then provide for per-process control of attached device power management states without intervention by the processor and without losing the historical evaluation state when a process is switched out. The device controller can control power-saving states of connected devices in conformity with the usage evaluation without processor intervention and across multiple process execution slices. The device controller may be a memory controller and the controlled devices memory modules or banks within modules if individual banks can be power-managed. Local thresholds provide the decision-making mechanism for each controlled device. The thresholds may be history-based, fixed or adaptive and are generally set initially by the operating system and may be updated by the memory controller adaptively or using historical collected usage evaluation counts or alternatively by the operating system via a system processor.

Owner:IBM CORP

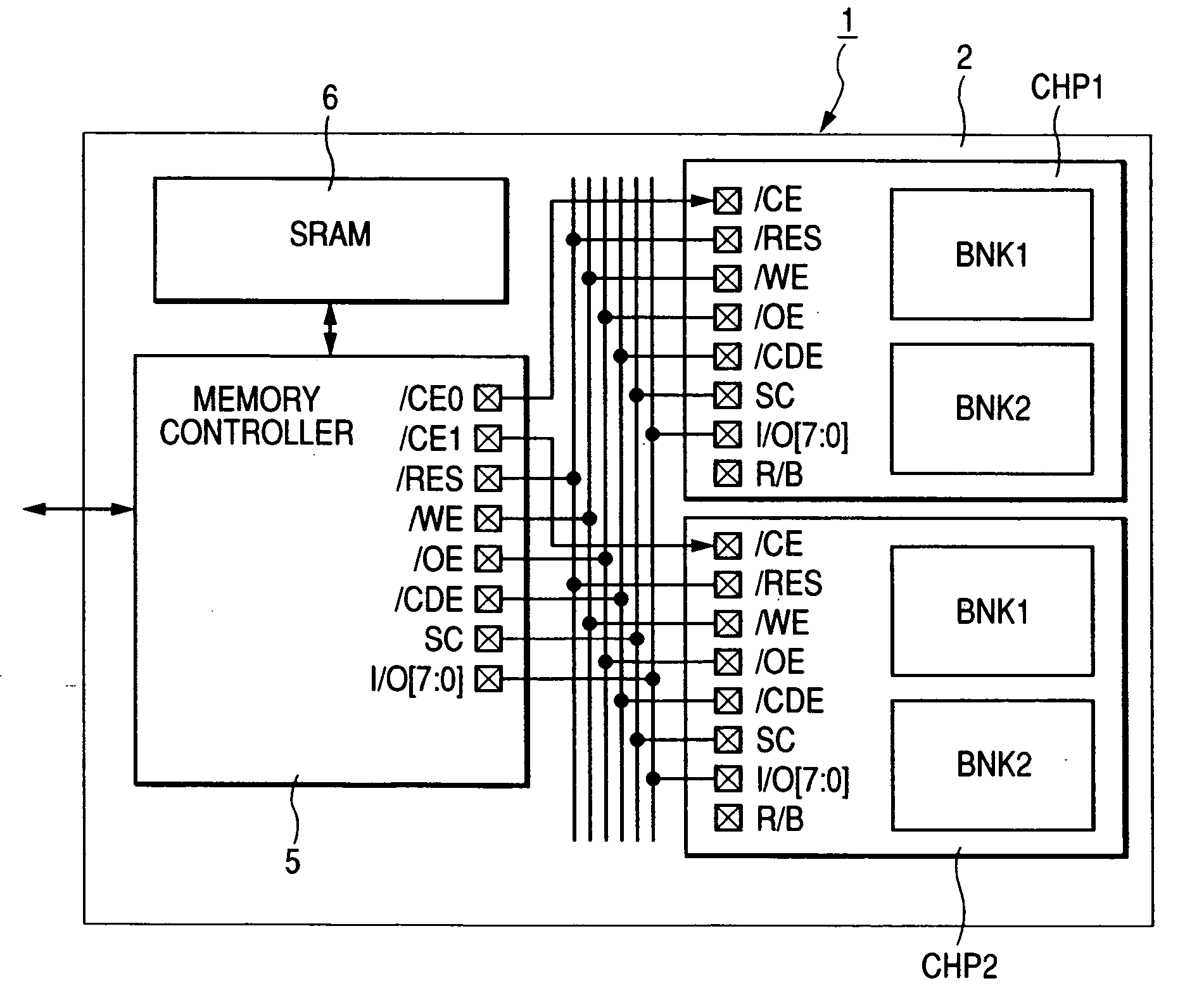

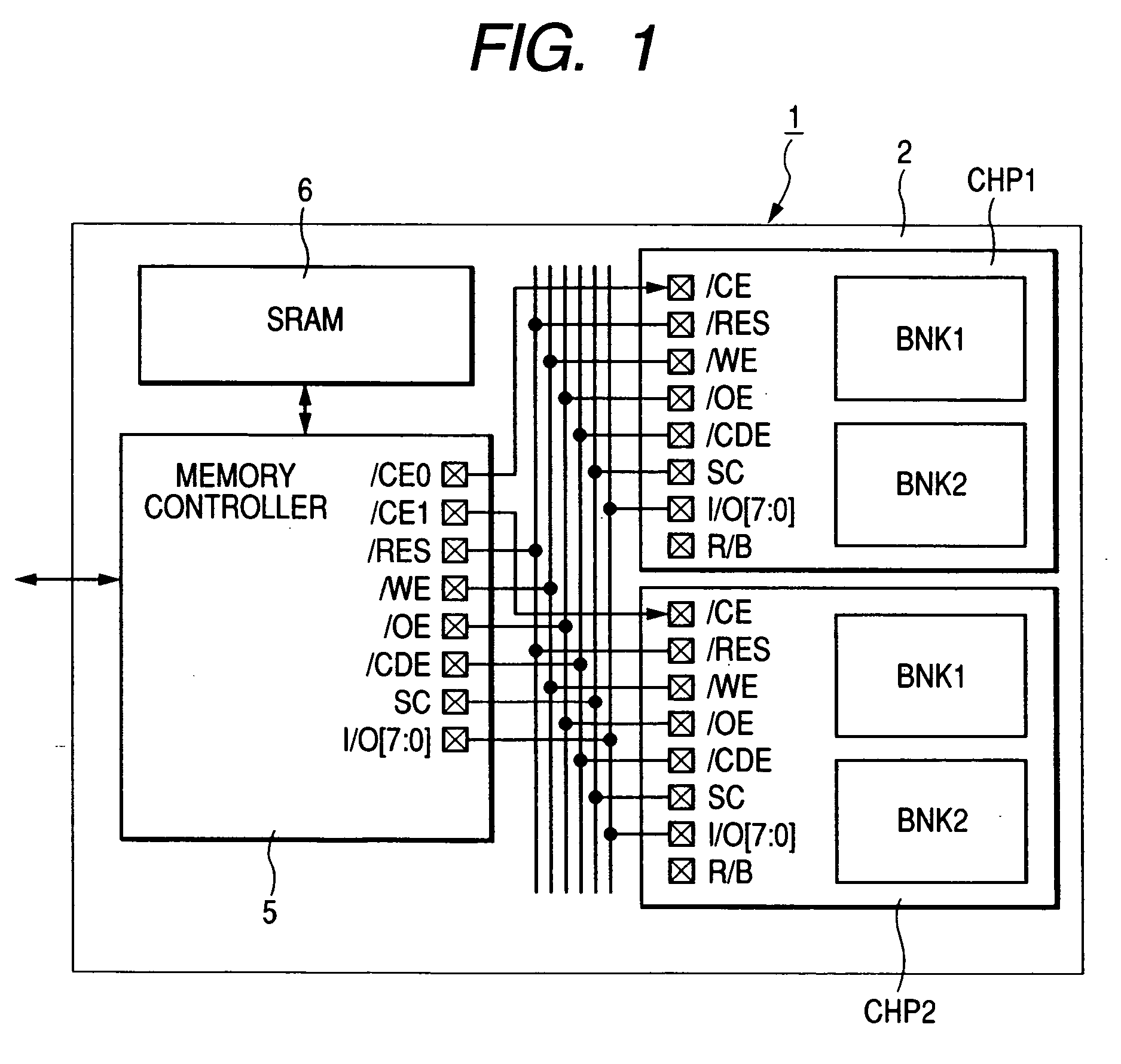

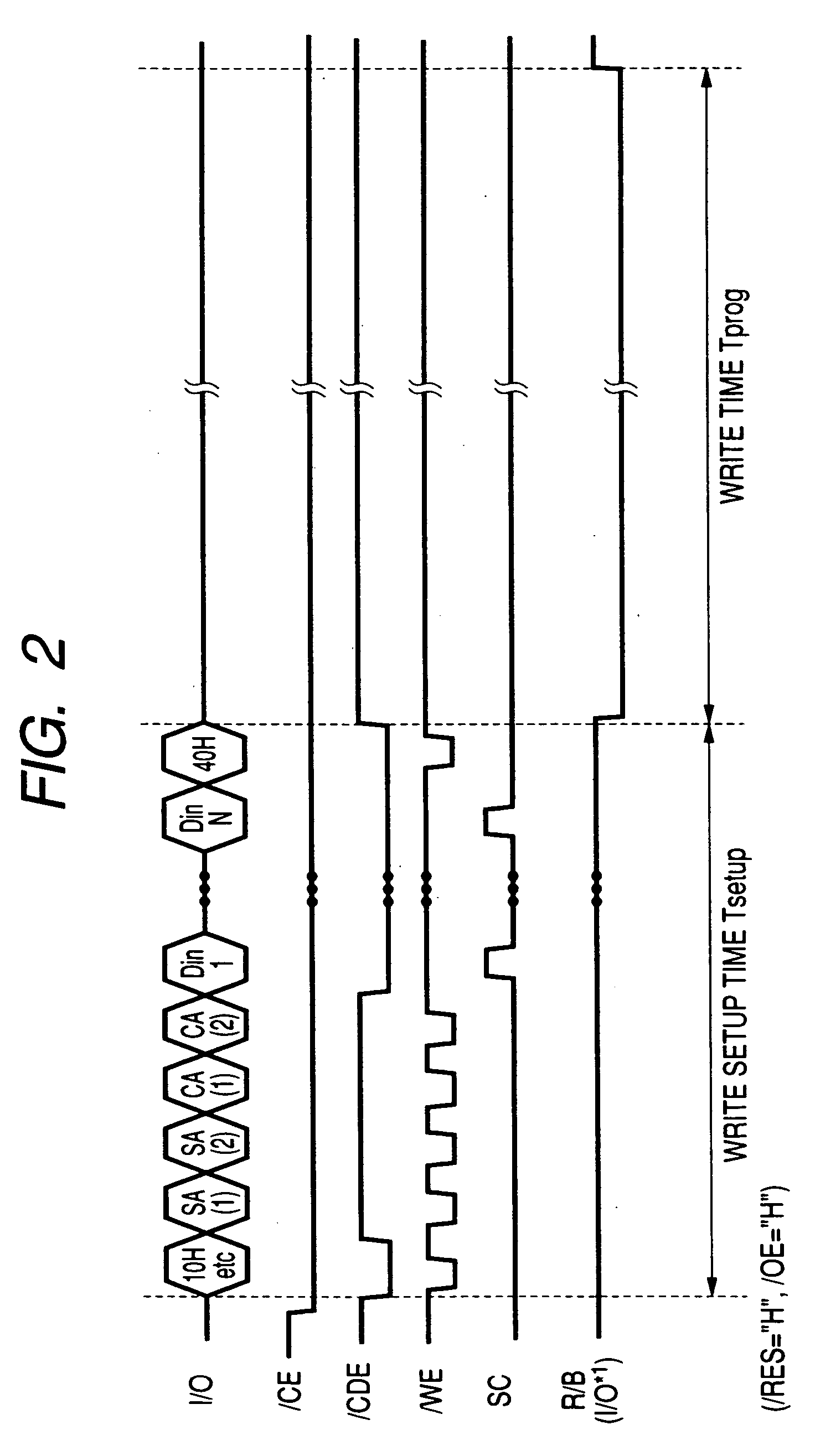

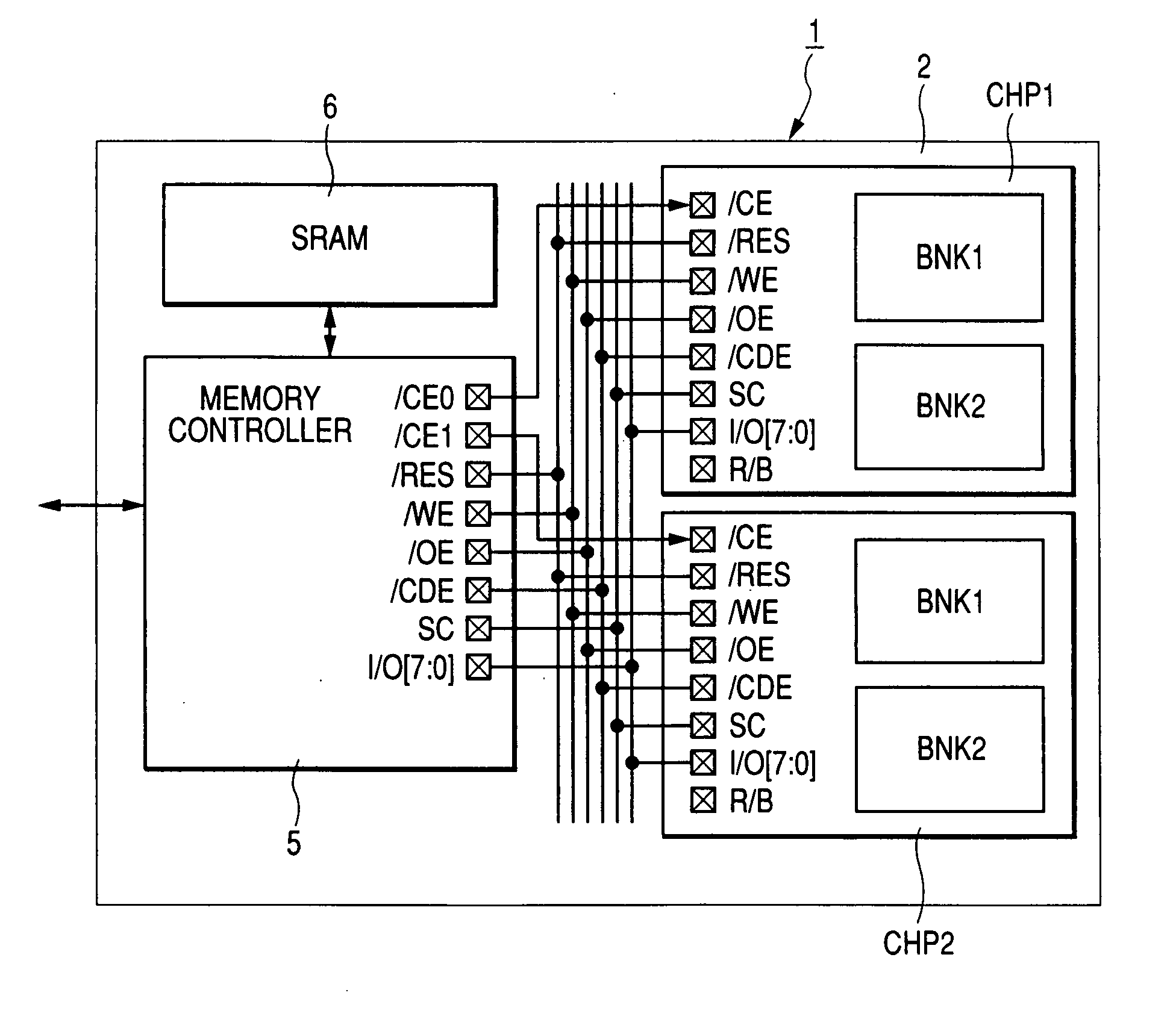

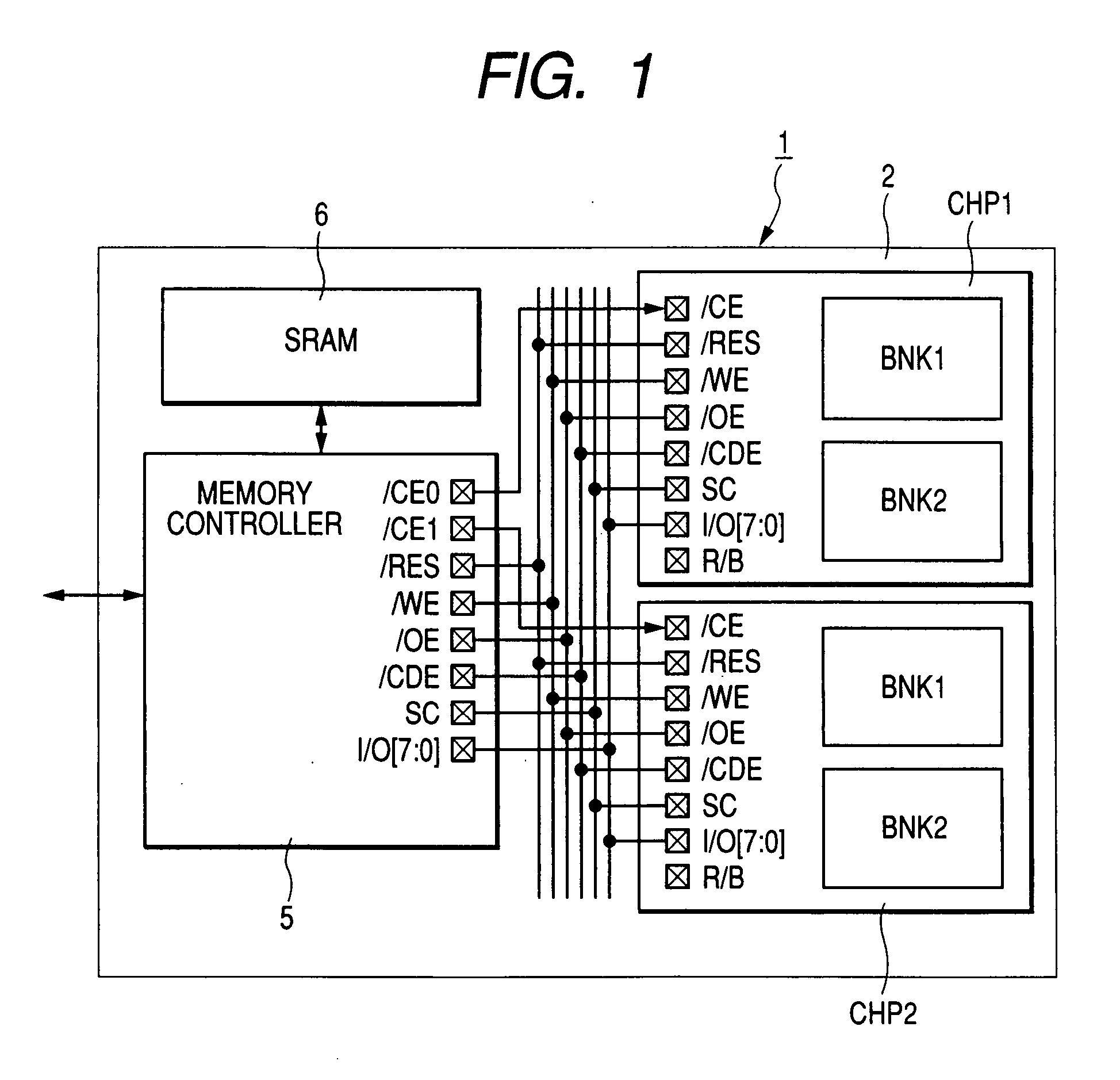

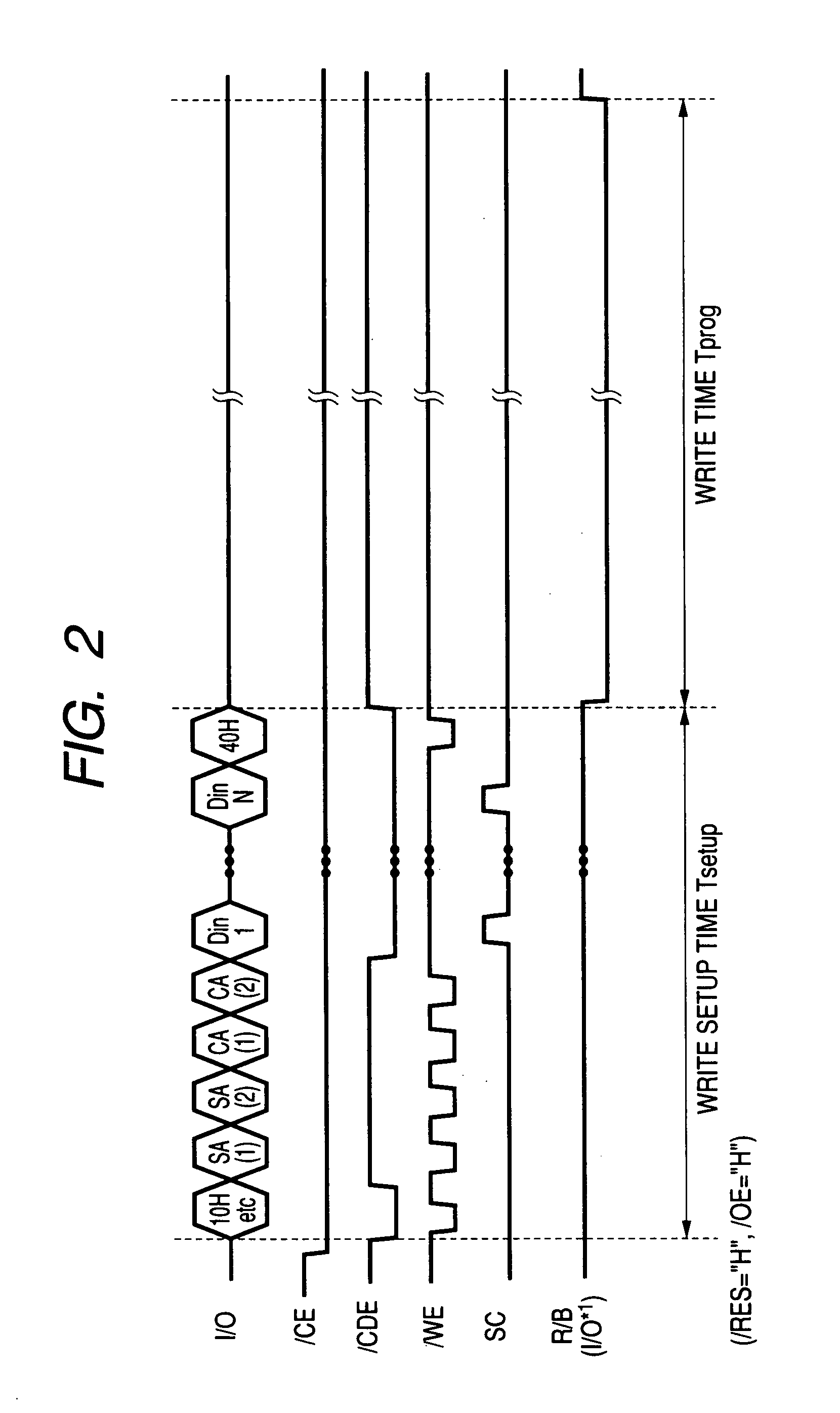

Memory system and memory card

InactiveUS20050015539A1Increase costIncrease speedMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:RENESAS ELECTRONICS CORP

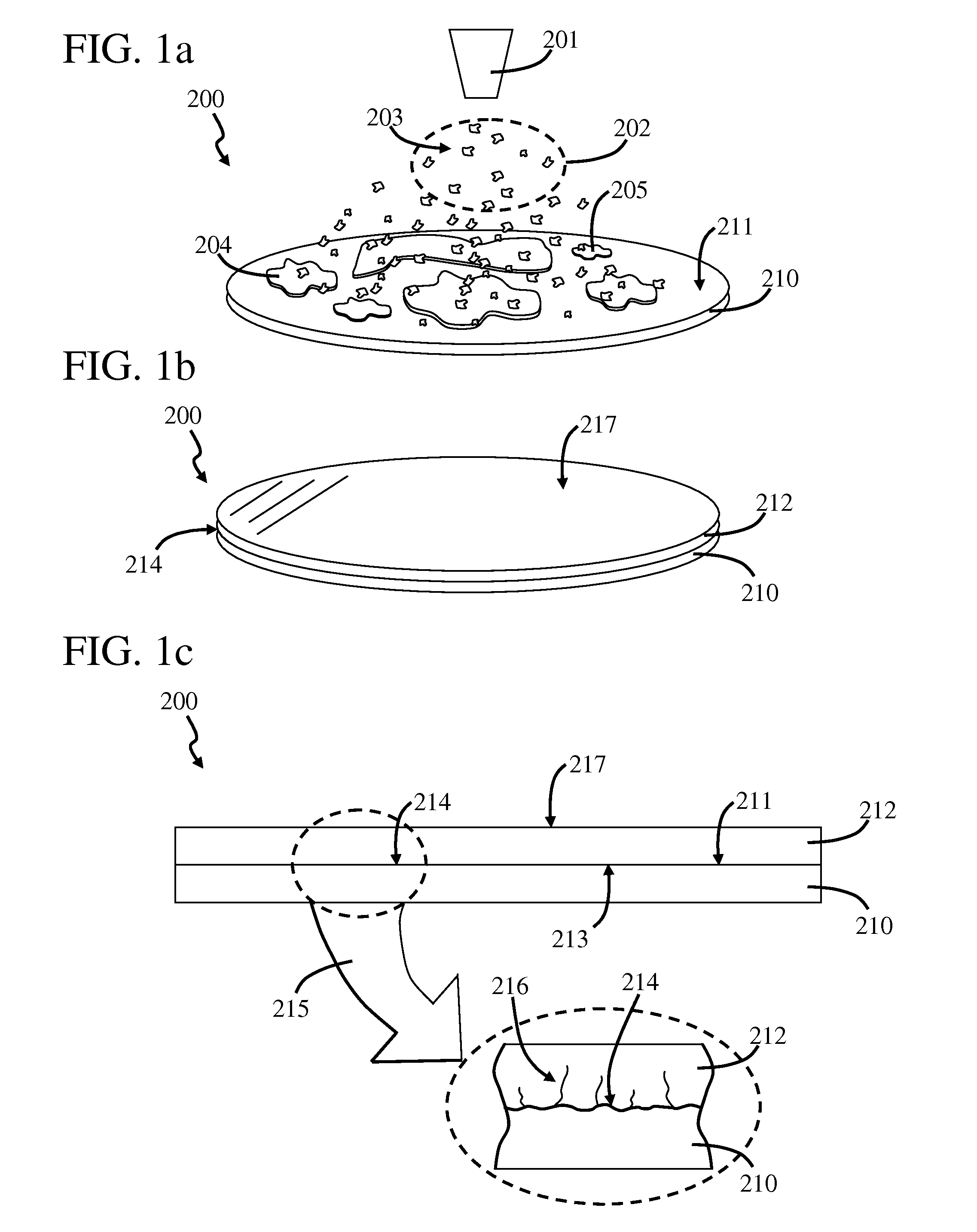

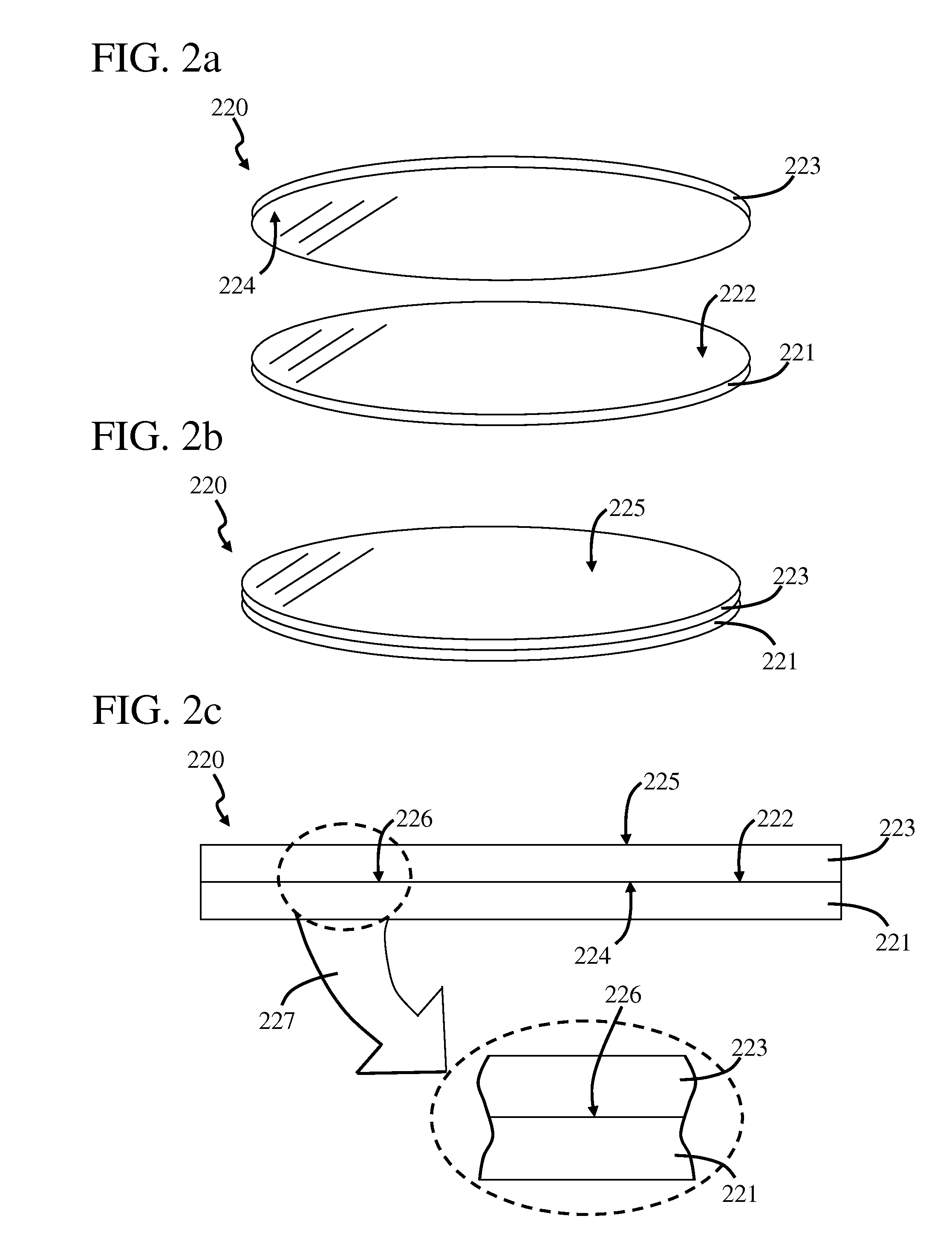

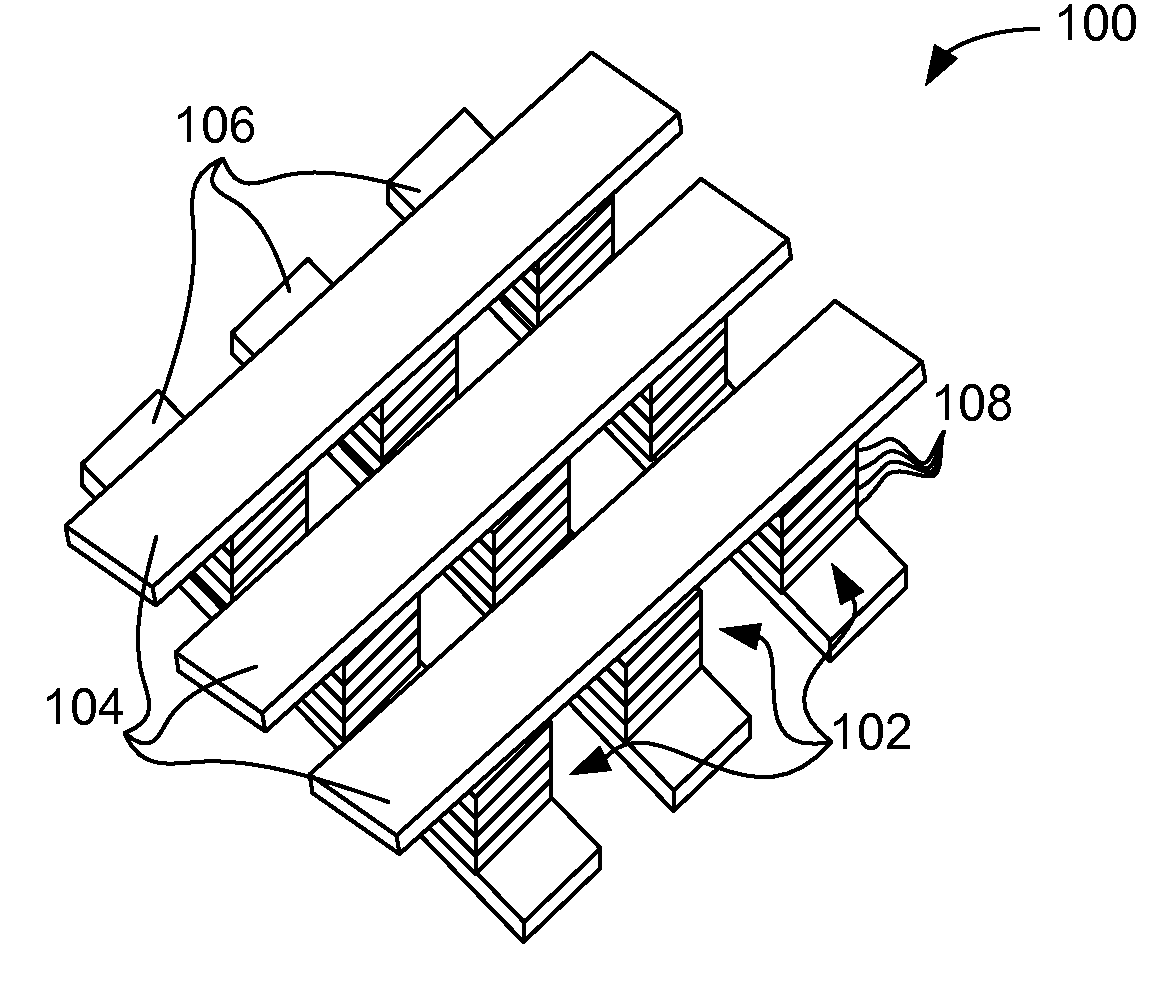

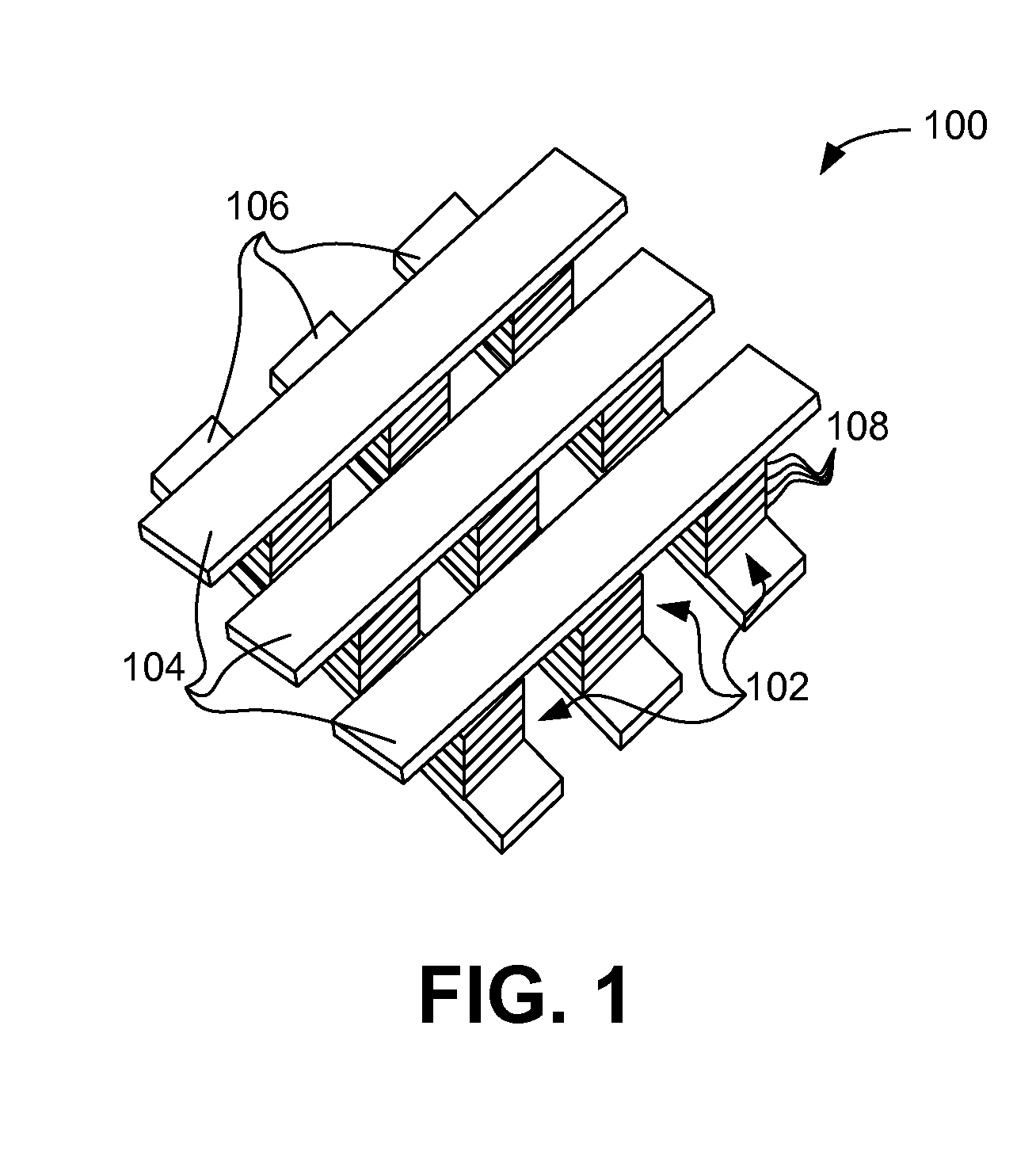

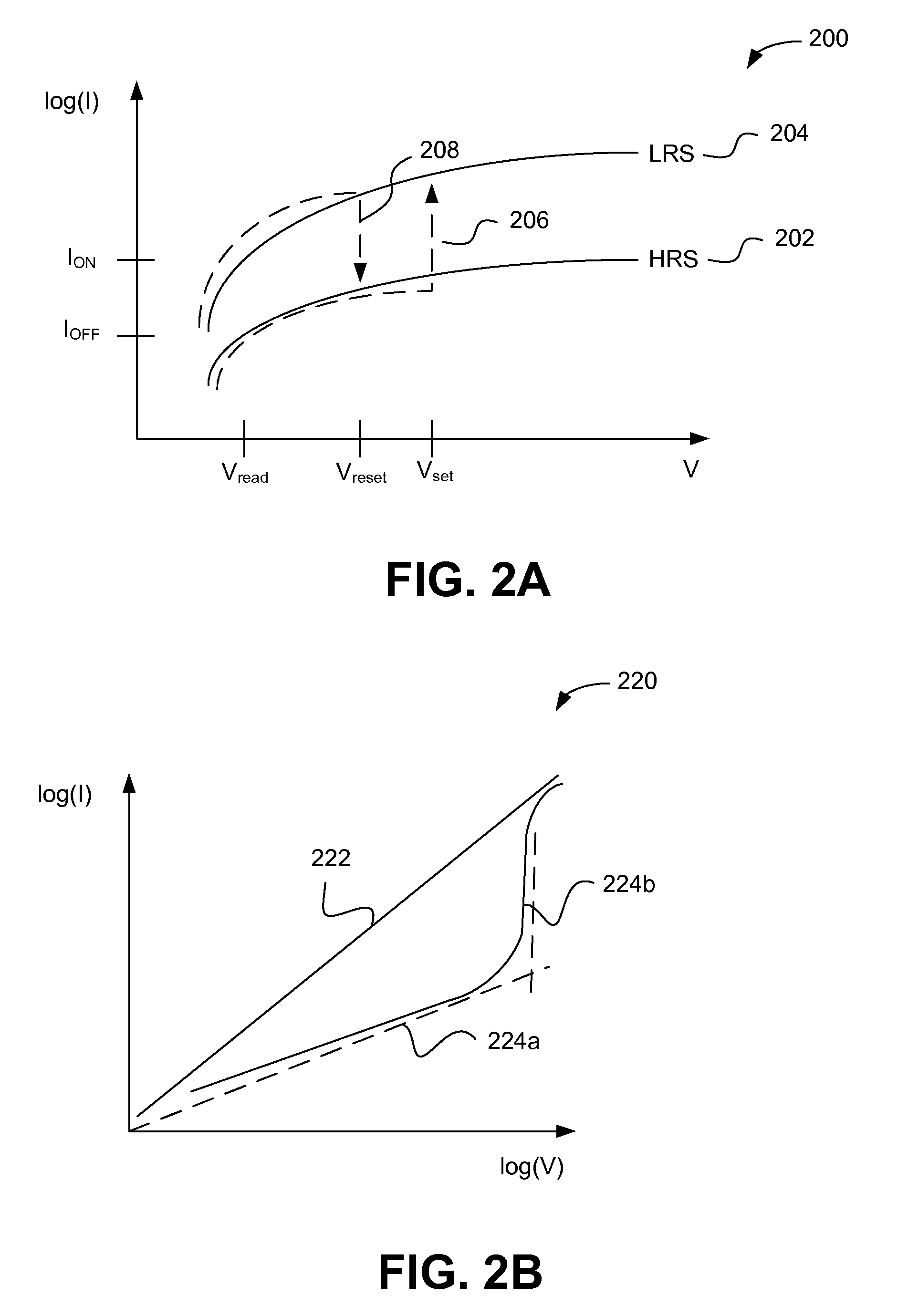

Controlled localized defect paths for resistive memories

ActiveUS20100243983A1Solid-state devicesSemiconductor/solid-state device manufacturingMaterials scienceMetal

Controlled localized defect paths for resistive memories are described, including a method for forming controlled localized defect paths including forming a first electrode forming a metal oxide layer on the first electrode, masking the metal oxide to create exposed regions and concealed regions of a surface of the metal oxide, and altering the exposed regions of the metal oxide to create localized defect paths beneath the exposed regions.

Owner:INTERMOLECULAR

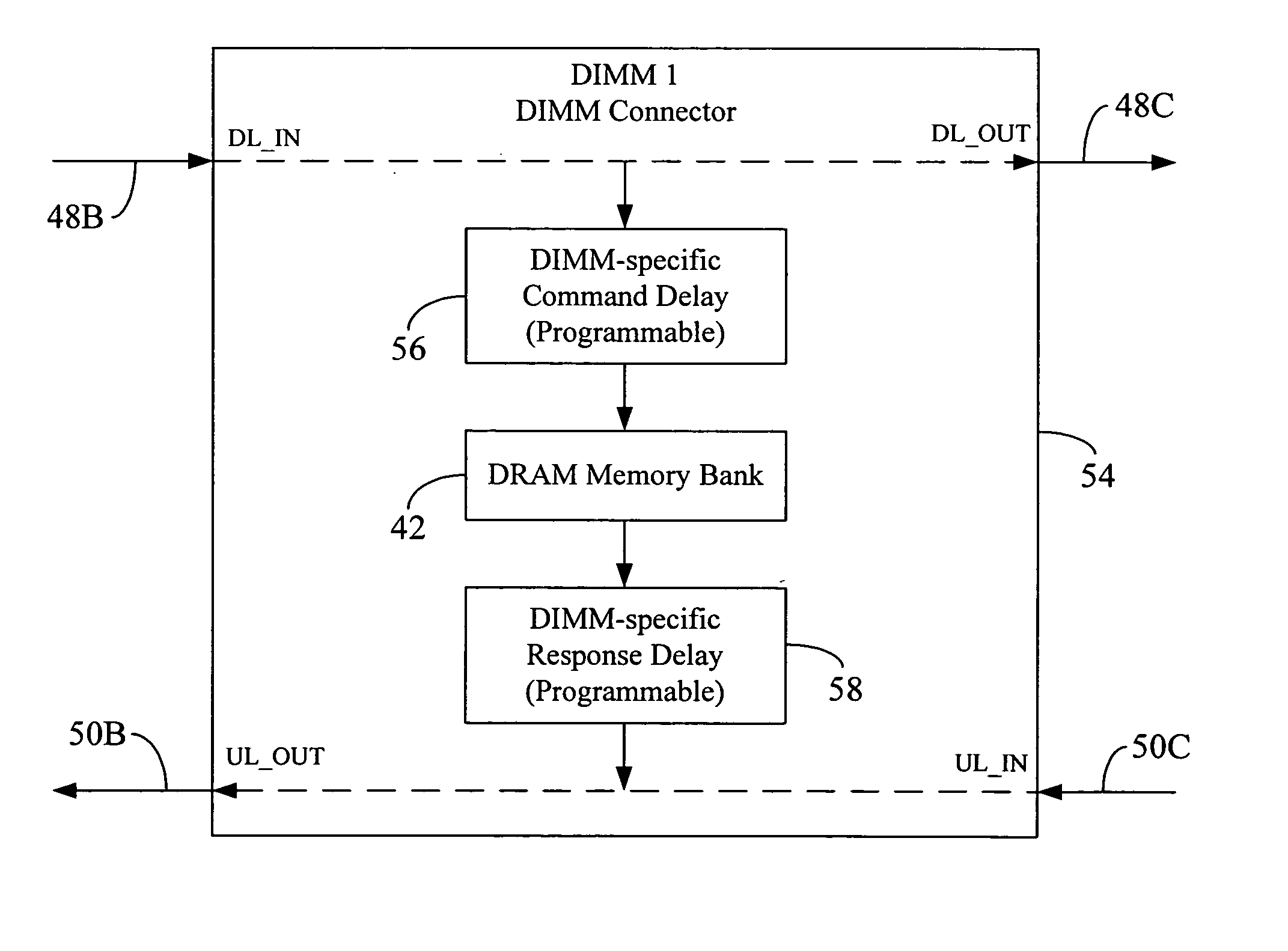

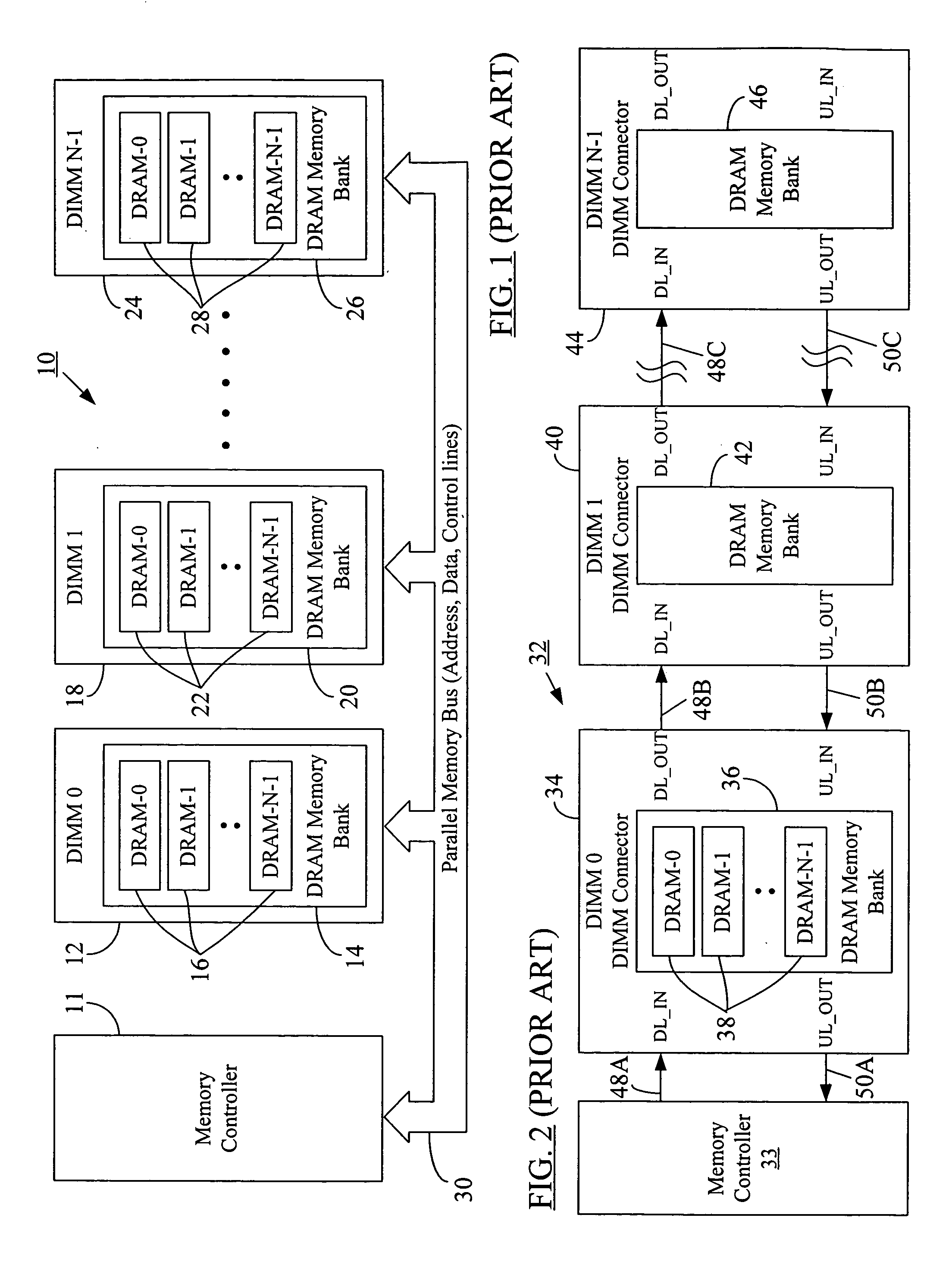

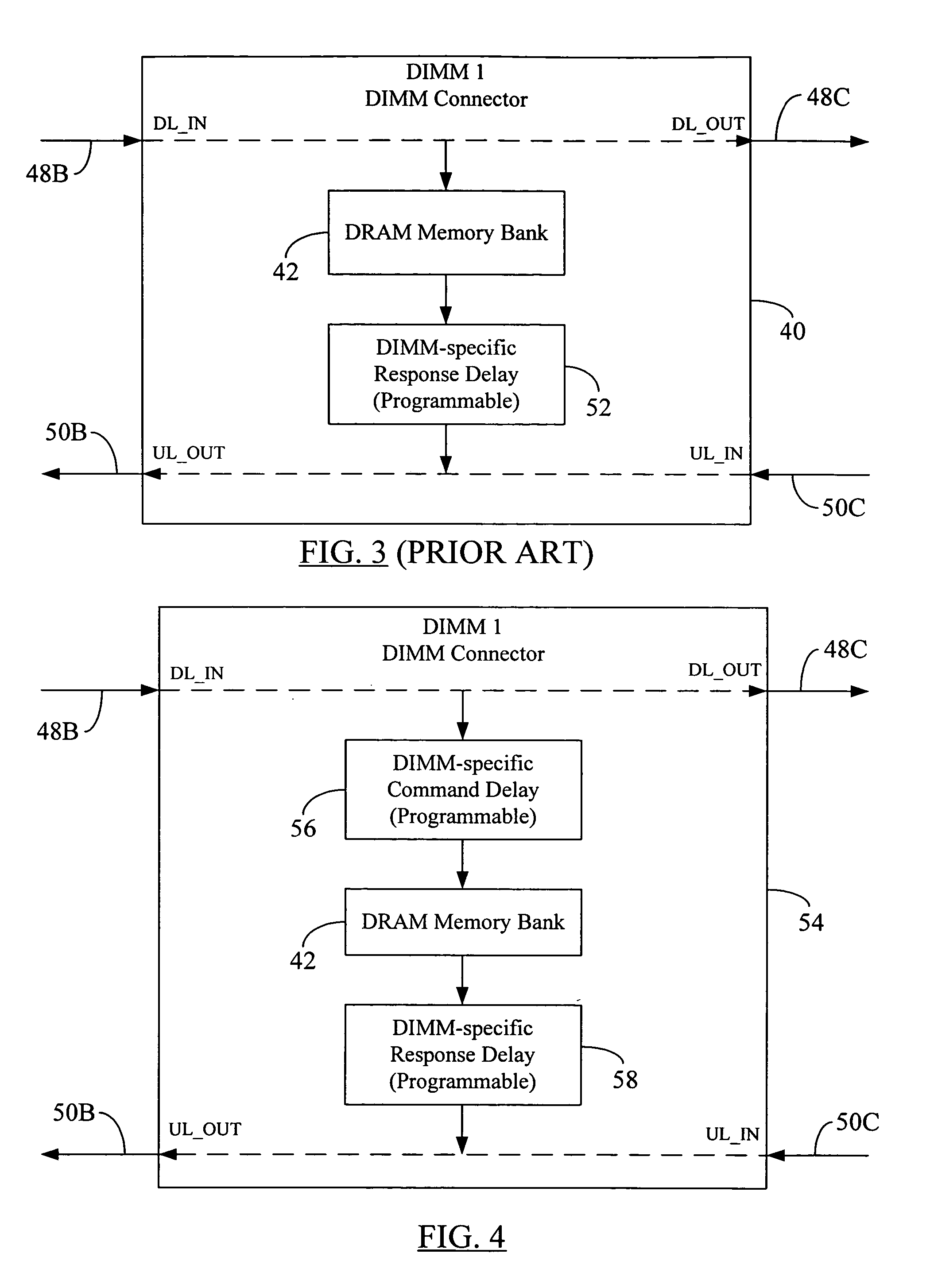

Memory command delay balancing in a daisy-chained memory topology

InactiveUS20060041730A1Effective predictionAccurately ascertainedEnergy efficient ICTDigital storageDIMMControl power

A methodology for a daisy-chained memory topology wherein, in addition to the prediction of the timing of receipt of a response from a memory module (DIMM), the memory controller can effectively predict when a command sent by it will be executed by the addressee DIMM. By programming DIMM-specific command delay in the DIMM's command delay unit, the command delay balancing methodology according to the present disclosure “normalizes” or “synchronizes” the execution of the command signal across all DIMMs in the memory channel. With such ability to predict command execution timing, the memory controller can efficiently control power profile of all the DRAM devices (or memory modules) on a daisy-chained memory channel. A separate DIMM-specific response delay unit in the DIMM may also be programmed to provide DIMM-specific delay compensation in the response path, further allowing the memory controller to accurately ascertain the timing of receipt of a response thereat, and, hence, to better manage further processing of the response.

Owner:ROUND ROCK RES LLC

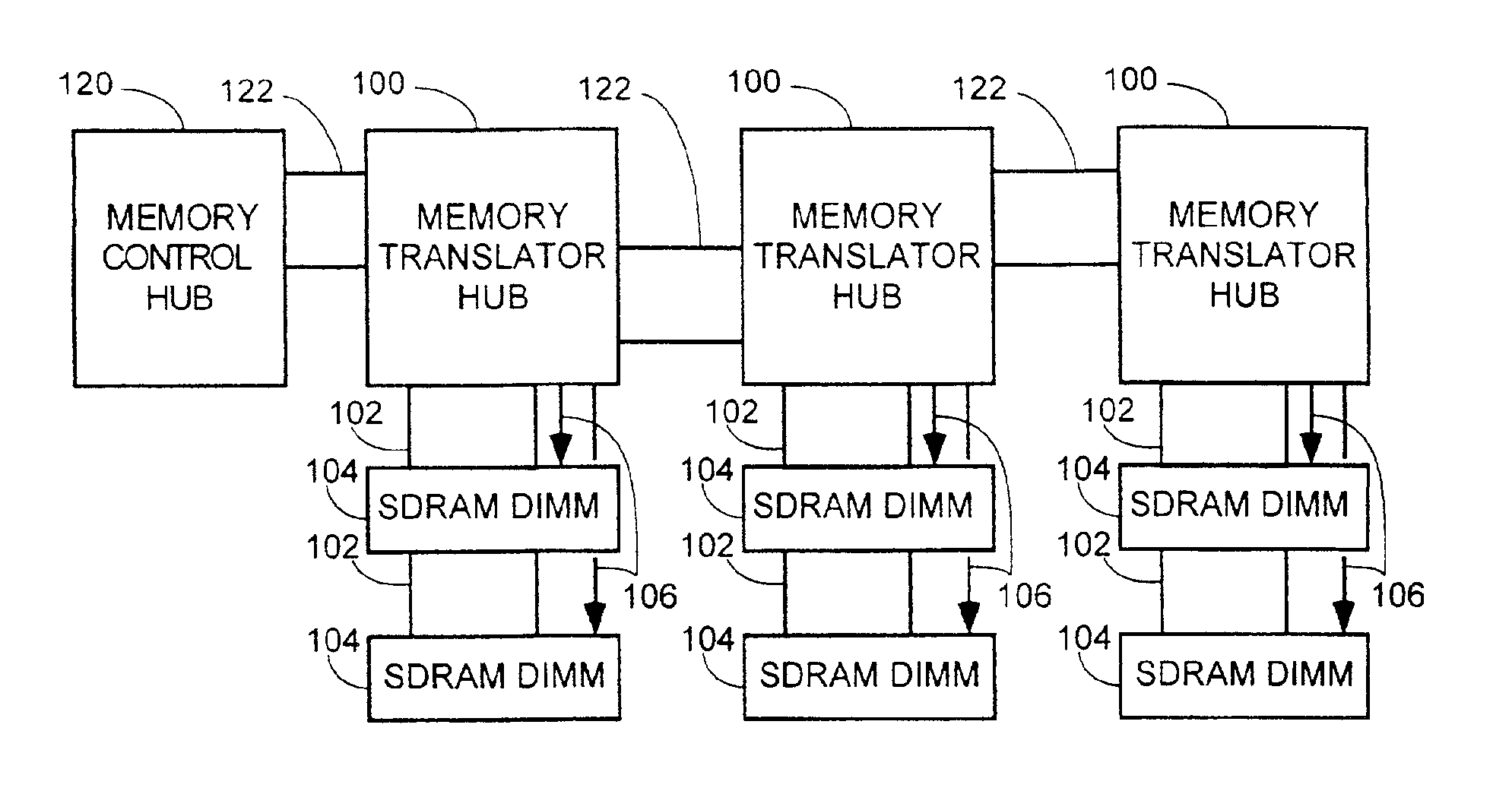

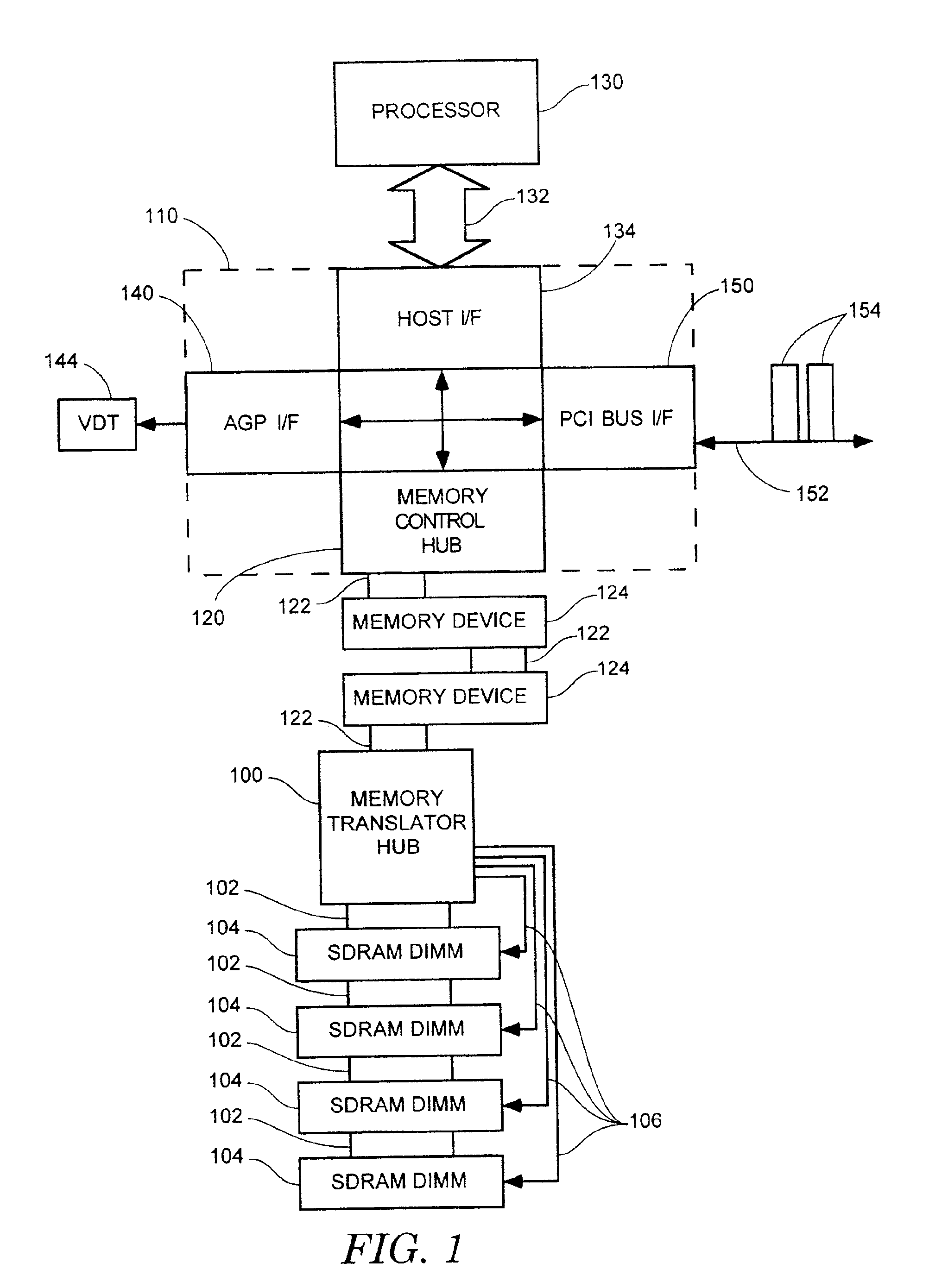

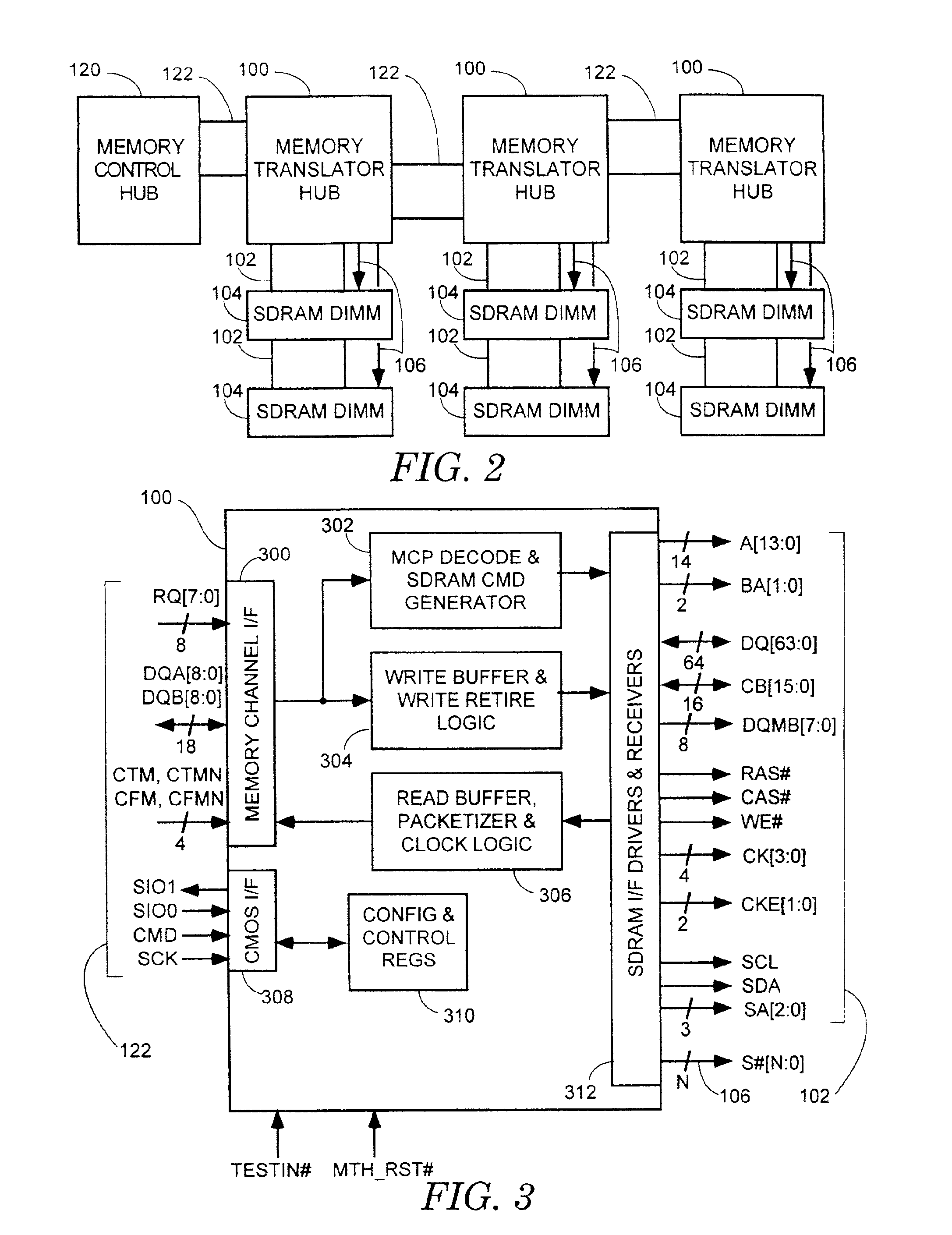

Method and apparatus for supporting SDRAM memory

A memory translation hub comprising a memory channel interface, a memory bus interface, and a command generator coupled to the memory channel interface and to the memory bus interface. The memory channel interface receives a memory control packet from a memory channel. The memory bus interface provides a memory bus. The command generator causes the memory bus interface to provide memory control signals on the memory bus responsive to the memory control packet.

Owner:INTEL CORP

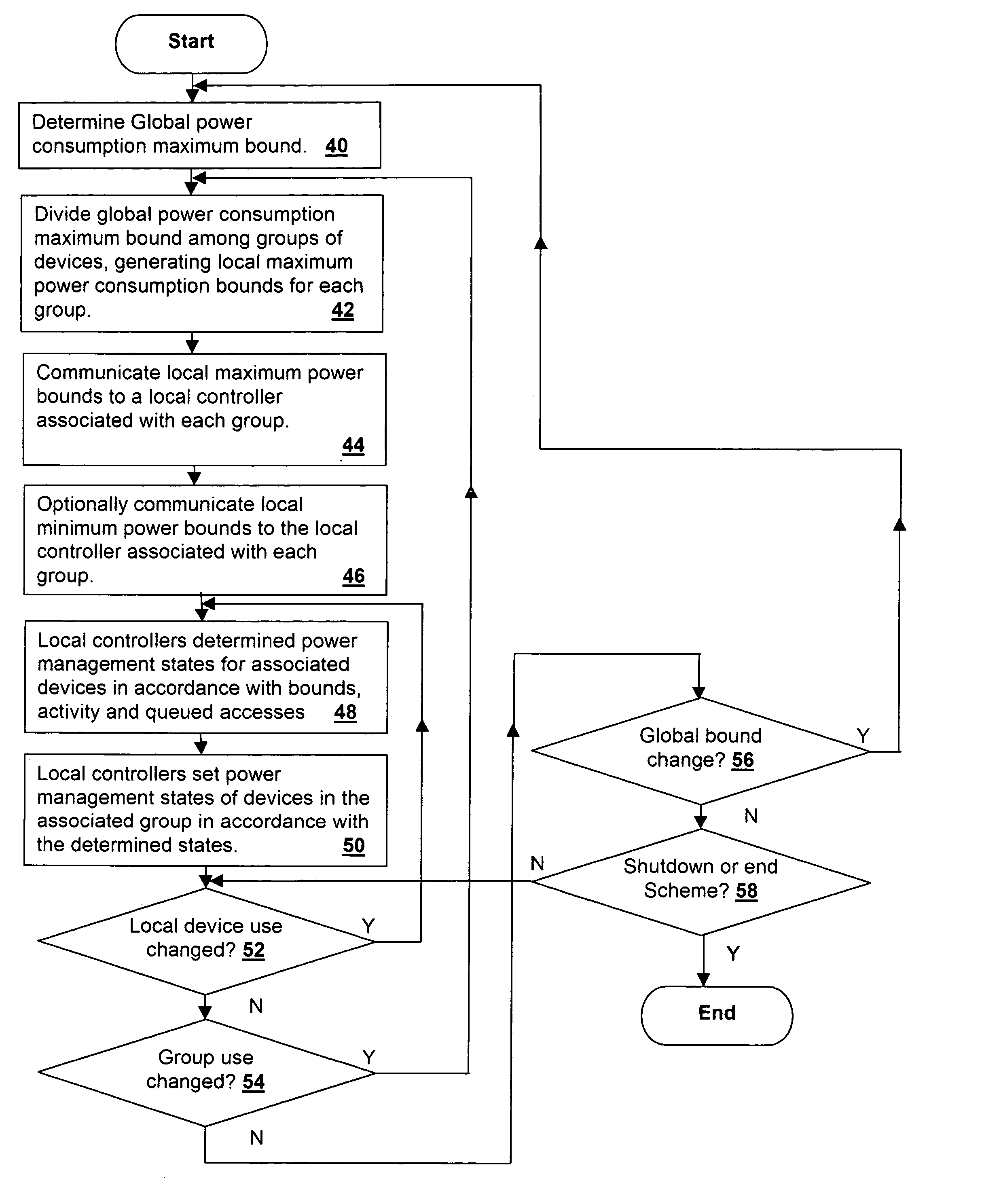

Method and system for power management including local bounding of device group power consumption

ActiveUS20050125703A1Inhibit currentSlow changeEnergy efficient ICTVolume/mass flow measurementMemory controllerGlobal system

A method and system for power management including local bounding of device group power consumption provides the responsiveness of local power control while meeting global system power consumption and power dissipation limits. At the system level, a global power bound is determined and divided among groups of devices in the system so that local bounds are determined that meet the global system bound. The local bounds are communicated to device controllers associated with each group of devices and the device controllers control the power management states of the associated devices in the group to meet the local bound. Thus, by action of all of the device controllers, the global bound is met. The controllers may be memory controllers and the devices memory modules, or the devices may be other devices within a processing system having associated local controllers. Alternatively or in concert, the devices may be entire processing systems and the associated controller a power management controller for associated processing systems, whereby multiple processing locales may be power-managed consistent with a global power consumption budget.

Owner:HUAWEI TECH CO LTD

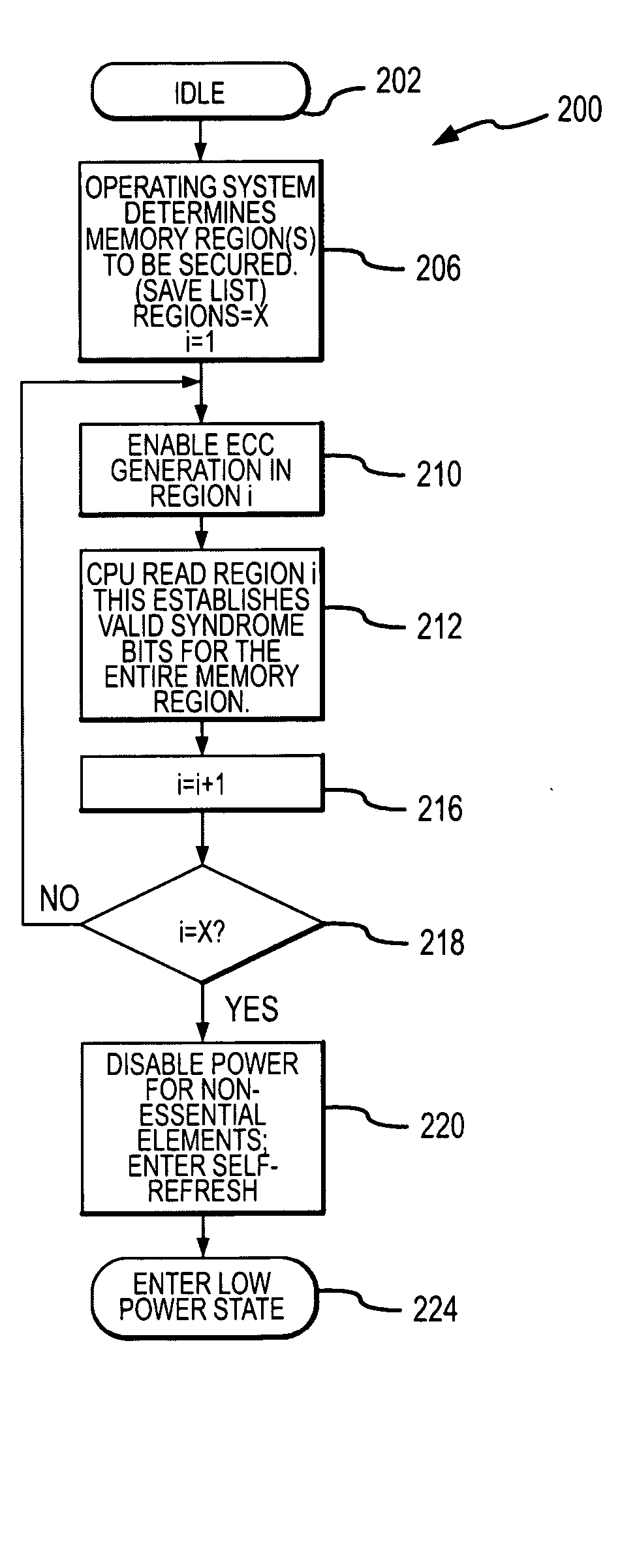

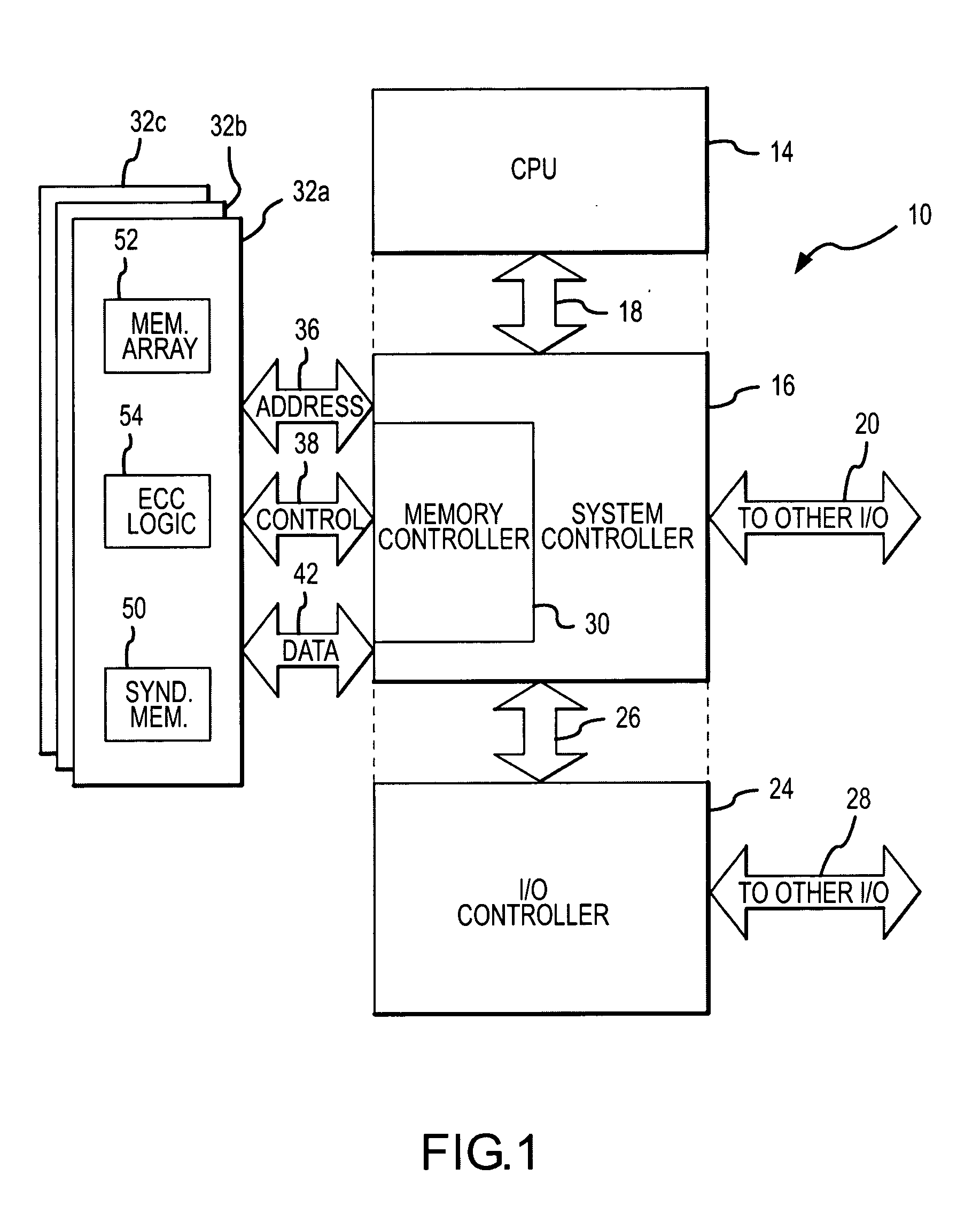

Memory system and method having selective ECC during low power refresh

InactiveUS20060010339A1Reduced power ratingMemory loss protectionError avoidanceError checkingMemory controller

A computer system includes a processor coupled to a DRAM through a memory controller. The processor switches the DRAM to a low power refresh mode in which DRAM cells are refreshed at a sufficiently low rate that data retention errors may occur. Prior to switching the DRAM to the low power refresh mode, the processor identifies a region of an array of DRAM cells that contains essential data that needs to be protected from such data retention errors. The processor then reads data from the identified region, and either the DRAM or the memory controller generates error checking and correcting syndromes from the read data. The syndromes are stored in the DRAM, and the low power refresh mode is then entered. Upon exiting the low power refresh mode, the processor again reads the data from the identified region, and the read data is checked and corrected using the syndromes.

Owner:MICRON TECH INC

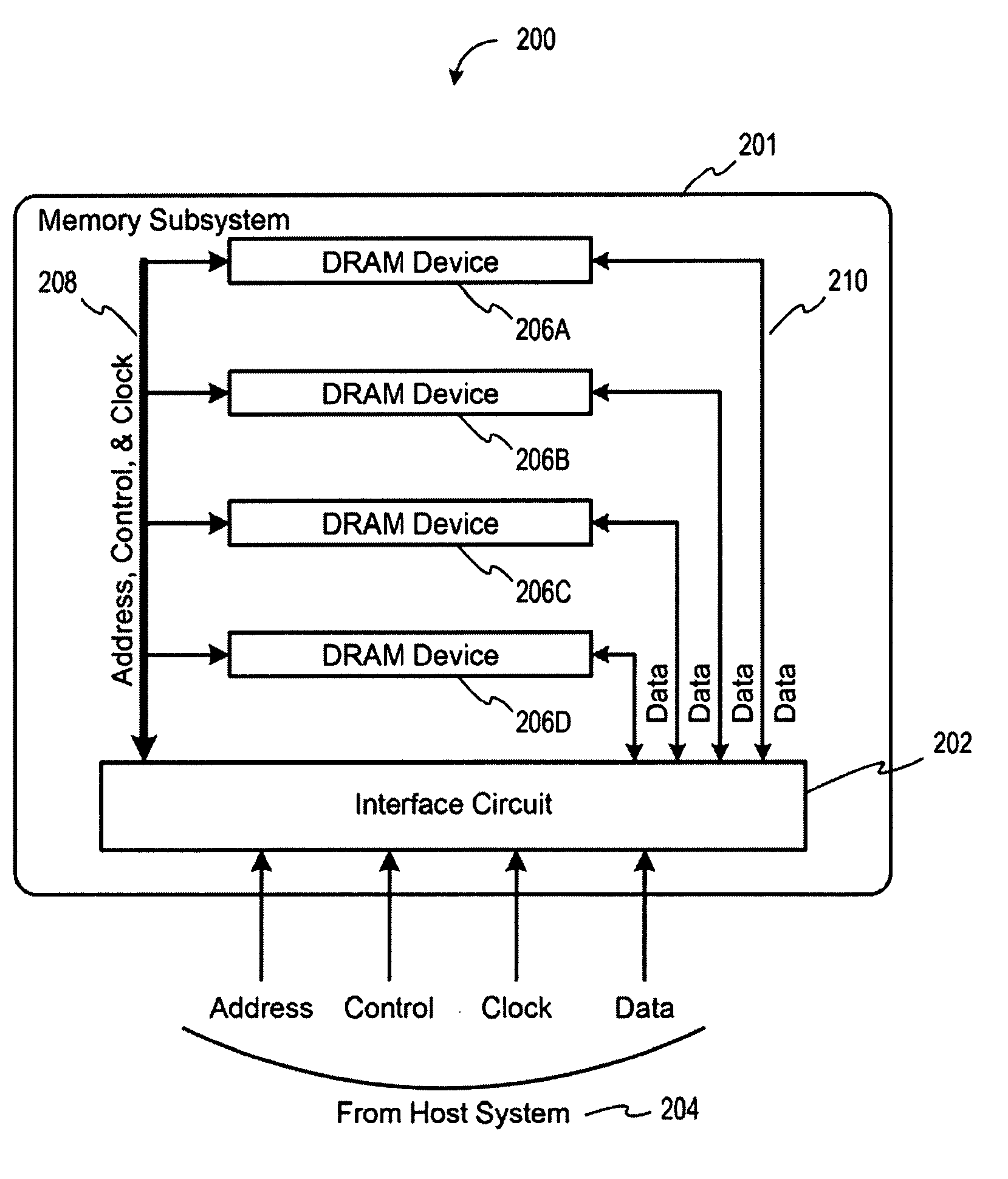

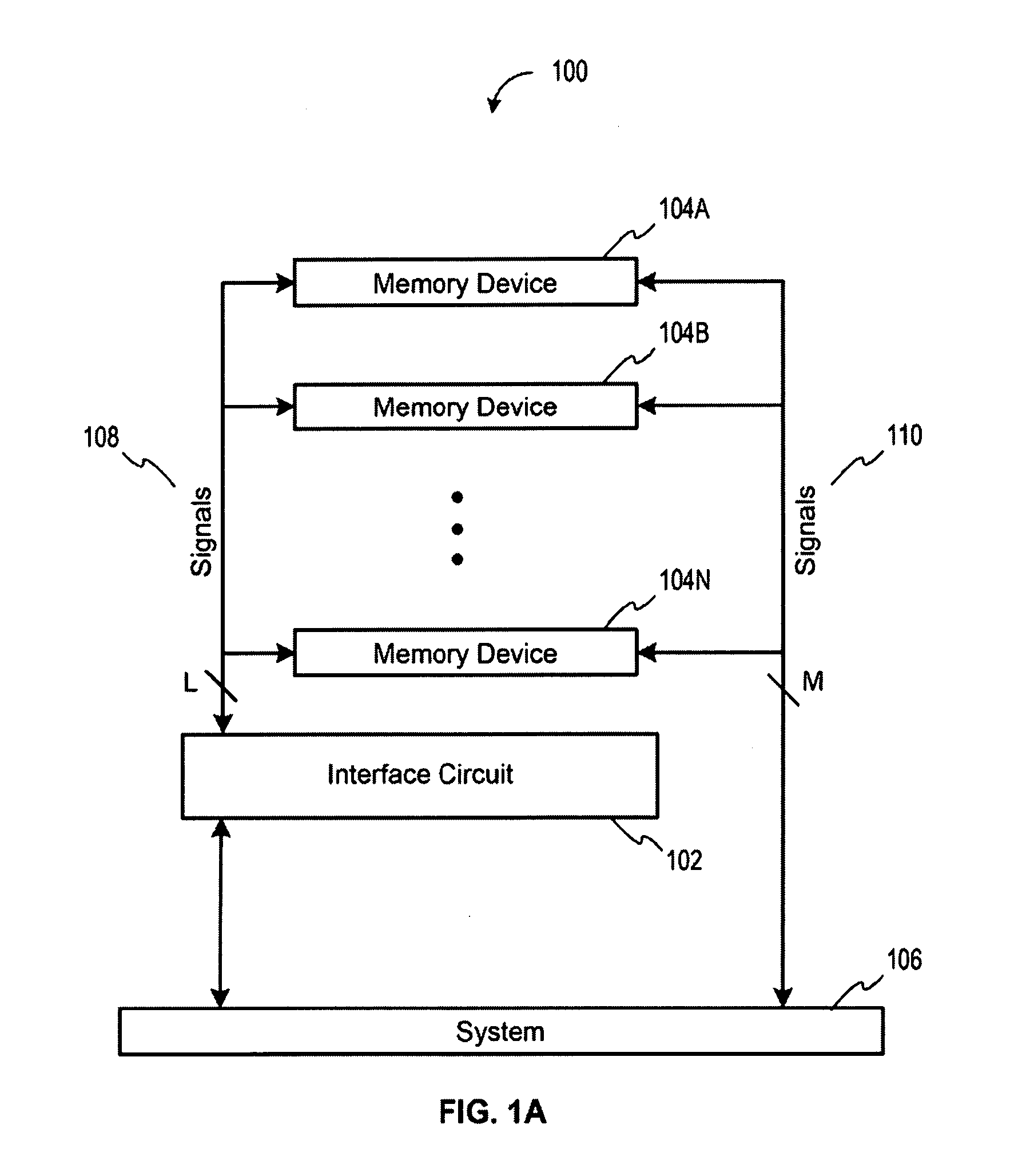

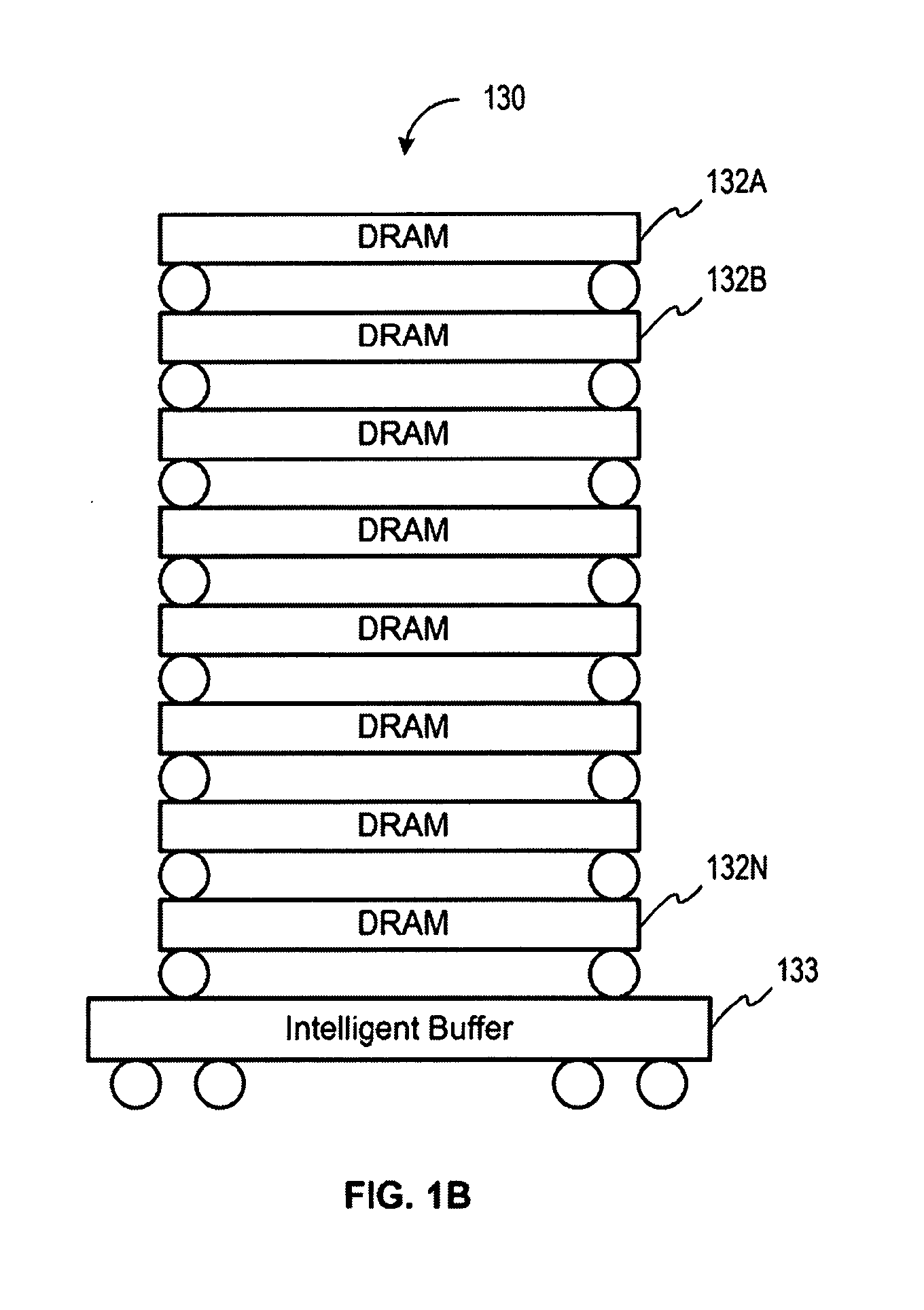

Method and apparatus for refresh management of memory modules

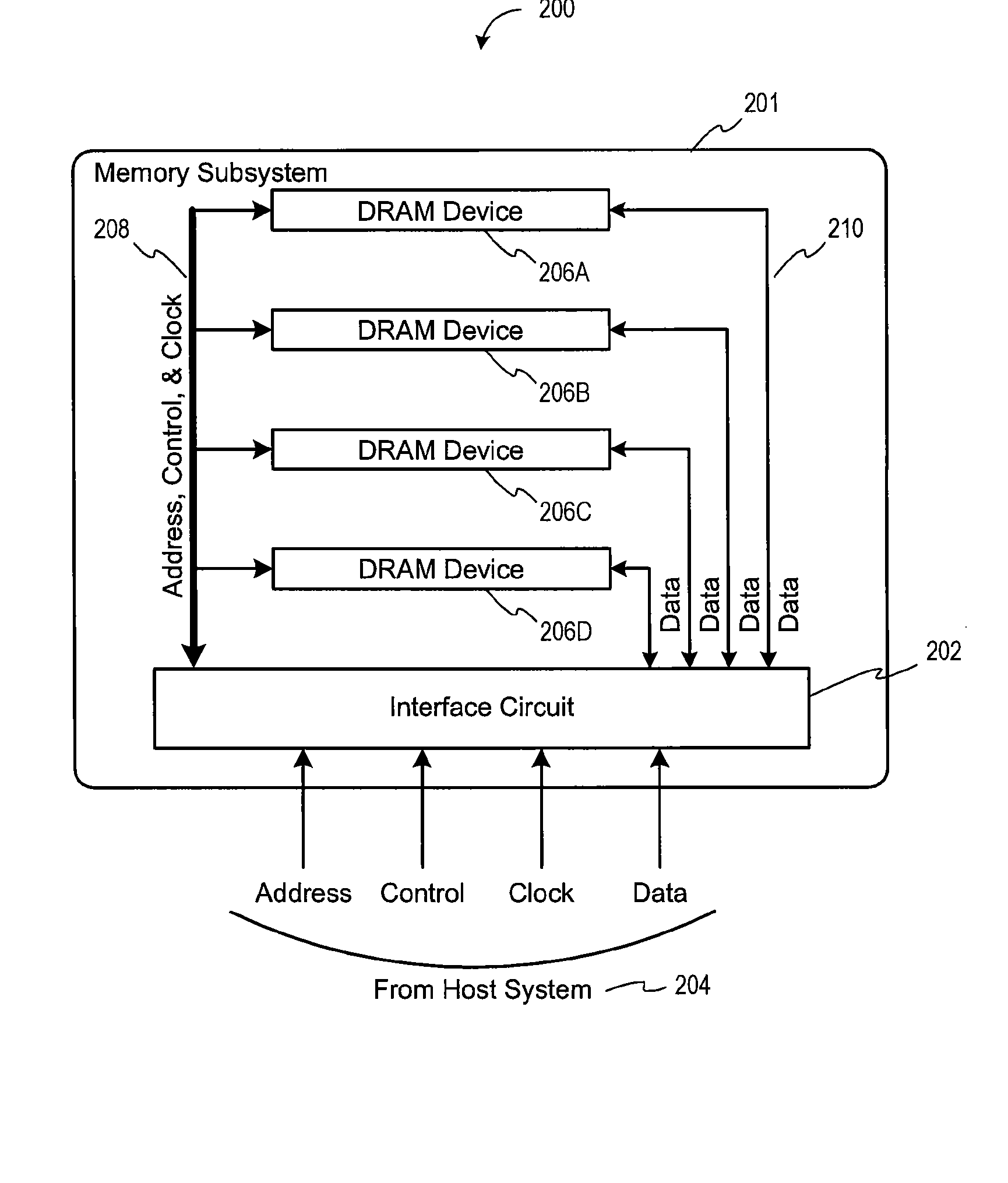

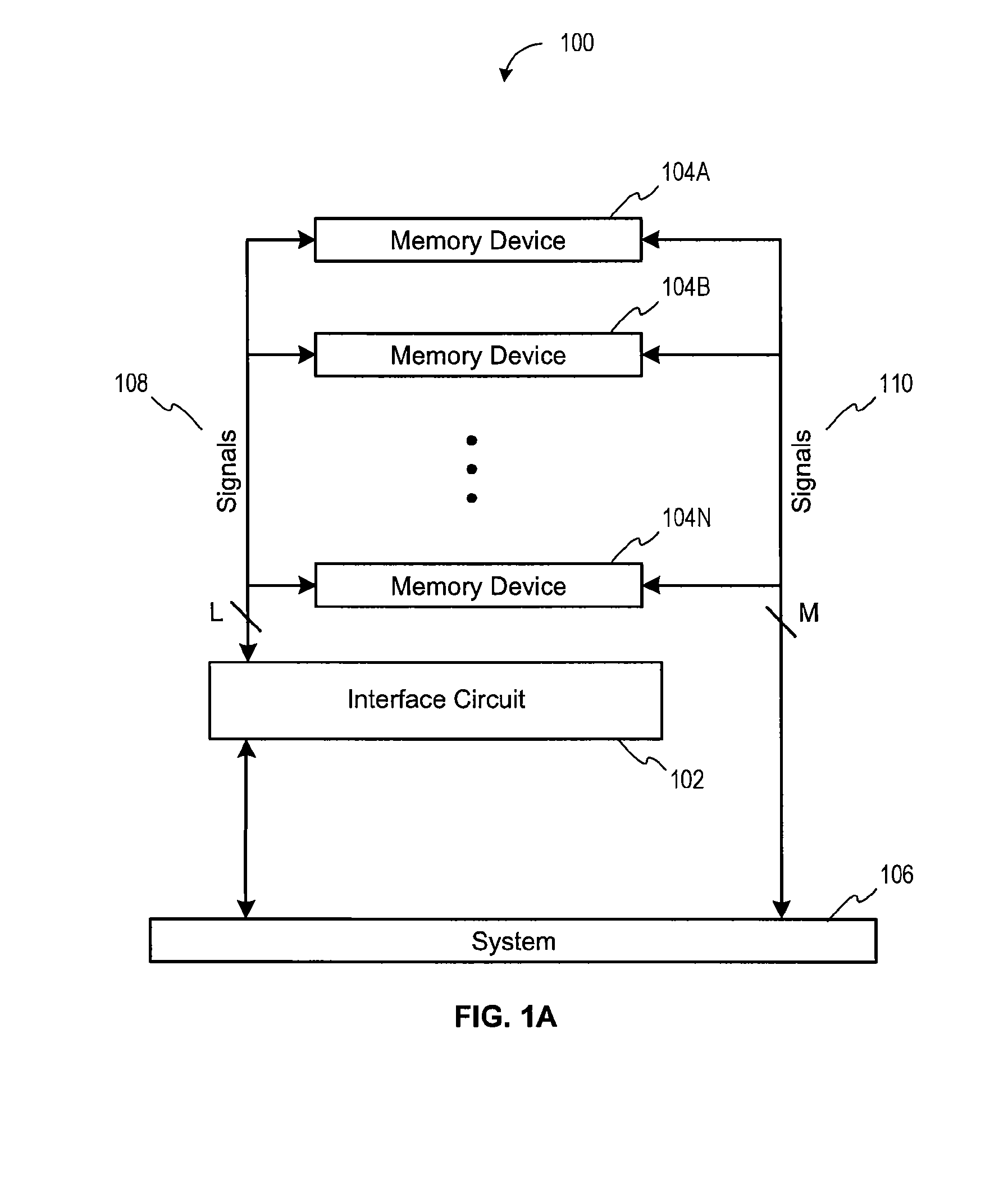

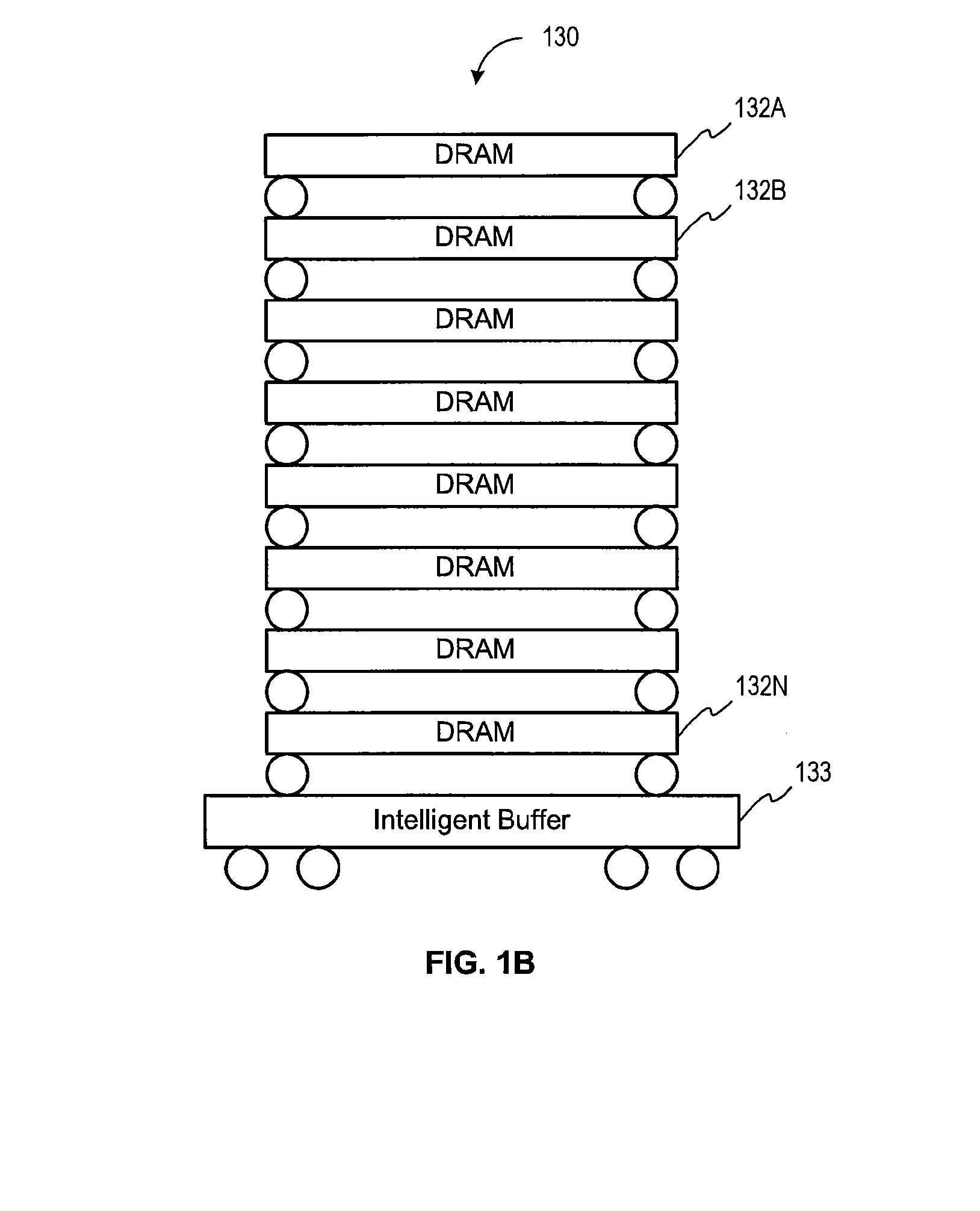

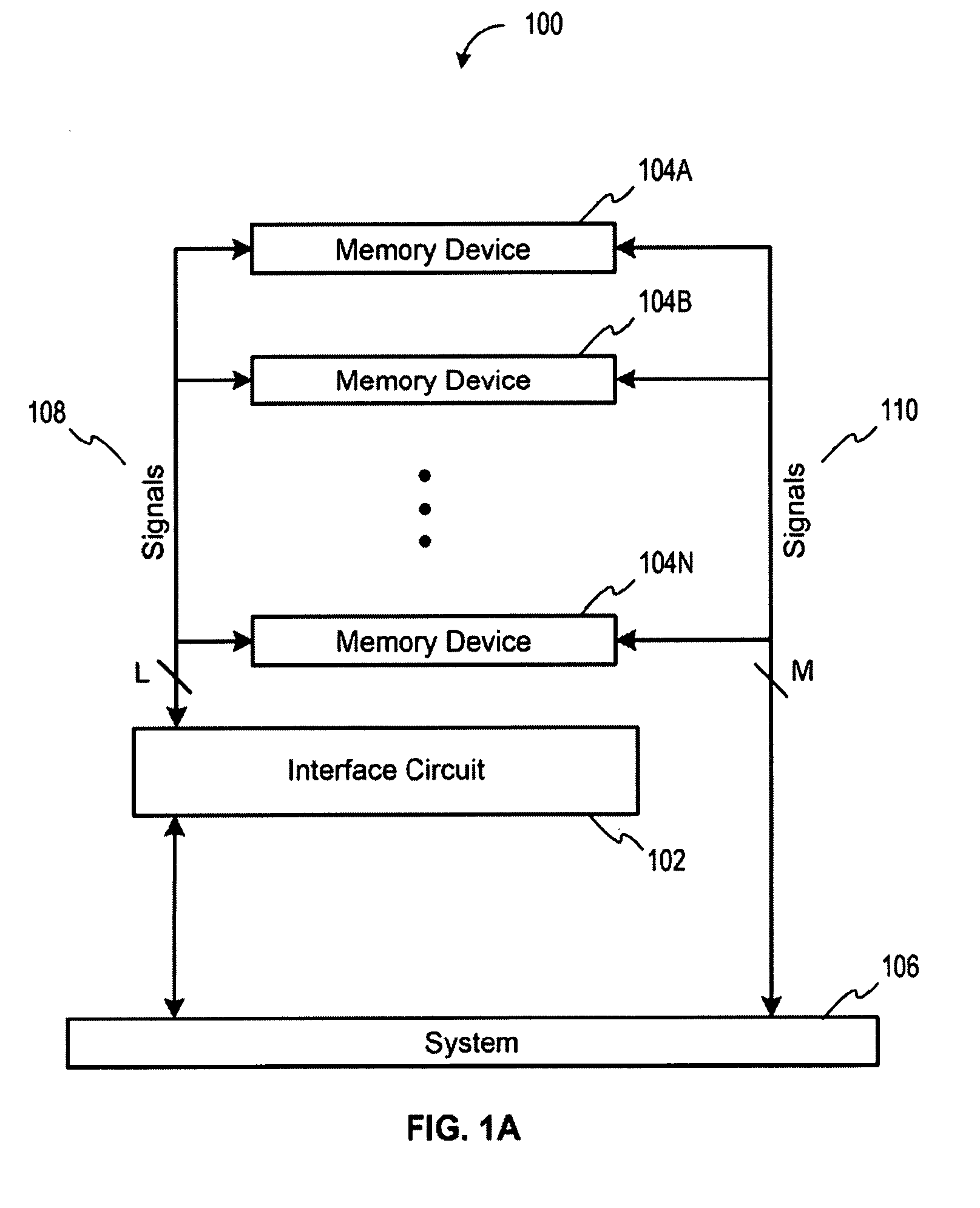

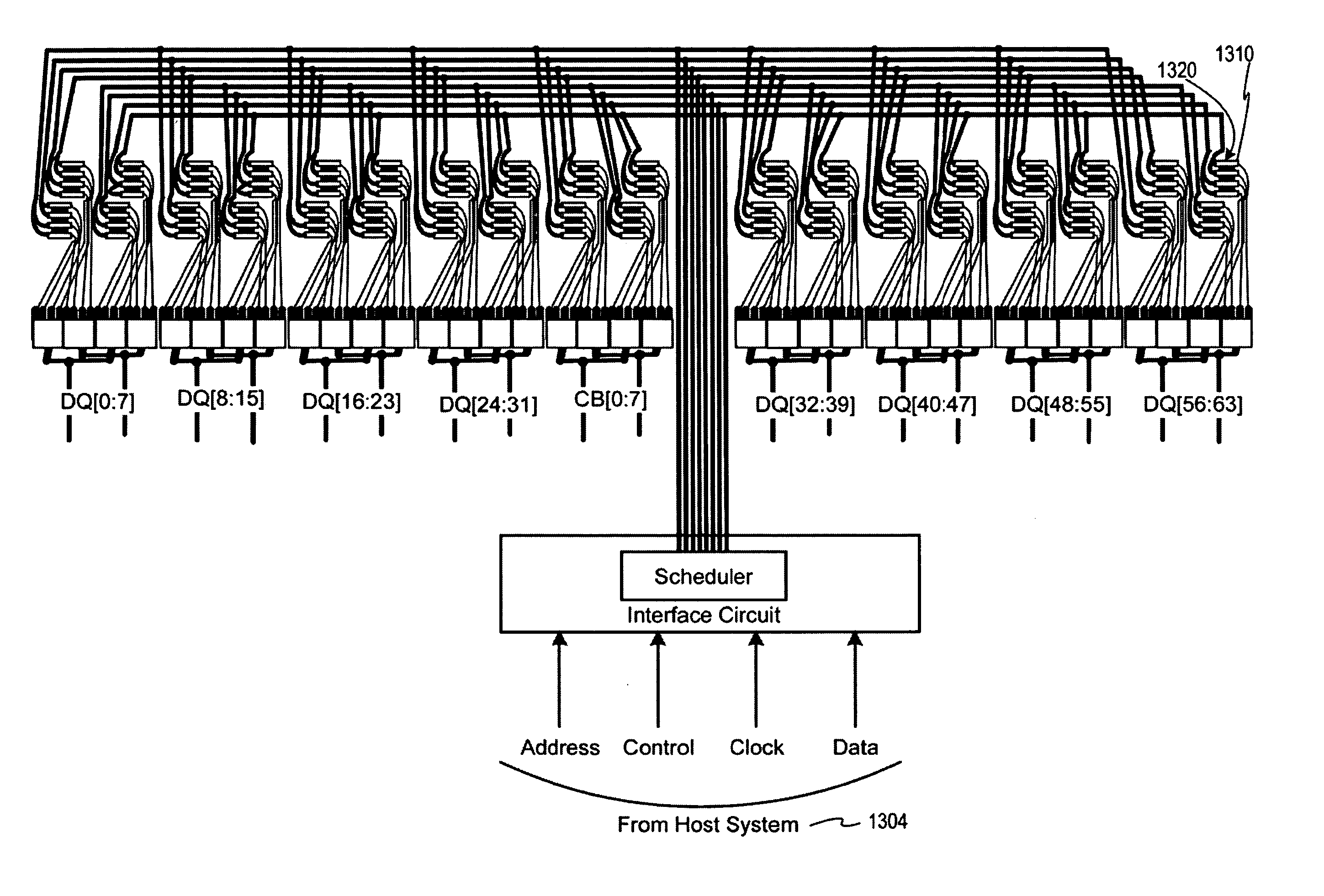

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, clock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller, and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

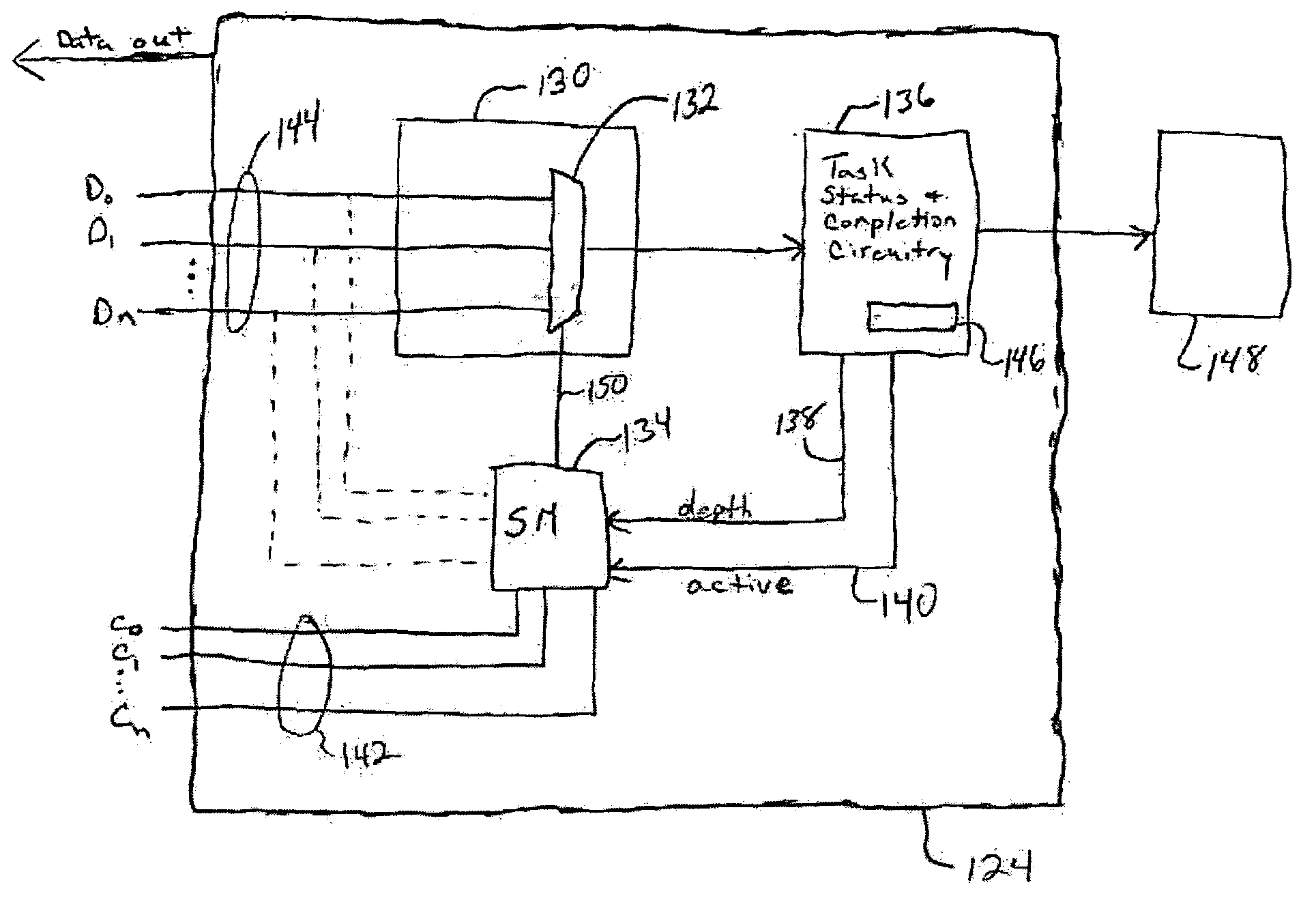

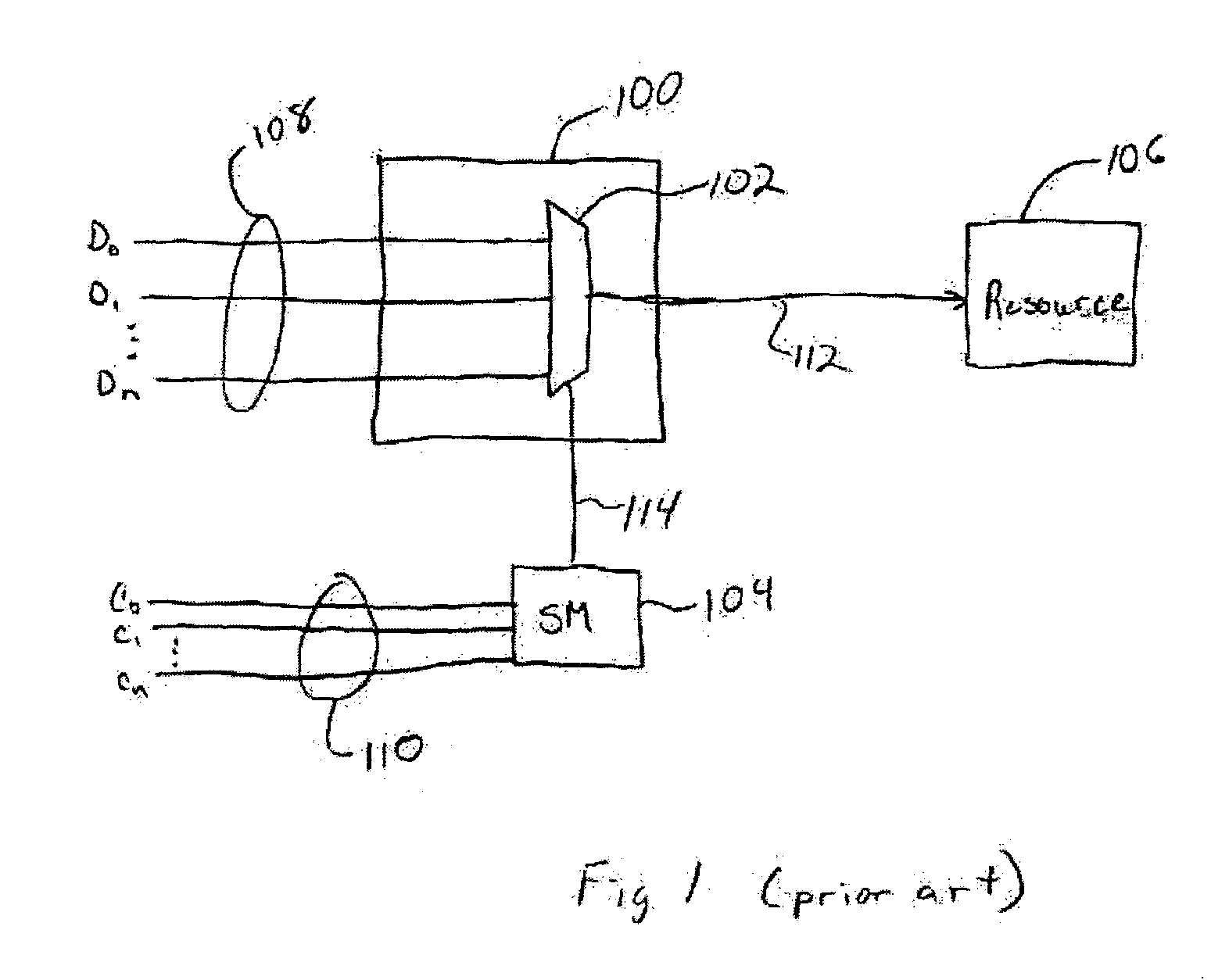

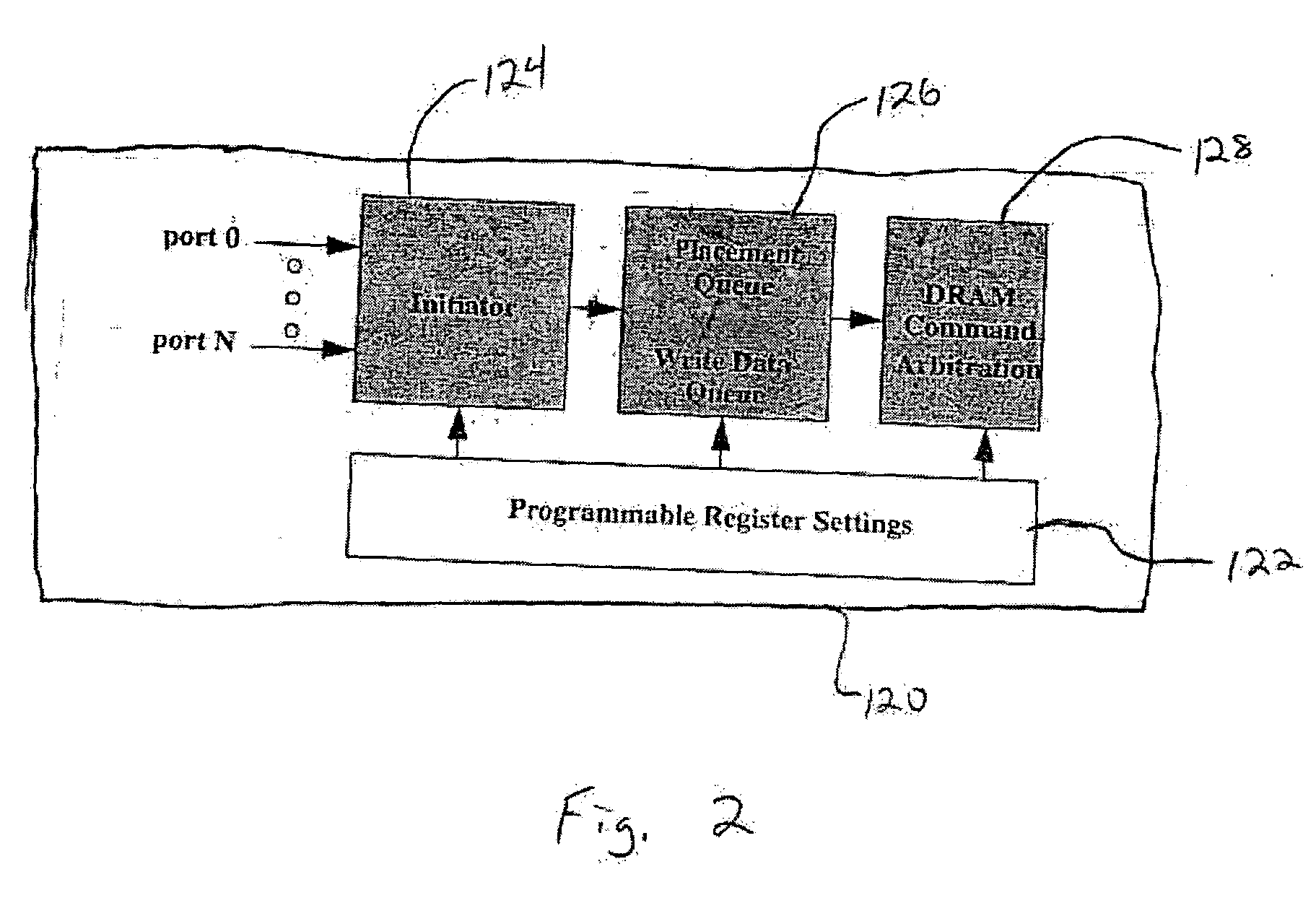

Method and apparatus for multi-port memory controller

A memory controller is provided. The memory controller includes an initiator block configured to arbitrate requests corresponding to data from multiple ports. The initiator block includes an arbitration module configured to consider a latency factor and a bandwidth factor associated with the data from a port to be selected for processing. A state machine is in communication with the arbitration module. The state machine is configured to generate a signal to the arbitration module that is configured to select the data associated with the port based upon the latency factor and the bandwidth factor. Task status and completion circuitry configured to calculate the bandwidth factor based upon previous data selected from the port is included in the initiator block. The task status and completion circuitry is further configured to transmit the calculated bandwidth factor to the state machine. A method for arbitrating across multiple ports is also provided.

Owner:CADENCE DESIGN SYST INC

Method and apparatus for refresh management of memory modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, dock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller. and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

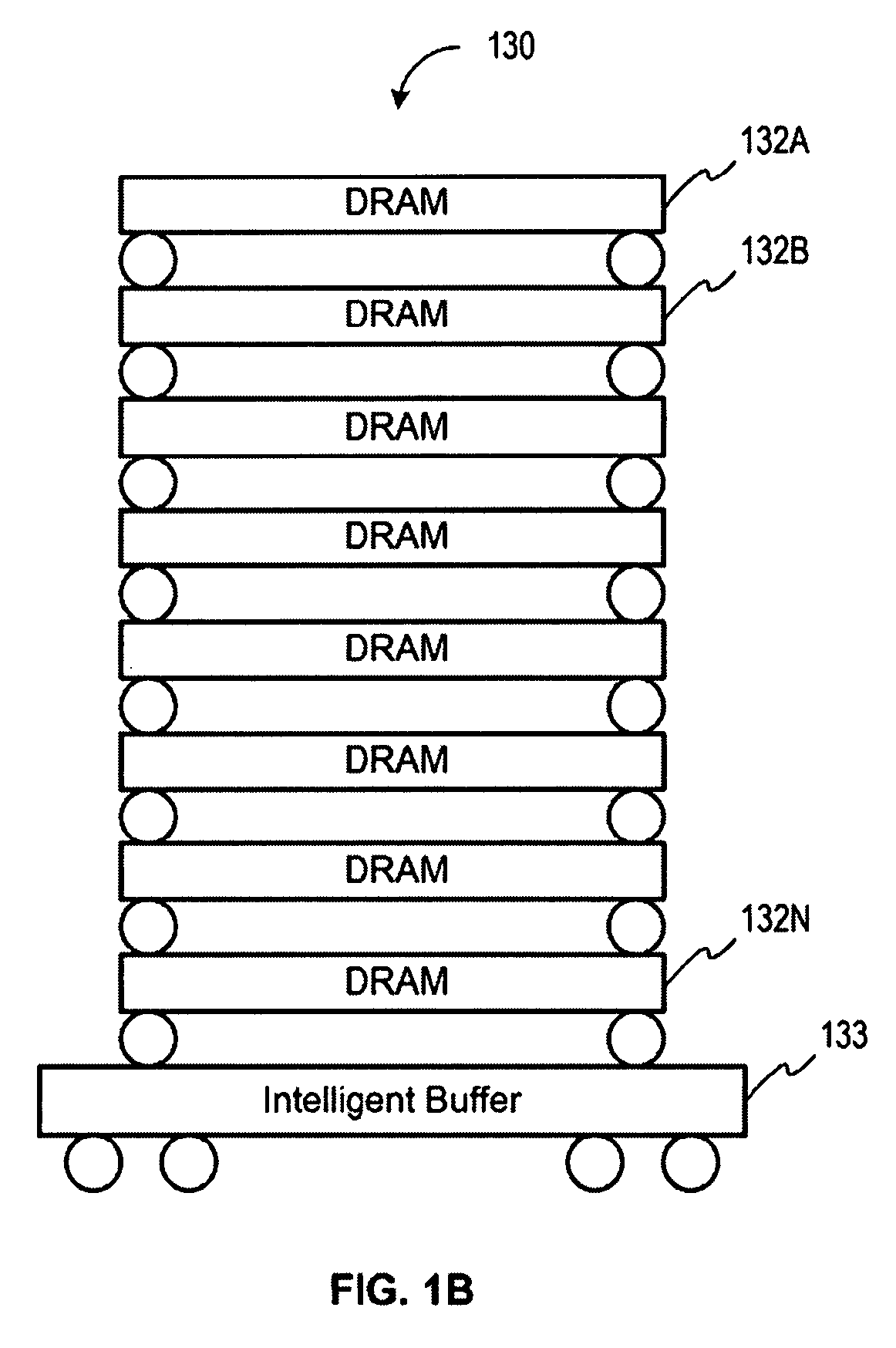

Memory module with a circuit providing load isolation and memory domain translation

A memory module includes a plurality of memory devices and a circuit. Each memory device has a corresponding load. The circuit is electrically coupled to the plurality of memory devices and is configured to be electrically coupled to a memory controller of a computer system. The circuit selectively isolates one or more of the loads of the memory devices from the computer system. The circuit comprises logic which translates between a system memory domain of the computer system and a physical memory domain of the memory module.

Owner:NETLIST INC

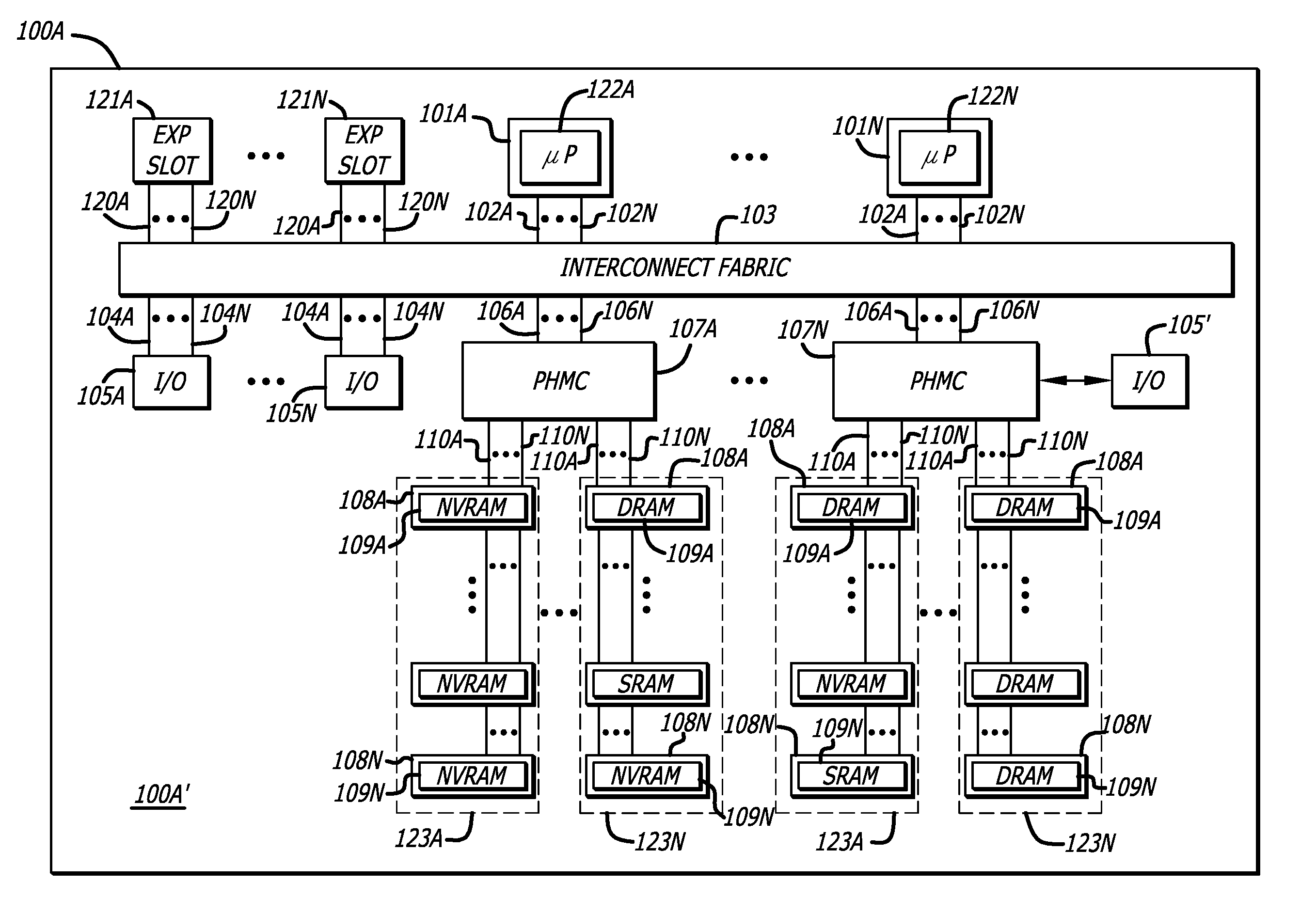

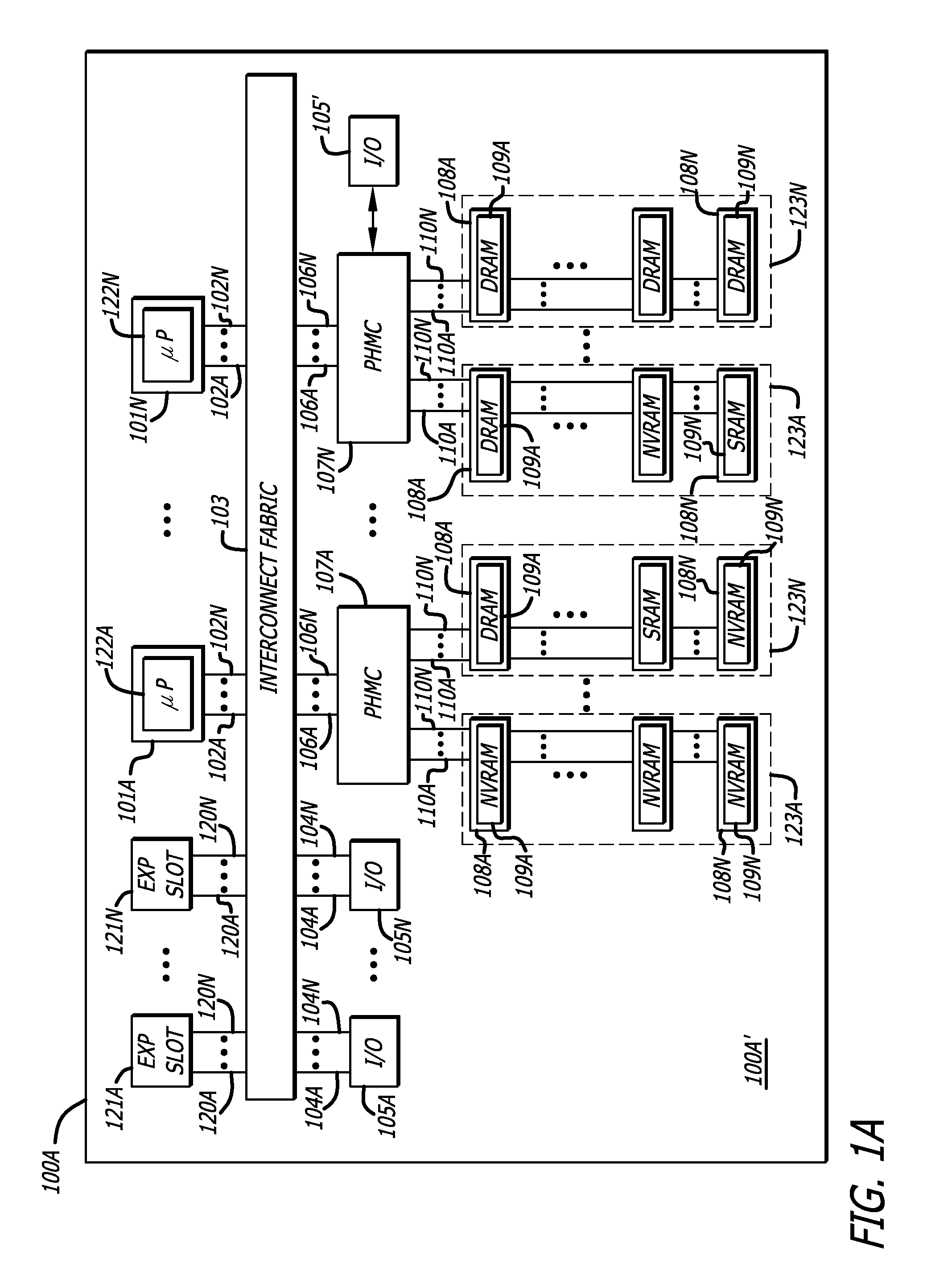

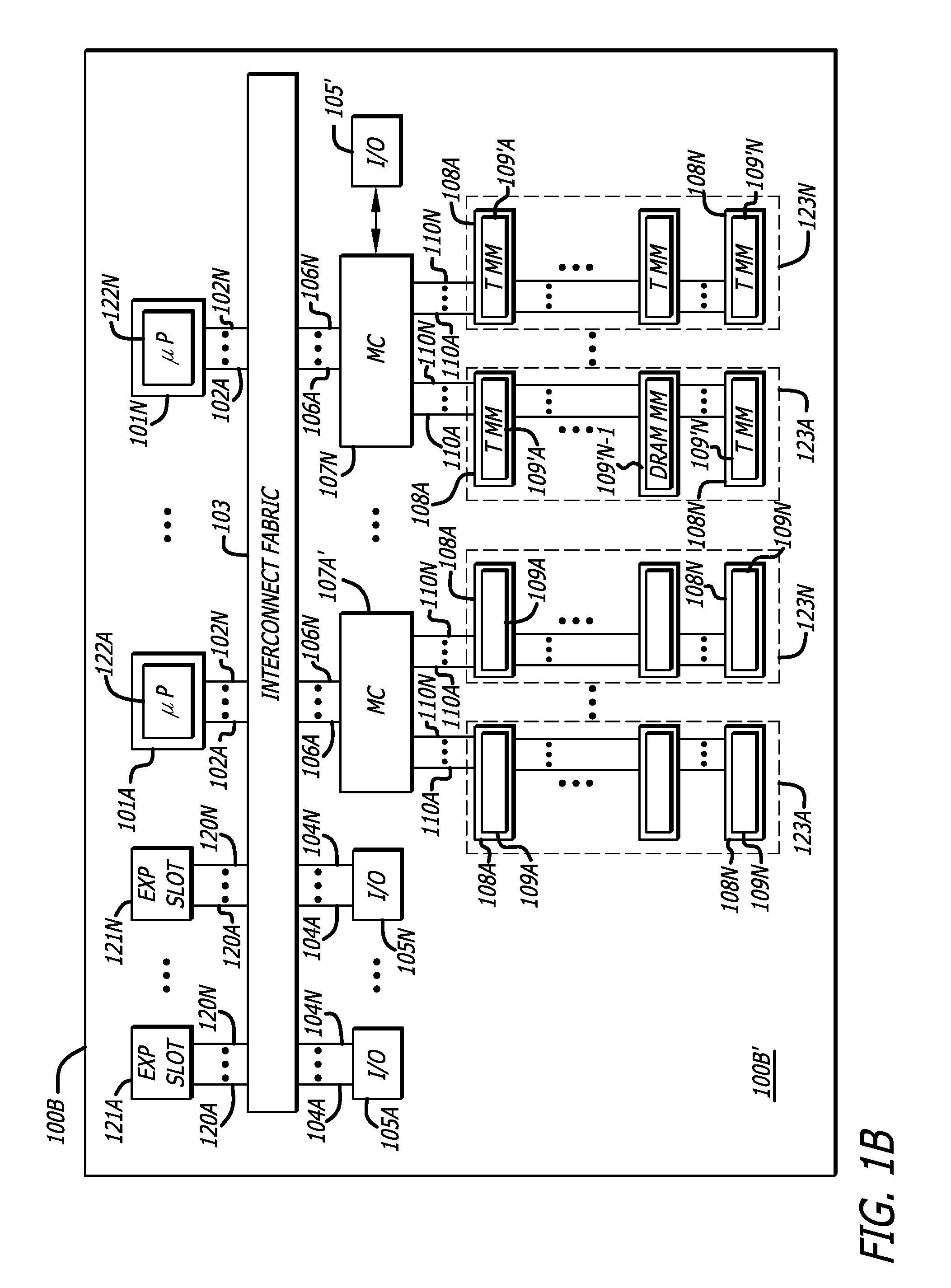

Systems and apparatus with programmable memory control for heterogeneous main memory

InactiveUS20080082766A1Memory architecture accessing/allocationEnergy efficient ICTParallel computingMemory controller

A computer system is disclosed including a printed circuit board (PCB) including a plurality of traces, at least one processor mounted to the PCB to couple to some of the plurality of traces, a heterogeneous memory channel including a plurality of sockets coupled to a memory channel bus of the PCB, and a memory controller coupled between the at least one processor and the heterogeneous memory channel. The heterogeneous memory channel includes a plurality of sockets coupled to a memory channel bus of the PCB. The plurality of sockets are configured to receive a plurality of different types of memory modules. The memory controller may be a programmable heterogeneous memory controller to flexibly adapt to the memory channel bus to control access to each of the different types of memory modules in the heterogeneous memory channel.

Owner:VIRIDENT SYST LLC

Method and apparatus for refresh management of memory modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, clock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller, and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

Memory system and memory card

InactiveUS20070198770A1Rise in cost is suppressedRequirement for numberMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:HORII TAKASHI +2

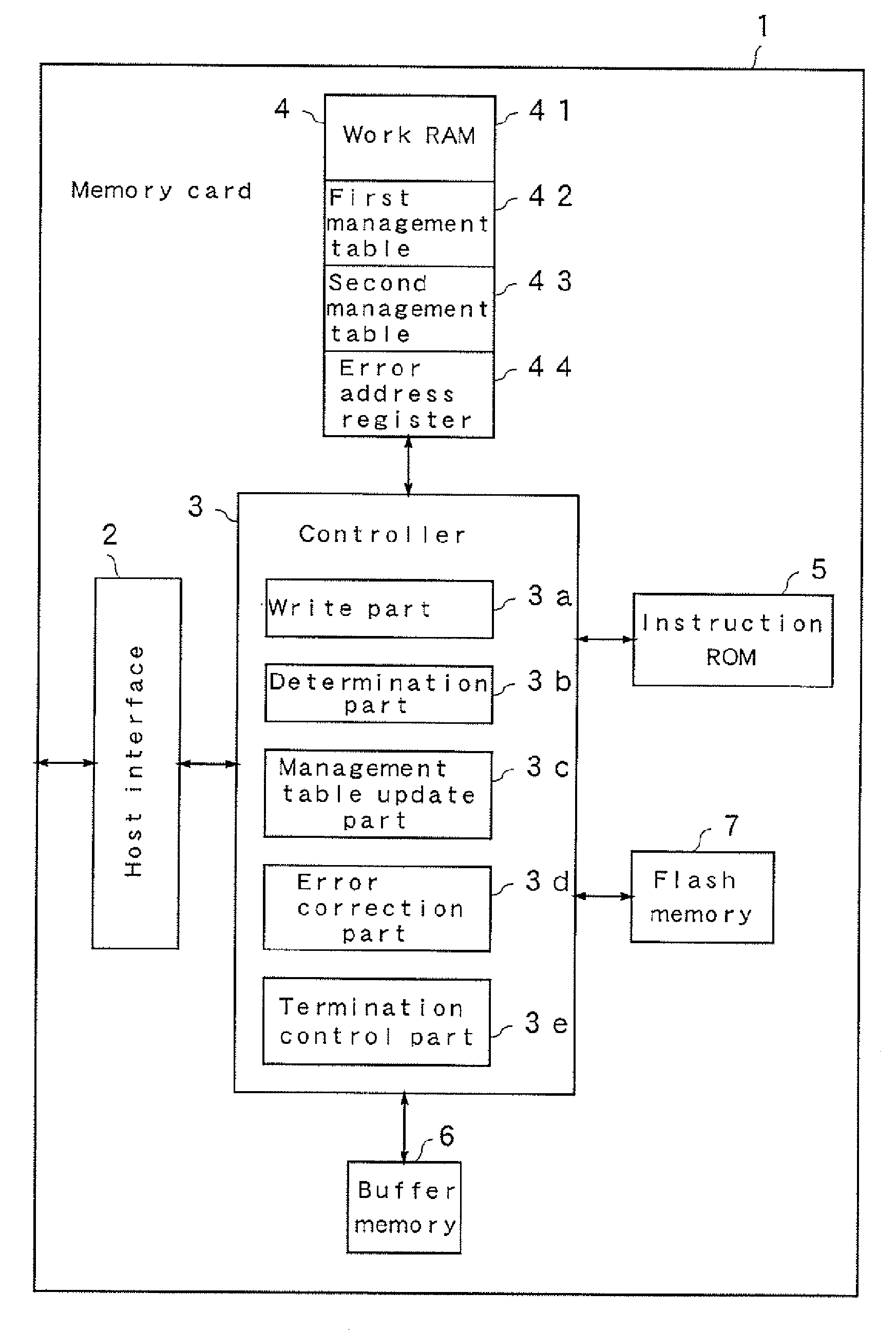

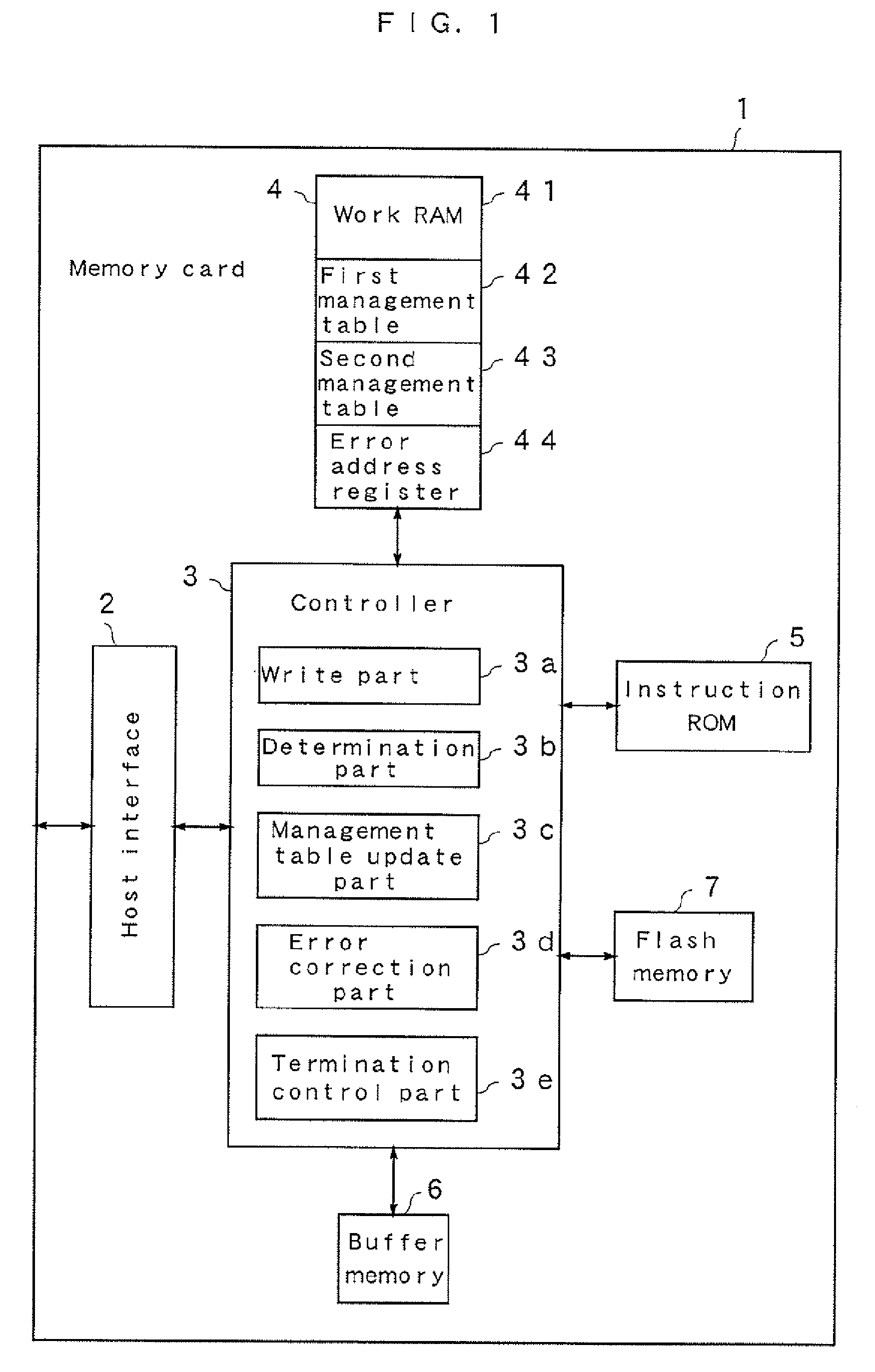

Memory Control Circuit, Nonvolatile Storage Apparatus, and Memory Control Method

InactiveUS20080049504A1Avoid elevationAddress rising pricesMemory loss protectionError detection/correctionError preventionControl circuit

An address at which a writing error occurs is held, and after a completion of a series of writings, the data of the held address is read. Then, a faulty-block processing is performed only for the addresses, for which it is determined that retry of writing is required, thereby preventing an increase of faulty-blocks. This can suppress the problem that when a writing is performed in a particular flash memory, a writing error frequently occurs and a large number of faulty blocks occur.

Owner:PANASONIC CORP

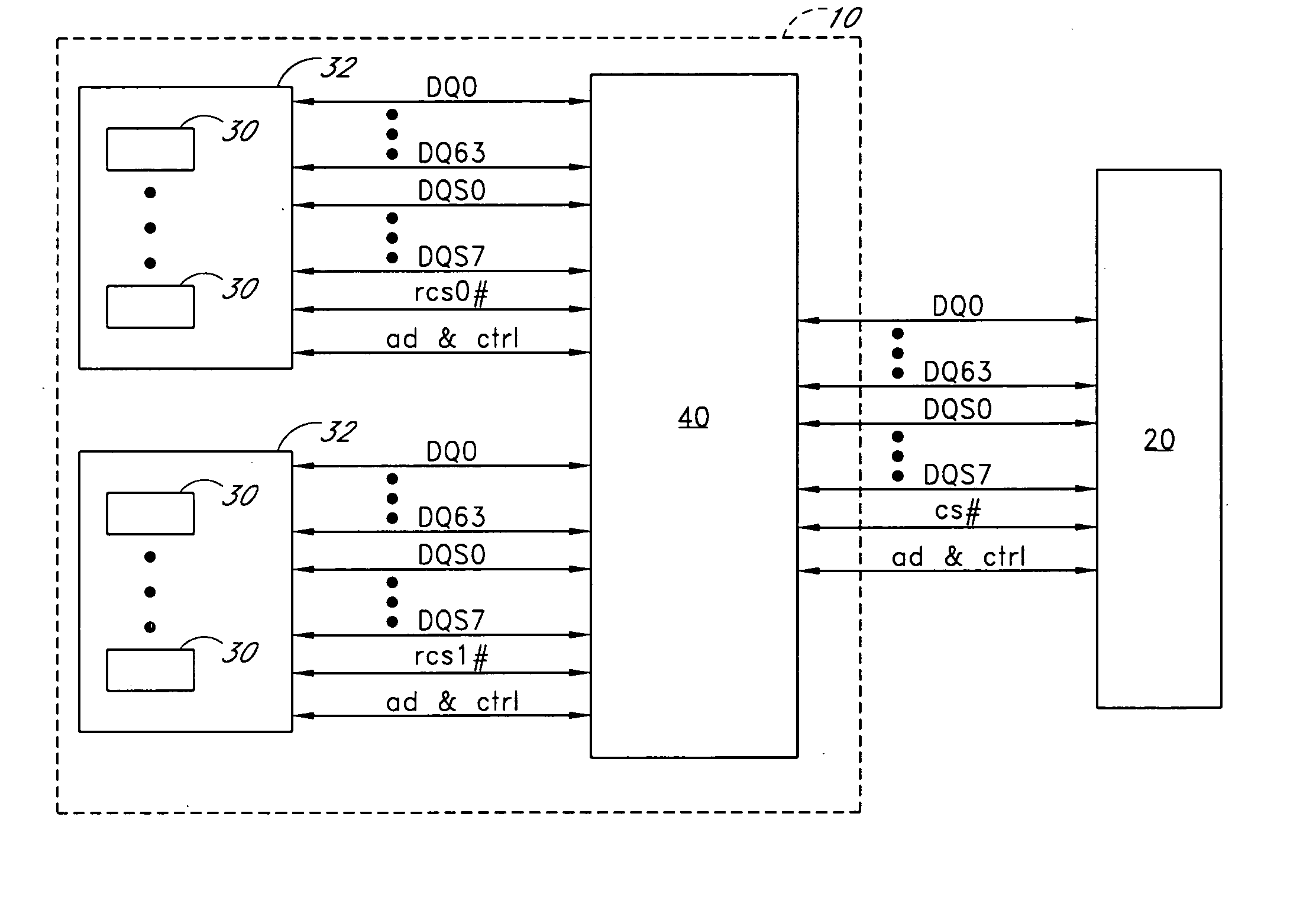

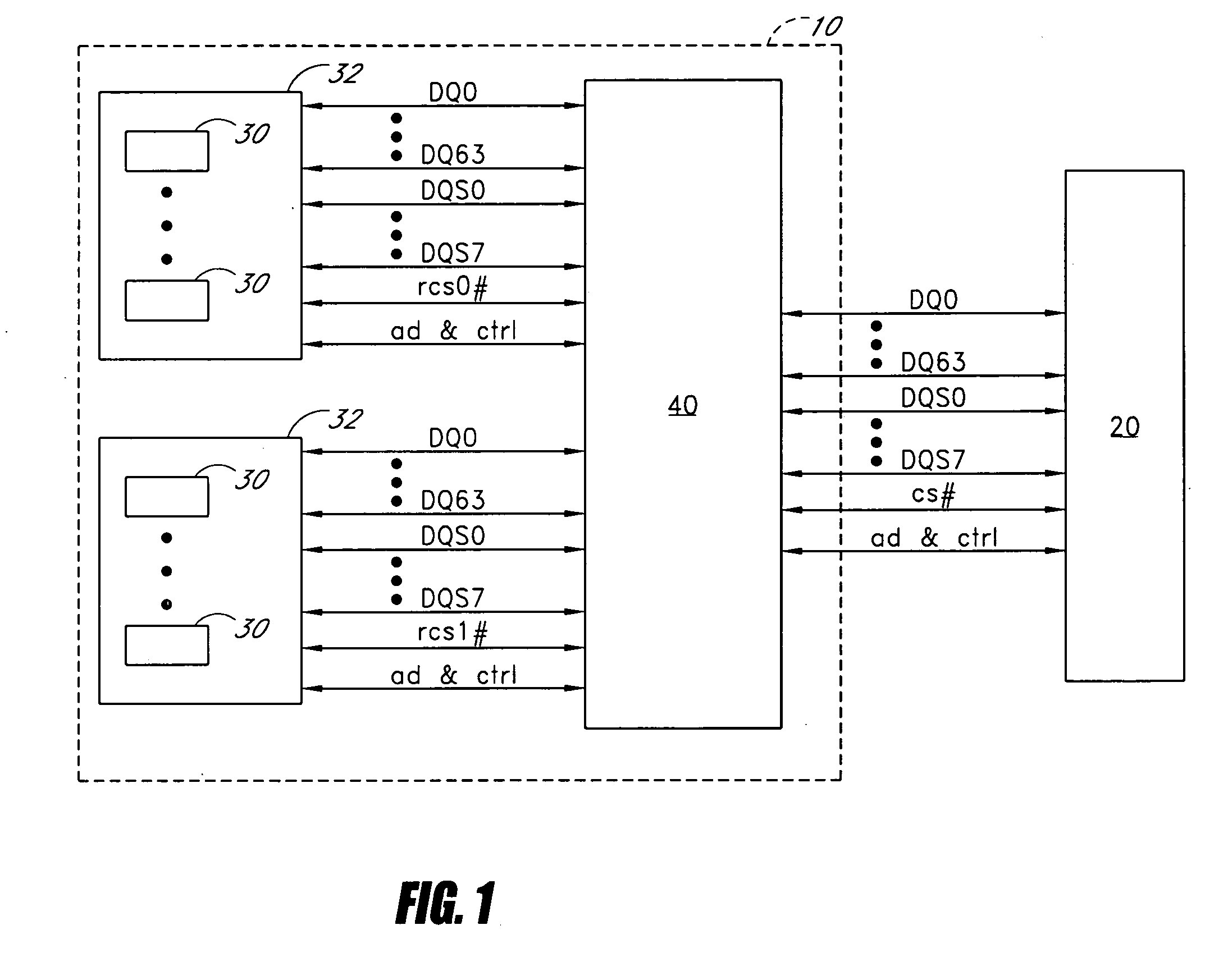

Transparent four rank memory module for standard two rank sub-systems

ActiveUS20060117152A1Memory adressing/allocation/relocationDigital storageParallel computingTerm memory

A transparent four rank memory module has a front side and a back side. The front side has a third memory rank stacked on a first memory rank. The back side has a fourth memory rank stacked on a second memory rank. An emulator coupled to the memory module activates and controls one individual memory rank from either the first memory rank, the second memory rank, the third memory rank, or the fourth memory rank based on the signals received from a memory controller.

Owner:SMART MODULAR TECH

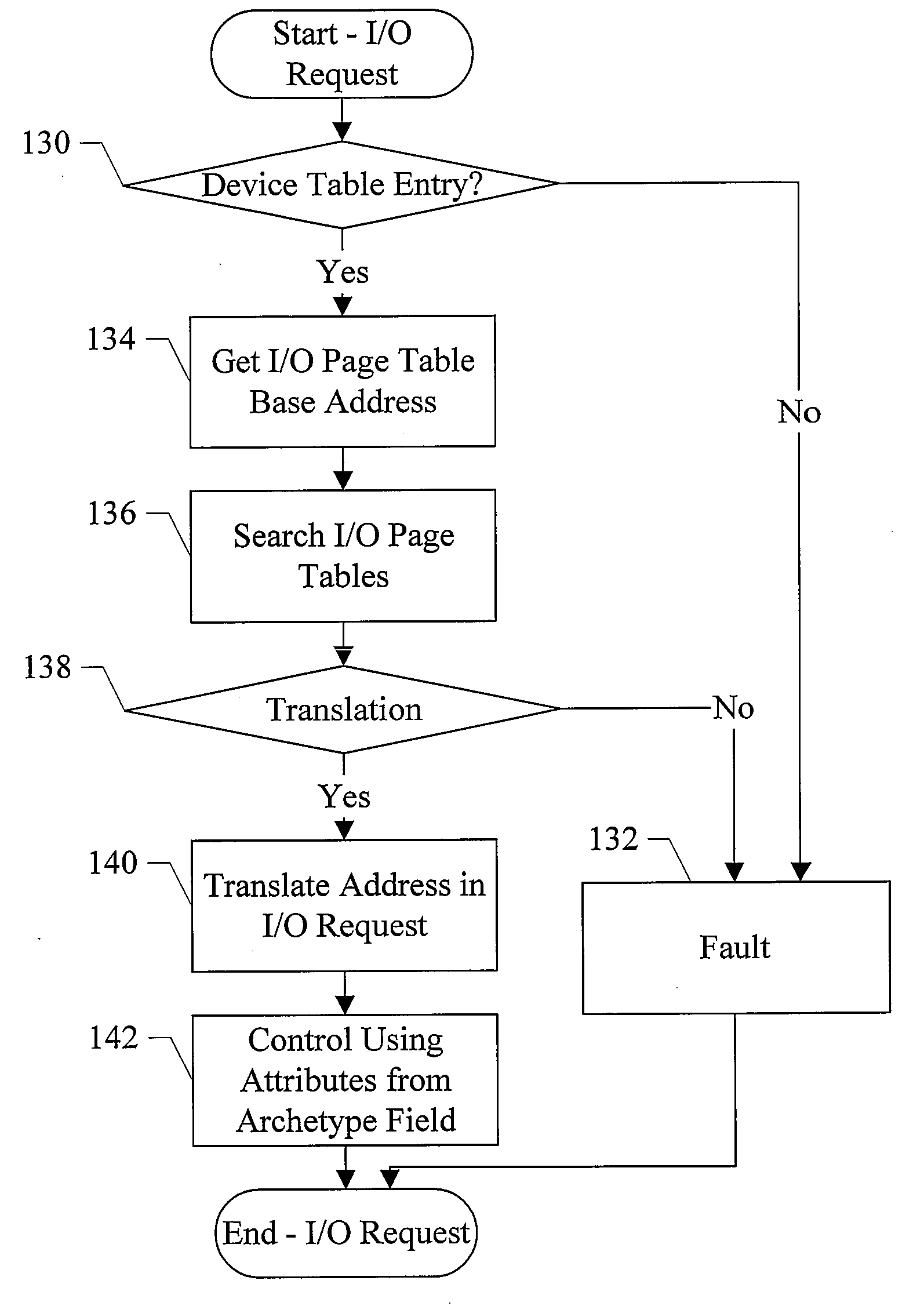

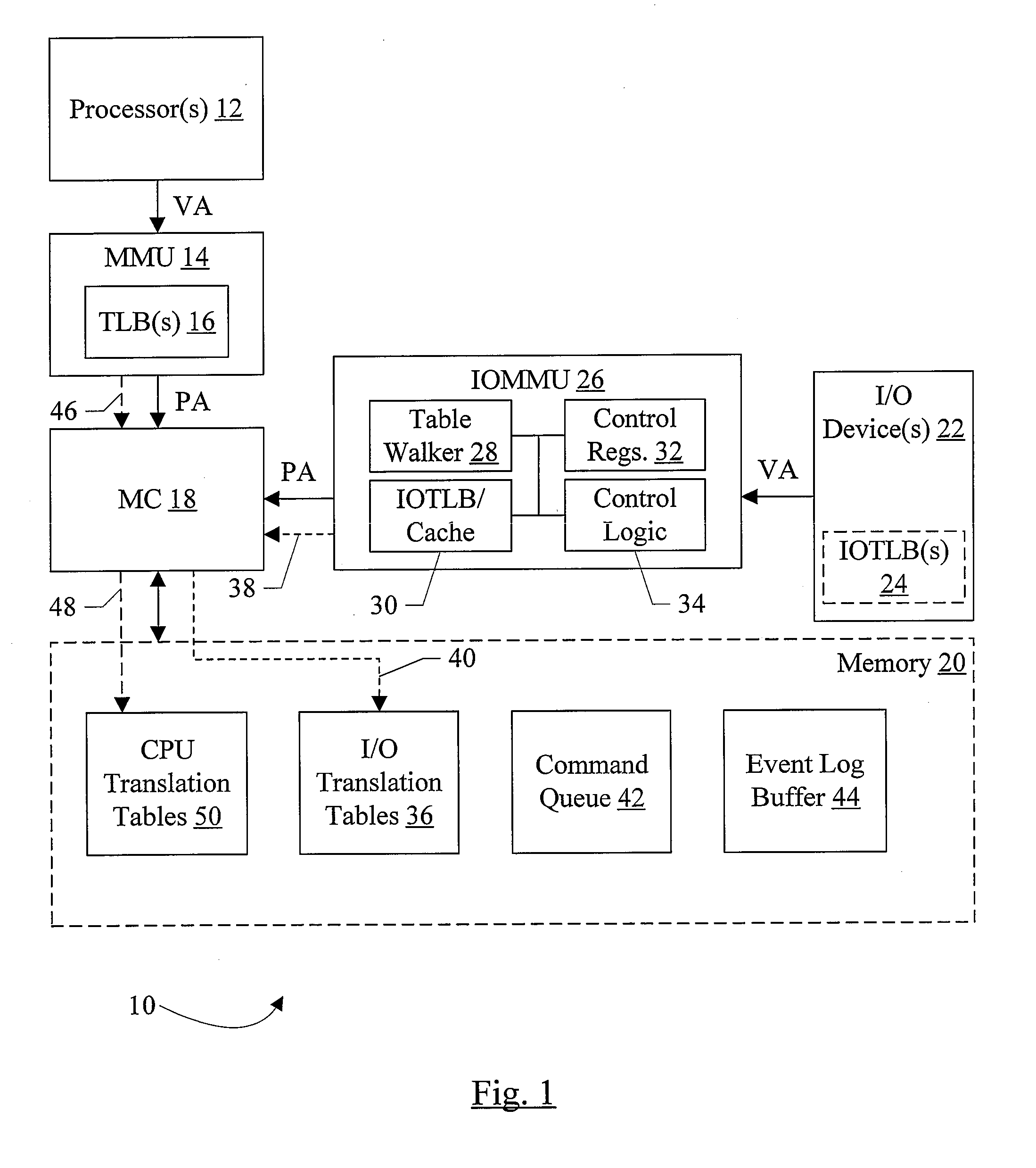

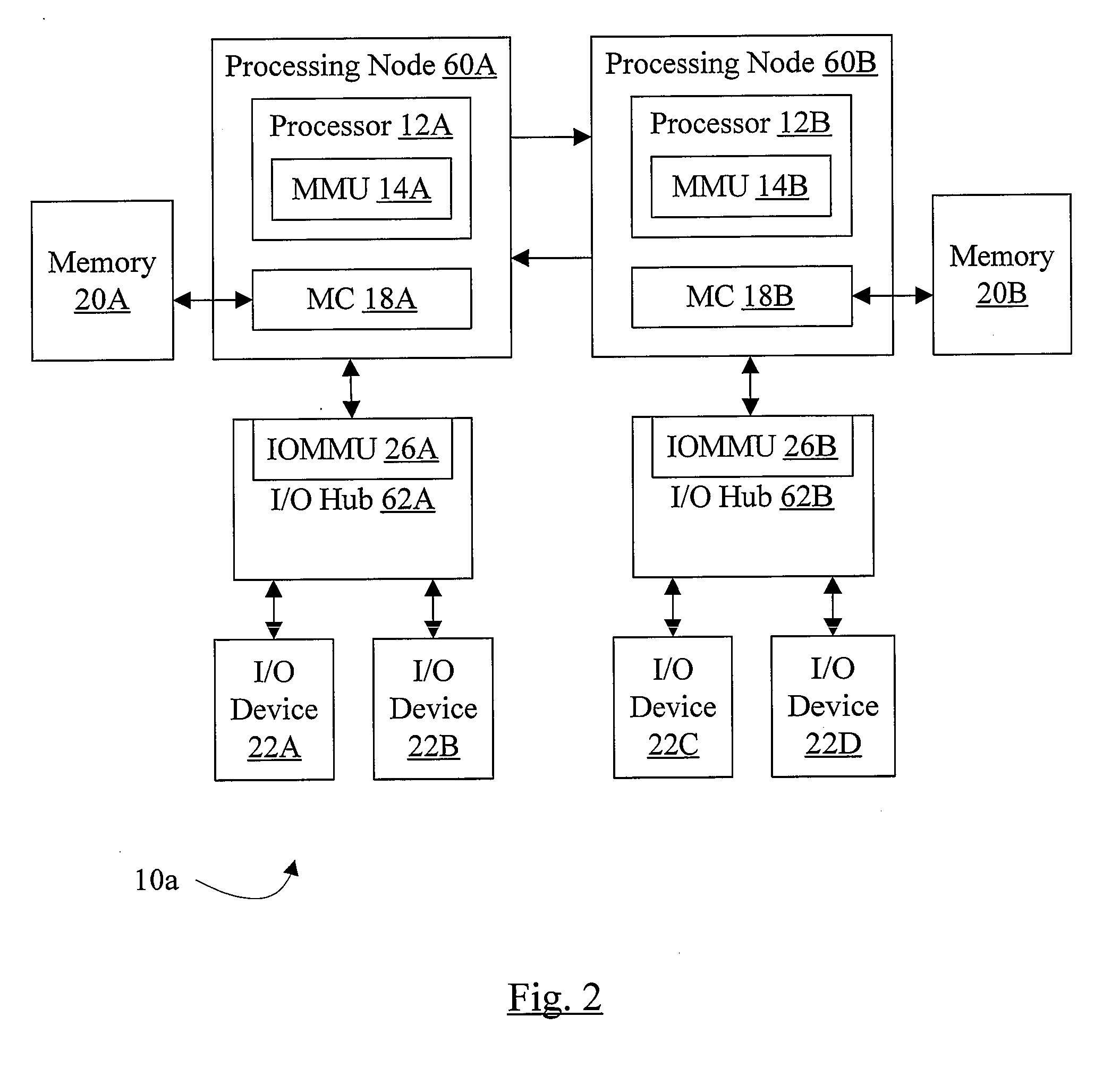

DMA Address Translation in an IOMMU

ActiveUS20070168643A1Memory architecture accessing/allocationMemory systemsPage tableMemory management unit

In an embodiment, an input / output (I / O) memory management unit (IOMMU) comprises at least one memory configured to store translation data; and control logic coupled to the memory and configured to translate an I / O device-generated memory request using the translation data. The translation data corresponds to one or more device table entries in a device table stored in a memory system of a computer system that includes the IOMMU, wherein the device table entry for a given request is selected by an identifier corresponding to the I / O device that generates the request. The translation data further corresponds to one or more I / O page tables, wherein the selected device table entry for the given request includes a pointer to a set of I / O page tables to be used to translate the given request.

Owner:MEDIATEK INC

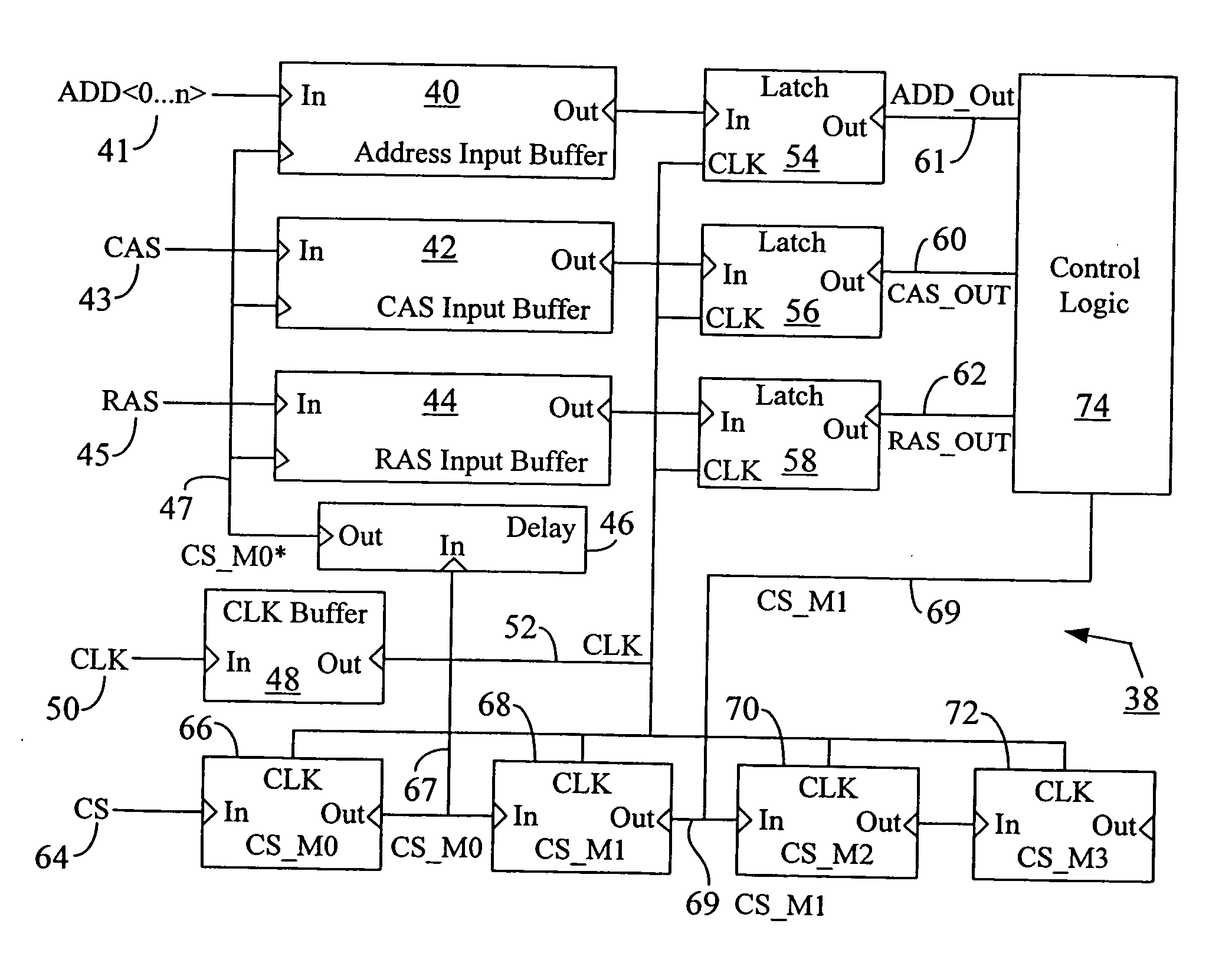

Low power chip select (CS) latency option

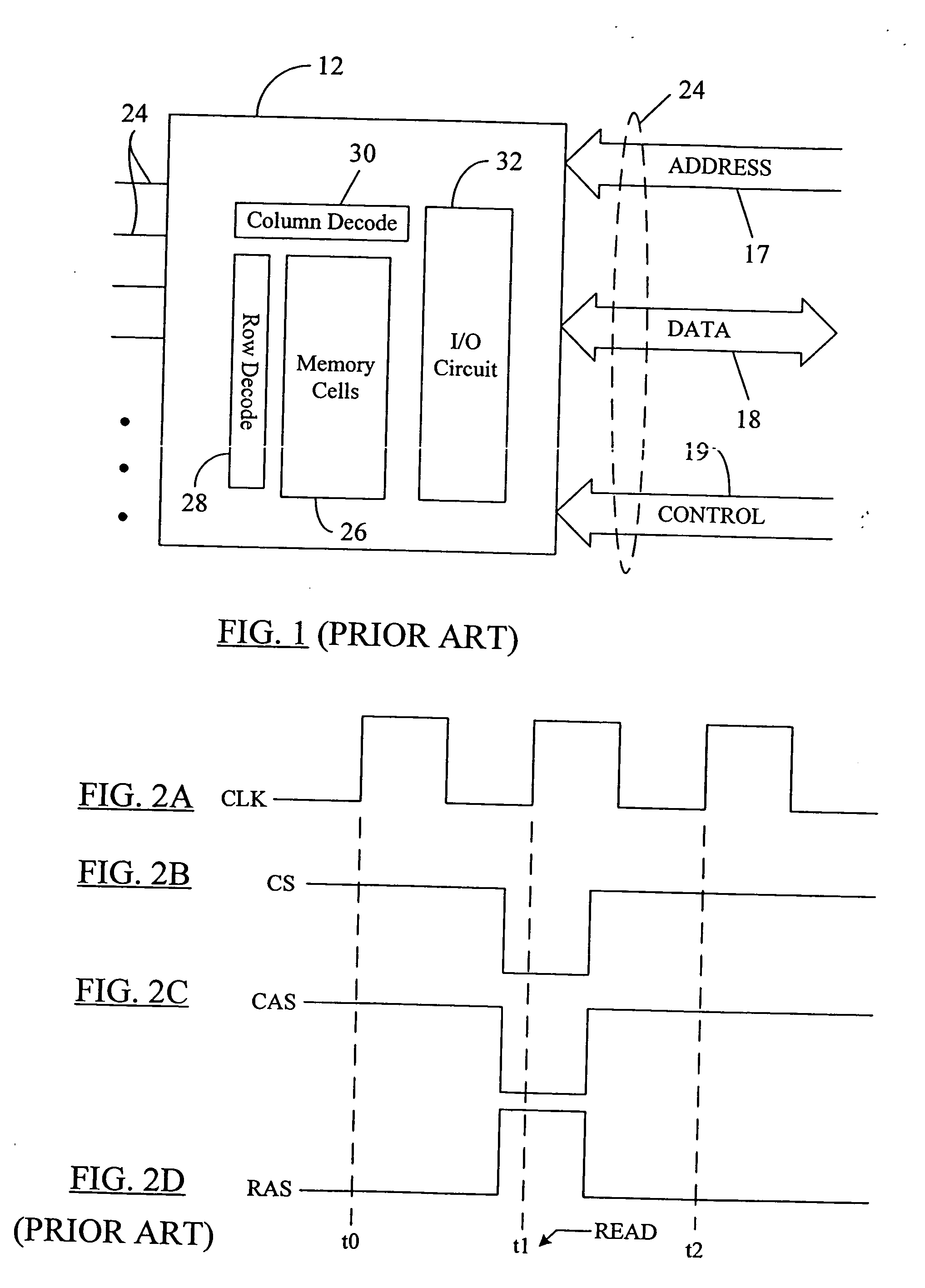

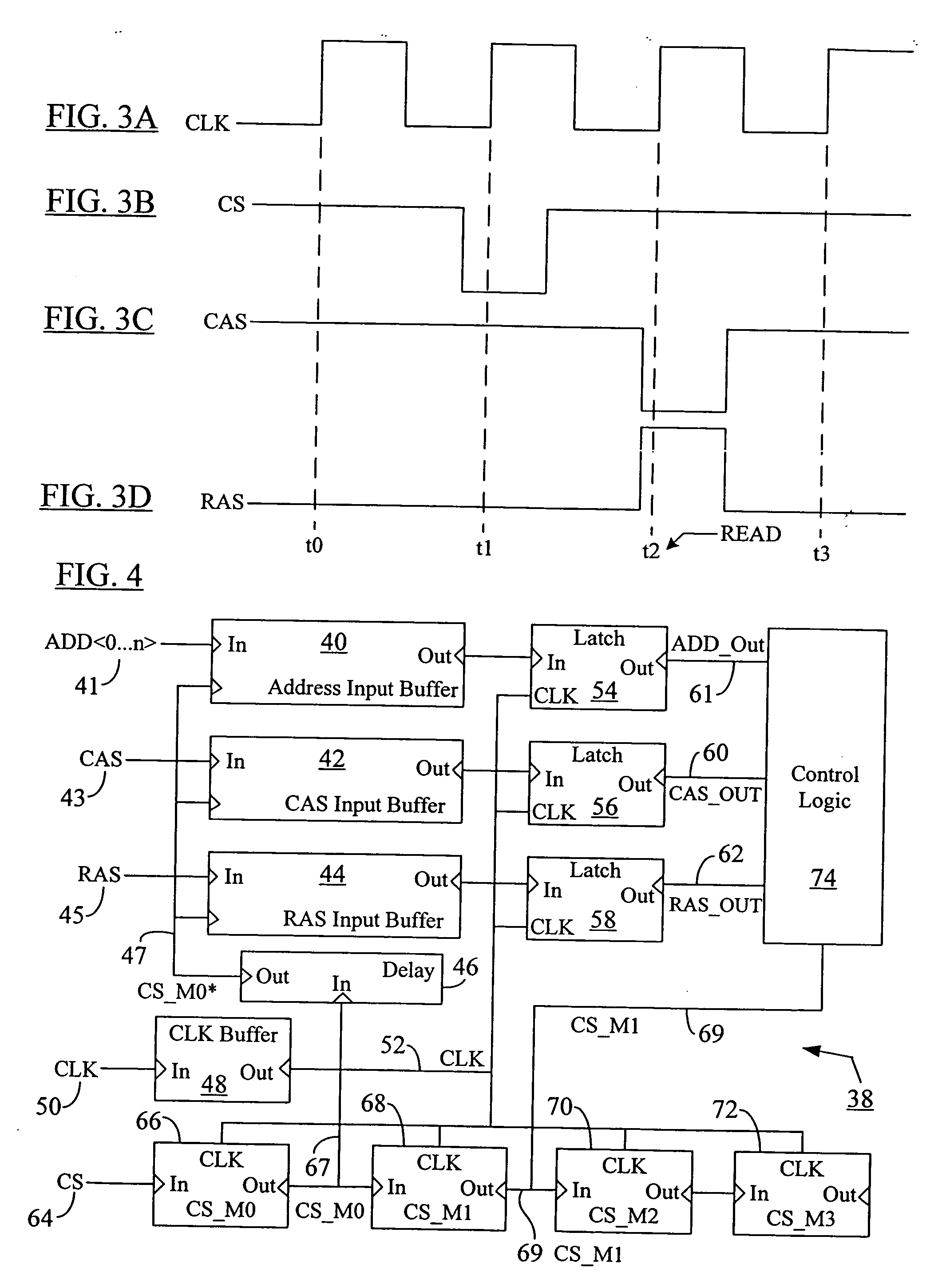

A system and method to reduce standby currents in input buffers in an electronic device (e.g., a memory device) is disclosed. The input buffers may be activated or deactivated by the state of a chip select (CS) signal. In case of a memory device, the active and precharge standby currents in memory input buffers may be reduced by turning off the input buffers when the CS signal is in an inactive state. A memory controller may supply the CS signal to the memory device at least one clock cycle earlier than other control signals including the RAS (row address strobe) signal, the CAS (column address strobe) signal, the WE (write enable) signal, etc. A modified I / O circuit in the memory device may internally delay the CS signal by at least one clock cycle to coincide its timing with the RAS / CAS signals for normal data access operation whereas the turning on / off of the memory input buffers may be performed by the CS signal received from the memory controller on the previous cycle. Thus, activation and deactivation of memory input buffers may be performed without forcing the memory device into power down mode and without employing complex circuits for power management. Because of the rules governing abstracts, this abstract should not be used to construe the claims.

Owner:ROUND ROCK RES LLC

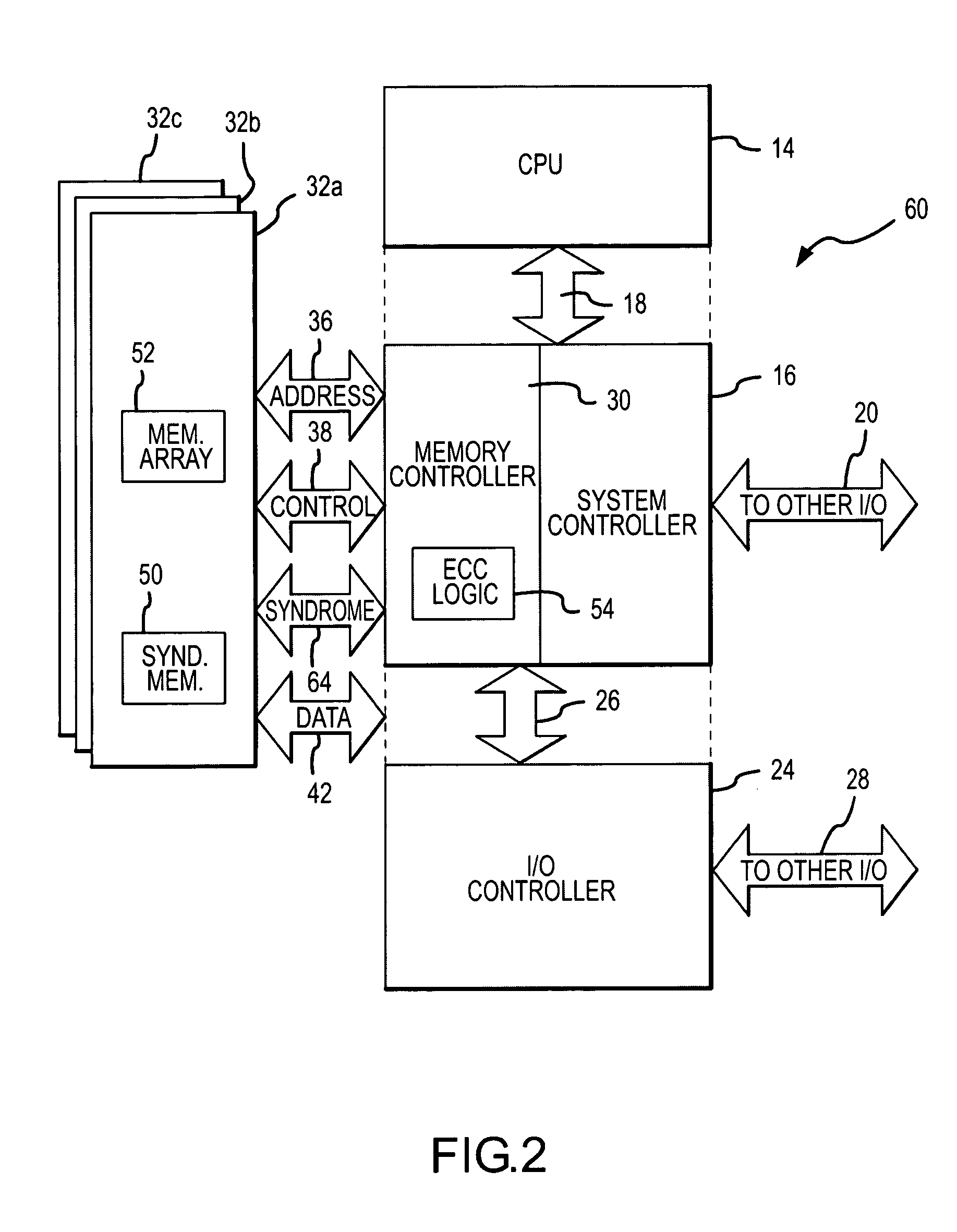

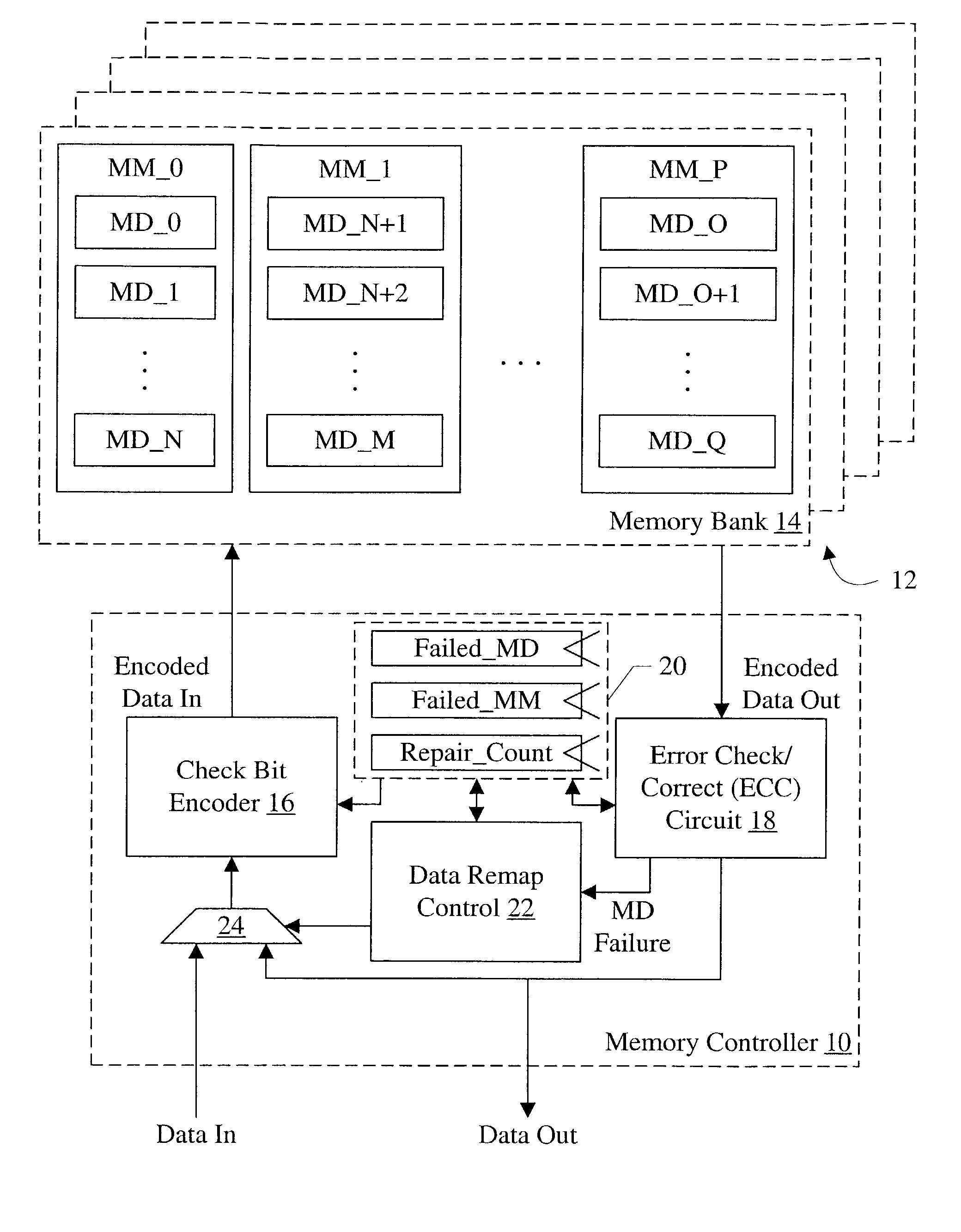

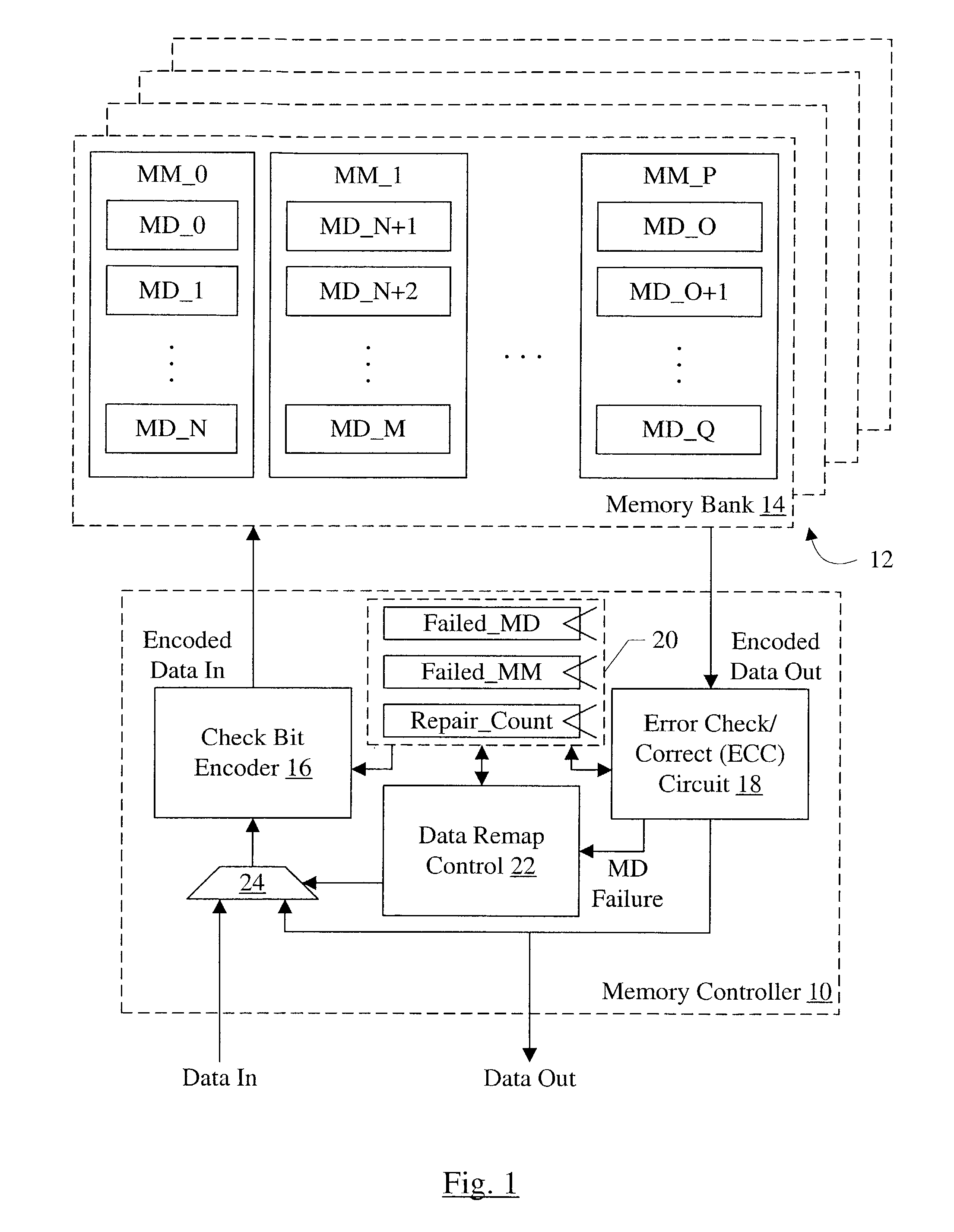

Error detection/correction code which detects and corrects component failure and which provides single bit error correction subsequent to component failure

A memory controller comprises a check bit encoder circuit and a check / correct circuit. The check bit encoder circuit is coupled to receive a data block to be written to a memory comprising a plurality of memory devices, and is configured to encode the data block with a plurality of check bits to generate an encoded data block. The plurality of check bits are defined to provide at least: (i) detection and correction of a failure of one of the plurality of memory devices; and (ii) detection and correction of a single bit error in the encoded data block following detection of the failure of one of the plurality of memory devices. The check / correct circuit is coupled to receive the encoded data block from the memory and is configured to decode the encoded data block and perform at least the detection of (i) and (ii) on the encoded data block.

Owner:ORACLE INT CORP

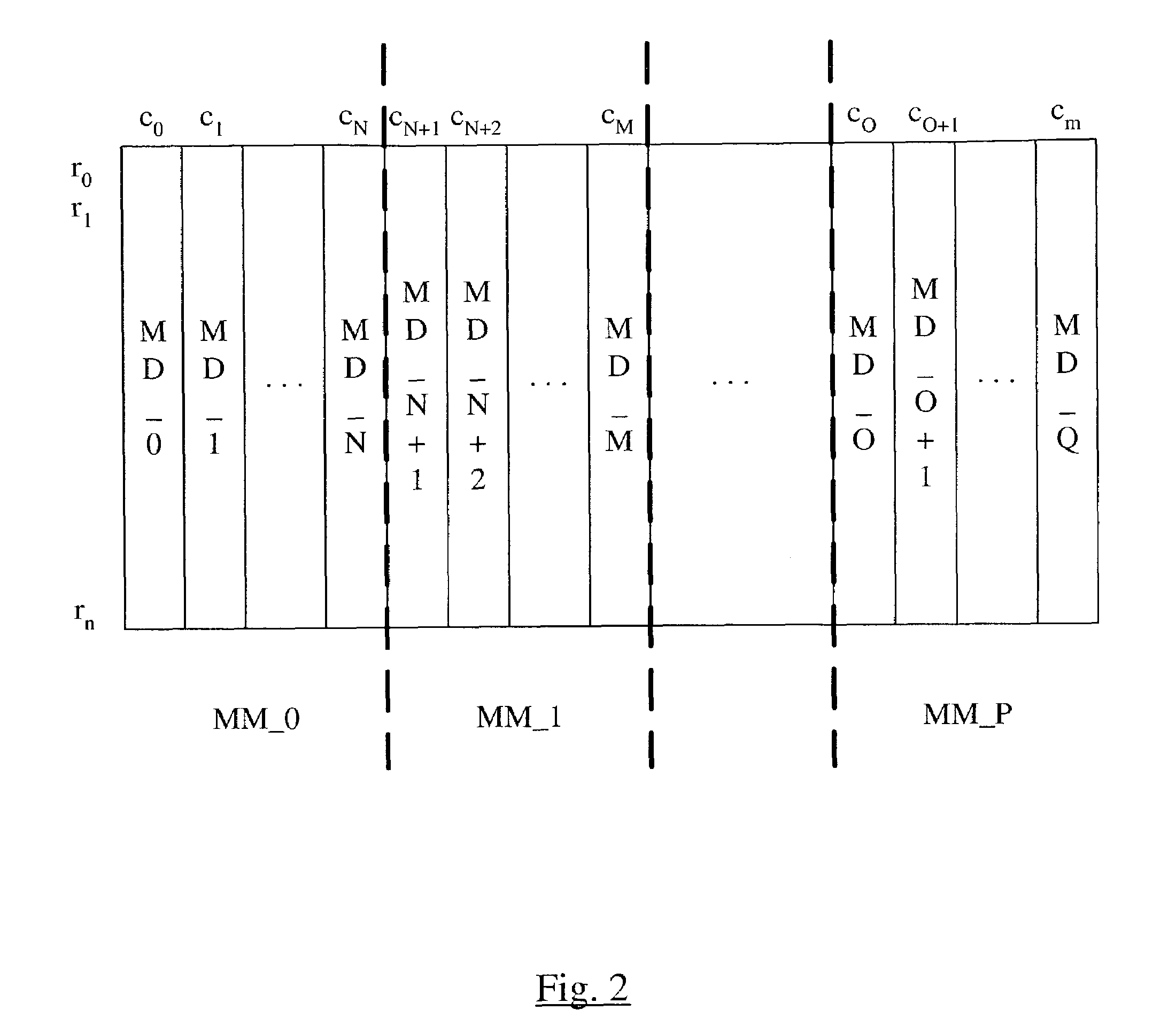

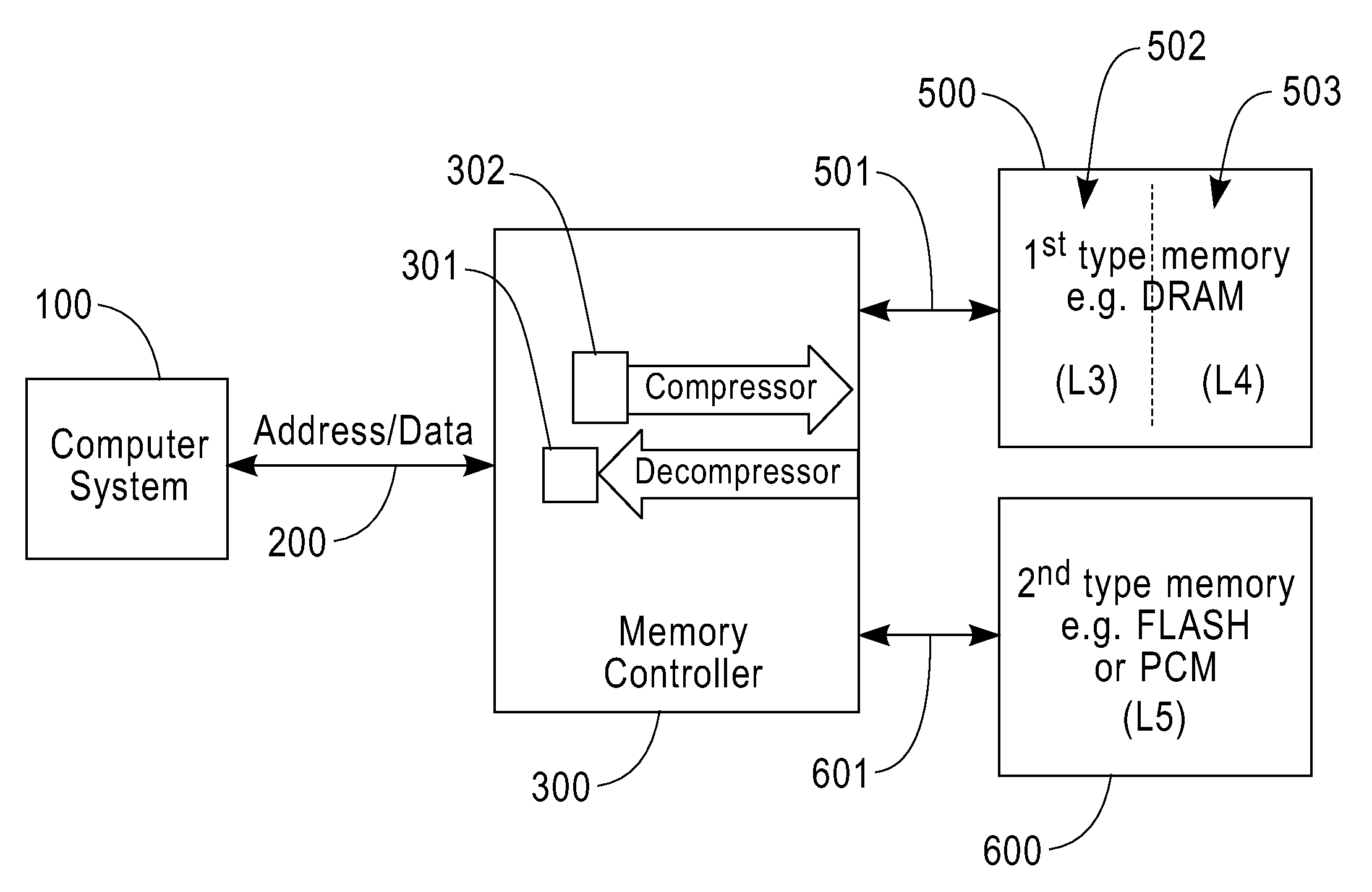

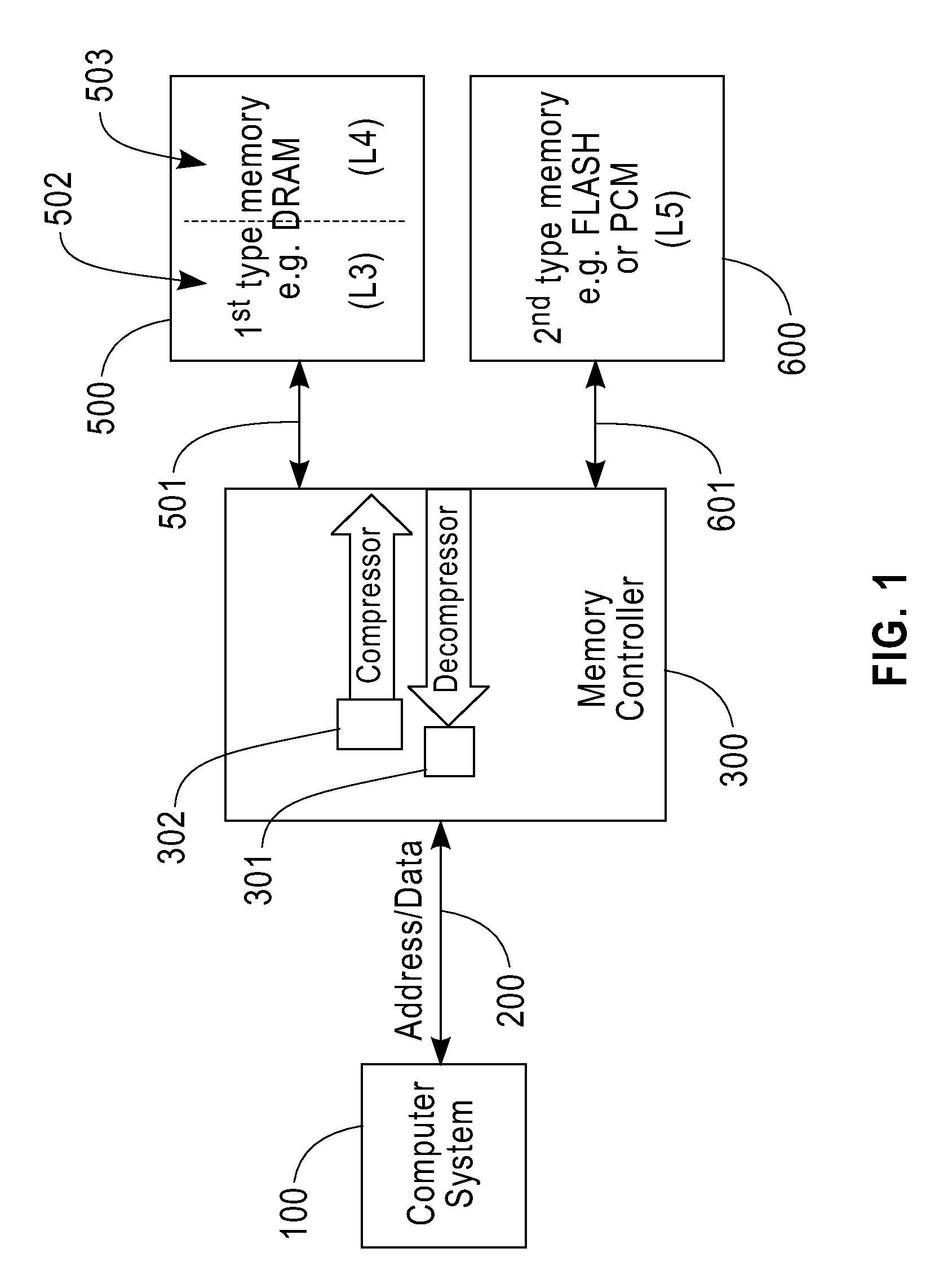

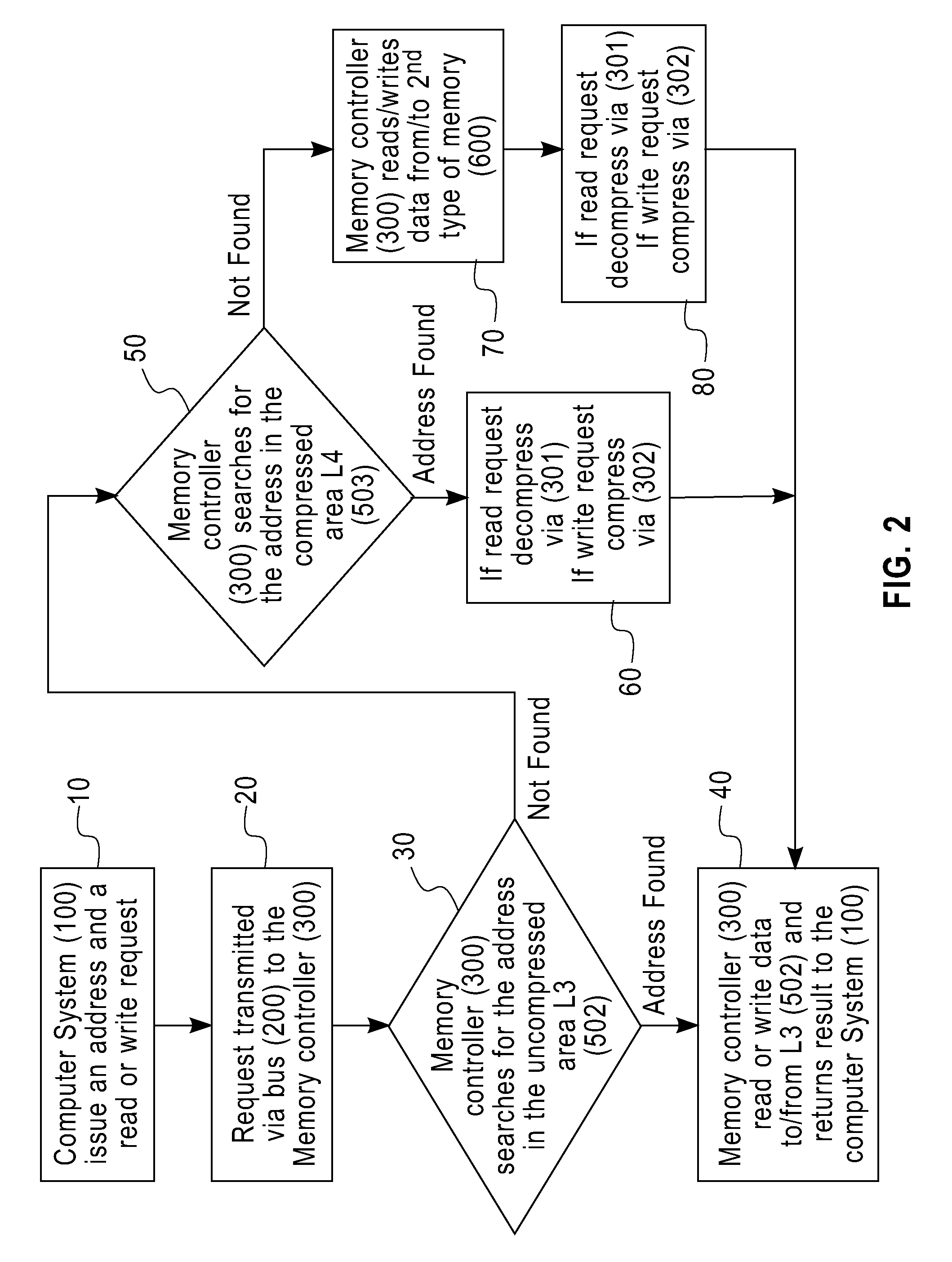

Bus attached compressed random access memory

InactiveUS20090254705A1Eliminate the problemLow costMemory architecture accessing/allocationMemory adressing/allocation/relocationThree levelMemory hierarchy

A computer memory system having a three-level memory hierarchy structure is disclosed. The system includes a memory controller, a volatile memory, and a non-volatile memory. The volatile memory is divided into an uncompressed data region and a compressed data region.

Owner:IBM CORP

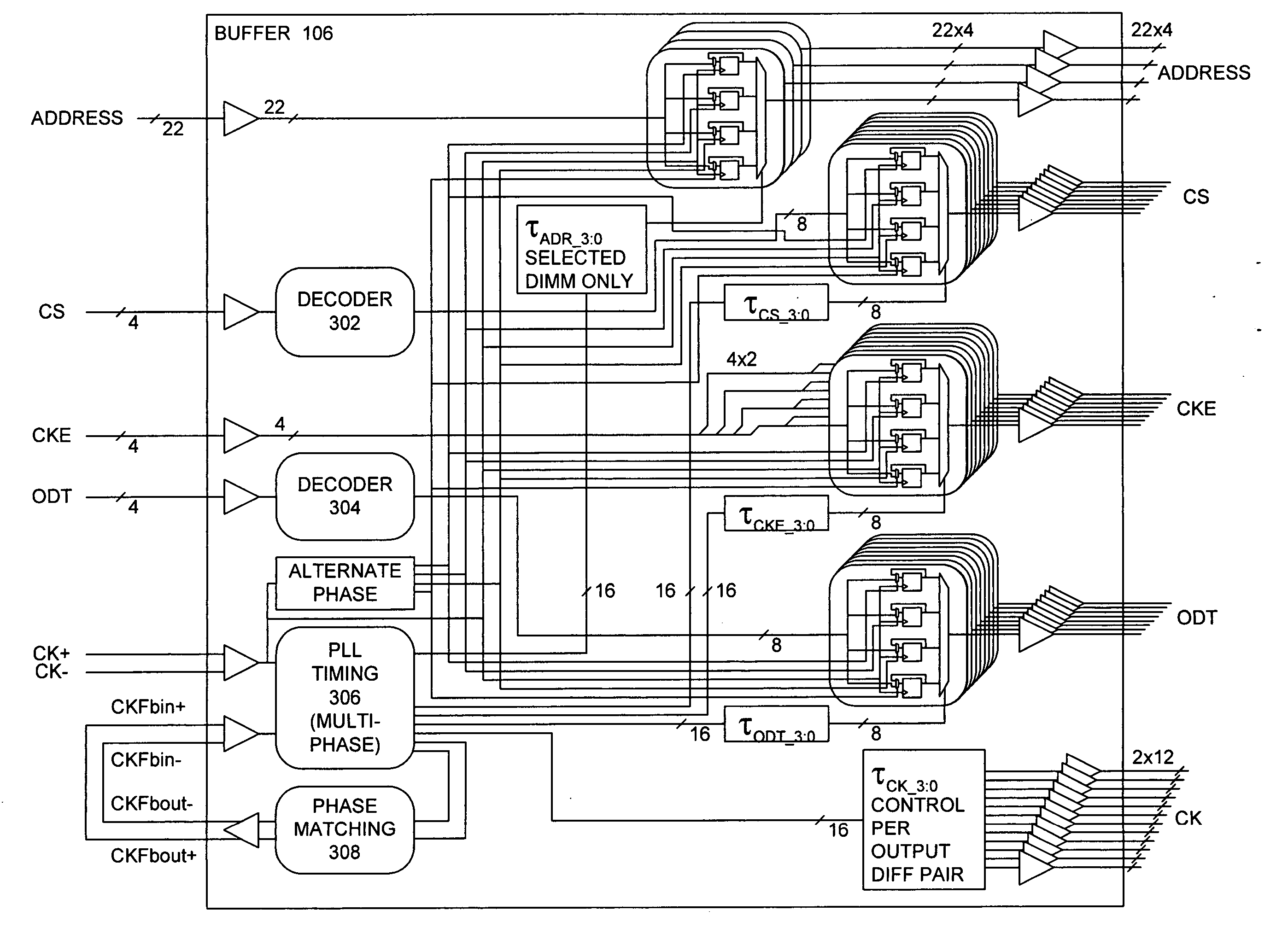

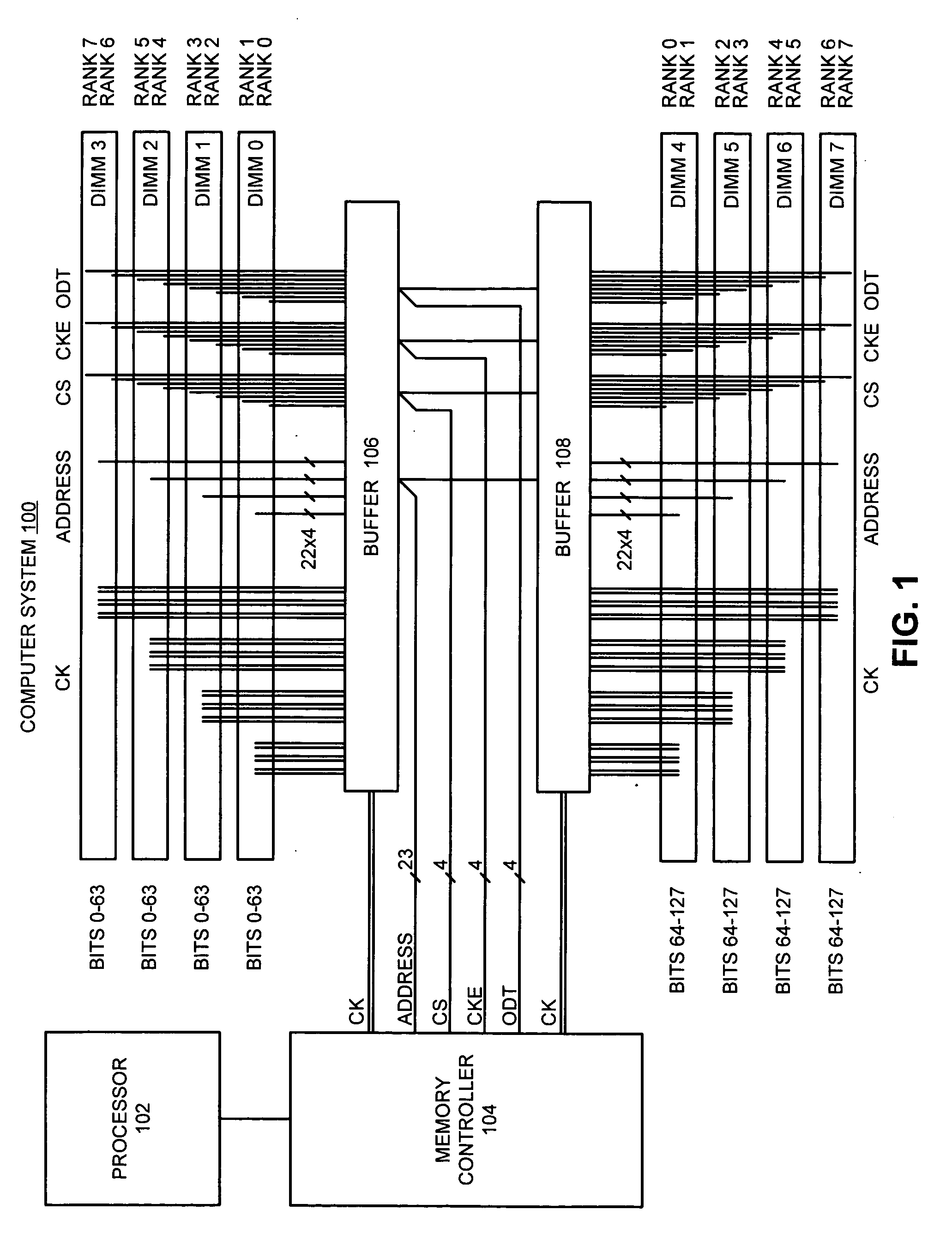

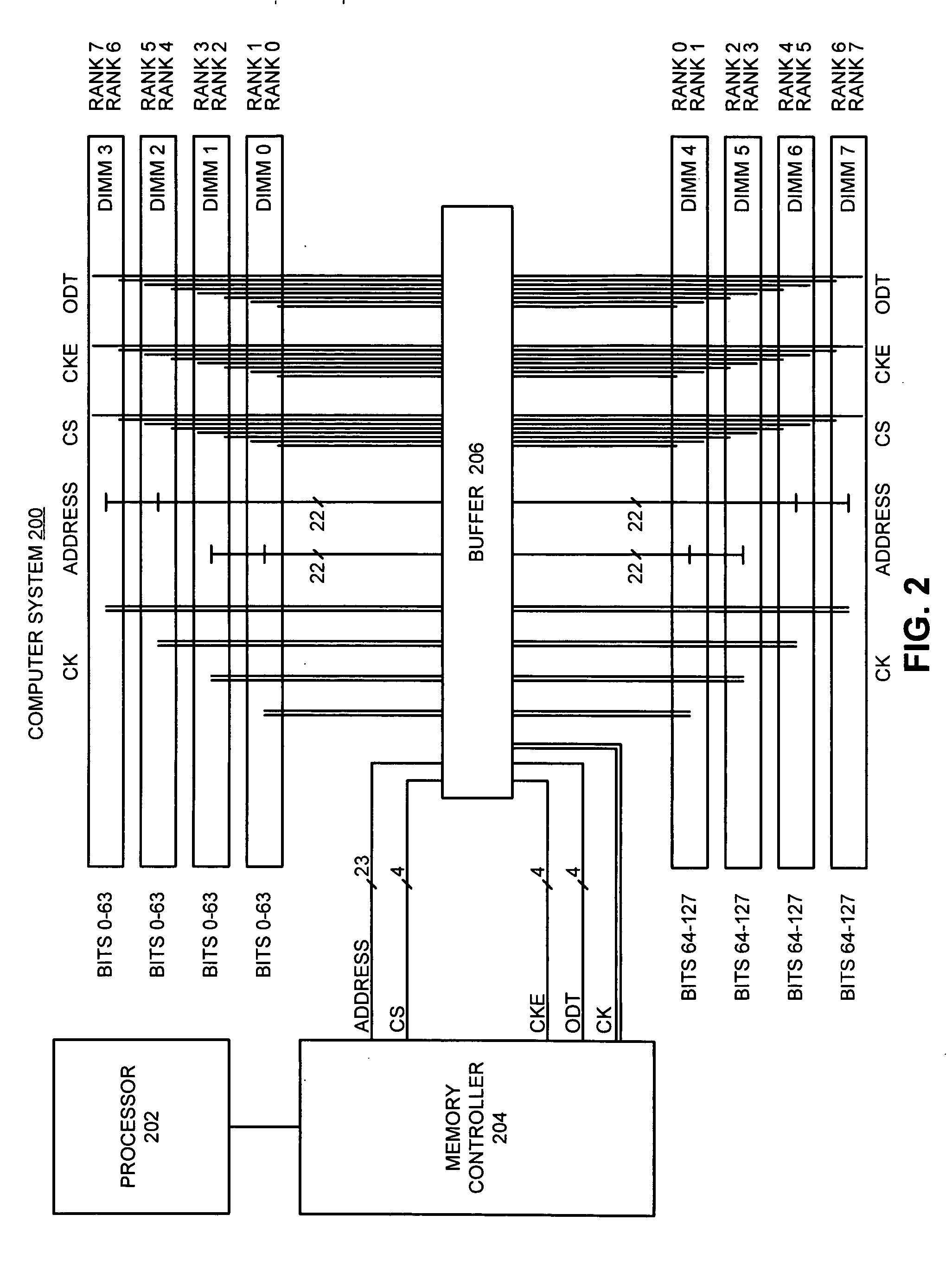

Reducing the number of power and ground pins required to drive address signals to memory modules

InactiveUS20060039205A1Reduced pin countReduce in quantityEnergy efficient ICTDigital storageChip selectEngineering

One embodiment of the present invention provides a system that reduces the number of power and ground pins required to drive address signals to system memory. During operation, the system receives address signals associated with a memory operation from a memory controller, wherein the address signals are received at a buffer chip, which is external the memory controller. The system also receives chip select signals associated with the memory operation at the buffer chip. Next, the system uses the chip select signals to identify an active subset of memory modules in the system memory, which are active during the memory operation. The system then uses address drivers on the buffer chip to drive the address signals only to the active subset of memory modules, and not to other memory modules in the system memory. In this way, the buffer chip requires fewer power and ground pins for the address drivers because the address signals are only driven to the active subset of memory modules, instead of being driven to all memory modules in the system memory.

Owner:APPLE INC

Method and system for energy management in a simultaneous multi-threaded (SMT) processing system including per-thread device usage monitoring

InactiveUS20050138442A1Lower latencyReduce power consumptionEnergy efficient ICTVolume/mass flow measurementDecision controlOperational system

A method and system for energy management in a simultaneous multi-threaded (SMT) processing system including per-thread device usage monitoring provides control of energy usage that accommodates thread parallelism. Per-device usage information is measured and stored on a per-thread basis, so that upon a context switch, the previous usage evaluation state can be restored. The per-thread usage information is used to adjust the thresholds of device energy management decision control logic, so that energy use can be managed with consideration as to which threads will be running in a given execution slice. A device controller can then provide for per-thread control of attached device power management states without intervention by the processor and without losing the historical evaluation state when a process is switched out. The device controller may be a memory controller and the controlled devices memory modules or banks within modules if individual banks can be power-managed. Local thresholds provide the decision-making mechanism for each controlled device and are adjusted by the operating system in conformity with the measured usage level for threads executing within the processing system. The per-thread usage information may be obtained from a performance monitoring unit that is located within or external to the device controller and the usage monitoring state is then retrieved and replaced by the operating system at each context switch.

Owner:IBM CORP