Patents

Literature

1495 results about "Memory management unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

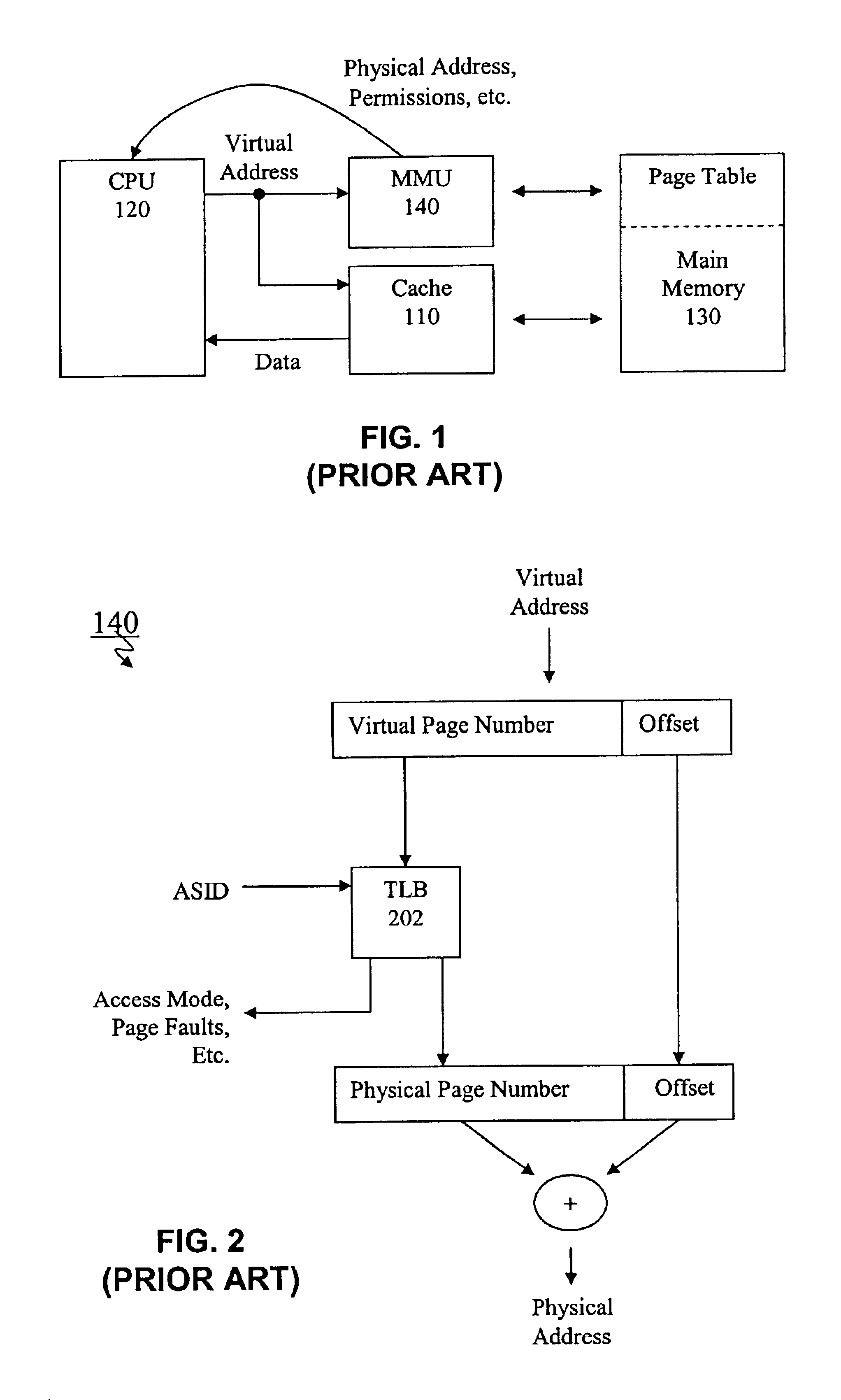

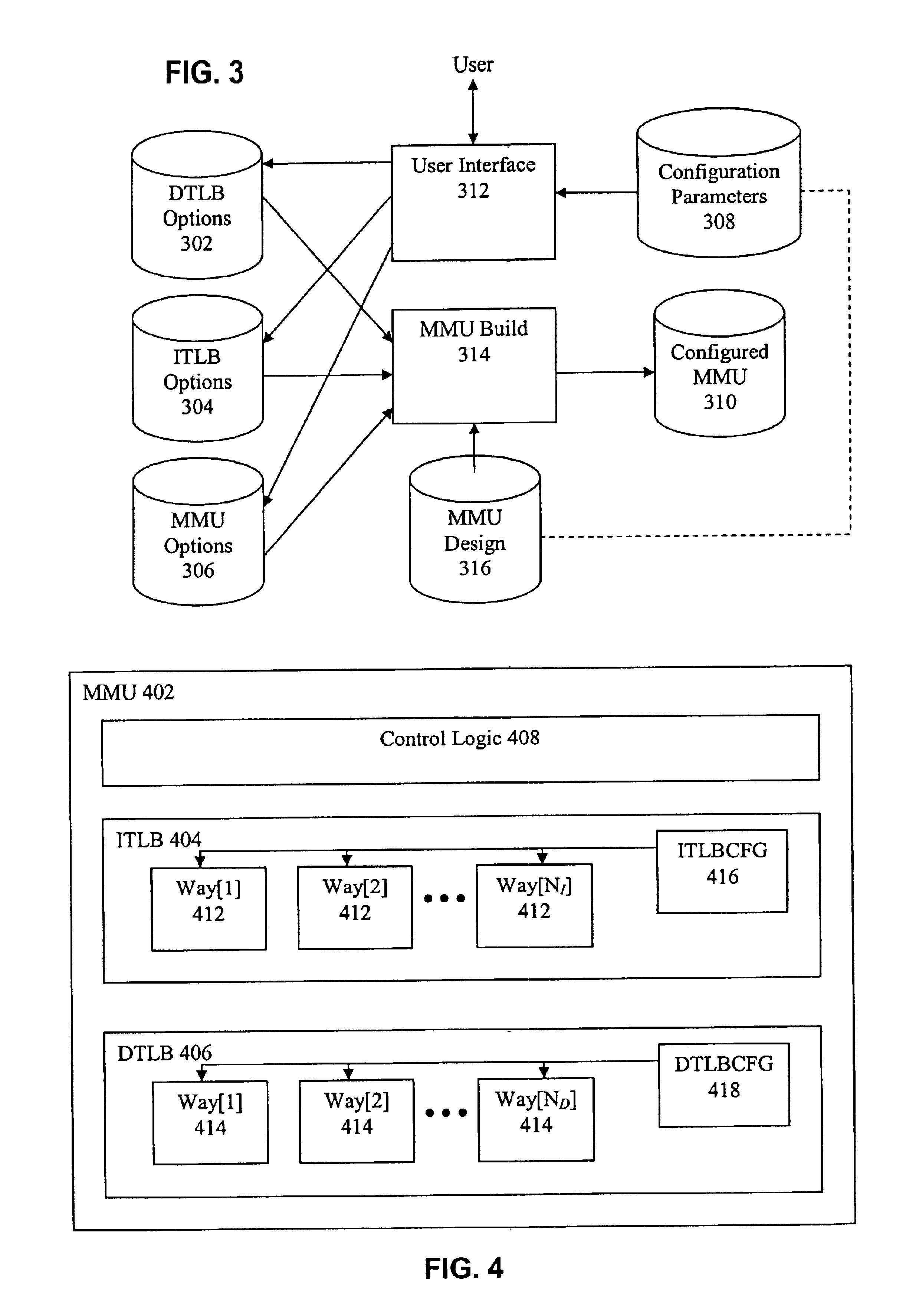

A memory management unit (MMU), sometimes called paged memory management unit (PMMU), is a computer hardware unit having all memory references passed through itself, primarily performing the translation of virtual memory addresses to physical addresses.

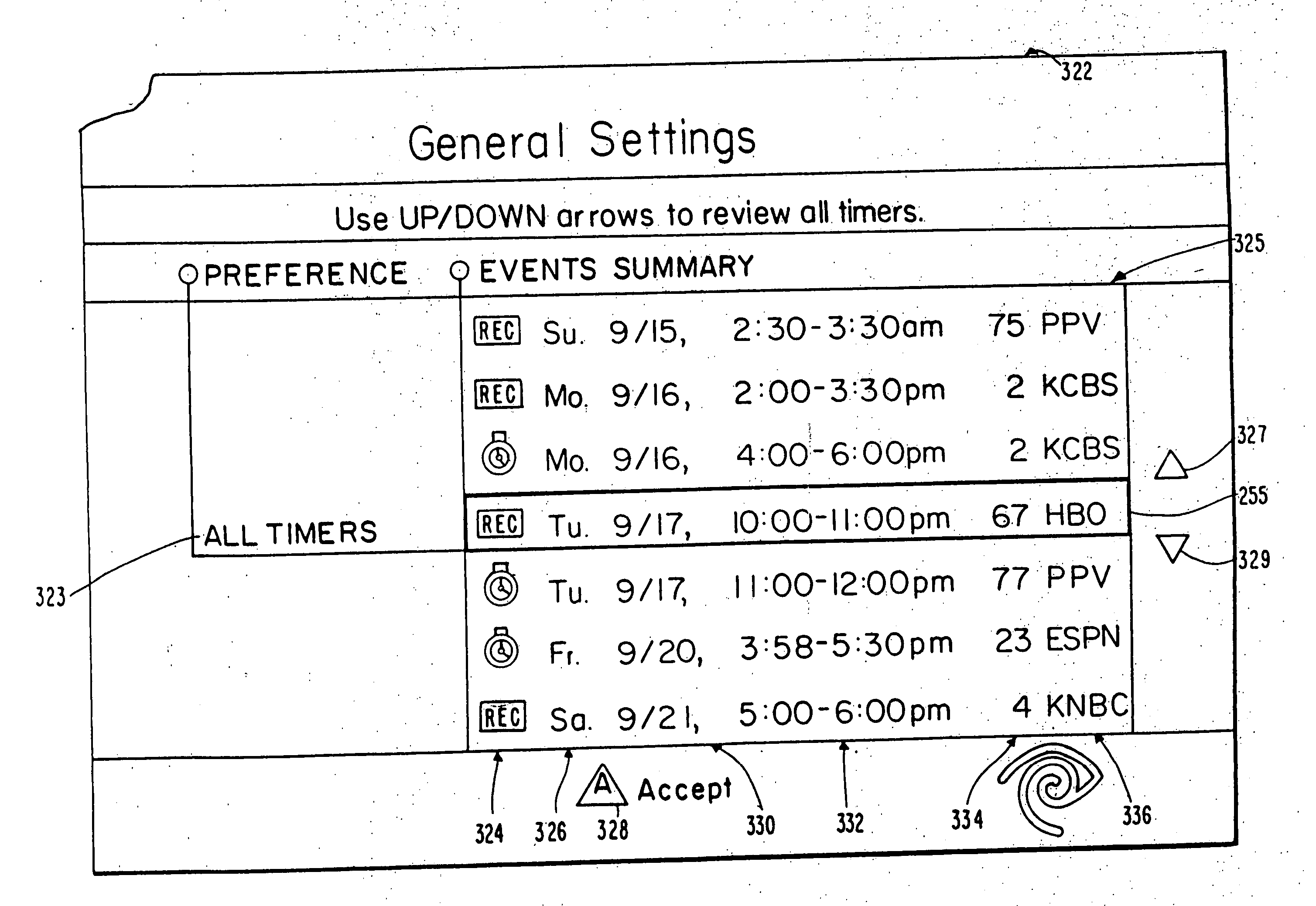

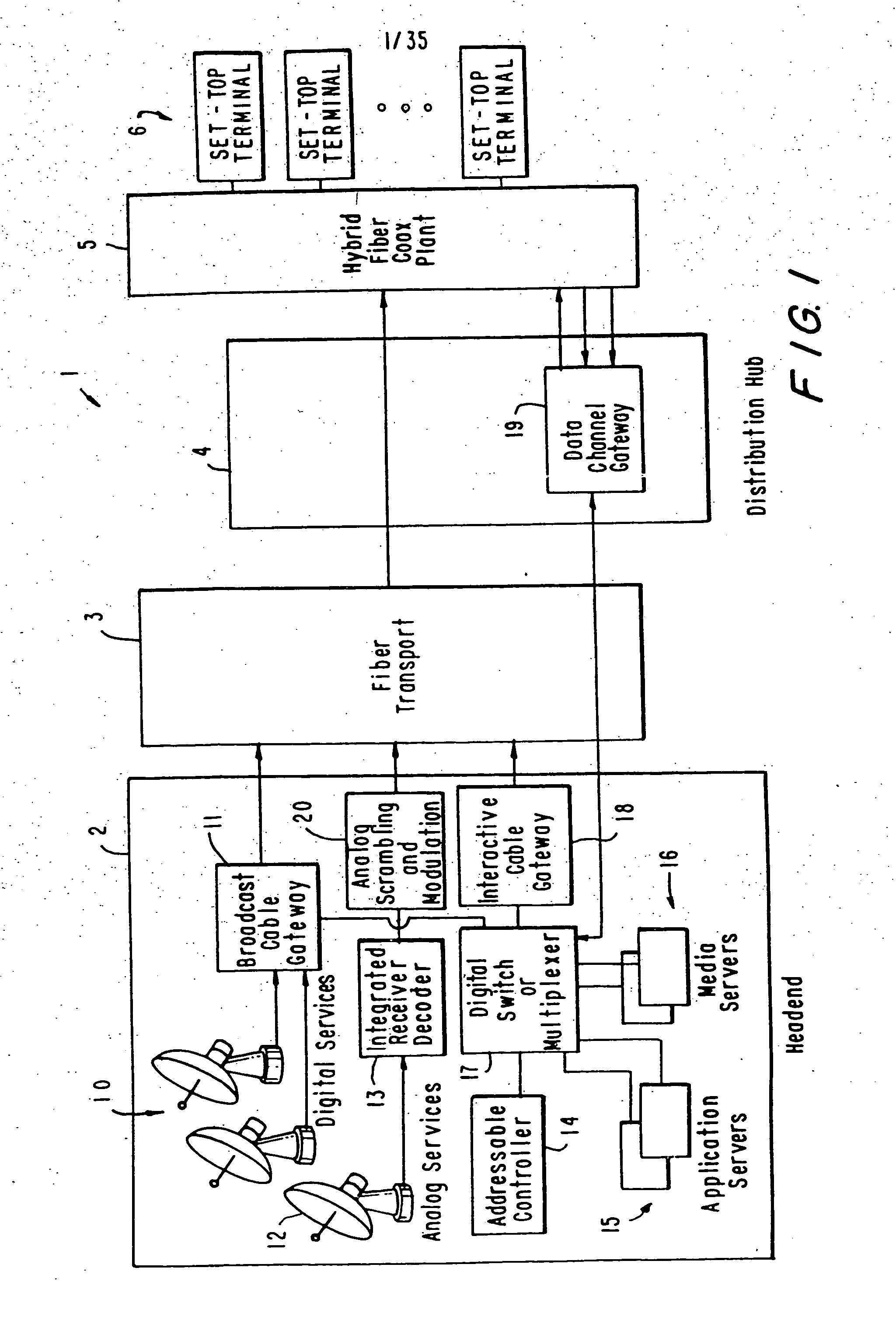

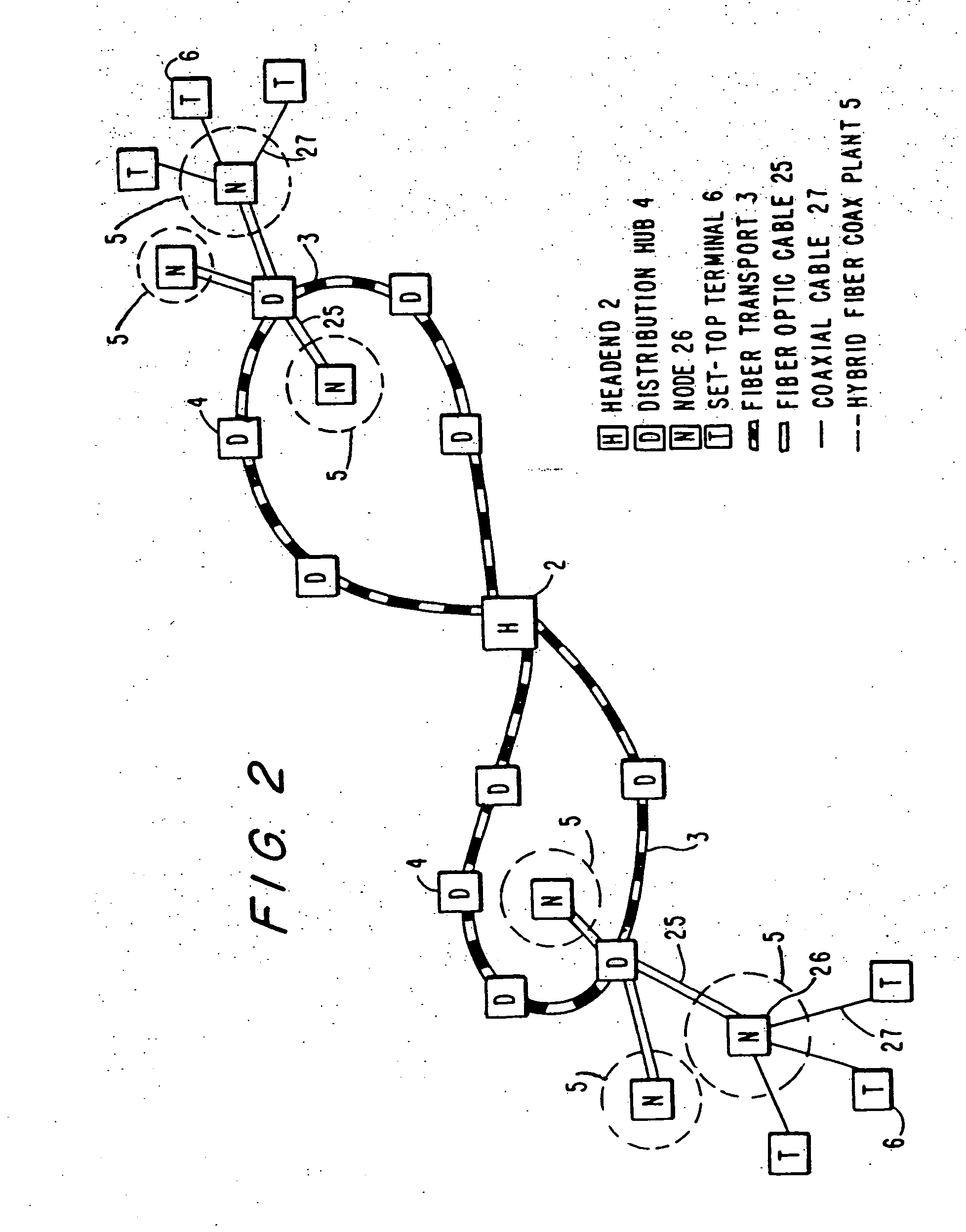

Interactive television program guide display

InactiveUS20050015804A1Increase the number ofEnhanced signalTelevision system detailsTelevision system scanning detailsThe InternetHybrid fibre-coaxial

A full service cable television system and method are provided. The system comprises a cable headend, at least one fiber transport, at least one distribution hub, at least one hybrid fiber coax plant, and a plurality of set-top terminals. The system delivers television programs, advanced cable services, and online services. Programs and services are transmitted to the set-top terminals in both digital and analog formats to maintain downward compatibility with existing systems. The set-top terminal includes a central processing unit, a unified memory architecture, a memory management unit, communications circuitry, I / O control circuitry, and audio and video output circuitry. Through these components, the set-top terminal provides advanced cable services such as a comprehensive channel navigator, an interactive program guide, impulse Pay-Per-View, Near-Video-On-Demand and Video-On-Demand programming, and advanced configuration controls. The set-top terminal also provides online services such as World Wide Web browsing, Internet e-mail, and home shopping.

Owner:TIME WARNER CABLE ENTERPRISES LLC

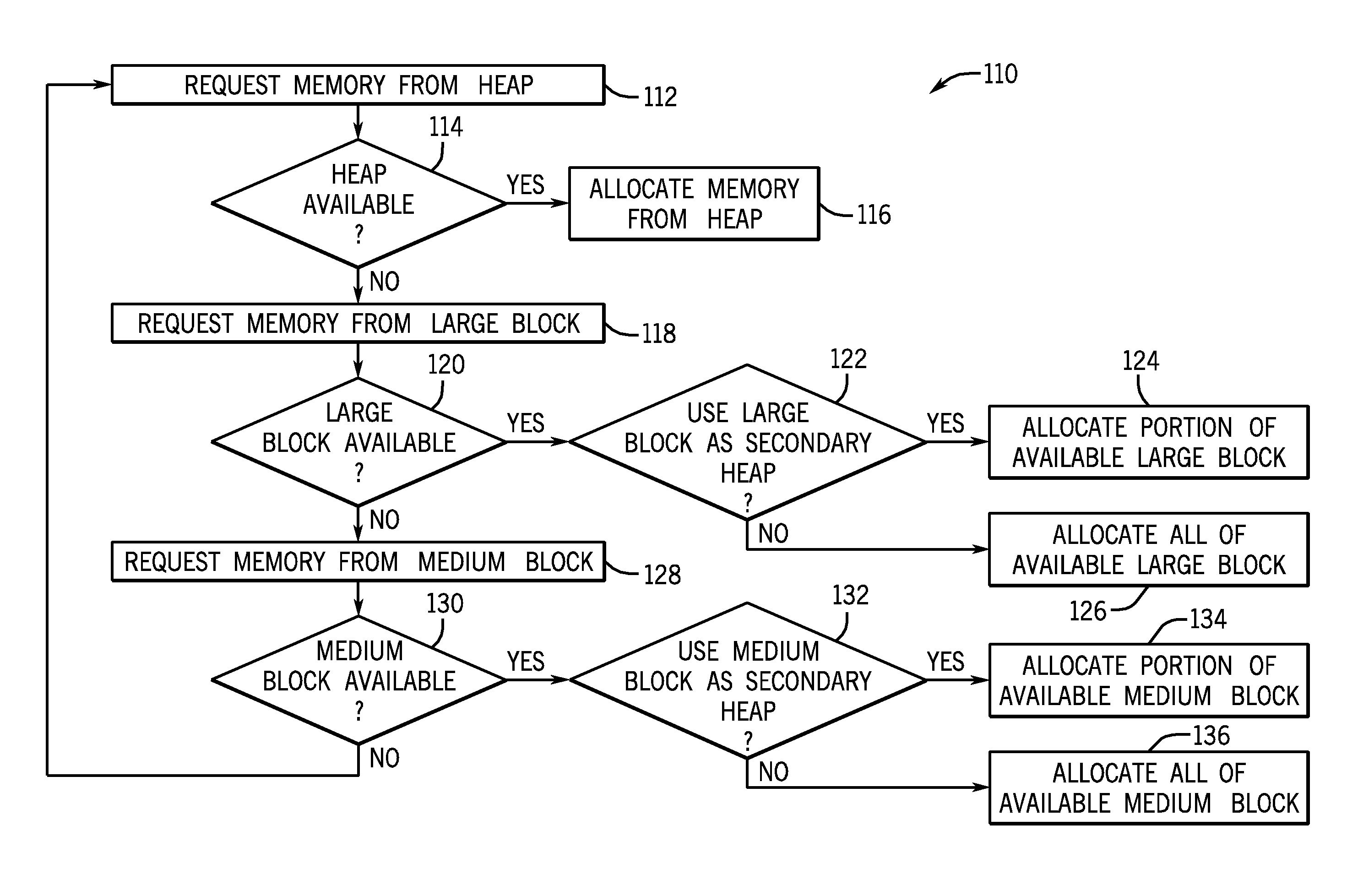

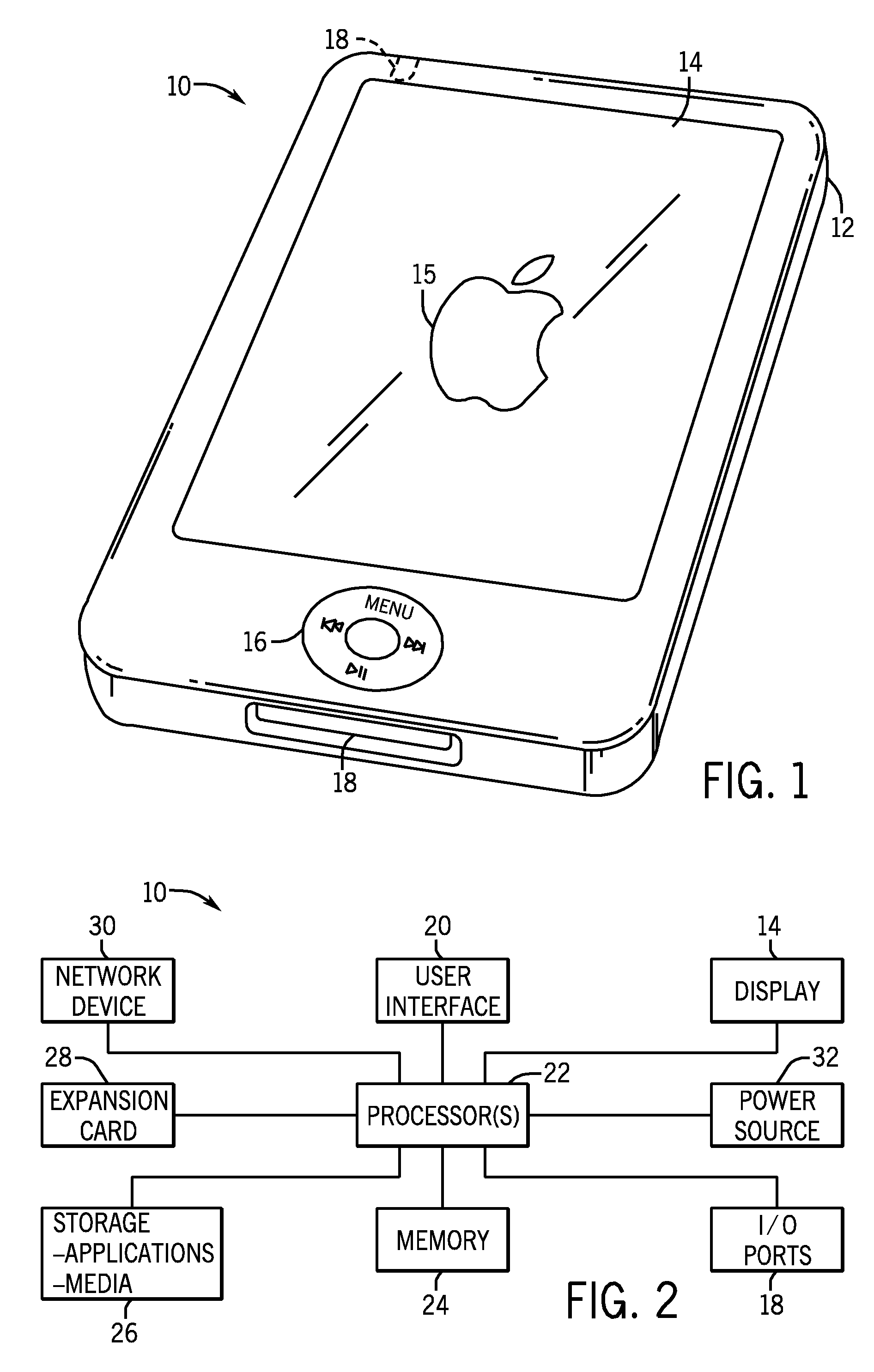

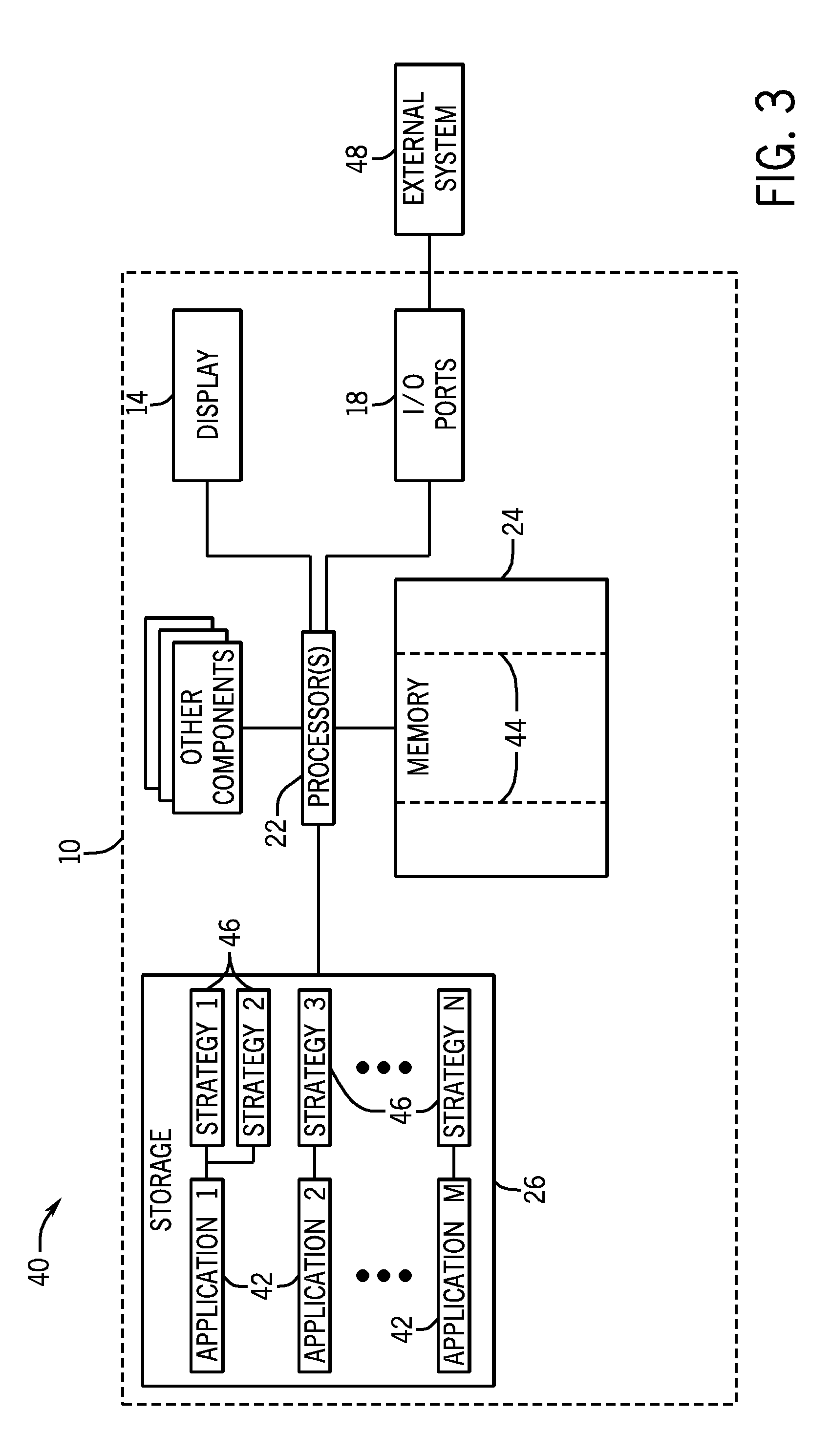

Memory management system and method

ActiveUS20100064113A1Facilitate memory allocationReduce frequencyMemory adressing/allocation/relocationParallel computingMemory management unit

Owner:APPLE INC

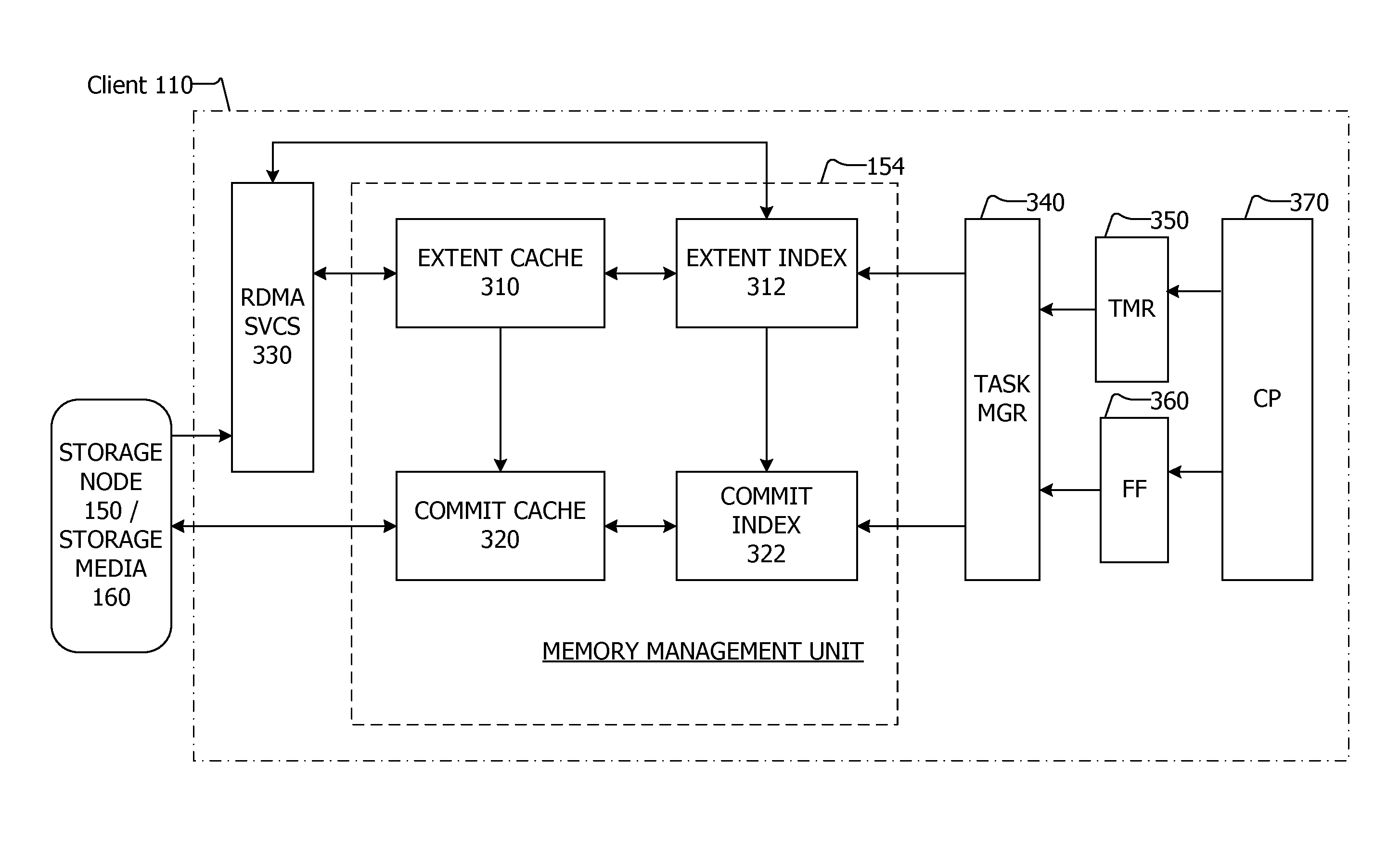

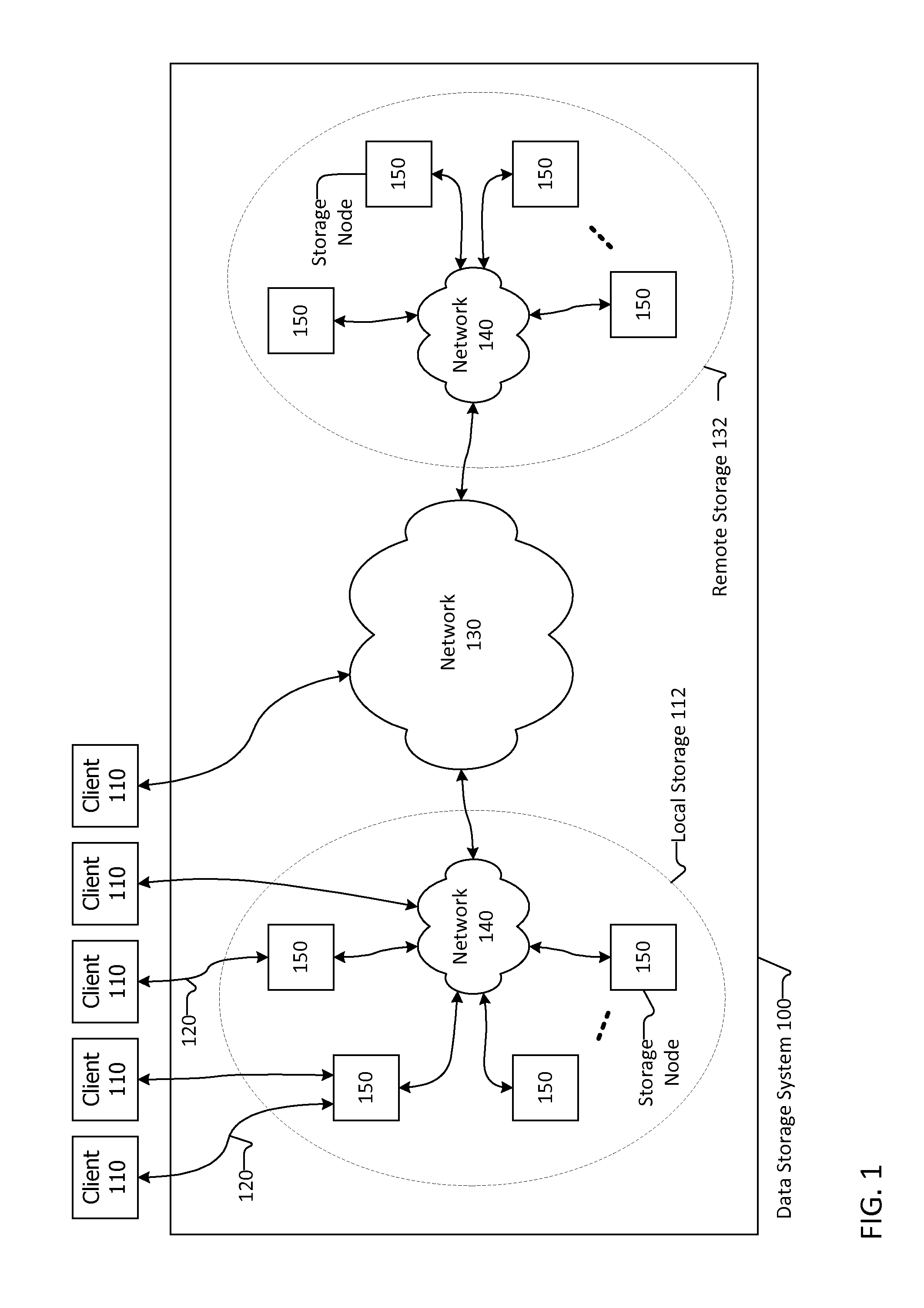

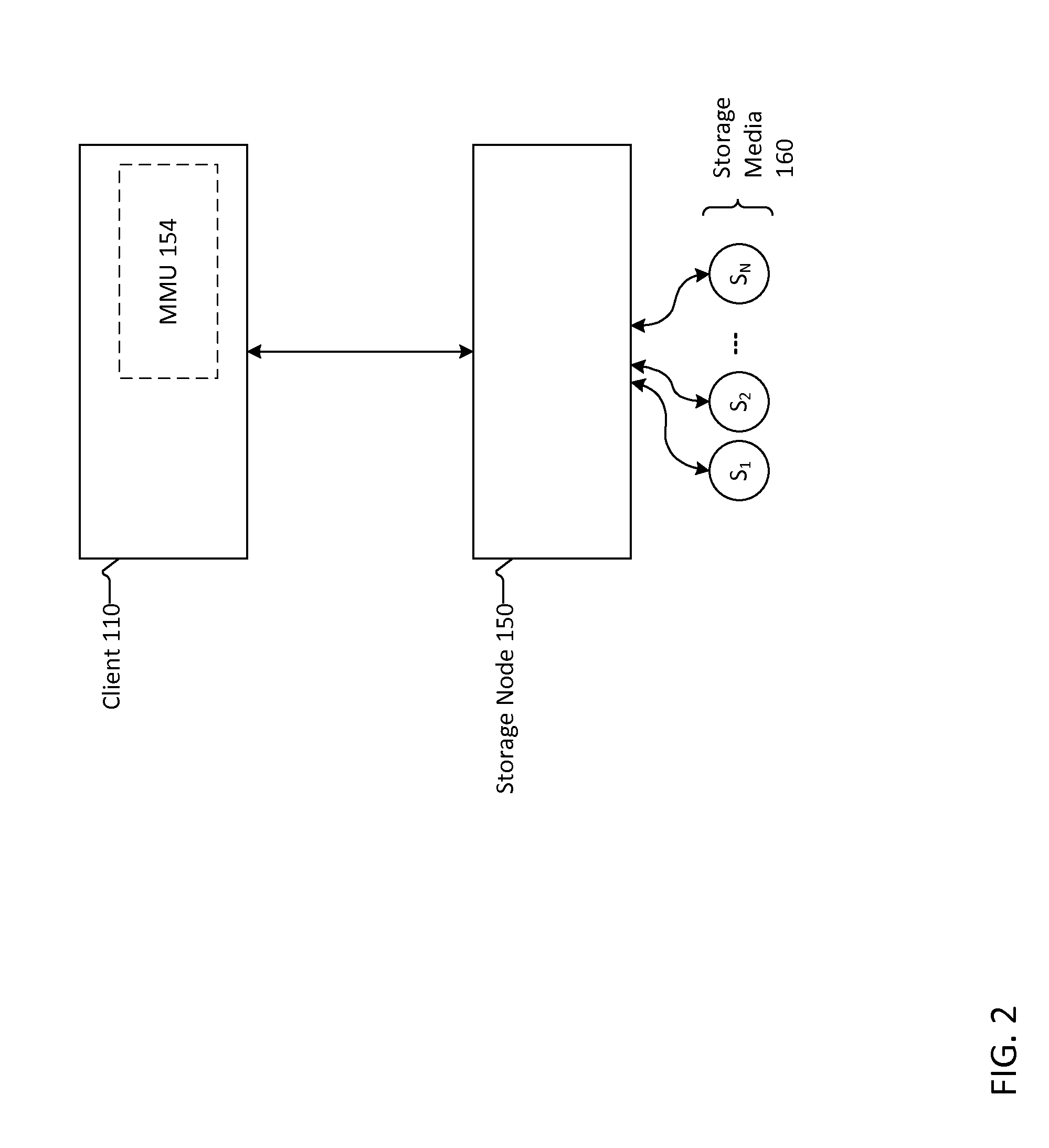

Reducing metadata in a write-anywhere storage system

ActiveUS9116819B2Memory architecture accessing/allocationMemory adressing/allocation/relocationManagement unitData retrieval

Systems and methods for reducing metadata in a write-anywhere storage system are disclosed herein. The system includes a plurality of clients coupled with a plurality of storage nodes, each storage node having a plurality of primary storage devices coupled thereto. A memory management unit including cache memory is included in the client. The memory management unit serves as a cache for data produced by the clients before the data is stored in the primary storage. The cache includes an extent cache, an extent index, a commit cache and a commit index. The movement of data and metadata is by an interval tree. Methods for reducing data in the interval tree increase data storage and data retrieval performance of the system.

Owner:DATADIRECT NETWORKS

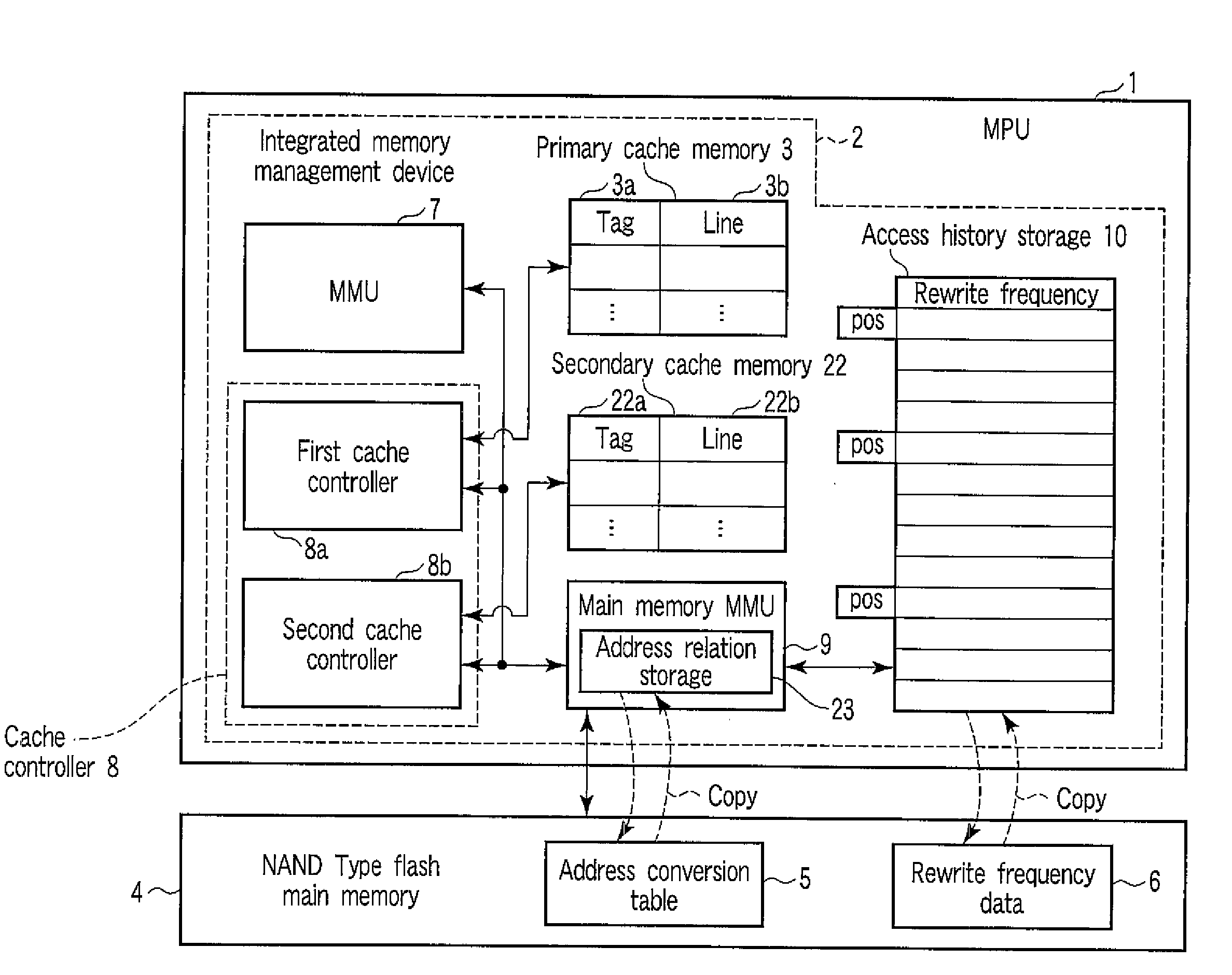

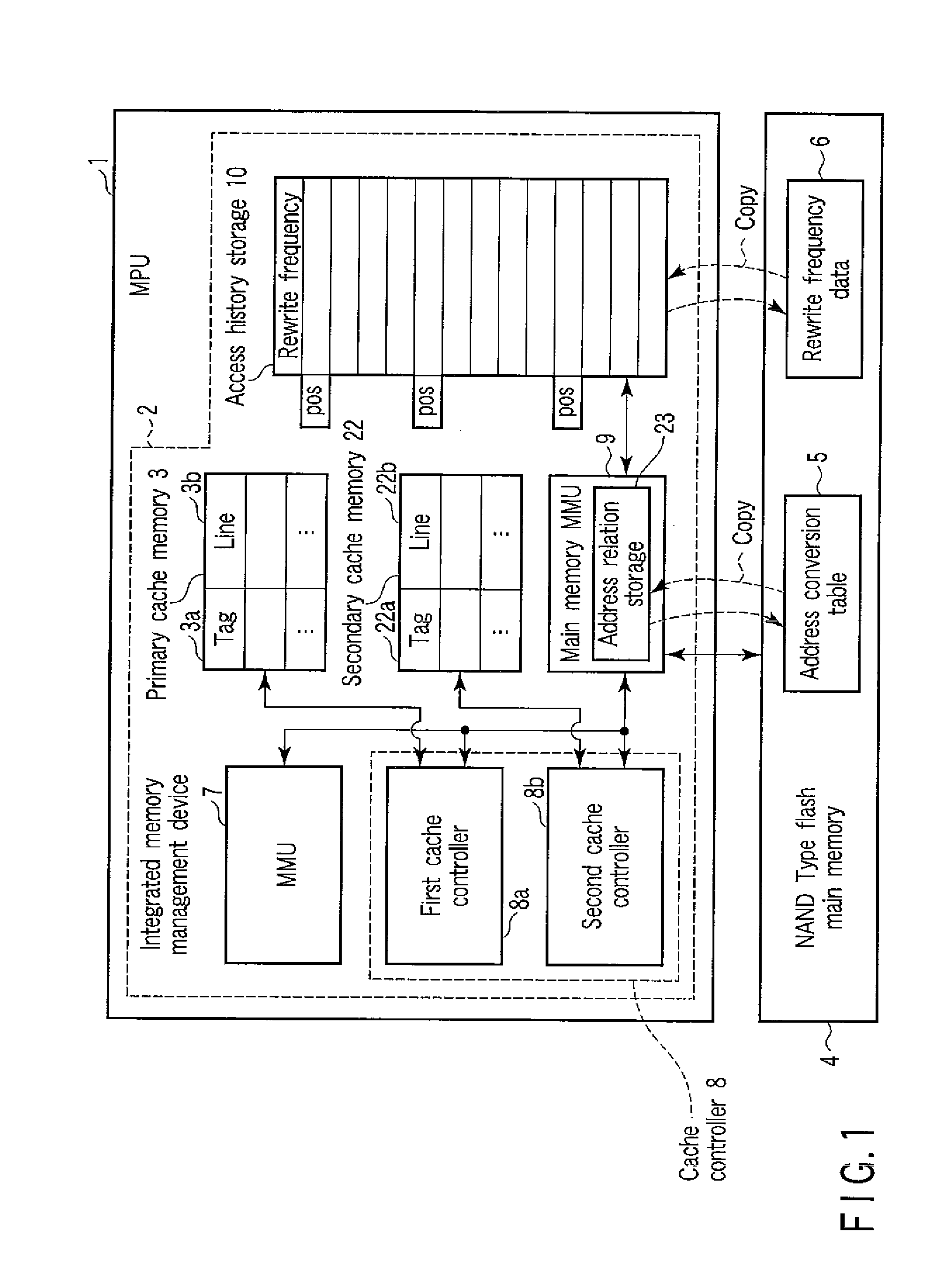

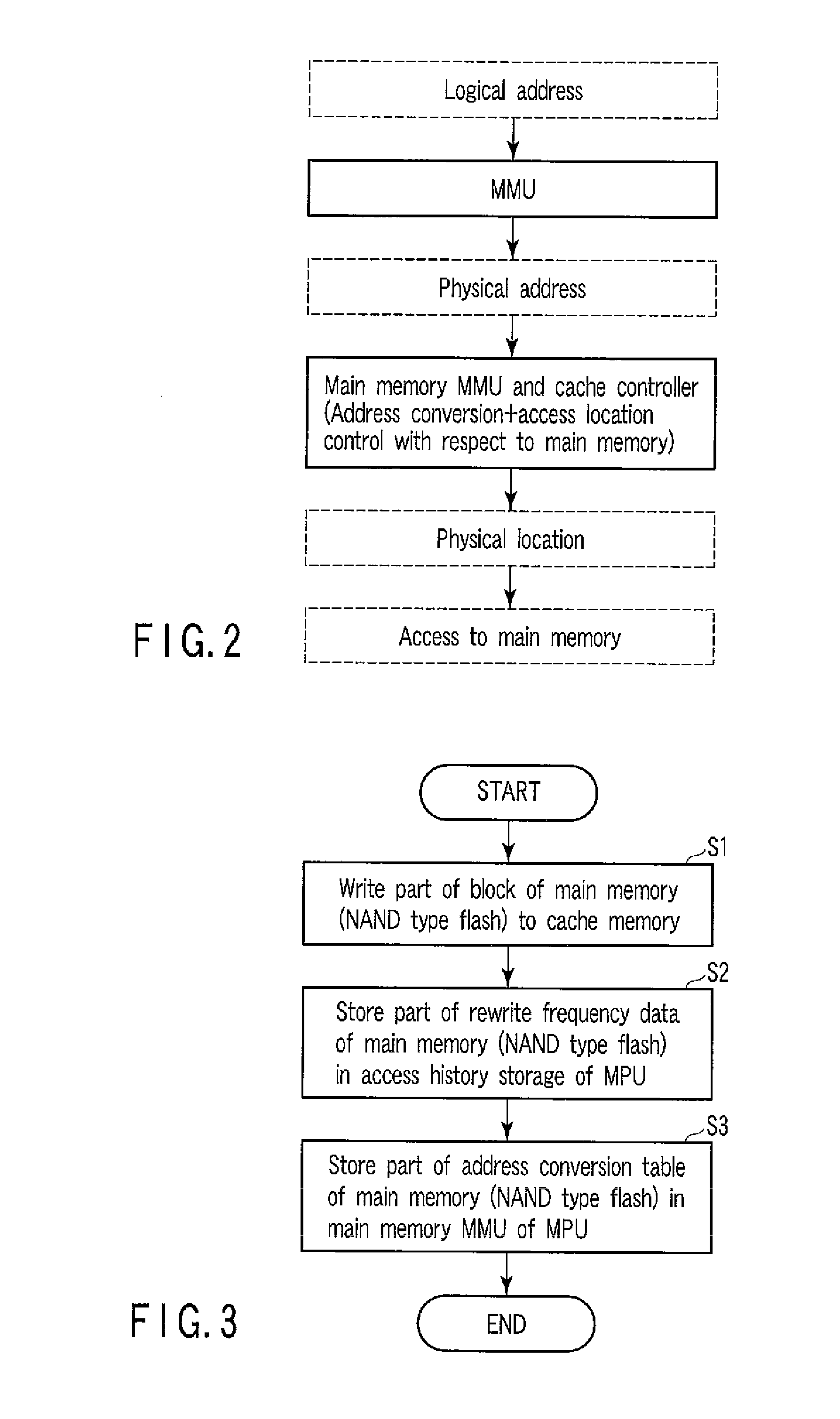

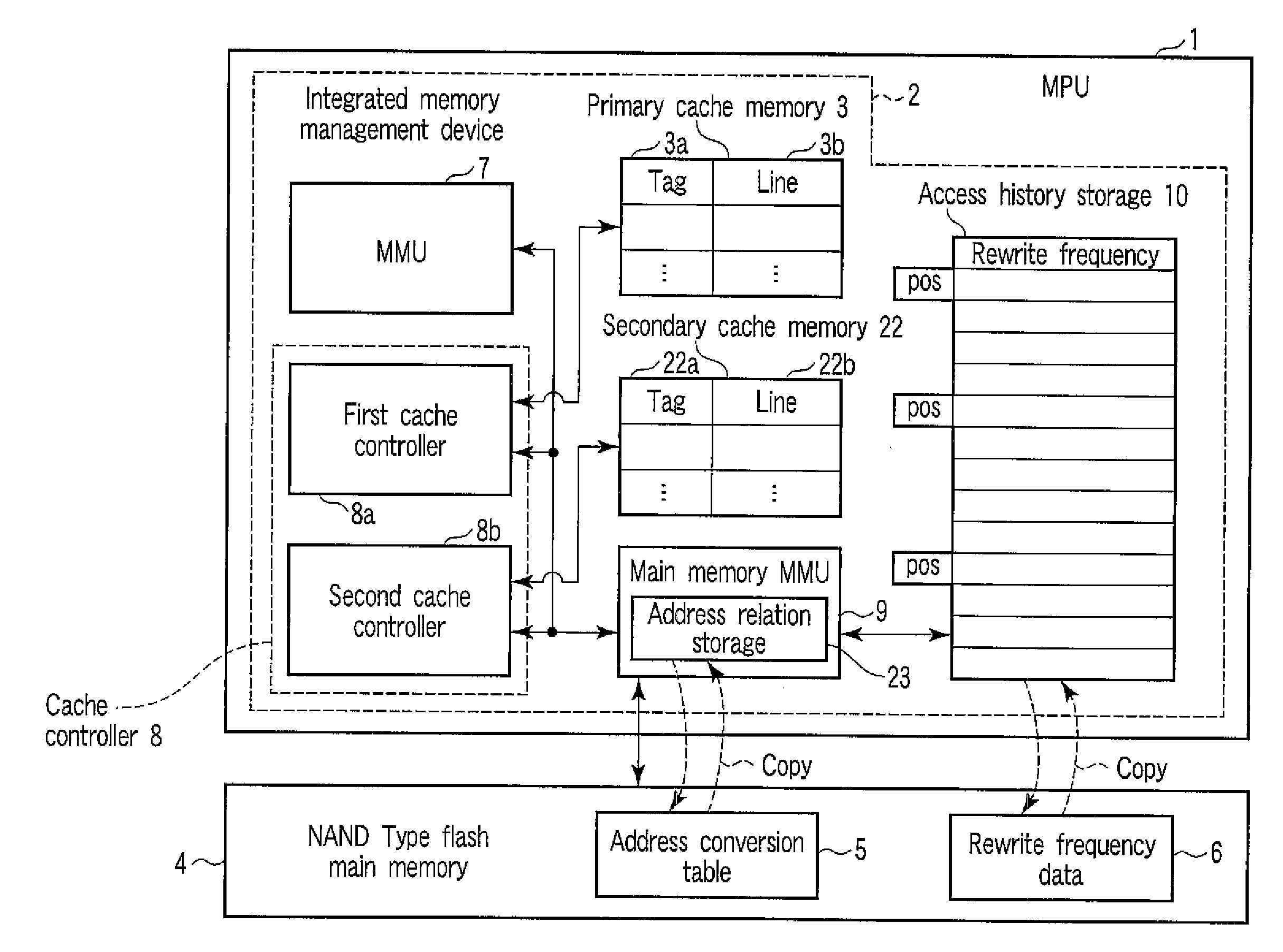

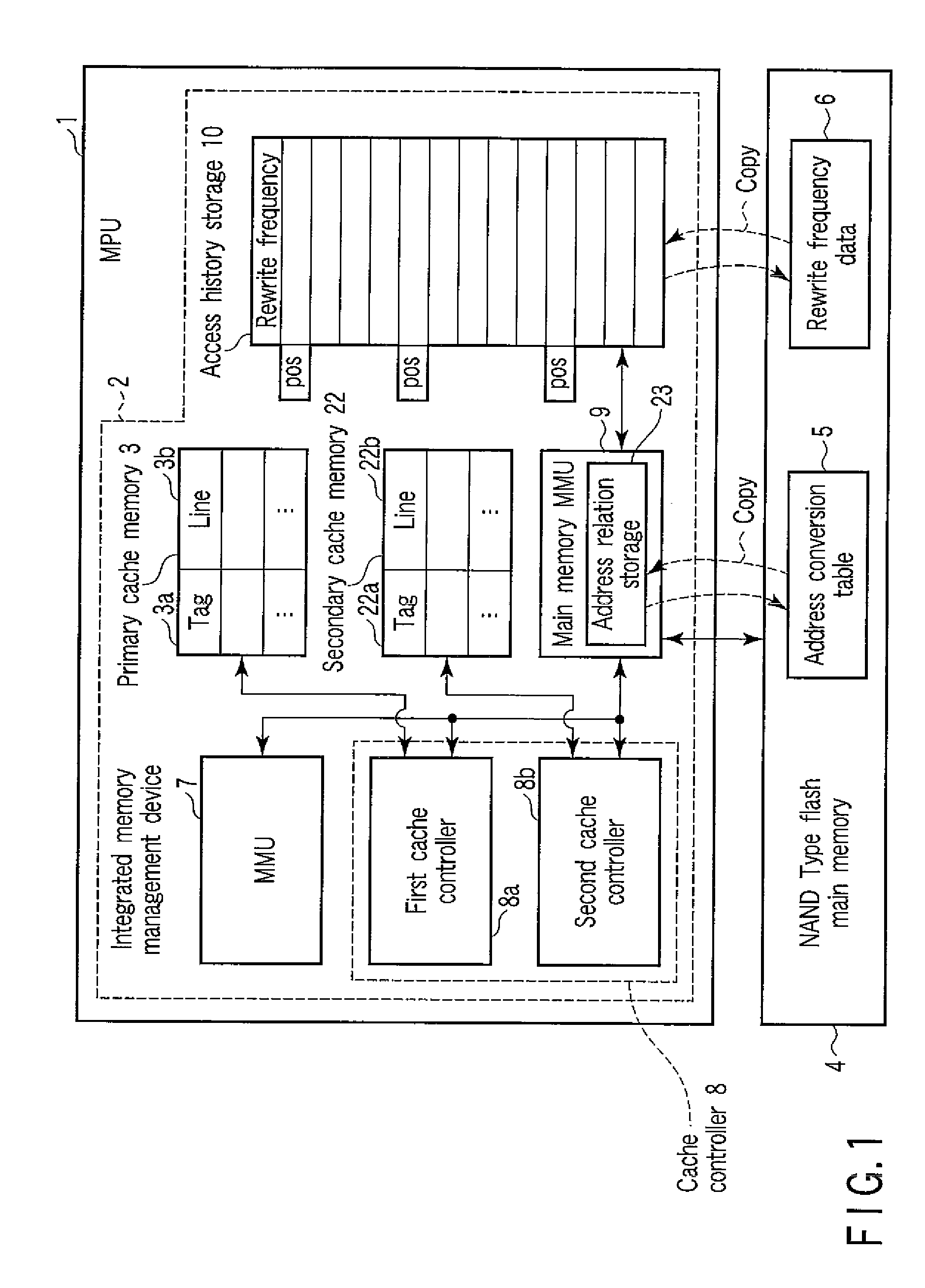

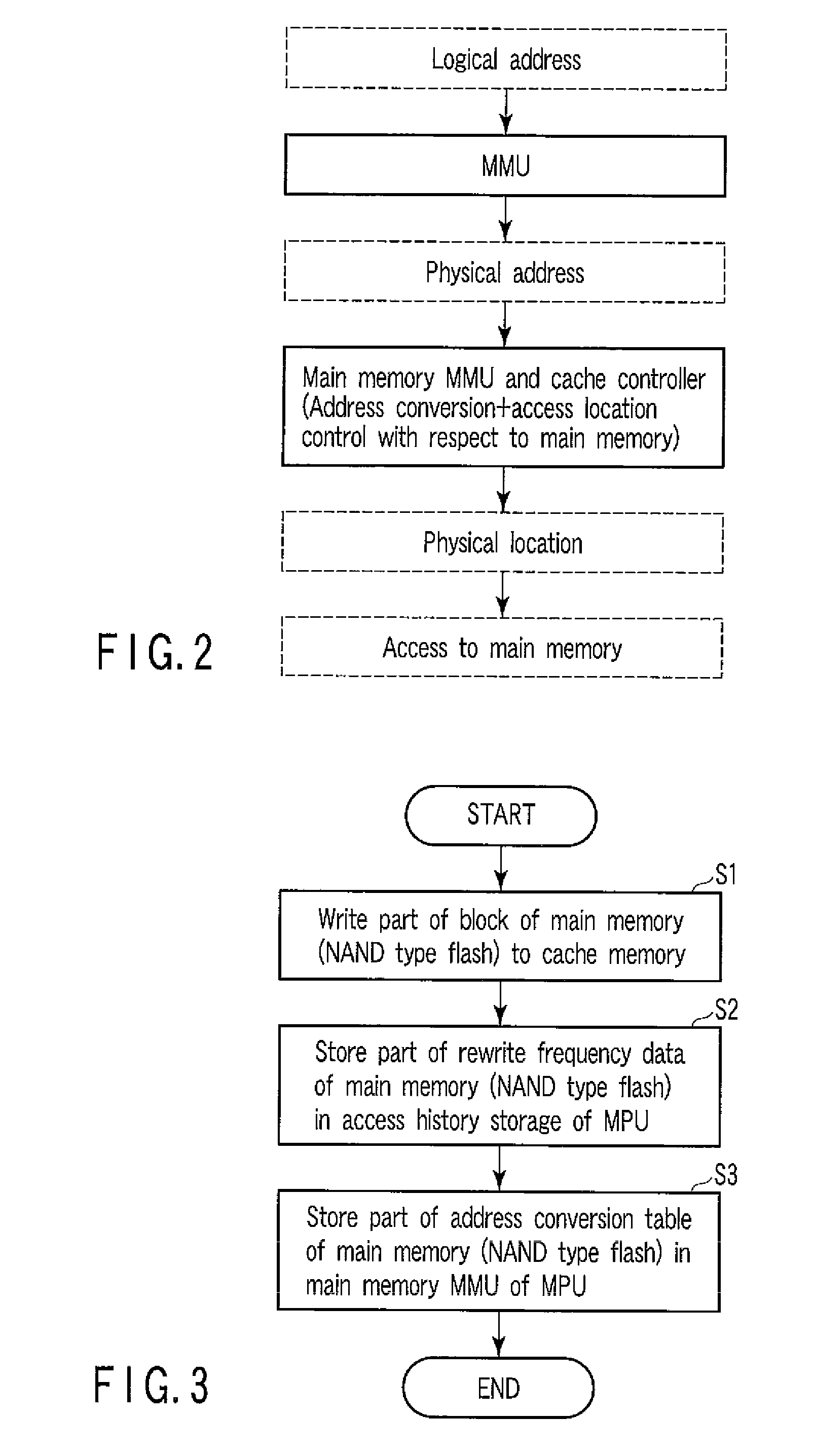

Integrated memory management and memory management method

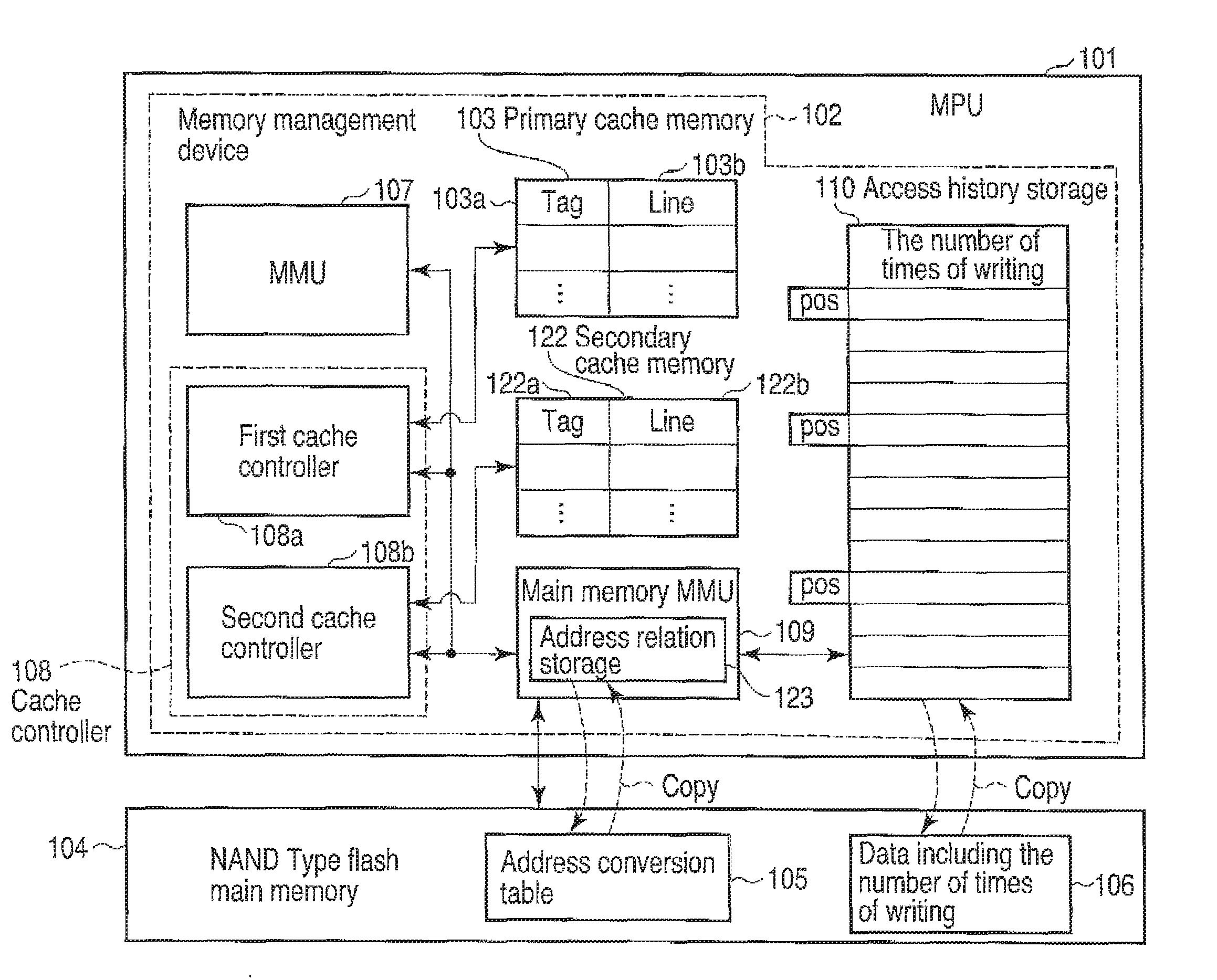

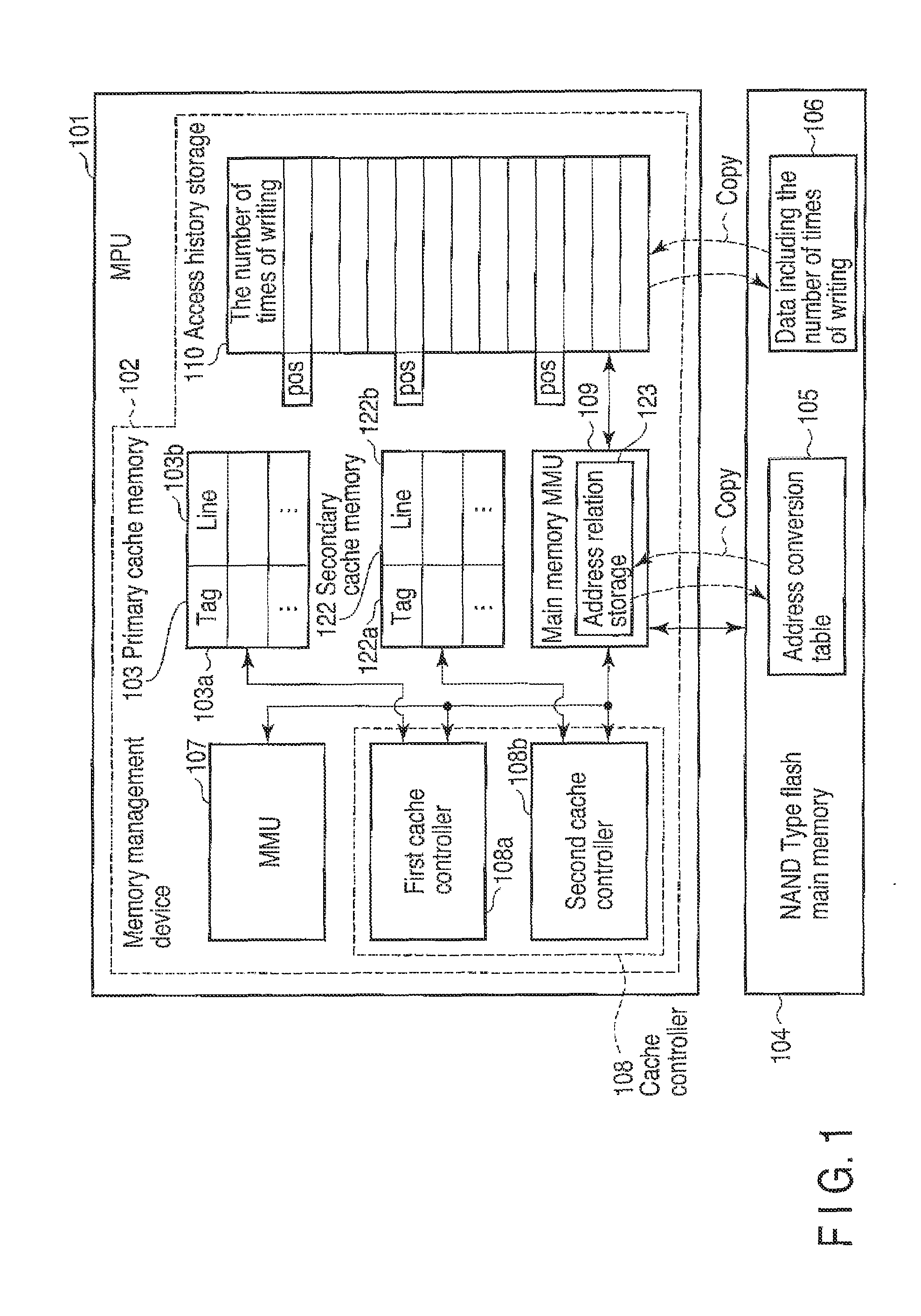

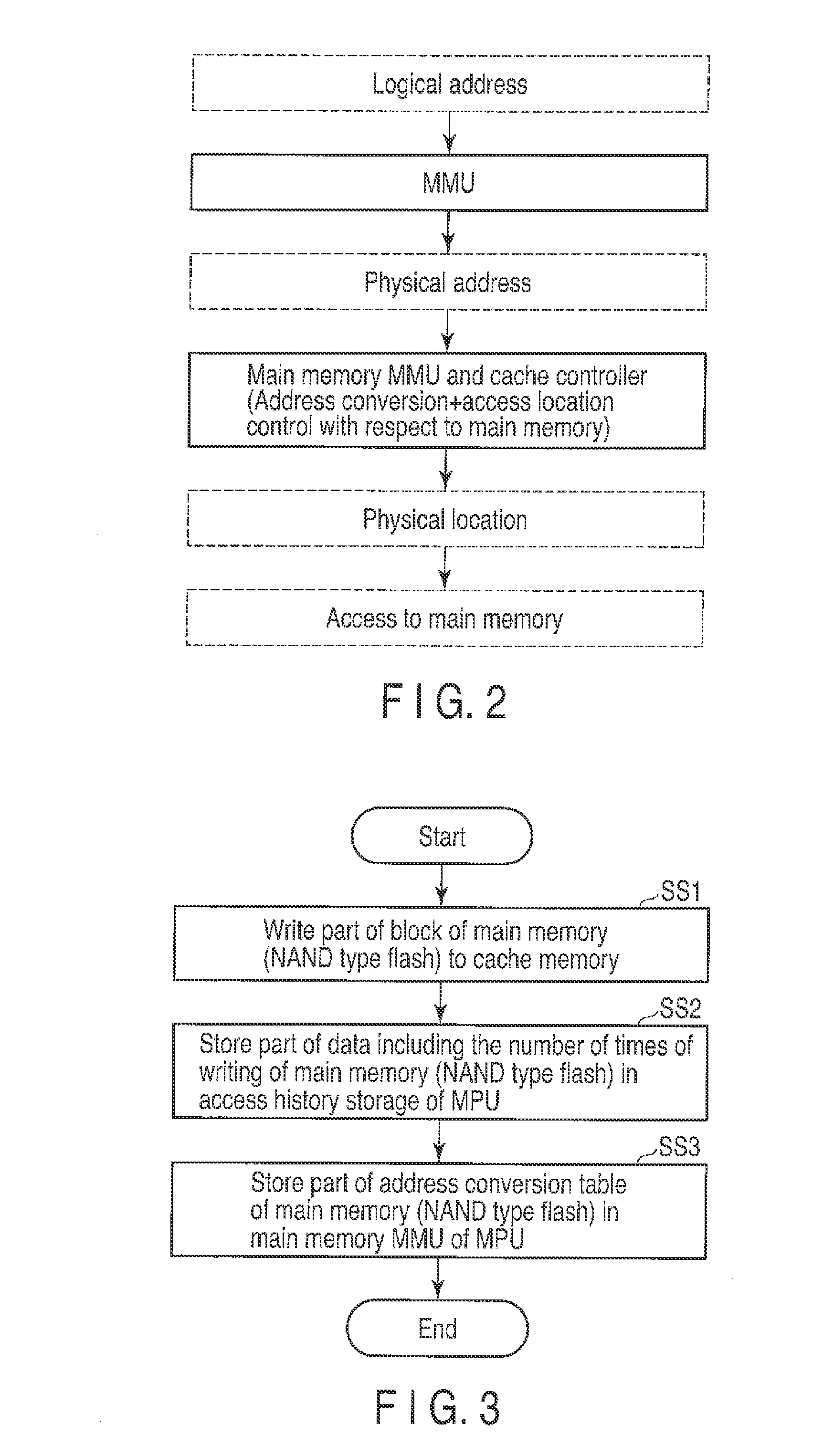

ActiveUS20090083478A1Memory architecture accessing/allocationMemory adressing/allocation/relocationData transmissionMemory management unit

An integrated memory management device according to an example of the invention comprises an acquiring unit acquiring a read destination logical address from a processor, an address conversion unit converting the read destination logical address into a read destination physical address of a non-volatile main memory, an access unit reading, from the non-volatile main memory, data that corresponds to the read destination physical address and has a size that is equal to a block size or an integer multiple of the page size of the non-volatile main memory, and transmission unit transferring the read data to a cache memory of the processor having a cache size that depends on the block size or the integer multiple of the page size of the non-volatile main memory.

Owner:KIOXIA CORP

Information processing device including memory management device managing access from processor to memory and memory management method

ActiveUS20100064111A1Memory architecture accessing/allocationMemory loss protectionInformation processingMemory management unit

A device according to an example of the invention comprises a section which accepts a write destination logical address and write target data from a processor, the write destination logical address indicating a write position to write the write target data into a composite memory which includes a first memory and a nonvolatile second memory, a section which determines a write destination physical address corresponding to the write destination logical address so that the number of times of access to the second memory is smaller than the number of times of access to the first memory, a section which stores, in a storage section, address conversion data associating the write destination logical address with the write destination physical address, and a section which writes the write target data into a position in the composite memory indicated by the write destination physical address.

Owner:KIOXIA CORP

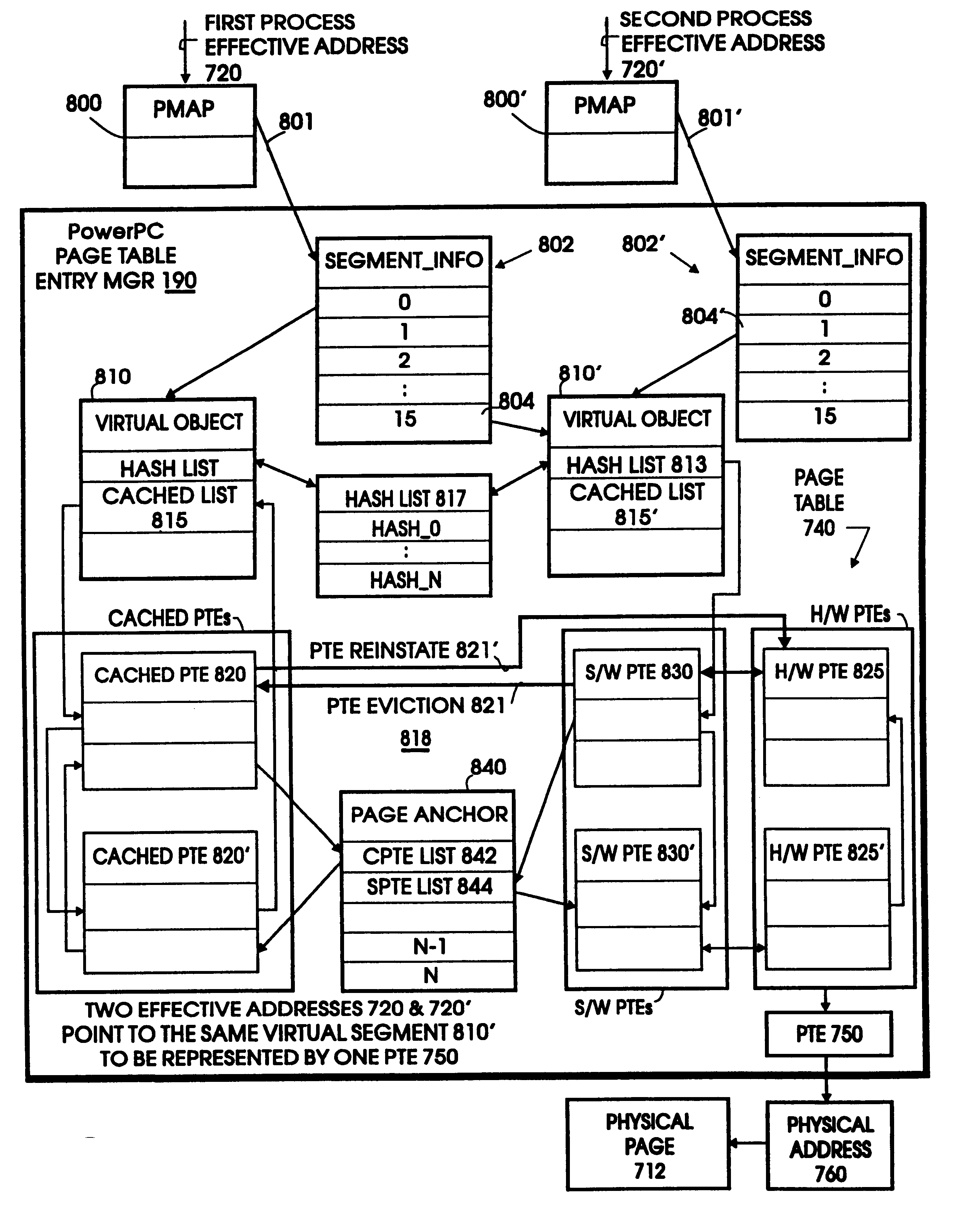

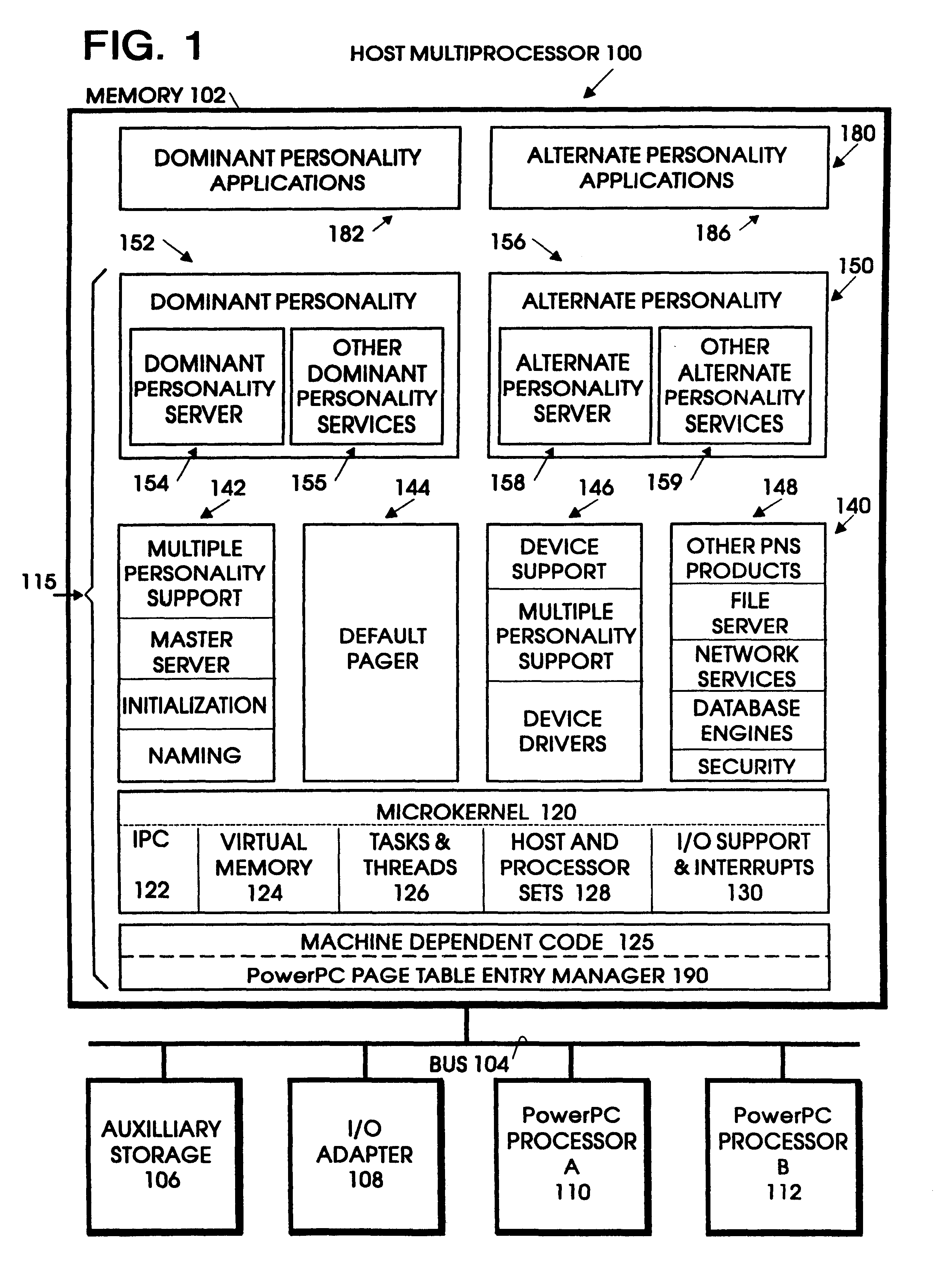

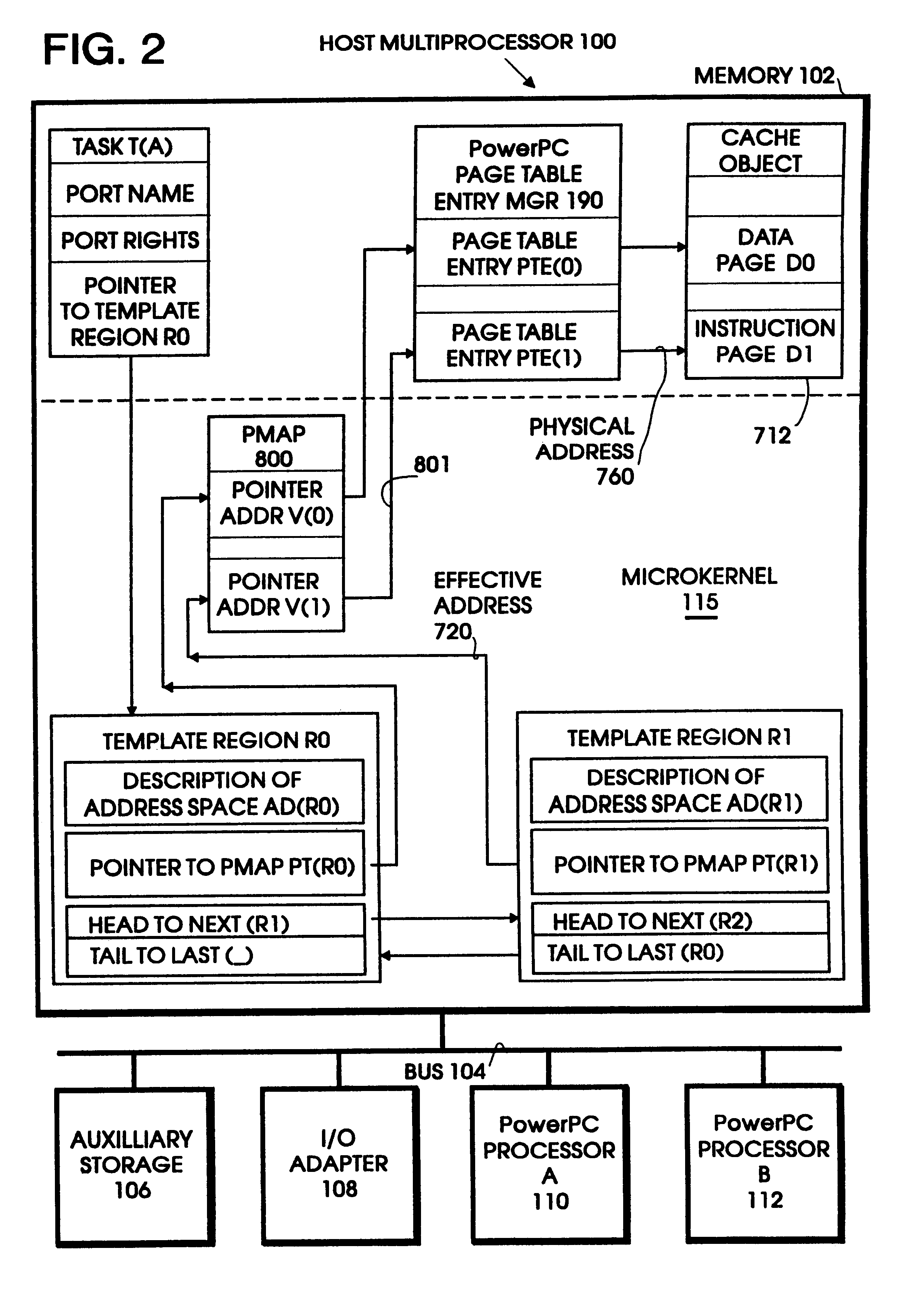

Page table entry management method and apparatus for a microkernel data processing system

InactiveUS6308247B1Maximize system performanceEasy to manageMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemManagement unit

A page table entry management method and apparatus provide the Microkernel System with the capability to program the memory management unit on the PowerPC family of processors. The PowerPC processors define a limited set of page table entries (PTEs) to maintain virtual to physical mappings. The page table entry management method and apparatus solves the problem of a limited number of PTEs by segment aliasing when two or more user processes share a segment of memory. The segments are aliased rather than duplicating the PTES. This significantly reduces the number of PTEs. In addition, the method provides for caching existing PTEs when the system actually runs out of PTEs. A cache of recently discarded PTEs provides a fast fault resolution when a recently used page is accessed again.

Owner:IBM CORP

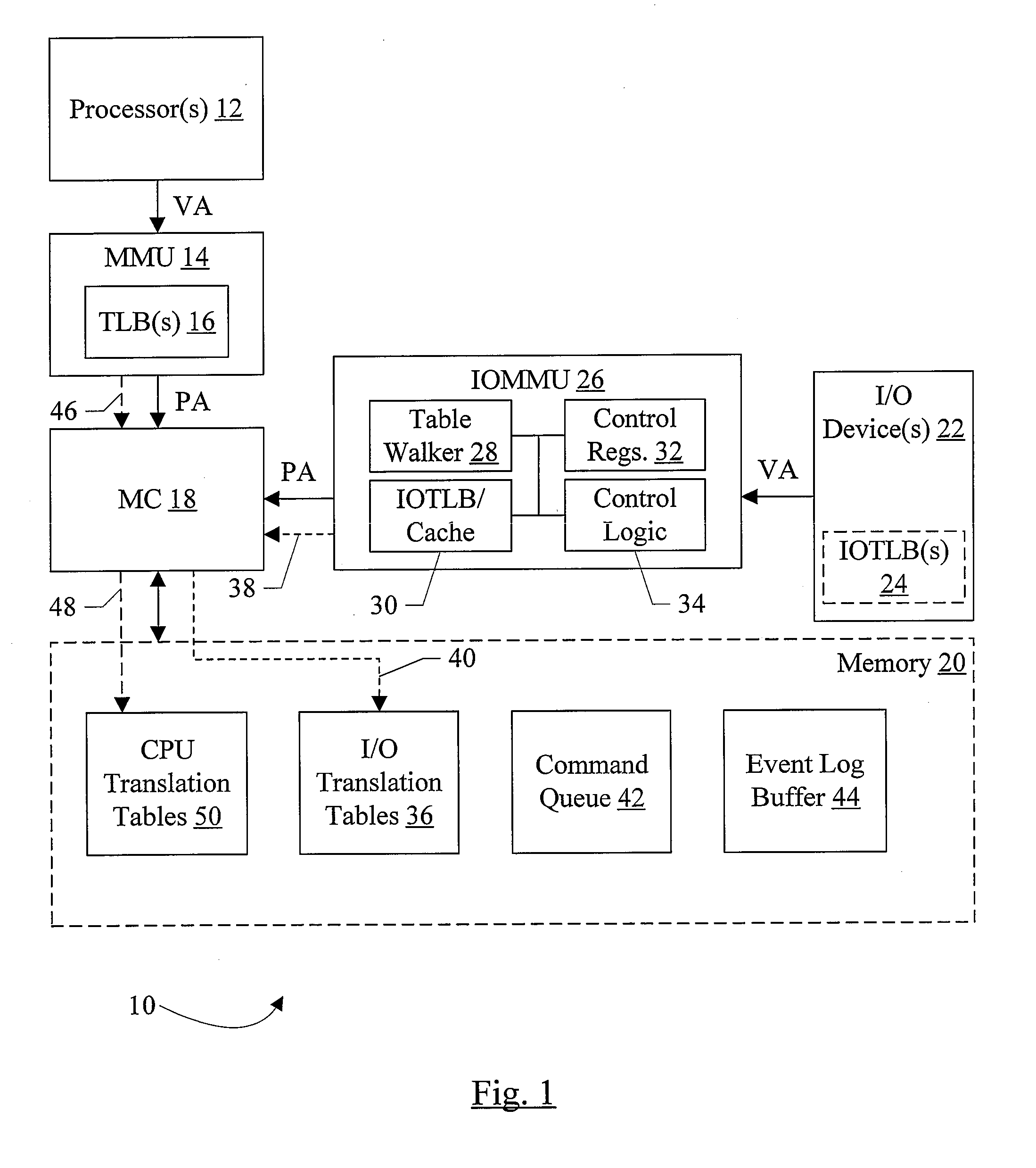

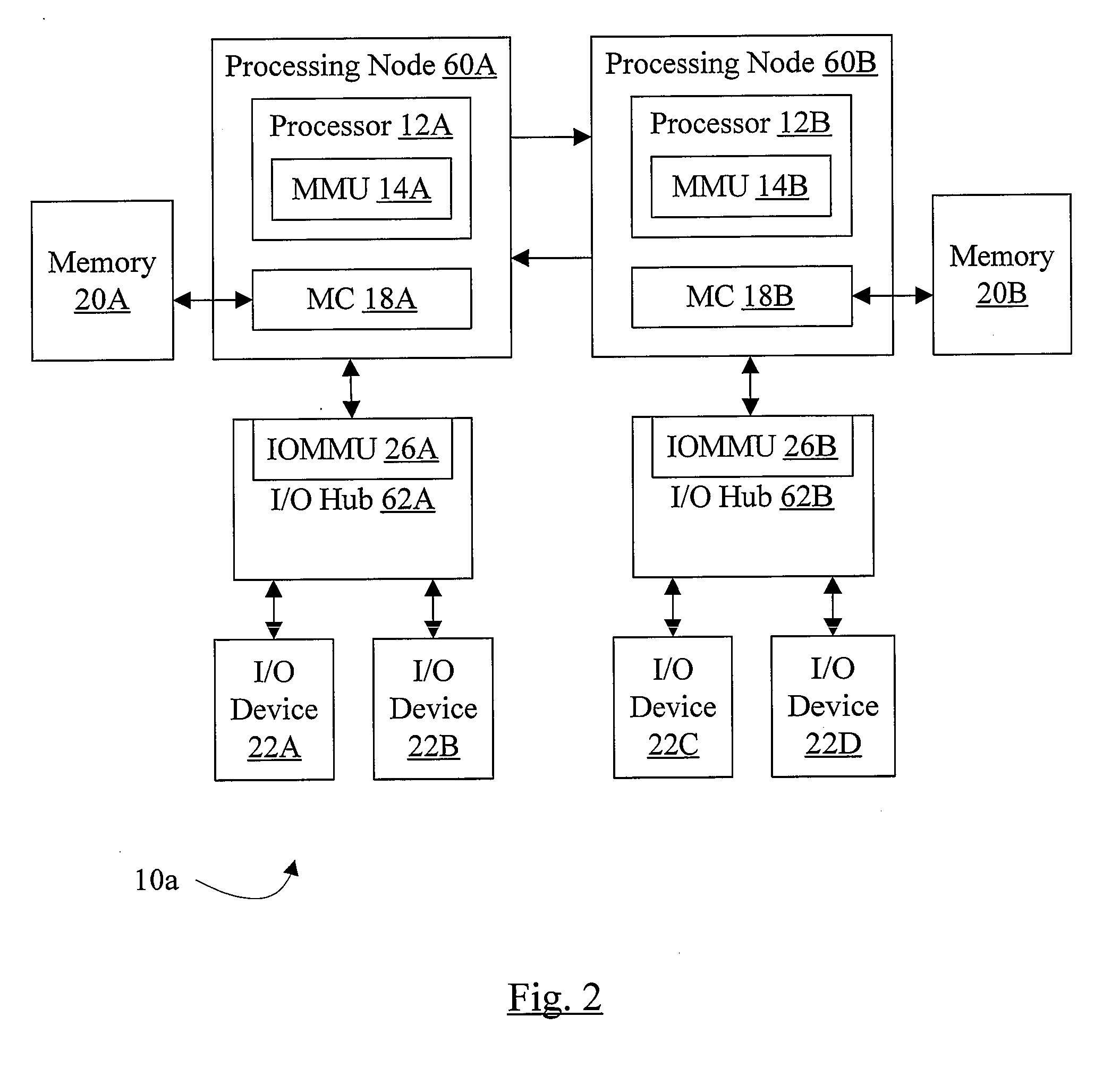

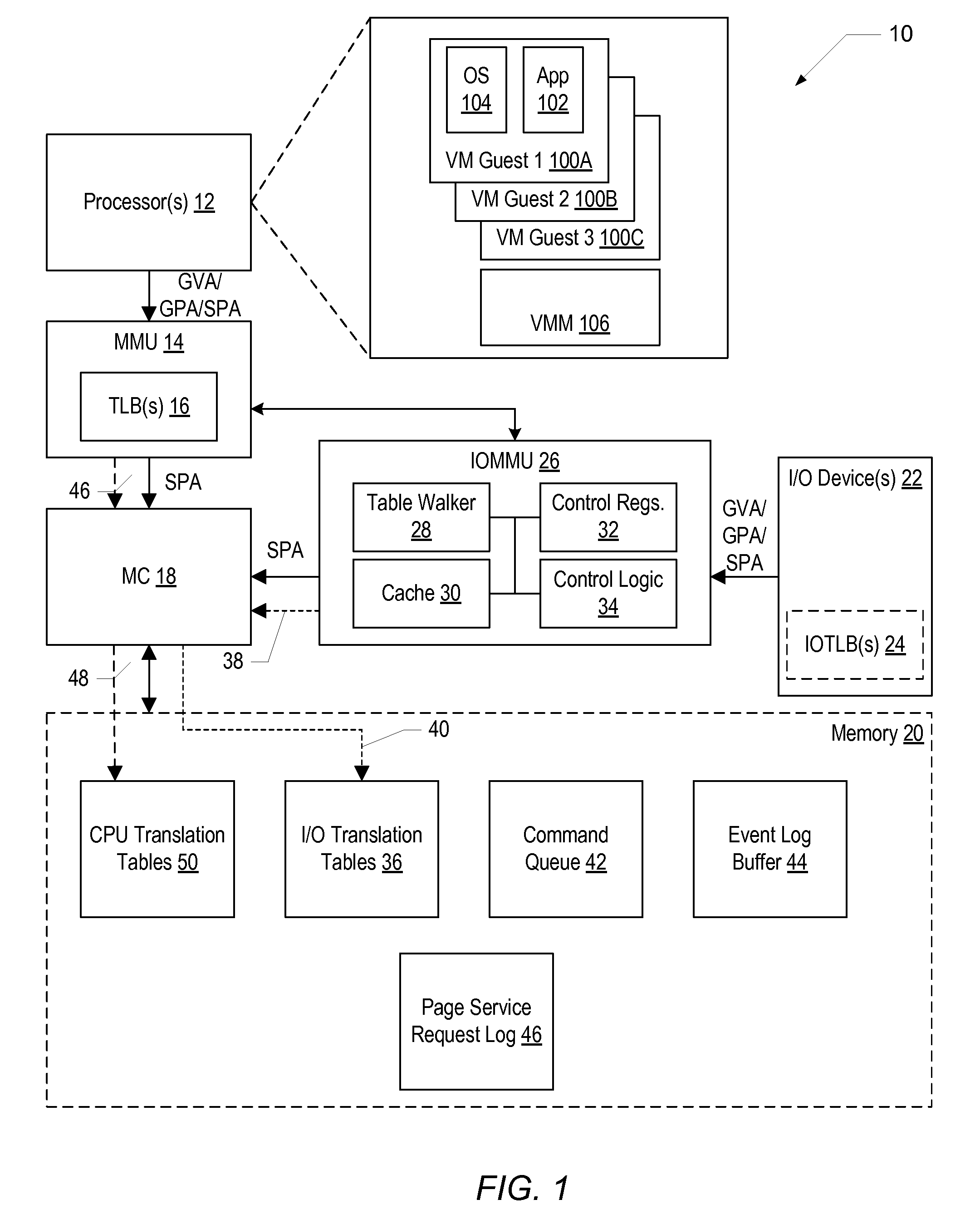

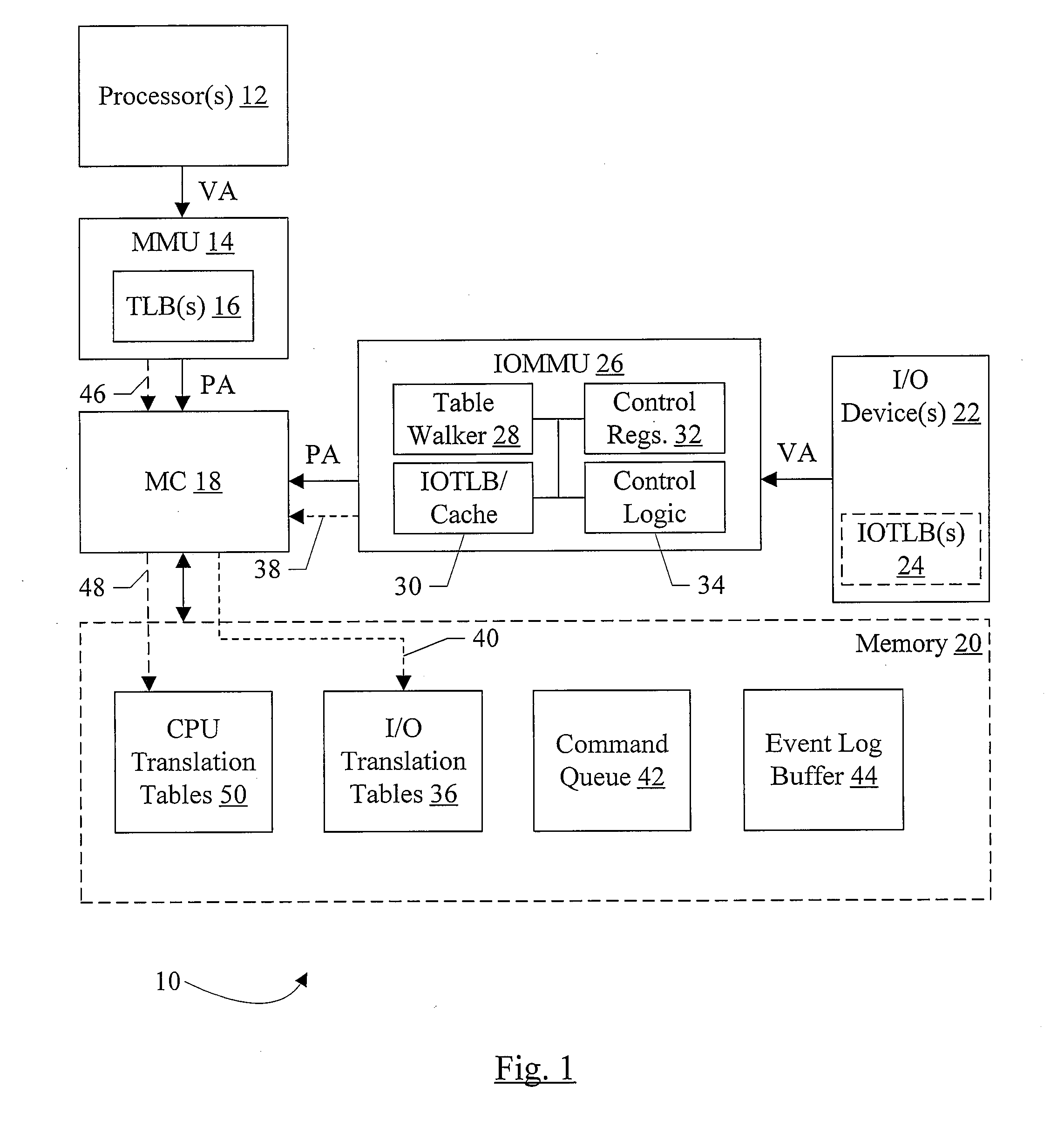

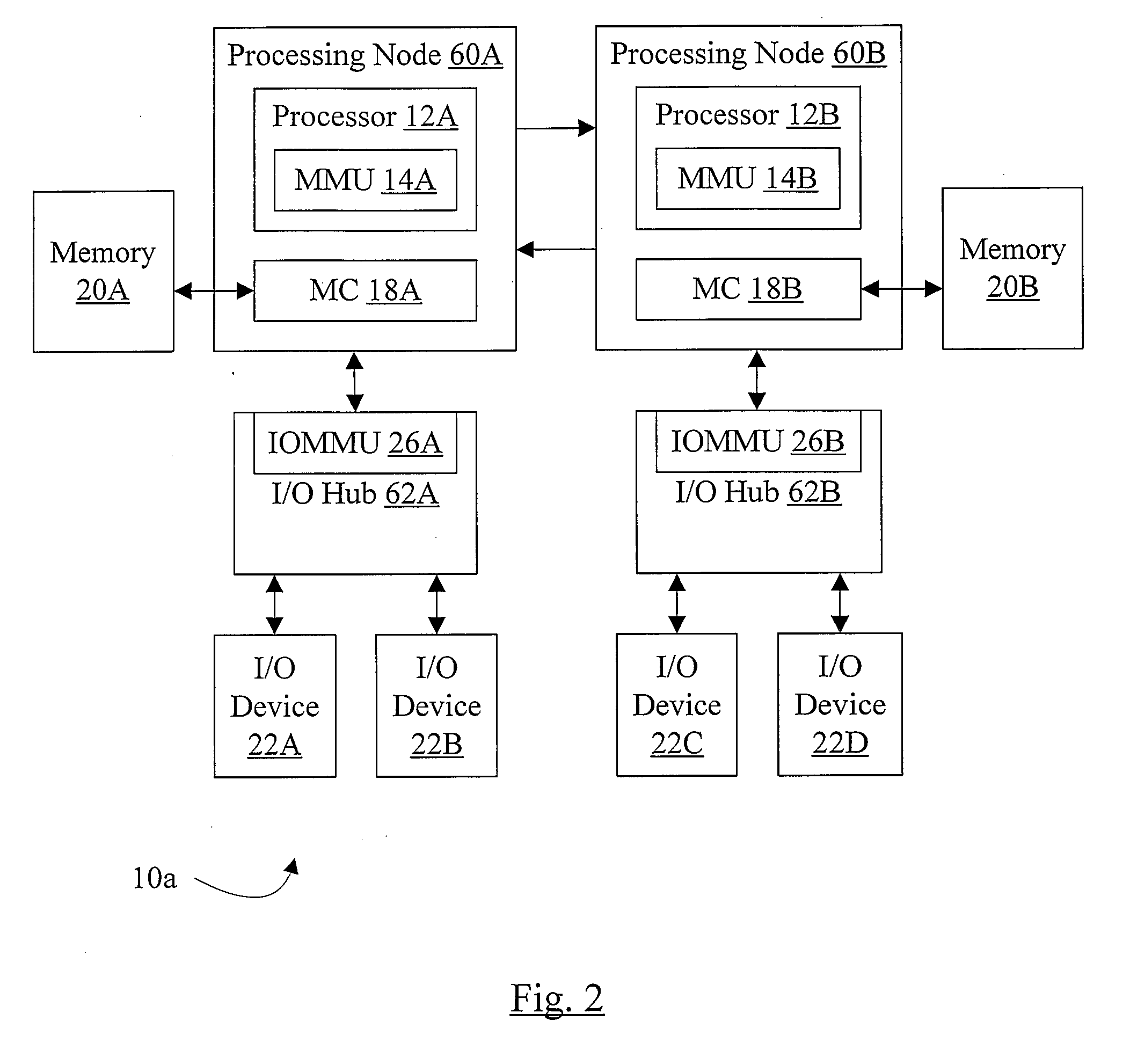

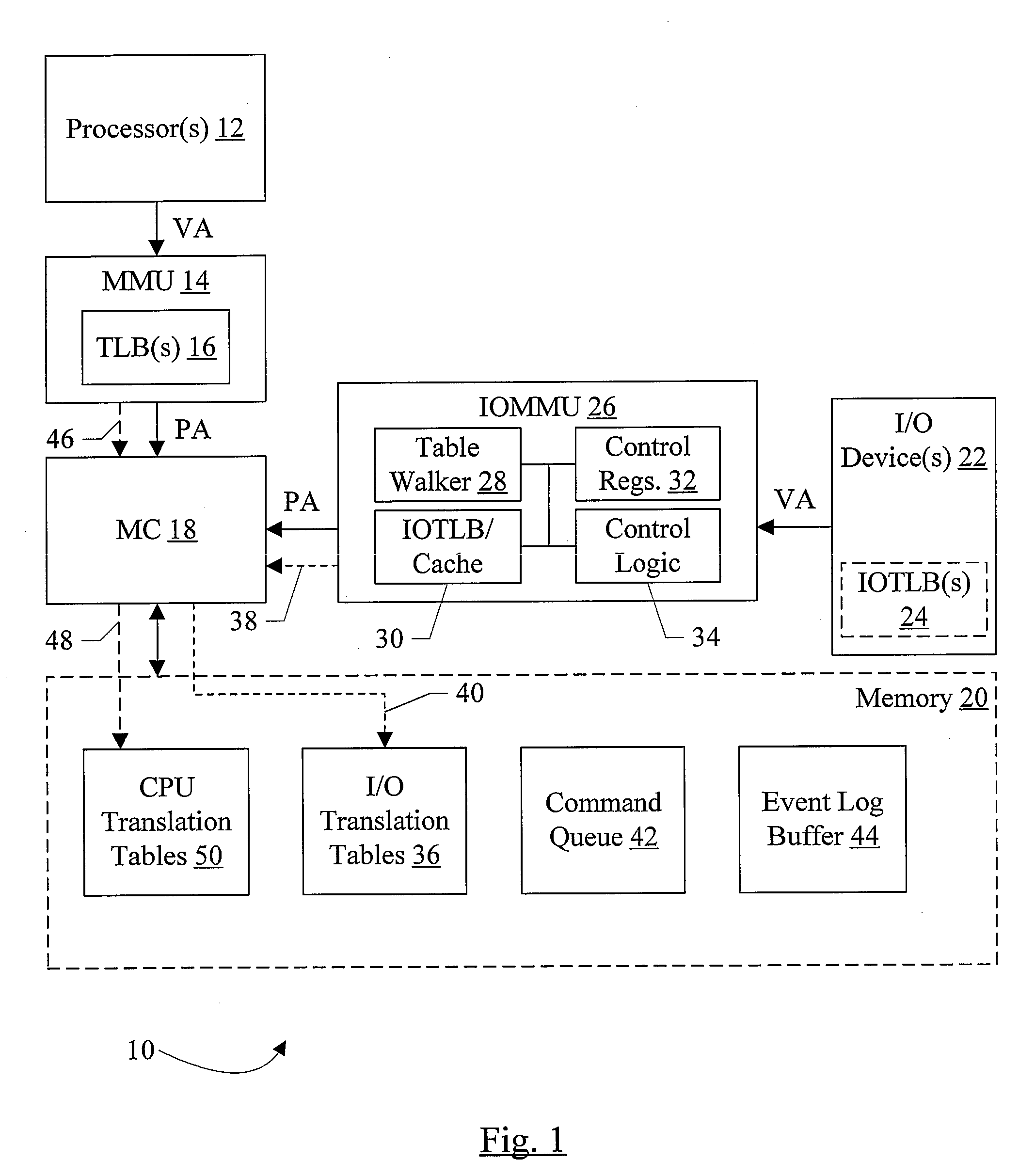

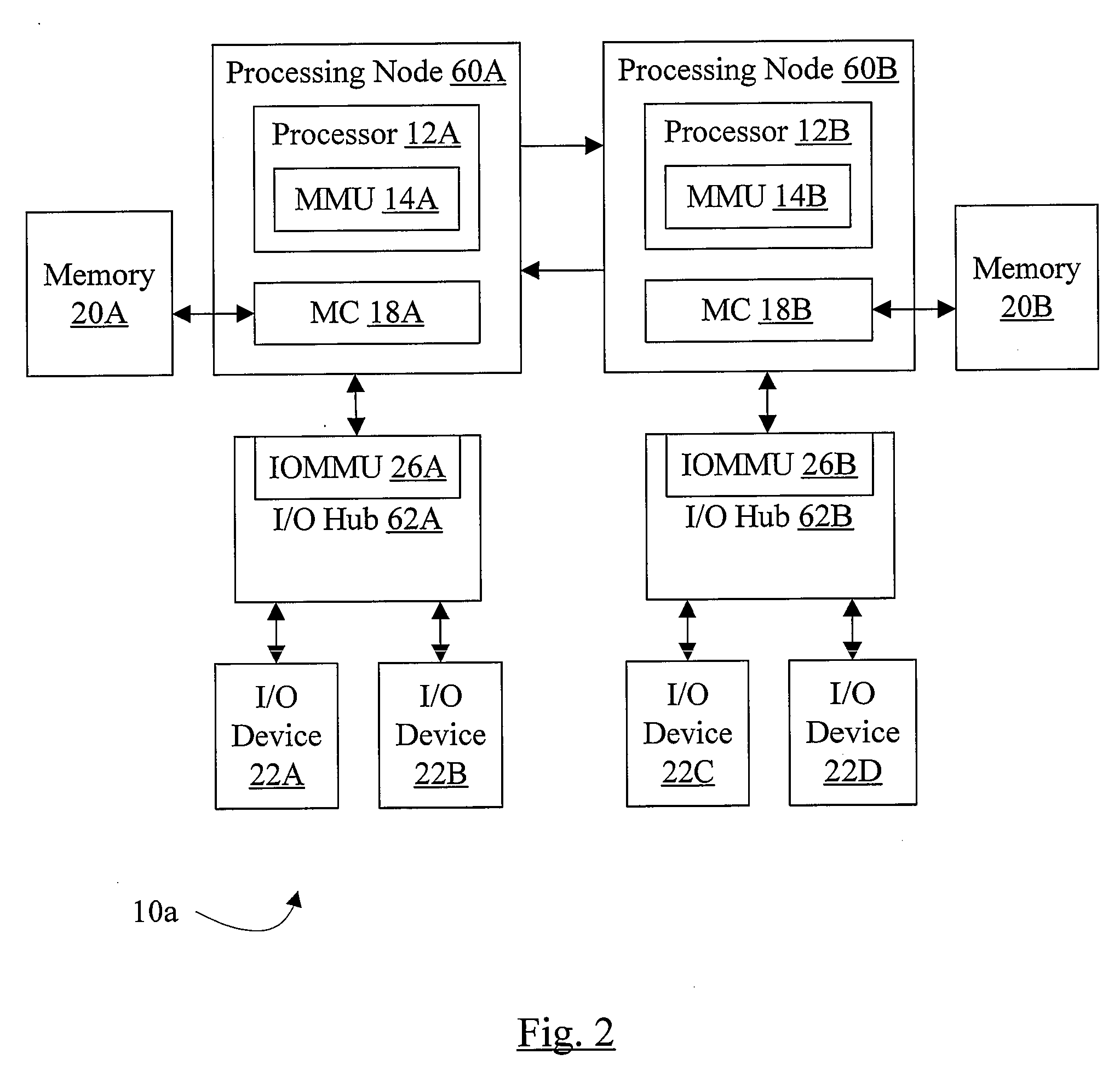

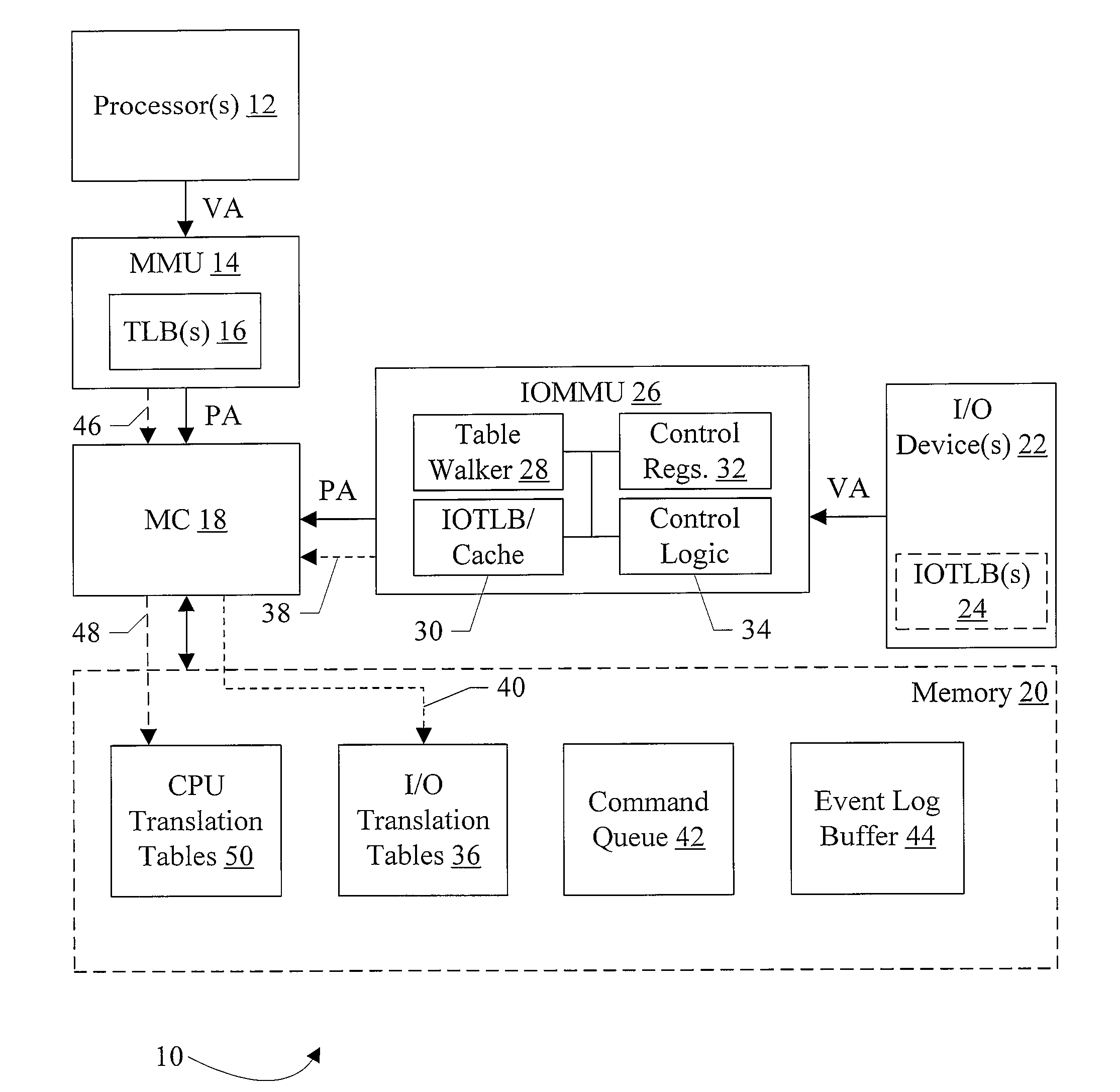

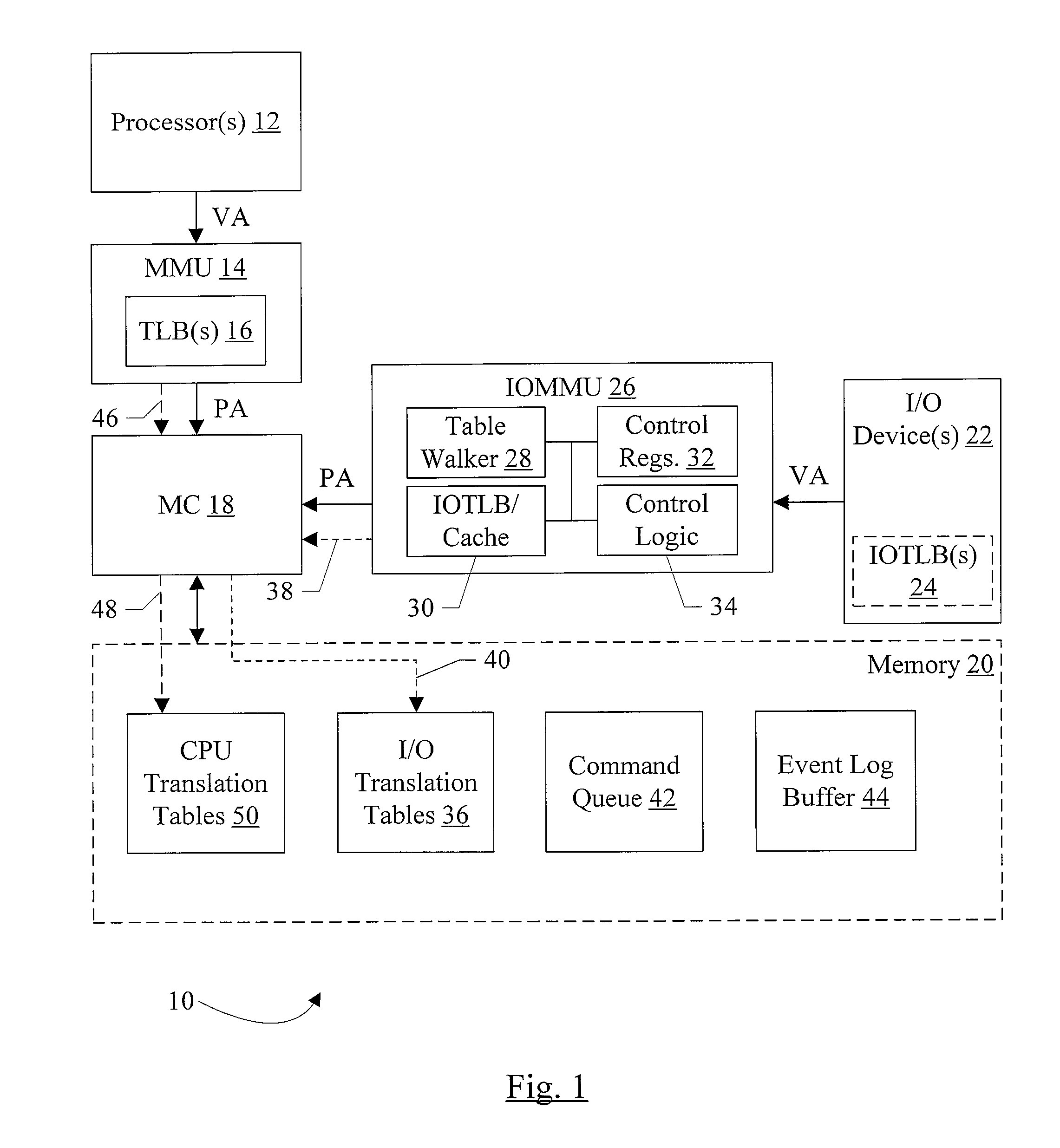

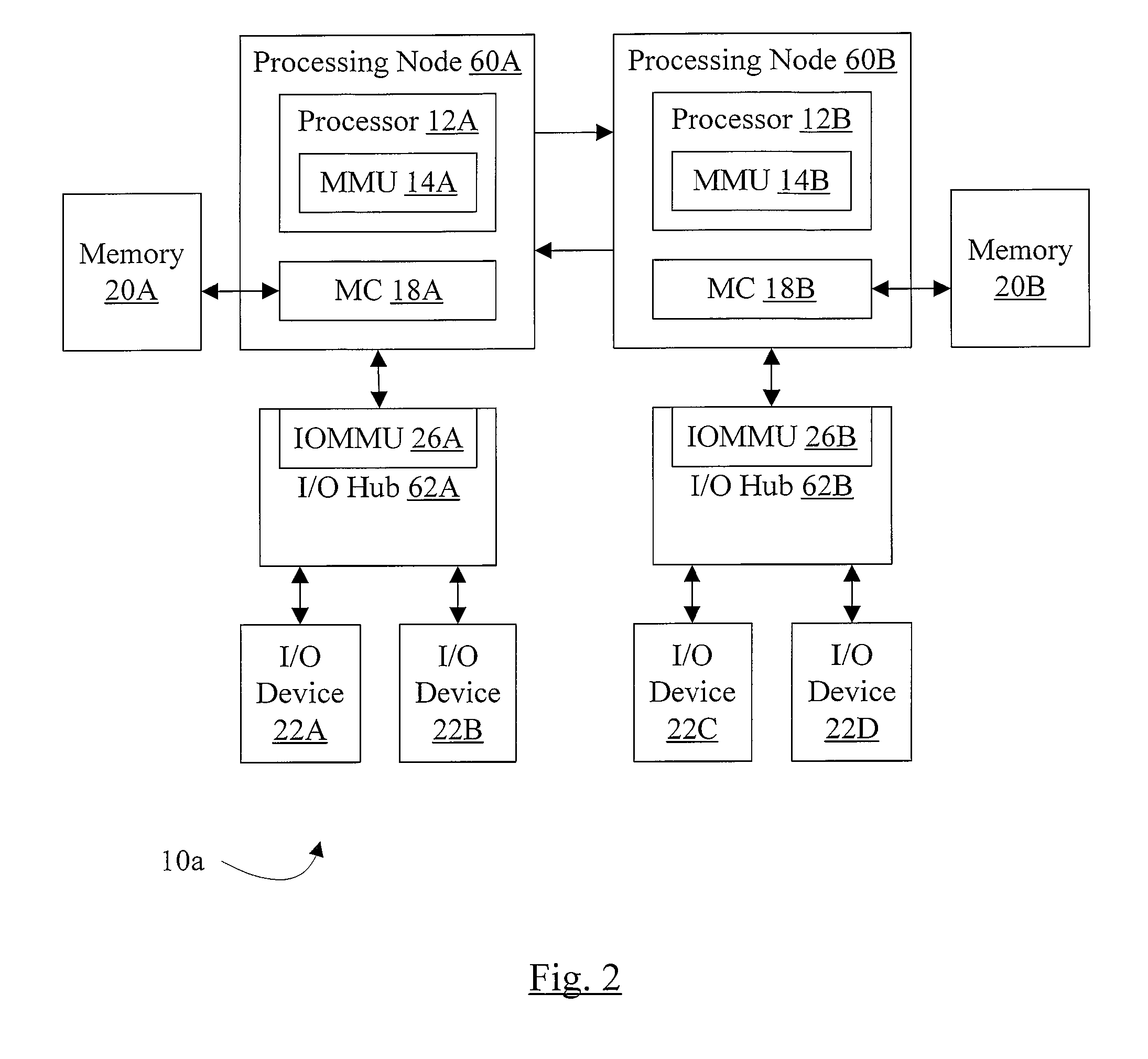

DMA Address Translation in an IOMMU

ActiveUS20070168643A1Memory architecture accessing/allocationMemory systemsPage tableMemory management unit

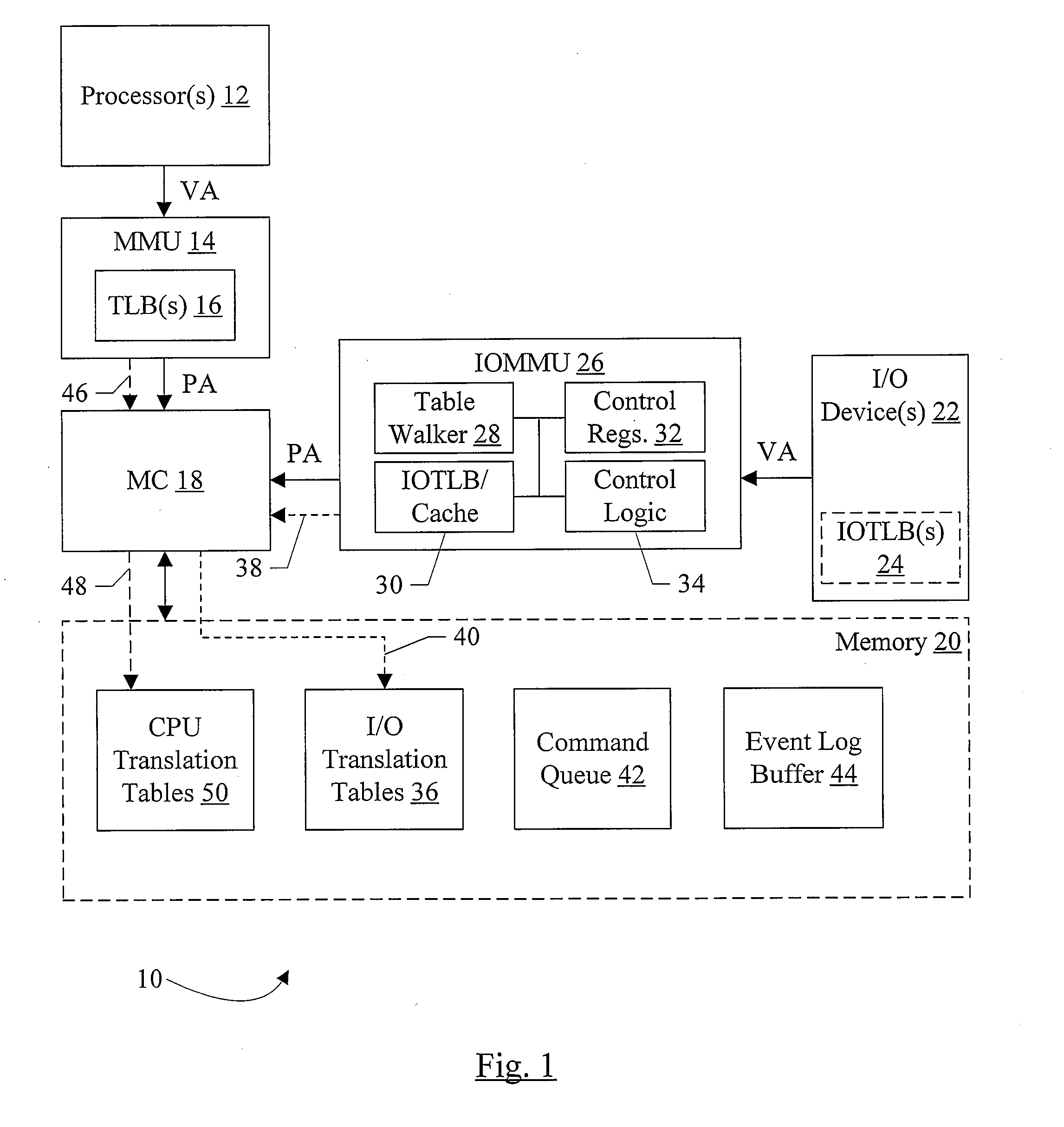

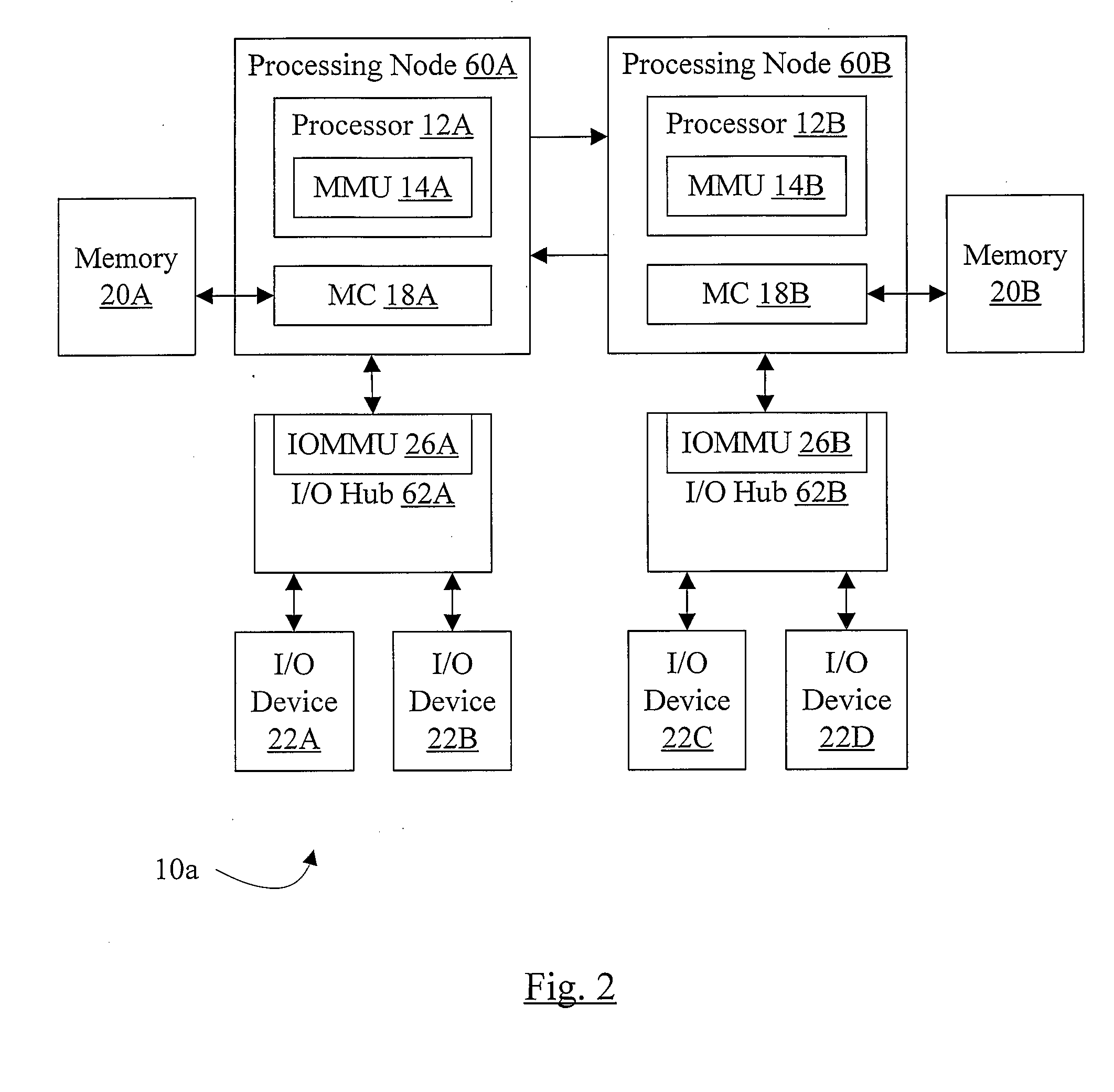

In an embodiment, an input / output (I / O) memory management unit (IOMMU) comprises at least one memory configured to store translation data; and control logic coupled to the memory and configured to translate an I / O device-generated memory request using the translation data. The translation data corresponds to one or more device table entries in a device table stored in a memory system of a computer system that includes the IOMMU, wherein the device table entry for a given request is selected by an identifier corresponding to the I / O device that generates the request. The translation data further corresponds to one or more I / O page tables, wherein the selected device table entry for the given request includes a pointer to a set of I / O page tables to be used to translate the given request.

Owner:MEDIATEK INC

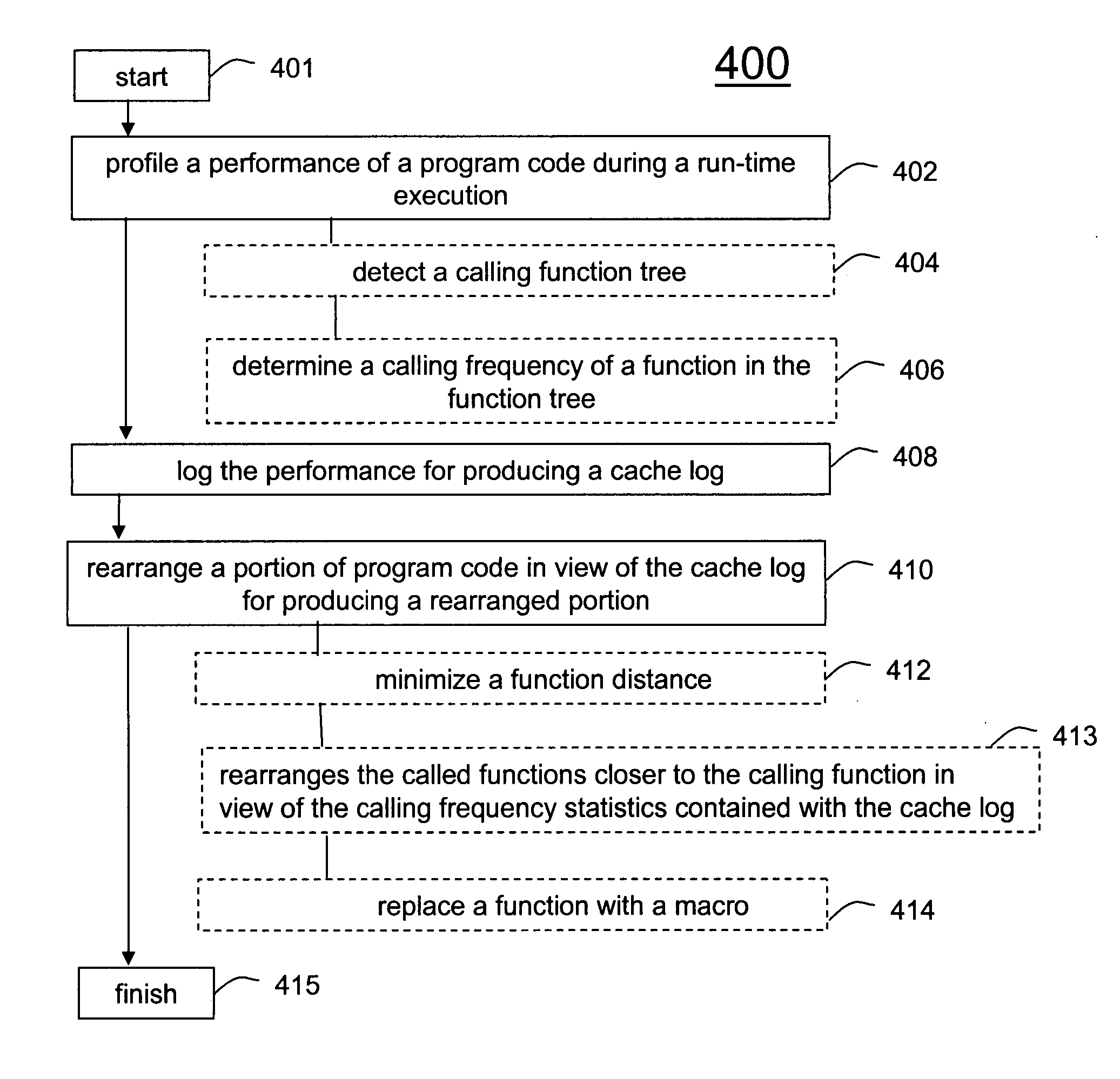

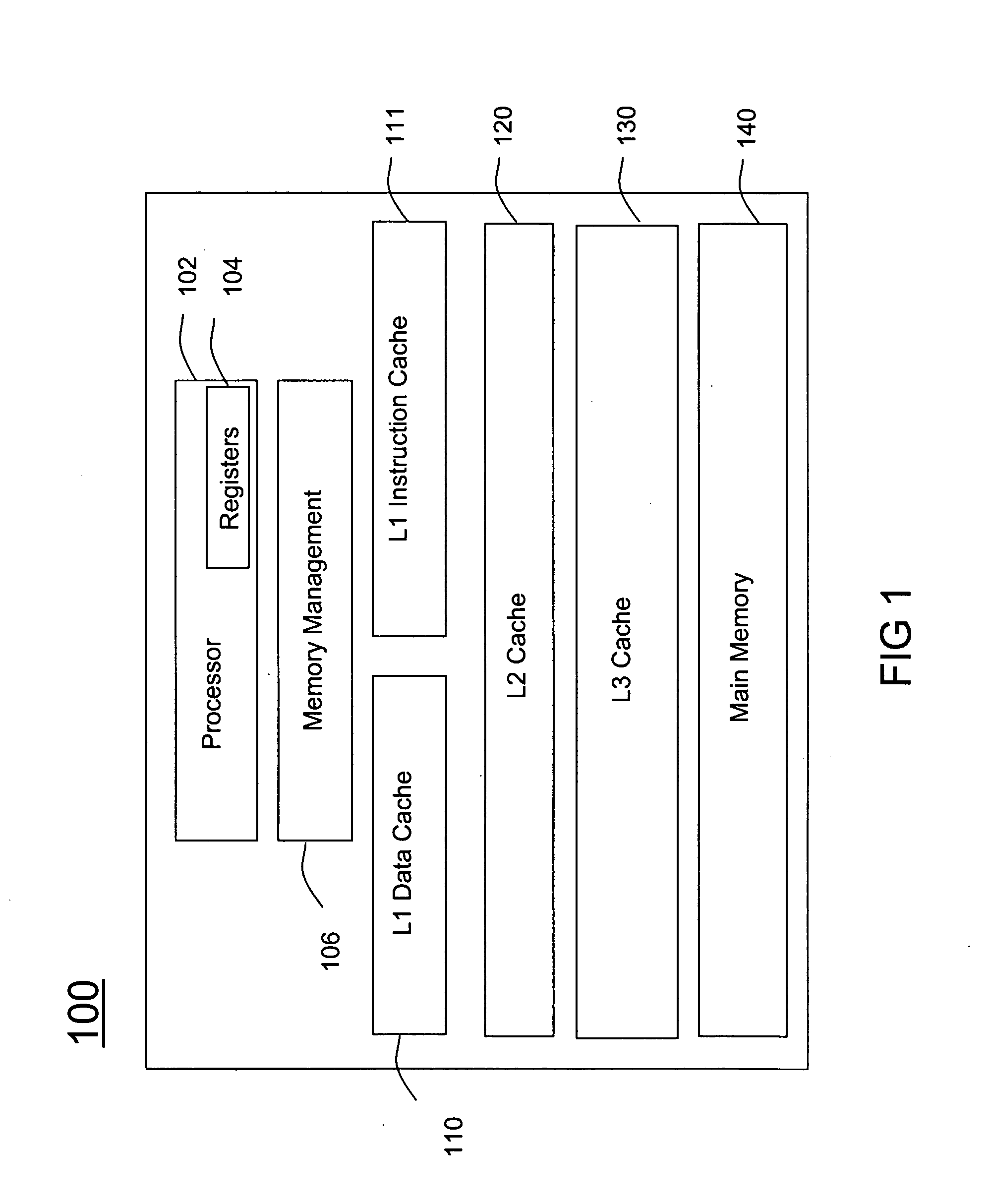

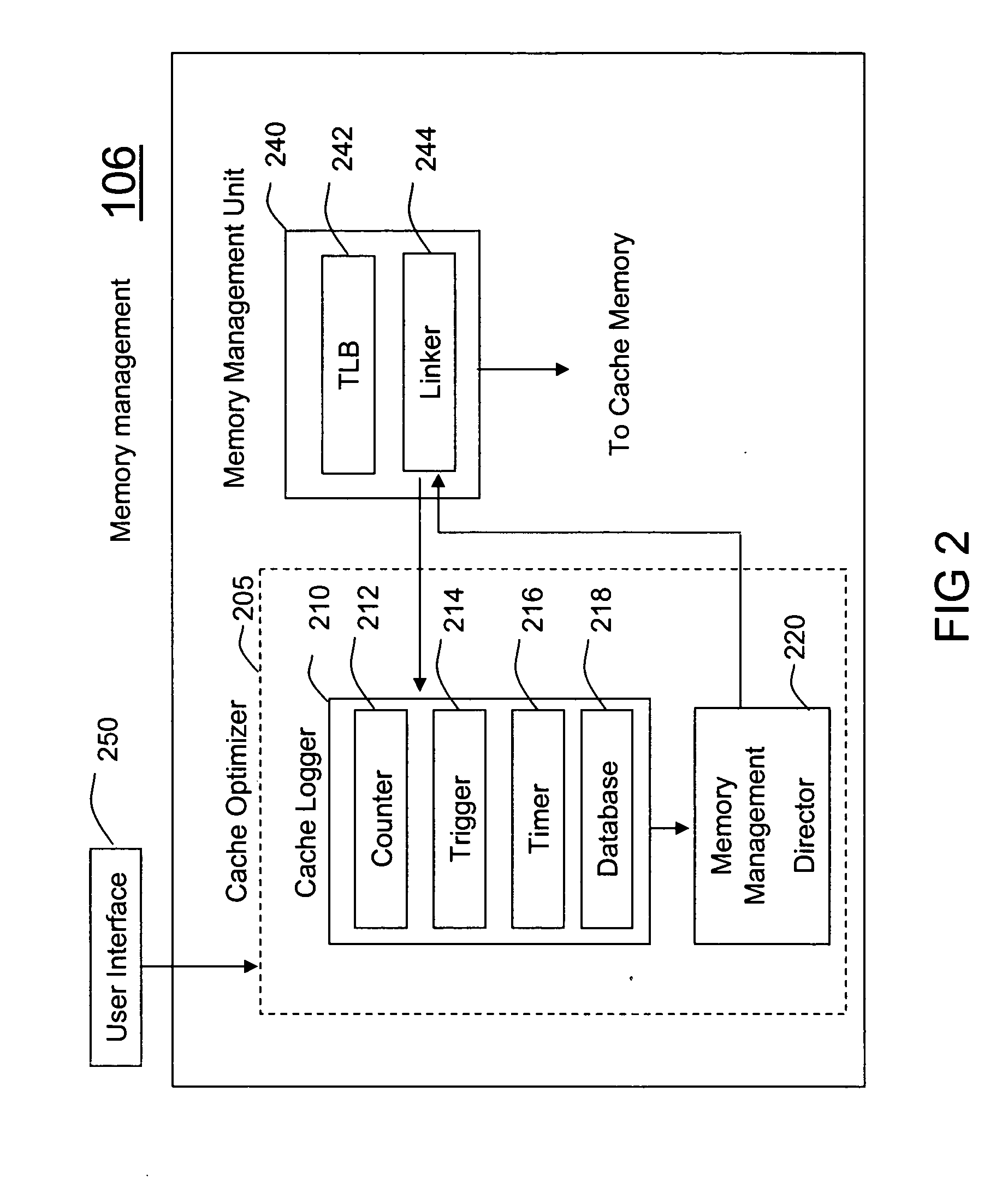

Method and system for run-time cache logging

InactiveUS20070150881A1Increase heightMaximize cache locality compile timeError detection/correctionSpecific program execution arrangementsCache optimizationParallel computing

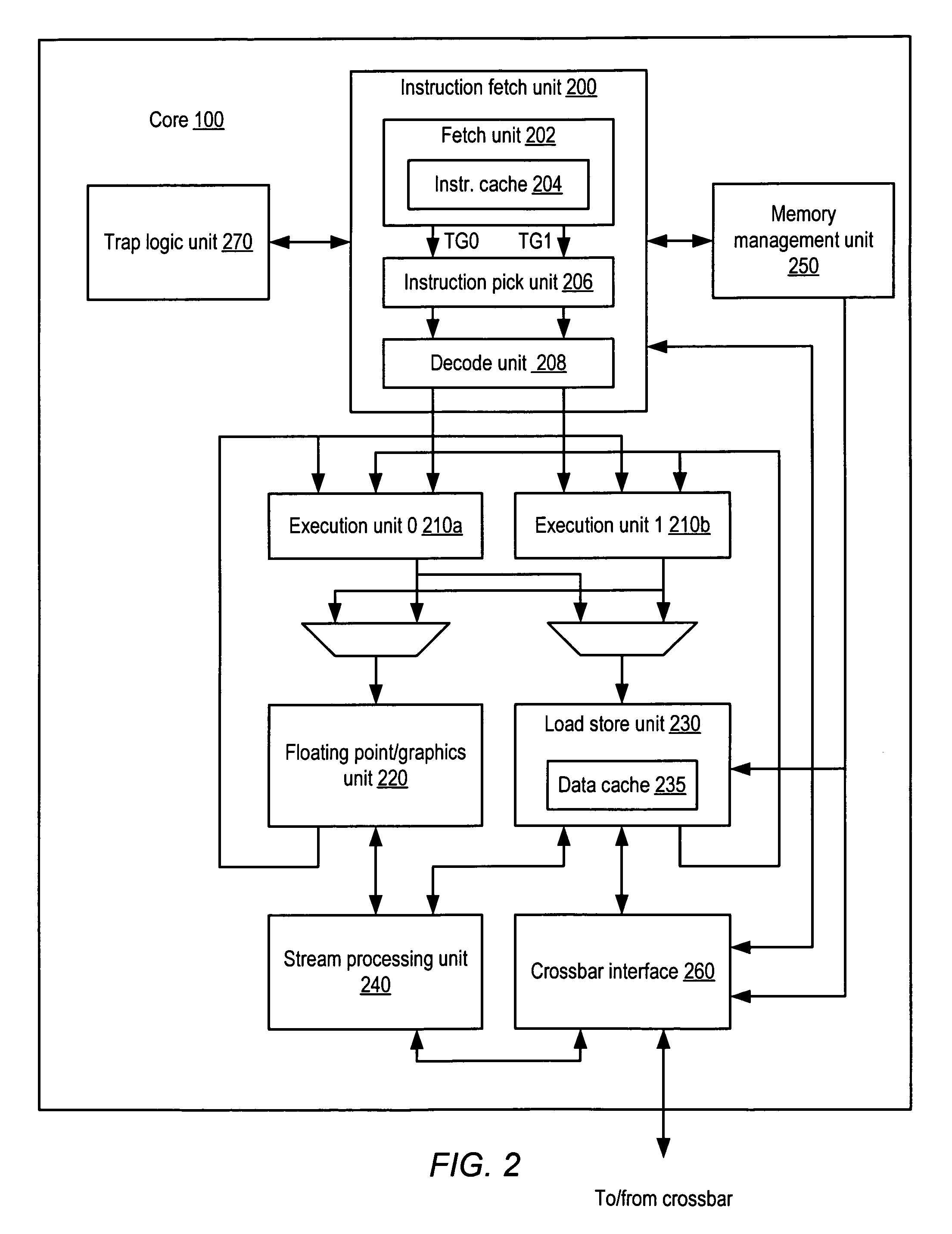

A method (400) and system (106) is provided for run-time cache optimization. The method includes profiling (402) a performance of a program code during a run-time execution, logging (408) the performance for producing a cache log, and rearranging (410) a portion of program code in view of the cache log for producing a rearranged portion. The rearranged portion is supplied to a memory management unit (240) for managing at least one cache memory (110-140). The cache log can be collected during a real-time operation of a communication device and is fed back to a linking process (244) to maximize a cache locality compile-time. The method further includes loading a saved profile corresponding with a run-time operating mode, and reprogramming a new code image associated with the saved profile.

Owner:MOTOROLA INC

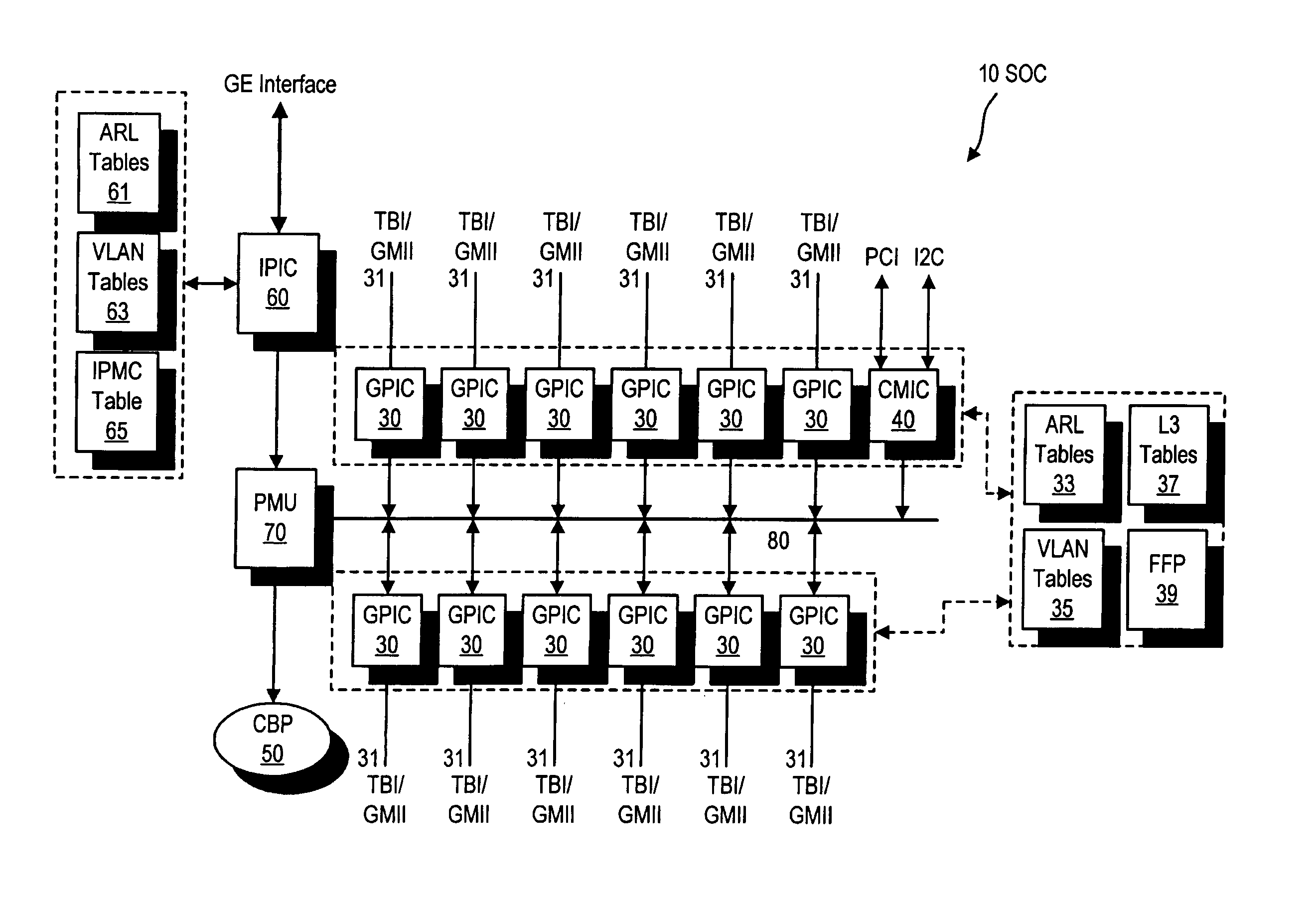

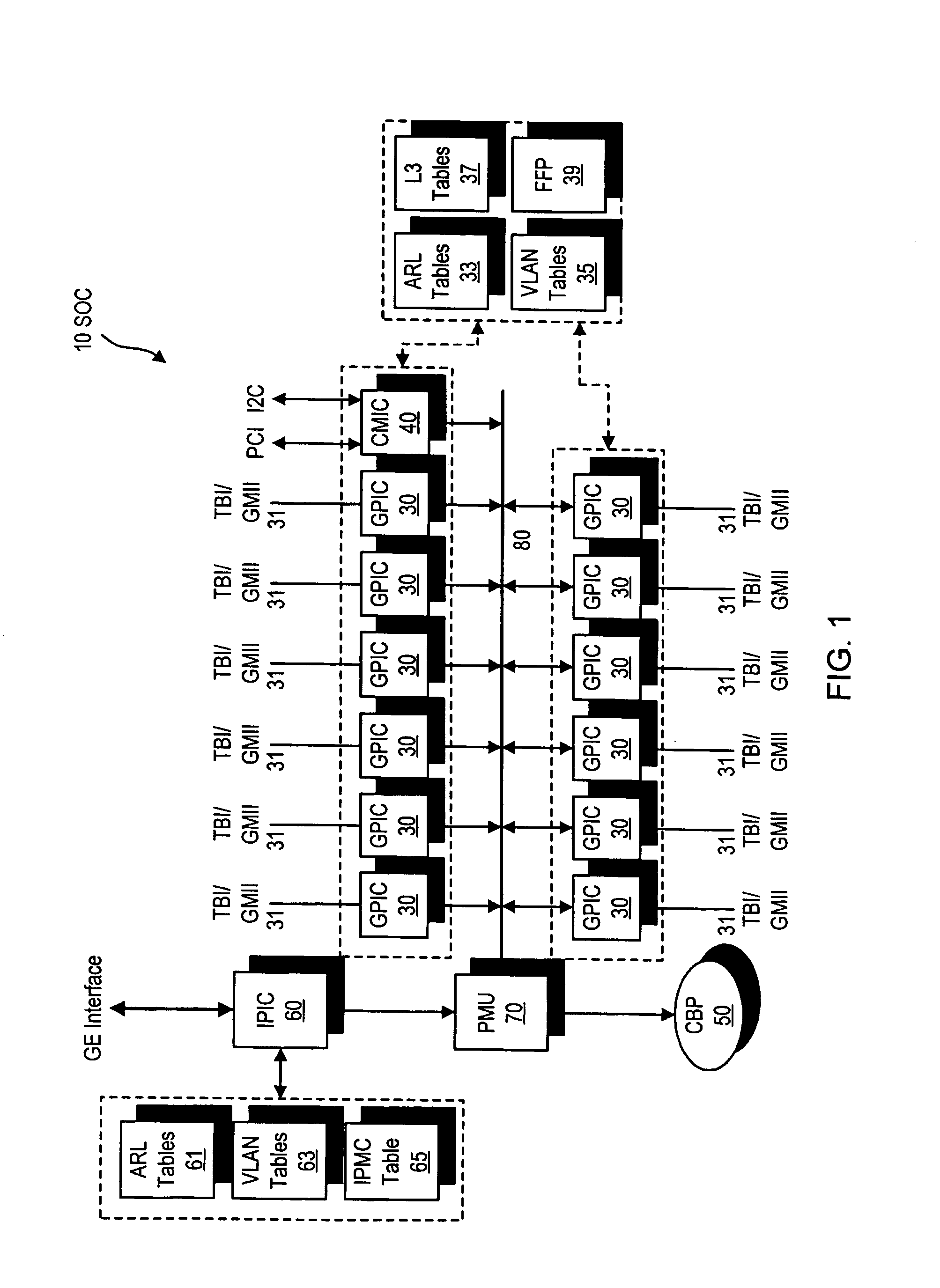

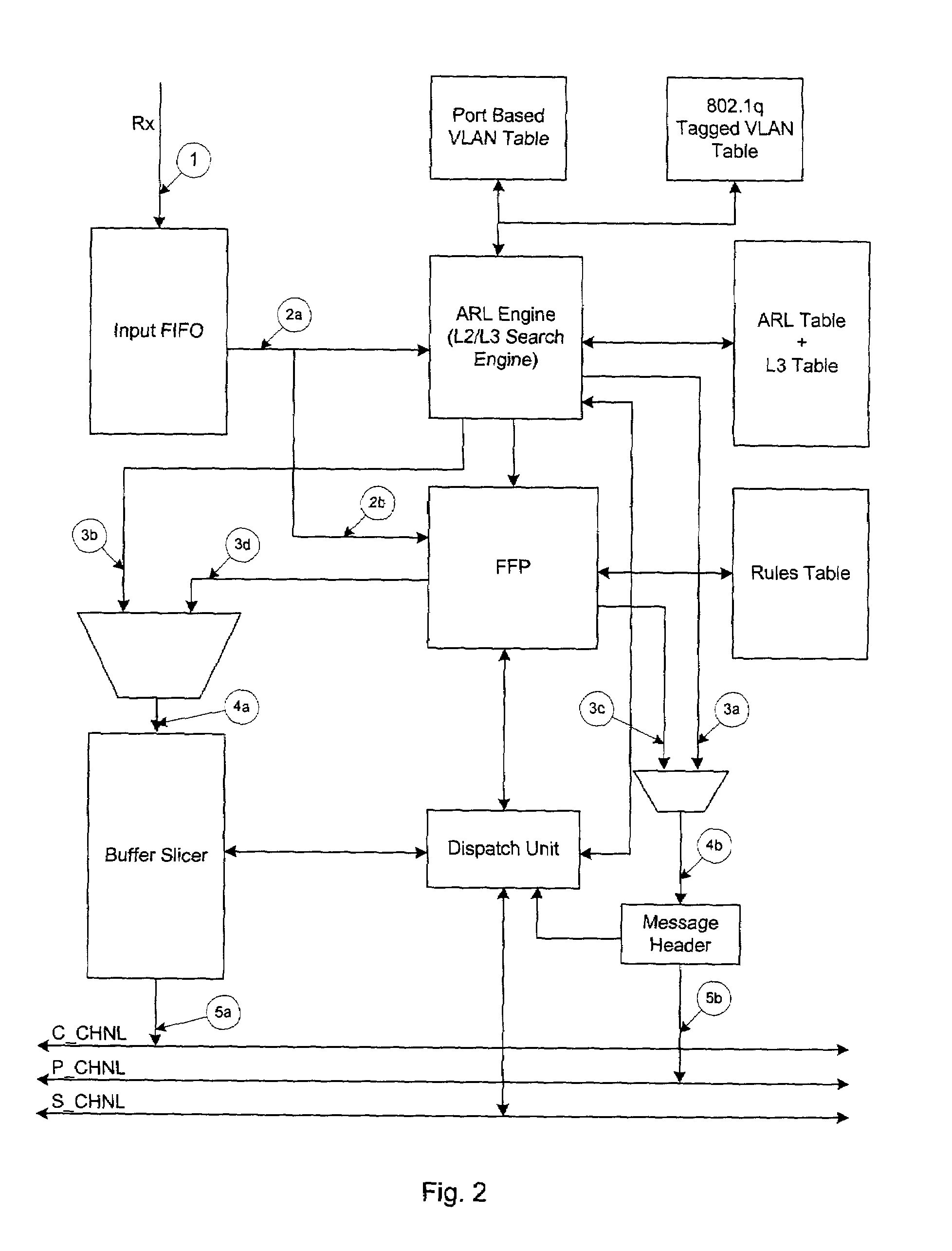

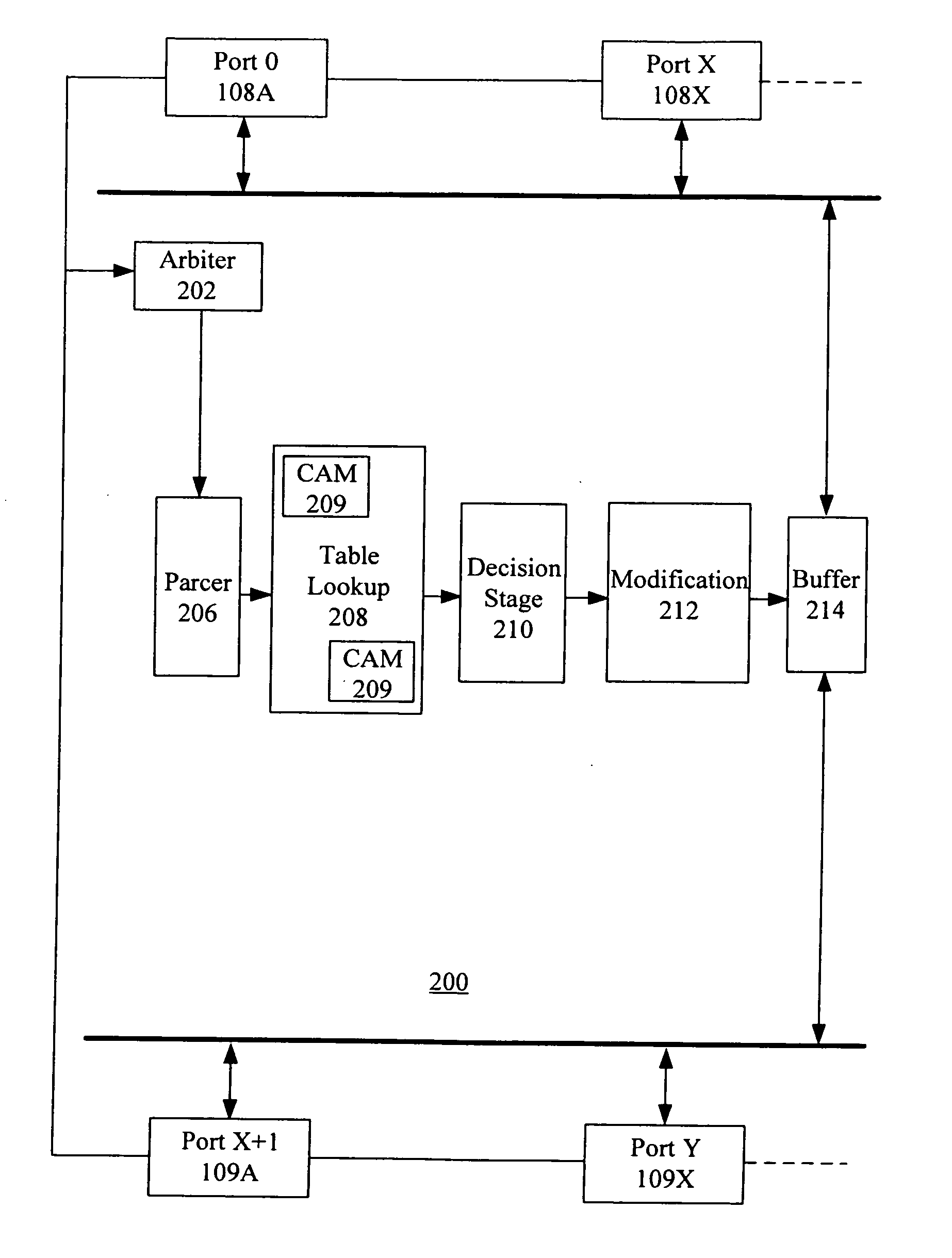

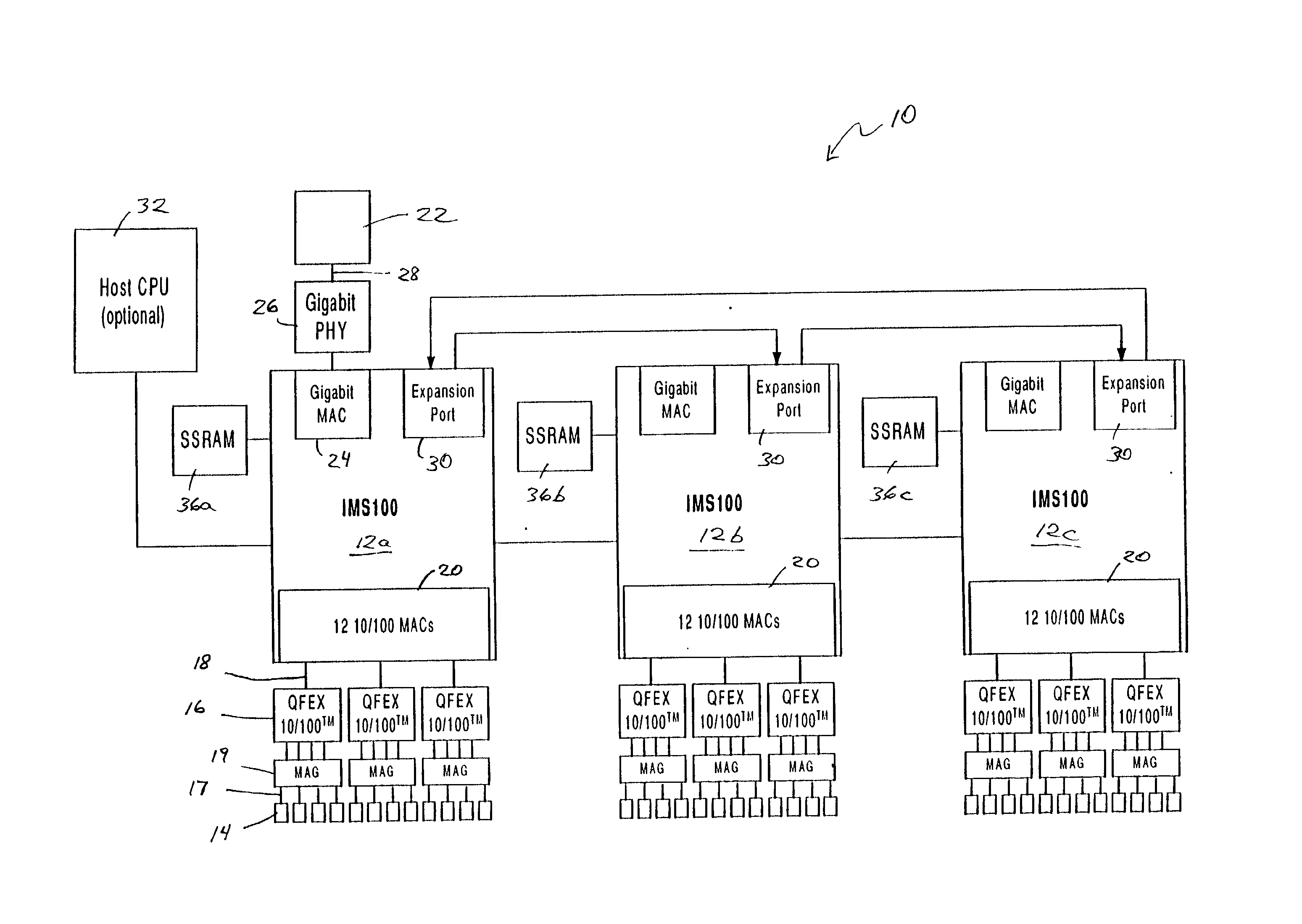

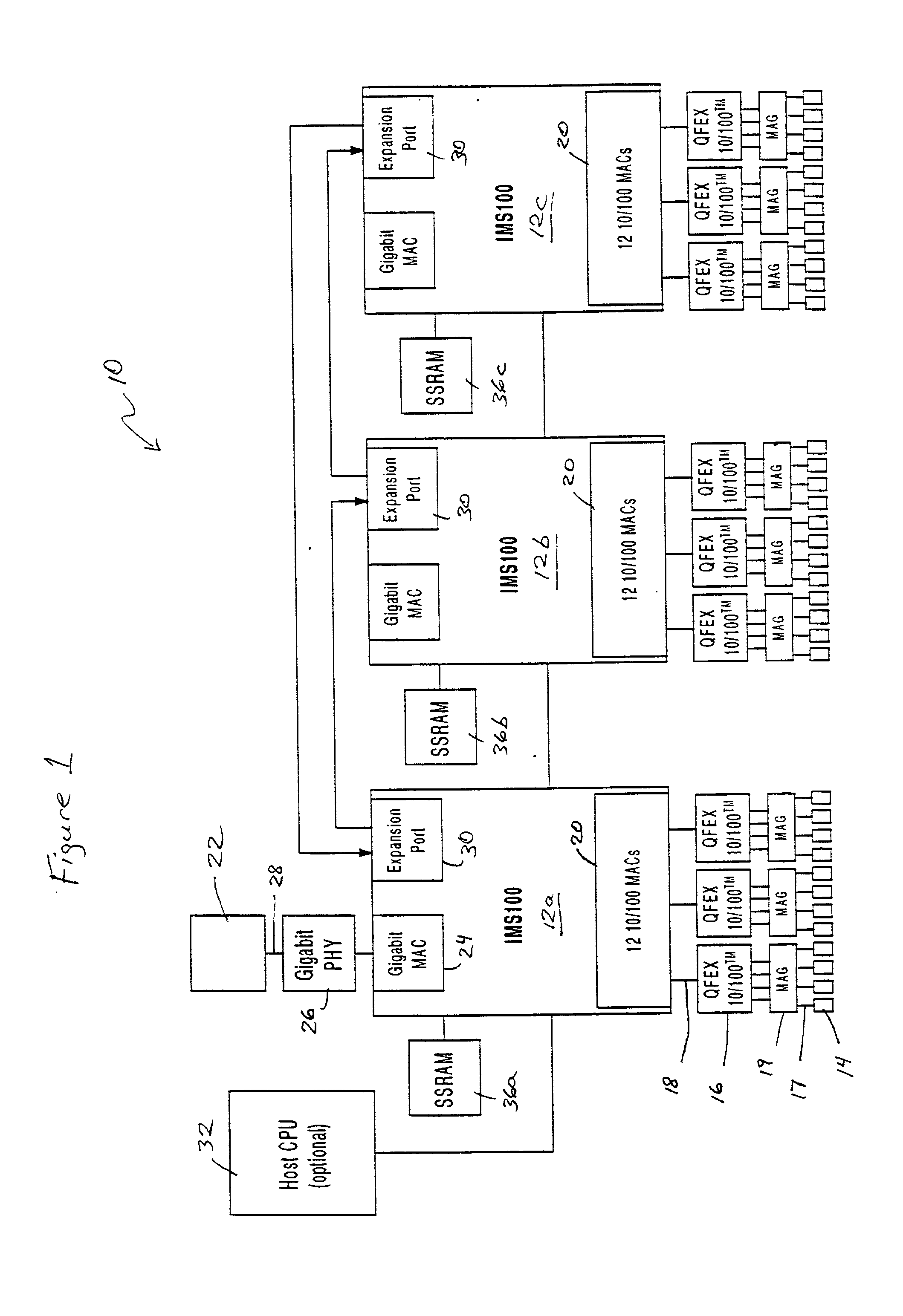

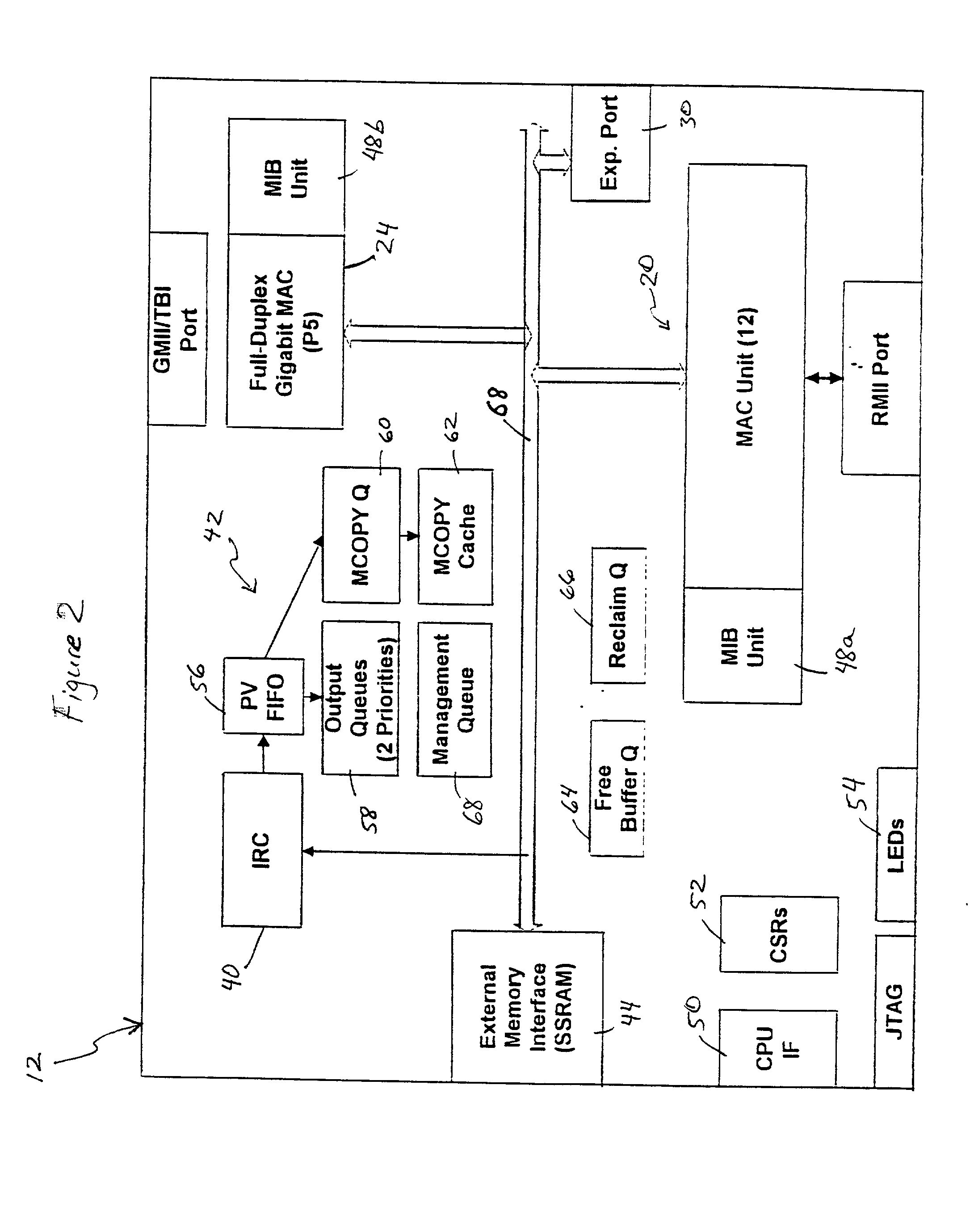

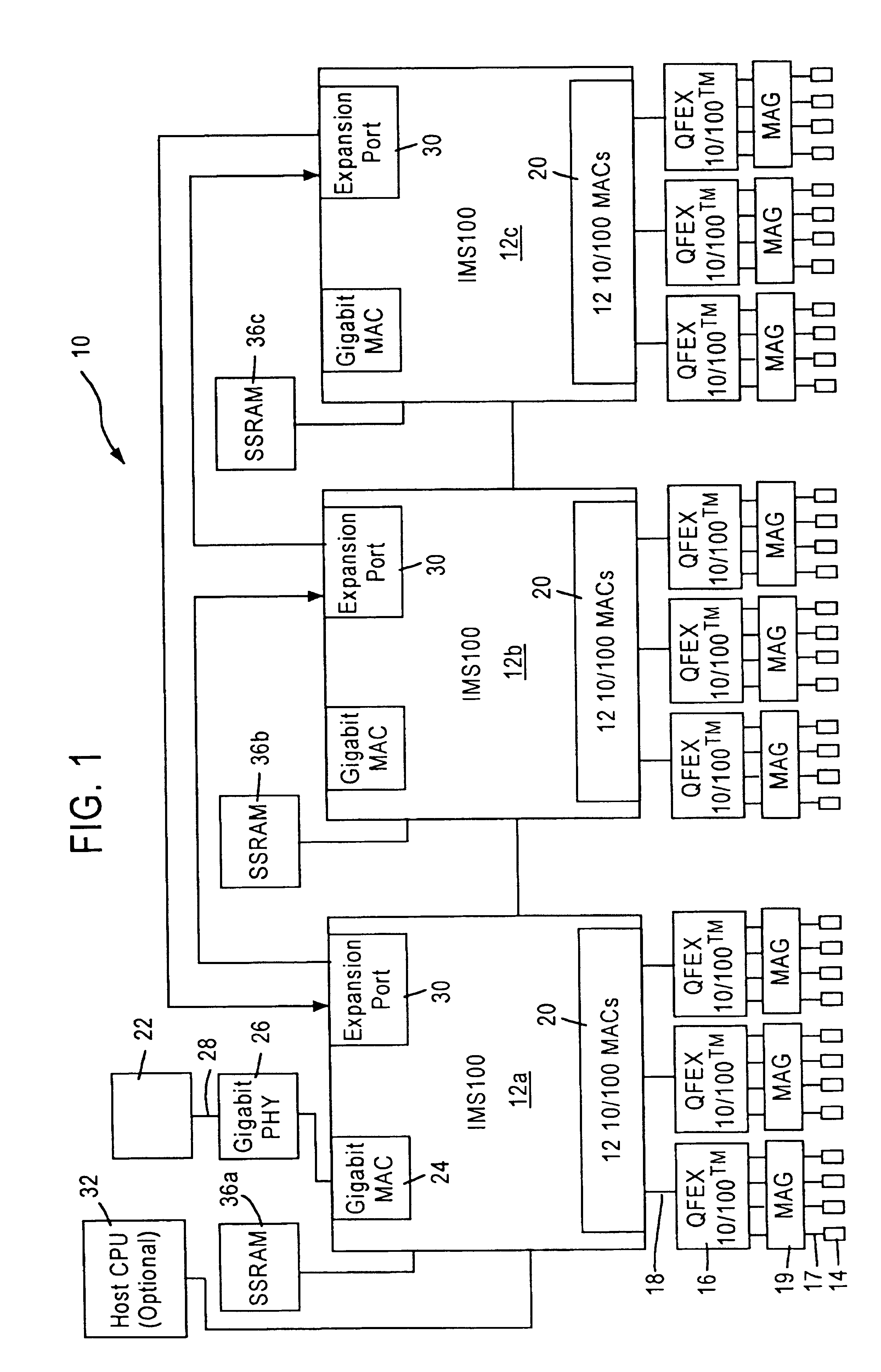

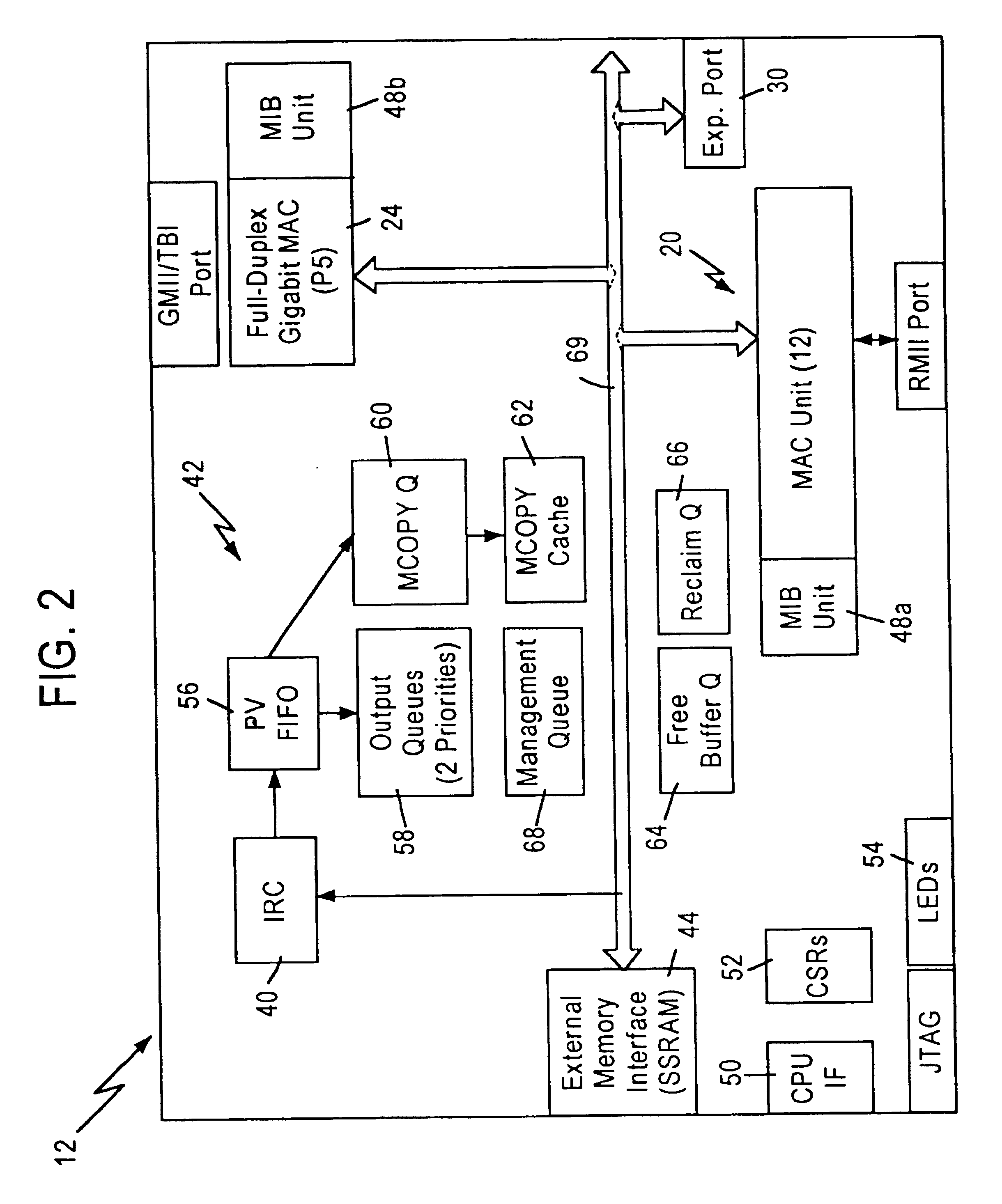

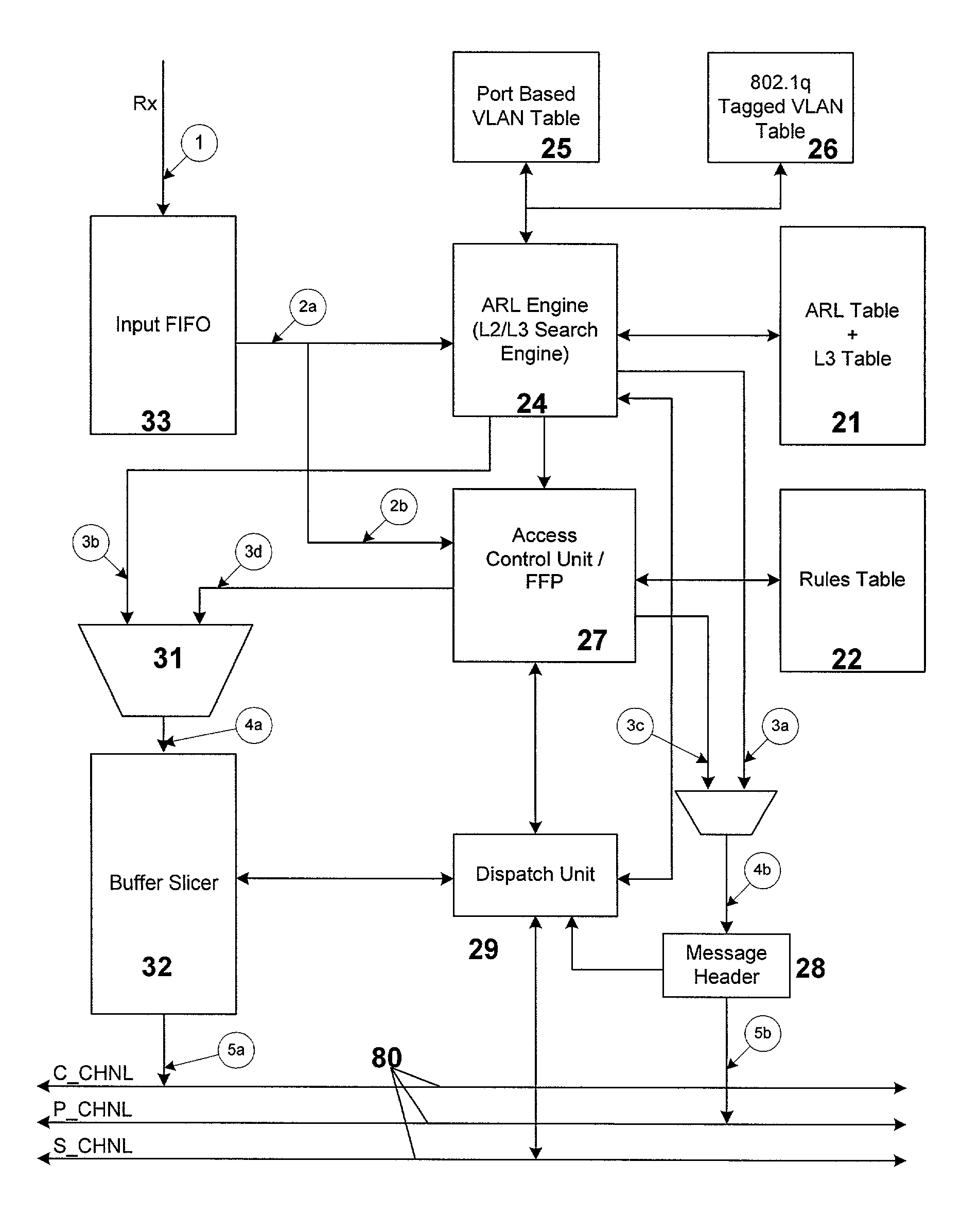

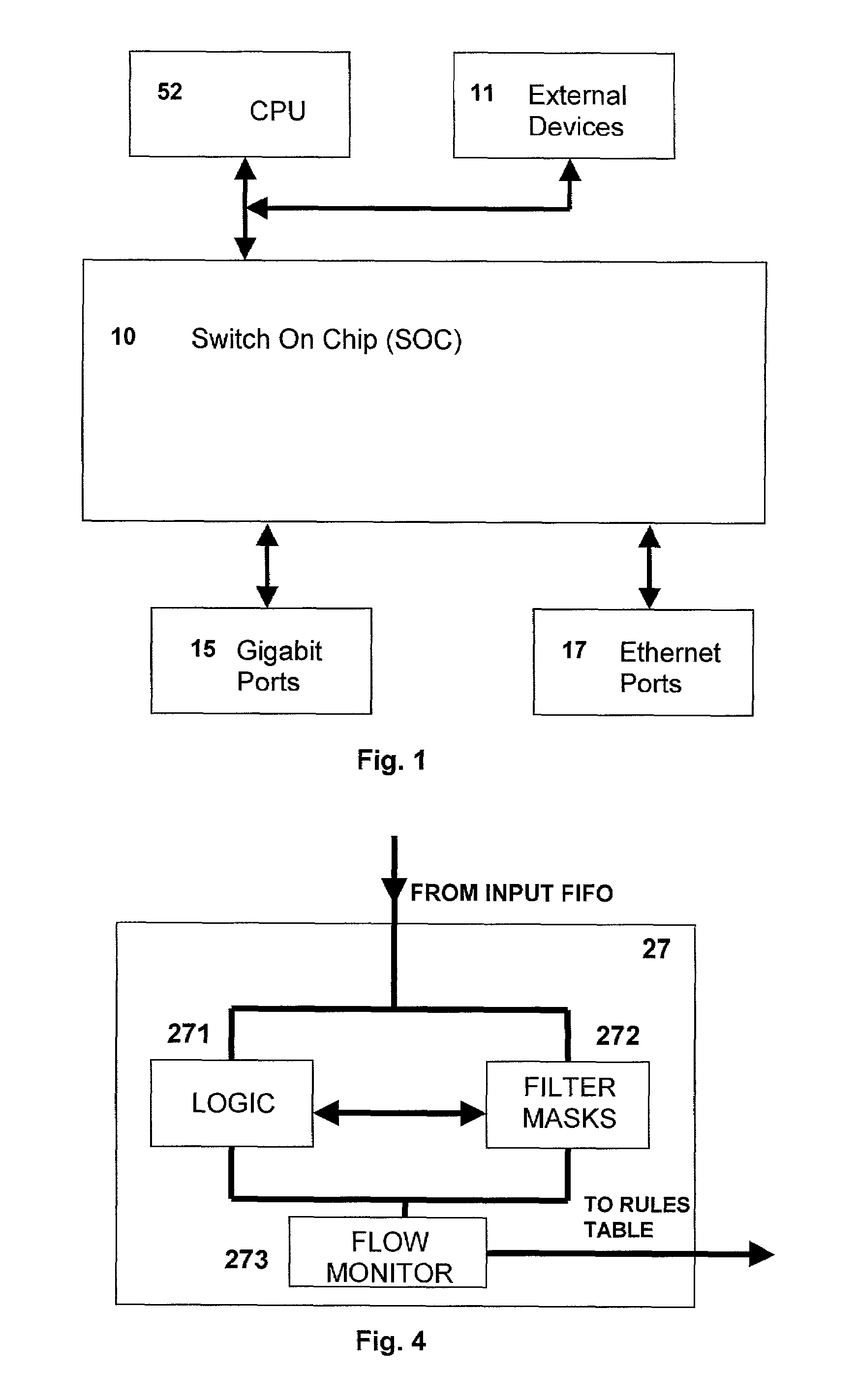

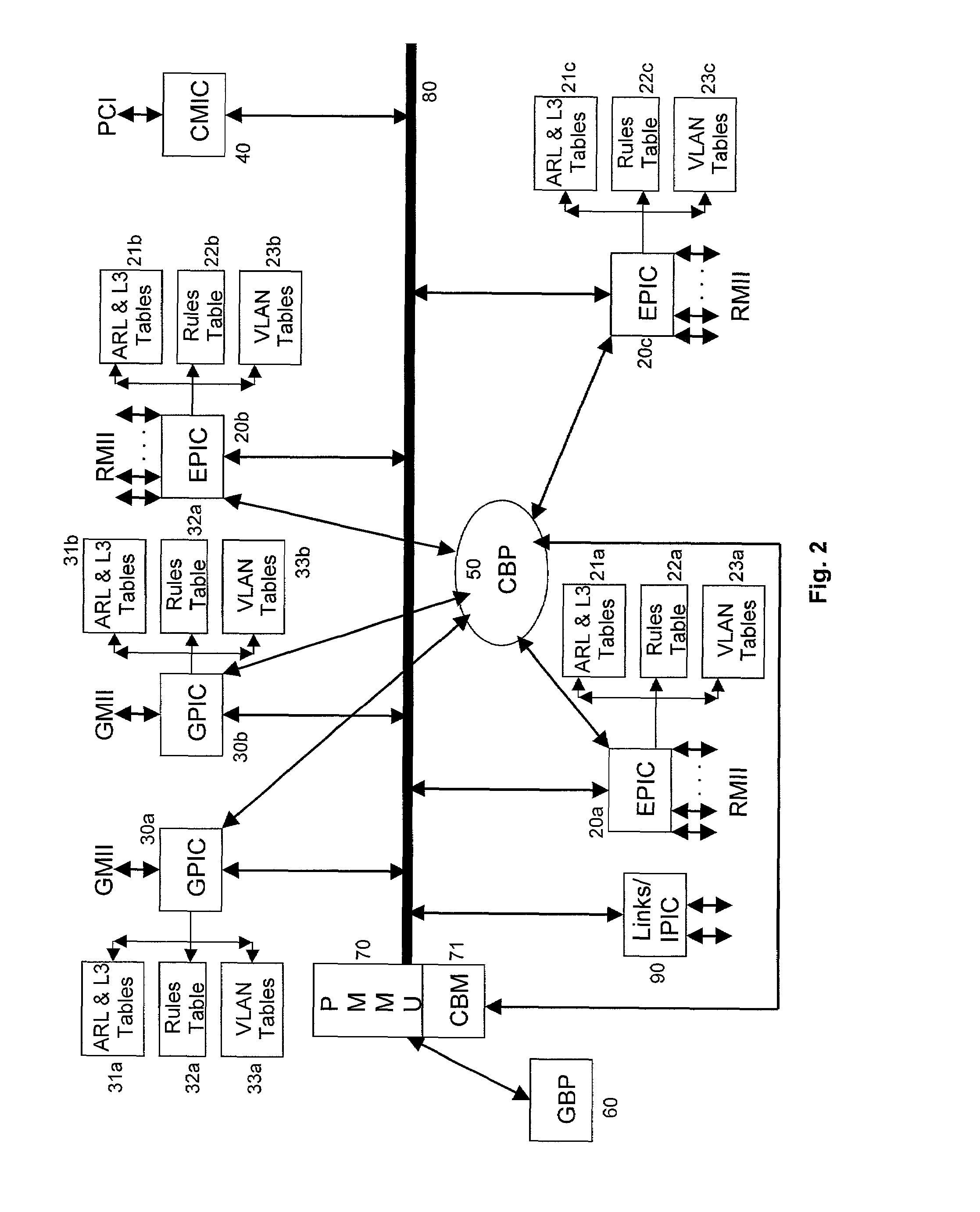

Gigabit switch supporting improved layer 3 switching

ActiveUS7009968B2Improved layer switchingEliminate needSpecial service provision for substationEnergy efficient ICTIP multicastNetwork communication

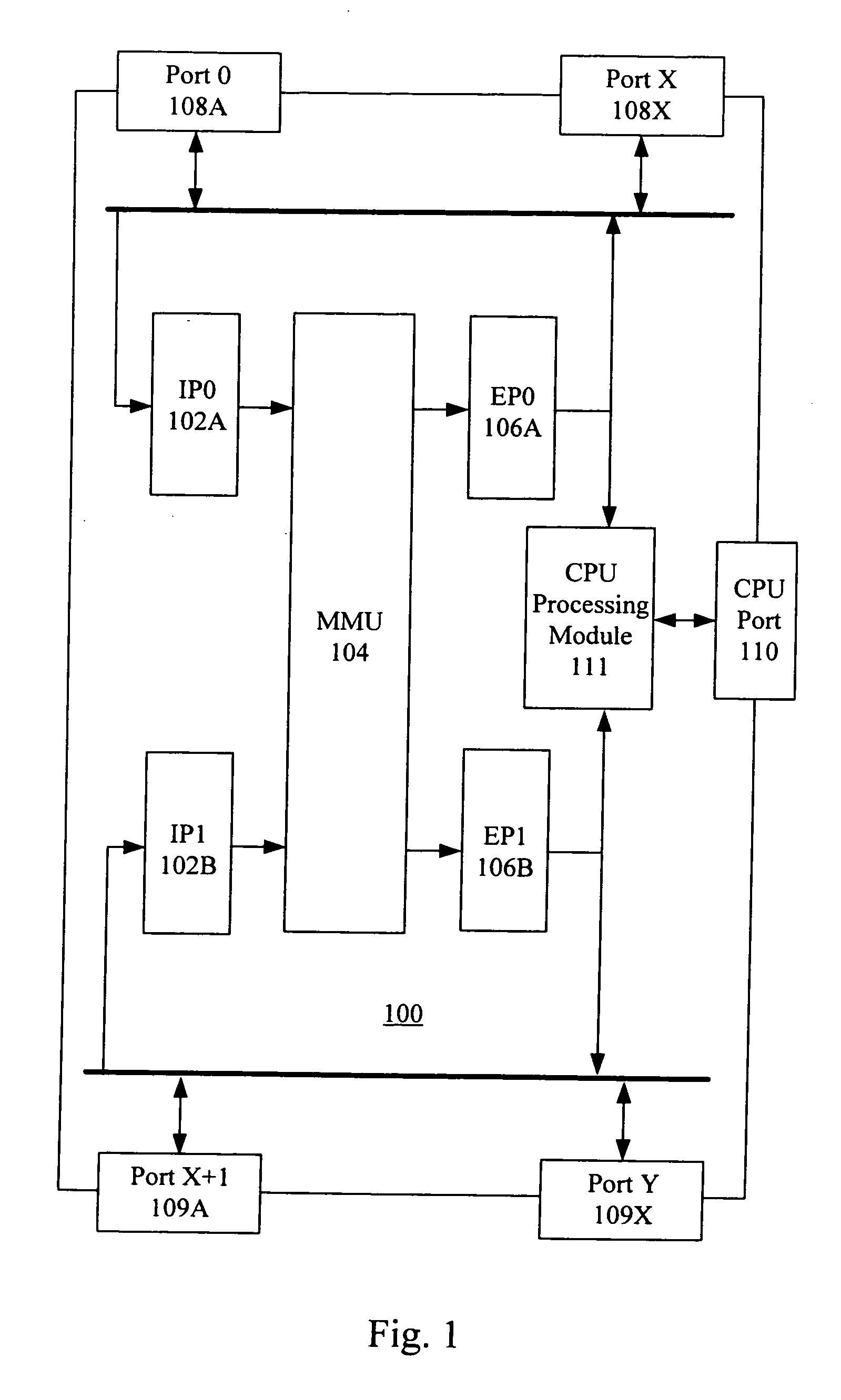

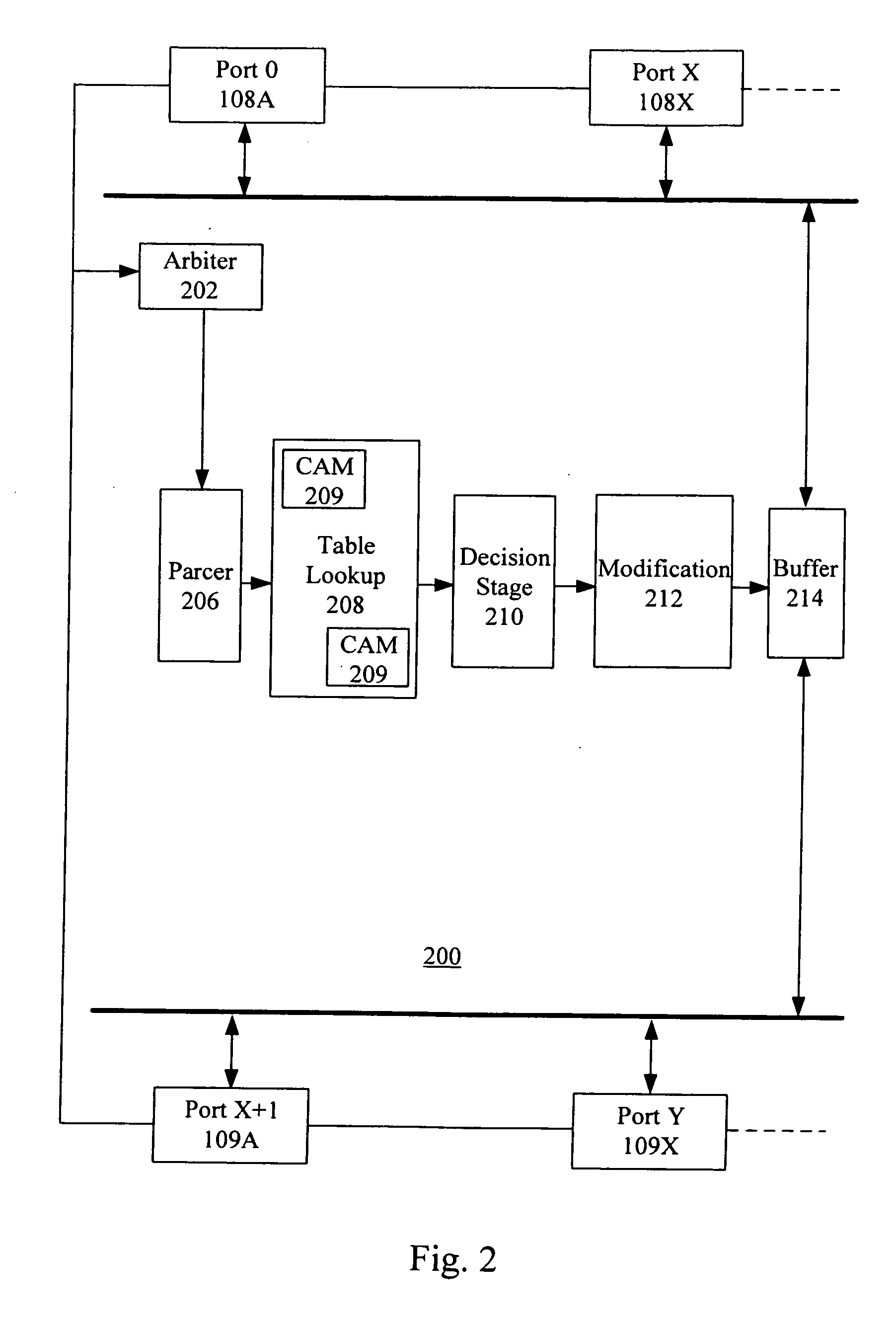

A network switch for network communications is disclosed. The switch includes a first data port interface, supporting at least one data port transmitting and receiving data at a first data rate and a second data port interface supporting a at least one data port transmitting and receiving data at a second data rate. The switch also has a CPU interface configured to communicate with a CPU and a memory management unit for communicating data from at least one of the first and second data port interfaces and a memory. It also has a communication channel for communicating data and messaging information between the first and second data port interfaces and the memory management unit and a plurality of semiconductor-implemented lookup tables including an address resolution lookup table, a layer three IP lookup table and VLAN tables. One of the first and second data port interfaces is configured to determine whether an incoming data packet is a unicast packet, a multicast packet or an IP multicast packet; and the address resolution lookup and layer three IP lookup tables are searched to find an egress port for the incoming data packet.

Owner:AVAGO TECH INT SALES PTE LTD

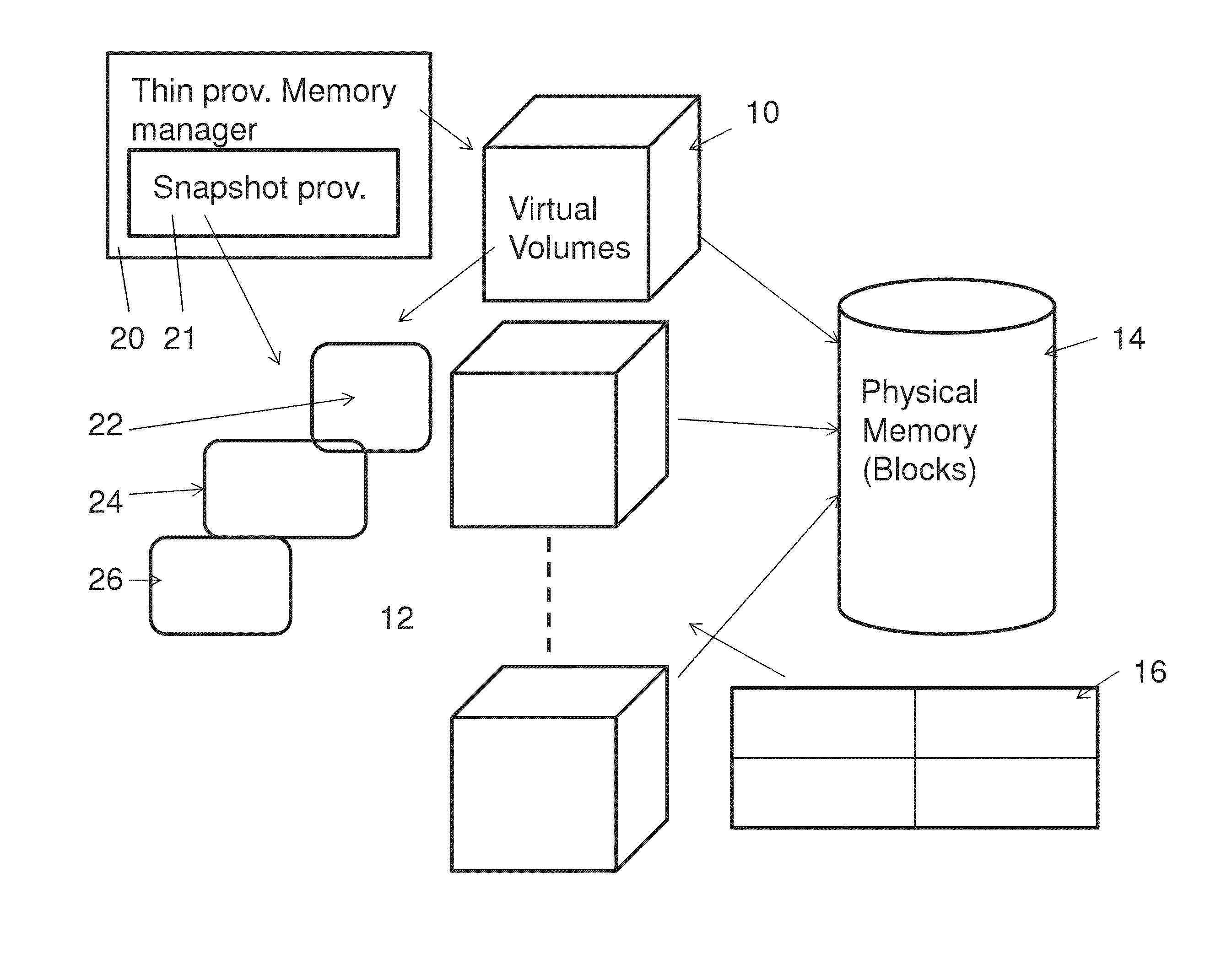

Snapshot mechanism

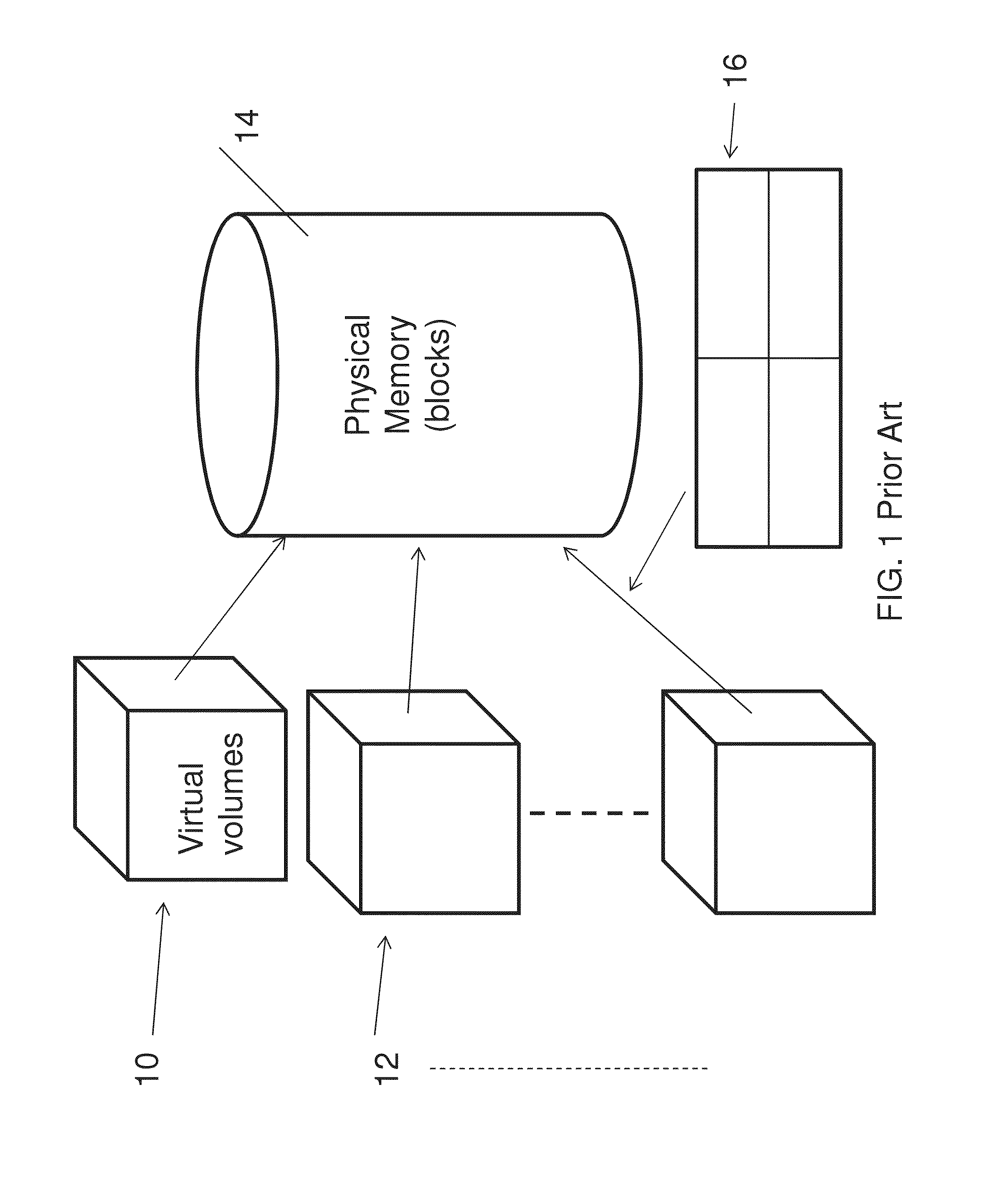

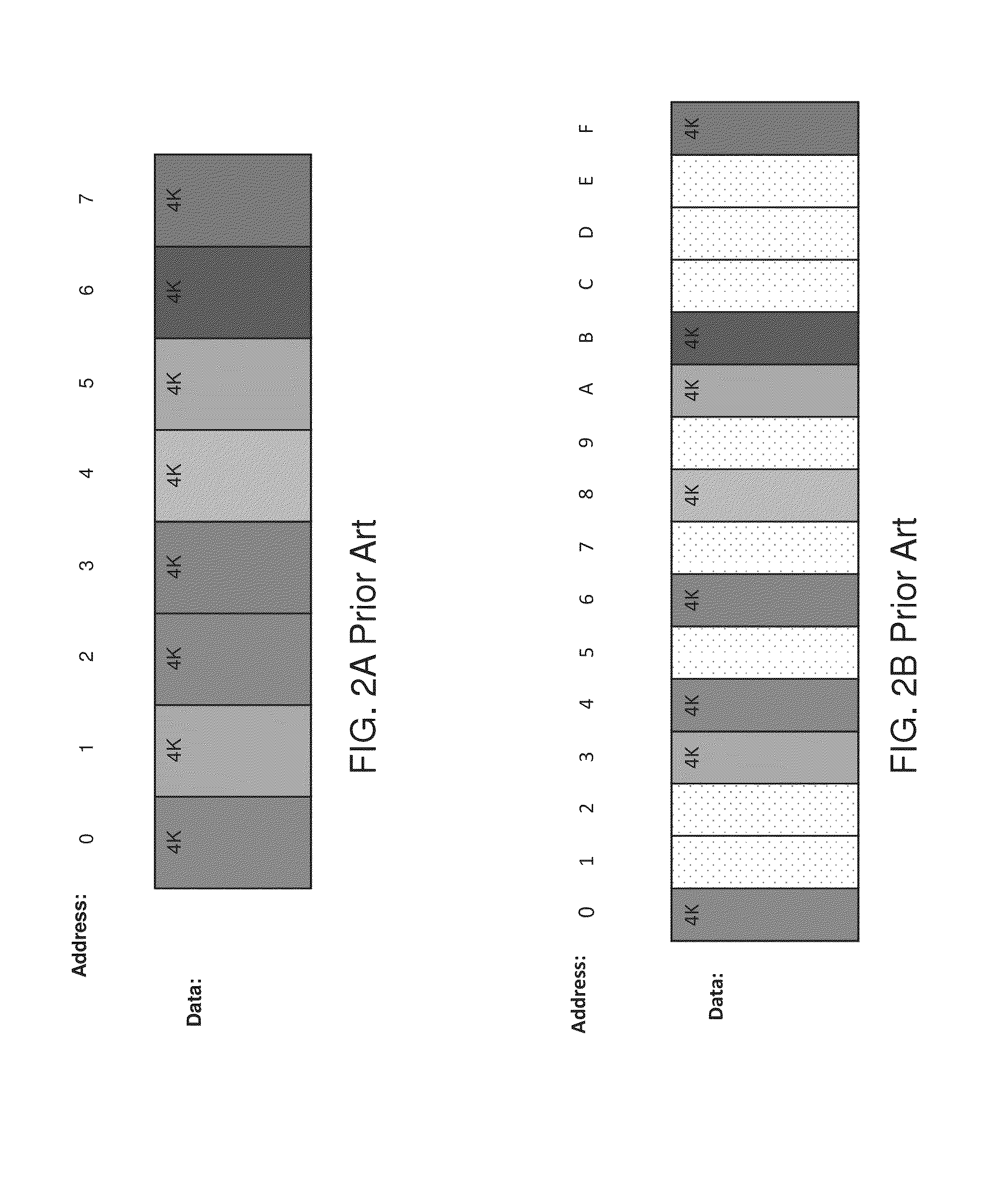

A memory management system for a thinly provisioned memory volume in which a relatively larger virtual address range of virtual address blocks is mapped to a relatively smaller physical memory comprising physical memory blocks via a mapping table containing entries only for addresses of the physical memory blocks containing data. The memory management system comprises a snapshot provision unit to take a given snapshot of the memory volume at a given time, the snapshot comprising a mapping table and memory values of the volume, the mapping table and memory values comprising entries only for addresses of the physical memory containing data. The snapshot is managed on the same thin provisioning basis as the volume itself, and the system is particularly suitable for RAM type memory disks.

Owner:EMC IP HLDG CO LLC

Processor and method for device-specific memory address translation

ActiveUS7487327B1Memory systemsInput/output processes for data processingMemory addressManagement unit

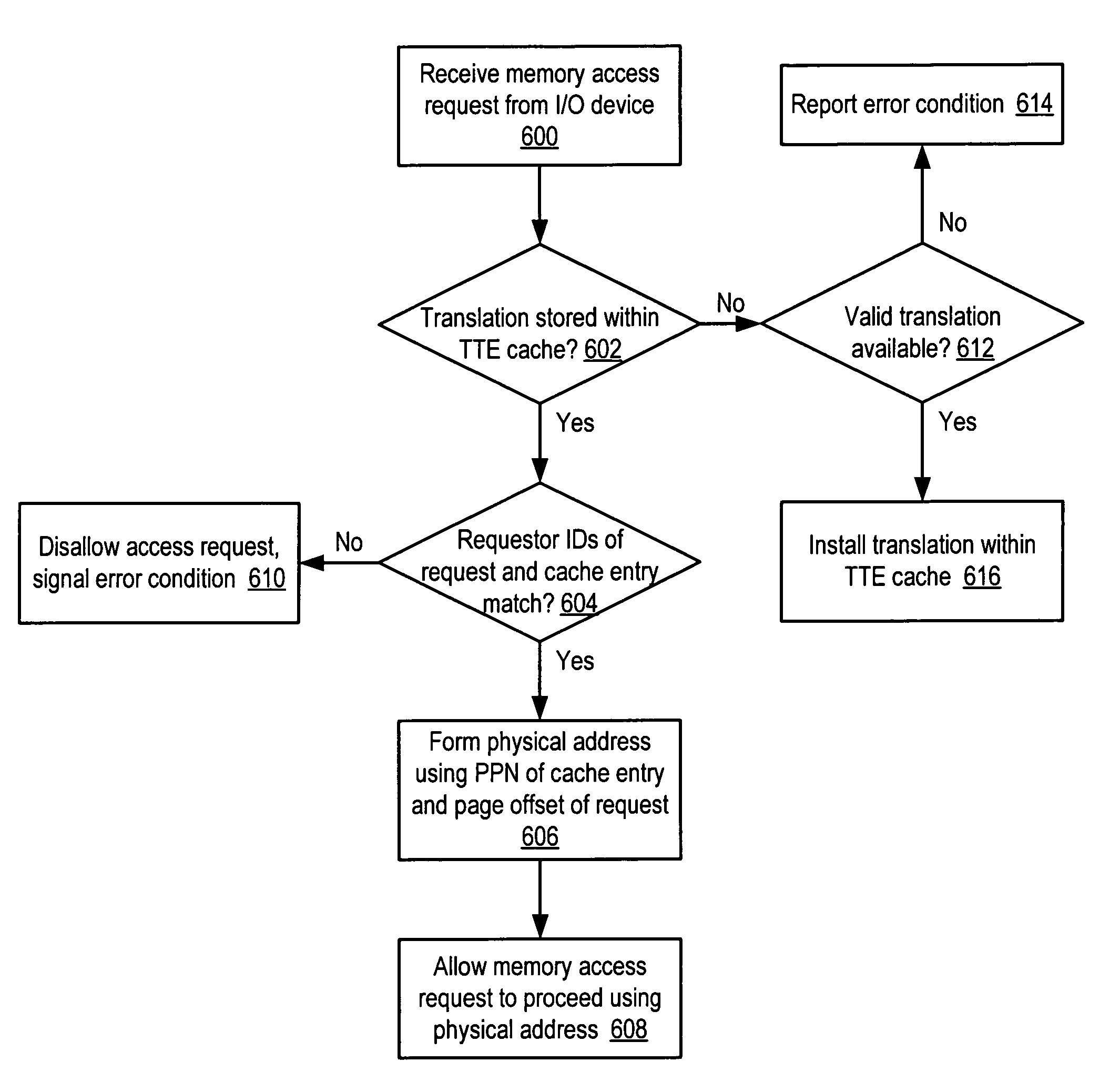

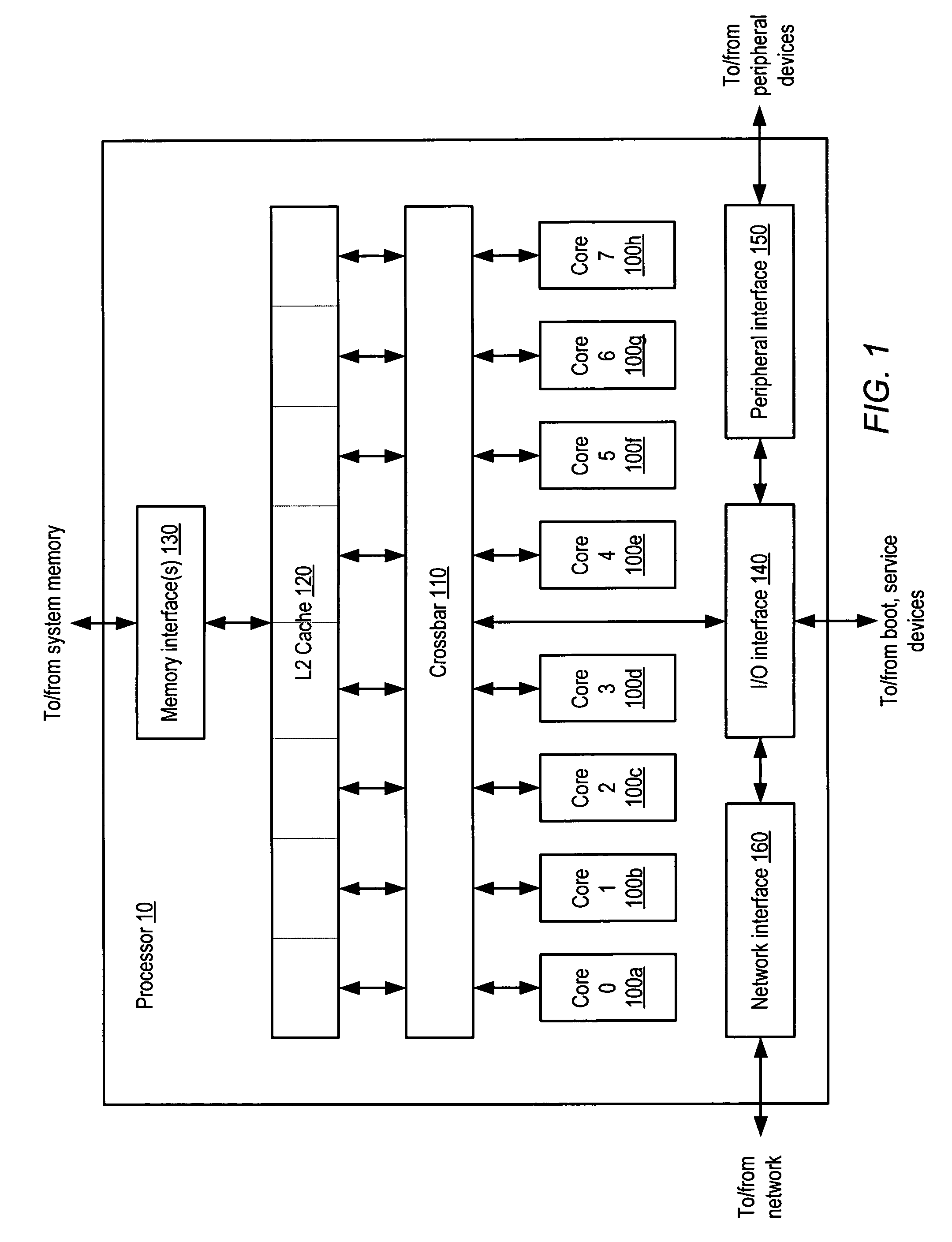

A processor employing device-specific memory address translation. In one embodiment, a processor may include a device interface configured to receive a memory access request from an input / output (I / O) device, where the request specifies a virtual memory address and a first requestor identifier (ID) that identifies the I / O device. The processor may also include an I / O memory management unit coupled to the device interface and configured to determine whether a virtual-to-physical memory address translation corresponding to the virtual memory address is stored within an I / O memory translation buffer. The I / O memory management unit may be further configured to determine whether a second requestor ID stored within the I / O memory translation buffer and corresponding to the memory address translation matches the first requestor ID. If the first and second requestor IDs do not match, the I / O memory management unit may disallow the memory access request and to signal an error condition.

Owner:ORACLE INT CORP

Apparatus and method for managing access to a memory

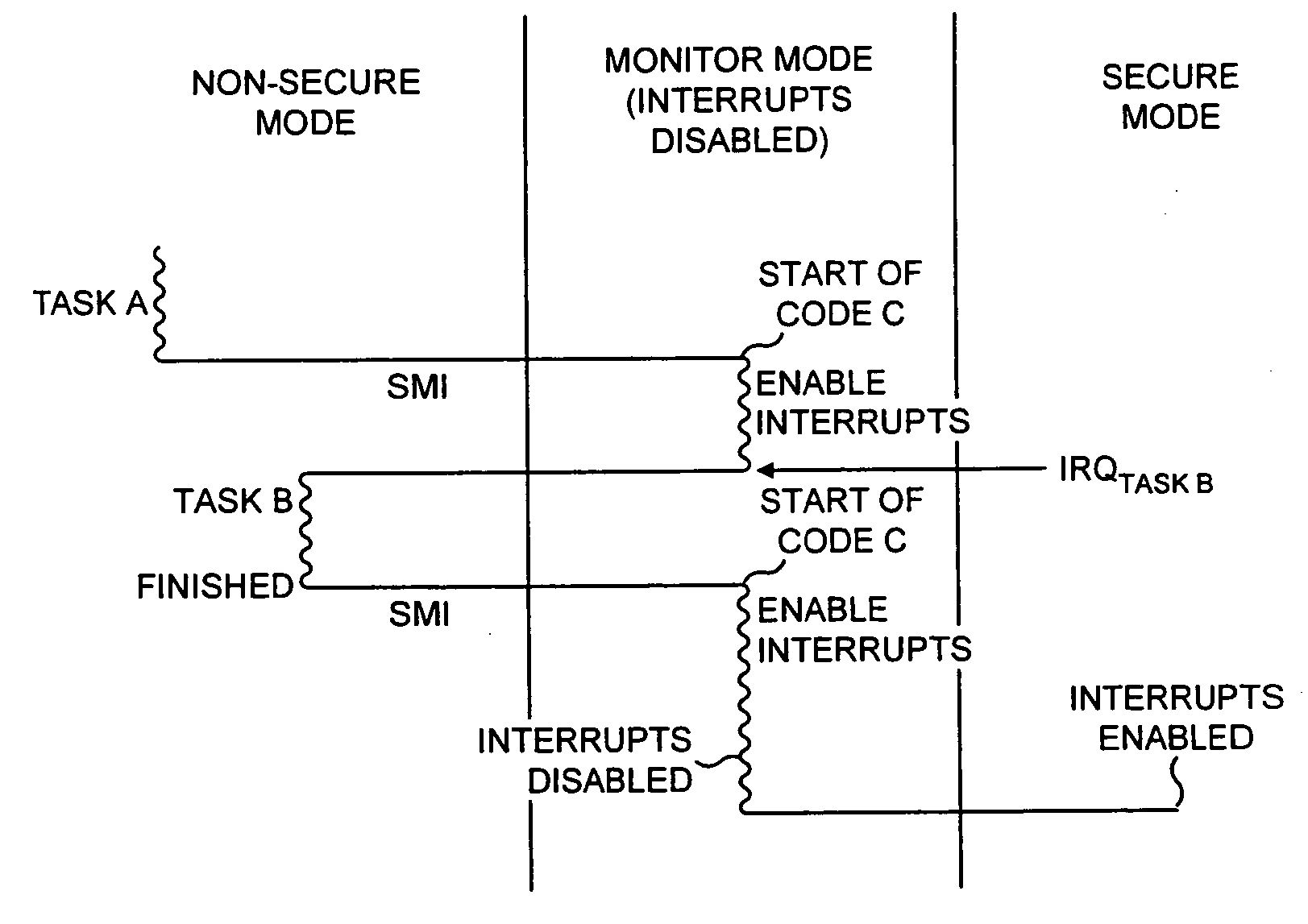

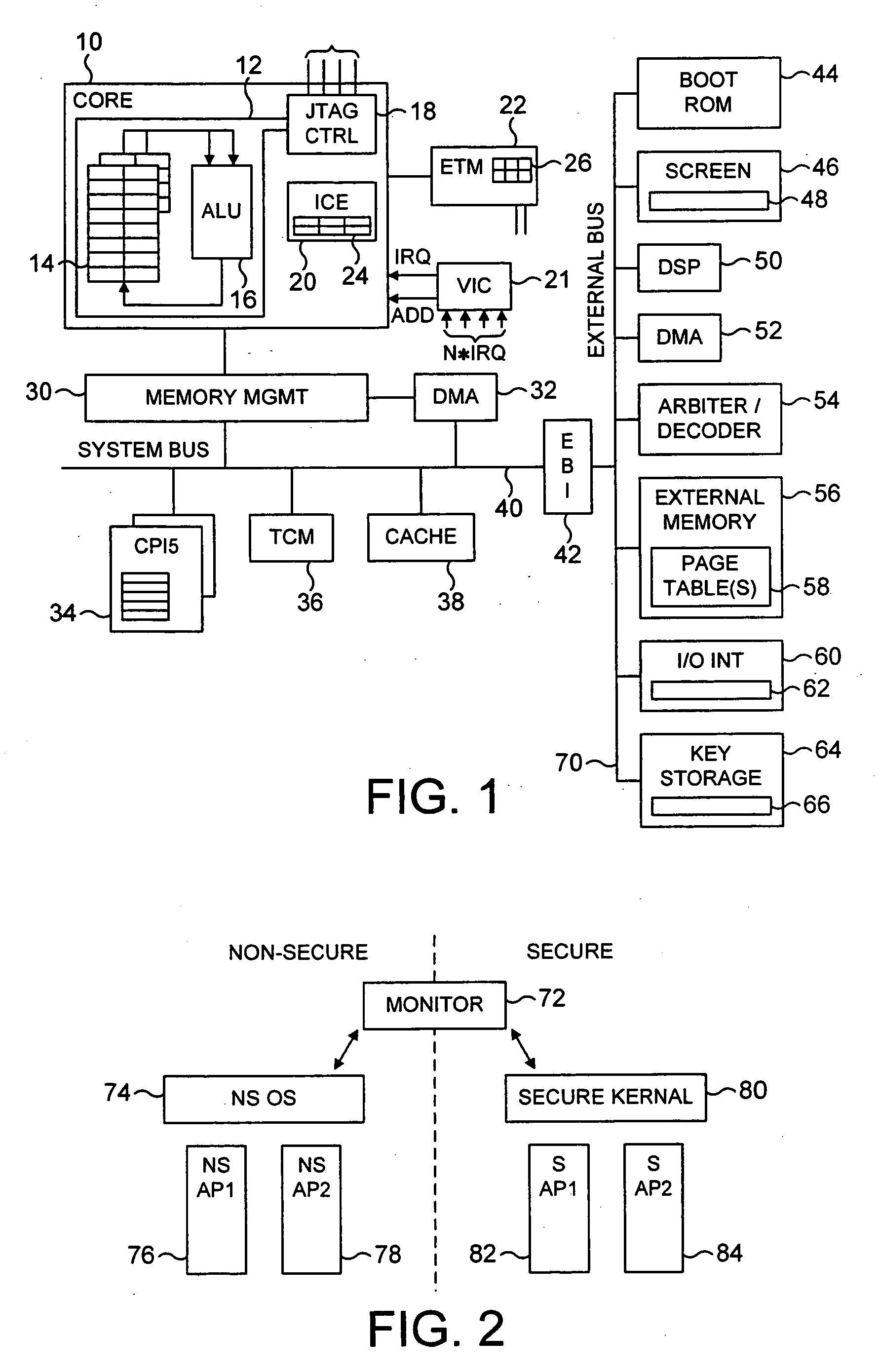

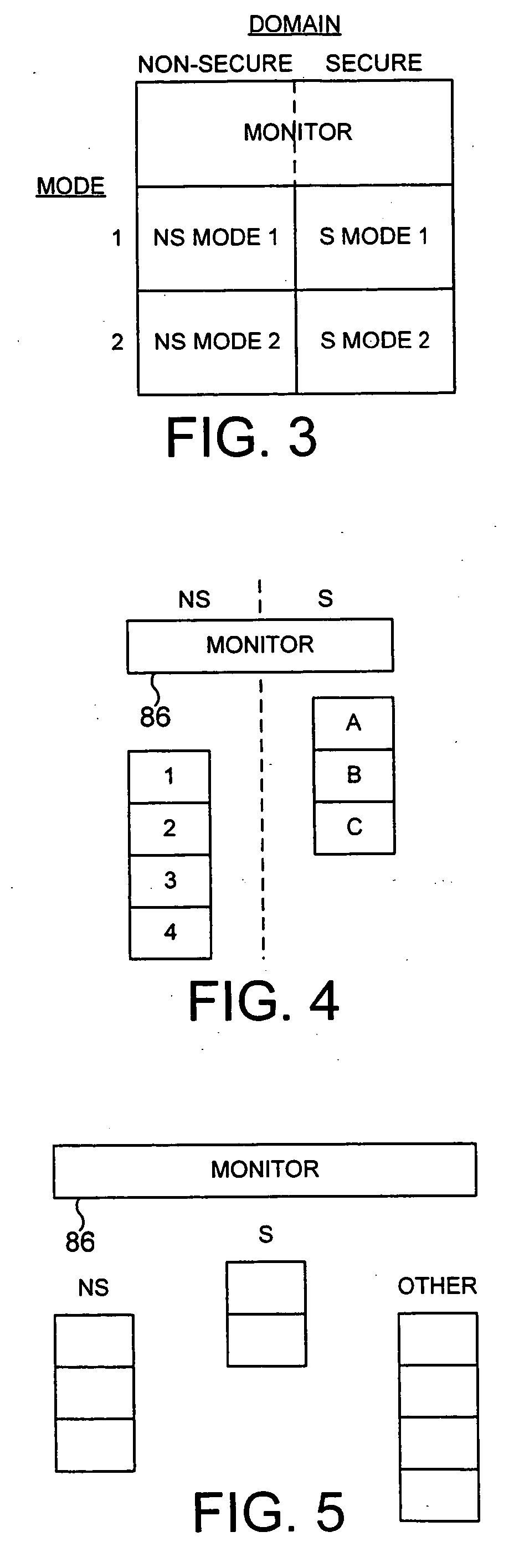

ActiveUS20040177269A1Performance is not affectedEasy to operateMemory architecture accessing/allocationDigital data processing detailsManagement unitMultiple modes

The present invention provides a data processing apparatus and method for managing access to a memory within the data processing apparatus. The data processing apparatus comprises a processor operable in a plurality of modes and a plurality of domains, said plurality of domains comprising a secure domain and a non-secure domain, said plurality of modes including at least one non-secure mode being a mode in the non-secure domain and at least one secure mode being a mode in the secure domain, said processor being operable such that when executing a program in a secure mode said program has access to secure data which is not accessible when said processor is operating in a non-secure mode. Further, a memory is provided for storing data required by the processor, and consists of secure memory for storing secure data and non-secure memory for storing non-secure data. The memory further contains a non-secure table and a secure table, the non-secure table being within the non-secure memory and arranged to contain for each of a number of first memory regions an associated descriptor, and the secure table being within the secure memory and arranged to contain for each of a number of second memory regions an associated descriptor. When access to an item of data in the memory is required by the processor, the processor issues a memory access request, and a memory management unit is provided to perform one or more predetermined access control functions to control issuance of the memory access request to the memory. The memory management unit comprises an internal storage unit operable to store descriptors retrieved by the memory management unit from either the non-secure table or the secure table, and in accordance with the present invention the internal storage unit comprises a flag associated with each descriptor stored within the internal storage unit to identify whether that descriptor is from the non-secure table or the secure table. By this approach, when the processor is operating in a non-secure mode, the memory management unit is operable to perform the predetermined access control functions for the memory access request with reference to access control information derived from the descriptors in the internal storage unit retrieved from the non-secure table. In contrast, when the processor is operating in a secure mode, the memory management unit is operable to perform the predetermined access control functions for the memory access request with reference to access control information derived from the descriptors in the internal storage unit retrieved from the secure table. This approach enables different descriptors to be used for the control of accesses to memory in either the secure domain or the non-secure domain, whilst enabling such different descriptors to co-exist within the memory management unit's internal storage unit, thereby avoiding the requirement to flush the contents of such an internal storage unit when the operation of the processor changes from the secure domain to the non-secure domain, or vice versa.

Owner:ARM LTD

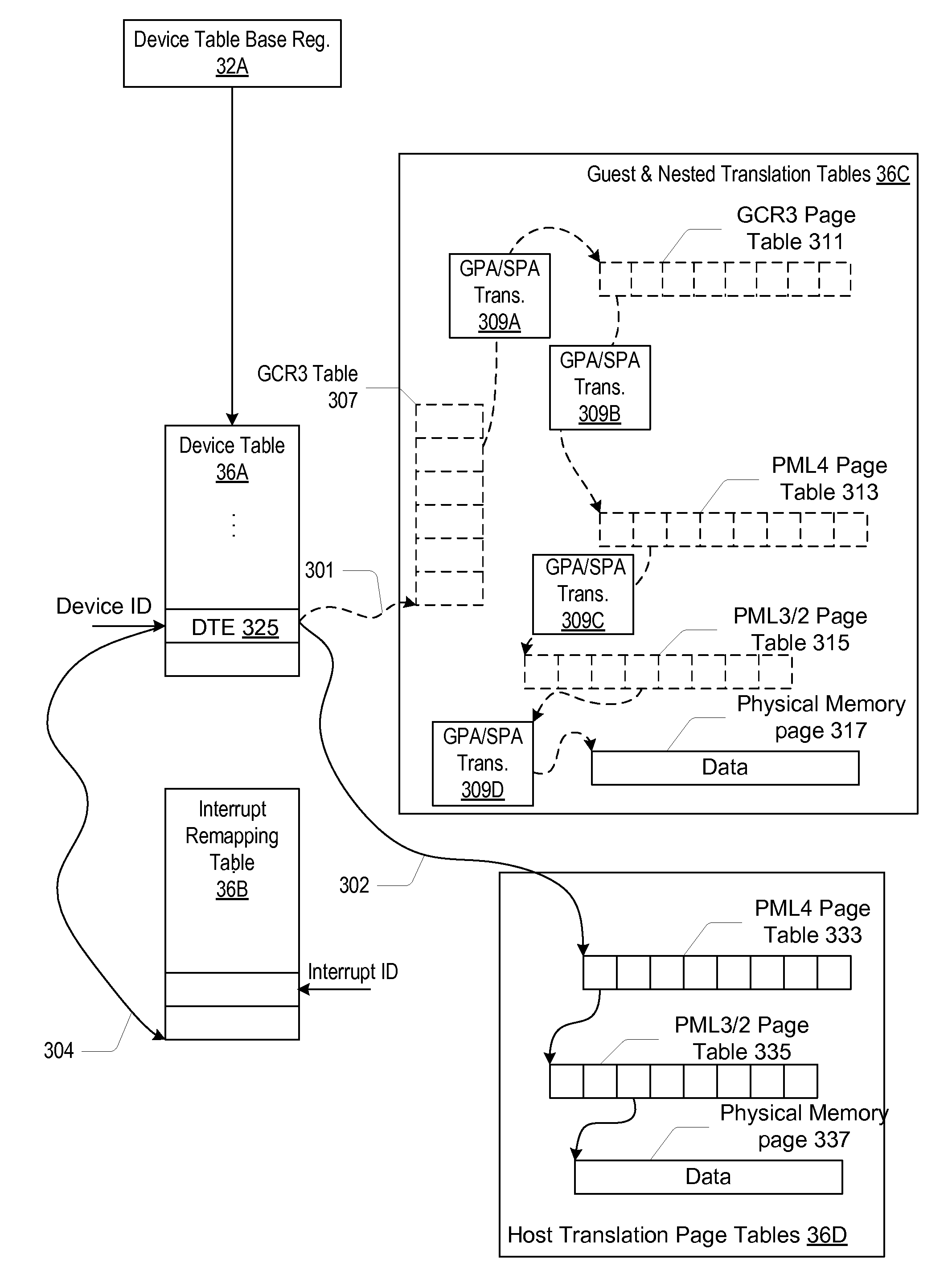

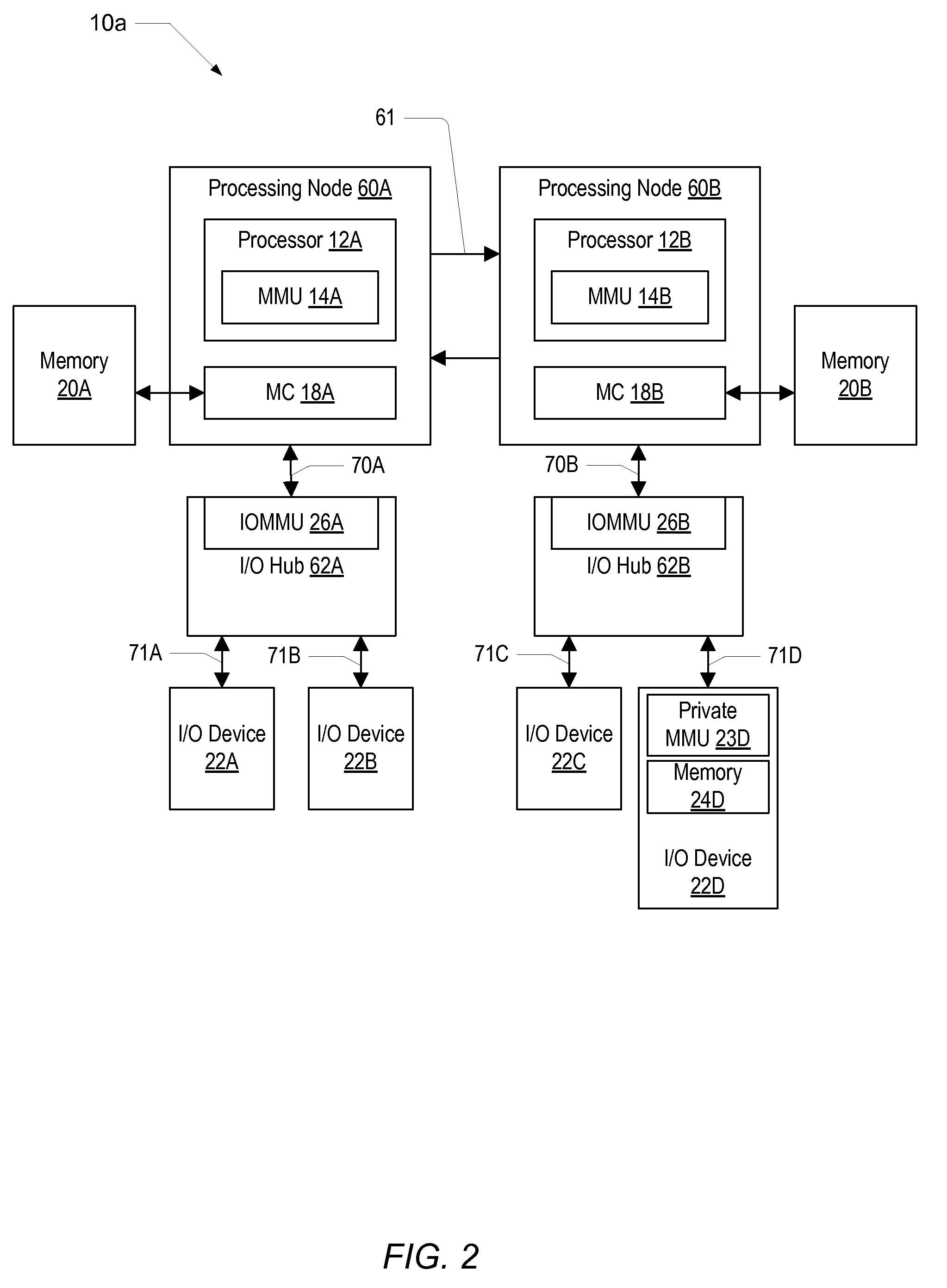

I/O memory management unit including multilevel address translation for I/O and computation offload

ActiveUS20110023027A1Memory architecture accessing/allocationMemory adressing/allocation/relocationTranslation tablePage table

An input / output memory management unit (IOMMU) configured to control requests by an I / O device to a system memory includes control logic that may perform a two-level guest translation to translate an address associated with an I / O device-generated request using translation data stored in the system memory. The translation data includes a device table having a number of entries. The control logic may select the device table entry for a given request by the using a device identifier that corresponds to the I / O device that generates the request. The translation data may also include a first set of I / O page tables including a set of guest page tables and a set of nested page tables. The selected device table entry for the given request may include a pointer to the set of guest translation tables, and a last guest translation table includes a pointer to the set of nested page tables

Owner:ADVANCED MICRO DEVICES INC

Interleaved processing of dropped packets in a network device

A network device for processing packets includes at least one ingress module for performing switching functions on a packet, a memory management unit for storing the packet and at least one egress module for transmitting the packet to at least one port. The at least one egress module is configured to maintain multiple queues for the at least one port, including a purge queue, and to store the packet in the purge queue when an error condition is determined when the end of the packet is received by the at least one ingress module.

Owner:AVAGO TECH INT SALES PTE LTD

Integrated memory management and memory management method

ActiveUS8135900B2Memory architecture accessing/allocationMemory adressing/allocation/relocationTerm memoryMemory management unit

An integrated memory management device according to an example of the invention comprises an acquiring unit acquiring a read destination logical address from a processor, an address conversion unit converting the read destination logical address into a read destination physical address of a non-volatile main memory, an access unit reading, from the non-volatile main memory, data that corresponds to the read destination physical address and has a size that is equal to a block size or an integer multiple of the page size of the non-volatile main memory, and transmission unit transferring the read data to a cache memory of the processor having a cache size that depends on the block size or the integer multiple of the page size of the non-volatile main memory.

Owner:KIOXIA CORP

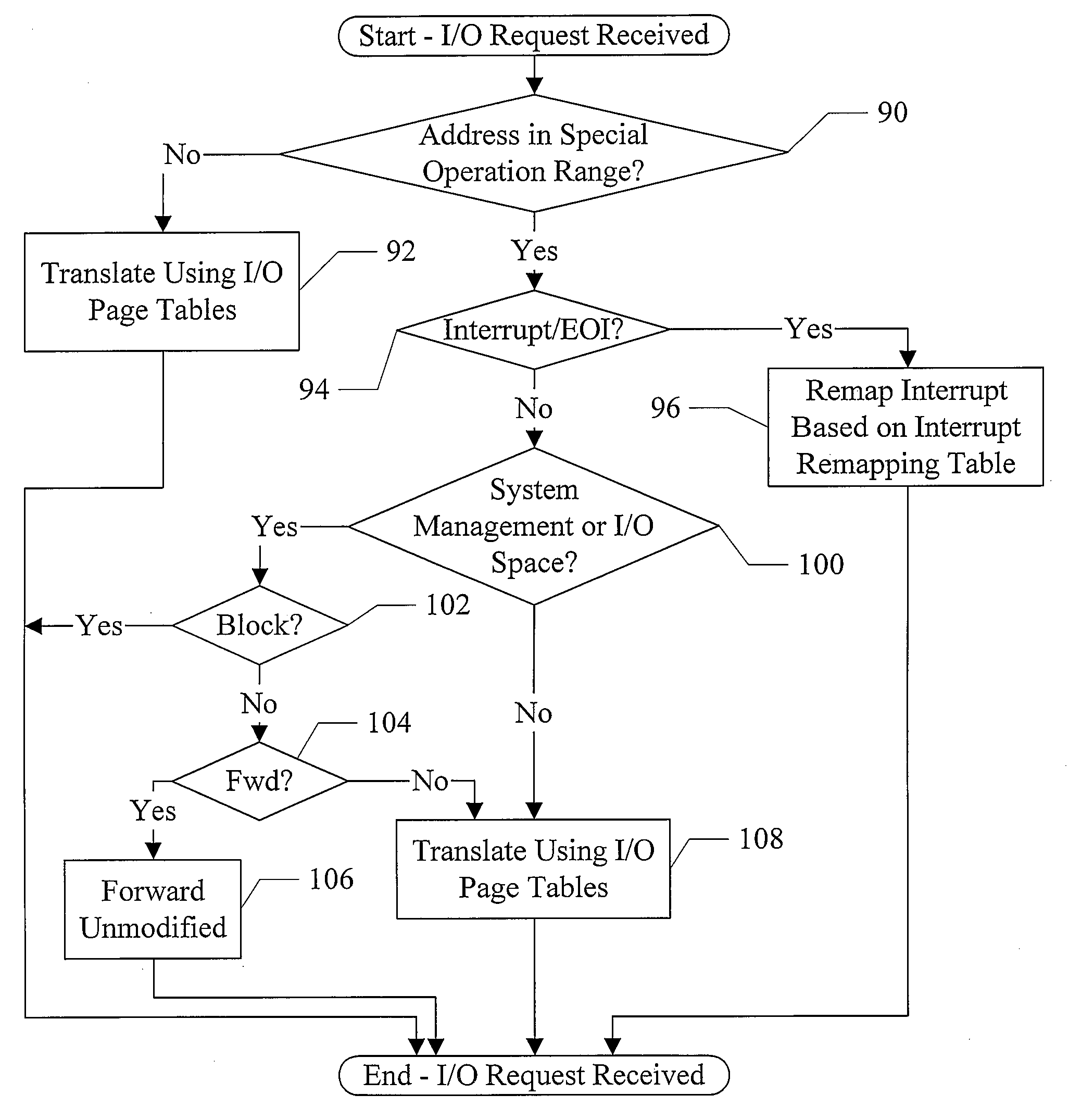

Filtering and Remapping Interrupts

ActiveUS20080114916A1Memory architecture accessing/allocationMemory systemsManagement unitProcessor register

In one embodiment, an input / output memory management unit (IOMMU) comprises a control register and control logic coupled to the control register. The control register is configured to store a base address of a device table, wherein a given input / output (I / O) device has an associated device identifier that selects a first entry in the device table. The first entry comprises a pointer to an interrupt remapping table. The control logic is configured to remap an interrupt specified by an interrupt request received by the IOMMU from the given I / O device if the interrupt remapping table includes an entry for the interrupt.

Owner:MEDIATEK INC

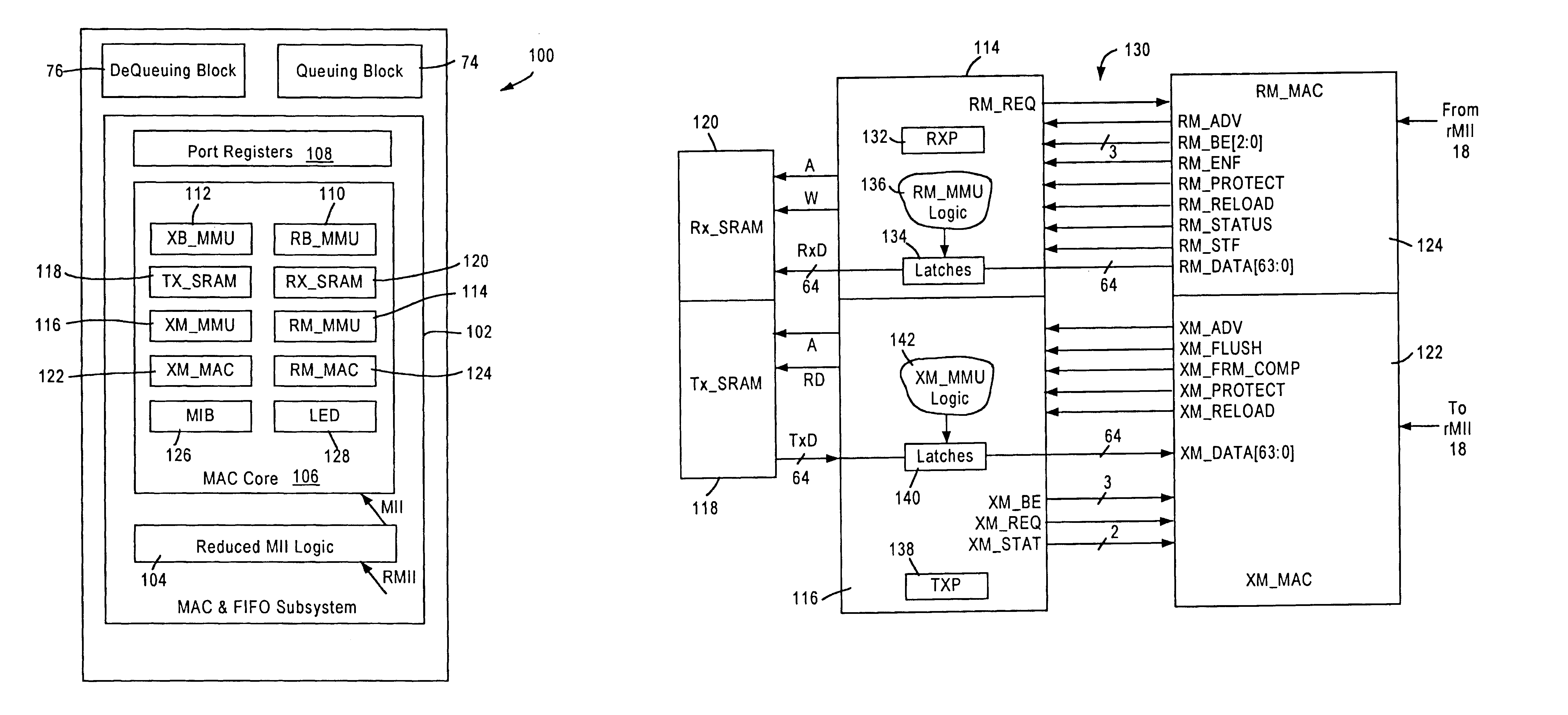

Apparatus and method in a network switch port for transferring data between buffer memory and transmit and receive state machines according to a prescribed interface protocol

InactiveUS20030072316A1Reliable dataReliable transmissionDigital computer detailsMultiprogramming arrangementsManagement unitInterface protocol

A network switch in a packet switched network includes a plurality of network switch ports, each configured for sending and receiving data packets between a medium interface and the network switch. The network switch port includes an IEEE 802.3 compliant transmit state machine and receive state machine configured for transmitting and receiving network data to and from a medium interface, such as a reduced medium independent interface, respectively. The network switch port also includes a memory management unit configured for selectively transferring the network data between the transmit and receive state machines and a random access transmit buffer and a random access receive buffer, respectively. The memory management unit transfers the network data between the transmit and receive state machines and the respective buffers based on prescribed interface protocol signals between the memory management unit and the transmit and receive state machines. Hence, the memory management unit and the transmit and receive state machines transfer data according to a prescribed interface protocol, where a request-based protocol enables data transfers to be performed independent of different clock domains encountered within the network switch port.

Owner:GLOBALFOUNDRIES INC

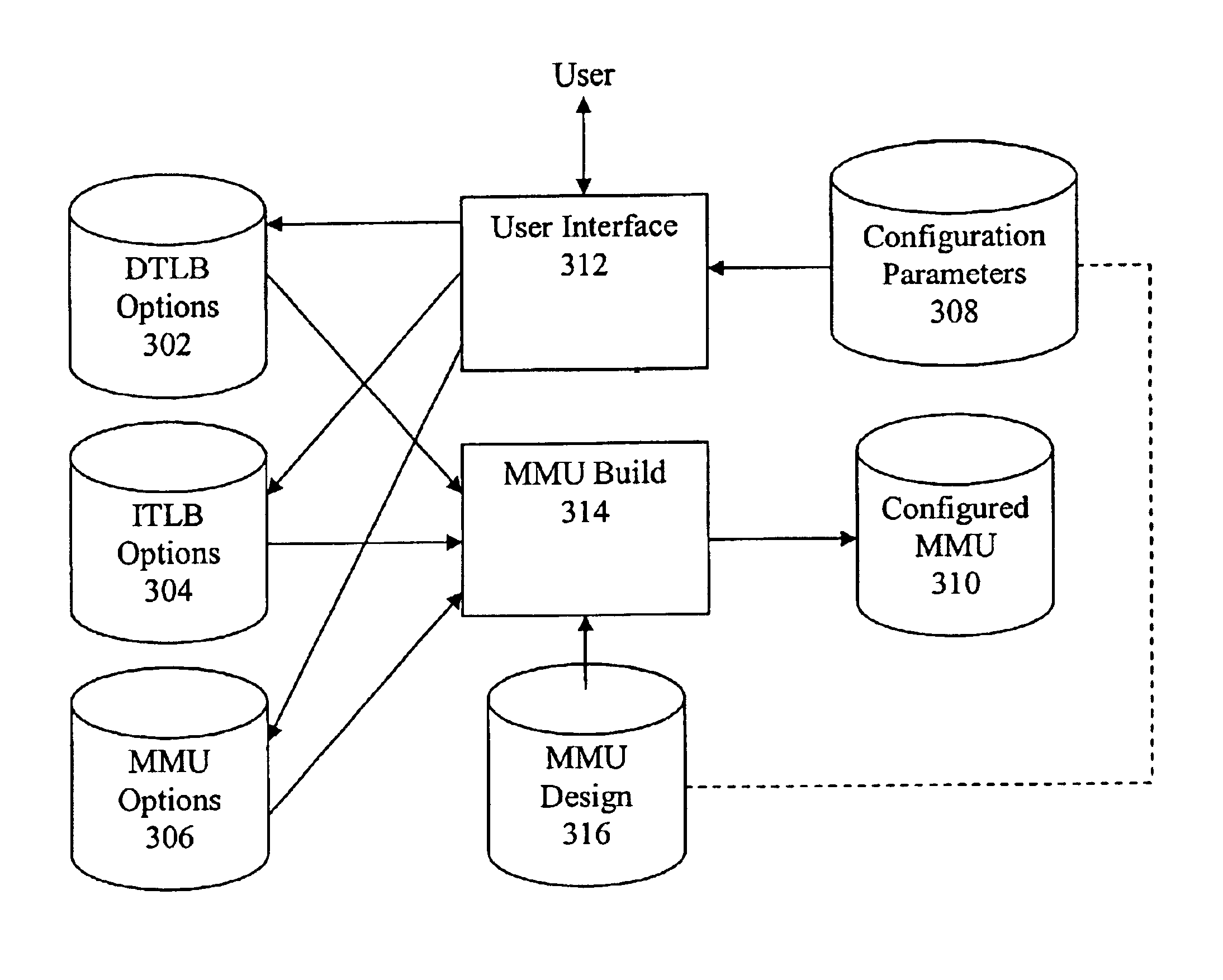

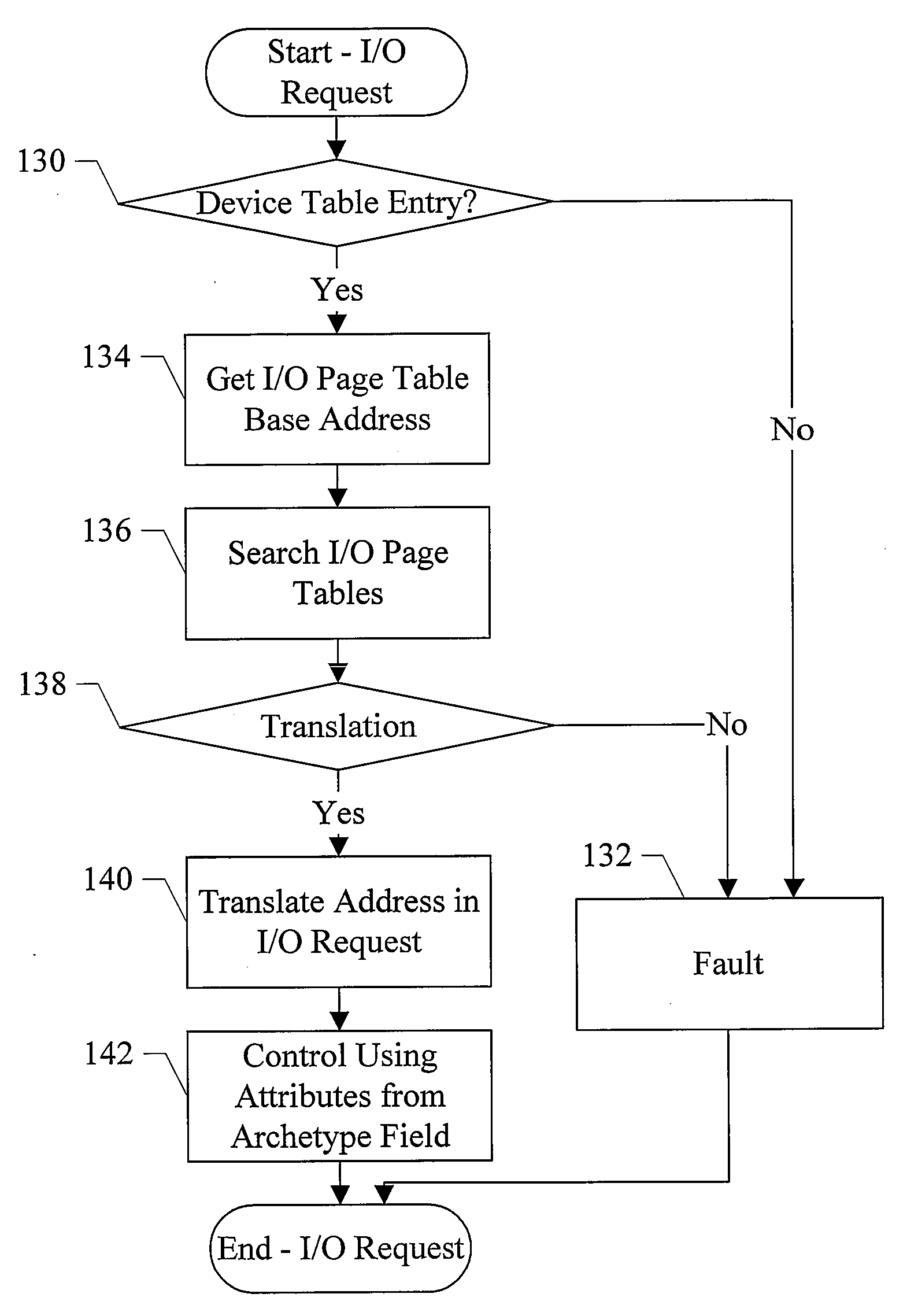

Configurable memory management unit

InactiveUS6854046B1Memory systemsMicro-instruction address formationSystems designApplication software

An MMU provides services at a cost more directly proportional to the needs of the system. According to one aspect, the MMU provides both address translation and sophisticated protection capabilities. Translation and protection are desirable when applications running on the processor are not completely debugged or trustable, for example. According to another aspect, a system for configuring the MMU design according to user specifications and system needs is provided. The MMU configurability aspects enable the system designer to configure MMUs having run-time programmability features that span the range from completely static to completely dynamic. In addition, the MMU can be configured to support variable page sizes, multiple protection and sharing rings, demand paging, and hardware TLB refill, for example.

Owner:TENSILICA

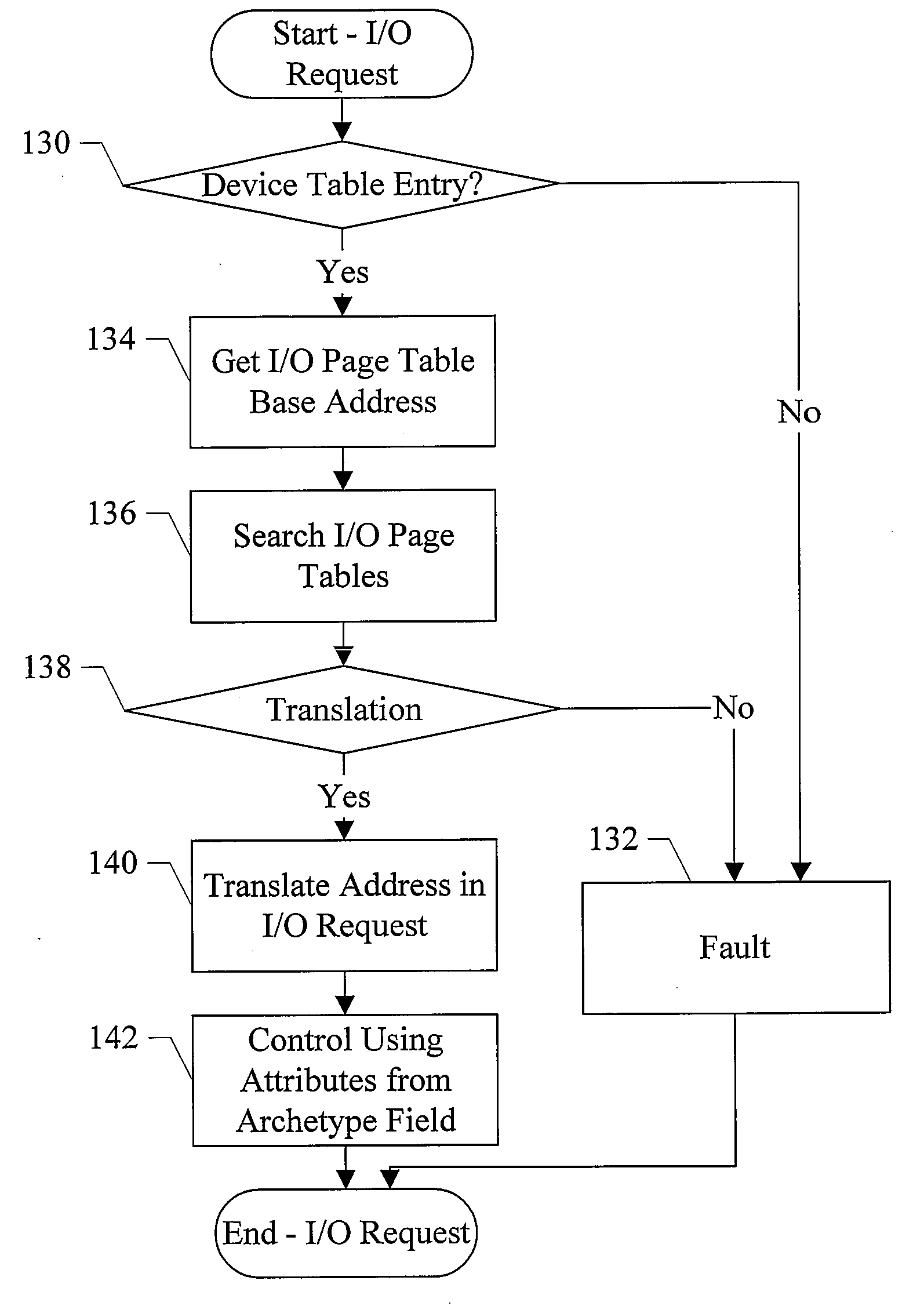

Using an IOMMU to Create Memory Archetypes

ActiveUS20070168644A1Memory architecture accessing/allocationMemory systemsManagement unitComputerized system

In one embodiment, an input / output (I / O) memory management unit (IOMMU) comprises at least one memory and control logic coupled to the memory. The memory is configured to store translation data corresponding to one or more I / O translation tables stored in a memory system of a computer system that includes the IOMMU. The control logic is configured to translate an I / O device-generated memory request using the translation data. The translation data includes a type field indicating one or more attributes of the translation, and the control logic is configured to control the translation responsive to the type field.

Owner:ADVANCED MICRO DEVICES INC

Apparatus and method in a network switch port for transferring data between buffer memory and transmit and receive state machines according to a prescribed interface protocol

InactiveUS6625157B2Reliable dataReliable transmissionDigital computer detailsMultiprogramming arrangementsManagement unitInterface protocol

A network switch in a packet switched network includes a plurality of network switch ports, each configured for sending and receiving data packets between a medium interface and the network switch. The network switch port includes an IEEE 802.3 compliant transmit state machine and receive state machine configured for transmitting and receiving network data to and from a medium interface, such as a reduced medium independent interface, respectively. The network switch port also includes a memory management unit configured for selectively transferring the network data between the transmit and receive state machines and a random access transmit buffer and a random access receive buffer, respectively. The memory management unit transfers the network data between the transmit and receive state machines and the respective buffers based on prescribed interface protocol signals between the memory management unit and the transmit and receive state machines. Hence, the memory management unit and the transmit and receive state machines transfer data according to a prescribed interface protocol, where a request-based protocol enables data transfers to be performed independent of different clock domains encountered within the network switch port.

Owner:GLOBALFOUNDRIES INC

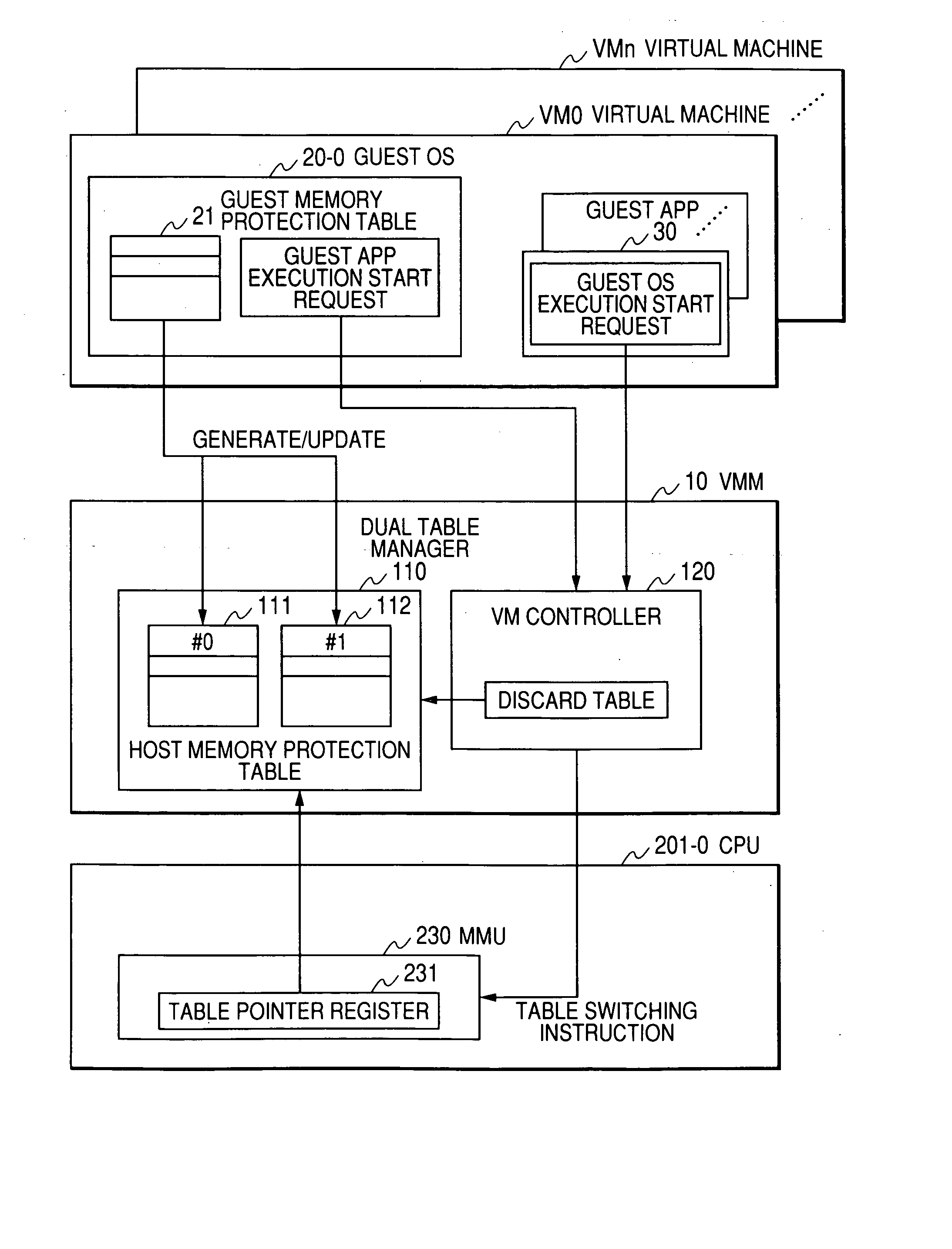

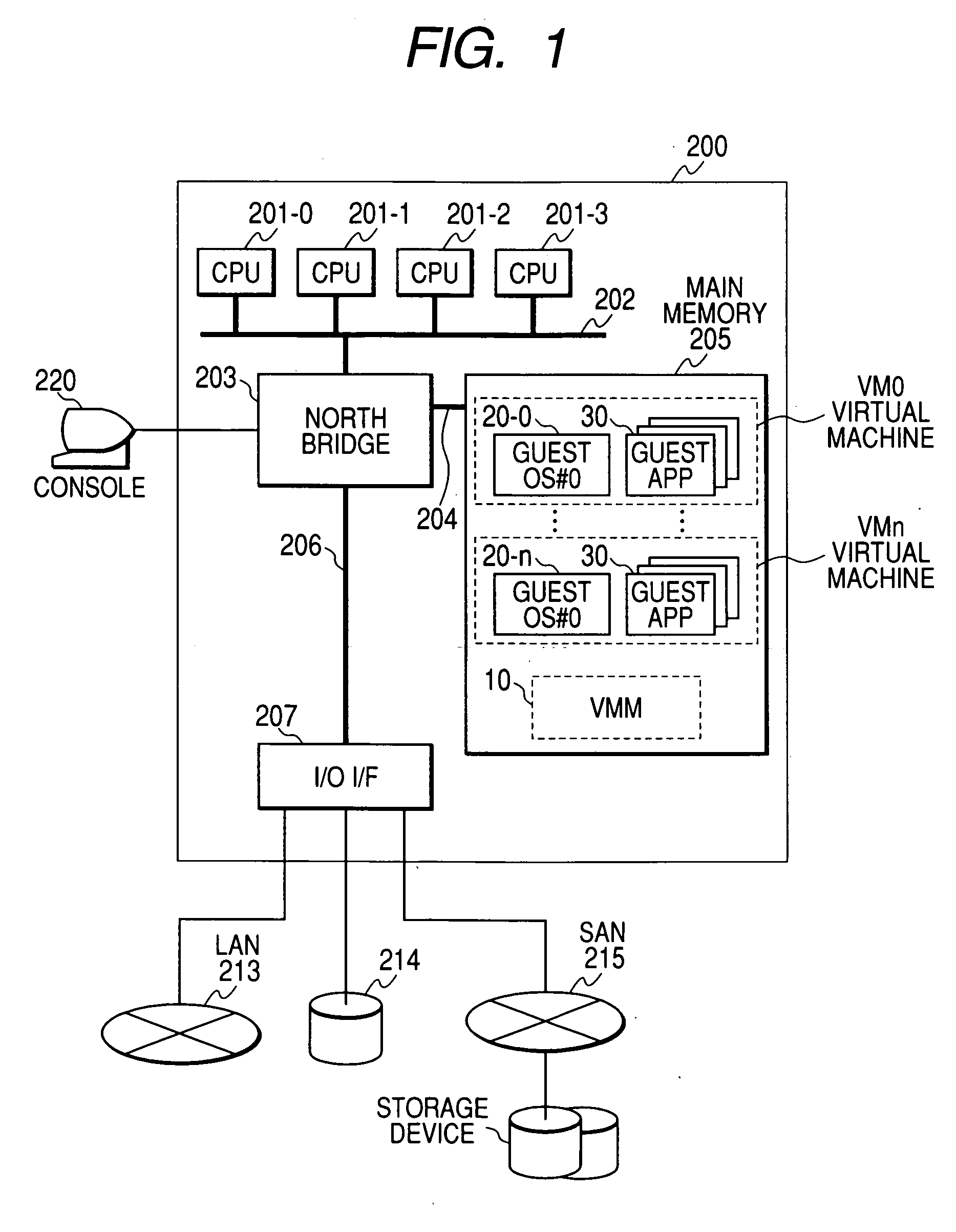

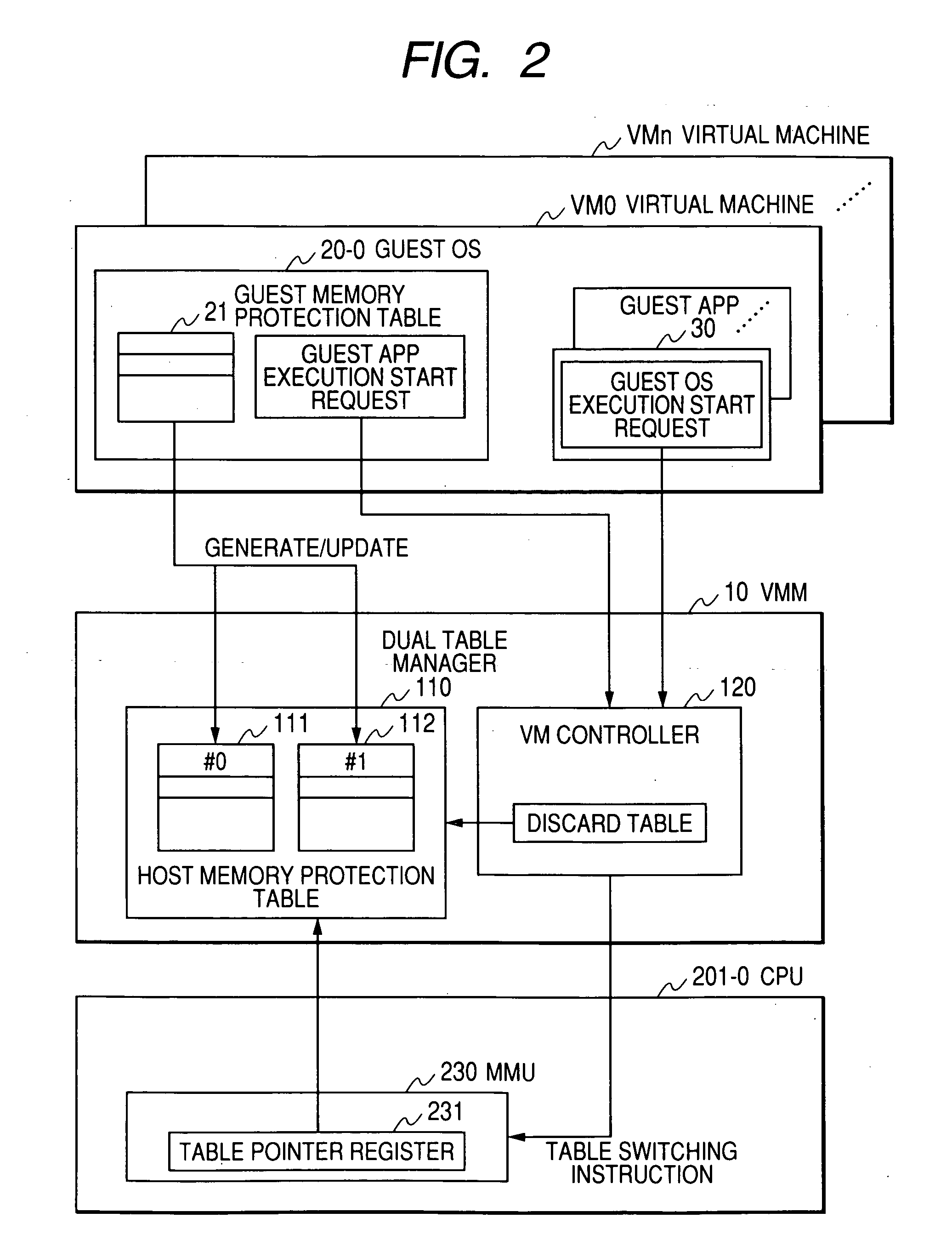

Virtual machine control method and program thereof

InactiveUS20060294519A1Highly reliable virtual machine systemImprove protectionSoftware simulation/interpretation/emulationMemory systemsTerm memoryMemory management unit

Disclosed is a virtual machine control method for switching and executing multiple programs jointly shared between at least one CPU and memory. The method is comprised of a process for setting a first memory protection table for defining a memory area accessible by a first program executed on the CPU, a process for setting a second memory protection table for defining a memory area accessible by a second program executed on the CPU, a process for detecting the start of execution of the first or the second program, a process for selecting and switching to either of a first or the second memory protection table according to the detected first or the second program, and a process for checking the first or the second memory protection table with the memory management unit for the CPU, and protecting the memory area defined in the first or the second memory protection table.

Owner:HITACHI LTD

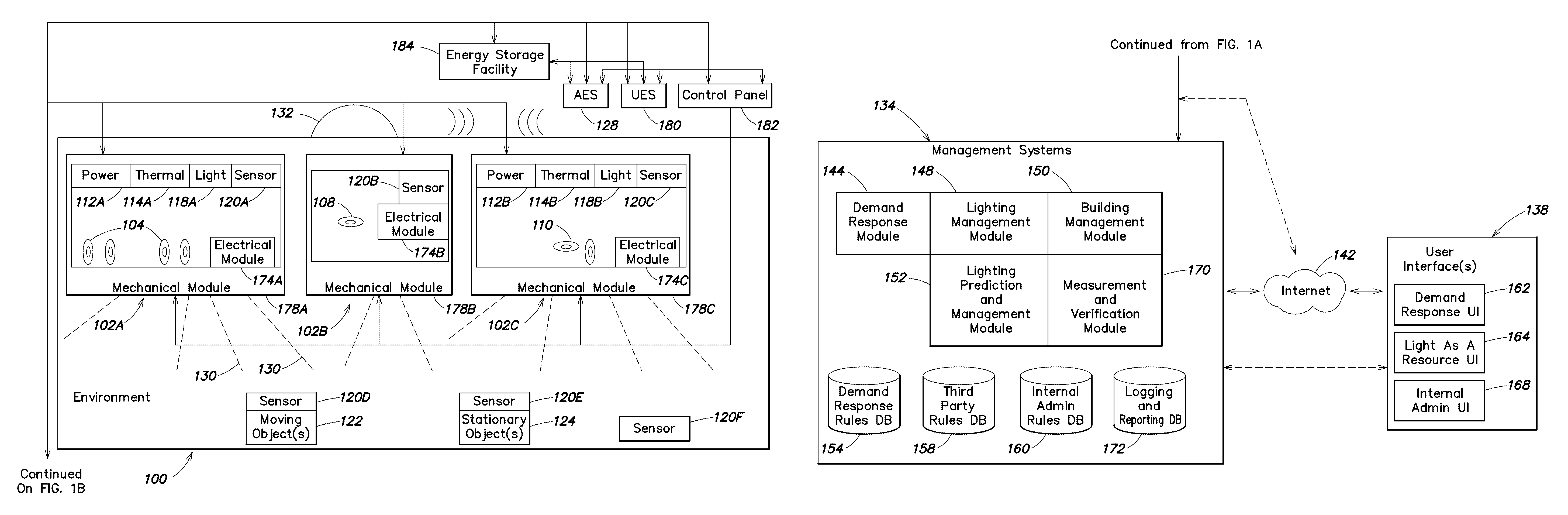

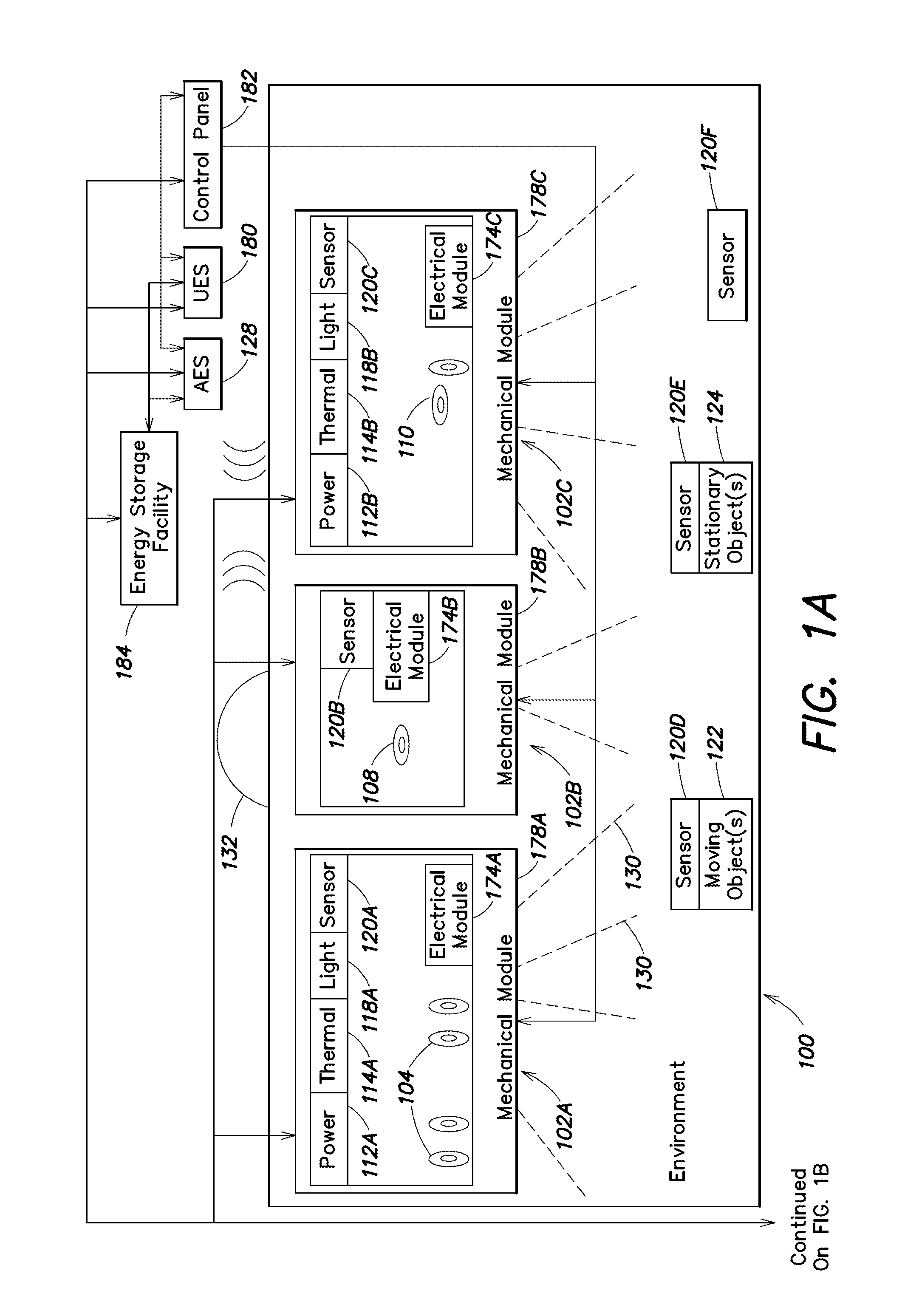

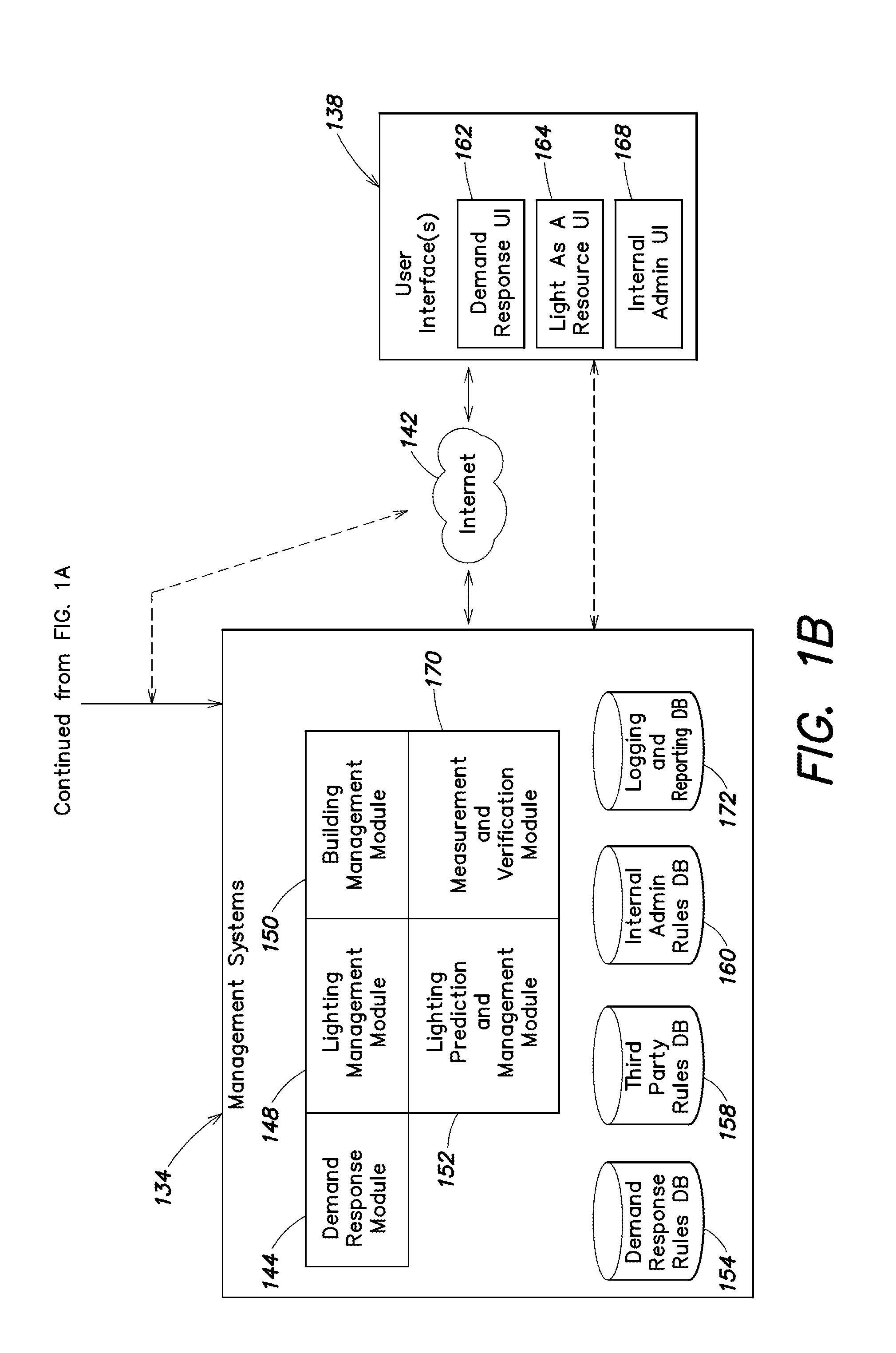

Power management unit with ballast interface

ActiveUS8552664B2Electrical apparatusElectric light circuit arrangementSmart lightingPower Management Unit

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

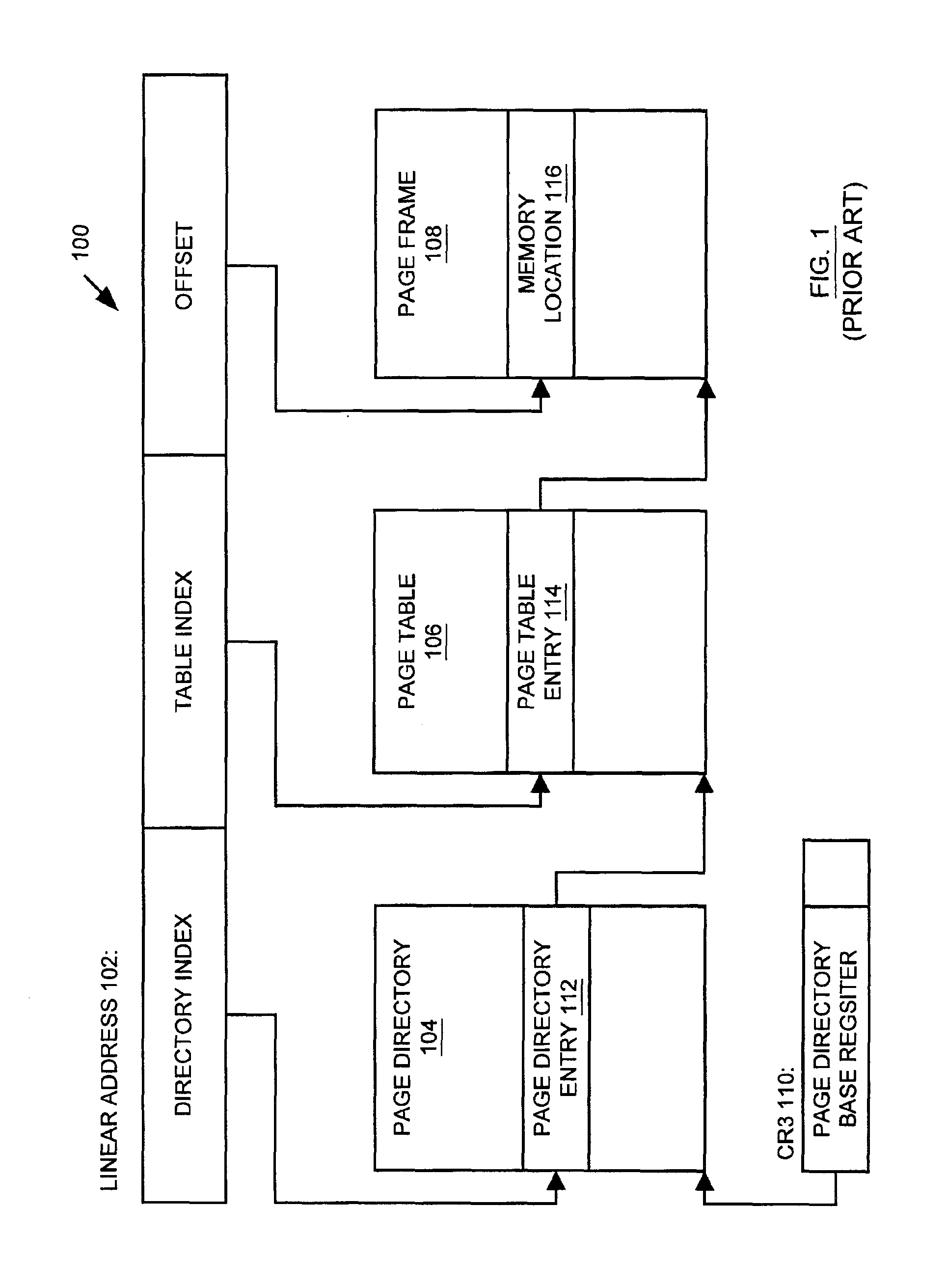

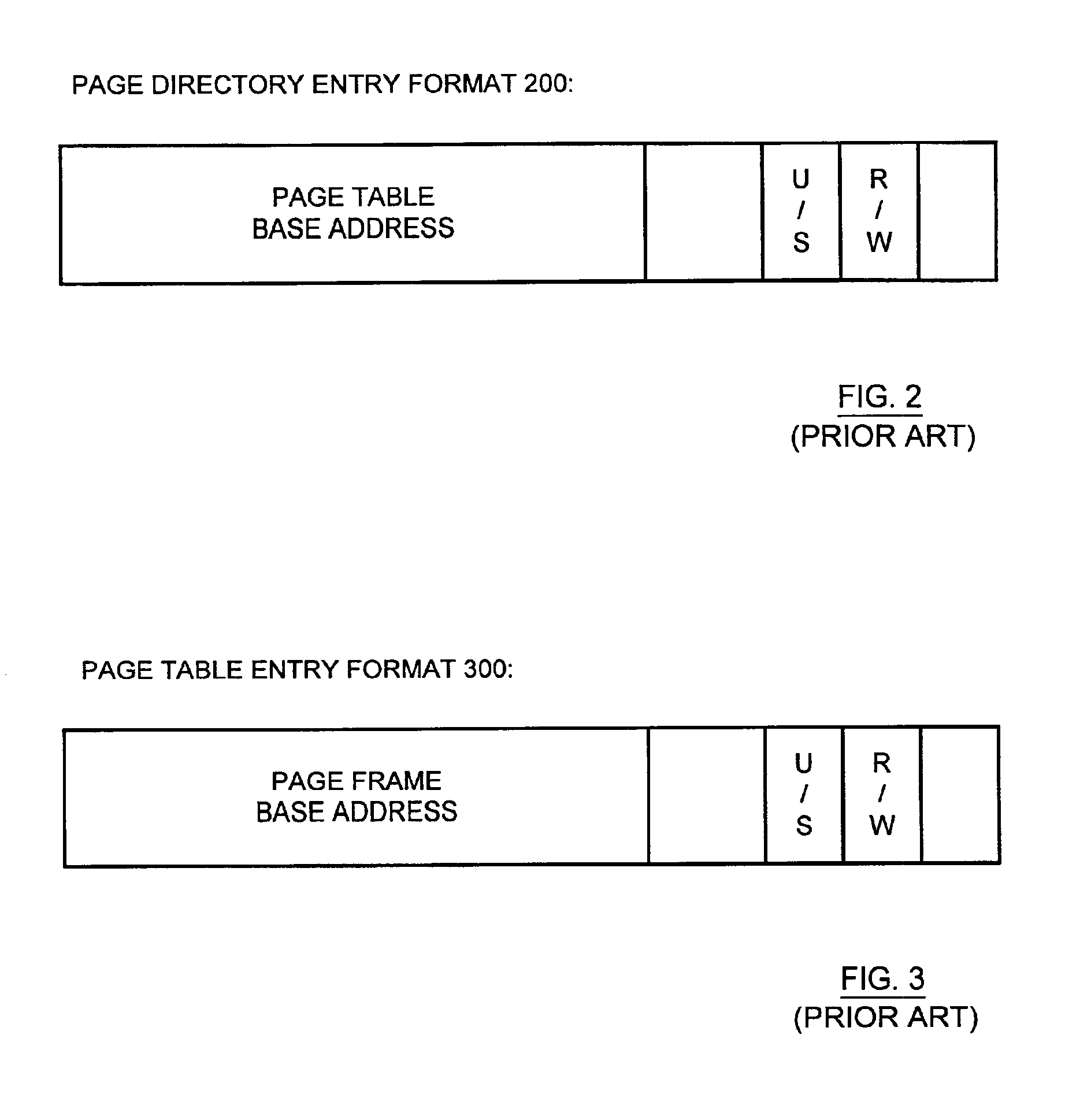

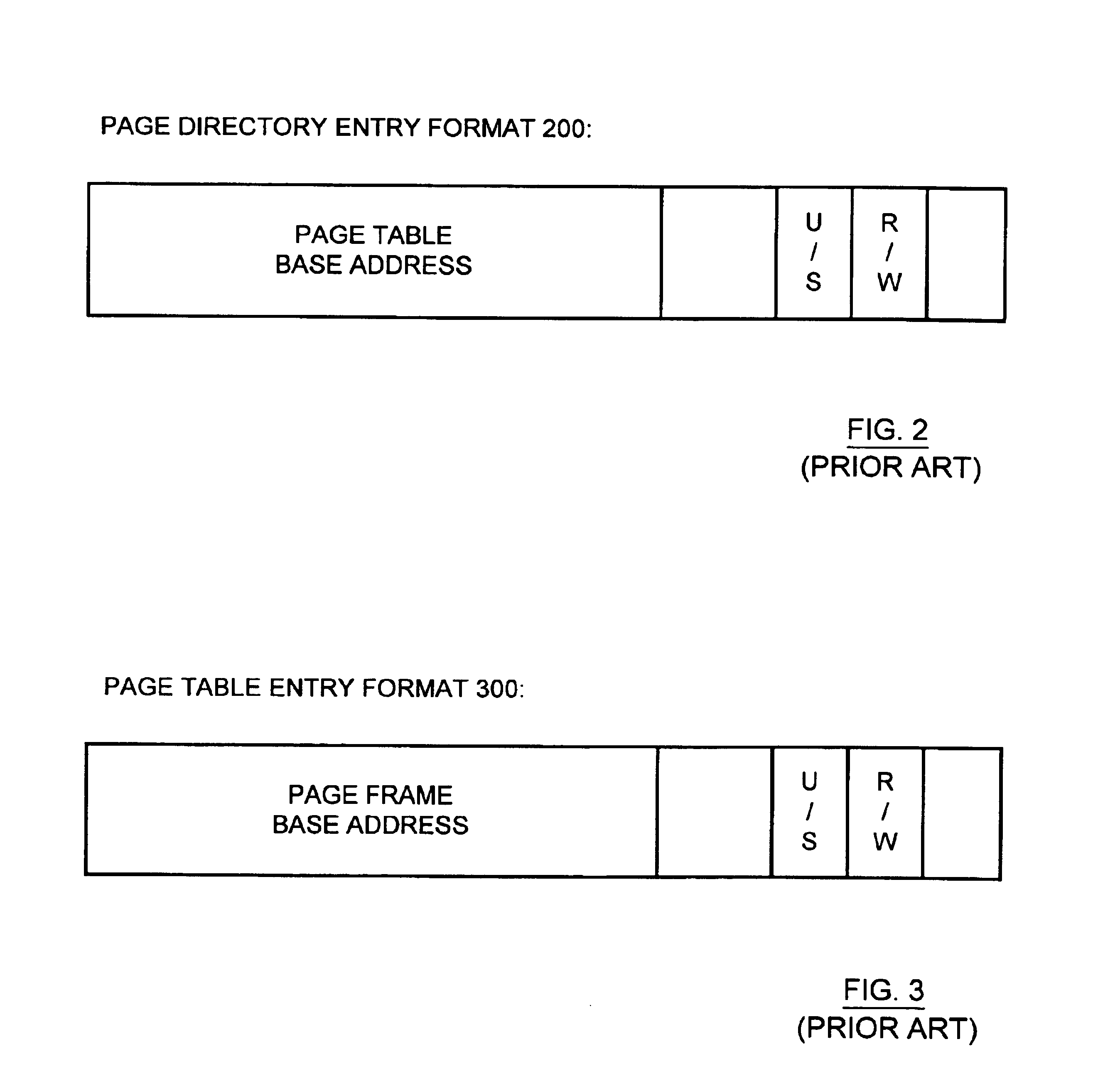

Memory management system and method providing increased memory access security

Owner:GLOBALFOUNDRIES INC

Method and apparatus for enabling access on a network switch

A data switch for network communications includes a data port interface which supports at least one data port which transmits and receives data. The switch also includes a CPU interface, where the CPU interface is configured to communicate with a CPU, and a memory management unit, including a memory interface for communicating data from the data port interface to the switch memory. A communication channel is also provided, communicating data and messaging information between the data port interface, the CPU interface, the switch memory, and the memory management unit. The data port interface also includes an access control unit that filters the data coming into the data port interface and takes selective action on the data by applying a set of filter rules such that access to the switch is controlled by the set of filter rules.

Owner:AVAGO TECH INT SALES PTE LTD

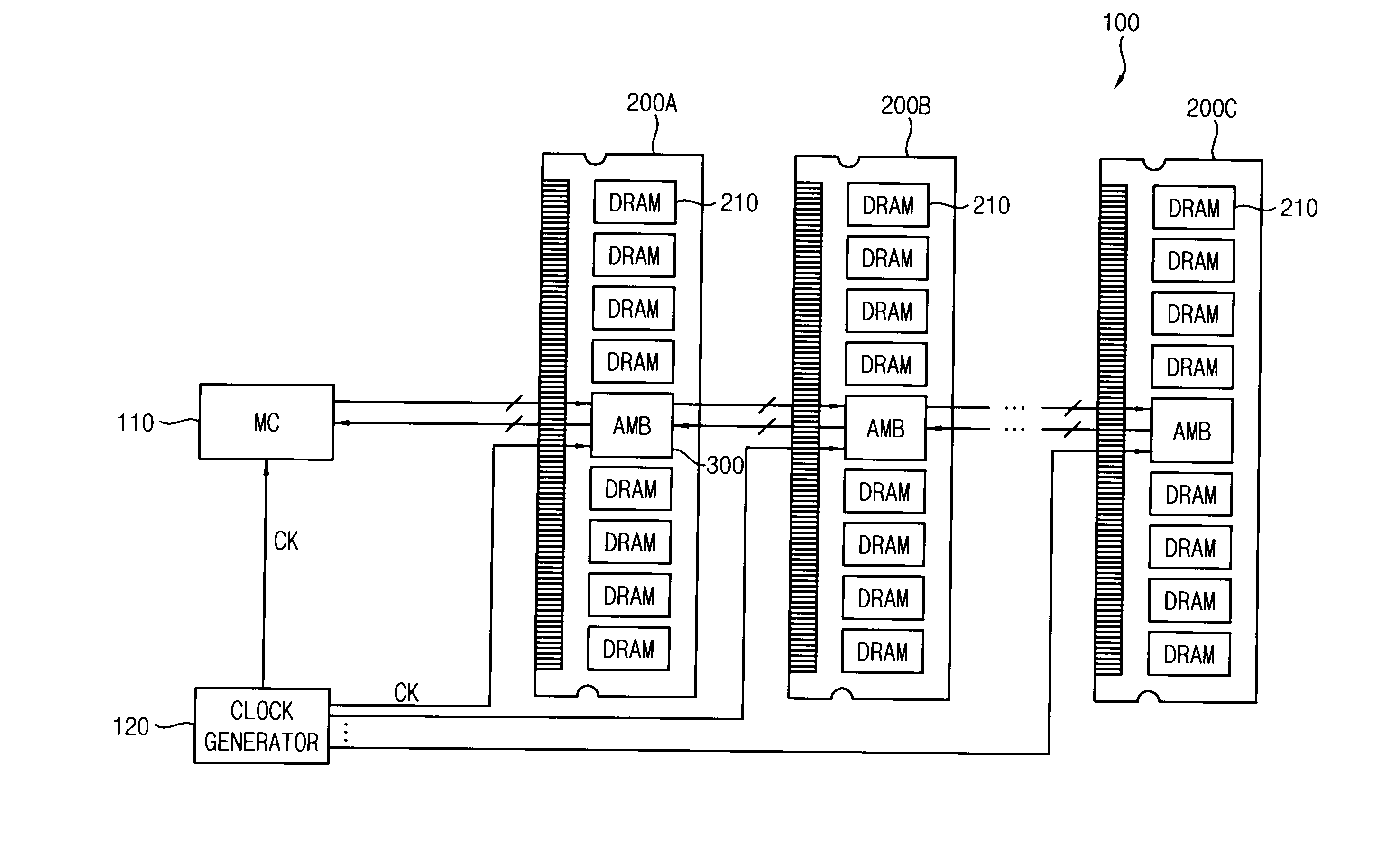

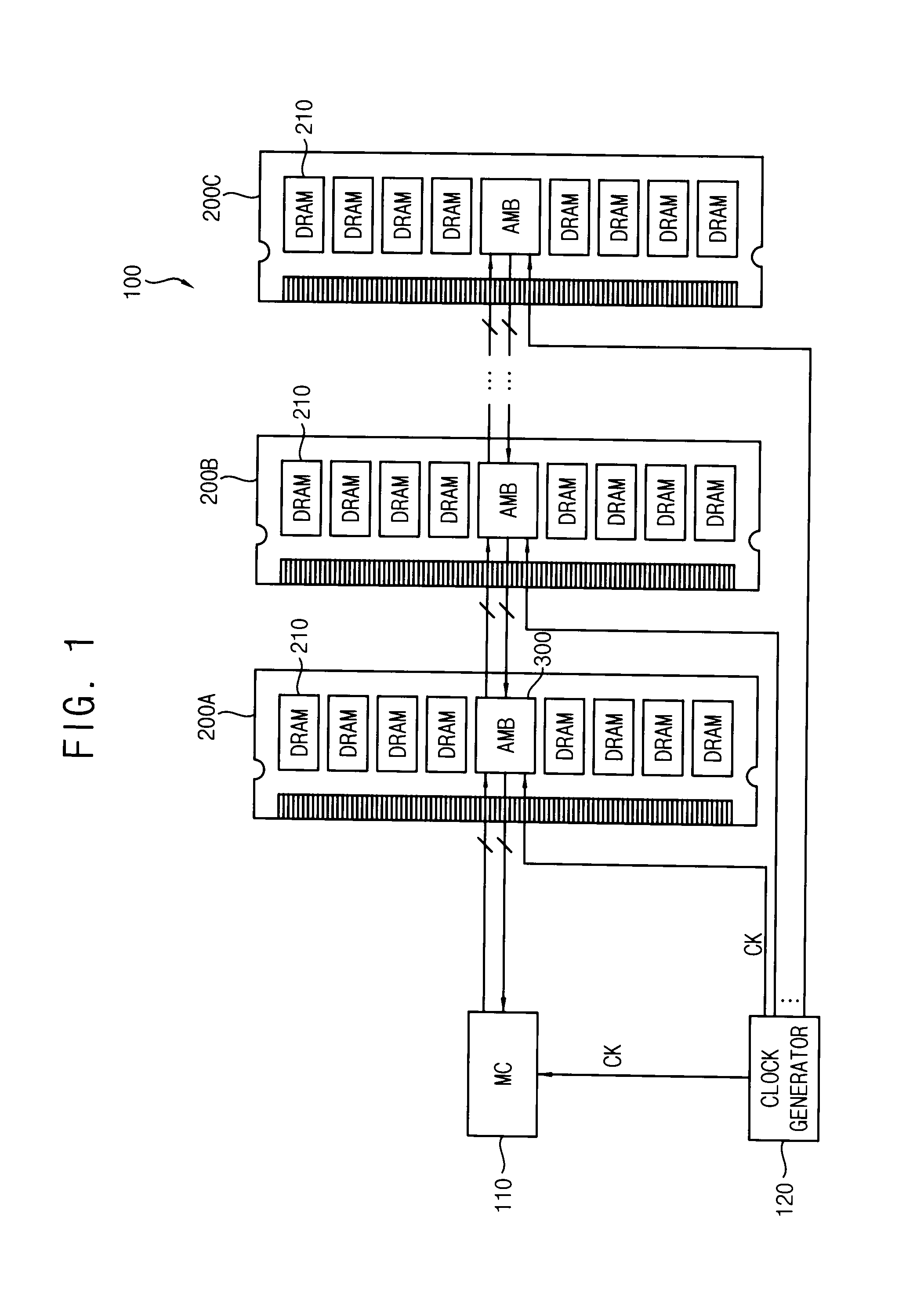

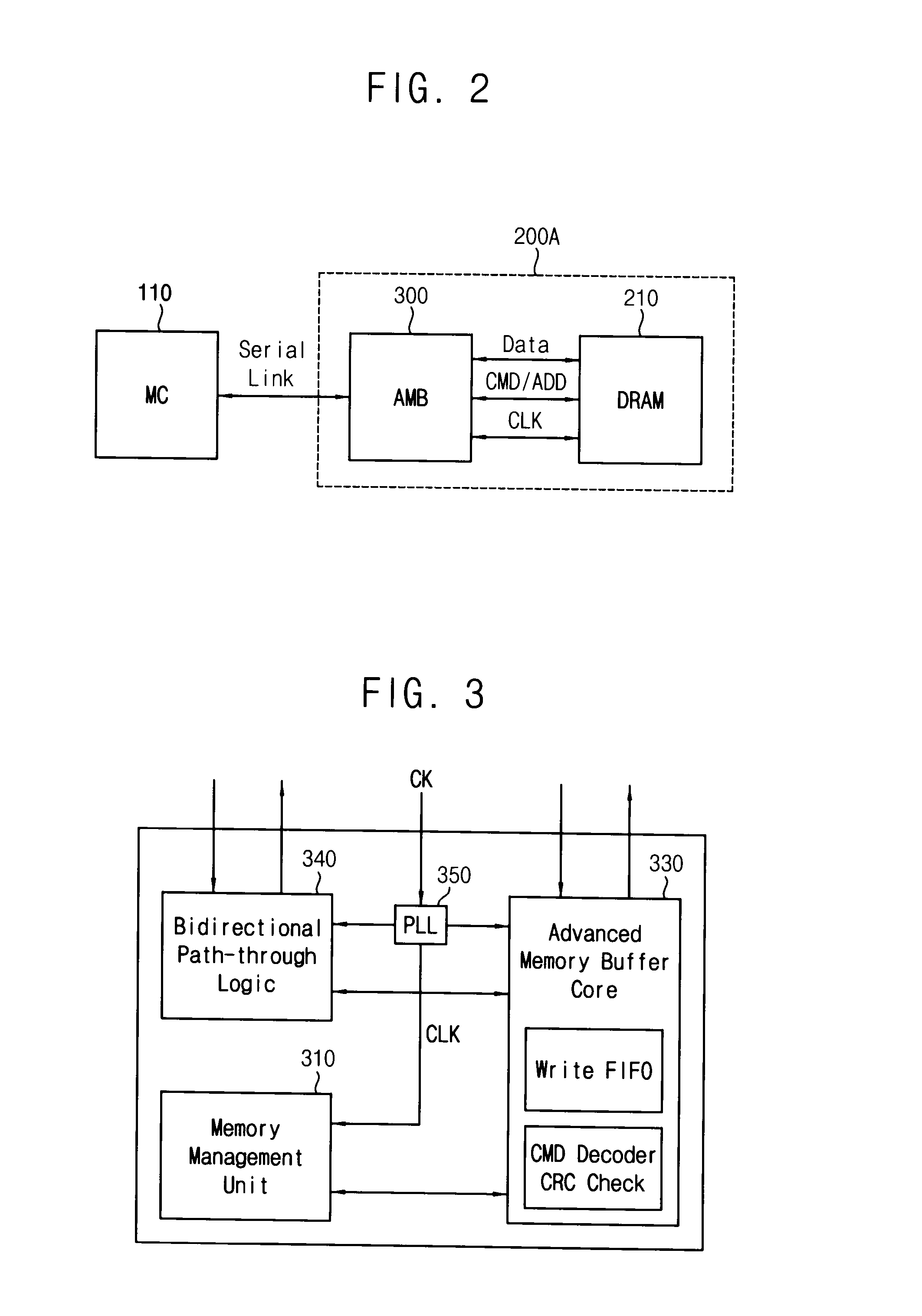

Memory modules and memory systems

ActiveUS20140146624A1Improve performanceReduced footprintError detection/correctionDigital storageMemory management unitMemory module

In one example embodiment, a memory module includes a plurality of memory devices and a buffer chip configured to manage the plurality of memory device. The buffer chip includes a memory management unit having an error correction unit configured to perform error correction operation on each of the plurality of memory devices. Each of the plurality of memory devices includes at least one spare column that is accessible by the memory management unit, and the memory management unit is configured to correct errors of the plurality of memory devices by selectively using the at least one spare column based on an error correction capability of the error correction unit.

Owner:SAMSUNG ELECTRONICS CO LTD

Translation Data Prefetch in an IOMMU

ActiveUS20080209130A1Memory architecture accessing/allocationMemory adressing/allocation/relocationDirect memory accessManagement unit

In an embodiment, a system memory stores a set of input / output (I / O) translation tables. One or more I / O devices initiate direct memory access (DMA) requests including virtual addresses. An I / O memory management unit (IOMMU) is coupled to the I / O devices and the system memory, wherein the IOMMU is configured to translate the virtual addresses in the DMA requests to physical addresses to access the system memory according to an I / O translation mechanism implemented by the IOMMU. The IOMMU comprises one or more caches, and is configured to read translation data from the I / O translation tables responsive to a prefetch command that specifies a first virtual address. The reads are responsive to the first virtual address and the I / O translation mechanism, and the IOMMU is configured to store data in the caches responsive to the read translation data.

Owner:GLOBALFOUNDRIES US INC

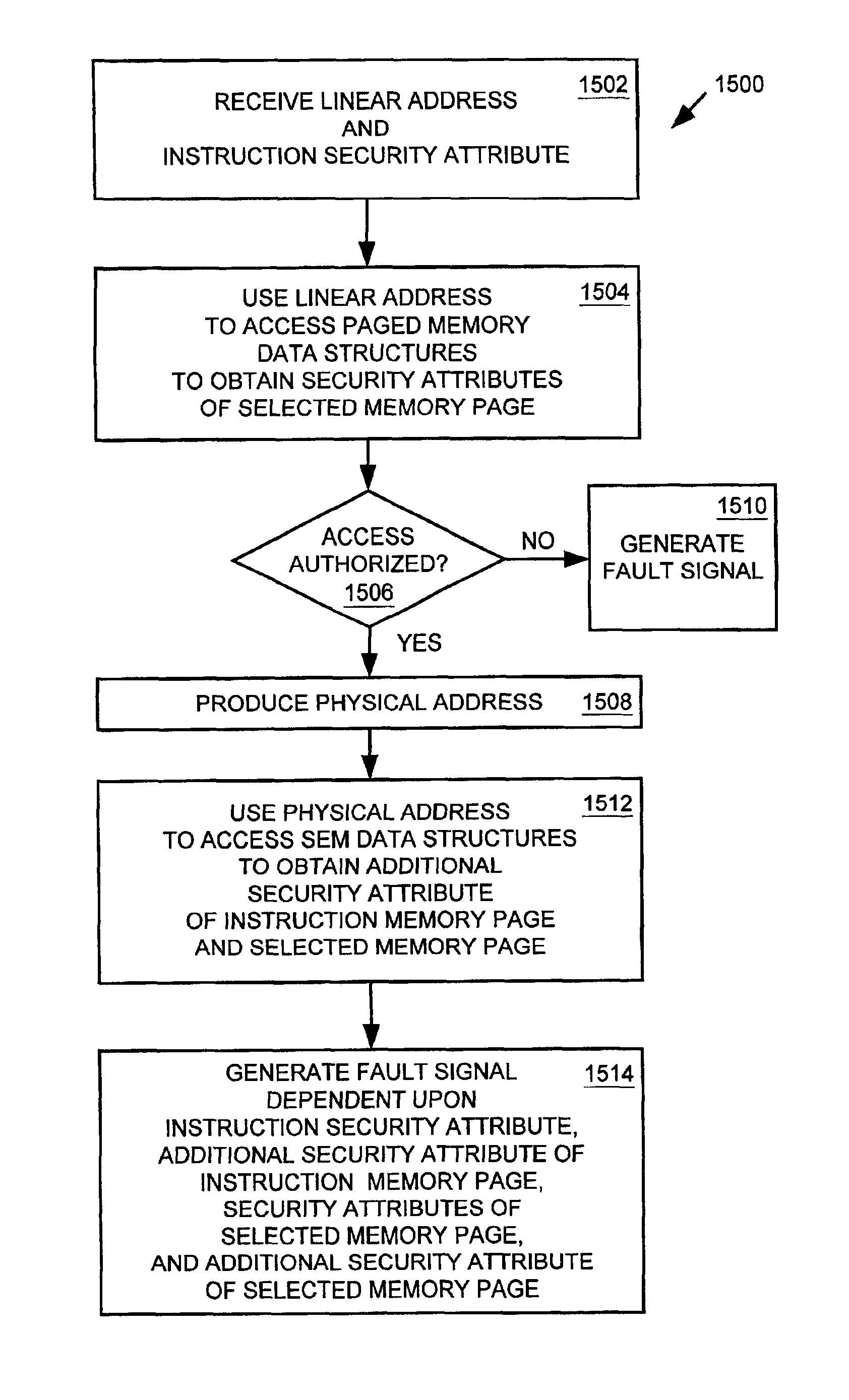

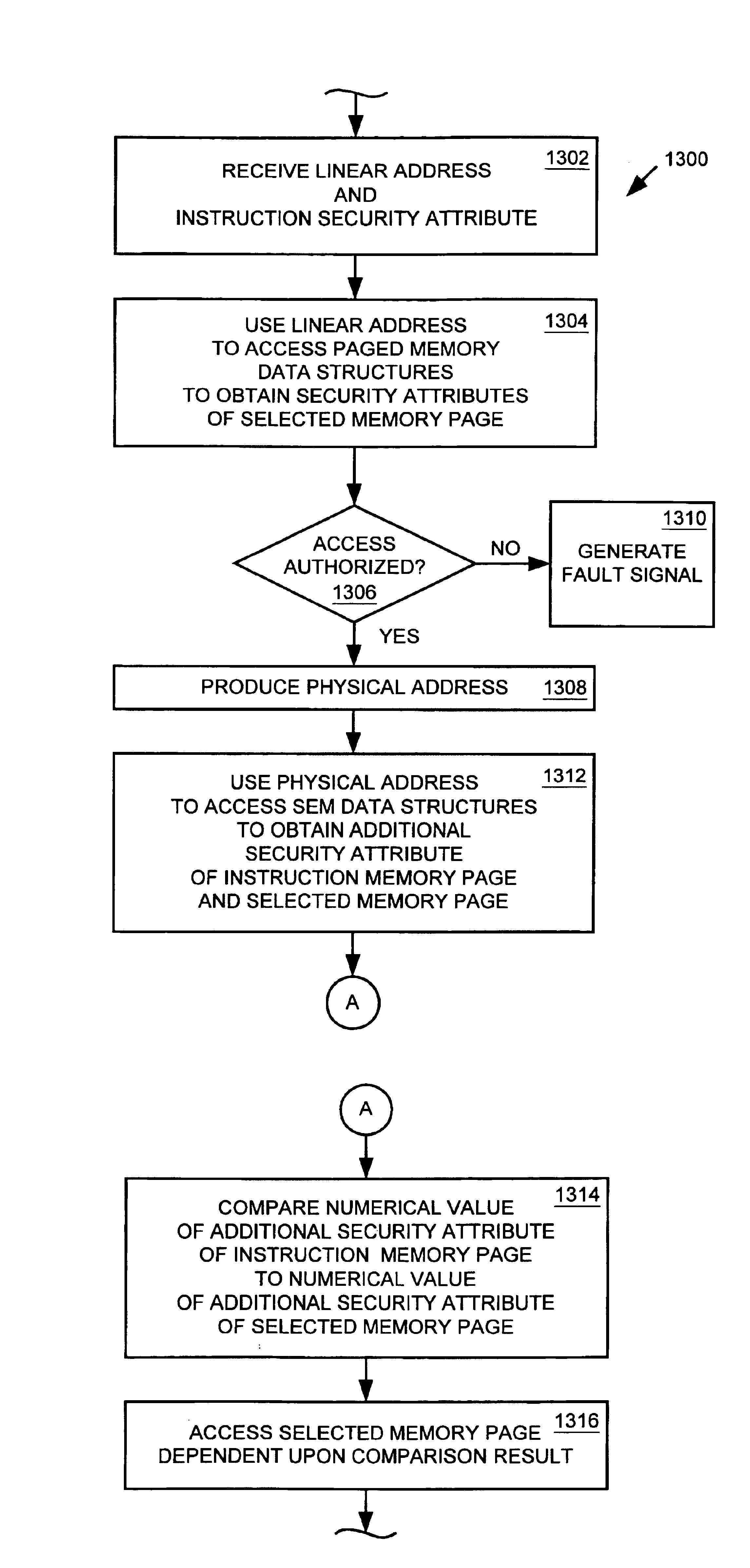

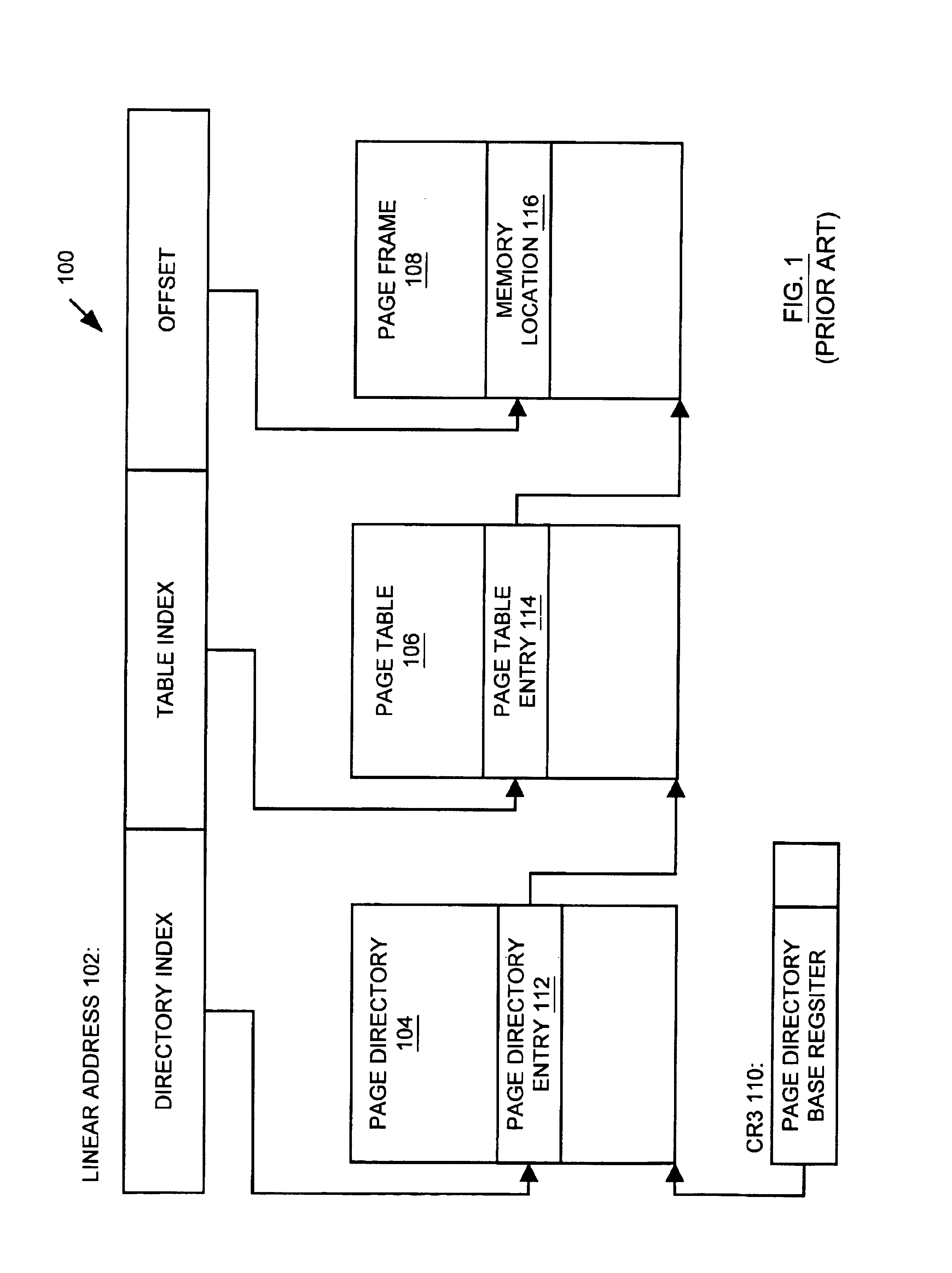

Memory management system and method for providing physical address based memory access security

InactiveUS6823433B1Memory adressing/allocation/relocationUnauthorized memory use protectionManagement unitComputerized system

A memory management unit (MMU) is disclosed for managing a memory storing data arranged within a plurality of memory pages. The MMU includes a security check unit (SCU) receiving a physical address generated during execution of a current instruction. The physical address resides within a selected memory page. The SCU uses the physical address to access one or more security attribute data structures located in the memory to obtain a security attribute of the selected memory page, compares a numerical value conveyed by a security attribute of the current instruction to a numerical value conveyed by the security attribute of the selected memory page, and produces an output signal dependent upon a result of the comparison. The MMU accesses the selected memory page dependent upon the output signal. The security attribute of the selected memory page may include a security context identification (SCID) value indicating a security context level of the selected memory page. The security attribute of the current instruction may include an SCID value indicating a security context level of a memory page containing the current instruction. A central processing unit (CPU) is described including an execution unit and the MMU. A computer system is described including the memory, the CPU, and the MMU. A method is described for providing access security for a memory used to store data arranged within a plurality of memory pages. The method may be embodied within the MMU.

Owner:GLOBALFOUNDRIES US INC +1

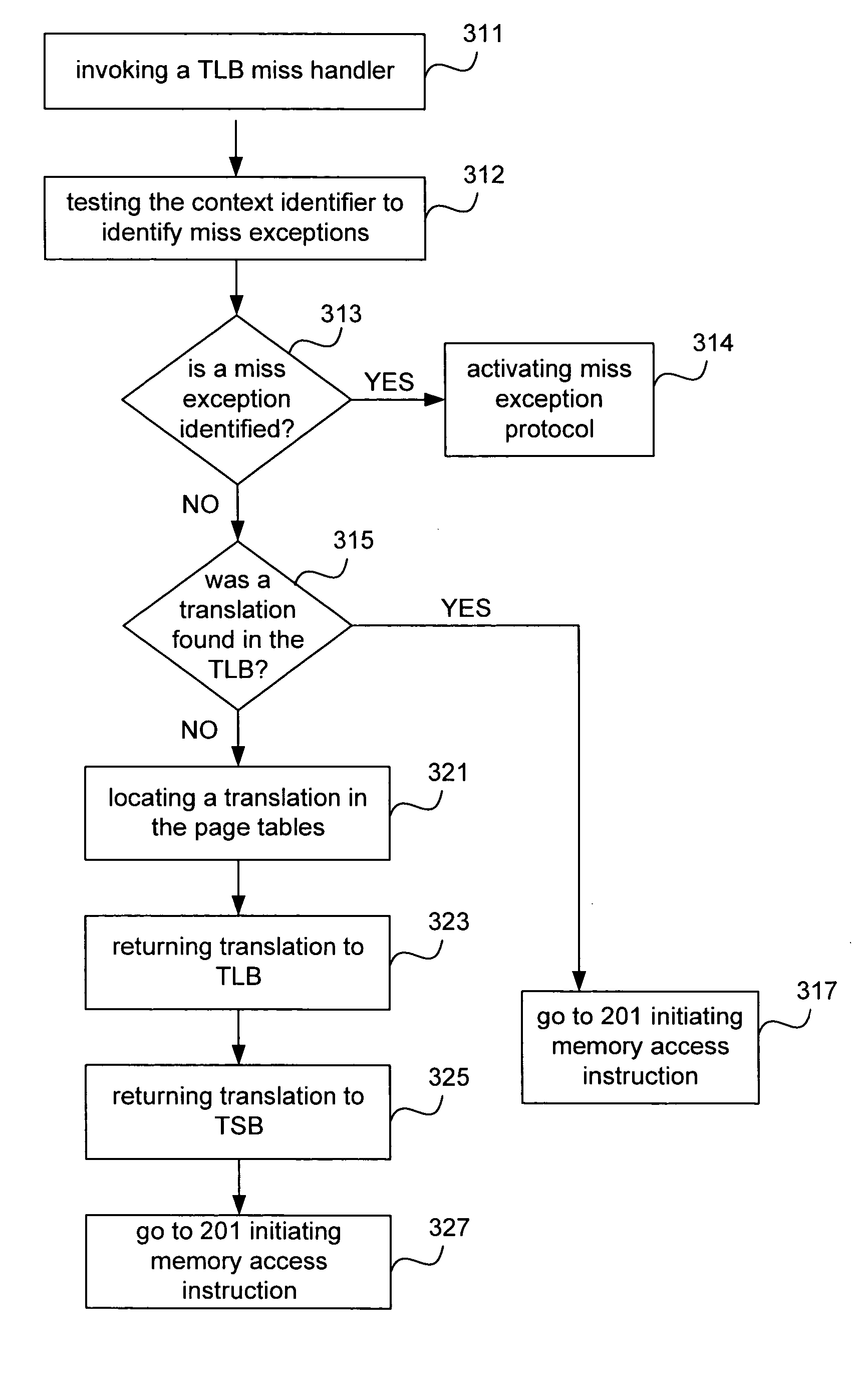

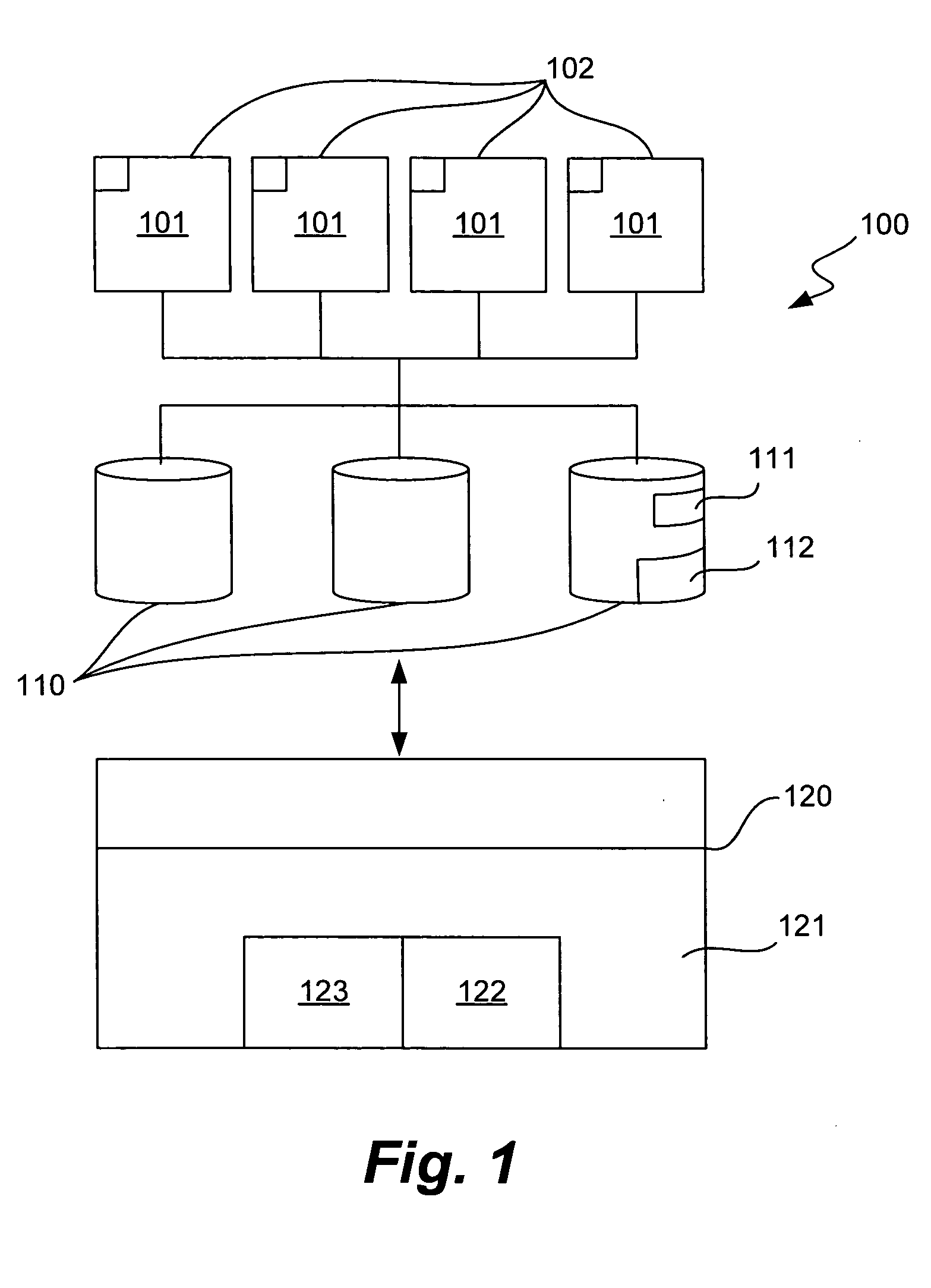

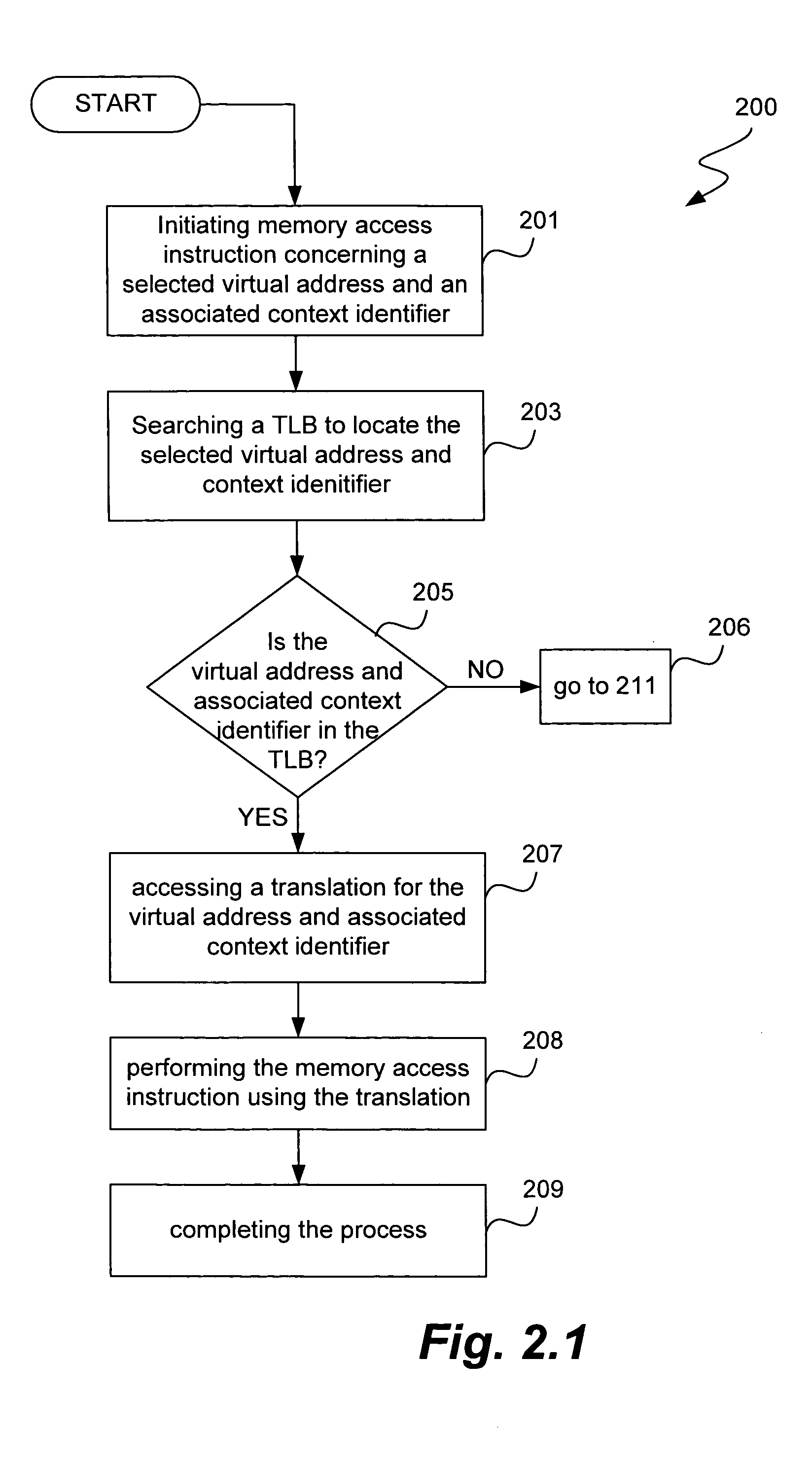

Method and apparatus for memory management in a multi-processor computer system

ActiveUS20050172099A1Avoid accessMemory architecture accessing/allocationMemory adressing/allocation/relocationManagement unitMulti processor

Improved techniques and systems for accommodating TLB shootdown events in multi-processor computer systems are disclosed. A memory management unit (MMU) having a TLB miss handler and miss exception handler is provided. The MMU receives instructions relative to a virtual address. A TLB is searched for the virtual address, if the virtual address is not found in the TLB, secondary memory assets are searched for a TTE that corresponds to the virtual address and its associated context identifier. The context identifier is tested to determine if the TTE is available. Where the TTE is available, the TLB and secondary memory assets are updated as necessary and the method initiates memory access instructions. Where the TTE is unavailable, the method either resolves the unavailability or waits until the unavailability is resolved and then initiates memory access instructions, thereby enabling the desired virtual address information to be accessed.

Owner:ORACLE INT CORP

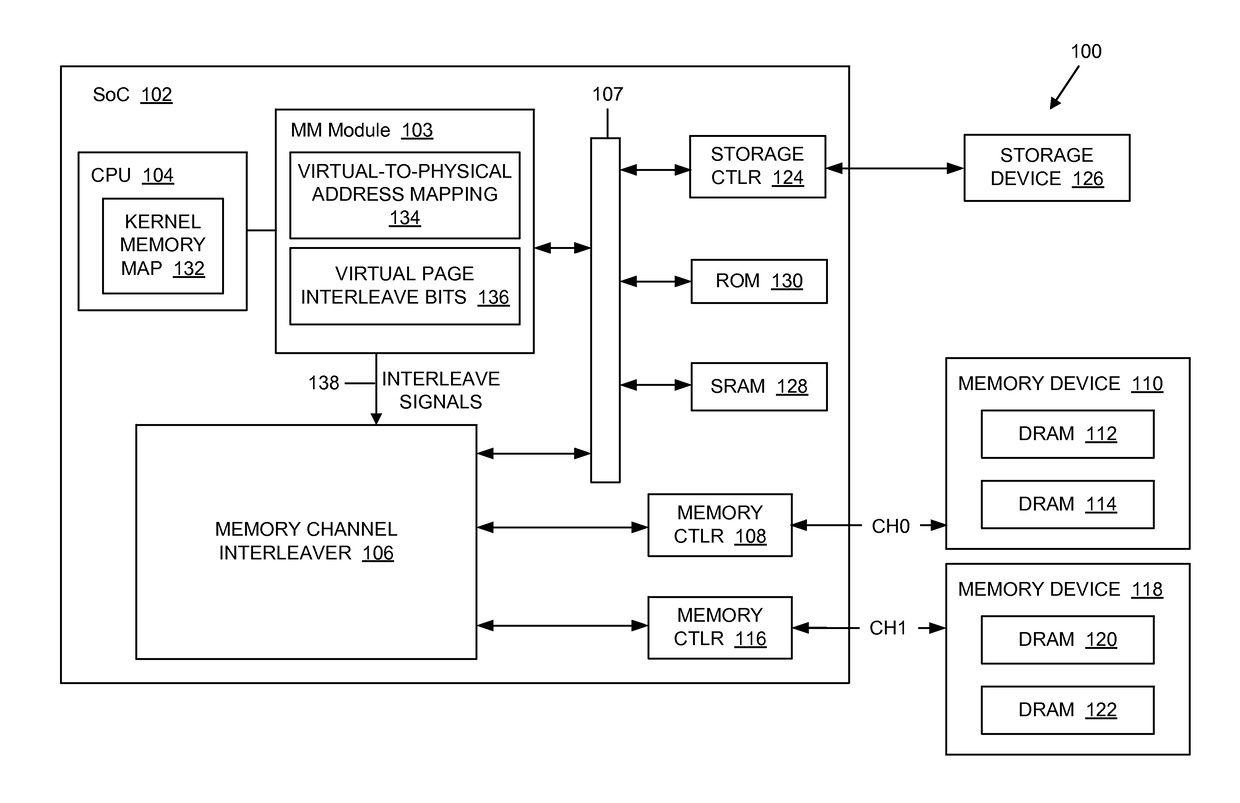

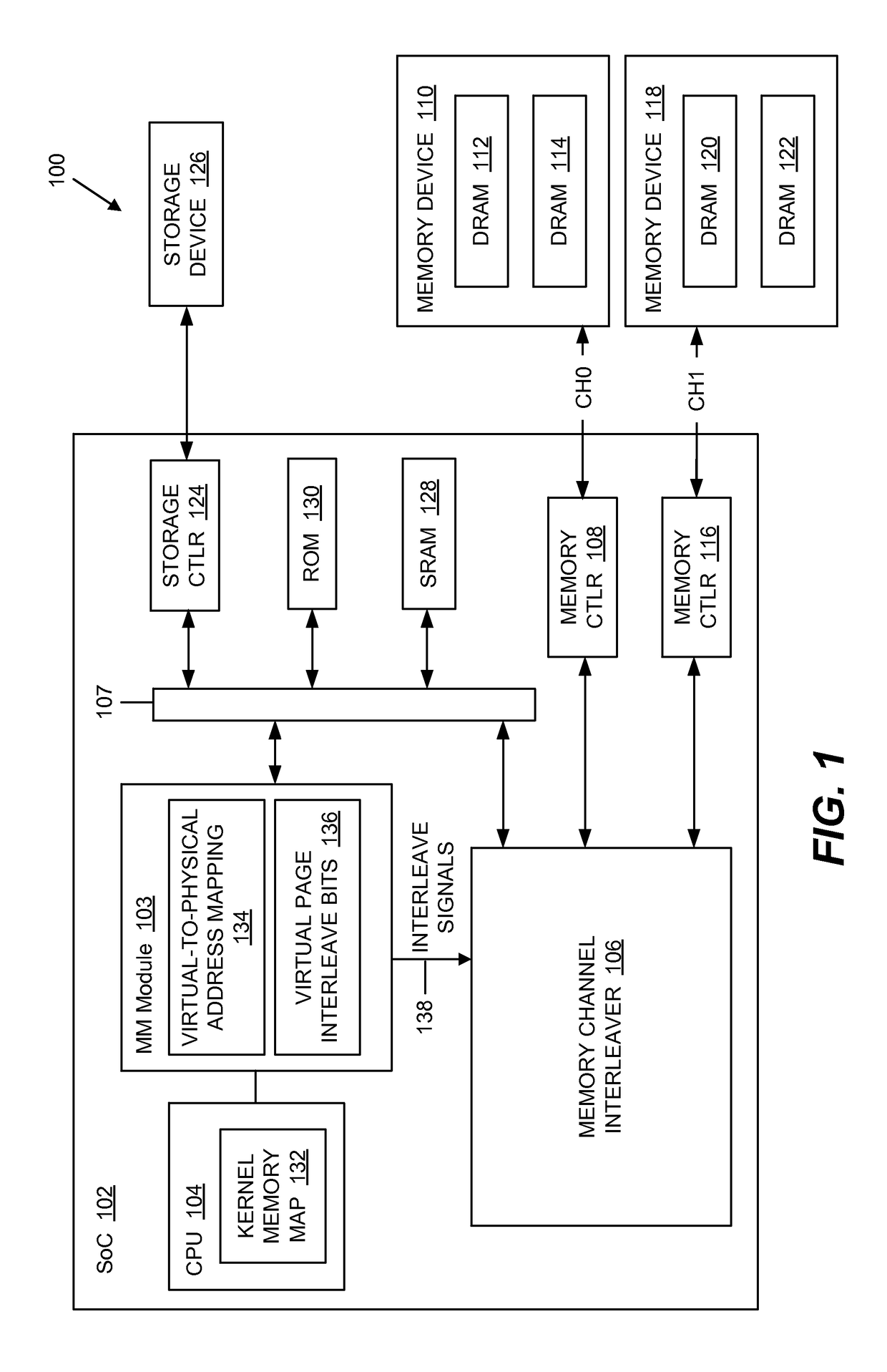

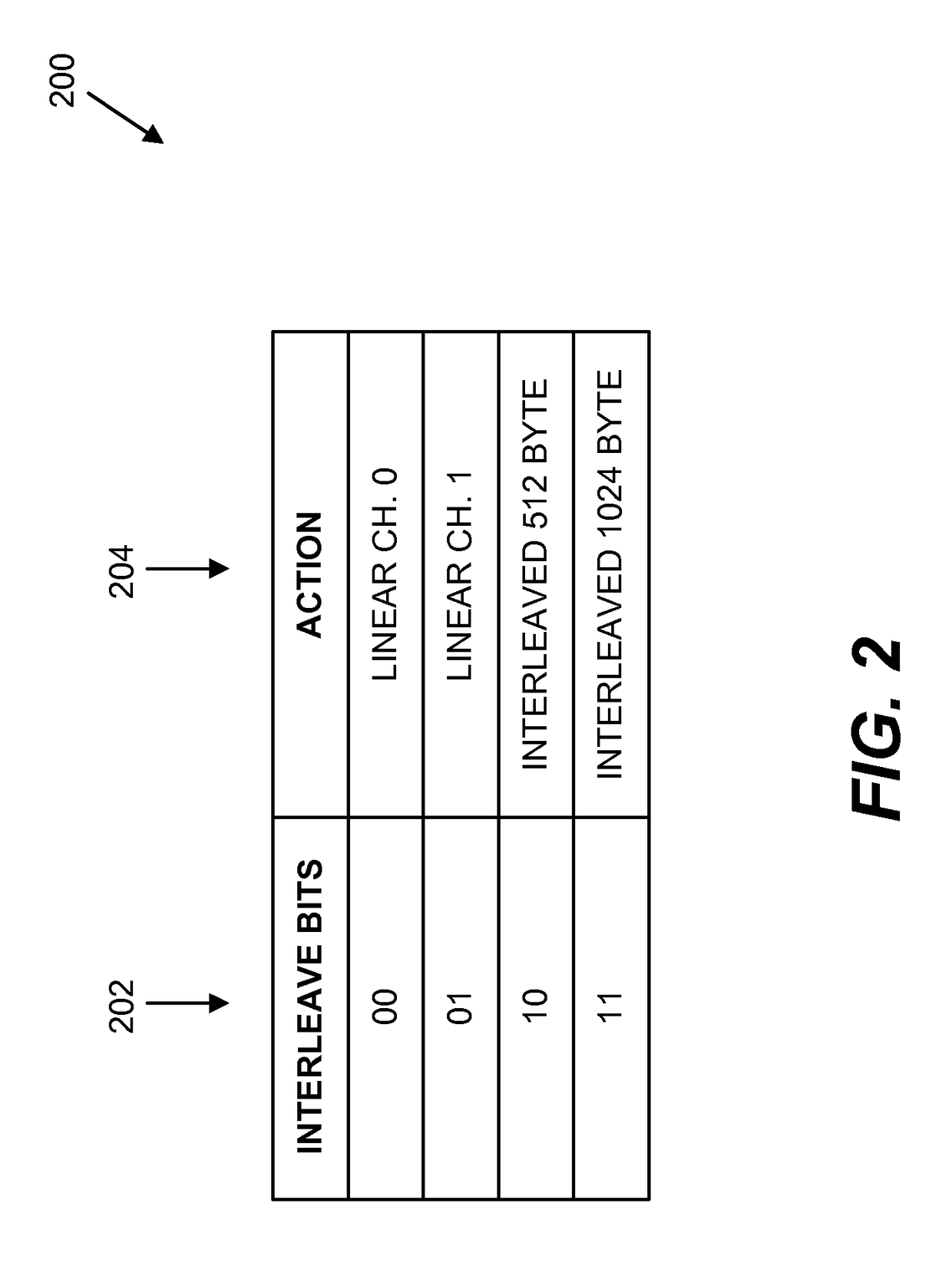

System and method for memory management using dynamic partial channel interleaving

InactiveUS20170162235A1Low powerReduce power consumptionMemory architecture accessing/allocationInput/output to record carriersComputer scienceMemory management unit

Systems and methods are disclosed for providing memory channel interleaving with selective power / performance optimization. One such method comprises configuring an interleaved zone for relatively higher performance tasks, a linear address zone for relatively lower power tasks, and a mixed interleaved-linear zone for tasks with intermediate performance requirements. A boundary is defined among the different zones using a sliding threshold address. The zones may be dynamically adjusted, and / or new zones dynamically created, by changing the sliding address in real-time based on system goals and application performance preferences. A request for high performance memory is allocated to a zone with lower power that minimally supports the required performance, or may be allocated to a low power memory zone with lower than required performance if the system parameters indicate a need for aggressive power conservation. Pages may be migrated between zones in order to free a memory device for powering down.

Owner:QUALCOMM INC

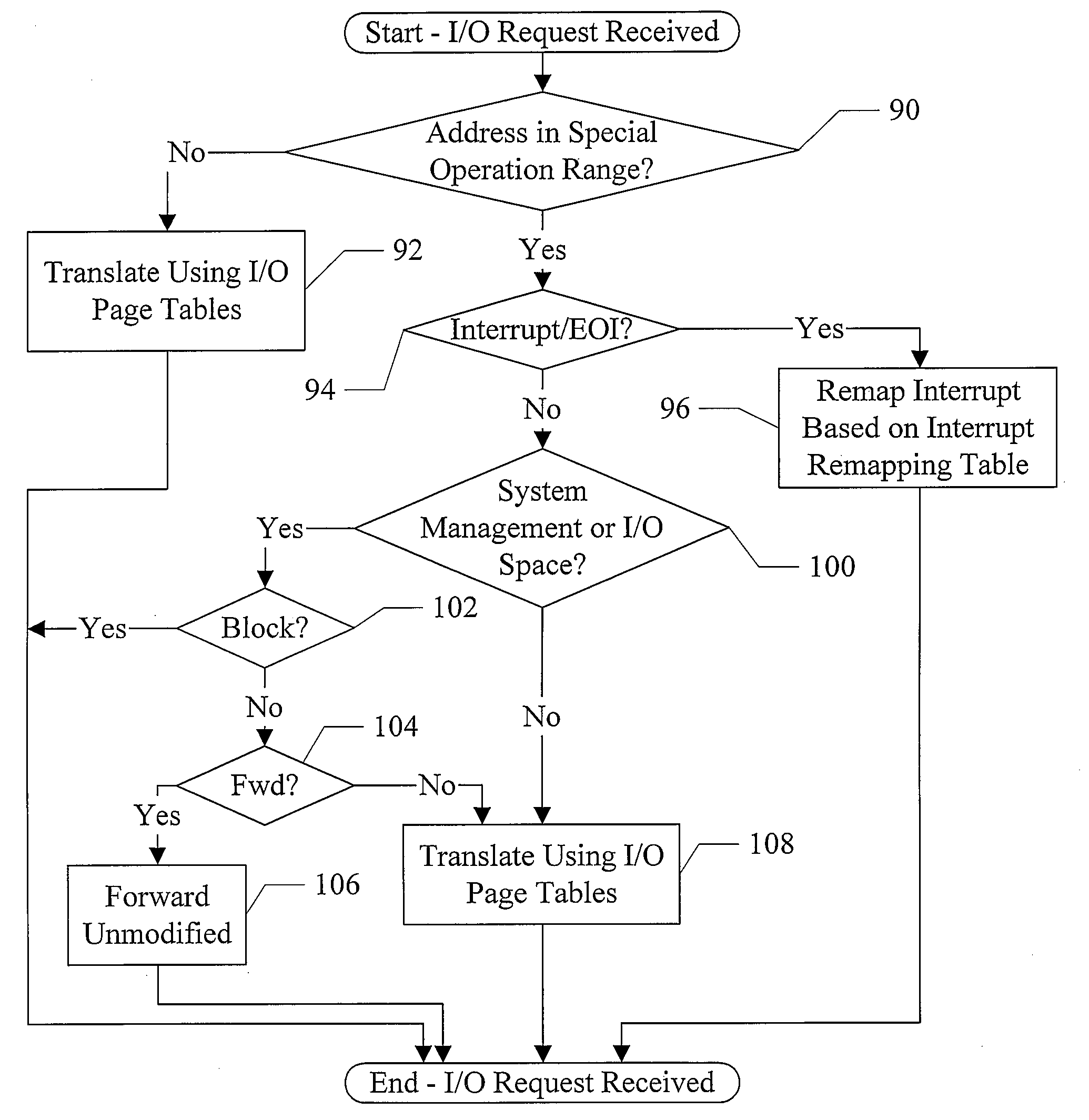

Efficiently Controlling Special Memory Mapped System Accesses

ActiveUS20080114906A1Memory architecture accessing/allocationMemory systemsManagement unitControl register

In one embodiment, an input / output memory management unit (IOMMU) comprises a control register configured to store a base address of a set of translation tables and control logic coupled to the control register. The control logic is configured to respond to an input / output (I / O) device-initiated request having an address within an address range of an address space corresponding to a peripheral interconnect. One or more operations other than a memory operation are associated with the address range, and the control logic is configured to translate the address to a second address outside of the address range if the translation tables specify a translation from the address to the second address, whereby a memory operation is performed in response to the request instead of the one or more operations associated with the address range.

Owner:ADVANCED MICRO DEVICES INC