Patents

Literature

167 results about "PowerPC" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

PowerPC (with the backronym Performance Optimization With Enhanced RISC – Performance Computing, sometimes abbreviated as PPC) is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple–IBM–Motorola alliance, known as AIM. PowerPC, as an evolving instruction set, has since 2006 been named Power ISA, while the old name lives on as a trademark for some implementations of Power Architecture-based processors.

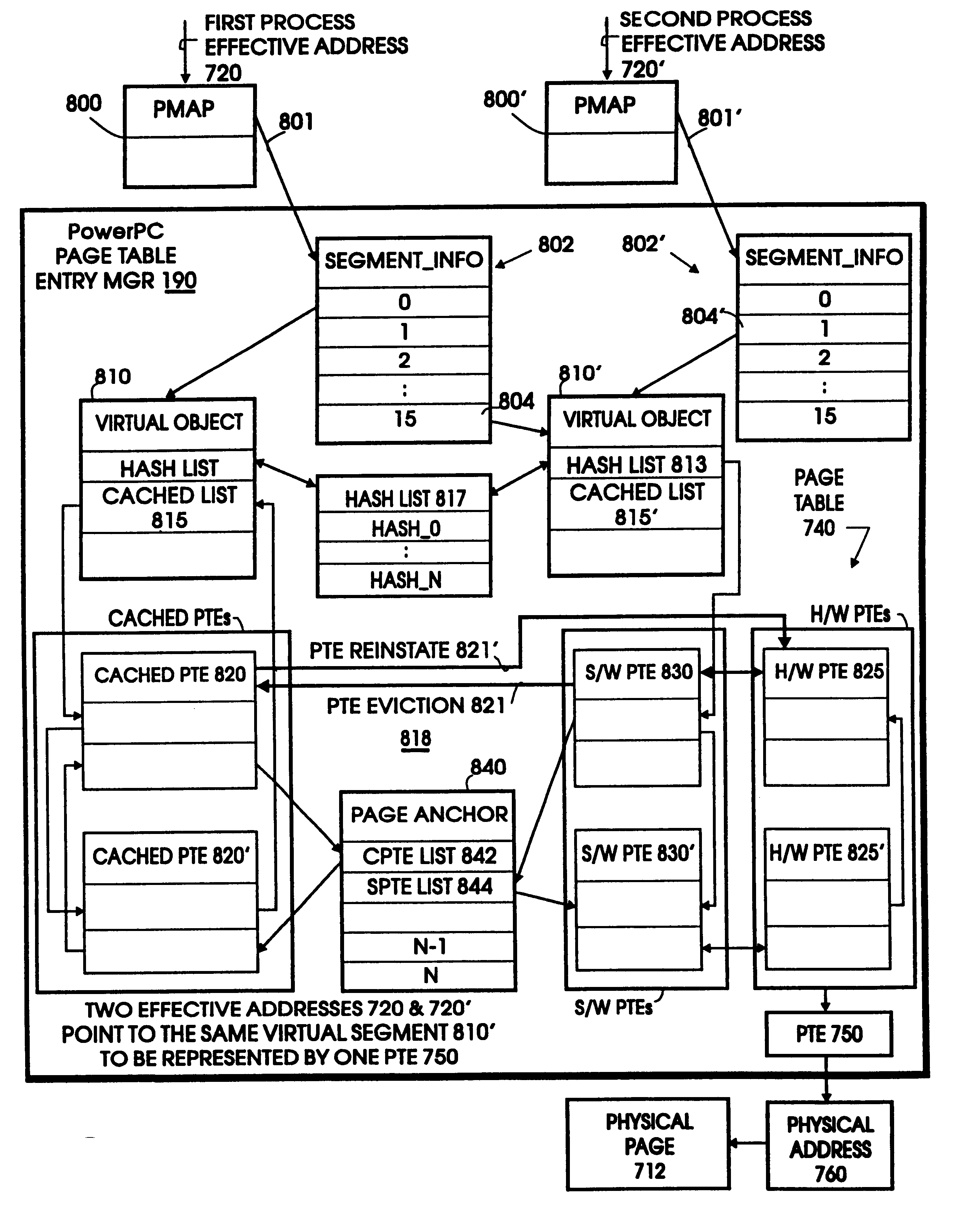

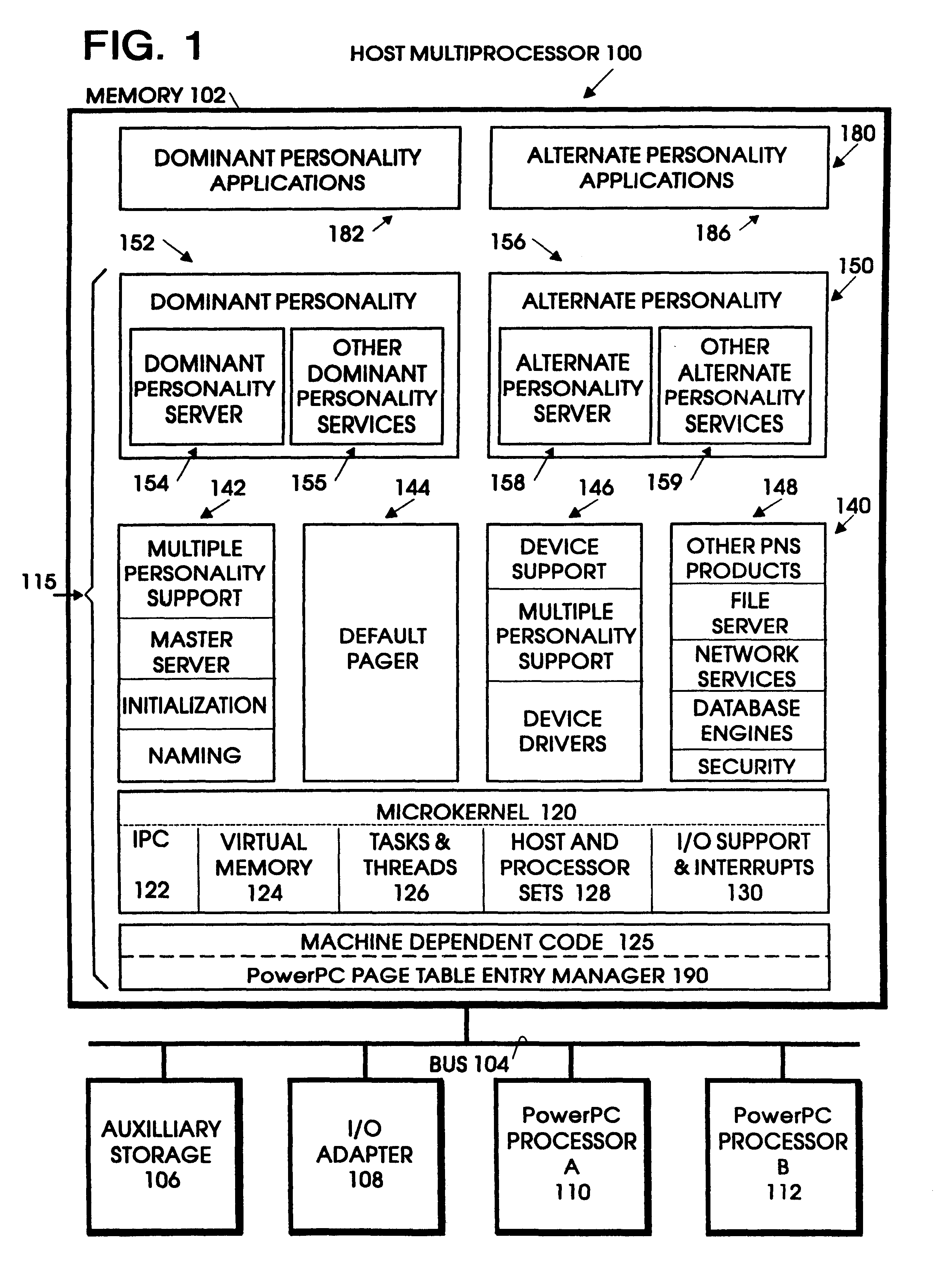

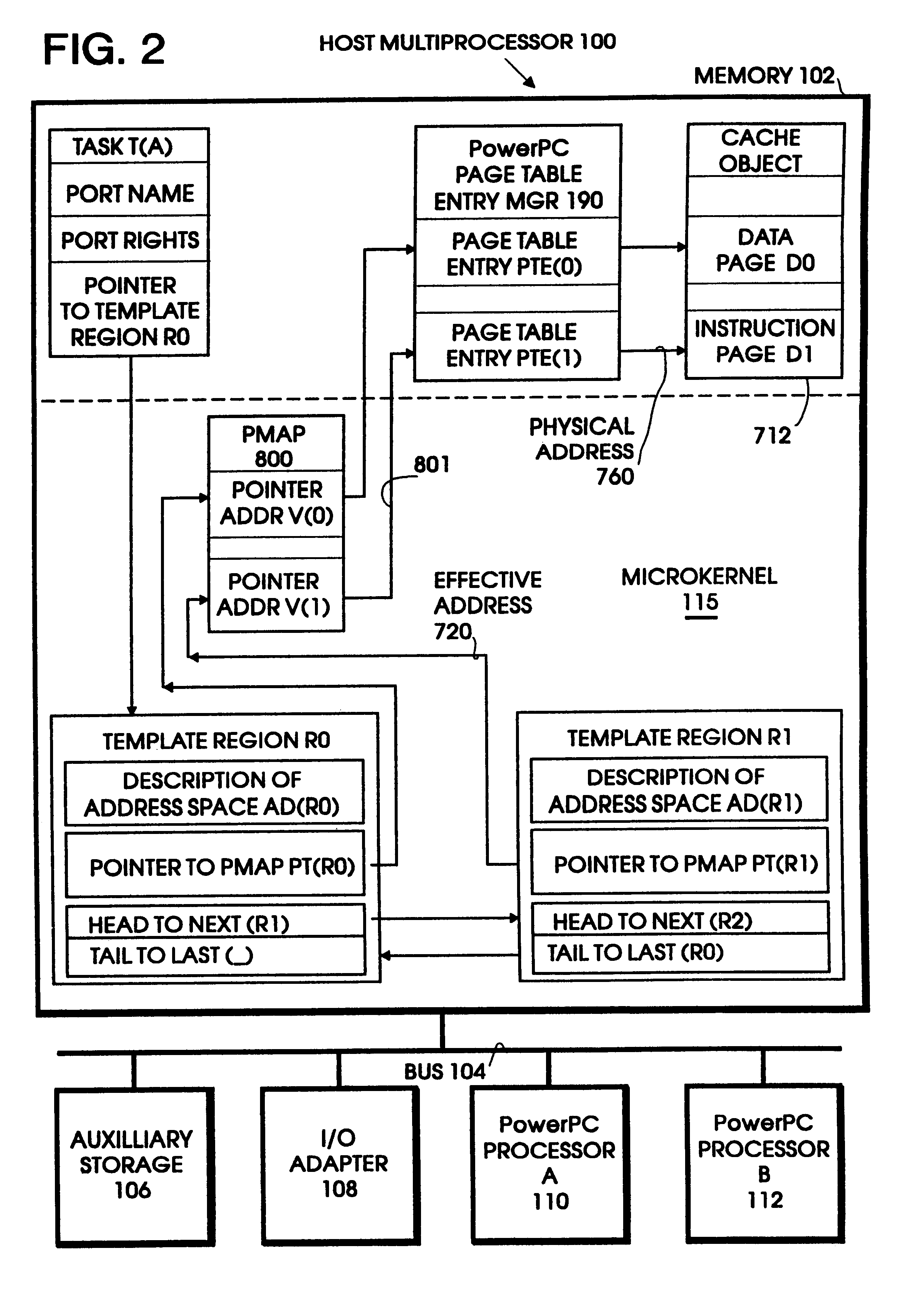

Page table entry management method and apparatus for a microkernel data processing system

InactiveUS6308247B1Maximize system performanceEasy to manageMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemManagement unit

A page table entry management method and apparatus provide the Microkernel System with the capability to program the memory management unit on the PowerPC family of processors. The PowerPC processors define a limited set of page table entries (PTEs) to maintain virtual to physical mappings. The page table entry management method and apparatus solves the problem of a limited number of PTEs by segment aliasing when two or more user processes share a segment of memory. The segments are aliased rather than duplicating the PTES. This significantly reduces the number of PTEs. In addition, the method provides for caching existing PTEs when the system actually runs out of PTEs. A cache of recently discarded PTEs provides a fast fault resolution when a recently used page is accessed again.

Owner:IBM CORP

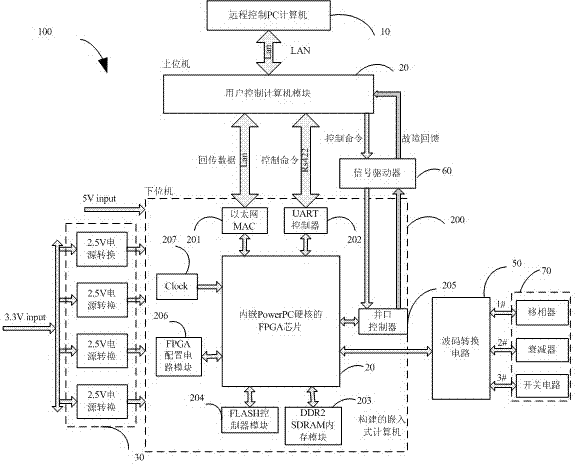

Phased array radar antenna beam control device

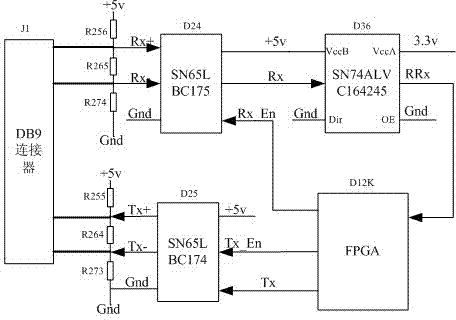

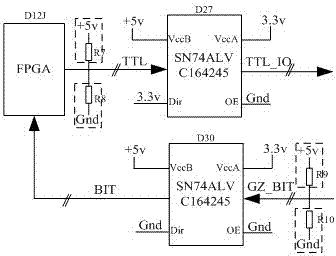

ActiveCN102495565AImprove reliabilityMeet developmentProgramme controlWave based measurement systemsDouble data rateUniversal asynchronous receiver/transmitter

The invention relates to a phased array radar antenna beam control device. The phased array radar antenna beam control device comprises a remote control PC (Personal Computer) computer, a user control computer module, a power supply management module, a FPGA (Field Programmable Gate Array) chip, a signal driver, a wave control conversion circuit and a controlled device which is electrically connected with the wave control conversion circuit, wherein the user control computer module remotely communicates with the remote control PC computer and are electrically connected with the FPGA chip, thepower supply management module and the wave control conversion circuit, respectively. The FPGA chip is embedded with a PowerPC hardcore and used for constructing an embedded computer; the embedded computer also comprises an Ethernet (Media Access Control), a UART (Universal Asynchronous Receiver Transmitter) controller, a DDR2SDRAM (Double Data Rate 2 Synchronous Dynamic Random Access Memory) memory module, a FLASH controller module, a parallel controller, a FPGA configuration circuit module and a clock generating circuit module. The phased array radar antenna beam control device provided by the invention has the advantage of high reliability.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

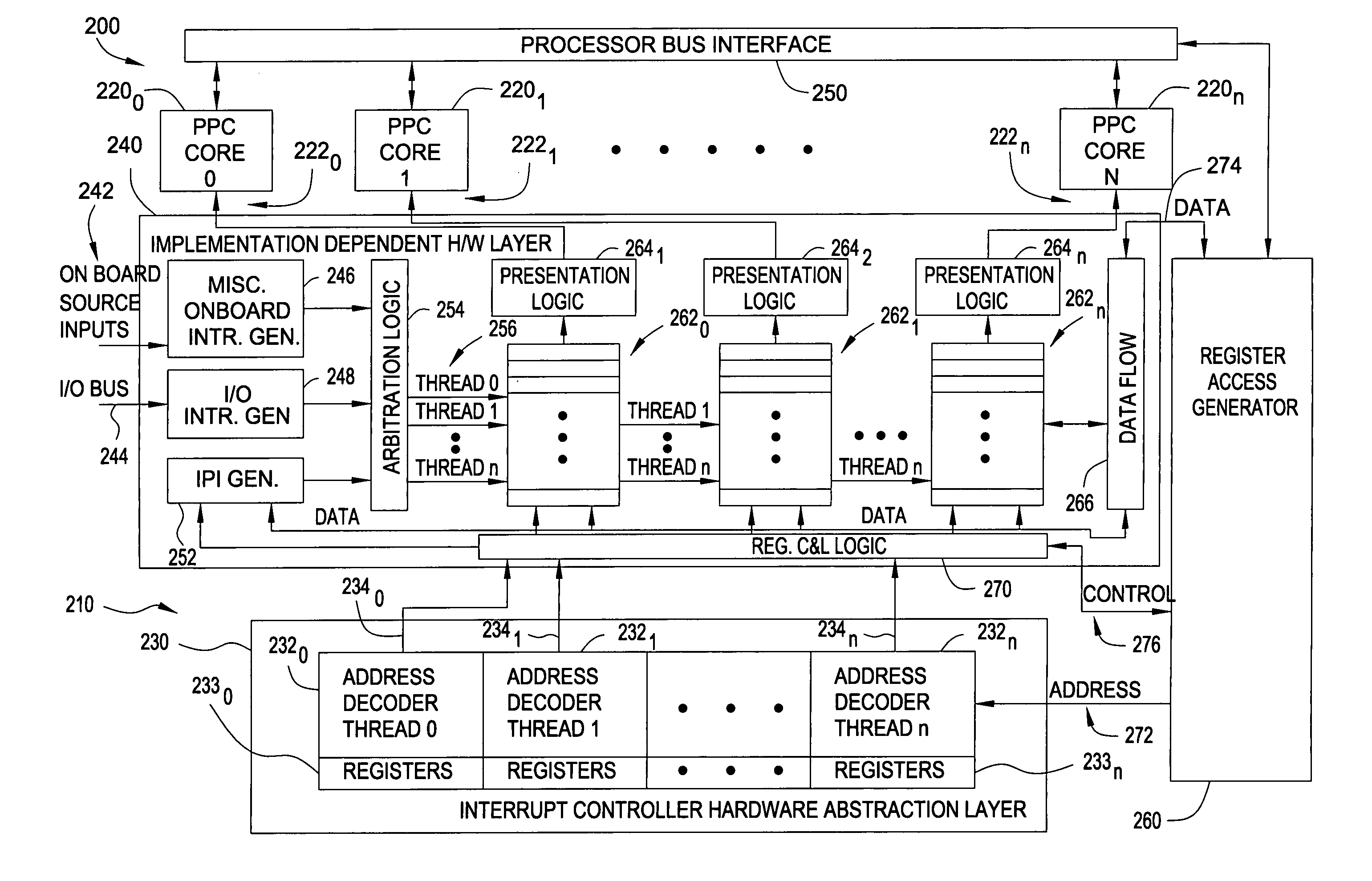

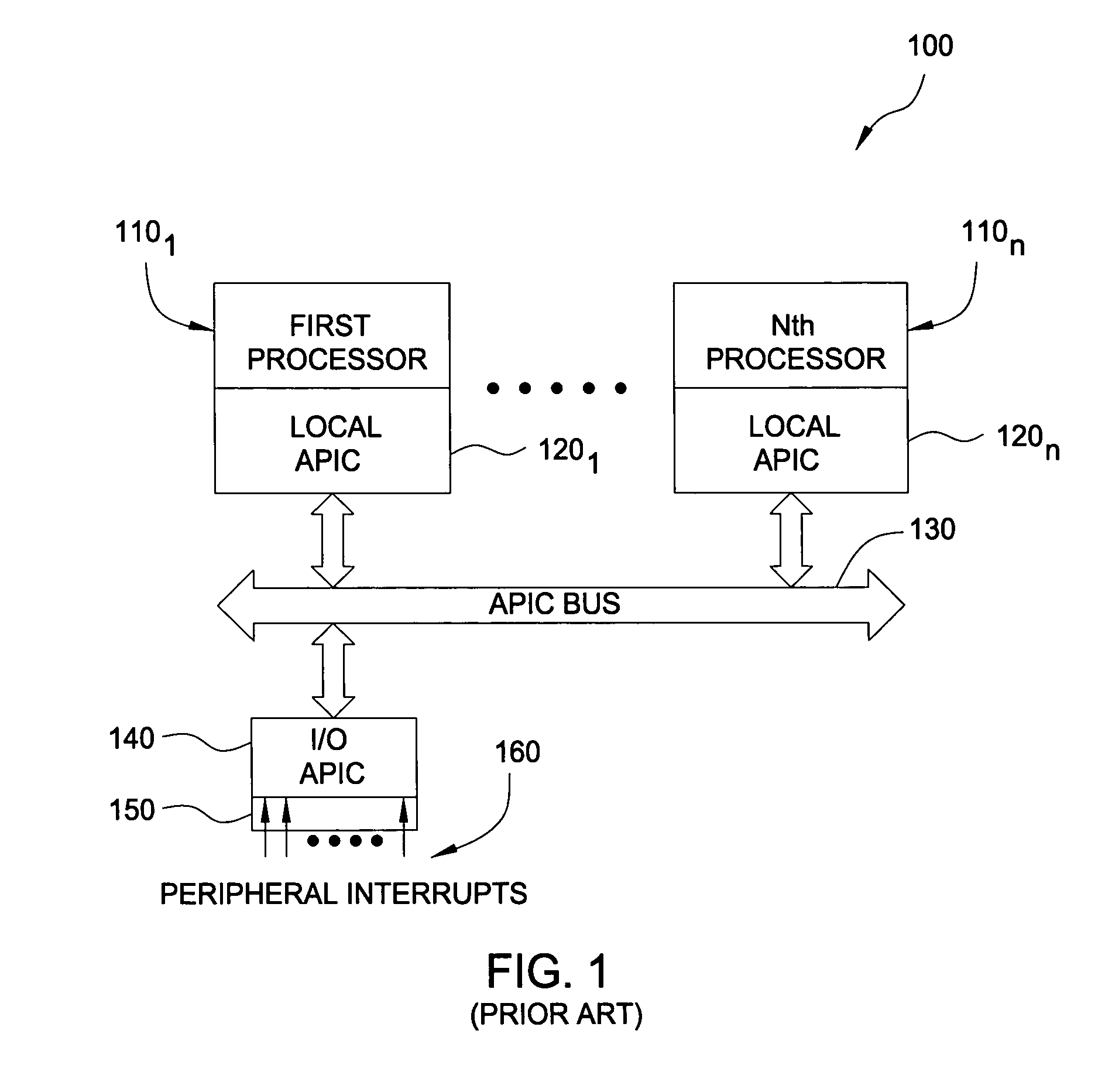

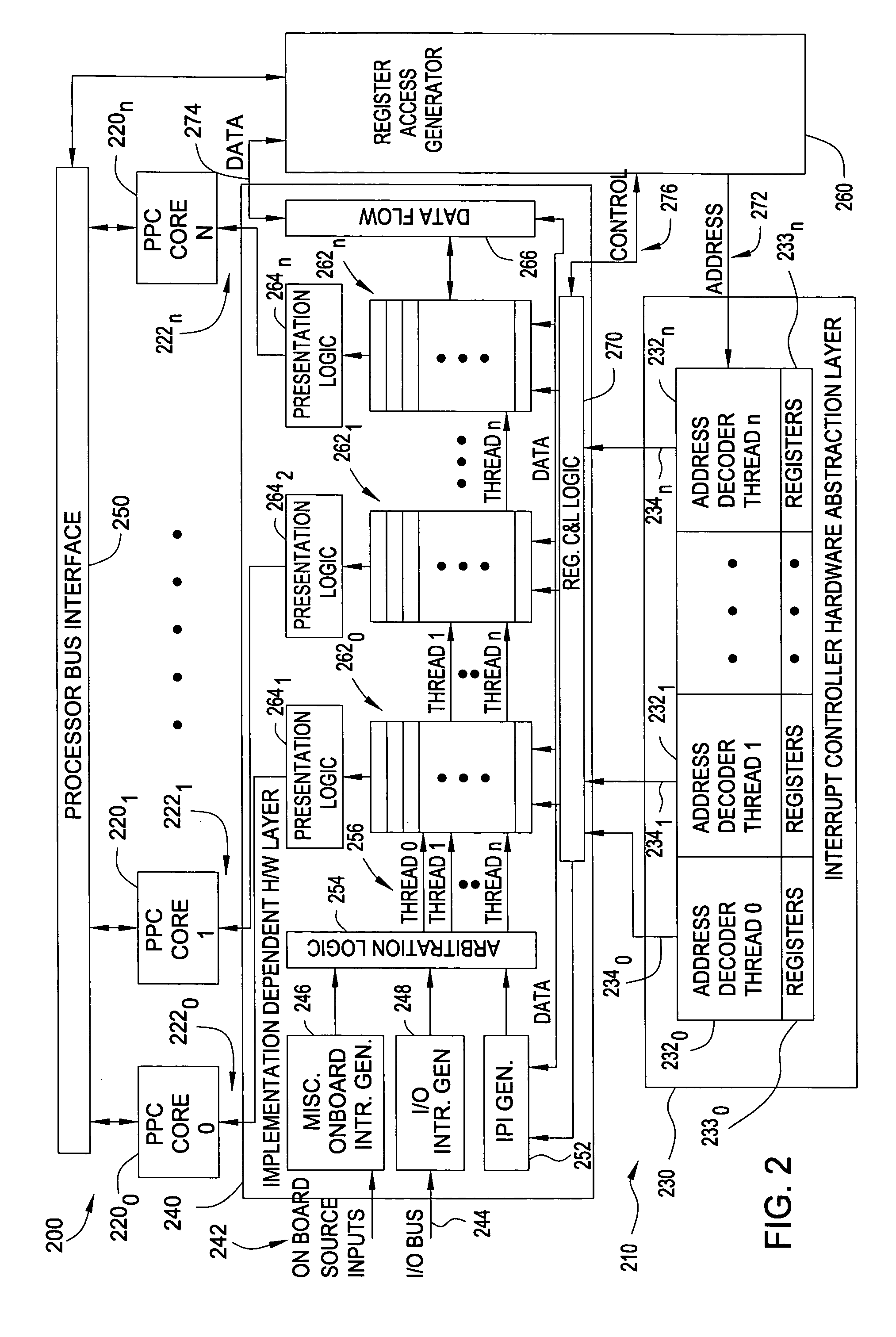

Method and apparatus for supporting interrupt devices configured for a particular architecture on a different platform

Method and apparatus for supporting interrupt devices configured for a specific architecture (e.g., APIC-based software and hardware) on a different platform (e.g., a PowerPC platform). One embodiment provides an apparatus for passing interrupts from one or more devices configured for a specific interrupt architecture to one or more processors not designed for the specific interrupt architecture, comprising: an abstraction layer comprising a first plurality of registers conforming to the specific interrupt architecture; and an implementation dependent layer, disposed in communication between the abstraction layer and the one or more processors, comprising a second plurality of registers which correspond to the first plurality of registers, wherein the implementation dependent layer is configured to receive interrupts and forward received interrupts to the one or more processors and to read and write data to the second plurality of registers in response to interrupts processed through the one or more processor.

Owner:INT BUSINESS MASCH CORP

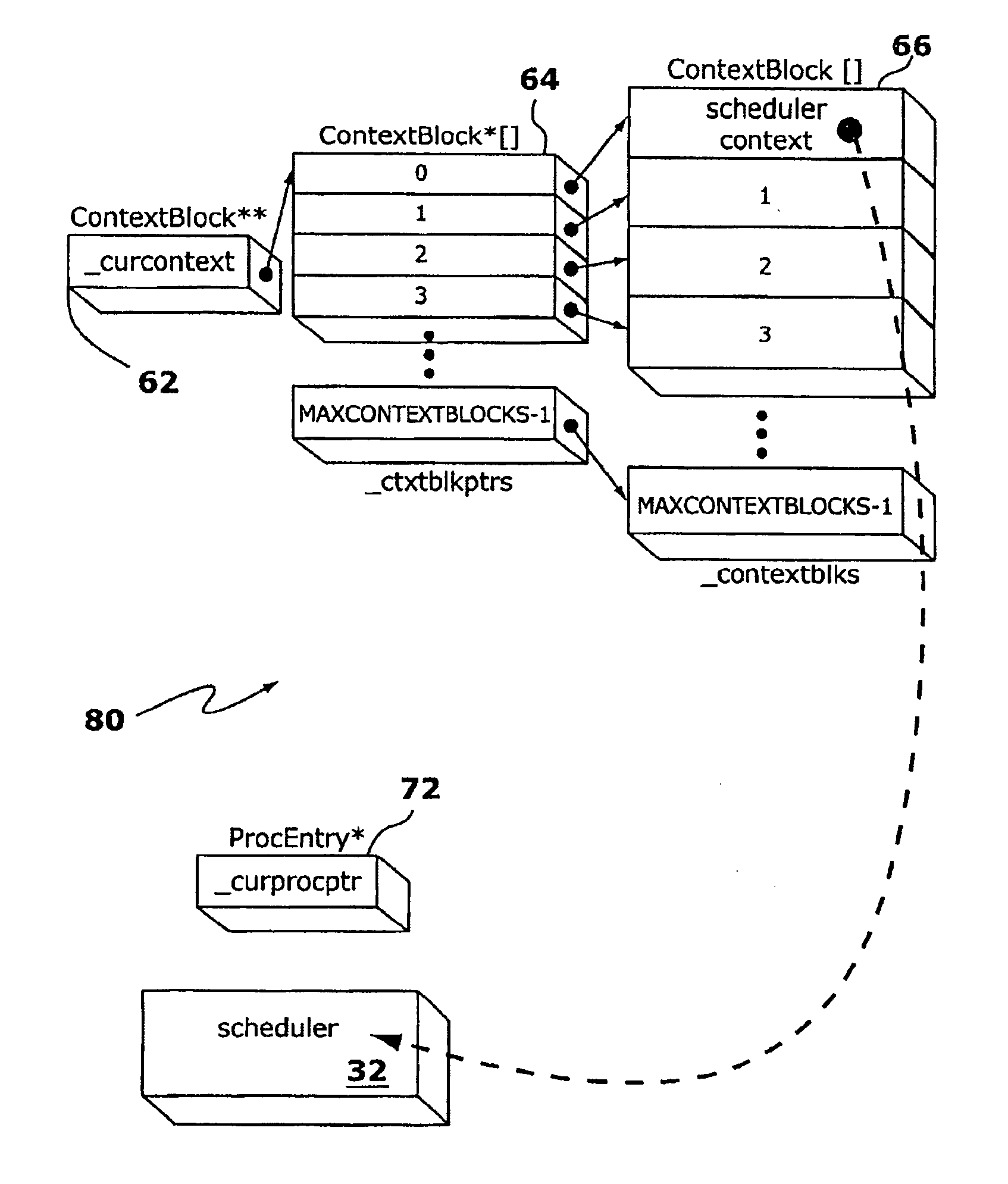

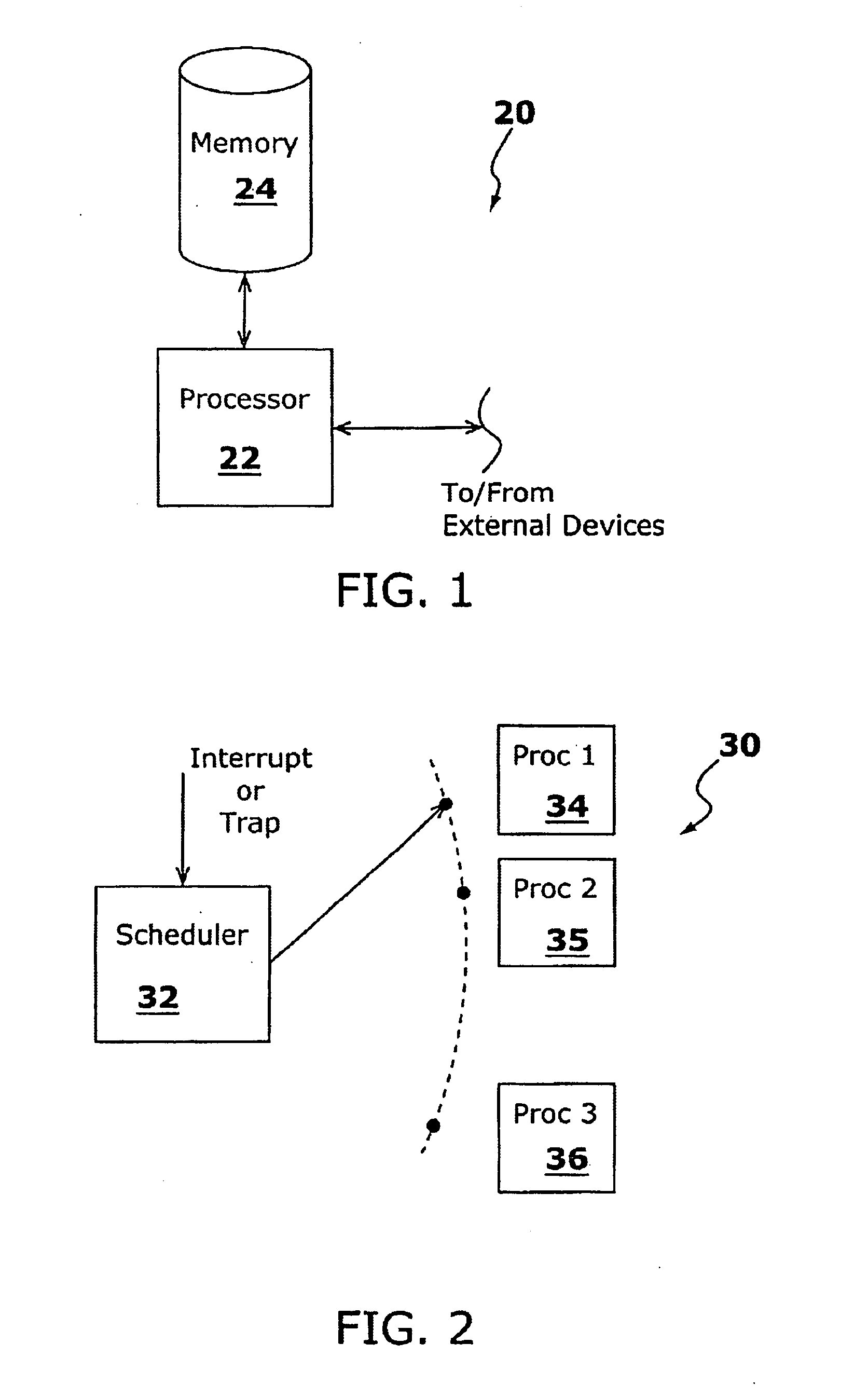

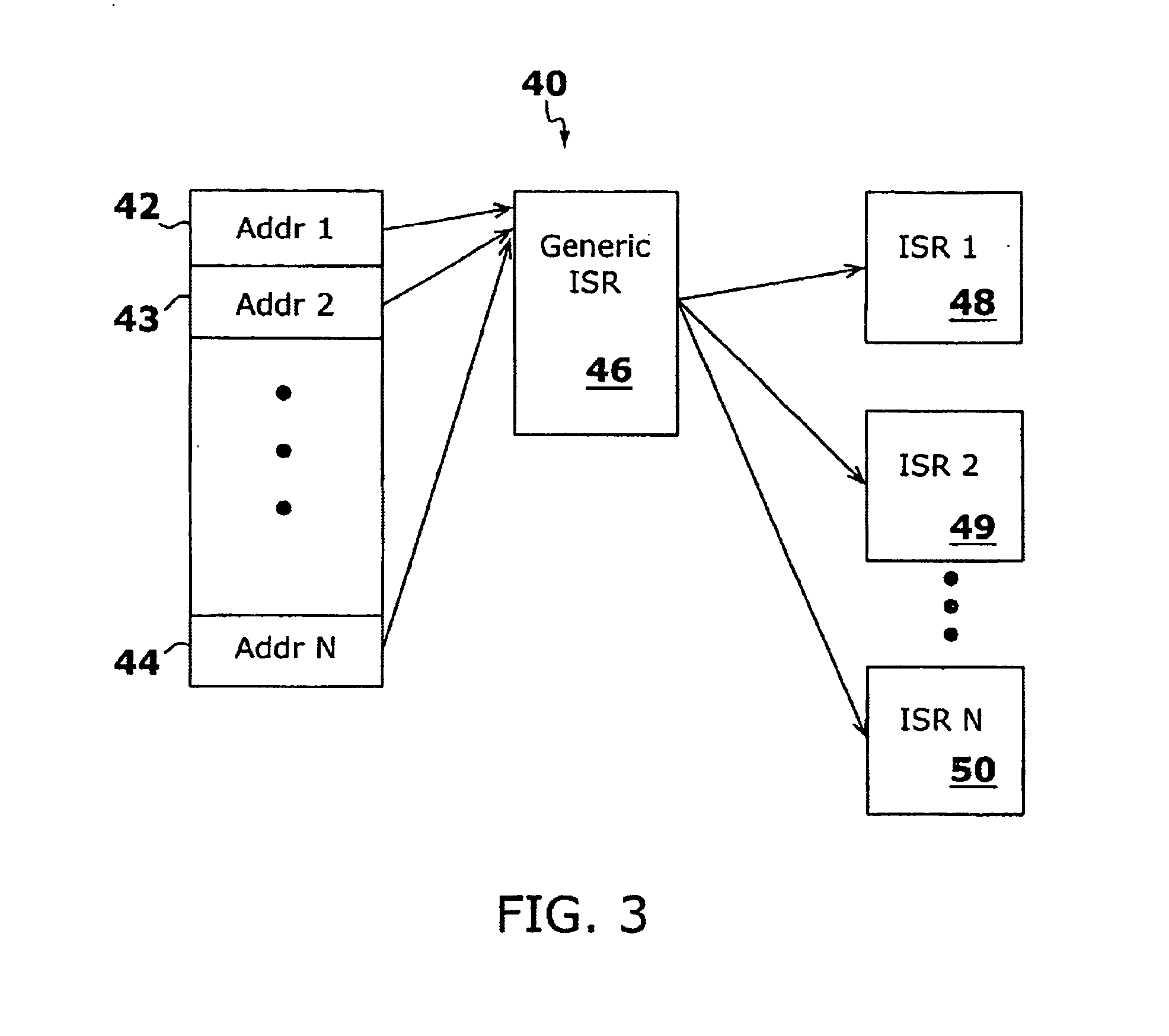

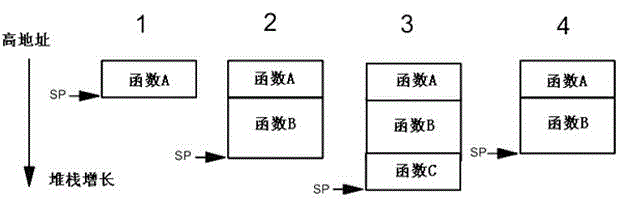

Replaceable scheduling algorithm in multitasking kernel

InactiveUS7296271B1Reduce needEnhancing kernel portabilityProgram synchronisationDigital computer detailsPowerPCProgram counter

Disclosed is providing one of a plurality of schedulers for a multitasking system for a processor that includes choosing a particular one of the schedulers, setting a program counter to an address corresponding to code of the particular one of the schedulers, and the processor executing code at an address corresponding to the program counter. Also included may be setting a stack pointer to an address corresponding to stack space for the particular one of the schedulers and the processor using the stack space at the stack pointer after executing code at the address corresponding to the program counter. The system described herein provides a small kernel that can run on a variety of hardware platforms, such as a PowerPC based Symmetrix adapter board used in a Symmetrix data storage device provided by EMC Corporation of Hopkinton, Ma. The core kernel code may be written for the general target platform, such as the PowerPC architecture. Since the PowerPC implementation specific modules are well defined, the system may be quite portable between PowerPC processors (such as the 8260 and 750), and should prove relatively easy to port to any PowerPC based Symmetrix adapter board / CPU combination. The kernel may also be ported to run on other RISC machines (Hitachi SH series) and can be ported to CISC architectures.

Owner:EMC IP HLDG CO LLC

Selective omission of endian translation to enhance emulator performance

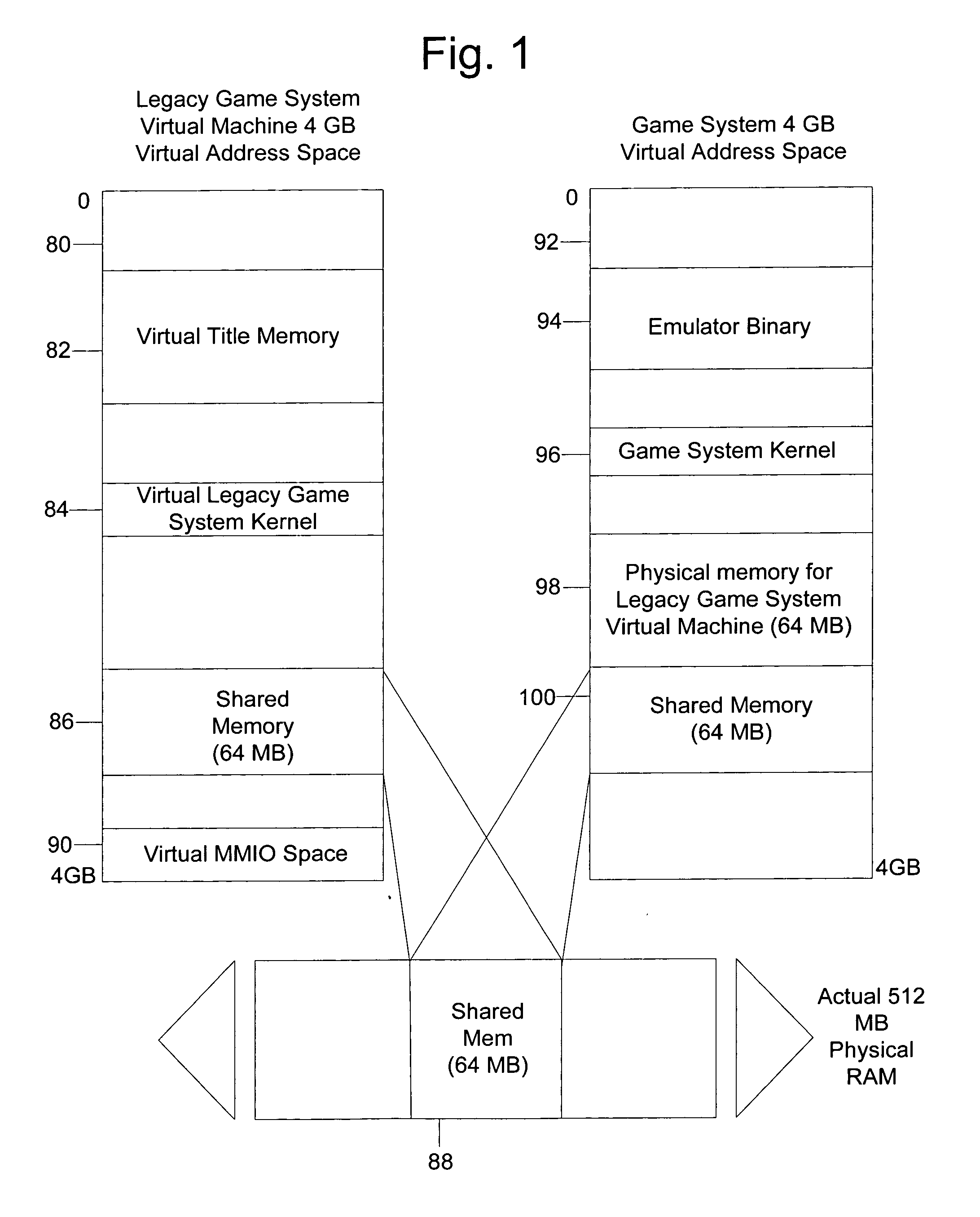

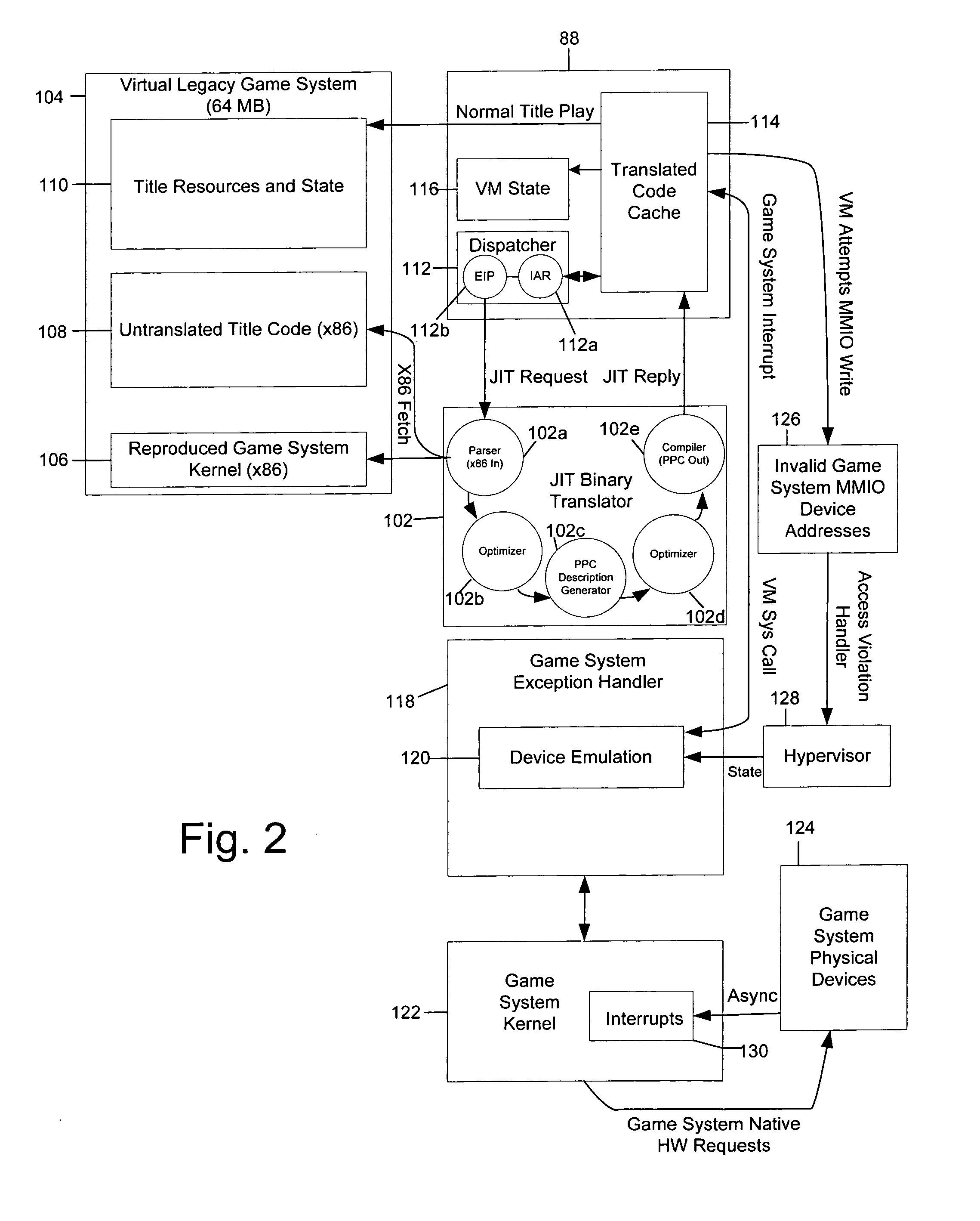

A JIT binary translator examines code to determine if a conversion from big-endian to little-endian can be omitted. For example, the conversion may be omitted when data is merely being loaded and stored. The conversion from big-endian to little-endian may also be omitted when storing certain constructs and numbers. A third example is loading of floating point values. If a conversion from big-endian to little-endian is performed, this could result in four instructions in PowerPC, seven if double precision. However, if floating point values are access consistently as big-endian, the result is only one PowerPC instruction. Optimizations, such as these result in a tighter emulated binary.

Owner:MICROSOFT TECH LICENSING LLC

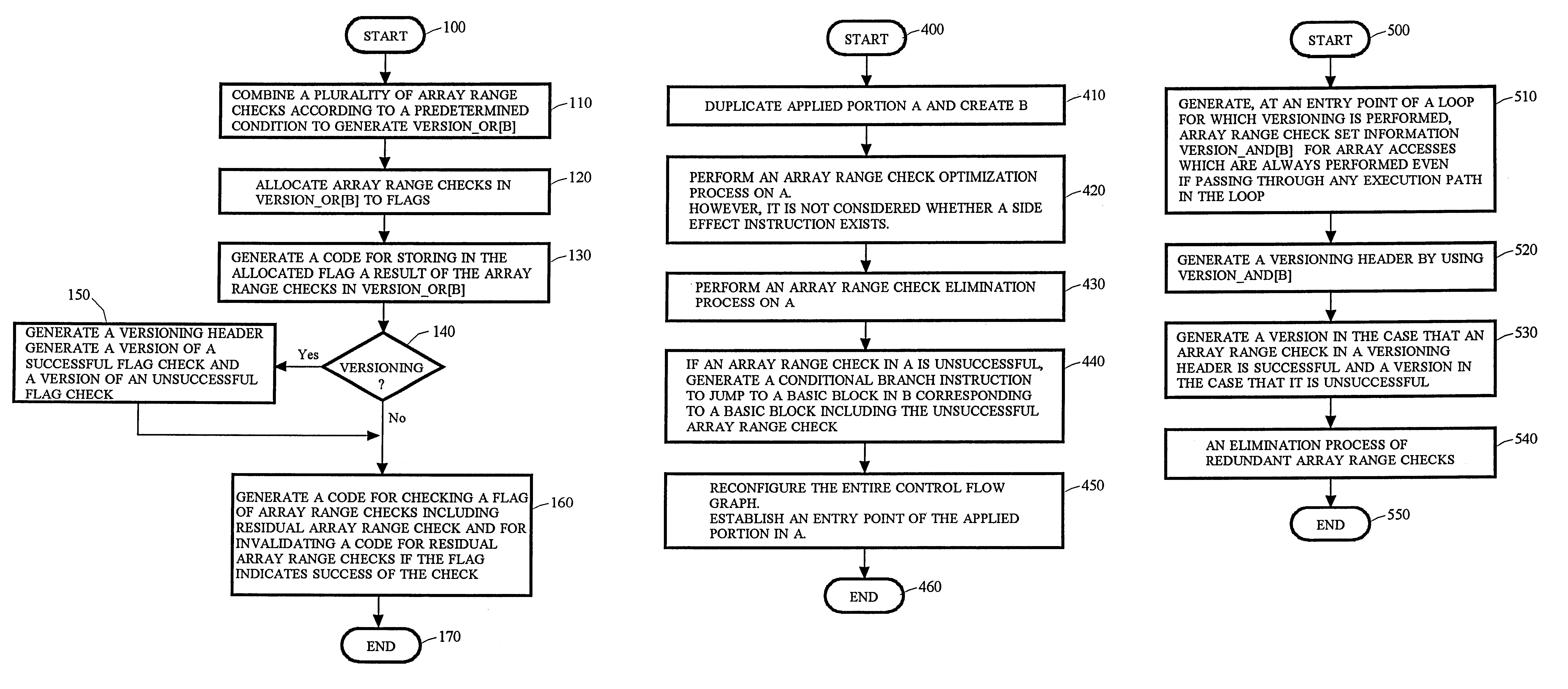

Method and apparatus for generating code for array range check and method and apparatus for versioning

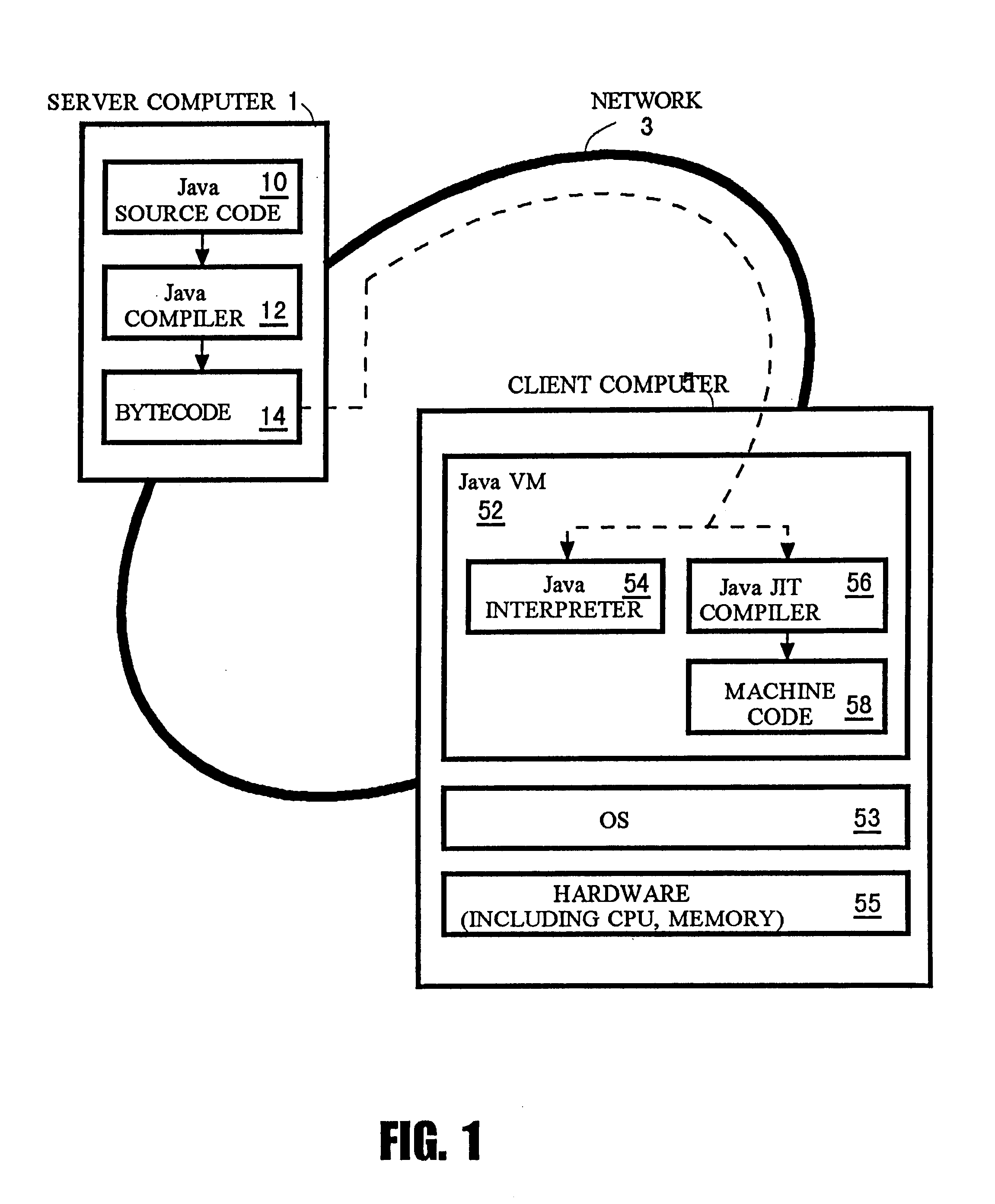

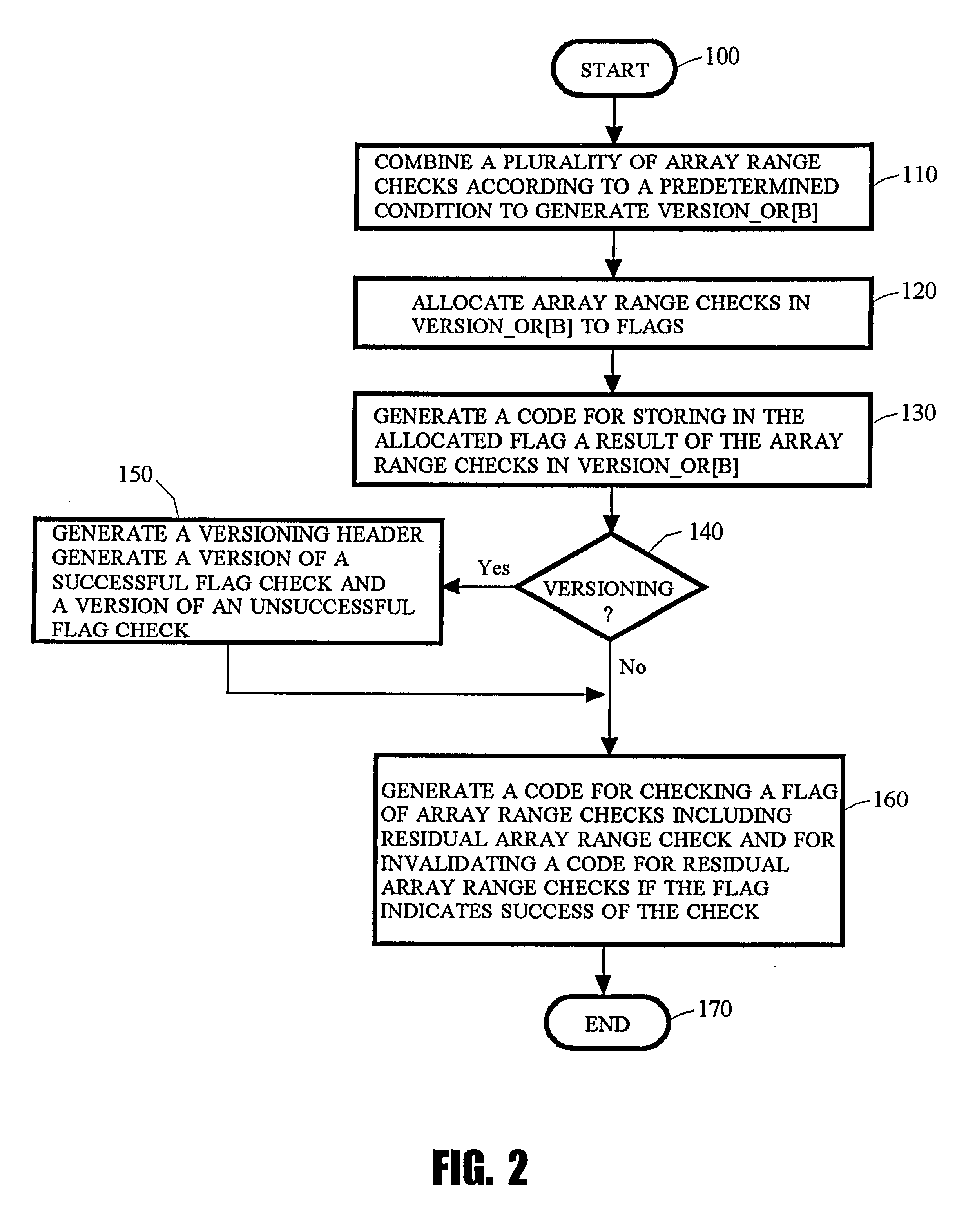

InactiveUS6665864B1Reduce in quantityIncrease speedSoftware engineeringSpecific program execution arrangementsArray data structurePowerPC

The present invention eliminates redundant array range checks. A two-phased check is performed, namely a wide range check is performed by combining a plurality of array range checks, and a strict range check is unsuccessful, so as to reduce the number of range checks at execution time and allow execution at high speed. For instance, it is possible with a processor such as PowerPC, by using a flag, to invalidate a code for performing an array range check at high speed without increasing a code size. Consequently, the number of array range checks to be executed can be reduced so as to allow execution at high speed. Also, for instance, a plurality of array range checks can be combined without considering existence of instructions which cause a side effect. Consequently, the number of array range checks to be executed can be reduced so as to allow execution at high speed. In addition, a versioning is performed by using, as array access information for versioning, information of array access information for versioning information of array accesses which are always performed even if passing through any execution path in a loop so that there are fewer cases where it goes to a version with a larger number of array range checks at execution time.

Owner:GOOGLE LLC

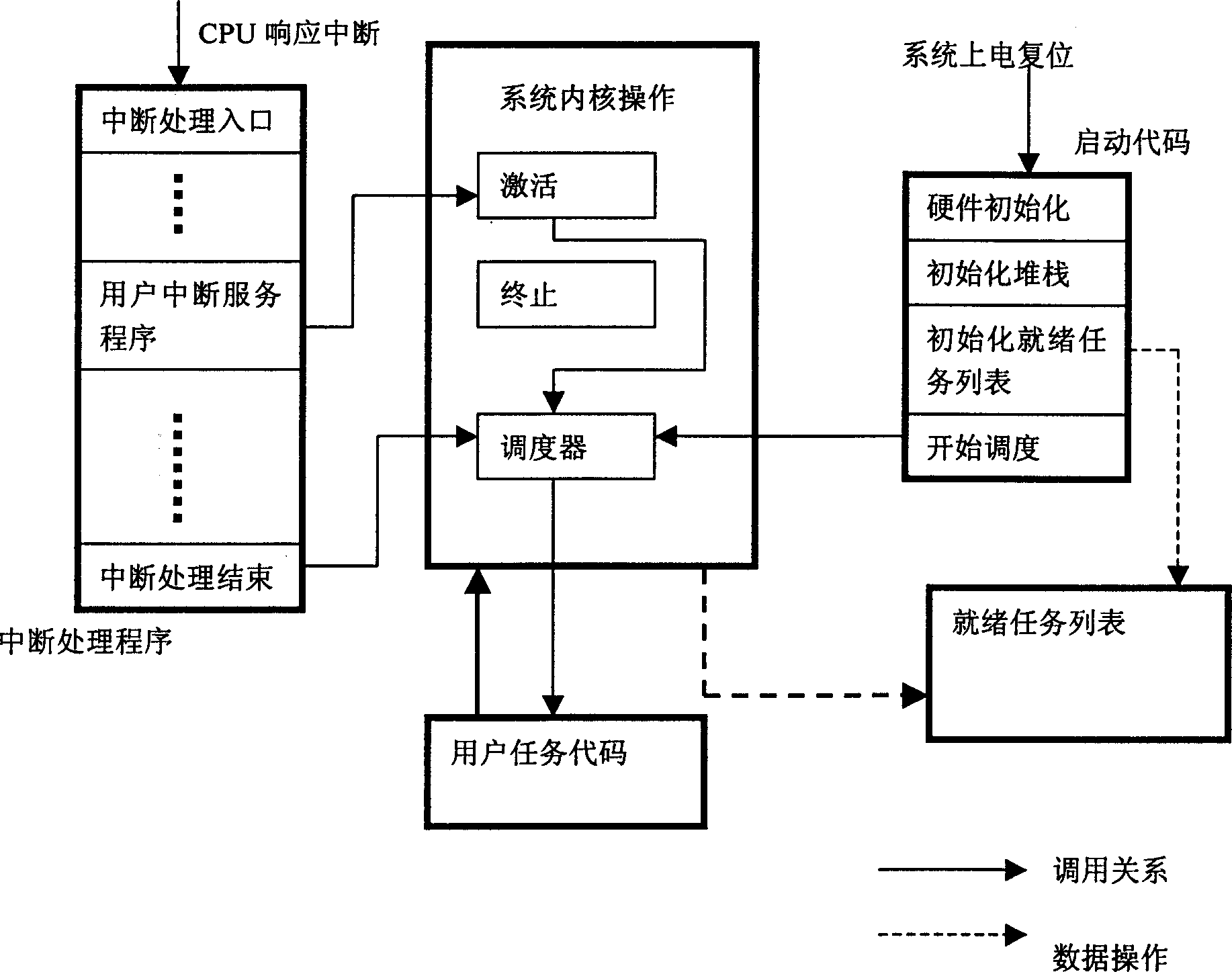

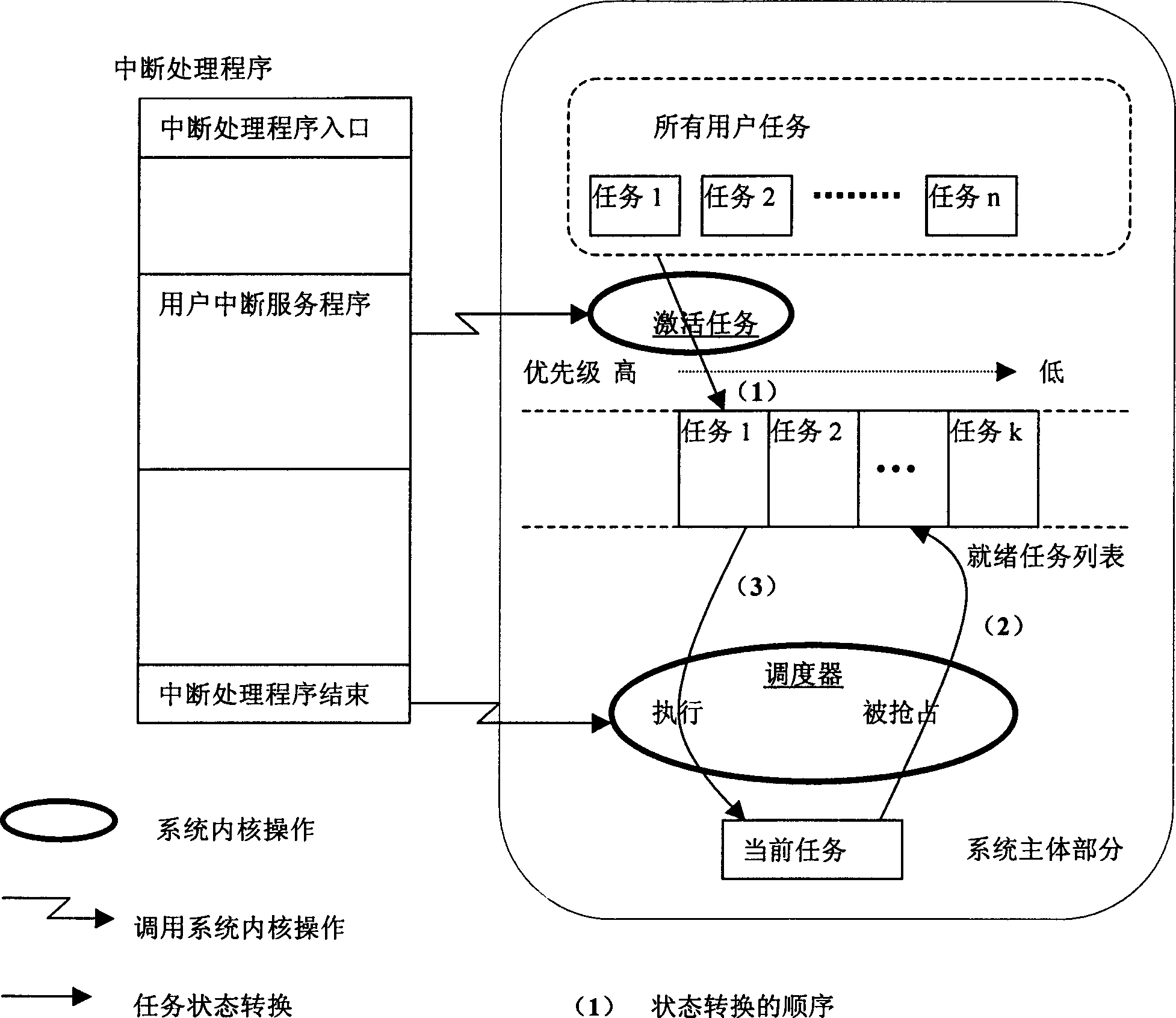

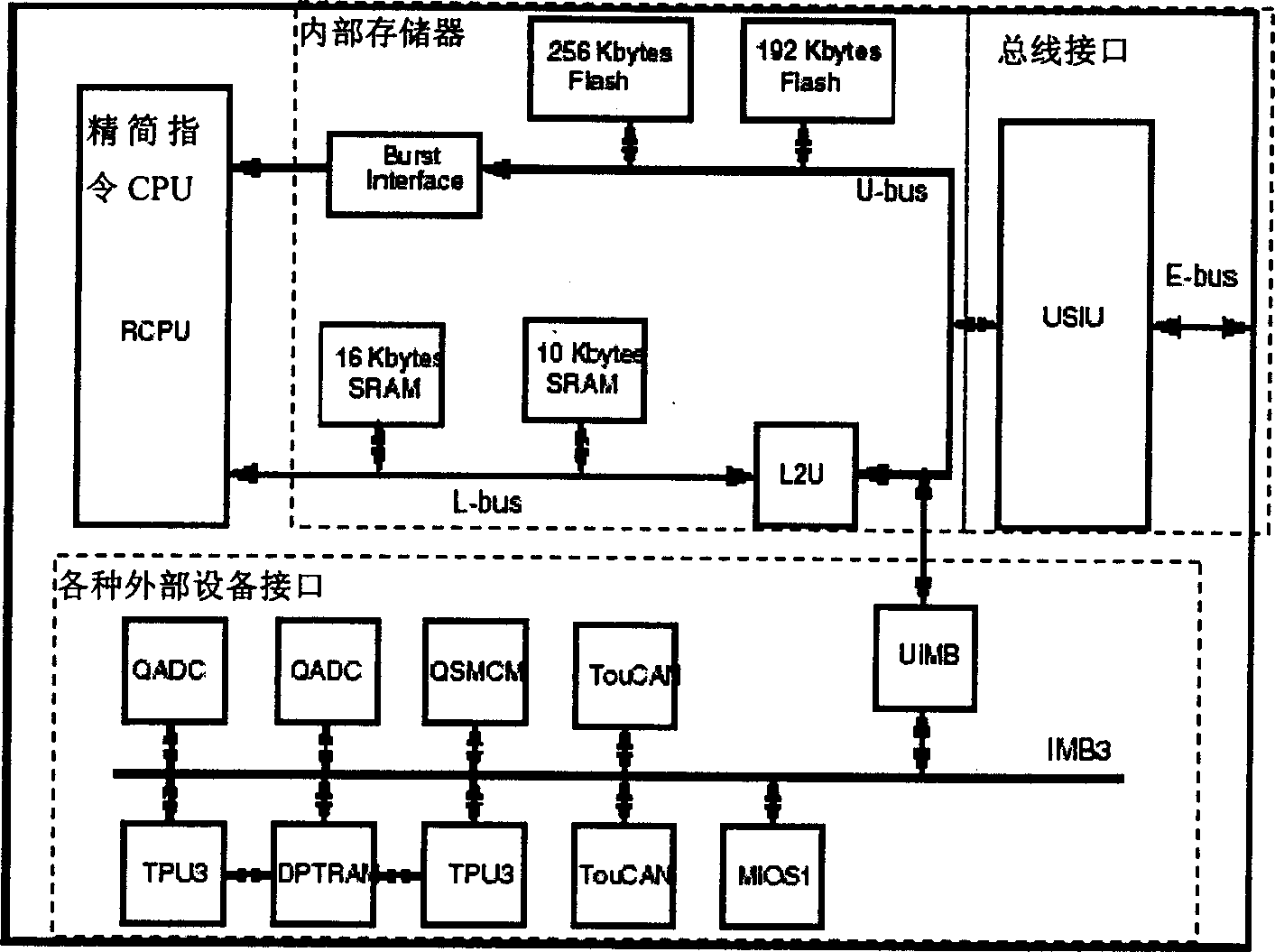

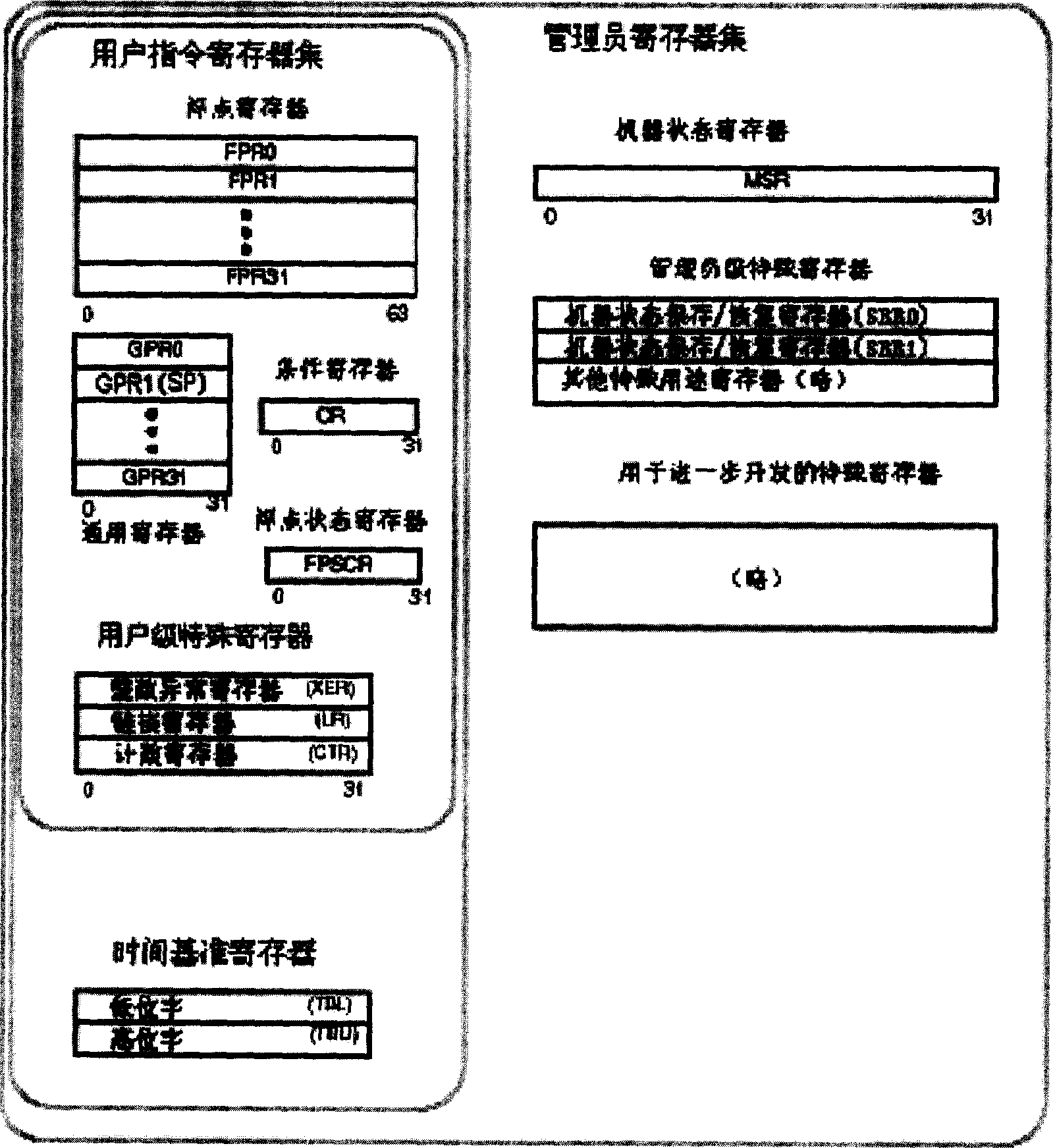

Graded task switching method based on PowerPC processor structure

InactiveCN1490722AShorten the timeImprove the efficiency of task switchingProgram initiation/switchingOperational systemPowerPC

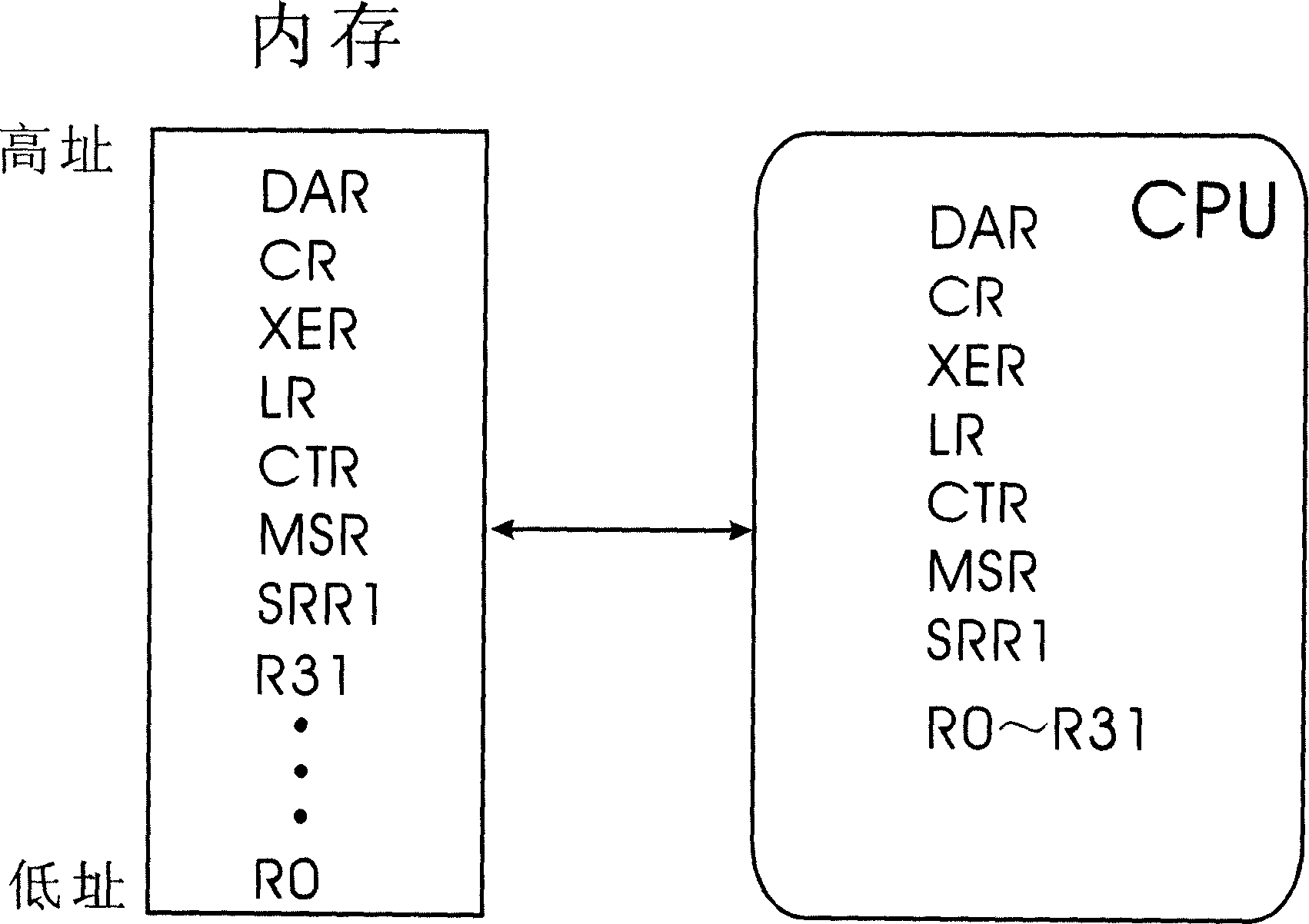

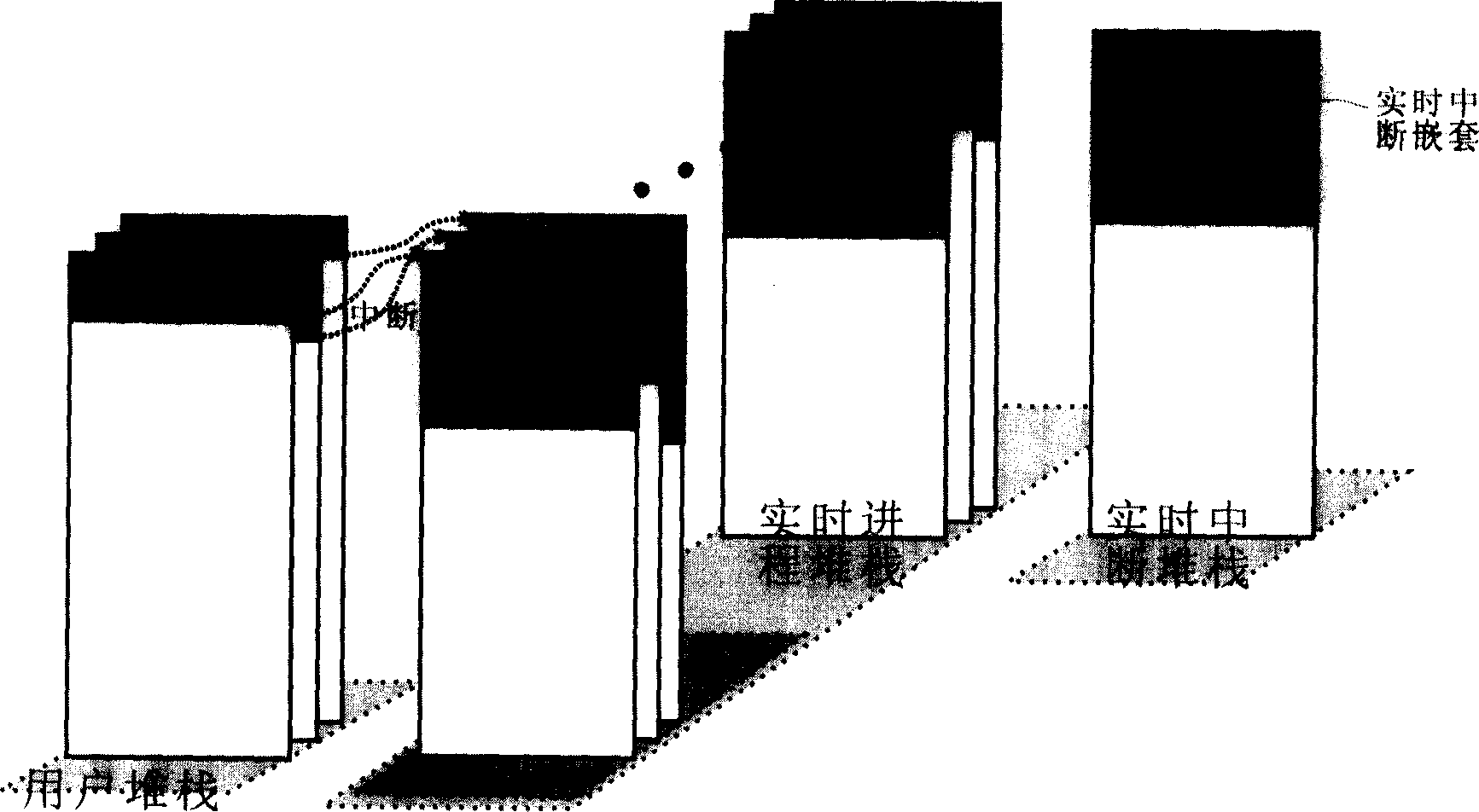

The method has the following characteristics: the task contex of the user can be divided into three parts of basic, expansion and selectable according to speciality of Power PC processor structure. In interruption process, only three stack entering modes of basic, basicand expansion as well as all context part are applied according to condition of system disposal and task dispatching. The basic part stack entering is executed first. After interruption process is finished the nature of task dispatching is judged for selecting to execute the next stage of stack entering operation, to call dispatcher or to return to the user task in order to reduce unnecessary stacking operation.

Owner:TSINGHUA UNIV

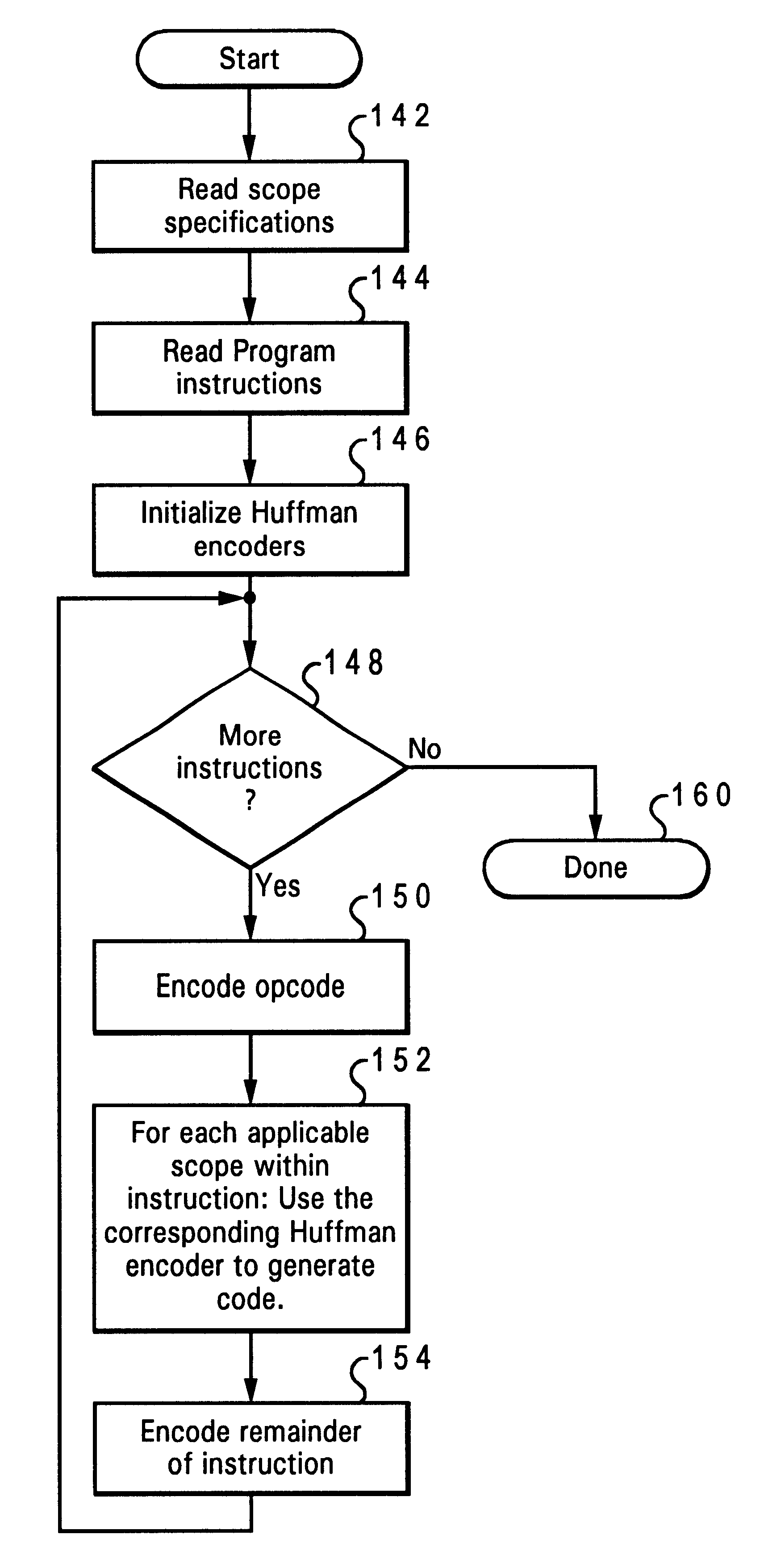

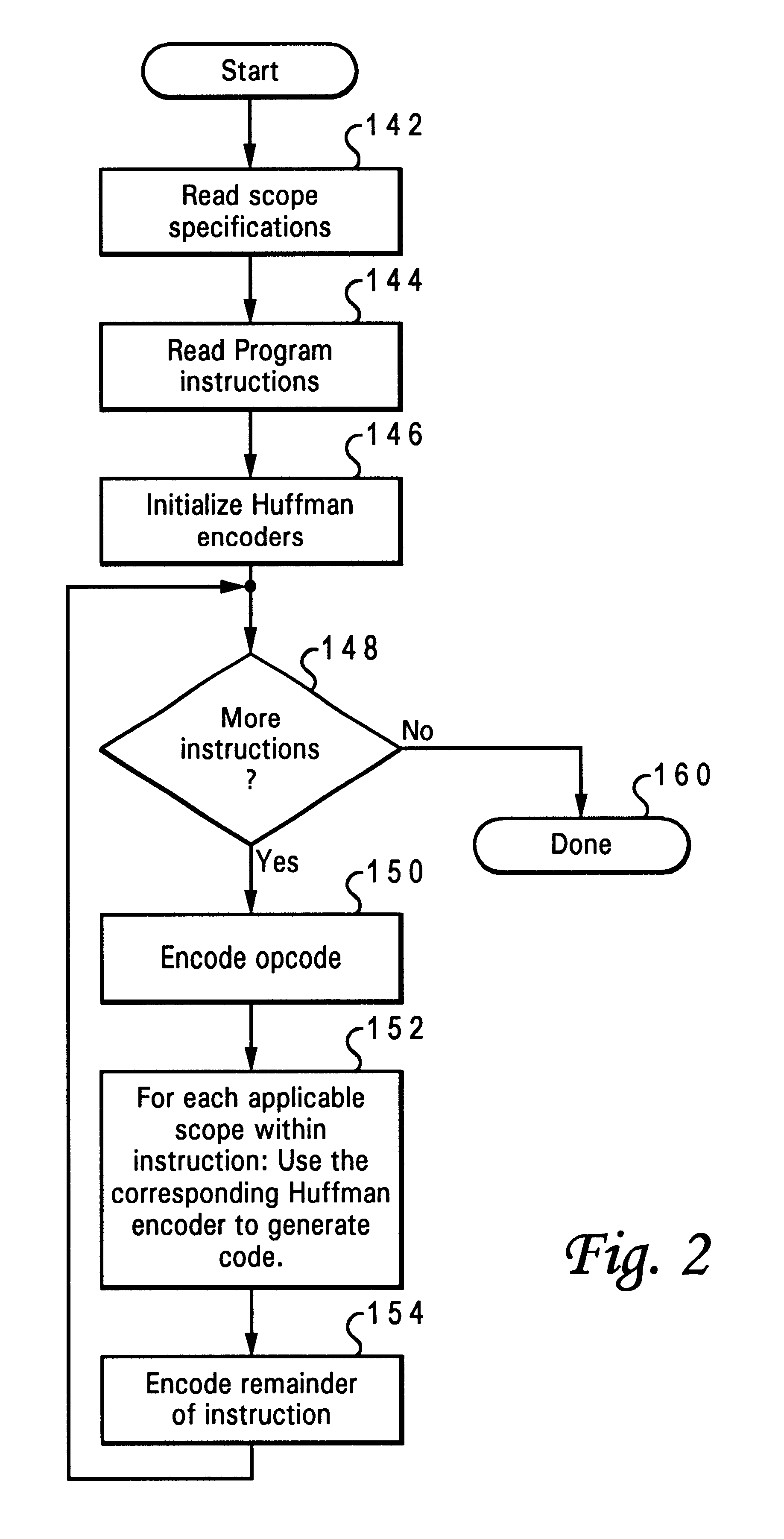

Method and system for scope-based compression of register and literal encoding in a reduced instruction set computer (RISC)

InactiveUS6233674B1Easy to compressEasily discerns the high pattern of usingSoftware engineeringRuntime instruction translationPowerPCProcessor register

A compression scheme for program executables that run in a reduced instruction set computer (RISC) architecture such as the PowerPC is disclosed. The method and system utilize scope-based compression for increasing the effectiveness of conventional compression with respect to register and literal encoding. First, discernible patterns are determined by exploiting instruction semantics and conventions that compilers adopt in register and literal usage. Additional conventions may also be set for register usage to facilitate compression. Using this information, separate scopes are created such that in each scope there is a more prevalent usage of a limited set of registers or literal value ranges, or there is an easily discernible pattern of register or literal usage. Each scope then is compressed separately by a conventional compressor. The resulting code is more compact because the small number of registers and literals in each scope makes the encoding sparser than when the compressor operates on the global scope that includes all instructions in a program. Additionally, scope-based compression reveals more frequent patterns within each scope than when considering the entire instruction stream as an opaque stream of bits.

Owner:IBM CORP

High performance network tester and the testing method thereof

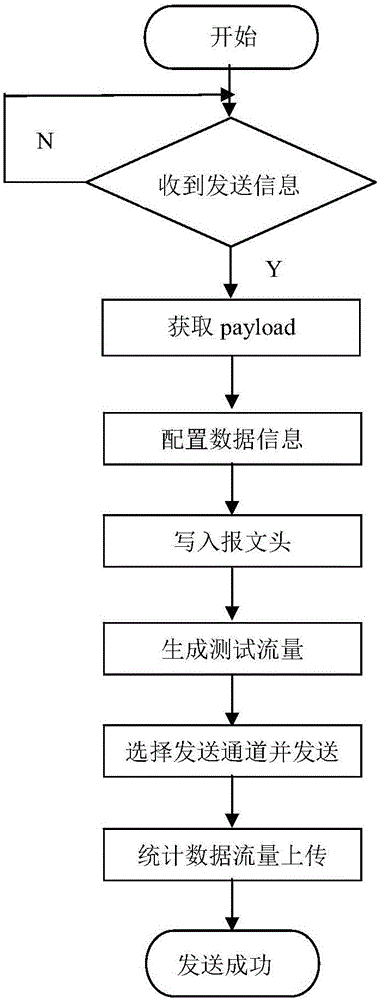

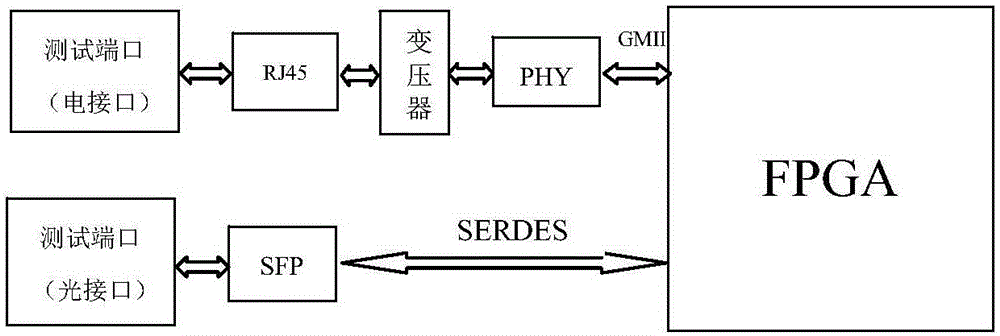

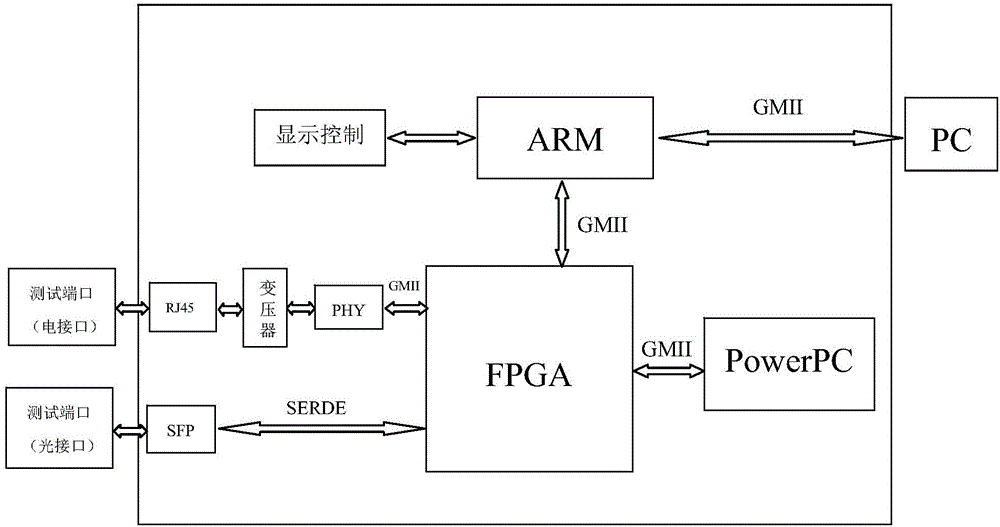

ActiveCN105099828ASupport parsingEasy compatibilityData switching networksTraffic capacityNetworking protocol

The invention discloses a high performance network tester and a testing method of the high performance network tester with the adoption of a FPGA+PowerPC+ARM framework. The network tester comprises a RJ45 interface, a transformer, a physical interface (PHY), an optical interface SFP, an FPGA, a PowerPC, an ARM and a display control device. The FPGA completes the generation and reception of testing flows, conducts analysis of a first layer message and a second layer message, controls the FPGA and surveys the first layer message and the second layer message; the PowerPC conducts analysis of a network protocol on a third layer or layers above; the ARM communicates with a computer to realize the display and control of entire equipment. According to the invention, the network tester puts together the advantages of three processors. The network tester is provided with high flexibility and is cost-effective to make. The tester is also compatible with a variety of interfaces and has strong expansibility.

Owner:NANJING UNIV OF SCI & TECH +1

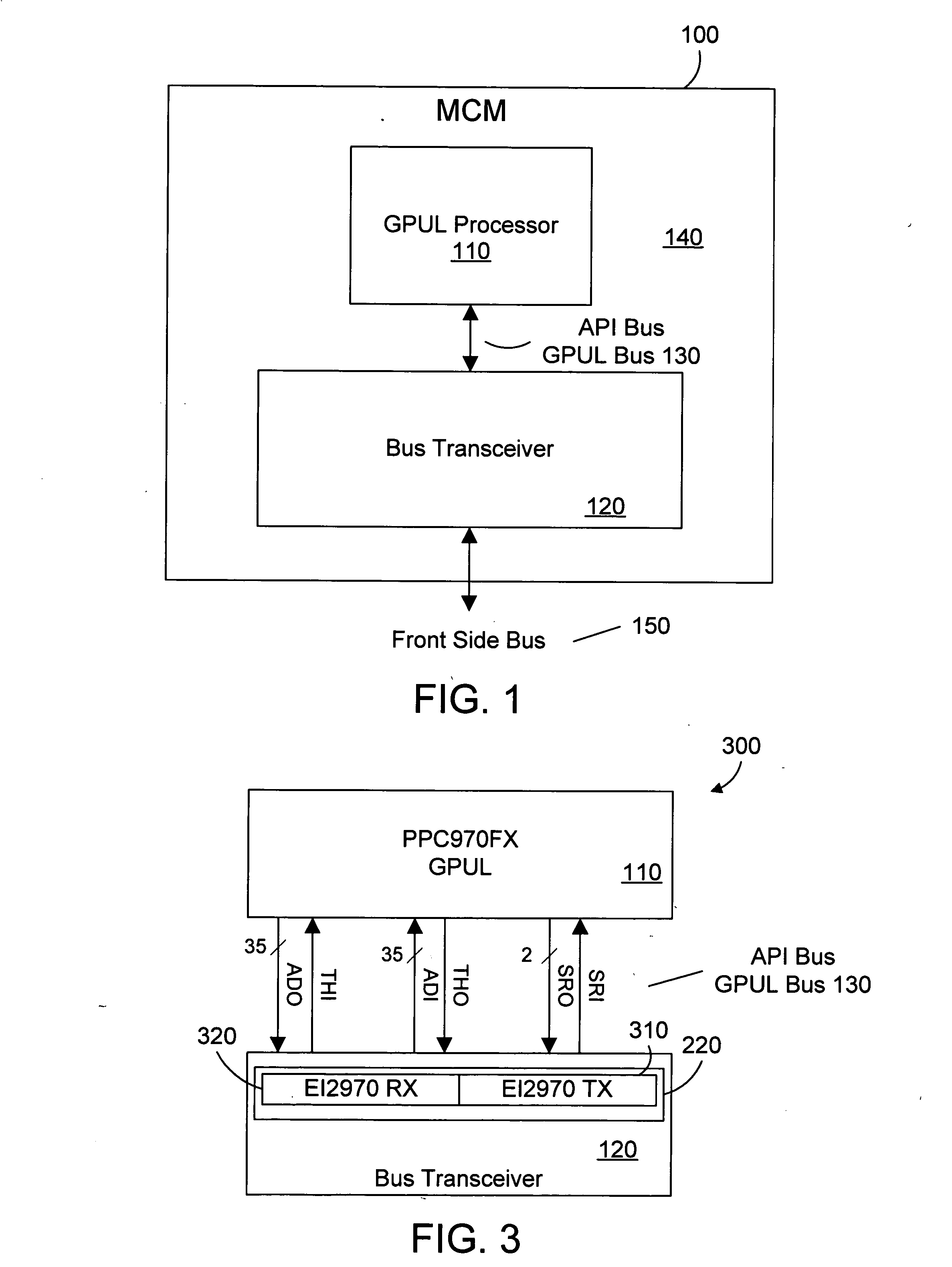

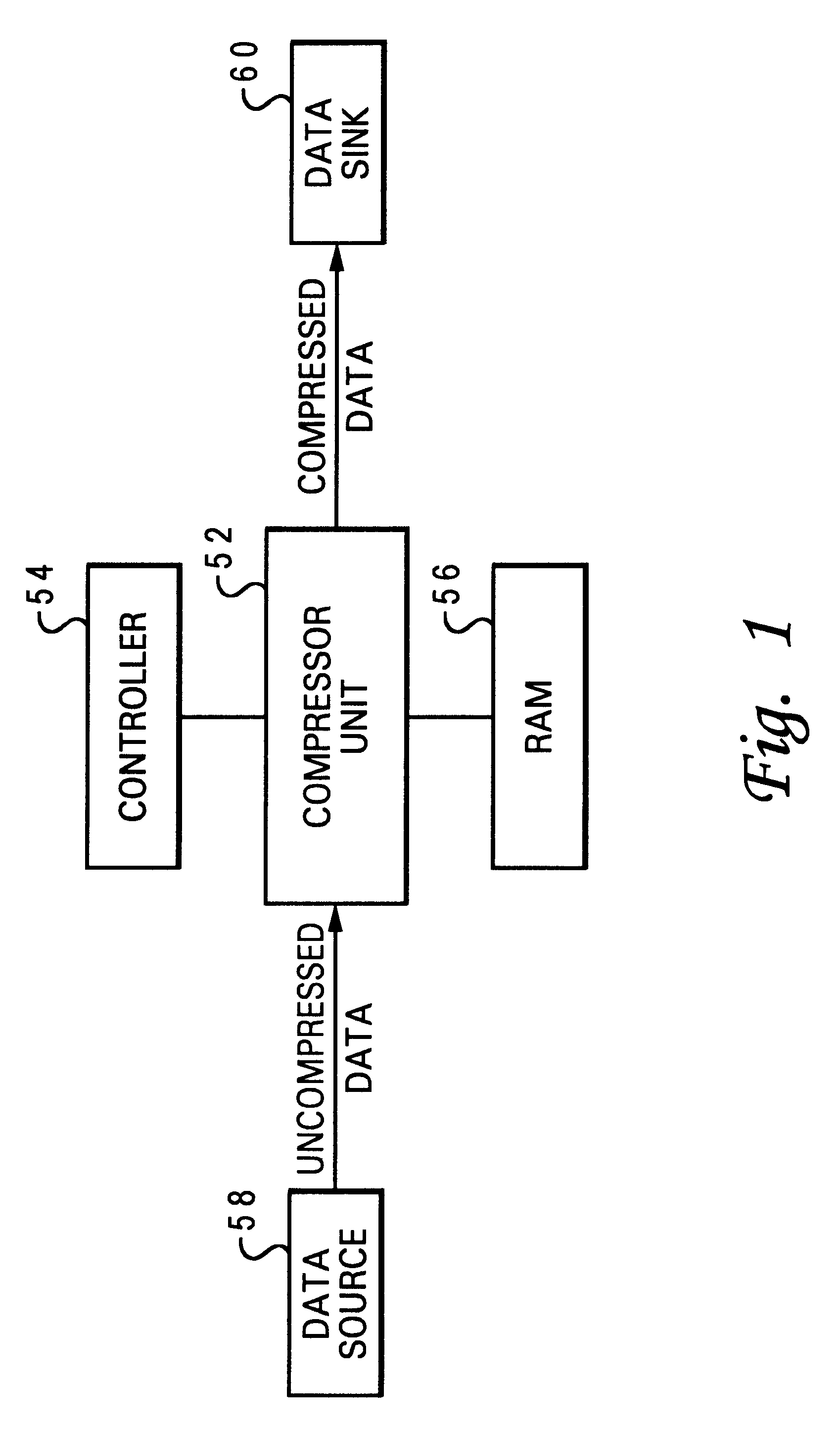

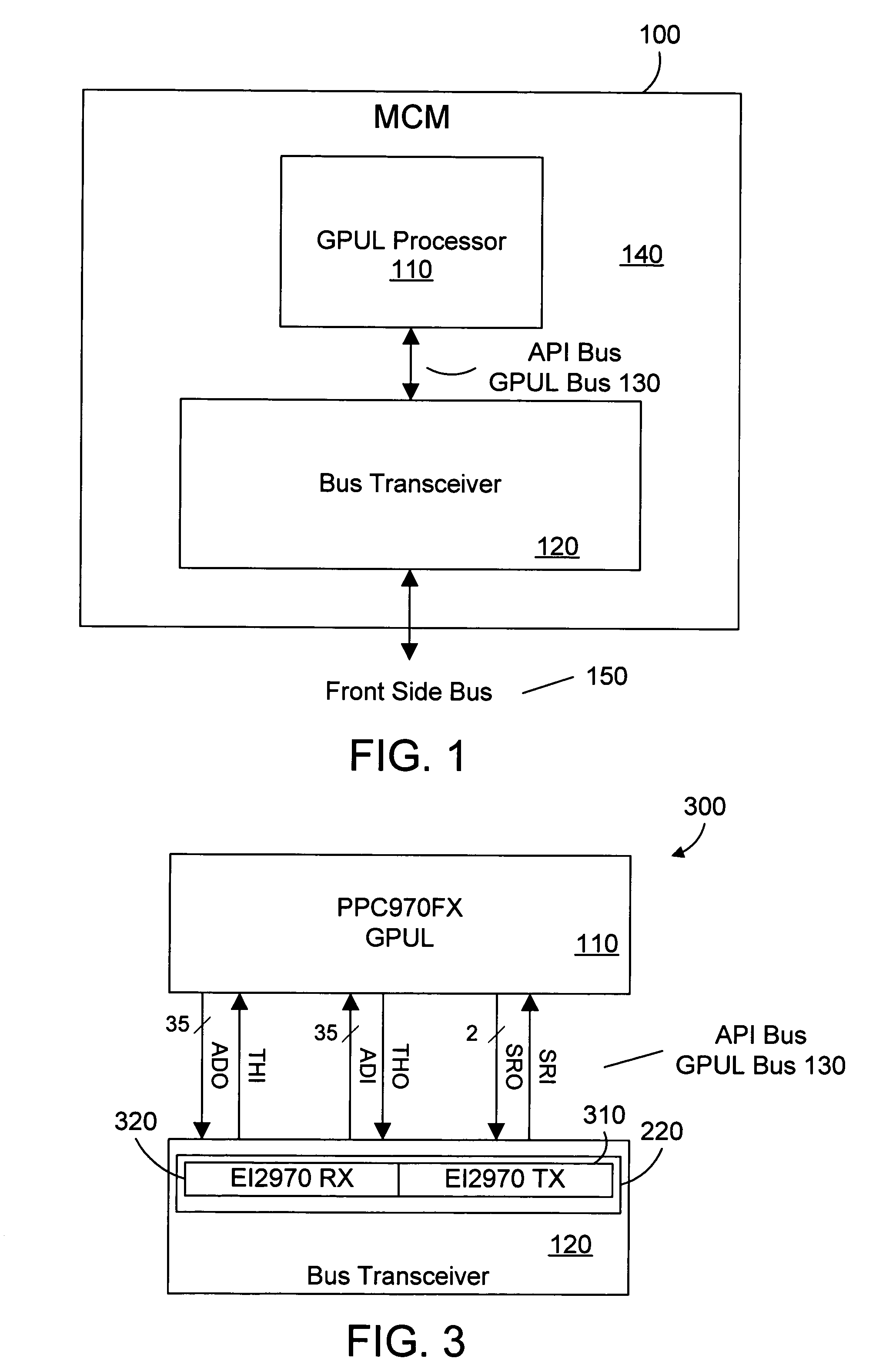

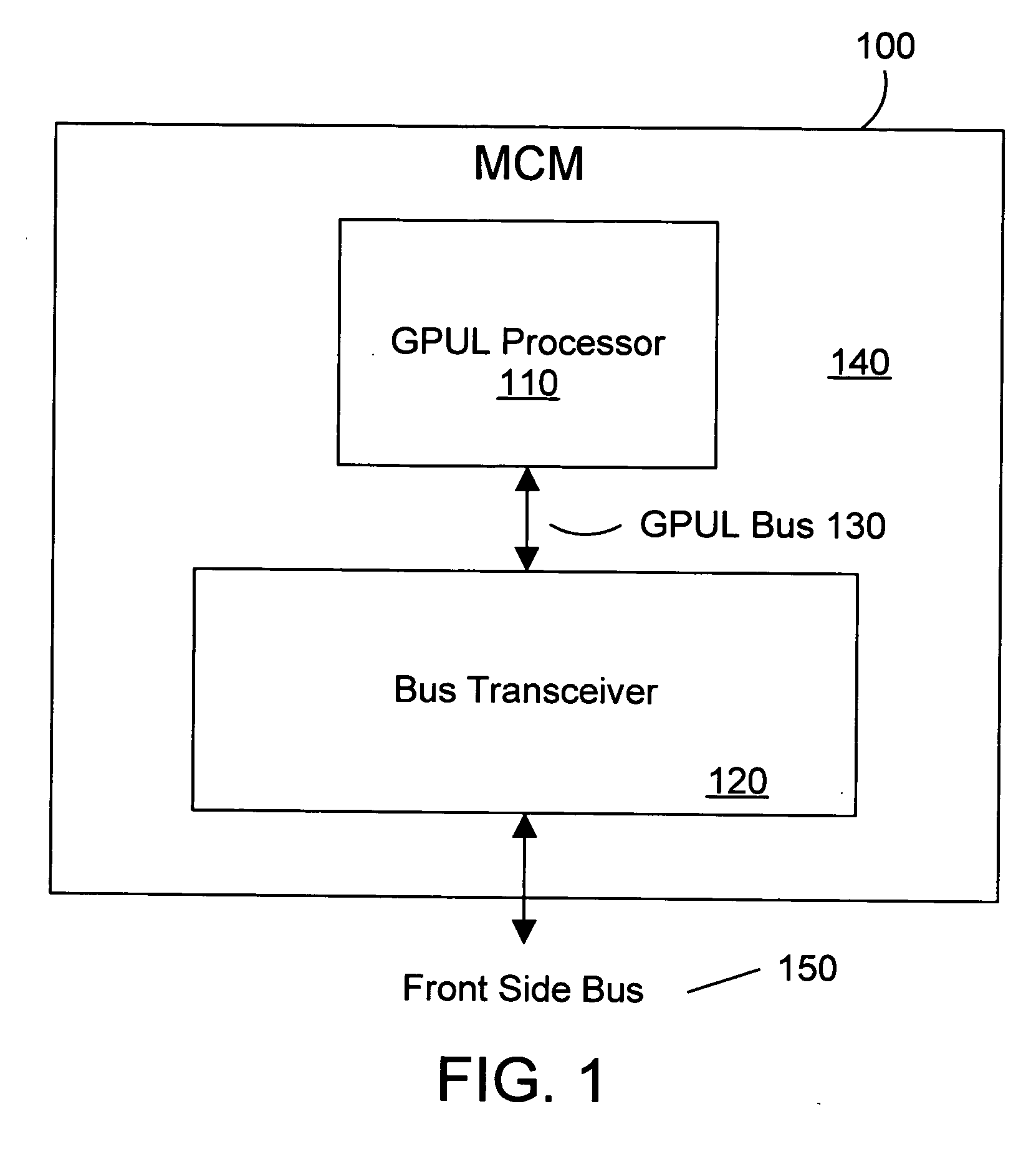

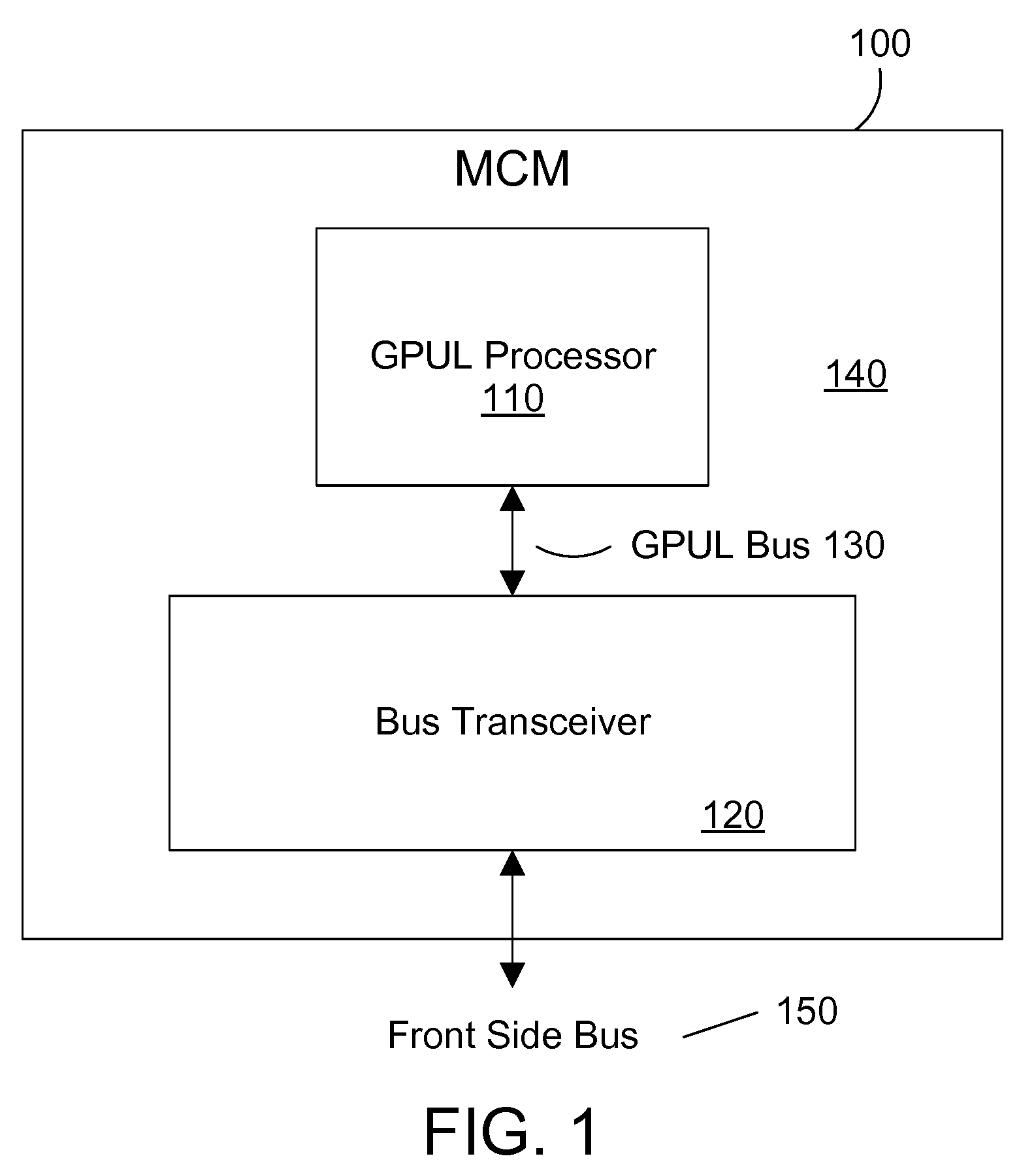

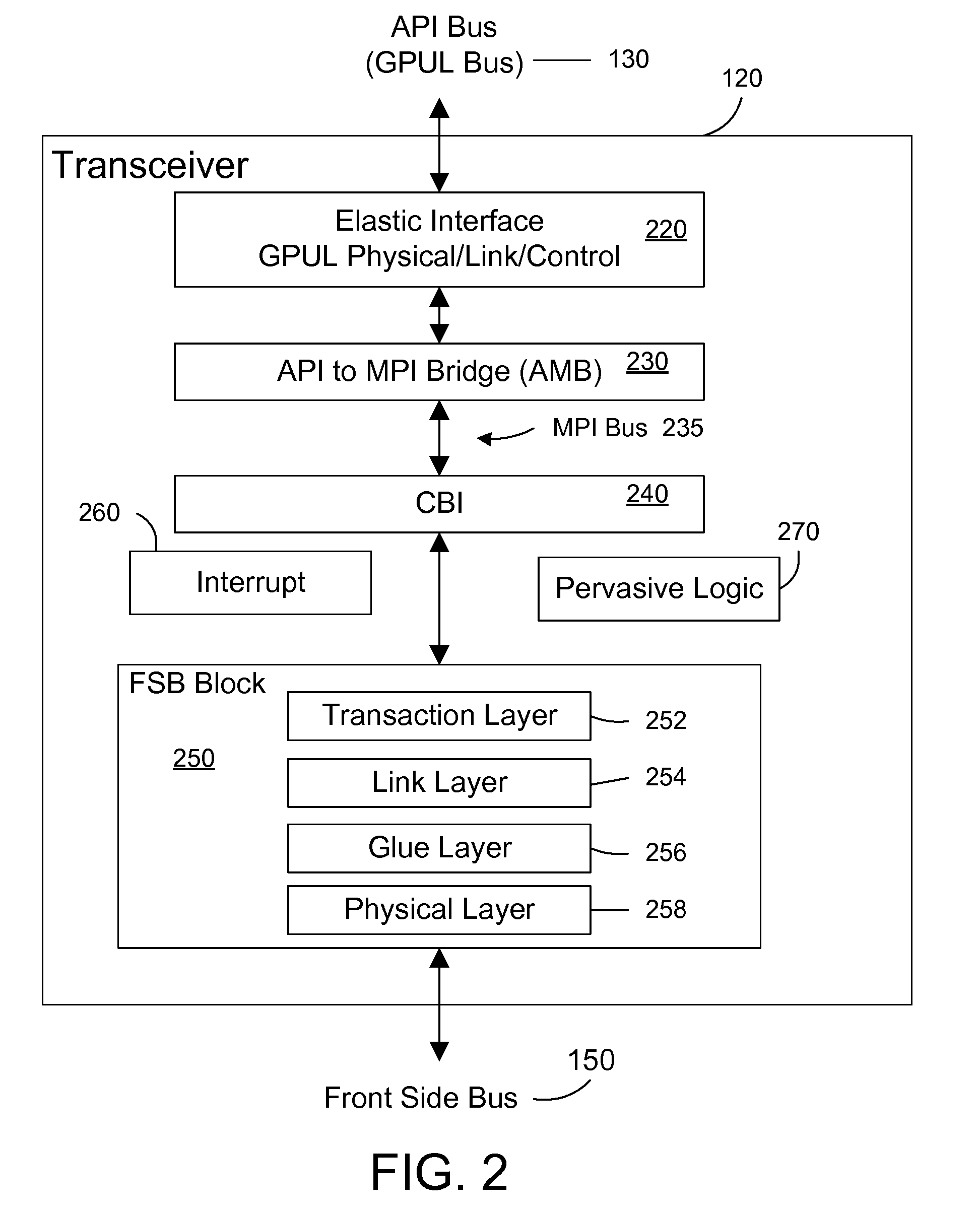

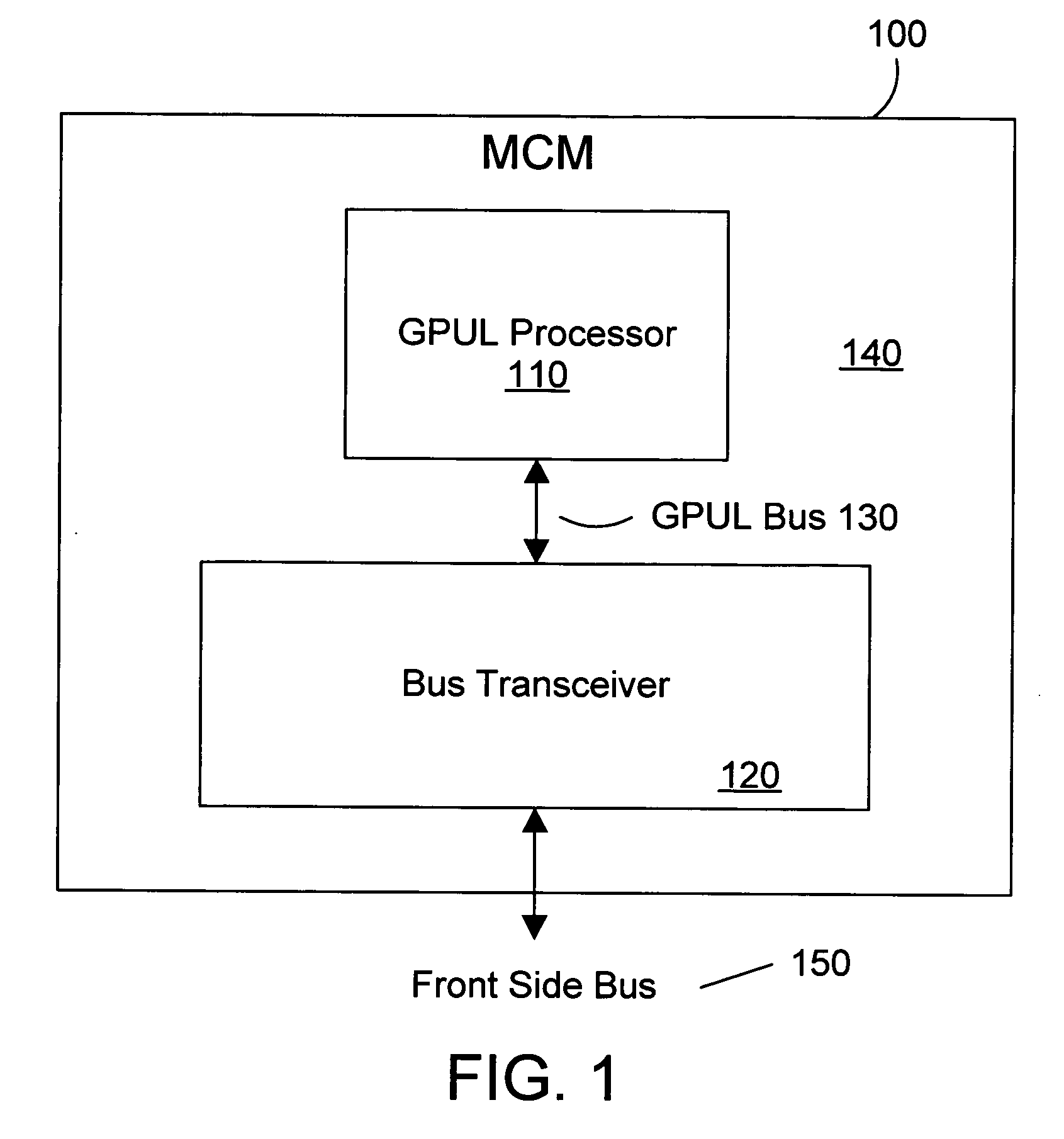

Computer system architecture

A high speed computer processor system has a high speed interface for a graphics processor. A preferred embodiment combines a PowerPC microprocessor called the Giga-Processor Ultralite (GPUL) 110 from International Business Machines Corporation (IBM) with a high speed interface on a multi-chip module.

Owner:IBM CORP

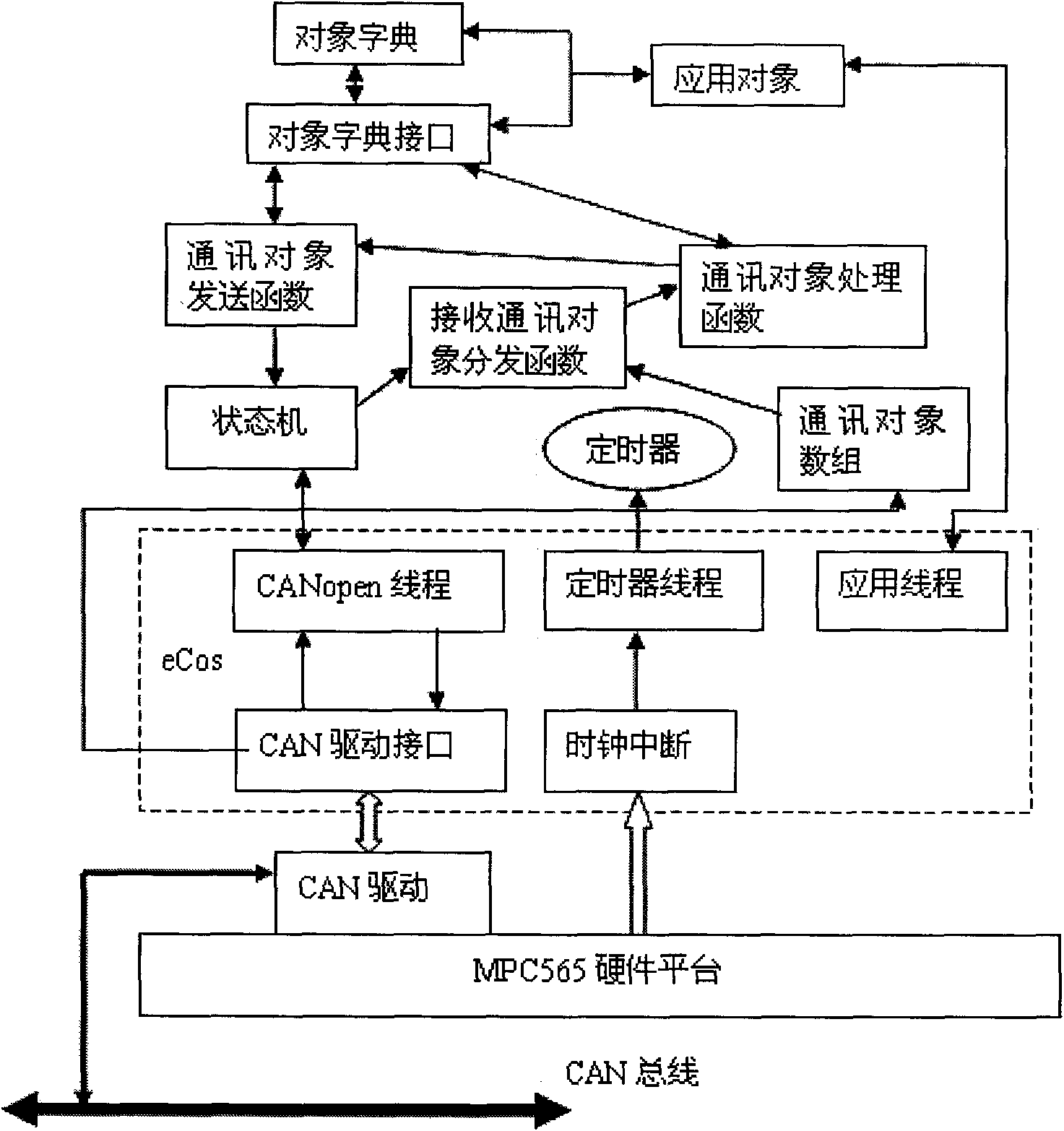

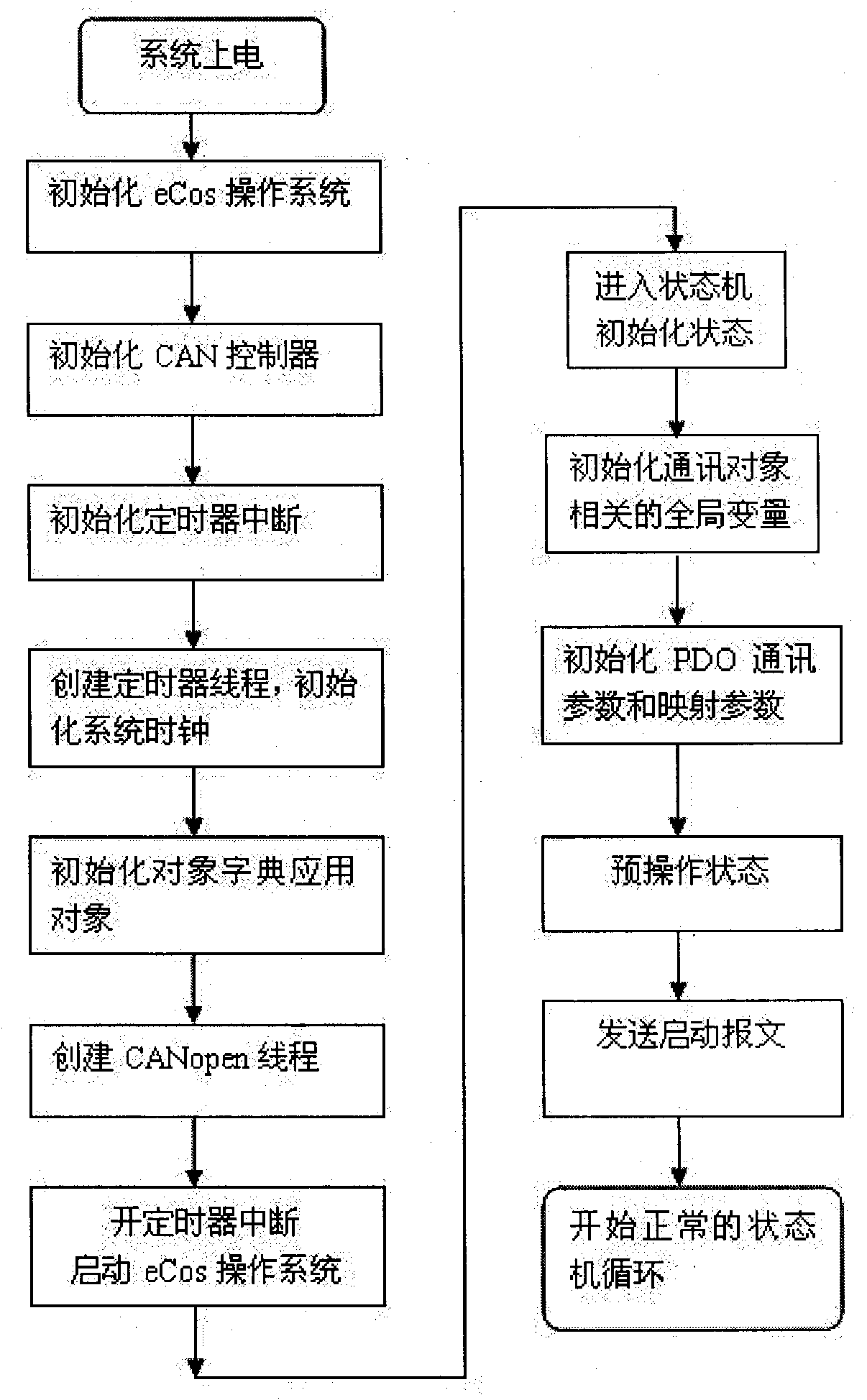

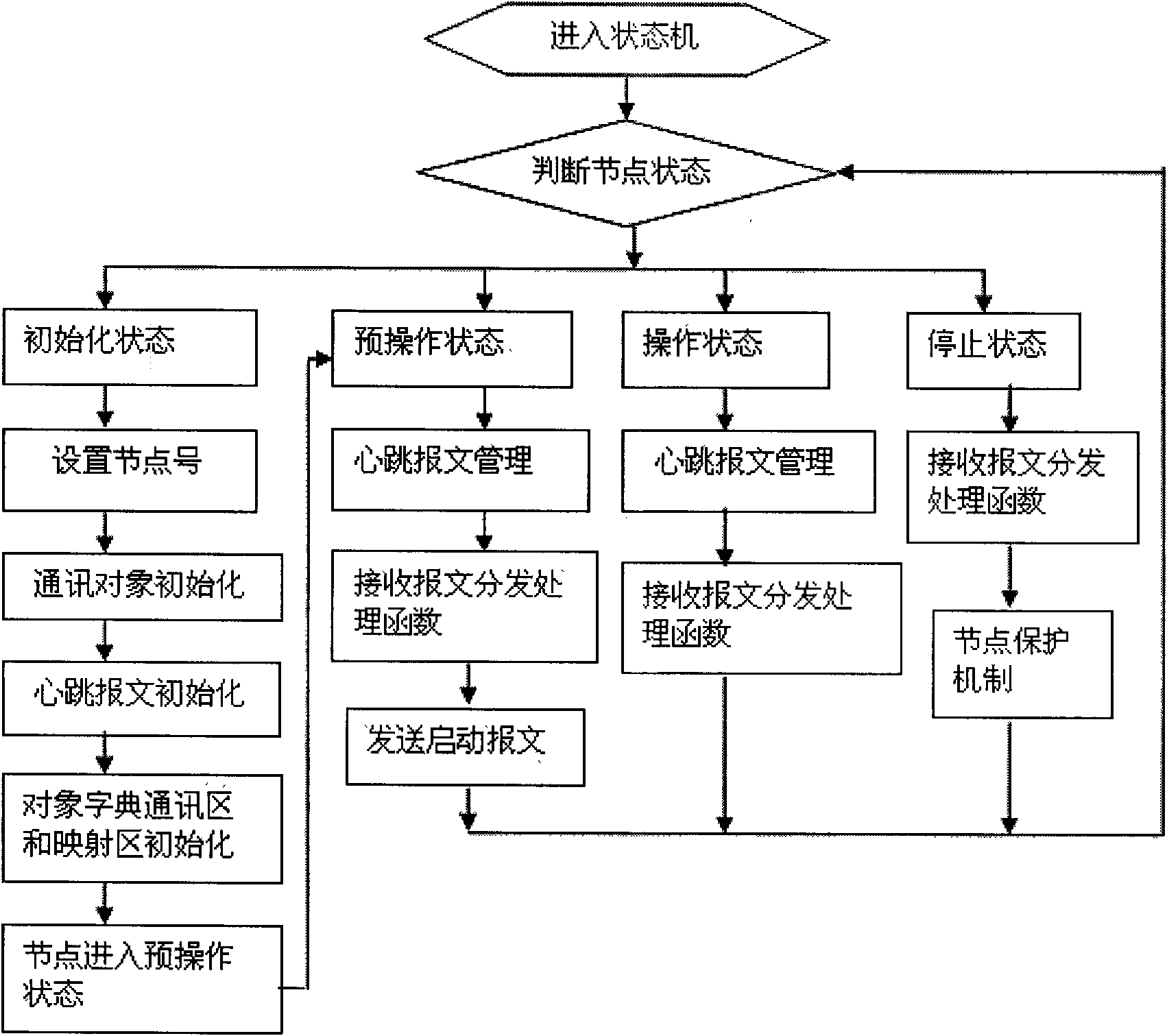

Method for realizing CANopen slave station

InactiveCN101854300AEnsure real-time requirementsNarrow searchBus networksOperational systemReal-time data

The invention relates to a method for realizing a CANopen slave station, which is characterized in that: a hardware platform realized by the slave station is a PowerPC-based processor; a multi-thread system is constructed on an eCos operating system and comprises a CANopen state machine thread, a timer thread and message reading interruption; the state machine thread is used for managing CANopen basic tasks such as switching the state of the slave station, receiving CAN message, receiving and transmitting CAN messages, PDO messages and SDO messages, processing the PDO, SDO, NMT and synchronous messages and the like; and an earliest deadline first (EDF) dynamic scheduling algorithm is introduced into the synchronous PDO messages for transmitting real-time data so as to ensure the requirement of low-priority messages on instantaneity and improve the communication characteristic of a bus. The eCos embedded real-time operating system is applied to the design of the slave station, so the instantaneity and concurrent processing capacity are high; the dynamic scheduling algorithm is introduced into the design of the synchronous PDO messages in the CANopen slave station, so the requirement of the low-priority messages on instantaneity is ensured; and an object dictionary meets the flexible configuration of a network, and objects in the object dictionary are changed according to the dynamic change of a master station.

Owner:BEIJING UNIV OF TECH

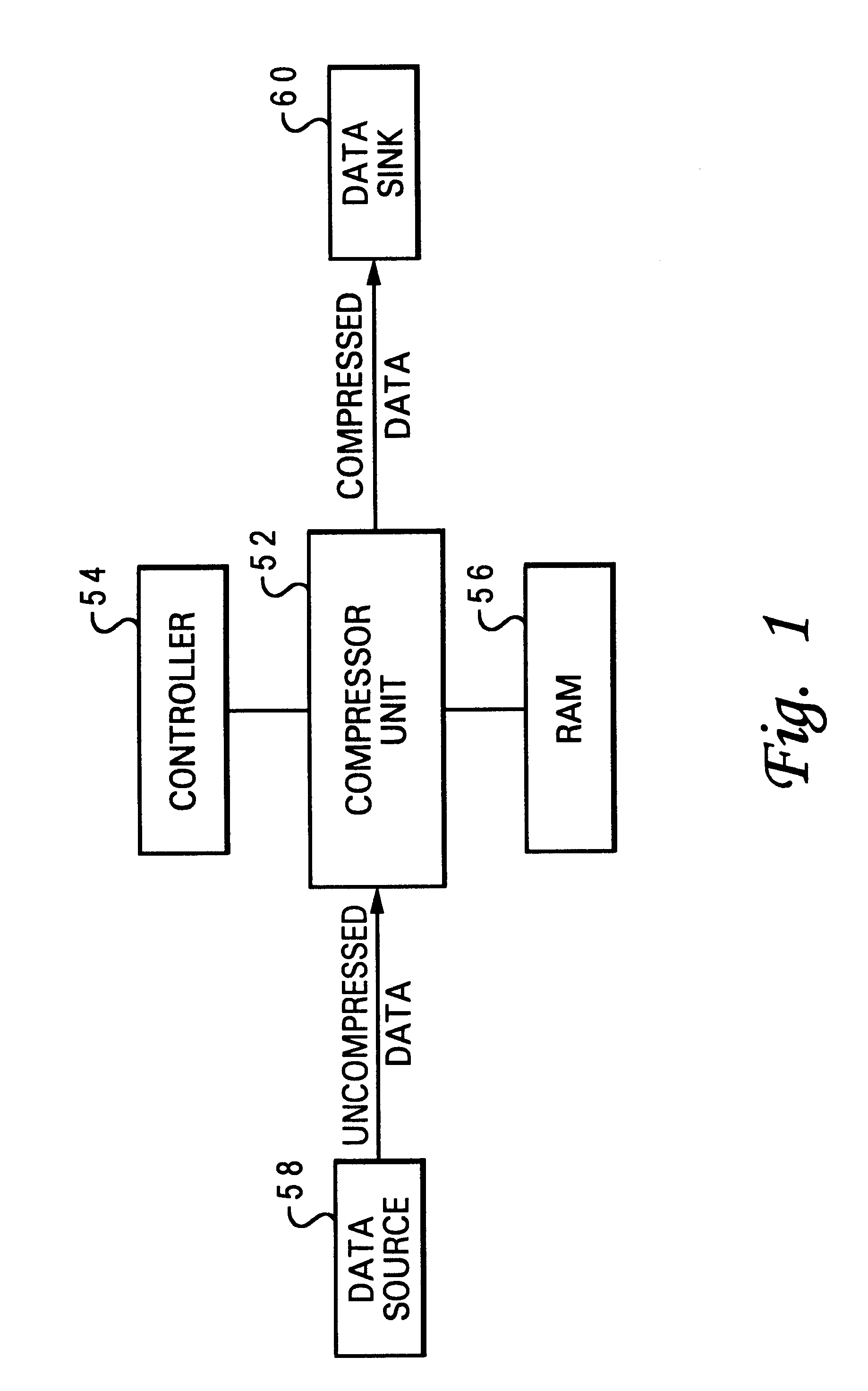

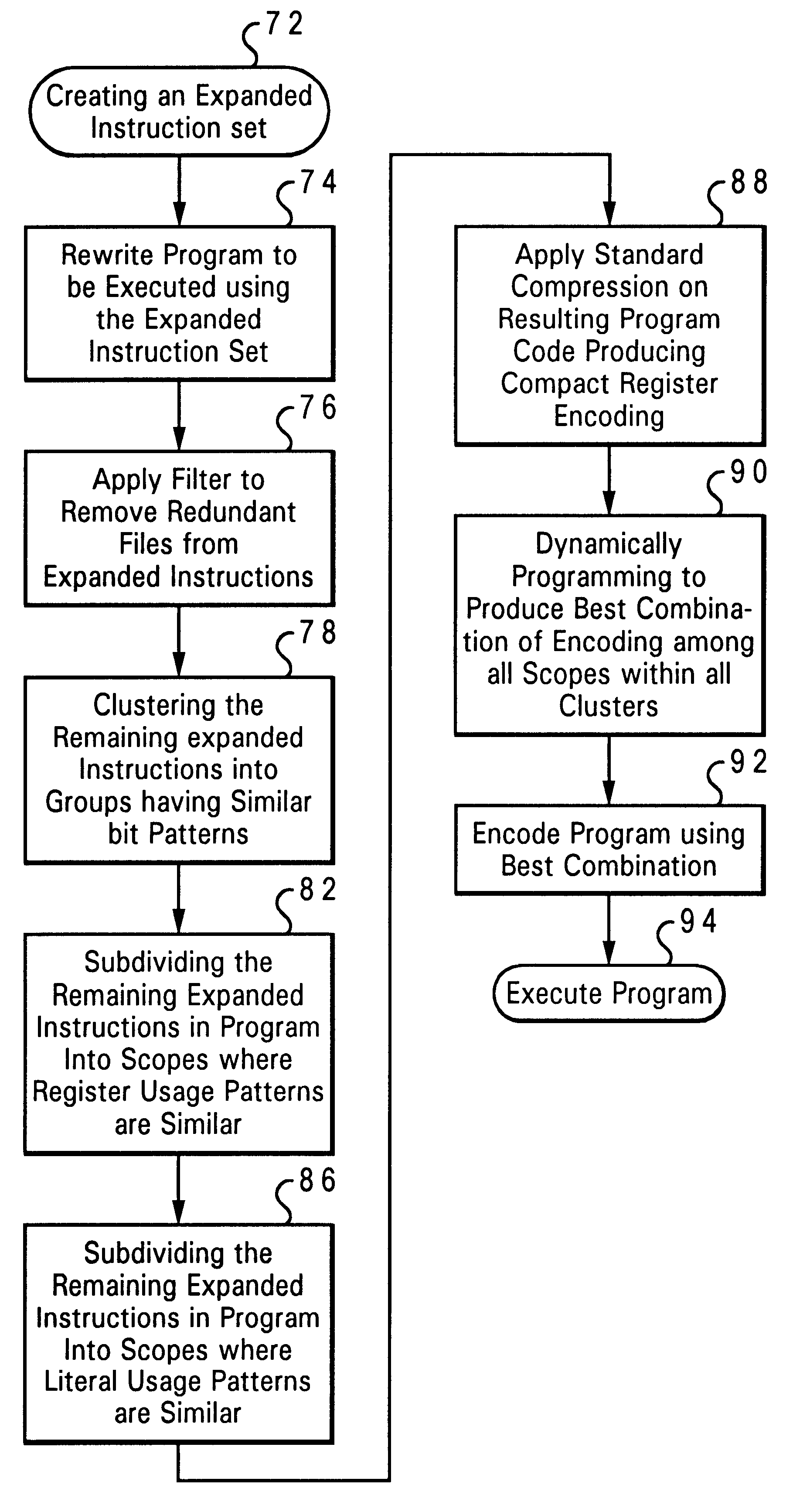

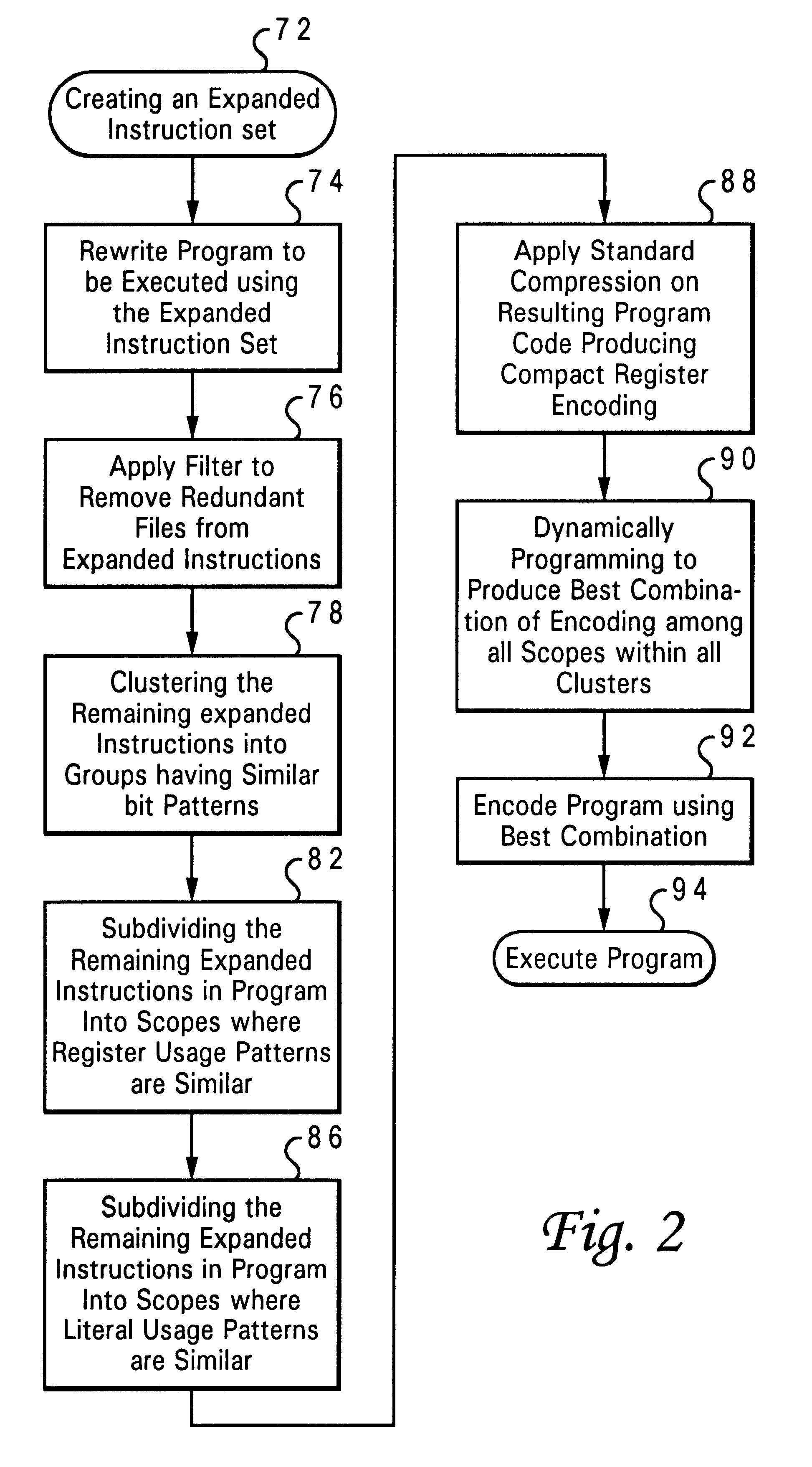

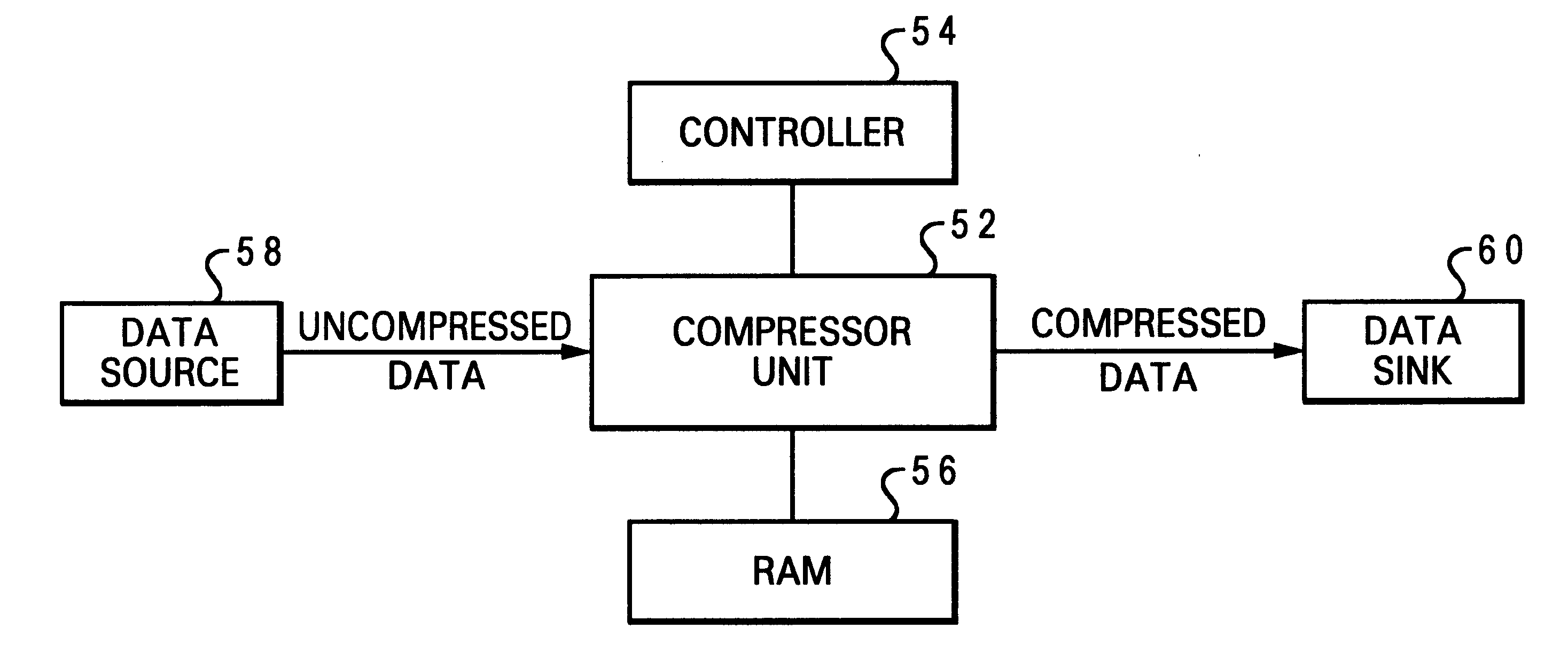

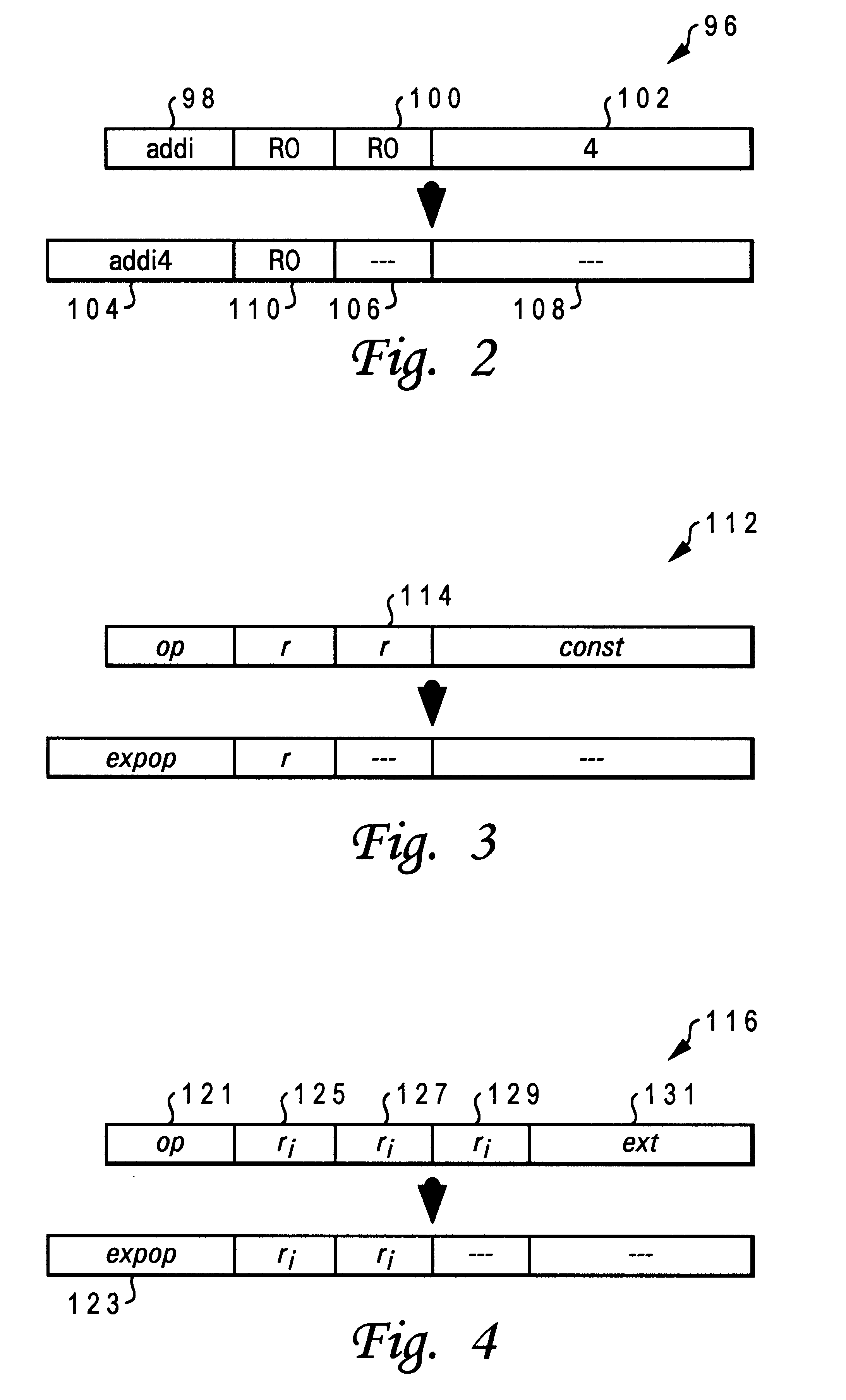

Method and system for compressing reduced instruction set computer (RISC) executable code

InactiveUS6442680B1Eliminate redundancySoftware engineeringDigital computer detailsPowerPCProcessor register

A method and system for a compression scheme used with program executables that run in a reduced instruction set computer (RISC) architecture such as the PowerPC is disclosed. Initially, a RISC instruction set is expanded to produce code that facilitates the removal of redundant fields. The program is then rewritten using this new expanded instruction set. Next, a filter is applied to remove redundant fields from the expanded instructions. The expanded instructions are then clustered into groups, such that instructions belonging to the same cluster show similar bit patterns. Within each cluster, the scopes are created such that register usage patterns within each scope are similar. Within each cluster, more scopes are created such that literals within each instruction scope are drawn from the same range of integers. A conventional compression technique such as Huffman encoding is then applied on each instruction scope within each cluster. Dynamic programming techniques are then used to produce the best combination of encoding among all scopes within all the different clusters. Where applicable, instruction scopes are combined that use the same encoding scheme to reduce the size of the resulting dictionary. Similarly instruction clusters are combined that use the same encoding scheme to reduce the size of the resulting dictionary.

Owner:IBM CORP

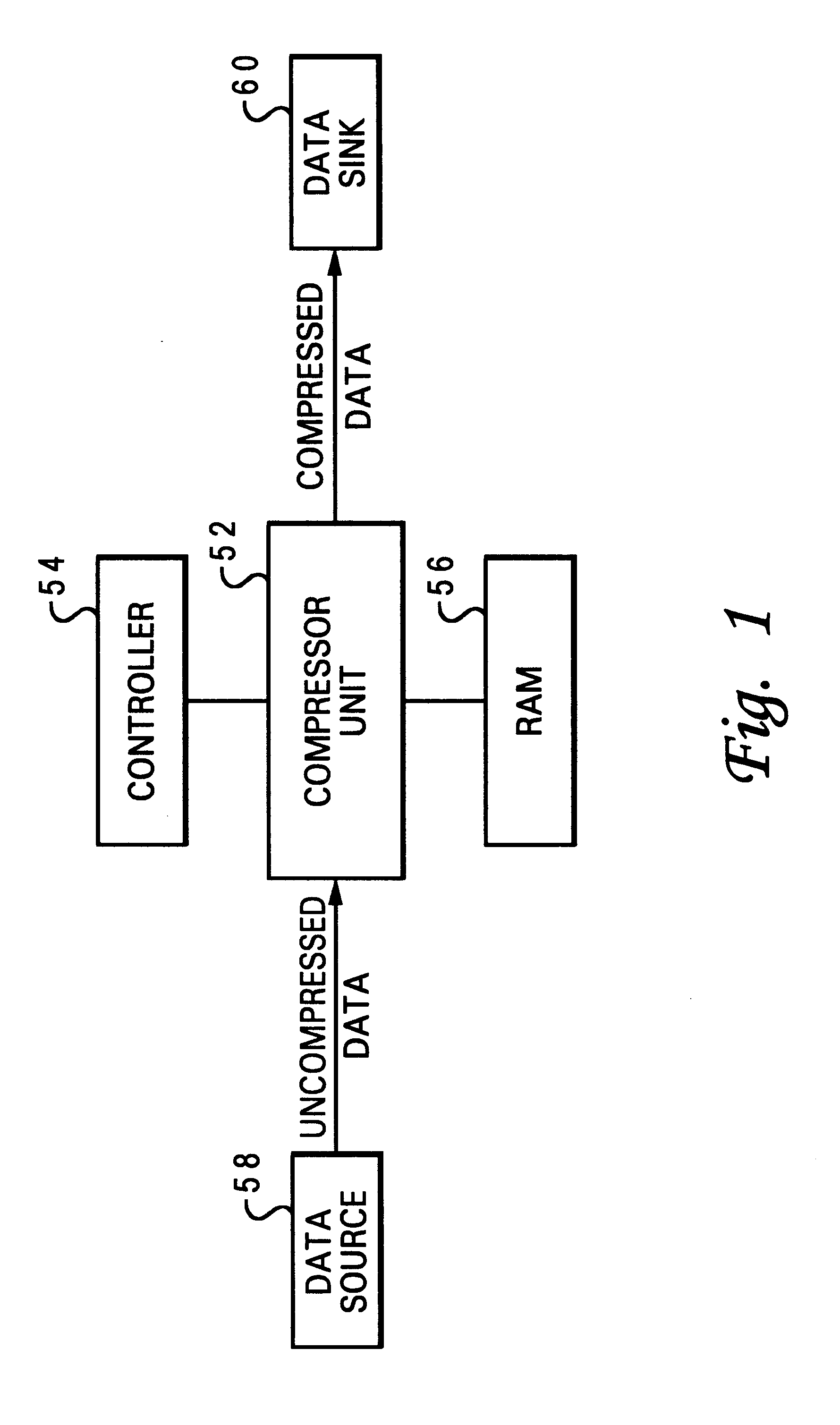

Method and system for compressing reduced instruction set computer (RISC) executable code through instruction set expansion

A compression scheme is disclosed for program executables that run on Reduced Instruction Set Computer (RISC) processors, such as the PowerPC architecture. The RISC instruction set is expanded by adding opcodes to produce code that facilitates the removal of redundant fields. To compress a program, a compressor engine rewrites the executable using the new expanded instruction set. Next, a filter is applied to remove the redundant fields from the expanded instructions. A conventional compression technique such as Huffman encoding is then applied on the resulting code.

Owner:IBM CORP

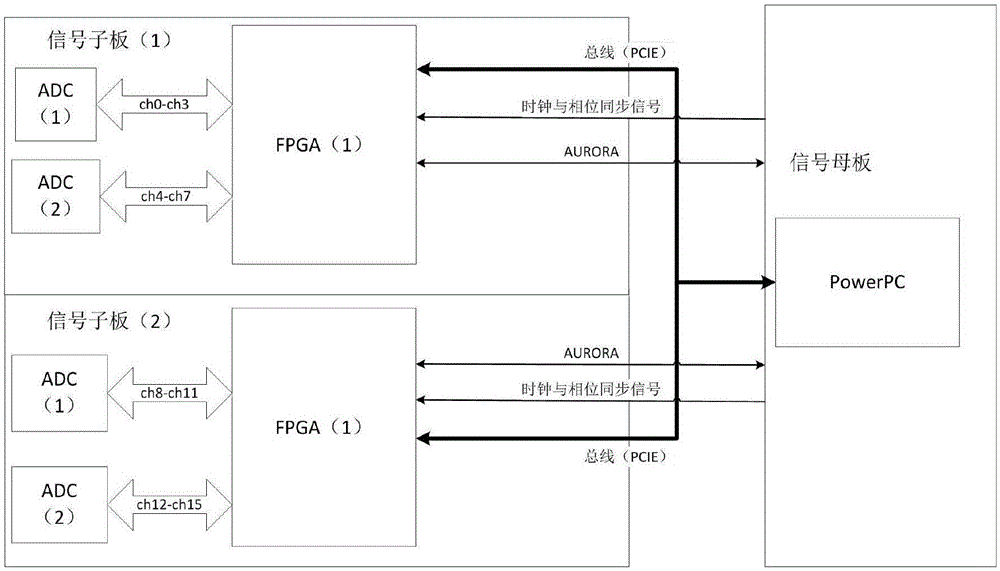

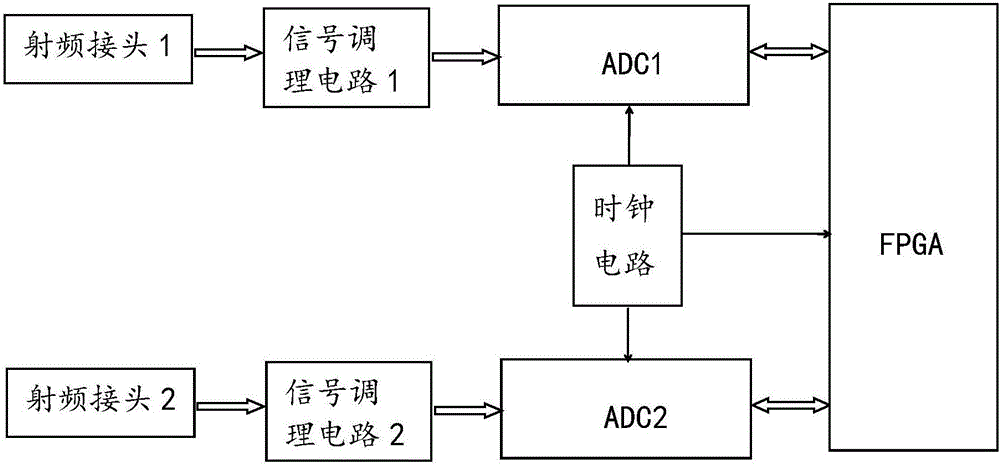

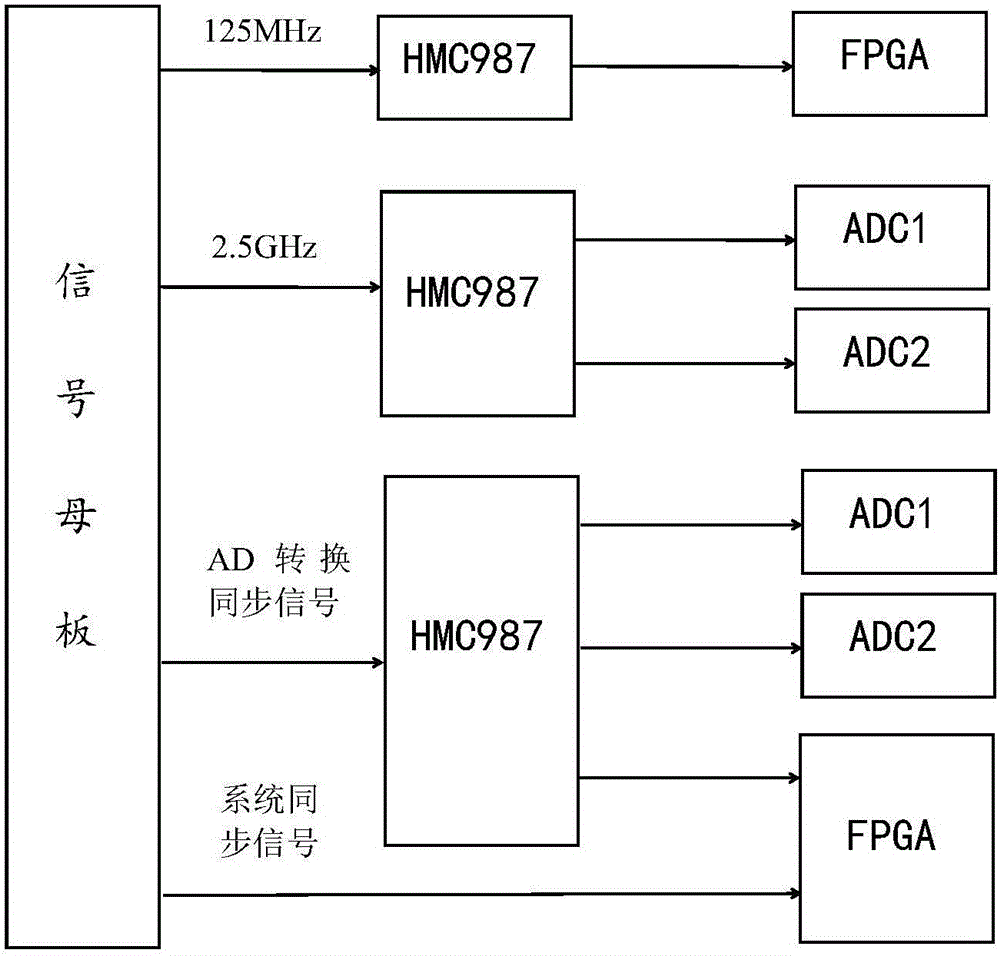

Multi-channel high-speed AD system based on FPGA and PowerPC

InactiveCN106374927ALarge wiring error toleranceImprove portabilityAnalogue-digital convertersPowerPCOperation mode

The invention relates to a multi-channel high-speed AD system based on an FPGA and a PowerPC. The system comprises a signal mother board based on the PowerPC and at least two signal daughter boards based on the FPGA, which are connected to the signal mother board, wherein the signal mother board provides synchronization pulse for the signal daughter boards, configuring ADC sampling parameters and sending an instruction of switching a synchronization operation and an actual sampling work mode; the signal daughter boards complete switching of the sampling operation mode and the synchronization operation according to the received instruction and transmit the collected data to the signal mother board through an SERDES interface, and the different signal daughter boards remain synchronous after the signal daughter boards return the data to the mother board. The system can stably work at a sampling frequency of 1.25 G, the synchronization error between the boards and in the boards can be within 80 ps, the system can be widely used in the fields with higher requirements for the sampling frequency and the need of precise synchronization of multi-channel signals, and meanwhile, the system has the characteristics of high transportability and large hardware routing error margin.

Owner:CHENGDU GOLDENWAY ELECTRONICS

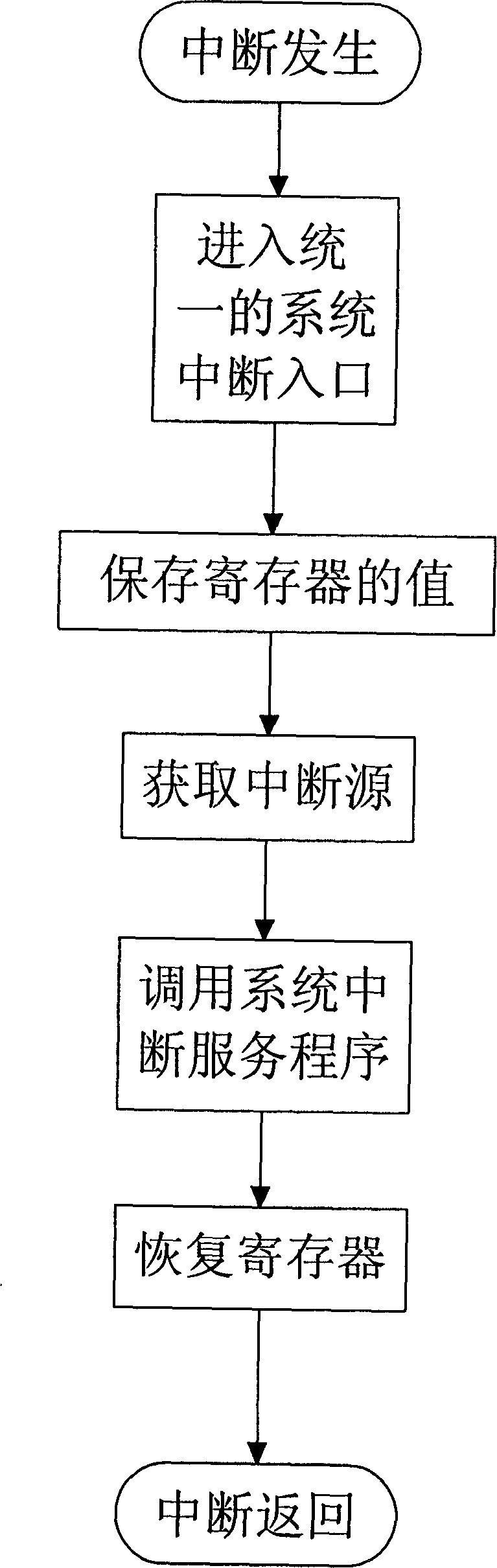

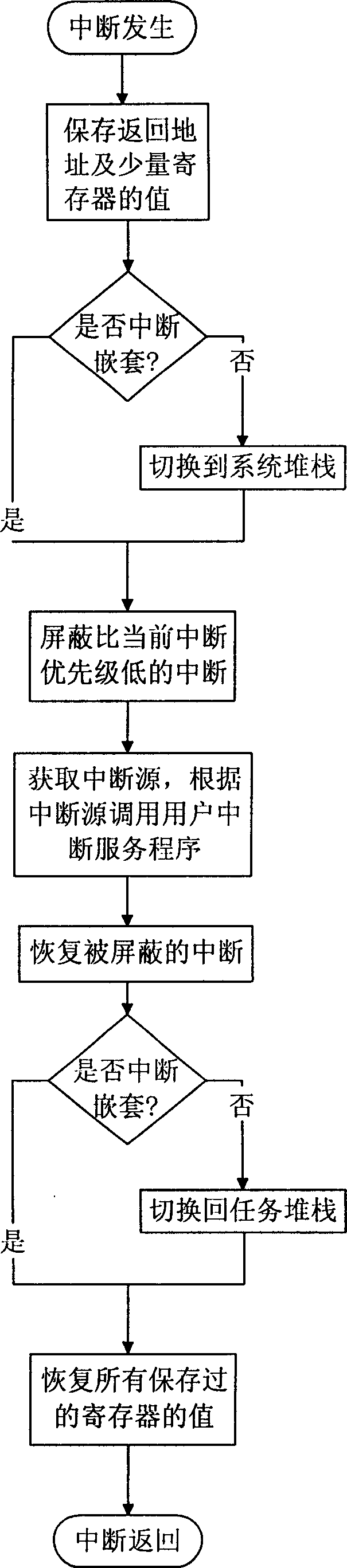

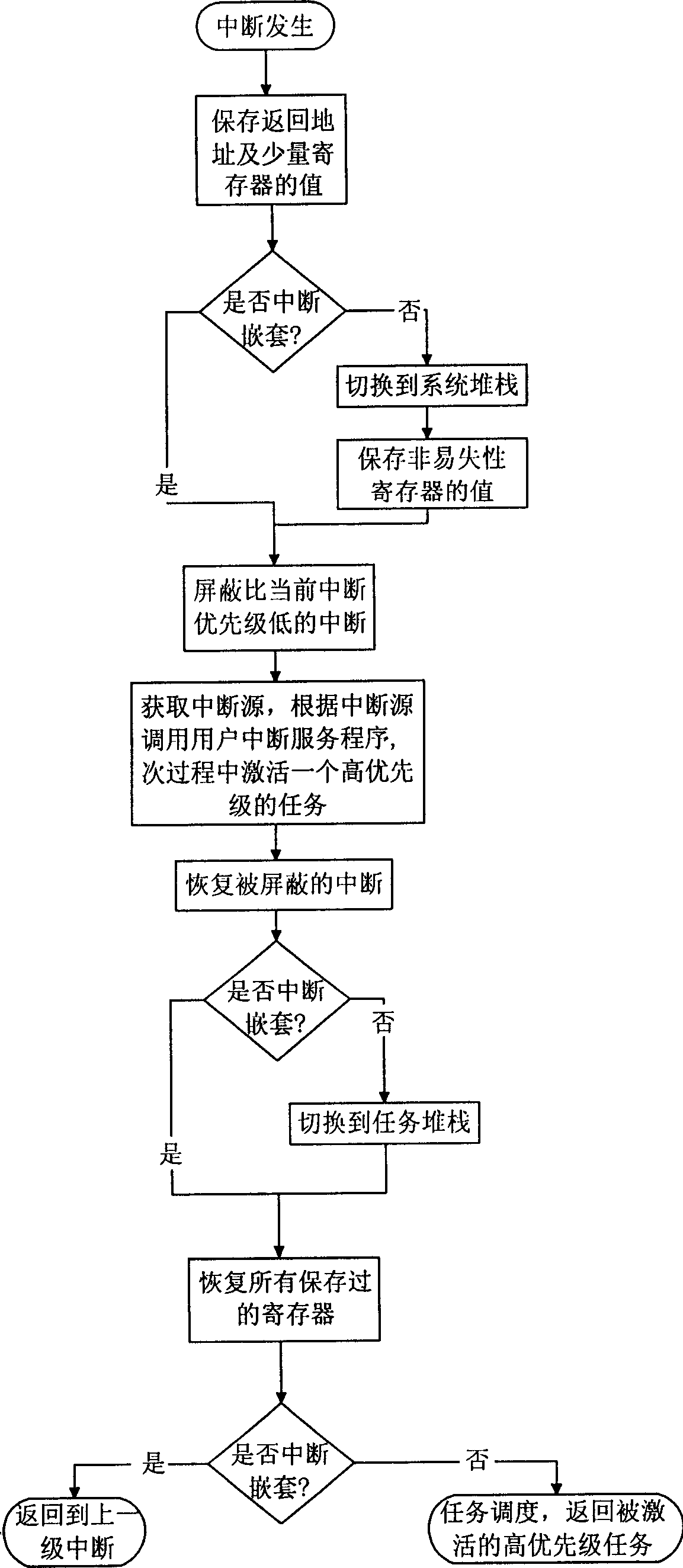

Interrupt managing method for embedded operation system based on PowerPC system structure

InactiveCN1783020APrevent executionImprove execution efficiencyProgram initiation/switchingOperational systemPowerPC

The interrupt management method for embedded operation system based on PowerPC system structure includes the following steps: dividing interrupts into two classes of system interrupt and user interrupt and dividing user interrupt service programs into class-I interrupt service program and class-II interrupt service program; first hardware responding the user interrupt; then, maintaining the context, stack switching and interrupt nesting for resuming the interrupted task after interrupt treatment; finding out and calling corresponding interrupt service program from the user interrupt vector list via the interrupt source; and maintaining the interrupt nesting and stack switching, restoring the context for the treater to resume the interrupted task. The present invention has the advantages of raised interrupt executing efficiency, raised interrupt utilizing efficiency, convenient interrupt control and use, raised user stack size controllability and predicting property.

Owner:ZHEJIANG UNIV

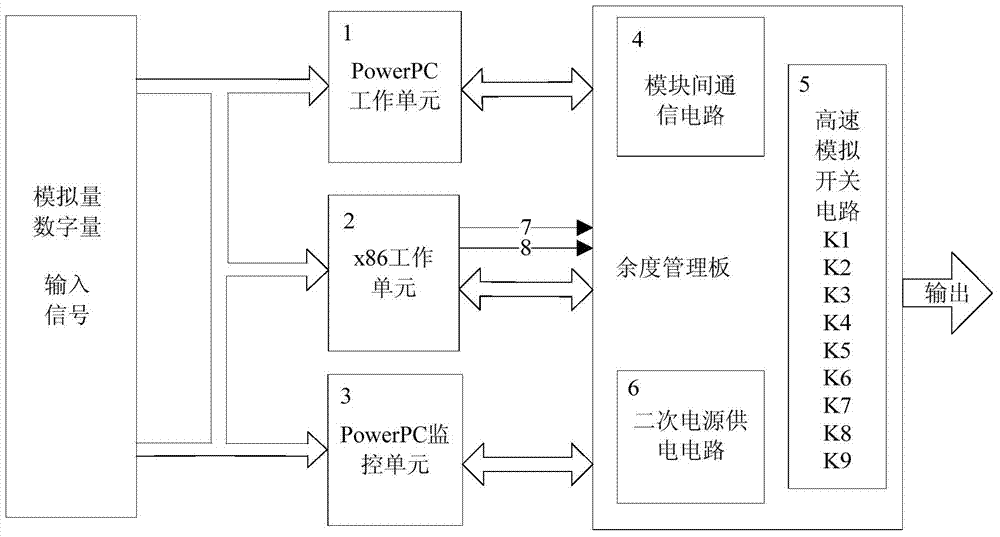

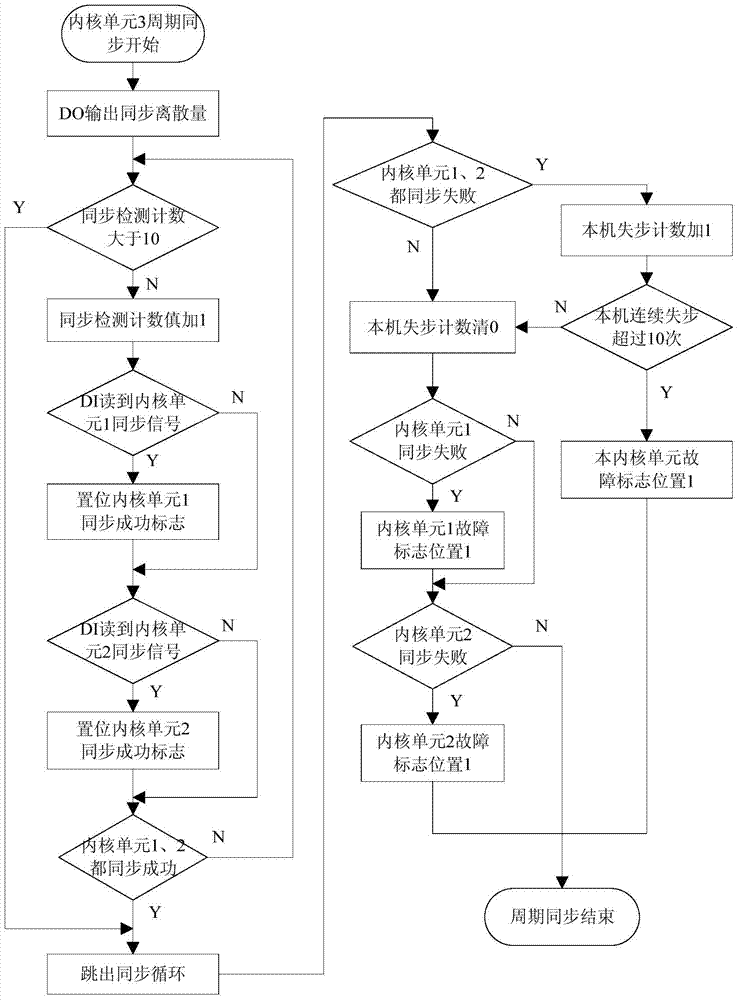

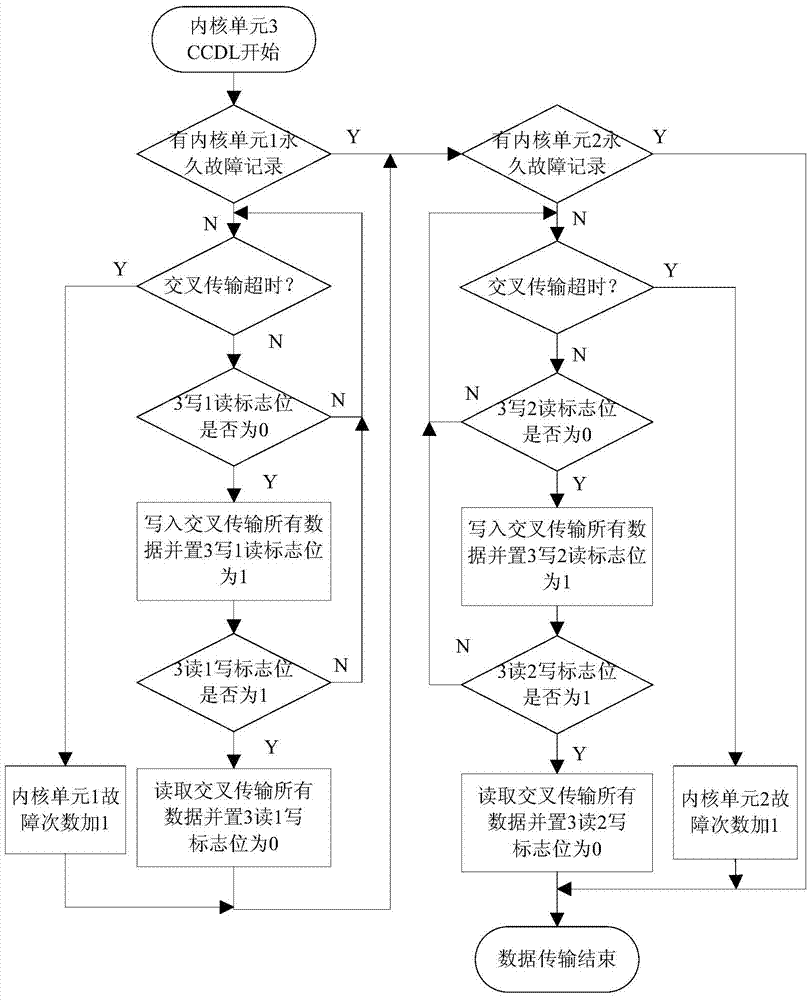

PowerPC and x86 based hybrid tri-redundancy UAV flying control computer and core design method

InactiveCN104749949AAvoiding Common State Fault ProblemsAvoid random failure problemsSafety arrangmentsFly controlPowerPC

The invention provides a PowerPC and x86 based hybrid tri-redundancy UAV flying control computer and a core design method. The PowerPC and x86 based hybrid tri-redundancy UAV flying control computer is that the hardware comprises three flying control computer core units and a redundancy managing plate, wherein the three flying control computer core units adopt 32-bit processors MPC565 and 80486 as the control cores; the redundancy managing plate comprises an inter-module communication circuit, a high-speed analog switch circuit and a secondary power supply circuit; the three flying control computer core units share the external input / output interfaces and devices; the sensor data are synchronously acquired in each control cycle so as to perform control rules resolving; the inter-module communication circuit performs data exchange; a monitoring core unit performs validity arbitration or the data according to the arbitration algorithm, then the high-speed analog switch controls some core unit output as a control signal of a performing mechanism. The computer is applied to the flying control of an UAV under an onboard environment and has the characteristics of being convenient to detect fault, accurate to position the fault, reliable in data exchange, and high in performance, stability and reliability of the system in three-machine parallel operation.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

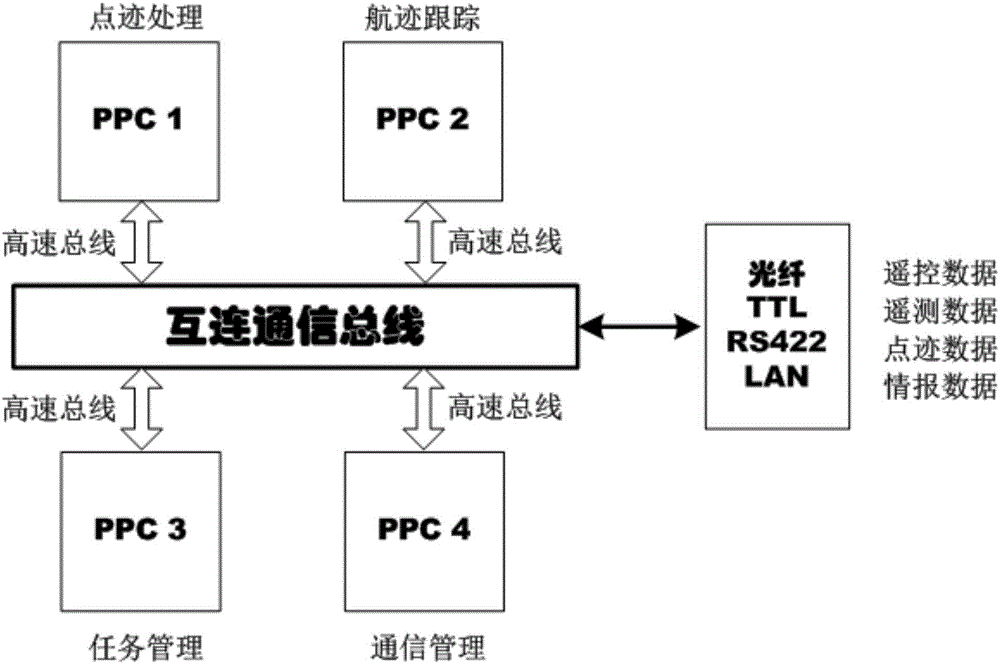

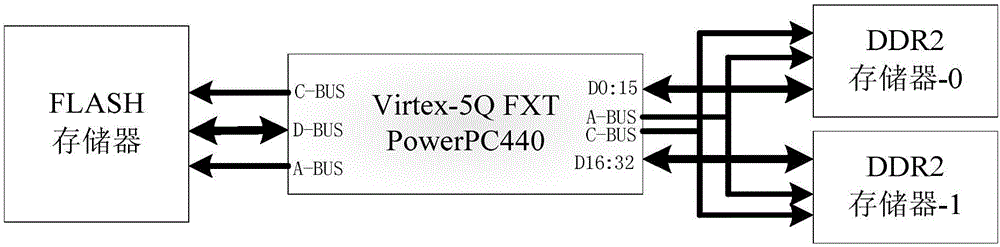

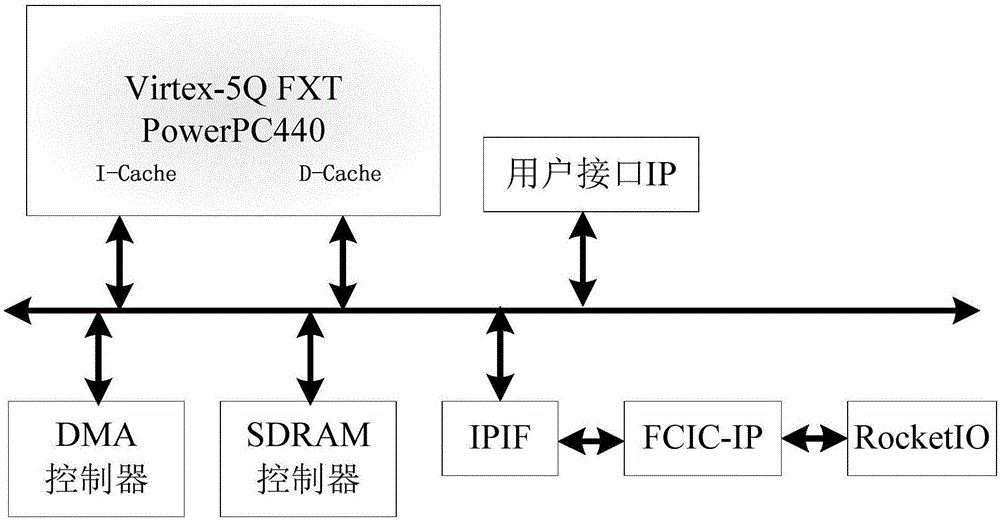

Spaceborne radar data processing and controlling device based on VPX bus

ActiveCN106502957AHigh track processing capabilityArchitecture with single central processing unitElectric digital data processingFault toleranceData processing system

The invention discloses a spaceborne radar data processing and controlling device based on a VPX bus. Two identical processing computers are adopted for a data processing system and a controlling system, and each processing computer comprises two isomorphic PowerPC 440 cores. The two systems form two working modes through the four isomorphic PowerPC 440 cores. According to the parallel mode, the four isomorphic PowerPC 440 cores independently work, but interconnection channels are formed between the four isomorphic PowerPC 440 cores through interconnection communication buses. According to the fault-tolerance mode, the four isomorphic PowerPC 440 cores carry out fault tolerance in a four-mode redundancy mode. The device aims at achieving the purposes of high spaceborne radar data processing point flight path processing capacity, coordinate transformation of radar information data, trace point and flight path rough correlation, trace point and temporary flight path correlation, flight path correlation, trace point fusion and flight path filtering, and short prediction processing time and solving the problem that the spaceflight use environment is severe.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

PowerPC processor based vehicular operating system interrupt management method

InactiveCN1655124AReduce stack usage requirementsProgram initiation/switchingOperational systemPowerPC

Owner:TSINGHUA UNIV

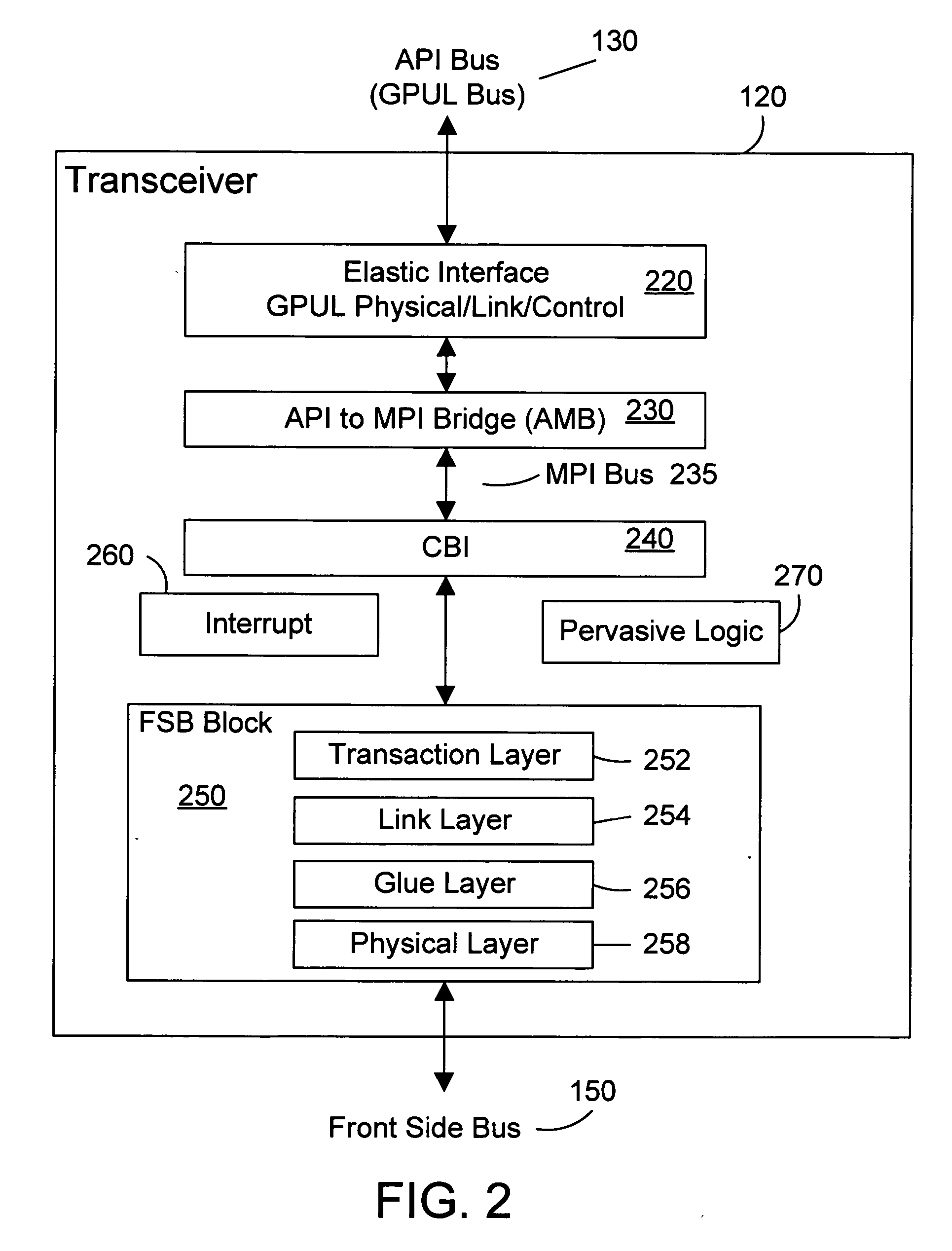

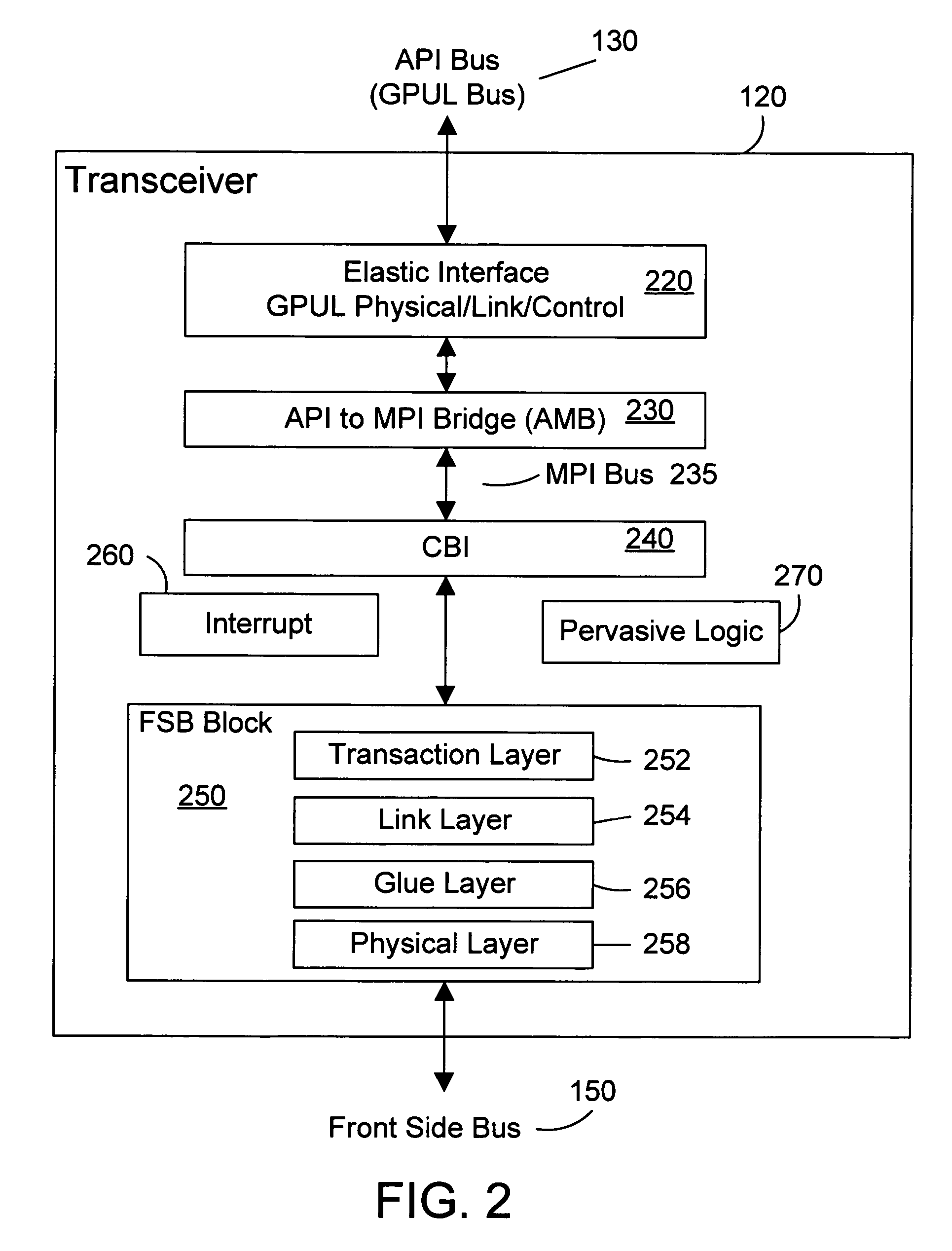

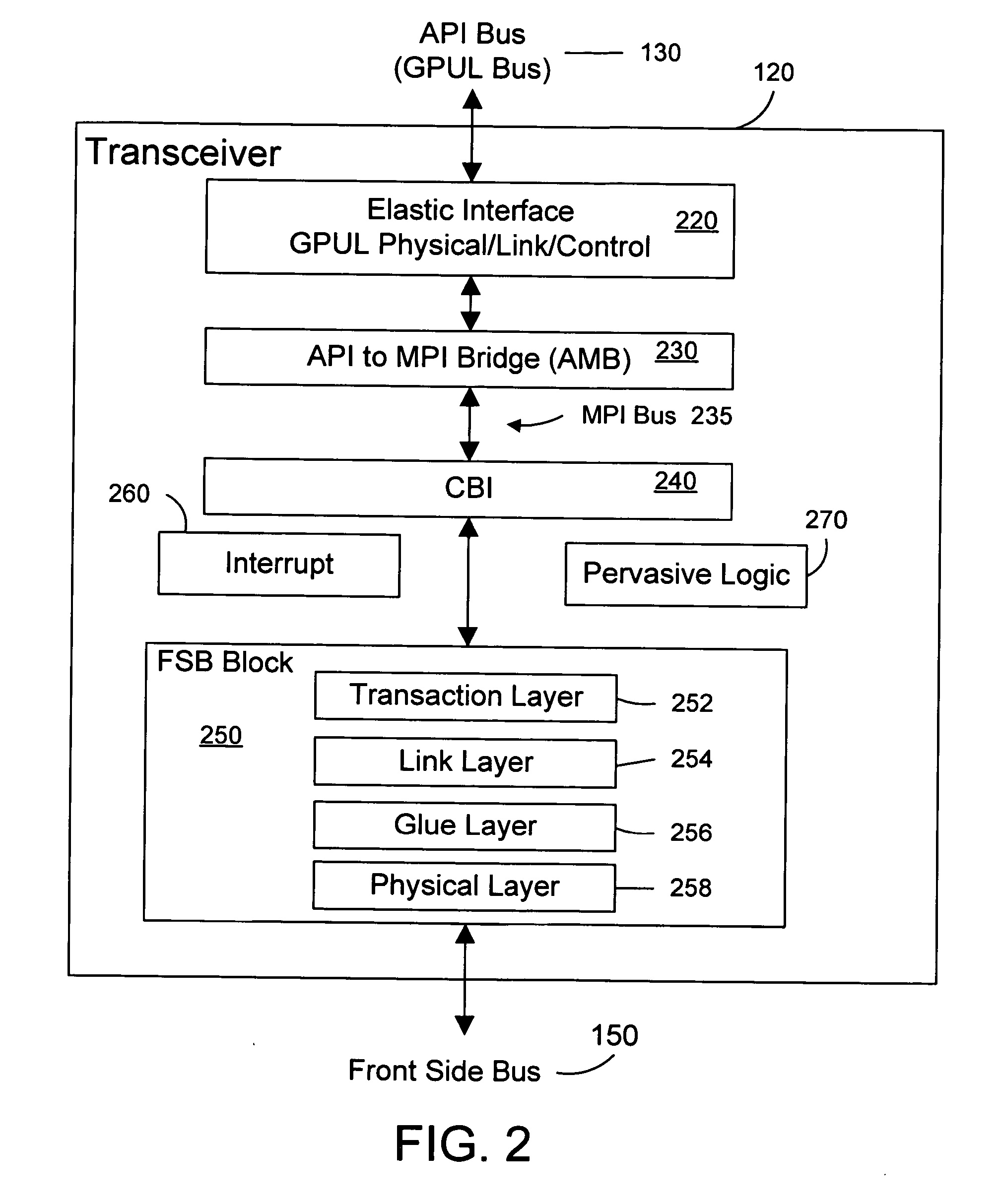

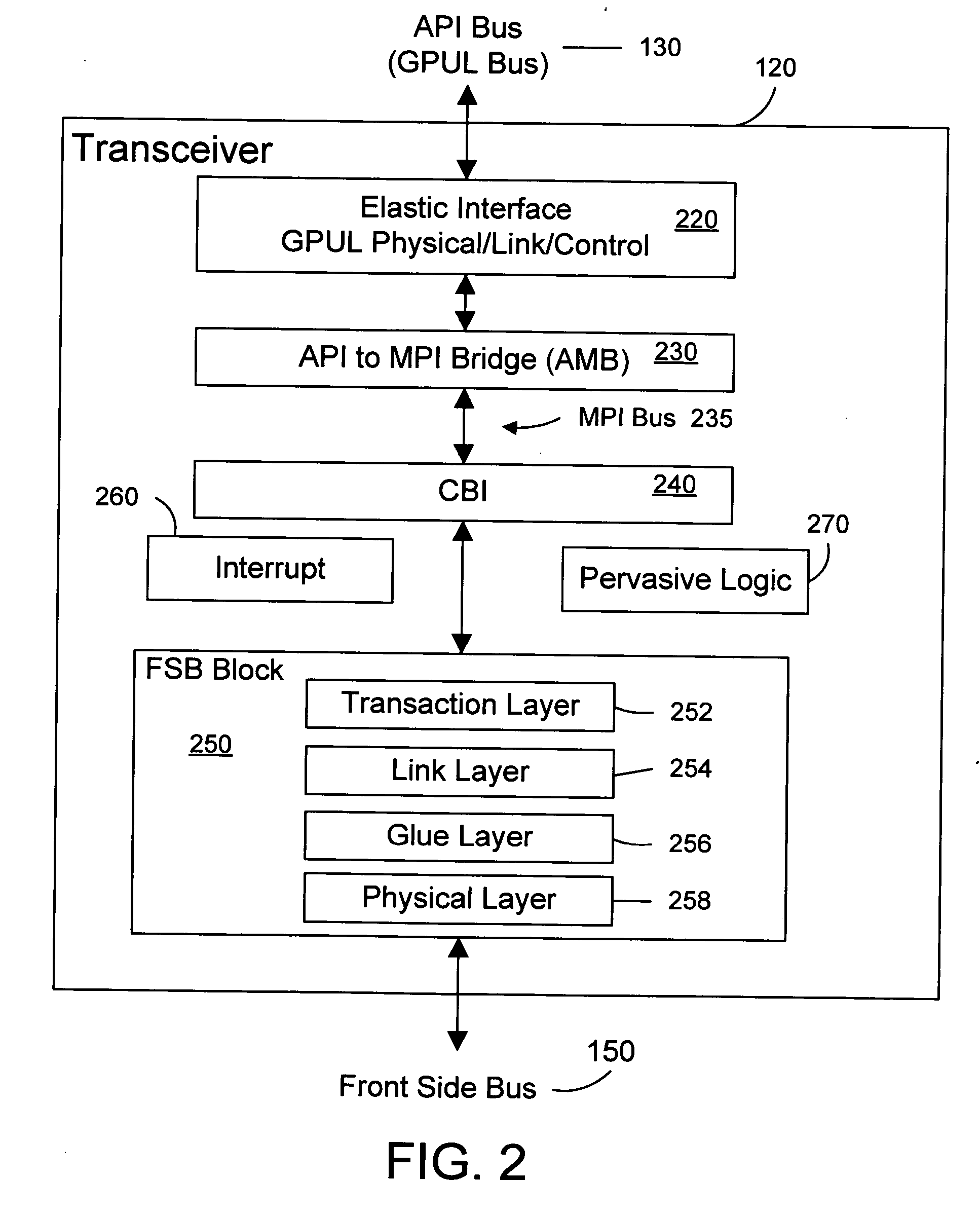

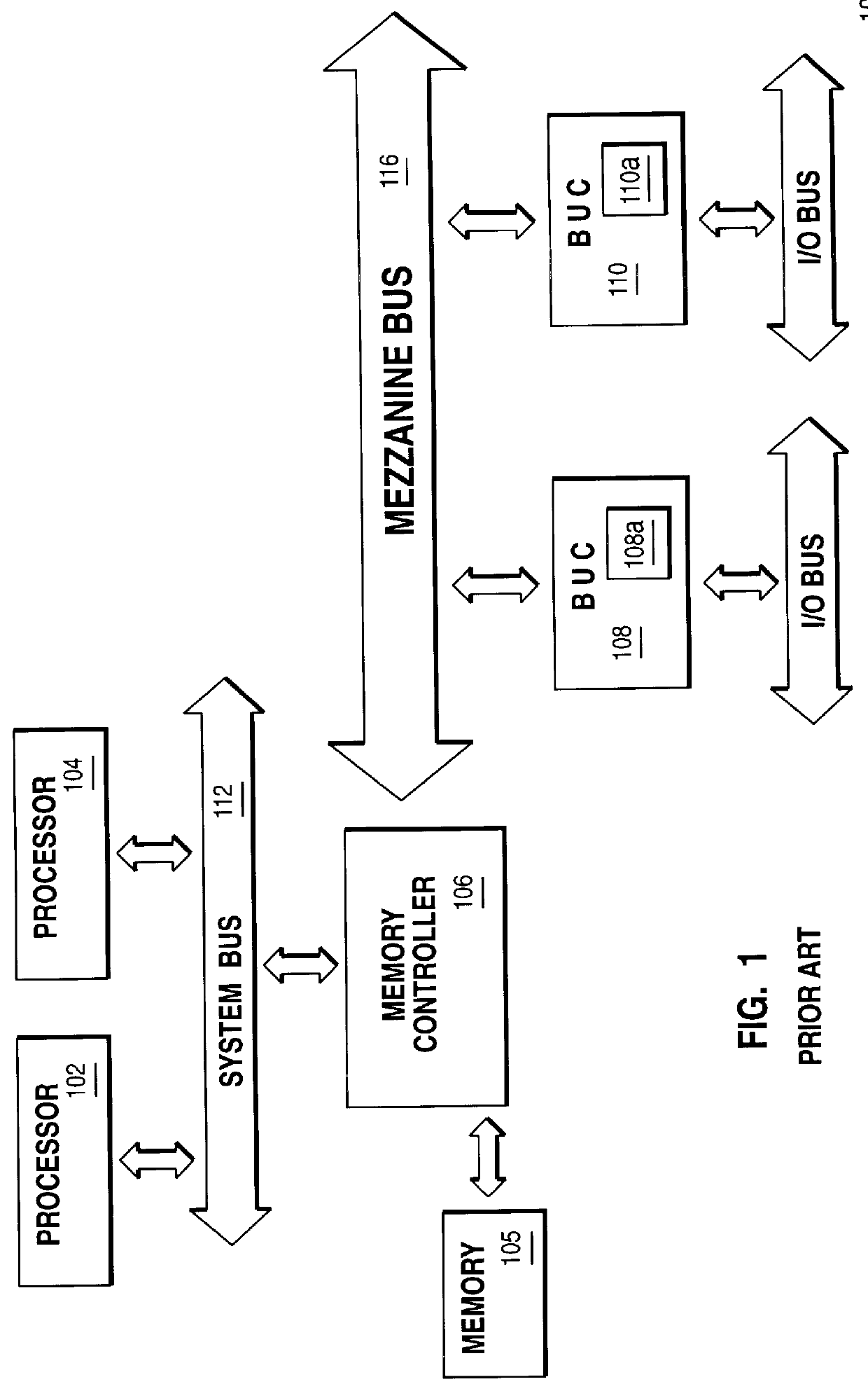

Computer system architecture for a processor connected to a high speed bus transceiver

A high speed computer processor system has a high speed interface for a graphics processor. A preferred embodiment combines a PowerPC microprocessor called the Giga-Processor Ultralite (GPUL) 110 from International Business Machines Corporation (IBM) with a high speed interface on a multi-chip module.

Owner:INT BUSINESS MASCH CORP

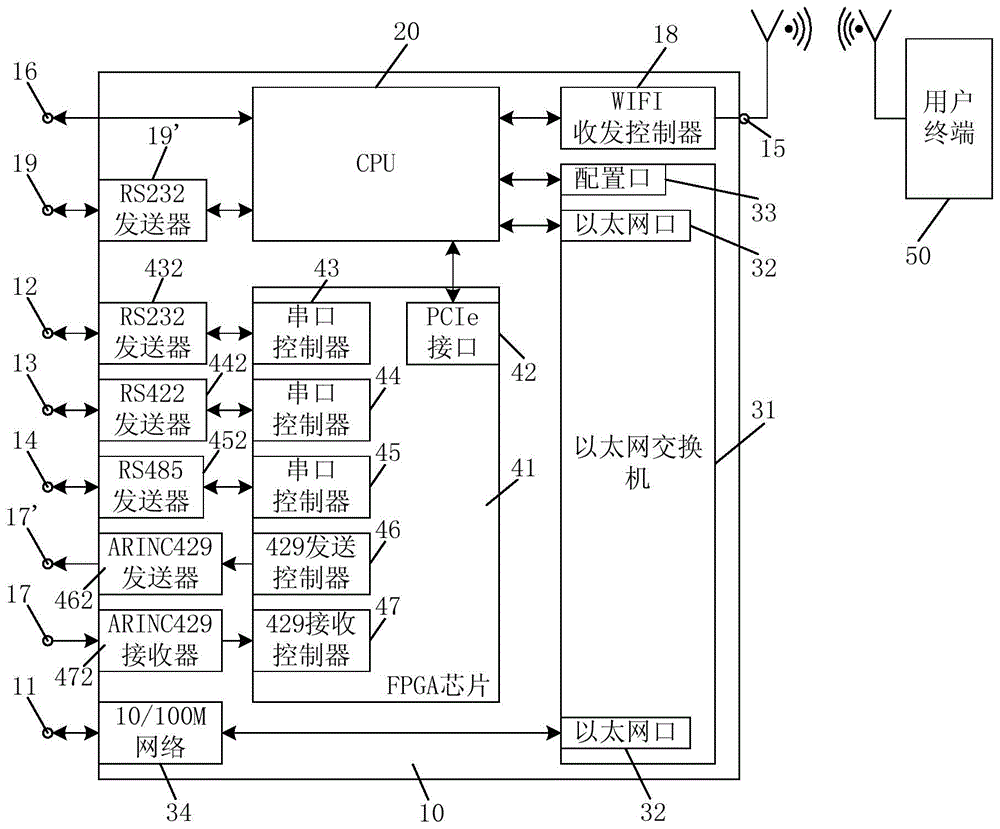

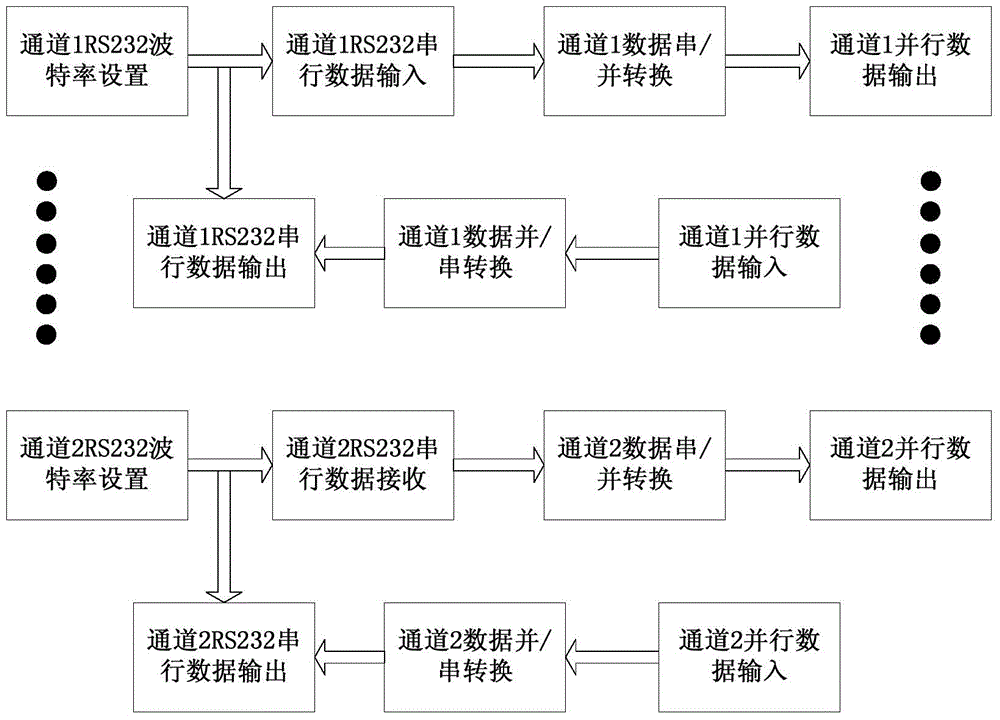

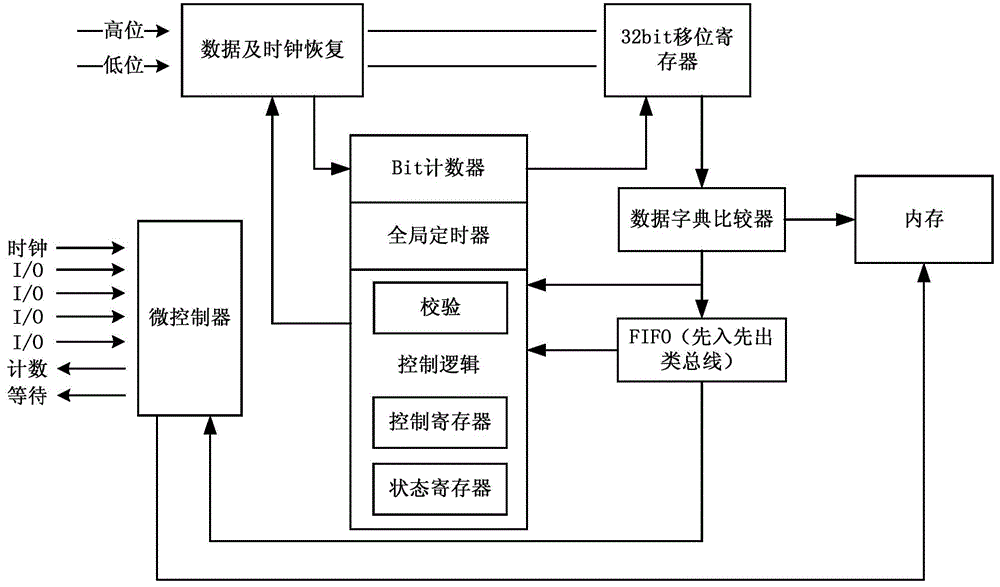

Multipurpose wireless data converter

ActiveCN104063347ARich means of useSufficient quantityElectric digital data processingBus networksWireless dataData interface

The invention relates to a converter, in particular to a multipurpose wireless data converter. The multipurpose wireless data converter comprises a converter body; the converter body is provided with a power supply output interface and a variety of data interfaces; the converter body is internally provided with a CPU (Central Processing Unit), and a WiFi (Wireless Fidelity) module and a serial port module which are in communication connection with the CPU respectively; the converter body is also provided with an external USB (Universal Serial Bus) module; the CPU adopts a PowerPC QorIQ series communication processor; the WiFi module adopts a wireless router chip which is provided with a wireless interface and integrated with an internal configurable Ethernet switch; the WiFi module communicates with the CPU by virtue of the Ethernet switch; the serial port module adopts an FPGA (Field Programmable Gate Array) chip integrated with a plurality of various serial buses; the USB module adopts a USB peripheral control unit; the CPU, the WiFi module and the serial port module are respectively in communication connection with respective corresponding data interfaces. The multipurpose wireless data converter disclosed by the invention integrates the serial port to WiFi function, the wireless router function and the ARINC429 avionics bus wireless transmission function, and has the advantages of large interface number, interface concentration, high equipment generality and the like.

Owner:CETC AVIONICS

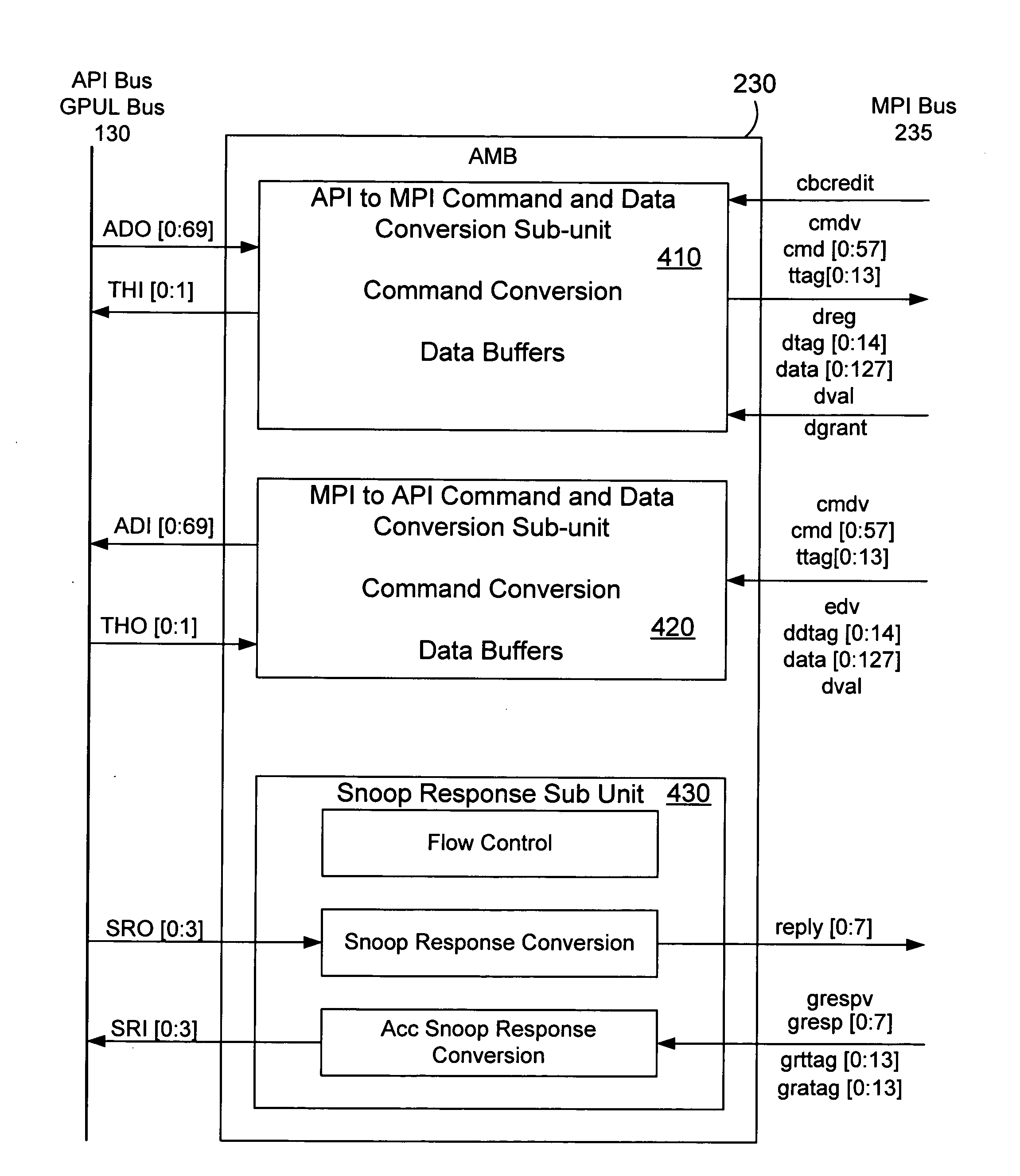

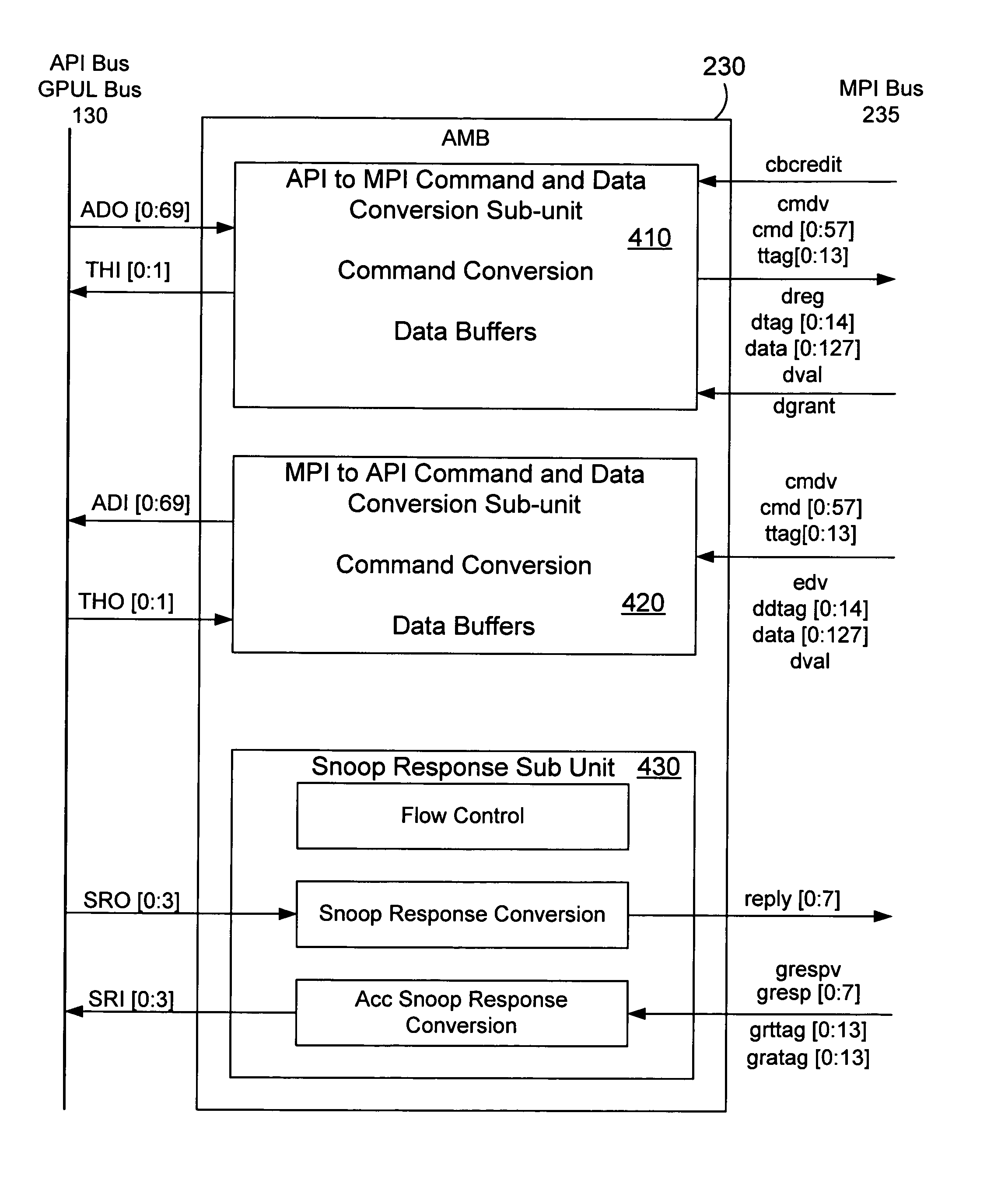

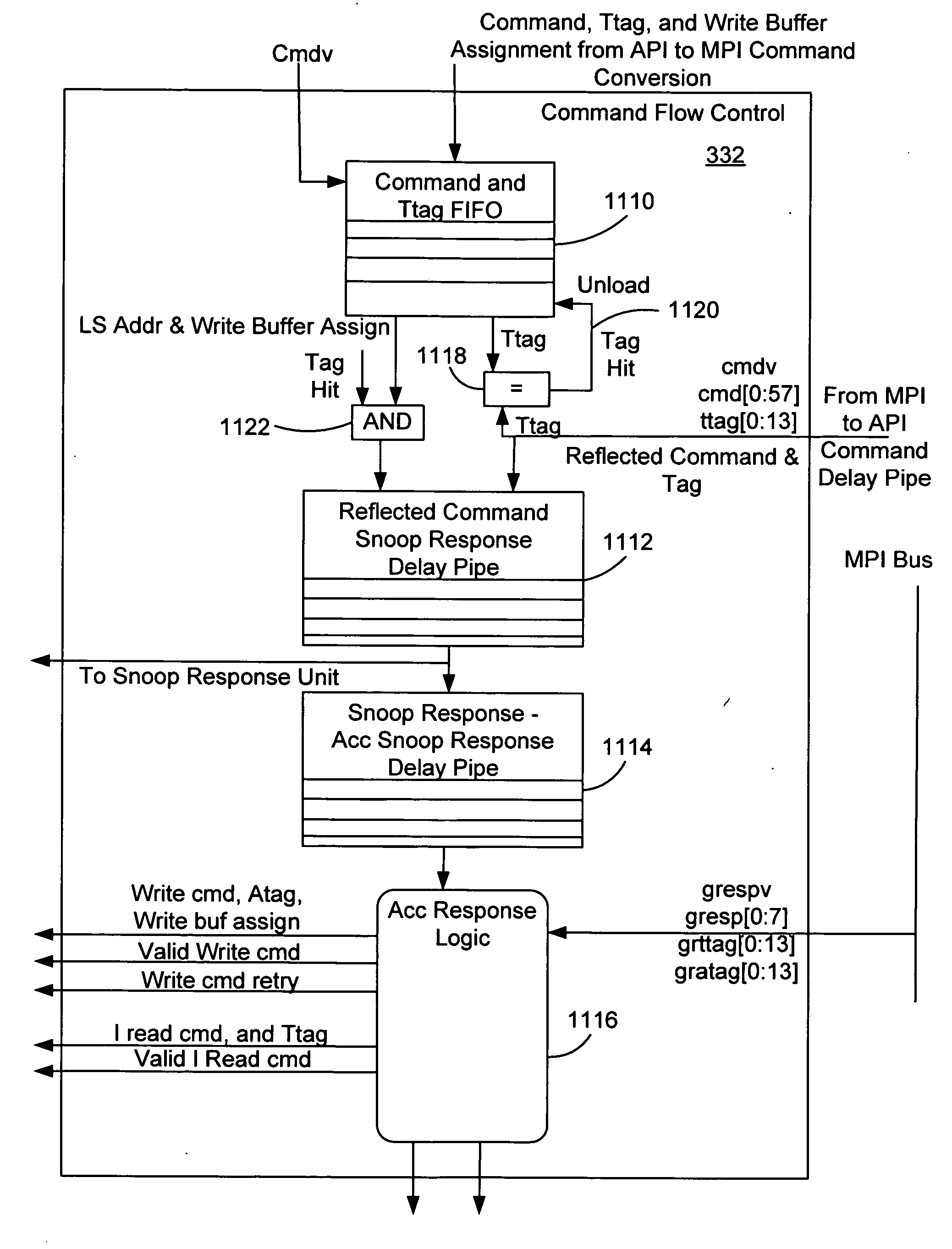

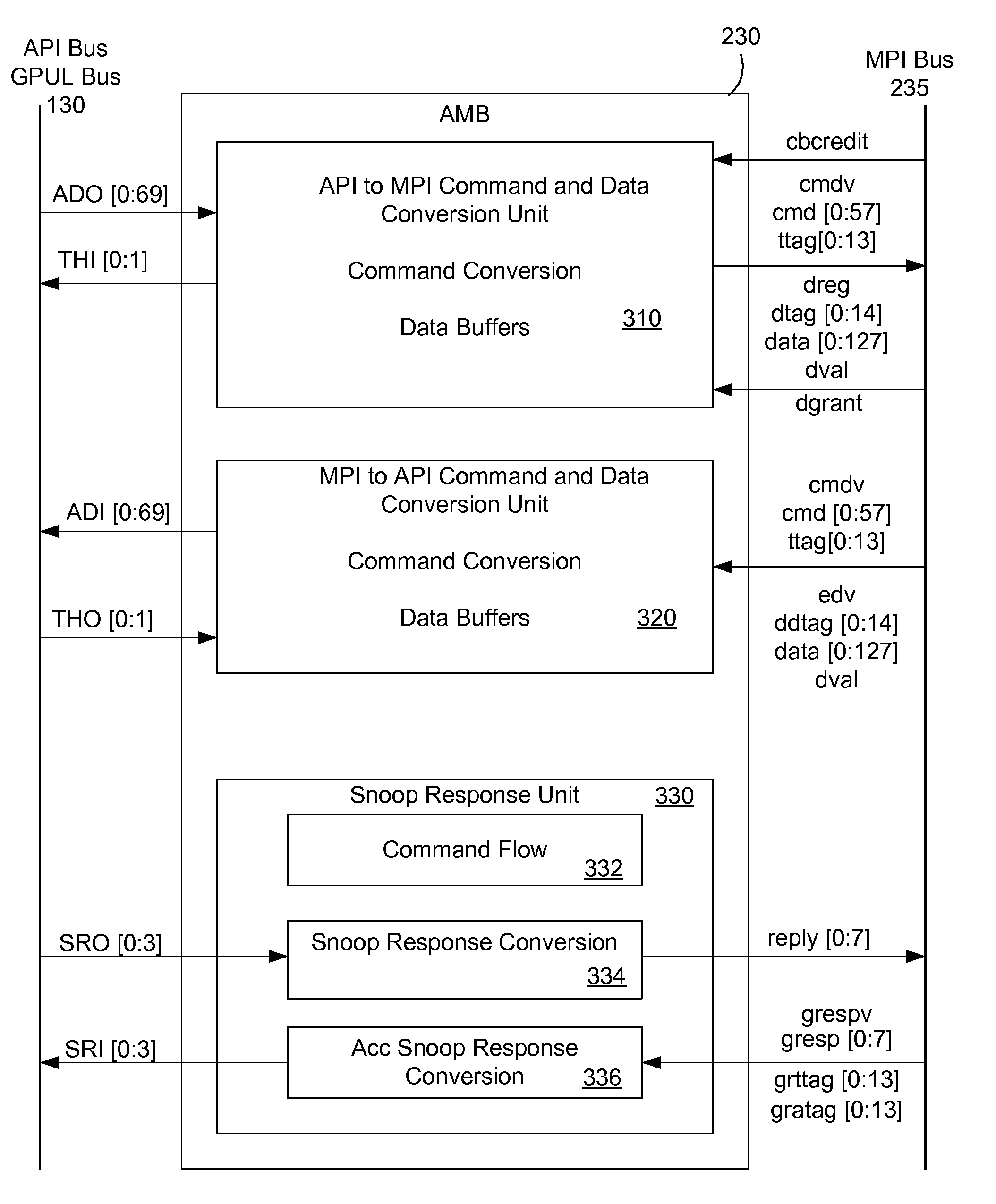

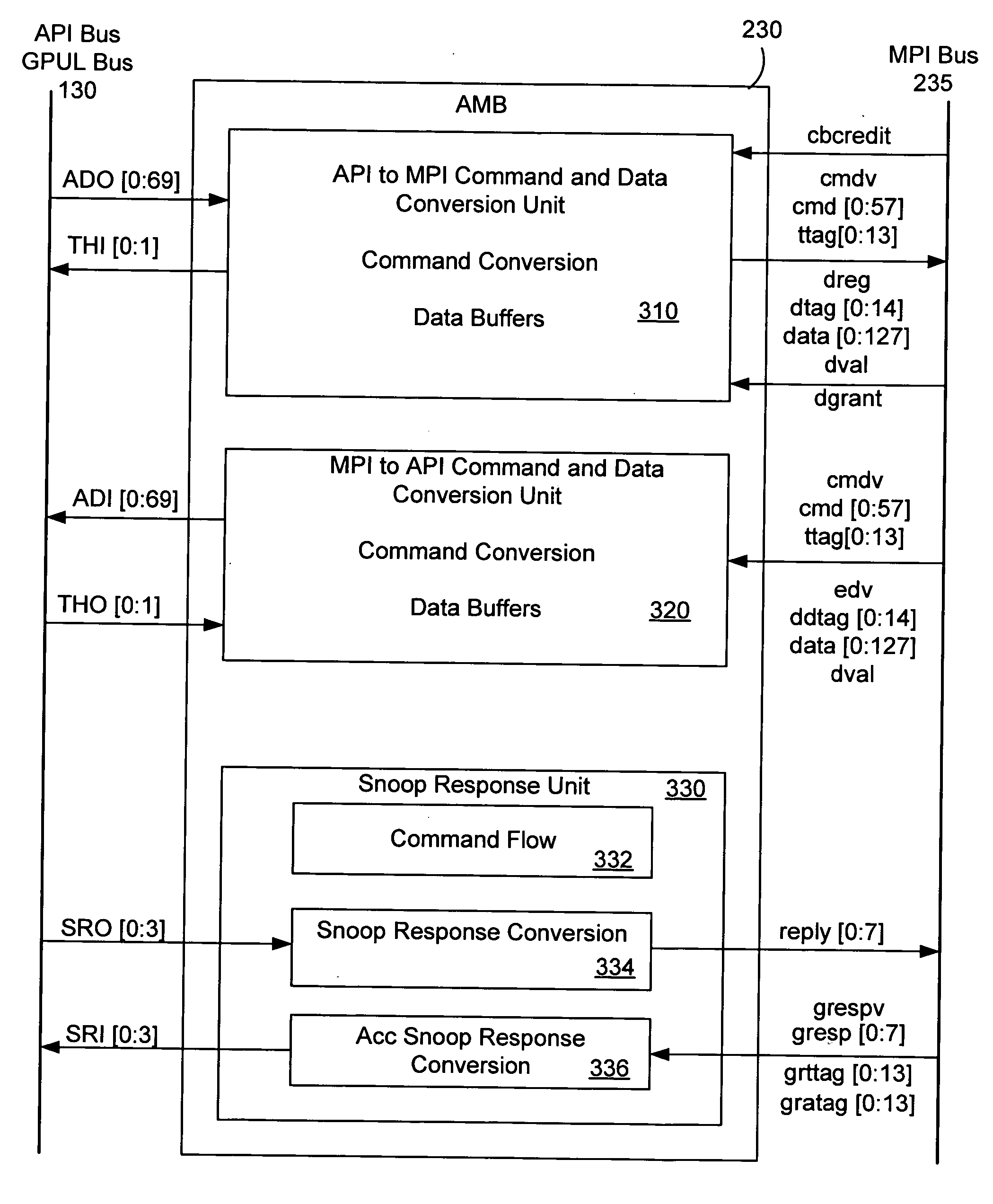

Transaction flow control mechanism for a bus bridge

A transaction flow control mechanism is disclosed for a bus bridge in a high speed computer system with a high speed interface for a graphics processor. A preferred embodiment provides a flow control mechanism for the bus bridge between a GPUL bus for a GPUL PowerPC microprocessor from International Business Machines Corporation (IBM) and a high speed interface. A preferred embodiment of the invention is a bus transceiver on a multi-chip module.

Owner:GOOGLE LLC

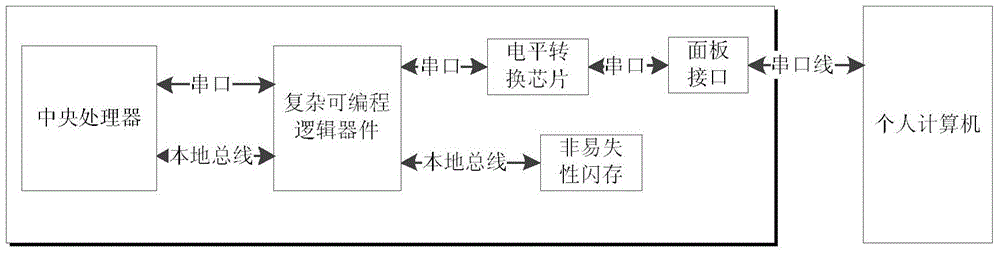

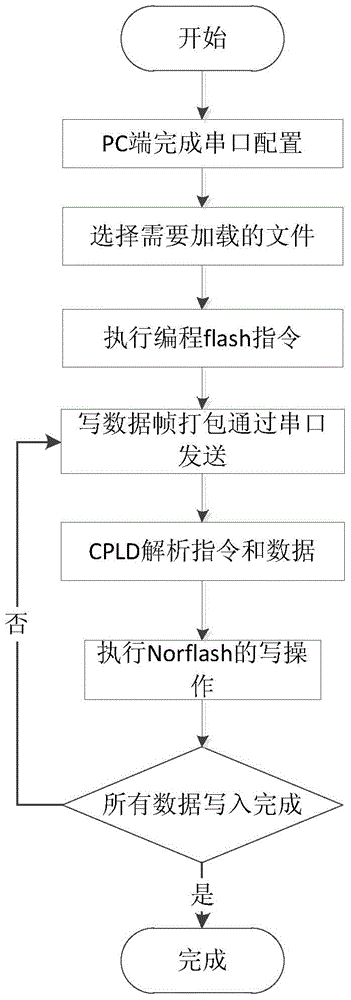

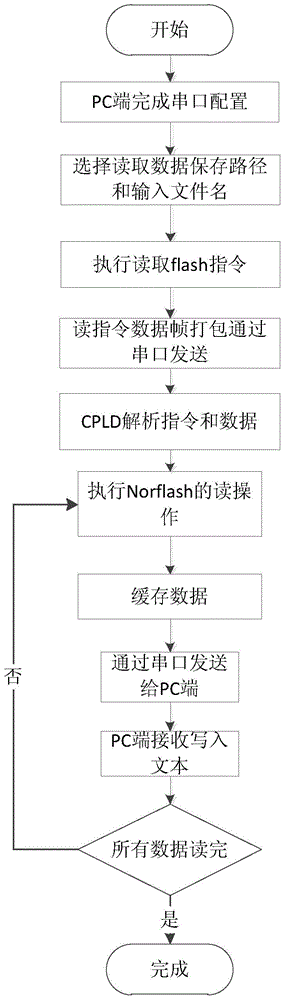

System and method for loading PowerPC system guide file through serial port

ActiveCN104133705ASimple loading processProgramming Speed GuaranteedProgram loading/initiatingPowerPCLogic implementation

The invention discloses a system and method for loading a PowerPC system guide file through a serial port. The method includes the steps of circuit board design of a loading scheme, logic implement of a CPLD and design of loading software of a PC end; after the requirements of the three modules are met, the file is sent to the CPLD through the serial port through the loading software at the PC end, and the file is programmed to a Norflash through the logic in the CPLD so that the system guide file loading can be completed. The invention provides the simple system loading method. The logic of Norflash programming is achieved on the CPLD instead of achieving a programming algorithm on the software of the PC end, and therefore the programming speed is ensured; meanwhile, due to the scheme, the software at the PC end can be quietly easily developed by reading the file to be loaded and then sending the file through the serial port according to the well-defined packaging data frame in the frame format. In addition, the system replaces a special simulator and a special programming environment, the loading process of the system guide file is simplified, and the debugging efficiency in the early period is improved.

Owner:WUHAN POST & TELECOMM RES INST CO LTD

Computer system bus bridge

InactiveUS20080307147A1Memory adressing/allocation/relocationInput/output processes for data processingTransceiverPowerPC

A bus bridge between a high speed computer processor bus and a high speed output bus. The preferred embodiment is a bus bridge between a GPUL bus for a GPUL PowerPC microprocessor from International Business Machines Corporation (IBM) and an output high speed interface (MPI). Another preferred embodiment is a bus bridge in a bus transceiver on a multi-chip module.

Owner:IBM CORP

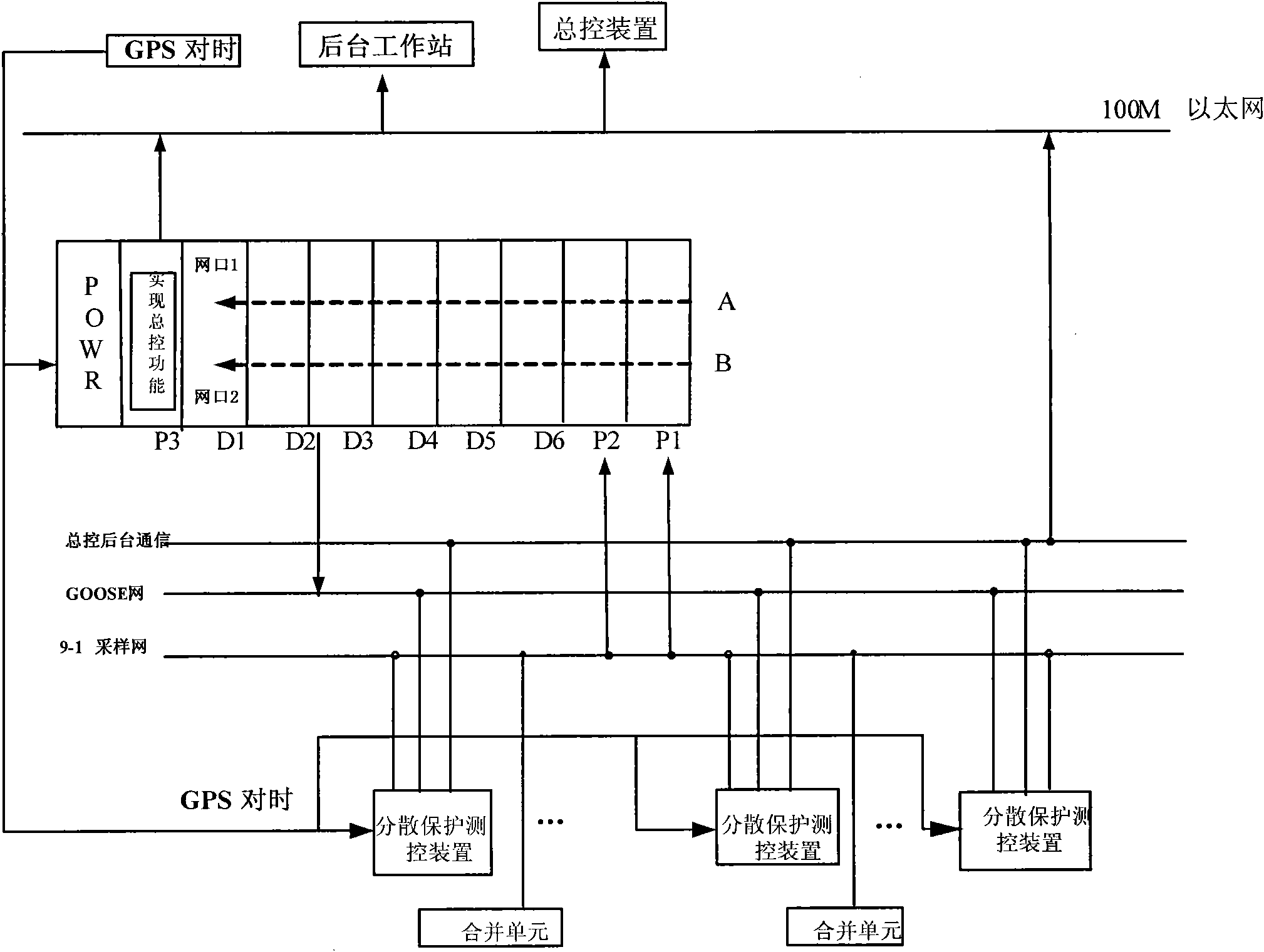

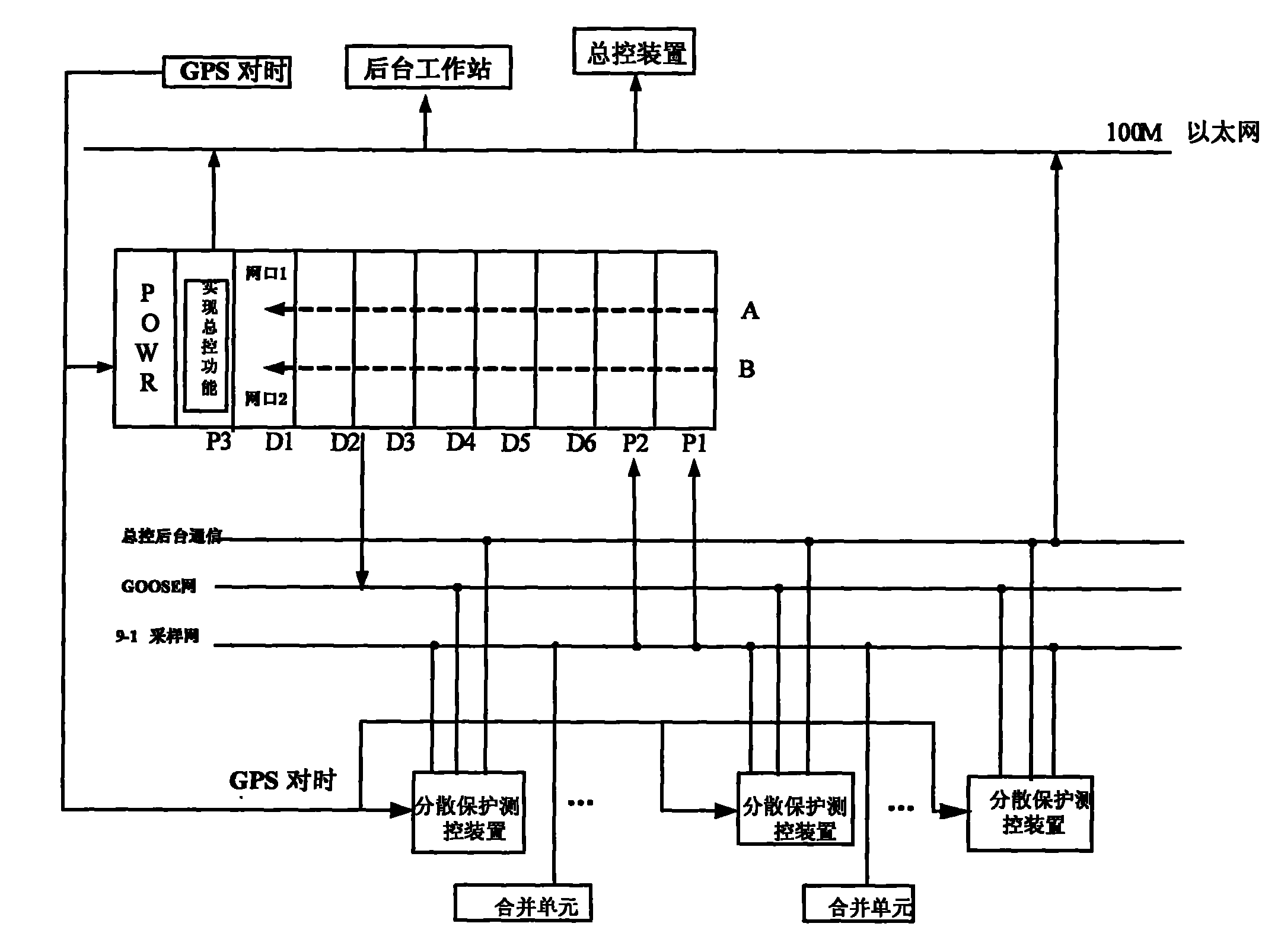

Centralized protection, measurement and control device and realizing method thereof

ActiveCN101841189AReduce construction and maintenance costsFriendly supplementEmergency protective circuit arrangementsLiquid-crystal displayPowerPC

The invention discloses a centralized protection, measurement and control device which comprises the following functional plug-ins: a PowerPC board, a master control PowerPC board, a CPU board, a high-speed serial bus board and a liquid crystal display board, wherein the PowerPC board is arranged on the high-speed serial bus board by plug-in connection, comprises a sampling PowerPC board and receives a sampling packet from a merging unit or sent from the protection, measurement and control device through a sampling network on process level; the master control PowerPC board communicates with a background and a master controller through the network; the CPU board is arranged on the high-speed serial bus board by plug-in connection and used for realizing the data calculation and the protection function of all intervals; the high-speed serial bus board is an access board for all the plug-ins and used for data transmission among the plug-ins; and the liquid crystal display board is connected with the master control PowerPC board through a built-in network port. The device can reduce the complex wiring among all the intervals on the secondary side of a substation and reduce the work of design, manufacture and maintenance of secondary equipment of an automatic system of the substation.

Owner:NARI TECH CO LTD +1

Computer system bus bridge

A bus bridge between a high speed computer processor bus and a high speed output bus. The preferred embodiment is a bus bridge between a GPUL bus for a GPUL PowerPC microprocessor from International Business Machines Corporation (IBM) and an output high speed interface (MPI). Another preferred embodiment is a bus bridge in a bus transceiver on a multi-chip module.

Owner:IBM CORP

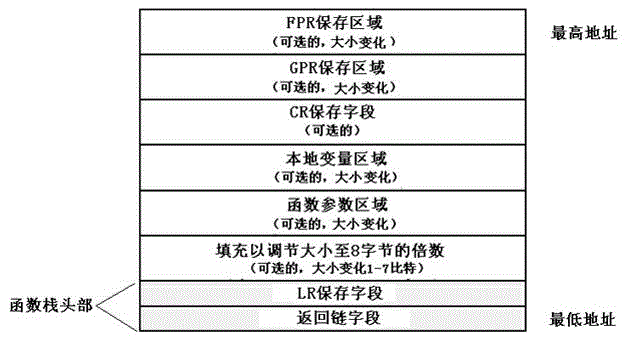

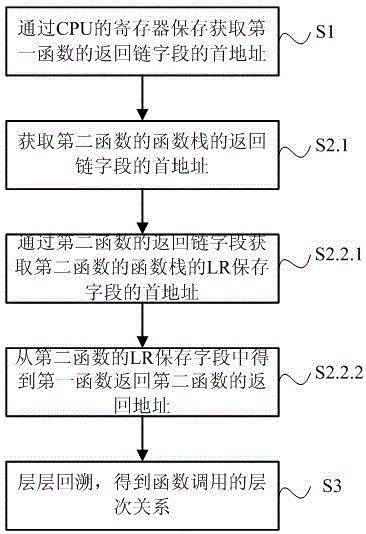

Stack recalling method

InactiveCN104484179AIncrease the probability of full backtrackingEasy to trace backSpecific program execution arrangementsMemory systemsPowerPCComputer science

The invention discloses a stack recalling method. A recalling function according to the stack recalling method has a PPC (PowerPC) stack frame structure. The stack recalling method comprises the following steps: analyzing a stack frame of a present function; seeking and recalling an upper layer function calling for the present function; recalling the function layer by layer, thereby acquiring a hierarchical relation of the function calling. The function stack recalling is performed according to the characteristics of a PPC internal storage stack frame structure, so that the probability of PPC complete recalling is increased and a low-level developer can conveniently recall information about the hierarchical relation of the function.

Owner:PHICOMM (SHANGHAI) CO LTD

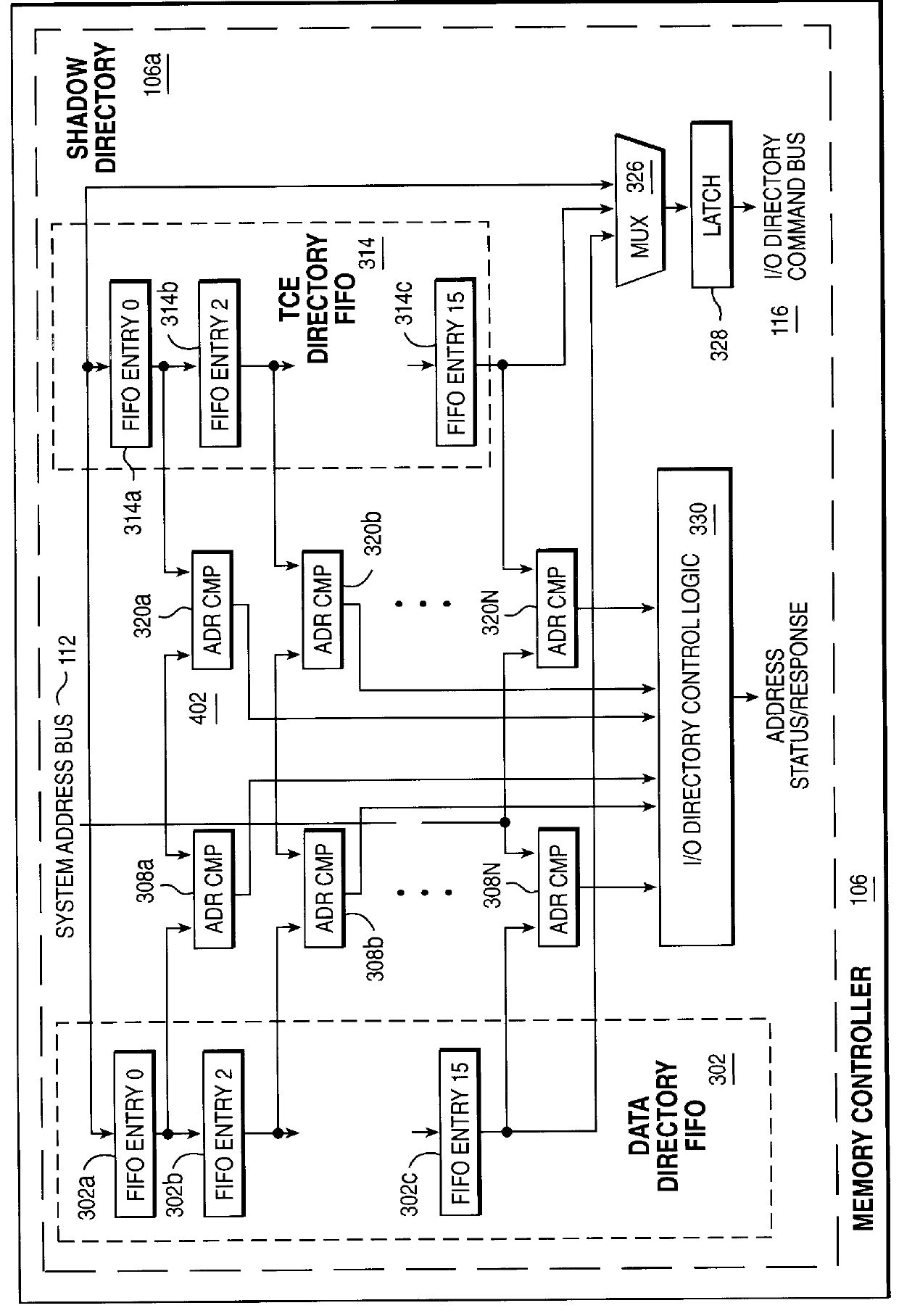

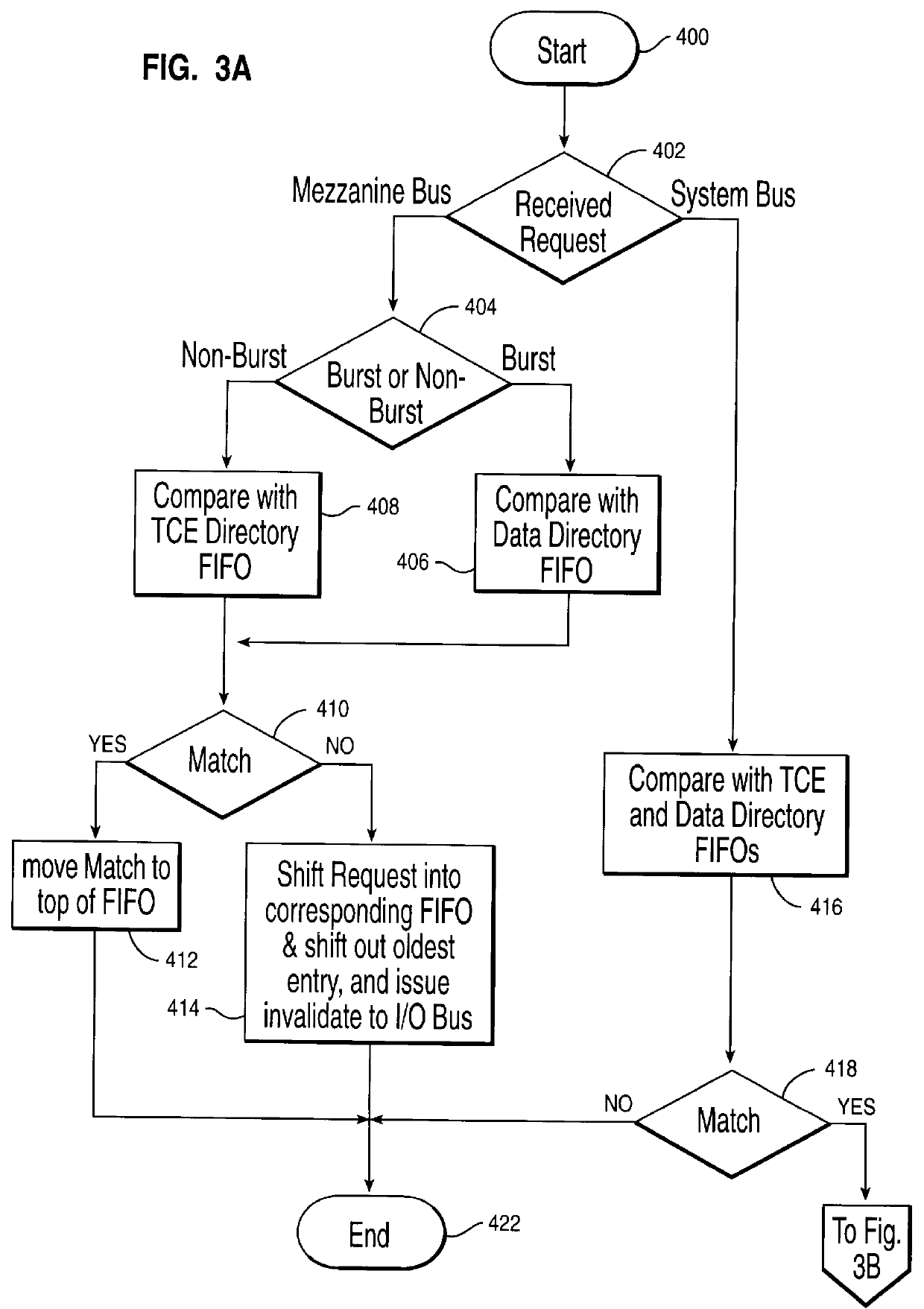

Method and apparatus for reducing system snoop latency

In multi-processor systems which have separated the system bus from the I / O bus, a Shadow Directory is introduced into the memory controller for reducing bottlenecks that occur from the processors snooping data cache in the I / O devices residing on the I / O bus. This Shadow Directory is advantageously employed in a system, such as the PowerPc architecture which distinguishes between the types of data that can be cached in I / O devices. The Shadow Directory uses two First In First Out (FIFO) stacks for two different types of data. These FIFO stacks are then used for addresses placed on the system bus and I / O bus in order to reduce snoop latency times.

Owner:GOOGLE LLC

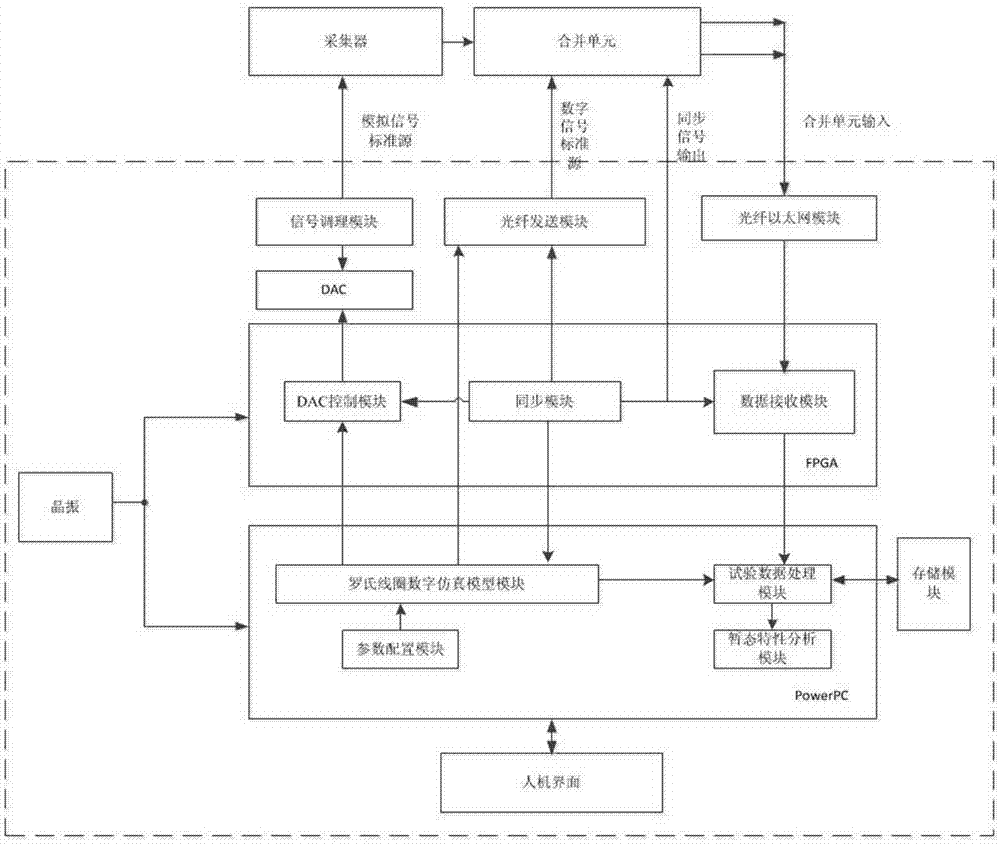

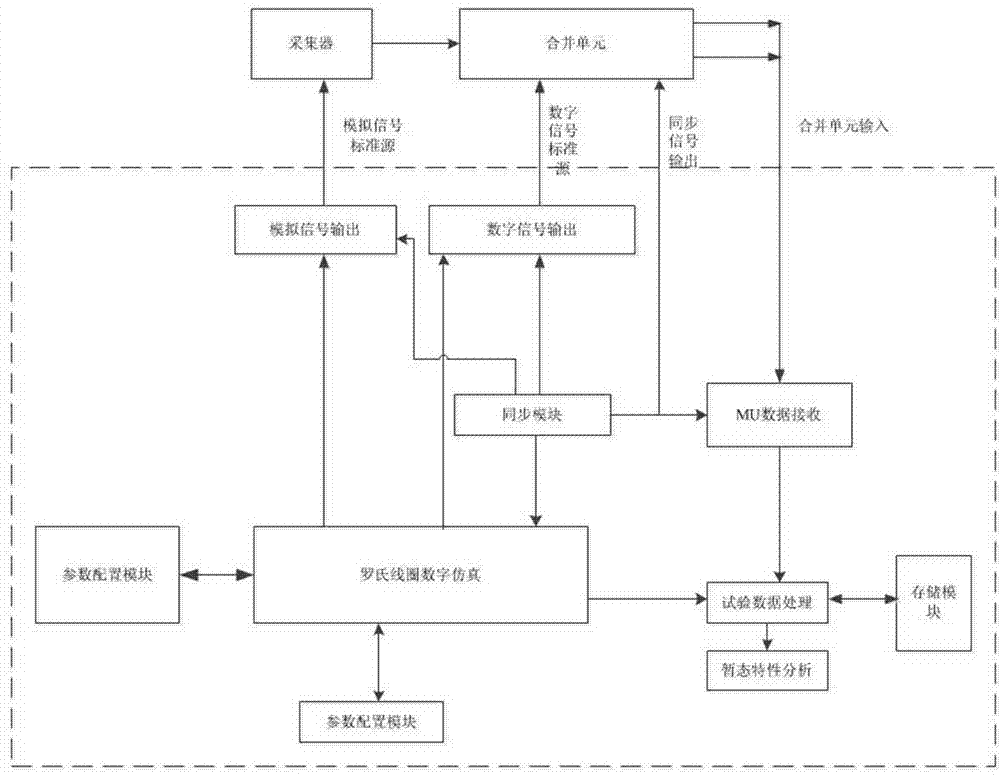

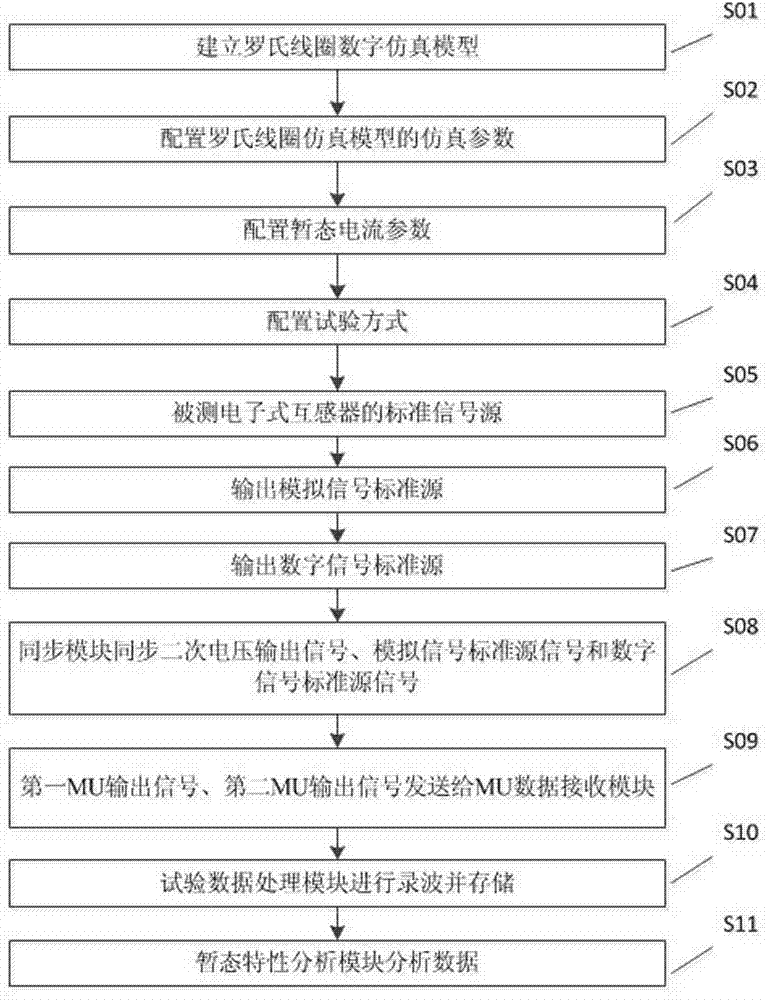

Transient characteristic test system and method of mutual inductor based on digital simulation of Rogowski coil

InactiveCN103969536APerformance pros and consRealize differential signal outputElectrical testingSpecial data processing applicationsHuman–machine interfaceEngineering

The invention discloses a transient characteristic test system of a mutual inductor based on digital simulation of a Rogowski coil. The system comprises a signal conditioning module, an optical fiber sending module, an optical fiber Ethernet module, a digital analog converter, an FPGA (Field Programmable Gate Array), a POWERPC, a crystal oscillator, a human-computer interface and a storage module, wherein the crystal oscillator is connected with the FPGA and the POWERPC, the FPGA is connected with the digital analog converter, the optical fiber sending module, the optical fiber Ethernet module and the POWERPC, the POWERPC is connected with the storage module and the human-computer interface, and the digital analog converter is connected with the signal conditioning module. The FPGA comprises a synchronization module, a data receiving module and a DAC (Digital-to-Analog Converter) control module. The POWERPC comprises a digital simulation model module of the Rogowski coil, a parameter configuration module, a test data processing module and a transient characteristic analyzing module. Based on an ideal Rogowski coil model, a differential signal output is established for all-digital simulation test to be not limited in individual professional laboratories. Advantages of hardware integration and software integration can be compared, and all-around simulation test of transient characteristics of the electronic mutual inductor can be realized.

Owner:ELECTRIC POWER SCI RES INST OF GUIZHOU POWER GRID CO LTD

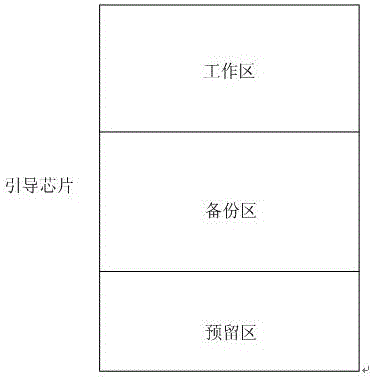

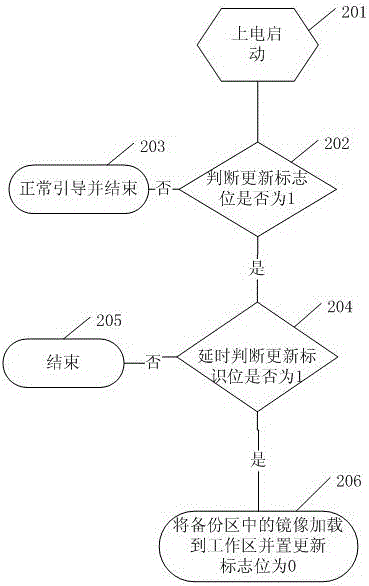

Method for updating PowerPC motherboard guide chip online

ActiveCN106598654AAvoid cumbersome operation proceduresImprove securityProgram loading/initiatingSoftware deploymentElectricityPowerPC

The invention provides a method for updating a PowerPC motherboard guide chip online. The method comprises the following steps: electrifying the system, and maintaining an update flag bit by a programmable logic device FPGA; transmitting a bootrom mirror image file to the system by an upper computer through a serial port in an update flow, and receiving and checking whether mirror image contents are correct by an update program; writing the checked mirror image contents in an FPGA operable address space, writing the mirror image contents in a working area by the FPGA, and meanwhile backing up the current mirror image; and starting the system again to accomplish the present update in the system, and otherwise rolling back the backup data in a backup area.

Owner:中国兵器装备集团自动化研究所有限公司

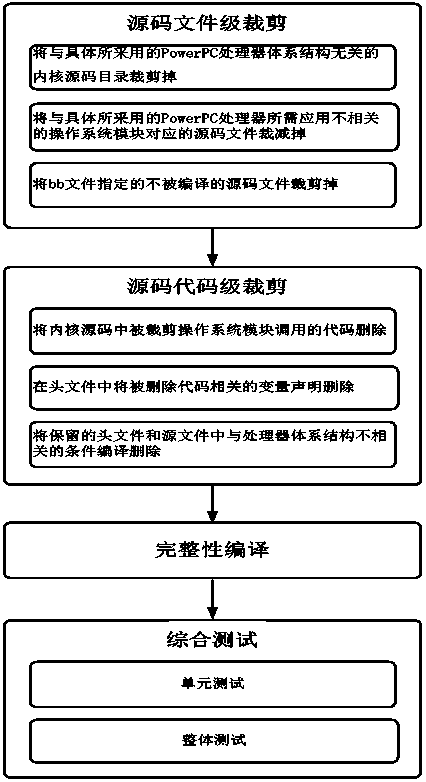

Embedded Linux operation system trimming customization method

InactiveCN104199713AGuaranteed autonomyEnsure controllabilityProgram controlMemory systemsHardware architectureSource code file

The invention discloses an embedded Linux operation system trimming customization method and belongs to the technical field of operation system trimming. The problems that an existing embedded Linux operation system code number based on a PowerPC hardware architecture is too large, the number of redundant modules is too large, and reading and modifying are not easy are solved. According to the technical scheme, an embedded Linux operation system based on the PowerPC hardware architecture is subjected to trimming and customization, the method comprises the steps that the embedded Linux operation system in the PowerPC hardware architecture is subjected to source code file level trimming; the embedded Linux operation system in the PowerPC hardware architecture is subjected to source code level trimming; source codes of the trimmed embedded Linux operation system are subjected to integral compiling, and embedded Linux operation system nucleus files are generated; and the compiled embedded Linux operation system nucleus files are used and are programmed into a storage of a main board in the PowerPC hardware architecture, then comprehensiveness testing is carried out, and whether the function or the performance of the trimmed embedded Linux operation system is normal is verified.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD