Patents

Literature

77 results about "Giga-" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Giga (/ˈɡɪɡə/ or /ˈdʒɪɡə/) is a unit prefix in the metric system denoting a factor of a (short-form) billion (10⁹ or 1000000000). It has the symbol G. Giga is derived from the Greek word γίγας, meaning "giant." The Oxford English Dictionary reports the earliest written use of giga in this sense to be in the Reports of the IUPAC 14th Conference in 1947: "The following prefixes to abbreviations for the names of units should be used: G giga 10⁹×."

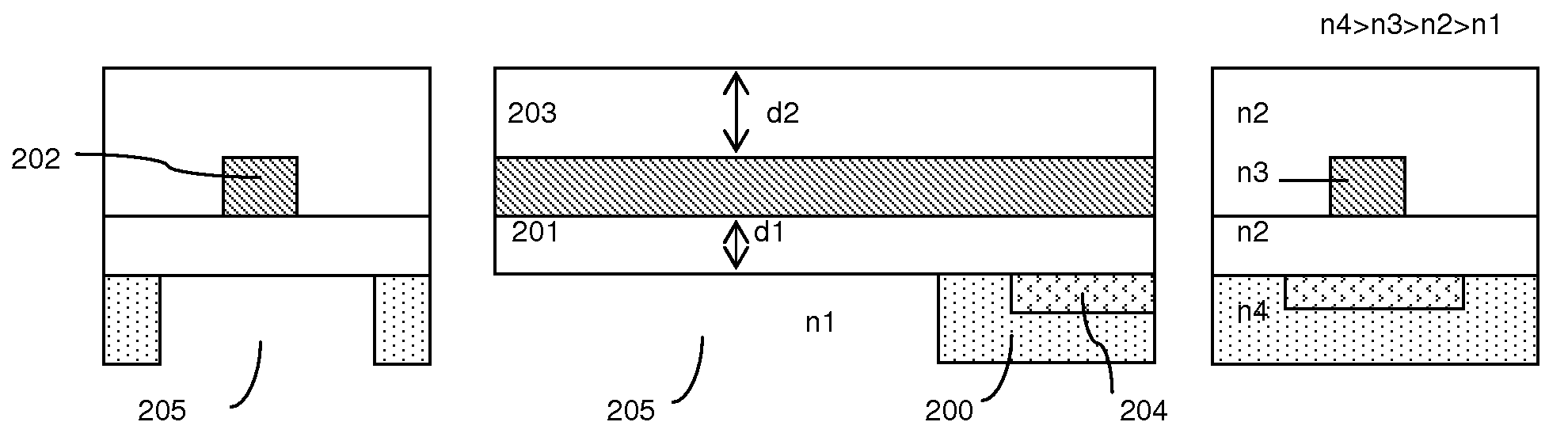

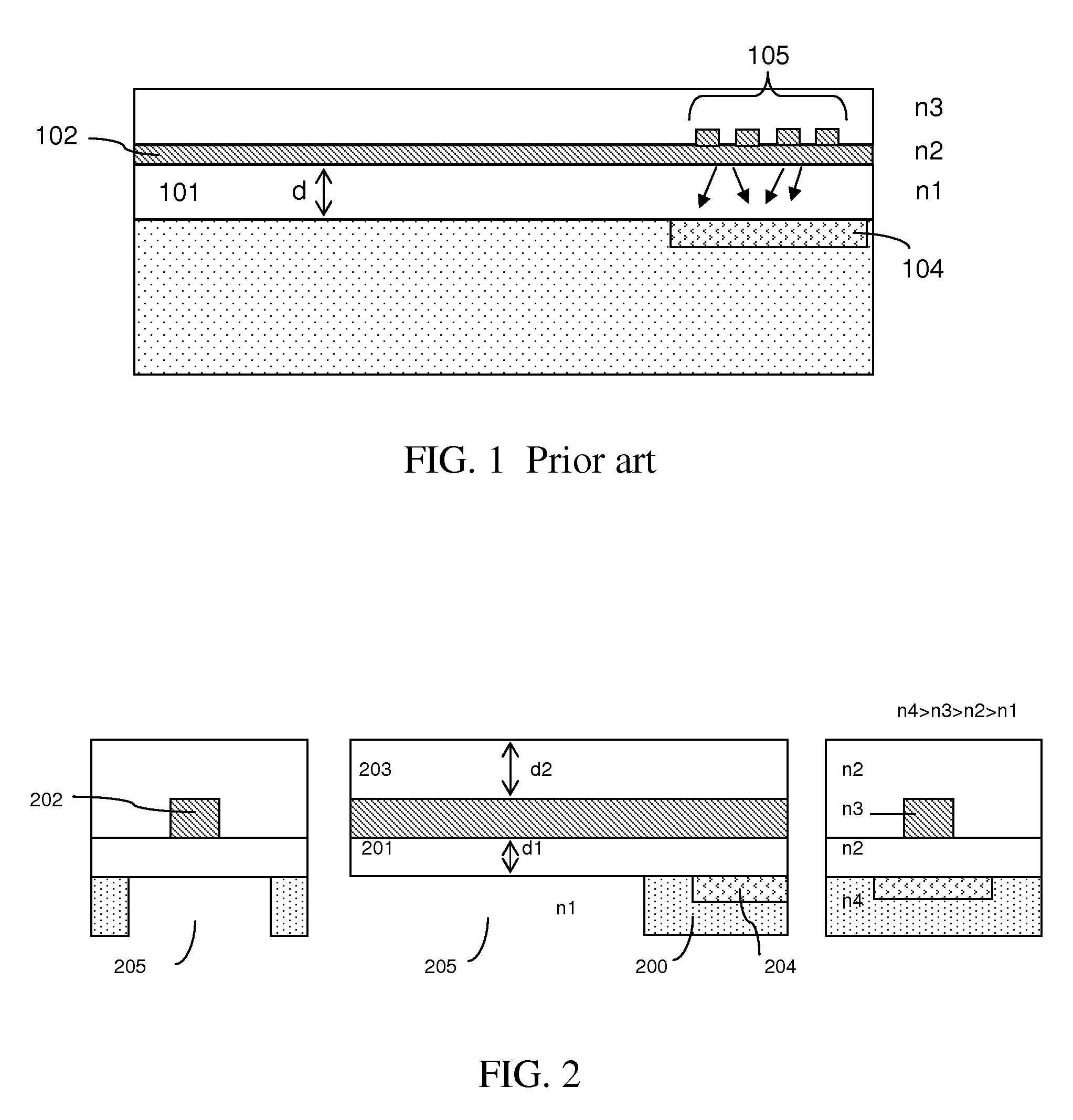

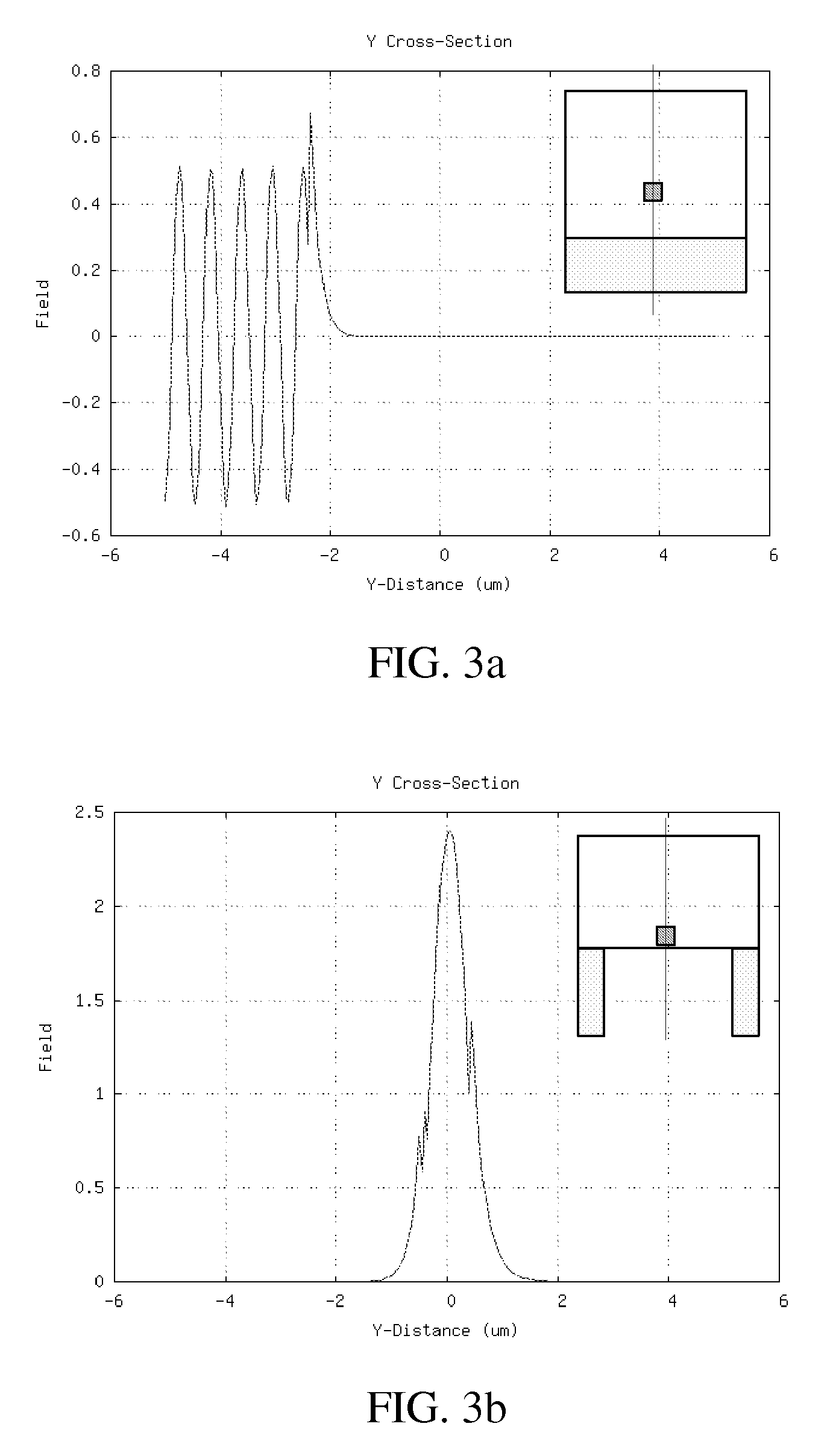

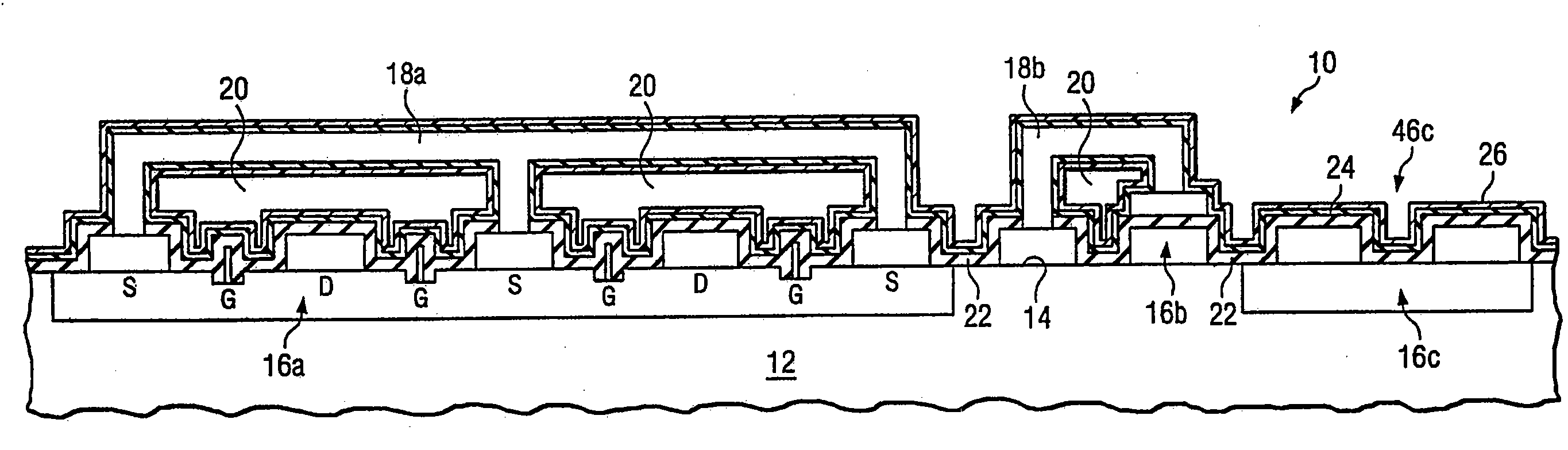

Planar lightwave circuits with air filled trenches

InactiveUS20090087137A1Easy to integrateReduce light lossMaterial analysis by optical meansNanoopticsPhotovoltaic detectorsPhotodetector

An air filled trench is formed underneath the waveguide to reduce propagation loss, which in turn allowing the waveguide to be in the close proximity of on-chip devices, such as a photodetector. The air filled trench is formed from the back side of the substrate; hence it would not disturb the integration and the formation of components on the front side of the substrate. In another embodiment, for silicon-on-insulator (SOI) based device, with an air filled trench and a metal electrode, a back gate is formed. In yet another embodiment, air filled trench also reduces the substrate loss of RF passive components and passive antenna operating in Giga Hertz range. Air filled trenches can be used for both photonic and electronic circuits in a planar lightwave circuit. Finally, another embodiment is for the trench to effectively guide gases and fluids to pass through the detection area.

Owner:DOAN MY THE

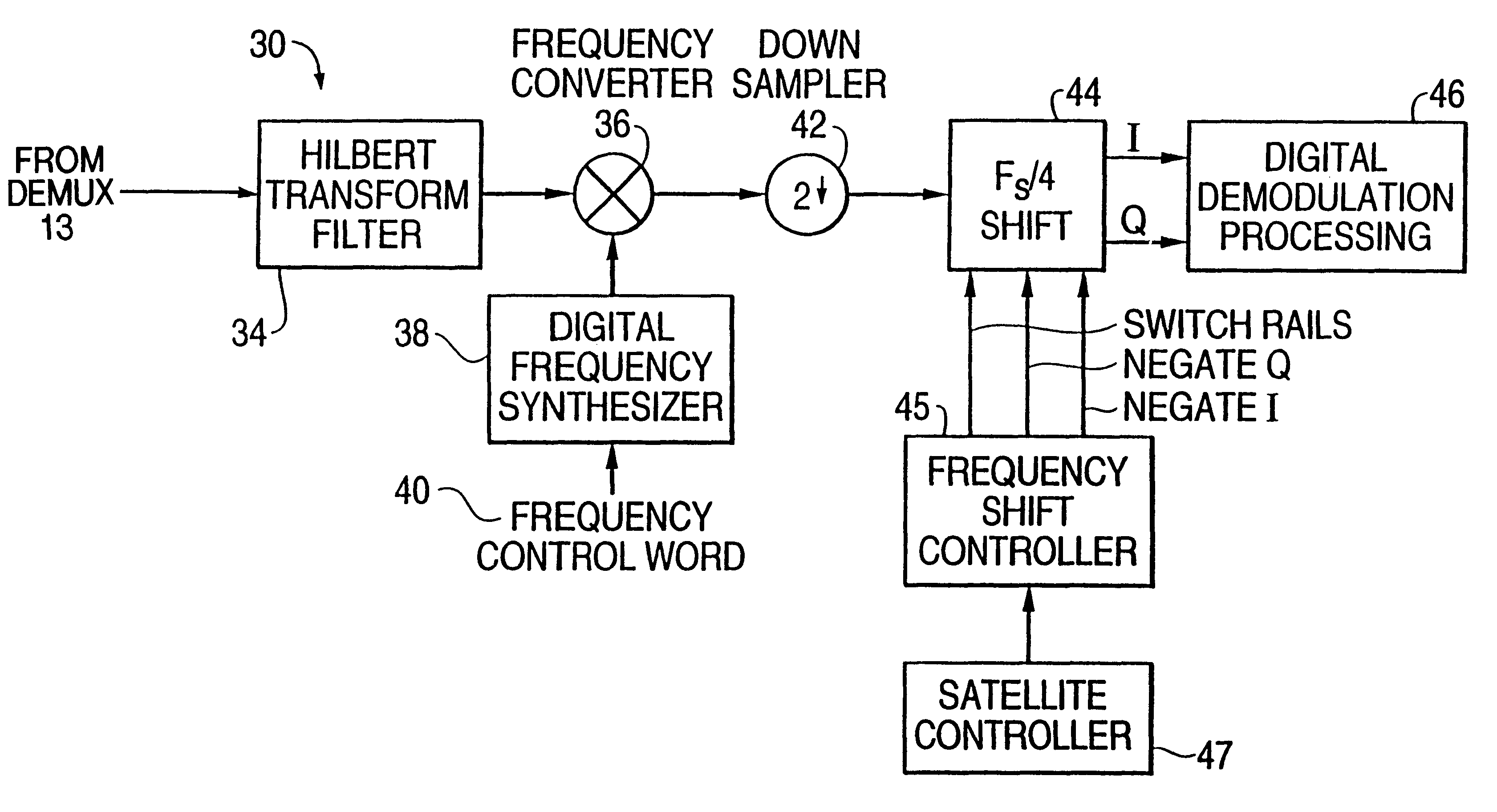

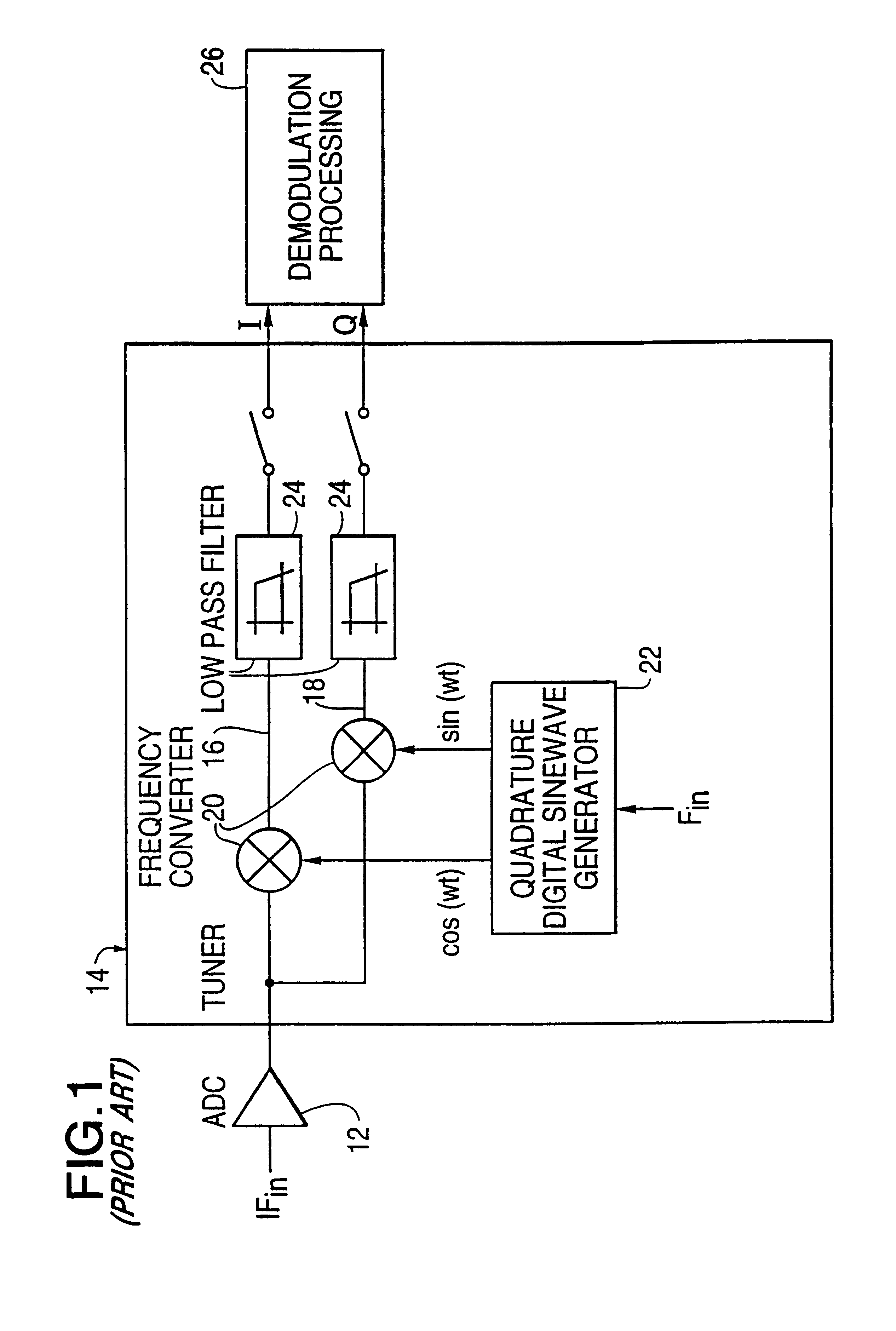

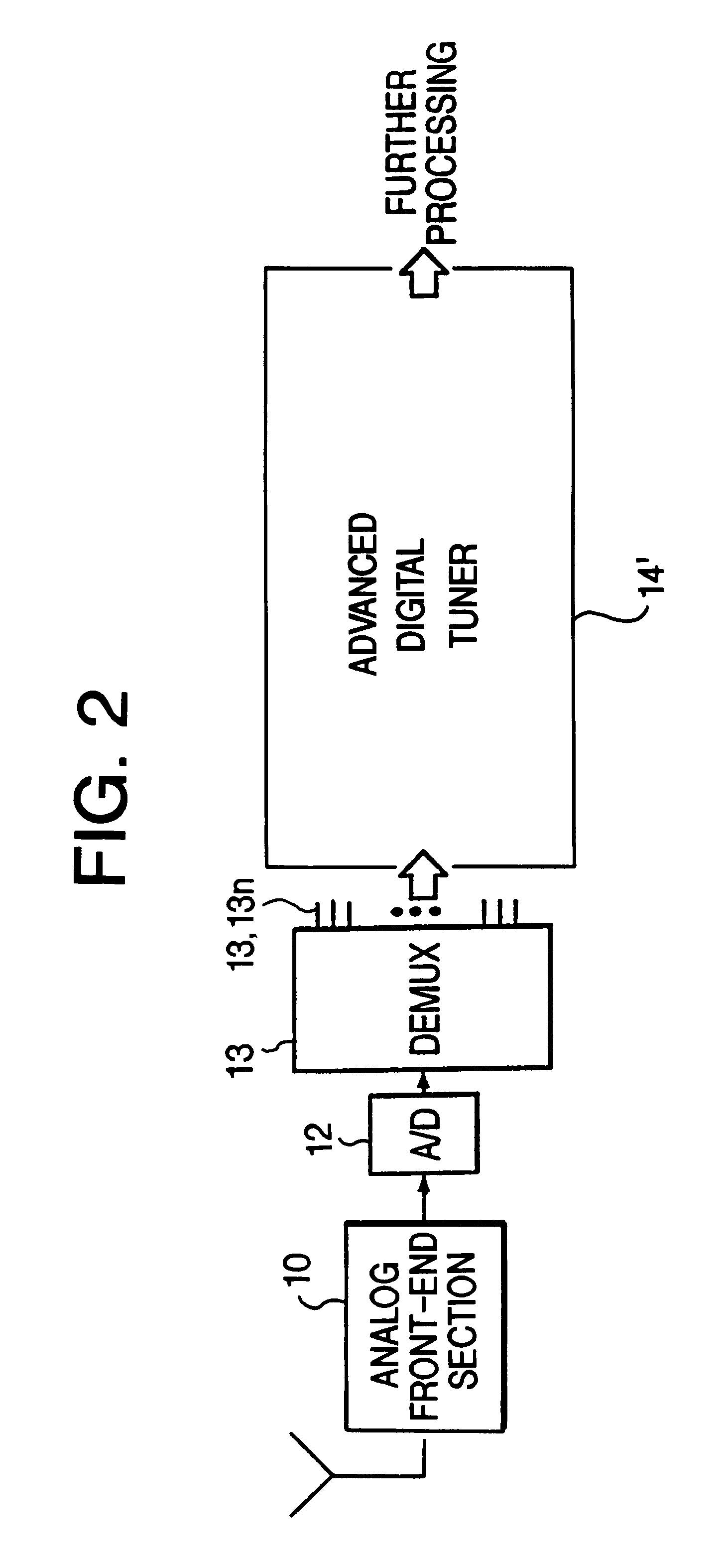

Wideband parallel processing digital tuner

InactiveUS6263195B1High speed data rateAvoid disadvantagesPolarisation/directional diversityPhase-modulated carrier systemsDigital dataFrequency spectrum

A wideband digital tuner (14') has an analog front-end section (10), a high speed analog-to-digital converter (12), demultiplexer (13) and a plurality of filters (341-342) arranged in a parallel input architecture to process wideband digital data received at extremely high sampling rates, such as at 2 Gsps (giga-samples per second). The tuner greatly attenuates an undesired spectral half of the wide bandwidth digital spectrum of the incoming digital signal using a complex band-pass filter, such as a Hilbert Transform filter. The tuner places the remaining half of the wide bandwidth digital spectrum of the incoming digital signal at complex baseband and down samples by 2. The architecture of the tuner can be partitioned into two separate halves which are hardware copies of each other.

Owner:NORTHROP GRUMMAN SYST CORP

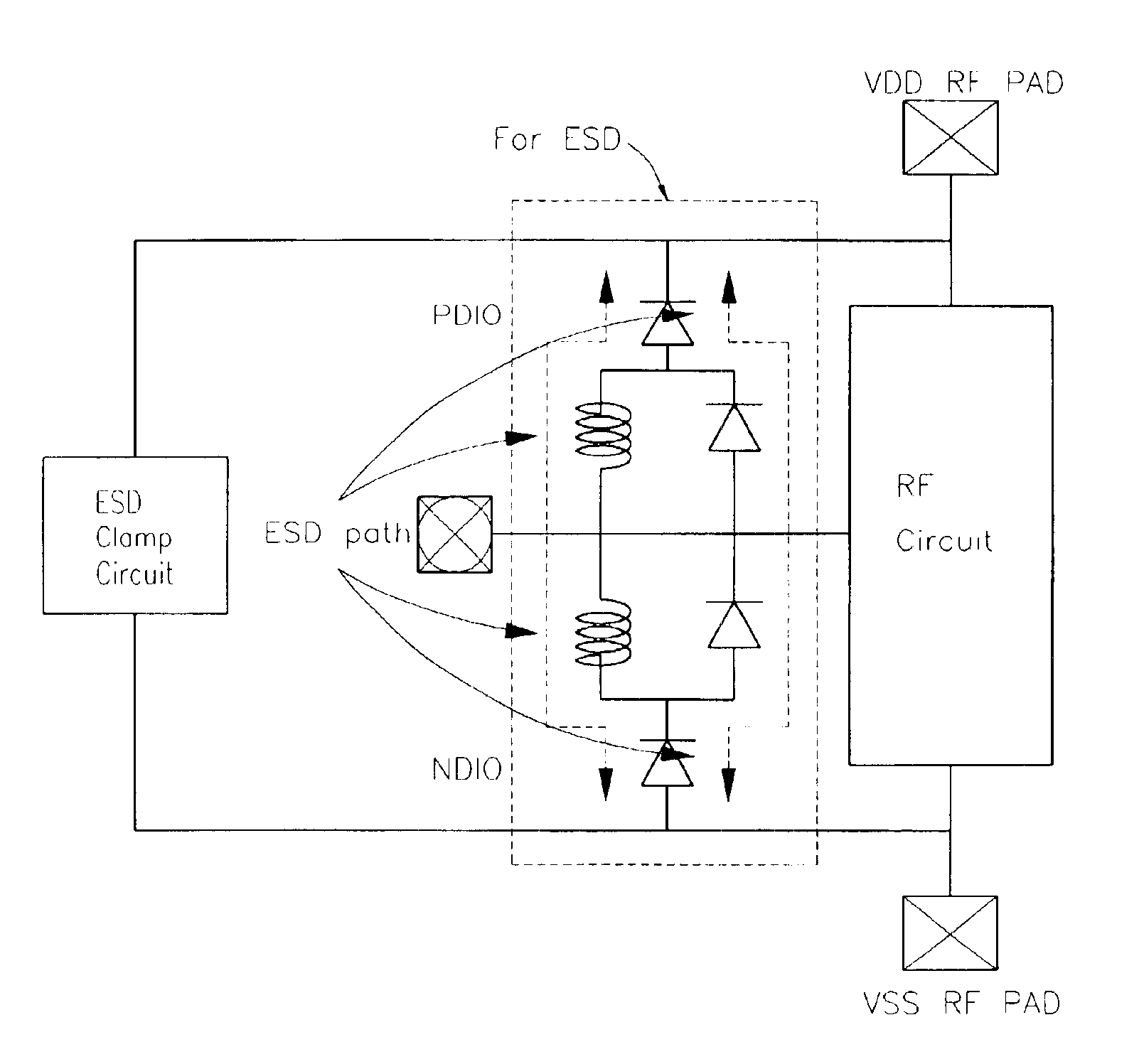

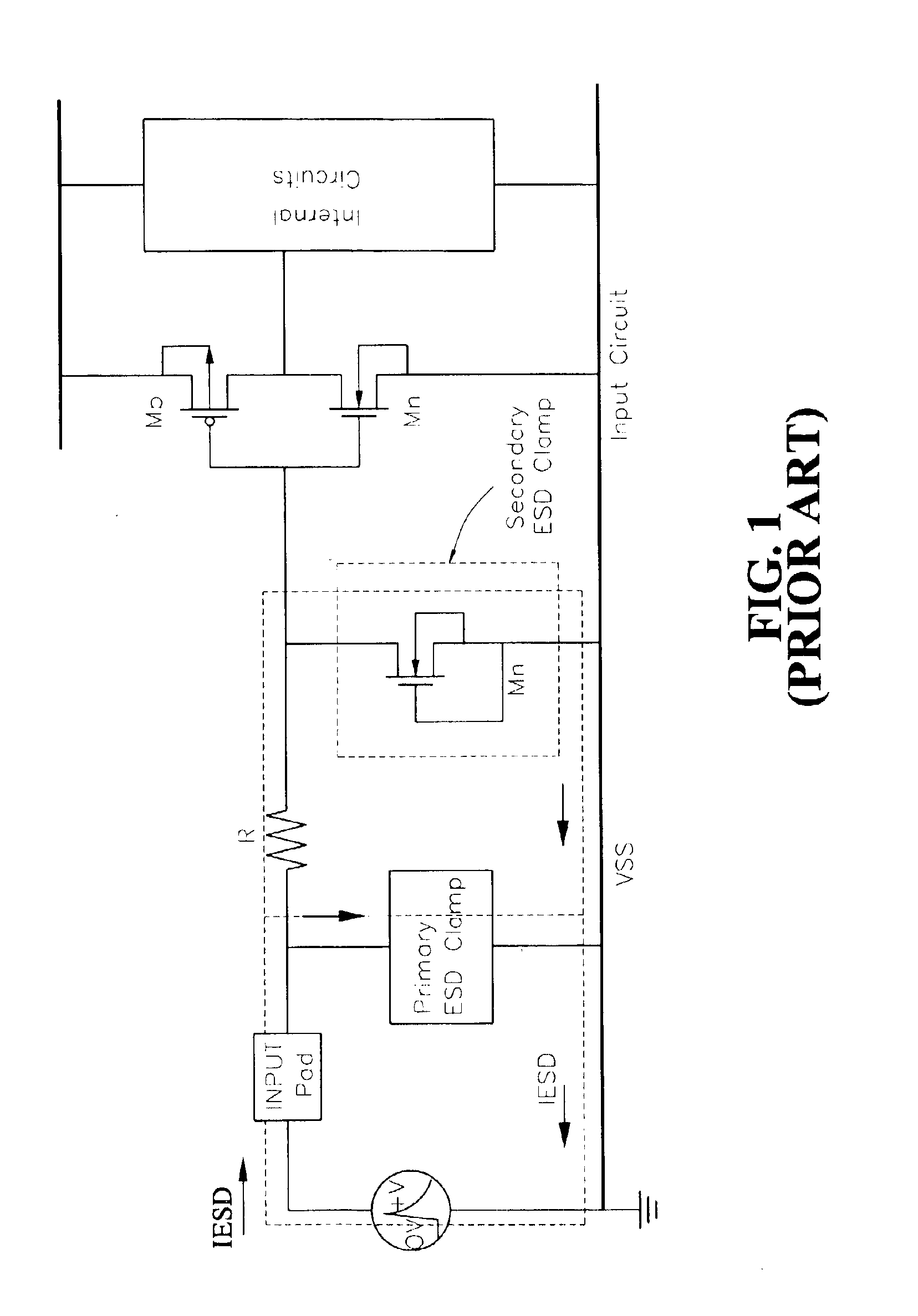

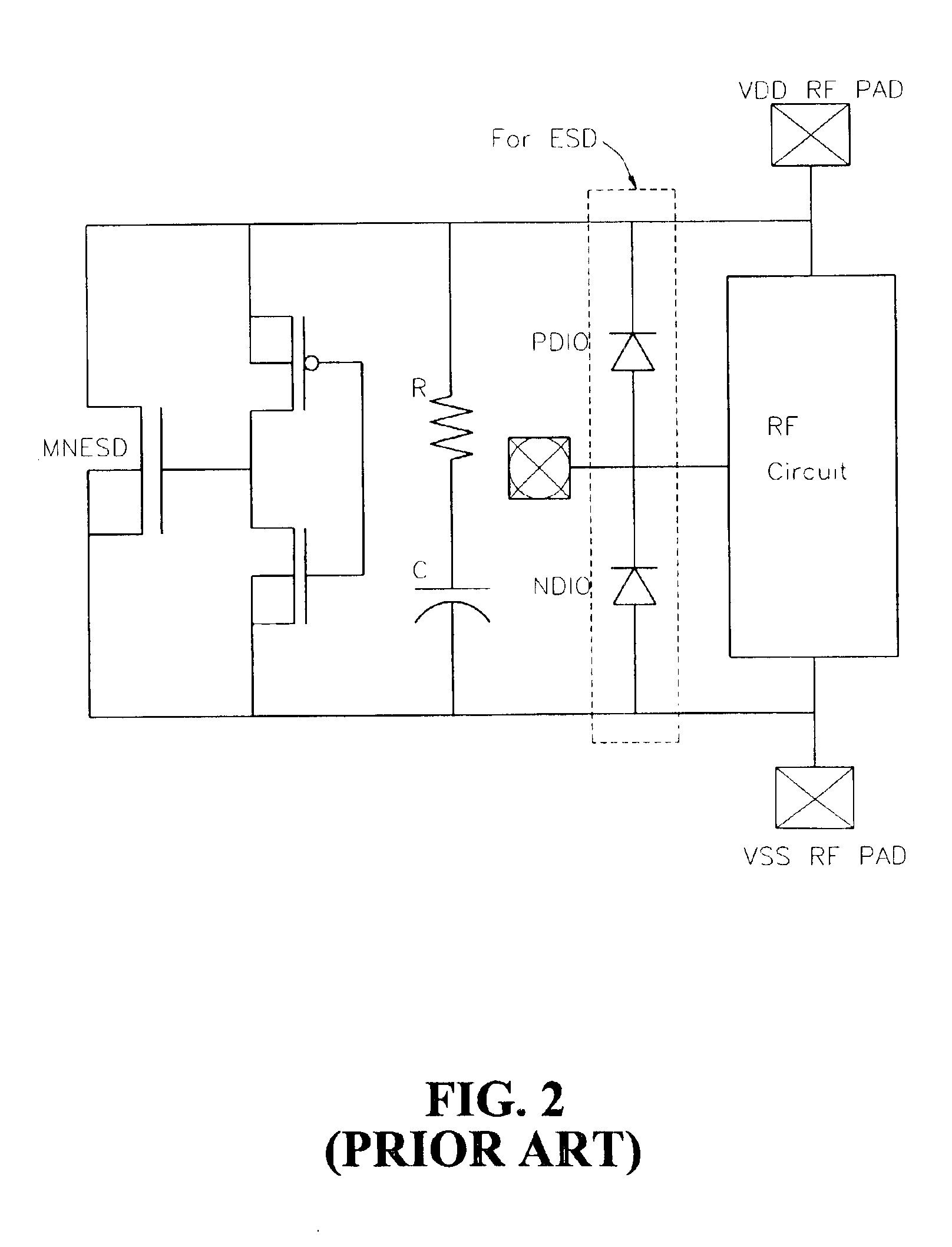

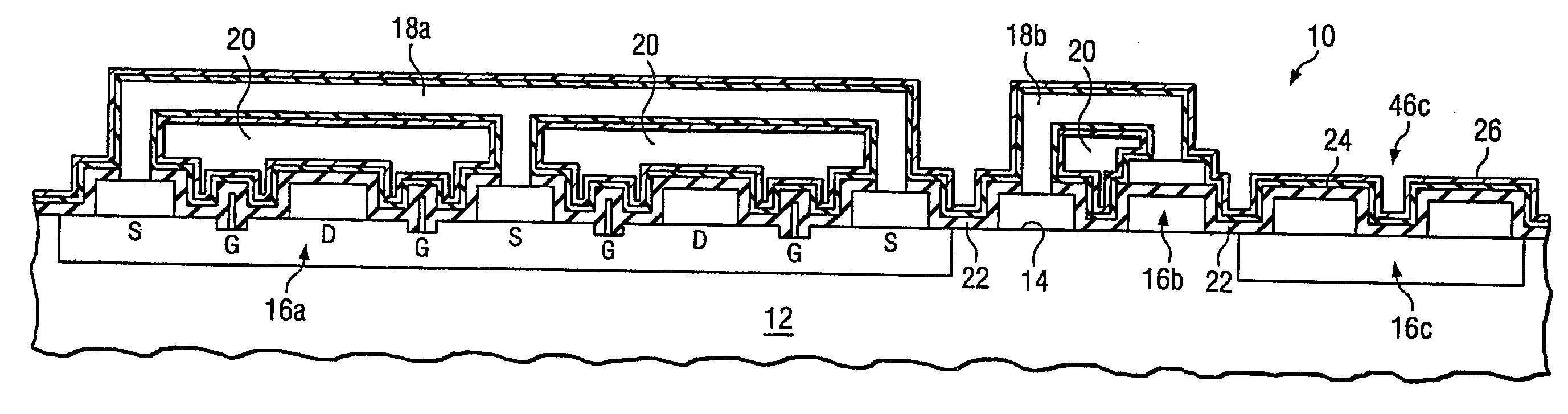

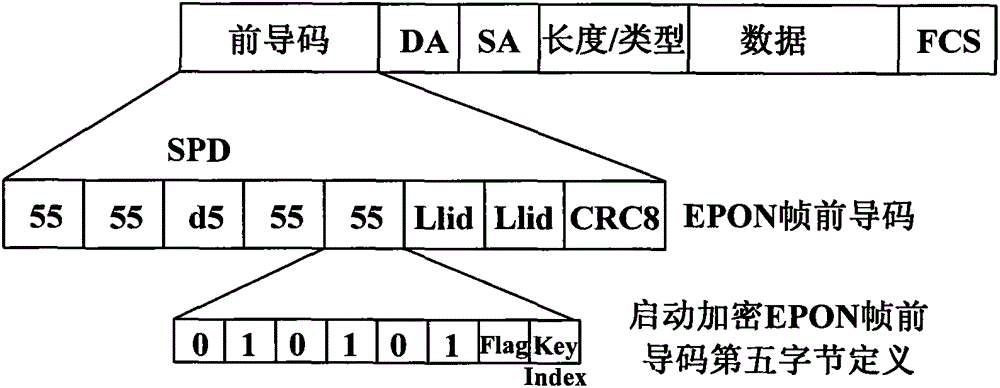

Electrostatic discharge protection device for giga-hertz radio frequency integrated circuits with varactor-LC tanks

InactiveUS6885534B2Solution value is not highHigh ESD levelSolid-state devicesEmergency protective arrangement detailsImpedance matchingEngineering

The present invention relates to a device for protecting high frequency RF integrated circuits from ESD damage. The device comprises at least one varactor-LC circuit tank stacked to avoid the power gain loss by the parasitic capacitance of ESD circuit. The varactor-LC tank could be designed to resonate at the RF operating frequency to avoid the power gain loss from the parasitic capacitance of ESD circuit. Multiple LC-tanks could be stacked for further reduction in the power gain loss. A reverse-biased diode is used as the varactor for both purposes of impedance matching and effective ESD current discharging. Because the inductor is made of metal, both the inductor and the varactor can discharge ESD current when ESD condition happens. It has a high enough ESD level to prevent ESD discharge.

Owner:LIBERTY PATENTS LLC

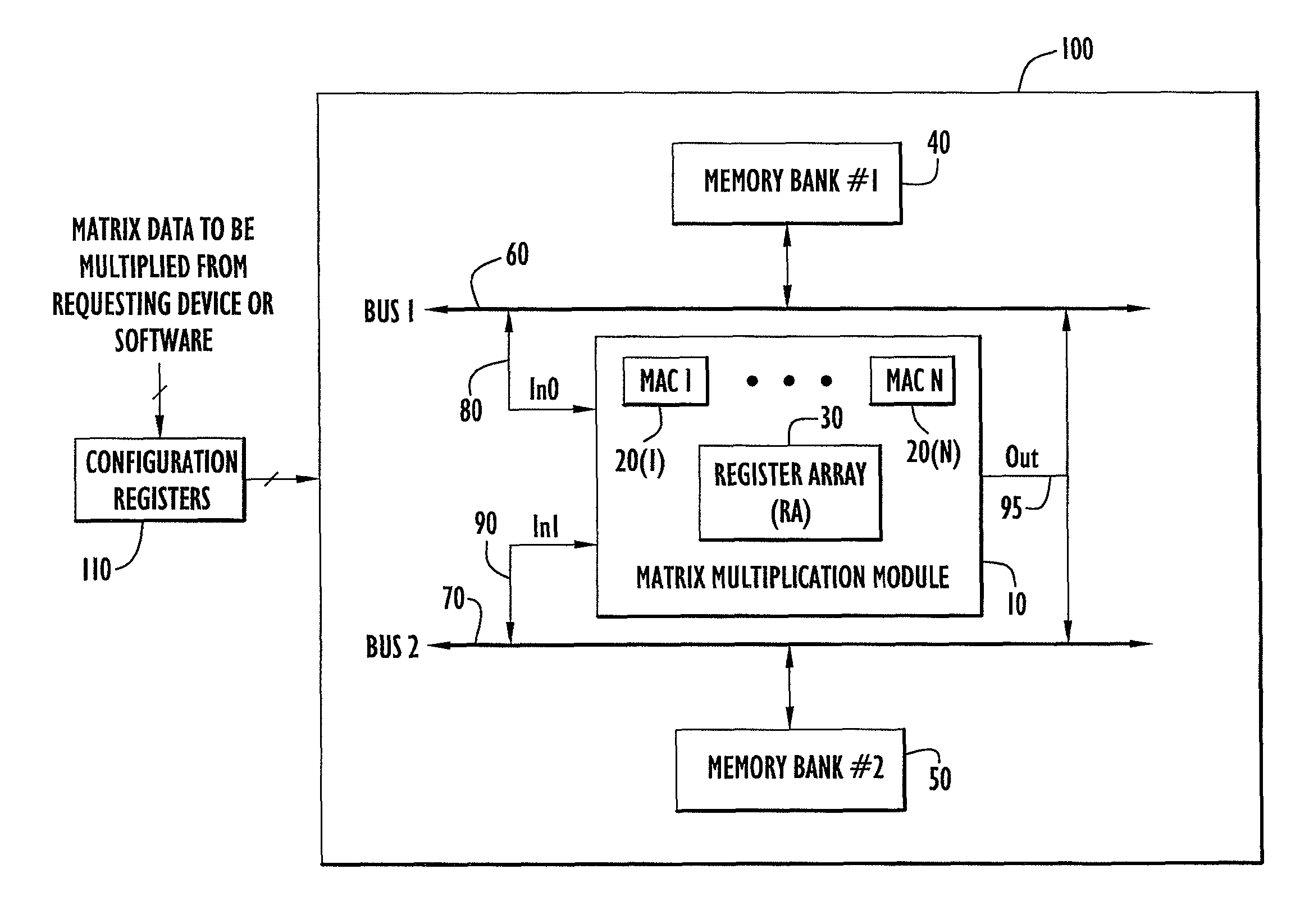

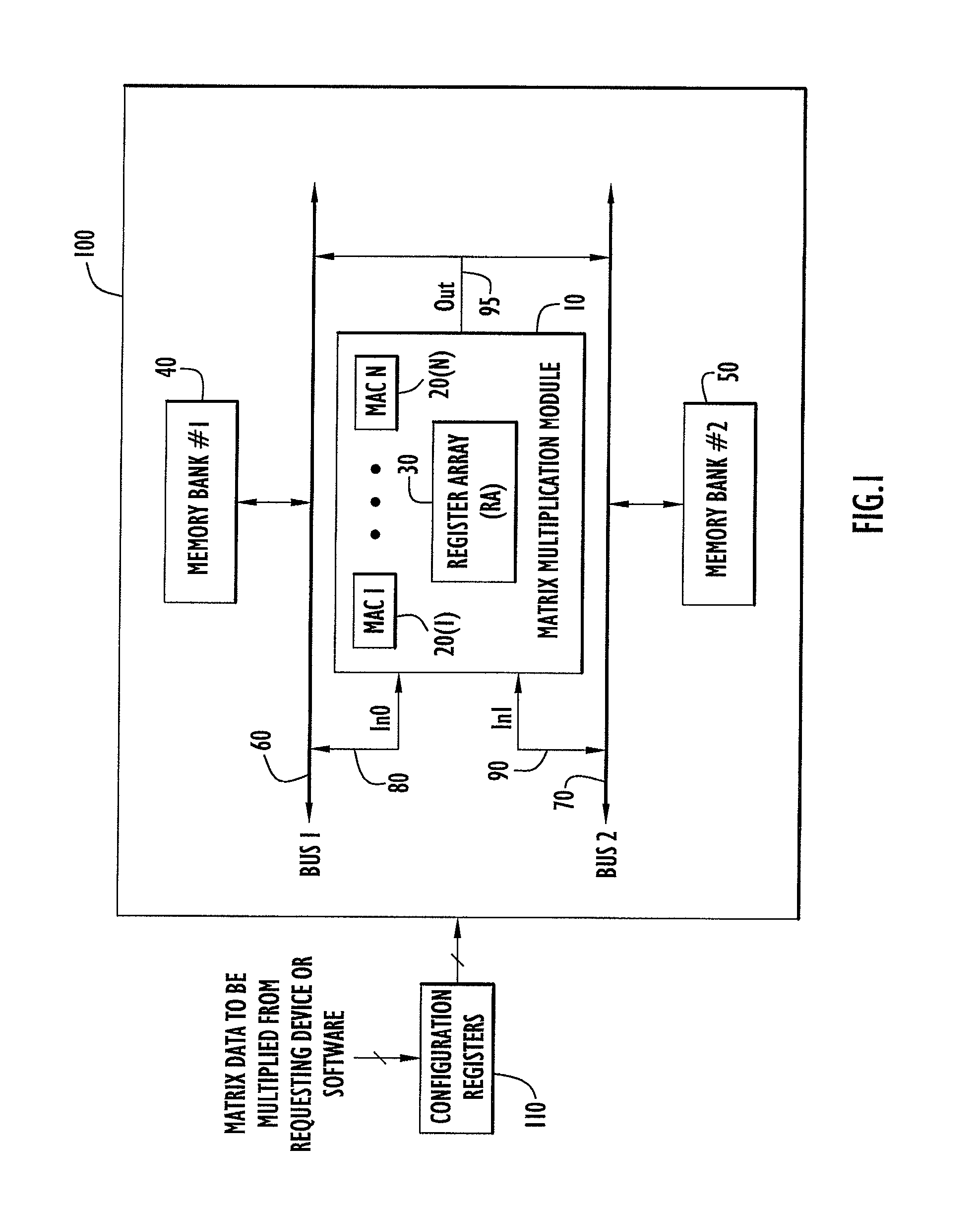

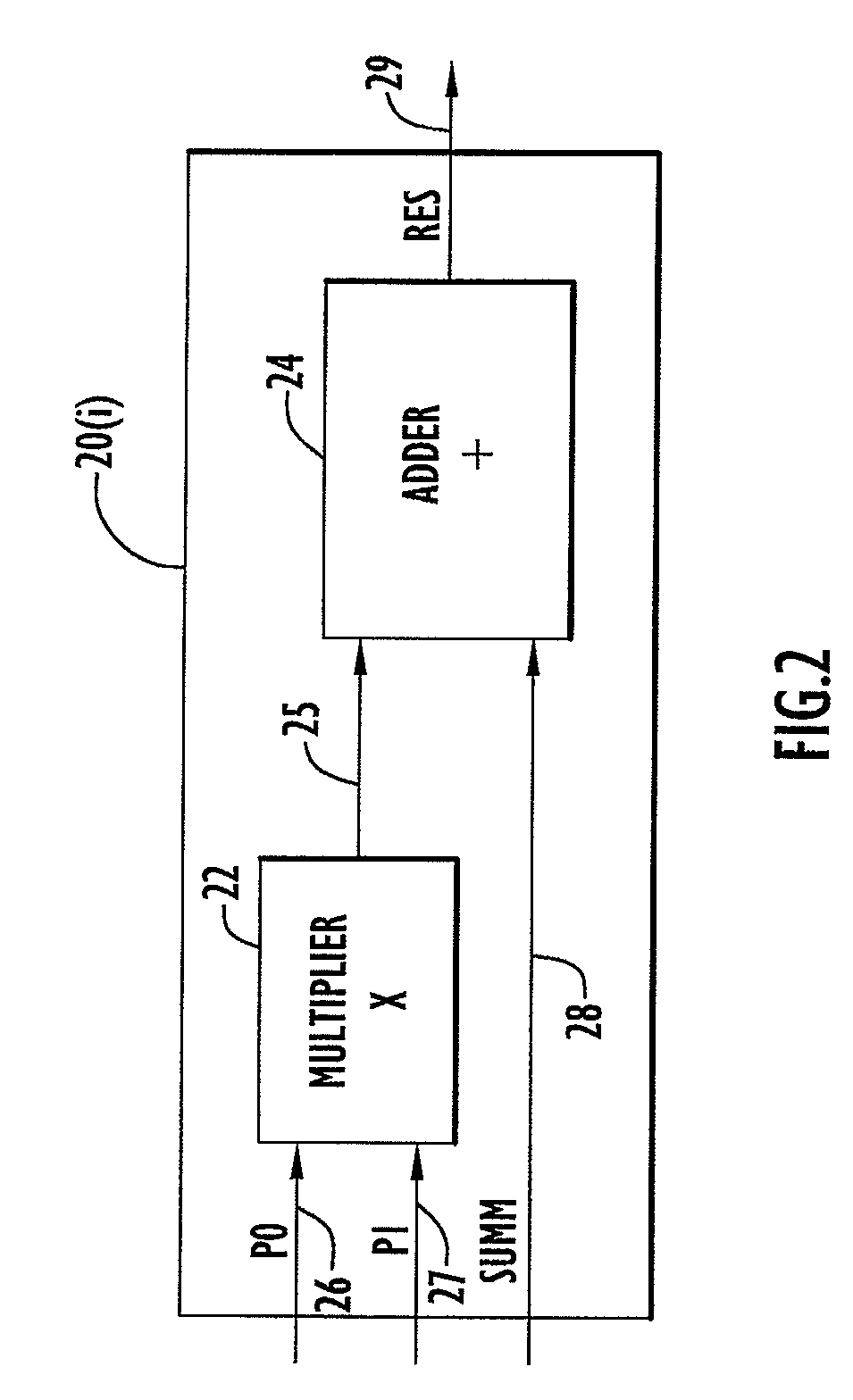

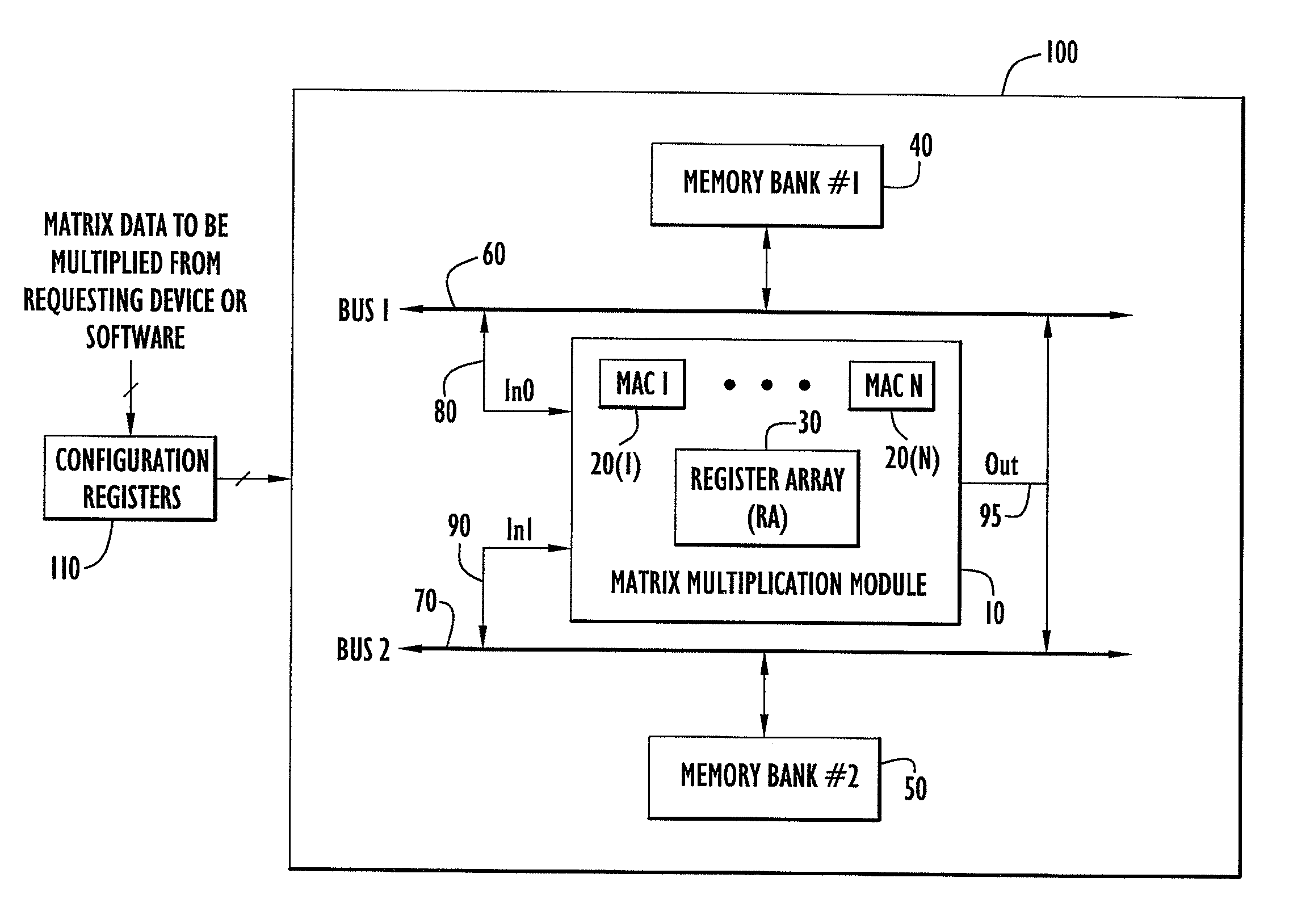

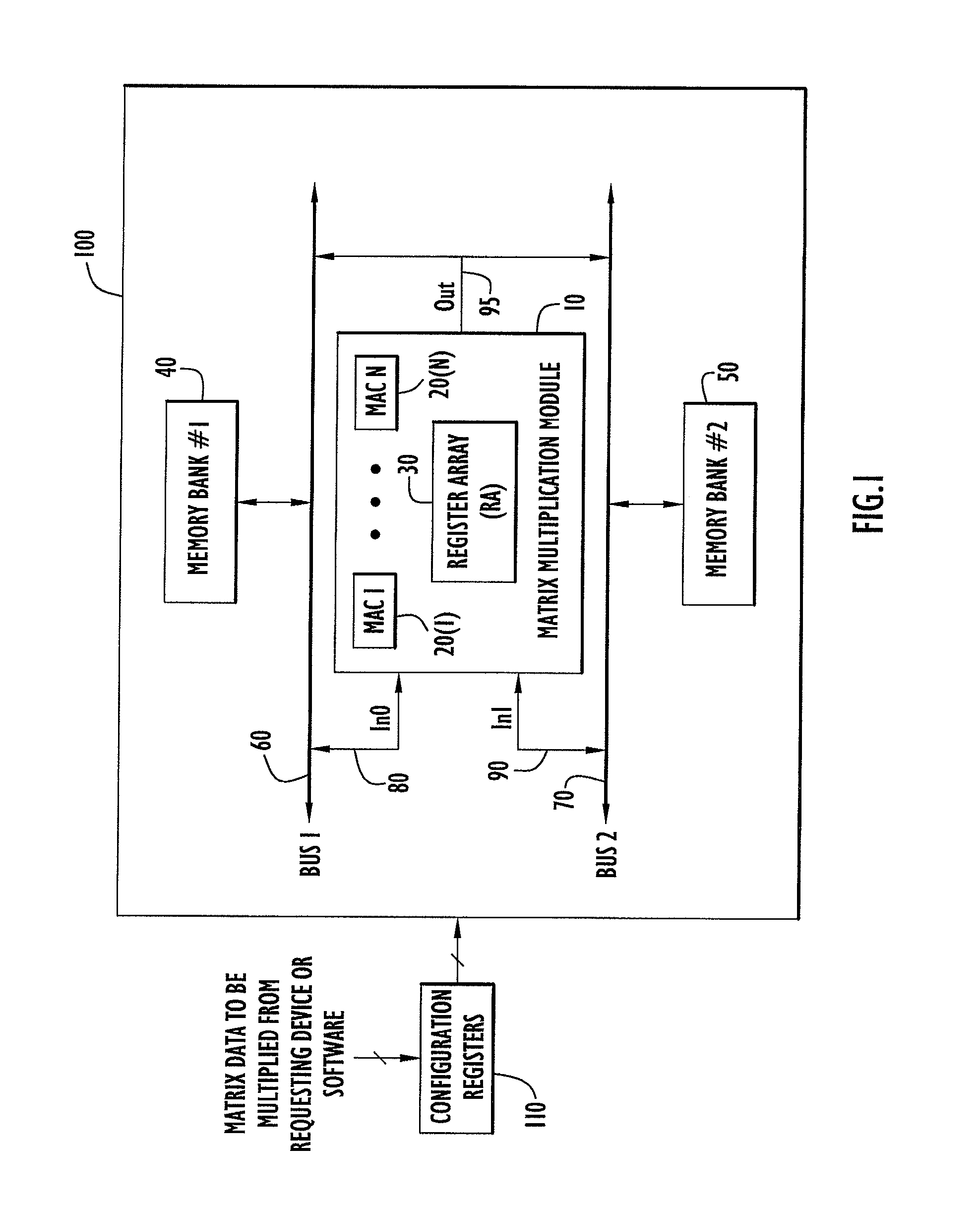

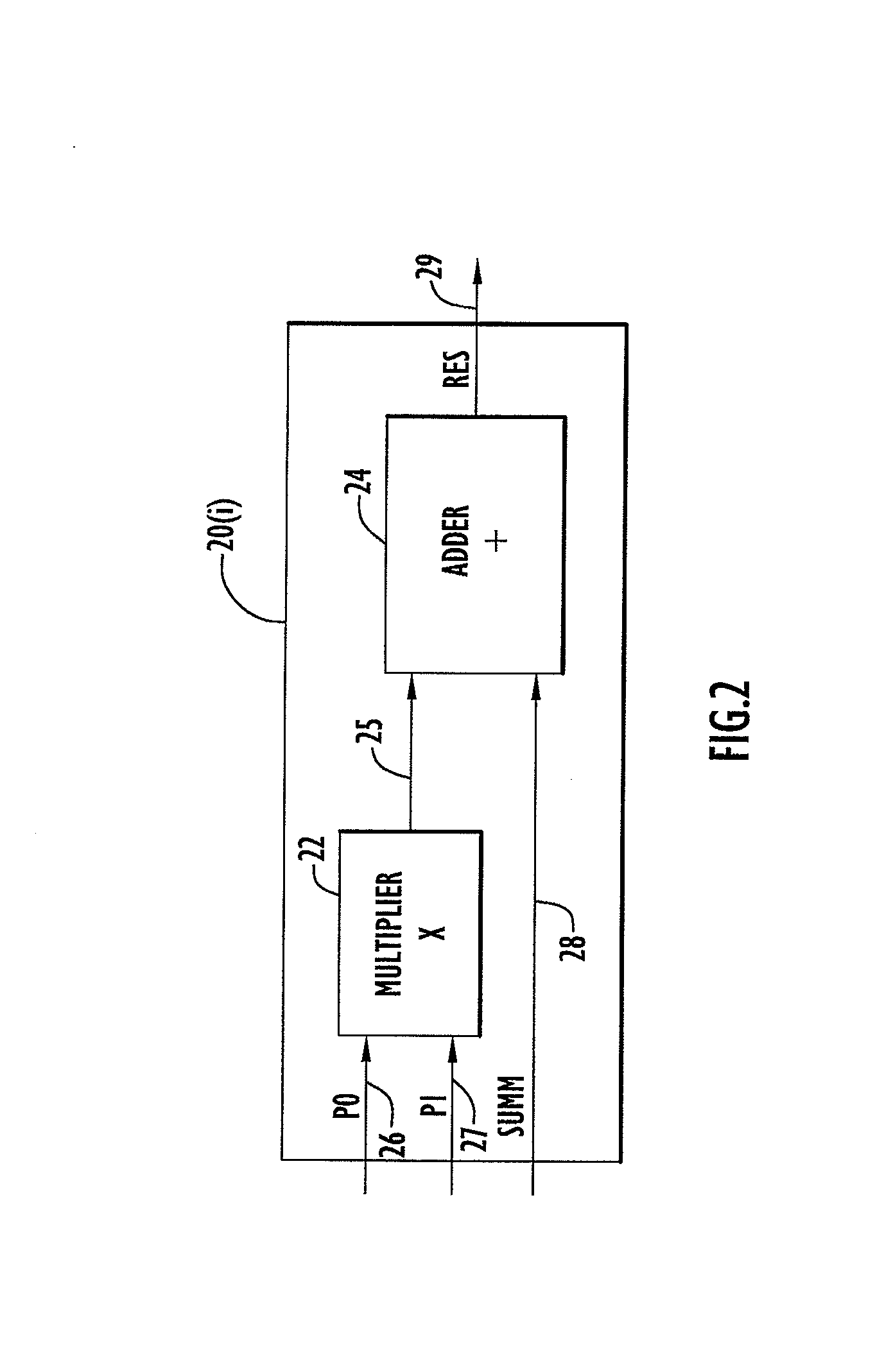

High speed and efficient matrix multiplication hardware module

ActiveUS8051124B2Computation using non-contact making devicesProgram controlClock rateComputer module

A matrix multiplication module and matrix multiplication method are provided that use a variable number of multiplier-accumulator units based on the amount of data elements of the matrices are available or needed for processing at a particular point or stage in the computation process. As more data elements become available or are needed, more multiplier-accumulator units are used to perform the necessary multiplication and addition operations. To multiply an N×M matrix by an M×N matrix, the total (maximum) number of used MAC units is “2*N−1”. The number of MAC units used starts with one (1) and increases by two at each computation stage, that is, at the beginning of reading of data elements for each new row of the first matrix. The sequence of the number of MAC units is {1, 3, 5, . . . , 2*N−1} for computation stages each of which corresponds to reading of data elements for each new row of the left hand matrix, also called the first matrix. For the multiplication of two 8×8 matrices, the performance is 16 floating point operations per clock cycle. For an FPGA running at 100 MHz, the performance is 1.6 Giga floating point operations per second. The performance increases with the increase of the clock frequency and the use of larger matrices when FPGA resources permit. Very large matrices are partitioned into smaller blocks to fit in the FPGA resources. Results from the multiplication of sub-matrices are combined to form the final result of the large matrices.

Owner:HARRIS CORP

Dedicated private network service method having backup and loads-balancing functions

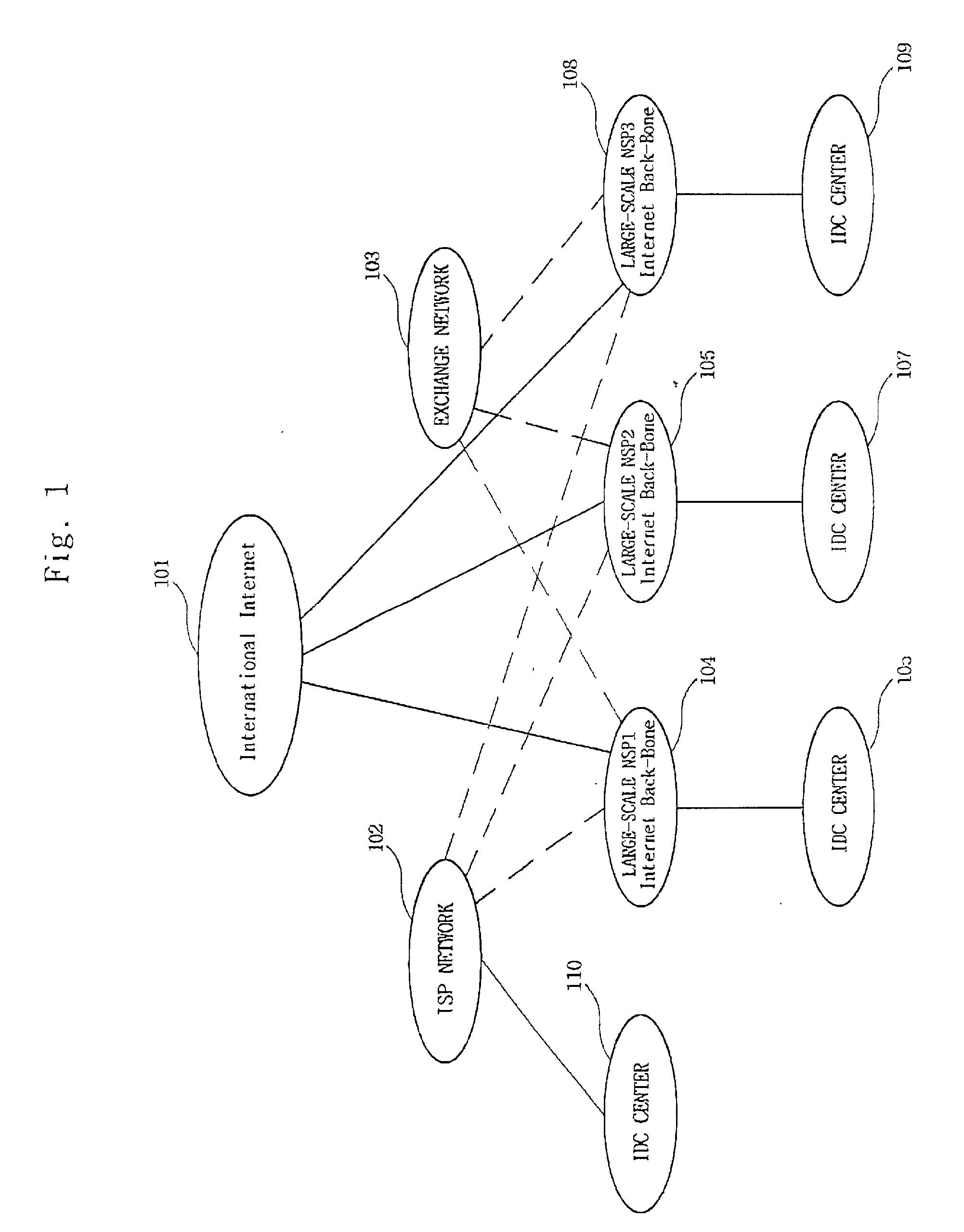

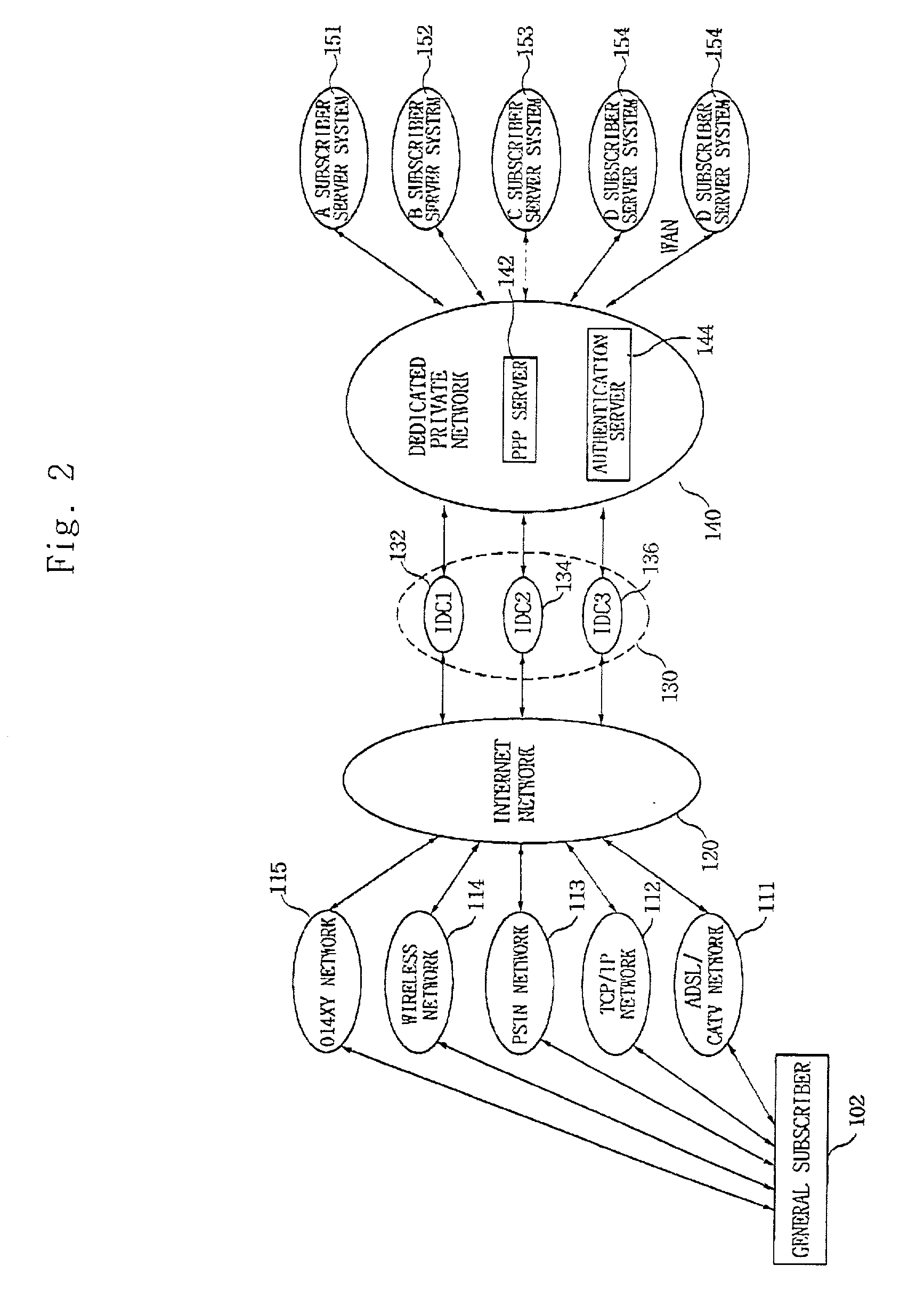

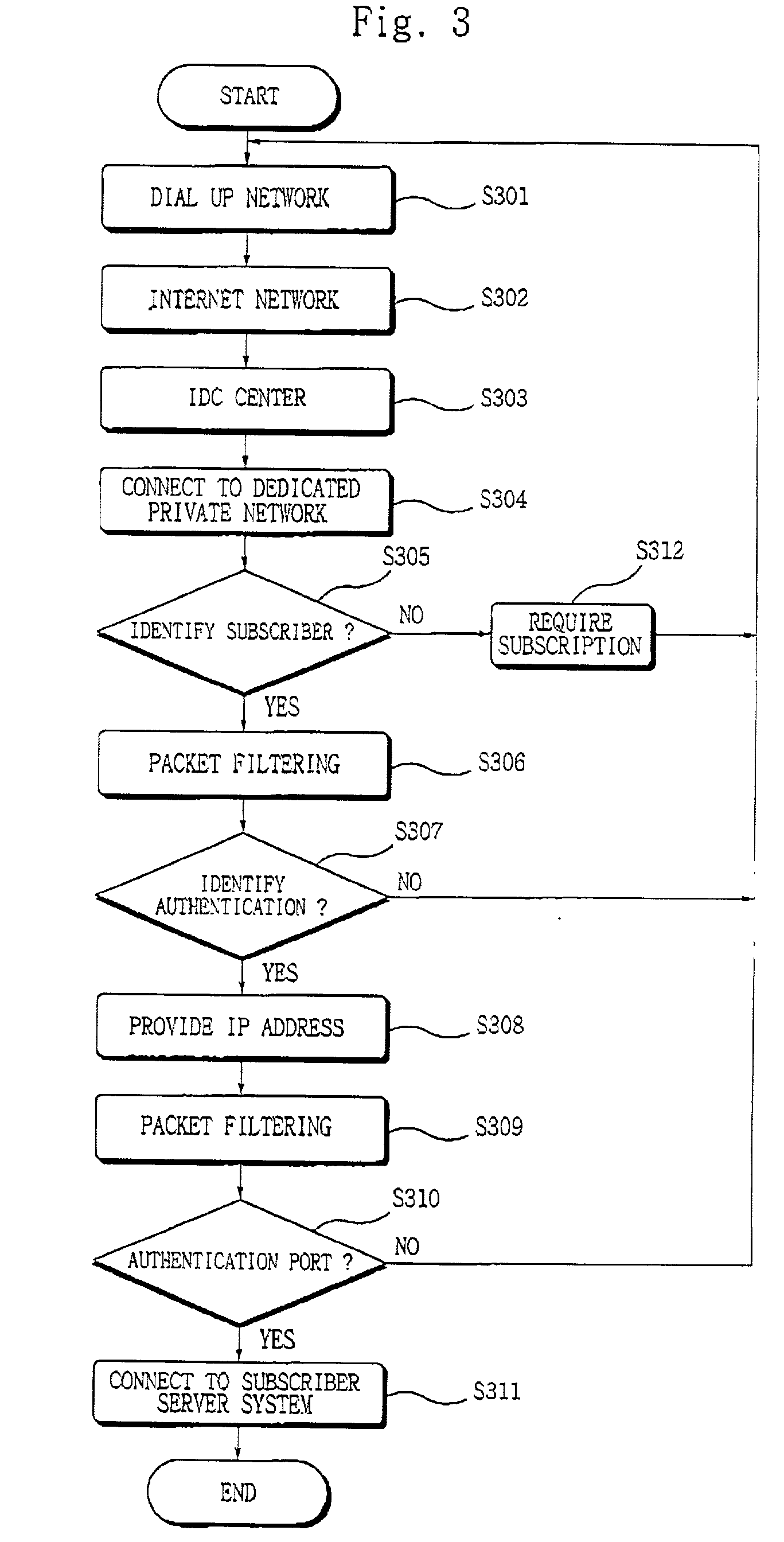

InactiveUS20010047414A1Reduce line costsSecures their privacyDigital data processing detailsDigital computer detailsTraffic capacityPrivate IP

The present invention relates to a service method for a construction of networks having automatic backup and load-balancing upon failures to networks and systems, and more particularly to a dedicated private network service method having a load-balancing function wherein the network backup is available since a bypass path is made to normally operating IDC centers upon failures to a specific IDC of the IDCs dispersed in plural places in a public IP networks by GLB servers, and load-balancing as to entire servers is available by constructing network equipment changeable into a private IP network in case of connecting to the IDC centers, connecting the network equipment by Giga lines, and using dispersed IDCs as a network constructed in one place. Further, the present invention, in a dedicated private network, comprises steps of (1) performing a bypass connection to an IDC normally operated upon a failure of a specific IDC by connecting a user by IDC center in a public IP network by a GLB server upon a user's connection; (2) changing a public IP address to a private IP address upon a connection to the dedicated private network; (3) load-balancing traffic to plural IDC centers after interactively connecting the respective IDC centers by constructing a ring-shape network with the IDC centers of private IP networks connected by Giga lines; and (4) performing the load balancing of servers by identifying server states at SLB servers in the respective IDC centers.

Owner:NITGEN TECH

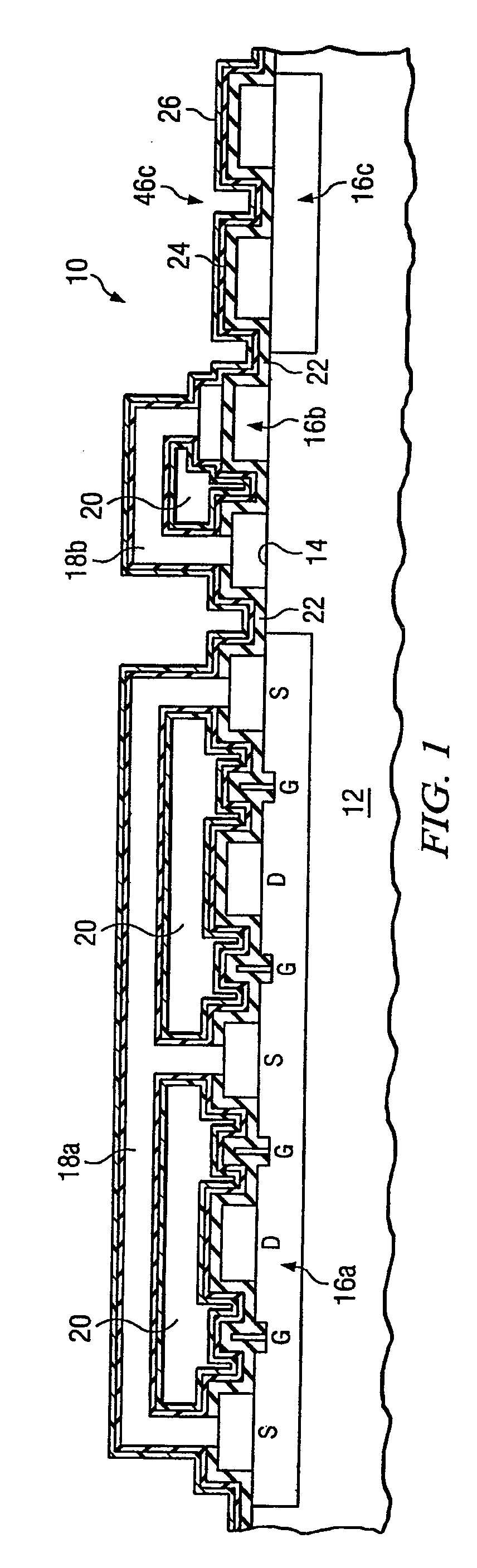

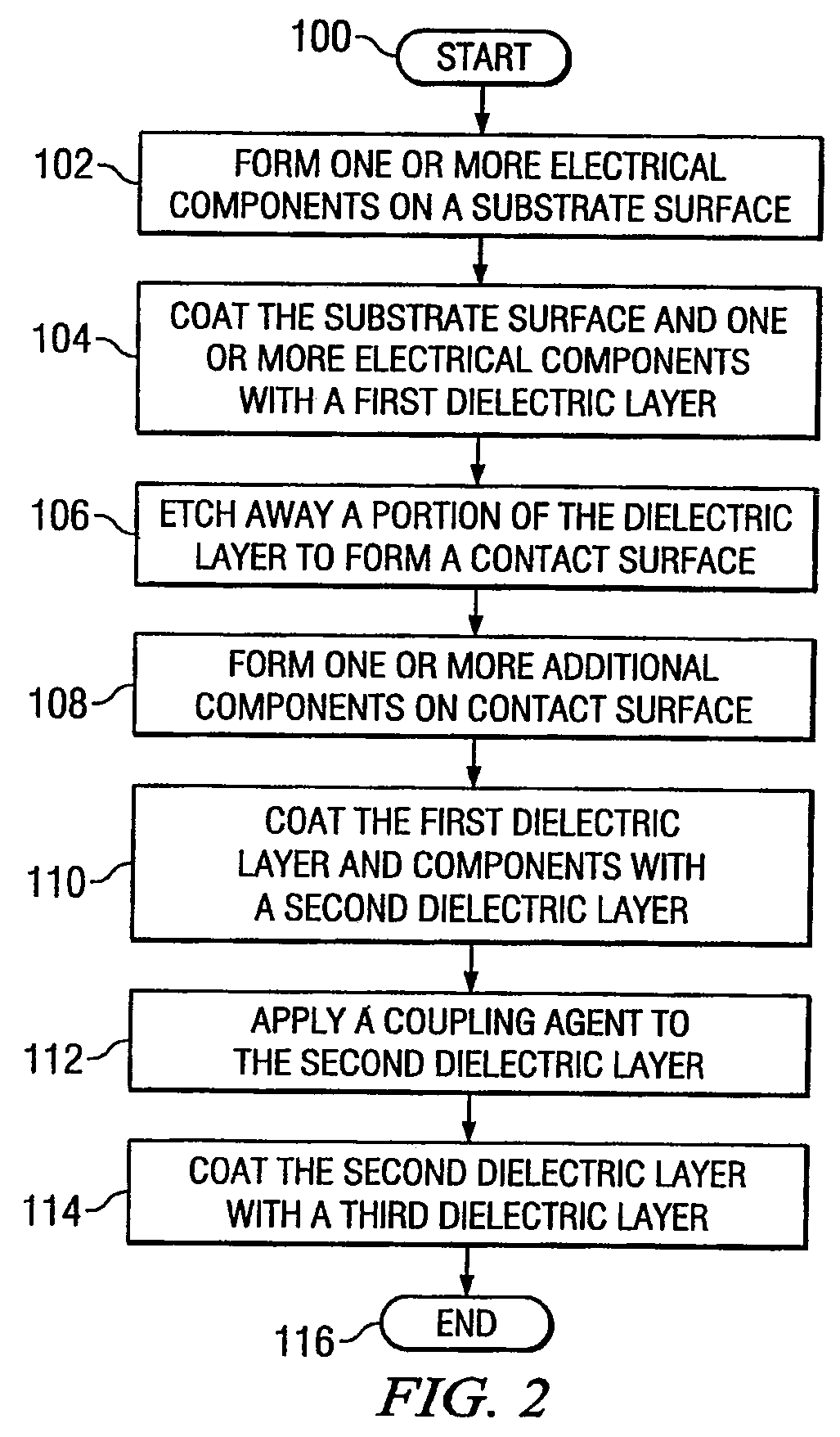

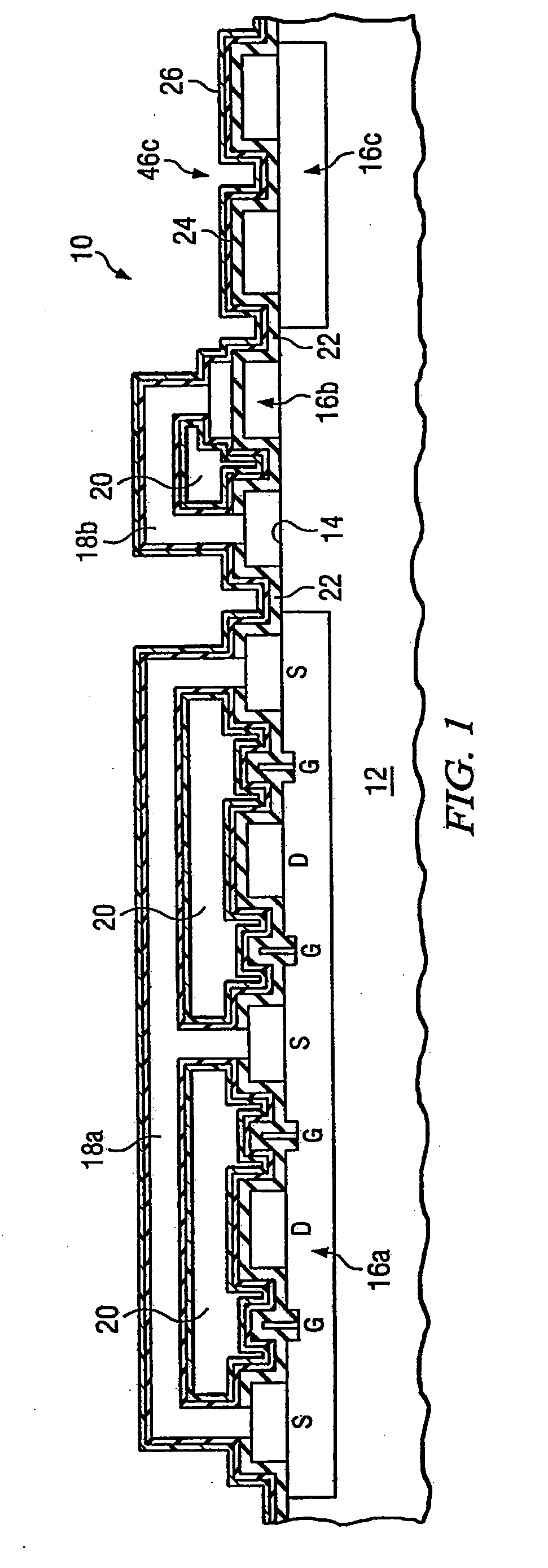

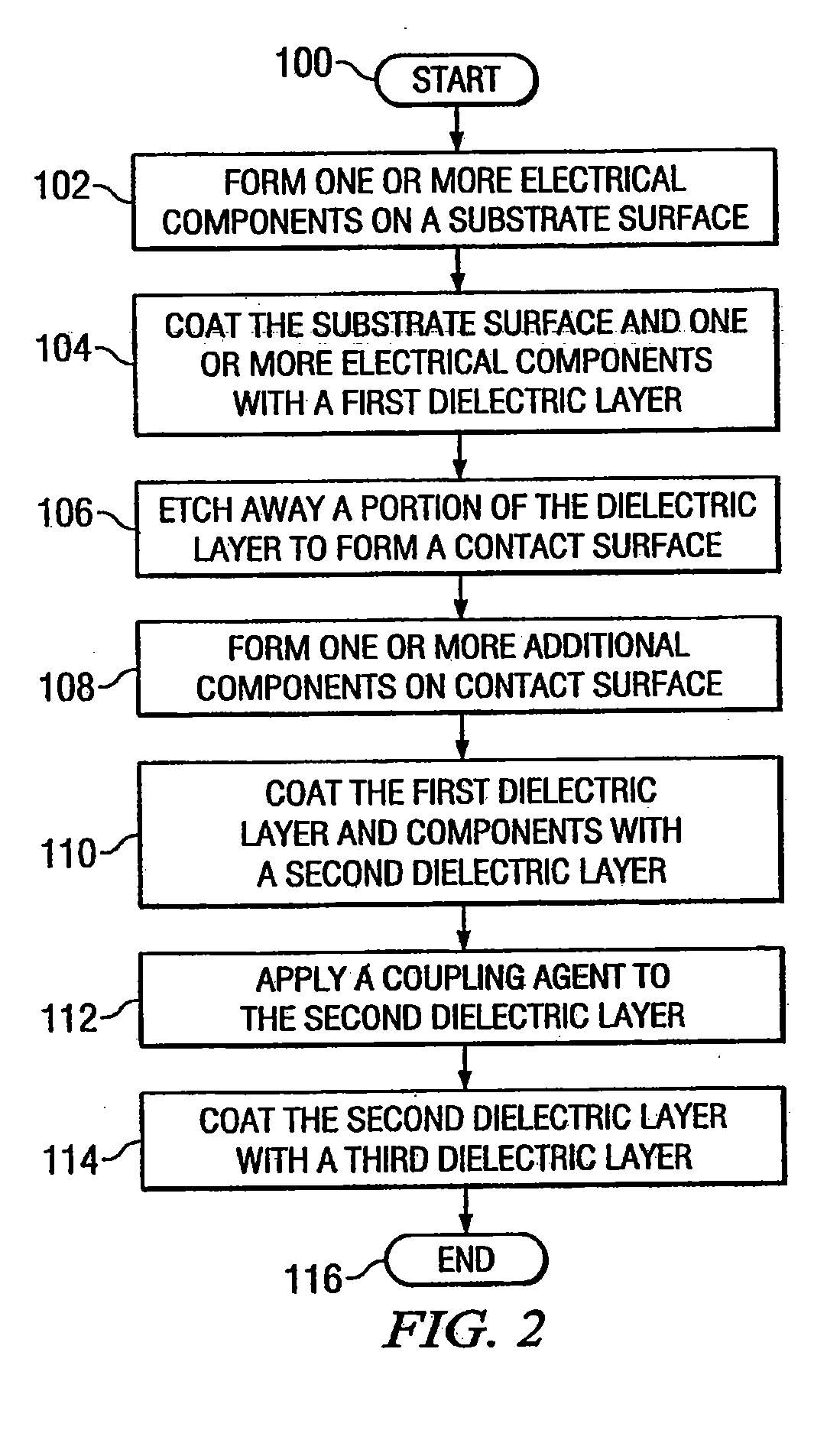

Environmental Protection Coating System and Method

ActiveUS20080185173A1Improve electrical performanceGood mechanical protectionPrinted circuit assemblingSemiconductor/solid-state device detailsDielectric lossCoating system

According to one embodiment of the disclosure, an environmental protection coating comprises a circuit assembly having a first protective dielectric layer and a second dielectric layer. The circuit assembly has an outer surface on which a plurality of discrete electrical components are attached. The first protective dielectric layer overlays the circuit assembly. The second dielectric layer overlays the first protective dielectric layer and is made of a dielectric material having modulus of elasticity less than 3.5 Giga-Pascal (GPa), dielectric constant less than 2.7, dielectric loss less than 0.008, breakdown voltage strength in excess of 2 million volts / centimeter (MV / cm), temperature stability to 3000 Celsius, defect densities less than 0.5 / centimeter, pinhole free in films greater than 50 Angstroms, capable of being deposited conformally over and under 3D structures with thickness uniformity less than or equal to 10%.

Owner:RAYTHEON CO

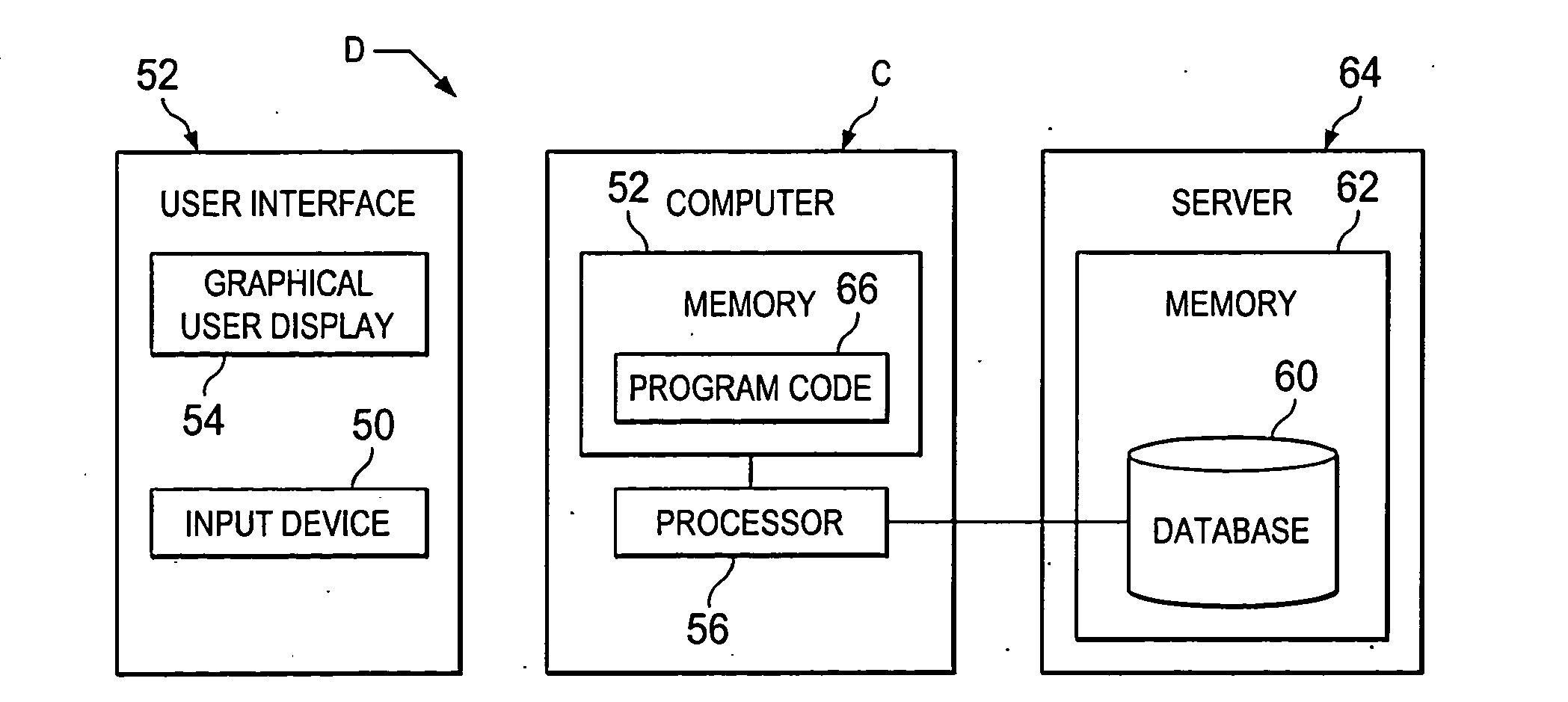

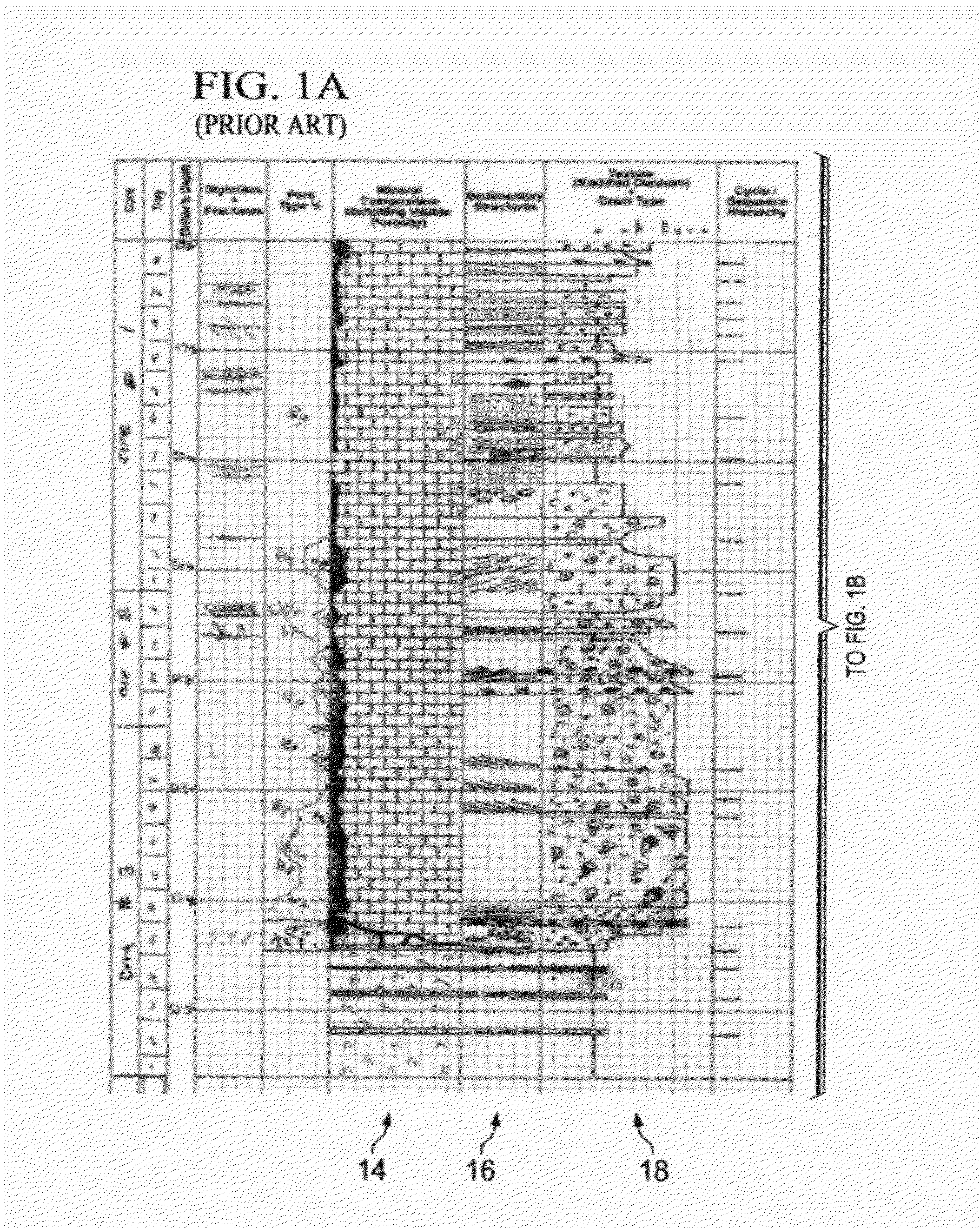

Core-plug to giga-cells lithological modeling

Well core data descriptions are received as input digital data for computer lithofacies modeling. Digital templates are established for carbonate and clastic core description based on reservoir rock formation analysis. Description criteria of the template for carbonate rock can include texture, mineral composition, grain size, and pore type. For clastic rock, the criteria in the template can include grain size, sedimentary structure, lithology, and visual porosity. The data and observations regarding these criteria are entered into a computer 3D geological modeling system directly. Wireline log data are integrated to calibrate with well core description to derive lithofacies. The lithofacies are exported in digital format to be entered into the 3D geological modeling system. A geologically realistic model of the reservoir can be established.

Owner:SAUDI ARABIAN OIL CO

High Speed and Efficient Matrix Multiplication Hardware Module

ActiveUS20090024685A1Computation using non-contact making devicesProgram controlClock rateParallel computing

A matrix multiplication module and matrix multiplication method are provided that use a variable number of multiplier-accumulator units based on the amount of data elements of the matrices are available or needed for processing at a particular point or stage in the computation process. As more data elements become available or are needed, more multiplier-accumulator units are used to perform the necessary multiplication and addition operations. To multiply an N×M matrix by an M×N matrix, the total (maximum) number of used MAC units is “2*N−1”. The number of MAC units used starts with one (1) and increases by two at each computation stage, that is, at the beginning of reading of data elements for each new row of the first matrix. The sequence of the number of MAC units is {1, 3, 5, . . . , 2*N−1} for computation stages each of which corresponds to reading of data elements for each new row of the left hand matrix, also called the first matrix. For the multiplication of two 8×8 matrices, the performance is 16 floating point operations per clock cycle. For an FPGA running at 100 MHz, the performance is 1.6 Giga floating point operations per second. The performance increases with the increase of the clock frequency and the use of larger matrices when FPGA resources permit. Very large matrices are partitioned into smaller blocks to fit in the FPGA resources. Results from the multiplication of sub-matrices are combined to form the final result of the large matrices.

Owner:HARRIS CORP

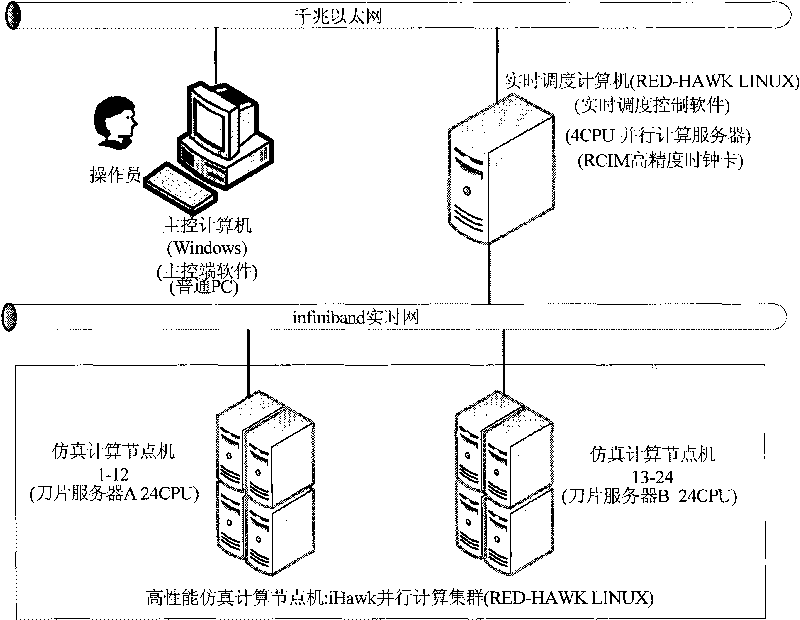

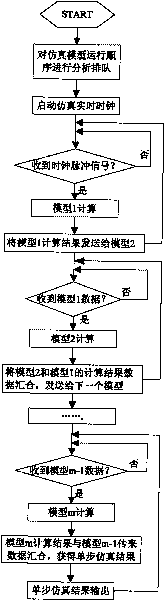

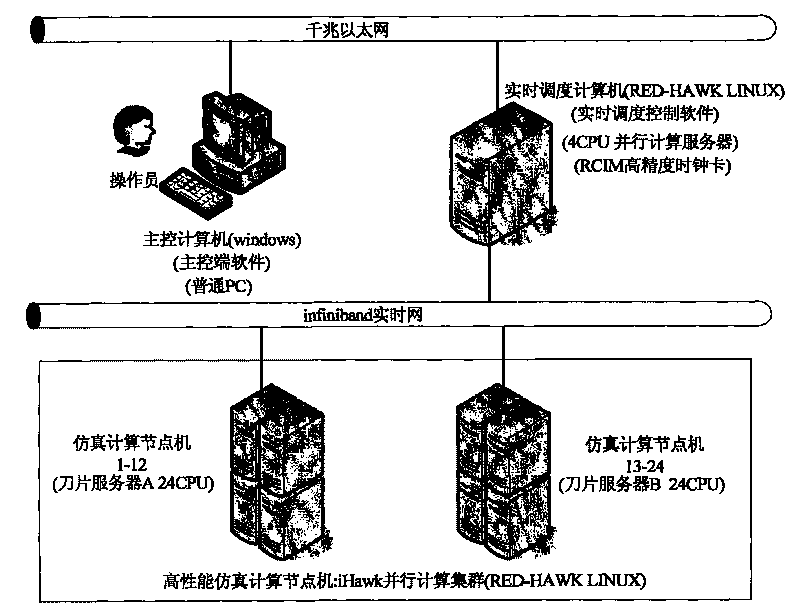

Parallel computation management-based autonomous navigation simulation and scheduling management system

ActiveCN101719078AGuaranteed real-timeGuaranteed parallelismMultiprogramming arrangementsSoftware simulation/interpretation/emulationOperational systemSoftware system

The invention discloses a parallel computation management-based autonomous navigation simulation and scheduling management system, which consists of a hardware system and a software system, wherein the hardware system consists of a master control computer, a real-time scheduling computer, a simulation computing node, a real-time communication network and a clock card; the real-time communication network consists of a giga Ethernet network and an infiniband high-performance real-time network; and the software system consists of a supporting operating system, master control end software and real-time scheduling control software. The parallel computation management-based autonomous navigation simulation and scheduling management system ensures the real-time property of a simulation system due to the adoption of the infiniband high-performance real-time network and an REDHAWK real-time operating system, ensures the possibility that the system realizes parallel computations in terms of hardware due to the adoption of a computing server and a blade server, realizes the parallel computations among simulation system models based on a data driving asynchronous pipeline parallel real-time scheduling algorithm, and in combination with the hardware, greatly speeds up the computation of the simulation system and ensures the parallelism and the real-time property of the complex simulation system.

Owner:BEIJING INST OF SPACECRAFT SYST ENG

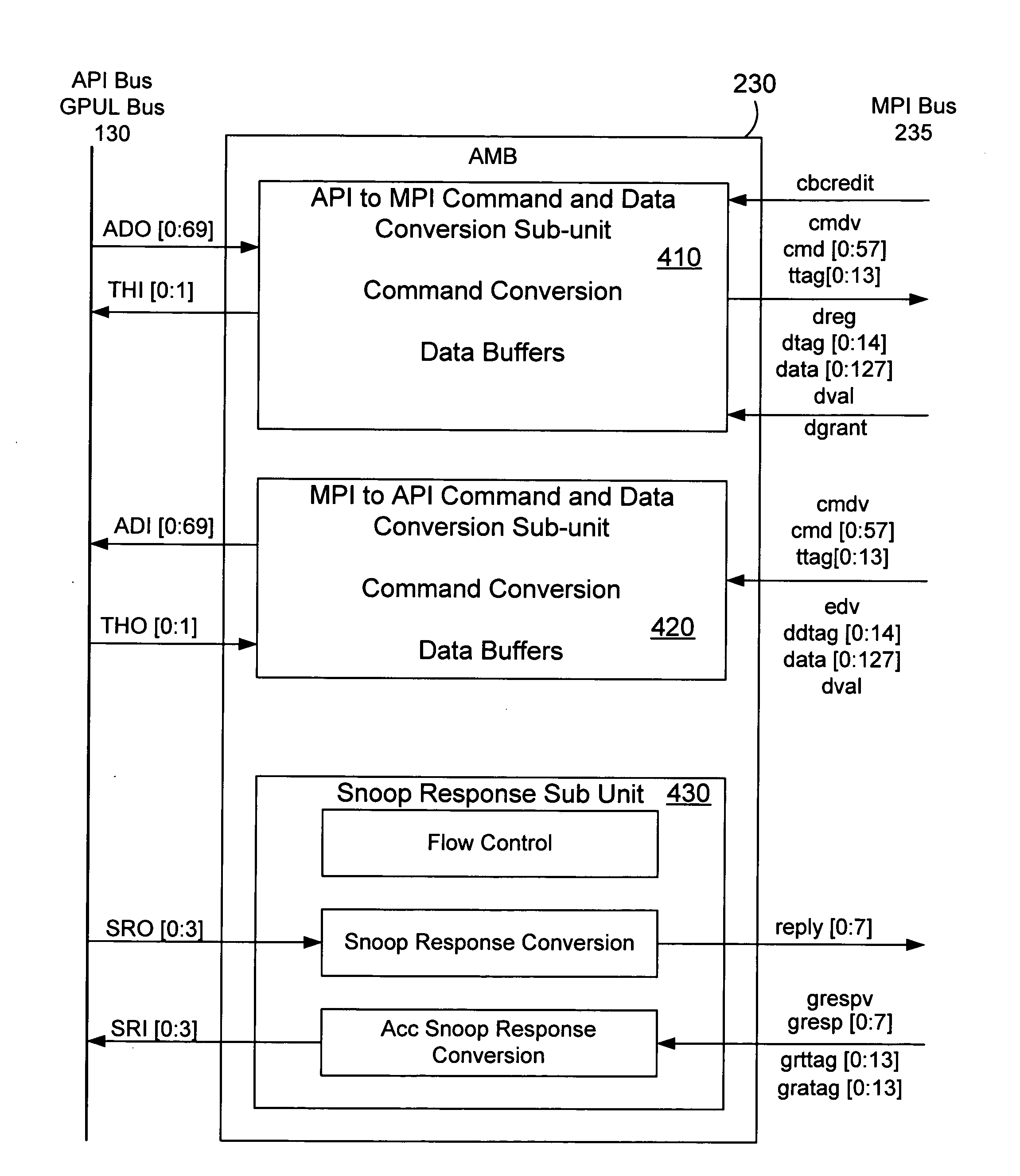

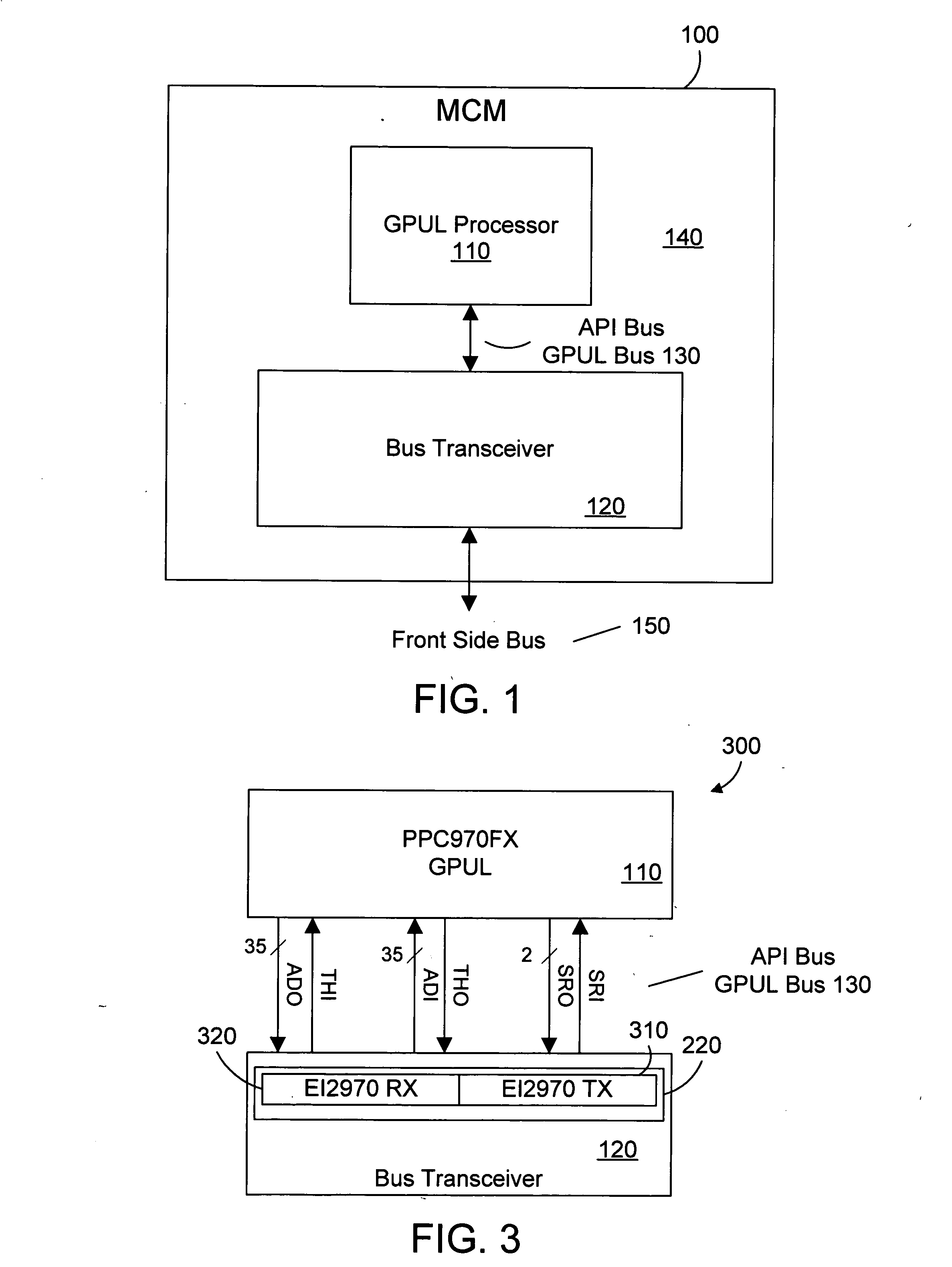

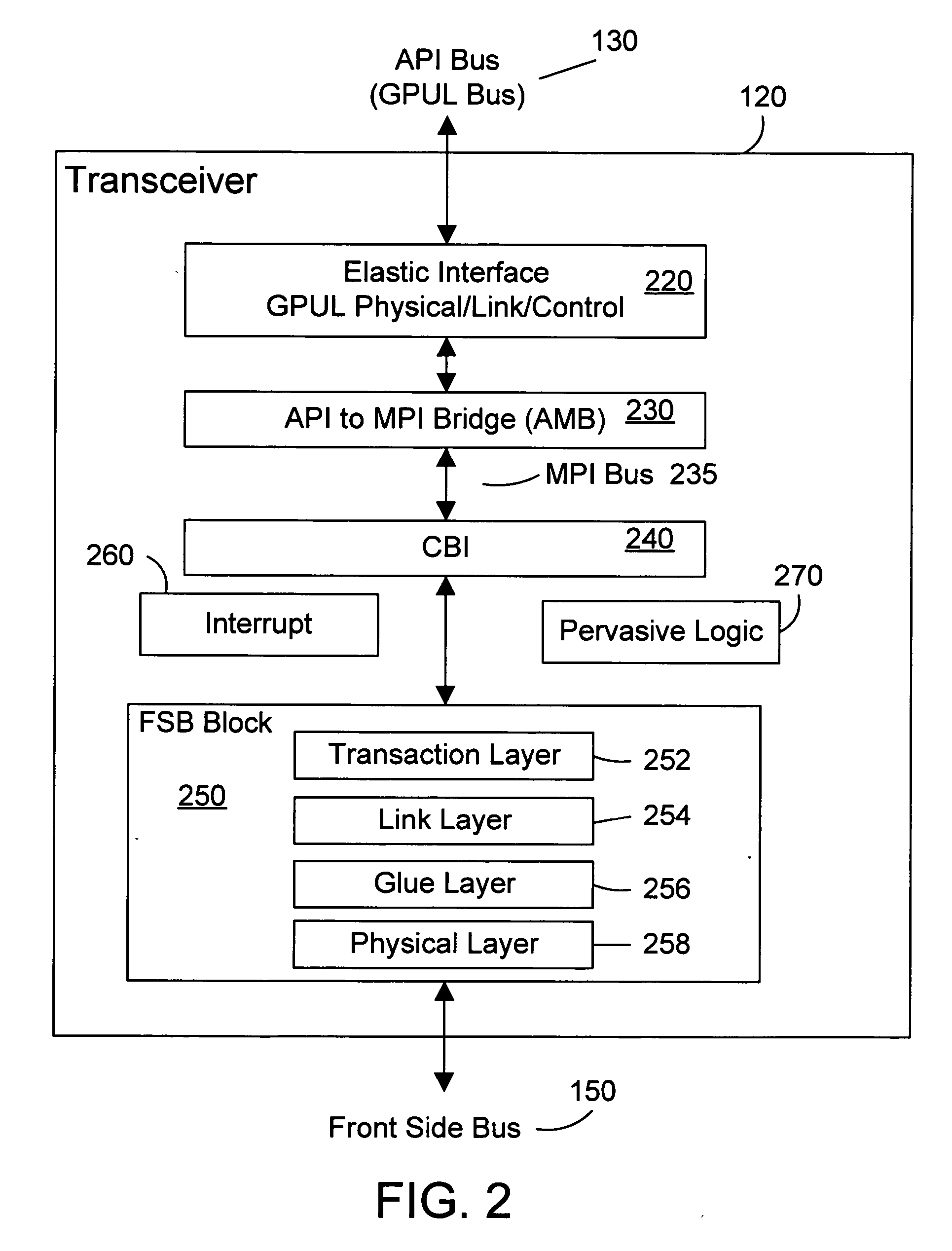

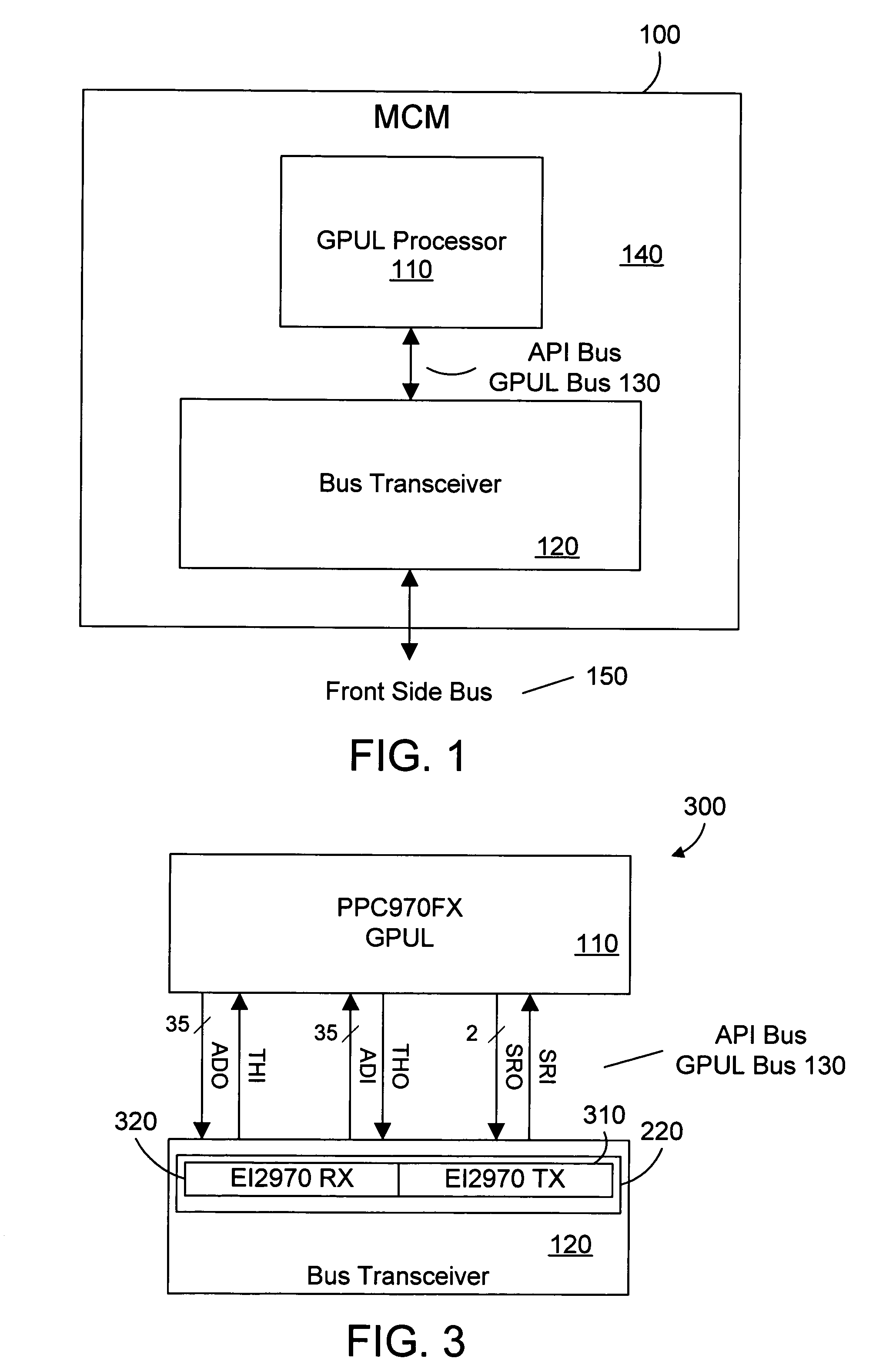

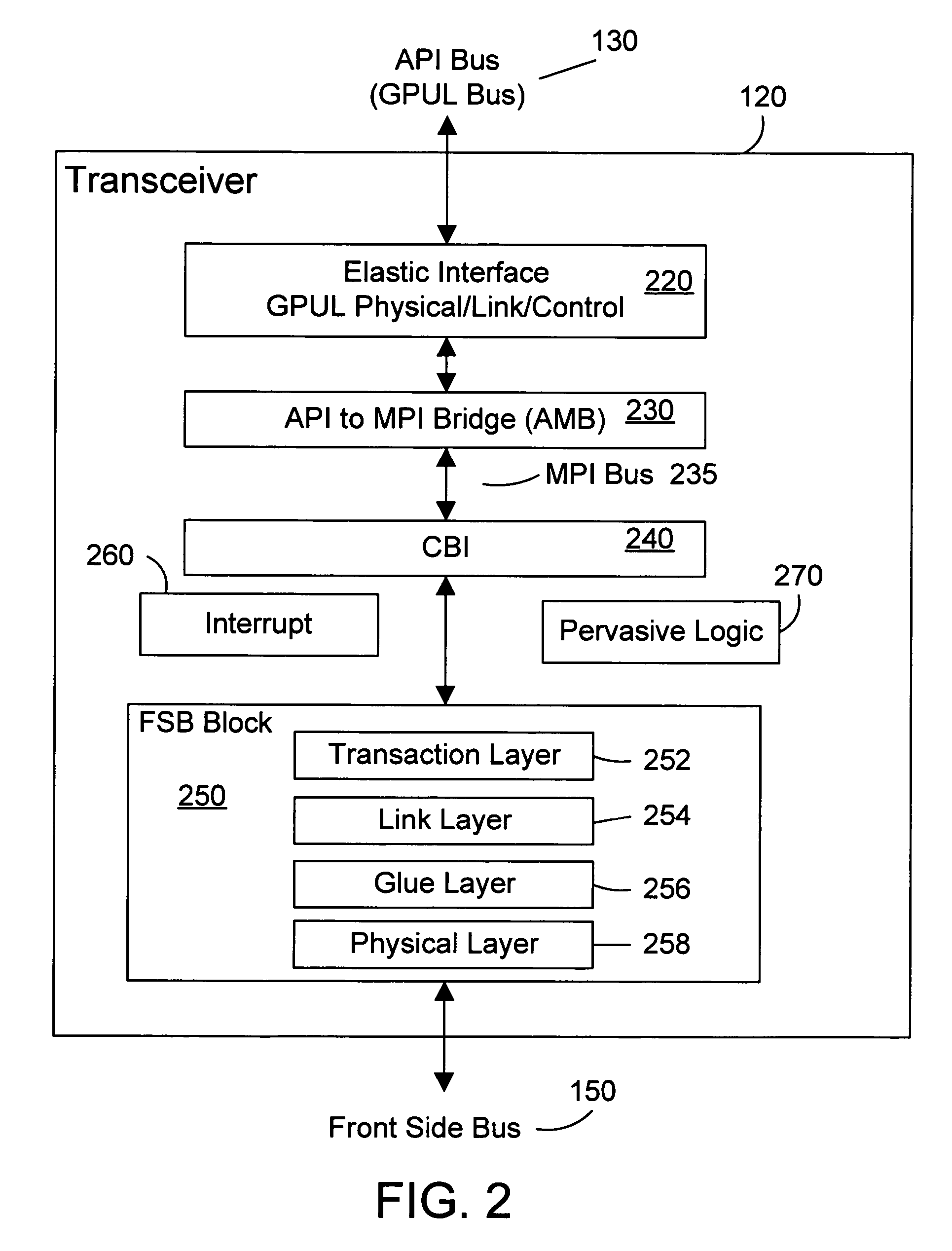

Computer system architecture

A high speed computer processor system has a high speed interface for a graphics processor. A preferred embodiment combines a PowerPC microprocessor called the Giga-Processor Ultralite (GPUL) 110 from International Business Machines Corporation (IBM) with a high speed interface on a multi-chip module.

Owner:IBM CORP

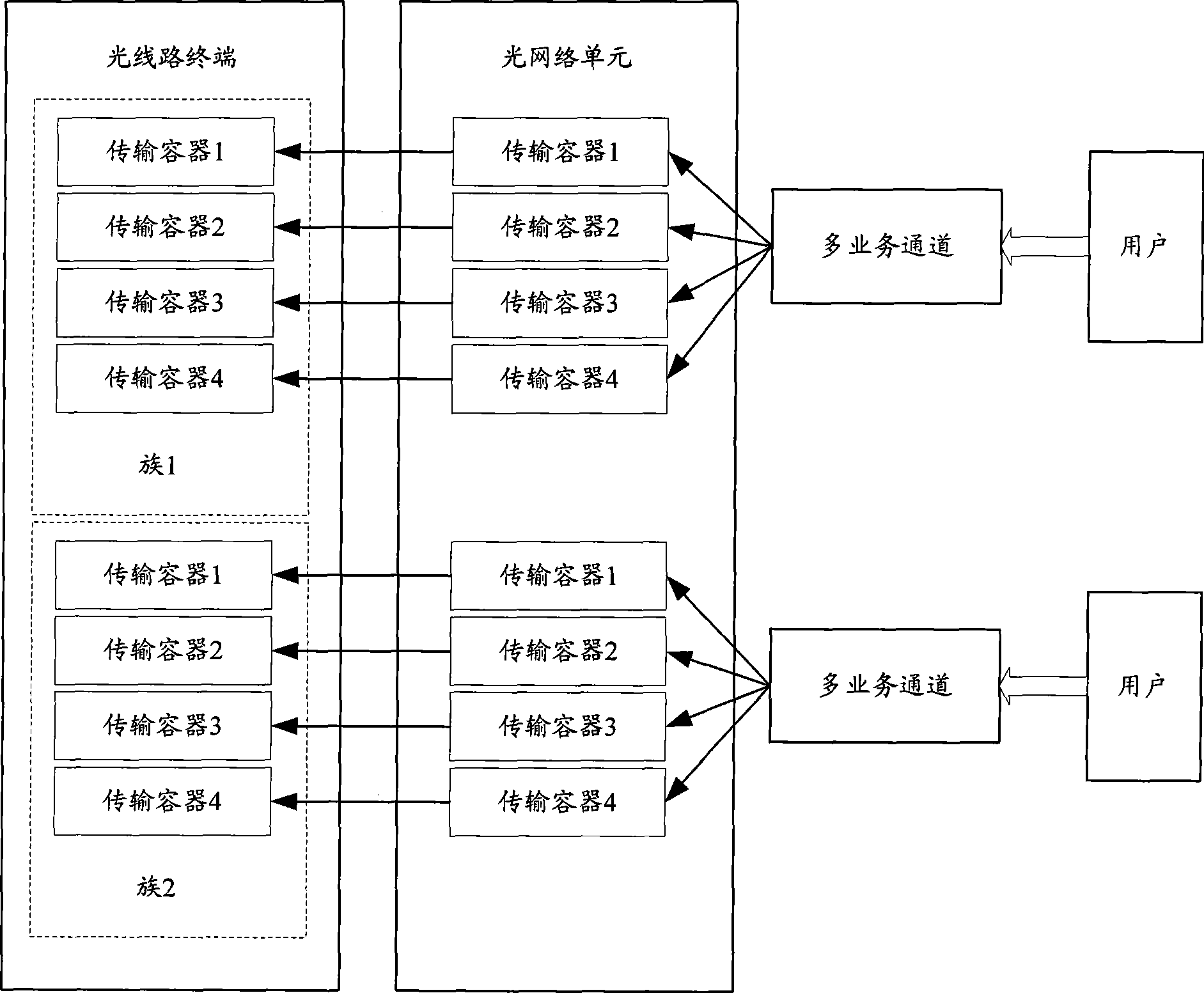

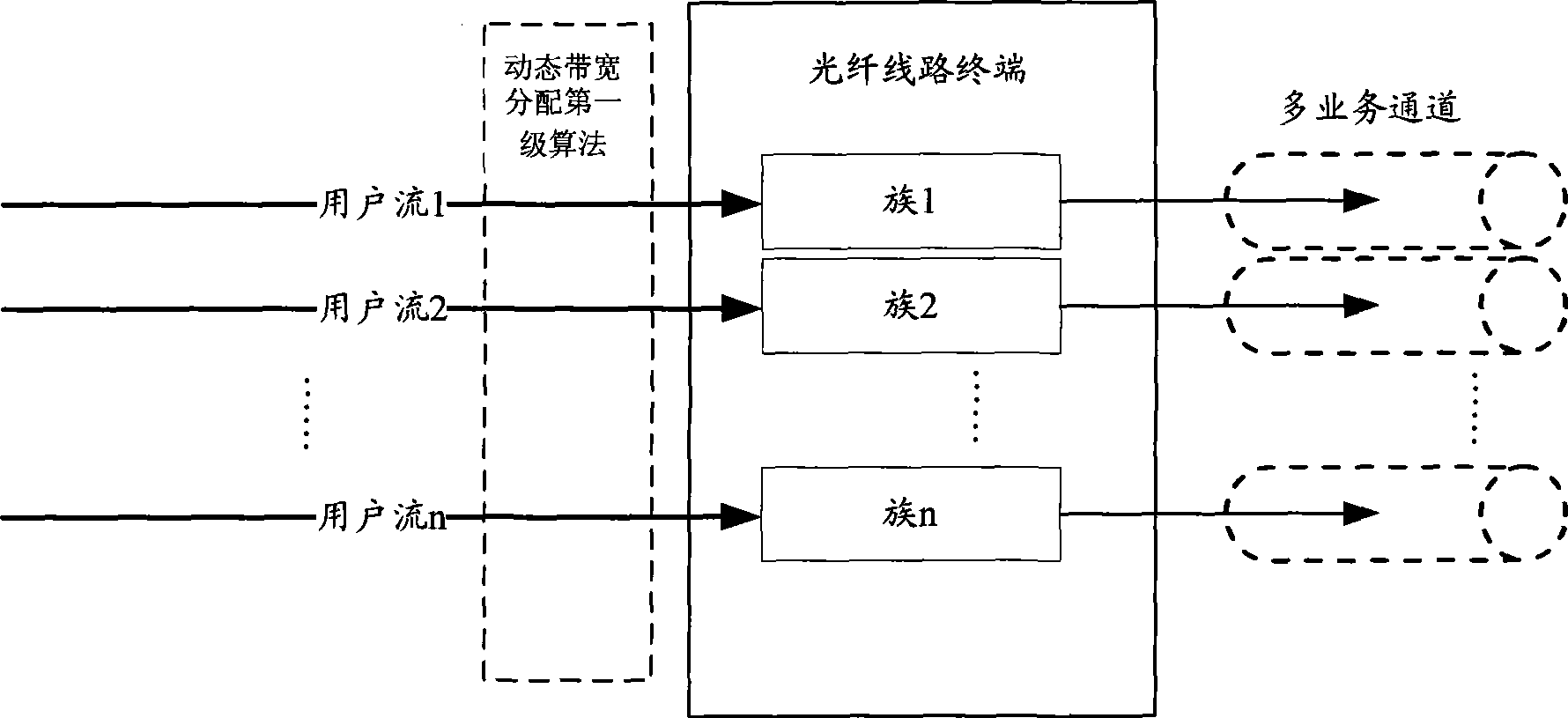

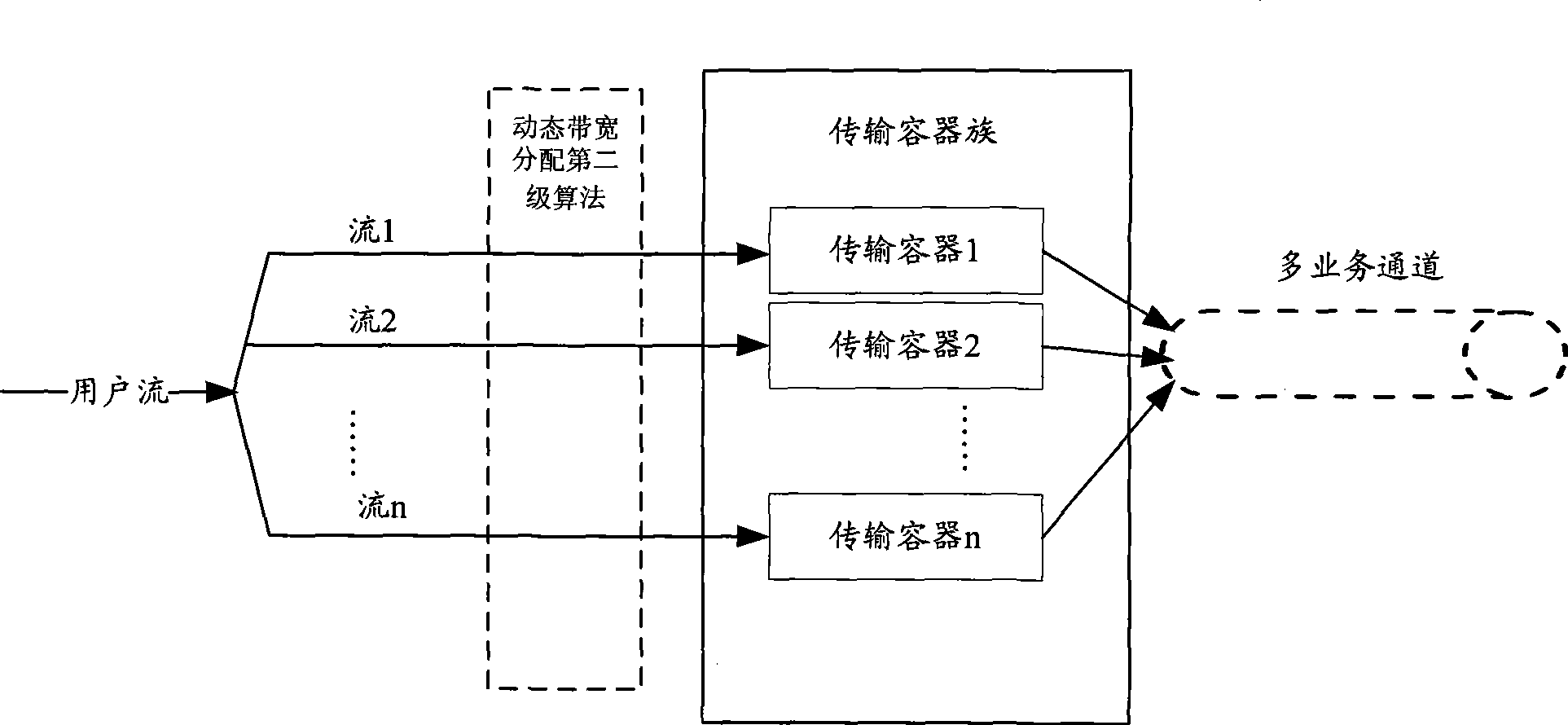

Uplink bandwidth management method for Giga passive optical network

ActiveCN101399758AReduce complexityFlexible bandwidth managementMultiplex system selection arrangementsData switching by path configurationService flowScheduling function

The invention discloses a GPON uplink bandwidth management method; a group is established basing on a plurality of same or different T-CONTs of an ONU by setting four basic T-CONTs and the T-CONT group becomes the logical bandwidth management unit; the T-CONT group and T-CONTs in the group are all provided with SLA parameters to execute two-stage DBA scheduling; the T-CONT group logically integrates the service flows born by different T-CONTs to represent the capability of GPON of providing multi-services and all-round services for users; moreover, DBA can participate in the scheduling of different data alignments in the ONU, thus being conducive to keeping down the scheduling function of the internal alignments of the ONU and reducing the complexity of the DBA policy.

Owner:ZTE CORP

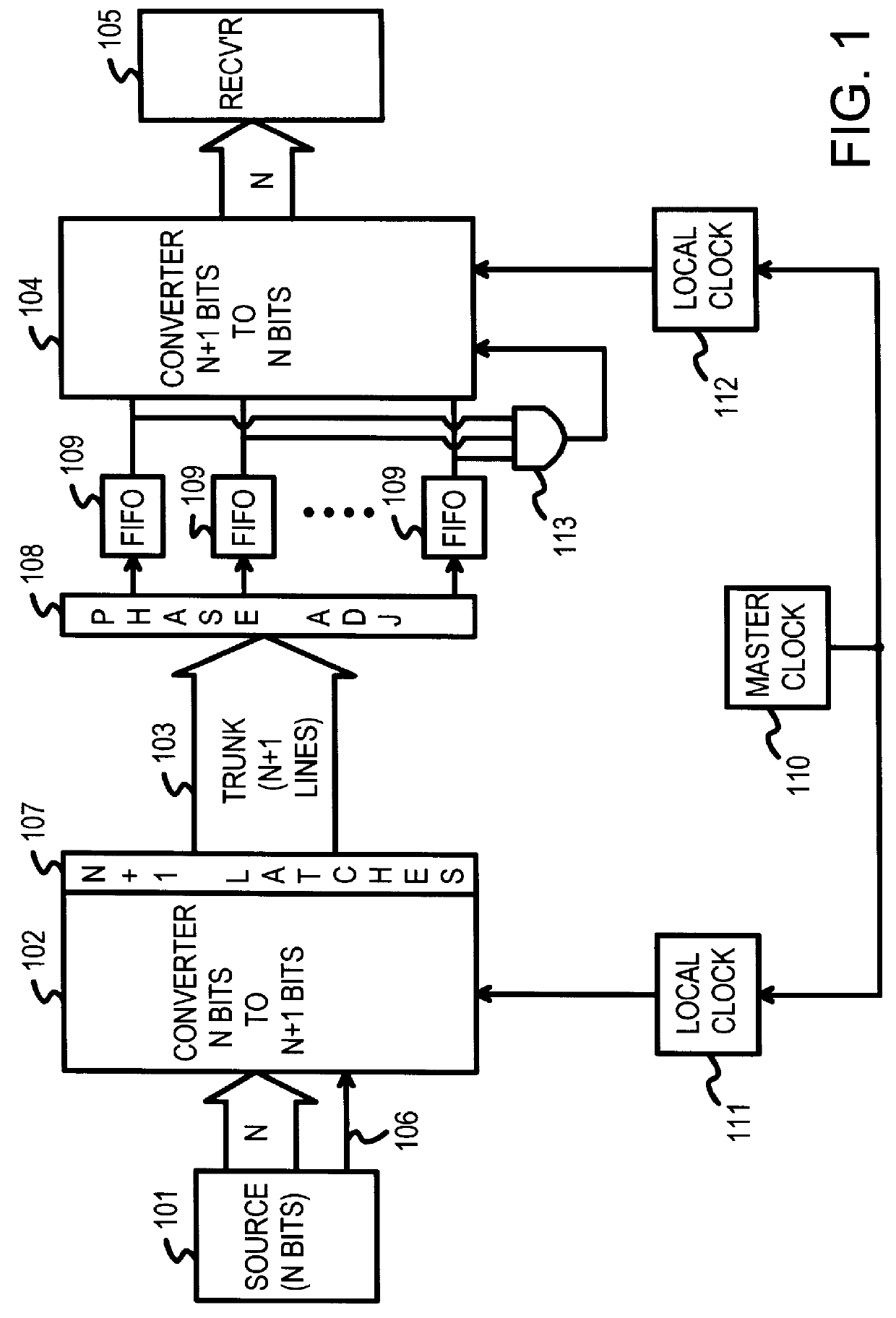

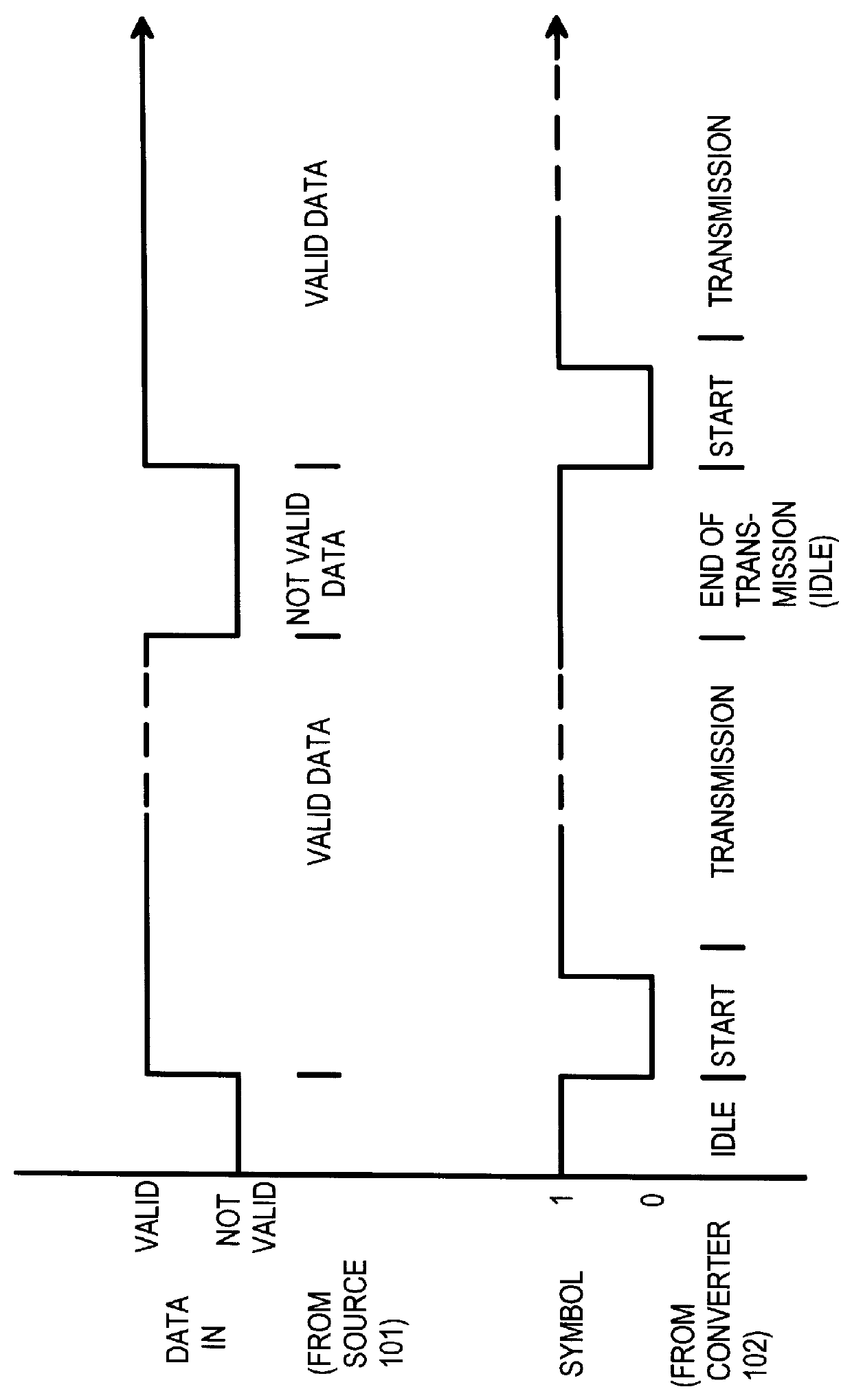

Hybrid interface for packet data switching

InactiveUS6128319ATime-division multiplexSynchronisation signal speed/phase controlSerial transferDigital data

A hybrid data parallel / serial data transfer system with phase adjustment and symbol coding for switching digital data packets in order to facilitate massive high speed transfer of information with a limited number of signal lines. Much higher data transfer is possible than in a conventional serial data transfer. Multi-giga bits or Tera bits can be transferred easily over a long distance using this invention. Data transmission apparatus is described in which data is transmitted over a communication link or trunk consisting of a plurality of lines. Each message is transmitted as a sequence of groups of data bits, the bits in each group being transmitted in parallel over the trunk. Each line or path carries a signal and each message is preceded by a serial start pattern. The receiver comprises a plurality of decoders for receiving data signals from the trunk. These signals are fed to a separate buffer. The contents of the buffer are then read out in parallel. The arrangement overcomes the problem of data skew due to different transmission times over the lines of the trunk.

Owner:NETWORK EXCELLENCE FOR ENTERPRISES CORP

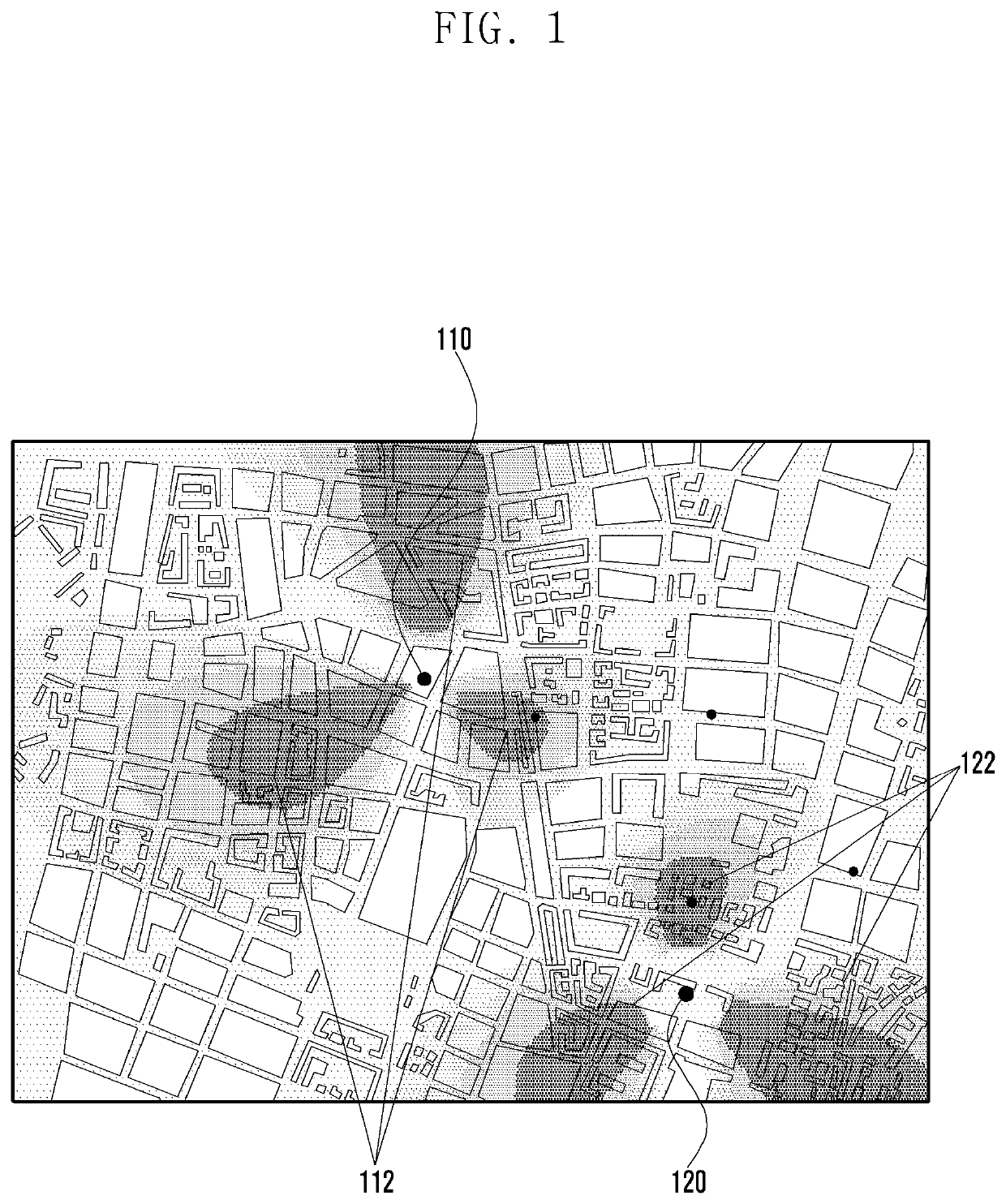

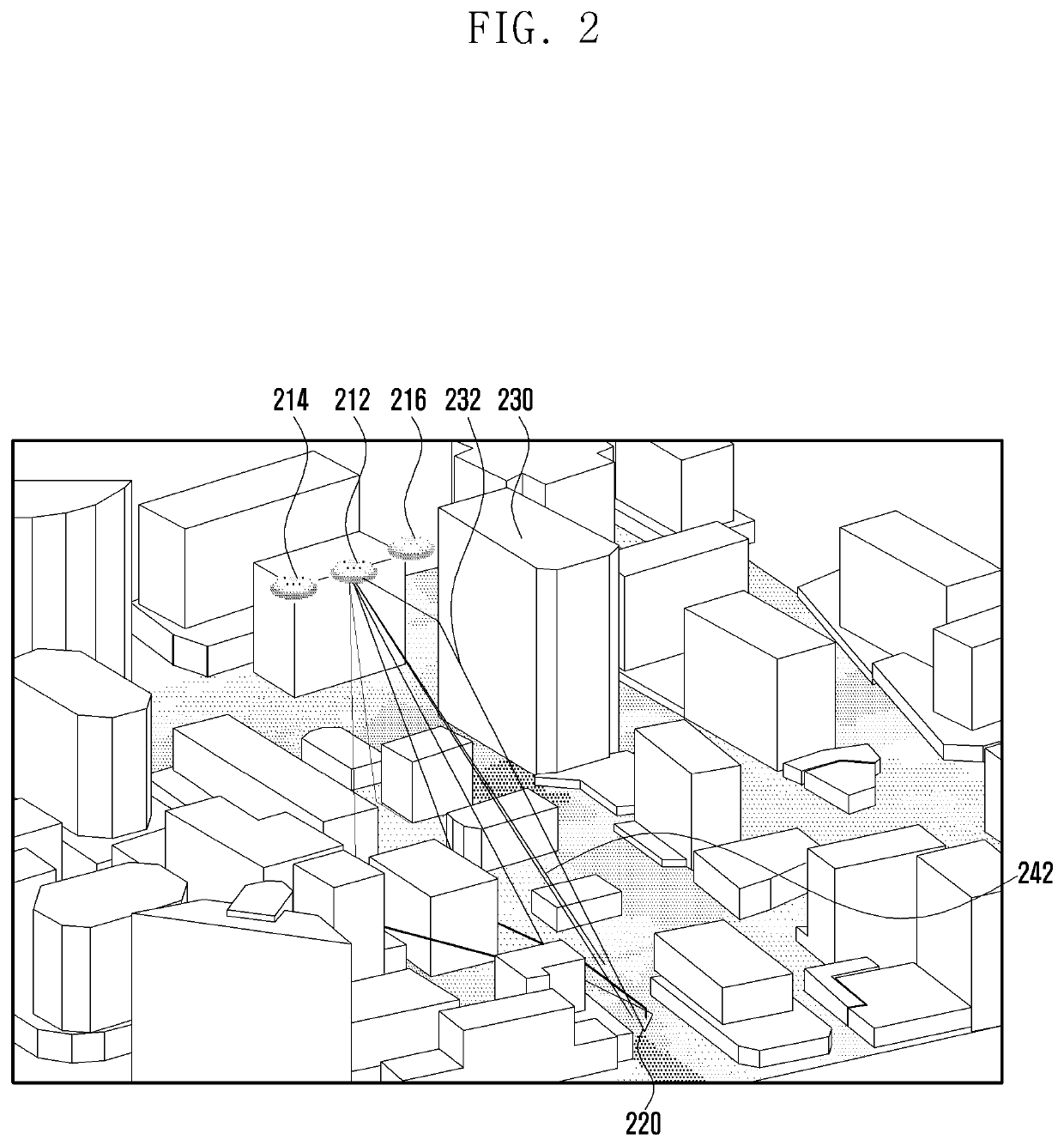

Method and device for analyzing communication channels and designing wireless networks, in consideration of information relating to real environments

ActiveUS20190342763A1Improve accuracyReduce the amount of calculationReceivers monitoringNetwork planningCommunications systemInformation analysis

The present disclosure relates to a communication technique for fusing, with an IoT technology, a 5G communication system for supporting a higher data transmission rate than a 4G system, and a system therefor. The present disclosure may be applied to intelligent services, such as smart homes, smart buildings, smart cities, smart cars or connected cars, health care, digital education, retail businesses, and security and safety related services, on the basis of 5G communication technologies and I-T-related technologies. A method for analyzing signal transmission properties in a wireless communication system, according to one embodiment of the present specification, comprises: obtaining first information comprising three-dimensional map information; obtaining second information comprising real environment information from image information relating to the three-dimensional map information; determining locations of a plurality of transmitter candidates on the basis of at least one of the first information and the second information; and performing a ray tracing simulation on the basis of the first information and the second information. The preset research was carried out with the support of the “Cross-ministry Giga Korea Project” of the Ministry of Science, ICT and Future Planning, of the Republic of Korea.

Owner:SAMSUNG ELECTRONICS CO LTD

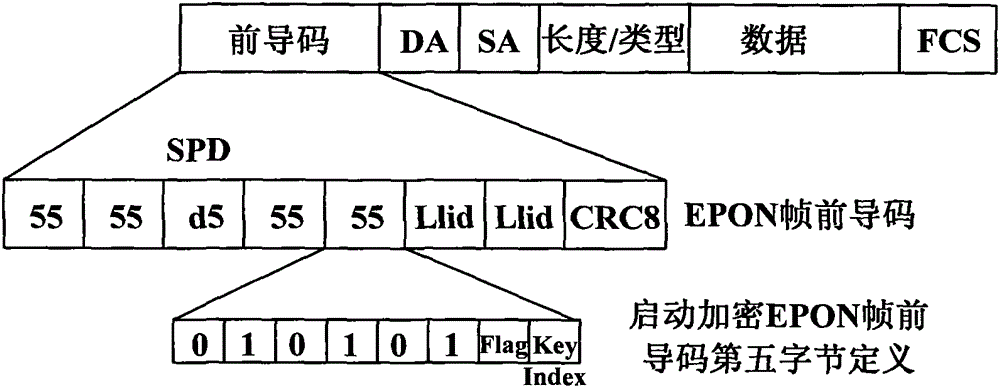

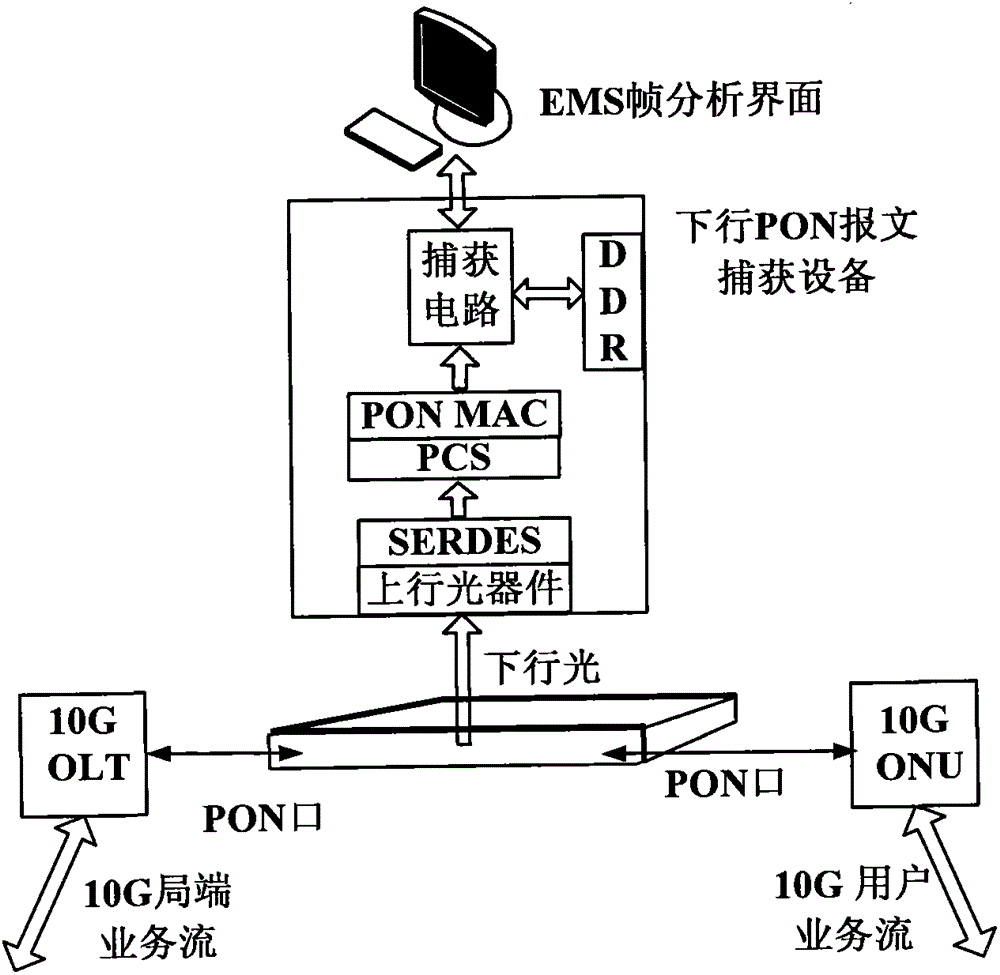

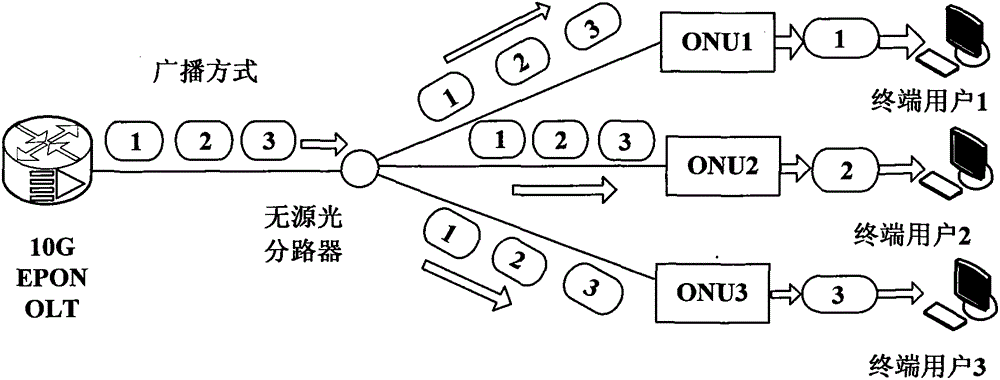

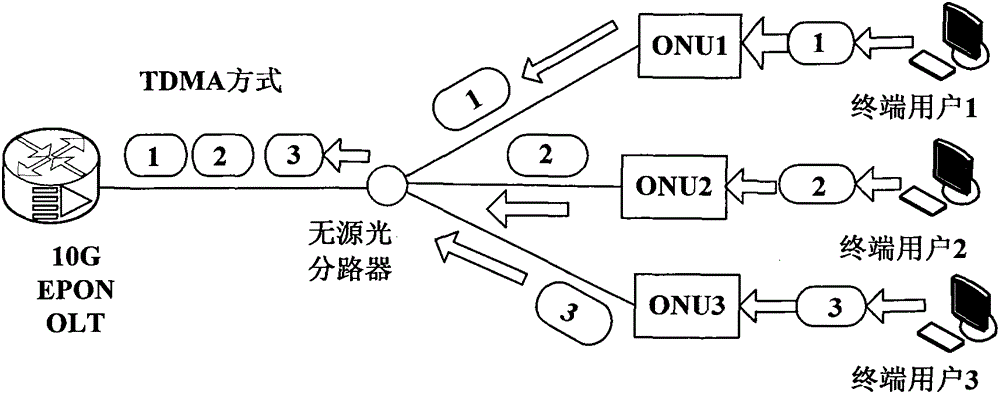

Timing device and method for automatically capturing 10G EPON (10 Giga Ethernet Passive Optical Network) message

ActiveCN102752211AAchieve captureAccurate timeMultiplex system selection arrangementsData switching networksOptical network unitEthernet passive optical network

The invention discloses a timing device and method for automatically capturing a 10G EPON (10 Giga Ethernet Passive Optical Network) message and relates to the field of communication. The timing method comprises the following steps: after starting the automatic capturing, counting for a preset time by an absolute clock subjected to time correction of a user / OLT (Optical Line Terminal) / ONU (Optical Network Unit) under an absolute timing capturing mode; starting the 10G EPON message capturing and writing into a capturing cache according to screening conditions; under a relative timing capturing mode, detecting a frame content and a frame state captured by specific starting; starting to count by a timing clock till reaching the time preset by the user; and starting a packet grabbing process and writing into the capturing cache according to screening conditions. According to the timing method provided by the invention, the 10G EPON message can be automatically and accurately captured and analyzed; the space for storing the captured message is reduced by designing accurate timing and filtering conditions; the performance and the use efficiency of a remote dispatcher are promoted; and the intercommunication capacity of different equipment factories is enhanced.

Owner:FENGHUO COMM SCI & TECH CO LTD +1

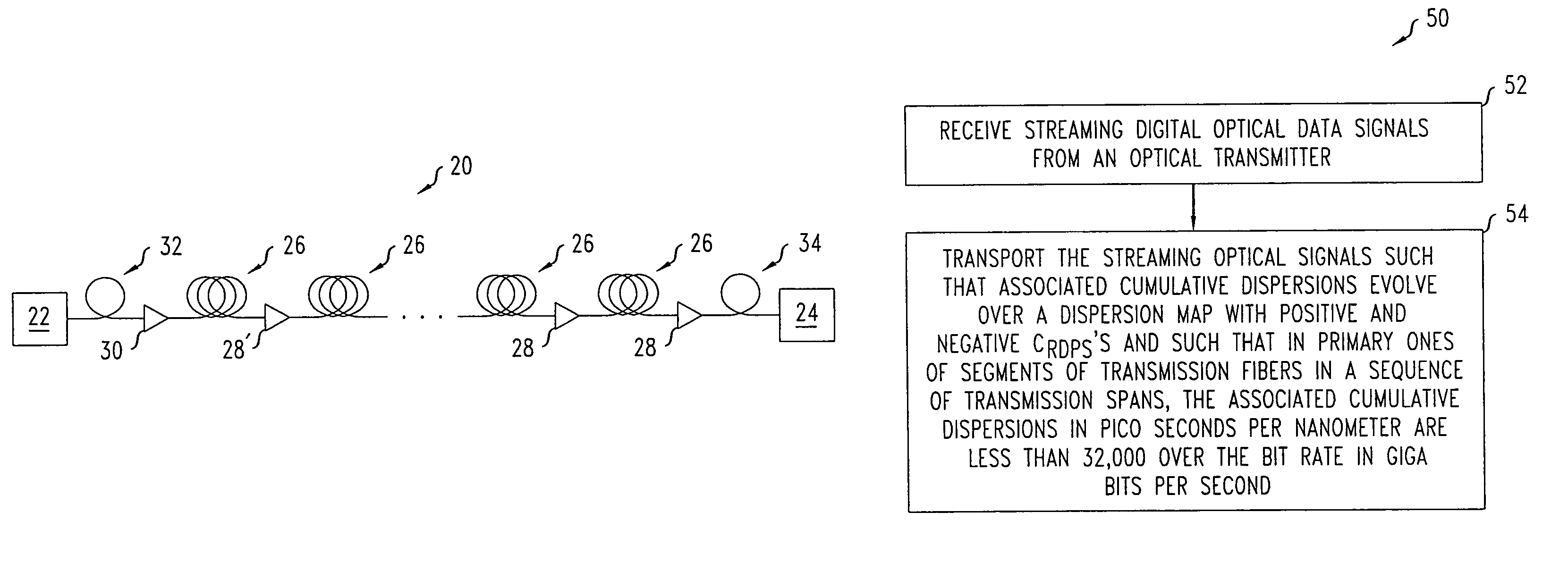

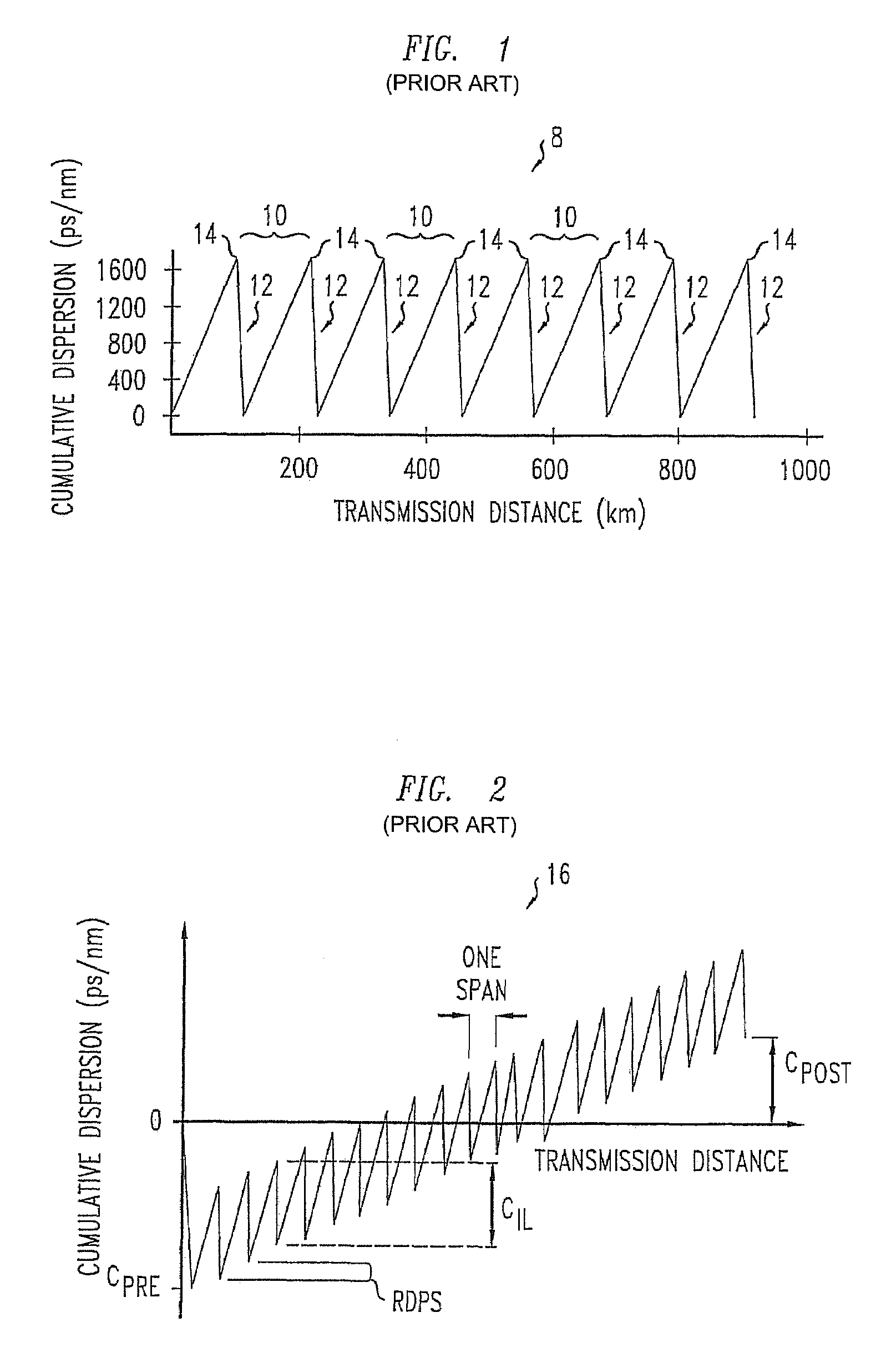

Low total excursion dispersion maps

InactiveUS7280765B2Reduce pulse degradationIncrease power levelMultimode transmissionDigital dataData signal

A process optically transports digital data over an all-optical long-haul communication path. The process includes transporting digital optical data signals at a selected bit rate and a selected wavelength over a sequence of transmission spans. The sequence includes 70 percent or more of the spans of the long-haul all-optical communication path. Each span of the sequence has a primary local maximum optical power point for the wavelength on a transmission fiber and nearest to an input of the span. The transporting causes a cumulative dispersion of each signal to evolve such that residual dispersions per span are positive over some of the spans and are negative over other of the spans. At the primary local maximum power points, magnitudes of cumulative dispersions of the signals in pico seconds per nanometer remain at less than 32,000 times the inverse of the bit rate in giga bits per second.

Owner:LUCENT TECH INC

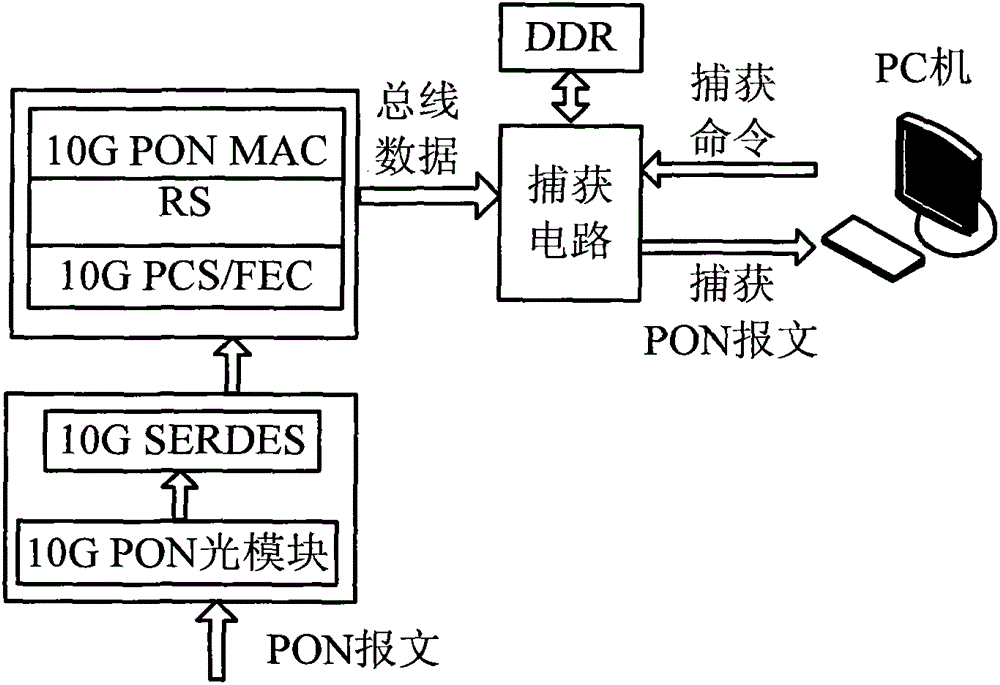

Capturing circuit and writing control method of 10G EPON (10 Giga Ethernet Passive Optical Network) message

ActiveCN102752674AImproved packet capture methodLow costMultiplex system selection arrangementsData switching networksOptical ModuleByte

The invention discloses a capturing circuit and a writing control method of 10G EPON (10 Giga Ethernet Passive Optical Network) messages. The writing control method comprises the following steps: receiving EPON messages interacting among 10G EPON OLT (Optical Line Terminal) and ONU (Optical Network Unit) through an optical module and a 10G SERDES (Serializer / Deserializer); combining and triggering message capturing according to set conditions after the decoding at a PCS (Physical Coding Sub-layer); writing the captured message into capturing cache, wherein the steps and formats for storing the capturing frames are as follows: writing 128bit frame data at an even number clock period while a frame envelope is valid; and writing the frame head byte number, the frame end byte number, the reaching time, the frame error indication, CRC (Cyclic Redundancy Check) verification error indication and frame boundary symbol of the frame within a clock period at the frame end. With the adoption of the capturing circuit and the writing control method, continuous EPON messages of 10 G can be captured and analyzed rapidly and precisely; the storage space of the captured message is reduced through specific triggering and screening conditions; the performance and the use efficiency of the remote scheduling are improved; and the inter-compatibility of factories of different equipment is enhanced.

Owner:FENGHUO COMM SCI & TECH CO LTD +1

Environmental Protection Coating System and Method

ActiveUS20090288876A1Small impactPrinted circuit detailsPrinted electric component incorporationCoating systemDielectric loss

A circuit board assembly includes a circuit board having an outer surface that is configured with a plurality of discrete electrical components that are each manufactured independently of one another. The circuit board assembly further includes a first protective dielectric layer overlying the outer surface, and a second dielectric layer overlying the first protective dielectric layer and the discrete electrical components. The second dielectric layer includes a dielectric material having modulus of elasticity less than 3.5 Giga-Pascal (GPa), a dielectric constant less than 3.0, a dielectric loss less than 0.008, a moisture absorption less than 0.04 percent, a breakdown voltage strength in excess of 2 million volts / centimeter (MV / cm), a temperature stability to 300° Celsius, pinhole free in films greater than 50 Angstroms, hydrophobic with a wetting angle greater than 45 degrees, capable of being deposited conformally over and under 3D structures with thickness uniformity less than or equal to 30%.

Owner:RAYTHEON CO

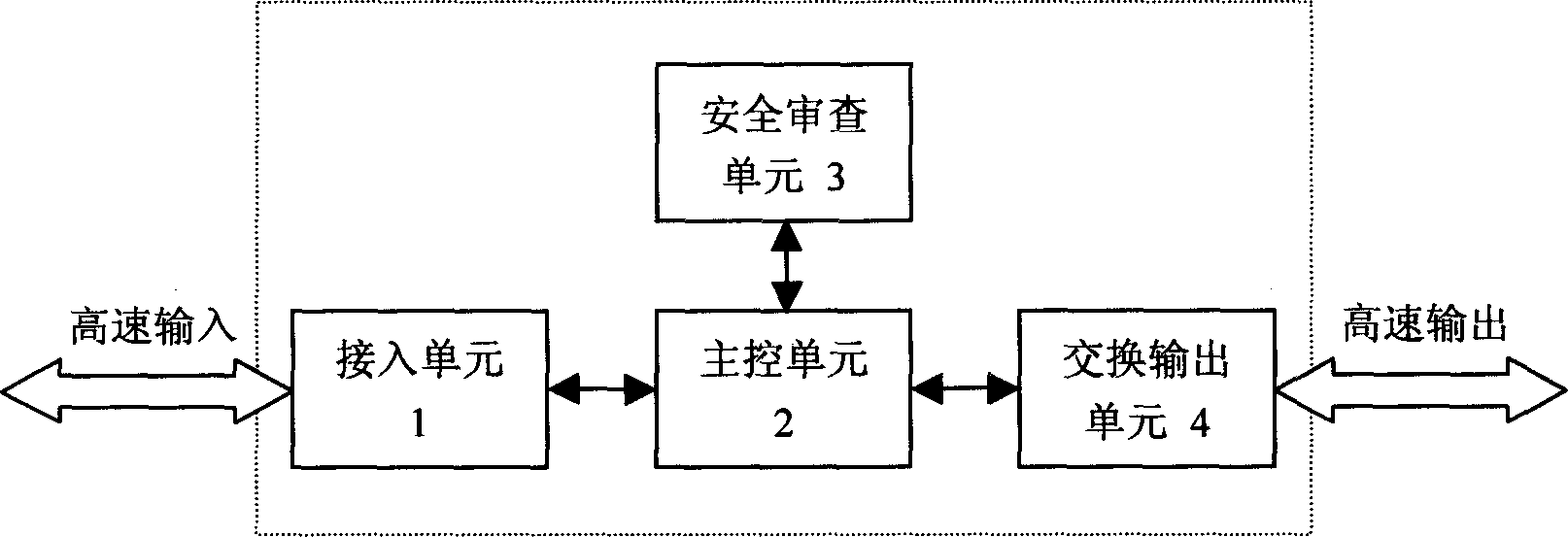

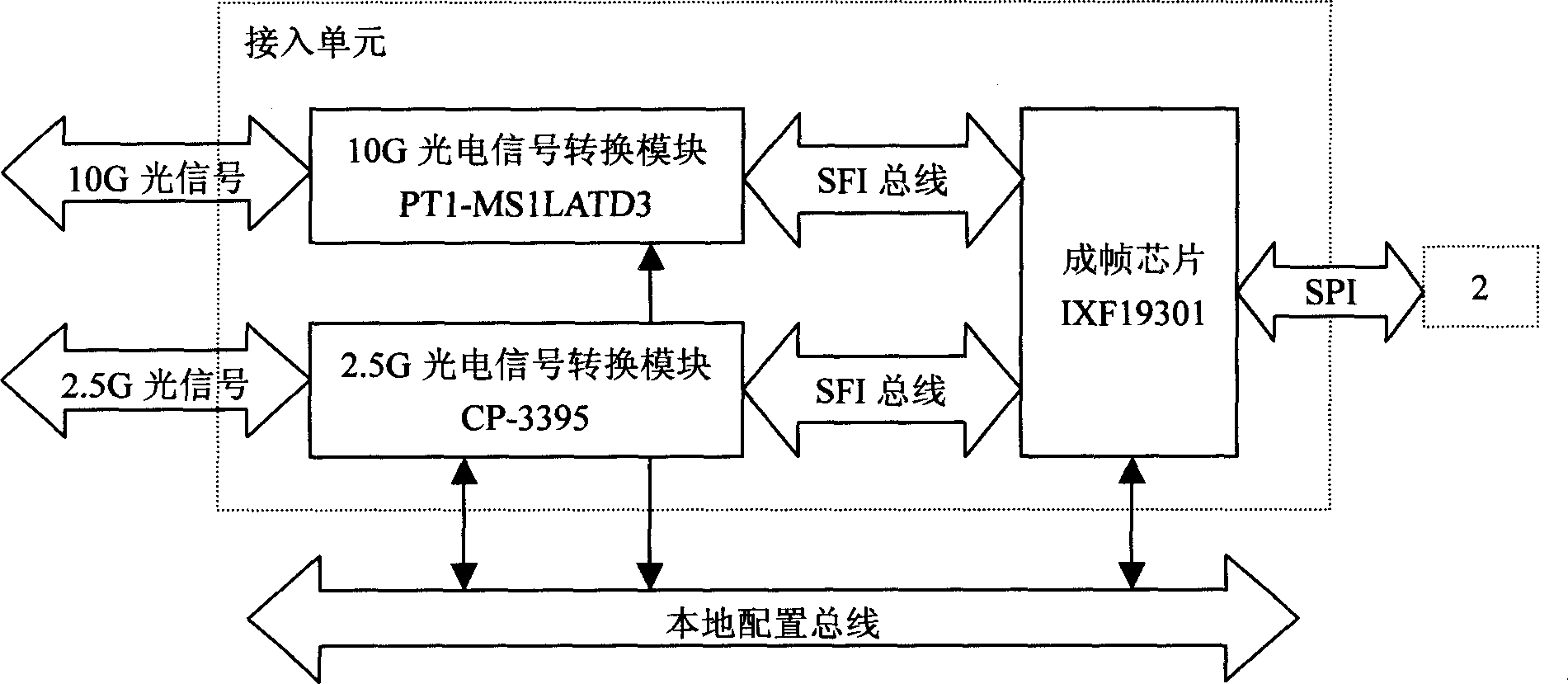

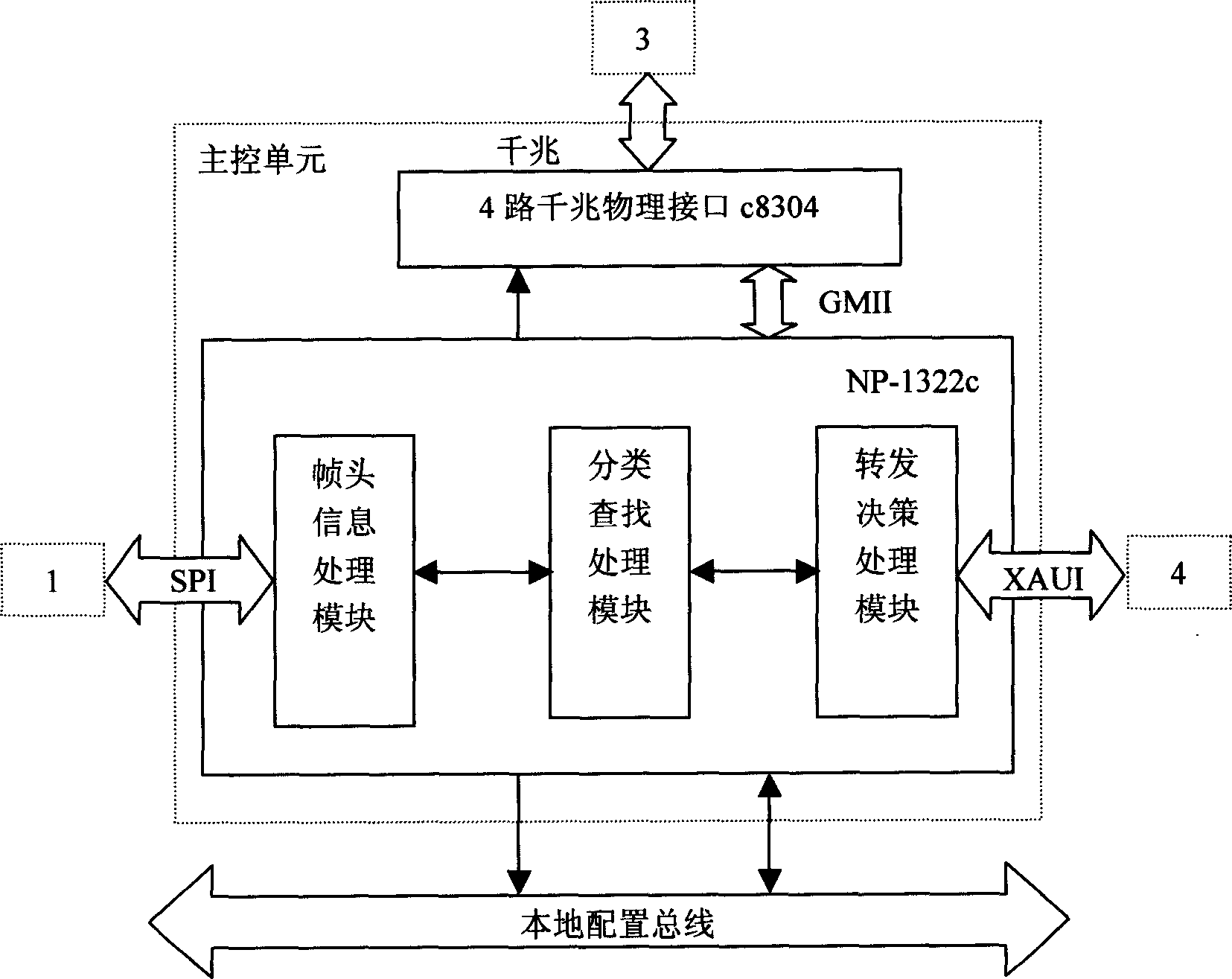

Safety filtering current shunt of exchange structure based on network processor and CPU array

InactiveCN1610335ARelieve work stressImprove work efficiencyData switching networksData transmissionNetwork processor

The safe filtering flow divider consists of access unit, main control unit, safety examination unit and exchange output unit connected together. The access unit consists of 10G photoelectronic signal converting module, 2.5G POS photoelectronic signal converting module and frame forming chip; the main control unit consists of network processor unit and four channels of giga level physical interfaces; the safety examination unit consists of four standard CPU processing modules with giga level electric interface; and the exchange output unit consists of giga level main exchange control module, giga level electric interface module and giga level optical interface module. The safety examination unit returns the examining result to the main control unit, and the main control unit makes the data flow dividing policy based on the filtering result and distributes the data flow dividing policy to the exchange output unit for data transmission.

Owner:上海光华如新信息科技股份有限公司

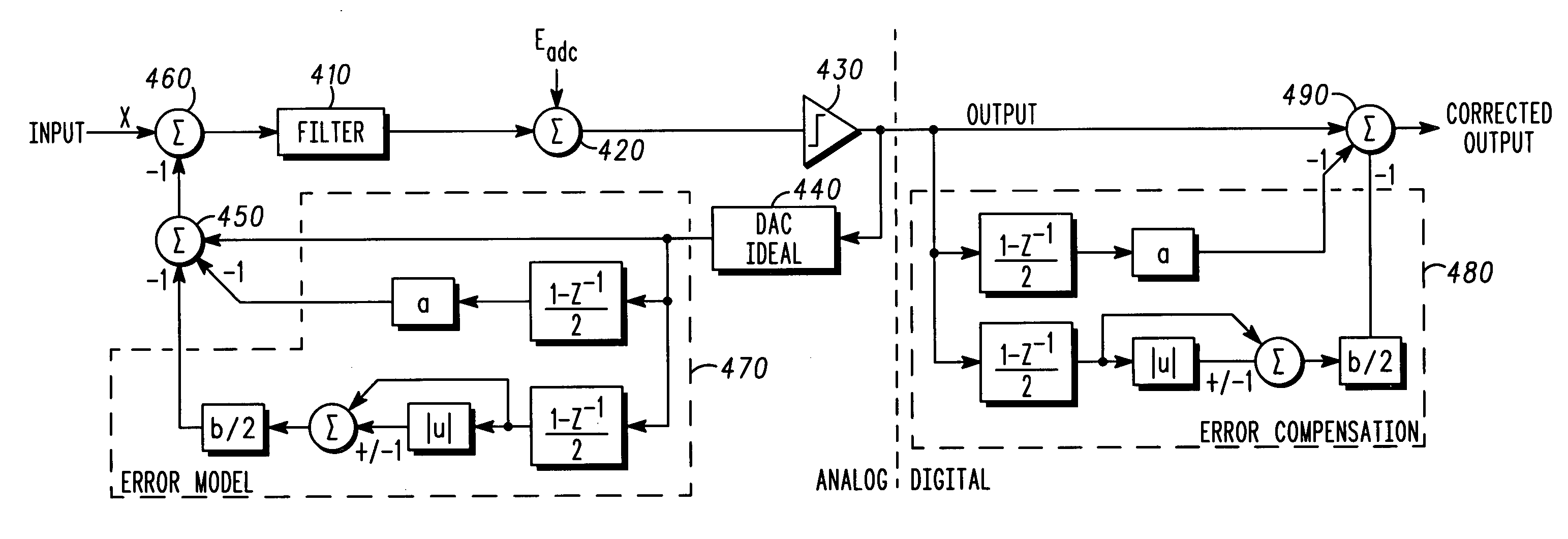

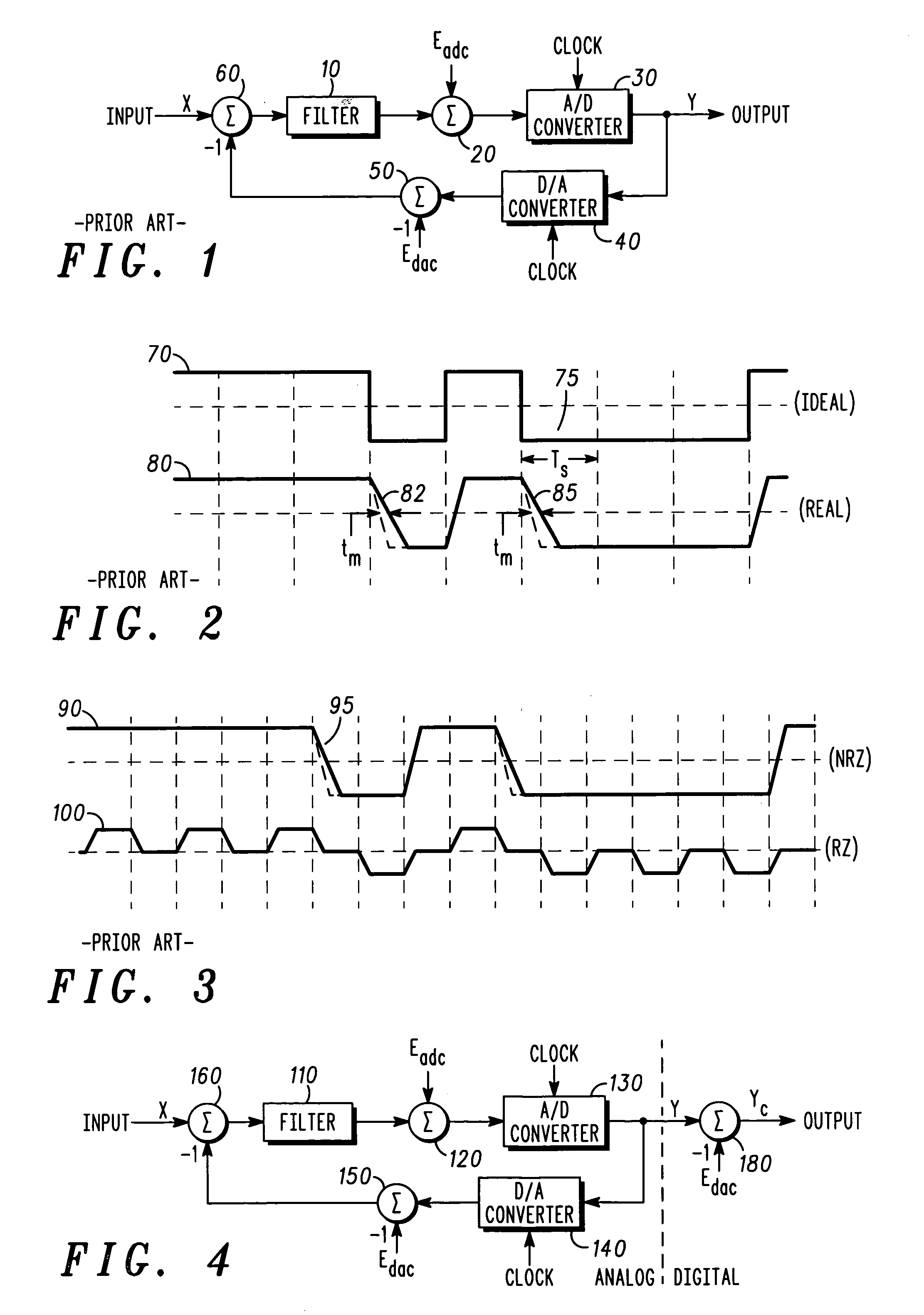

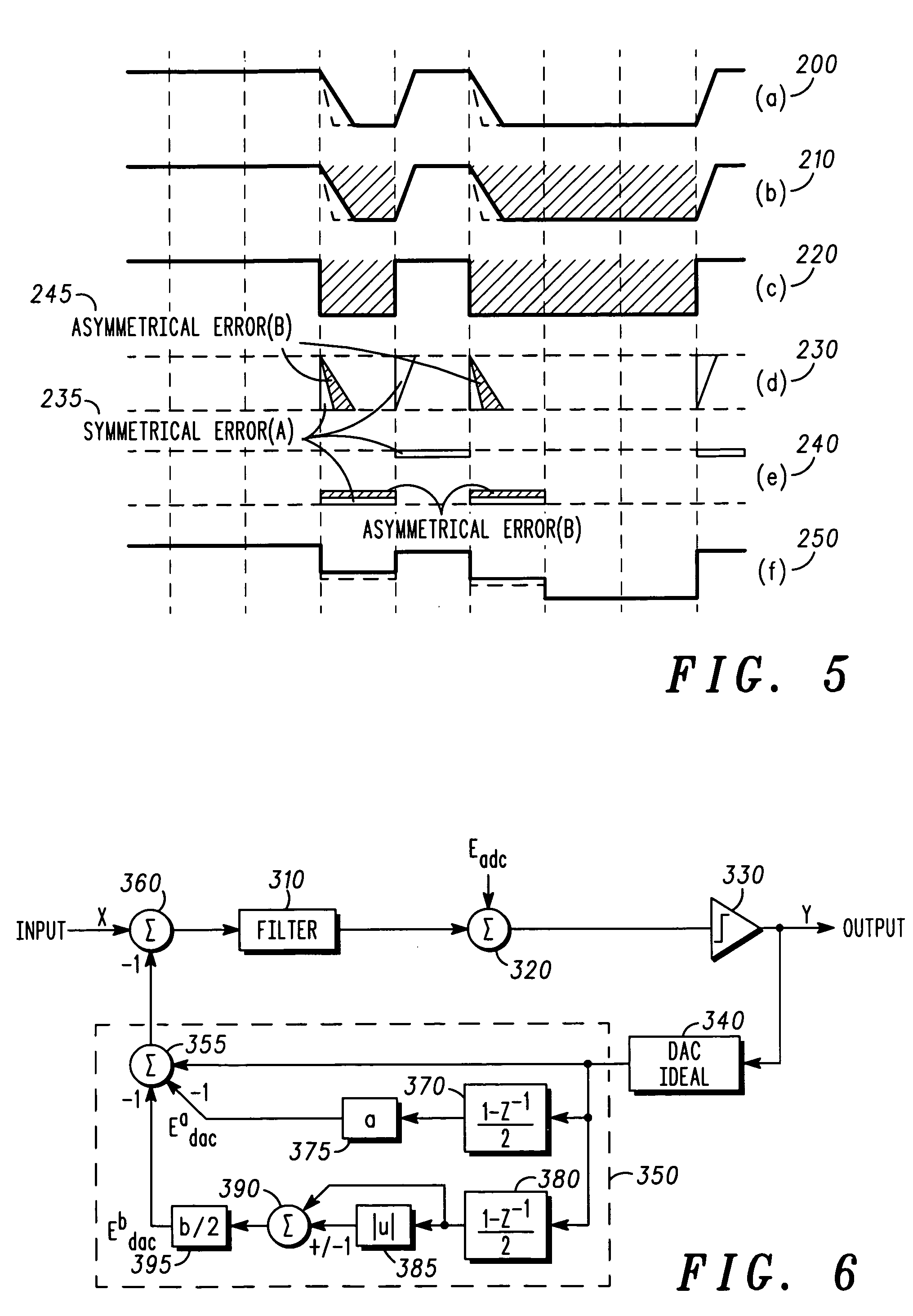

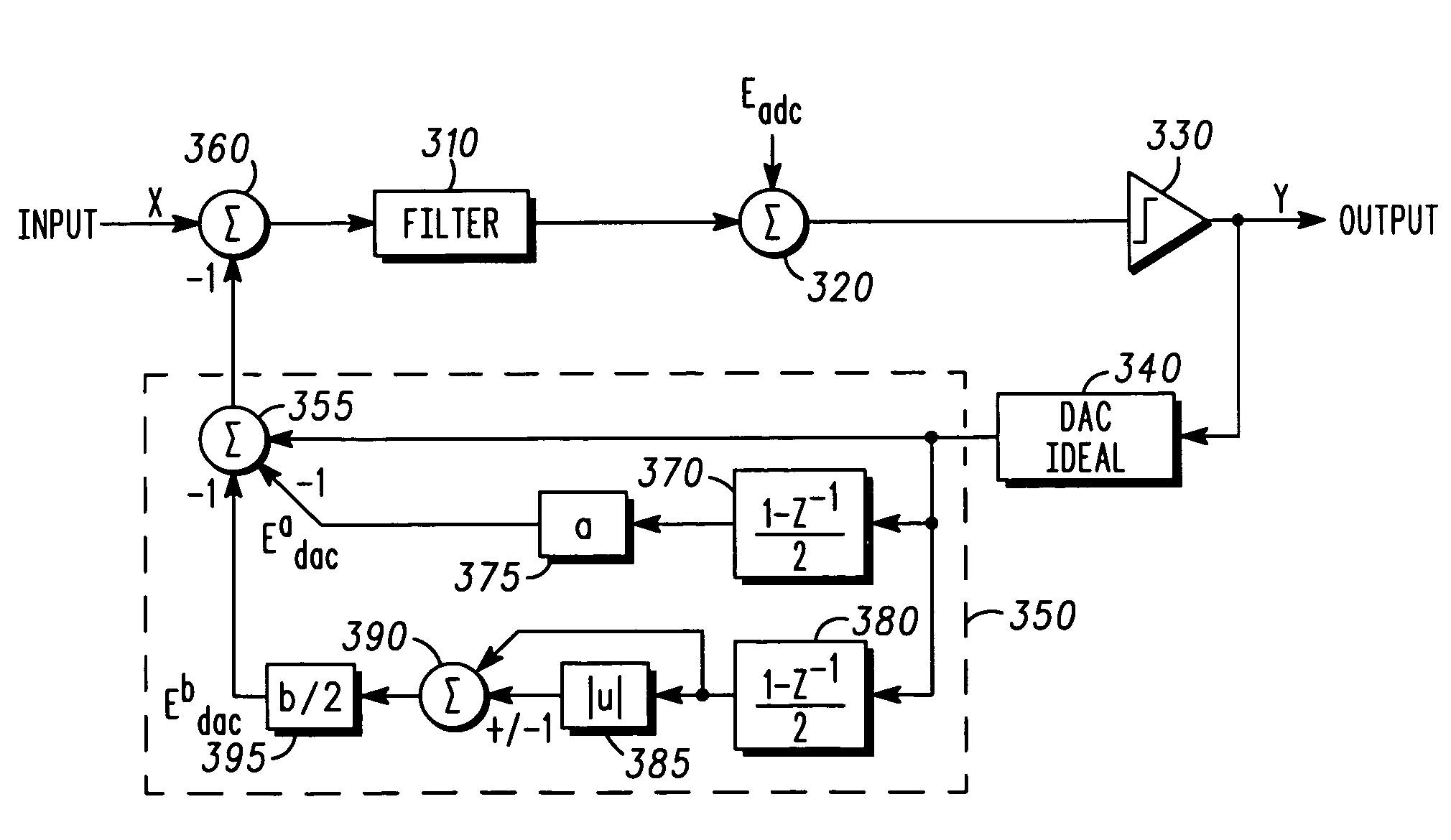

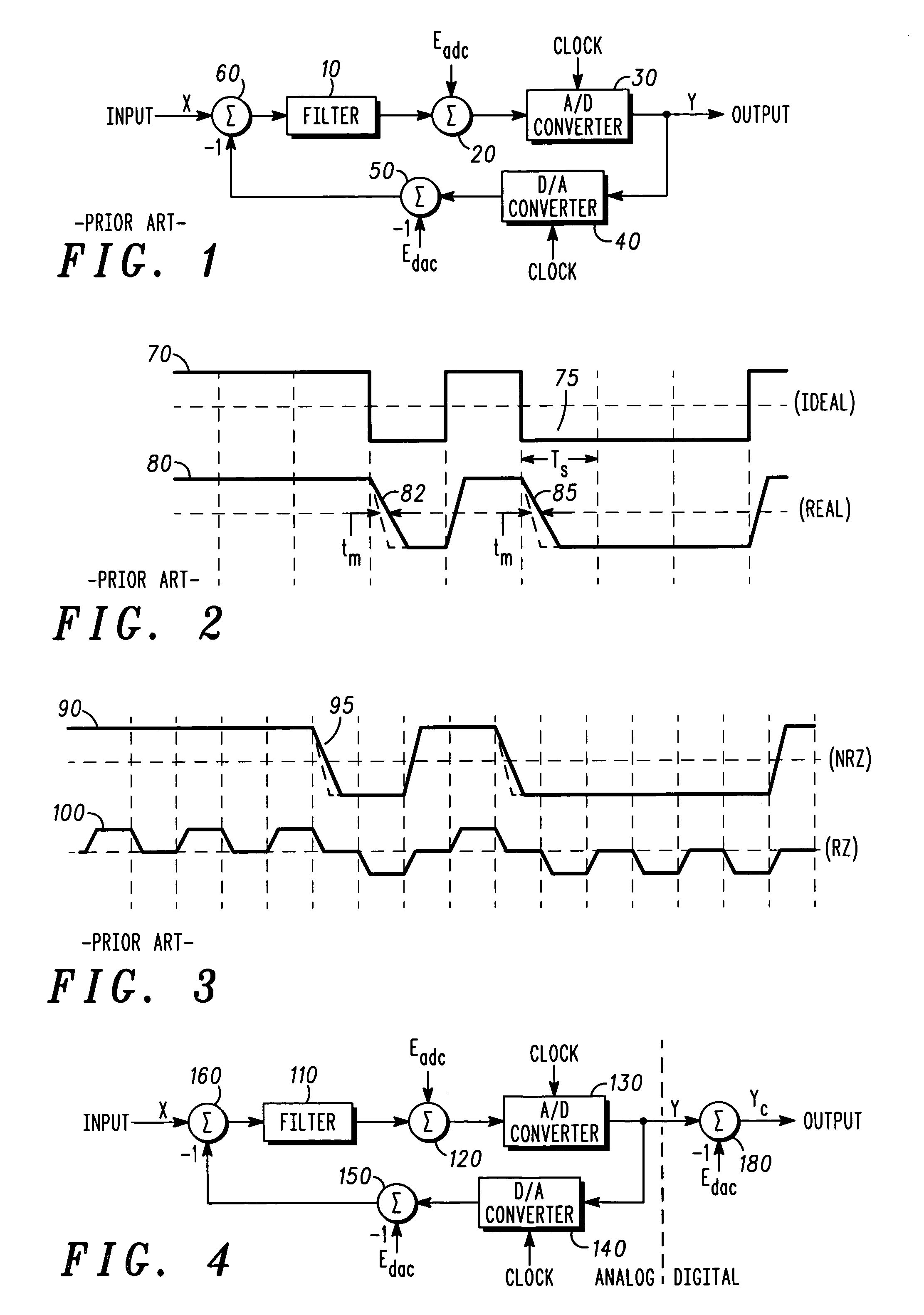

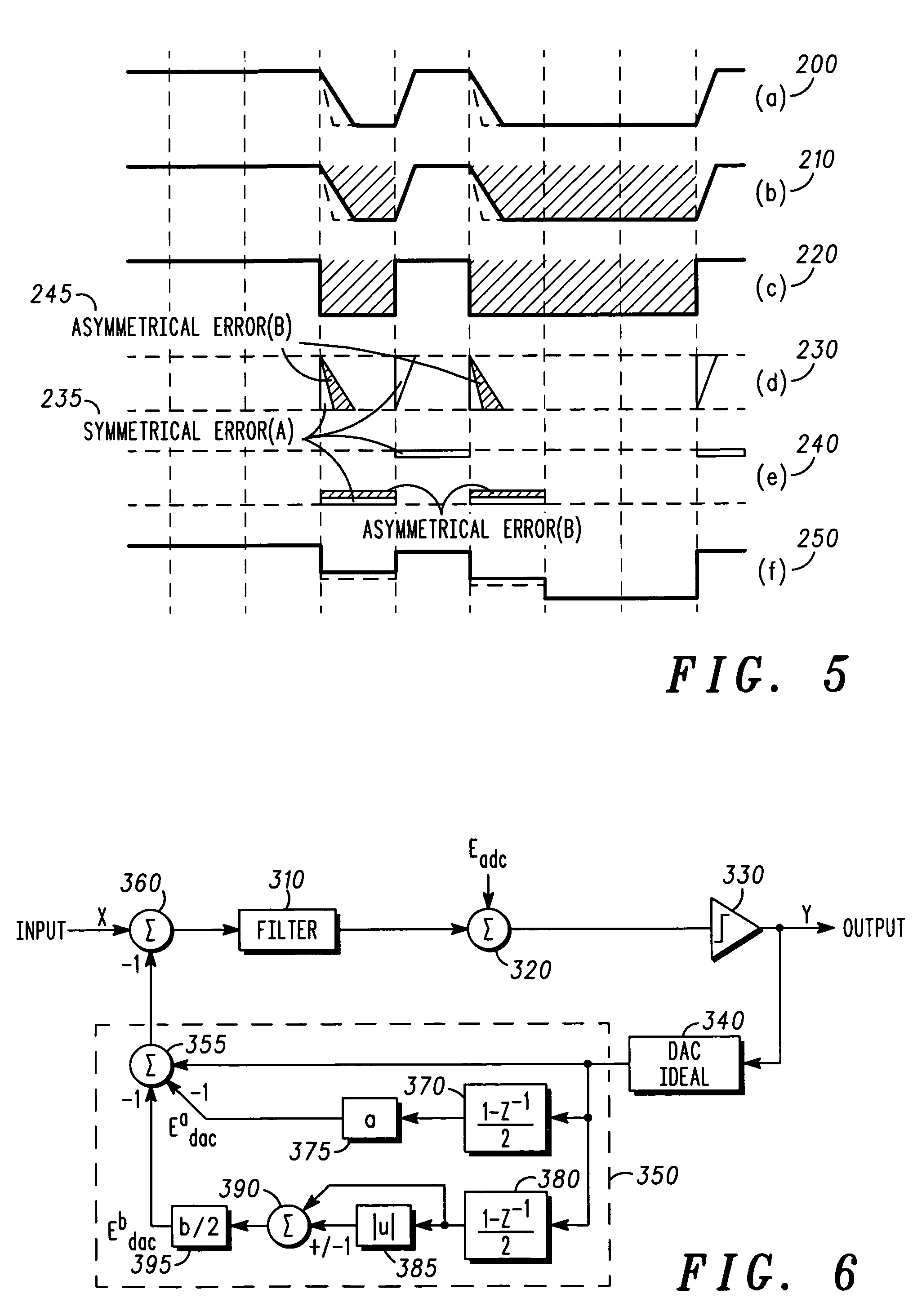

Converter, circuit and method for compensation of non-idealities in continuous time sigma delta converters

InactiveUS20060012499A1Effective compensationStraightforward integrationAnalogue conversionGreek letter sigmaSigma delta converters

A continuous time sigma delta converter has a filter and converter components having known non-ideal characteristics. A compensation circuit has error modelling components arranged to model the non-ideal characteristics of the converter. A summation block combines a compensation signal from the compensation circuit with a non-ideal output signal from the converter in order to provide a compensated output signal. This has substantially no effect on other modulator performance characteristics and contributes to the implementation of giga sample-per-second Continuous Time sigma deltas having the dynamic range capabilities of traditional DT sigma deltas.

Owner:NORTH STAR INNOVATIONS

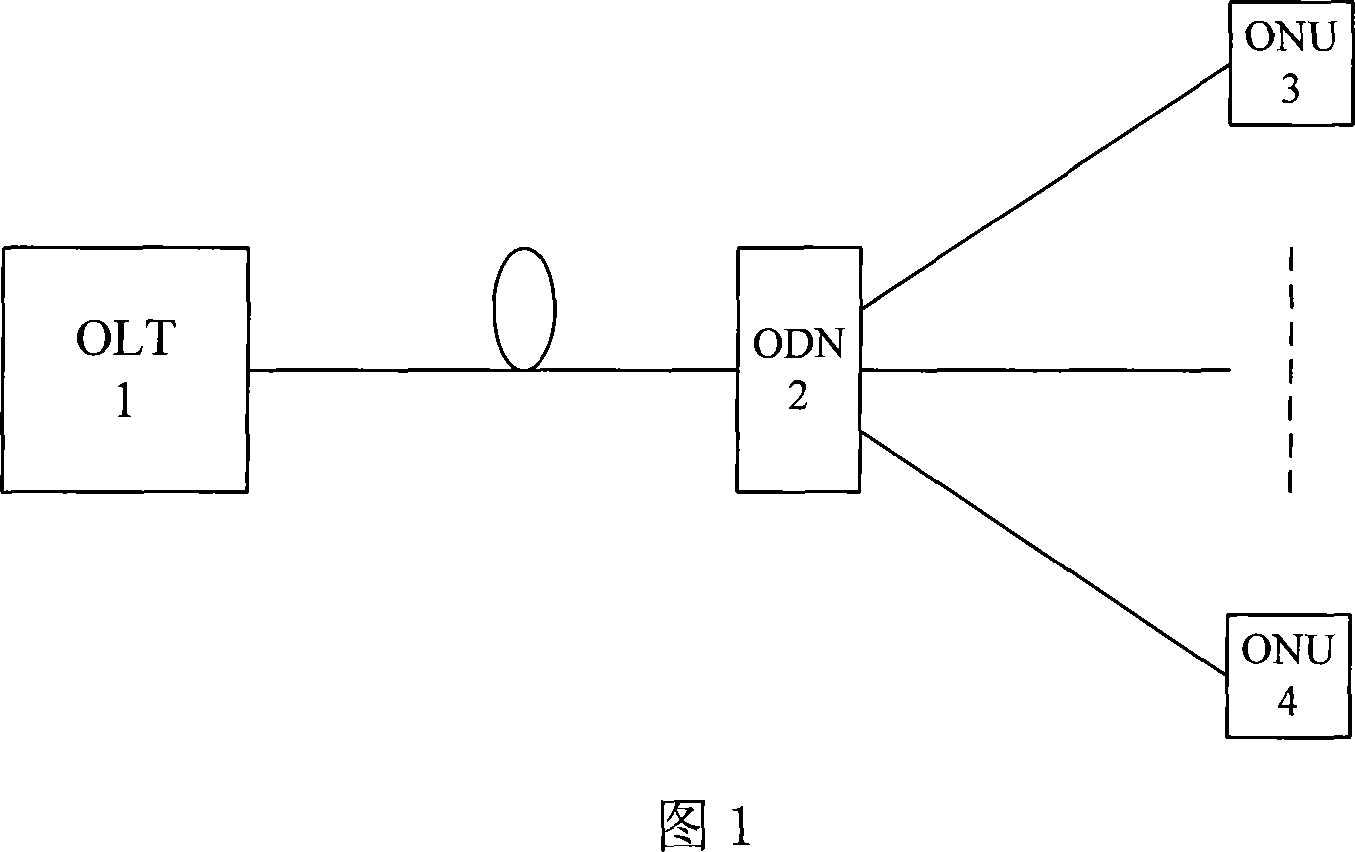

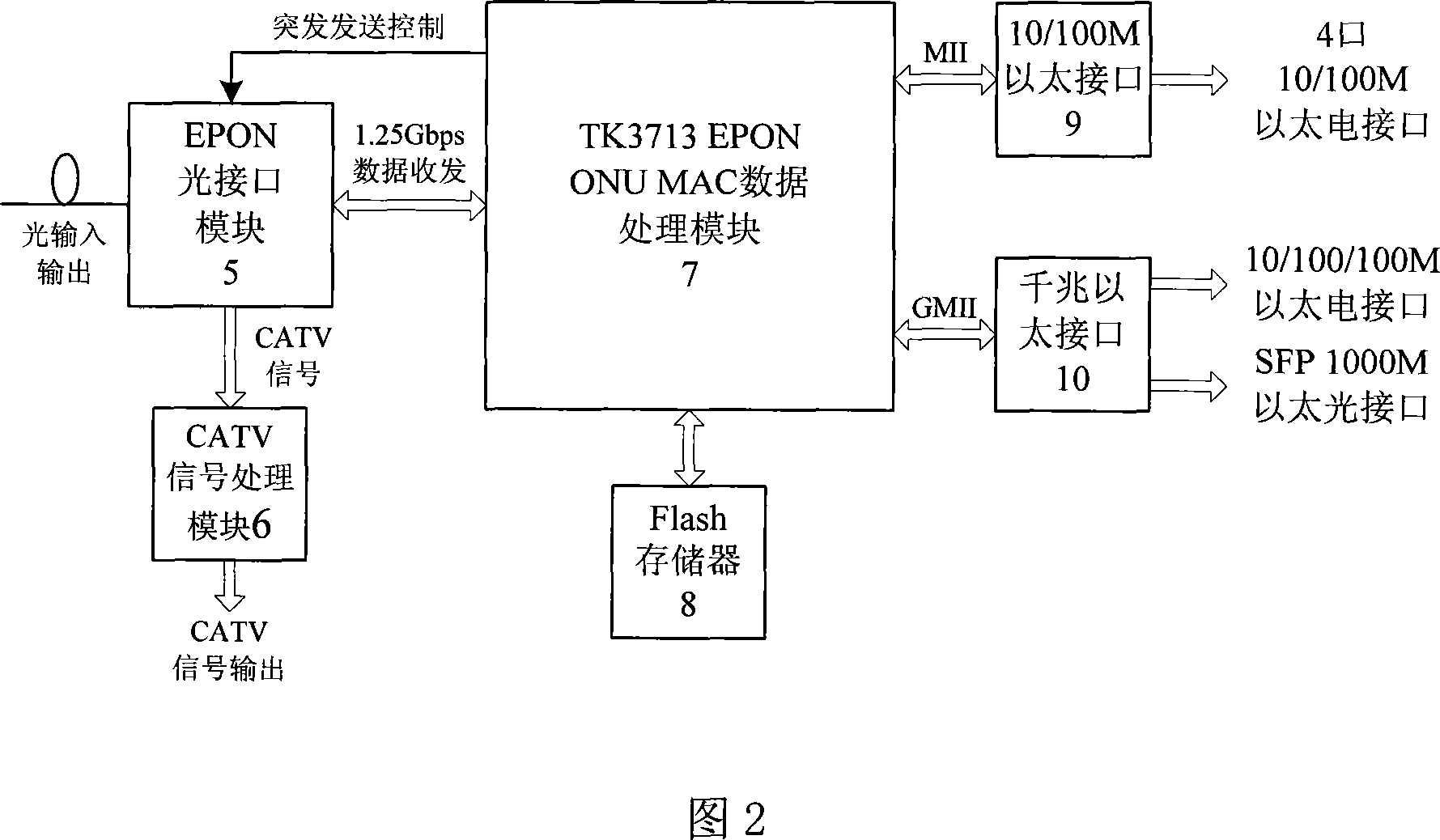

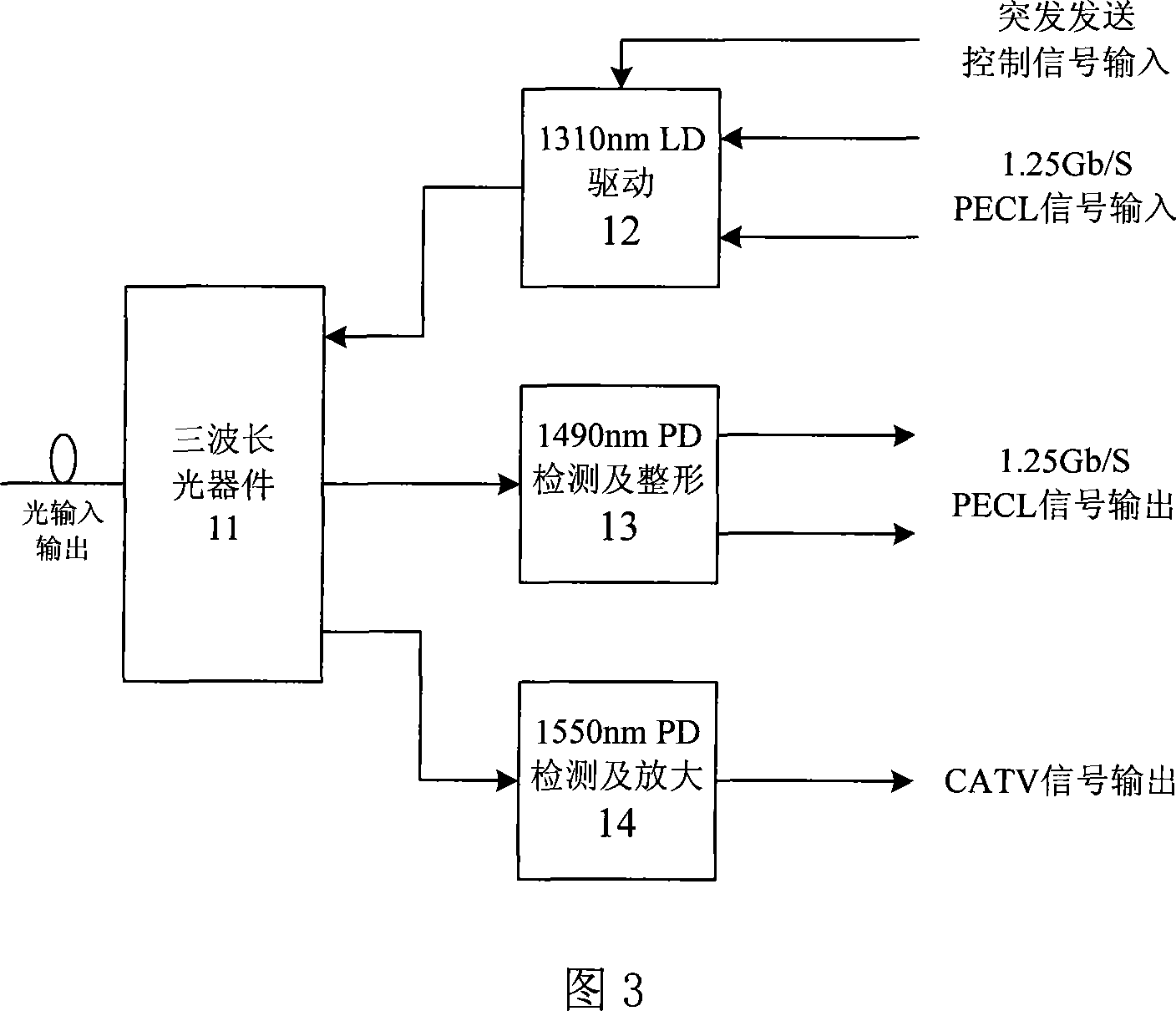

Optical network unit of Ethernet passive optical network

InactiveCN101075853AReduce volumeFirmly connectedMultiplex system selection arrangementsData switching by path configurationOptical ModuleNetwork integration

The optical network unit thereof has CATV-signal outputting function while realizing the transmission of Ethernet data transmission so as to realizing the transmission of TV signal in EPON, and can be used in realizing EPON-based three-network integration. The invention uses an optical module integrated with three wave lengths and an ONU MAC process chip so as to improve the reliability of ONU and to reduce the cost, and is equipped with mega bytes and giga bytes Ethernet I / O interfaces so as to improve the adaptability of ONU.

Owner:SHANGHAI UNIV

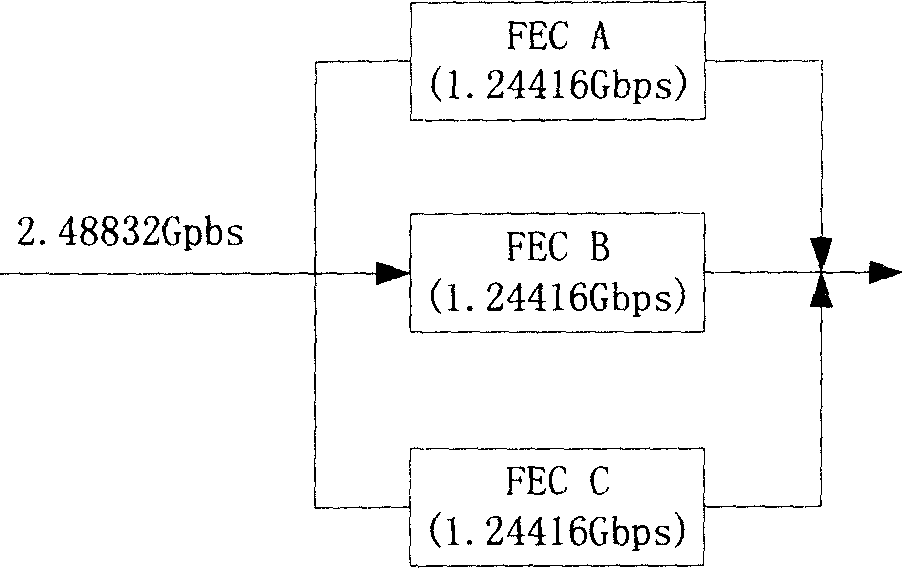

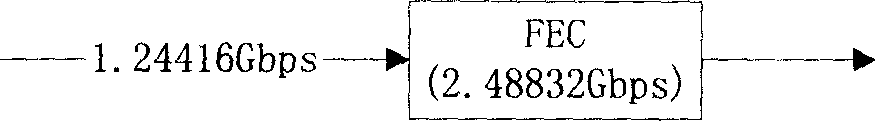

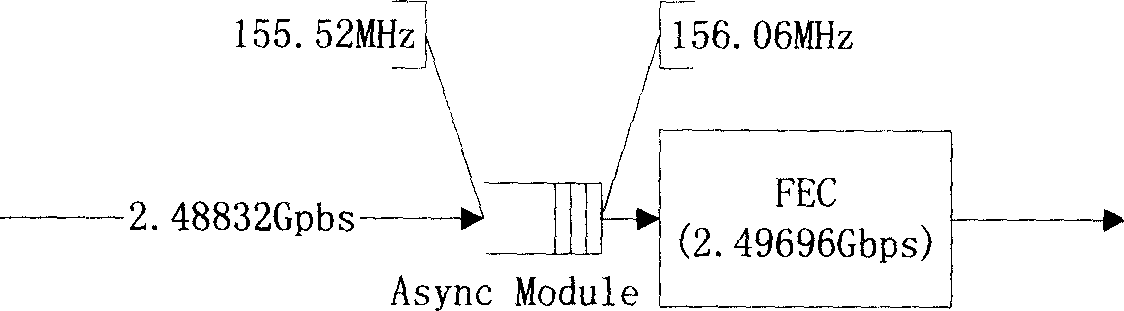

Method and system for reducing downlink forward error correction process of kilomega passive optical network

InactiveCN1913410AReduce codec performance requirementsReduce complexityMultiplex system selection arrangementsError preventionProcess moduleClock rate

This invention relates to a method and a device for forward error correction process to down data in a giga passive optical network GPON, in which, the method includes: a specific byte in the dowm data is set to be a fixed datum, the FEC process module adds said datum to the tail of the down data frame while coding and casts off said fixed datum when decoding, which casts aside the effective data of255 residual part in the GPON down frame and the system can work without adding FEC process modules and performances or altering the system clock frequency.

Owner:HUAWEI TECH CO LTD

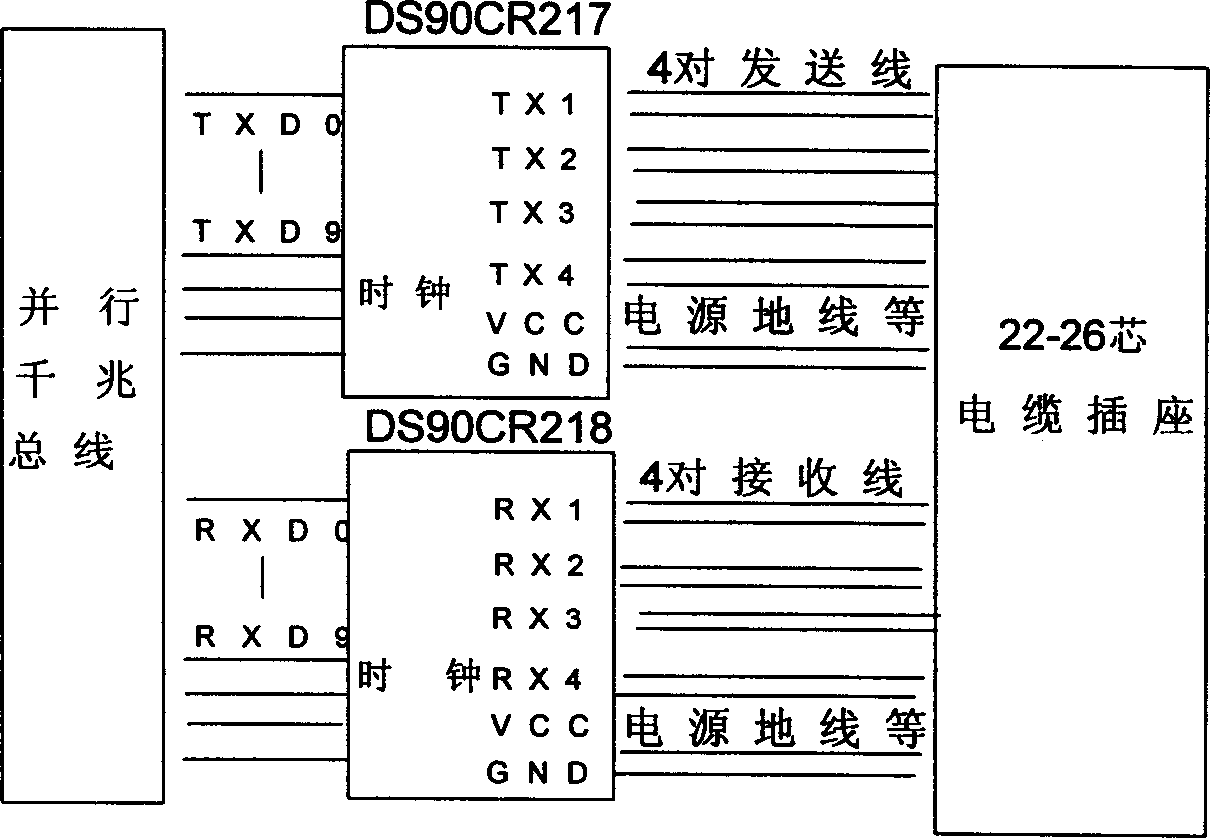

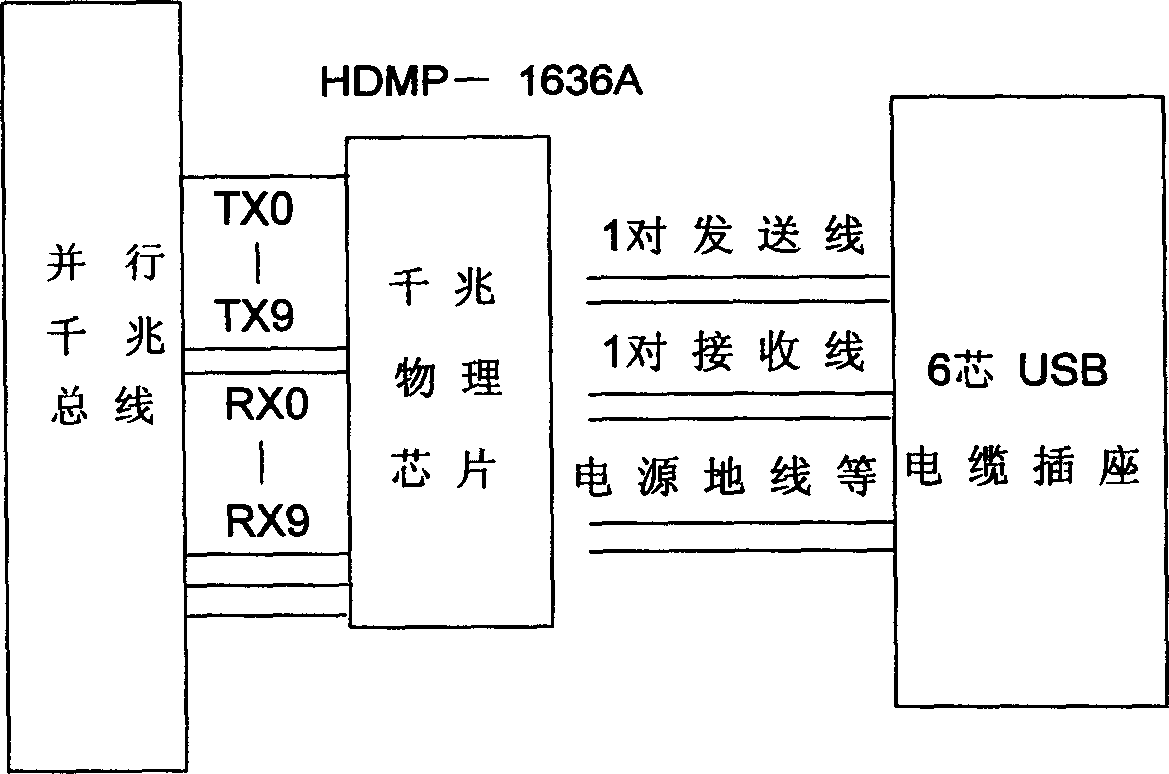

Method for implementing Ethernet exchange piling

The method for implementing Ethernet exhcnage stacking includes the following steps: converting the giga-parallel signal outputted by Ethernet exchanger into giga-serial signal by means of conversioncircuit, transferring said giga-serial signal into another Ethernet exchange to be stakced with the above-mentioned Ethernet exchanger by means of cable, and when the Ethernet exchange is used for receiving giga-serial signal transferred from another Ethernet exchanger, converting the giga-serial signal into giga-parallel signal by means of conversion circuit, and connecting it into said Ethernetexchanger.

Owner:HUAWEI TECH CO LTD

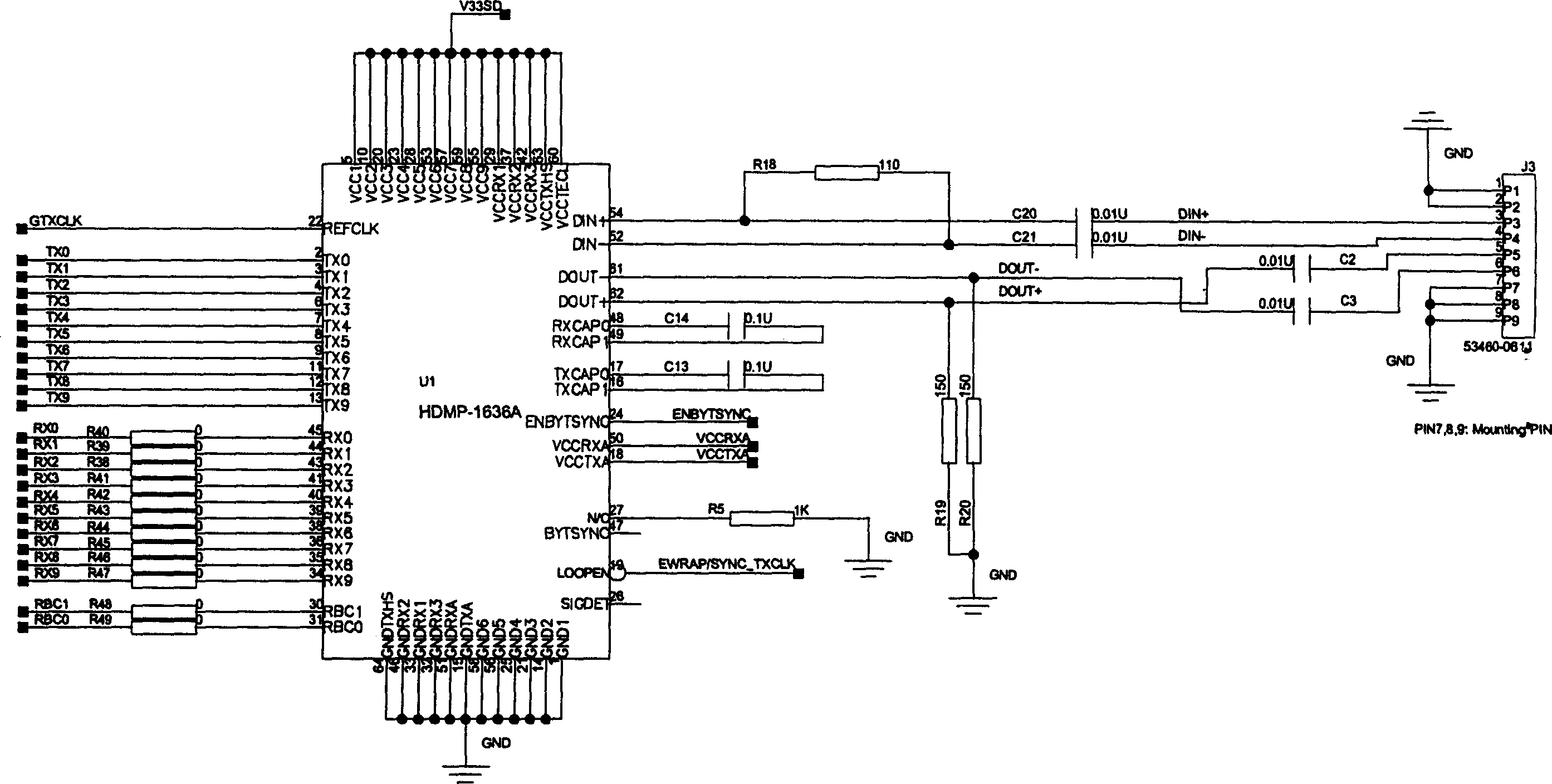

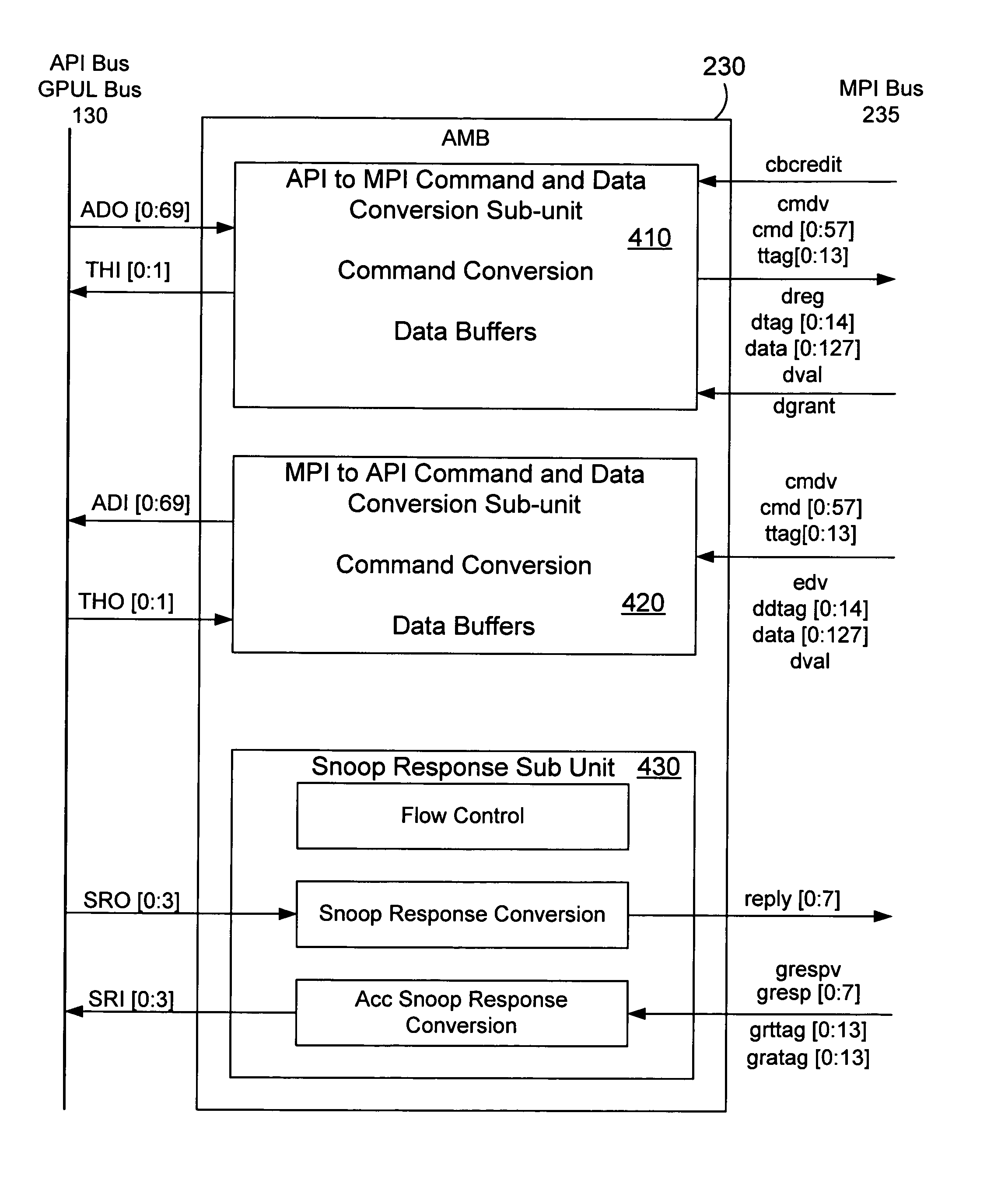

Computer system architecture for a processor connected to a high speed bus transceiver

A high speed computer processor system has a high speed interface for a graphics processor. A preferred embodiment combines a PowerPC microprocessor called the Giga-Processor Ultralite (GPUL) 110 from International Business Machines Corporation (IBM) with a high speed interface on a multi-chip module.

Owner:INT BUSINESS MASCH CORP

Converter, circuit and method for compensation of non-idealities in continuous time sigma delta converters

InactiveUS7245246B2Effective compensationStraightforward integrationElectric signal transmission systemsAnalogue conversionSigma delta convertersDynamic range

A continuous time sigma delta converter has a filter and converter components having known non-ideal characteristics. A compensation circuit has error modelling components arranged to model the non-ideal characteristics of the converter. A summation block combines a compensation signal from the compensation circuit with a non-ideal output signal from the converter in order to provide a compensated output signal. This has substantially no effect on other modulator performance characteristics and contributes to the implementation of giga sample-per-second Continuous Time sigma deltas having the dynamic range capabilities of traditional DT sigma deltas.

Owner:NORTH STAR INNOVATIONS

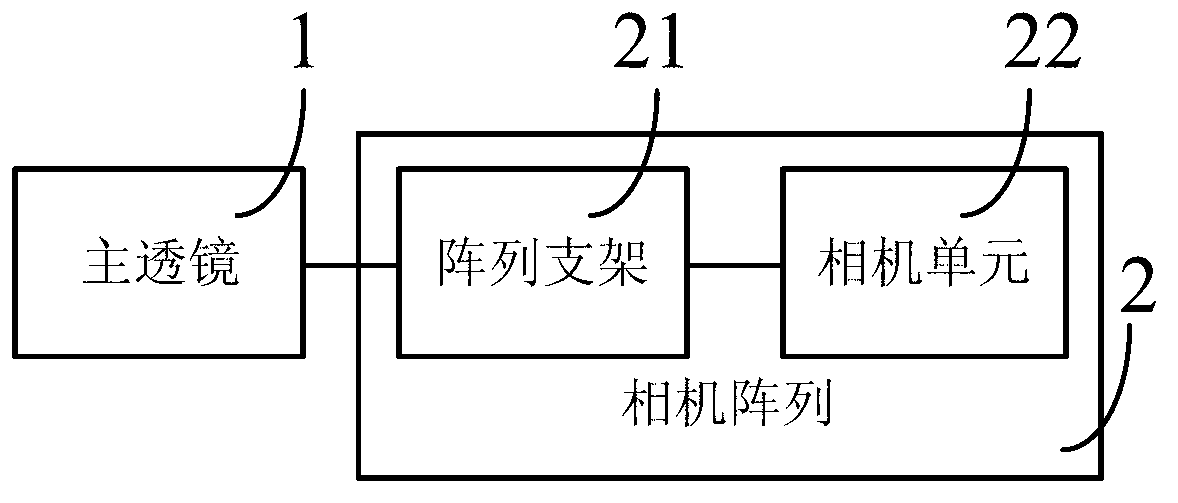

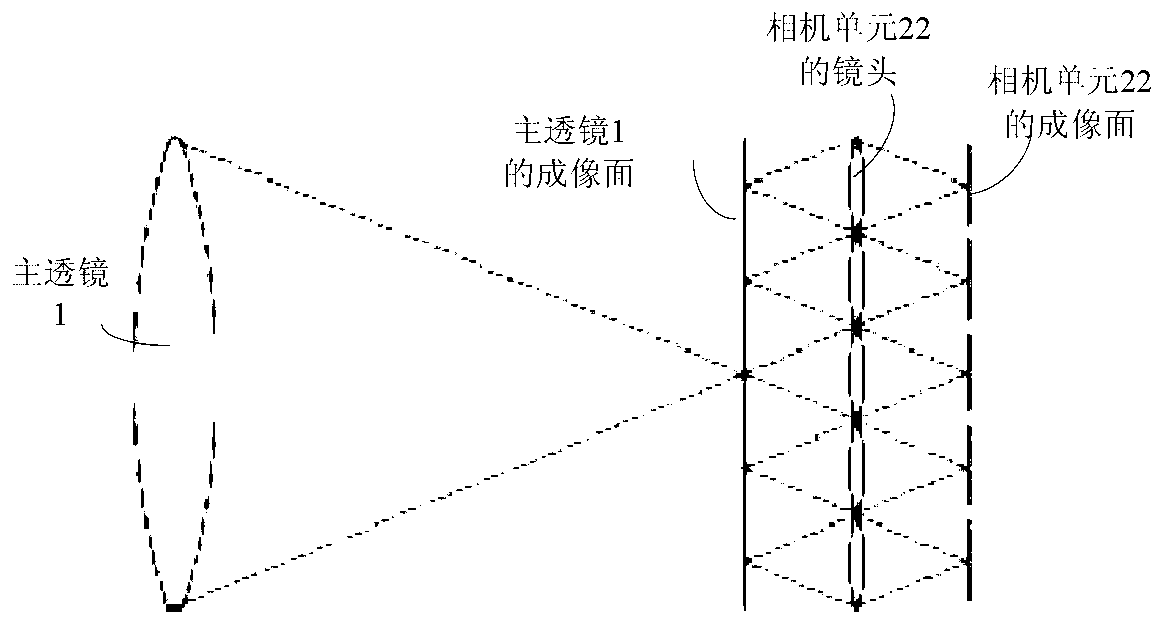

Giga-pixel video collecting device

InactiveCN103281484AHigh resolutionTelevision system detailsColor television detailsCamera lensImage resolution

The invention provides a giga-pixel video collecting device which comprises a main lens and a camera array. The camera array is distributed in a spherical mode. The position of a sphere center is the position of the main lens. The camera array comprises an array support and a plurality of camera units, wherein the array support comprises a plurality of round holes which are used for placing and fixing the camera units. According to the giga-pixel video collecting device, the camera units are arranged to form the array, the front end of the array projects a scene to each camera lens through the main lens, each camera unit, as one unit, collects a part of the scene, the parts are composited through software into a complete giga-resolution-ratio picture, and the picture is displayed on a screen in real time. Detailed local parts can be seen and a broad view angle can be obtained through amplifying and minifying, the conflict between a field angle and a resolution ratio is solved, and the giga-pixel video collecting device has the advantages of being large in field angle and high in resolution ratio.

Owner:TSINGHUA UNIV

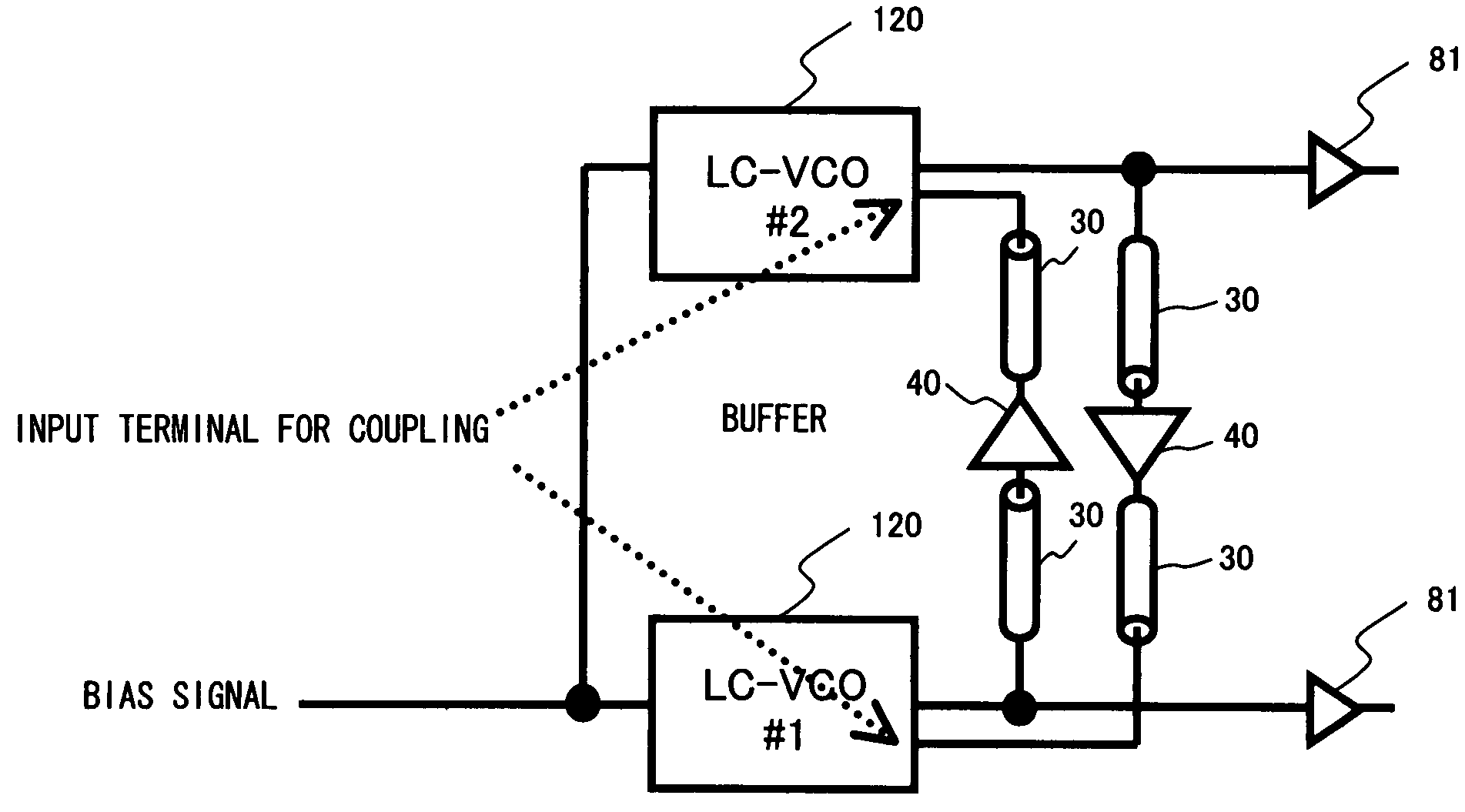

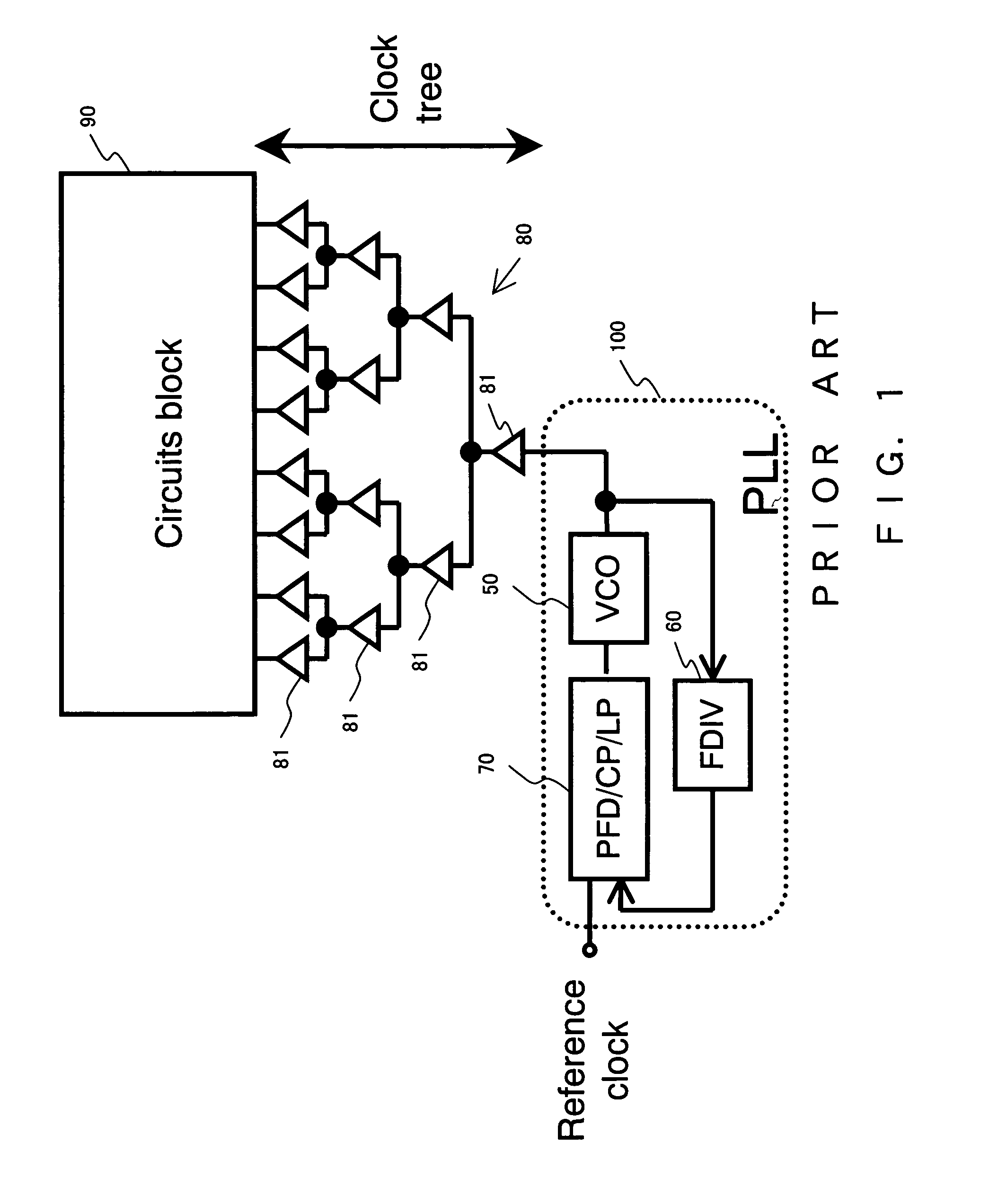

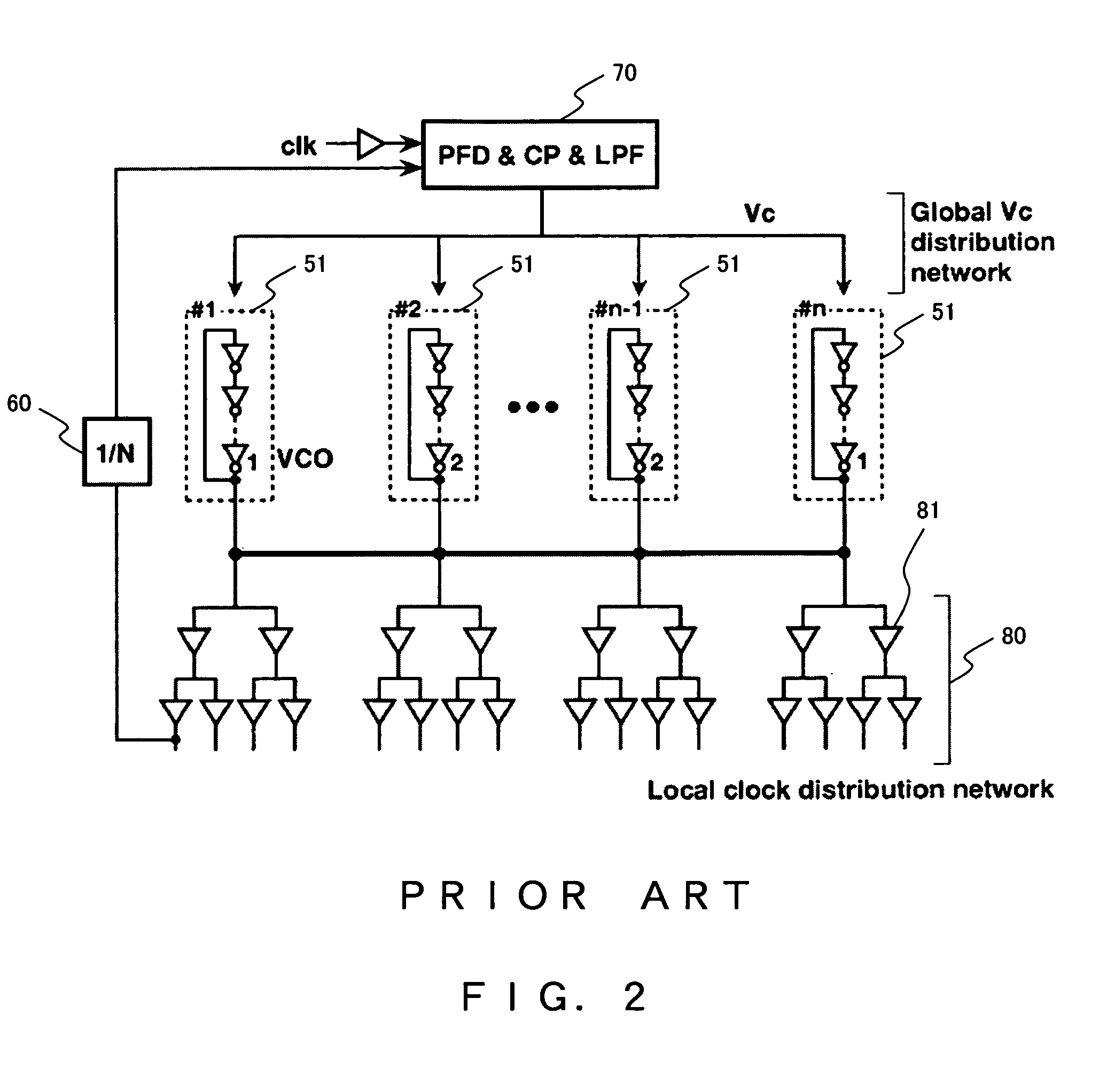

Clock signal generating and distributing apparatus

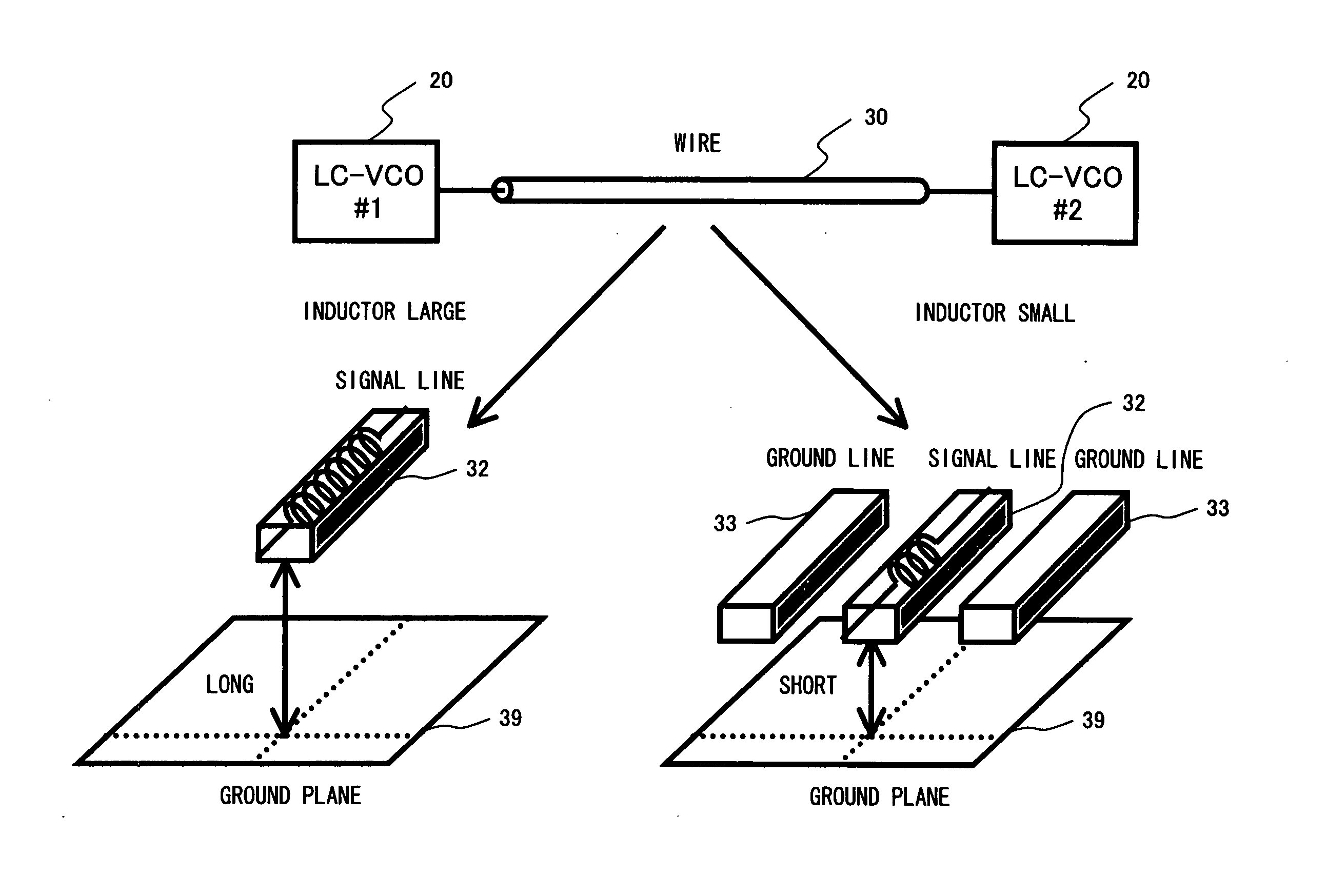

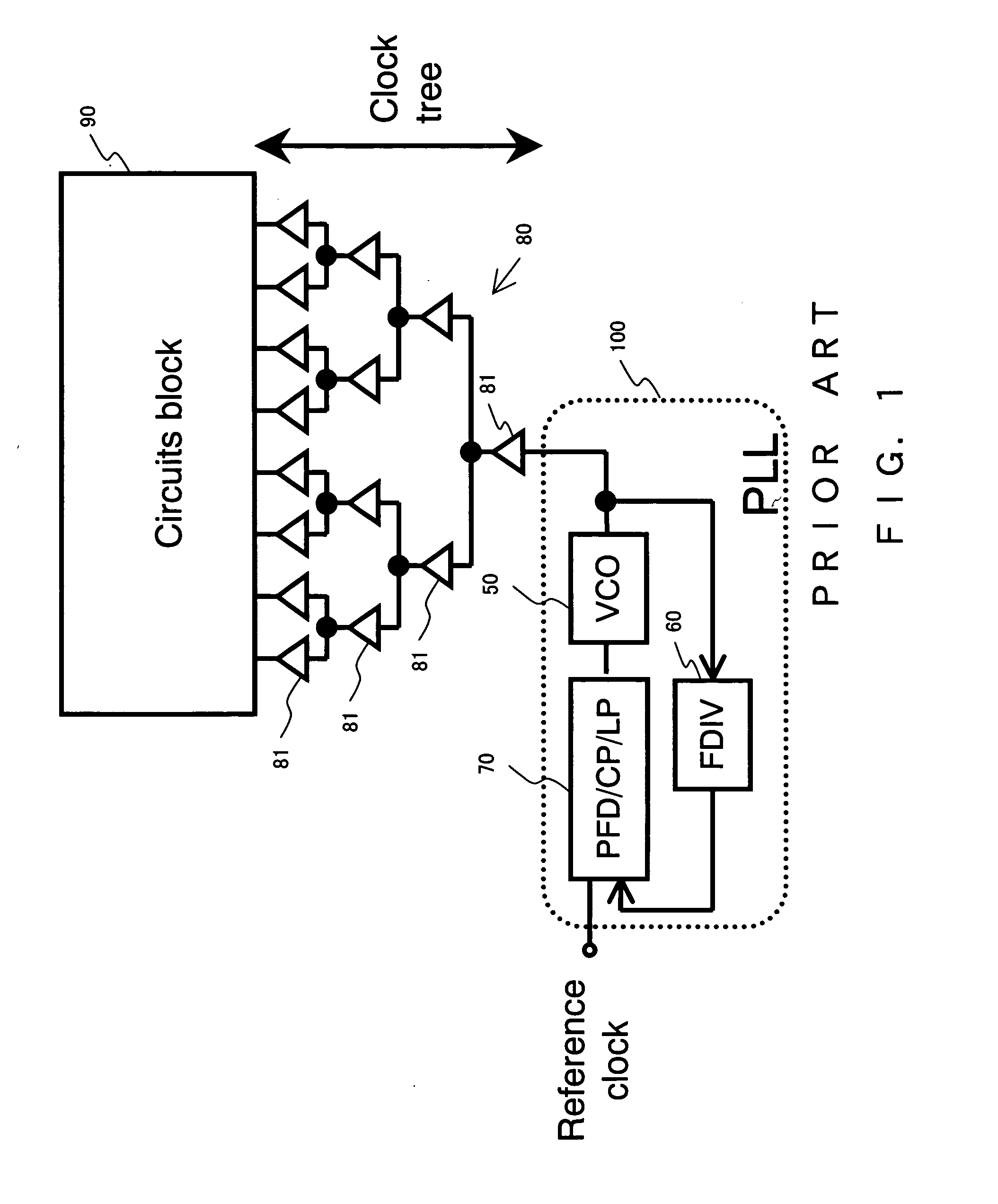

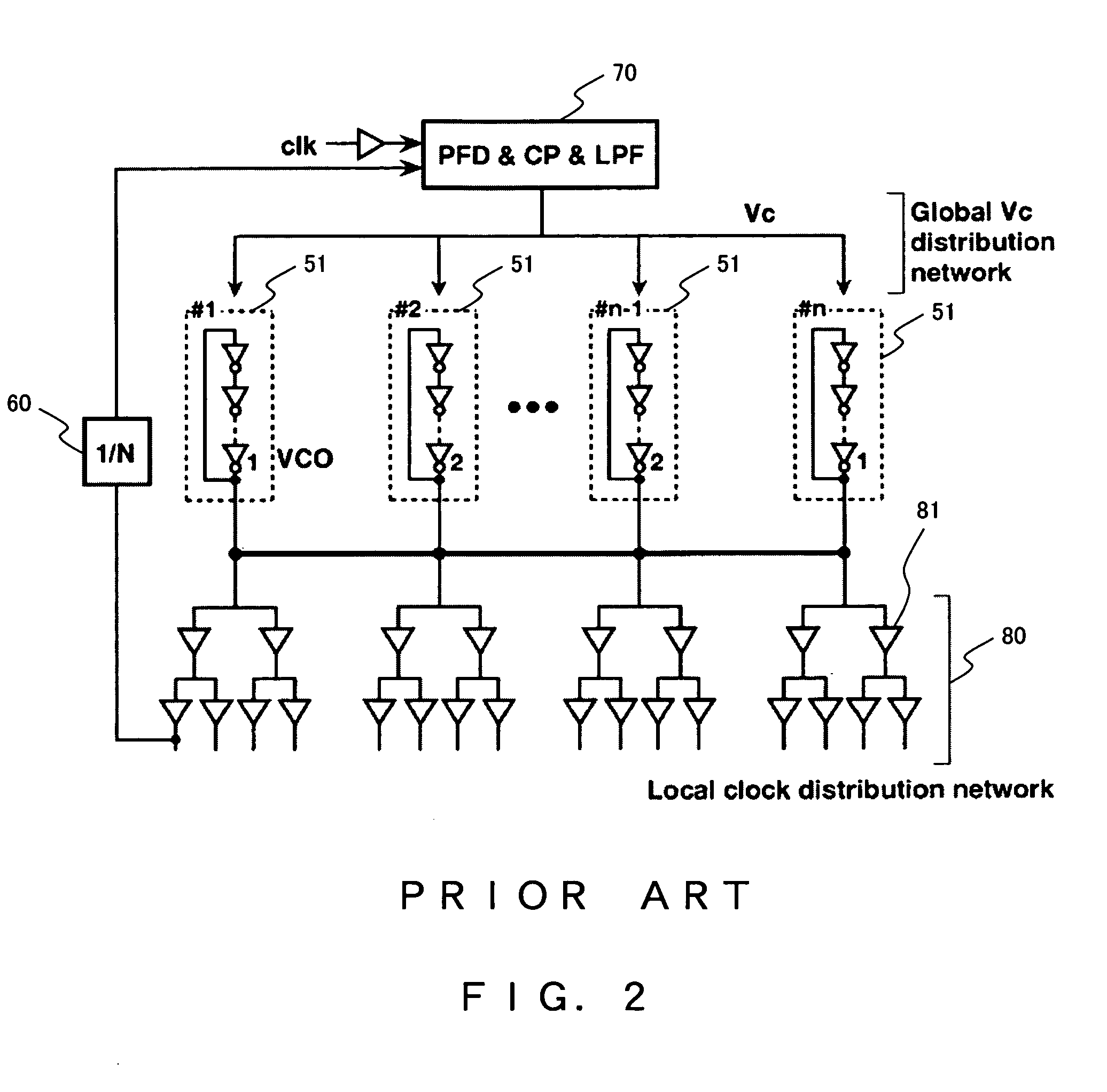

InactiveUS7863987B2Improve accuracyMore stablyPulse automatic controlGenerating/distributing signalsInjection lockedEngineering

LC resonant voltage control oscillators are adopted as voltage control oscillators for the purpose of providing a clock generating and distributing apparatus that can generate and distribute a clock signal of high precision even in a high-frequency region of several giga hertz or higher, and of providing a distributive VCO-type clock generating and distributing apparatus in which voltage control oscillators oscillate in the same phase, and which can generate a clock signal of a desired frequency and distributes a high-frequency clock signal to each part within a chip more stably even in a high-frequency region reaching 20 GHz. Furthermore, an inductor component of a wire connecting the oscillation nodes of the oscillators is made relatively small, or the LC resonant oscillators are oscillated in synchronization by using injection locking, whereby the LC resonant voltage control oscillators stably oscillate in the same phase.

Owner:FUJITSU LTD

Clock signal generating and distributing apparatus

InactiveUS20070063779A1Improve accuracyMore stablyPulse automatic controlGenerating/distributing signalsInjection lockedEngineering

LC resonant voltage control oscillators are adopted as voltage control oscillators for the purpose of providing a clock generating and distributing apparatus that can generate and distribute a clock signal of high precision even in a high-frequency region of several giga hertz or higher, and of providing a distributive VCO-type clock generating and distributing apparatus in which voltage control oscillators oscillate in the same phase, and which can generate a clock signal of a desired frequency and distributes a high-frequency clock signal to each part within a chip more stably even in a high-frequency region reaching 20 GHz. Furthermore, an inductor component of a wire connecting the oscillation nodes of the oscillators is made relatively small, or the LC resonant oscillators are oscillated in synchronization by using injection locking, whereby the LC resonant voltage control oscillators stably oscillate in the same phase.

Owner:FUJITSU LTD

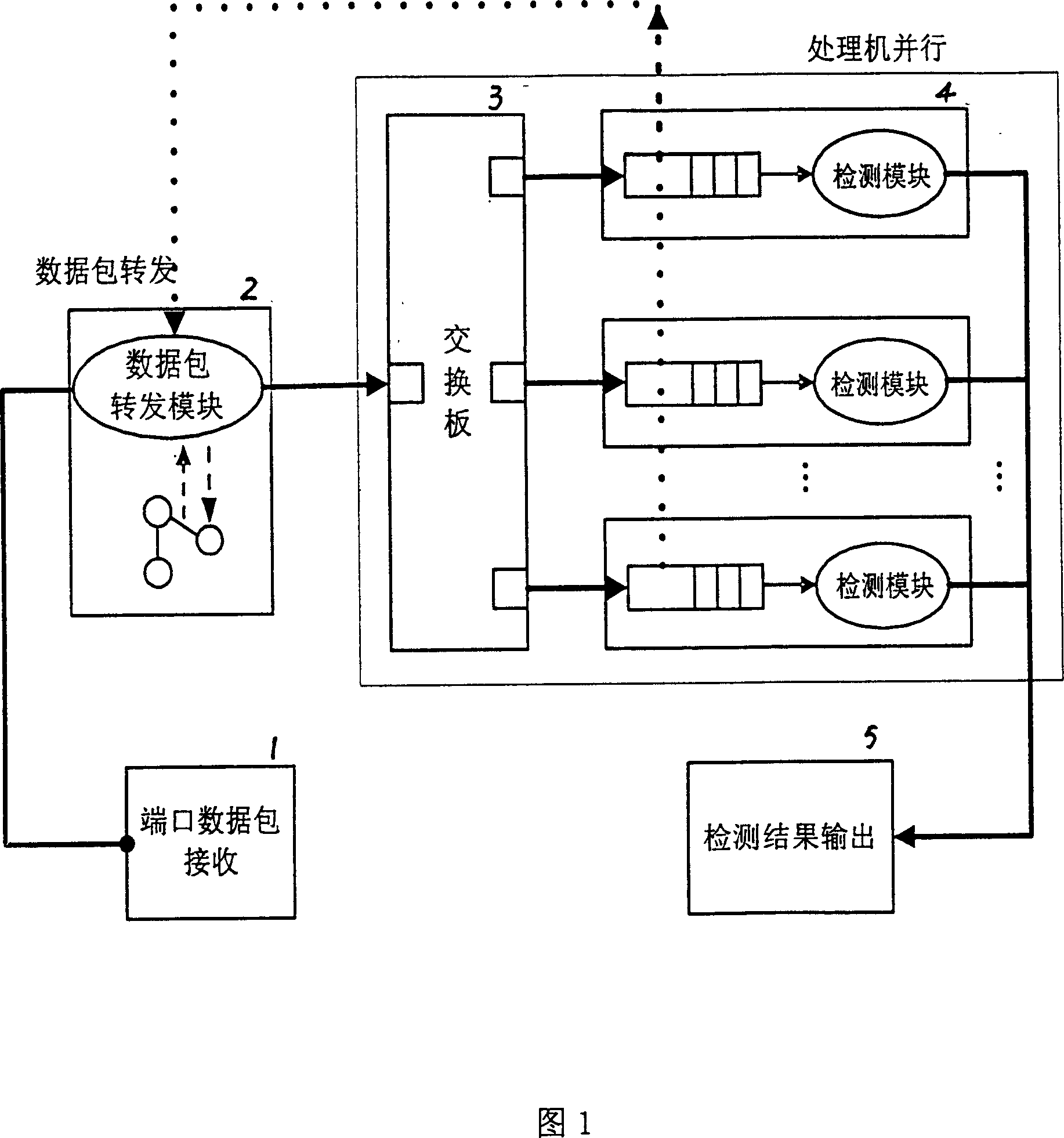

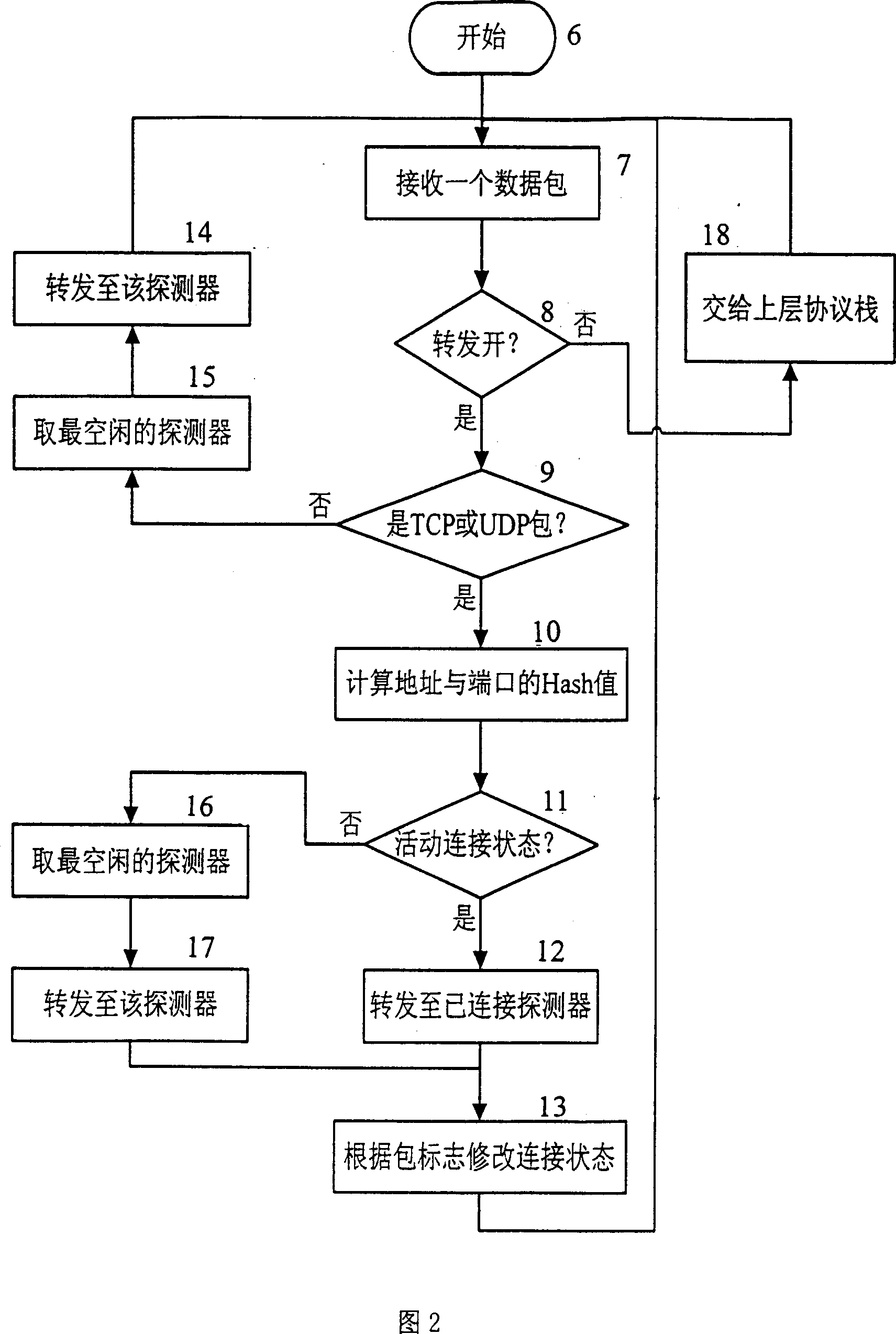

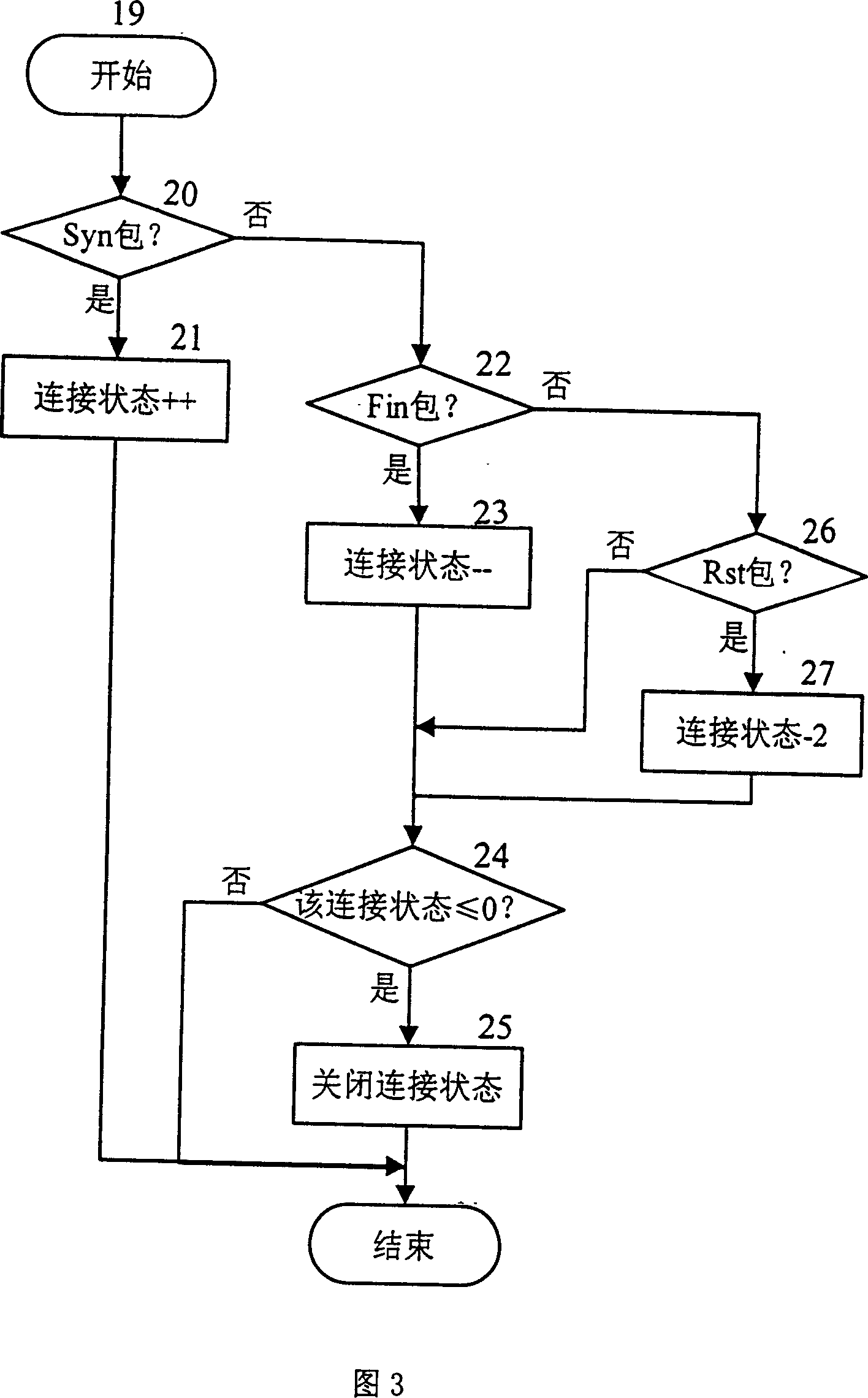

A method for kilomega NIDS parallel processing based on NP and BS

The relative giga-level NIDS paralleled process method based on NP and BS comprises: receiving all data package from target network by a translator; dividing high-speed network data flow into multiple low-speed data flow, and determining target detector; changing target MAC of data package into detector MAC, and sending to the detector by a exchange board; with two complementary threads, acquiring data, analyzing protocol, and matching feature; and forming a detection result on console. This invention improves process capacity of whole system, and reduces package-missing rate.

Owner:NANJING UNIV

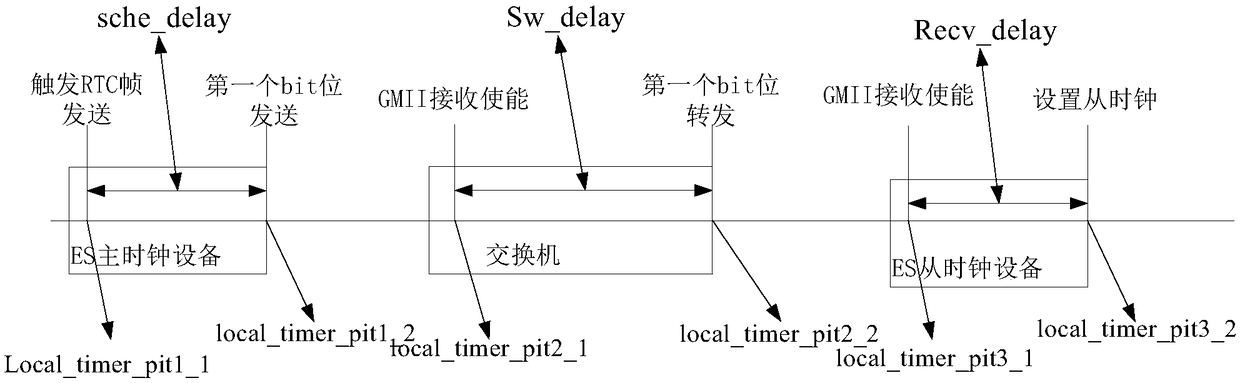

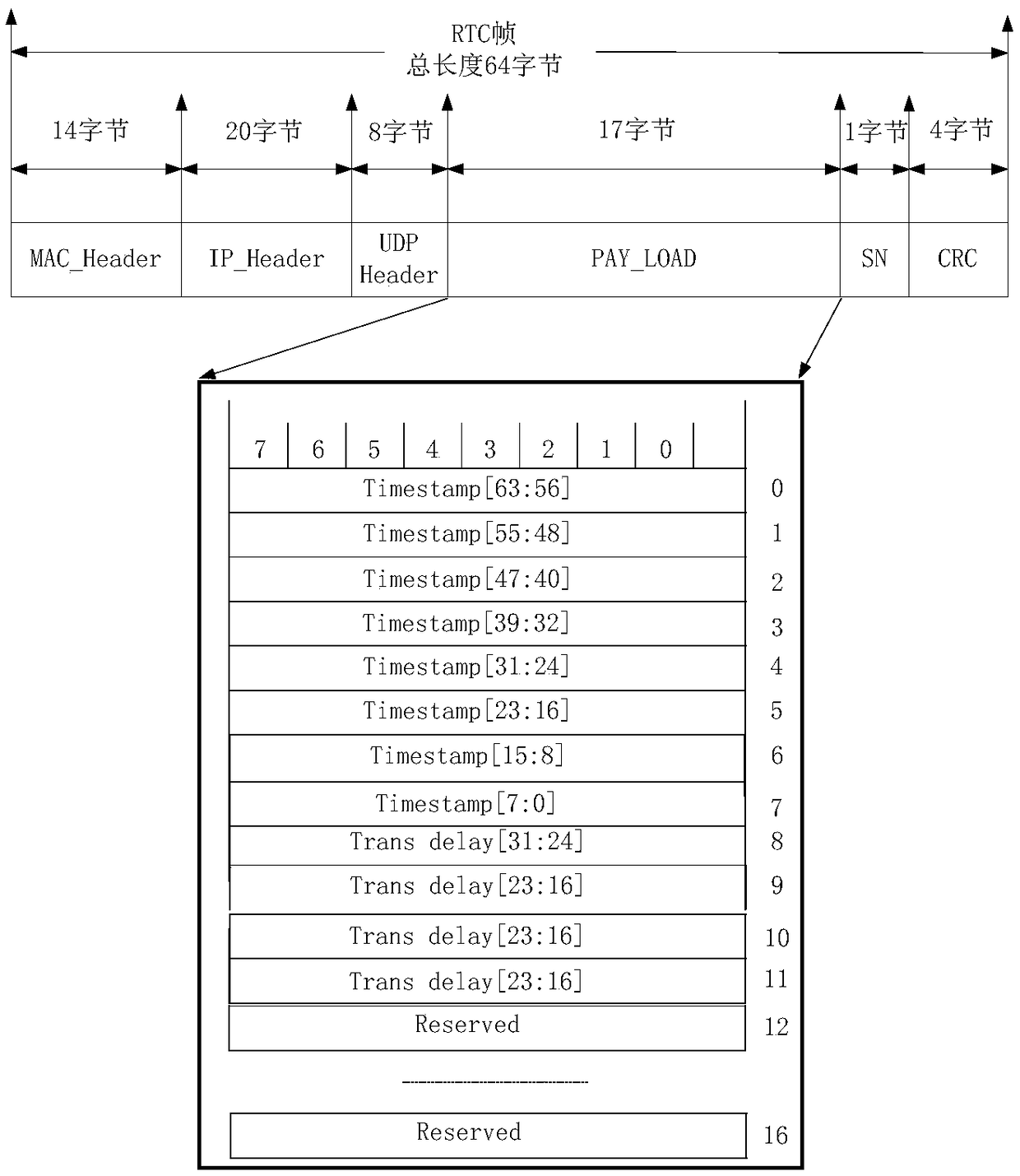

Implementation method of high-precision time service timing system based on giga AFDX network

The present invention provides an implementation method of high-precision time service timing system based on a giga-AFDX network. The method comprises the steps of: taking the sum of delay parametersas real delay of a RTC frame from a time service terminal to a time served terminal to compensate the clock of the time service through recording of dispatching delay of the RTC frame at a main clocksource device, forward delay of a path switch and technical delay received and processed from the clock device, adding a main timestamp value in the RTC frame extraction frame of time service received by the time served terminal to the calculated and obtained actual delay value transmitted by the RTC frame, and writing the main timestamp value and the actual delay value into a local clock timer,wherein the difference of the main clock timer and the slave clock timer value cannot exceed 100ns in an implementation mode, namely, the synchronous time service precision can reach submicrosecond precision. The implementation method of high-precision time service timing system based on the giga-AFDX network can change the forwarding output mode of the switch of the RTC system in the network system, can change the frame load content at the forwarding port and can recalculate CRC so as to achieve the high-precision performance.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

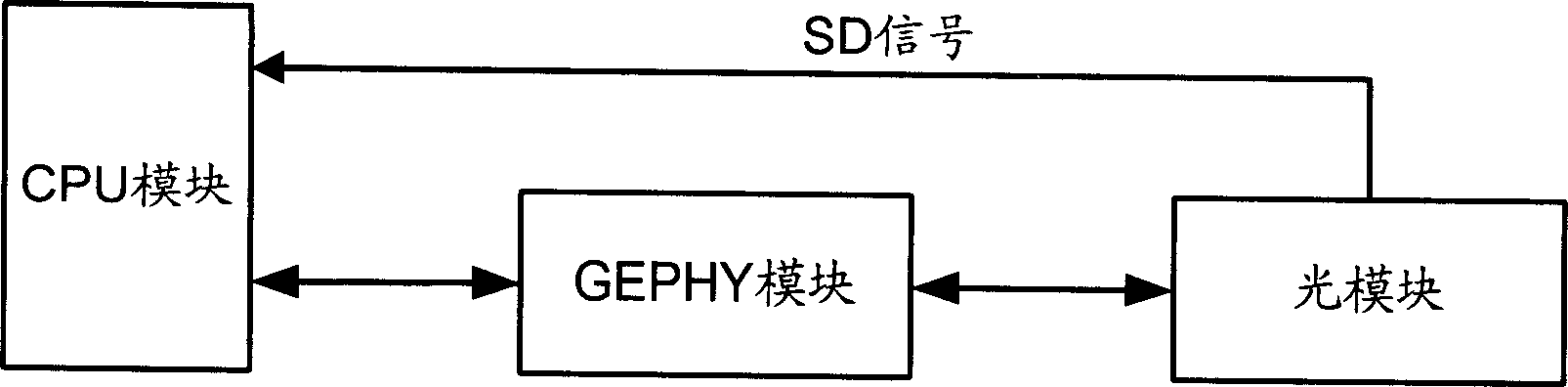

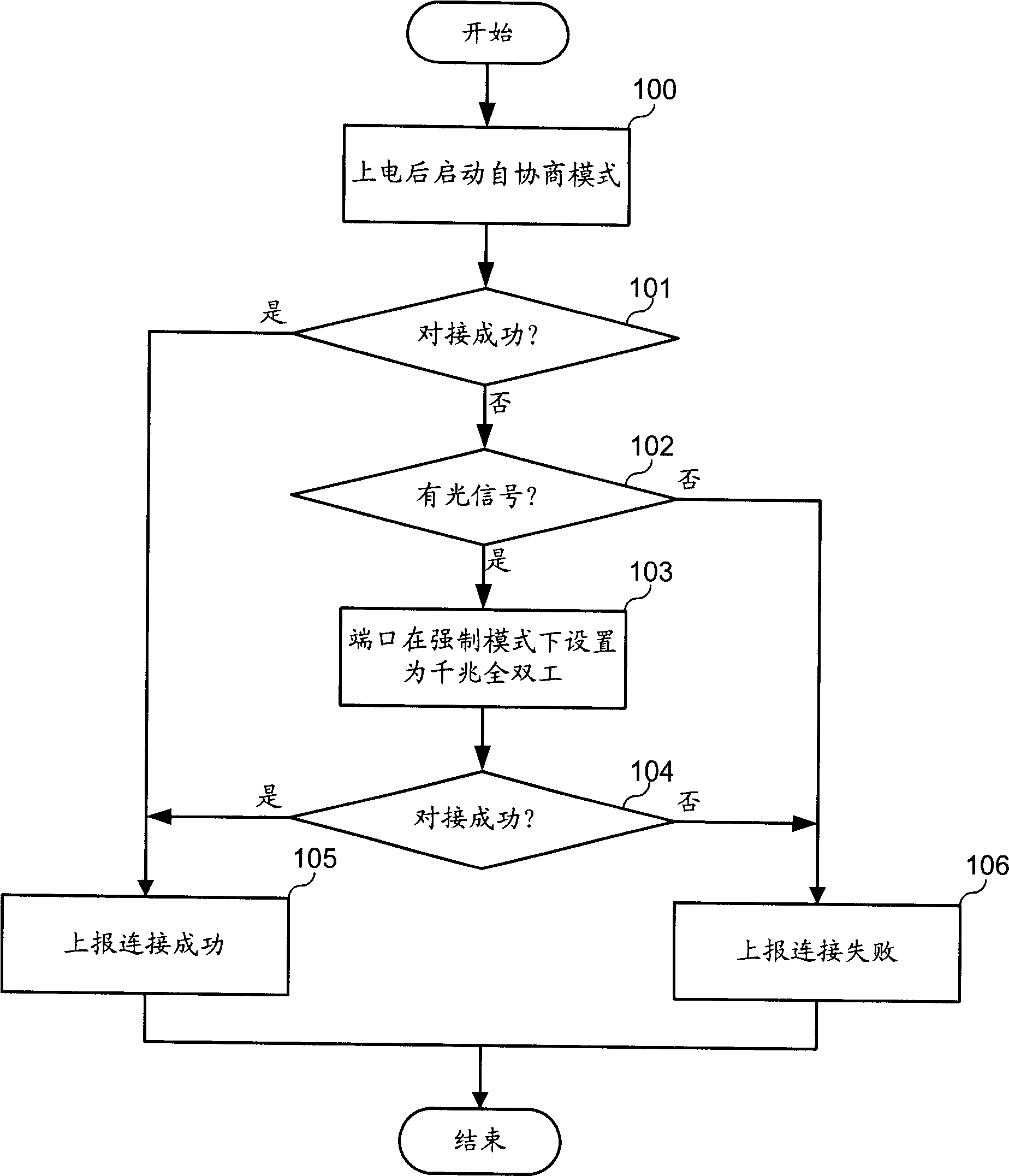

Kilomega Ethernet port butt method

InactiveCN1835466ASolve the problem of not being able to connect automaticallyImprove adaptabilityNetworks interconnectionGigabitEngineering

The invention can build connection between two GE (Giga Ethernet) ports having different configuration modes. The method comprises: a control process is added, which firstly configures the GE ports into a self-negotiation mode and tries to build connection, if the connection is failure, then configures the ports to Gigabits full duplex at a force mode; before the ports is configured into a force mode, firstly making detection to decide if there is a optical signal, if yes, then configuring the ports to force mode.

Owner:HUAWEI TECH CO LTD