Patents

Literature

941 results about "Timing system" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

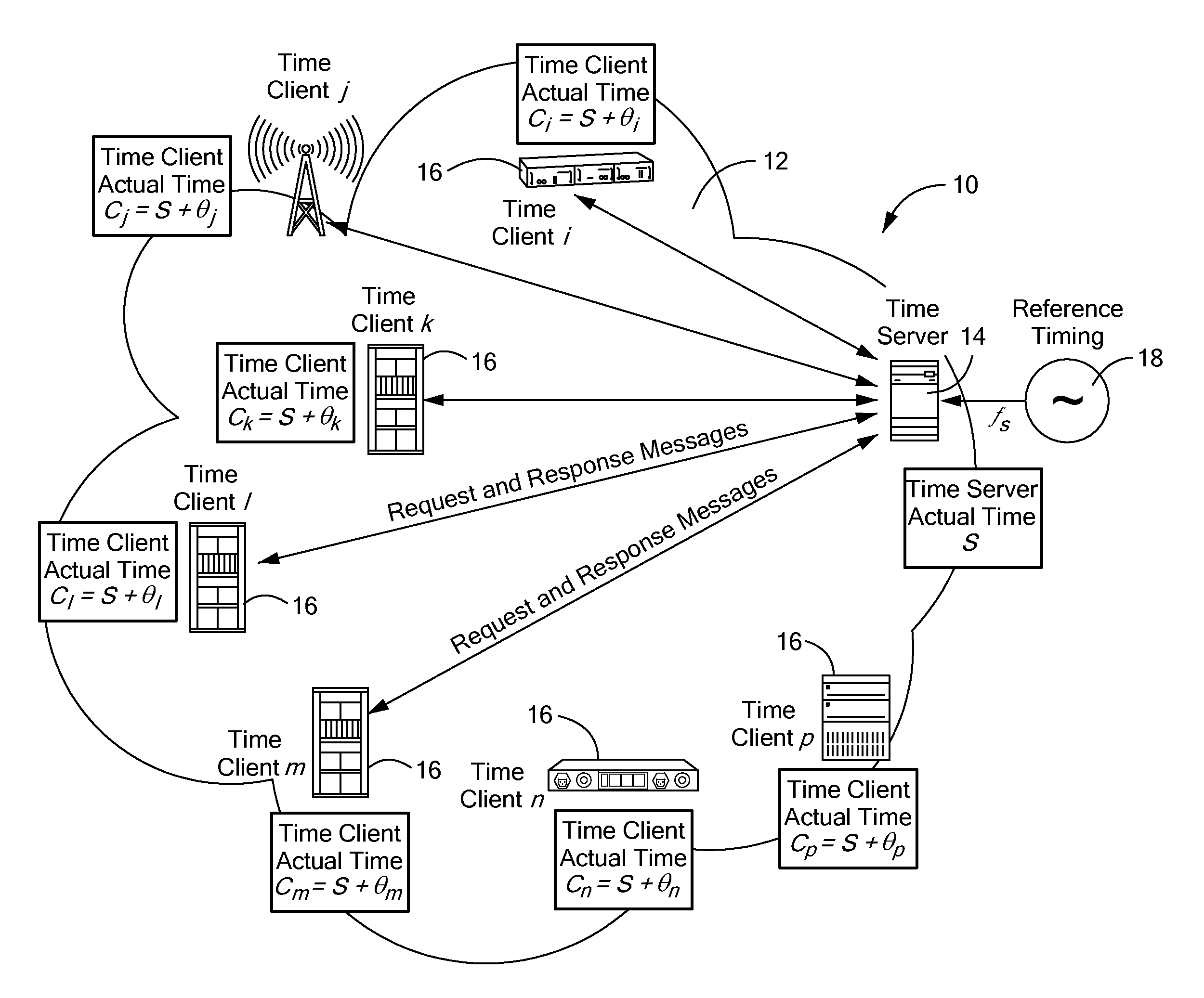

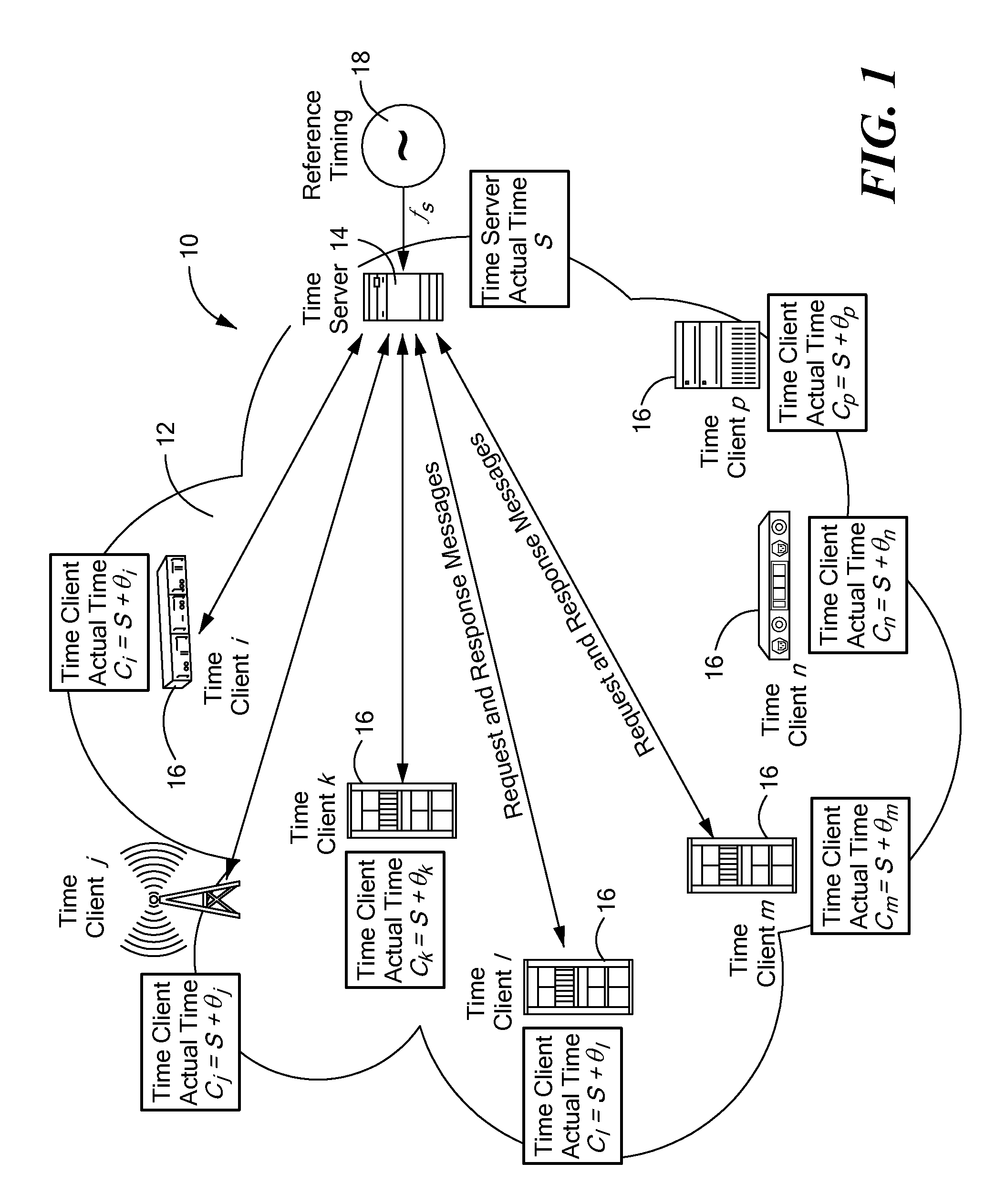

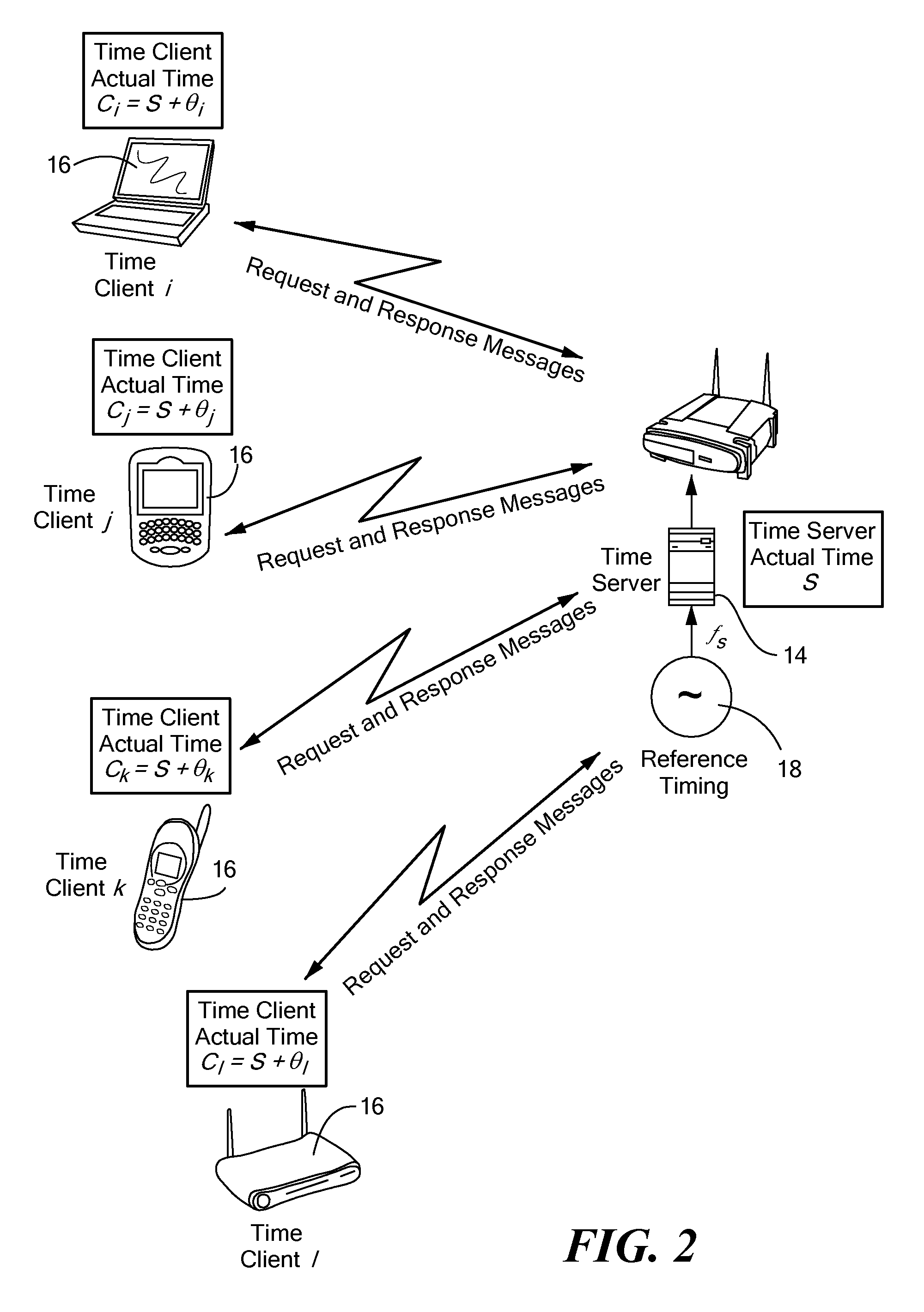

Method and apparatus for time and frequency transfer in communication networks

A timing system for time synchronization between a time server and a time client over a packet network. The timing system includes a time server for generating current timestamp information and a time client having a phase-locked loop driven client clock counter. The time client periodically exchanges time transfer protocol messages with the time server over the packet network, and calculates an estimated client time based on the timestamp information. The phase-locked loop in the time client receives periodic signals representing the estimated server time as its input and calculates a signal which represents the error difference between the estimated server time and the time indicated by the time client clock counter. The error difference eventually converges to zero or a given error range indicating the time presented by the client clock counter, which is driven by the phase-locked loop having locked onto the time of the time server.

Owner:RPX CLEARINGHOUSE +1

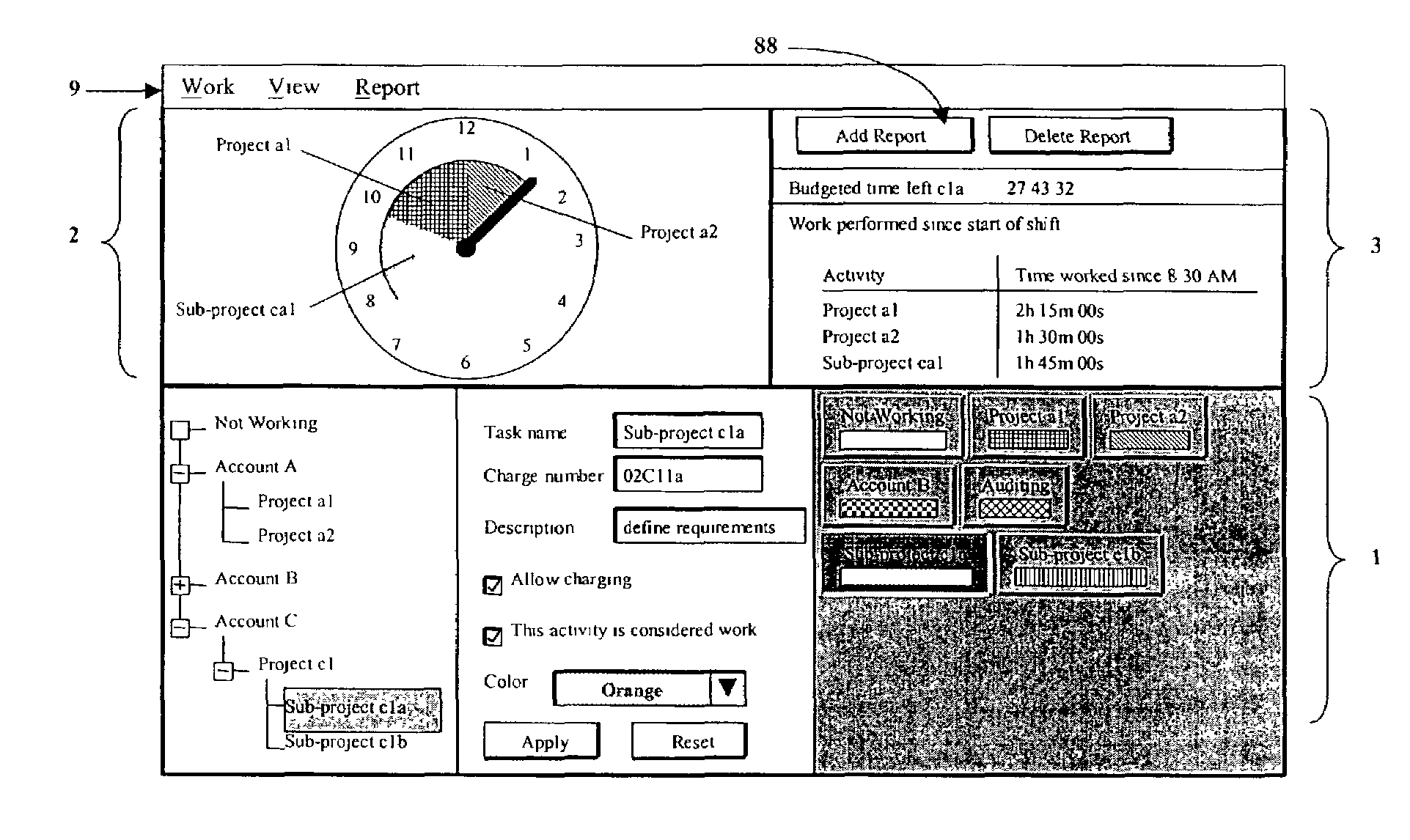

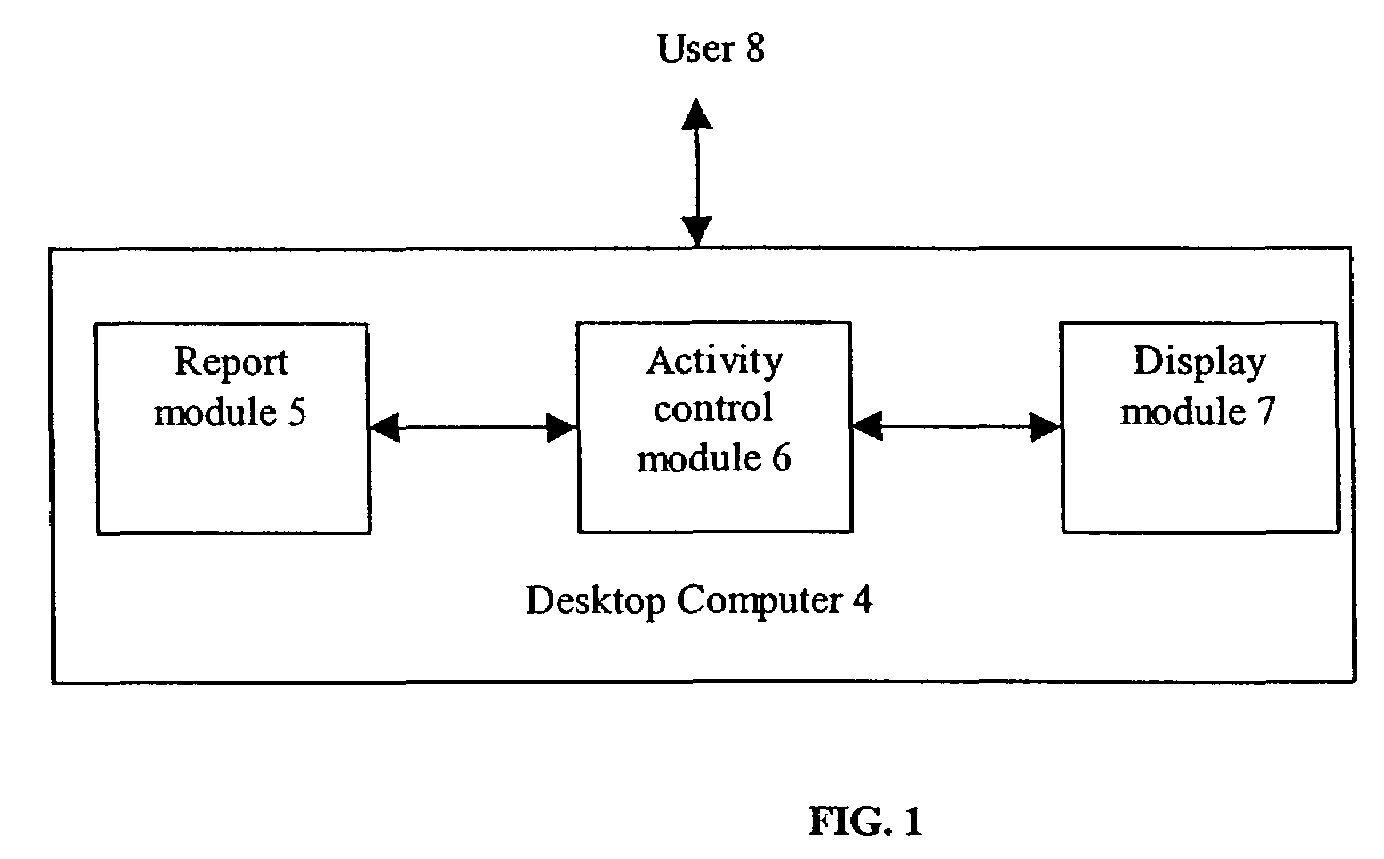

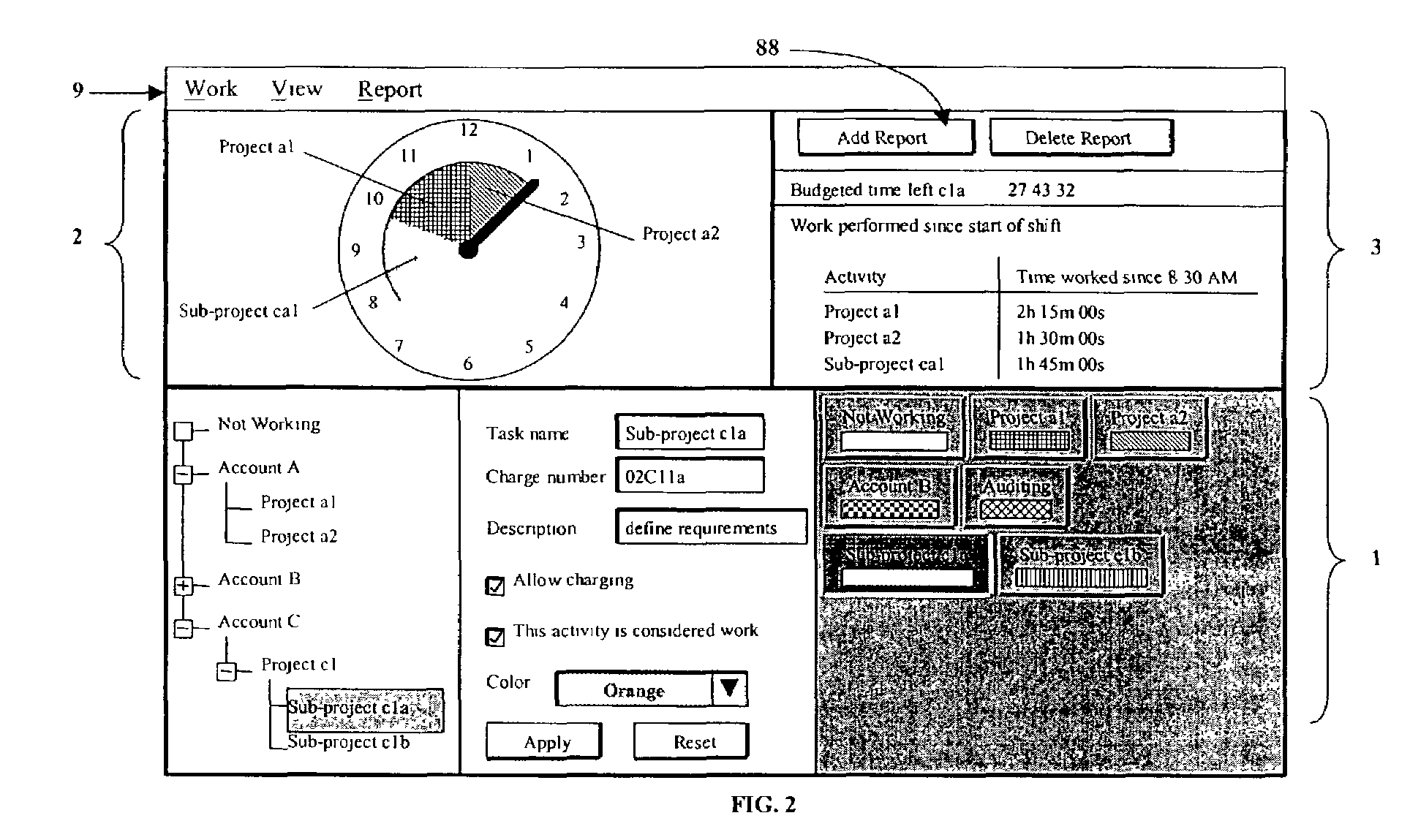

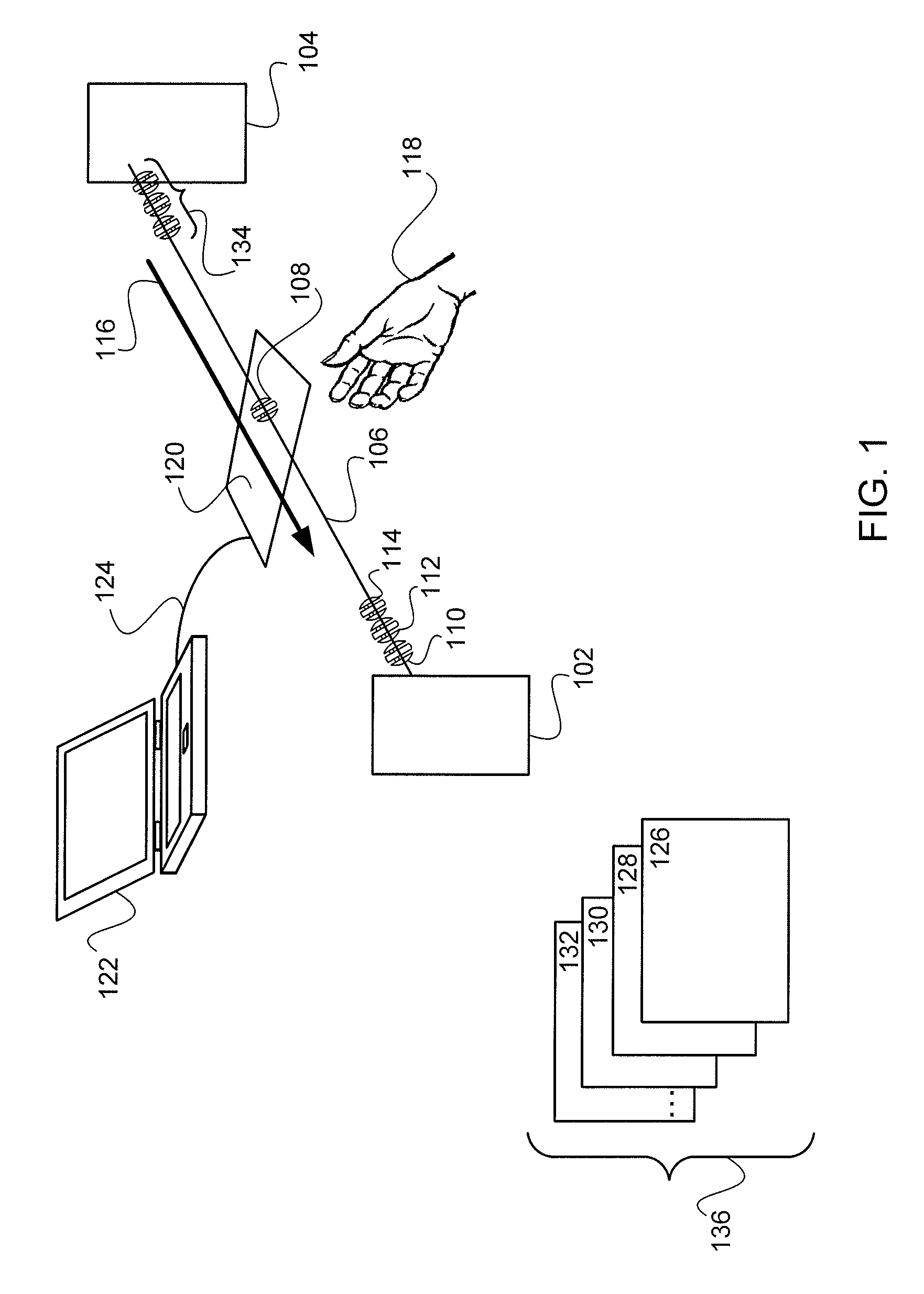

Timekeeping system and method for graphically tracking and representing activities

A timekeeping system and method is provided for enabling users to graphically represent one or more activities, as well as the time that has been allocated to each. A graphical display uniquely identifies activities or events based on different visual indicators (e.g., colors), as well as a dimension (e.g., length, area, etc.) that visually represents the duration of the activities or events. At least one dimension of the visual indicator changes in real time to represent the elapsed time of an activity. A report module comprising a report generator and report editor is provided to enable users to account for and summarize the time that has been spent on various activities.

Owner:DAVID PETER

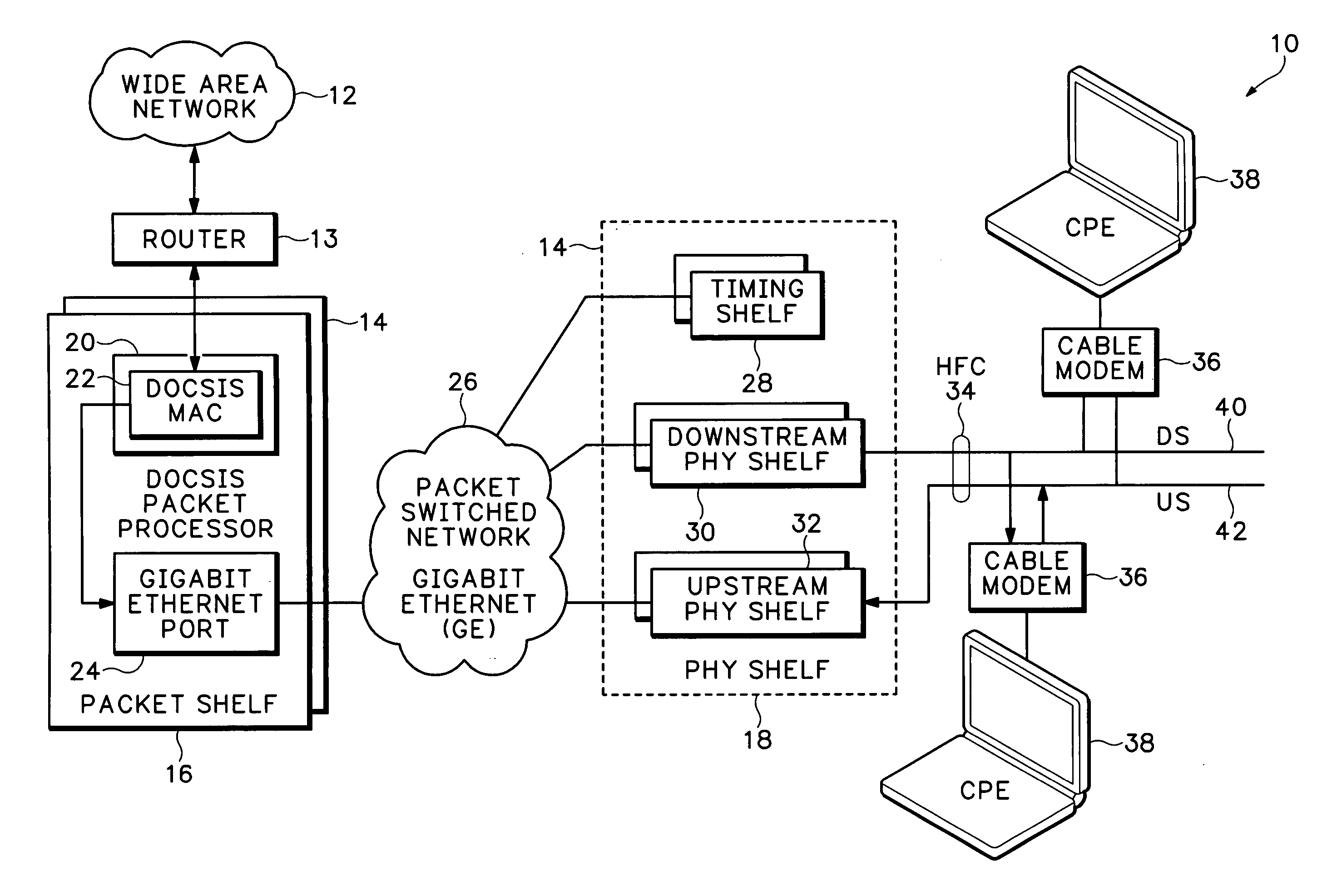

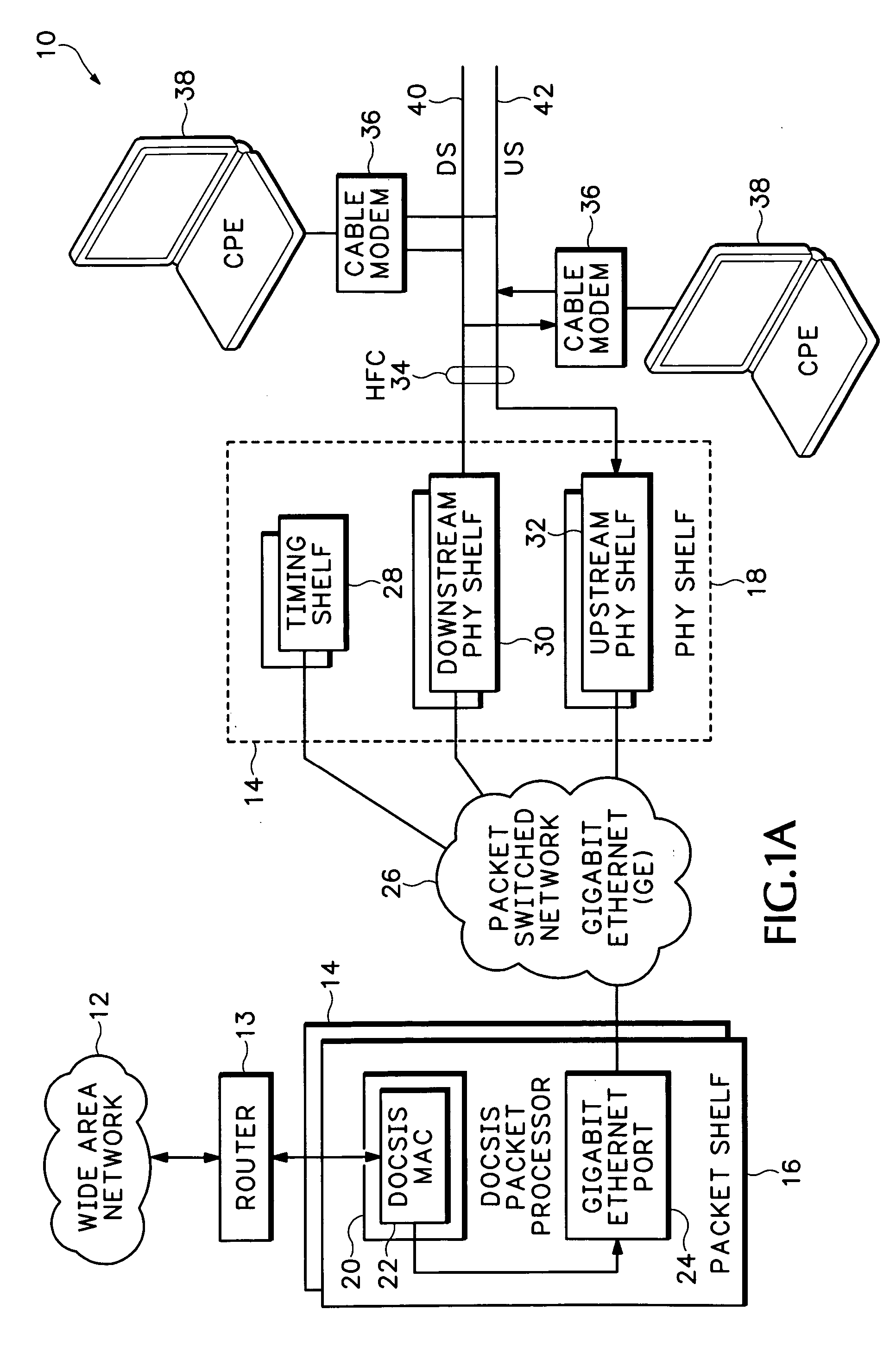

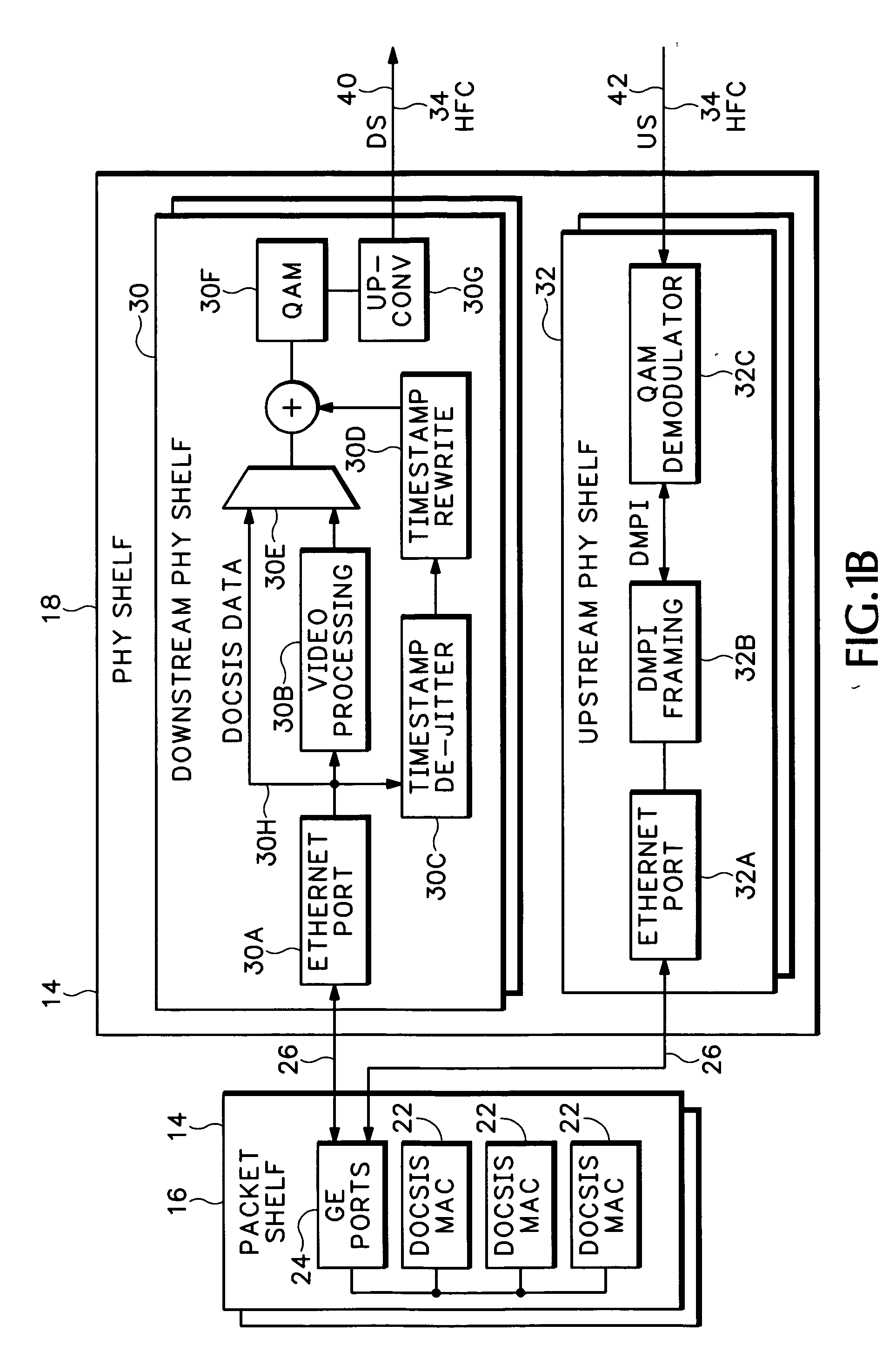

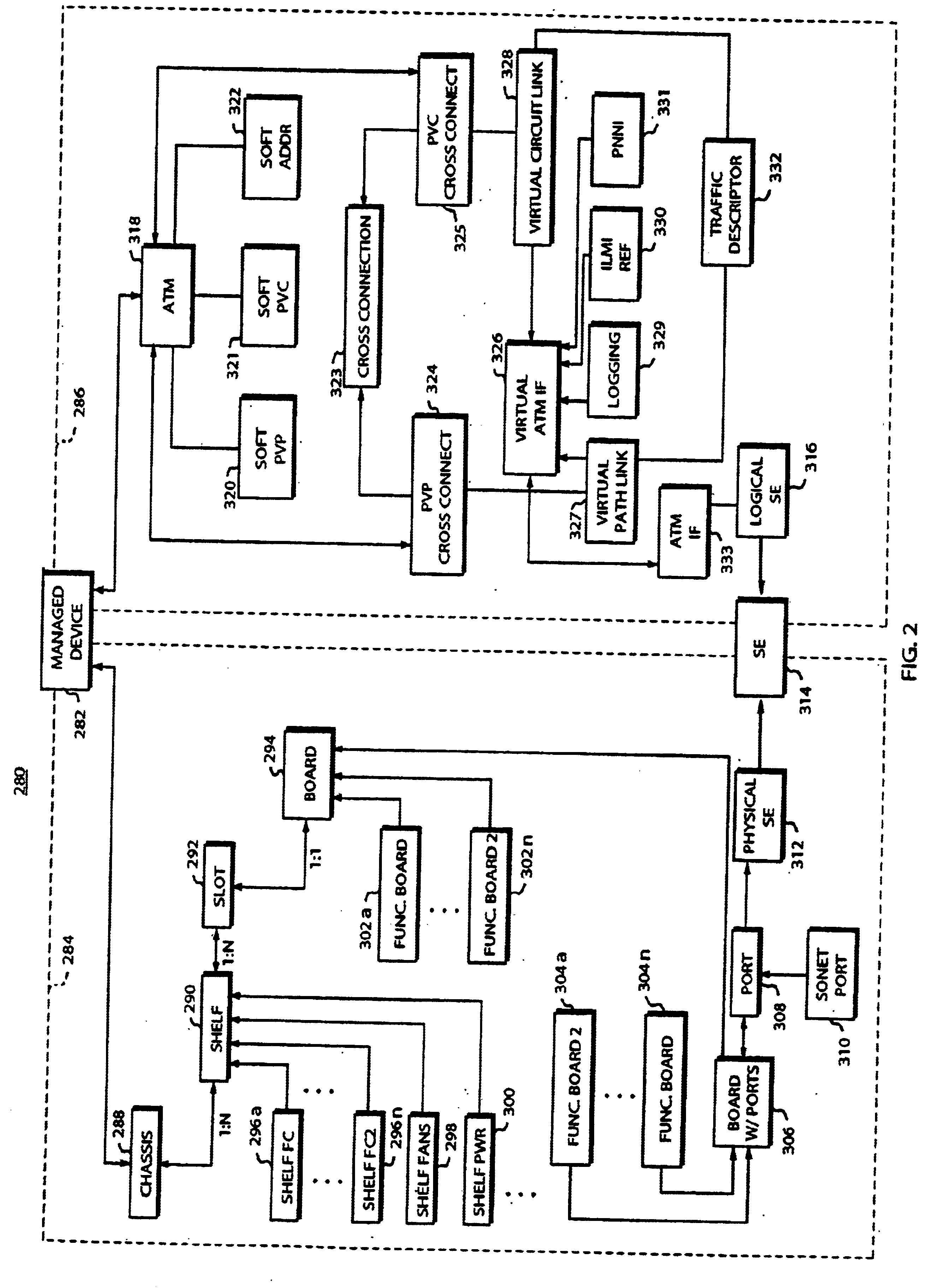

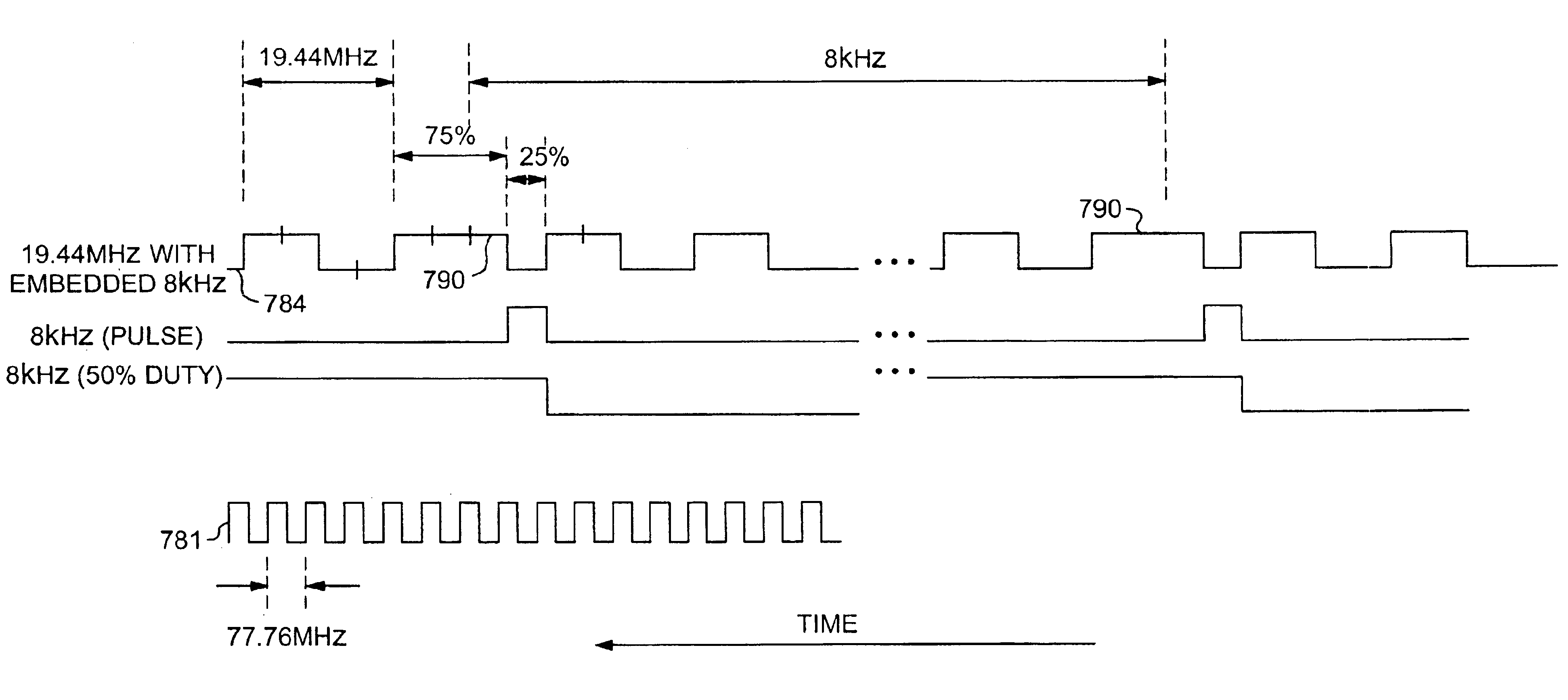

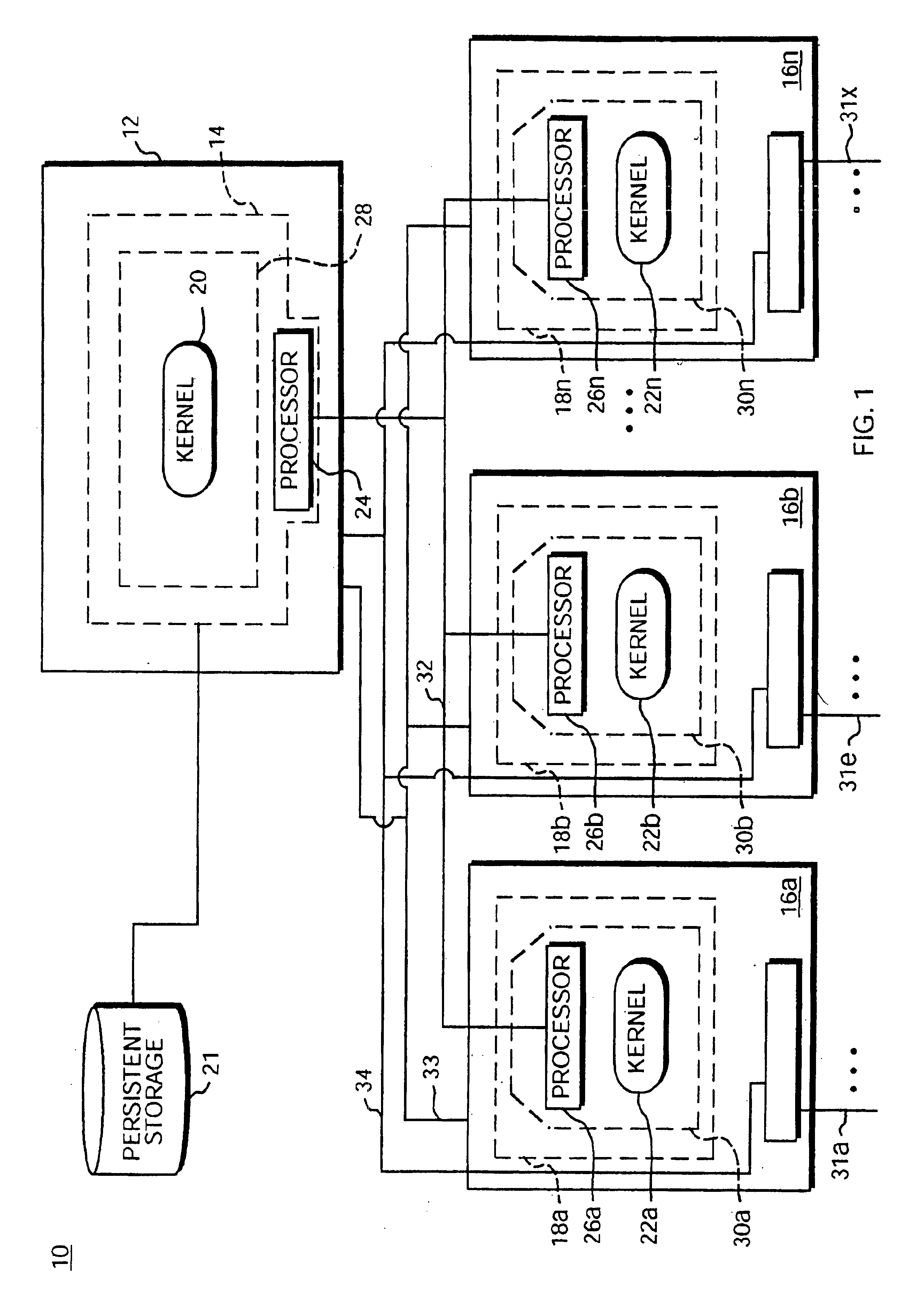

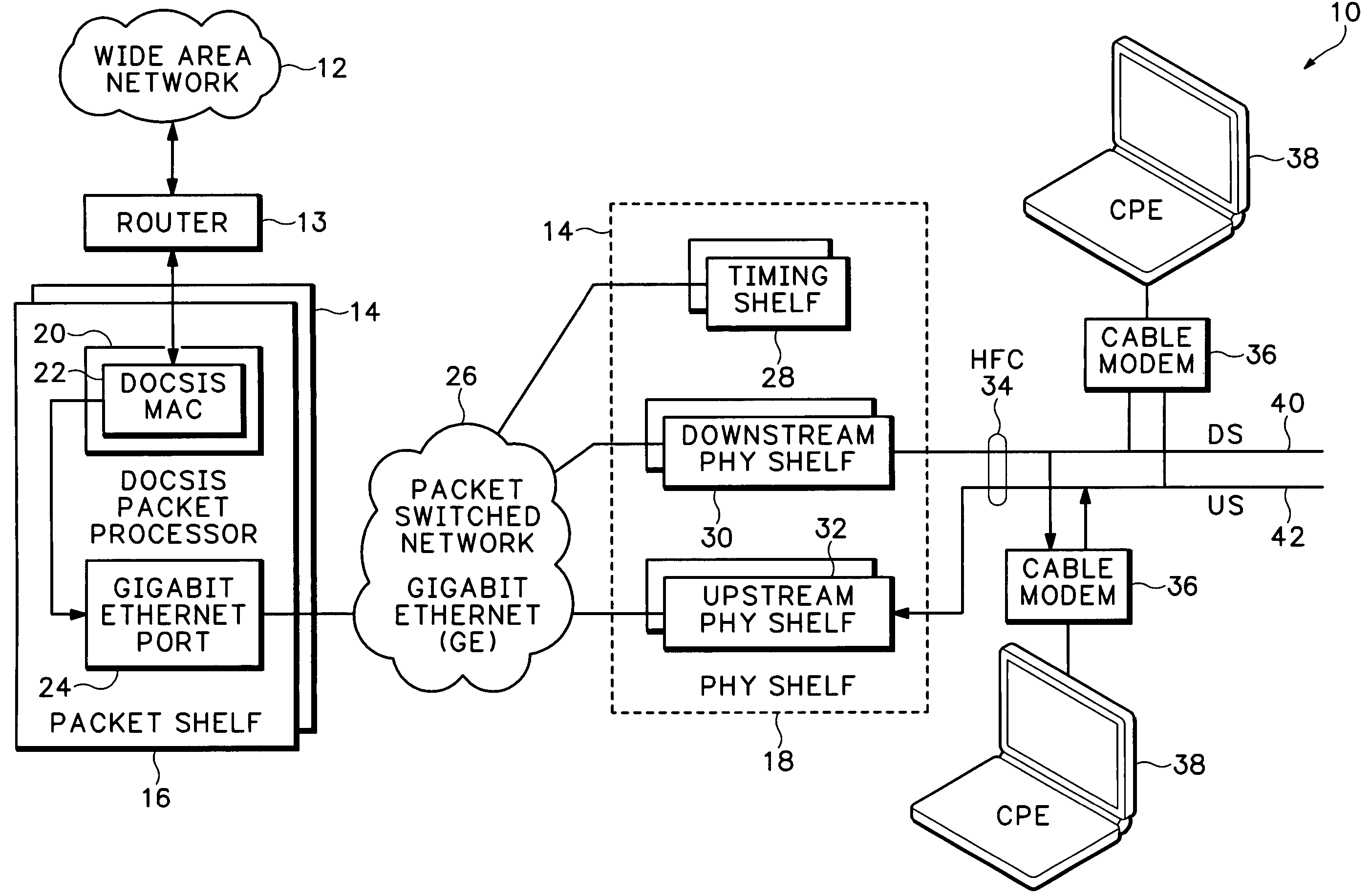

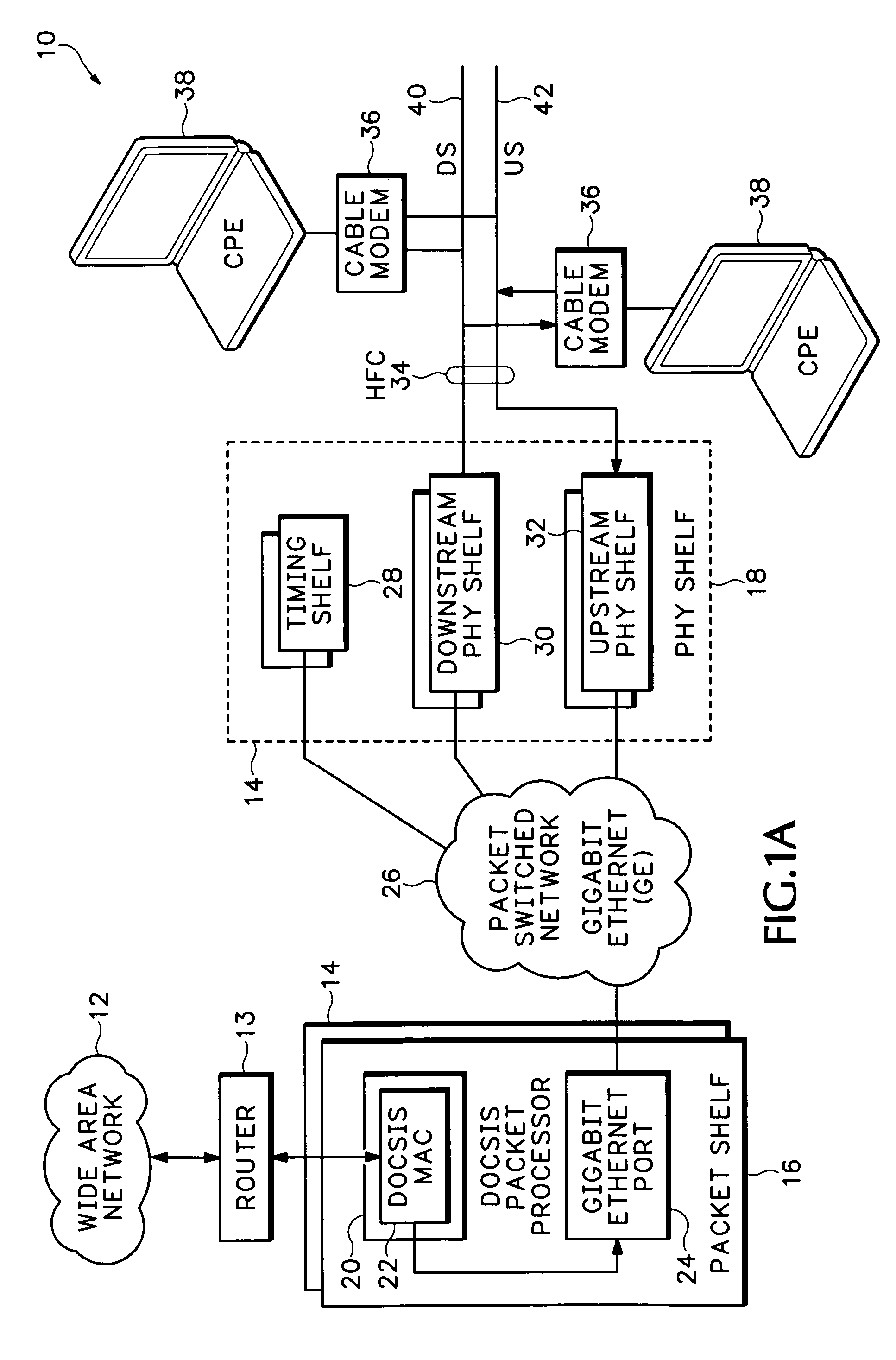

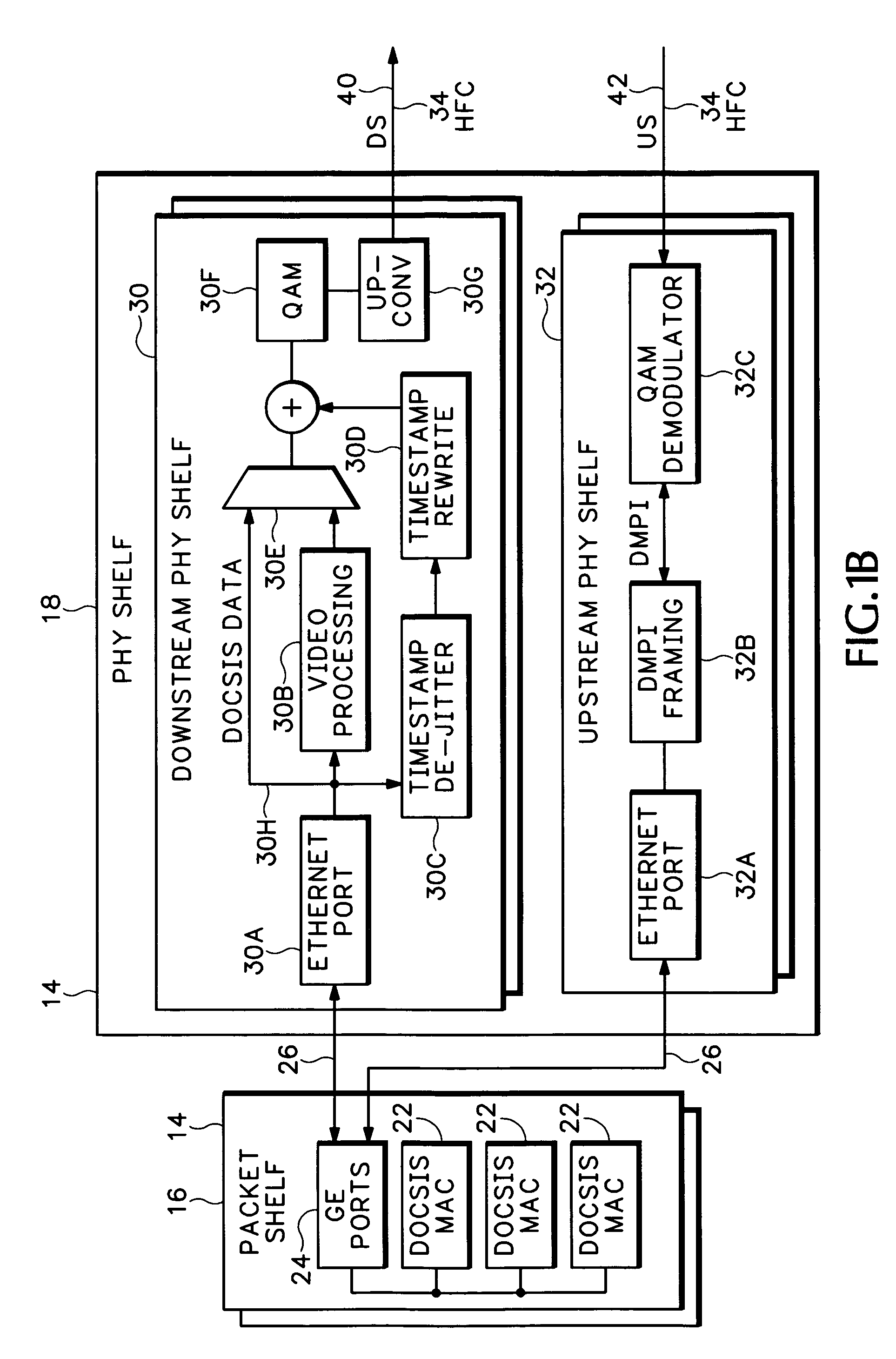

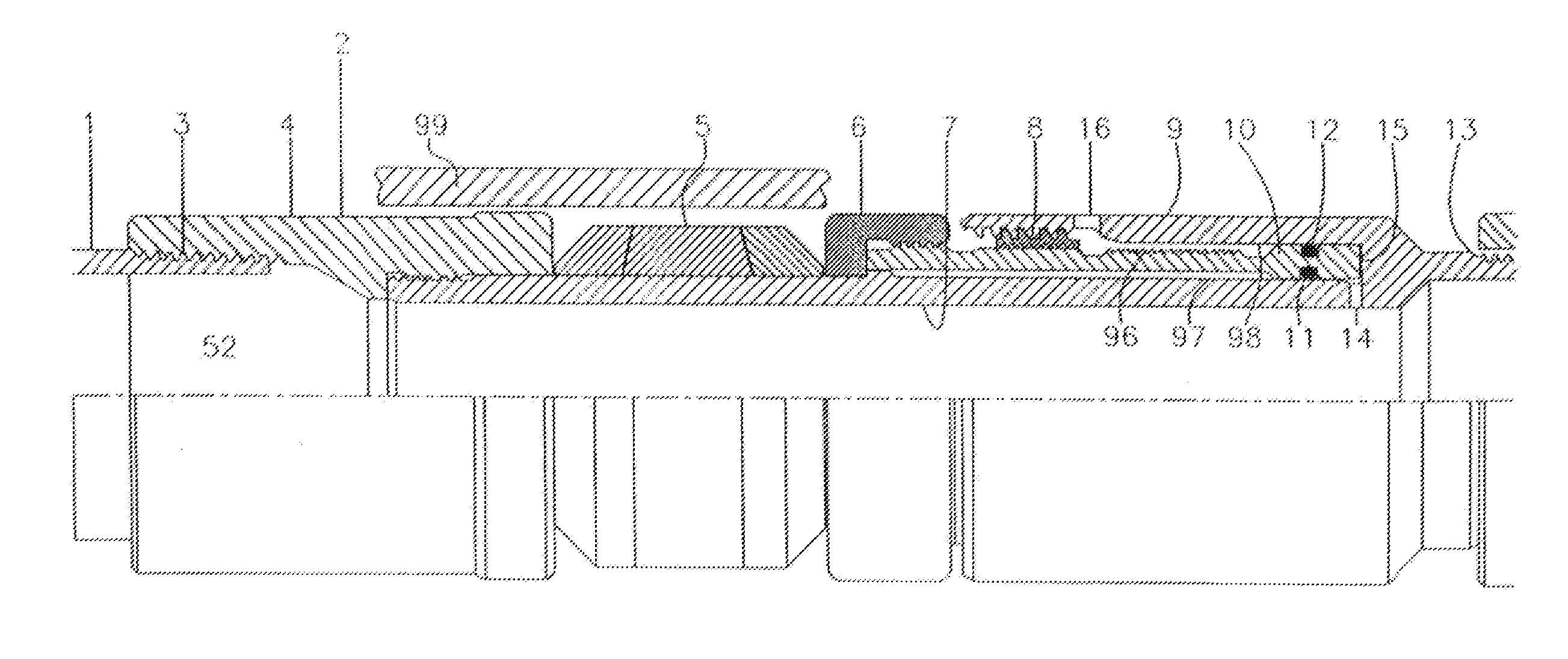

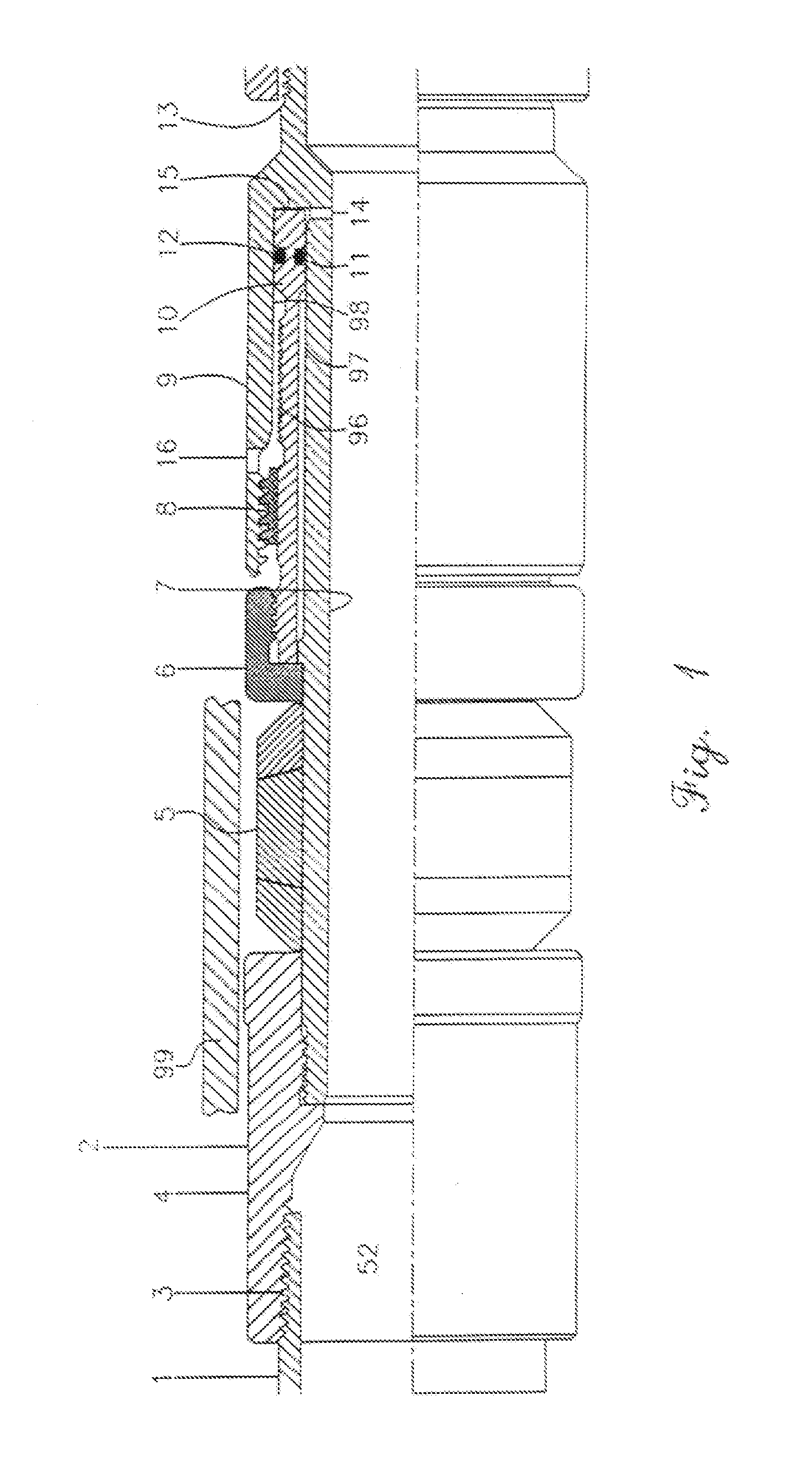

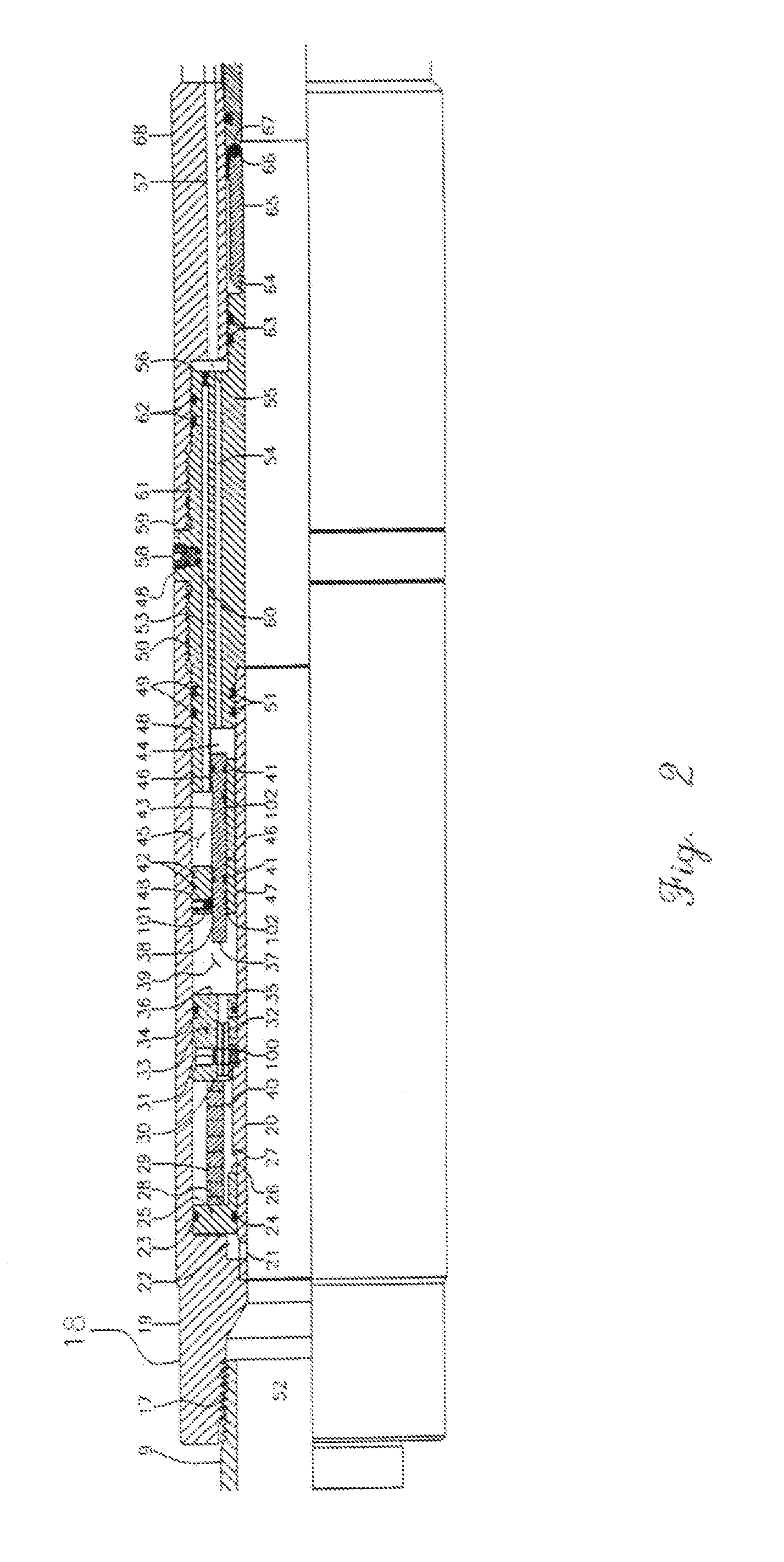

Timing system for modular cable modem termination system

InactiveUS20060168612A1Synchronisation information channelsBroadcast transmission systemsDigital subscriber lineModem device

A modular Cable Modem Termination System (CMTS) includes a packet shelf operating a Data Over Cable Service Interface Specifications (DOCSIS) Media Access Control (MAC) framer. One or more downstream Physical Interface (PHY) shelves receive DOCSIS data from the packet shelf over a packet switched network and modulate the DOCSIS data for sending on a downstream path of a cable plant. One or more upstream PHY shelves send DOCSIS data received from an upstream path of the cable plant over the packet switched network to the packet shelf. By separating the PHY components from the MAC and from the system software, the PHY components for a Hybrid Fiber Coax (HFC) plant may be replaced with different PHY components for other access technologies such as wireless, Digital Subscriber Lines (DSL), Ethernet-to-the-Home, Fiber-to-the-Home, or fiber Passive Optical Networks (PONs).

Owner:CISCO TECH INC

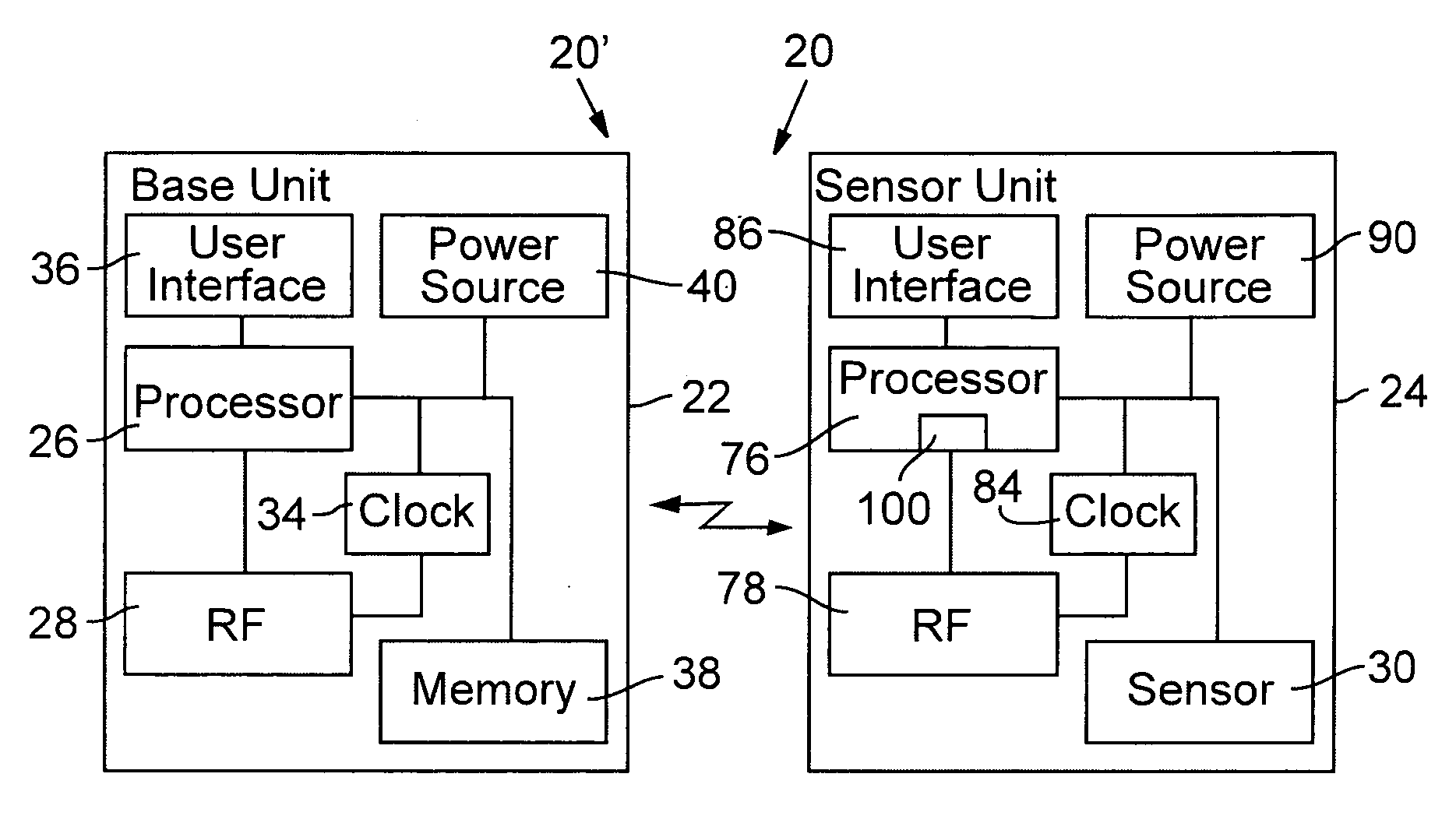

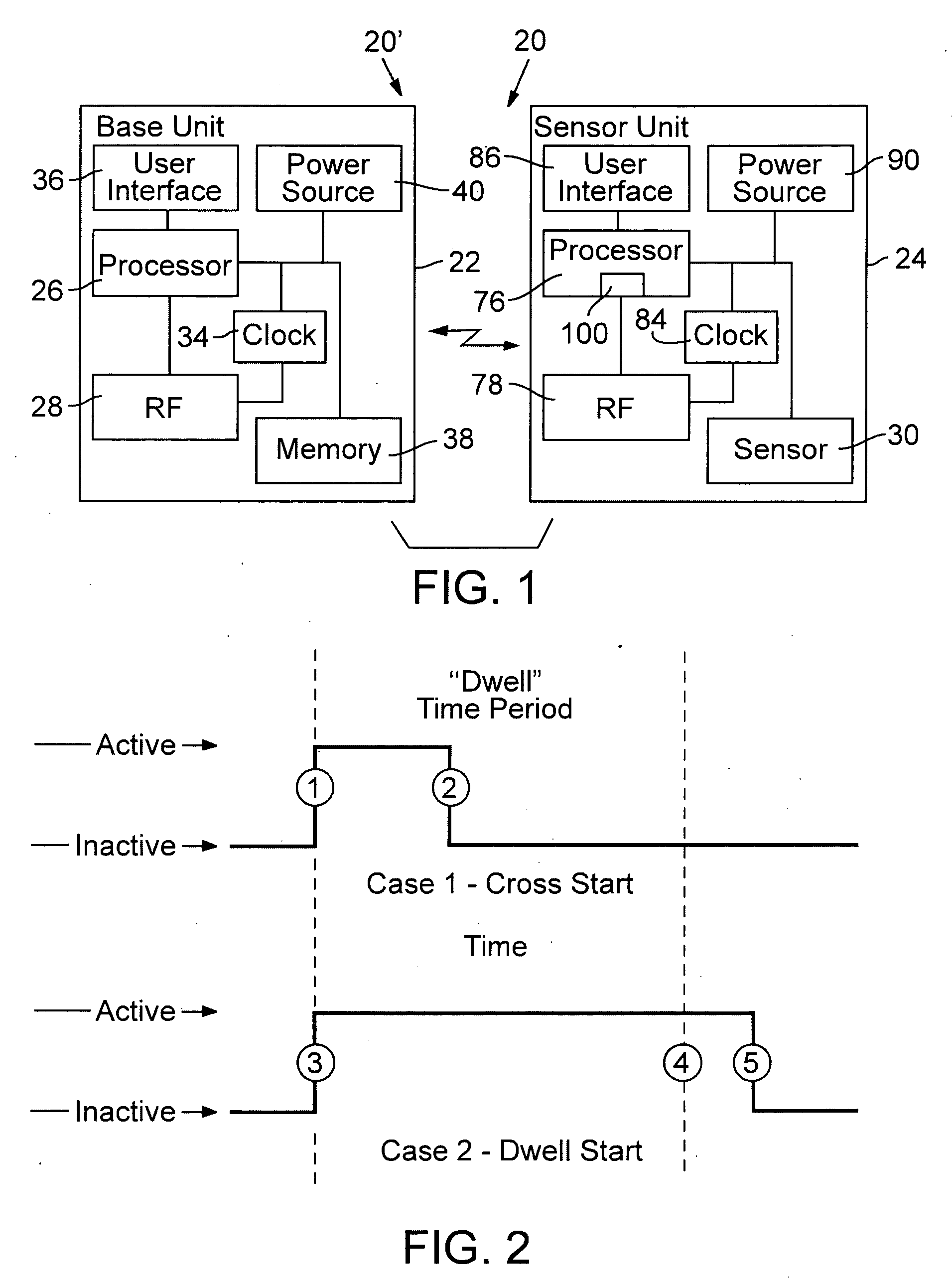

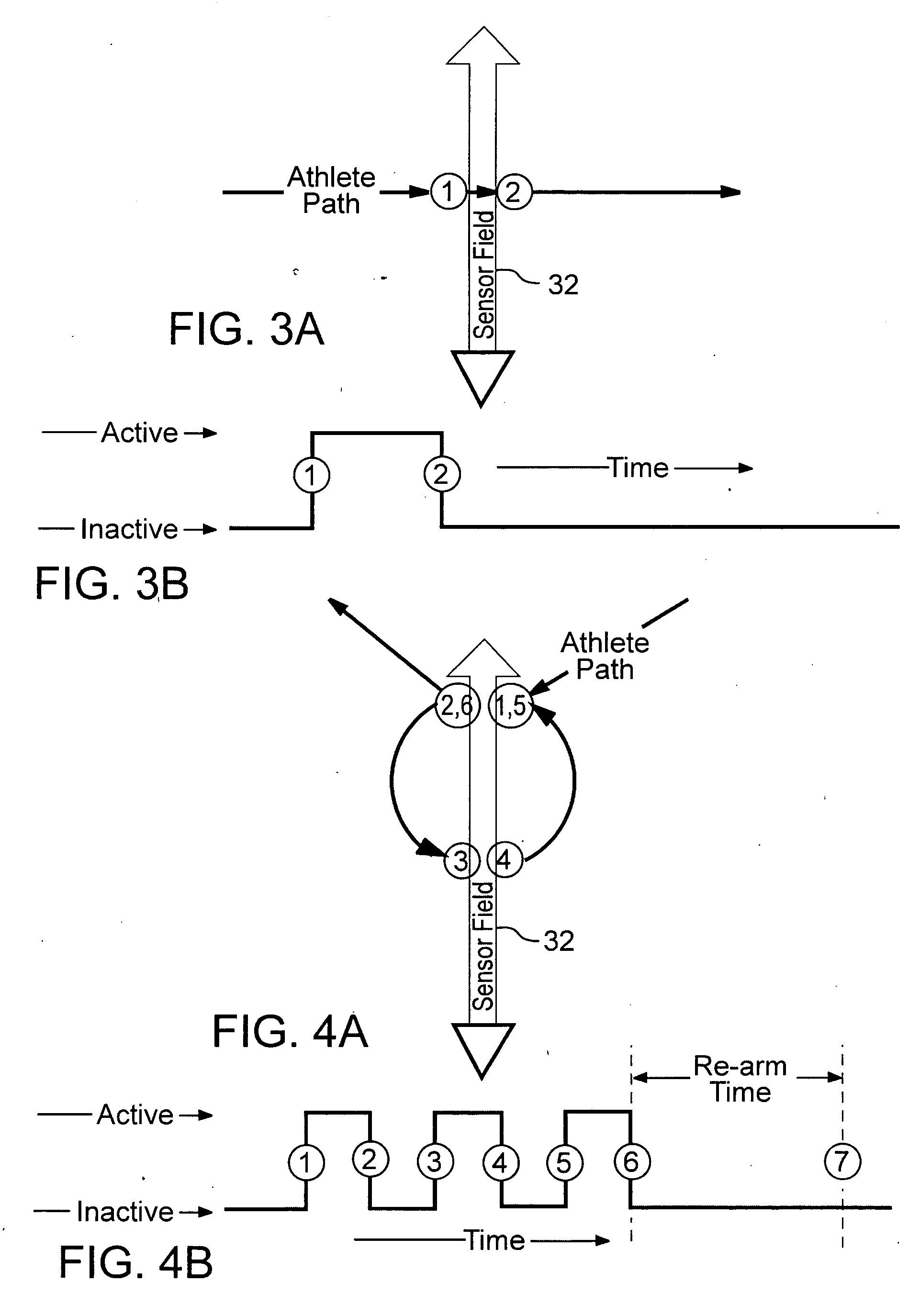

Athleticism rating and performance measuring systems

ActiveUS20070272011A1Quick and easy and accurate collectionRegistering/indicating time of eventsDigital data processing detailsRating systemExercise performance

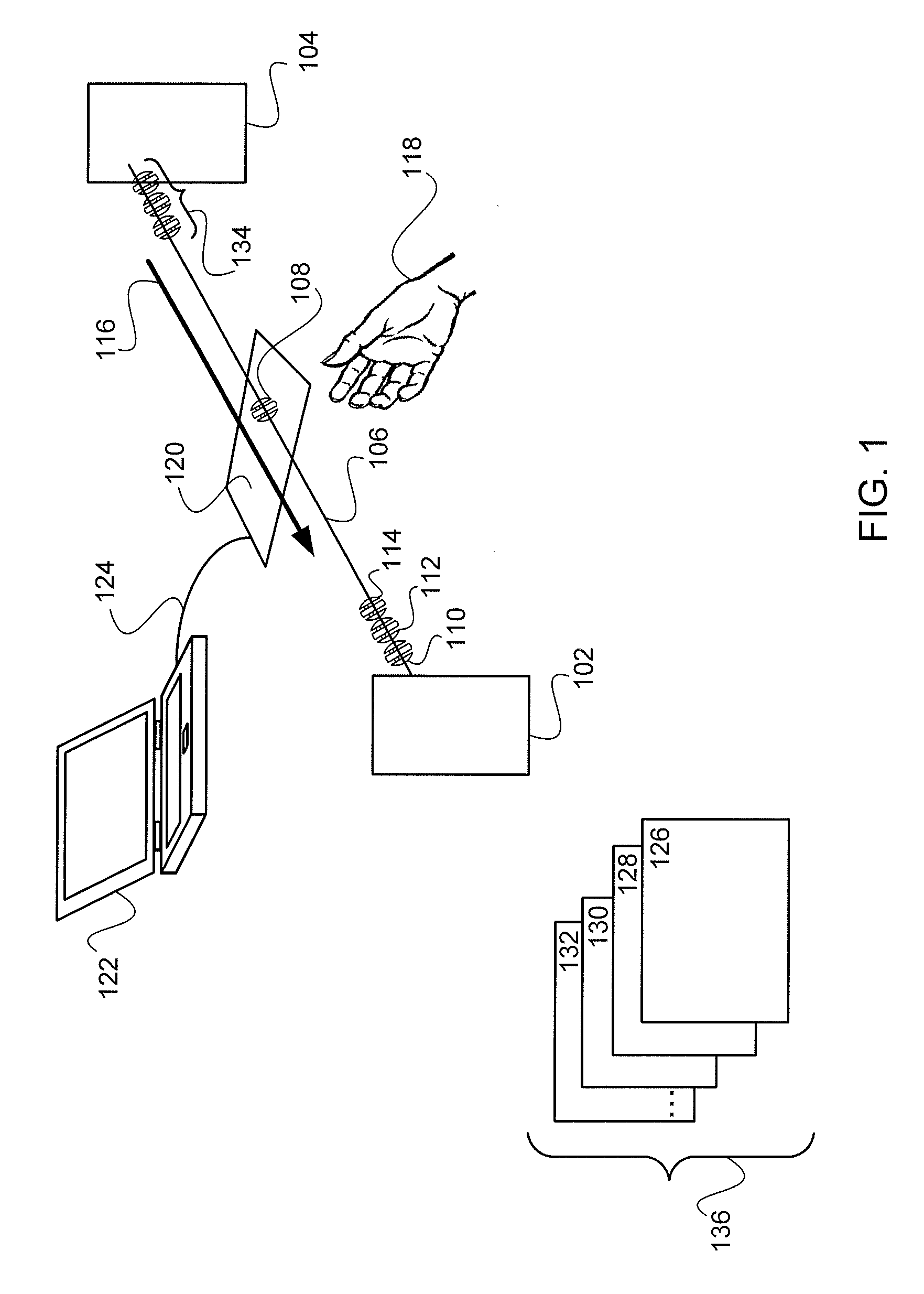

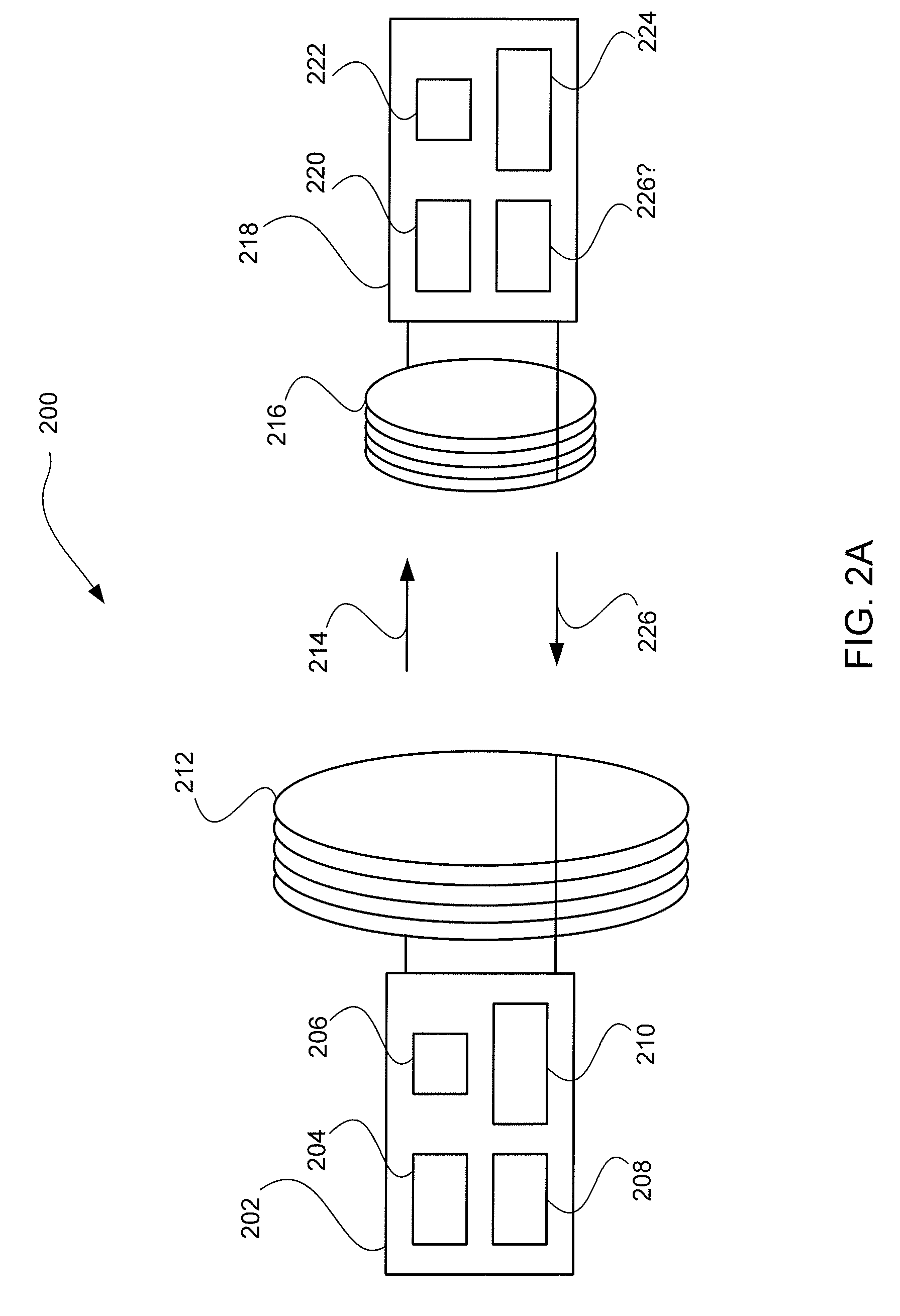

A universal athleticism rating system and related athletic performance measuring systems for accurately detecting and recording athletic performance are disclosed. The athleticism rating system evaluates individual athletes against a common, standardized, set of athletic performance tests. Each athlete performs the athletic tests and his or her scores in the individual tests are entered into a standardized calculation to produce a single athletic performance score. The related performance measuring system is preferably a timing system that ensures quick, easy, and accurate collection of athletic event timing related data without the need for the athlete to wear any special detection devices or the like. In a preferred embodiment, the performance measuring system integrates with the rating system to provide seamless athletic data collection and rating of athletes.

Owner:NIKE INC

Tracking and timing system

InactiveUS20060176216A1Increase opportunitiesRapid positioningRegistering/indicating time of eventsGymnastic exercisingCommunications systemCentral database

An apparatus and methods for tracking an object is disclosed. The apparatus and methods provide for GPS tracking, and can include a communication system that transmits the position of the object to a central database. Software can track the object and provide updates as to the position, speed, course, and other items of interest.

Owner:HIPSKIND JASON C

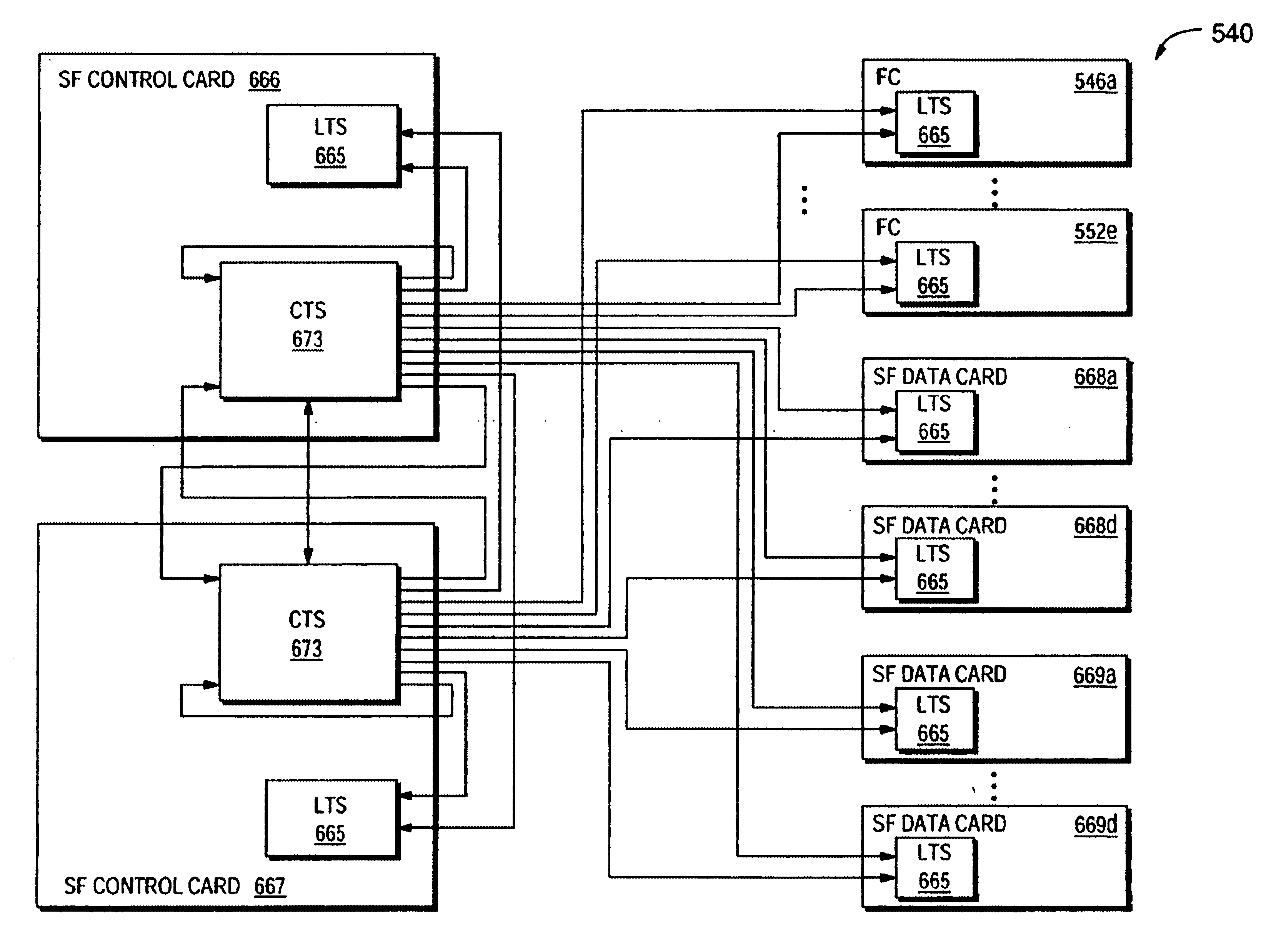

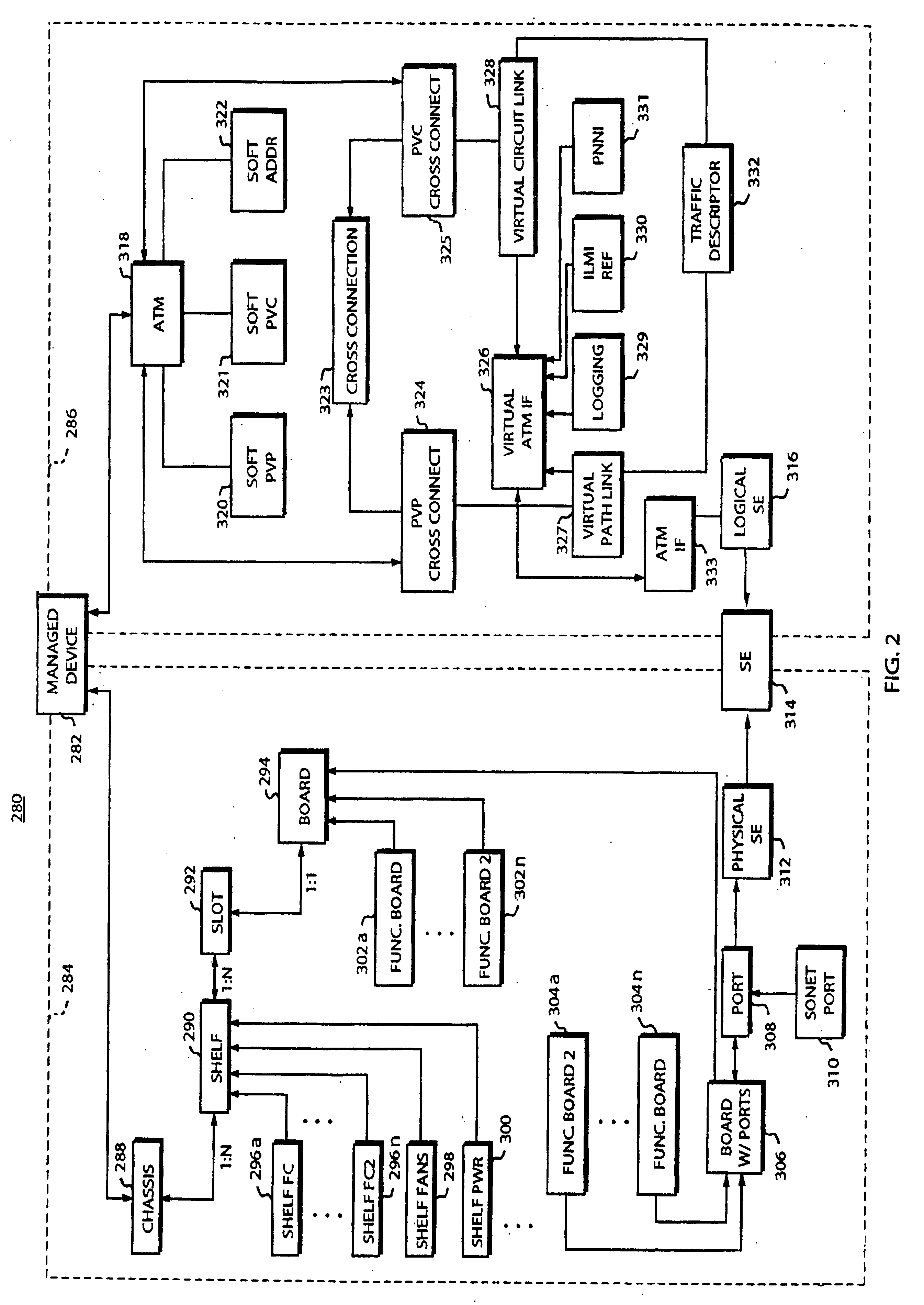

Network device with a distributed switch fabric timing system

InactiveUS6876652B1Low costMultiplex system selection arrangementsSynchronisation information channelsEngineeringTiming system

The present invention provides a central switch fabric timing subsystem and distributed switch fabric timing subsystems. Distributed switch fabric subsystems reduce the cost of a minimally configured network device by providing a network device with a distributed switch fabric. Such a network device locates a portion of the switch fabric functionality on each forwarding card allowing the minimal network device configuration to include less than the entire switch fabric functionality. The cost of the minimal configuration is, therefore, reduced allowing network service providers to more quickly recover the initial cost of the network device. As new services are requested, additional functionality, including both forwarding cards and universal port cards may be added to the network device to handle the new requests, and the fees for the new services may be applied to the cost of the additional functionality. Consequently, the cost of the network device more closely tracks the service fees received by network providers.

Owner:CIENA

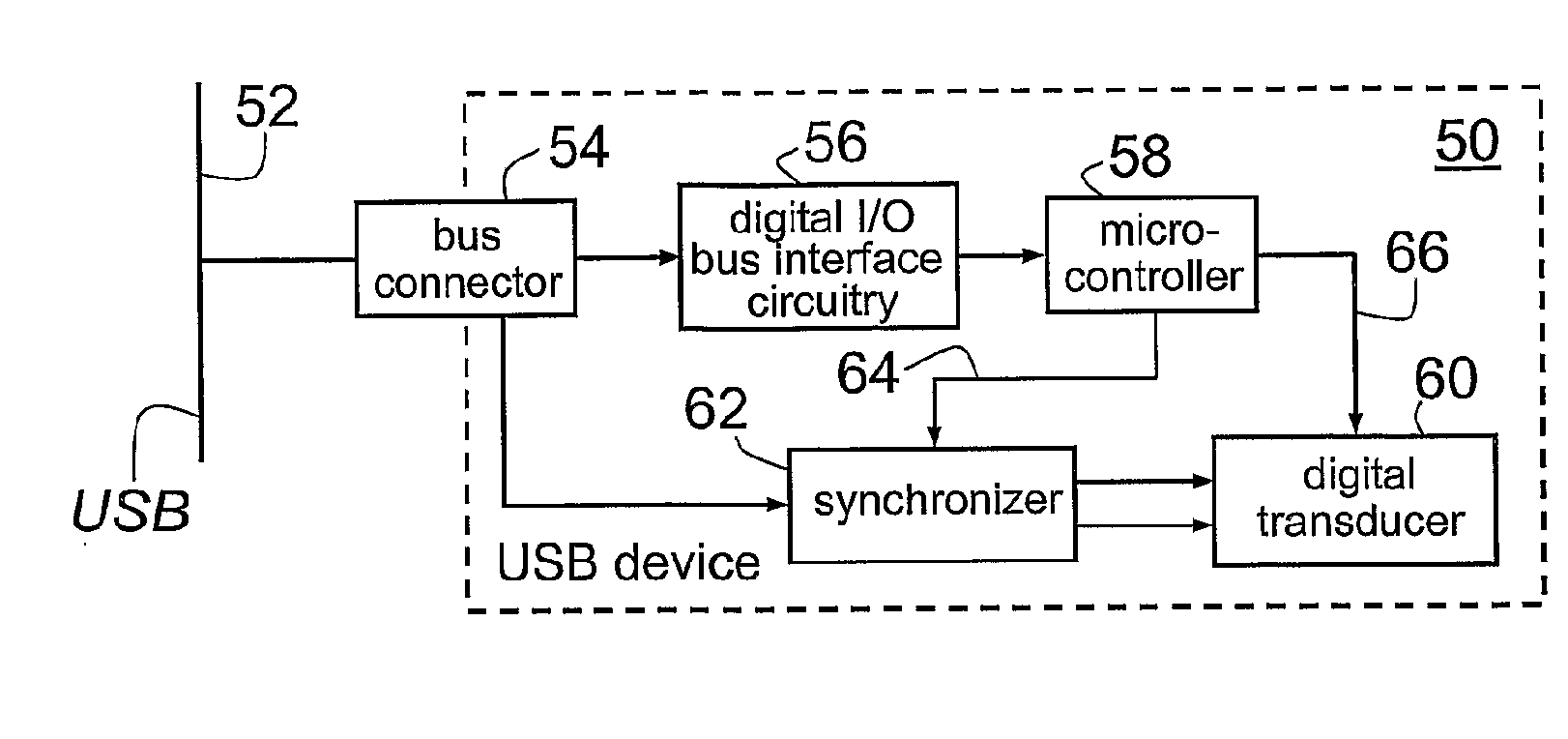

Distributed synchronization and timing system

InactiveUS20090222685A1Highly accurate time-stampingImprove accuracyGenerating/distributing signalsTransmission path multiple useClock rateTiming system

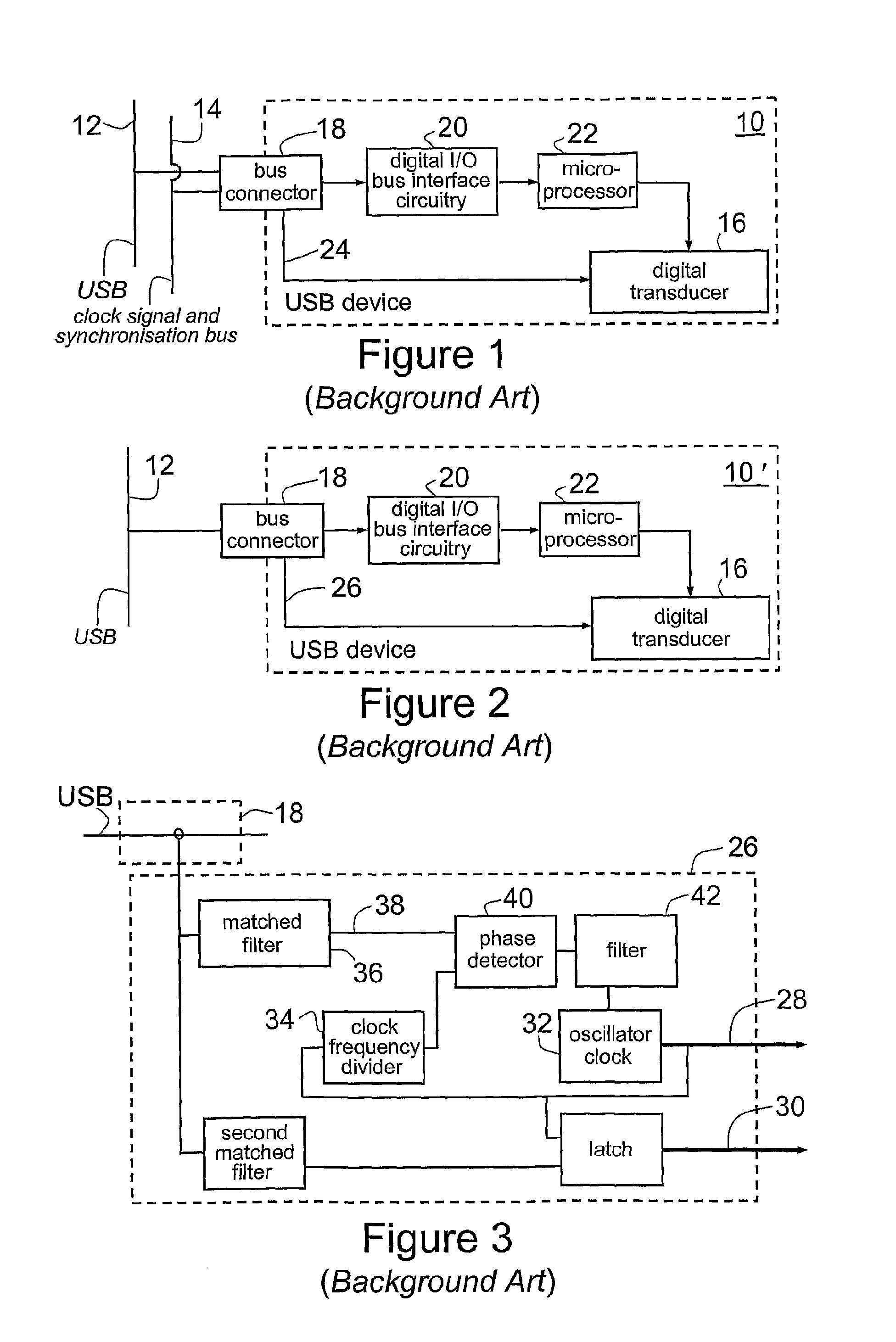

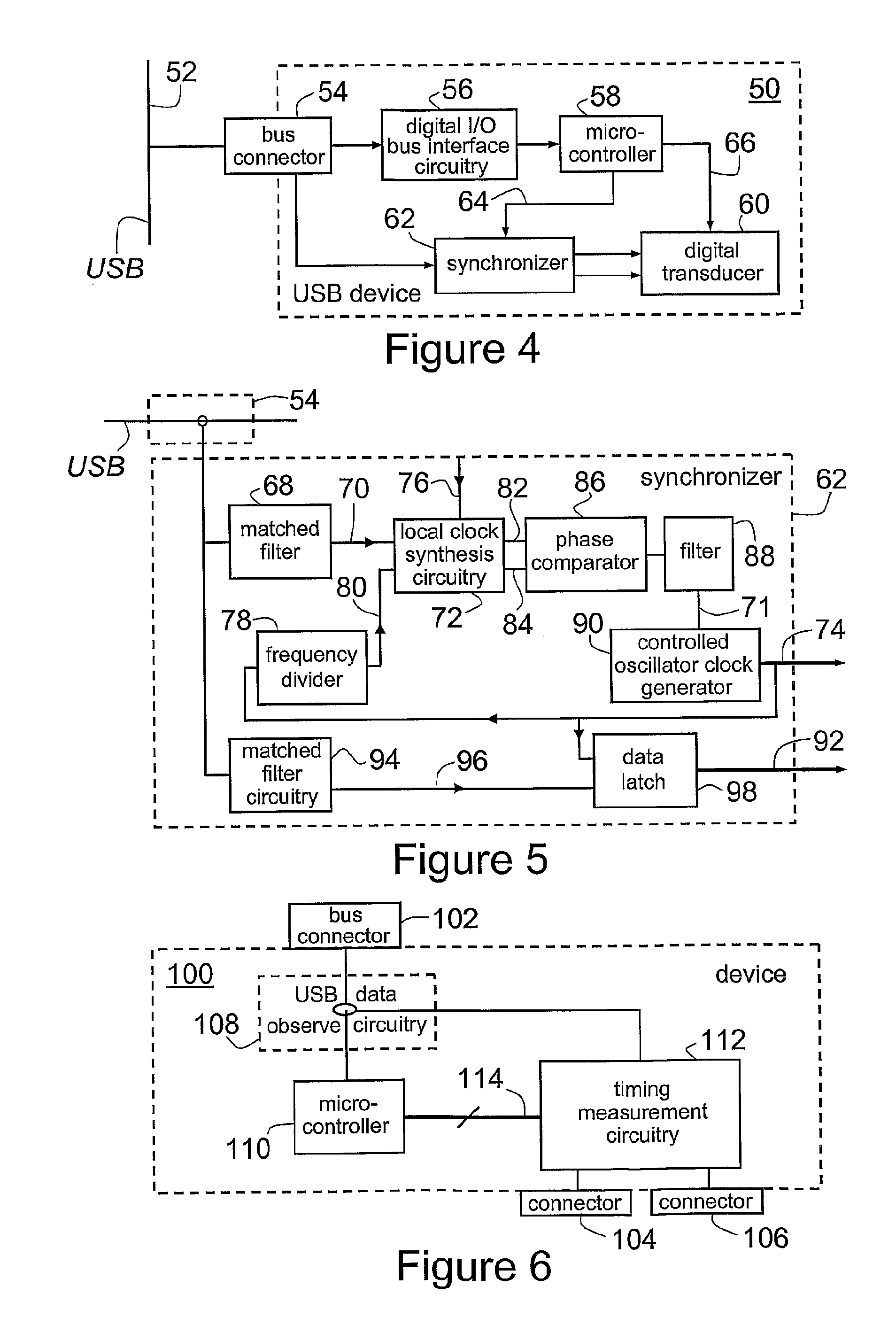

A method and apparatus for controlling the phase and frequency of the local clock of a USB device, the apparatus comprising circuitry for observing USB traffic and decoding from the USB traffic a periodic data structure containing information about the frequency and phase of a distributed clock frequency, and phase and circuitry for receiving the periodic data structure and generating from at least the periodic data structure a local clock signal locked in both frequency and phase to the periodic data structure. The circuitry for receiving the periodic data structure and generating the local clock signal can generate the local clock signal with a frequency that is a non-integral multiple of a frequency of the periodic data structure.

Owner:CHRONOLOGIC PTY LTD

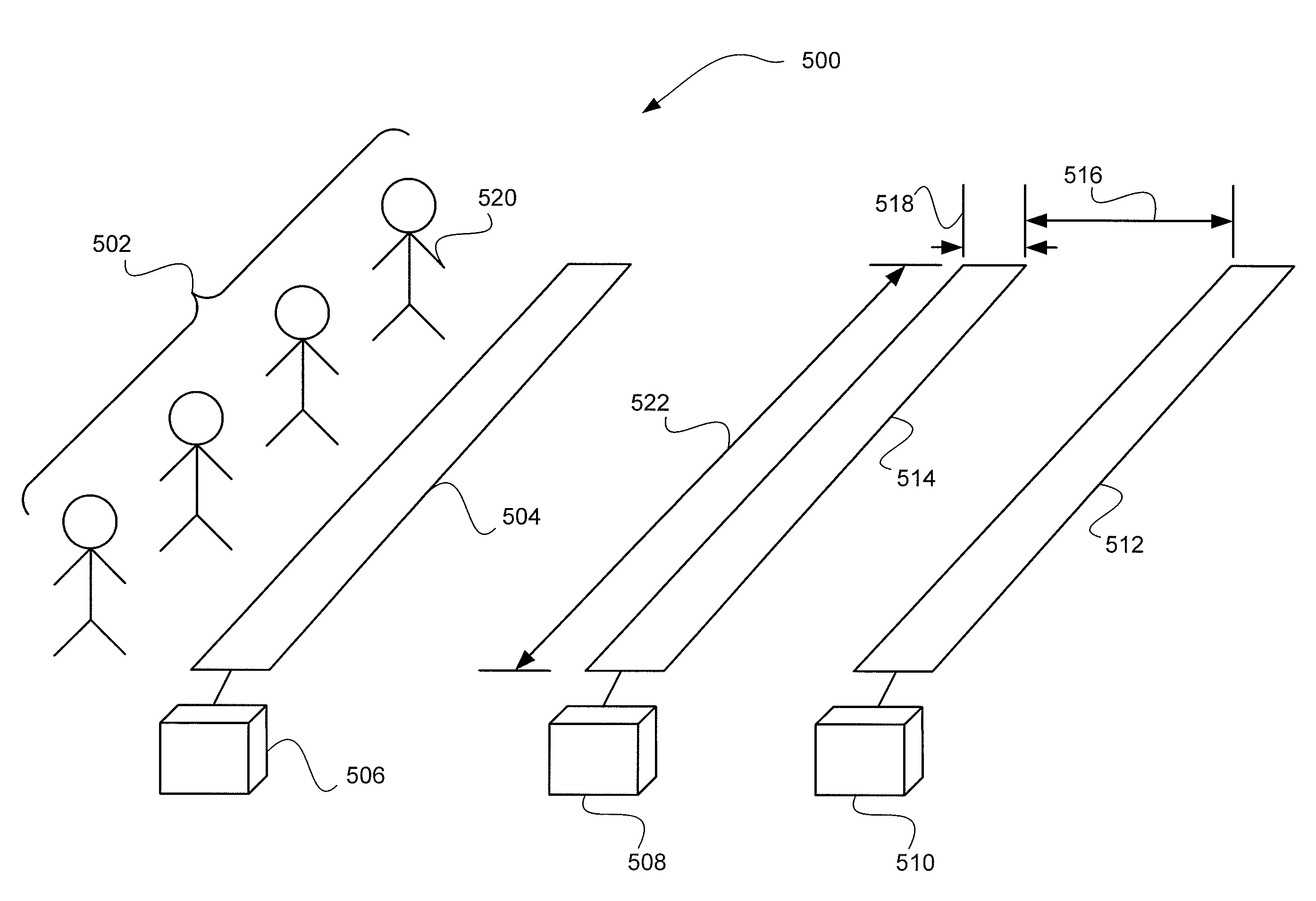

Uhf timing system for participatory athletic events

ActiveUS20090184806A1Digital data processing detailsGymnastic exercisingTiming systemComputer science

A participatory athletic event timing system based on backscattering modulation in the UHF band and including wirelessly encoding writable data tags with participant's bib numbers or a calculated derivative thereof for timing participants in a participative athletic event, and attaching the data tags to the participant's bibs for distribution of the bibs and data tags to participants so as to eliminate the need for matching data tags with bibs and maintaining the sequenced order of the matched data tags and bibs. In a preferred embodiment, when participants register for the event, they are assigned an ID number and a bib printed with that number and having attached to the bib one or more data tag encoded in the tags memory the ID number or a calculated derivative thereof. Before the start of the event, the athlete pulls the data tag from the bib and attaches it to their shoe. Antennas suitably designed and adapted for use with the data tags in participative athletic events are used to communicate with the data tags.

Owner:CHRONOTRACK SYST

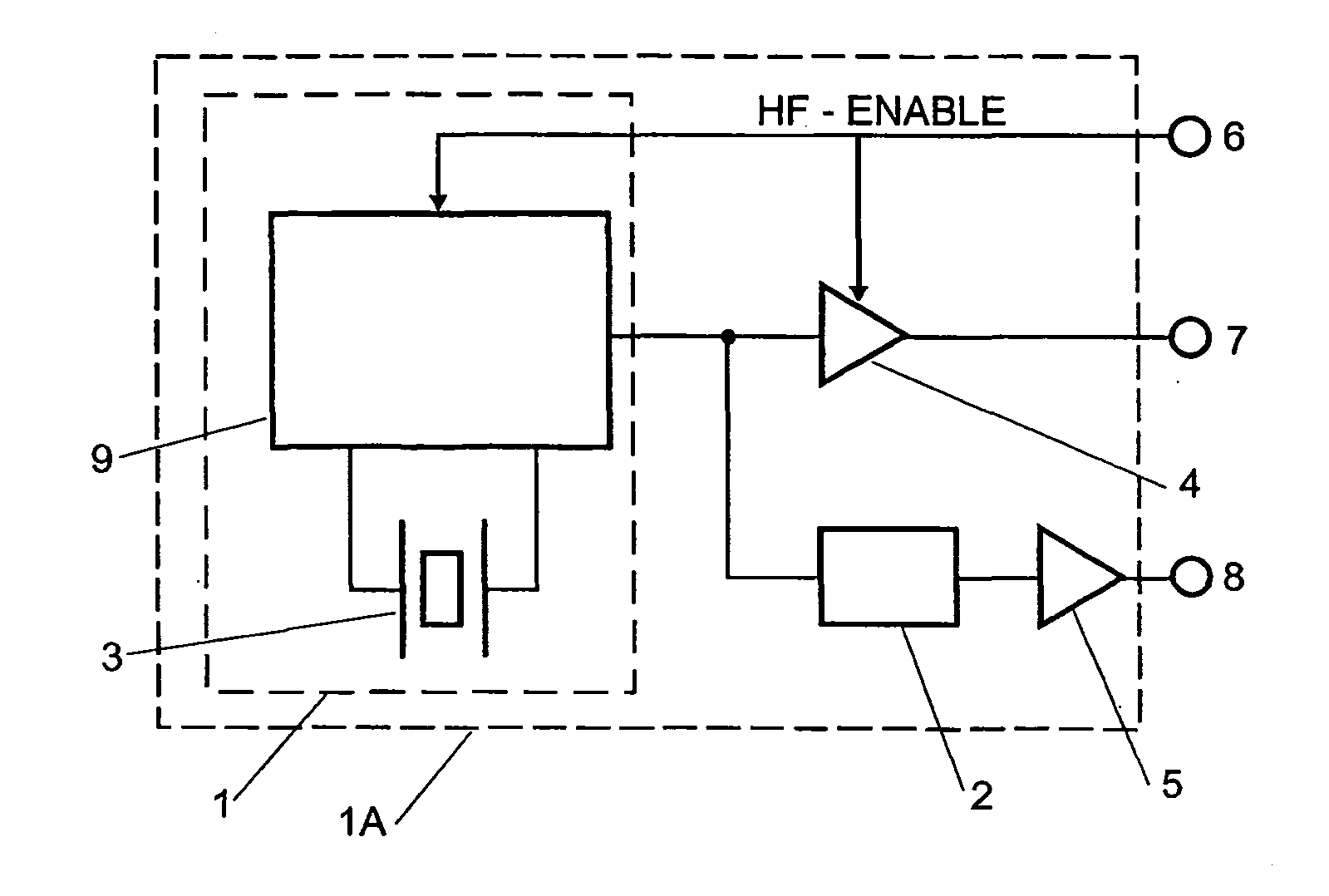

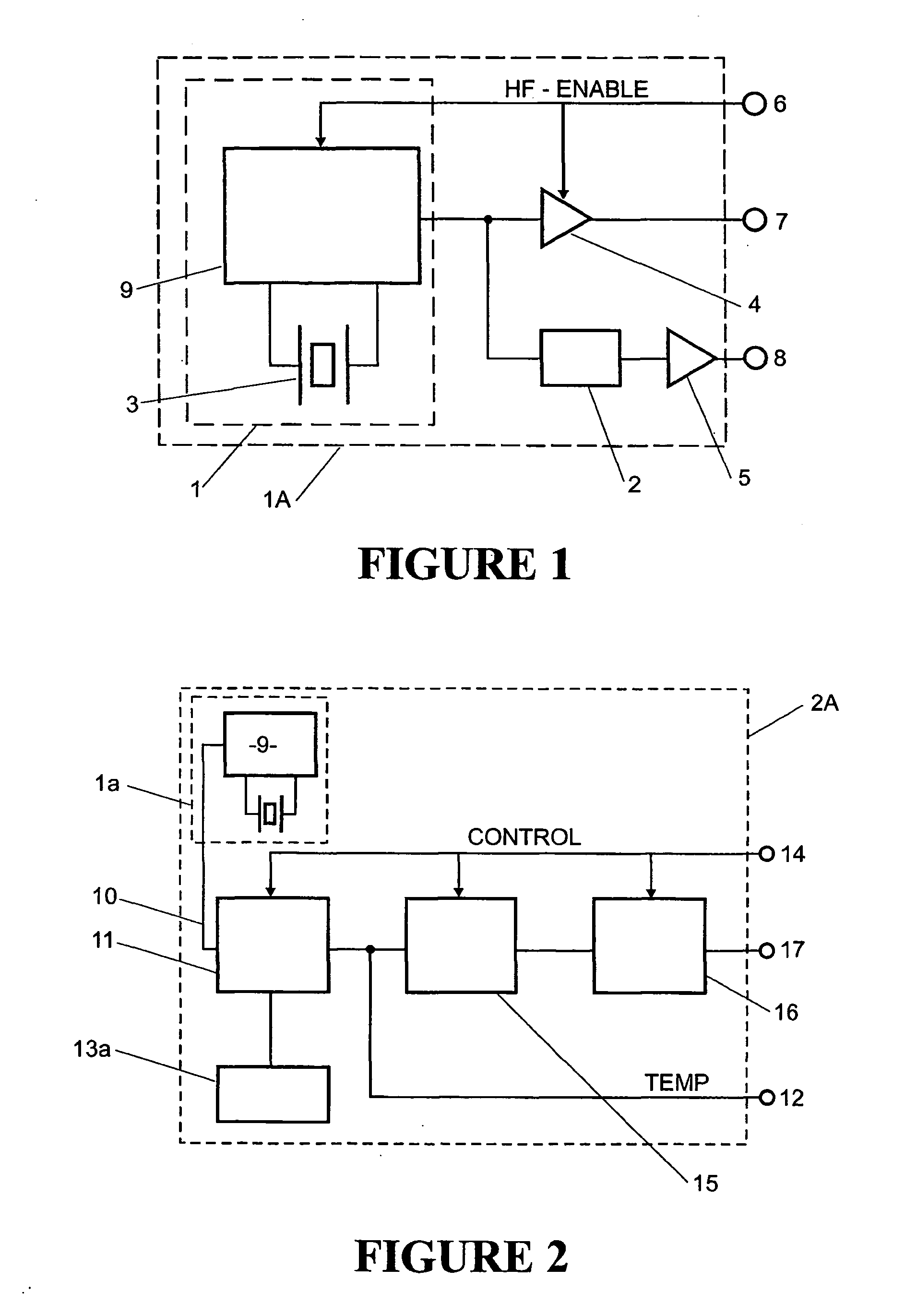

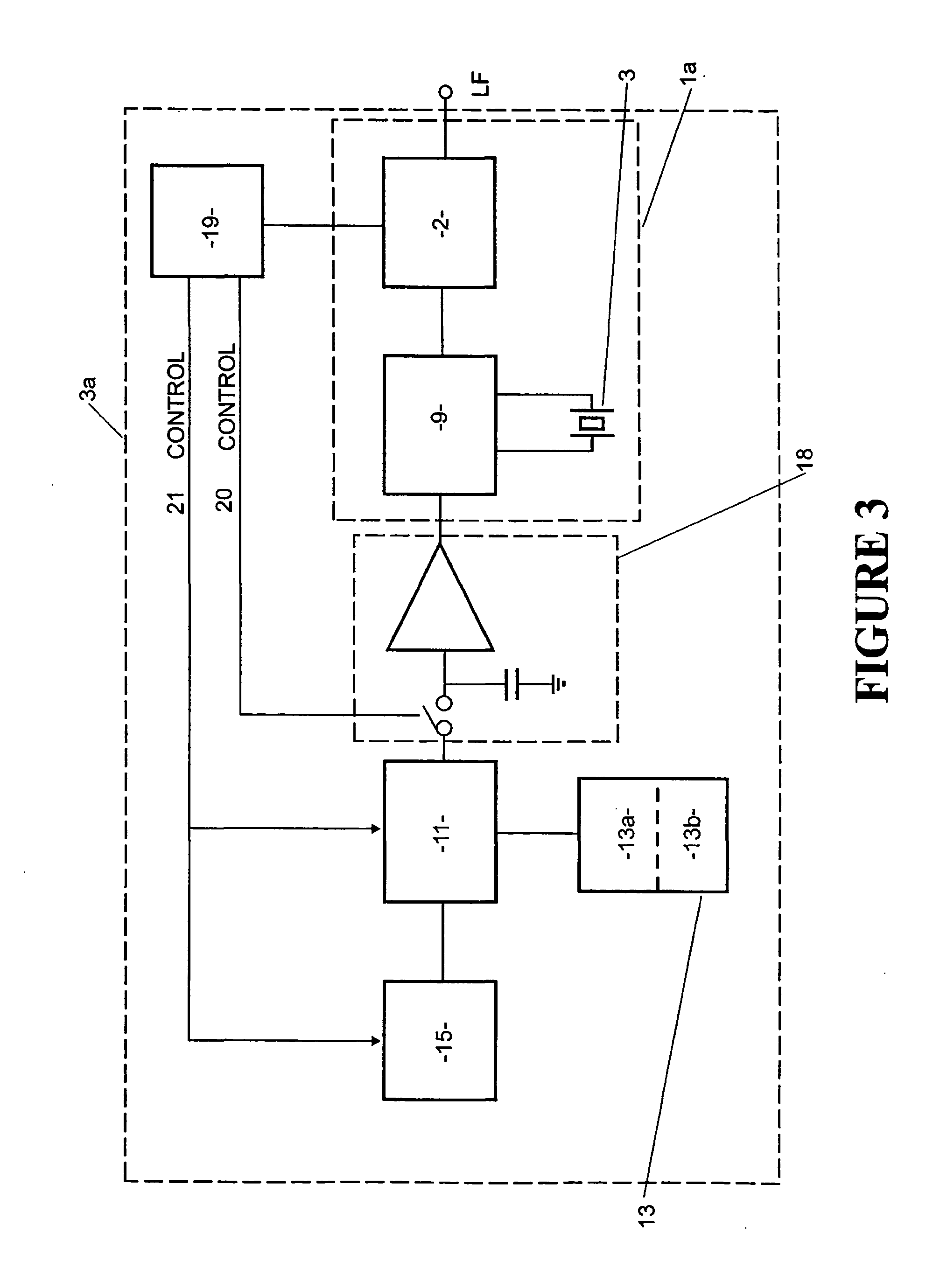

Low power crystal oscillator

InactiveUS20050007205A1Reduce frequencyReduce bias currentGenerator stabilizationOscillations generatorsPhase noiseEngineering

The present invention relates to a timing system including an integrated circuit having an oscillator that provides both high and low frequency clock signals from a single high frequency crystal without the necessity of a tuning fork crystal. The low frequency signal is available for time-keeping applications, with low power consumption during “idle” periods. The high performance high frequency signal is available on demand for clock and frequency reference use. The oscillator of the present invention provides improved time-keeping accuracy, whilst size, cost and component count is reduced. Furthermore, phase noise and other critical parameters of the high frequency oscillator are not compromised. Shock vulnerability, a known problem for tuning fork crystals, is reduced.

Owner:RAKON

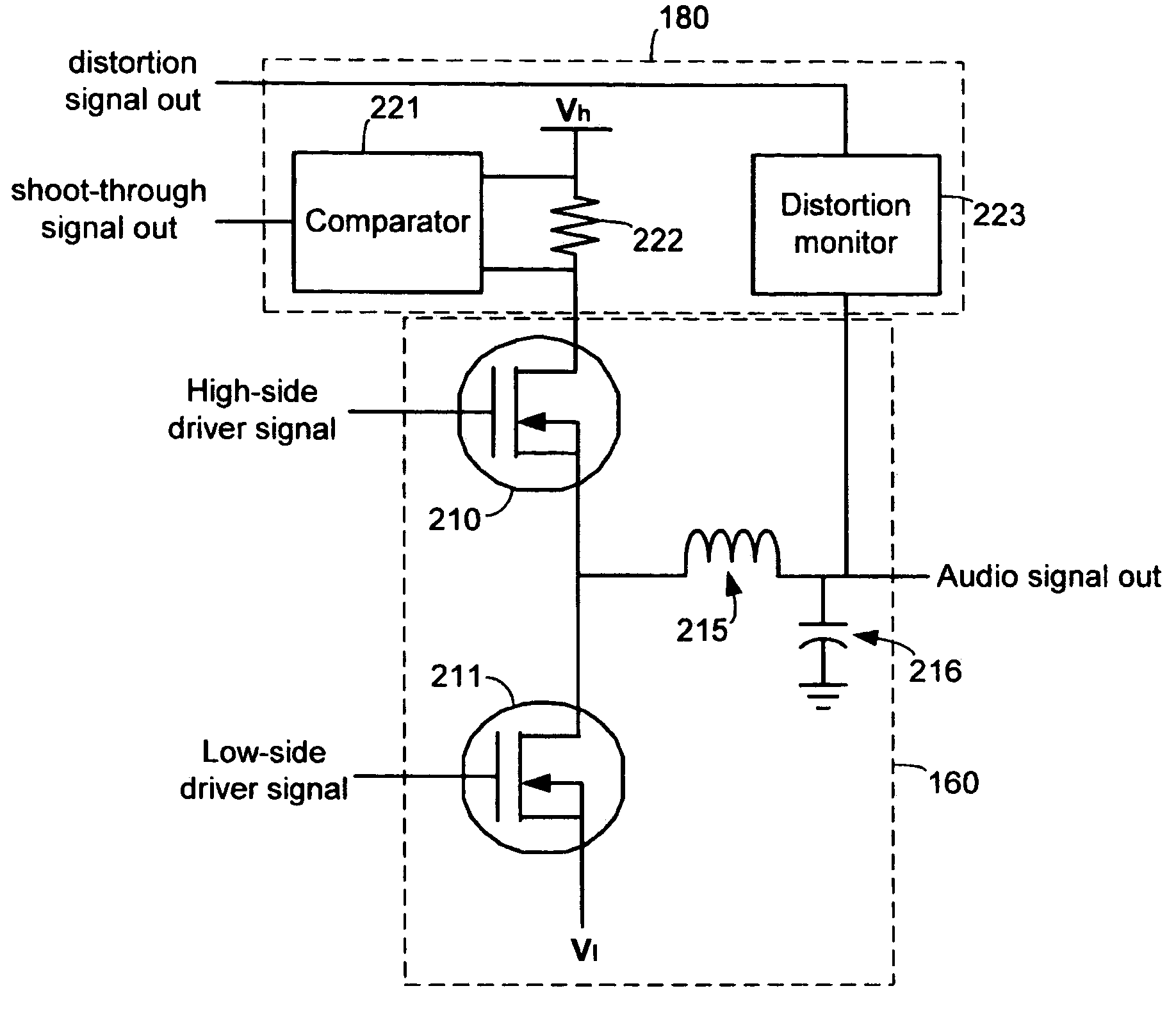

Systems and methods for automatically adjusting channel timing

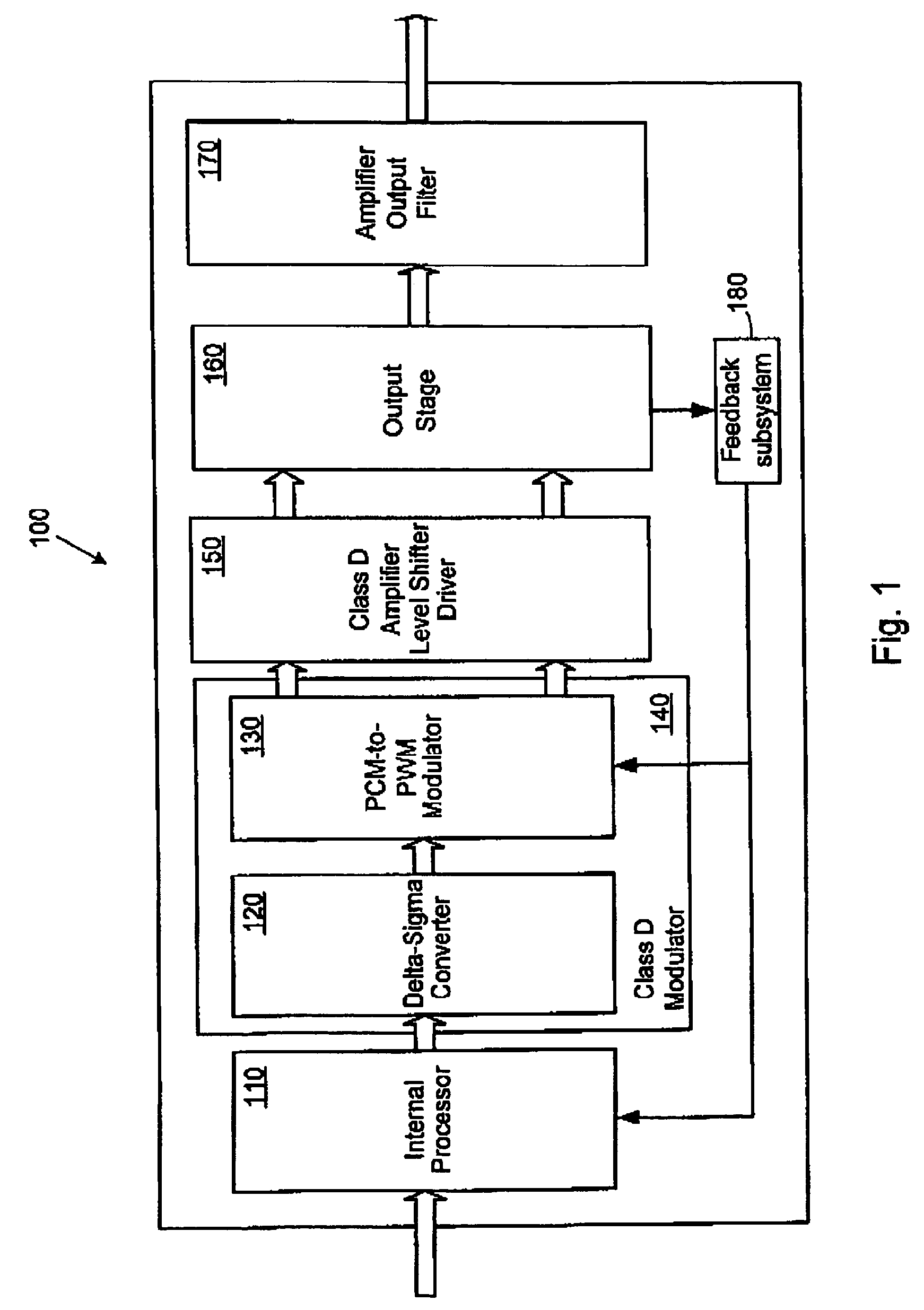

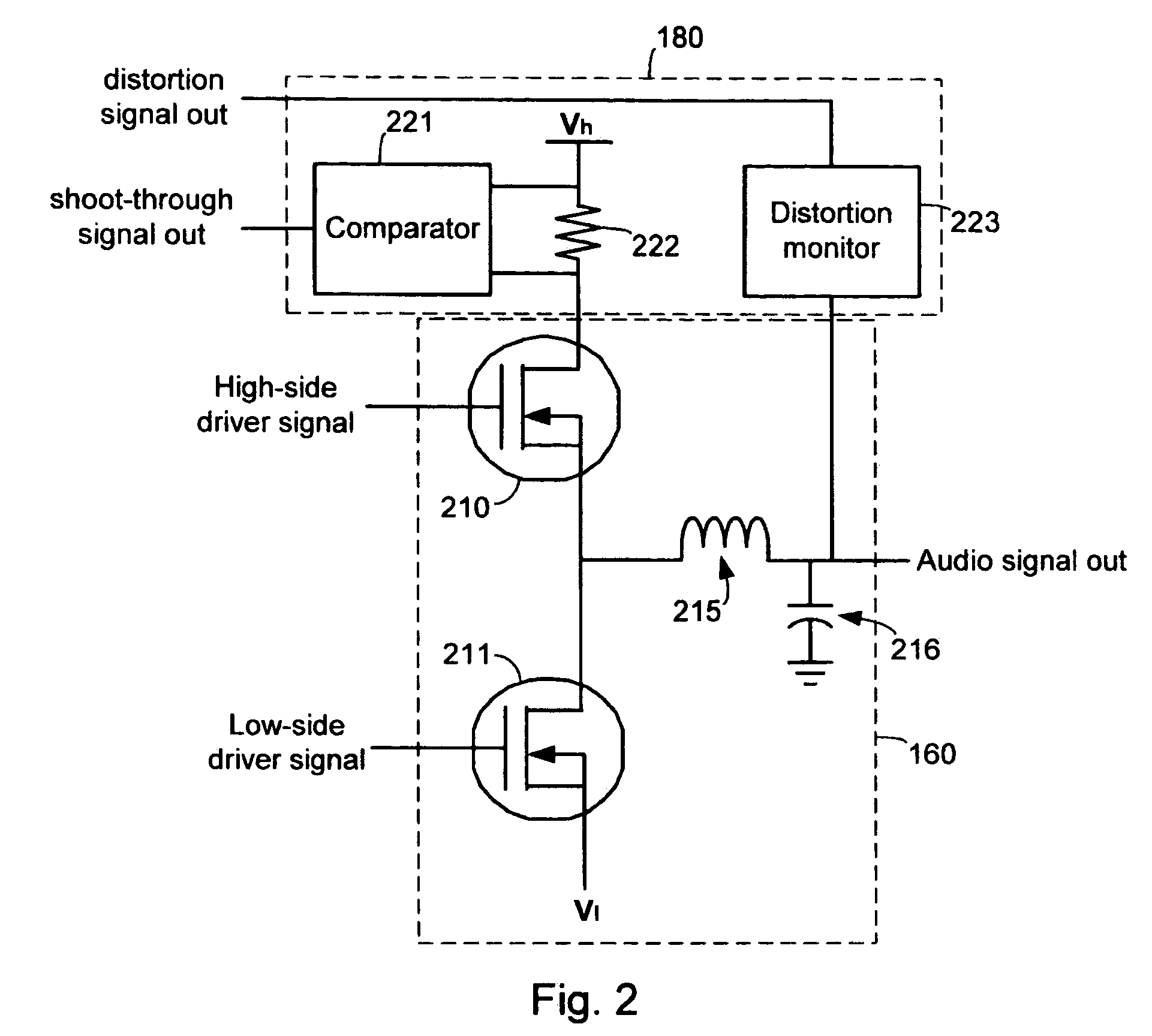

ActiveUS7023268B1Extended dead timeImprove shoot-through conditionAmplifier modifications to reduce non-linear distortionLow frequency amplifiersAuto regulationAudio power amplifier

Systems and methods for automatically adjusting the alignment of high-side and low-side pulse width modulated signals to improve dead time and shoot-through conditions. In one embodiment, a system includes a digital amplifier controller, an amplifier output stage coupled to the controller and configured to receive audio signals from the controller, and one or more sensors coupled to the output stage. The sensors are configured to detect and / or measure various parameters, such as shoot-through current and distortion, which are associated with the operation of the output stage. The sensors provide feedback to an internal processor or modulator of the controller, which then adjusts the timing of the high-side and low-side signals to improve the operating conditions of the output stage by minimizing shoot-through current and / or distortion.

Owner:INTERSIL INC

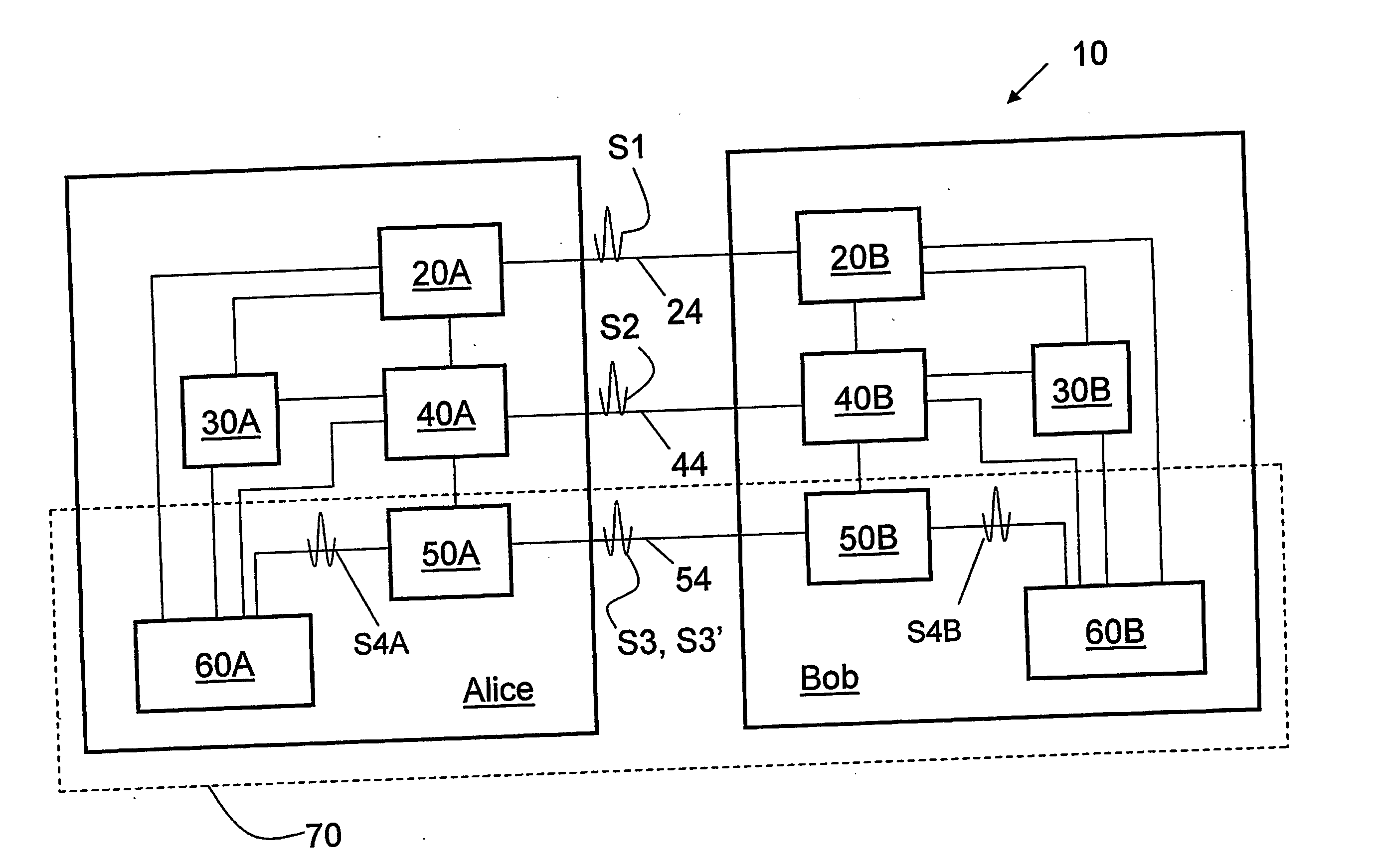

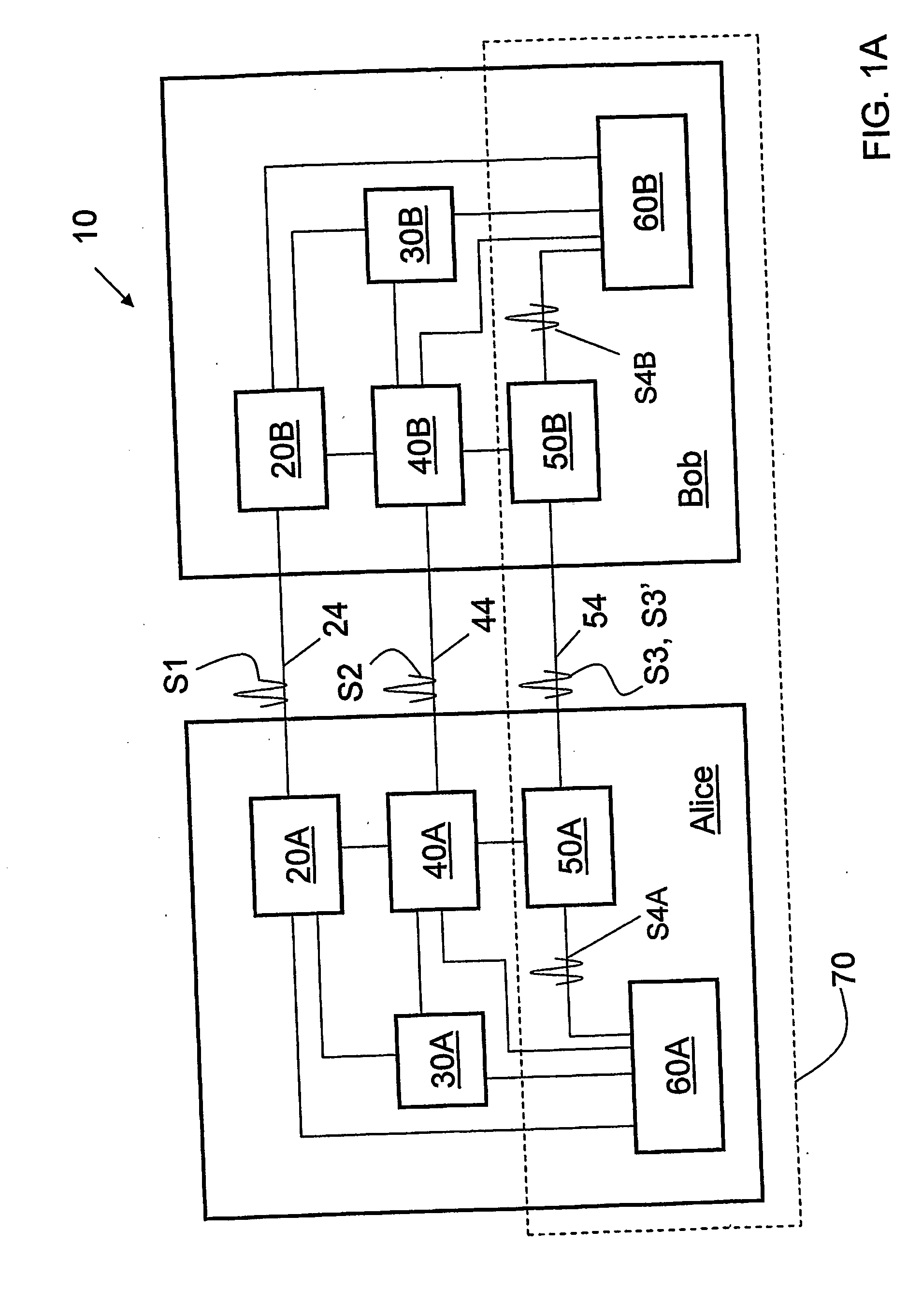

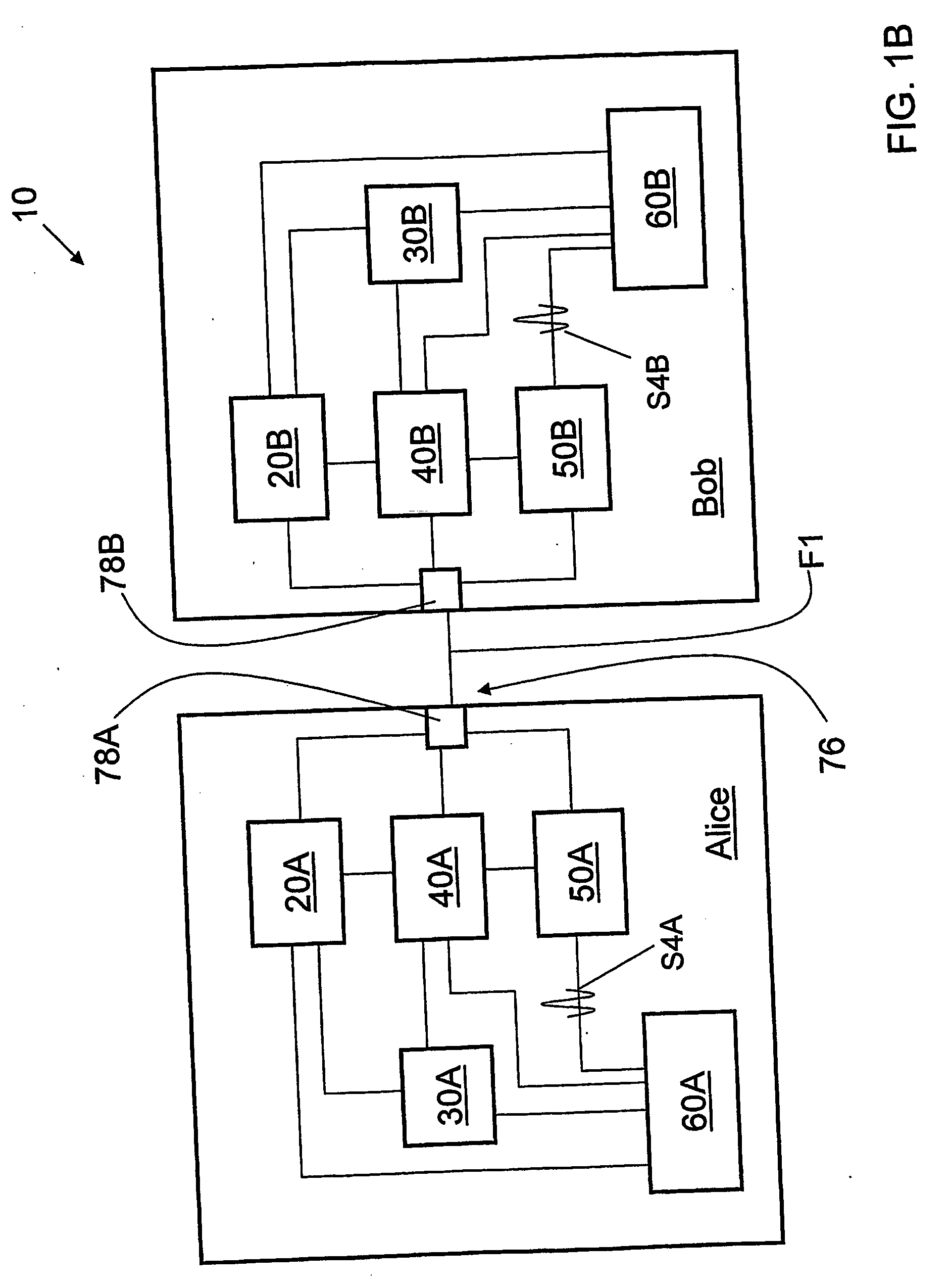

Kd systems with robust timing

QKD systems having timing systems and timing method that allow for QKD to be performed in actual field conditions associated with practical commercial applications of quantum cryptography. The QKD system includes optical modems in each QKD station. Each modem has a circulator with an optical receiver and an optical transmitter coupled to it. One of the optical modems includes two phase lock loops and the other optical modem includes a phase lock loop and a transmit clock. Synchronization pulses are exchanged between the optical modems over a timing channel to synchronize the operation of the QKD system. The phase lock loops serve to lock a receive timing domain to a transmit time domain to ensure proper encoding and detection of weak quantum signals exchanged between the QKD stations.

Owner:MAGIQ TECH INC

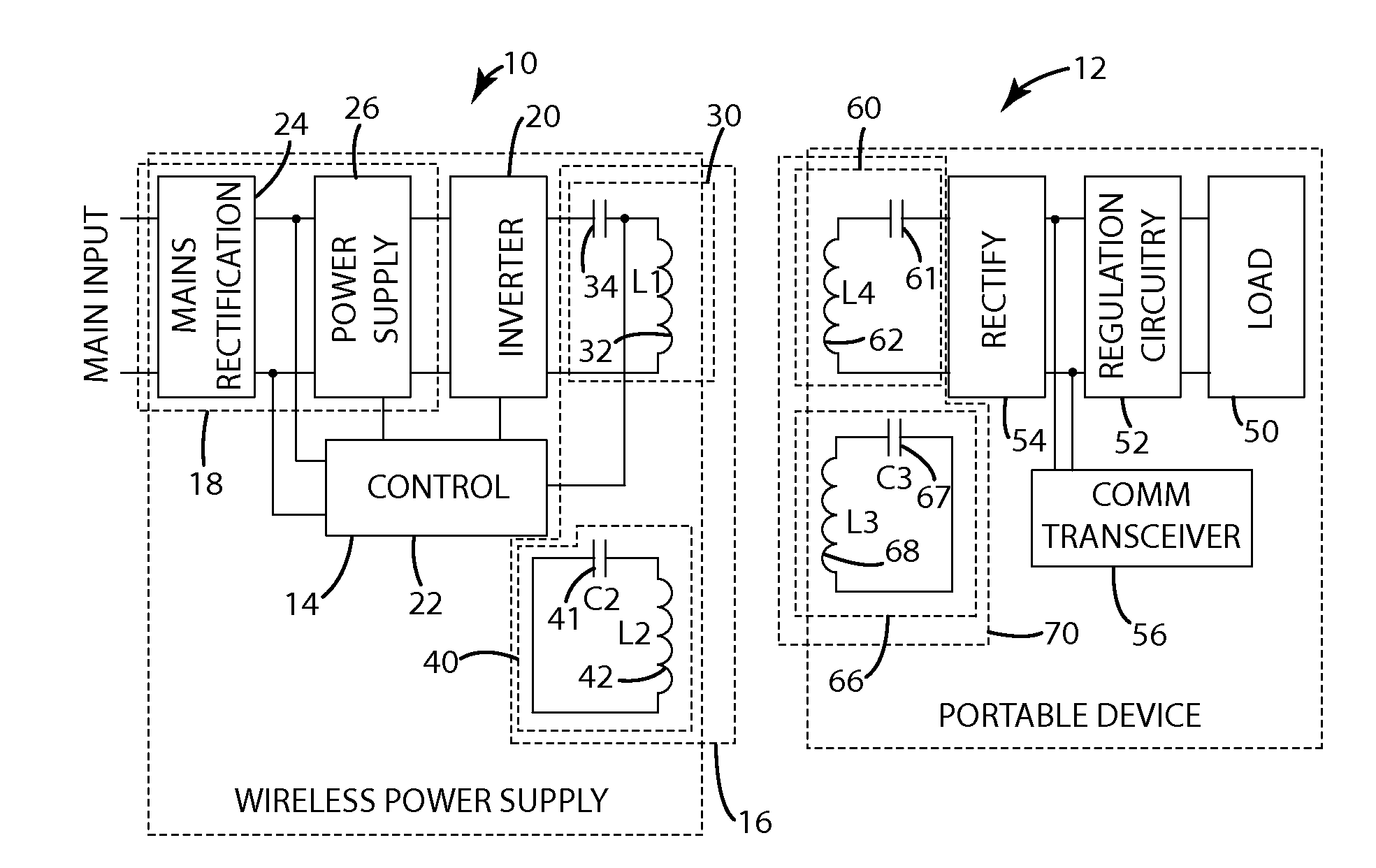

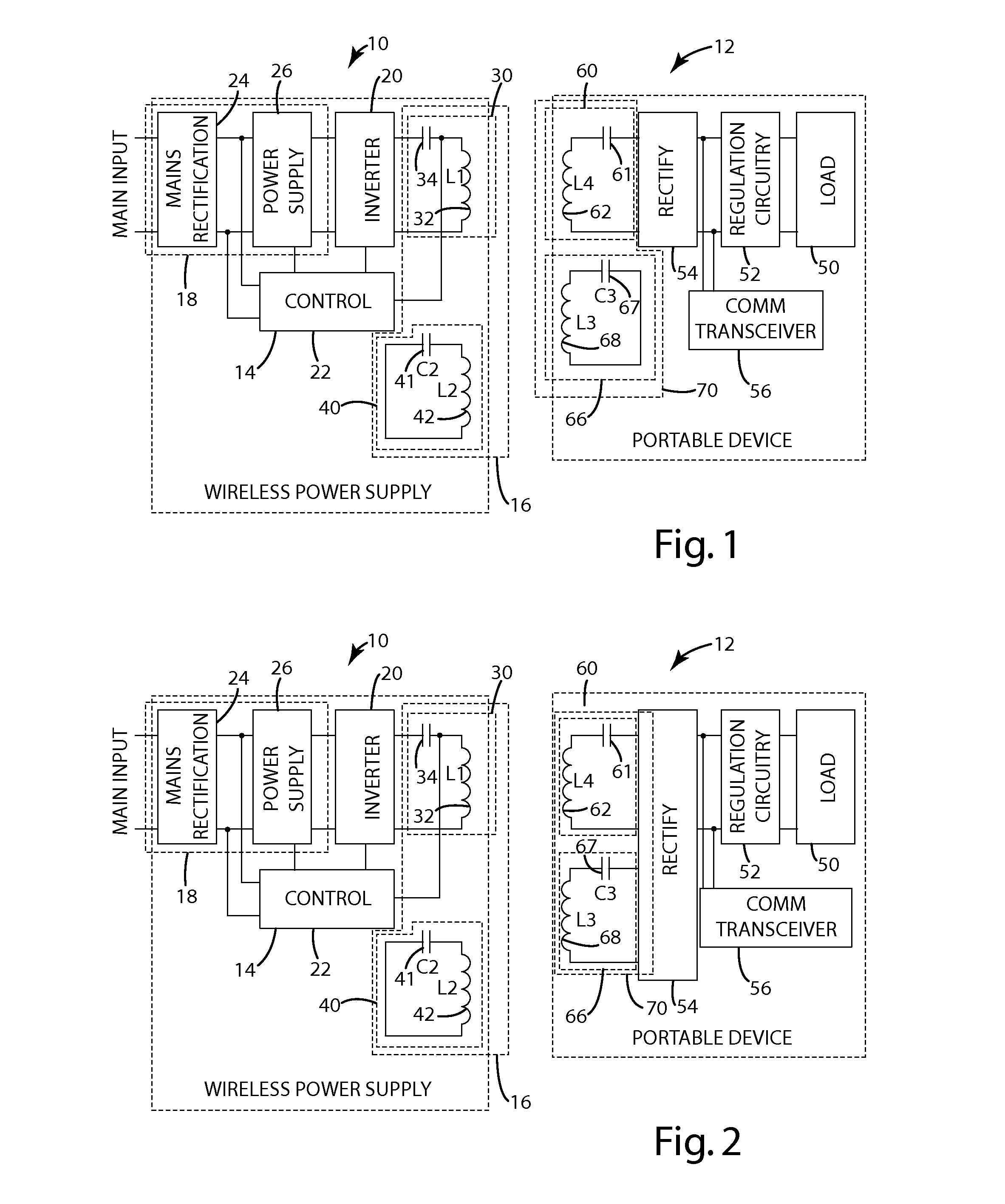

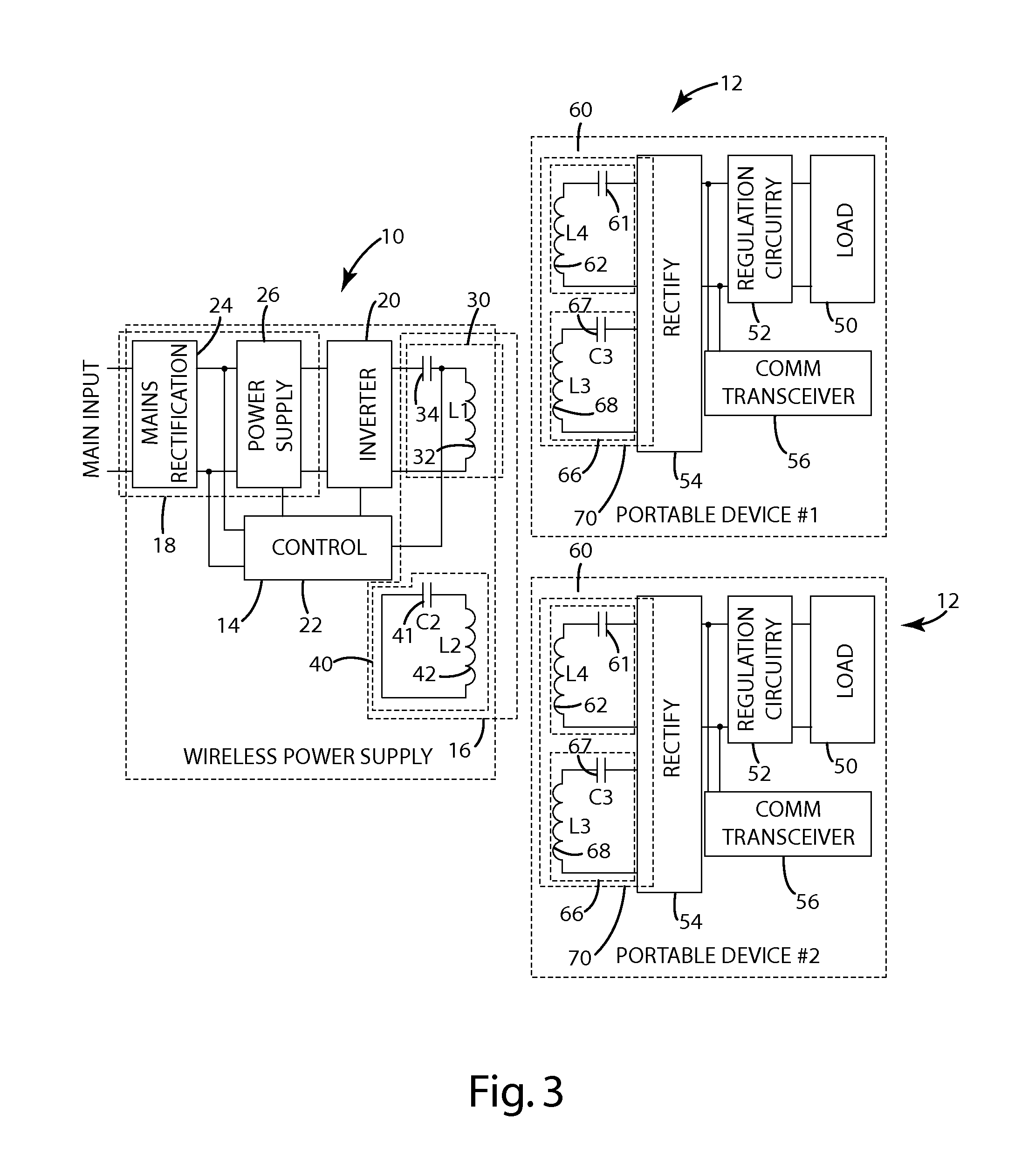

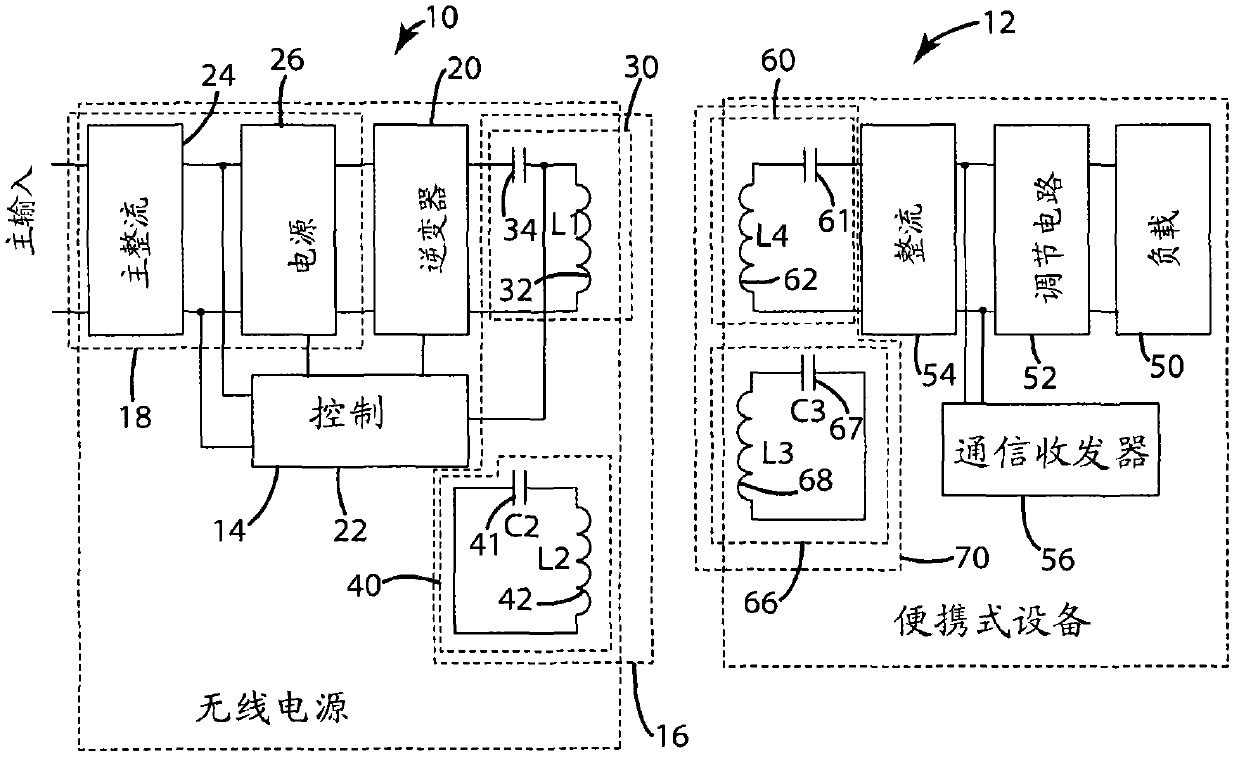

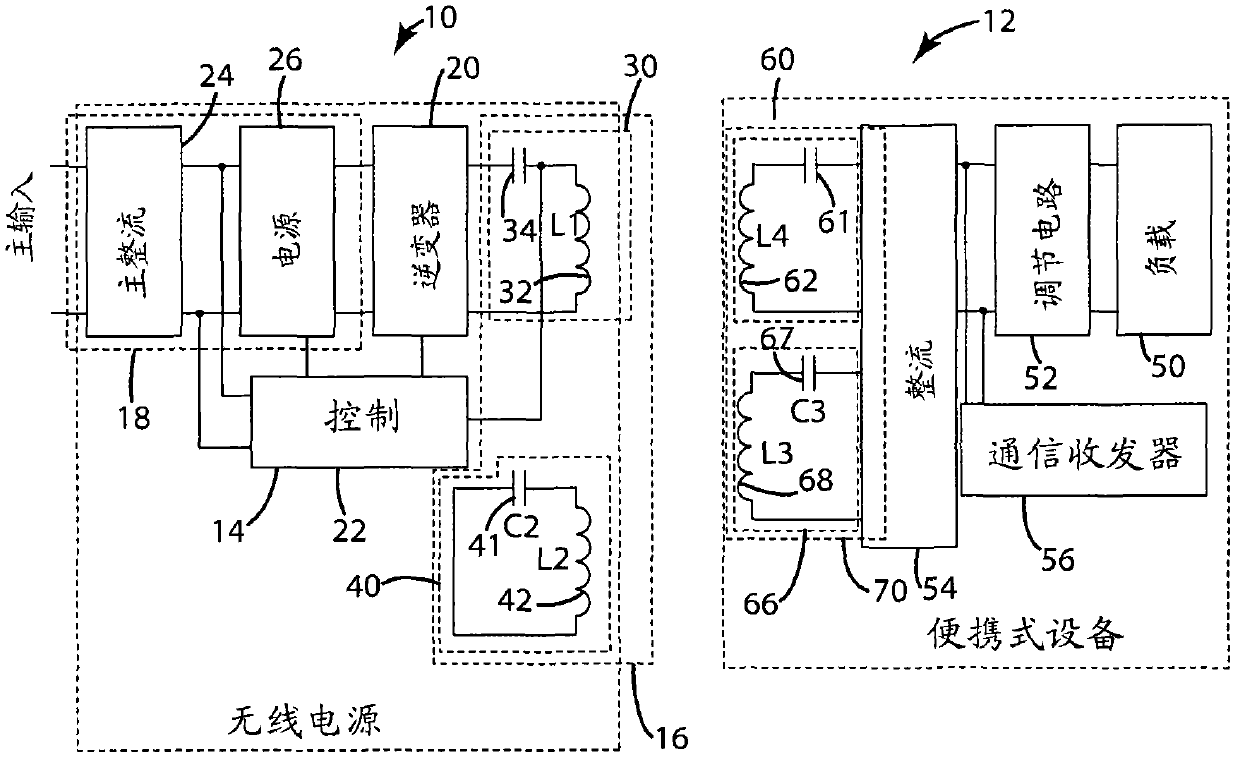

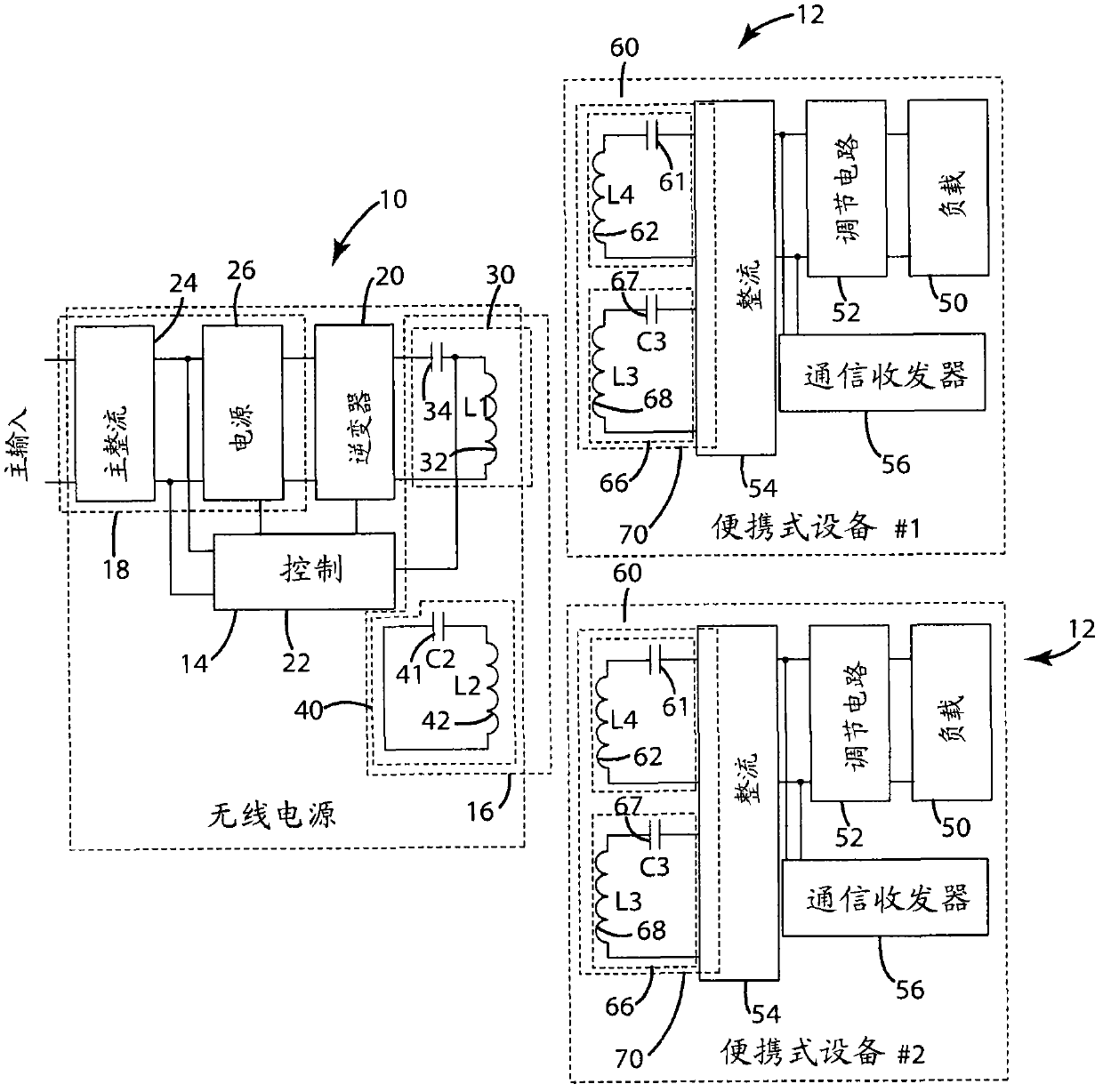

System and method for communication in wireless power supply systems

ActiveUS20150194814A1Avoid Data ConflictsFacilitate communicationDc network circuit arrangementsNear-field transmissionTelecommunicationsCommunication issues

The present invention relates to wireless power supplies adapted to supply power and communicate with one or more remote devices. The systems and methods of the present invention generally relate to a communication timing system that may ensure information being communicated does not overlap with that of another device, preventing data collisions and information from going undetected. With information being communicated in a way that addresses or avoids potential communication issues in multiple device systems, the wireless power supply may control operation to effectively supply wireless power.

Owner:PHILIPS IP VENTURES BV

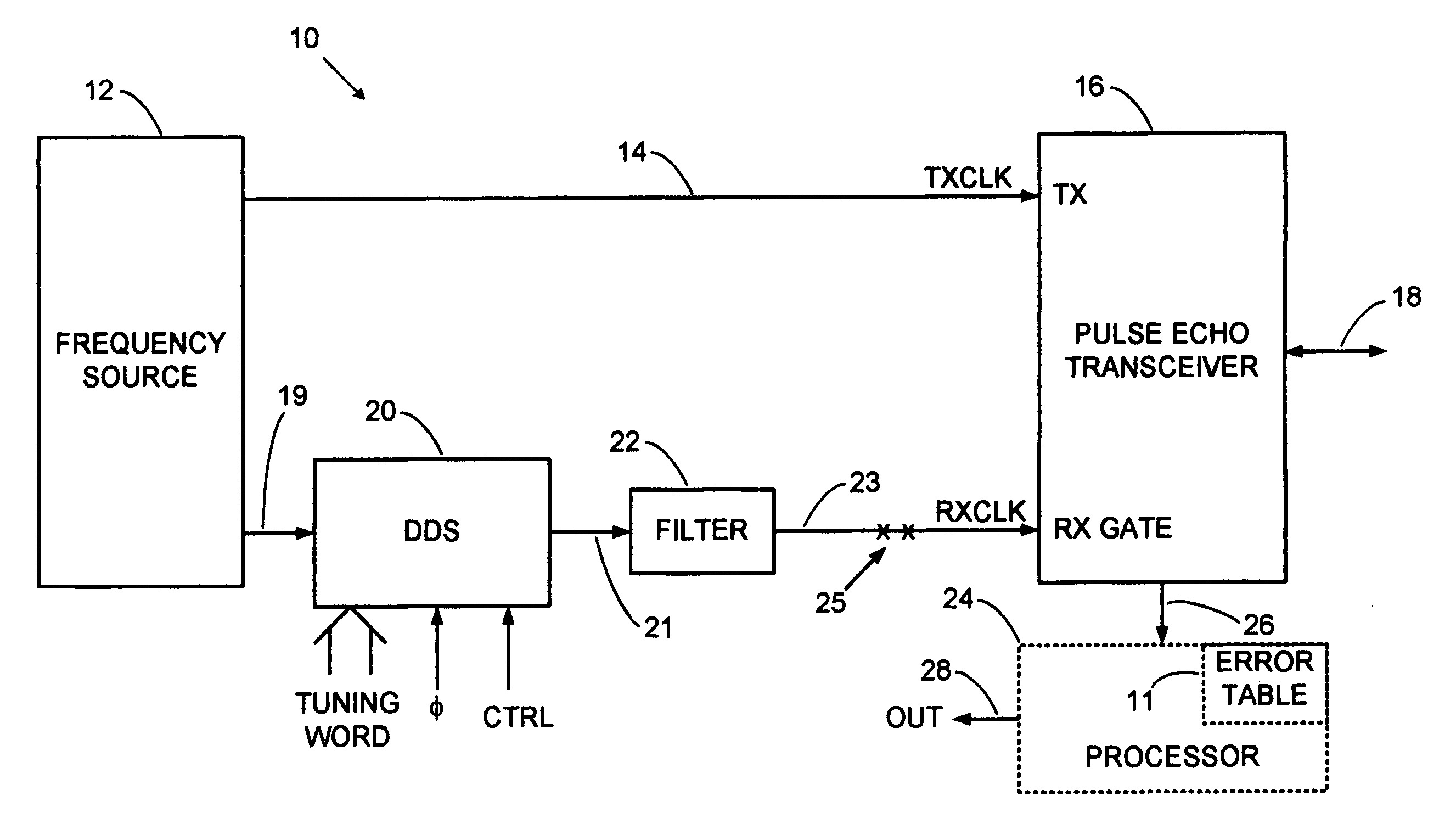

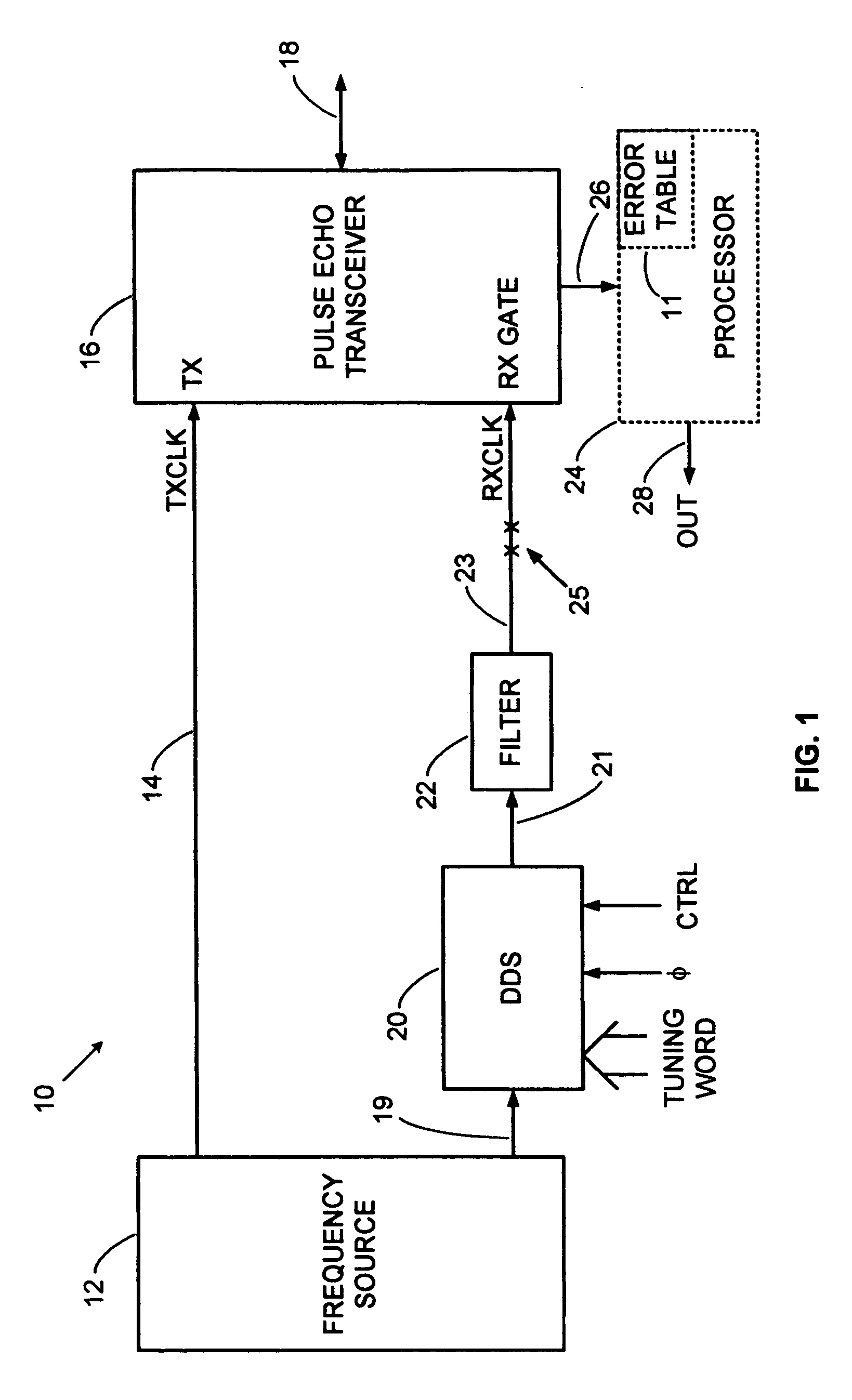

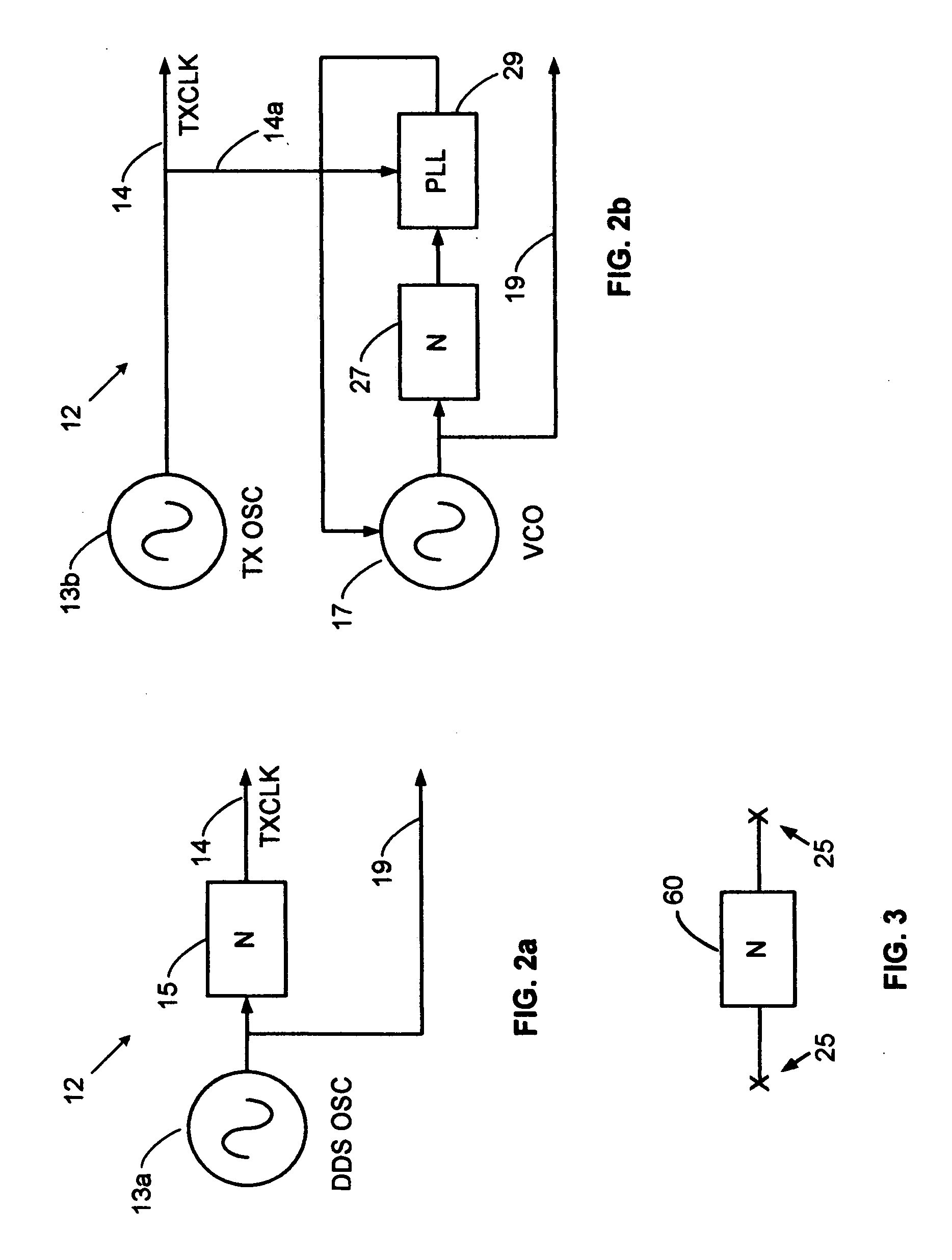

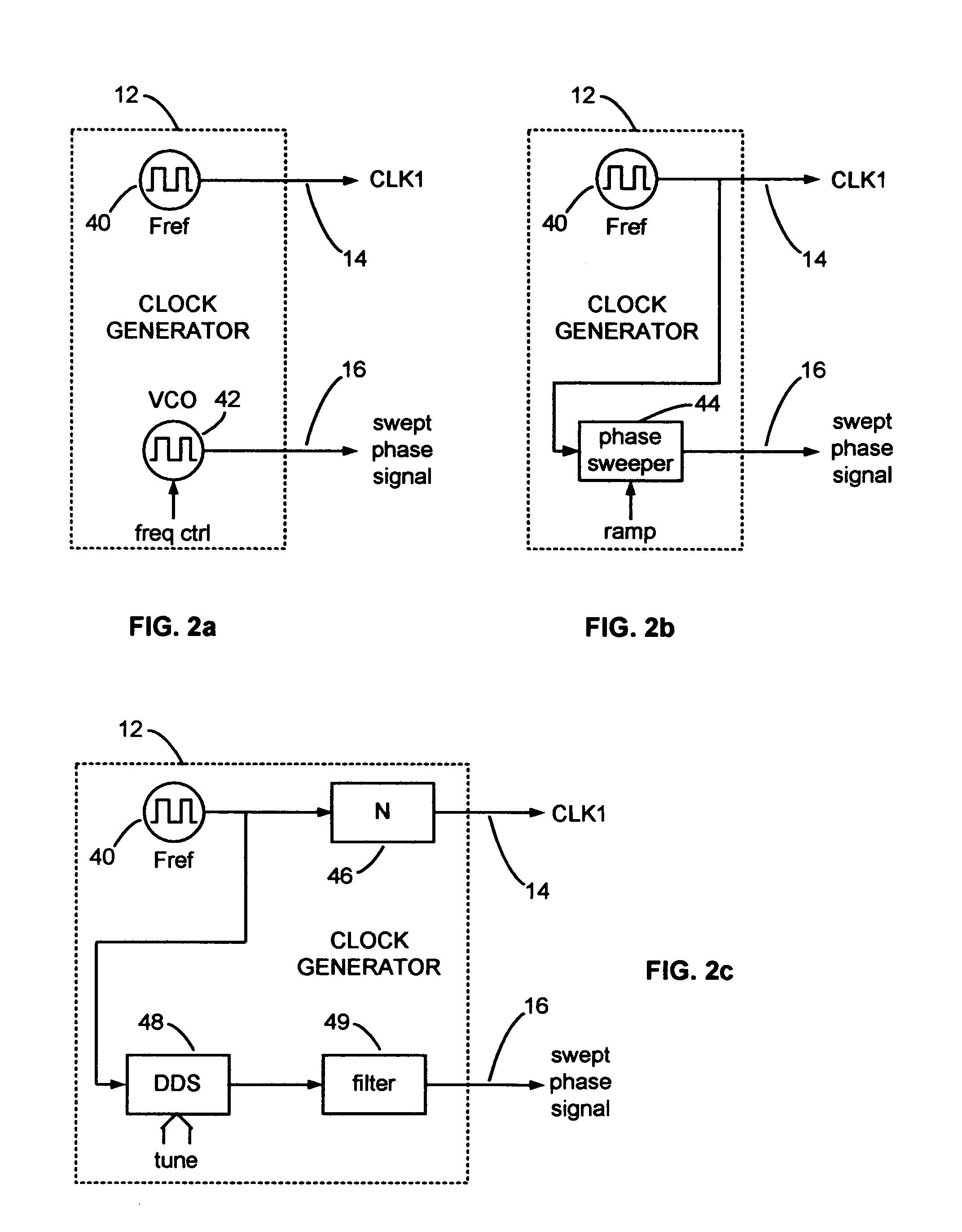

Direct digital synthesis radar timing system

InactiveUS20070192391A1Reducing timing system errorImprove stabilityWave based measurement systemsDigital function generatorsAccuracy improvementRadar

A direct digital synthesizer (DDS) drives a receive sampling gate at a frequency that is offset from a transmit pulse frequency to produce an expanded time sampled echo signal. The frequency offset generates a smoothly slipping phase between realtime received echoes and the sampling gate that stroboscopically expands the apparent time of the sampled echoes with an exemplary factor of 1-million and a range accuracy of 1-centimeter. The flexibility and repeatability of the digitally synthesized timing system is a quantum leap over analog prior art. The rock solid stability of the DDS allows further accuracy improvement via an error correction table.

Owner:MCEWAN TECH

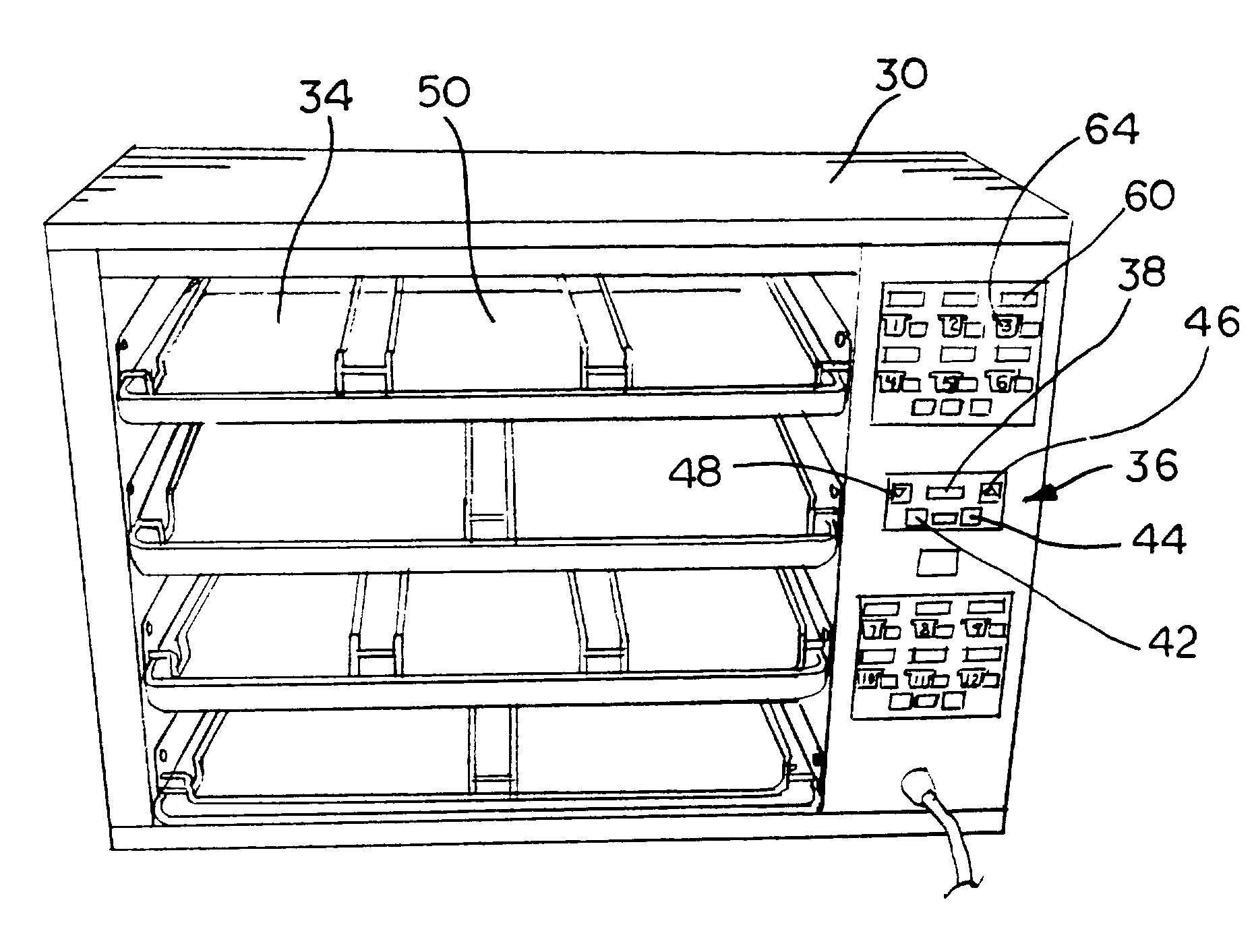

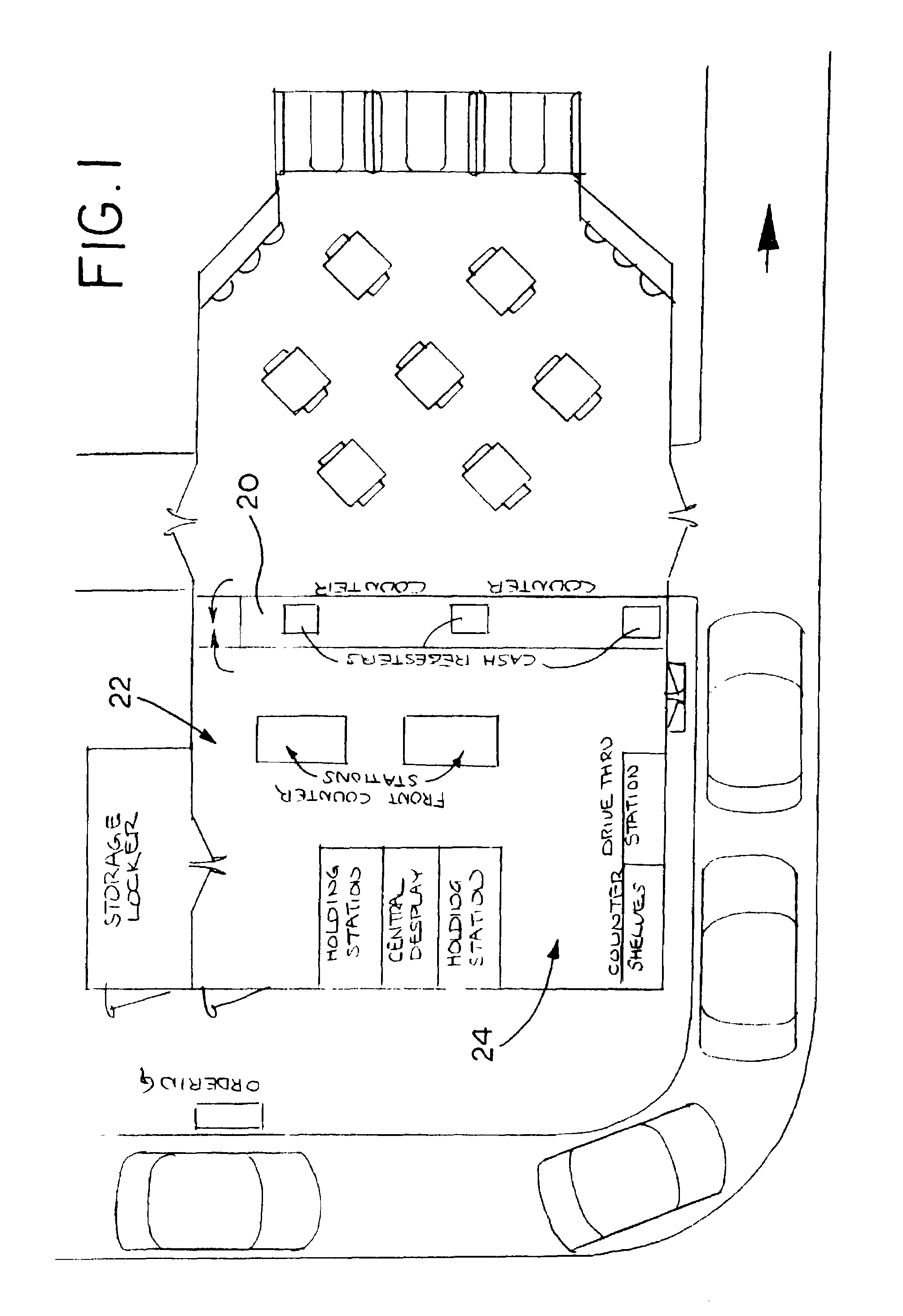

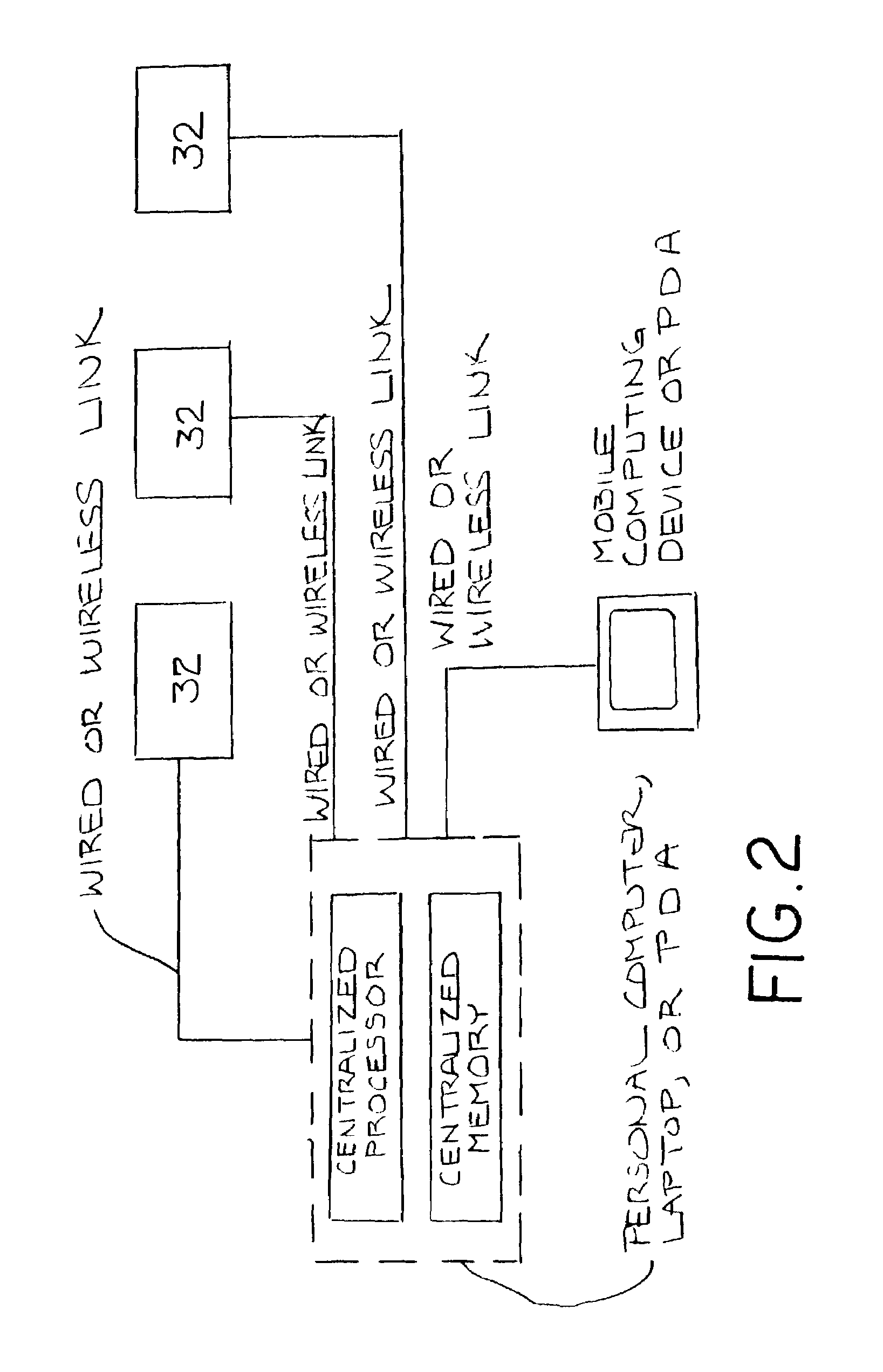

Food product timing system

A food timing system is disclosed that includes a number of timer modules associated with food holding devices in a restaurant. The timer modules are connected in a network for communicating information about the food being held in food holding compartments of the food holding devices. Each timer module includes a plurality of timers, with each timer being associated with a food holding compartment of a food holding device. The timers measure the holding time of food in each food holding compartment and are capable of transferring the holding time to another timer when the food is transferred to a holding compartment associated with the other timer.

Owner:MARMON FOODSERVICE TECH INC

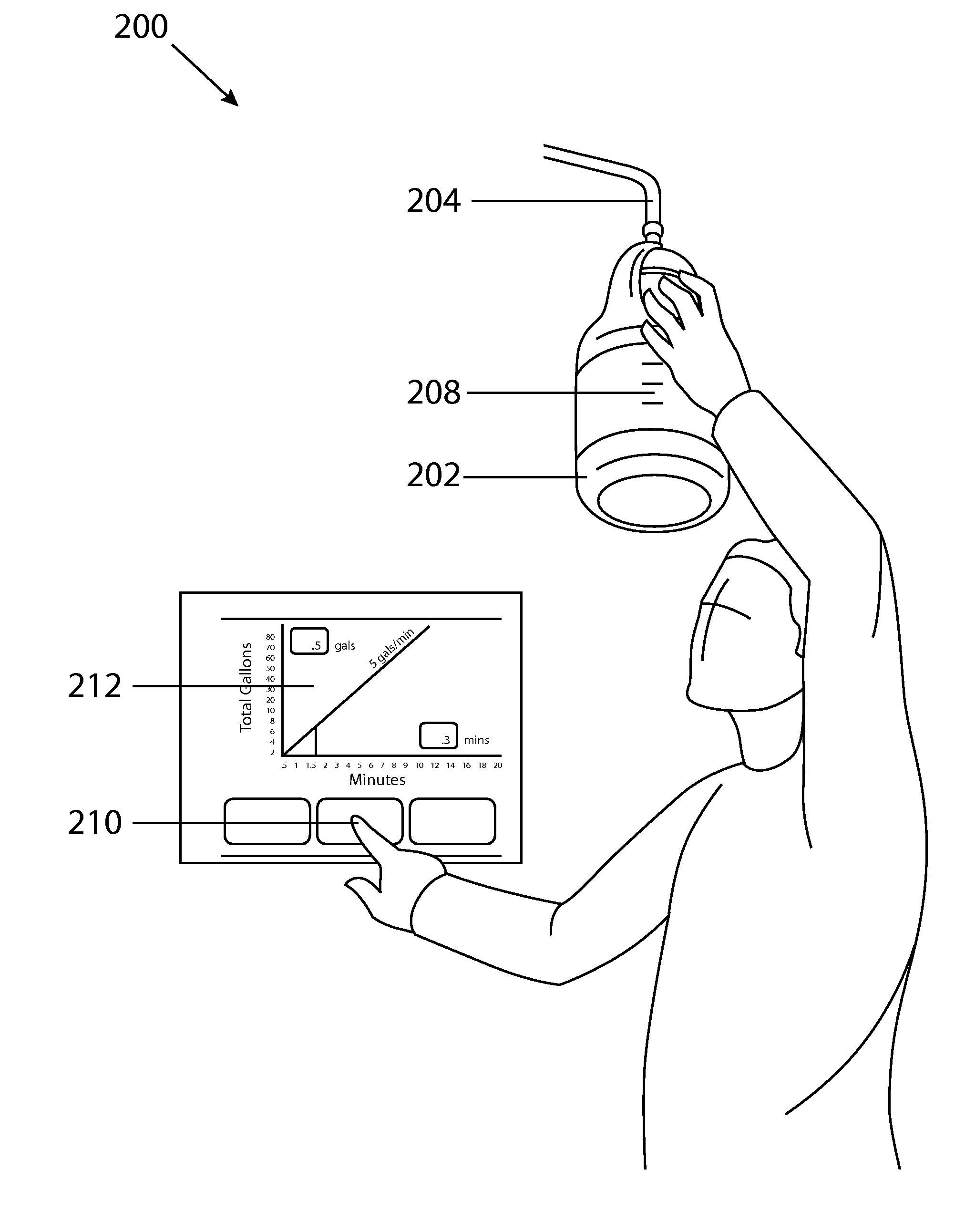

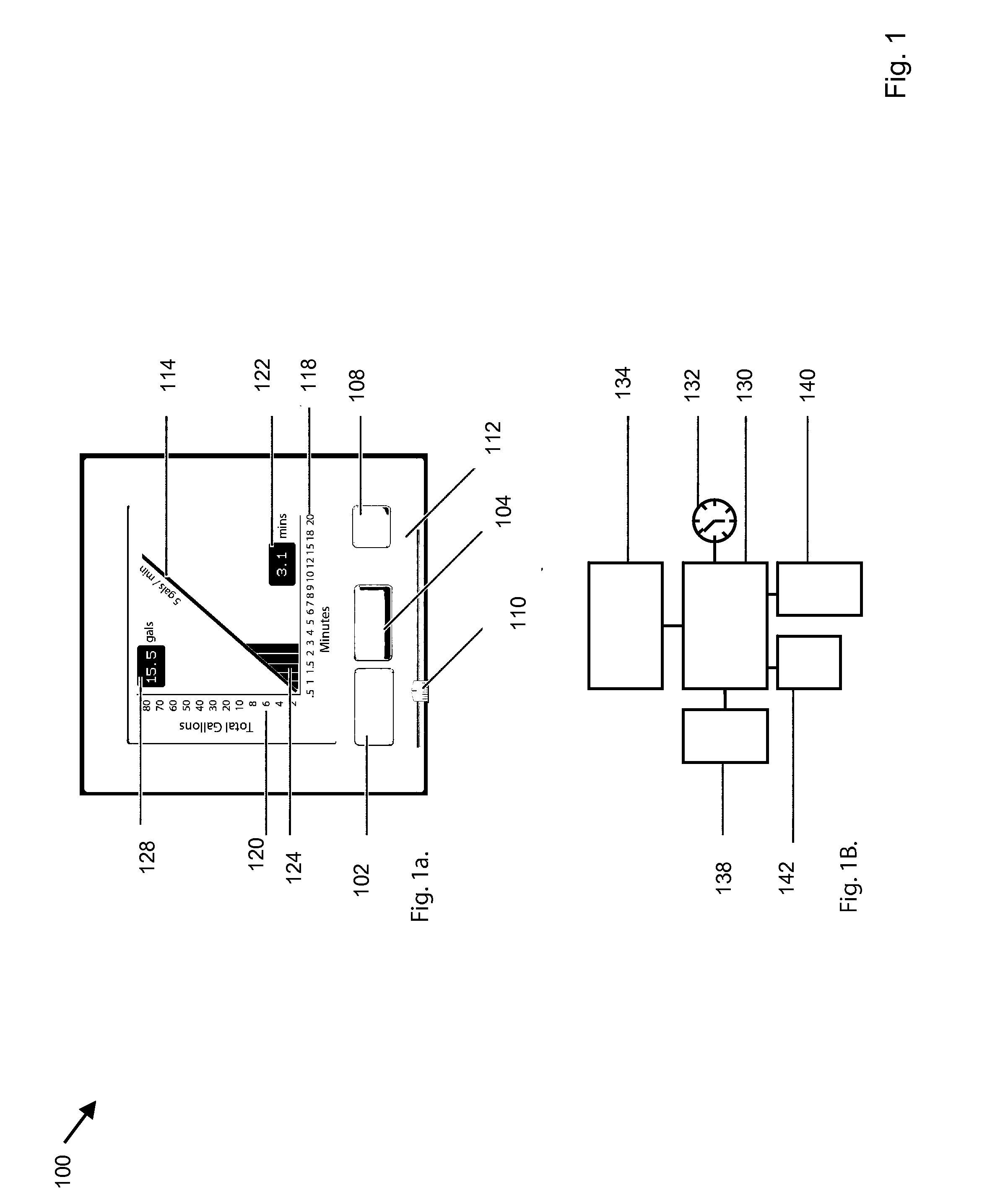

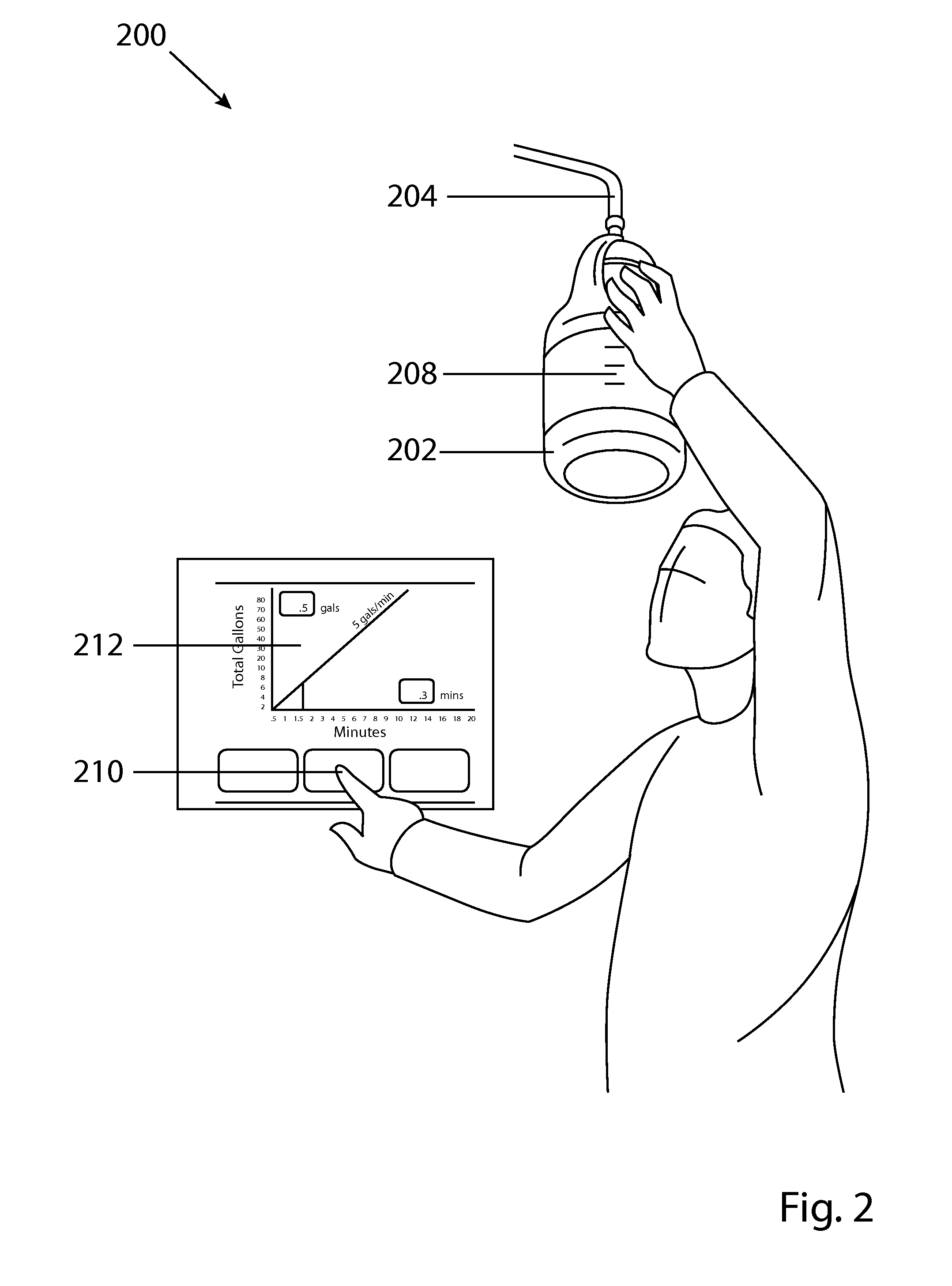

Faucet flow timing system that monitors volume of water usage

InactiveUS20080262755A1Temperature control without auxillary powerTesting/calibration apparatusWater useLow voltage

A battery powered, low voltage faucet flow timer, water usage calculator, and energy consumption awareness meter is simple to install and calibrate and may enable a user to understand the water usage associated with showering, bathing or other open faucet water use activity. The device may provide a simple method for calculating the flow characteristics for a shower, bath or other faucet and entering this flow rate into the timing device so that the timer provides an accurate calculation of water usage indicating both the time spent with the water running and approximate total water usage.

Owner:UMAGINATION LABS

UHF timing system for participatory athletic events

A participatory athletic event timing system based on backscattering modulation in the UHF band and including wirelessly encoding writable data tags with participant's bib numbers or a calculated derivative thereof for timing participants in a participative athletic event, and attaching the data tags to the participant's bibs for distribution of the bibs and data tags to participants so as to eliminate the need for matching data tags with bibs and maintaining the sequenced order of the matched data tags and bibs. In a preferred embodiment, when participants register for the event, they are assigned an ID number and a bib printed with that number and having attached to the bib one or more data tag encoded in the tags memory the ID number or a calculated derivative thereof. Before the start of the event, the athlete pulls the data tag from the bib and attaches it to their shoe. Antennas suitably designed and adapted for use with the data tags in participative athletic events are used to communicate with the data tags.

Owner:CHRONOTRACK SYST

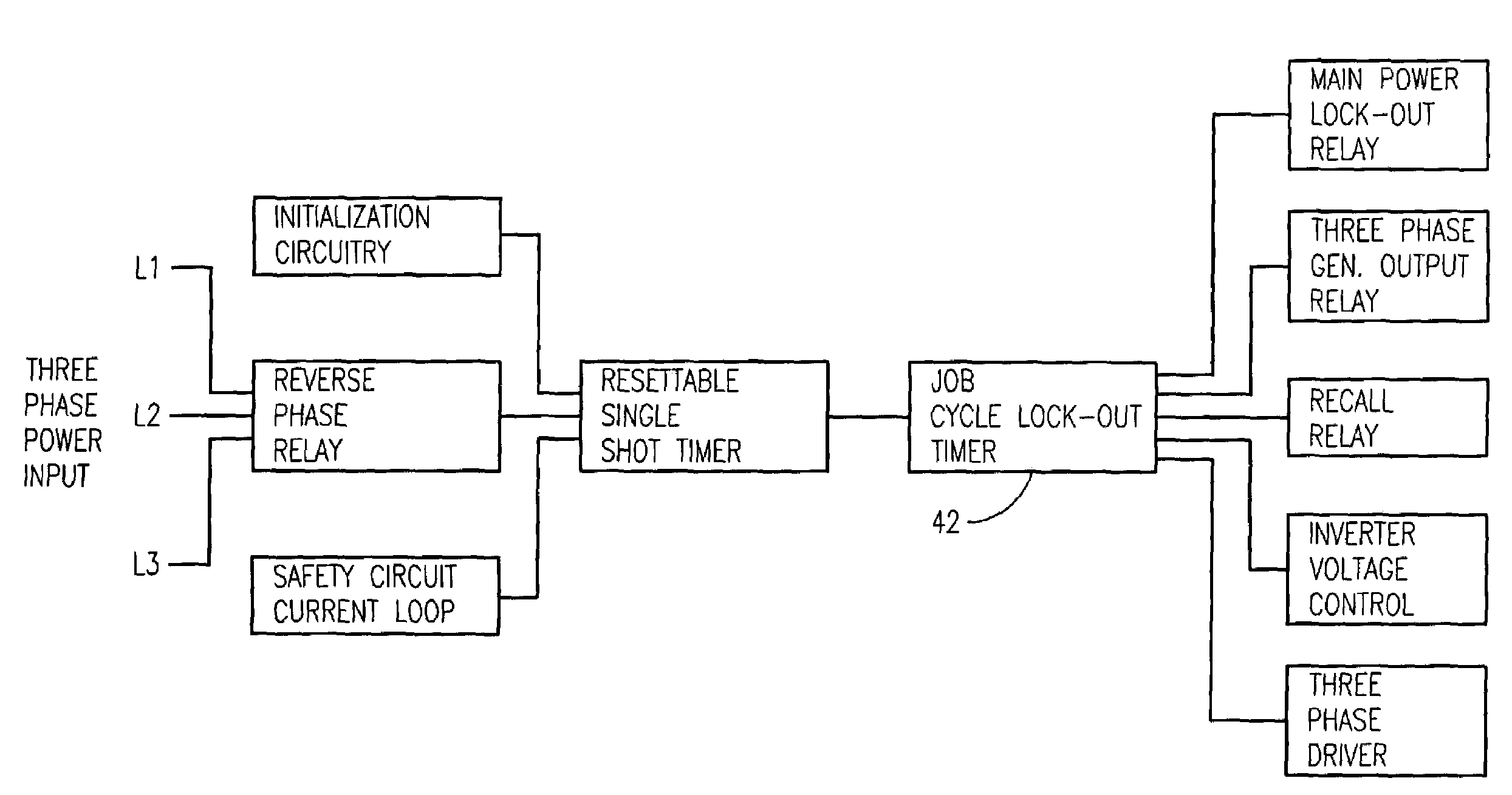

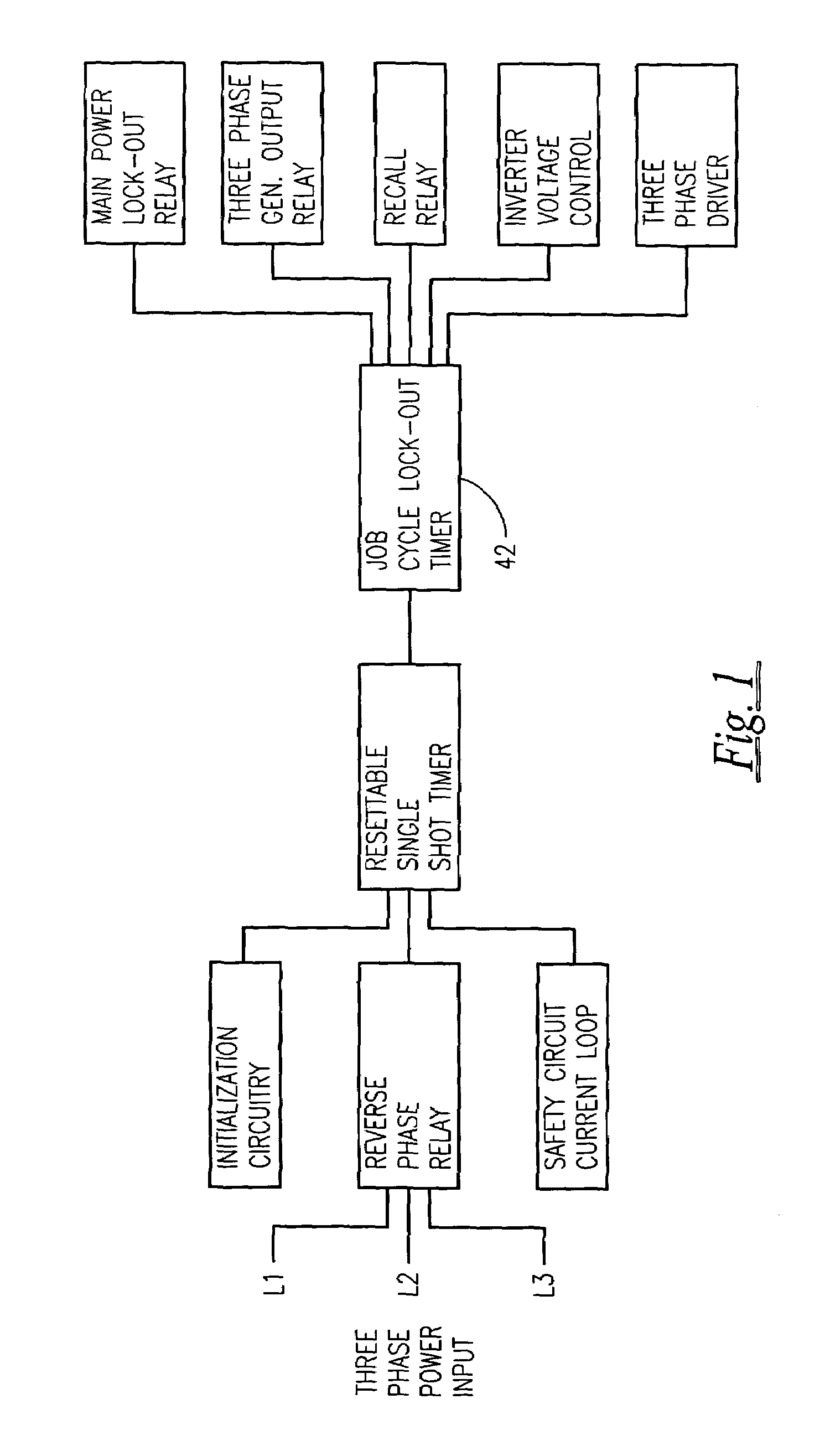

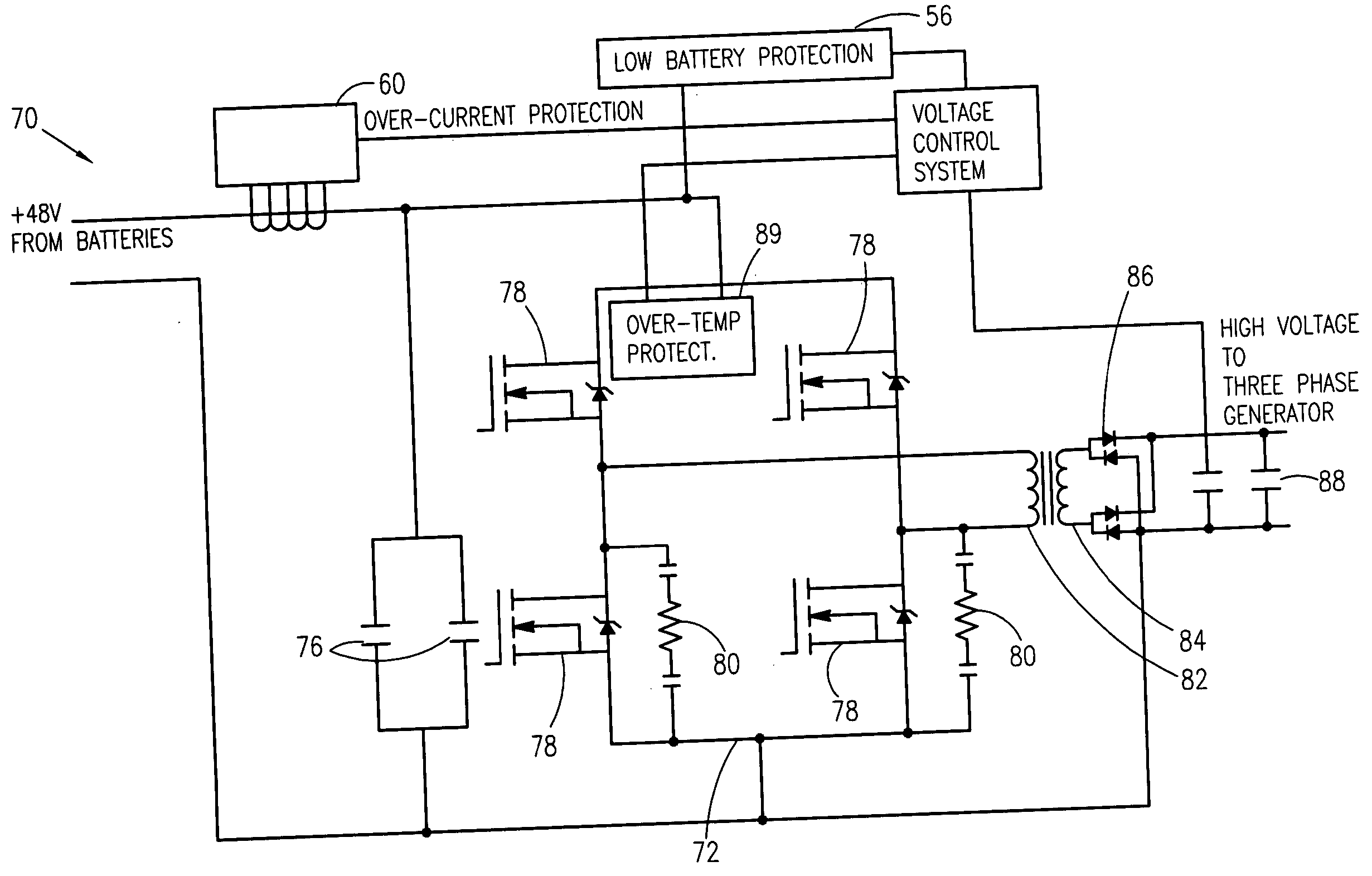

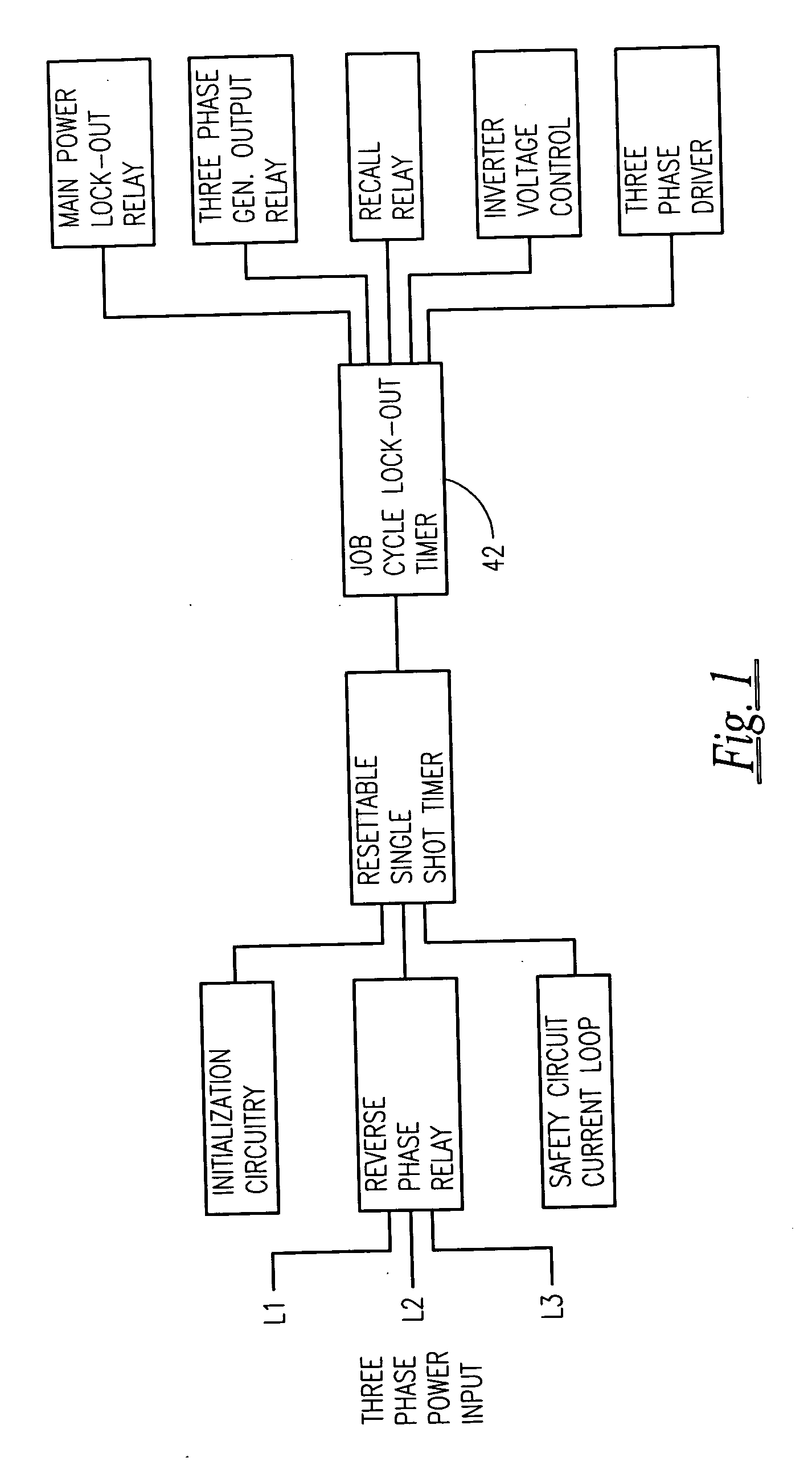

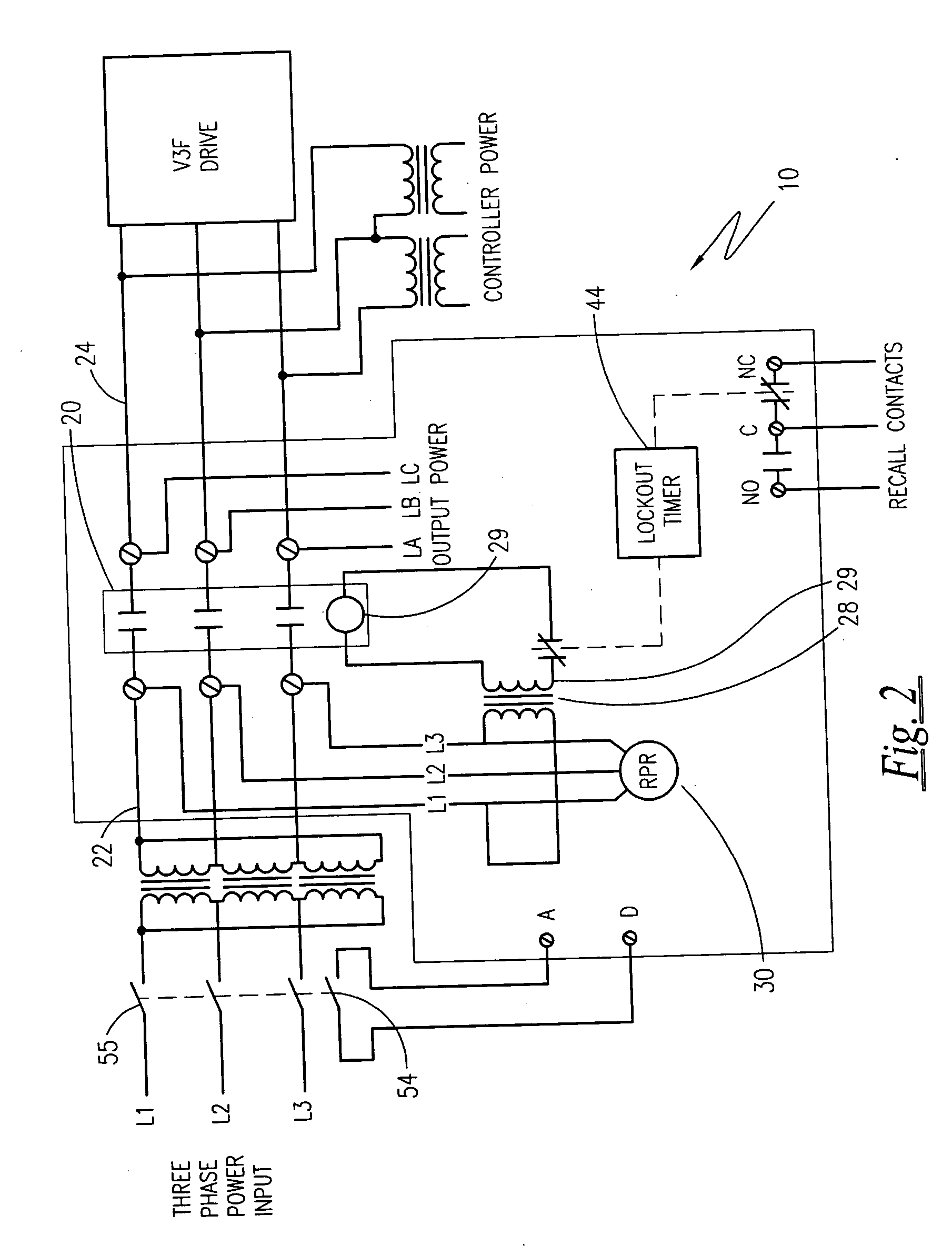

Traction elevator back-up power system with inverter timing

A back-up power system for a traction elevator includes a power sensing device to sense a power loss or irregularity of the normal control power. An inverter timing system is connected to the power loss sensing device. The inverter timing system receives a power sensing signal from the power sensing device. A back-up power generating system communicates with the inverter timing system and generates an output to provide back-up power to the elevator system.

Owner:REYNOLDS & REYNOLDS ELECTRONICS

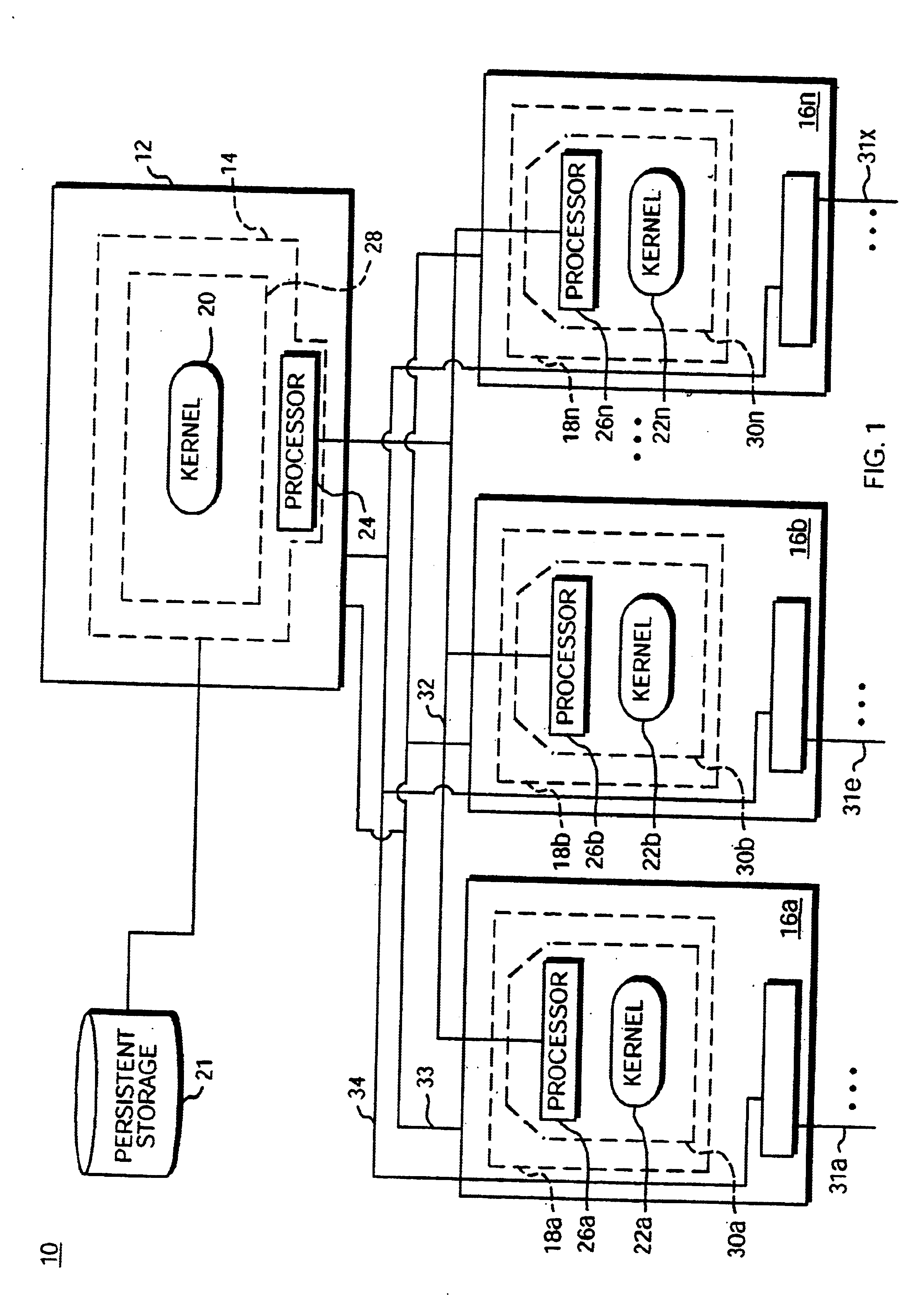

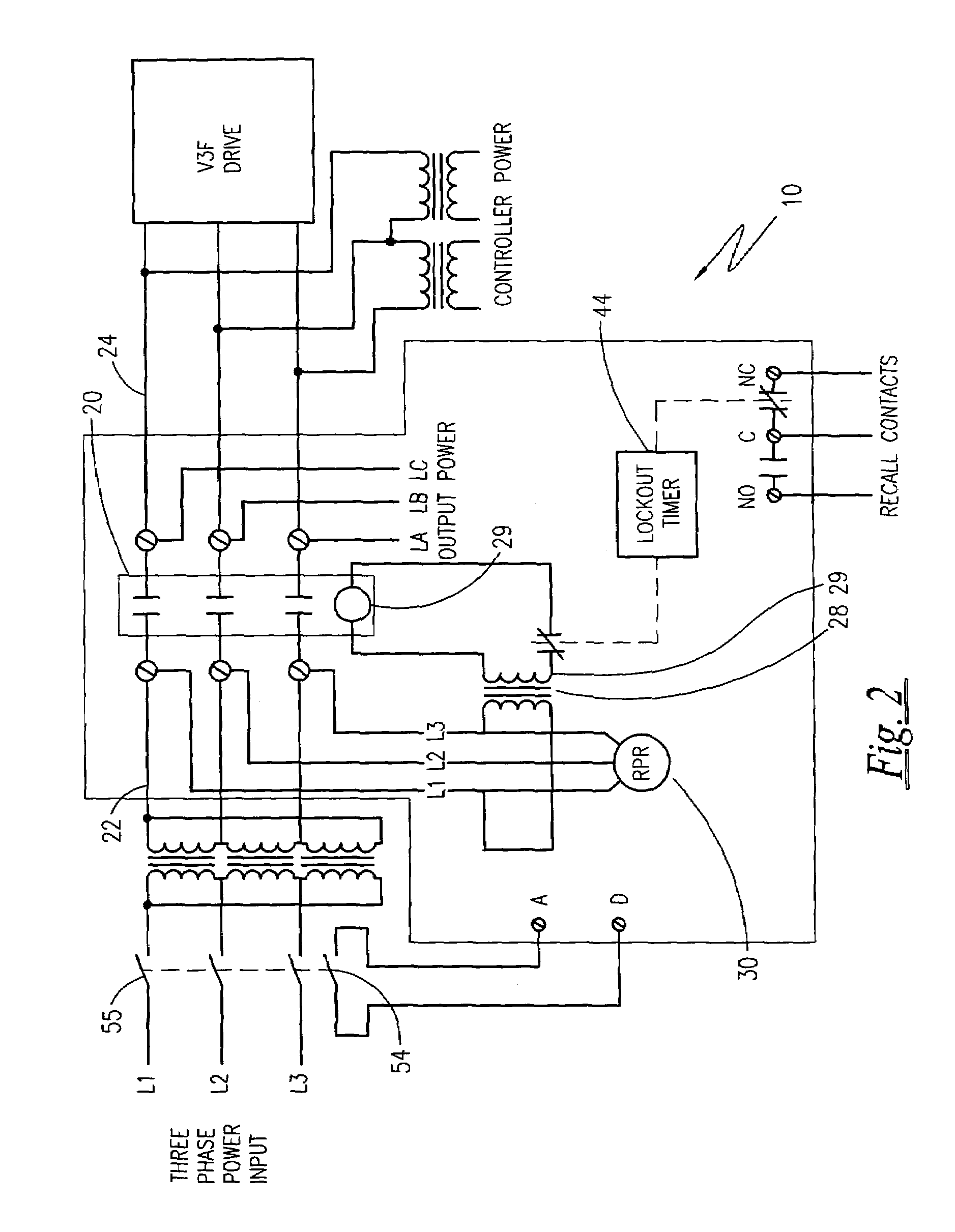

Network device with embedded timing synchronization

InactiveUS6868092B1Reduced resourceLess design timeSynchronisation information channelsTime-division multiplexData synchronizationNetwork data

The present invention provides a network device including a central timing subsystem for distributing one or more timing reference signals including a main timing signal and an embedded timing signal. Embedding one timing signal within another reduces the routing resources necessary to route the timing signal(s) within the network device. In addition, one central timing system, as opposed to two or more, may be used to provide multiple different synchronous clock signals. In one embodiment, the main timing signal is used for network data transfer while the embedded signal is used at least for processor synchronization. Consequently, a separate central timing subsystem is not required for generation and distribution of processor timing reference signals, and separate routing resources are not required for the processor timing reference signals. In addition, separate local timing subsystems for both the central timing and processor timing are not necessary. Embedding the processor timing reference signal within a highly accurate, redundant external timing reference signal also provides a highly accurate and redundant processor timing reference signal, and having a common local timing subsystem is more efficient resulting in less design time, less debug time, less risk, design re-use and simulation re-use.

Owner:CIENA

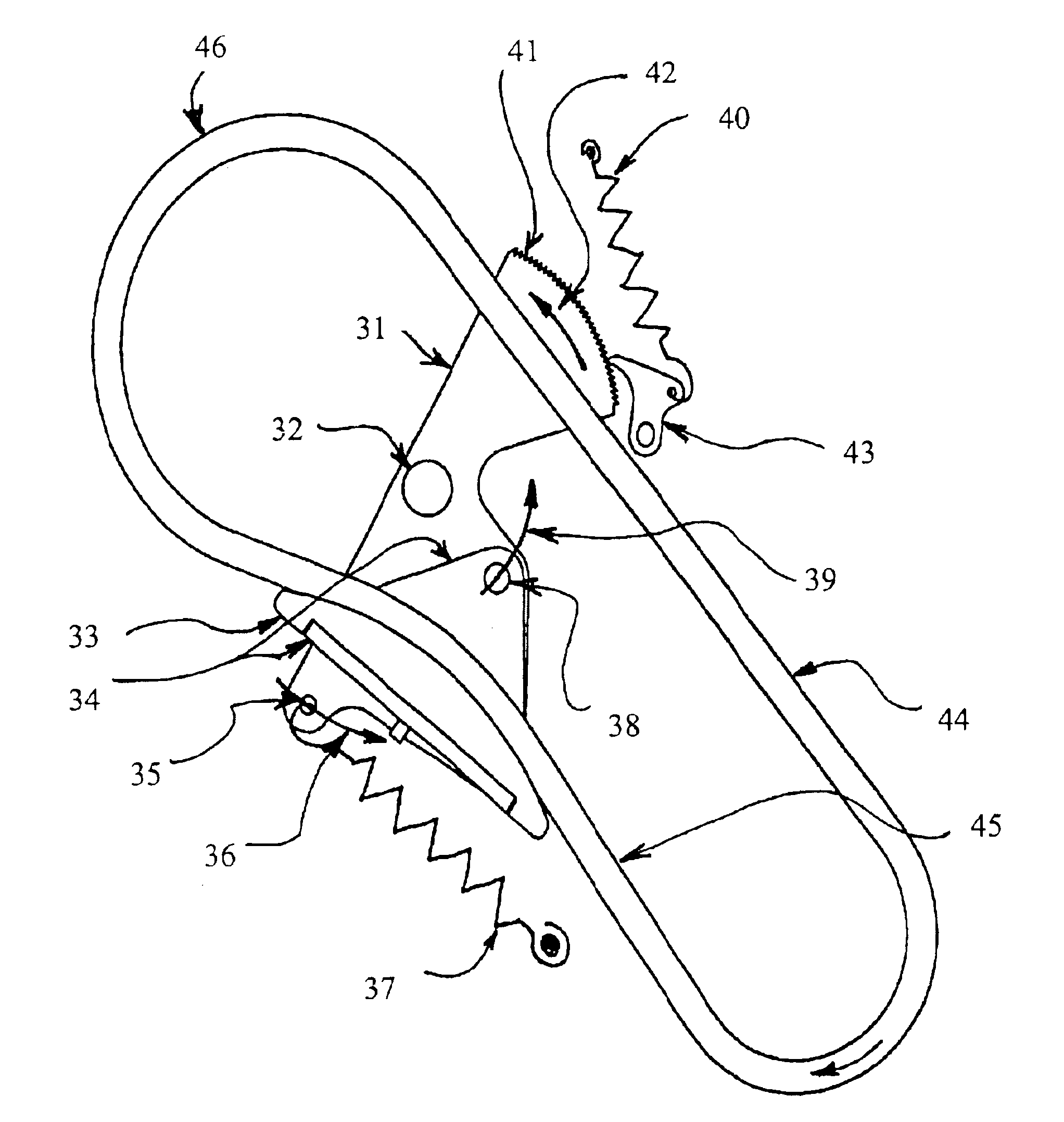

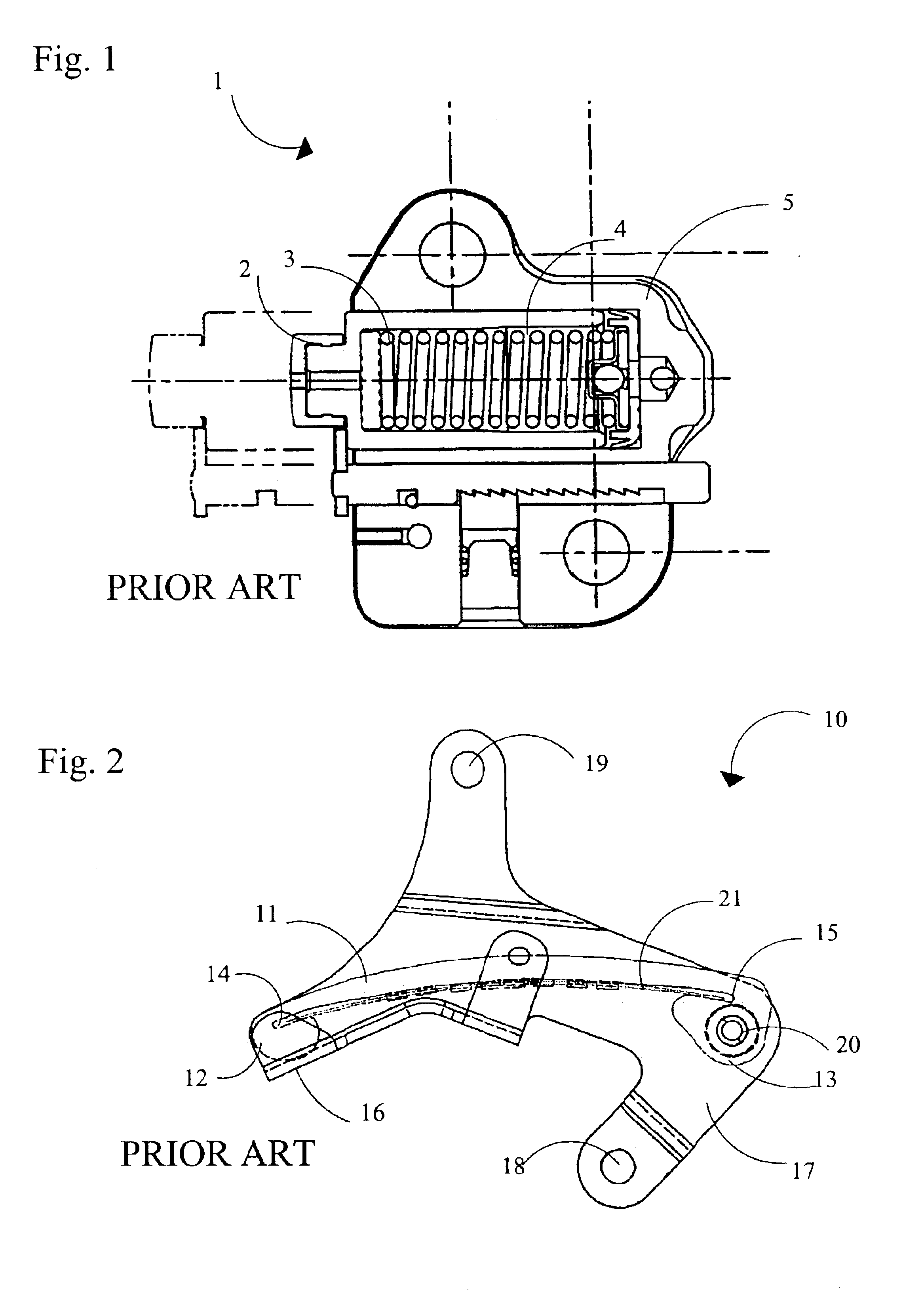

Ratcheting pivot arm tensioner with backlash

An engine chain or belt tensioning system includes a tensioner pivot arm with a ratcheting means that includes backlash in an engine timing system. The tensioner system includes a tensioner pivot arm having a fixed pin, ratchet teeth, and a connection for a rotation-causing device, all being spaced radially outward from a pivoting feature. The pivoting feature and the fixed pin are positioned between two strands of a chain. An arm carrying a shoe extended outside the strands of chain and positioned to contact an outside portion of chain is pivotally mounted to the fixed pin. Rotation of the pivot arm causes the arm and shoe to draw inwards, imparting tension to the chain strand. The ratchet teeth allow free rotation of the tensioner arm in one direction, but not the other.

Owner:BORGWARNER INC

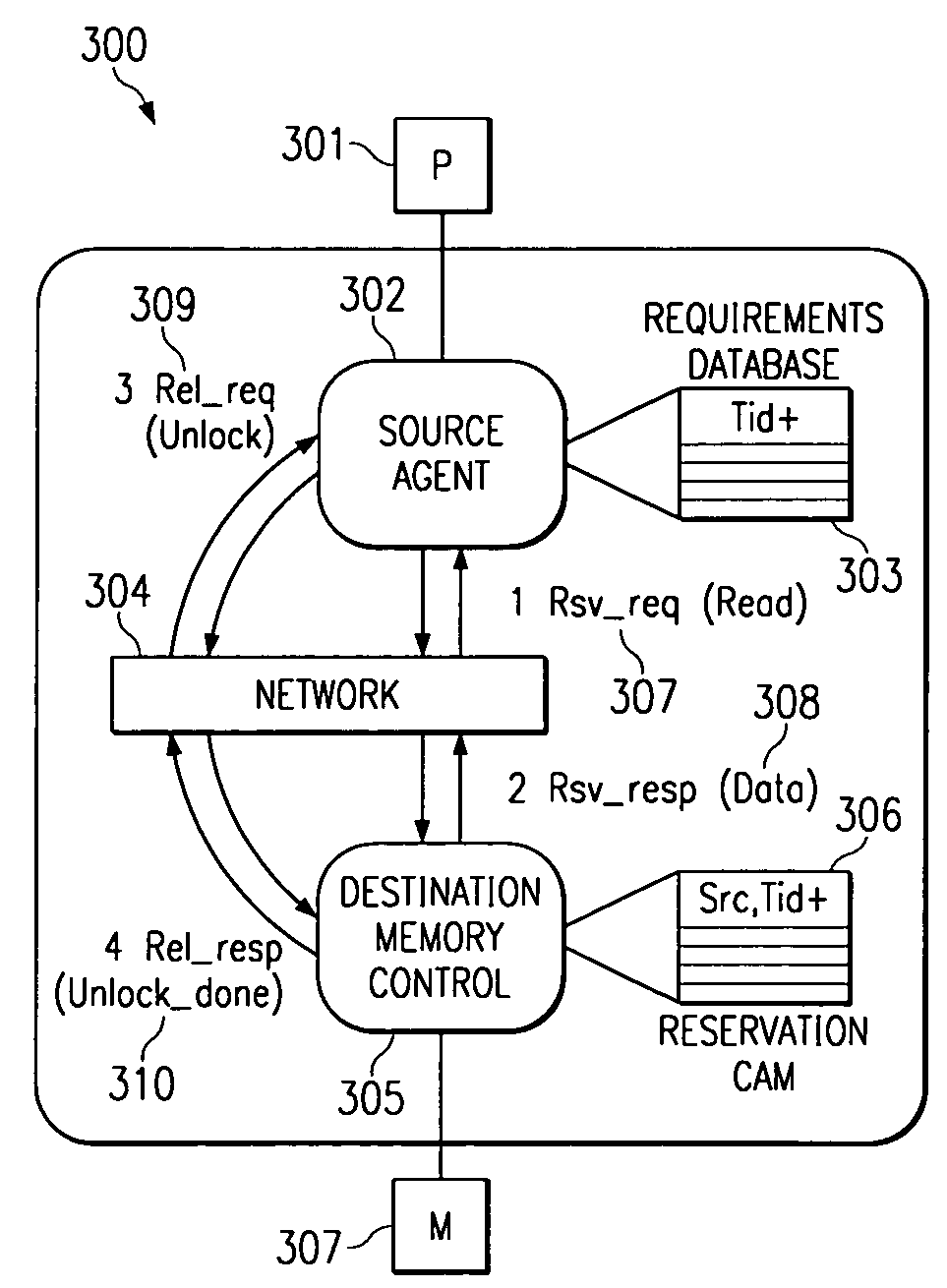

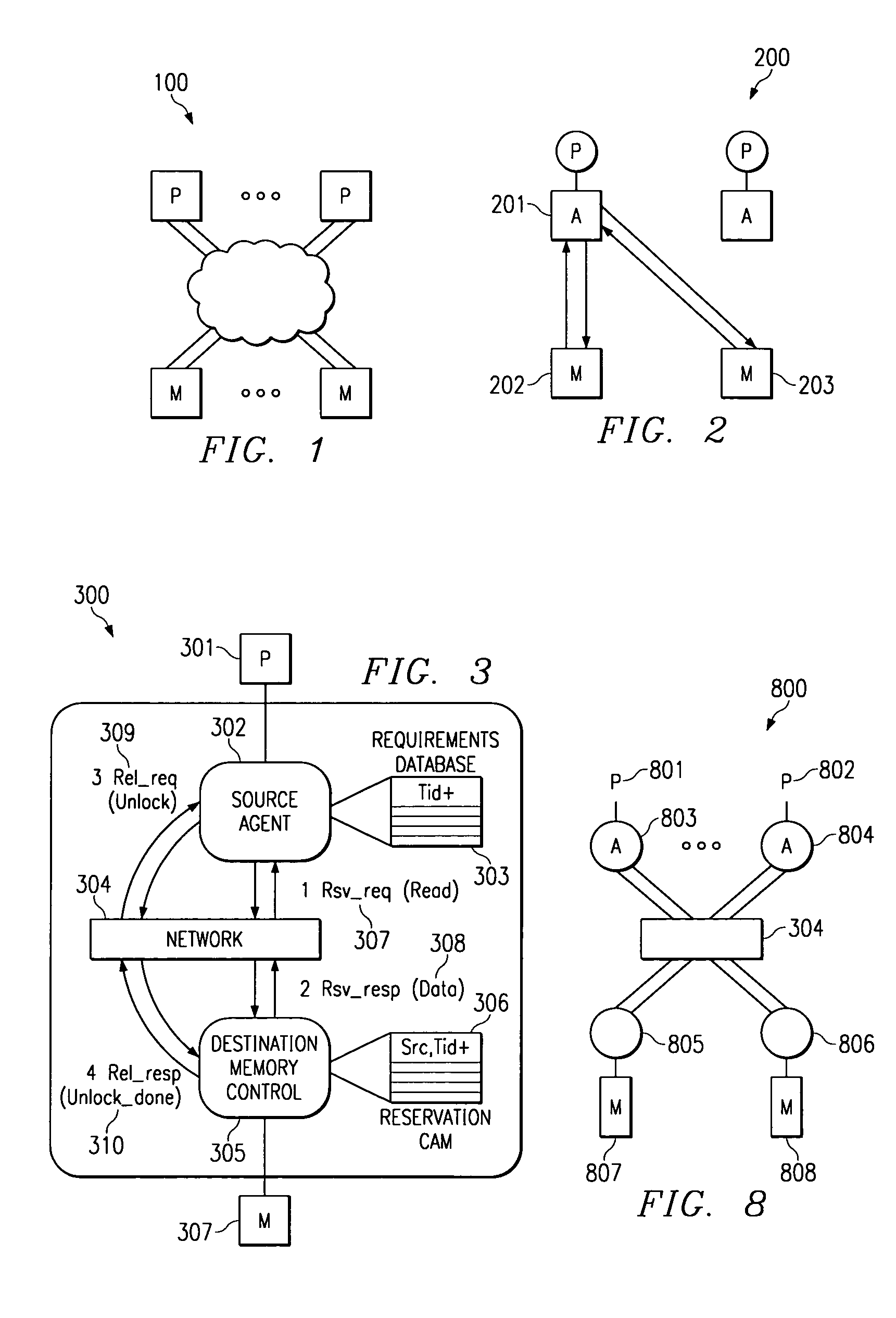

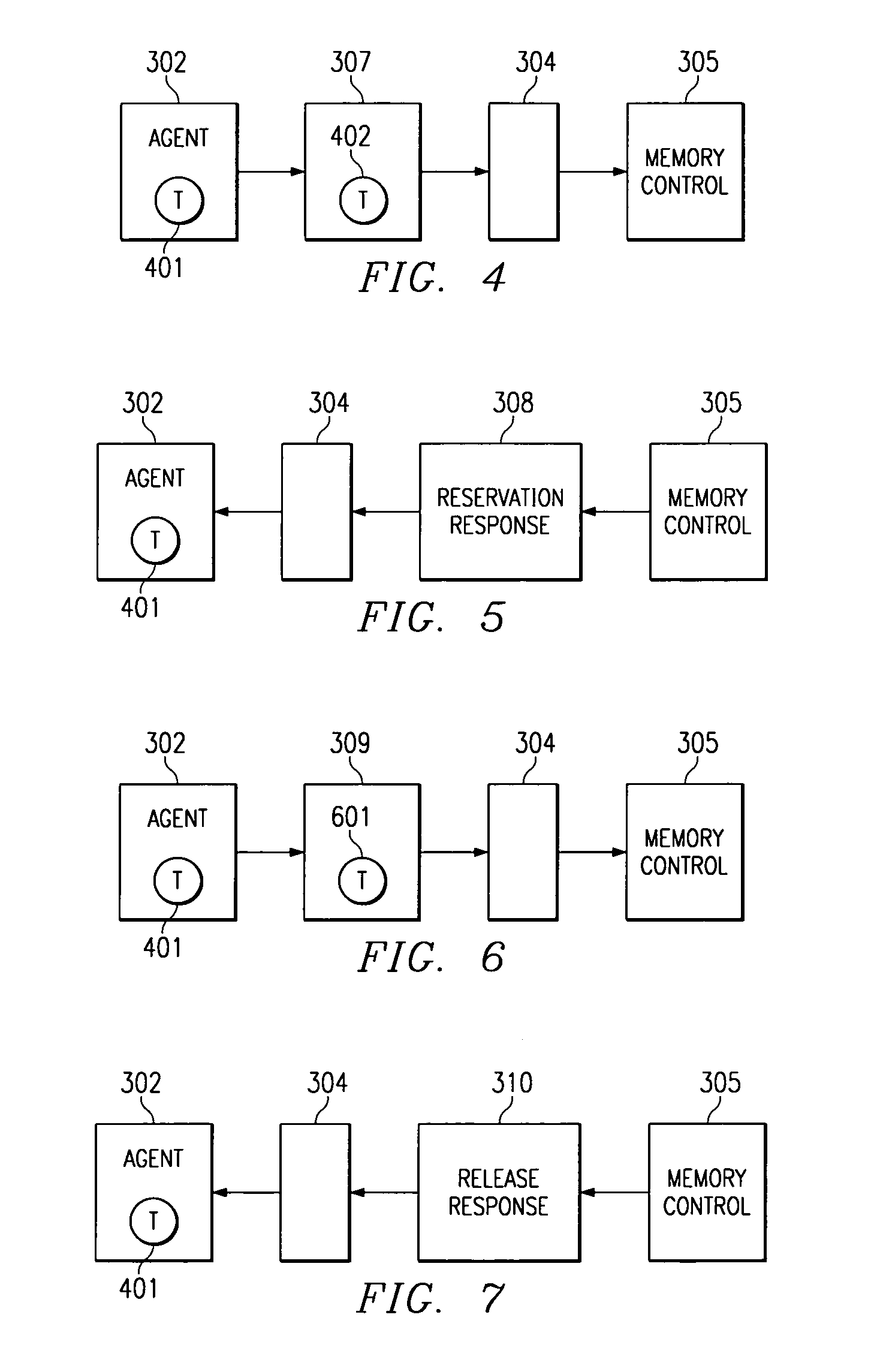

Protocol for insuring exactly once semantics of transactions across an unordered, unreliable network

InactiveUS7249192B1Completely successfulAvoid performanceError detection/correctionDigital data processing detailsNetwork connectionNetwork link

The present invention implements a mechanism for reliably communicating transaction messages between source and destination devices connected across an unreliable network, where a transaction is an operation requested by a source device of a destination device and where a plurality of messages are exchanged between source and destination in order to ensure completion of the transaction. Because the network linking the source and destination is unreliable, the source and destination operate to preserve data regarding the transaction messages which they have received and transmitted. If responsive messages are not timely received, they are generally resent. A dual timing system is preferably implemented to ensure that there are never two identical messages simultaneously in transmission through the network.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

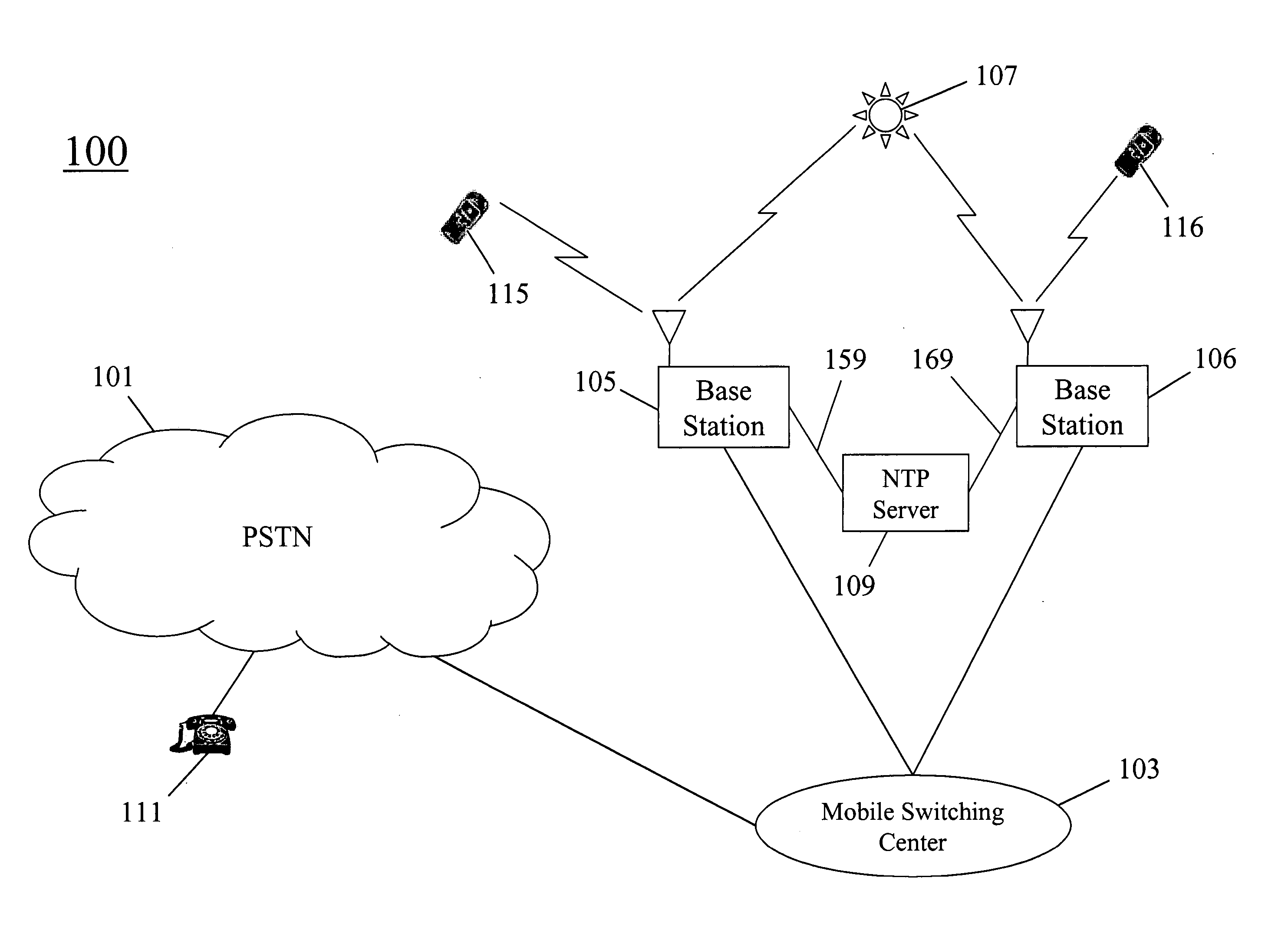

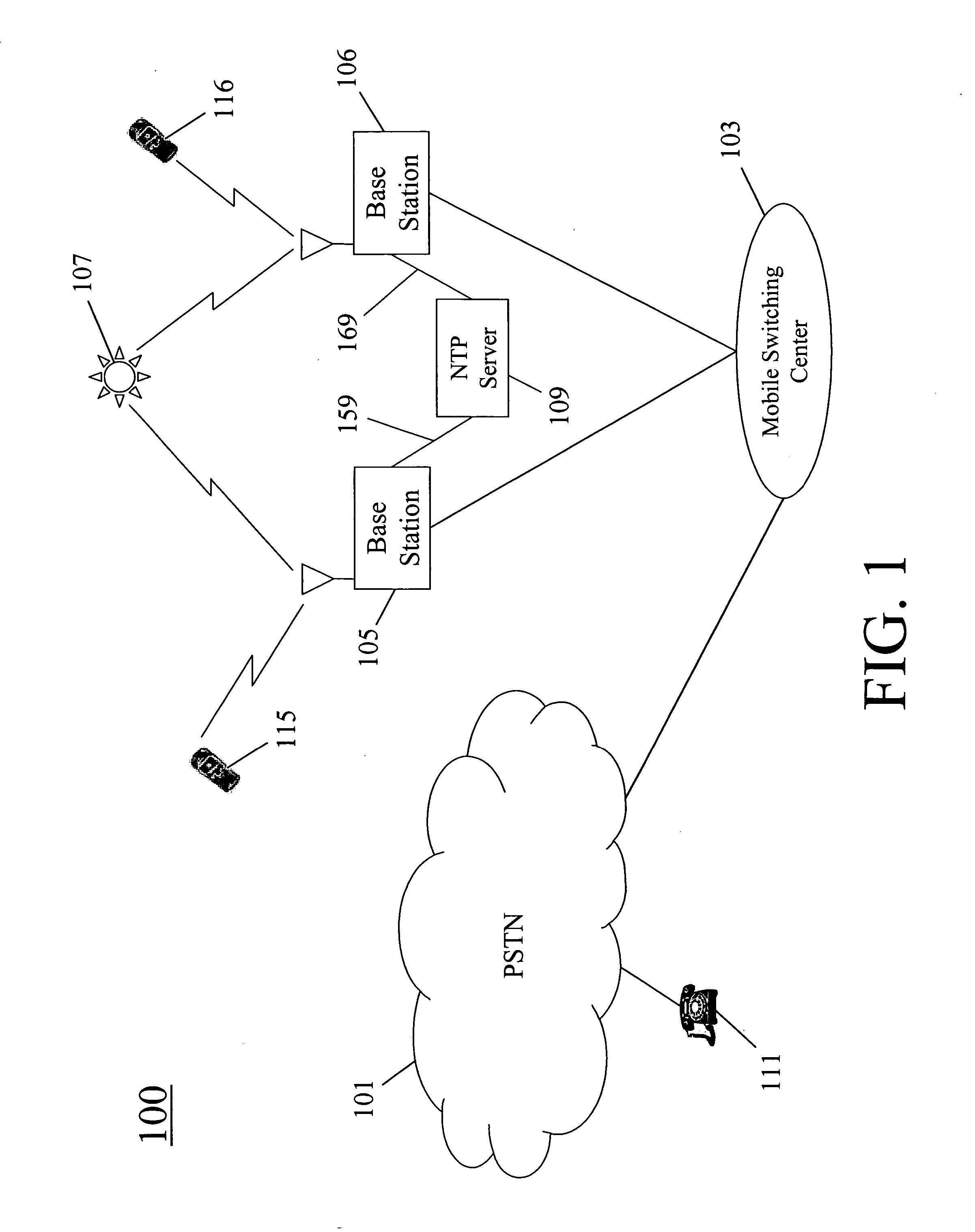

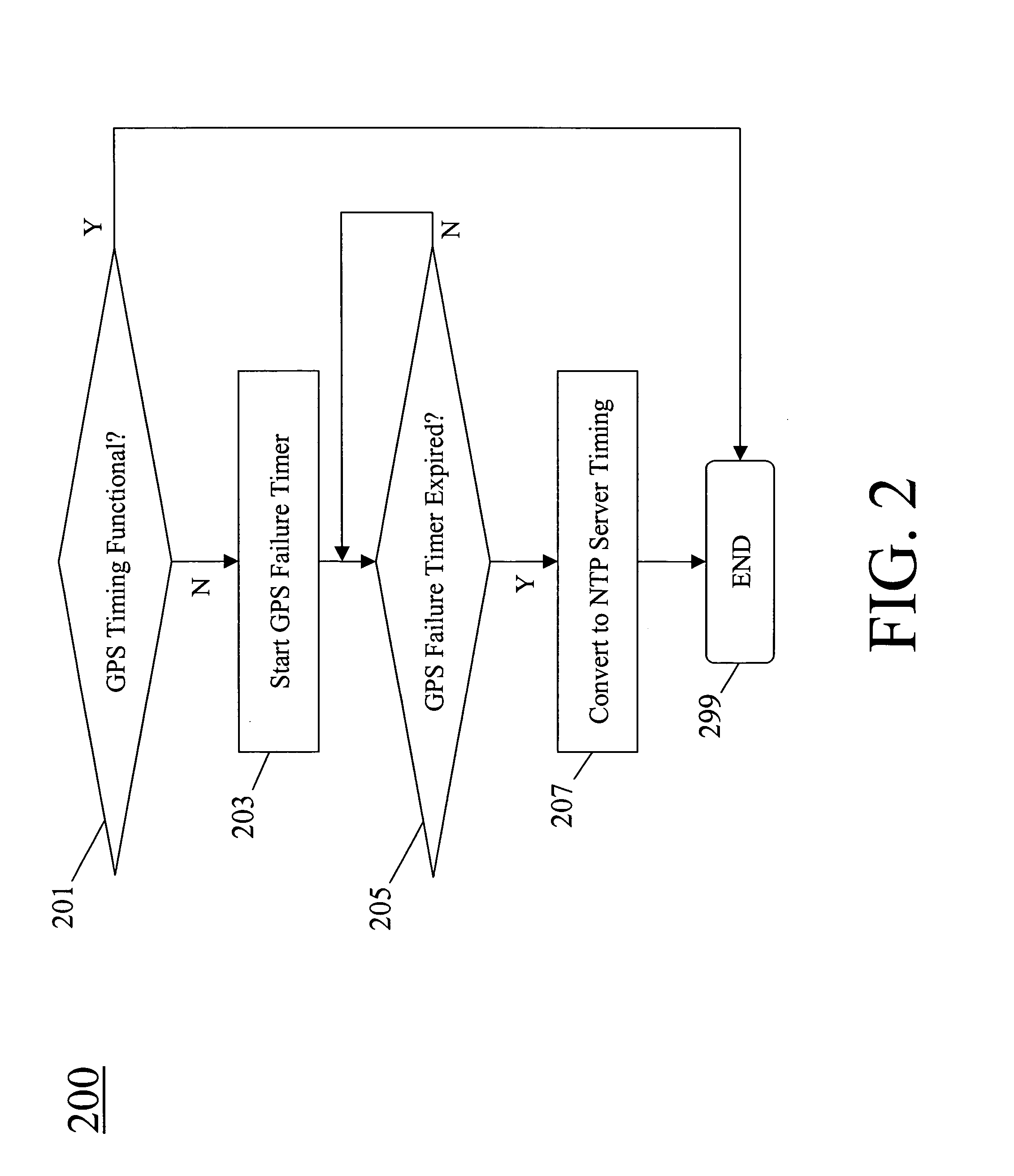

Method for utilizing a backup timing source when GPS becomes nonfunctional

InactiveUS20070177605A1Maintenance operationError preventionTransmission systemsCommunications systemTiming system

The present invention provides a method for utilizing a backup timing source in digital communication systems when GPS becomes nonfunctional. When a base station fails to receive an expected signal from a GPS satellite, a GPS failure timer is started. If the base station does not receive a signal from the GPS satellite prior to the expiration of the timer, the wireless communication system switches to a backup timing system, such as NTP (Network Time Protocol).

Owner:LUCENT TECH INC

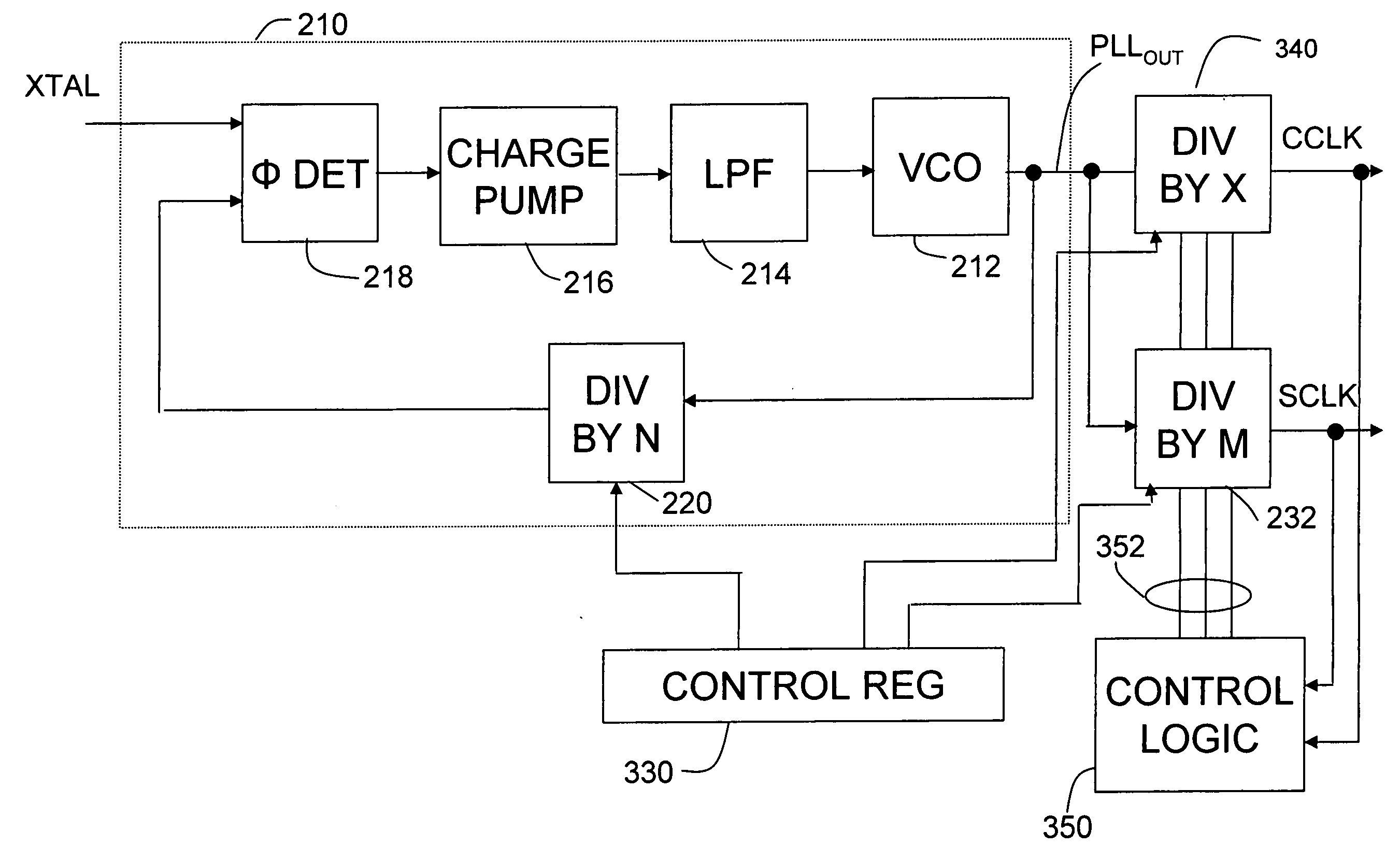

Microprocessor with power saving clock

ActiveUS20050184773A1Reduce clock frequencyEnergy efficient ICTPulse automatic controlDigital dataElectric force

A data processing chip with a flexible timing system and method for supplying clocks to a digital data processing system useful for power conservation. A phase locked loop generates a master clock from which a core clock and a system clock are derived. The frequency of each of the core and system clocks is independently controllable relative to the master clock and can be changed on the fly with glitch free and jitter free operation. The data processing chip is well suited for use in hand held electronic devices where power management is a concern. Power can be saved by lowering the frequency of the core clock, even for short intervals of time.

Owner:ANALOG DEVICES INC

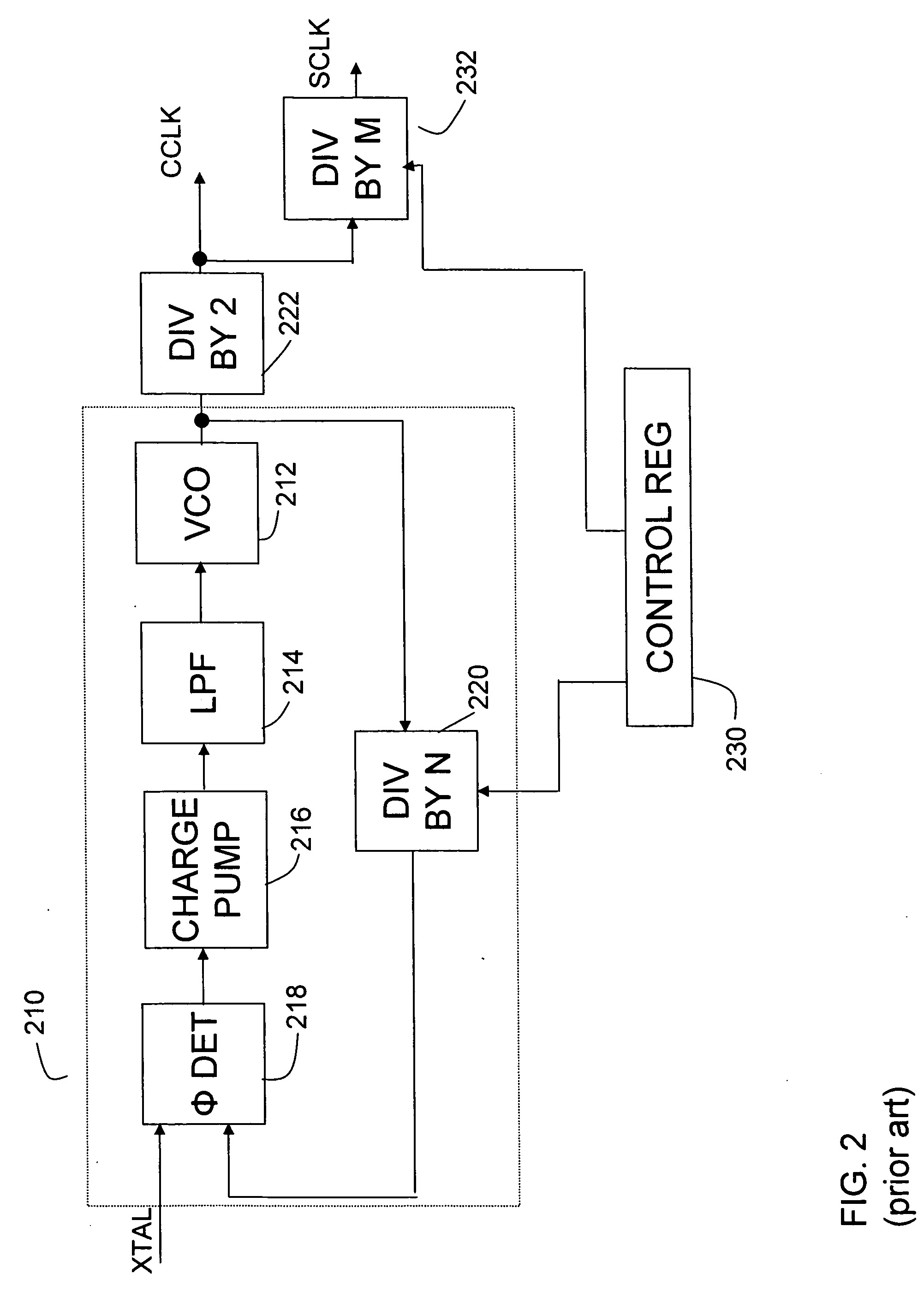

Timing system for modular cable modem termination system

InactiveUS7539208B2Synchronisation information channelsBroadcast transmission systemsFiberDigital subscriber line

A modular Cable Modem Termination System (CMTS) includes a packet shelf operating a Data Over Cable Service Interface Specifications (DOCSIS) Media Access Control (MAC) framer. One or more downstream Physical Interface (PHY) shelves receive DOCSIS data from the packet shelf over a packet switched network and modulate the DOCSIS data for sending on a downstream path of a cable plant. One or more upstream PHY shelves send DOCSIS data received from an upstream path of the cable plant over the packet switched network to the packet shelf. By separating the PHY components from the MAC and from the system software, the PHY components for a Hybrid Fiber Coax (HFC) plant may be replaced with different PHY components for other access technologies such as wireless, Digital Subscriber Lines (DSL), Ethernet-to-the-Home, Fiber-to-the-Home, or fiber Passive Optical Networks (PONs).

Owner:CISCO TECH INC

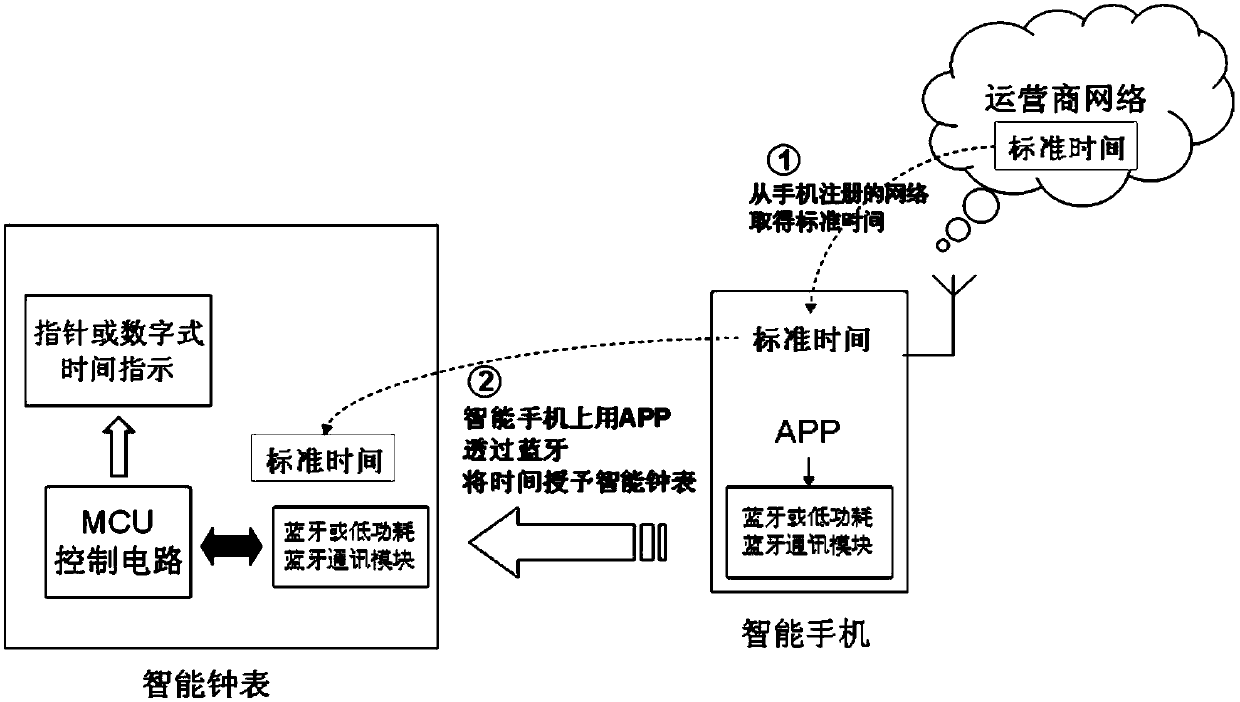

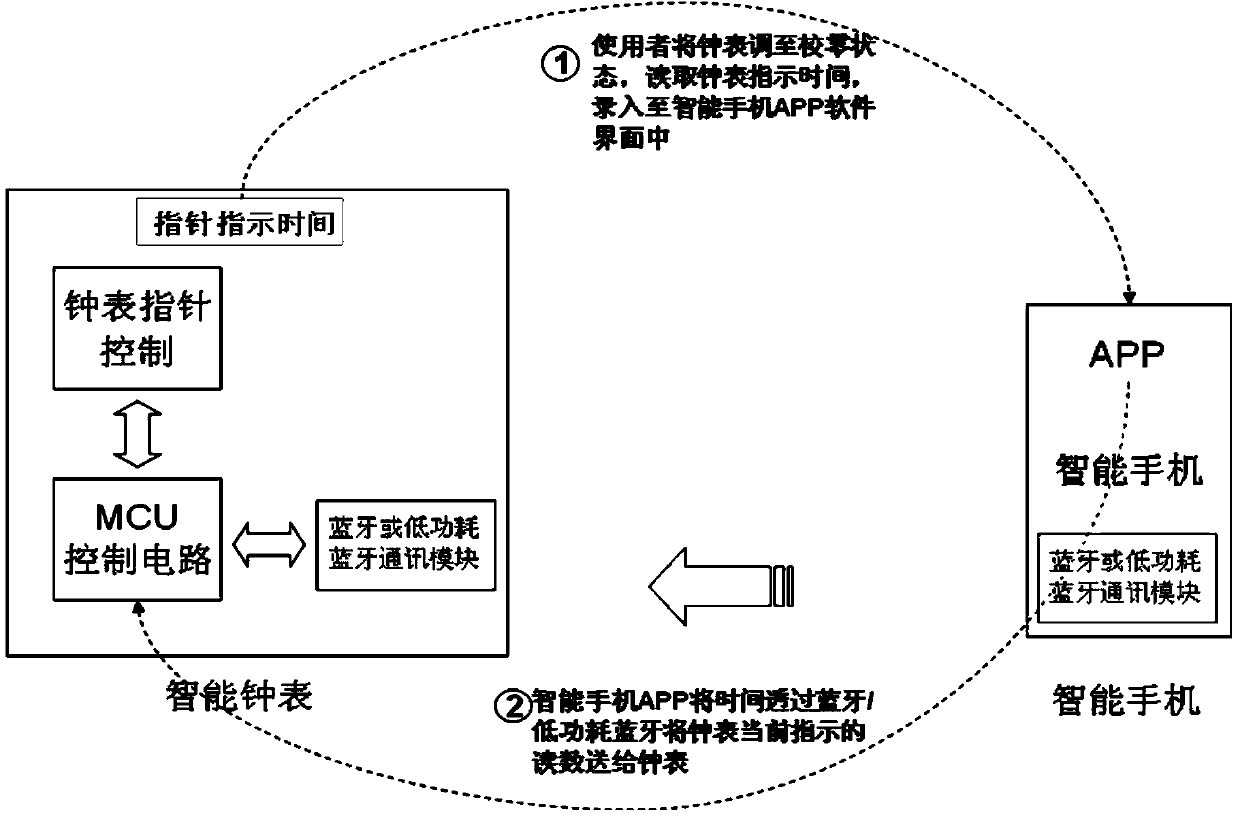

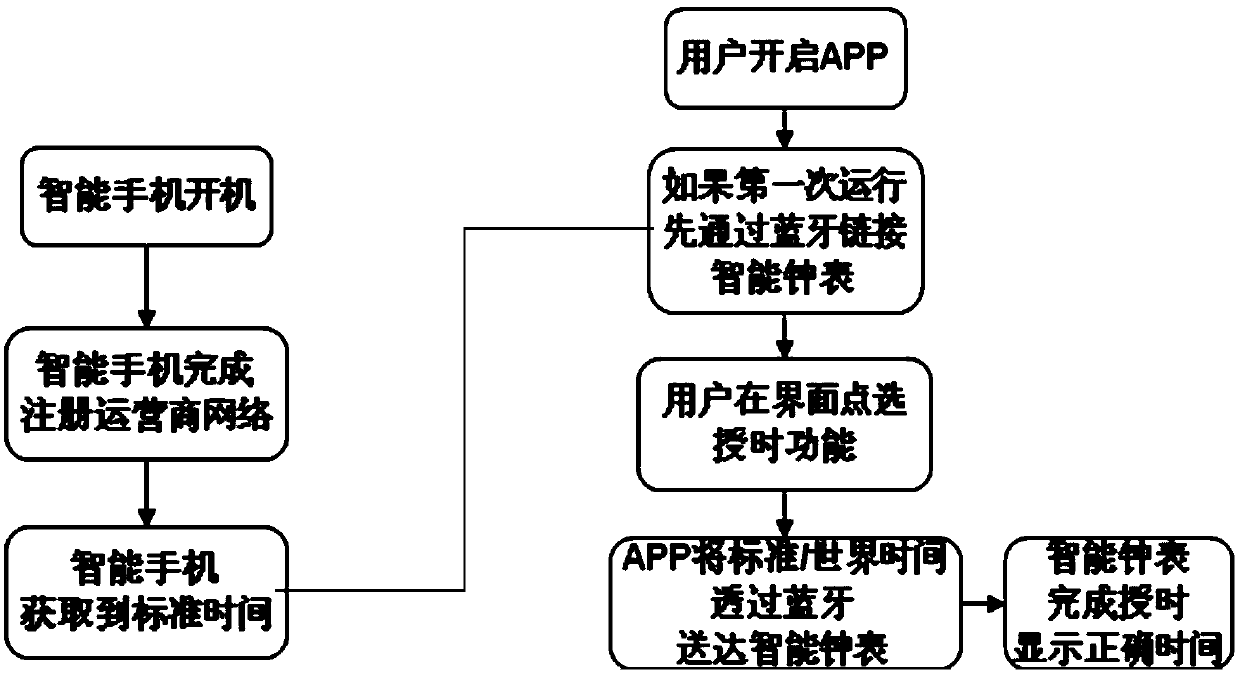

Bluetooth radio wave zero calibration and timing system and method

ActiveCN103995461AReduce labor intensityEasy to operateSynchronisation arrangementRadio-controlled time-piecesComputer moduleTime zone

The invention provides a Bluetooth radio wave zero calibration and timing system and method. The system comprises a display portion, an MCU circuit, an electric motor and a BLE communication module, wherein the display portion is an LCD display screen or a time indicating pointer and the LCD display screen, the BLE communication module is a Bluetooth module or a BLE module, the MCU circuit is adopted as a control circuit, the time calibration structure of most traditional radio wave clocks can be removed, cost can be reduced, meanwhile, the clocks can be made to be more durable, timing and calibration can be automatically achieved for a long time at regular intervals, the daily rate can be corrected, a precise deviation rectification mechanism can be built in an internal chip of each clock, labor cost and labor intensity can be greatly reduced, and the clocks with the low cost can obtain the time precision identical to that of a clock with the high cost. The problem that the radio wave clocks cannot accurately display time under the state without the radio wave signals is solved, and meanwhile the aim that when a user reaches different countries, adjustment of different time zones can be performed is easily achieved.

Owner:SHENZHEN TIANHAIBA WACTHES CO LTD

System and method for communication in wireless power supply systems

ActiveCN103427499AThe received power changesPrevent or reduce lossEnergy efficient ICTNear-field transmissionTelecommunicationsEngineering

The present invention relates to wireless power supplies adapted to supply power and communicate with one or more remote devices. The systems and methods of the present invention generally relate to a communication timing system that may ensure information being communicated does not overlap with that of another device, preventing data collisions and information from going undetected. With information being communicated in a way that addresses or avoids potential communication issues in multiple device systems, the wireless power supply may control operation to effectively supply wireless power.

Owner:PHILIPS IP VENTURES BV

Back-up power system for a traction elevator

A back-up power system for a traction elevator is provided with a power sensing device to sense a power loss or irregularity of the normal control power; an inverter timing system connected to the power loss sensing device, where the inverter timing system receives a power sensing signal from the power sensing device; and a back-up power generating system communicating with the inverter timing system, where the back-up power generating system generates an output to provide back-up power to the elevator system.

Owner:REYNOLDS & REYNOLDS ELECTRONICS

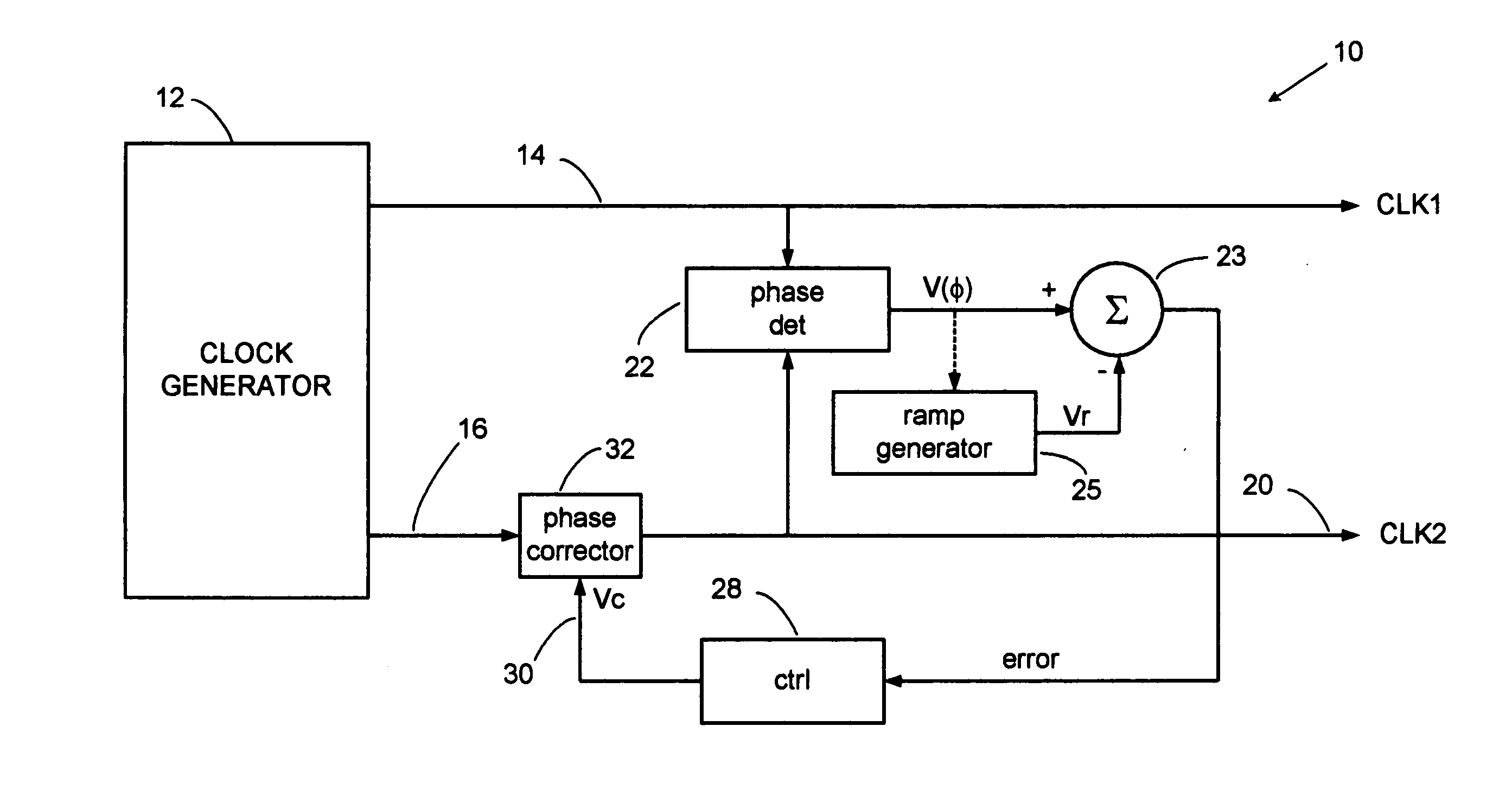

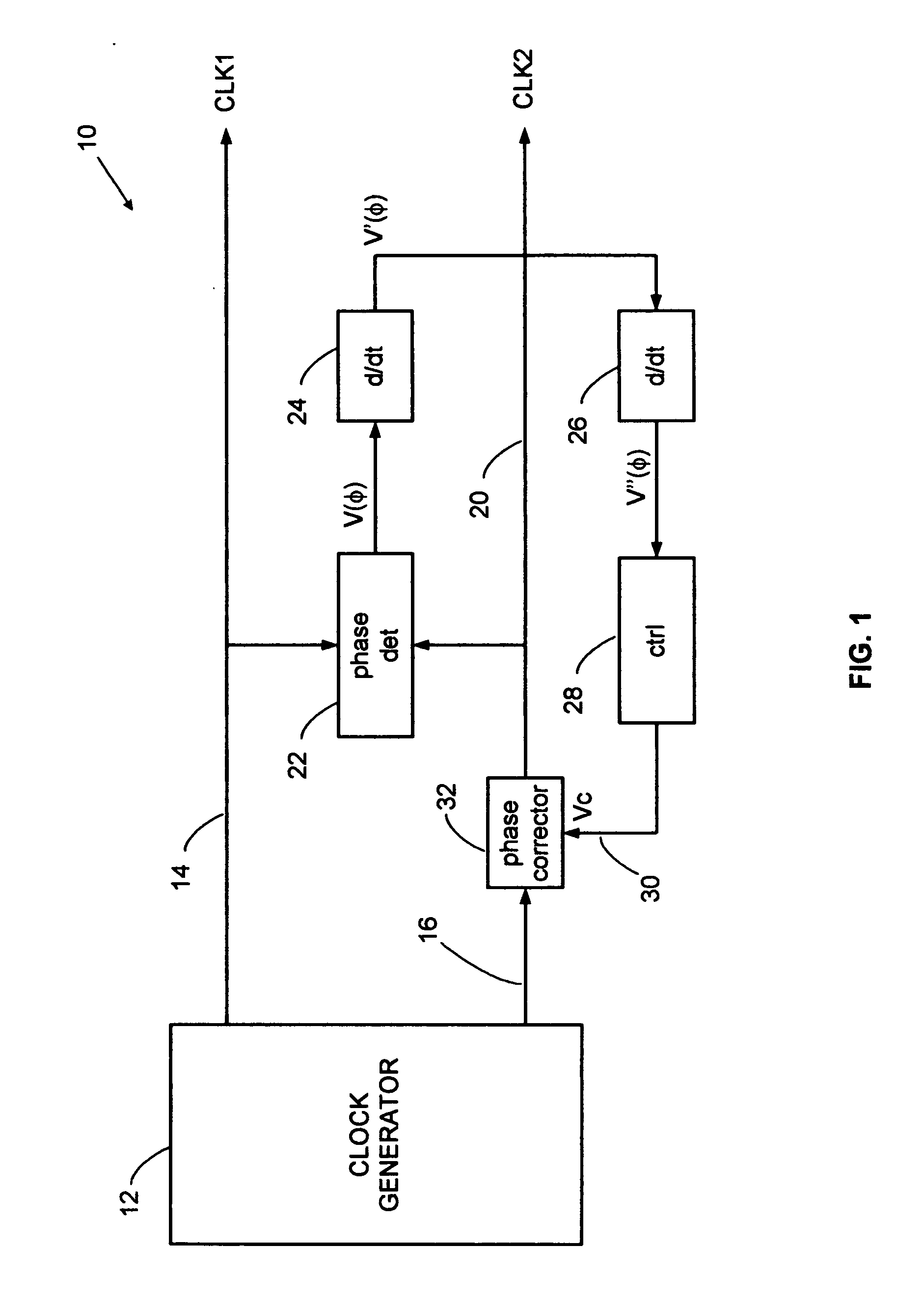

Error corrector for radar timing systems

InactiveUS20070210955A1Reduce biasOvercome limitationsRadio wave reradiation/reflectionPhase correctionRadar

A feedback loop corrects timing errors by reducing deviations from a constant radar sweep rate. Errors are detected and fed back to a phase corrector in a high gain feedback system. A precision radar rangefinder can be implemented with a direct digital synthesizer (DDS) that includes feedback error correction for reducing range errors by, for example, 100 times, or to 0.1 mm. An error-corrected DDS swept timing system can enable a new generation of highly flexible, repeatable and accurate radar, laser and guided wave rangefinders.

Owner:MCEWAN TECH

Method and Apparatus for Single-Trip Time Progressive Wellbore Treatment

ActiveUS20120138311A1Improve conductivityShorten the timeFluid removalWell/borehole valve arrangementsEngineeringTiming system

A single trip multizone time progressive well treating method and apparatus that provides a means to progressively stimulate individual zones through a cased or open hole well bore. The operator can use pre-set timing devices to progressively treat each zone up the hole. At each zone the system automatically opens a sliding sleeve and closes a frangible flapper, at a preselected point in time. An adjustable preset timing device is installed in each zone to allow preplanned continual frac operations for all zones. An optional “Stand-Down-Mode” can be integrated into the timing system so that if pumping stops the timers go into a sleep mode until the pumping resumes. The apparatus can consist of three major components: a packer, a timing pressure device, and a sliding sleeve / isolation device. The packer may be removed.

Owner:COMPLETION TOOL DEV

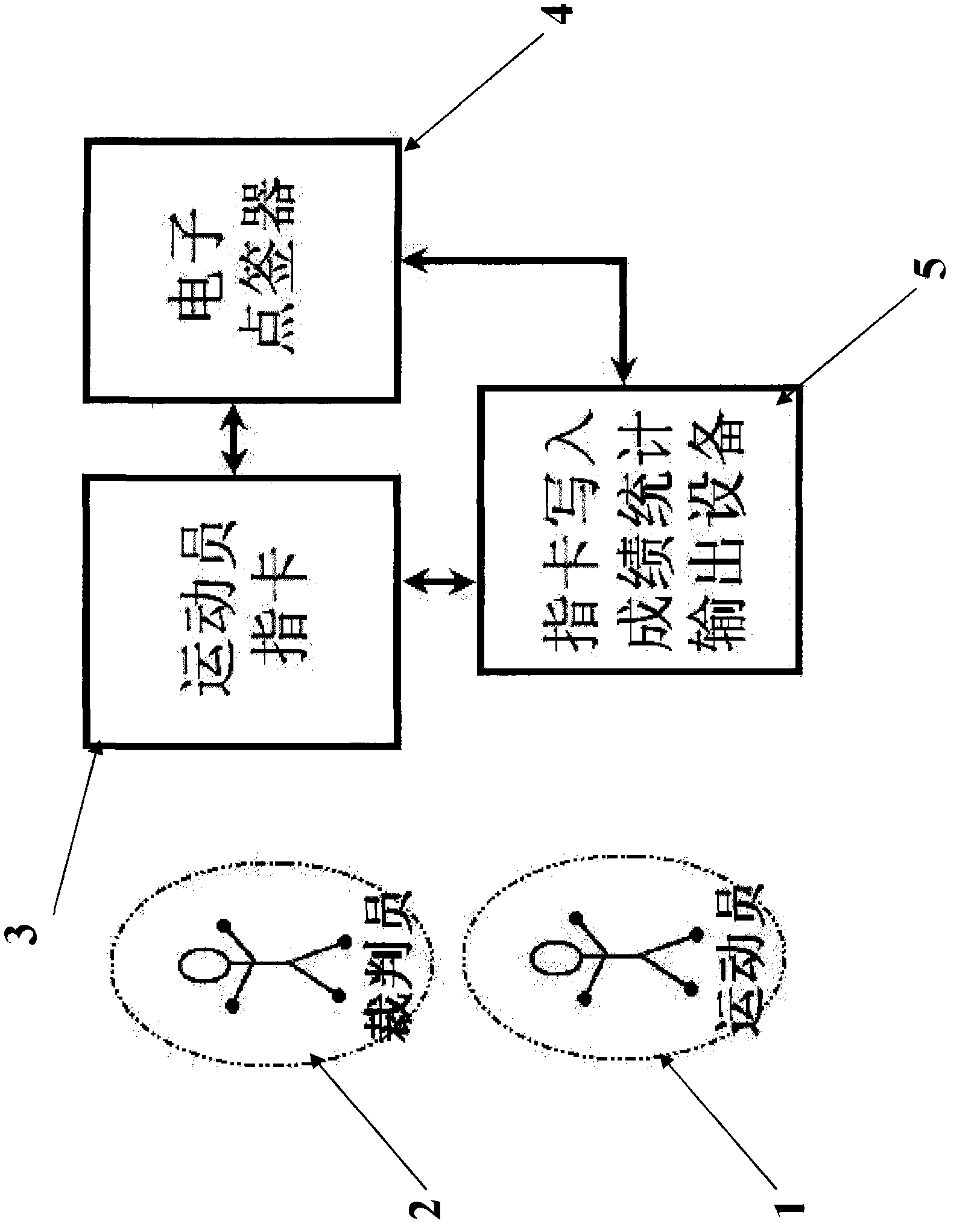

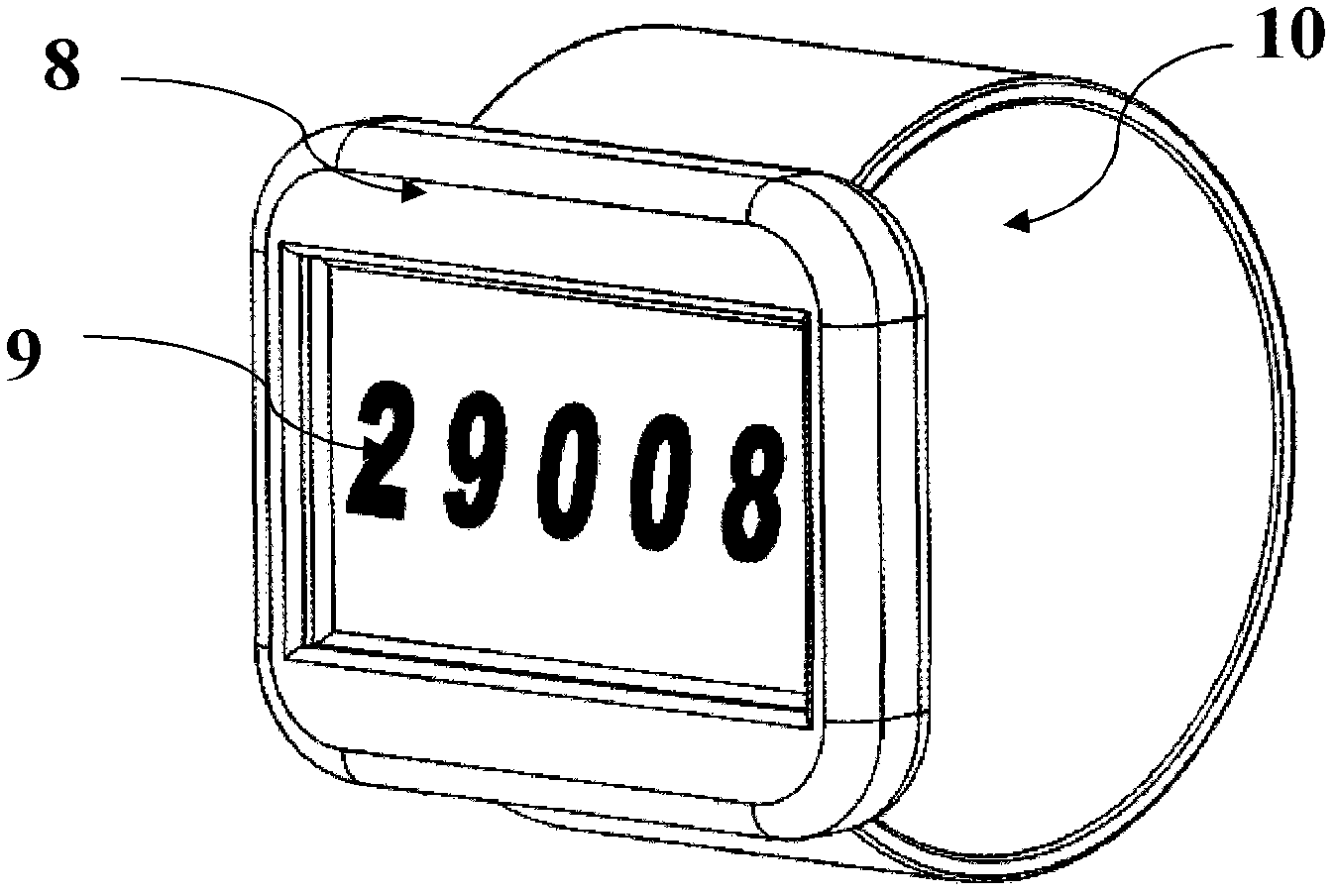

Orienteering and direction-finding fixed station and fingerprint identity identification electronic timing system

ActiveCN102999952AReduce constructionReduce construction costsRegistering/indicating time of eventsSports activityTiming system

The invention relates to a sports competition information collection and result calculation device, and especially relates to an orienteering and direction-finding fixed station and fingerprint identity identification electronic timing system. The device can collect information (comprising athlete personal information, competition information and the like) and result (comprising athlete personal competition information value, result validity and the like) statistics in orienteering and radio direction-finding competition activities. The system has the advantages of punch-card station construction in orienteering and radio direction-finding competitions, substantially-reduced maintenance cost, suitableness for the extensive and batch construction of permanent punch-card stations, and realization of the very easy implementation of mass sports activities. Simultaneously the system has the athlete fingerprint collection, storage and comparison functions, can fundamentally avoid and awe cheat phenomena comprising running for an another person and the like existing in the competition activities for a long term, and maintains the justice and the seriousness of the competition activities.

Owner:北京乐恩嘉业体育发展有限公司

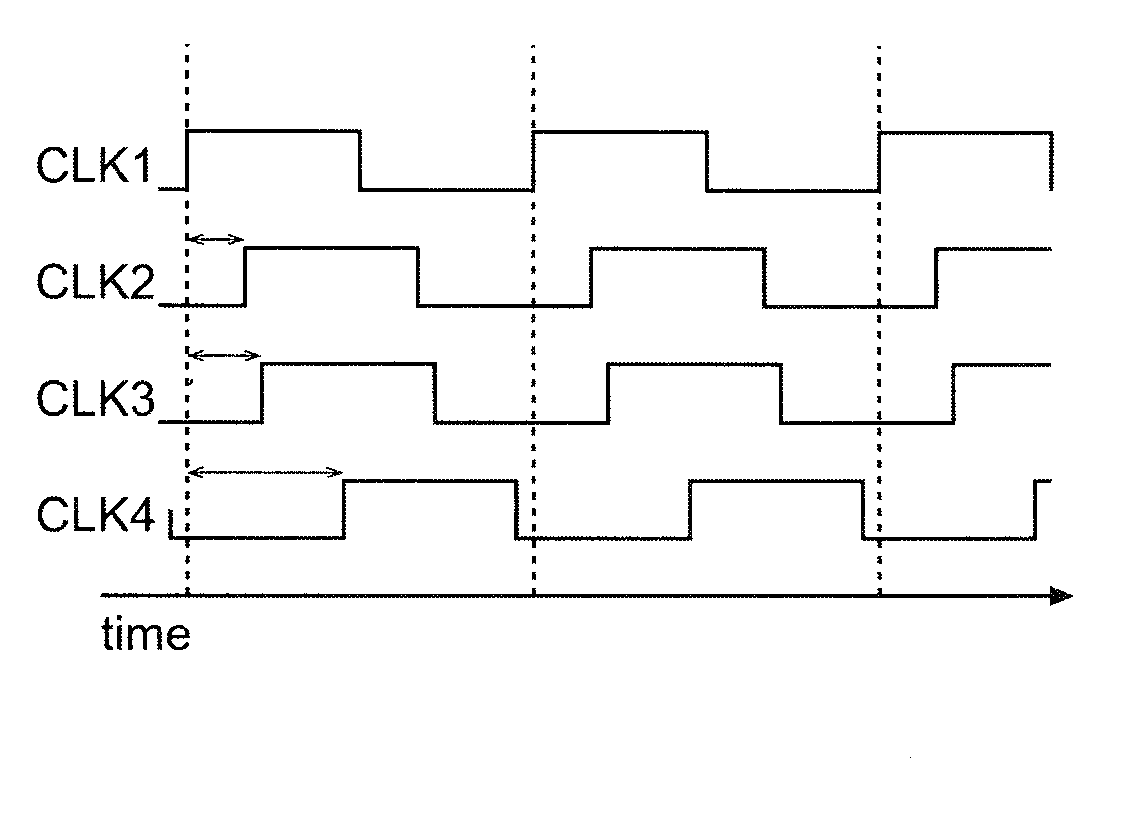

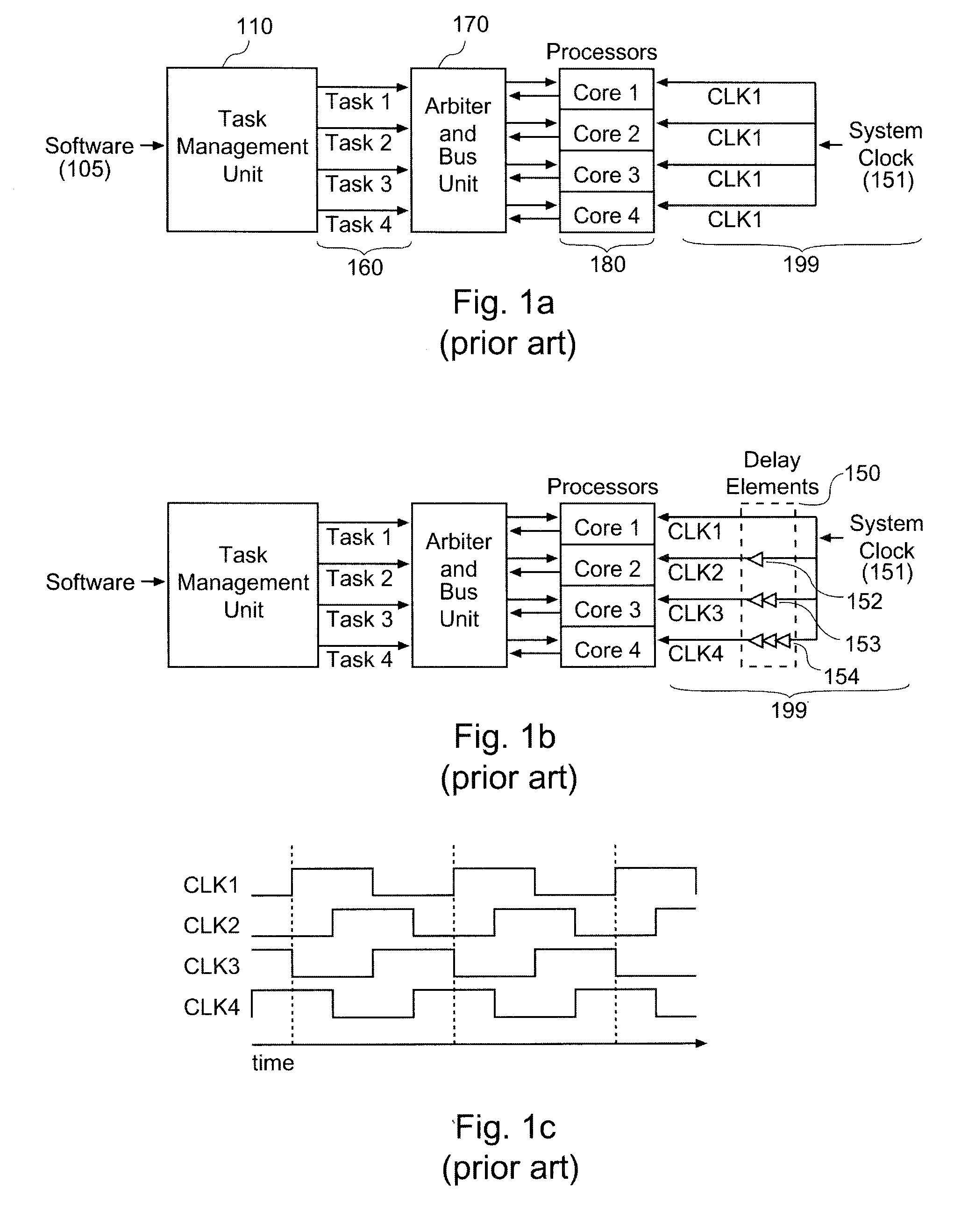

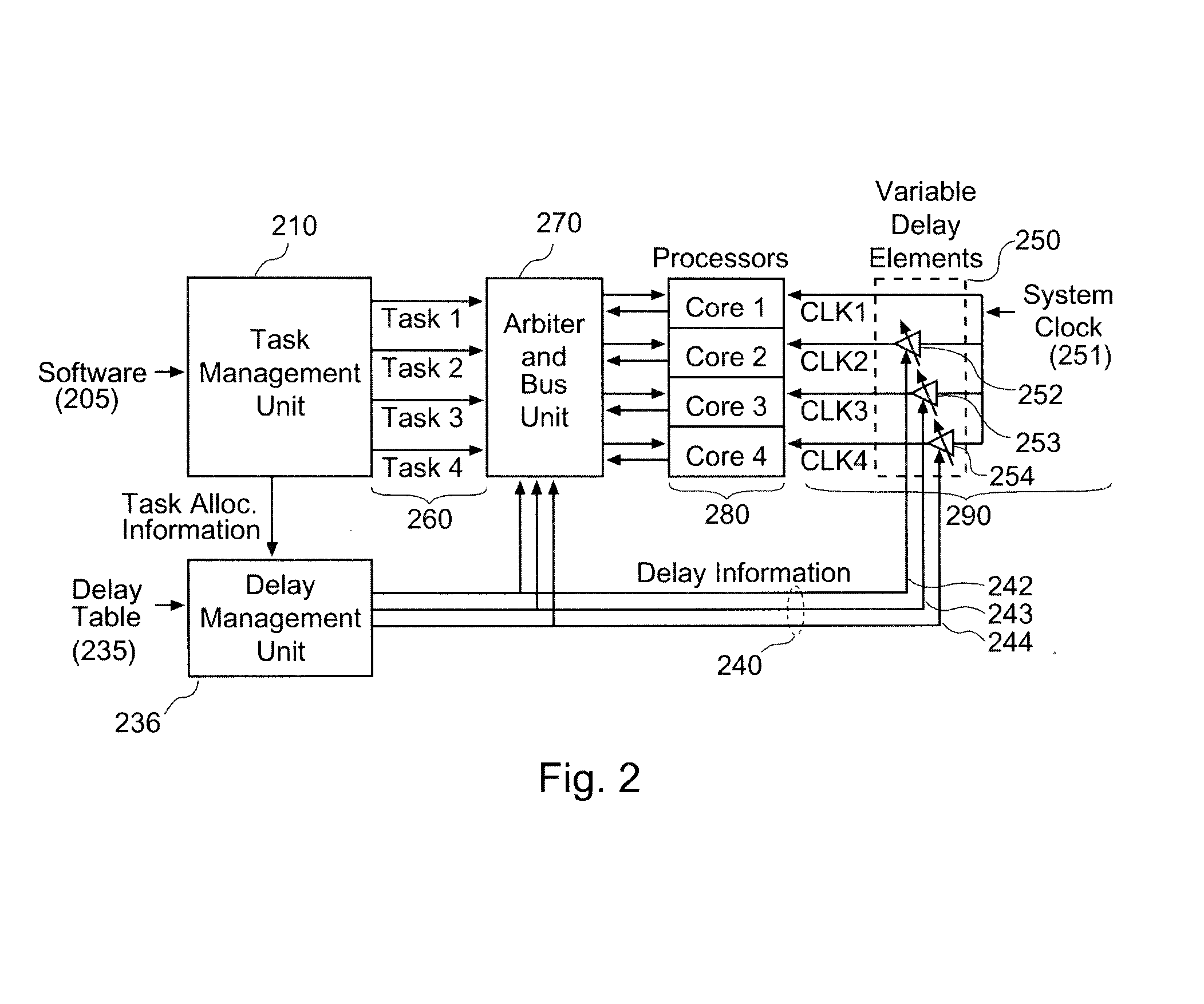

Systems and Methods for Reducing di/dt Using Clock Signals Having Variable Delays

InactiveUS20080141062A1Generating/distributing signalsTransmission path multiple useManagement unitEngineering

Systems and methods for managing power consumption in an integrated circuit to reduce the rate of change of current (di / dt) in the integrated circuit. One embodiment comprises a system having multiple processor cores. A timing system provides each of the processor cores with a corresponding operating clock signal. The timing system uses variable delay elements to impart variable delays to the clock signals. A delay management unit determines the delays that should be used by the task processing units in executing their assigned tasks and provides this information to the variable delay elements to set the appropriate delays in each of these elements. The delay information is also provided to a task management unit, which assigns the tasks to specific processor cores based upon the delays selected by the delay management unit, so that consecutively fired processor cores are not adjacent to each other.

Owner:KK TOSHIBA