Patents

Literature

301787results about How to "Improve reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

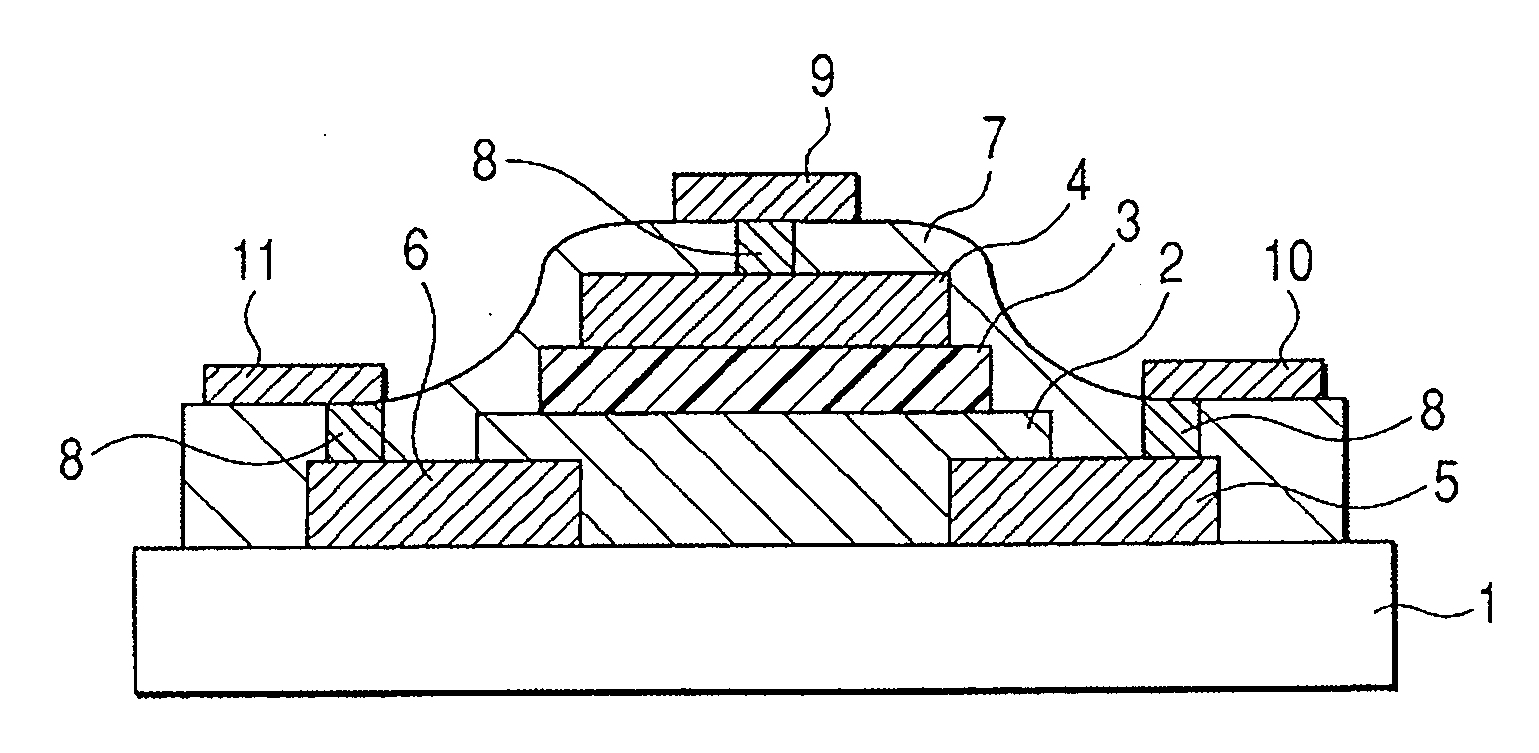

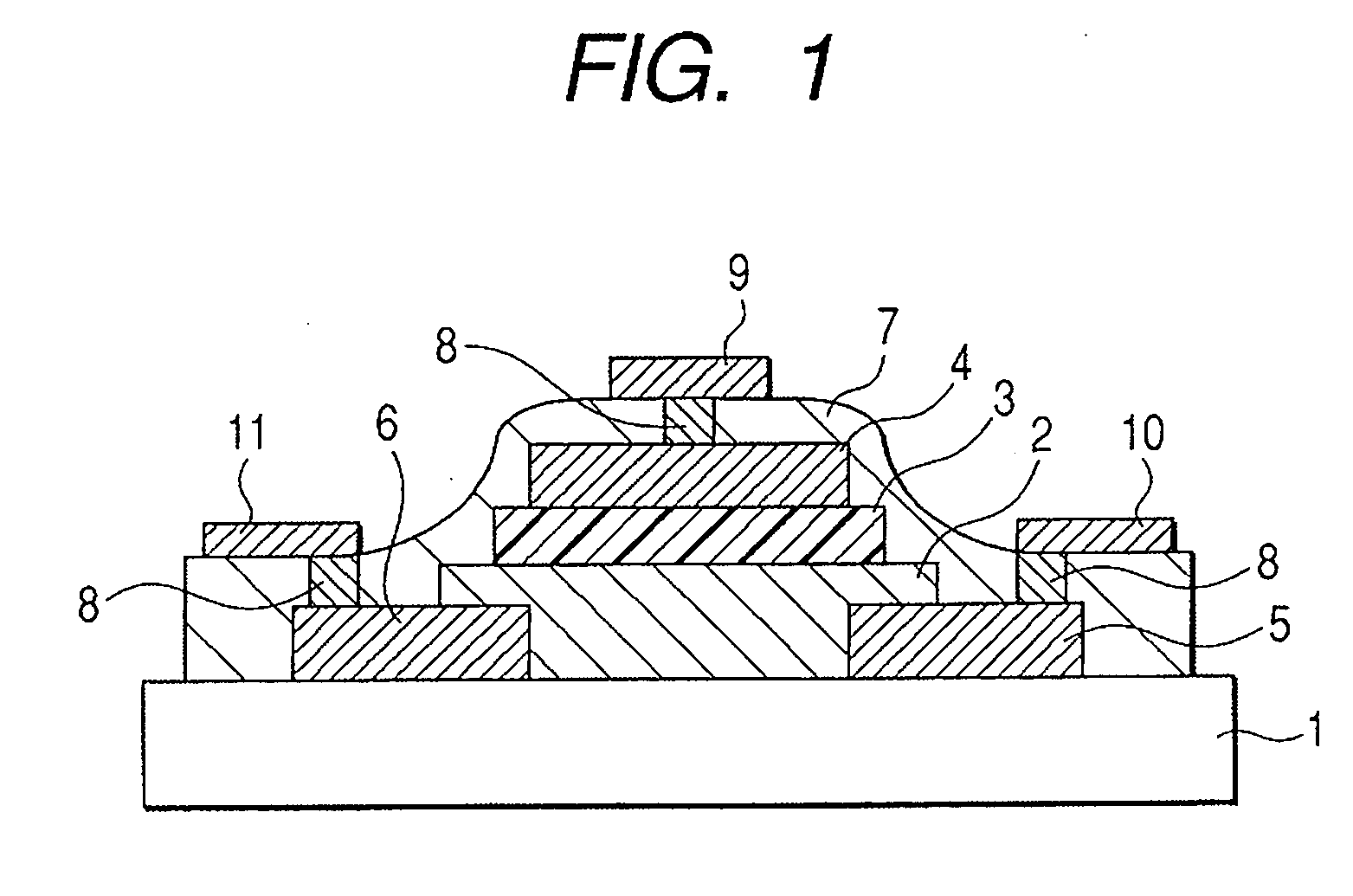

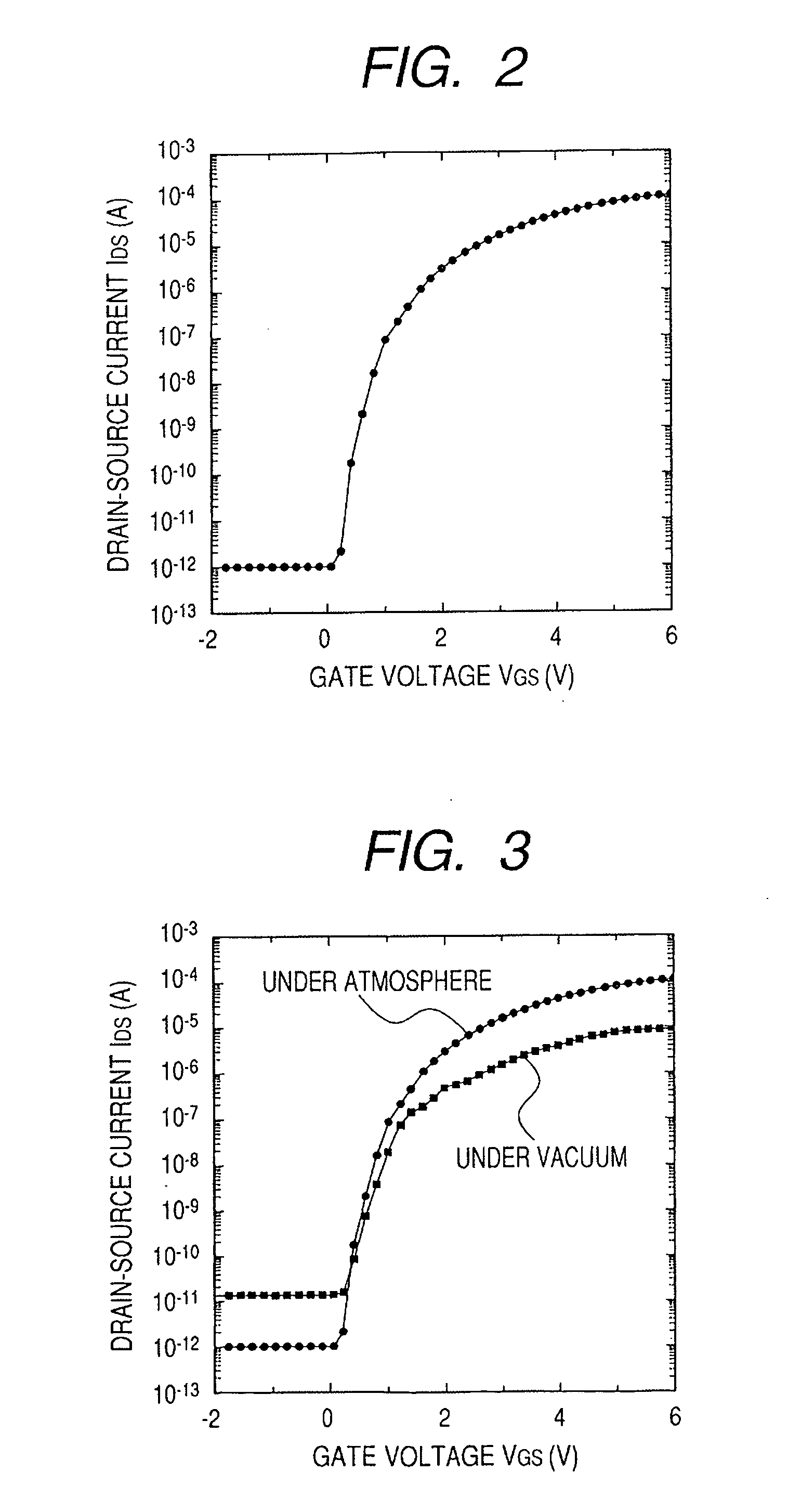

Oxide semiconductor thin film transistor and method of manufacturing the same

InactiveUS20070052025A1Improve reliabilityUnstability of may lessenSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Provided is a thin film transistor comprising a channel layer comprised of an oxide semiconductor containing In, M, Zn, and O, M including at least one selected from the group consisting of Ga, Al, and Fe. The channel layer is covered with a protective film.

Owner:CANON KK

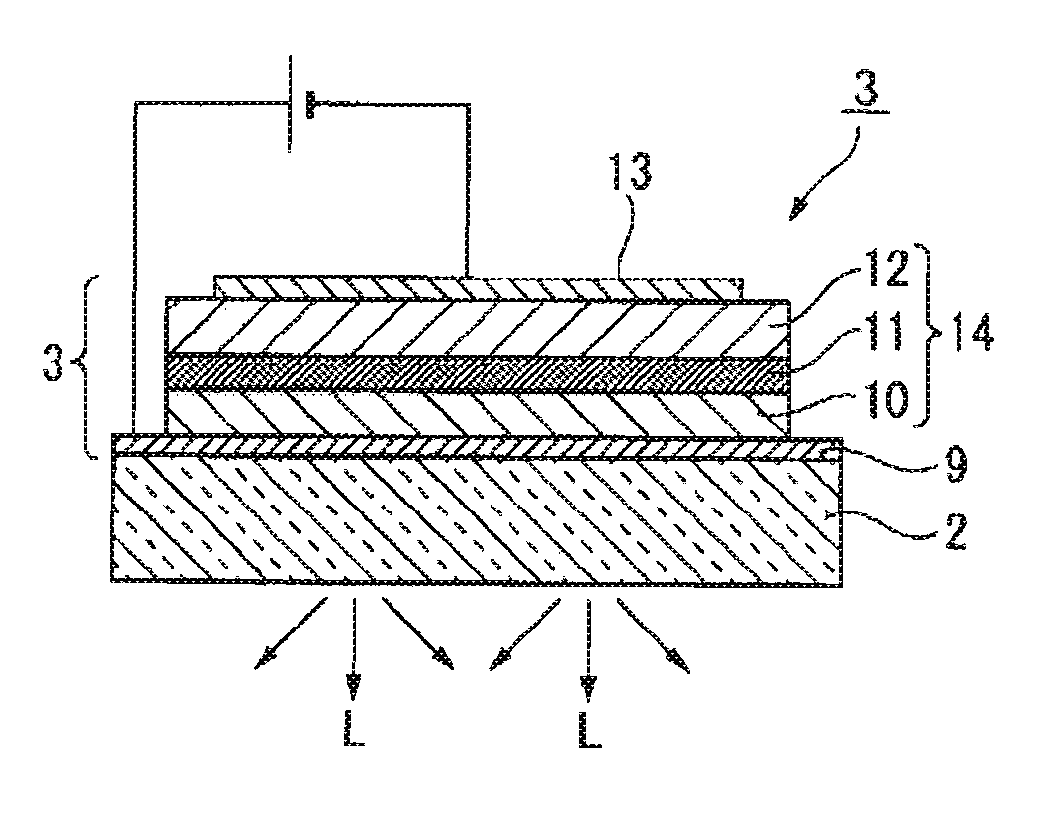

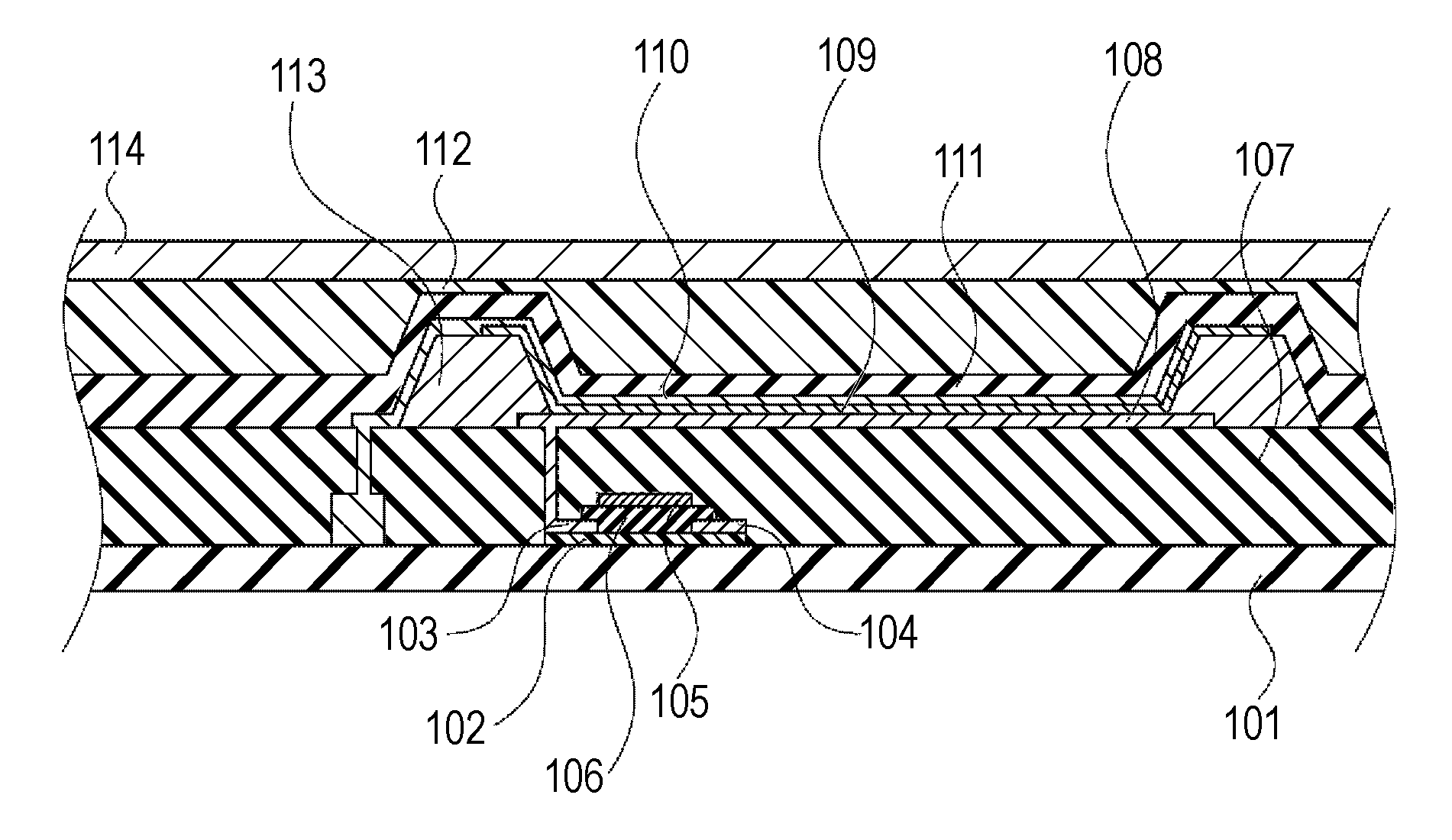

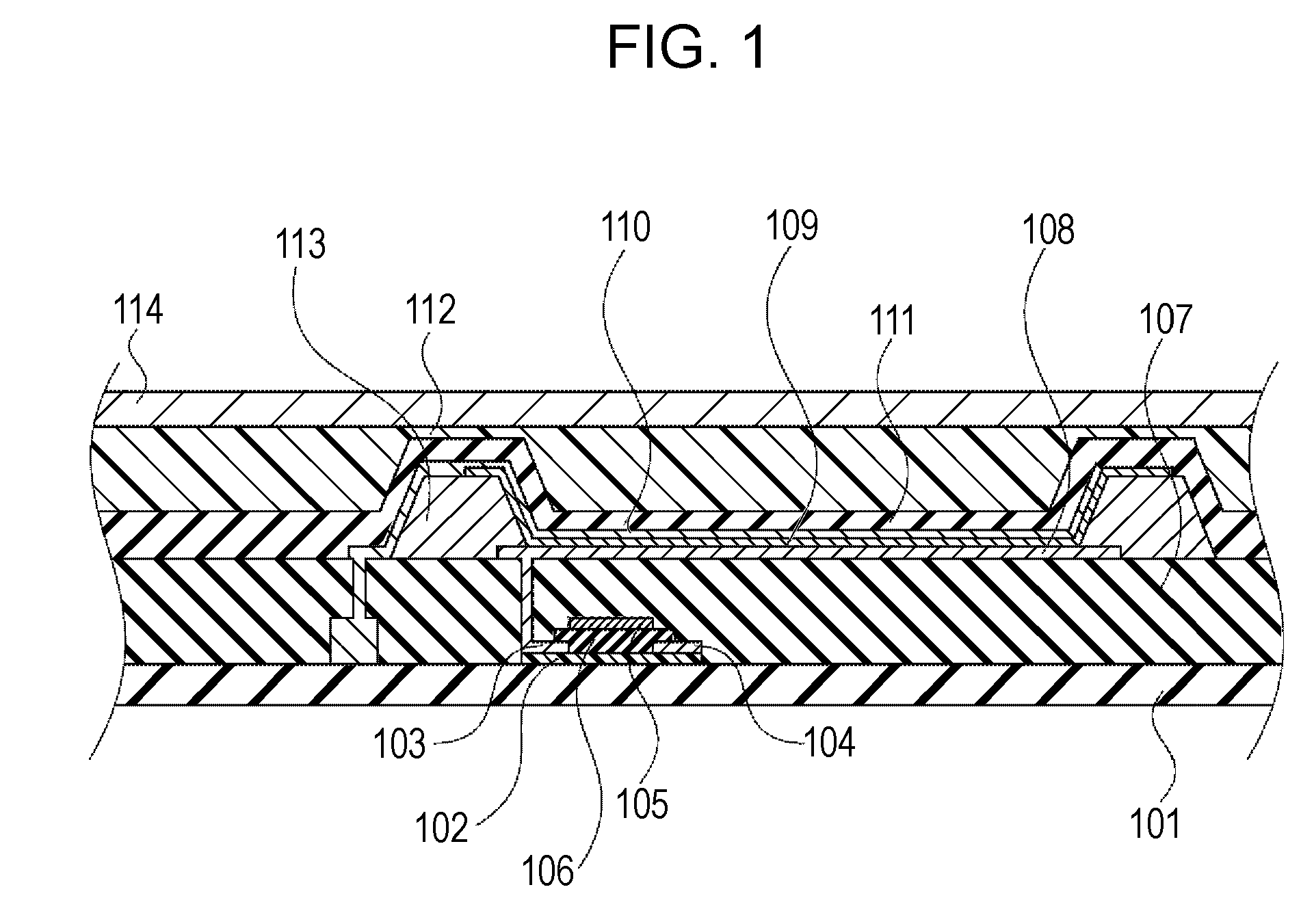

Electronic device, organic electroluminescence device, and organic thin film semiconductor device

InactiveUS20080106191A1Easy to manufactureImprove reliabilityCellsDischarge tube luminescnet screensSolid state electrolyteElectrolysis

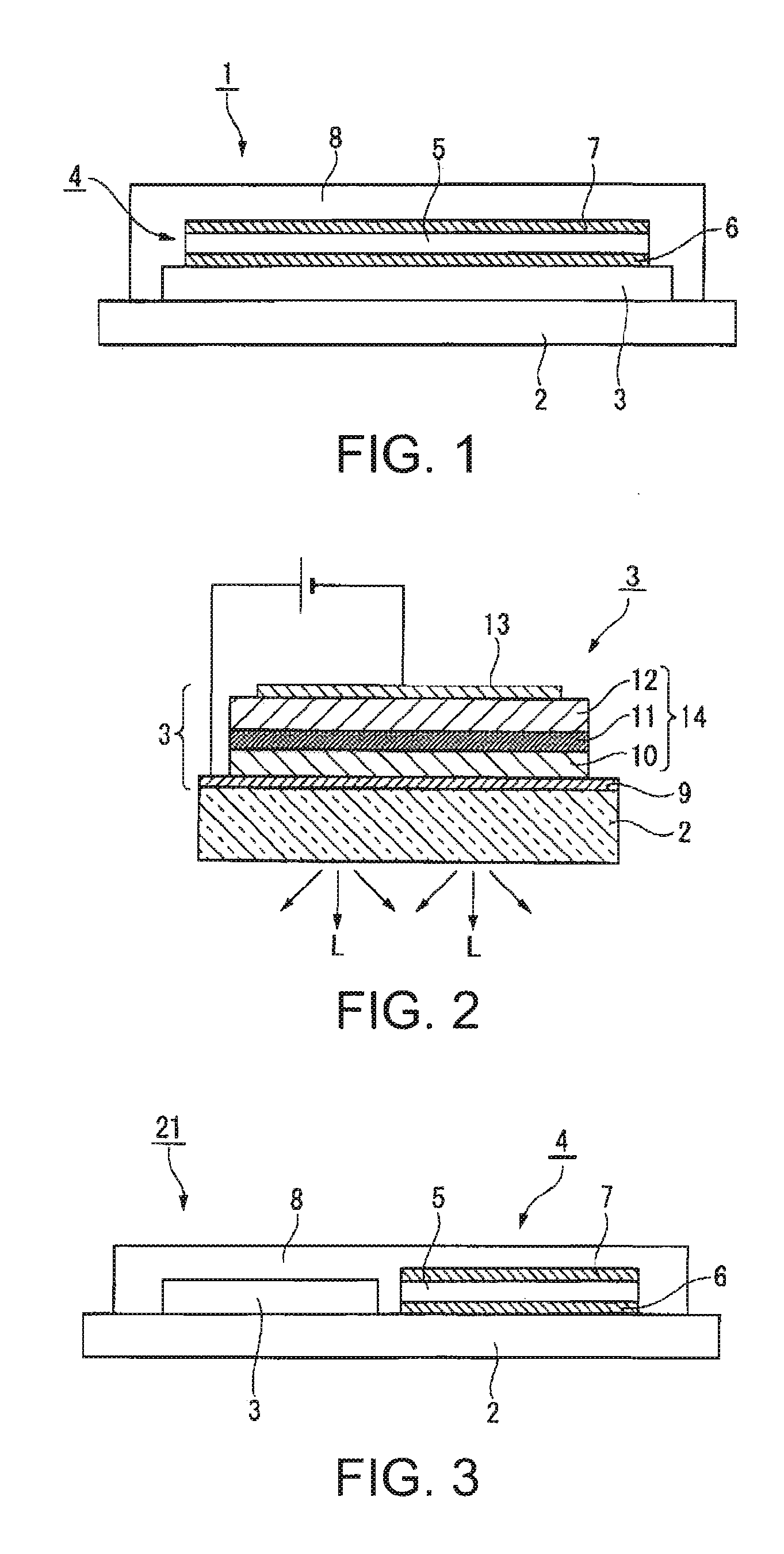

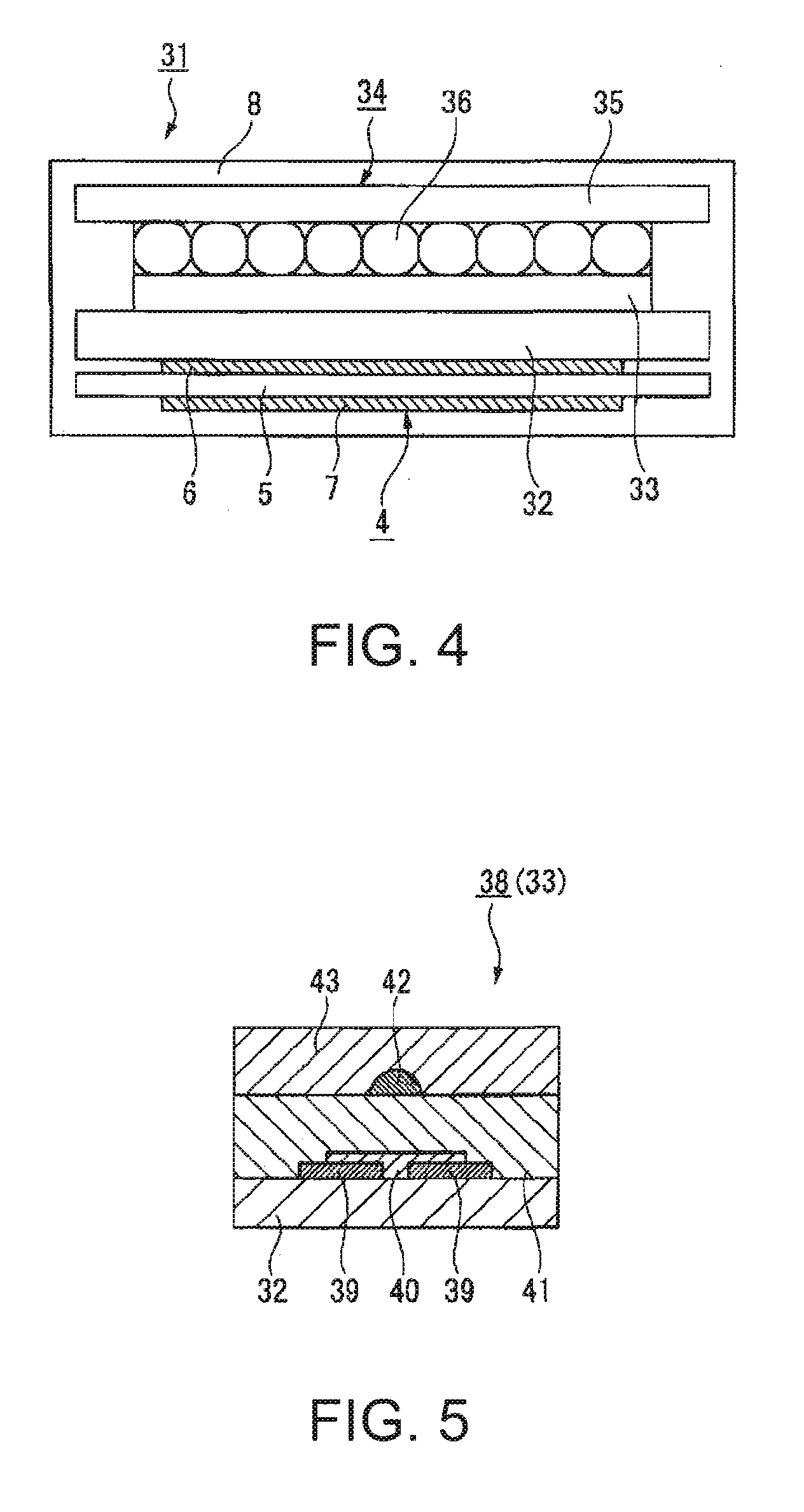

An electronic device includes a substrate, a functional element formed on the substrate, an electrolytic element provided on at least one of a side of the substrate on which the functional element is formed and a side of the substrate opposite to the side on which the functional element is formed, configured including a solid-state electrolyte layer and a pair of electrodes for holding the solid-state electrolyte layer in between, and capable of applying electrolysis to water, and a sealing member for sealing the functional element and the electrolytic element.

Owner:SEIKO EPSON CORP

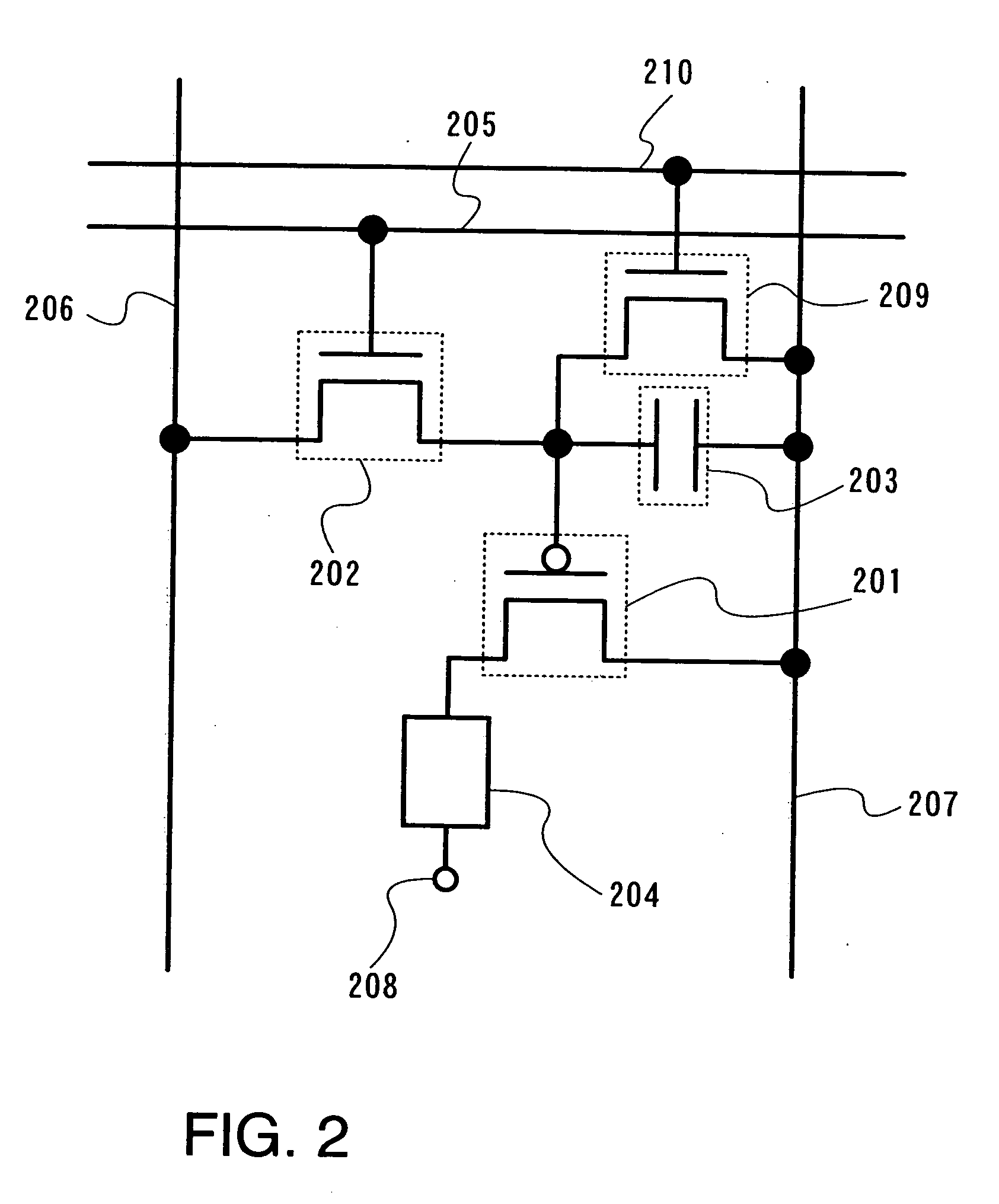

Semiconductor device and display device

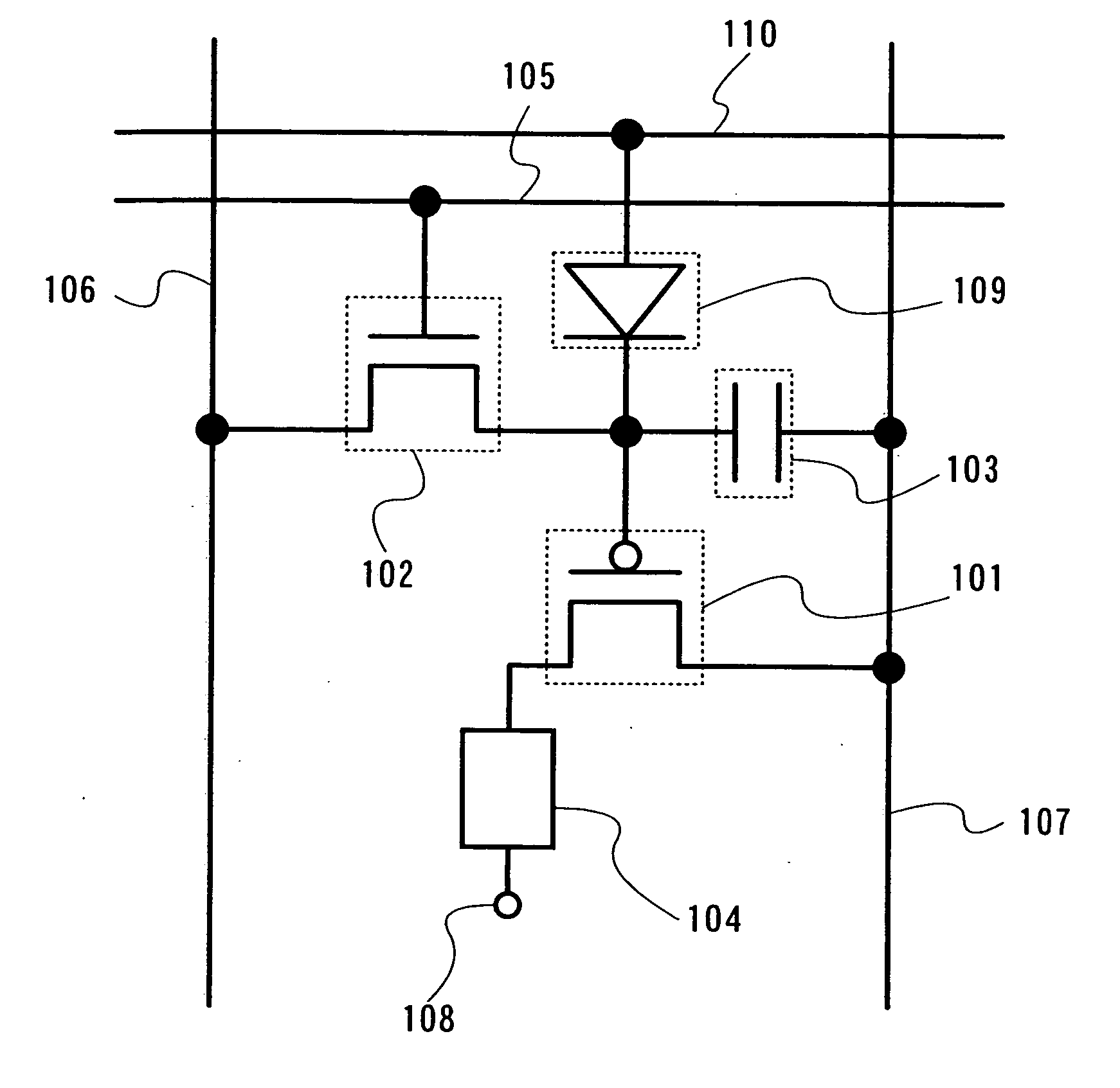

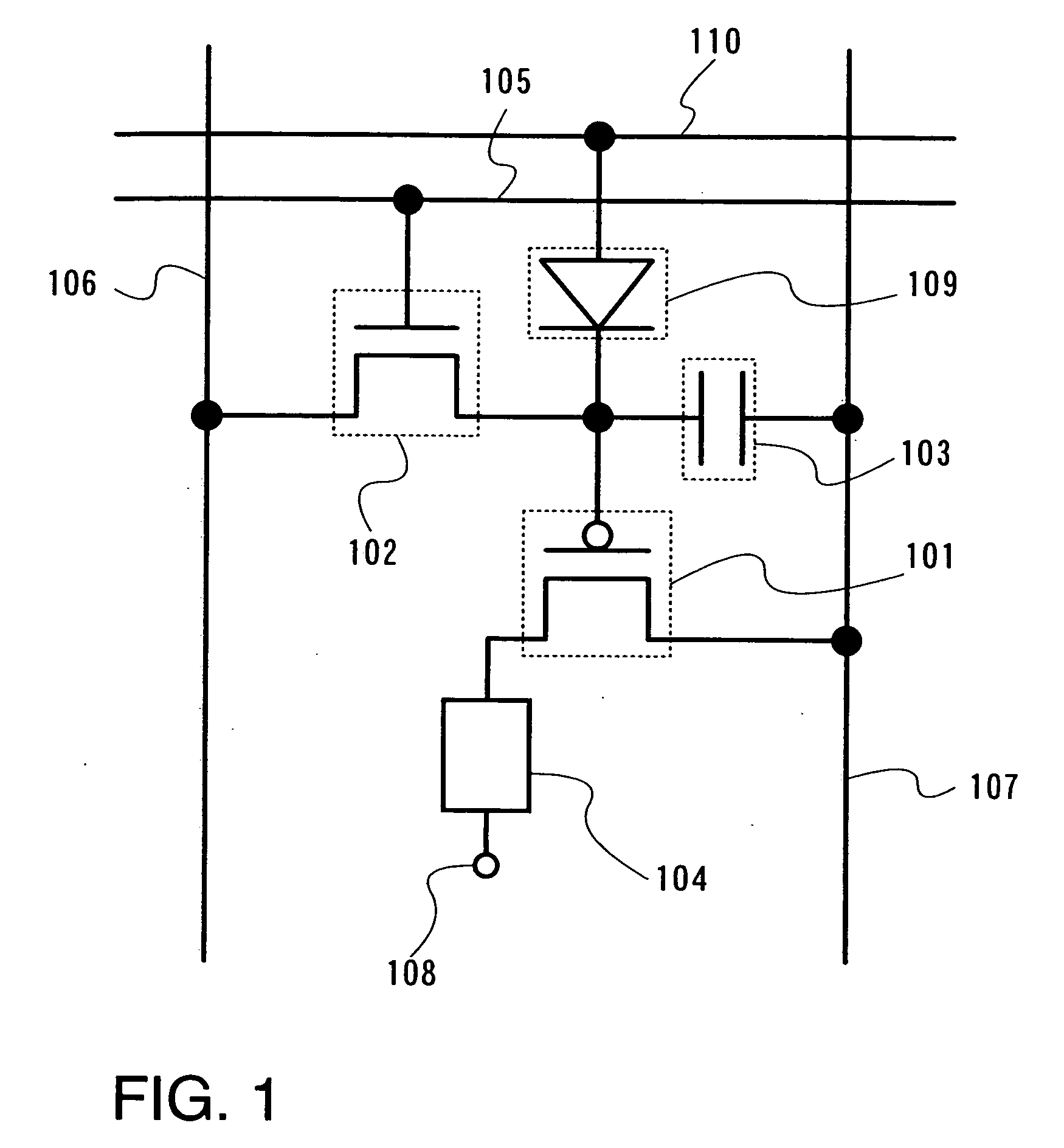

InactiveUS20060238135A1Total current dropReduce trafficElectrical apparatusElectroluminescent light sourcesDevice materialScan line

When a signal inputted to a pixel is erased by setting potentials of a gate terminal and a source terminal of a driving transistor to be equal, a current slightly flows through the driving transistor in some cases, which leads to occur a display defect. The invention provides a display device which improves the yield while suppressing the increase in manufacturing cost. When a potential of a scan line for erasure is raised, a potential of the gate terminal of the driving transistor is raised accordingly. For example, the scan line and the gate terminal of the driving transistor are connected through a rectifying element.

Owner:SEMICON ENERGY LAB CO LTD

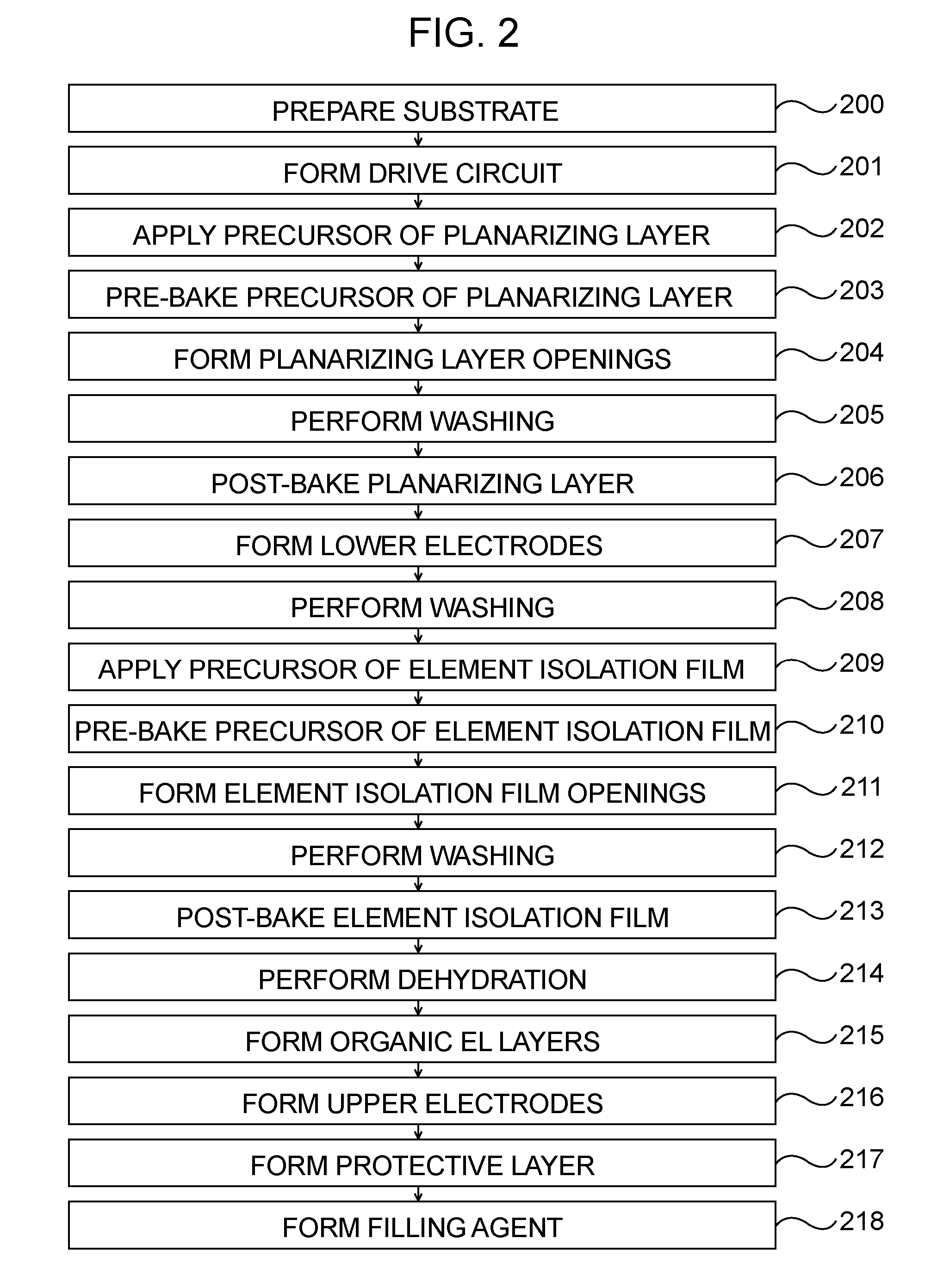

Organic electroluminescent display device and manufacturing method thereof

ActiveUS20070046191A1Maintain its level of performanceEnhance layeringDischarge tube luminescnet screensElectroluminescent light sourcesOligomerEngineering

The present invention provides an organic EL display device having a planarizing layer, which is prevented from being distorted. The above organic EL display device has a planarizing layer, which retains 5% or less the oligomer used to form this layer.

Owner:CANON KK

Semiconductor device, electronic device, and method of manufacturing semiconductor device

InactiveUS20060169973A1Stable formationImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialDisplay device

To provide a semiconductor device and a display device which can be manufactured through a simplified process and the manufacturing technique. Another object is to provide a technique by which a pattern of wirings or the like which is partially constitutes a semiconductor device or a display device can be formed with a desired shape with controllability.

Owner:SEMICON ENERGY LAB CO LTD

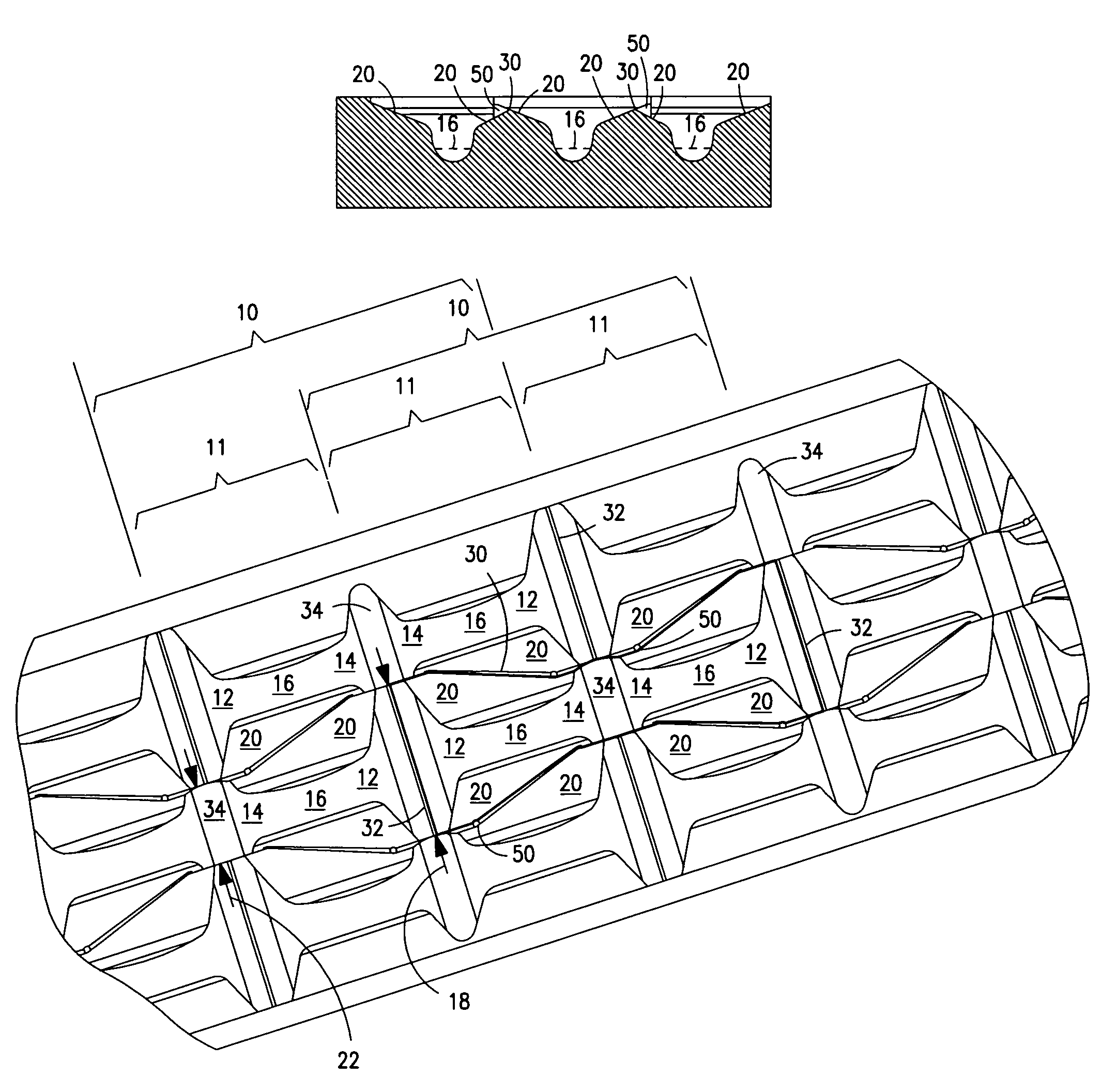

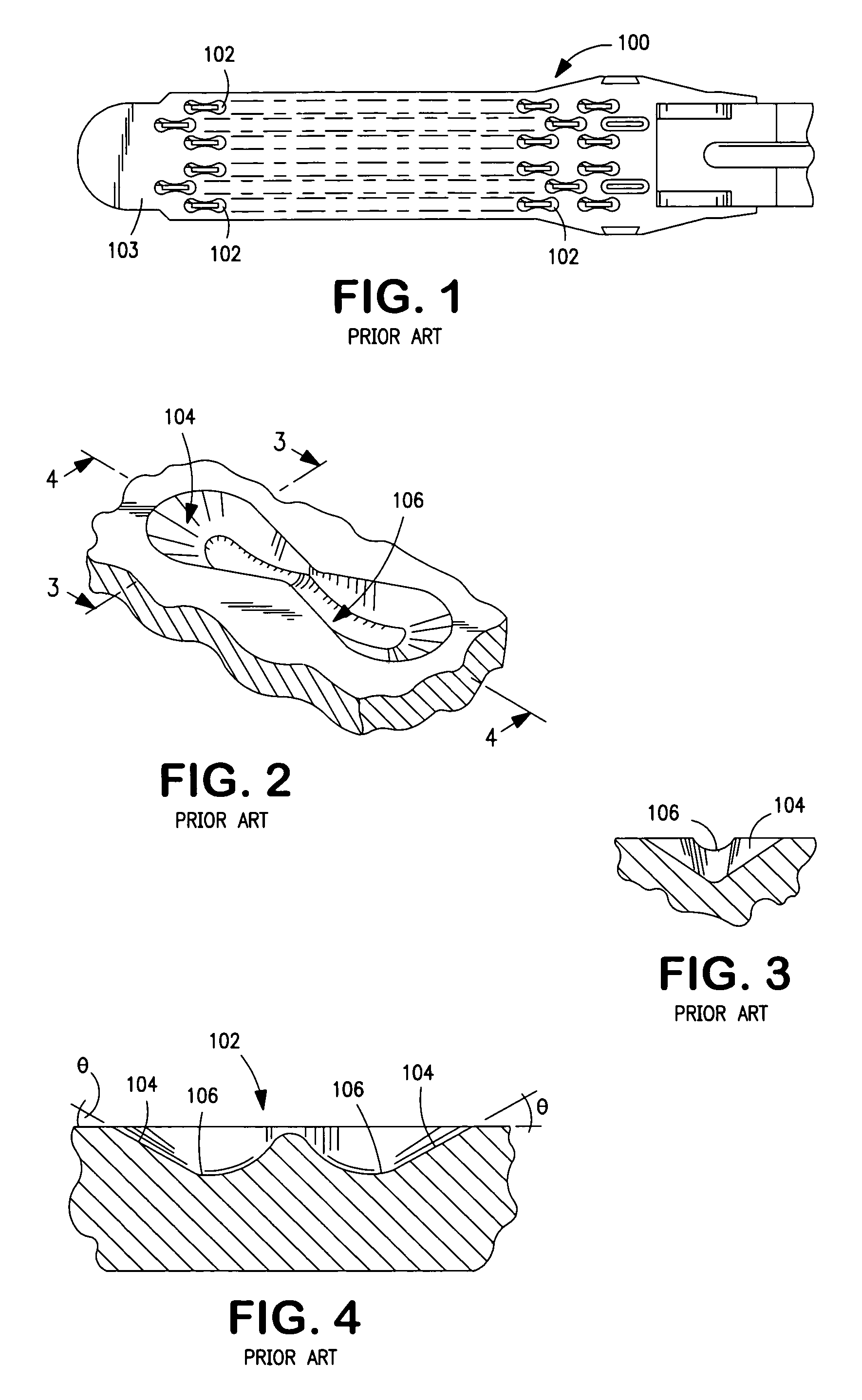

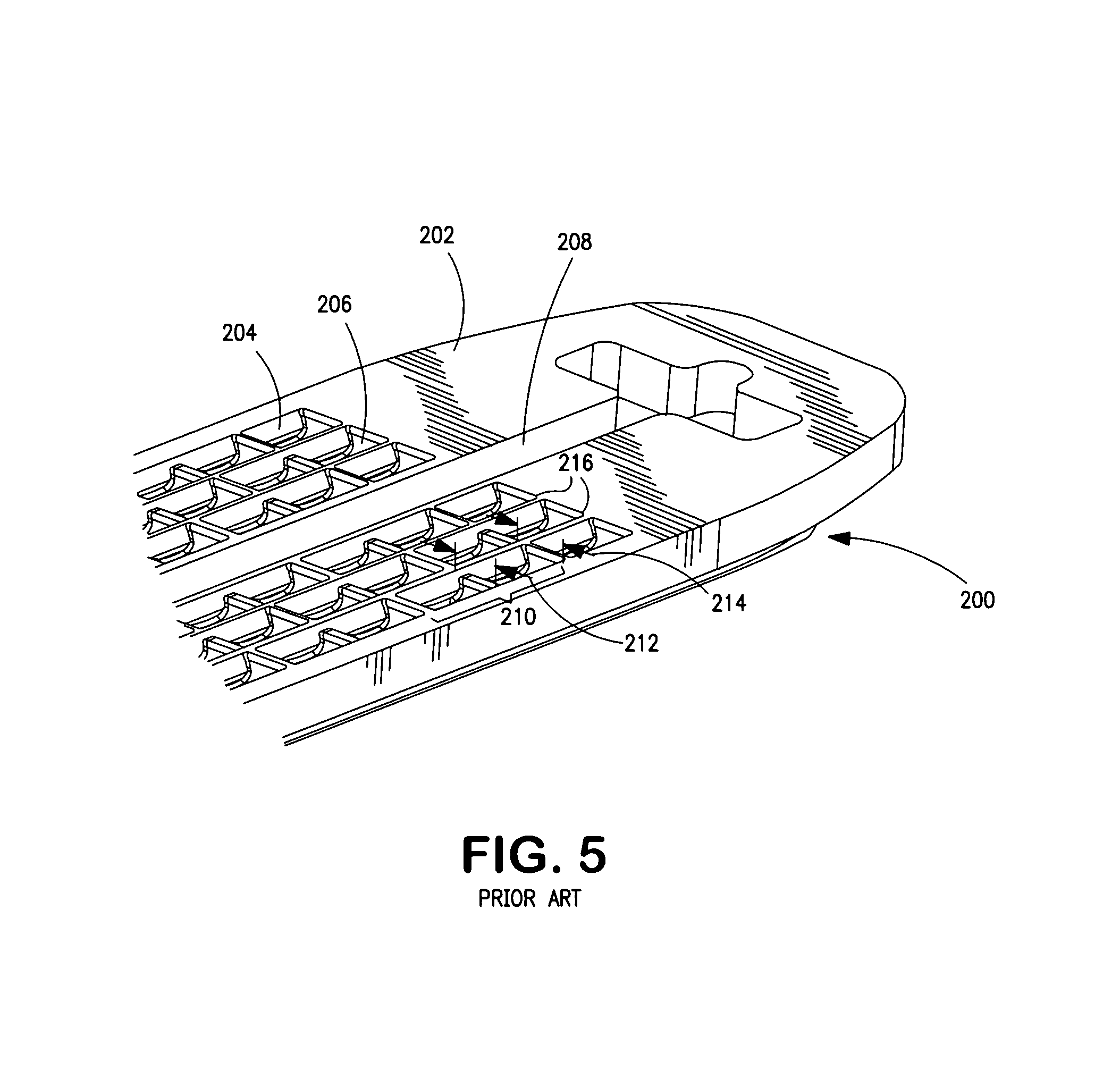

Surgical stapler anvil with nested staple forming pockets

InactiveUS6953138B1Increased lateral widthLittle lateral spaceSuture equipmentsStapling toolsMirror imageBiomedical engineering

A surgical stapler anvil provides an expanded leg-receiving target area for a staple forming pocket in a compact staggered array by narrowing the lateral width of the leg-clinching portion of a laterally adjacent pocket. Advantageously, the lateral spacing between adjacent rows of staple forming pockets can remain small, while the leg-receiving target area for laterally adjacent rows of pockets is significantly expanded. The staple forming pockets include two mirror image leg-forming cups. The cups are longitudinally aligned with their respective ascending leg clinching portions adjoining in the center of the pocket. Laterally spaced guide surfaces extend upwardly and outwardly from the clinching surface at the bottom of the cup to define an expanded leg-receiving target area at the distal ends of the pocket. Substantially planar laterally outward portions of the guide surface intersect with the guide surface of a laterally adjacent pocket to form a non-linear ridge.

Owner:DWORAK FR W

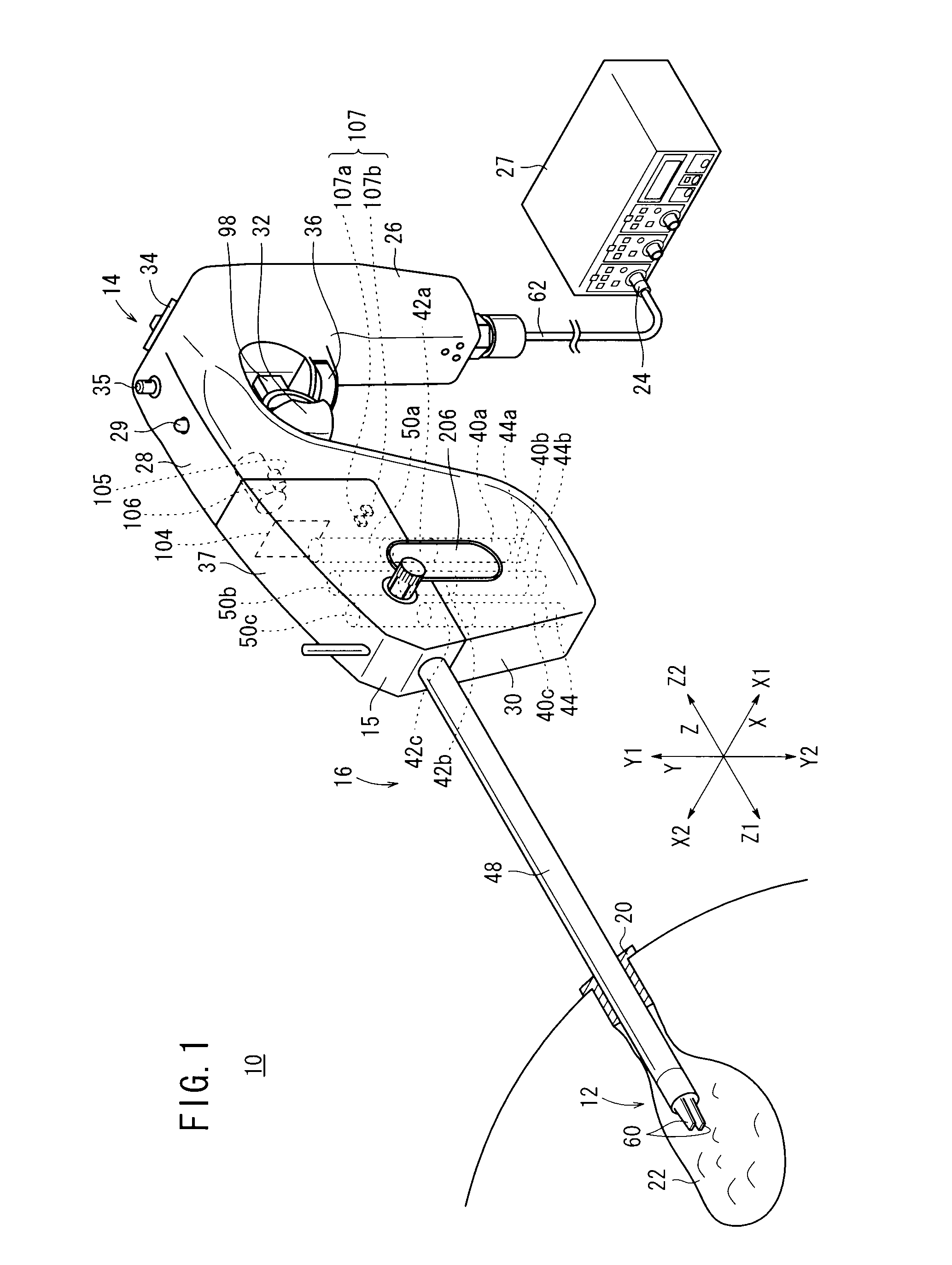

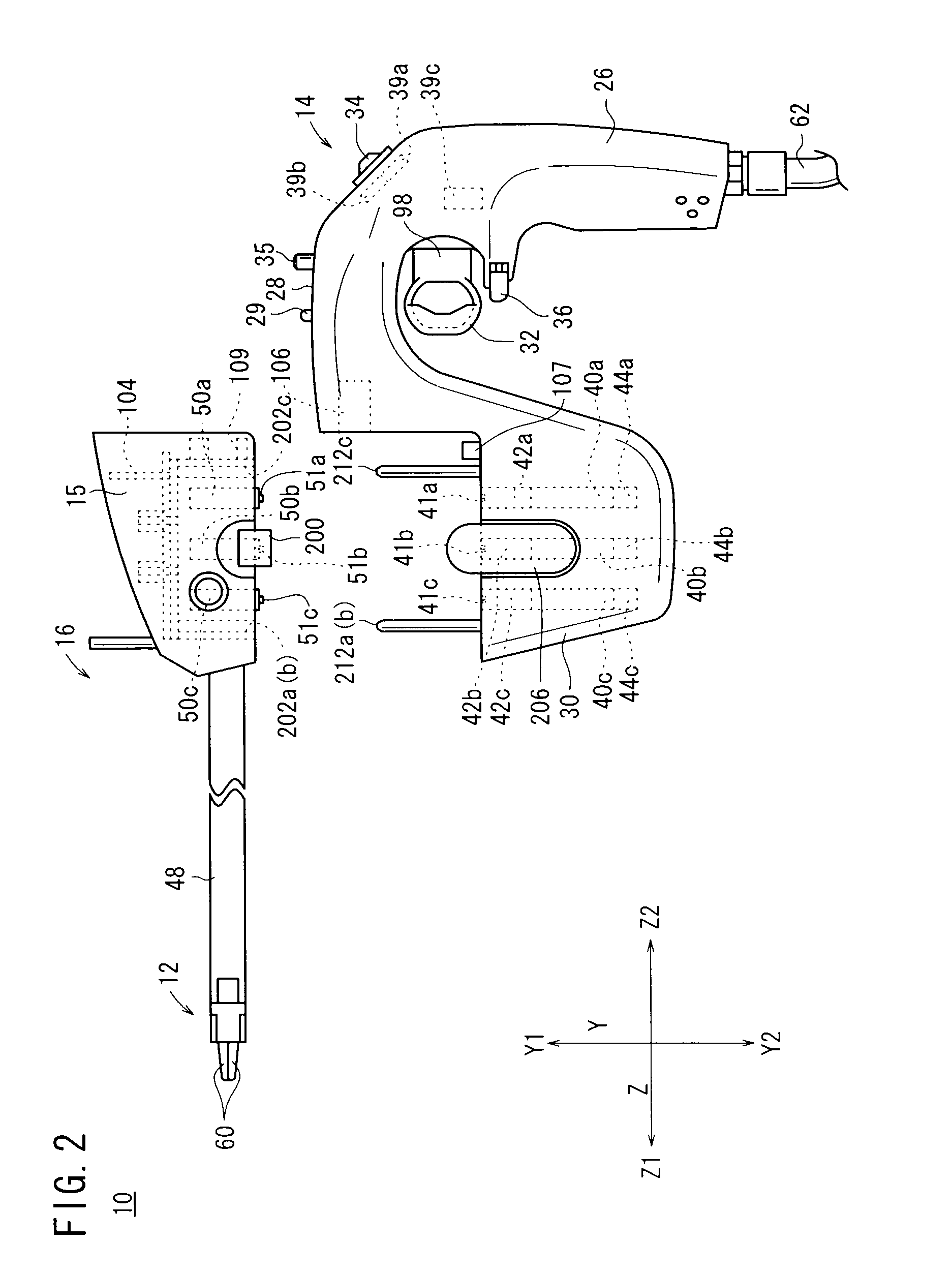

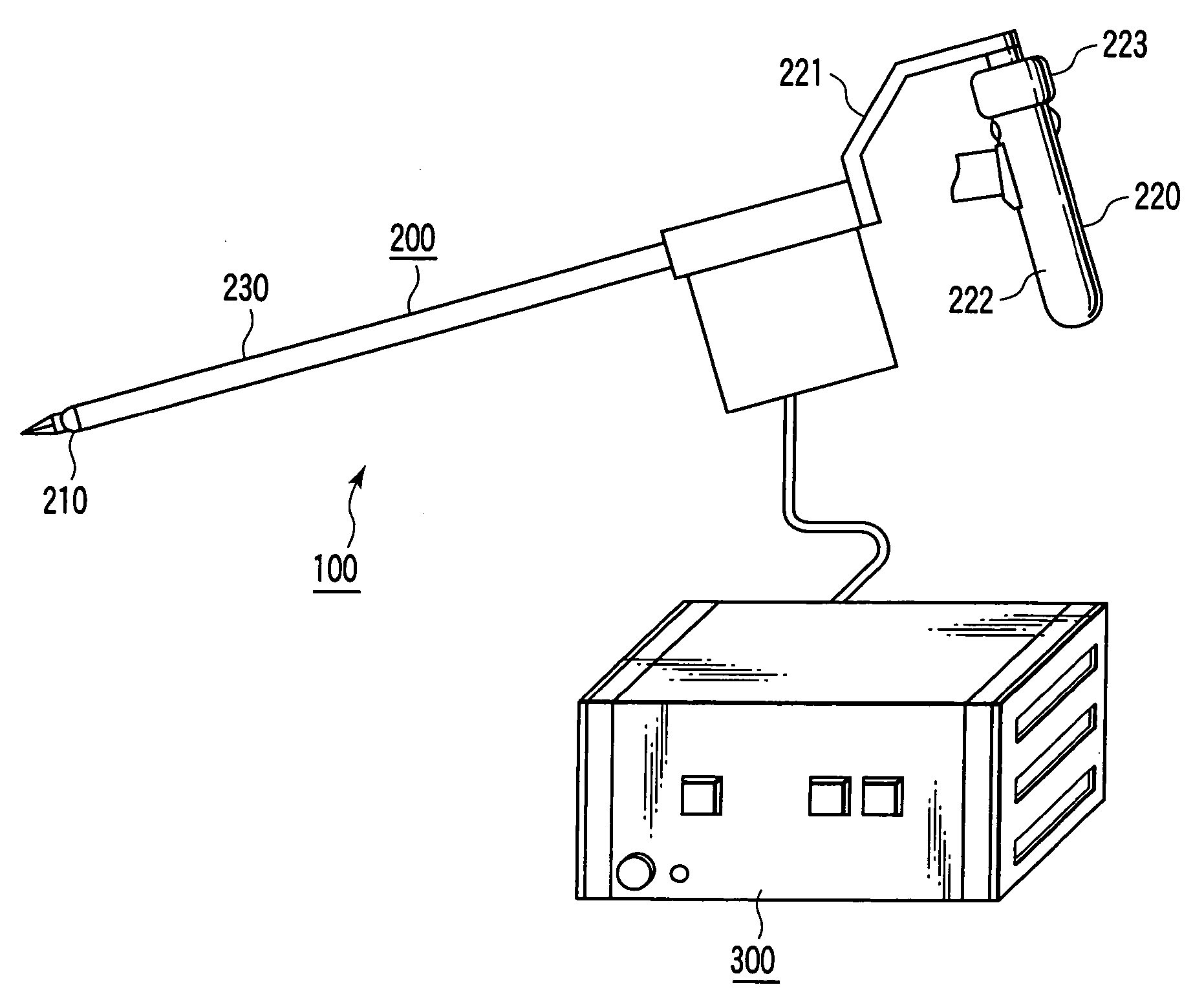

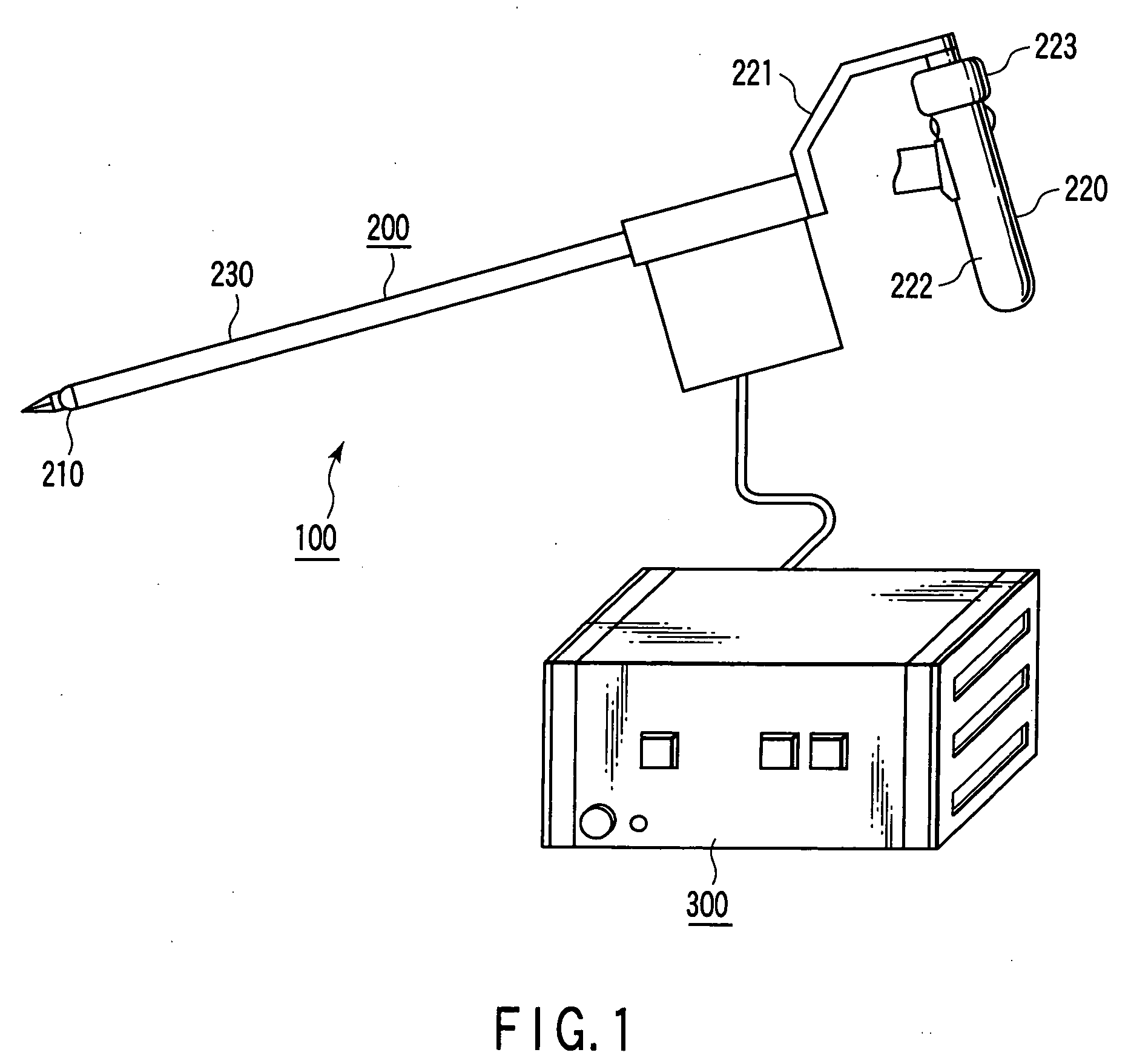

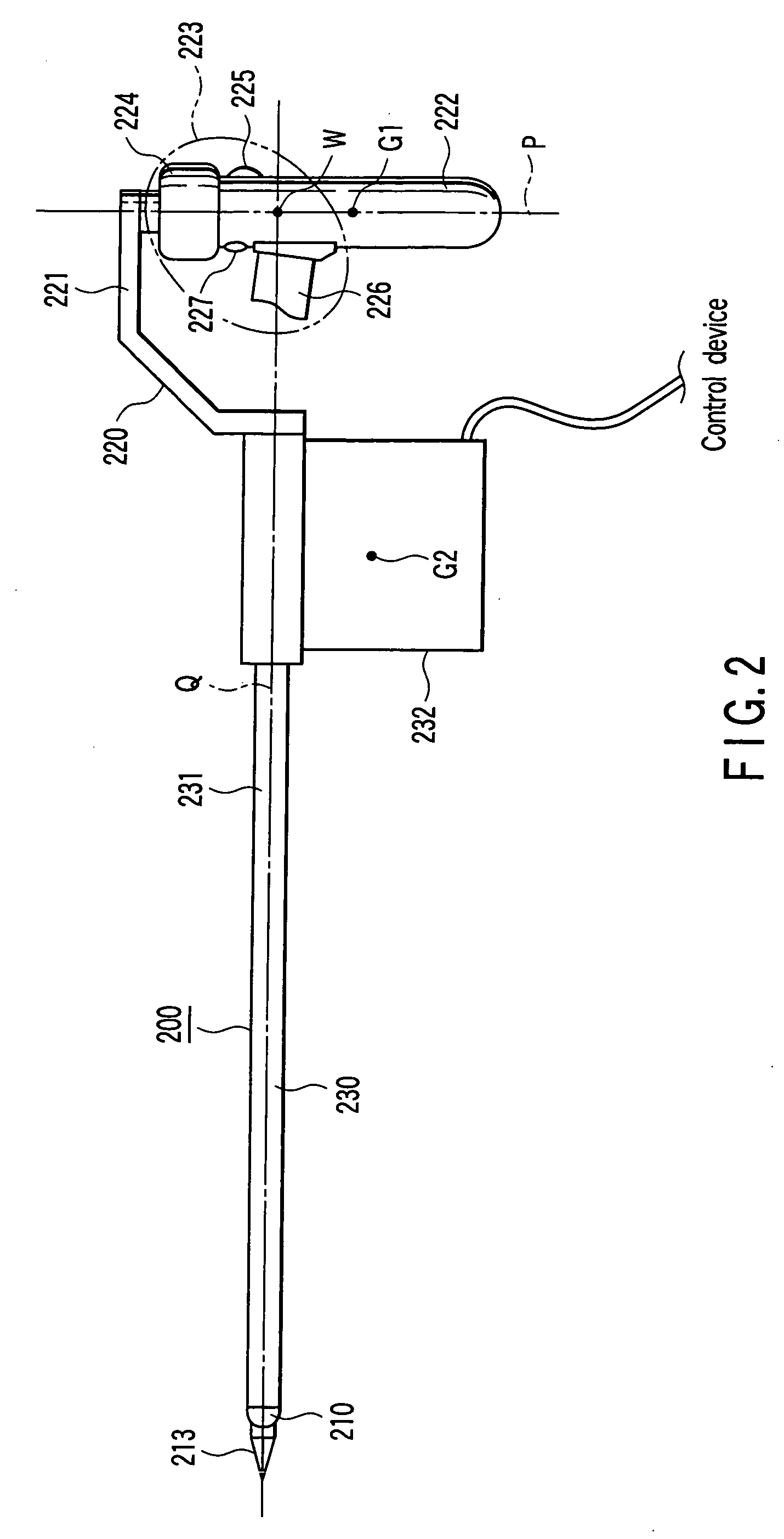

Manipulator

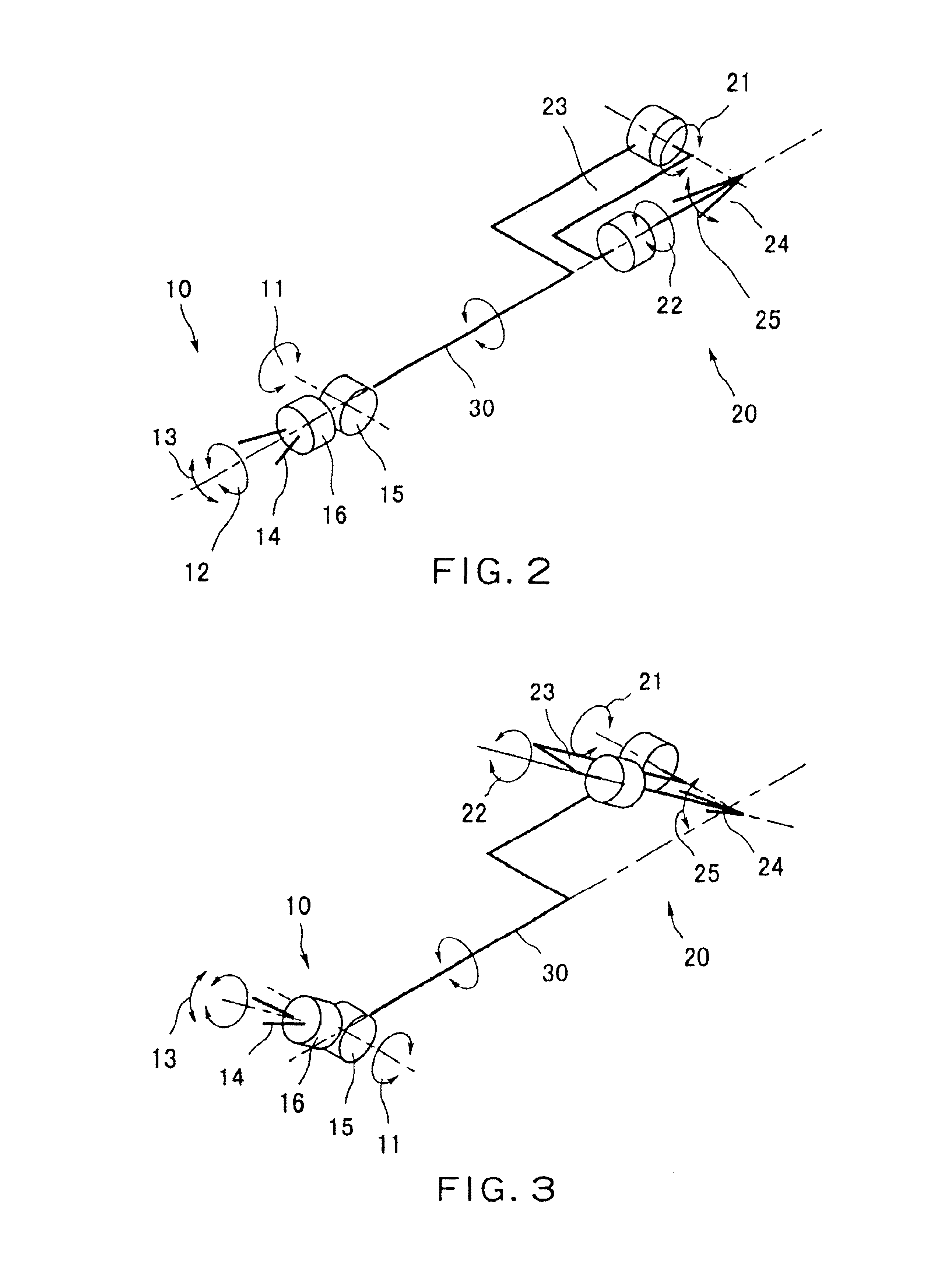

A manipulator comprises an operation command unit provided with an attitude adjusting unit and an end effector control unit, a connecting unit having one end connected to the operation command unit, a working unit connected to the other end of the connecting unit and provided with an end effector and a support unit supporting the end effector for motions, and a control unit that transmits an operation command provided by the attitude adjusting unit to the support unit to adjust the attitude of the end effector and transmits an operation command provided by the end effector control unit to the end effector to operate the end effector. The support unit includes a first joint capable of turning about a first axis perpendicular to the center axis of the connecting unit, and a second joint capable of turning about a second axis perpendicular to the first axis. The end effector can be turned for rolling about an axis substantially parallel to the second axis of the second joint. The attitude adjusting unit has a third joint having a third axis perpendicular to the center line of the connecting unit. The end effector control unit is formed such that the fingers of an operator gripping operating members included in the end effector control unit extend substantially in parallel to the fourth axis.

Owner:KARL STORZ GMBH & CO KG

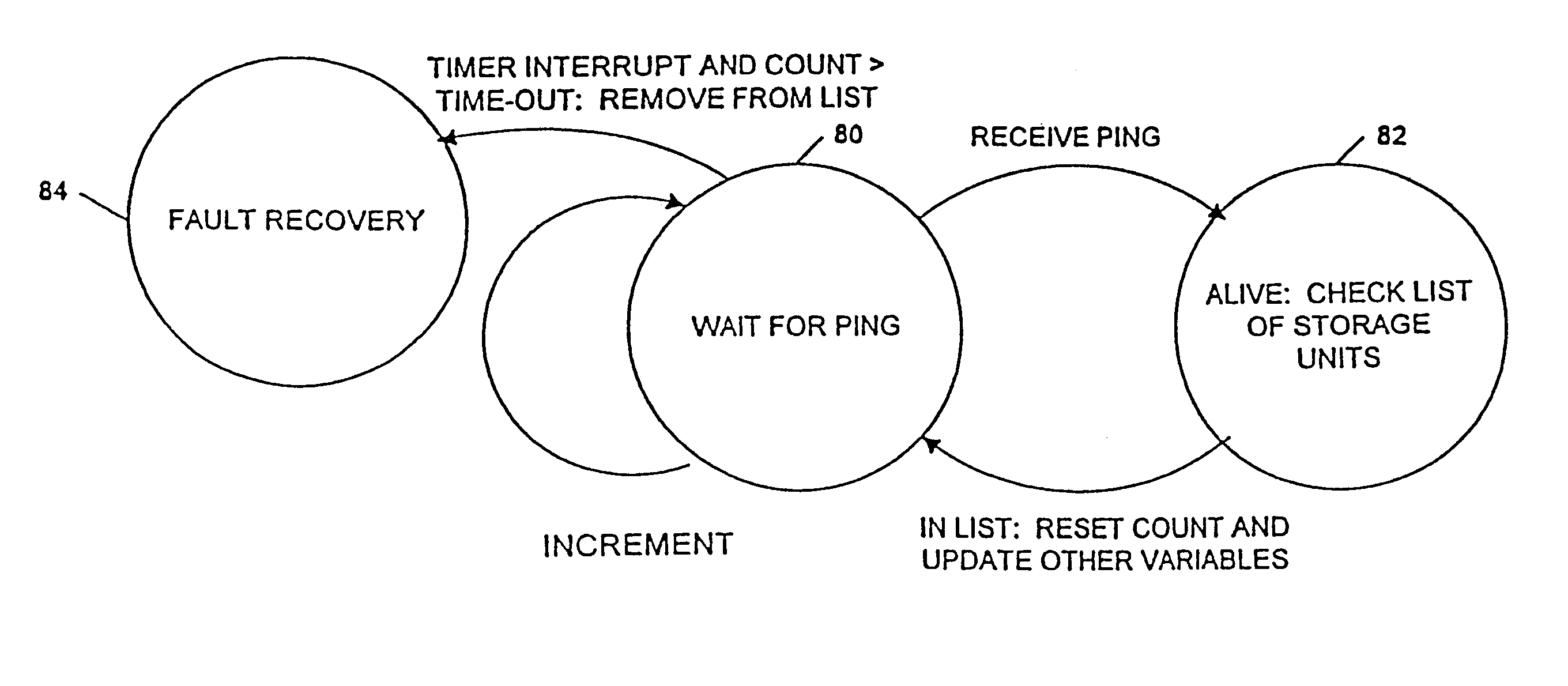

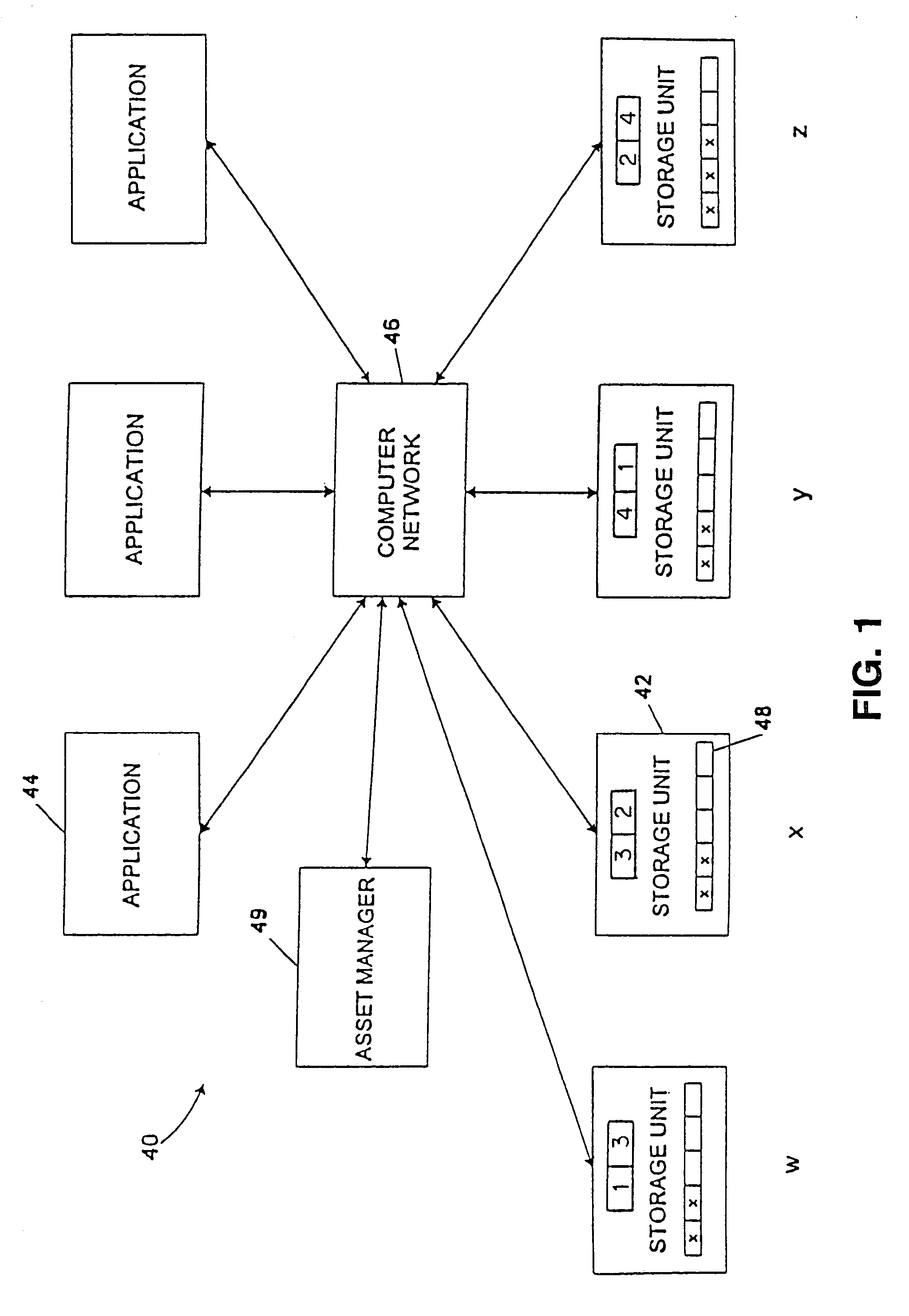

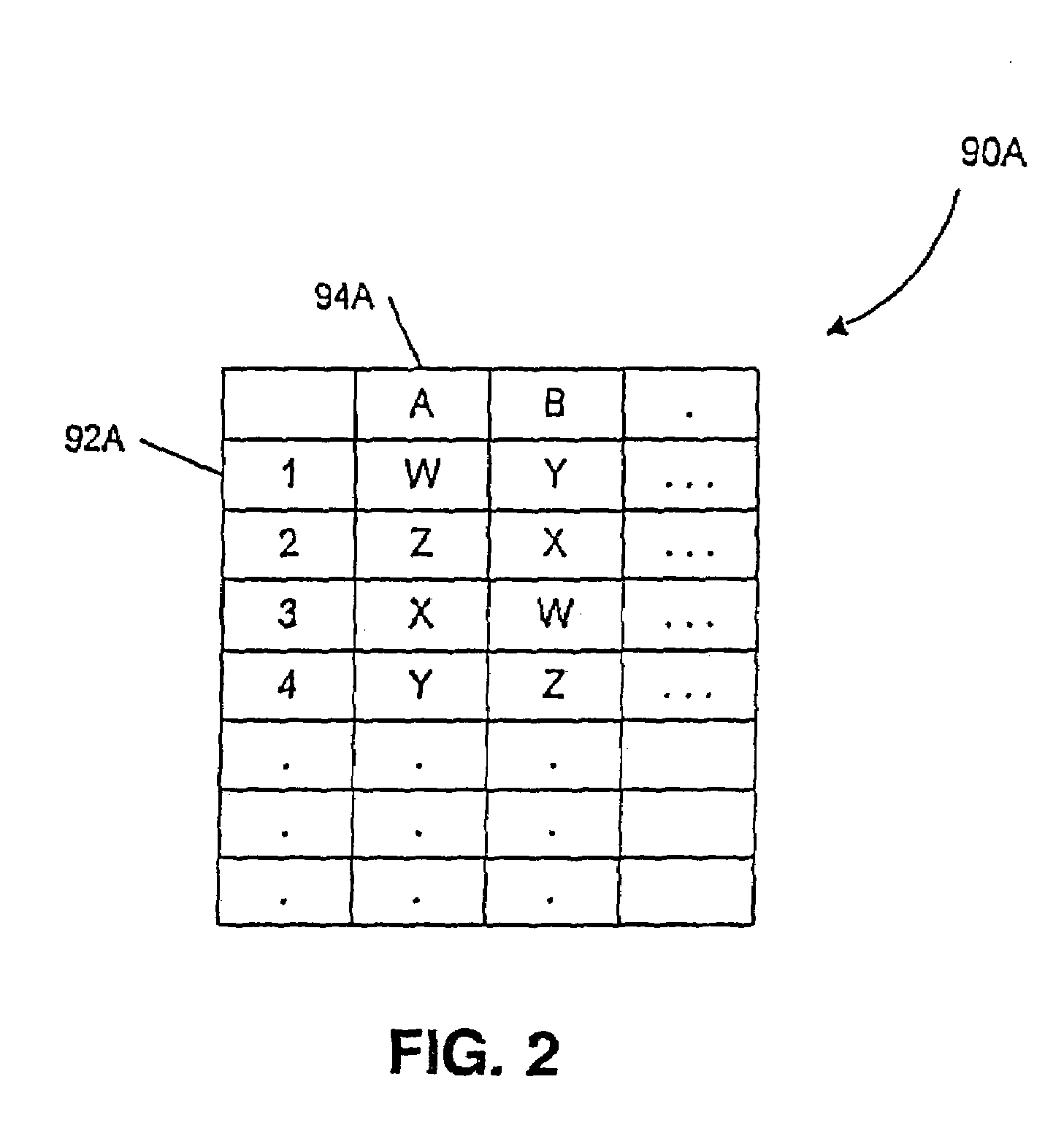

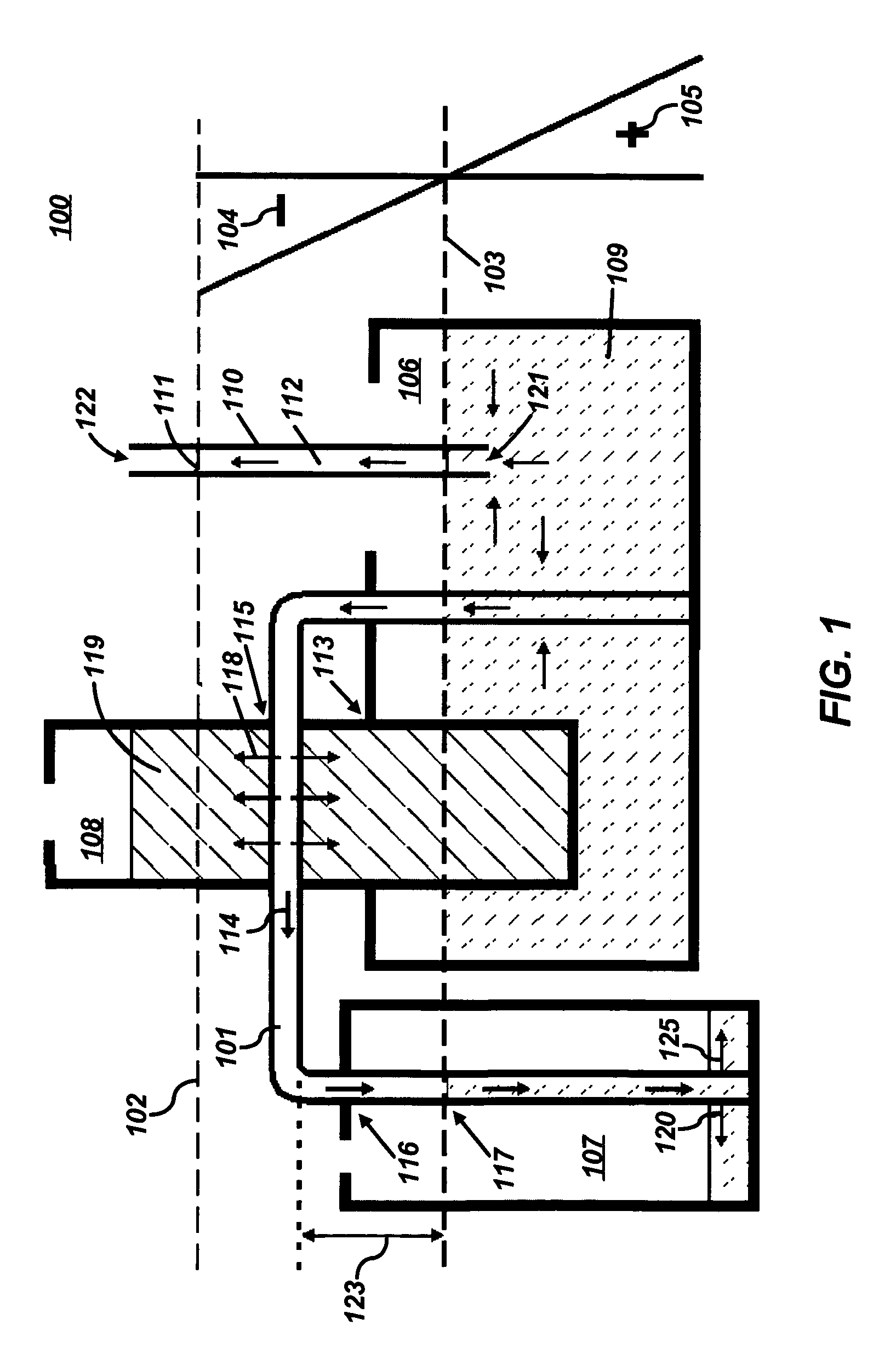

Computer system and process for transferring multiple high bandwidth streams of data between multiple storage units and multiple applications in a scalable and reliable manner

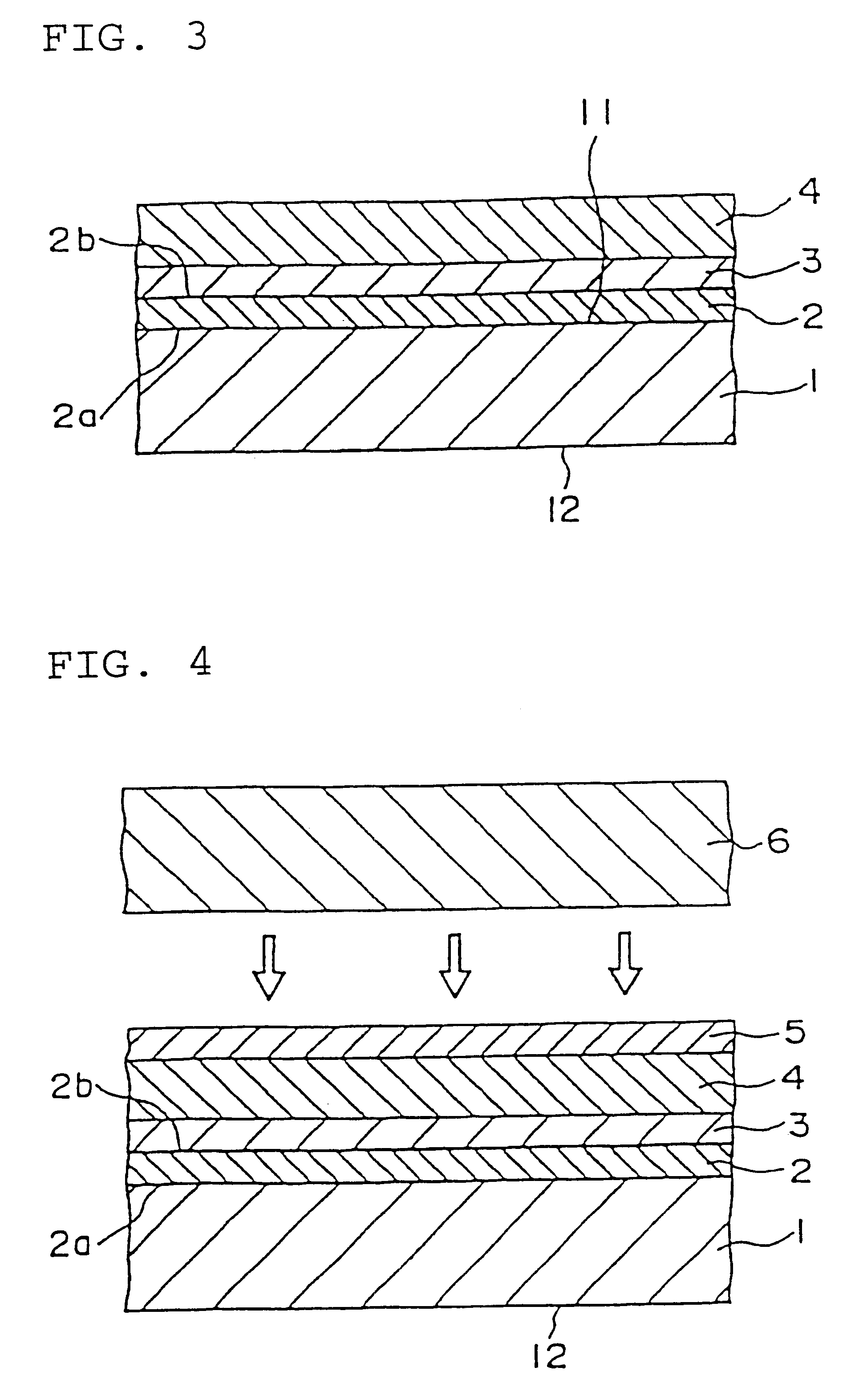

InactiveUS7111115B2Improve reliabilityImprove scalabilityInput/output to record carriersData processing applicationsHigh bandwidthData segment

Multiple applications request data from multiple storage units over a computer network. The data is divided into segments and each segment is distributed randomly on one of several storage units, independent of the storage units on which other segments of the media data are stored. At least one additional copy of each segment also is distributed randomly over the storage units, such that each segment is stored on at least two storage units. This random distribution of multiple copies of segments of data improves both scalability and reliability. When an application requests a selected segment of data, the request is processed by the storage unit with the shortest queue of requests. Random fluctuations in the load applied by multiple applications on multiple storage units are balanced nearly equally over all of the storage units. This combination of techniques results in a system which can transfer multiple, independent high-bandwidth streams of data in a scalable manner in both directions between multiple applications and multiple storage units.

Owner:AVID TECHNOLOGY

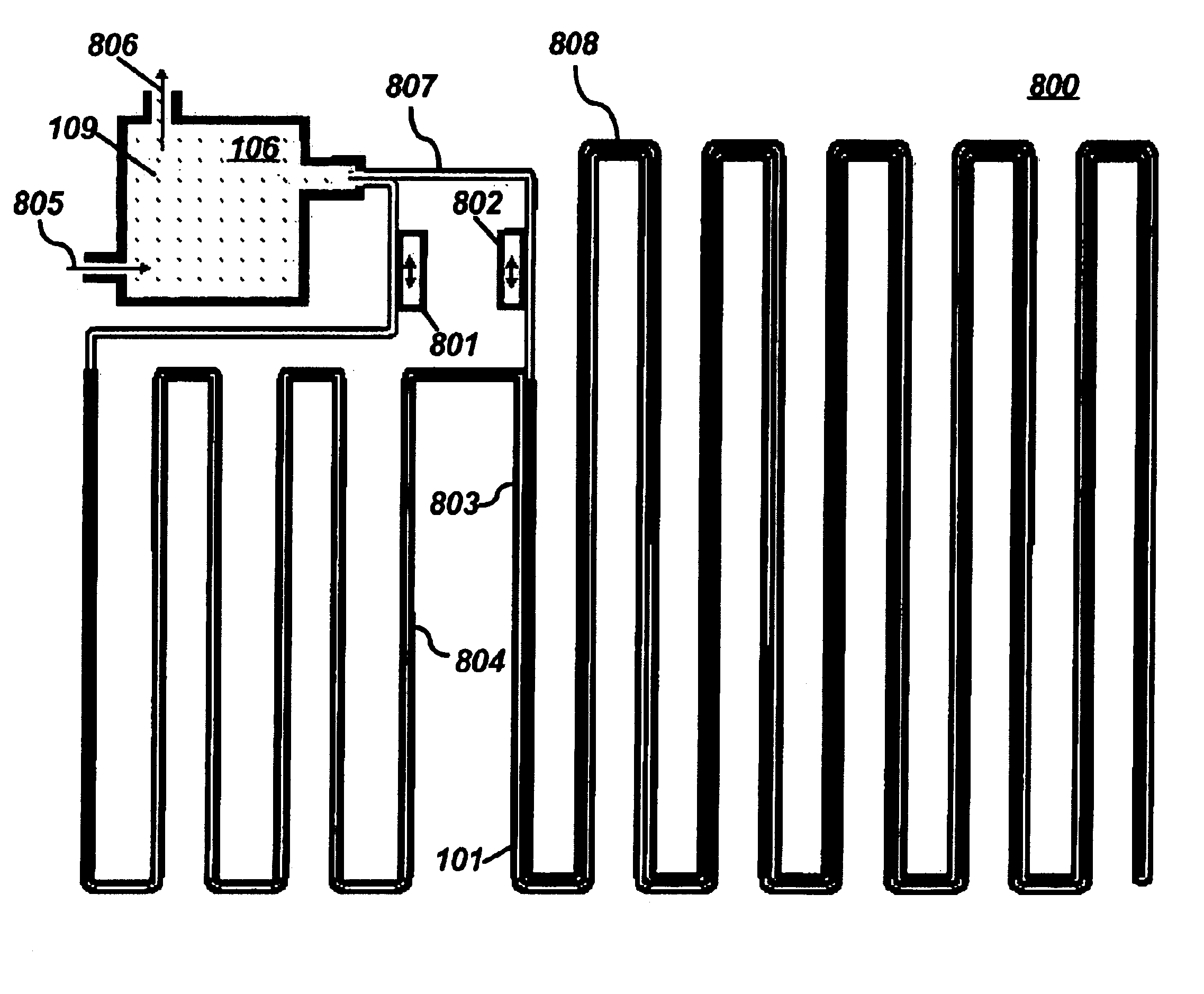

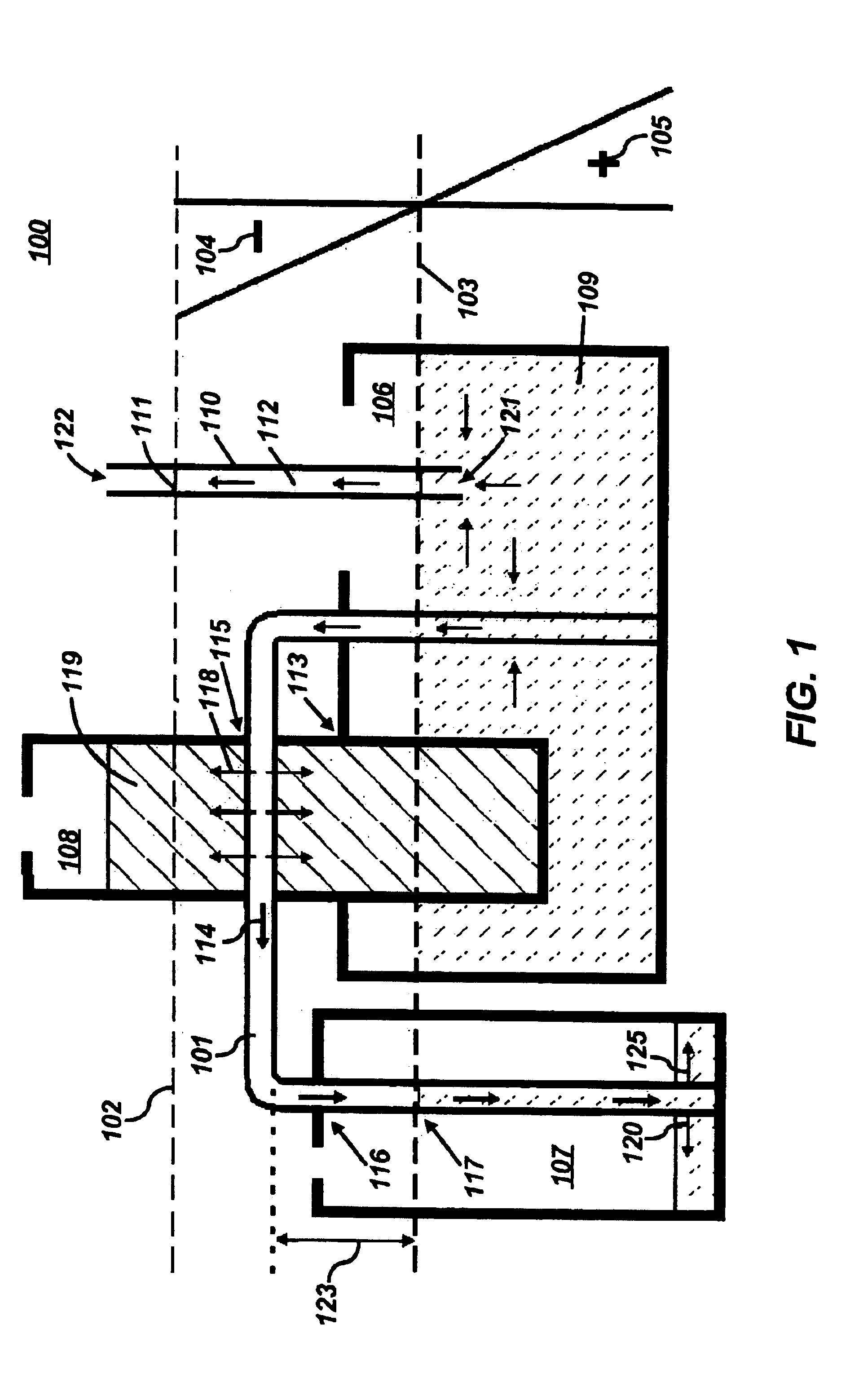

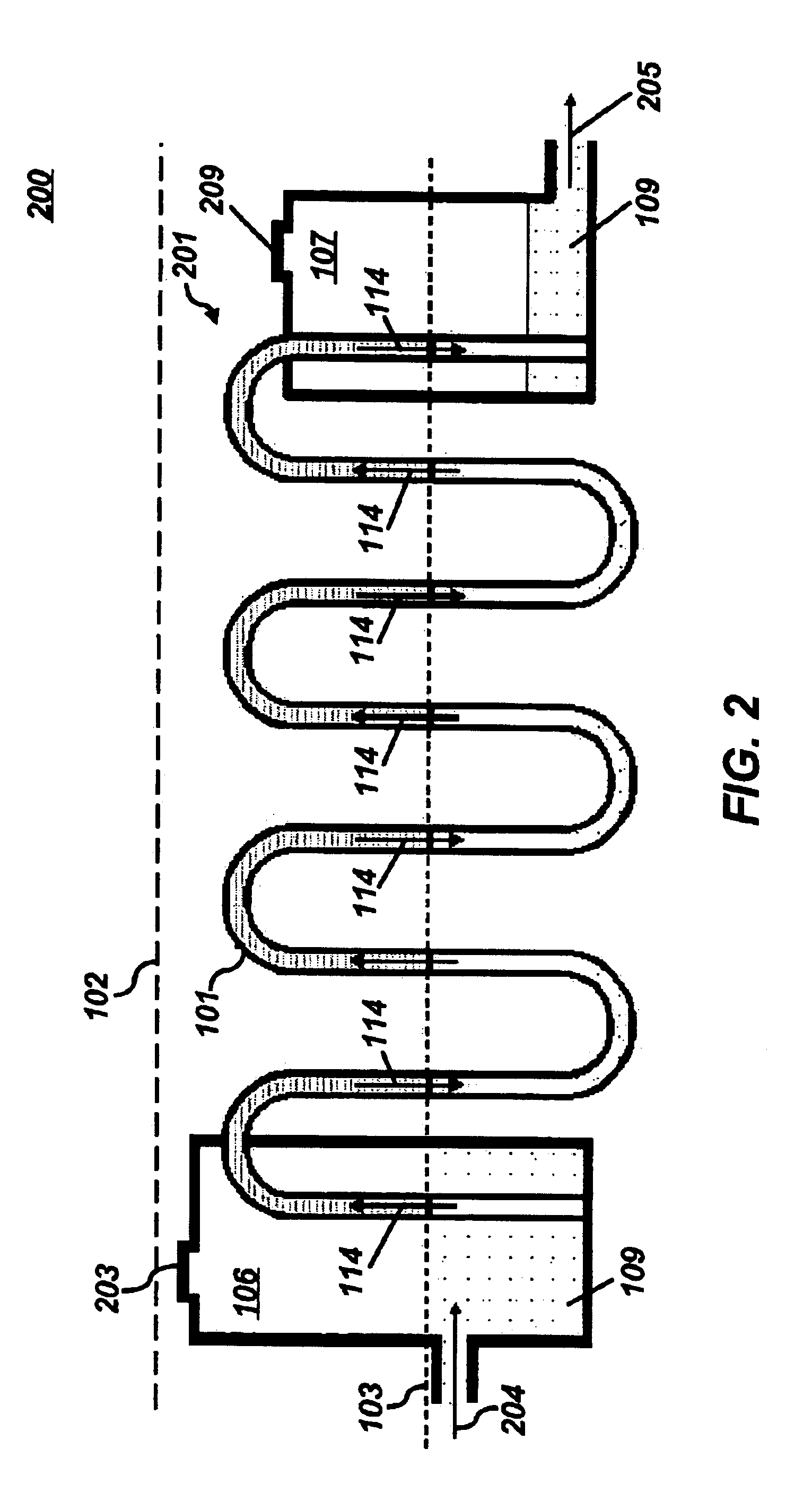

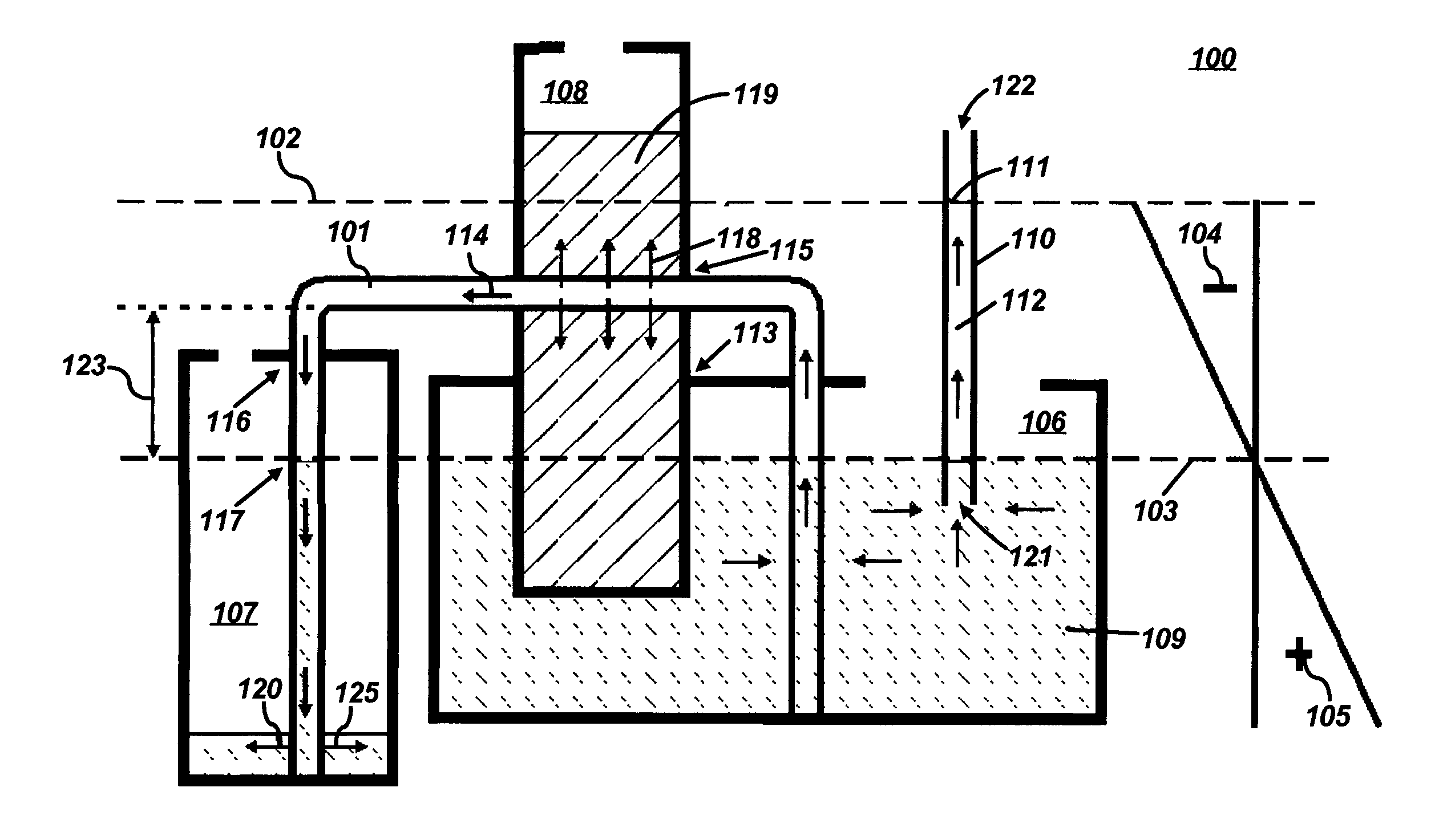

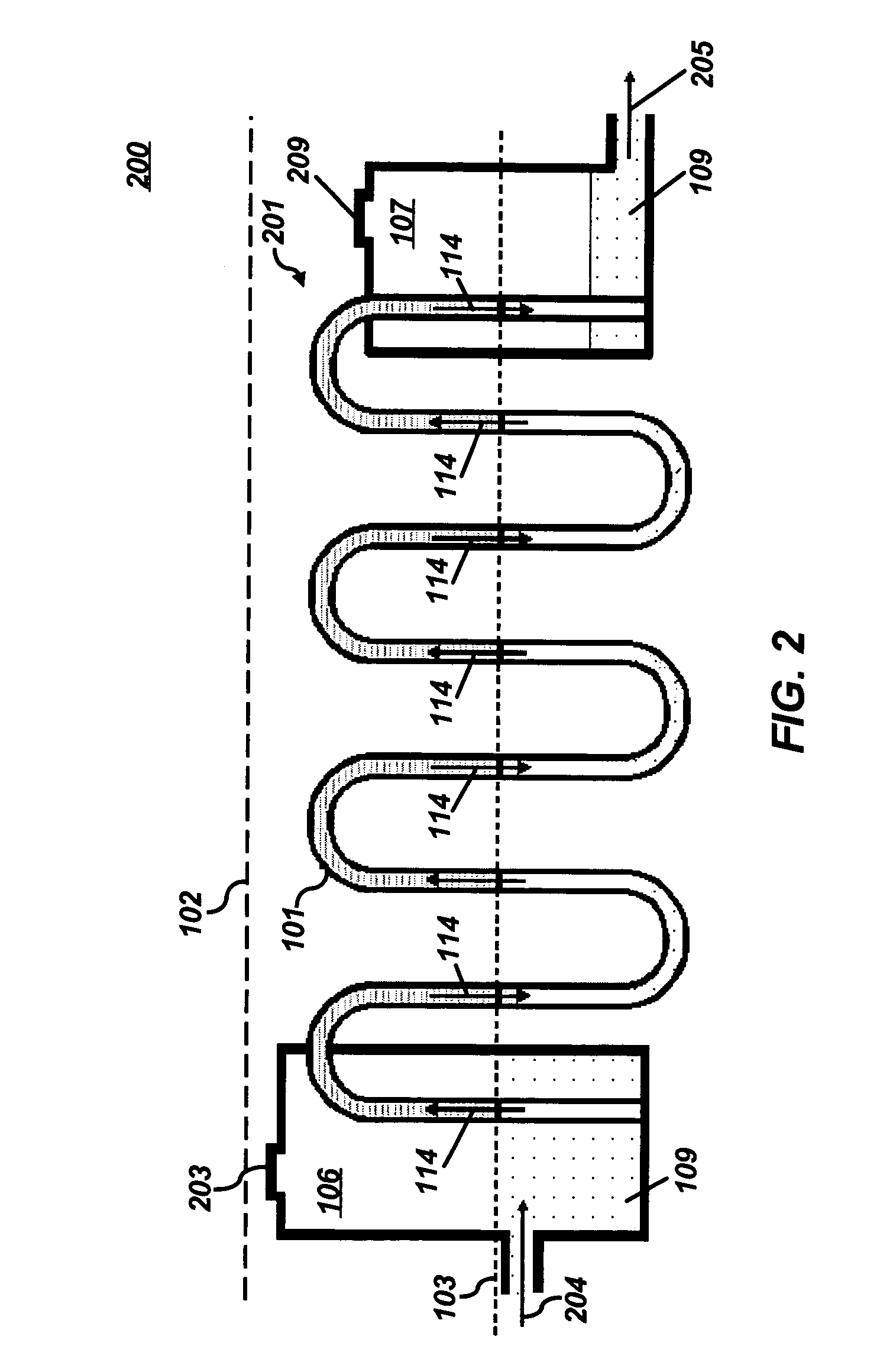

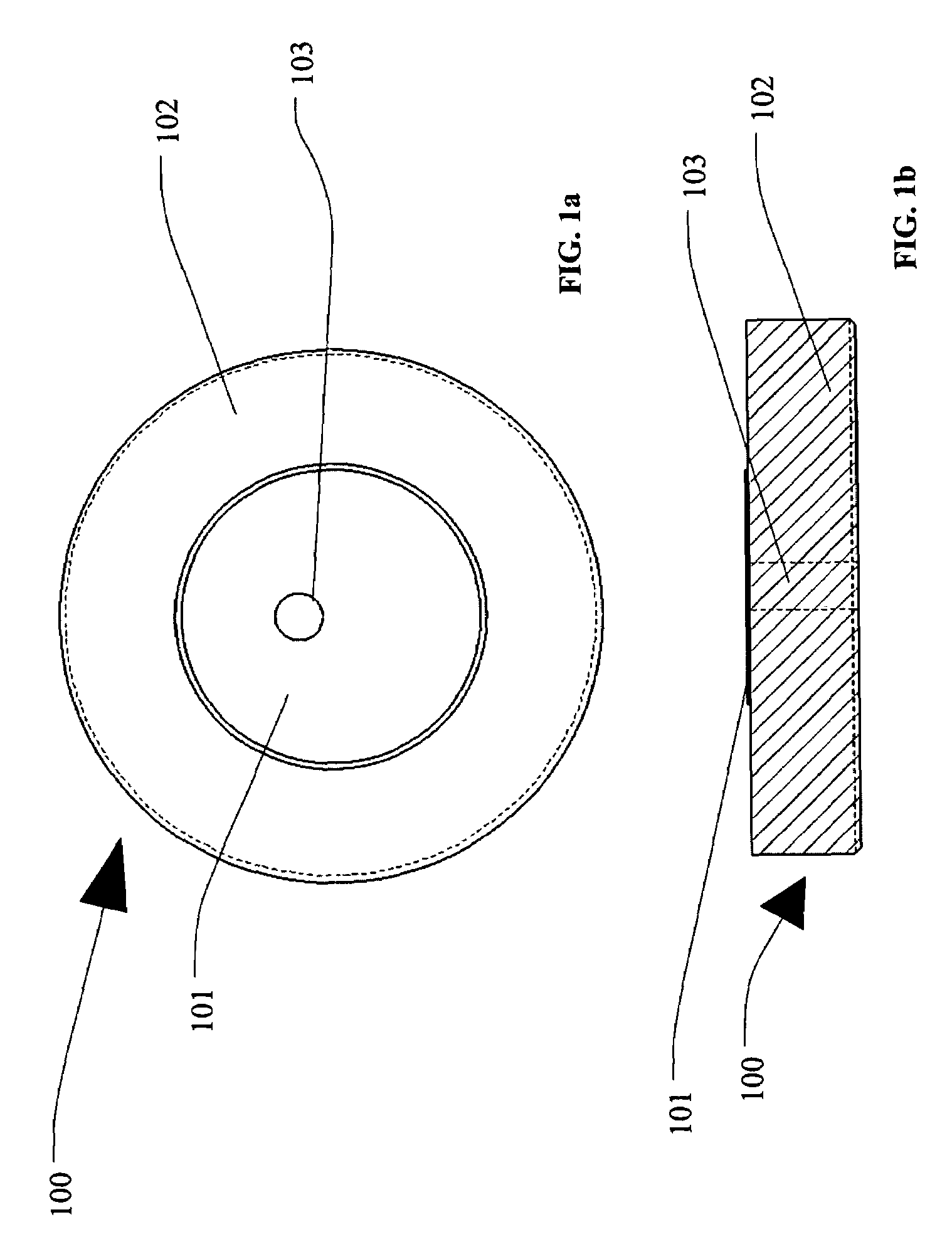

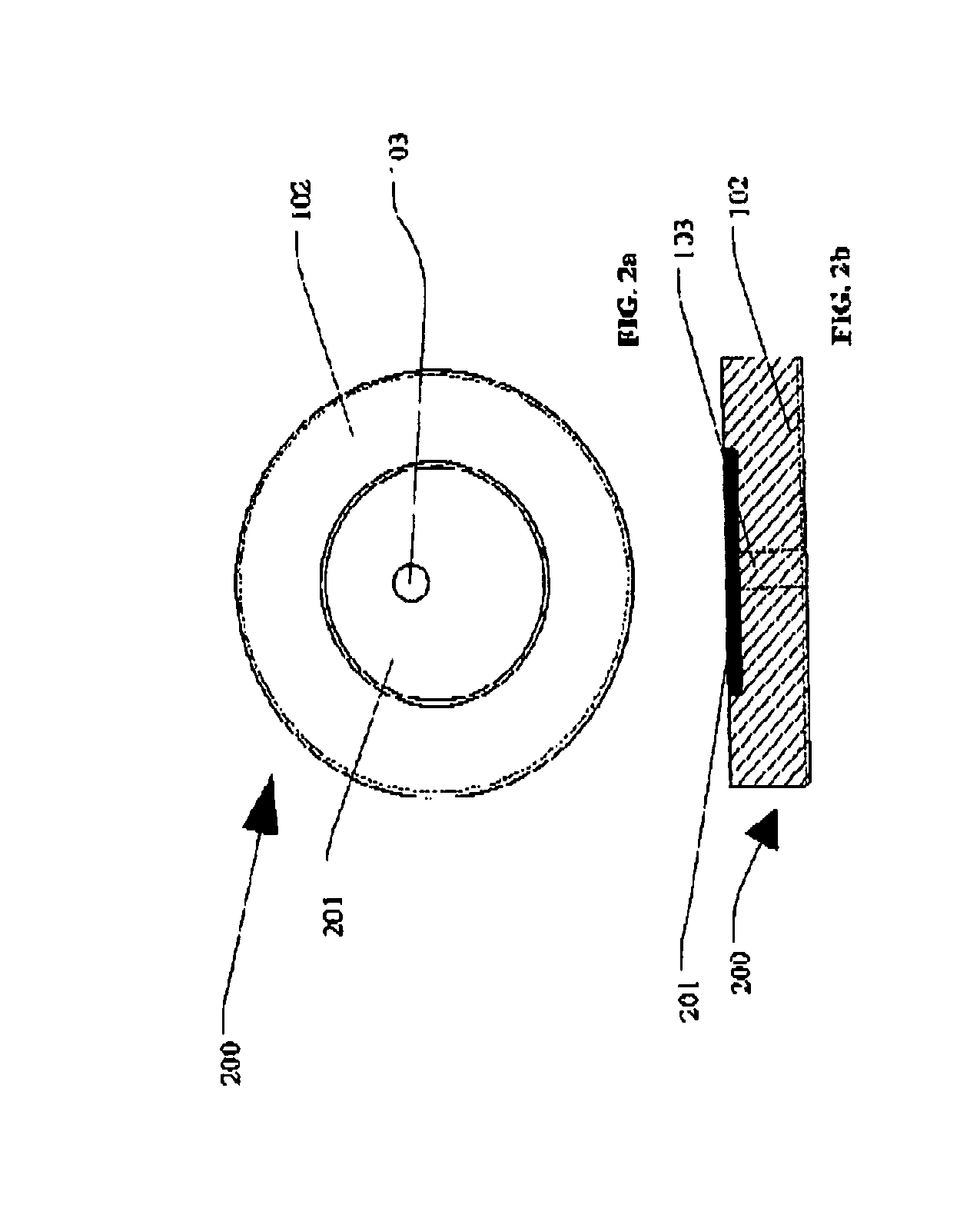

Irrigation and drainage based on hydrodynamic unsaturated fluid flow

InactiveUS6918404B2Improve the level ofHigh porosityPipeline systemsMachines/enginesEnvironmental engineeringPorous microstructure

Irrigation and drainage systems are disclosed, including a saturated zone and at least one pipe in communication with the saturated zone. The pipe(s) can be configured to comprise a tubarc porous microstructure for conducting water from the saturated zone to an unsaturated zone in order to drain the water from the saturated zone. The water can be delivered from the saturated zone to the unsaturated zone through the tubarc porous microstructure, thereby permitting the water to be harnessed for irrigation or drainage through the hydrodynamic movement of the water from one zone of saturation or unsaturation to another.

Owner:TUBARC TECH

Ink refill and recharging system

InactiveUS7066586B2Improve reliabilityPrecise deliveryPipeline systemsPrintingEngineeringPrint-through

Ink refill systems are disclosed. In general, an ink source comprising a saturated zone and a tubarc porous microstructure for conducting ink from the saturated zone to an unsaturated zone are provided. The ink can be delivered from the saturated zone to the unsaturated zone through the tubarc porous microstructure, thereby permitting the ink to be harnessed for ink writing and / or printing through the unsaturated hydrodynamic flow of the ink from one zone of saturation or unsaturation to another.

Owner:TUBARC TECH

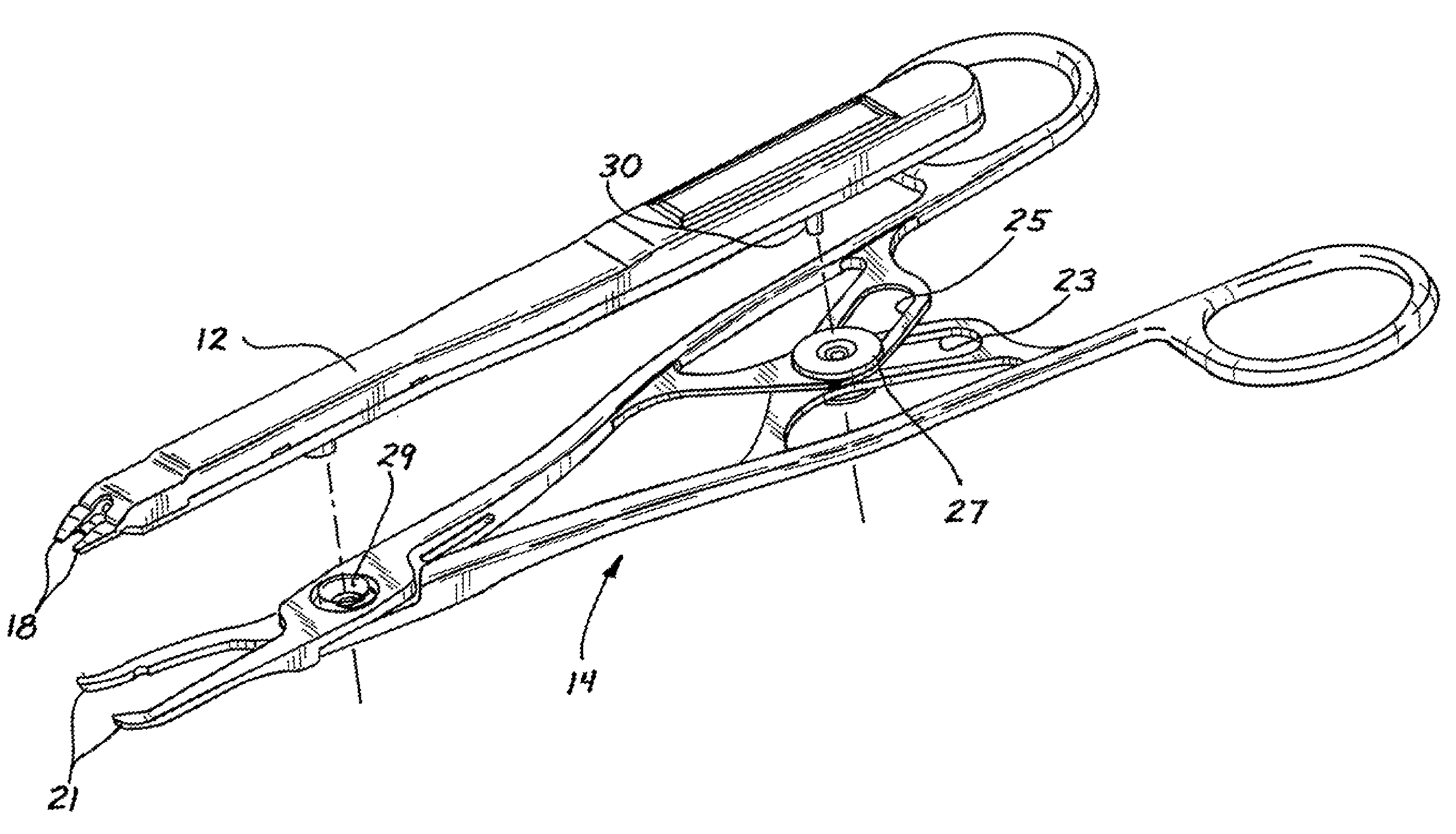

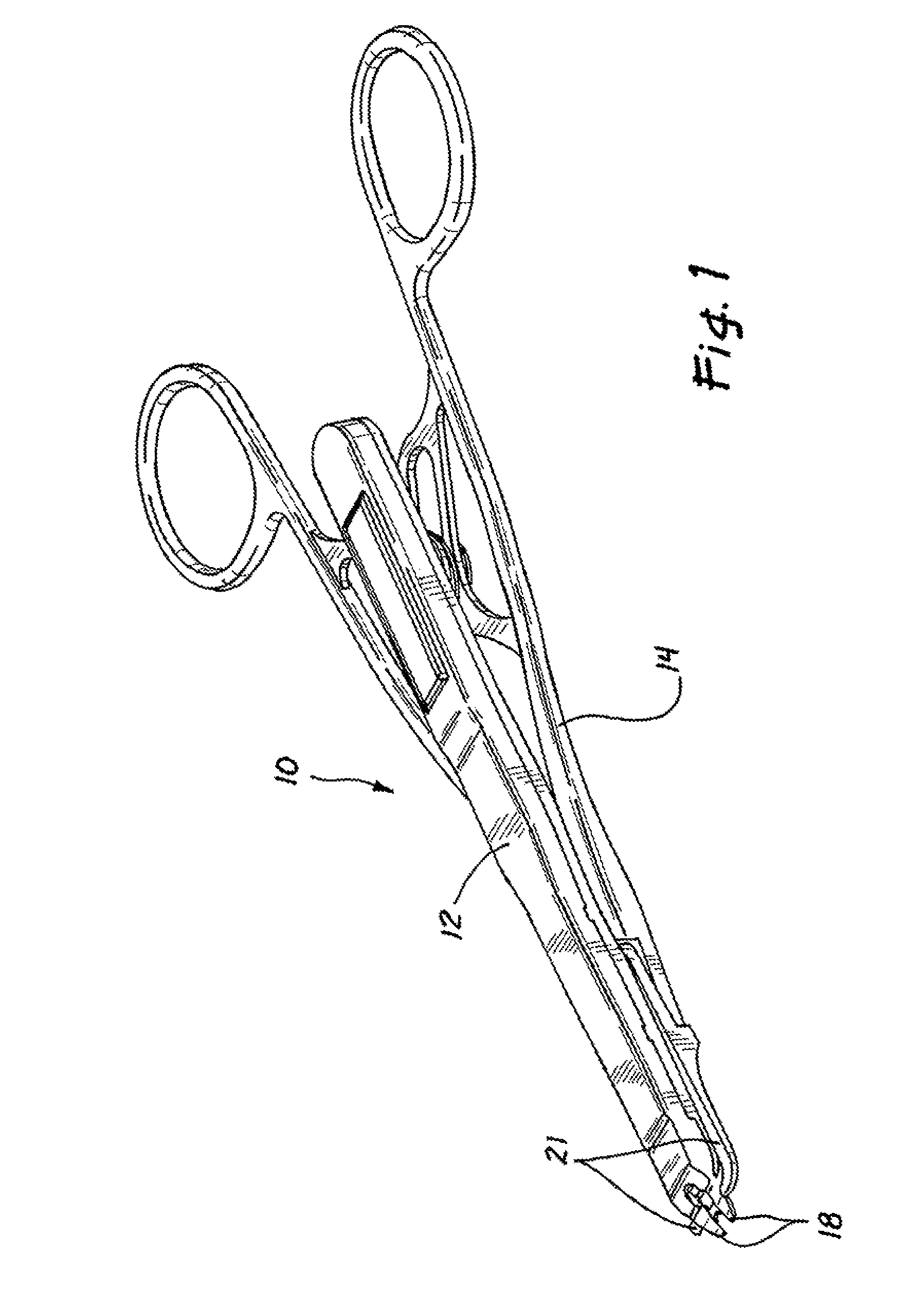

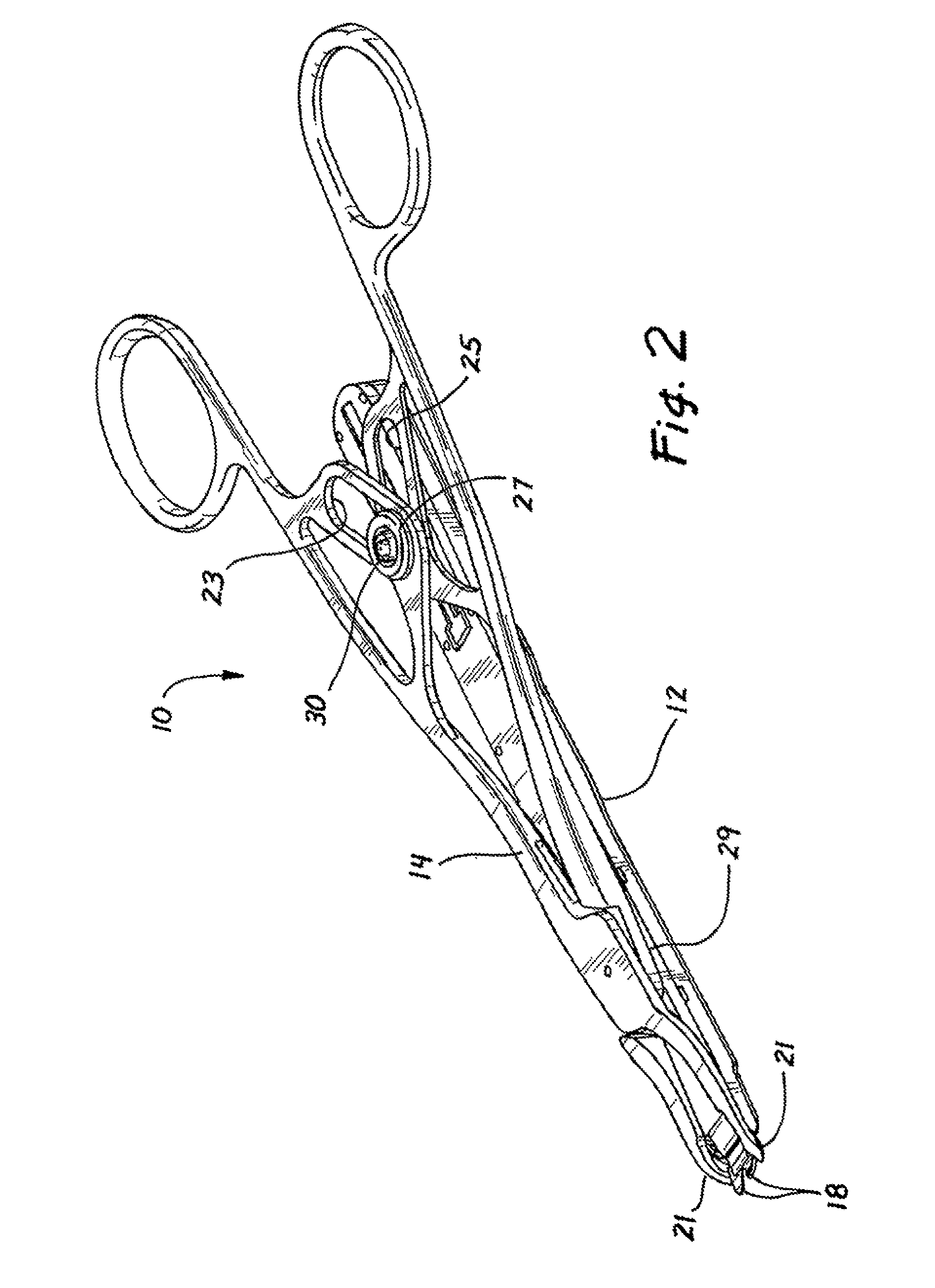

Multiple clip applier apparatus and method

InactiveUS8529588B2High degreeOptimization mechanismSuture equipmentsStapling toolsEngineeringRisk stroke

A surgical clip applier includes a train of clips disposed in a plane with a single clip removed from the train of clips and disposed in a staging position. A pair of jaws are adapted to receive the single clip from the staging position by operation of a jaw loader moveable outside the plane of the train of clips. In an associate method, a handle assembly is provided which is moveable in an open stroke and a closed stroke. A source of surgical clips are provided along with a pair of jaws which are adapted to receive one of the clips as the handle assembly is moved in an open stroke, the jaws are open to receive the clip. Following the opening of the jaws, a jaw loader is extended to a position between the jaws to move the clip into the jaws. The handle assembly is moveable in a closed stroke during which the jaws are closed to crimp the clip. Prior to this closing of the jaws, the jaw loader is retracted from the position between the jaws leaving the clip in the jaws.

Owner:APPL MEDICAL RESOURCES CORP

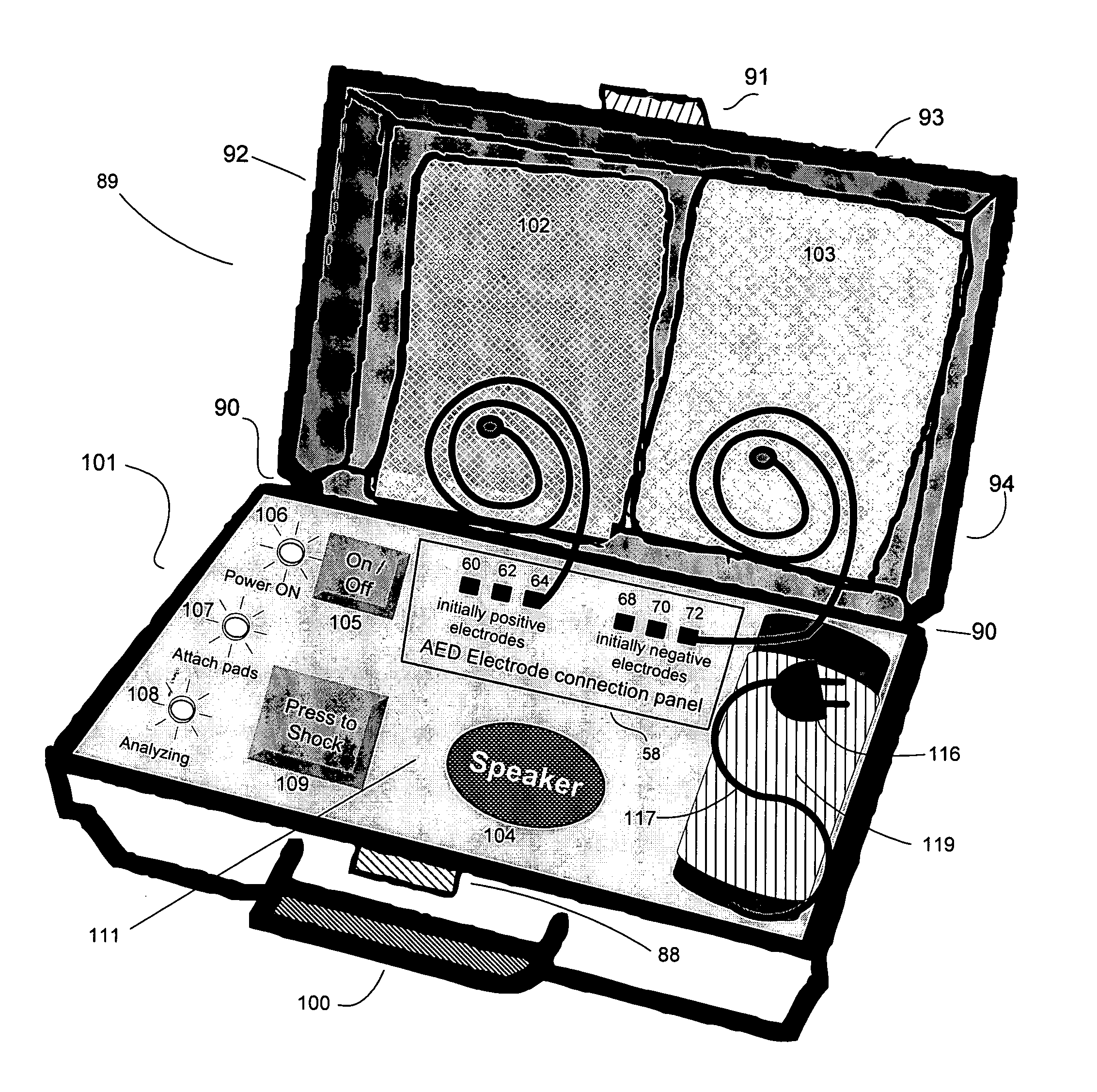

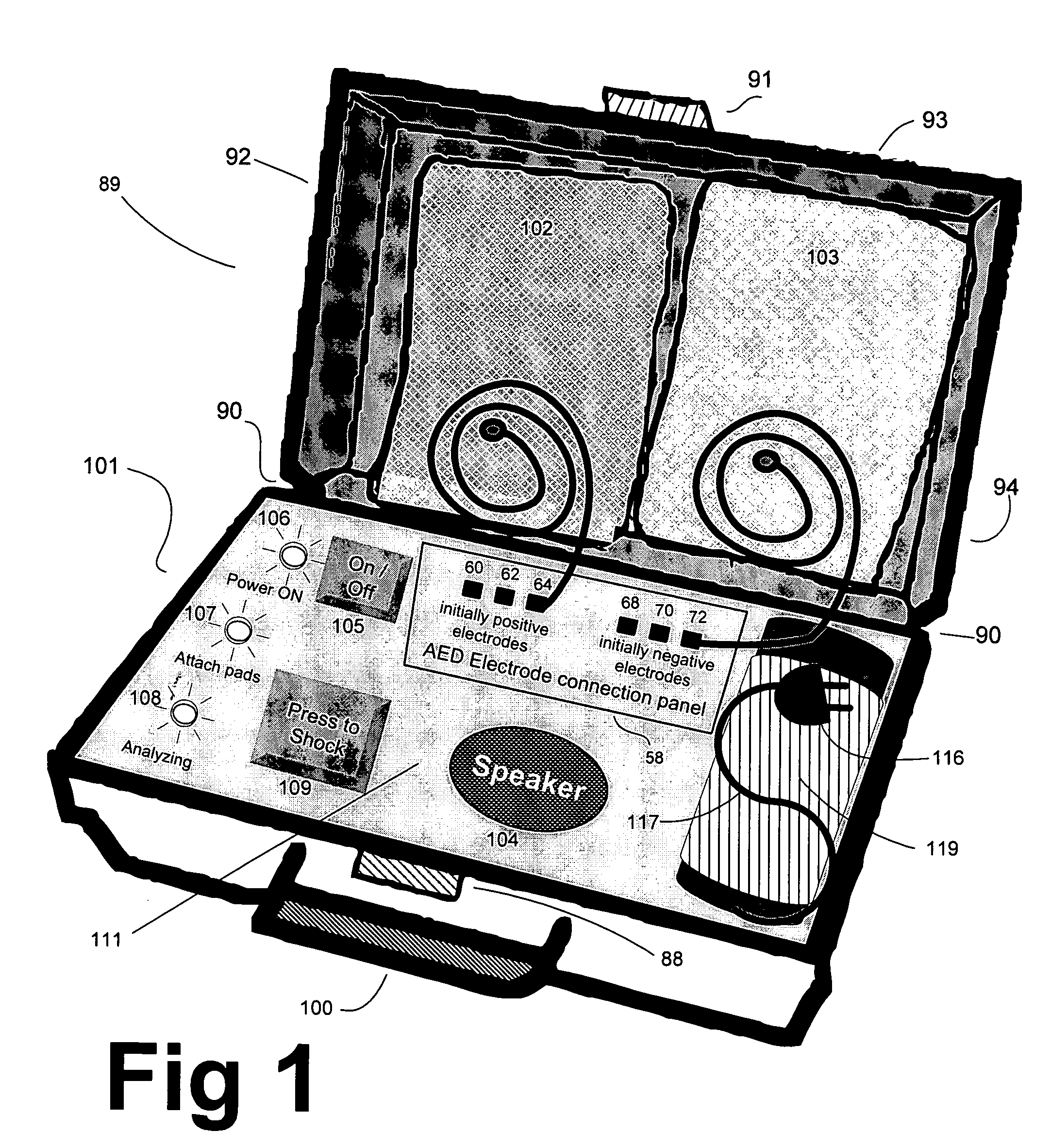

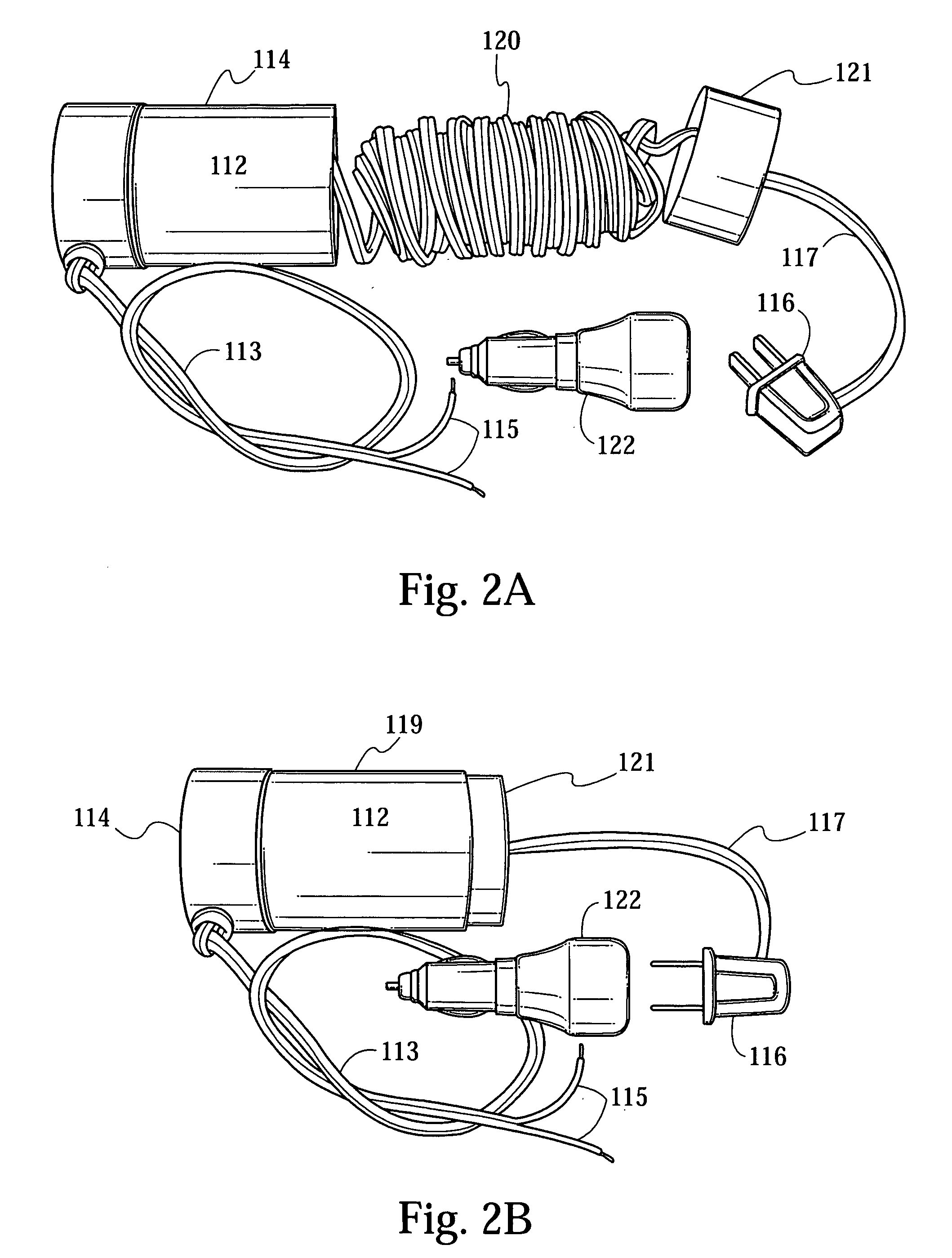

Advanced automatic external defibrillator powered by alternative and optionally multiple electrical power sources and a new business method for single use AED distribution and refurbishment

InactiveUS20040143297A1Improve reliabilityRapid and easy deploymentData processing applicationsHeart defibrillatorsEngineeringAutomatic external defibrillator

An AED being powered by 120 / 240 VAC electrical power alone, being powered by external DC power alone, or any in combination with or without internal-integral battery power, and further an AED access service business method for sales of access to AEDs. The inventive AED, in addition to the defibrillator circuitry comprises a long, tangle free power access cord to be plugged into an external source of AC or DC power and optionally, additional sets of body surface and alternative electrodes positioned in the esophagus and / or heart. The AED has additional advanced capabilities including the ability to deliver rapid sequential shocks through one or more sets of patient electrodes, and the optional mode of shock delivery whereby the shock is delayed while the AED continues to analyze the patients ECG waveform and delays the defibrillation shock or sequence of shocks until the ECG analysis indicates conditions are optimum for successful defibrillation.

Owner:RAMSEY MAYNARD III

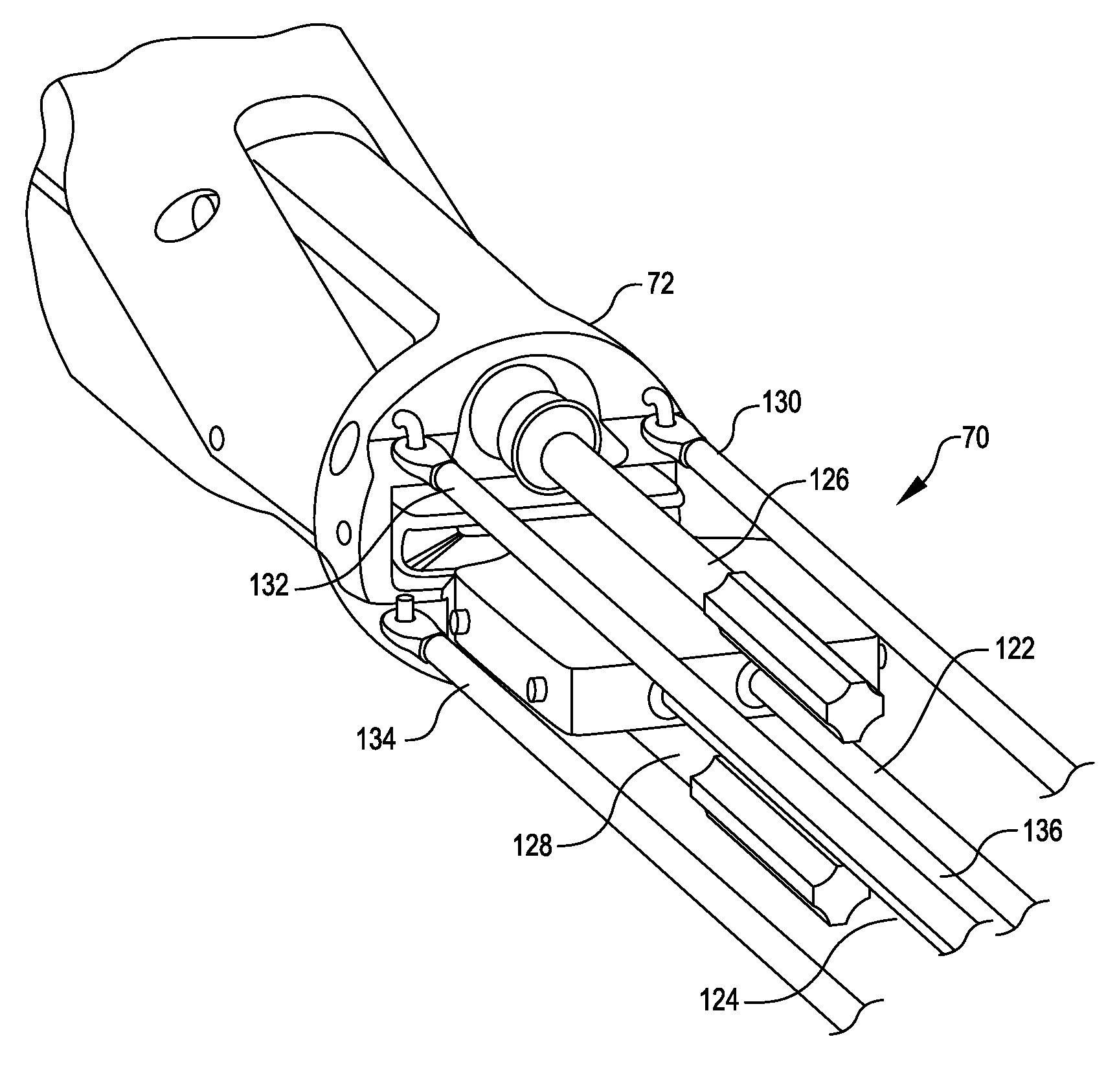

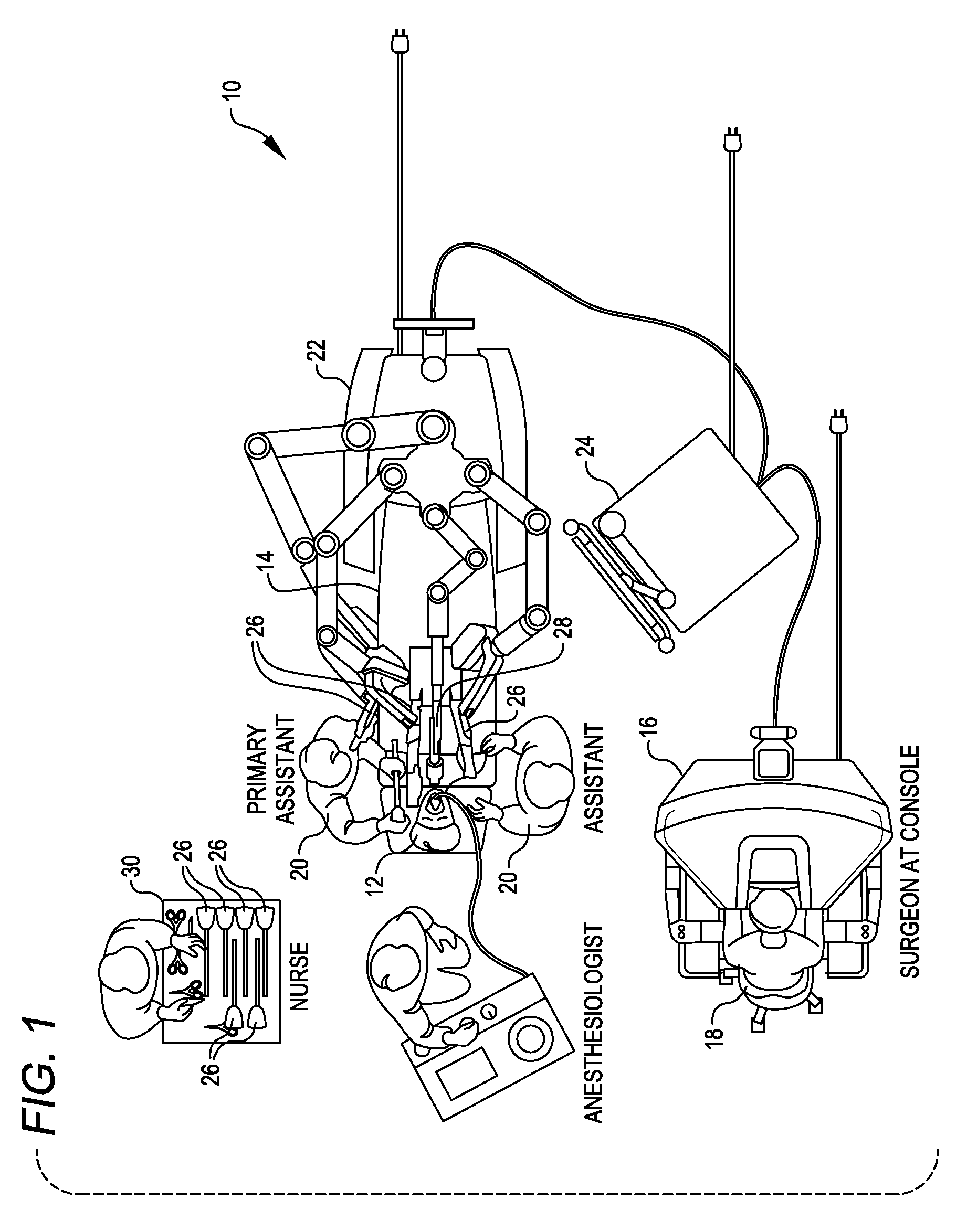

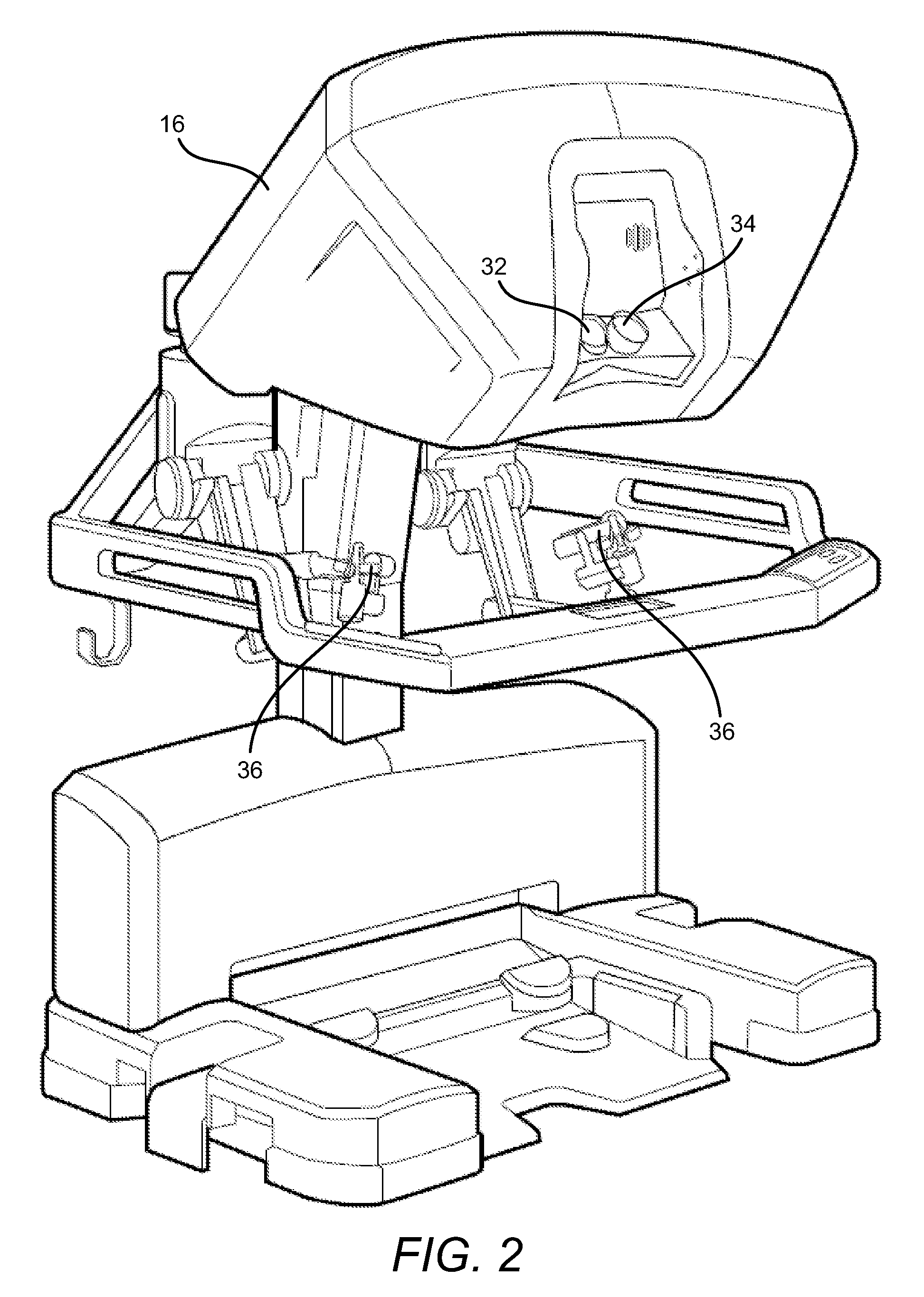

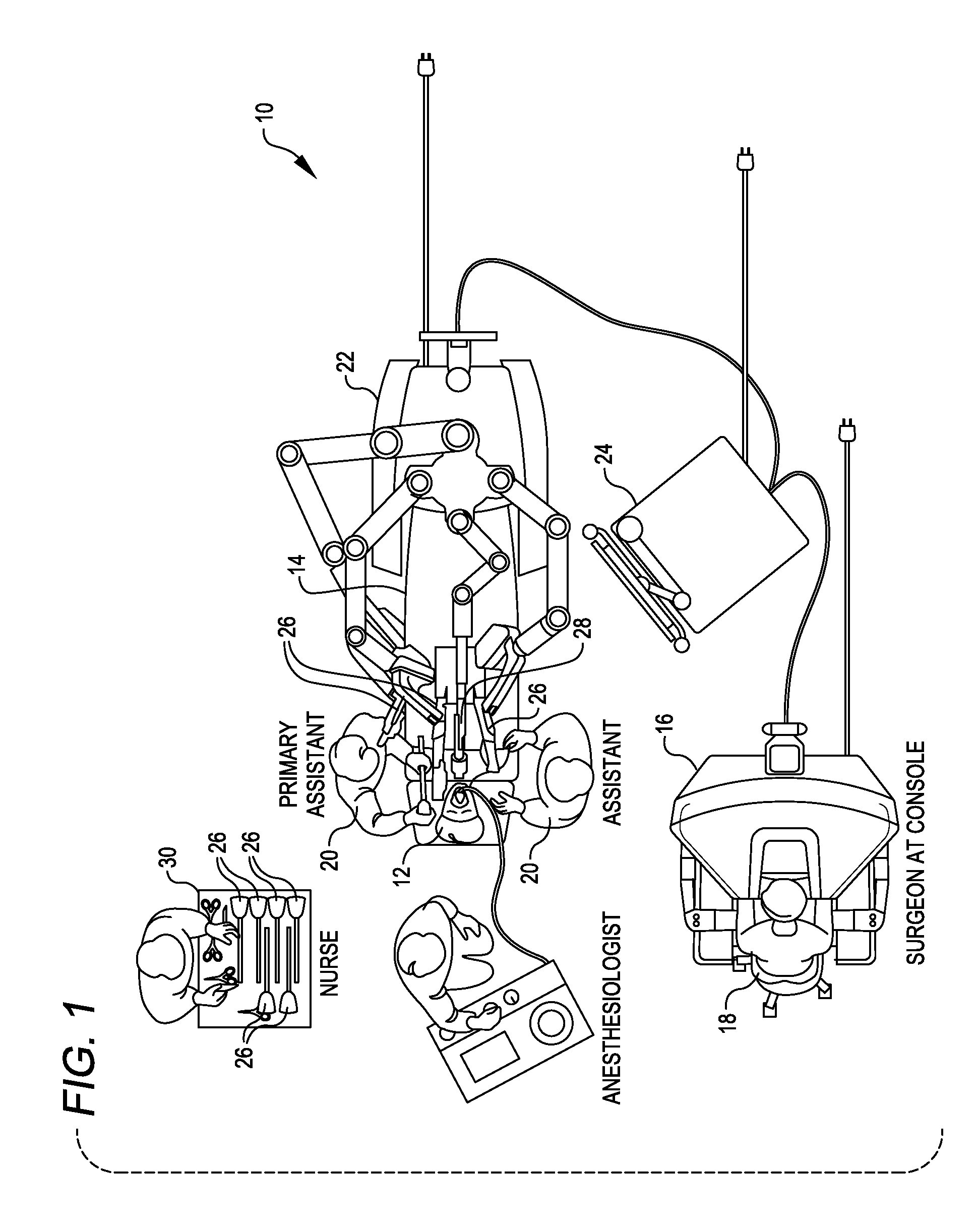

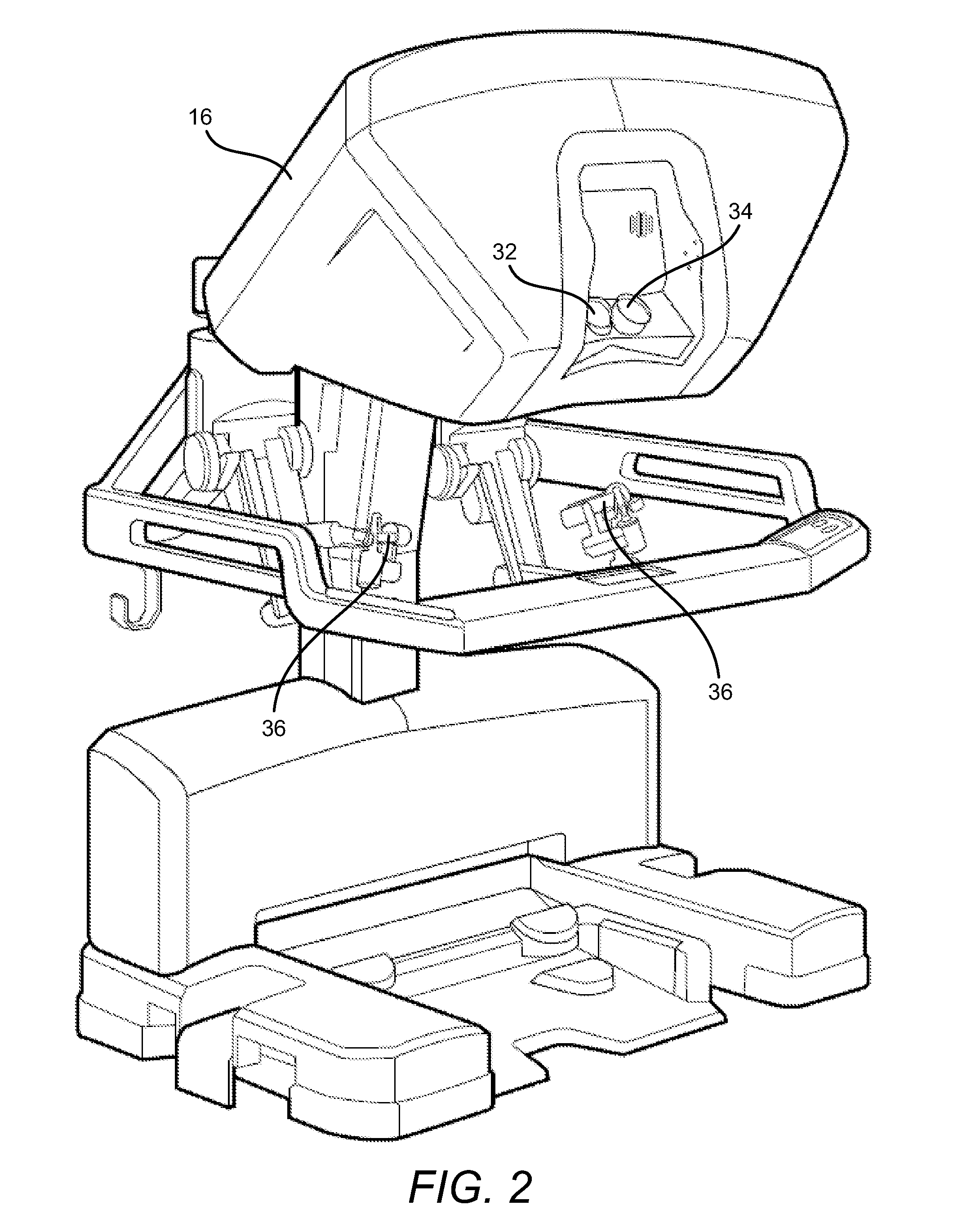

Surgical tool with a two degree of freedom wrist

ActiveUS8852174B2Amount of maneuverabilityShorten the lengthYielding couplingDiagnosticsDrive shaftAngular degrees

Surgical tools having a two degree-of-freedom wrist, wrist articulation by linked tension members, mechanisms for transmitting torque through an angle, and minimally invasive surgical tools incorporating these features are disclosed. An elongate intermediate wrist member is pivotally coupled with a distal end of an instrument shaft so as to rotate about a first axis transverse to the shaft, and an end effector body is pivotally coupled with the intermediate member so as to rotate about a second axis that is transverse to the first axis. Linked tension members interact with attachment features to articulate the wrist. A torque-transmitting mechanism includes a coupling member, coupling pins, a drive shaft, and a driven shaft. The drive shaft is coupled with the driven shaft so as to control the relative orientations of the drive shaft, the coupling member, and the driven shaft.

Owner:INTUITIVE SURGICAL OPERATIONS INC

Enzyme electrode structure

InactiveUS6071391AEasy to manufactureEasy to measureImmobilised enzymesBioreactor/fermenter combinationsEnzyme electrodeWorking electrode

A biosensor comprises a space part for sucking and housing a sample formed of two upper and lower plates, the two plates being stuck together by an adhesive layer, the space part for sucking and housing the sample being constituted so as to be partially opened in the peripheral part and partially closed by the adhesive layer, and has a working electrode having at least glucose oxidase immobilized thereon and a counter electrode on the same plane of the plate.

Owner:ABBOTT DIABETES CARE INC

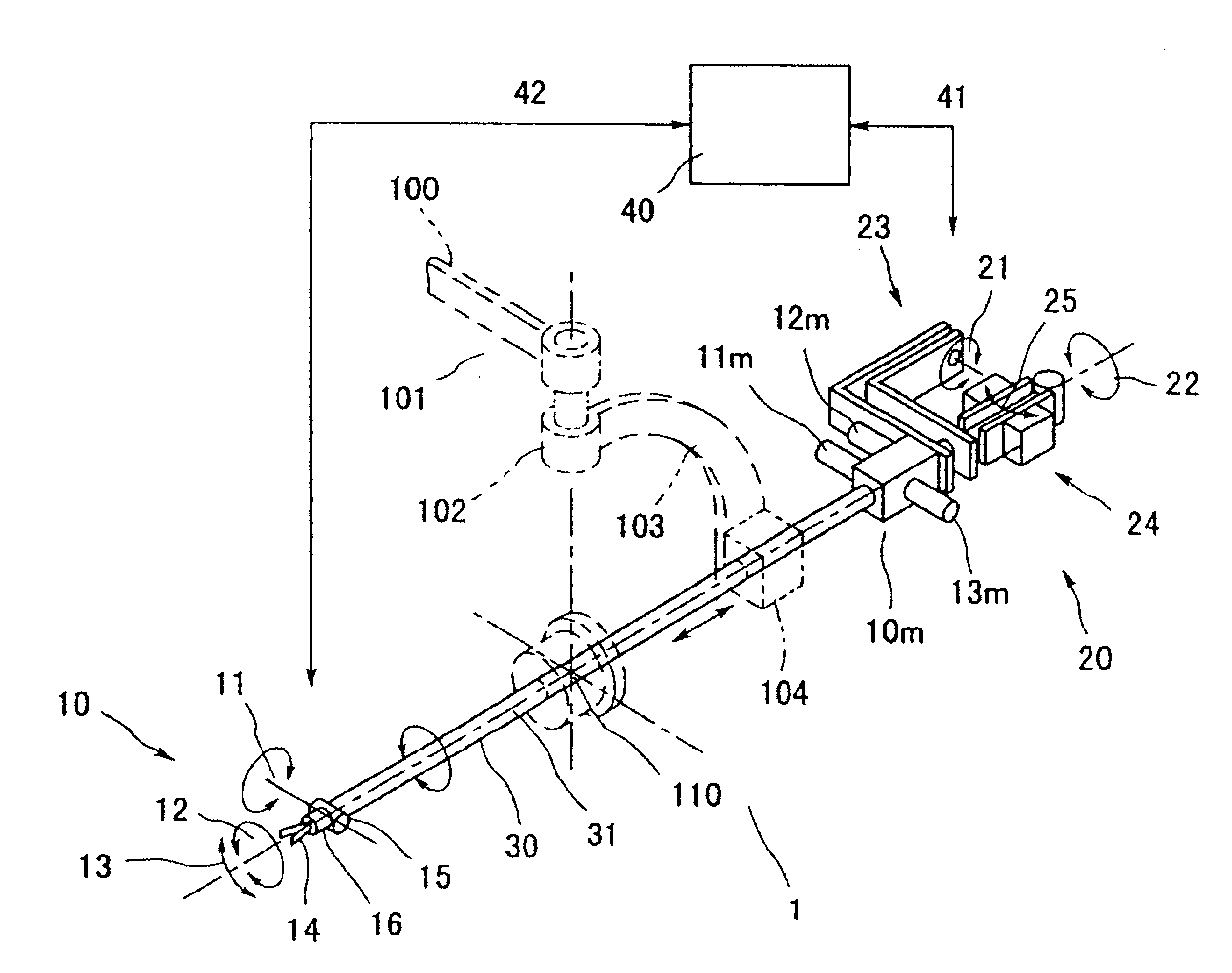

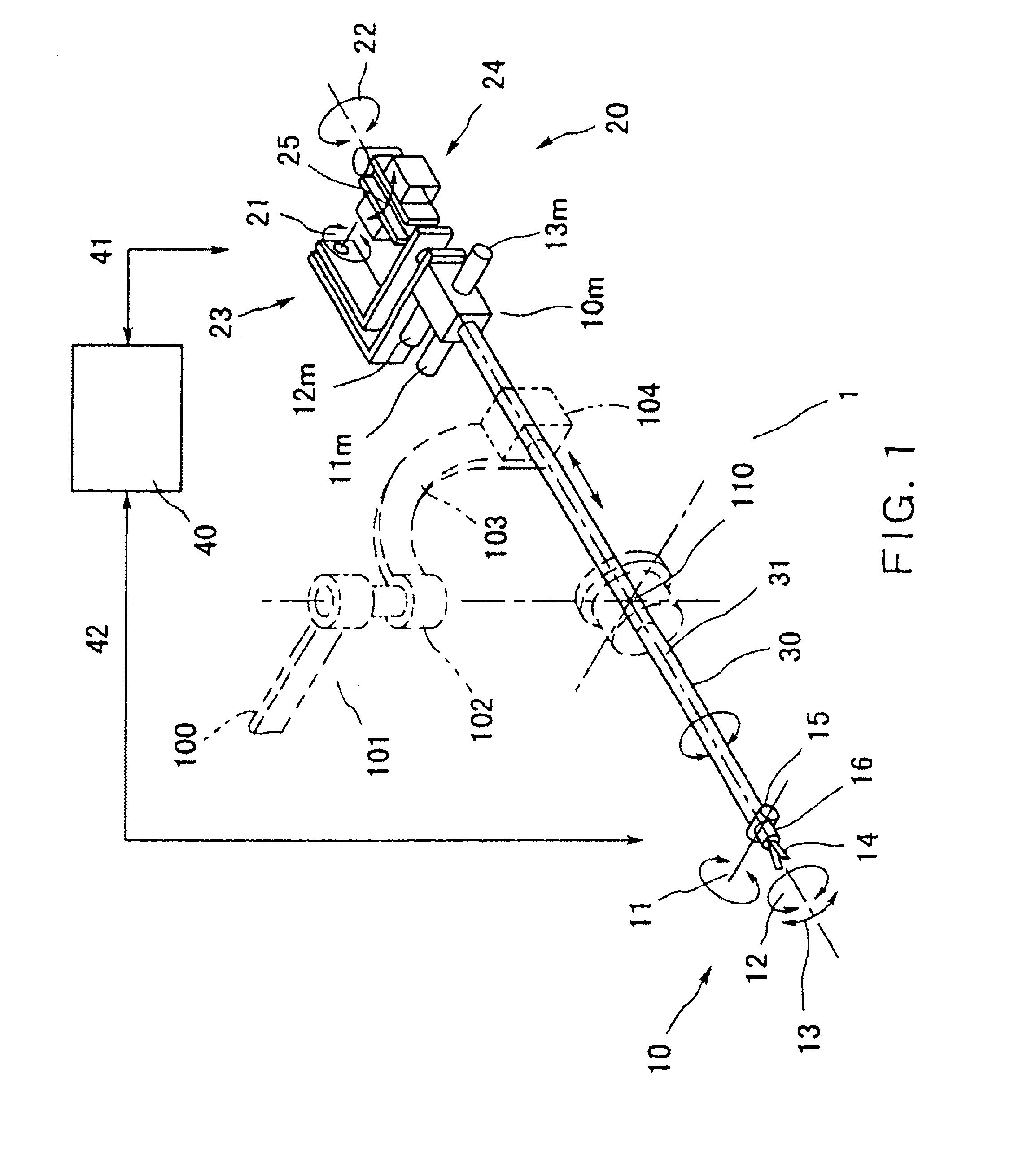

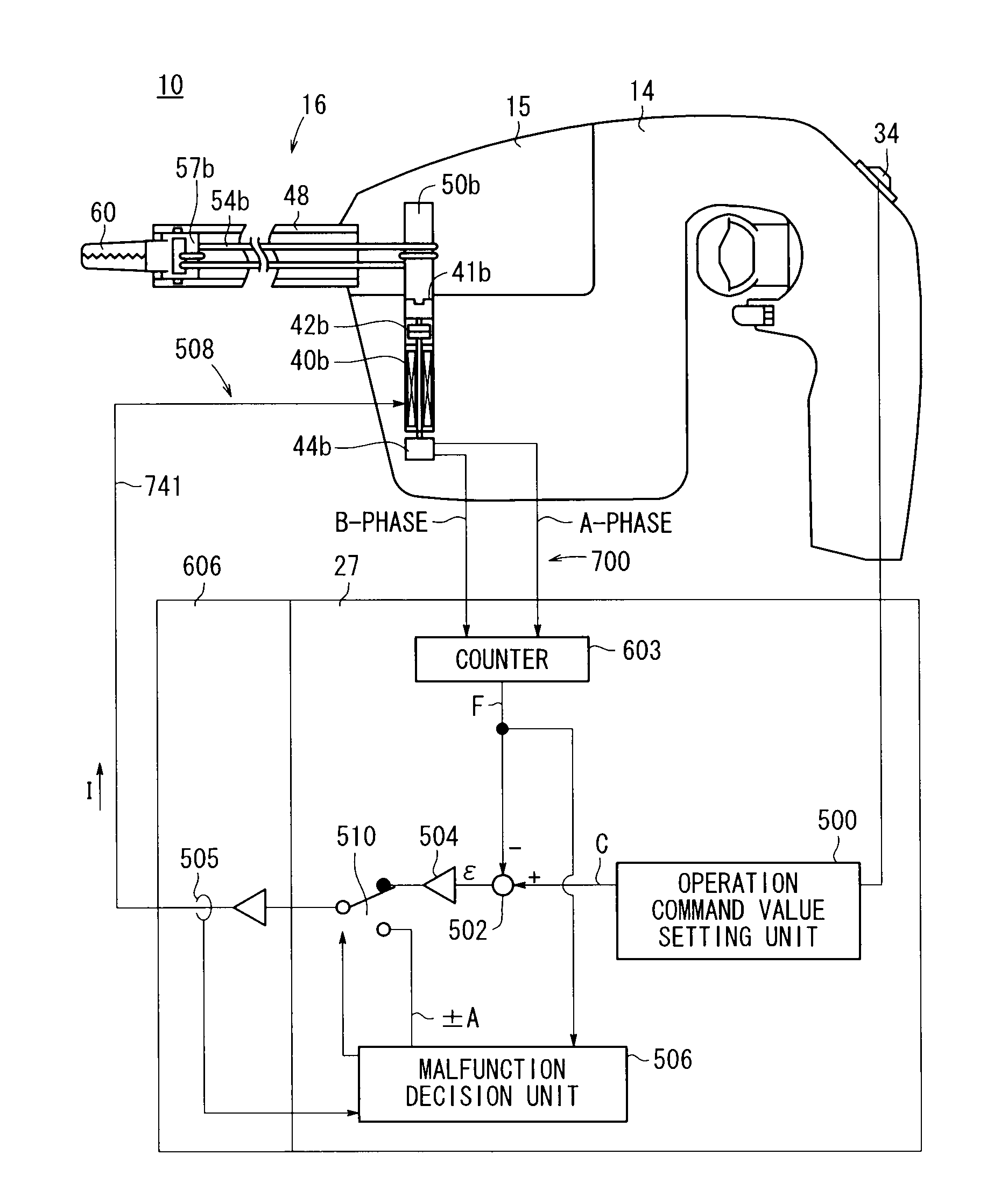

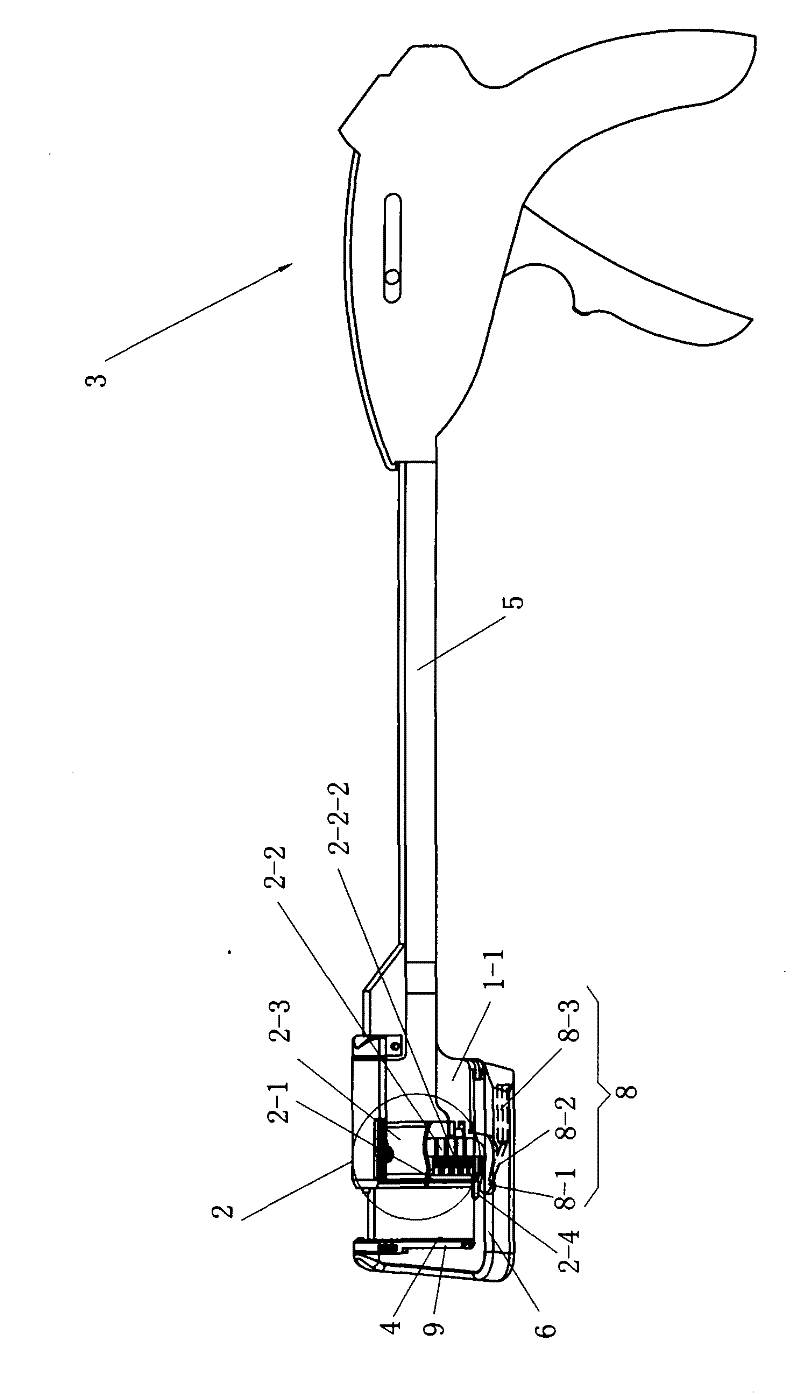

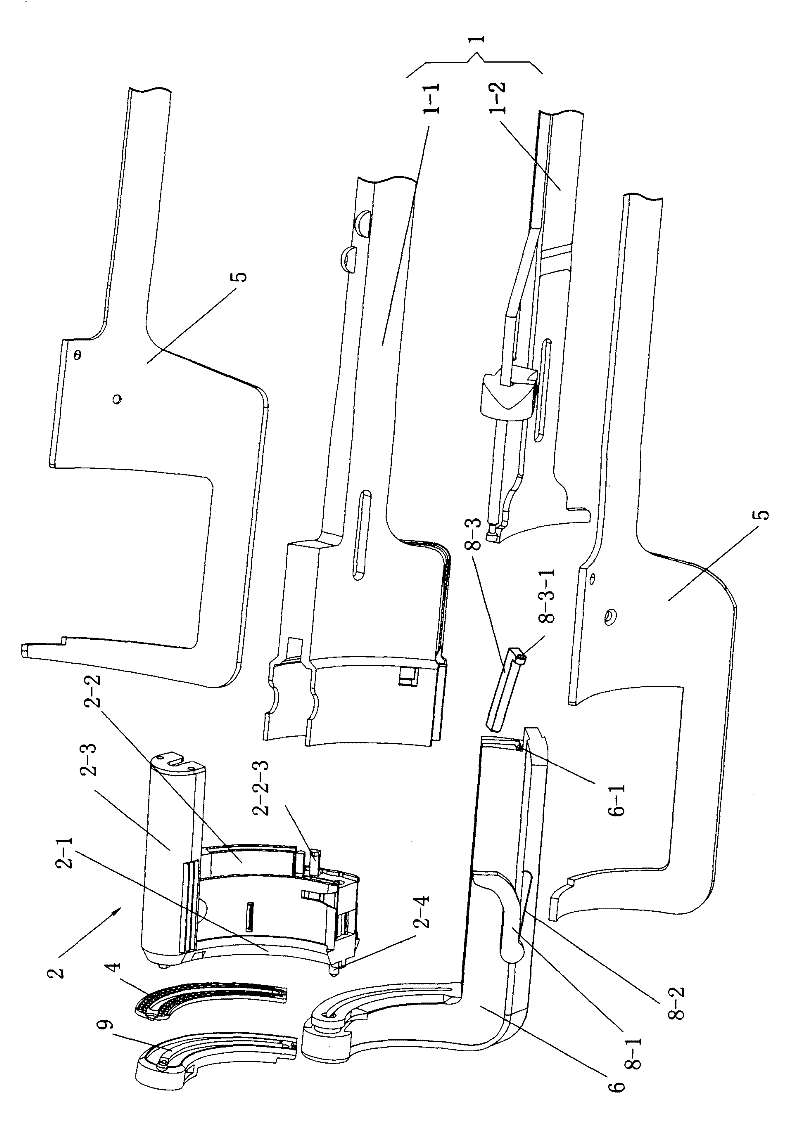

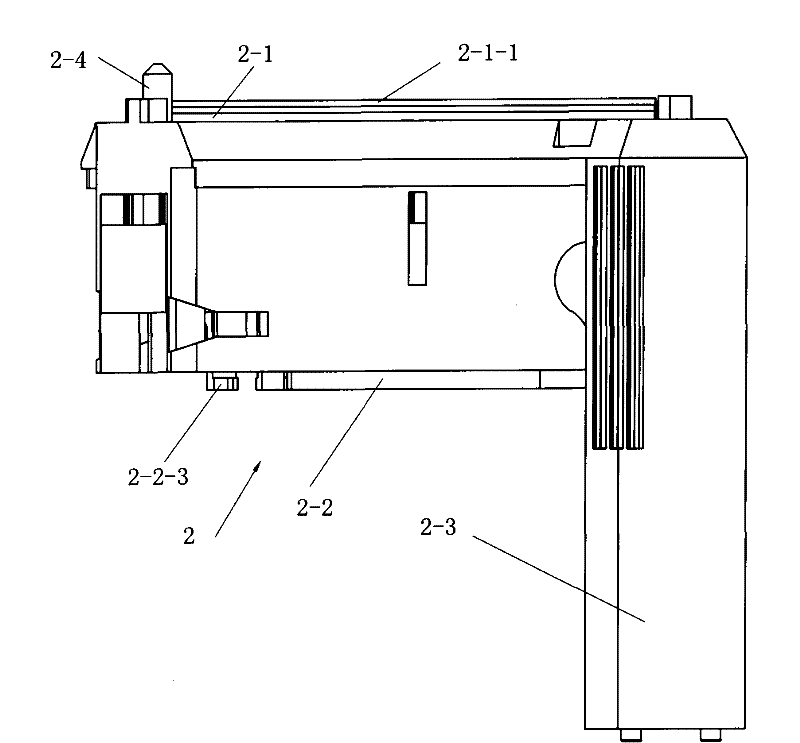

Medical manipulator

ActiveUS8154239B2Improve reliabilityAccurately respondProgramme-controlled manipulatorComputer controlEngineeringActuator

A medical manipulator includes an actuator block having a motor, a coupler detachably mounted on the actuator block and having a rotor connected to a rotatable shaft of the motor, a distal-end working unit mounted on a distal end of a joint shaft, which extends from the coupler and is operatively connected to the rotor by a wire, an encoder for detecting an angular displacement of the motor, and a controller for reading a signal from the encoder and comparing the read signal with an operation command value for energizing the motor through a feedback loop. The controller outputs a signal having a level greater than the resolution of the encoder and a lower operation limit of the motor within a range in which the distal-end working unit remains still, and monitors the angular displacement of the motor for thereby determining whether the feedback loop is malfunctioning or not.

Owner:KARL STORZ GMBH & CO KG

Manipulator apparatus

InactiveUS20050222587A1High operability , reliability and safetyMinimizing affectionDiagnosticsSurgical manipulatorsManipulatorEngineering

A manipulator apparatus comprises a surgical treatment section to be inserted into a subject body, a supporting section which turnably supports the surgical treatment section around a first axis and a second axis, an arm section having the supporting section connected to a distal end side thereof, a manipulating section provided at a proximal end side of the arm section, a manipulating lever provided at the manipulating section, the manipulating lever being turnably supported around a third axis provided at the proximal end side of the arm section, and a manipulating device provided at the manipulating lever, the manipulating device causing the surgical treatment section to turn around the first axis and the second axis.

Owner:TERUMO KK

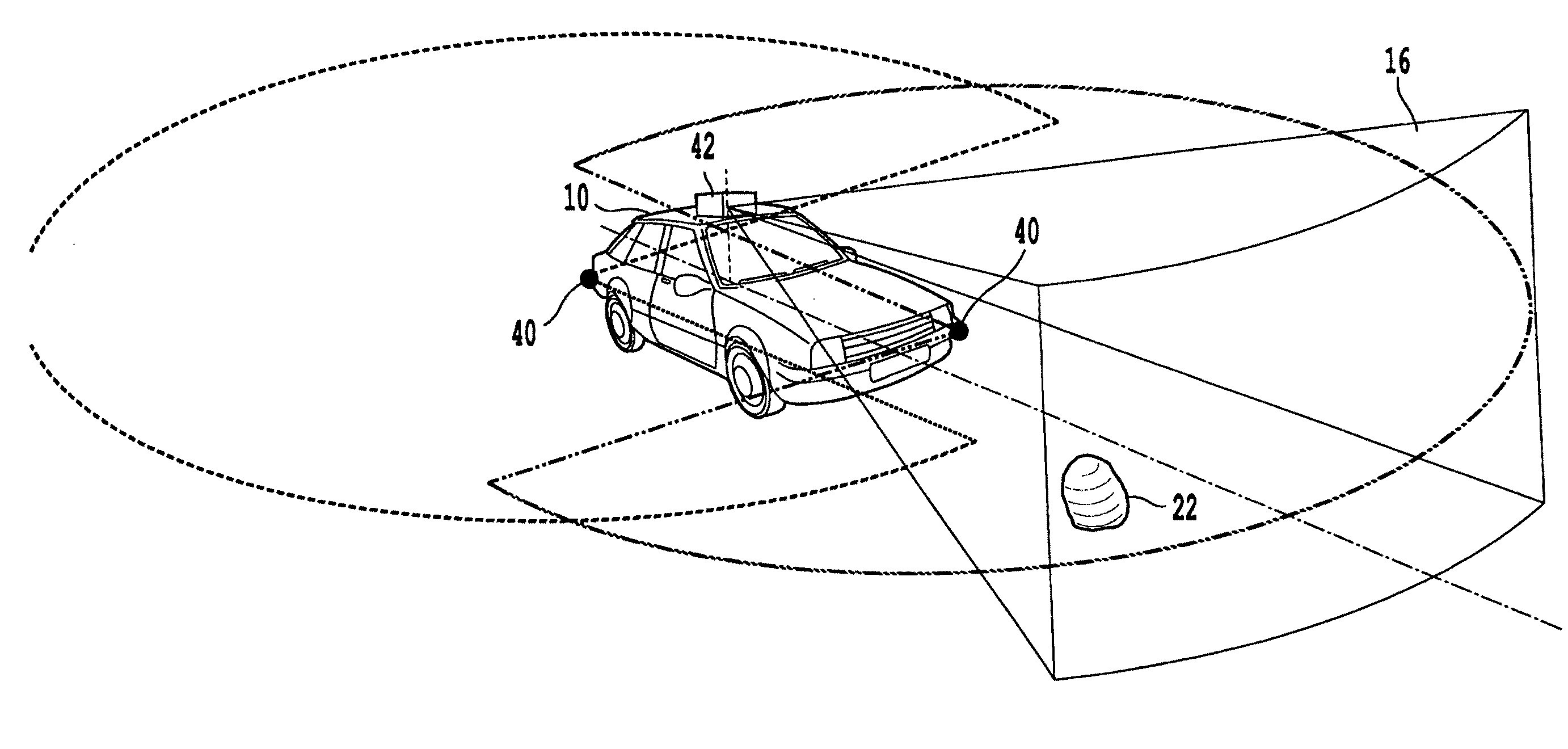

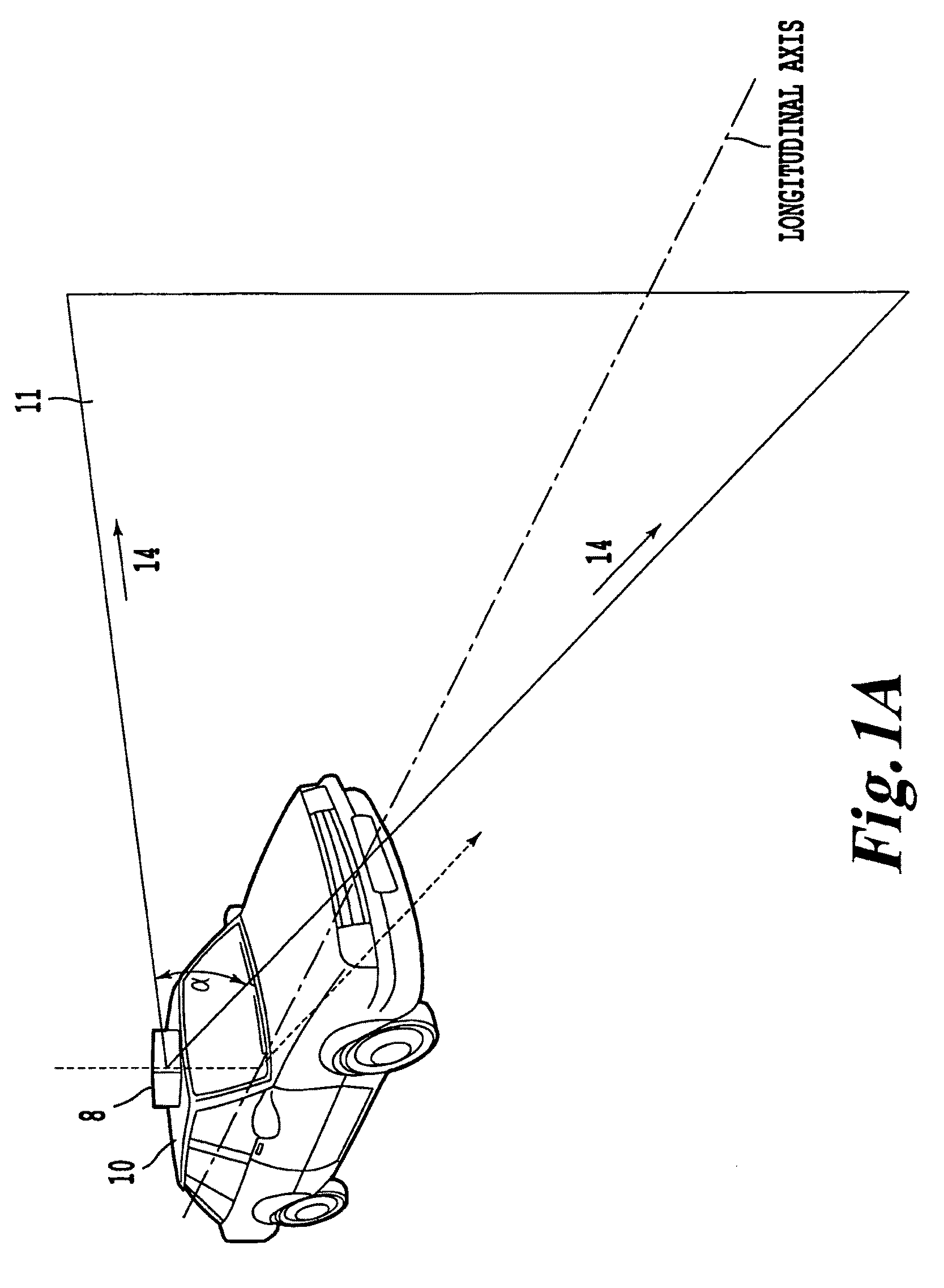

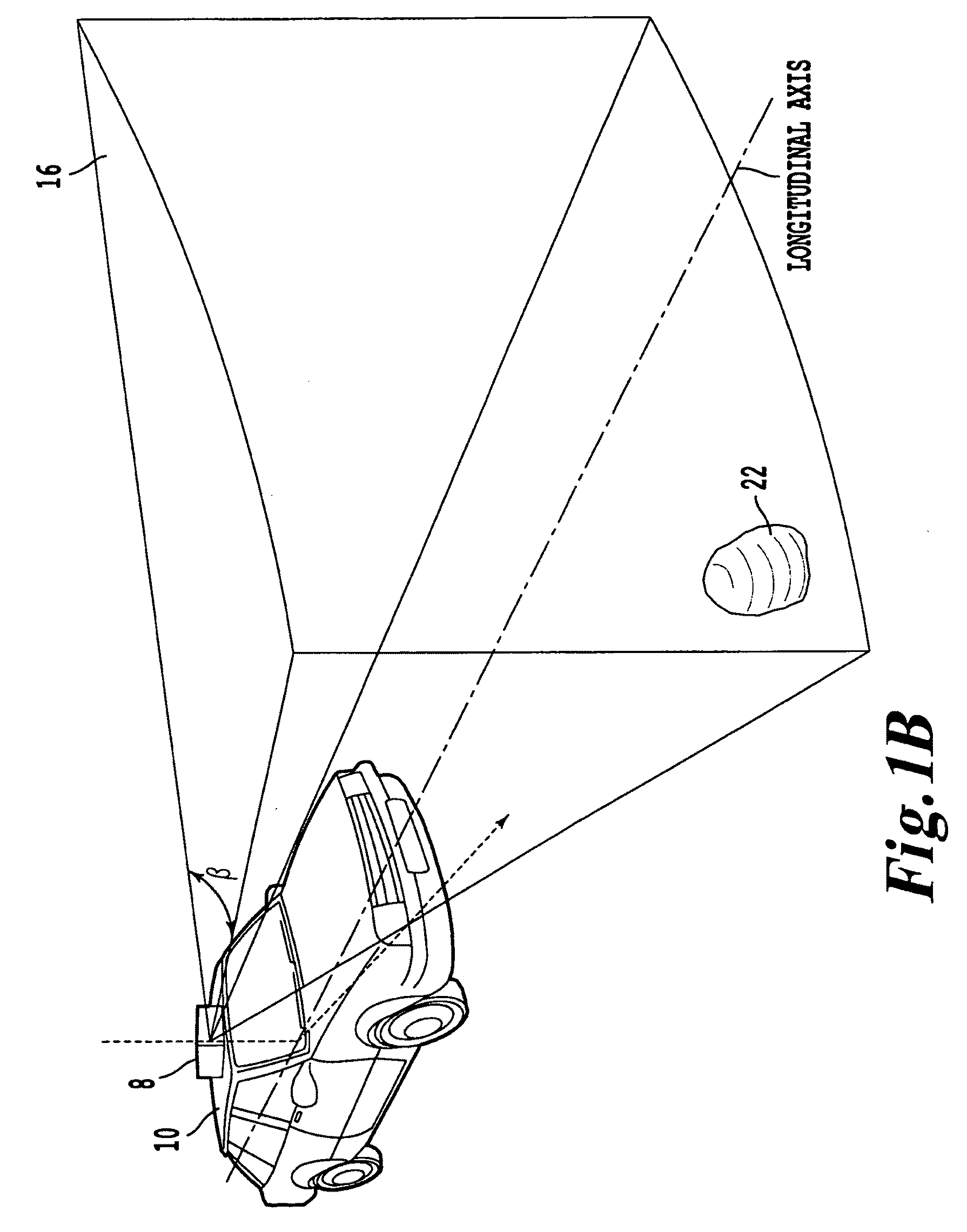

Control and systems for autonomously driven vehicles

ActiveUS20100106356A1Reduce complexityImprove reliabilityAnti-collision systemsElectromagnetic wave reradiationControl systemControl signal

A navigation and control system including one or more position sensors configured to generate position signals indicative of the location and heading of a vehicle. The system includes one or more operation control mechanisms having inputs and producing outputs which control an operation of the vehicle and includes a self-contained autonomous controller disposed remote from the operation control mechanisms. The autonomous controller includes a processor configured to receive the position signals from the position sensors and to generate operation control signals defining an updated travel path for the vehicle, and a programmable interface providing communication among the position sensors, the operation control mechanisms, and the processor. The programmable interface is configured to normalize inputs to the processor from the position sensors and to generate compatible operation control signals applied as the inputs to the operation control mechanisms, whereby the self-contained autonomous controller is configurable for operation with a variety of different sensors and different operation control mechanisms.

Owner:SAMSUNG ELECTRONICS CO LTD

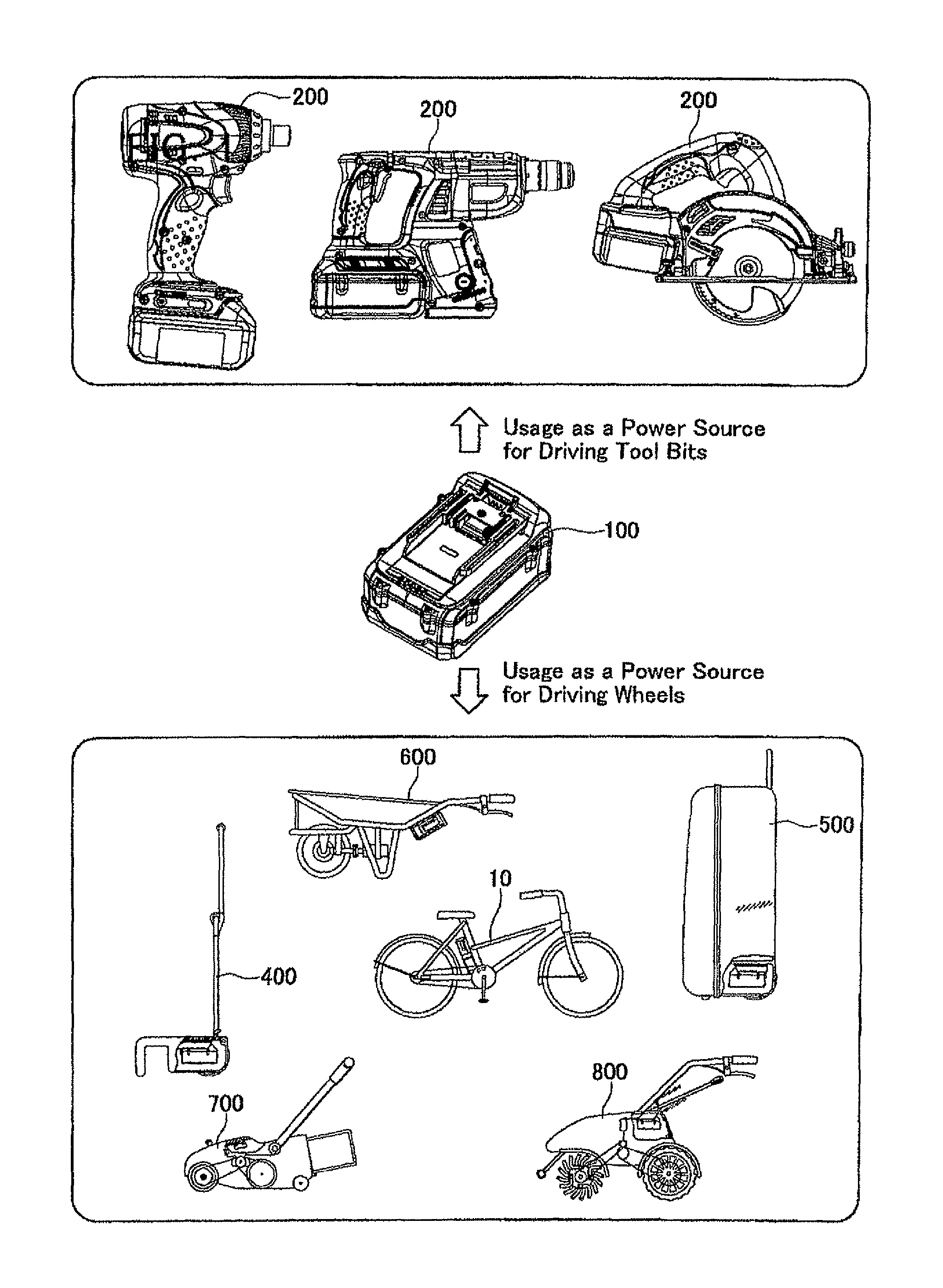

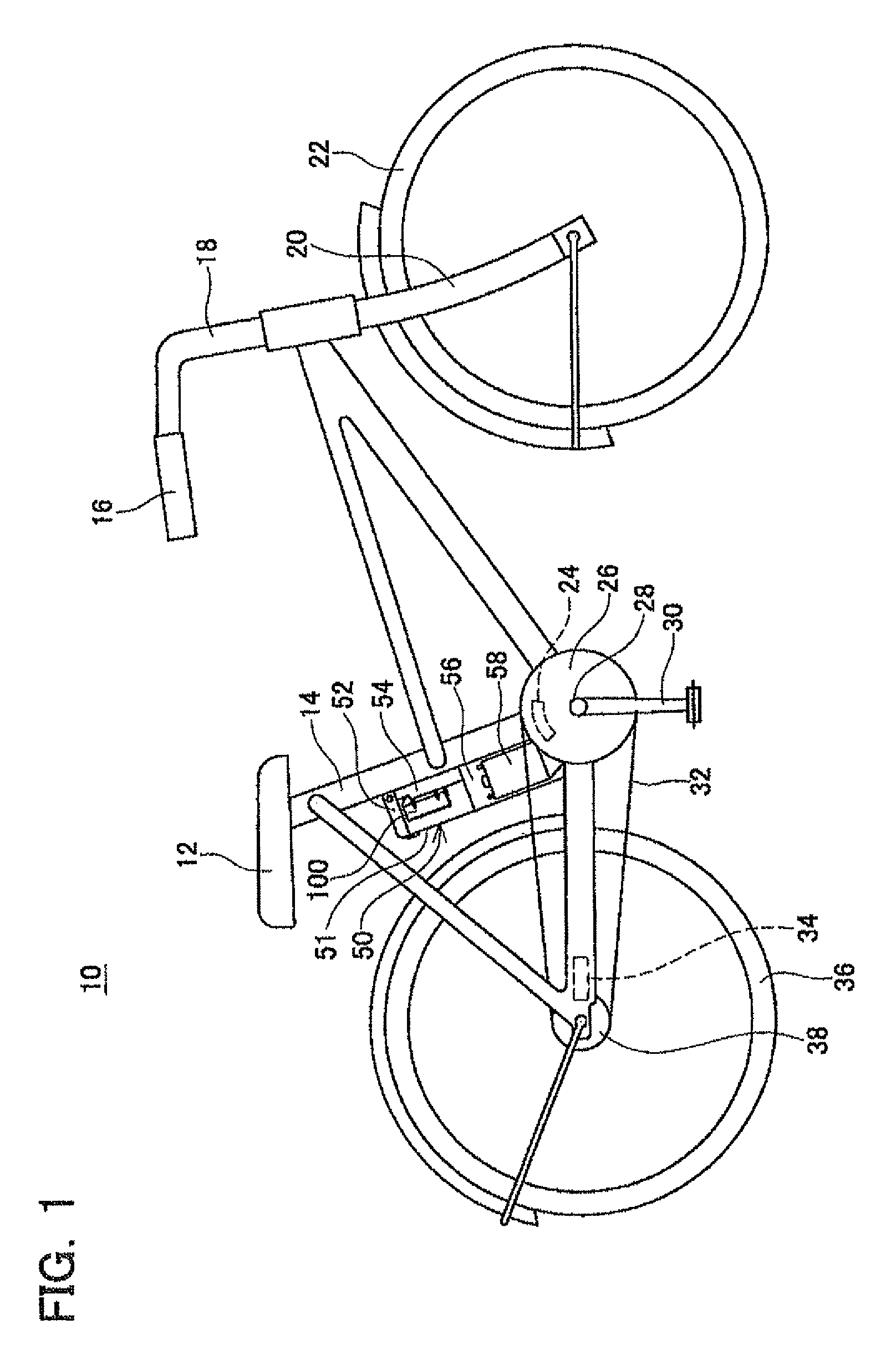

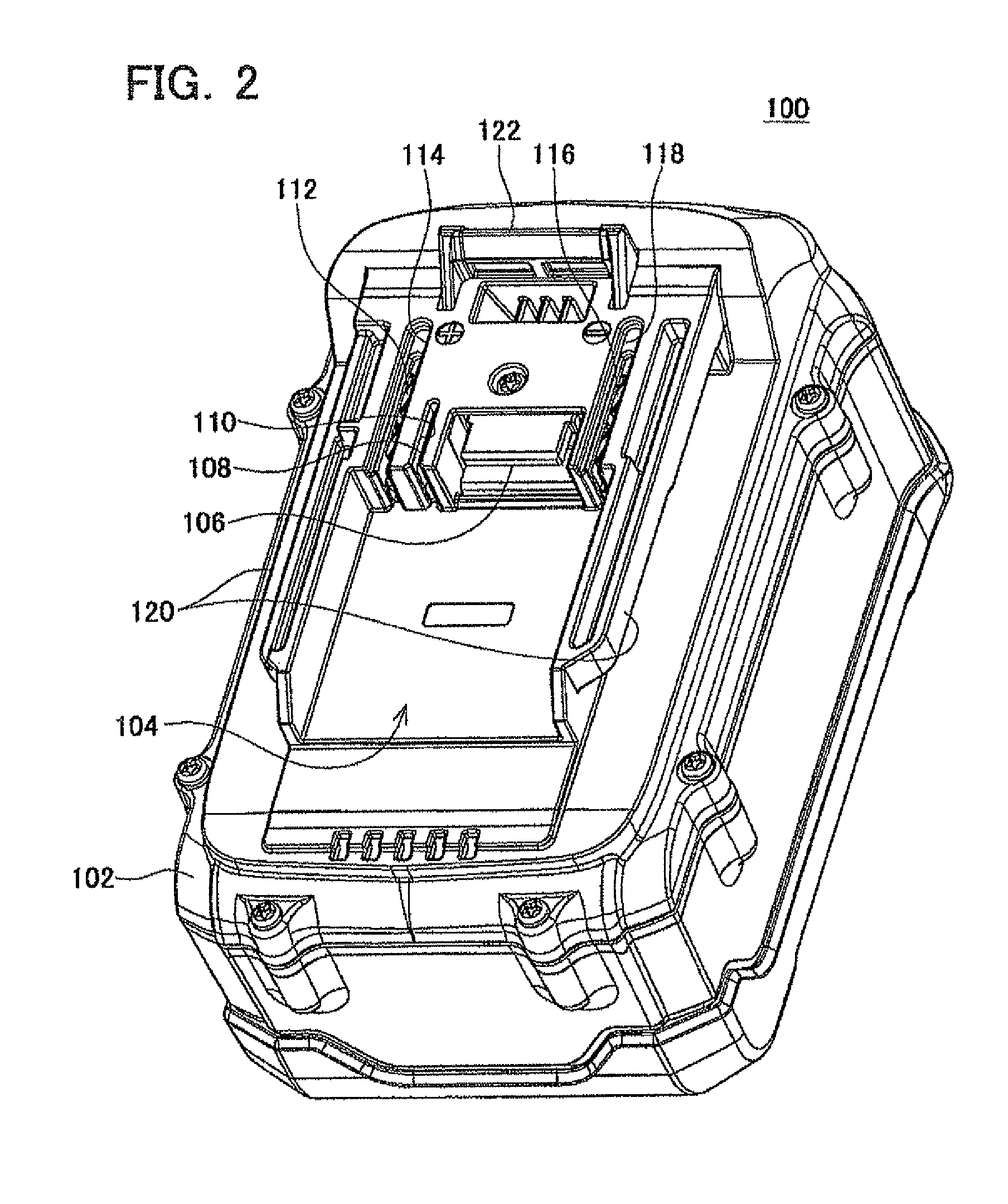

Electric wheeled apparatus

ActiveUS8851215B2Increase the output voltageLarge capacityMowersTilling equipmentsElectricityElectric power system

Owner:MAKITA CORP

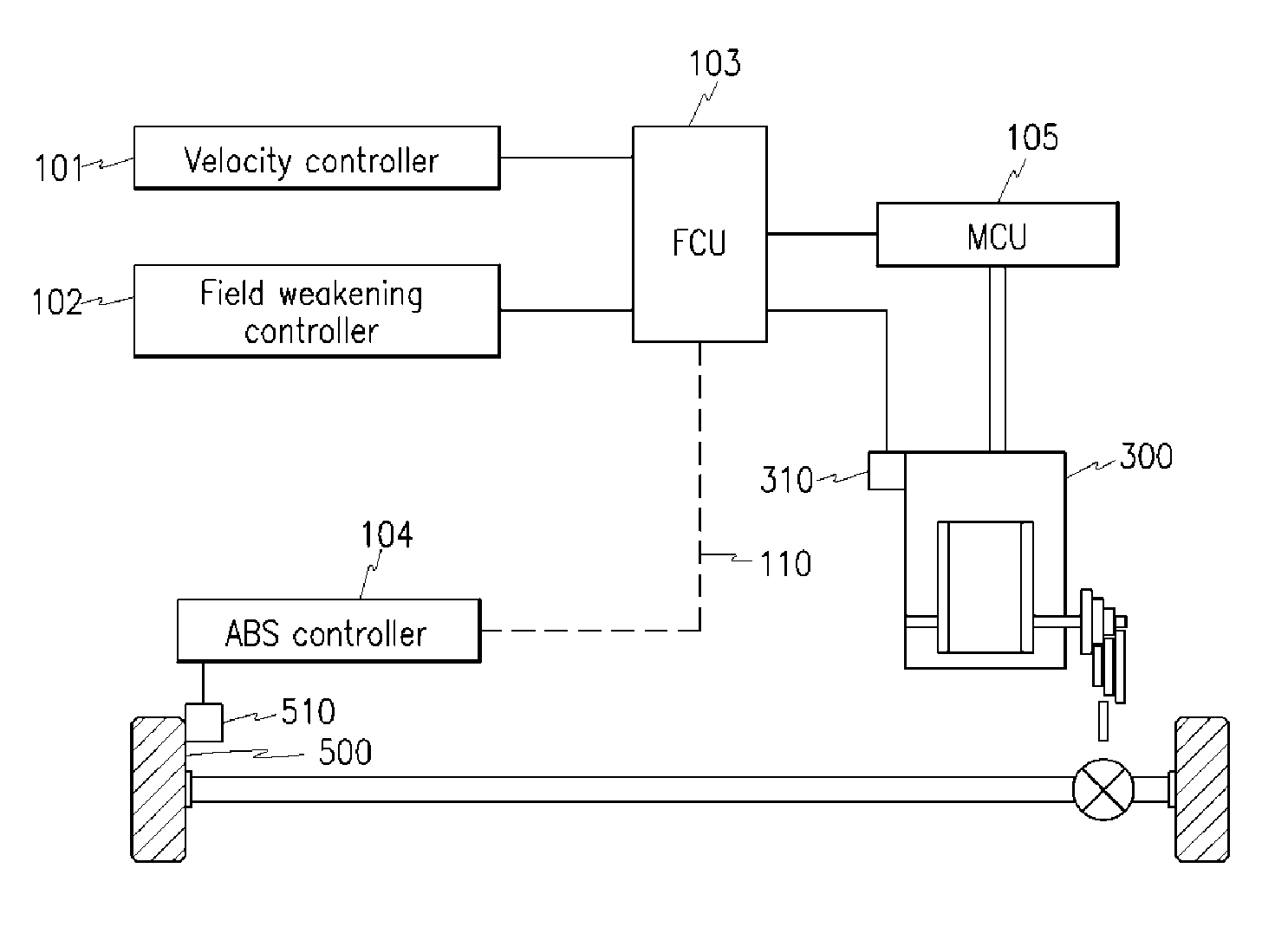

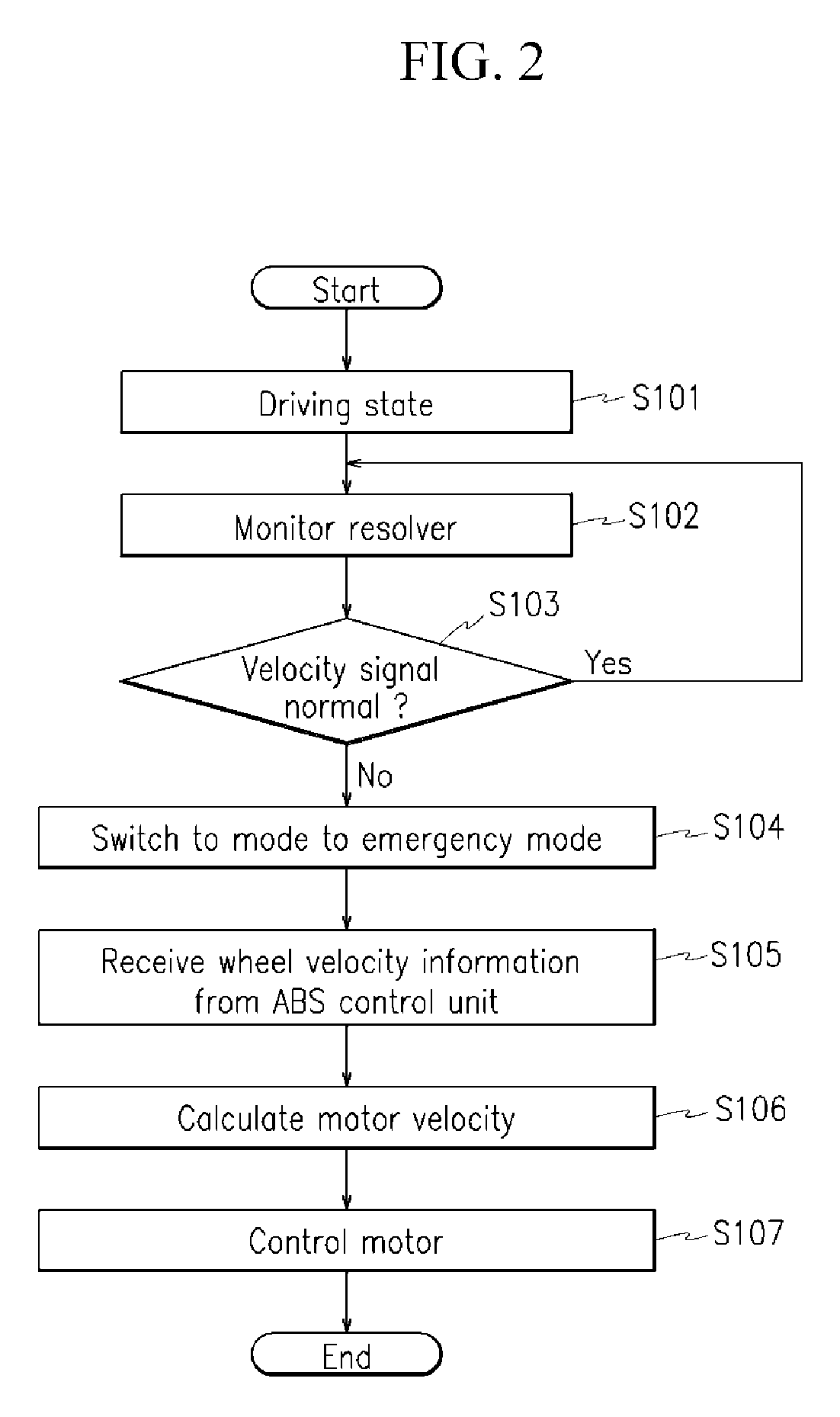

Apparatus and method of compensating for motor velocity of fuel cell vehicle

ActiveUS9233610B2Improve stabilityImprove reliabilitySpeed controllerElectric devicesData controlFuel cells

A method and apparatus that compensates for a velocity of a motor of fuel cell vehicle when a resolver is determined to have failed is provided. In particular, a wheel velocity sensor is configured to detect a wheel velocity of a driving wheel, and an ABS controller is configured to calculate an average wheel velocity and transmit the calculated average to a fuel cell controller (FCU). The FCU is configured to receive information related to the wheel velocity upon detecting that the resolver has failed, and control driving of the motor based on the data related to the wheel velocity so that the motor may maintain operation.

Owner:HYUNDAI MOTOR CO LTD

Data processing system and method

InactiveUS6215898B1Reduce overheadHigh sensitivityImage enhancementImage analysisStatic random-access memoryHigh memory

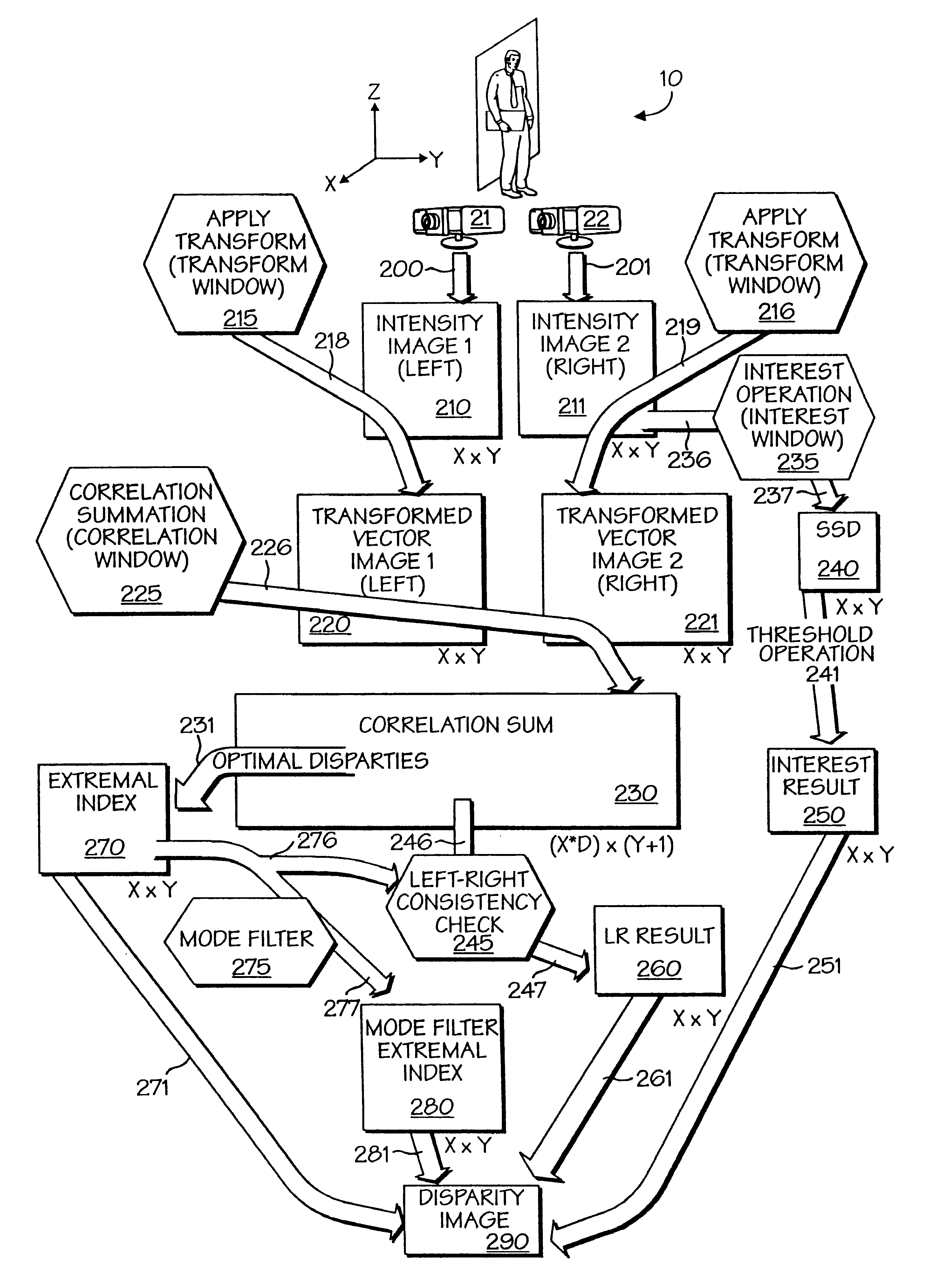

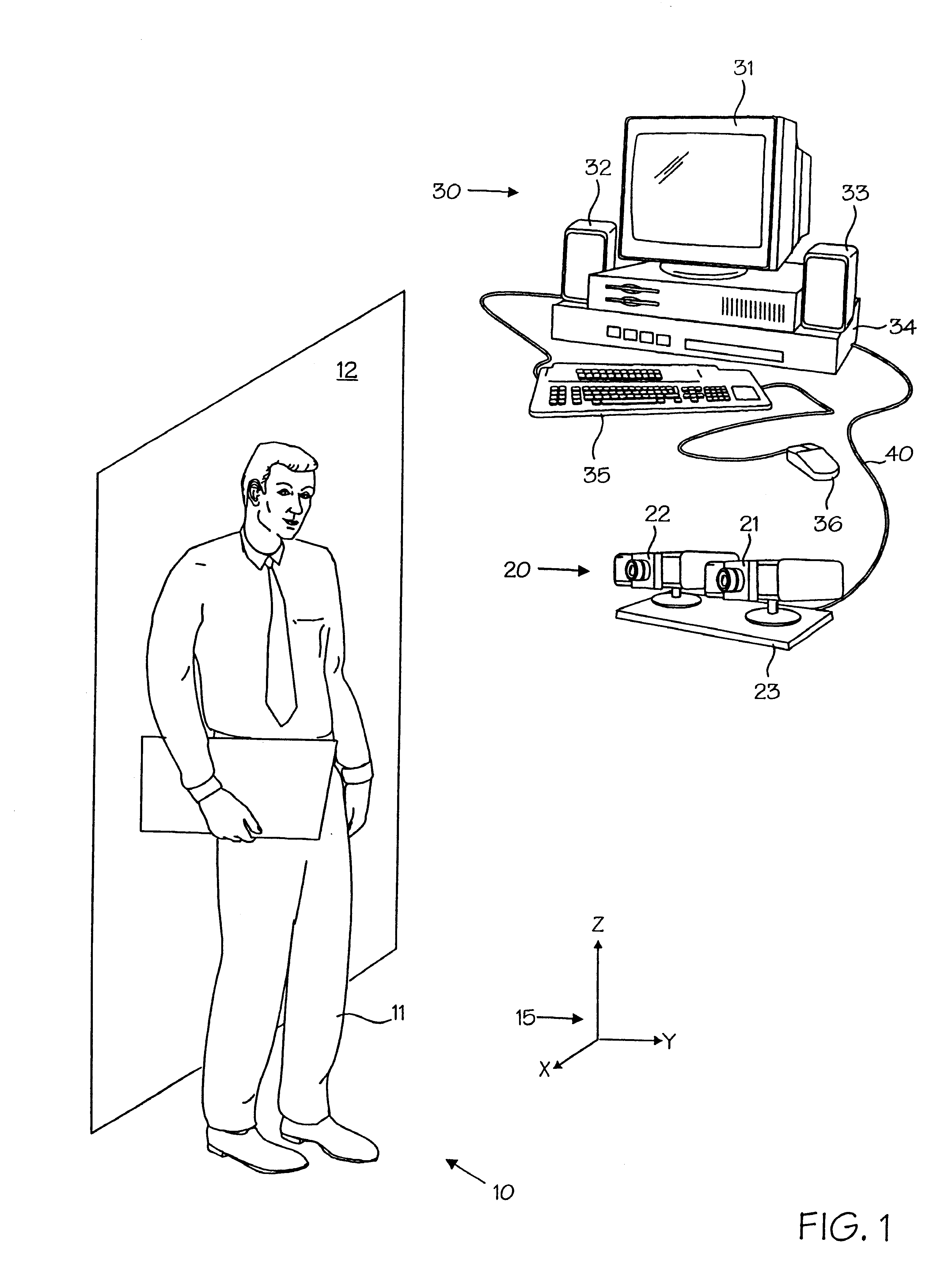

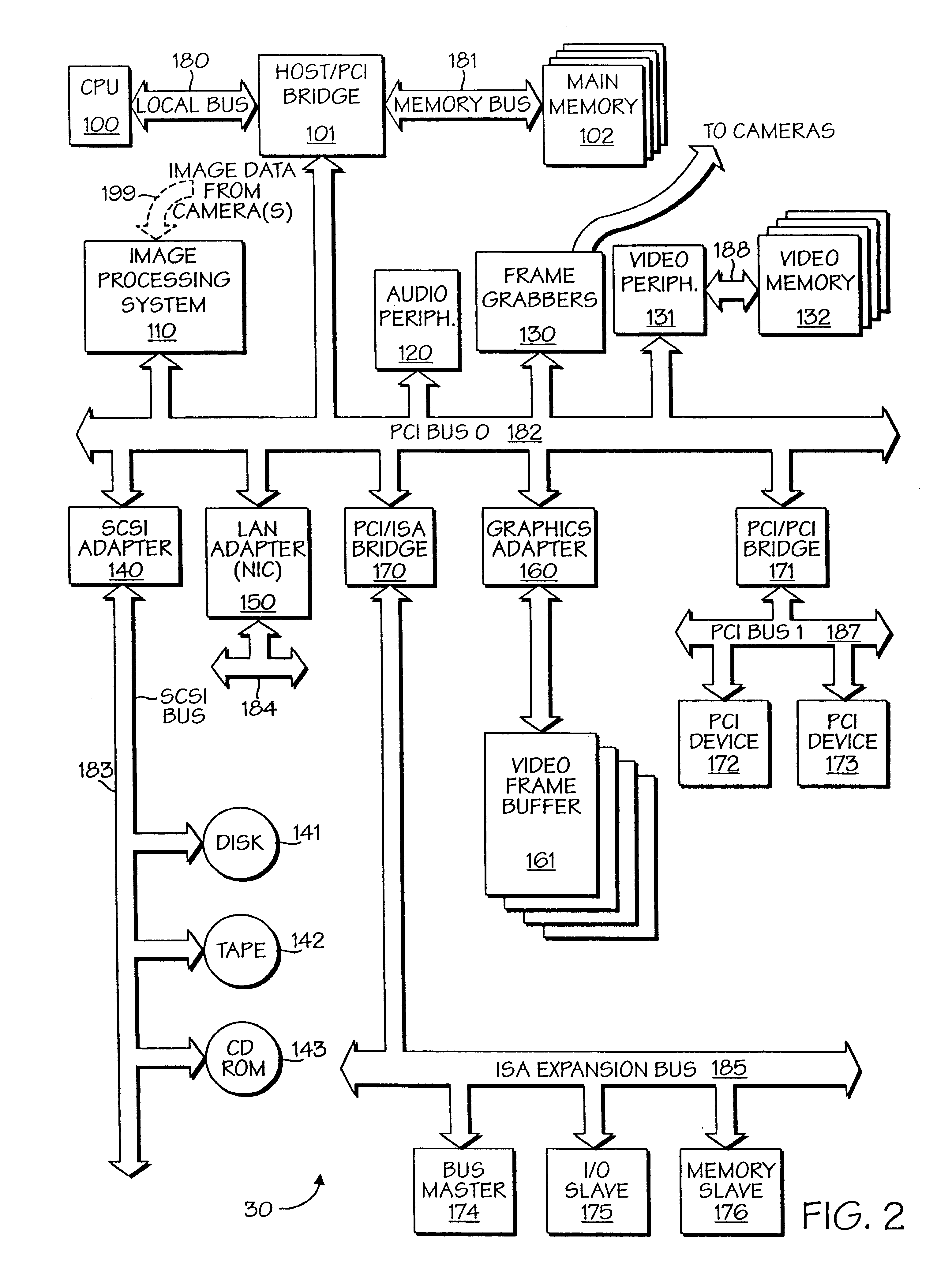

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

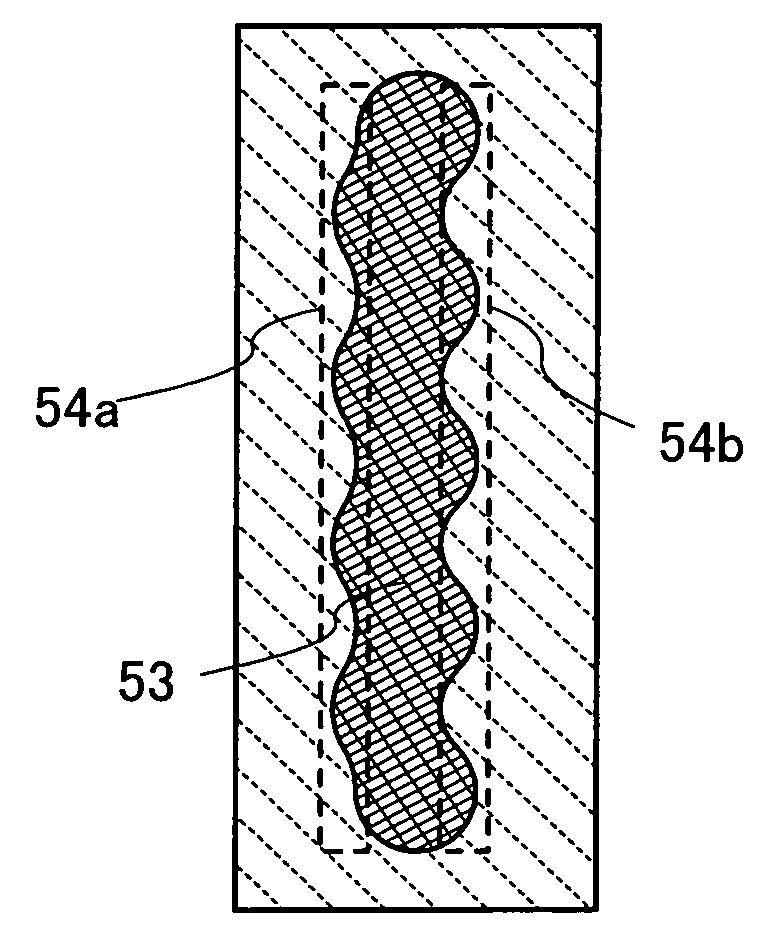

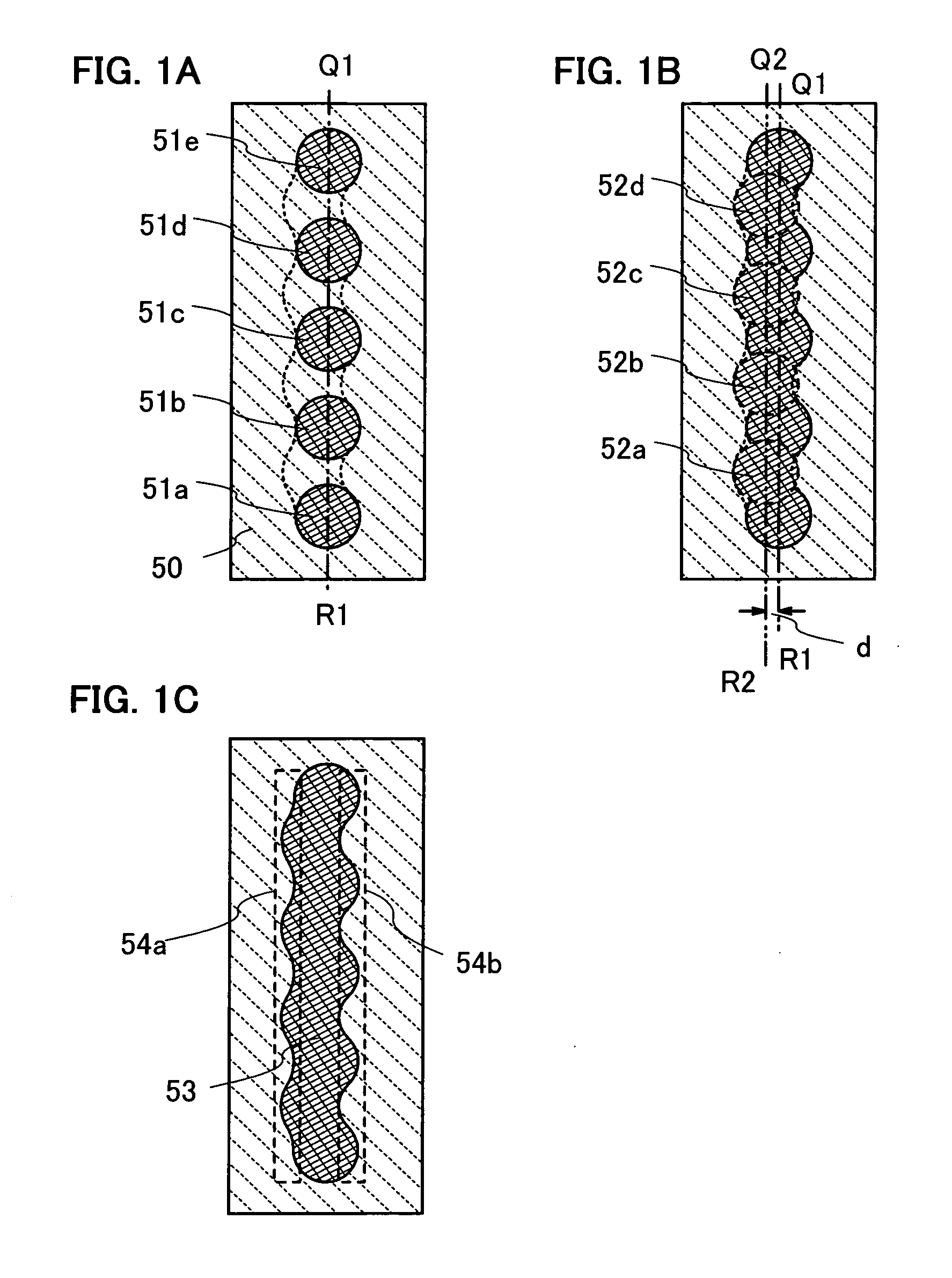

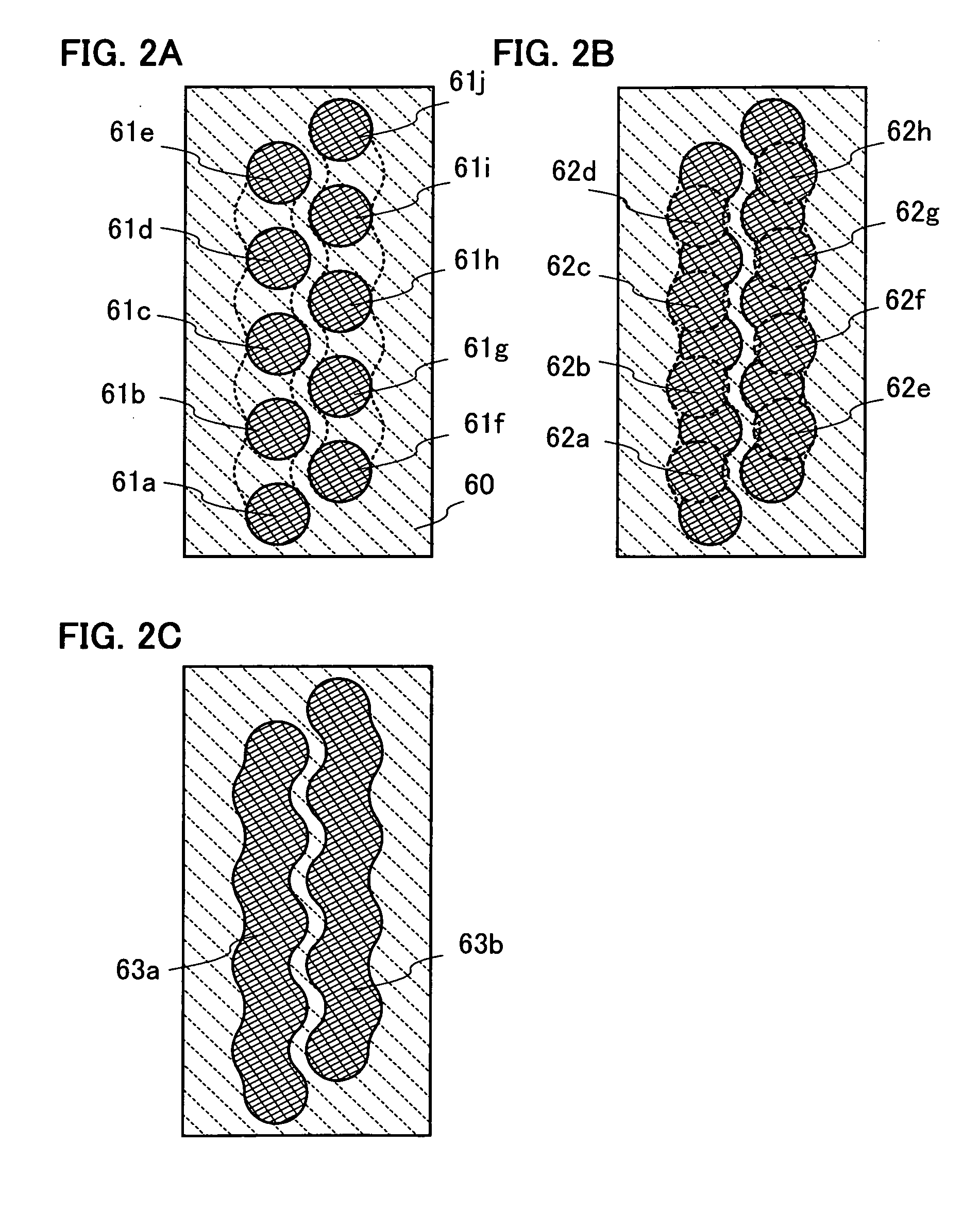

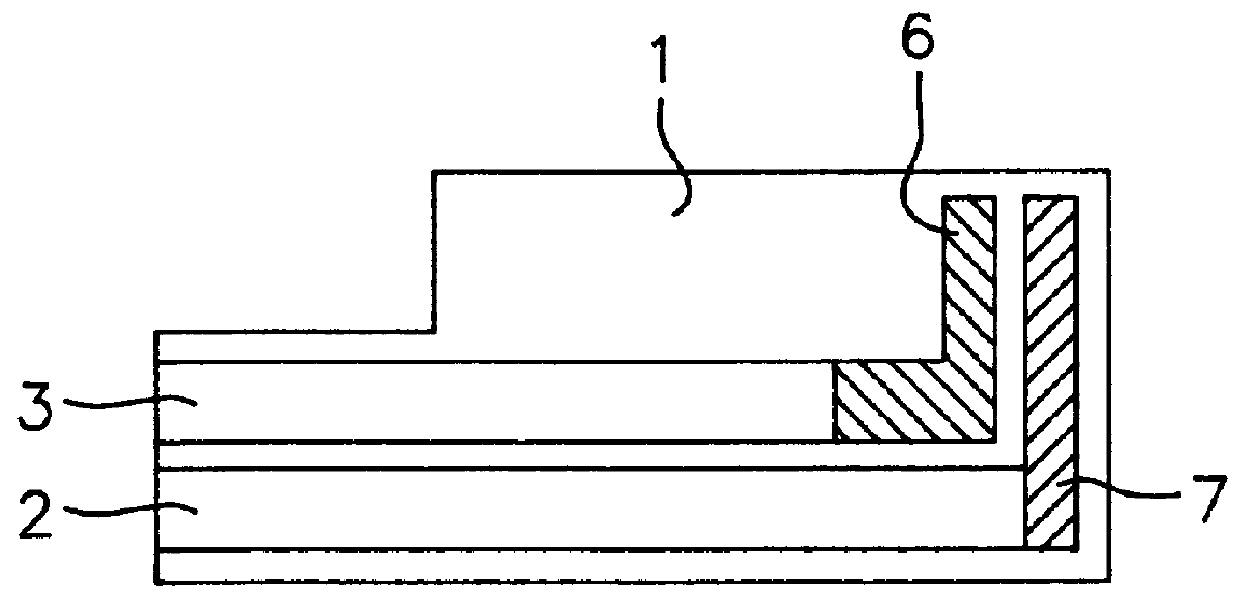

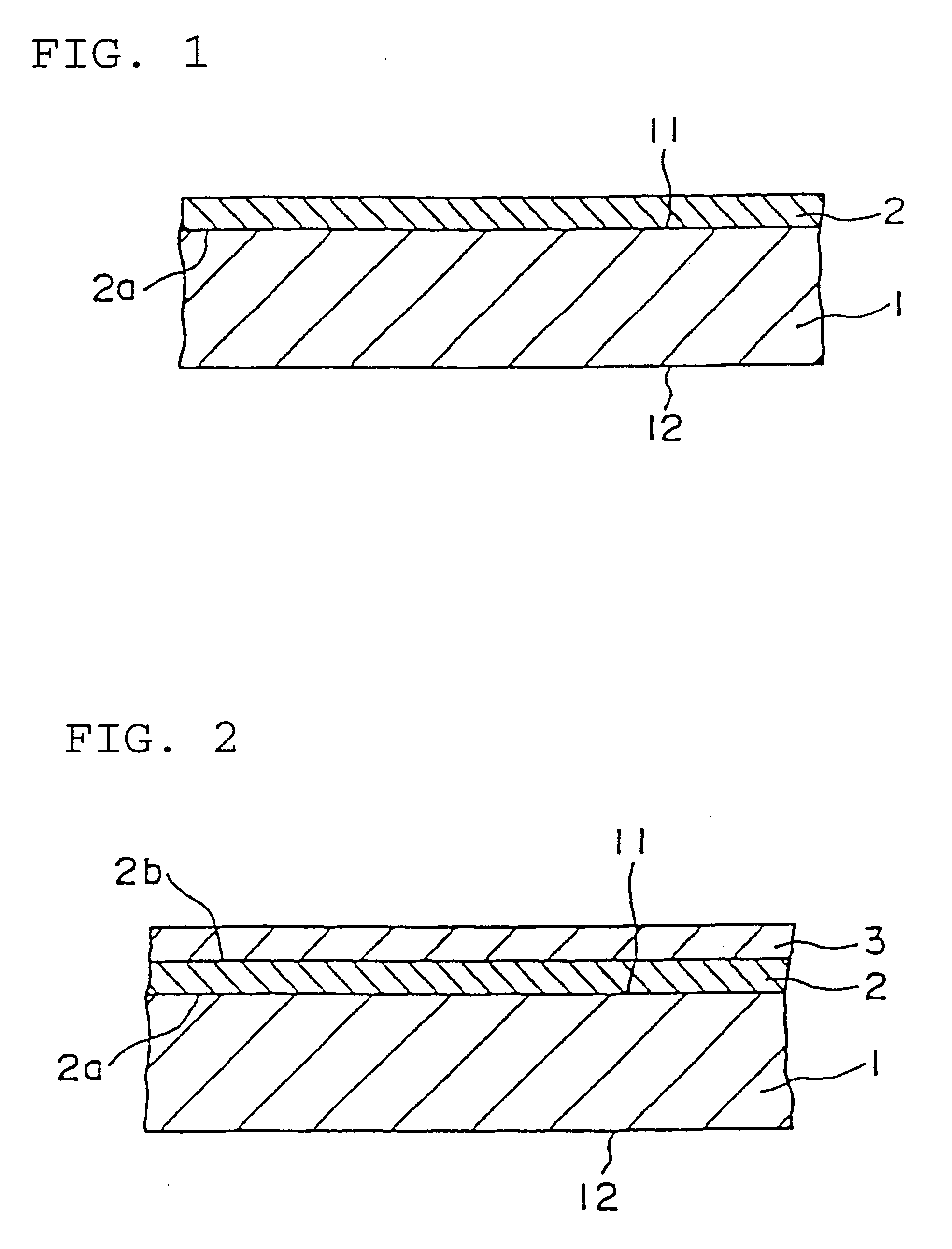

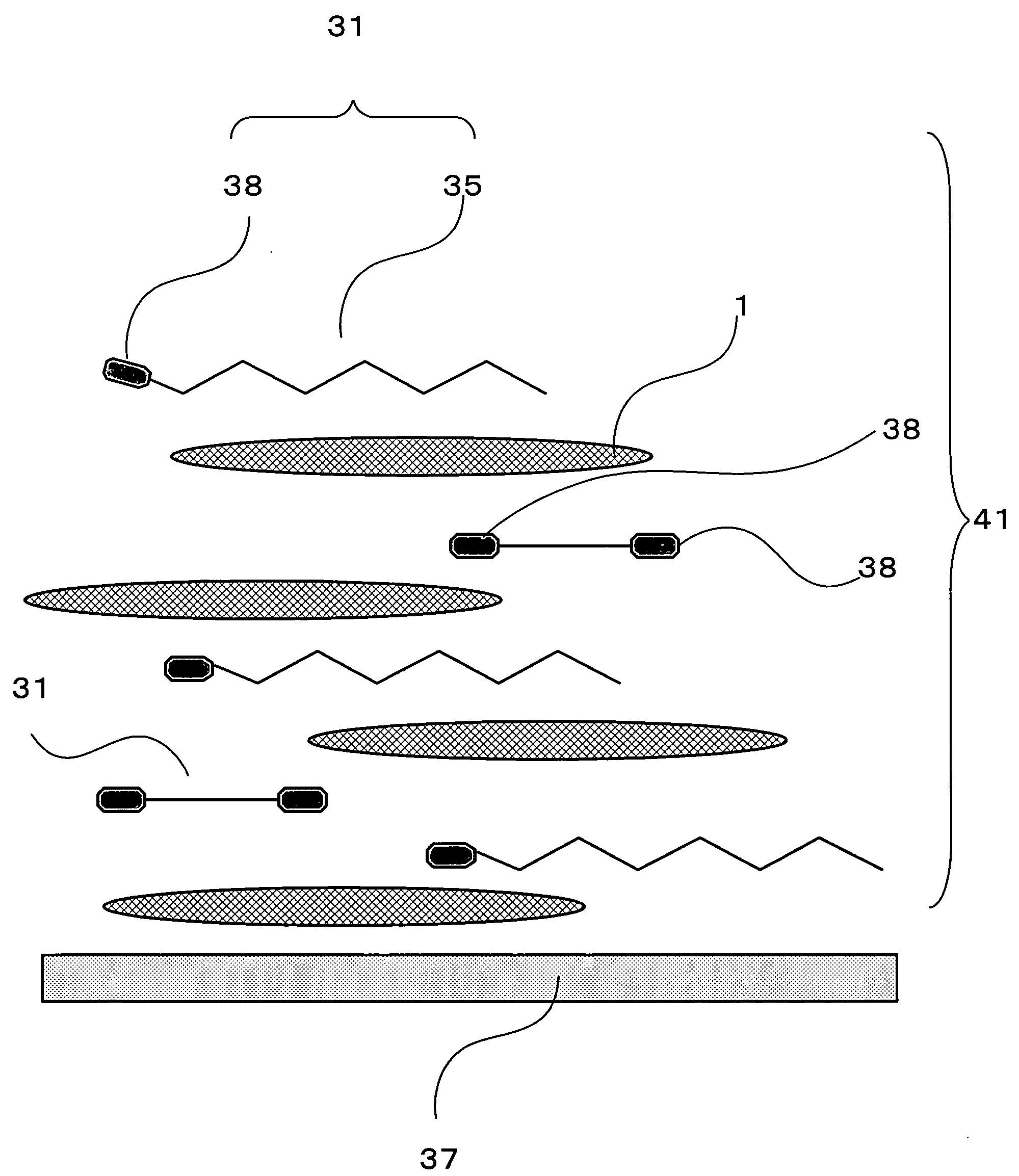

Exfoliating method, transferring method of thin film device, and thin film device, thin film integrated circuit device and liquid crystal display device produced by the same

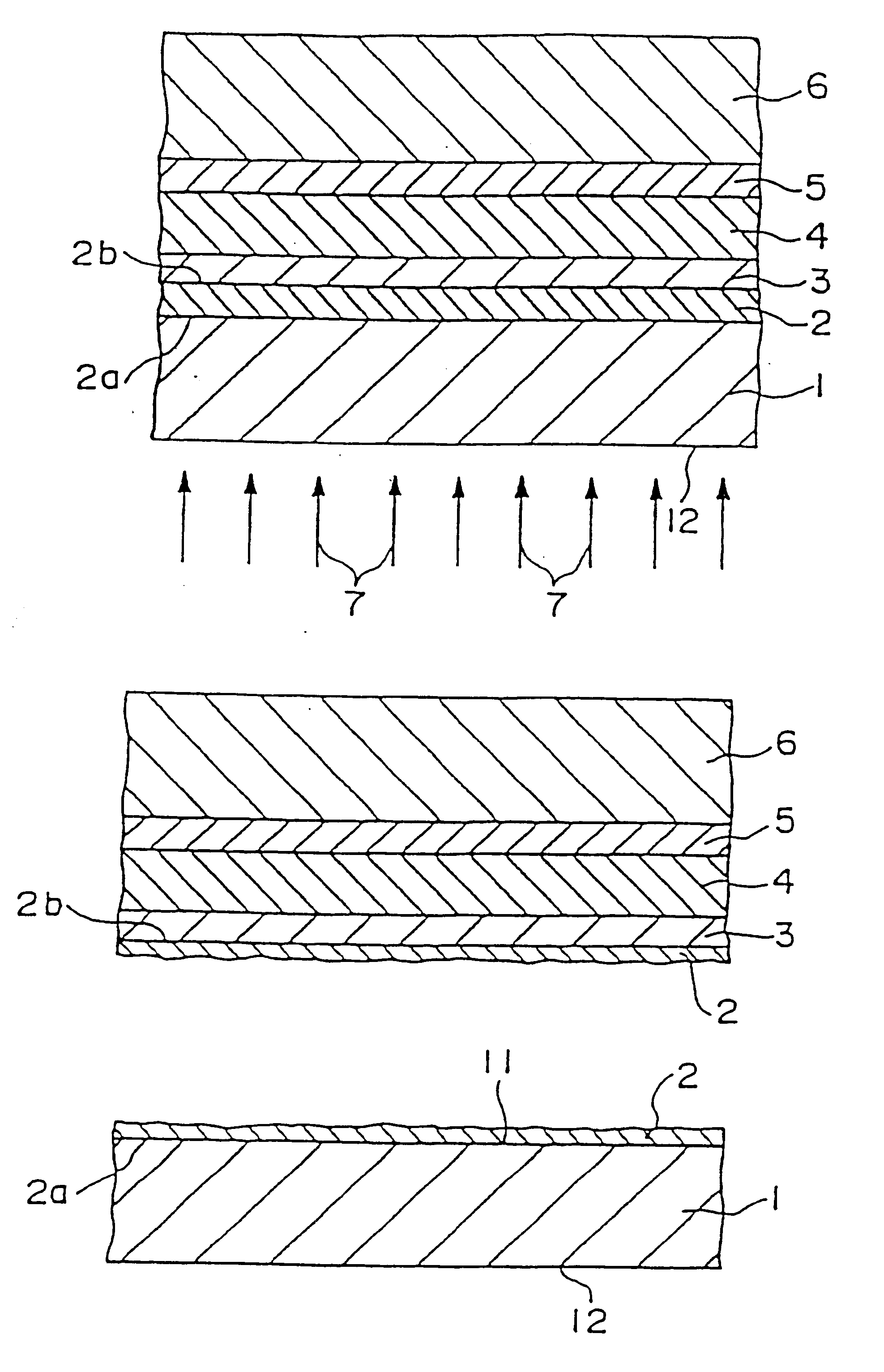

InactiveUS6645830B2Improve reliabilityReduce adhesionSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayPellicle membrane

A method for transferring a thin film device on a substrate onto a transfer member, includes a step for forming a separation layer on the substrate, a step for forming a transferred layer including the thin film device on the separation layer, a step for adhering the transferred layer including the thin film device to the transfer member with an adhesive layer therebetween, a step for irradiating the separation layer with light so as to form internal and / or interfacial exfoliation of the separation layer, and a step for detaching the substrate from the separation layer.

Owner:SAMSUNG ELECTRONICS CO LTD

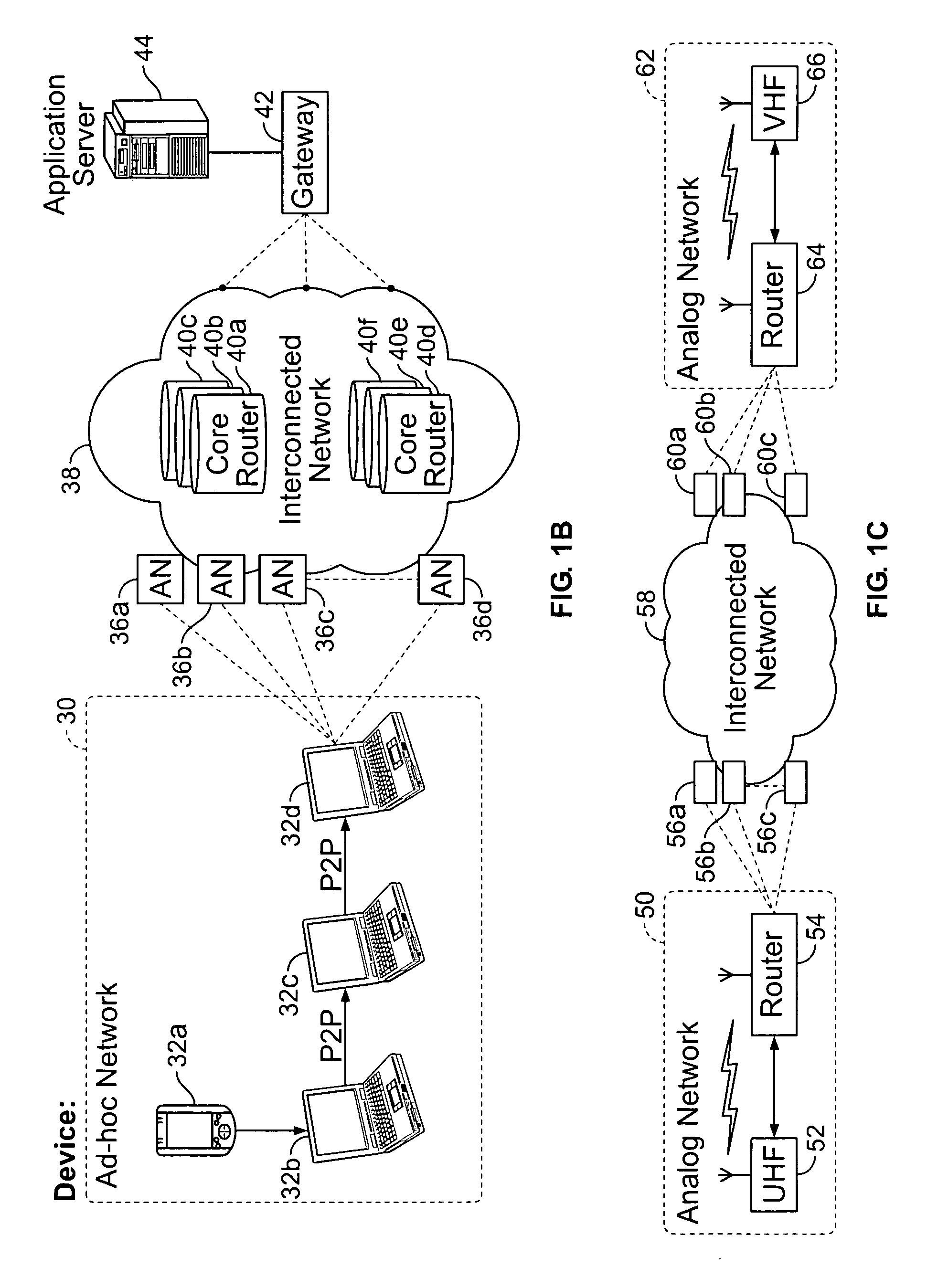

Multi-access terminal with capability for simultaneous connectivity to multiple communication channels

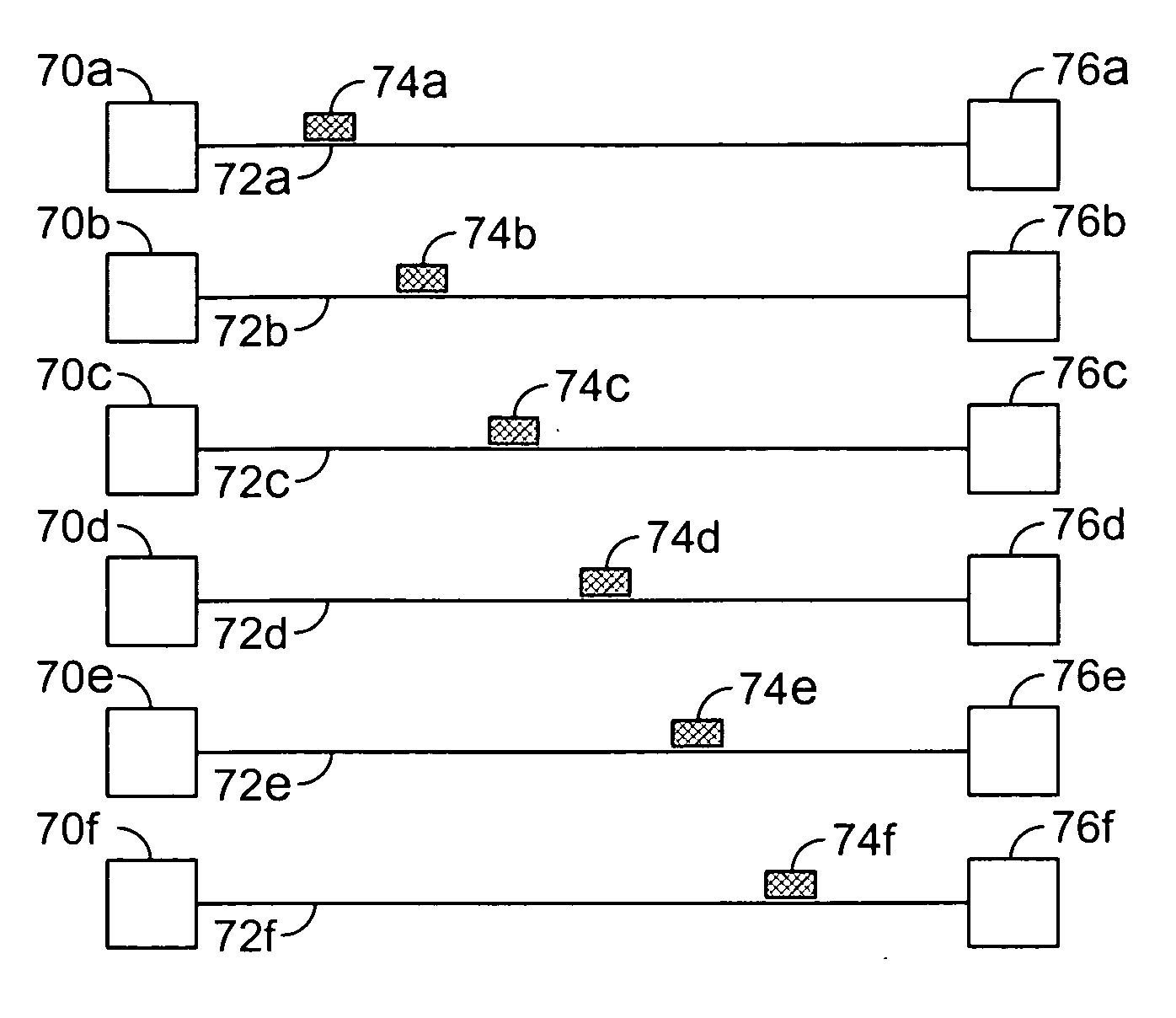

ActiveUS20060193295A1Improve reliabilityImprove behaviorNetwork traffic/resource managementTime-division multiplexTransceiverOperational system

An apparatus is disclosed for permitting a mobile terminal having multiple, heterogeneous network connections (e.g., multiple wired or wireless transceivers of various types) to set up and maintain virtual connections over multiple networks to either the same or to multiple destinations. The mobile terminal can “load-share” traffic, i.e., it can distribute segments of traffic over a full set of heterogeneous networks, significantly improving the reliability and availability of communications. In a first embodiment, a mobile terminal is configured with multiple radio frequency (RF) transceivers. Operating system software is provided for dynamically establishing and maintaining traffic flow for user applications over multiple communications paths, and for automatically adapting to variations in the networking environment, application traffic flow requirements, end user preferences, or mobility. In a second embodiment, a software-defined radio is used to implement the physical layer protocols for each desired network, eliminating the need for multiple transceivers.

Owner:TRUSTEES OF STEVENS INST OF TECH THE

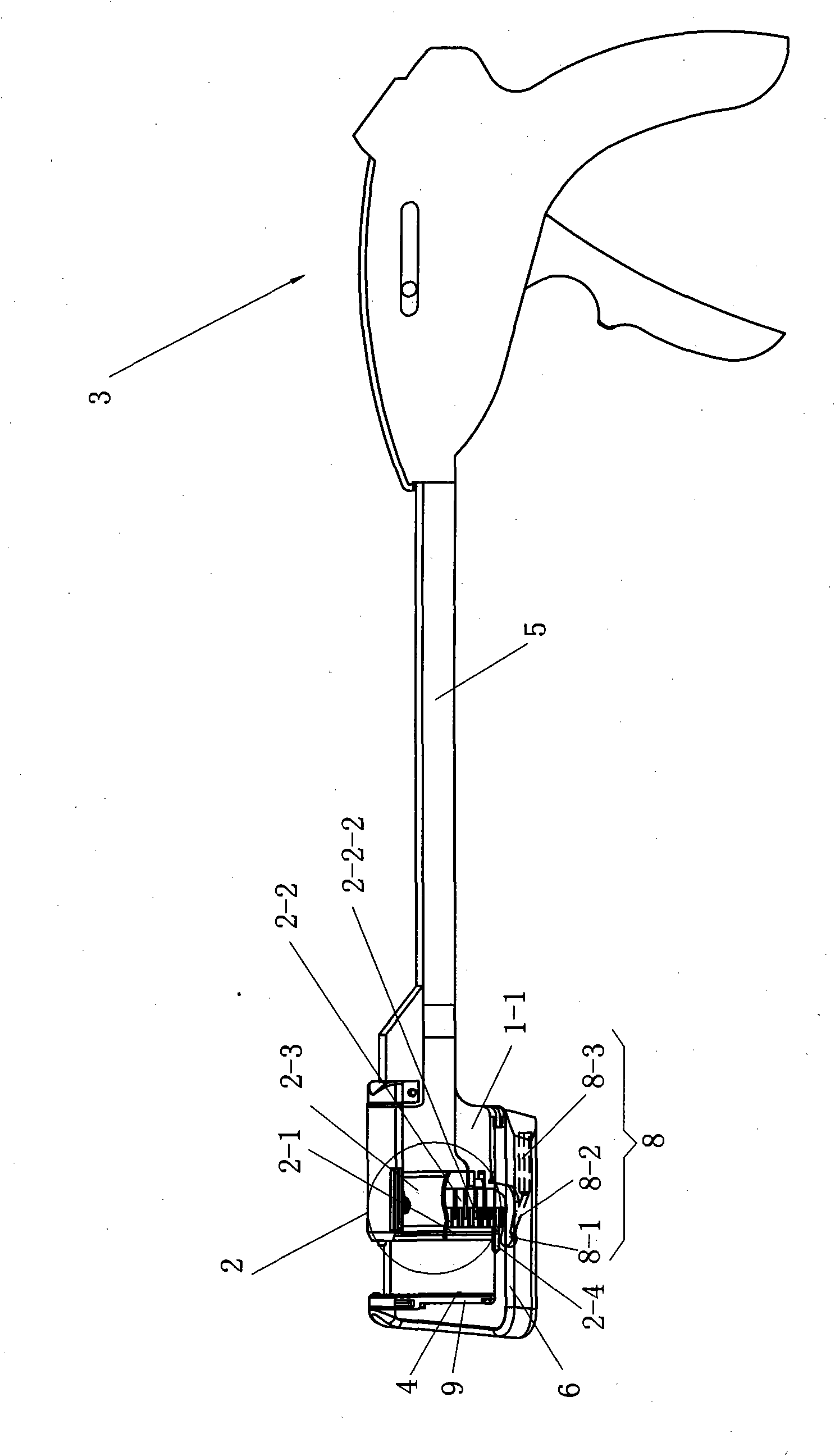

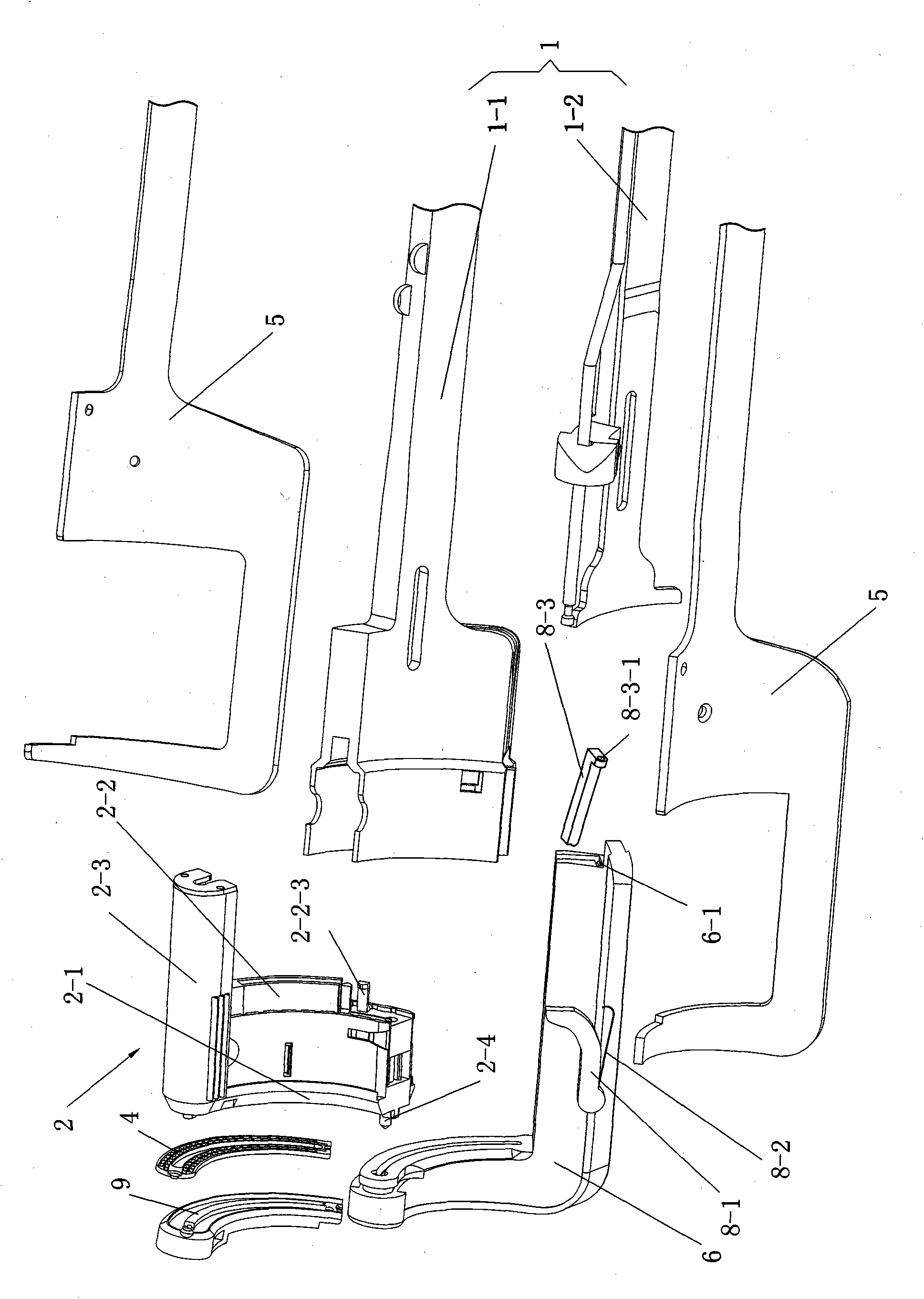

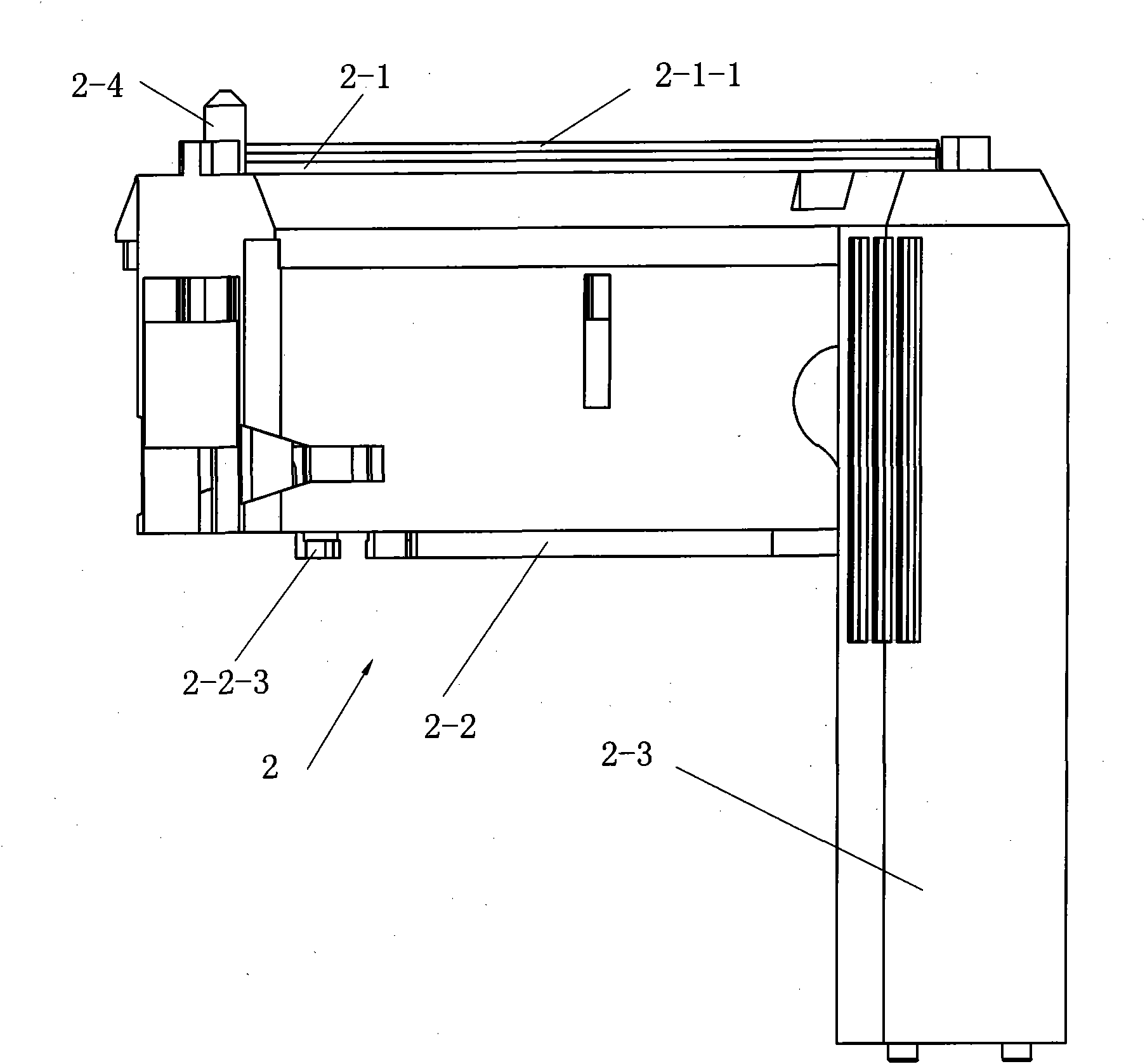

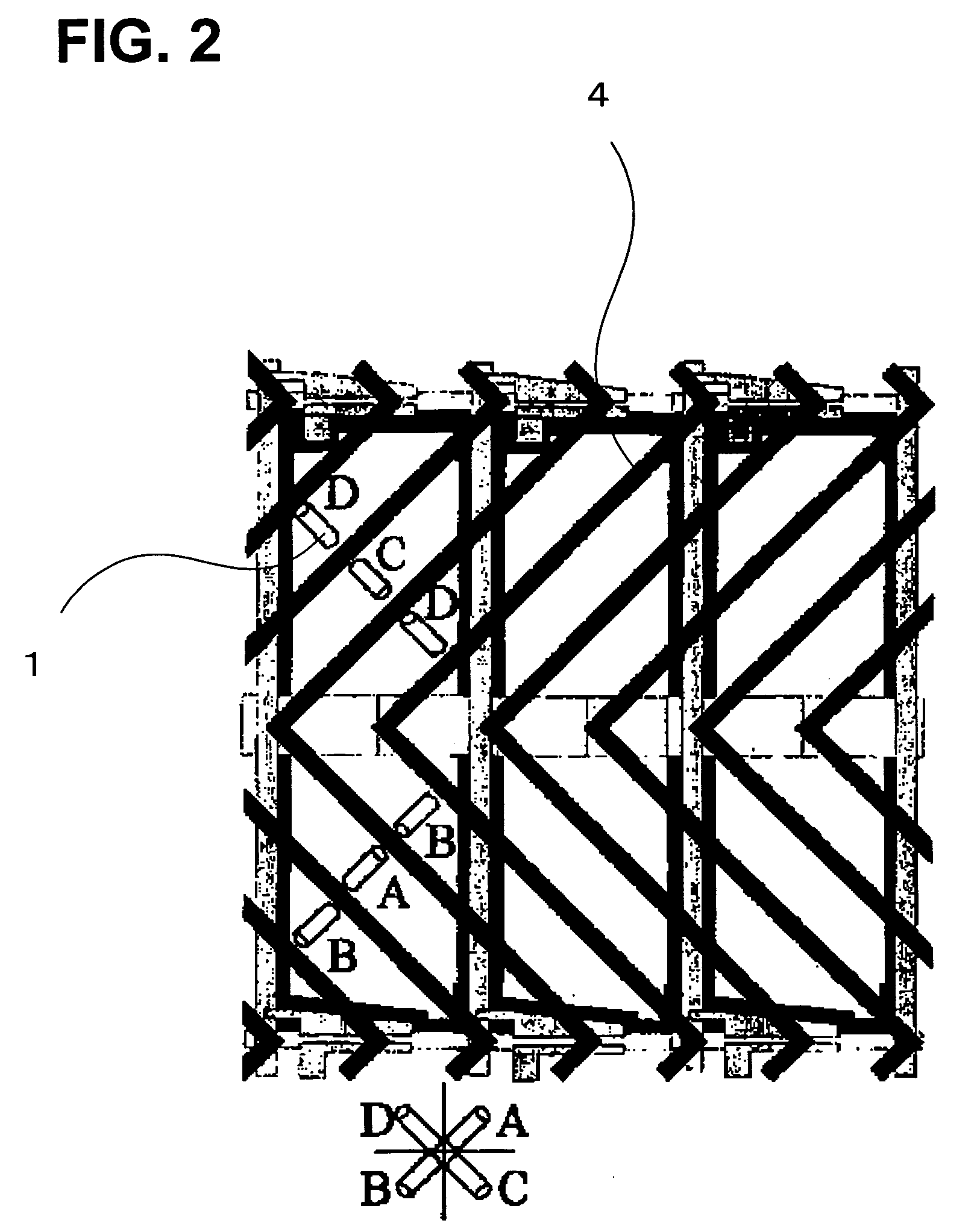

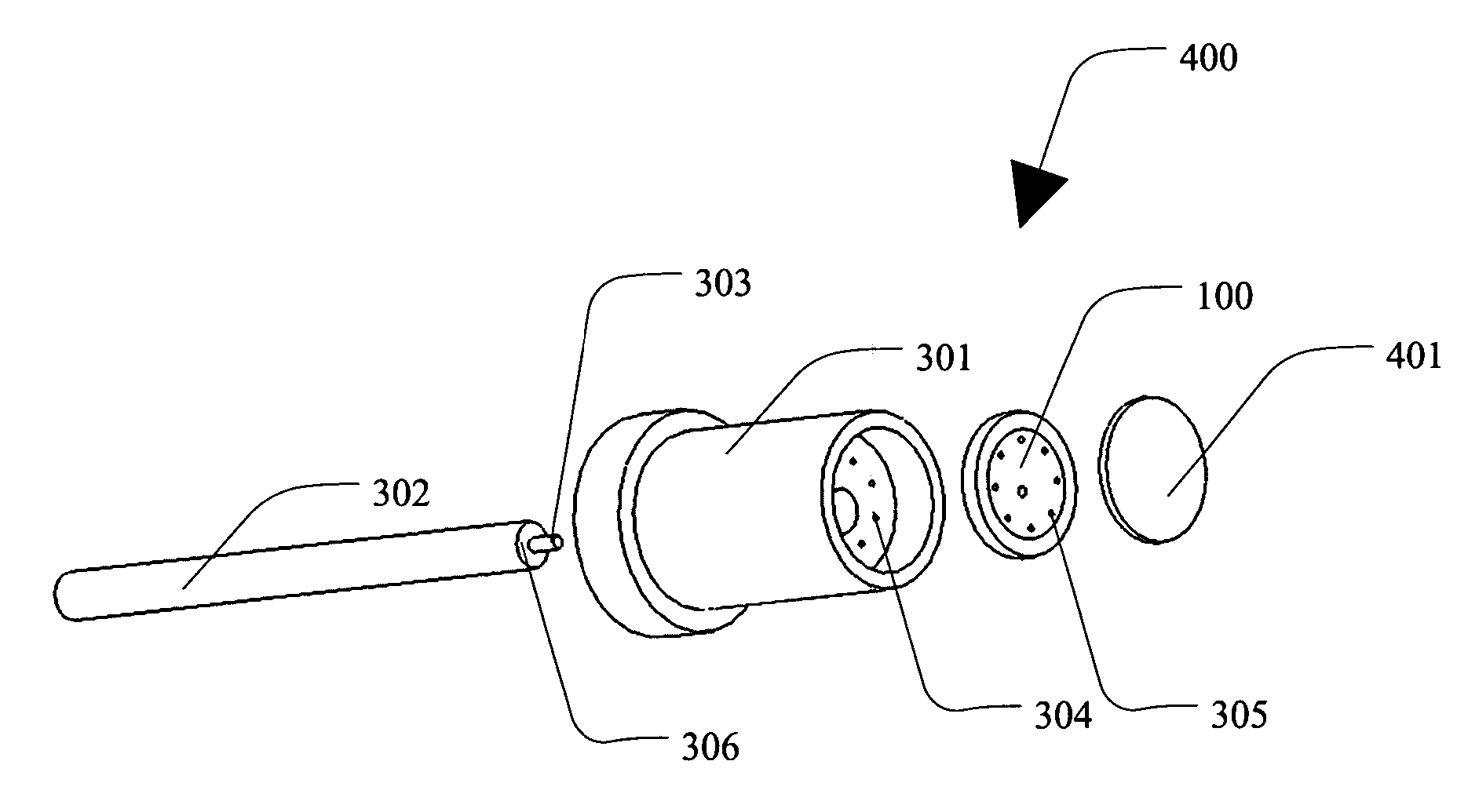

Arc-shaped cutting anastomat

ActiveCN101912284AGood assembly firmnessImprove reliabilitySurgical staplesDistal anastomosisEngineering

The invention relates to an arc-shaped cutting anastomat comprising an anastomosis nail shaping mechanism, a nail pushing assembly, a trigger handle, a nail supporting seat, a base of the nail supporting seat, a knife cushioning ring and two splints, wherein the nail pushing assembly comprises a cutting knife, a nail pushing sheet, a nail bin and a guide post; the end of the nail pushing sheet and both sides of the cutting knife are respectively provided with a plurality of inner nail pushing dental sheets which are near the cutting knife and a plurality of outer nail pushing dental sheets which are far away from the cutting knife; the cutting knife and the nail pushing sheet are injected and molded at a time to be fixed together; the outer side of the each outer nail pushing dental sheet on the nail pushing sheet is provided with a reinforcing rib; the inner side of each nail pushing dental sheet on the nail pushing sheet is provided with a reinforcing rib; both ends of the first guide surfaces of the nail pushing dental sheets are respectively connected with the first contact surfaces and the second contact surfaces of the nail pushing dental sheets through concave arc-shaped connecting surfaces, and both ends of the second guide surfaces thereof are respectively connected with the first contact surfaces and the second contact surfaces through the concave arc-shaped connecting surfaces; and the first contact surfaces and the second contact surfaces are respectively in contact with the inner walls of the nail pushing dental sheet holes of the nail bin. The invention has the advantages of good trigger anastomosis shaping effect and high safety.

Owner:CHANGZHOU JIANRUIBAO MEDICAL DEVICES

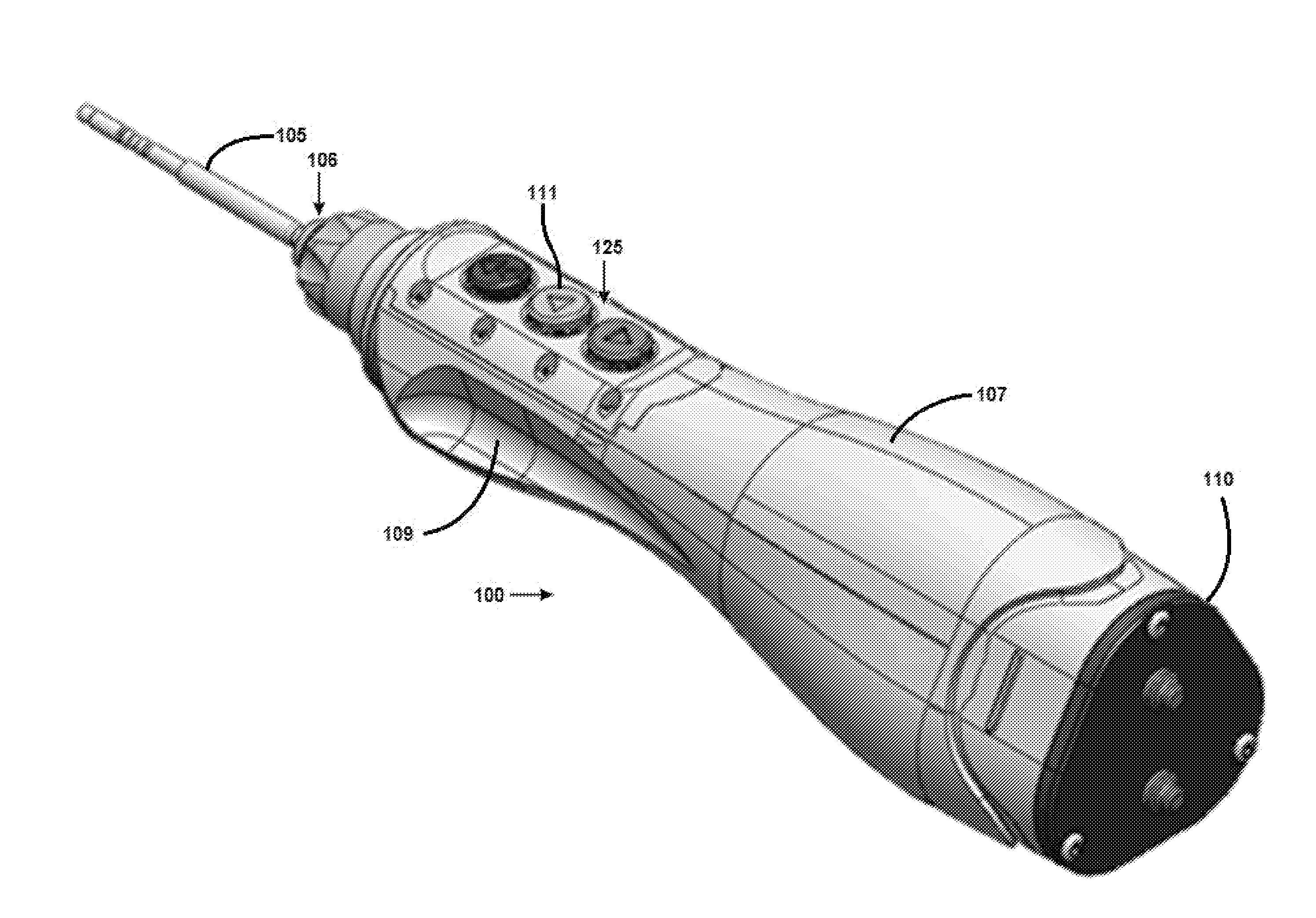

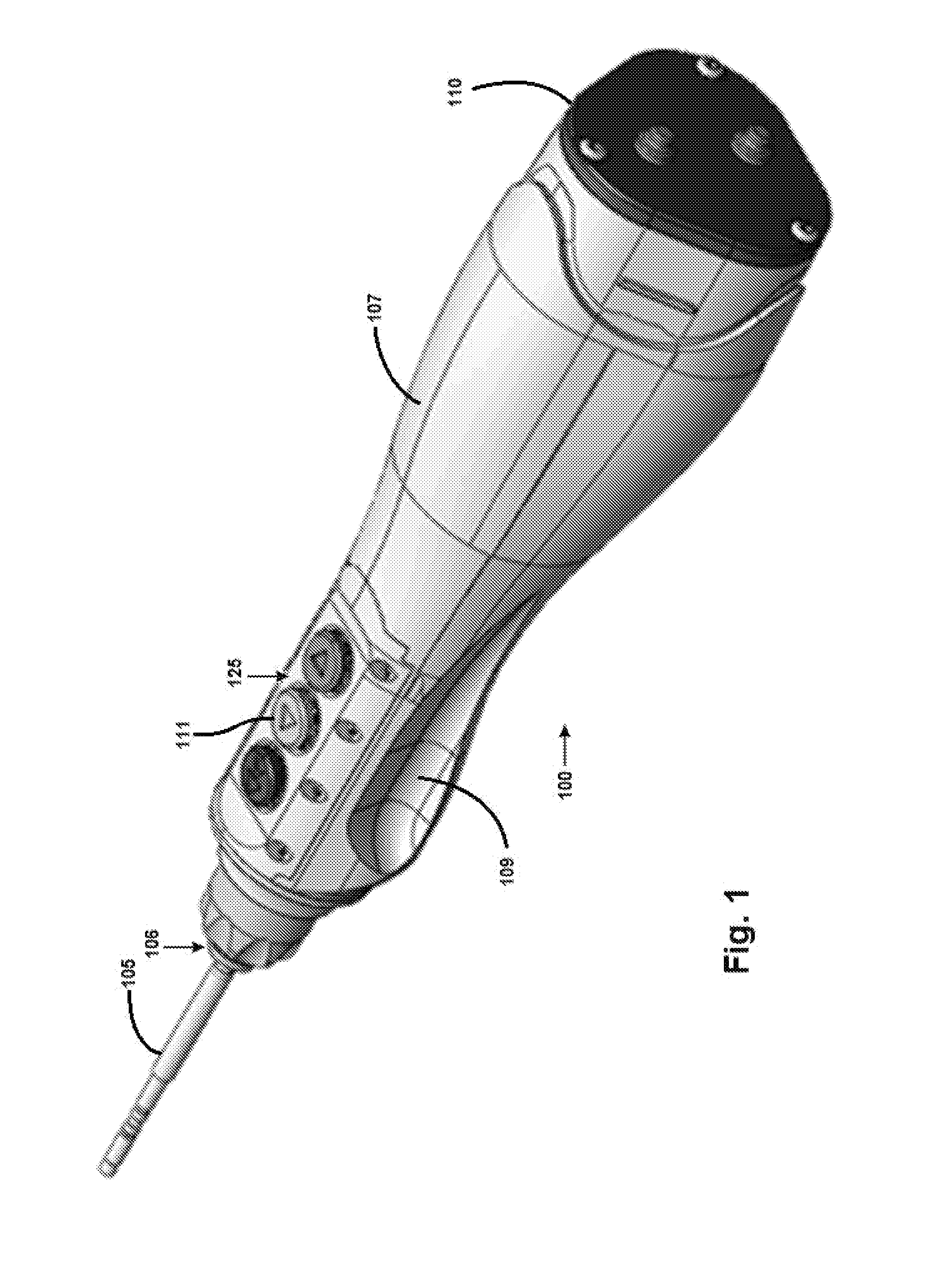

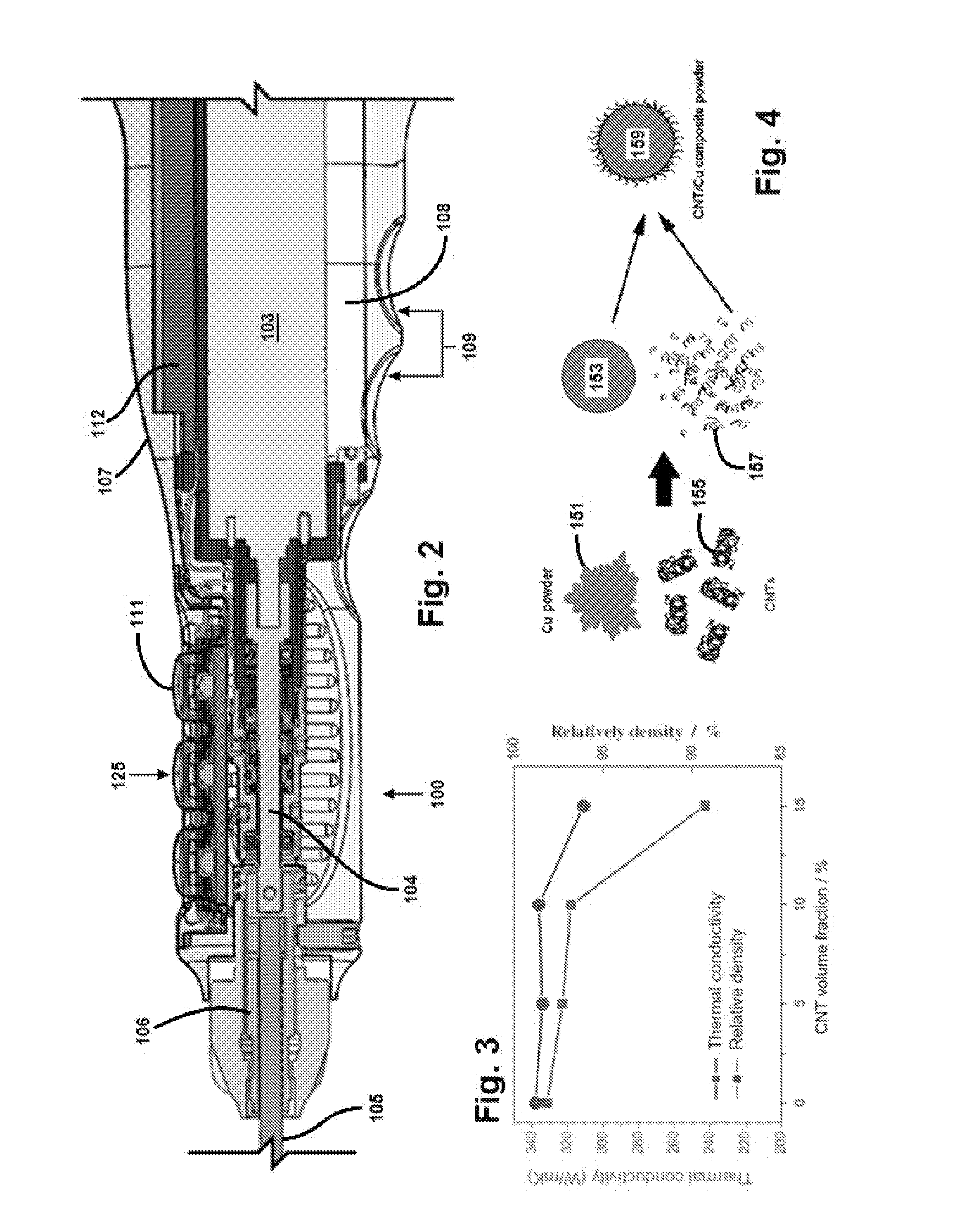

Surgical Handpiece

InactiveUS20150201918A1Improve operationIncreased durabilityDental implantsDiagnosticsSurgical instrumentationEngineering

Embodiments of the present invention provide a unique surgical handpiece having improved operation, durability and reliability. In one embodiment, the present invention provides a motorized handheld surgical instrument having one or more sensors for sensing motion, position, pressure, humidity, and various other environmental conditions relevant to the operation and maintenance of the surgical instrument.

Owner:OSSEODYNE SURGICAL SOLUTIONS LLC

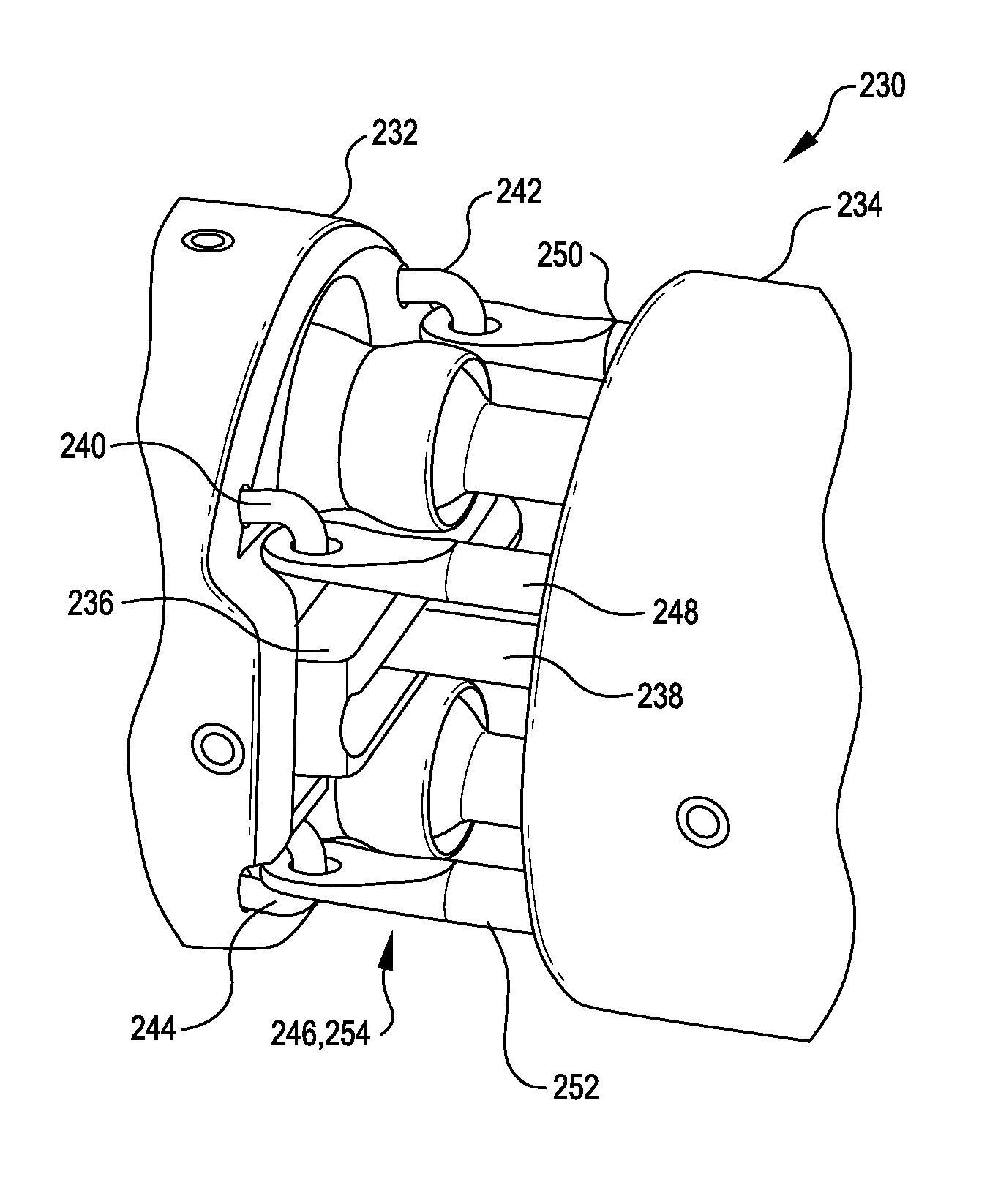

Wrist articulation by linked tension members

ActiveUS9259275B2Amount of maneuverabilityShorten the lengthDiagnosticsSurgical manipulatorsDrive shaftEngineering

Owner:INTUITIVE SURGICAL OPERATIONS INC

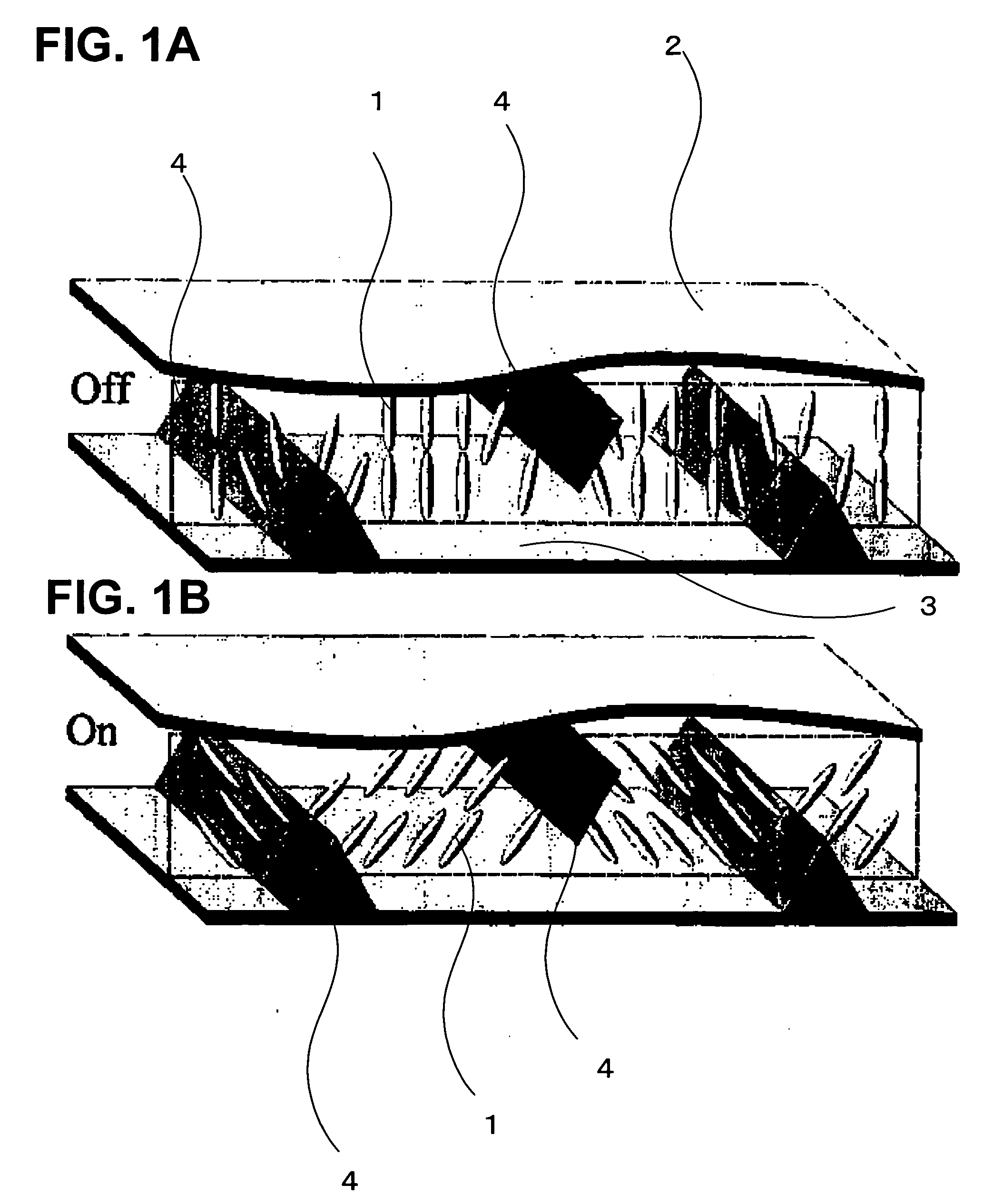

Liquid crystal display device and method of manufacture of the same

InactiveUS20060103804A1Improve reliabilityLittle and no tendency to exhibit white lineLiquid crystal compositionsNon-linear opticsLiquid-crystal displayReduced contrast volume

A liquid crystal composition, comprising a liquid crystal and a polymerizable compound capable of polymerization by means of light, heat, or a combination thereof, is placed in the gap between two parallel substrates on which are formed a pair of electrodes, and the polymerizable compound is polymerized to form a liquid crystal layer and a resin film. A liquid crystal display device is manufactured accordingly. The polymerizable compound comprises a monofunctional polymerizable compound, and the dipole moment of the monofunctional polymerizable compound is 4 debyes or lower. Thus, a liquid crystal display device, with high reliability, and of excellent quality with little or no contrast reduction due to white lines, is provided.

Owner:SHARP KK

Arc-shaped cutting anastomat

The invention relates to an arc-shaped cutting anastomat comprising an anastomosis nail shaping mechanism, a nail pushing assembly, a trigger handle, a nail supporting seat, a base of the nail supporting seat, a knife cushioning ring and two splints, wherein the nail pushing assembly comprises a cutting knife, a nail pushing sheet, a nail bin and a guide post; the end of the nail pushing sheet and both sides of the cutting knife are respectively provided with a plurality of inner nail pushing dental sheets which are near the cutting knife and a plurality of outer nail pushing dental sheets which are far away from the cutting knife; the cutting knife and the nail pushing sheet are injected and molded at a time to be fixed together; the outer side of the each outer nail pushing dental sheeton the nail pushing sheet is provided with a reinforcing rib; the inner side of each nail pushing dental sheet on the nail pushing sheet is provided with a reinforcing rib; both ends of the first guide surfaces of the nail pushing dental sheets are respectively connected with the first contact surfaces and the second contact surfaces of the nail pushing dental sheets through concave arc-shaped connecting surfaces, and both ends of the second guide surfaces thereof are respectively connected with the first contact surfaces and the second contact surfaces through the concave arc-shaped connecting surfaces; and the first contact surfaces and the second contact surfaces are respectively in contact with the inner walls of the nail pushing dental sheet holes of the nail bin. The invention has the advantages of good trigger anastomosis shaping effect and high safety.

Owner:CHANGZHOU JIANRUIBAO MEDICAL DEVICES

Microstrip patch antenna for high temperature environments

ActiveUS7283096B2Improve performanceImprove reliabilitySimultaneous aerial operationsAntenna adaptation in movable bodiesMicrostrip patch antennaSpray coating

A patch antenna for operation within a high temperature environment. The patent antenna typically includes an antenna radiating element, a housing and a microwave transmission medium, such as a high temperature microwave cable. The antenna radiating element typically comprises a metallization (or solid metal) element in contact with a dielectric element. The antenna radiating element can include a dielectric window comprising a flame spray coating or a solid dielectric material placed in front of the radiating element. The antenna element is typically inserted into a housing that mechanically captures the antenna and provides a ground plane for the antenna. Orifices or passages can be added to the housing to improve high temperature performance and may direct cooling air for cooling the antenna. The high temperature microwave cable is typically inserted into the housing and attached to the antenna radiator to support the communication of electromagnetic signals between the radiator element and a receiver or transmitter device.

Owner:MEGGITT SA

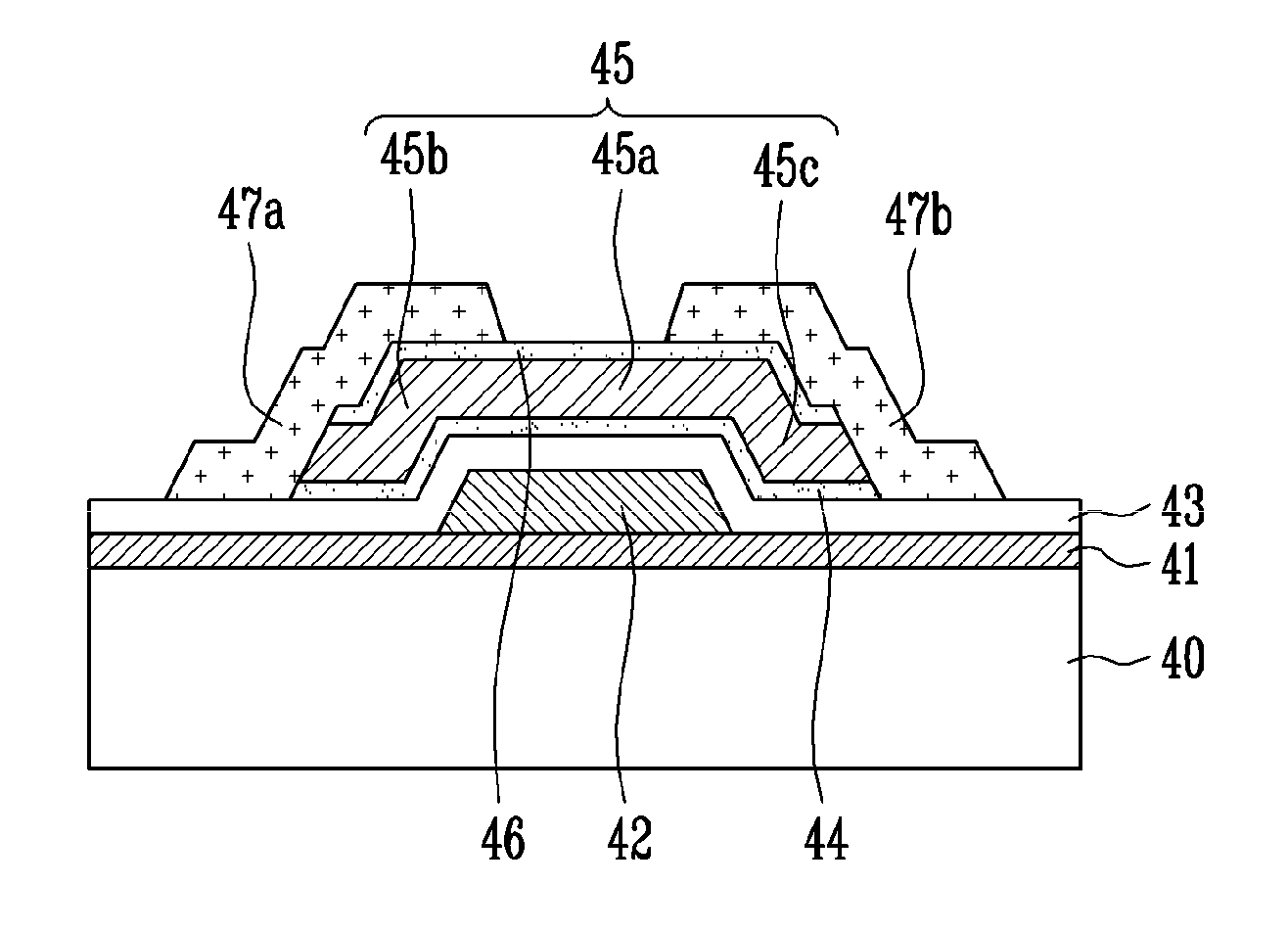

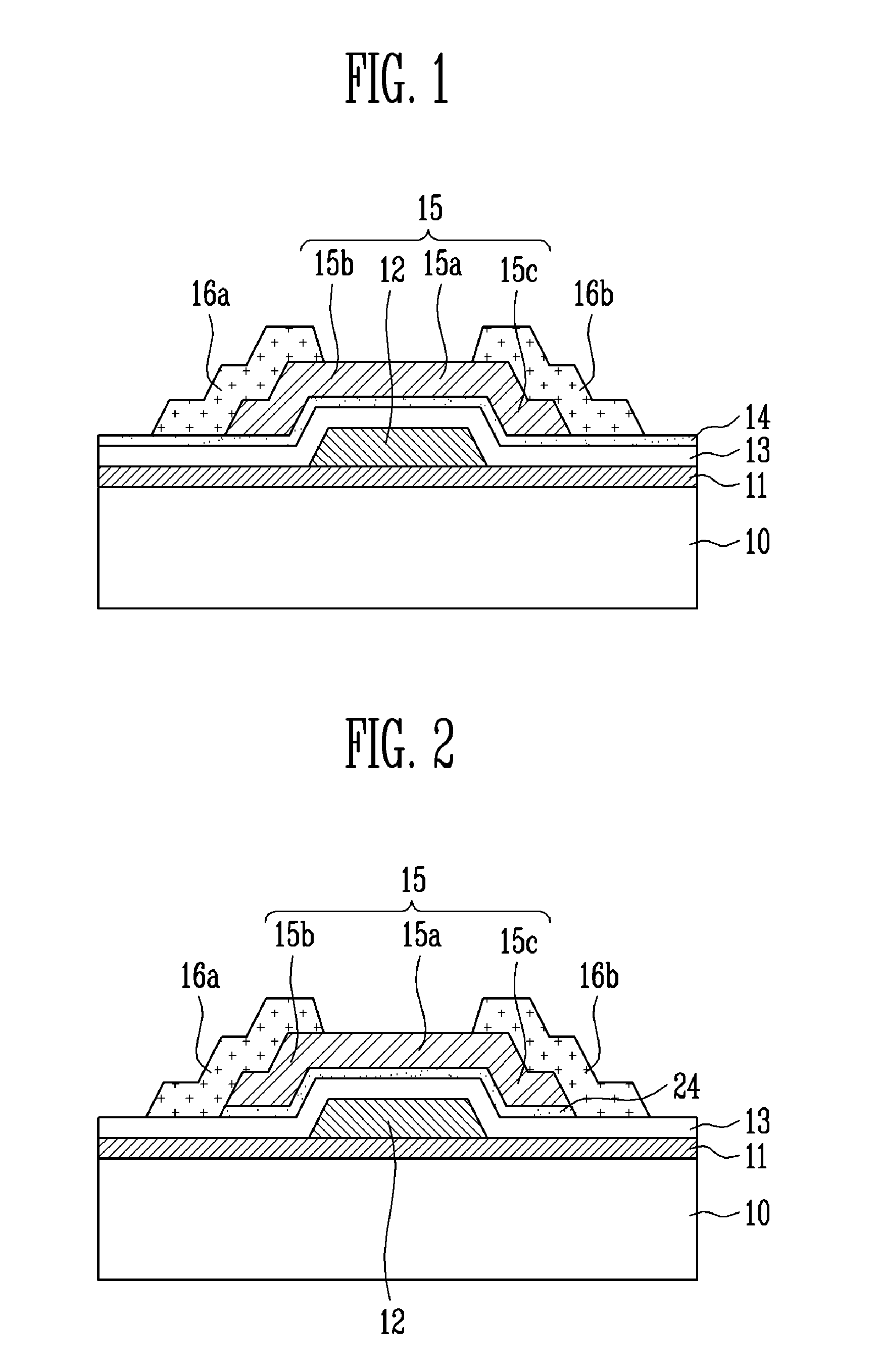

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS8148779B2Improve featuresAvoid chargingSolid-state devicesSemiconductor/solid-state device manufacturingTrappingEngineering

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include a gate electrode formed on a substrate; an active layer made of an oxide semiconductor and insulated from the gate electrode by a gate insulating layer; source and drain electrodes coupled to the active layer; and an interfacial stability layer formed on one or both surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristic as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

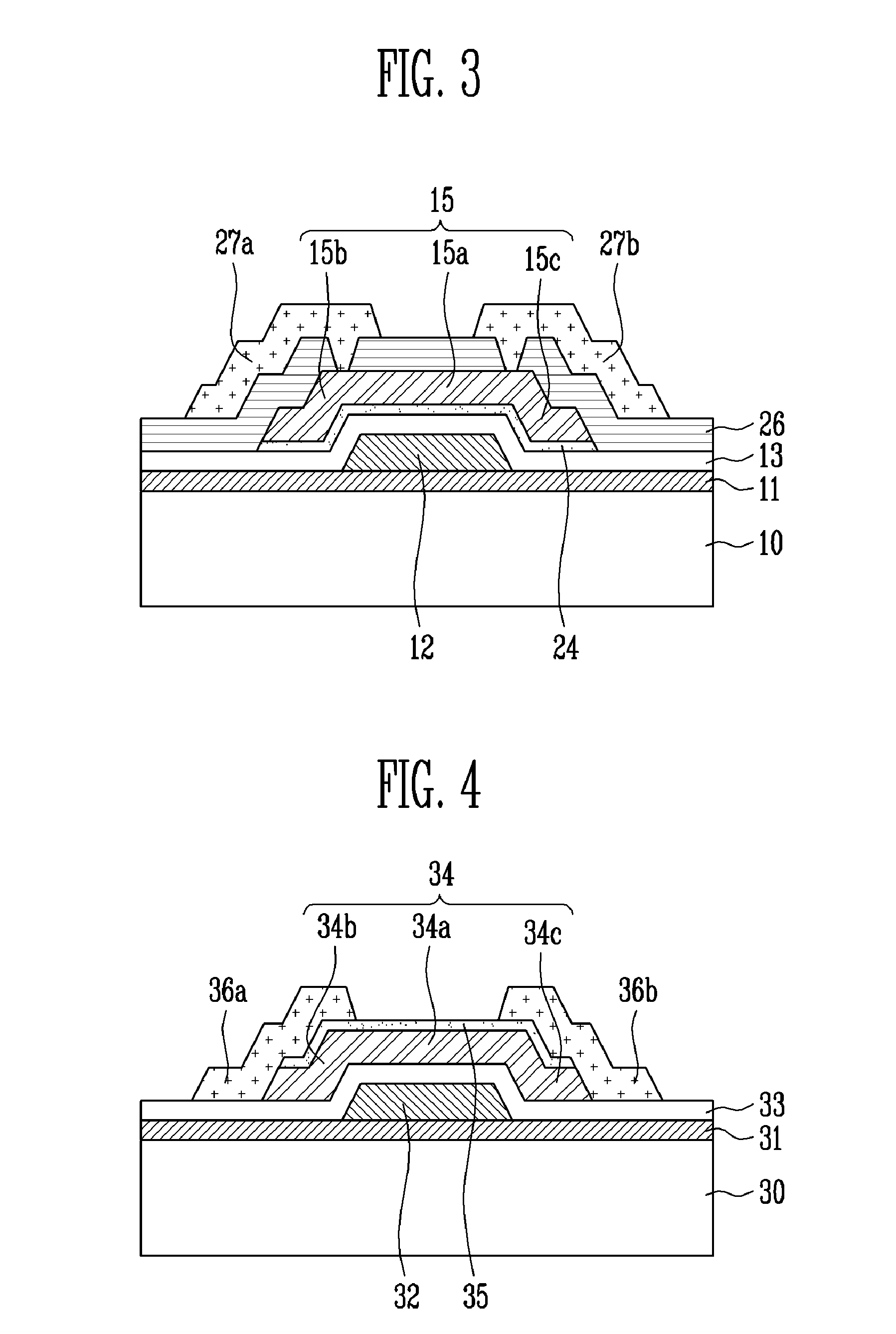

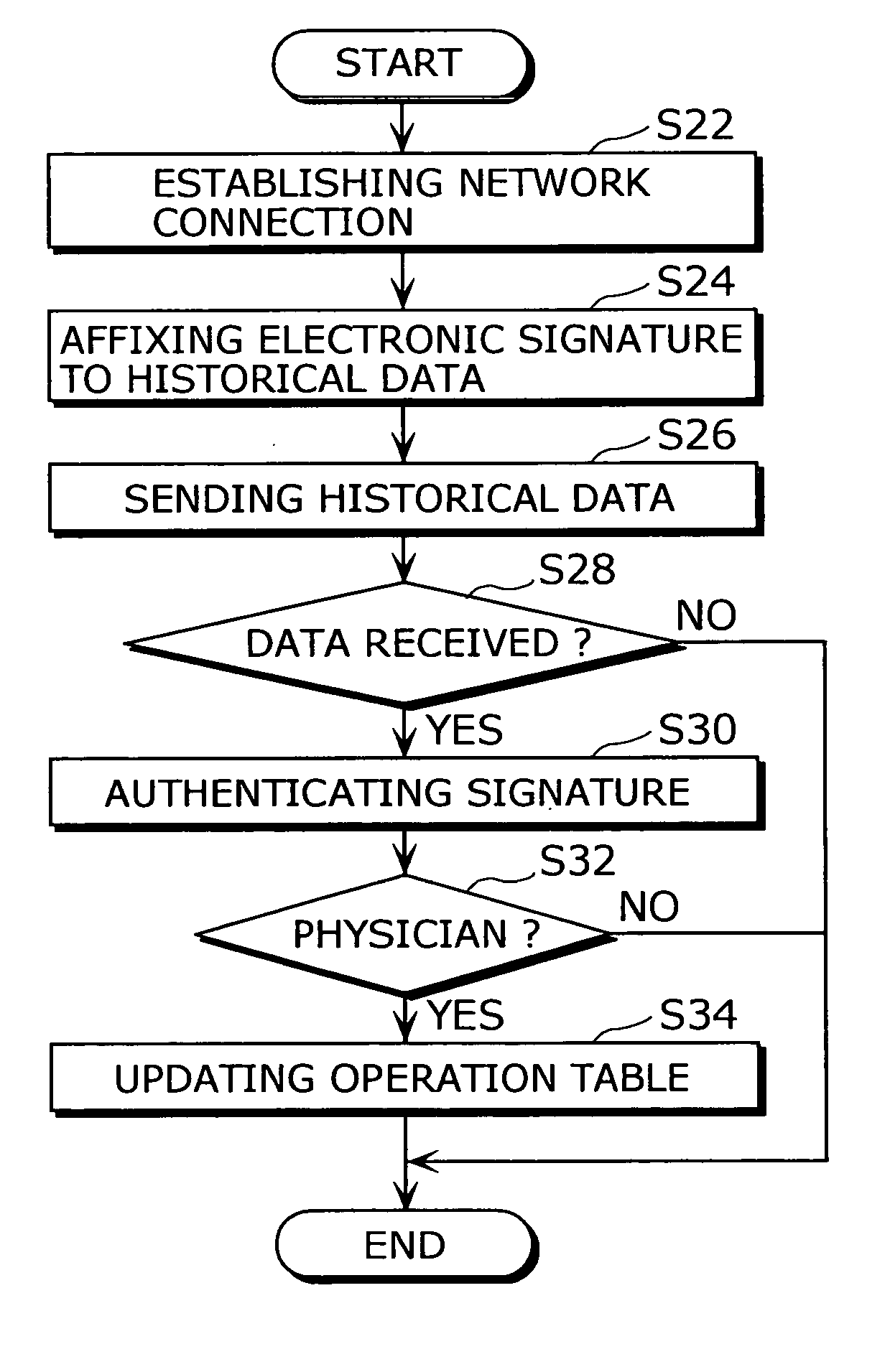

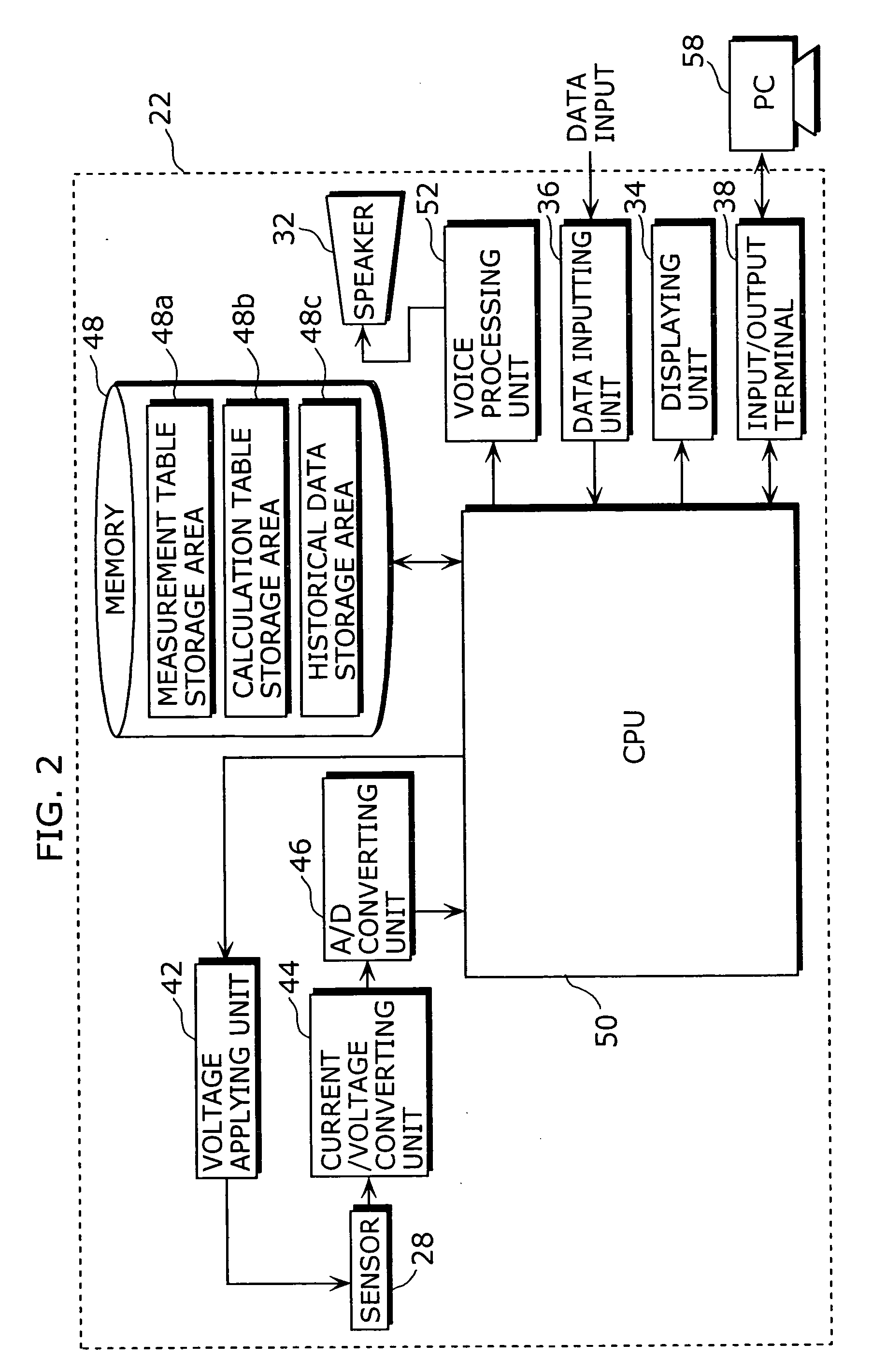

Dosage determination supporting device, injector, and health management supporting system

InactiveUS20050177398A1Improve reliabilityImprove portabilityData processing applicationsInfusion syringesSupporting systemMedicine

A dosage determination supporting apparatus, which is able to precisely determine a dosage in accordance with the health condition of a user, is provided with: a sensor (28) for measuring the blood sugar level obtained from the blood of the user; a memory (48) for storing an operation table showing a correspondence between the blood sugar level and the amount of insulin; a CPU (50) for calculating the amount of insulin corresponding to the blood sugar level, with reference to the operation table stored in the memory (48); a displaying unit (34) for displaying the amount of insulin; and a voice processing unit (52) for performing the voice processing on the amount of insulin and outputting the voice through a speaker (32).

Owner:PANASONIC CORP