Patents

Literature

6059 results about "Ground plane" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

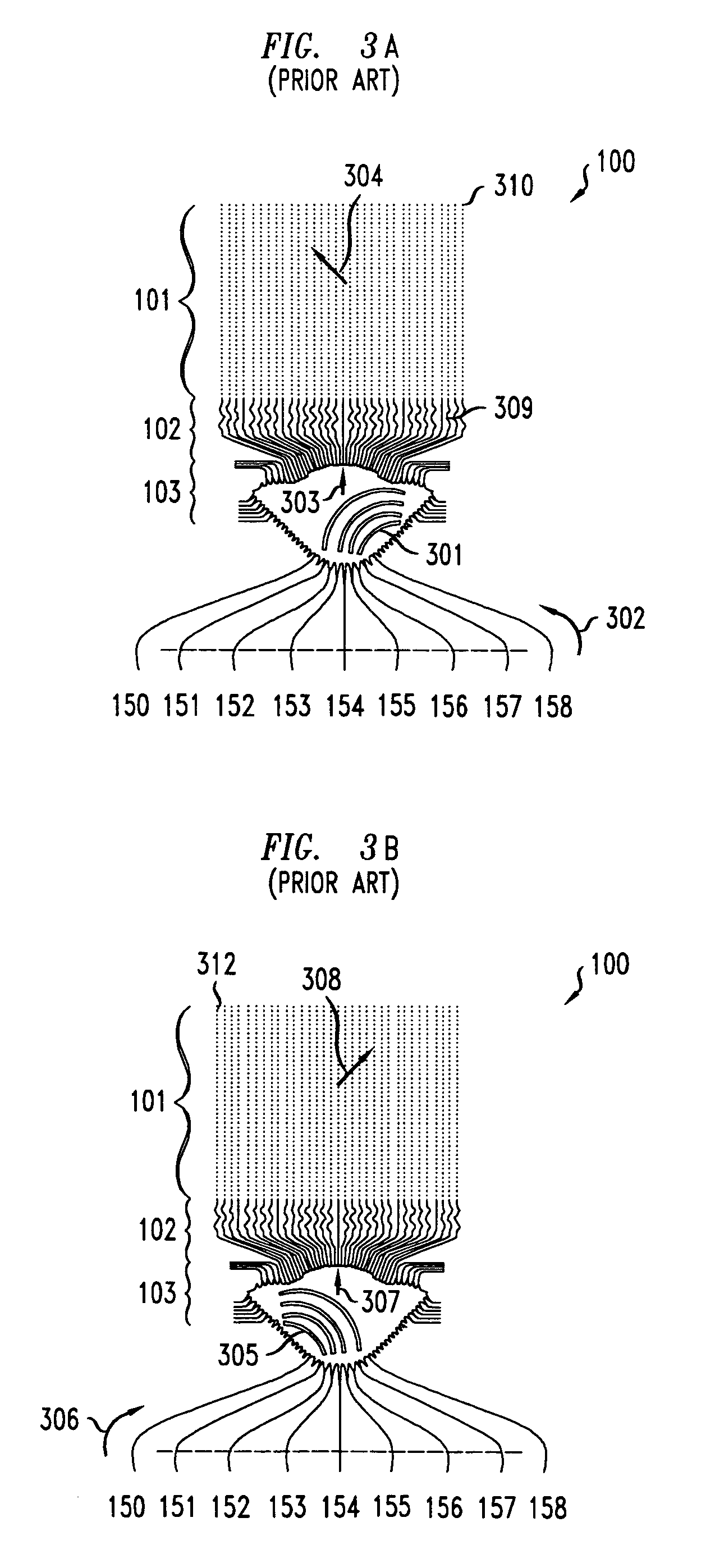

In electrical engineering, a ground plane is an electrically conductive surface, usually connected to electrical ground. The term has two different meanings in separate areas of electrical engineering. In antenna theory, a ground plane is a conducting surface large in comparison to the wavelength, such as the Earth, which is connected to the transmitter's ground wire and serves as a reflecting surface for radio waves. In printed circuit boards, a ground plane is a large area of copper foil on the board which is connected to the power supply ground terminal and serves as a return path for current from different components on the board.

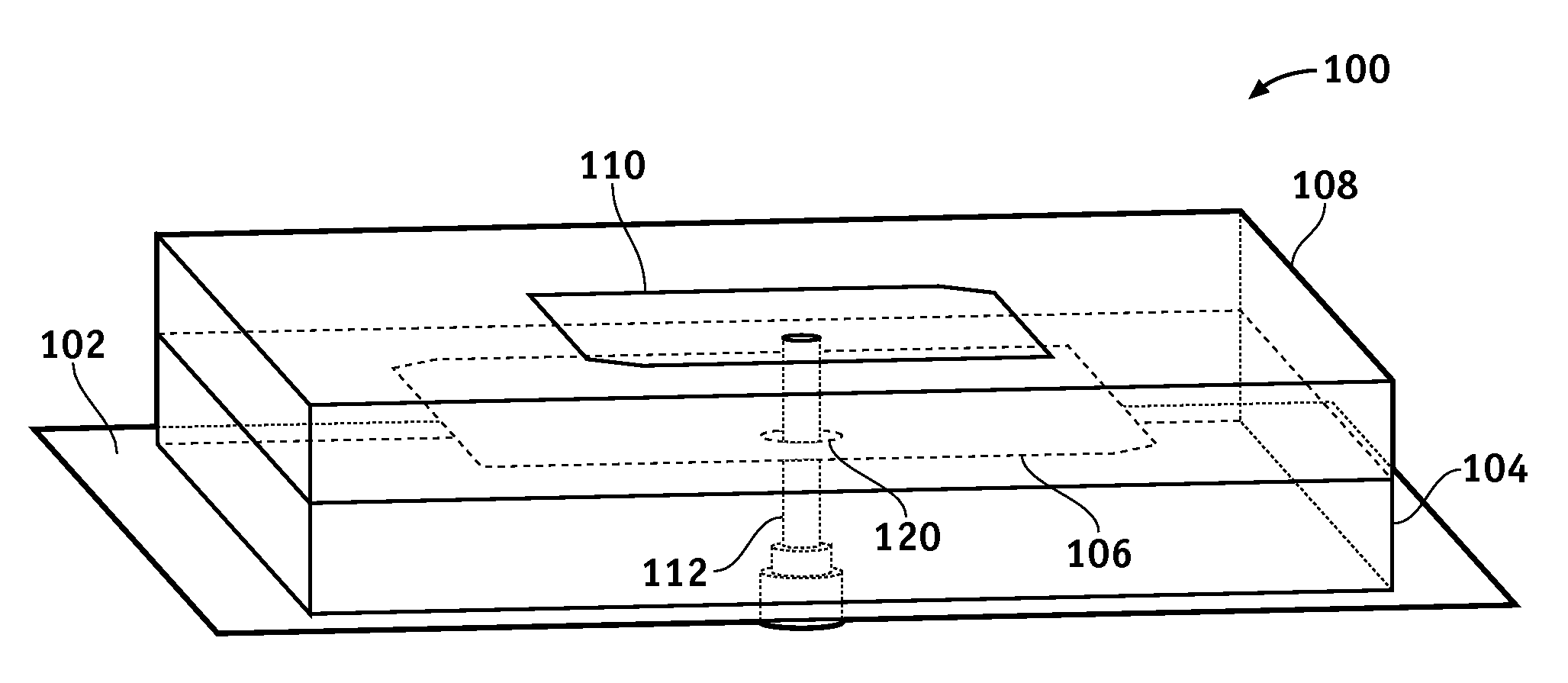

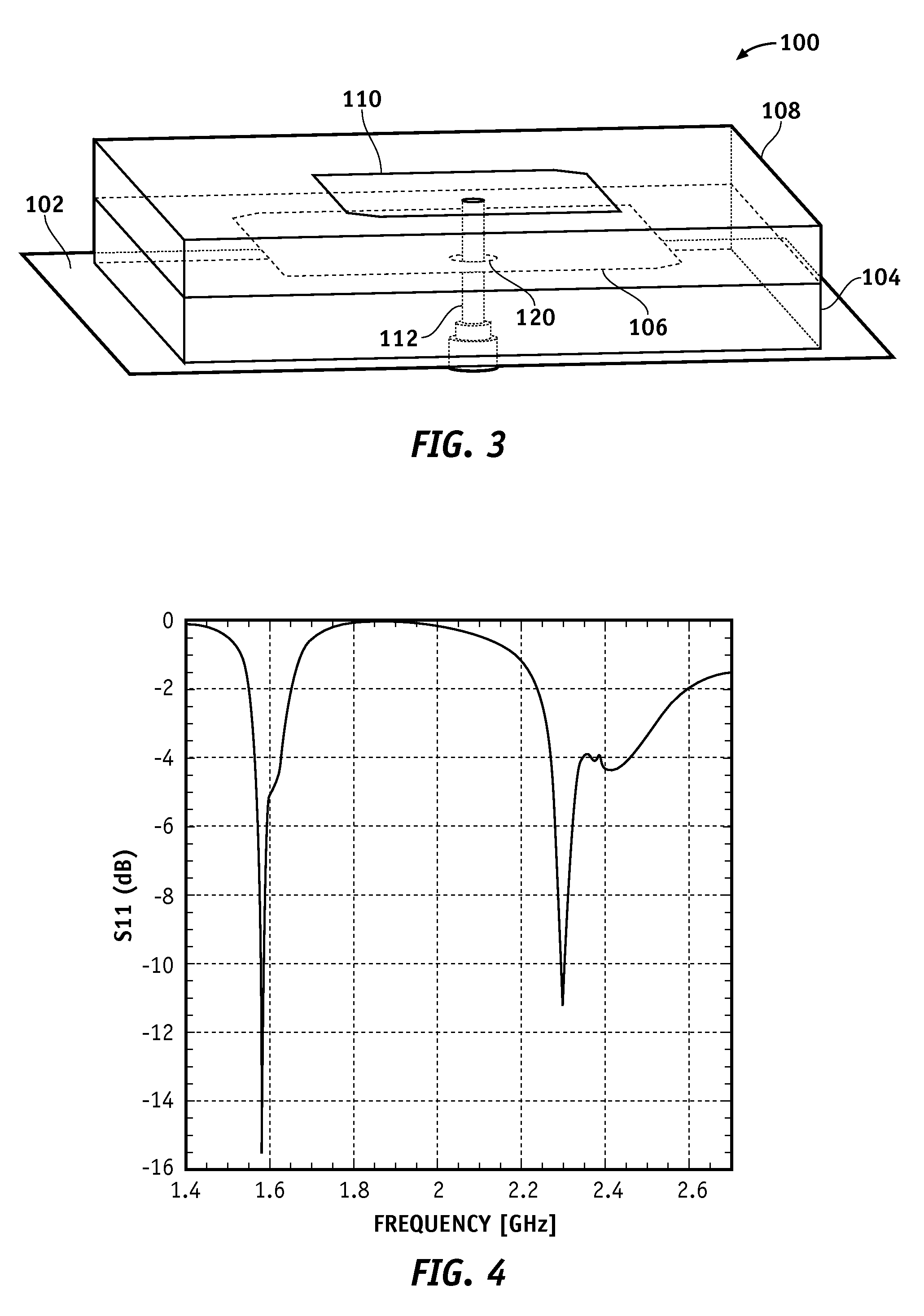

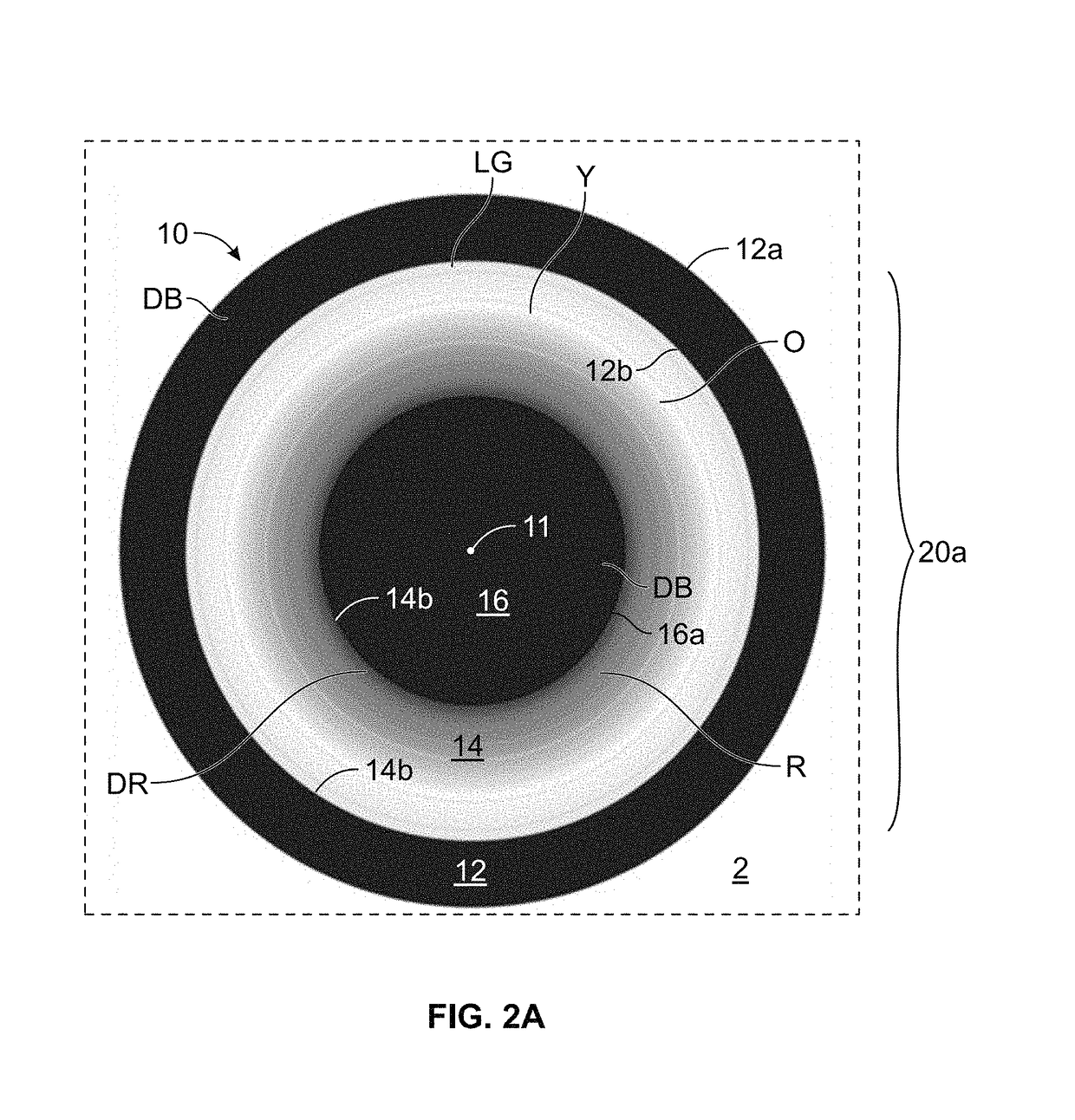

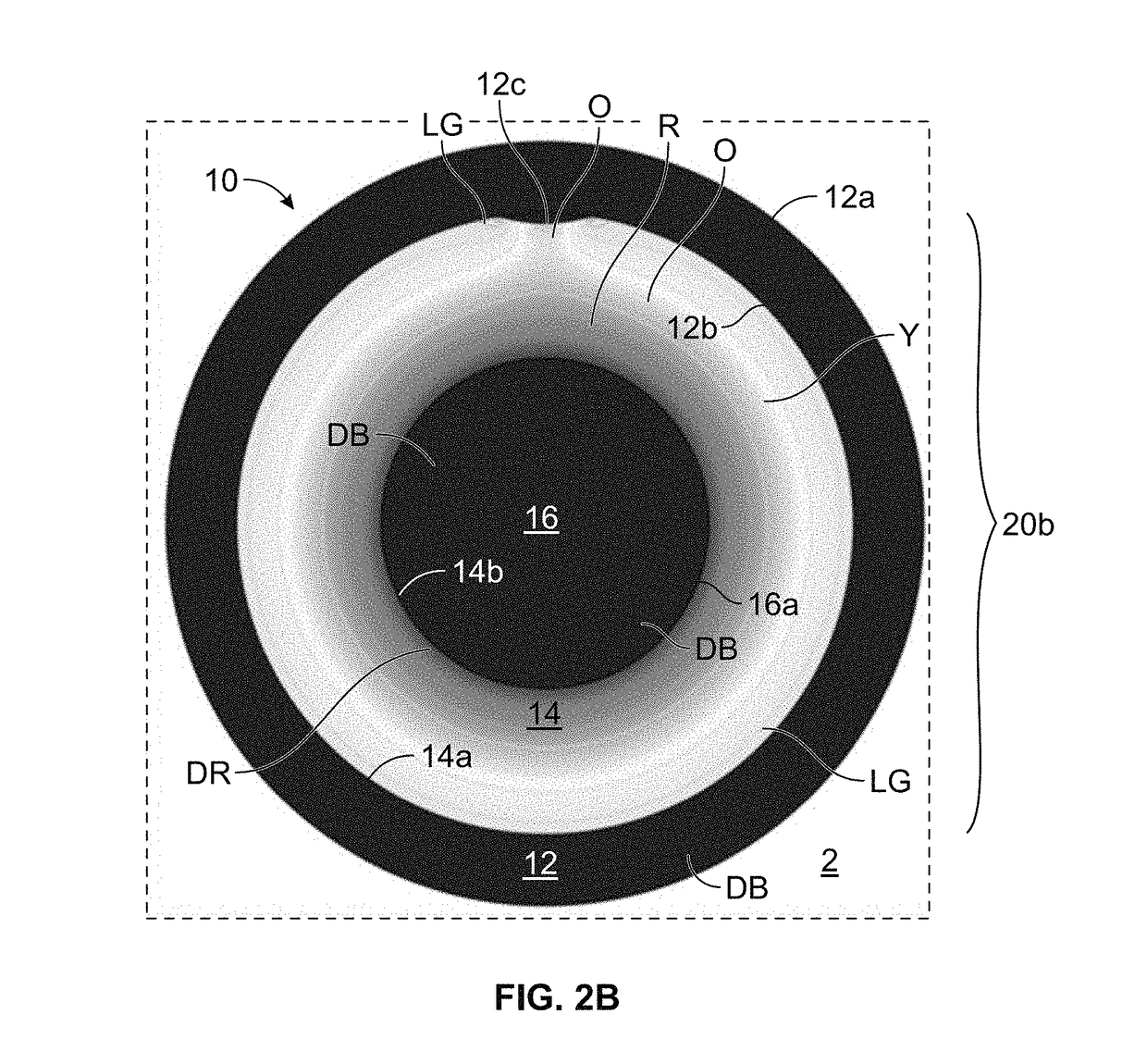

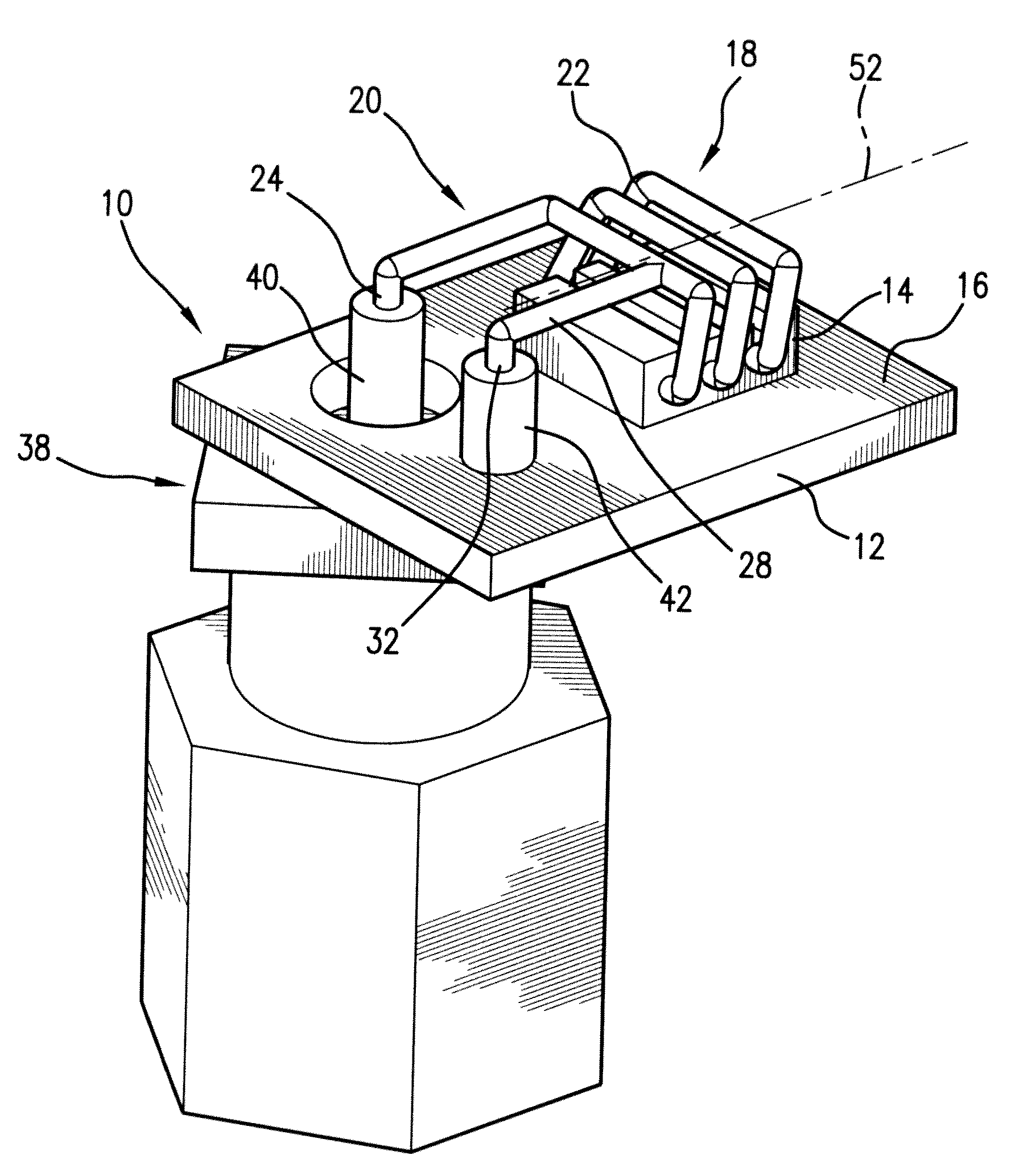

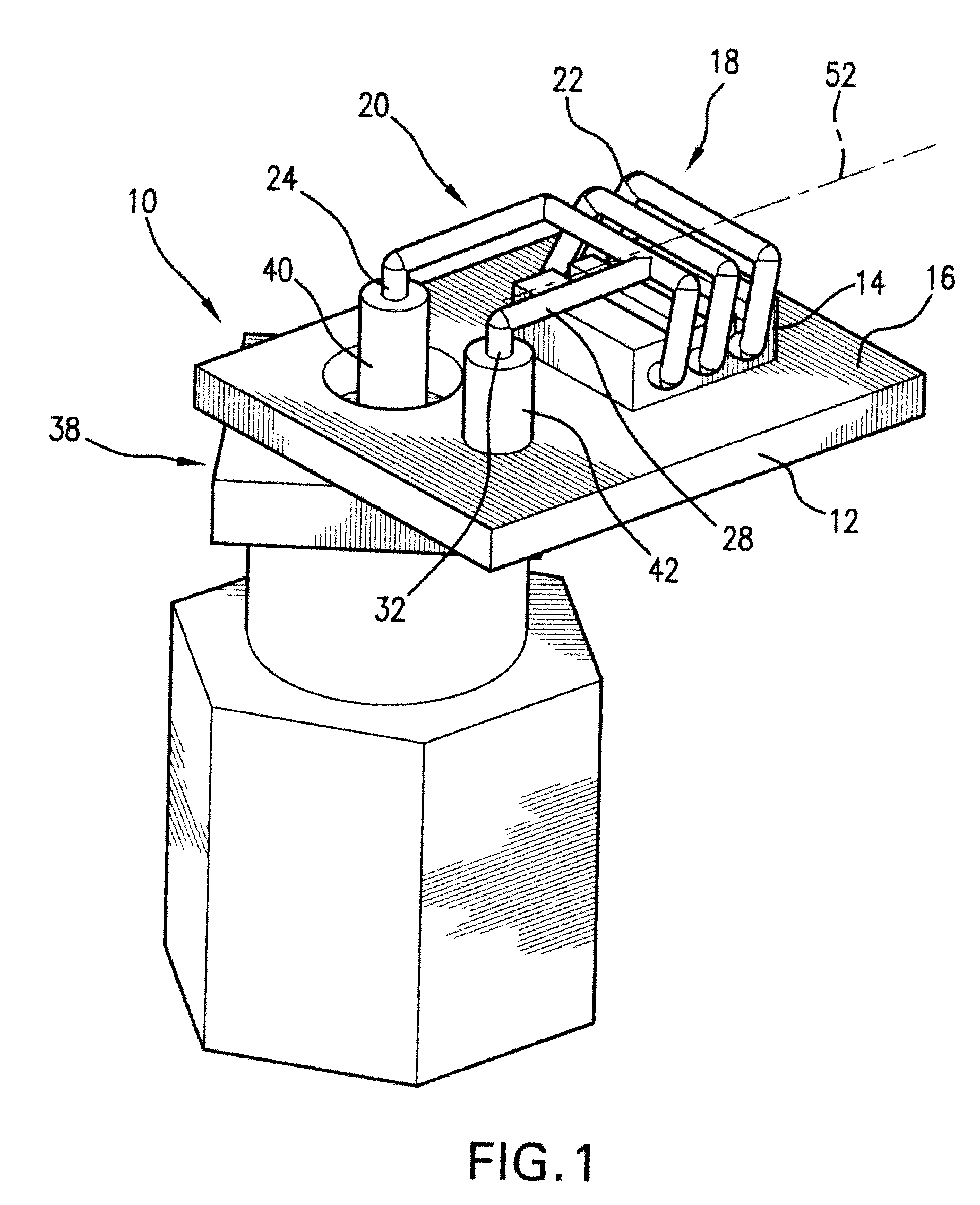

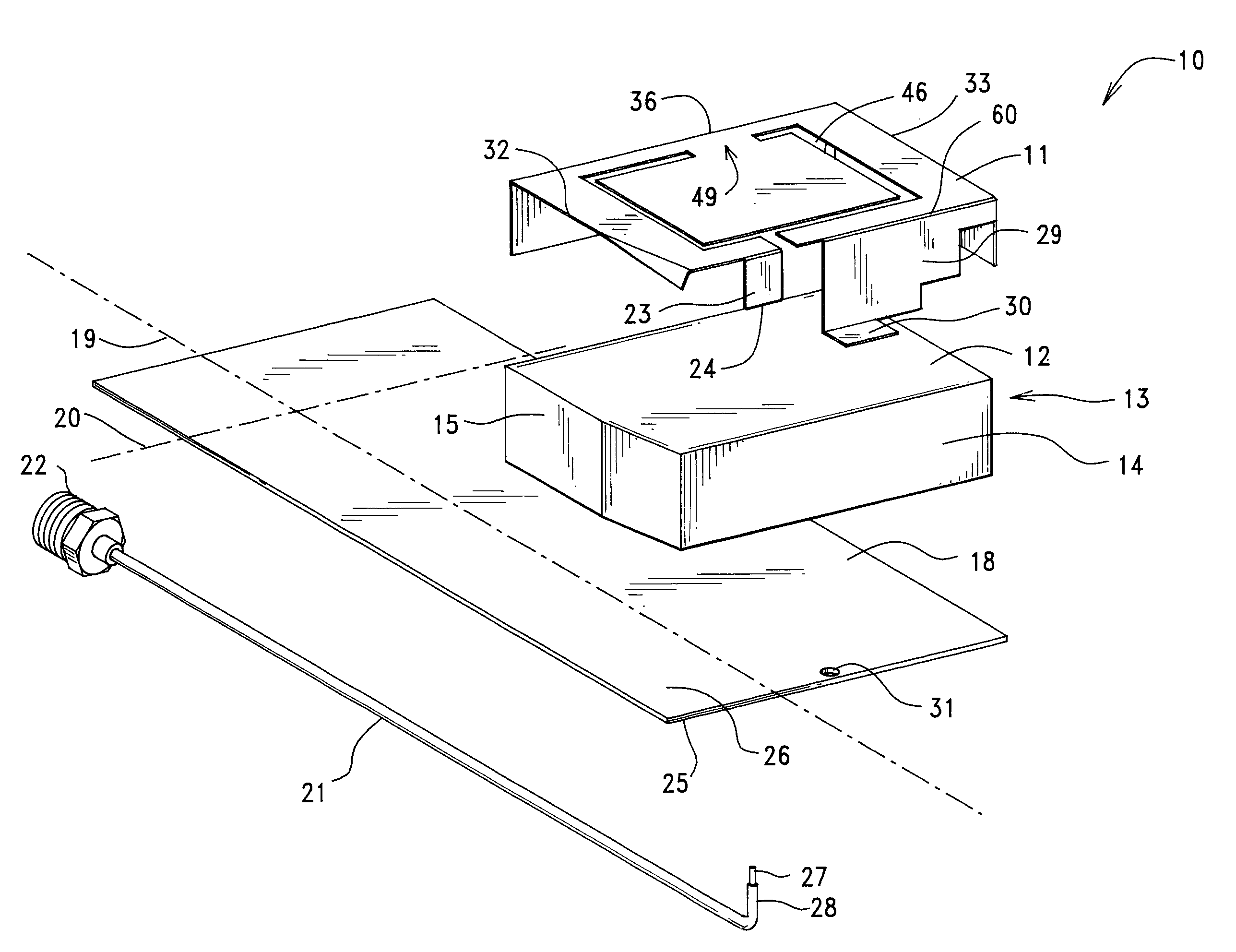

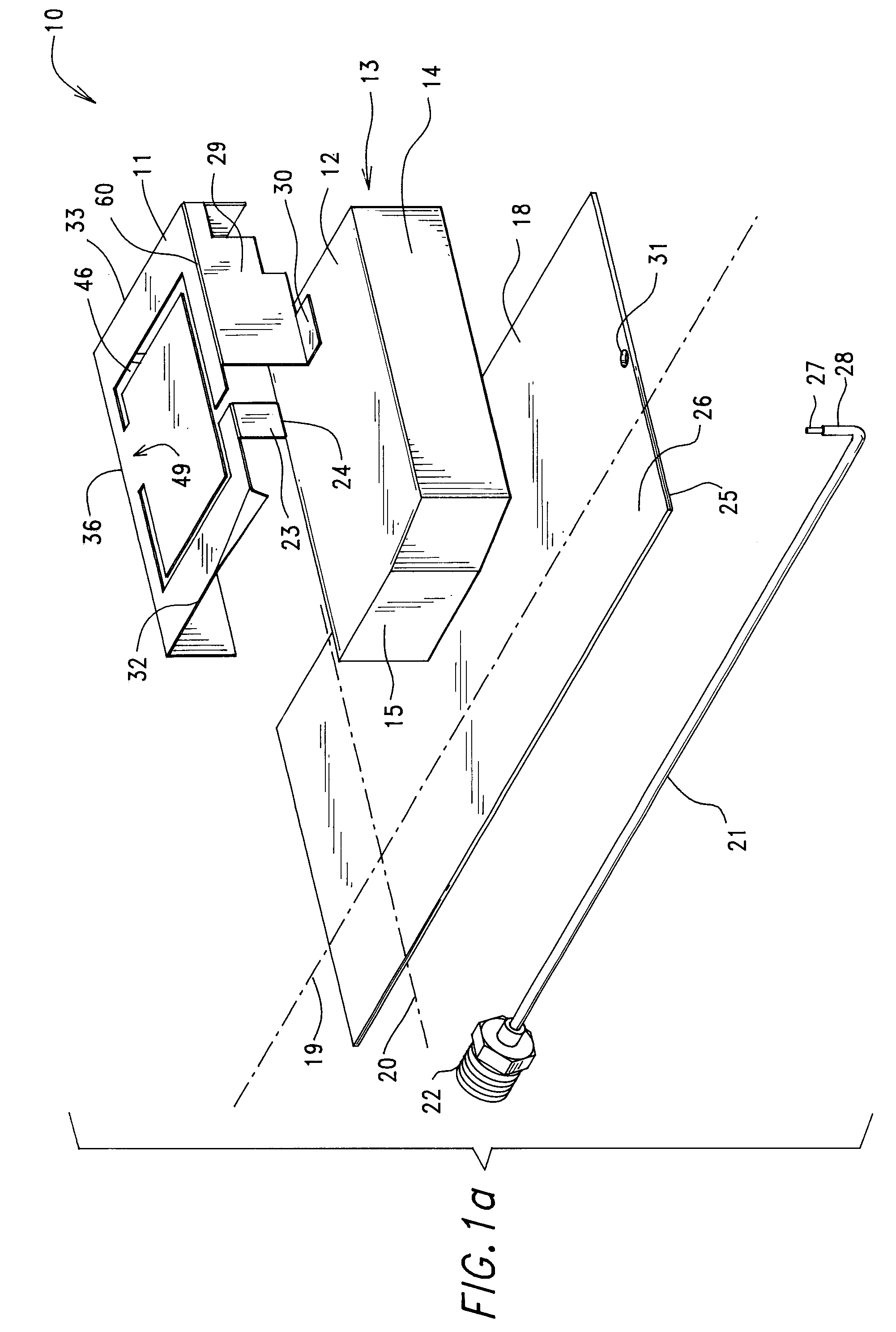

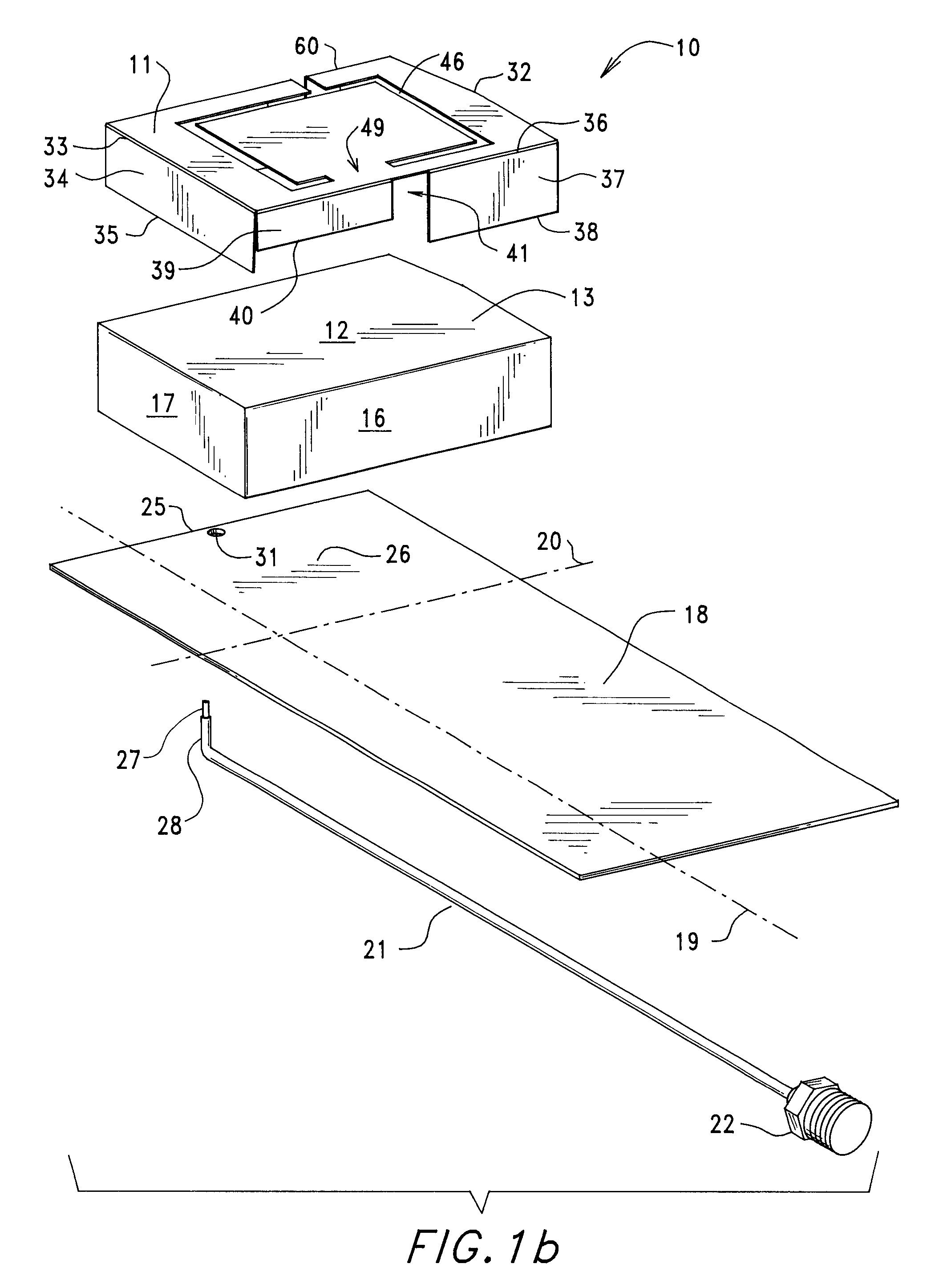

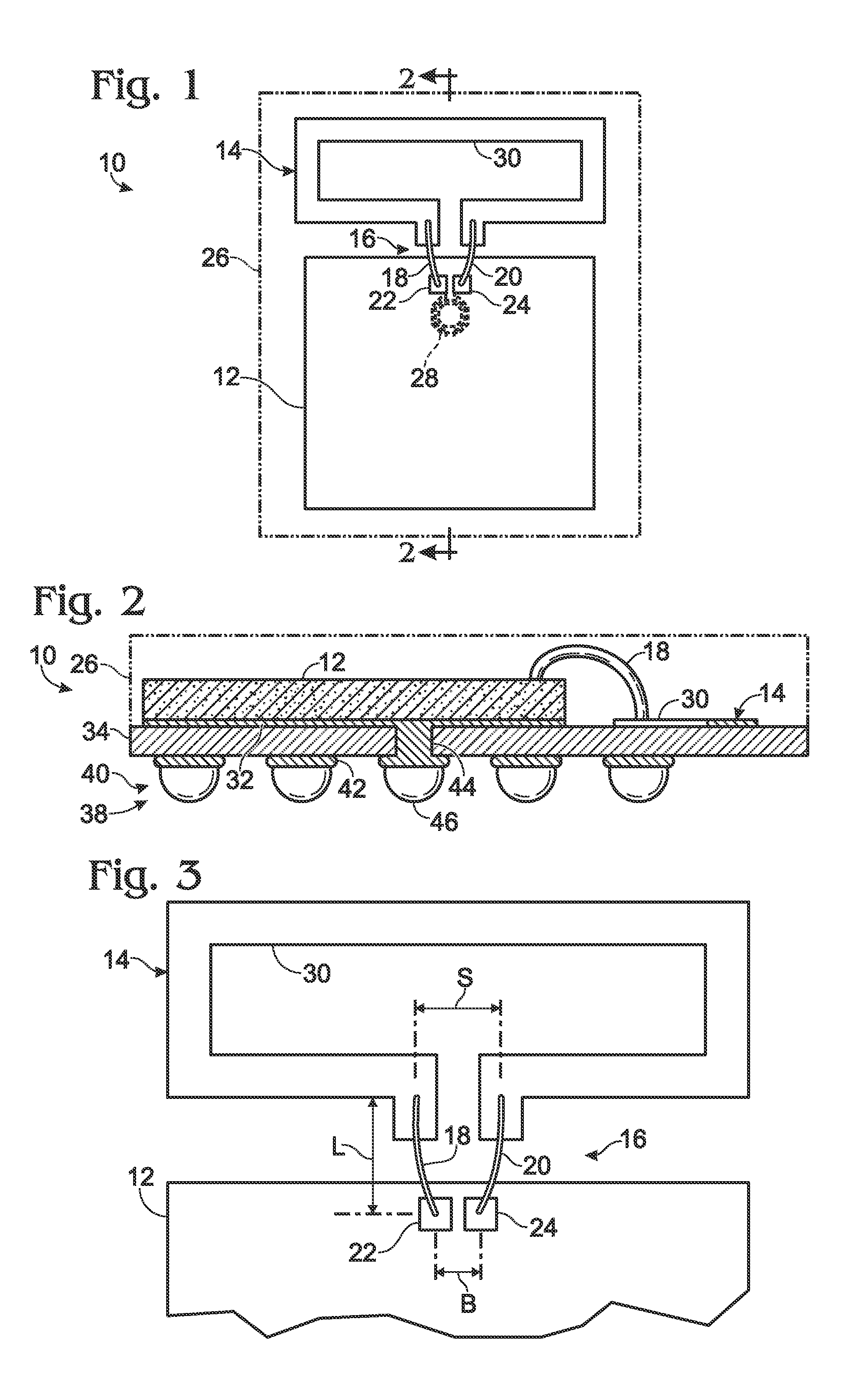

Microstrip patch antenna for high temperature environments

ActiveUS7283096B2Improve performanceImprove reliabilitySimultaneous aerial operationsAntenna adaptation in movable bodiesMicrostrip patch antennaSpray coating

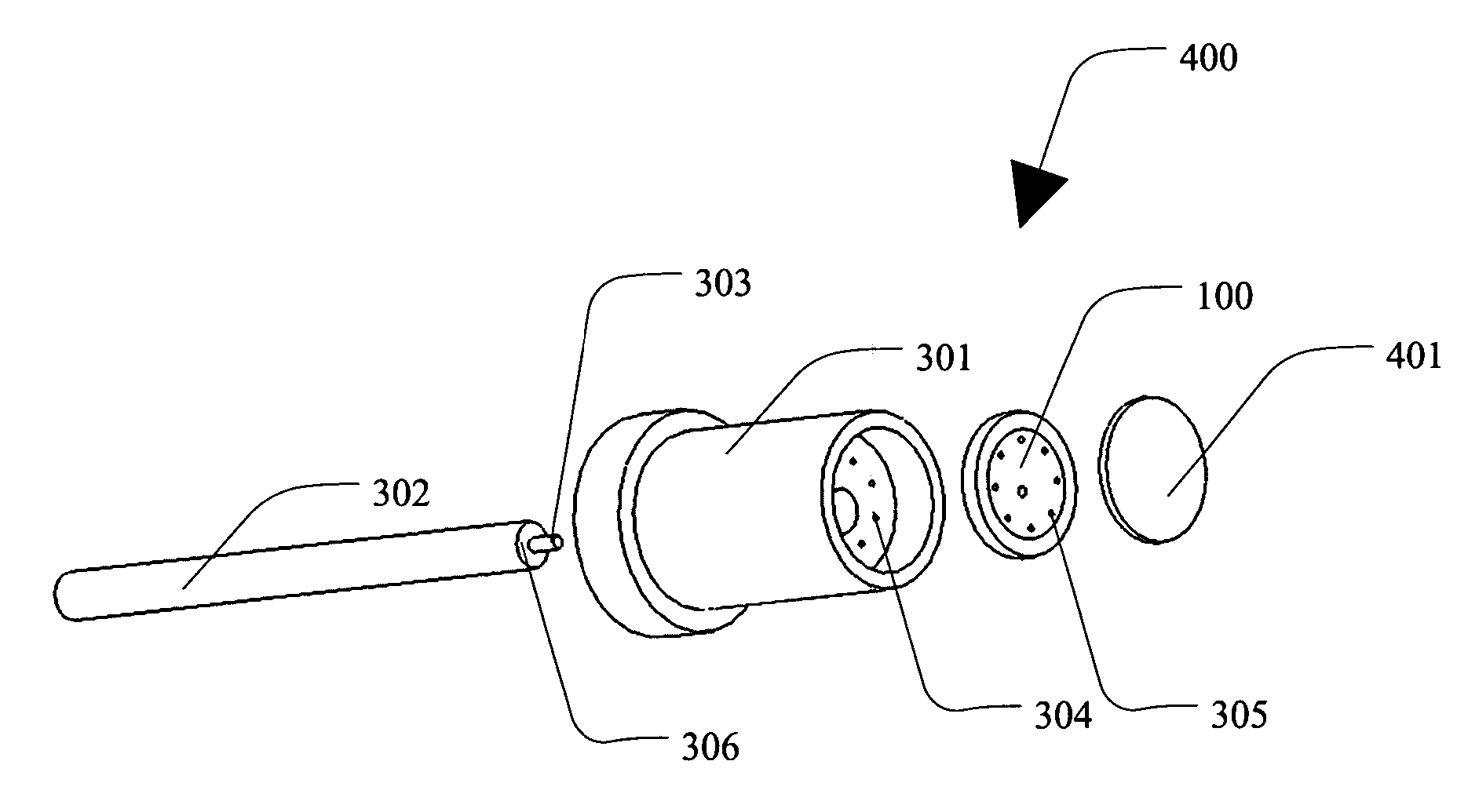

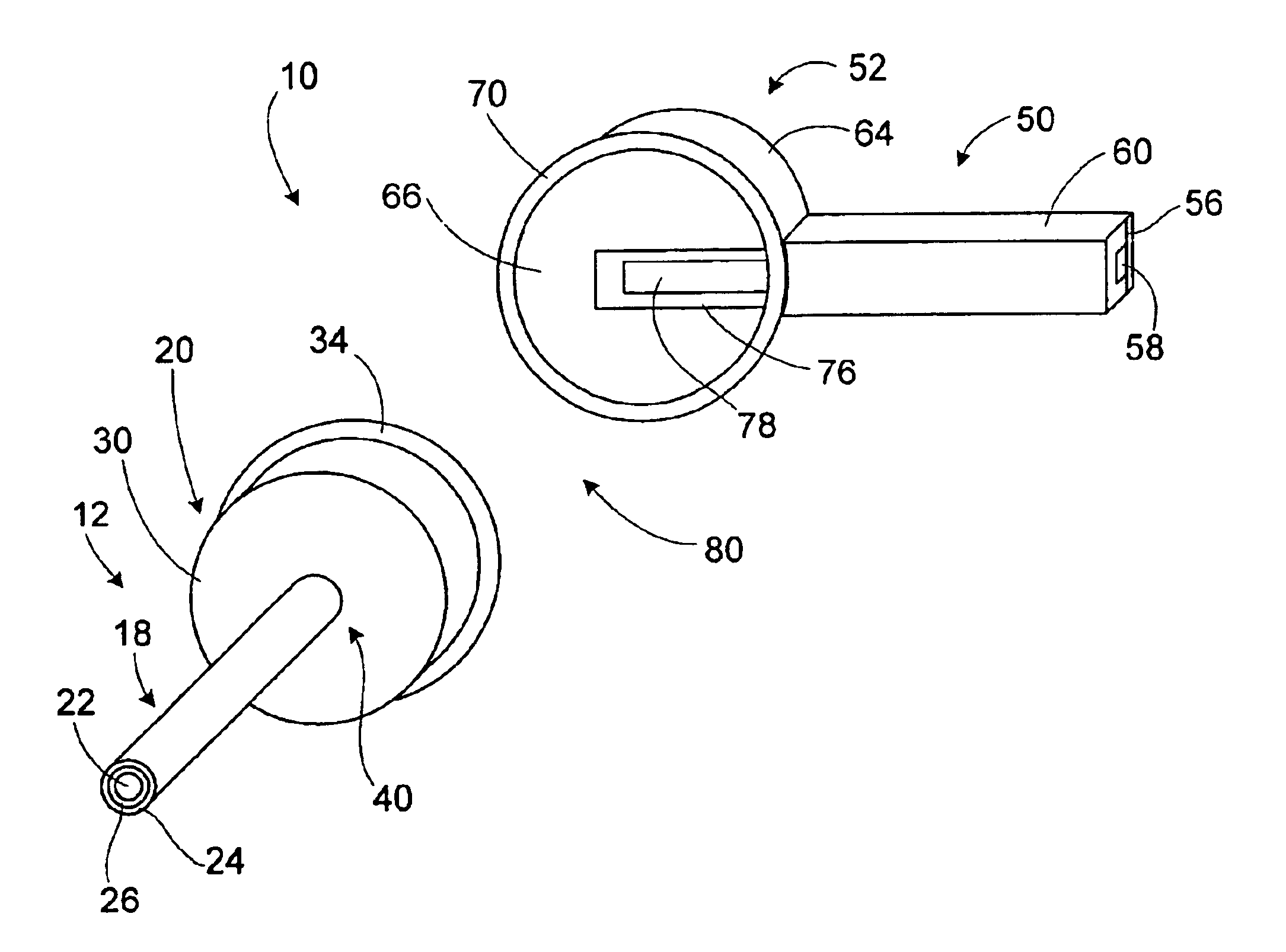

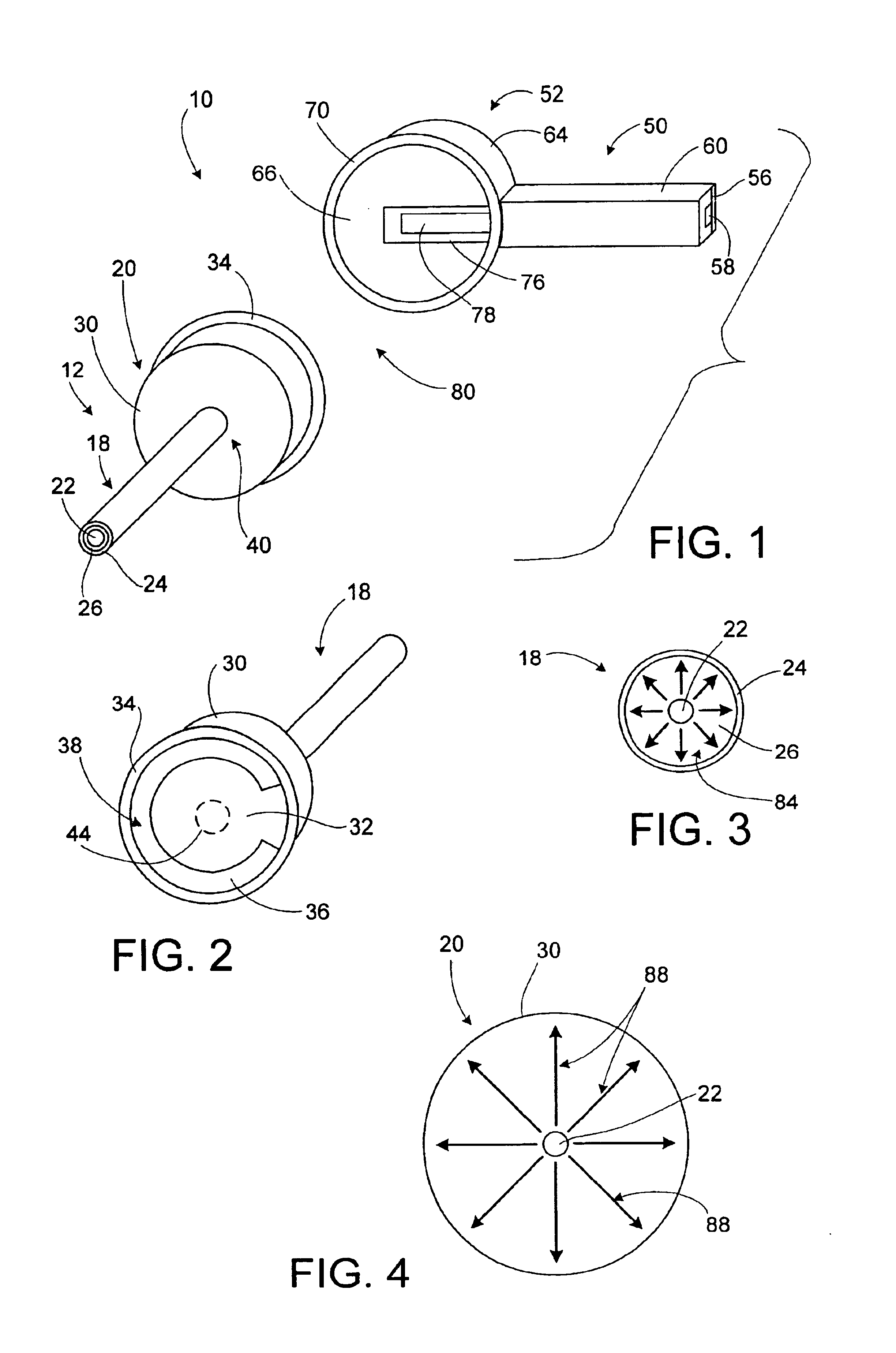

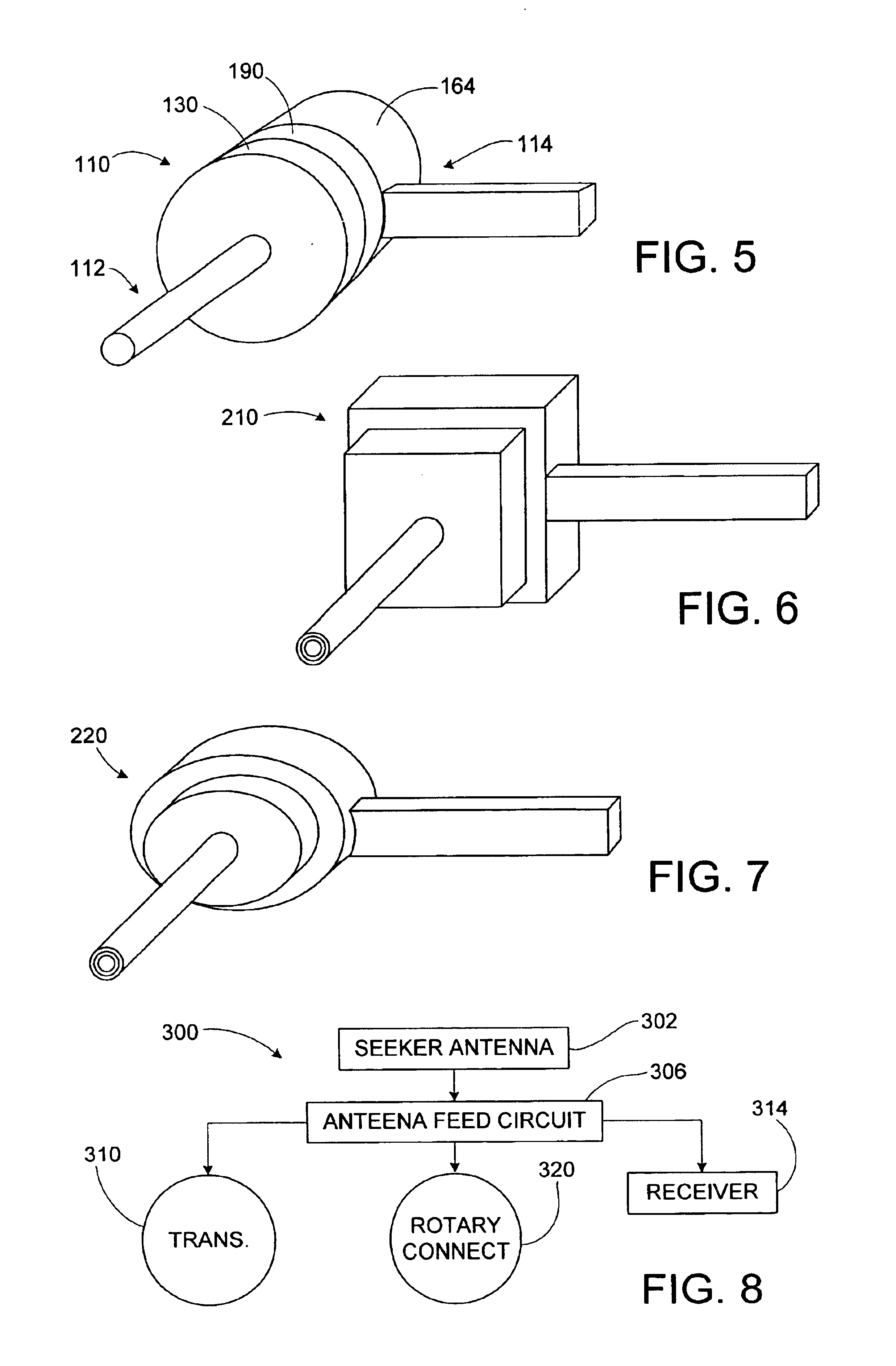

A patch antenna for operation within a high temperature environment. The patent antenna typically includes an antenna radiating element, a housing and a microwave transmission medium, such as a high temperature microwave cable. The antenna radiating element typically comprises a metallization (or solid metal) element in contact with a dielectric element. The antenna radiating element can include a dielectric window comprising a flame spray coating or a solid dielectric material placed in front of the radiating element. The antenna element is typically inserted into a housing that mechanically captures the antenna and provides a ground plane for the antenna. Orifices or passages can be added to the housing to improve high temperature performance and may direct cooling air for cooling the antenna. The high temperature microwave cable is typically inserted into the housing and attached to the antenna radiator to support the communication of electromagnetic signals between the radiator element and a receiver or transmitter device.

Owner:MEGGITT SA

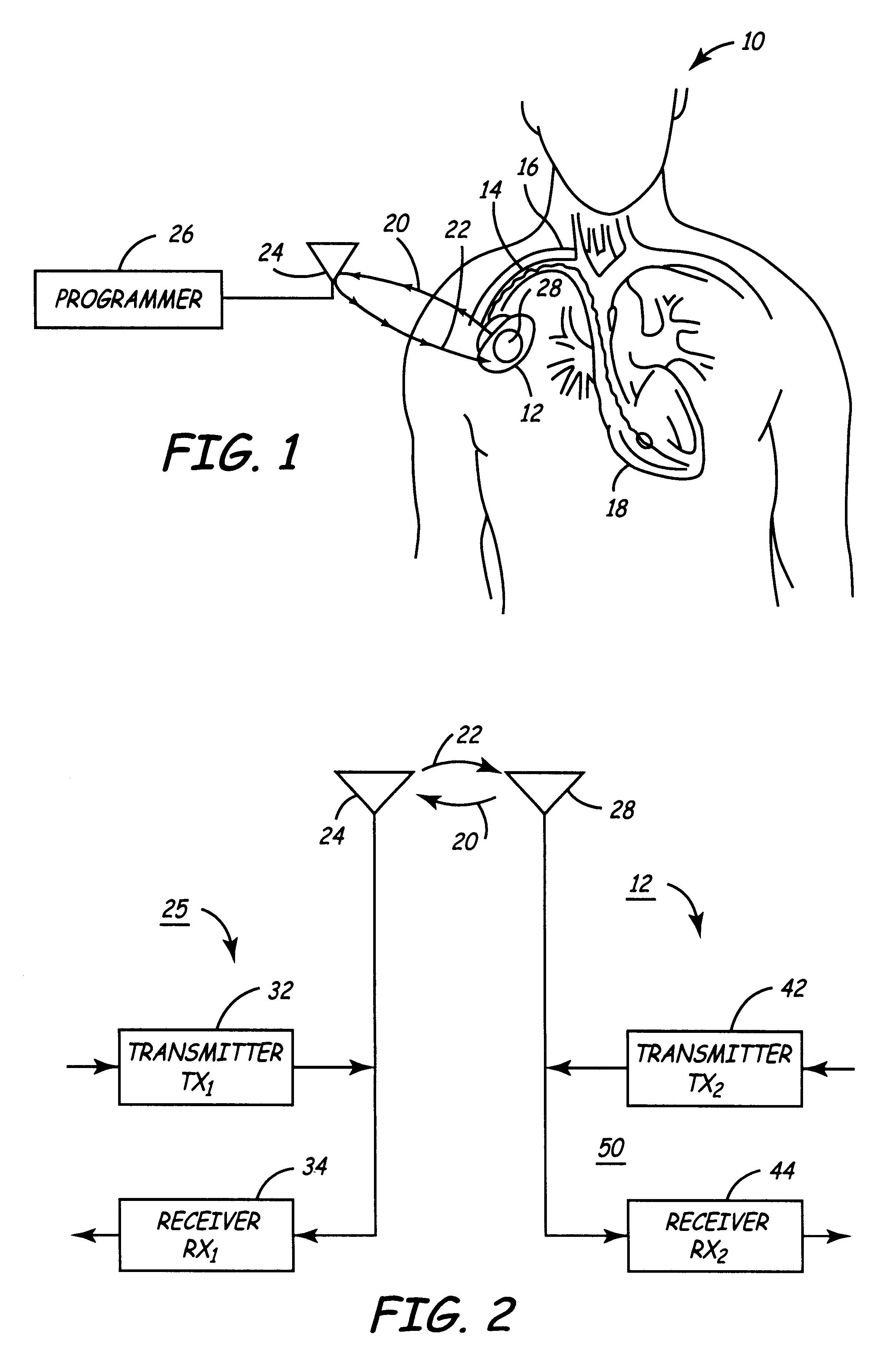

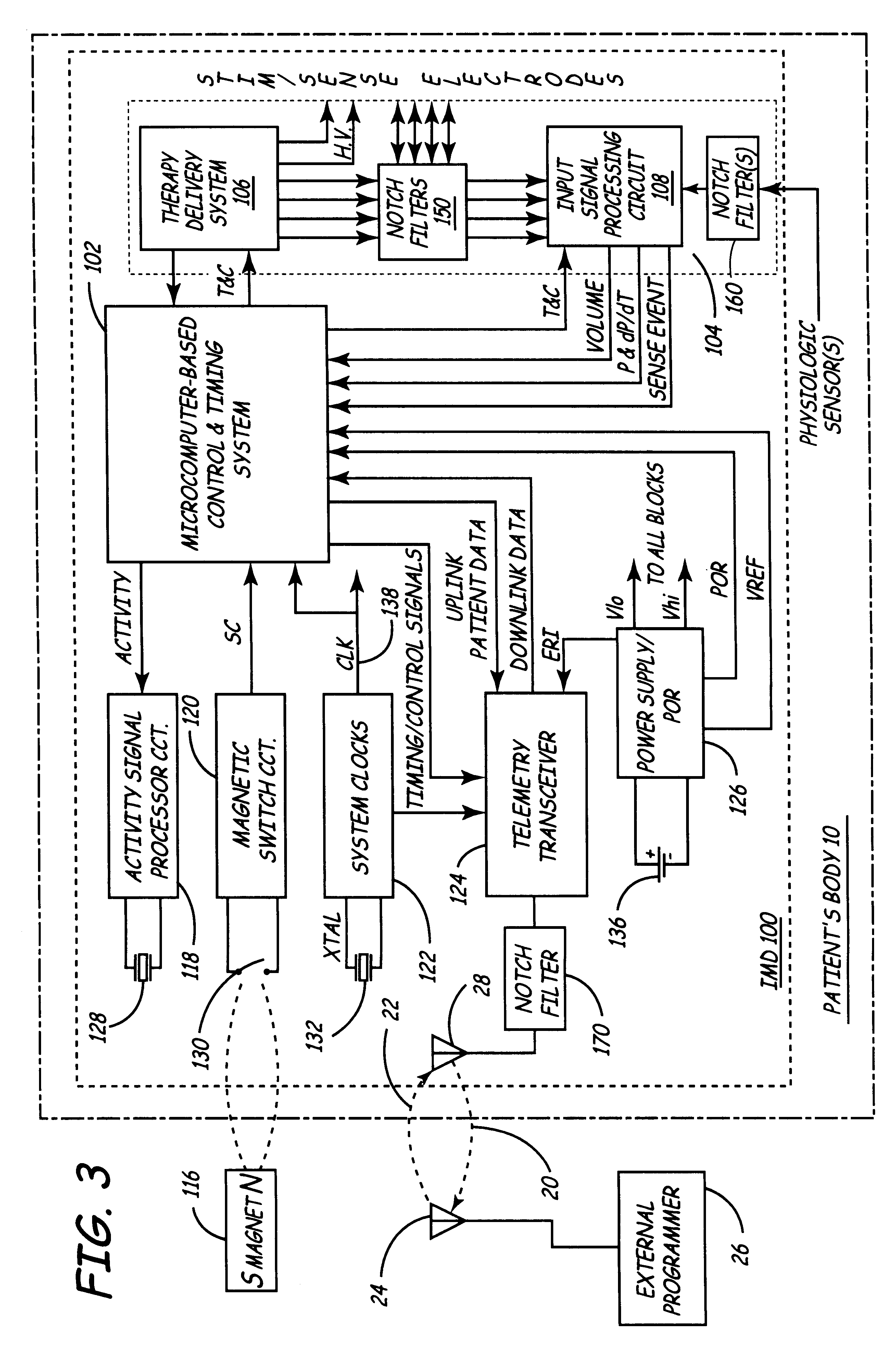

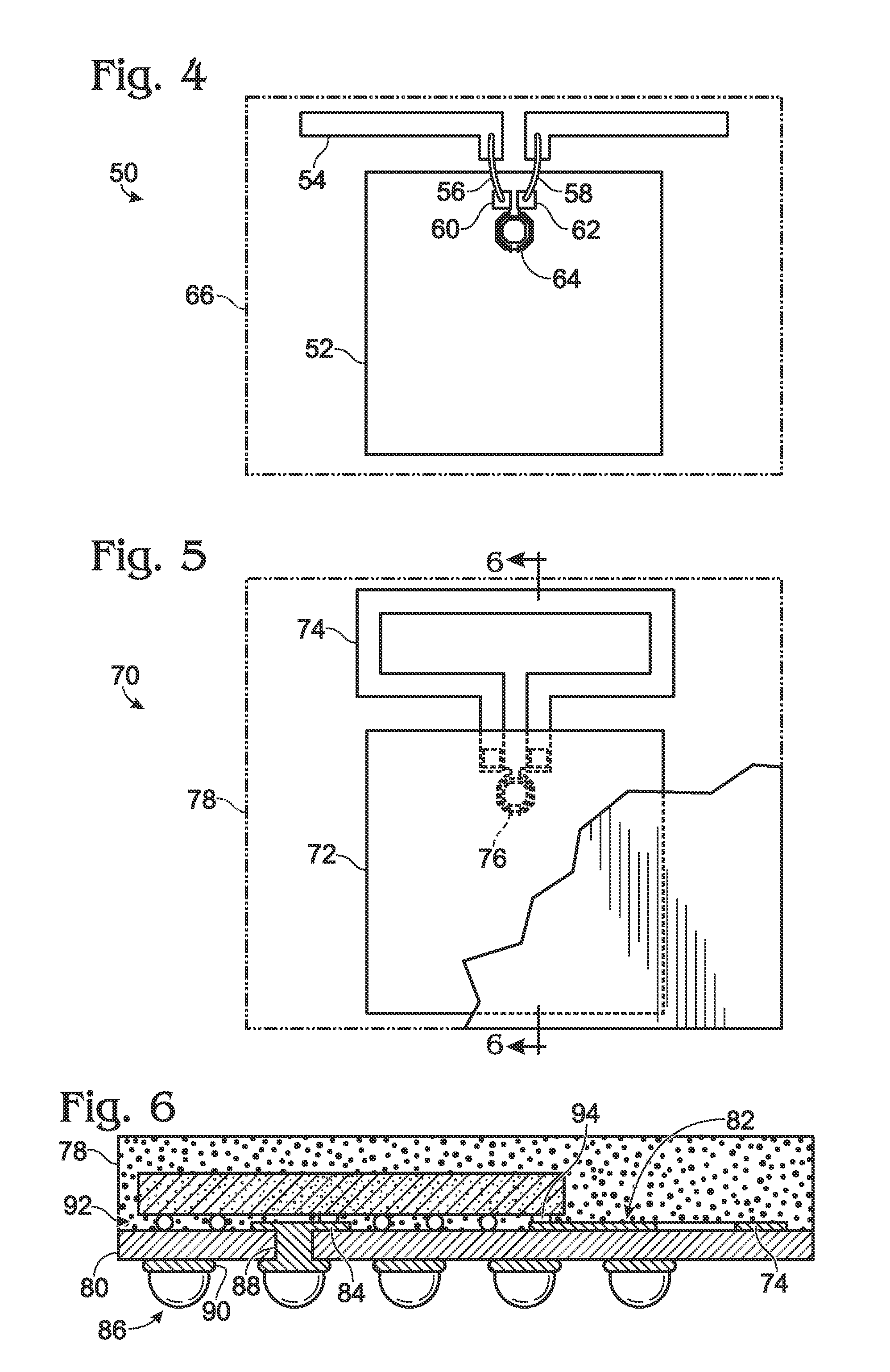

Implantable medical device incorporating integrated circuit notch filters

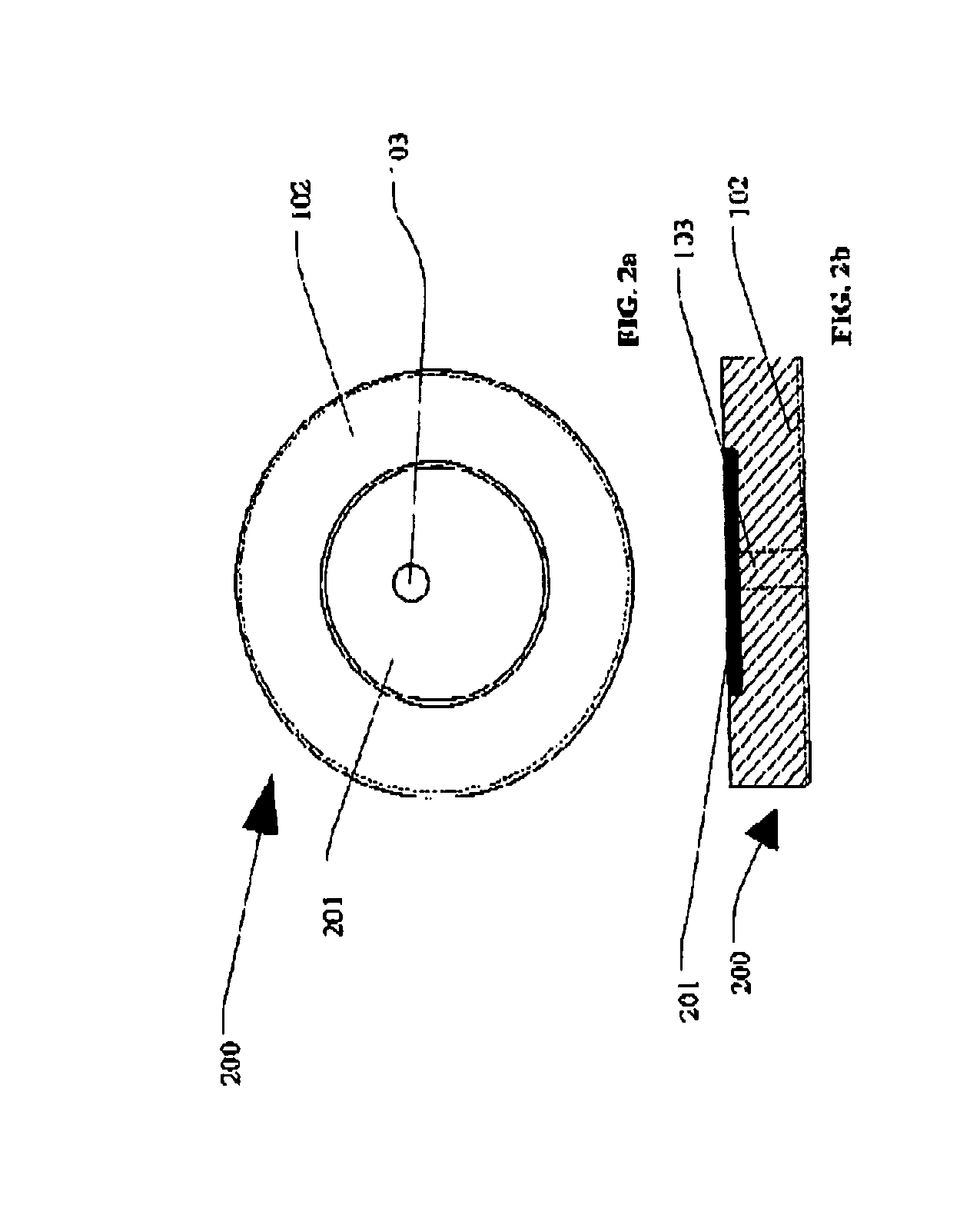

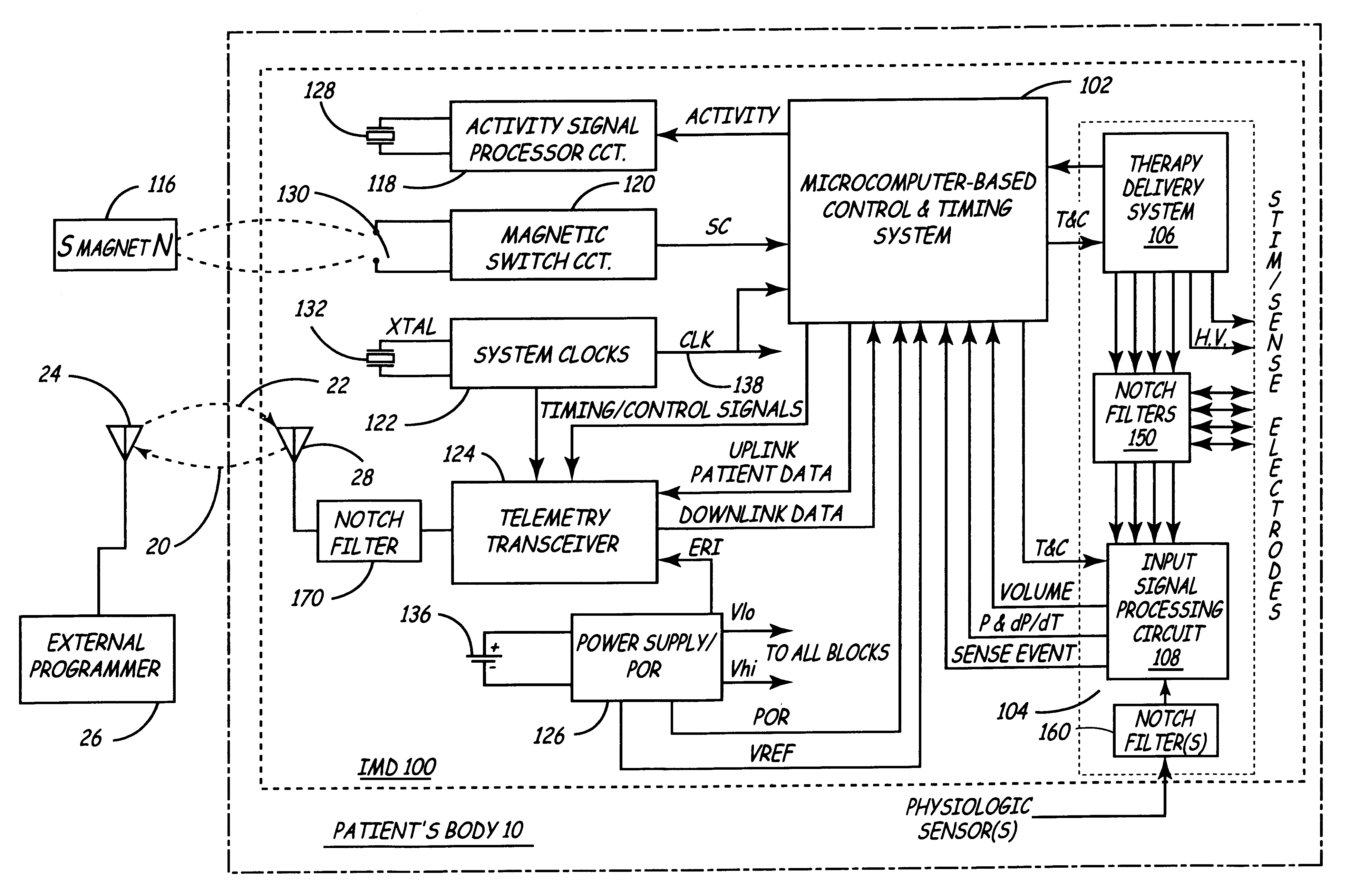

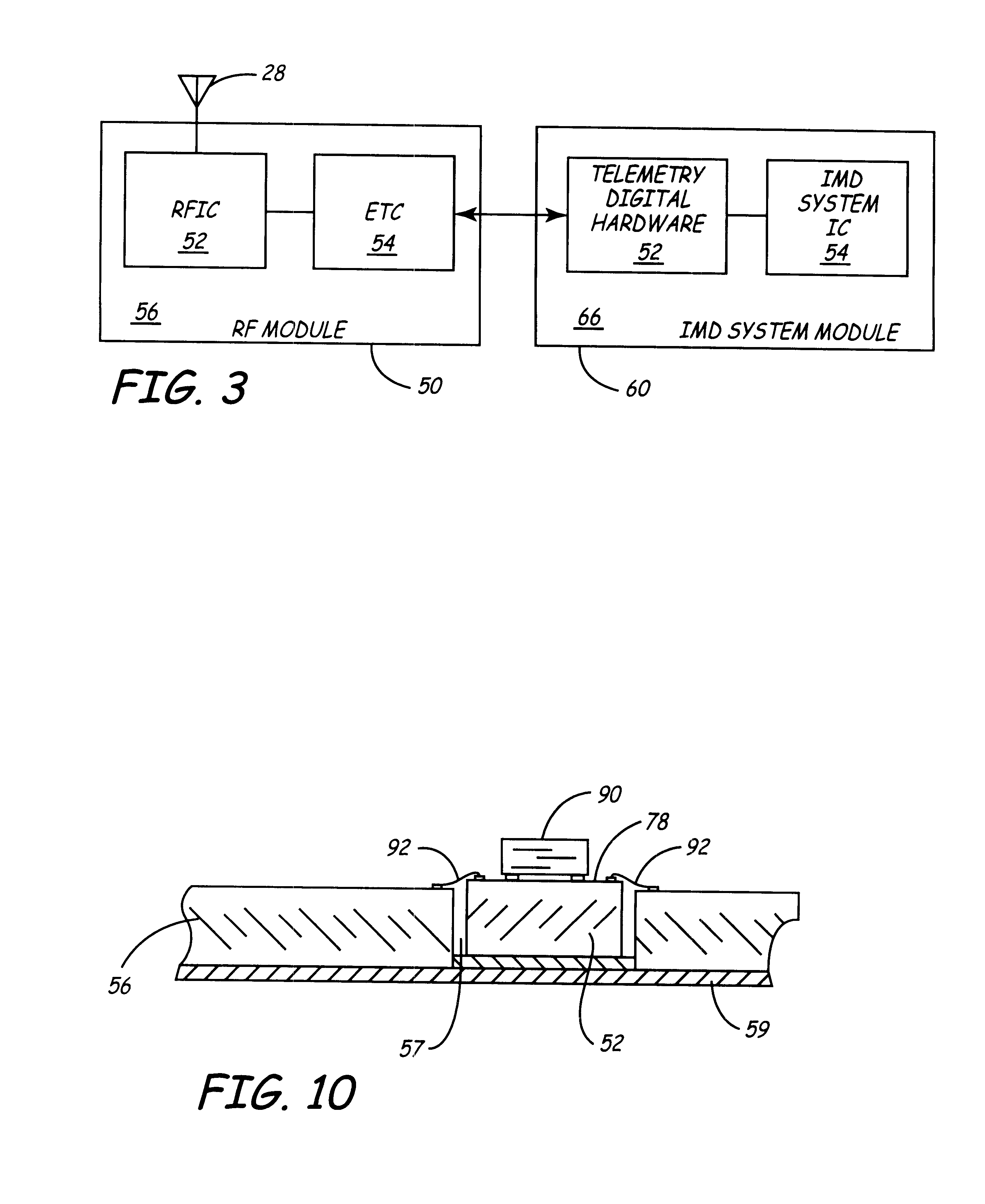

Implantable medical devices (IMDs) having sense amplifiers for sensing physiologic signals and parameters, RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming and interrogation commands to and from an external programmer or other medical device are disclosed. At least one IC chip and discrete components have a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include forming notch filters of MEMS structures or forming discrete circuit notch filters by one or more of: (1) IC fabricating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The IC fabricated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the IC chip substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

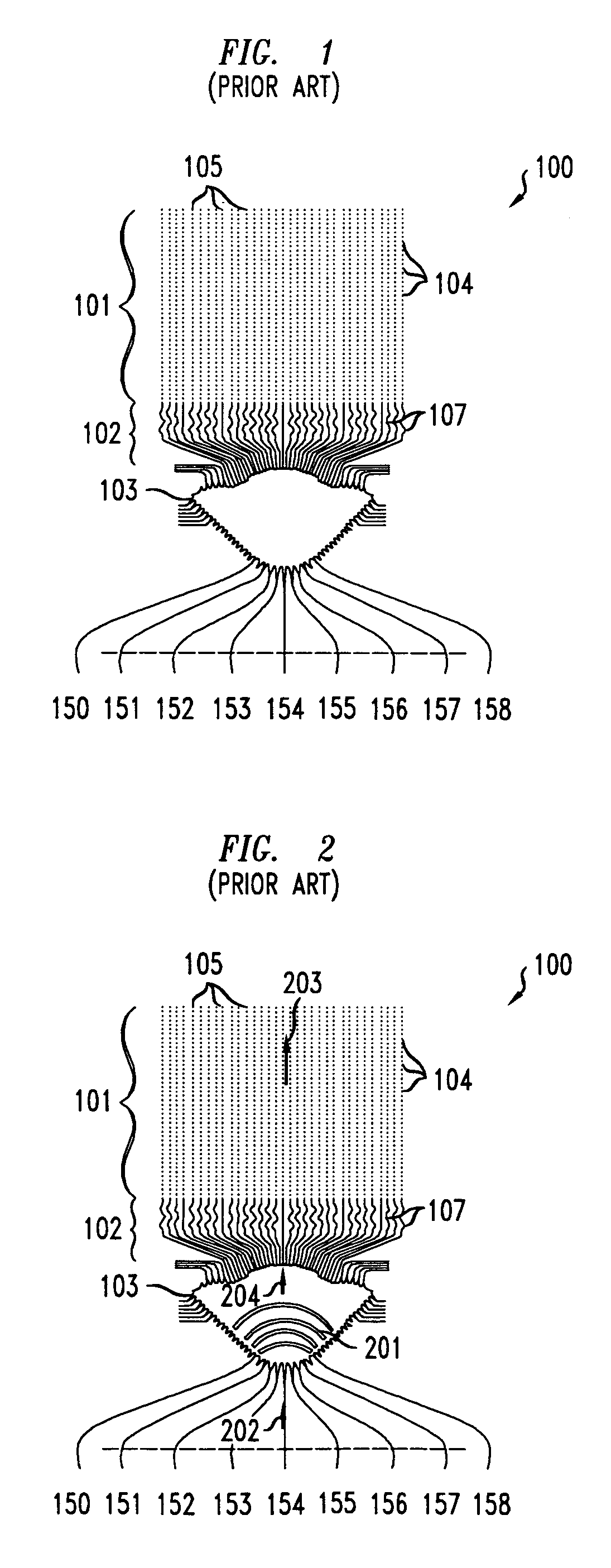

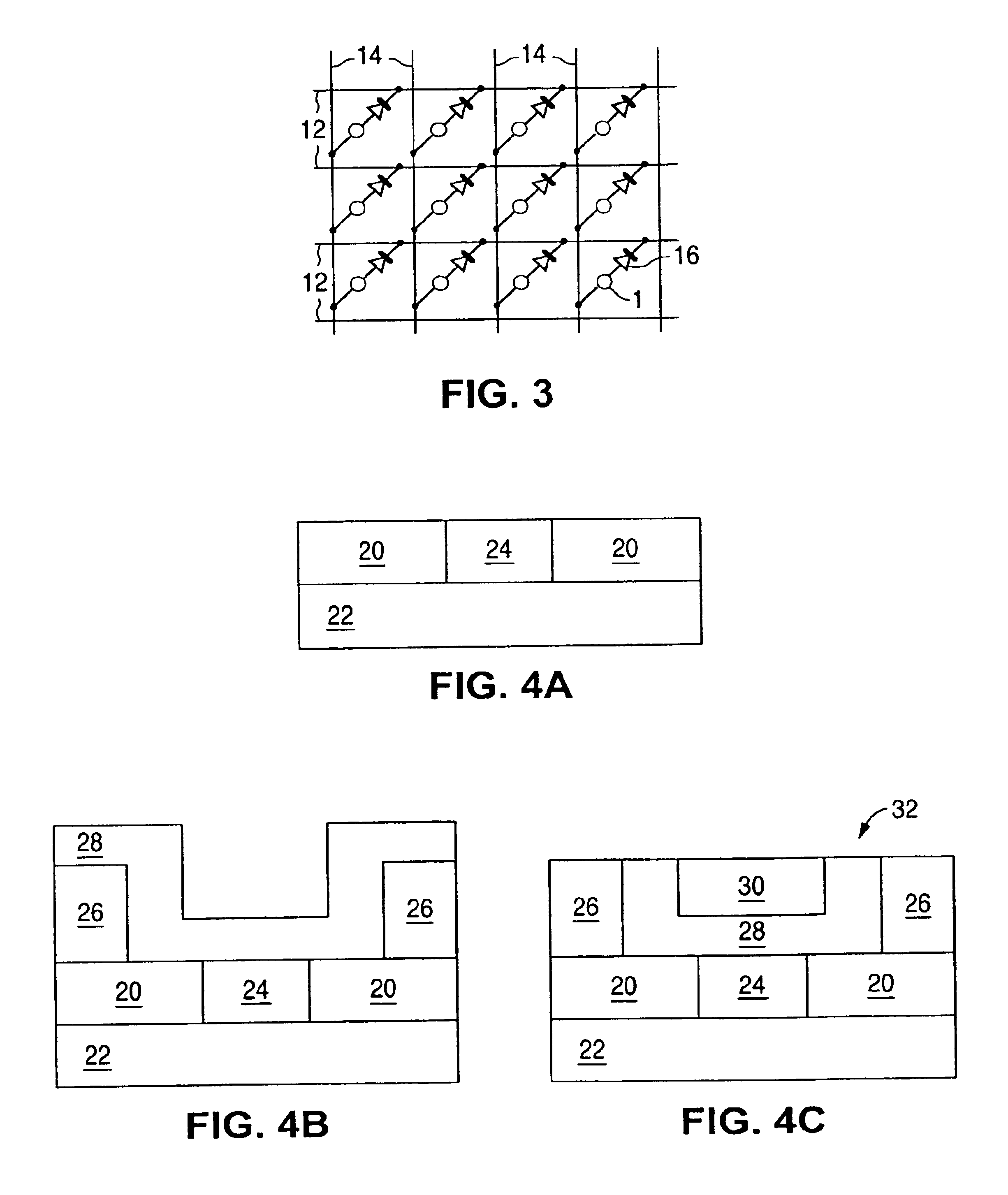

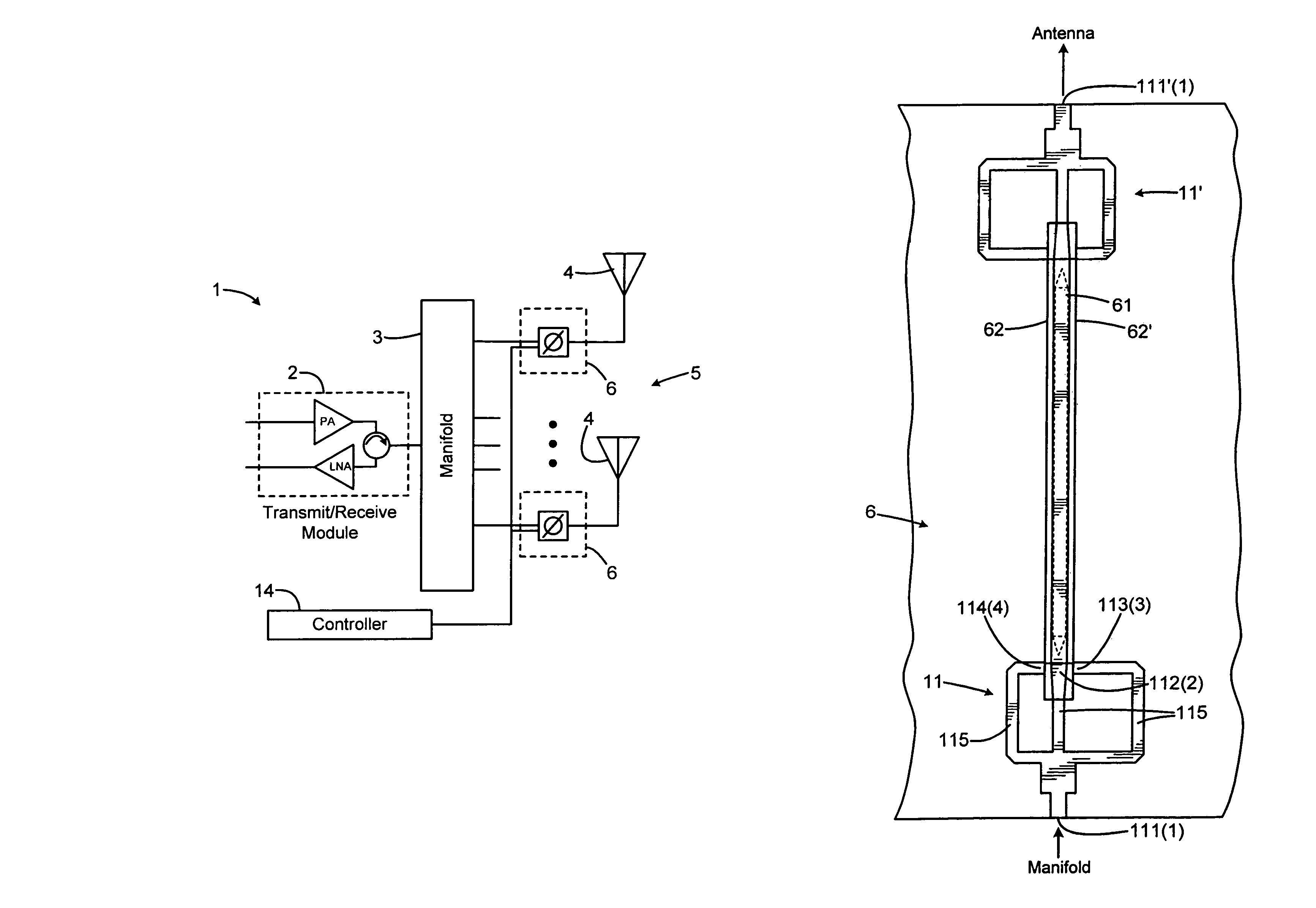

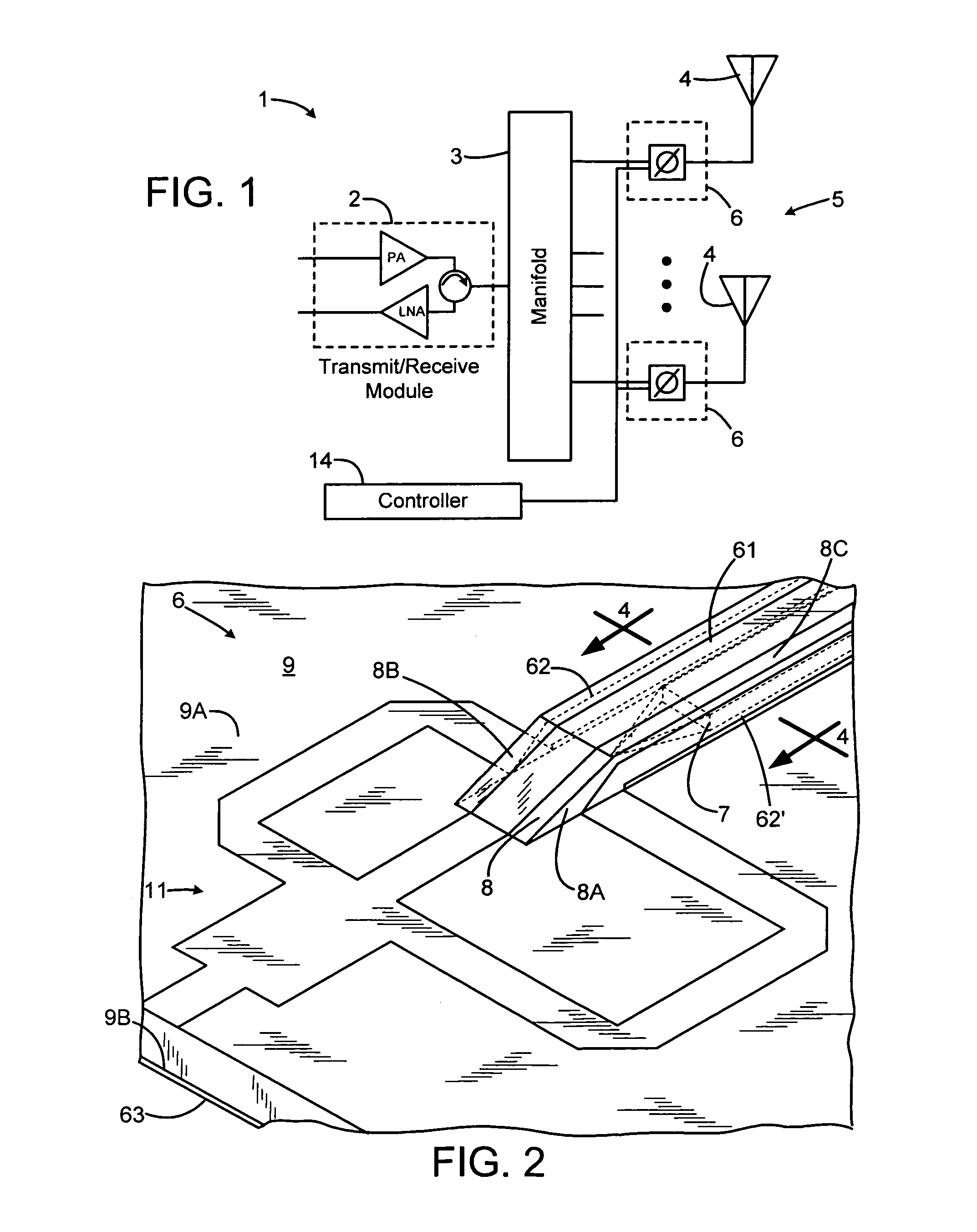

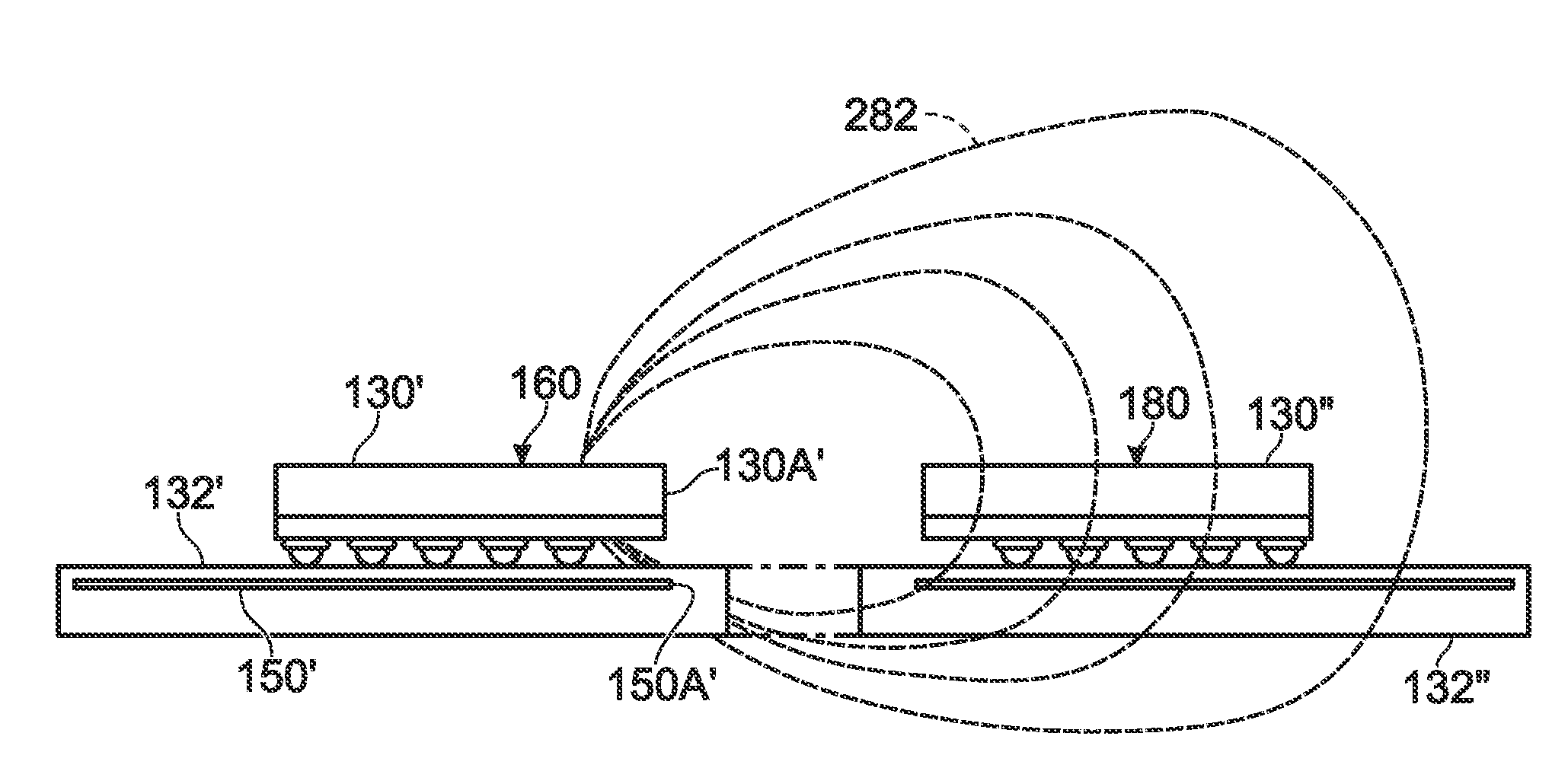

Phased array metamaterial antenna system

ActiveUS6958729B1Reduce sidelobeIncrease amplitude performanceSimultaneous aerial operationsRadiating elements structural formsSolid substratePhased array

An efficient, low-loss, low sidelobe, high dynamic range phased-array radar antenna system is disclosed that uses metamaterials, which are manmade composite materials having a negative index of refraction, to create a biconcave lens architecture (instead of the aforementioned biconvex lens) for focusing the microwaves transmitted by the antenna. Accordingly, the sidelobes of the antenna are reduced. Attenuation across microstrip transmission lines may be reduced by using low loss transmission lines that are suspended above a ground plane a predetermined distance in a way such they are not in contact with a solid substrate. By suspending the microstrip transmission lines in this manner, dielectric signal loss is reduced significantly, thus resulting in a less-attenuated signal at its destination.

Owner:LUCENT TECH INC

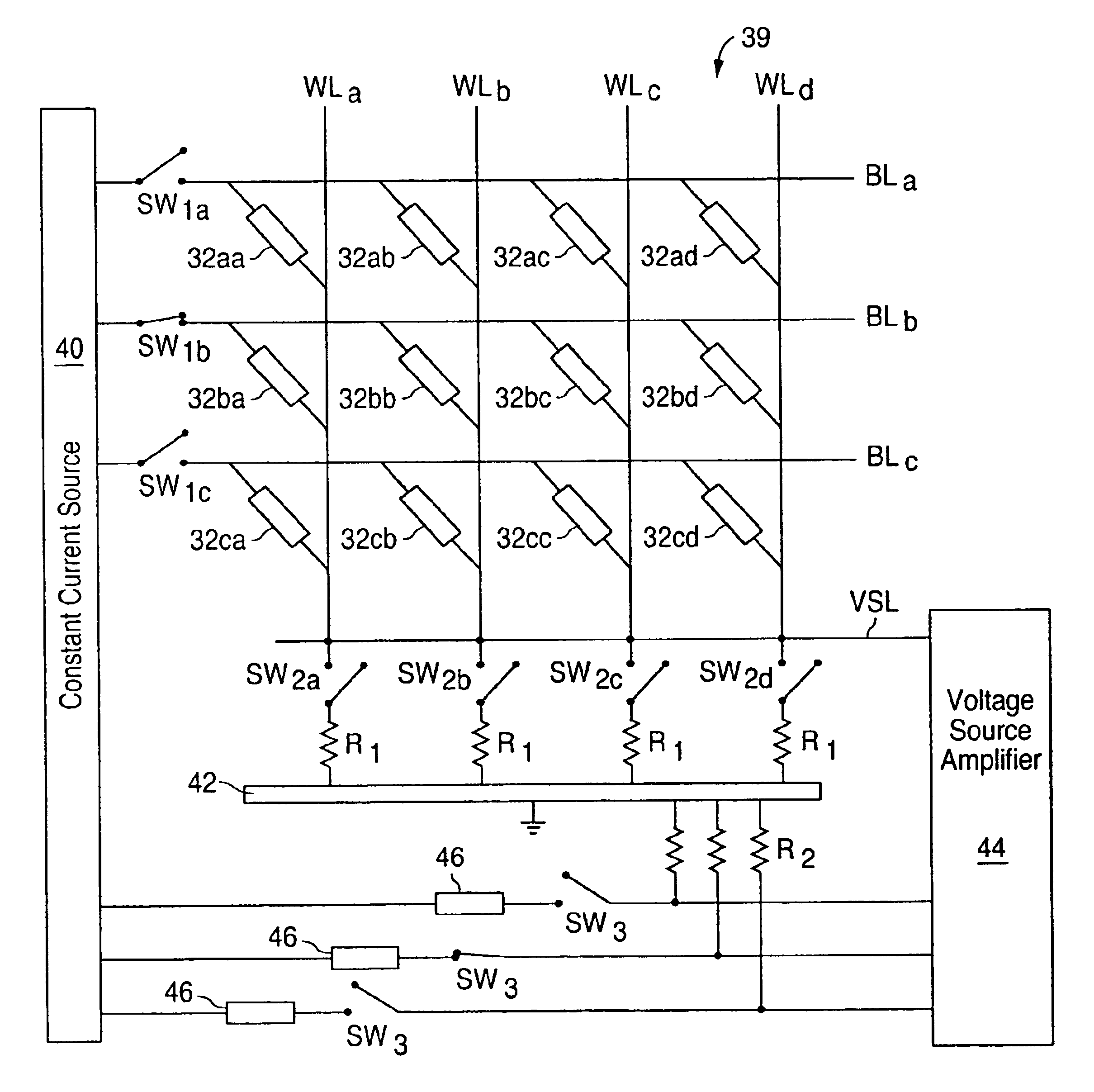

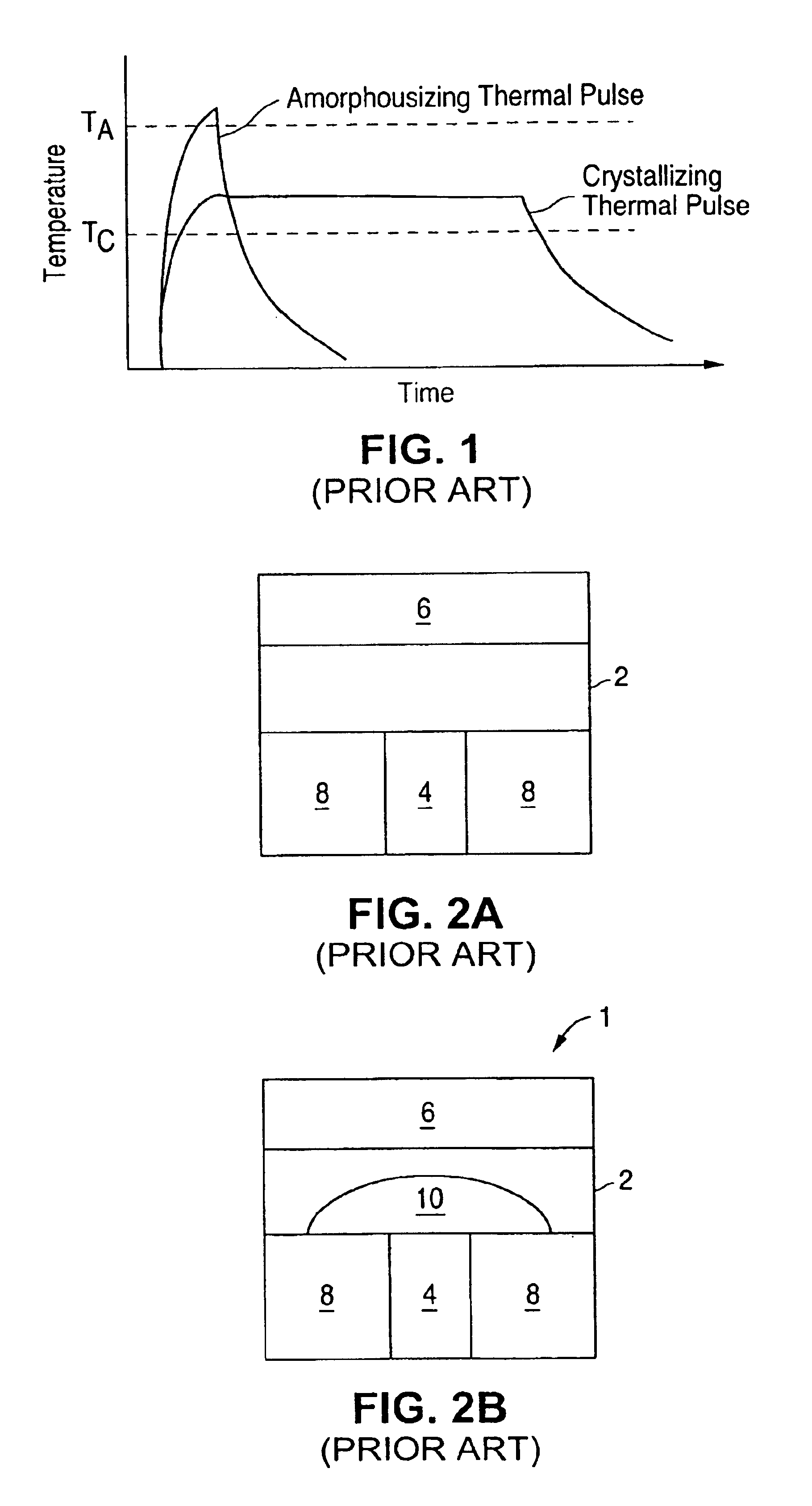

Memory device and method of operating same

An array of phase changing memory cells that includes a current source, a voltage sensor, a plurality of conductive bit lines electrically connected to the current source, a plurality of conductive word lines each electrically connected to a ground plane via a first resistor and to the voltage sensor, and a plurality of memory cells. Each memory cell is connected between one of the bit lines and one of the word lines and includes phase change memory material. One of the memory cells is selected by turning on switches just on the bit line and word line connected thereto, or by turning a switch connected in series between the corresponding bit and word lines, where the read current flows through the selected memory cell and the voltage sensor measures a voltage drop across the selected memory cell.

Owner:SILICON STORAGE TECHNOLOGY

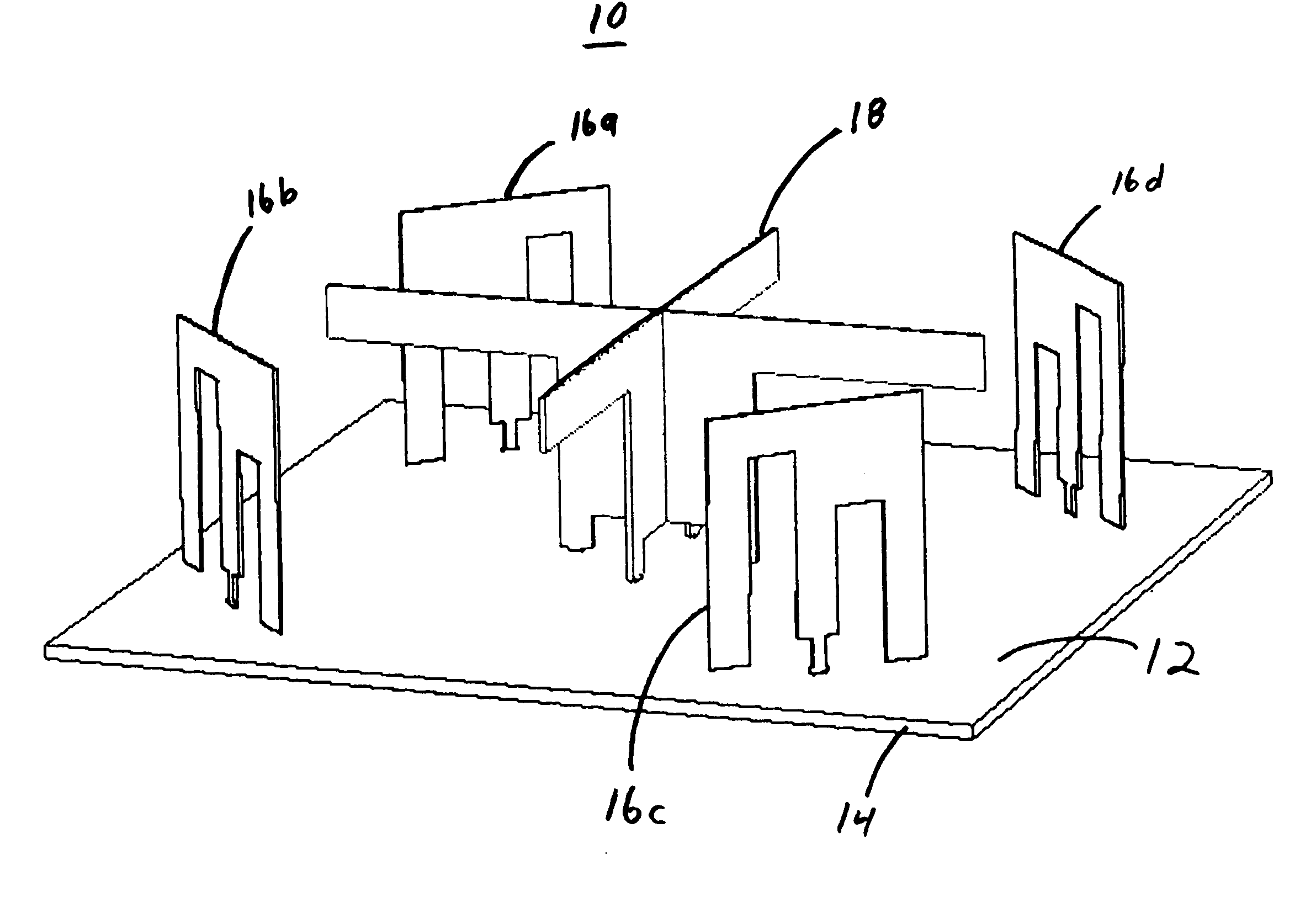

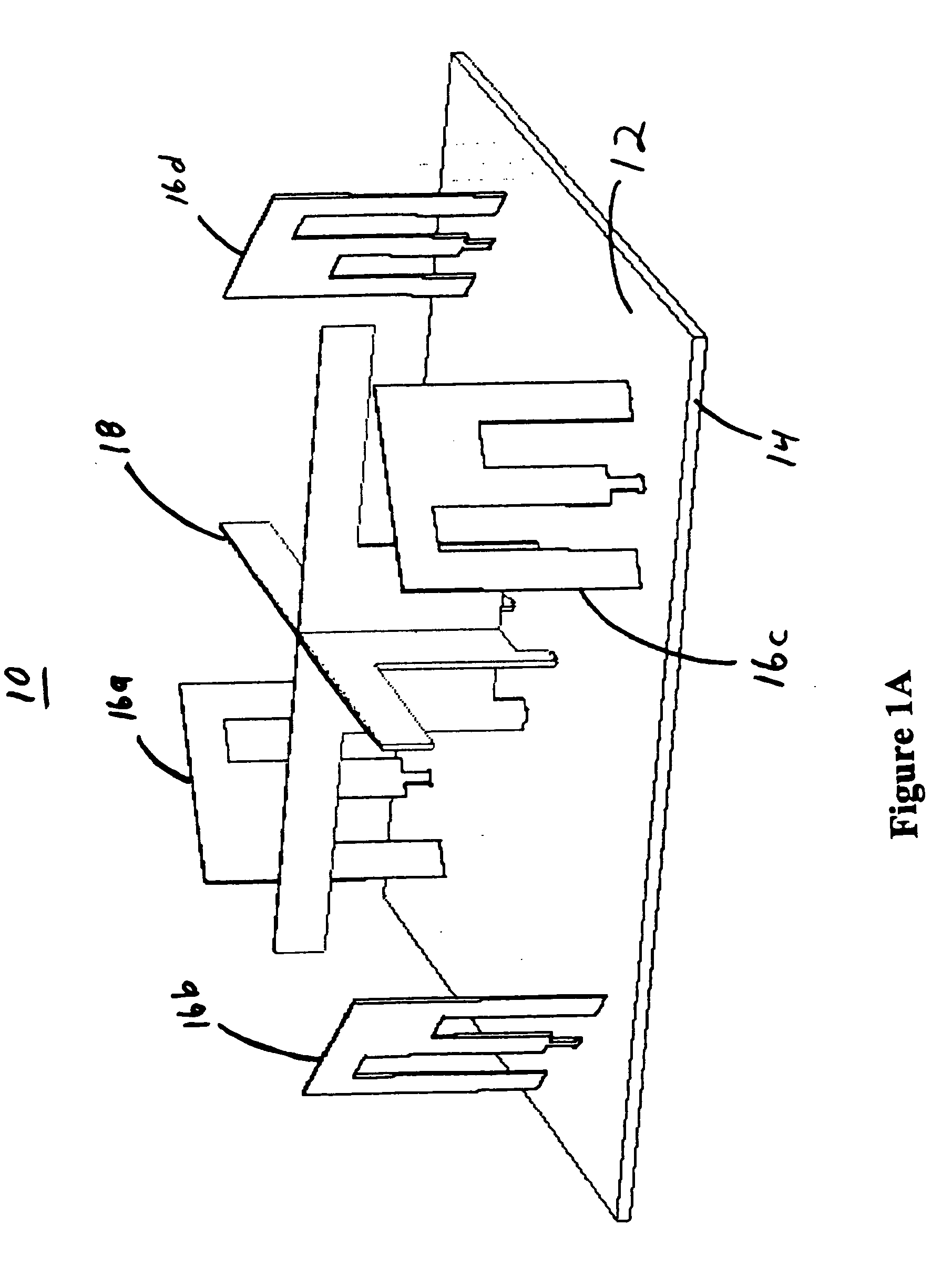

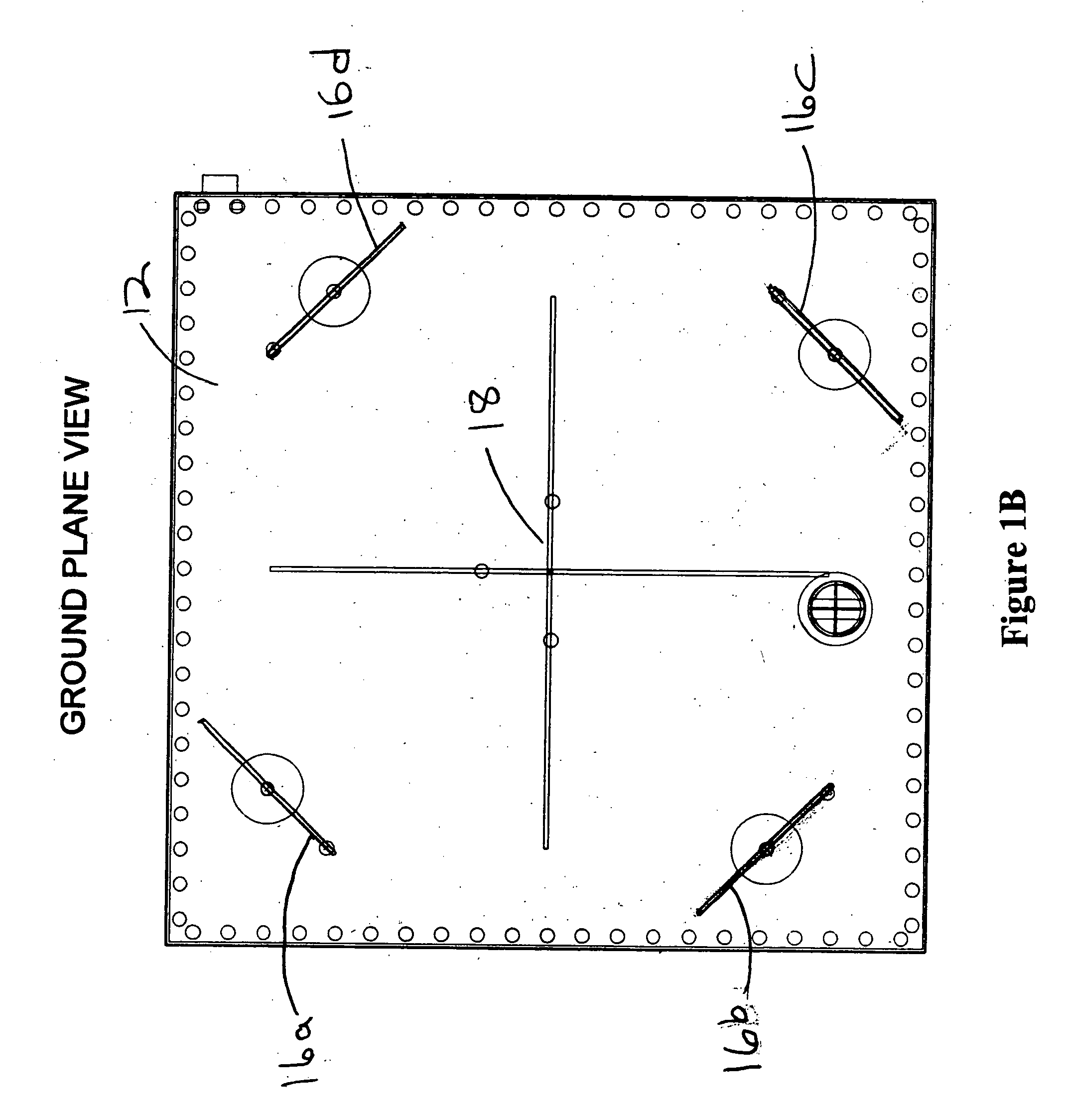

Switched multi-beam antenna

InactiveUS20050237258A1Reduce lossesRadiating elements structural formsAntenna earthingsCapacitanceCapacitive coupling

An antenna assembly includes a common reflector and multiple monopole type antenna elements positioned on a ground plane and fed with a switch assembly. The switch assembly is capable of feeding individual antennas as well as combining multiple antennas for improved radiation pattern coverage. Multiple antenna elements are placed around the common reflector to cover sectors of space around the antenna assembly to provide transmission and reception of radio frequency (RF) signals for mobile communication devices in a wireless network. The ground plane can be grounded or capacitively coupled to an existing circuit board or metal surface, allowing for reduced ground plane dimensions.

Owner:AIRGAIN INC

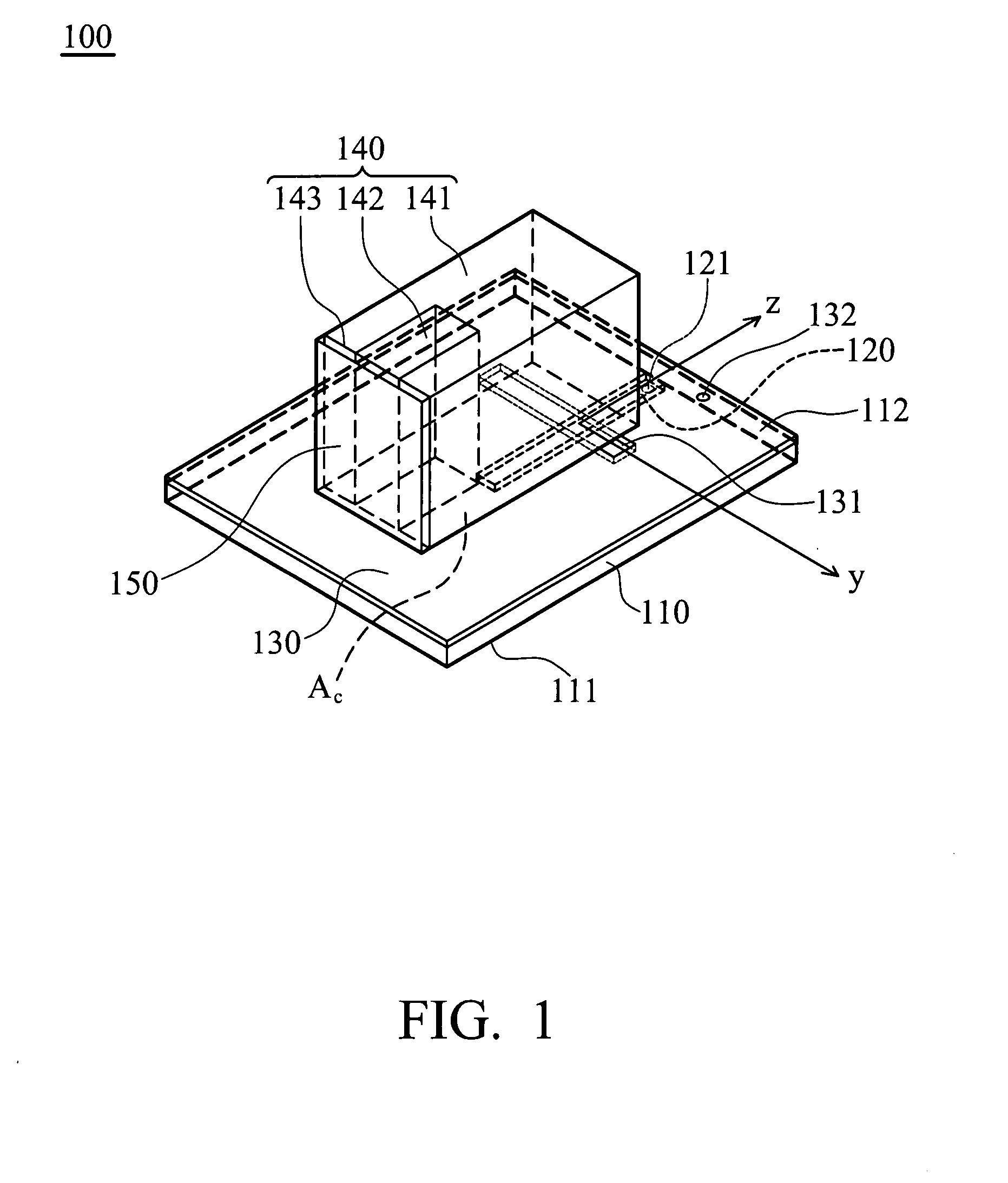

Wideband dielectric resonator antenna

InactiveUS20080278378A1Easy to manufactureReduces attrition rateSimultaneous aerial operationsRadiating elements structural formsDielectric resonator antennaGround plane

Owner:NAT TAIWAN UNIV

Dual Band Stacked Patch Antenna

InactiveUS20090058731A1Reduce manufacturing costHigh gainSimultaneous aerial operationsRadiating elements structural formsDual frequencyDual band antenna

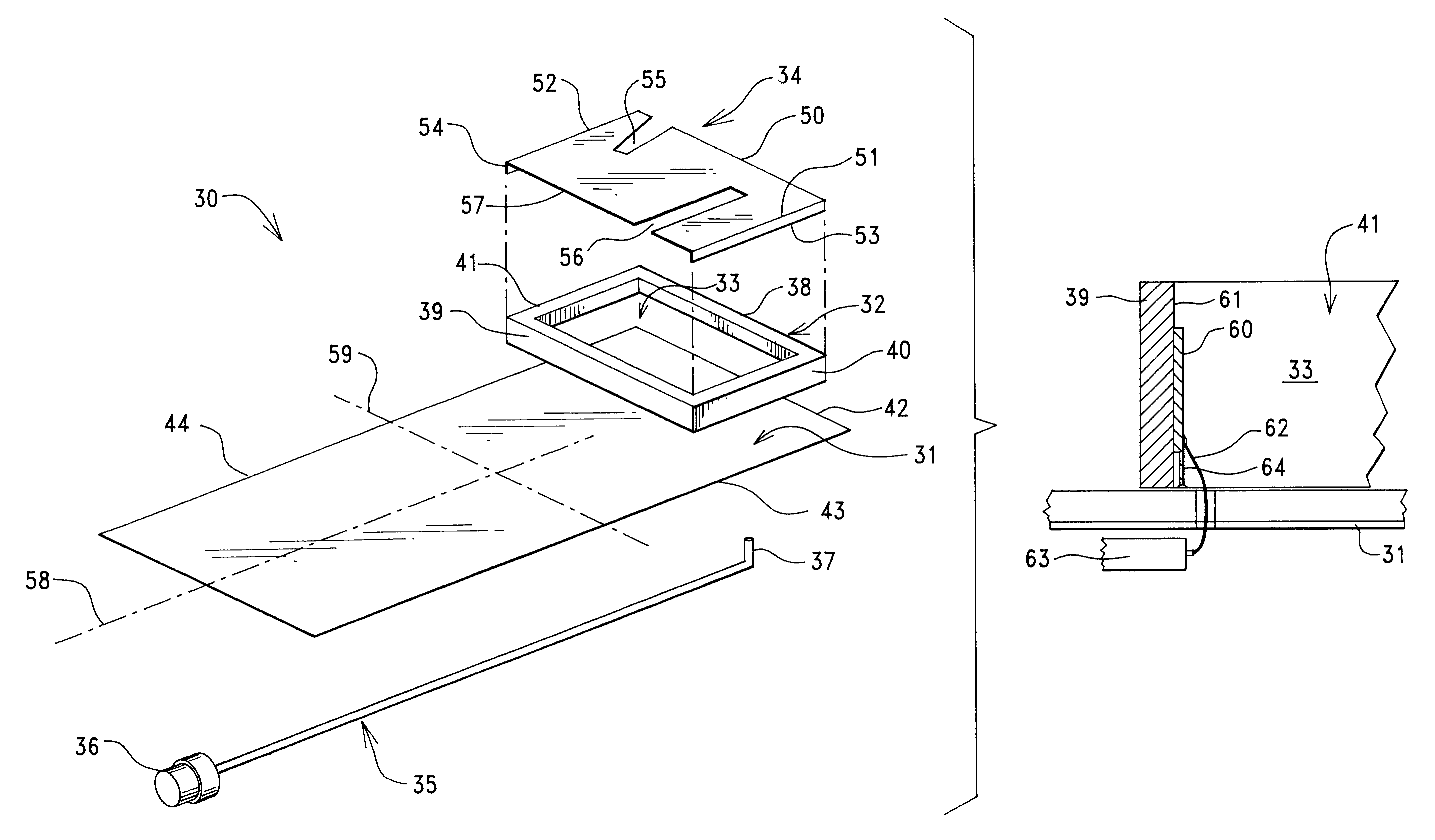

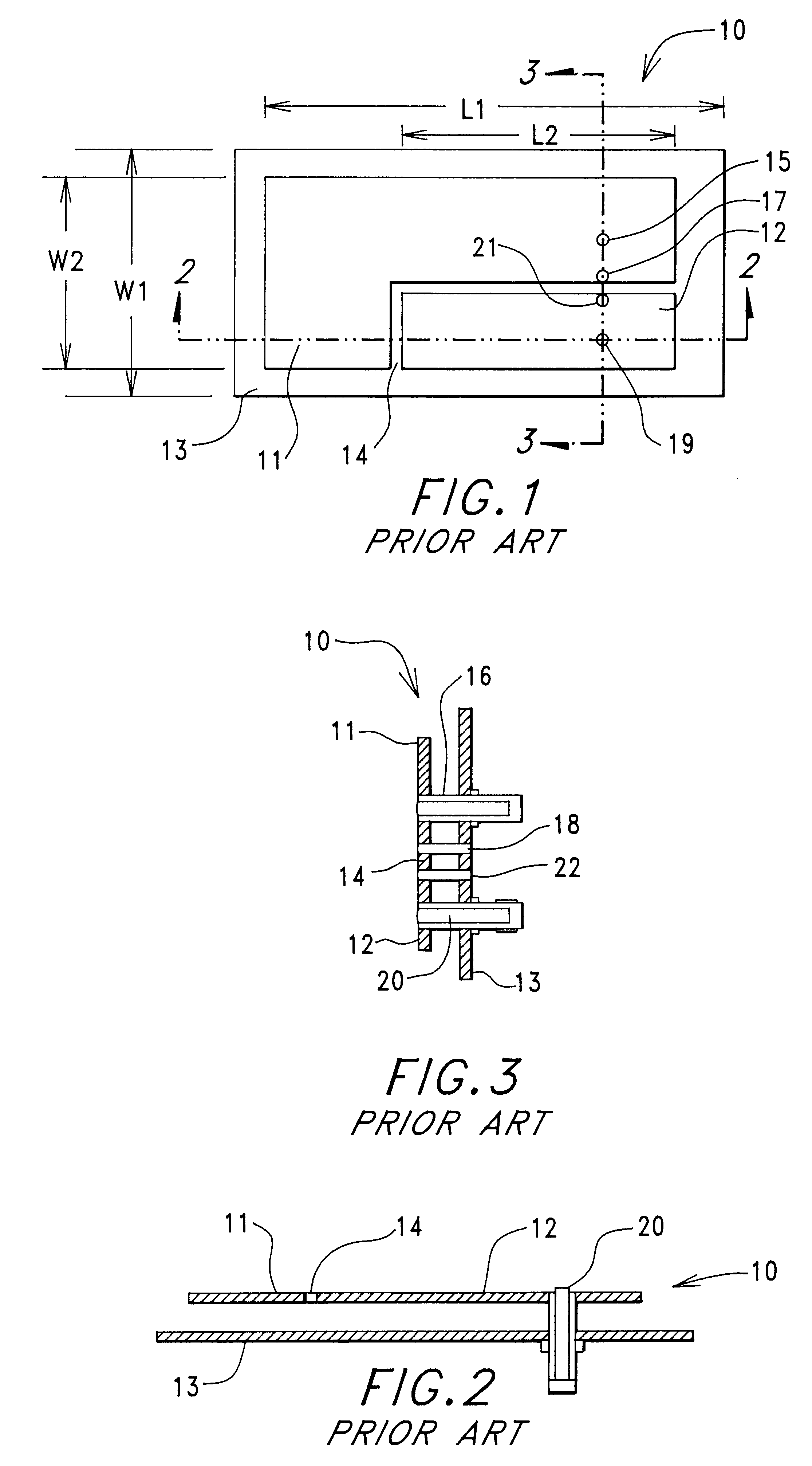

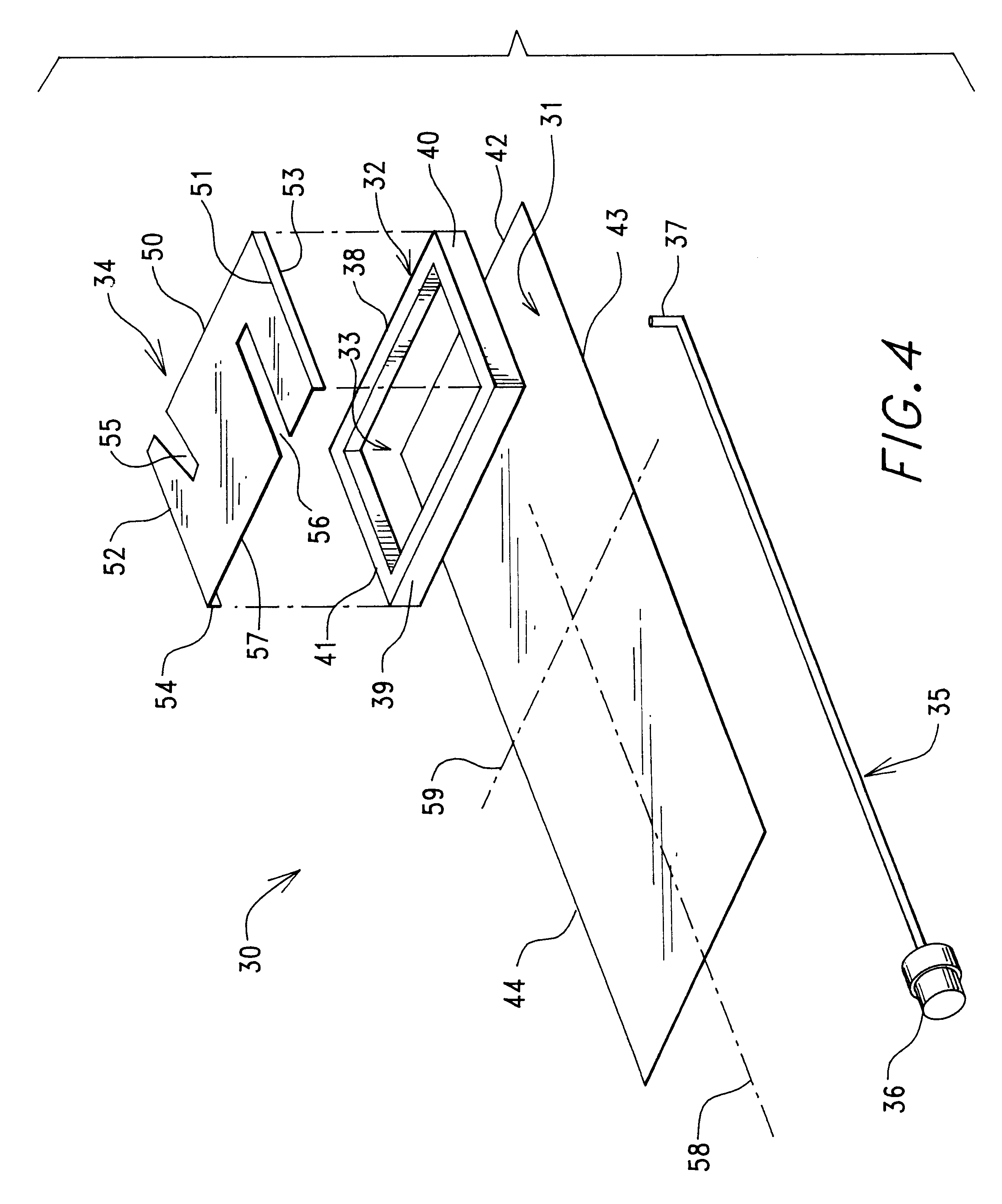

One or more of the embodiments of a dual band stacked patch antenna described herein employ an integrated arrangement of a global positioning system (GPS) antenna and a satellite digital audio radio service (SDARS) antenna. The dual band antenna receives right hand circularly polarized GPS signals in a first frequency band, left hand circularly polarized SDARS signals in a second frequency band, and vertical linear polarized SDARS signals in the second band. The dual band antenna includes a ground plane element, an upper radiating element (which is primarily utilized to receive SDARS signals), dielectric material between the ground plane element and the upper radiating element, and a lower radiating element (which is primarily utilized to receive GPS signals) surrounded by the dielectric material. The dual band antenna uses only one conductive signal feed to receive both GPS and SDARS signals.

Owner:GM GLOBAL TECH OPERATIONS LLC

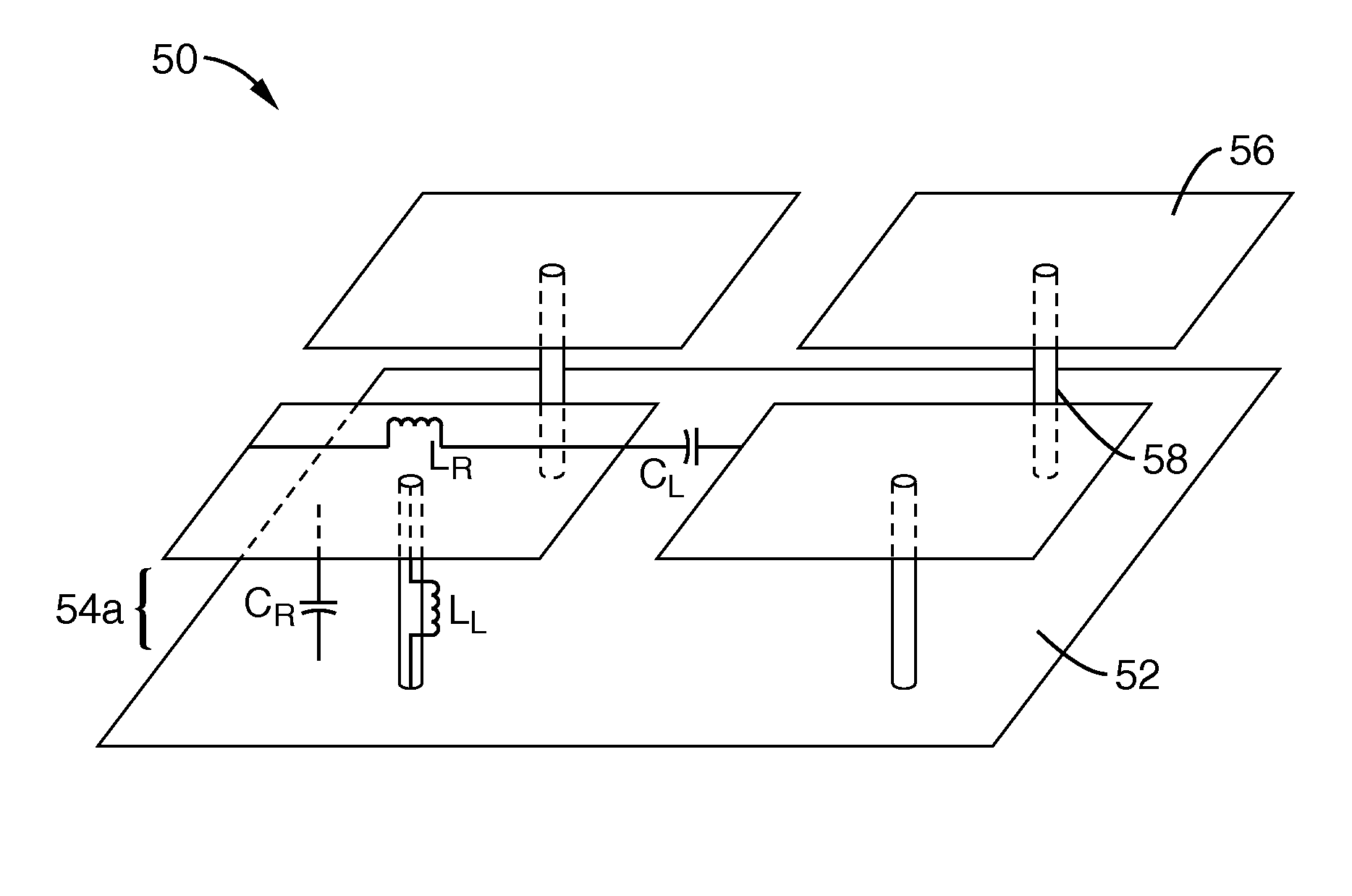

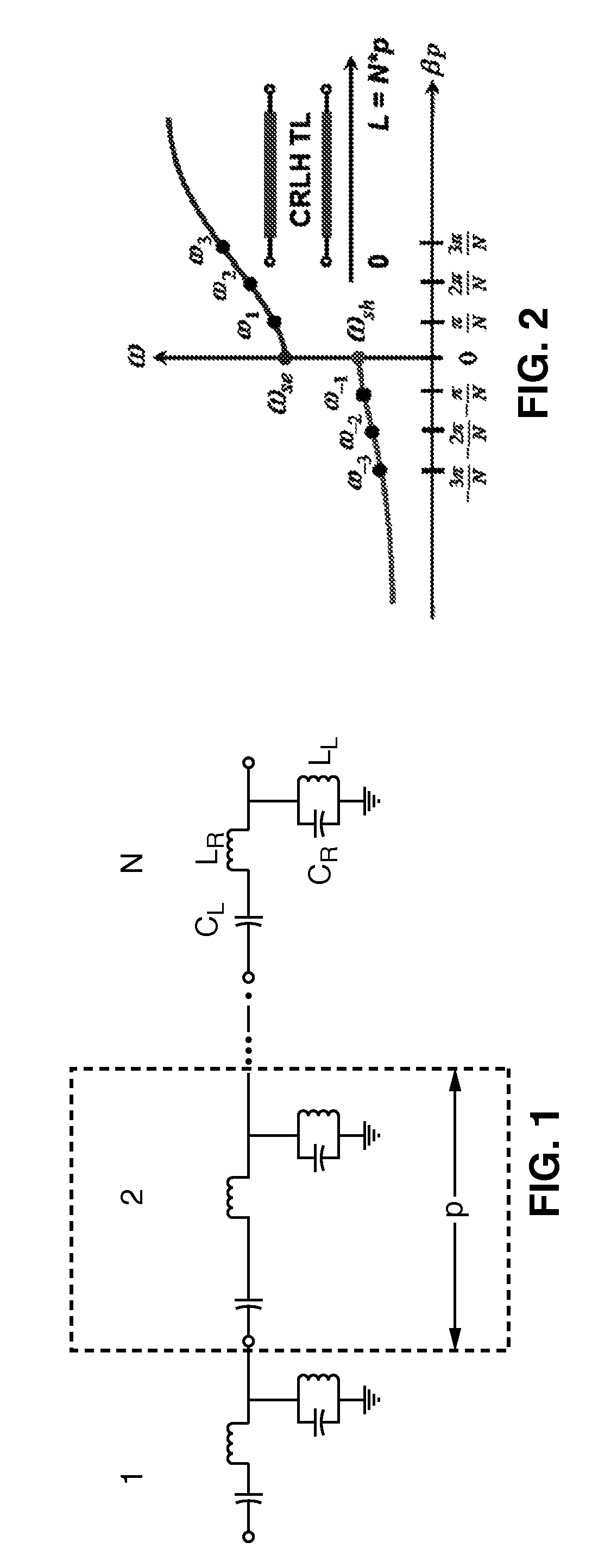

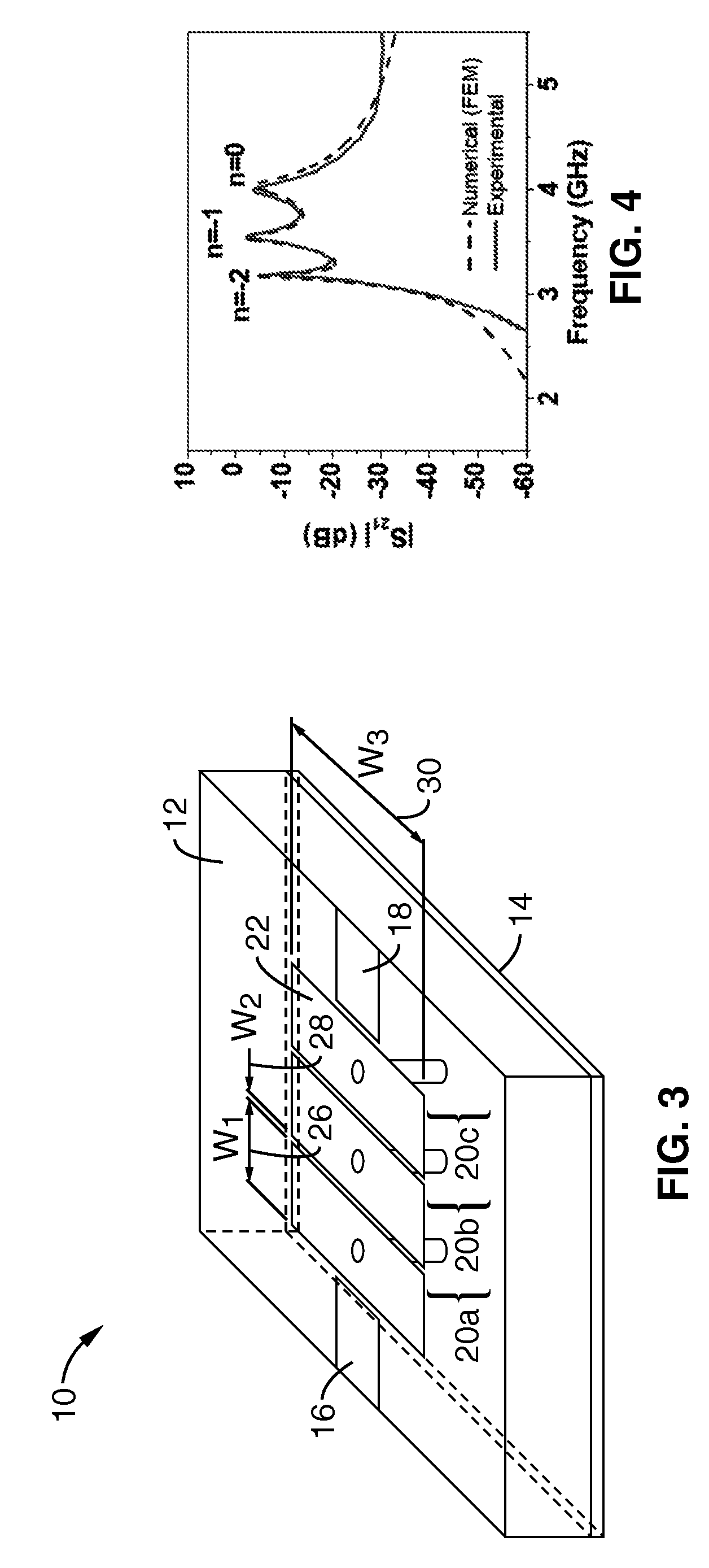

Multi-band radiating elements with composite right/left-handed meta-material transmission line

ActiveUS7911386B1Simultaneous aerial operationsRadiating elements structural formsMulti bandHarmonic

Dual-band and multi-band radiating elements are described based on composite right / left-handed (CRLH) meta-material transmission line (TL). These elements can operate as resonators and / or antennas depending on feed-line configuration. The radiating elements are based on the fundamental backward wave supported by a composite right / left-handed (CRLH) meta-material transmission line (TL). Unit-cells of the transmission line comprise conductive patches coupled through vias to a ground plane. The physical size and operational frequencies of the radiating element is determined by the unit cell of the CRLH meta-material. This radiating element is configured for monopolar radiation at a first resonant frequency and patch-like radiation at a second resonant frequency. The first and second resonant frequencies are not constrained to a harmonic relationship.

Owner:RGT UNIV OF CALIFORNIA

Dual band, low profile omnidirectional antenna

InactiveUS7042403B2Simultaneous aerial operationsAntenna supports/mountingsOmnidirectional antennaDual band antenna

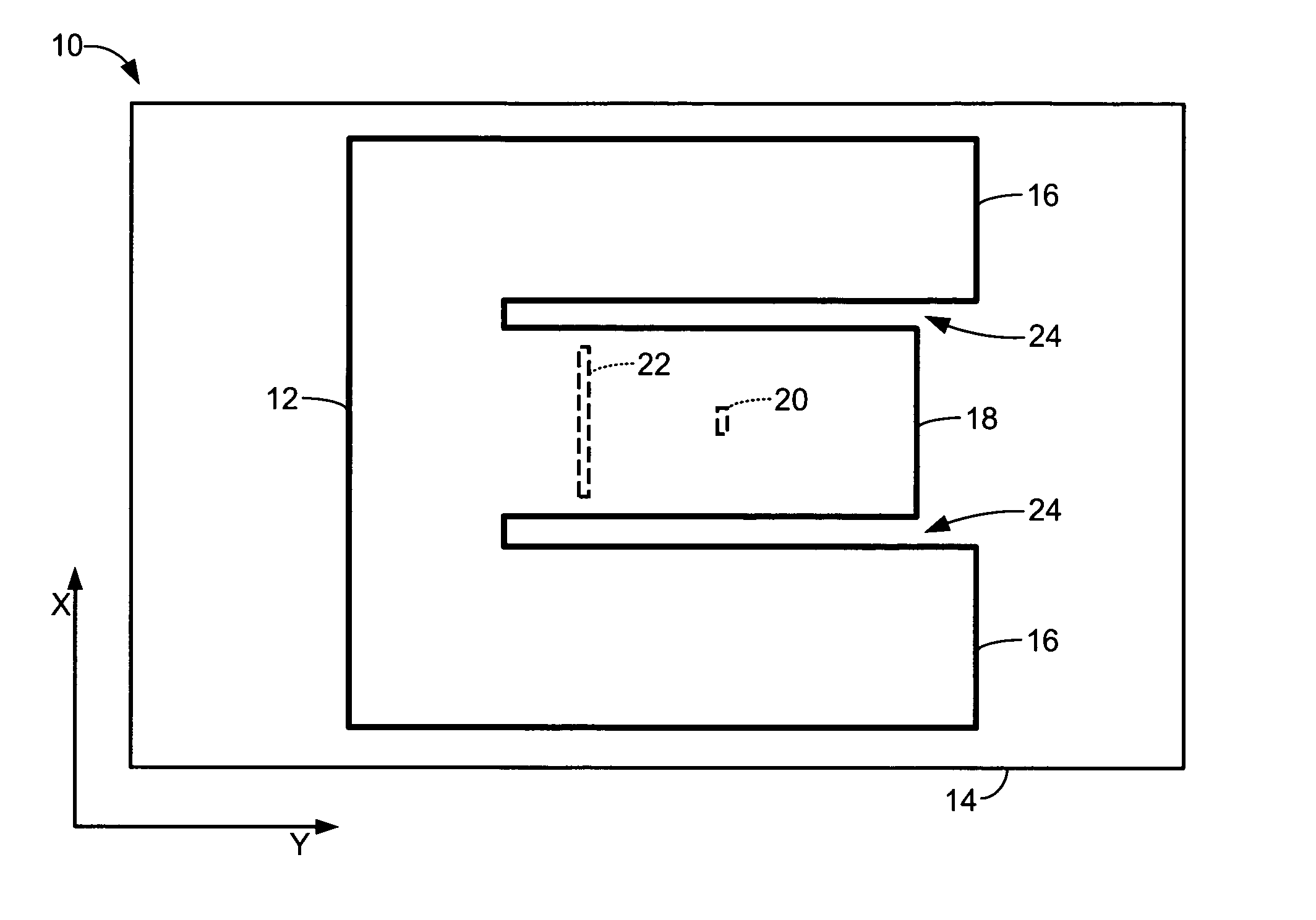

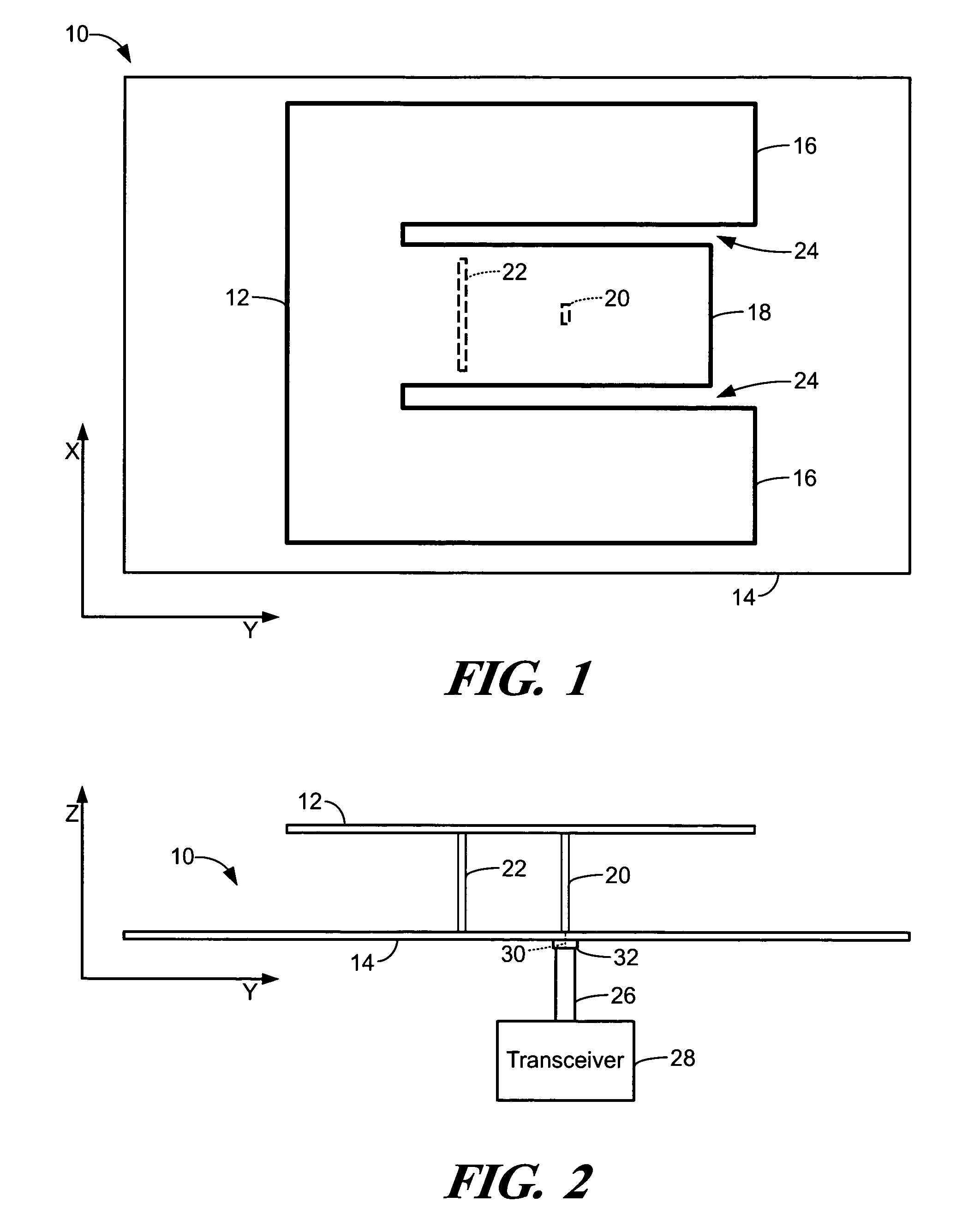

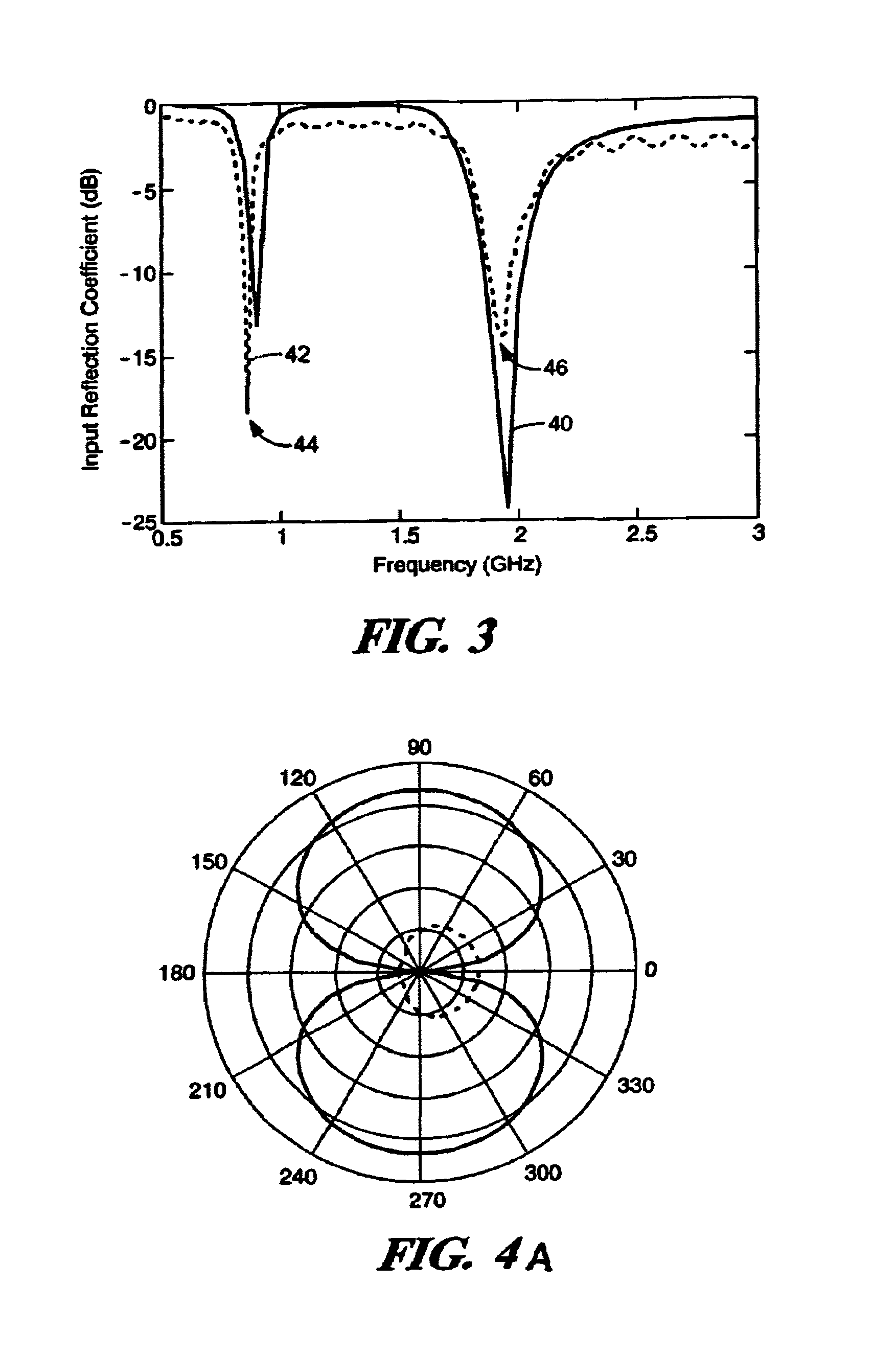

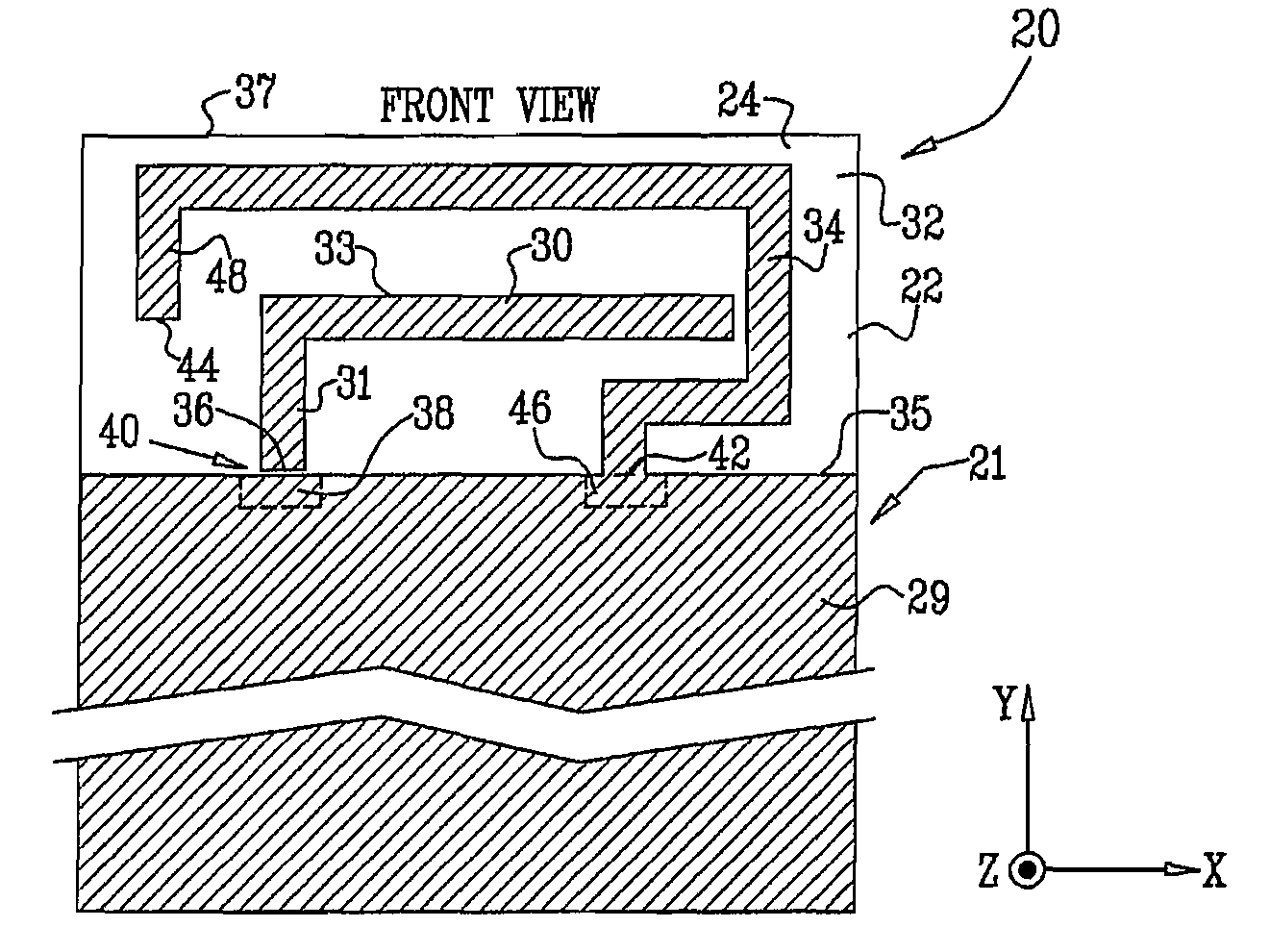

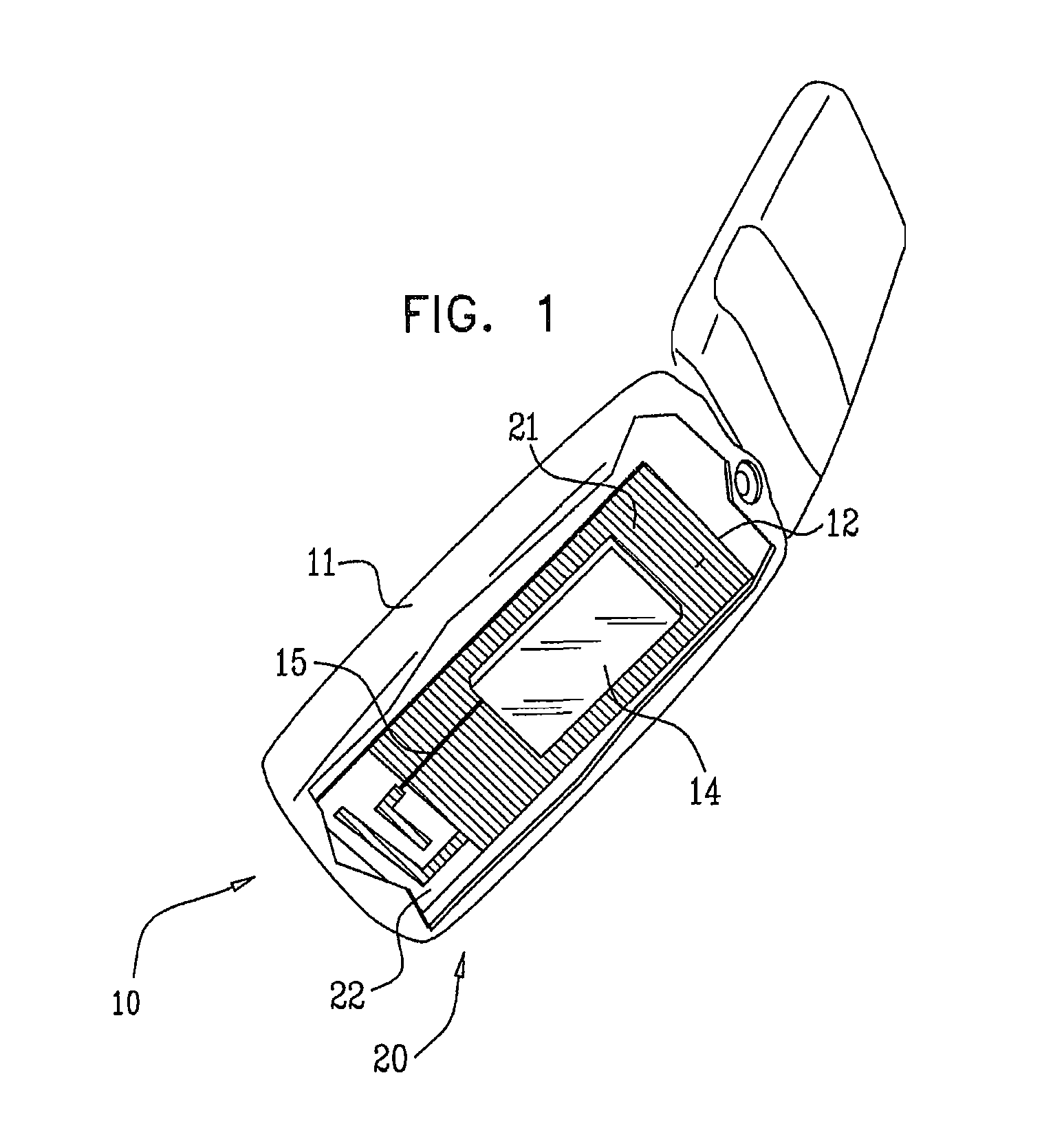

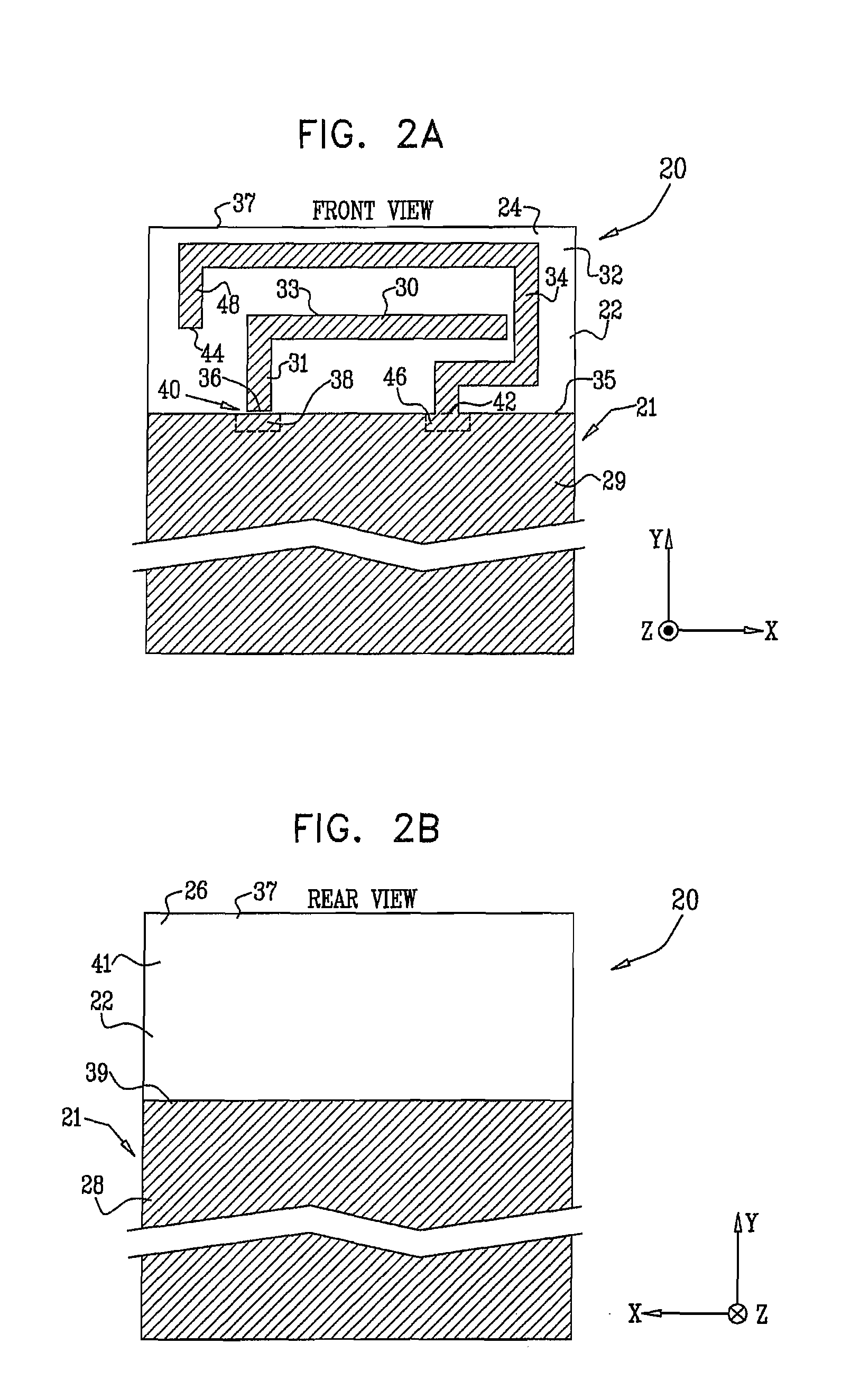

A low-profile dual-band antenna includes a ground plane. An “E”-shaped metal plate is located a first distance from the ground plane and includes first and second outer extensions and an inner extension of the metal plate. A feed tab connects the inner extension and the ground plane. A shorting tab connects the inner extension and the ground plane. The low-profile dual-band antenna communicates first radio frequency (RF) signals in a first RF band and second RF signals in a second RF band. The first RF signals and the second RF signals are vertical polarized signals. The low-profile dual-band antenna produces a radiation pattern that is omnidirectional in the azimuth plane and vertically polarized in a horizontal plane when communicating the first RF signals and the second RF signals. The first RF band and the second RF band can be independently tuned.

Owner:GM GLOBAL TECH OPERATIONS LLC

Wideband circularly polarized hybrid dielectric resonator antenna

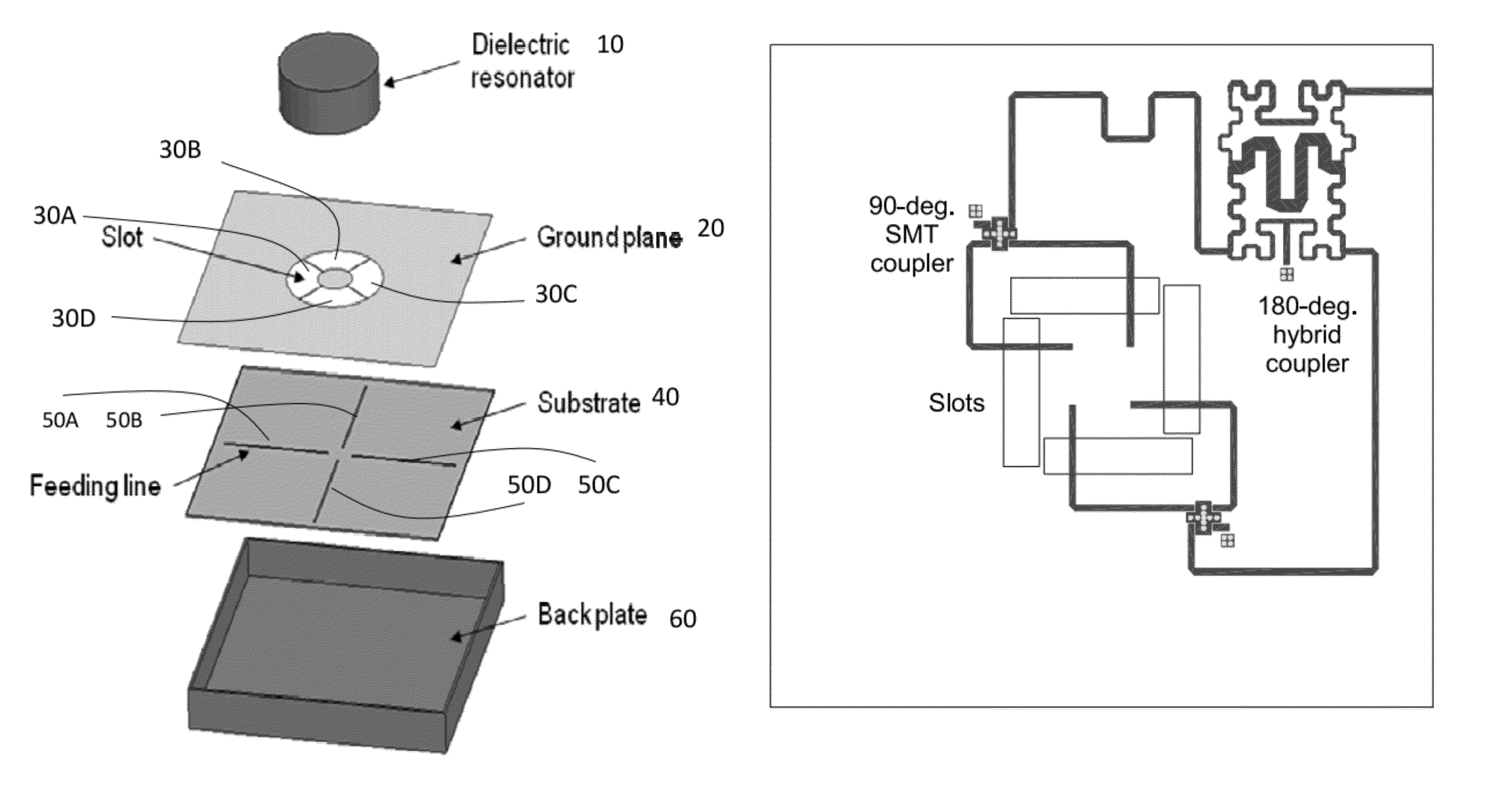

ActiveUS8928544B2High bandwidthCompact geometryAntenna supports/mountingsAntennas earthing switches associationDielectric resonator antennaPhase difference

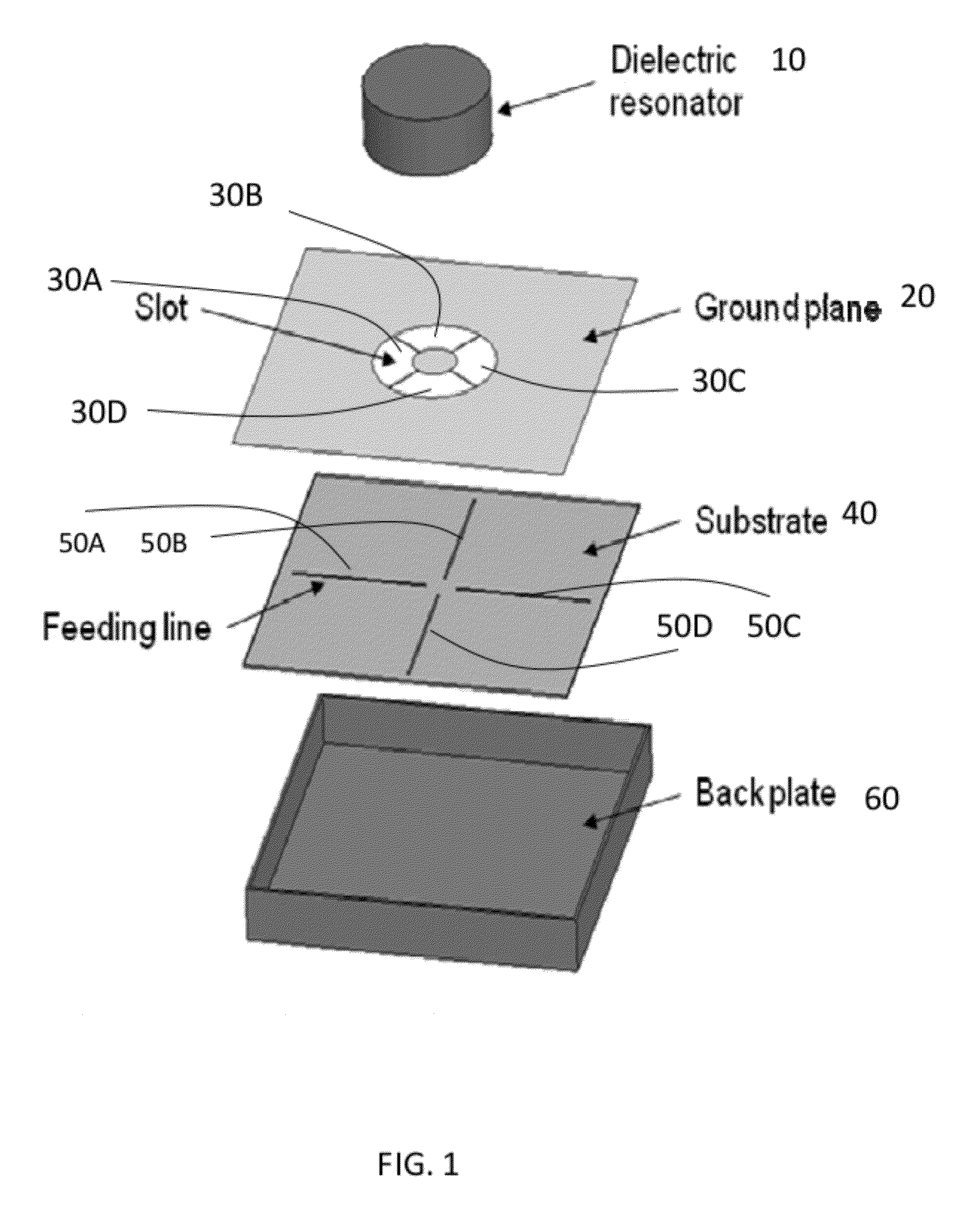

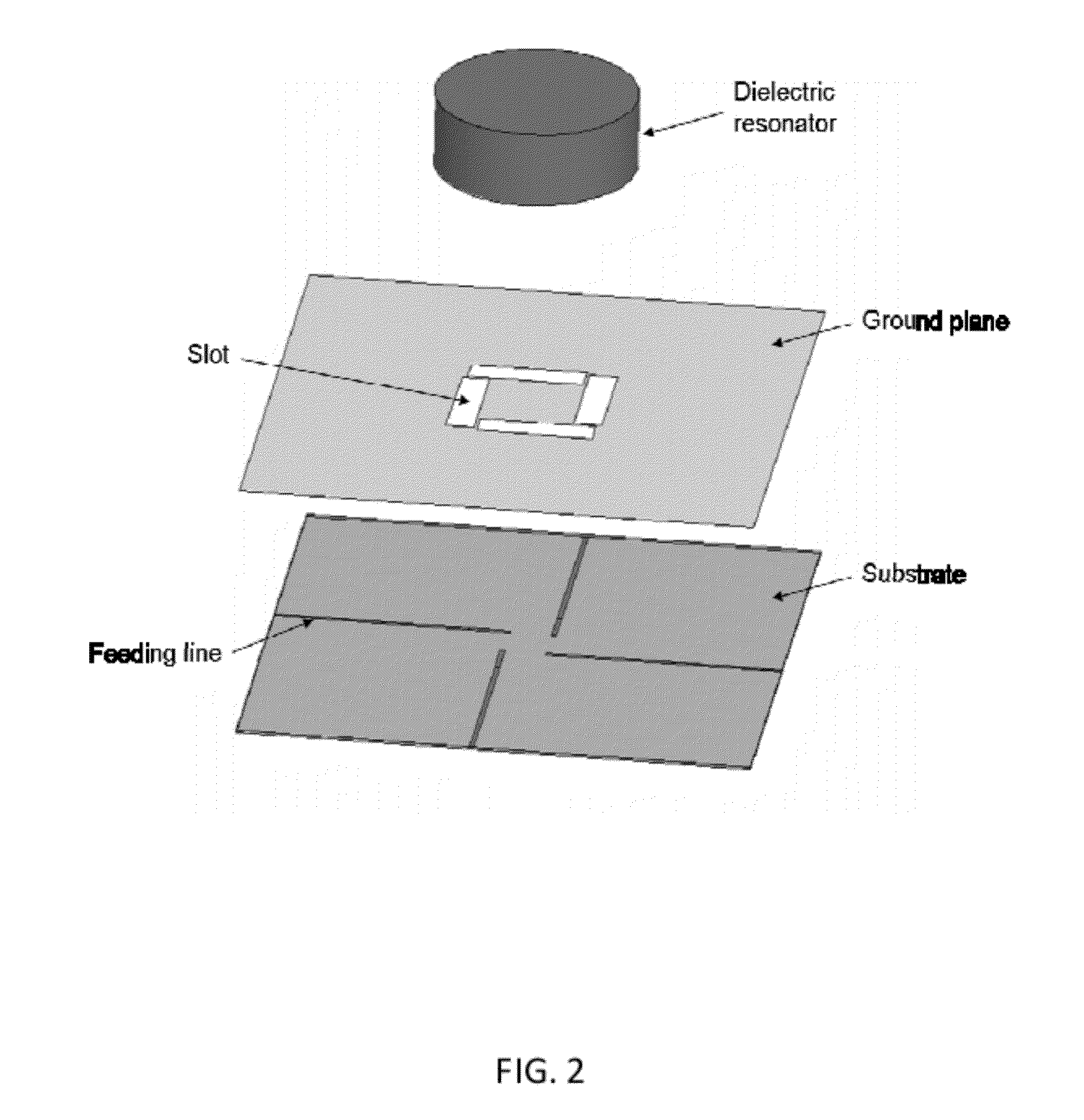

The present invention provides a dielectric resonator antenna comprising: a dielectric resonator; a ground plane, operatively coupled with the dielectric resonator, the ground plane having four slots; and a substrate, operatively coupled to the ground plane, having a feeding network consisting of four microstrip lines; wherein the four slots are constructed and geometrically arranged to ensure proper circular polarization and coupling to the dielectric resonator; and wherein the antenna feeding network combines the four microstrip lines with a 90 degree phase difference to generate circular polarization over a wide frequency band.

Owner:HER MAJESTY THE QUEEN AS REPRESENTED BY THE MINIST OF NAT DEFENCE OF HER MAJESTYS CANADIAN GOVERNMENT

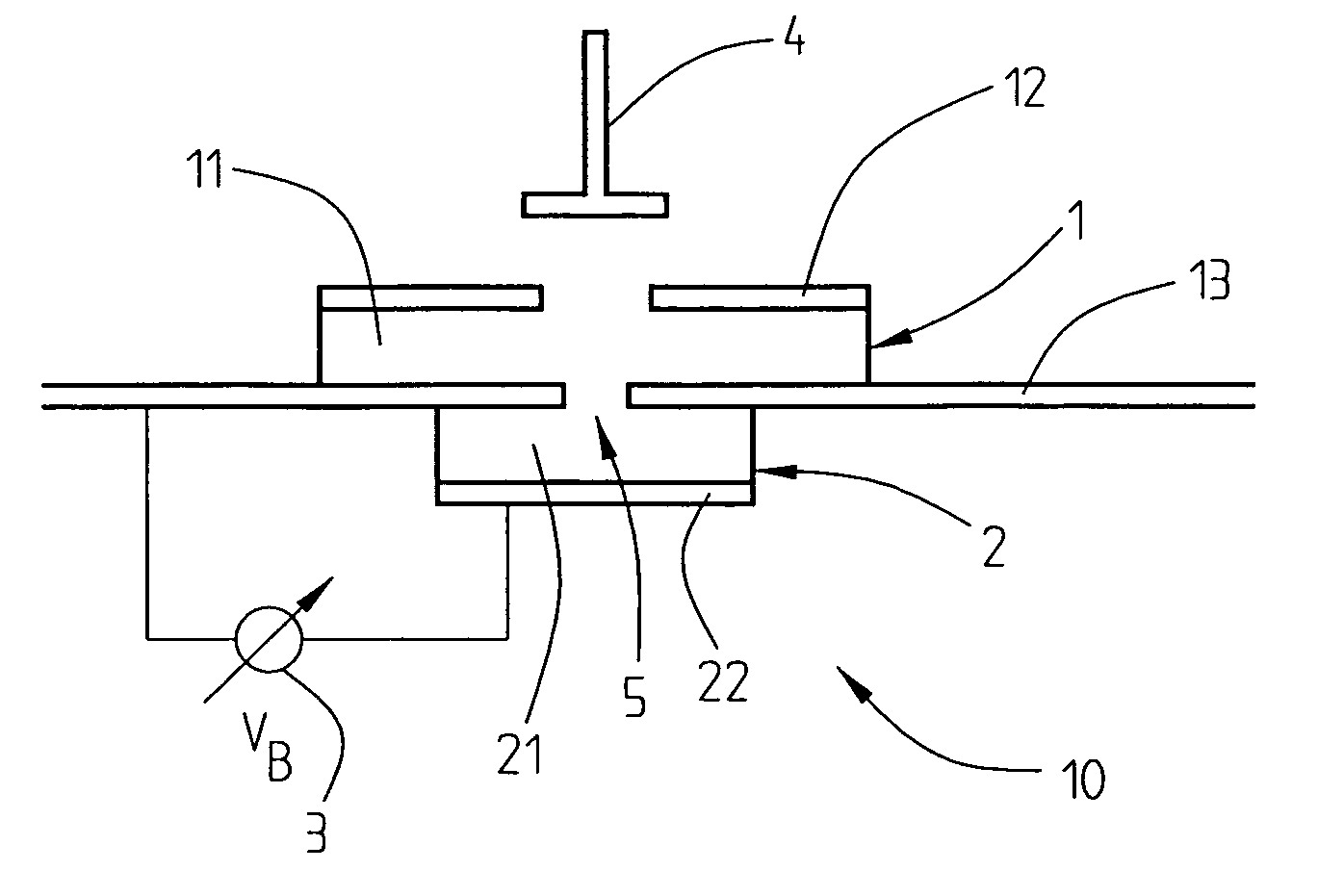

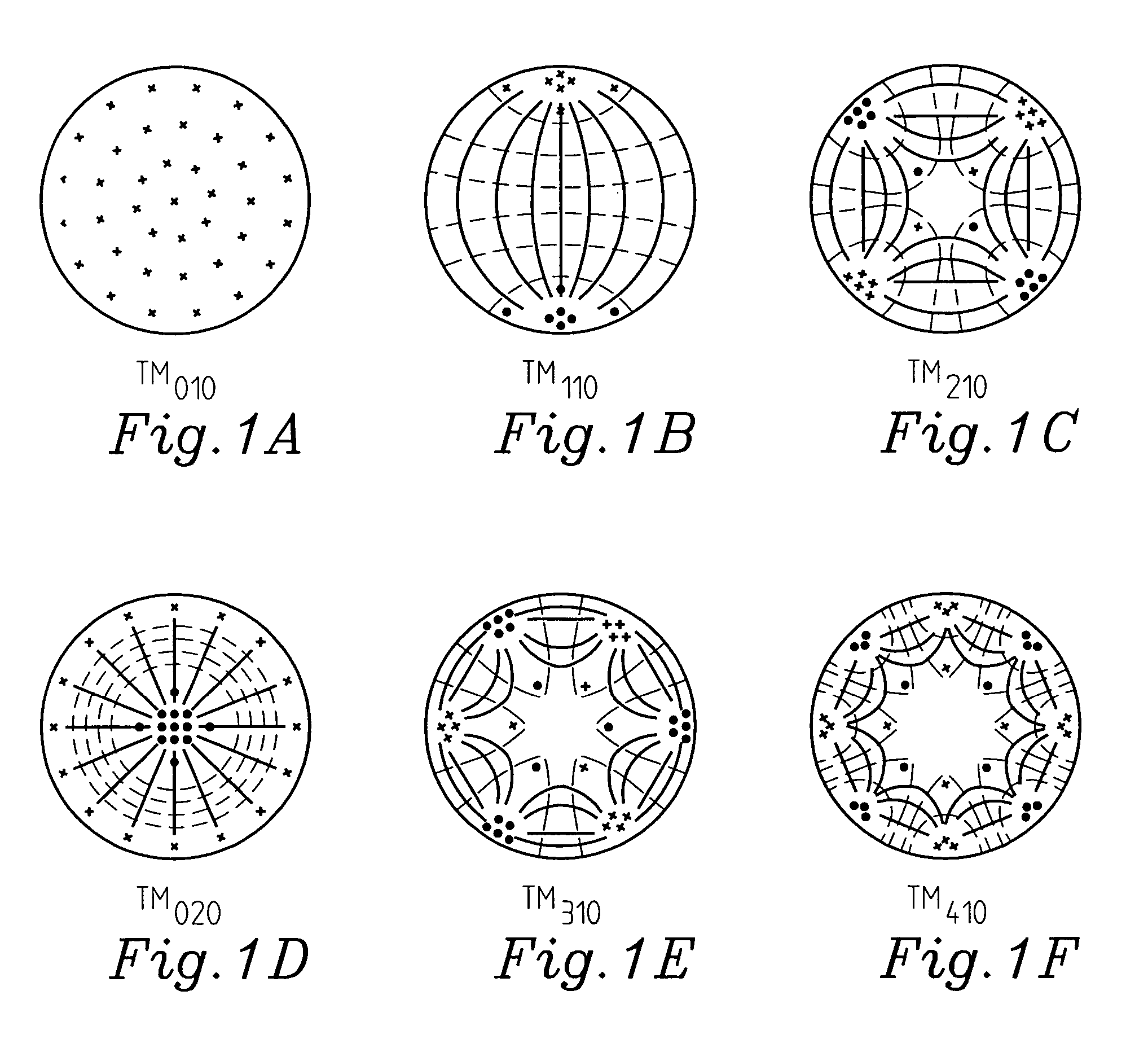

Electromagnetic coupling

InactiveUS6850128B2Improve power performanceLow profileMultiple-port networksOne-port networksElectricityElectromagnetic coupling

An orthogonal electrical coupling relies on electromagnetic coupling for the inner connection, as opposed to direct contact between conductors. A conductor on one of the lines is connected to a ground plane which is adjacent to a resonant slot. Microwave energy is coupled to the slot, thereby exciting the slot. A second conductor is on the opposite side of the ground plane from the first conductor. Microwave energy from the excited resonant slot passes to the second conductor, thereby allowing contactless interconnection between the first conductor and the second conductor. The coupling may emphasize certain modes of propagation relative to other possible modes of propagation. Specifically, the ground plane and slot may be enclosed in a cavity of a size such that the cavity does not support any natural mode propagation inside the cavity. Instead, the coupling may have a cavity in which a transverse electromagnetic (TEM) mode is propagated.

Owner:RAYTHEON CO

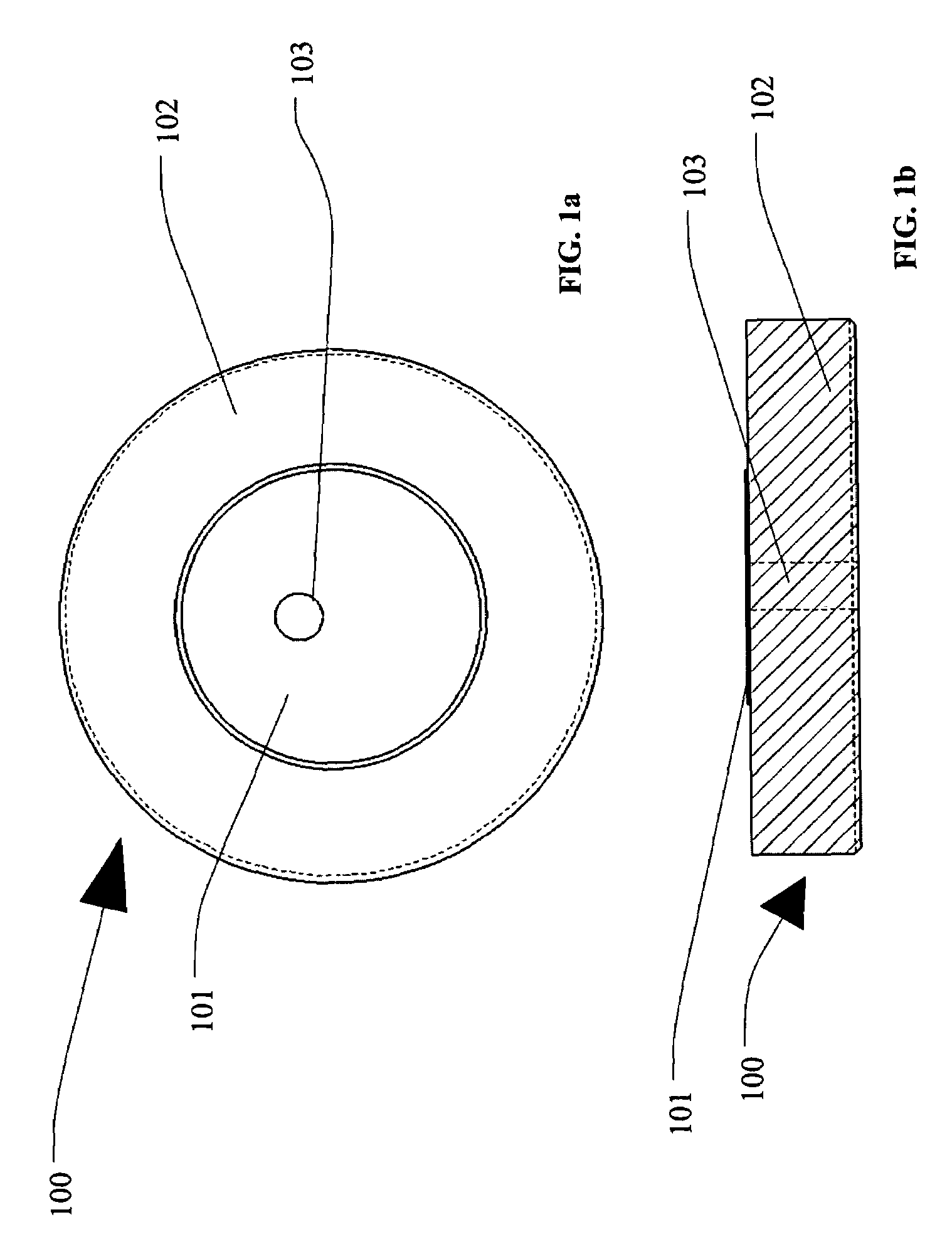

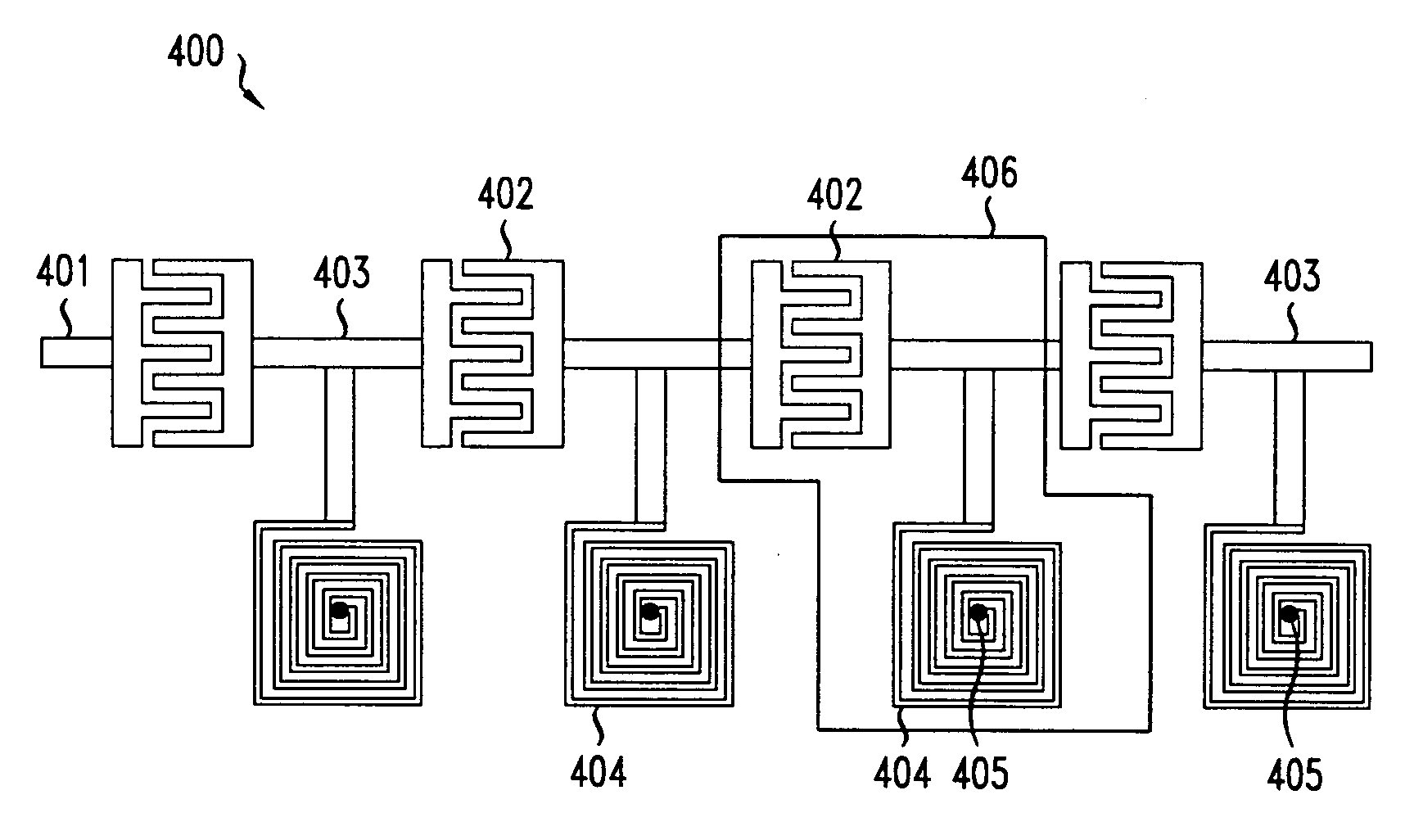

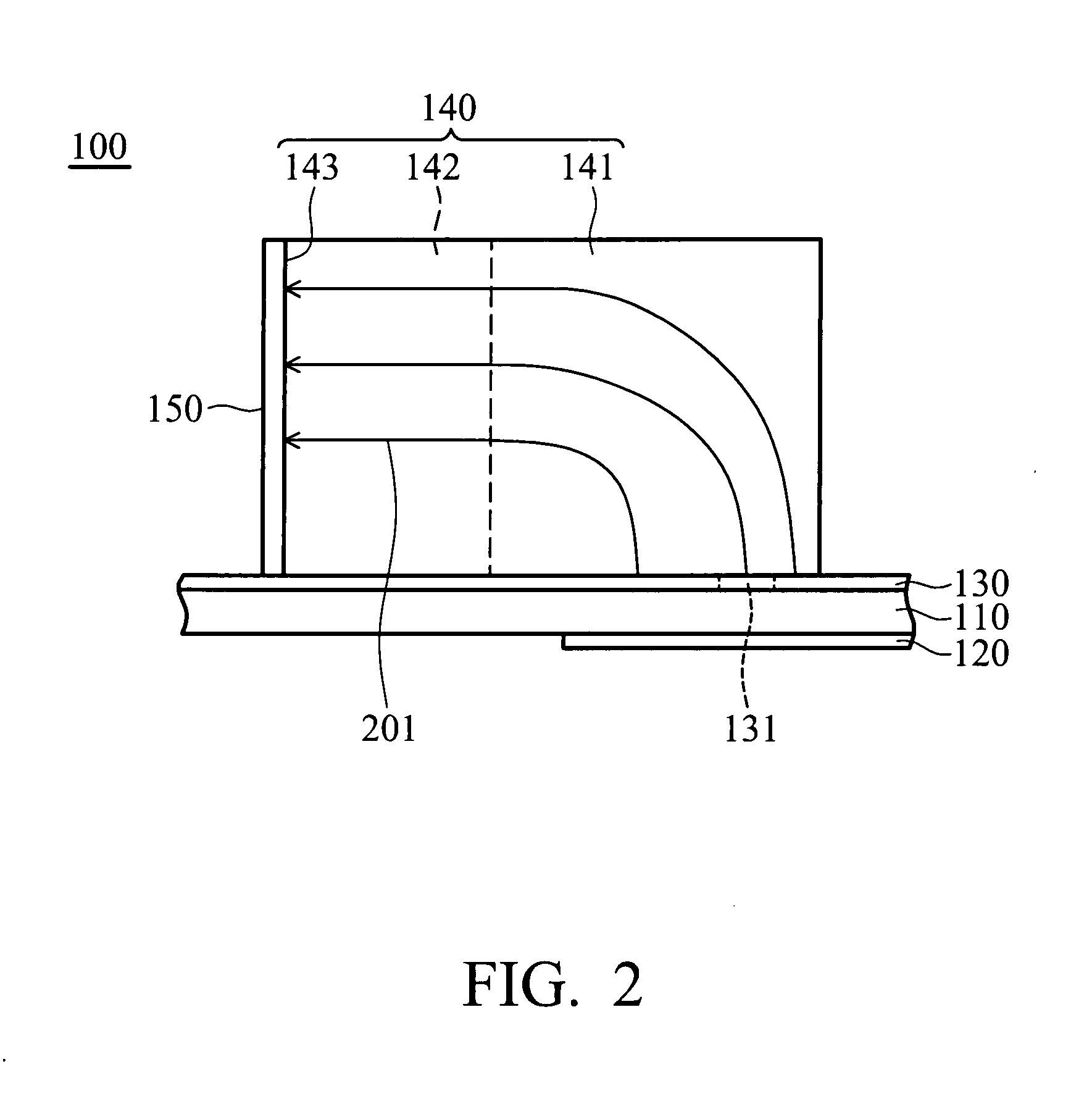

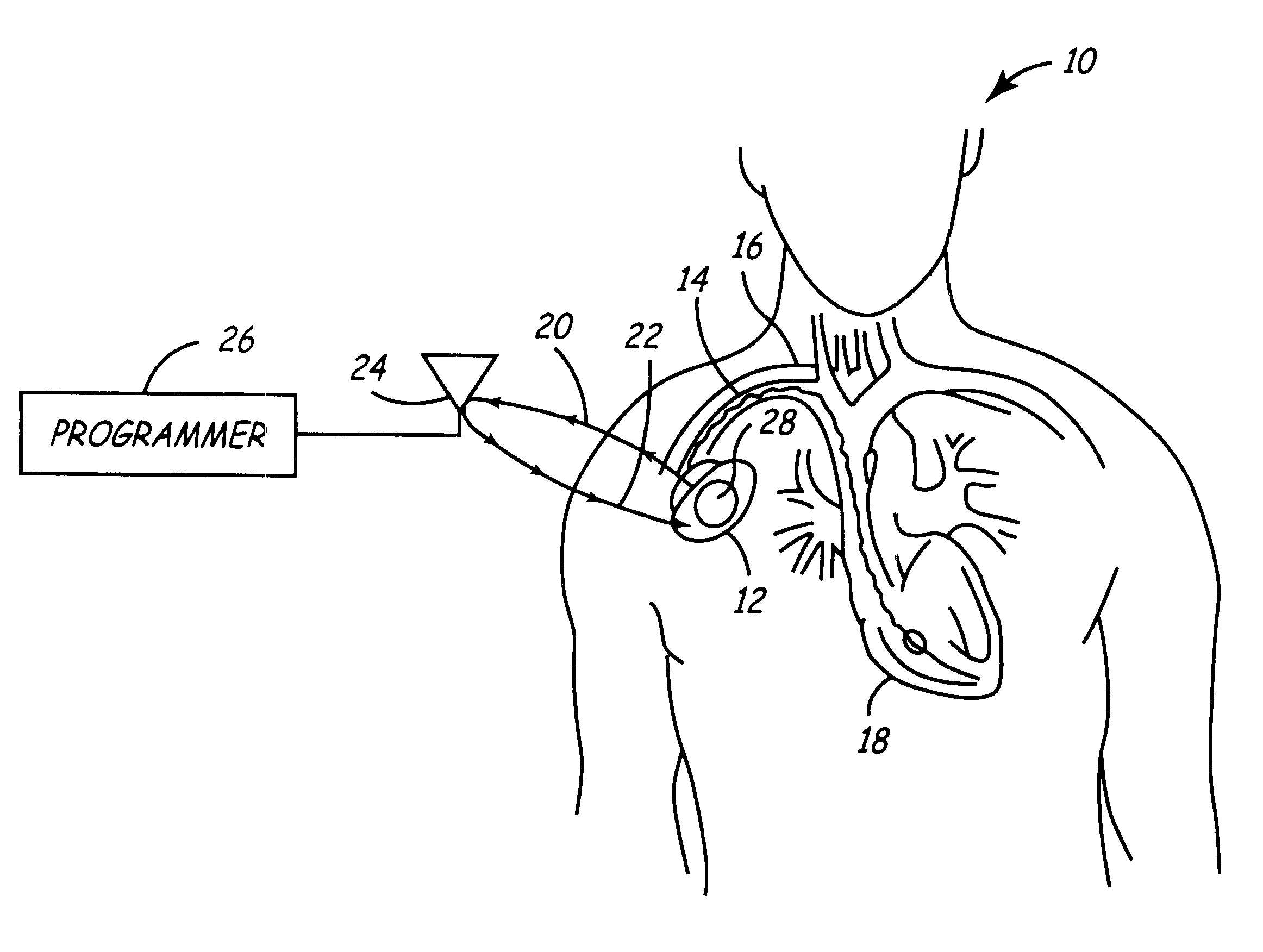

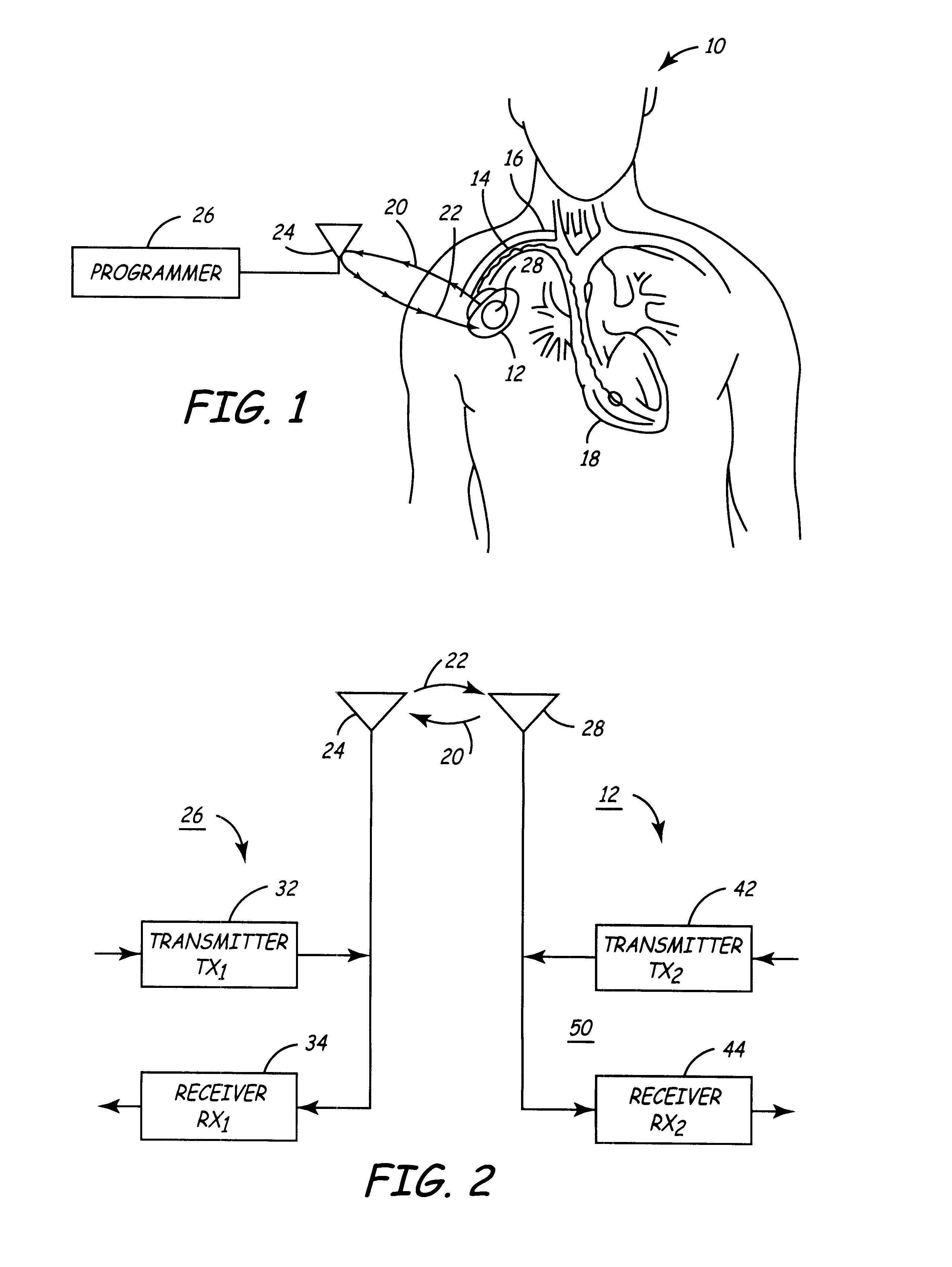

Implantable medical device incorporating miniaturized circuit module

Implantable medical devices (IMDS) having RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming commands to and from an external programmer having an improved RF module configured to occupy small spaces within the IMD housing to further effect the miniaturization thereof. An RF module formed of an RF module substrate and at least one IC chip and discrete components has a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include: (1) integrating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The integrated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the RF module substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

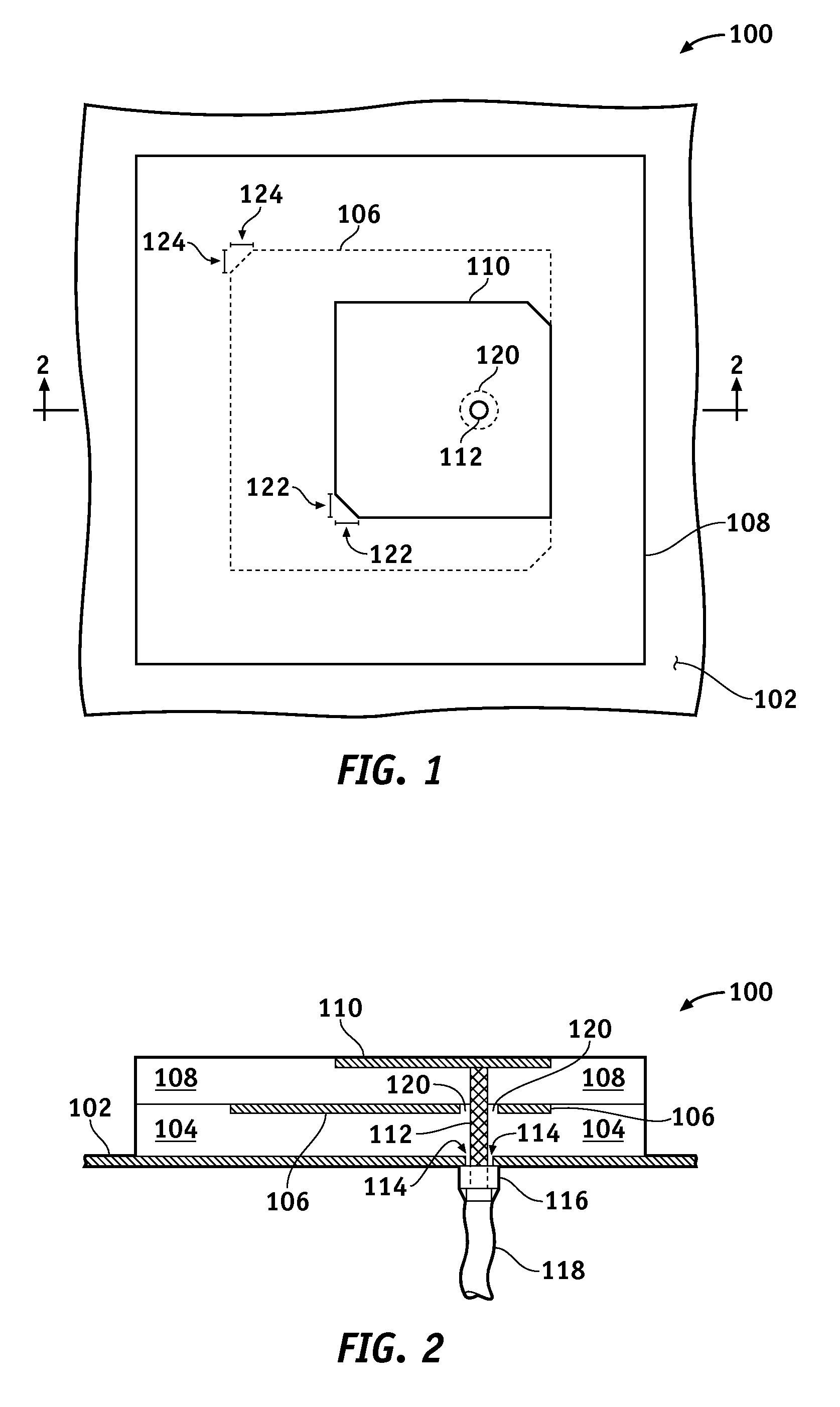

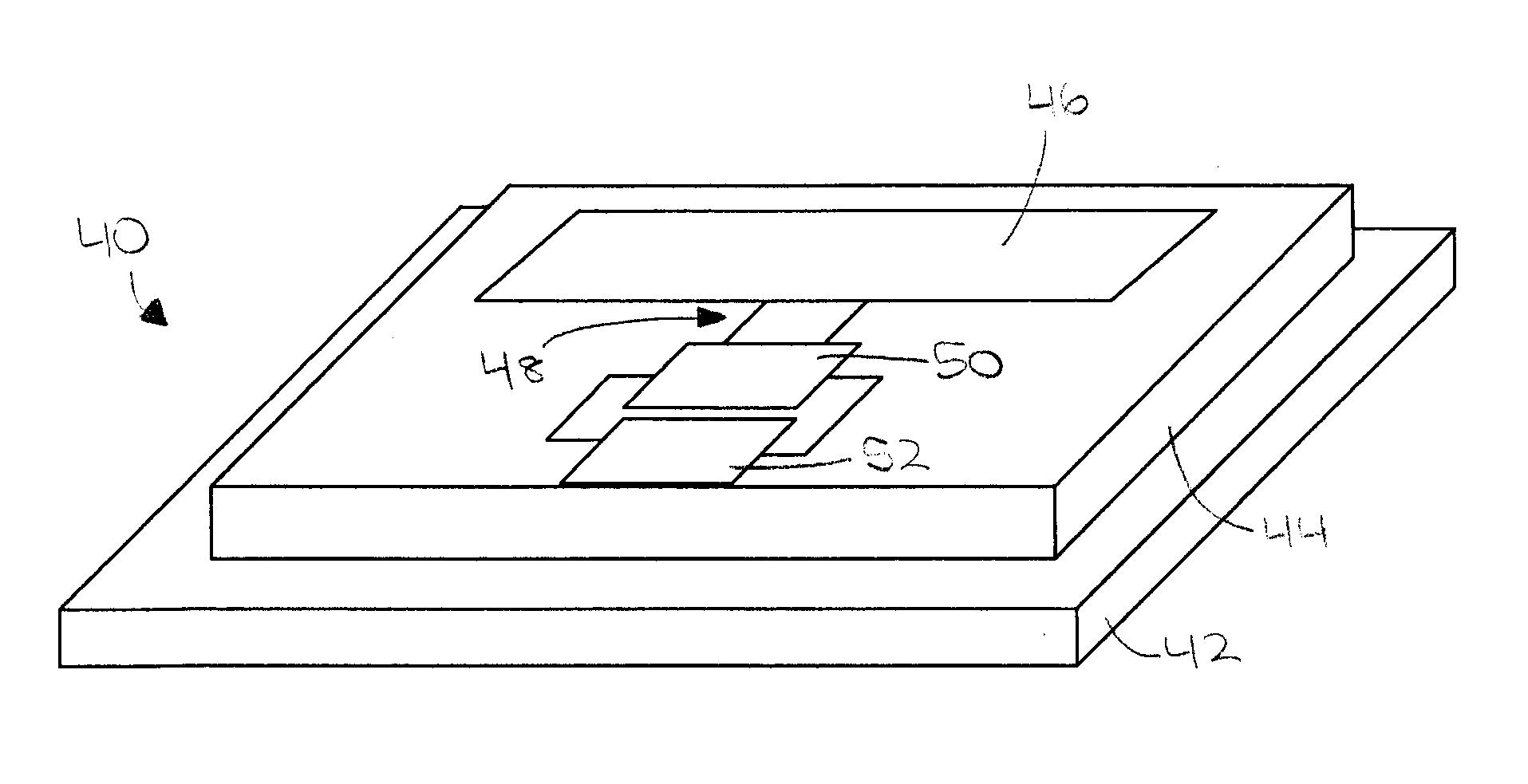

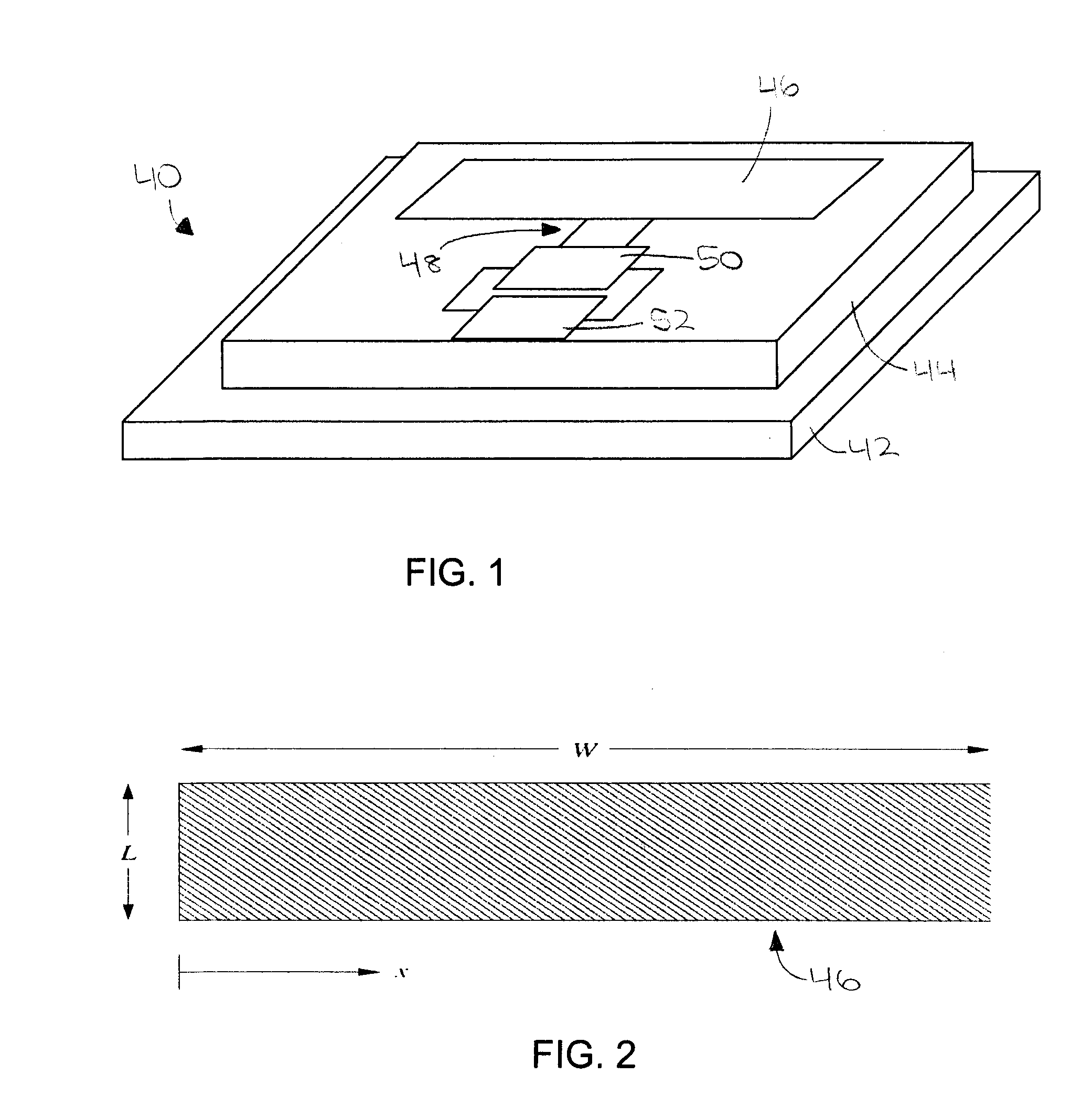

Microstrip antenna for RFID device

InactiveUS20070164868A1Low costEliminate needSimultaneous aerial operationsAntenna supports/mountingsMicrostrip patch antennaAntenna design

Microstrip patch antenna (46), feed structure (48), and matching circuit (50) designs for an RFID tag (10). A balanced feed design using balanced feeds coupled by a shorting stub (56) to create a virtual short between the two feeds so as to eliminate the need for physically connecting substrate to the ground plane. A dual feed structure design using a four-terminal IC can be connected to two antennas (46a,46b) resonating at different frequencies so as to provide directional and polarization diversity. A combined near / field-far / field design using a microstrip antenna providing electromagnetic coupling for far-field operation, and a looping matching circuit providing inductive coupling for near-field operation. A dual-antenna design using first and second microstrip antennas providing directional diversity when affixed to a cylindrical or conical object, and a protective superstrate (66). An annual antenna (46c) design for application to the top of a metal cylinder around a stem.

Owner:UNIVERSITY OF KANSAS

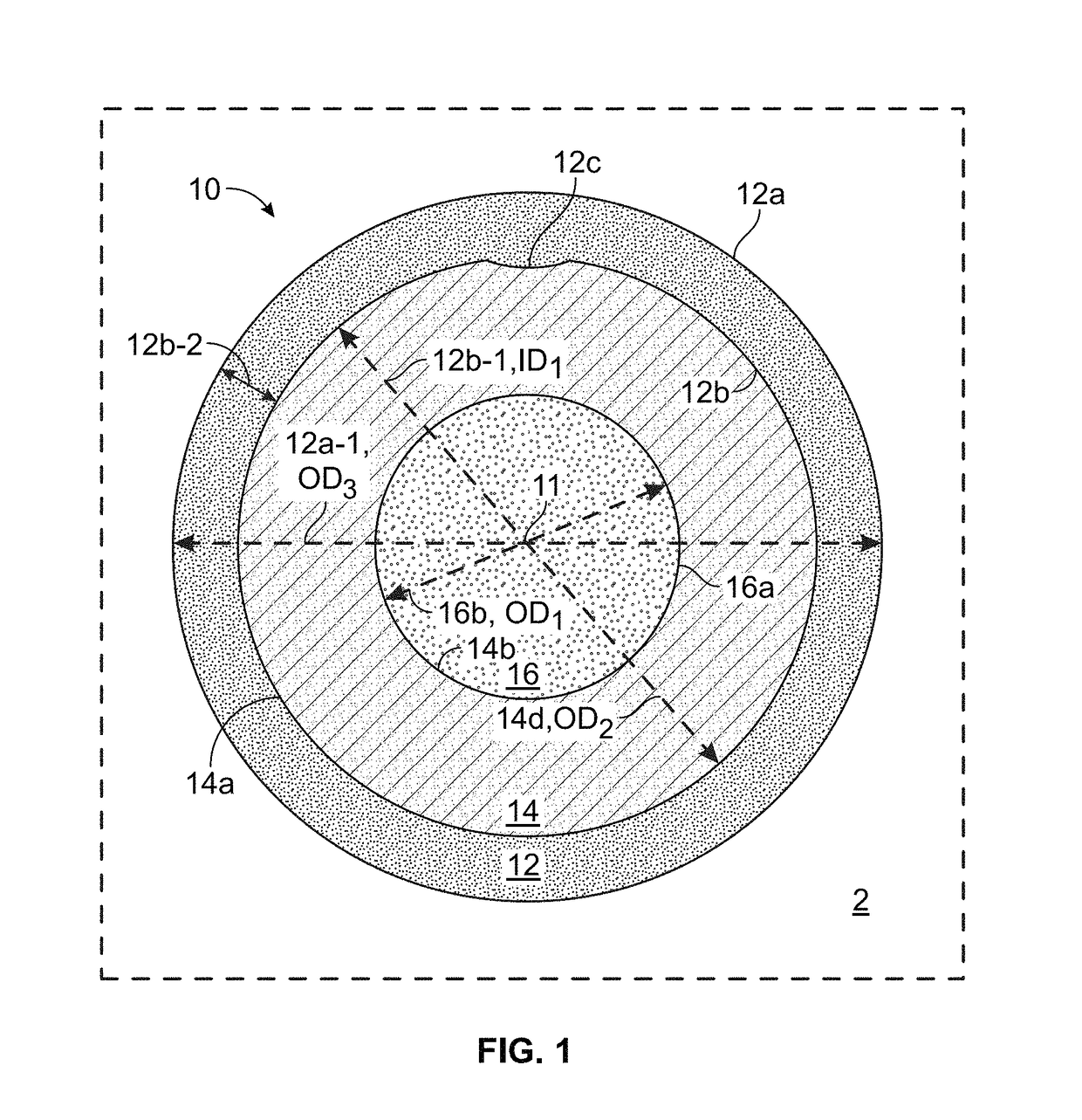

Stress control cones for downhole electrical power system tubing encapsulated power cables

ActiveUS20190089143A1Reduce electrical stressElectrically conductive connectionsDrilling rodsInsulation layerPower cable

A stress cone for reducing electrical stresses is disclosed for use on terminated ends of tubing encapsulated power cable used in surface applications in a subsurface well power system employing electric submersible pumps (ESPs). The stress cone comprises an annular section about a longitudinal axis for receiving a terminated end of the TEPC in its first end and for abutting the terminated metal TEPC end against a metal shoulder at its second end therein, and an insulation chamber axially aligned with and connected to the annular section. The chamber comprises a metal interior surface symmetrical about the axis. The insulated TEPC core (without outer metal sheath) passes through the insulation chamber along the axis and then exits. The ID of the TEPC metal sheath and the inside metal surface of the chamber form a smooth ground plane transition surface. Insulation material surrounds the TEPC insulation layer within the insulation chamber.

Owner:ARTIFICIAL ELEVATOR

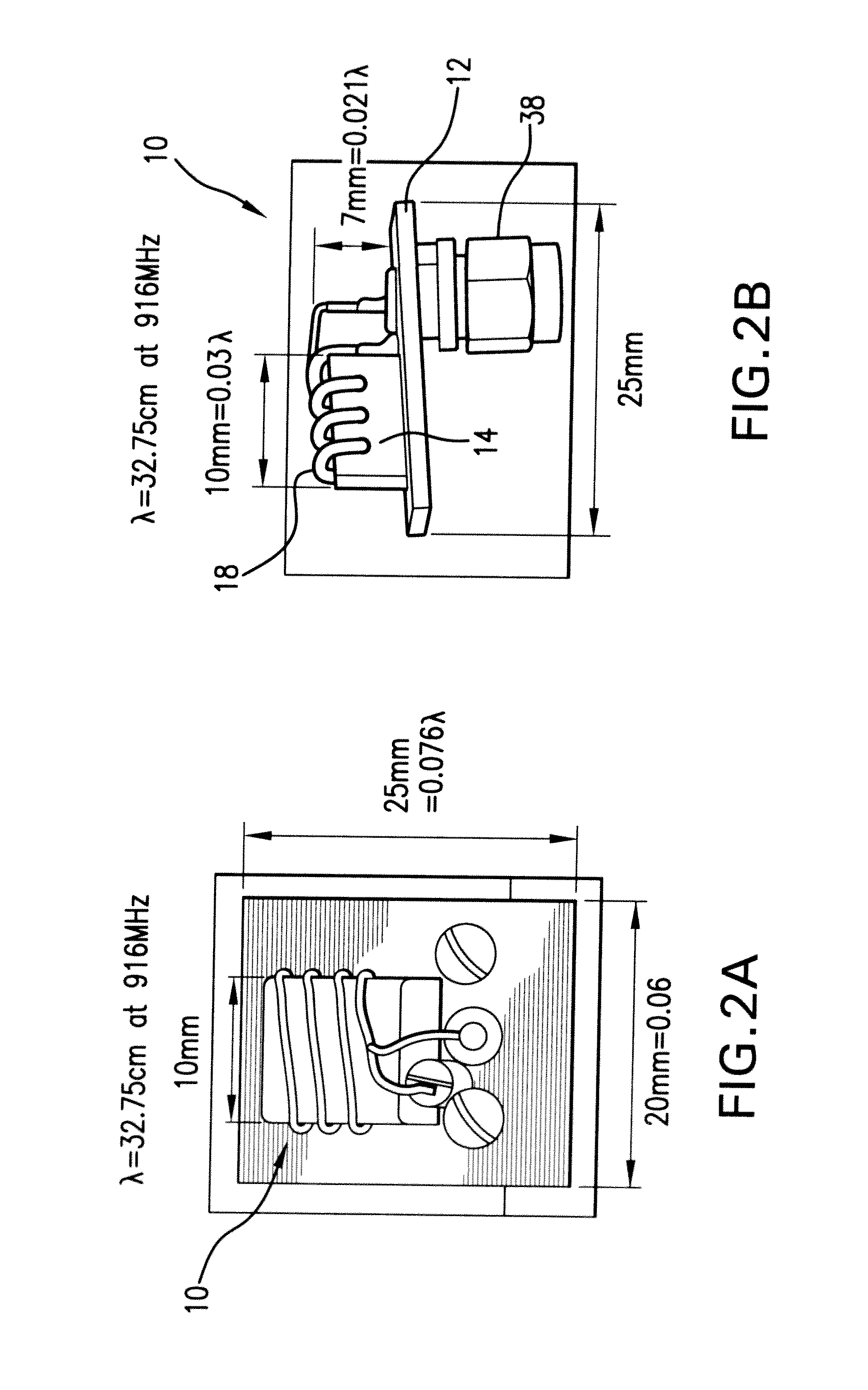

F-inverted compact antenna for wireless sensor networks and manufacturing method

InactiveUS20100026605A1Effective bandwidthLow profileRadiating elements structural formsHelical antennasDielectricCopper wire

An F-inverted compact antenna for ultra-low volume Wireless Sensor Networks is developed with a volume of 0.024λ×0.06λ×0.076λ, ground plane included, where λ is a resonating frequency of the antenna. The radiation efficiency attained is 48.53% and the peak gain is −1.38 dB. The antenna is easily scaled to higher operating frequencies up to 2500 MHz bands with comparable performance. The antenna successfully transmits and receives signals with tolerable errors. It includes a standard PCB board with dielectric block thereon and helically contoured antenna wound from a copper wire attached to the dielectric block and oriented with the helix axis parallel to the PCB. The antenna demonstrates omnidirectional radiation patterns and is highly integratable with WSN, specifically in Smart Dust sensors. The antenna balances the trade offs between performance and overall size and may be manufactured with the use of milling technique and laser cutters.

Owner:UNIV OF MARYLAND

Switched multi-beam antenna

InactiveUS7215296B2Reduce lossesRadiating elements structural formsAntenna earthingsCapacitanceCapacitive coupling

Owner:AIRGAIN INC

Multi-band antenna

ActiveUS7148849B2Excellent high-frequency characteristic and electromagnetic compatibilityMiniaturizationSimultaneous aerial operationsAntenna supports/mountingsMulti bandImpedance matching

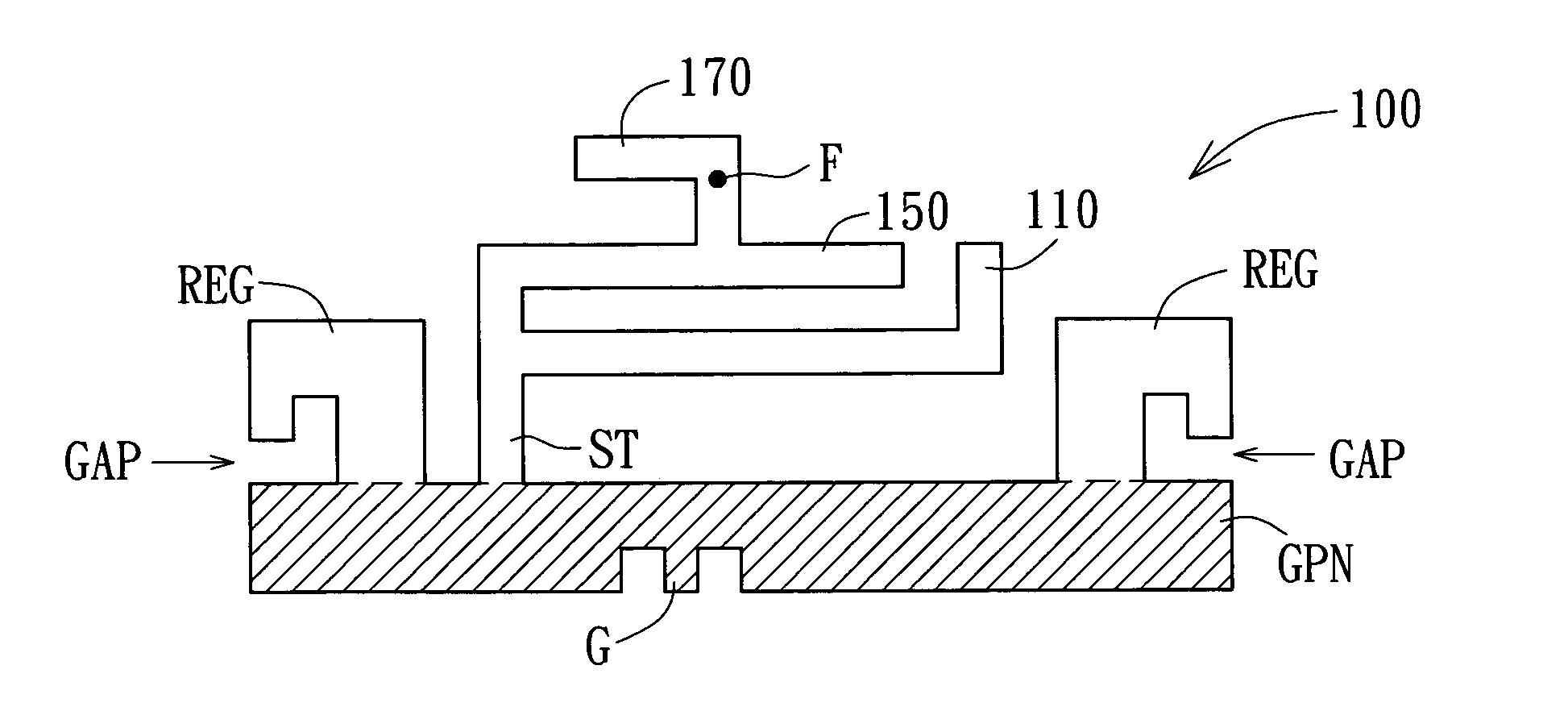

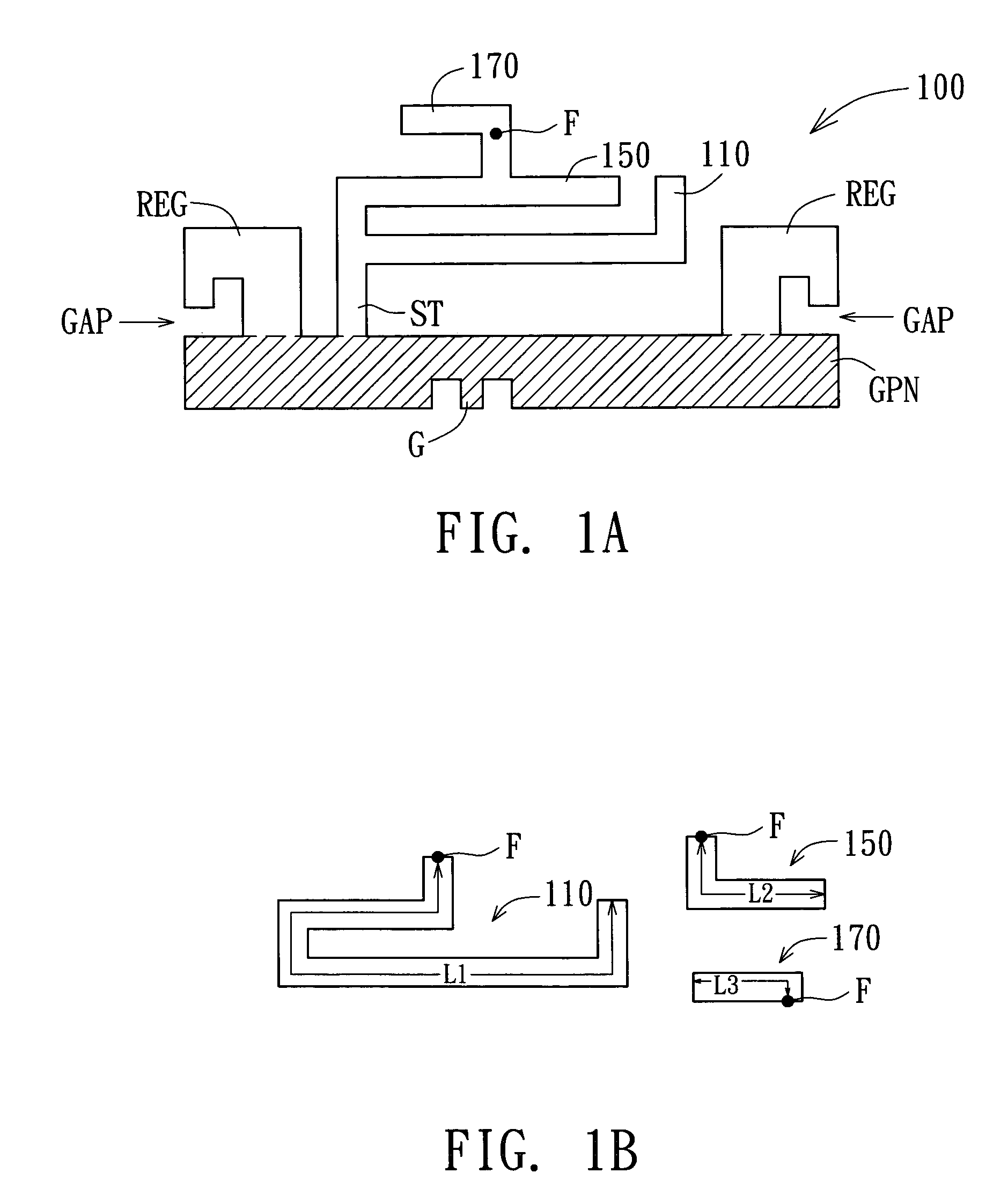

A multi-band antenna having a low frequency operating band and a high frequency operating band is provided. The multi-band antenna includes a radiating element, a grounding plane, a short-circuiting element and a short-circuiting regulator. The radiating element has a feed-in point for transmitting signals and several radiation arms. The first and the second radiation arms respectively have a first resonant mode and a second resonant mode which jointly generate a high frequency operating band, while the third radiation arm has a third resonant mode which generates a low frequency operating band. The grounding plane is connected to the radiating element via the short-circuiting element to miniaturize the scale of the antenna. The short-circuiting regulator of the grounding plane enhances the impedance matching when high frequency resonance occurs.

Owner:QUANTA COMPUTER INC

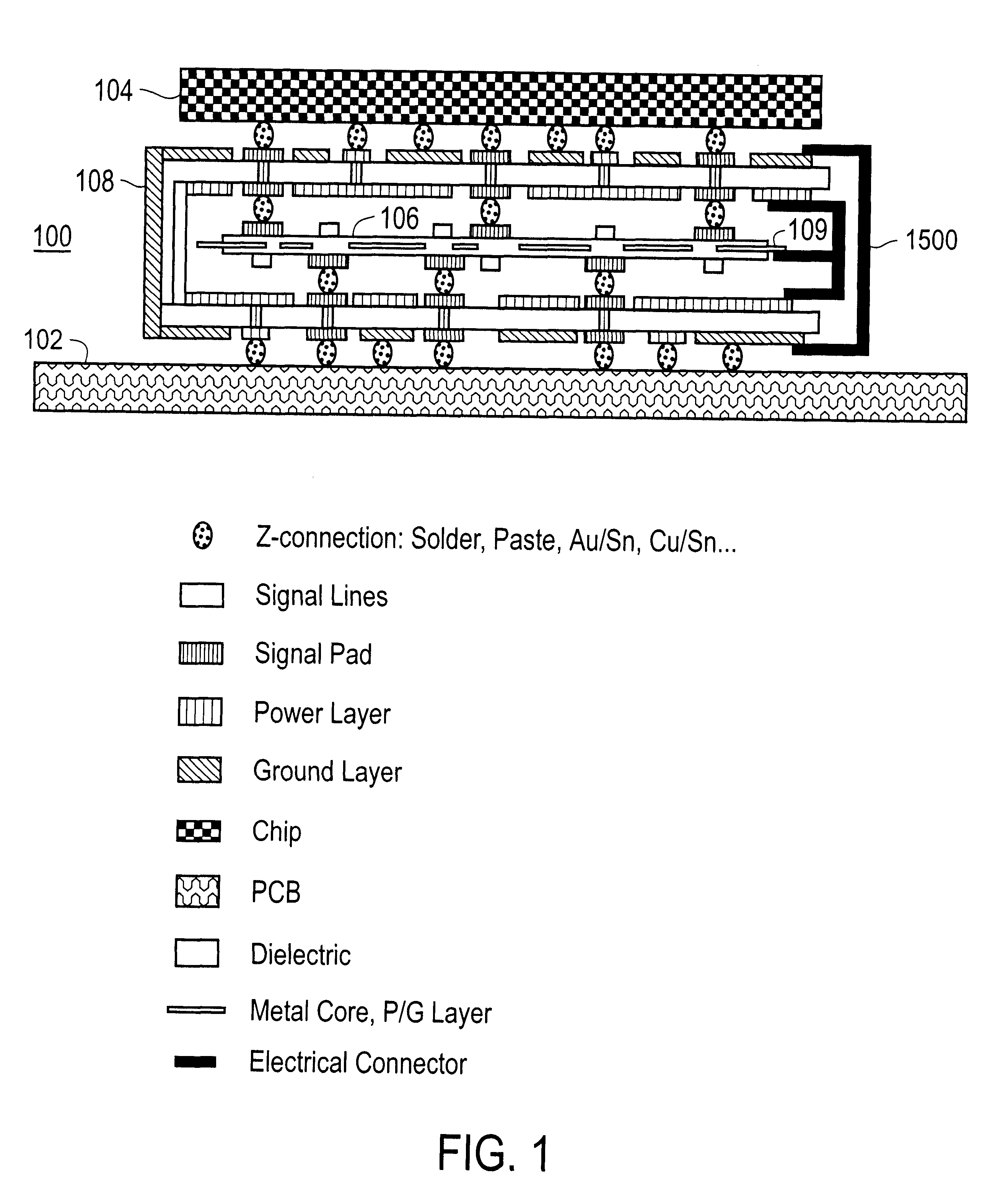

Composite interposer and method for producing a composite interposer

InactiveUS6521530B2Cross-talk/noise/interference reductionSemiconductor/solid-state device detailsEpoxyFilling materials

A composite interposer for providing power and signal connections between an integrated circuit chip or chips and a substrate. The interposer includes a signal core formed from a conductive power / ground plane positioned between two dielectric layers. A method for fabricating a composite interposer comprising disposing a silicon layer on a substrate, and selectively etching the silicon layer down to the substrate to develop silicon openings with a silicon profile, and to expose part of the substrate. Vias are formed through the exposed part of the substrate. The method additionally includes filling the vias and the silicon openings with a filler material (e.g., a high-aspect-ratio-capable photodefinable epoxy polymer) to form filled silicon openings and filled vias, forming first openings through the filled silicon openings and through the filled vias, forming second opening through filler material to expose semiconductor devices on the silicon layer, and interconnecting electrically, through the first openings and through the second openings, the exposed semiconductor devices with pads disposed against a bottom of the substrate.

Owner:FUJITSU LTD

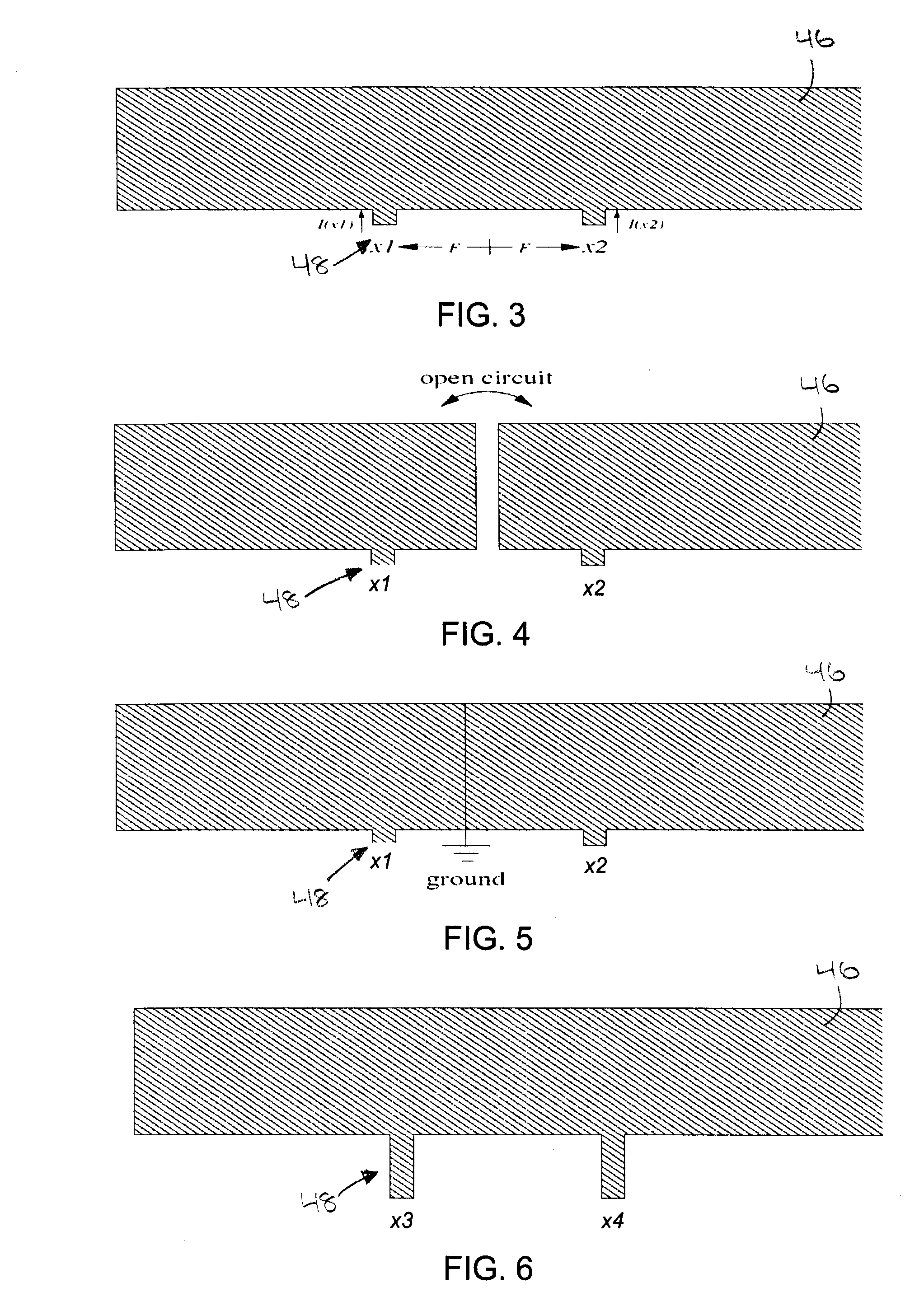

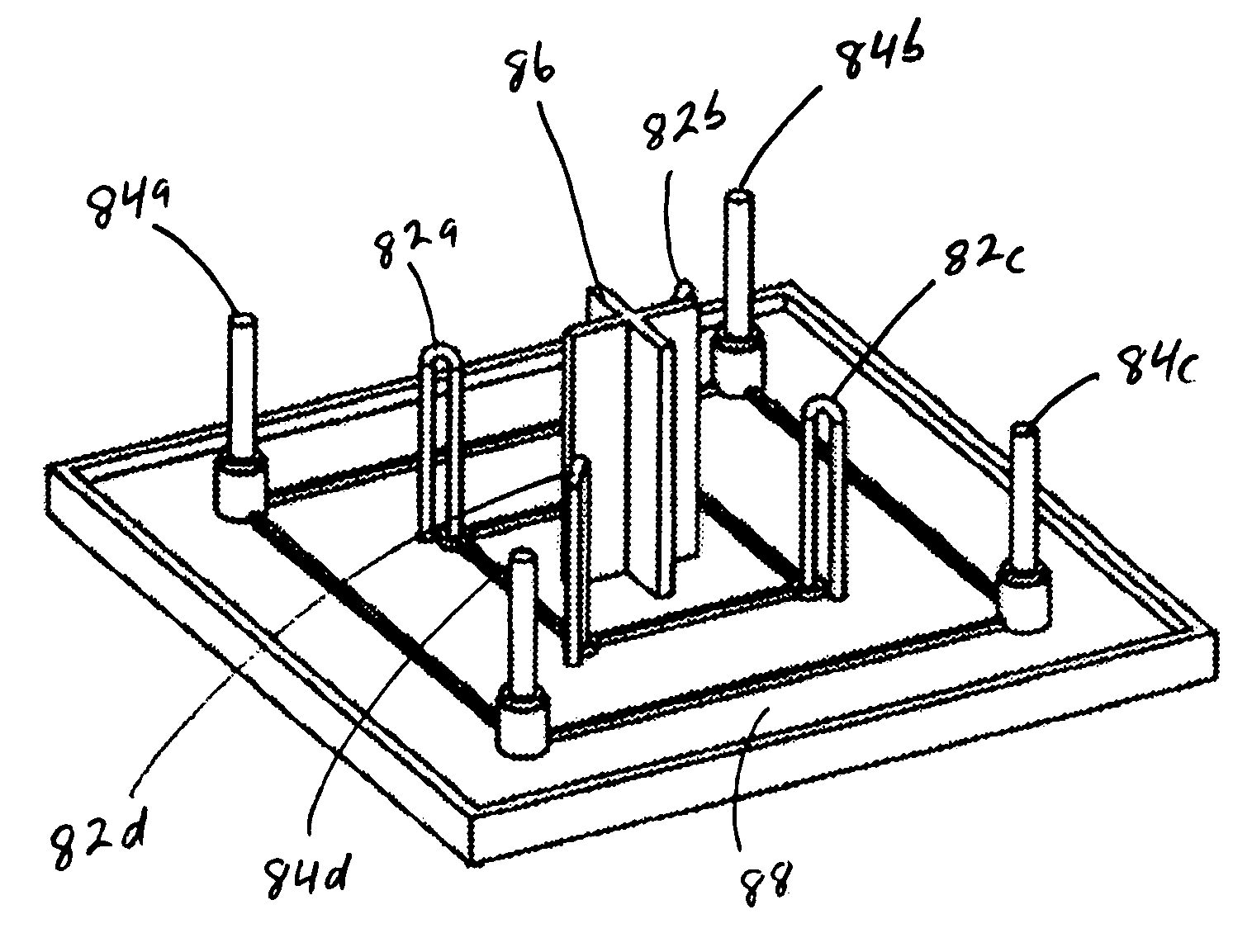

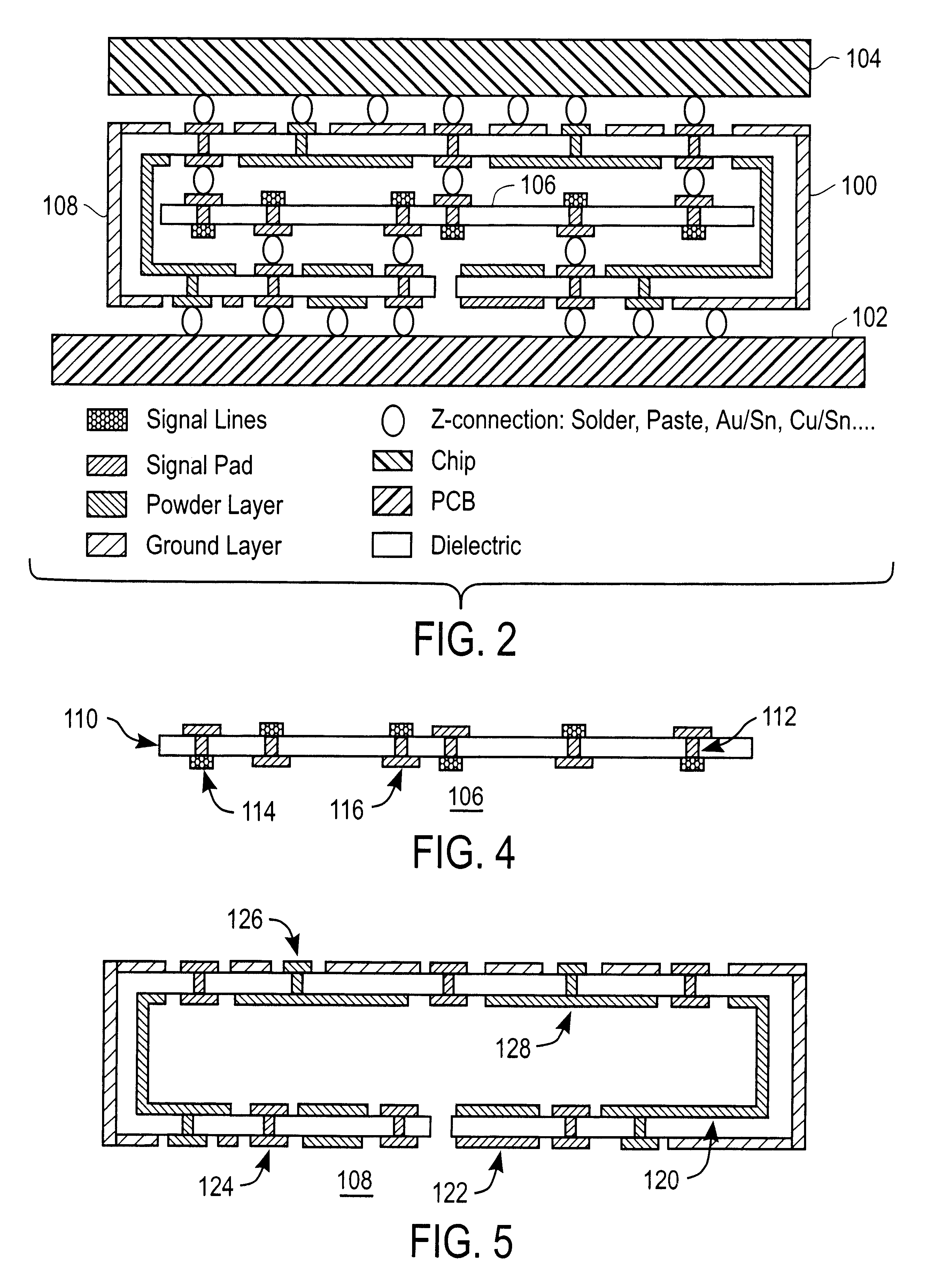

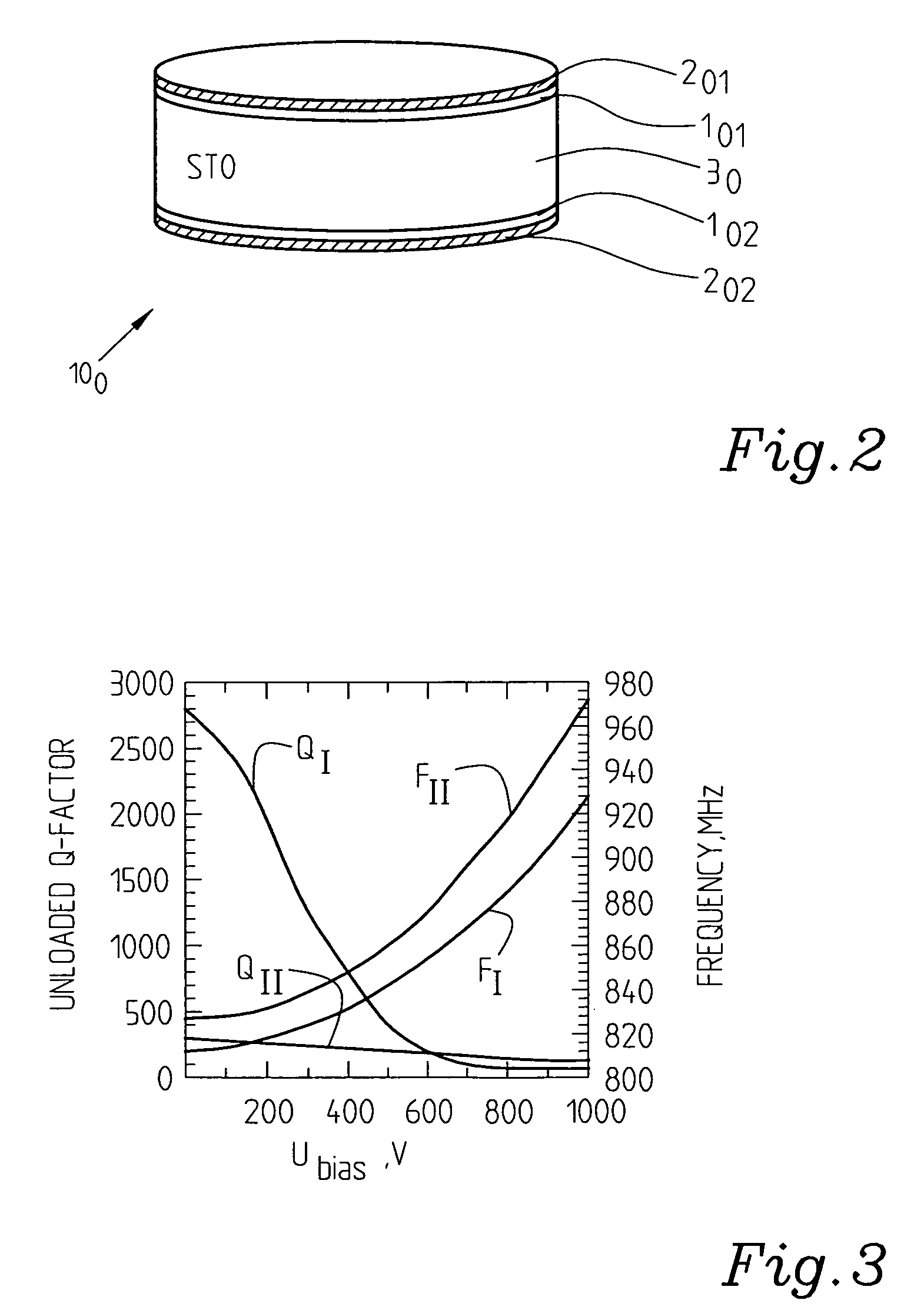

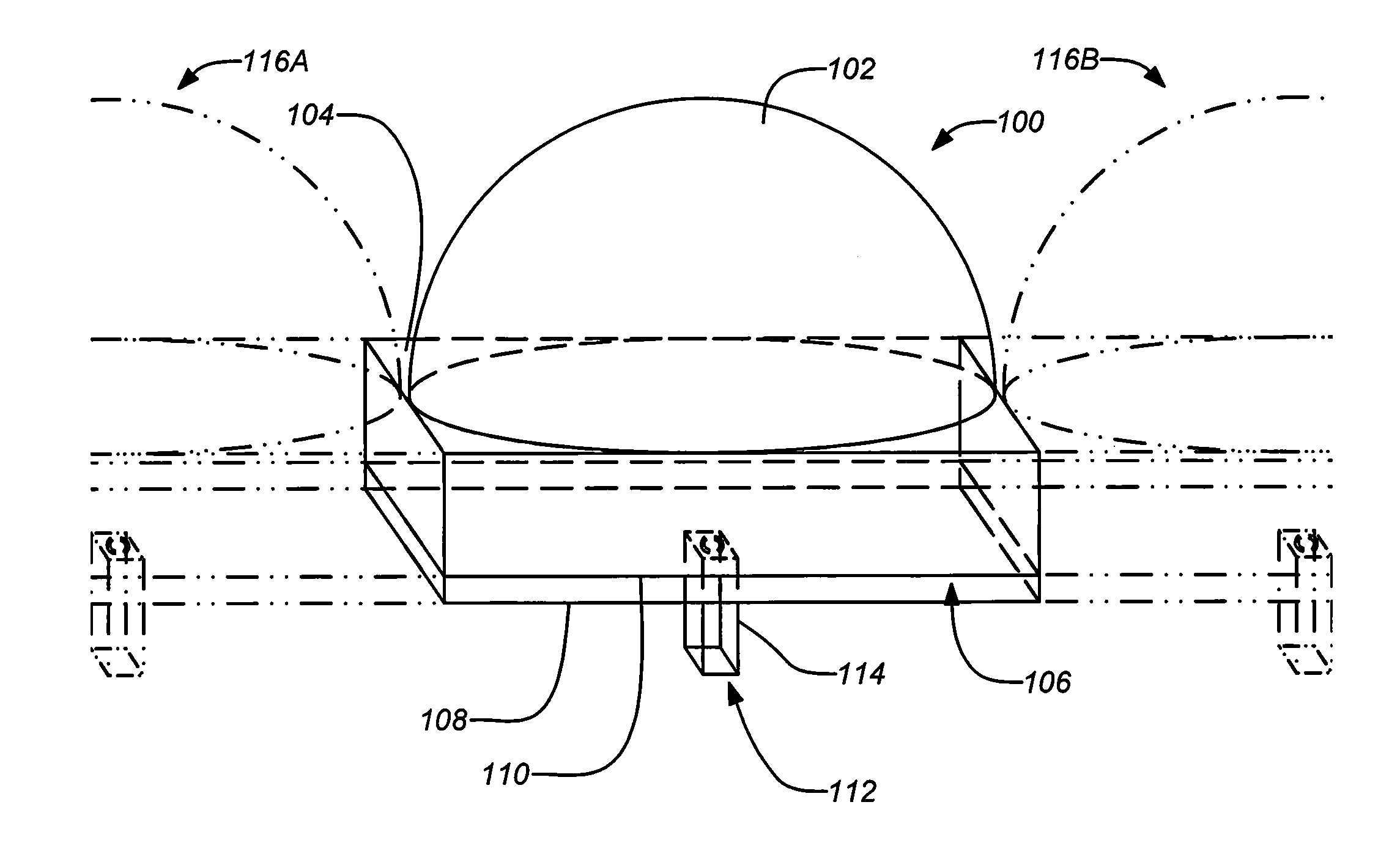

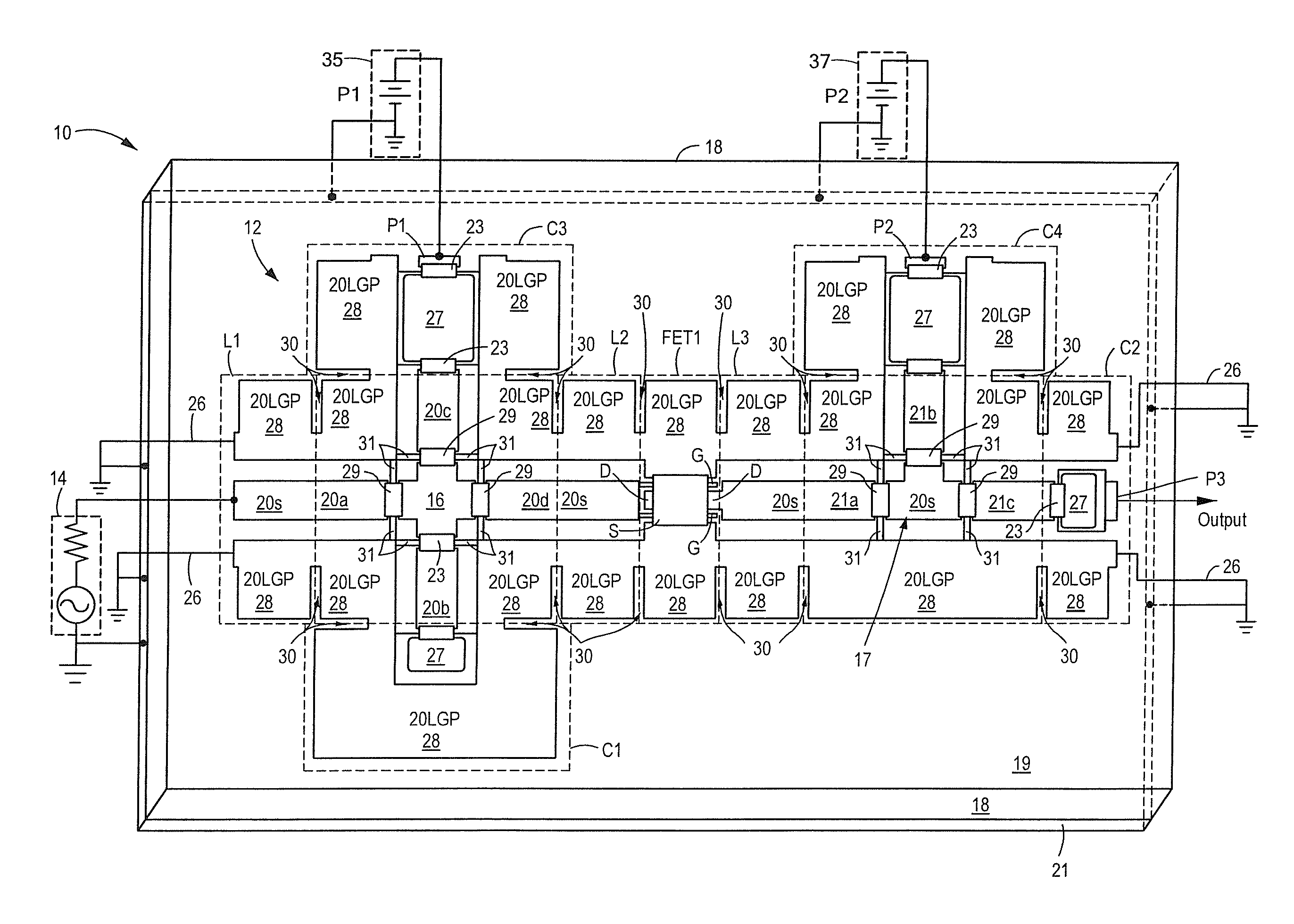

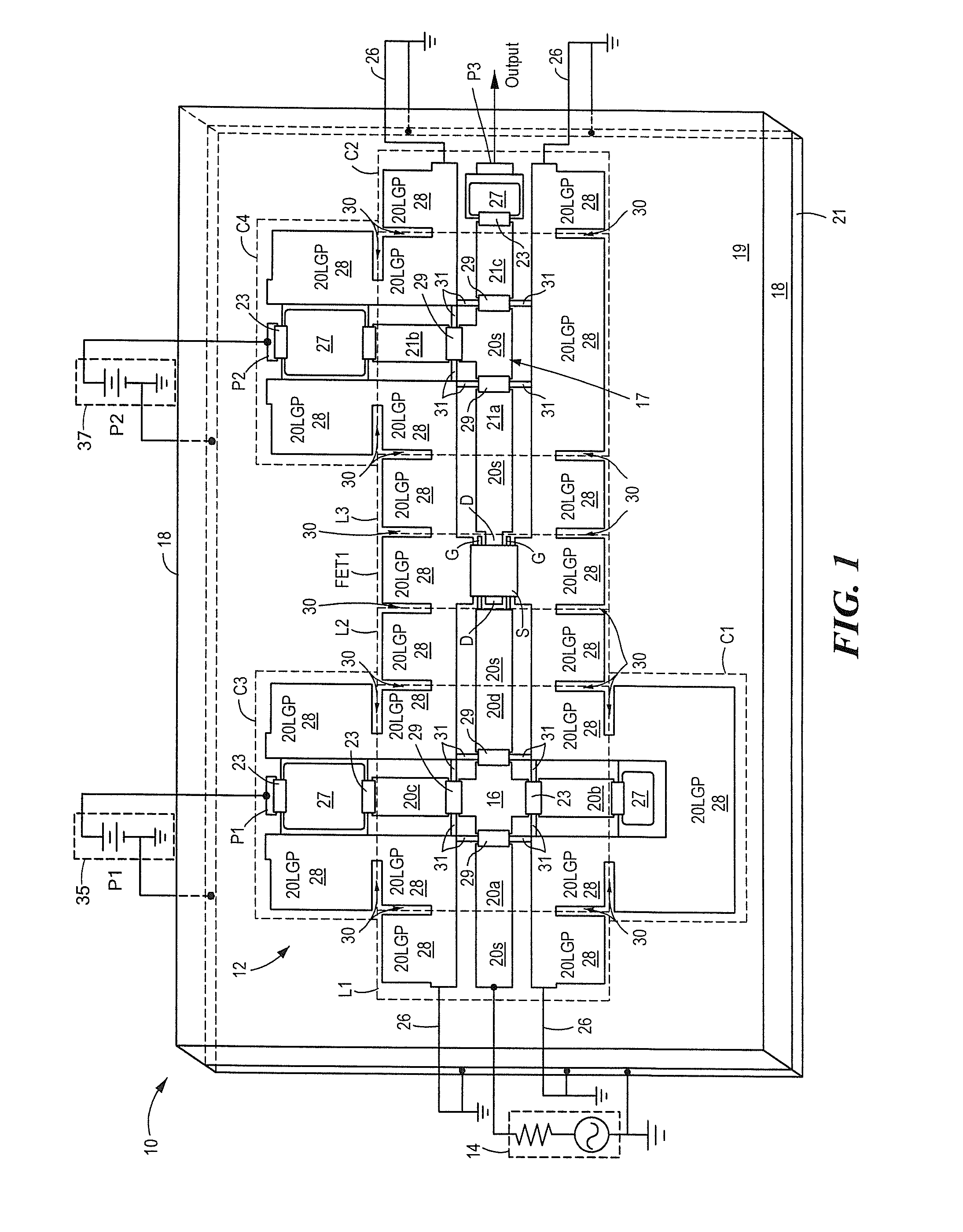

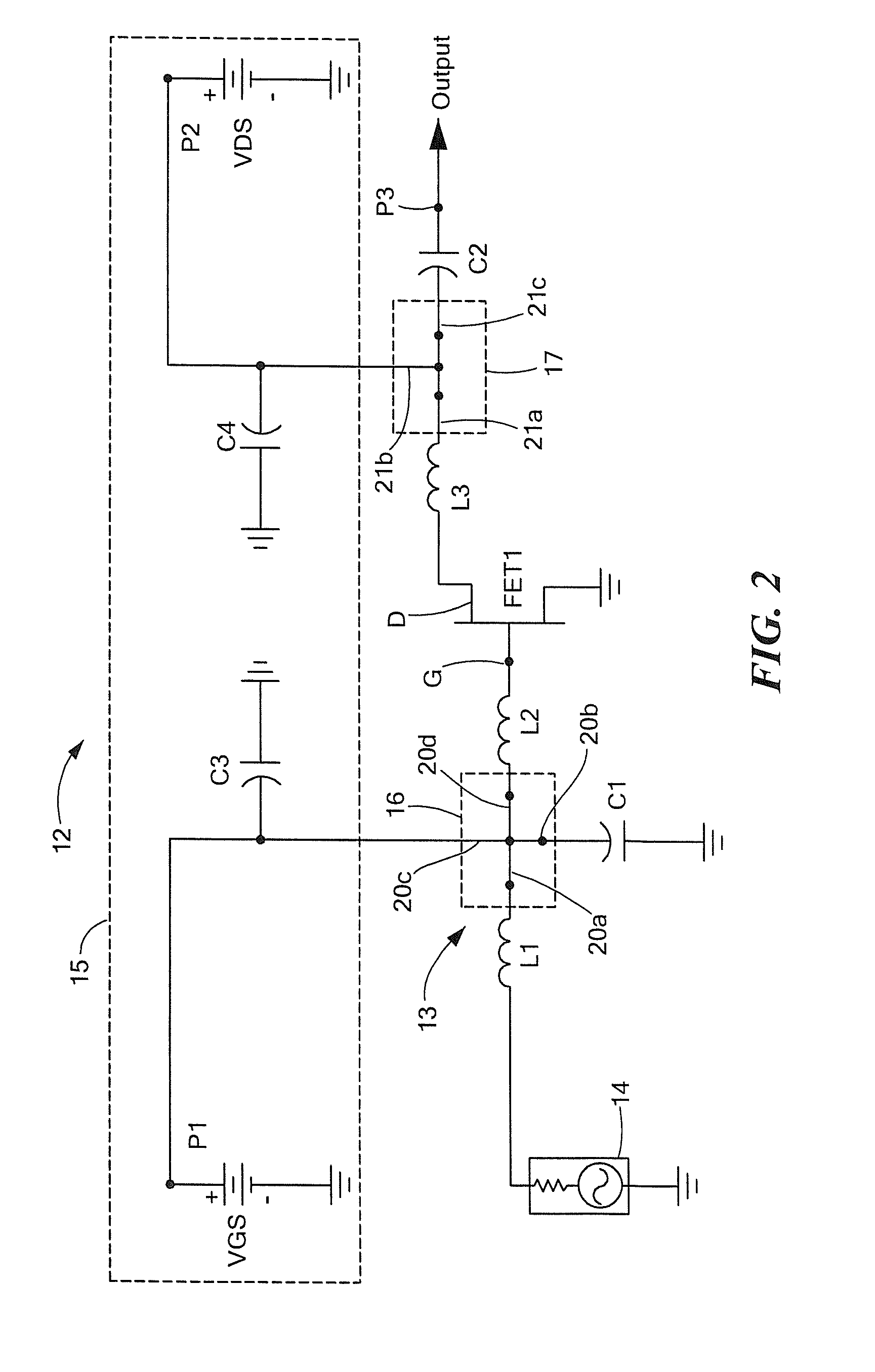

Tunable ferroelectric resonator arrangement

InactiveUS7069064B2Efficiency tuningGuaranteed uptimeSuperconductors/hyperconductorsSuperconductor devicesCouplingEnergy coupling

The present invention relates to a tunable resonating arrangement comprising a resonator apparatus (10), input / output coupling (4) means for coupling electromagnetic energy into / out of the resonator apparatus, and a tuning device (3) for application of a biasing voltage / electric field to the resonator apparatus. The resonator apparatus comprises a first resonator (1) and a second resonator (2). Said first resonator is non-tunable and said second resonator is tunable and comprises a ferroelectric substrate (21). Said first and second resonators are separated by a ground plane (13) which is common for said first and second resonators, and coupling means (5) are provided for providing coupling between said first and second resonators. For tuning of the resonator apparatus, the biasing voltage / electric field is applied to the second resonator (2).

Owner:TELEFON AB LM ERICSSON (PUBL)

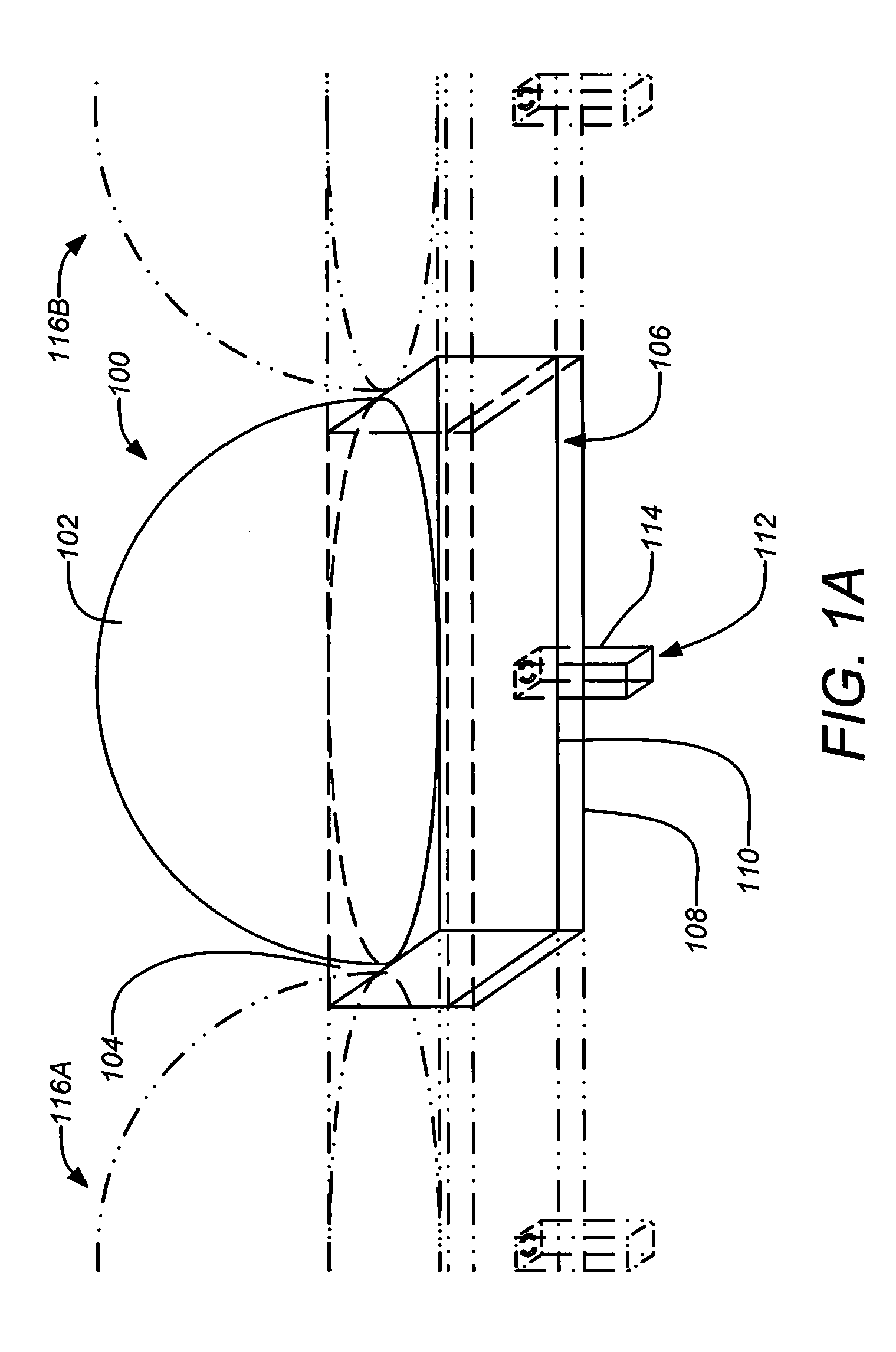

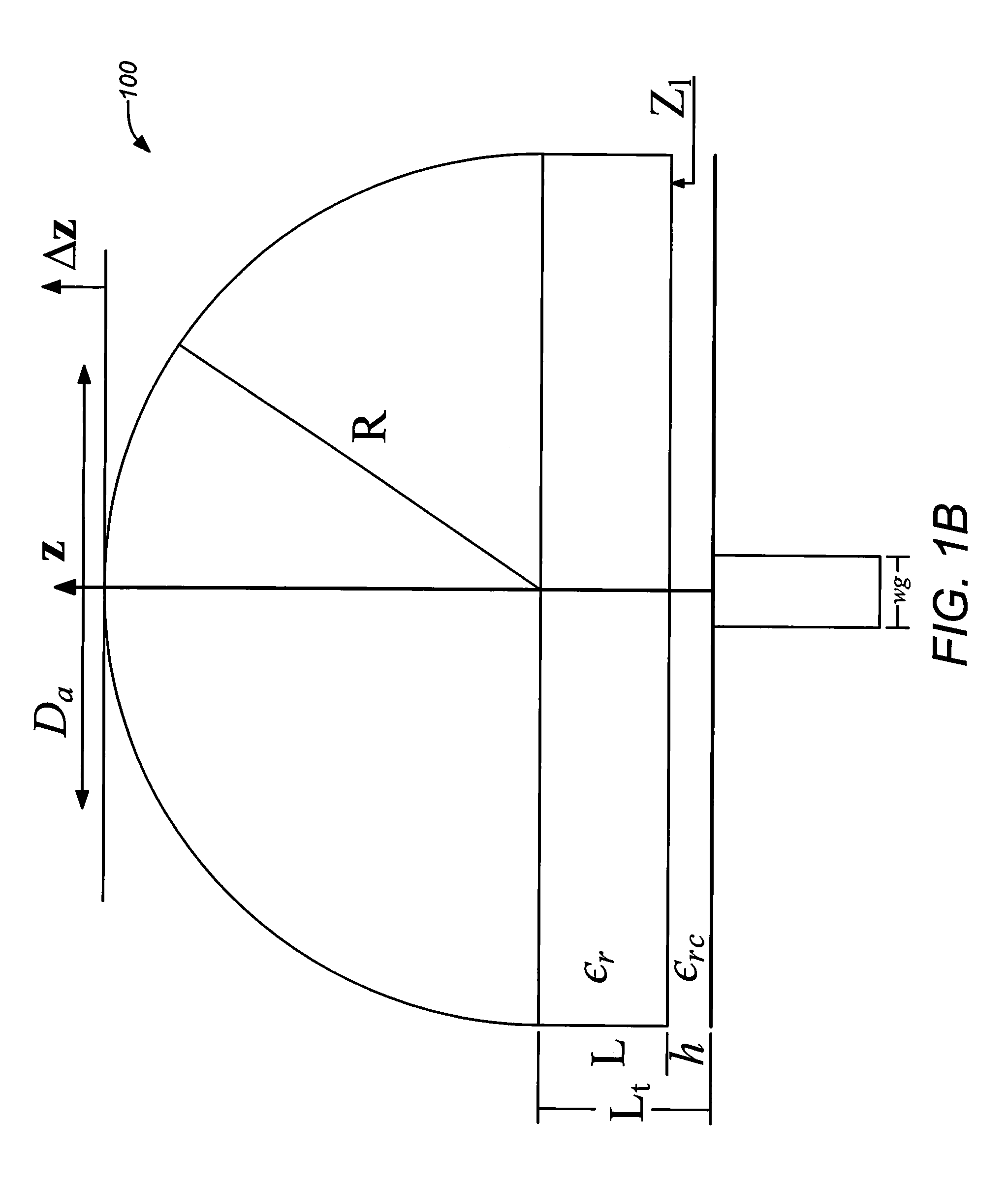

Dielectric covered planar antennas

An antenna element suitable for integrated arrays at terahertz frequencies is disclosed. The antenna element comprises an extended spherical (e.g. hemispherical) semiconductor lens, e.g. silicon, antenna fed by a leaky wave waveguide feed. The extended spherical lens comprises a substantially spherical lens adjacent a substantially planar lens extension. A couple of TE / TM leaky wave modes are excited in a resonant cavity formed between a ground plane and the substantially planar lens extension by a waveguide block coupled to the ground plane. Due to these modes, the primary feed radiates inside the lens with a directive pattern that illuminates a small sector of the lens. The antenna structure is compatible with known semiconductor fabrication technology and enables production of large format imaging arrays.

Owner:CALIFORNIA INST OF TECH

Monolithic microwave integrated circuits (MMICs) having conductor-backed coplanar waveguides and method of designing such MMICs

Owner:RAYTHEON CO

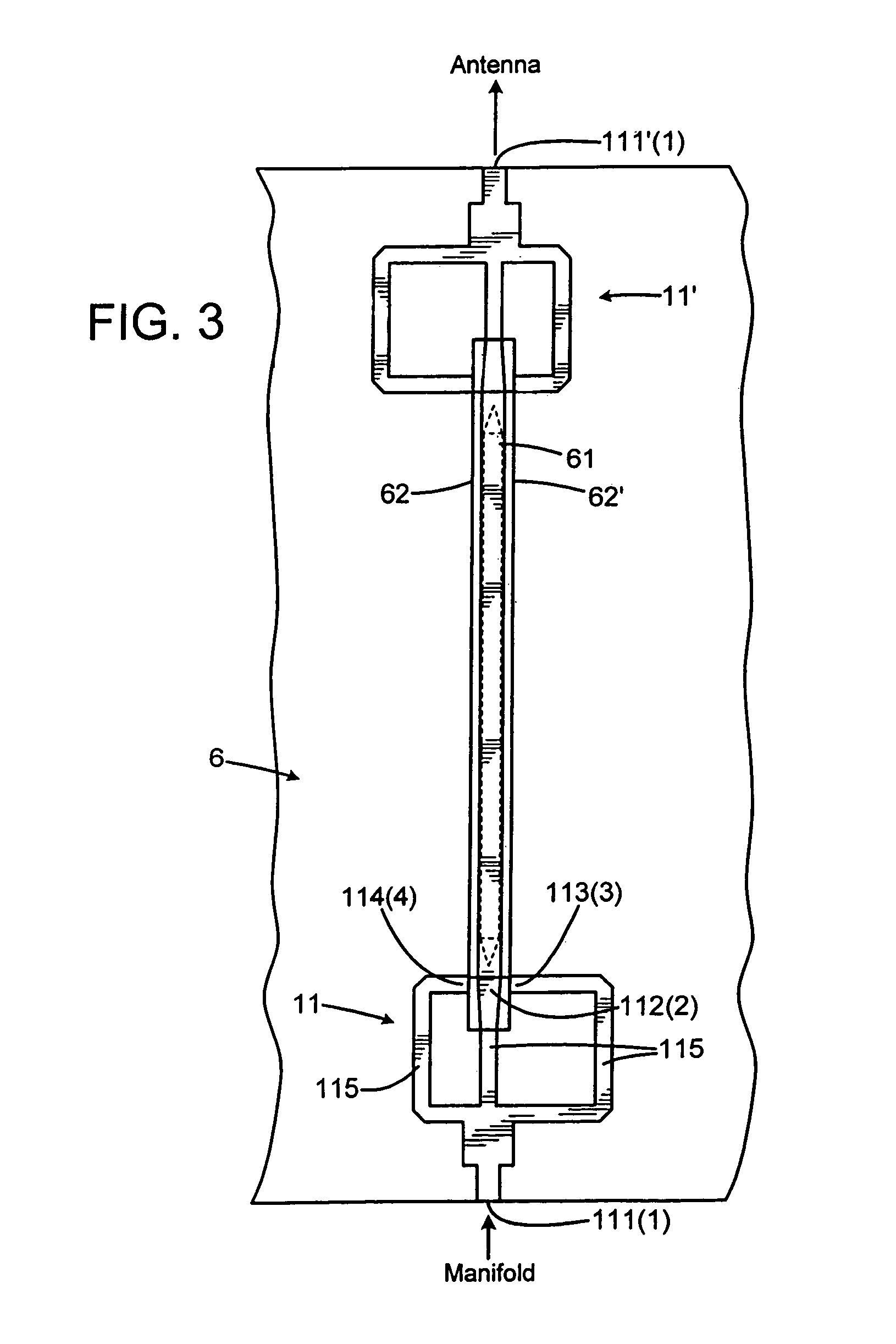

Ferrite phase shifter and phase array radar system

A phase shifter comprises a substrate, a ground plane formed on a first surface of the substrate, a support structure positioned on a second surface of the substrate opposite the first surface, three parallel, non-co-planar microstrip lines supported by the support structure above the second surface of the substrate, a ferrite element supported by the support structure between the second surface of the substrate and the three non-co-planar microstrip lines, and means for applying a magnetic field to the ferrite element.

Owner:RAYTHEON CO

Planar Inverted-F-Antenna (PIFA) having a slotted radiating element providing global cellular and GPS-bluetooth frequency response

InactiveUS6741214B1Simultaneous aerial operationsAntenna supports/mountingsPlanar inverted f antennaResonance

Owner:LAIRDTECH INC

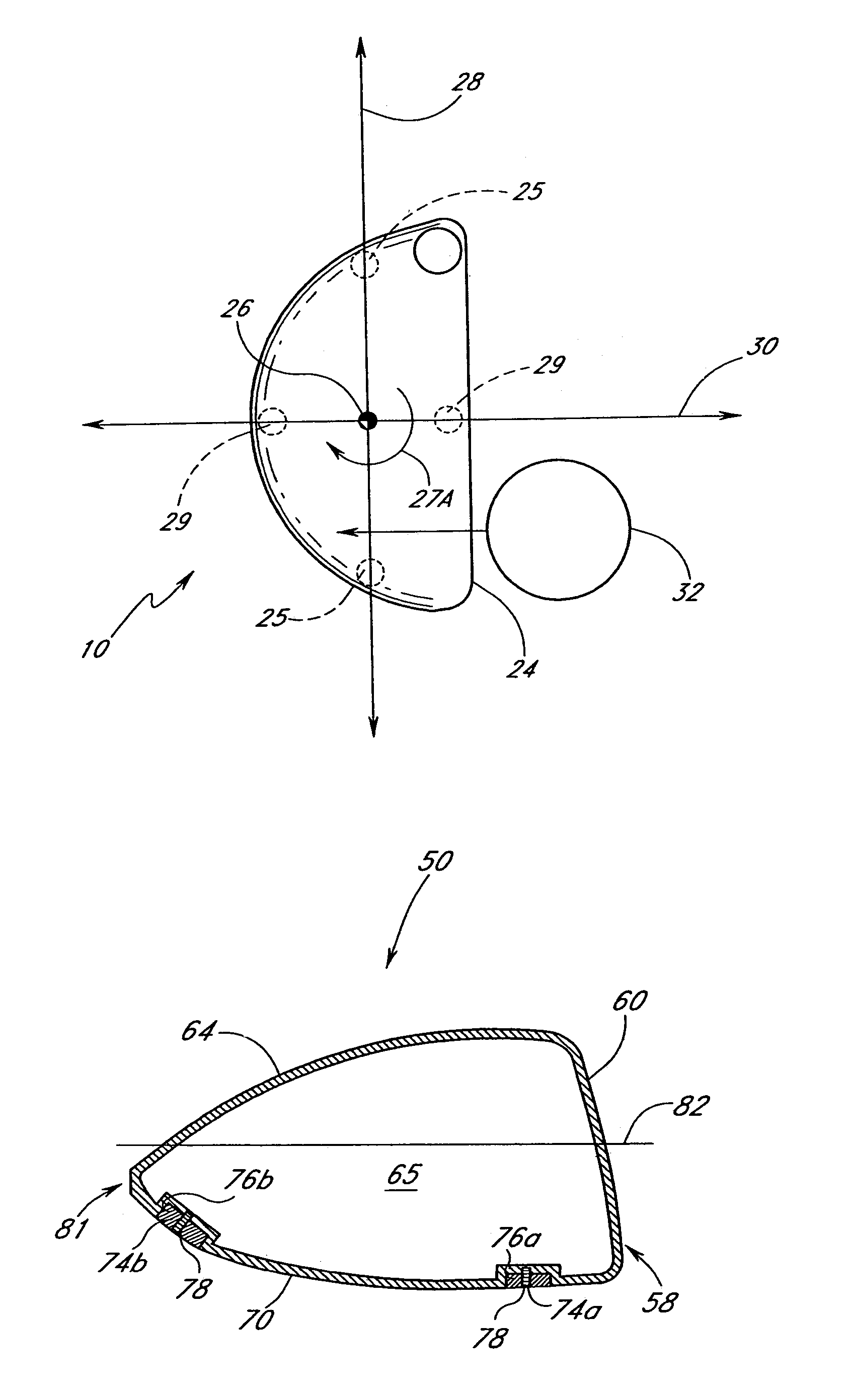

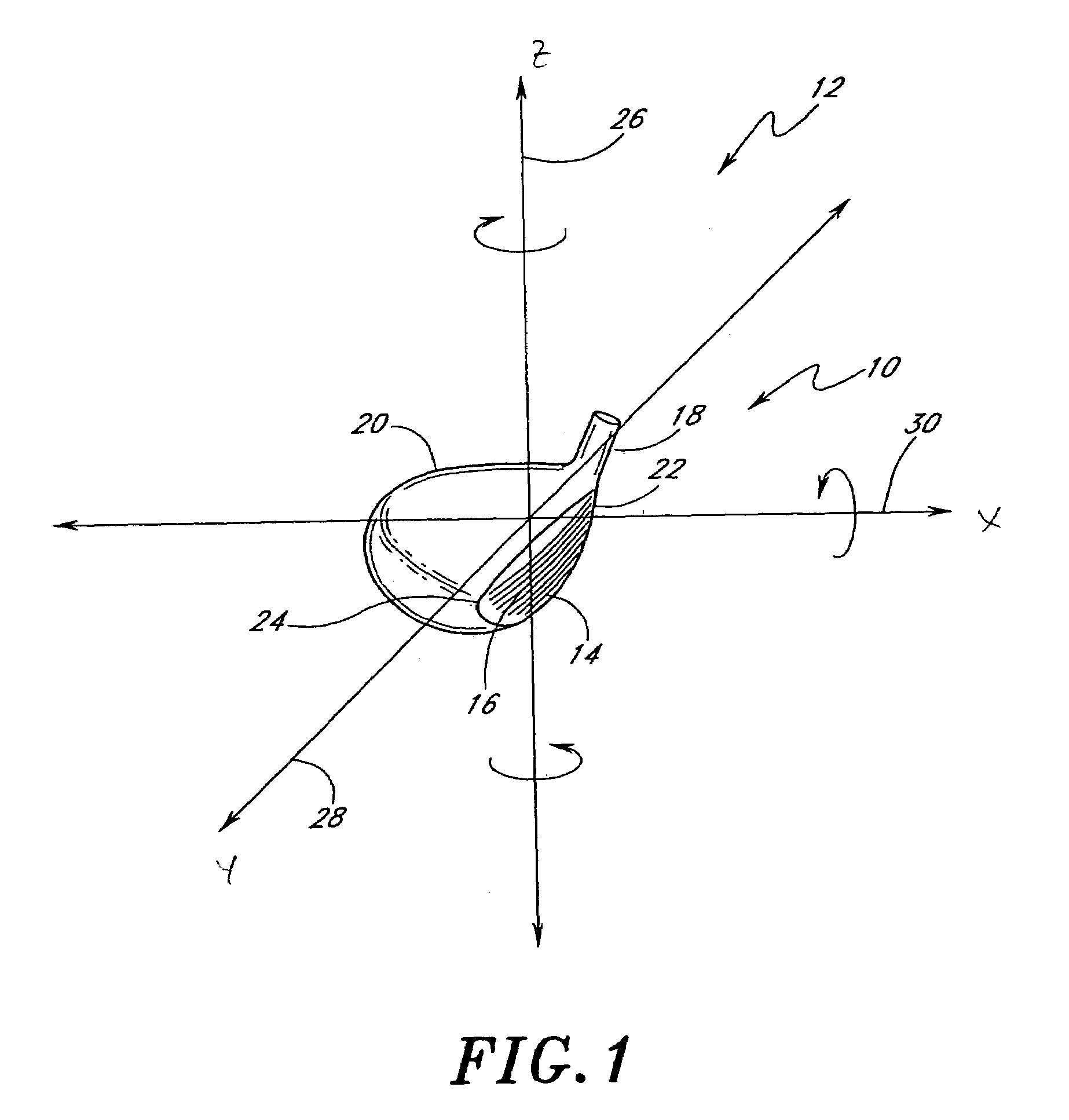

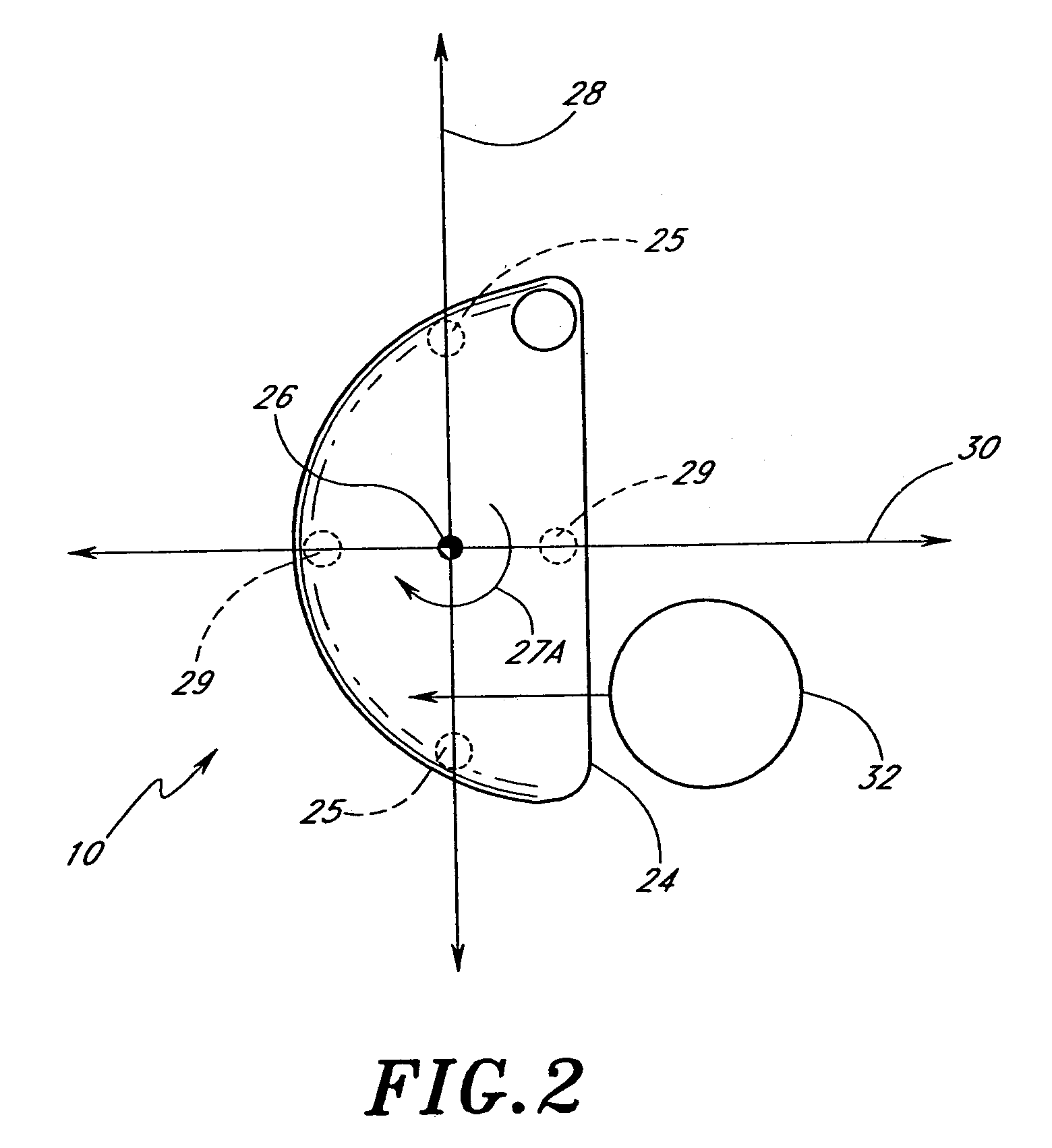

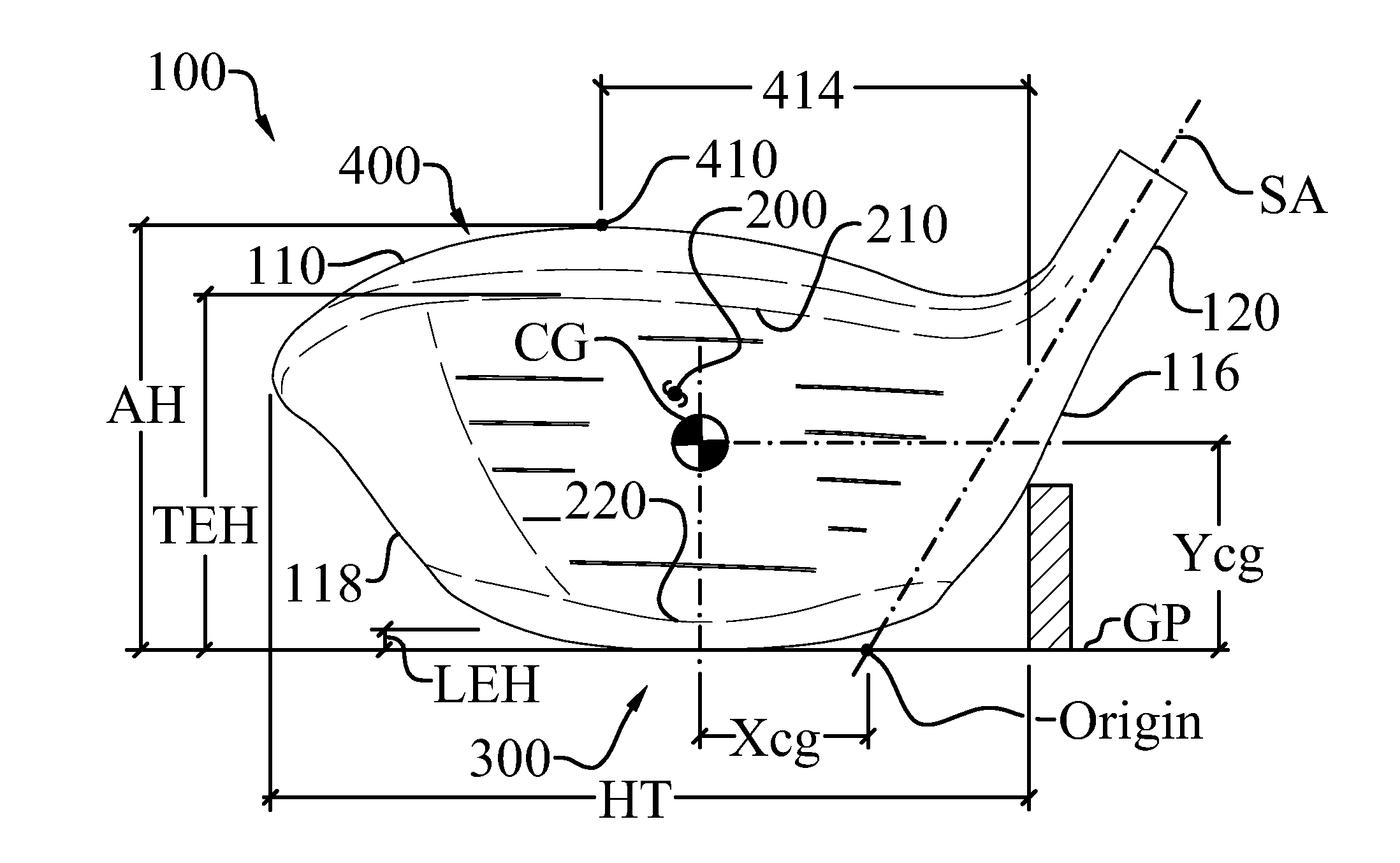

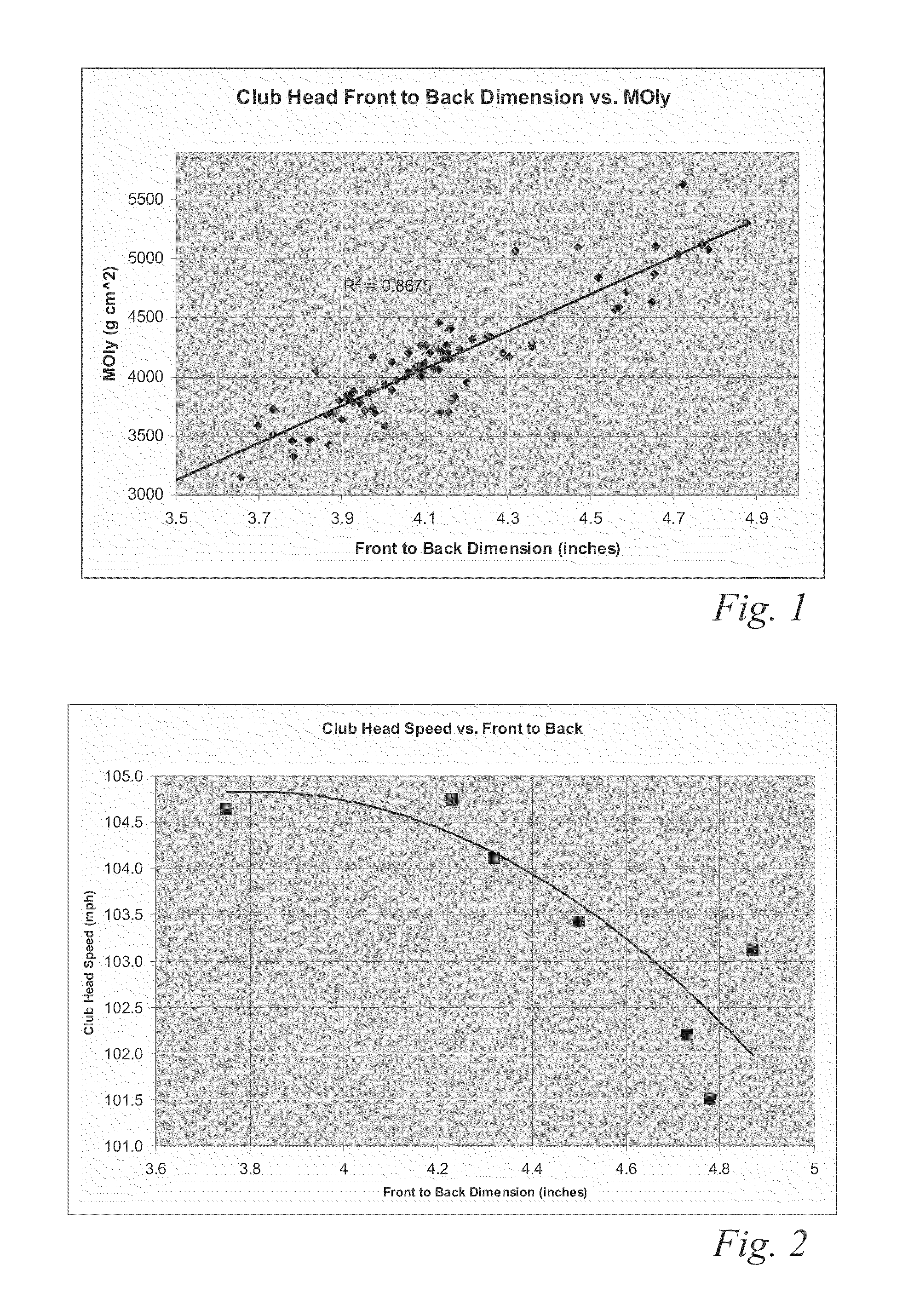

Golf club head

A golf club head comprising an outer shell and a strike plate having a strike face. The outer shell and the strike face define a club head volume. A heel / toe axis extends through the center of gravity of the club head. The heel / toe axis is generally parallel to the strike face and generally horizontal relative to a ground plane when the club head is at an address position. The rotational moment of inertia about the heel / toe axis is related to the club head volume by the equation Ixx ≧,46*HV+77, where Ixx is the rotational moment of inertia about the heel / toe axis in units of kg-mm2 and HV is the club head volume in units of cm3.

Owner:TAYLOR MADE GOLF

Compact antenna

ActiveUS20080180333A1Improve antenna performanceReducing antennas reflection coefficientSimultaneous aerial operationsAntenna supports/mountingsCouplingDielectric substrate

An antenna, including a planar dielectric substrate and a conductive ground plane formed on the substrate. A conductive monopole is formed on the substrate and has an end point located in proximity to a feed region of the ground plane. A conductive coupling element is formed on the substrate and is coupled to the ground plane at a coupling region of the ground plane. The coupling element is folded around the monopole.

Owner:GALTRONICS USA INC

Integrated circuit with electromagnetic communication

ActiveUS20120263244A1Baseband system detailsModulated-carrier systemsElement spaceElectrical conductor

A system for transmitting or receiving signals may include an integrated circuit (IC), a transducer operatively coupled to the IC for converting between electrical signals and electromagnetic signals; and insulating material that fixes the locations of the transducer and IC in spaced relationship relative to each other. The system may further include a lead frame providing external connections to conductors on the IC. An electromagnetic-energy directing assembly may be mounted relative to the transducer for directing electromagnetic energy in a region including the transducer and in a direction away from the IC. The directing assembly may include the lead frame, a printed circuit board ground plane, or external conductive elements spaced from the transducer. In a receiver, a signal-detector circuit may be responsive to a monitor signal representative of a received first radio-frequency electrical signal for generating a control signal that enables or disables an output from the receiver.

Owner:MOLEX INC

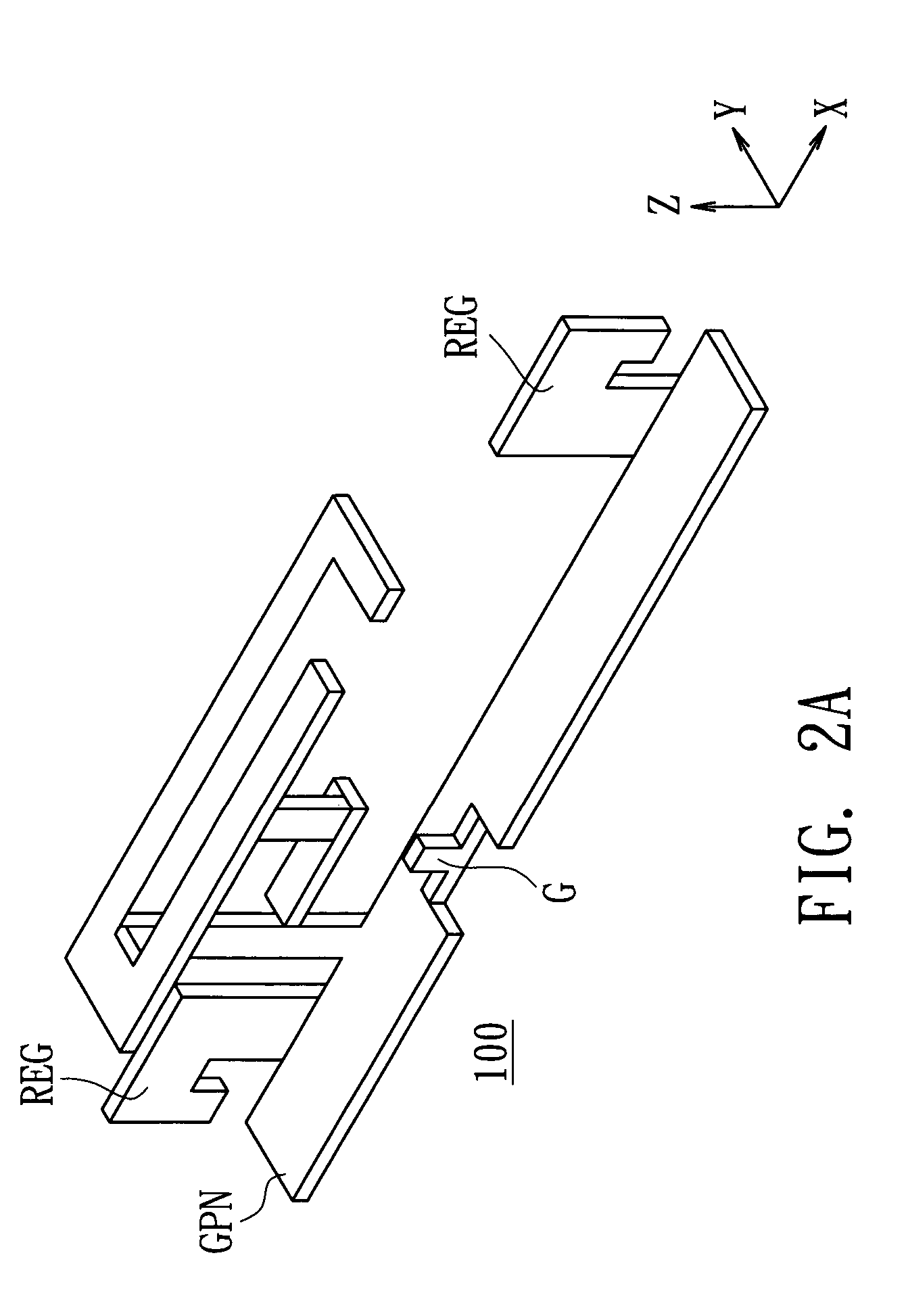

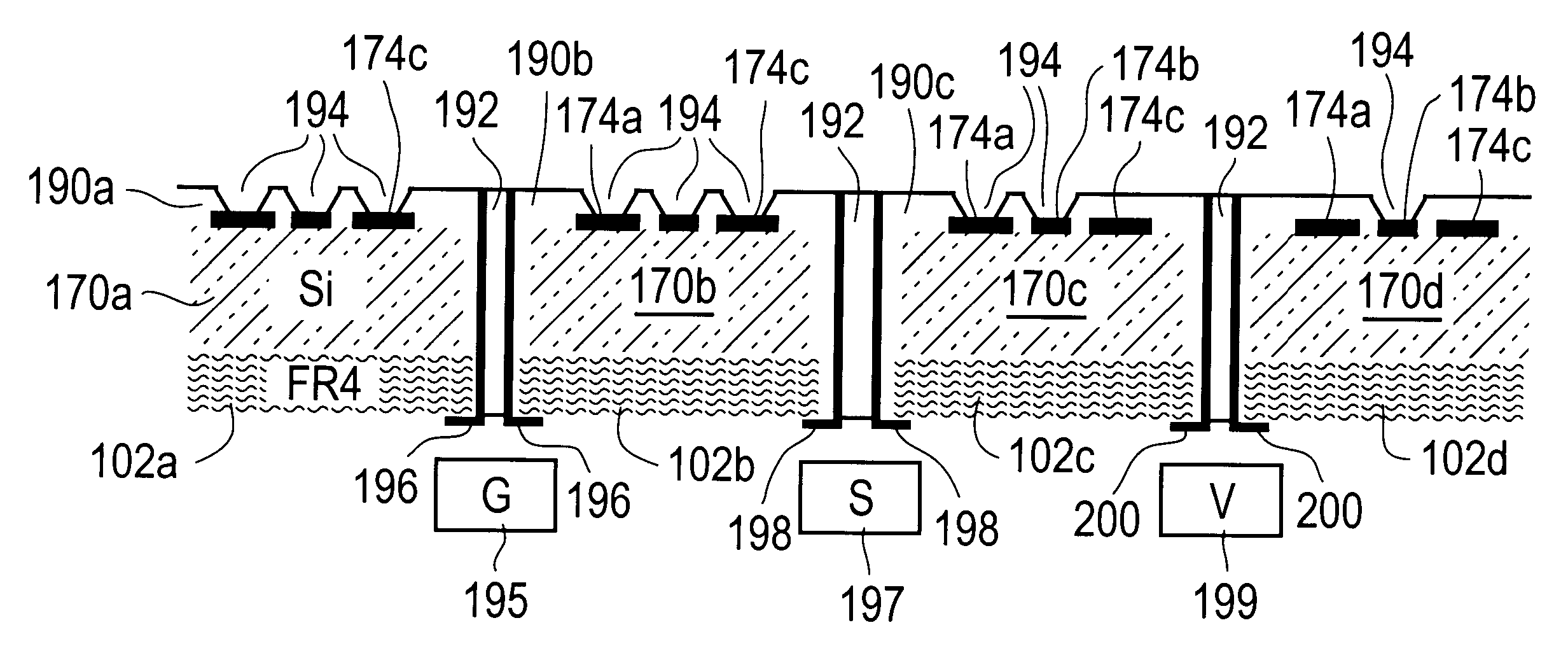

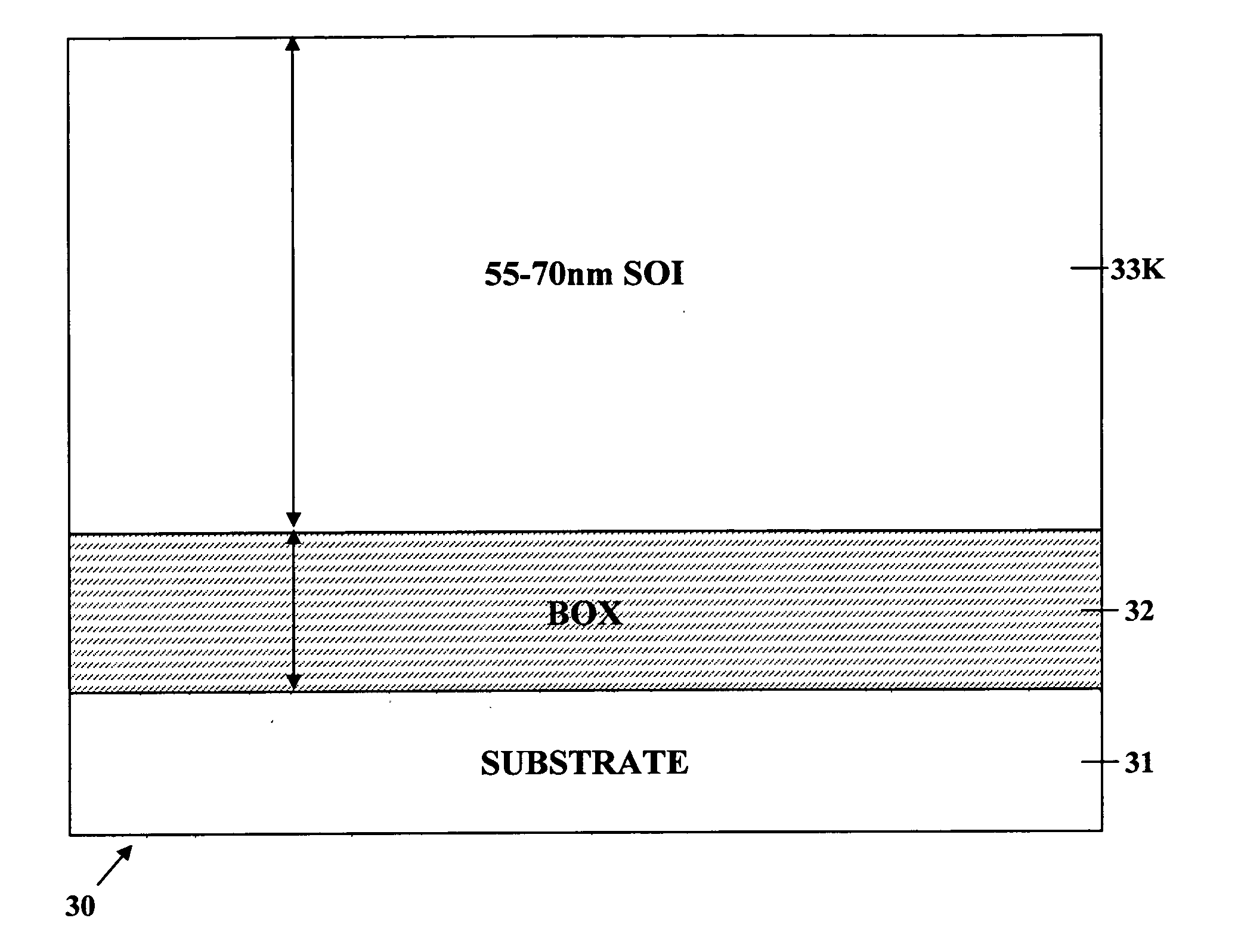

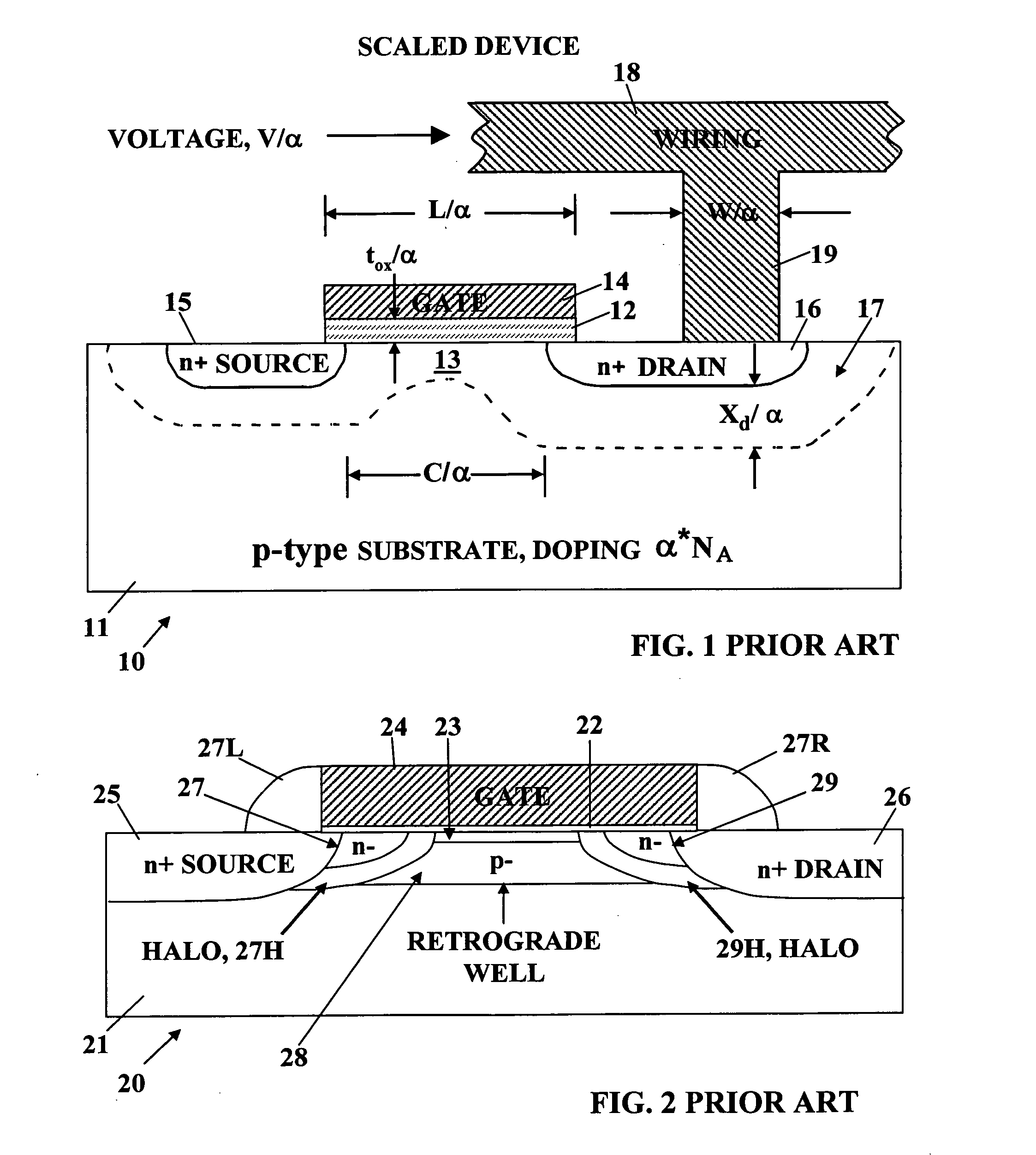

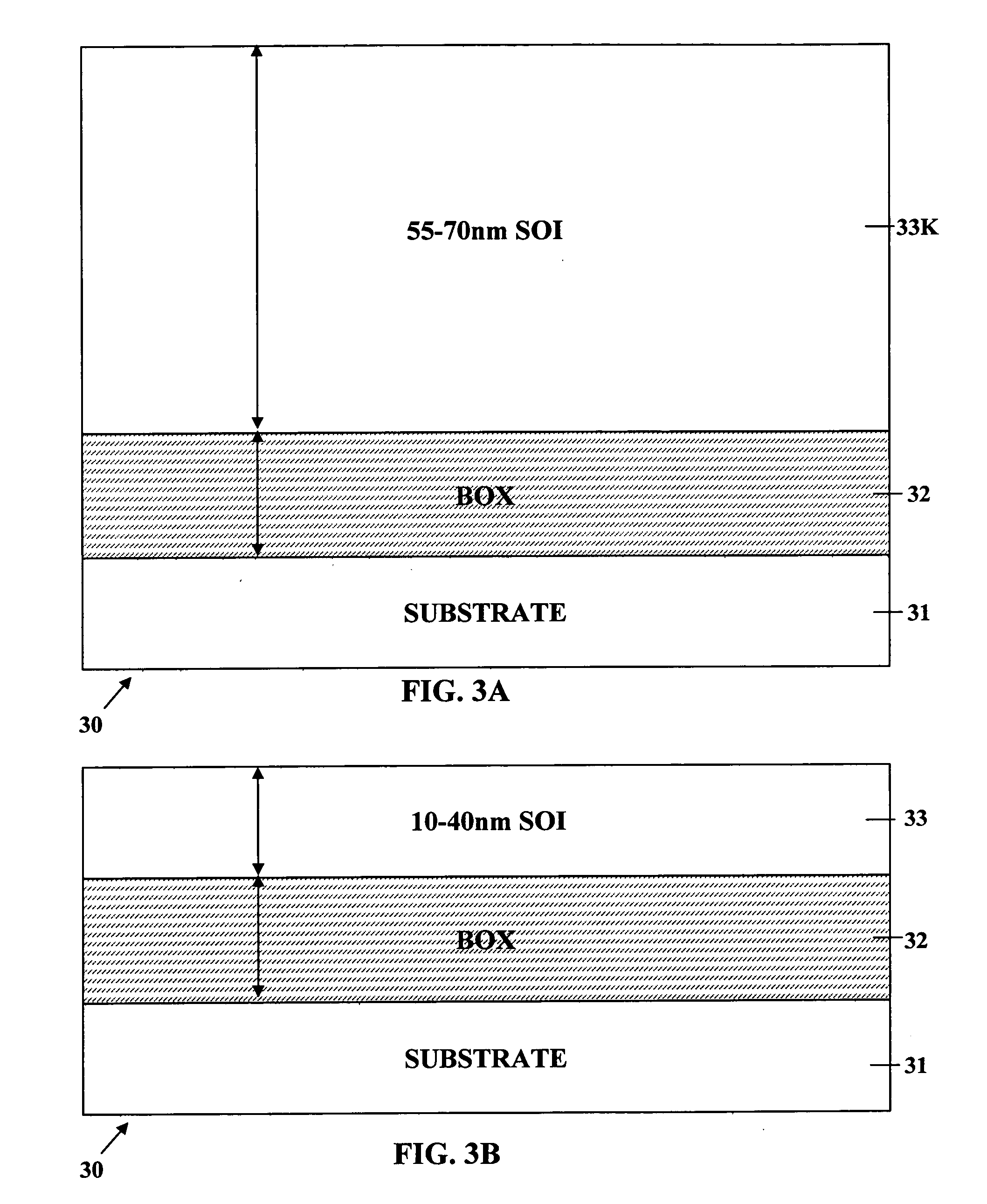

Ultra-thin body super-steep retrograde well (SSRW) FET devices

ActiveUS20060022270A1Minimize space-charge related fluctuationReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

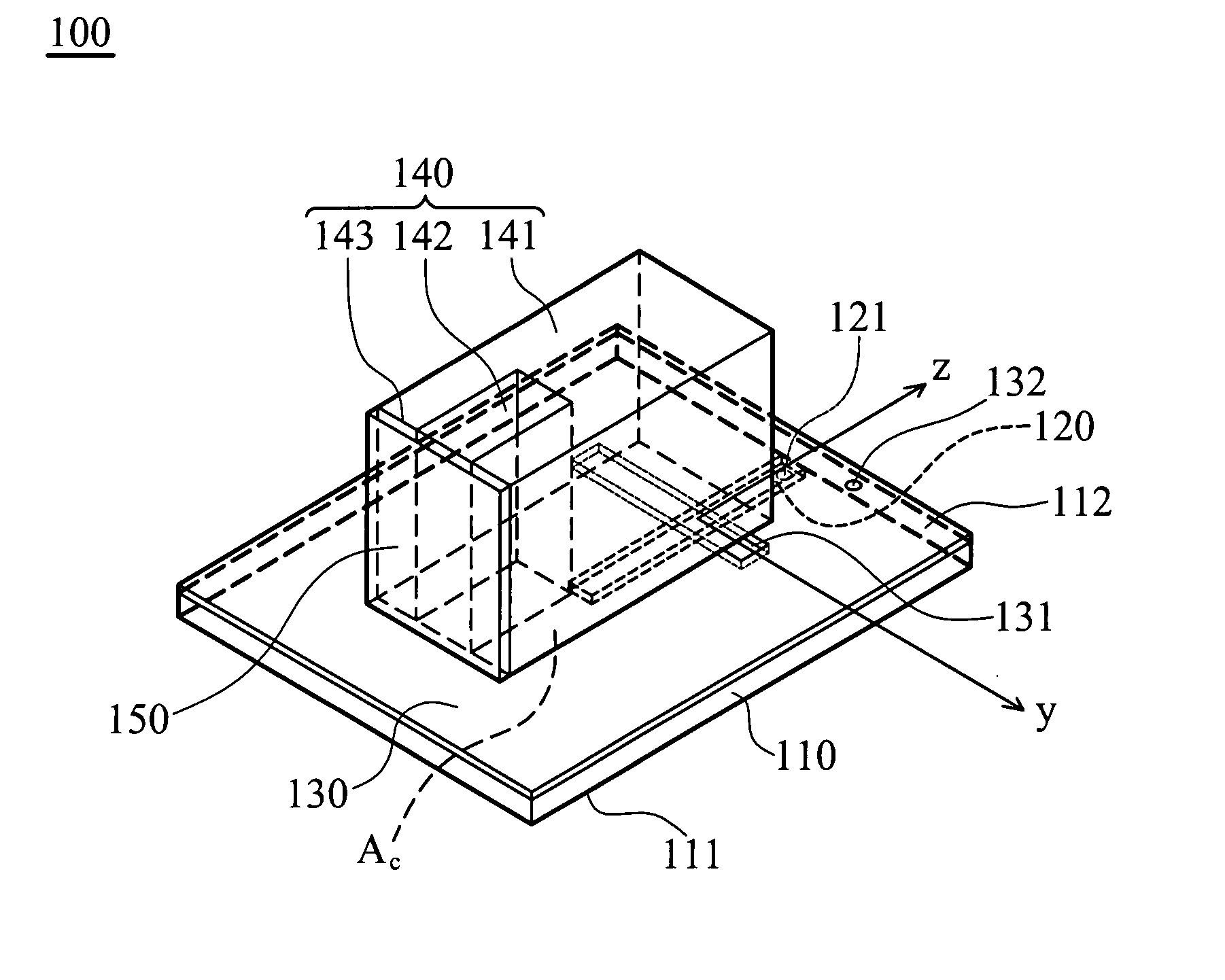

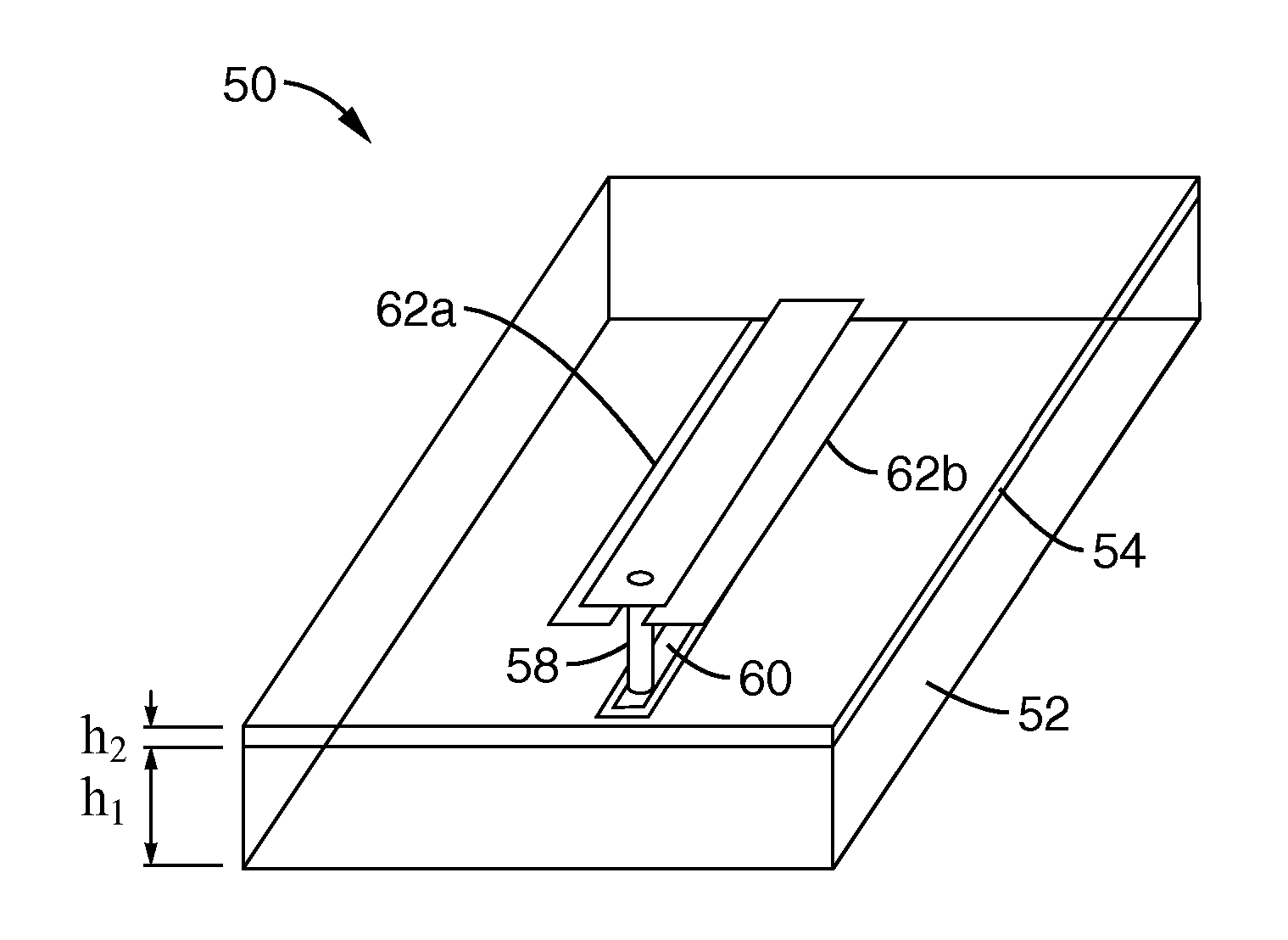

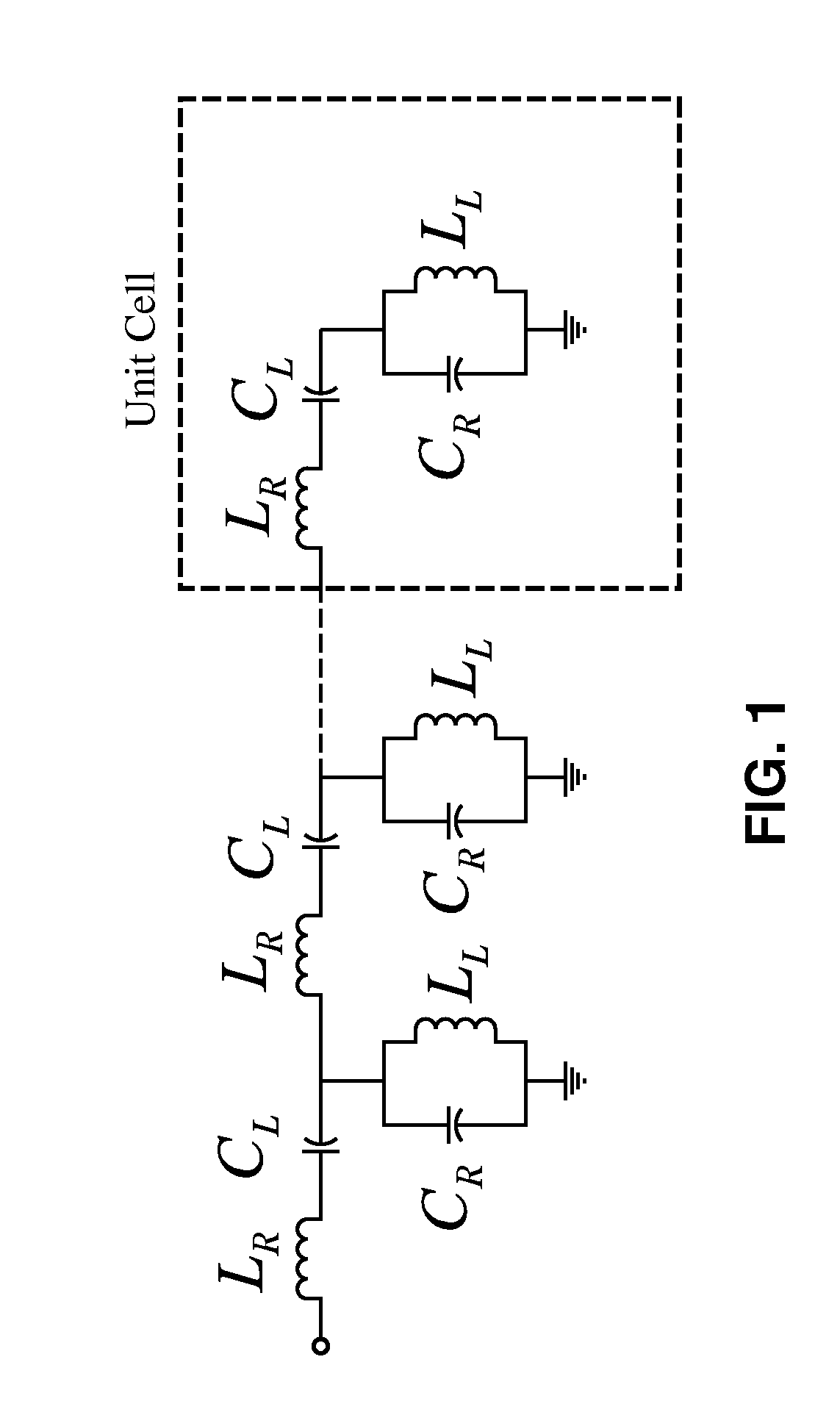

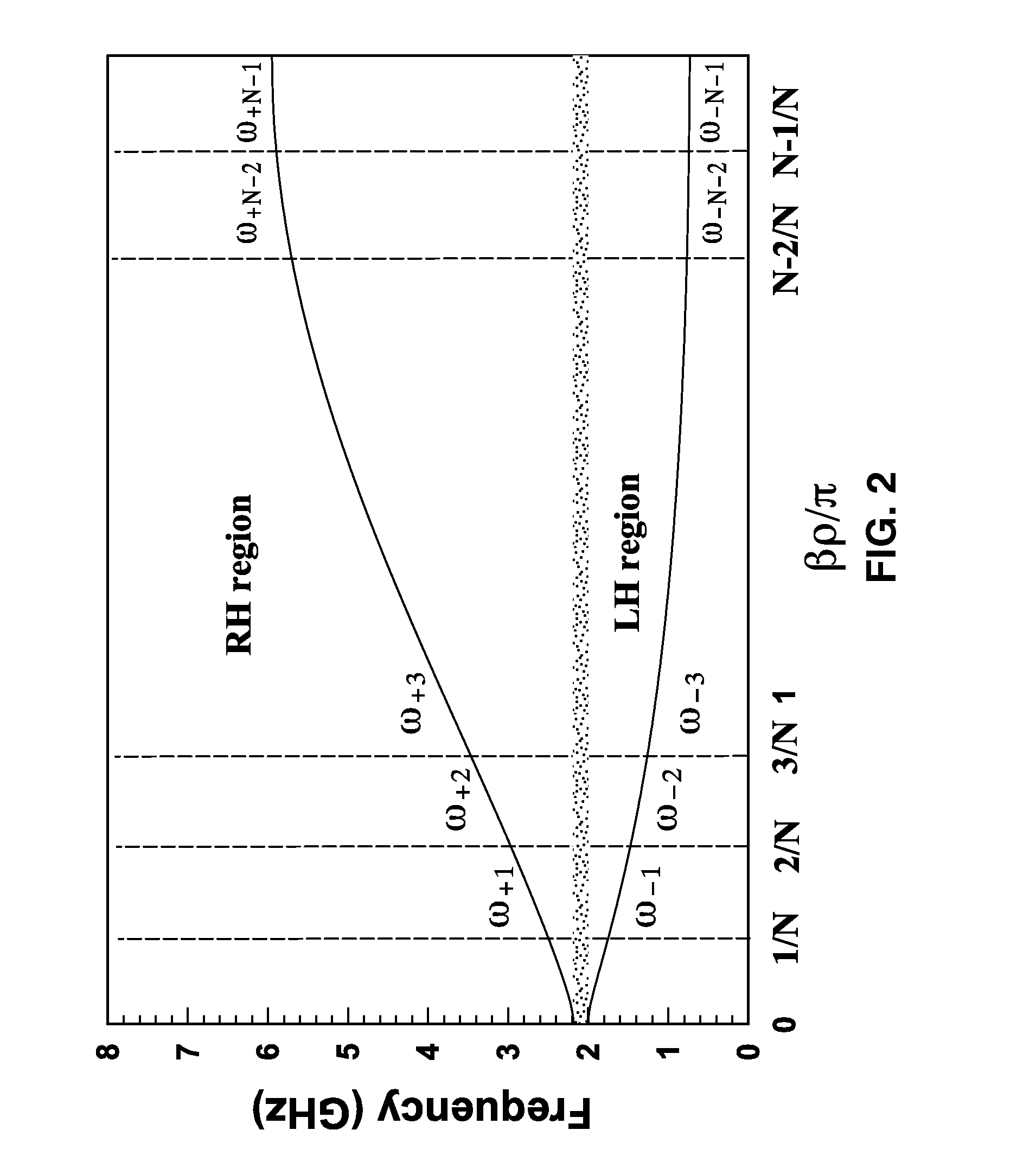

Composite right/left-handed transmission line based compact resonant antenna for RF module integration

ActiveUS20070176827A1Improve efficiencyAccurate manufacturing capabilitySimultaneous aerial operationsRadiating elements structural formsMetal-insulator-metalShunt capacitors

An apparatus based on composite right-handed or left-handed (CRLH) principles to provide a transmission line or antenna structure having a plurality of cells to which one or more feed ports are attached. The apparatus is based on an equivalent circuit Right-Hand (RH) series induction (LR) and shunt capacitor (CR), and Left-Hand (LH) series capacitor (CL) and induction (LL), in which effective permittivity (e) and permeability (m) of the structure are manipulated by the choice of CR, LR, CL, and LL. One embodiment describes mushroom antenna cells (1D or 2D array) in which vias extend up from a feed network on a ground plane through at least one dielectric region to each of a first plurality of conductive elements (plates or strips). Optionally, a second plurality of conductive elements are disposed between first and second dielectric layers to form metal-insulator-metal (MIM) capacitors to lower resonance frequency.

Owner:RGT UNIV OF CALIFORNIA

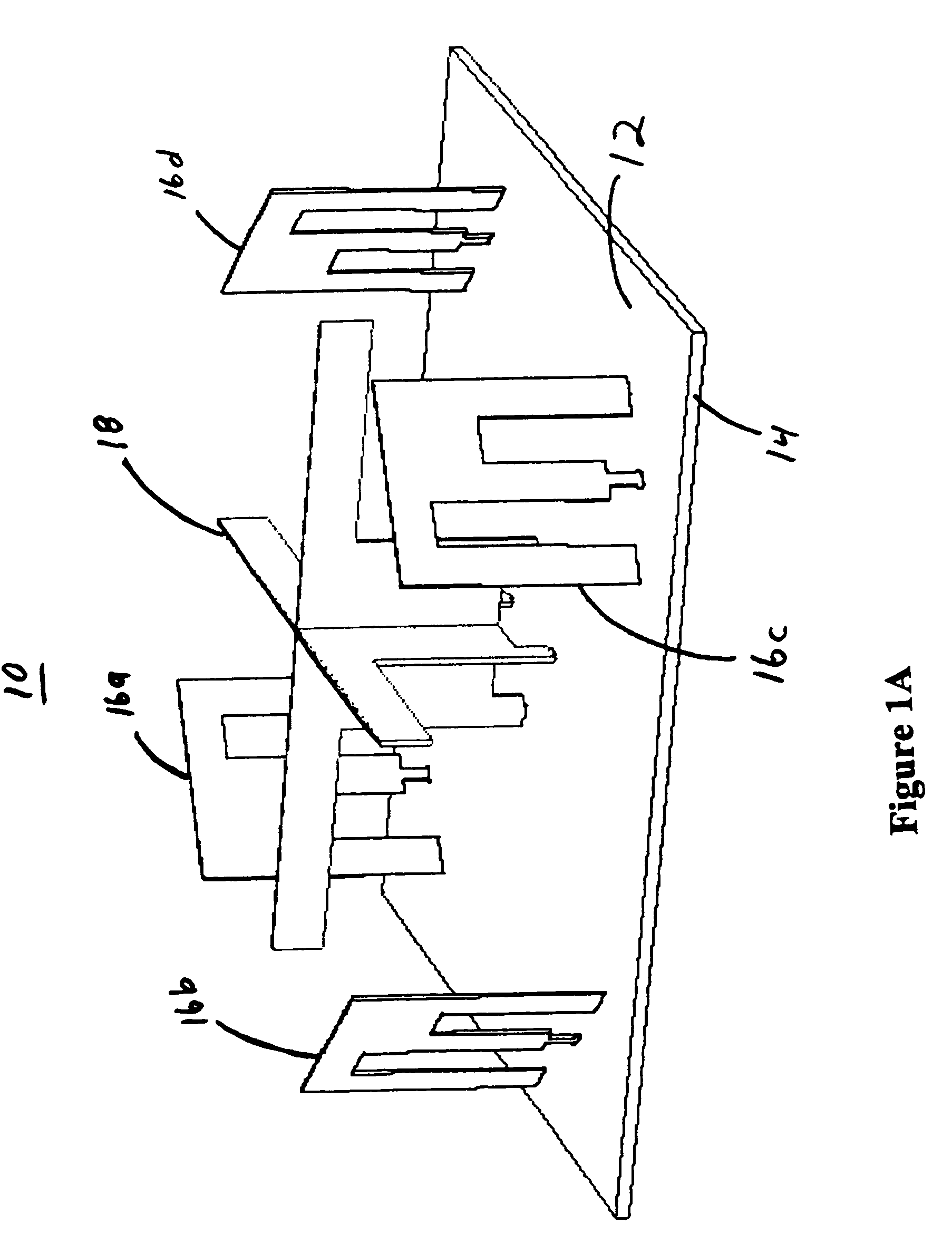

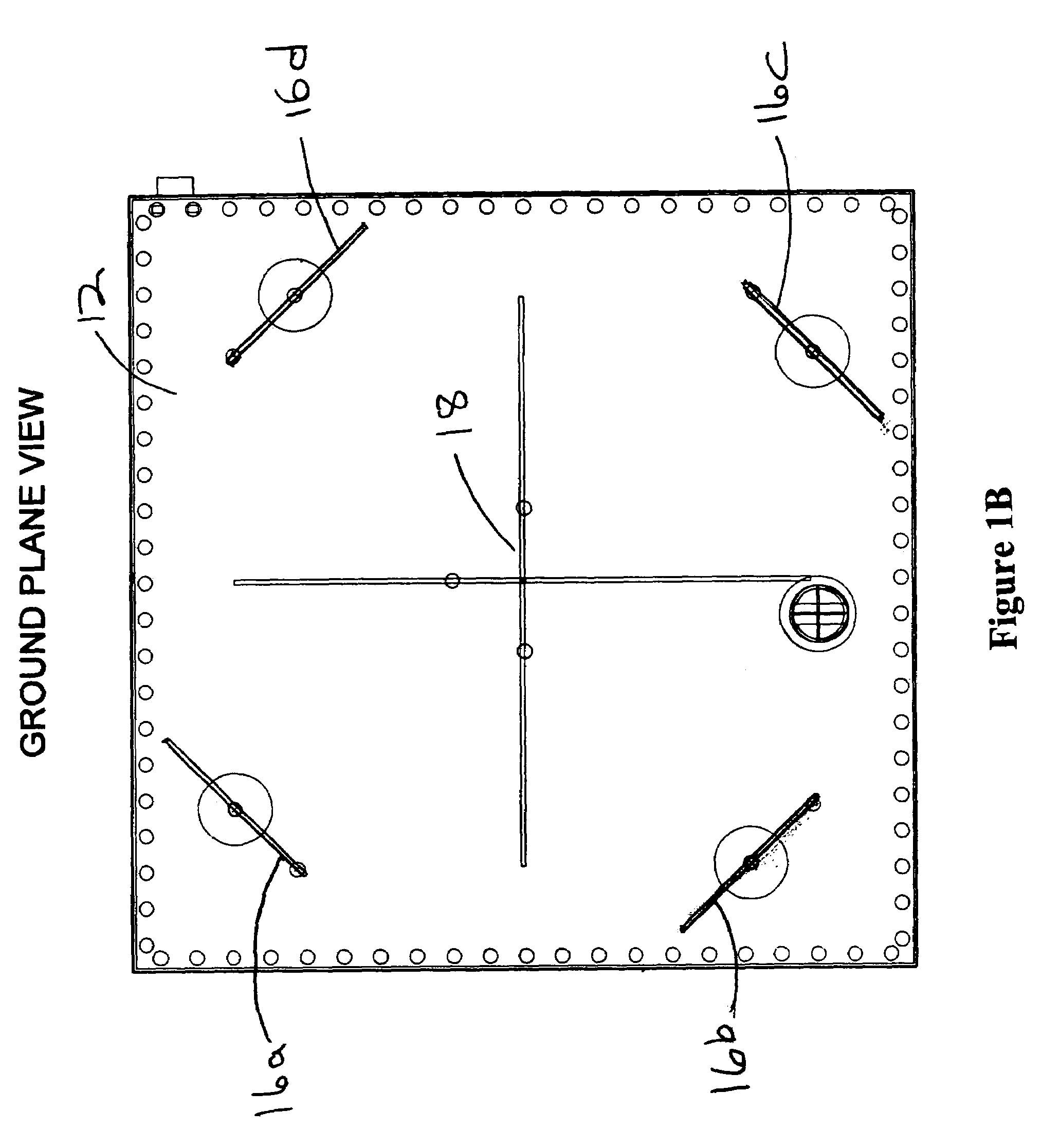

Dual feel multi-band planar antenna

InactiveUS6670923B1Reduce Design ComplexityCompromise performanceSimultaneous aerial operationsAntenna supports/mountingsMulti bandPlanar inverted f antenna

A three-band, two-antenna, assembly includes a planar inverted-F antenna (PIFA) having a radiating / receiving element that is spaced from and extends generally parallel to a ground plane element. The planar radiating / receiving element of an inverted-F antenna (IFA) is located in an open space that exists between the radiating / receiving element of the PIFA and the ground plane element. The radiating / receiving element of the IFA extends either perpendicular to, or parallel to, the radiating / receiving element of the PIFA. The radiating / receiving element of the PIFA includes one or more open slot configurations that operate to provide dual resonant frequencies for the IPFA (AMPS / PCS or GSM / DCS). The radiating / receiving element of the IFA operates in a non-cellular frequency band (ISM or GPS).

Owner:LAIRD CONNECTIVITY LLC

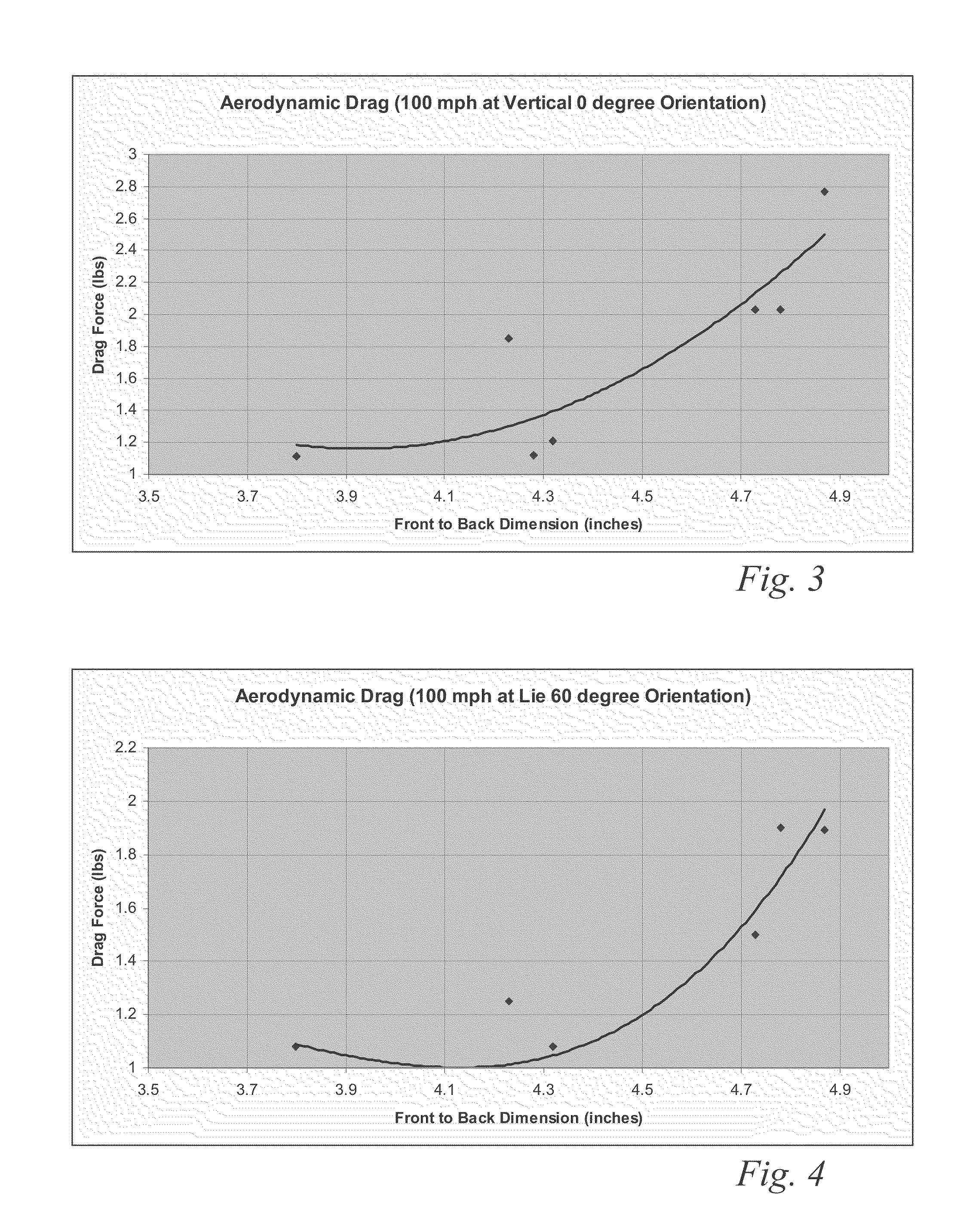

High volume aerodynamic golf club head

ActiveUS8083609B2Improve aerodynamic performanceIncrease volumeGolf clubsRacket sportsAerodynamic dragGround plane

A high volume aerodynamic golf club head with a club head volume of at least 400 cc and a front-to-back dimension of at least 4.4 inches producing a face-on normalized aerodynamic drag force of less than 1.5 lbf when exposed to a 100 mph wind parallel to the ground plane and oriented at the front of the club head. The club head has a crown section having a crown apex located an apex height above a ground plane, wherein a portion of the crown section between the crown apex and the face has an apex-to-front radius of curvature that is less than 3 inches. An apex ratio of the apex height to a maximum face top edge height is at least 1.13. The apex height and location of the crown apex obtain desirable airflow reattachment close to the face and improve airflow attachment to the crown section.

Owner:TAYLOR MADE GOLF