Patents

Literature

599 results about "Metal-insulator-metal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Metal-insulator-metal (MIM) diode is a type of nonlinear device very similar to a semiconductor diode that is capable of very fast operation. Depending on the geometry and the material used for fabrication, the operation mechanisms are governed either by quantum tunnelling or thermal activation.

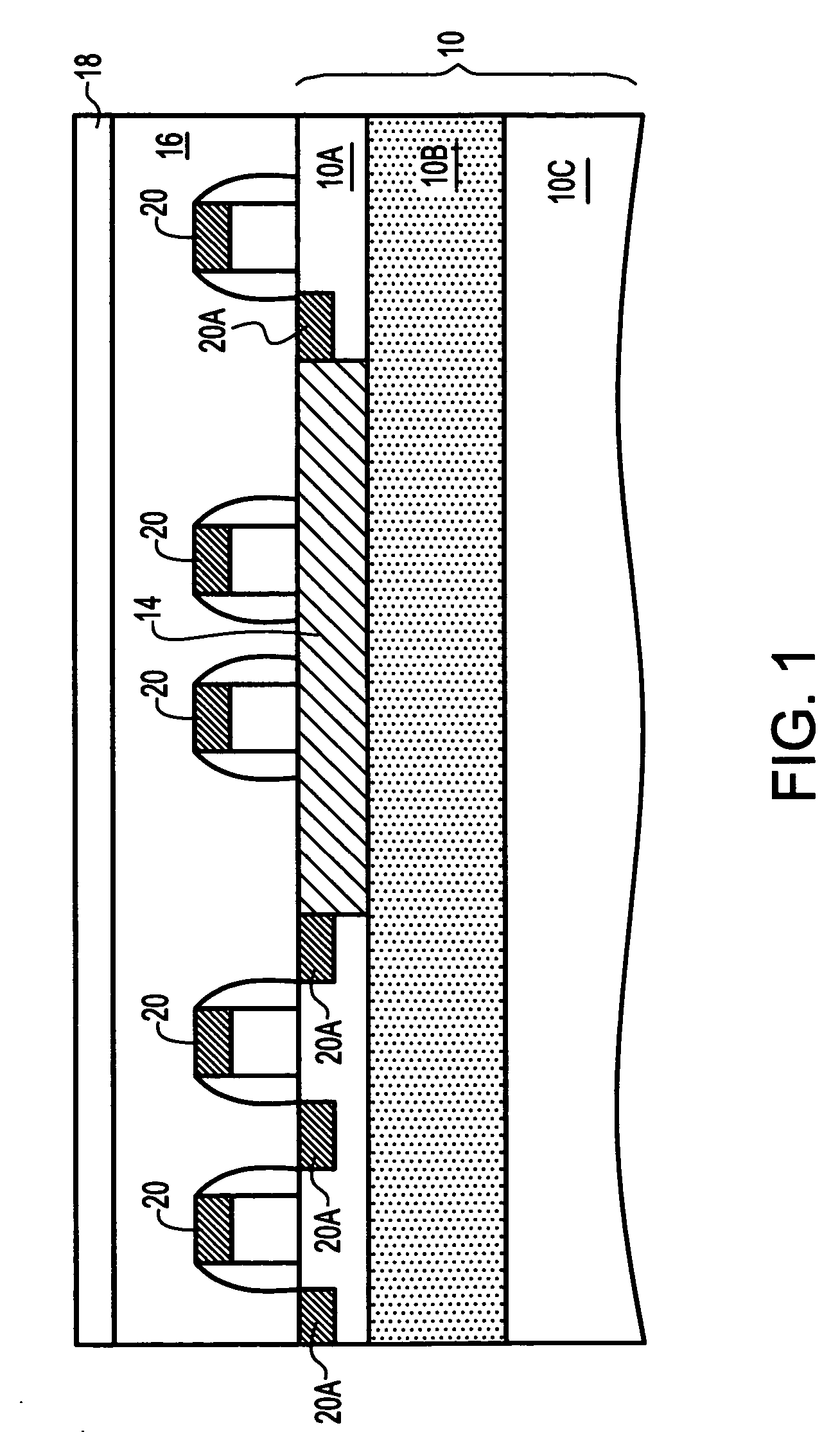

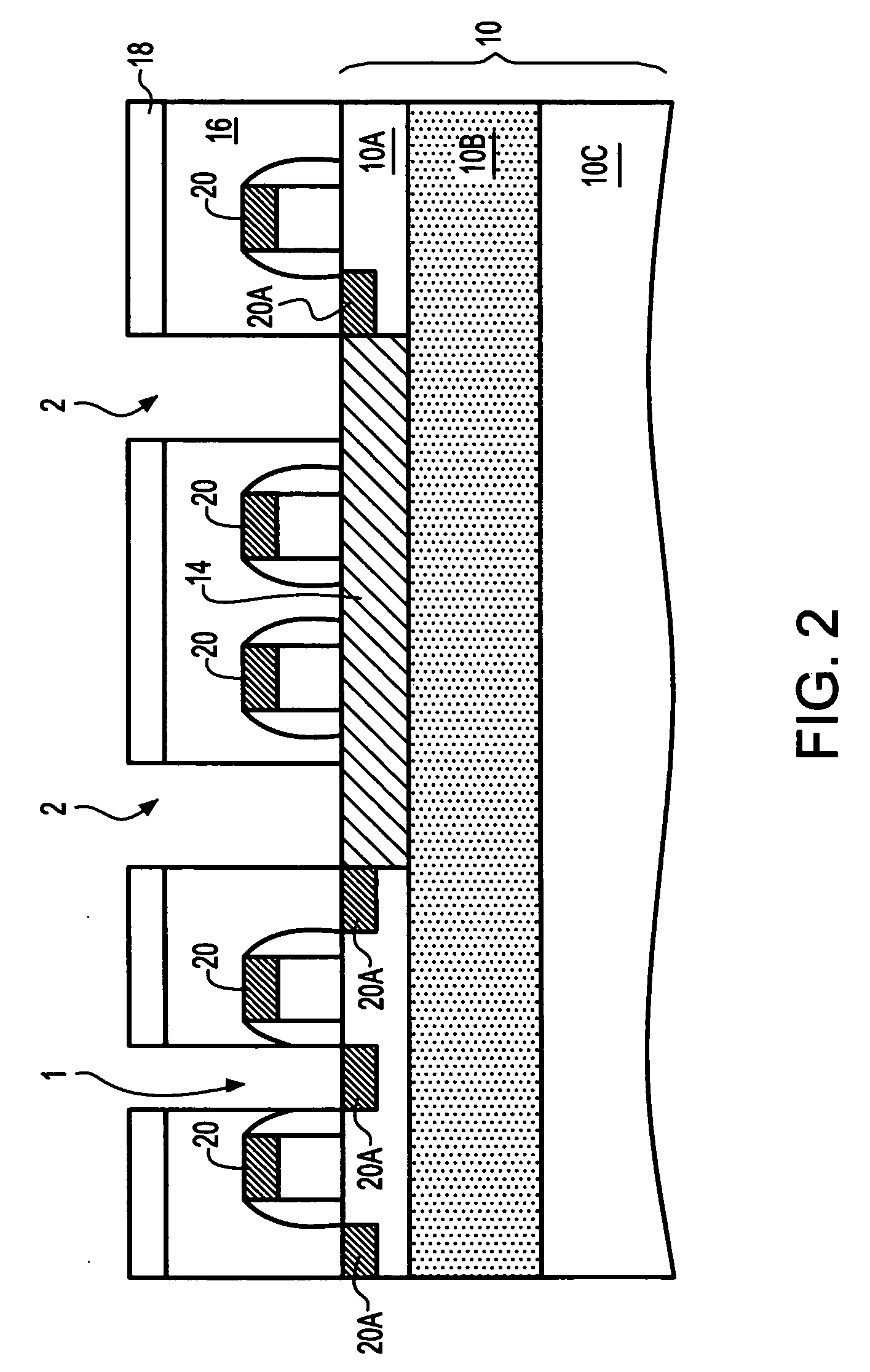

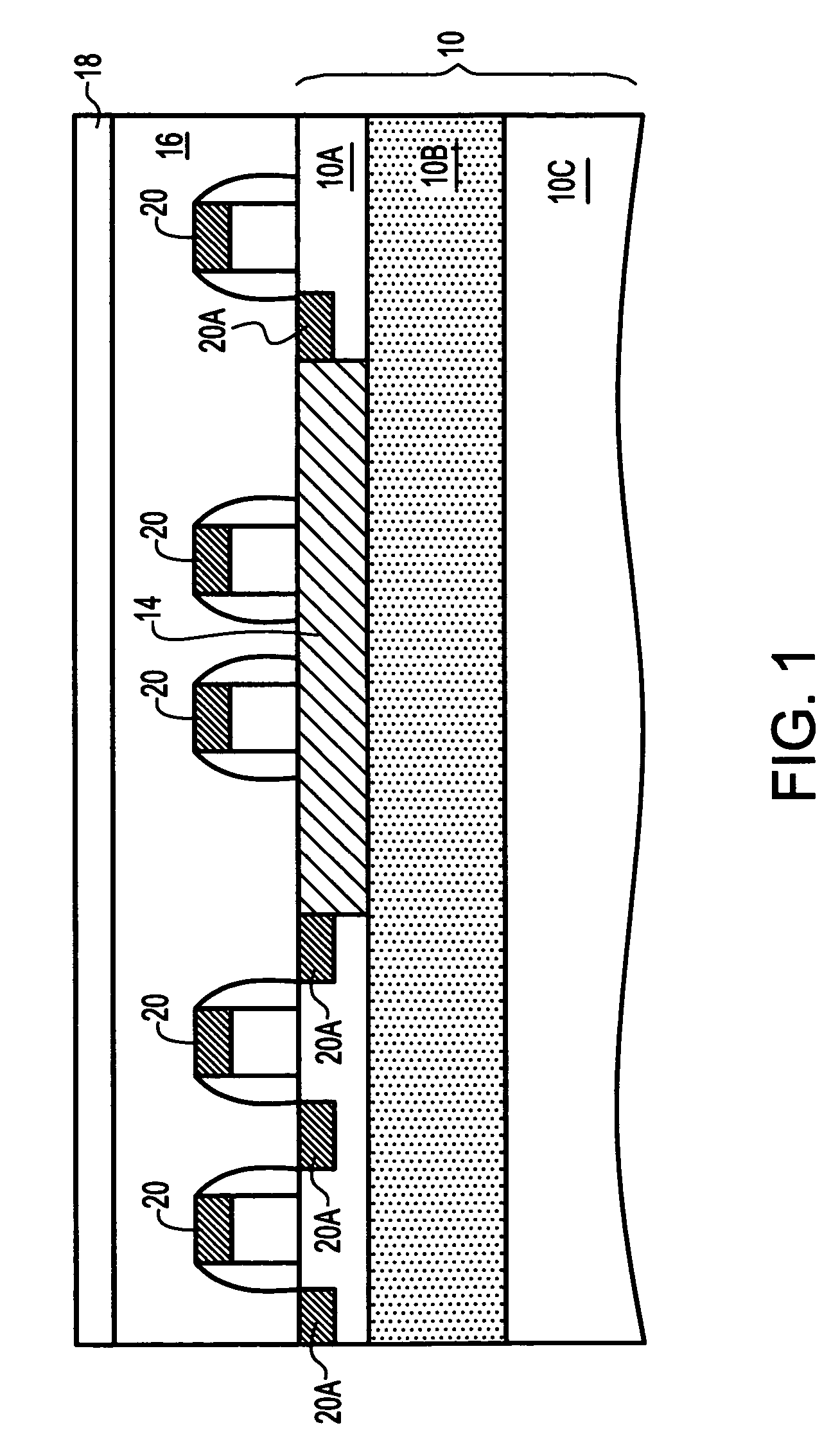

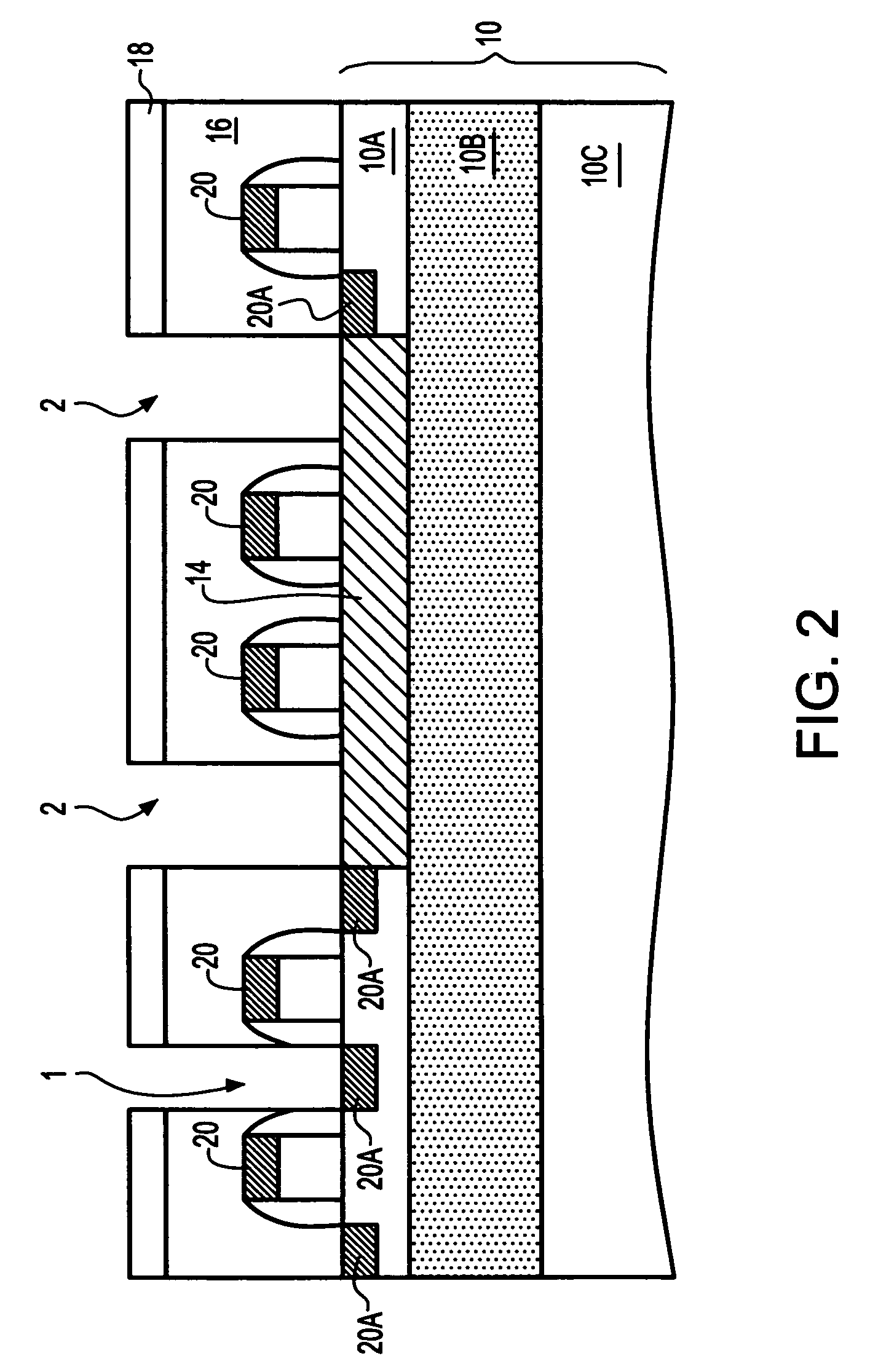

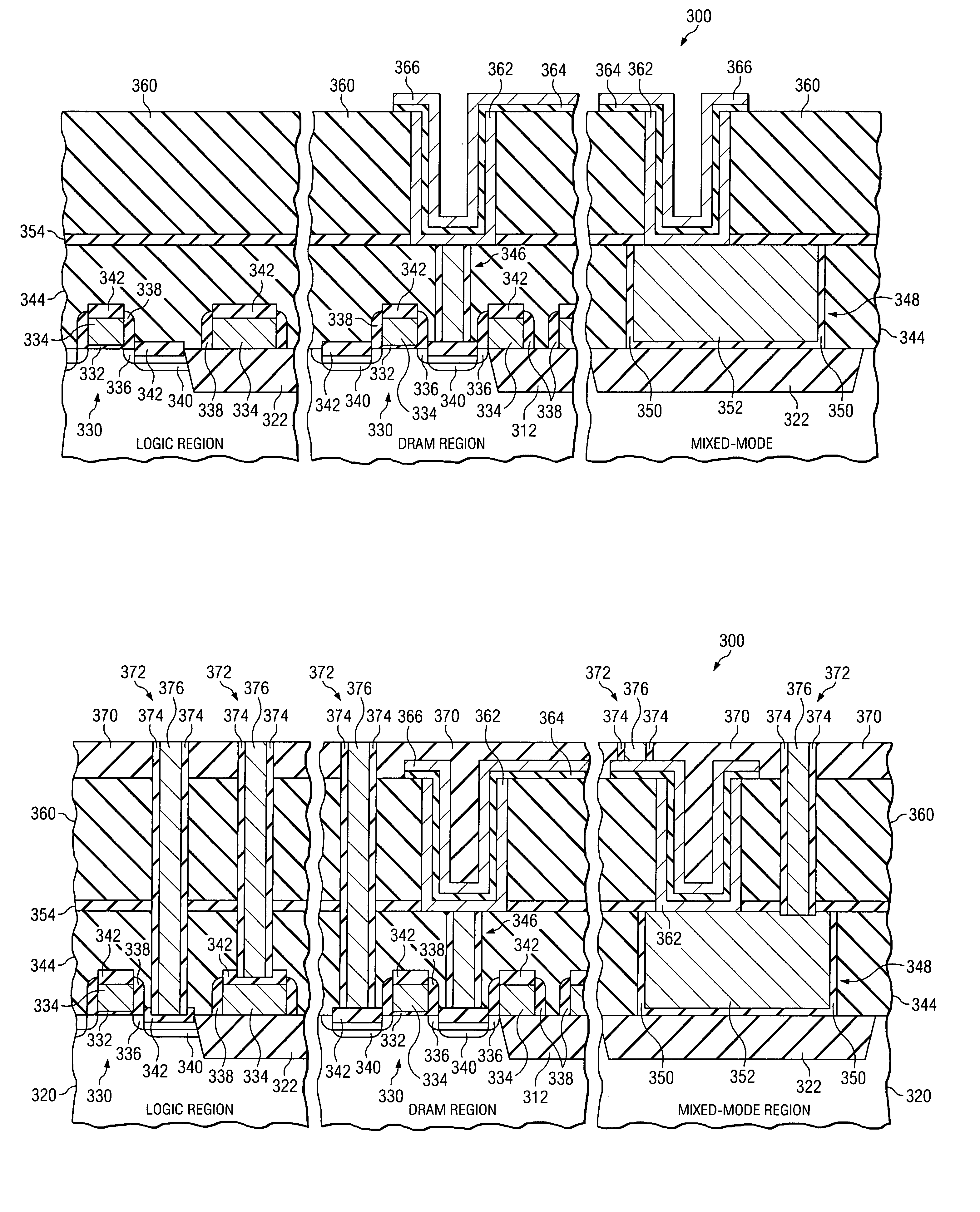

Method and structure for a 1T-RAM bit cell and macro

InactiveUS7425740B2Increase capacitanceTransistorSolid-state devicesMetal-insulator-metalCapacitance

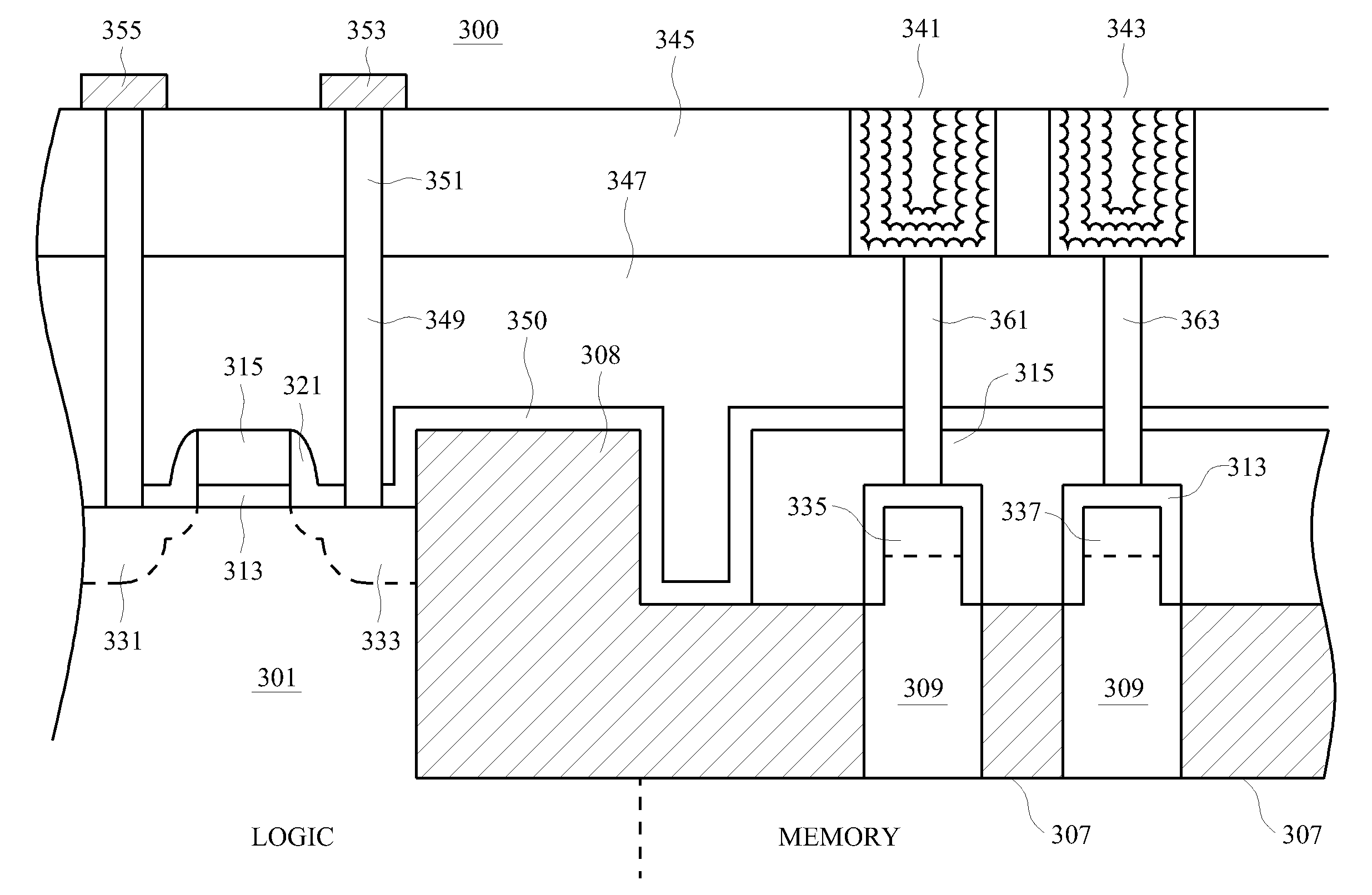

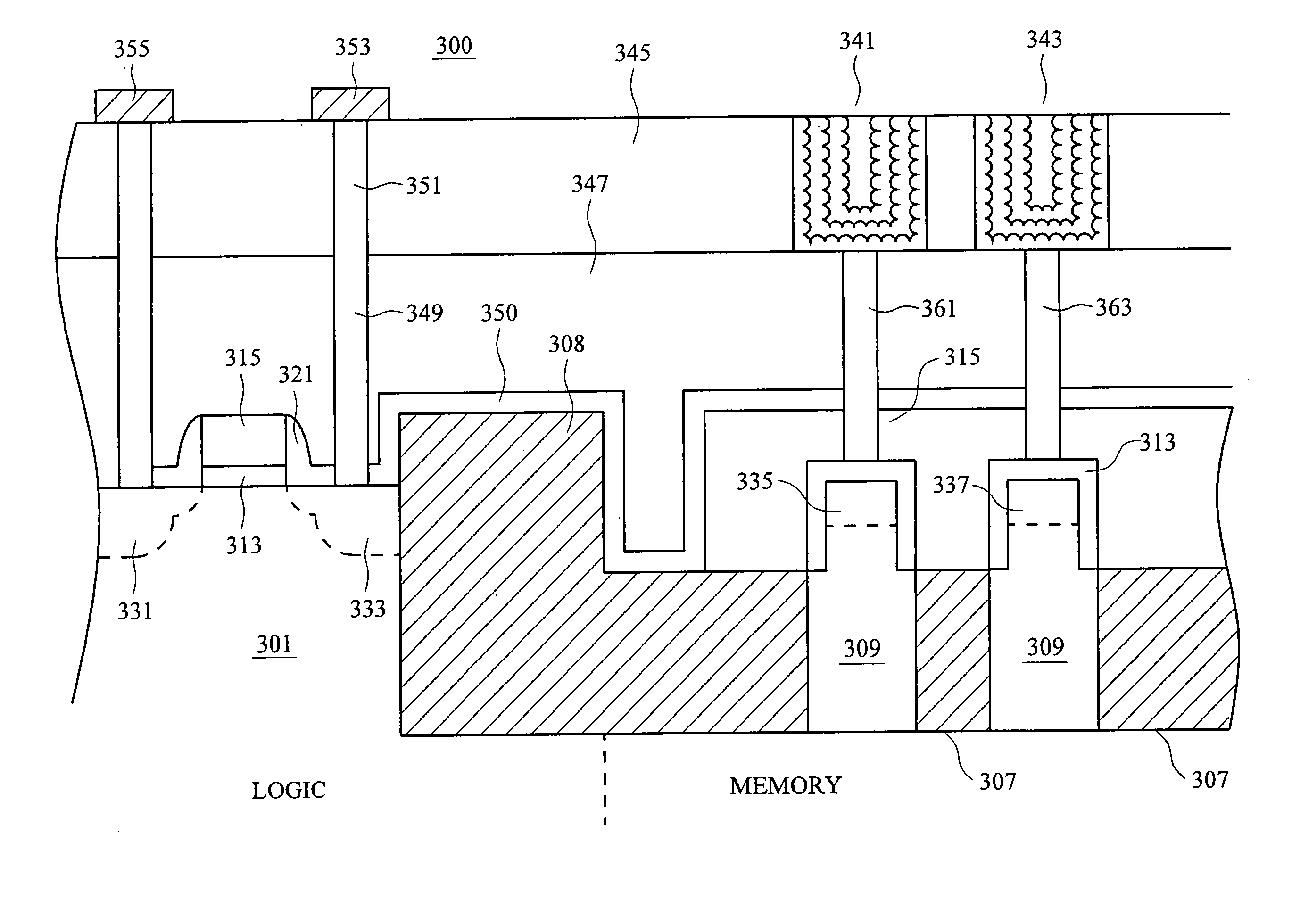

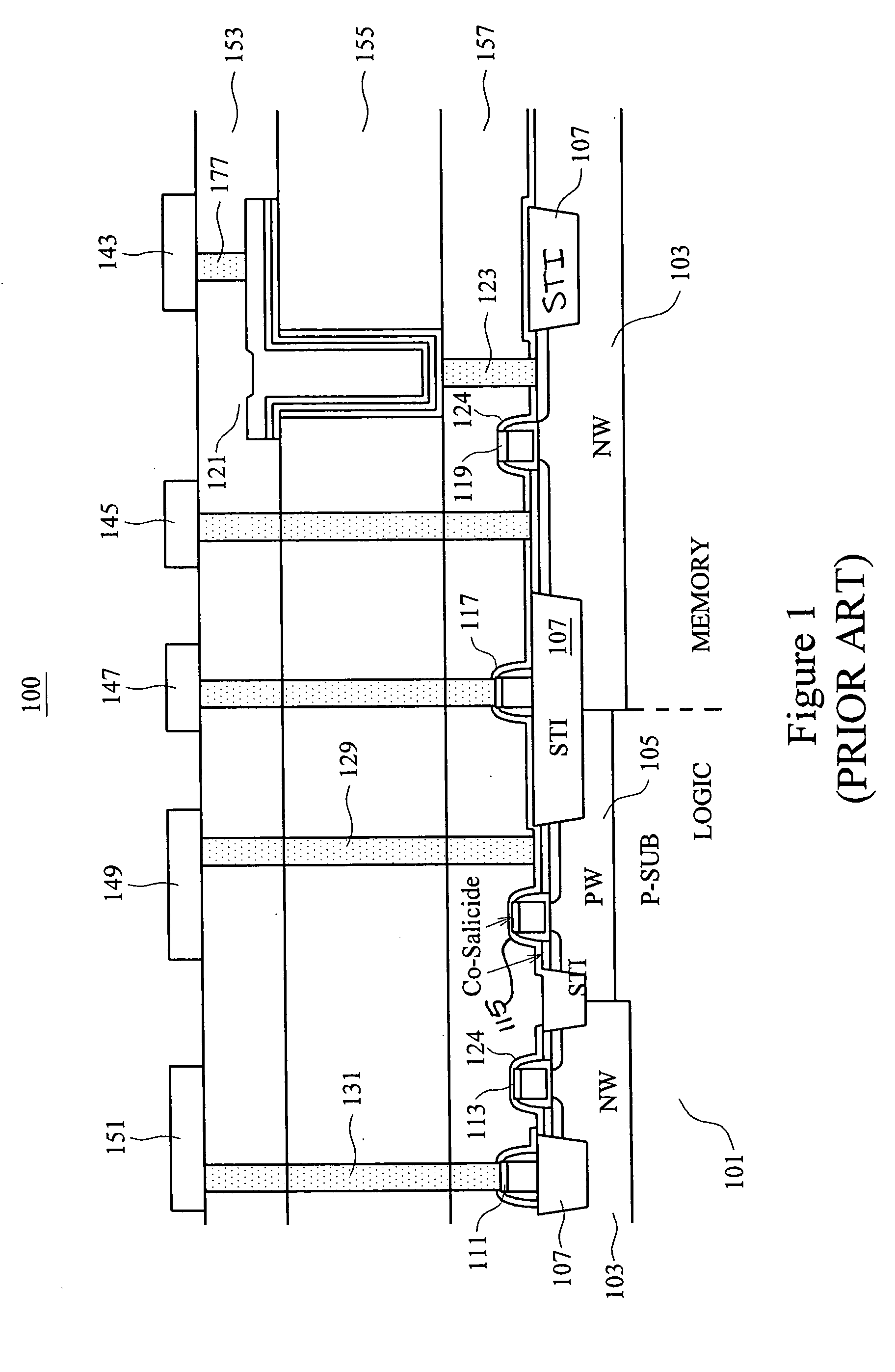

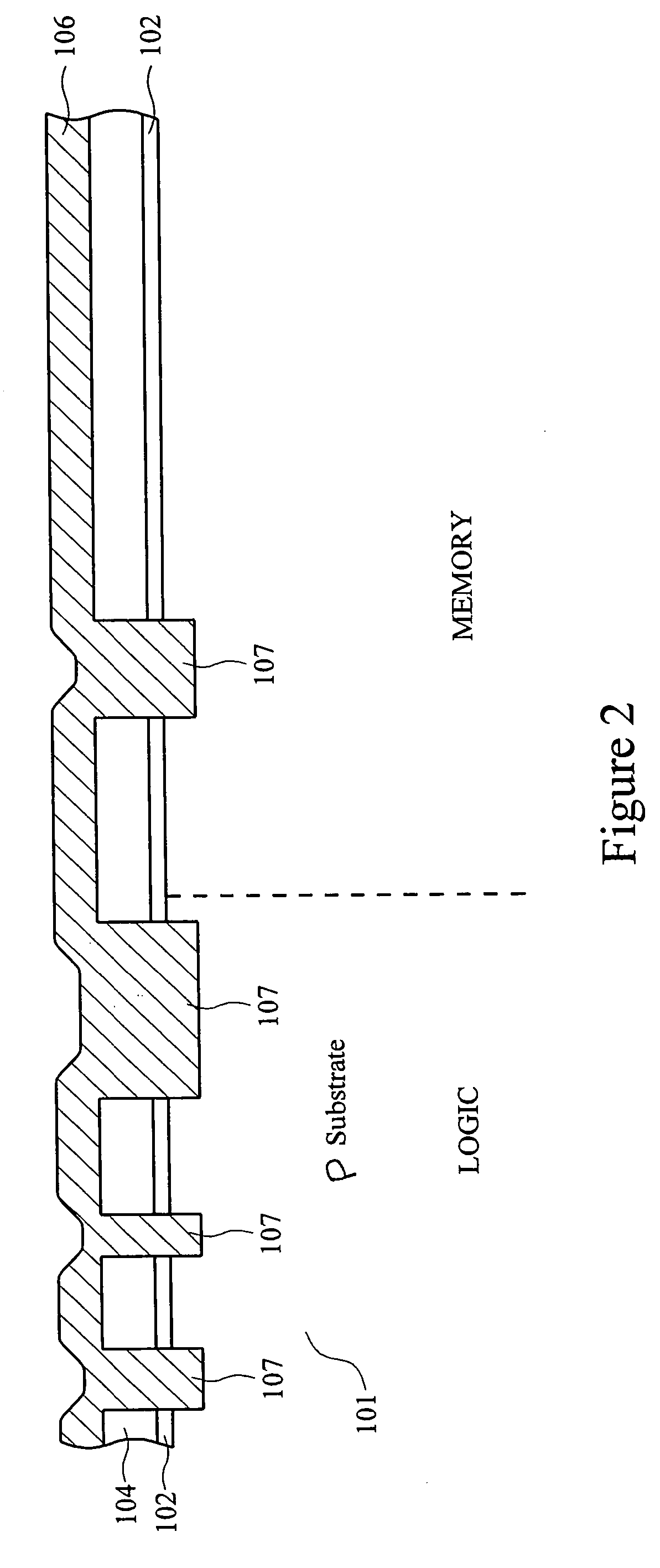

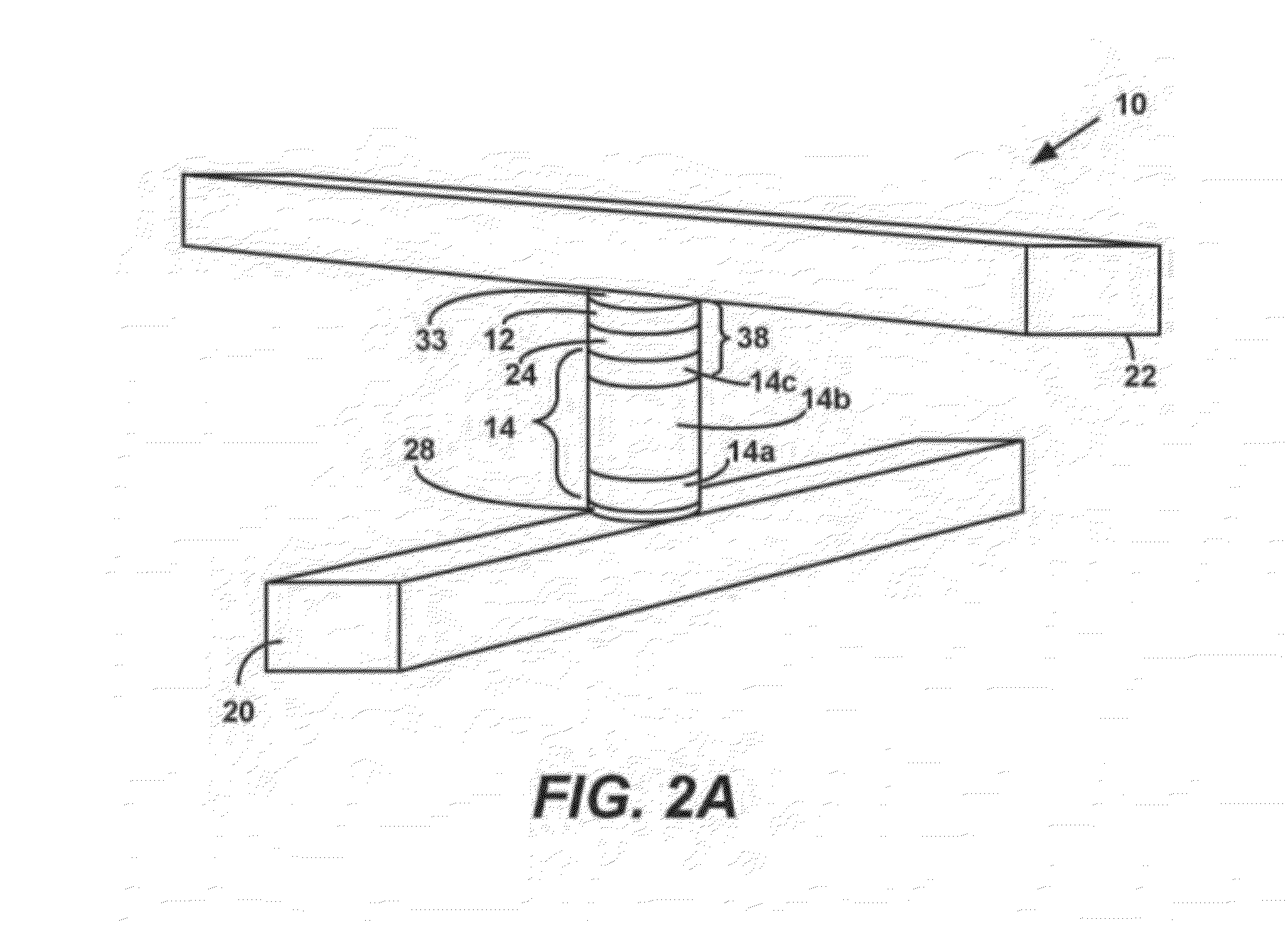

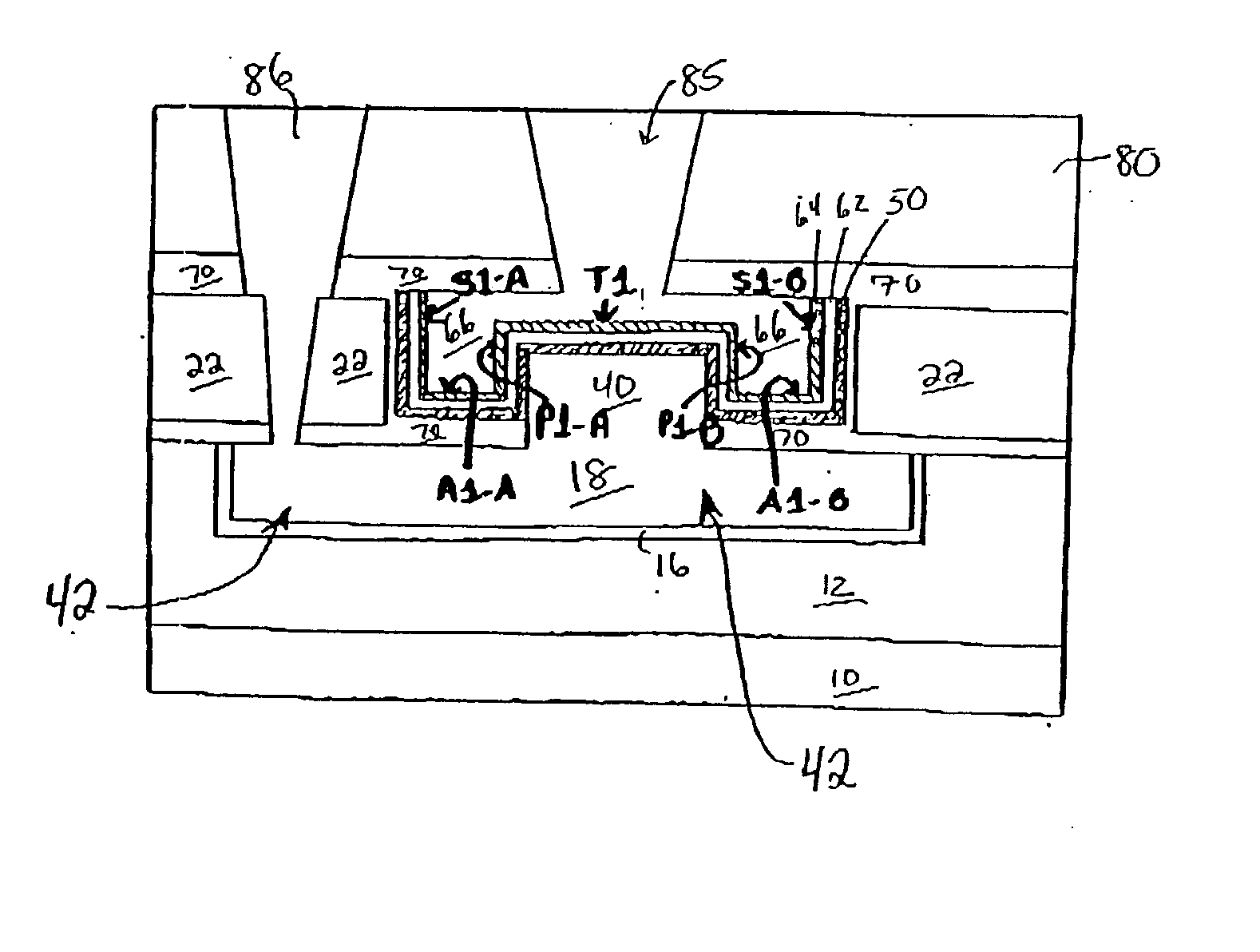

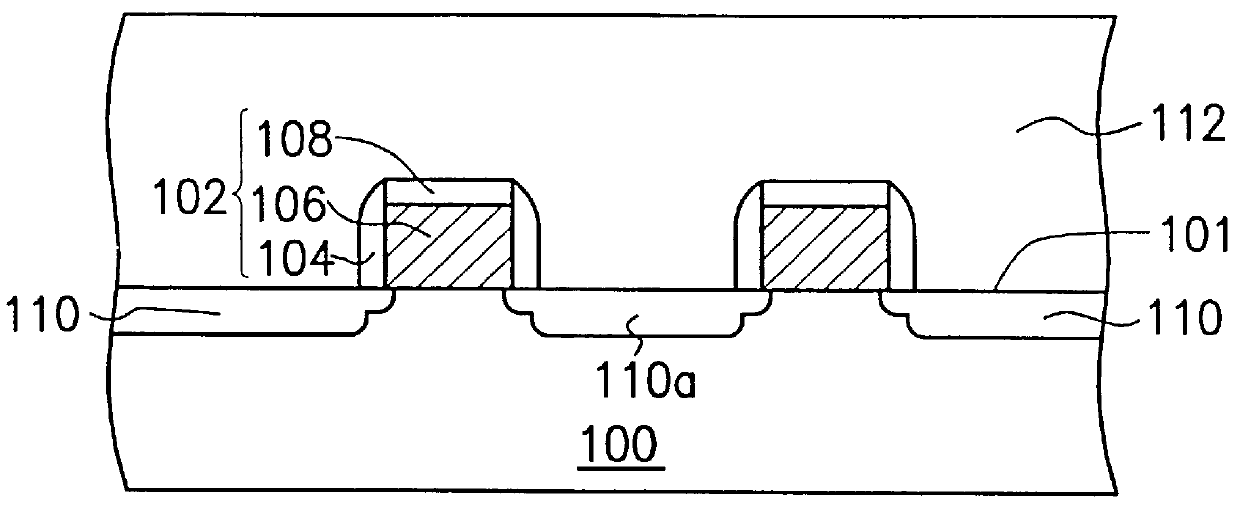

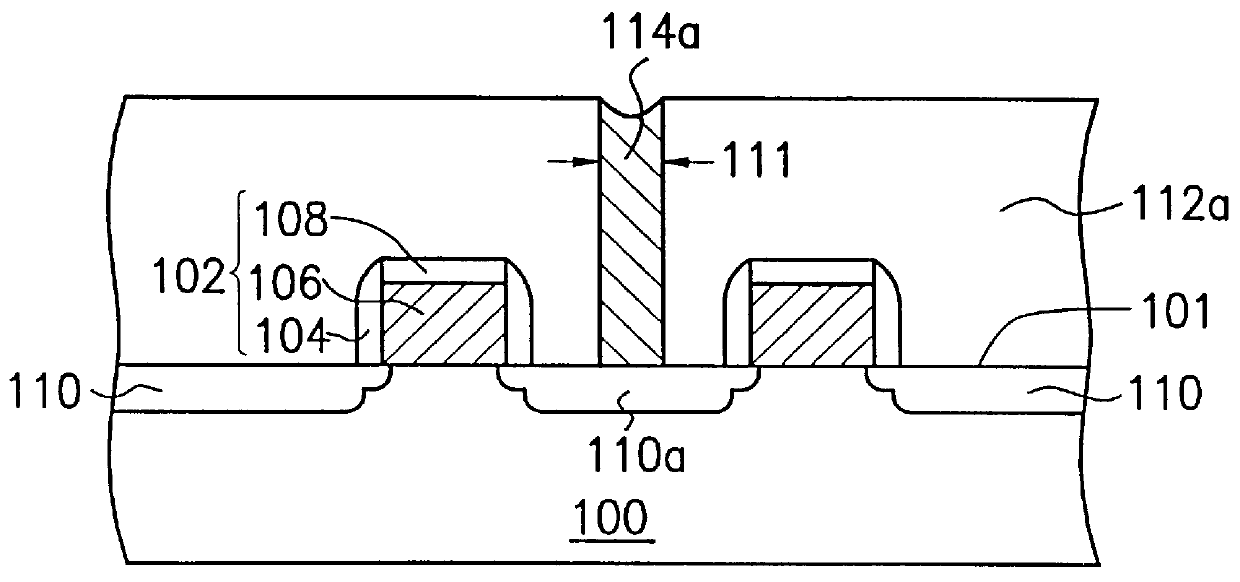

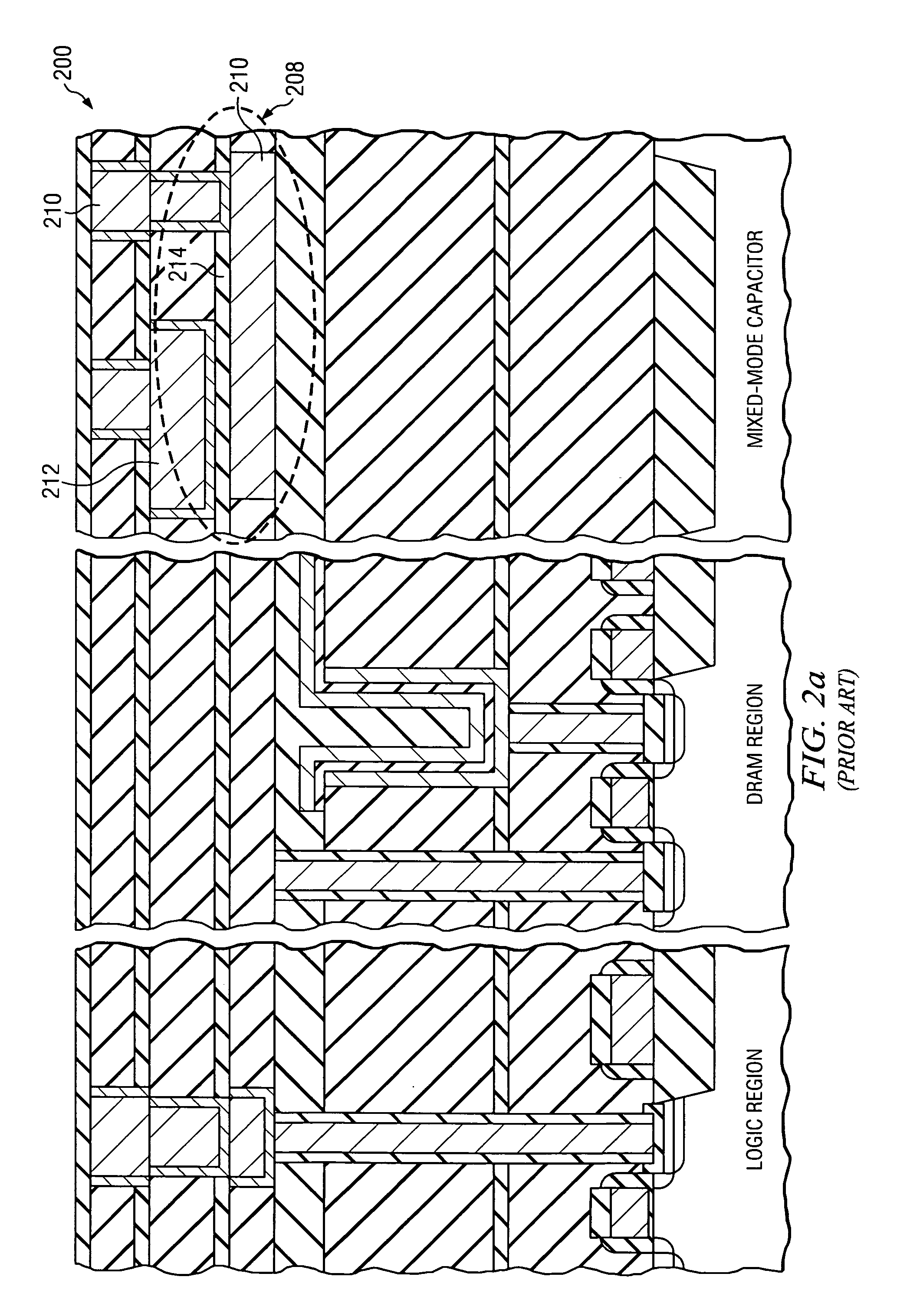

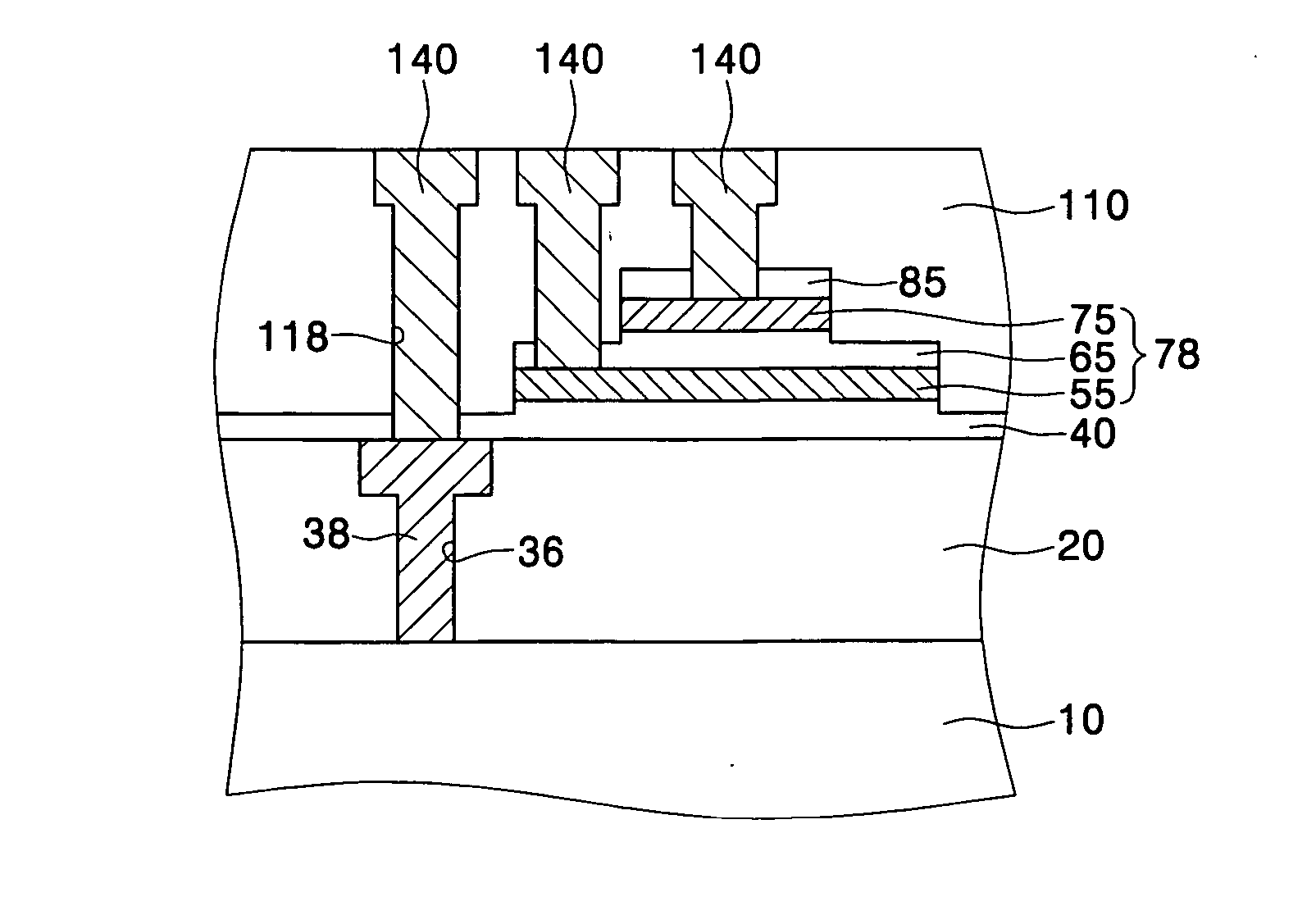

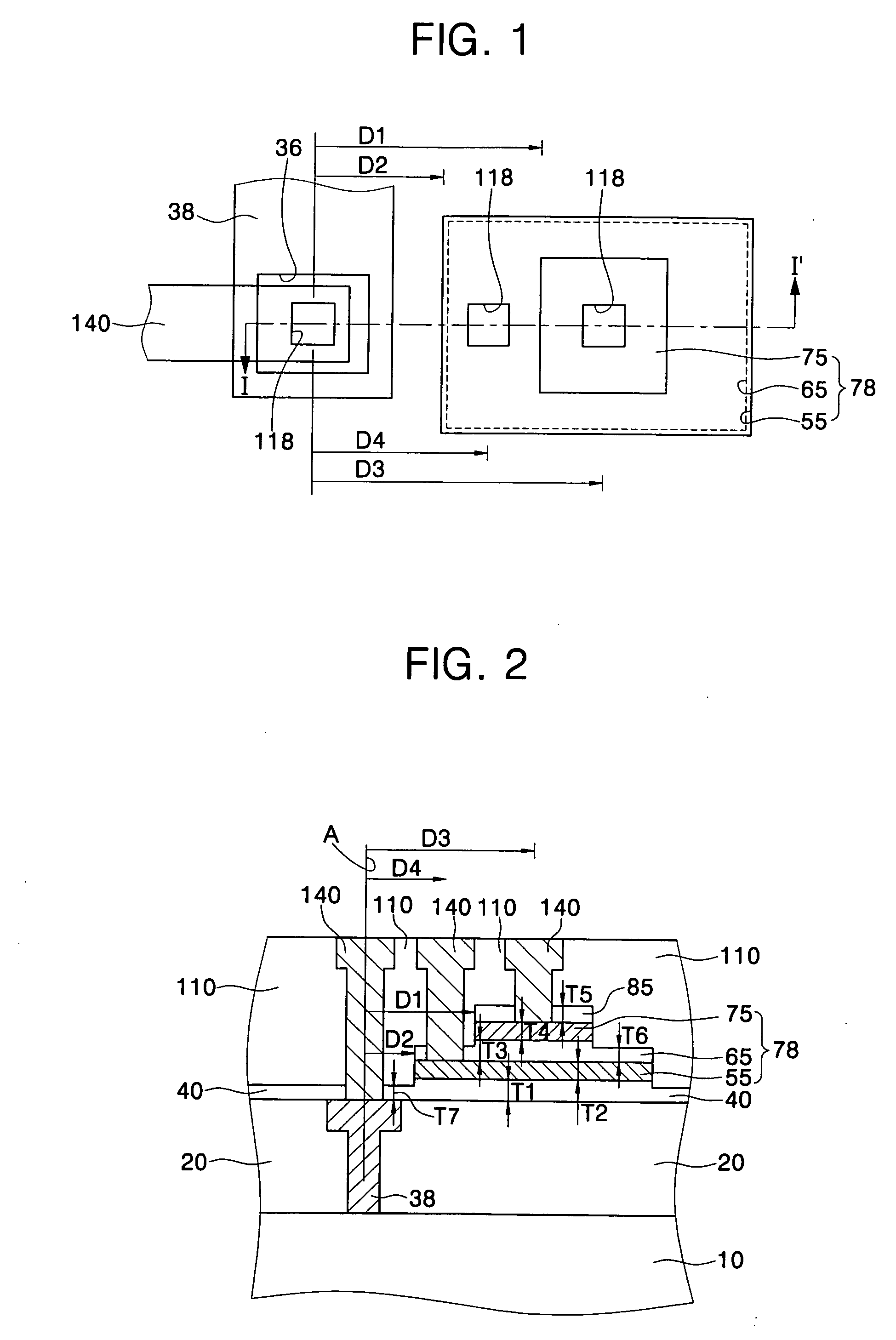

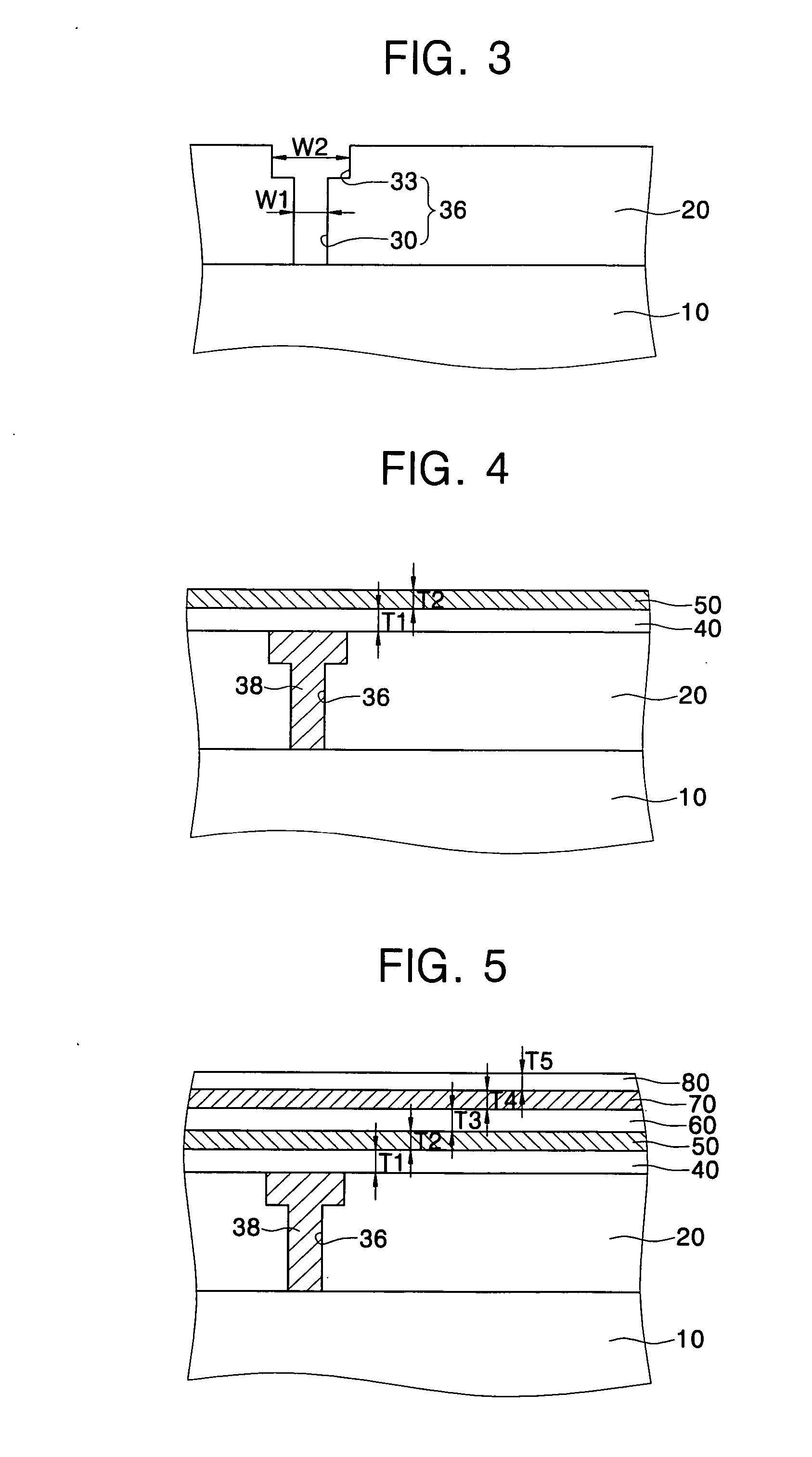

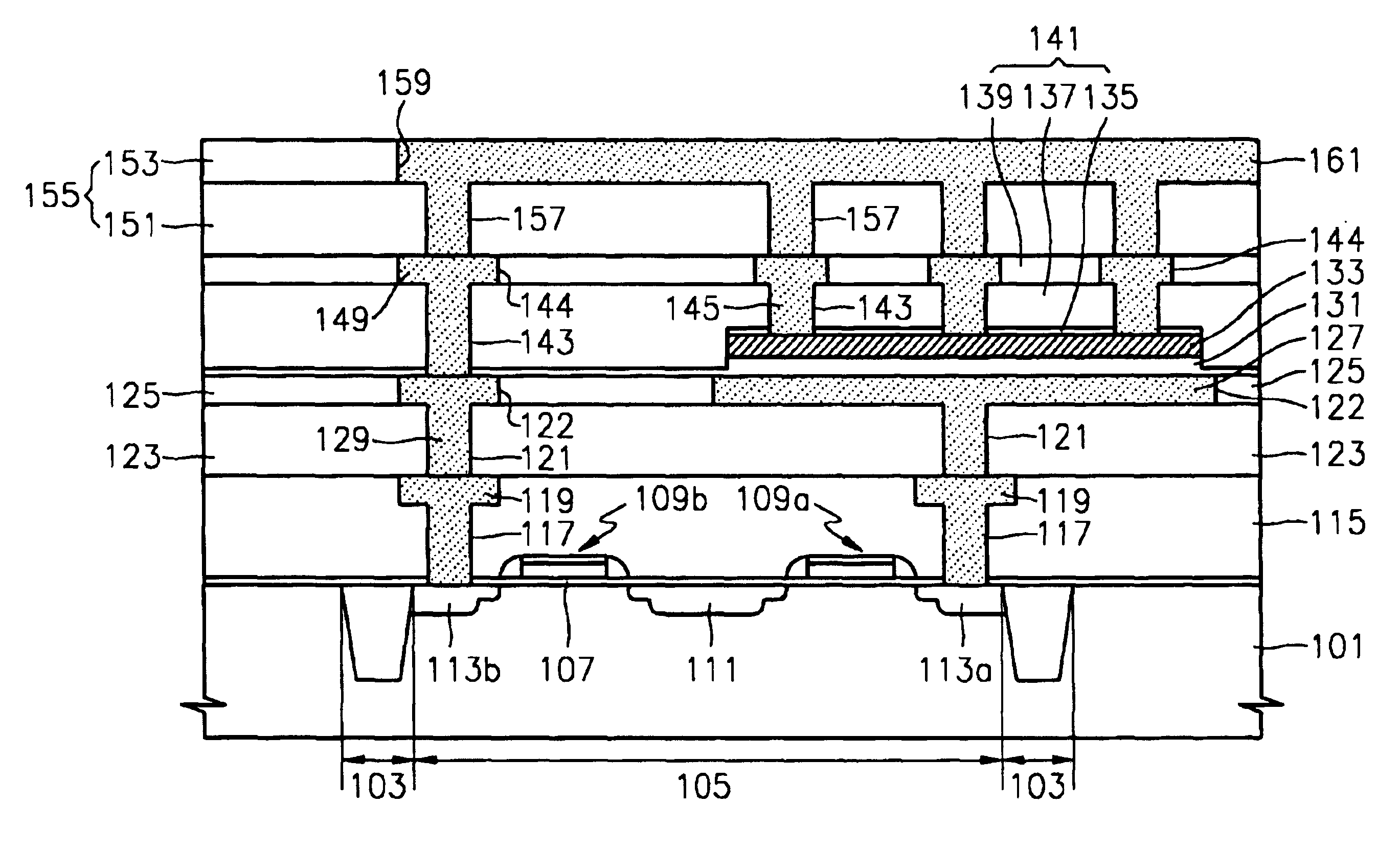

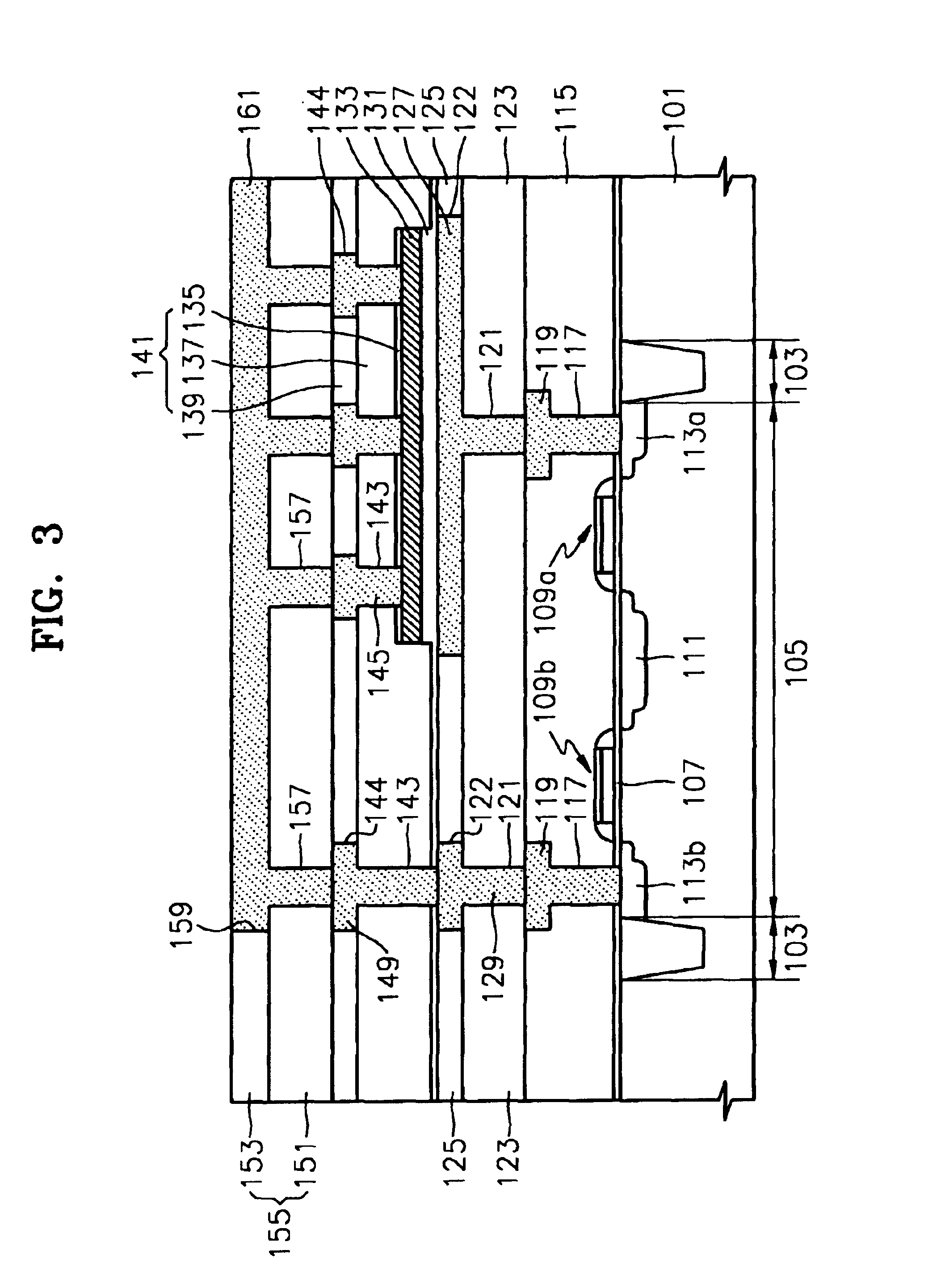

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

Composite right/left-handed transmission line based compact resonant antenna for RF module integration

ActiveUS20070176827A1Improve efficiencyAccurate manufacturing capabilitySimultaneous aerial operationsRadiating elements structural formsMetal-insulator-metalShunt capacitors

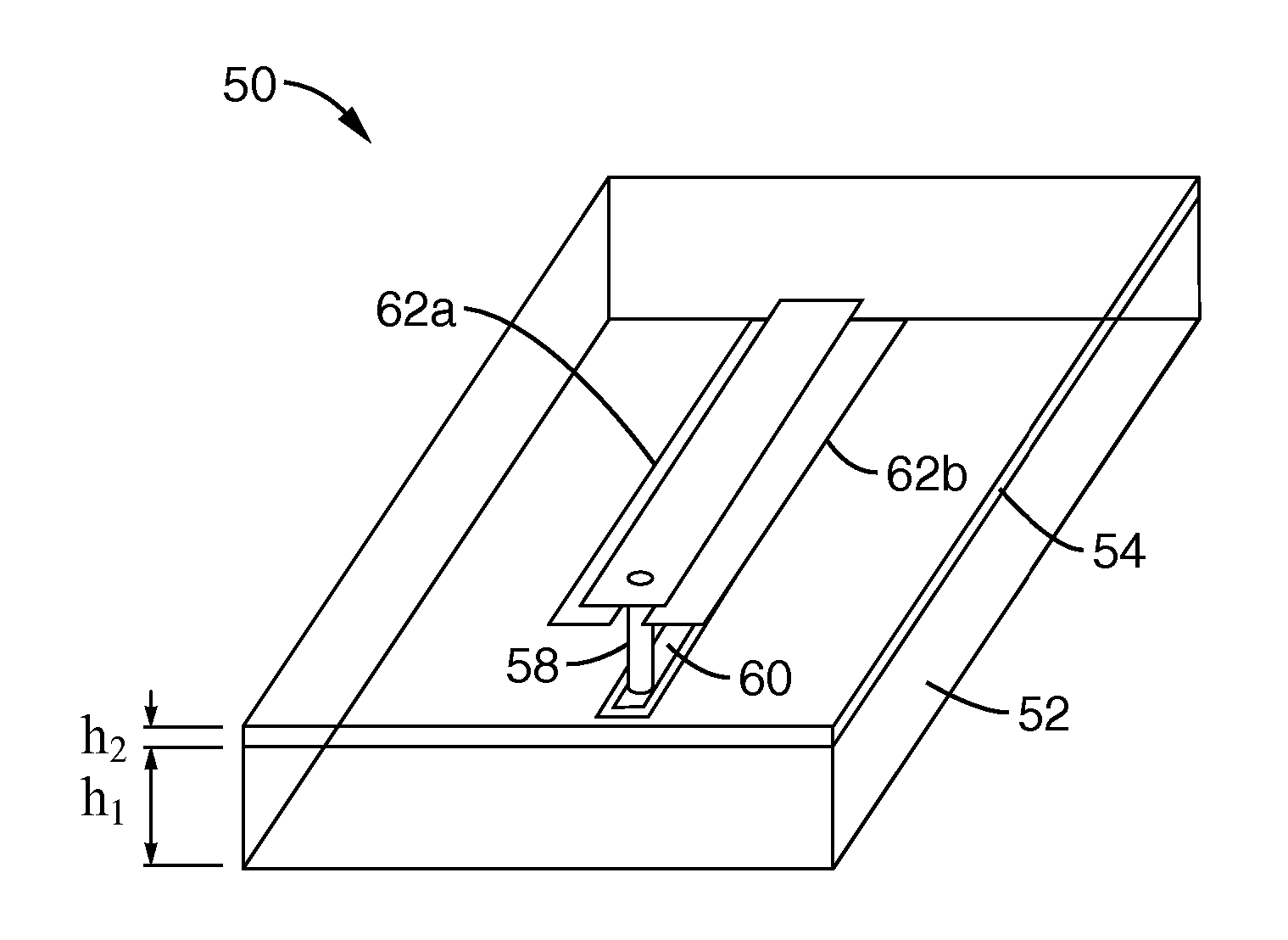

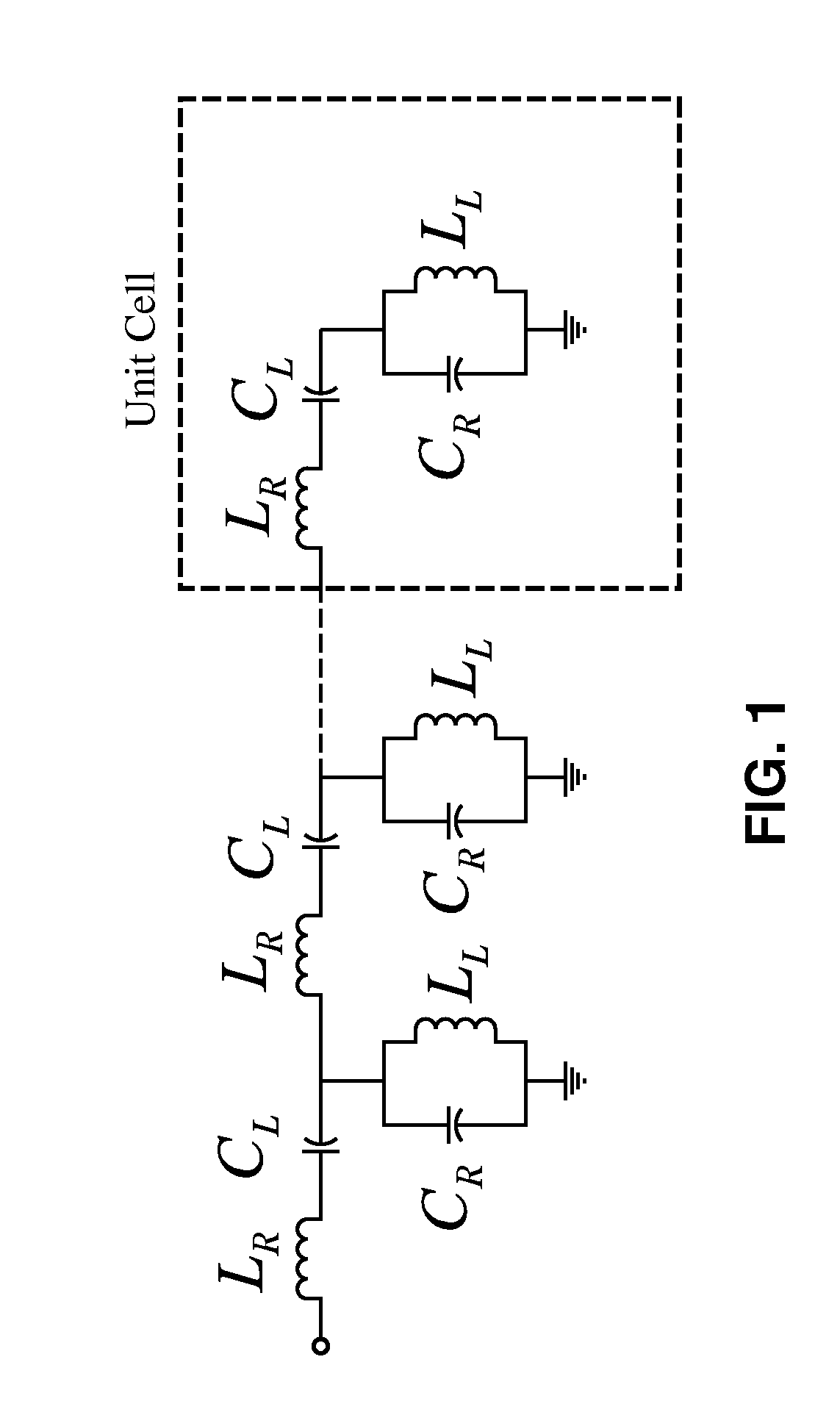

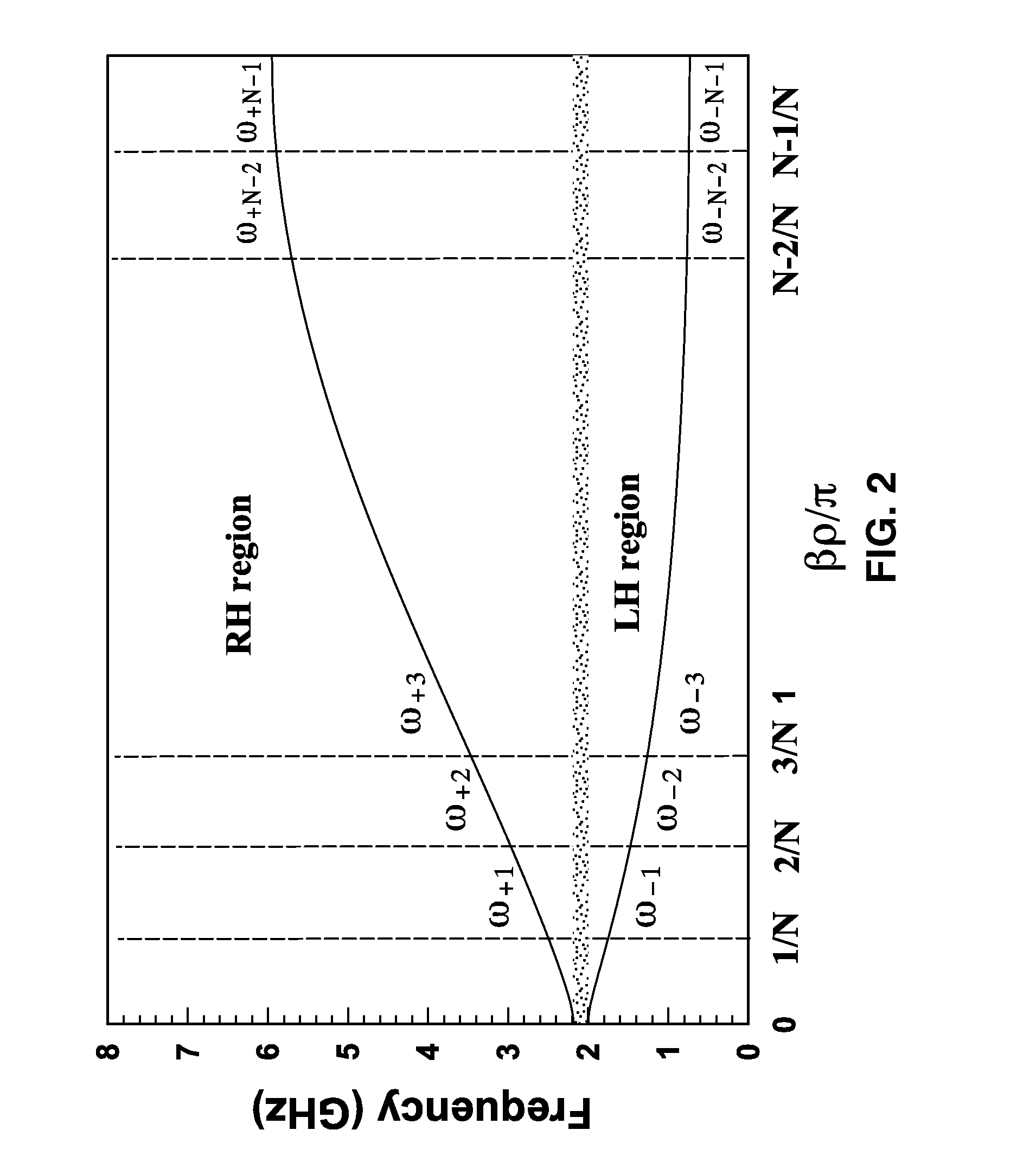

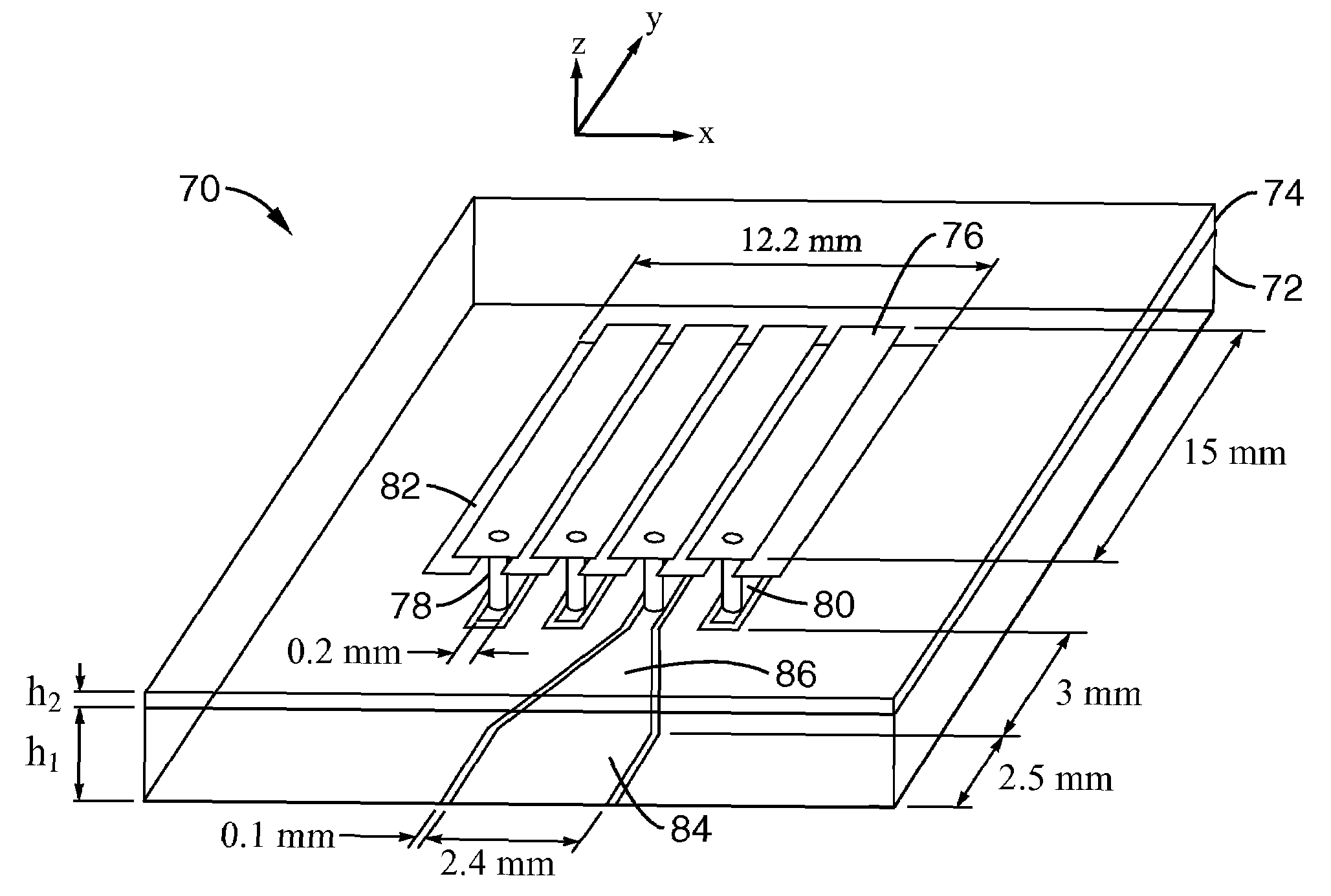

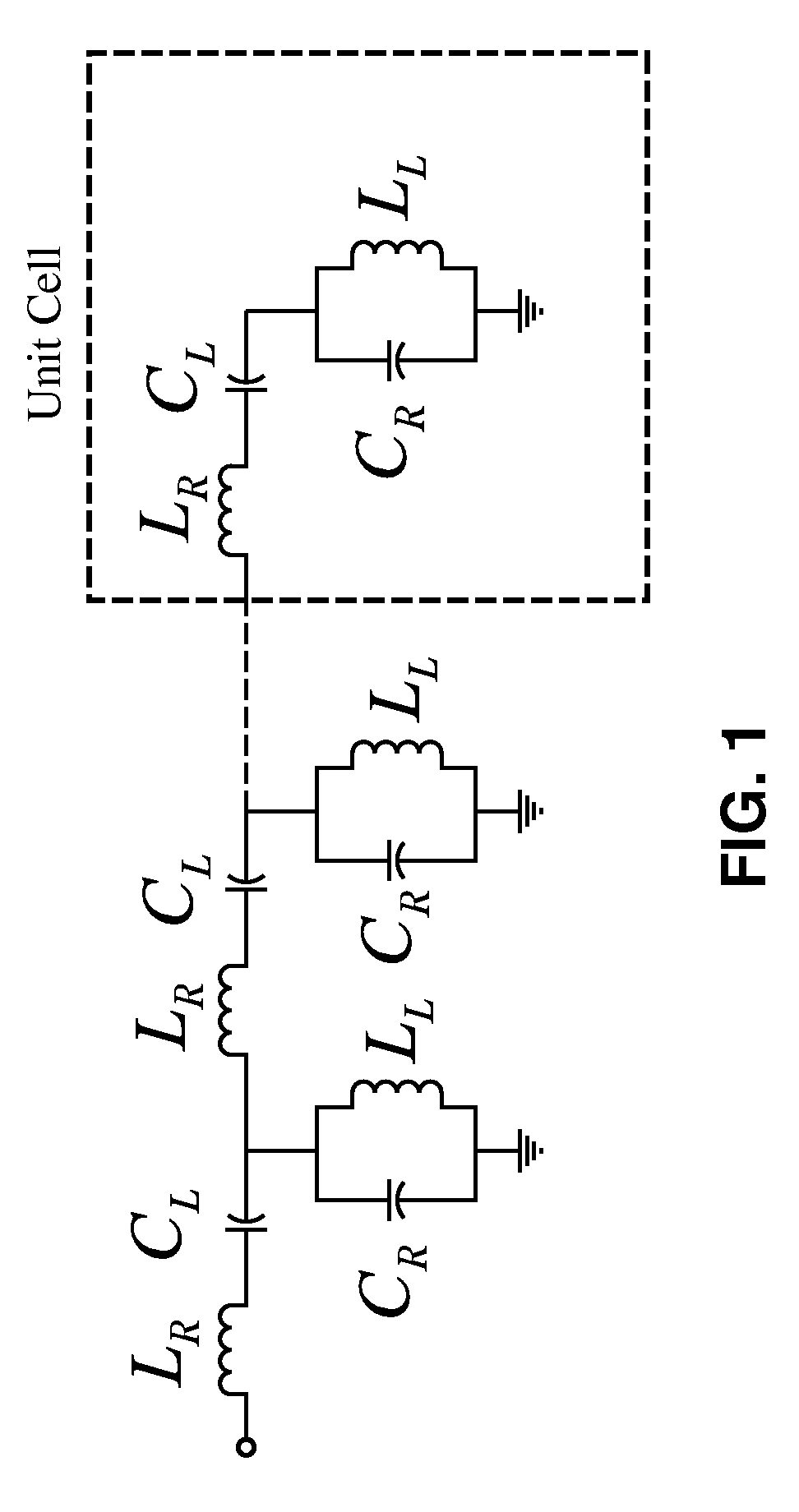

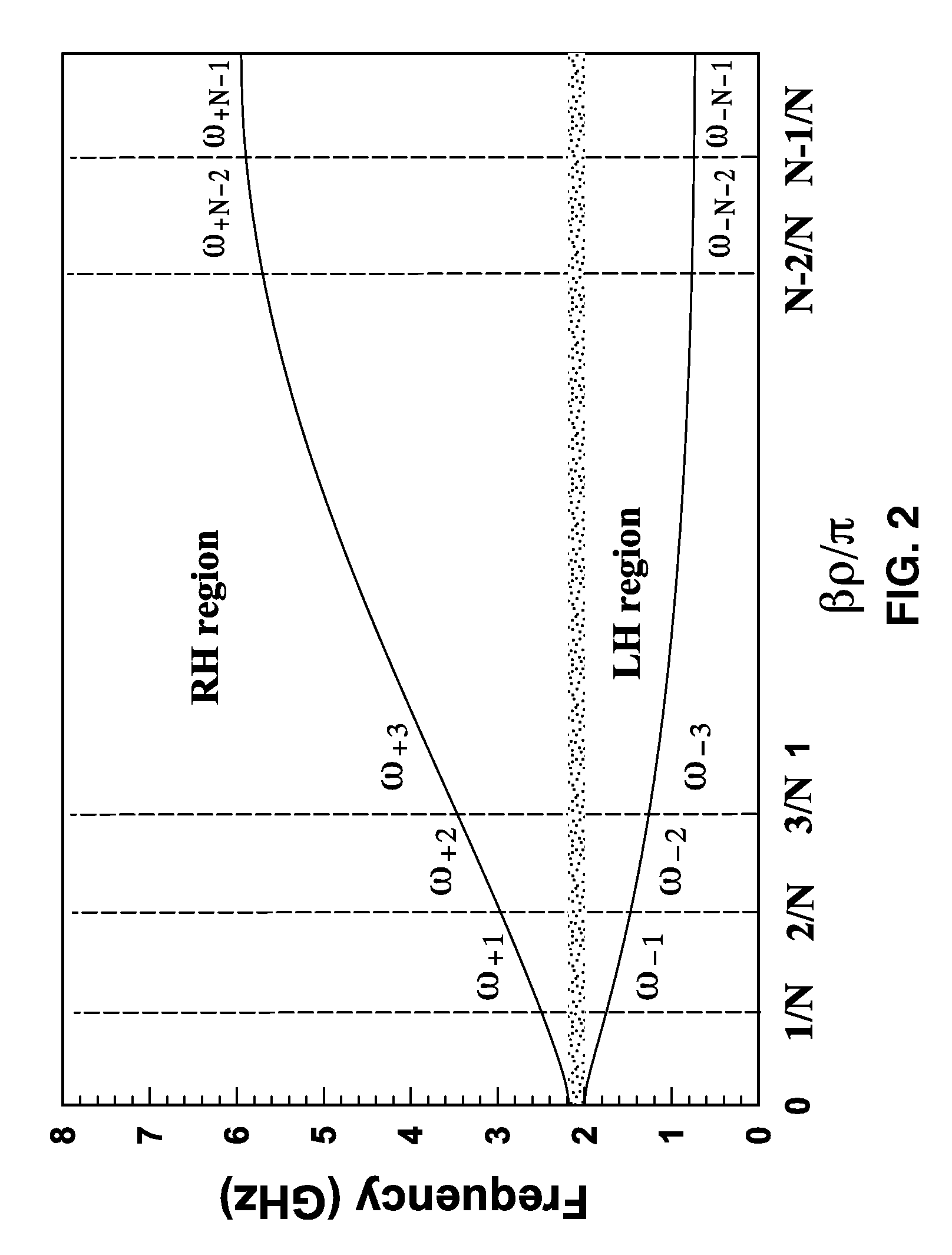

An apparatus based on composite right-handed or left-handed (CRLH) principles to provide a transmission line or antenna structure having a plurality of cells to which one or more feed ports are attached. The apparatus is based on an equivalent circuit Right-Hand (RH) series induction (LR) and shunt capacitor (CR), and Left-Hand (LH) series capacitor (CL) and induction (LL), in which effective permittivity (e) and permeability (m) of the structure are manipulated by the choice of CR, LR, CL, and LL. One embodiment describes mushroom antenna cells (1D or 2D array) in which vias extend up from a feed network on a ground plane through at least one dielectric region to each of a first plurality of conductive elements (plates or strips). Optionally, a second plurality of conductive elements are disposed between first and second dielectric layers to form metal-insulator-metal (MIM) capacitors to lower resonance frequency.

Owner:RGT UNIV OF CALIFORNIA

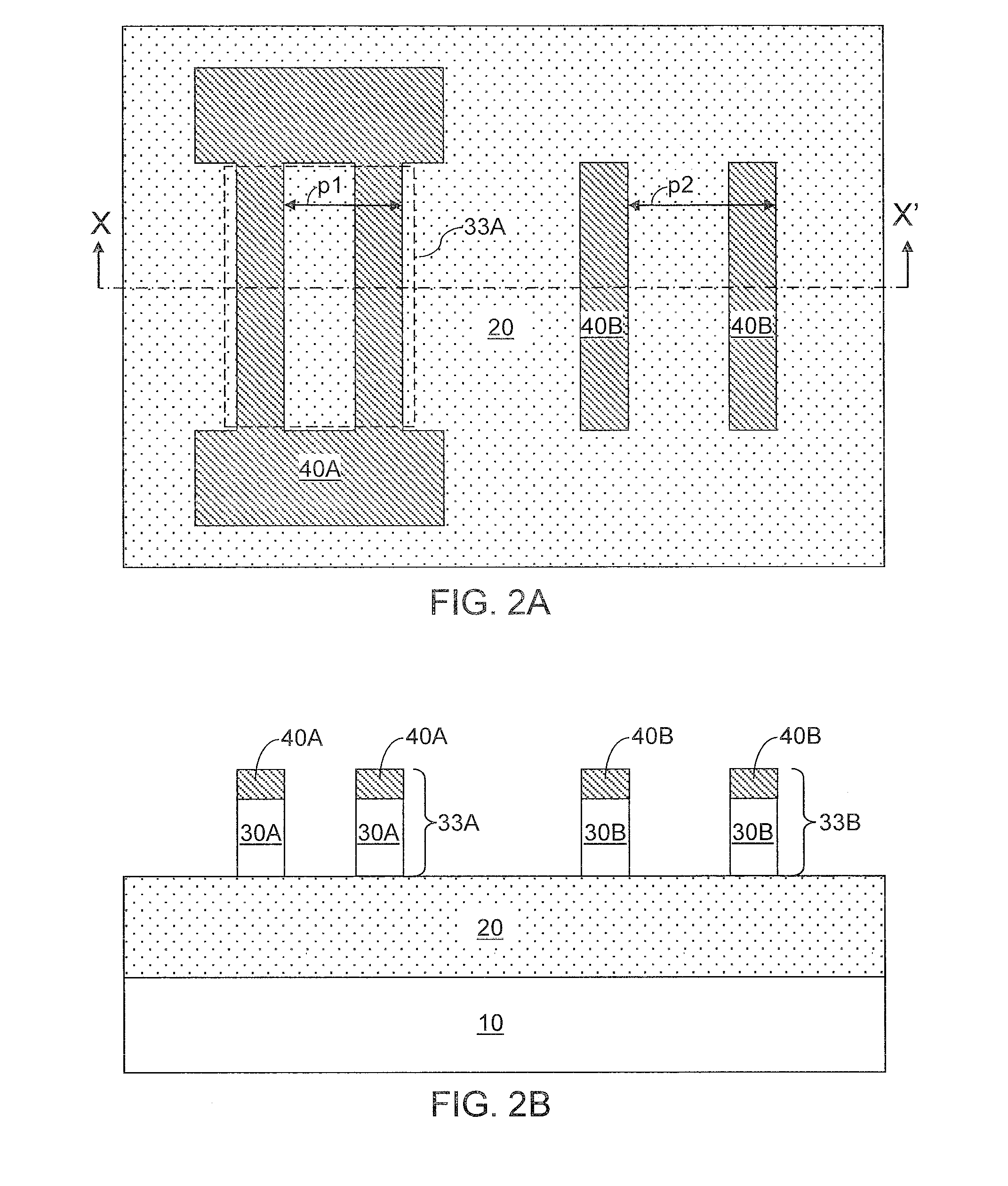

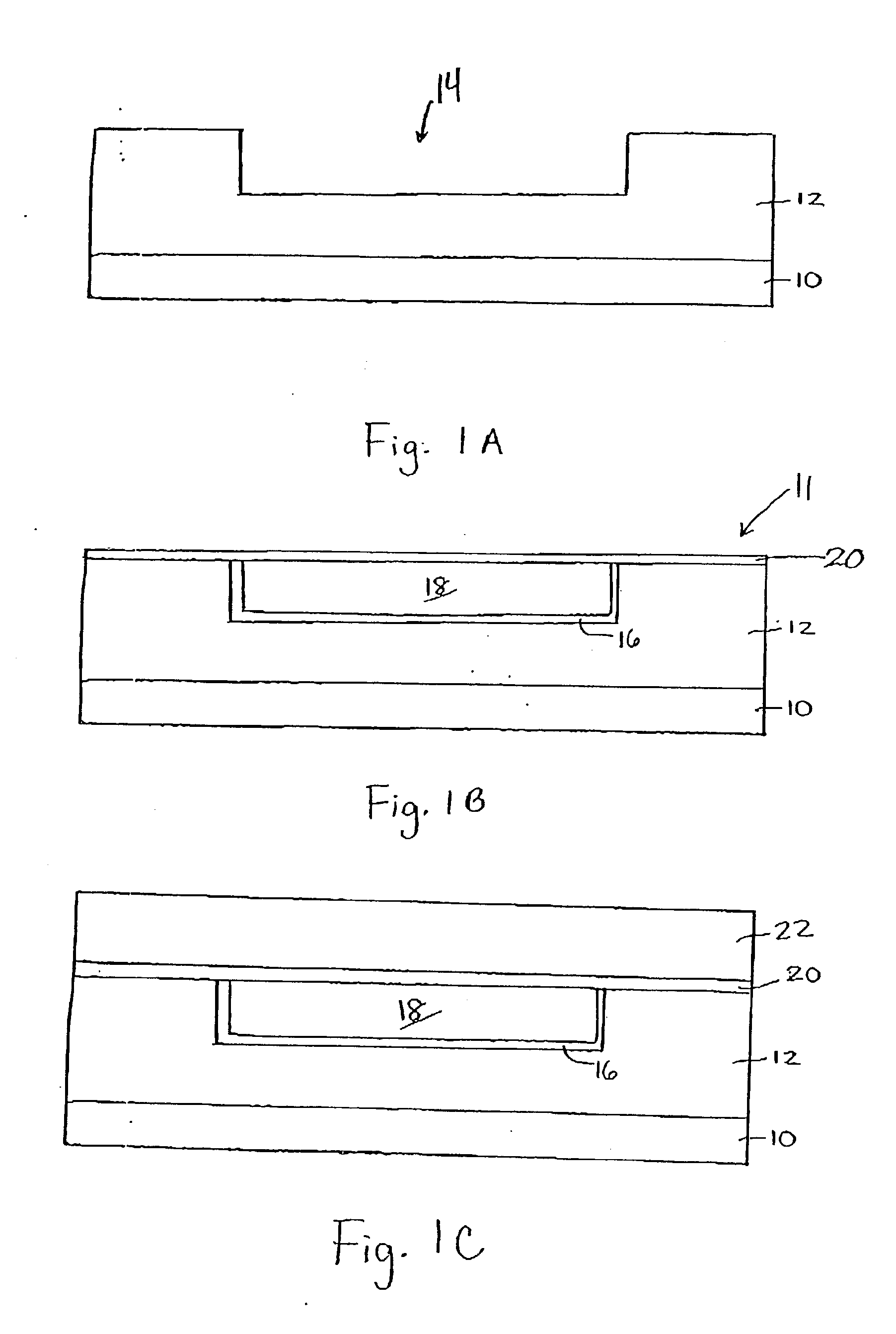

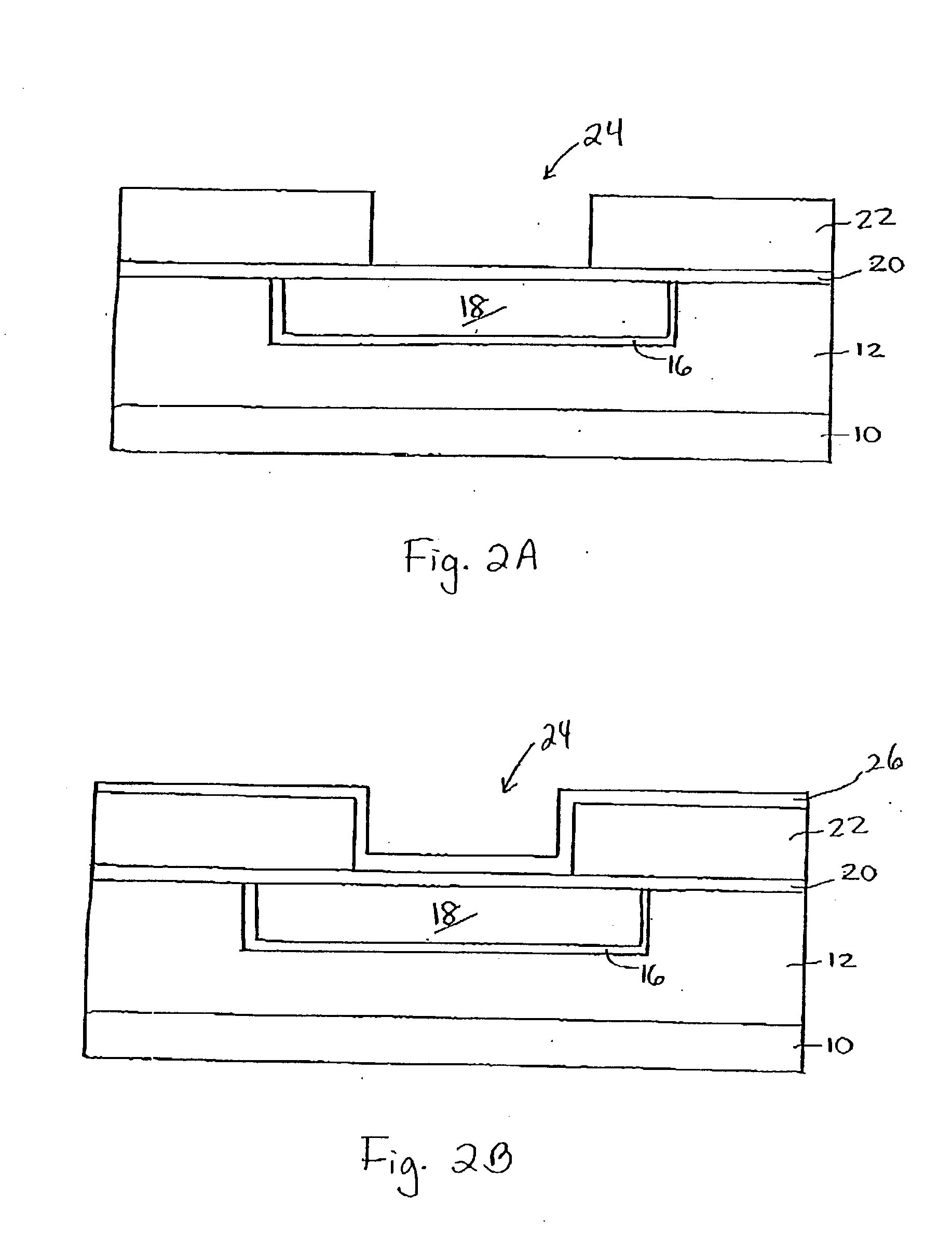

Finfet-compatible metal-insulator-metal capacitor

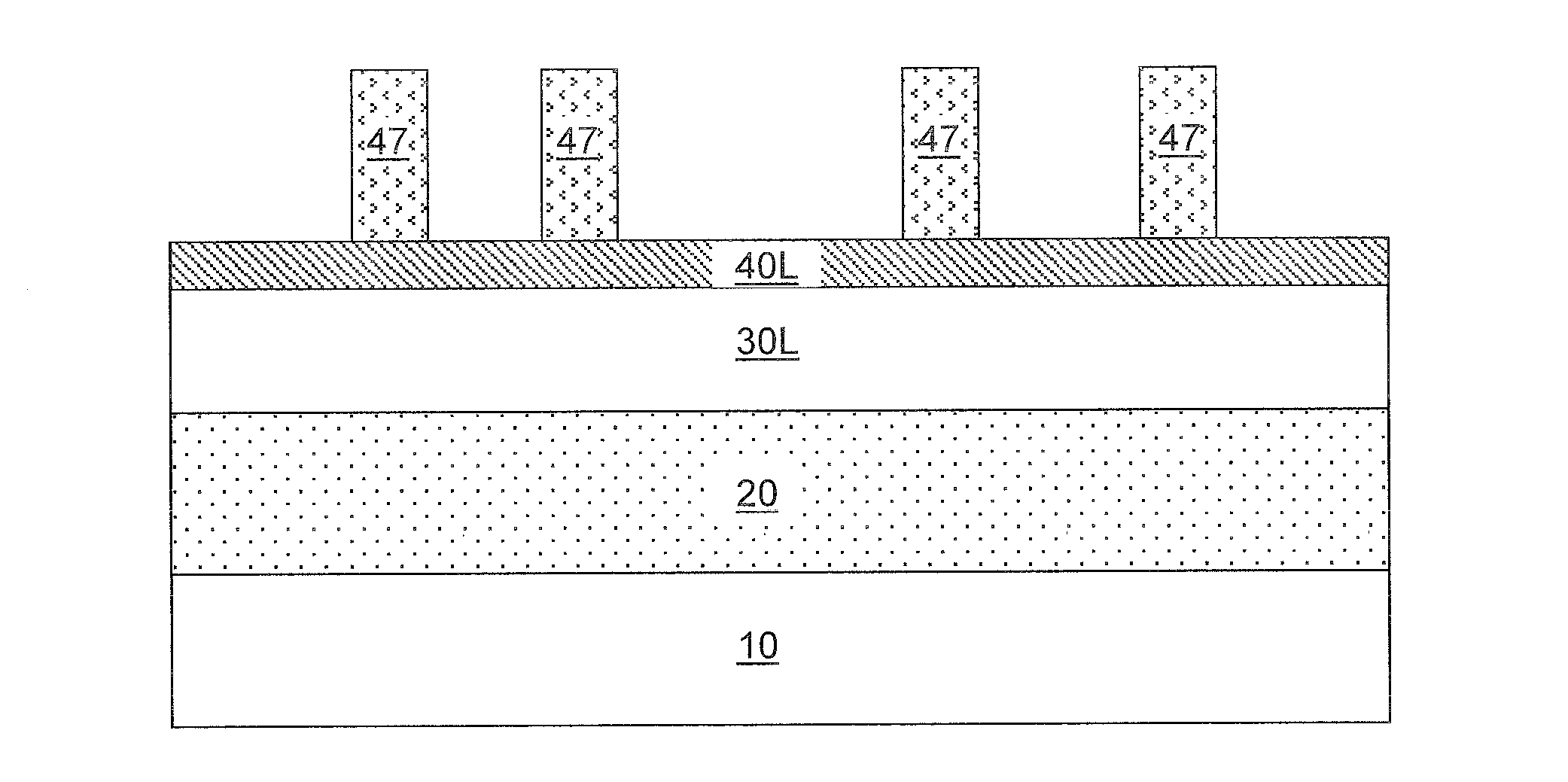

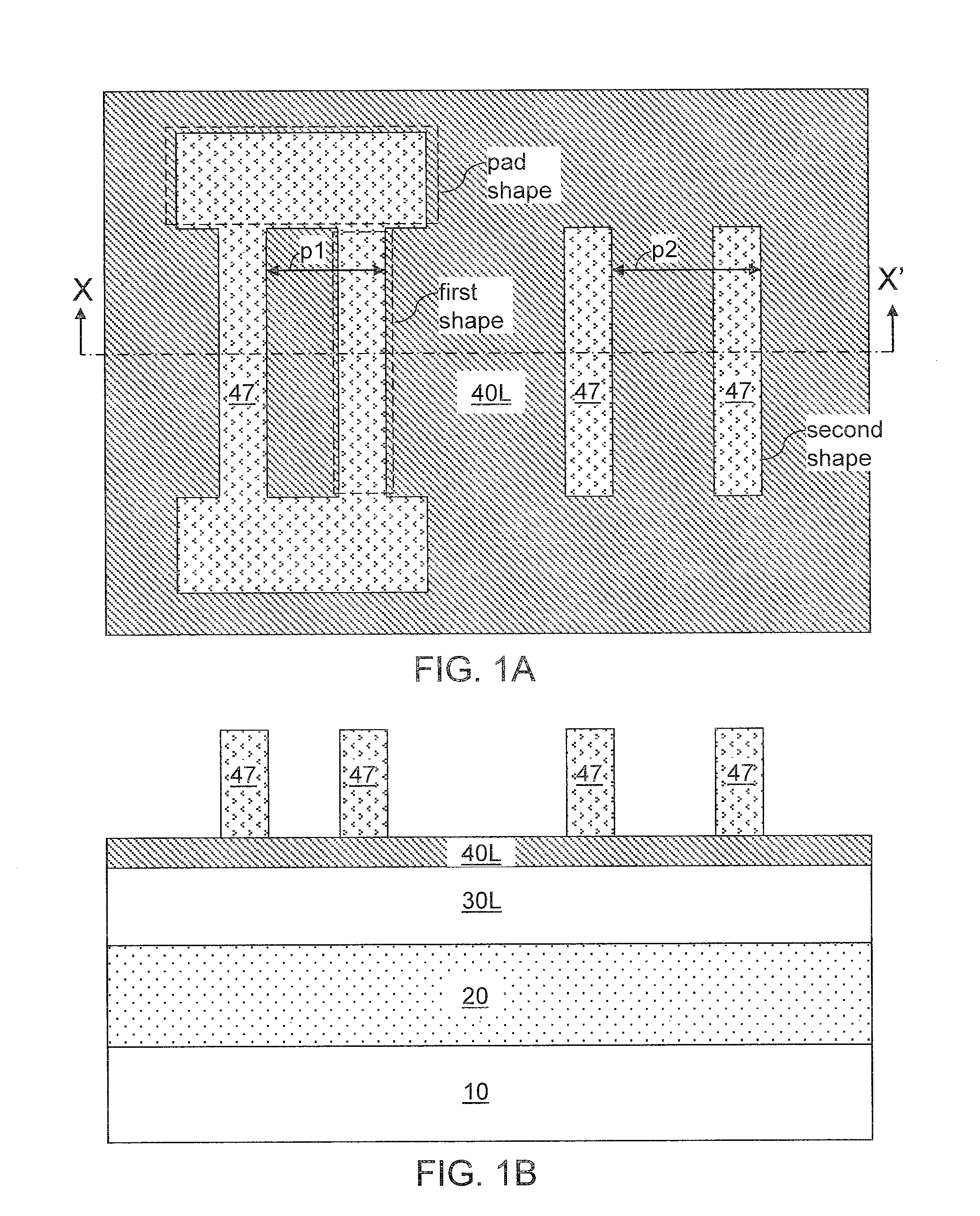

At least one semiconductor fin for a capacitor is formed concurrently with other semiconductor fins for field effect transistors. A lower conductive layer is deposited and lithographically patterned to form a lower conductive plate located on the at least one semiconductor fin. A dielectric layer and at least one upper conductive layer are formed and lithographically patterned to form a node dielectric and an upper conductive plate over the lower conductive plate as well as a gate dielectric and a gate conductor over the other semiconductor fins. The lower conductive plate, the node dielectric, and the upper conductive plate collectively form a capacitor. The finFETs may be dual gate finFETs or trigate finFETs. A buried insulator layer may be optionally recessed to increase the capacitance. Alternately, the lower conductive plate may be formed on a planar surface of the buried insulator layer.

Owner:GLOBALFOUNDRIES US INC

Metal-insulator-metal capacitor for copper damascene process and method of forming the same

A capacitor structure formed on a semiconductor substrate may include a first interconnect wiring (such as copper damascene) and a first conductive barrier layer in contact with the first interconnect wiring. A first capacitor plate, a capacitor dielectric structure and a second capacitor plate may also be included over the first conductive barrier layer. A second conductive barrier layer may be formed on the second capacitor plate and a second planar insulating structure may be formed over the second capacitor plate. Finally, a second interconnect wiring may be embedded within a second planar insulator structure.

Owner:IBM CORP

Composite right/left-handed transmission line based compact resonant antenna for RF module integration

ActiveUS7446712B2Improve efficiencyAccurate manufacturing capabilitySimultaneous aerial operationsRadiating elements structural formsMetal-insulator-metalShunt capacitors

Owner:RGT UNIV OF CALIFORNIA

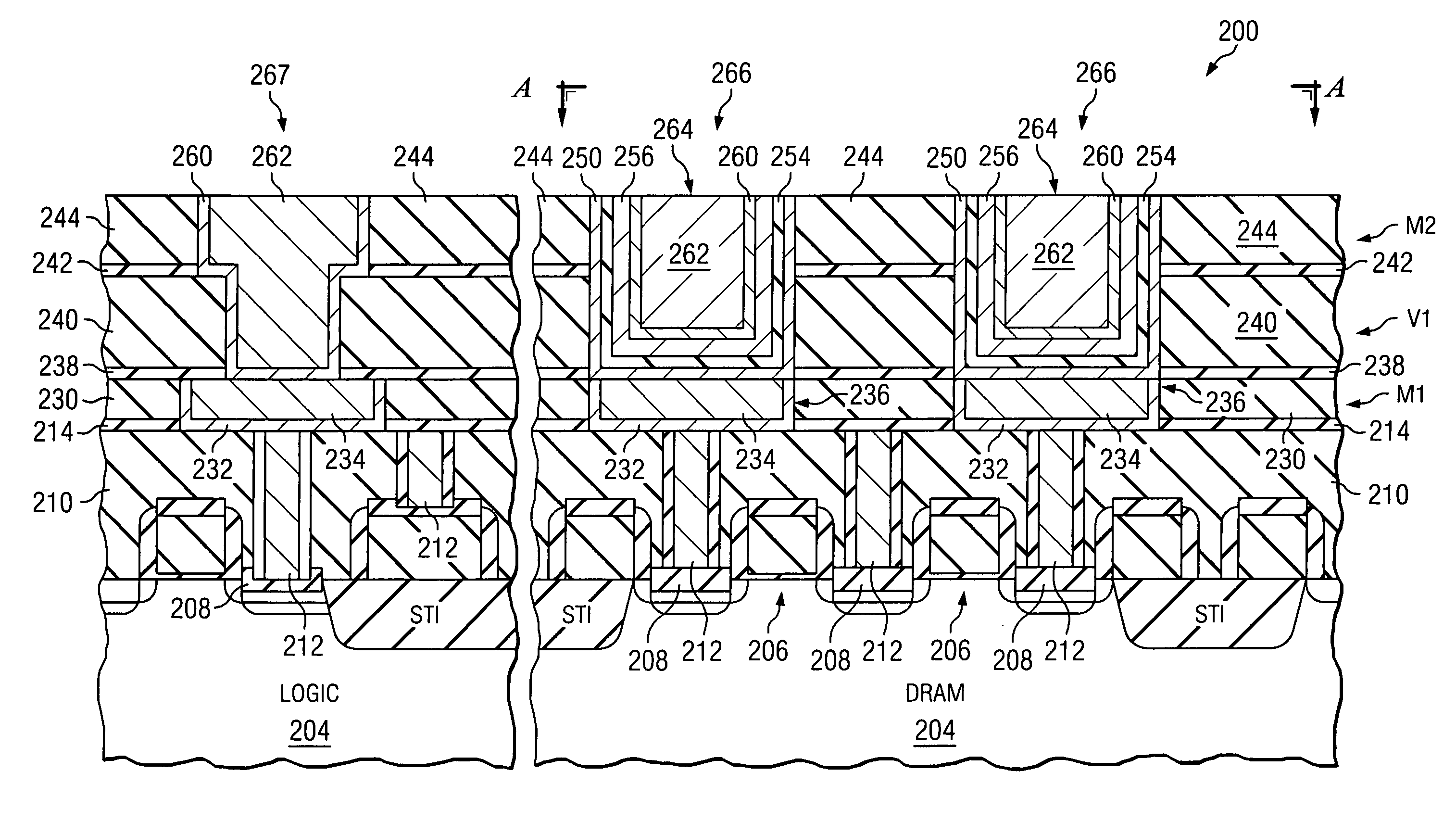

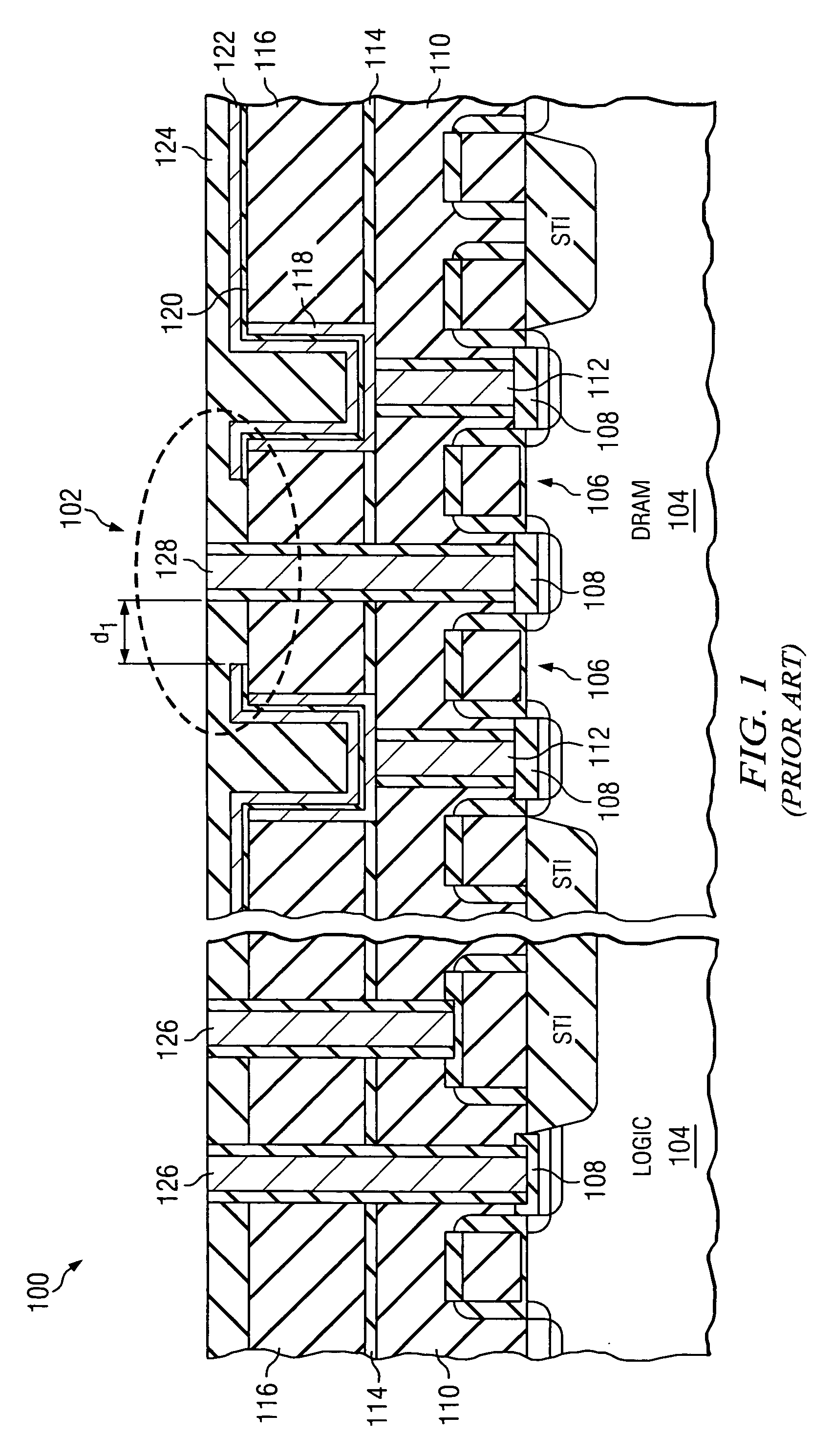

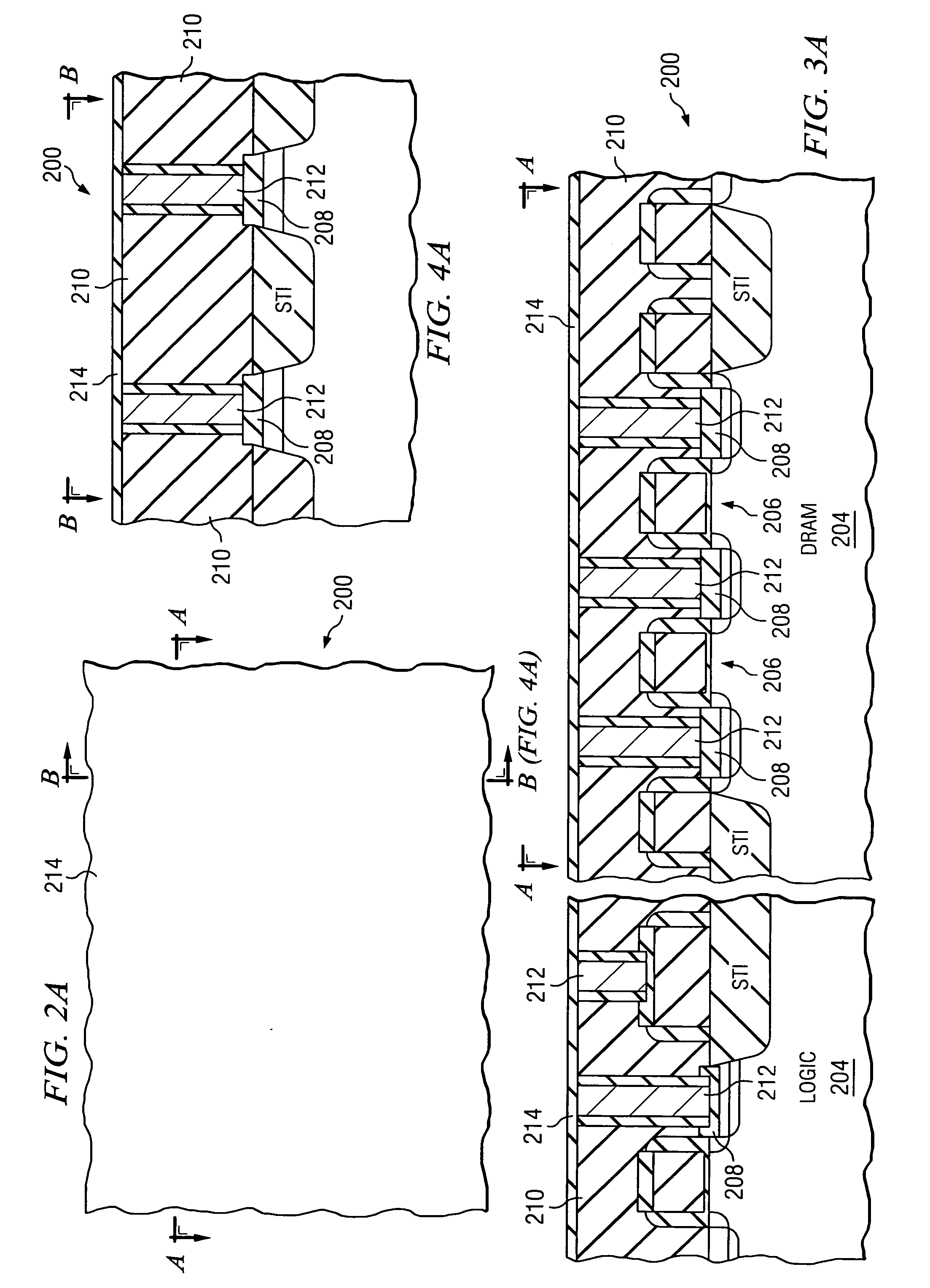

Method and structure for a 1T-RAM bit cell and macro

InactiveUS20070080387A1Function increaseIncrease capacitanceTransistorSolid-state devicesMetal-insulator-metalMOSFET

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

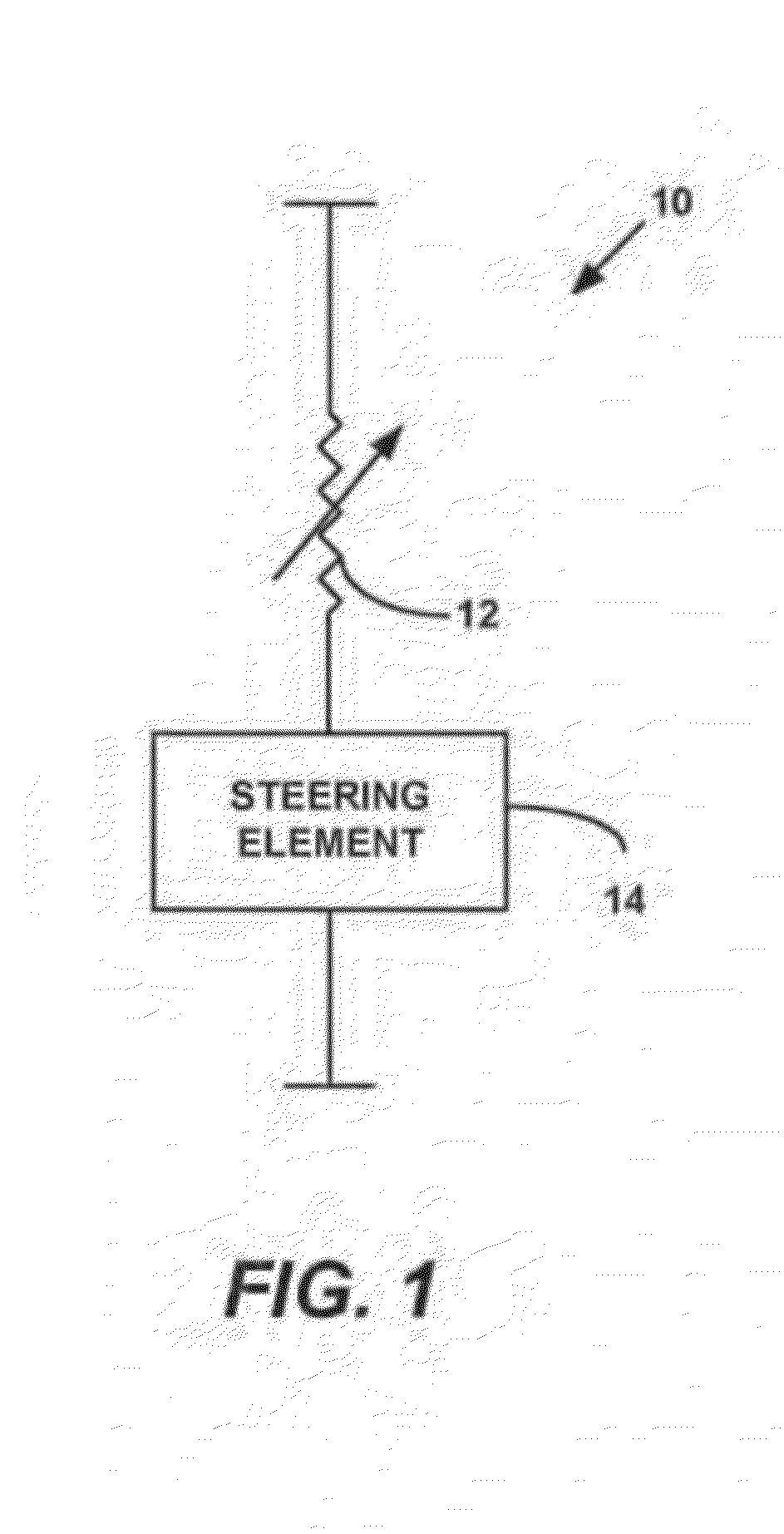

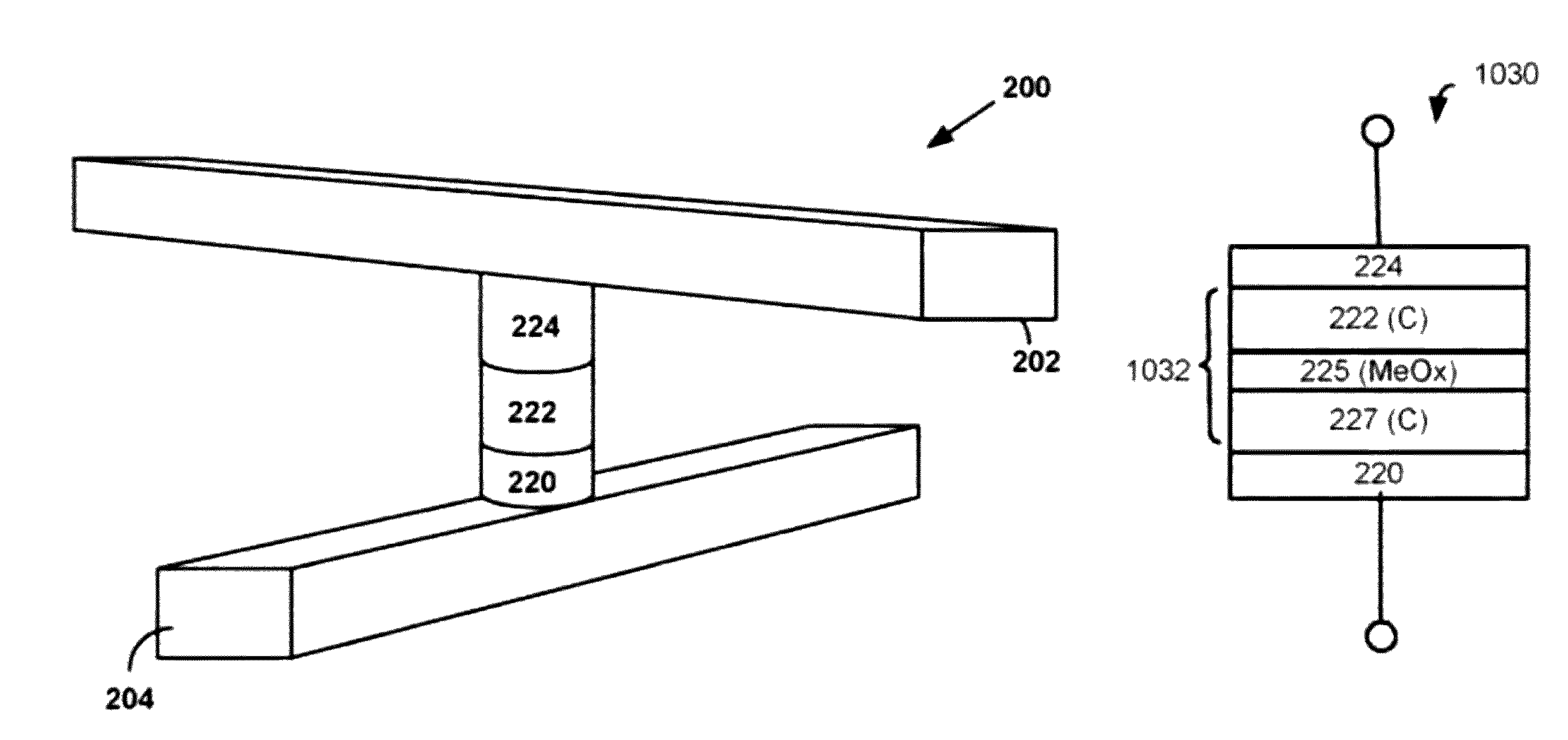

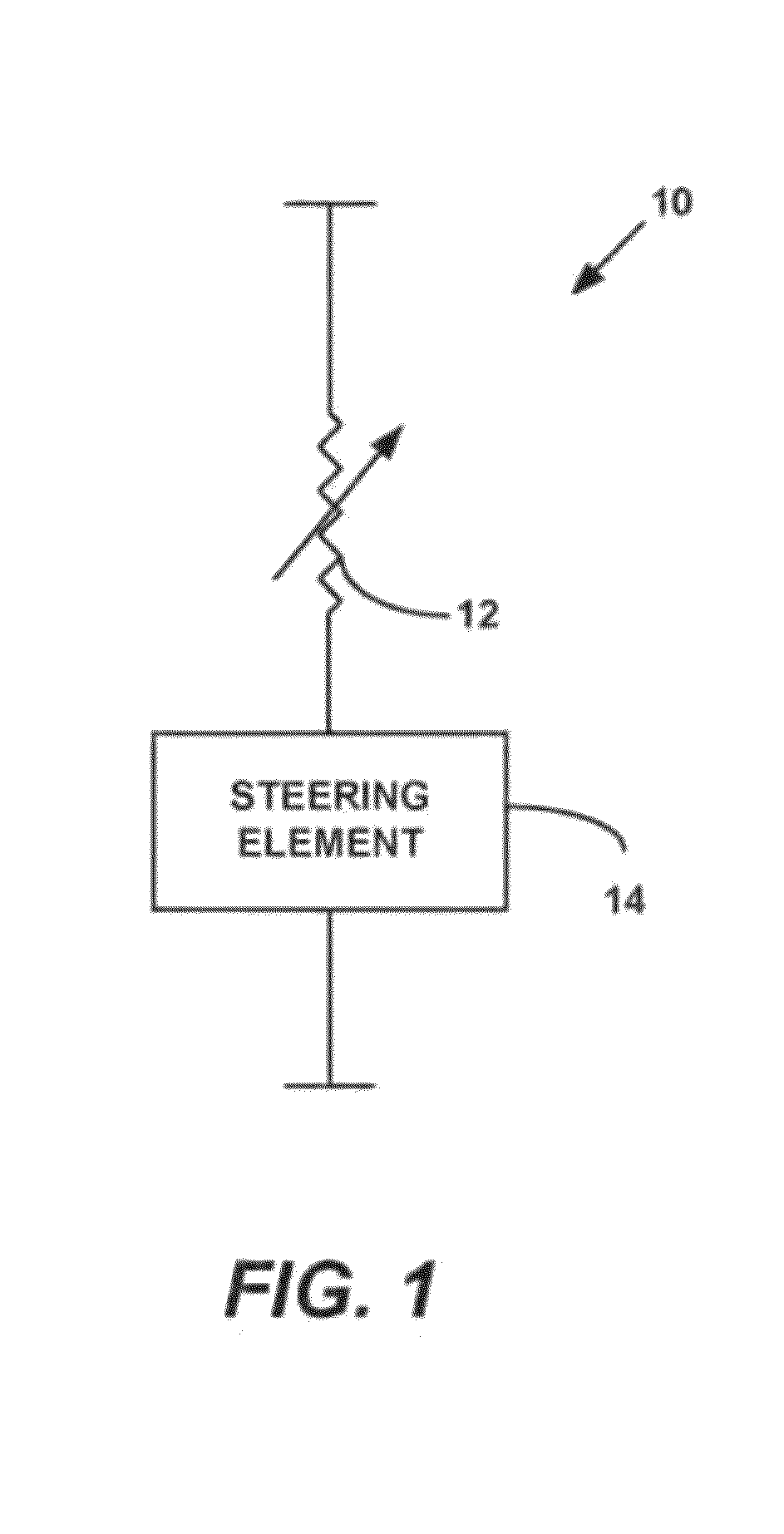

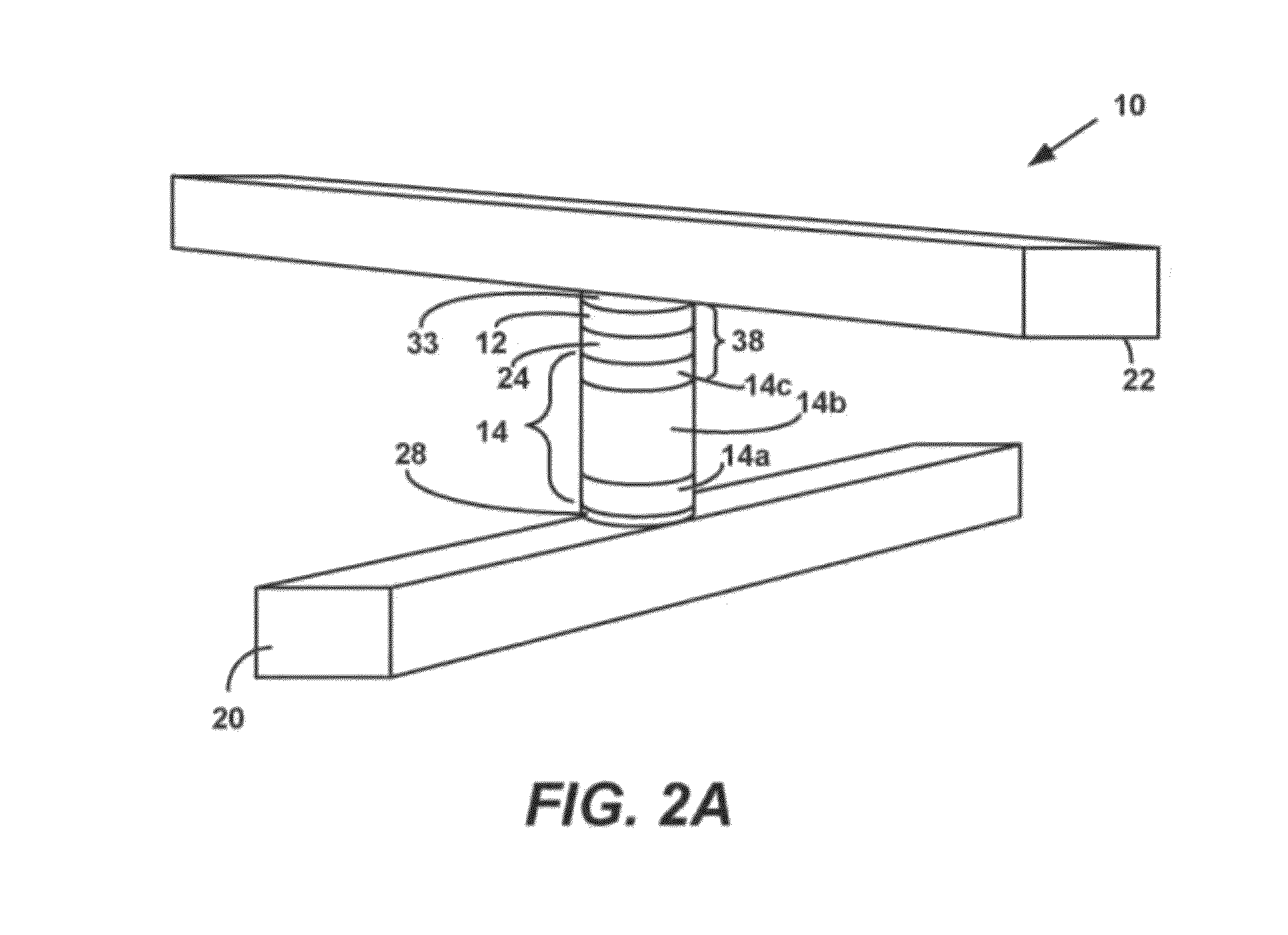

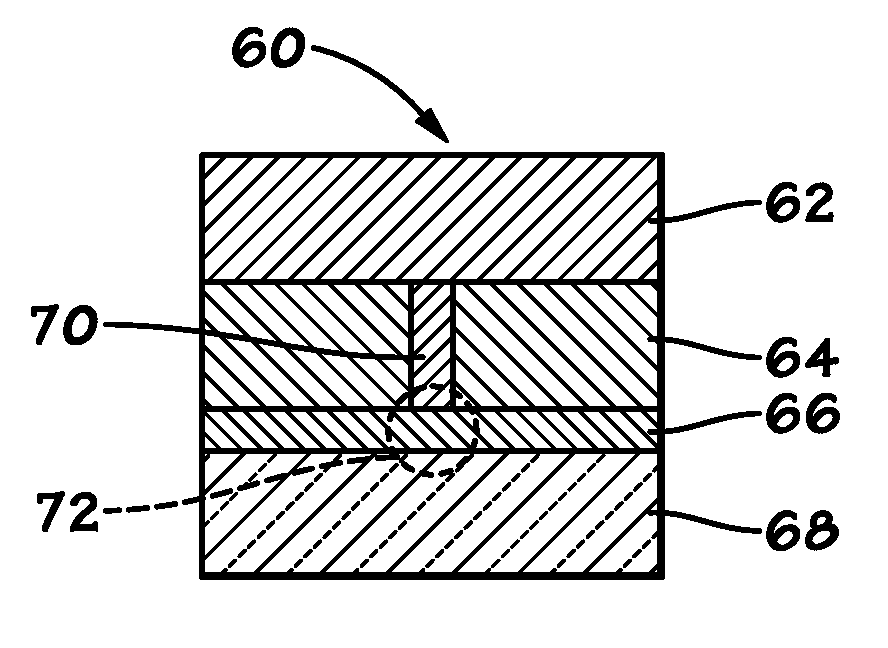

Non-Volatile Storage System Using Opposite Polarity Programming Signals For MIM Memory Cell

A reversible resistance-switching metal-insulator-metal (MIM) stack is provided which can be set to a low resistance state with a first polarity signal and reset to a higher resistance state with a second polarity signal. The first polarity signal is opposite in polarity than the second polarity signal. In one approach, the MIM stack includes a carbon-based reversible resistivity switching material such as a carbon nanotube material. The MIM stack can further include one or more additional reversible resistivity switching materials such as metal oxide above and / or below the carbon-based reversible resistivity switching material. In another approach, a metal oxide layer is between separate layers of carbon-based reversible resistivity switching material.

Owner:SANDISK TECH LLC

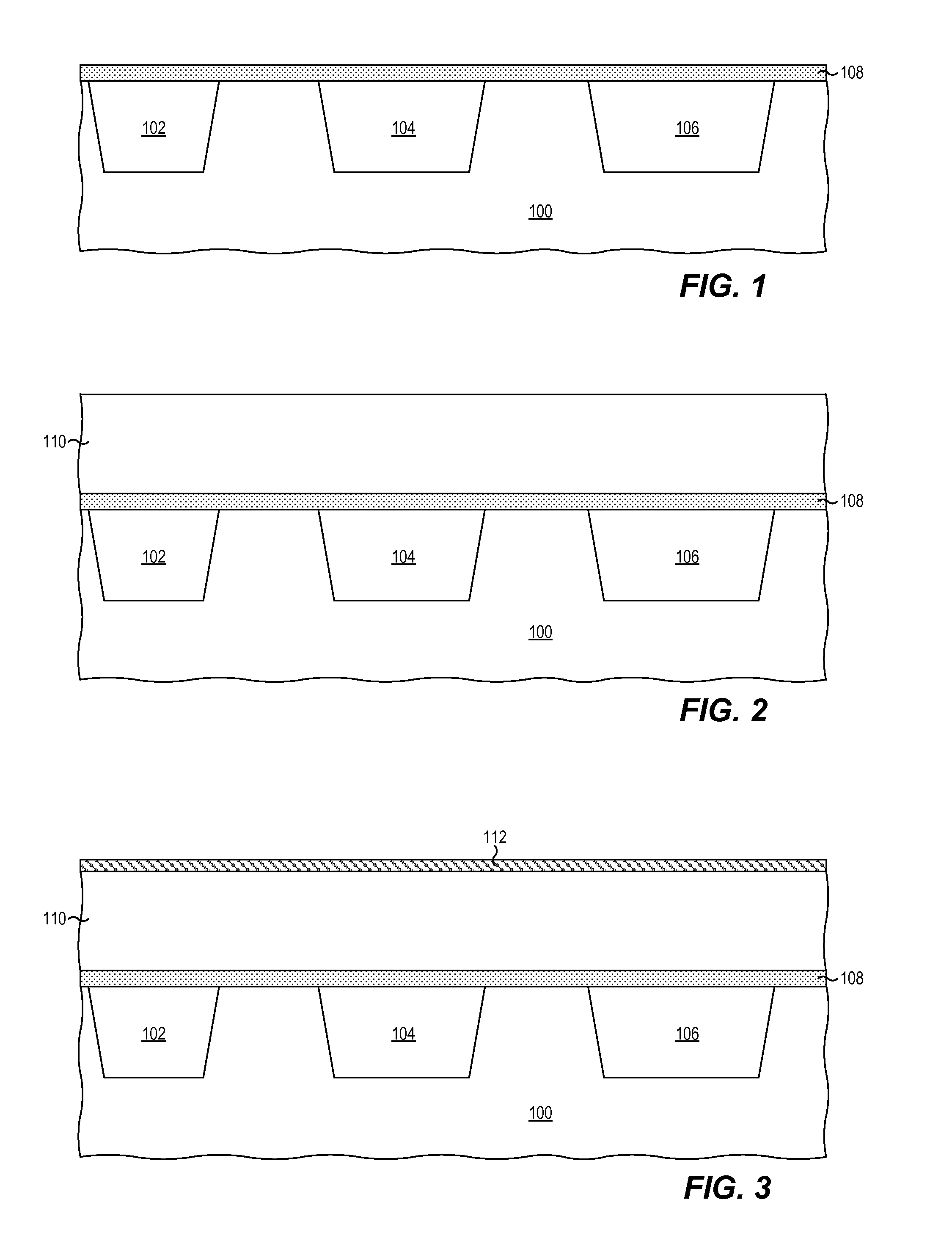

Damascene integration scheme for developing metal-insulator-metal capacitors

InactiveUS20040113235A1Increase capacitanceSave chip areaTransistorSolid-state devicesMetal-insulator-metalGas phase

The invention is directed to unique high-surface area BEOL capacitor structures with high-k dielectric layers and methods for fabricating the same. These high-surface area BEOL capacitor structures may be used in analog and mixed signal applications. The capacitor is formed within a trench with pedestals within the trench to provide additional surface area. The top and bottom electrodes are created using damascene integration scheme. The dielectric layer is created as a multilayer dielectric film comprising for instance Al2O3, Al2O3 / Ta2O5, Al2O3 / Ta2O5 / Al2O3 and the like. The dielectric layer may be deposited by methods like atomic layer deposition or chemical vapor deposition. The dielectric layer used in the capacitor may also be produced by anodic oxidation of a metallic precursor to yield a high dielectric constant oxide layer.

Owner:GLOBALFOUNDRIES US INC

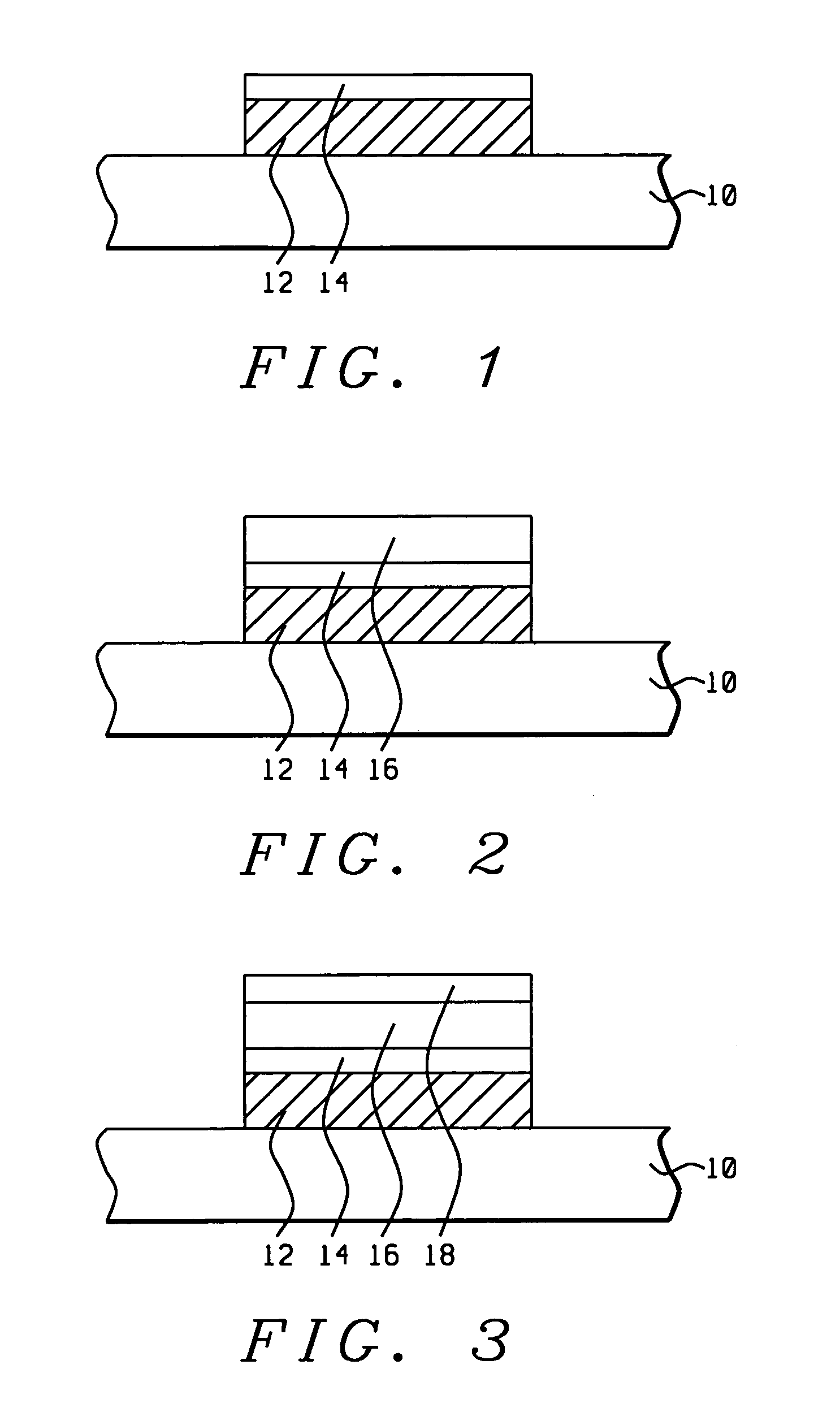

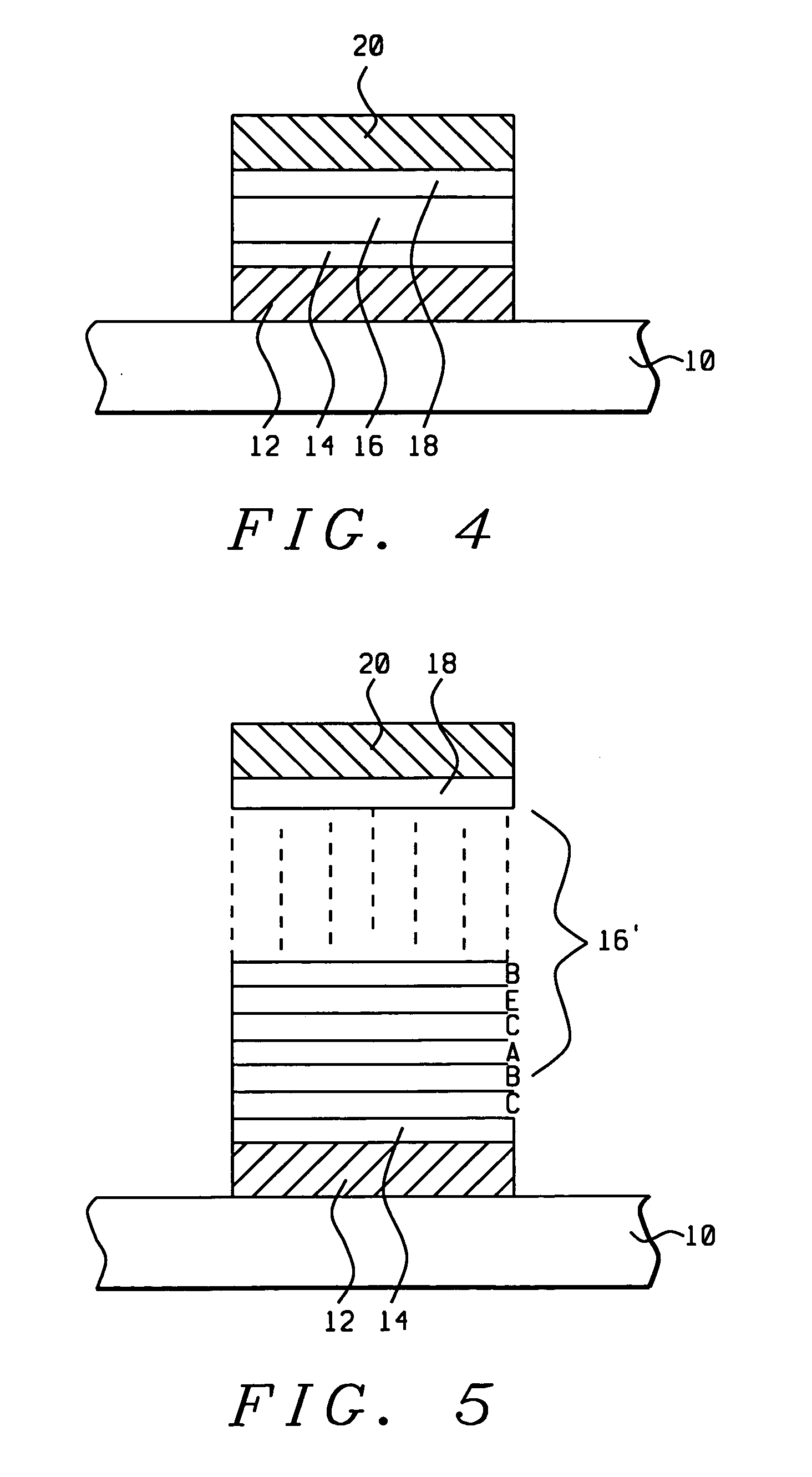

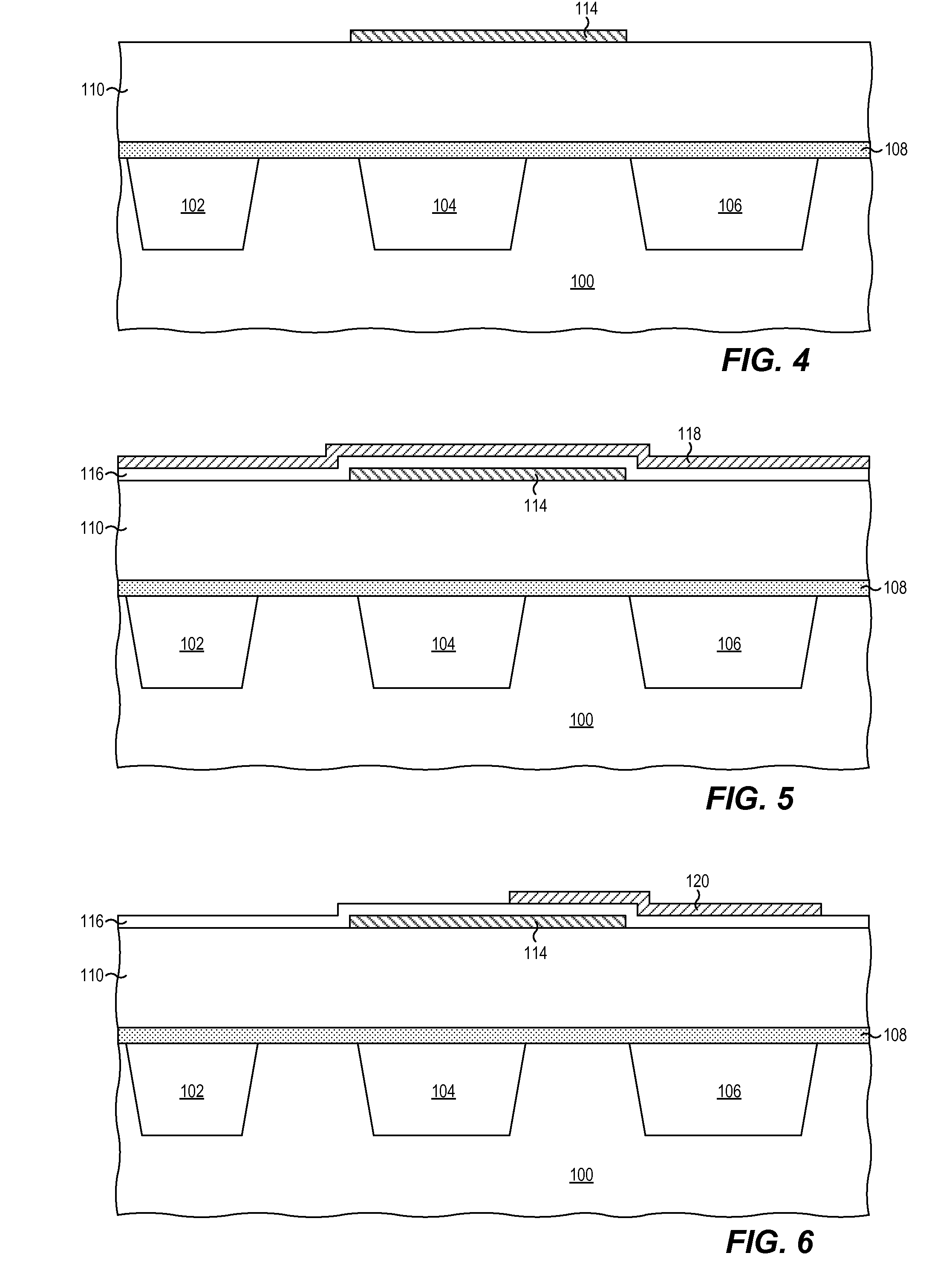

MIM capacitor structure and method of manufacture

ActiveUS20050082586A1Increase capacitanceIncrease process marginTransistorSolid-state devicesMetal-insulator-metalDevice material

A metal-insulator-metal (MIM) capacitor structure and method of manufacturing thereof. A plurality of MIM capacitor patterns is formed in two or more insulating layers. The insulating layers may comprise a via layer and a metallization layer of a semiconductor device. A top portion of the top insulating layer is recessed in a region between at least two adjacent MIM capacitor patterns. When the top plate material of the MIM capacitors is deposited, the top plate material fills the recessed area of the top insulating layer between the adjacent MIM capacitor pattern, forming a connecting region that couples together the top plates of the adjacent MIM capacitors. A portion of the MIM capacitor bottom electrode may be formed in a first metallization layer of the semiconductor device.

Owner:TAIWAN SEMICON MFG CO LTD

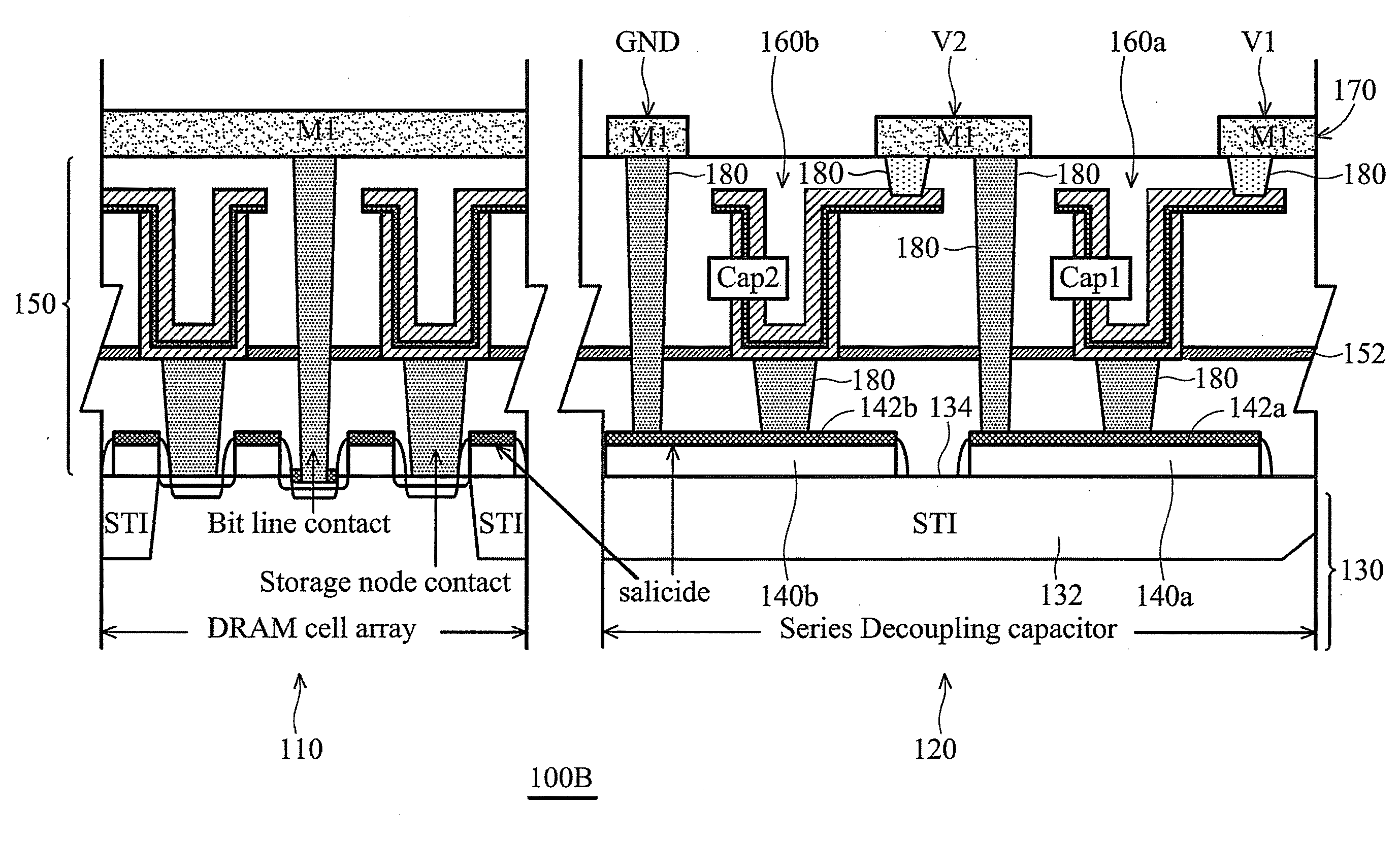

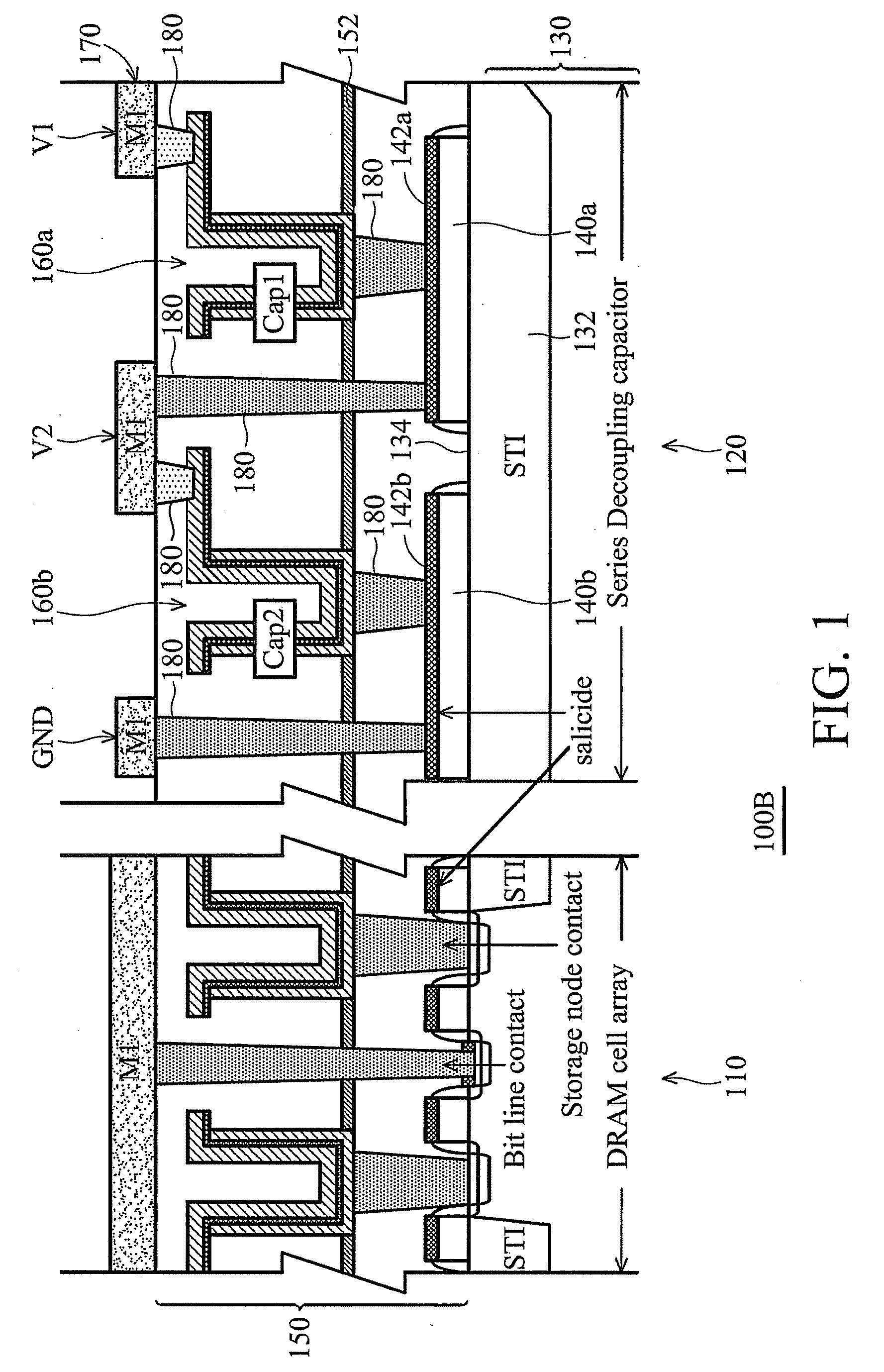

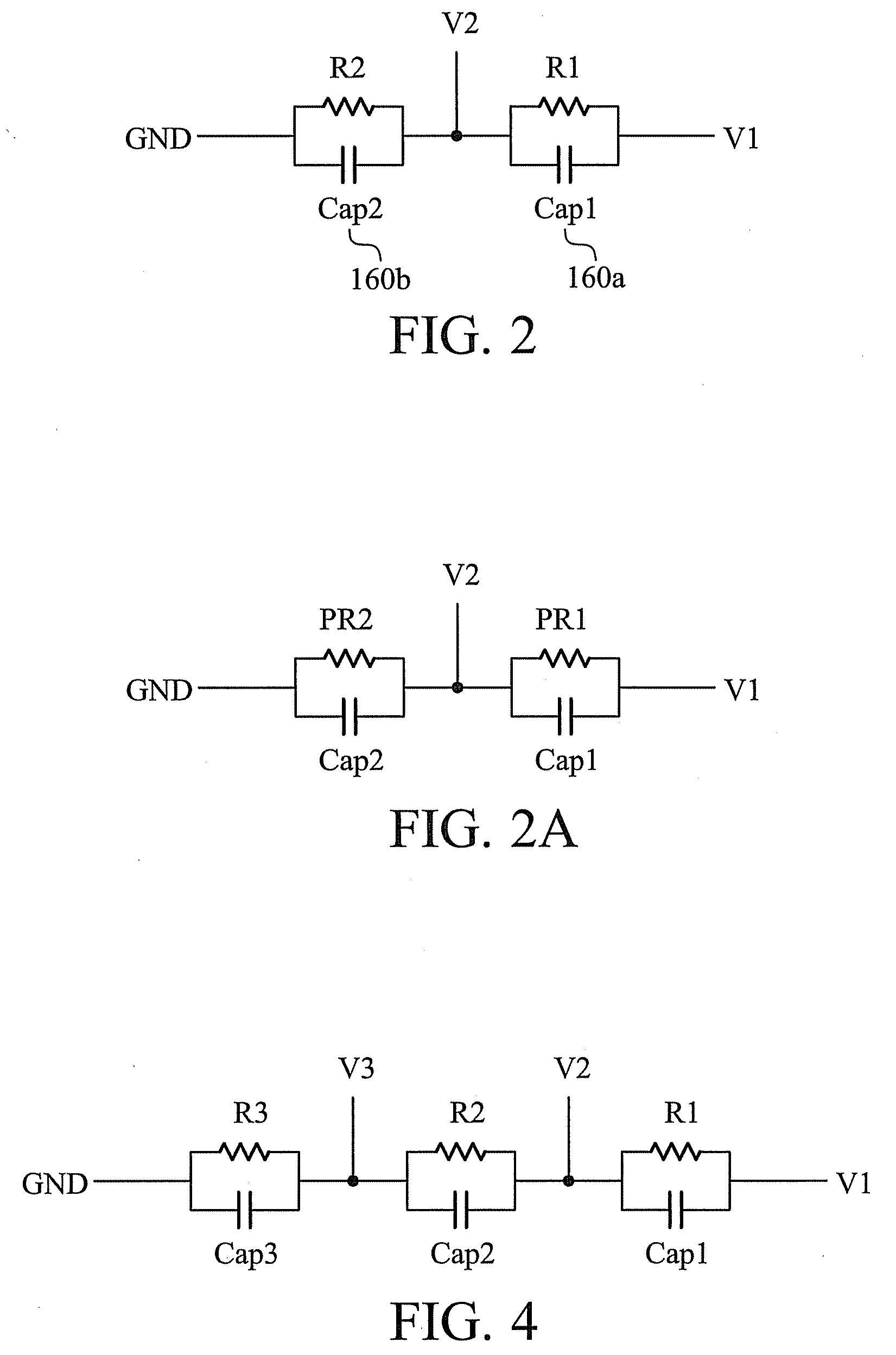

Semiconductor device with decoupling capacitor design

ActiveUS20100065944A1Reduce voltage stressTransistorSemiconductor/solid-state device detailsMetal-insulator-metalCapacitance

An integrated circuit includes a circuit module having a plurality of active components coupled between a pair of supply nodes, and a capacitive decoupling module coupled to the circuit module. The capacitive decoupling module includes a plurality of metal-insulator-metal (MiM) capacitors coupled in series between the pair of supply nodes, wherein a voltage between the supply nodes is divided across the plurality of MiM capacitors, thereby reducing voltage stress on the capacitors.

Owner:TAIWAN SEMICON MFG CO LTD

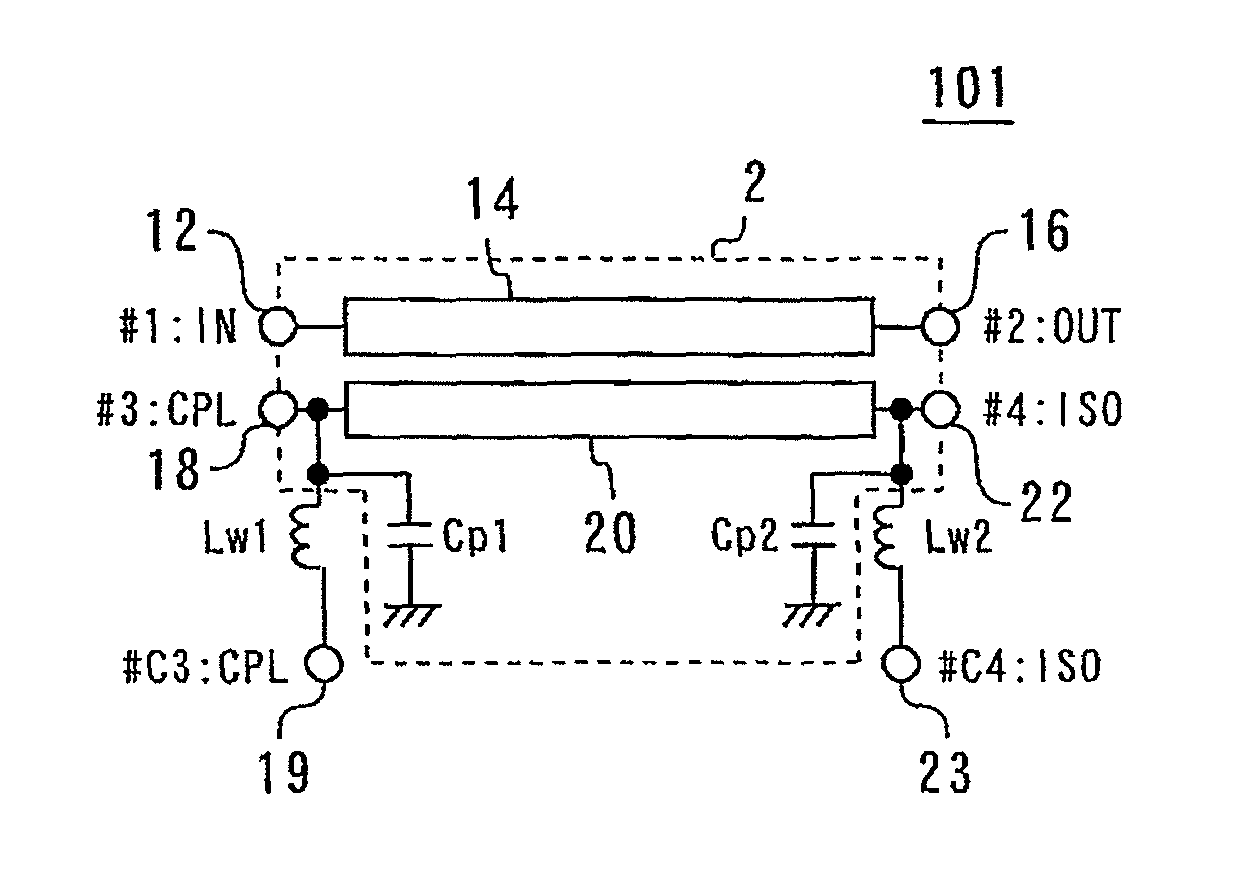

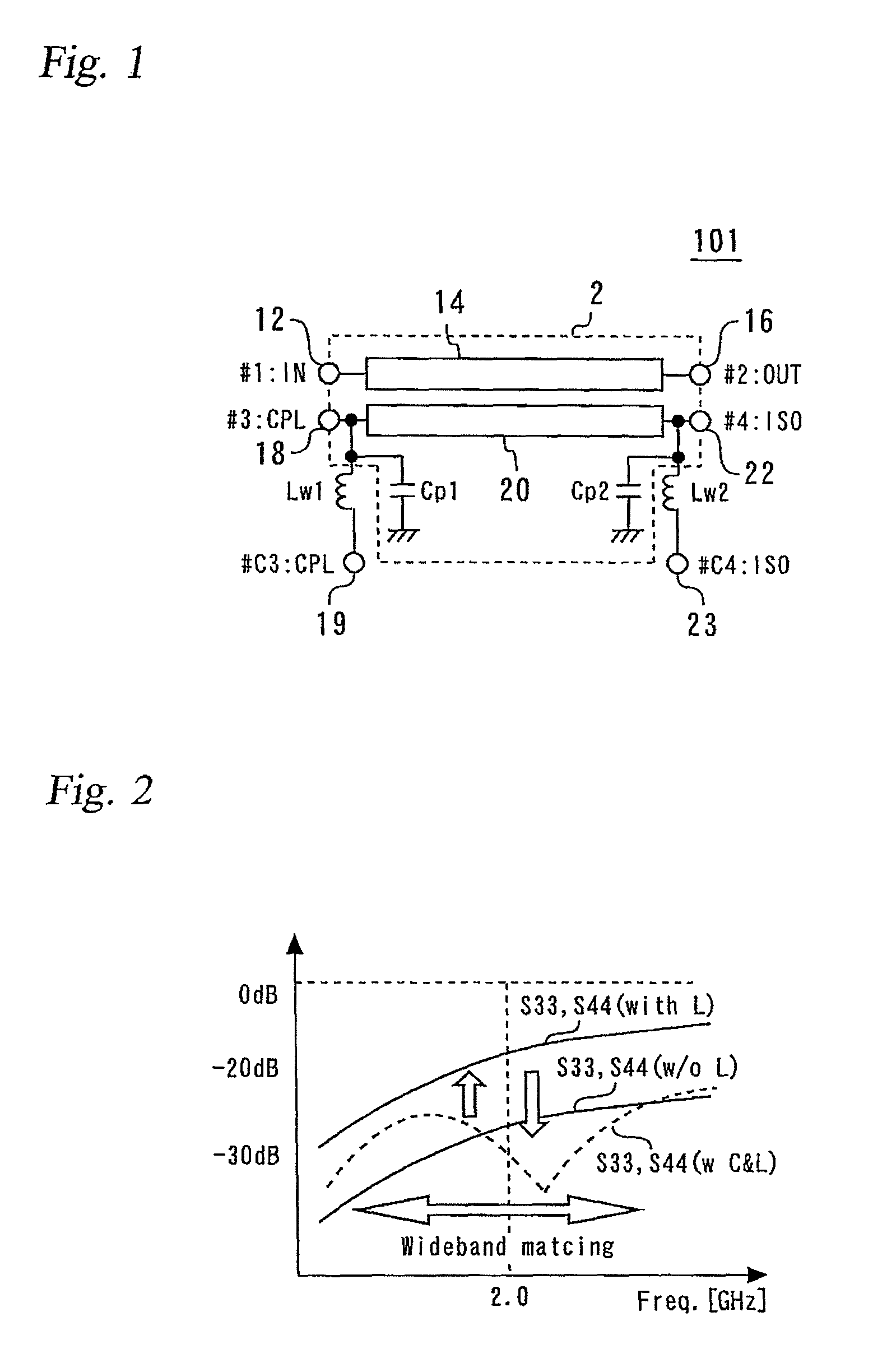

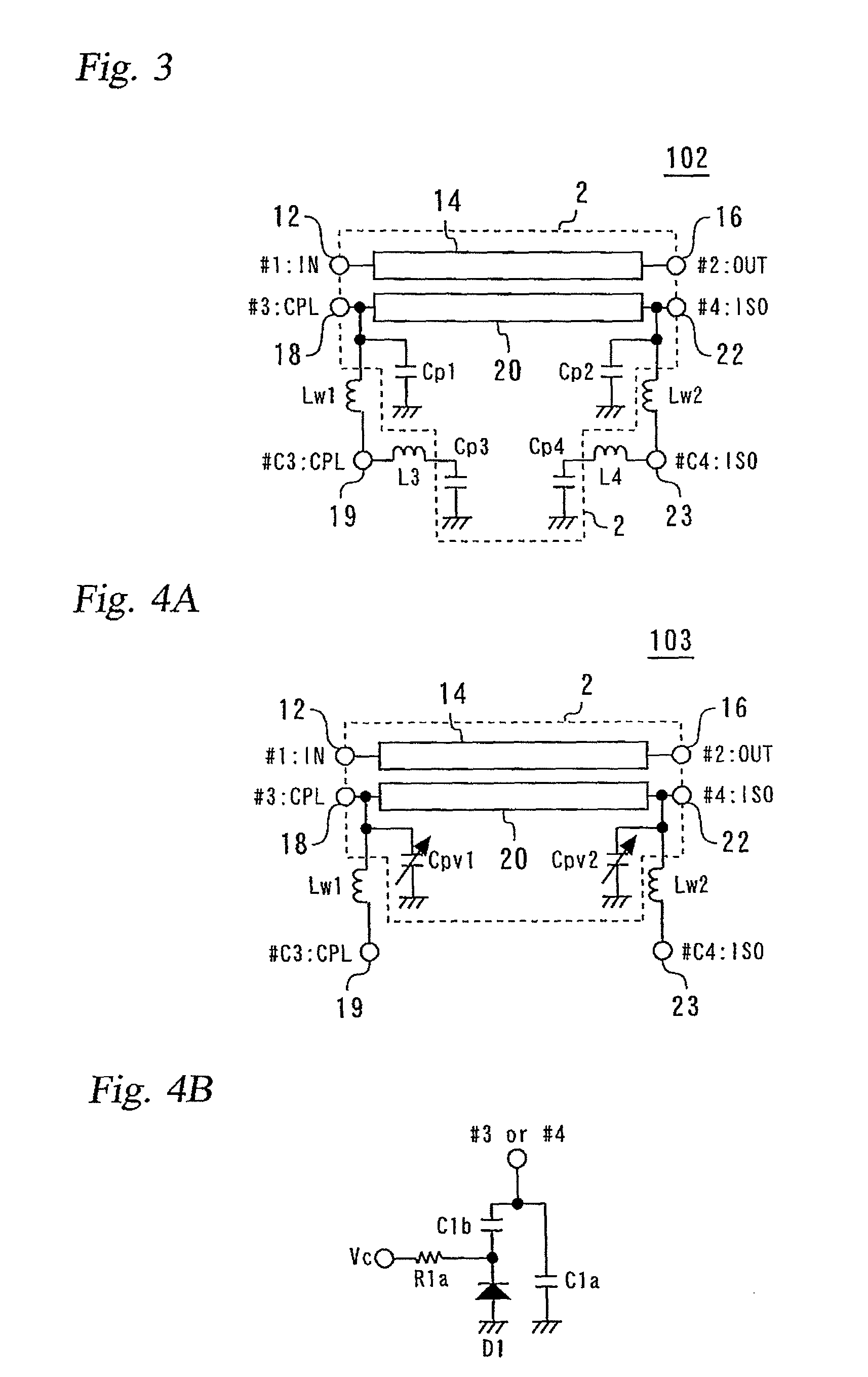

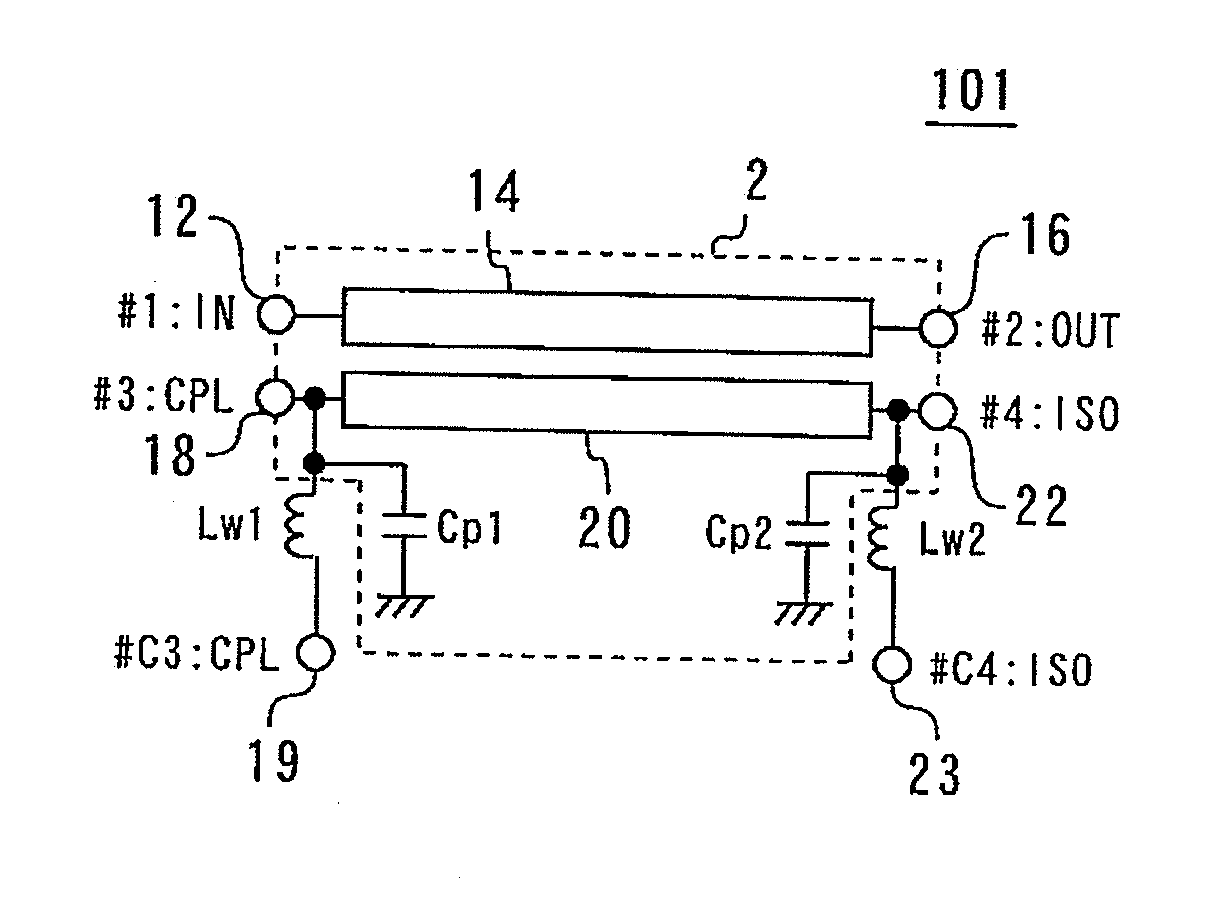

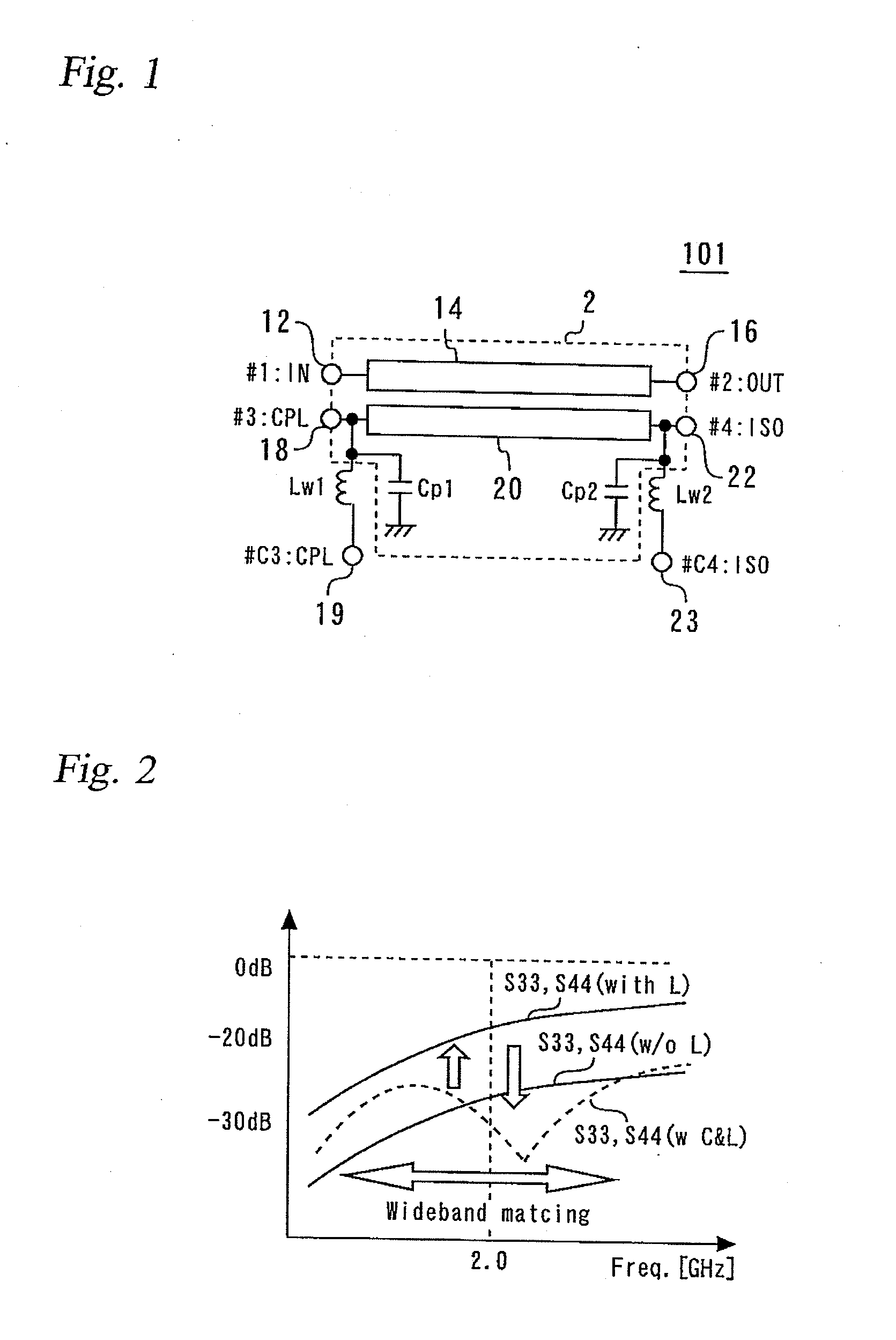

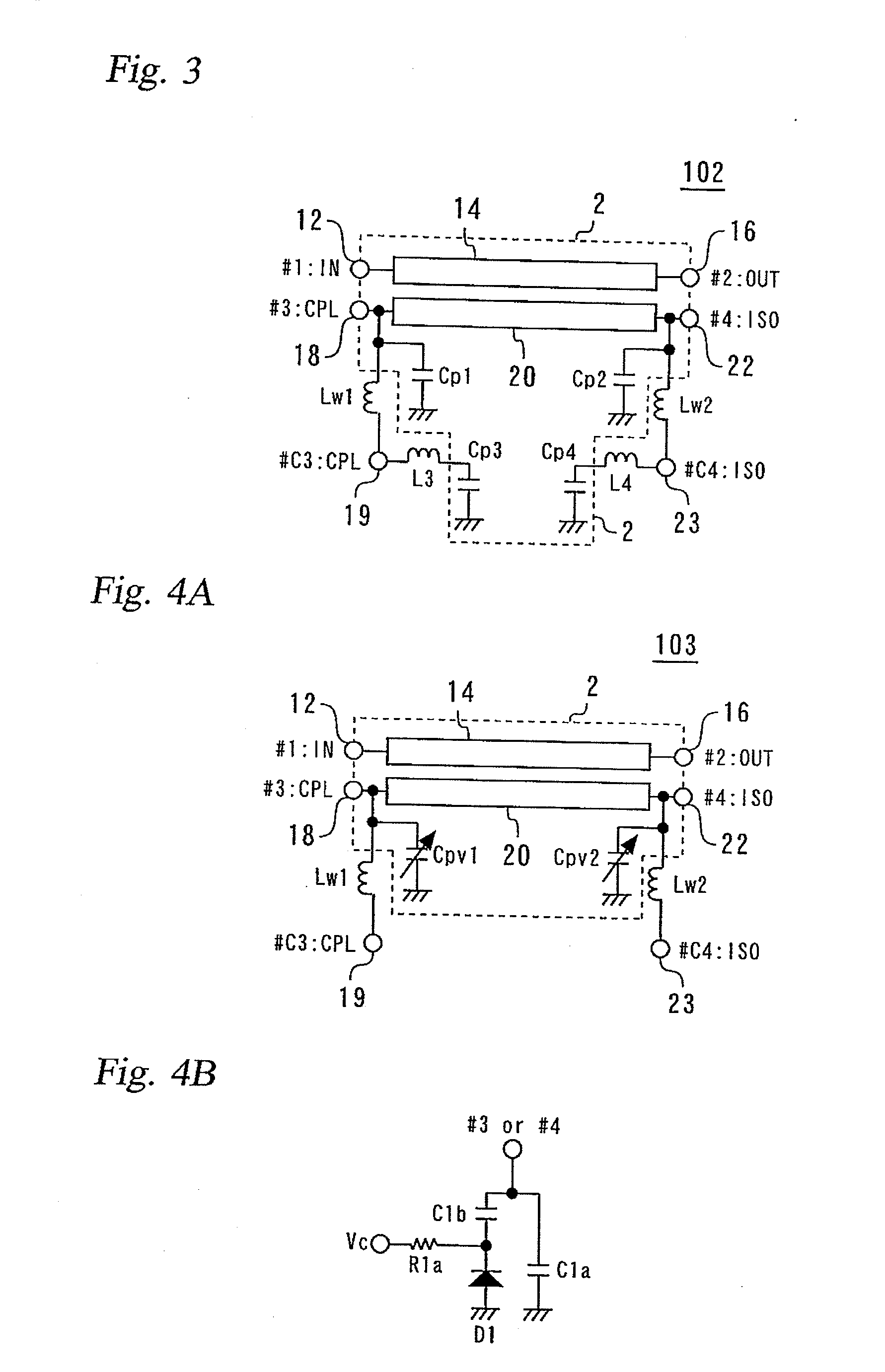

Directional coupler

ActiveUS8289102B2Improved reflection loss characteristicGood reflection loss characteristicWaveguidesCoupling devicesMetal-insulator-metalCapacitance

A directional coupler includes capacitive elements electrically connected to a coupled port and an isolated port, respectively, for a coupled line on a chip (on-chip). The capacitive elements serve as matching capacitive elements and may be MIM (Metal Insulator Metal) capacitors on a substrate. A first end of a first of the capacitive elements is connected between the coupled port and the coupled line and a second end is grounded. A first end of a second of the capacitive elements is connected between the isolated port and the coupled line and a second end is grounded.

Owner:MURATA MFG CO LTD

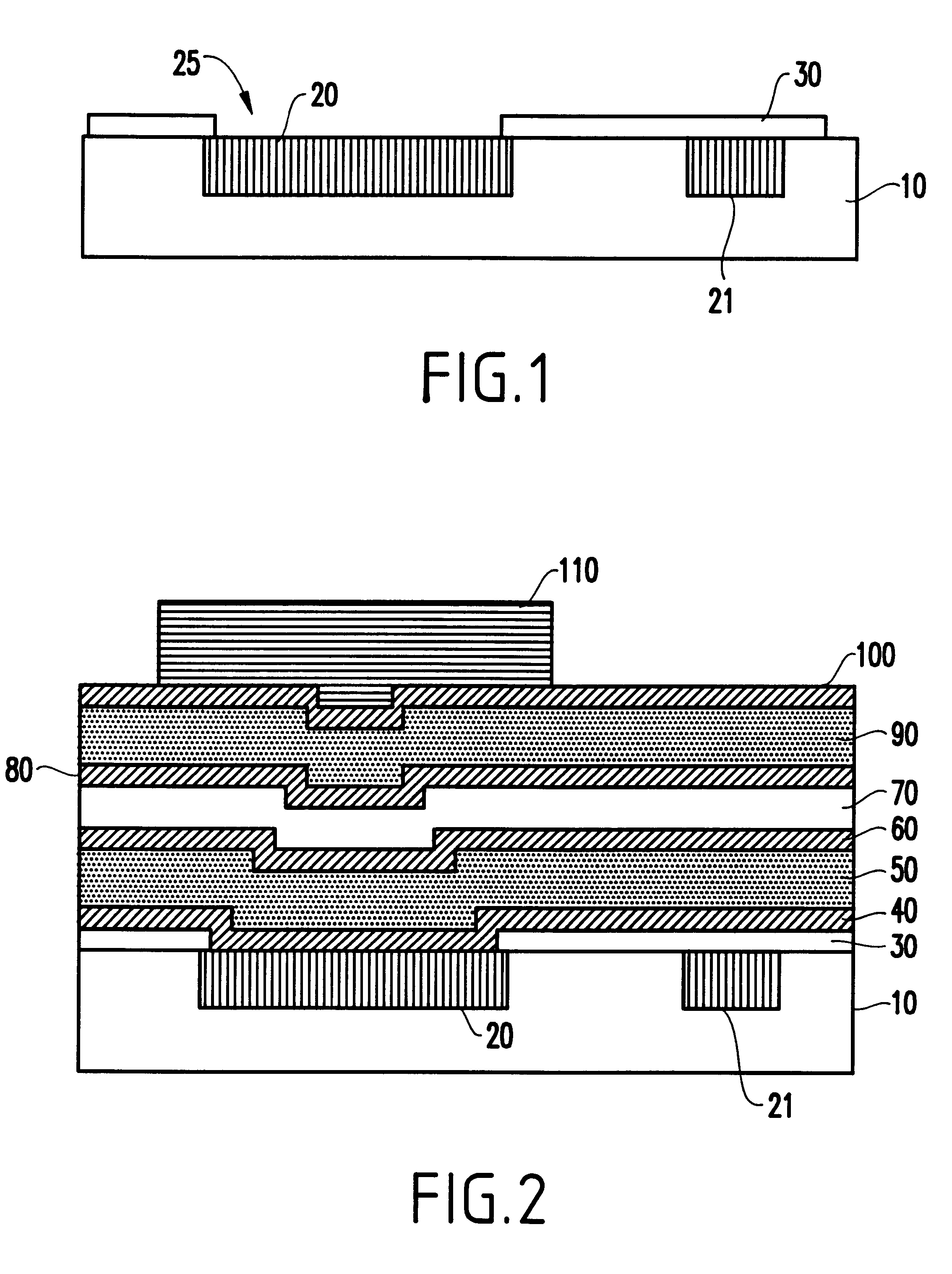

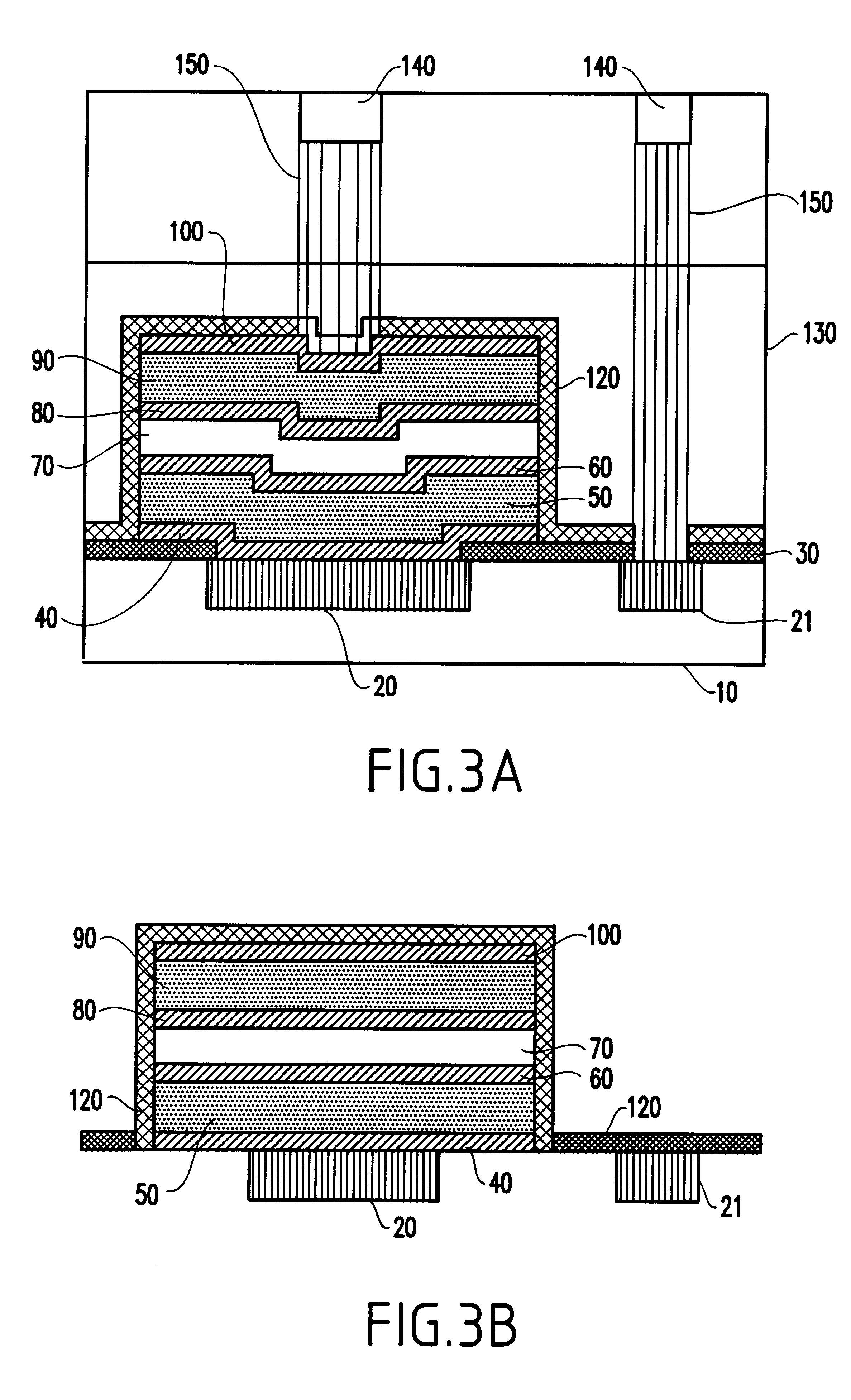

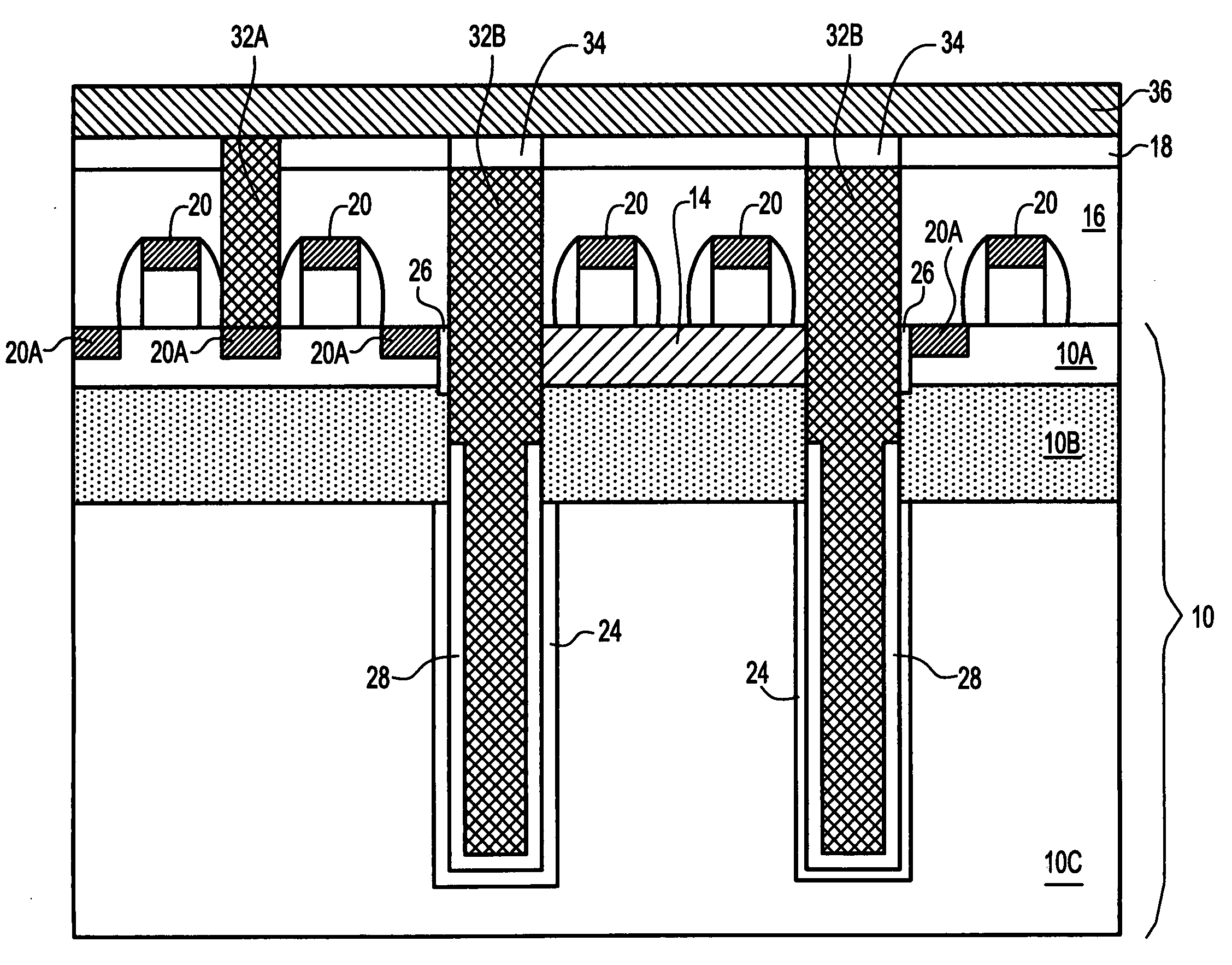

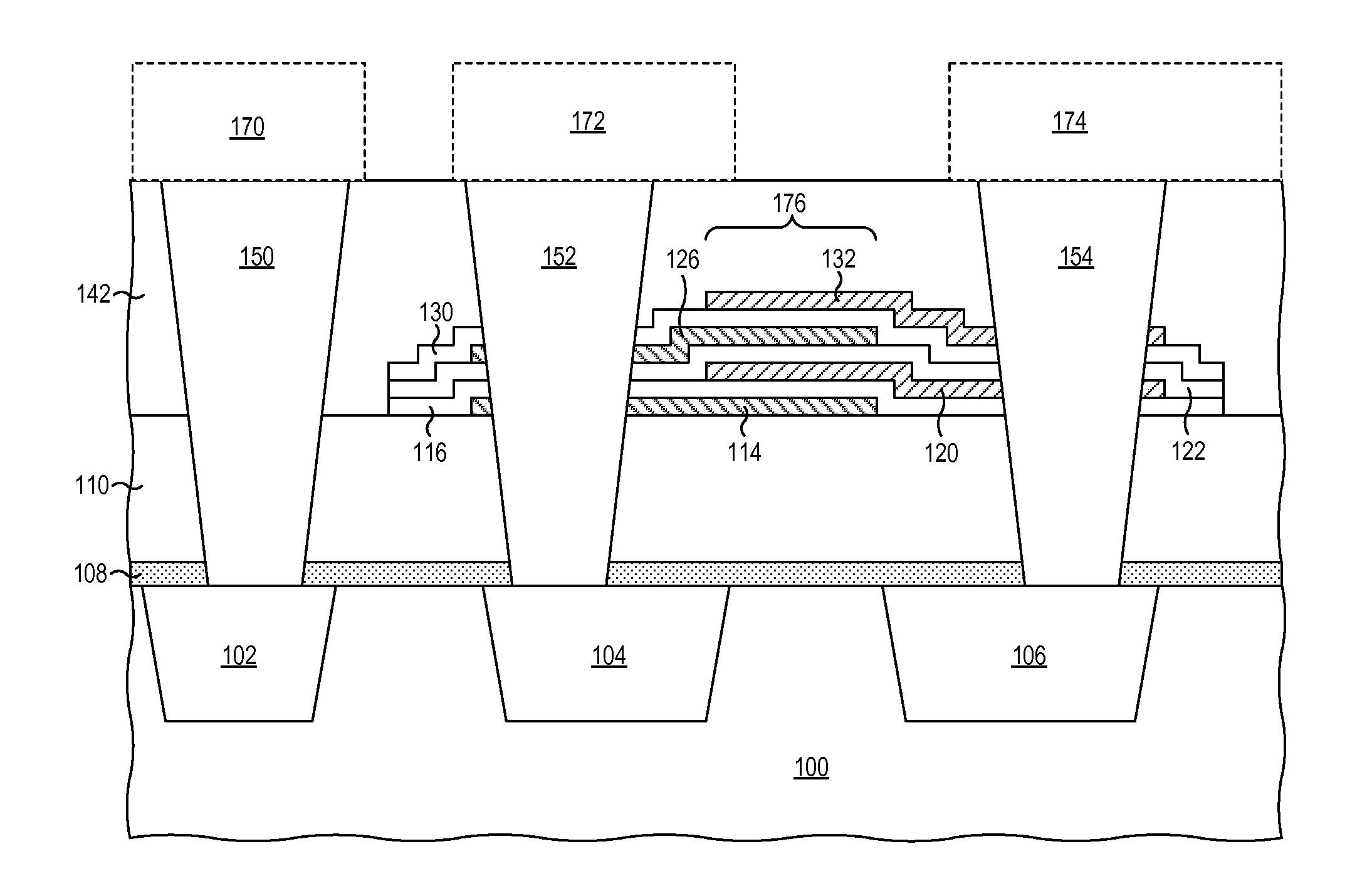

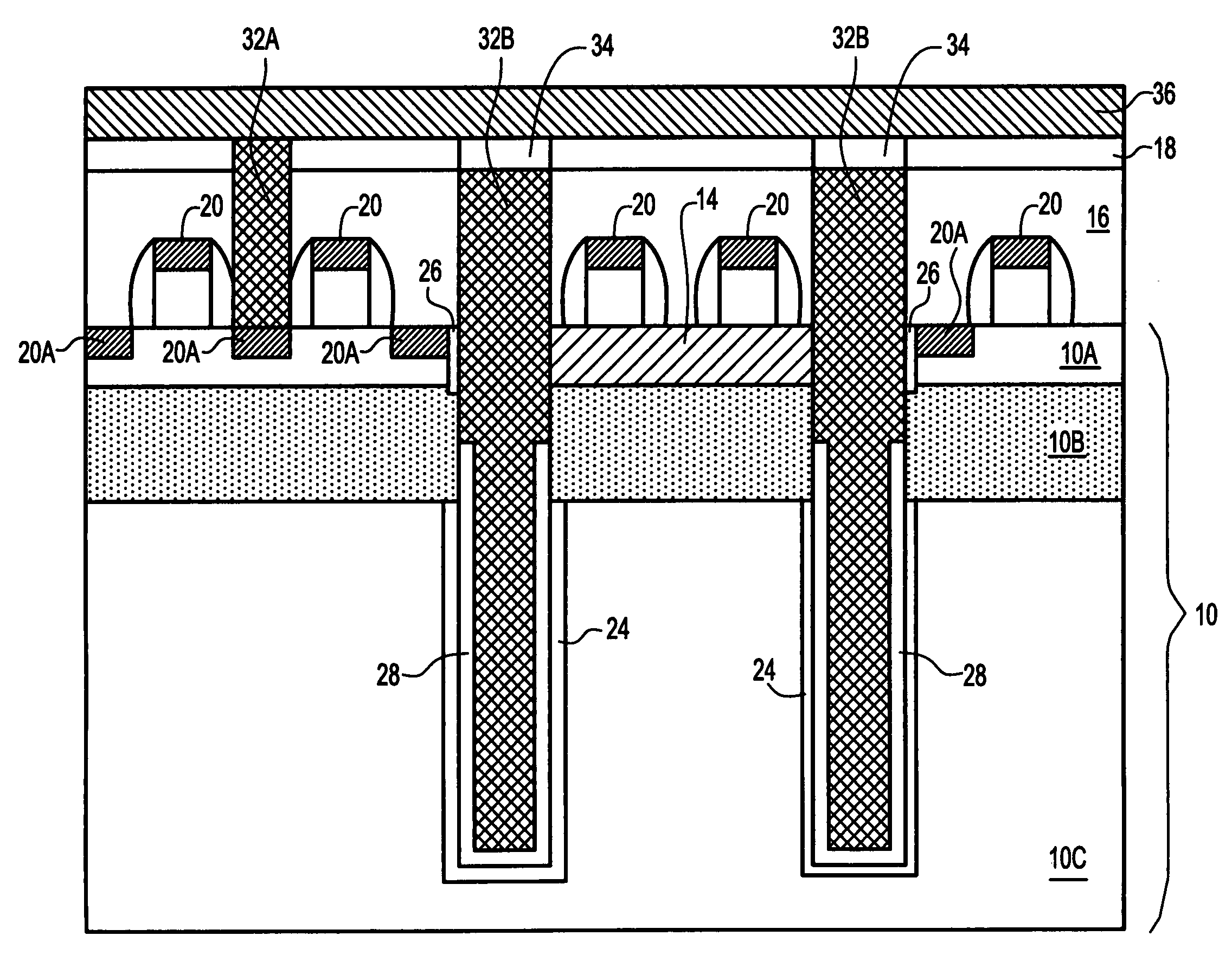

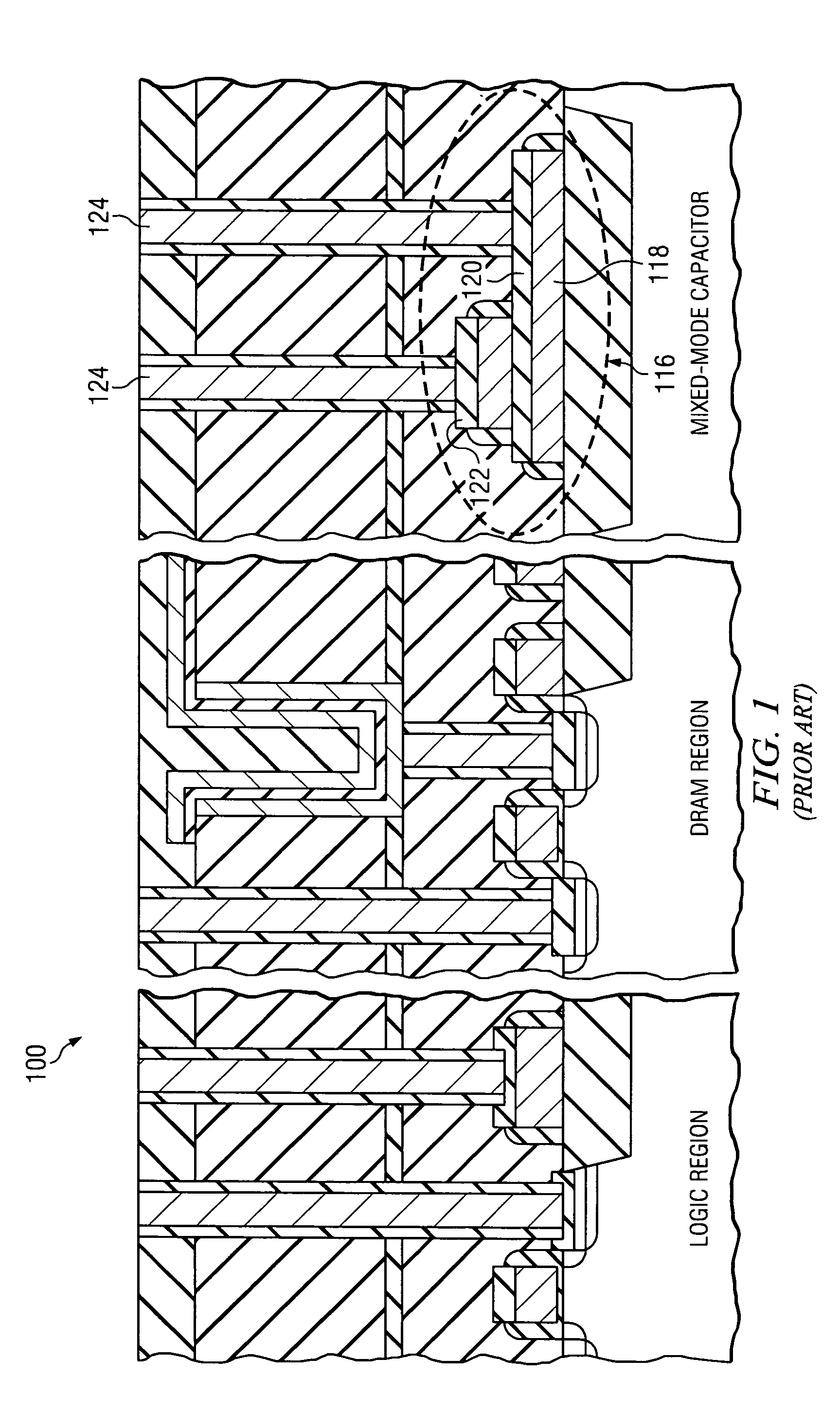

Trench metal-insulator-metal (MIM) capacitors integrated with middle-of-line metal contacts, and method of fabricating same

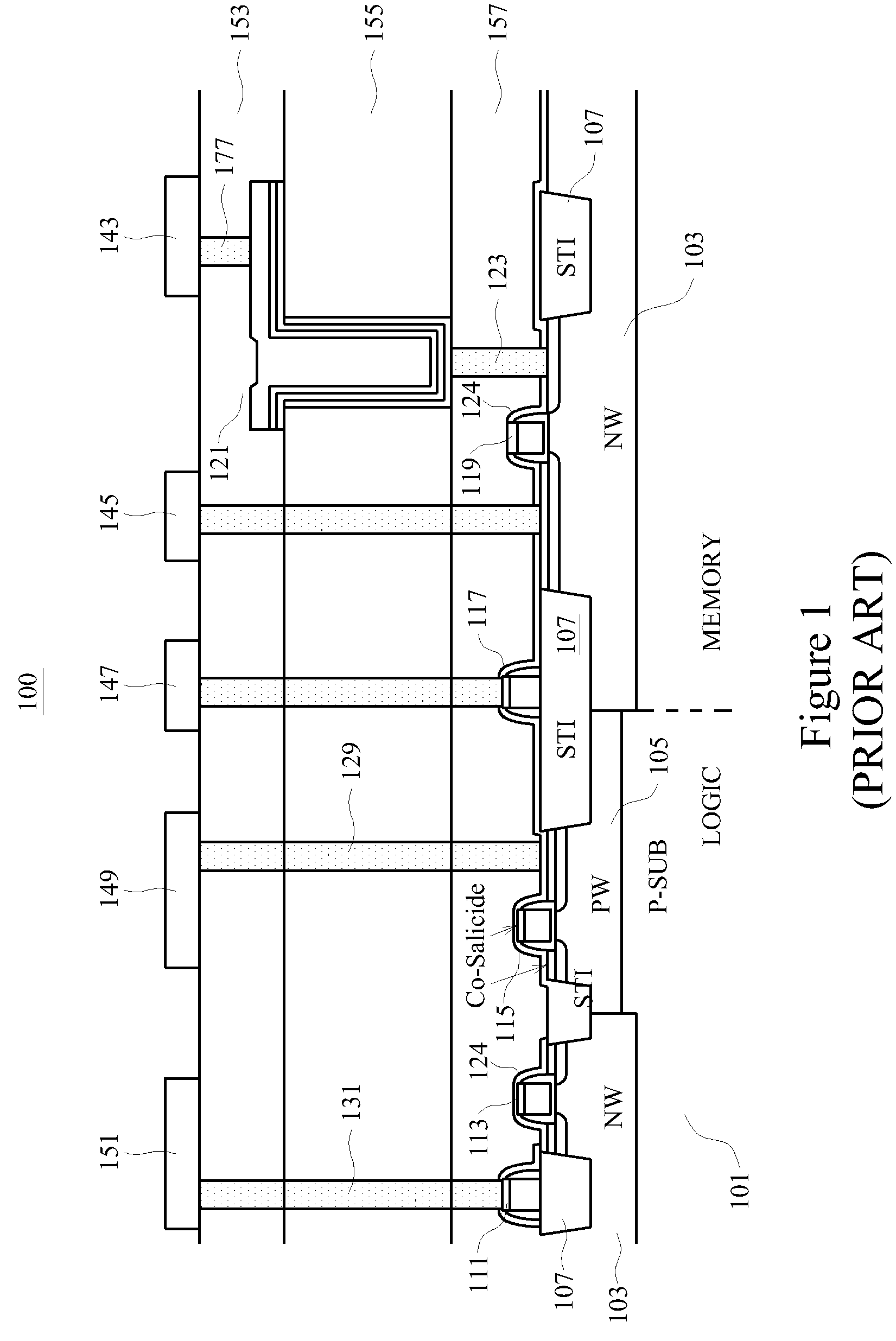

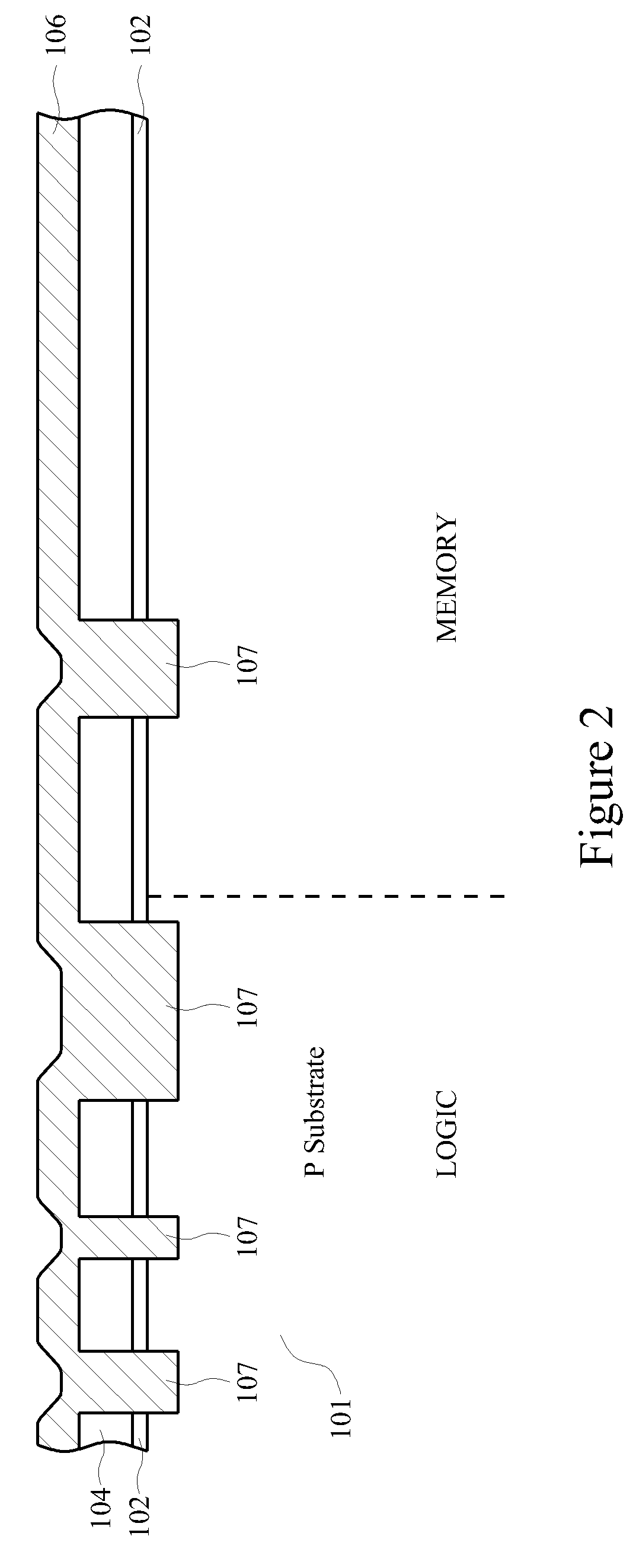

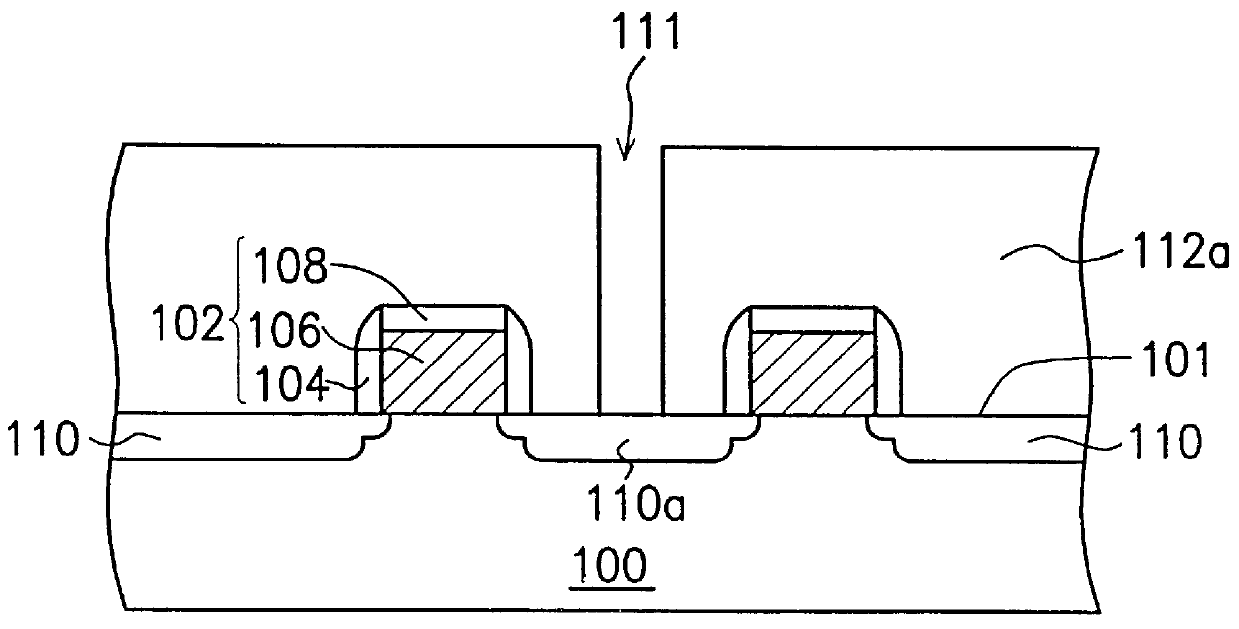

The present invention relates to a semiconductor device that contains at least one trench metal-oxide-metal (MIM) capacitor and at least one other logic circuitry component, preferably at least one field effect transistor (FET). The trench MIM capacitor is located in a trench in a substrate and comprises inner and outer metallic electrode layers with a dielectric layer therebetween. The FET comprises a source region, a drain region, a channel region, and at least one metal contact connected with the source or drain region. The present invention also relates to a fabrication process, which integrates the processing steps for fabricating the trench MIM capacitor with the conventional middle-of-line processing steps for fabricating metal contacts, so that the inner metallic electrode layer of the trench MIM capacitor and the metal contact of the FET or other logic circuitry components are formed by a single middle-of-line processing step and comprise essentially the same metallic material.

Owner:GLOBALFOUNDRIES INC

Directional coupler

ActiveUS20110057746A1Good reflection loss characteristicImproved reflection loss characteristicWaveguidesCoupling devicesMetal-insulator-metalCapacitance

A directional coupler includes capacitive elements electrically connected to a coupled port and an isolated port, respectively, for a coupled line on a chip (on-chip). The capacitive elements serve as matching capacitive elements and may be MIM (Metal Insulator Metal) capacitors on a substrate. A first end of a first of the capacitive elements is connected between the coupled port and the coupled line and a second end is grounded. A first end of a second of the capacitive elements is connected between the isolated port and the coupled line and a second end is grounded.

Owner:MURATA MFG CO LTD

Structure of a capacitor in a semiconductor device having a self align contact window which has a slanted sidewall

InactiveUS6078492ATransistorFixed capacitor electrodesHigh dielectric permittivityMetal-insulator-metal

A structure of a capacitor includes two gates and a commonly used source / drain region on a substrate. Then, a pitted self align contact window (PSACW) partly exposes the commonly used source / drain region. Then an glue / barrier layer and a lower electrode of the capacitor are over the PSACW. Then a dielectric thin film with a material having high dielectric constant is over the lower electrode. Then, an upper electrode is over the dielectric thin film to complete a capacitor, which has a structure of metal insulator metal with a shape like the PSACW.

Owner:UNITED MICROELECTRONICS CORP

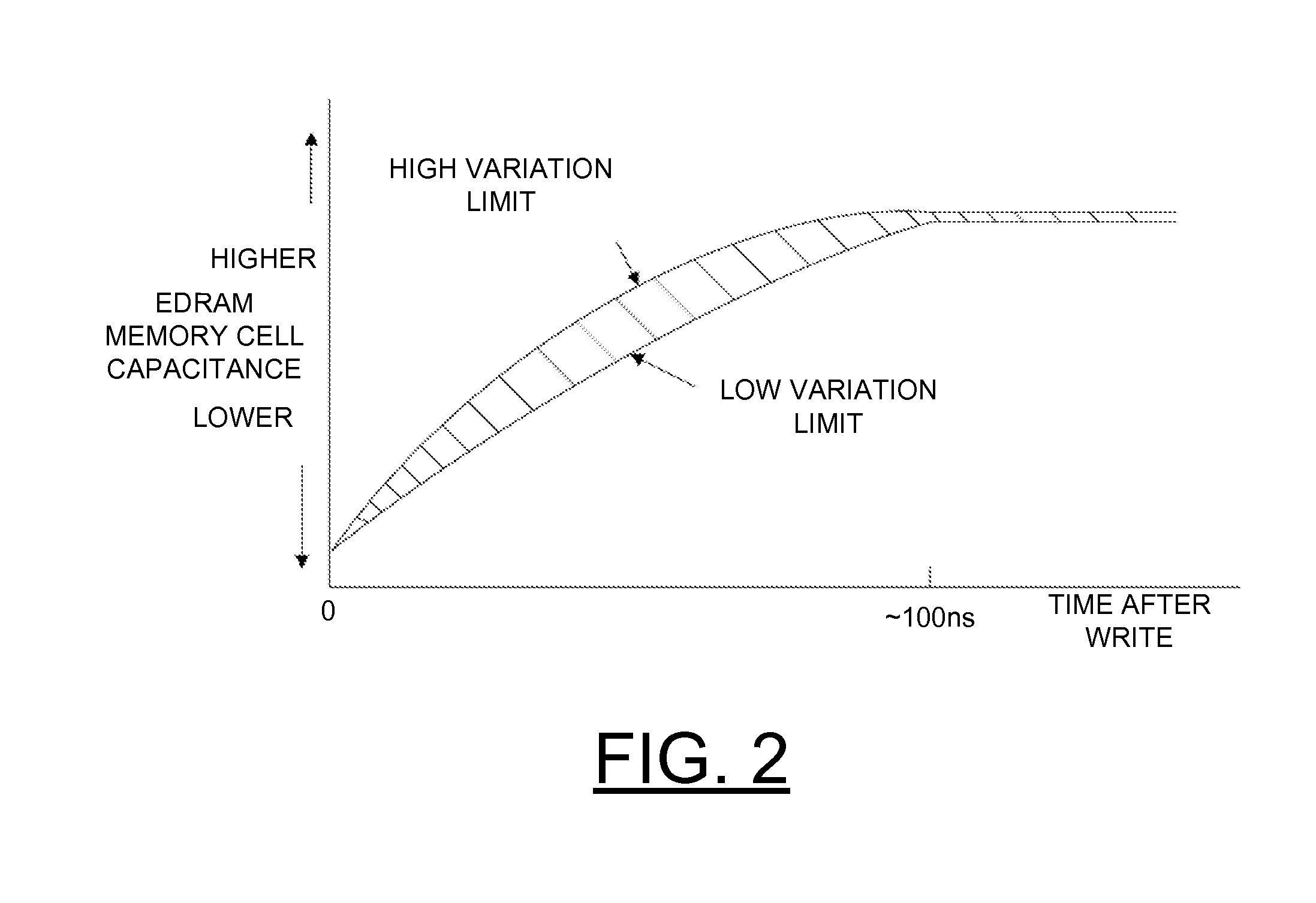

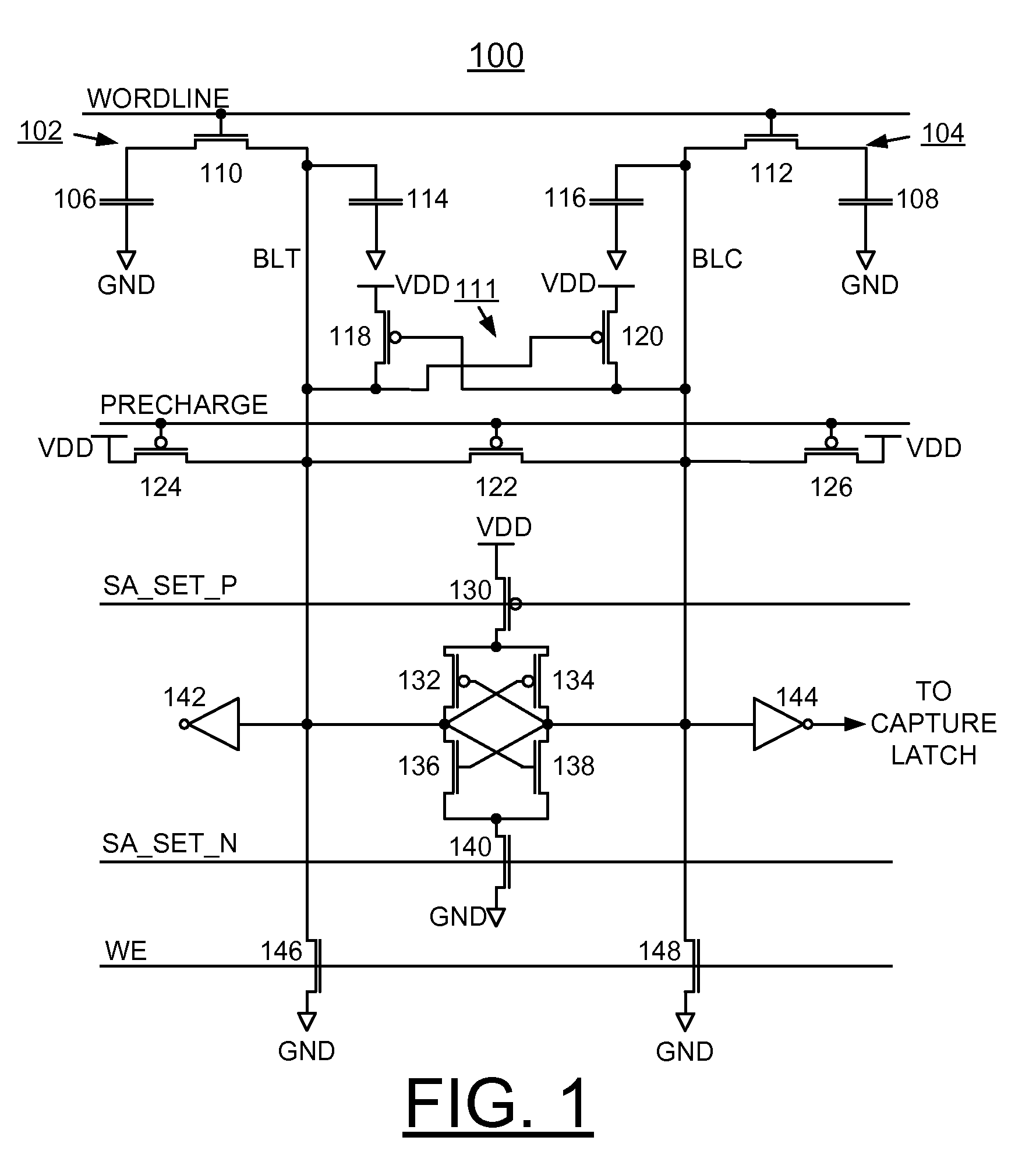

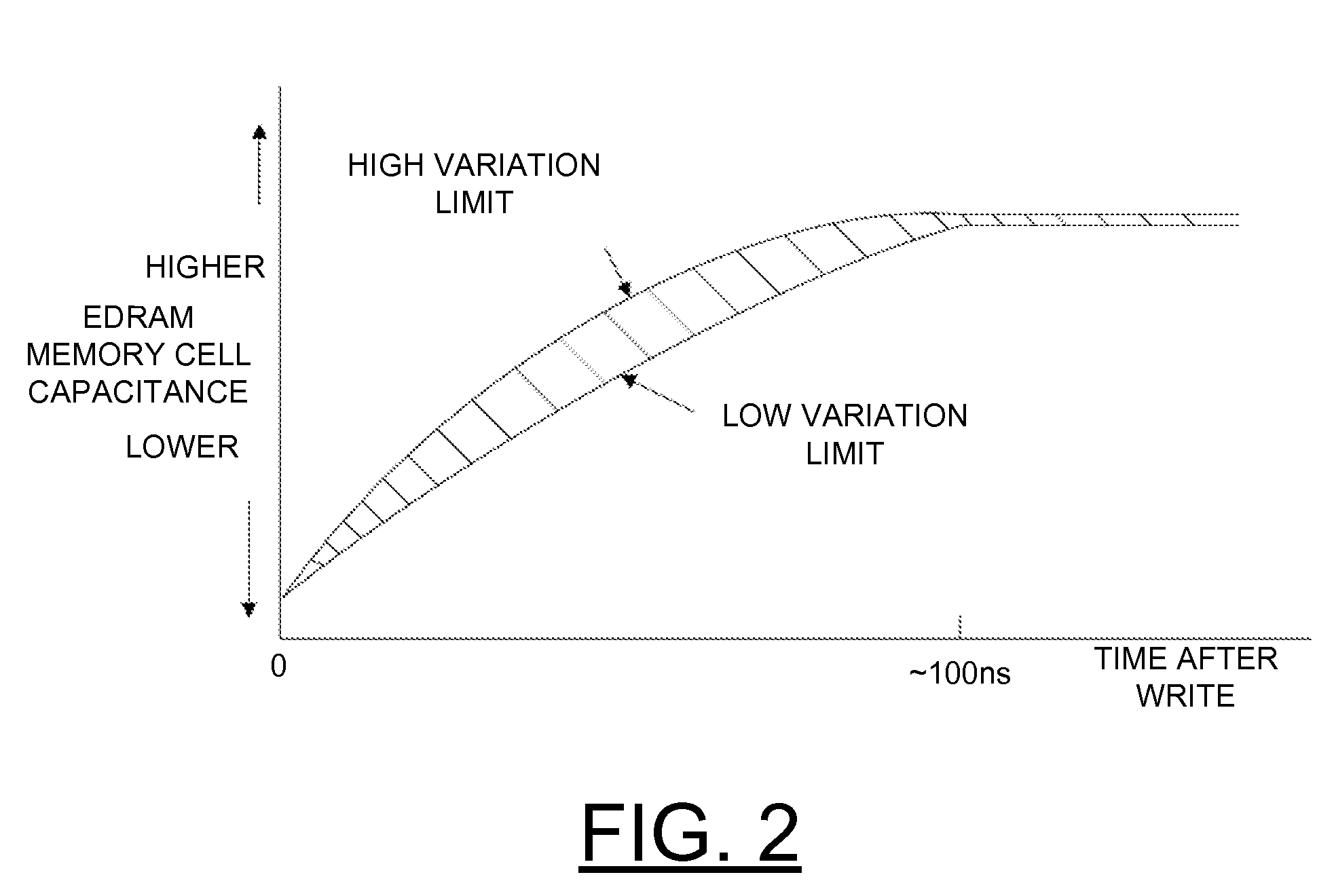

Implementing physically unclonable function (PUF) utilizing edram memory cell capacitance variation

ActiveUS20120106235A1Overcome disadvantagesDigital data processing detailsDigital storageCapacitanceMetal-insulator-metal

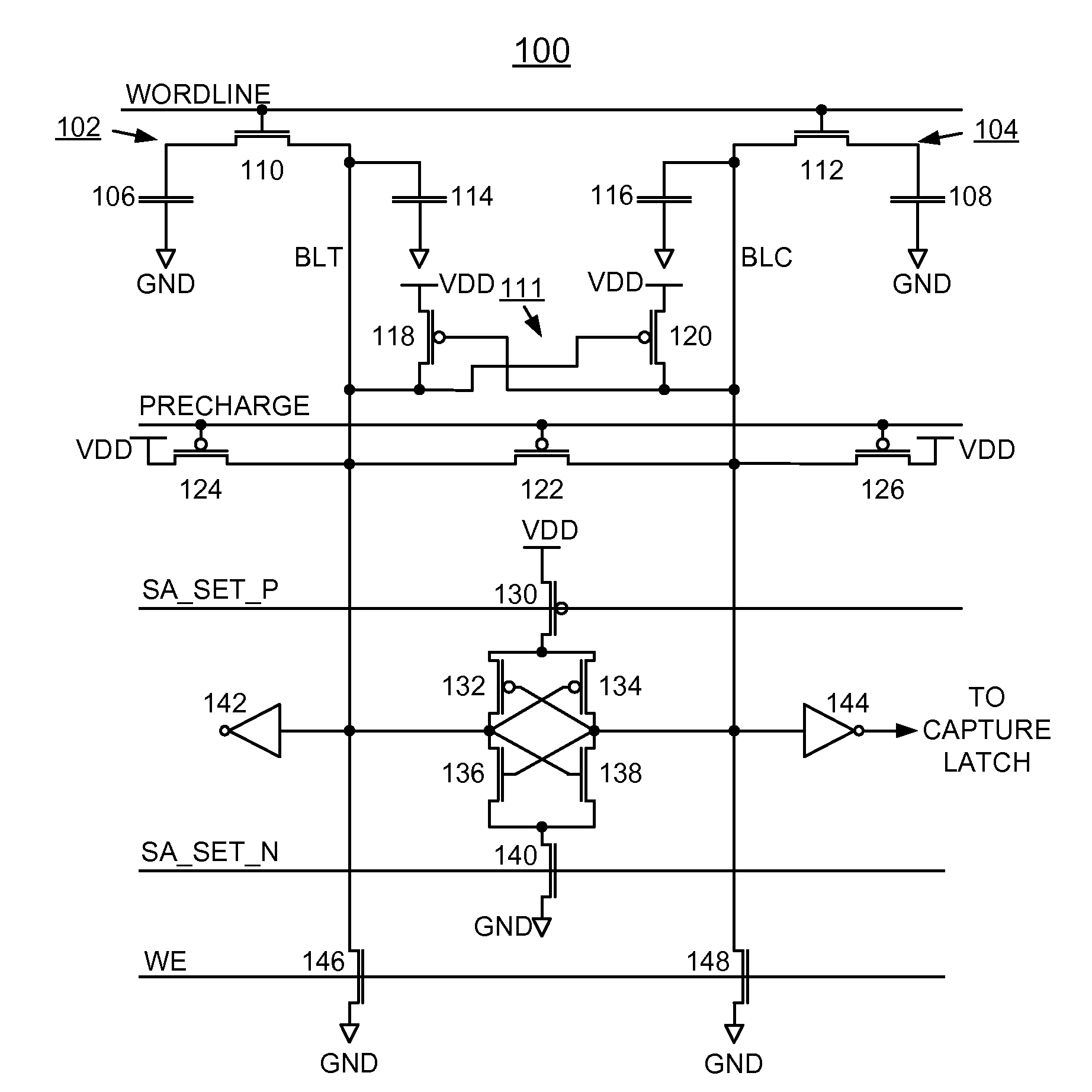

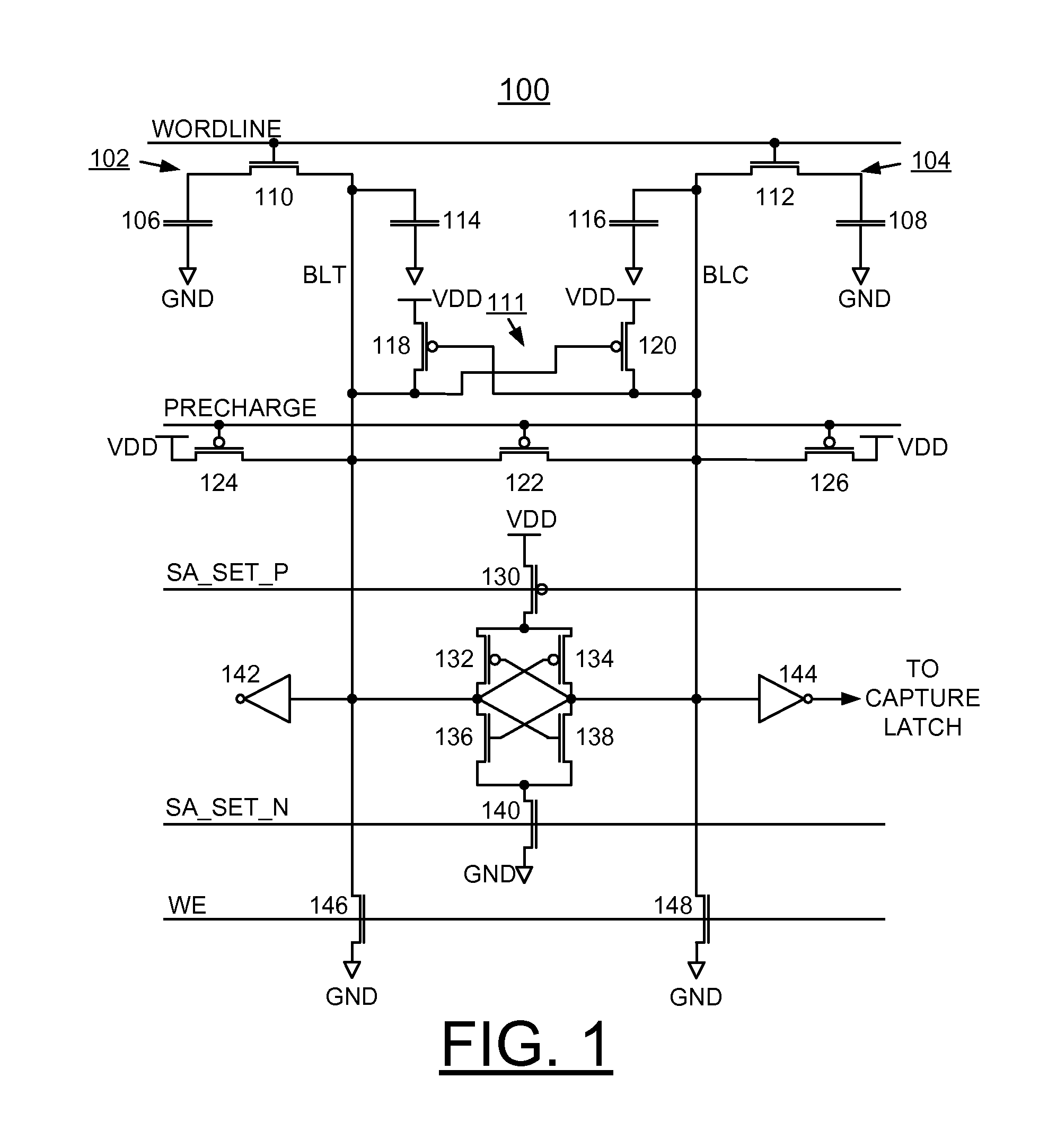

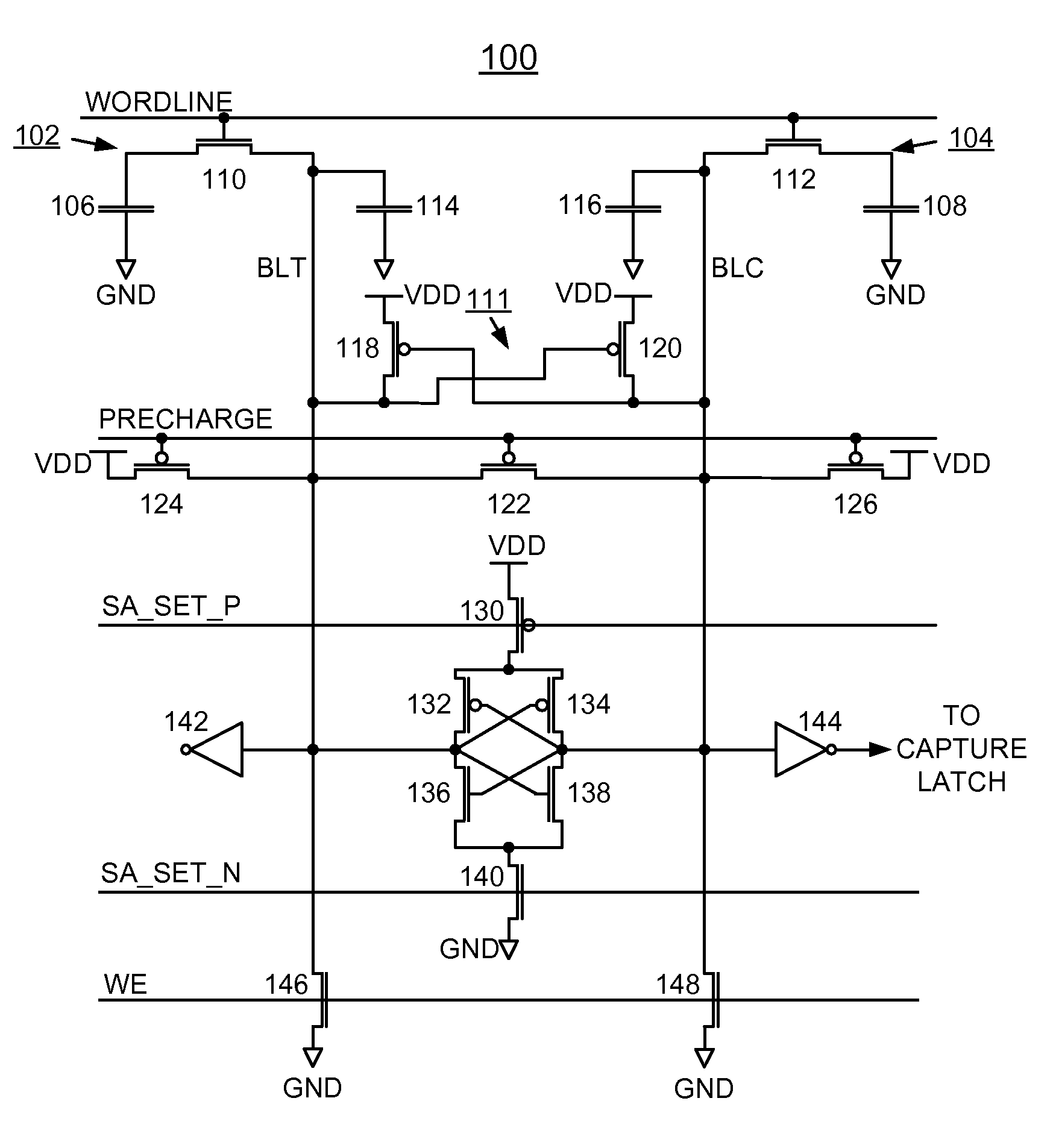

A method and embedded dynamic random access memory (EDRAM) circuit for implementing a physically unclonable function (PUF), and a design structure on which the subject circuit resides are provided. An embedded dynamic random access memory (EDRAM) circuit includes a first EDRAM memory cell including a memory cell true storage capacitor and a second EDRAM memory cell including a memory cell complement storage capacitor. The memory cell true storage capacitor and the memory cell complement storage capacitor include, for example, trench capacitors or metal insulator metal capacitors (MIM caps). A random variation of memory cell capacitance is used to implement the physically unclonable function. Each memory cell is connected to differential inputs to a sense amplifier. The first and second EDRAM memory cells are written to zero and then the first and second EDRAM memory cells are differentially sensed and the difference is amplified to consistently read the same random data.

Owner:MARVELL ASIA PTE LTD

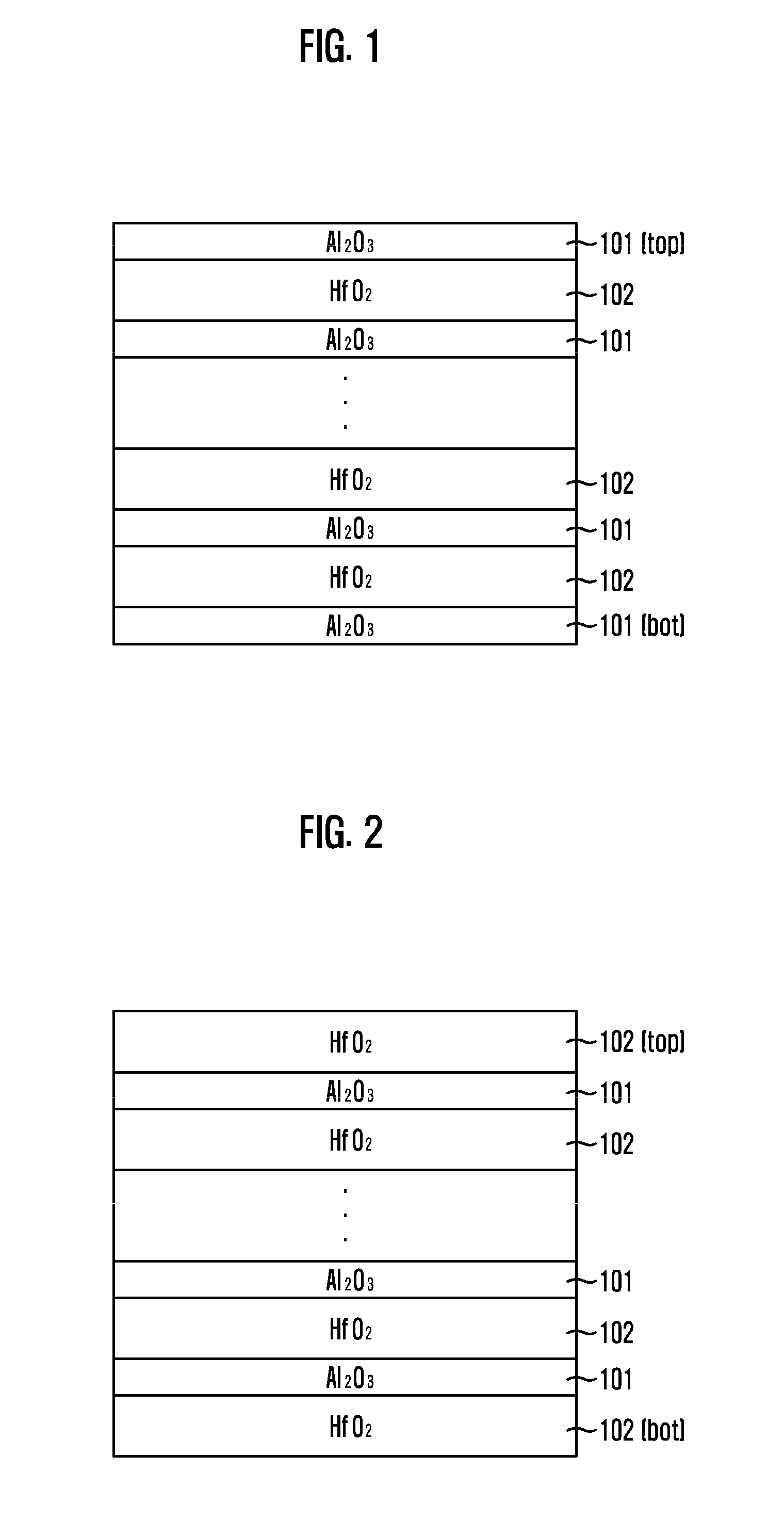

Method for making metal capacitors with low leakage currents for mixed-signal devices

InactiveUS20050132549A1Reduce leakage currentHigh capacitance per unit areaElectrolytic capacitorsSemiconductor/solid-state device manufacturingCapacitanceMetal-insulator-metal

A method for making metal-insulator-metal (MIM) capacitors having insulators with high-dielectric-constant and sandwiched between wide-band-gap insulators resulting in low leakage currents and high capacitance per unit area is achieved. The high-k layer increases the capacitance per unit area for next generation mixed-signal devices while the wide-band-gap insulators reduce leakage currents. In a second embodiment, a multilayer of different high-k materials is formed between the wide-band-gap insulators to substantially increase the capacitance per unit area. The layer materials and thicknesses are optimized to reduce the nonlinear capacitance dependence on voltage.

Owner:TAIWAN SEMICON MFG CO LTD

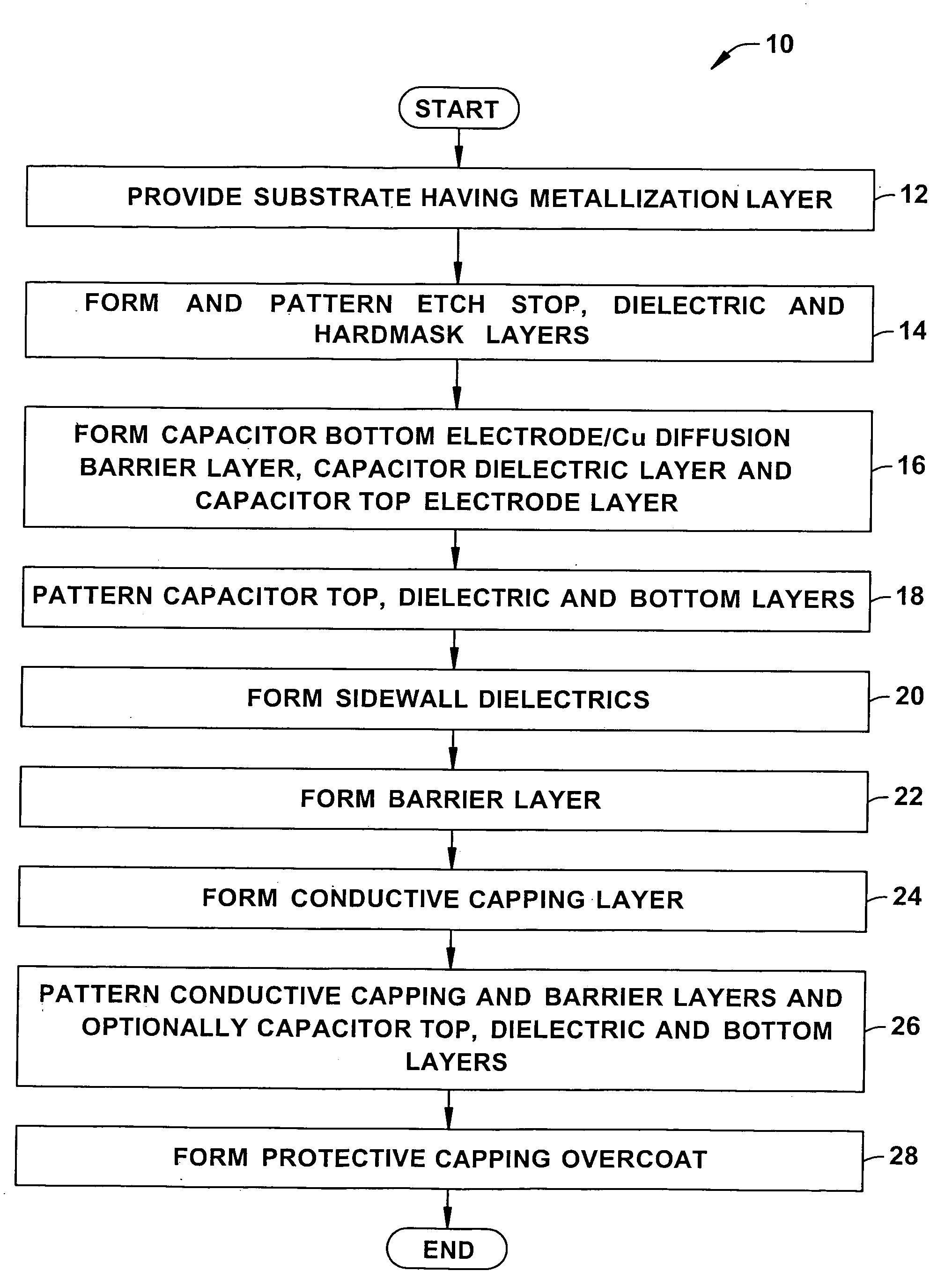

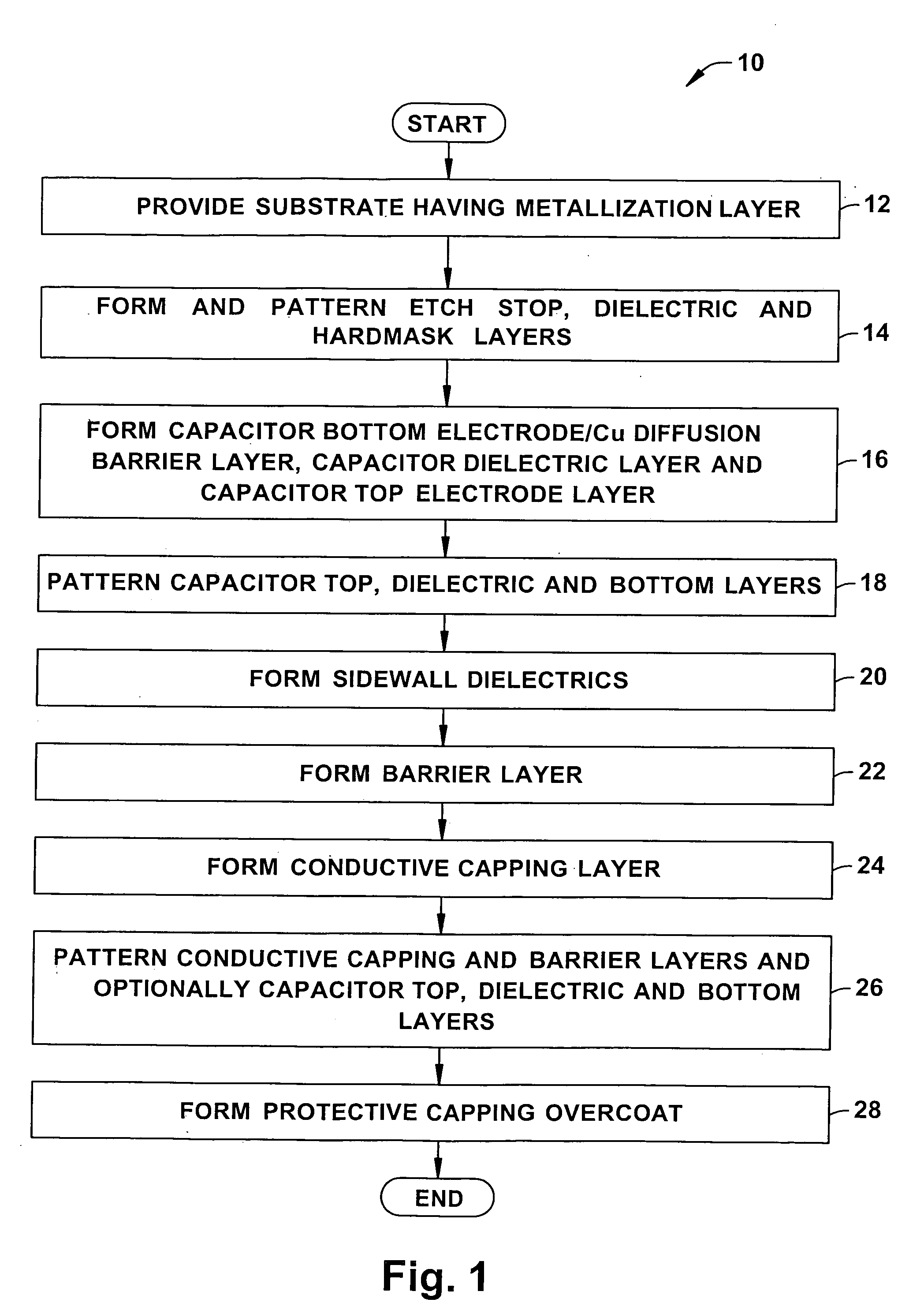

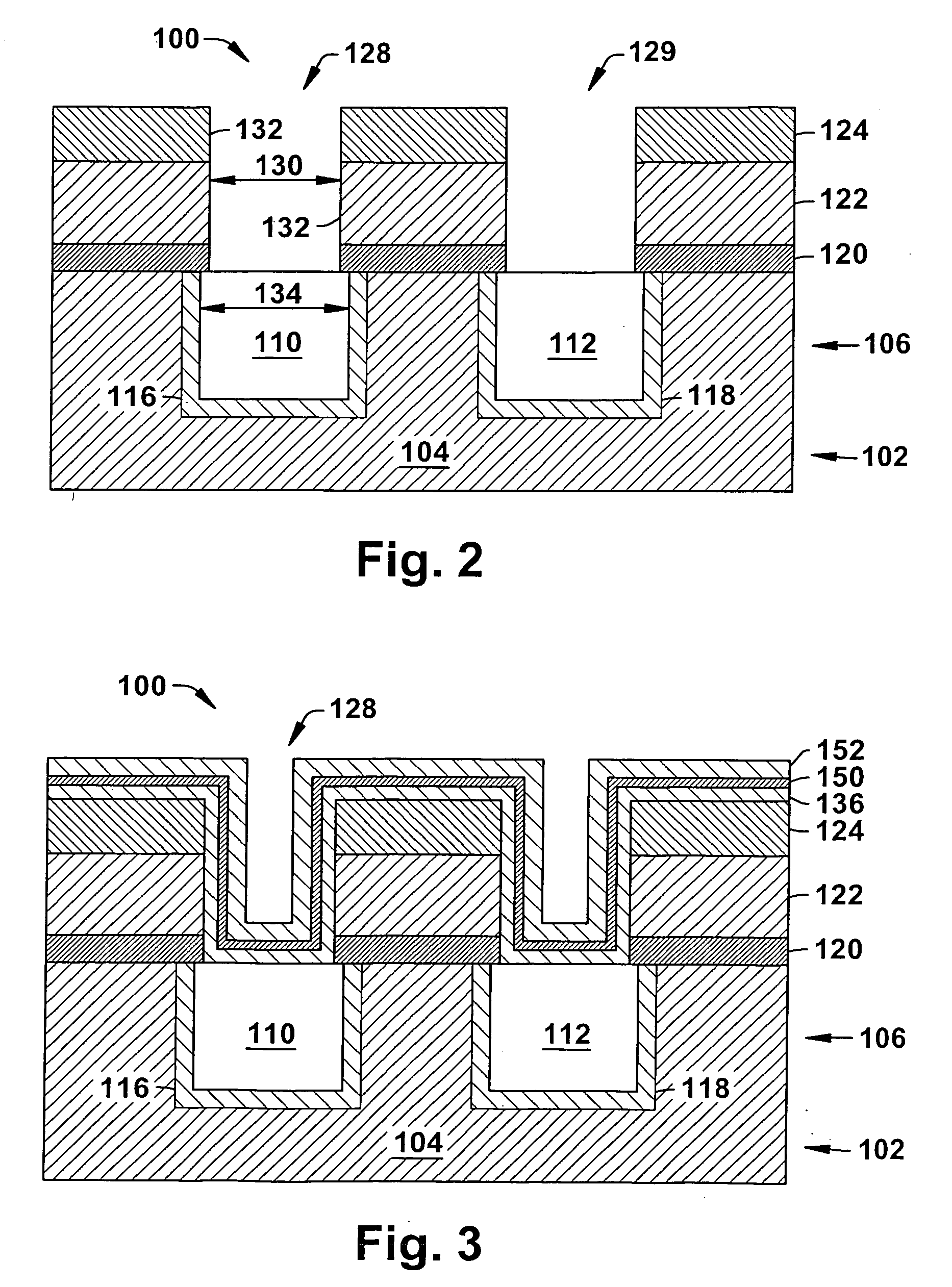

Metal insulator metal (MIM) capacitor fabrication with sidewall spacers and aluminum cap (ALCAP) top electrode

ActiveUS20060024899A1Facilitates device scalingReduce adverse effectsSemiconductor/solid-state device detailsSolid-state devicesMetal-insulator-metalCopper

A method (10) of forming a MIM (metal insulator metal) capacitor is disclosed whereby adverse affects associated with copper diffusion are mitigated even as the capacitor is scaled down. A sidewall spacer (156) is formed against an edge (137) of a layer of bottom electrode / copper diffusion barrier material (136), an edge (151) of a layer of capacitor dielectric material (150) and at least some of an edge (153) of a layer of top electrode material. The sidewall spacer (156) is dielectric or non-conductive and mitigates “shorting” currents that can develop between the plates as a result of copper diffusion. Bottom electrode diffusion barrier material (136) mitigates copper diffusion and / or copper drift, thereby reducing the likelihood of premature device failure.

Owner:TEXAS INSTR INC

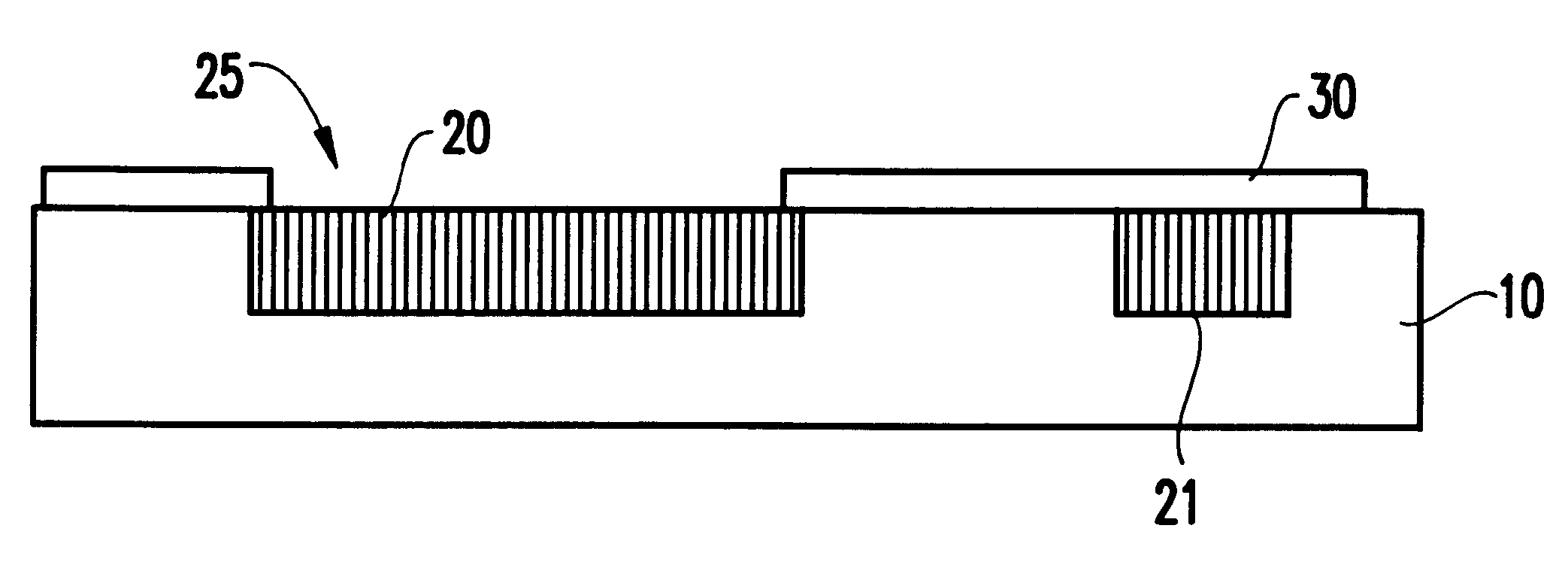

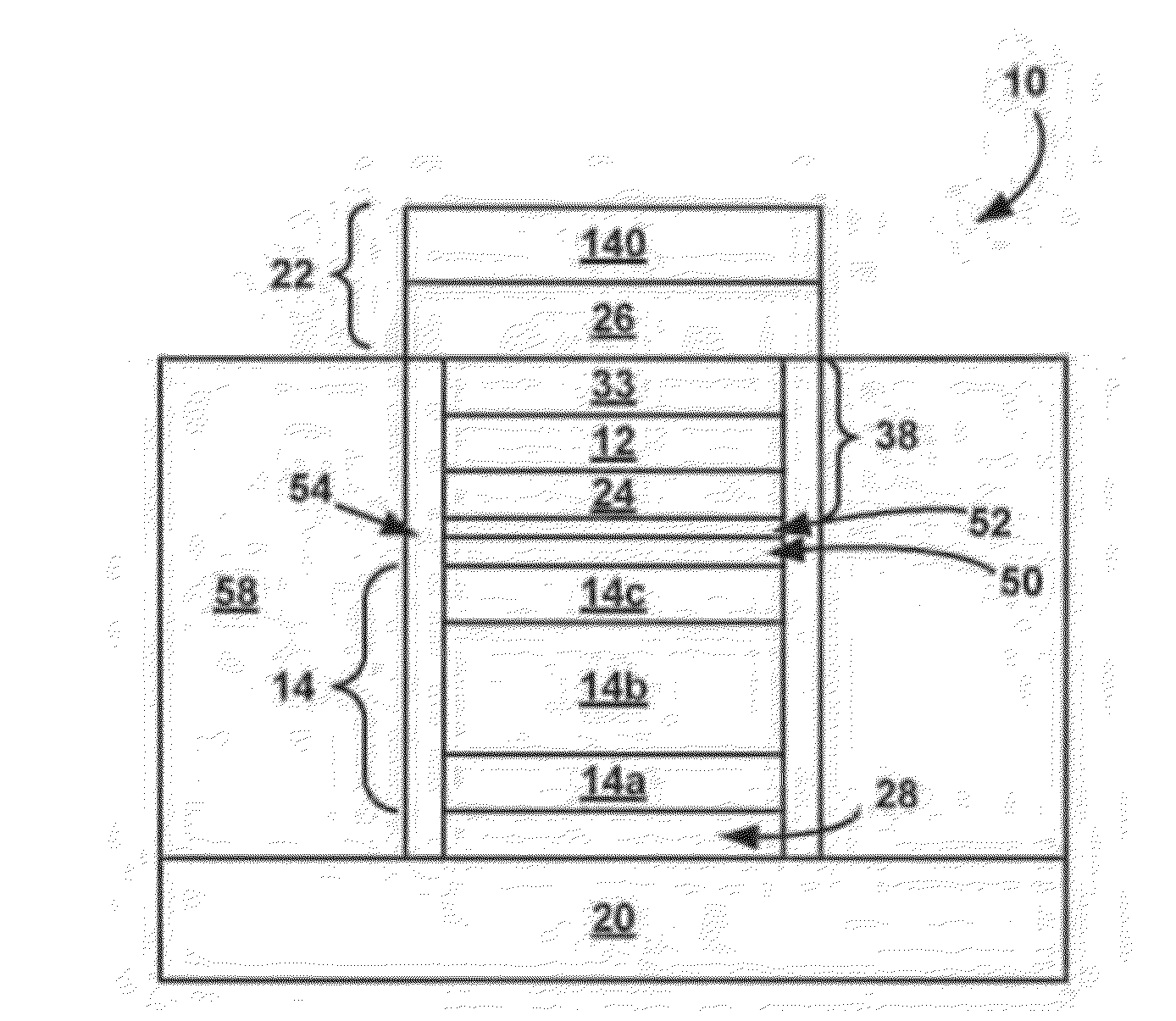

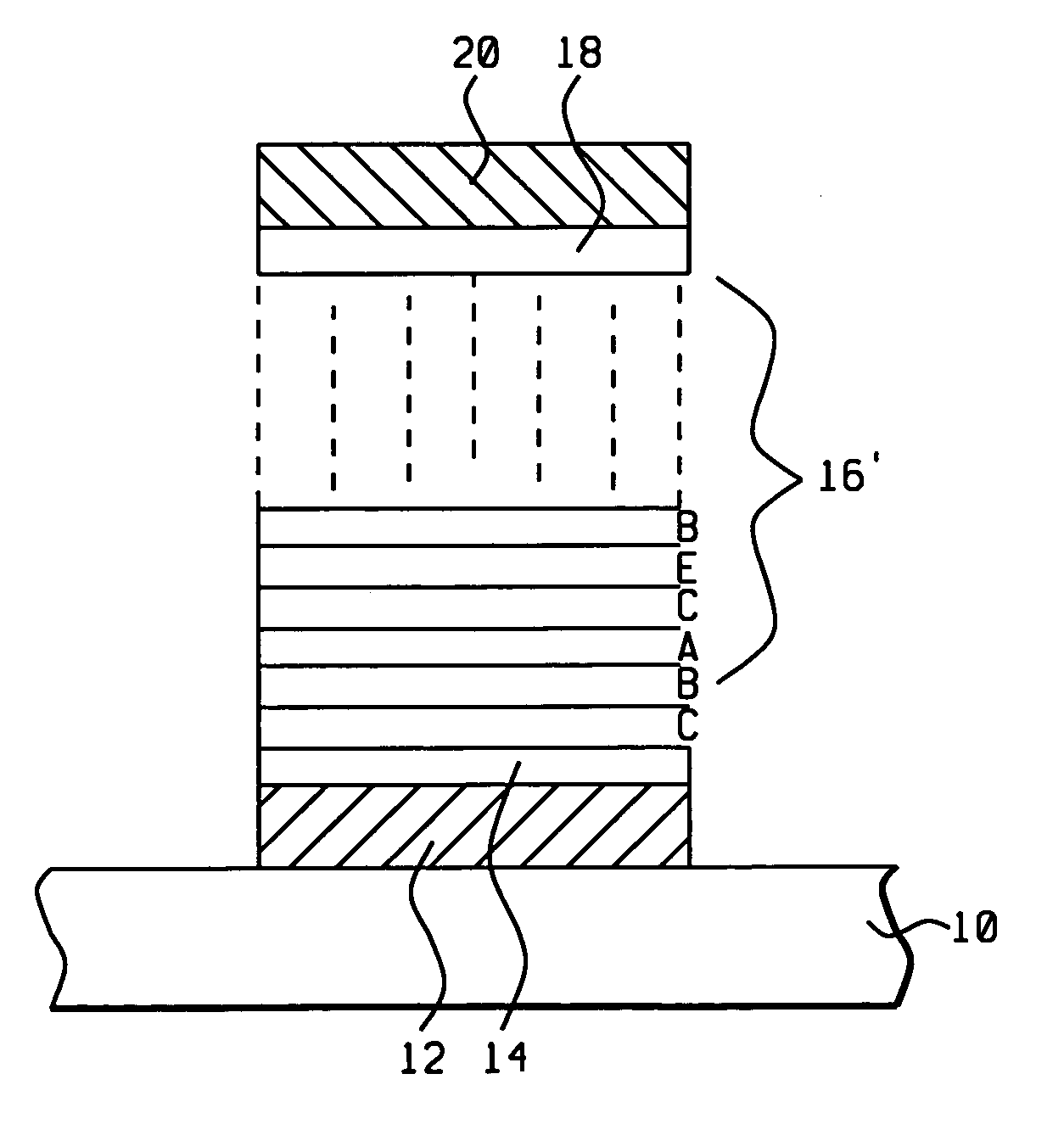

High-density stacked planar metal-insulator-metal capacitor structure and method for manufacturing same

InactiveUS20140159200A1High on-chip capacitance densityWeakening rangeSemiconductor/solid-state device detailsSolid-state devicesMetal-insulator-metalElectrical connection

An embodiment of a high-density, stacked, planar metal-insulator-metal (MIM) capacitor structure includes a stack of planar electrodes and interposing dielectric layers. Vertically-alternating electrodes are horizontally-staggered, and vias are formed through the multiple electrodes, so that electrical connection is made circumferentially through the via sidewalls to multiple electrodes through which a given via passes. An MIM capacitor incorporating a multiple-level capacitor stack may be fabricated by repeated usage of the same mask operation for each incremental capacitor stack level, and without requiring additional masks beyond those utilized for the first such level.

Owner:ADVANCED MICRO DEVICES INC

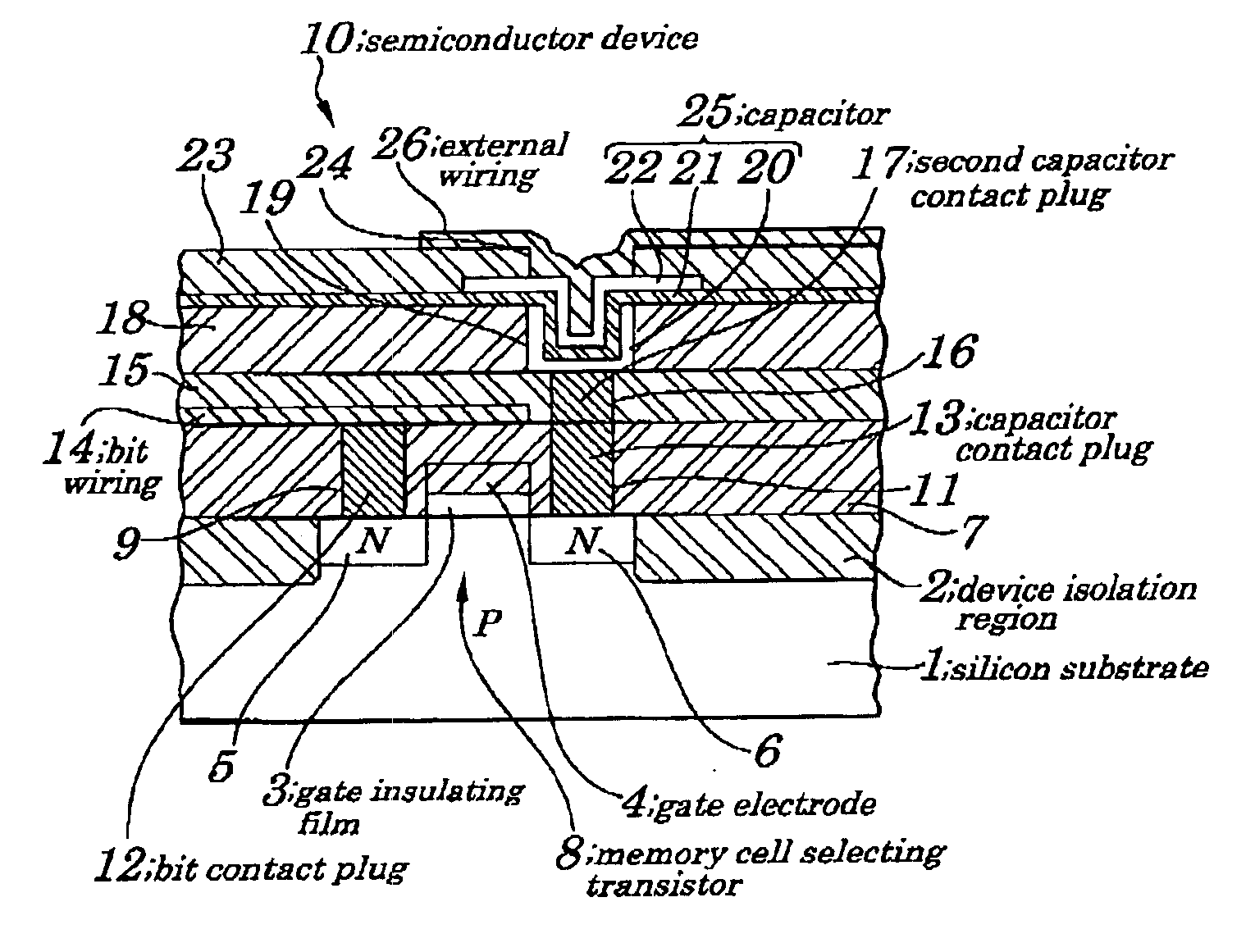

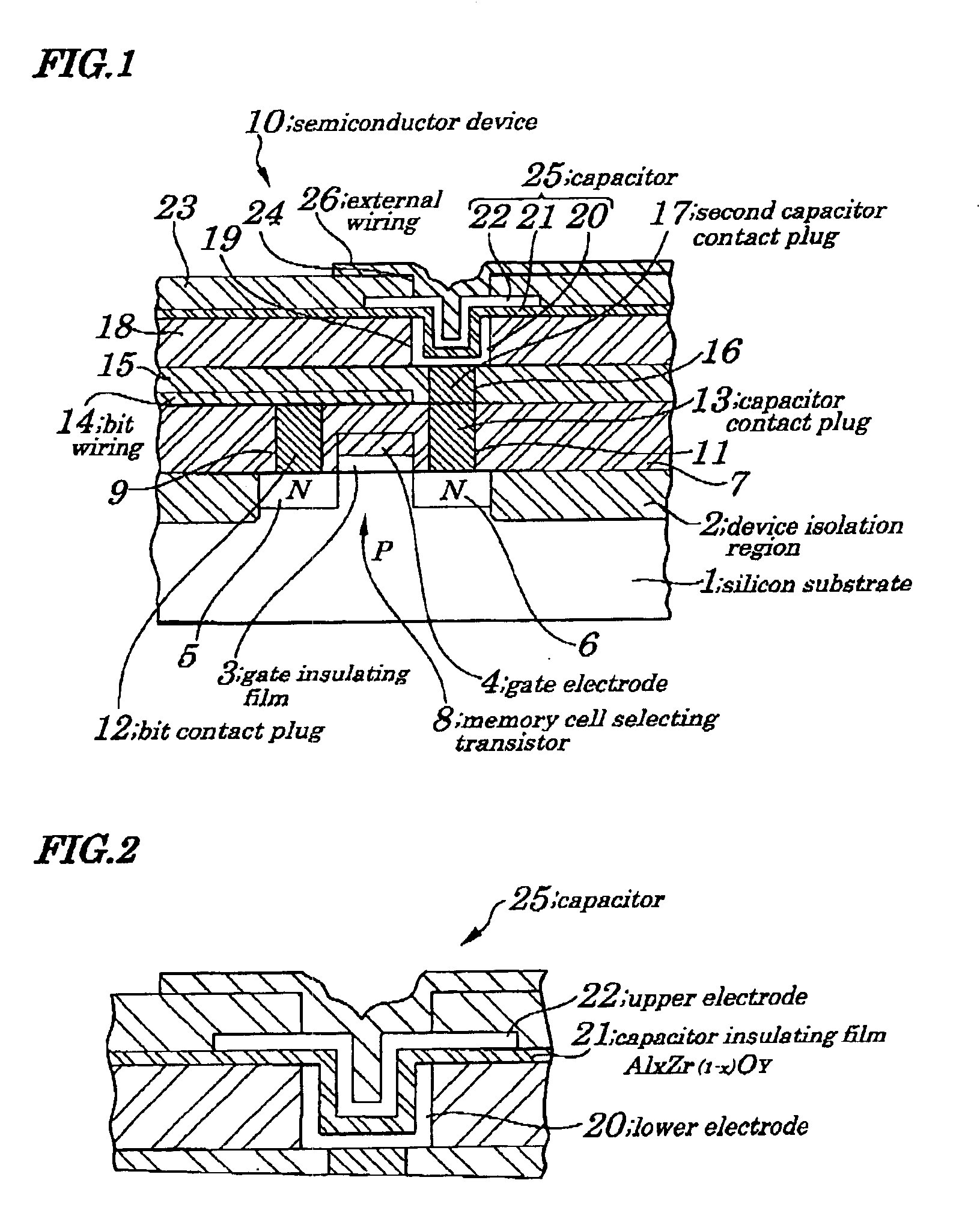

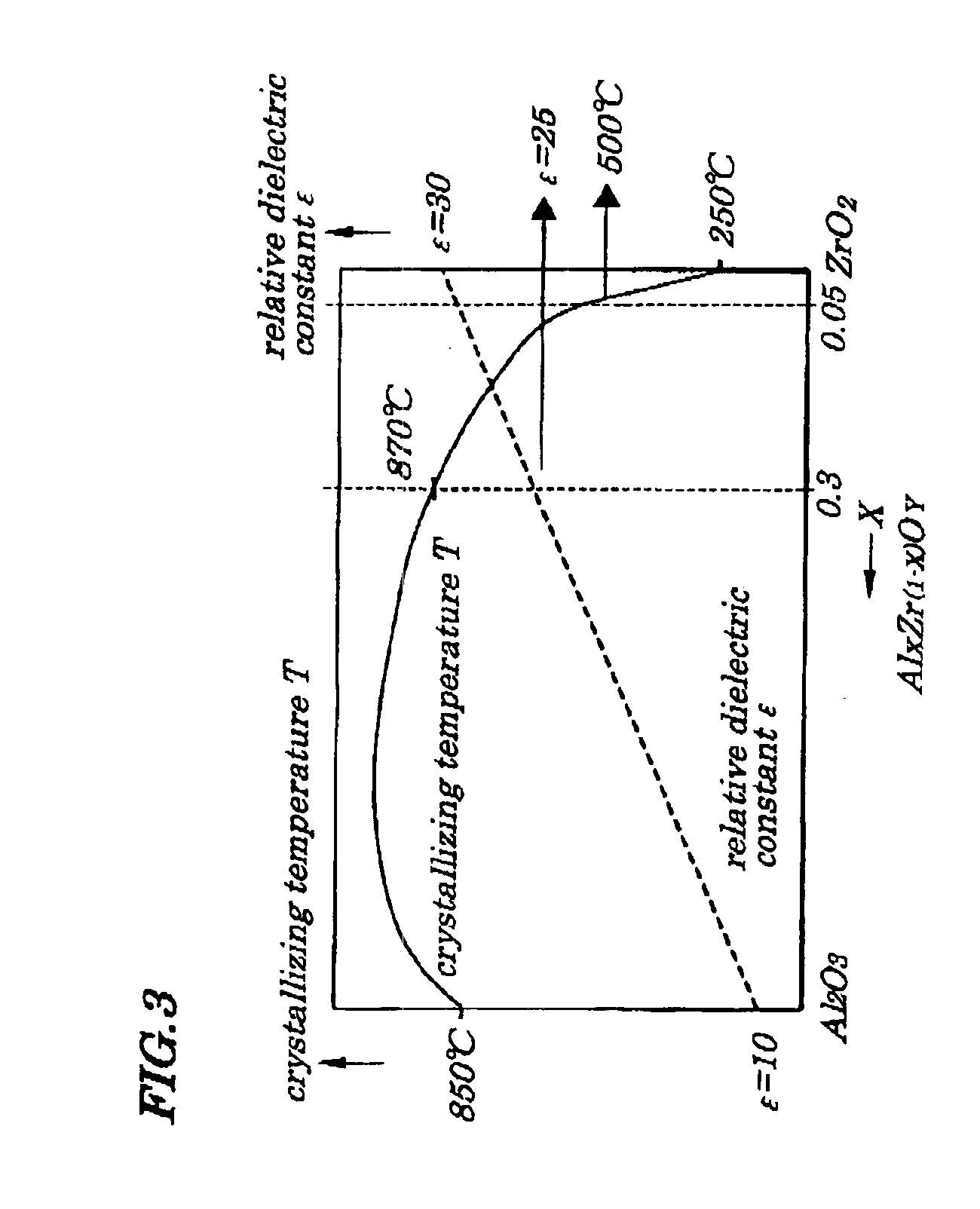

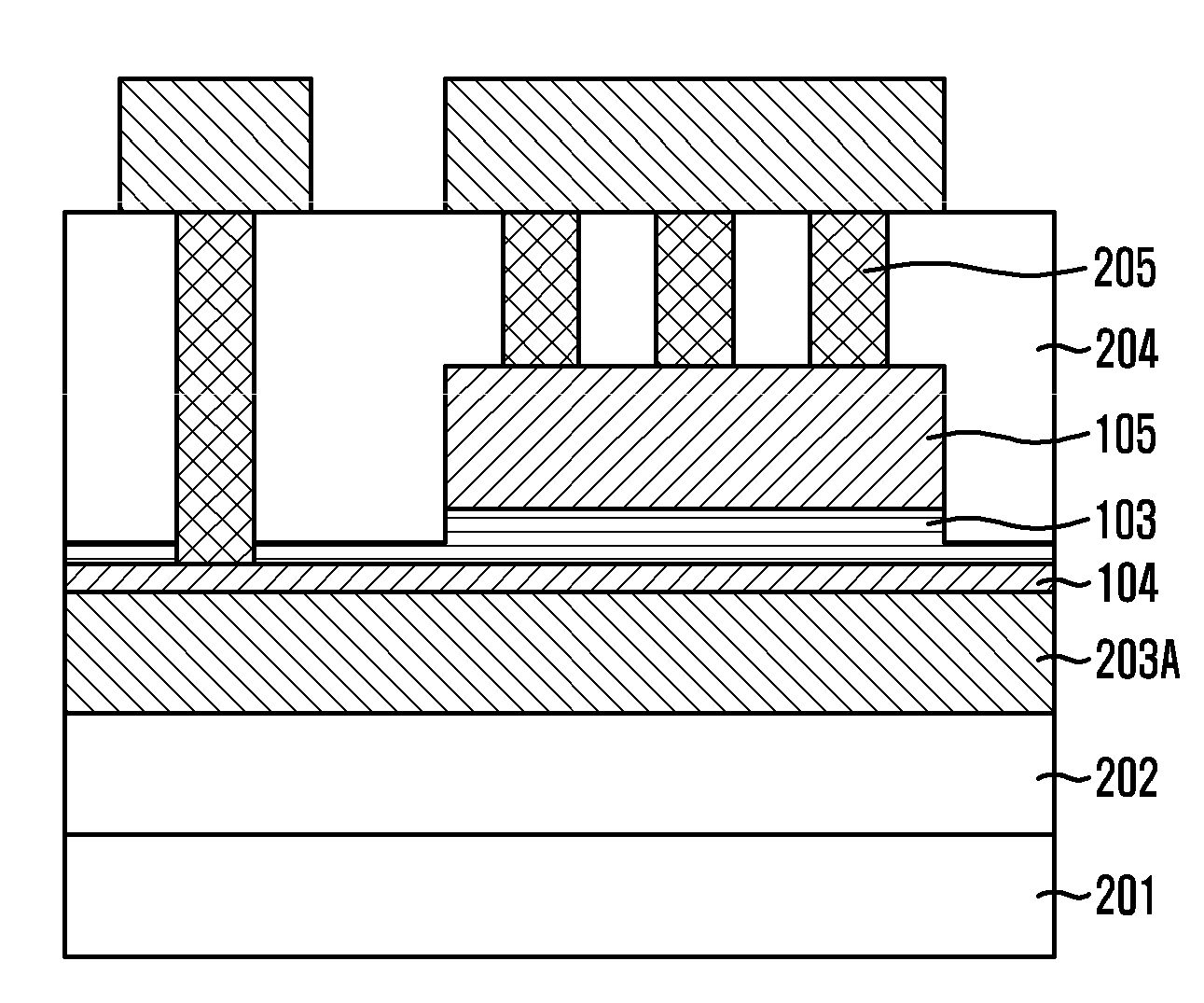

Semiconductor device and method for manufacturing same

ActiveUS6903398B2High dielectric constantQuality improvementTransistorSolid-state devicesMetal-insulator-metalDielectric

A semiconductor device is provided which has a capacitor insulating film made up of zirconium aliminate being an amorphous film obtained by having crystalline dielectric contain amorphous aluminum oxide and having its composition of AlXZr(1-X)OY(0.05≦x≦0.3), hereby being capable of preventing, in a process of forming a capacitor of MIM (Metal Insulator Metal) structure, dielectric breakdown of a capacitor insulating film while a relative dielectric constant of a metal oxide film used as the capacitor insulating film is kept high.

Owner:RENESAS ELECTRONICS CORP

Trench metal-insulator-metal (MIM) capacitors integrated with middle-of-line metal contacts, and method of fabricating same

The present invention relates to a semiconductor device that contains at least one trench metal-oxide-metal (MIM) capacitor and at least one other logic circuitry component, preferably at least one field effect transistor (FET). The trench MIM capacitor is located in a trench in a substrate and comprises inner and outer metallic electrode layers with a dielectric layer therebetween. The FET comprises a source region, a drain region, a channel region, and at least one metal contact connected with the source or drain region. The present invention also relates to a fabrication process, which integrates the processing steps for fabricating the trench MIM capacitor with the conventional middle-of-line processing steps for fabricating metal contacts, so that the inner metallic electrode layer of the trench MIM capacitor and the metal contact of the FET or other logic circuitry components are formed by a single middle-of-line processing step and comprise essentially the same metallic material.

Owner:GLOBALFOUNDRIES INC

Semiconductor device having a metal-insulator-metal capacitor

A method for manufacturing a semiconductor device having a metal-insulator-metal (MIM) capacitor comprises the steps of forming a first dielectric film on a substrate, forming a MIM capacitor on the first dielectric film, forming a second dielectric film covering the MIM capacitor, selectively removing the first and second dielectric films to expose the substrate surface, surface treating using a hydrochloric acid solution, forming a third dielectric film on the second dielectric film and the substrate, and forming a transistor on the third dielectric film. The second dielectric film protects the capacitor insulator film of the MIM capacitor.

Owner:NEC CORP

Phase shift device

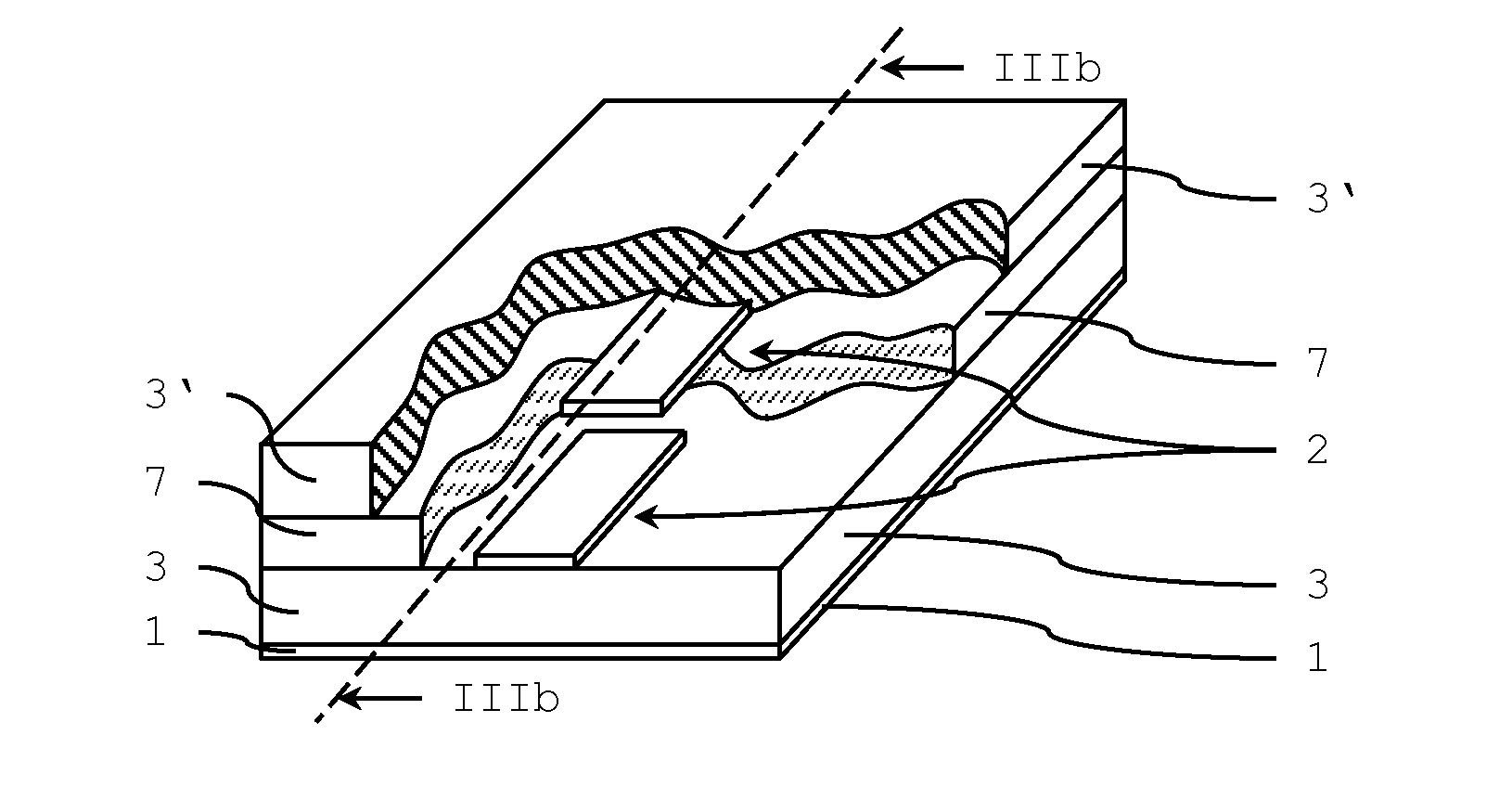

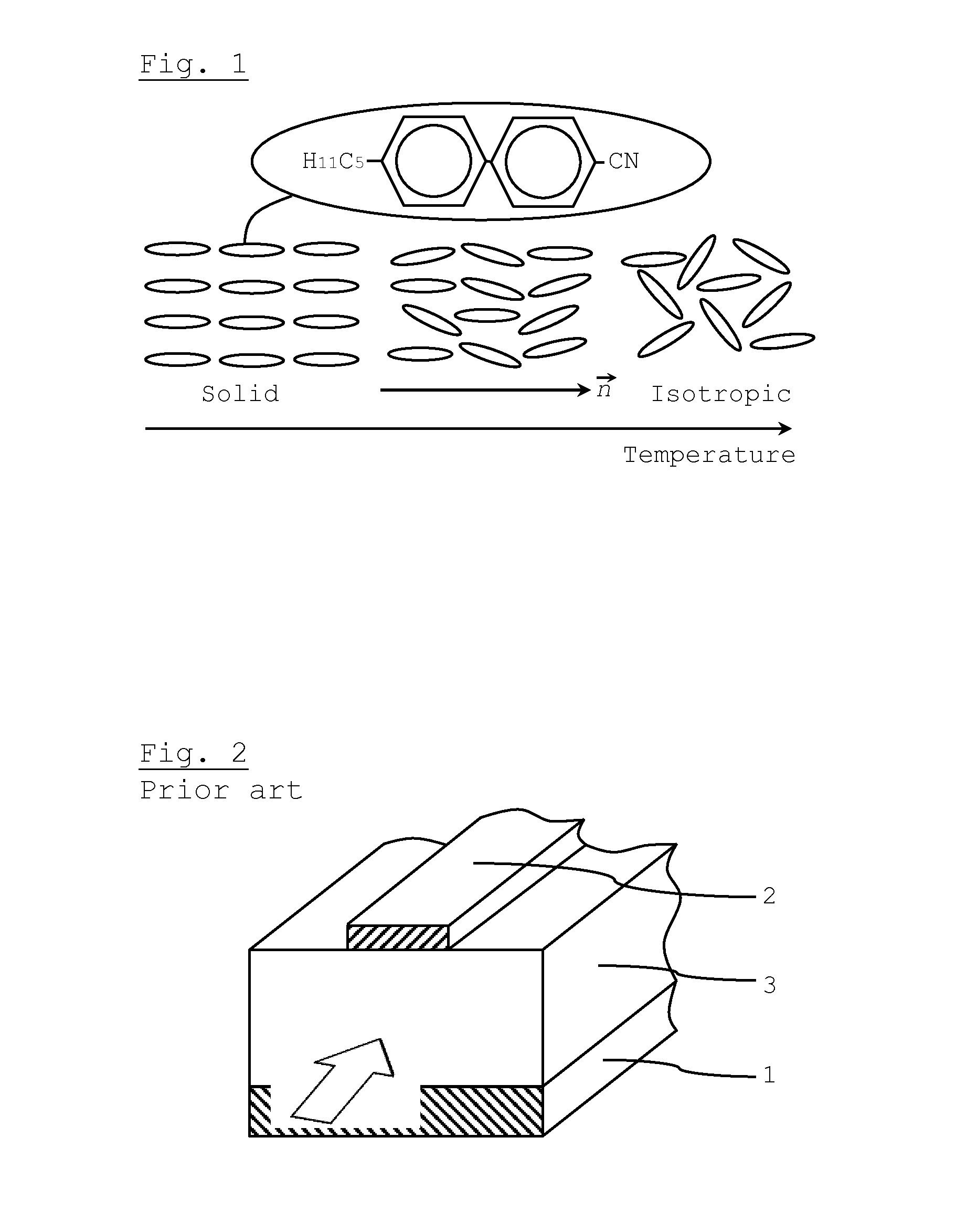

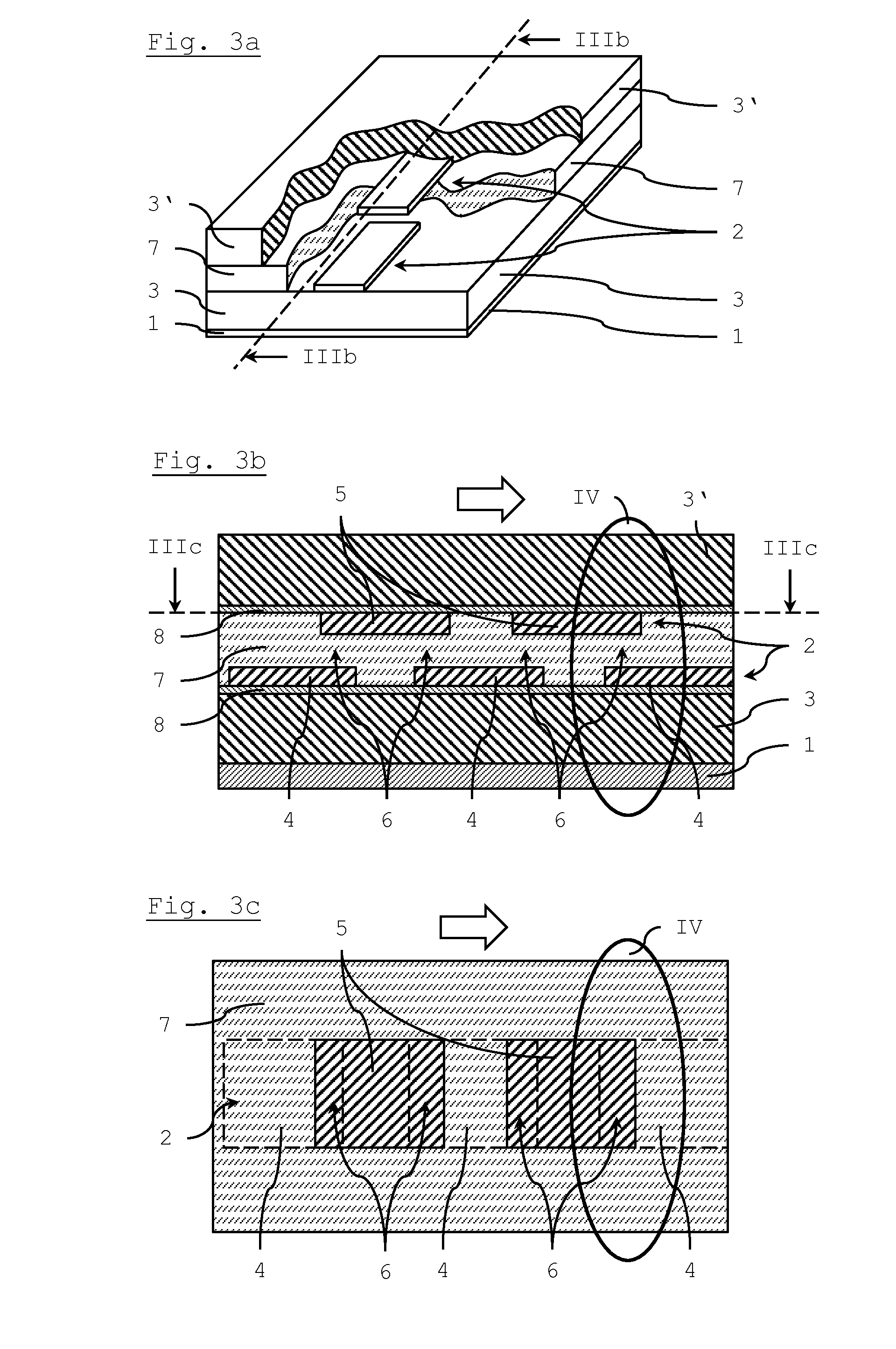

ActiveUS20150380789A1Easy and cost-saving fabricationFast and cheap fabricationCapacitor with voltage varied dielectricDelay linesMetal-insulator-metalElectricity

A phase shift device includes a planar transmission line that is formed by a signal electrode and a ground electrode which are separated by a dielectric substance, whereby the signal electrode of the planar transmission line is divided into several pieces and includes overlapping areas of adjacent pieces that are filled with a tunable liquid crystal material, thereby forming a dielectric tunable component (varactor) with a metal-insulator-metal type capacitor. The several pieces of the signal electrode are arranged at two or more different distance levels with respect to the ground electrode. The tunable liquid crystal material is arranged as a continuous layer between several pieces of the signal electrode that are arranged at two different distance levels.

Owner:ALCAN SYST GMBH

Non-volatile storage system using opposite polarity programming signals for MIM memory cell

A reversible resistance-switching metal-insulator-metal (MIM) stack is provided which can be set to a low resistance state with a first polarity signal and reset to a higher resistance state with a second polarity signal. The first polarity signal is opposite in polarity than the second polarity signal. In one approach, the MIM stack includes a carbon-based reversible resistivity switching material such as a carbon nanotube material. The MIM stack can further include one or more additional reversible resistivity switching materials such as metal oxide above and / or below the carbon-based reversible resistivity switching material. In another approach, a metal oxide layer is between separate layers of carbon-based reversible resistivity switching material.

Owner:SANDISK TECH LLC

Metal-insulator-metal capacitors

A metal-insulator-metal (MIM) capacitor is provided. The bottom electrode of the MIM capacitor is electrically connected to a connection node. The connection node may be, for example, a contact formed in an interlayer dielectric, a polysilicon connection node, a doped polysilicon or silicon region, or the like. A contact provides an electrical connection between the connection node and components formed above the connection node. A second contact provides an electrical connection to the top electrode.

Owner:TAIWAN SEMICON MFG CO LTD

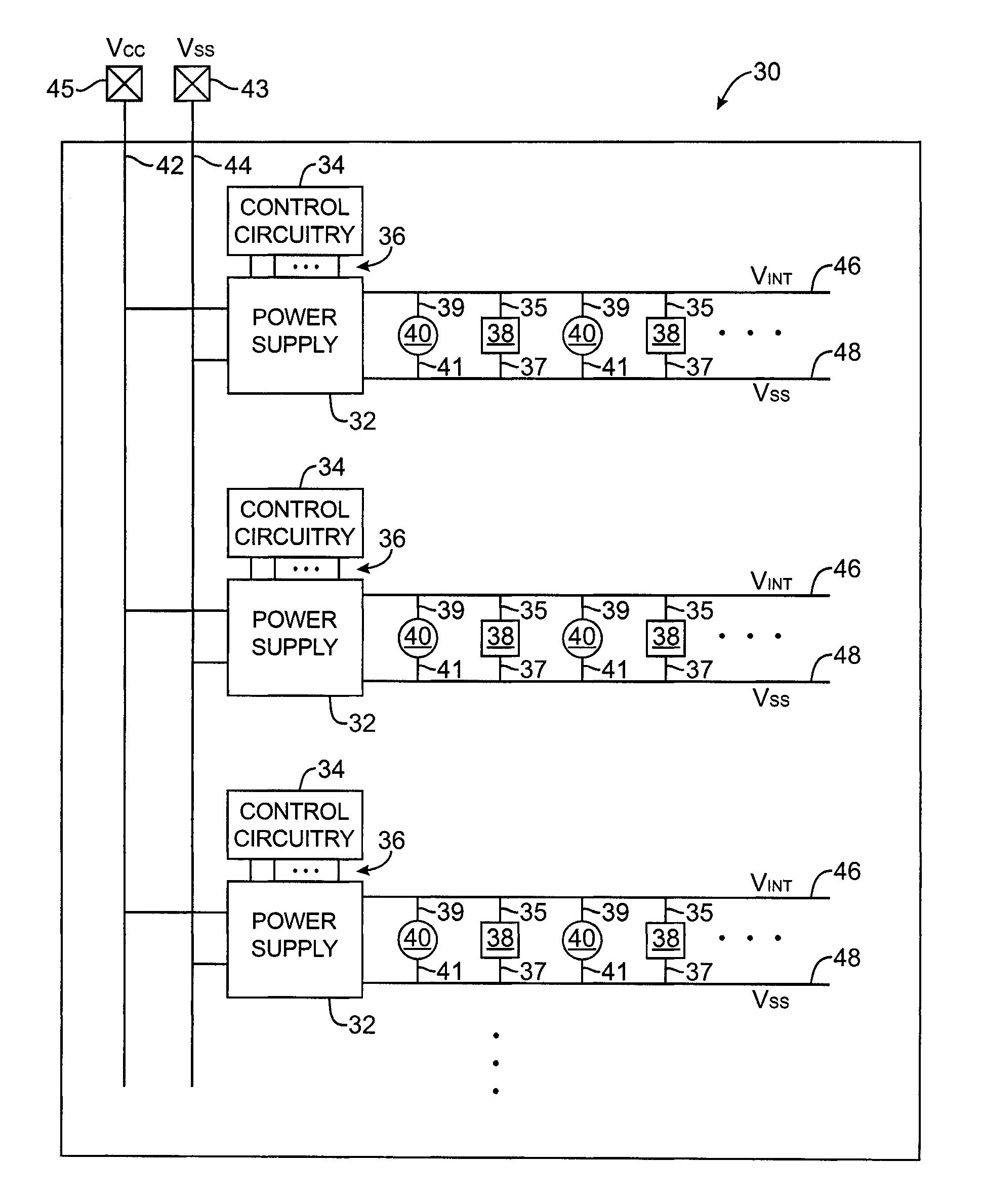

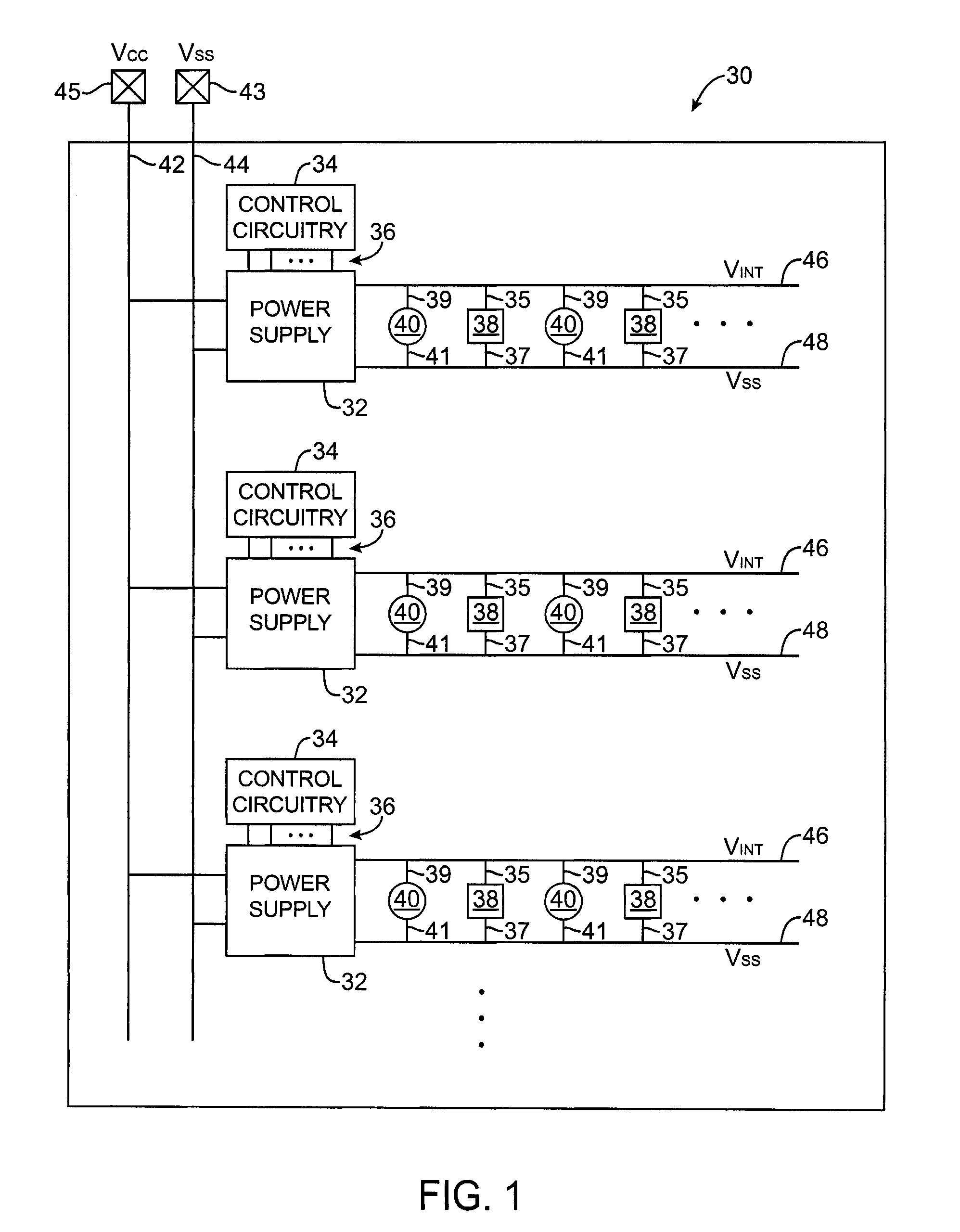

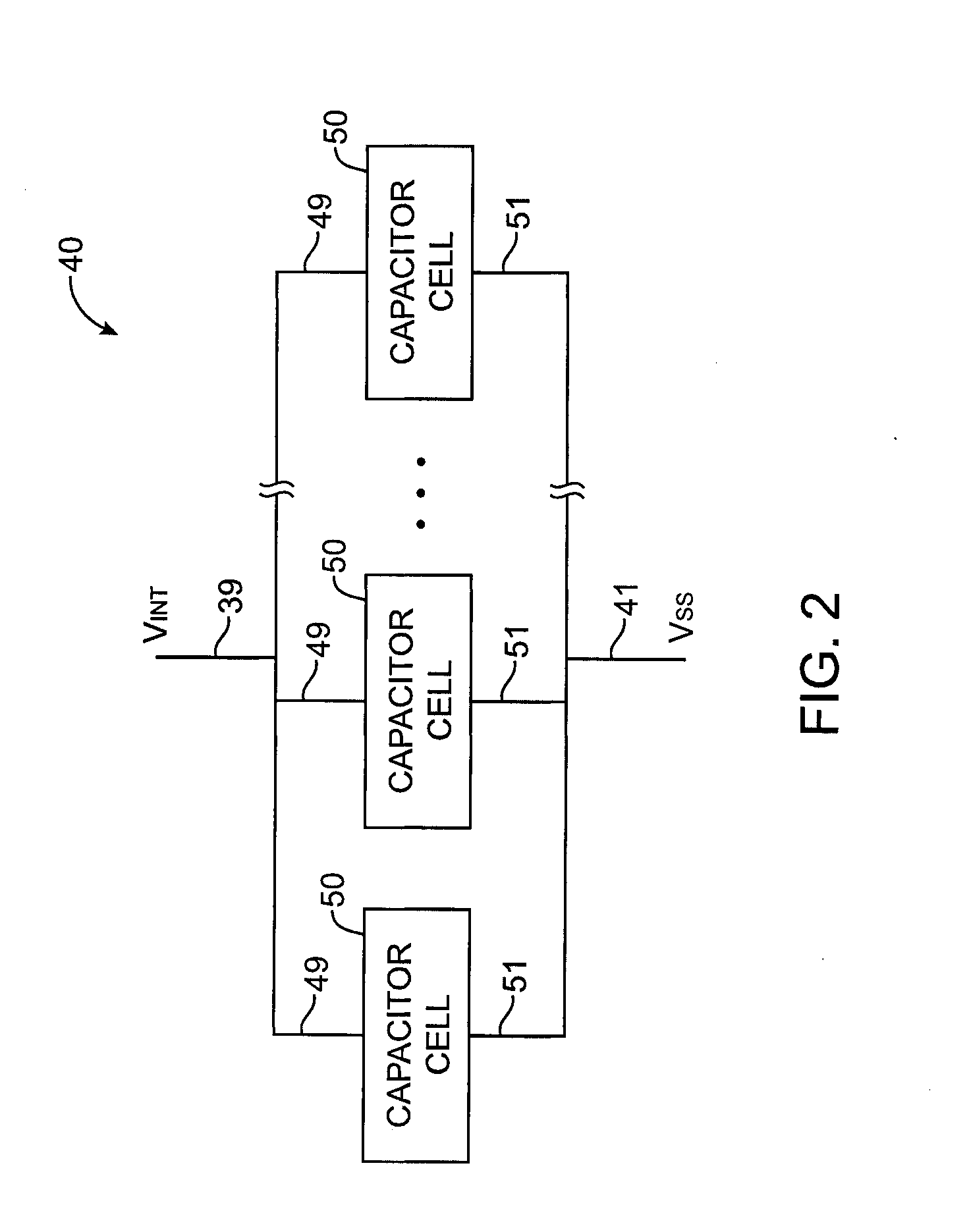

Integrated circuit decoupling capacitors

ActiveUS20100148304A1Control flowReduce the overall decoupling capacitorSemiconductor/solid-state device detailsSolid-state devicesMetal-insulator-metalEngineering

Power supply decoupling capacitors are provided for integrated circuits. The decoupling capacitors may be distributed in clusters amongst powered circuit components. Each cluster may contain a number of individual capacitor cells that are connected in parallel. Each capacitor cell may contain a capacitor and a resistor connected in series with the capacitor. The capacitors may be metal-insulator-metal (MIM) capacitors. The resistor in each cell may limit the current through an individual capacitor in the event of a short in the capacitor due to a dielectric defect.

Owner:ALTERA CORP

Metal-insulator-metal capacitors and methods of forming the same

InactiveUS20060183280A1Simple processSimplify the manufacturing processSolid-state devicesSemiconductor/solid-state device manufacturingMetal-insulator-metalSemiconductor

There are provided metal-insulator-metal (MIM) capacitors and methods of forming the same. The capacitors and the formation methods thereof provide a way of simplifying semiconductor fabrication processes, using component elements of the capacitor and insulating layers around the capacitor. To this end, lower and upper electrodes are sequentially stacked on a semiconductor substrate. A dielectric layer pattern is interposed between the upper and lower electrodes. An etch stop layer pattern and an etch buffer layer are disposed on the upper electrode and under the lower electrode, respectively. The upper and lower electrodes are disposed to expose the dielectric layer pattern and the etch buffer layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Implementing physically unclonable function (PUF) utilizing EDRAM memory cell capacitance variation

Owner:MARVELL ASIA PTE LTD

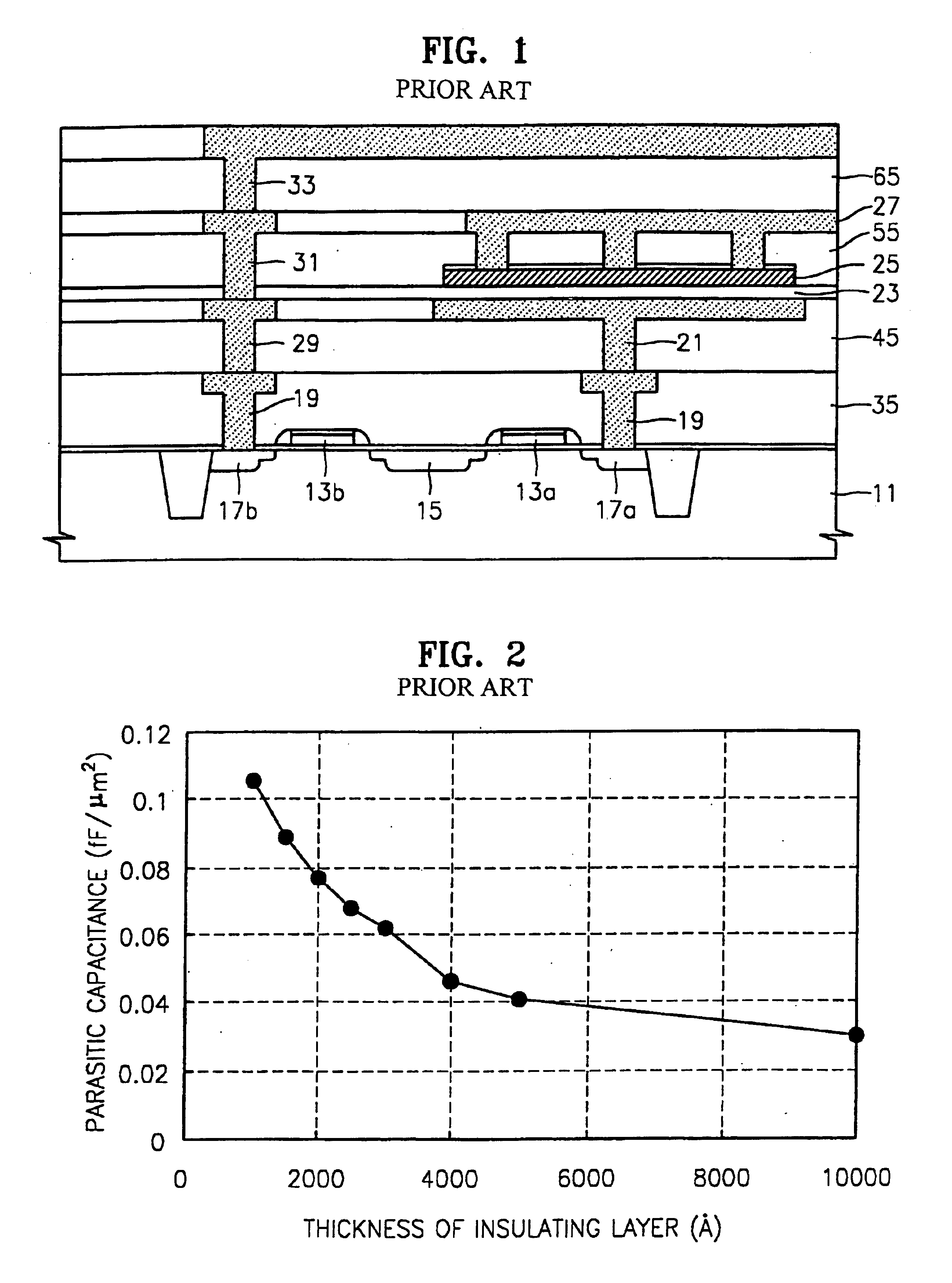

Integrated circuit devices including a MIM capacitor

ActiveUS6940114B2TransistorSemiconductor/solid-state device detailsMetal-insulator-metalOptoelectronics

Integrated circuit devices include an integrated circuit substrate and a conductive lower electrode layer of a Metal-Insulator-Metal (MIM) capacitor on the integrated circuit substrate. A dielectric layer is on the lower electrode layer and a conductive upper electrode layer of the MIM capacitor is on the dielectric layer. A first intermetal dielectric layer is on the upper electrode layer. The first intermetal dielectric layer includes at least one via hole extending to the upper electrode layer. A first conductive interconnection layer is on the at least one via hole of the first intermetal dielectric layer. A second intermetal dielectric layer is on the first intermetal dielectric layer. The second intermetal dielectric layer includes at least one via hole extending to the first conductive interconnection layer and at least partially exposing the at least one via hole of the first intermetal dielectric layer. A second conductive interconnection layer is provided in the at least one via hole of the second intermetal dielectric layer that electrically contacts the first conductive interconnection layer.

Owner:SAMSUNG ELECTRONICS CO LTD

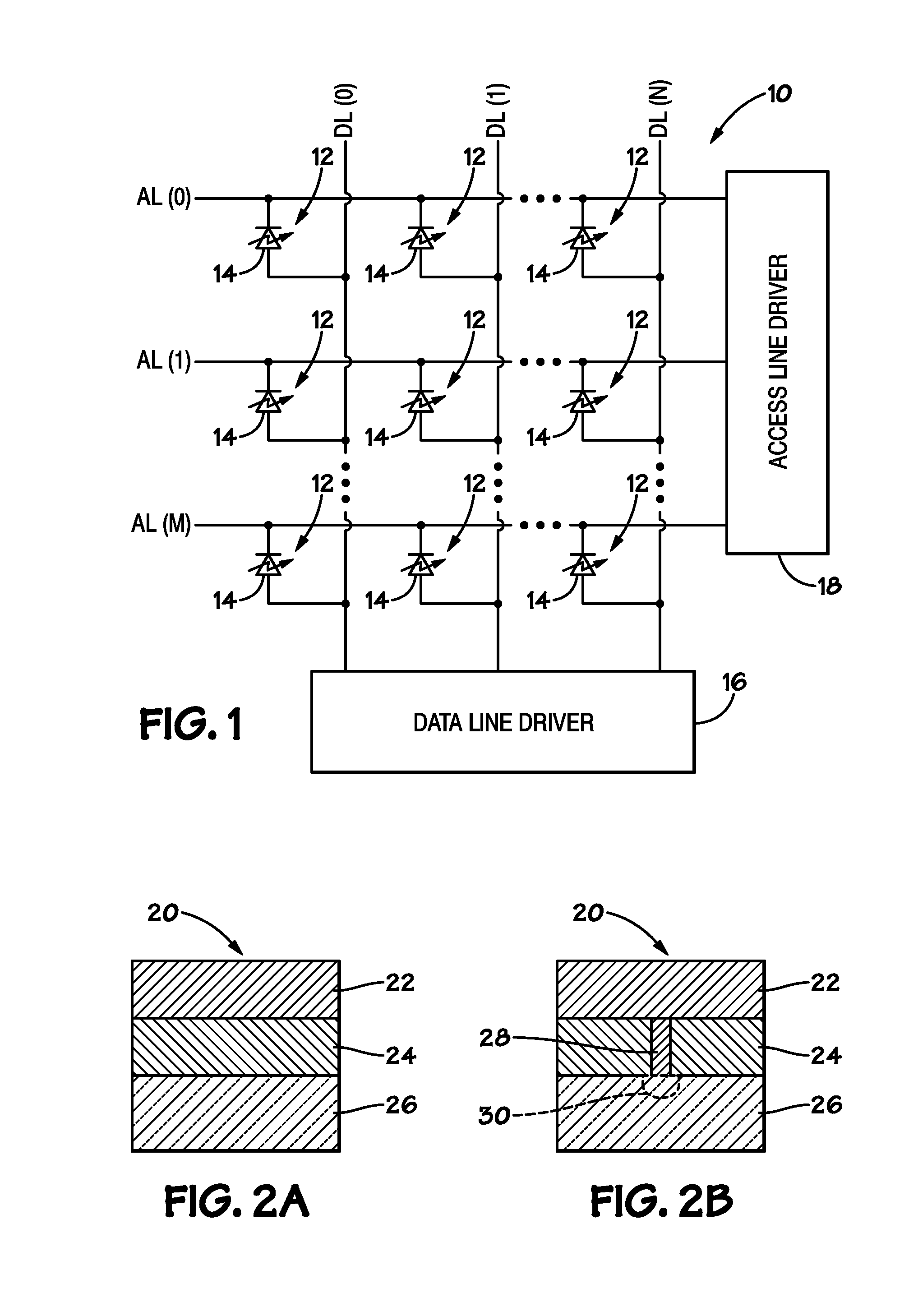

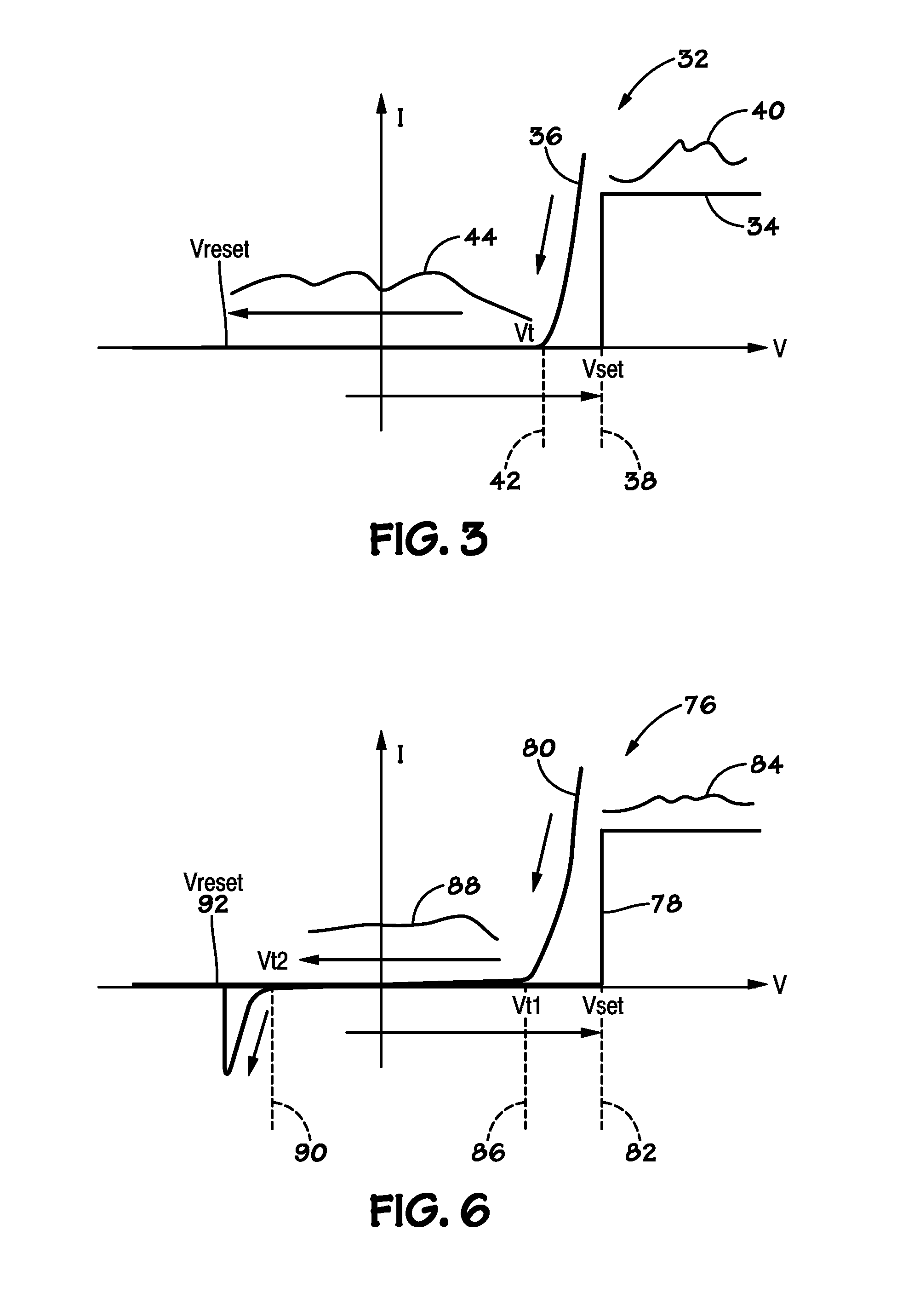

Bipolar Switching Memory Cell With Built-in "On" State Rectifying Current-Voltage Characteristics

ActiveUS20120168705A1Semiconductor/solid-state device manufacturingDigital storageMetal-insulator-metalElectrical resistance and conductance

A memory array is disclosed having bipolar current-voltage (IV) resistive random access memory cells with built-in “on” state rectifying IV characteristics. In one embodiment, a bipolar switching resistive random access memory cell may have a metal / solid electrolyte / semiconductor stack that forms a Schottky diode when switched to the “on” state. In another embodiment, a bipolar switching resistive random access memory cell may have a metal / solid electrolyte / tunnel barrier / electrode stack that forms a metal-insulator-metal device when switched to the “on” state. Methods of operating the memory array are also disclosed.

Owner:OVONYX MEMORY TECH LLC

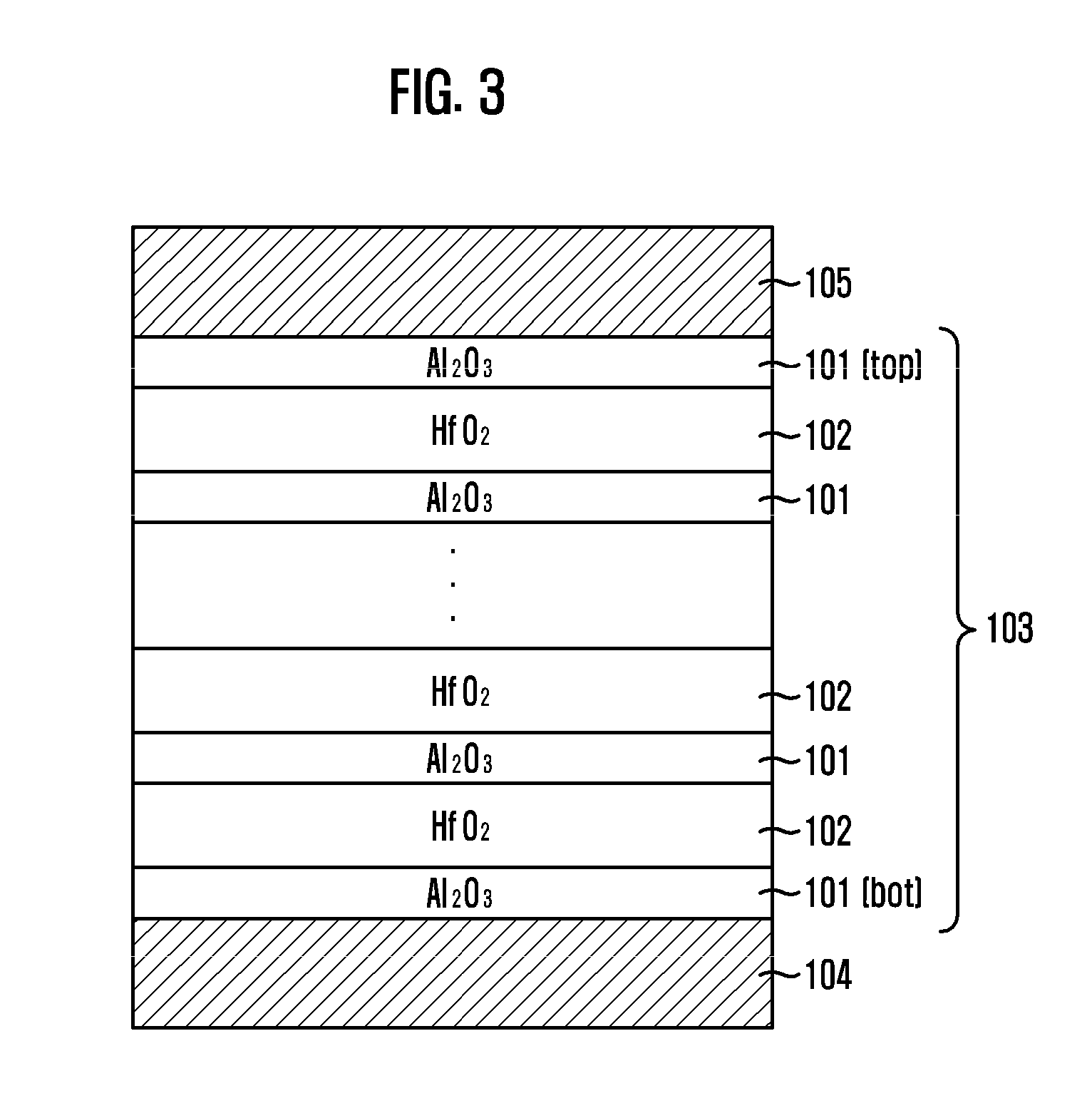

Insulator, capacitor with the same and fabrication method thereof, and method for fabricating semionductor device

ActiveUS20100091428A1High capacitanceGood leakage current characteristicSemiconductor/solid-state device detailsSolid-state devicesEngineeringMetal-insulator-metal

Disclosed is a multilayer insulator, a metal-insulator-metal (MIM) capacitor with the same, and a fabricating method thereof. The capacitor includes: a first electrode; an insulator disposed on the first electrode, the insulator including: a laminate structure in which an aluminum oxide (Al2O3) layer and a hafnium oxide (HfO2) layer are laminated alternately in an iterative manner and a bottom layer and a top layer are formed of the same material; and a second electrode disposed on the insulator.

Owner:KEY FOUNDRY CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com