Patents

Literature

737 results about "Bit cell" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A bit cell is the length of tape, the area of disc surface, or the part of an integrated circuit in which a single bit is recorded. The smaller the bit cells are, the better the storage density of the medium is.

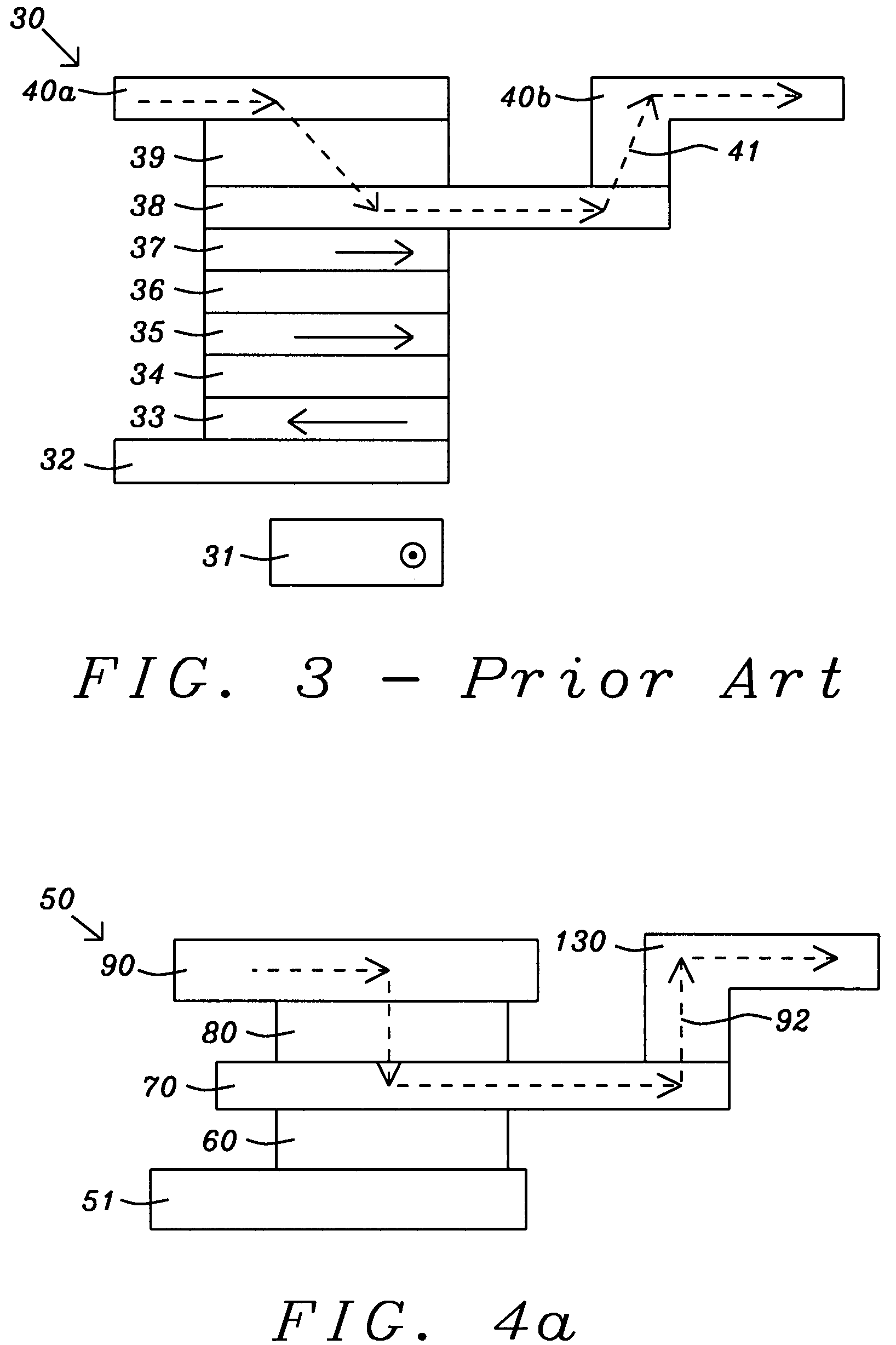

Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory

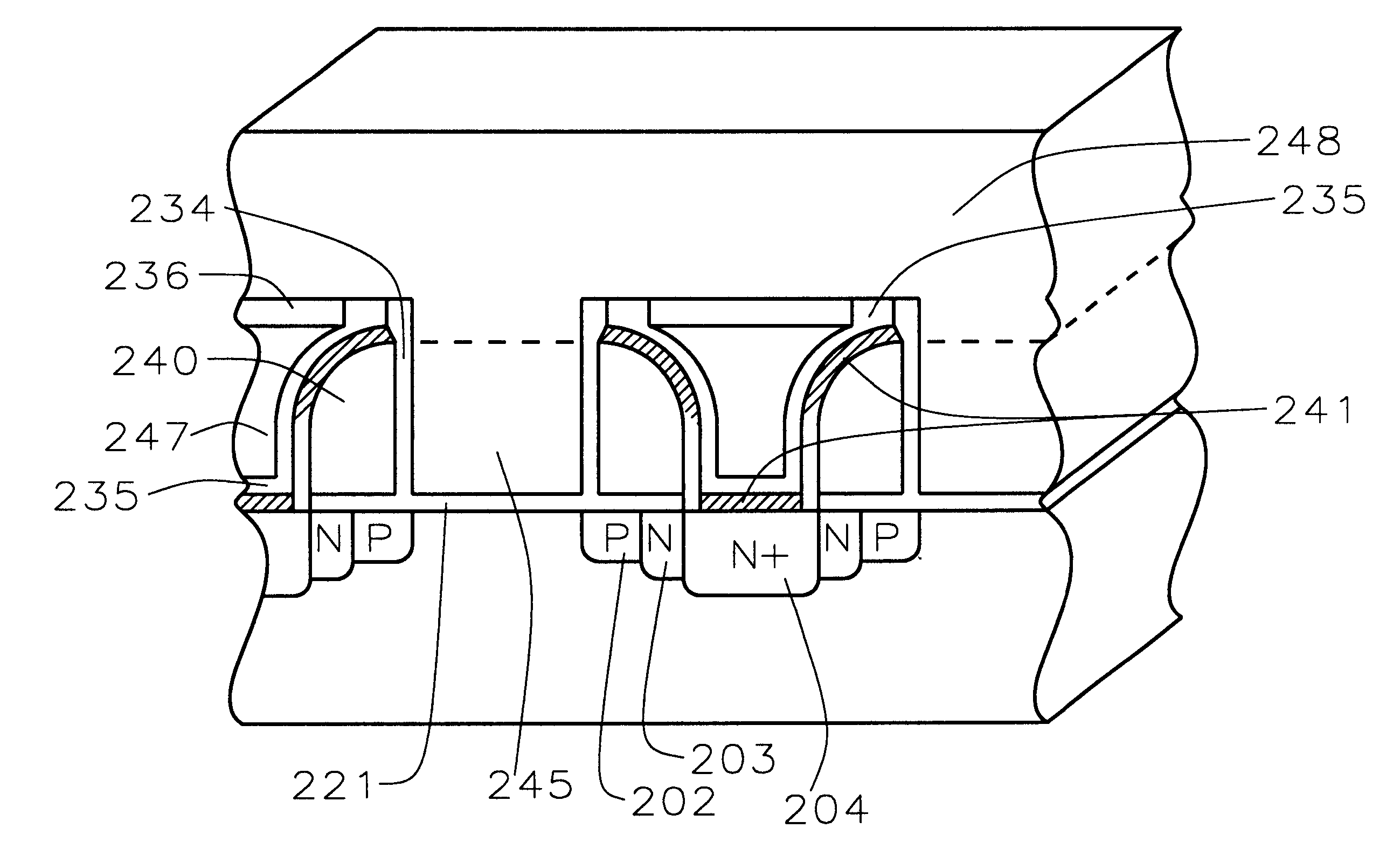

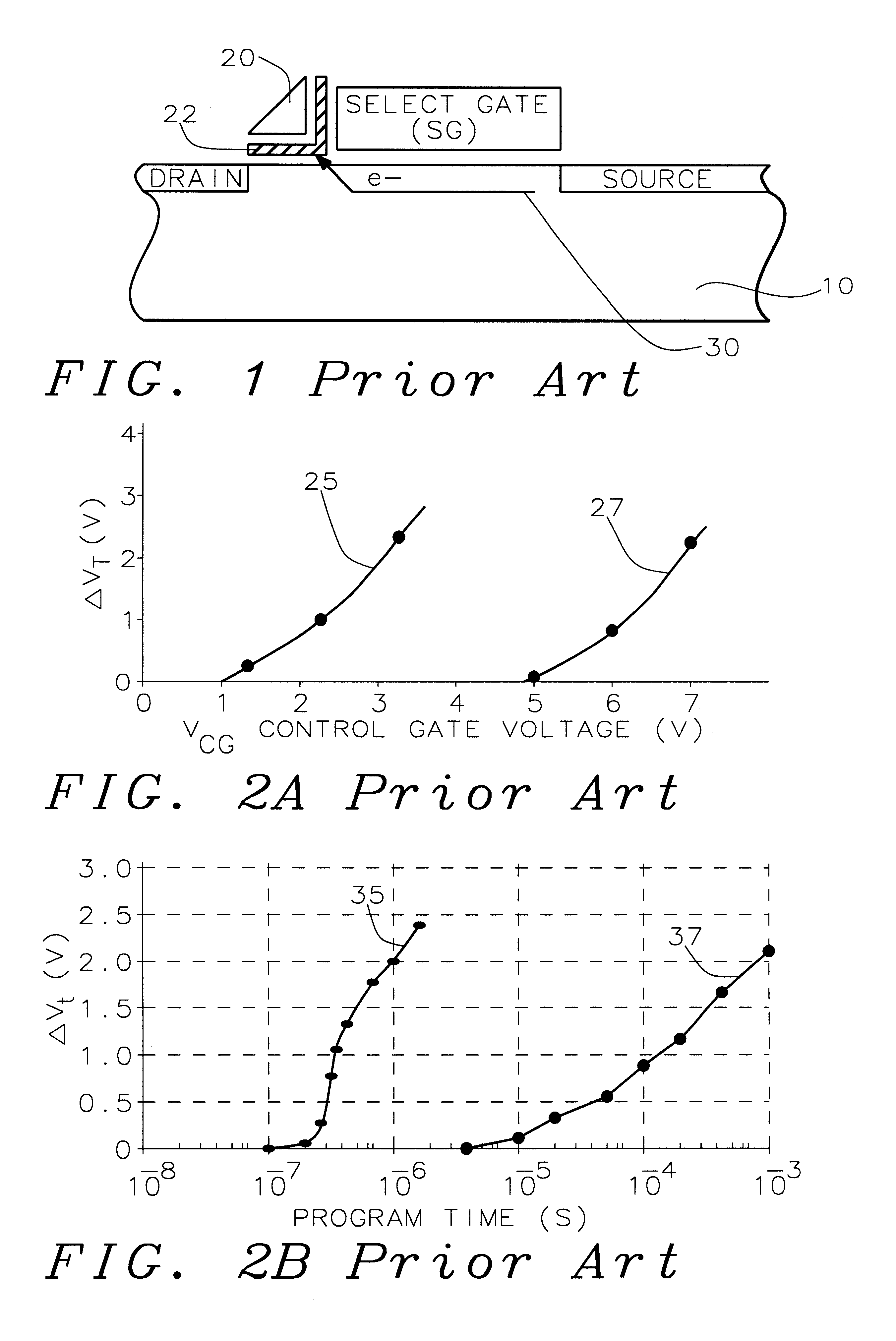

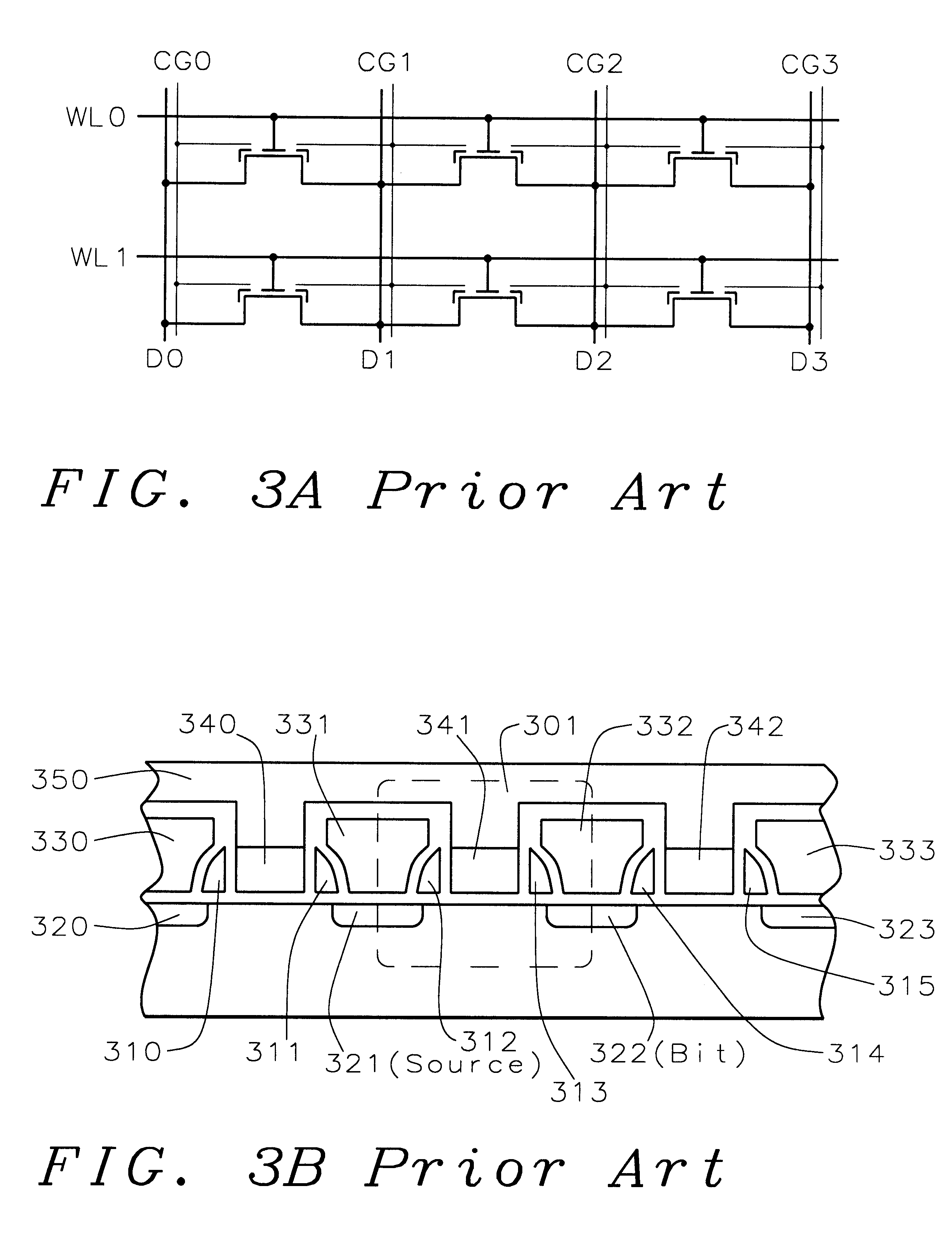

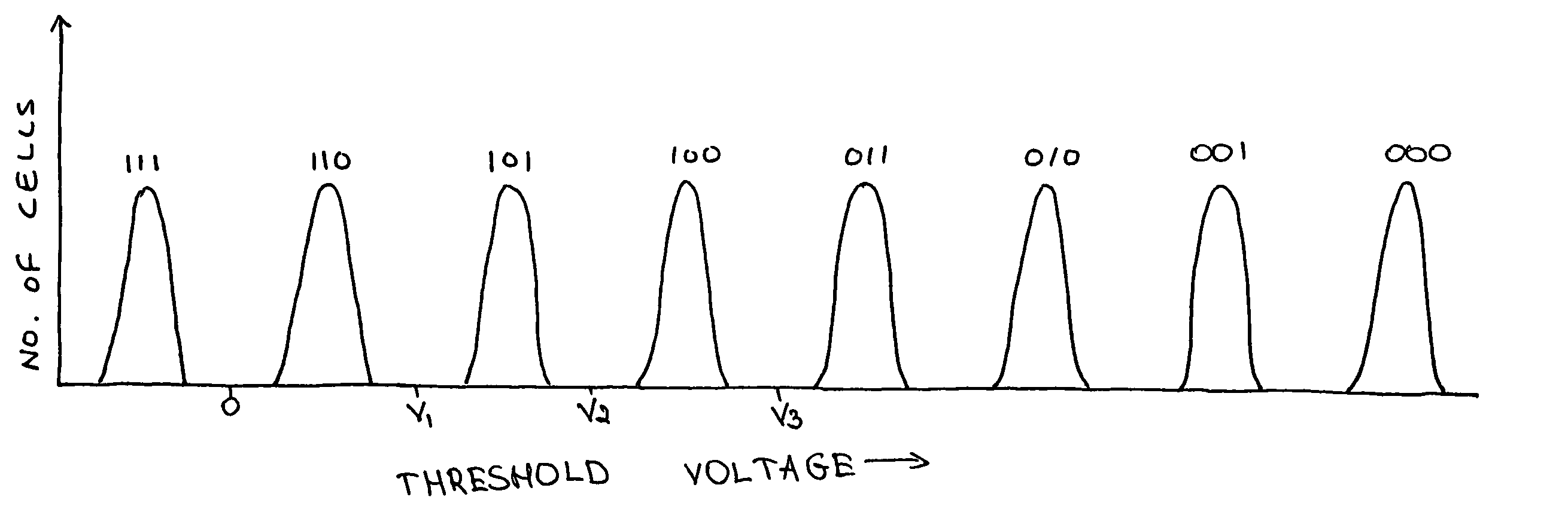

A fast low voltage ballistic program, ultra-short channel, ultra-high density, dual-bit multi-level flash memory is described with a two or three polysilicon split gate side wall process. The structure and operation of this invention is enabled by a twin MONOS cell structure having an ultra-short control gate channel of less than 40nm, with ballistic injection which provides high electron injection efficiency and very fast program at low program voltages of 3~5V. The cell structure is realized by (i) placing side wall control gates over a composite of Oxide-Nitride-Oxide (ONO) on both sides of the word gate, and (ii) forming the control gates and bit diffusion by self-alignment and sharing the control gates and bit diffusions between memory cells for high density. Key elements used in this process are: 1) Disposable side wall process to fabricate the ultra short channel and the side wall control gate with or without a step structure, and 2) Self-aligned definition of the control gate over the storage nitride and the bit line diffusion, which also runs in the same direction as the control gate. The features of fast program, low voltage, ultra-high density, dual-bit, multi-level MONOS NVRAM of the present invention include: 1) Electron memory storage in nitride regions within an ONO layer underlying the control gates, 2) high density dual-bit cell in which there are two nitride memory storage elements per cell, 3) high density dual-bit cell can store multi-levels in each of the nitride regions, 4) low current program controlled by the word gate and control gate, 5) fast, low voltage program by ballistic injection utilizing the controllable ultra-short channel MONOS, and 6) side wall control poly gates to program and read multi-levels while masking out memory storage state effects of the unselected adjacent nitride regions and memory cells. The ballistic MONOS memory cell is arranged in the following array: each memory cell contains two nitride regions for one word gate, and ½ a source diffusion and ½ a bit diffusion. Control gates can be defined separately or shared together over the same diffusion. Diffusions are shared between cells and run in parallel to the side wall control gates, and perpendicular to the word line.

Owner:HALO LSI INC

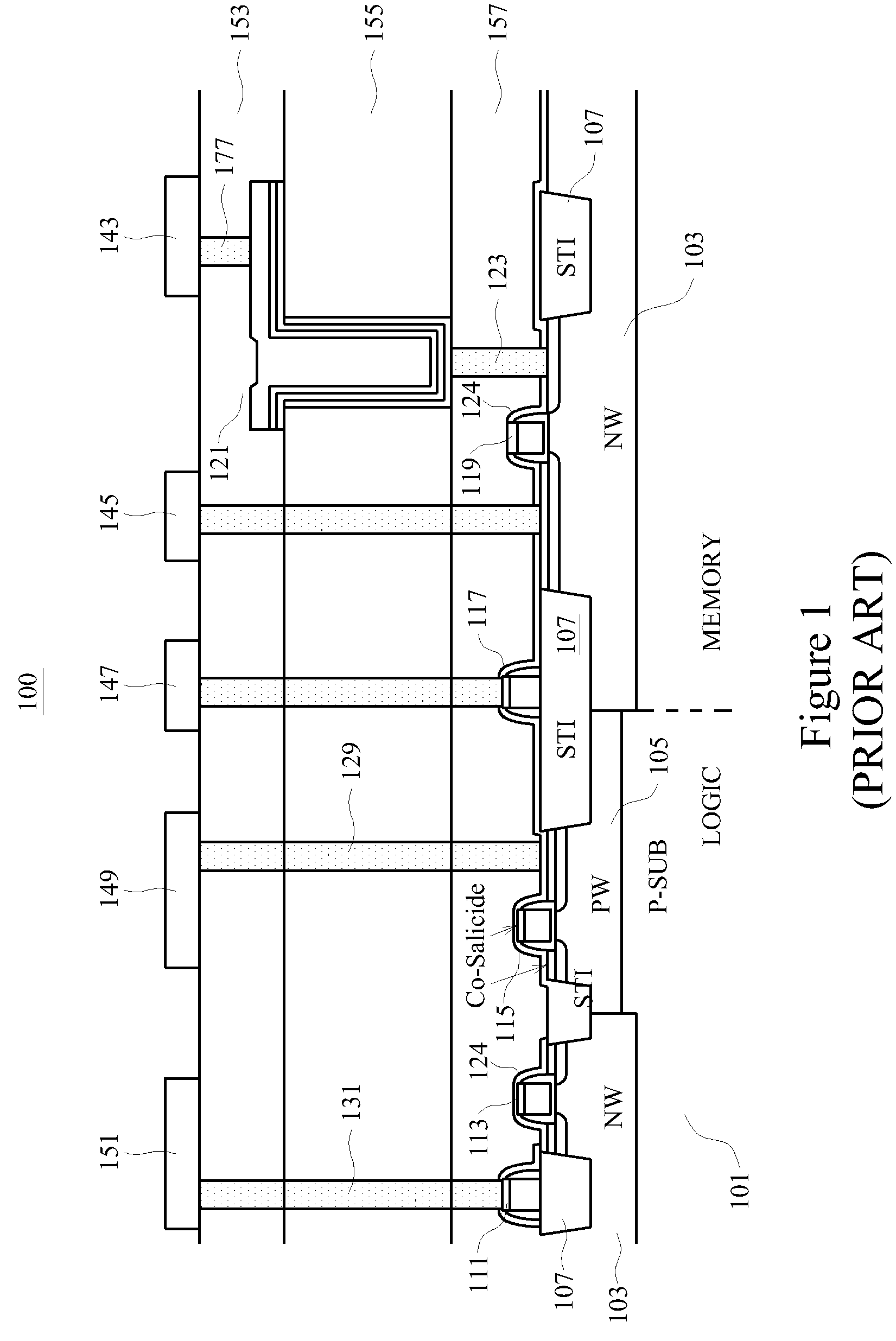

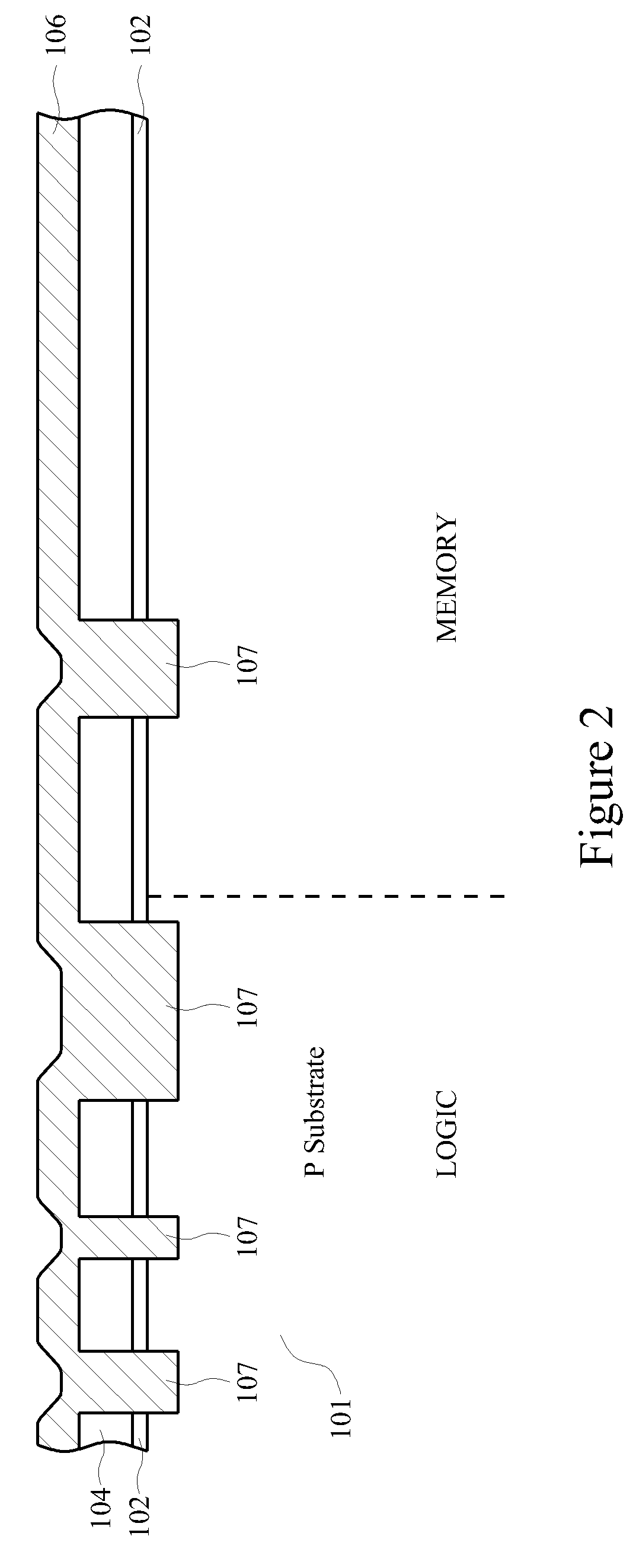

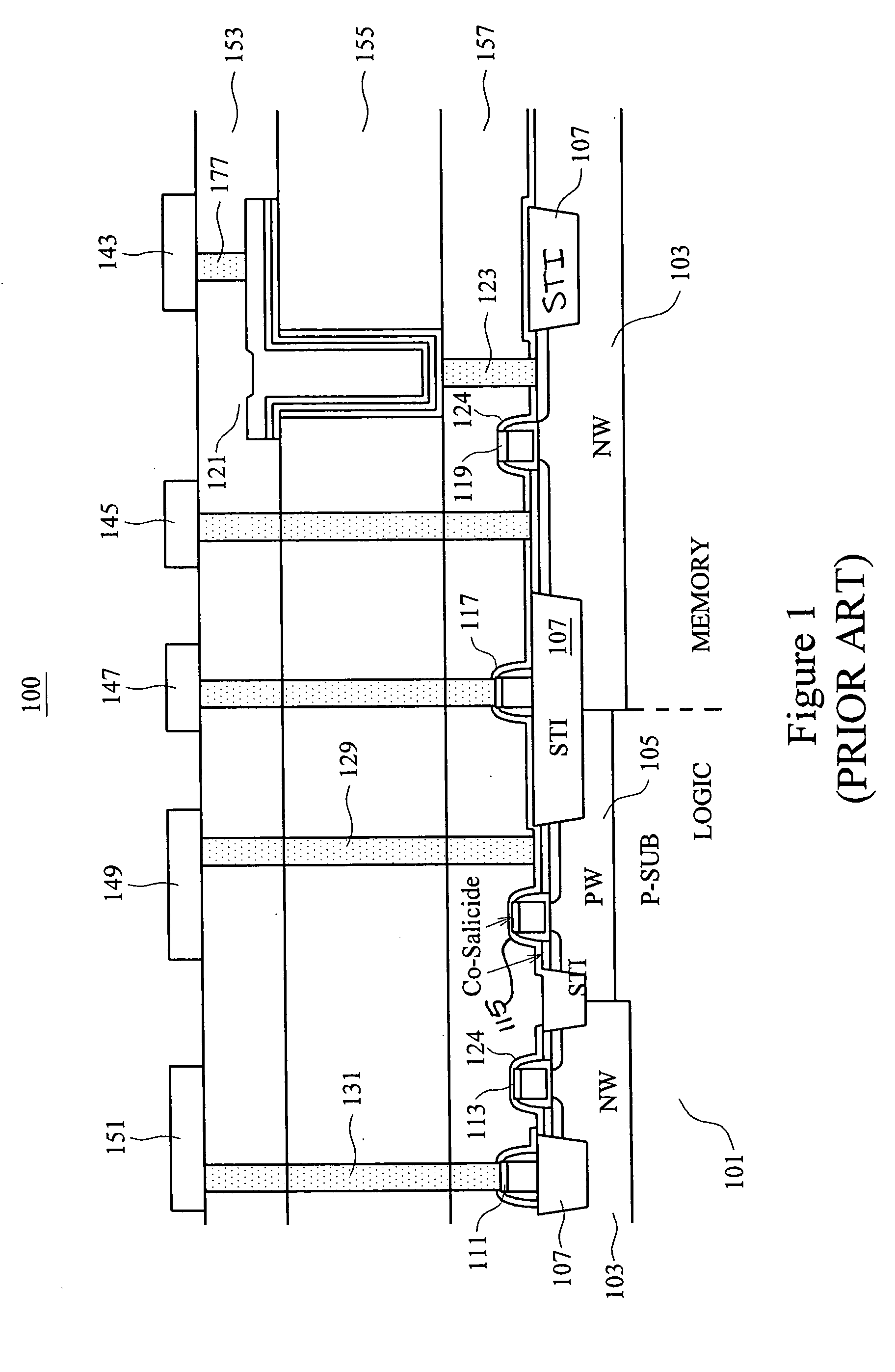

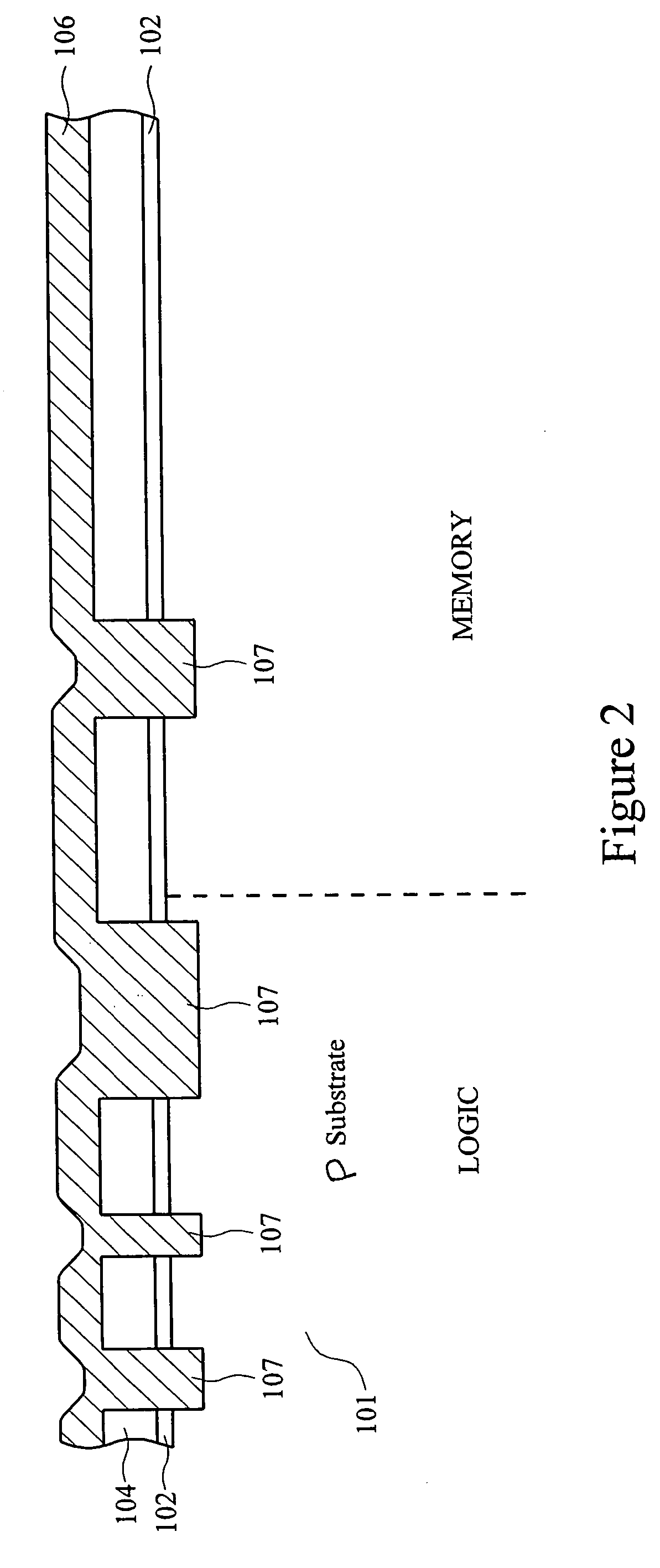

Method and structure for a 1T-RAM bit cell and macro

InactiveUS7425740B2Increase capacitanceTransistorSolid-state devicesMetal-insulator-metalCapacitance

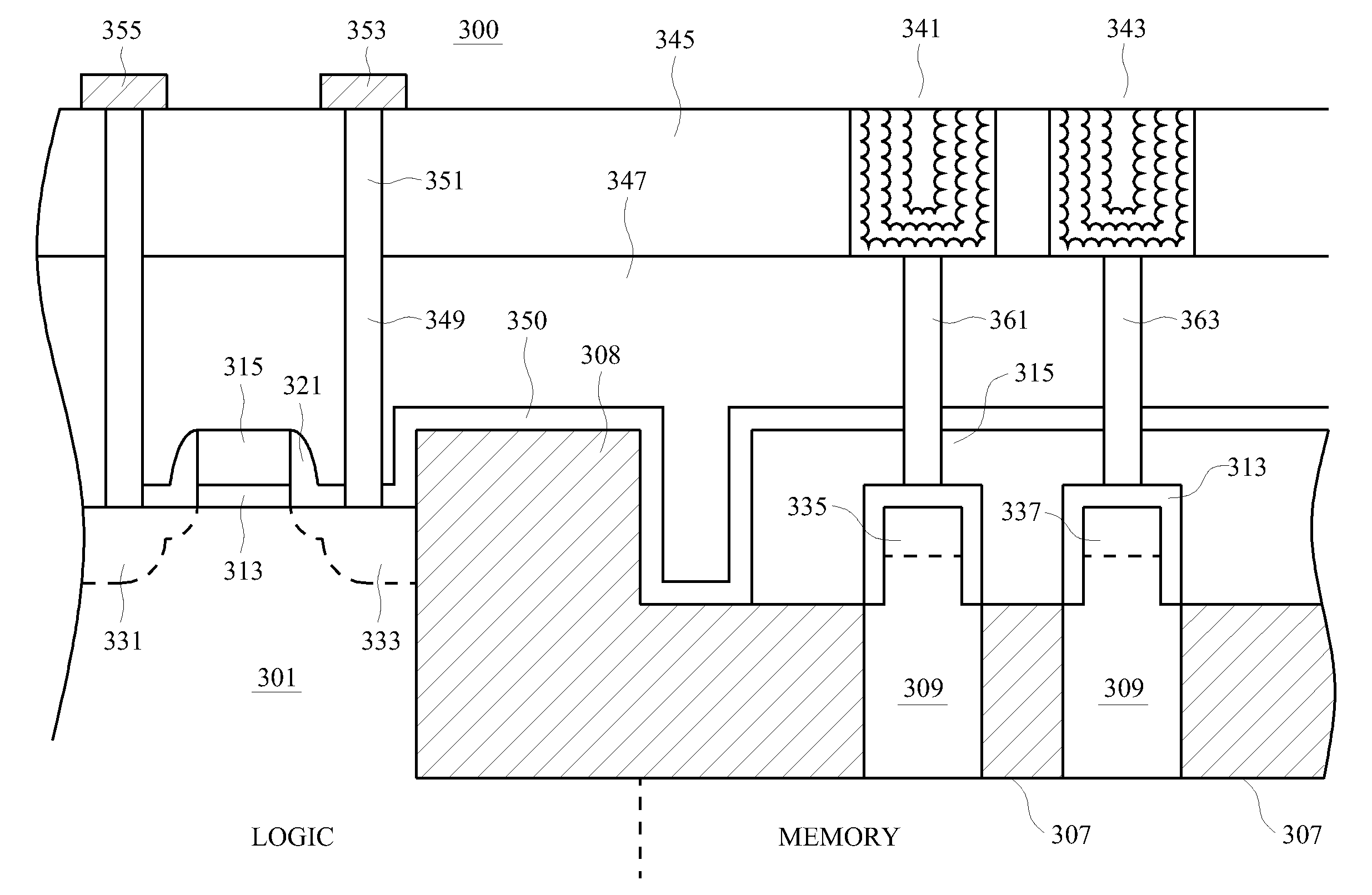

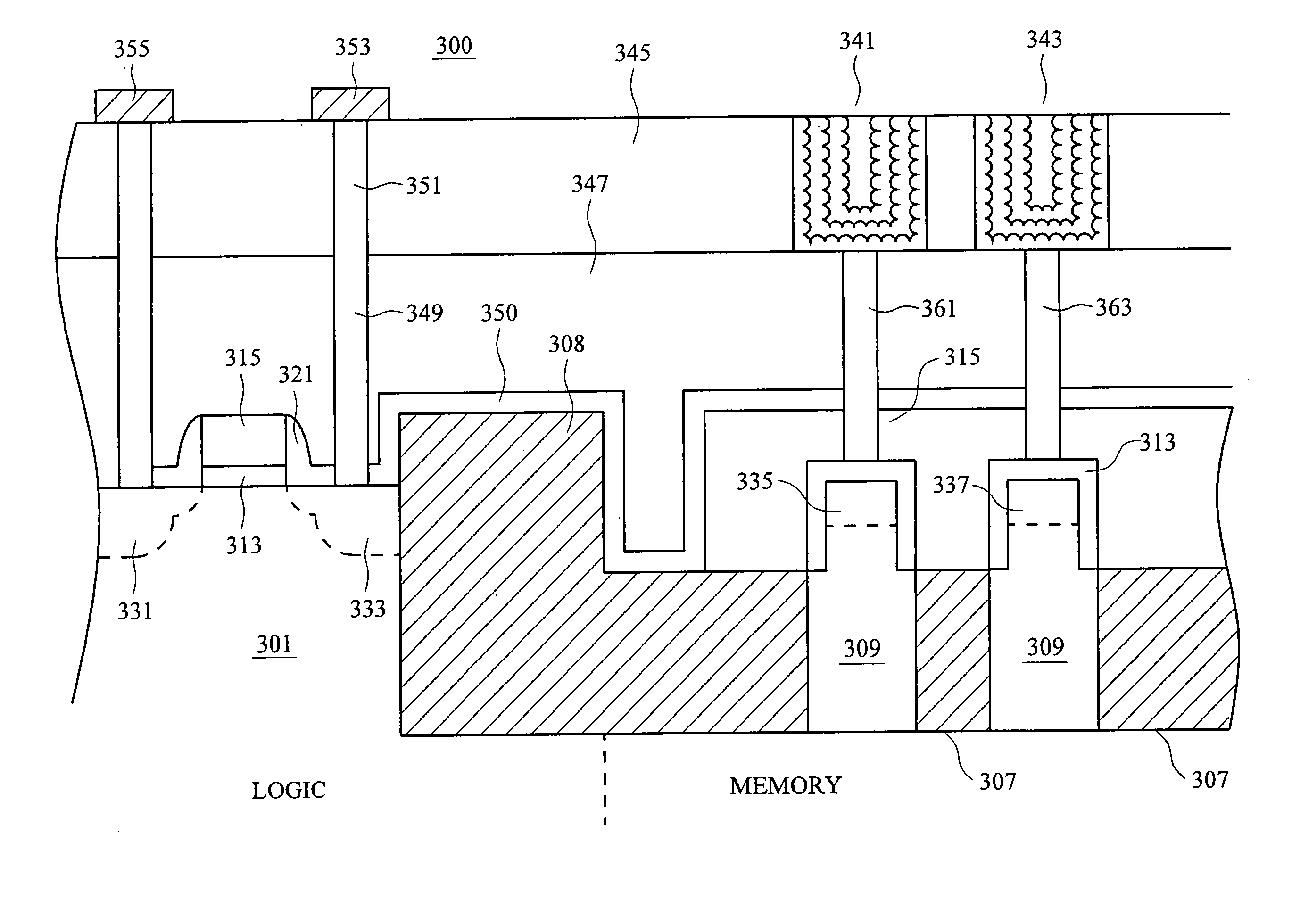

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

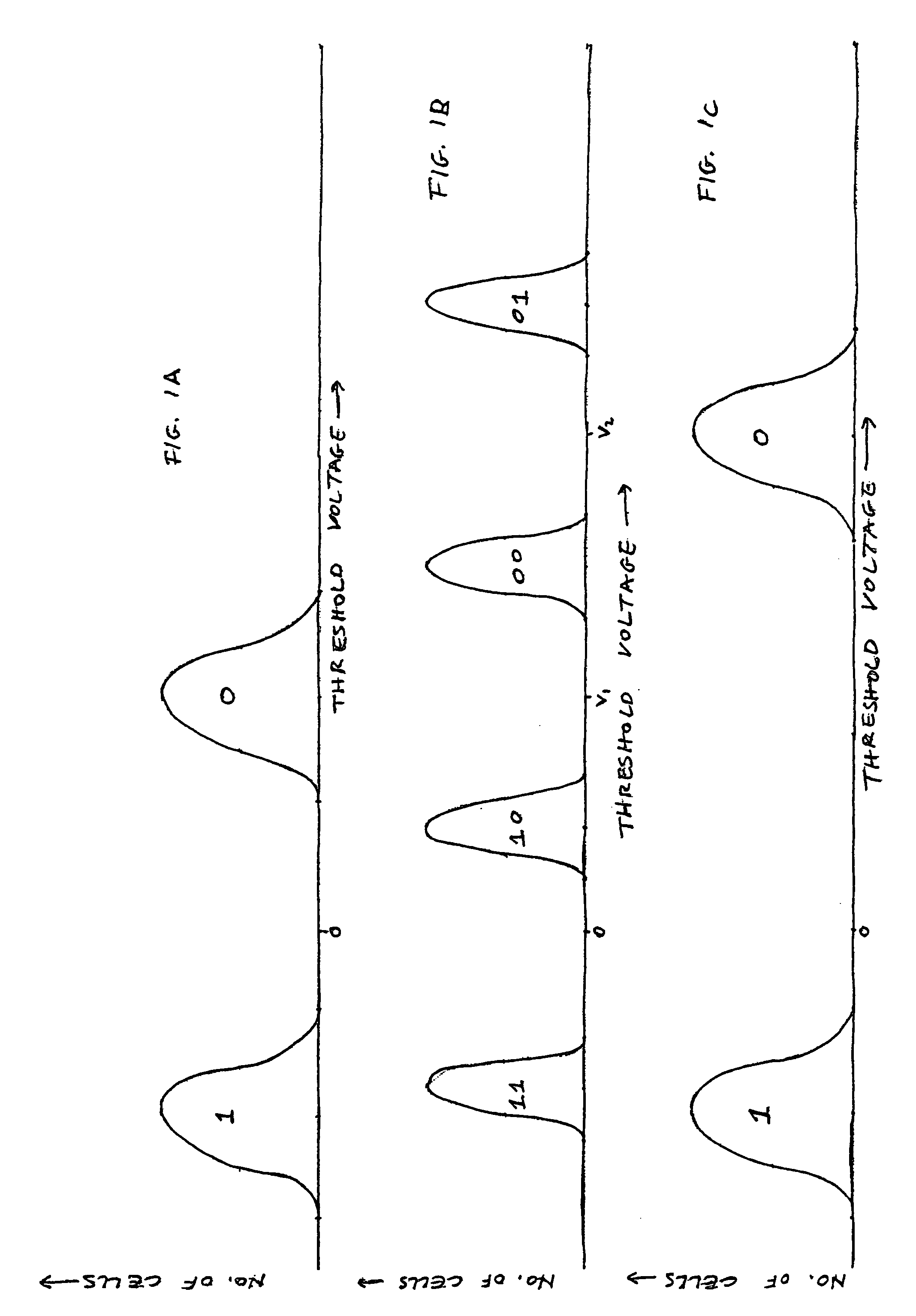

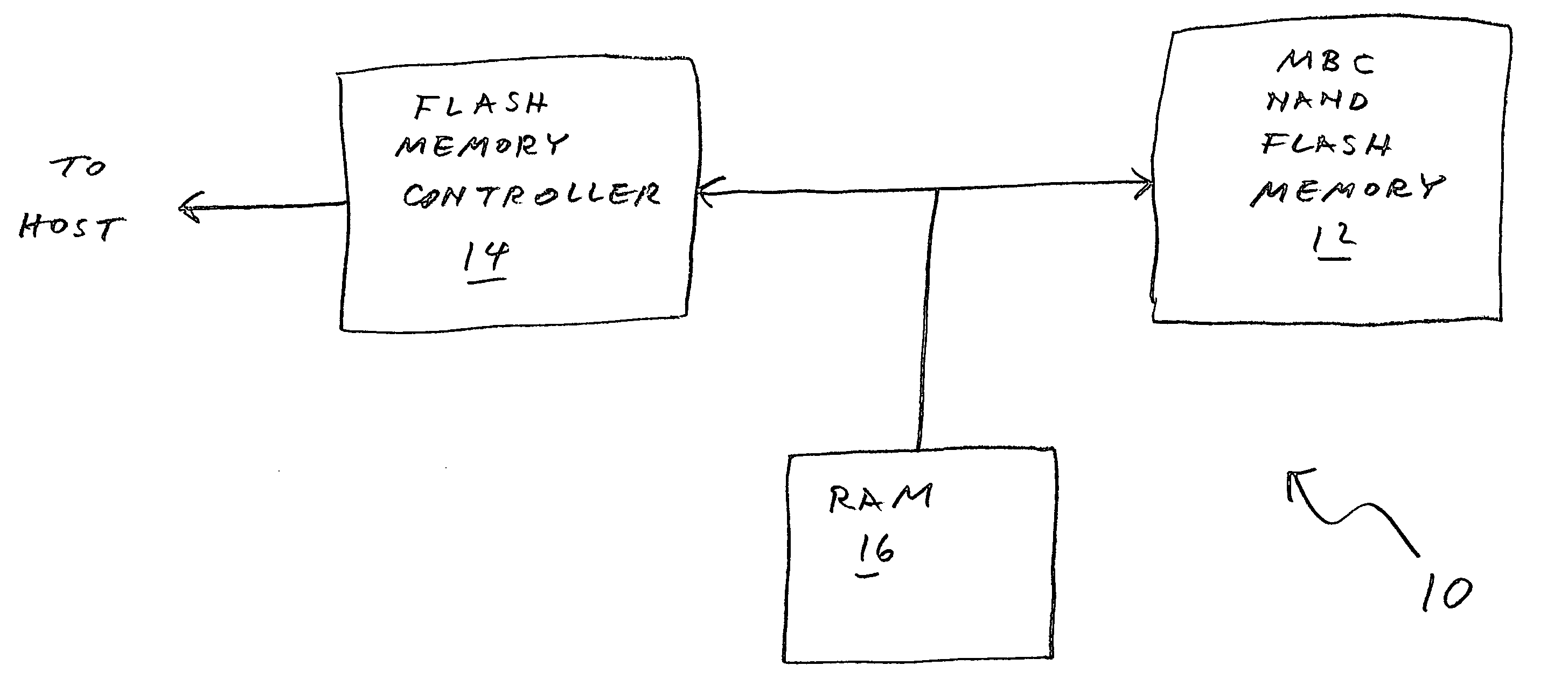

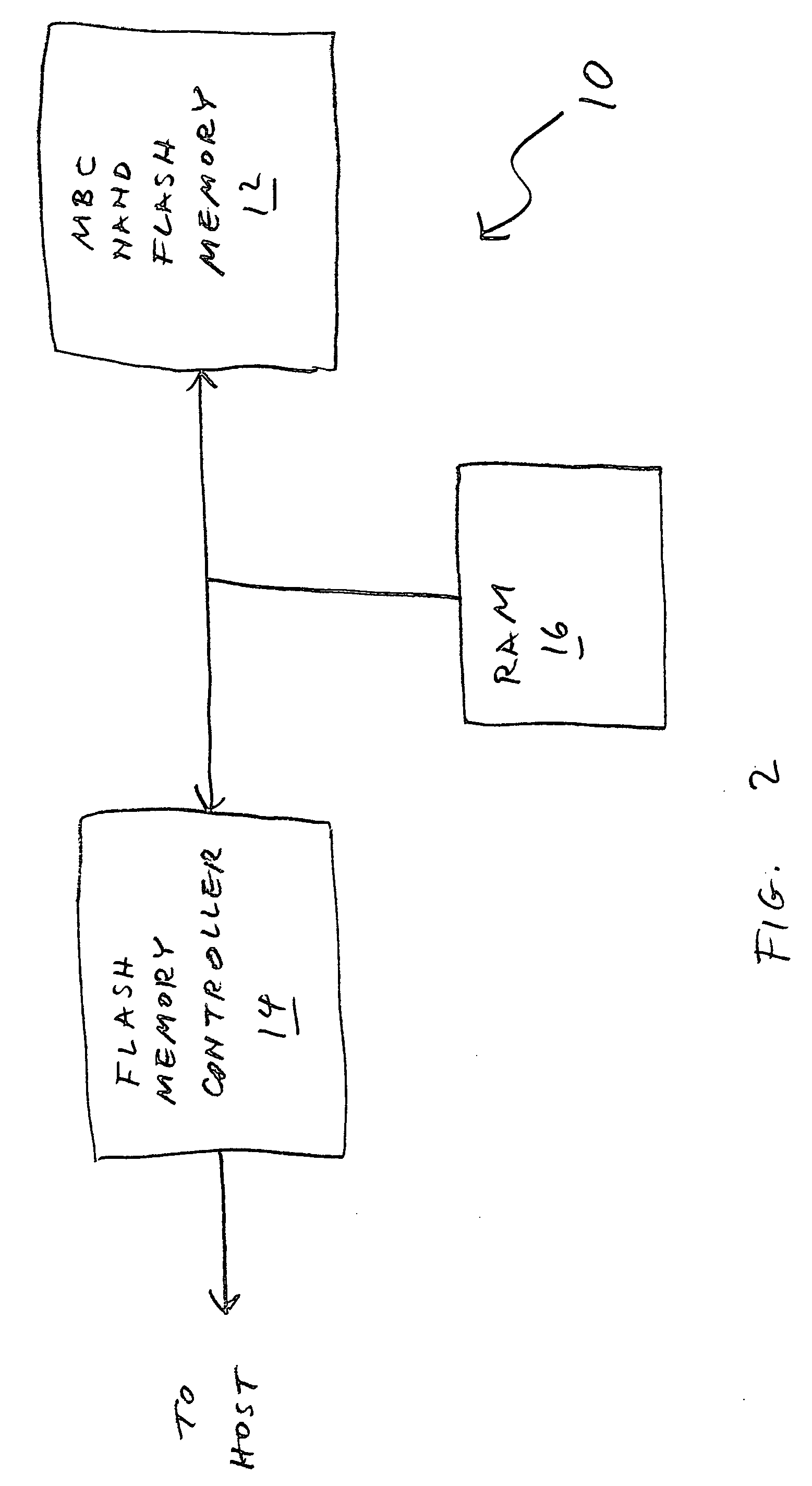

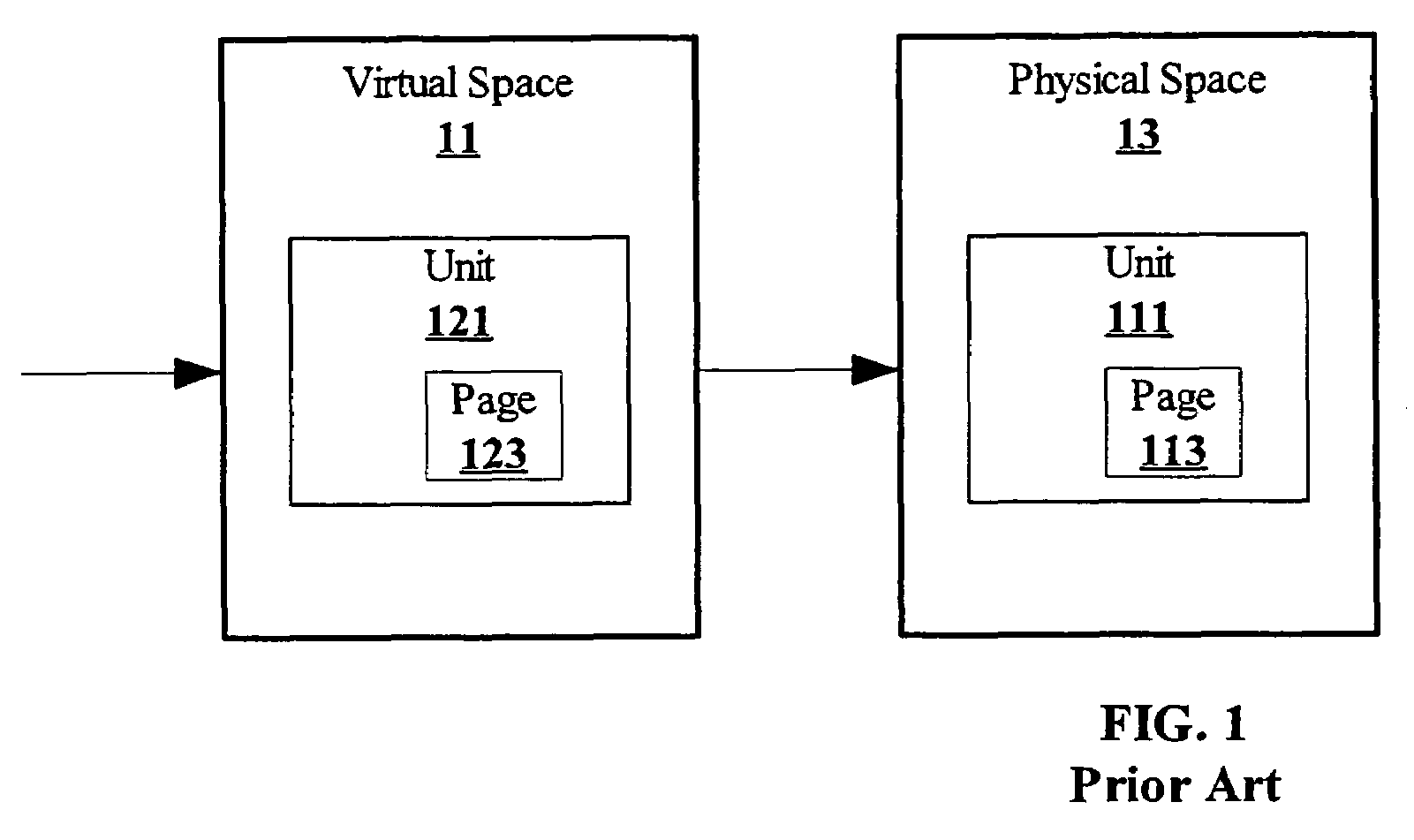

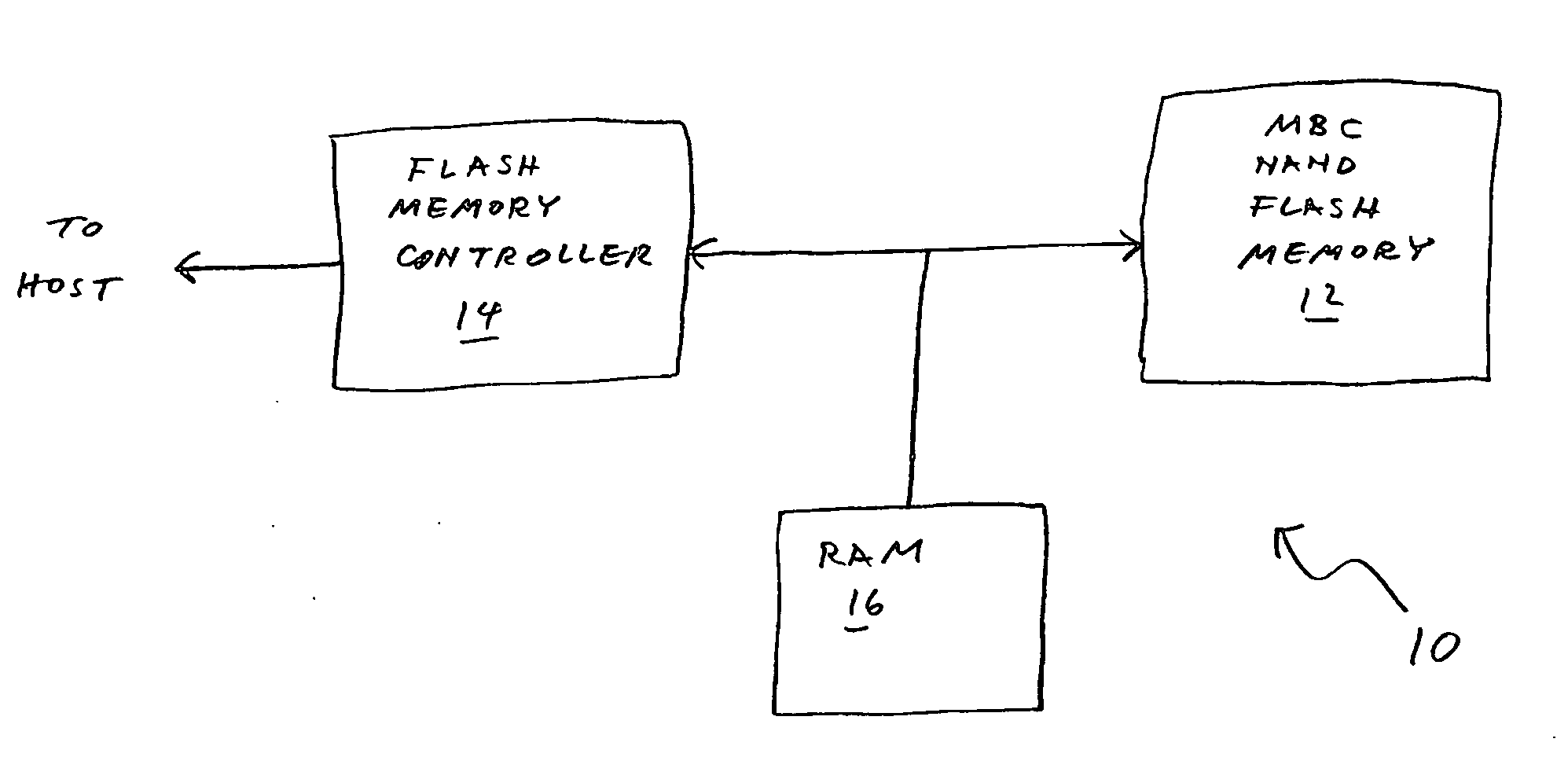

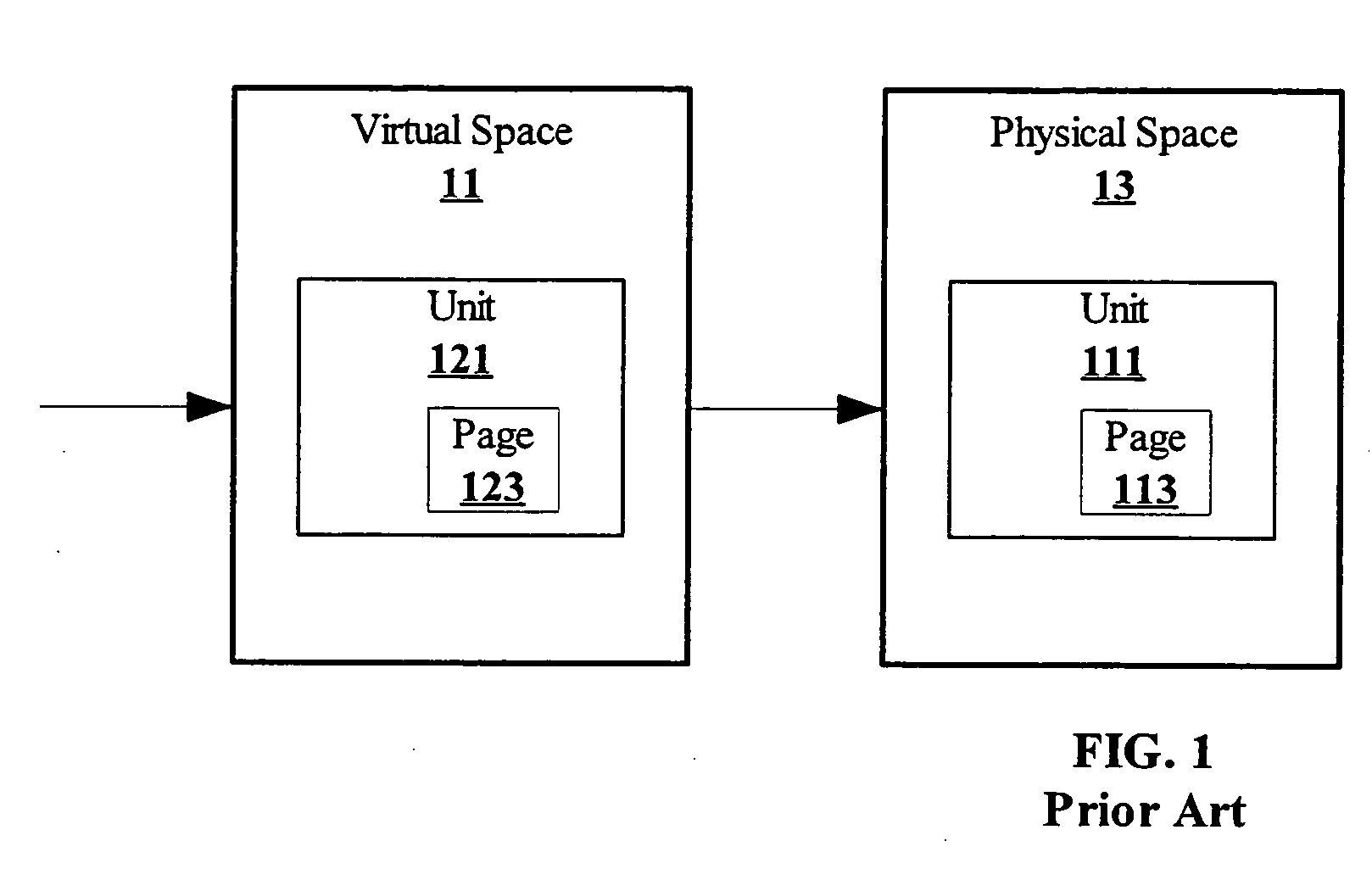

Method of managing a multi-bit-cell flash memory

A flash memory is managed by reserving one or more cells as flag cells to represent the number N of bits to store in the cells of a memory block, selecting the value of N from at least three candidates, and programming the flag cell(s) to represent the selected value. A flash memory is managed by selecting a value of the number N>2 of bits to store in the cells of a portion (e.g. a block or page) of the memory, reserving one other cell of the memory as a flag cell to represent how many bits actually are stored in each cell of the portion, and, as the cells of the portion are successively programmed with 1≦n≦N bits, programming the flag cell to represent n.

Owner:WESTERN DIGITAL ISRAEL LTD

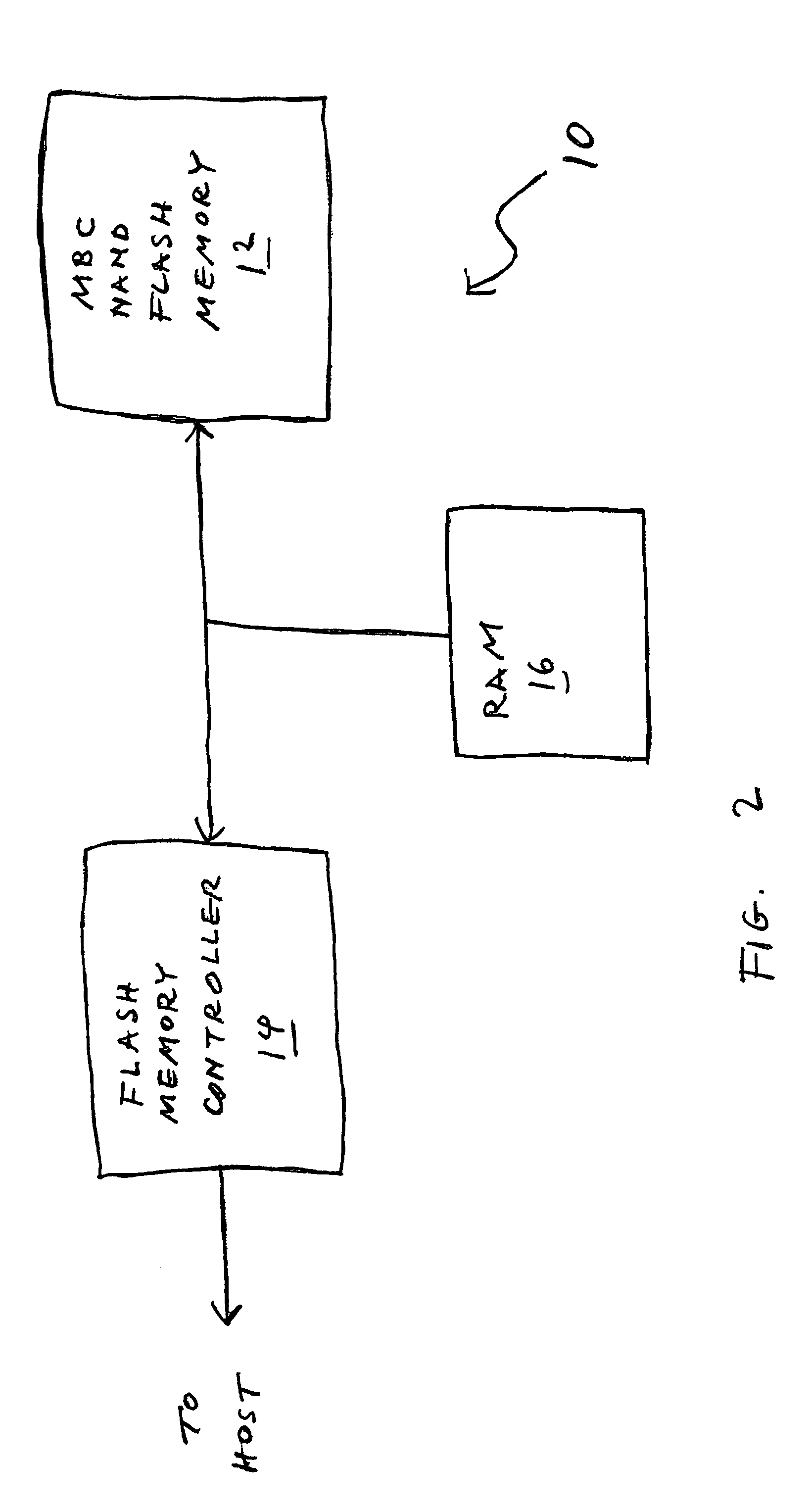

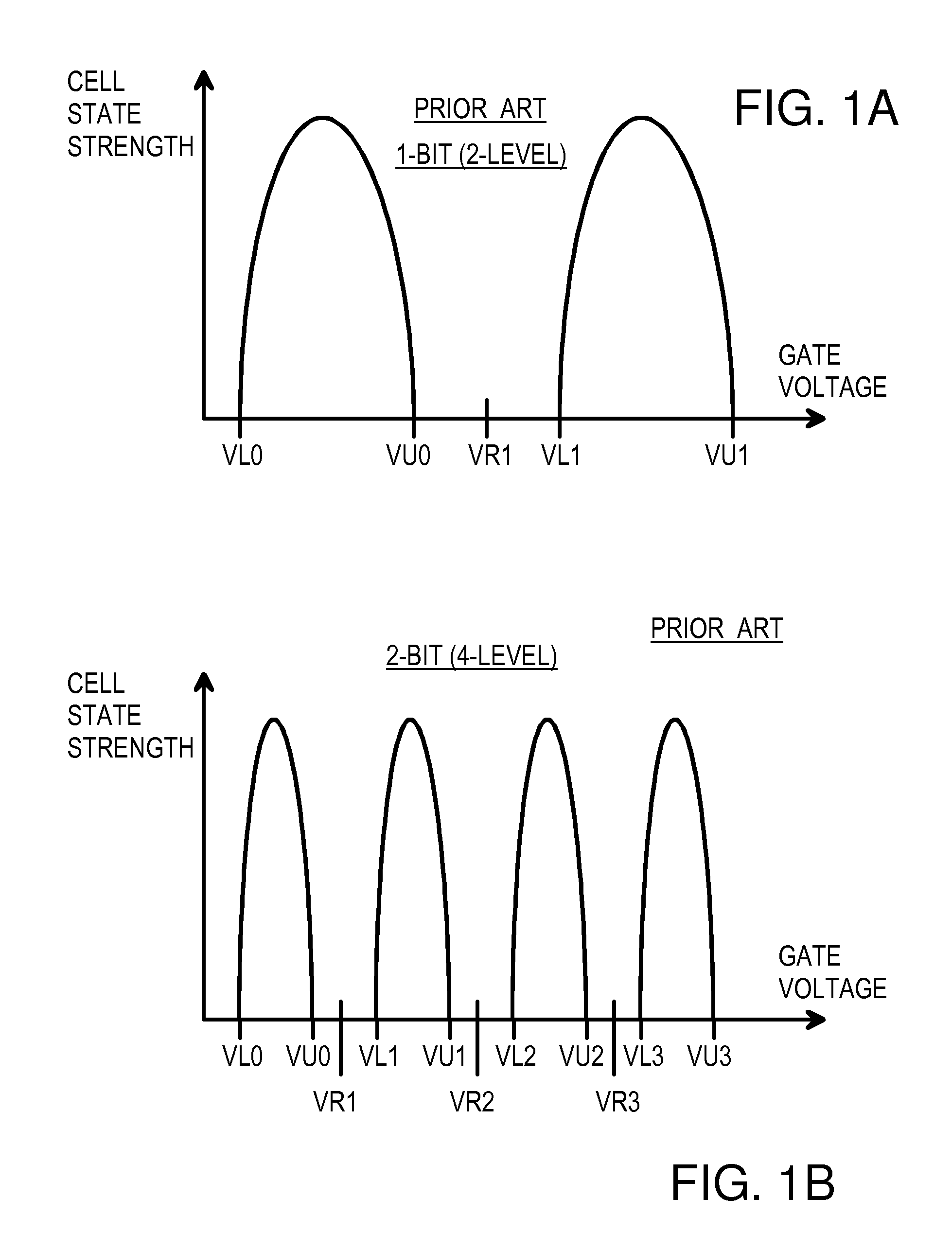

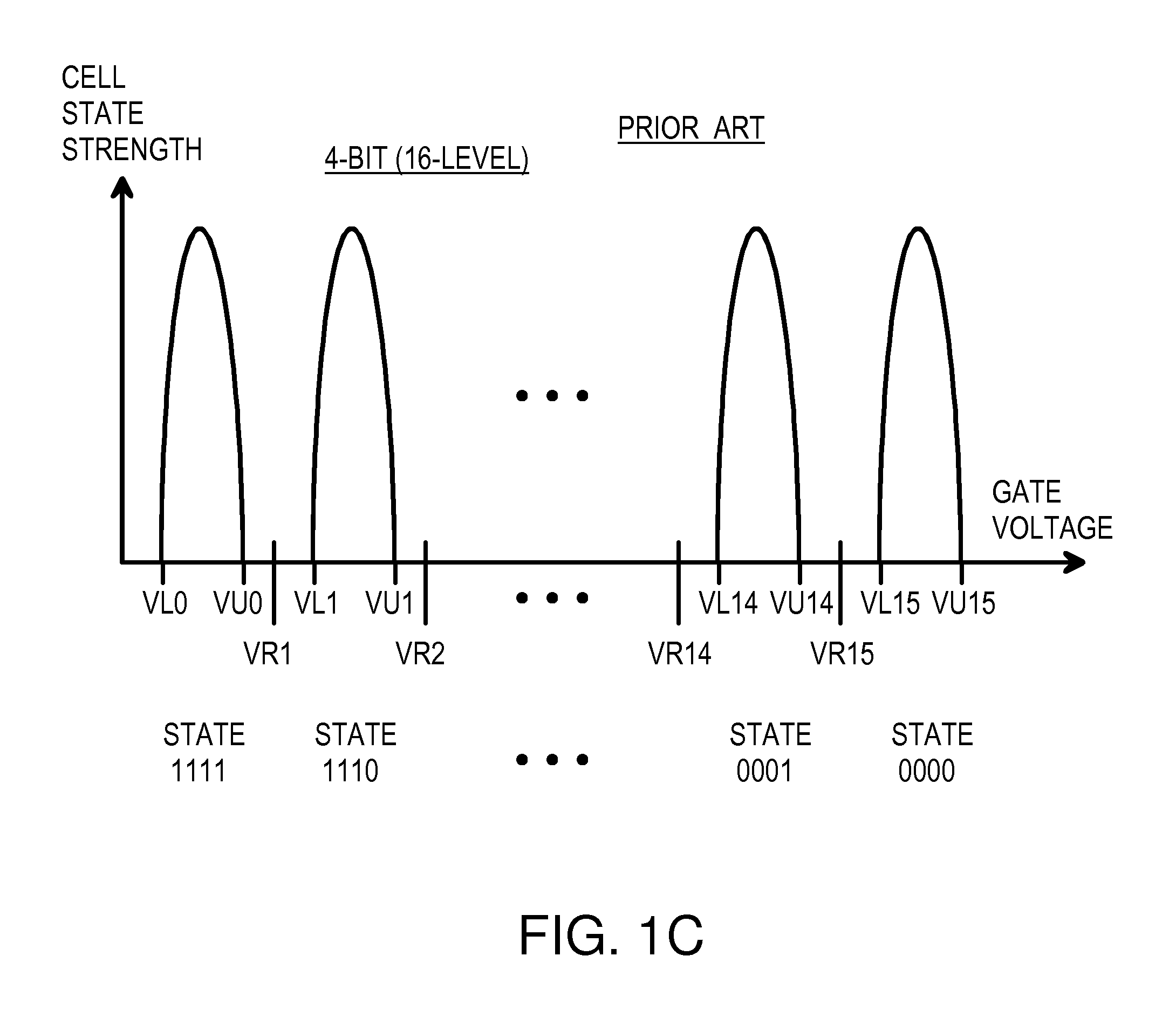

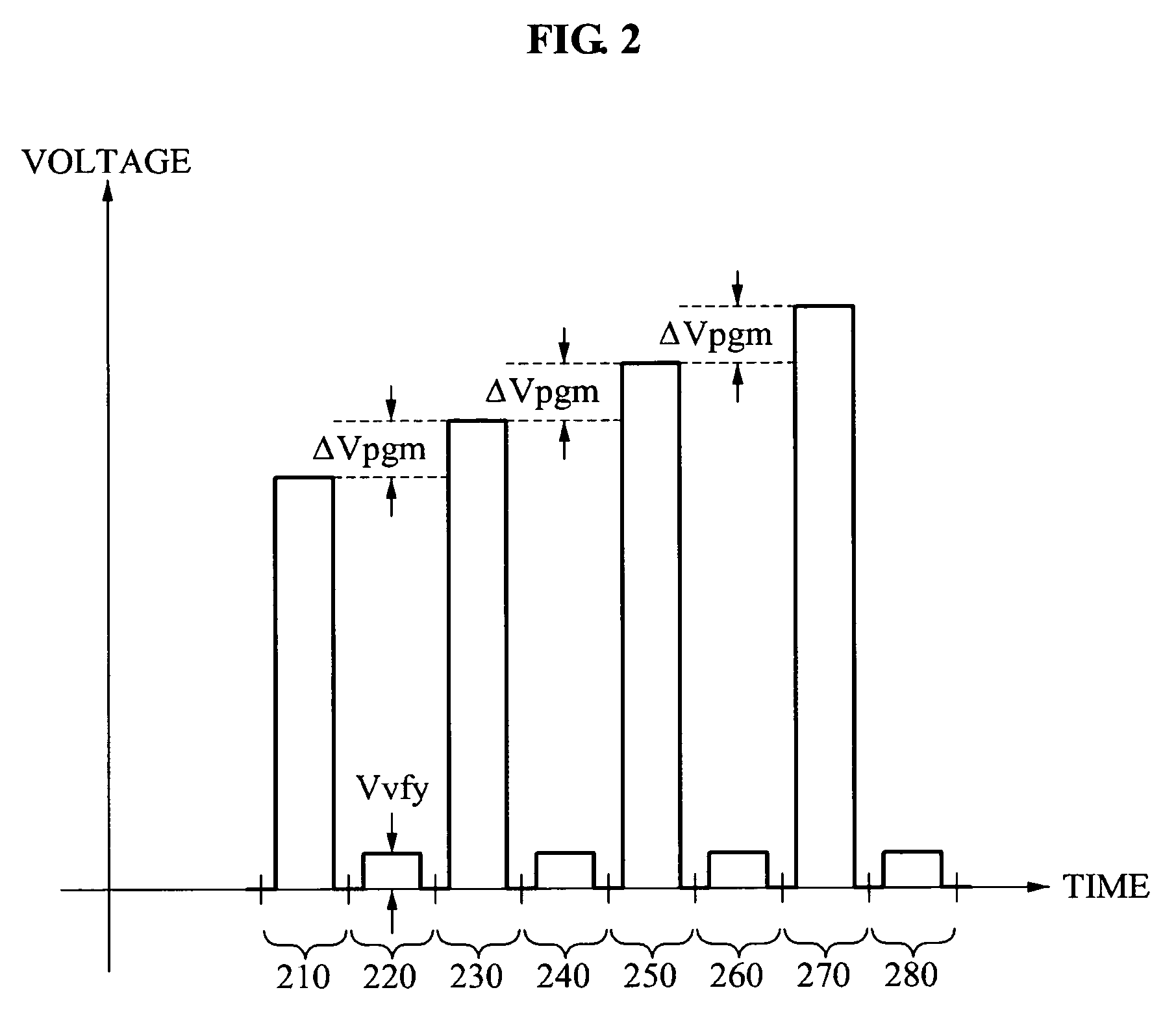

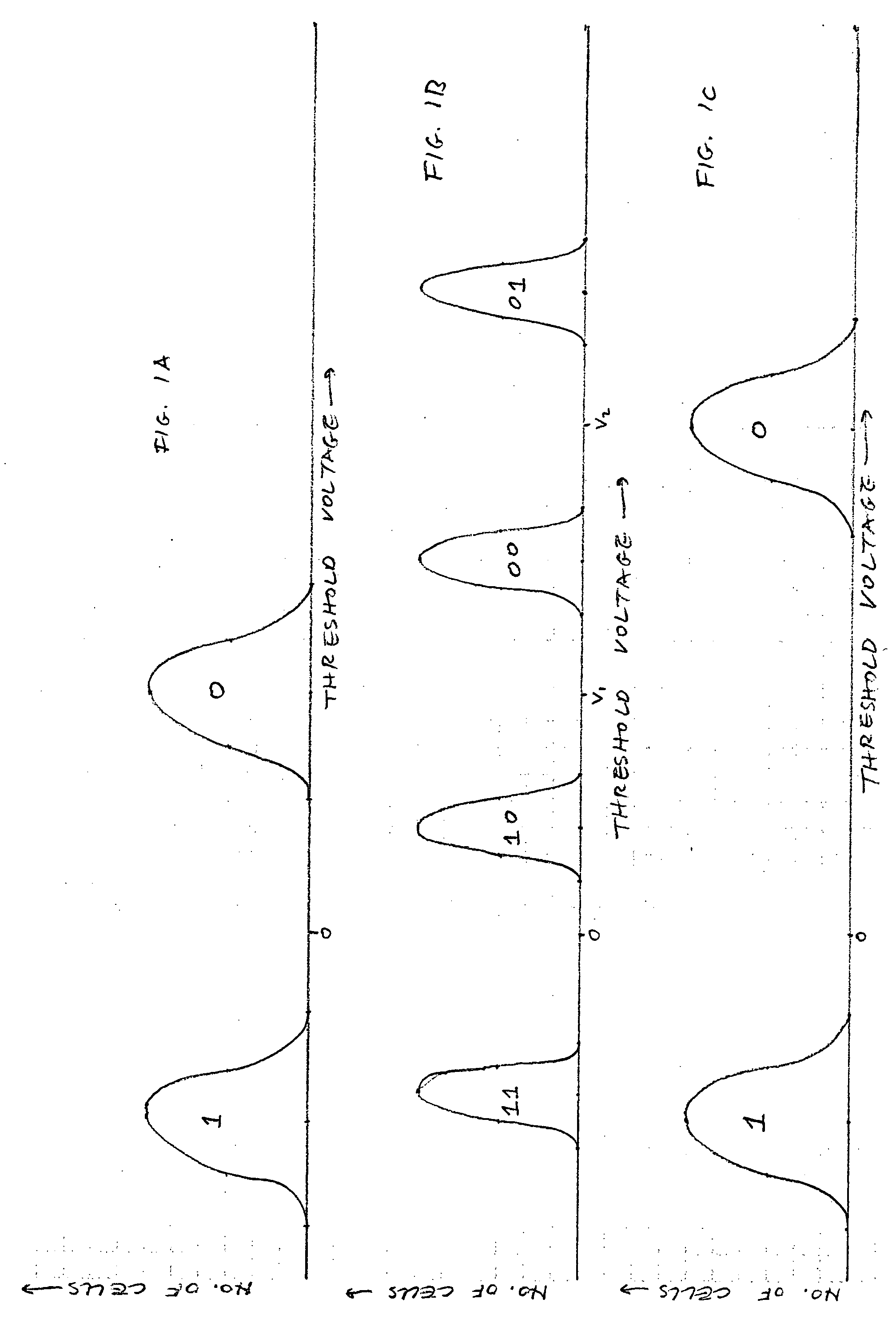

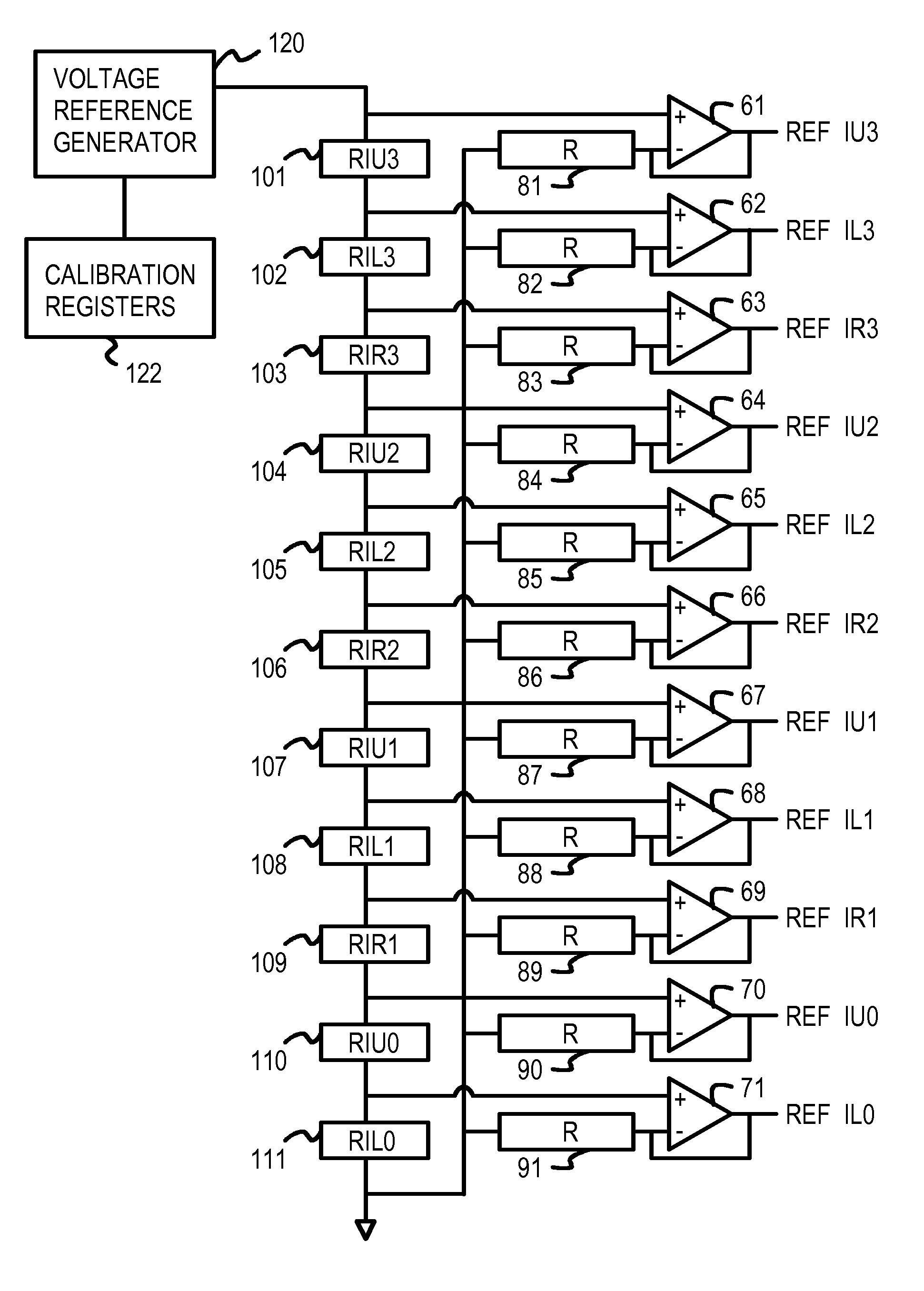

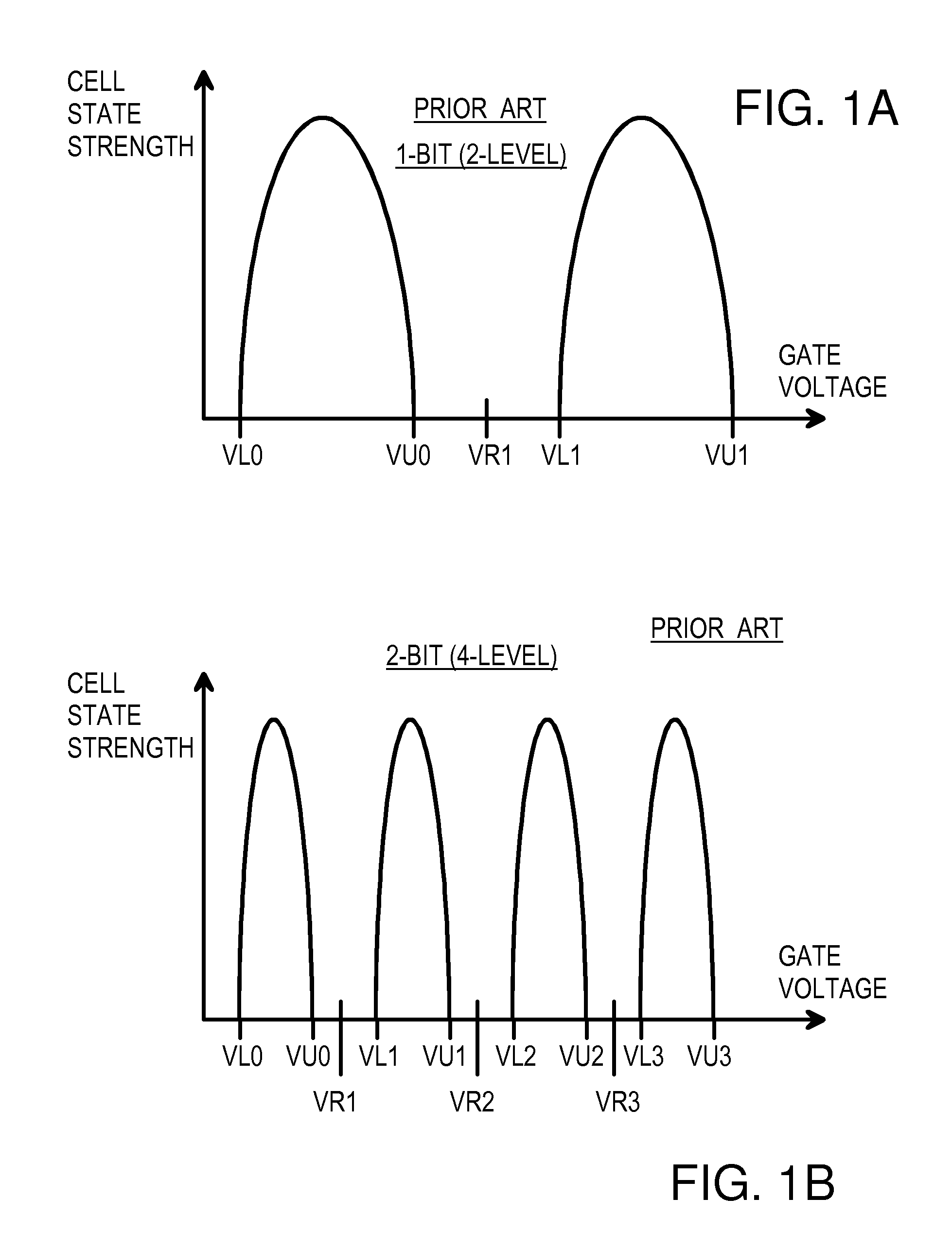

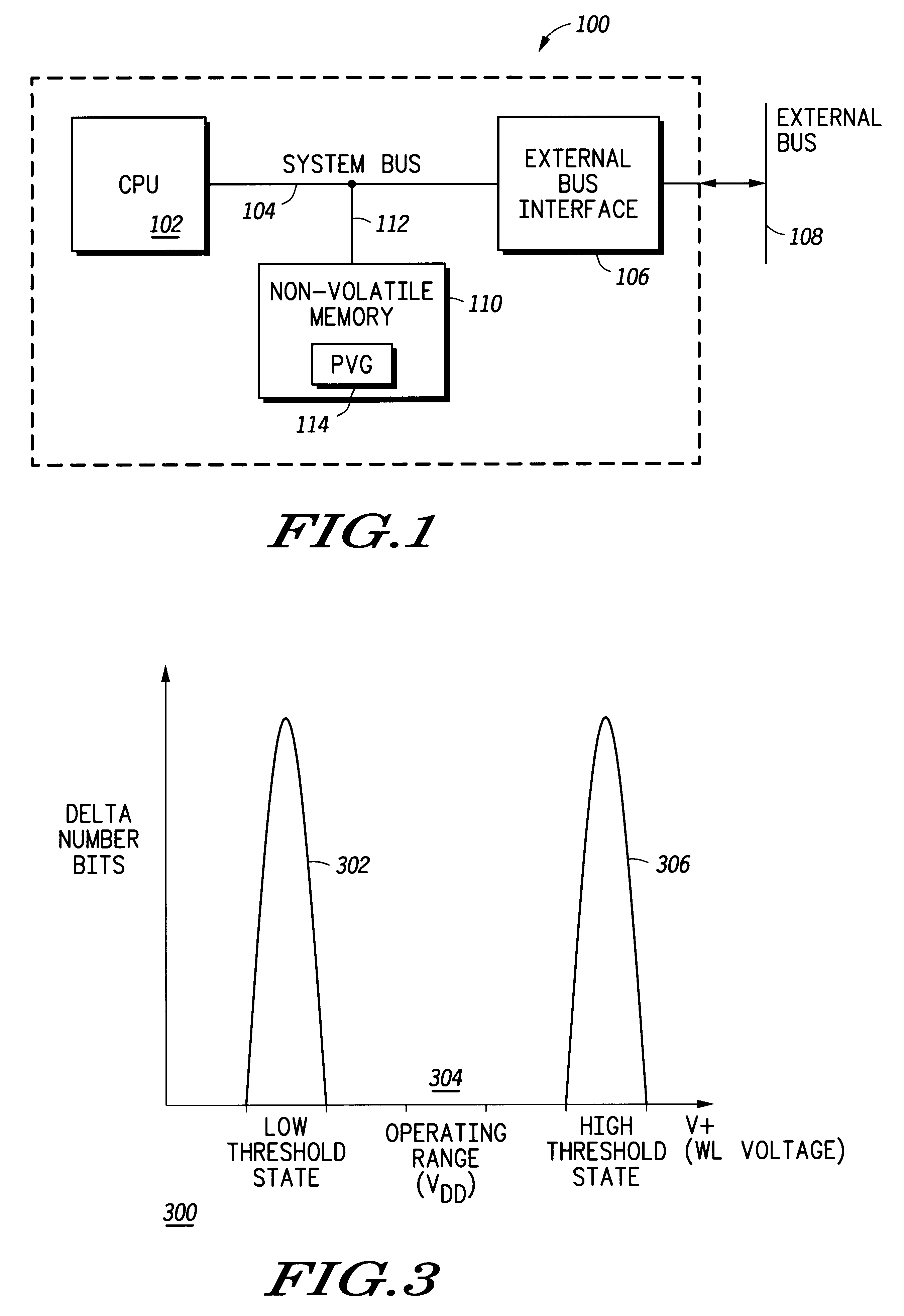

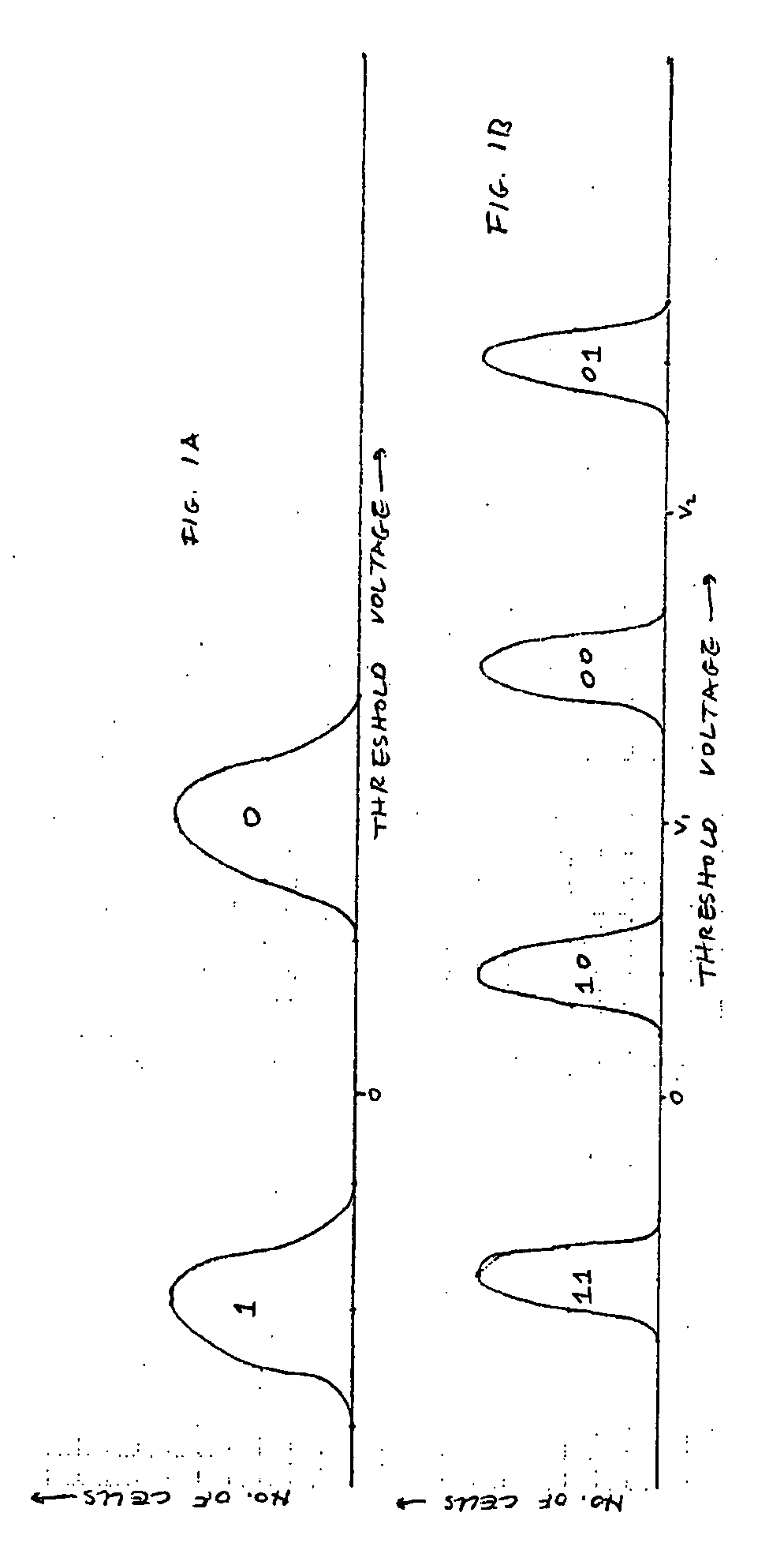

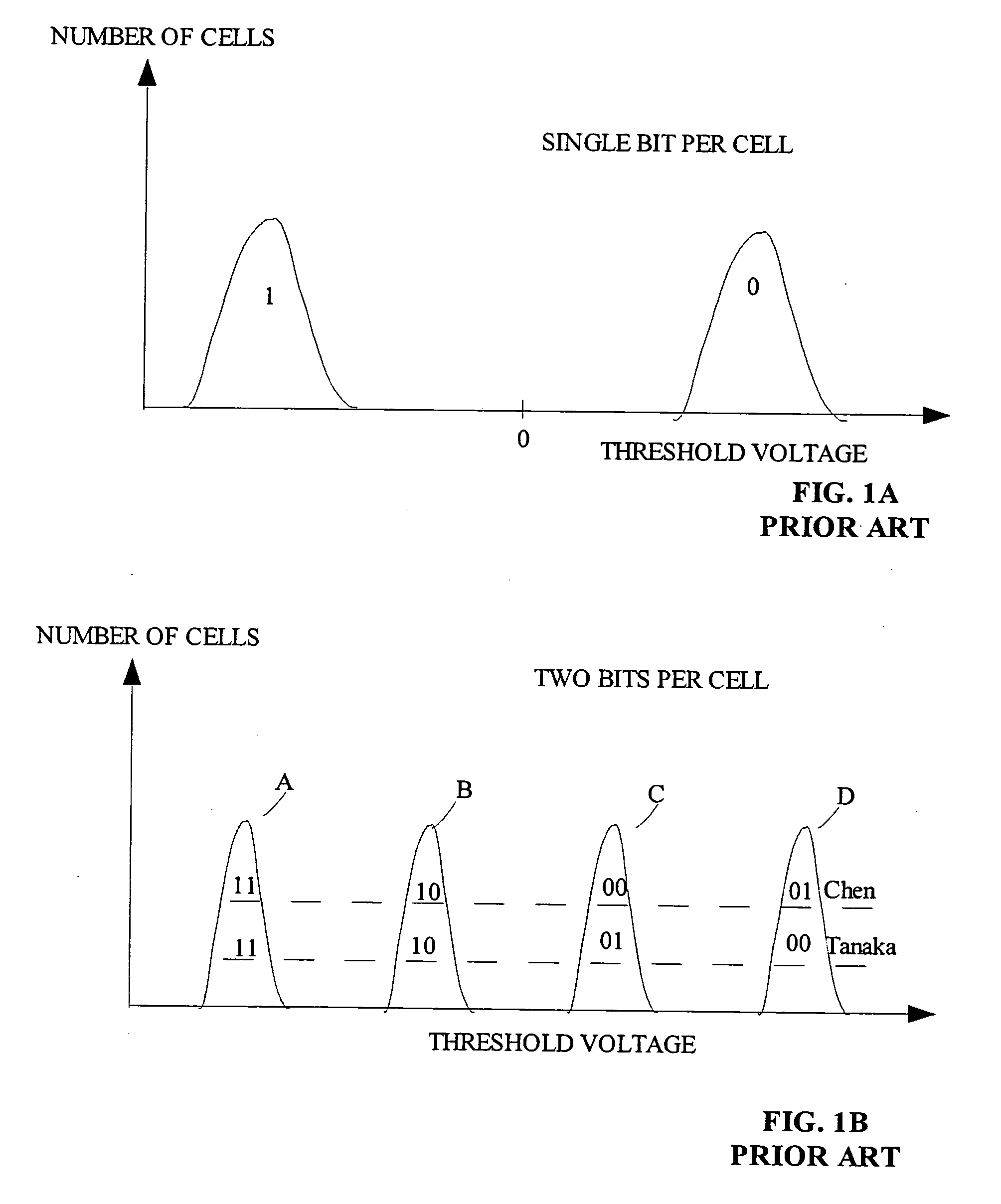

Cell-Downgrading and Reference-Voltage Adjustment for a Multi-Bit-Cell Flash Memory

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

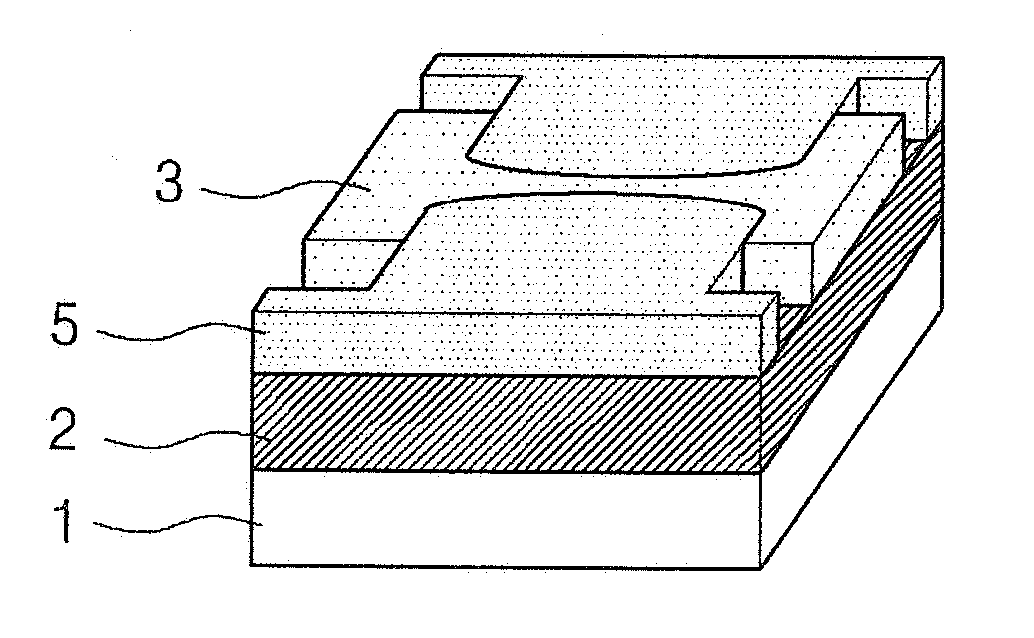

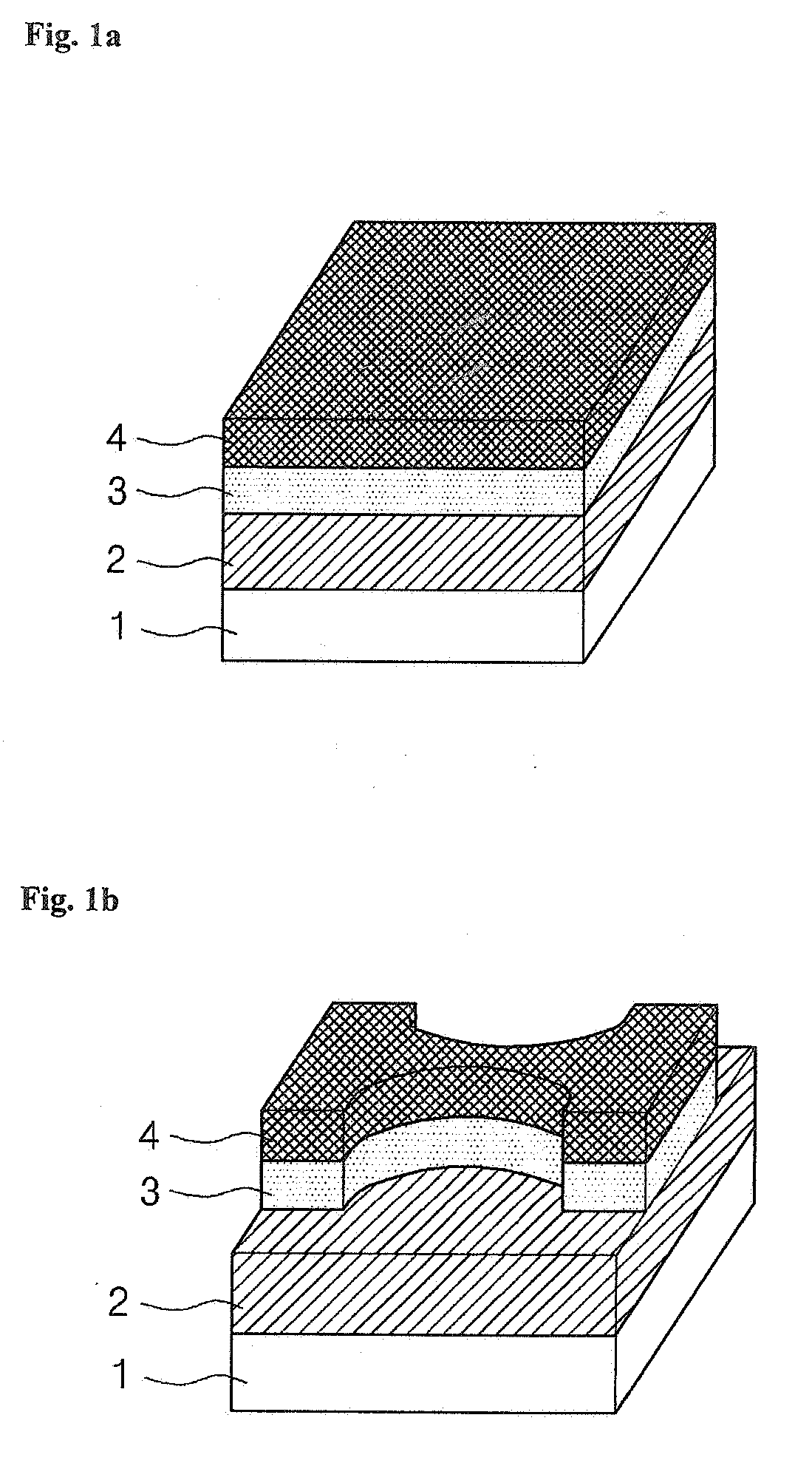

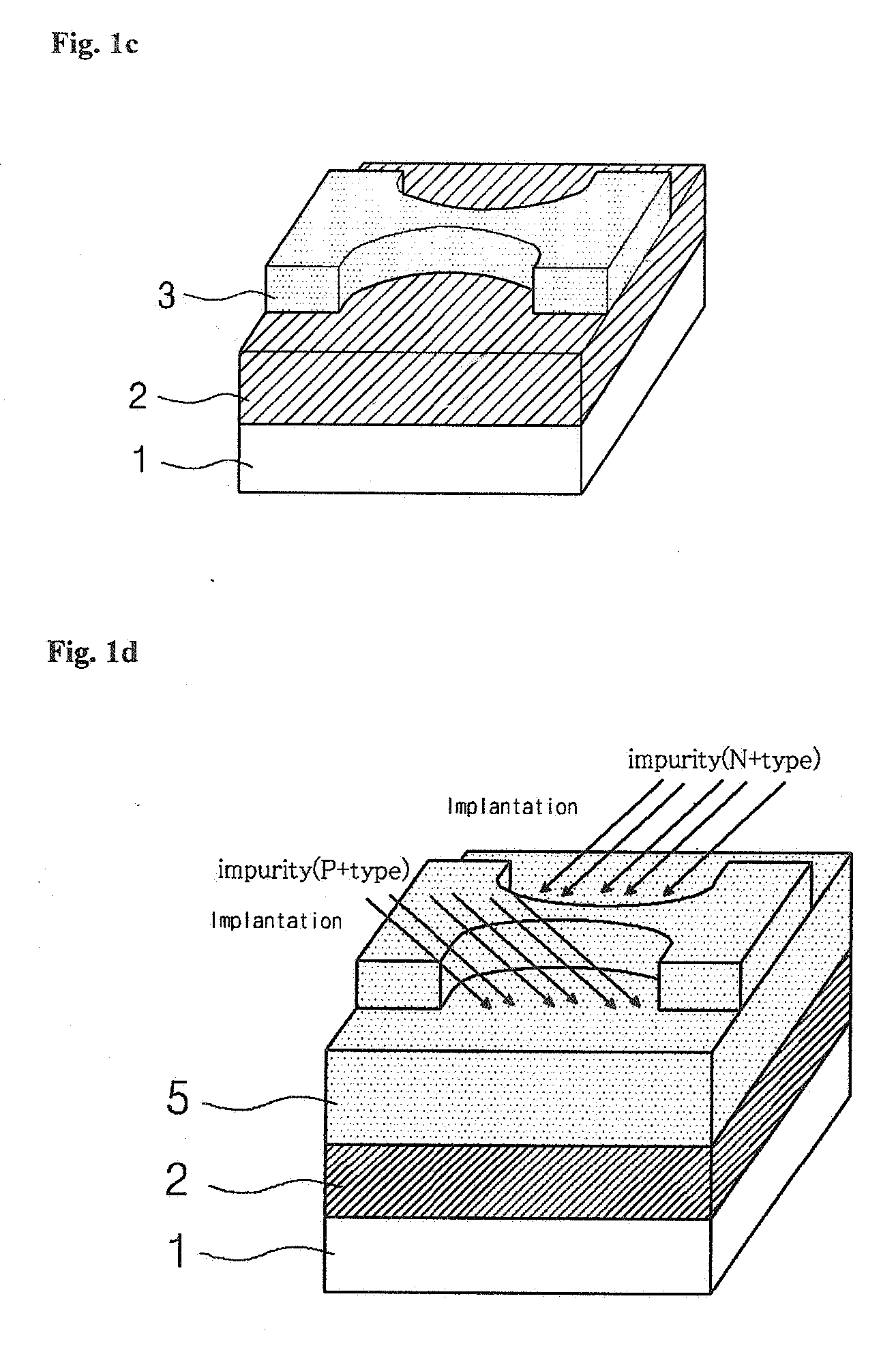

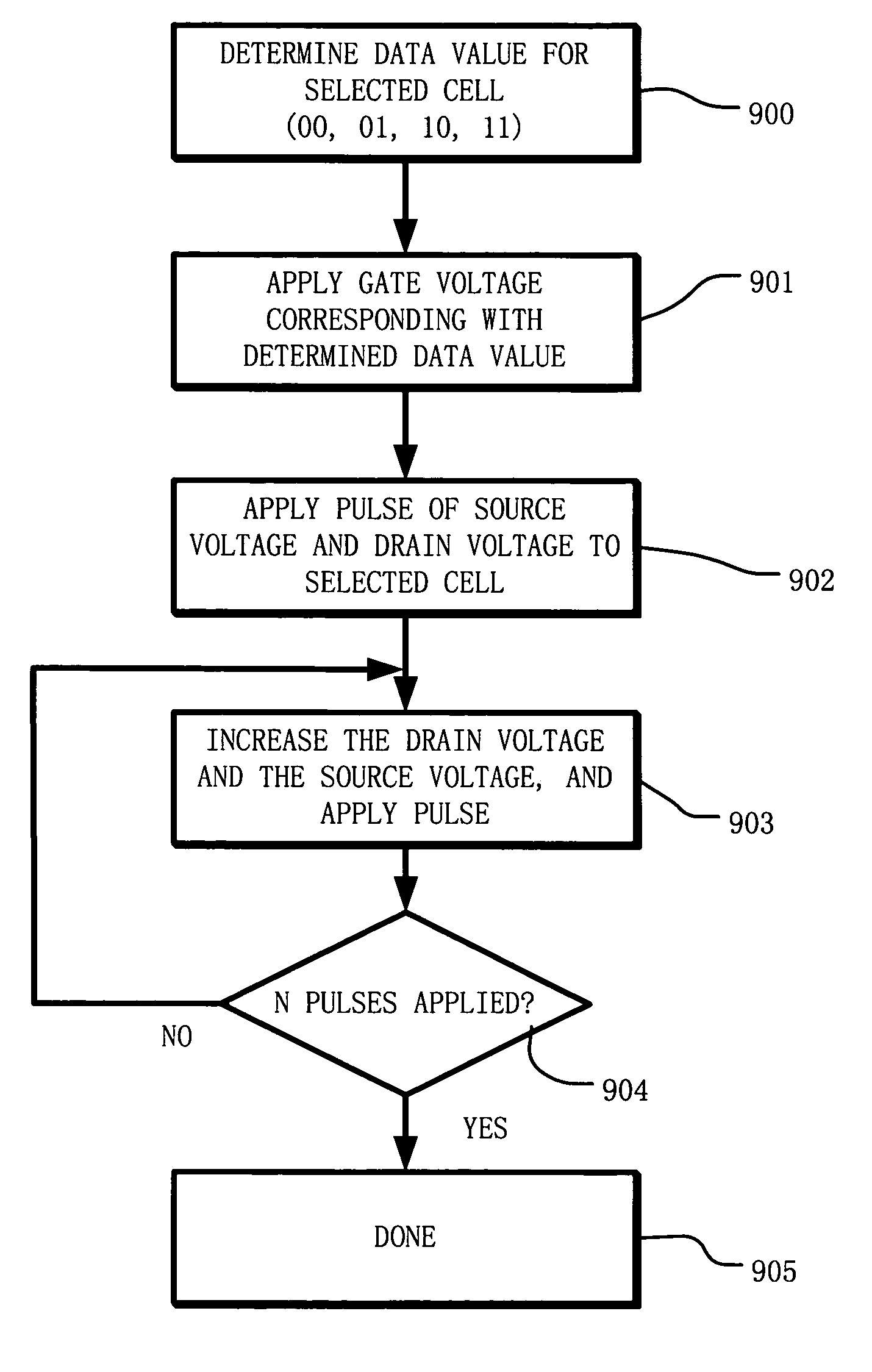

Multi-bit non-volatile memory device having a dual-gate and method of manufacturing the same, and method of multi-bit cell operation

ActiveUS20060237777A1Eliminate the effects ofTransistorNanoinformaticsEngineeringNon-volatile memory

The present invention relates to a multi-bit non-volatile memory device having a dual gate employing local charge trap and method of manufacturing the same, and an operating method for a multi-bit cell operation.

Owner:KOREA ADVANCED INST OF SCI & TECH

Circuit and method for programming charge storage memory cells

ActiveUS6937511B2Increases the effective thresholdHot electron injection efficiencySolid-state devicesRead-only memoriesEngineeringGate voltage

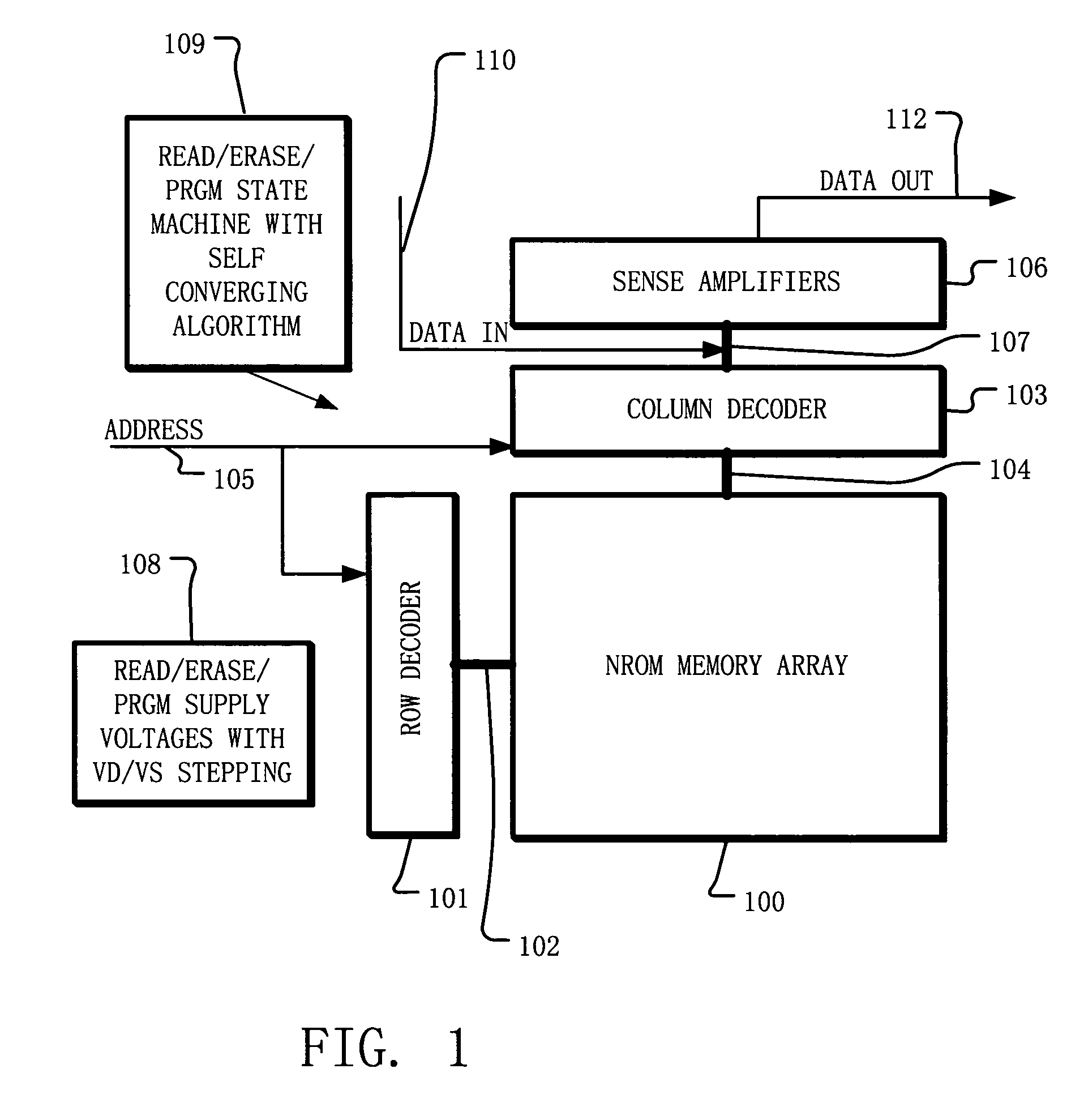

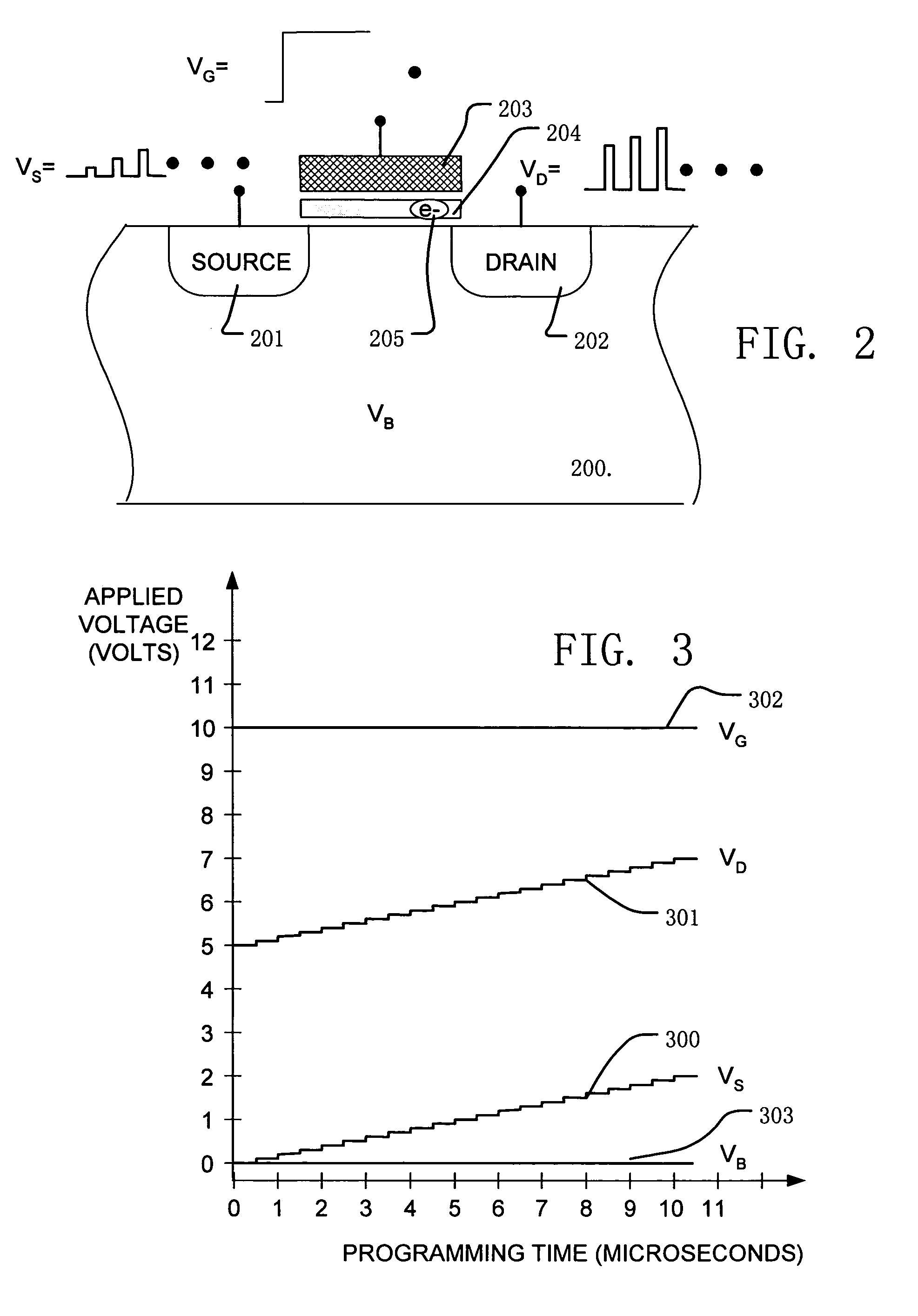

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash, having a source and a drain in a substrate, a charge storage element and a control gate. The method includes applying source voltage, inducing a body effect that increases the effective threshold, and increasing the source voltage along with the drain voltage to moderate hot electron injection efficiency during the program operation, at least during a portion of the program operation in which convergence on a target threshold occurs. A selected gate voltage is applied during the operation to establish the target threshold voltage. In multiple bit cells, the gate voltage is set according to the data values to be stored, enabling self-convergence at more than one target threshold.

Owner:MACRONIX INT CO LTD

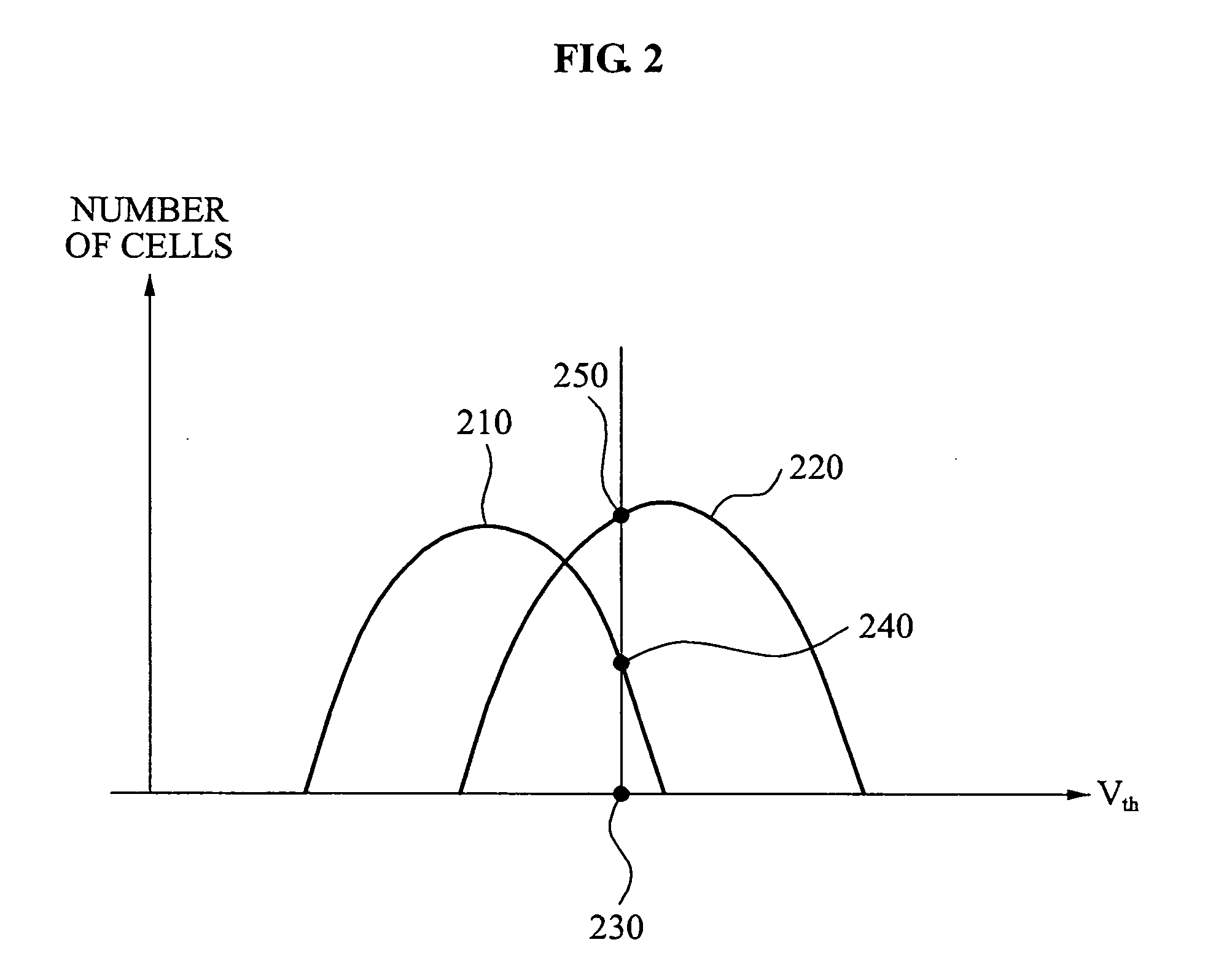

Memory device and memory programming method

ActiveUS20090296466A1Reduce distribution widthReduce errorsRead-only memoriesDigital storageParallel computingThreshold voltage

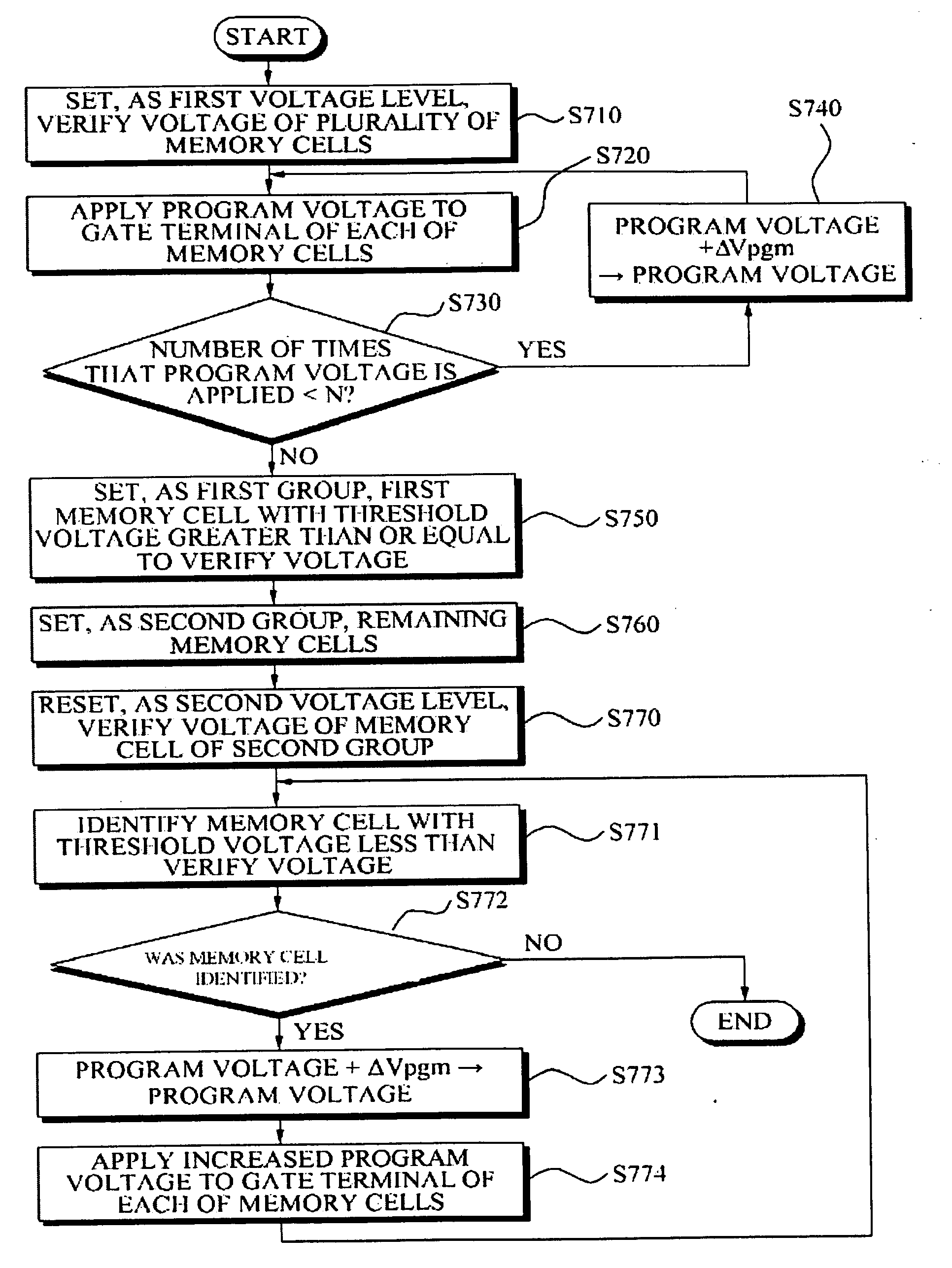

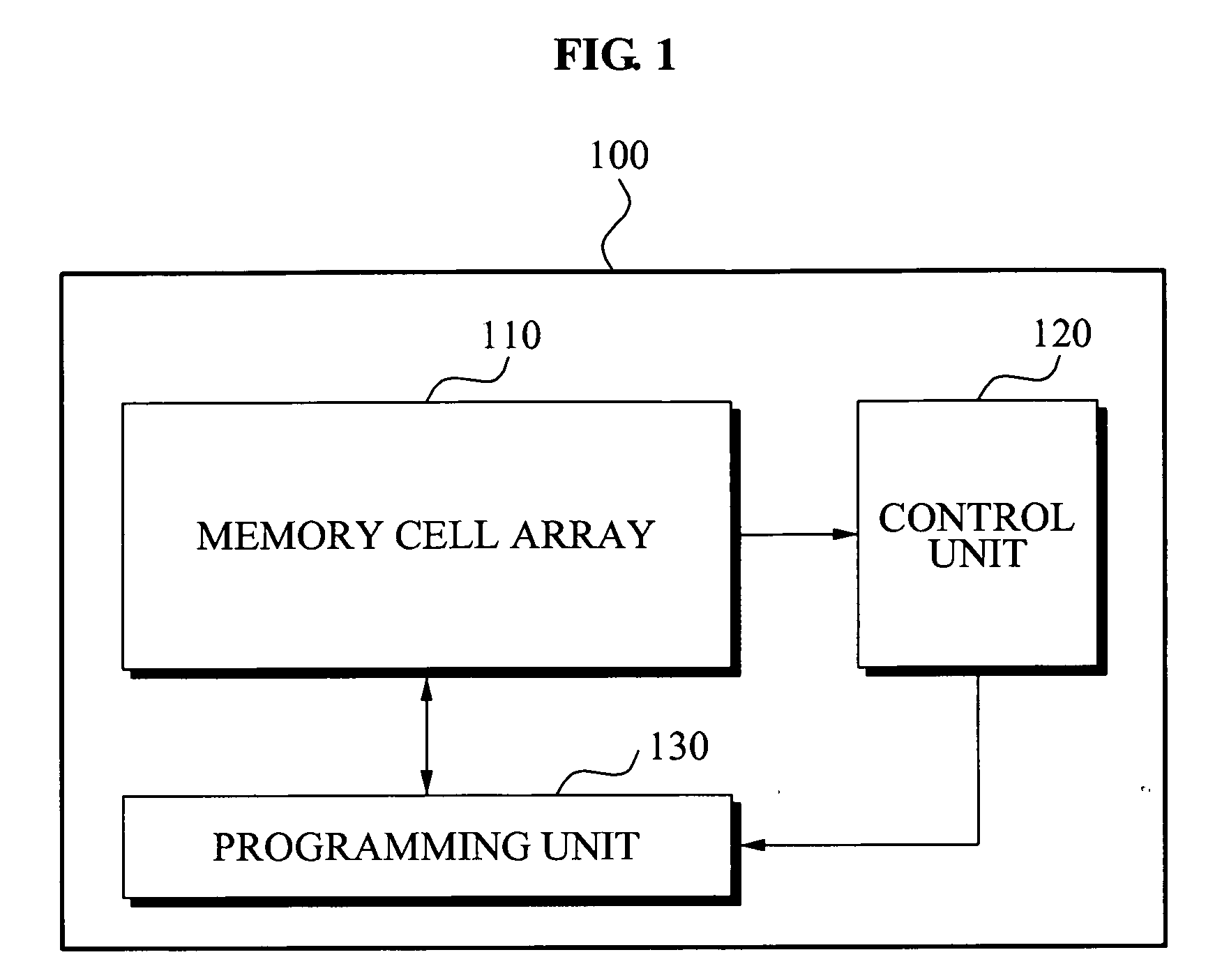

Provided are memory devices and memory programming methods. A memory device may include: a multi-bit cell array that includes a plurality of memory cells; a controller that extracts state information of each of the memory cells, divides the plurality of memory cells into a first group and a second group, assigns a first verify voltage to memory cells of the first group and assigns a second verify voltage to memory cells of the second group; and a programming unit that changes a threshold voltage of each memory cell of the first group until the threshold voltage of each memory cell of the first group is greater than or equal to the first verify voltage, and changes a threshold voltage of each memory cell of the second group until the threshold voltage of each memory cell of the second group is greater than or equal to the second verify voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of managing a multi-bit-cell flash memory

A flash memory that supports N>1-bit programming is managed by, for at least one block of the memory, selecting the value of N to use for the block, designating one or more cells of the block as flag cells, and programming the flag cells to represent the selected value of N. Preferably, N is encoded according to whether the threshold voltages of the flag cells are greater or less than a reference voltage common to all values of N. The other cells of the block then are programmed in accordance with the selected value of N. N and its flag cells are selected when the block is first used to store data. Subsequent to an erasure of the block, a different value of N may be selected.

Owner:WESTERN DIGITAL ISRAEL LTD

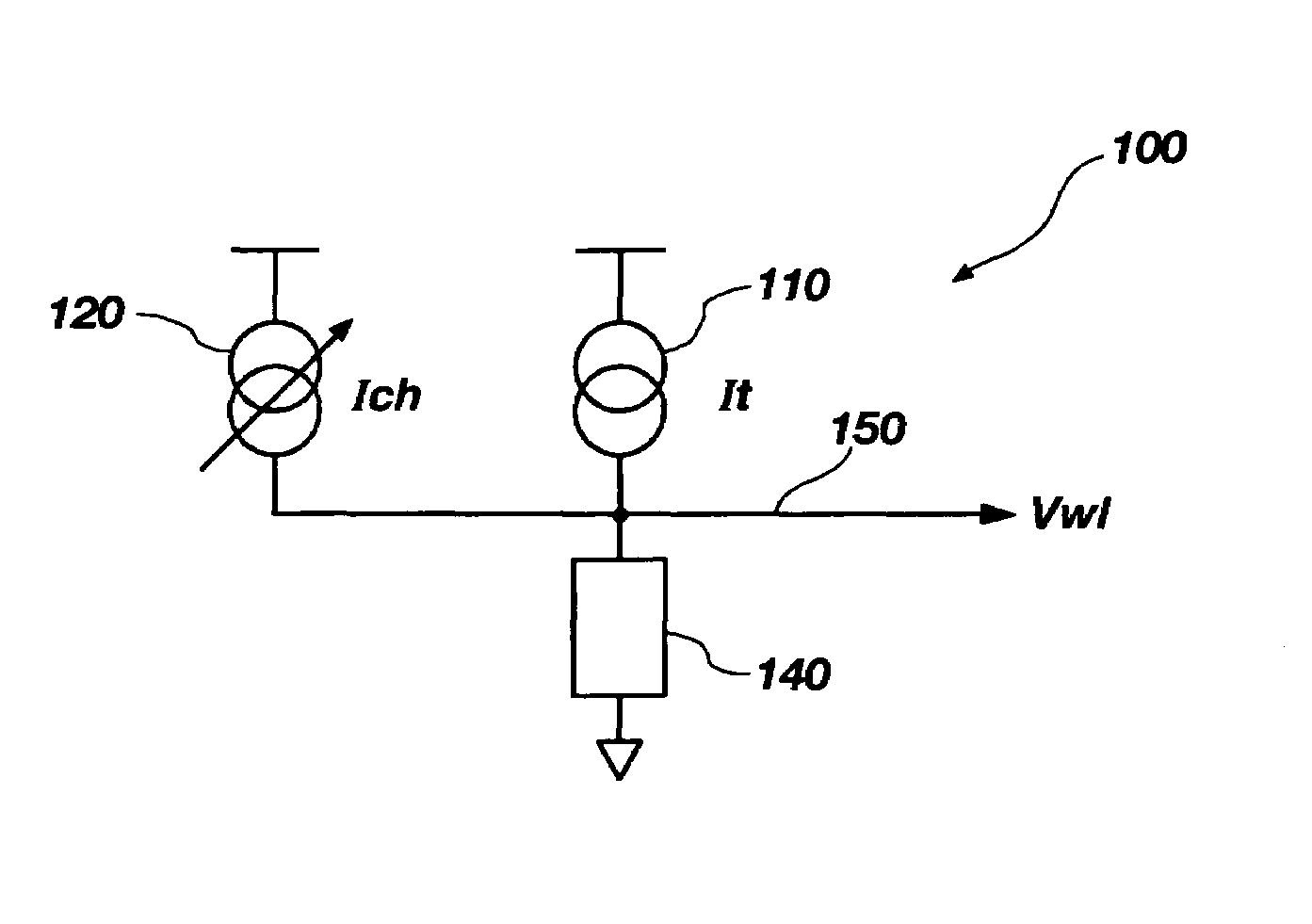

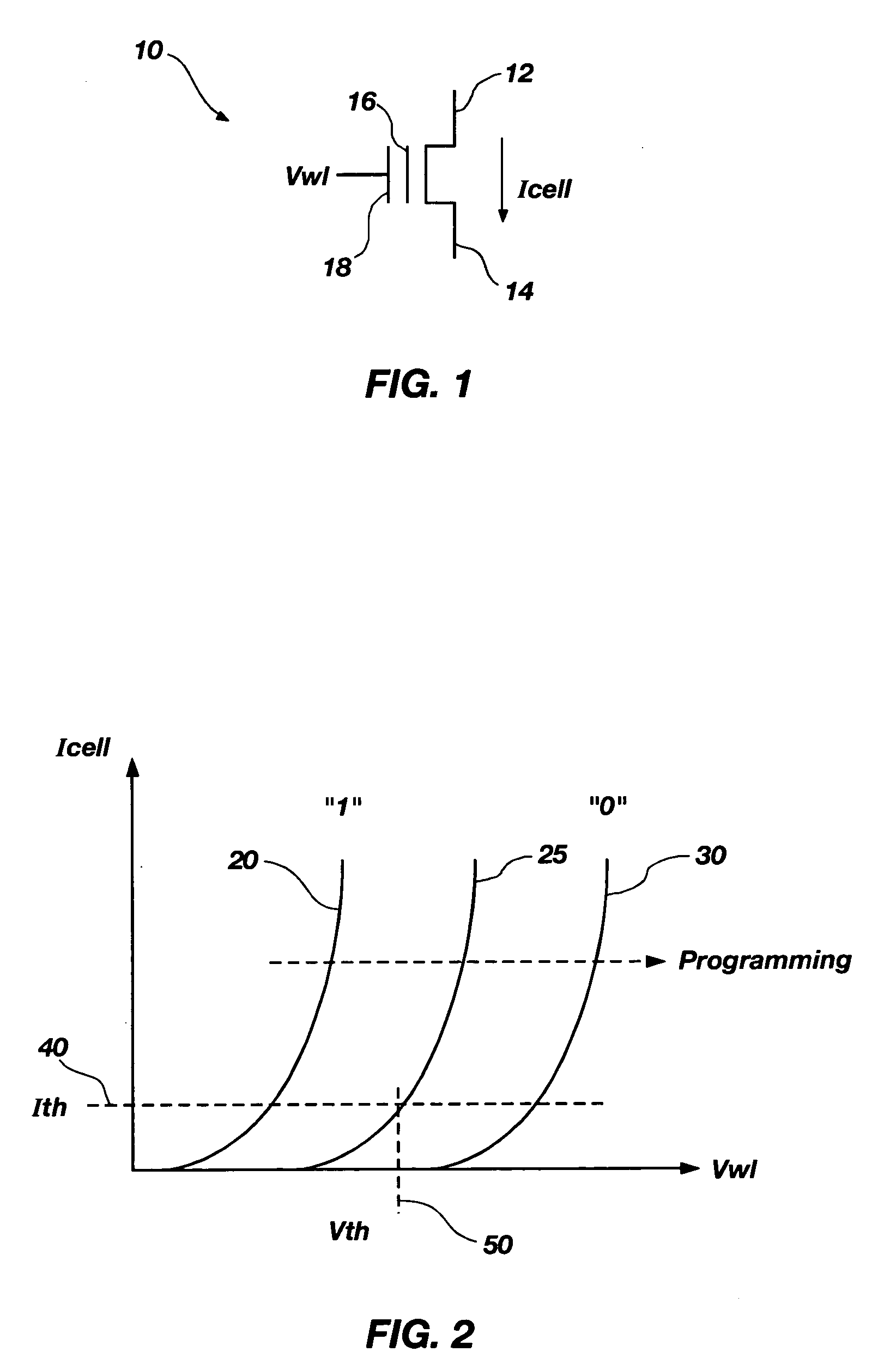

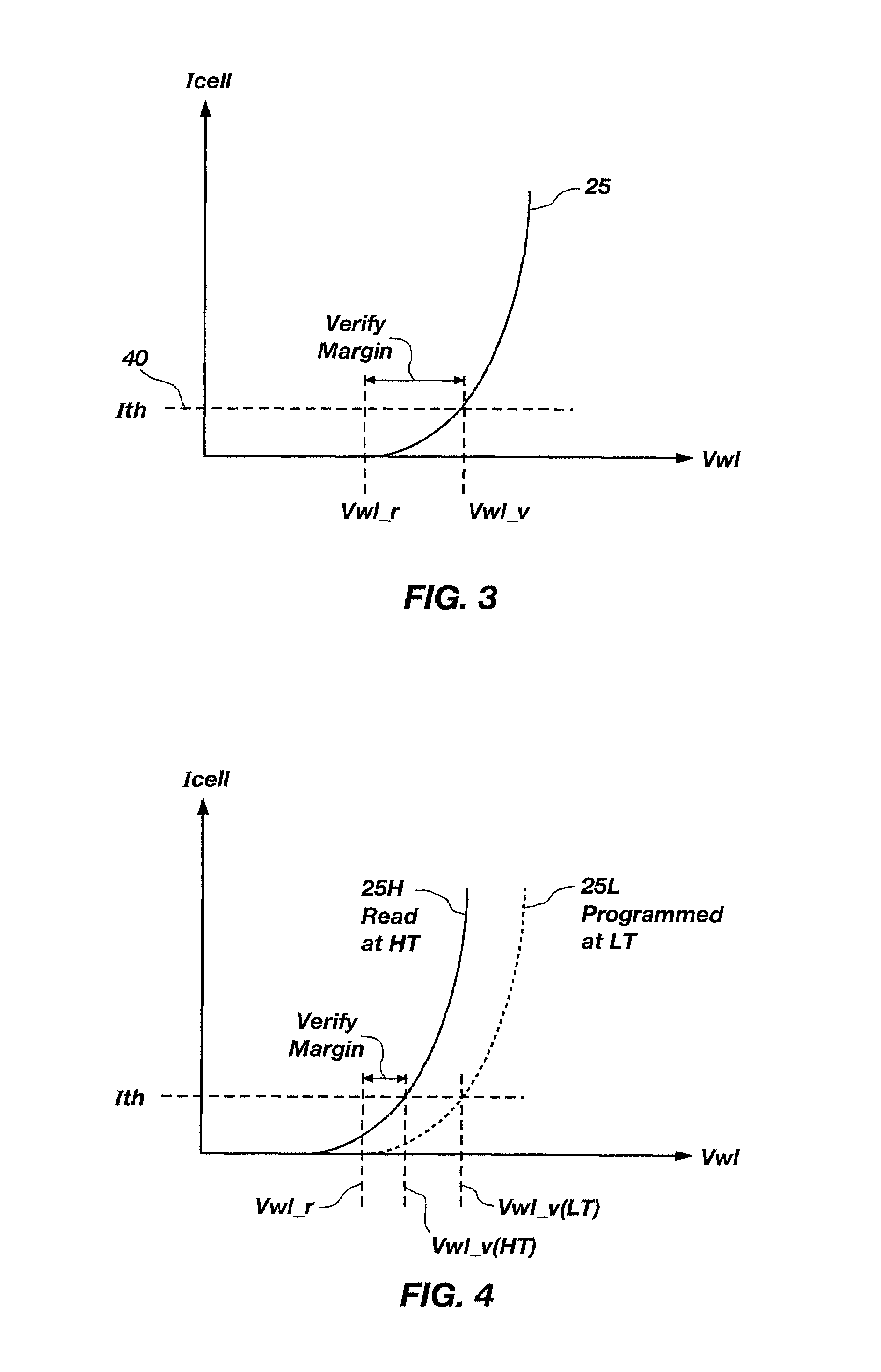

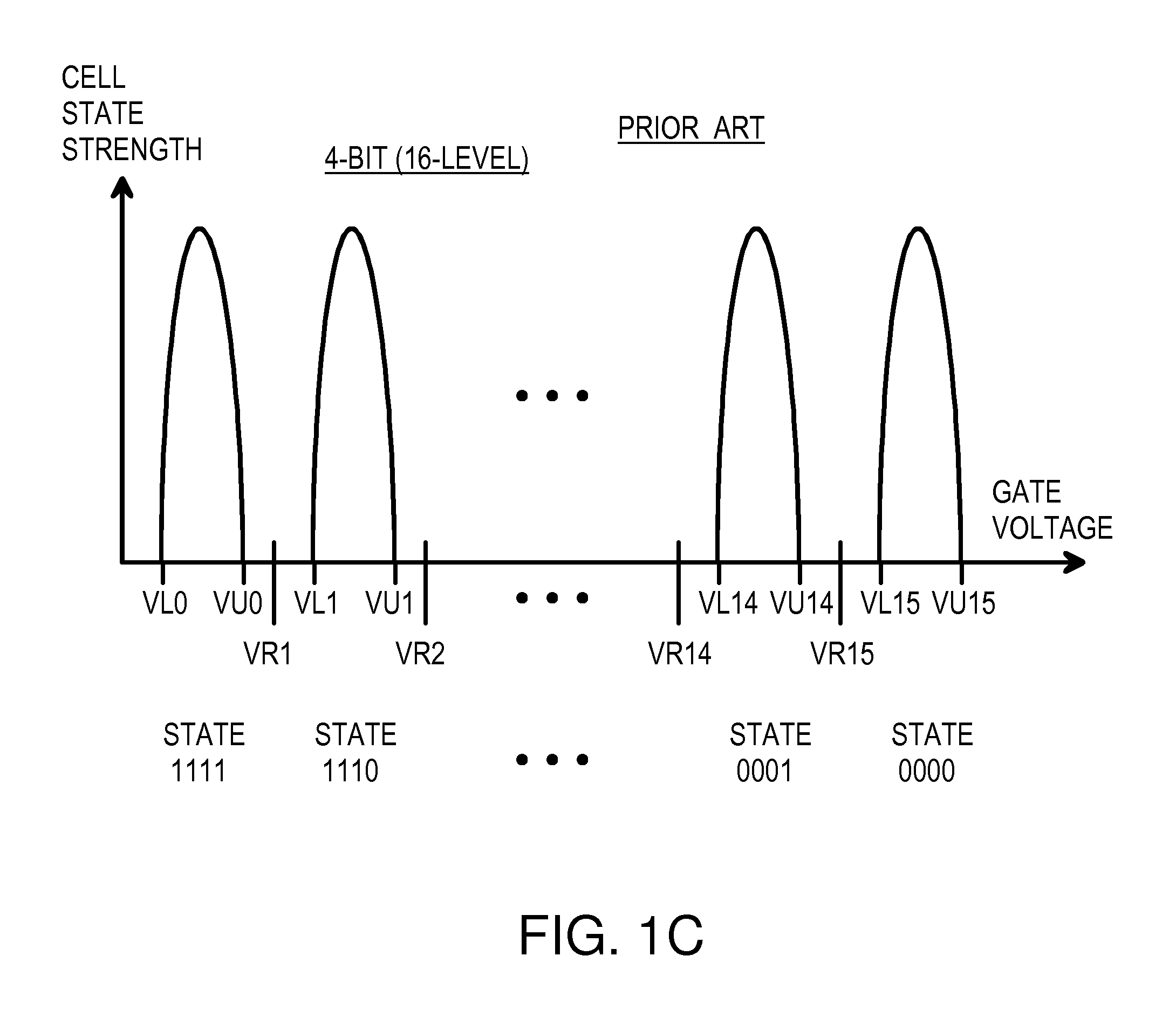

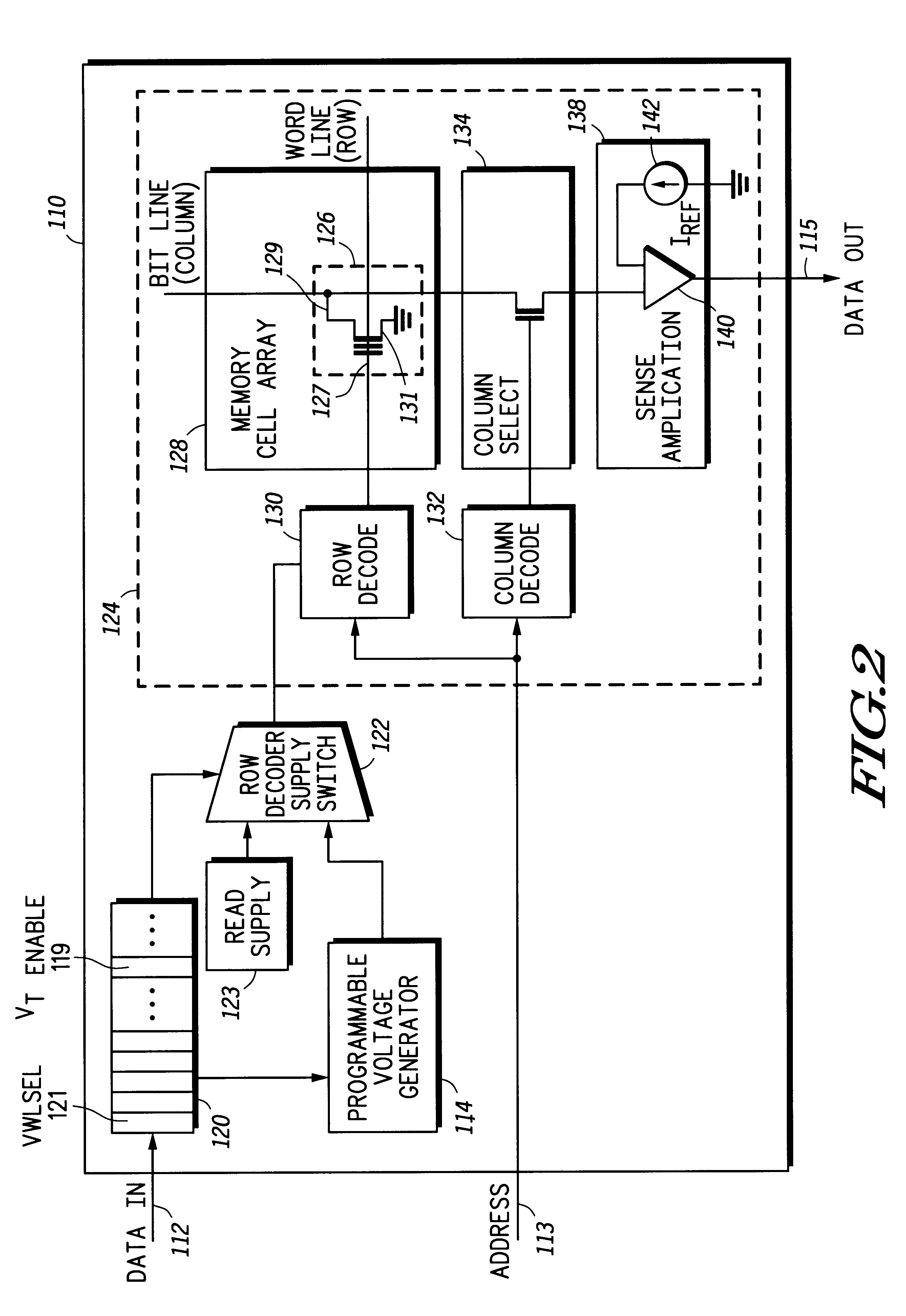

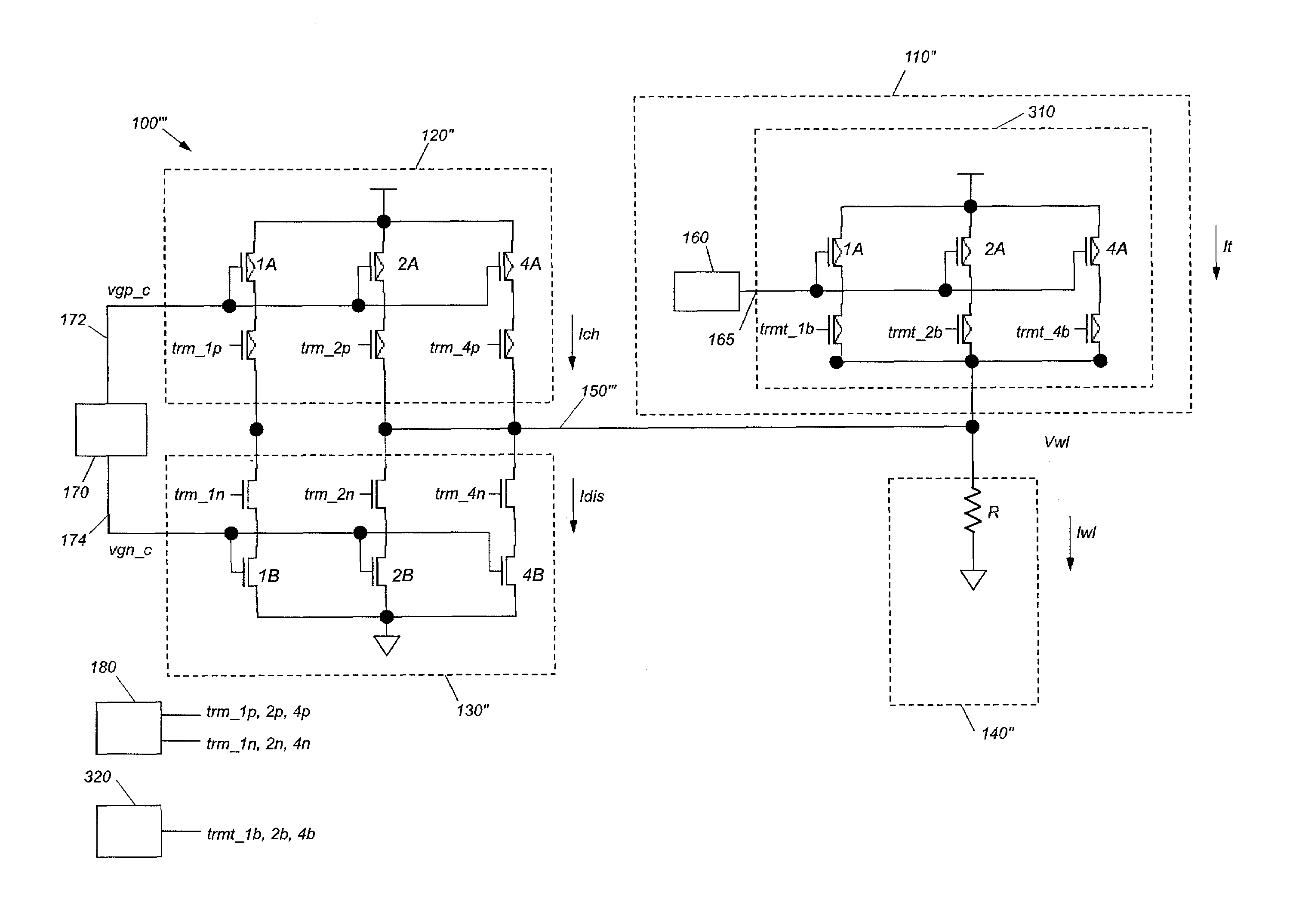

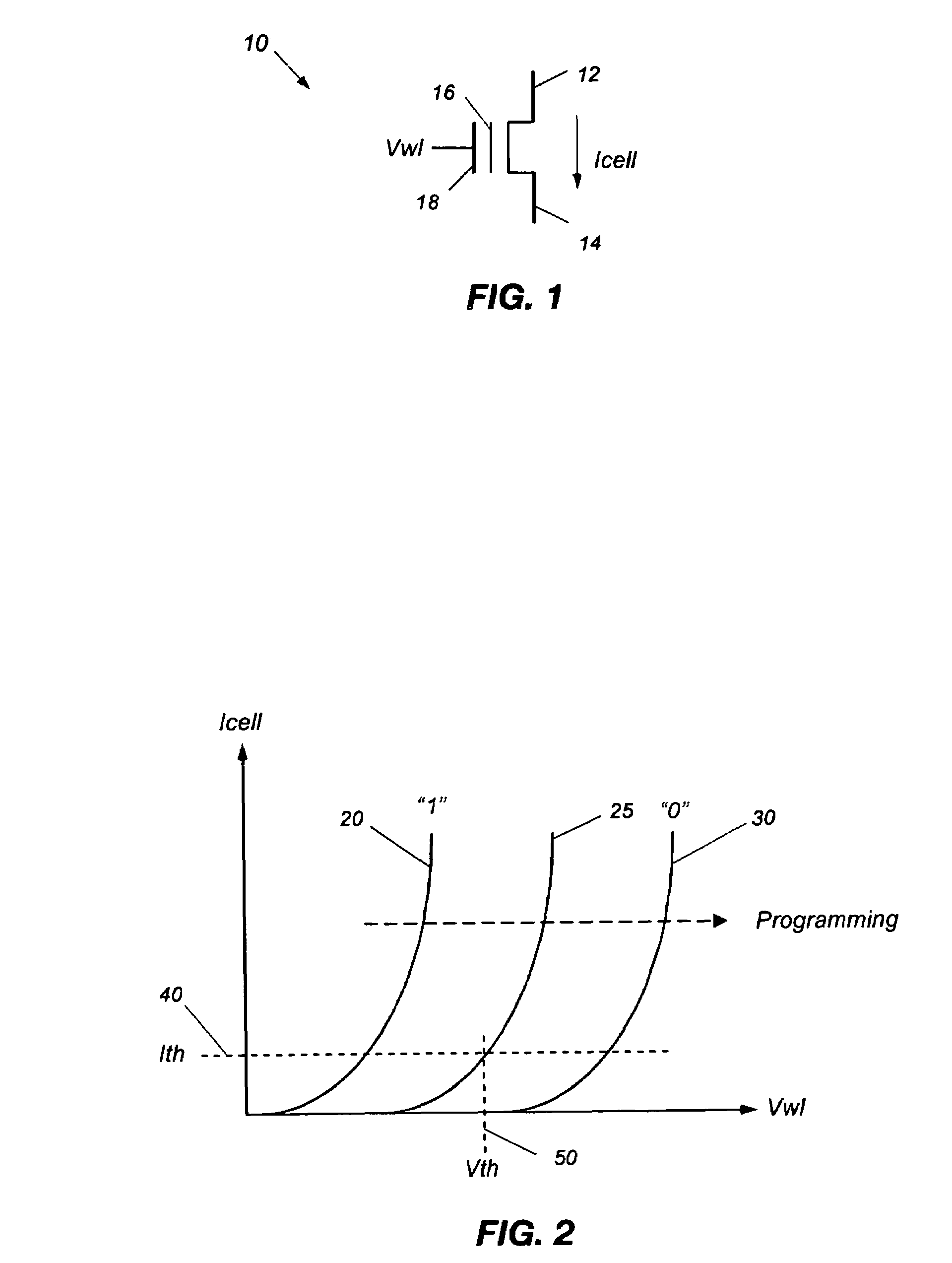

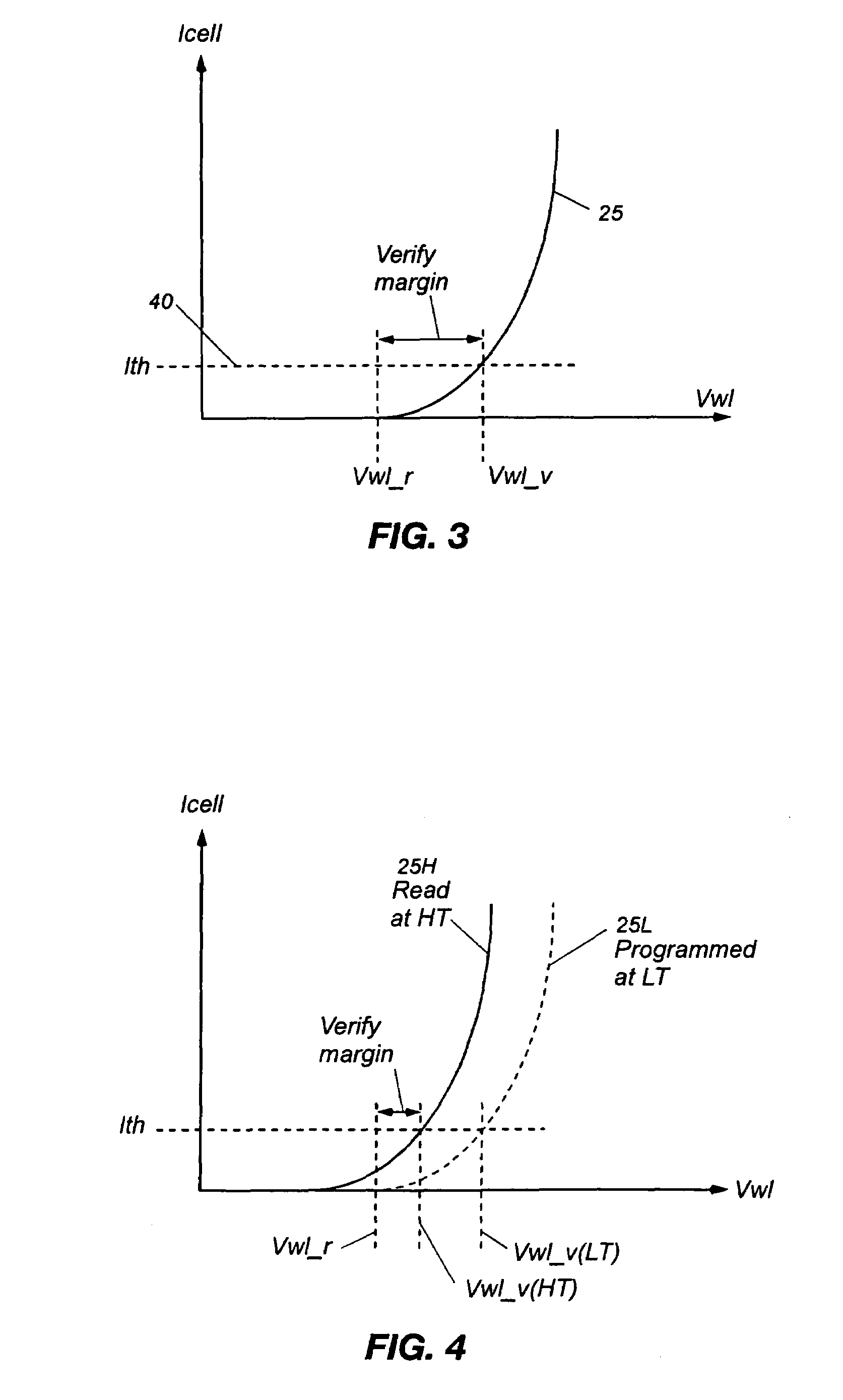

Method and apparatus for generating temperature-compensated read and verify operations in flash memories

Methods and an apparatuses for generating a word-line voltage are disclosed. A word-line voltage generator includes a first current source, an adjustable current source, adjustable current sink, and a voltage converter, all operably coupled to a current sum node. The first current source generates a first current having a temperature coefficient substantially equal to a temperature coefficient of at least one bit cell. The adjustable current source generates a second current that is substantially independent of a temperature change. The adjustable current sink sinks a third current that is substantially independent of a temperature change. The voltage converter is configured for generating a word-line signal having a word-line voltage proportional to a reference current, wherein the reference current comprises the first current, plus the second current, and minus the third current.

Owner:MICRON TECH INC

Method and structure for a 1T-RAM bit cell and macro

InactiveUS20070080387A1Function increaseIncrease capacitanceTransistorSolid-state devicesMetal-insulator-metalMOSFET

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

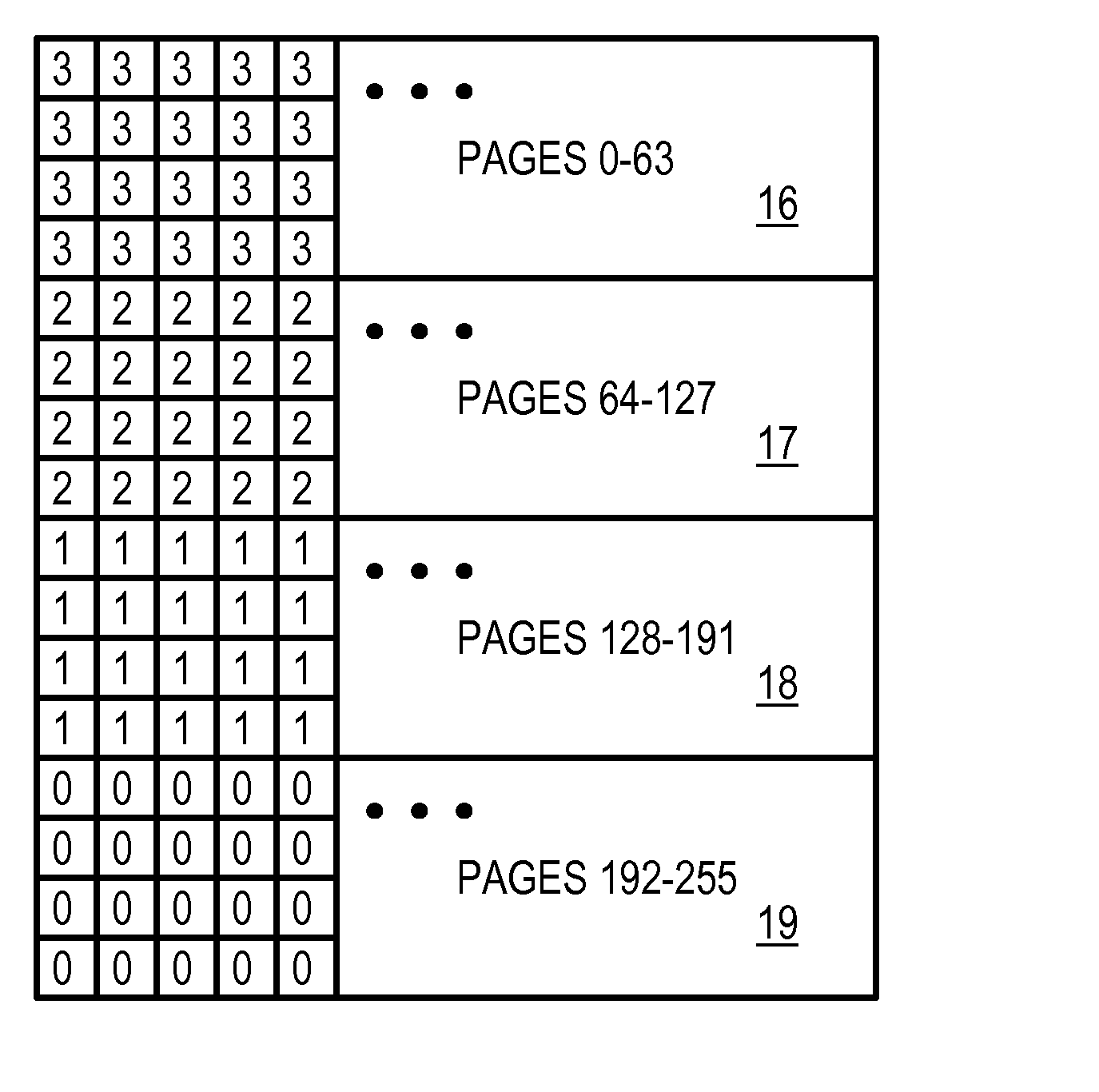

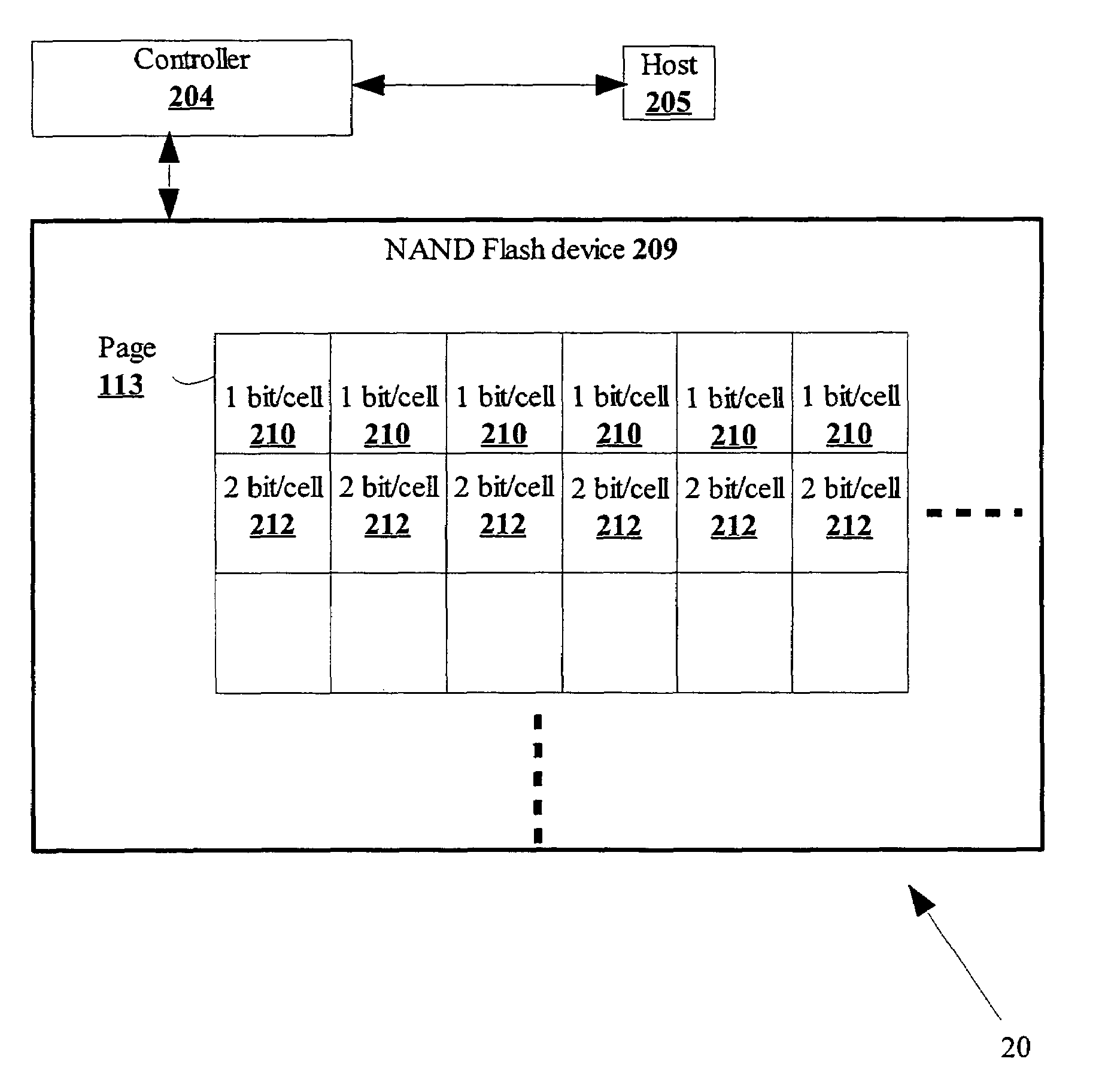

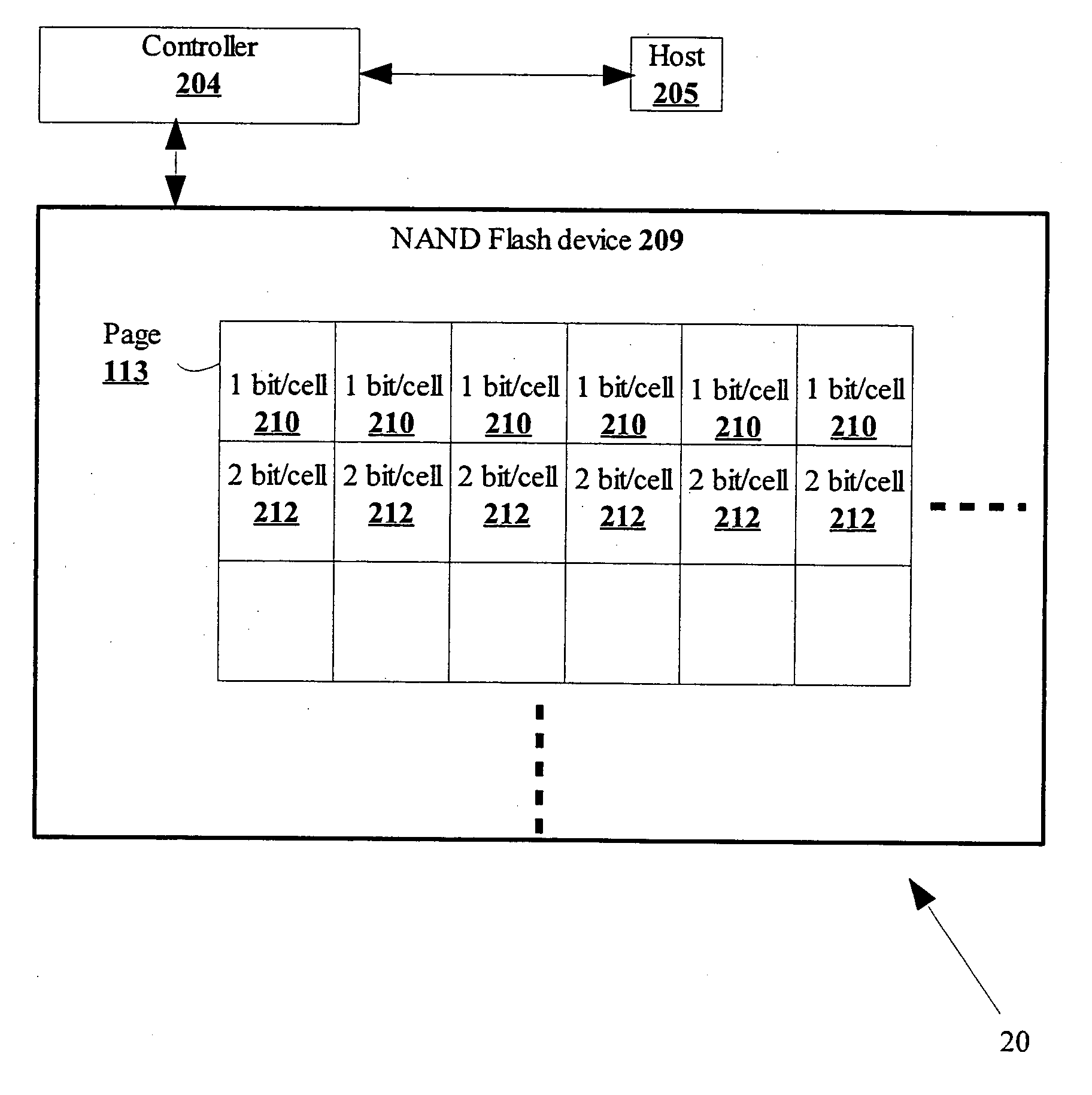

Method of managing a multi-bit cell flash memory with improved reliablility and performance

A method of storing data by providing a flash memory device including a plurality of memory cells; each of the memory cells is capable of storing data bits. First data bits are stored into memory cells used for storing M bits per cell, the memory cells are allocated to a page of the memory. Second data bits are stored into other memory cells, the other memory cells used for storing N bits per cell are allocated to the page and upon storing of the first data bits and upon storing the second data bits, the page uses at the same time at least one of the memory cells with M bits per cell and at least one of the other memory cells with N bits per cell with N less than M.

Owner:WESTERN DIGITAL ISRAEL LTD

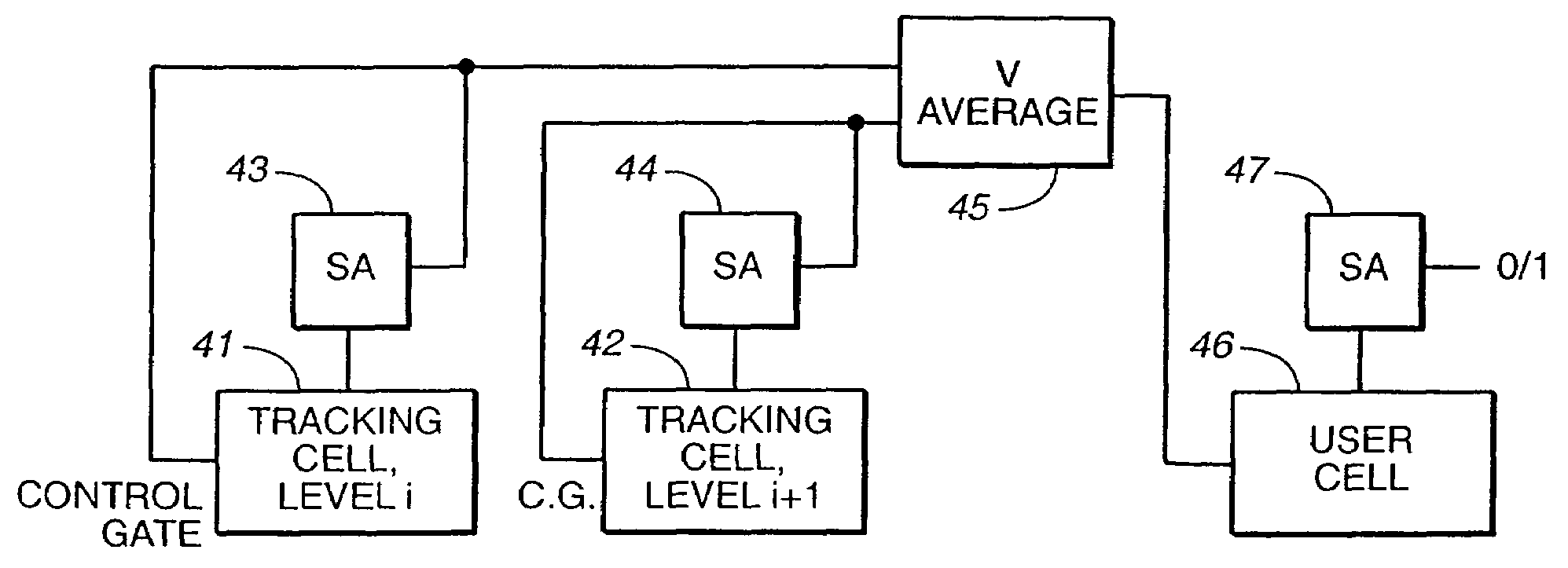

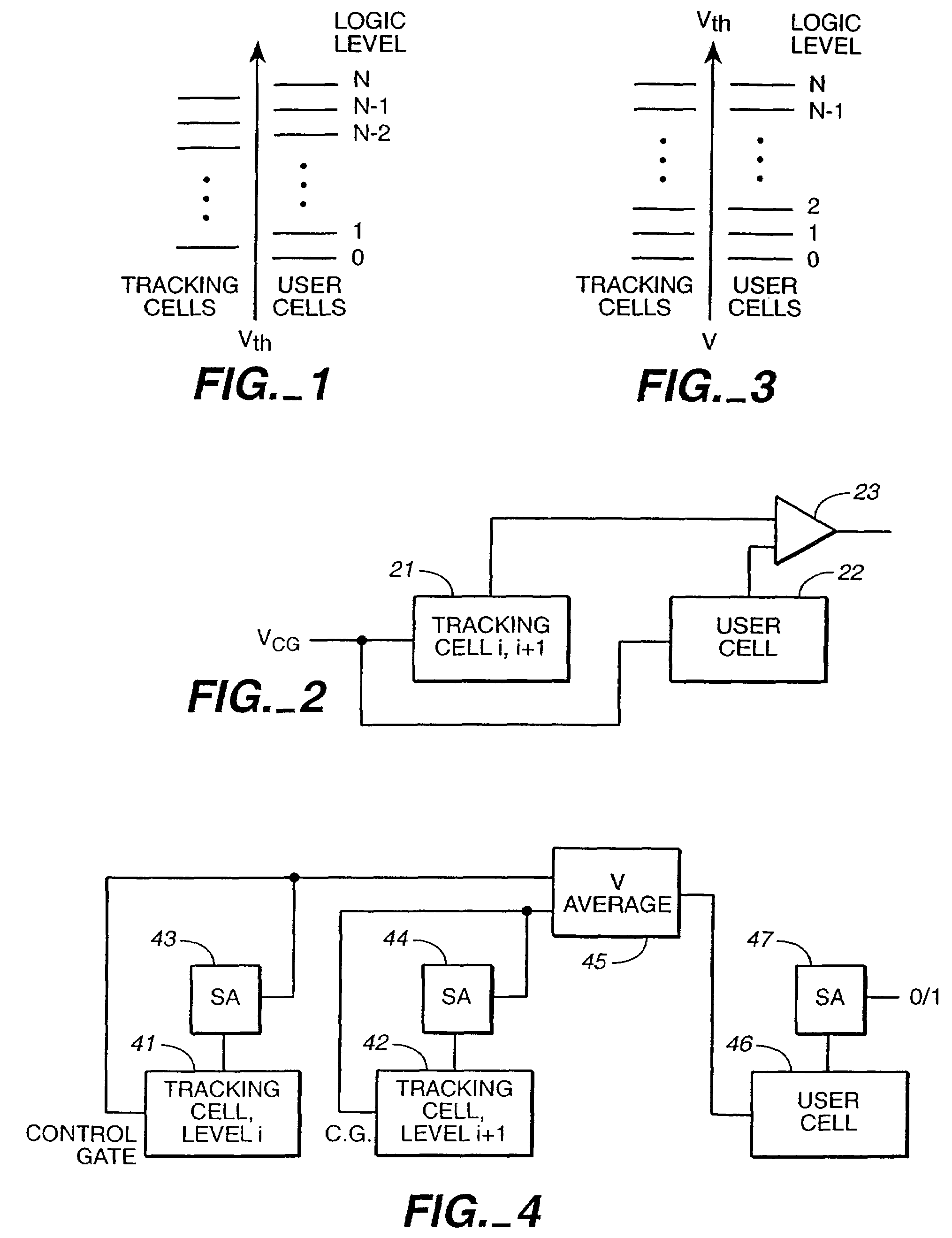

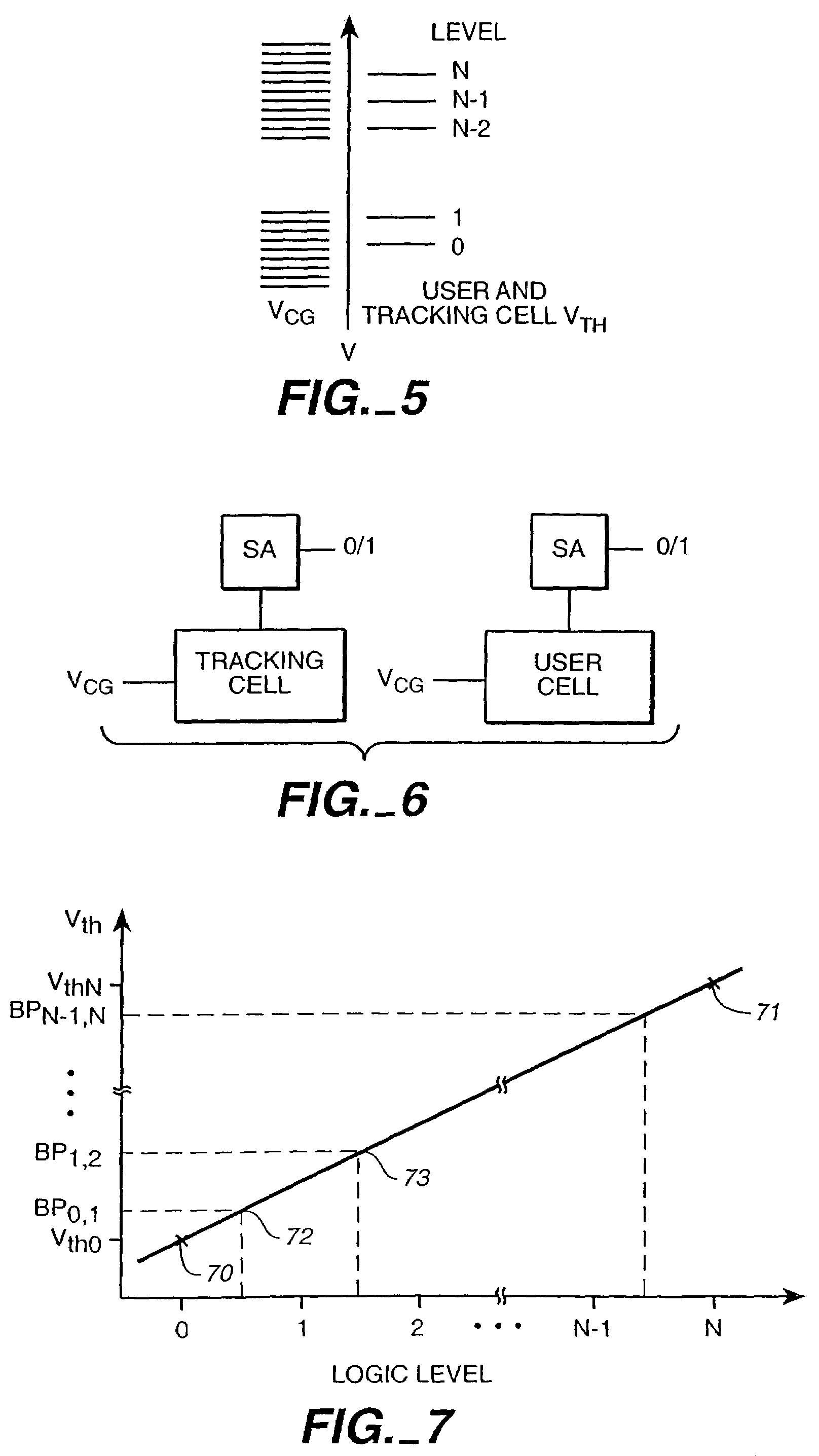

Writable tracking cells

ActiveUS20050169051A1Less uncertaintyReduce reference cell threshold uncertaintyElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

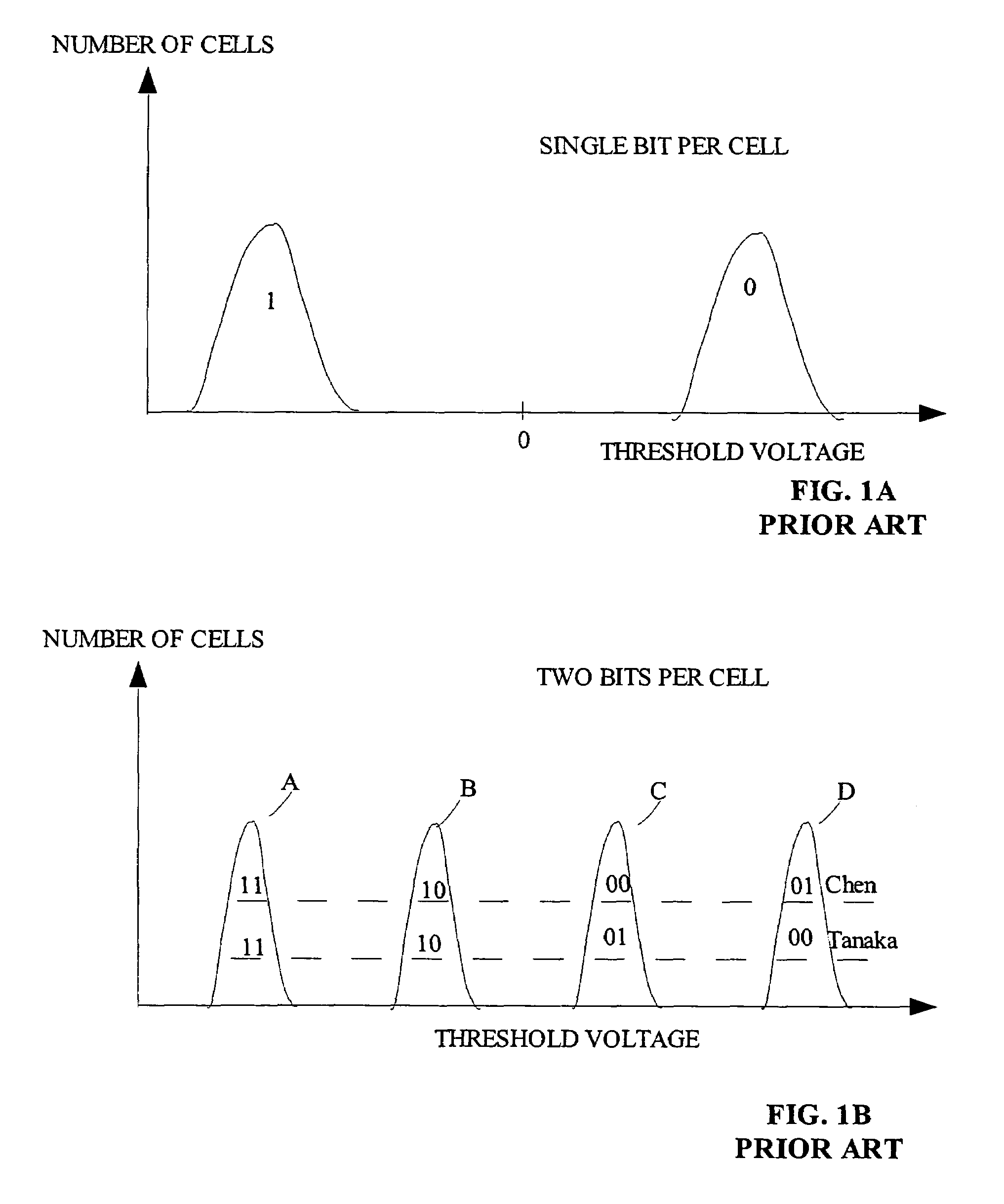

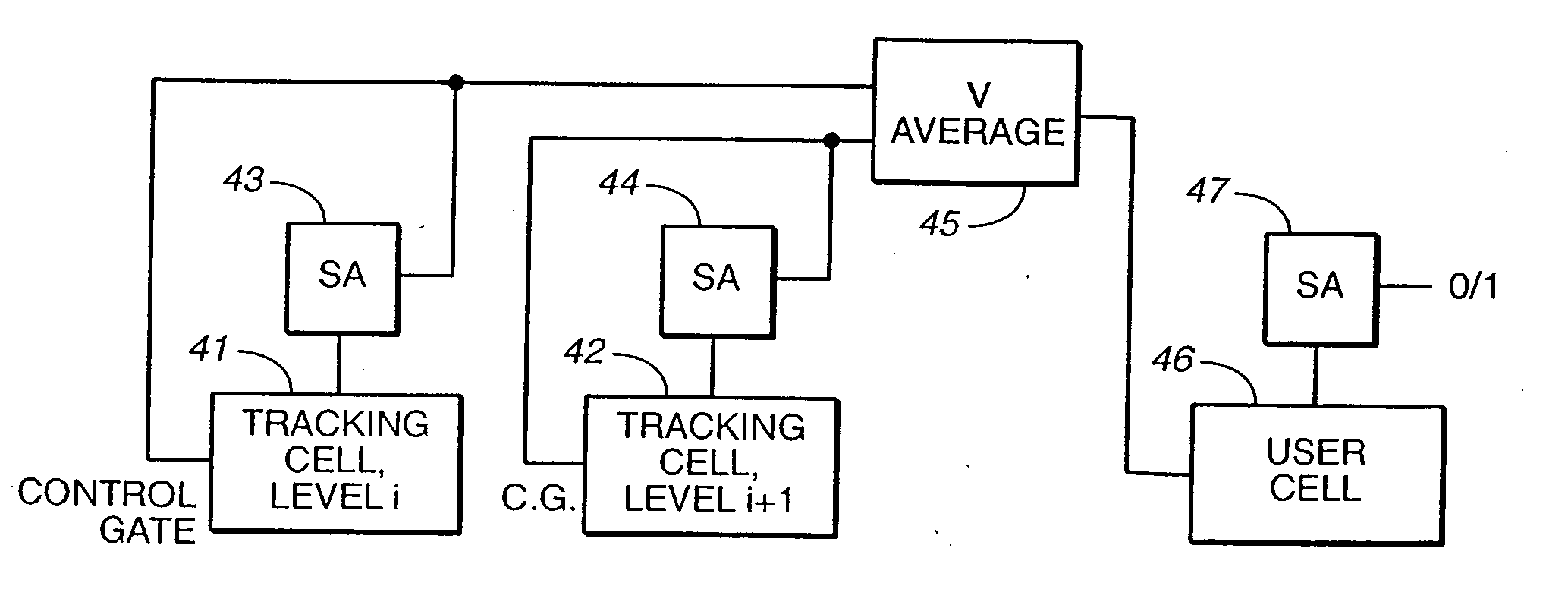

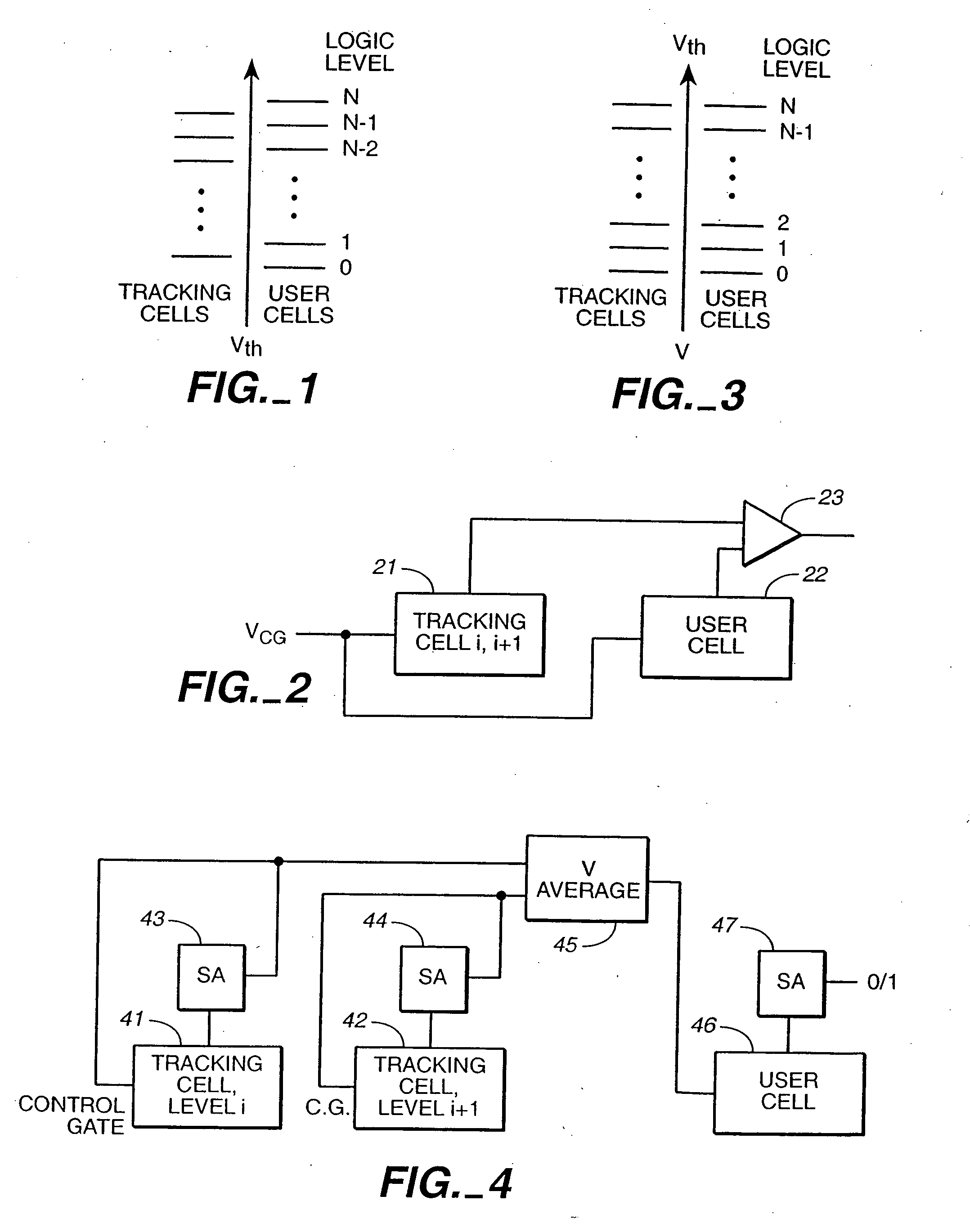

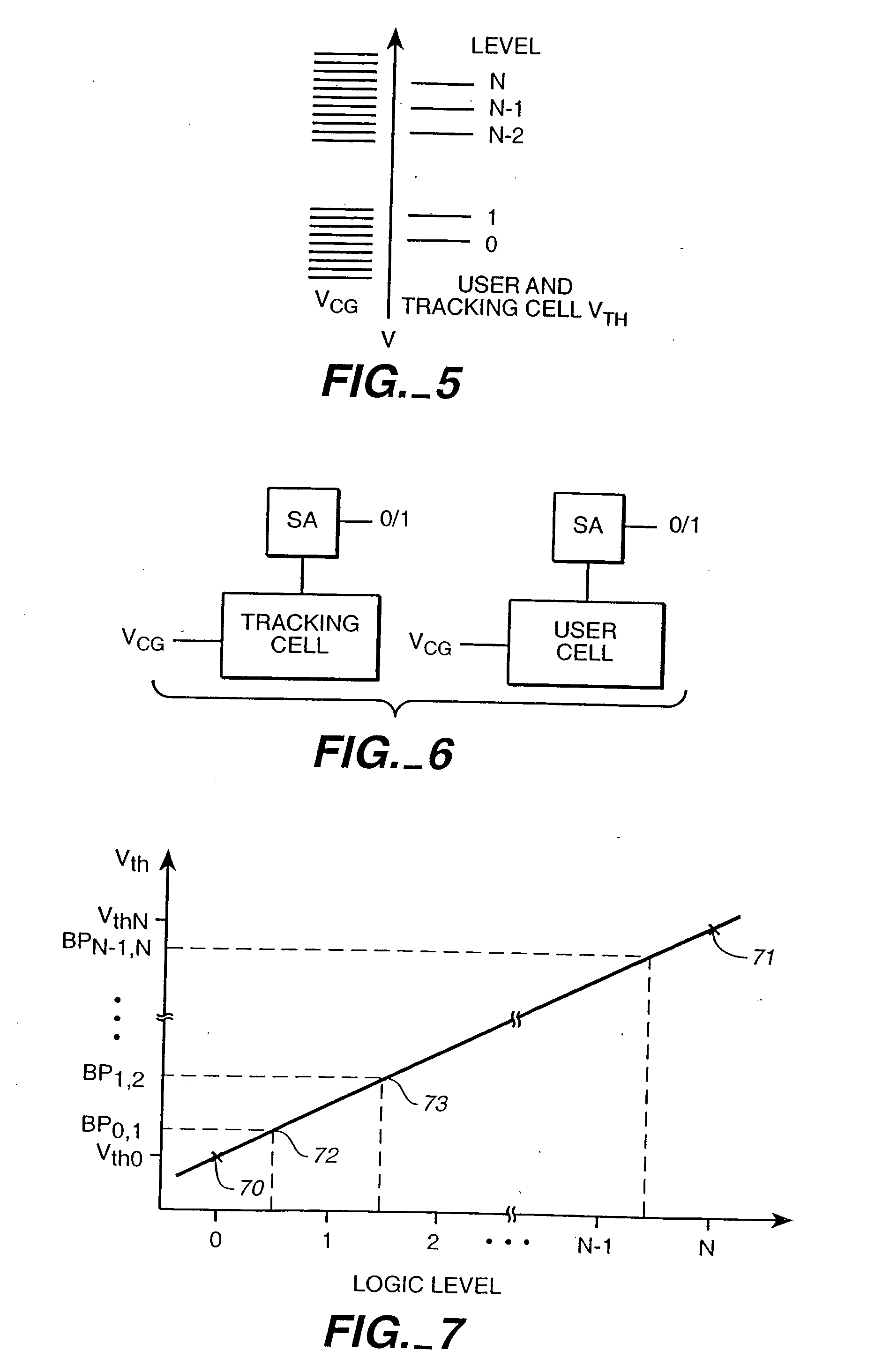

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

Writable tracking cells

InactiveUS7301807B2Less uncertaintyReduced referenceElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

Cell-downgrading and reference-voltage adjustment for a multi-bit-cell flash memory

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

In-circuit memory array bit cell threshold voltage distribution measurement

InactiveUS6226200B1Early detectionElectronic circuit testingMemory loss protectionTest powerOperation mode

An apparatus and method for operating a non-volatile memory including an array of bit cells. A selection is made between an operational power supply and a test power supply, the test power supply being on-chip programmable. The non-volatile memory is operated in a operational mode if the operational power supply is selected, and in a test mode if the test power supply is selected.

Owner:PROGRESSIVE SEMICON SOLUTIONS

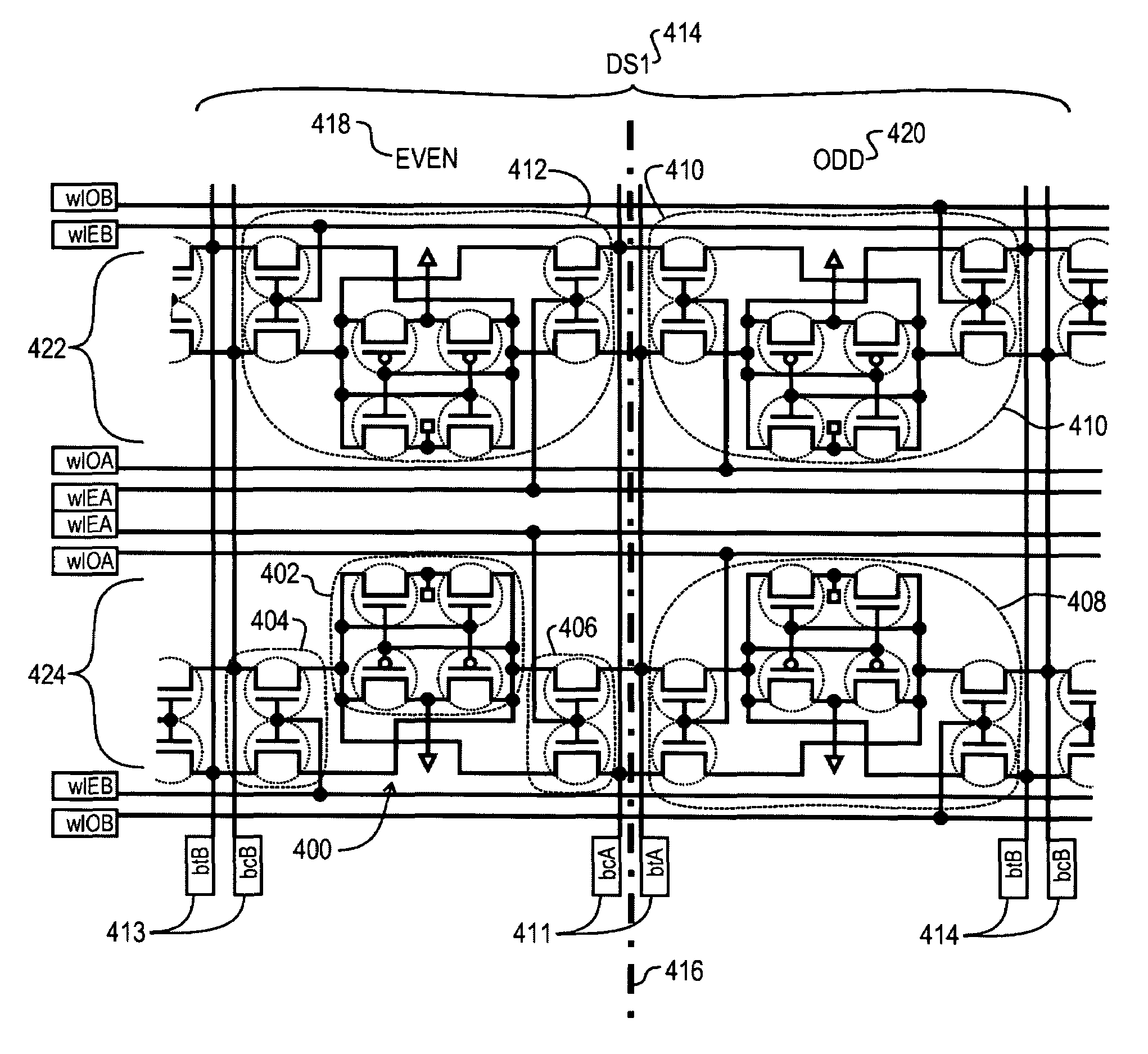

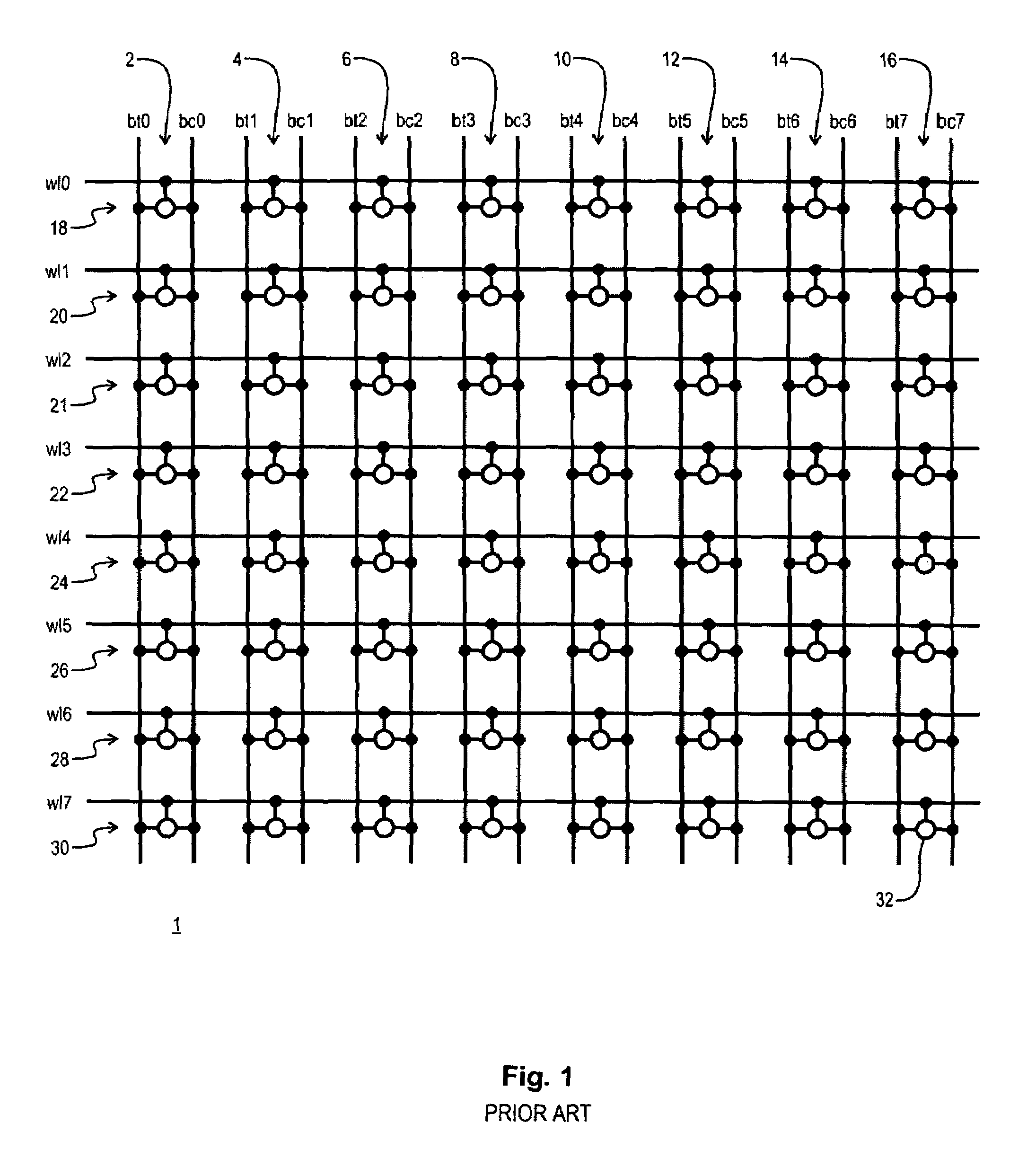

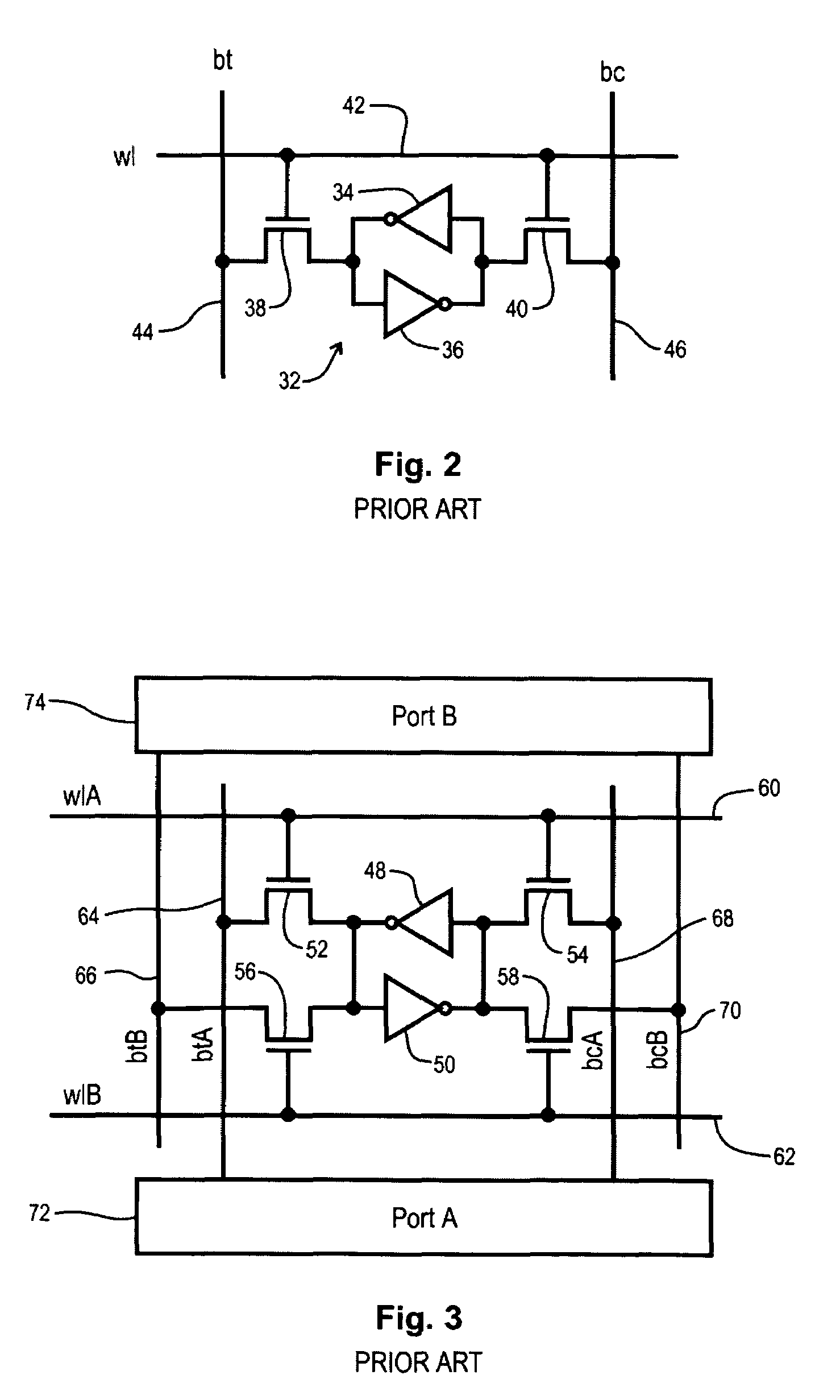

Shared bit line memory device and method

A memory array employing shared bit-lines. A memory is formed from an array of plural bit-cells organized as plural columns and plural rows. Plural word-lines are aligned with each for the rows, and each is electrically coupled to a discrete fraction of the bit-cells its corresponding row. The memory also includes plural bit-lines that are aligned with the plural columns. Every bit-line is electrically coupled to all of the bit-cells that lie along at least one column. In addition, at least a first one of the bit-lines is further electrically coupled to all of the bit-cells in an additional column. That bit-line is coupled such that every one of the plural bit-cells, that lie along any given row that are coupled to it, is coupled to a unique word-line from the other bit-cells coupled thereto. The shared bit-line invention is applicable to single and multiple port memory arrays. It is applicable to all memory array technologies including, but not limited to, SRAMs and DRAMs.

Owner:SHEPPARD DOUGLAS P

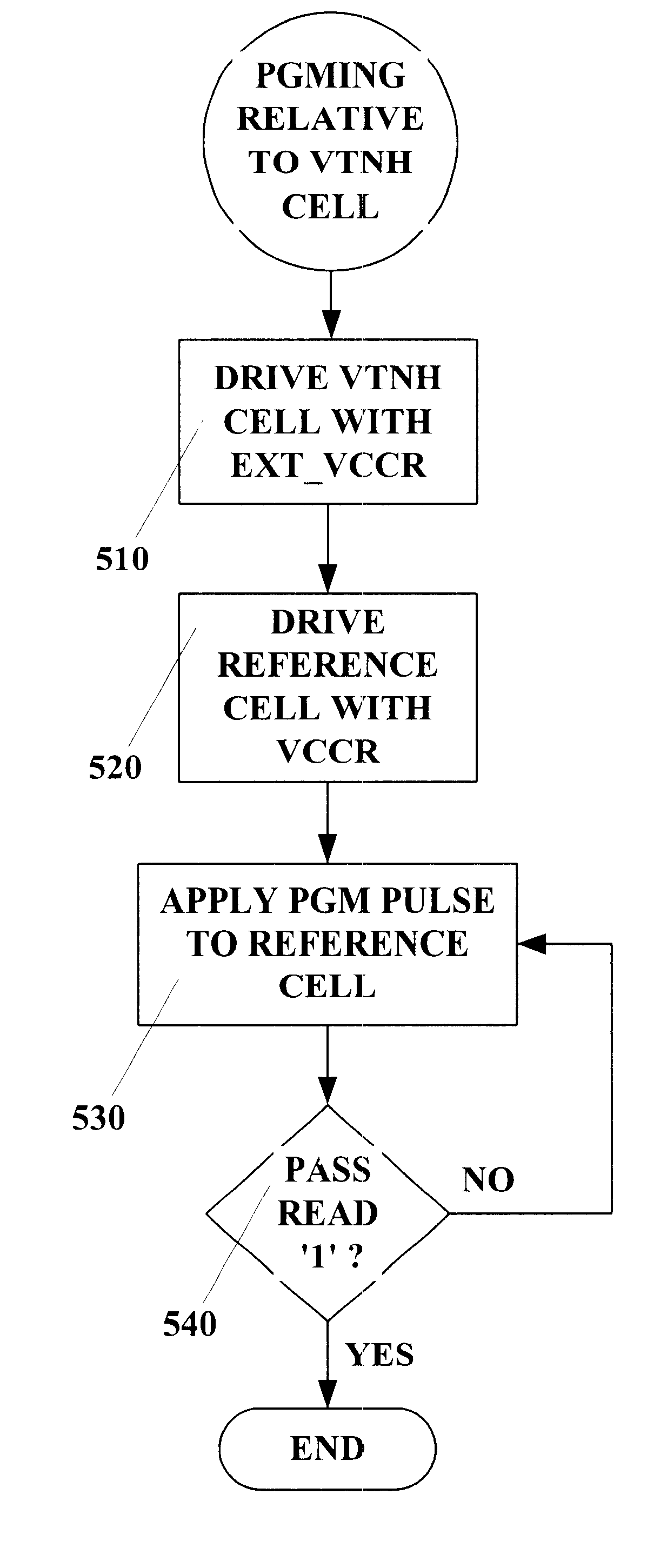

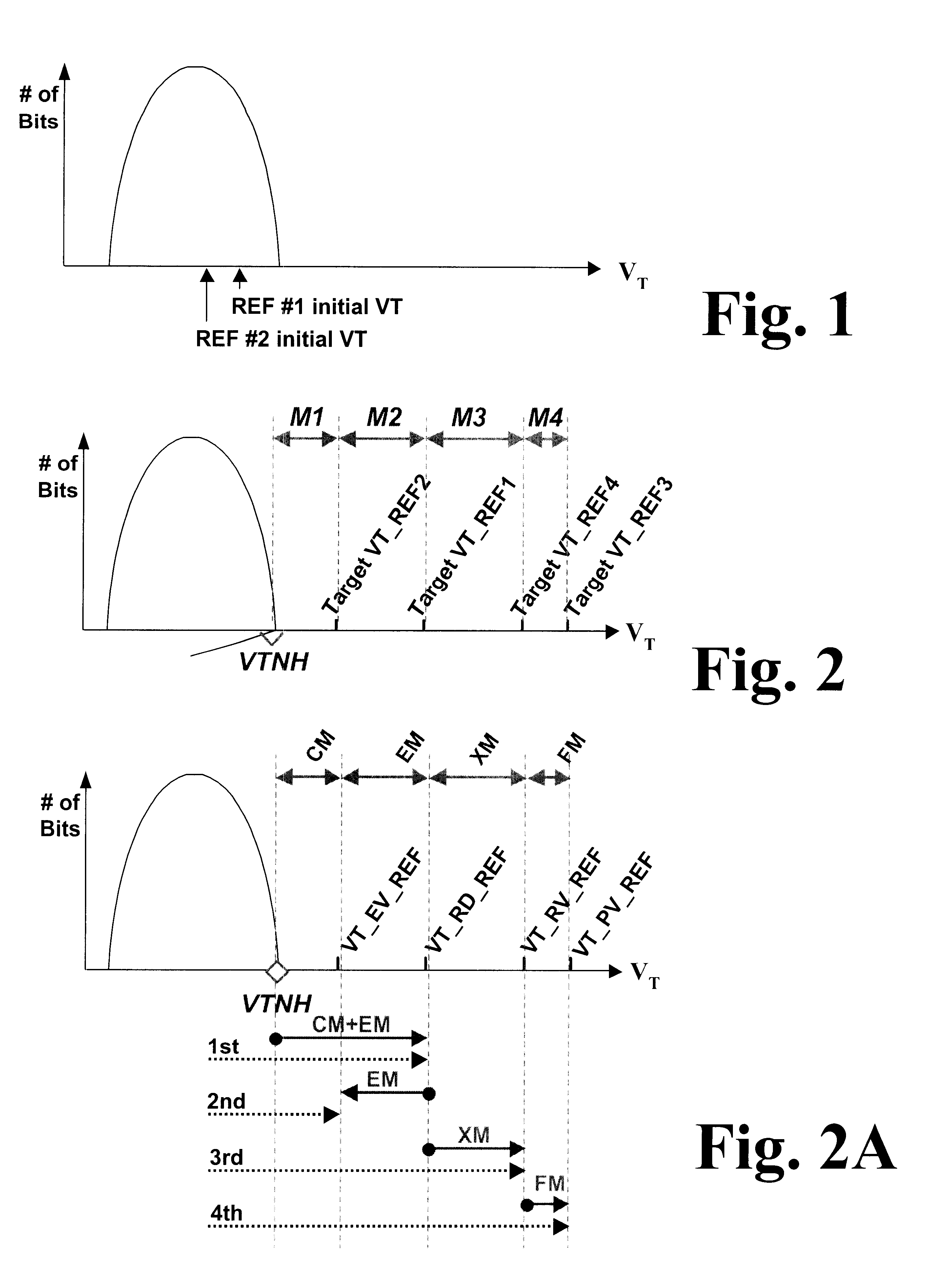

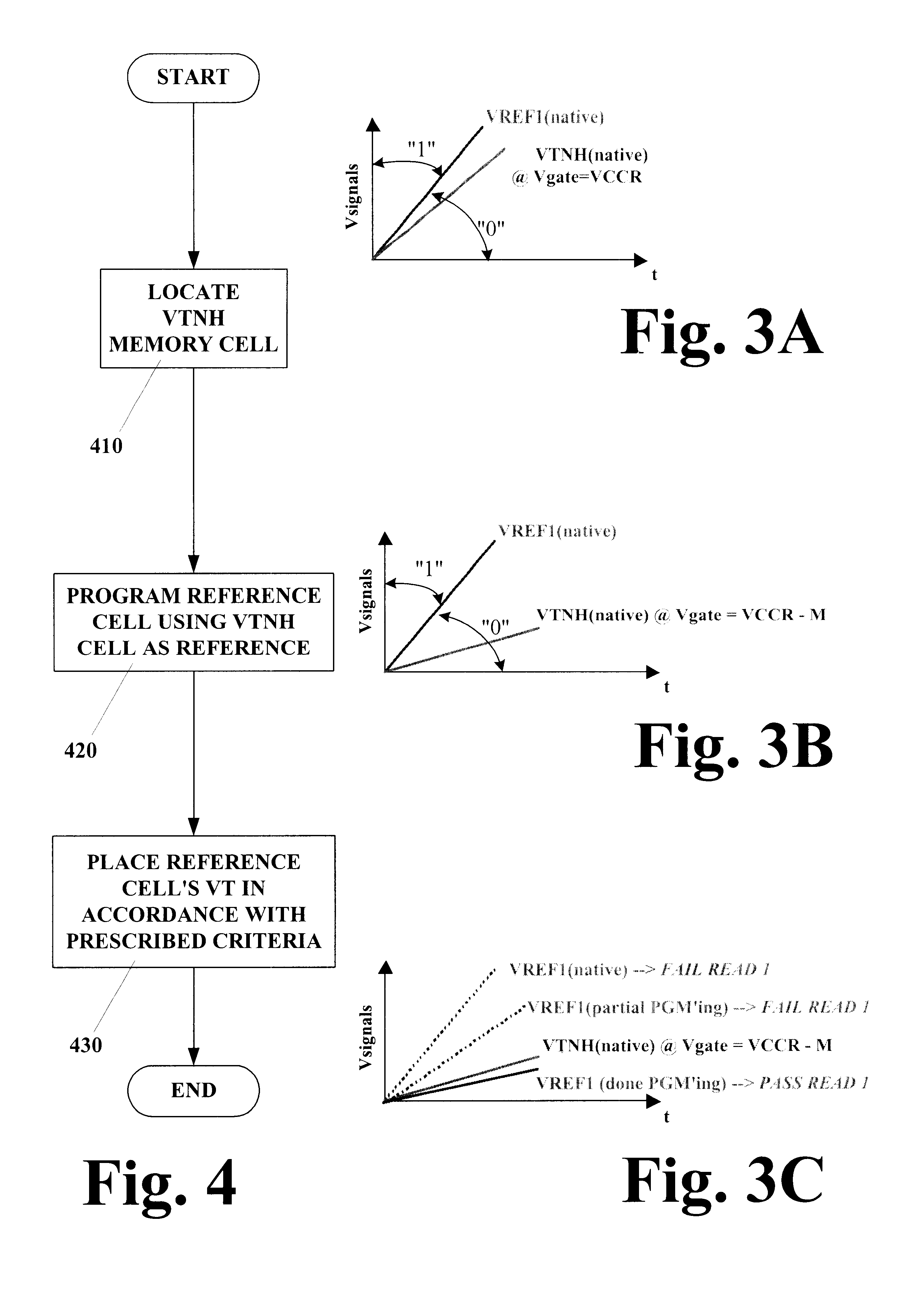

Method for programming a reference cell

InactiveUS6584017B2Accurately determinedRead-only memoriesDigital storageProgramming processComputer science

A method for programming one or more reference cells is described. The reference cell is programmed a predetermined amount, its program state is sensed relative to a prescribed cell on the same die (e.g., a memory cell or a golden bit cell), and the programming process continues until the reference cell fails a preselected read operation. In one preferred embodiment, the memory cell used during the reference cell programming process is the cell in the memory array having the highest native threshold value. In another preferred embodiment, the memory cell used during the reference cell programming process is a native cell that is onboard the die containing the memory array, but not a cell within the memory array.

Owner:SPANSION ISRAEL

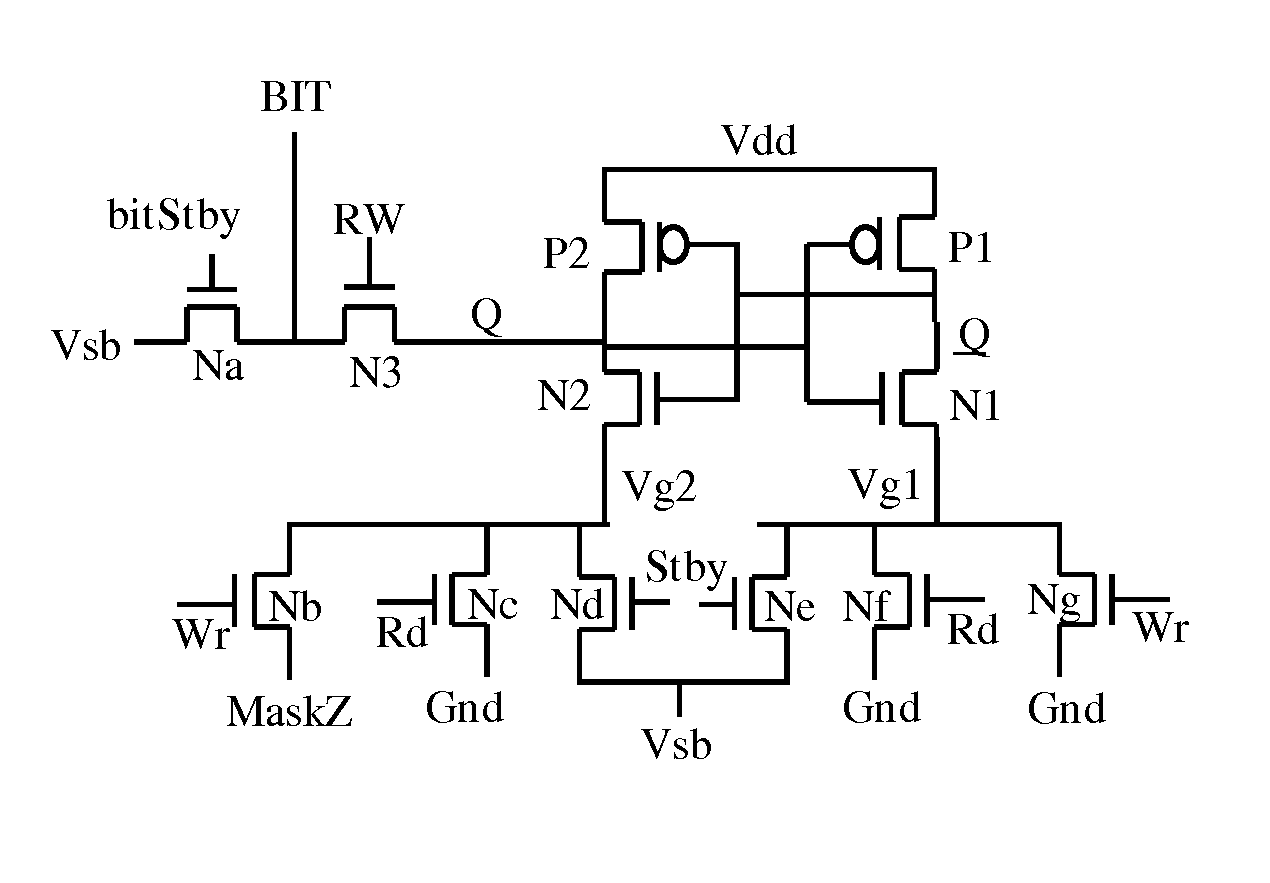

SRAM cell with common bit line and source line standby voltage

A high threshold five transistor SRAM bit cell with cross-coupled inverters has a single BIT line, a common logic 1 supply voltage, and two logic 0 virtual ground source voltages. The BIT line is coupled to the bit cell by a pass transistor. When BIT line and virtual ground lines are not otherwise being used, they are connected to a common standby voltage that substantially lowers bit cell standby leakage. Writing is performed by driving a data signal through the pass transistor and is facilitated by creating a voltage differential on the virtual ground lines. Reading is also performed through the pass transistor wherein the BIT line is initially at the standby voltage, and is then driven lower or higher depending upon the data value stored in the bit cell.

Owner:HOBSON RICHARD FREDERIC +1

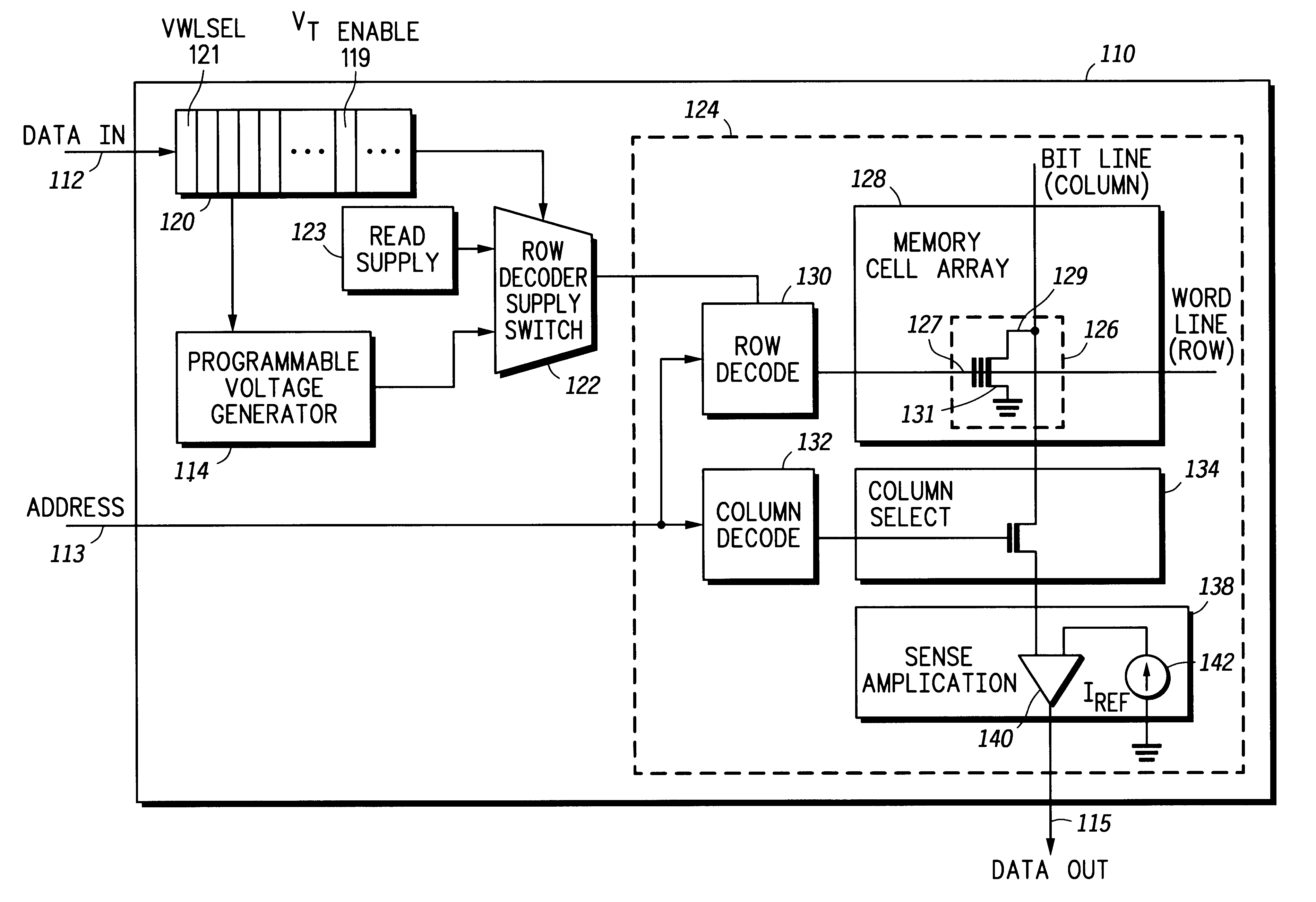

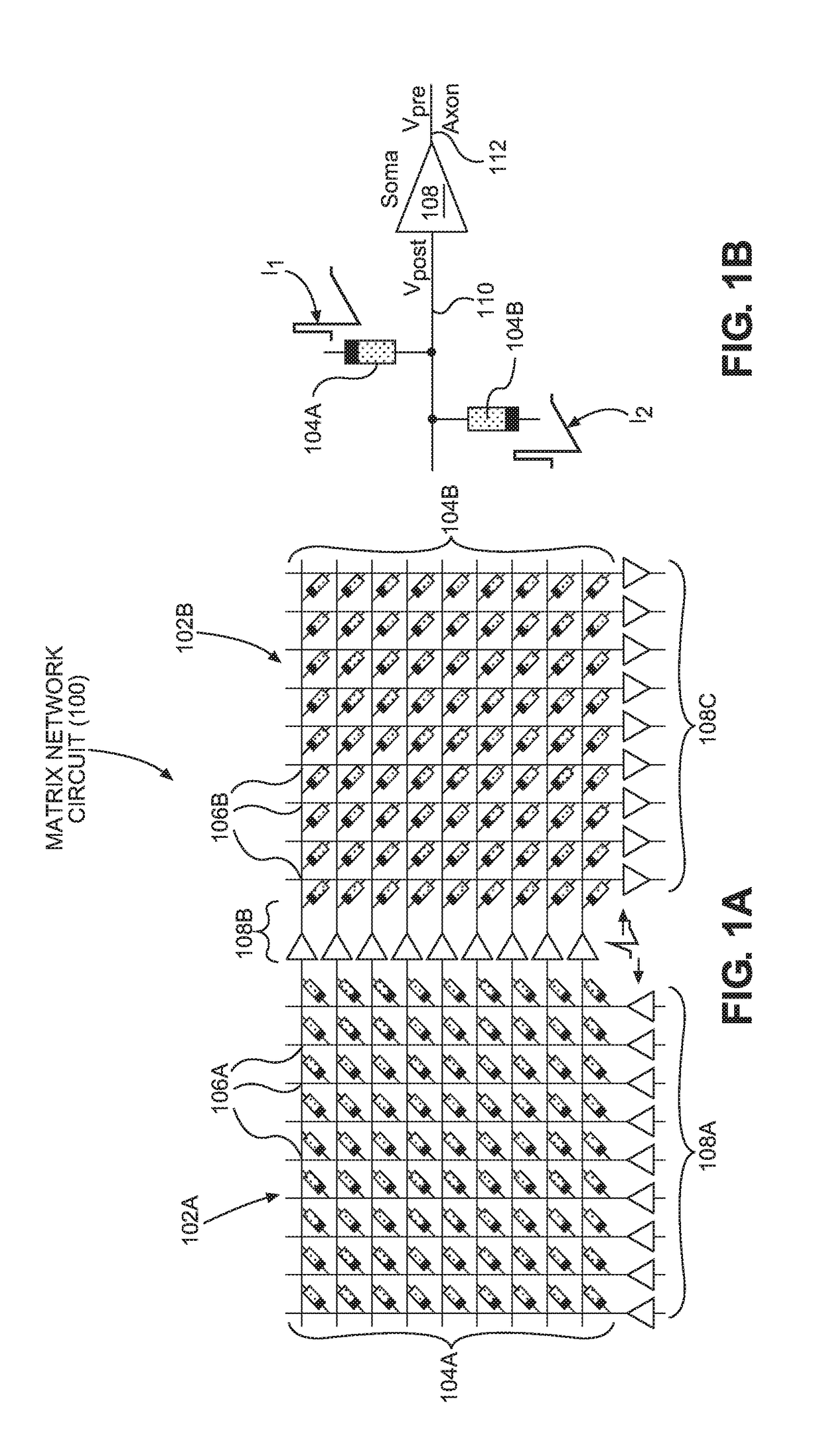

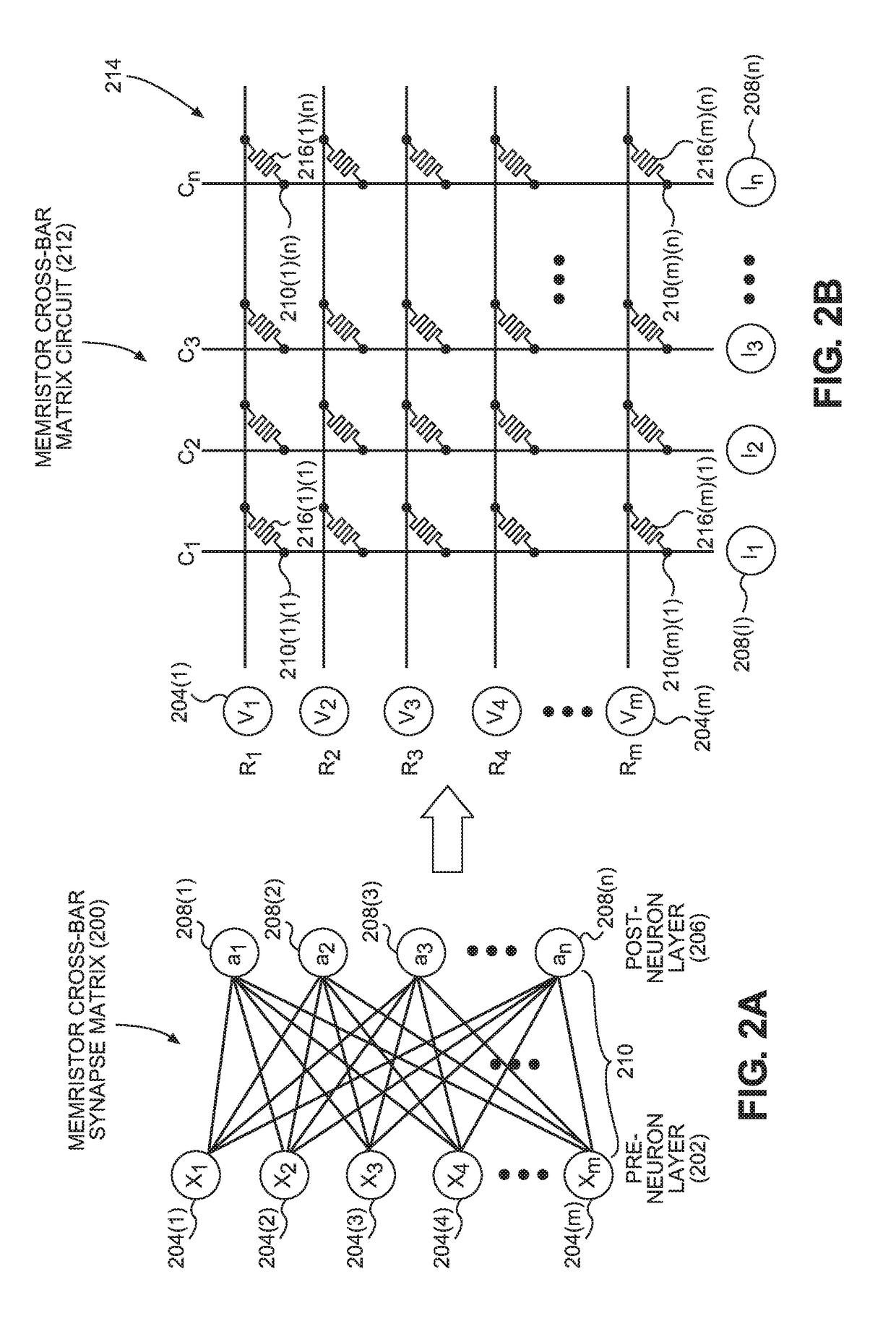

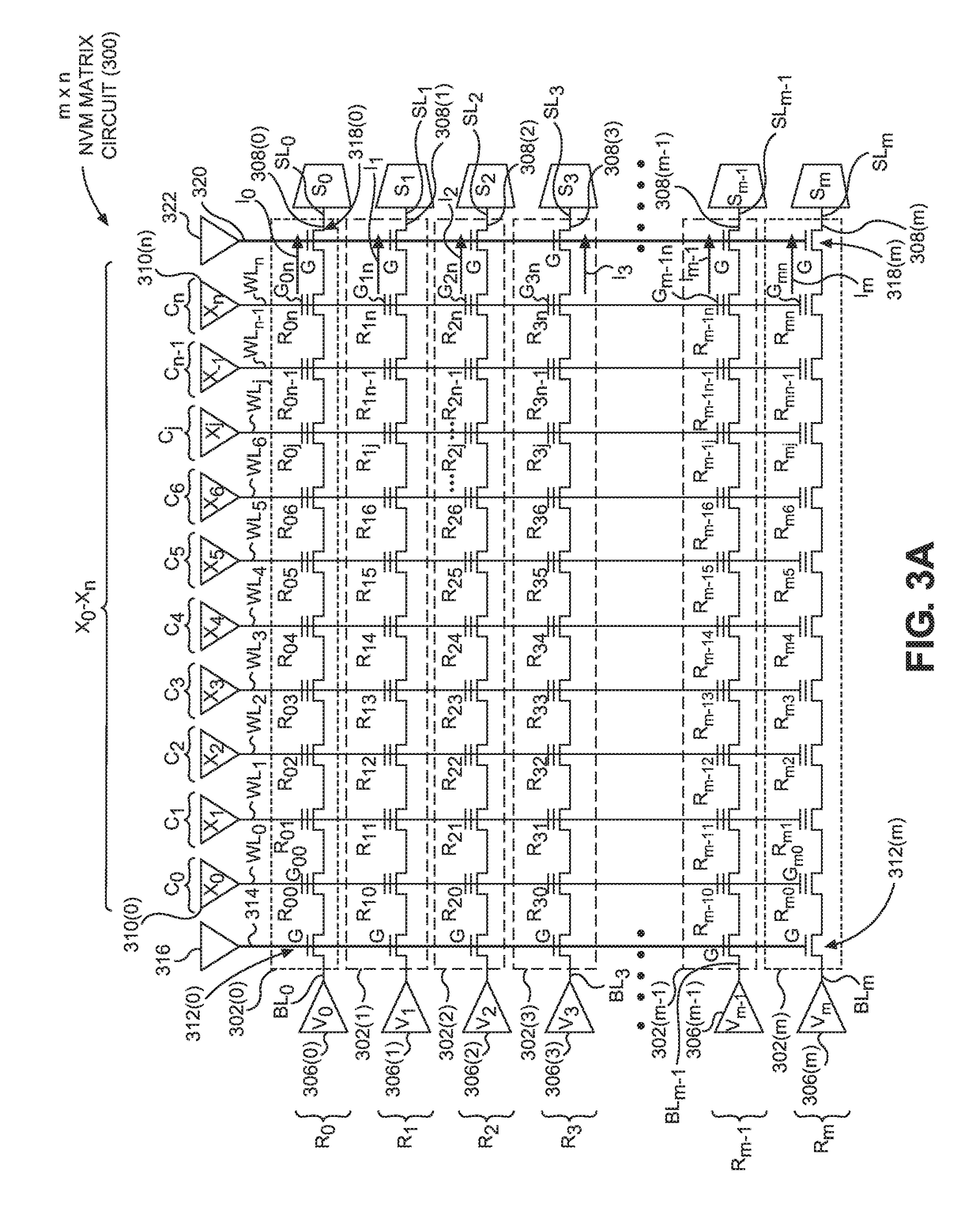

Multiple (multi-) level cell (MLC) non-volatile (NV) memory (NVM) matrix circuits for performing matrix computations with multi-bit input vectors

Multiple (multi-) level cell (MLC) non-volatile (NV) memory (NVM) matrix circuits for performing matrix computations with multi-bit input vectors are disclosed. An MLC NVM matrix circuit includes a plurality of NVM storage string circuits that each include a plurality of MLC NVM storage circuits each containing a plurality of NVM bit cell circuits each configured to store 1-bit memory state. Thus, each MLC NVM storage circuit stores a multi-bit memory state according to memory states of its respective NVM bit cell circuits. Each NVM bit cell circuit includes a transistor whose gate node is coupled to a word line among a plurality of word lines configured to receive an input vector. Activation of the gate node of a given NVM bit cell circuit in an MLC NVM storage circuit controls whether its resistance is contributed to total resistance of an MLC NVM storage circuit coupled to a respective source line.

Owner:QUALCOMM INC

Method of storing data in a multi-bit-cell flash memory

In writing to a block, of a flash memory, that includes pages with different write access or read access speeds, after writing first data to a first page that has fast access, at least one page that has slow access is skipped to write second data to a second page that has fast access.

Owner:WESTERN DIGITAL ISRAEL LTD

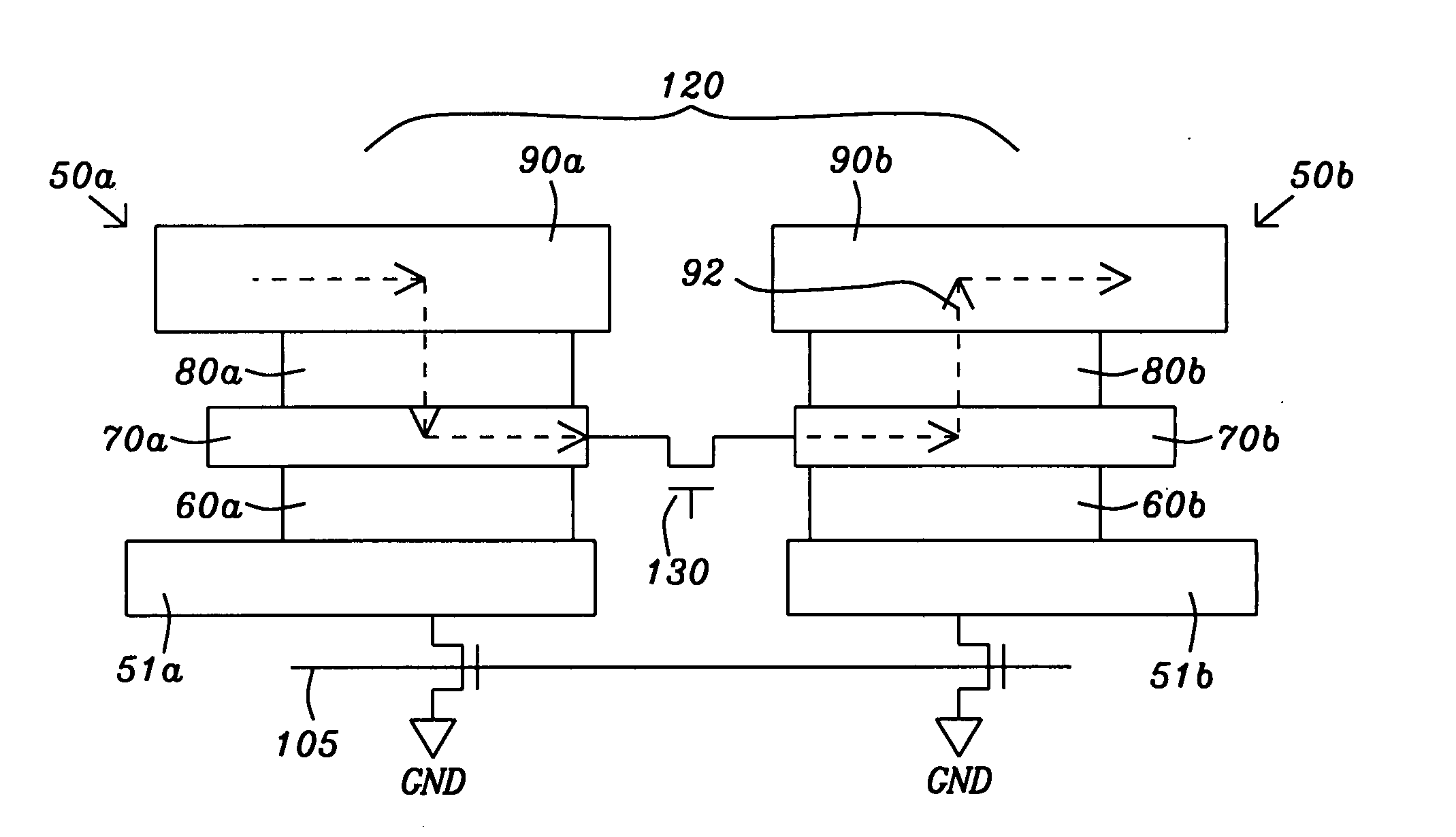

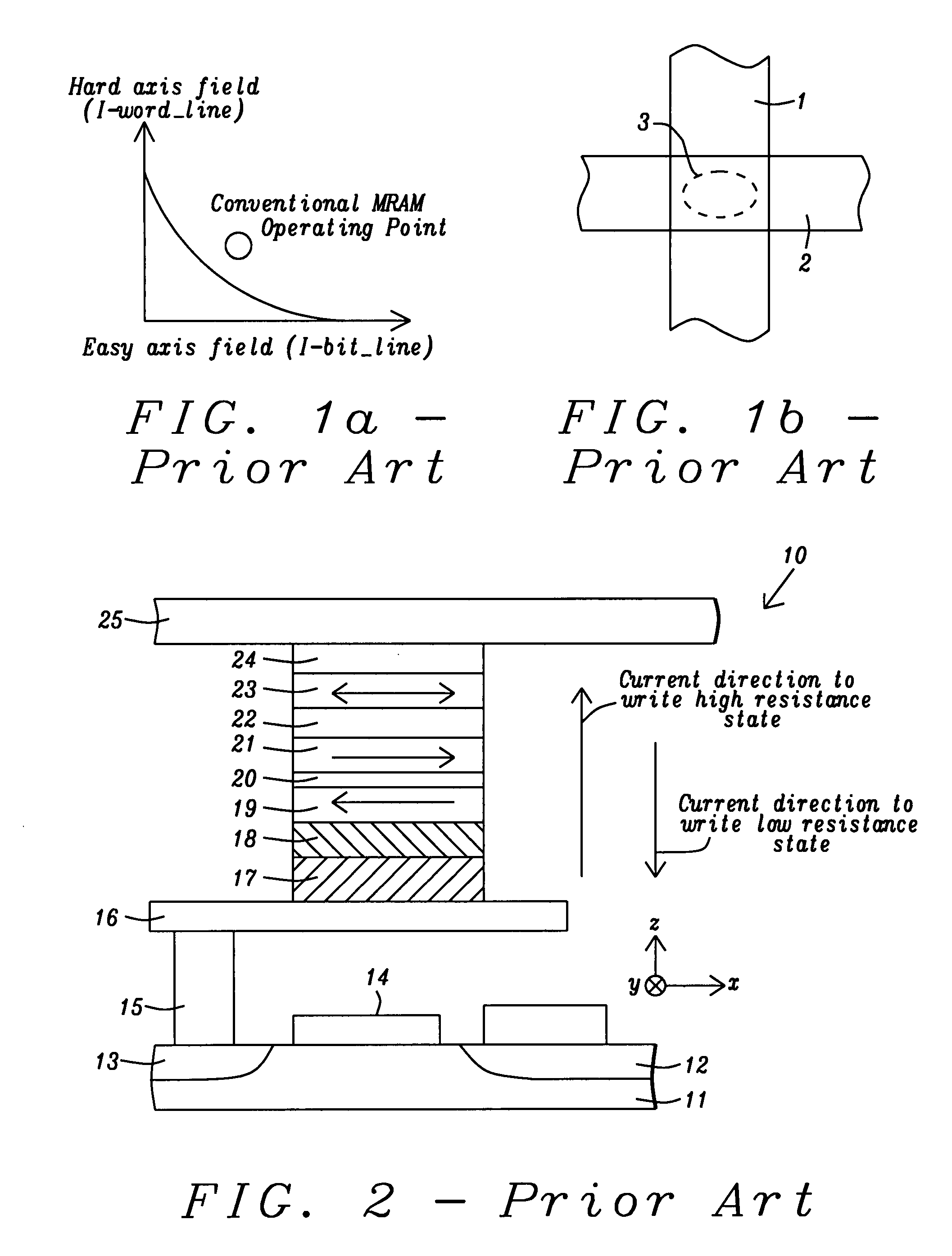

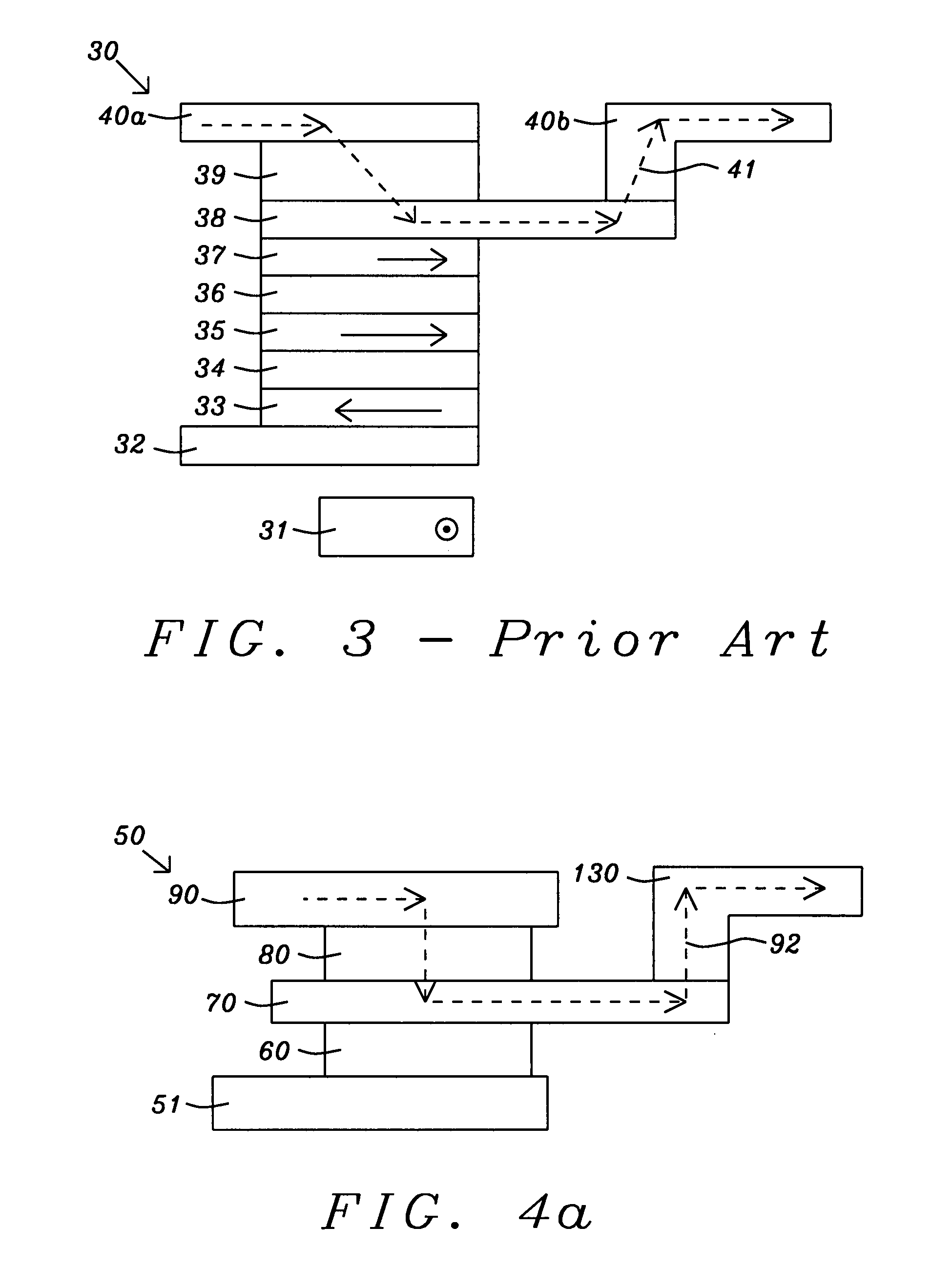

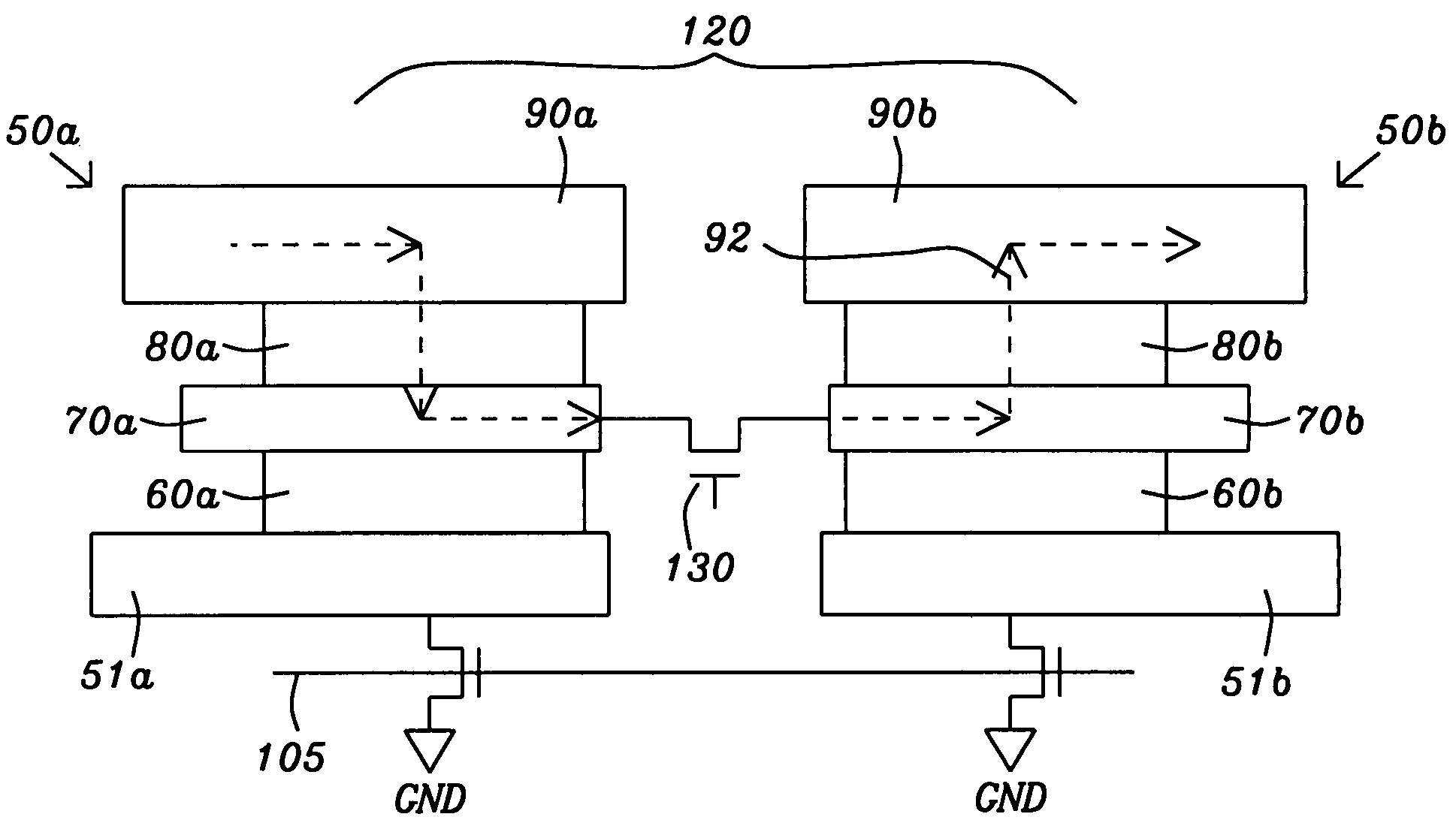

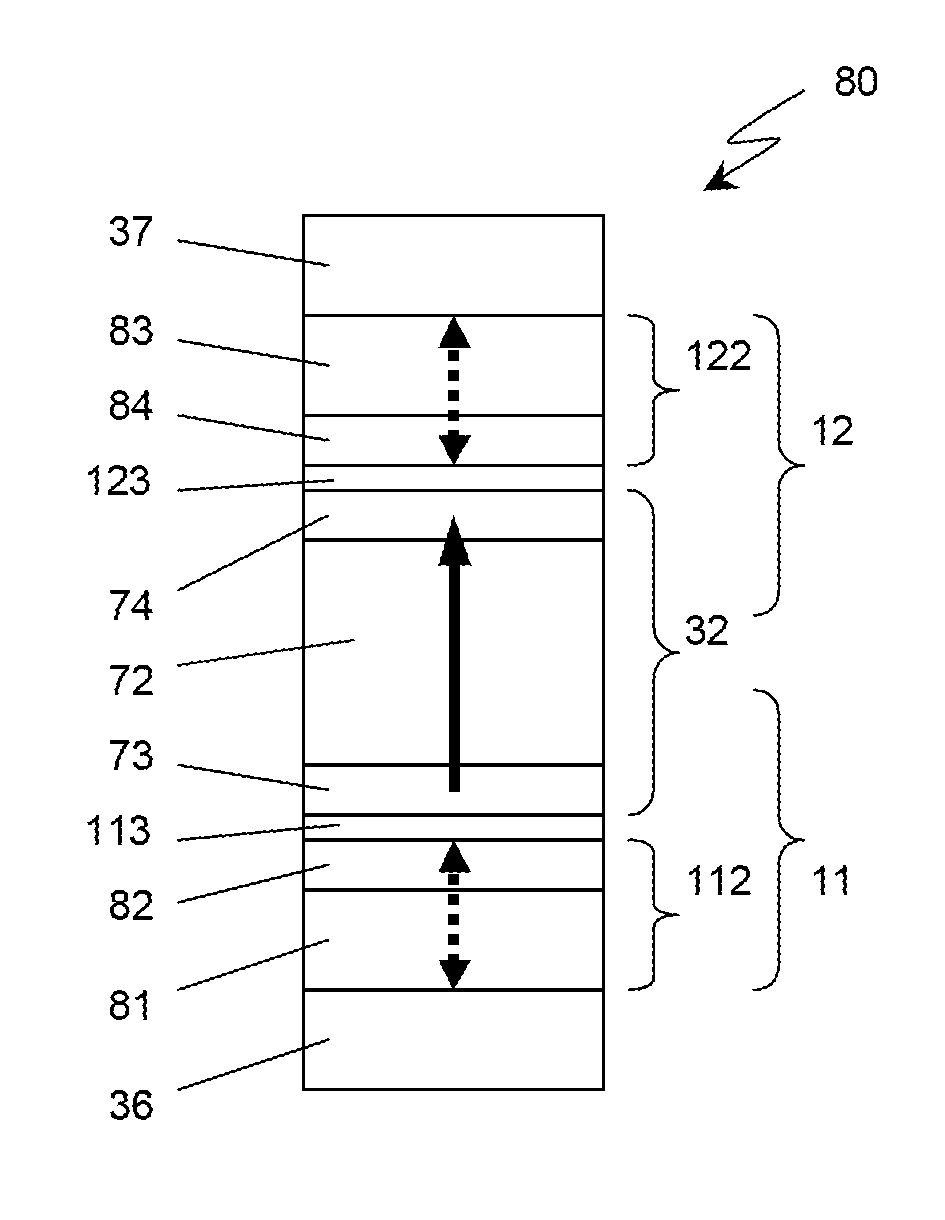

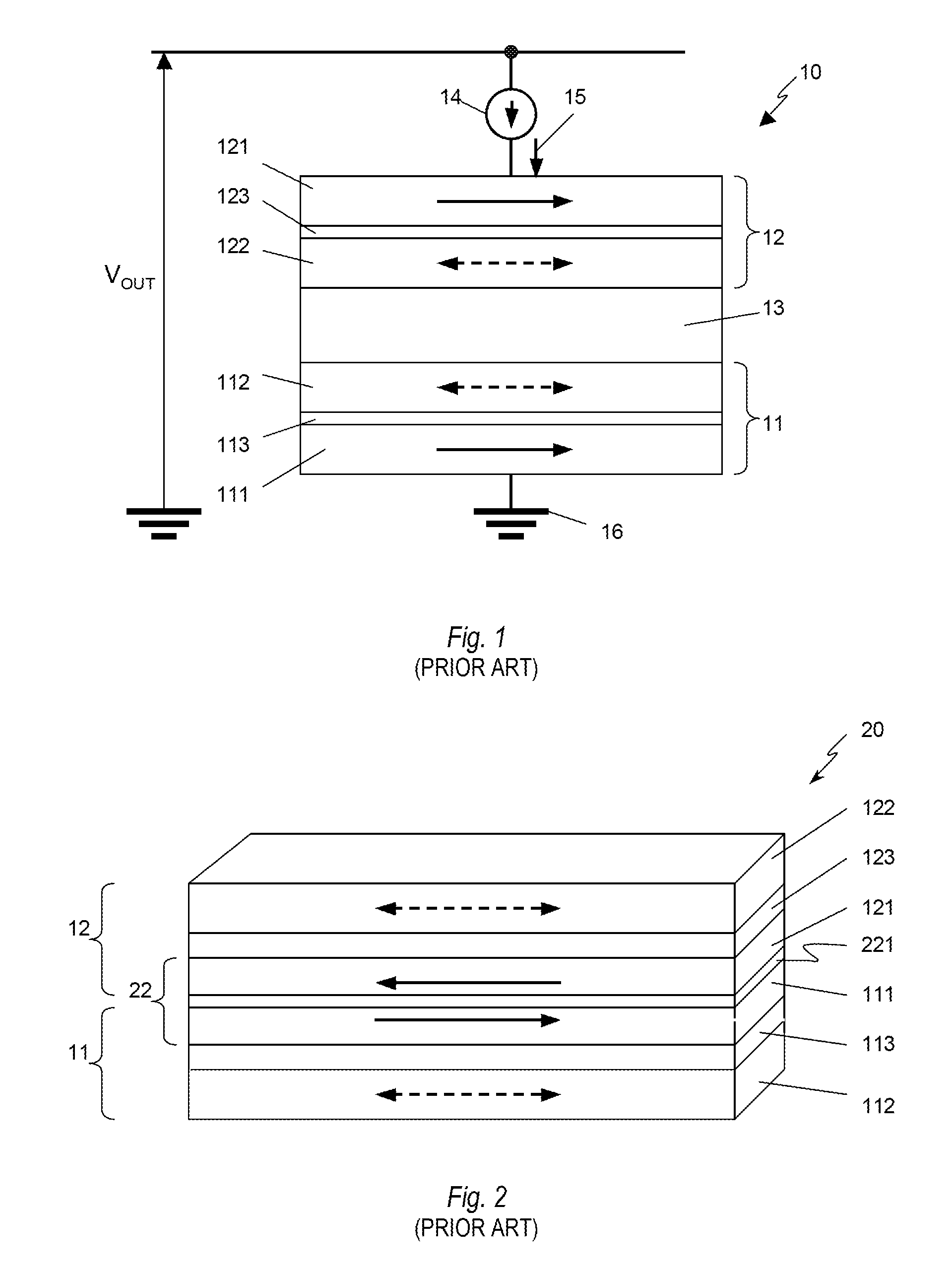

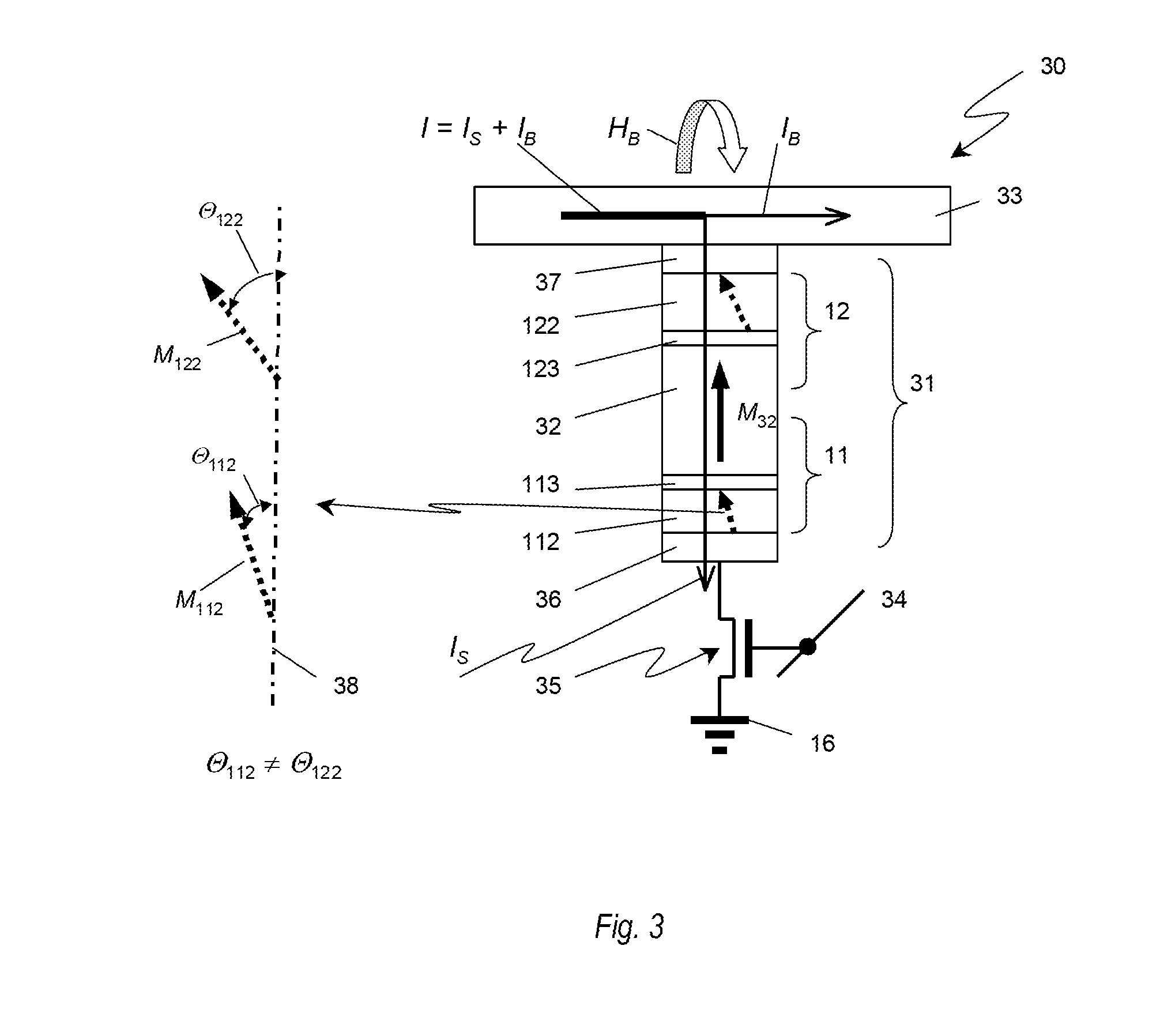

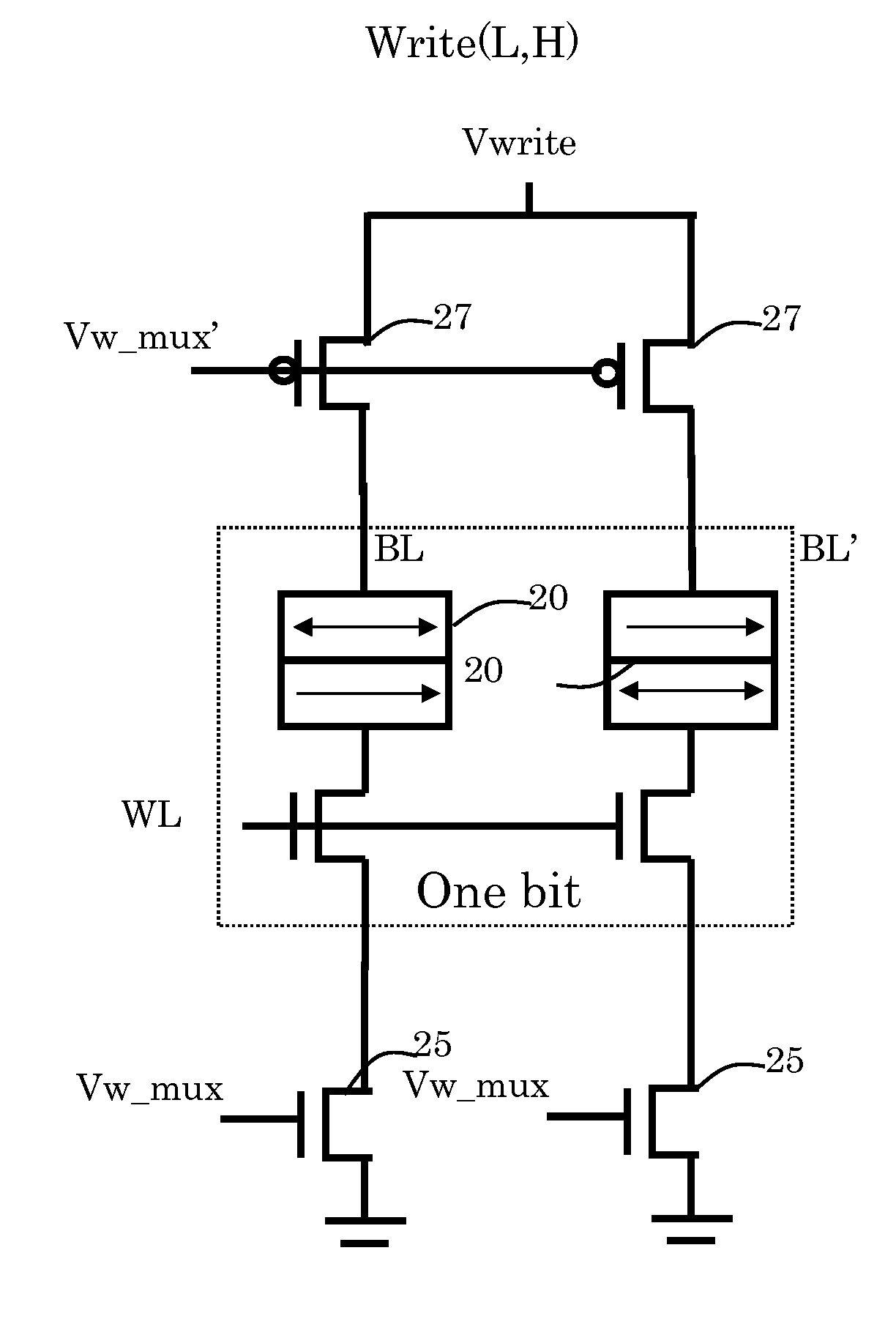

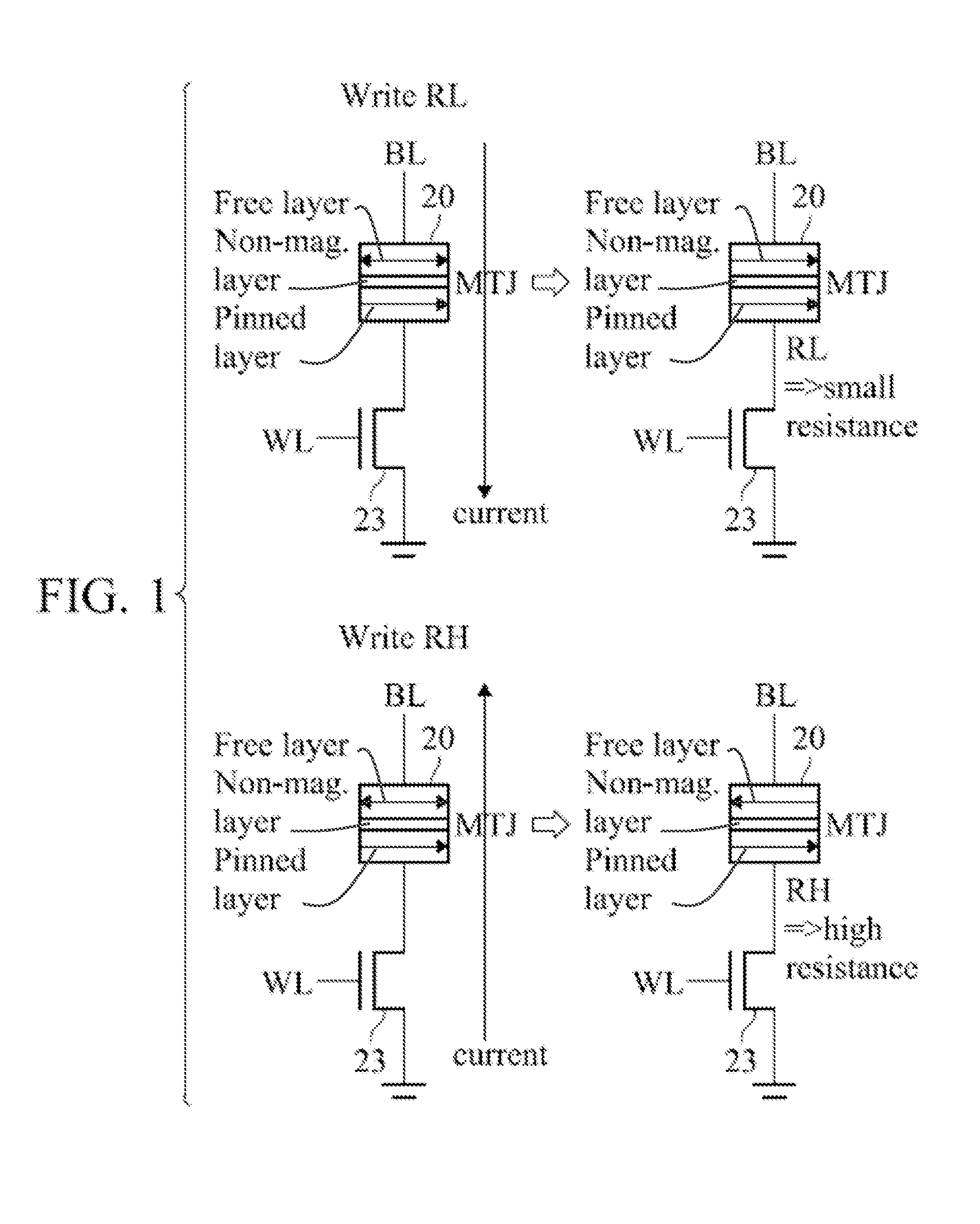

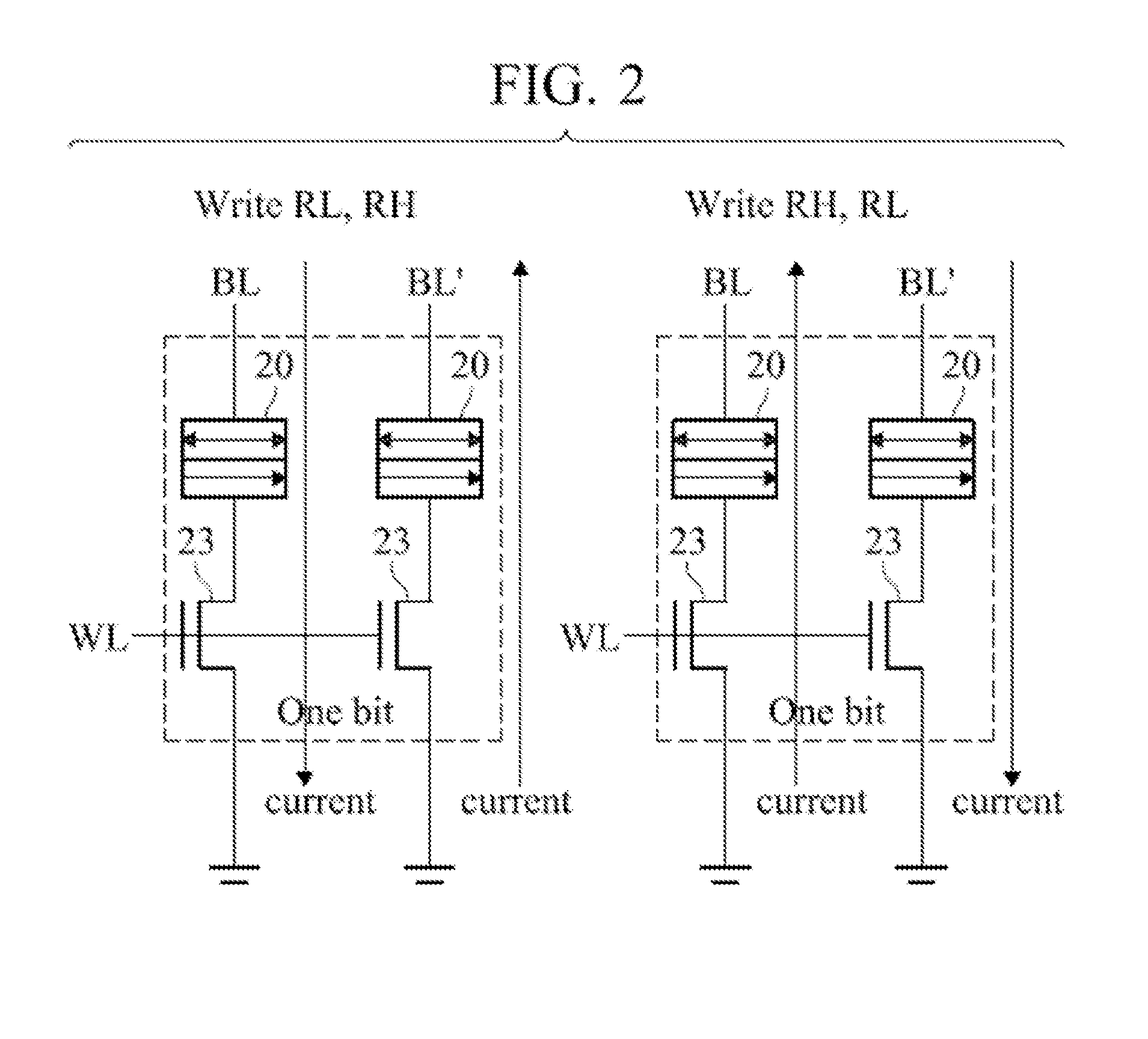

Spin transfer MRAM device with separated CPP assisted writing

ActiveUS20090129143A1Improve reading and writing efficiencyEasy to switchNanotechSolid-state devicesEngineeringSpin transfer

A spin-transfer MRAM is described that has two sub-cells each having a conductive spacer between an upper CPP cell and a lower MTJ cell. The two conductive spacers in each bit cell are linked by a transistor which is controlled by a write word line. The two CPP cells in each bit cell have different resistance states and the MTJ cell and CPP cell in each sub-cell have different resistance states. The MTJ free layer rotates in response to switching in the CPP free layer because of a large demagnetization field exerted by the CPP free layer. An improved circuit design is disclosed that enables a faster and more reliable read process since the reference is a second MTJ within the same bit cell. When RMTJ1>RMTJ2, the bit cell has a “0” state, and when RMTJ1<RMTJ2, the bit cell has a “1” state.

Owner:TAIWAN SEMICON MFG CO LTD

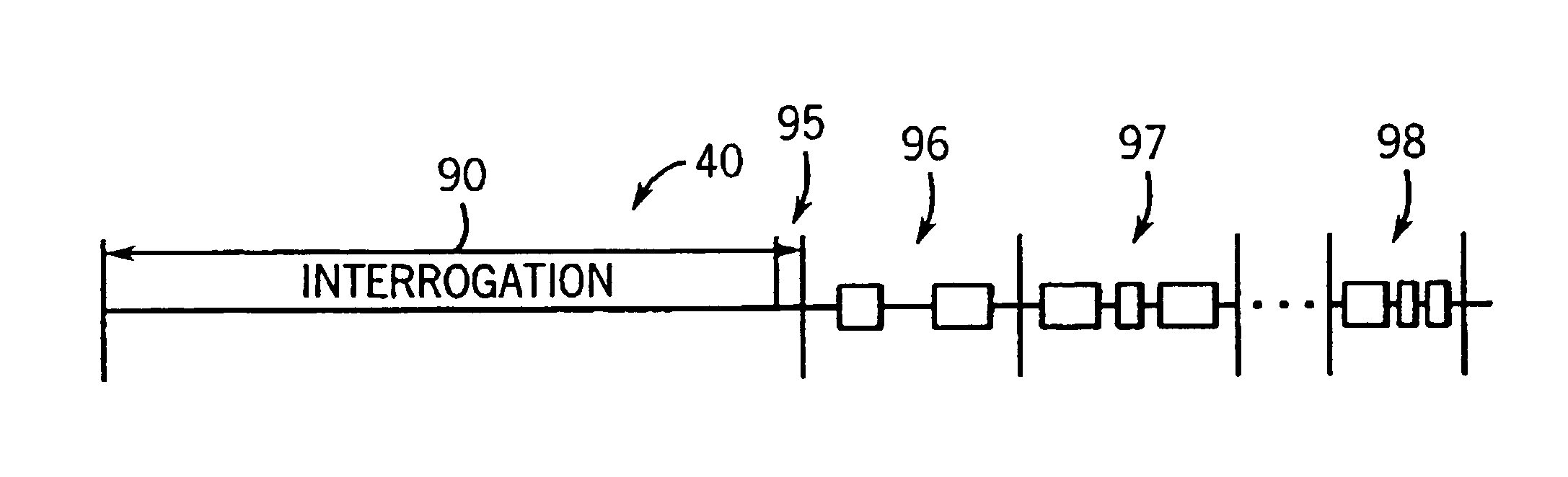

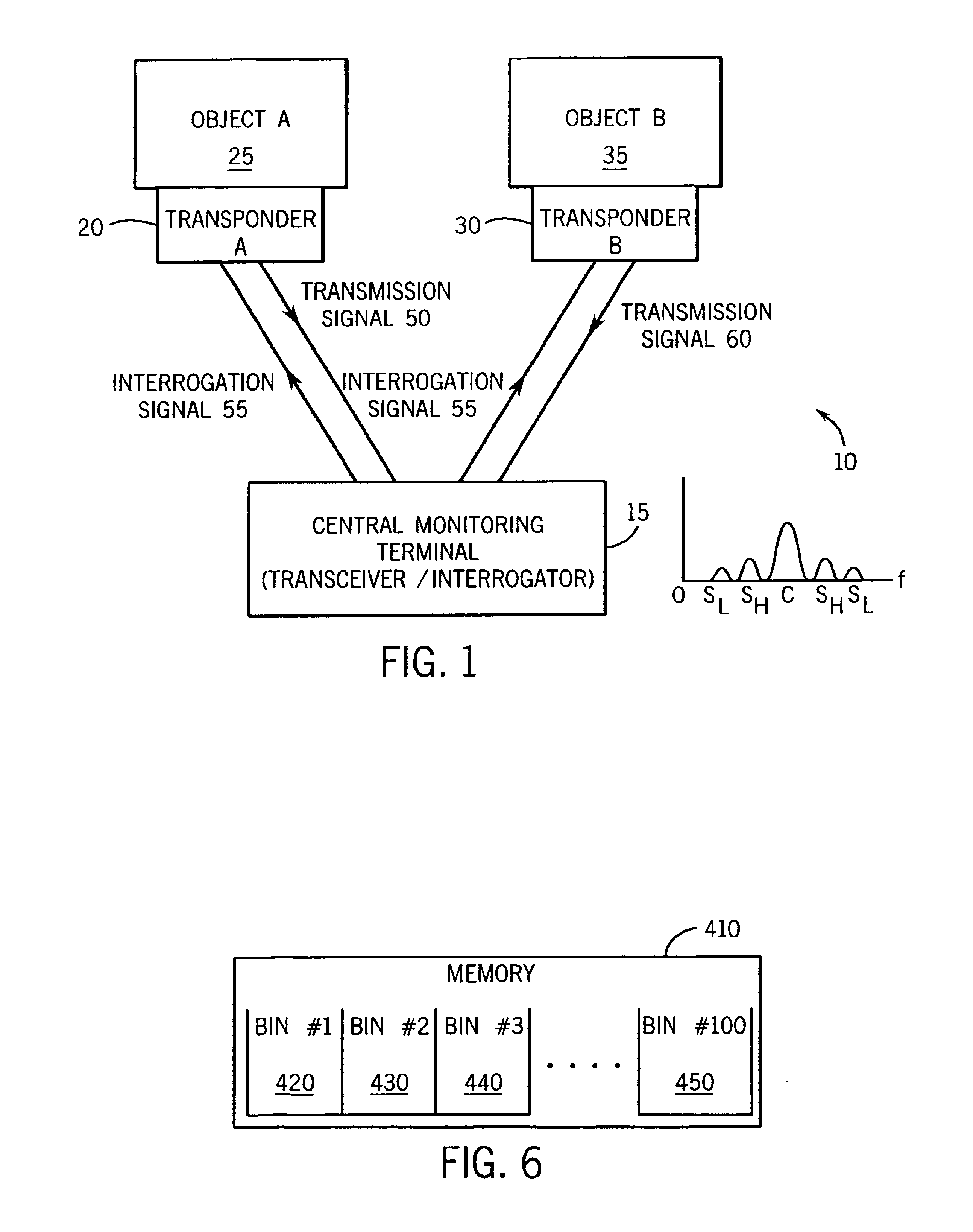

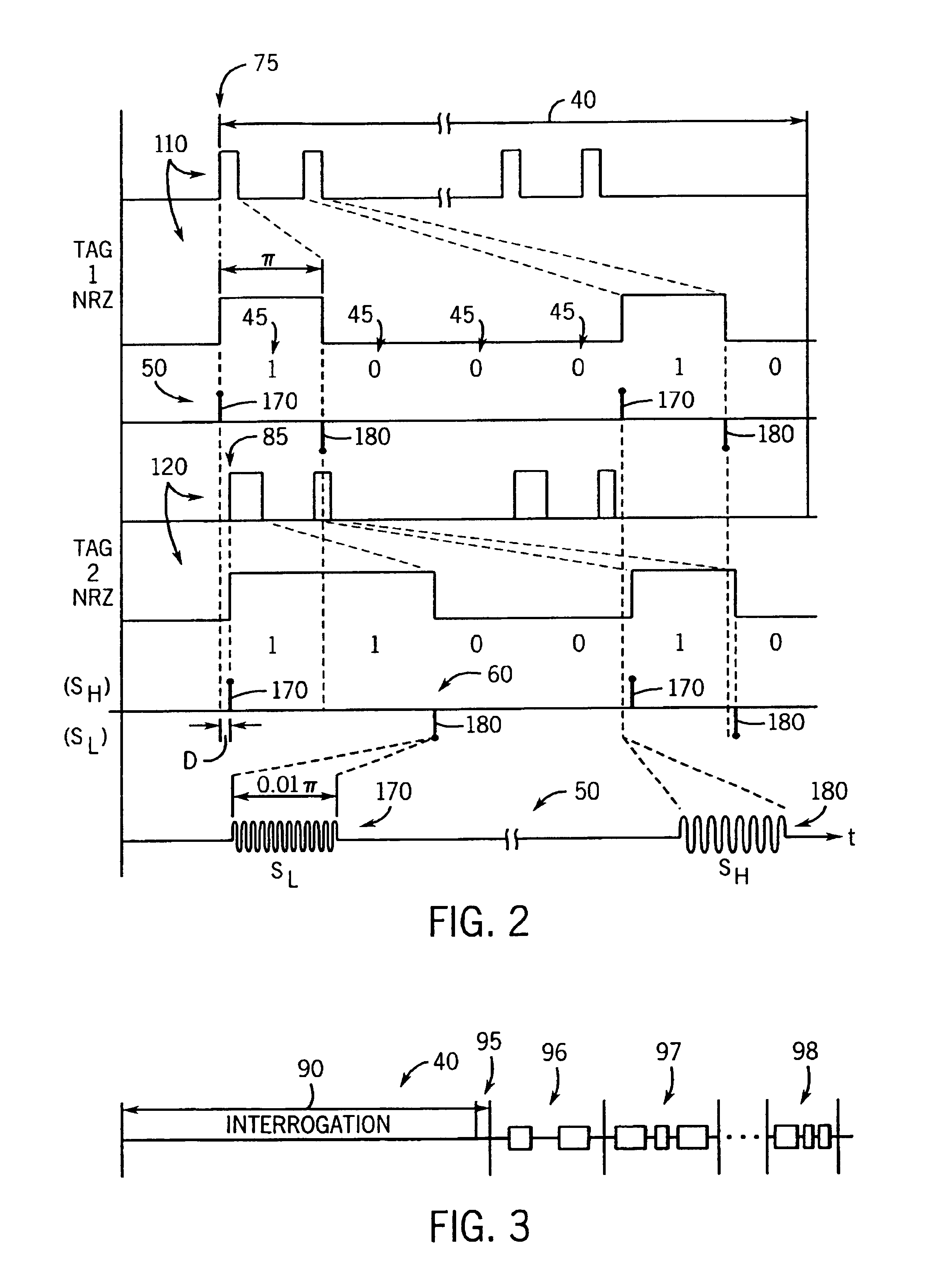

Method for communication between central terminal and multiple transponders

InactiveUS6975206B2Electric signal transmission systemsMemory record carrier reading problemsStart timeComputer terminal

A method of communicating information from first and second transponders (or multiple transponders) to a central monitoring device, and a communications apparatus, are disclosed. The method includes receiving a starting indication at the transponders, determining start times for the transponders in response to that indication, and transmitting first and second sets of bursts from the first and second transponders, respectively. The bursts of the first set occur at at least some of a first set of potential transmission times within an interrogation period, and the bursts of the second set occur at at least some of a second set of potential transmission times during that period. Each of the potential transmission times of the burst sets are respectively determined in relation to the start times of the respective transponders. The potential transmission times of the respective burst sets are separated from one another by one of a bit-cell period and a multiple thereof.

Owner:INTPROP LLC

Spin transfer MRAM device with separated CPP assisted writing

ActiveUS7577021B2Improve reading and writing efficiencyEasy to switchNanotechSolid-state devicesHemt circuitsEngineering

A spin-transfer MRAM is described that has two sub-cells each having a conductive spacer between an upper CPP cell and a lower MTJ cell. The two conductive spacers in each bit cell are linked by a transistor which is controlled by a write word line. The two CPP cells in each bit cell have different resistance states and the MTJ cell and CPP cell in each sub-cell have different resistance states. The MTJ free layer rotates in response to switching in the CPP free layer because of a large demagnetization field exerted by the CPP free layer. An improved circuit design is disclosed that enables a faster and more reliable read process since the reference is a second MTJ within the same bit cell. When RMTJ1>RMTJ2, the bit cell has a "0" state, and when RMTJ1<RMTJ2, the bit cell has a "1" state.

Owner:TAIWAN SEMICON MFG CO LTD

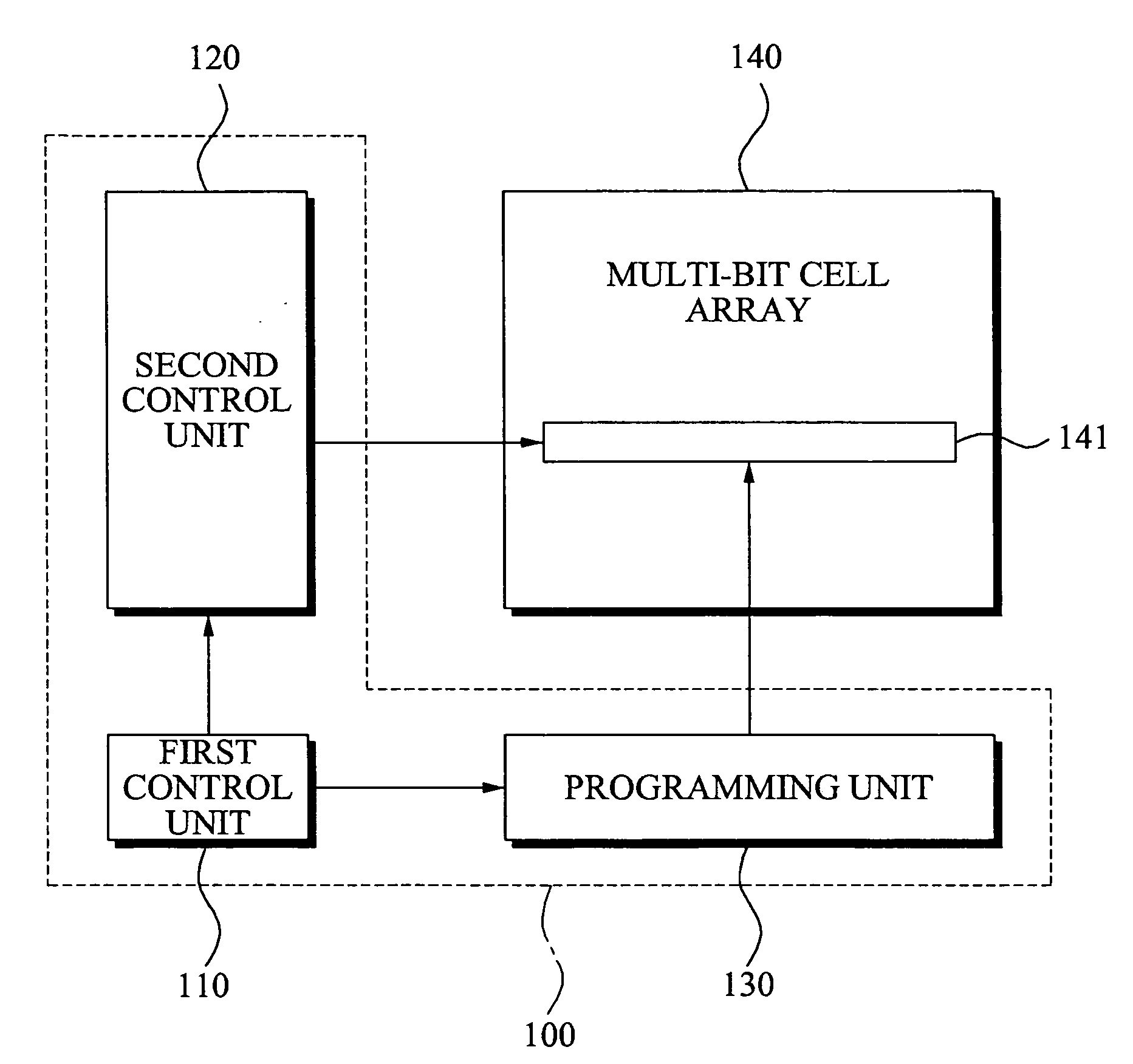

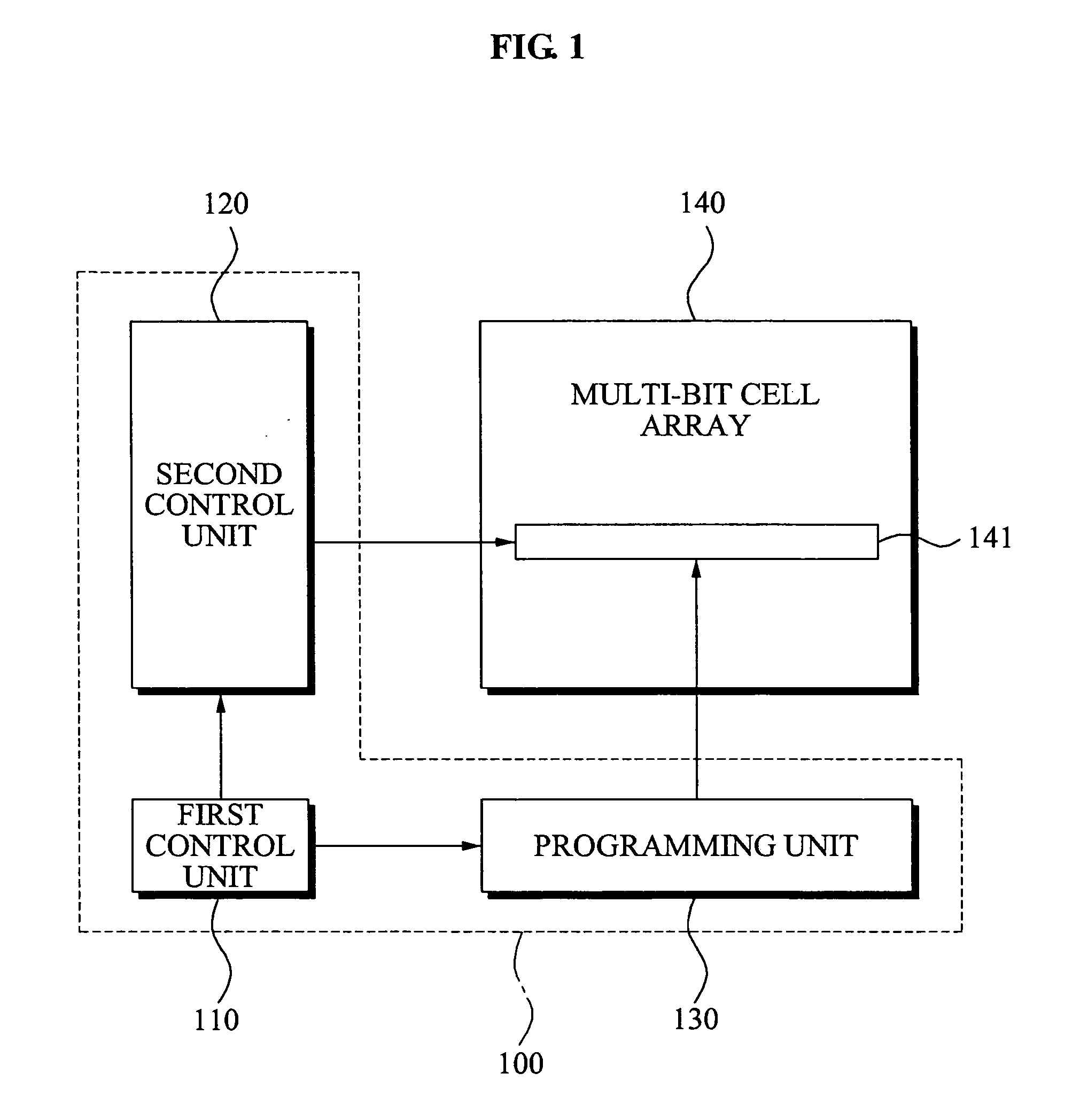

Apparatus and method of multi-bit programming

ActiveUS20090091990A1Reduce complexityReduce the valueProgram control using stored programsRead-only memoriesComputer scienceThreshold voltage

Disclosed are a multi-bit programming apparatus and a multi-bit programming method. The multi-bit programming apparatus may include a first control unit that may generates 2N threshold voltage states based on a target bit error rate (BER) of each of the page programming operations, a second control unit that may assign any one of the threshold voltage states to the N-bit data, and a programming unit that may program the assigned threshold voltage state in each of the at least one multi-bit cell to program the N-bit data.

Owner:SAMSUNG ELECTRONICS CO LTD

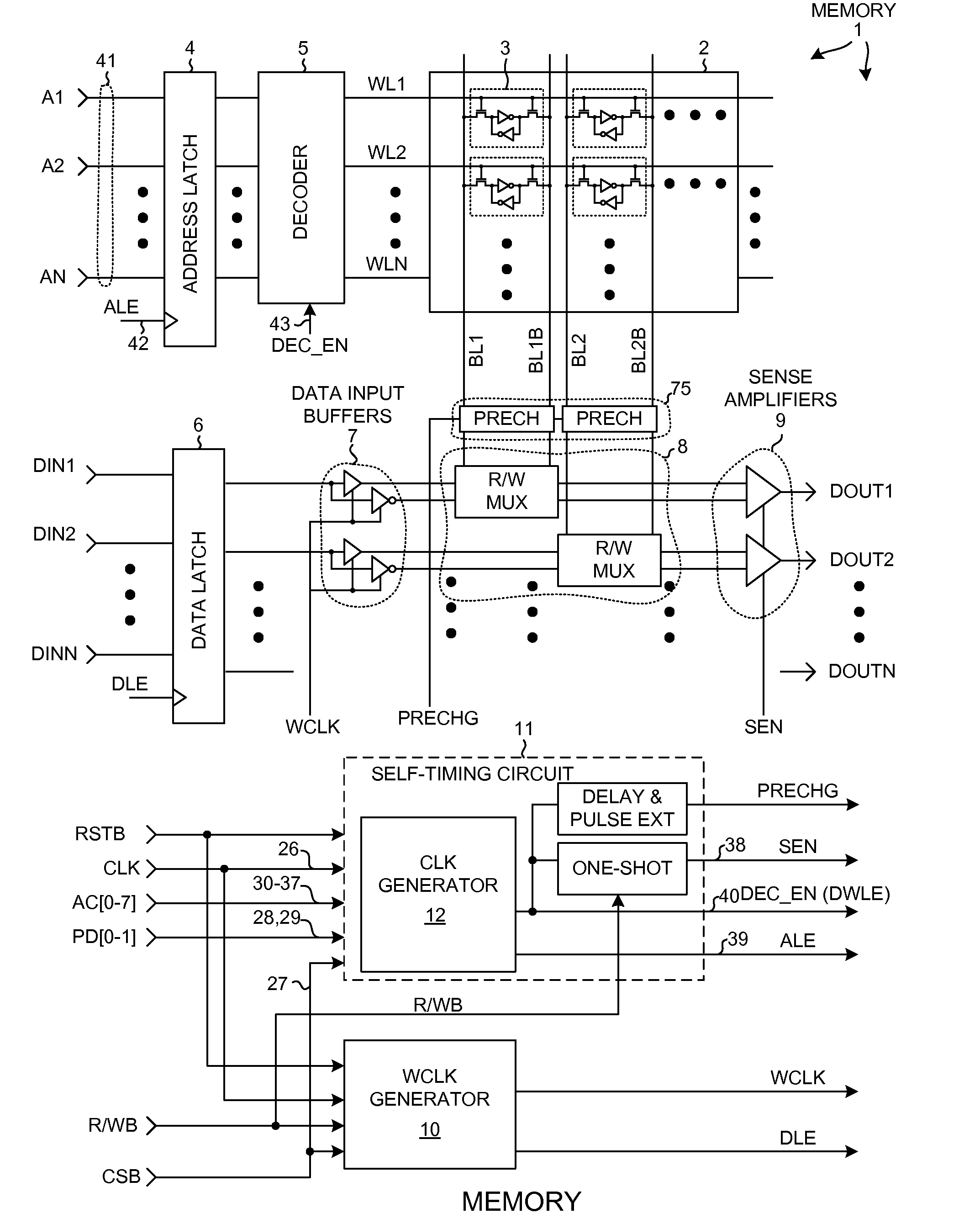

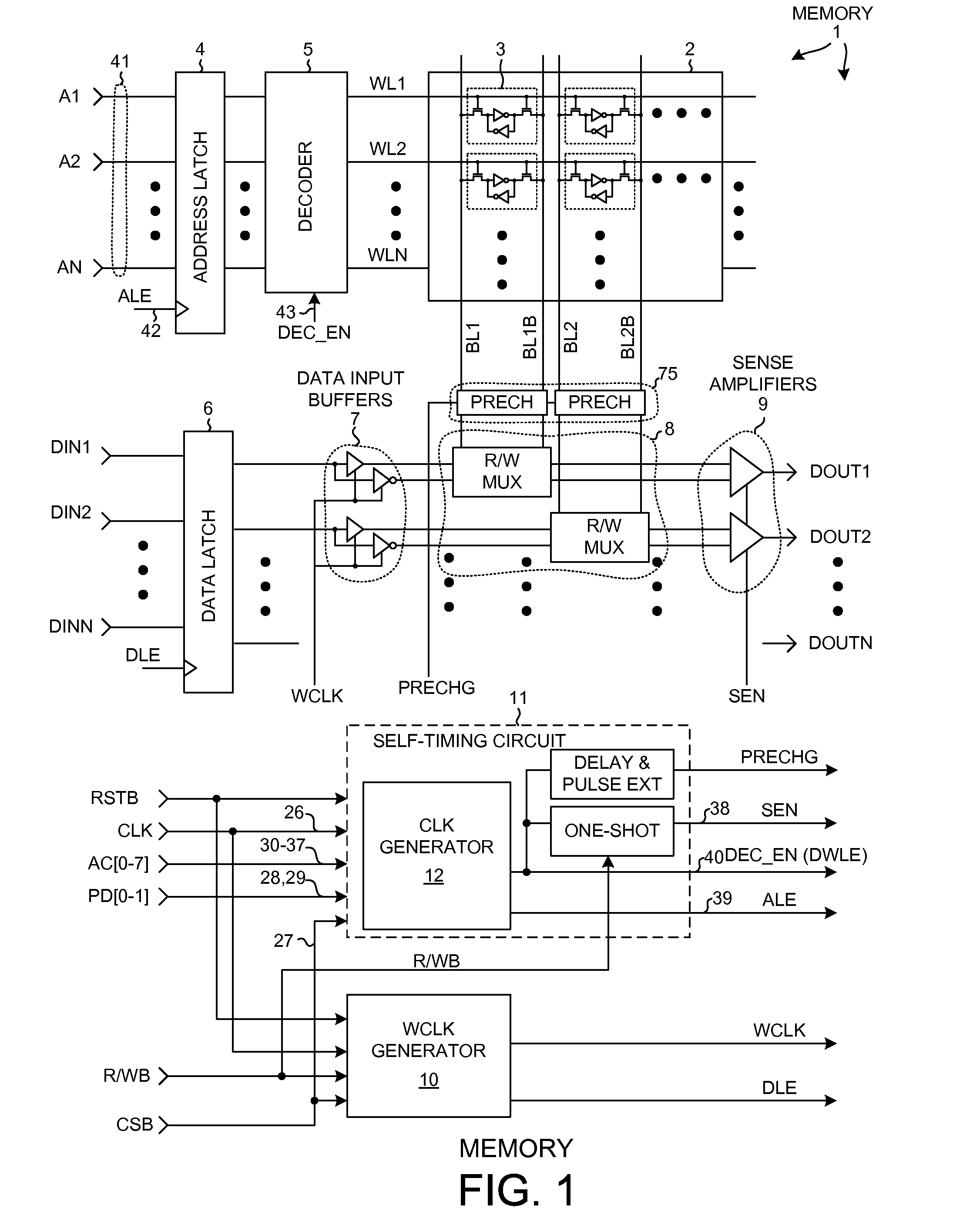

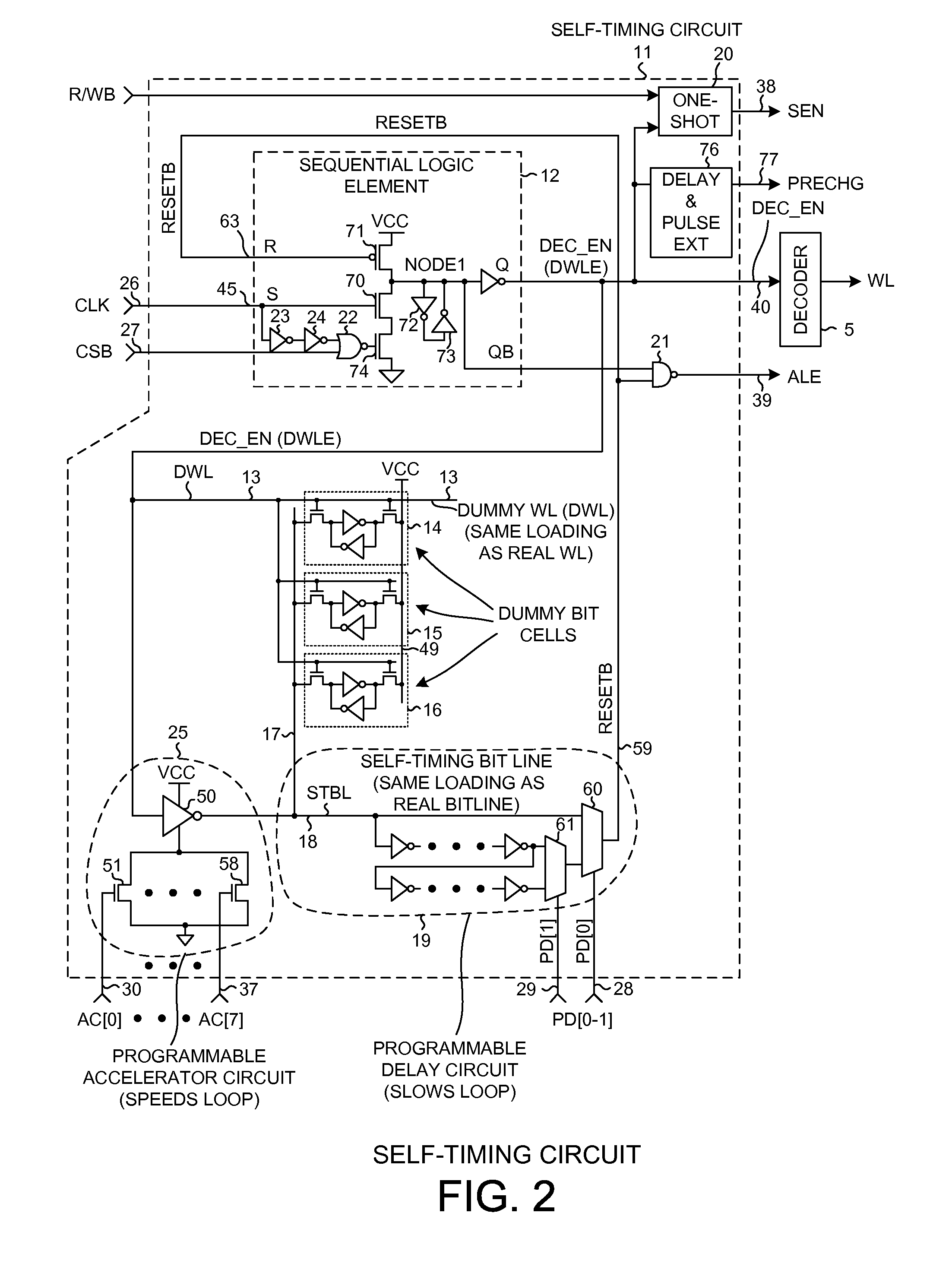

Self-timing circuit with programmable delay and programmable accelerator circuits

ActiveUS20080037338A1Shorten the timeFaster access timeDigital storageInternal memoryAudio power amplifier

A memory has a novel self-timing circuit that generates internal memory control signals. Control signals may include an address latch enable signal, a decoder enable signal, and a sense amplifier enable signal. The circuit has a timing loop whose timing mimics the timing of an access of the real memory. The timing loop includes dummy bit cells of identical construction to bit cells in the real array being accessed, a programmable delay circuit, and a programmable accelerator circuit. The dummy bit cells cause the timing of the control signals to track speed changes in the memory array being accessed. The programmable delay and accelerator circuits are usable to slow or speed the timing loop. The programmable delay and accelerator circuits are usable to achieve a desired yield to memory access speed tradeoff. Flexibility of the timing loop allows a memory to be designed before memory access timing characteristics are fixed.

Owner:QUALCOMM INC

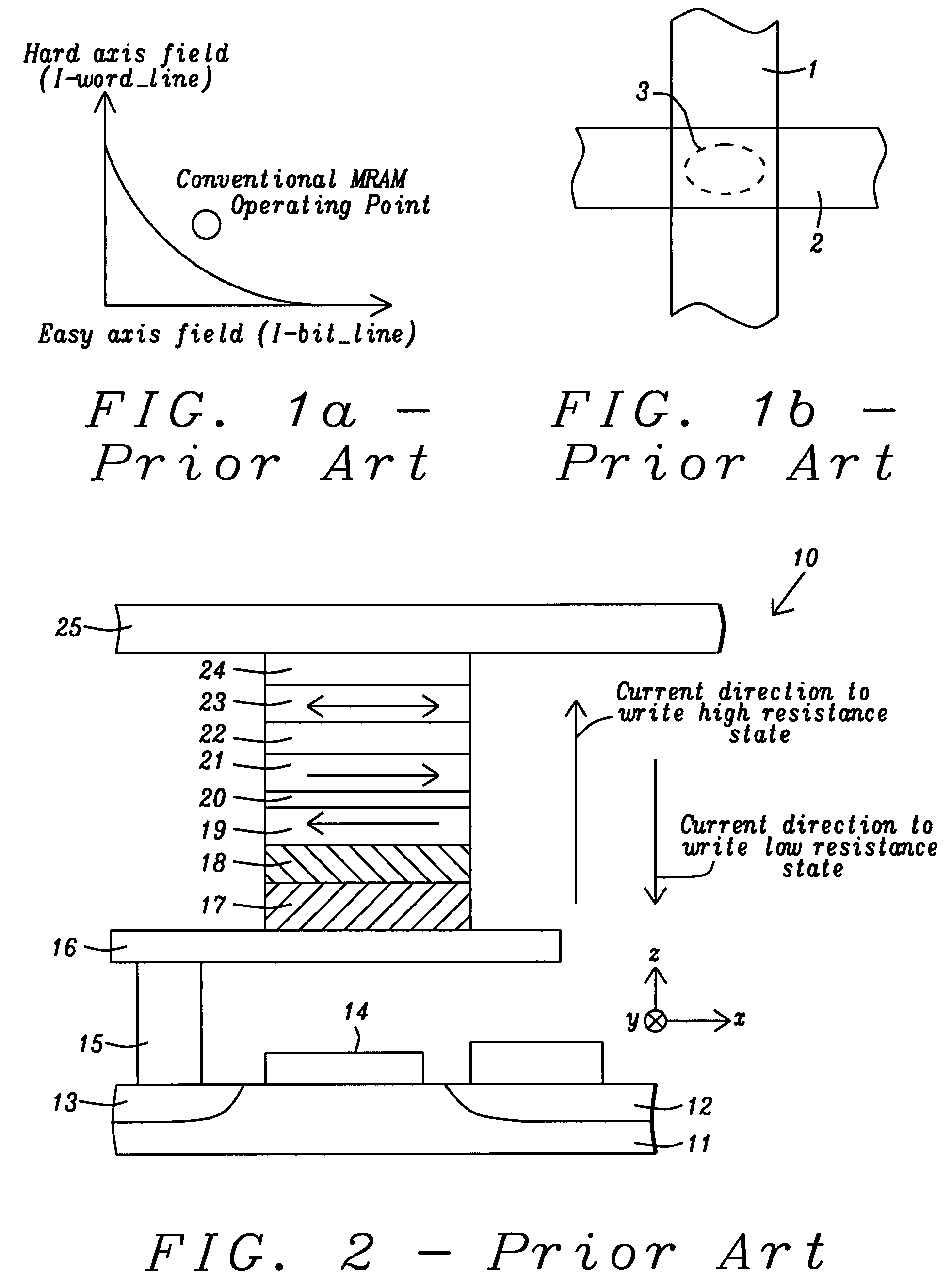

Multibit Cell of Magnetic Random Access Memory With Perpendicular Magnetization

ActiveUS20120155164A1Magnetic-field-controlled resistorsSolid-state devicesPerpendicular magnetizationBit line

A multi-bit cell of magnetic random access memory comprises a magnetic tunnel junction element including a first and second free layer comprising a changeable magnetization oriented substantially perpendicular to a layer plane in its equilibrium state and a switching current, a first and second tunnel barrier layer, and a pinned layer comprising a fixed magnetization oriented substantially perpendicular to a layer plane, the pinned layer is disposed between the first and second free layers and is separated from the free layers by one of the tunnel barrier layers, a selection transistor electrically connected to a word line, and a bit line intersecting the word line. The magnetic tunnel junction element is disposed between the bit line and the selection transistor and is electrically connected to the bit line and the selection transistor, wherein the first and second free layers have substantially different switching currents.

Owner:SHUKH ALEXANDER MIKHAILOVICH

Method and apparatus for generating read and verify operations in non-volatile memories

Method and apparatus for generating a word-line voltage are disclosed. A word-line voltage generator includes a first current source, an adjustable current source, and a voltage converter, all operably coupled to a current sum node. The first current source generates a first current wherein a voltage derived from the first current at least partially comprises a cell location-dependent temperature coefficient varying with a location of a memory cell in a string of interconnected bit cells. The adjustable current source generates a second current that is substantially independent of a temperature change. The voltage converter is configured for generating a word-line signal having a word-line voltage proportional to the first current.

Owner:MICRON TECH INC

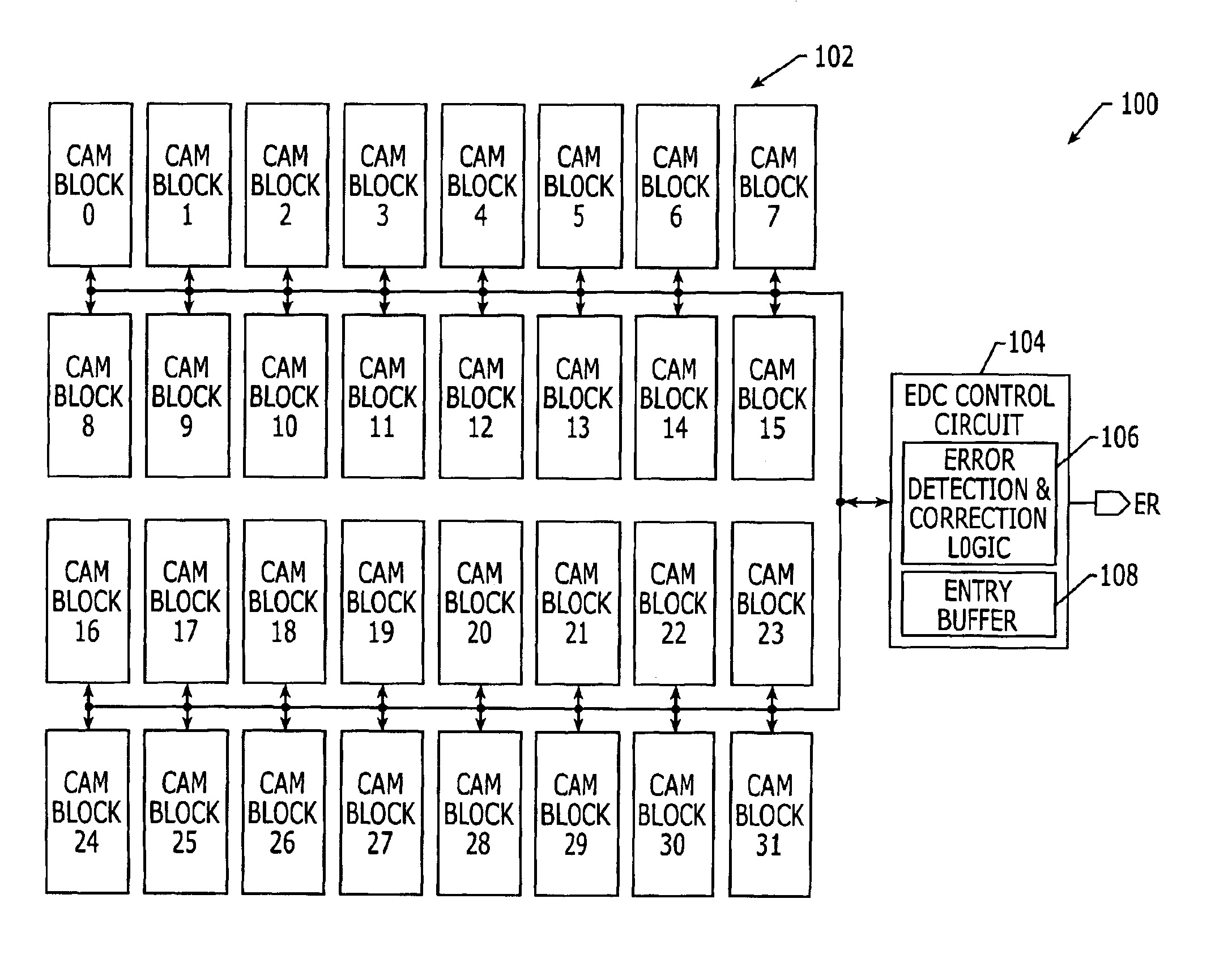

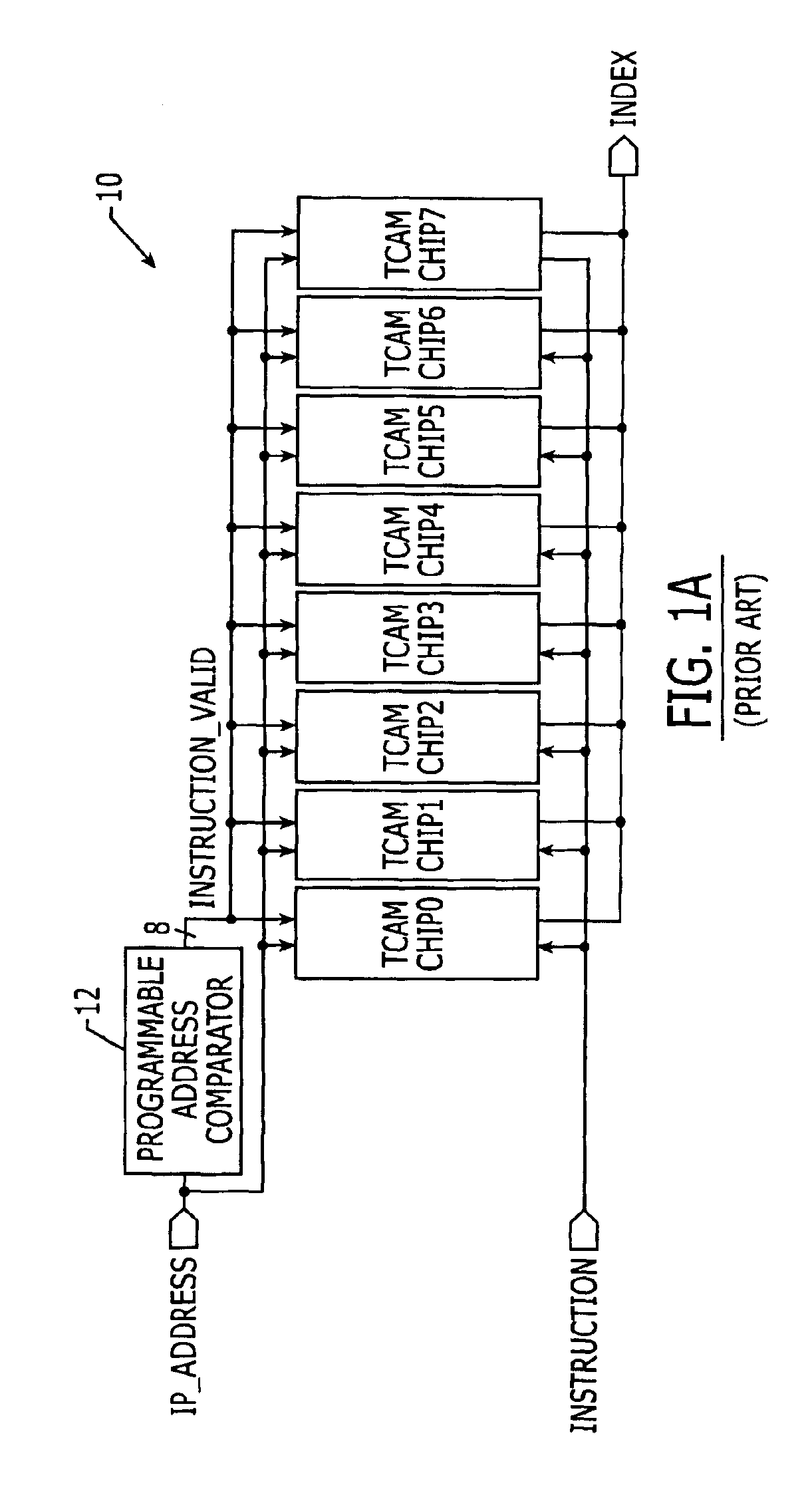

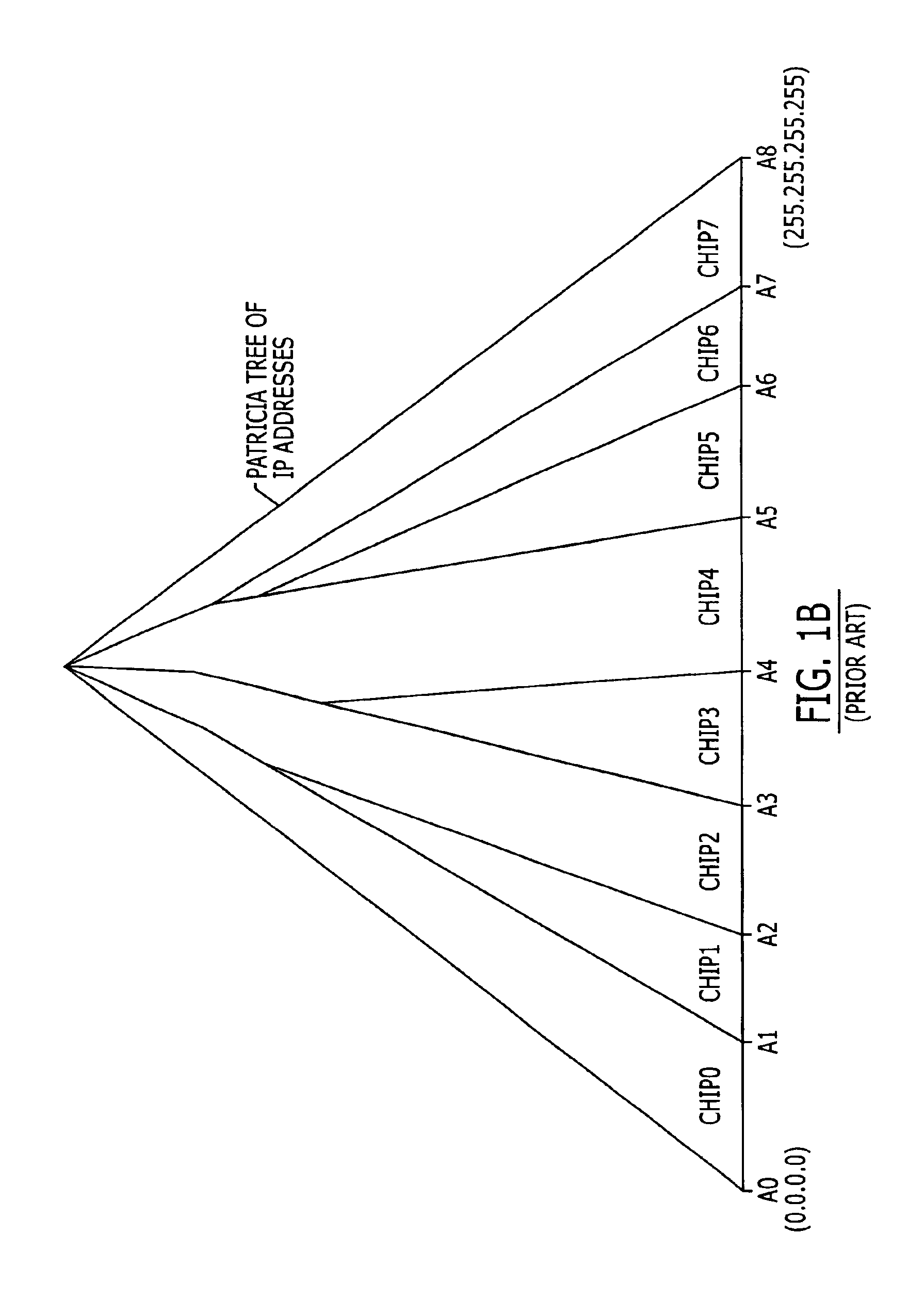

Content addressable memory (CAM) devices having error detection and correction control circuits therein and methods of operating same

Content addressable memory (CAM) devices include error detection and correction (EDC) control circuits therein. The EDC control circuit operates to correct soft errors in entries within a plurality of internal CAM array blocks with, at most, limited interruption to other operations performed by the CAM device. The EDC control circuit utilizes a multi-bit check word associated with each entry to detect a soft error and perform one-bit error correction on the entry. The EDC control circuit is configured to be active during a background mode of operation when the CAM array blocks are undergoing search operations in a foreground mode of operation. A CAM array block may also include a column of dual-function check bit cells that are configured to operate as a column of CAM cells when necessary to replace a defective column of CAM cells.

Owner:AVAGO TECH INT SALES PTE LTD

Method of managing a multi-bit cell flash memory with improved reliability and performance

A method of storing data by providing a flash memory device including a plurality of memory cells; each of the memory cells is capable of storing data bits. First data bits are stored into memory cells used for storing M bits per cell, the memory cells are allocated to a page of the memory. Second data bits are stored into other memory cells, the other memory cells used for storing N bits per cell are allocated to the page and upon storing of the first data bits and upon storing the second data bits, the page uses at the same time at least one of the memory cells with M bits per cell and at least one of the other memory cells with N bits per cell with N less than M.

Owner:WESTERN DIGITAL ISRAEL LTD

Differential MRAM structure with relatively reversed magnetic tunnel junction elements enabling writing using same polarity current

A magnetoresistive memory has first and second magnetic tunnel junction (MTJ) elements operated differentially, each with a pinned magnetic layer and a free magnetic layer that can have field alignments that are parallel or anti-parallel, producing differential high and low resistance states representing a bit cell value. Writing a high resistance state to an element requires an opposite write current polarity through the pinned and free layers, and differential operation requires that the two MTJ elements be written to different resistance states. One aspect is to arrange or connect the layers in normal and reverse order relative to a current bias source, thereby achieving opposite write current polarities relative to the layers using the same current polarity relative to the current bias source. The differentially operated MTJ elements can supplement or replace single MTJ elements in a nonvolatile memory bit cell array.

Owner:TAIWAN SEMICON MFG CO LTD