Patents

Literature

37results about How to "Faster access time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

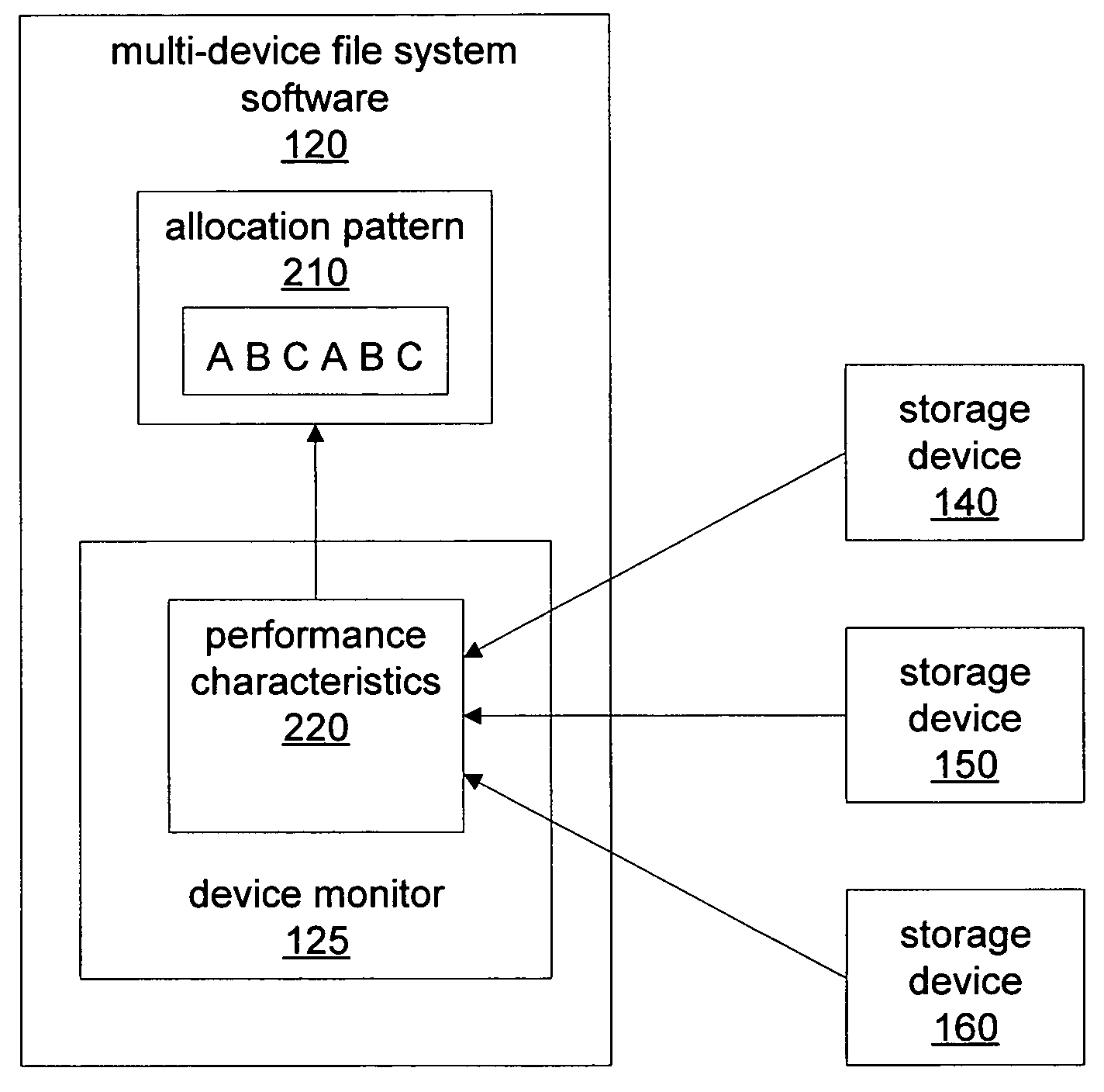

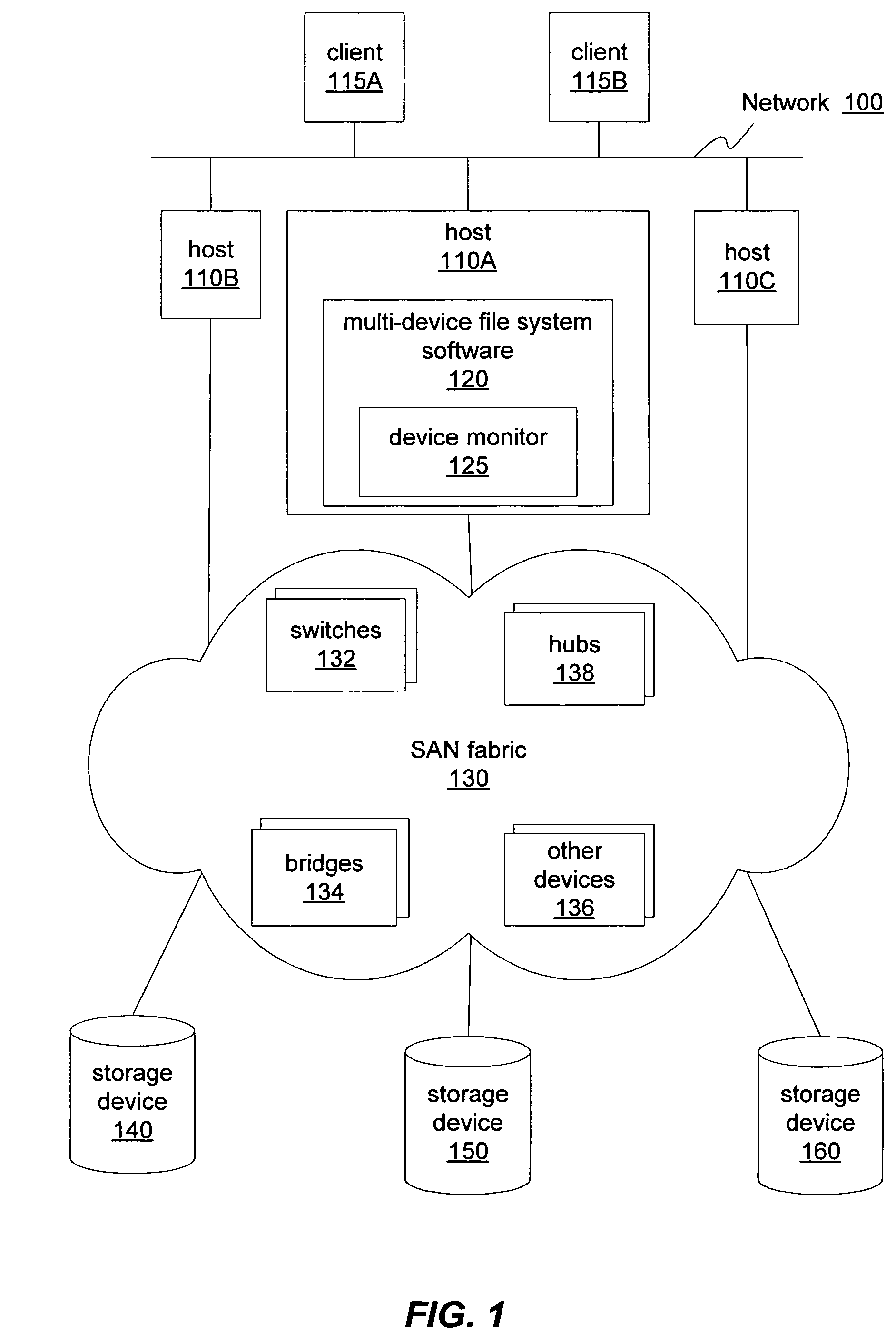

Performance-adjusted data allocation in a multi-device file system

InactiveUS7631023B1Faster access timeReduce throughputData processing applicationsError detection/correctionFile systemPerformance tuning

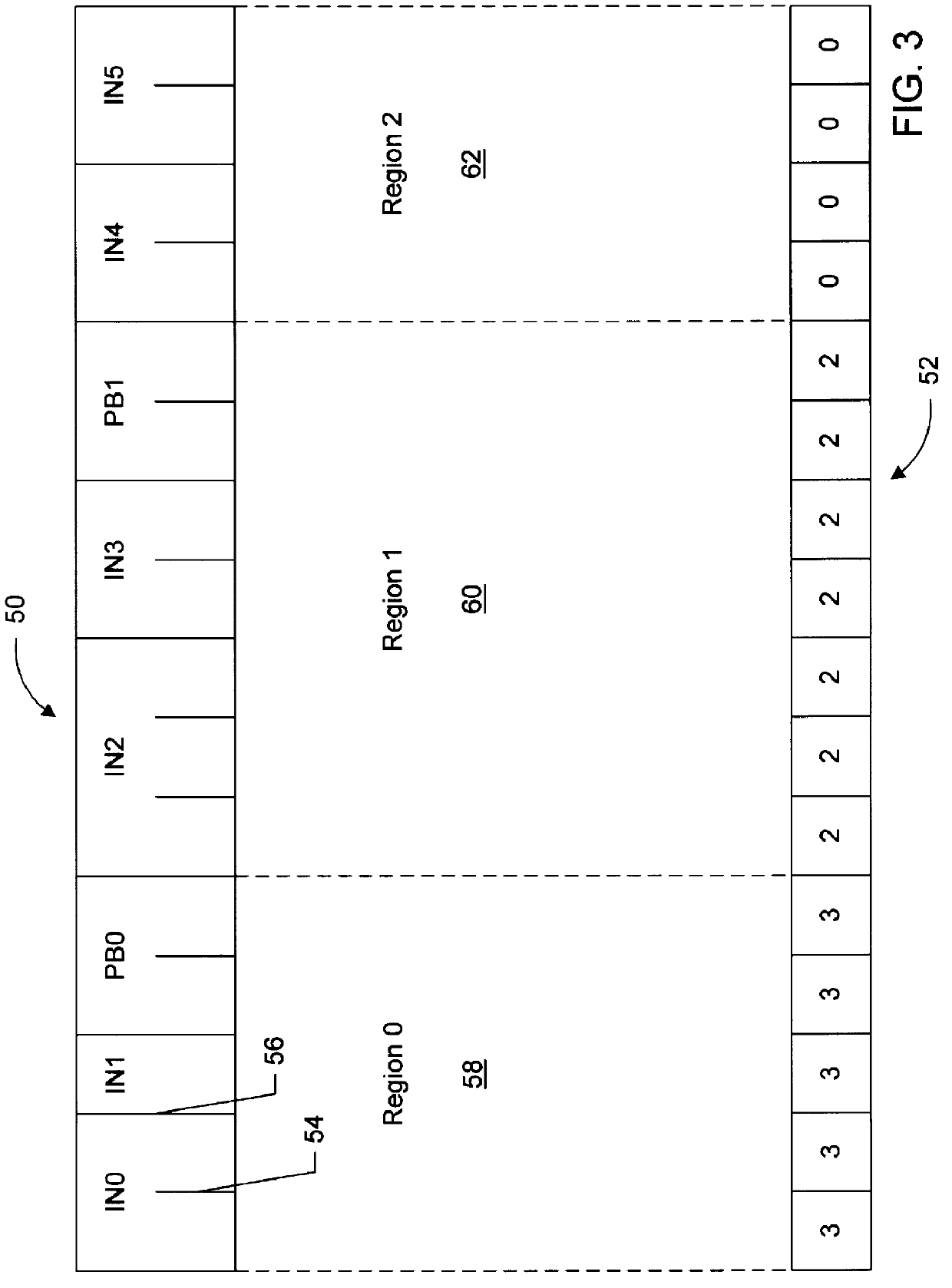

A file system may employ an enhanced or performance-adjusted allocation scheme when storing data to multiple storage devices. A file system may monitor one or more performance characteristics of storage devices. The file system may, in response to storage requests, select one or more of the storage devices for storing data associated storage requests based on differences among the respective monitored performance characteristics for the storage devices. Additionally, the file system may determine an allocation pattern for storing data to the storage devices and may modify the determined allocation pattern based on a detected change in the monitored performance characteristics of the storage devices. Further, the file system may store data based on both the allocation pattern and on data characteristics associated with a data storage request. The file system may also incorporate input specifying either new performance characteristics or a new allocation pattern.

Owner:SYMANTEC OPERATING CORP

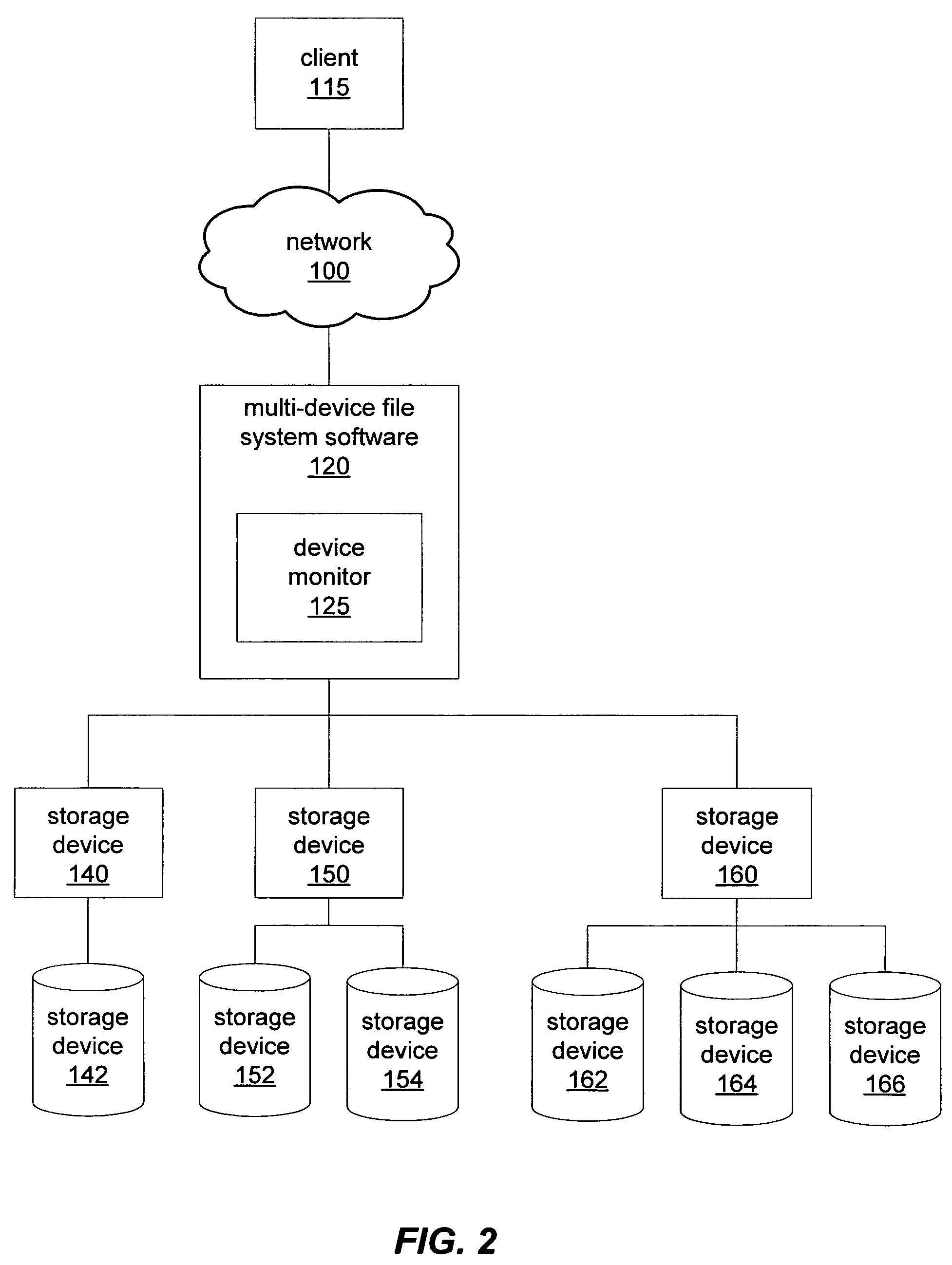

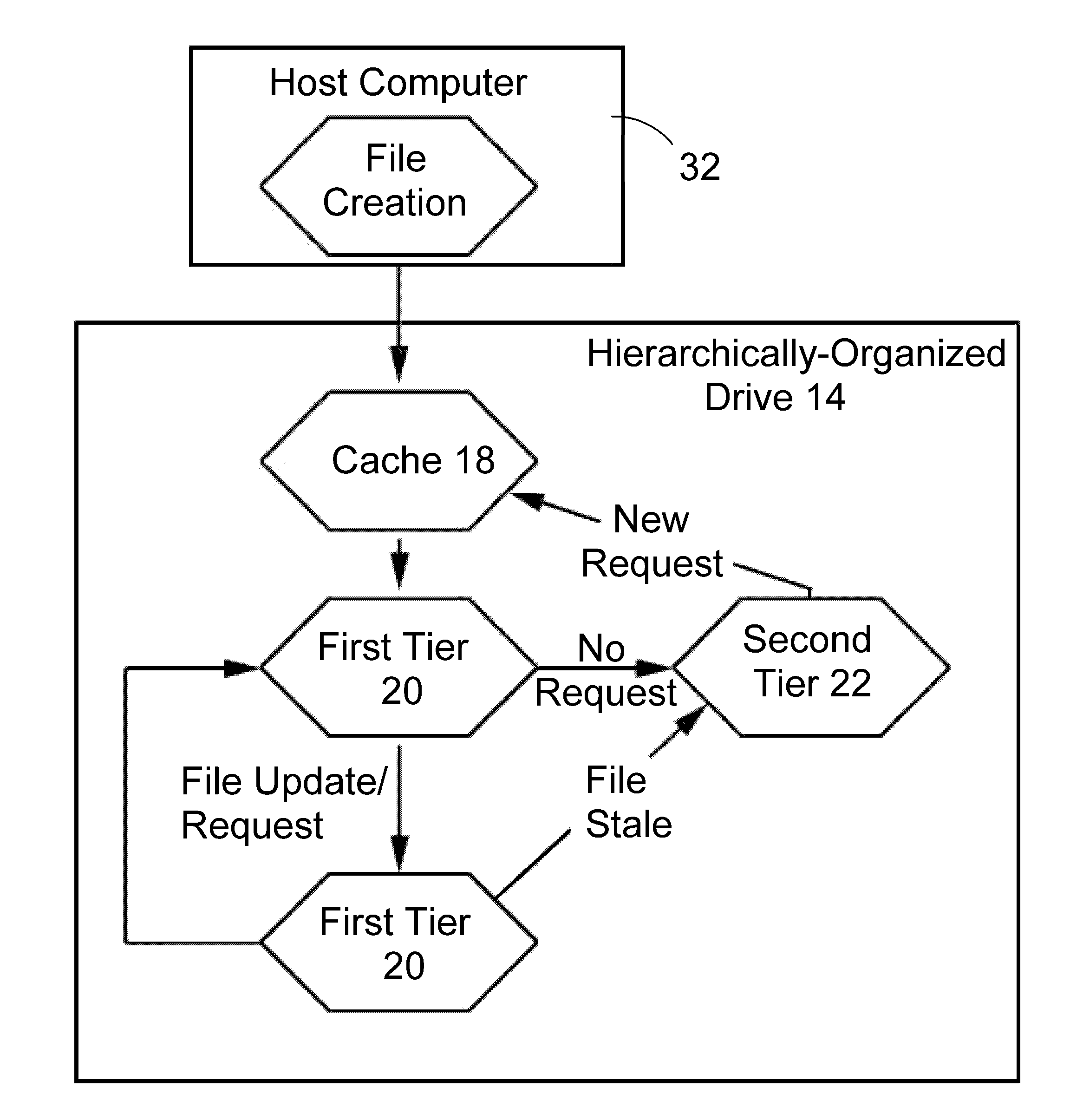

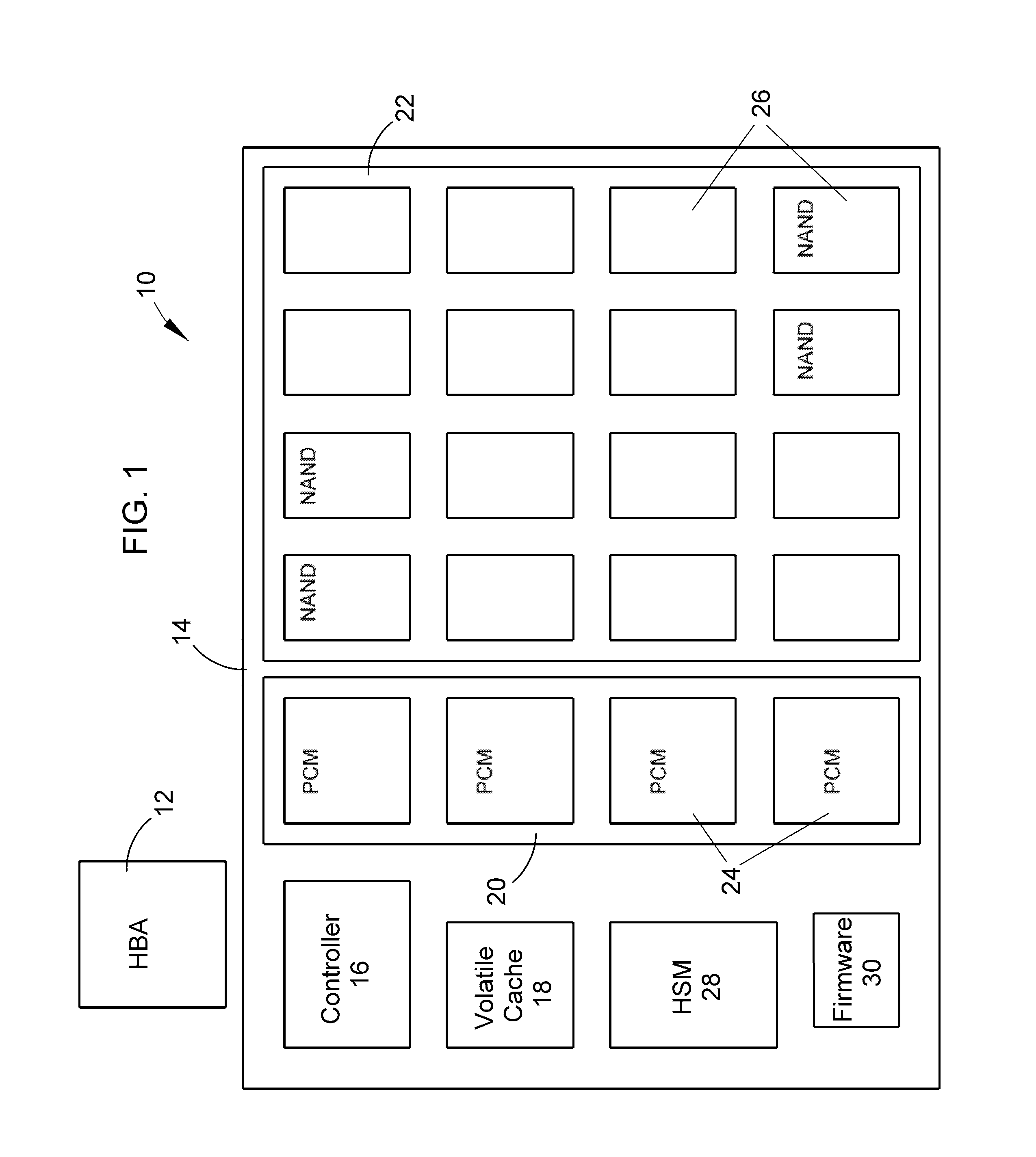

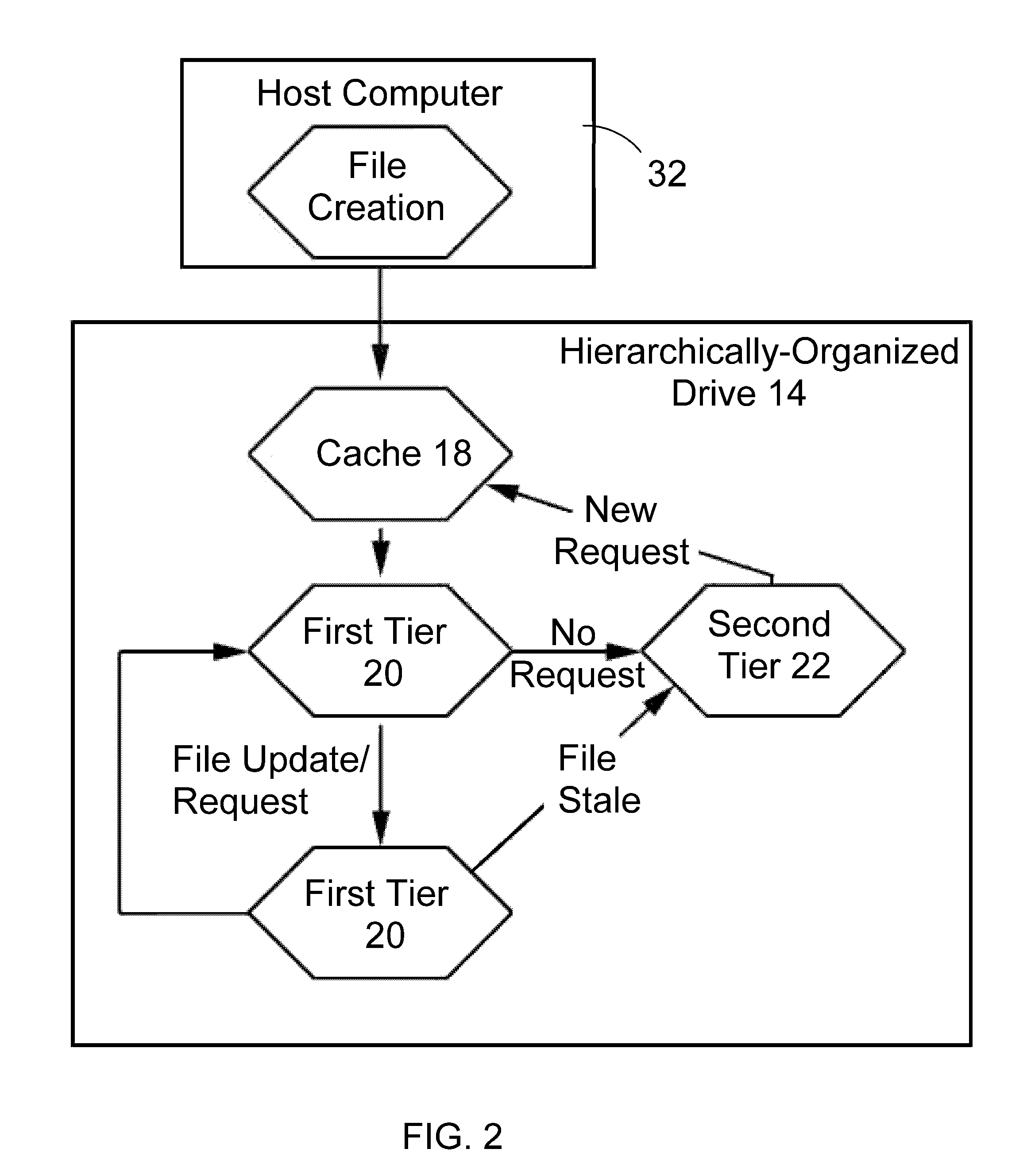

Hierarchically structured mass storage device and method

InactiveUS20100325352A1Faster access timeHigh write enduranceMemory architecture accessing/allocationMemory adressing/allocation/relocationAccess timeStorage management

A hierarchically-structured computer mass storage system and method. The mass storage system includes a mass storage memory drive, control logic on the mass storage memory drive that includes a controller and one or more devices for executing a hierarchical storage management technique, a volatile memory cache configured to be accessed by the control logic, and first and second non-volatile storage arrays on the mass storage memory drive and comprising, respectively, first and second non-volatile memory devices. The first and second non-volatile memory devices have properties including access times and write endurance, and at least one of the access time and the write endurance of the first non-volatile memory devices is faster or higher, respectively, than the second non-volatile memory devices. Desired data storage localities on the storage arrays are determined through access patterns and selectively utilizing the properties of the memory devices to match the data storage requirements.

Owner:OCZ STORAGE SOLUTIONS

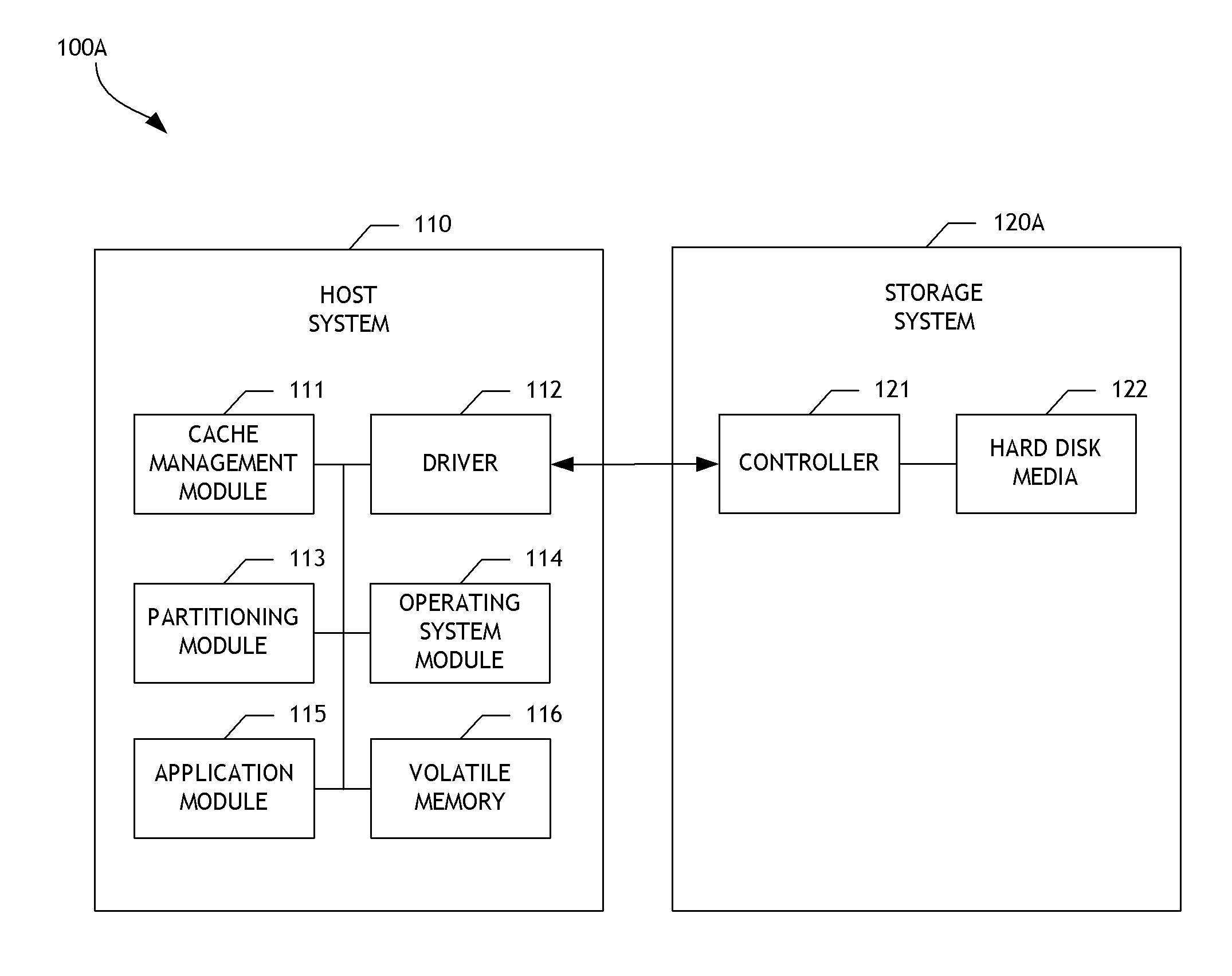

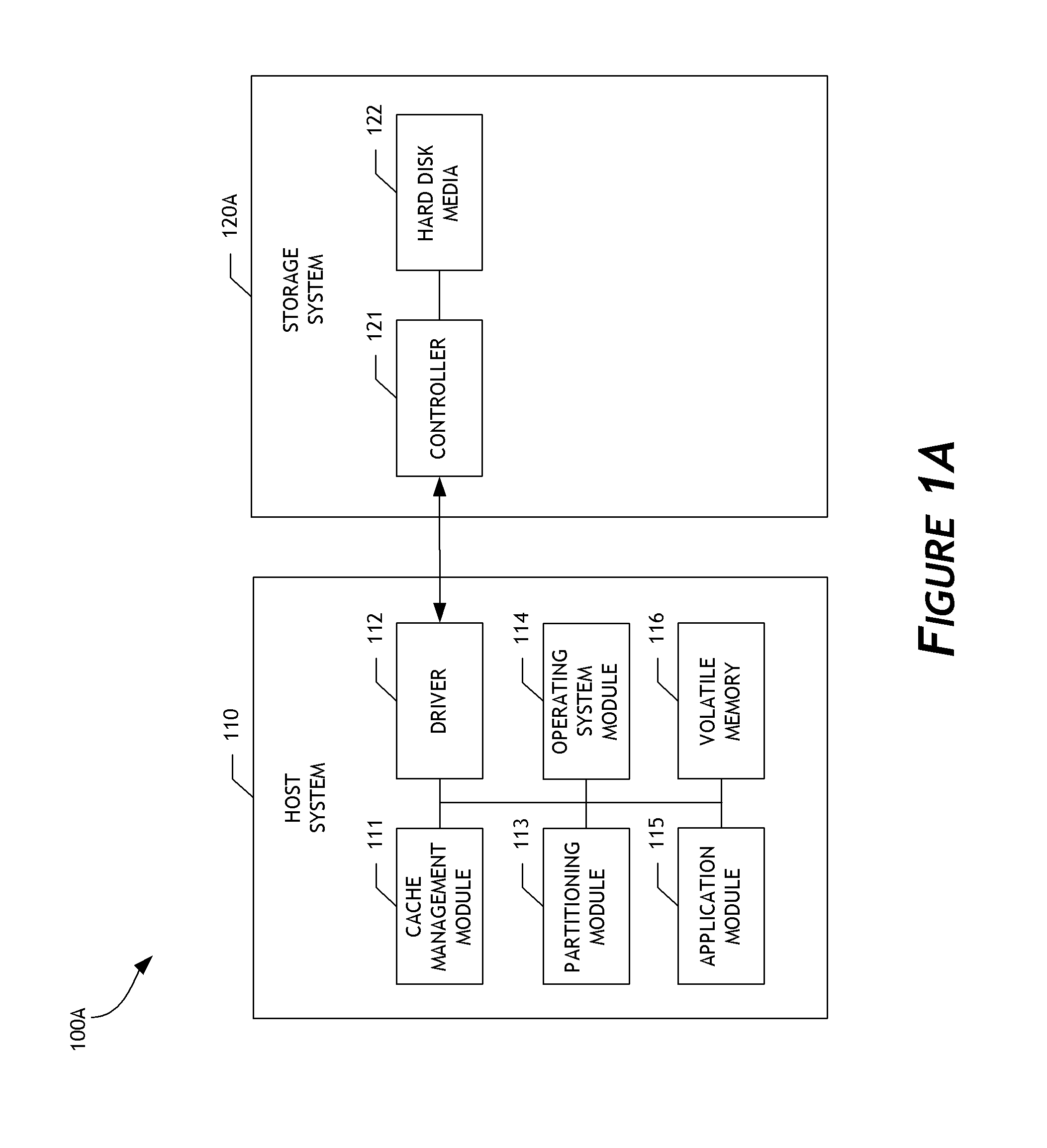

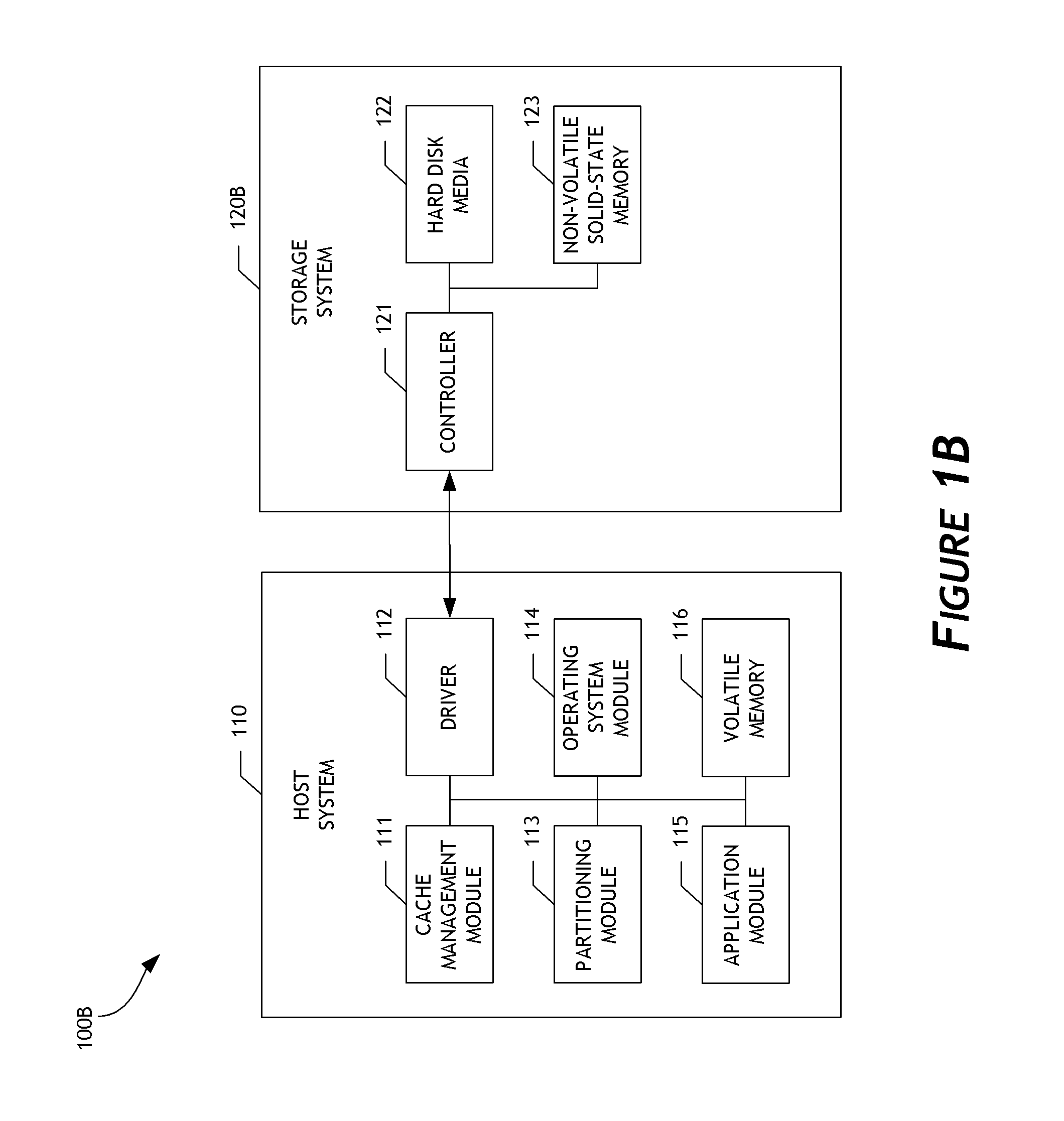

Caching data in a high performance zone of a data storage system

ActiveUS9280472B1Short response timeFaster access timeMemory architecture accessing/allocationMemory adressing/allocation/relocationCache managementData store

A combination of a host system and a storage system is disclosed that facilitates improved responsiveness of the host system to user requests. In one embodiment, the host system includes a cache management module, a partitioning module, and a driver. The cache management module determines write data to cache to a dedicated zone of a hard disk media of the storage system. The partitioning module partitions the hard disk media into one partition including the dedicated zone and another partition not including the dedicated zone. The driver transmits storage access commands to the storage system to cache data in and retrieve cached data from the one partition. Thereby, the host system can access the write data from the hard disk media more quickly than if the write data were cached in and accessed from another zone of the hard disk media.

Owner:WESTERN DIGITAL TECH INC

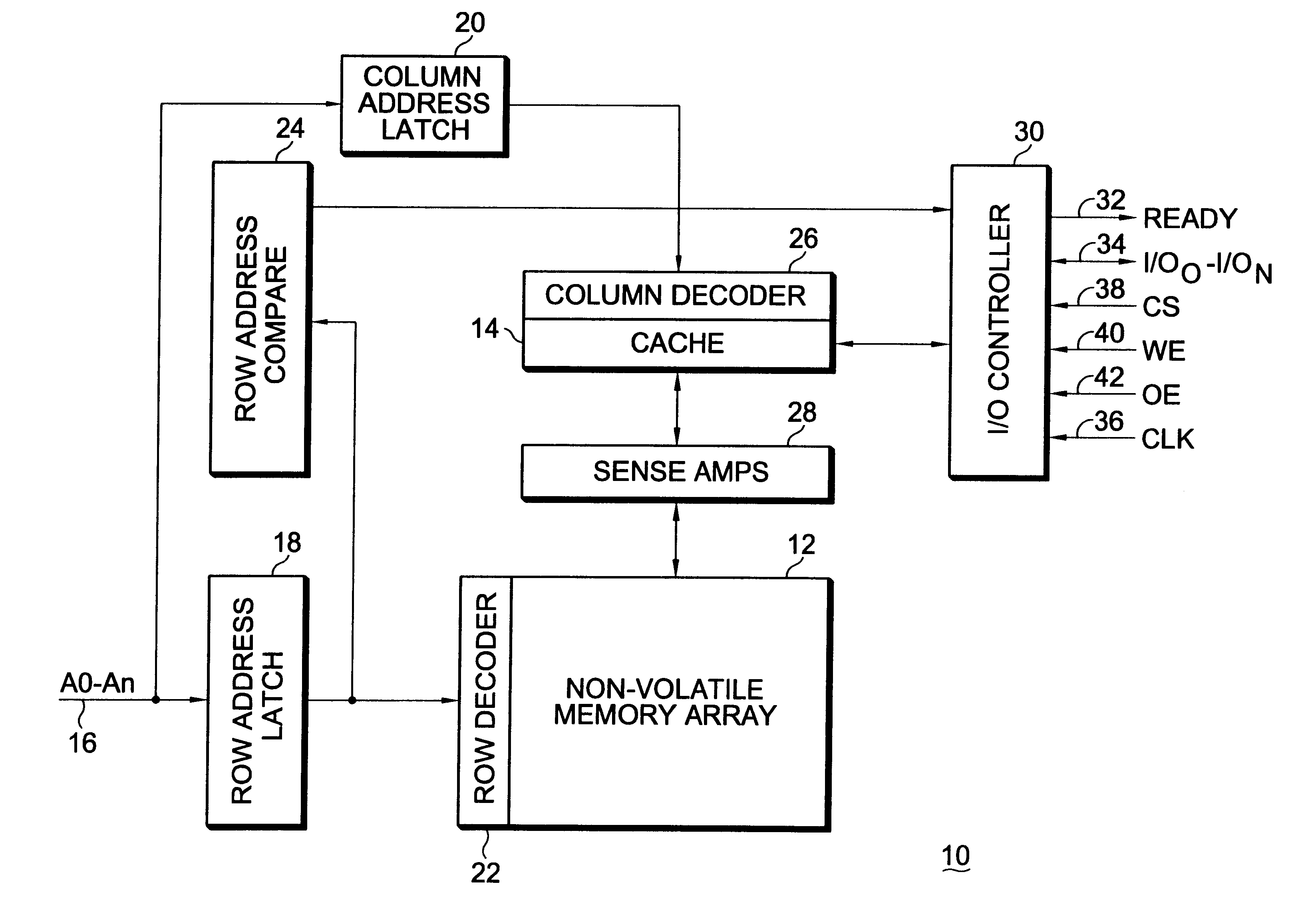

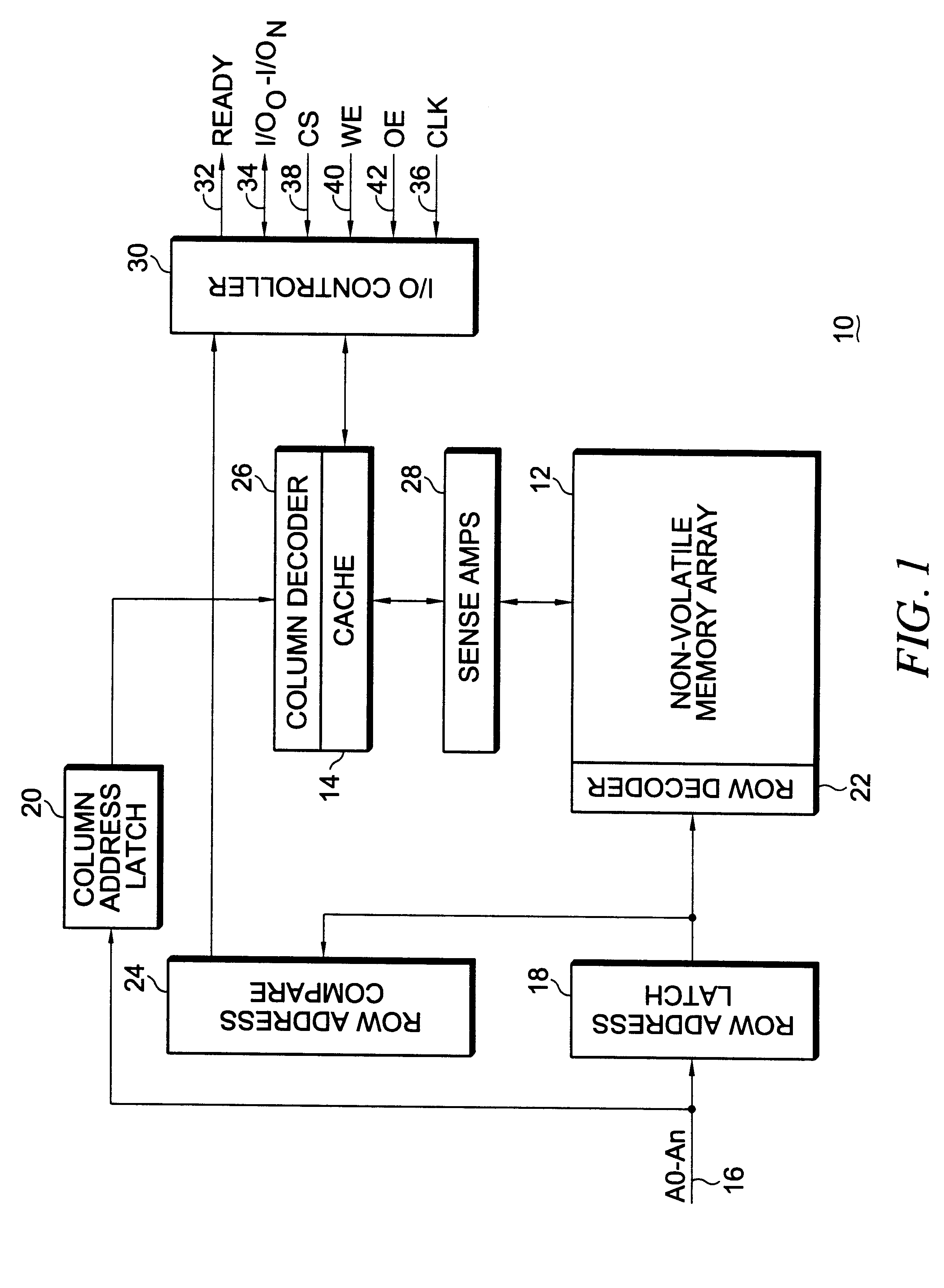

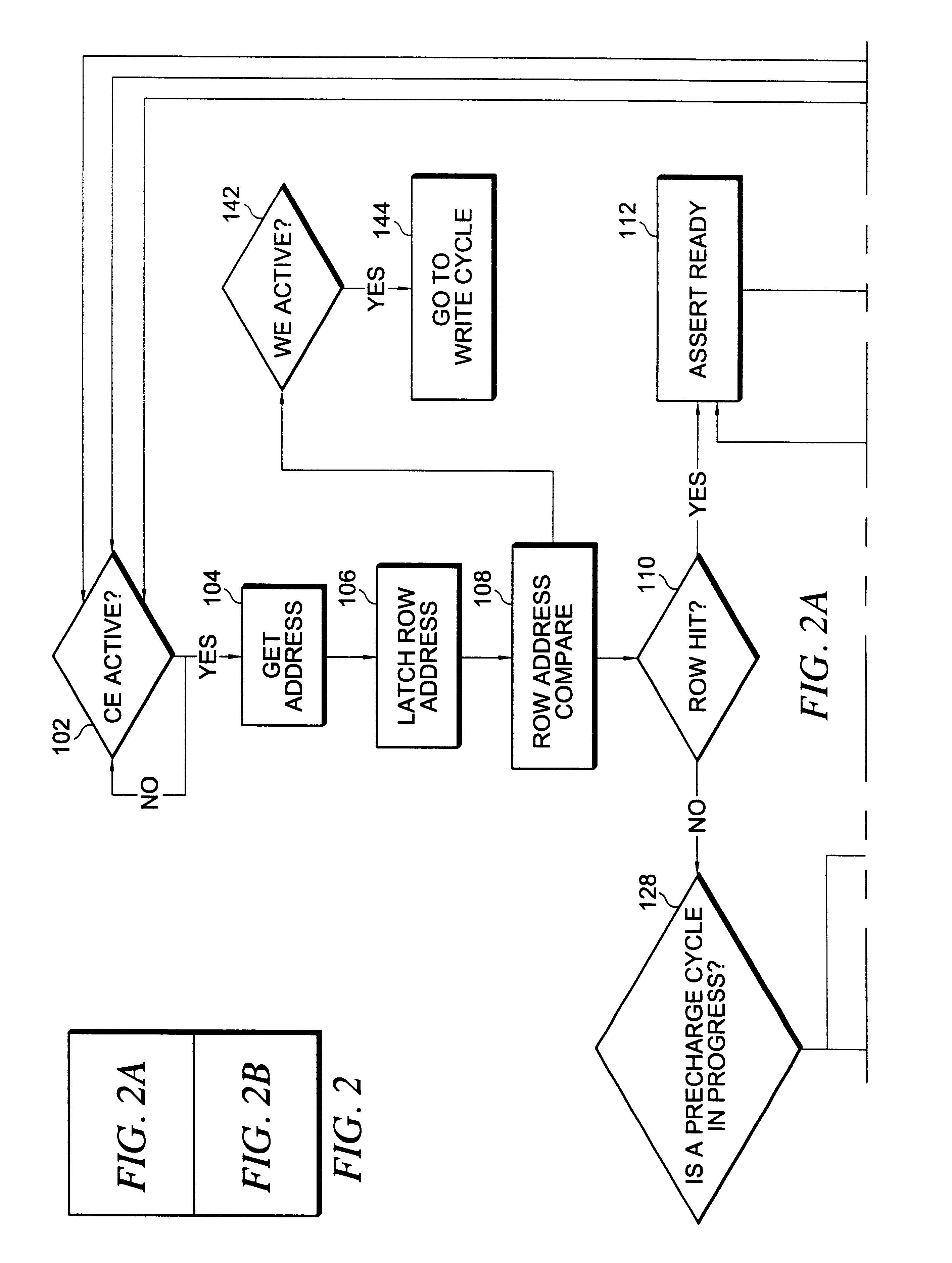

Integrated circuit memory device incorporating a non-volatile memory array and a relatively faster access time memory cache

InactiveUS6263398B1Increases access timeFaster access timeMemory architecture accessing/allocationMemory adressing/allocation/relocationStatic random-access memoryAccess time

An integrated circuit memory device incorporating a non-volatile memory array and a relatively faster access time memory cache integrated monolithically therewith improves the overall access time in page and provides faster cycle time for read operations. In a particular embodiment, the cache may be provided as static random access memory ("SRAM") and the non-volatile memory array provided as ferroelectric random access memory wherein on a read, the row is cached and the write back cycle is started allowing subsequent in page reads to occur very quickly. If in page accesses are sufficient the memory array precharge may be hidden and writes can occur utilizing write back or write through caching. In alternative embodiments, the non-volatile memory array may comprise electrically erasable read only memory ("EEPROM") or Flash memory in conjunction with an SRAM cache or a ferroelectric random access memory based cache which has symmetric read / write times and faster write times than either EEPROM or Flash memory.

Owner:MONTEREY RES LLC

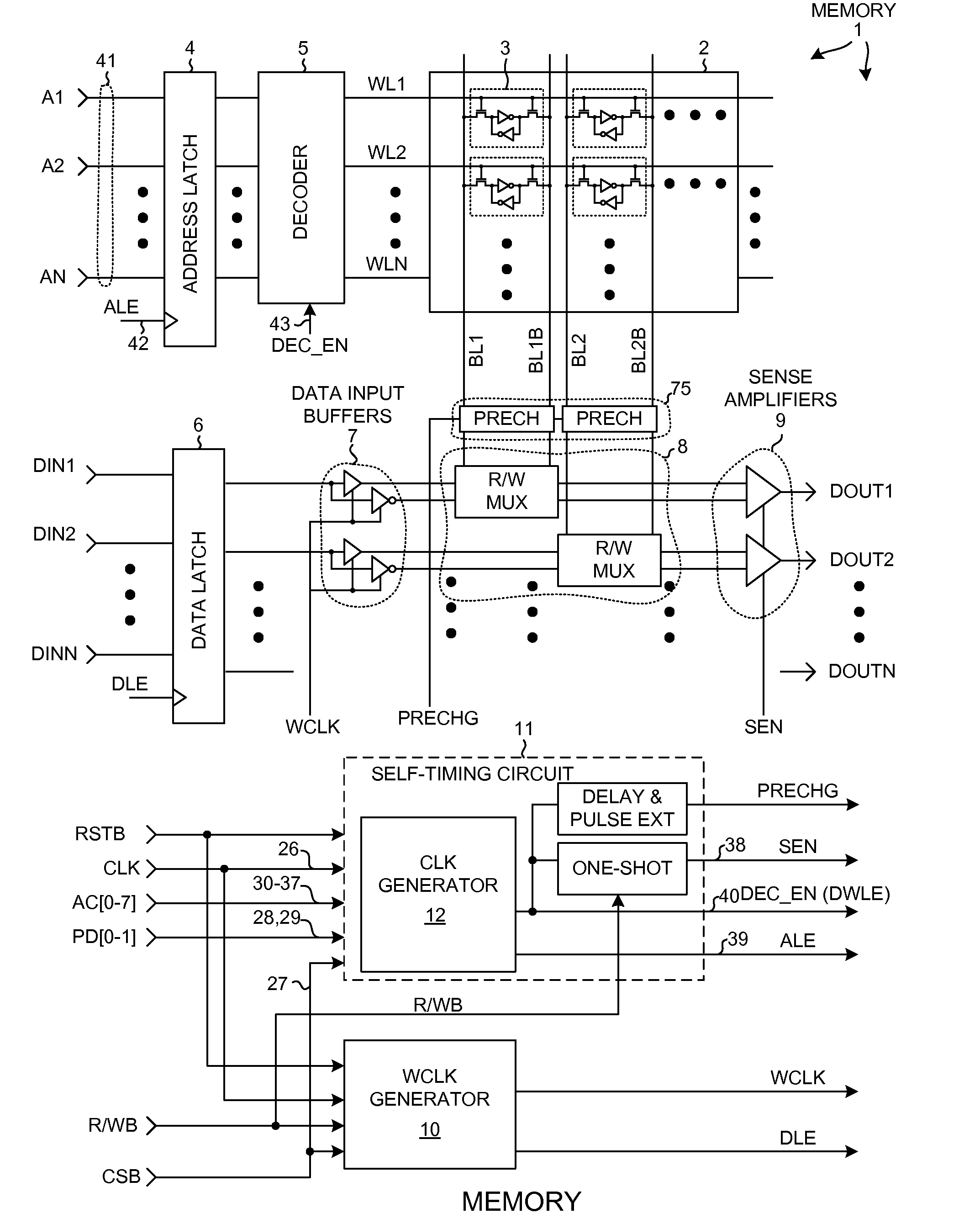

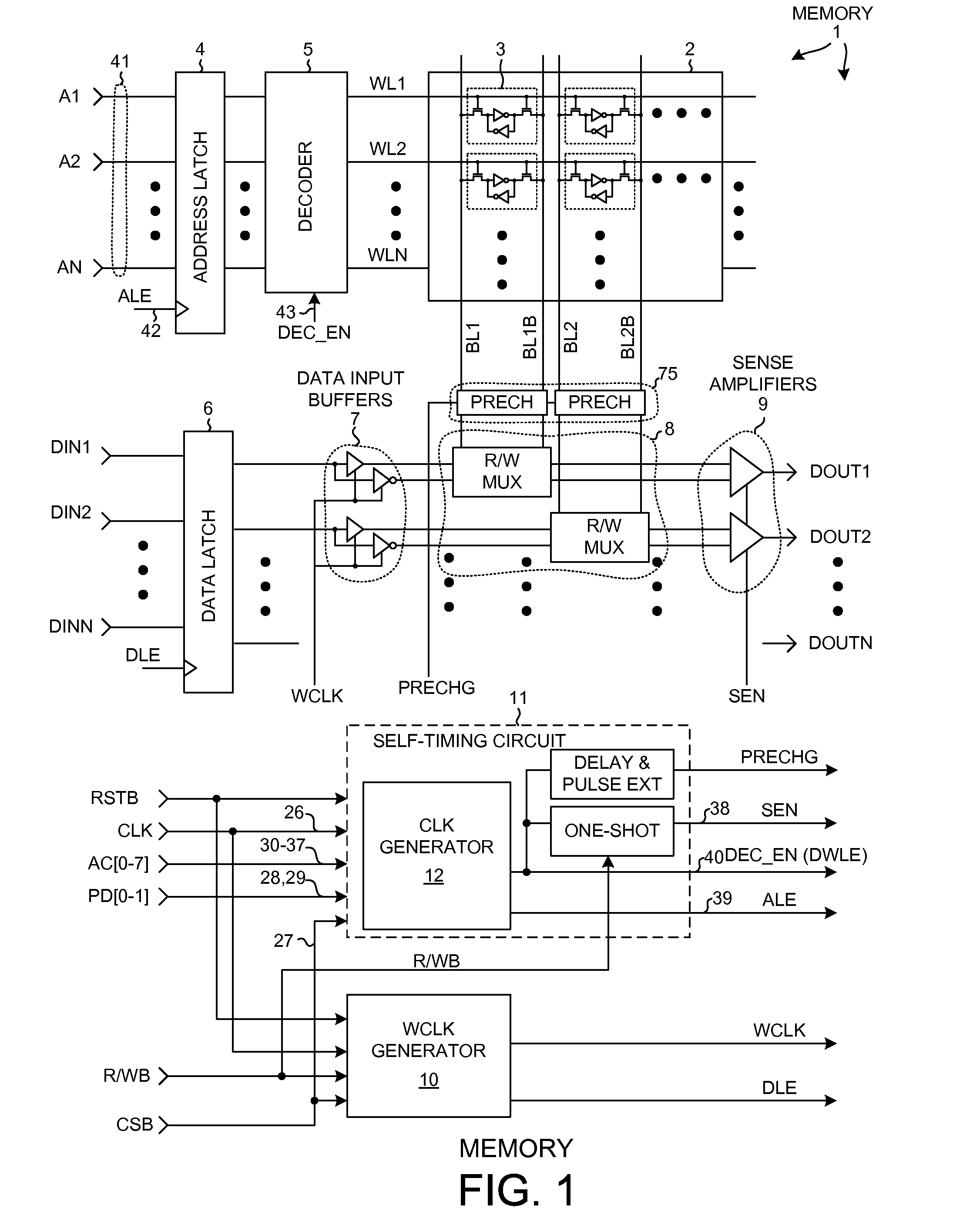

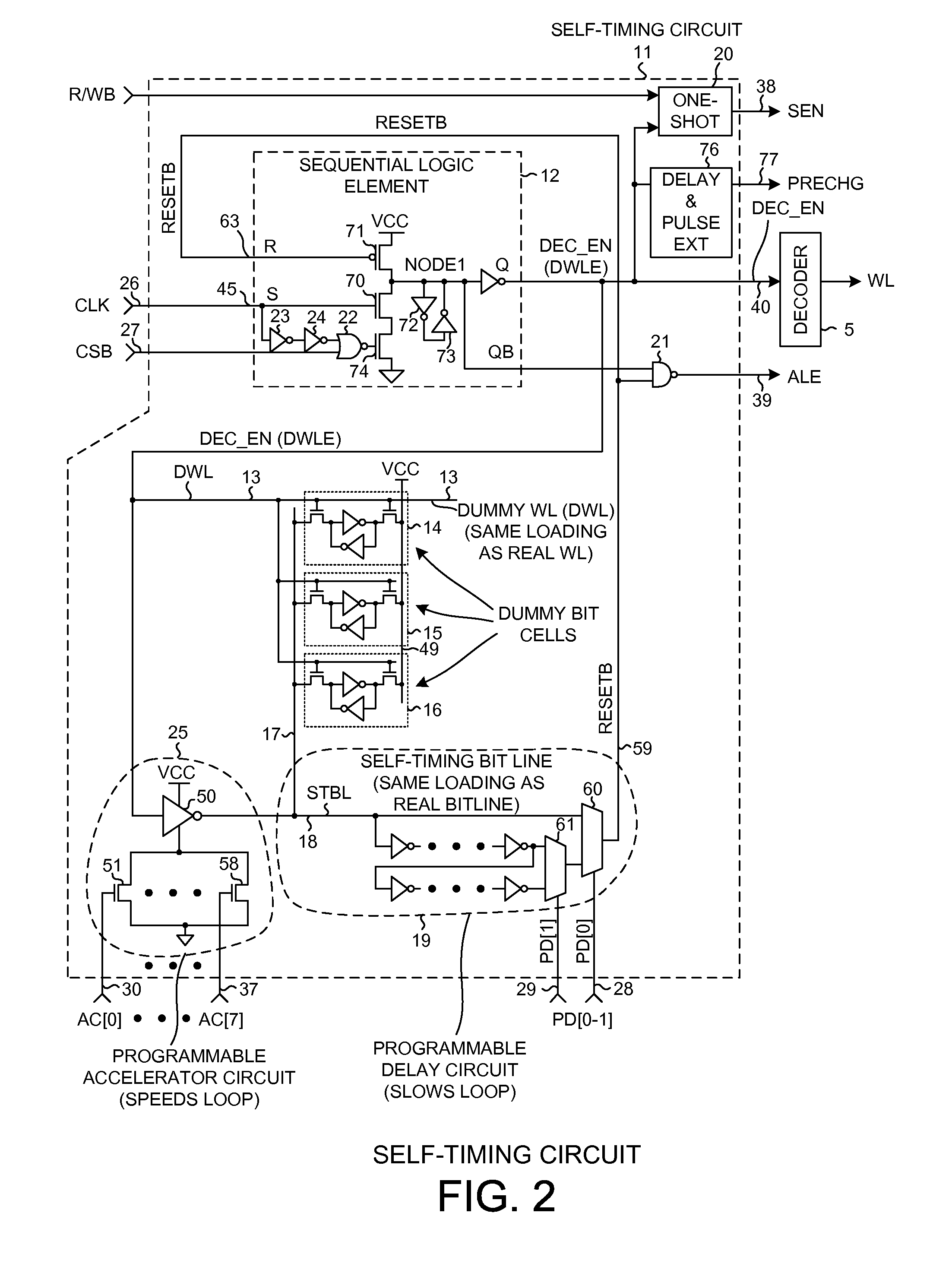

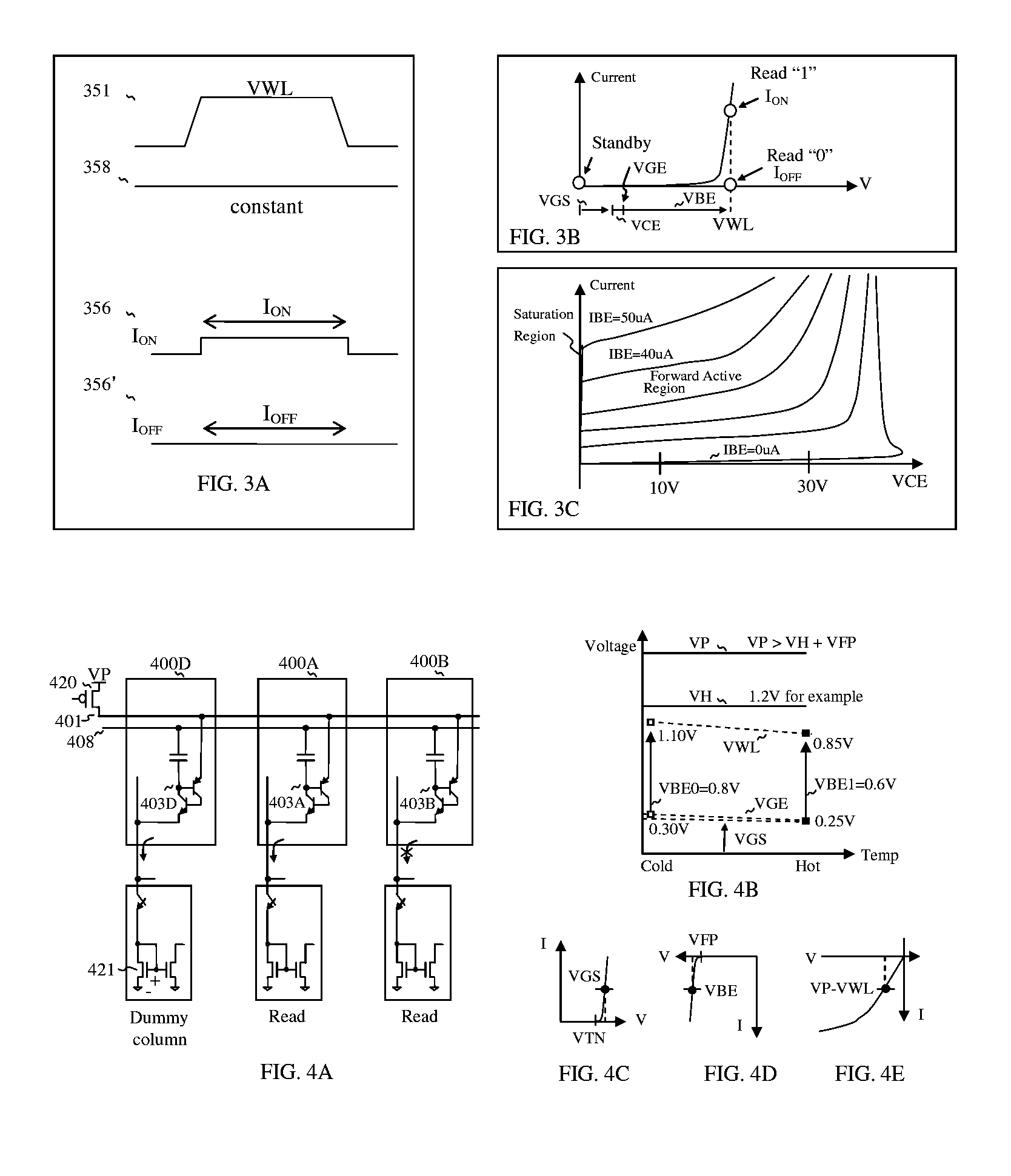

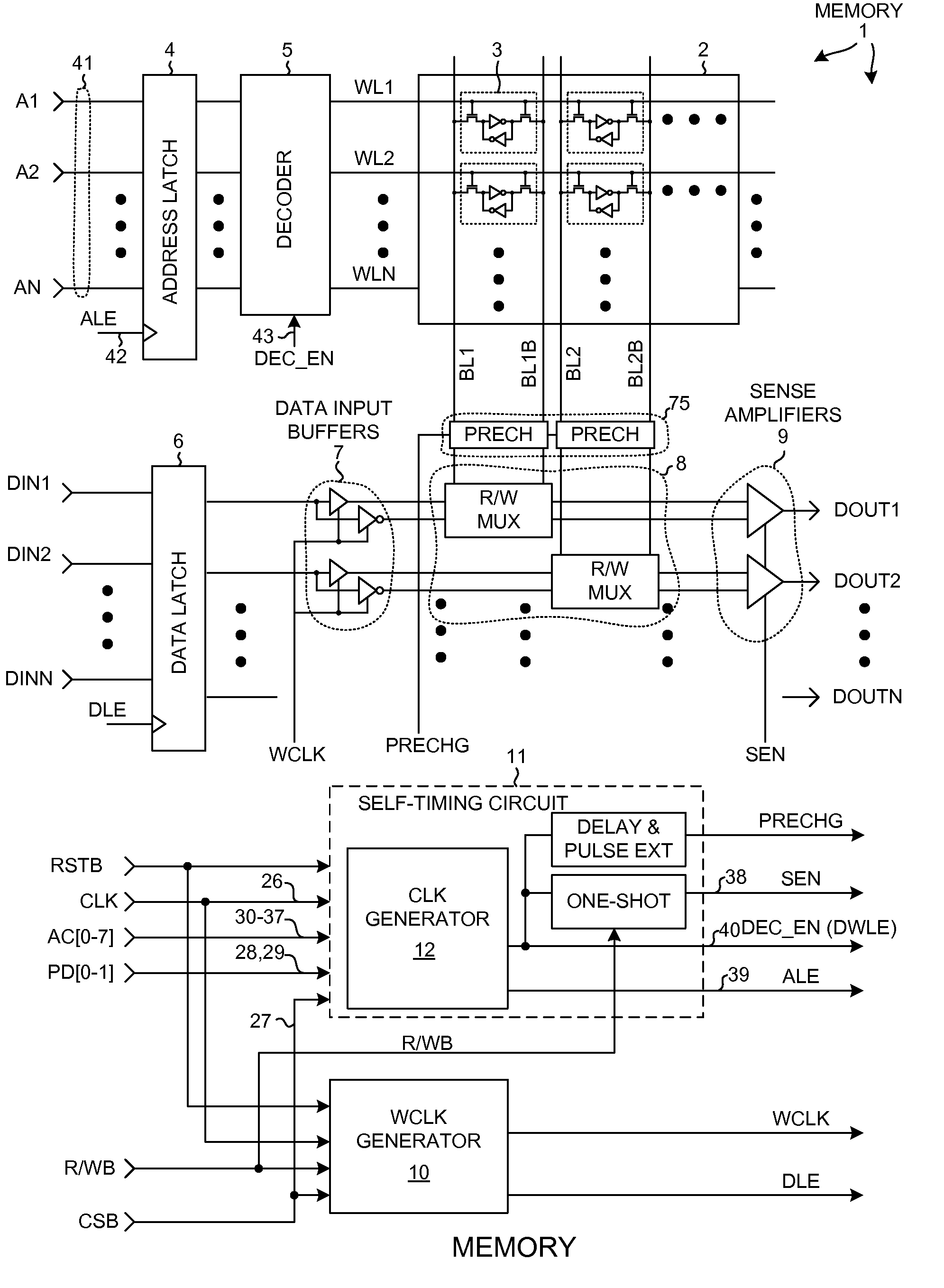

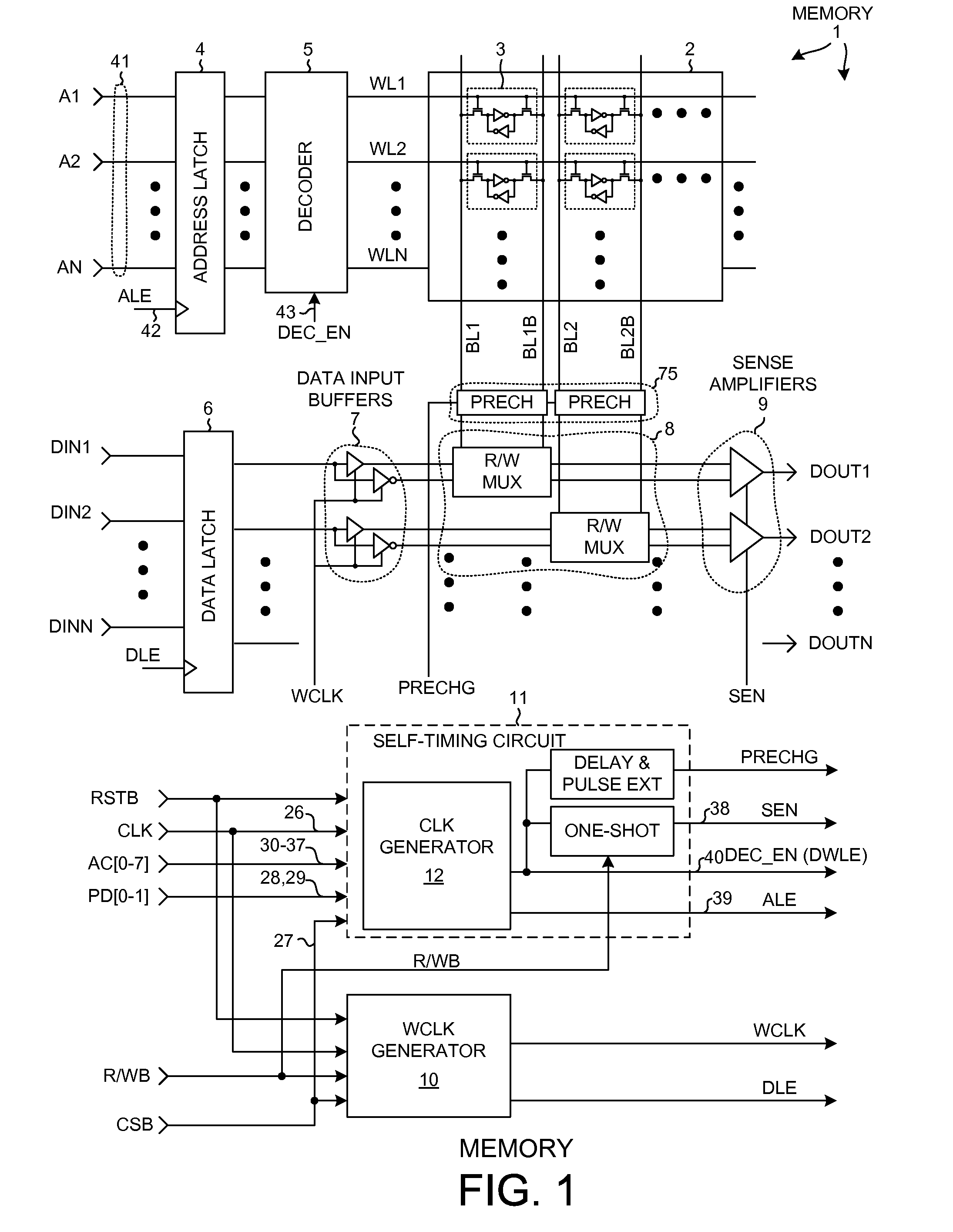

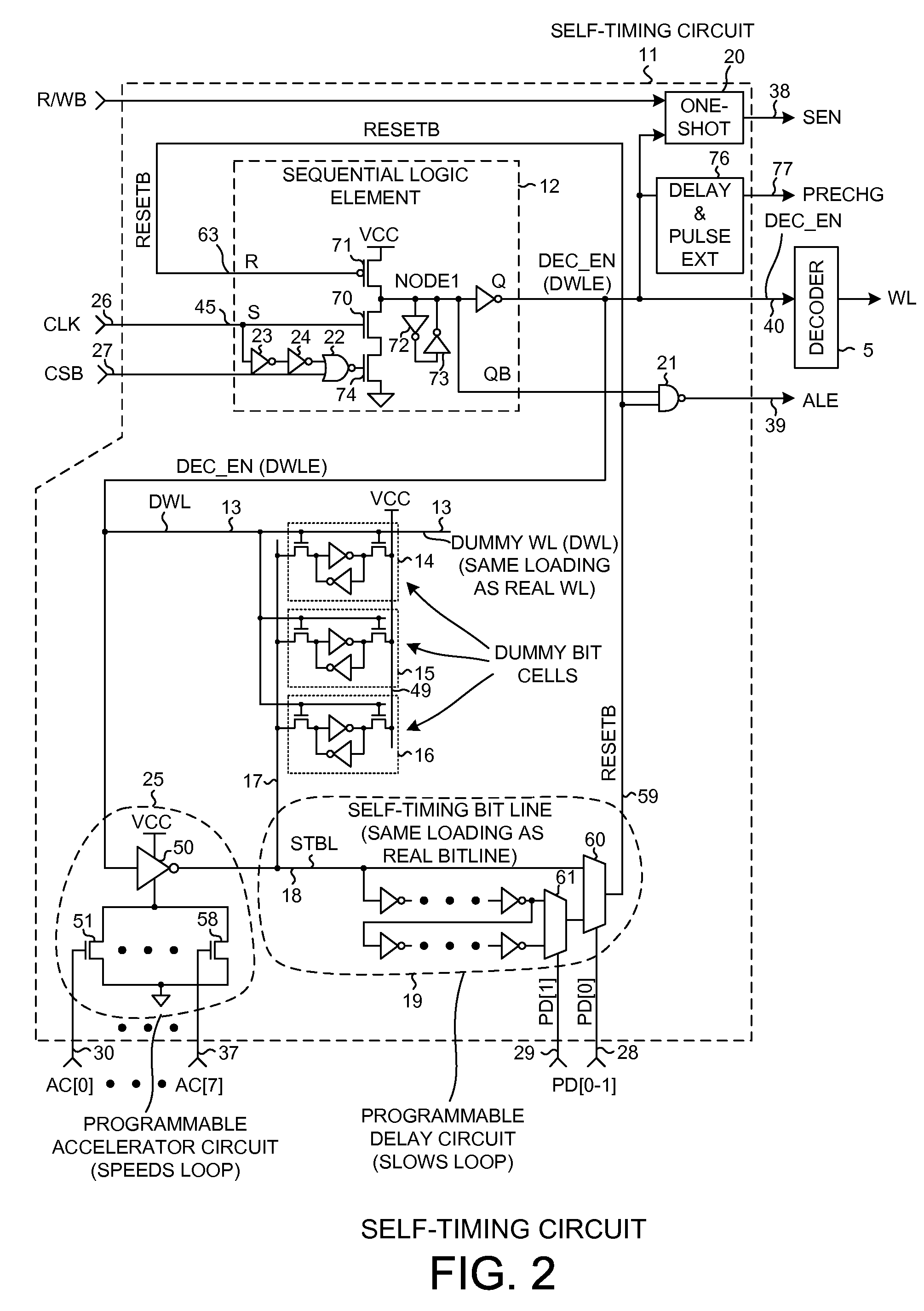

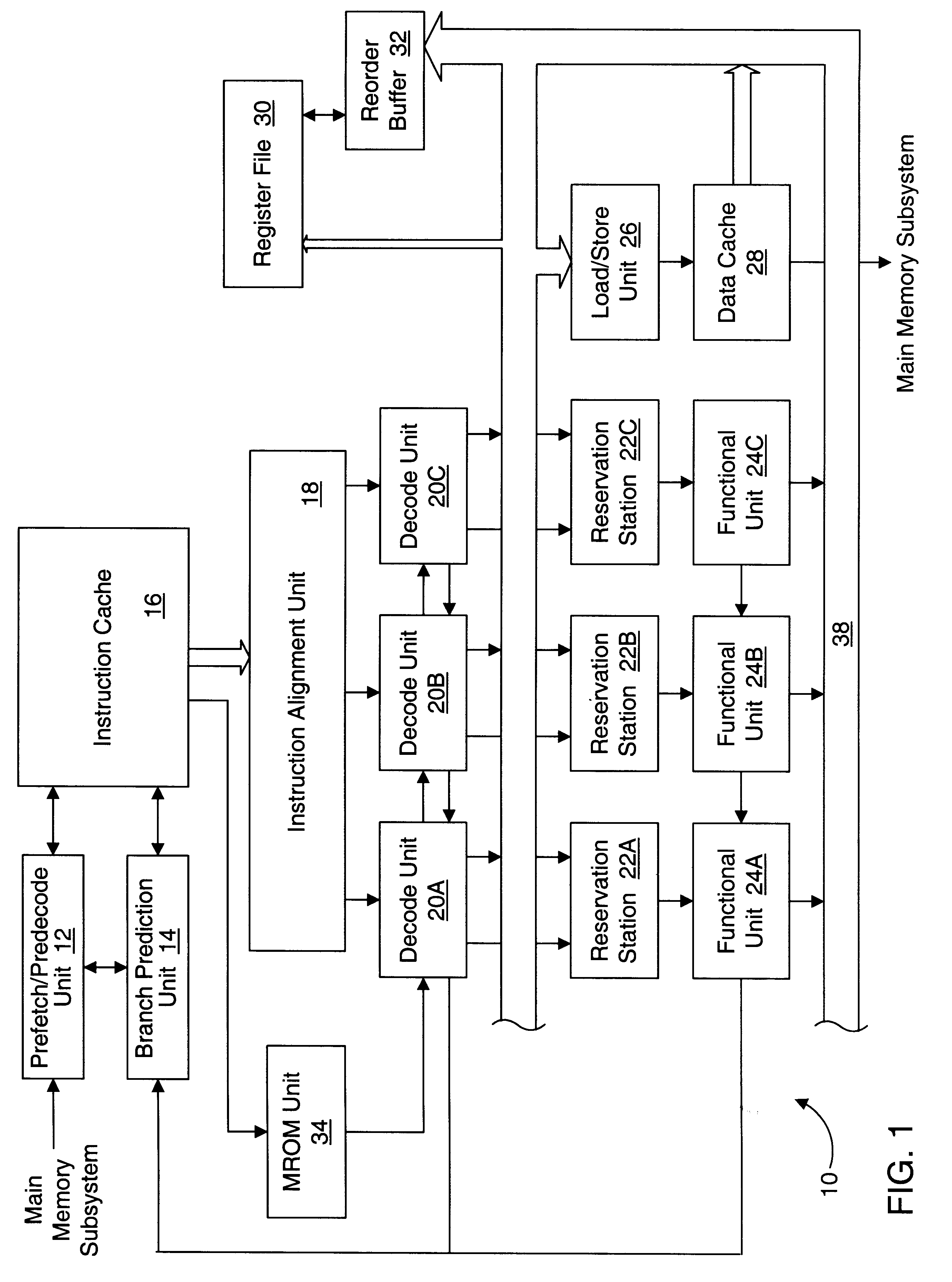

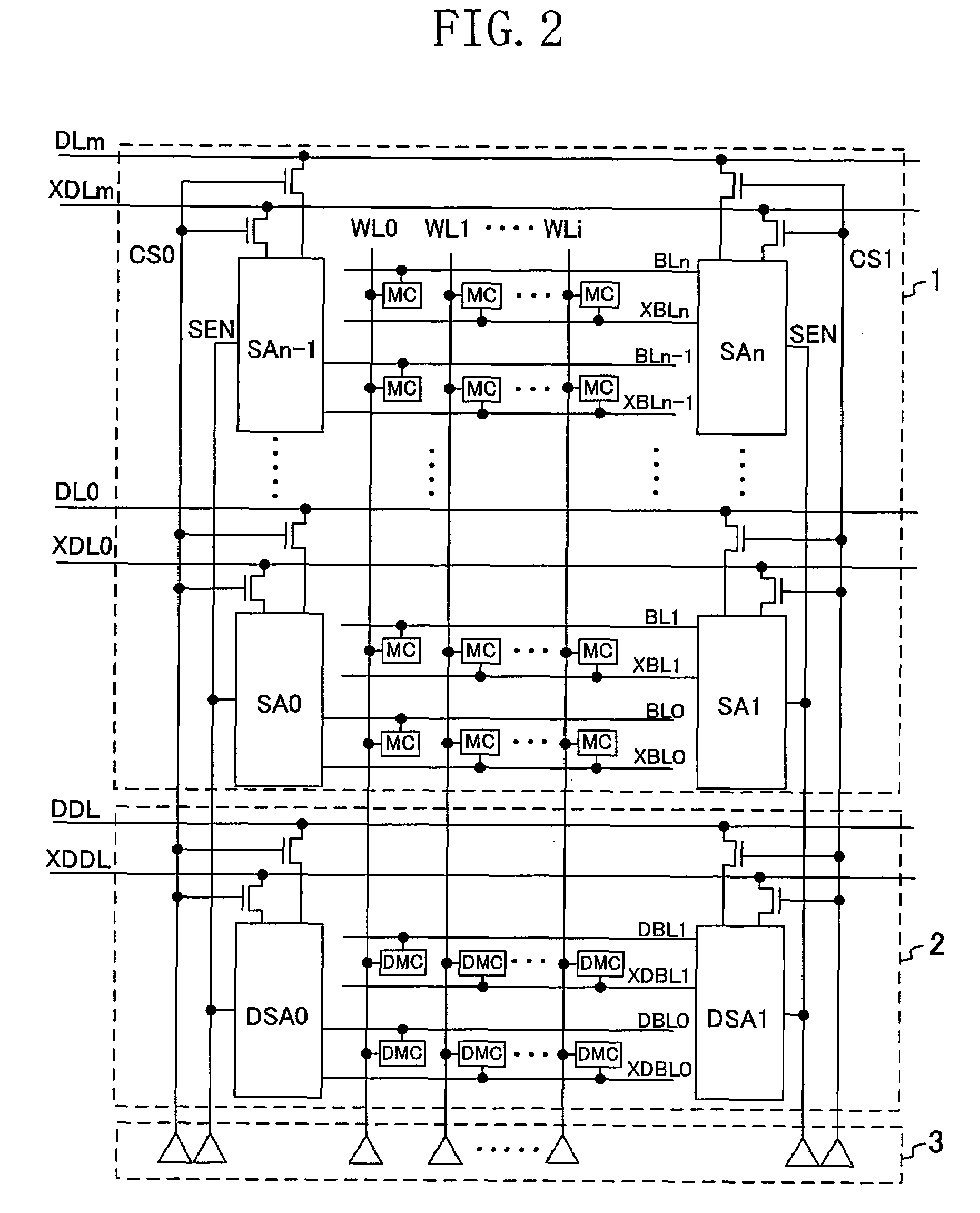

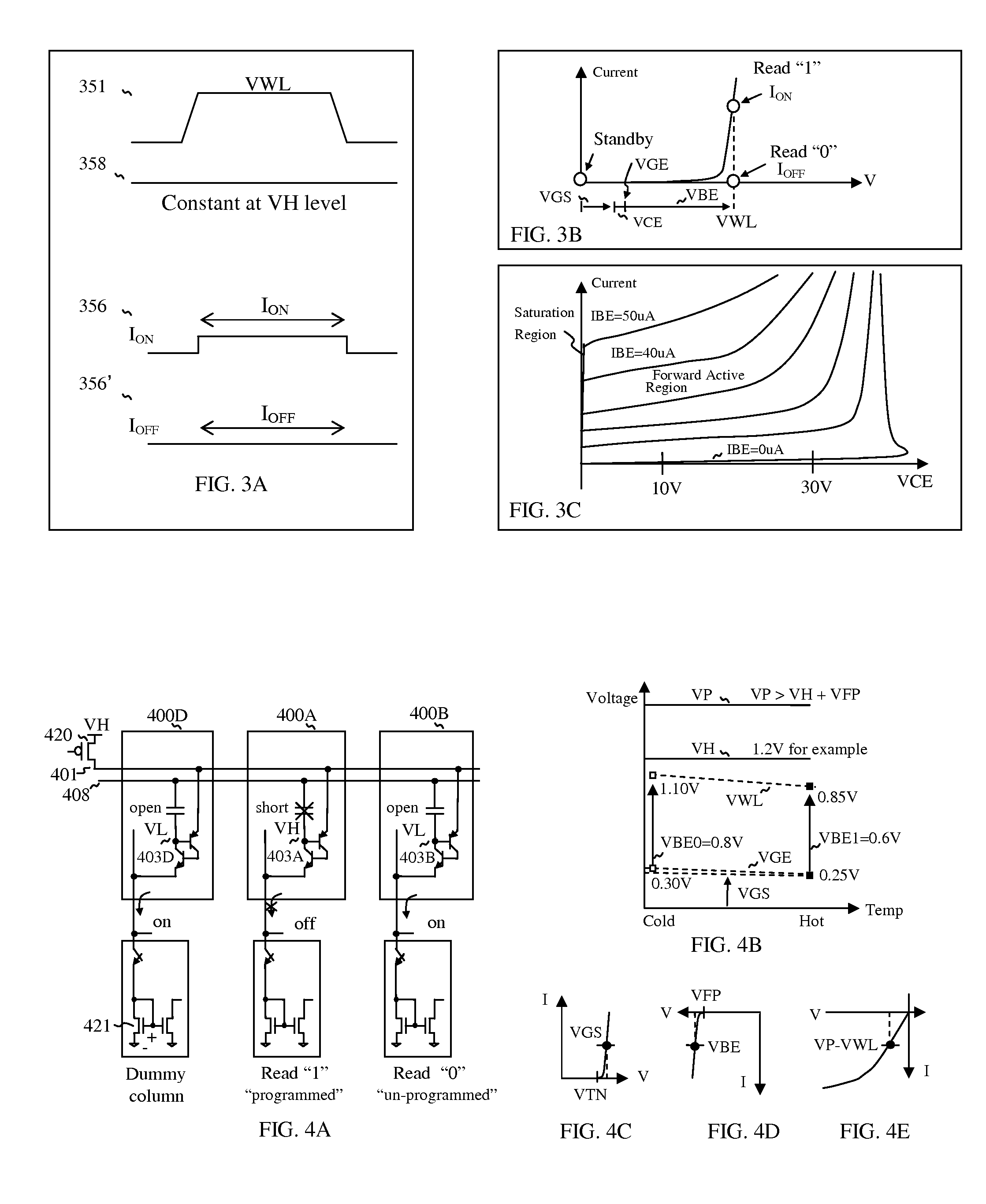

Self-timing circuit with programmable delay and programmable accelerator circuits

ActiveUS20080037338A1Shorten the timeFaster access timeDigital storageInternal memoryAudio power amplifier

A memory has a novel self-timing circuit that generates internal memory control signals. Control signals may include an address latch enable signal, a decoder enable signal, and a sense amplifier enable signal. The circuit has a timing loop whose timing mimics the timing of an access of the real memory. The timing loop includes dummy bit cells of identical construction to bit cells in the real array being accessed, a programmable delay circuit, and a programmable accelerator circuit. The dummy bit cells cause the timing of the control signals to track speed changes in the memory array being accessed. The programmable delay and accelerator circuits are usable to slow or speed the timing loop. The programmable delay and accelerator circuits are usable to achieve a desired yield to memory access speed tradeoff. Flexibility of the timing loop allows a memory to be designed before memory access timing characteristics are fixed.

Owner:QUALCOMM INC

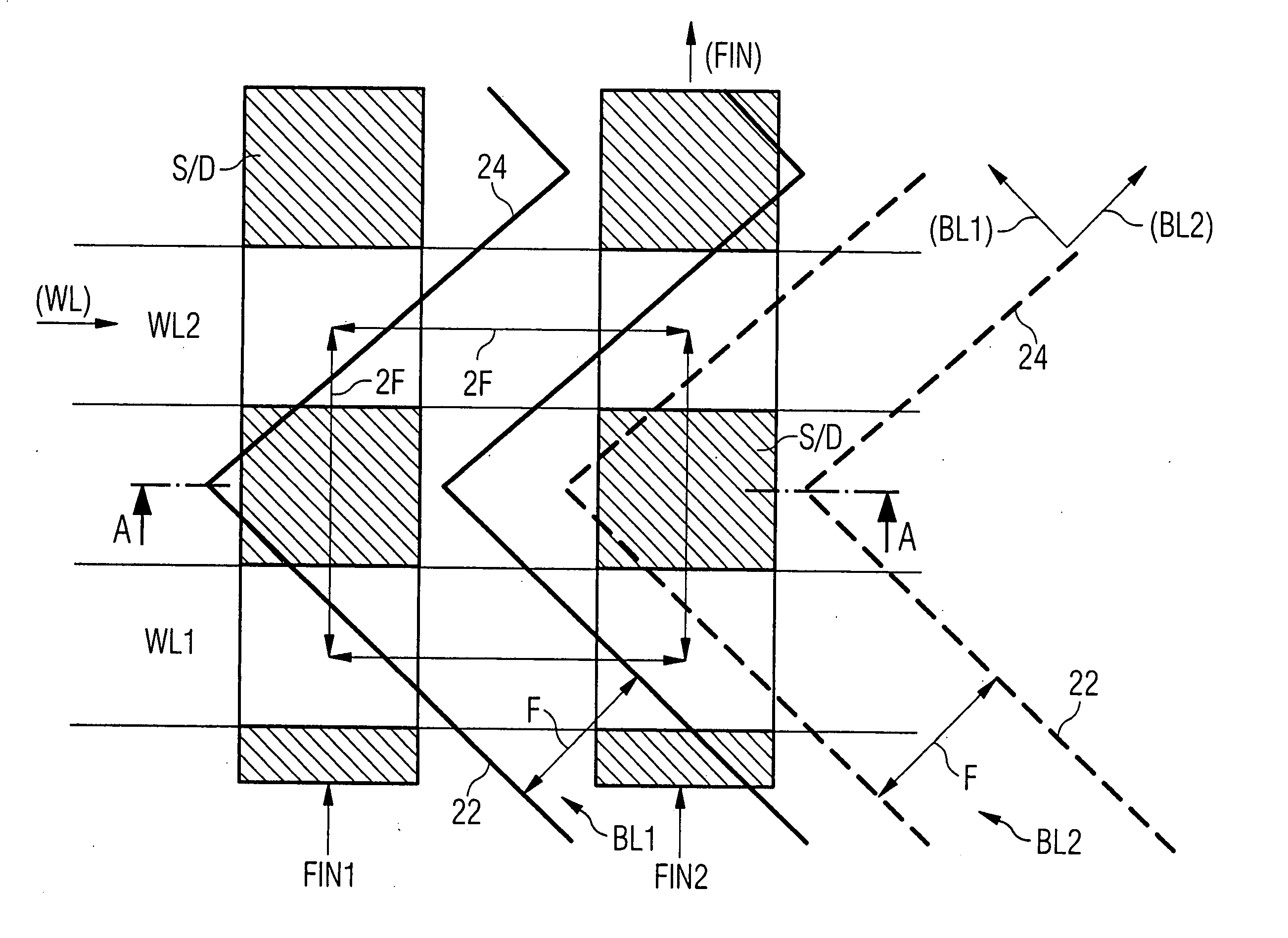

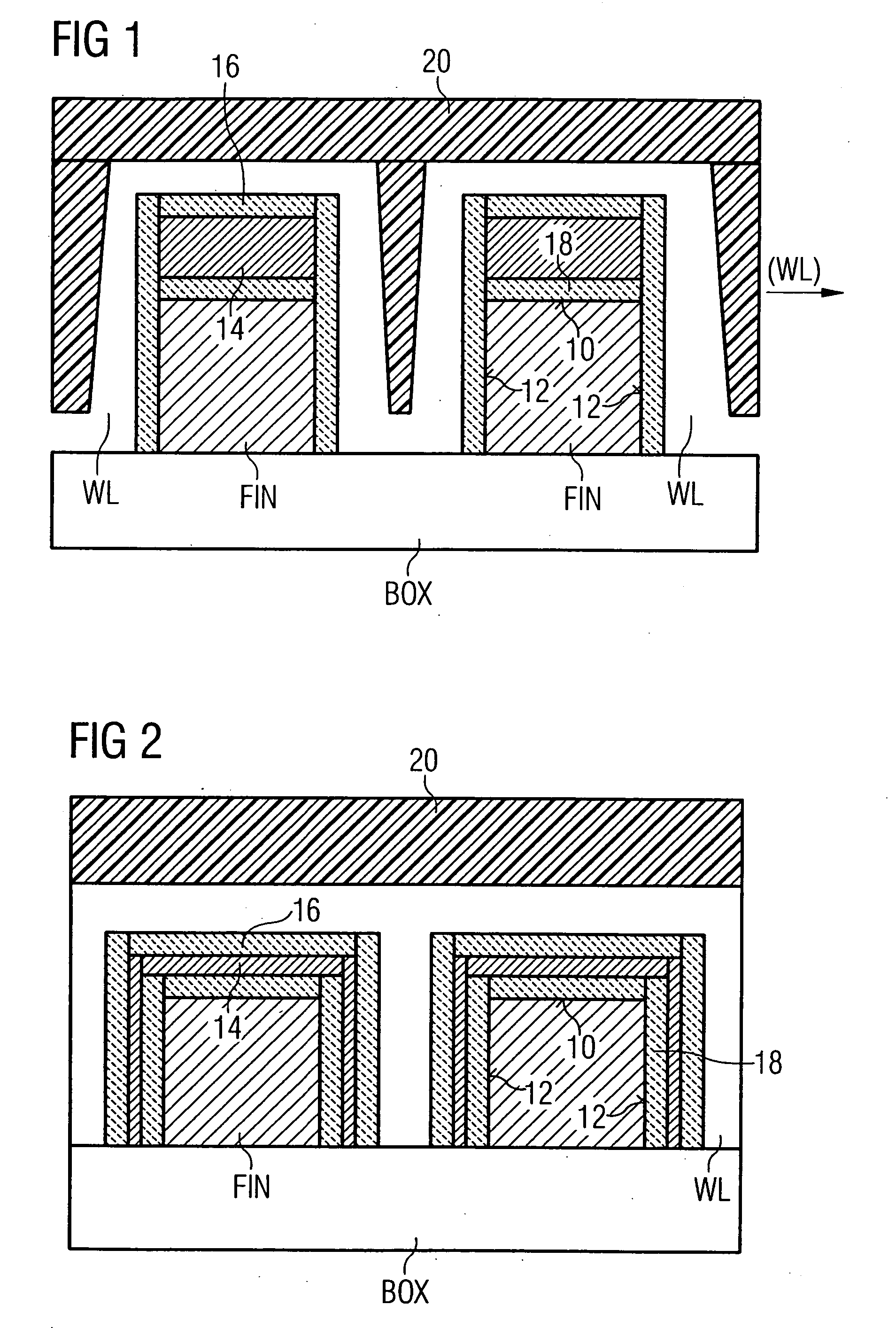

Word and bit line arrangement for a FinFET semiconductor memory

InactiveUS20050199913A1Improve good performanceImprove storage densityTransistorSolid-state devicesBit lineSemiconductor materials

The invention relates to a semiconductor memory having a multiplicity of fins made of semiconductor material which are spaced apart from one another, a multiplicity of channel regions and contact regions being formed in each of the fins, a multiplicity of word lines, a multiplicity of storage layers, at least one of the storage layers being arranged between each of the channel regions and the word line, and a multiplicity of bit lines, the longitudinal axes of first bit line portions running parallel to a first bit line direction and the longitudinal axes of second bit line portions running parallel to a second bit line direction, the second bit line direction being rotated relative to the first bit line direction, each of the bit lines being electrically connected to a multiplicity of the contact regions, wherein, between two contact regions of the same fin that are connected to one of the bit lines, a contact region is not connected to the respective bit line.

Owner:INFINEON TECH AG

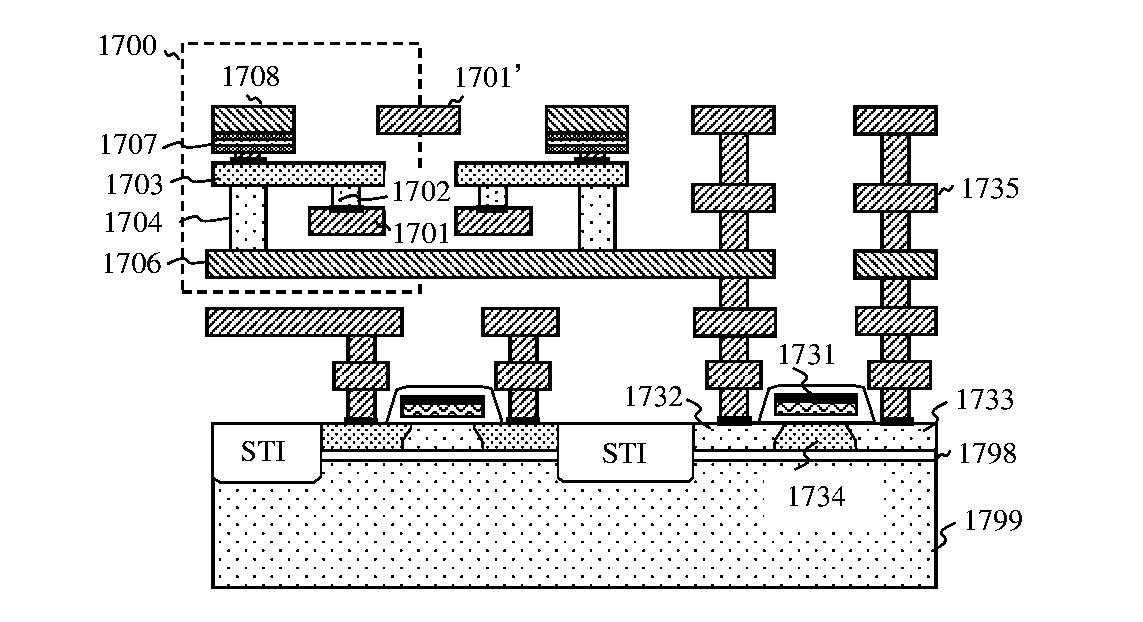

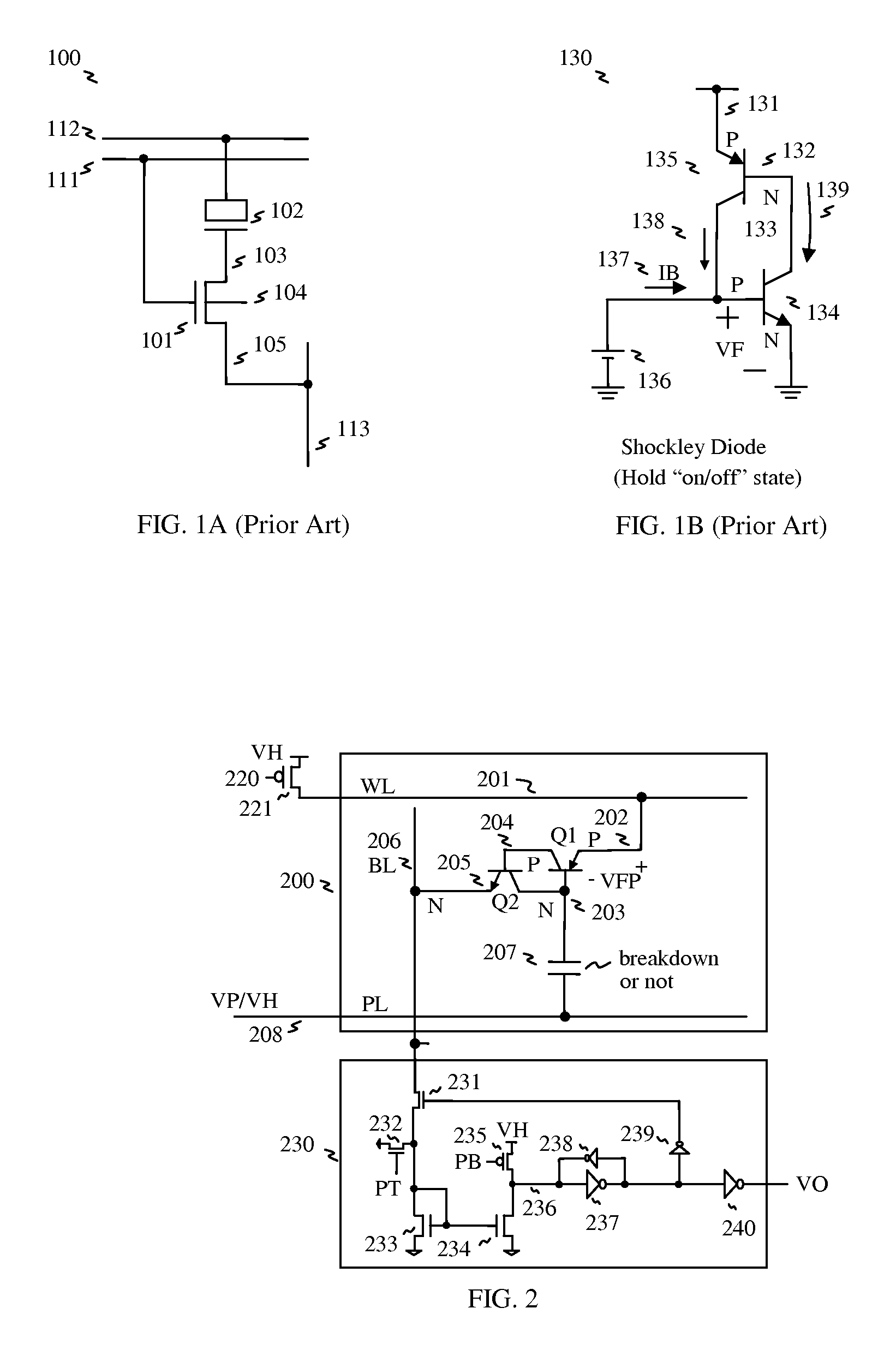

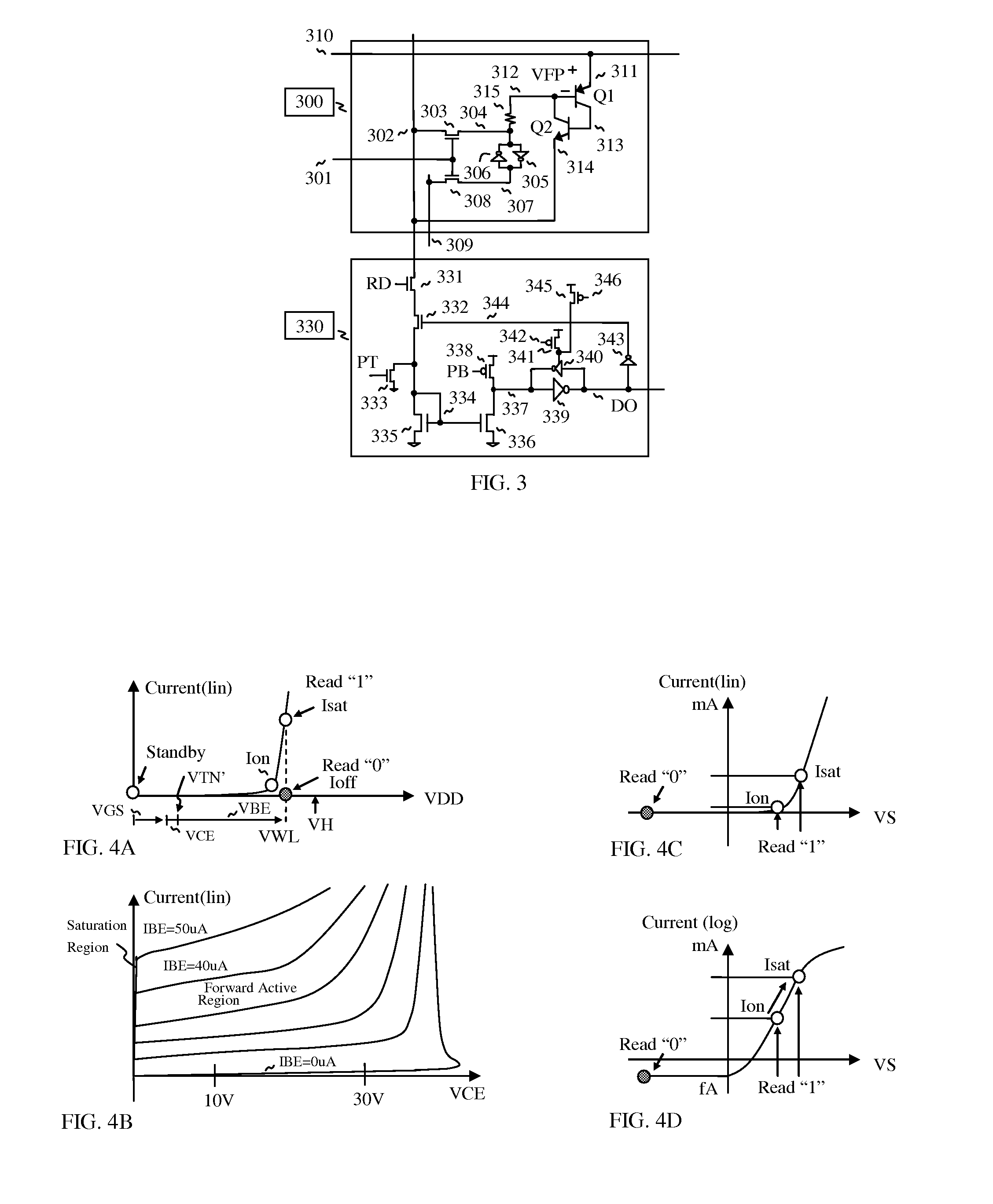

Stacked capacitor memory

InactiveUS20070183191A1Reduce chip areaLess complicated to fabricateSolid-state devicesDiodeEngineeringMulti port

Stacked capacitor memory is realized, wherein a capacitor stores data and a diode serves as an access device instead of MOS transistor, the first terminal is connected to a word line, the second terminal is connected to the first electrode of the capacitor which serves as a storage node while the second electrode is connected to a plate line, the third terminal is floating, and the fourth terminal is connected to a bit line. When write, the storage node is charged or not, depending on the conducting state of the diode which is controlled by the bit line. When read, the diode also serves as a sense amplifier to detect whether the storage node is forward bias or not, and it sends binary data to a latch device wherein includes a current mirror and a feedback loop which cuts off the current path after latching, thus it reduces active current, minimizes data pattern sensitivity, and also rejects coupling noise. And dummy rows and columns generate replica delay signals which guarantee timing margin and reduce cycle time. And its applications are extended to single port, multi port and content addressable memory. In addition, the memory cells are formed in between the routing layers, which memory cells can be stacked over the transistor or another capacitor memory cell.

Owner:KIM JUHAN

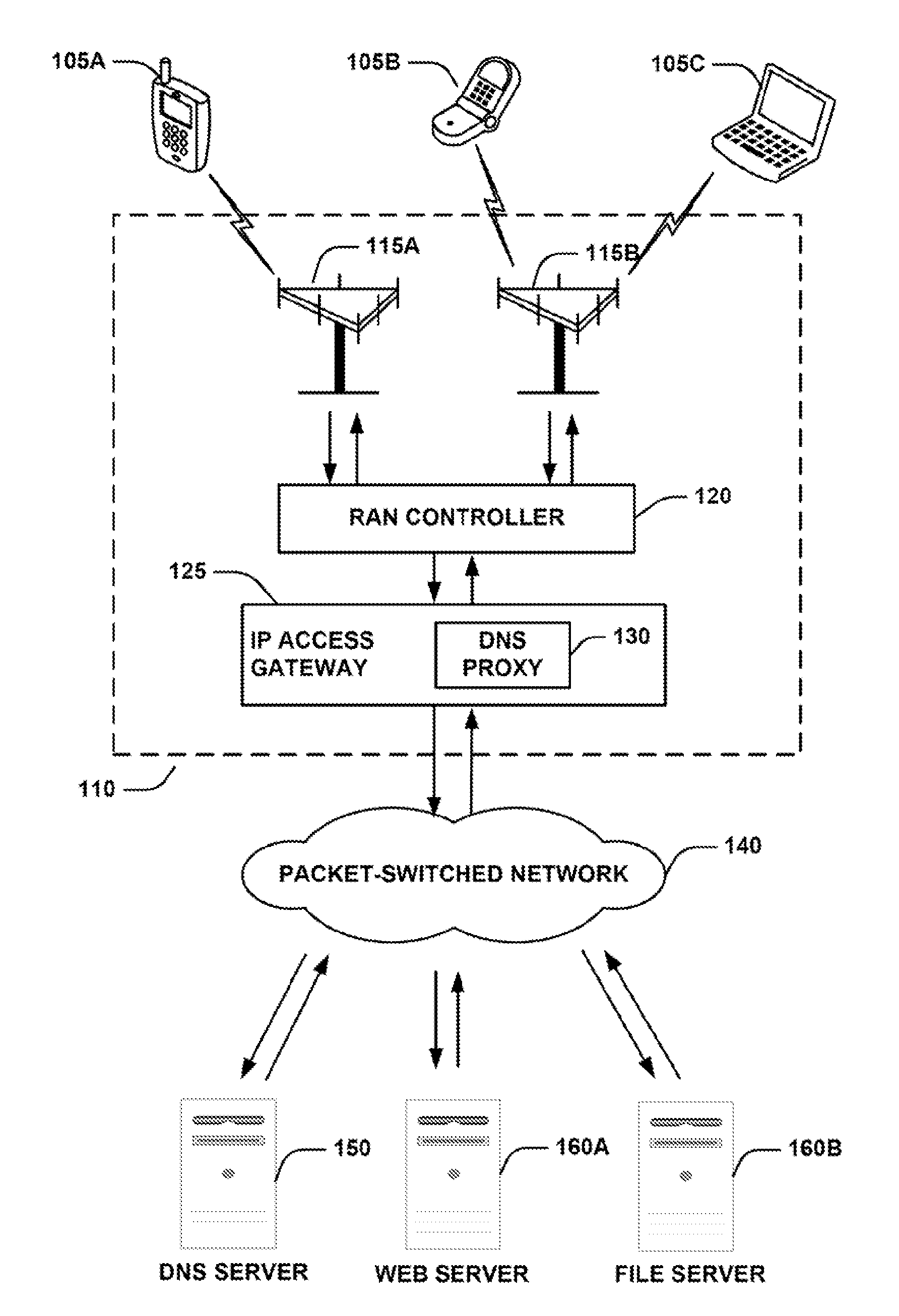

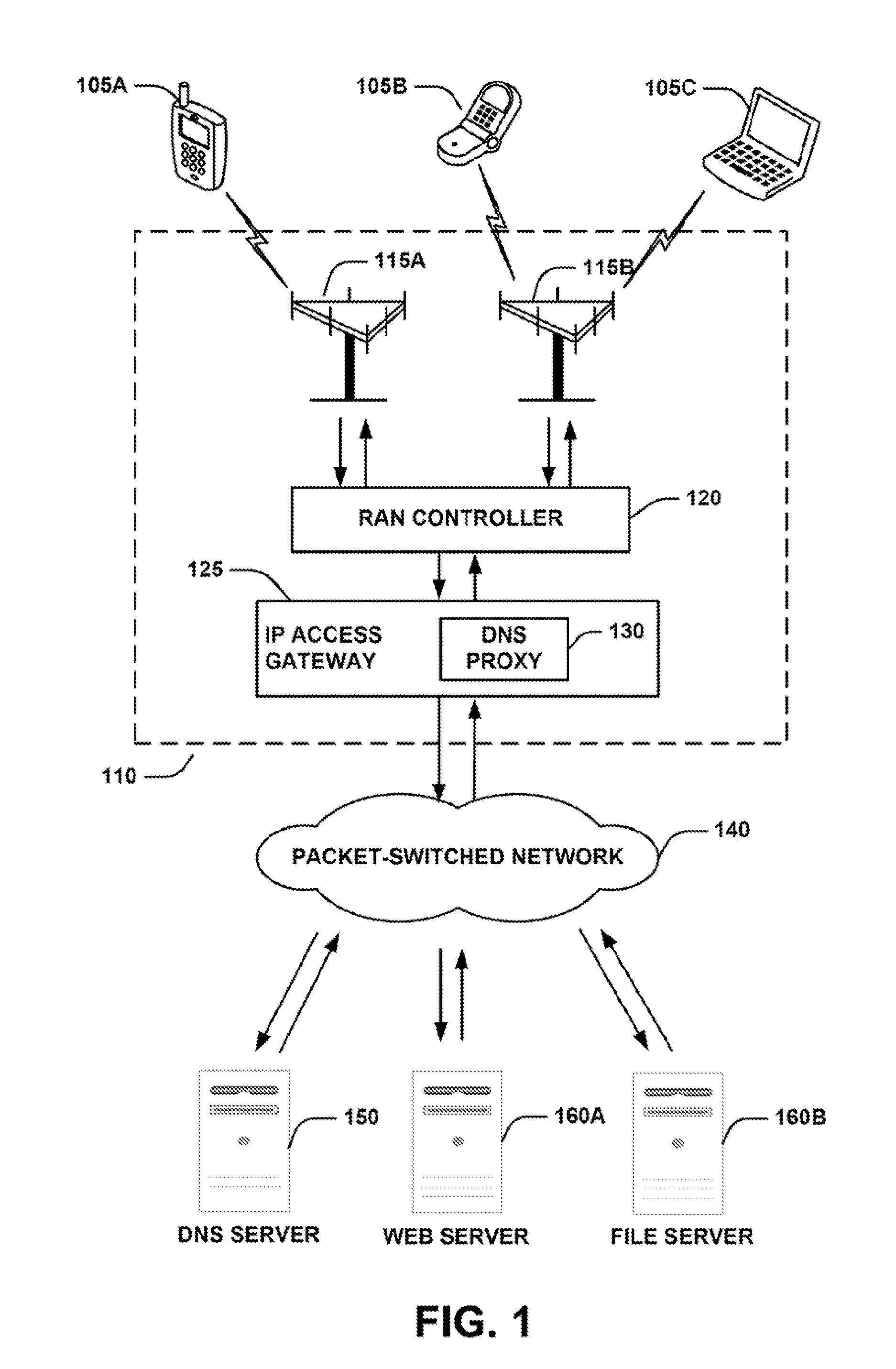

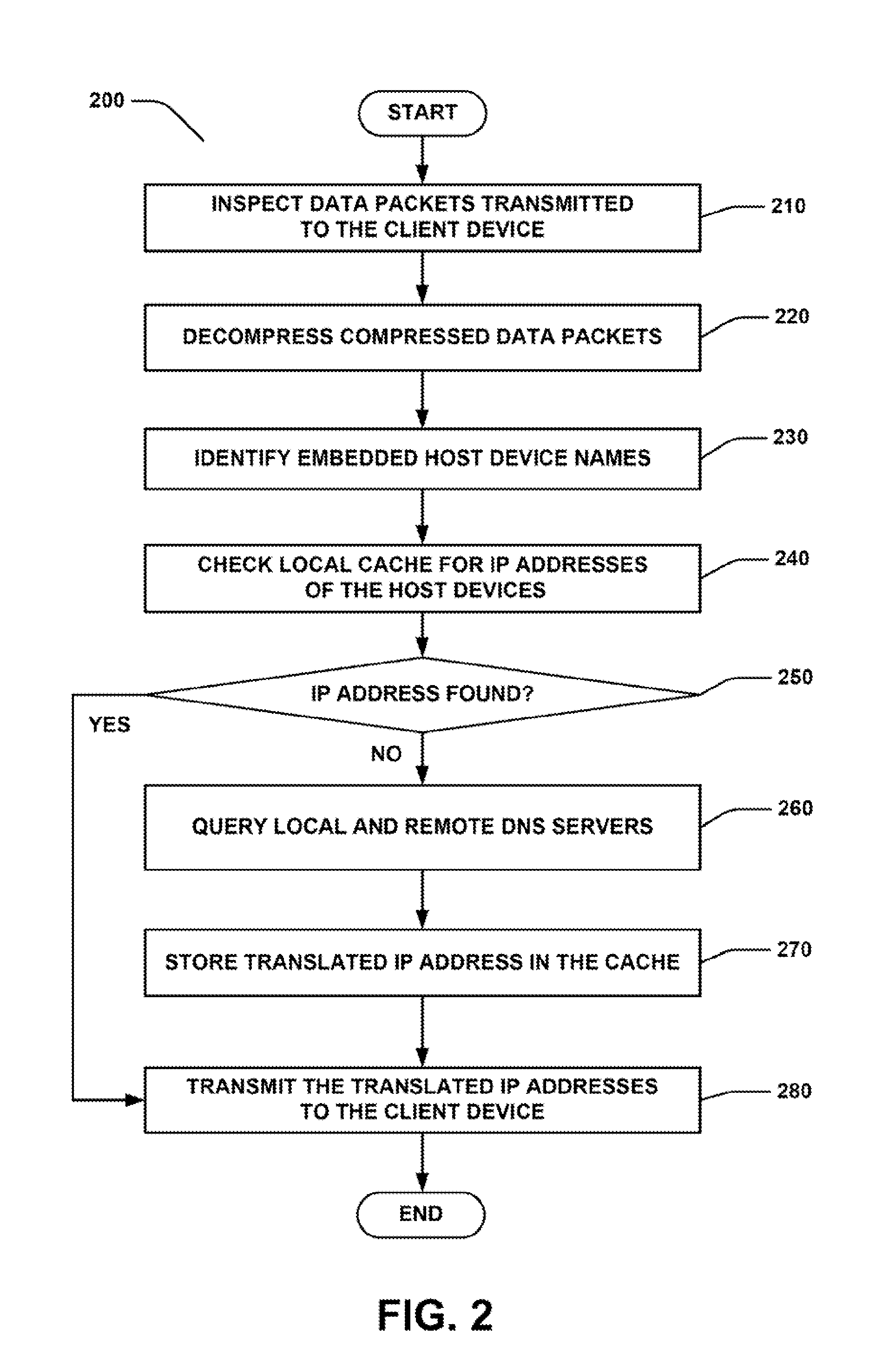

Systems and Methods for Preemptive DNS Resolution

InactiveUS20110153807A1Faster access timeEasy to operateMultiple digital computer combinationsTransmissionTelecommunications linkIp address

Disclosed are systems, methods and computer program products for preemptive DNS resolution. A DNS proxy is provided for inspecting data packets transmitted to a client device on a first communication link. The proxy identifies one or more host device names embedded in the inspected data packets and resolves IP addresses associated with the embedded host device names. The proxy device transmits the inspected data packets to the client device without alterations on a second communication link. The second communication link has significantly higher propagation latency than the first communication link. The proxy then transmits to the client device, independent of the inspected data packets, the one or more host device names and the associated resolved IP addresses for use by the client device to establish connections to the host devices identified in the inspected data packet.

Owner:QUALCOMM INC

Self-timing circuit with programmable delay and programmable accelerator circuits

ActiveUS7499347B2Shorten the timeFaster access timeDigital storageInternal memoryAudio power amplifier

Owner:QUALCOMM INC

Hybrid memory module structure and method of driving the same

InactiveUS20160110102A1Faster access timeInput/output to record carriersDigital storageWork memoryMemory module

A hybrid memory module structure includes a channel for receiving data from and transmitting data to a device external to the hybrid memory module structure, a first memory module connected to the channel, and a second memory module connected to the channel. The first memory module includes at least a first memory and a second memory, the first memory being a working memory and the second memory being a storage memory. The second memory module includes at least a third memory and a fourth memory, the third memory being a working memory and the fourth memory being a storage memory. The channel includes a first data line commonly connected to the first memory and the second memory, and a second data line commonly connected to the third memory and the fourth memory.

Owner:SAMSUNG ELECTRONICS CO LTD

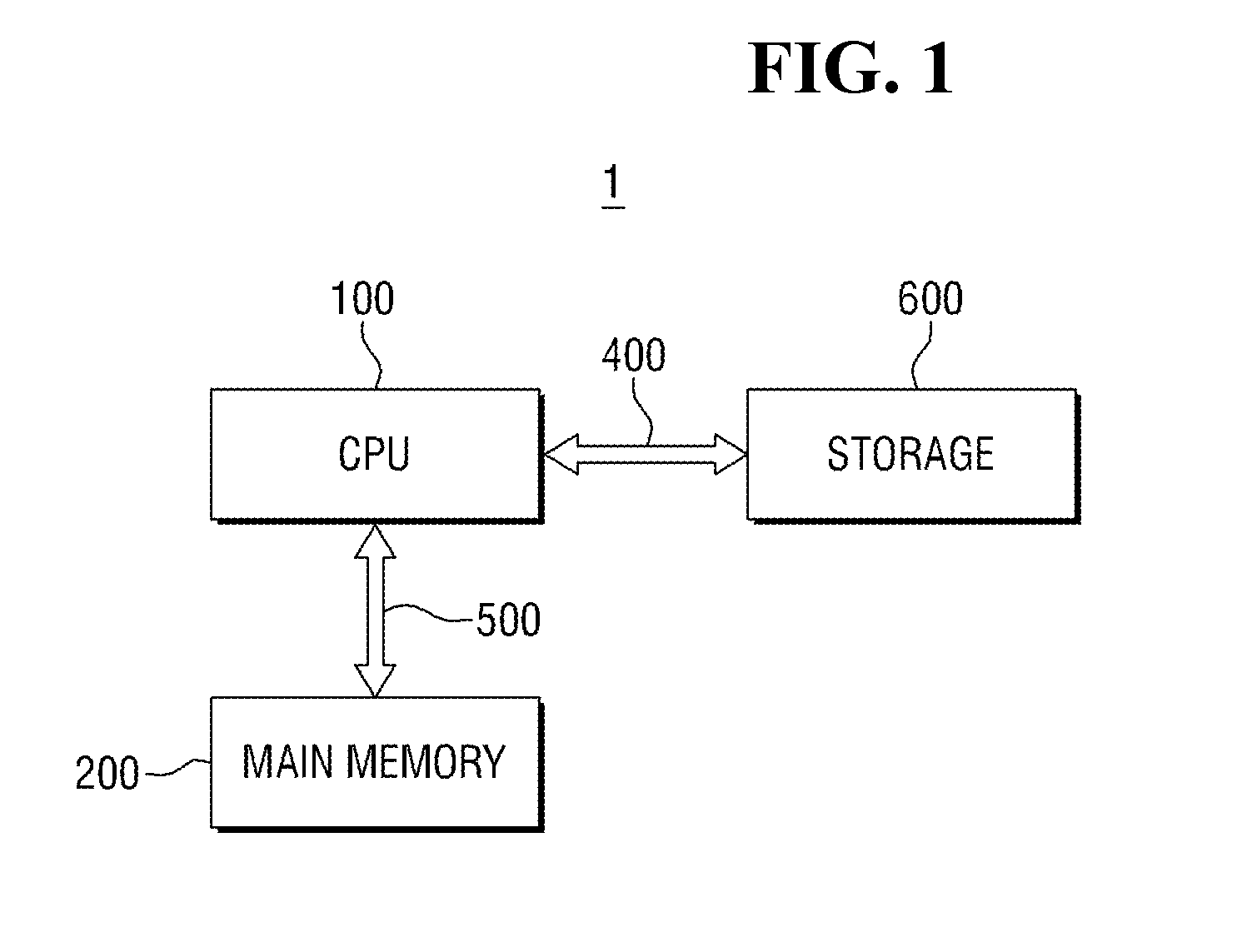

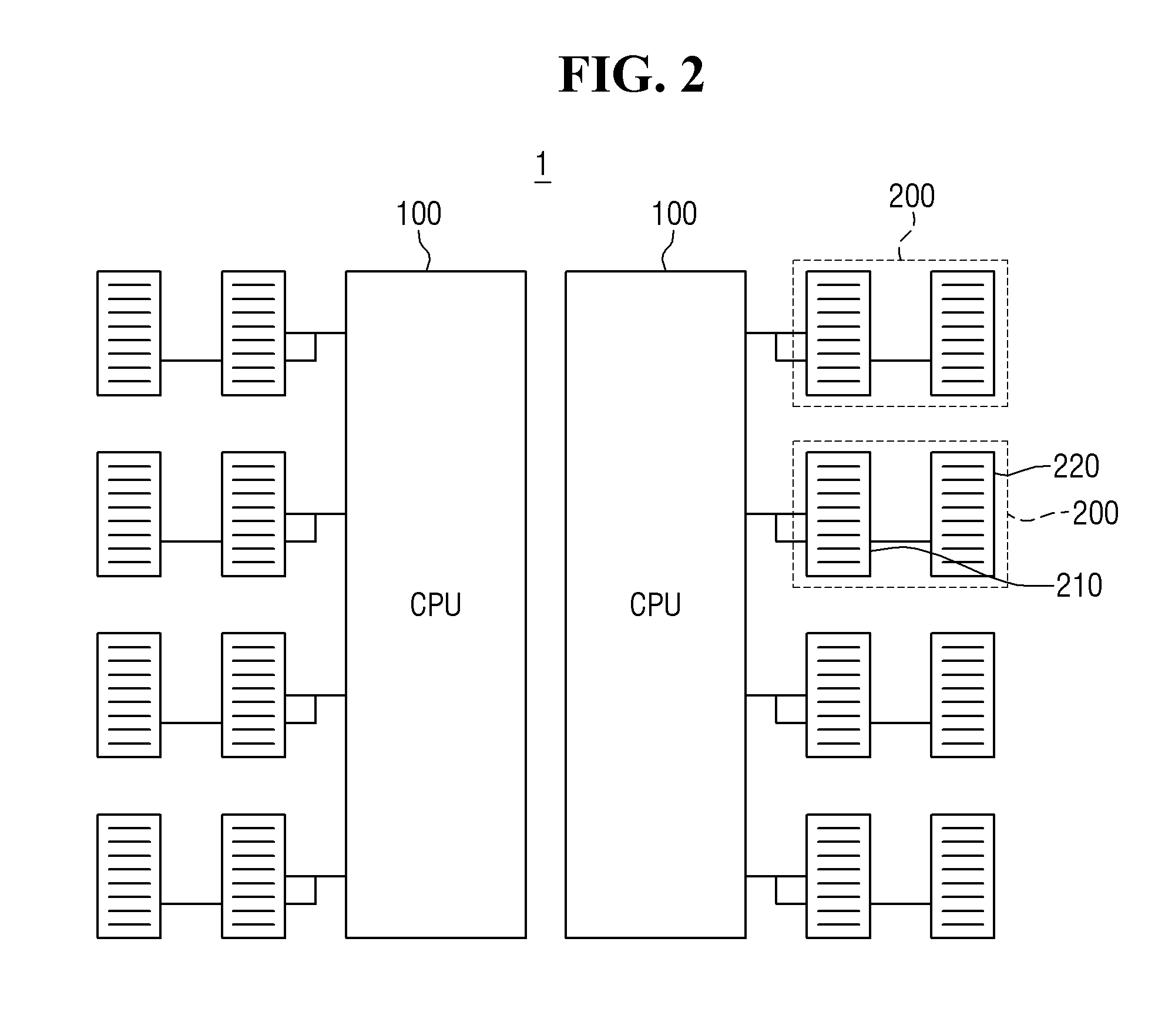

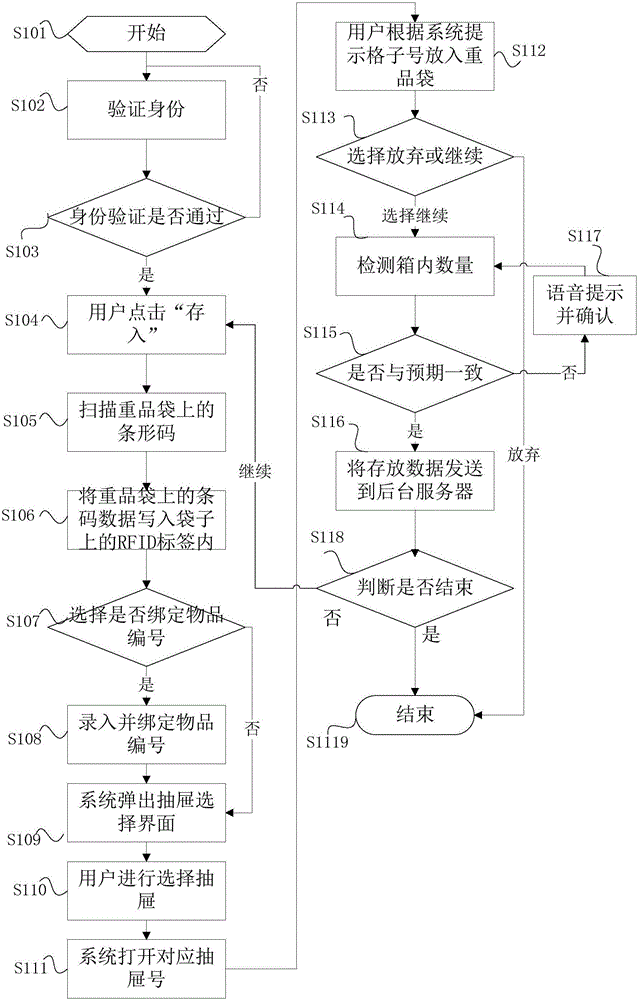

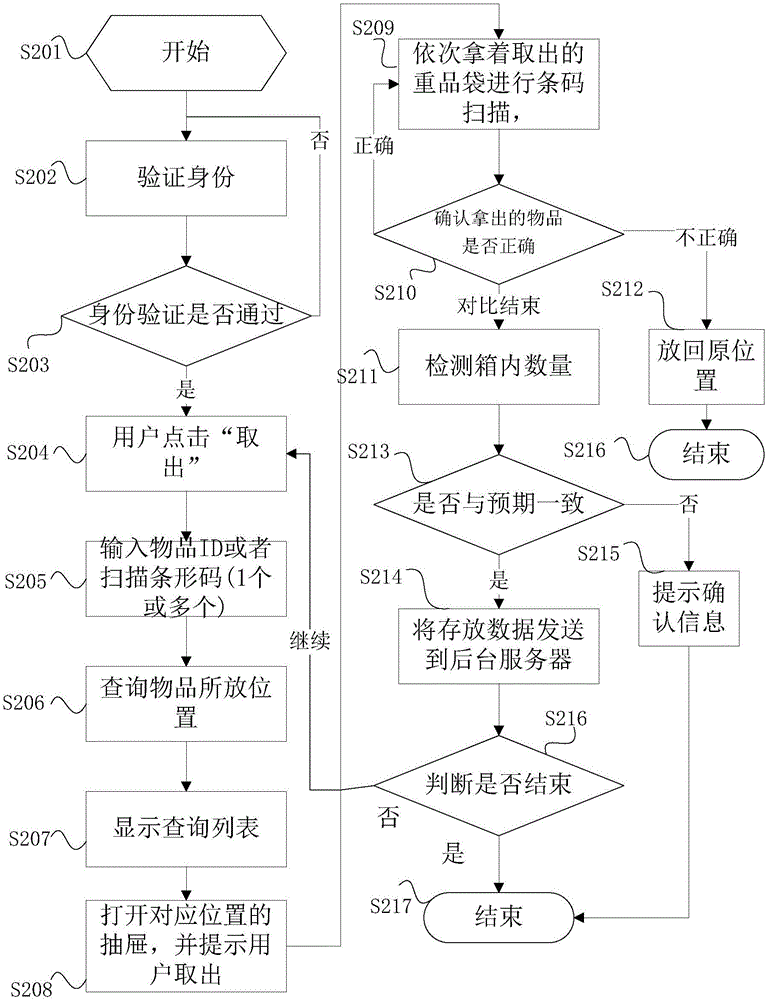

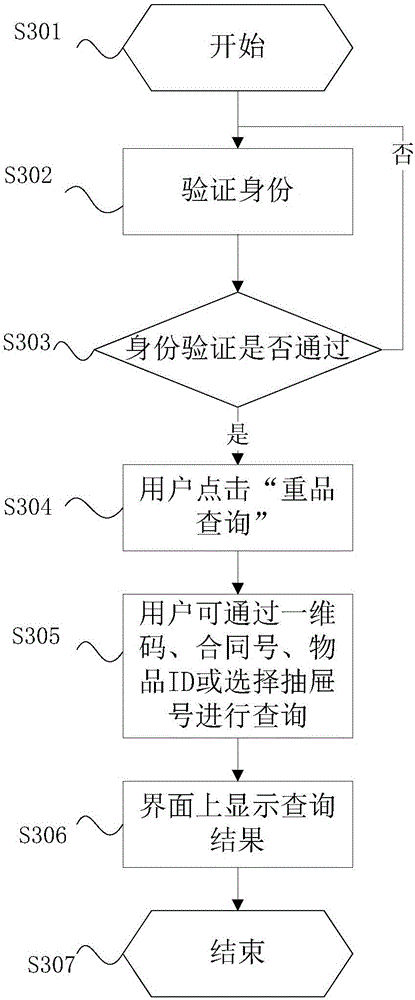

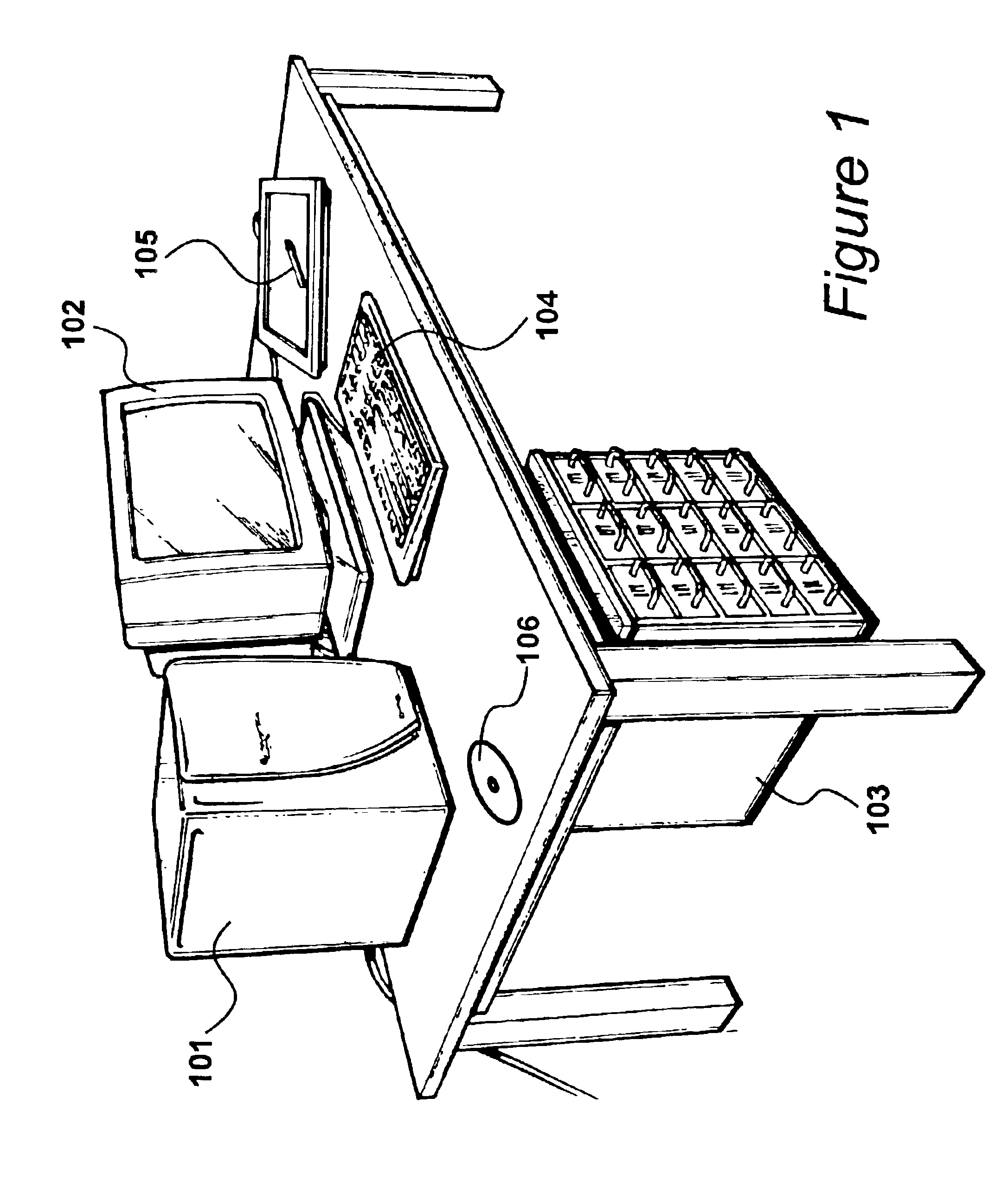

Important article keeping system, method and device

PendingCN106228292AFaster access timeImprove accuracyCo-operative working arrangementsIndividual entry/exit registersEngineeringLoudspeaker

The invention relates to an important article keeping system, method and device, and the system comprises a cabinet which is provided with a control assembly. The control assembly comprises a touch control display, a voice play loudspeaker, a bar code recognizer, a fingerprint device, an RFID reader-writer, and an RFID multichannel reader-writer. The central part of the cabinet is provided with an electronic cabinet door. The electronic cabinet door is provided with a cabinet door handle. The lower part of the cabinet is provided with an emergency lock. The electronic cabinet door is provided with an electronic lock. An inner wall of the electronic cabinet door is provided with a file label. According to the invention, the system is used for the management of important articles based on the advantages of biological feature recognition, and carries out the strict multistage electronized management and control. The articles in the cabinet are independently packaged and labeled. The system automatically generates an electronic list of the stored articles, and the inventory status of the stored articles can be obtained at a management background at any time. The system can find a situation of unauthorized taking, achieves the IT management of the inventory status, speeds up the storing and taking time, and improves the storing and taking accuracy.

Owner:邢德智 +1

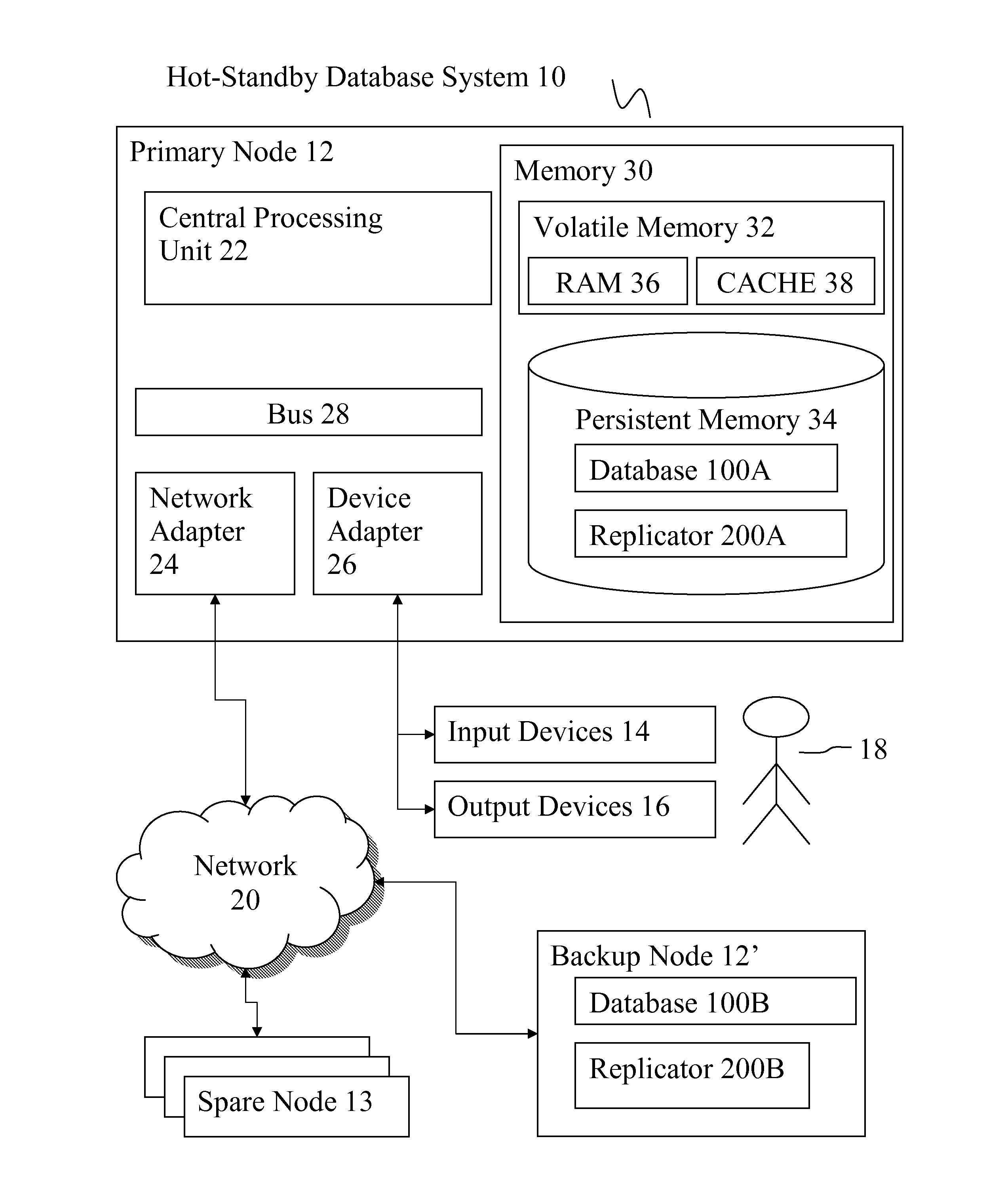

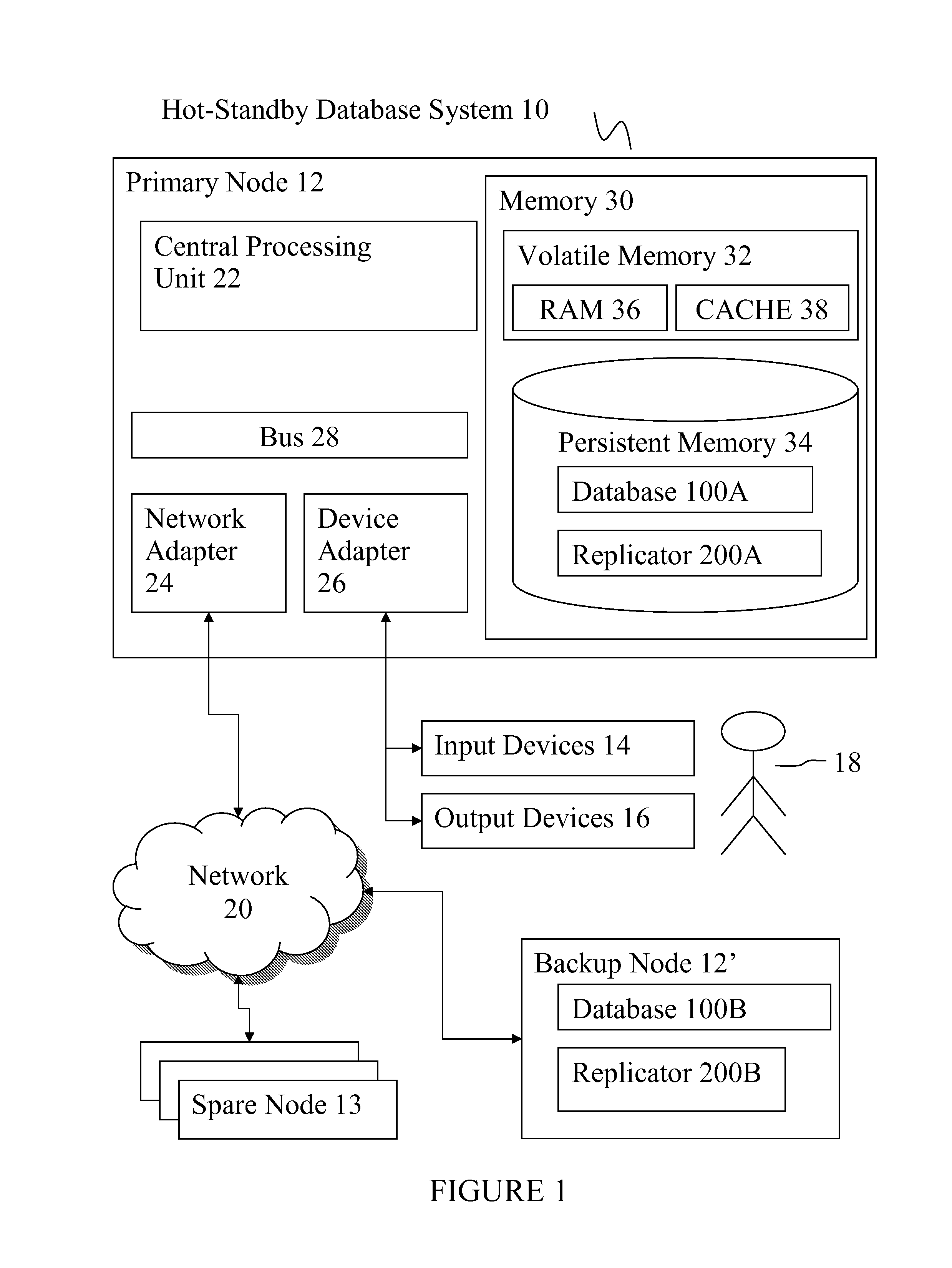

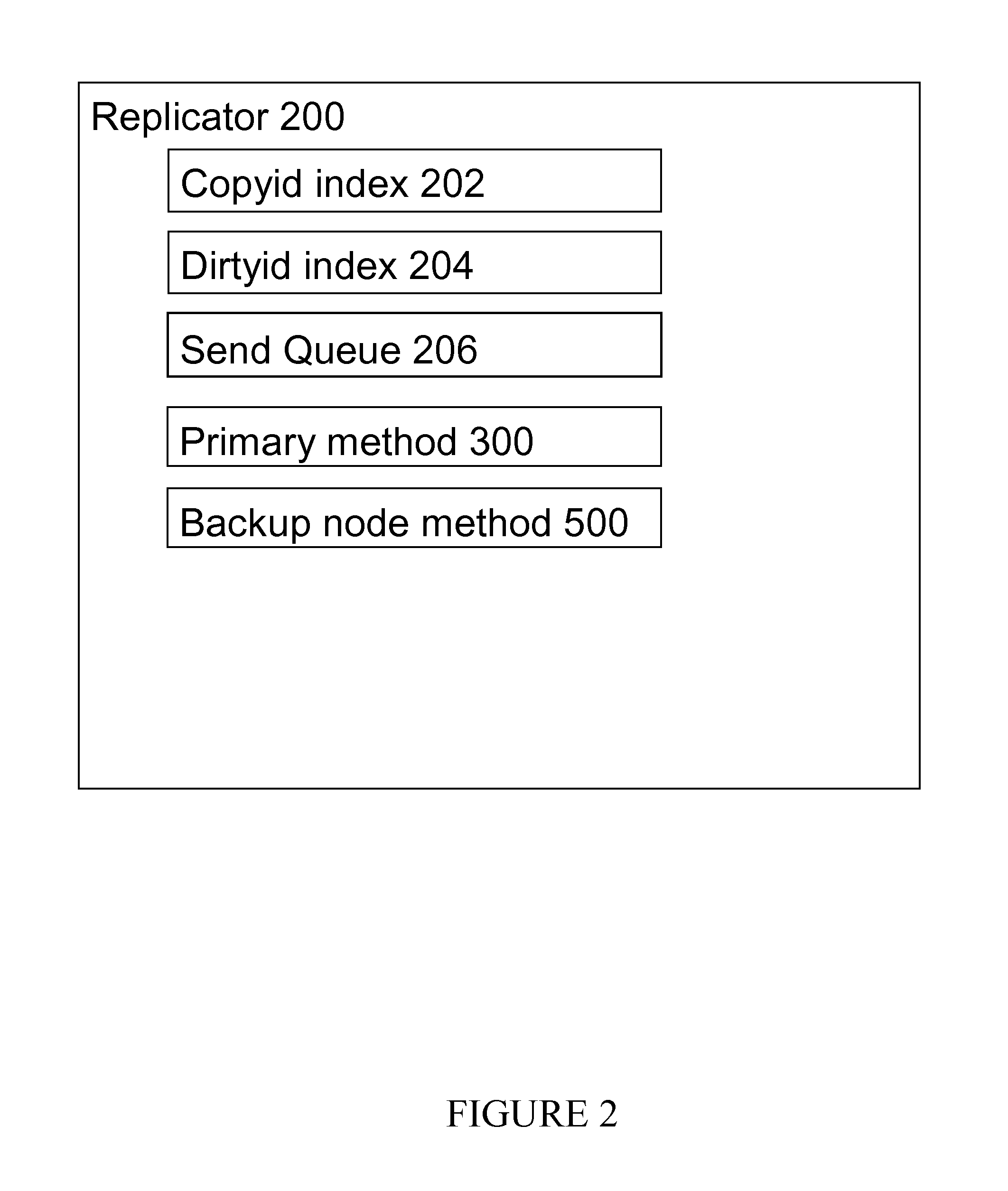

Replication for on-line hot-standby database

ActiveUS20150339366A1Reduce capacityLarge capacityError detection/correctionDigital data processing detailsComputerized systemDistributed database

A method, and corresponding computer program product and computer system, for replicating a database image in a distributed database environment comprises: defining a checkpoint image of the primary node including a database structure and a plurality of database pages; creating a replica database by initiating a backup node and saving the defined structure on the initiated backup node; sending each database page of the checkpoint image for saving on the backup node; saving every transaction on the primary node and creating a corresponding REDO transaction; identifying each data page operated on by each REDO transaction; sending each created REDO transaction to the backup node in the order in which the corresponding transaction occurred, and prioritizing each identified database page so that it arrives at the backup node before or substantially at the same time as a corresponding REDO transaction.

Owner:IBM CORP

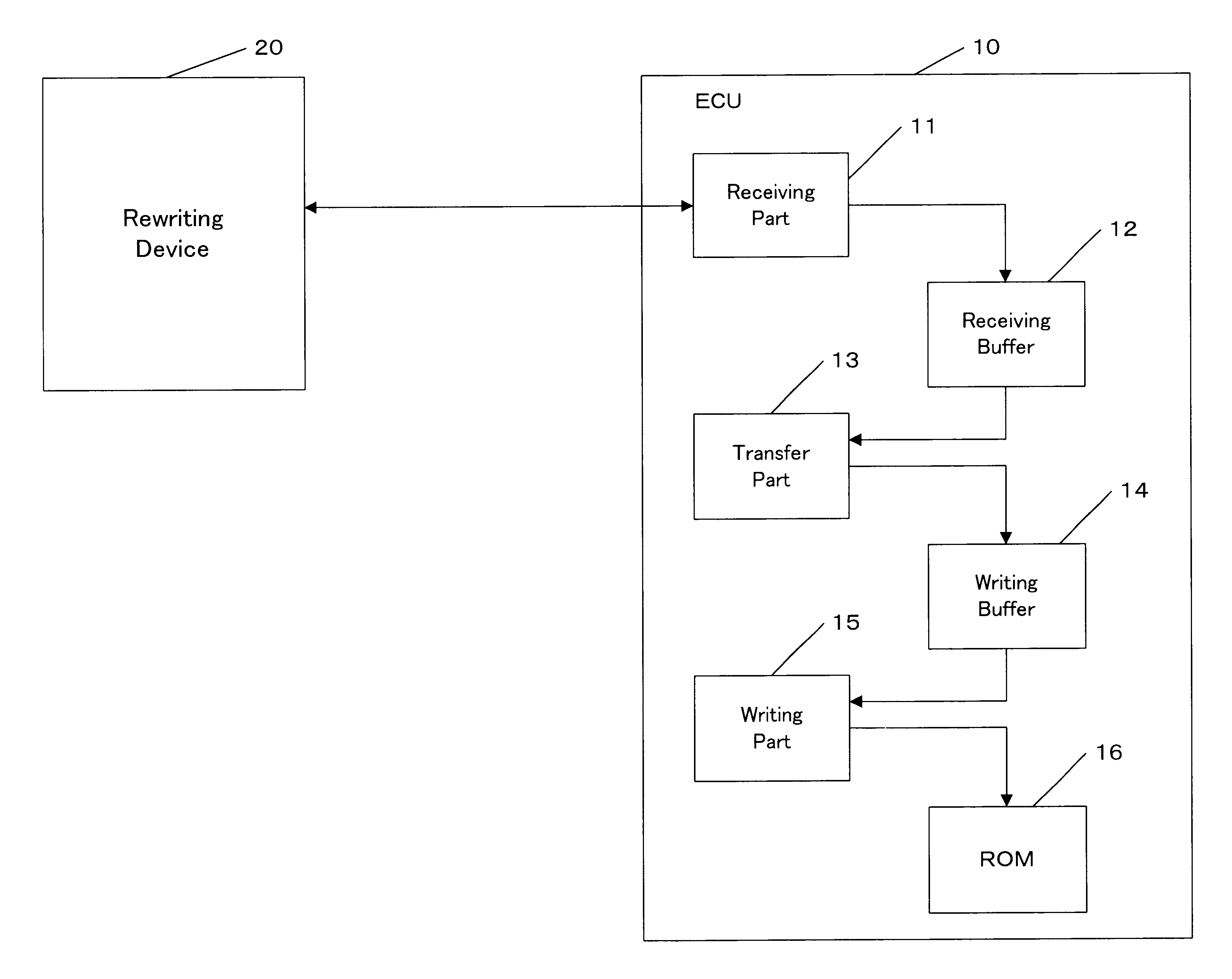

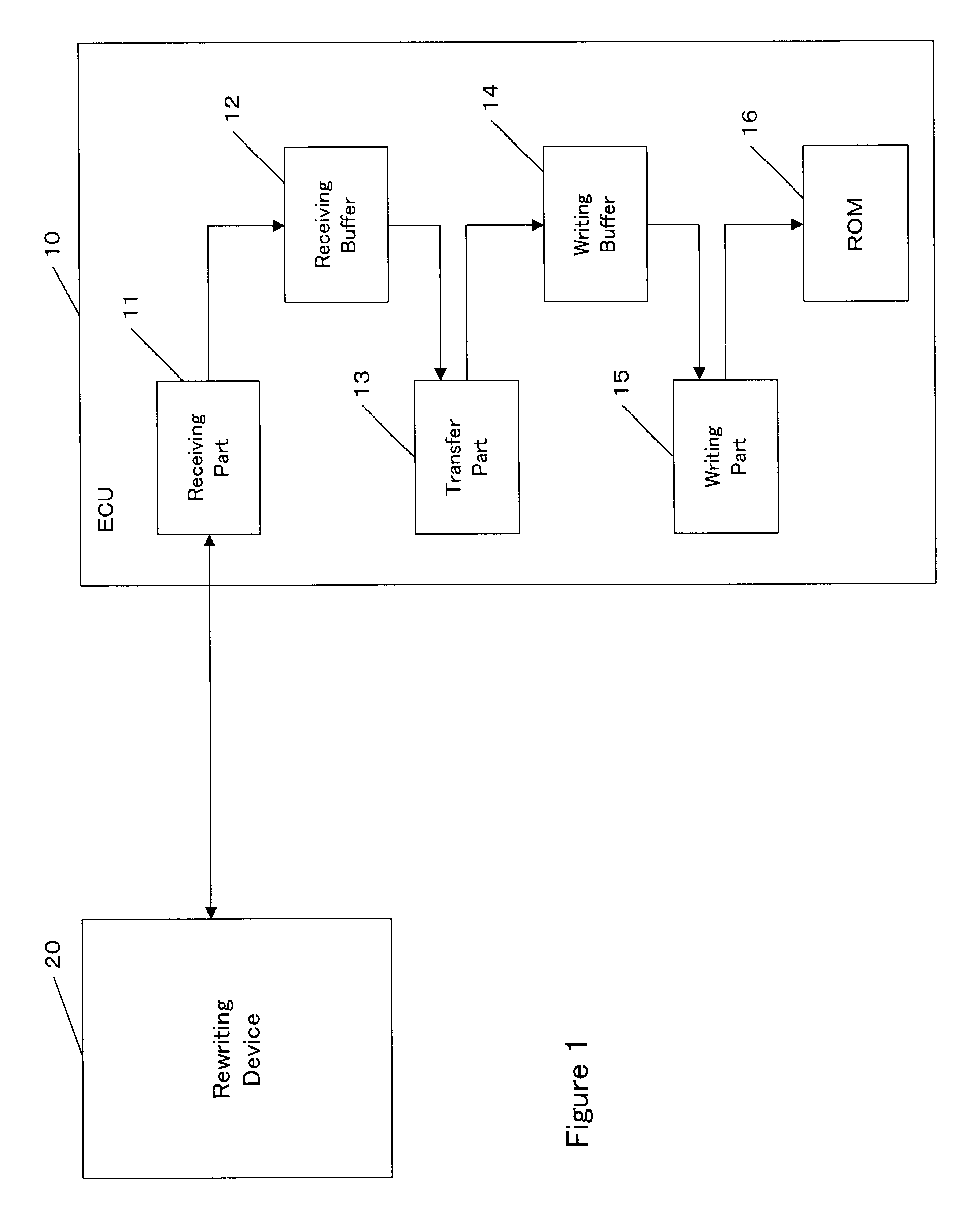

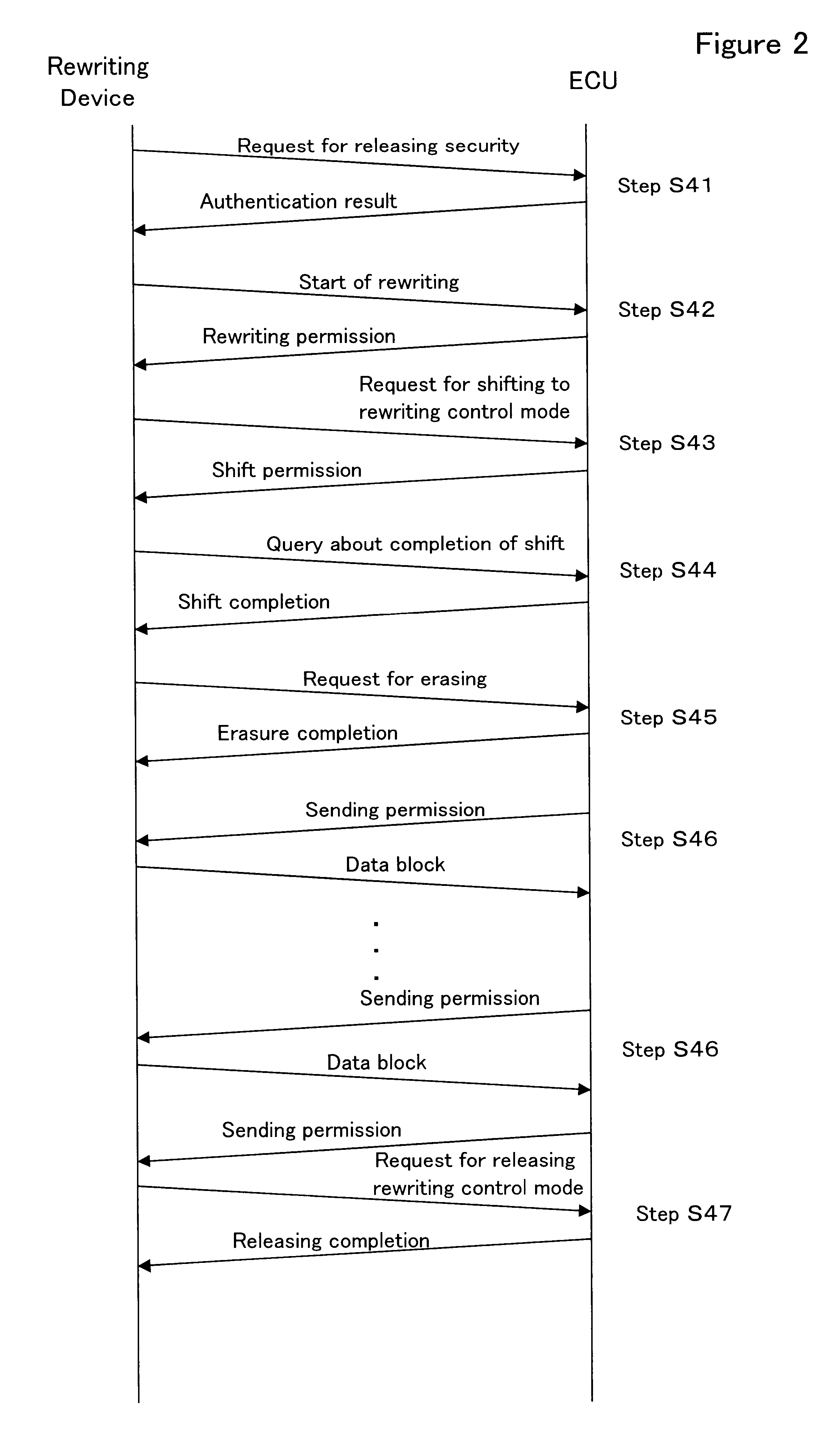

Vehicle controller for controlling rewriting data in a nonvolatile memory

InactiveUS6898490B2Reduce delaysShorten the timeElectrical controlComputer controlData storingData store

A vehicle controller comprises a first buffer for storing at least one data block, a second buffer for storing at least one data block, and a rewritable non-volatile memory for storing information for controlling a vehicle. The controller receives a data block from an external rewriting device to store it in the first buffer. The data block stored in the first buffer is transferred to the second buffer. The data block stored in the second buffer is written into the memory. When a first data block is written into the memory, a subsequent data block is received. Thus, the time required to rewrite data stored in the nonvolatile memory is reduced.

Owner:HONDA MOTOR CO LTD

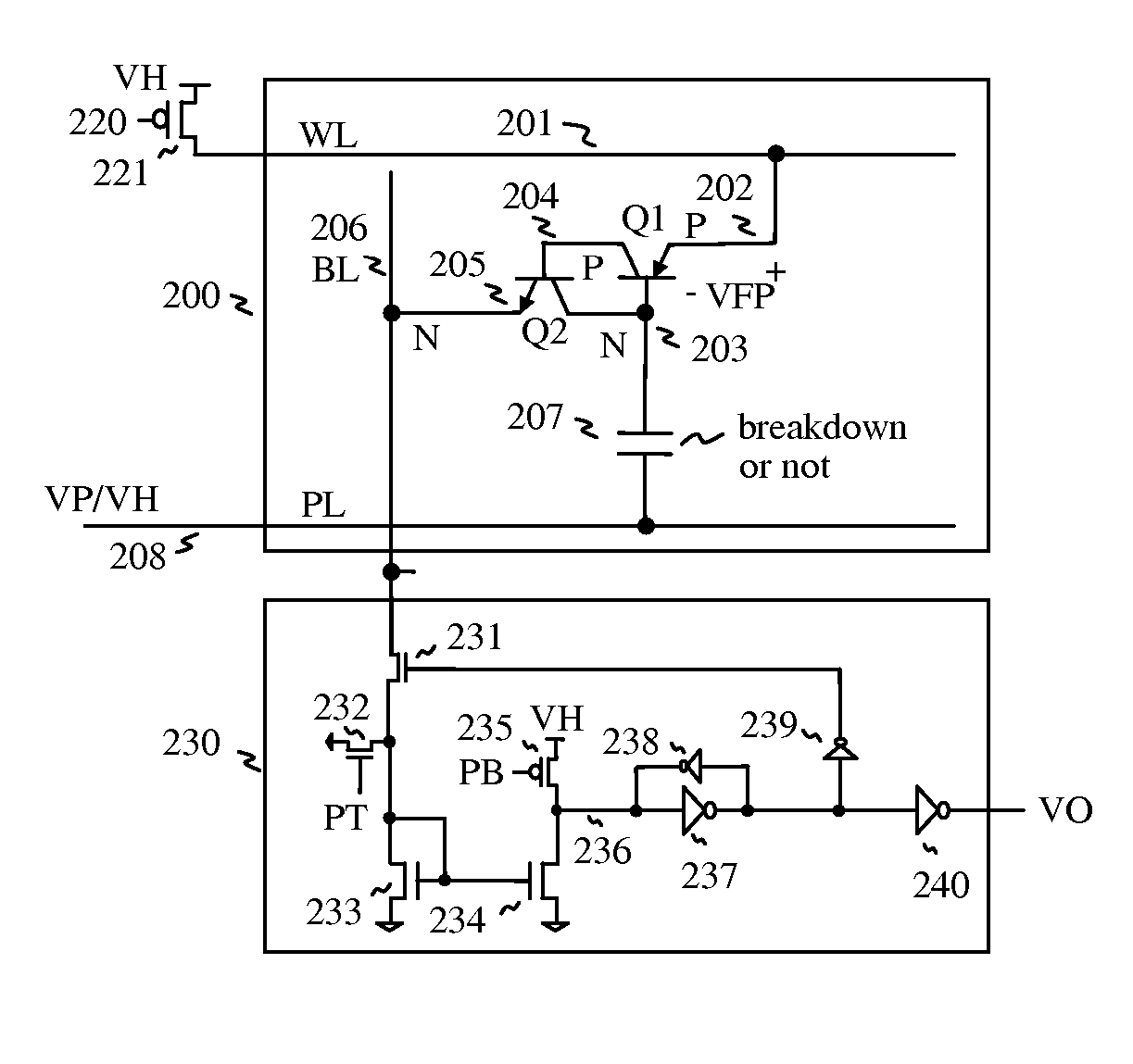

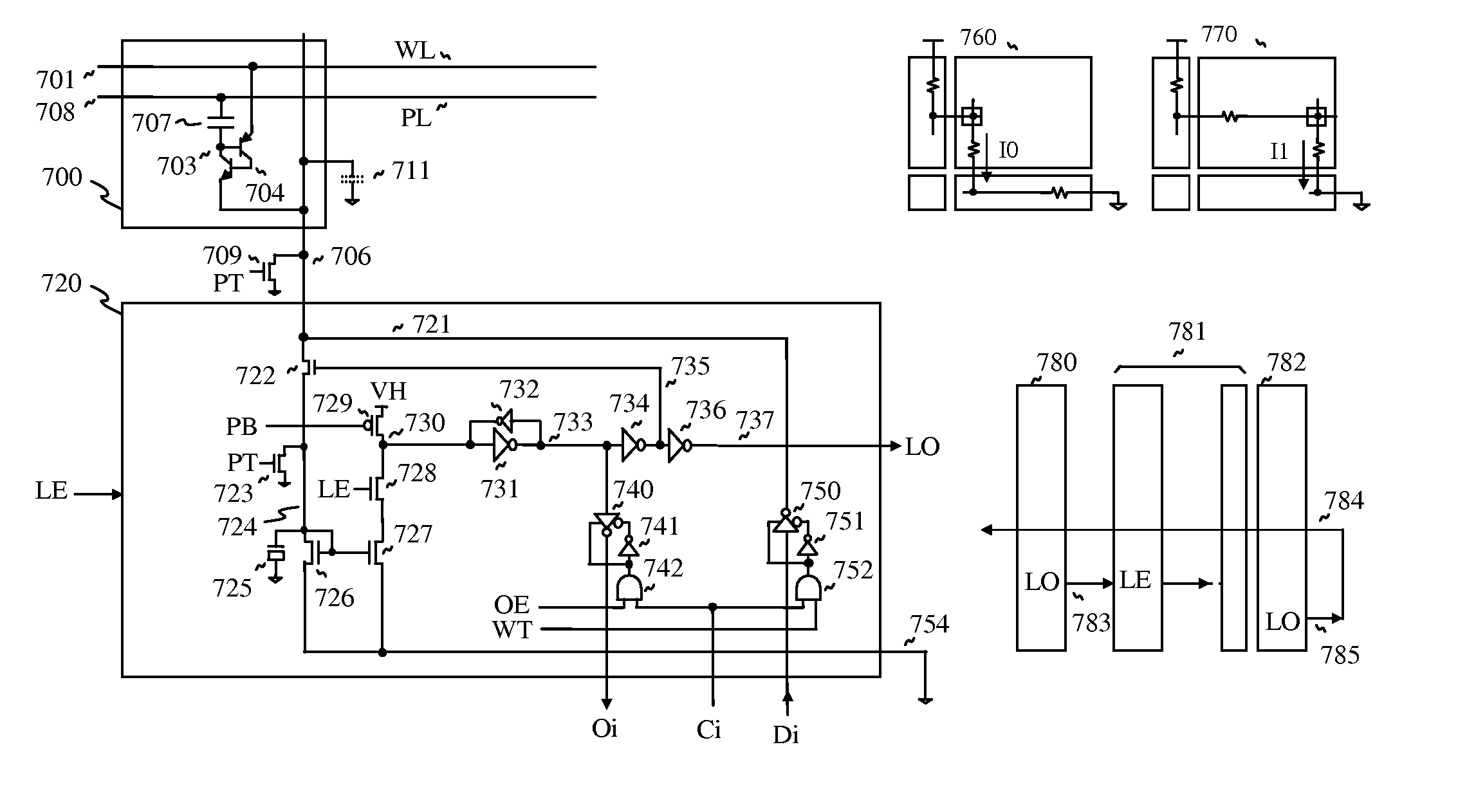

One-time programmable memory

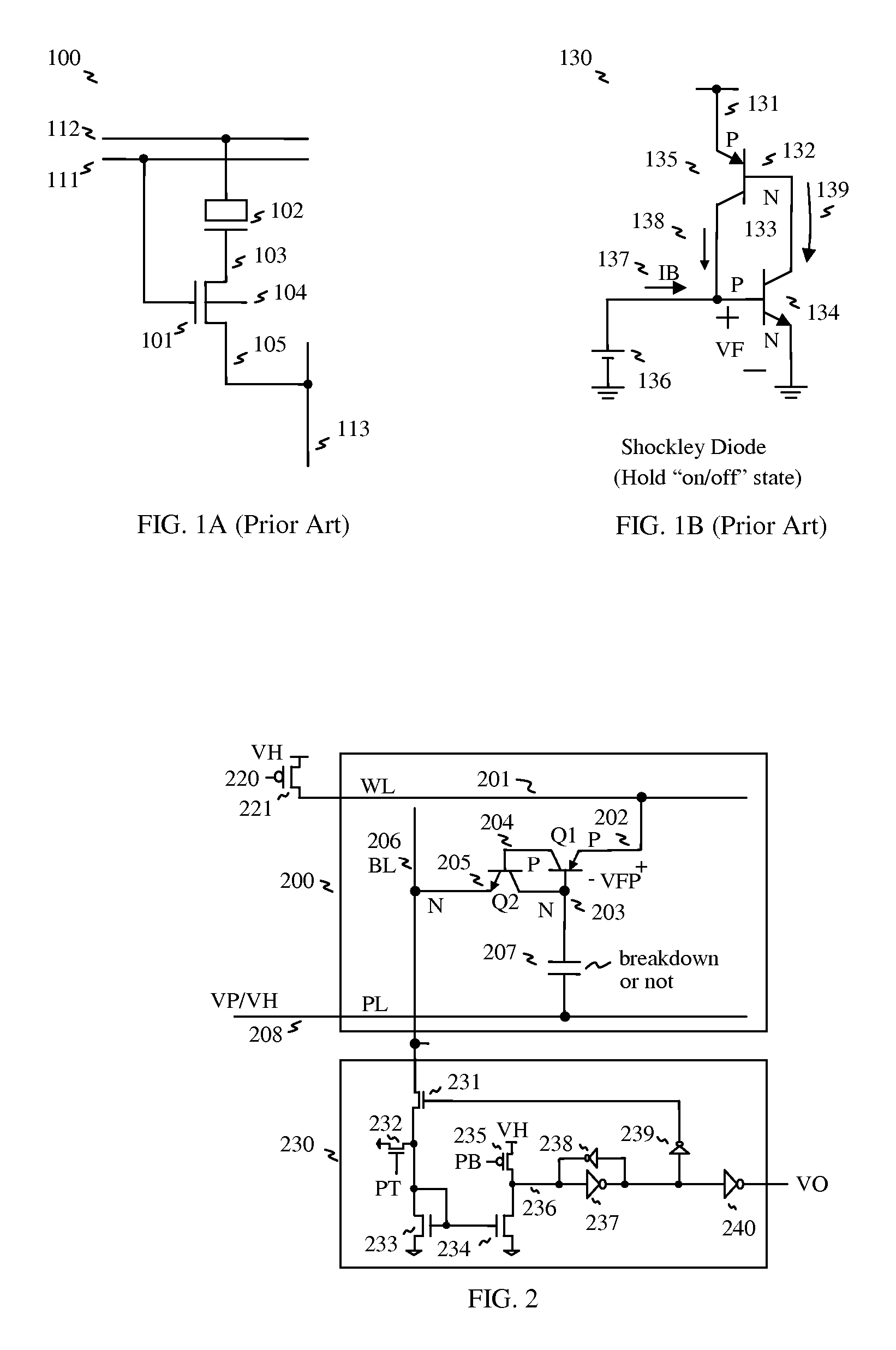

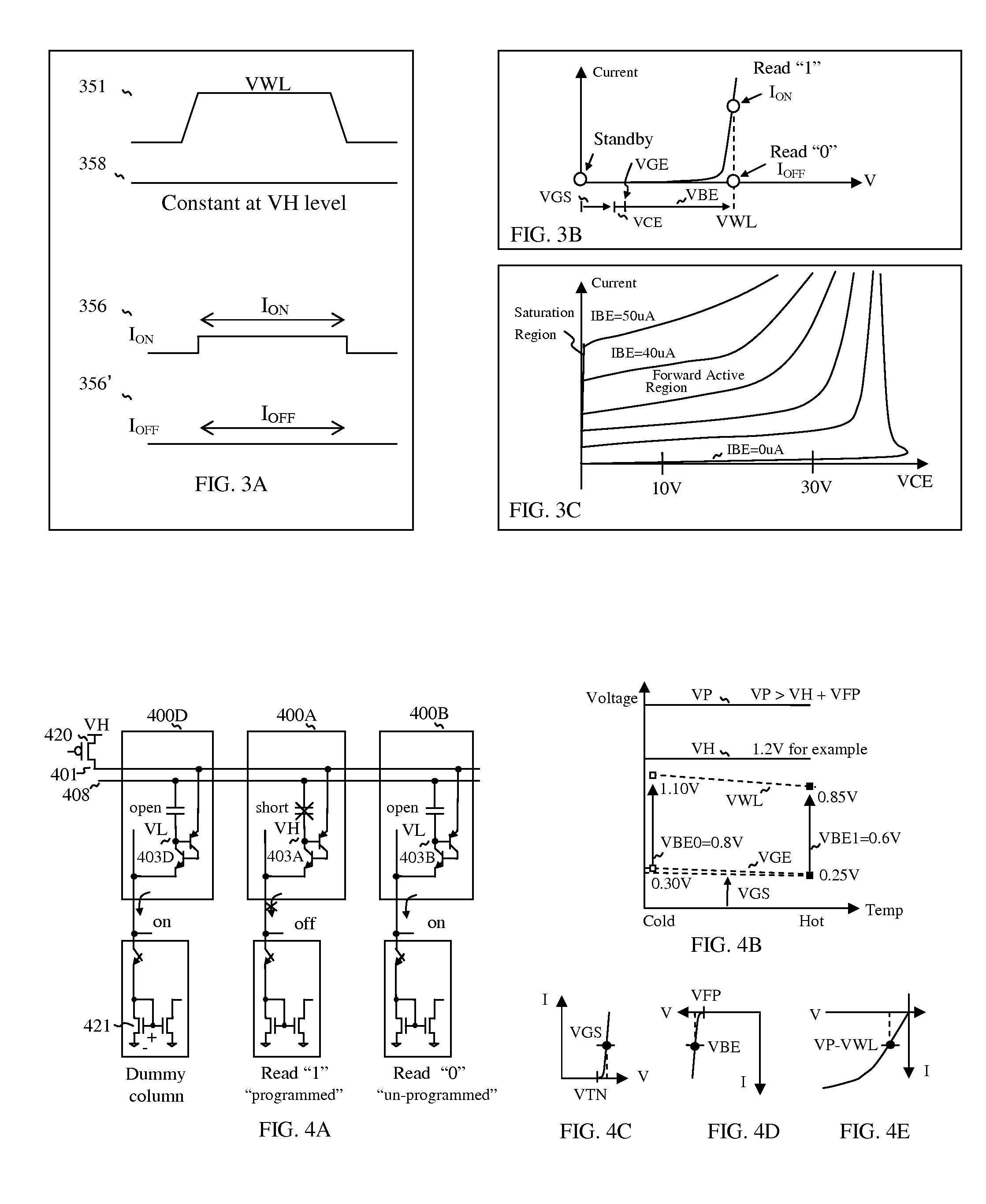

InactiveUS20070133259A1Reduce chip areaFlexibly fabricateSolid-state devicesRead-only memoriesPositive directionOne time programmable

In the present invention, one-time programmable memory includes a diode as an access device and a capacitor as a storage device, the diode includes four terminals, wherein the first terminal is connected to a word line, the second terminal is connected to one plate of the capacitor, the third terminal is floating, and the fourth terminal is connected to a bit line, and the capacitor includes two electrodes, wherein one of the capacitor plate serves as a storage node which is connected to the second terminal of the diode, and another plate of the capacitor is connected to a plate line, and the plate line is asserted to programming voltage which is higher than the regular supply voltage of the decoders and data latches, in order to breakdown the insulator of the capacitor when programming, but the plate line is connected to the regular supply voltage when read. And during read, the diode also serves as a sense amplifier to detect whether the storage node is forward bias or not, and it sends binary data to a latch device wherein includes a current mirror and a feedback loop, which cuts off the current path after latching. And dummy columns generate replica delay signals which guarantee timing margin and reduce cycle time. In addition, the memory cells are formed in between the routing layers, which memory cells can be stacked over the transistor or another capacitor memory cell.

Owner:KIM JUHAN

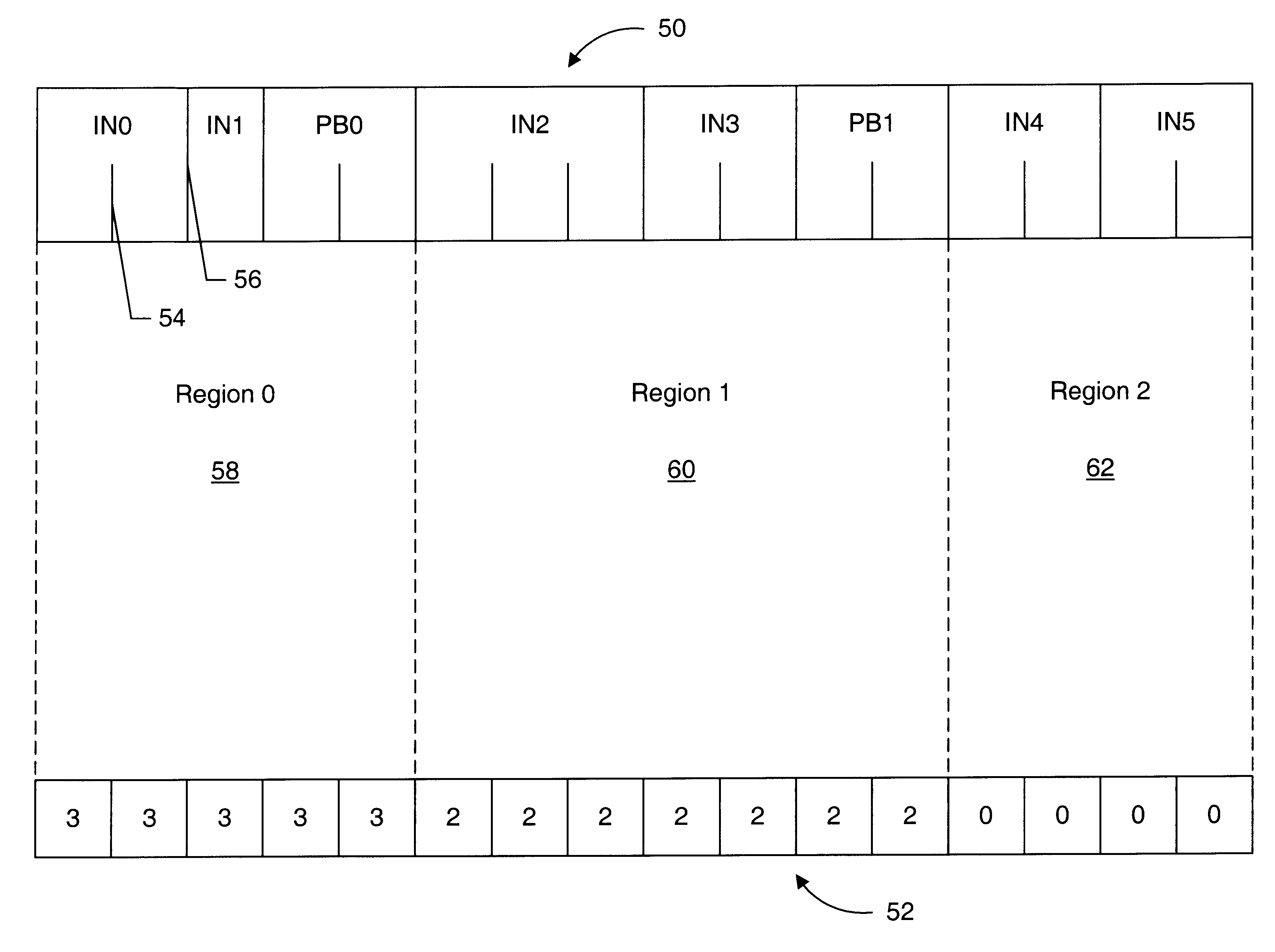

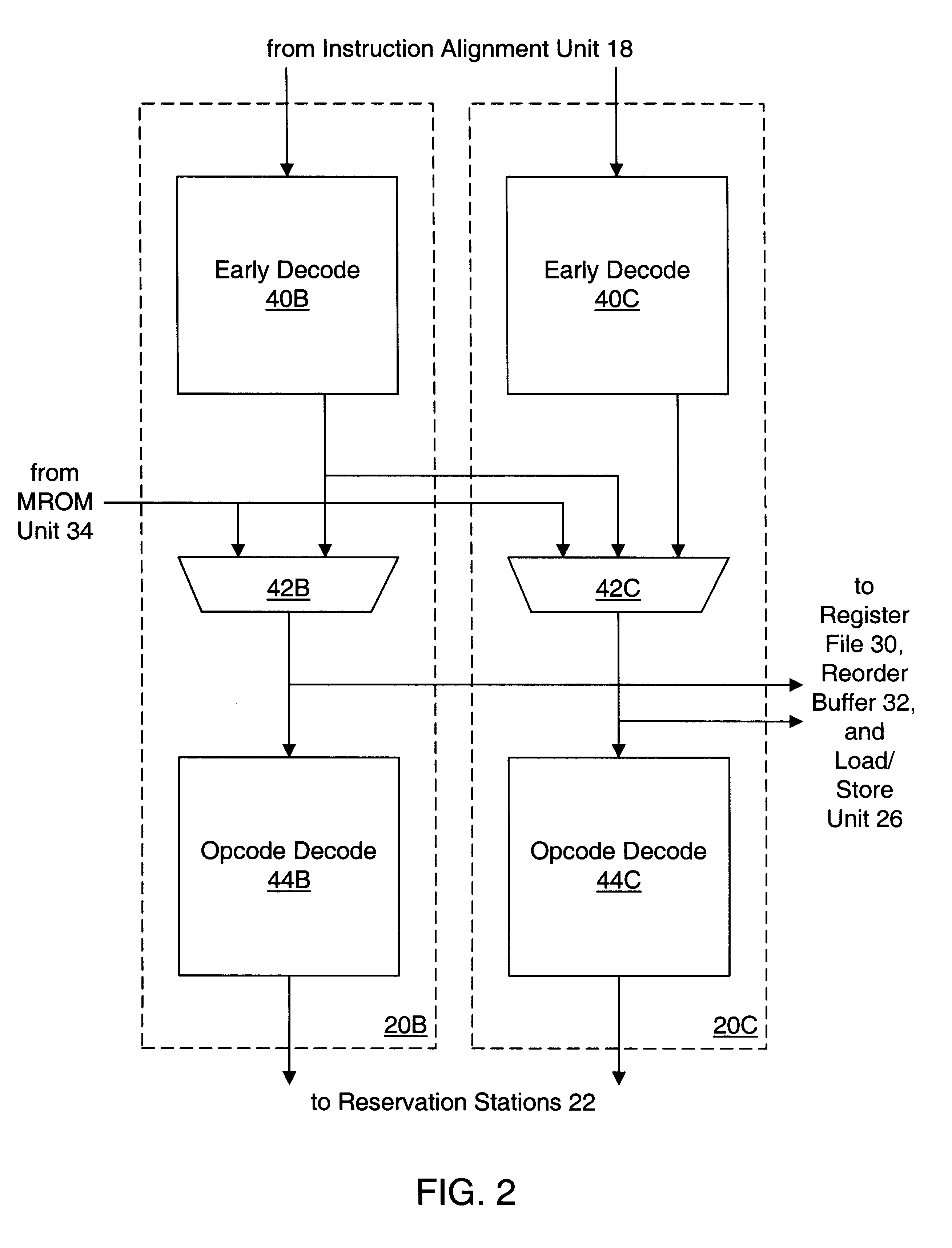

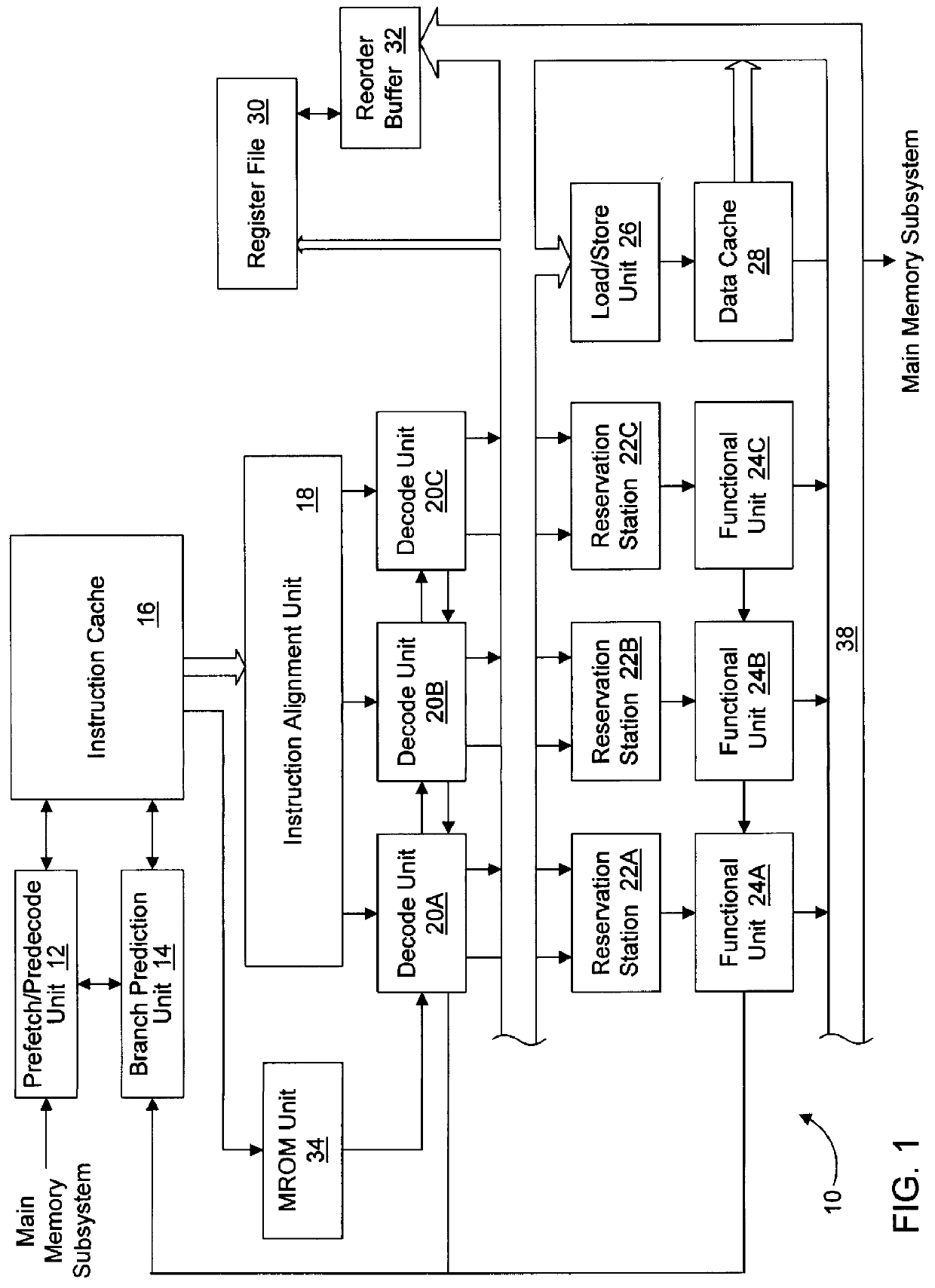

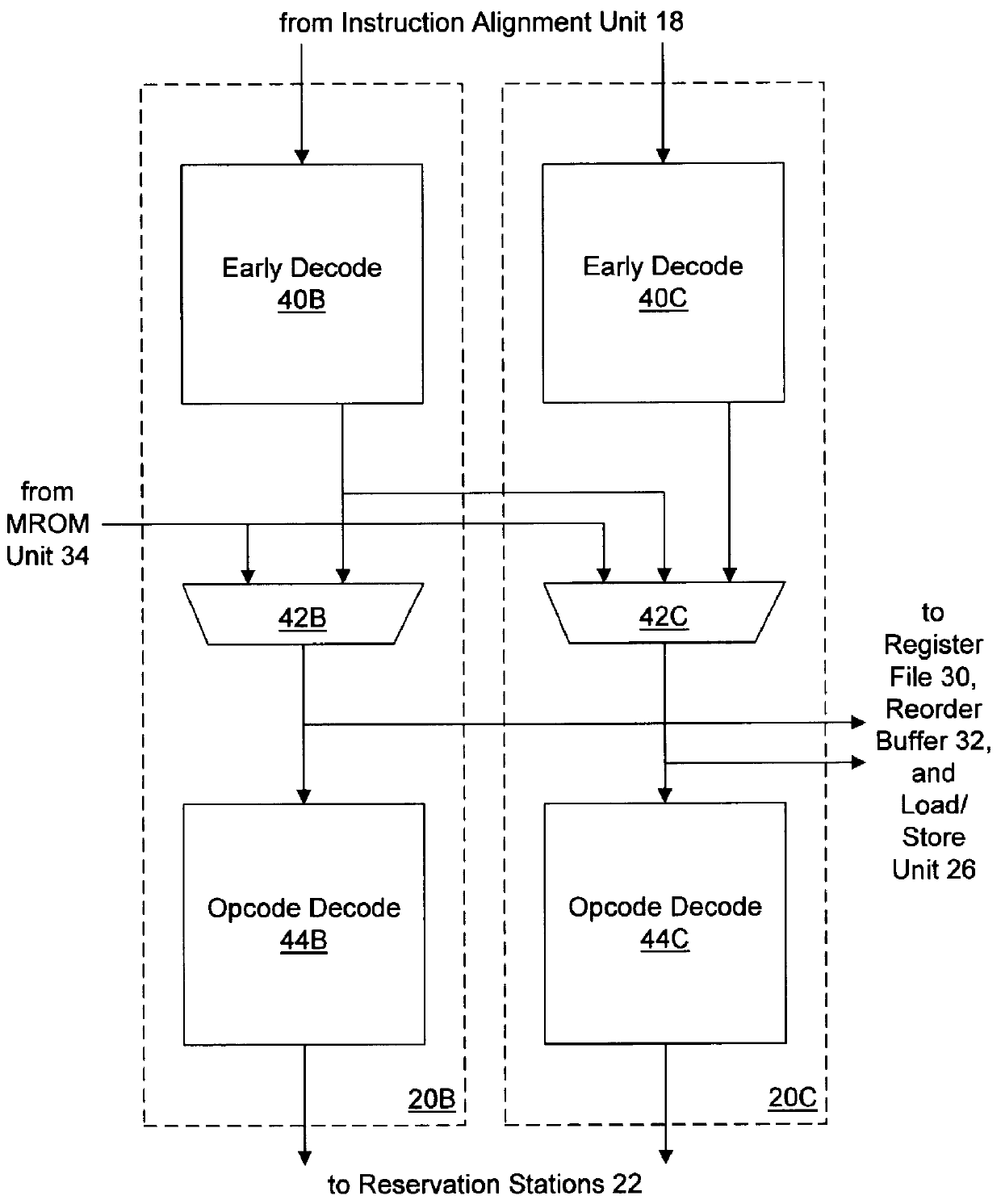

Branch selectors associated with byte ranges within an instruction cache for rapidly identifying branch predictions

InactiveUS6279107B1Minimize the numberSmall sizeDigital computer detailsNext instruction address formationByteInstruction set

Owner:GLOBALFOUNDRIES INC

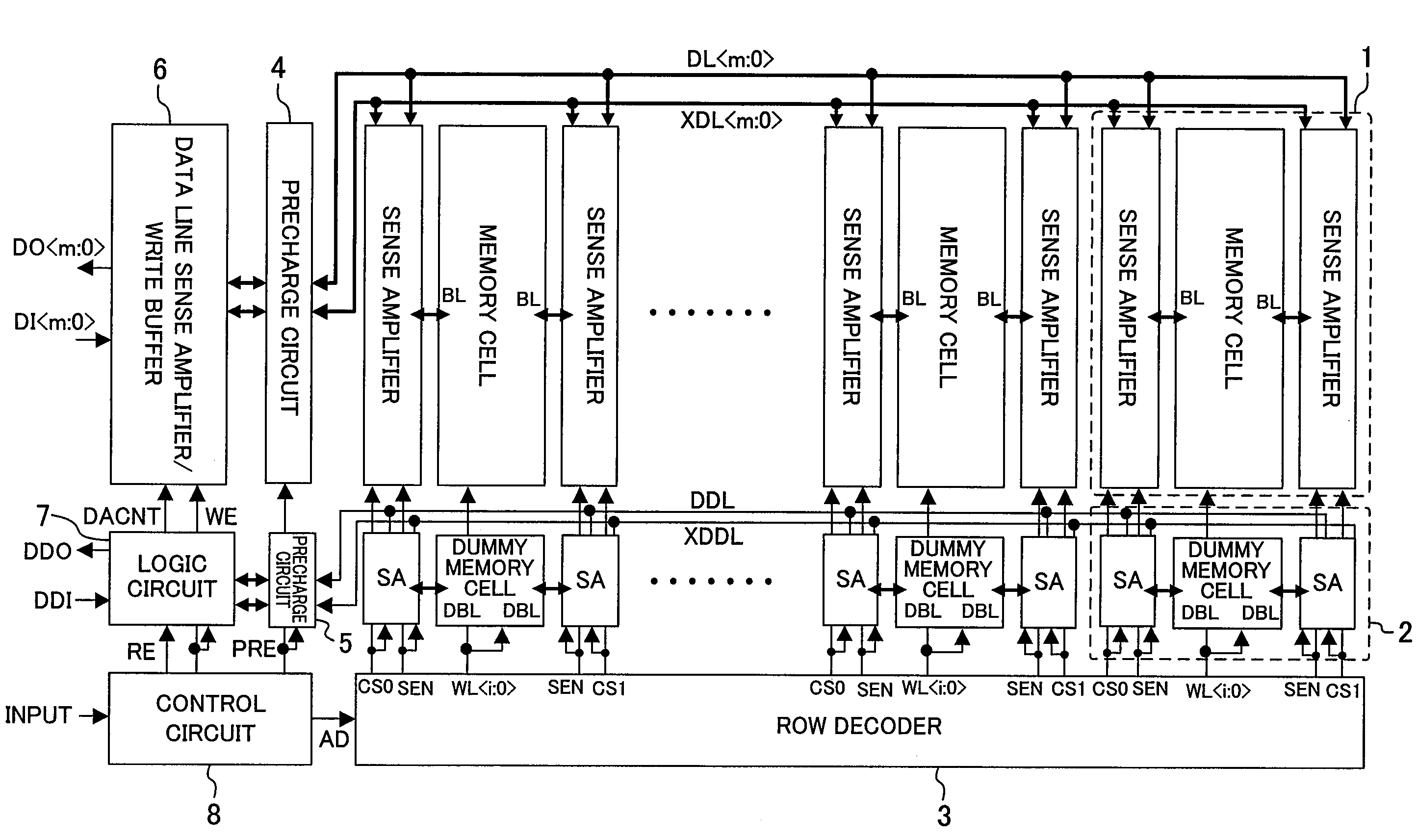

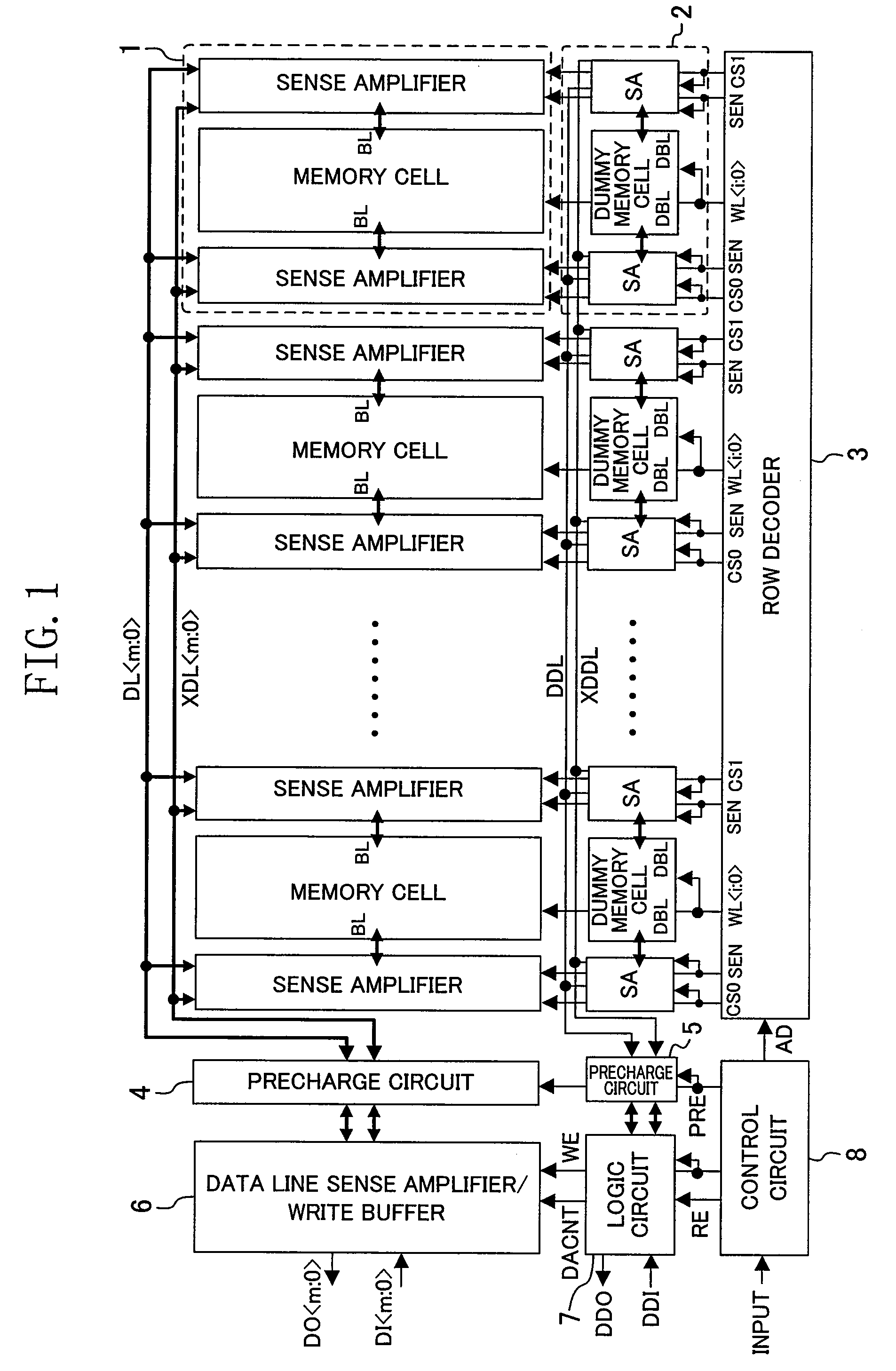

Semiconductor storage device

ActiveUS7656732B2Increase speedHindering operating speed and access timeDigital storageStatic random-access memoryControl signal

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

One-time programmable memory

InactiveUS7411810B2Manufacturing flexibilityReduce chip areaSolid-state devicesRead-only memoriesBit lineTiming margin

In the present invention, one-time programmable memory includes a diode as an access device and a capacitor as a storage device, the diode includes four terminals, wherein the first terminal is connected to a word line, the second terminal is connected to one plate of the capacitor, the third terminal is floating, and the fourth terminal is connected to a bit line, and the capacitor includes two electrodes, wherein one of the capacitor plate serves as a storage node which is connected to the second terminal of the diode, and another plate of the capacitor is connected to a plate line, and the plate line is asserted to programming voltage which is higher than the regular supply voltage of the decoders and data latches, in order to breakdown the insulator of the capacitor when programming, but the plate line is connected to the regular supply voltage when read. And during read, the diode also serves as a sense amplifier to detect whether the storage node is forward bias or not, and it sends binary data to a latch device wherein includes a current mirror and a feedback loop, which cuts off the current path after latching. And dummy columns generate replica delay signals which guarantee timing margin and reduce cycle time. In addition, the memory cells are formed in between the routing layers, which memory cells can be stacked over the transistor or another capacitor memory cell.

Owner:KIM JUHAN

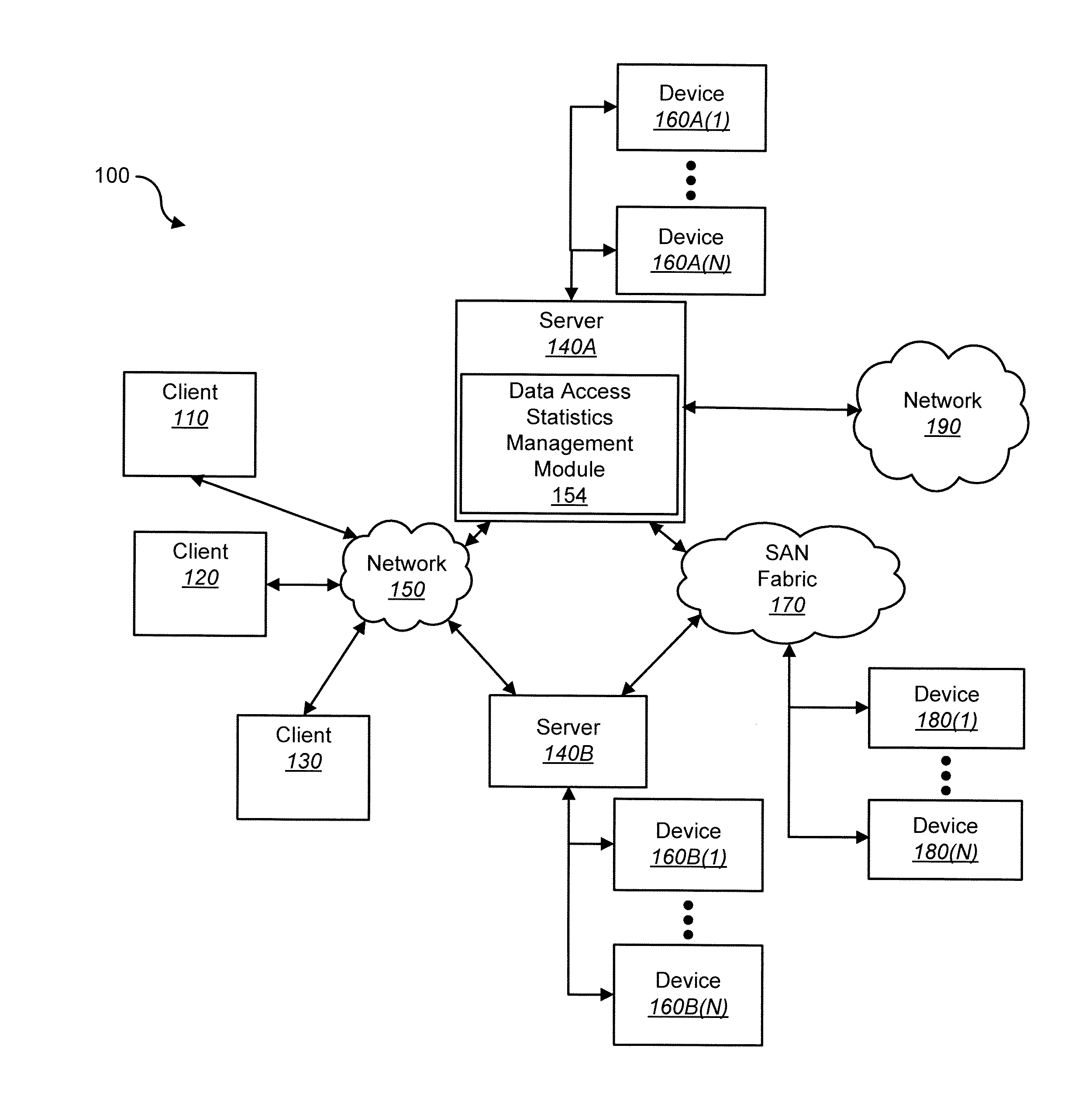

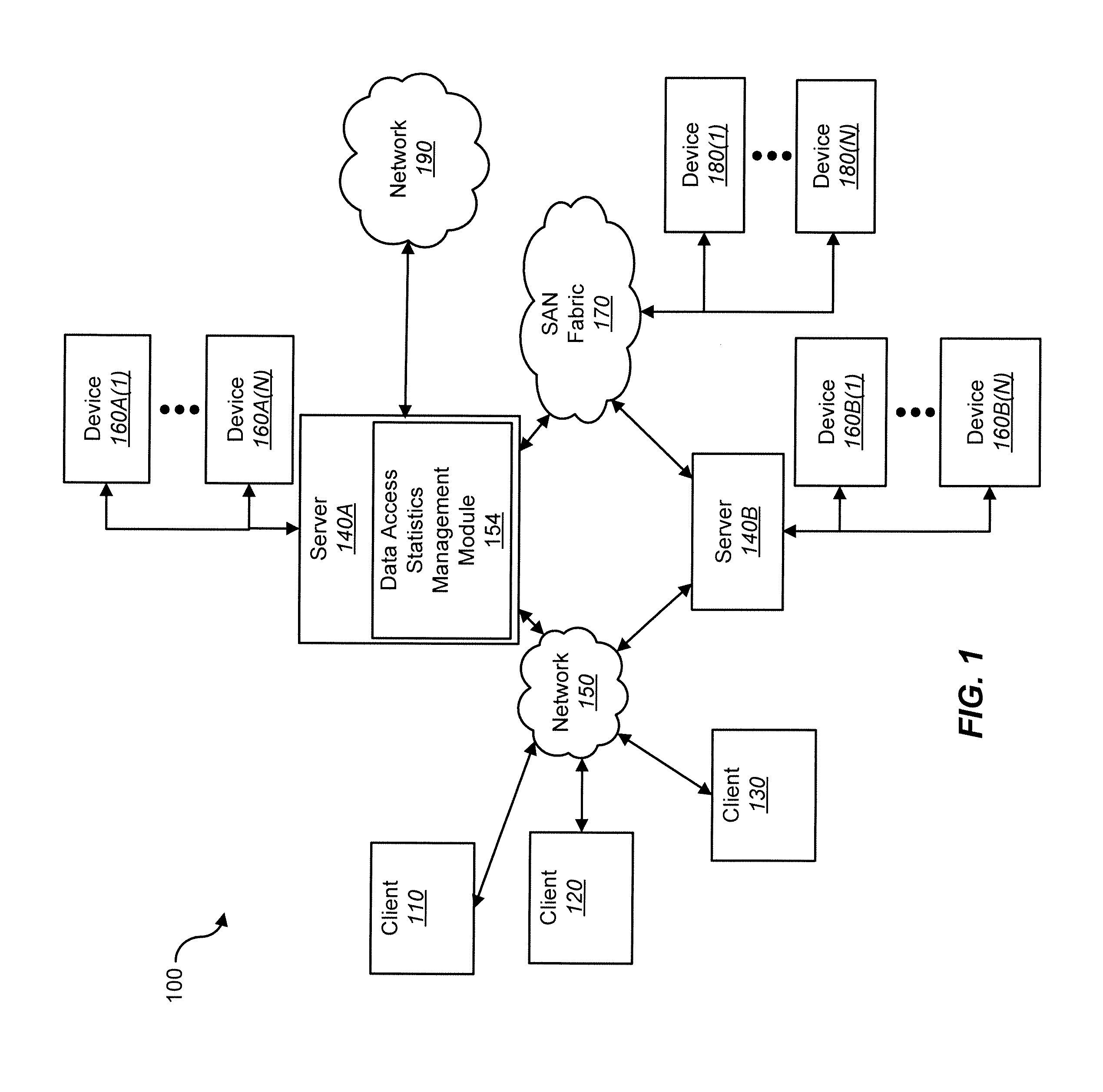

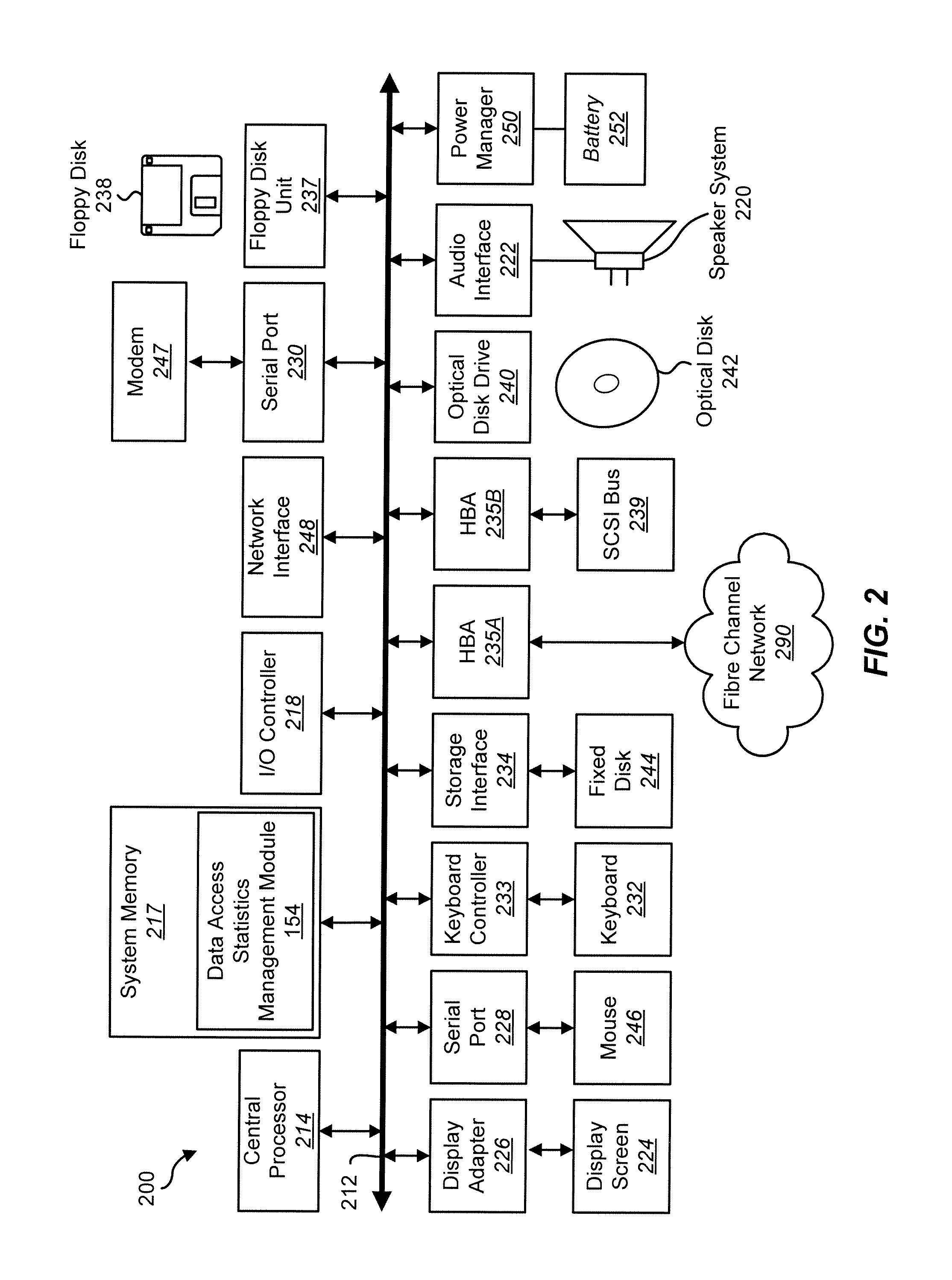

Techniques for deduplicated data access statistics management

ActiveUS9483484B1Faster access timeFaster seek timeDigital data information retrievalSpecial data processing applicationsData accessData deduplication

Techniques for data access statistics management are disclosed. In one particular embodiment, the techniques may be realized as a method for data access statistics management comprising determining that a portion of data has been deduplicated, and modifying access statistics of the portion of data for each reference to the portion of data.

Owner:VERITAS TECH

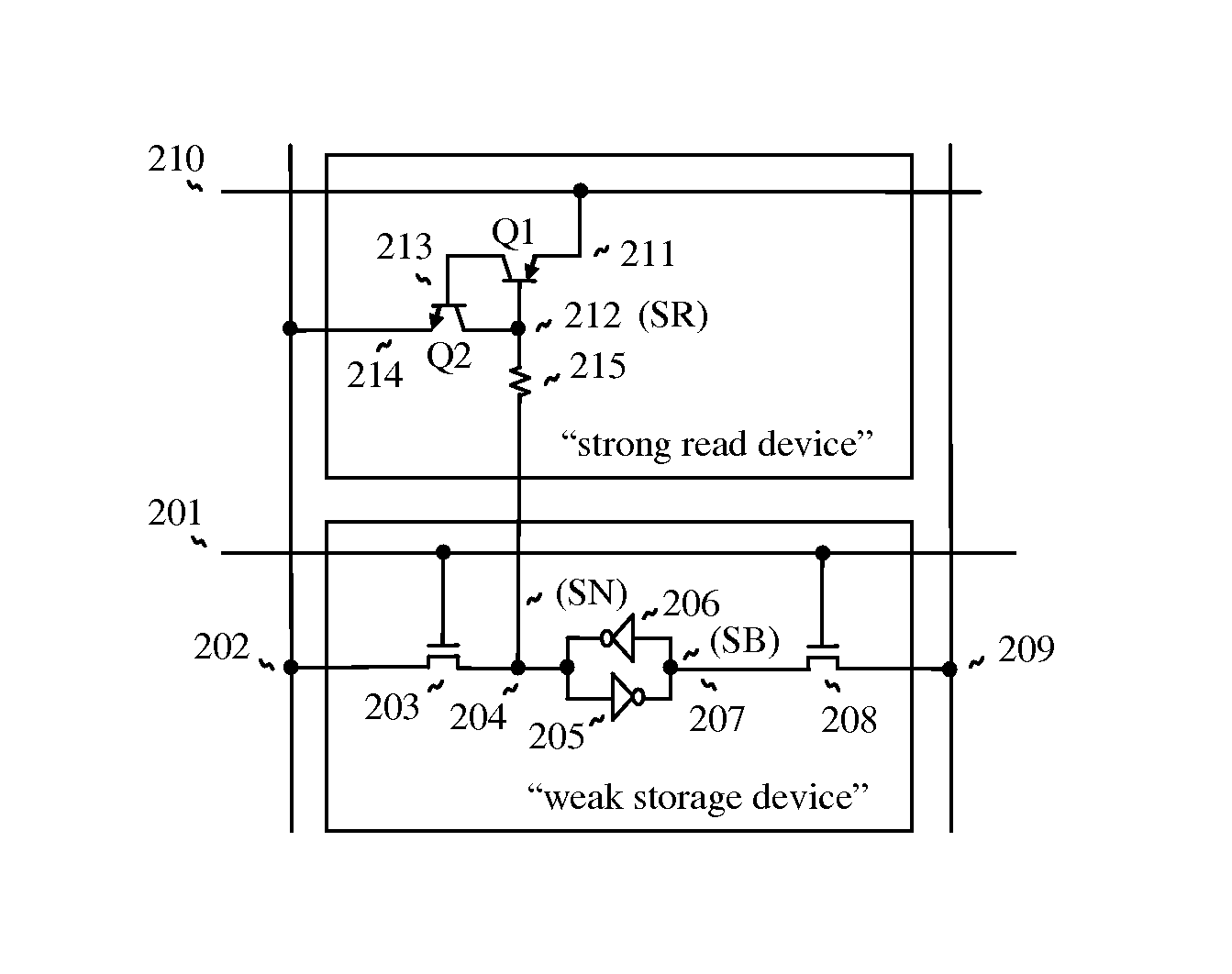

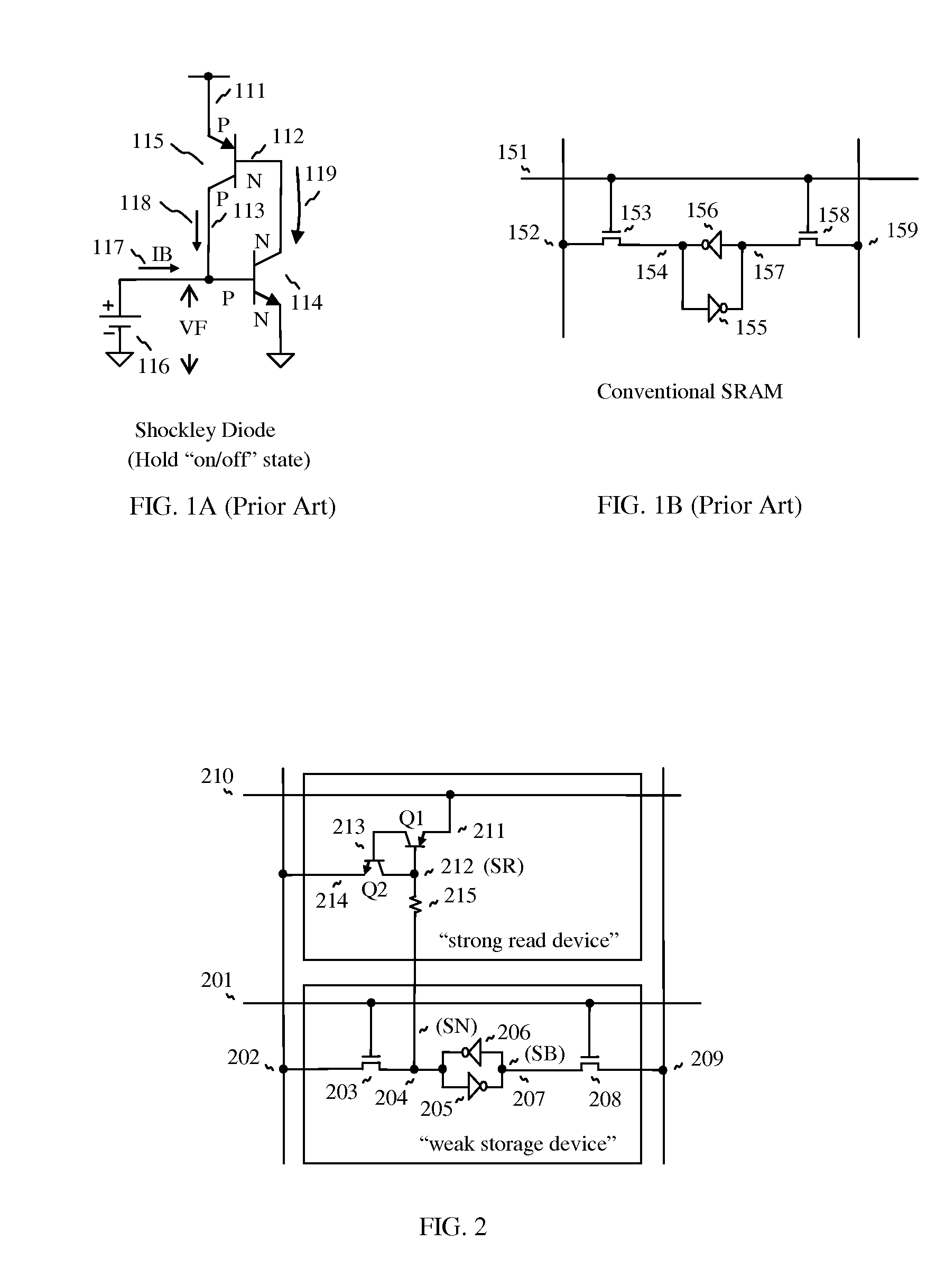

Static random access memory

InactiveUS20070217266A1Improve performanceGood write deviceRead-only memoriesDigital storageComputer architectureStatic random-access memory

SRAM cell includes a four-terminal diode as a read device wherein the first terminal is connected to a read word line, the second terminal is connected to a storage device through a resistor, the third terminal is floating, and the fourth terminal is connected to one of two bit lines; and two MOS transistors as a write device; and each MOS transistor is connected to the bit line respectively; and a latch including two cross-coupled inverters as the storage device; and the SRAM cell can be formed from thin-film layer, thus multiple memory cells are stacked; and the heavy routing lines are driven by the bipolar drivers which are part of the invention, hence the bipolar circuits and the control MOS transistors of the peripheral circuit can be formed from the deposited thin-film layers; consequently the whole chip can be stacked over the wafer, such as silicon, quartz and others; additionally it applications are extended to a multi port memory and a content addressable memory.

Owner:KIM JUHAN

Branch selectors associated with byte ranges within an instruction cache for rapidly identifying branch predictions

InactiveUS6141748AMinimize the numberSmall sizeDigital computer detailsNext instruction address formationByteInstruction set

A branch prediction unit stores a set of branch selectors corresponding to each of a group of contiguous instruction bytes stored in an instruction cache. Each branch selector identifies the branch prediction to be selected if a fetch address corresponding to that branch selector is presented. In order to minimize the number of branch selectors stored for a group of contiguous instruction bytes, the group is divided into multiple byte ranges. The largest byte range may include a number of bytes comprising the shortest branch instruction in the instruction set (exclusive of the return instruction). For example, the shortest branch instruction may be two bytes in one embodiment. Therefore, the largest byte range is two bytes in the example. Since the branch selectors as a group change value (i.e. indicate a different branch instruction) only at the end byte of a predicted-taken branch instruction, fewer branch selectors may be stored than the number of bytes within the group.

Owner:GLOBALFOUNDRIES INC

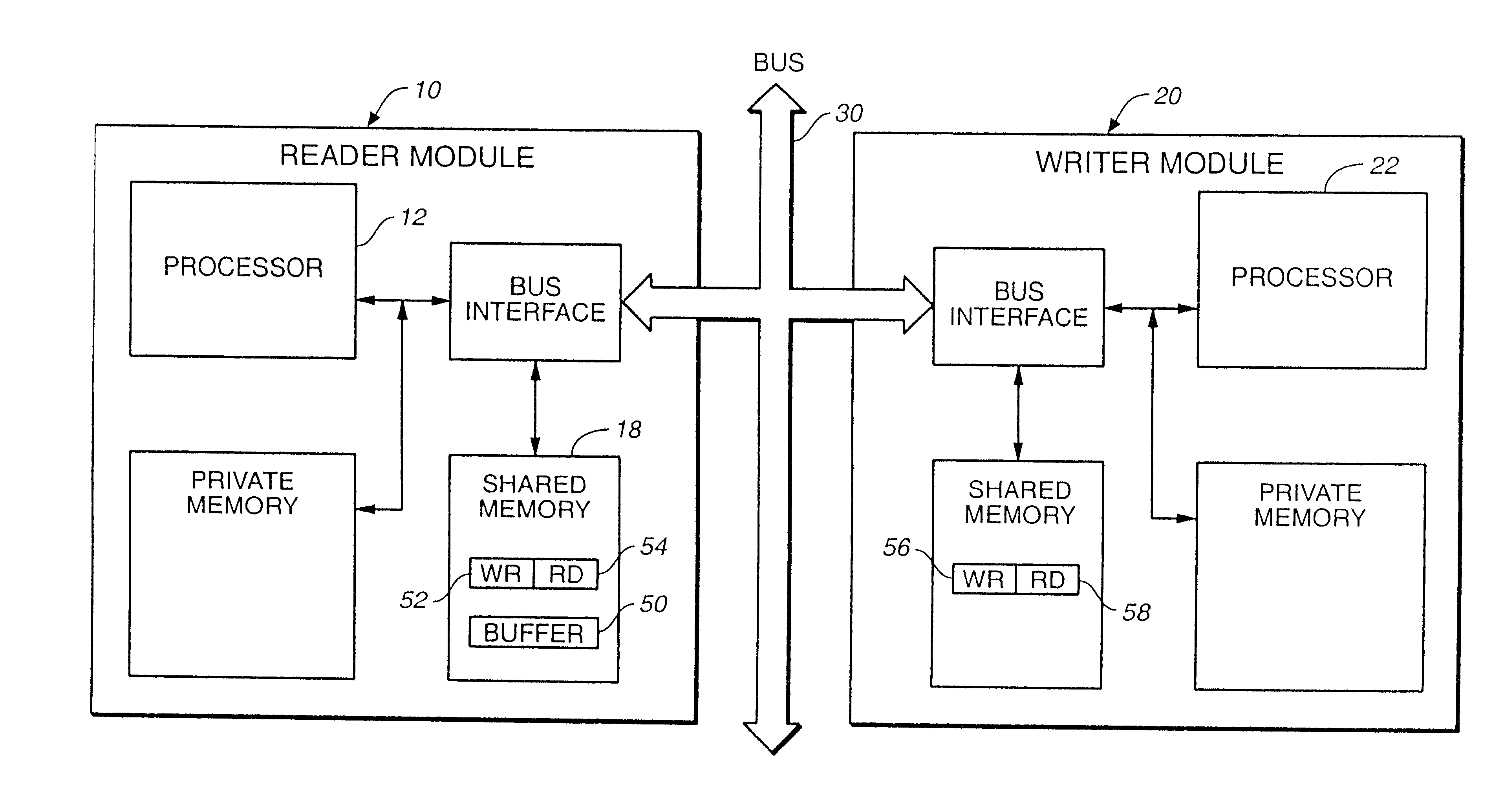

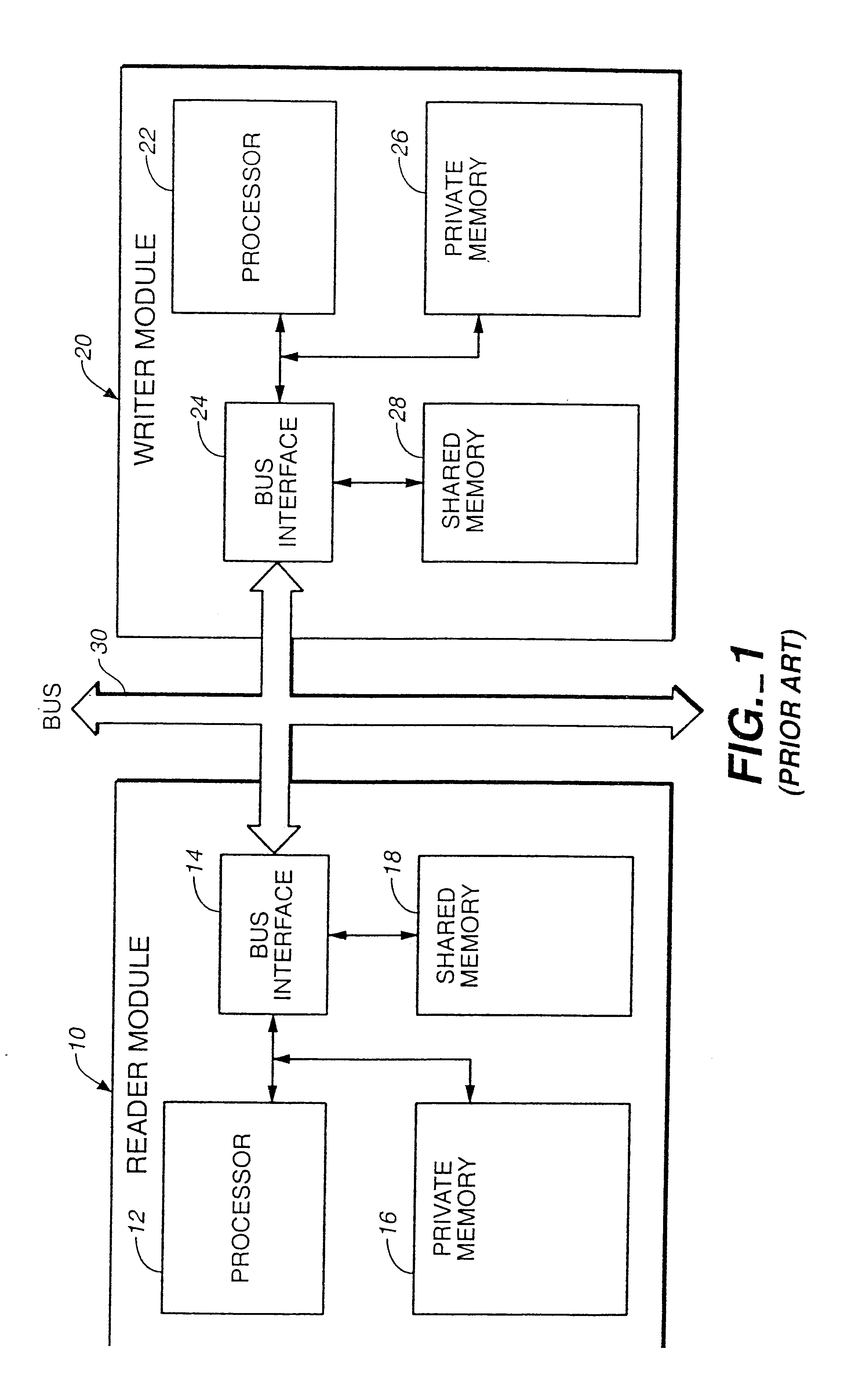

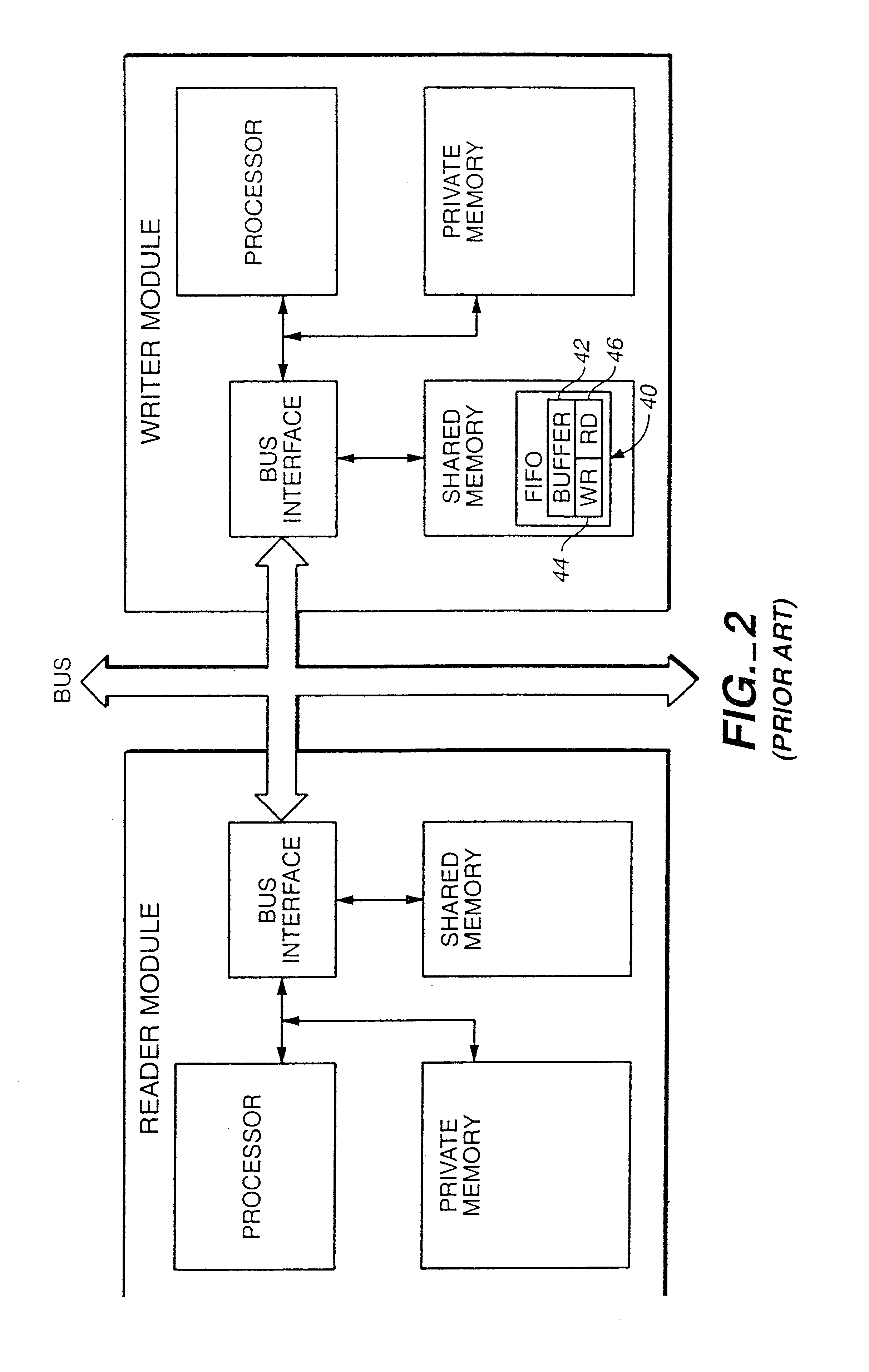

Efficient implementation of first-in-first-out memories for multi-processor systems

InactiveUS6615296B2Faster access timeEliminates performance bottleneckMultiple digital computer combinationsInput/output processes for data processingData valueOn board

To reduce FIFO access cycles across a system bus in a multi-processor system in which two processors communicate across a system bus through a FIFO, two separate FIFO descriptors are provided. The first descriptor is maintained by the processor located on-board with the FIFO, and the second descriptor is maintained by an off-board processor which communicates with the FIFO across the bus. When one processor performs a FIFO operation, the processor updates the other processor's descriptor via a memory access across the bus. Additionally, one module passes credits to the other to indicate that the latter has permission to perform a plurality of FIFO operations consecutively. In one embodiment a special non-valid data value is used to indicate an empty FIFO position.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

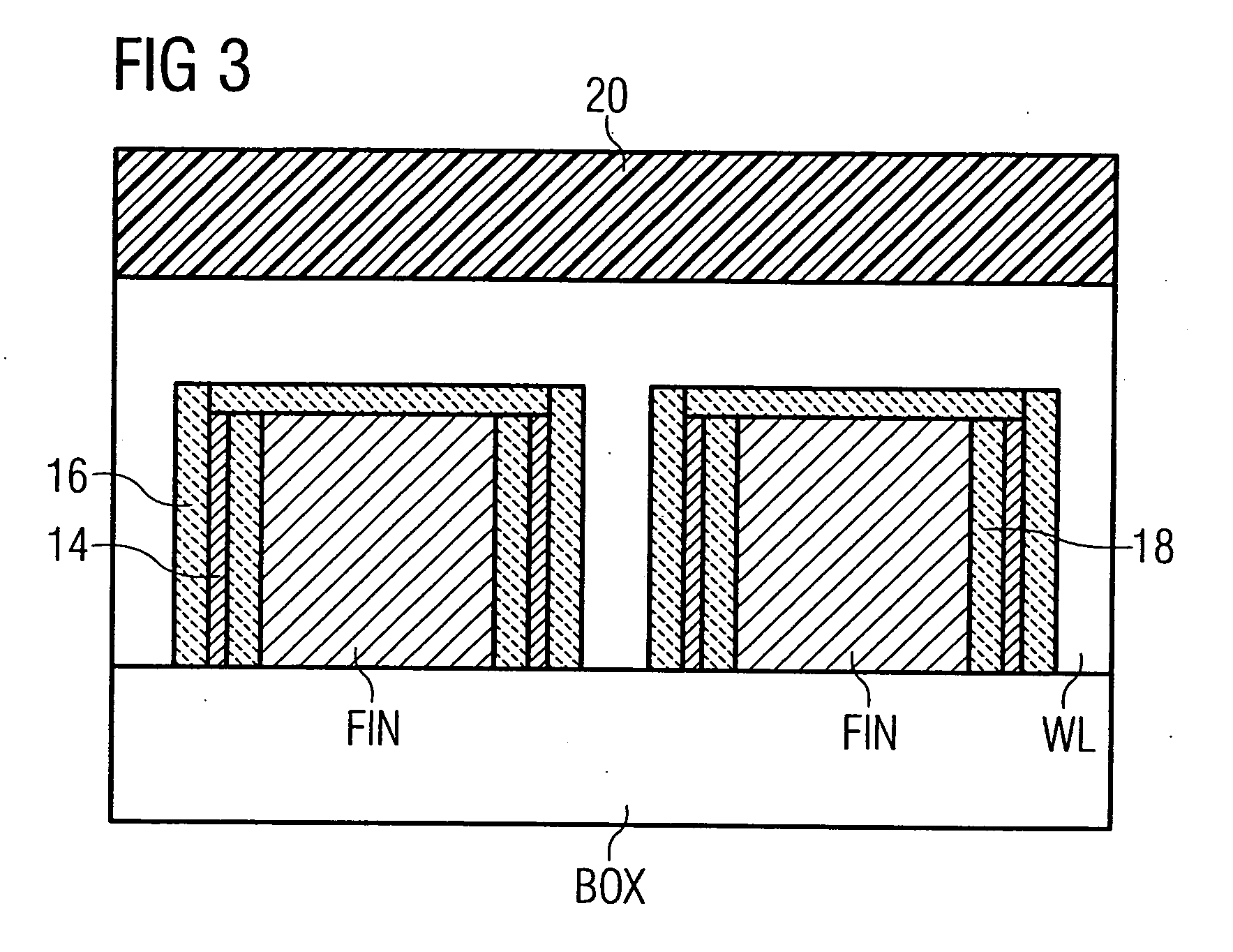

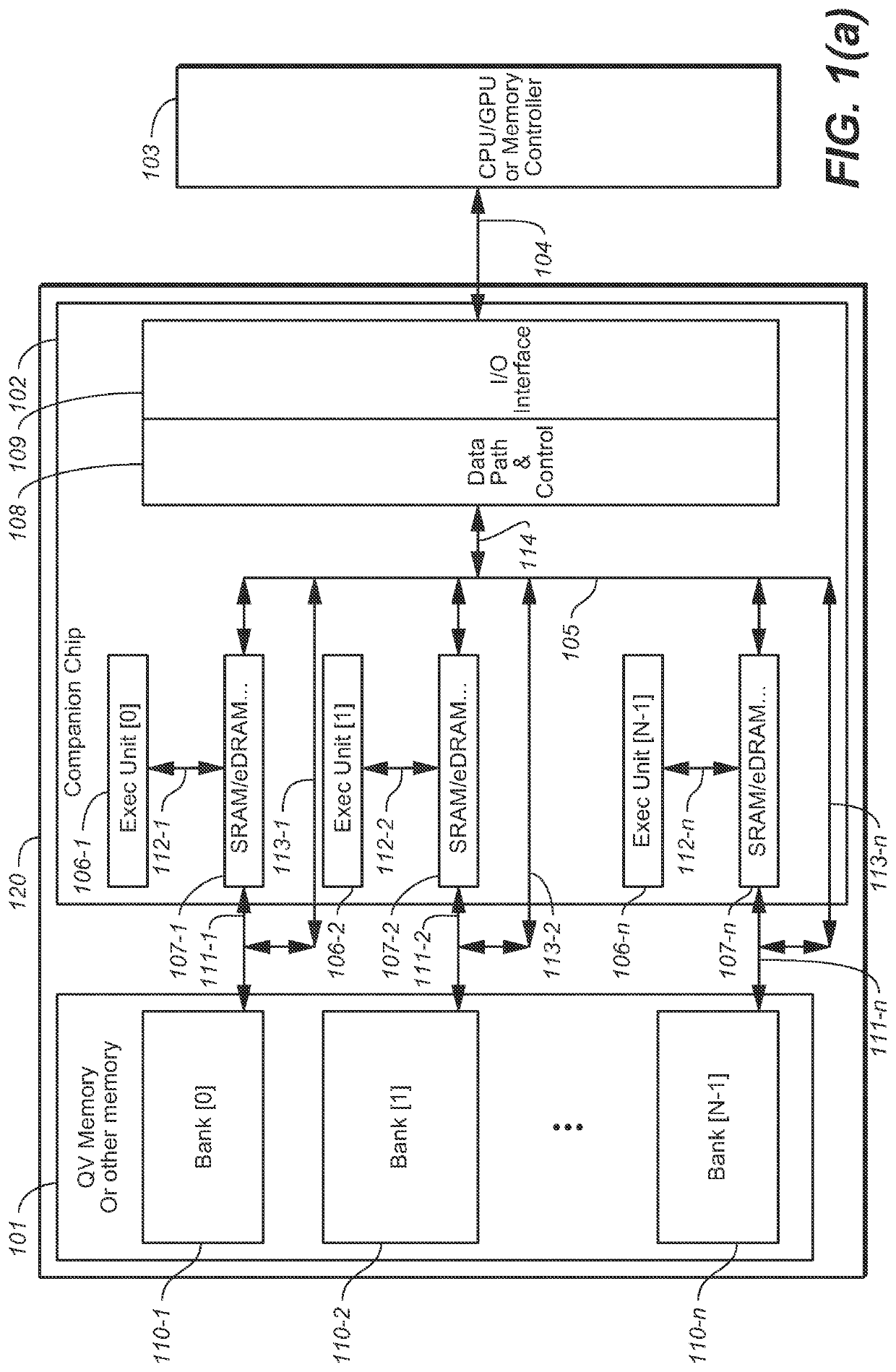

High capacity memory circuit with low effective latency

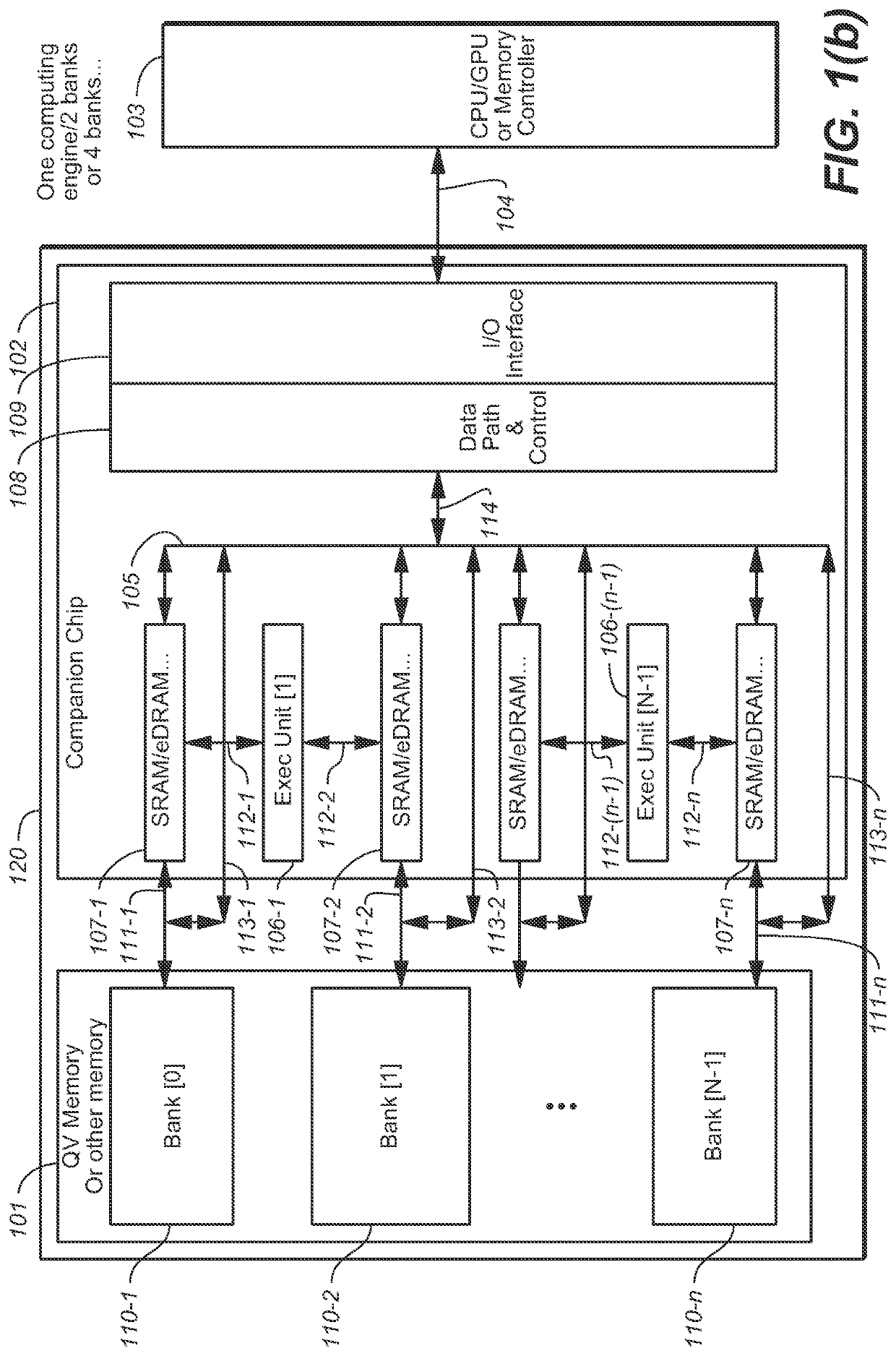

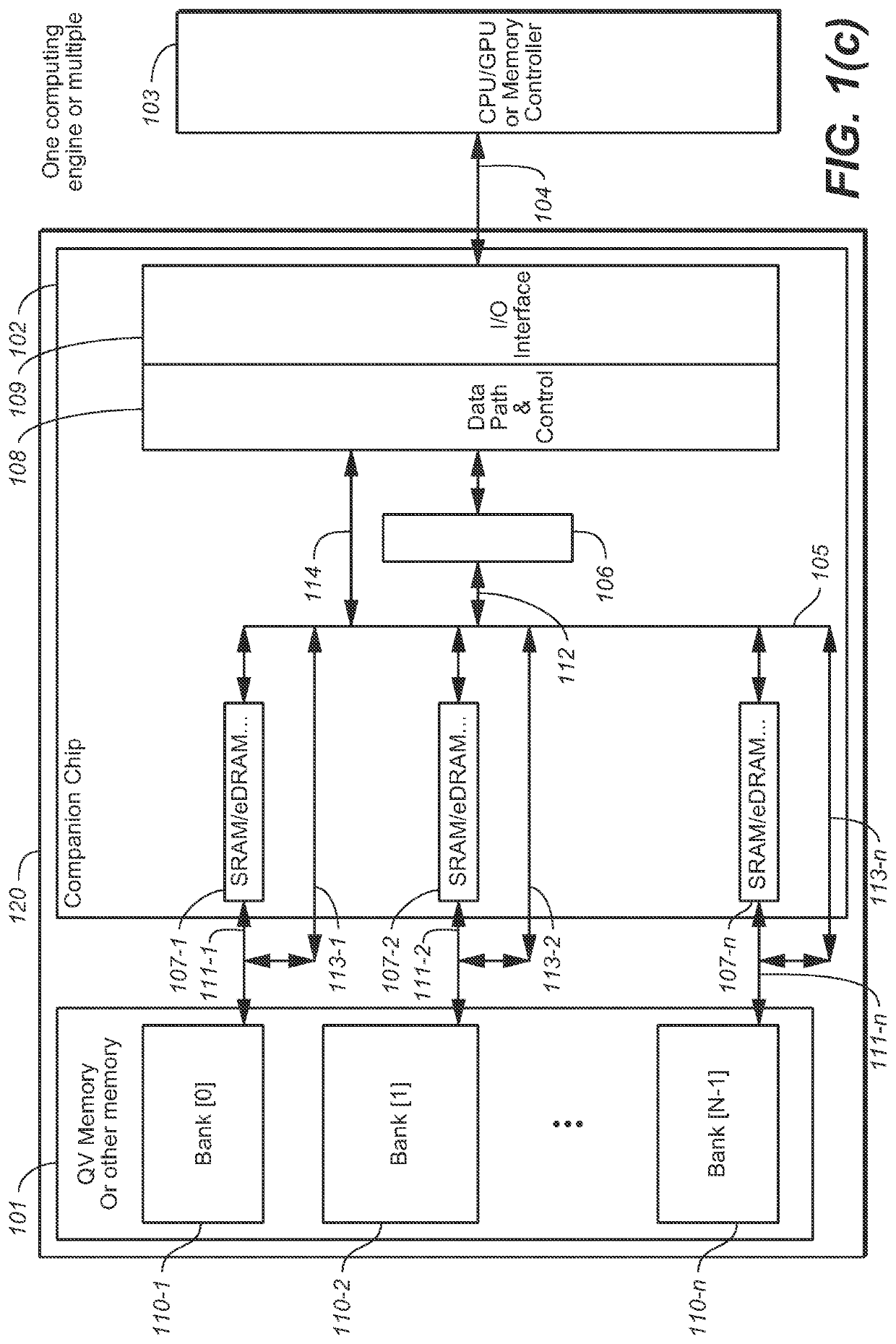

ActiveUS20210247910A1High data densityImprove staminaInput/output to record carriersSemiconductor/solid-state device detailsComputer architectureWafering

A first circuit formed on a first semiconductor substrate is wafer-bonded to a second circuit formed on a second memory circuit, wherein the first circuit includes quasi-volatile or non-volatile memory circuits and wherein the second memory circuit includes fast memory circuits that have lower read latencies than the quasi-volatile or non-volatile memory circuits, as well as logic circuits. The volatile and non-volatile memory circuits may include static random-access memory (SRAM) circuits, dynamic random-access memory (DRAM) circuits, embedded DRAM (eDRAM) circuits, magnetic random-access memory (MRAM) circuits, embedded MRAM (eMRAM), or any suitable combination of these circuits.

Owner:SUNRISE MEMORY CORP

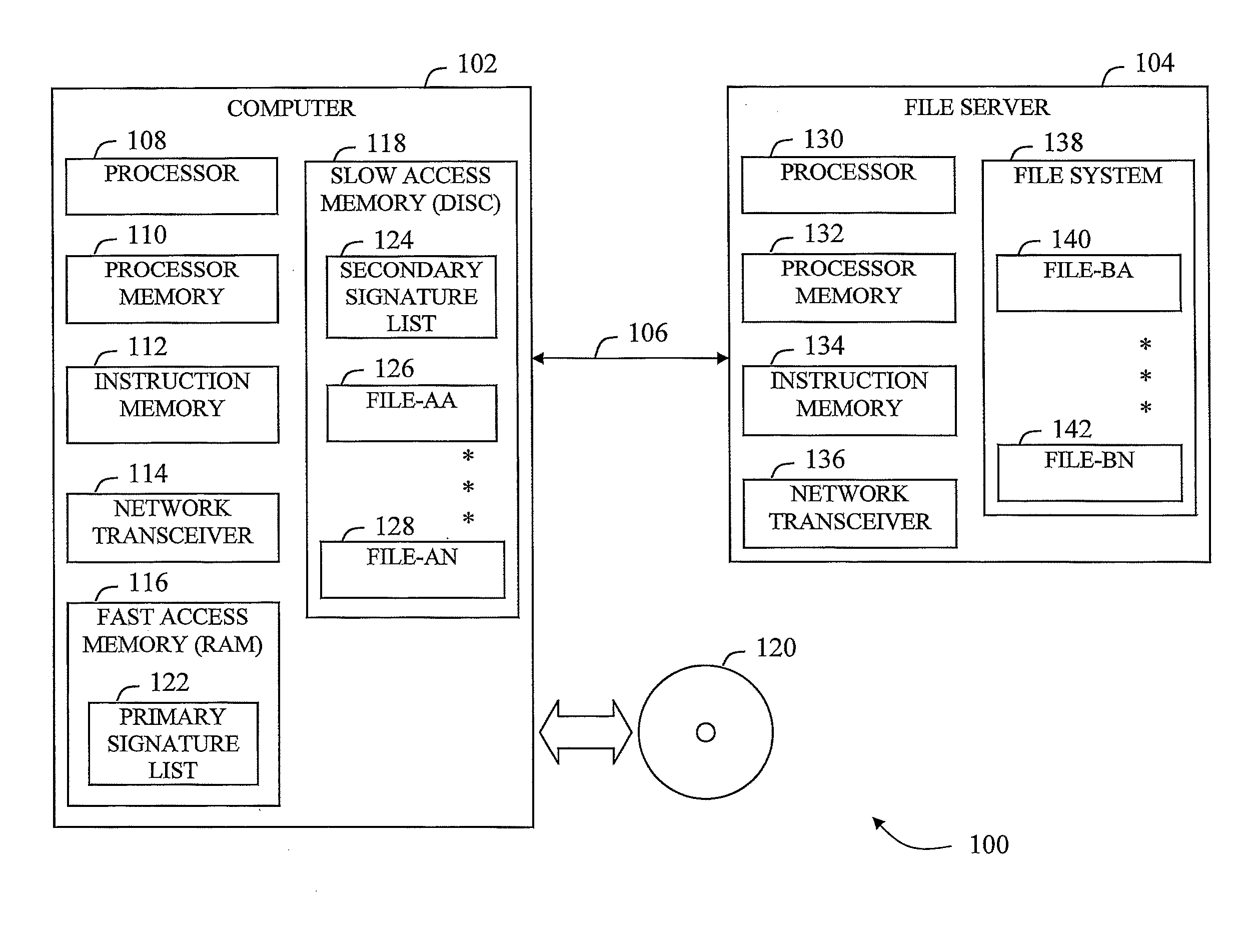

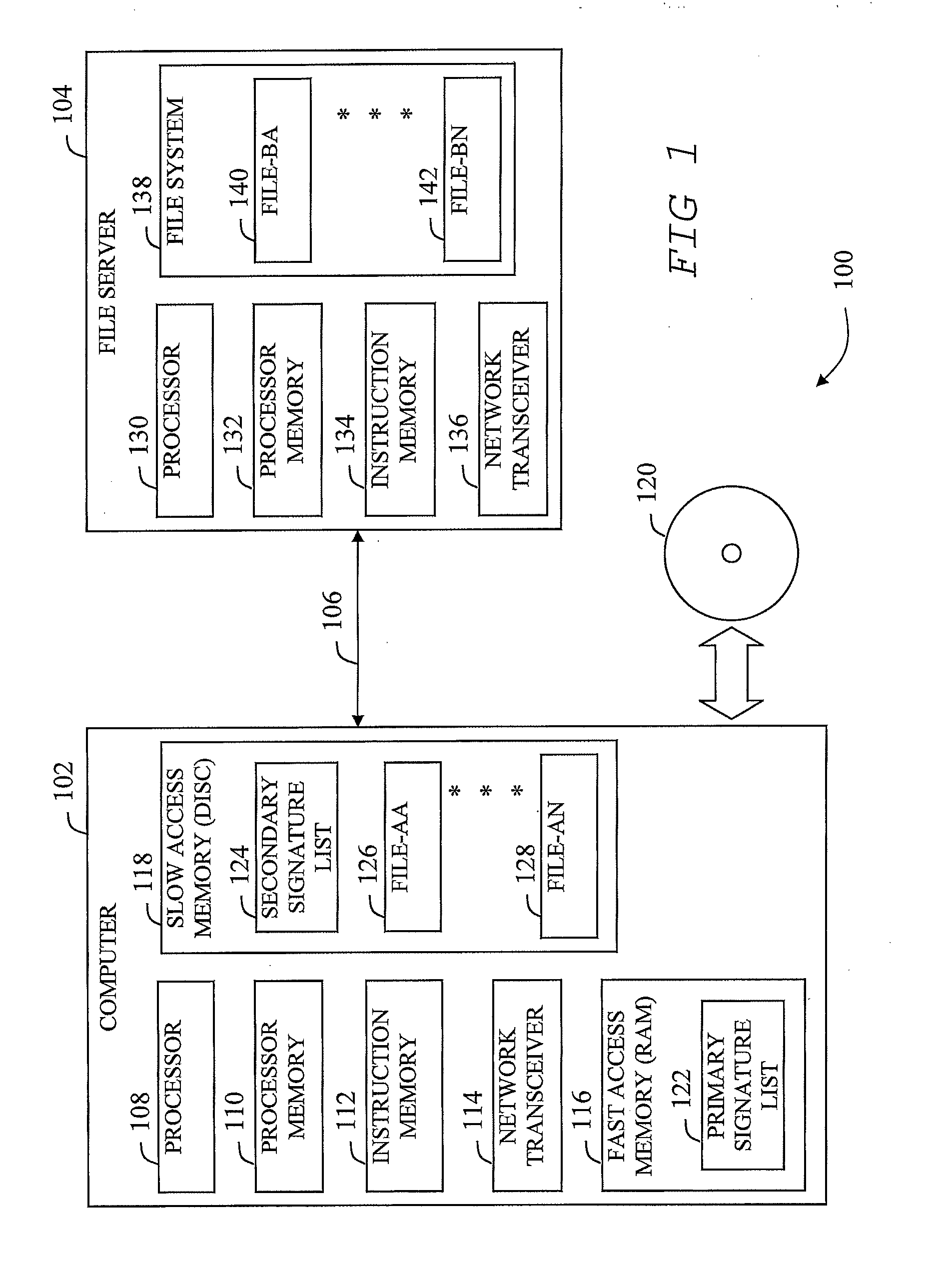

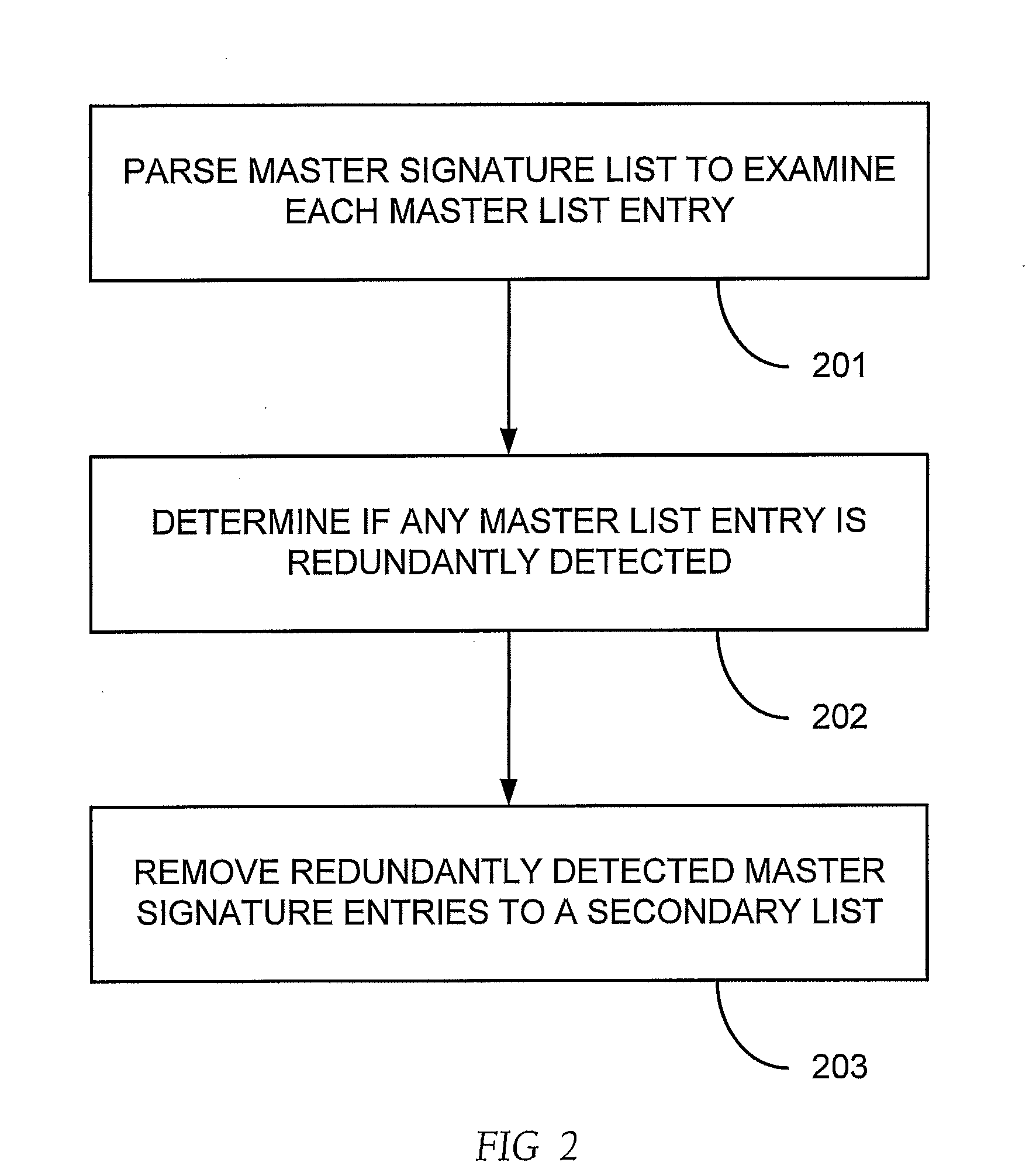

Anti-virus signature footprint

InactiveUS20080155264A1Reduced first memory size requirementFaster access timeUser identity/authority verificationAnti virusTheoretical computer science

A computer anti-virus system is disclosed. The computer anti-virus system can have multiple detection layers and can include a first memory and a second memory. The computer anti-virus system can have a reduced first memory size requirement for a fingerprint signature based anti-virus application program by putting off to the second memory those signatures that are redundantly detected on other layers. Thus, performance can be enhanced and / or costs can be reduced.

Owner:EEYE DIGITAL SECURITY

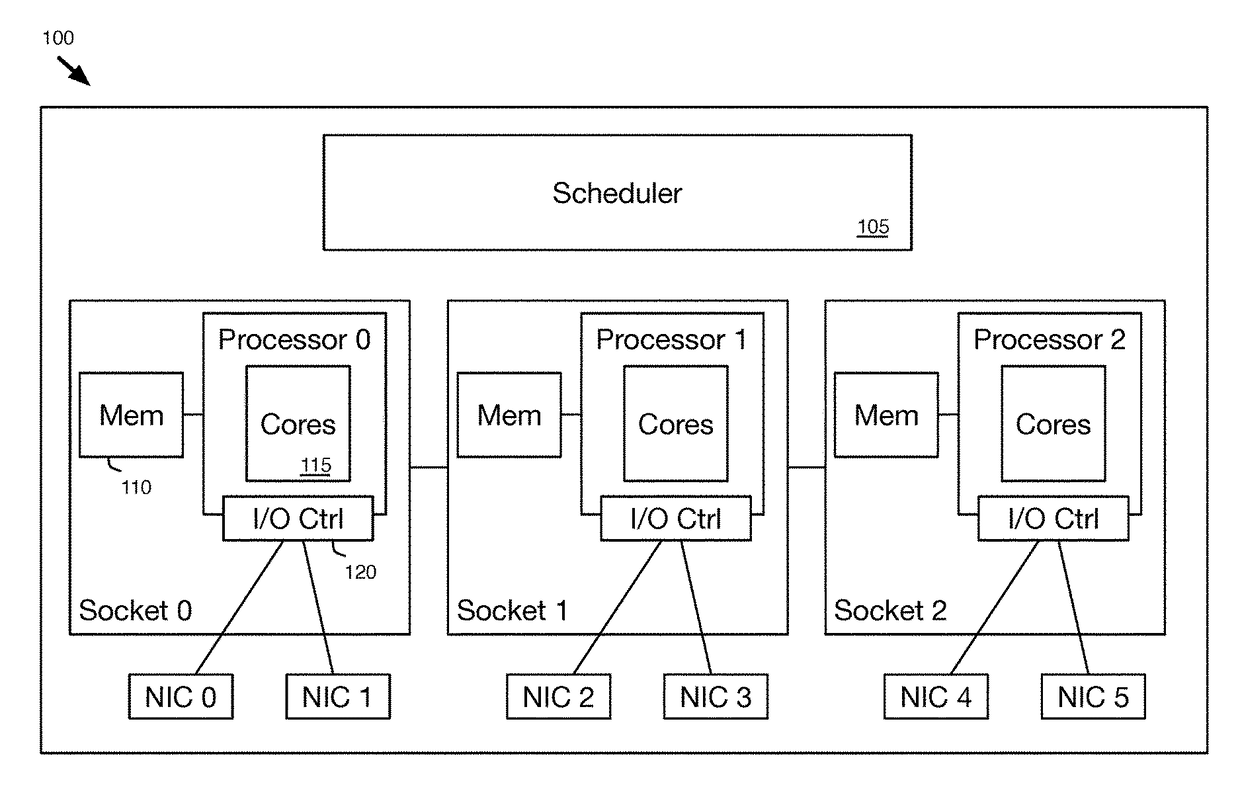

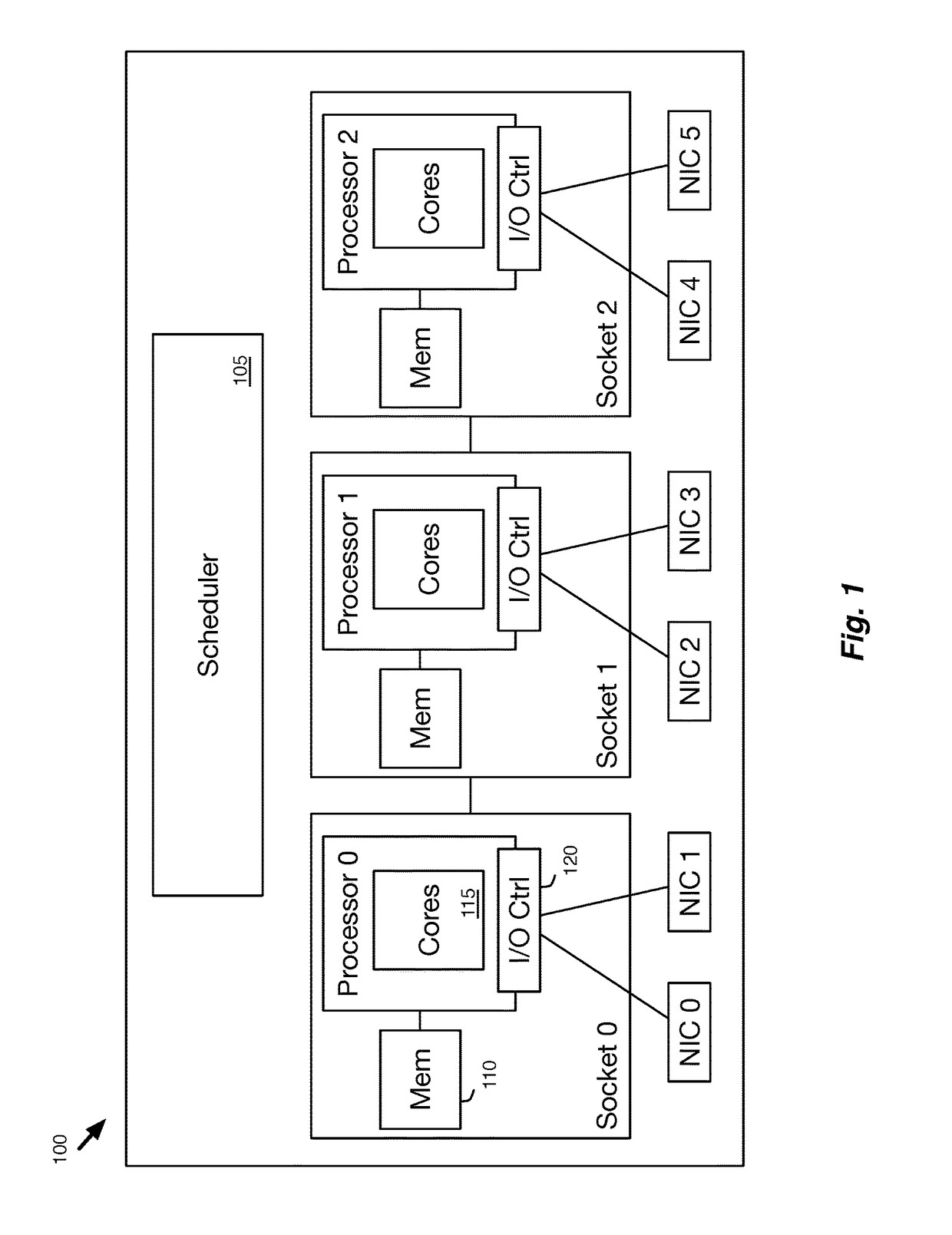

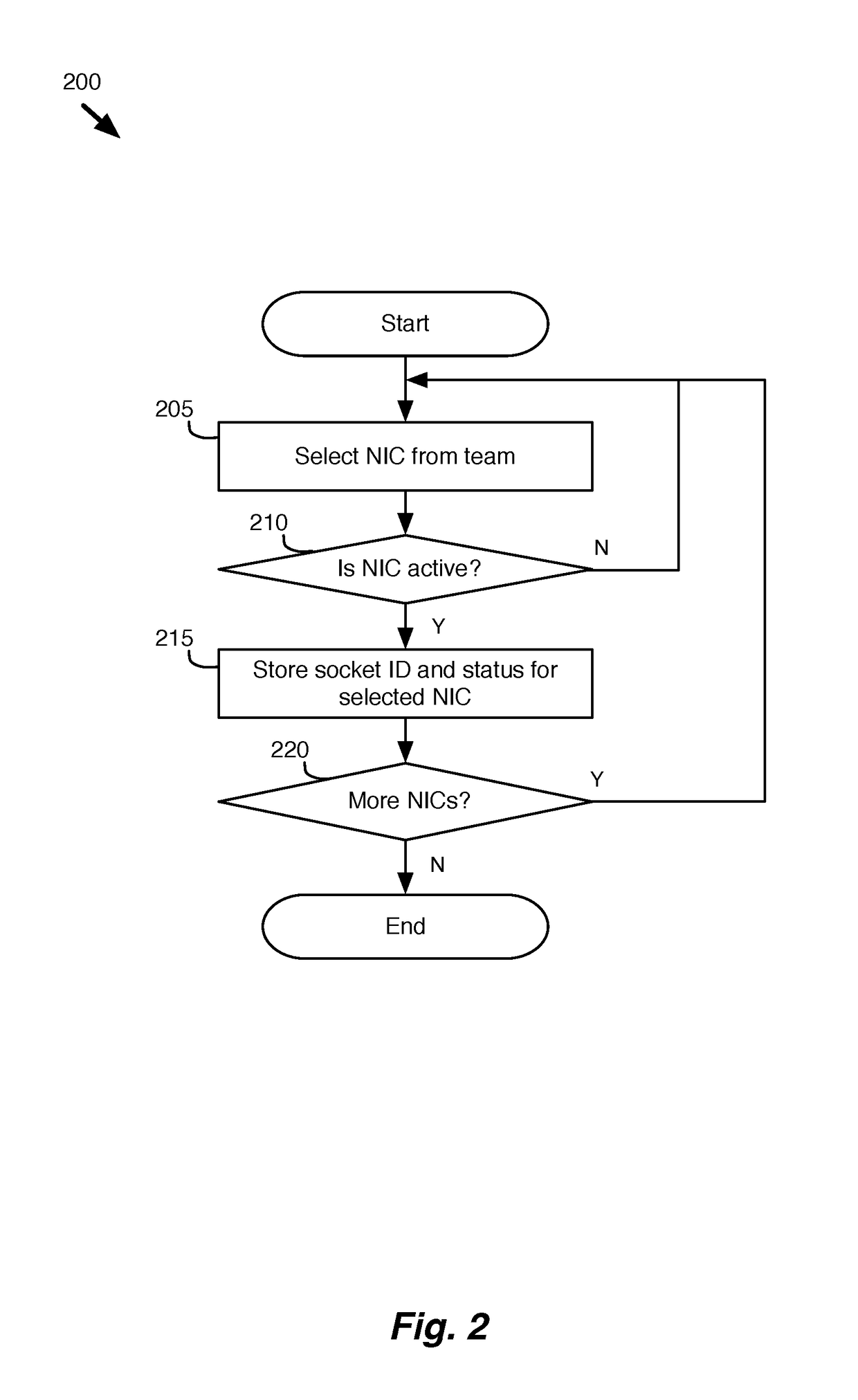

Locality-aware scheduling for nic teaming

ActiveUS20170315840A1Faster access timeAddressing slow performanceMemory architecture accessing/allocationProgram initiation/switchingTraffic capacityNetwork interface controller

Some embodiments provide a method for distributing packets processed at multiple sockets across a team of network interface controllers (NICs) in a processing system. The method of some embodiments uses existing distribution (or selection) algorithms for distributing traffic across NICs of a NIC team (across several sockets), but augments the method to prioritize local NICs over remote NICs. When active NICs local to a socket associated with a packet are available, the method of some embodiments uses the selection algorithm to select from an array of the active local NICs. When active NICs local to the socket are not available, the method of some embodiments uses the selection algorithm to select from an array of the active NICs of other NICs on the NIC team.

Owner:NICIRA

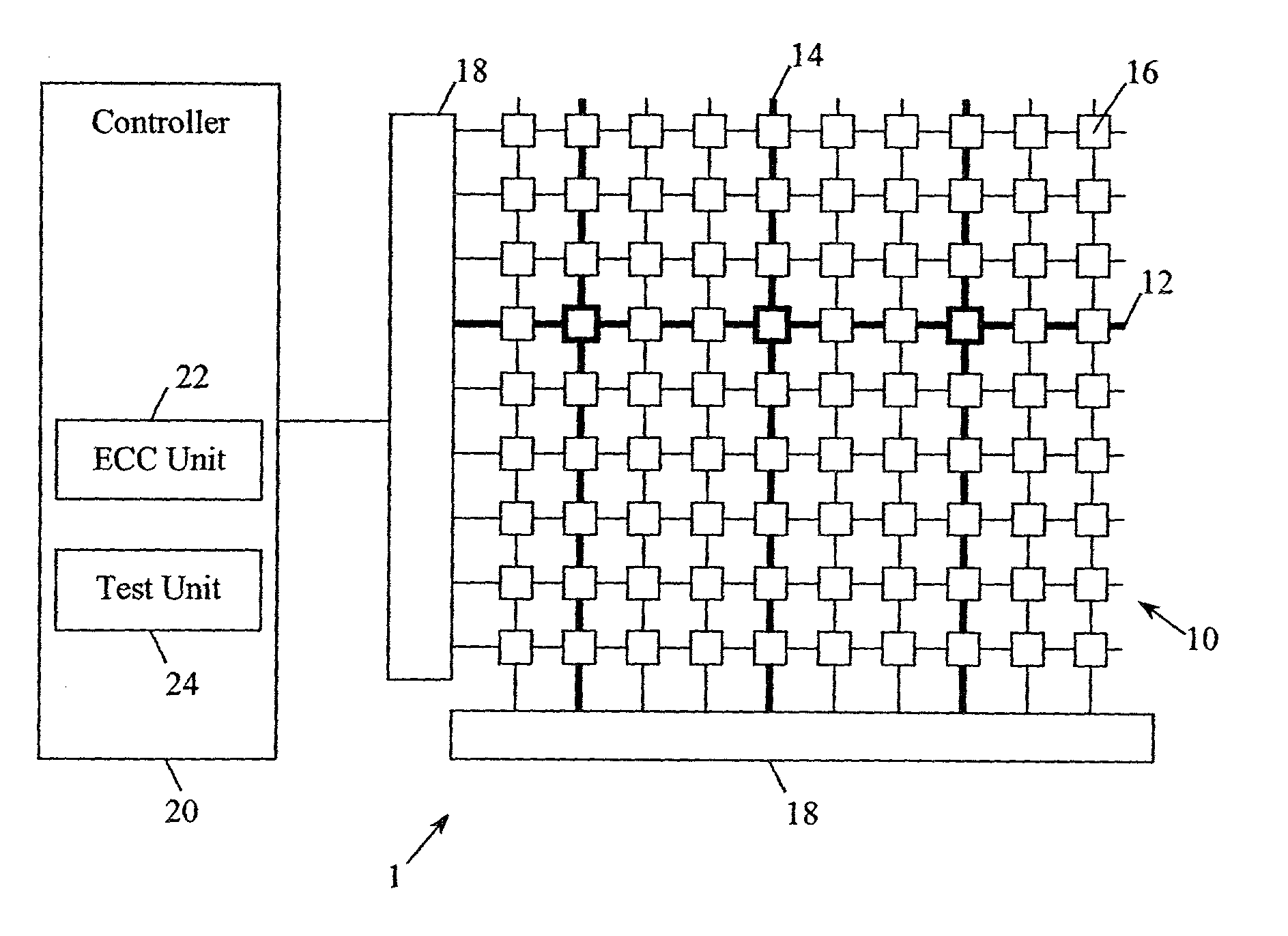

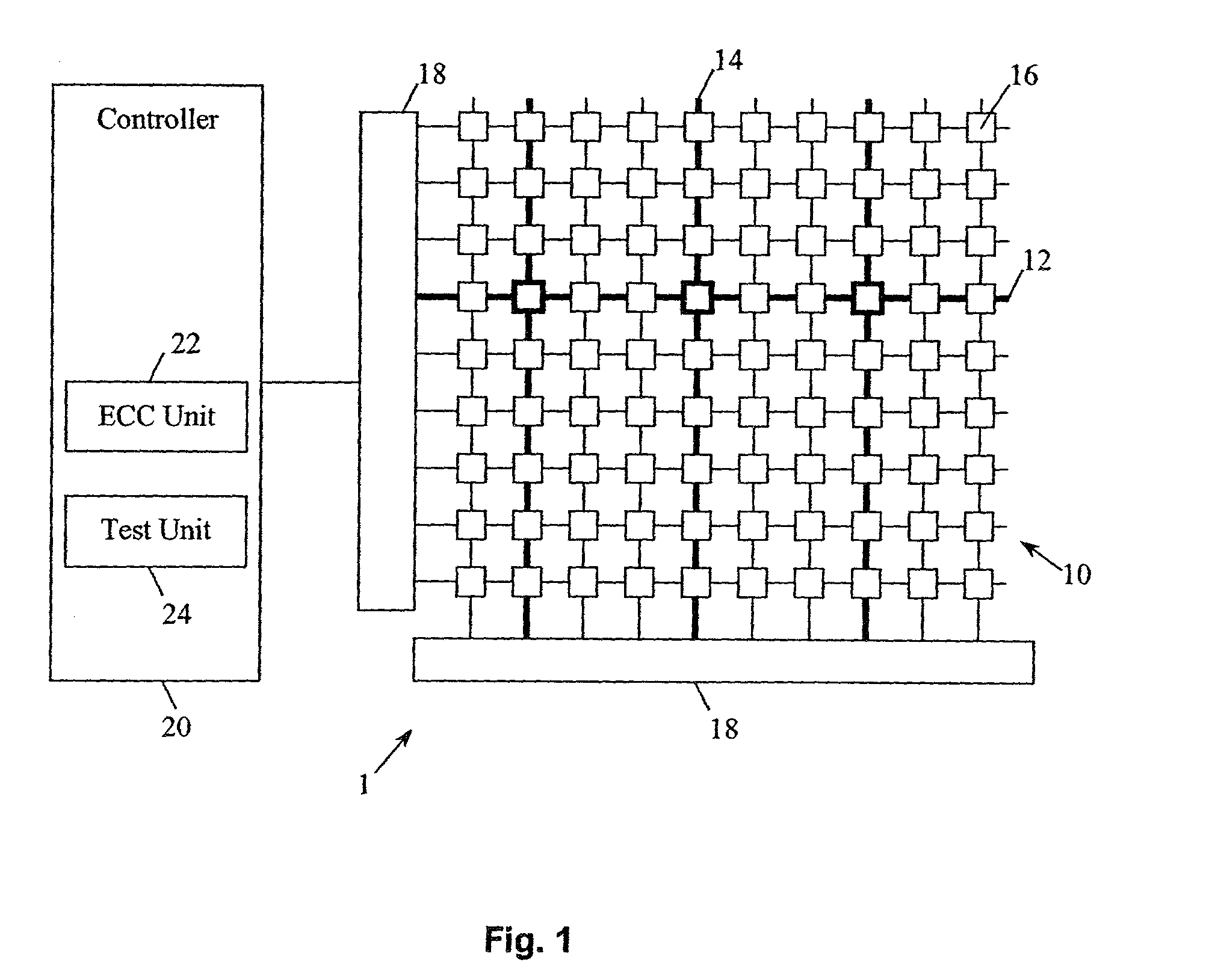

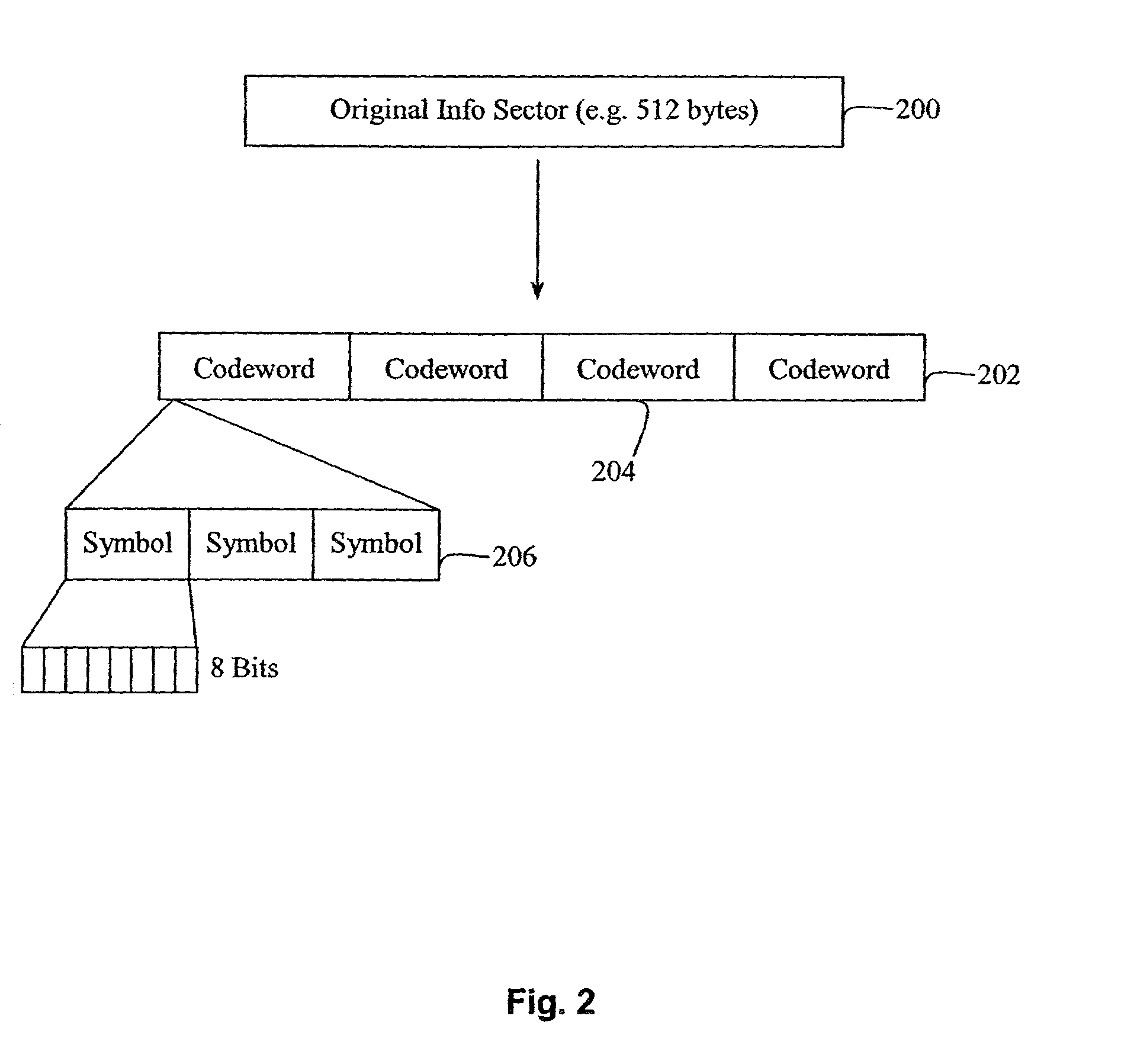

Manufacturing test for a fault tolerant magnetoresistive solid-state storage device

InactiveUS7107508B2Reliable calibrationReduce power consumptionMemory loss protectionError detection/correctionSolid-state storageMagnetic reluctance

A fault-tolerant magnetoresistive solid-state storage device (MRAM) in use performs error correction coding and decoding of stored information, to tolerate physical failures. At manufacture, the device is tested to confirm that each set of storage cells is suitable for storing ECC encoded data. The test comprises identifying failed cells where the failures will be visible in use for the generation of erasure information used in ECC decoding, by comparing parametric values obtained from the cells against one or more failure ranges, and includes performing a write-read-compare operation with test data to identify failed cells which will be hidden for the generation of erasure information in use. A failure count is formed based on both the visible failures and the hidden failures, to determine that the set of cells is suitable for storing ECC encoded data. The failure count is weighted, with hidden failures having a greater weighting than visible failures.

Owner:SAMSUNG ELECTRONICS CO LTD

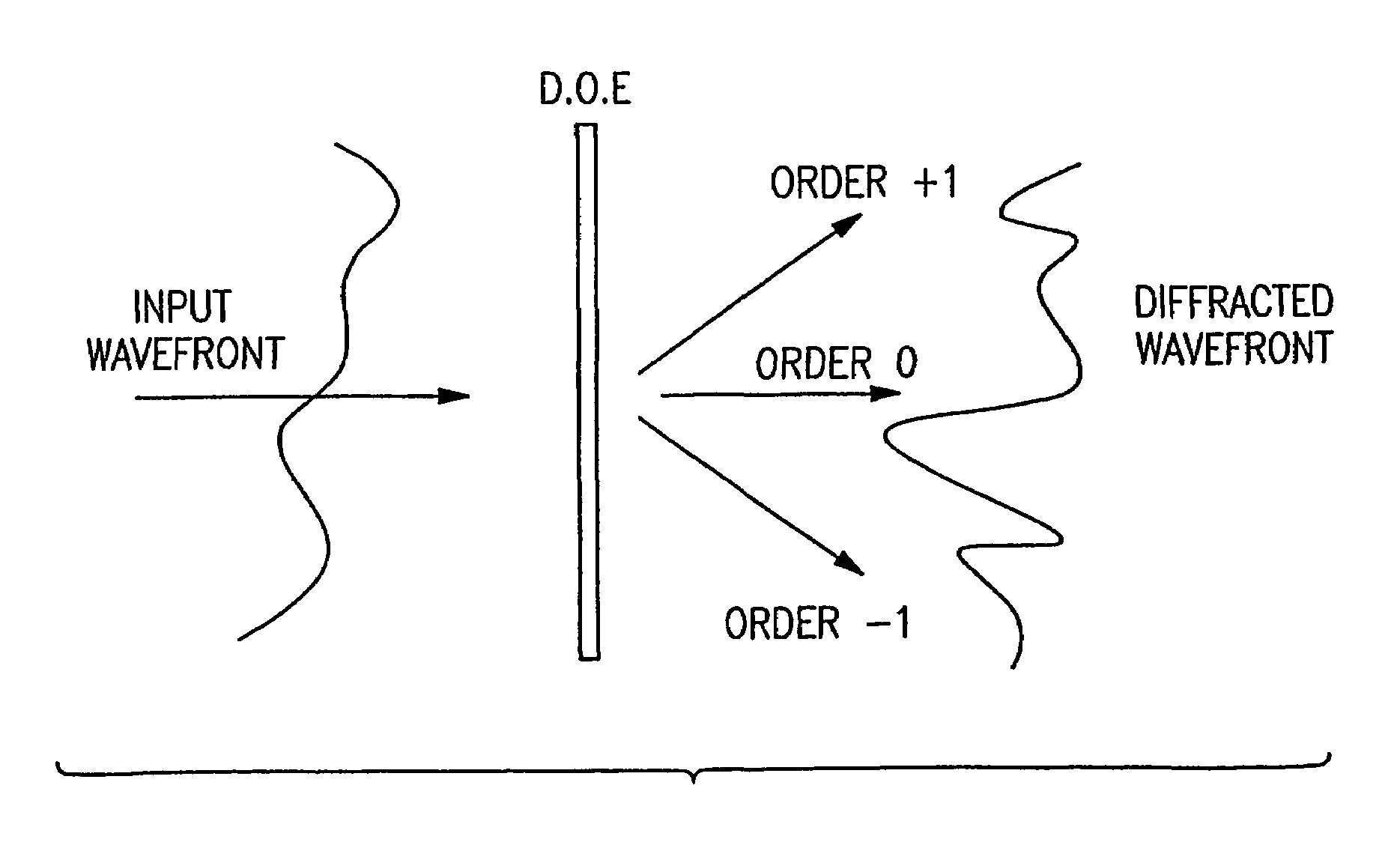

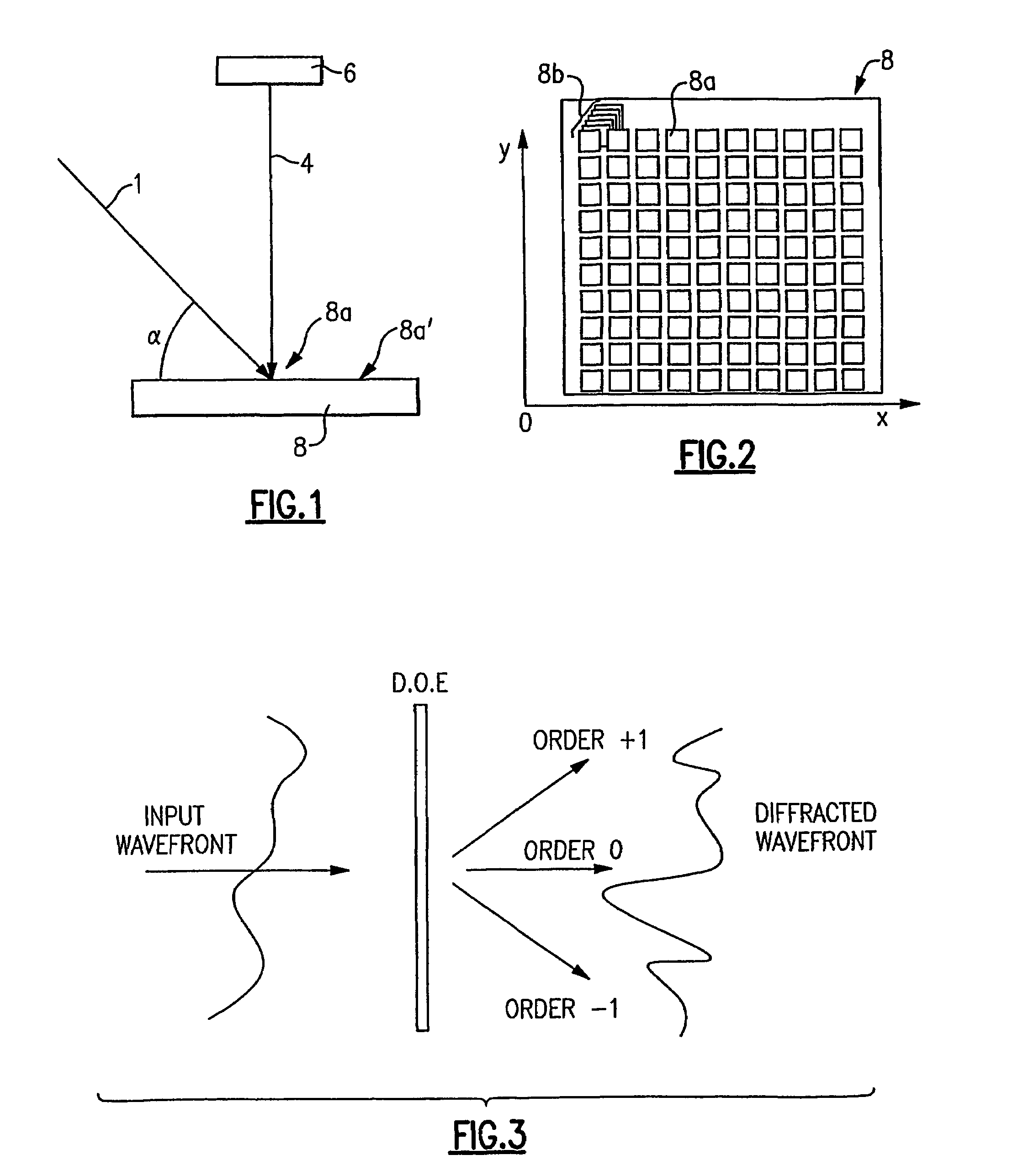

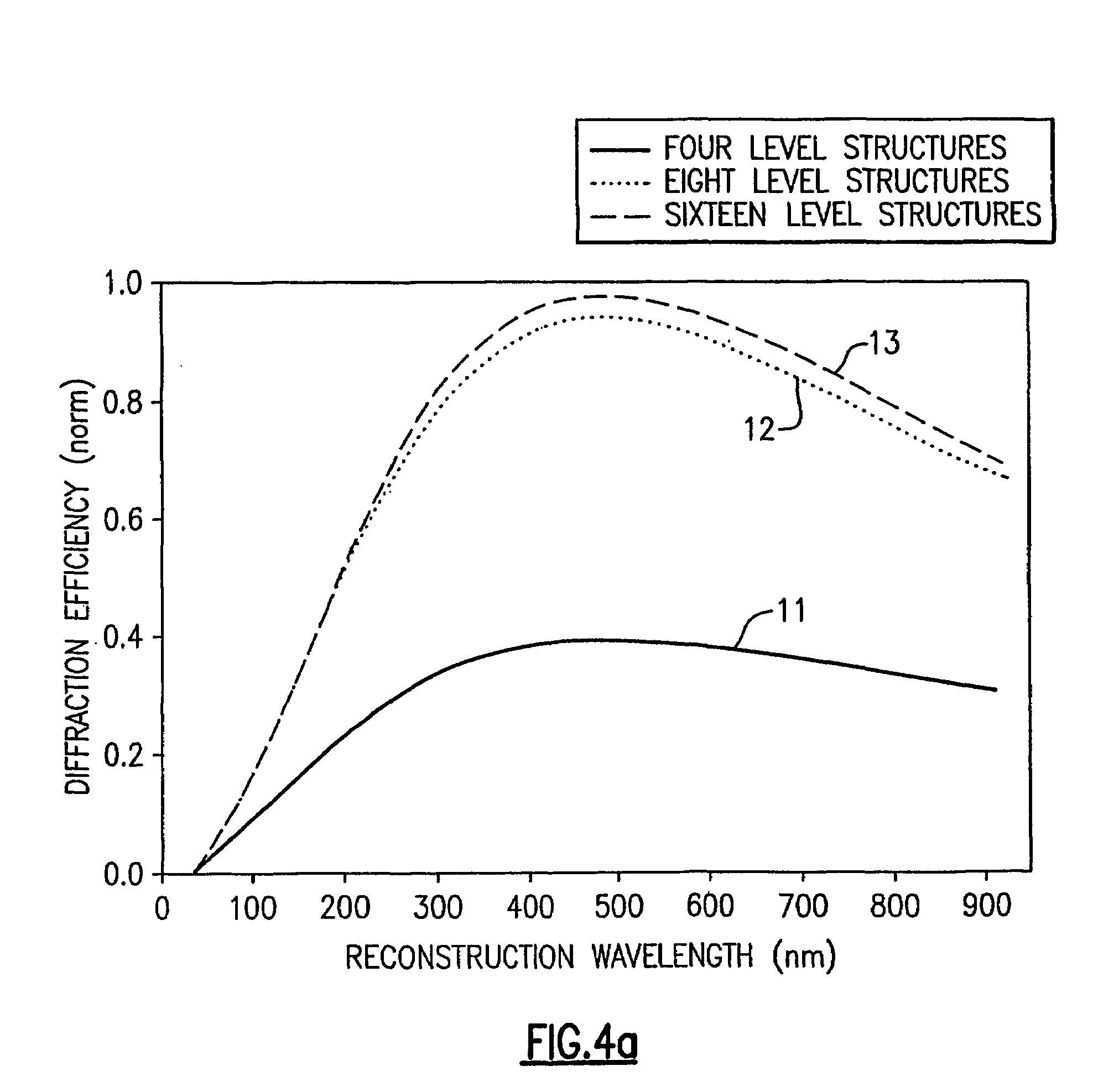

Dynamic solid state diffractive optics applied for reading a diffractive optics memory

InactiveUS7210628B2Faster access timeLong lastingRecord information storageOptical beam guiding meansComputer scienceDiffraction optics

Owner:RES INVESTMENT NETWORK

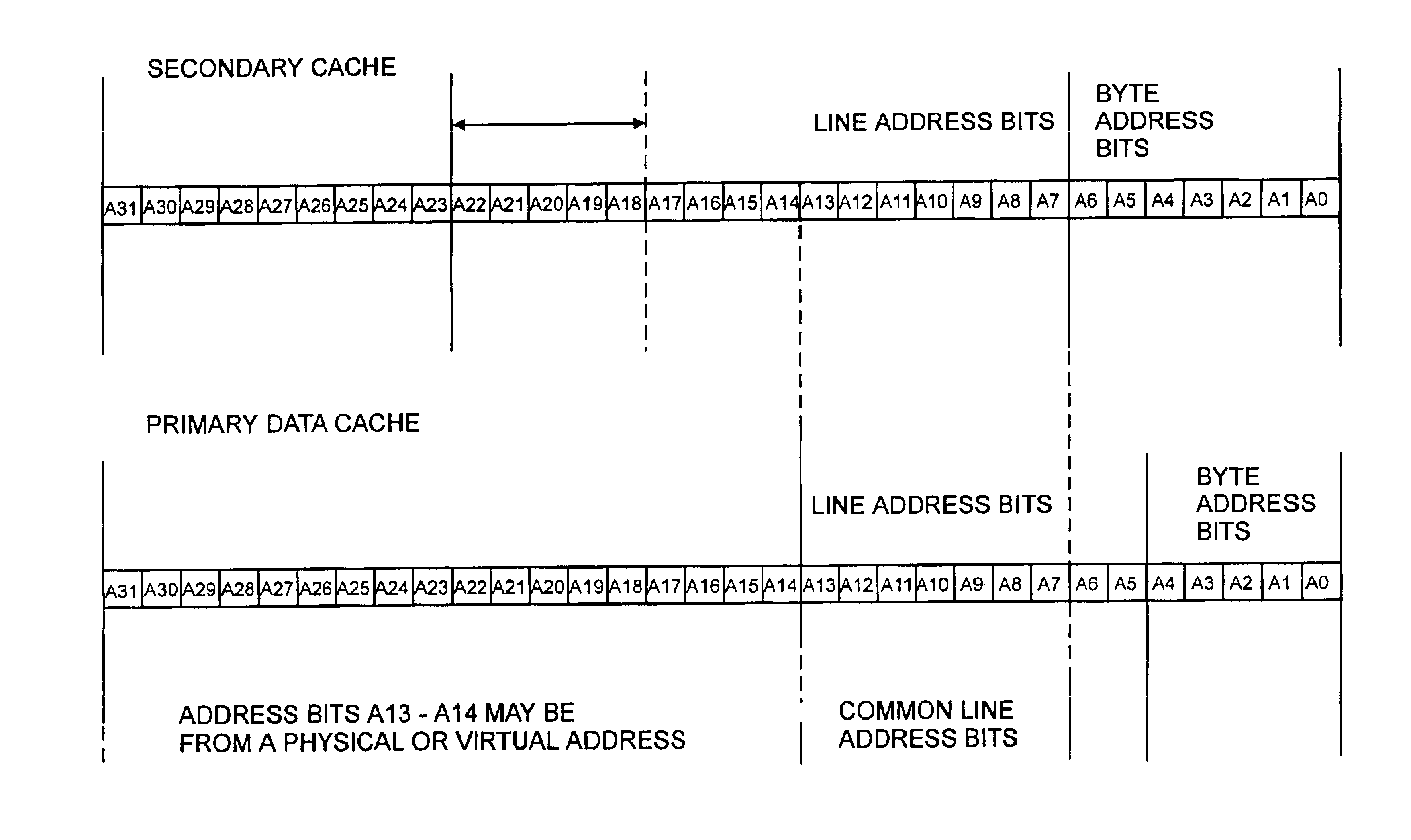

Addressing a cache

InactiveUS6977657B2Shorten the timeSolve large capacityMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemOperational system

A data processing system has main memory and one or more caches. Data from main memory is cached while mitigating the effects of address pattern dependency. Main memory physical addresses are translated into main memory virtual address under the control of an operating system. The translation occurs on a page-by-page basis such that some of the virtual address bits are the same as some of the physical address bits. A portion of the address bits that are the same are selected and cache offset values are generated from the selected portion. Data is written to the cache at offset positions derived from the cache offset values.

Owner:AUTODESK INC

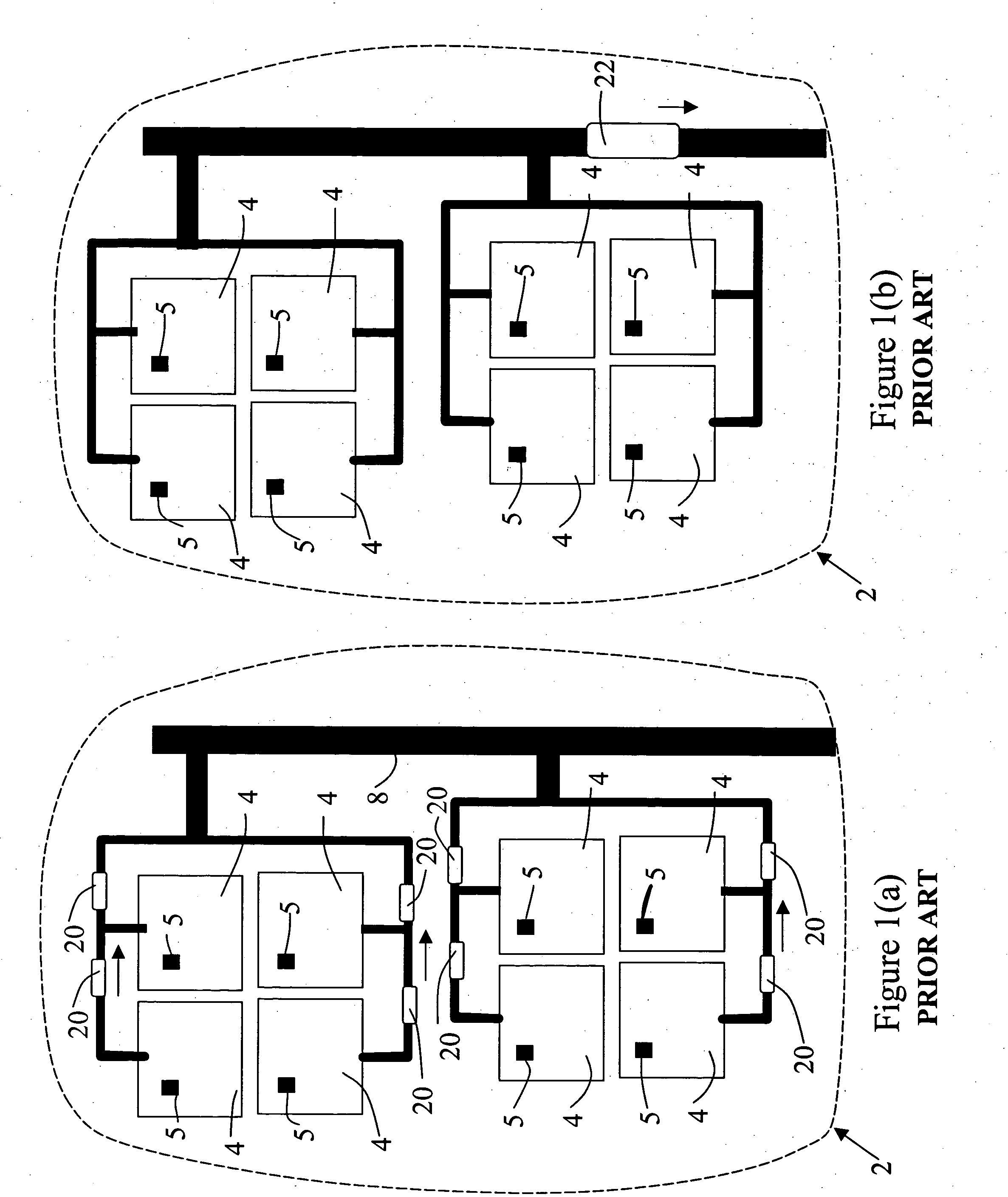

Power and signal line bussing method for memory devices

InactiveUSRE36490E1Reduce chip sizeReduce noiseSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGround line

A memory cell device having circuitry located between memory cell arrays comprises power and ground lines to the circuitry formed directly above the memory cell arrays. The power and ground lines are parallel and positioned in an adjacent alternating pattern such that a power line is positioned adjacent a ground line, which is positioned adjacent another power line and so on. Signal lines carrying signals to and from the circuitry are also formed directly above memory cell arrays.

Owner:SAMSUNG ELECTRONICS CO LTD

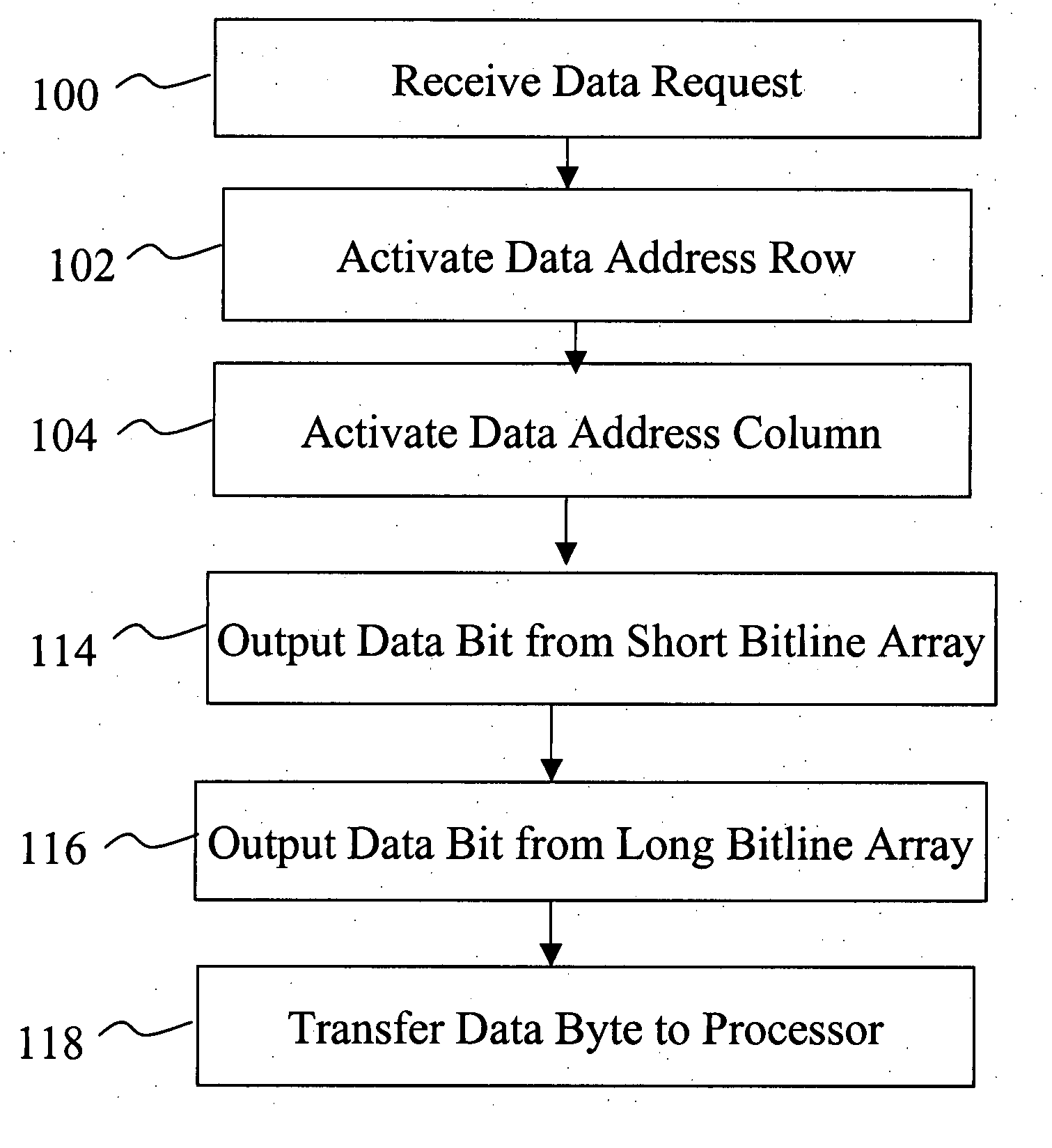

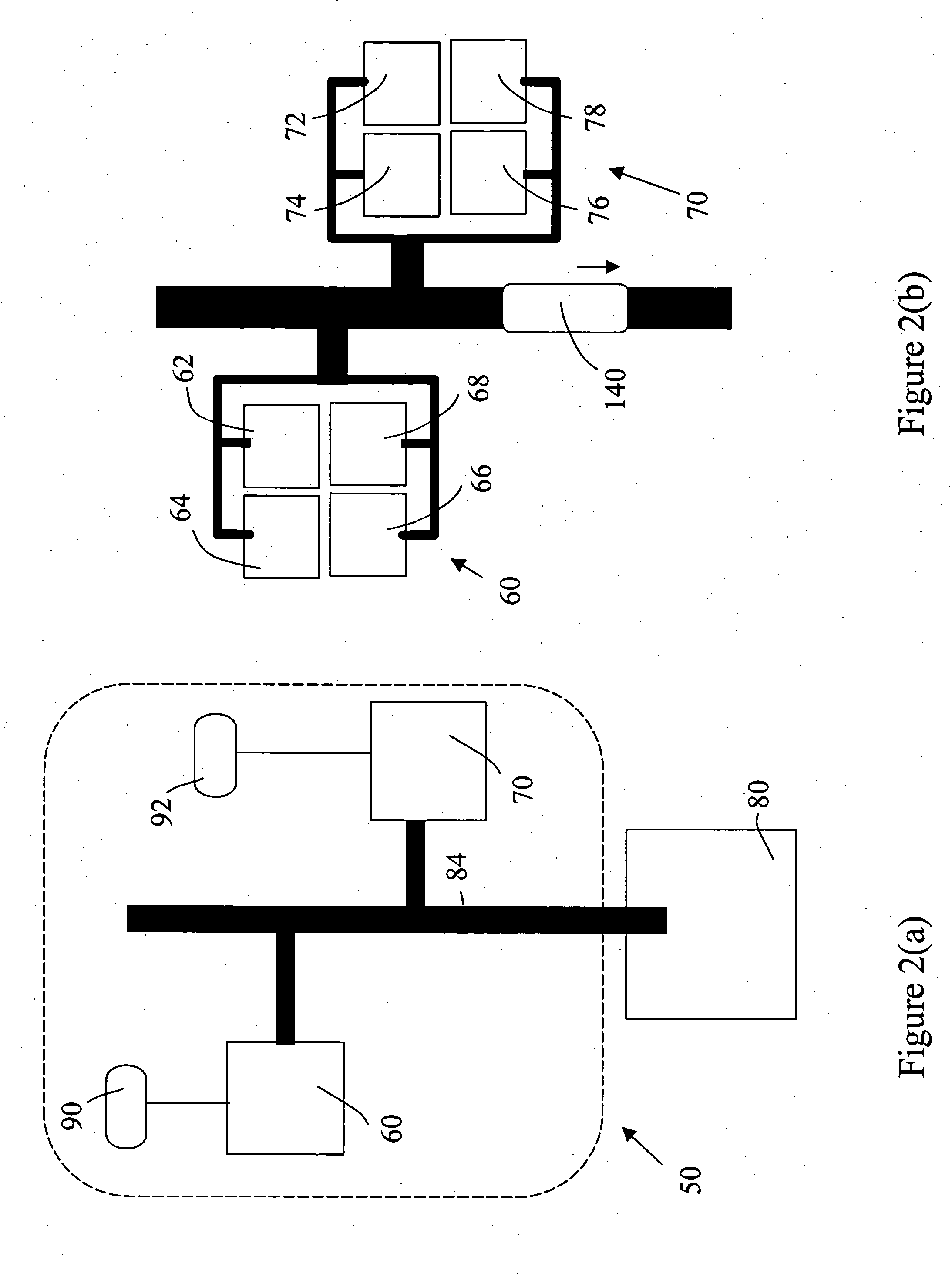

System and method for variable array architecture for memories

InactiveUS20050144373A1Increase heightWithout slowing down operation timeEnergy efficient ICTEnergy efficient computingData operationsParallel computing

A memory system that employs simultaneous activation of at least two dissimilar memory arrays, during a data manipulation, such as read or write operations is disclosed. An exemplary embodiment includes a memory system containing a plurality of arrays, each in communication with a common controller, wherein the arrays are activated by different supply voltage (Vdd). When a processor sends a command to retrieve or write data to the memory system, two or more arrays are addressed to supply the required data. By proper partitioning of the data between dissimilar arrays, the efficiency of data reading is improved.

Owner:IBM CORP +1

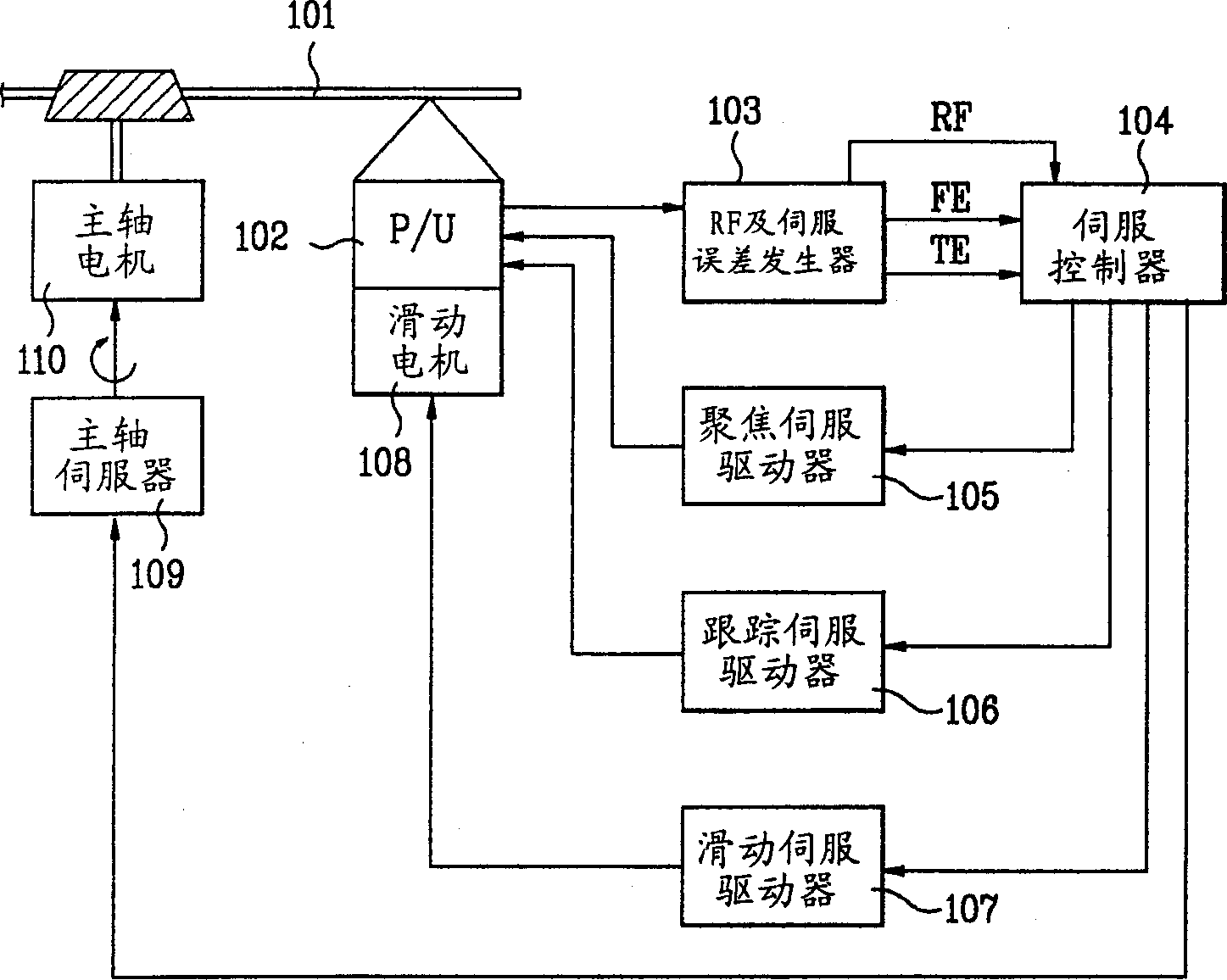

Tracking tab method and device for optical recording media

InactiveCN1484223AFaster access timeReduce transient responseTrack finding/aligningRecord information storageControl signalOptical recording

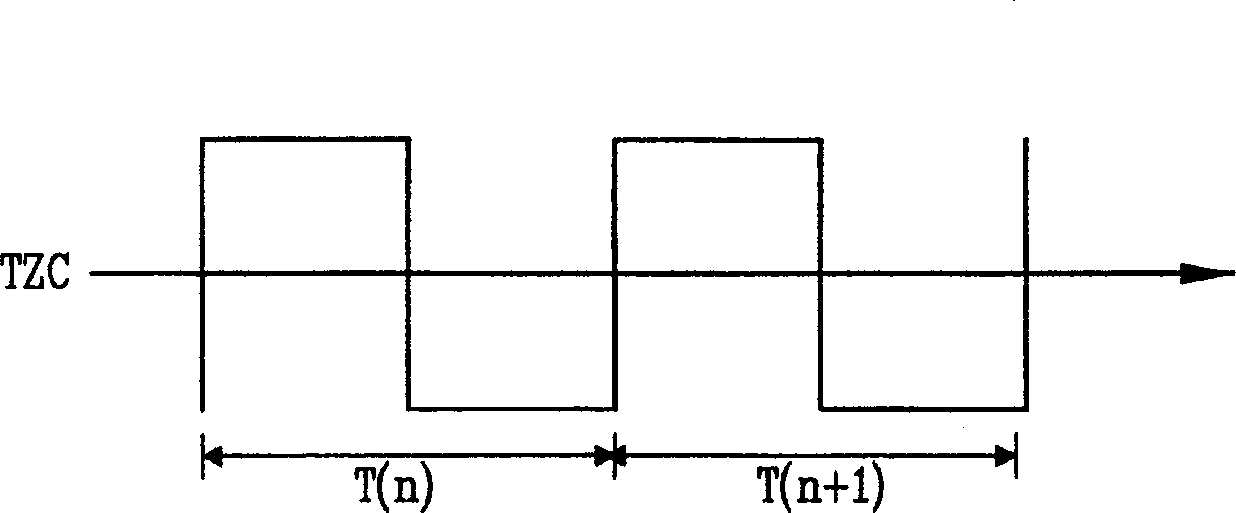

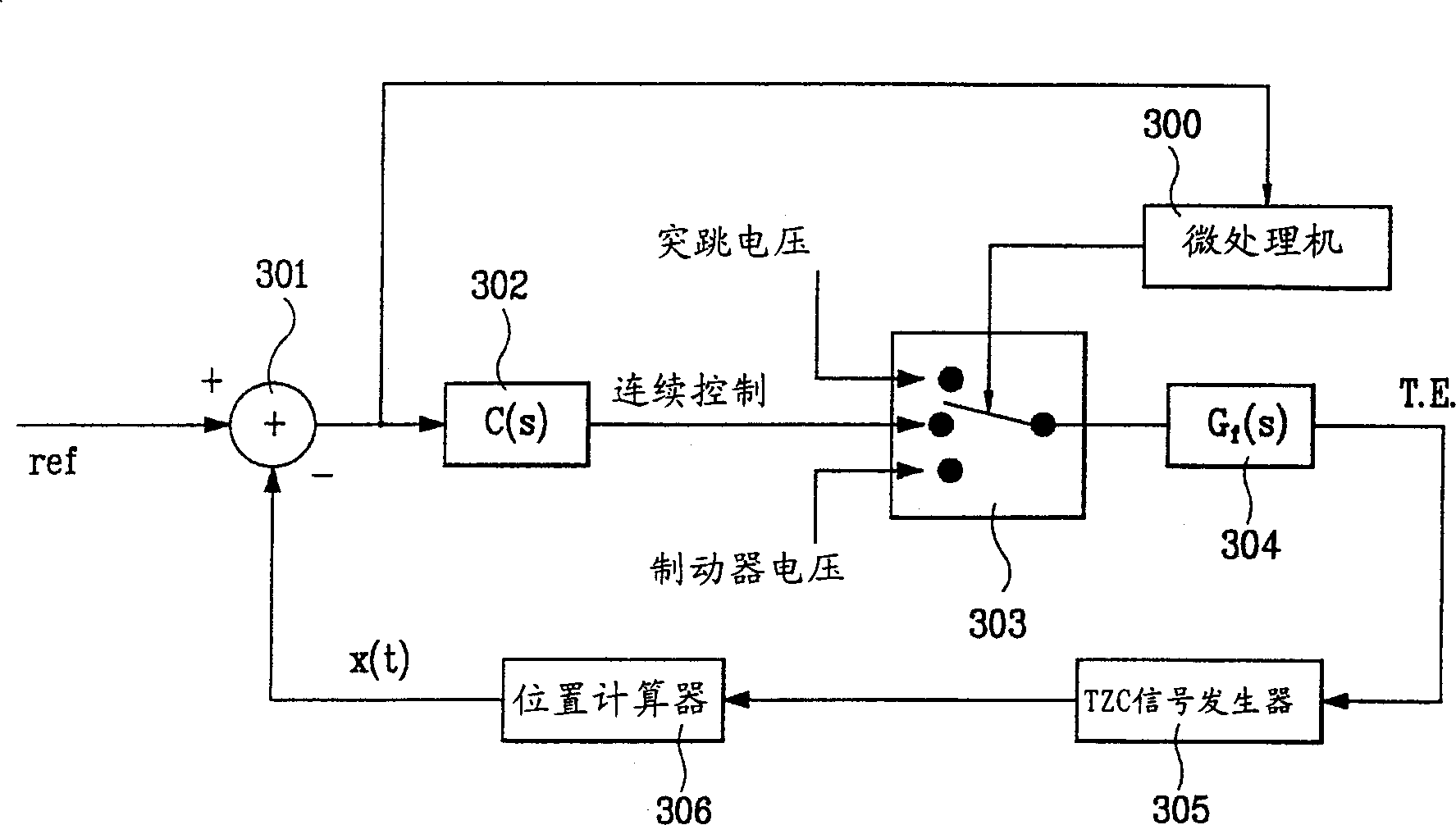

The invention is a kind of track jump method and the device of light recording media, which uses track adjustor to complete track jump. When input track order, then drives track adjustor, determines the track driver rate and position, namely the feedback step, it generate continuously input according to position and rate information, and drives the driver continuously to target according to the continuous control signal, when minutely examining, it may move the track number freely. The invention uses fixed track zero closed TZC signal, carries on feed back according to the position and rate information.

Owner:LEJIN GUANGDIAN ELECTRONIC CO LTD SHANGHAI