Patents

Literature

542results about How to "Reduce chip size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

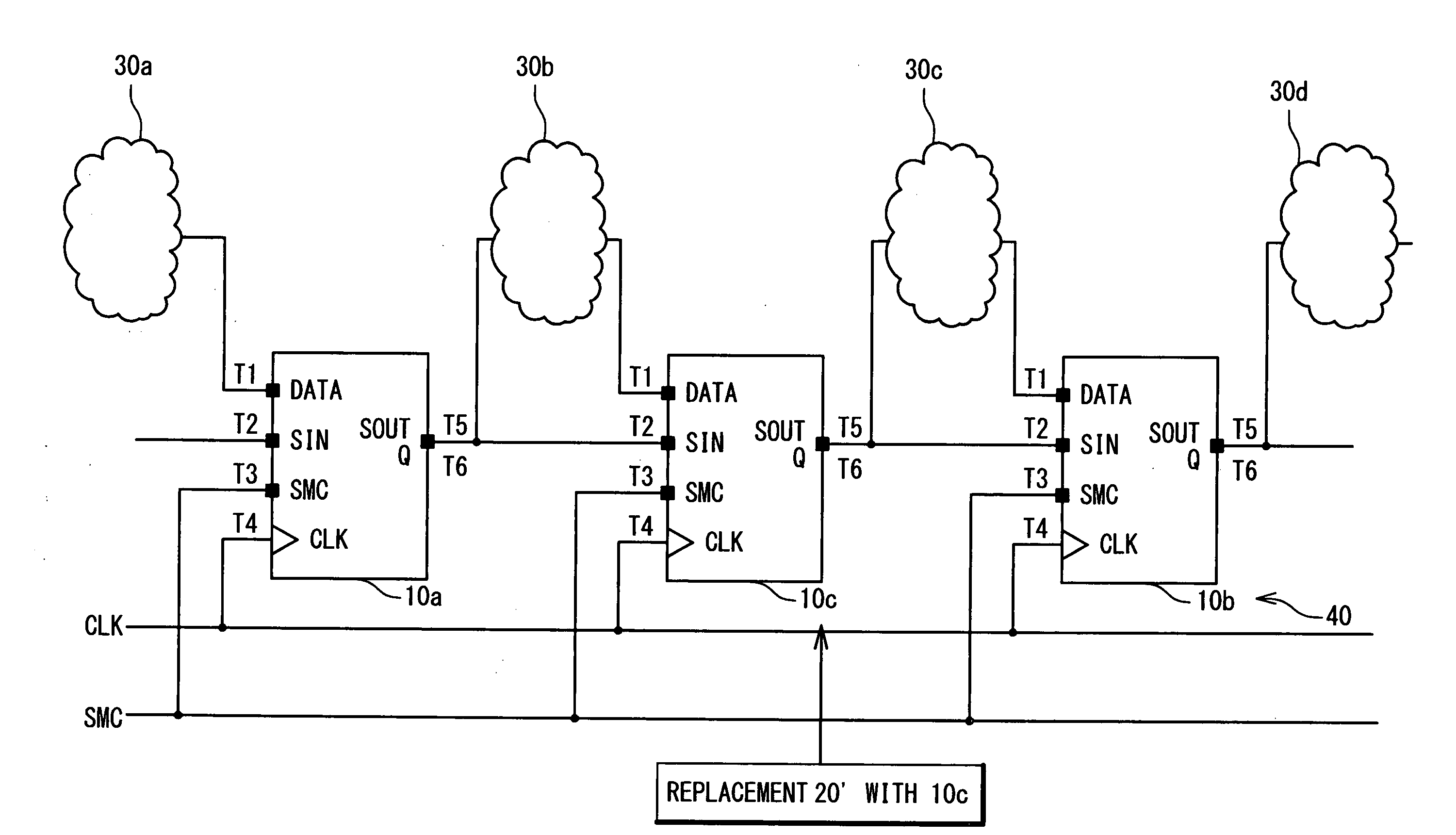

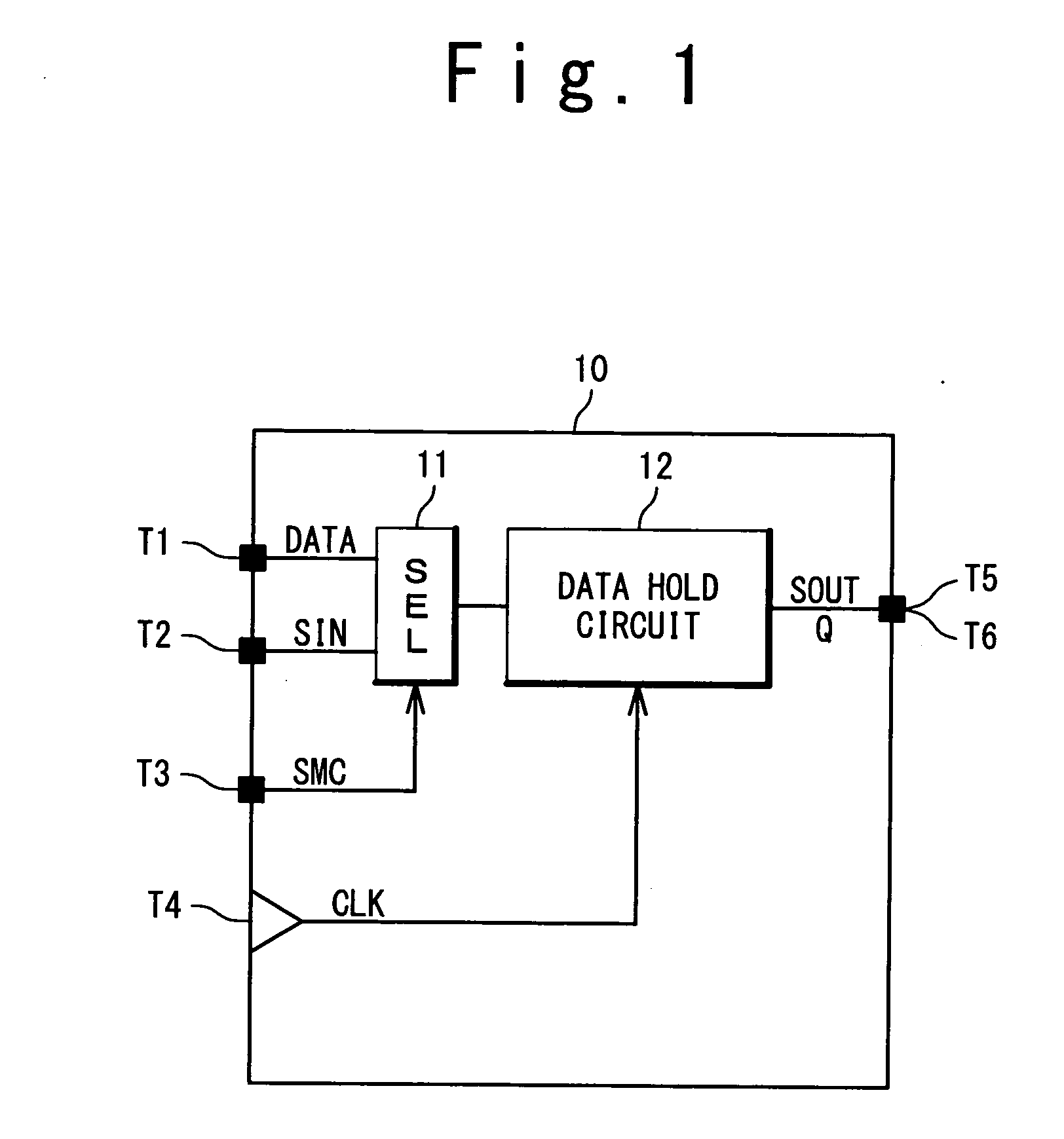

Integrated circuit design based on scan design technology

InactiveUS20090032899A1Effect of power consumption reduction is enhancedReduce power consumptionElectronic circuit testingSolid-state devicesEngineeringCircuit design

An integrated circuit is provided with a scan chain including a scan flip-flop and a dummy block. The dummy block has a clock terminal receiving a clock signal, a scan input terminal connected to a scan data line within the scan chain, and a scan output terminal connected to another scan data line within the scan chain. The dummy block is configured to output data on the scan output terminal in response to input data fed to the scan input terminal, not responsively to the clock signal.

Owner:RENESAS ELECTRONICS CORP

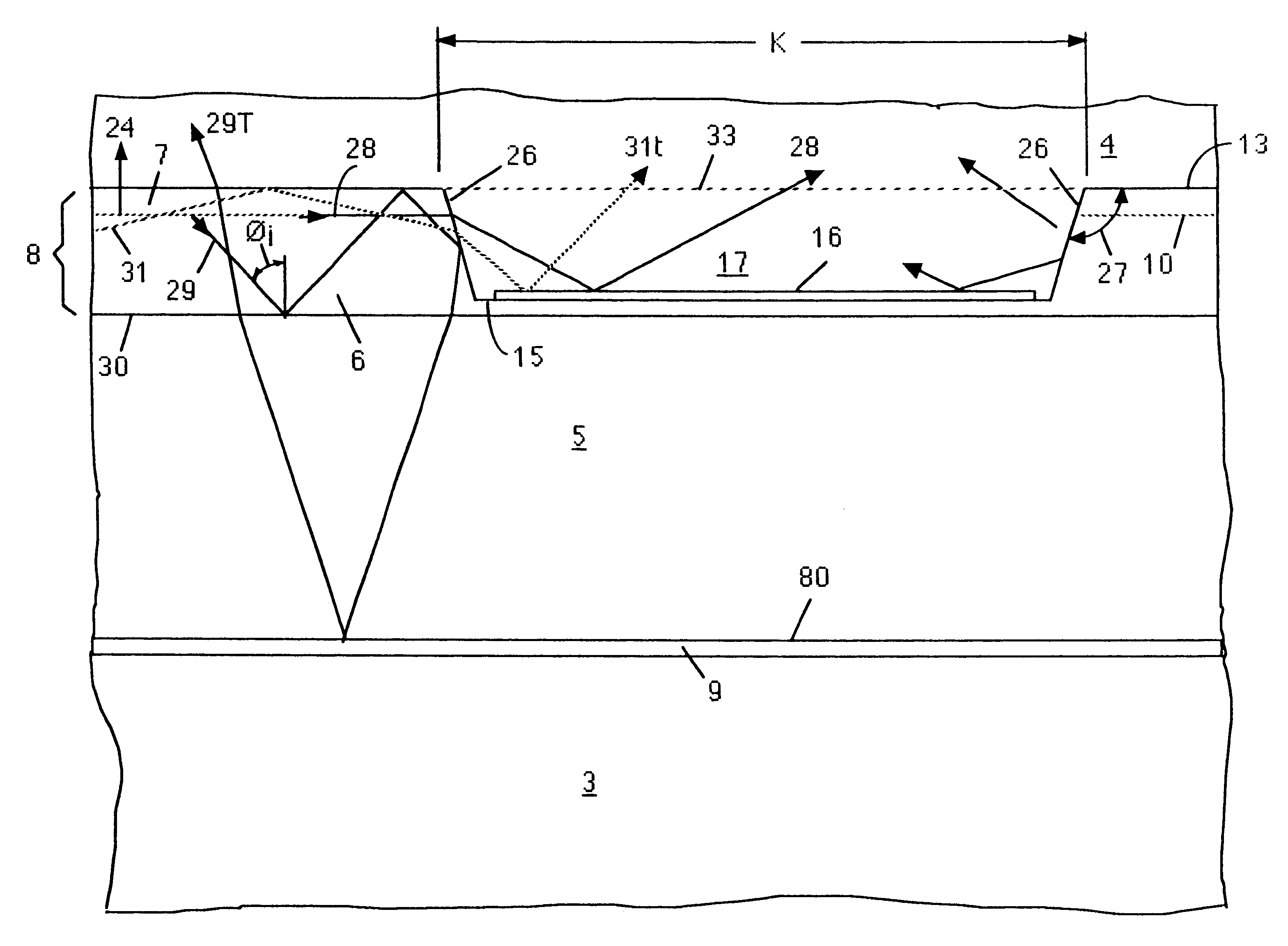

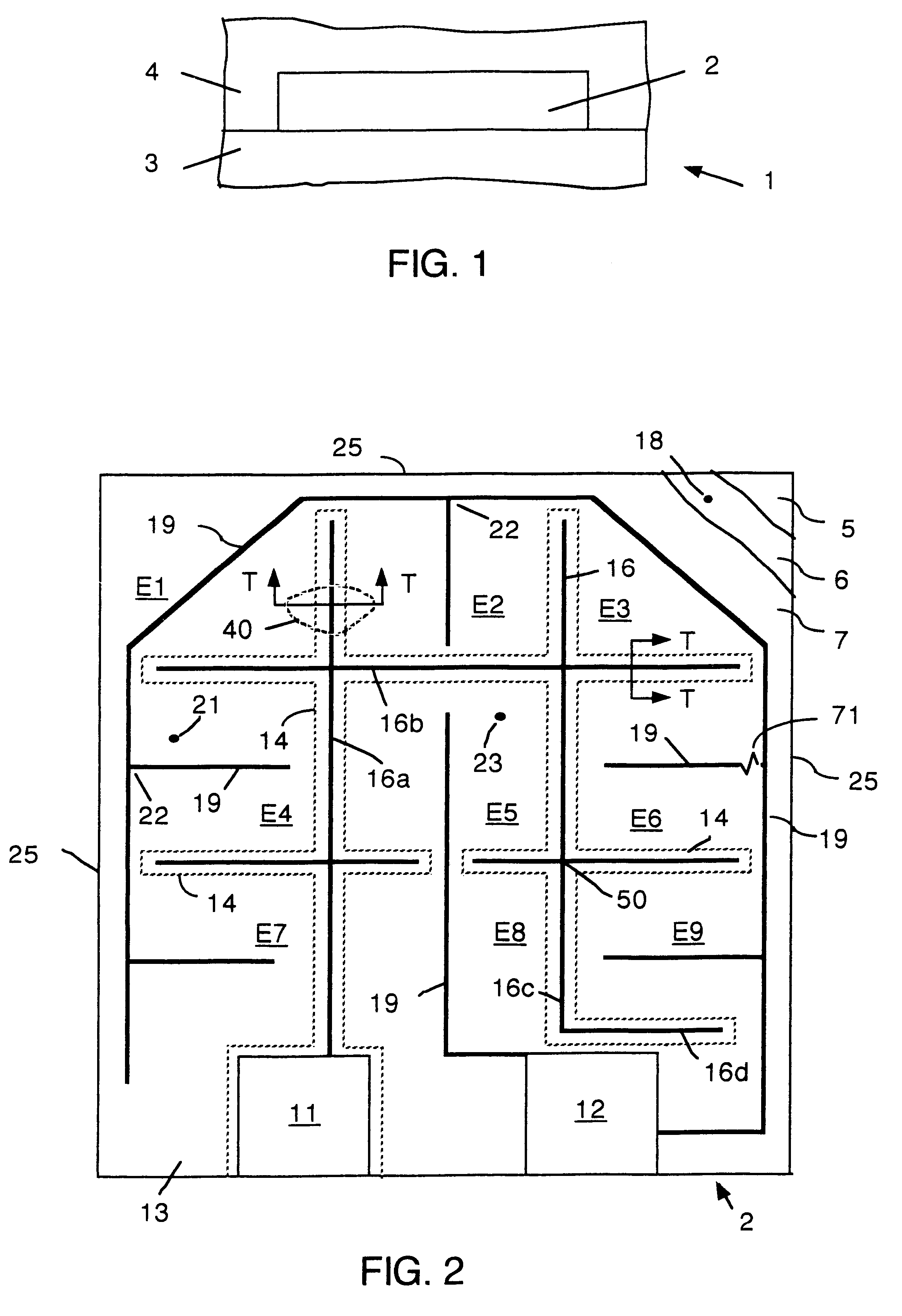

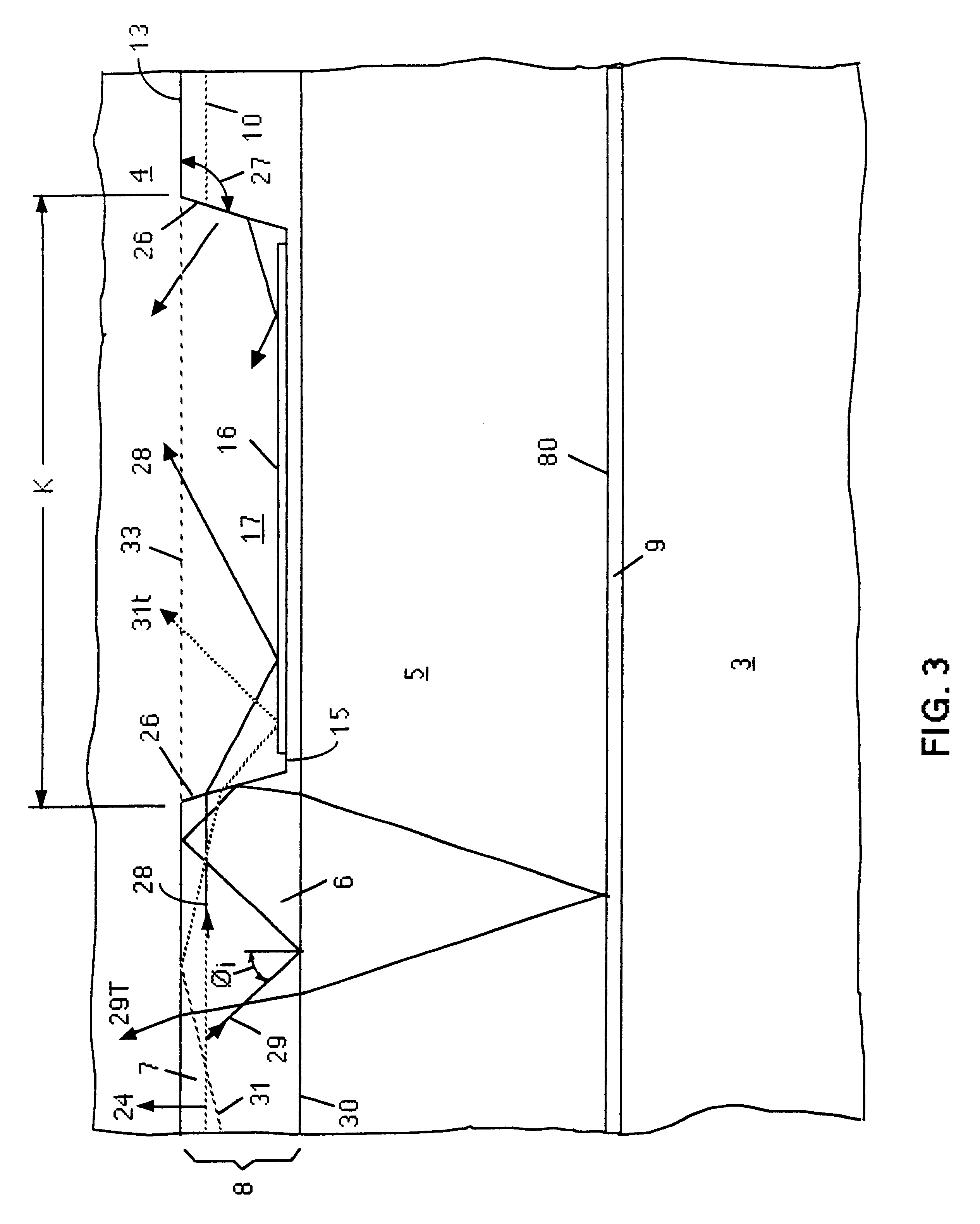

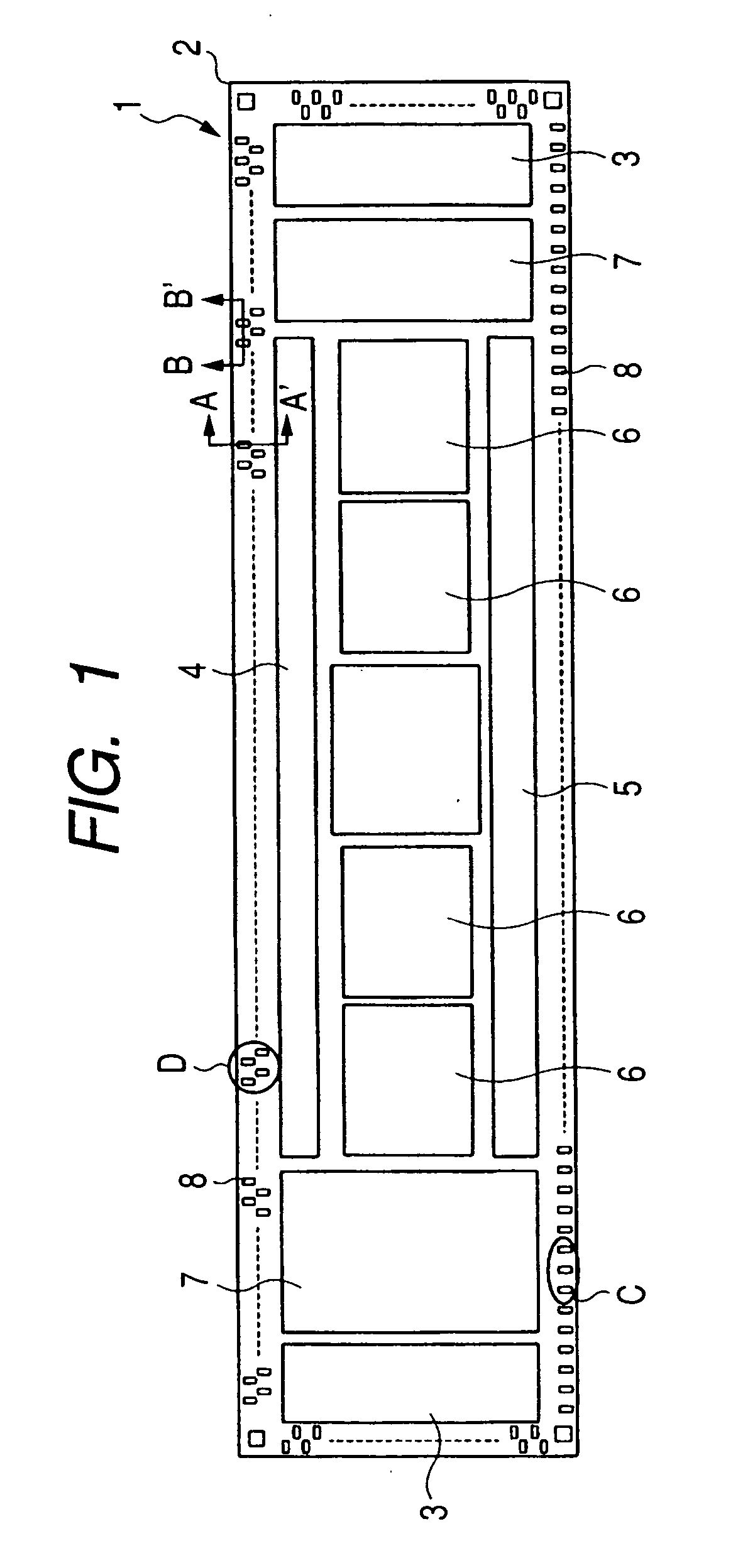

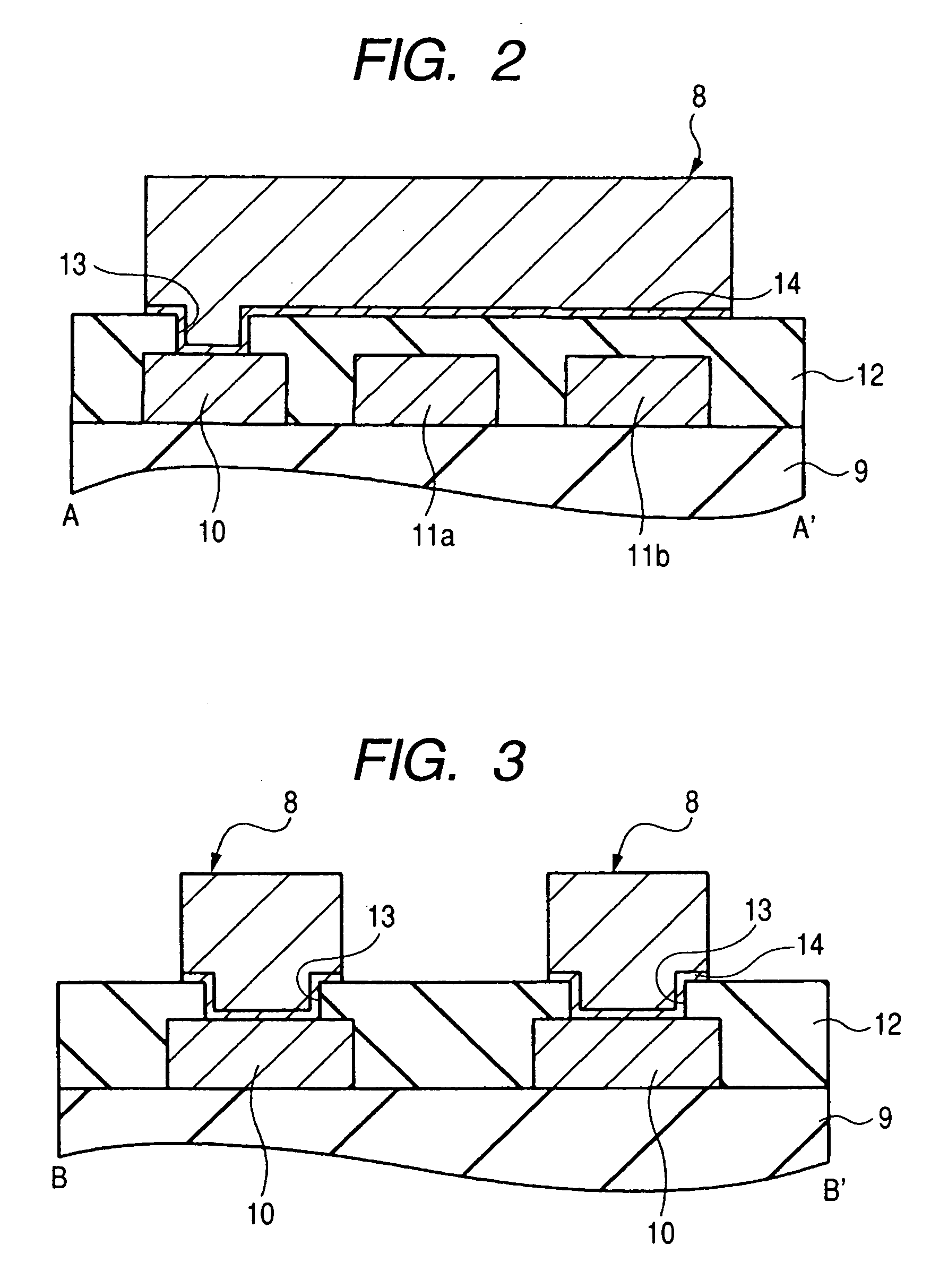

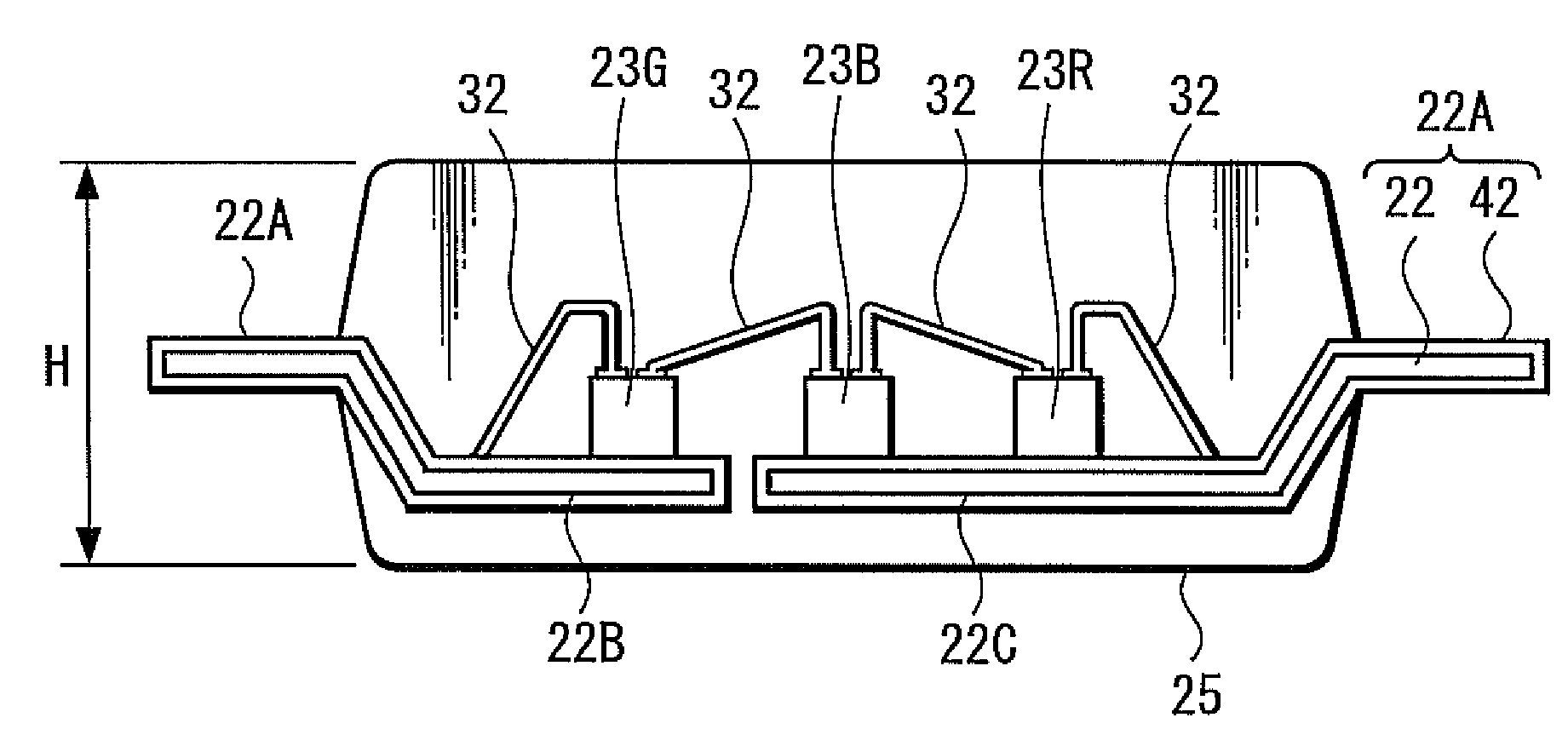

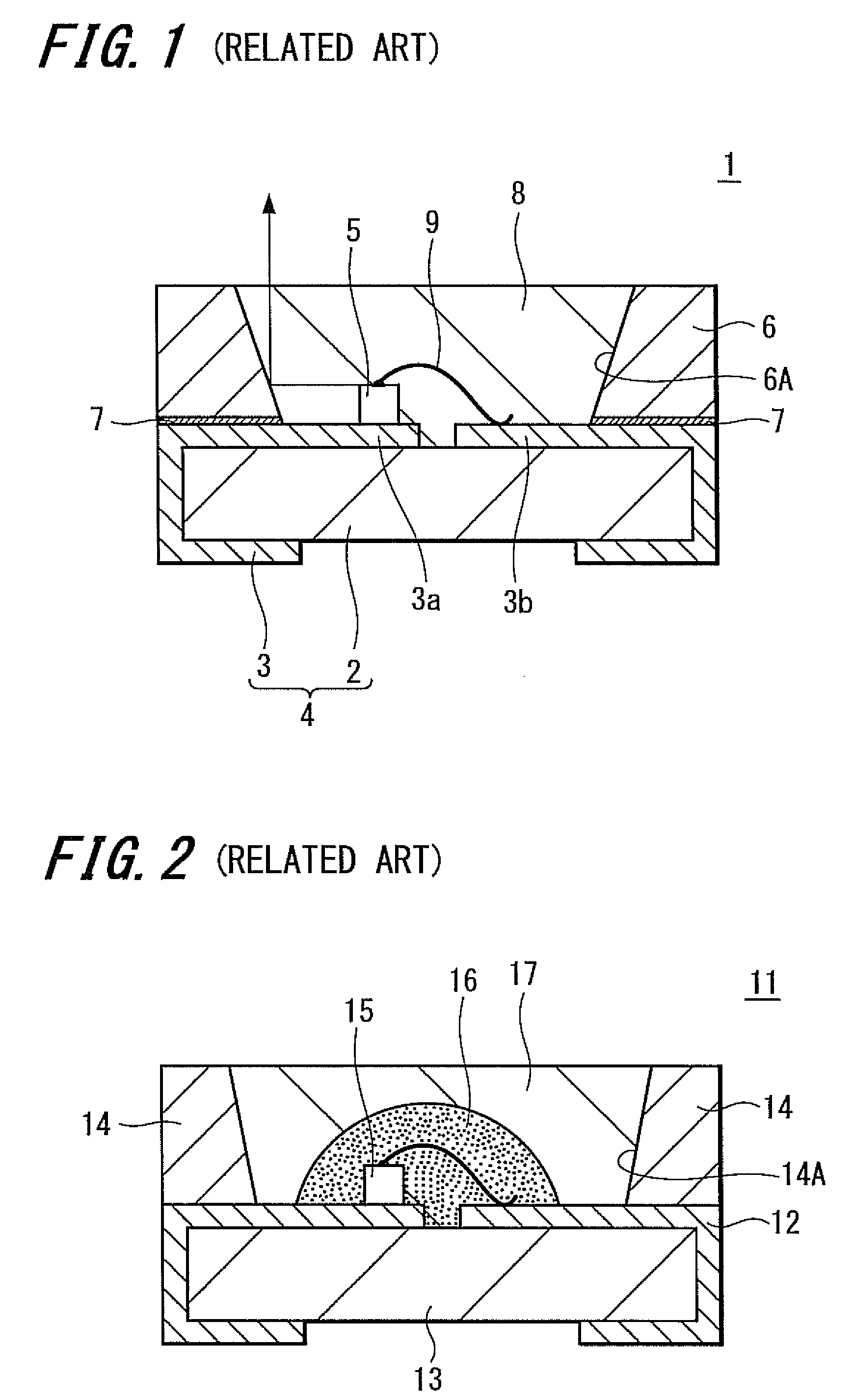

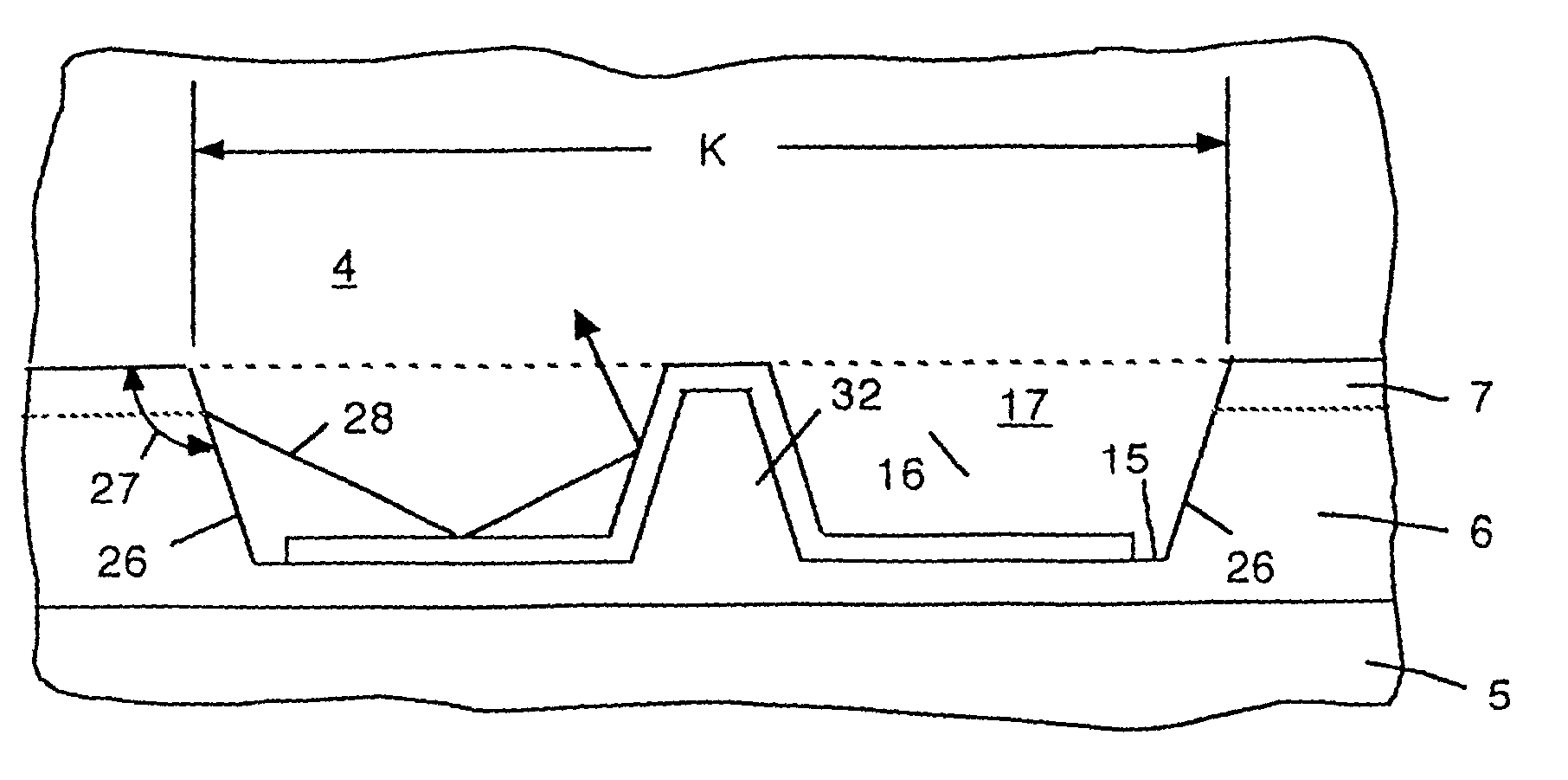

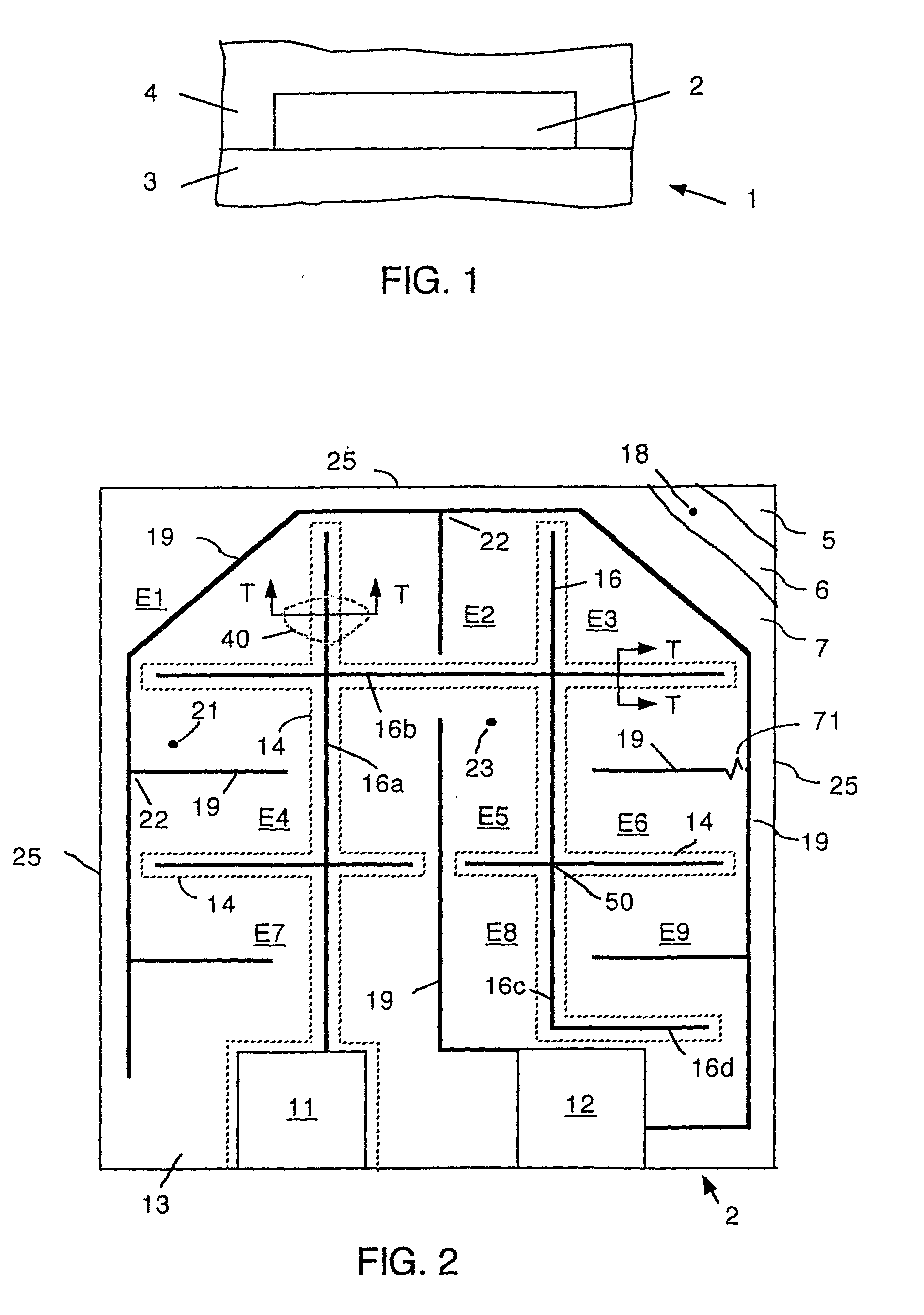

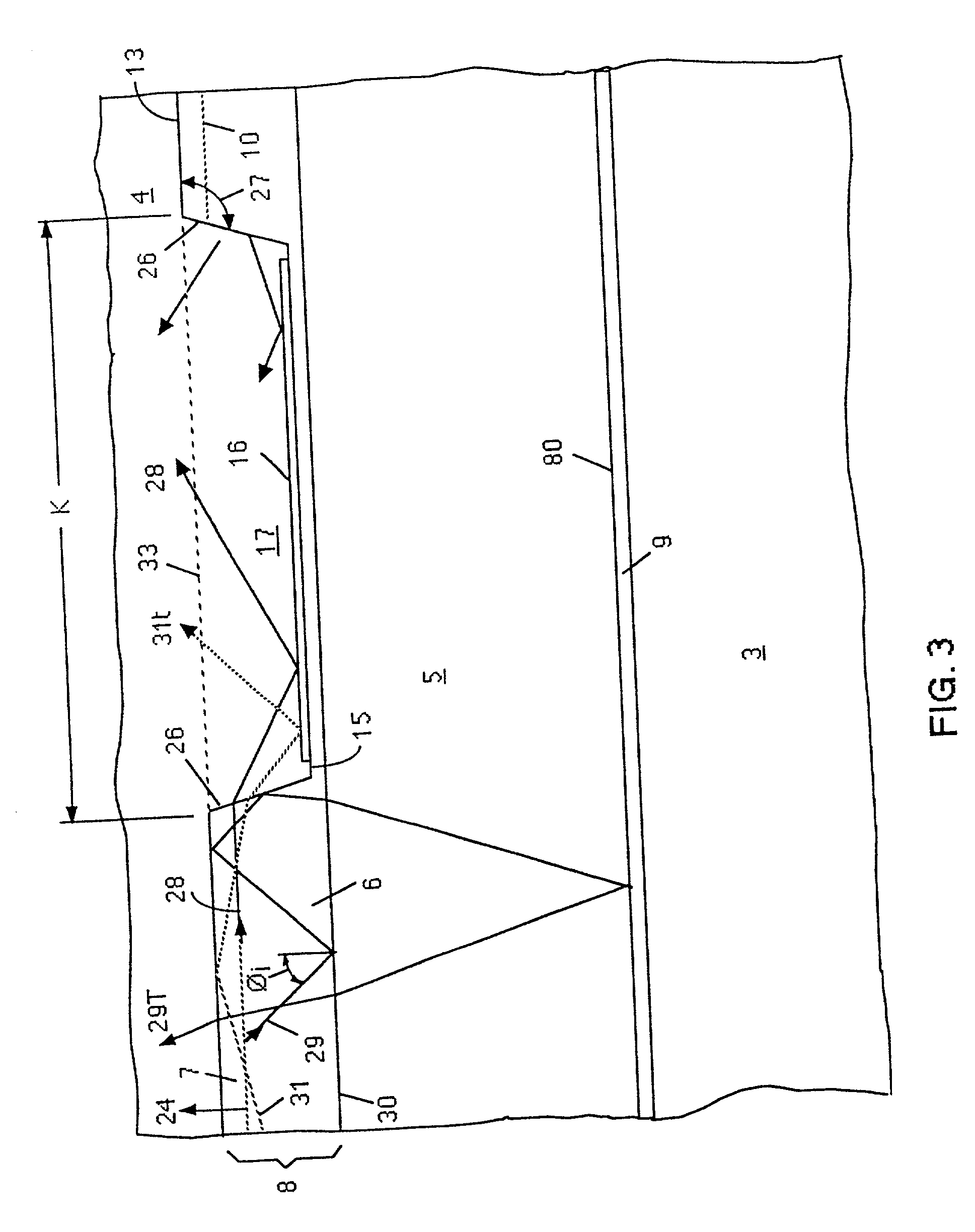

High power led lamp

InactiveUS6346771B1Improve uniformityReduce chip sizeDischarge tube luminescnet screensLamp detailsEngineeringLED lamp

A high-power LED lamp uses an LED chip that can be larger than 1mm square. The chip has trenches that can convert light trapped in the semiconductor into light that passes through a major surface of the chip. The trenches include light-reflecting tracks joined to a chip terminal and feeding a semiconductor layer. The chip can have triangular light emitting elements that improve light extraction from the semiconductor. The elements can be fused, resulting in improved manufacture yield of chips. A 25 watt single chip lamp with a heat sink very close to the active region is described.

Owner:EPISTAR CORP

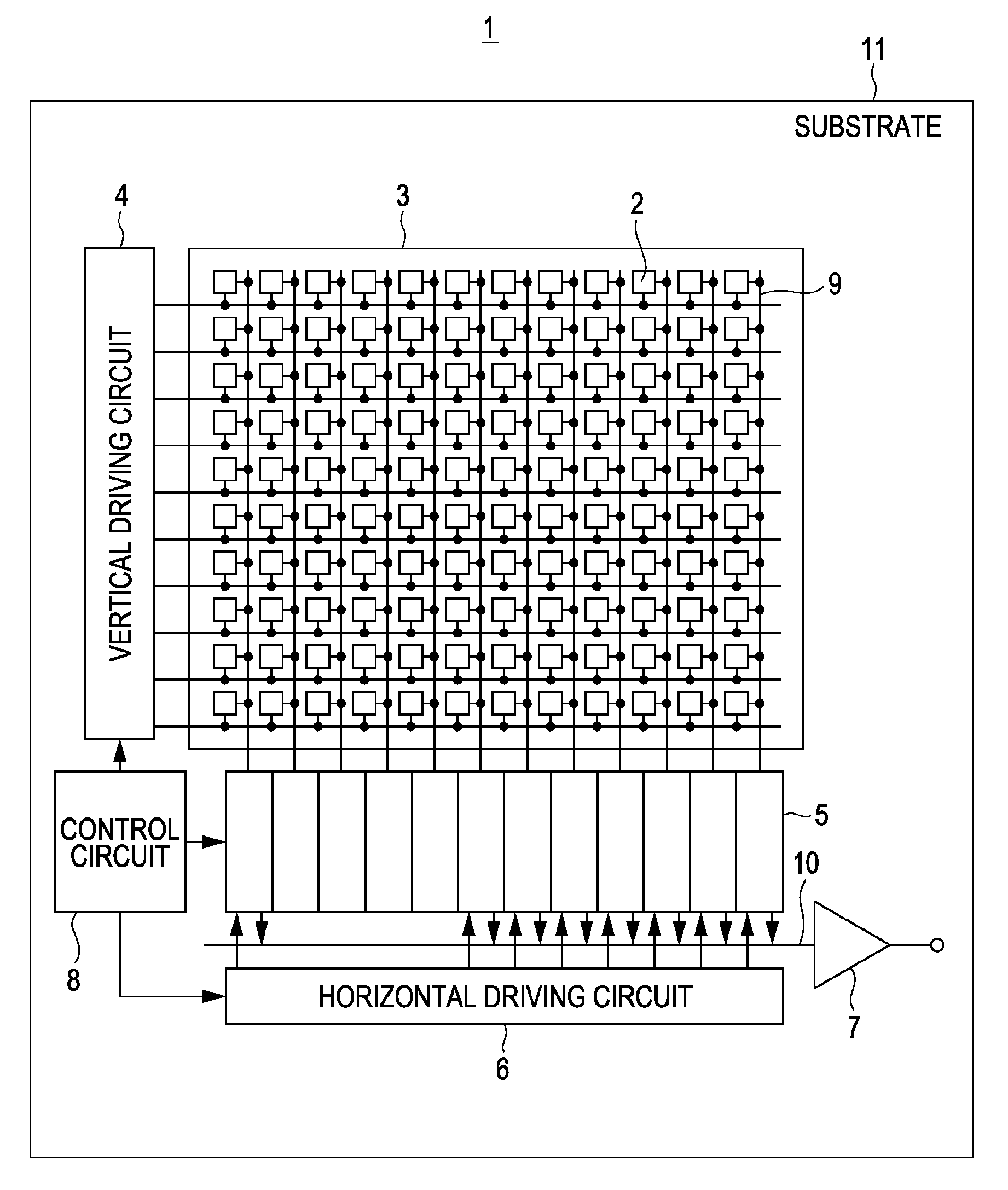

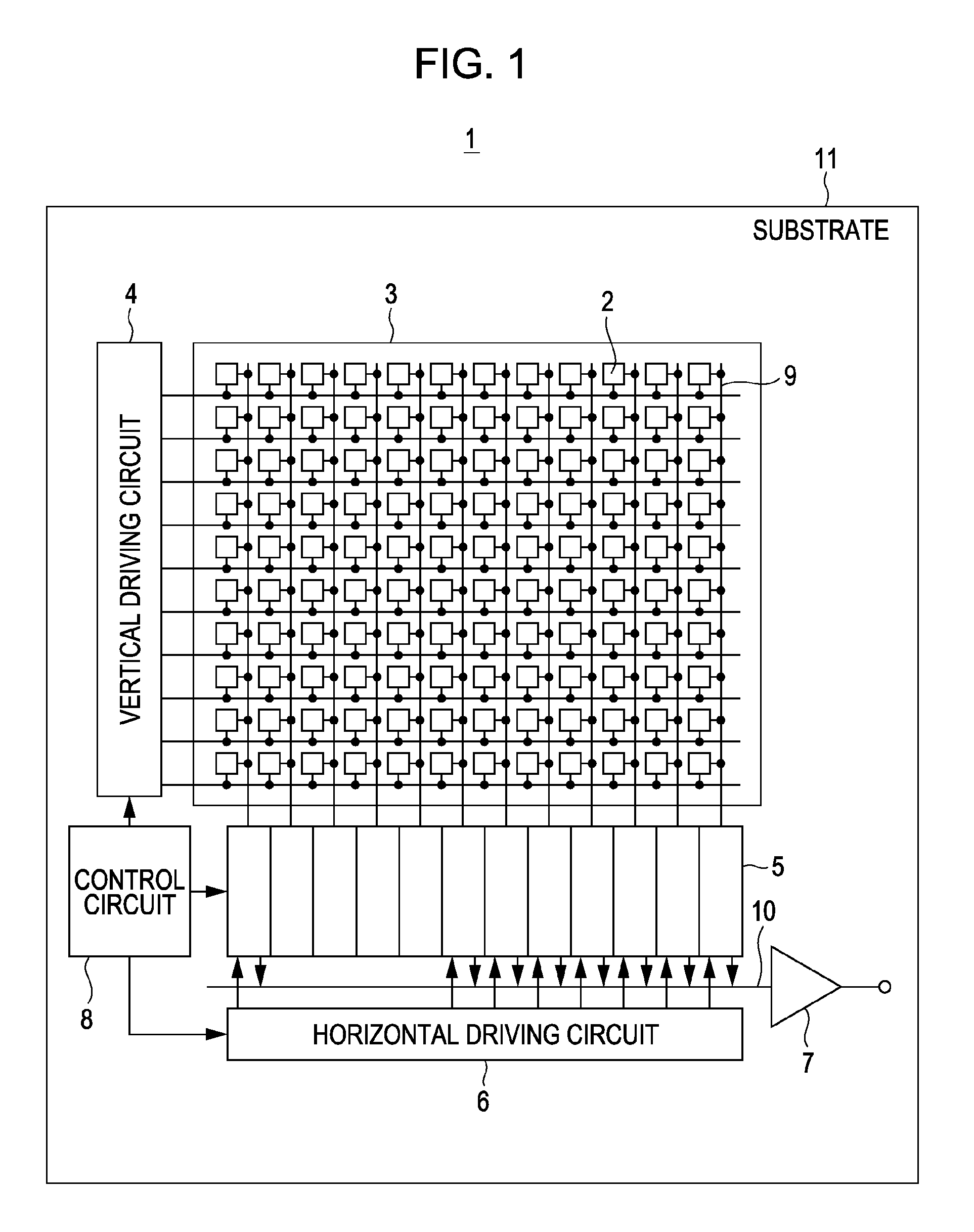

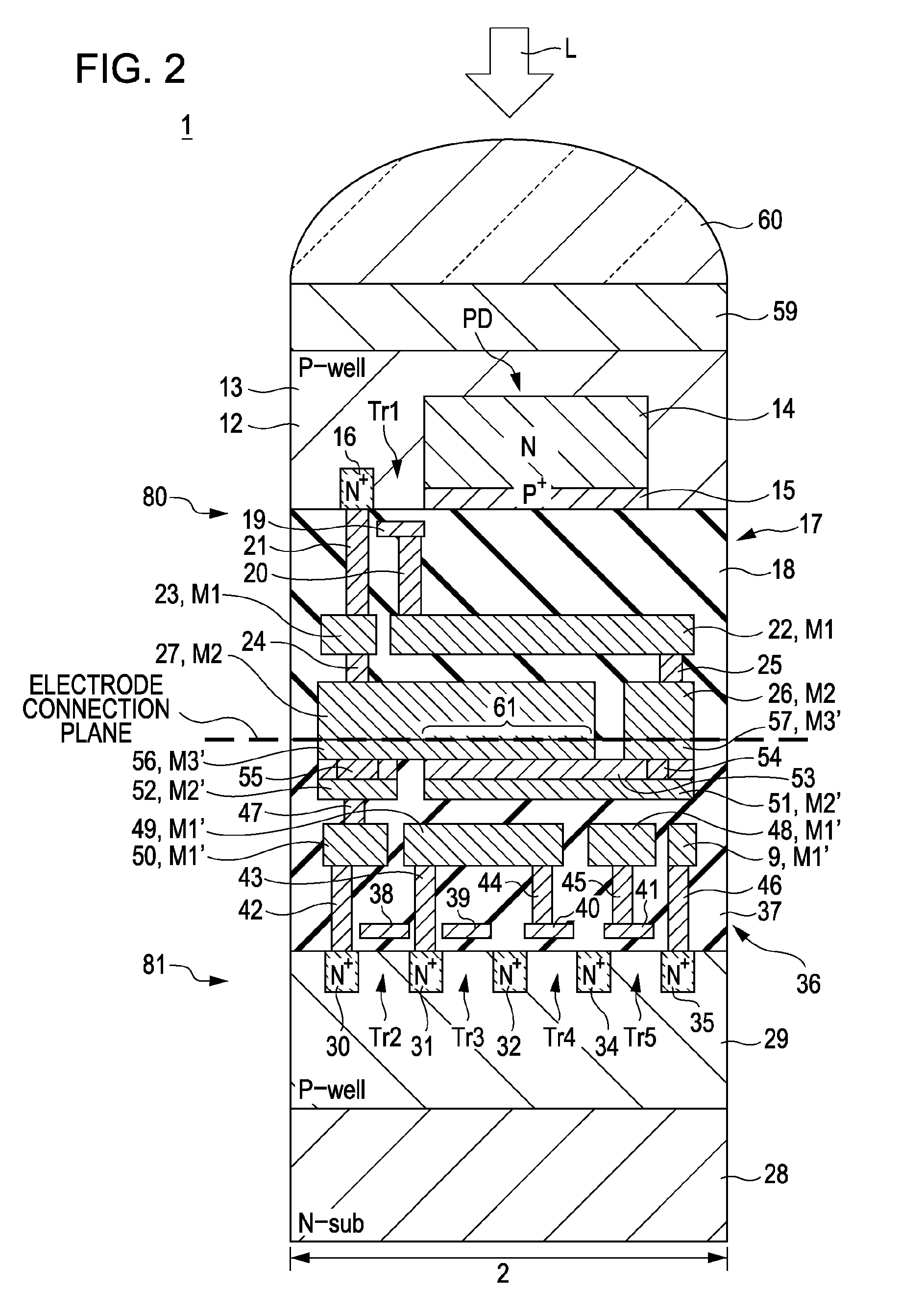

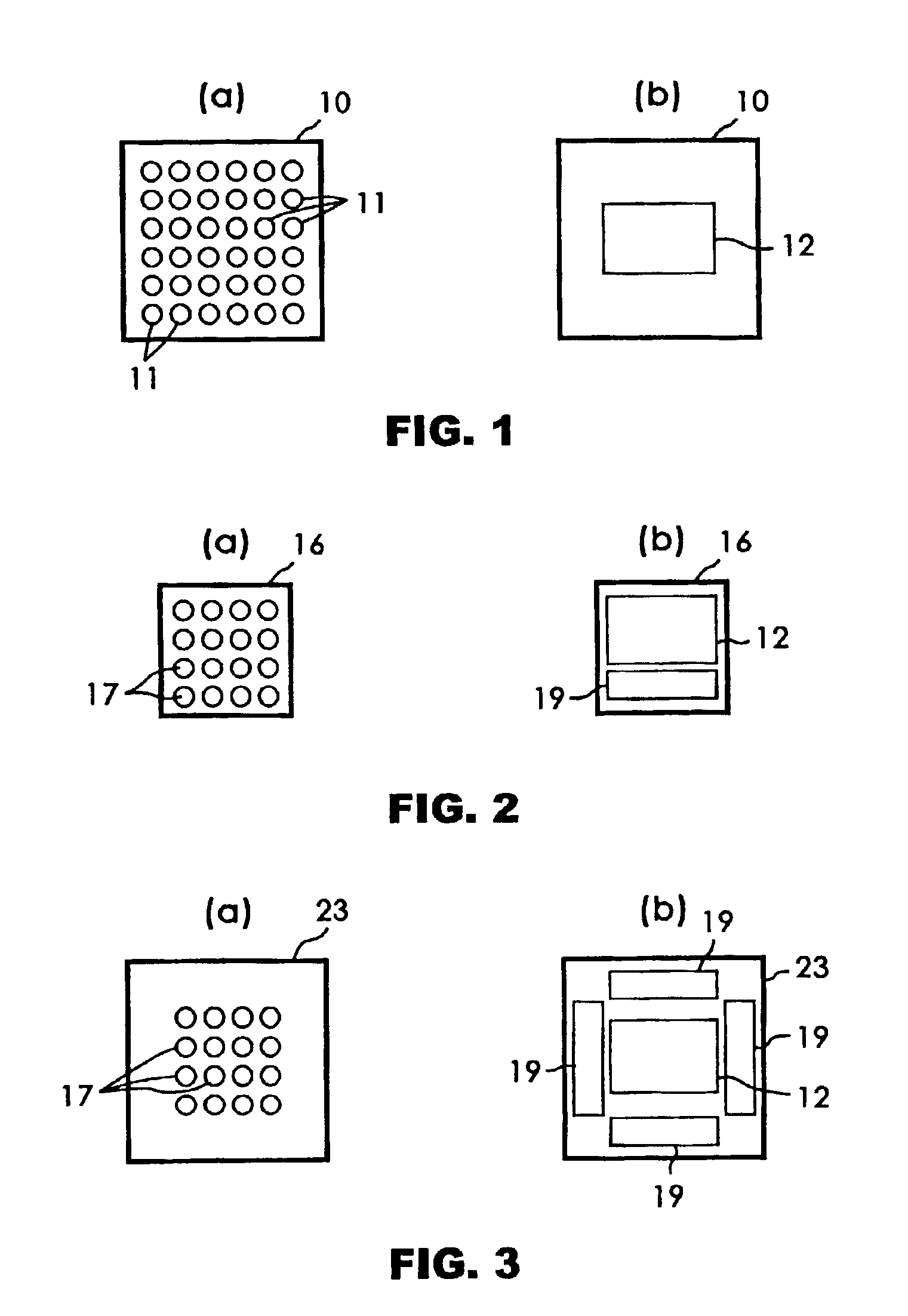

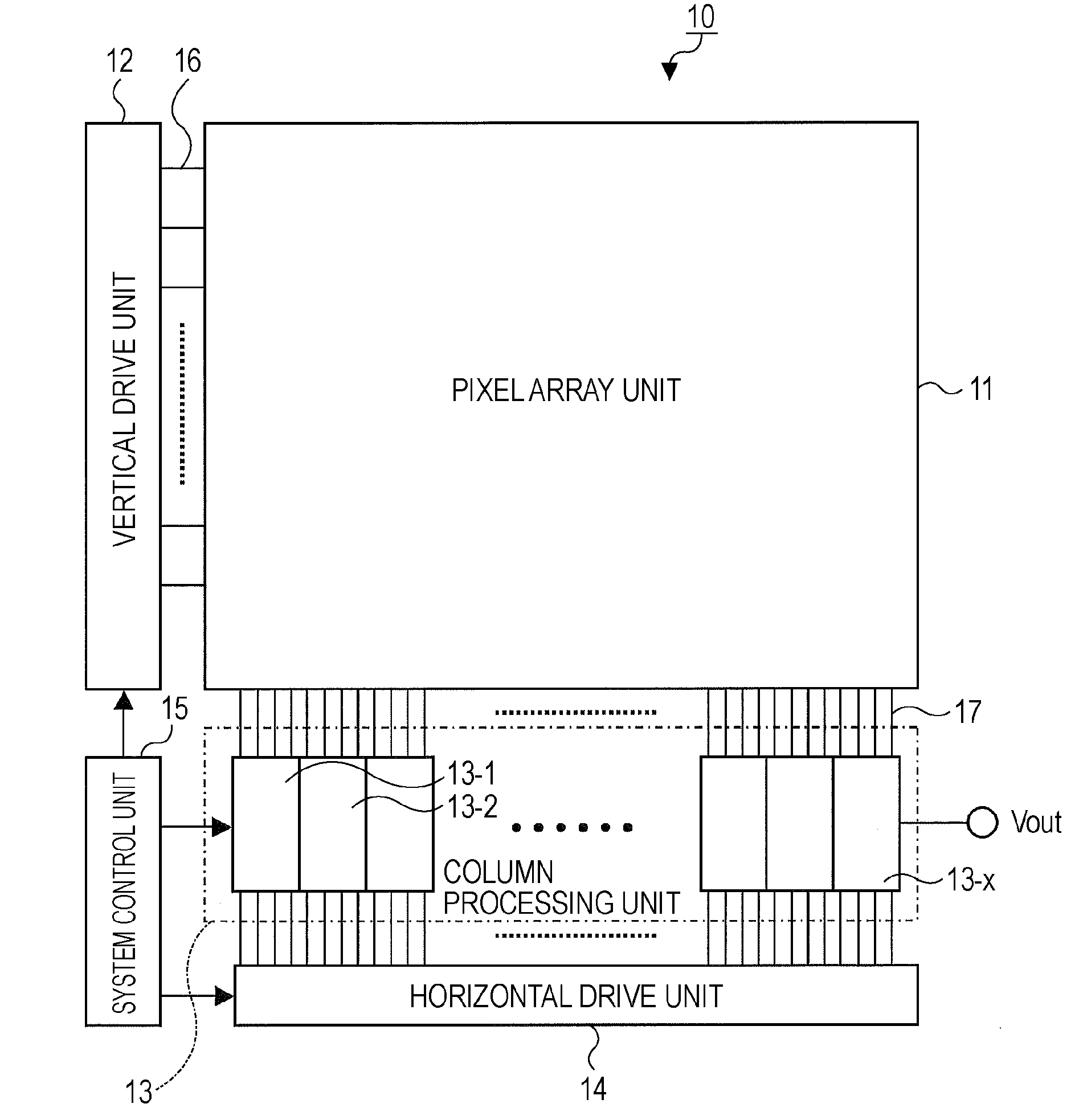

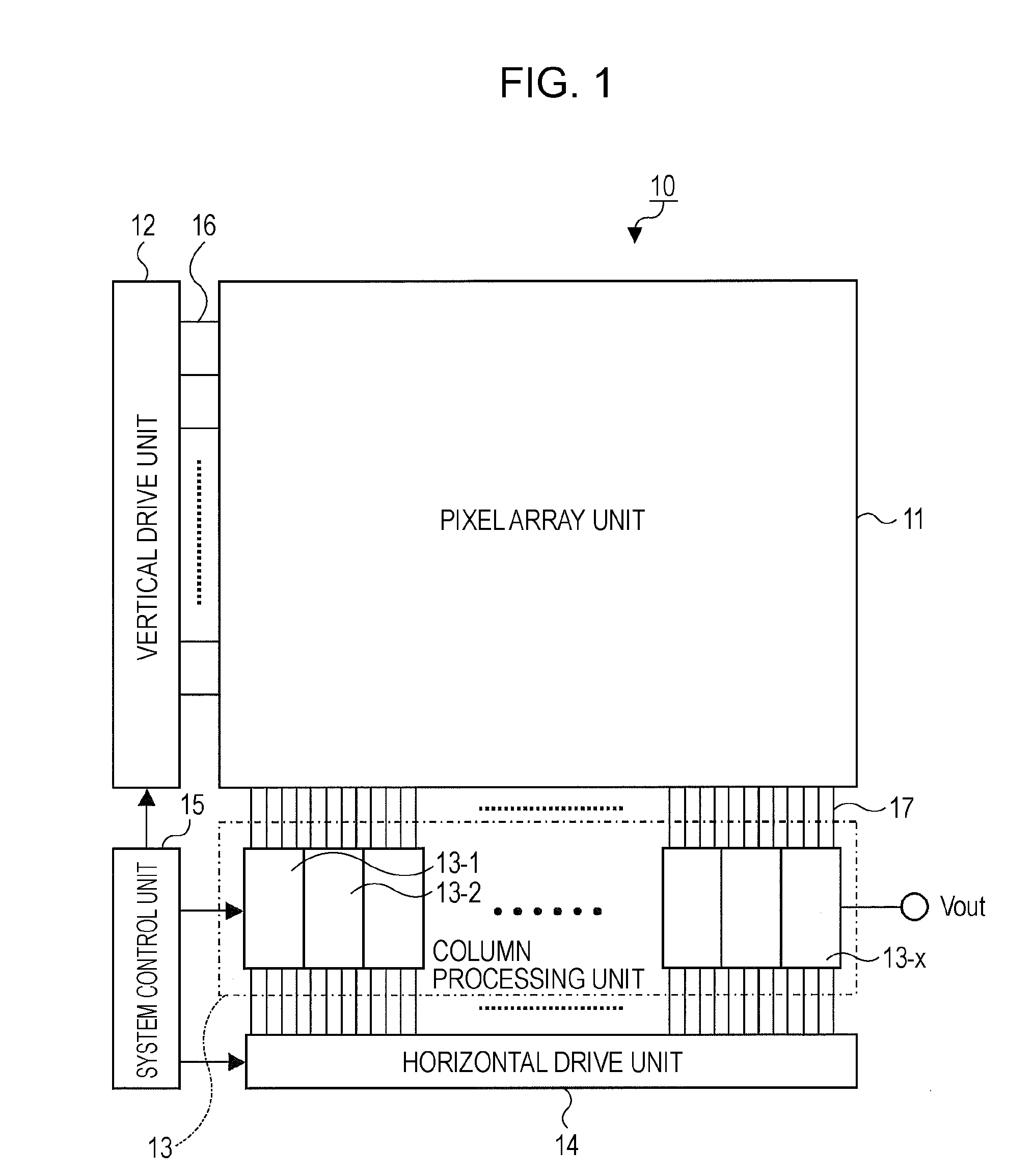

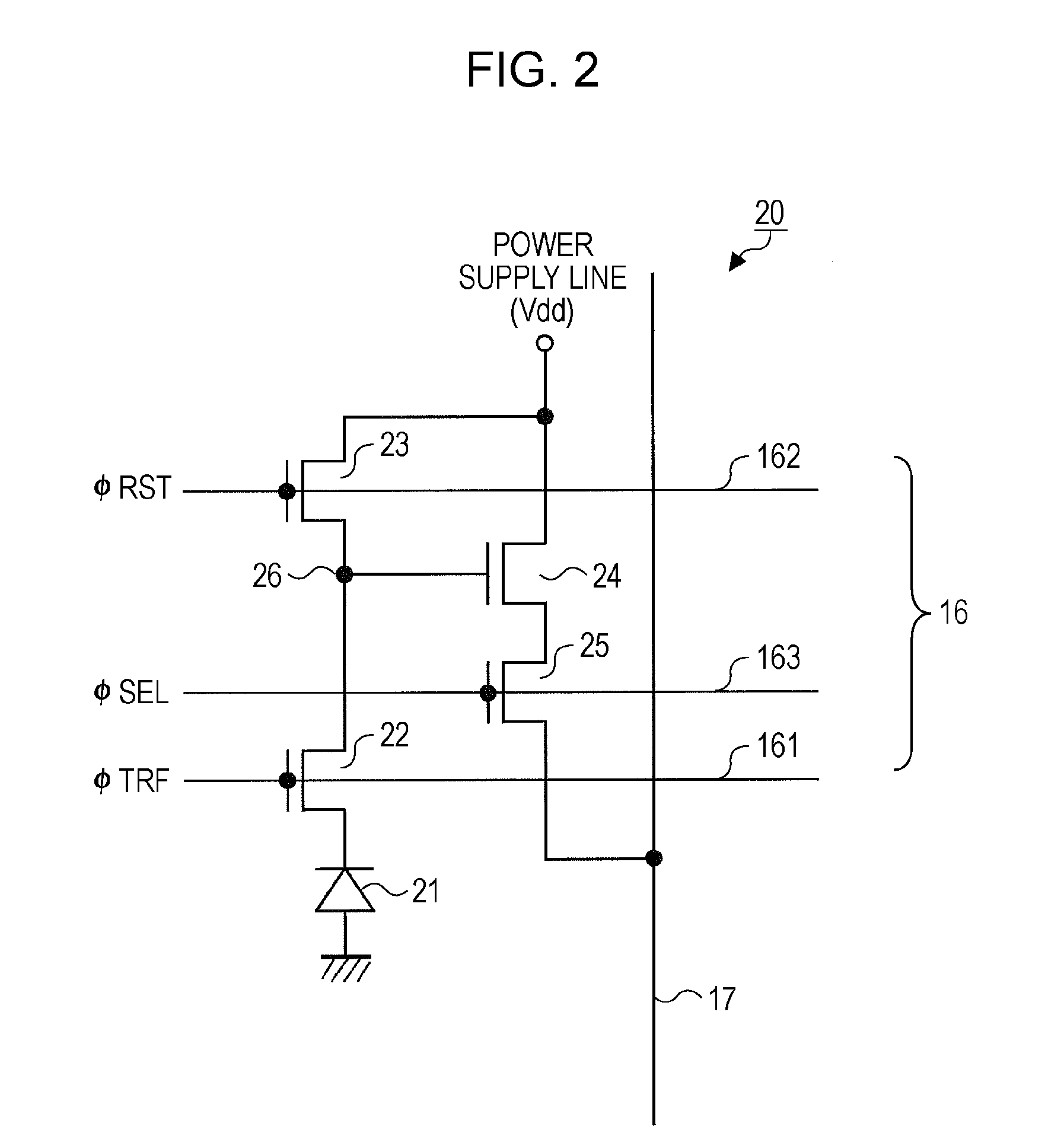

Solid-state imaging device, method of manufacturing the same, method of driving the same, and electronic apparatus

ActiveUS20100238334A1Reduce chip sizeReduce chip costTelevision system detailsTelevision system scanning detailsEngineeringElectron

A solid-state imaging device includes a plurality of pixels, each of which includes a photoelectric converter section formed on a first substrate to generate and accumulate signal charges corresponding to incident light, a charge accumulation capacitor section formed on the first substrate or a second substrate to temporarily hold the signal charges transferred from the photoelectric converter section, and a plurality of MOS transistors formed on the second substrate to transfer the signal charges accumulated in the charge accumulation capacitor section, connection electrodes formed on the first substrate, and connection electrodes formed on the second substrate and electrically connected to the connection electrodes formed on the first substrate.

Owner:SONY CORP

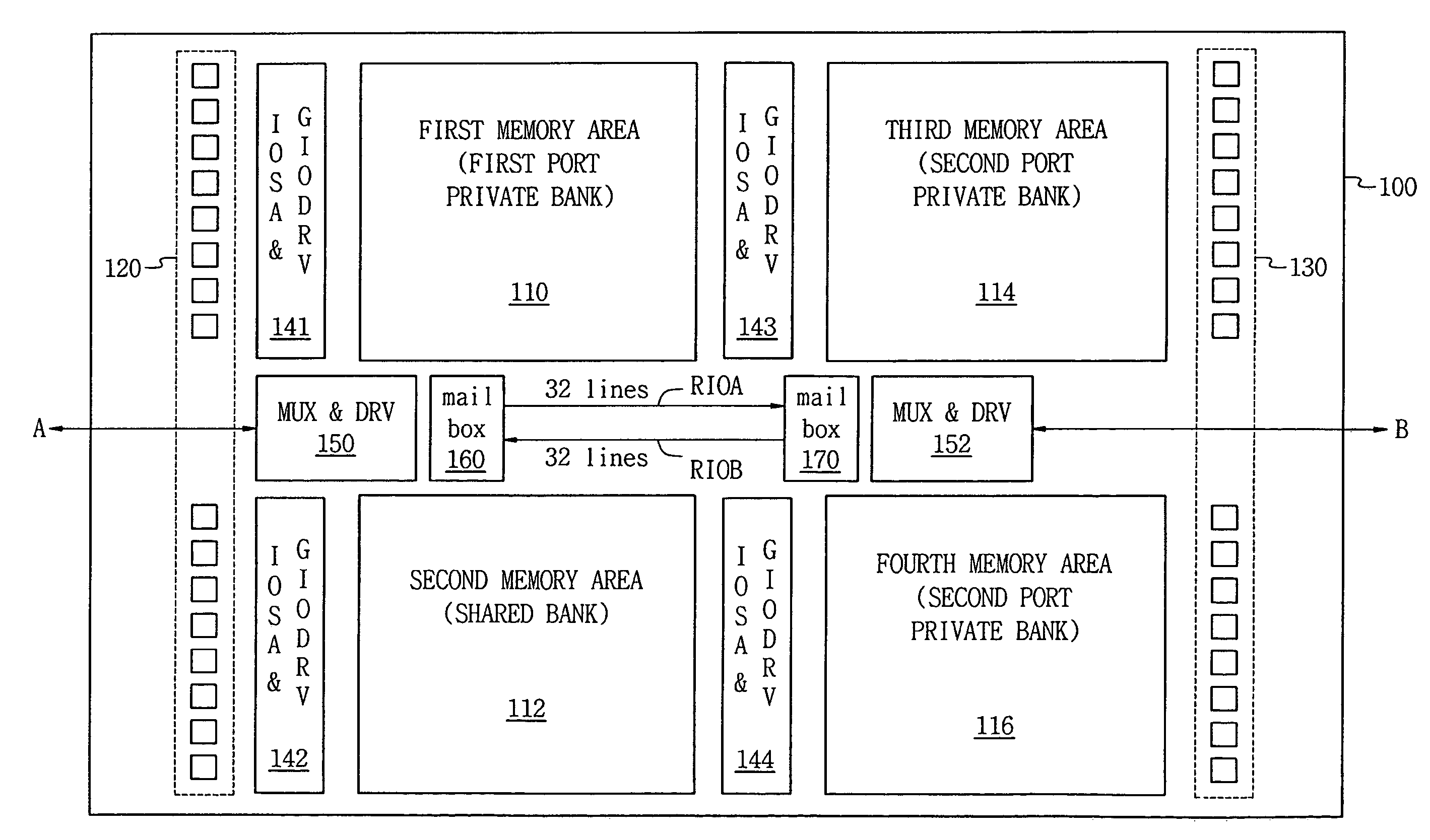

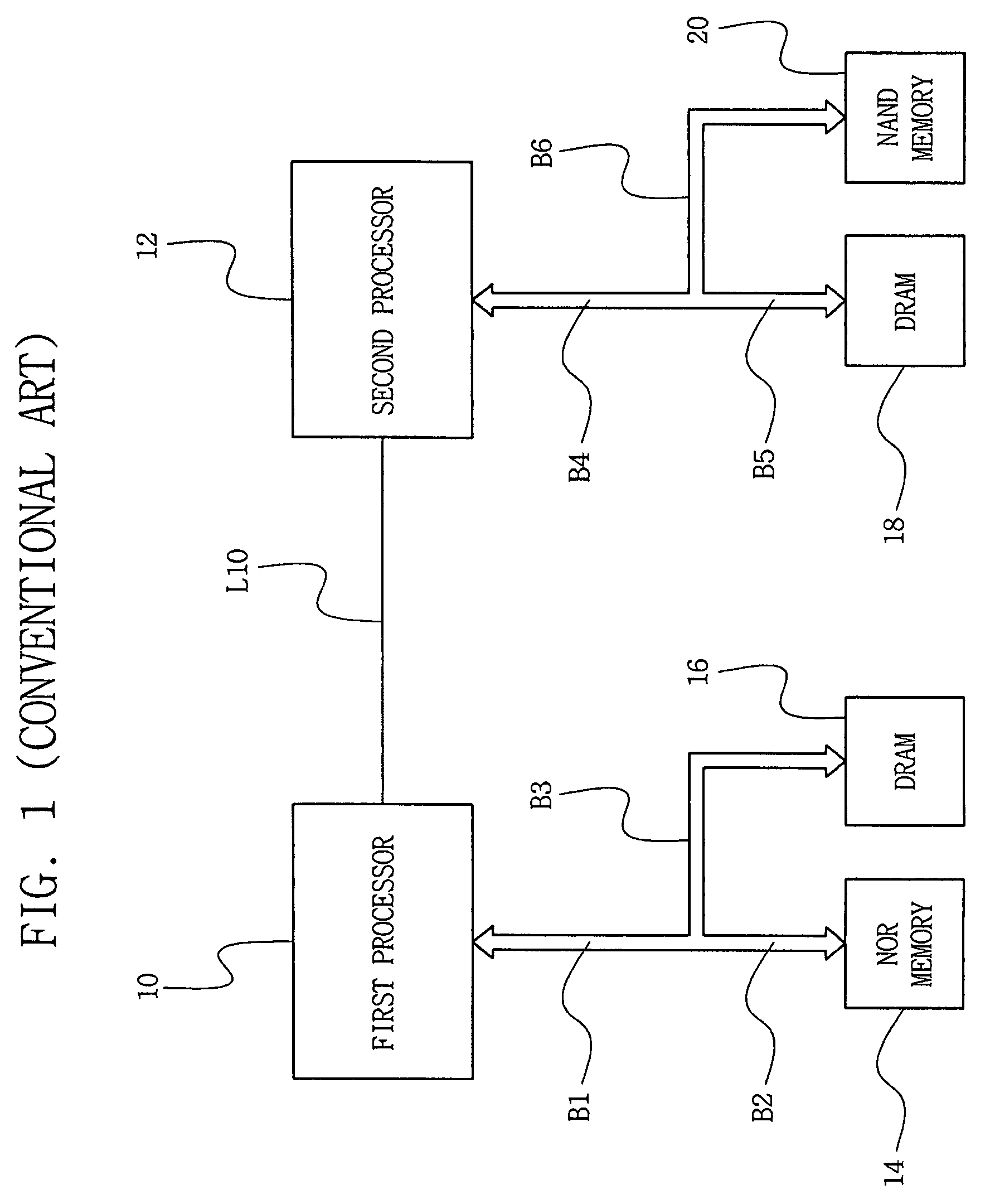

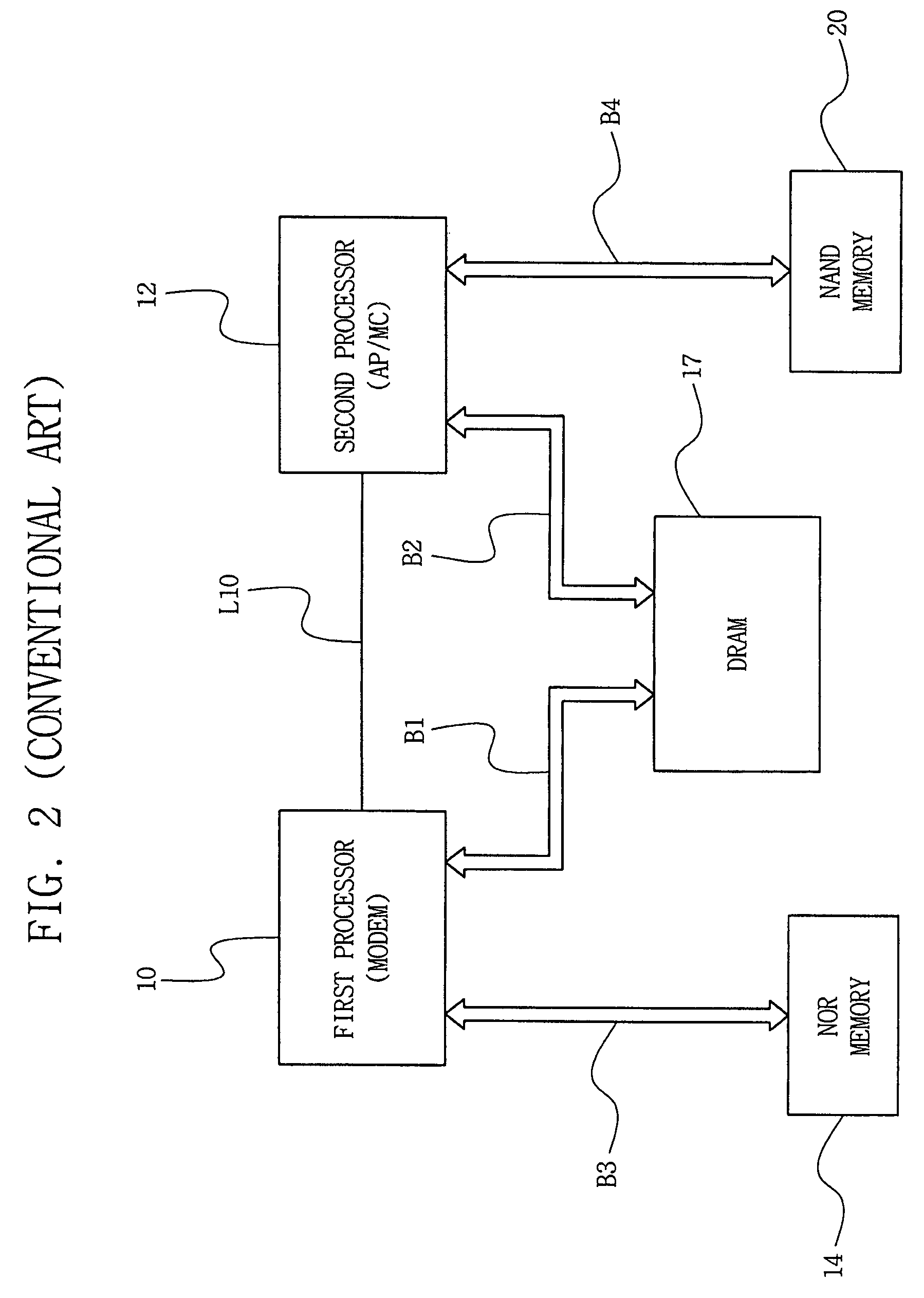

Multi-path accessible semiconductor memory device having mailbox areas and mailbox access control method thereof

InactiveUS7840762B2Reduce chip sizeReduce in quantityMemory adressing/allocation/relocationMultiple digital computer combinationsData accessMulti path

A multipath accessible semiconductor memory device having a mailbox area and a mailbox access control method thereof are provided. The semiconductor memory device includes N number of ports, at least one shared memory area allocated in a memory cell array, and N number of mailbox areas for message communication. The at least one shared memory area is operationally connected to the N number of ports, and is accessible through a plurality of data input / output lines to form a data access path between the at least one shared memory area and one port, having an access right to the at least one memory area, among the N number of ports. The N number of mailbox areas are provided in one-to-one correspondence with the N number of ports and are accessible through the plurality of data input / output lines when an address of a predetermined area of the at least one shared memory area is applied to the semiconductor memory device. An efficient layout of mailboxes and an efficient message access path can be obtained.

Owner:SAMSUNG ELECTRONICS CO LTD

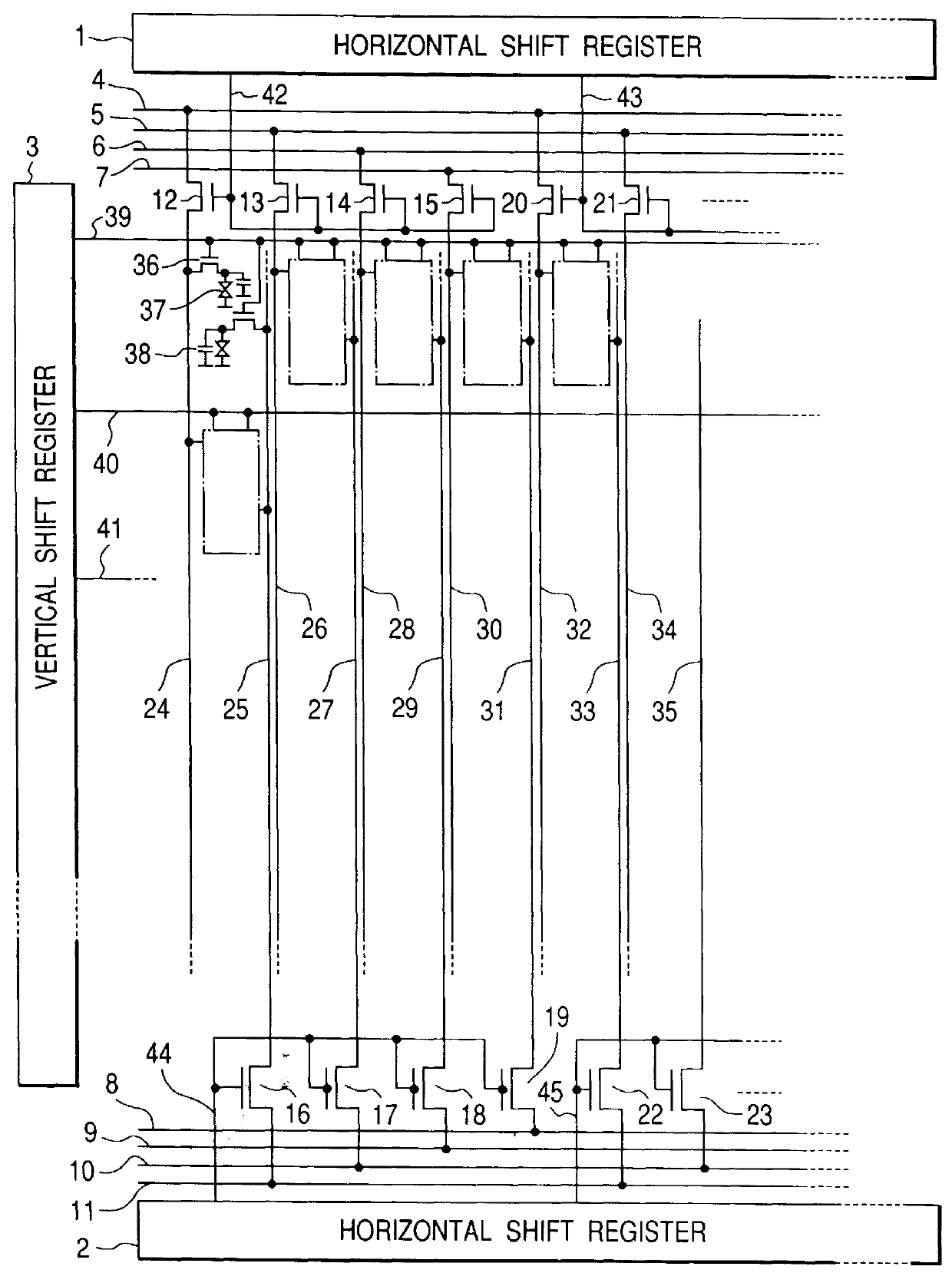

Matrix substrate, liquid-crystal device incorporating the matrix substrate, and display device incorporating the liquid-crystal device

InactiveUS6127998AReduce chip sizeReduce power consumptionStatic indicating devicesNon-linear opticsDisplay deviceEngineering

A matrix substrate comprises a plurality of pixel electrodes arrayed in a matrix pattern, a plurality of switching elements connected to the pixel electrodes, a plurality of signal lines for supplying video signals to the plurality of switching elements, a plurality of scanning lines for supplying scanning signals to the plurality of switching elements, a horizontal driving circuit for supplying the video signals to the plurality of signal lines, and a vertical driving circuit for supplying the scanning signals to the plurality of scanning lines, wherein the horizontal driving circuit is comprised of a dynamic type circuit and the vertical driving circuit is comprised of a static type circuit.

Owner:CANON KK

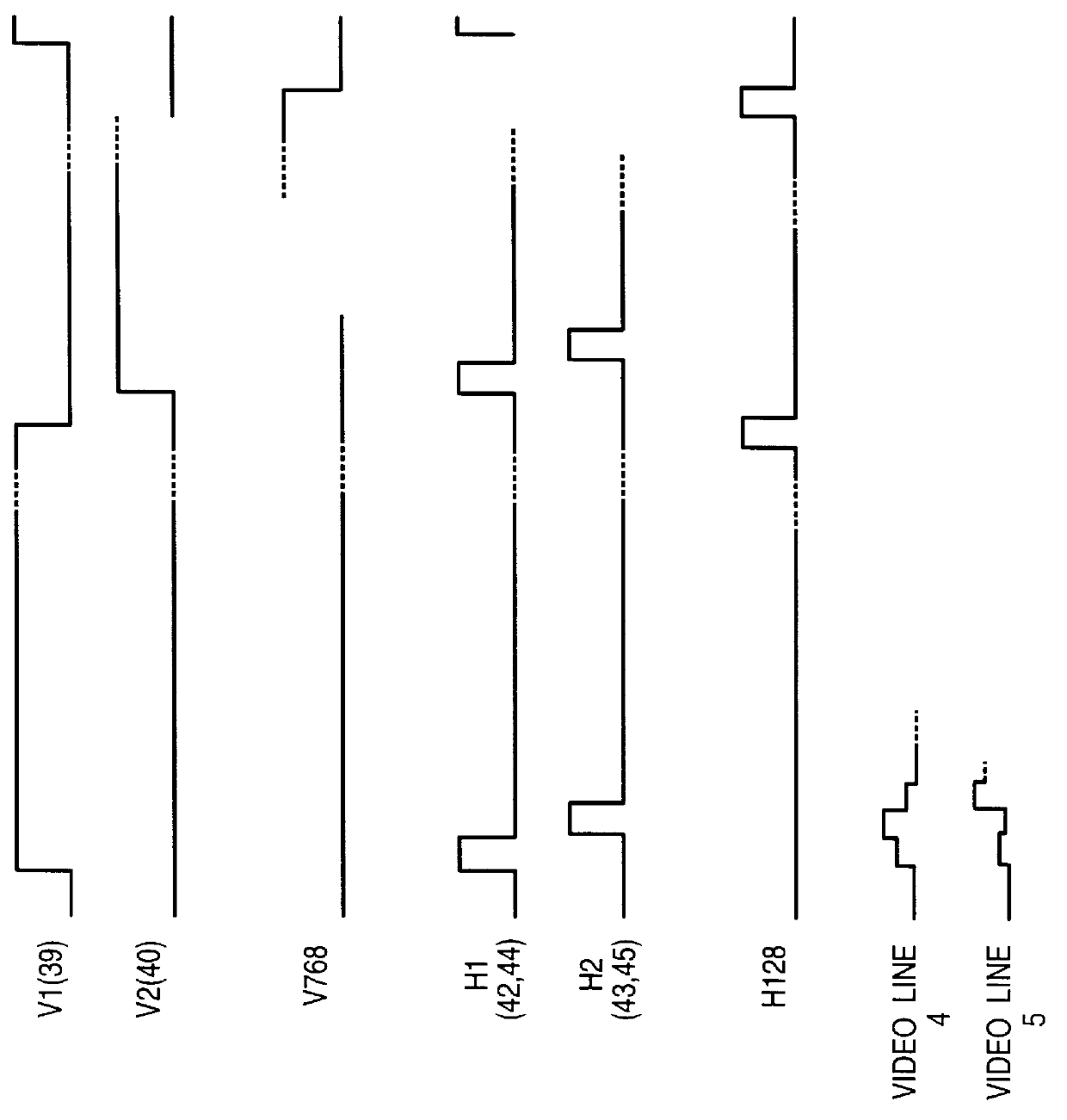

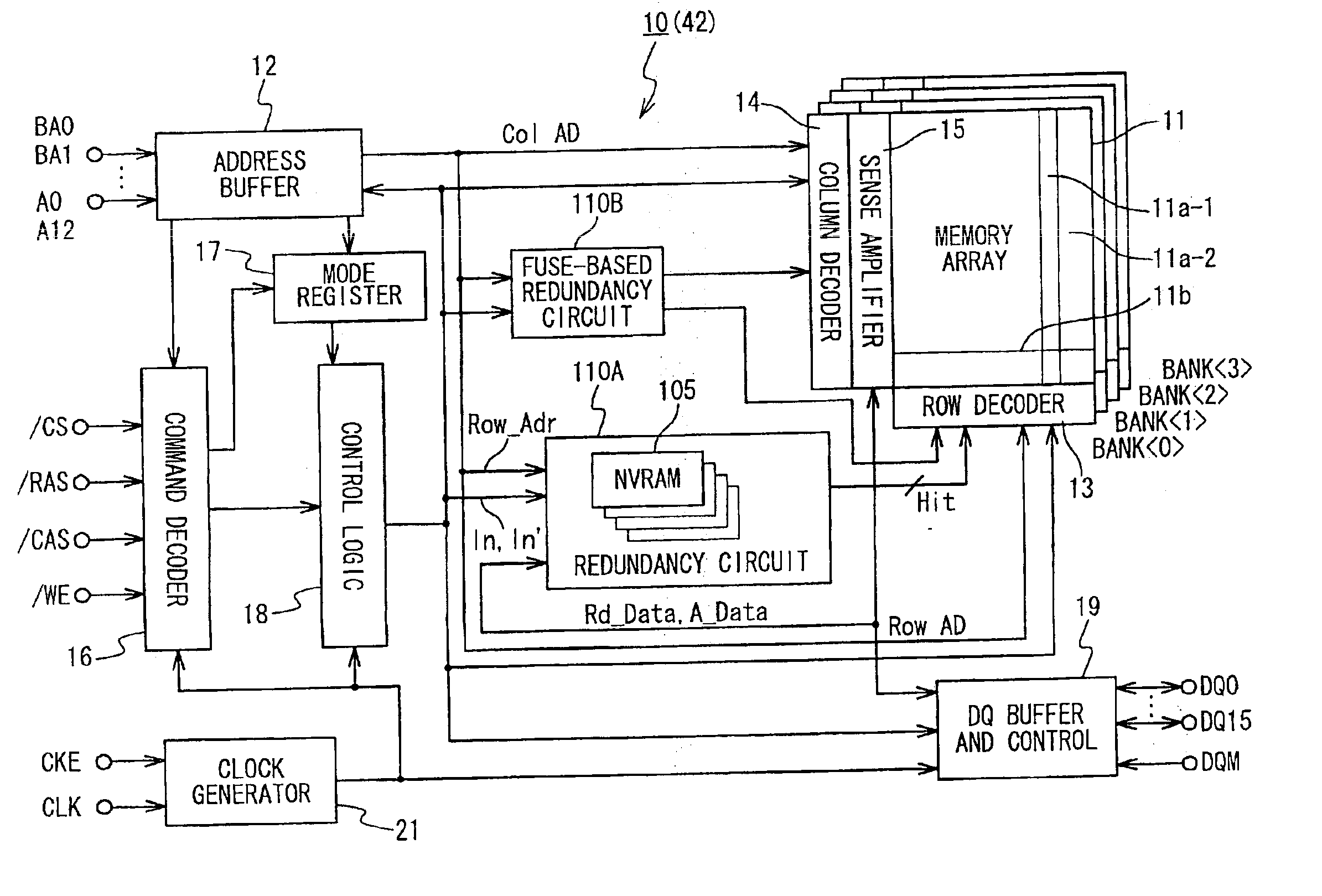

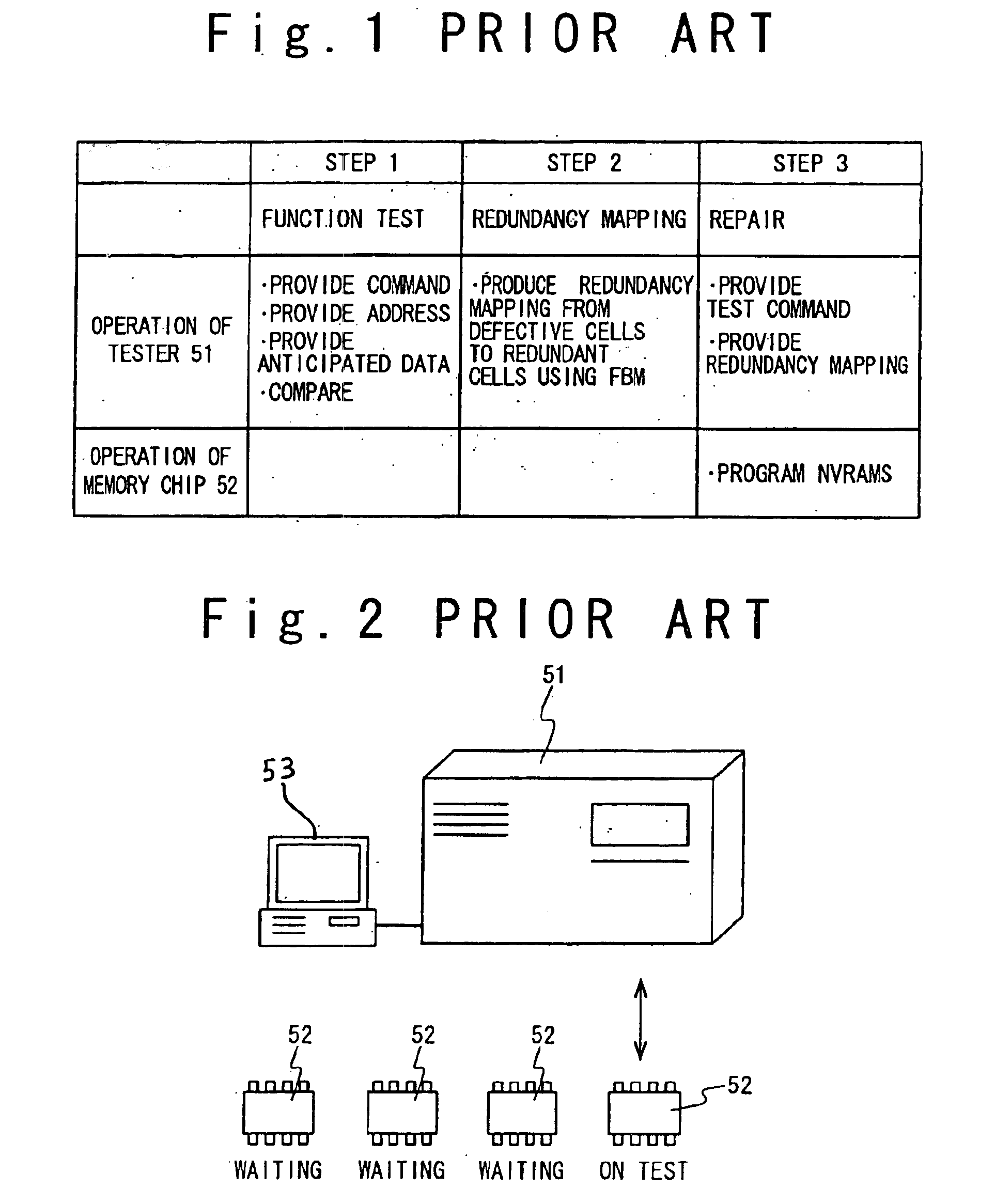

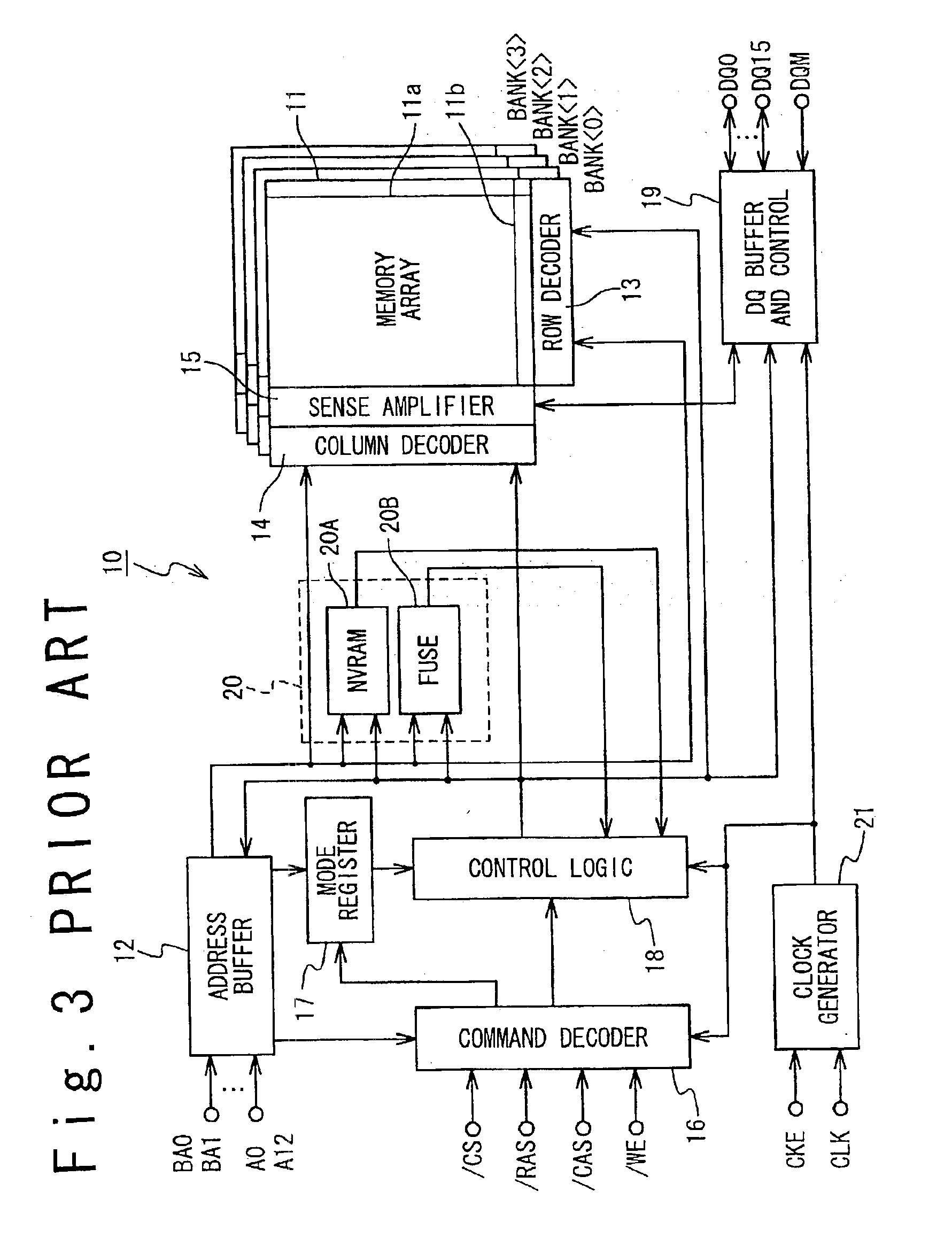

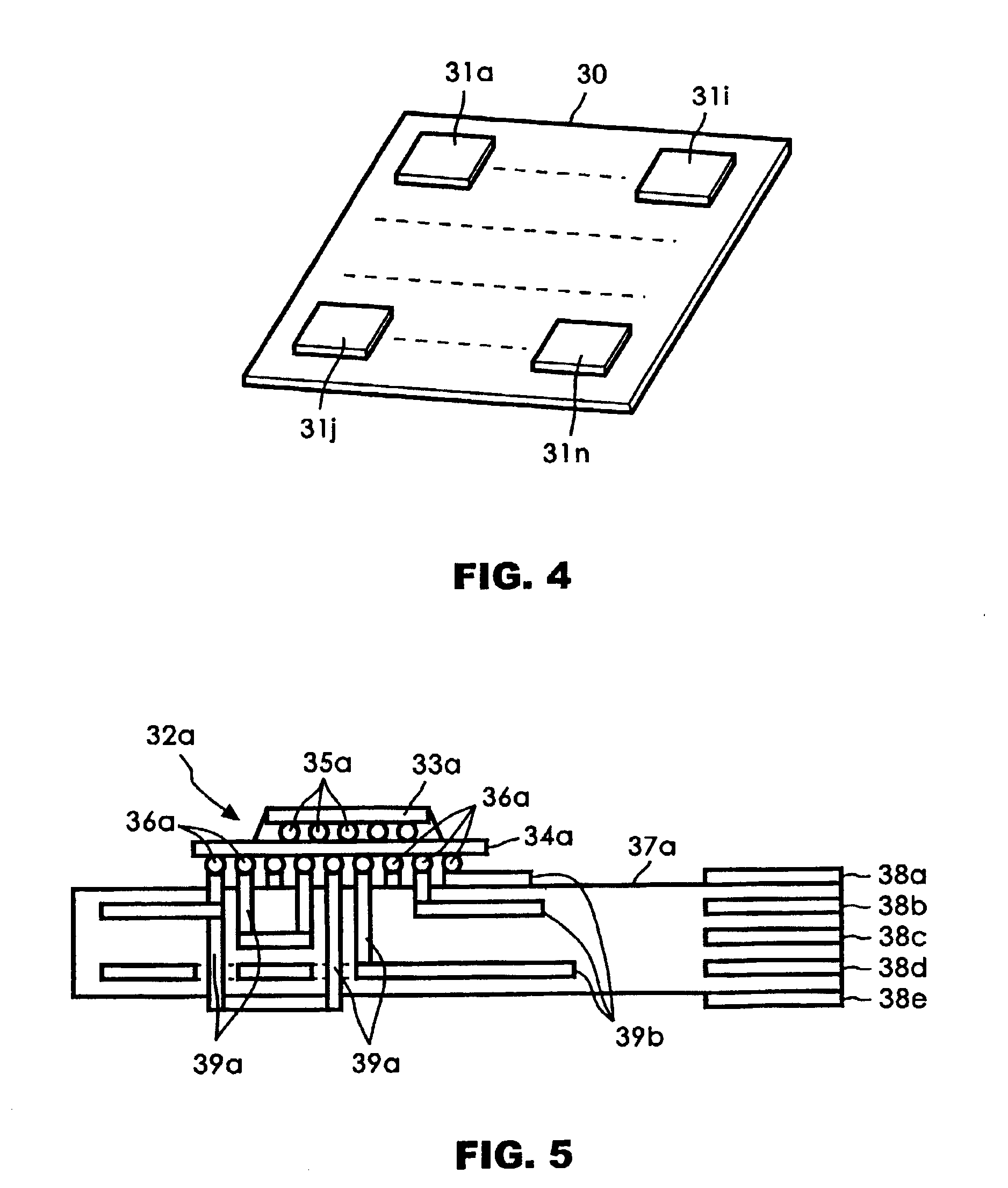

Redundancy architecture for repairing semiconductor memories

InactiveUS6967878B2Improve throughputReduce chip sizeElectronic circuit testingSolid-state devicesComputer scienceSemiconductor

A redundancy architecture for improving the throughput of testing and repairing the semiconductor memory after packaging. A memory device is composed of a memory cell array including memory cells and first redundant cells, a data comparator comparing read data received from the memory cell array with anticipated data provided by an external tester to produce a data mismatch signal, a redundancy mapping circuit responsive to the data mismatch signal for detecting a defective address of the memory cell array, a nonvolatile memory storing the detected defective address, and a redundancy circuitry repairing the memory cell array by replacing ones of the memory cells associated with the defective address with the first redundant cells.

Owner:LONGITUDE SEMICON S A R L

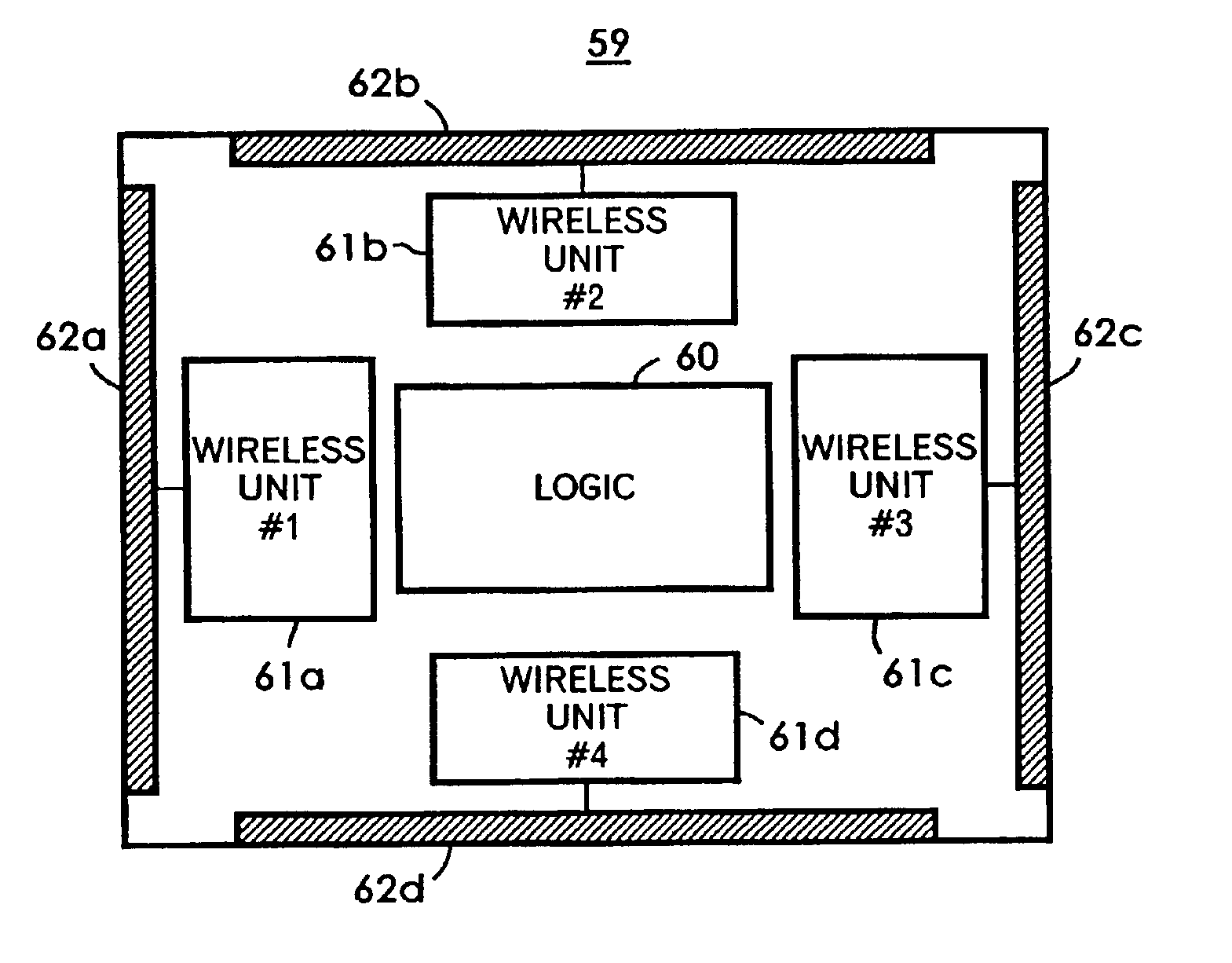

Data processing system and data processing method

InactiveUS6942157B2Reduce decreaseReduce chip sizeCircuit optical detailsPrinted circuit aspectsData processing systemΠ pad

An IC chip is provided with a wireless unit for inputting and outputting data by wireless communication, in addition to a logic section, so that the IC chip no longer needs I / O pads, leaving only power supply and ground pads. IC chips can input and output data with one another by wireless communications, which makes it possible to significantly improve the spacing relationships of various chips on a singular or even plurality of substrates.

Owner:GLOBALFOUNDRIES US INC

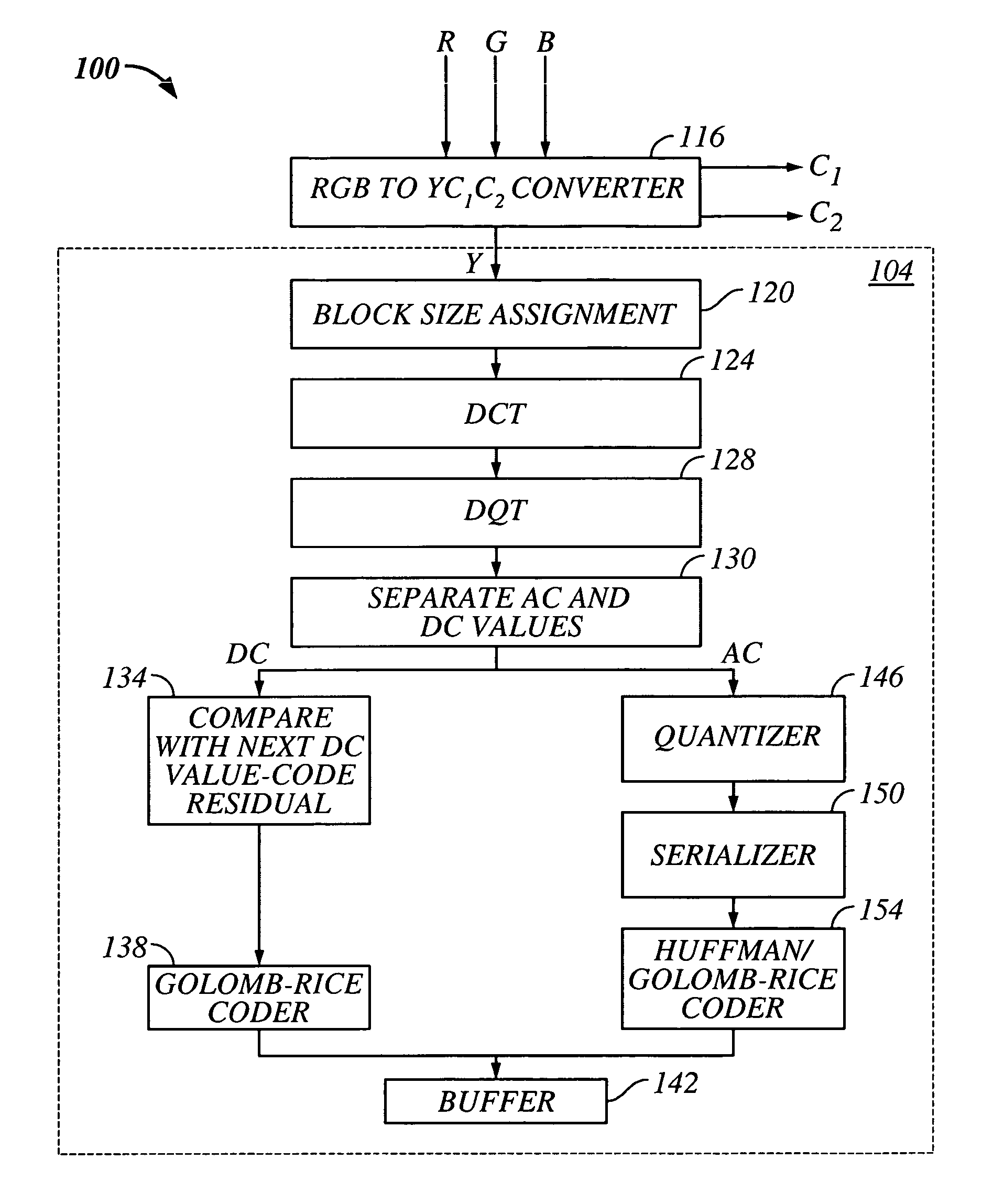

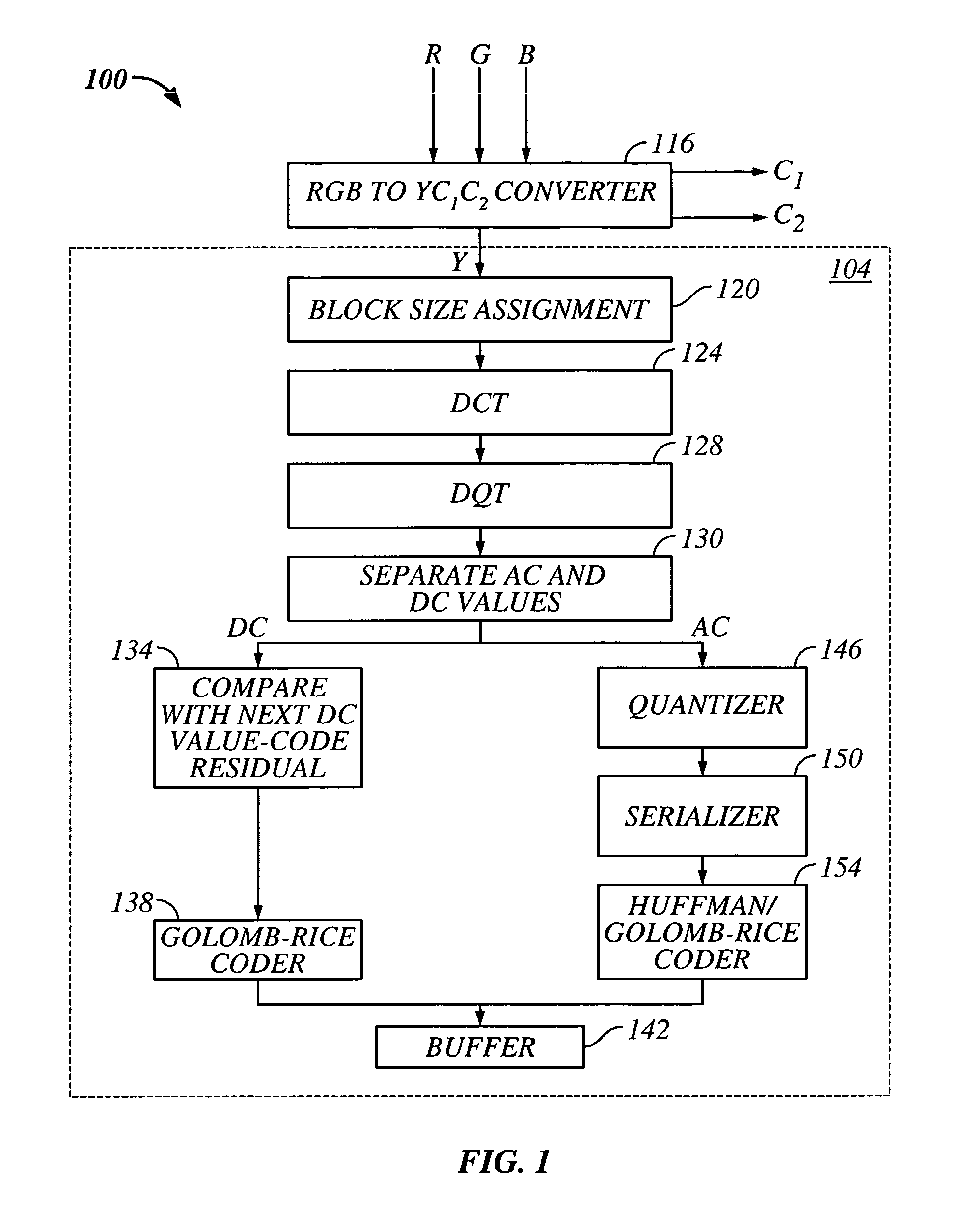

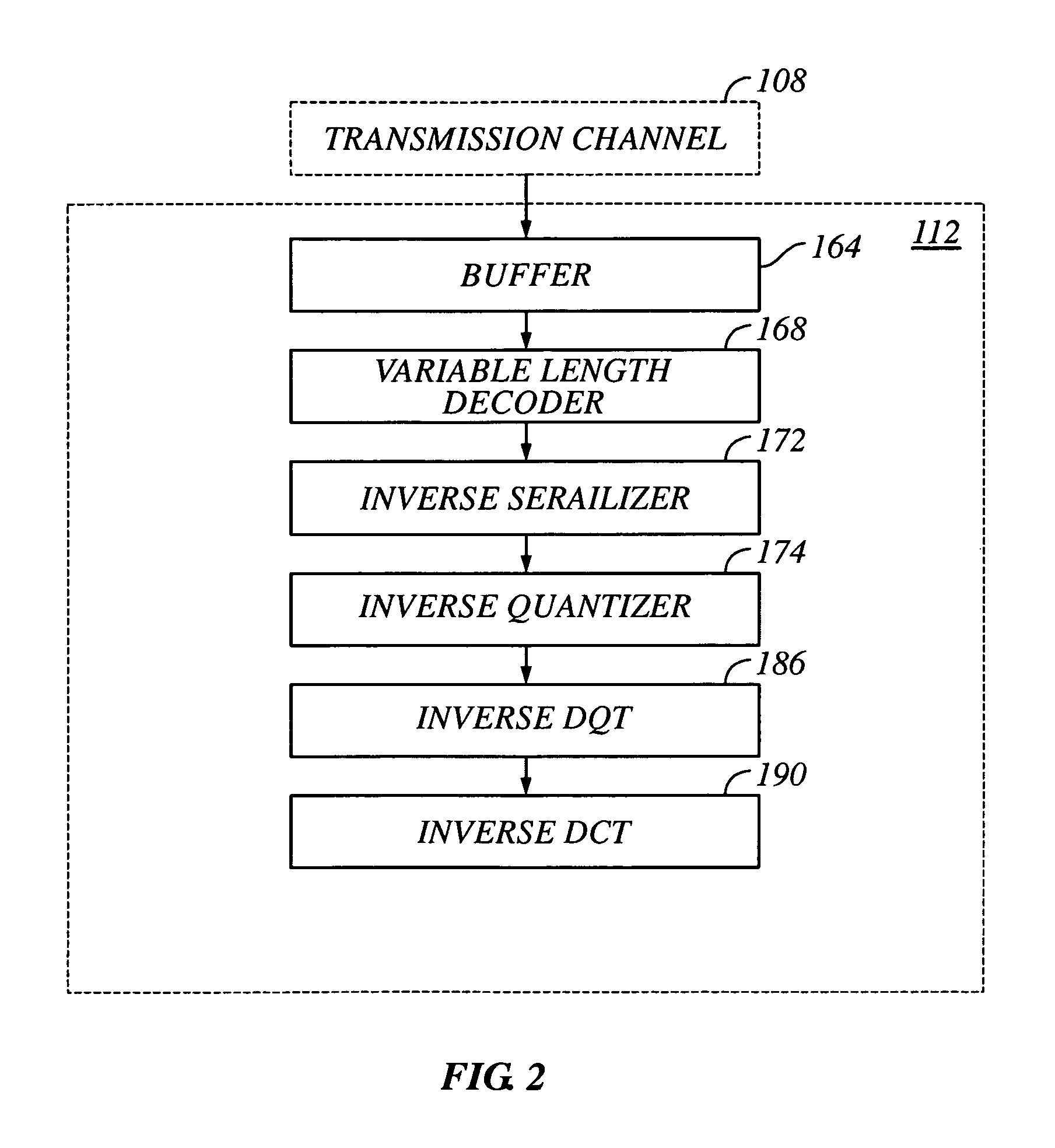

Apparatus and method for encoding digital image data in a lossless manner

ActiveUS7483581B2Weaken energyHigh compressionCode conversionCharacter and pattern recognitionOriginal dataData file

Owner:QUALCOMM INC

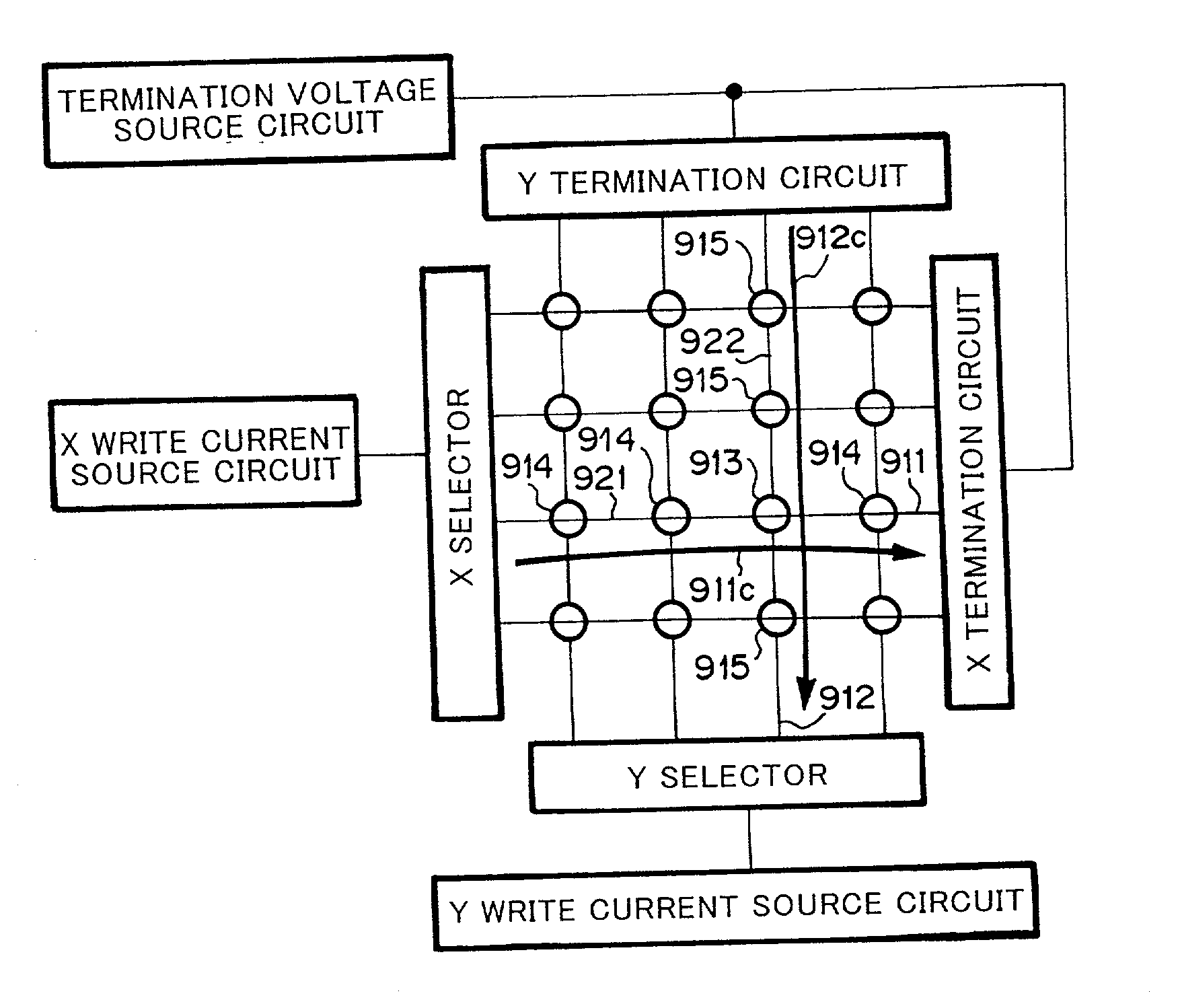

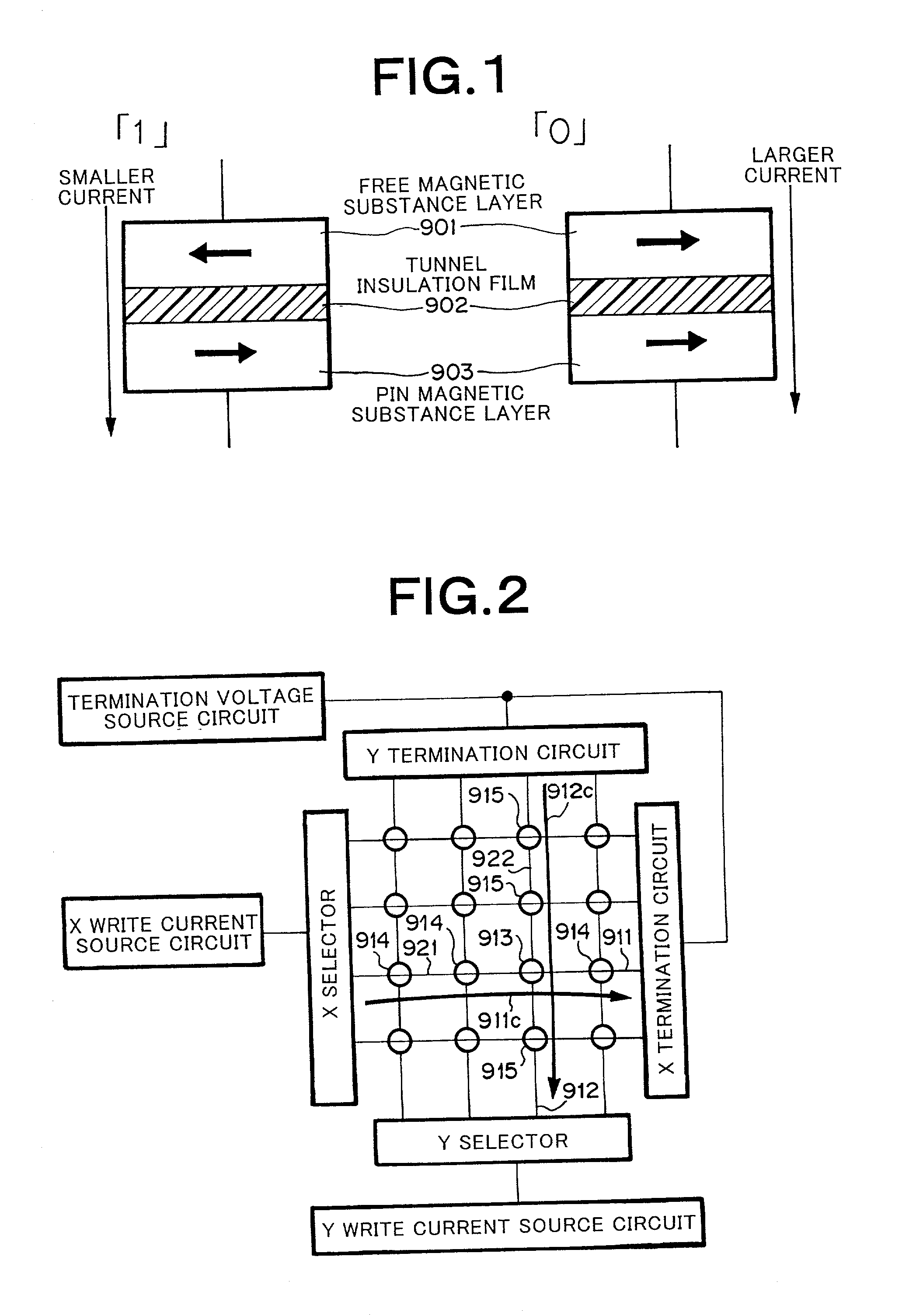

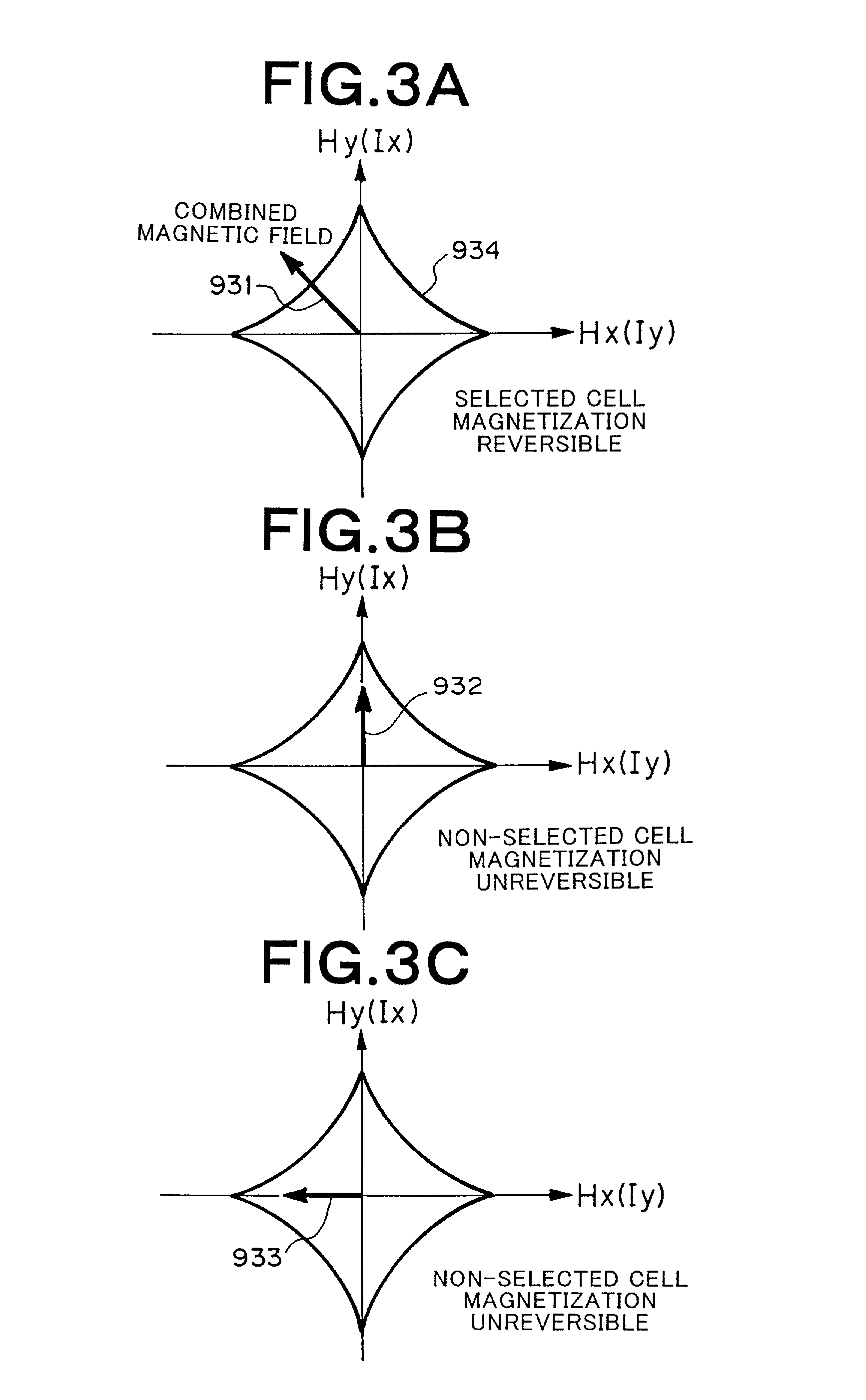

Semiconductor memory apparatus using tunnel magnetic resistance elements

InactiveUS20020126524A1Reduce chip sizeLow production costMagnetic-field-controlled resistorsSolid-state devicesSense amplifierIntegrator

A semiconductor memory apparatus using tunnel magnetic resistance elements comprises a plurality of cell arrays. When data is read from a cell in one of the cell array, a word line connected to the cell is connected to a voltage source, a bit line connected to the cell is connected to an input of a sense amplifier, word lines in the cell array concerned except for the word line connected to the cell and bit lines in the cell array concerned except for the bit line connected to the cell are isolated. A subtracter subtracts an offset current which is generated in another cell array from a current flowing from the bit line connected the cell. An integrator integrates the result of the subtraction. A comparator, a read current value register, and a reference value register performs self-reference reading method on the result of the integration.

Owner:NEC CORP

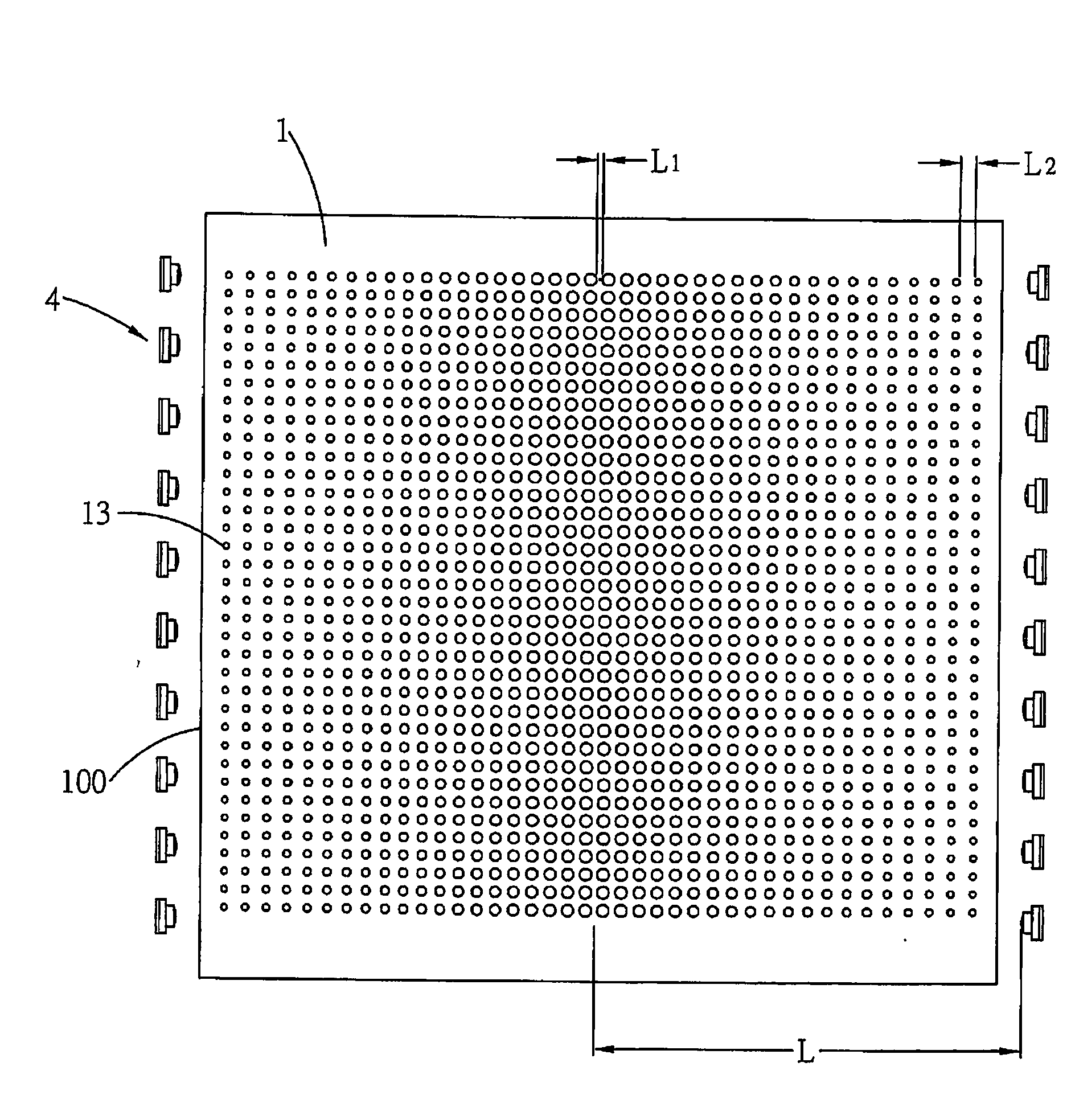

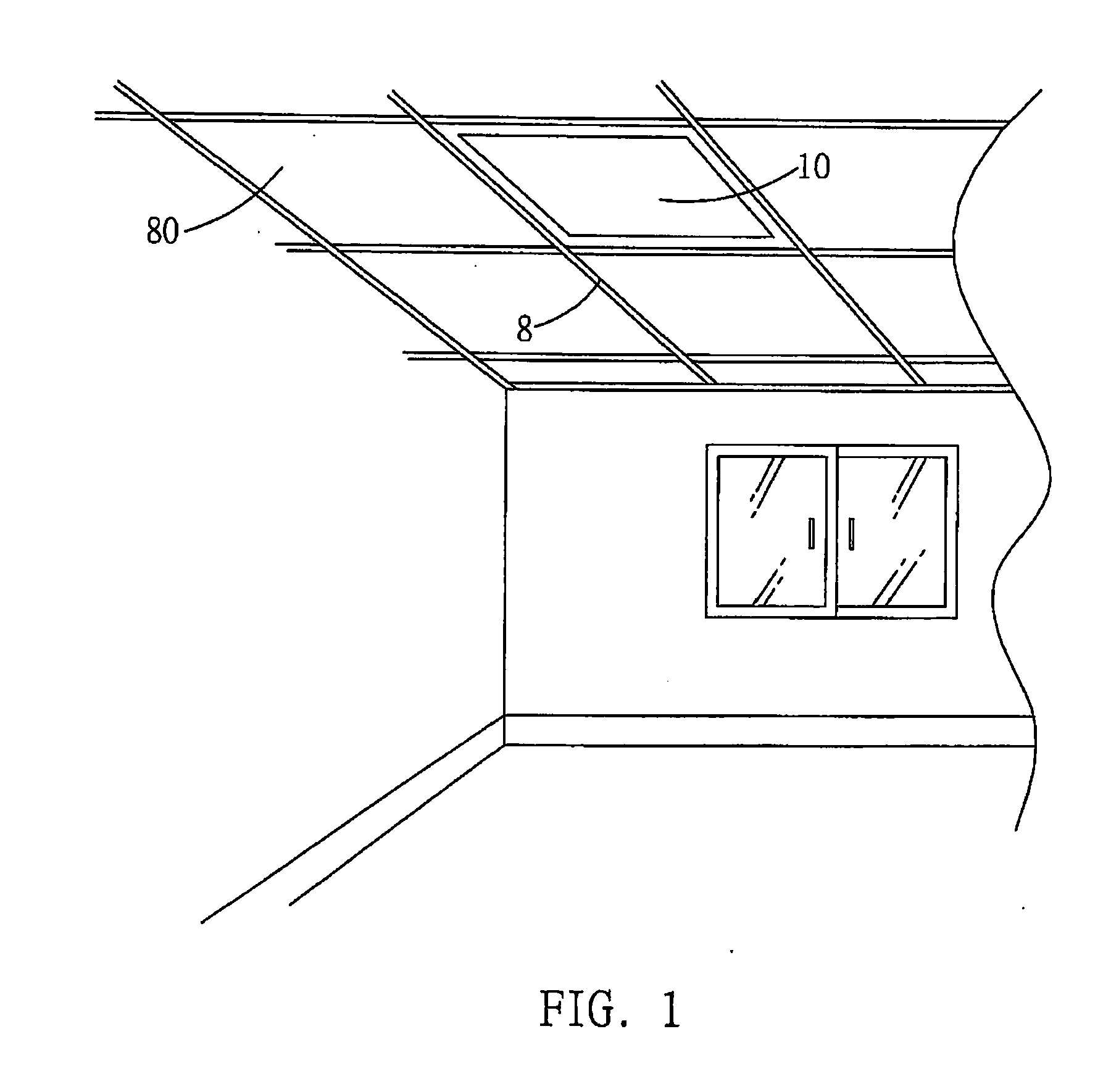

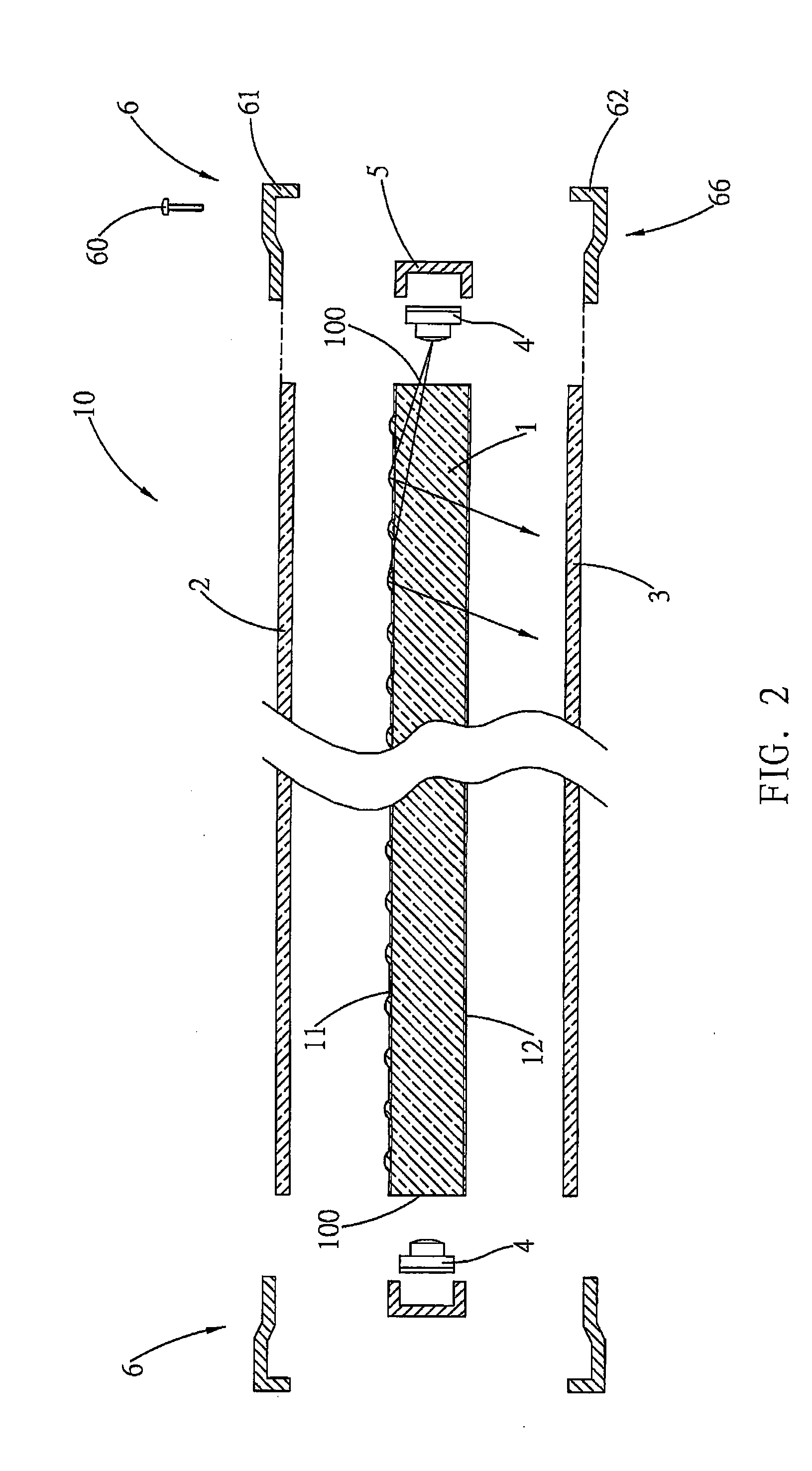

Refraction-type LED ceiling lamp

InactiveUS20100254121A1Effectively utilize lightUniform strengthPlanar light sourcesPoint-like light sourceFiberLight guide

A refraction-type LED ceiling lamp, especially a plate-type ceiling lamp which is used on an indoor ceiling, includes primarily a fiber light guide plate, a reflection surface of which is provided with multiple chip-shape reflection elements, distributed in arrays. A chip size of the reflection elements decreases gradually toward an entrance surface by a geometric series; whereas, a gap between the reflection elements increases gradually. A reflection curve of the reflection element allows light to be projected out uniformly and a required illumination angle to be achieved.

Owner:广东佳兆业佳云科技股份有限公司

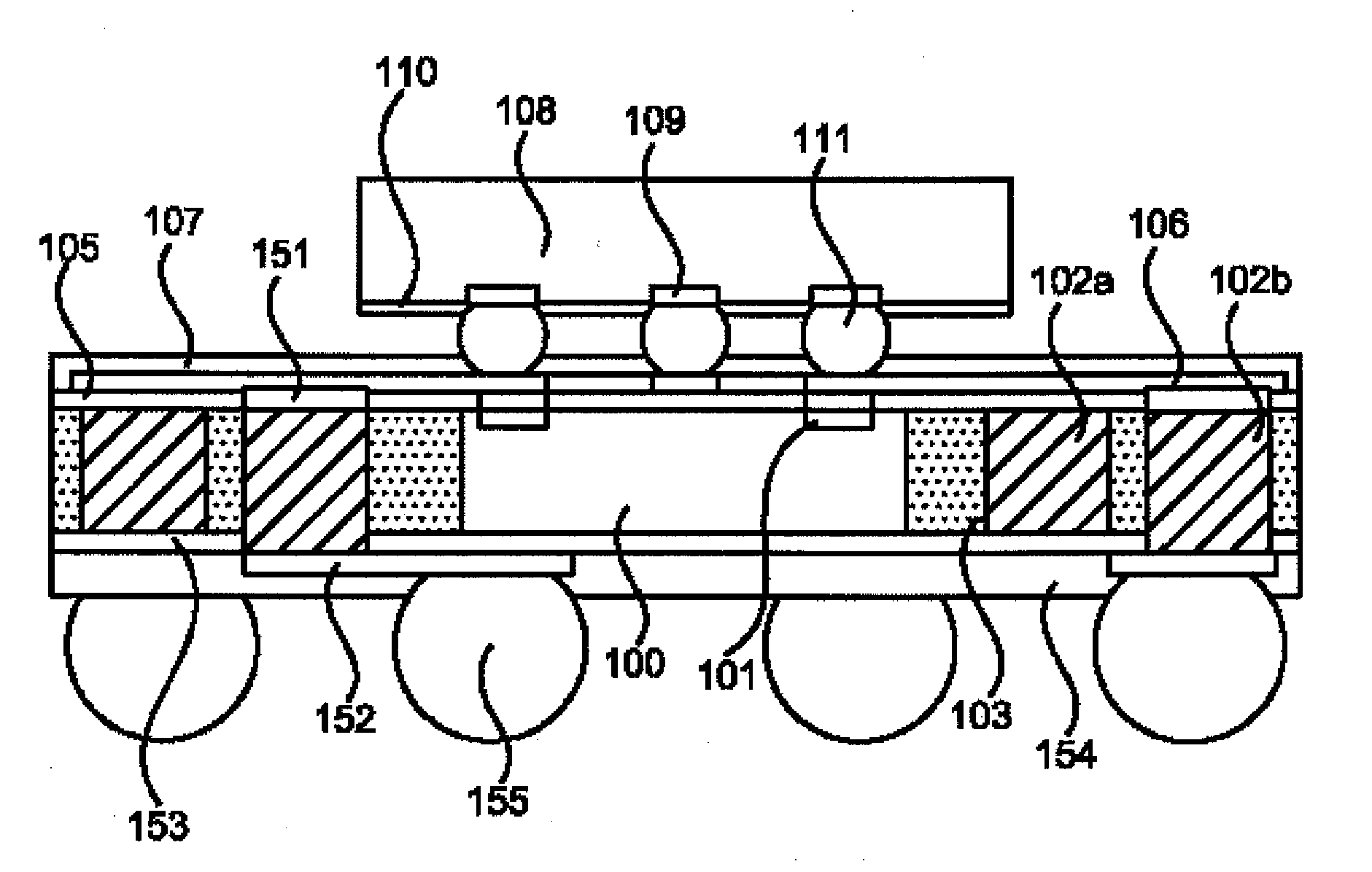

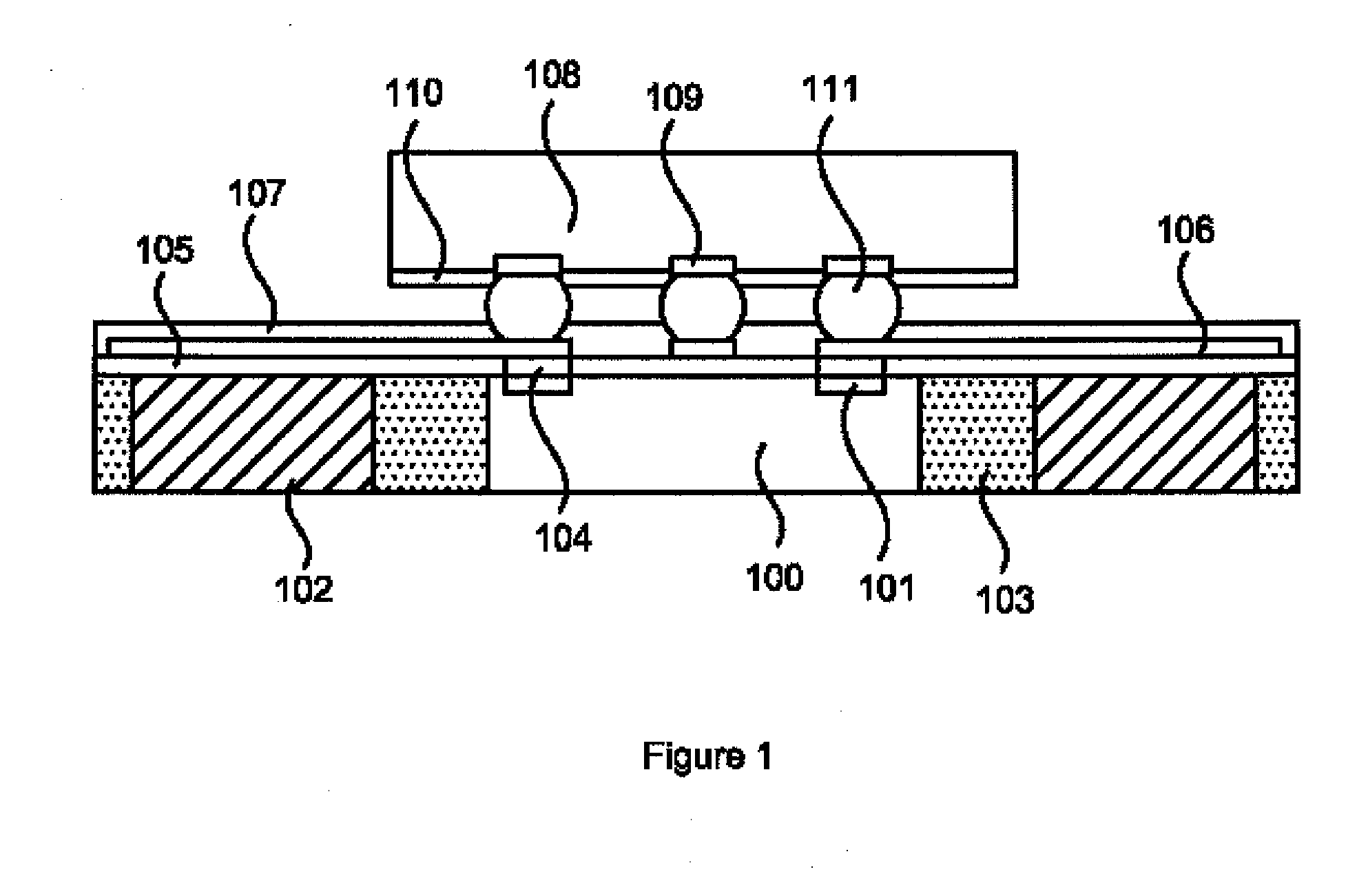

Semiconductor chip package and method for fabricating semiconductor chip

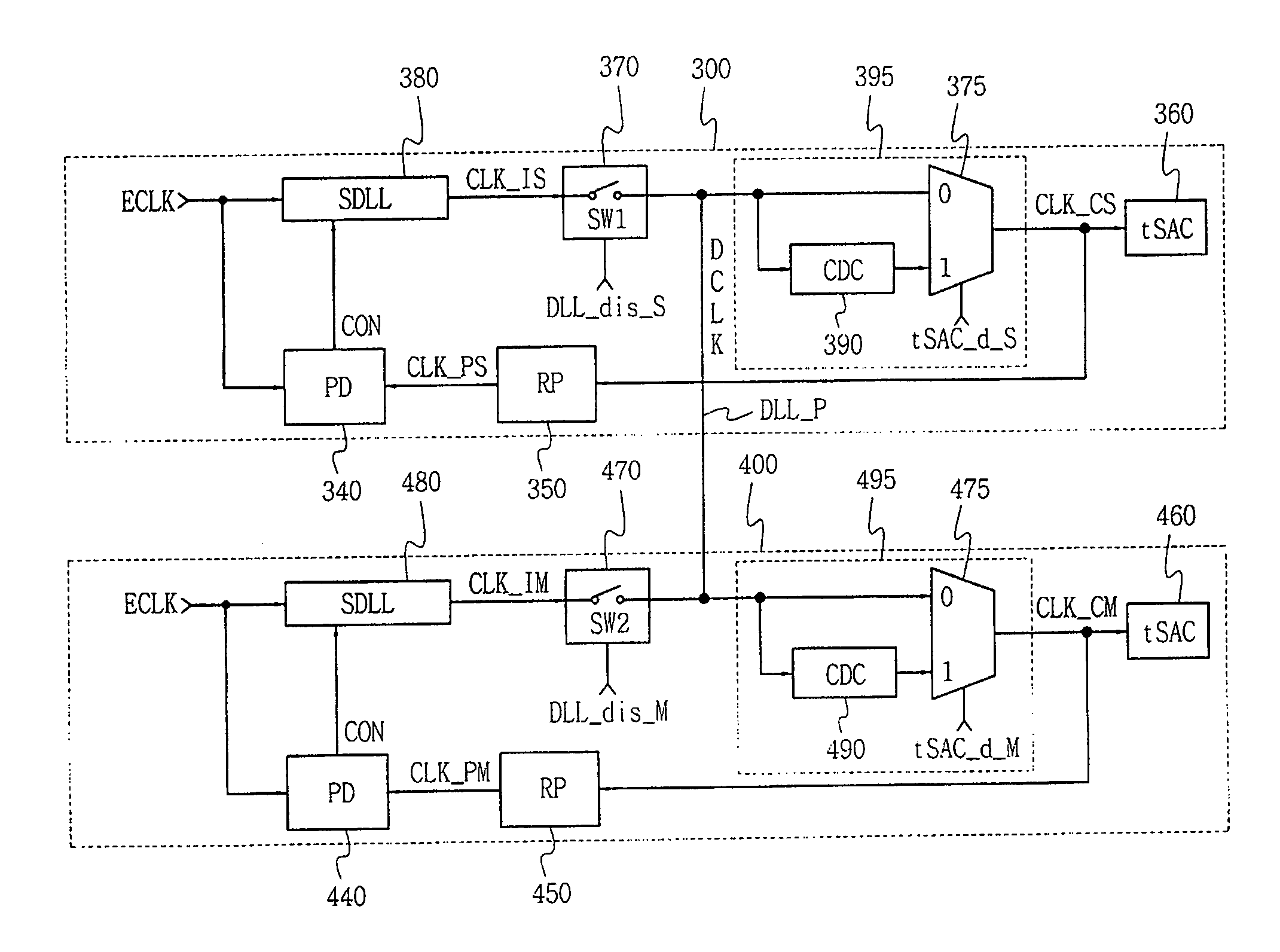

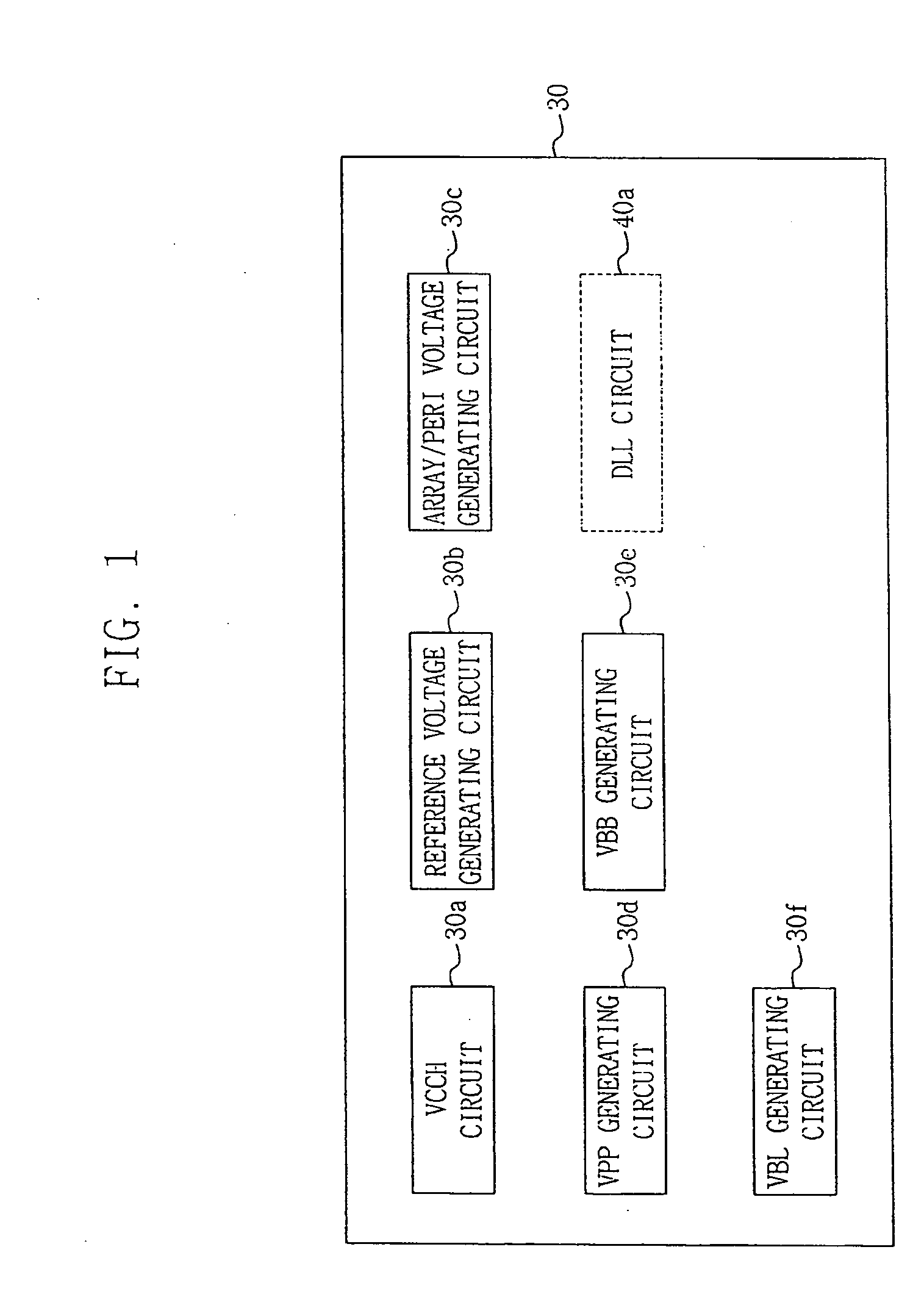

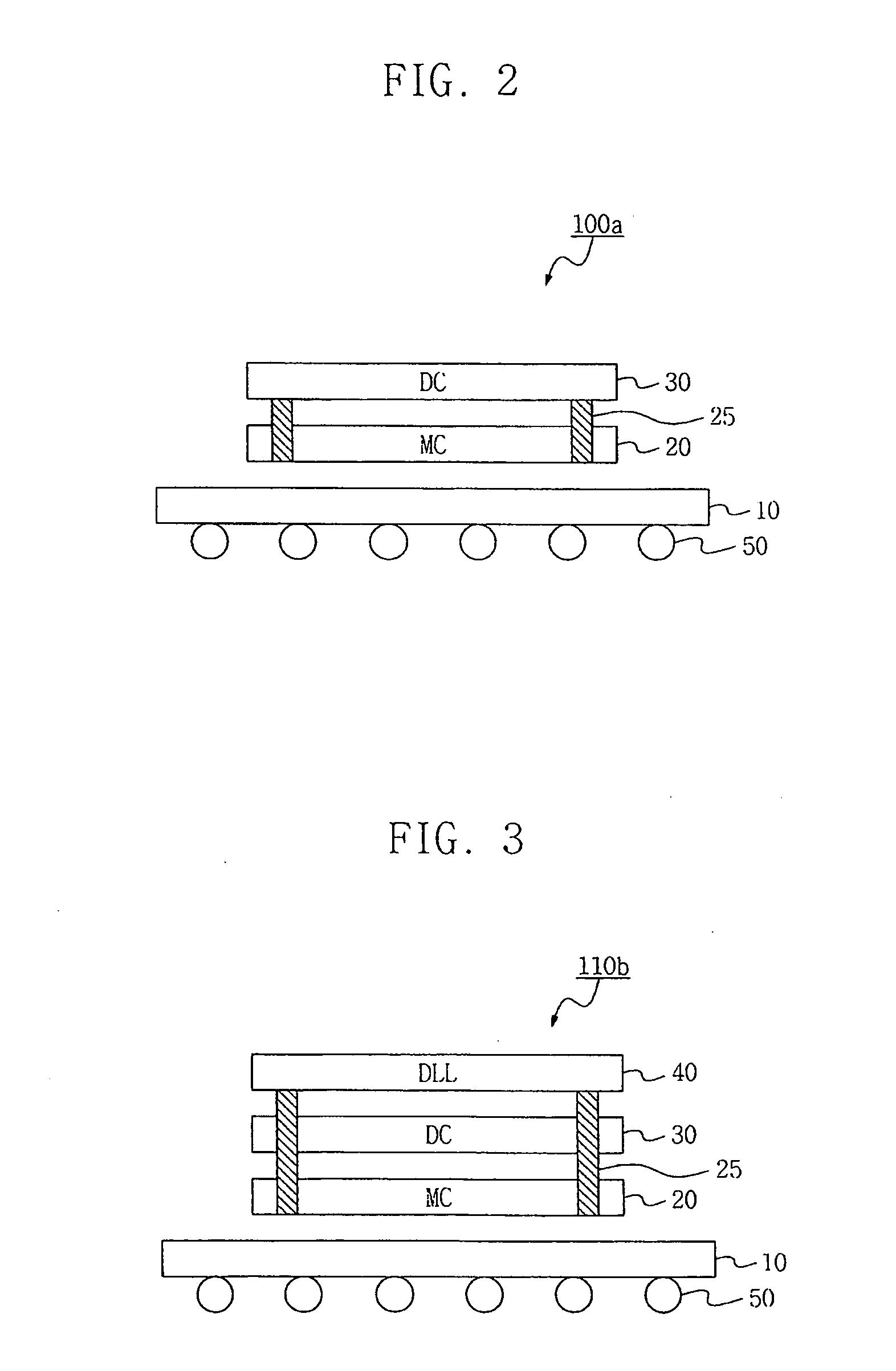

ActiveUS20080204091A1Increase in level trimming rangeReduce power consumptionPulse automatic controlSemiconductor/solid-state device detailsProduction rateEngineering

A semiconductor chip package and a semiconductor chip fabricating method are provided. A semiconductor chip package comprises at least two semiconductor chips having a stacked configuration, the semiconductor chips at least one of: sharing DC signals of DC generating circuits provided by one of the semiconductor chips; and sharing a DLL clock signal of a DLL circuit provided by the semiconductor chip having the DC generating circuits or provided by another semiconductor chip. Power consumption can be reduced, and sharing a DLL clock is valid. In addition, a stabilized DC supply can be guaranteed and an increase for level trimming range and productivity can be improved.

Owner:SAMSUNG ELECTRONICS CO LTD

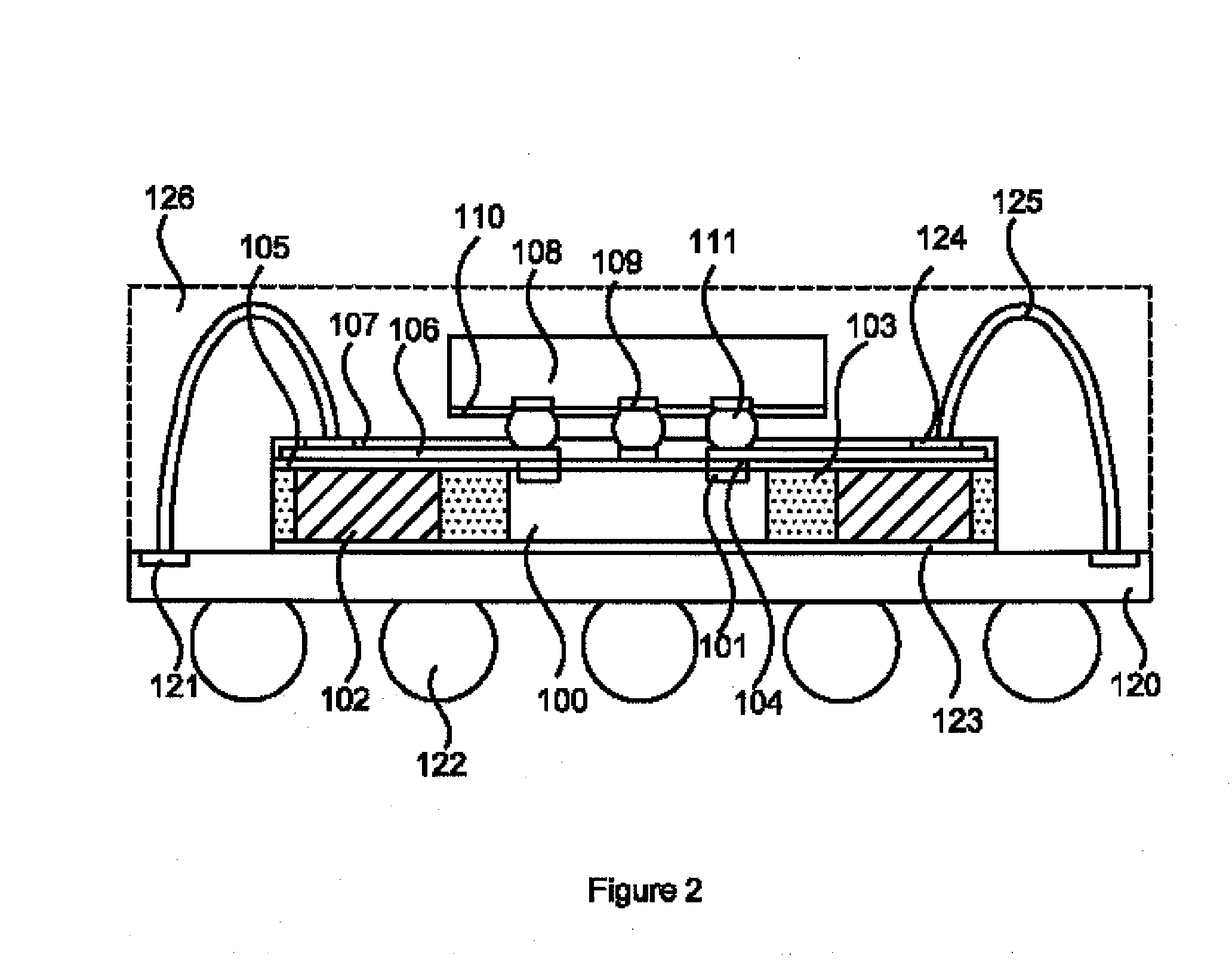

Semiconductor device and a method of manufacturing the same

InactiveUS20070080416A1Great latitudeReduce chip sizeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor device manufacturing technique which allows reduction of semiconductor chip size. First, a pad and other wires are formed over an insulating film. A surface protective film is formed over the insulating film including the pad and wires, and an opening is made in the surface protective film. The opening lies over the pad and exposes a surface of the pad. A bump electrode is formed over the surface protective film including the opening. Here, the pad is smaller than the bump electrode. Consequently, the wires are arranged just beneath the bump electrode in the same layer as the pad 10. In other words, the wires are arranged in space which becomes available because the pad is small enough.

Owner:RENESAS TECH CORP

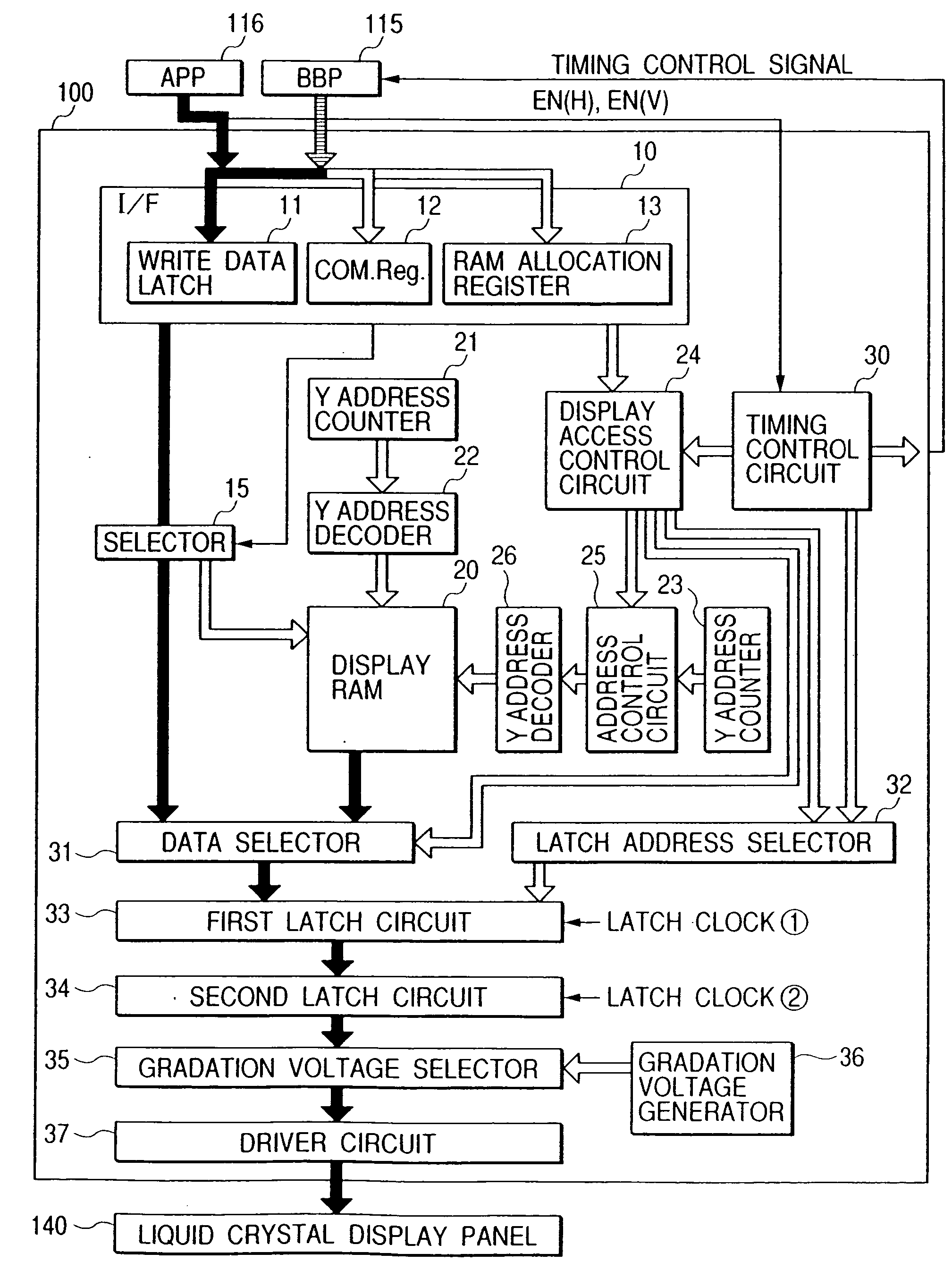

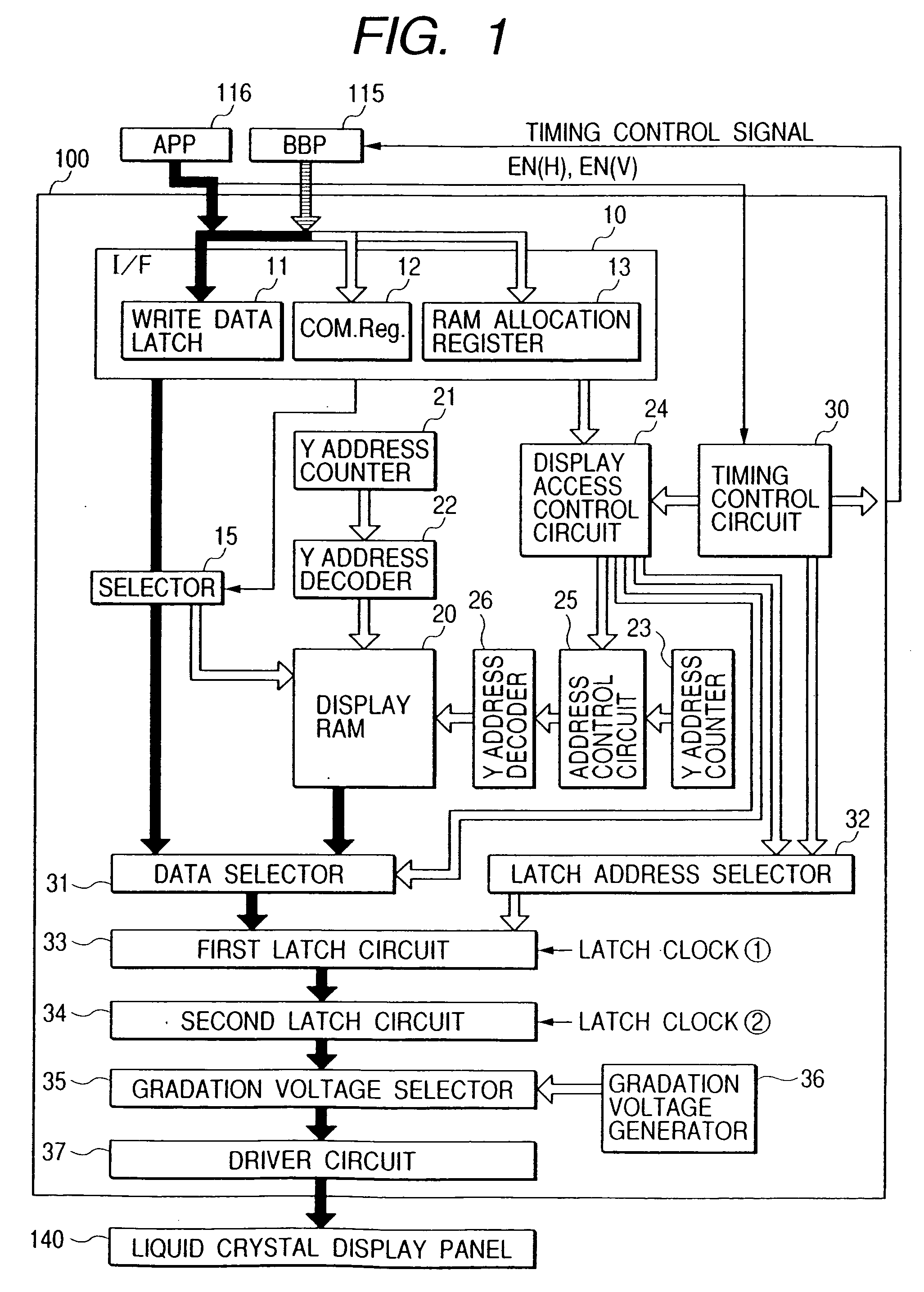

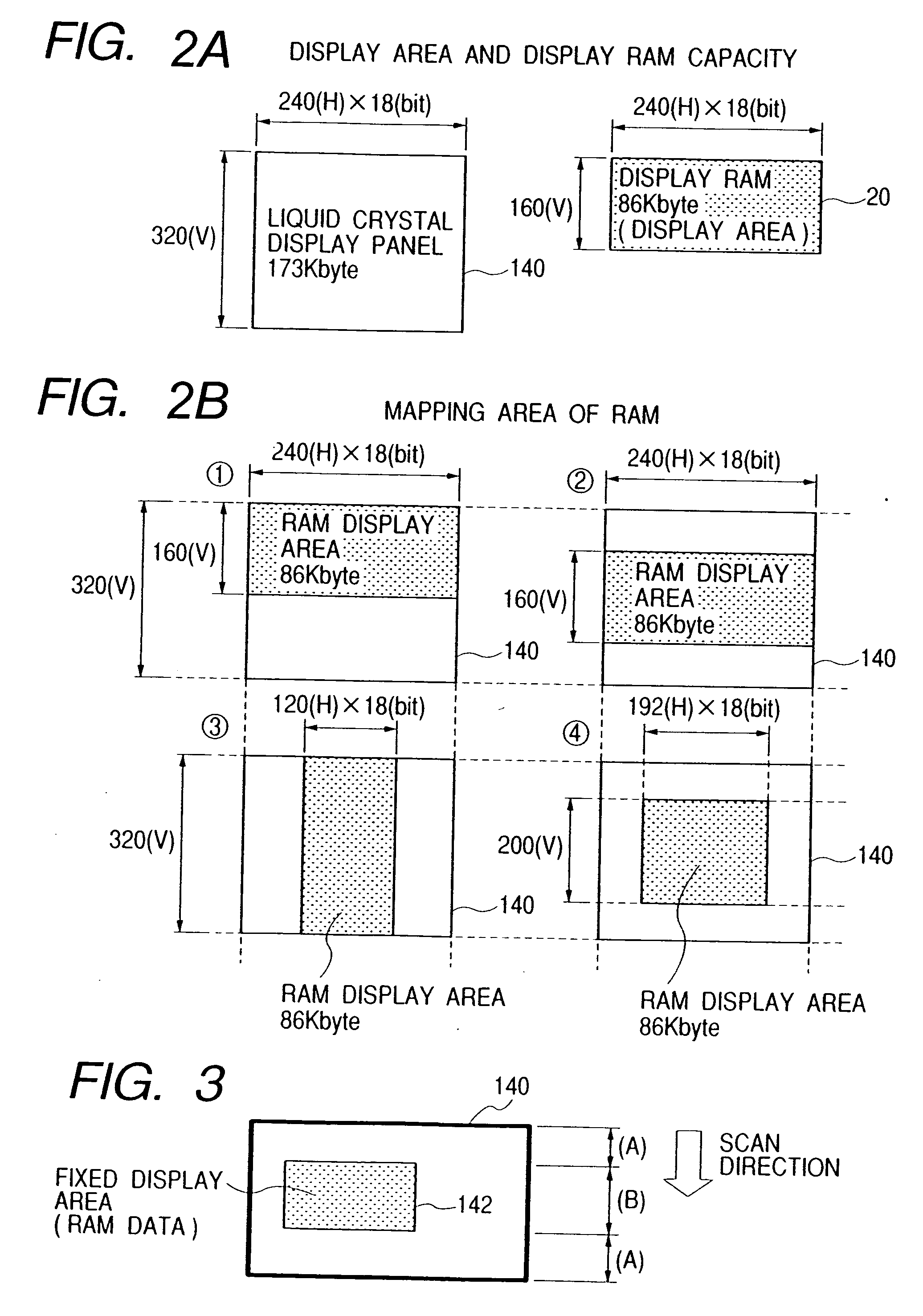

Display driver control circuit and electronic equipment with display device

InactiveUS20070035503A1Large capacityNumber of display colors are more and more increasingCathode-ray tube indicatorsControl circuitComputer science

There is provided a display driver control circuit which is just suitable for display drive including display with a small amount of change and display with a large amount of change and can realize saving of chip area and reduction of power consumption and cost. In this display driver control circuit, memory capacity of an internal display memory is set smaller than amount of data of one display picture of a display panel as the drive object, and the display data can be transferred with the system in which externally inputted display data is once stored in the display memory and is then sent of a drive circuit to output a drive signal and with the system in which the display data is sent in direct to the drive circuit by way of no display memory to output a drive signal. Moreover, both transfer methods can be executed on the time division basis.

Owner:KUROKAWA YASUHITO +4

Three-dimensional system-in-package package-on-package structure

ActiveUS20120161315A1Reduce CTE mismatchMinimize size of deviceSemiconductor/solid-state device detailsSolid-state devicesFilling materialsEngineering

The present invention provides a three-dimensional System-In-Package (SIP) Package-On-Package (POP) structure comprising a support element formed around a first electronic device. A filling material is filled between the first electronic device and the support element. Signal channels are coupled to first die pads of the first electronic device. Conductive elements form signal connection between the first end of the signal channels and the second die pads of a second electronic device.

Owner:ADL ENERGY CORP

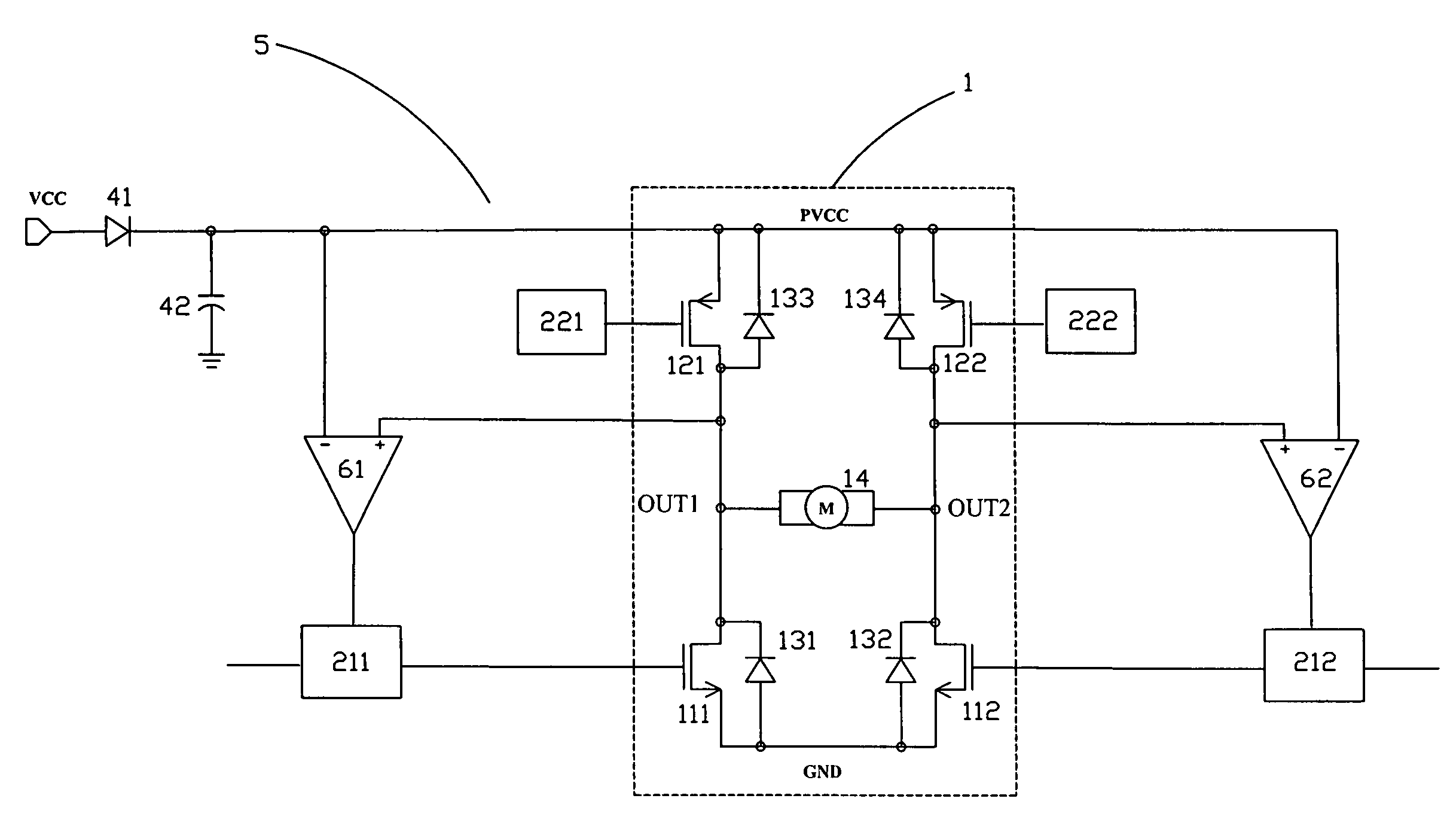

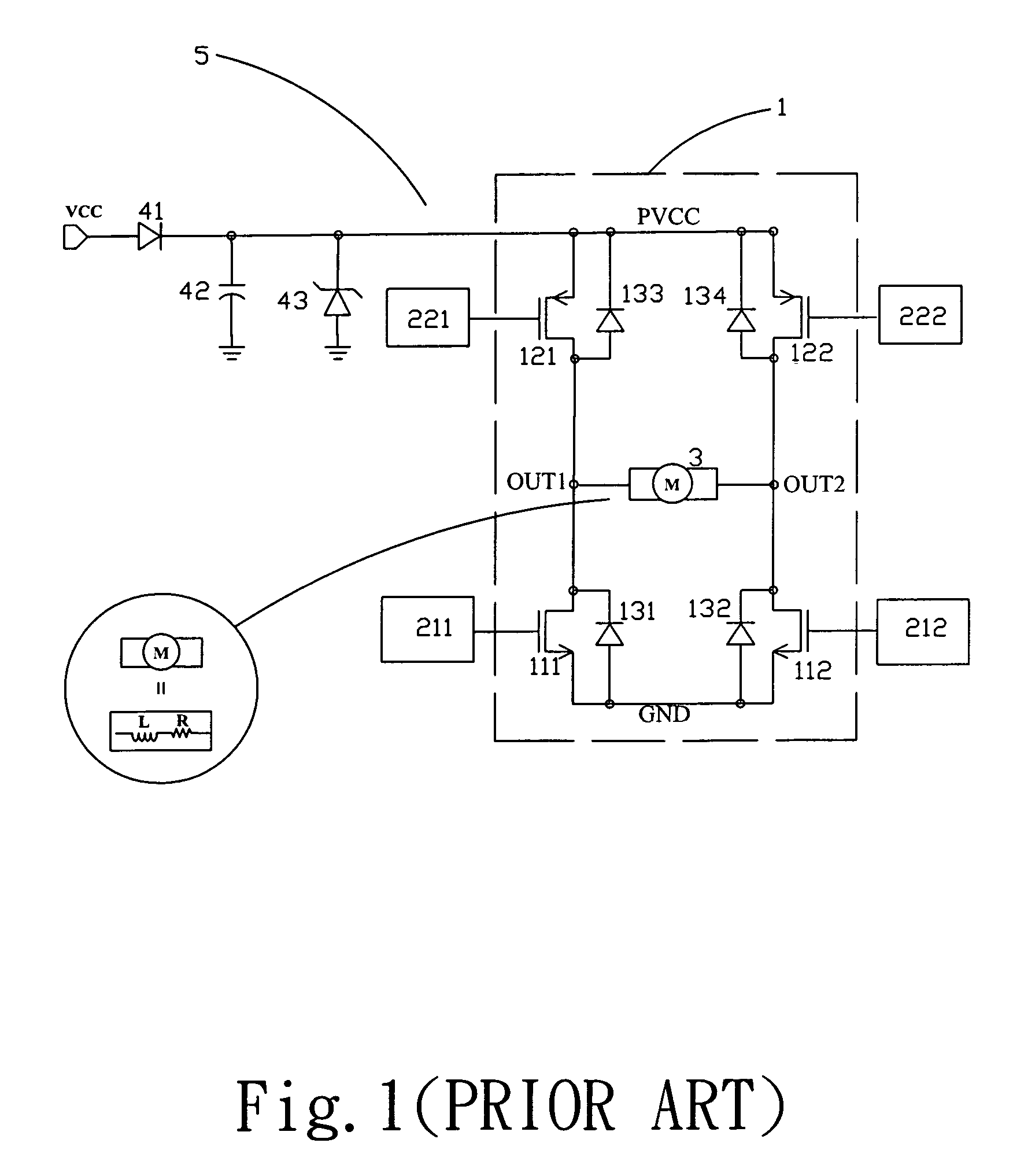

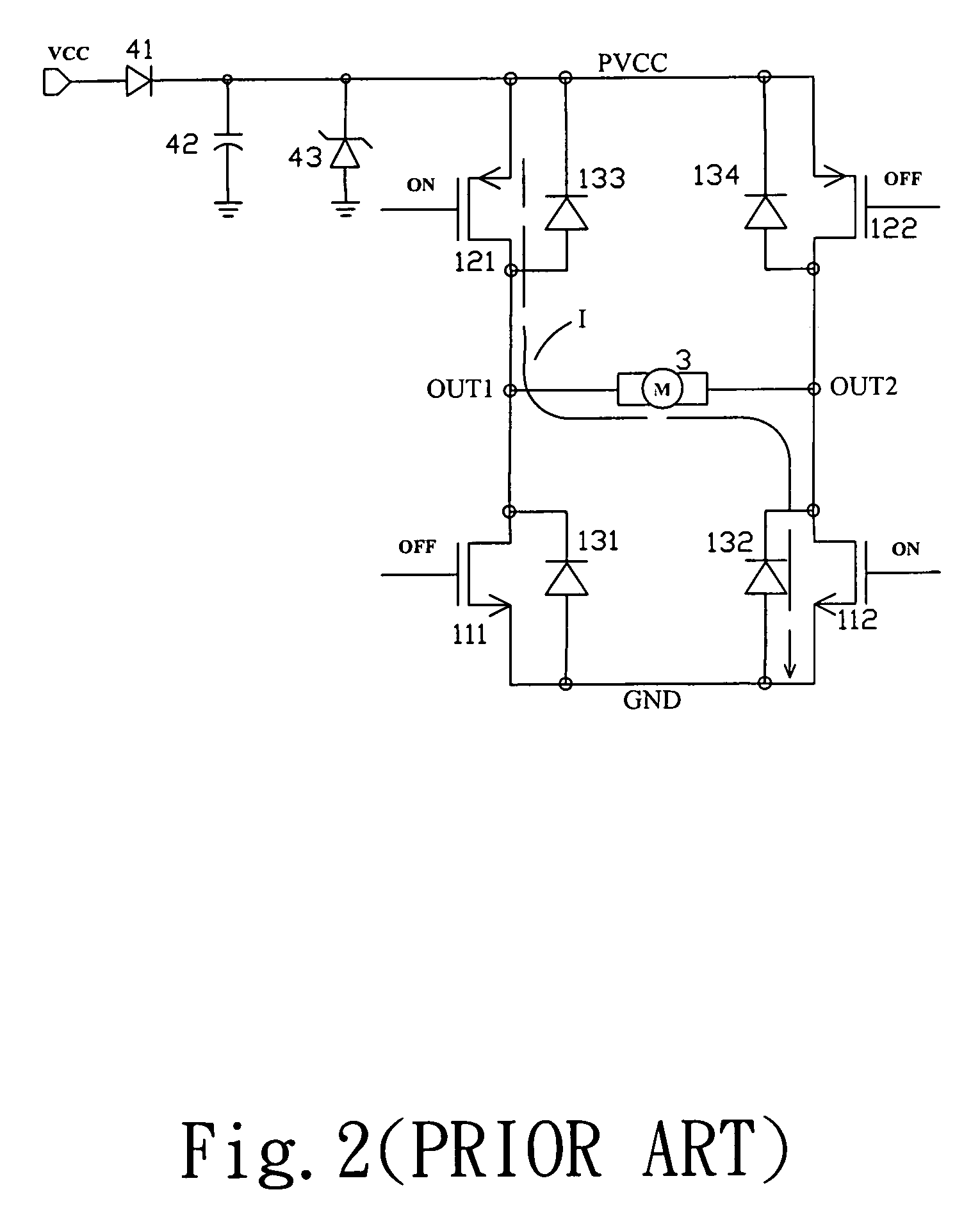

Drive circuit for reducing inductive kickback voltage

InactiveUS7639064B2Reduce voltageReduce chip sizeTransistorElectronic switchingTime segmentEngineering

In one embodiment a drive circuit includes two comparators which are adapted to sense kickback voltage generated in an inductive load and conduct two field-effect transistors connected to ground in a very short period of time so as to quickly reduce the kickback voltage to a minimum value. In another embodiment only one comparator is provided.

Owner:EUTECH MICROELECTRONICS

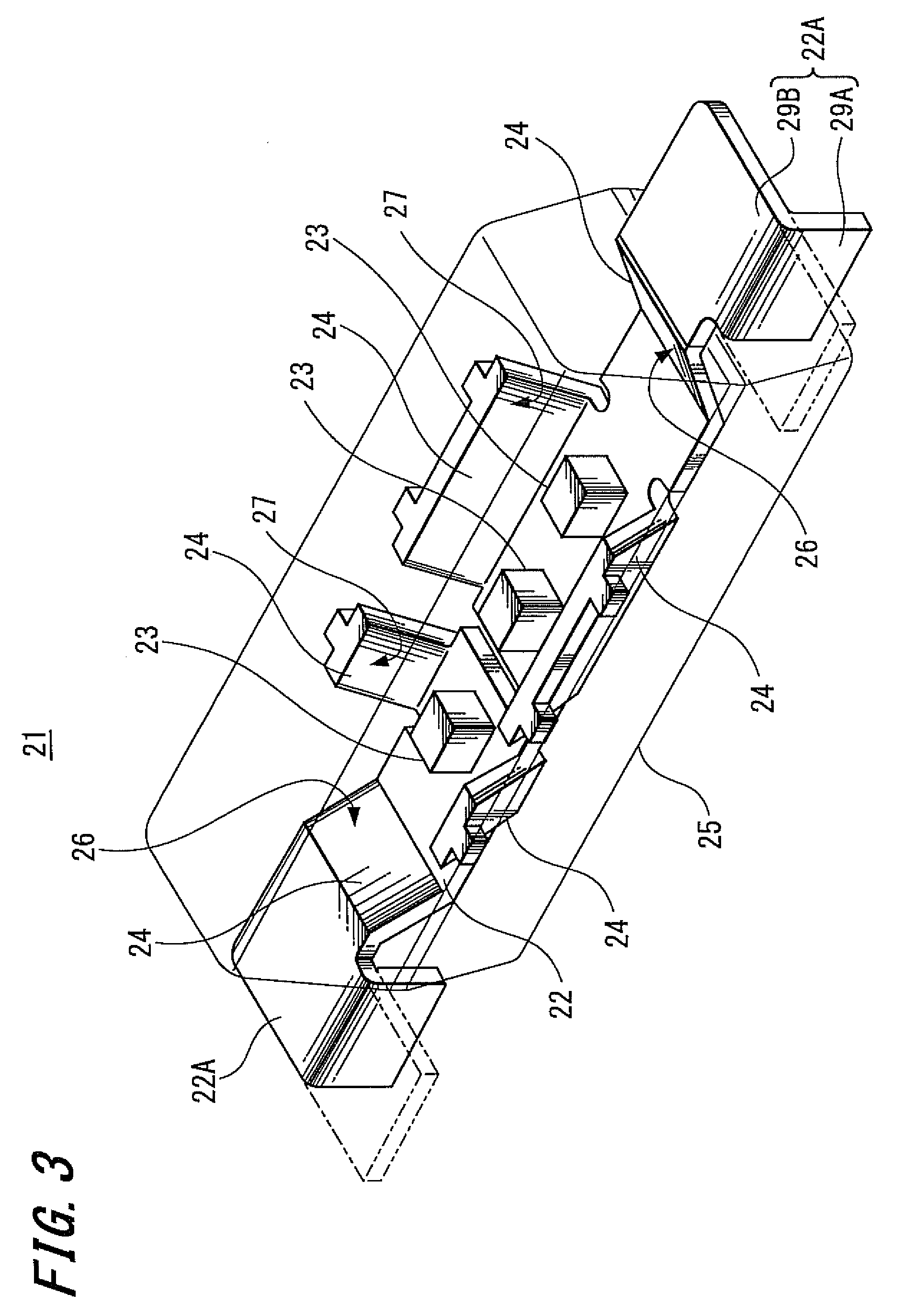

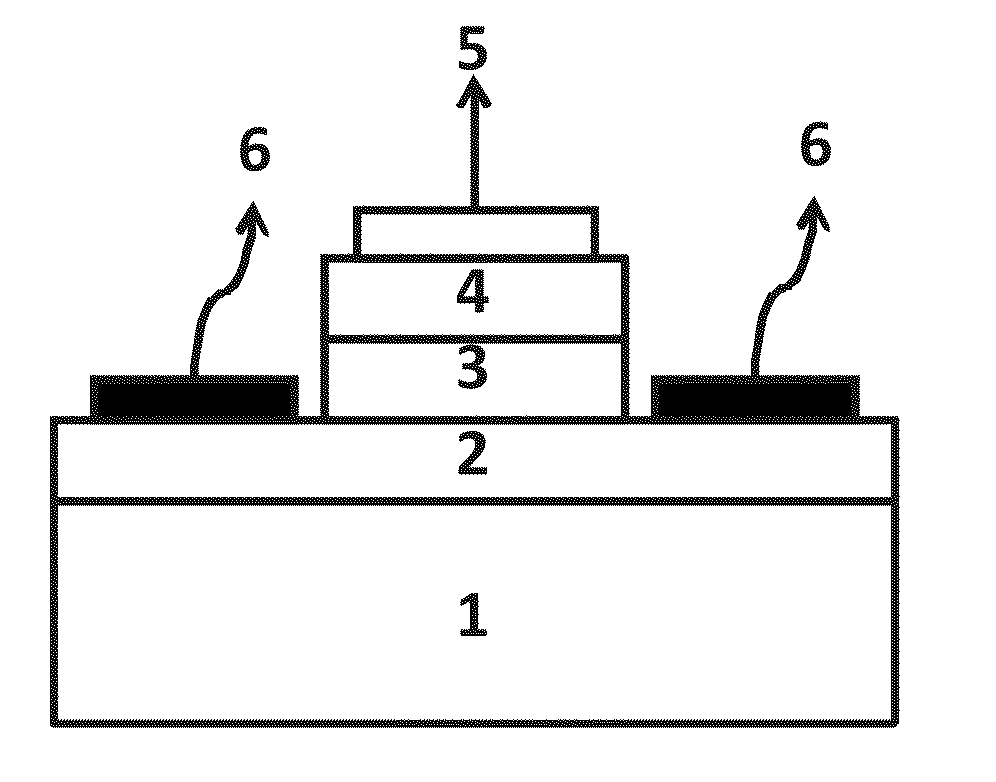

Semiconductor Light-Emitting Device

InactiveUS20080296592A1Structure can be simplified and minimizedNumber of partSolid-state devicesSemiconductor devicesEngineeringLead frame

A semiconductor light-emitting device includes: a light-emitting semiconductor element arranged on a lead frame; a transparent resin mold covering the light-emitting semiconductor element and the lead frame except a terminal portion of the lead frame; and a reflective surface formed on a bent portion of part of the lead frame. The terminal portion of the lead frame has a terminal structure, which can serve as a combination of a top-view type and a side-view type.

Owner:ACCELERATE DEVICE

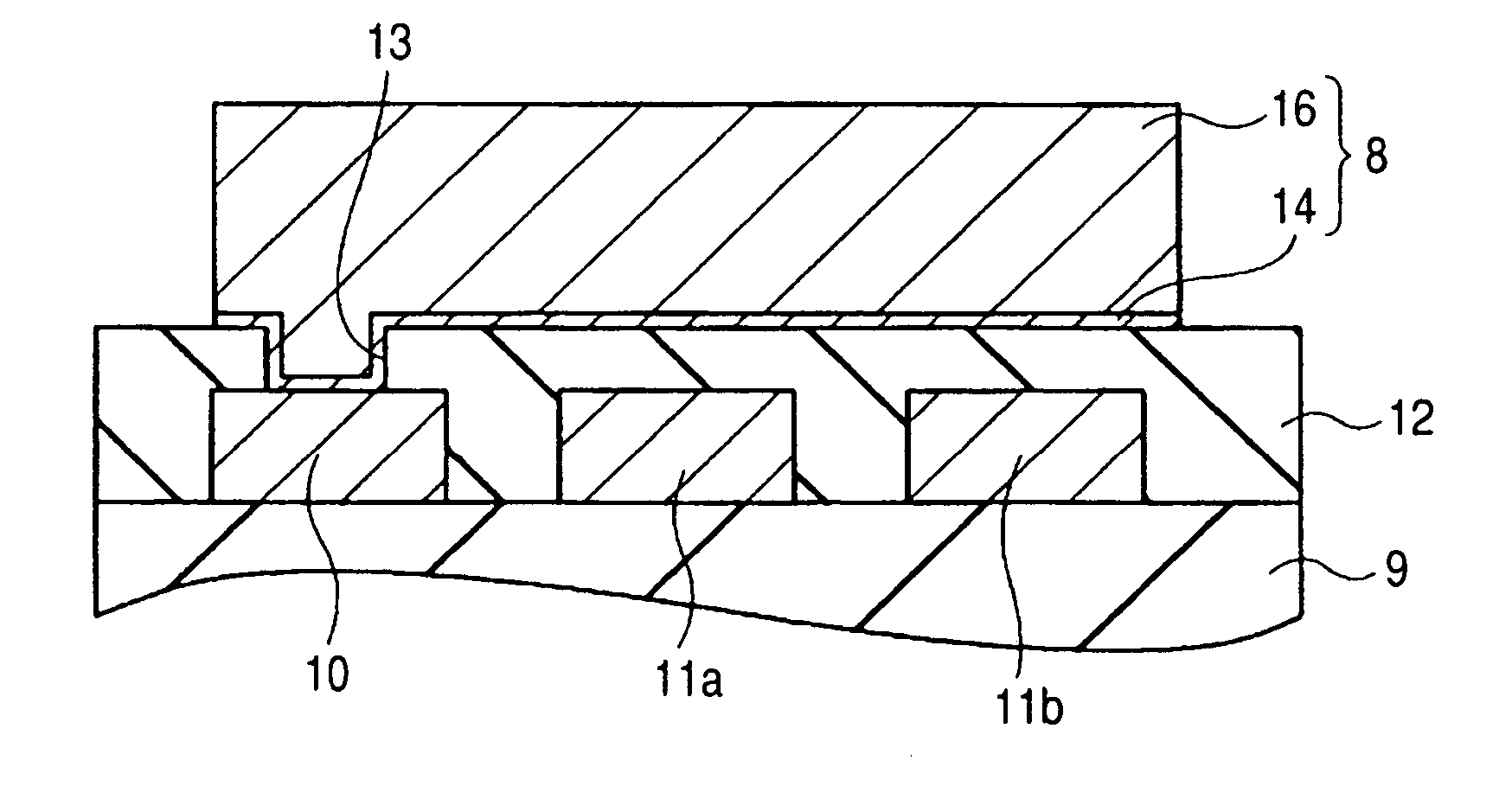

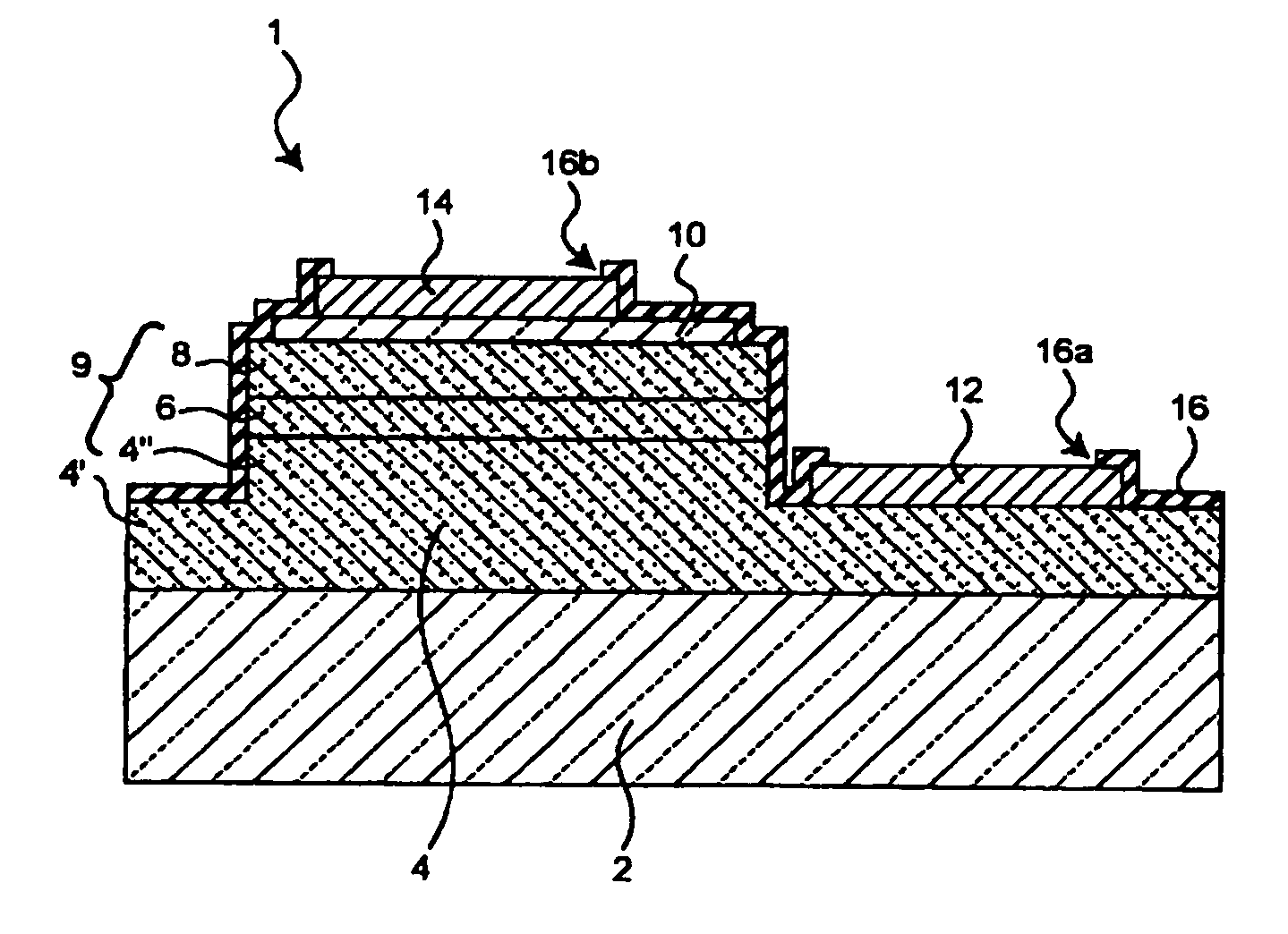

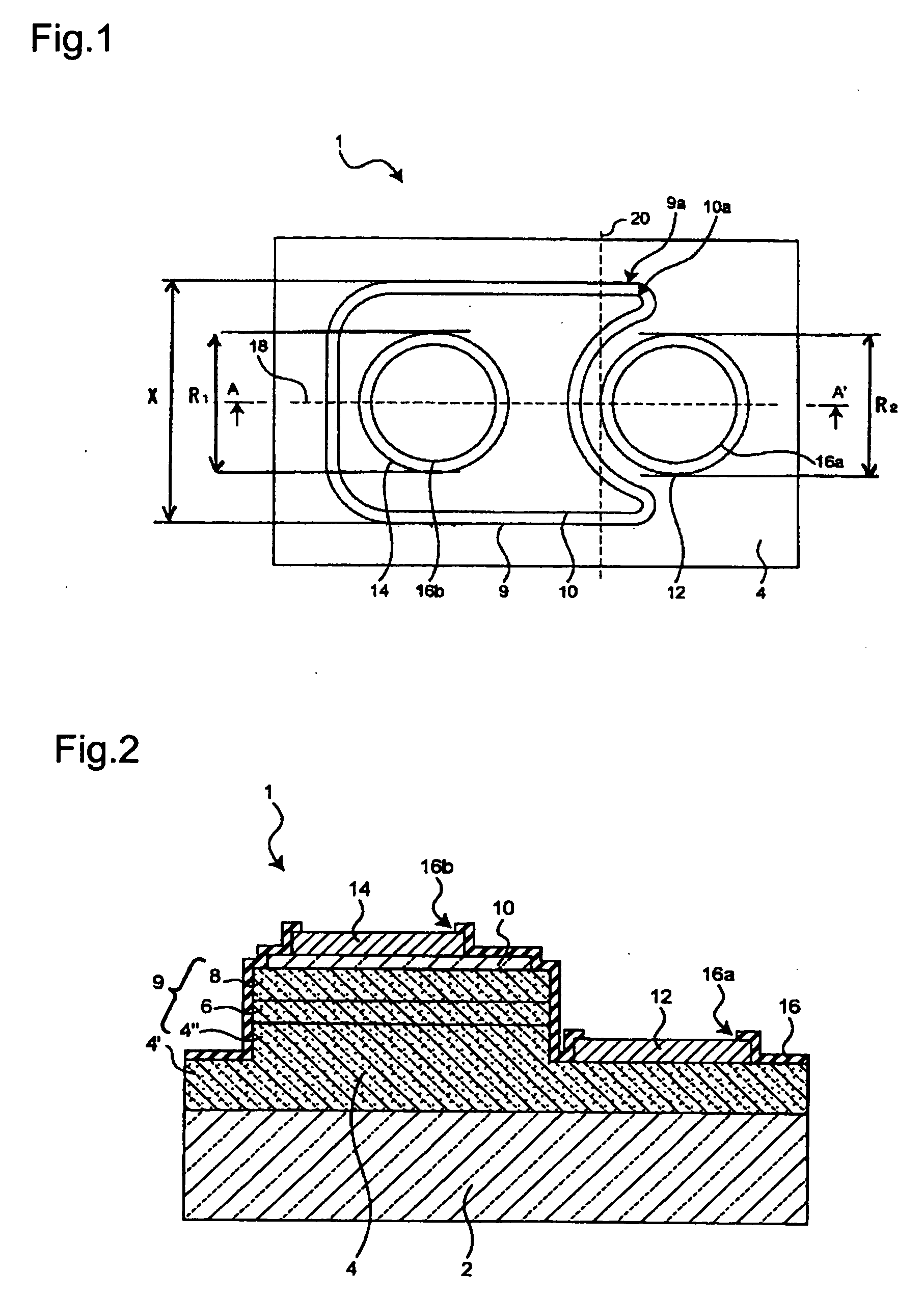

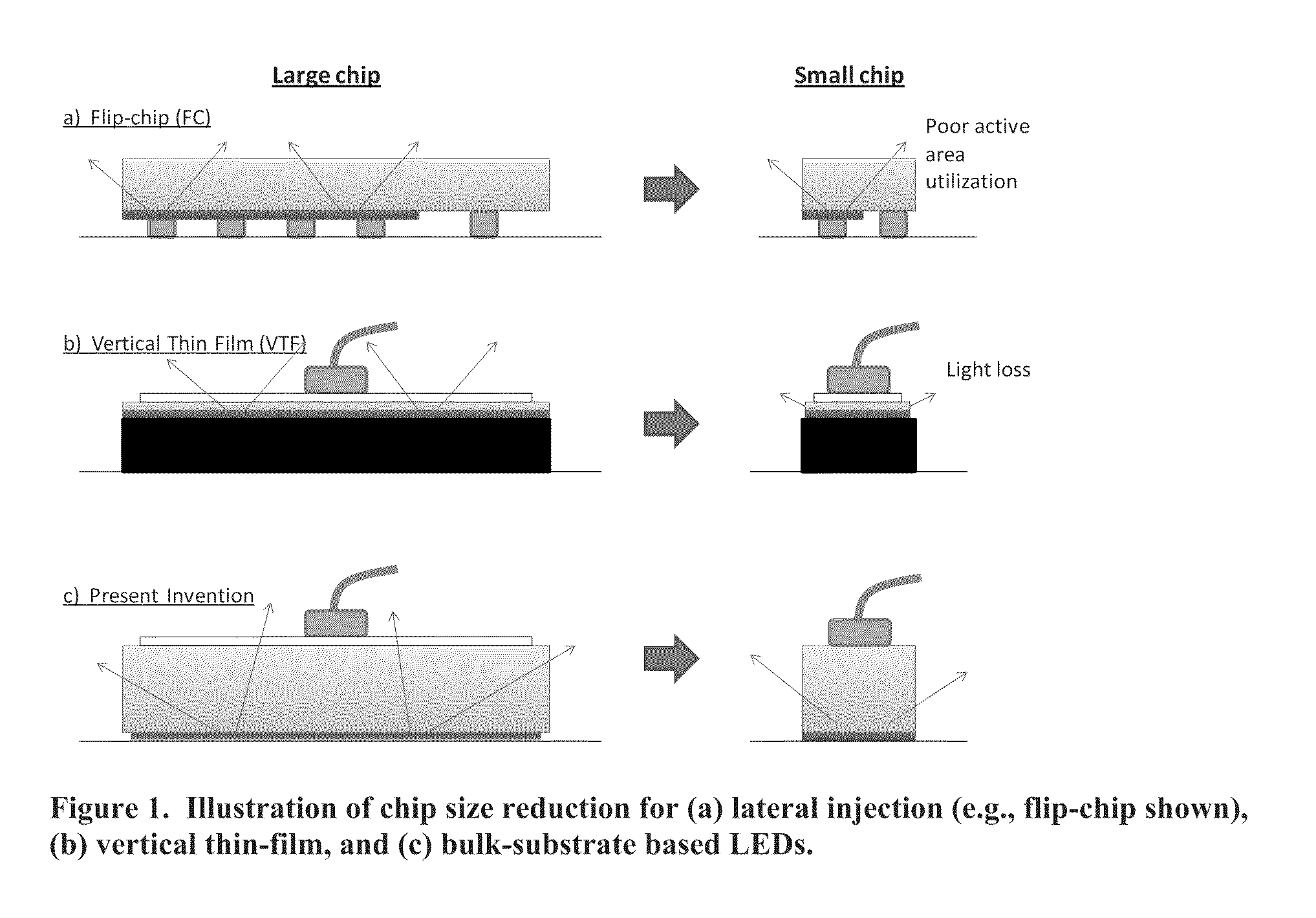

Nitride semiconductor light emitting device

ActiveUS20060017061A1Efficiently extract lightEfficient extractionSolid-state devicesSemiconductor/solid-state device manufacturingExternal circuitElectrode

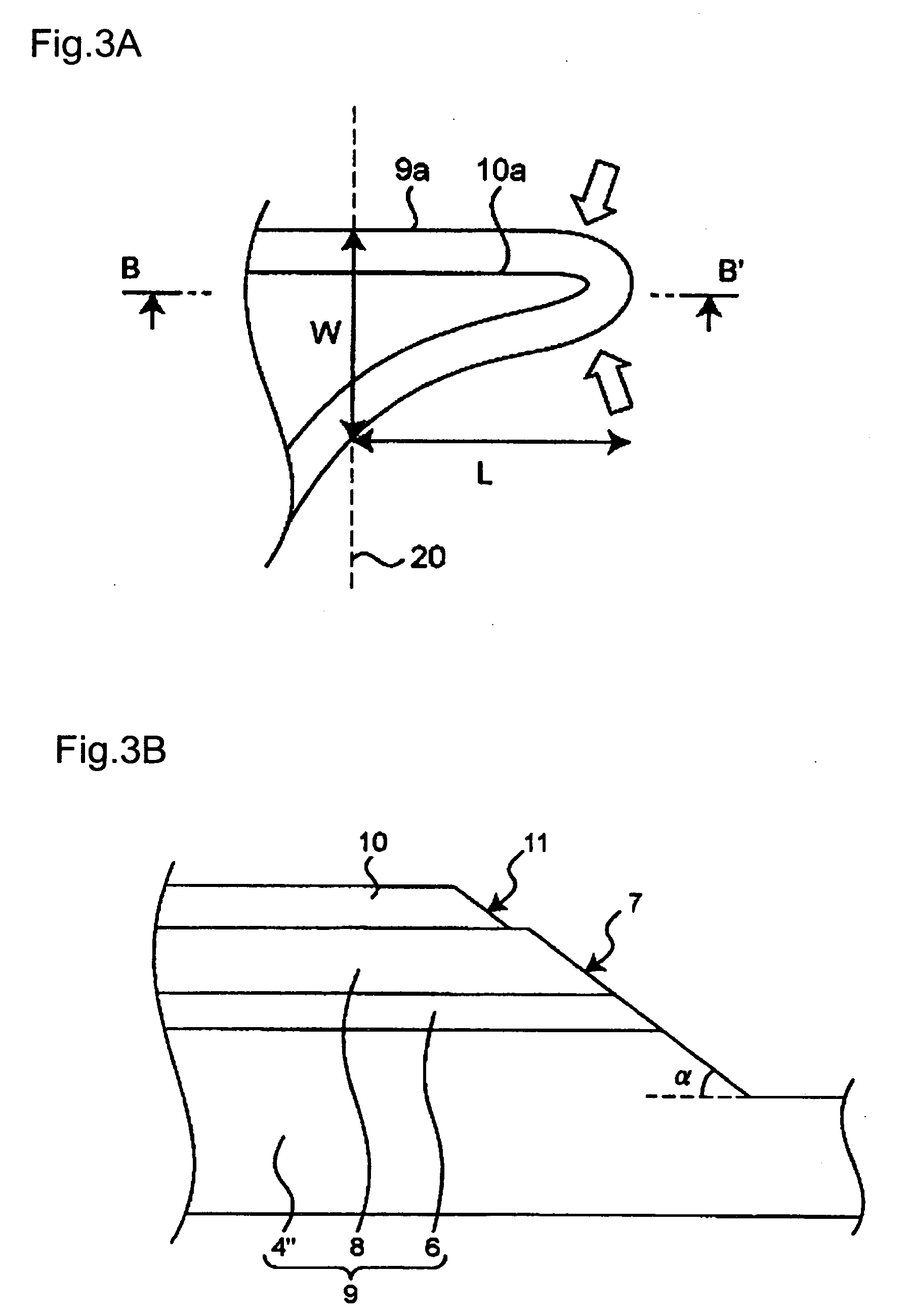

A nitride semiconductor light emitting device comprising an n-side nitride semiconductor layer and a p-side nitride semiconductor layer formed on a substrate, with a light transmitting electrode 10 formed on the p-side nitride semiconductor layer, and the p-side pad electrode 14 formed for the connection with an outside circuit, and the n-side pad electrode 12 formed on the n-side nitride semiconductor layer for the connection with the outside circuit, so as to extract light on the p-side nitride semiconductor layer side, wherein taper angles of end faces of the light transmitting electrode 10 and / or the p-side nitride semiconductor layer are made different depending on the position.

Owner:NICHIA CORP

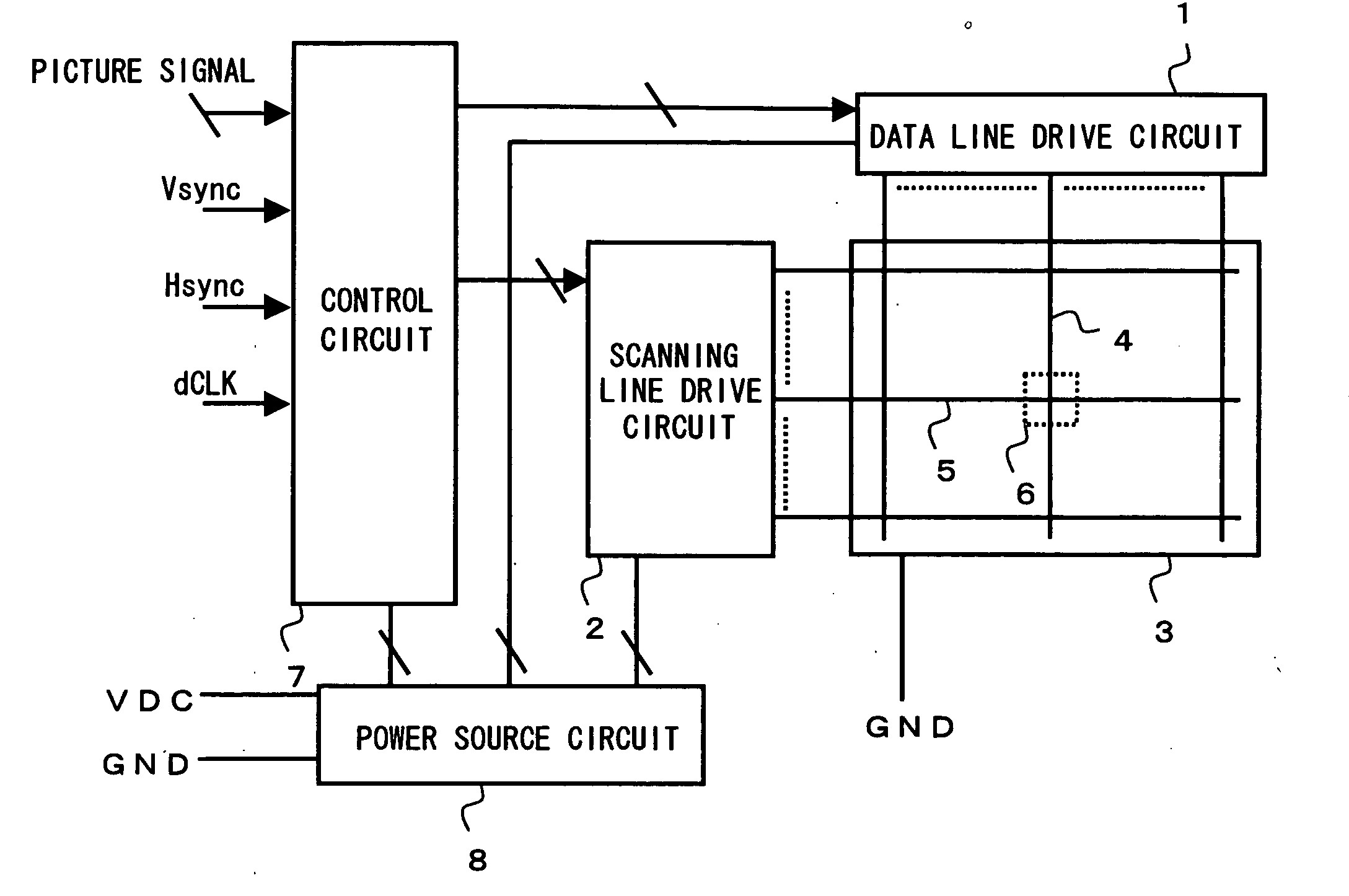

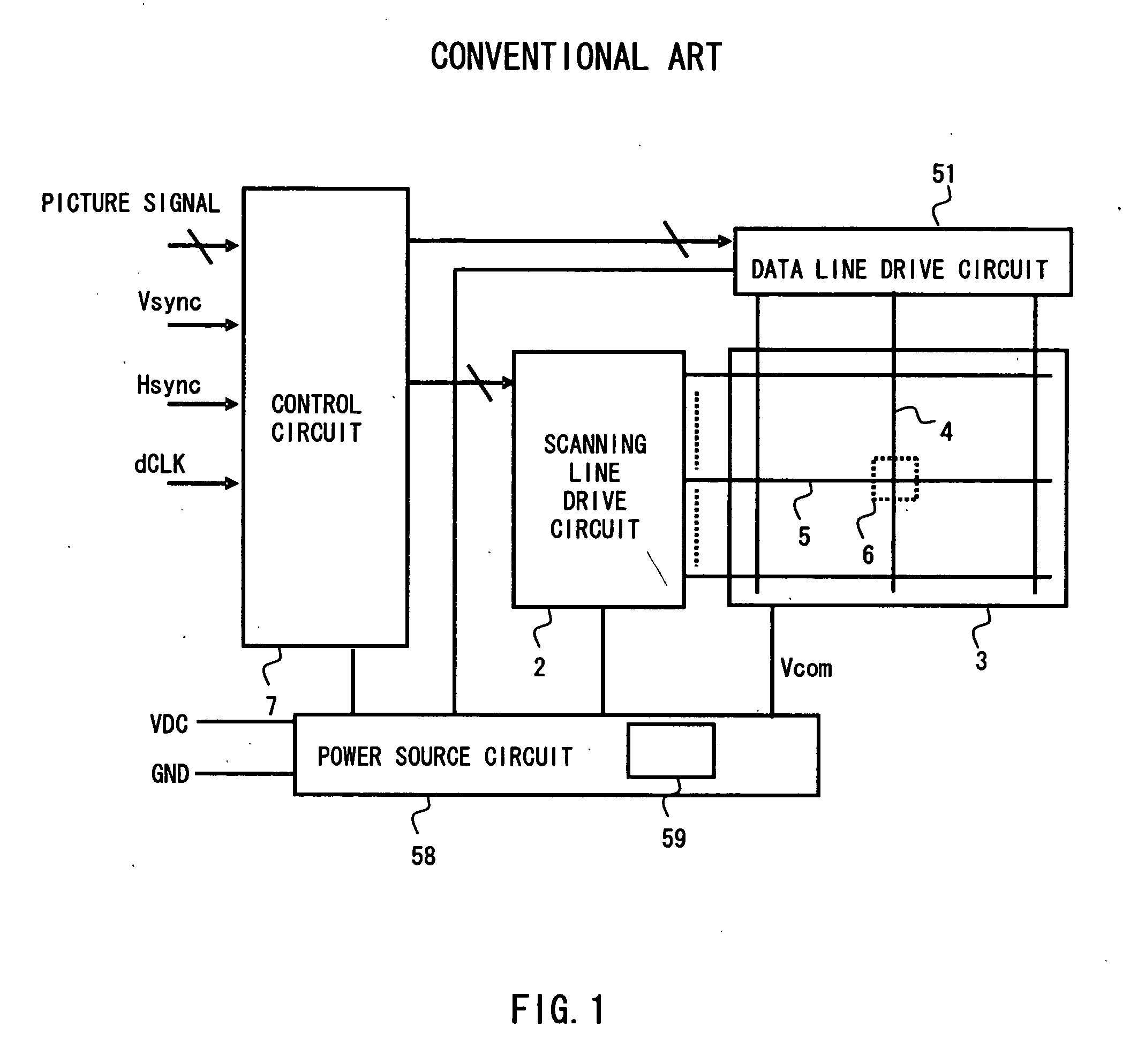

Liquid crystal display driver device and liquid crystal display system

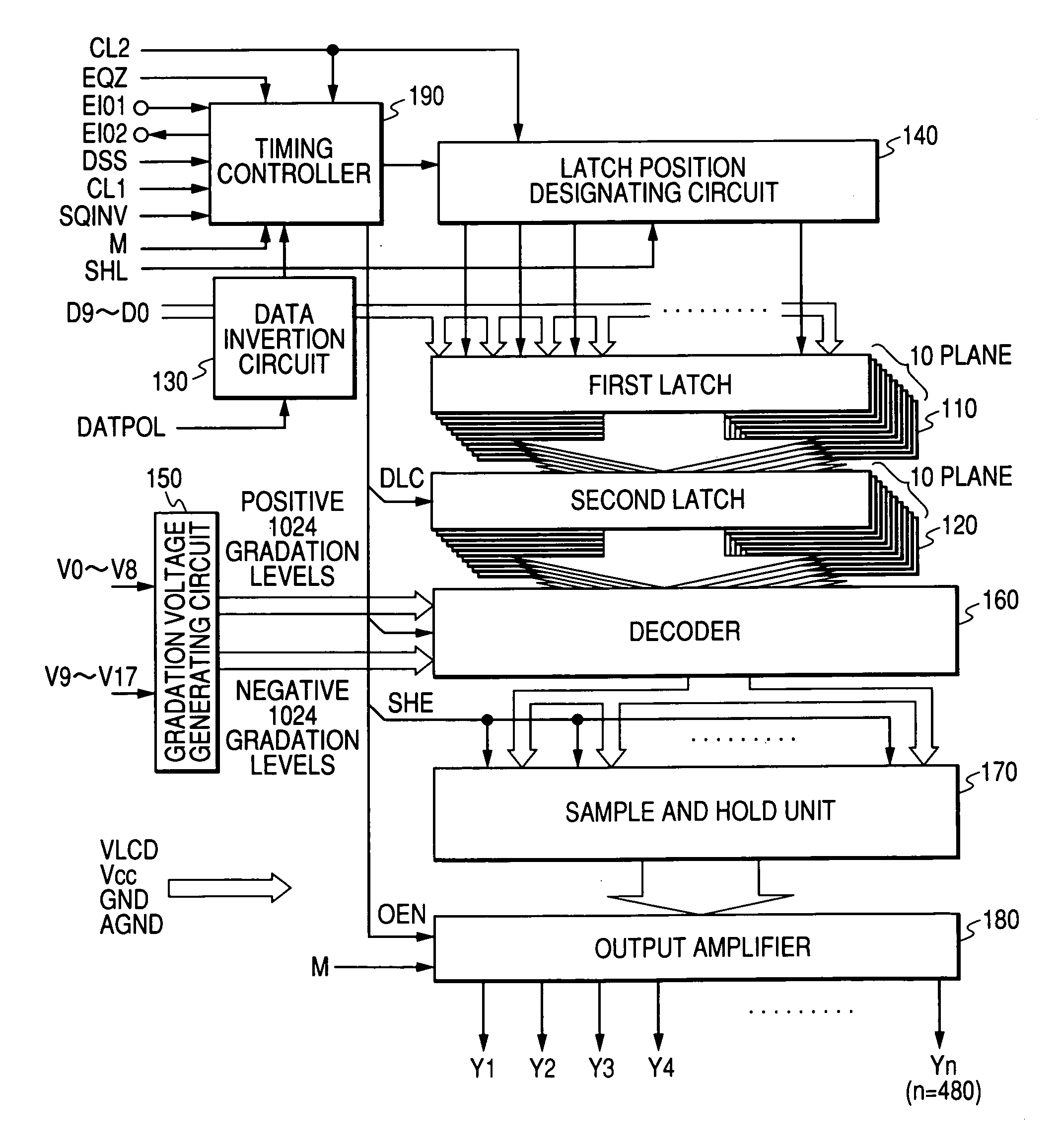

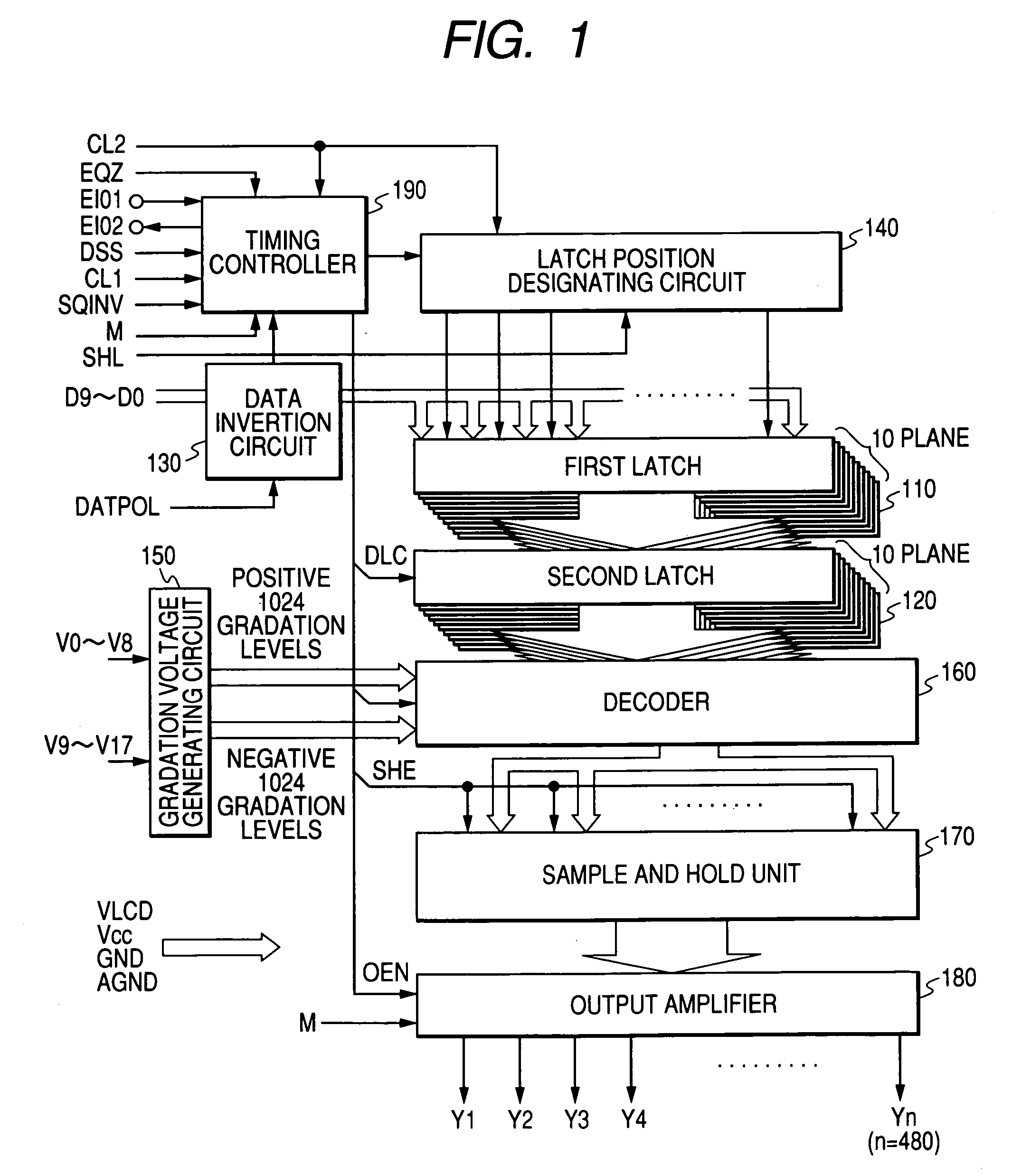

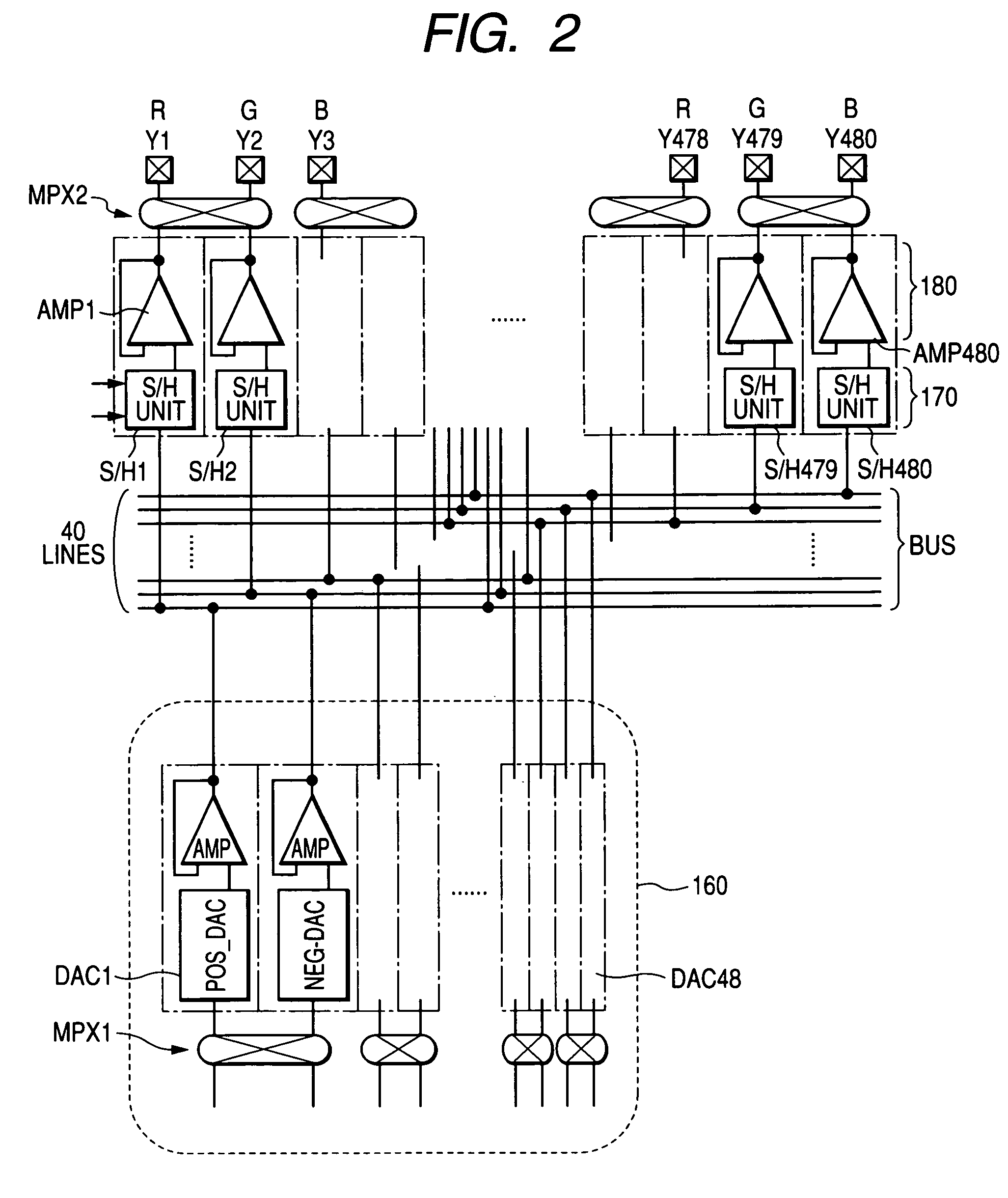

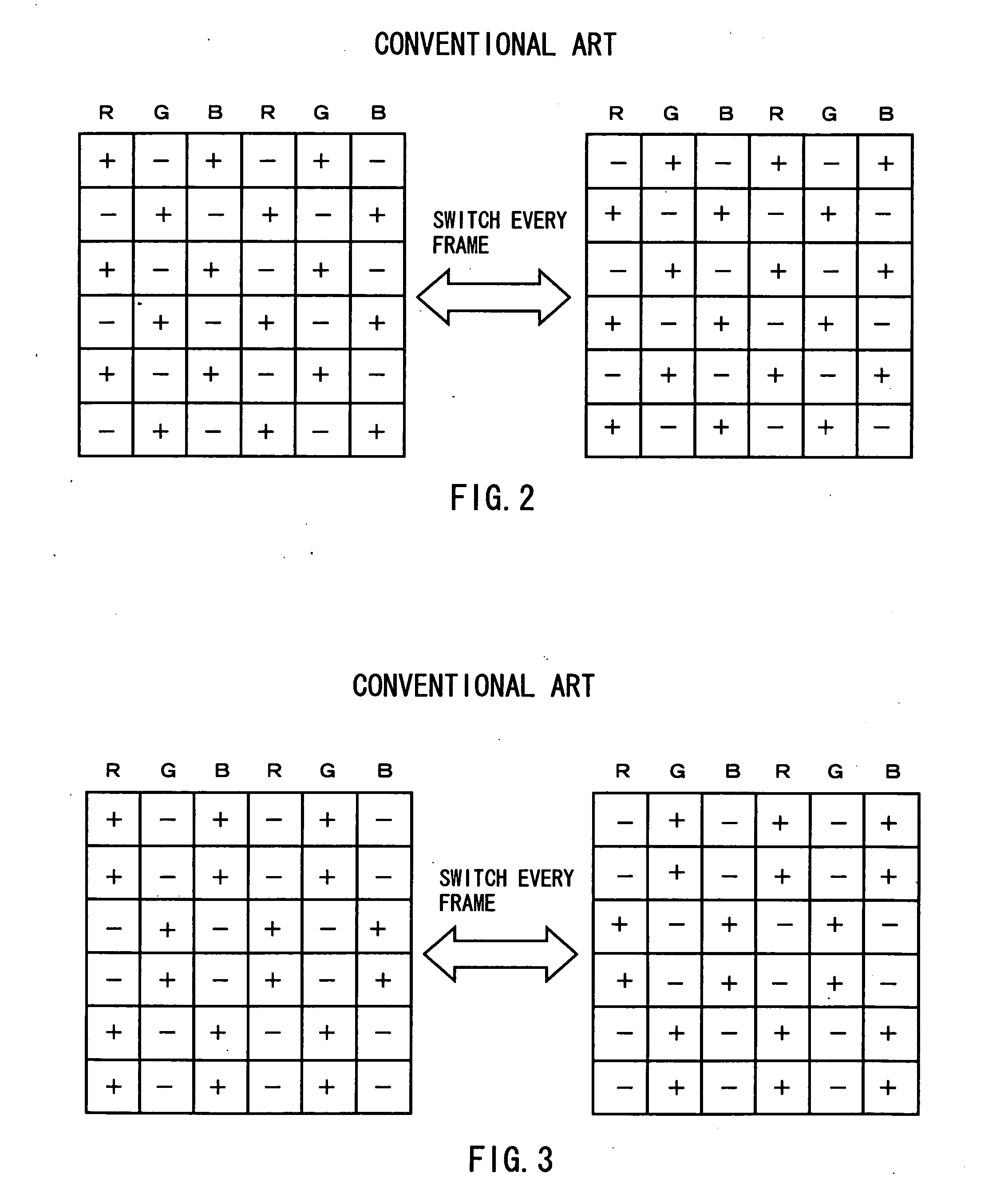

InactiveUS20050259058A1Reduce chip sizeExtended transfer timeStatic indicating devicesDisplay deviceEngineering

The present invention is directed to reduce the size of a liquid crystal driver (semiconductor integrated circuit for driving liquid crystal) having therein a D / A converting circuit, converting digital image data to analog gradation voltage, and outputting a voltage to be applied to a signal line (source line) of a color liquid crystal panel. Output amplifiers of the final stage for outputting an image signal converted to gradation voltage are divided into a plurality of groups. D / A converting circuits for converting image data to gradation voltage are provided as circuits common to the groups. While switching the group, the D / A converting circuit is operated in a time sharing manner. The output amplifiers in the final stage related to image signals of the same color are selected and grouped. A selector function is provided between the D / A converting circuit and the output amplifier, and an image signal converted to gradation voltage by the D / A converting circuit is supplied to a desired hold circuit.

Owner:RENESAS TECH CORP

Solid-state image sensing device, method for reading signal of solid-state image sensing device, and image pickup apparatus

ActiveUS20090190018A1Reduce circuit areaReduce chip sizeTelevision system detailsTelevision system scanning detailsCapacitanceAudio power amplifier

An image sensor includes a pixel array having vertical signal lines, each interconnected to one of columns of the pixel array, and a column processor including a unit readout circuit provided for each of sets of a predetermined number of columns. The unit readout circuit includes input switches, each connected to a corresponding one of the vertical signal lines and being sequentially turned on and off, an input capacitor having one end commonly connected to the input switches, a reference switch for selectively providing a reference voltage to the input capacitor, an operational amplifier connected to the other end of the input capacitor, a reset switch for selectively providing a short-circuit between input and output ends of the operational amplifier, and a feedback circuit provided for each of the columns and including a feedback switch and a feedback capacitor connected in series between the two ends of the operational amplifier.

Owner:SONY CORP

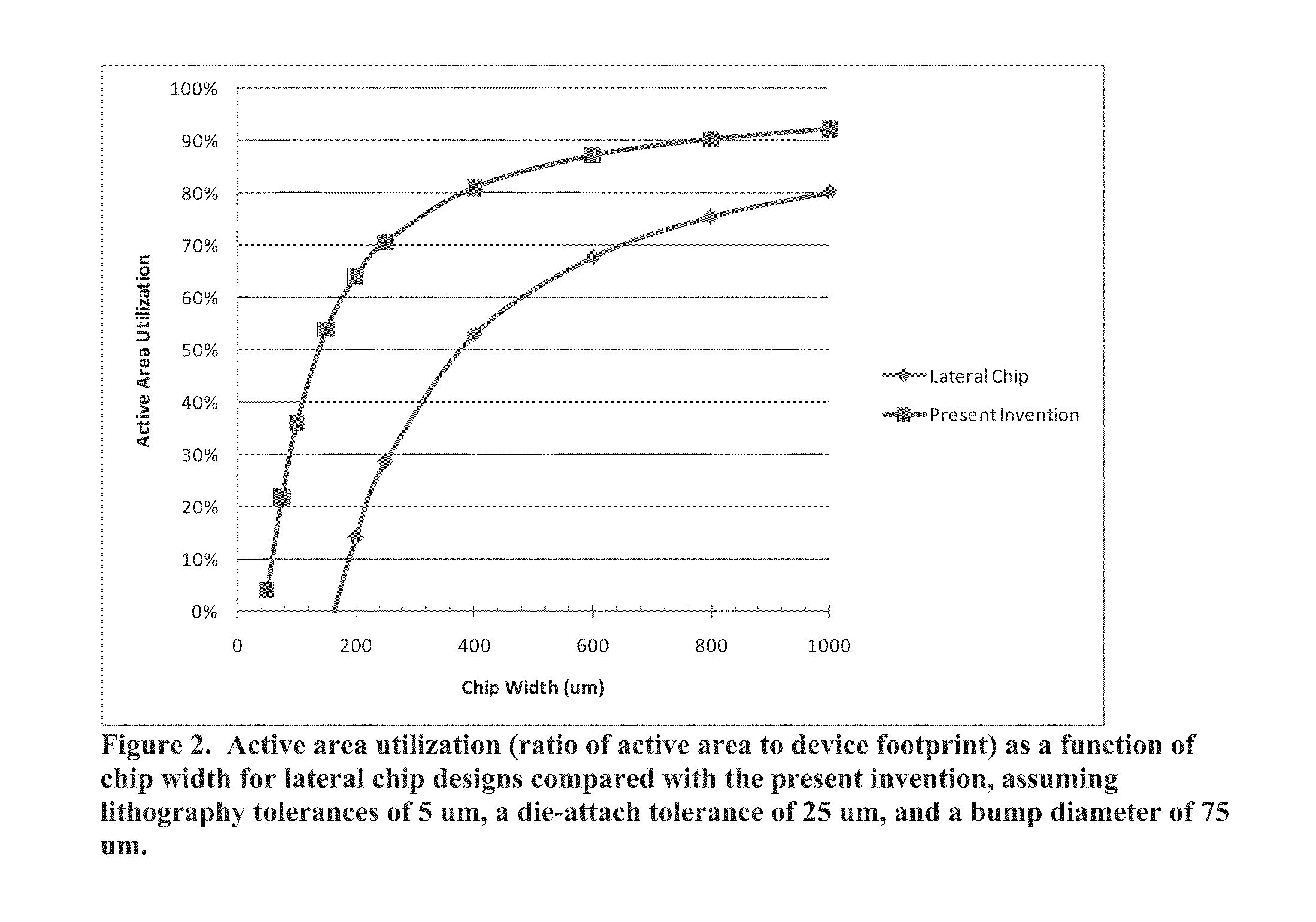

Power light emitting diode and method with current density operation

ActiveUS8502465B2Reduce chip areaLow costSolid-state devicesSemiconductor/solid-state device manufacturingQuantum efficiencyNitrogen

A light emitting diode device emitting at a wavelength of 390-415 nm has a bulk gallium and nitrogen containing substrate with an active region. The device has a current density of greater than about 175 Amps / cm2 and an external quantum efficiency with a roll off of less than about 5% absolute efficiency.

Owner:KORRUS INC

Drive circuit for display apparatus and display apparatus

InactiveUS20050206635A1Reduce circuit sizeReduce chip sizeVibration massageCathode-ray tube indicatorsDisplay deviceEngineering

A drive circuit that is an example of the present invention is a drive circuit of a display device for outputting in parallel the analog picture signals generated based on the digital picture signals inputted in serial. This circuit comprises a level shift circuit for converting the voltage level of the digital picture signals that were inputted in serial, a D / A conversion circuit for generating analog picture signals based on the digital picture signals that were subjected to level conversion with the level shift circuit, and an expansion circuit connected to the output side of the D / A conversion circuit or between the level shift circuit and the D / A conversion circuit and serving to expand and hold the inputted serial picture signals in parallel and output the picture signals in parallel. The level shift circuit is thus formed in the front stage of the picture signal register circuit.

Owner:RENESAS ELECTRONICS CORP

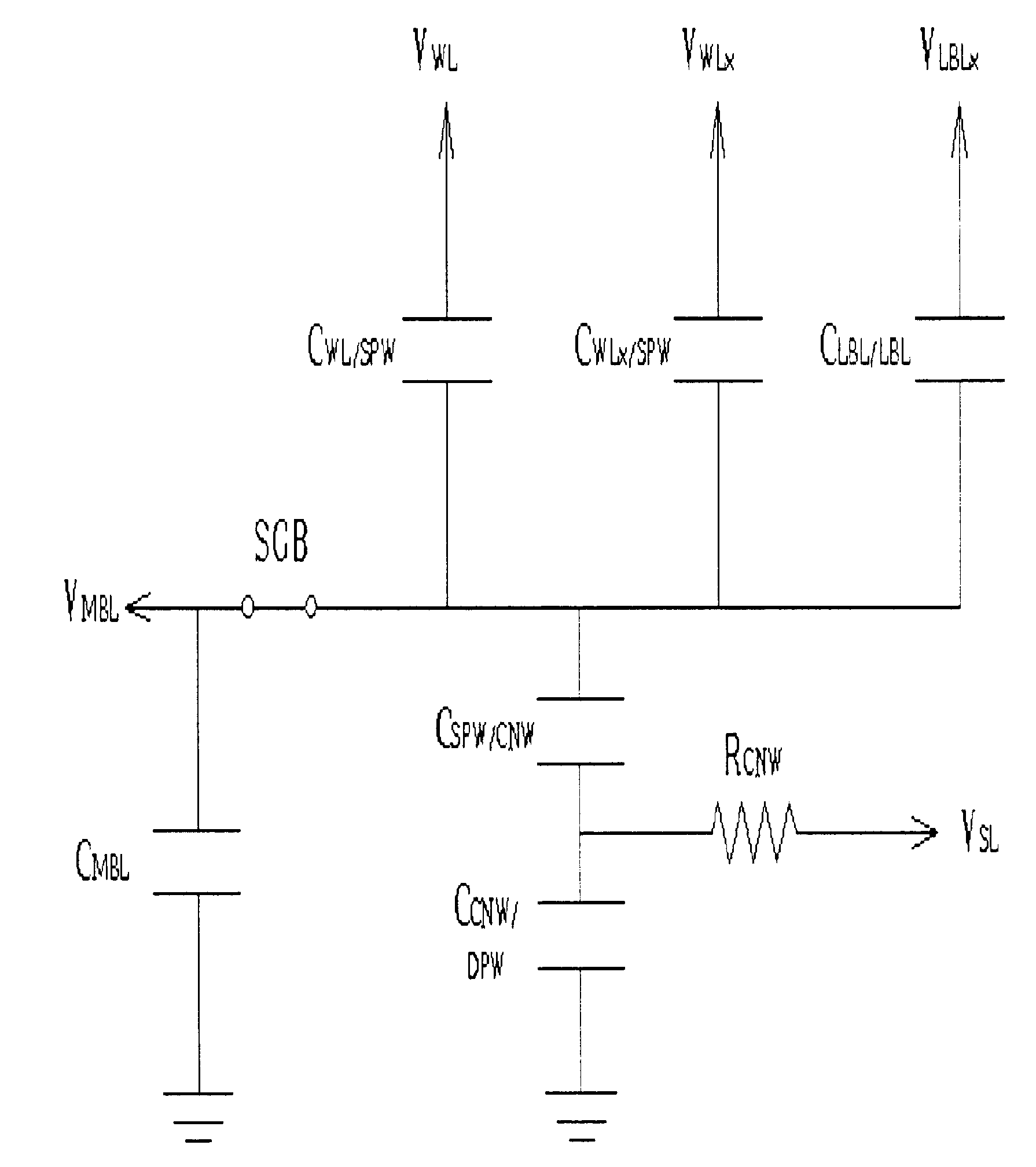

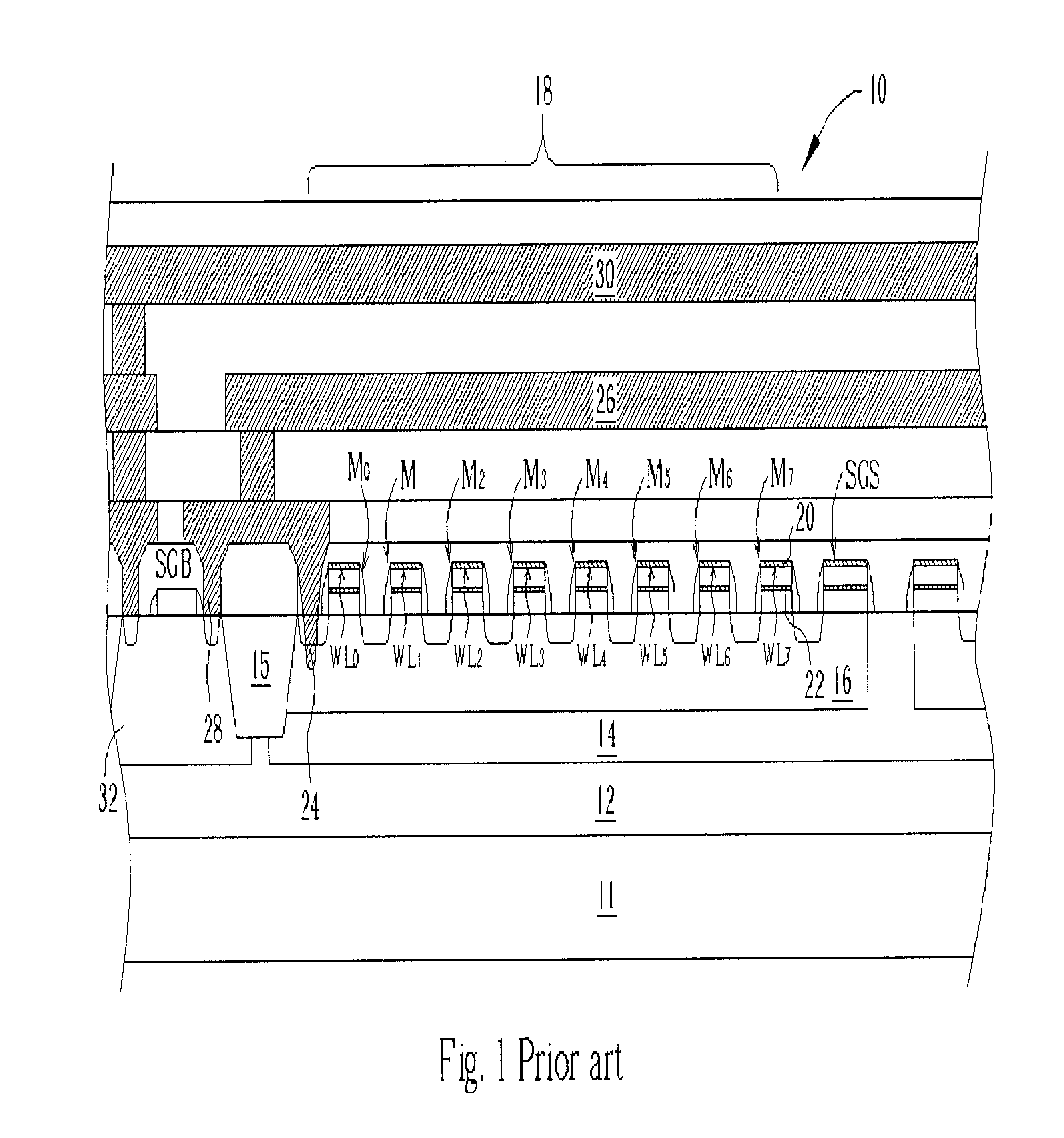

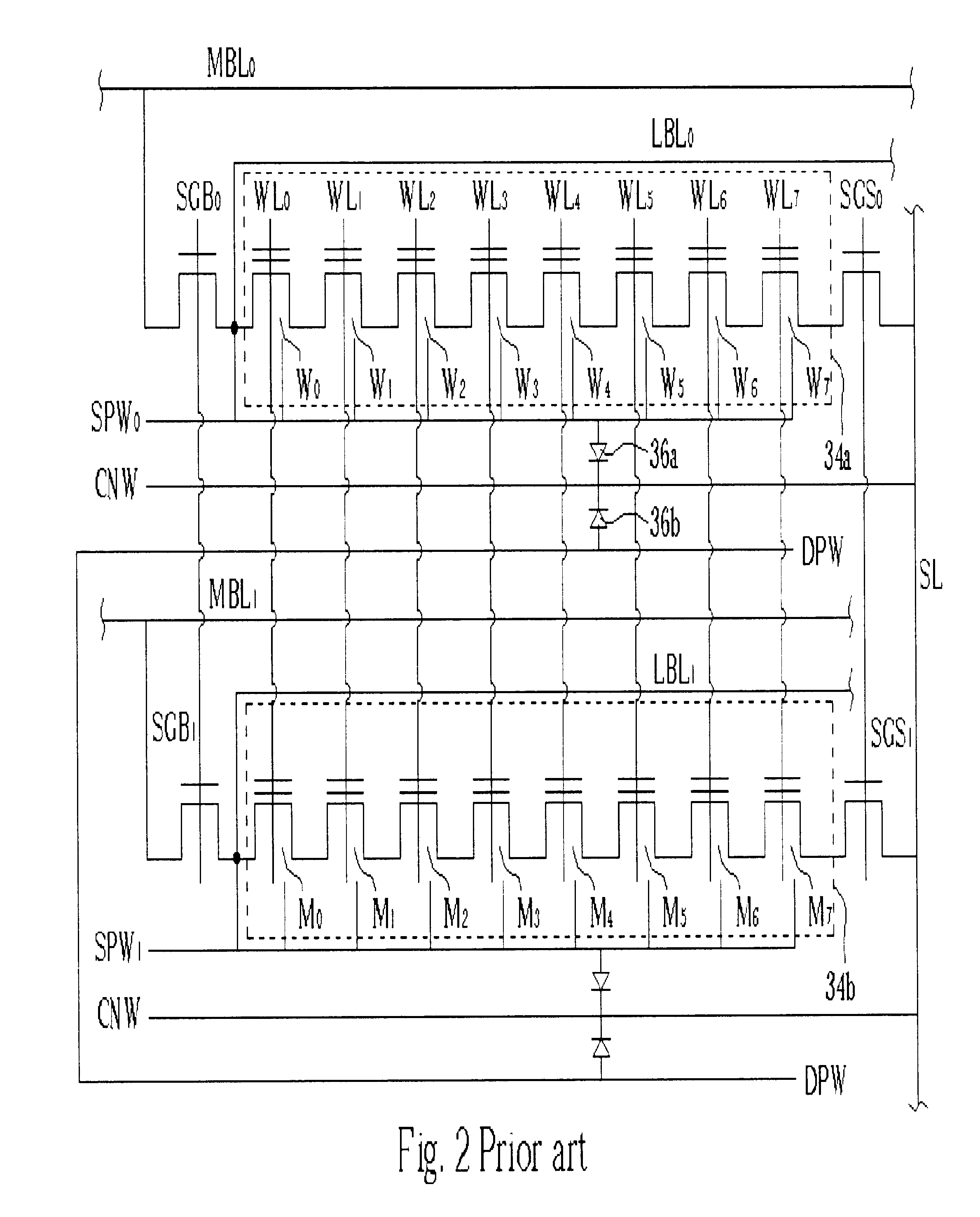

Method of programming a flash memory through boosting a voltage level of a source line

InactiveUS6898126B1Power requirement is easedLow costRead-only memoriesDigital storageBit lineCapacitance

A method of programming a flash memory through boosting a voltage level of a source line. The flash memory has n memory cell transistors cascaded in series, a local bit line positioned above the n memory cell transistors, a buried bit line positioned under the n memory cell transistors, and a source line positioned under the buried bit line. The method includes inputting a word line voltage to a control gate of a kth memory cell transistor, and after floating the local bit line, inputting a source line voltage to the source line for inducing an FN tunneling effect inside the kth memory cell transistor through capacitance coupling between the buried bit line and the source line.

Owner:POWERCHIP SEMICON CORP

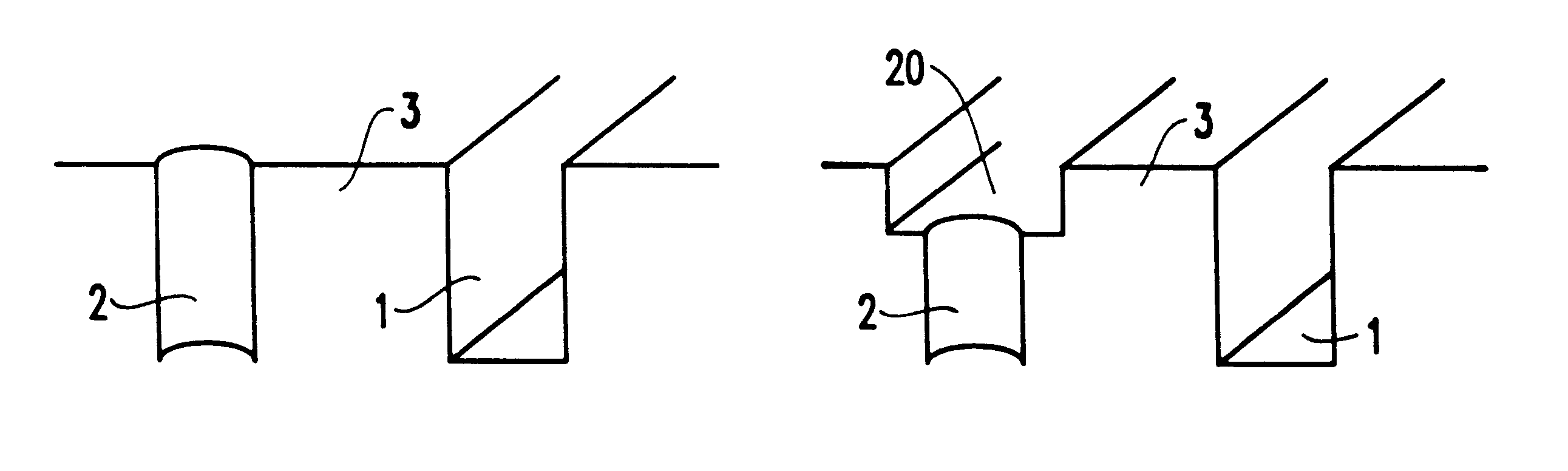

High power led lamp

InactiveUS20020063521A1Improve uniformityReduce chip sizeDischarge tube luminescnet screensLamp detailsEngineeringSingle chip

A high-power LED lamp uses an LED chip that can be larger than 1 mm square. The chip has trenches that can convert light trapped in the semiconductor into light that passes through a major surface of the chip. The trenches include light-reflecting tracks joined to a chip terminal and feeding a semiconductor layer. The chip can have triangular light emitting elements that improve light extraction from the semiconductor. The elements can be fused, resulting in improved manufacture yield of chips. A 25 watt single chip lamp with a heat sink very close to the active region is described.

Owner:EPISTAR CORP

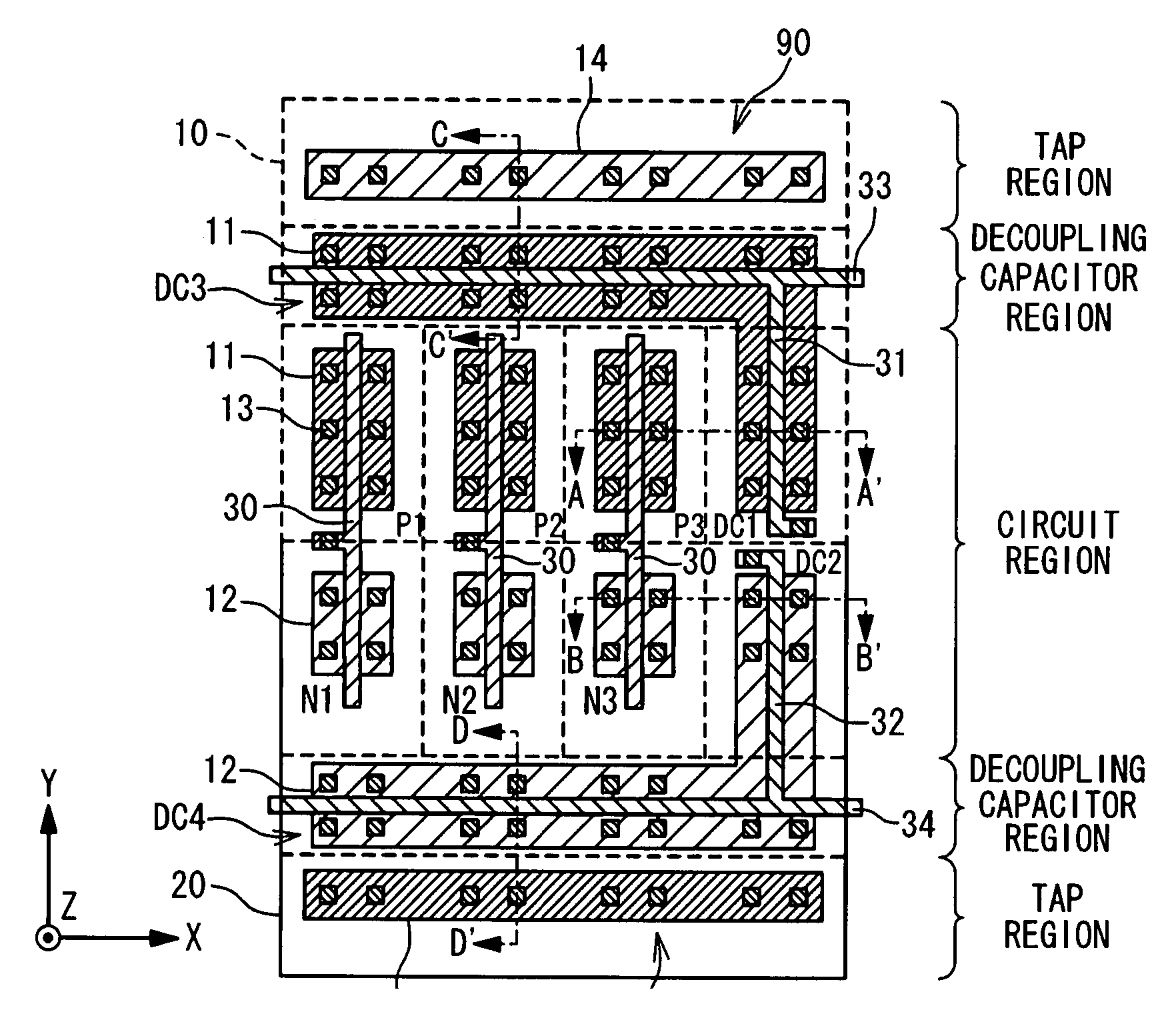

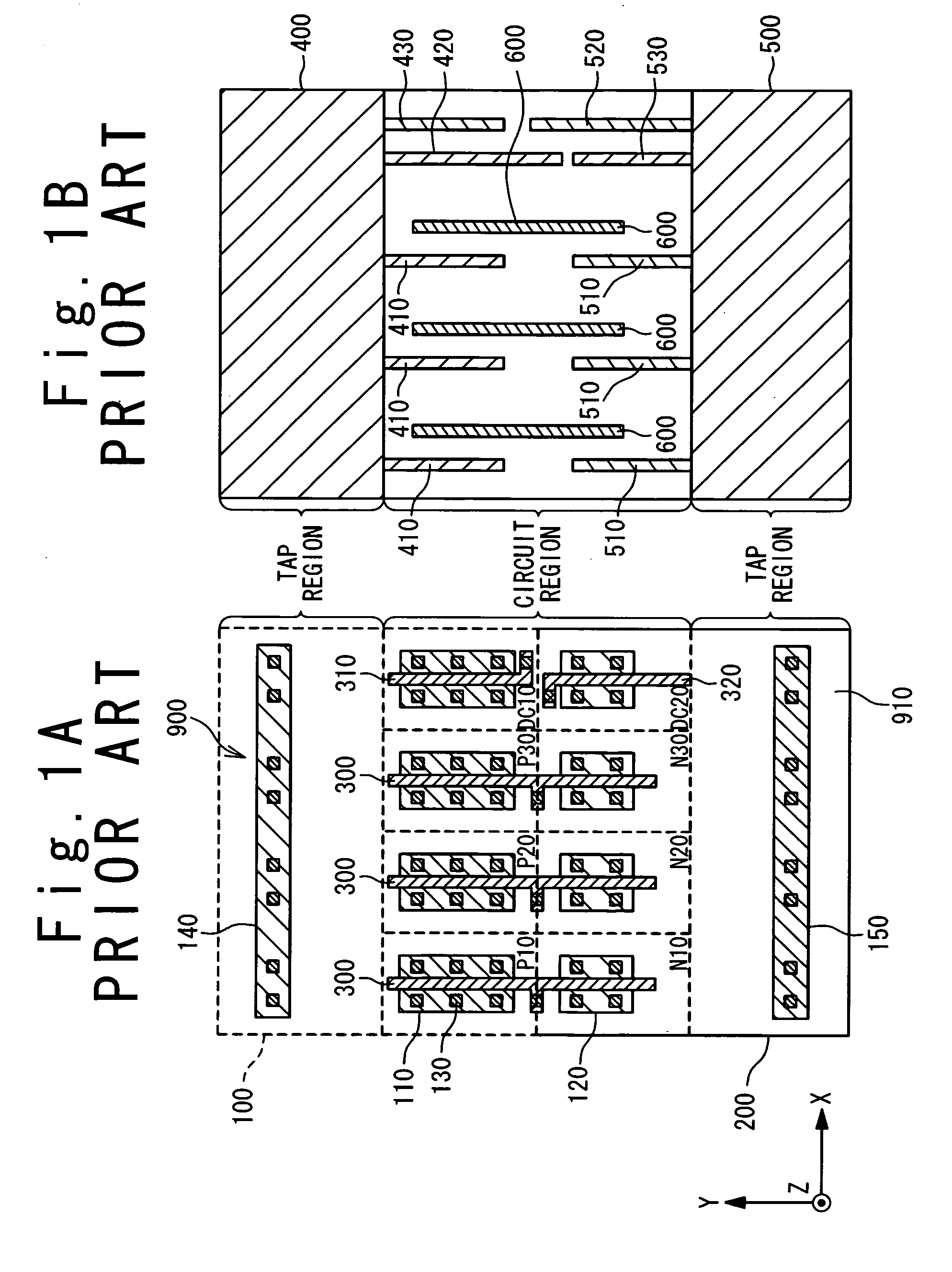

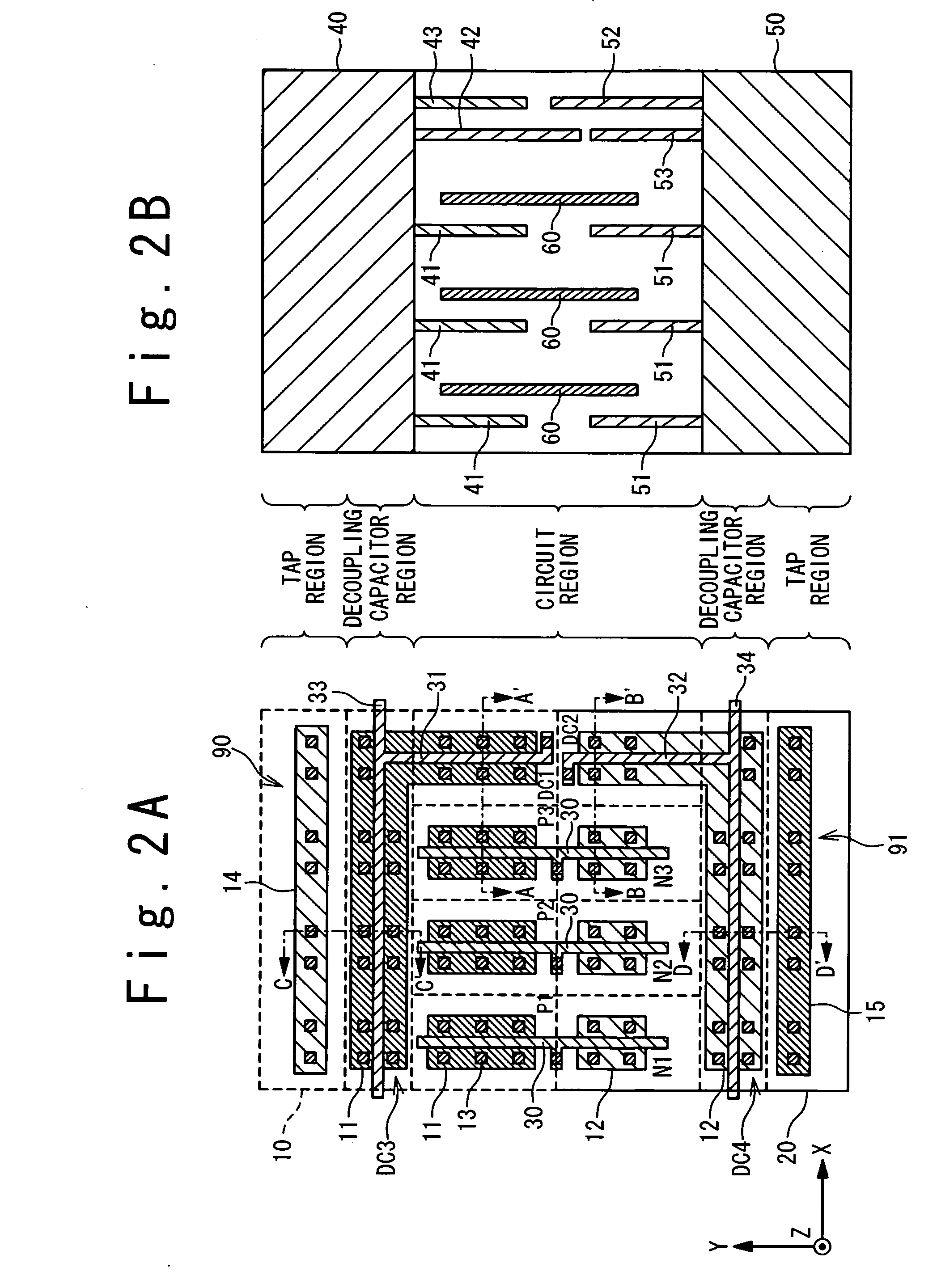

Integrated circuit incorporating decoupling capacitor under power and ground lines

A semiconductor device is composed of: an array of CMOS primitive cells provided in a circuit region; a power supply line extended along the array of the CMOS primitive cells and connected to the CMOS primitive cells; a ground line extended along the array of the CMOS primitive cells and connected to the CMOS primitive cells; a first decoupling capacitor provided under the power supply line; a second decoupling capacitor provided under the ground line. The first decoupling capacitor is formed of a PMOS transistor having a gate connected to the ground line. At least one of the source and drain of the PMOS transistor is connected to the power supply line. The second decoupling capacitor is formed of an NMOS transistor having a gate connected to the power supply line. At least one of the source and drain of the NMOS transistor is connected to the ground line.

Owner:RENESAS ELECTRONICS CORP

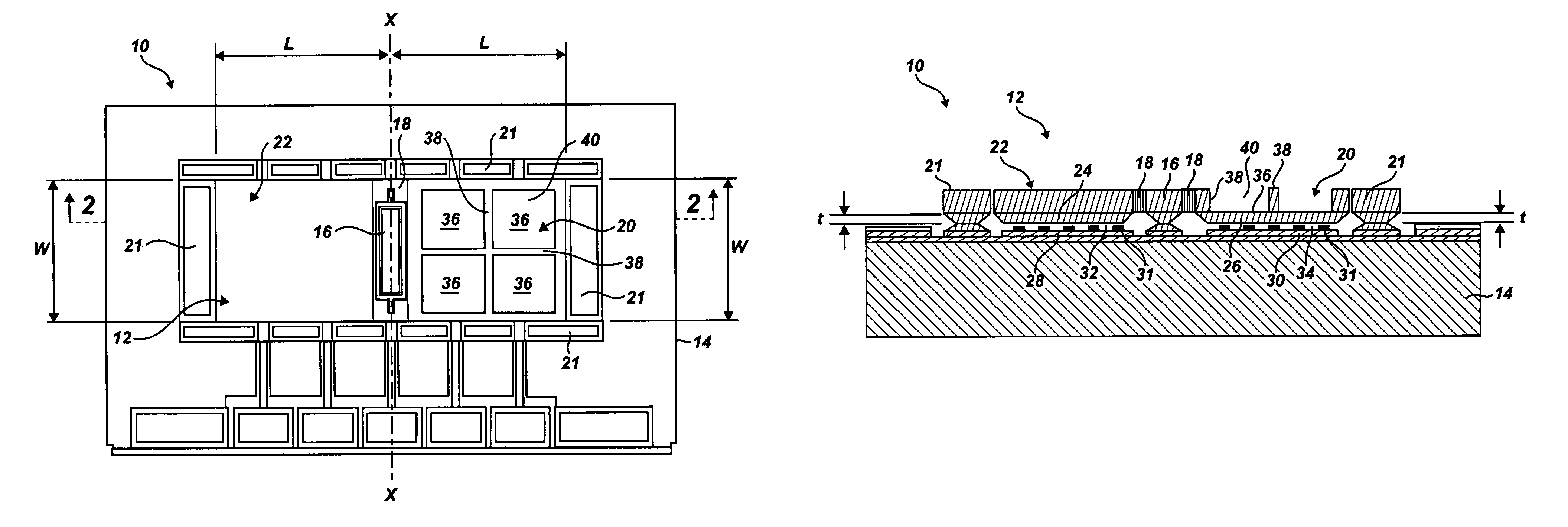

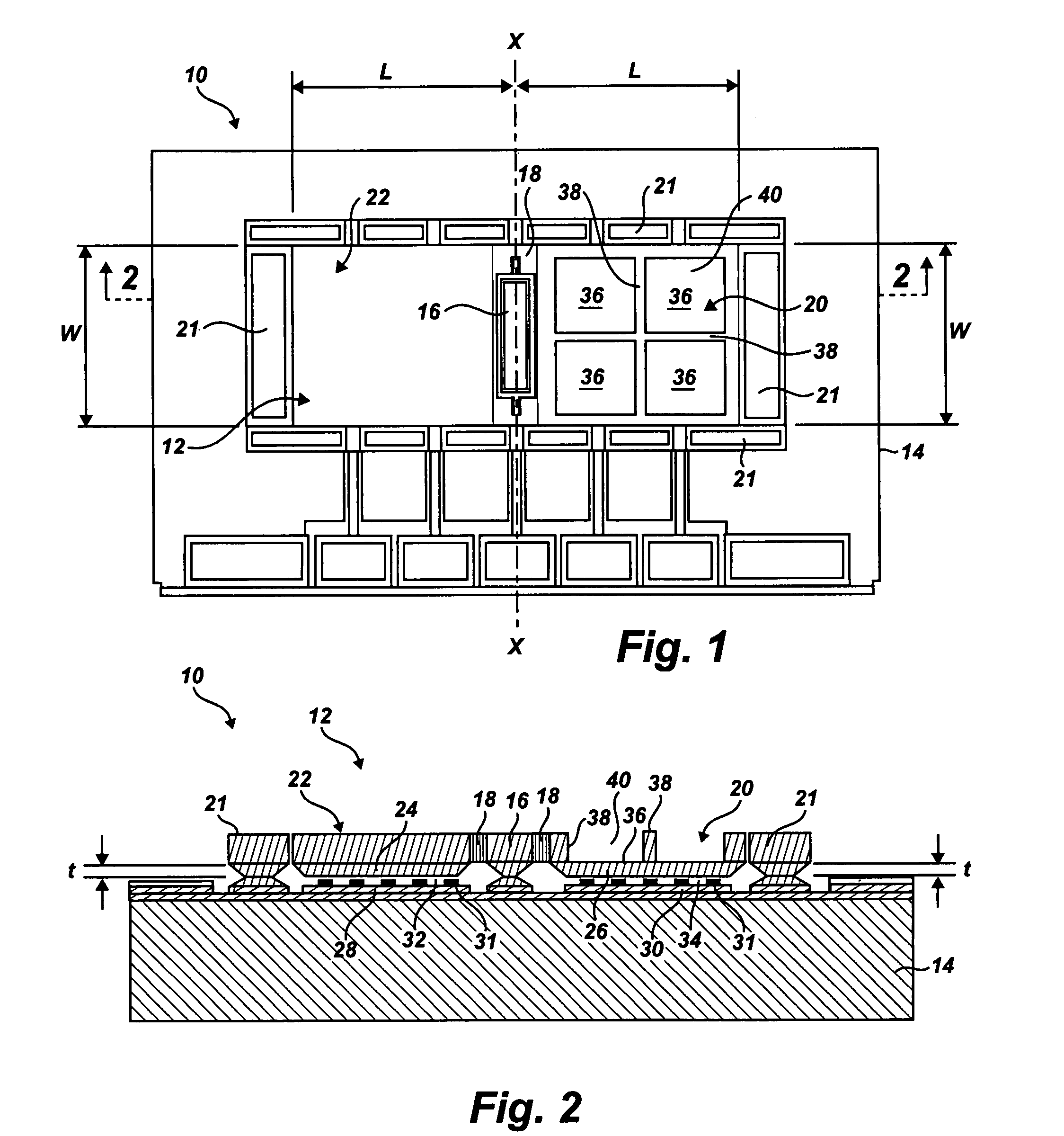

Pendulous accelerometer with balanced gas damping

A pendulous capacitive accelerometer including a substrate having a substantially planar upper surface with an electrode section, and a sensing plate having a central anchor portion supported on the upper surface of the substrate to define a hinge axis. The sensing plate includes a solid proof mass on a first side of the central anchor portion and a substantially hollow proof mass on a second side of the central anchor portion, providing for reduced overall chip size and balanced gas damping. The solid proof mass has a first lower surface with a first electrode element thereon, and the substantially hollow proof mass has a second lower surface with a second electrode element thereon. Both the solid proof mass and the hollow proof mass have the same capacitive sensing area. The sensing plate rotates about the hinge axis relative to the upper surface of the substrate in response to an acceleration.

Owner:ROSEMOUNT AEROSPACE

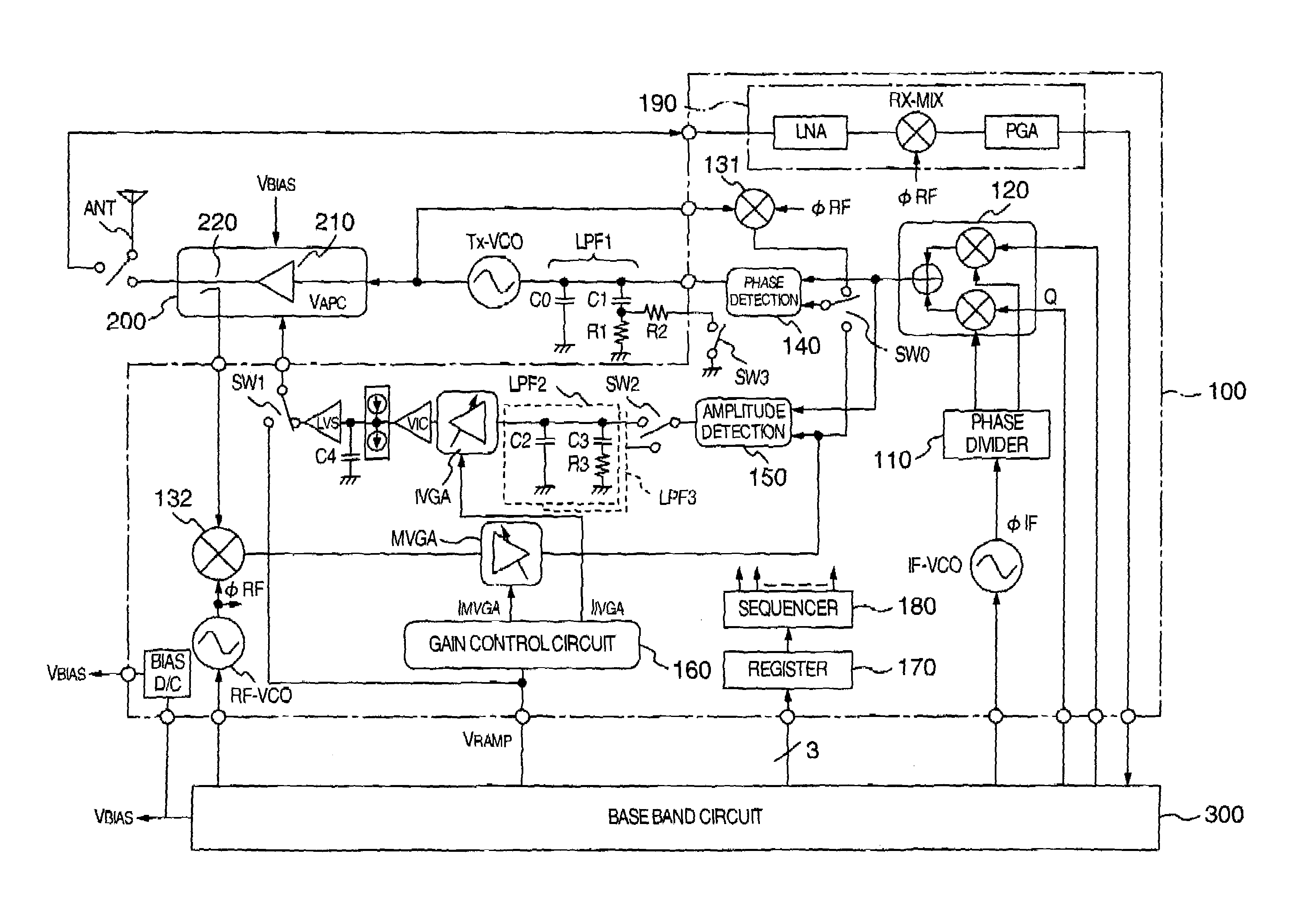

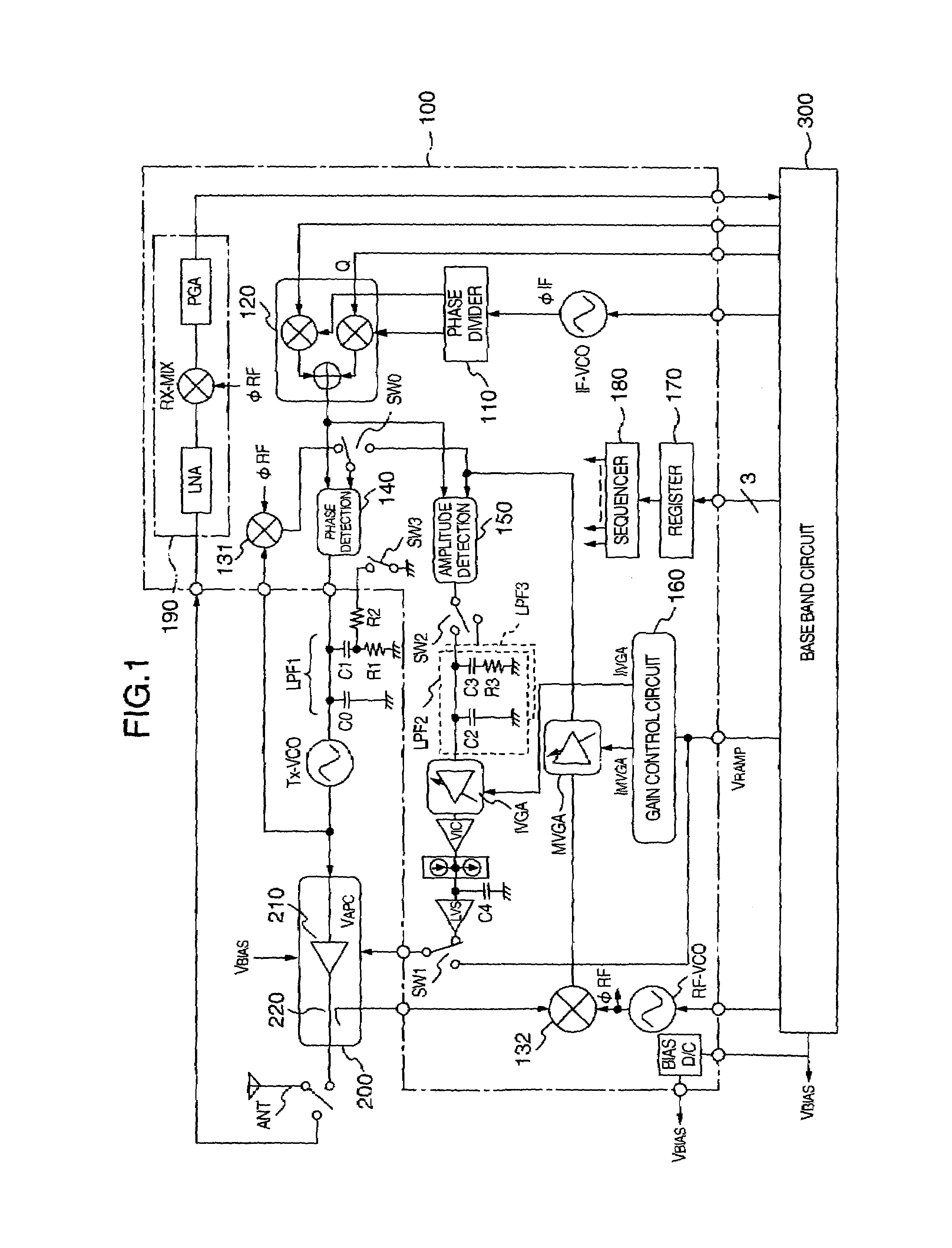

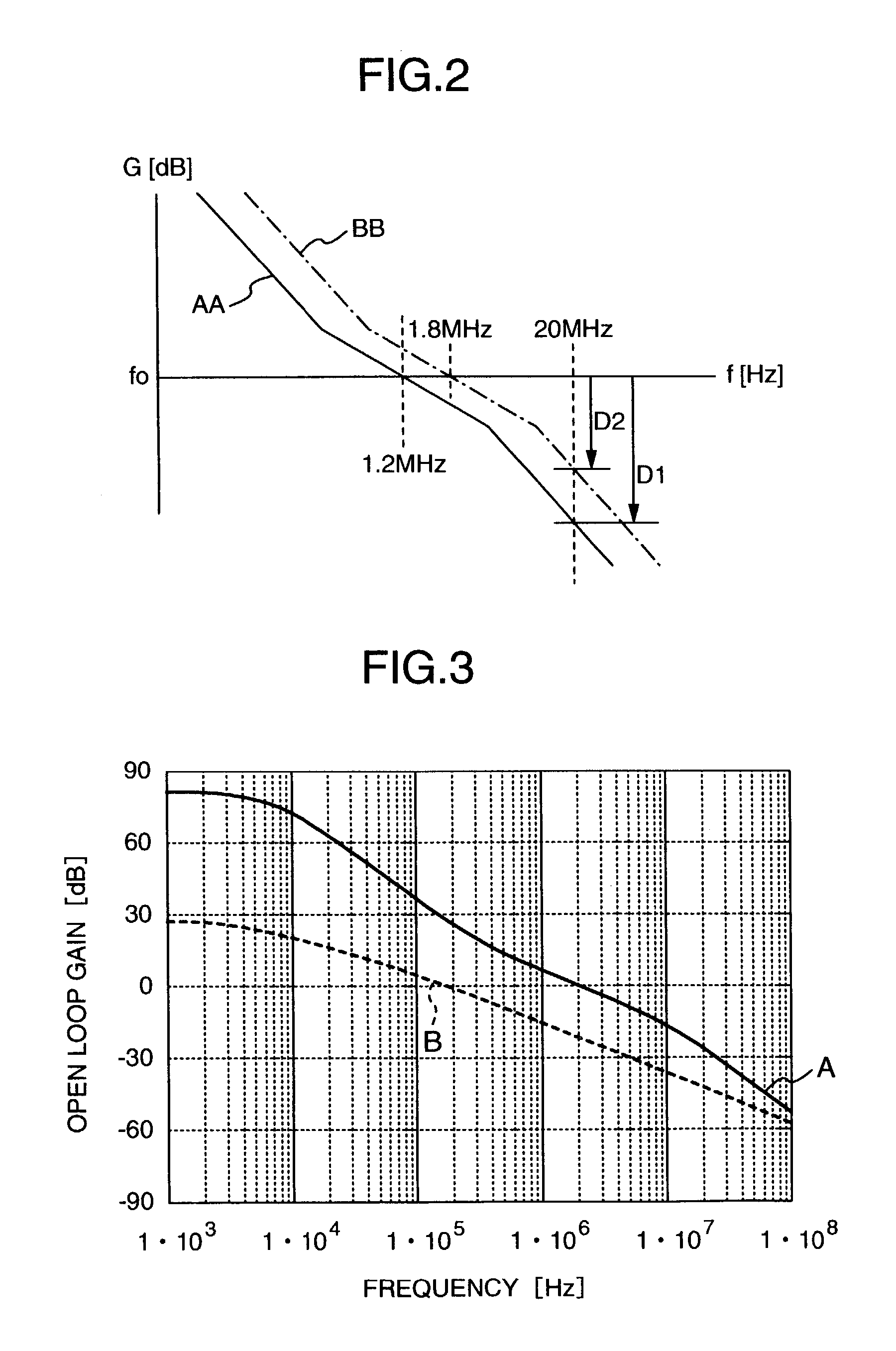

Transmitter having a phase control loop whose frequency bandwidth is varied in accordance with modulation modes

InactiveUS7085544B2Increase in error vector magnitudeSufficiently suppressPower amplifiersModulation with suppressed carrierLoop filterCarrier signal

A transmitter adopting a polar loop system including a phase control loop for controlling the phase of a carrier signal outputted from a transmitting oscillator and an amplitude control loop for controlling the amplitude of a transmitting output signal outputted from a power amplification circuit, and designed to be capable of performing transmission using a GMSK modulation mode and transmission using an 8-PSK modulation mode. In the transmitter, the phase control loop is shared as a phase control loop for use in the GMSK modulation mode and a phase control loop for use in the 8-PSK modulation mode. A component similar to any one of components constituting a loop filter is provided in parallel therewith so that the component can be connected or disconnected in accordance with the modulation mode, for example, by use of a switching element.

Owner:RENESAS ELECTRONICS CORP +2

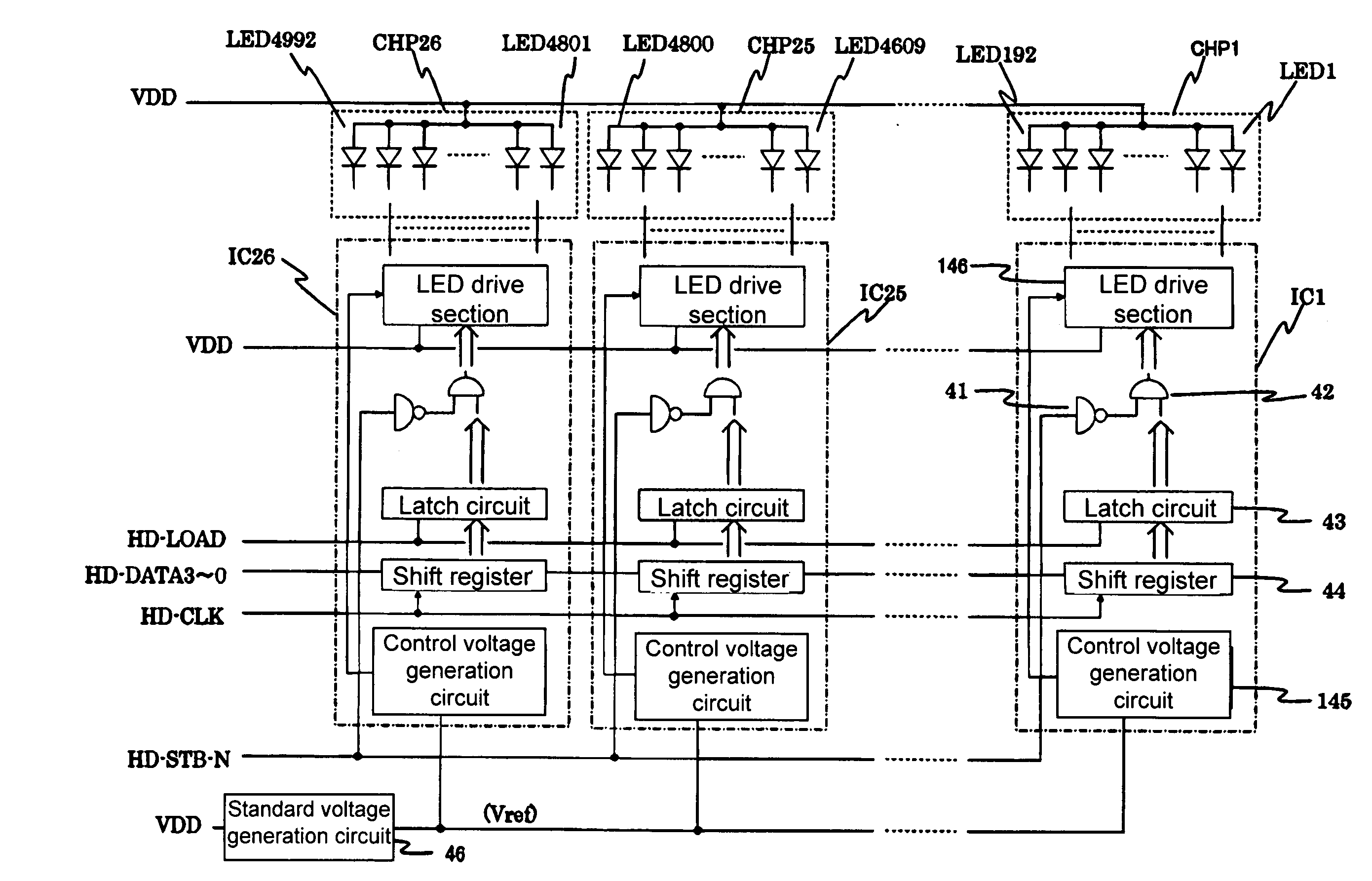

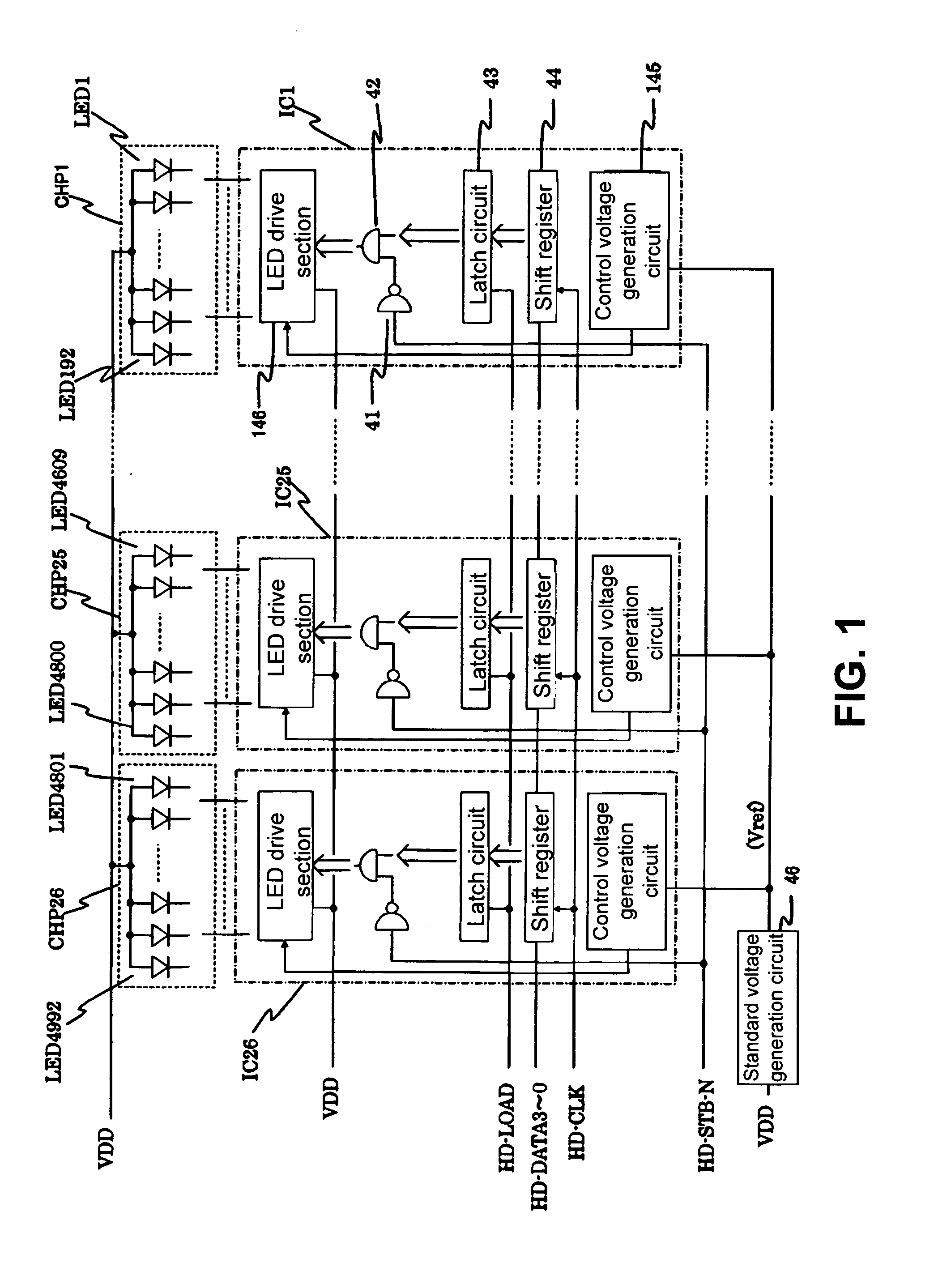

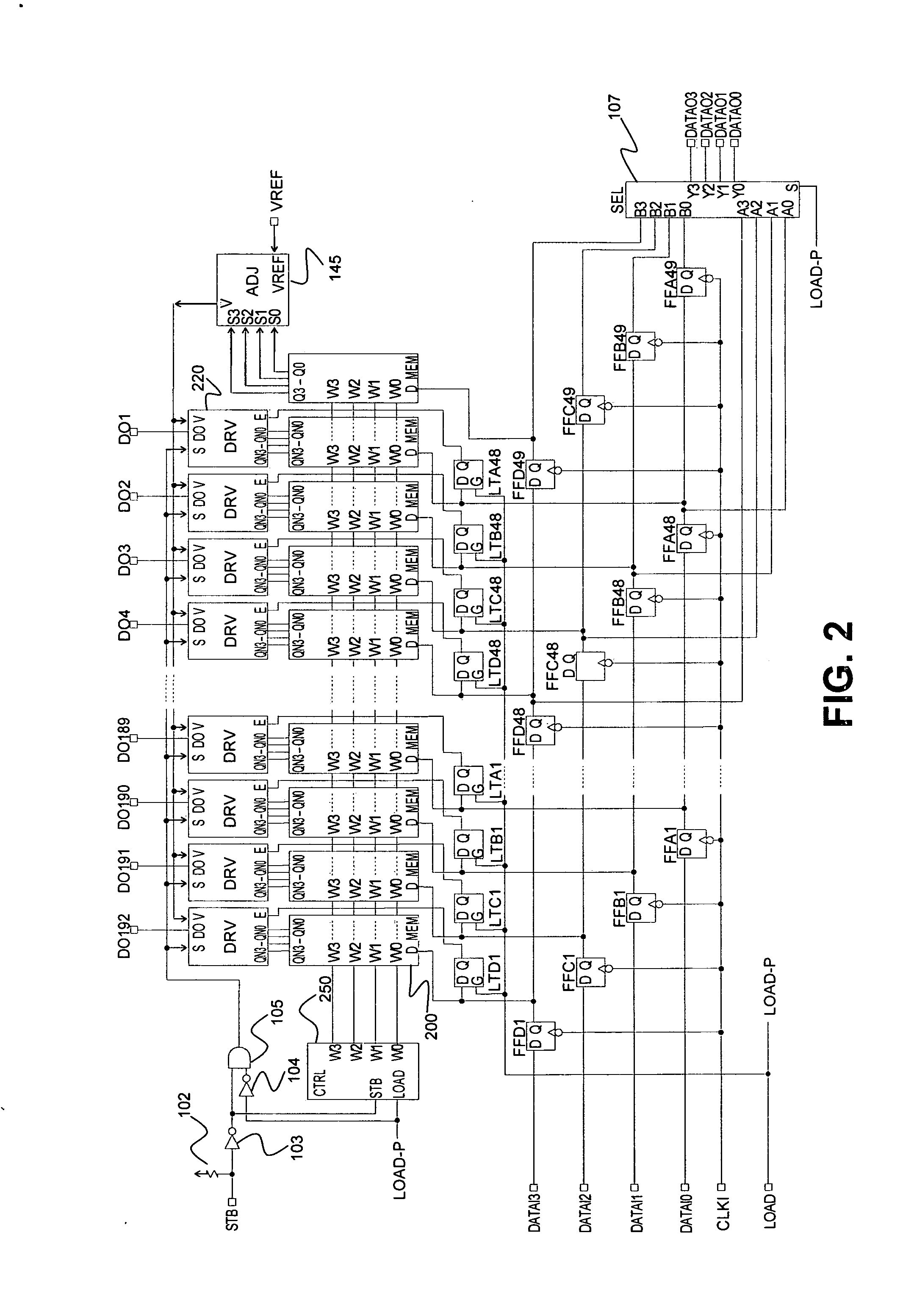

Drive circuit, light emitting diode head, and image forming apparatus

InactiveUS20080292344A1Transistor area can be reducedReduce power supply voltageStatic indicating devicesElectroluminescent light sourcesDriving currentAudio power amplifier

A drive circuit includes a drive element for driving a driven element; a correction data input section for adjusting a drive current of the driven element; a resistor having an end portion connected to ground; and a control voltage generation section for generating a direction value of the drive current. The control voltage generation section includes a calculation amplifier having a first input terminal for receiving a standard voltage, a second input terminal, and an output terminal; a first conductive type transistor having a first terminal, a second terminal connected to the ground, and a control terminal connected to the output terminal; and a current-mirror circuit including a control side transistor and a follower side transistor. The control side transistor has a current output terminal connected to the first terminal. The follower side transistor has a current output terminal connected to another end portion of the resistor and the second input terminal.

Owner:OKI DATA CORP

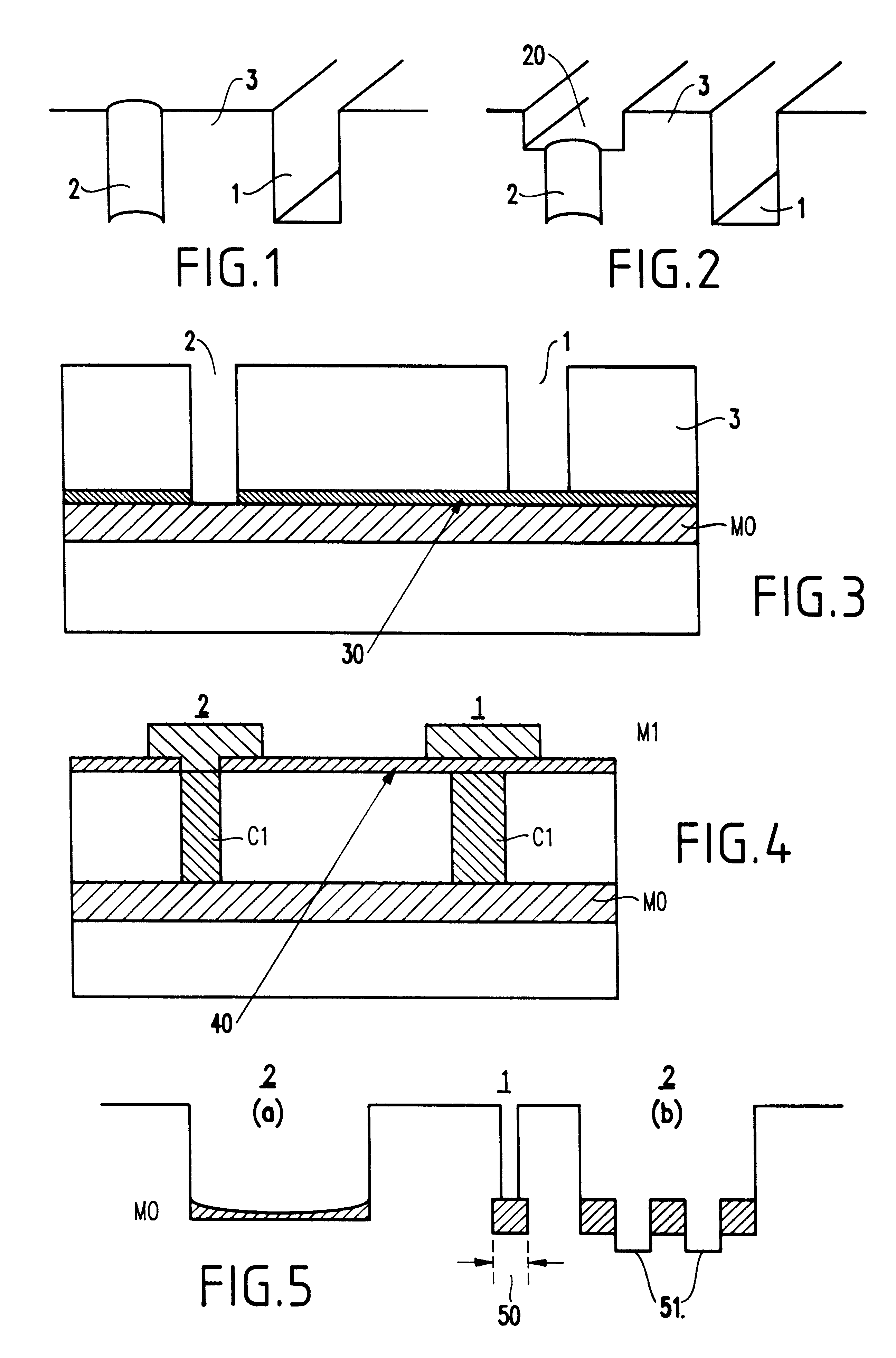

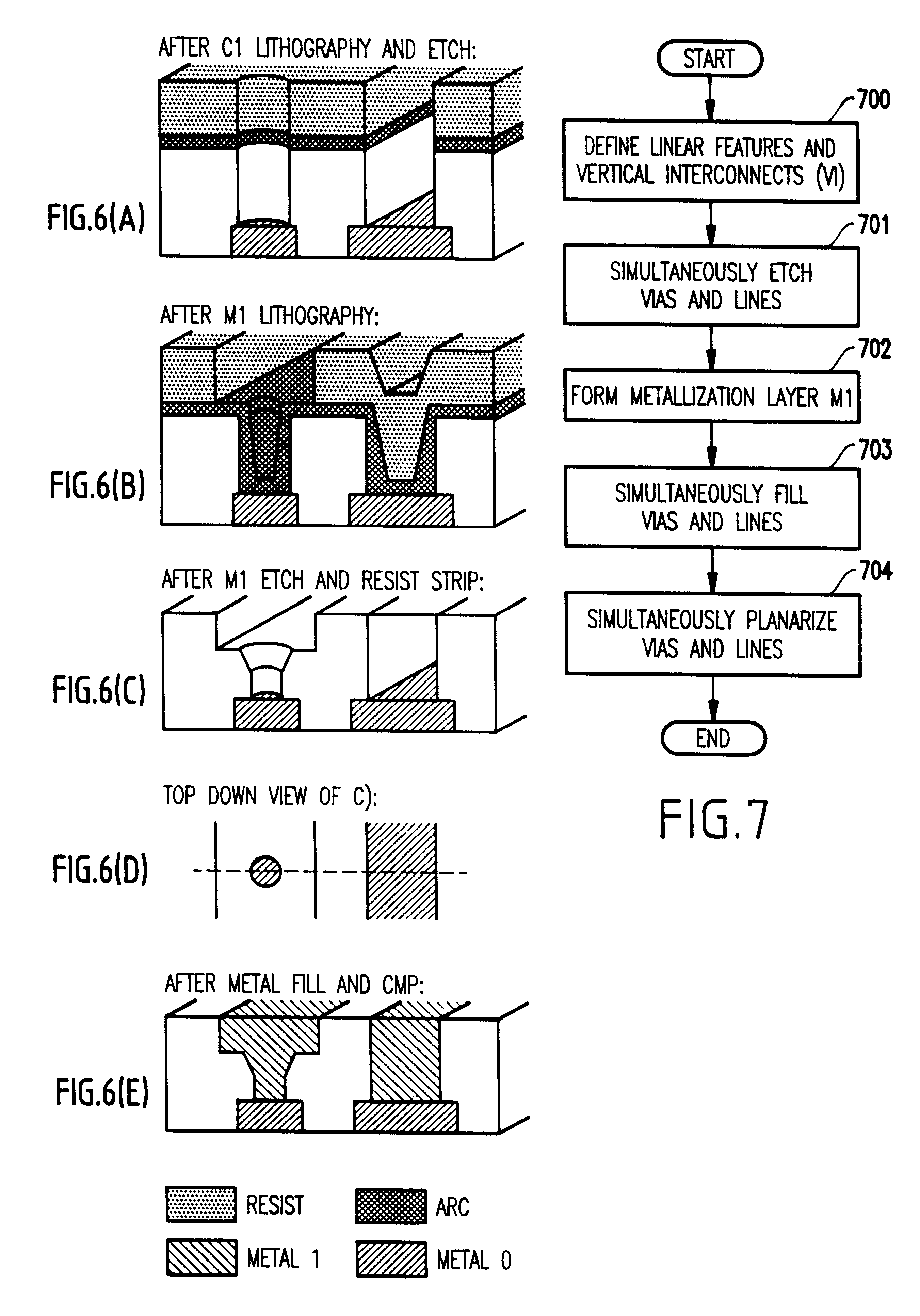

Slotted damascene lines for low resistive wiring lines for integrated circuit

InactiveUS6265308B1Reduce processing costsLow gradientSemiconductor/solid-state device detailsSolid-state devicesDielectricPhotonic integrated circuit

A process of forming a wiring in a semiconductor interlayer dielectric, include simultaneously patterning a via and a slotted line in the interlayer diectric, simultaneously etching the via and the slotted line, and simultaneously filling the via and the slotted line with a metal.

Owner:INFINEON TECH AG +1

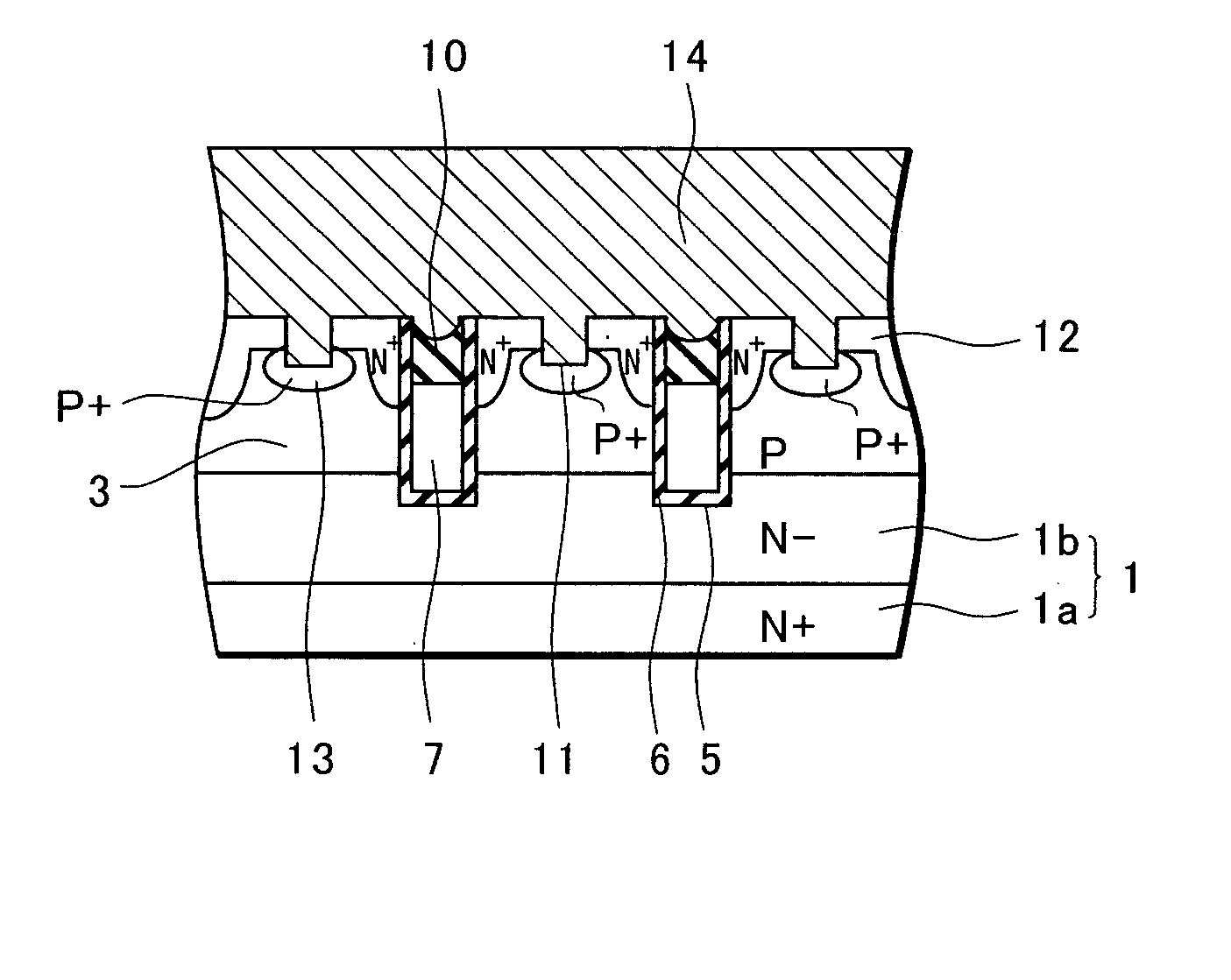

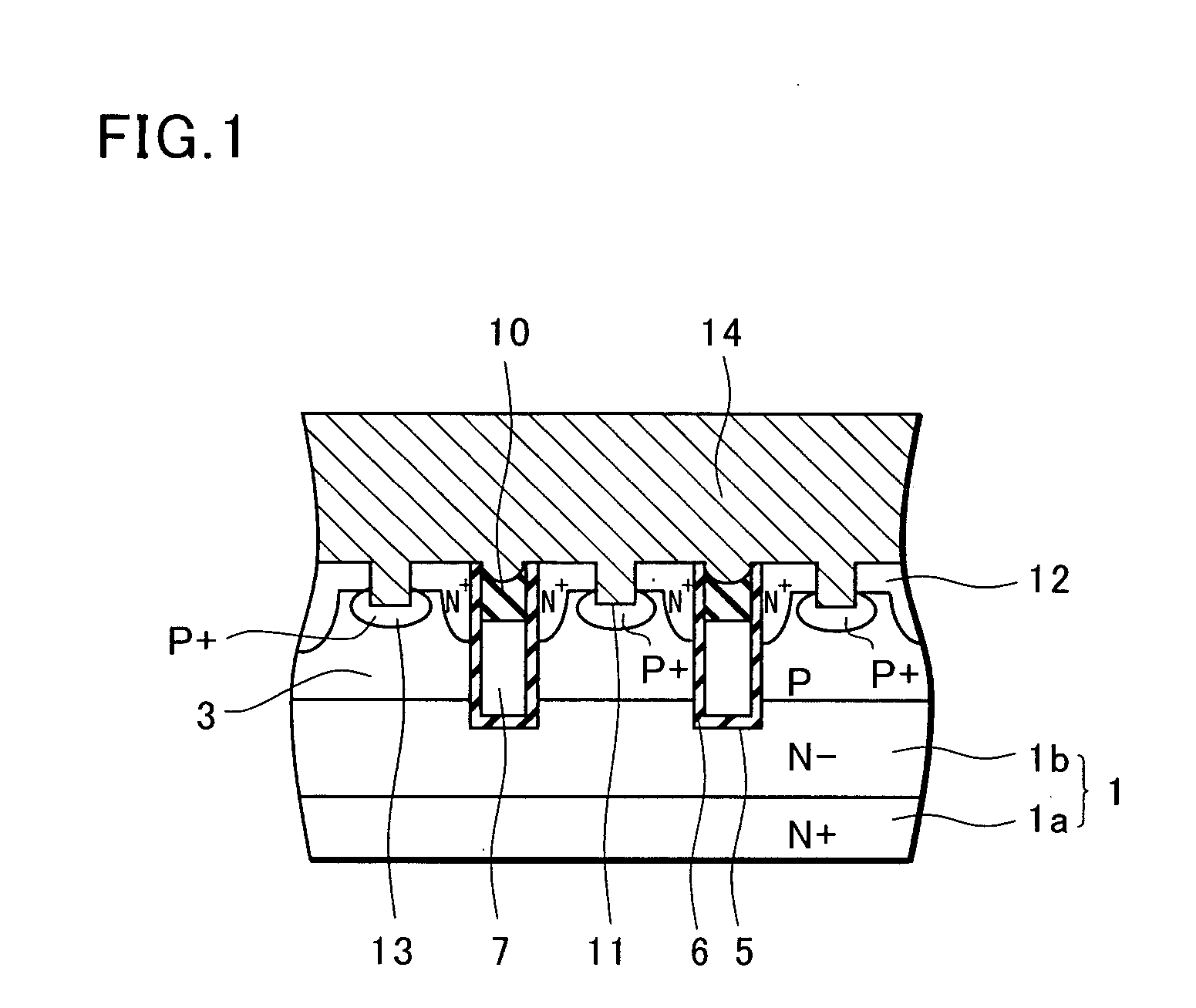

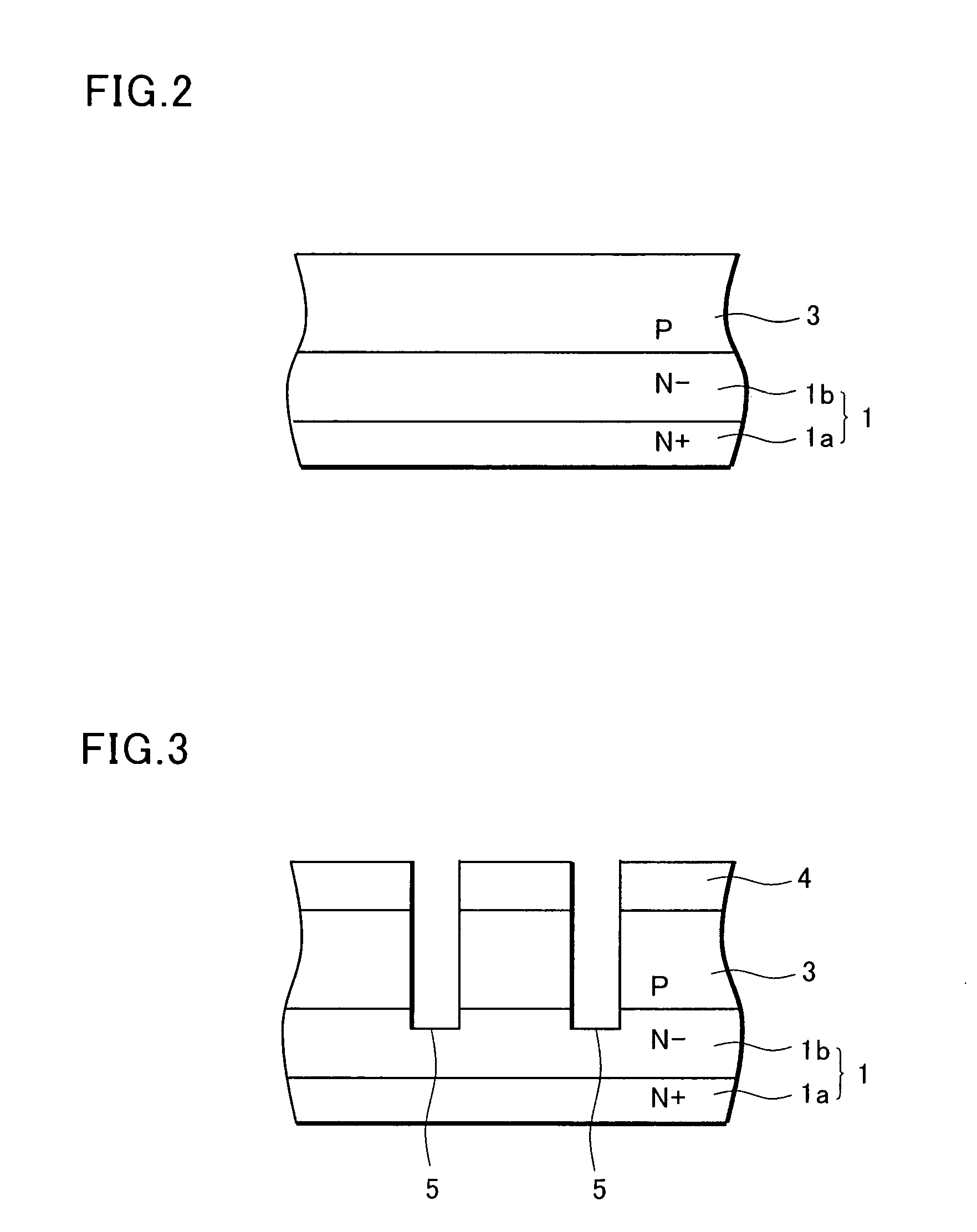

Insulated gate-type semiconductor device and manufacturing method of the same

ActiveUS20050167748A1DistanceOn-resistance is reducedTransistorSemiconductor/solid-state device manufacturingFailure causesBody region

An interlayer dielectric film is completely buried in a trench, and failures caused by step coverage is prevented because a source electrode can be formed substantially uniformly on an upper portion of a gate electrode. Also, in the processes of forming a source region, a body region and an interlayer dielectric film, only one mask is necessary so that the device size is reduced to account for placement error of only one mask alignment.

Owner:SEMICON COMPONENTS IND LLC

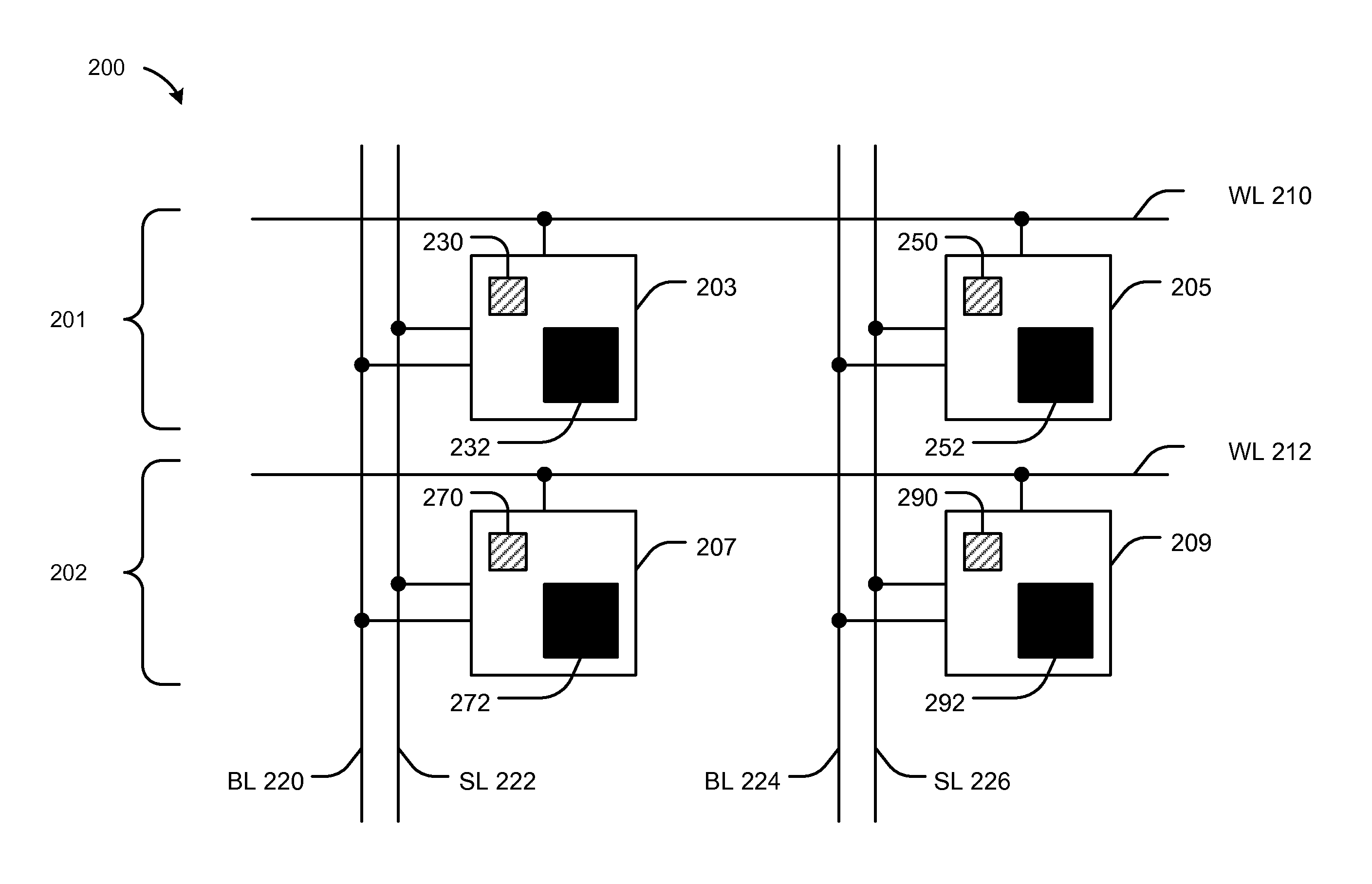

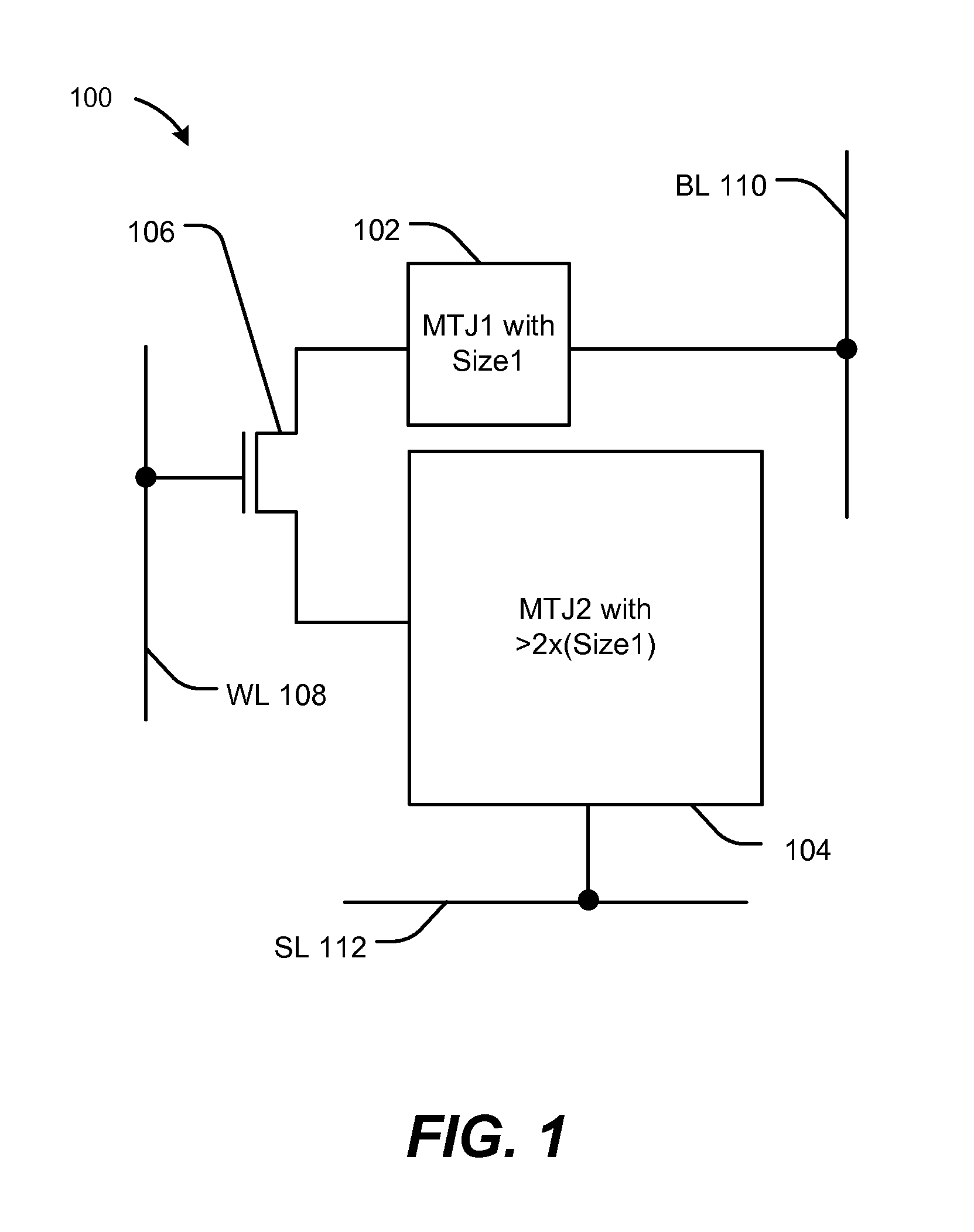

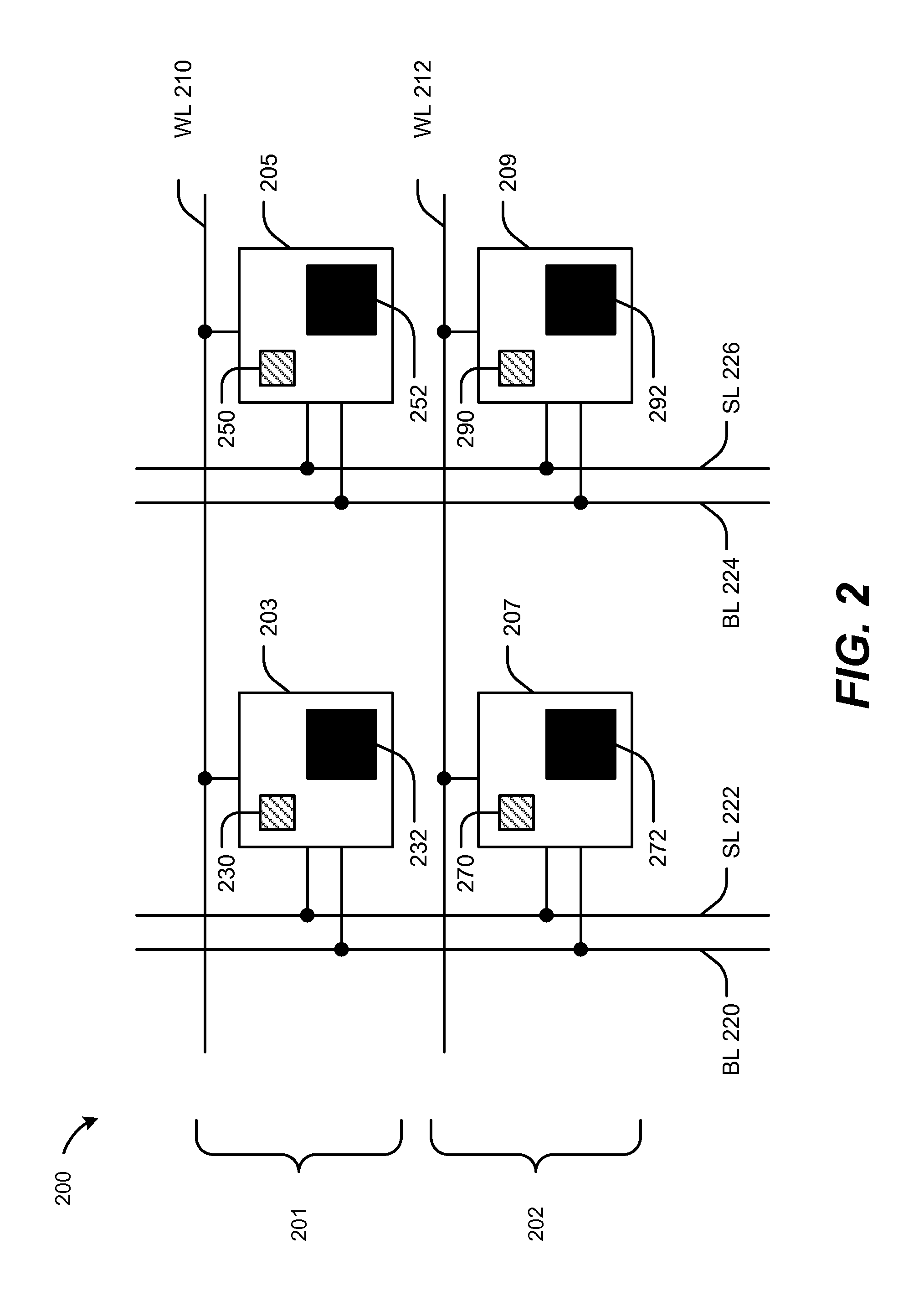

Multi-bit spin torque transfer magnetoresistive random access memory with sub-arrays

ActiveUS9437272B1Reduce chip sizeReduce power consumptionDigital storageMemory systemsMagnetic reluctanceEngineering

A device includes a first magnetic tunnel junction (MTJ) element having a first read margin and a second MTJ element having a second read margin. The first read margin is greater than twice the second read margin. The device also includes an access transistor coupled between the first MTJ element and the second MTJ element. A gate of the access transistor is coupled to a word line. The first MTJ element, the second MTJ element, and the access transistor form a multi-bit spin torque transfer magnetoresistive random access memory (STT-MRAM) memory cell.

Owner:QUALCOMM INC