Patents

Literature

1117results about How to "Reduce circuit size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

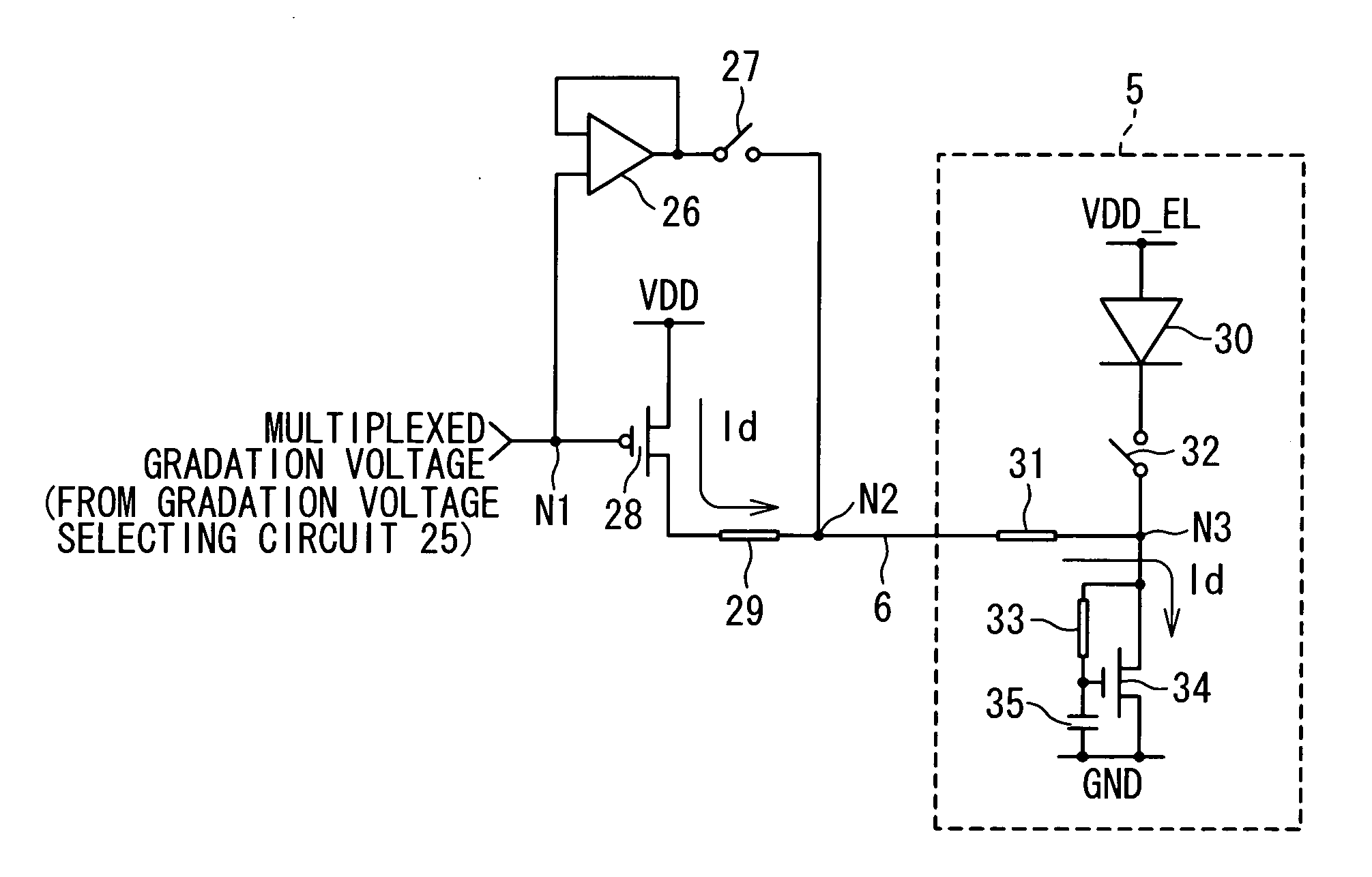

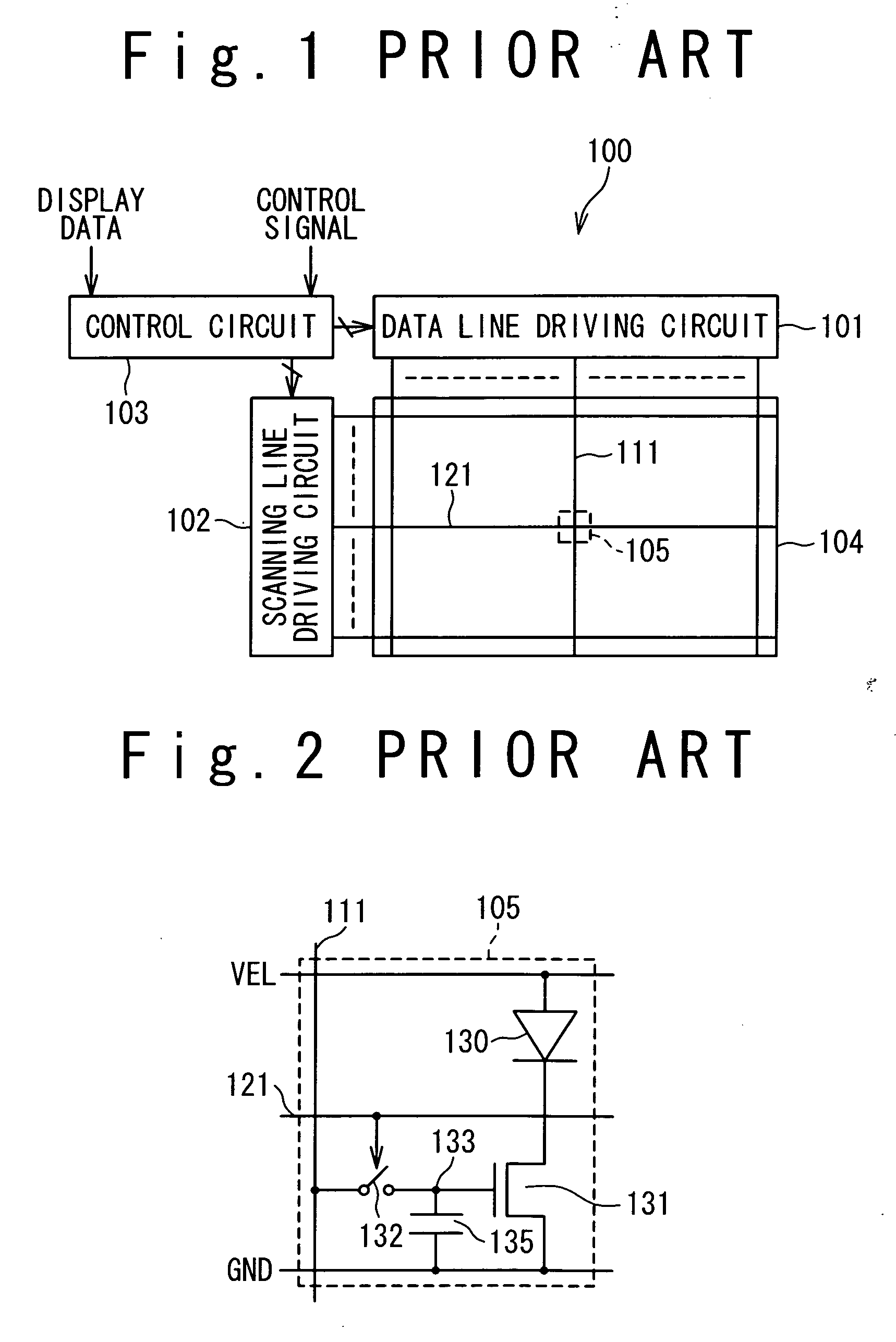

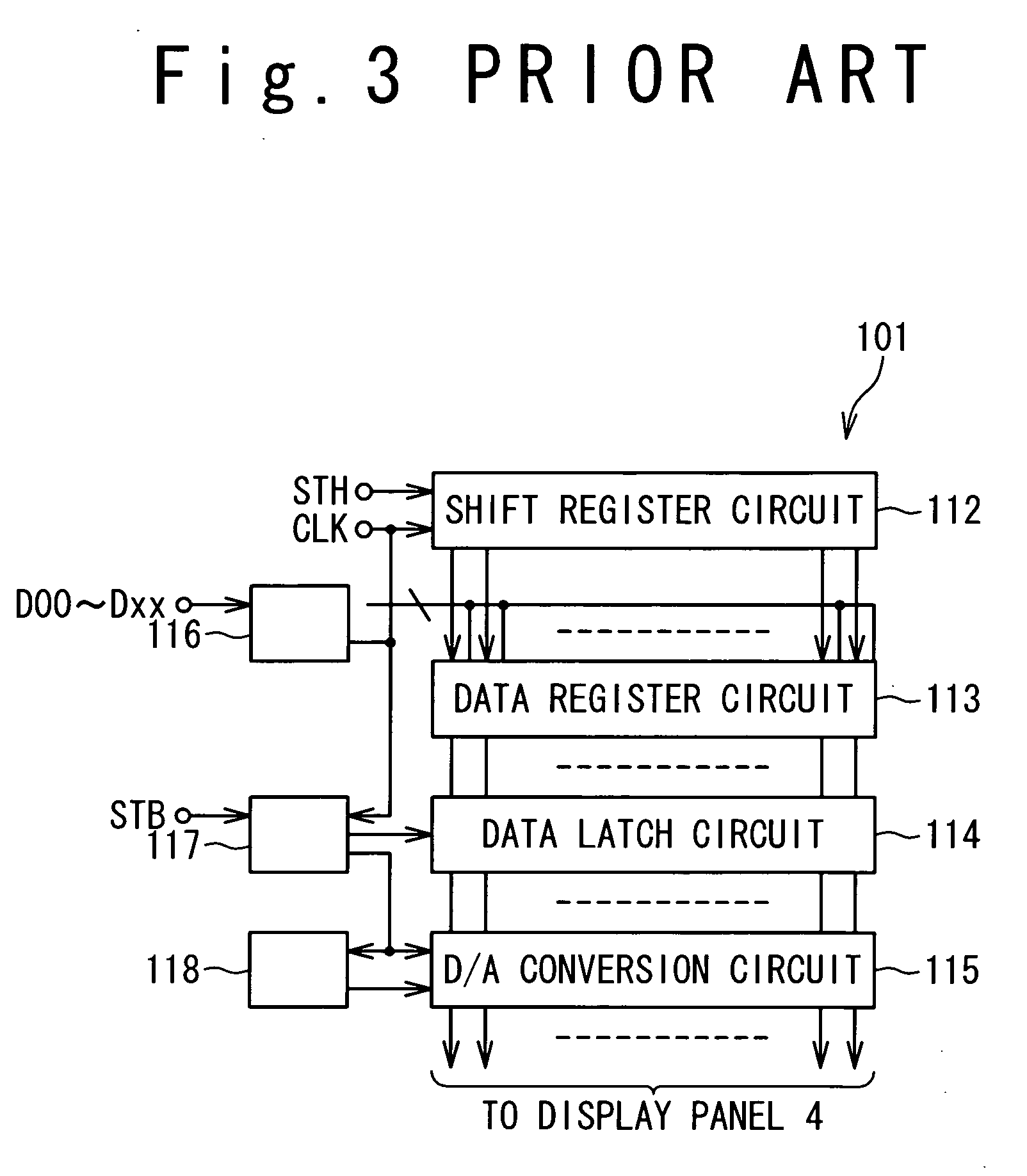

Display apparatus, and driving circuit for the same

ActiveUS20070001939A1Reduce the valueReduce circuit sizeStatic indicating devicesElectroluminescent light sourcesEngineeringDifferential amplifier

A drive circuit which outputs an output signal to an output terminal, includes a drive transistor configured to output a gradation current to the output terminal; a single differential amplifier; a resistance element connected with the drive transistor; and a plurality of switches. The plurality of switches are controlled such that a precharge voltage is outputted from the differential amplifier to the output terminal in a first period while blocking off an output from the drive transistor and such that a gradation current is outputted from the drive transistor to the output terminal in a second period after the first period.

Owner:RENESAS ELECTRONICS CORP

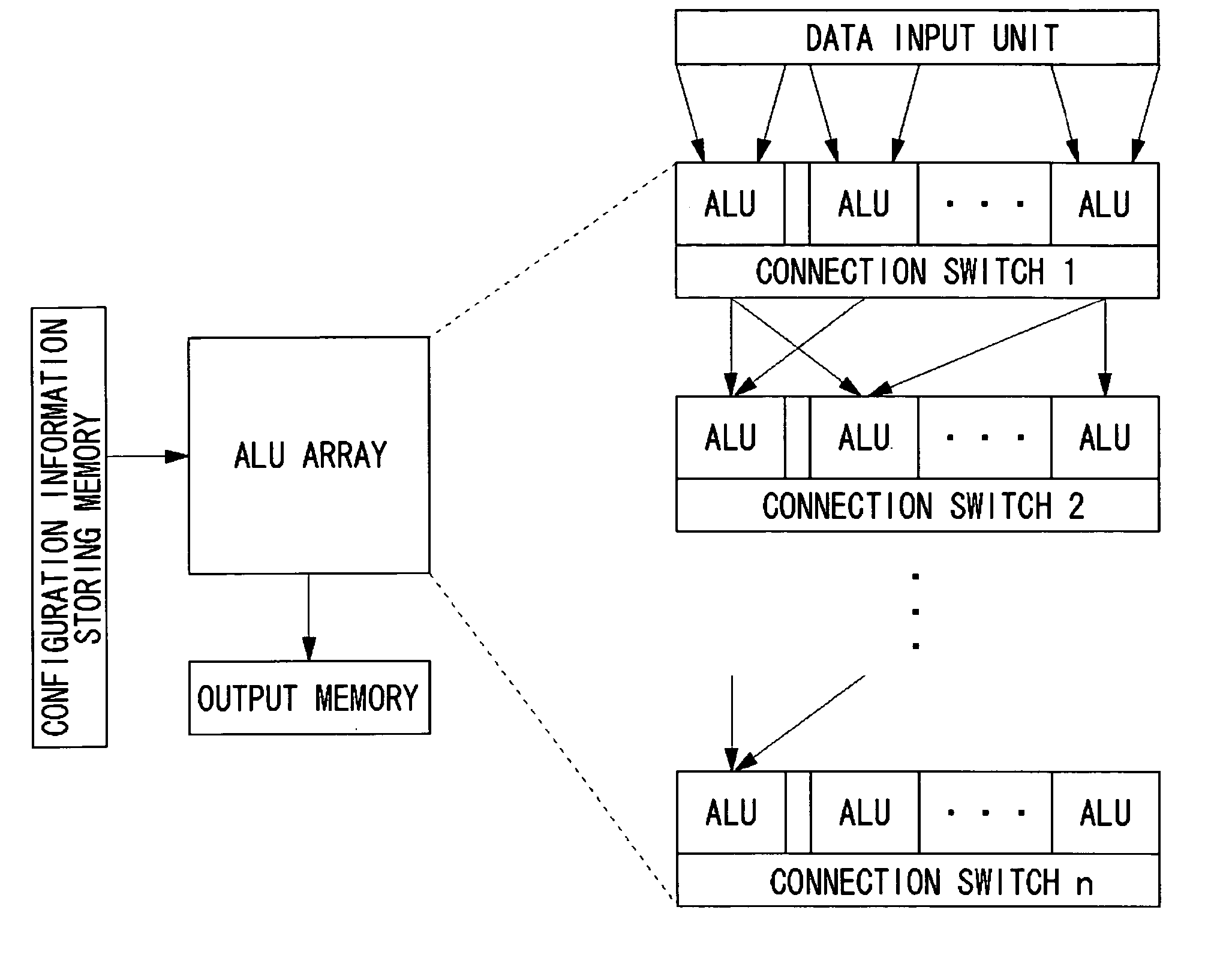

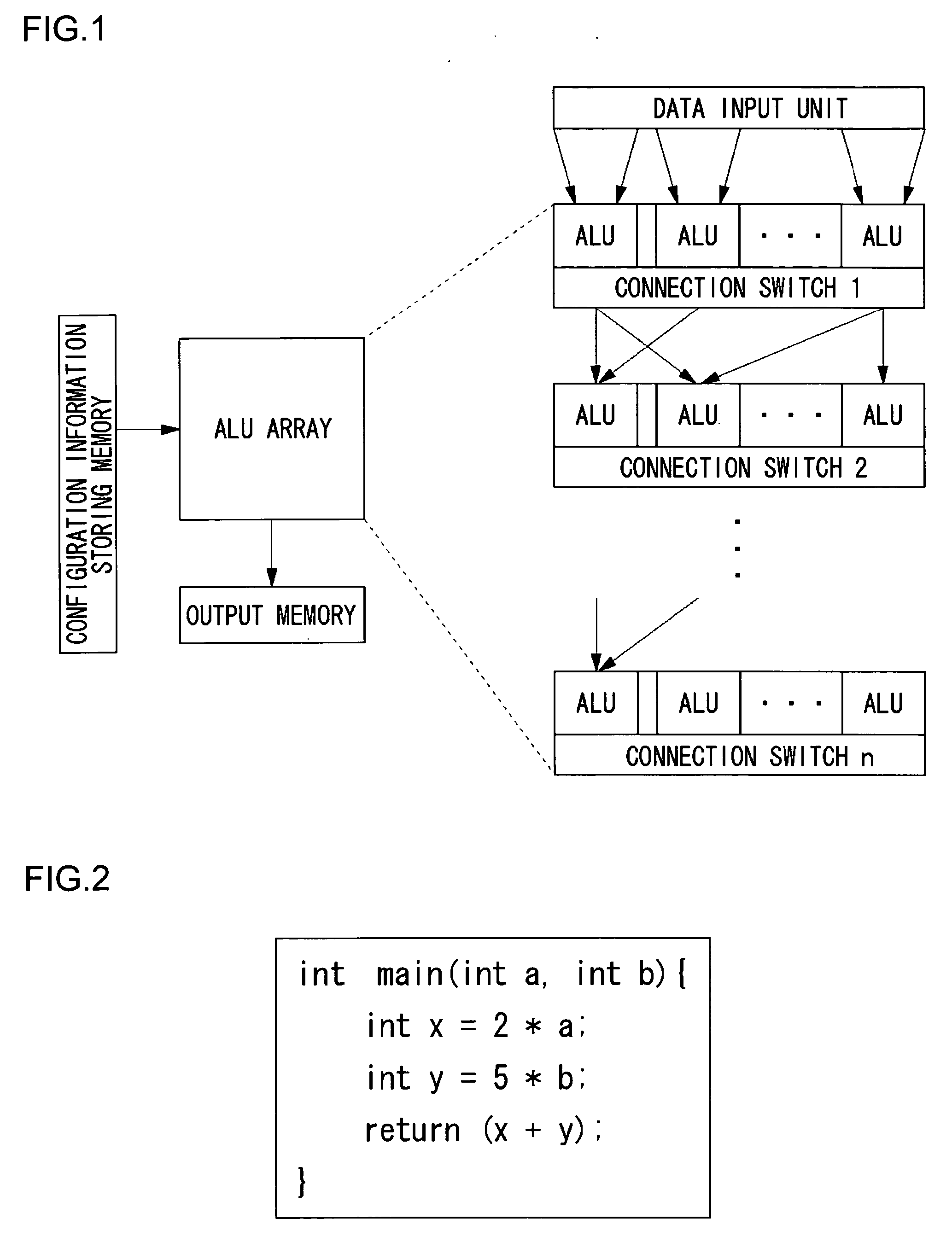

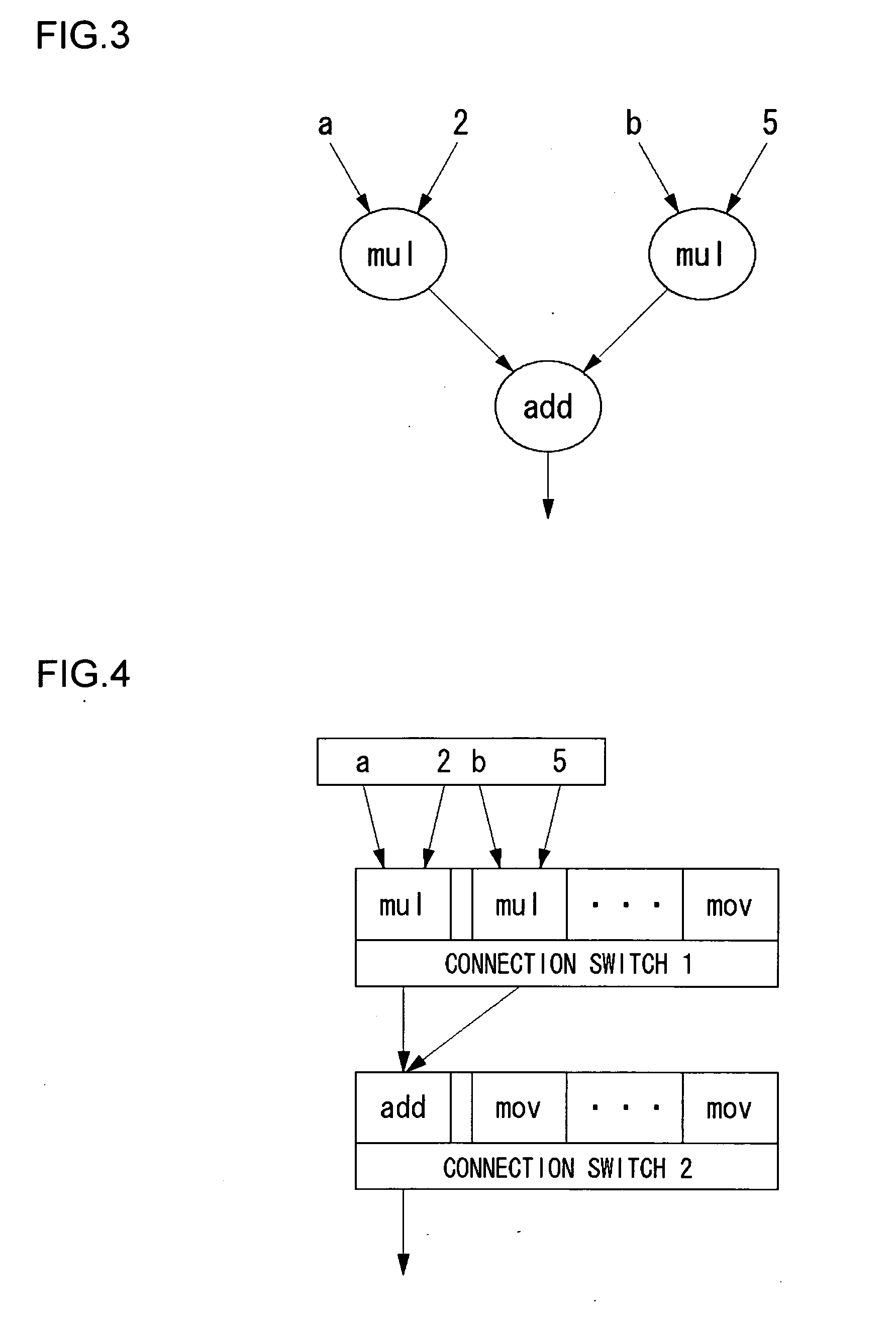

Reconfigurable circuit, processor having reconfigurable circuit, method of determining functions of logic circuits in reconfigurable circuit, method of generating circuit, and circuit

InactiveUS20050134308A1Reduce in quantityReduce switchingEnergy efficient ICTSemiconductor/solid-state device manufacturingLogical circuit

Owner:SANYO ELECTRIC CO LTD

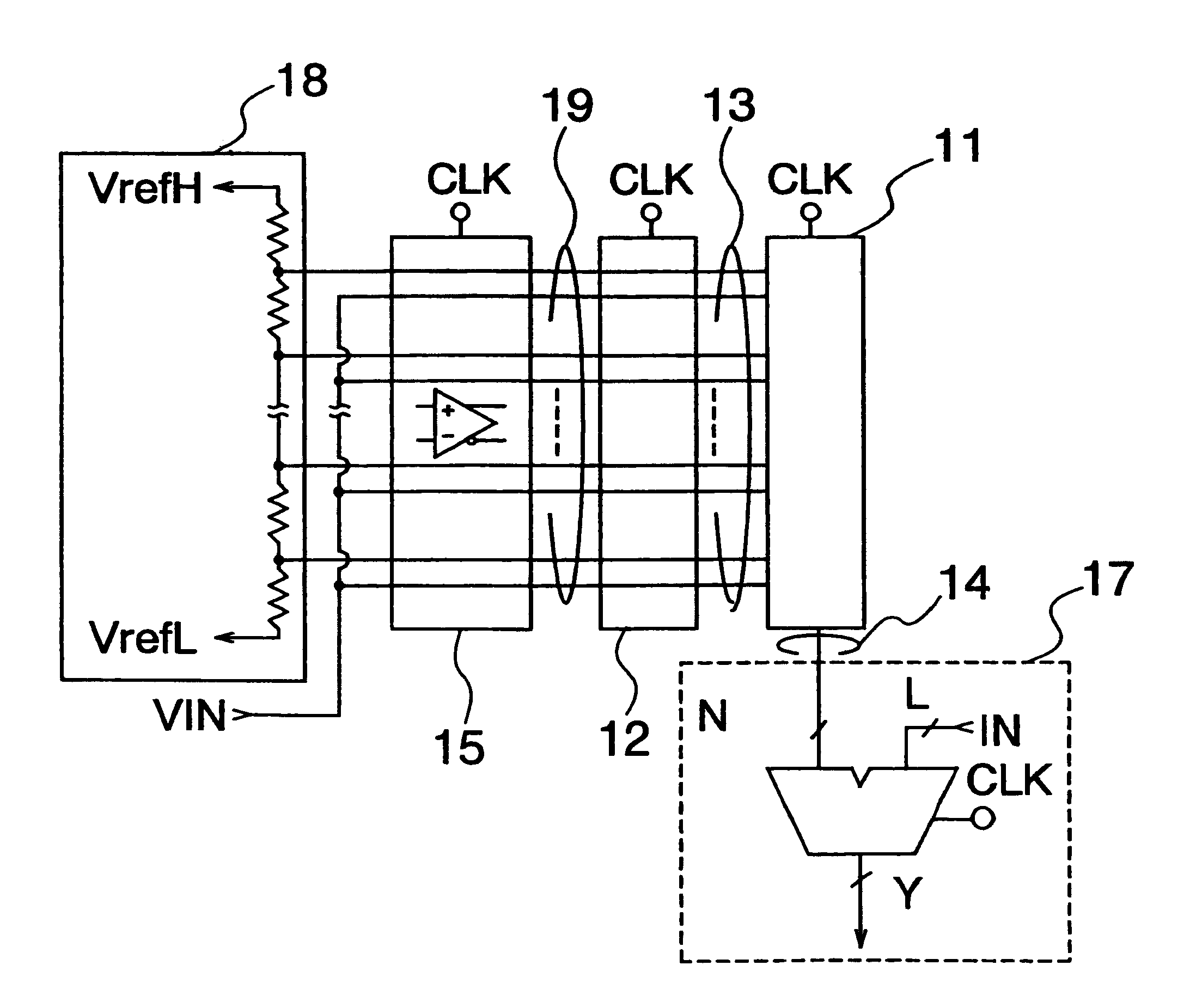

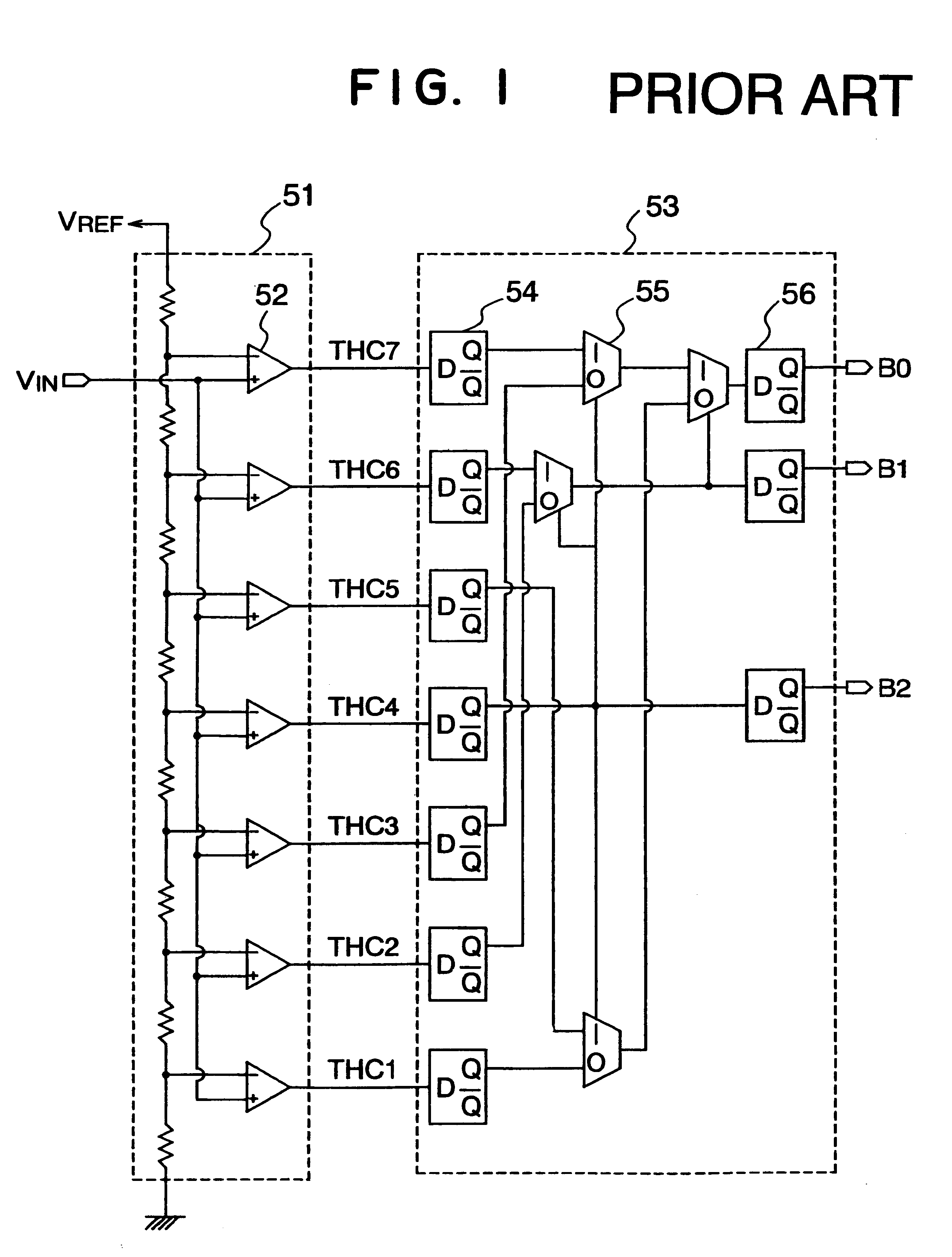

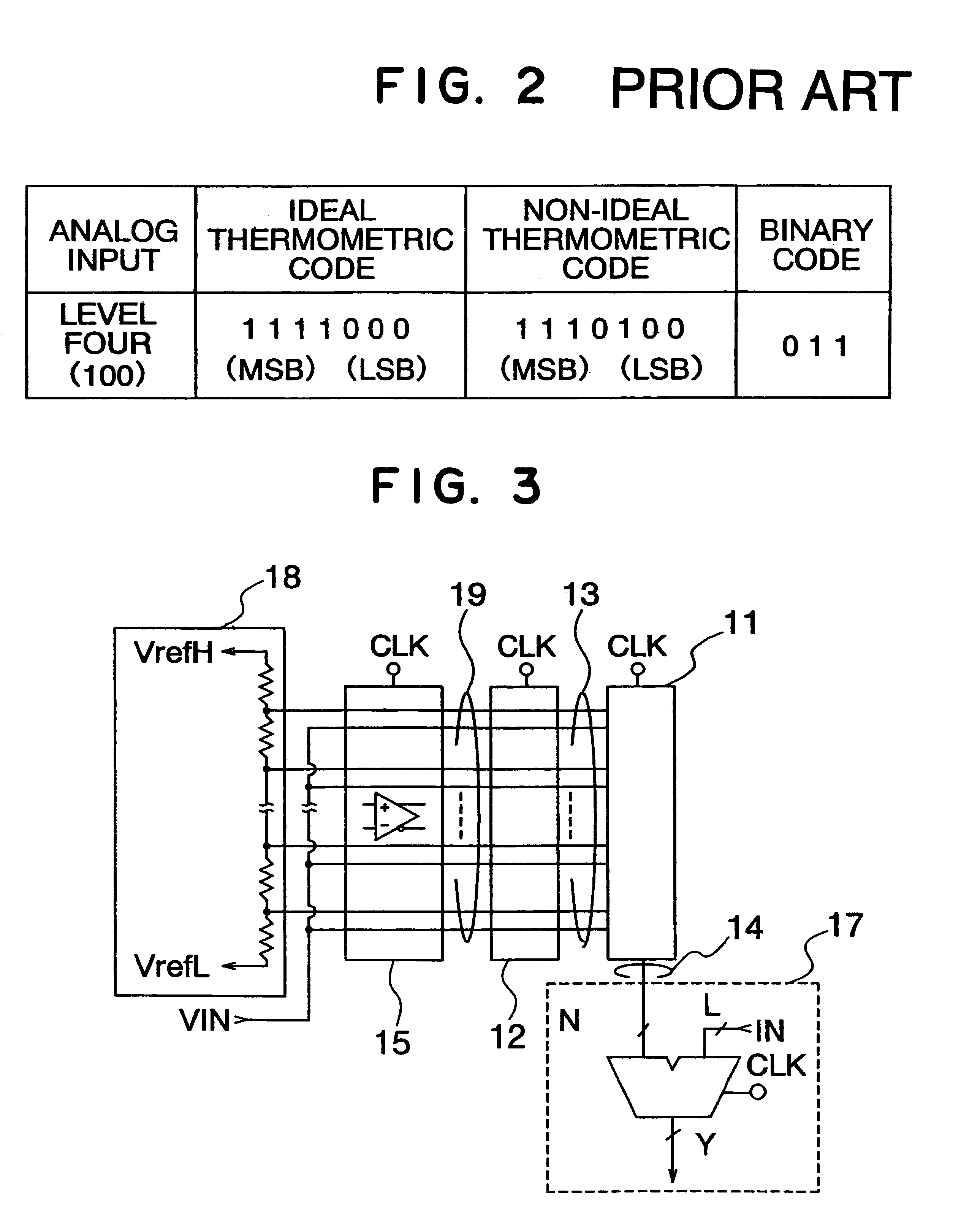

A/D converter having a dynamic encoder

InactiveUS6232908B1Increase speedReduce circuit sizeElectric signal transmission systemsAnalogue-digital convertersBuck converterA d converter

An A / D converter includes a resistor ladder for generating a plurality of reference potentials, a comparing section for comparing each of the reference potentials against an input analog signal to output a thermometric code, and a dynamic encoder composed of a combinational circuit to encode the thermometric code to a binary code by responding a clock signal. The A / D conversion is finished in a single clock cycle at a high speed, with a reduced number of elements and reduced power dissipation.

Owner:NEC ELECTRONICS CORP

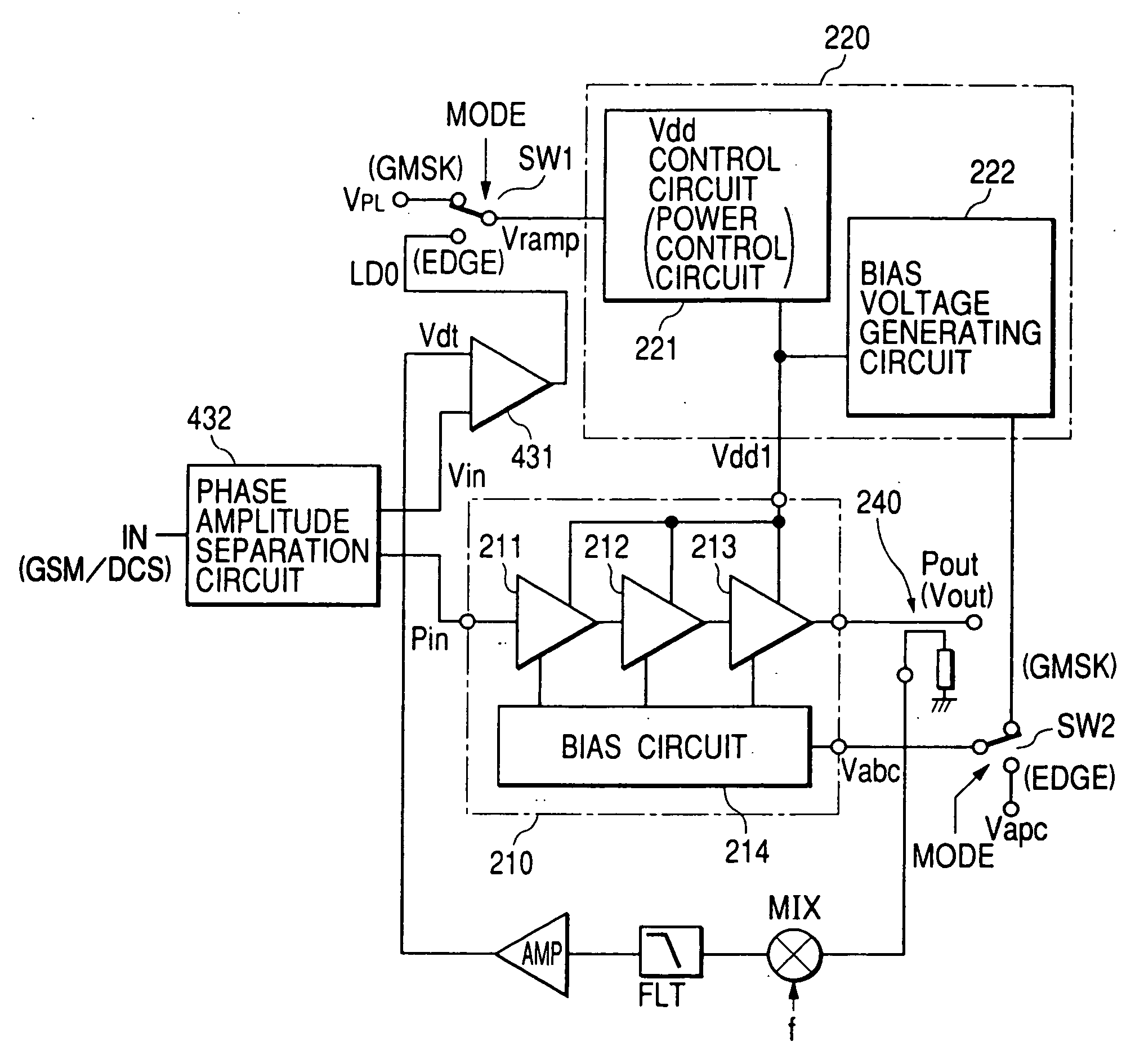

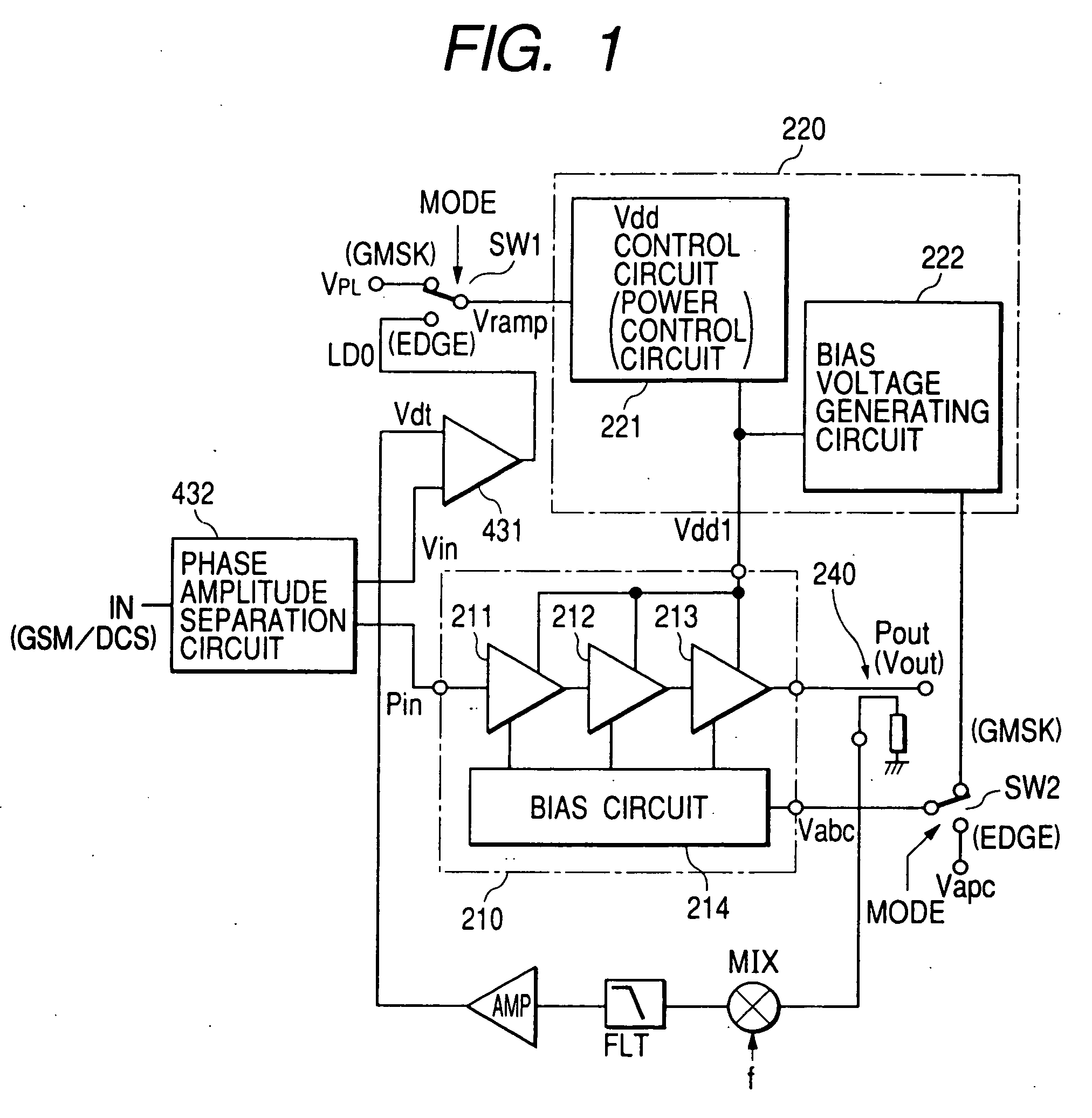

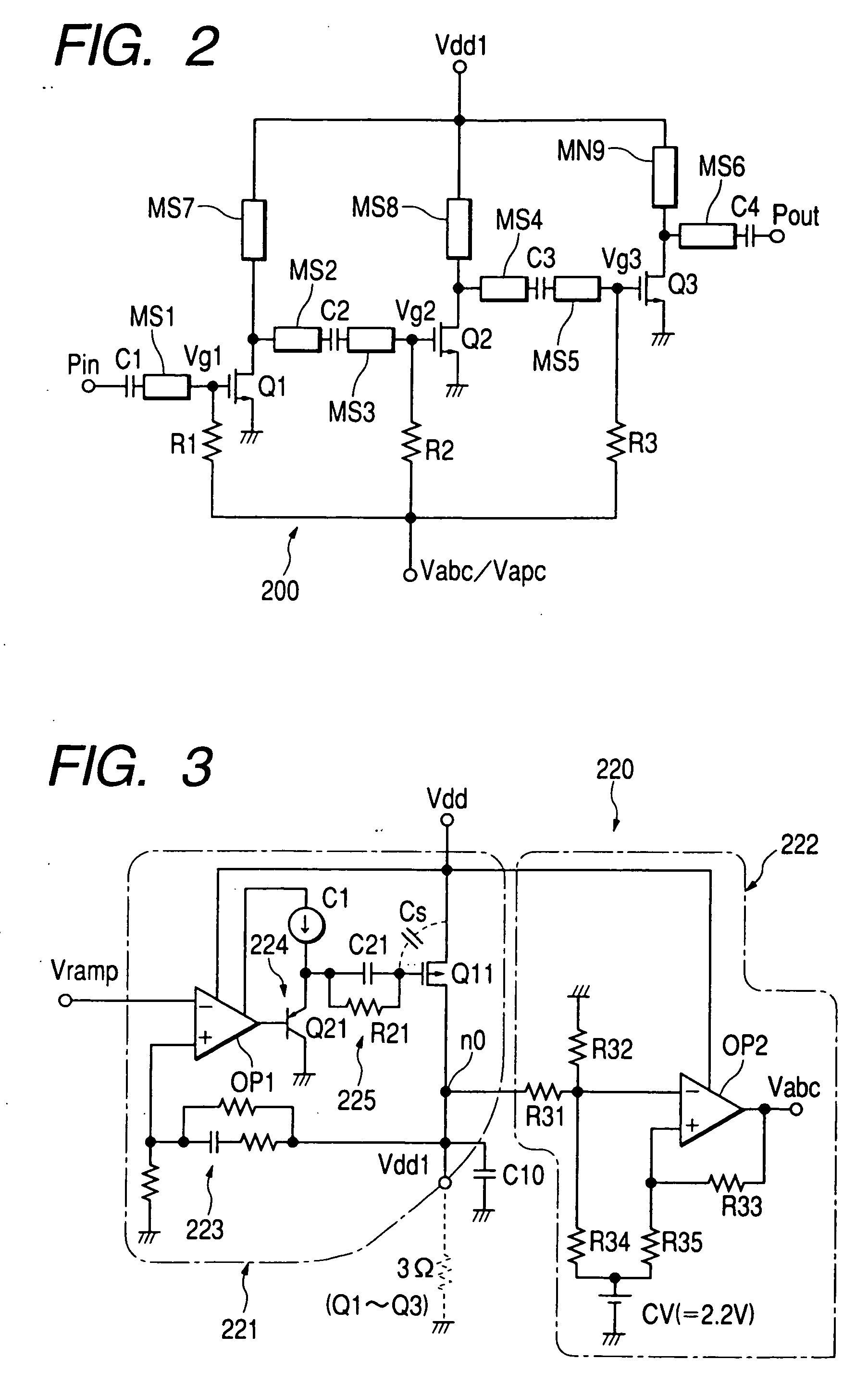

High frequency power amplifier and wireless communication module

InactiveUS20050200407A1Reduce circuit sizeReduce the packing densityAmplifier modifications to reduce non-linear distortionSolid-state devicesAudio power amplifierHigh frequency power

The present invention provides a high frequency power amplifier of an open-loop type, which outputs a signal having a level corresponding to an output level required under control of a power supply voltage for each output power FET, based on a control signal for the output level. The high frequency power amplifier is provided with a bias voltage generating circuit which generates a gate bias voltage of each output power FET according to an output voltage of a power control circuit for controlling the power supply voltage for the output power FET, based on the control signal for the output level.

Owner:MURATA MFG CO LTD

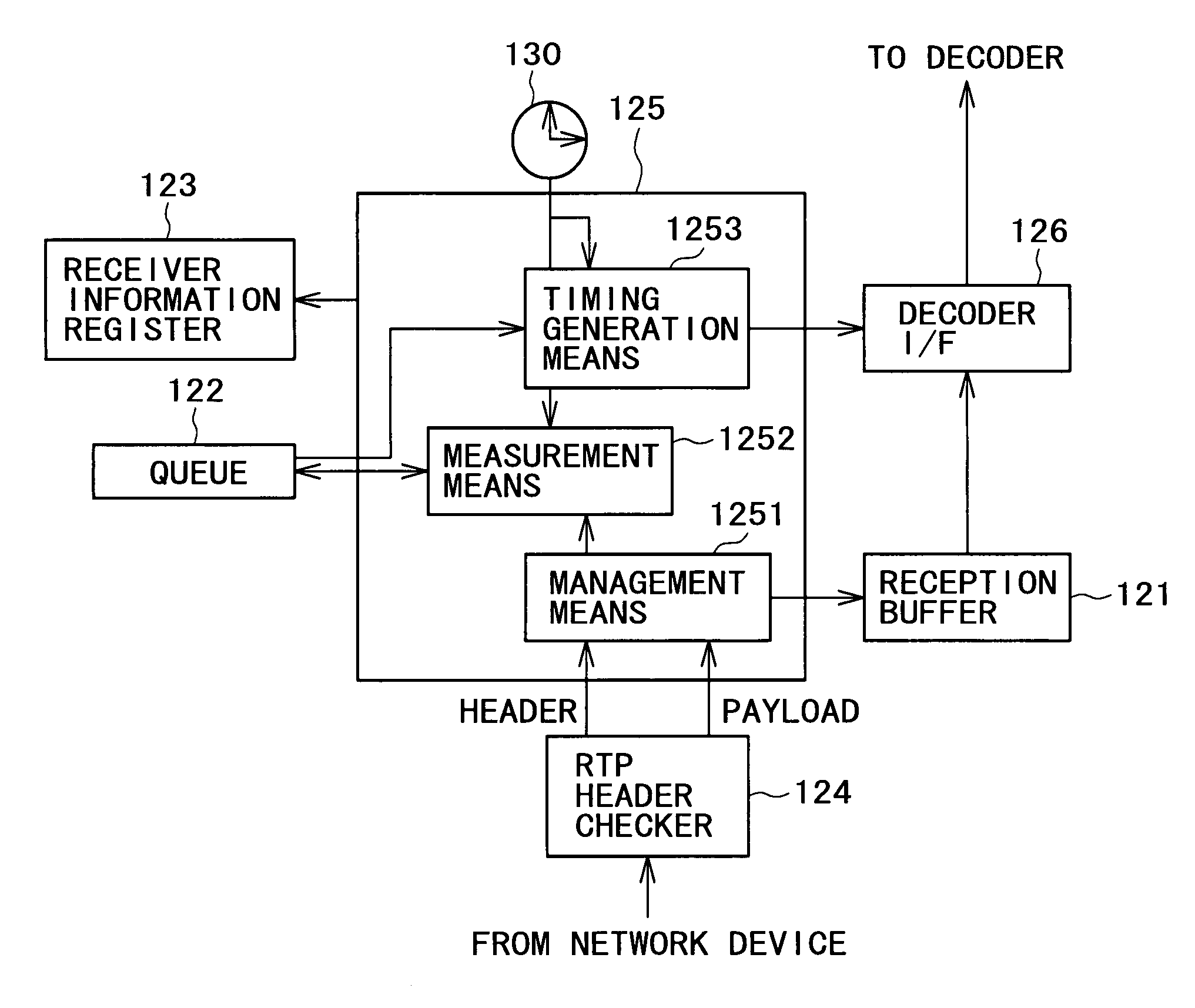

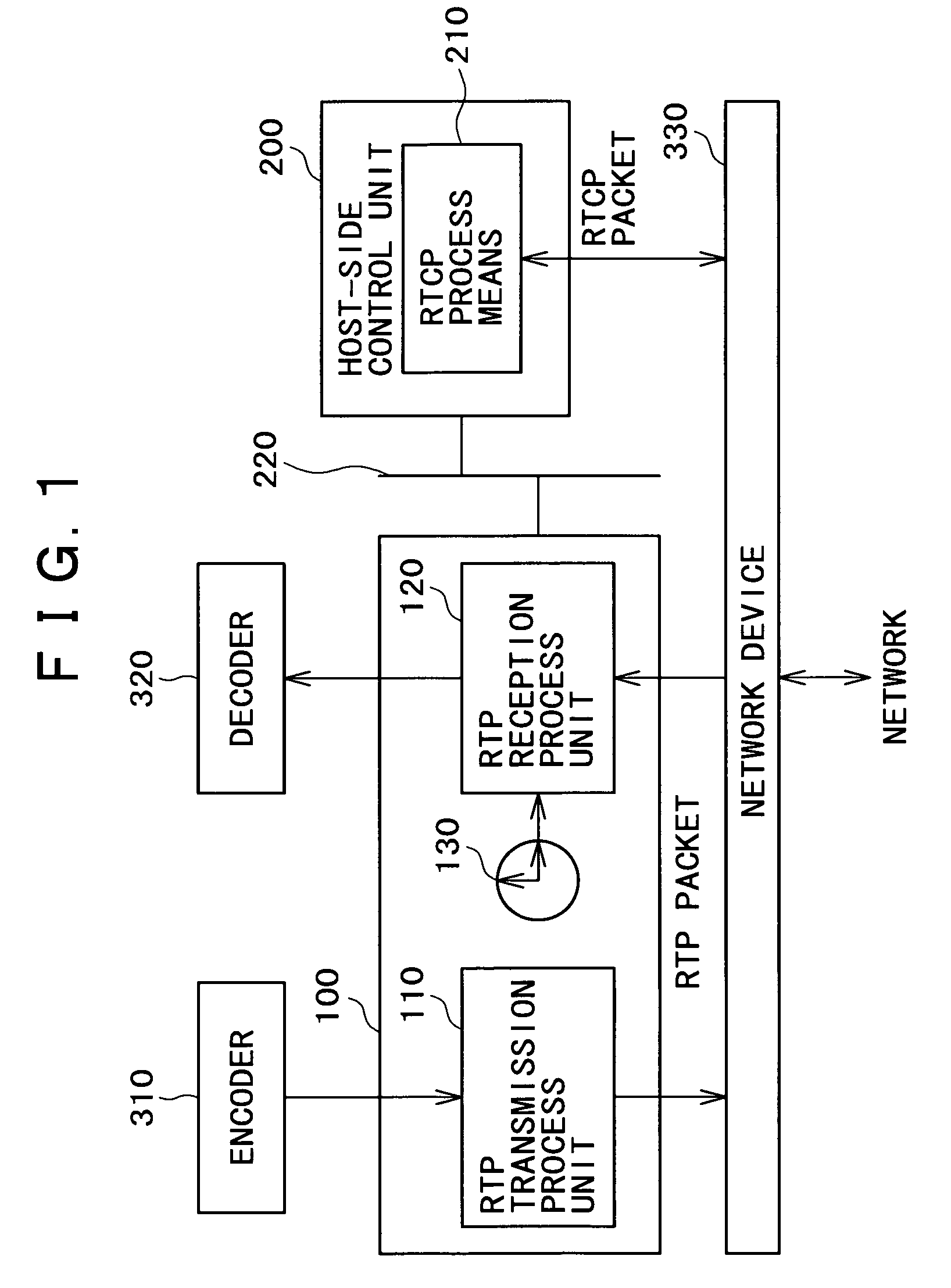

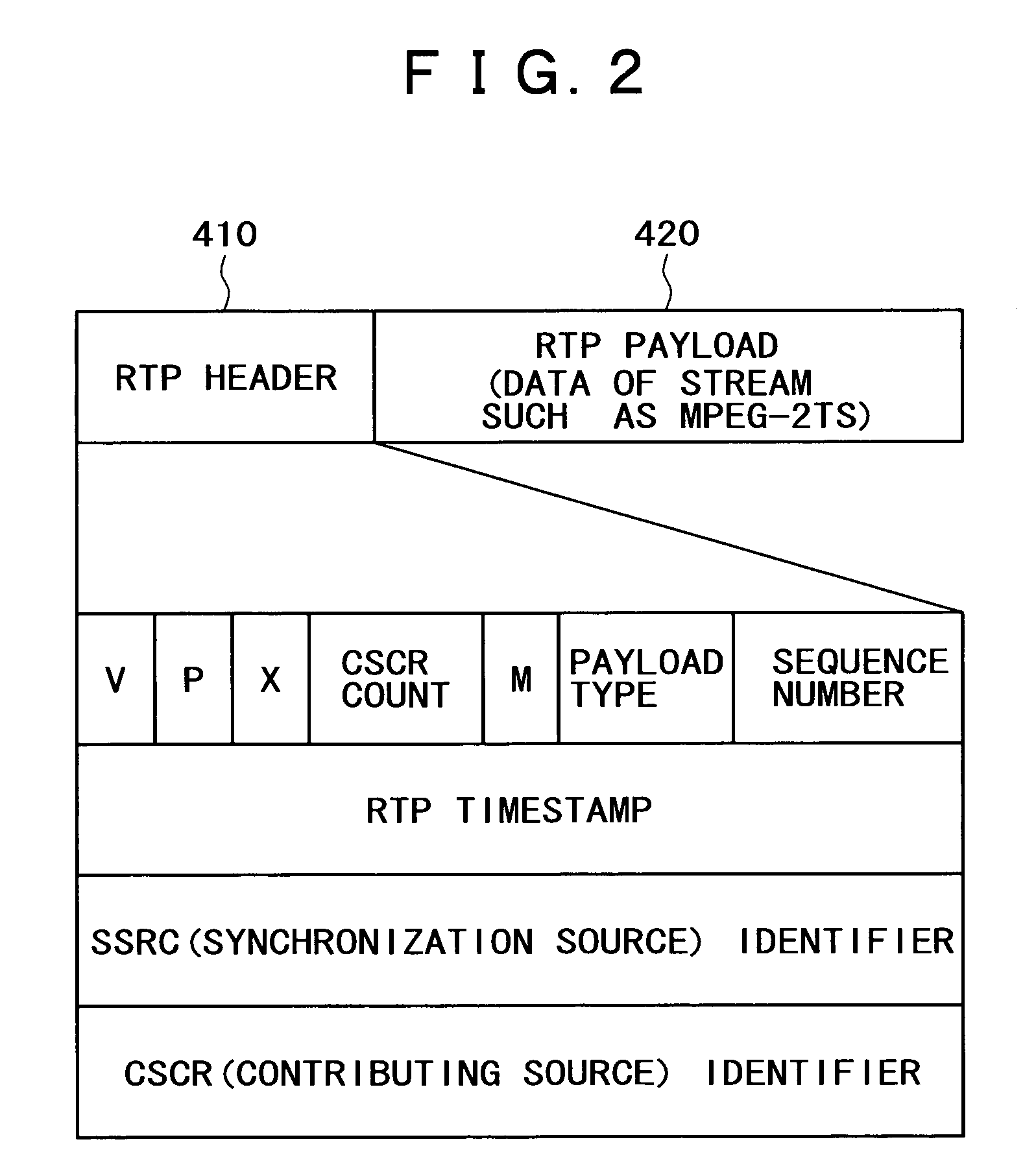

Communication apparatus, transmission apparatus and reception apparatus

InactiveUS7447164B2High streaming qualityReduce circuit sizeError preventionFrequency-division multiplex detailsMPEG transport streamControl unit

Upon reception of a transport stream of information data from an encoder, an RTP transmission process unit employed in an RTP process circuit is activated to packetize the transport stream in an RTP packet. A network device then outputs the resulting RTP packet to a network. At that time, sender information for the transmission is created and stored. On the other hand, an RTP reception process unit employed in the RTP process circuit depacketizes an RTP packet received from the network through the network device to obtain a transport stream and supplies the transport stream to a decoder. At that time, receiver information for the reception is created and stored. An RTCP process means employed in a control unit on the host side acquires the sender information and the receiver information through an internal bus and uses them to create an RTCP packet to be output to the network by way of the network device. As a result, the streaming quality can be assured independently of the state of the control unit on the host side.

Owner:SONY CORP

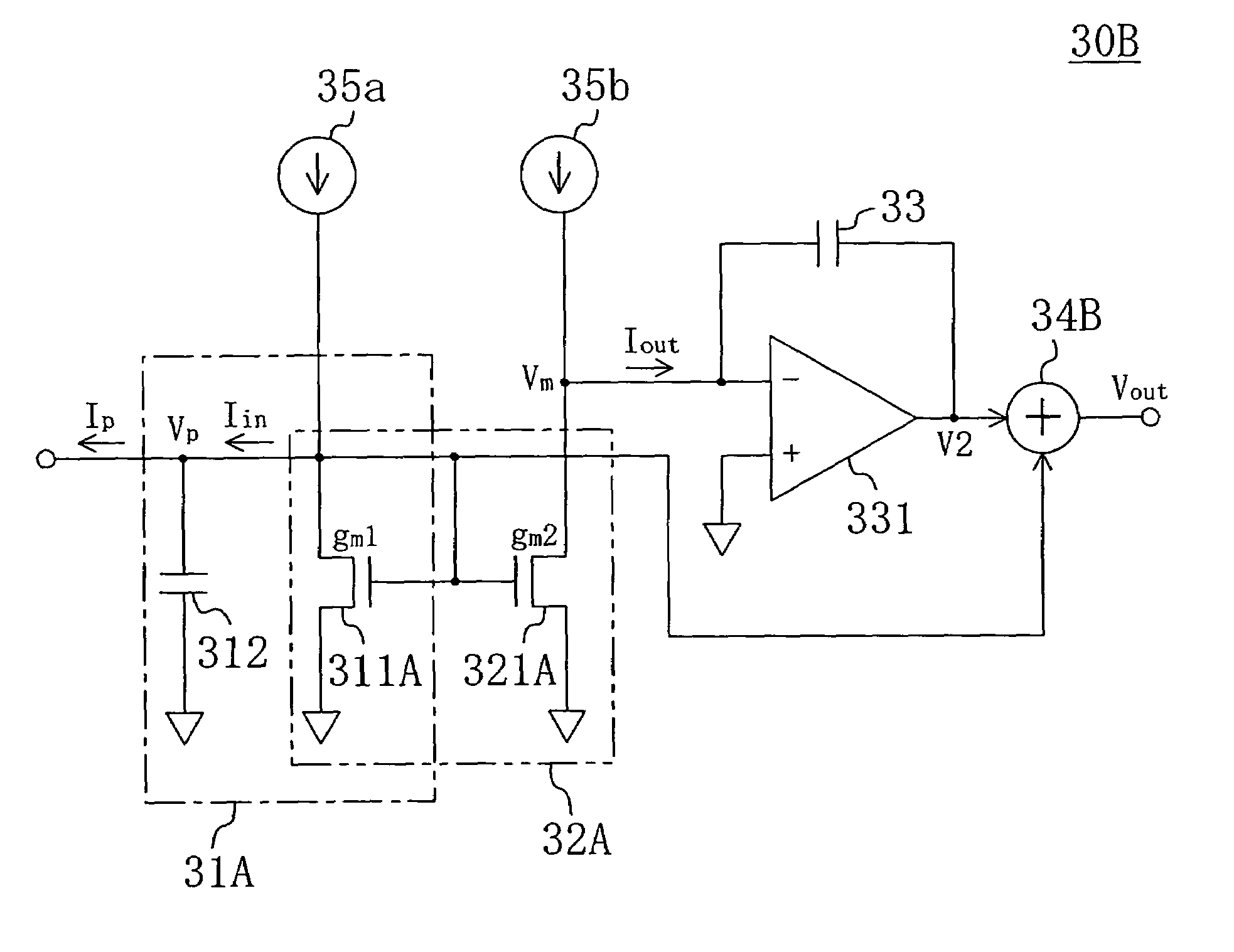

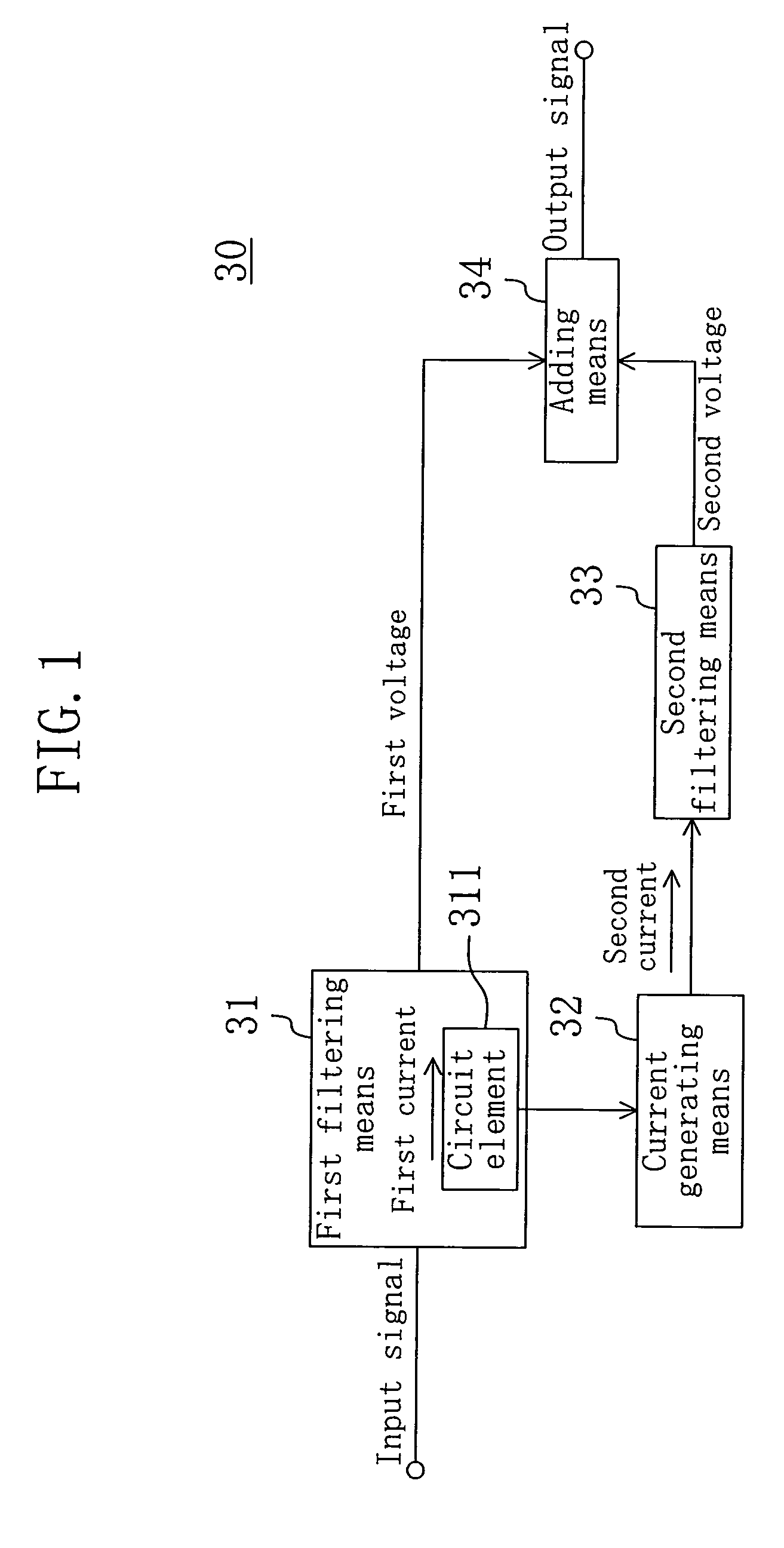

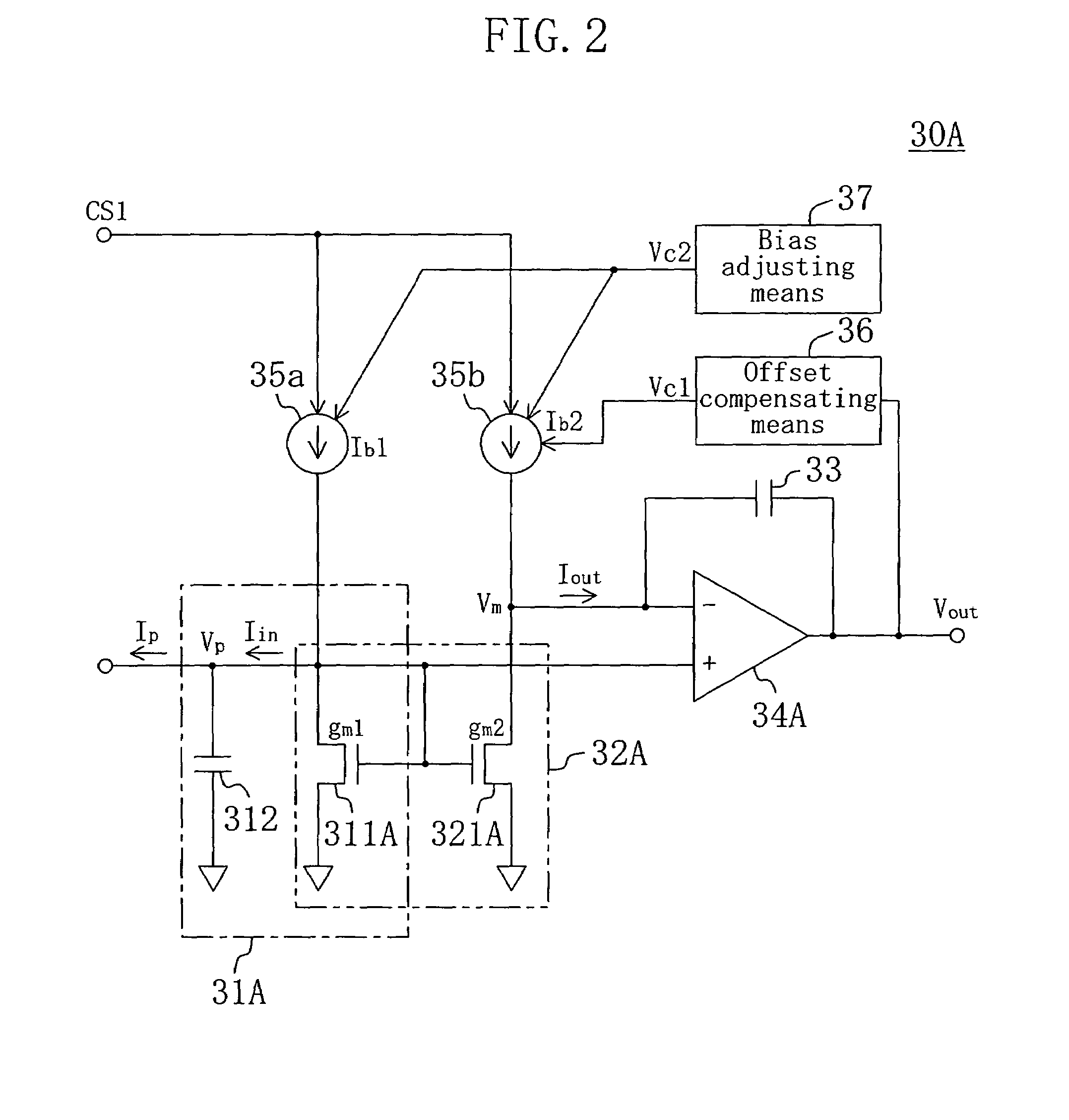

Low-pass filter for a PLL, phase-locked loop and semiconductor integrated circuit

InactiveUS7030688B2Reduce circuit sizeReduce circuit areaPulse automatic controlOscillations generatorsLoop filterBand-pass filter

The invention provides a low-pass filter suitably used as a loop filter for a PLL or a DLL that has a filtering characteristic equivalent to that of a conventional one and can be realized in a smaller circuit area. The low-pass filter includes first filtering means (31) for accepting, as an input, an input signal to the low-pass filter and outputting a first voltage; a circuit element (311) included in the first filtering means (31) for allowing a first current to flow in accordance with the first voltage; current generating means (32) for generating a second current at a given rate to the first current; second filtering means (33) for accepting, as an input, the second current and outputting a second voltage; and adding means (34) for adding the first voltage and the second voltage and outputting an output signal of the low-pass filter, in which the second current is set to be smaller than the first current.

Owner:PANASONIC CORP

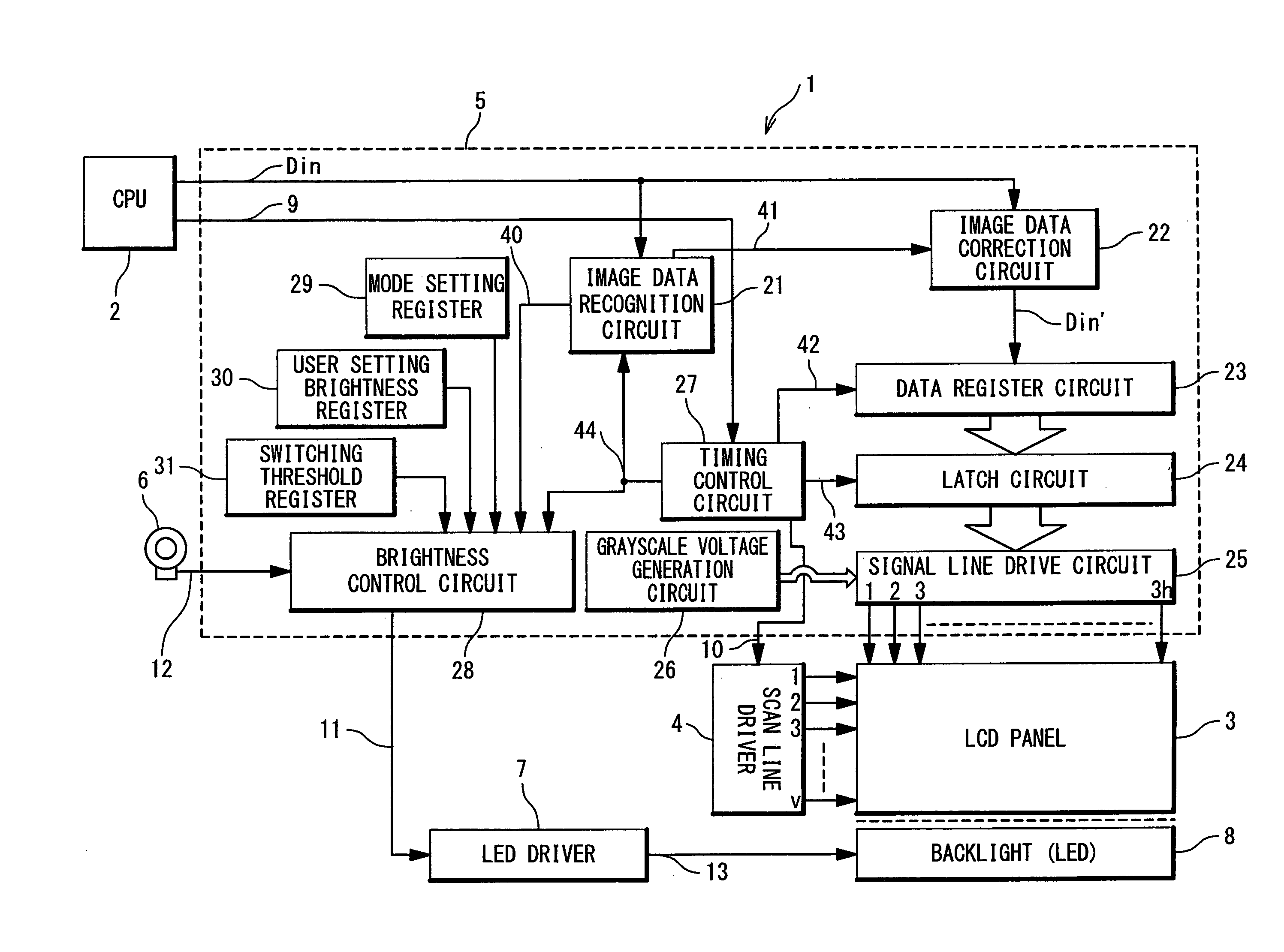

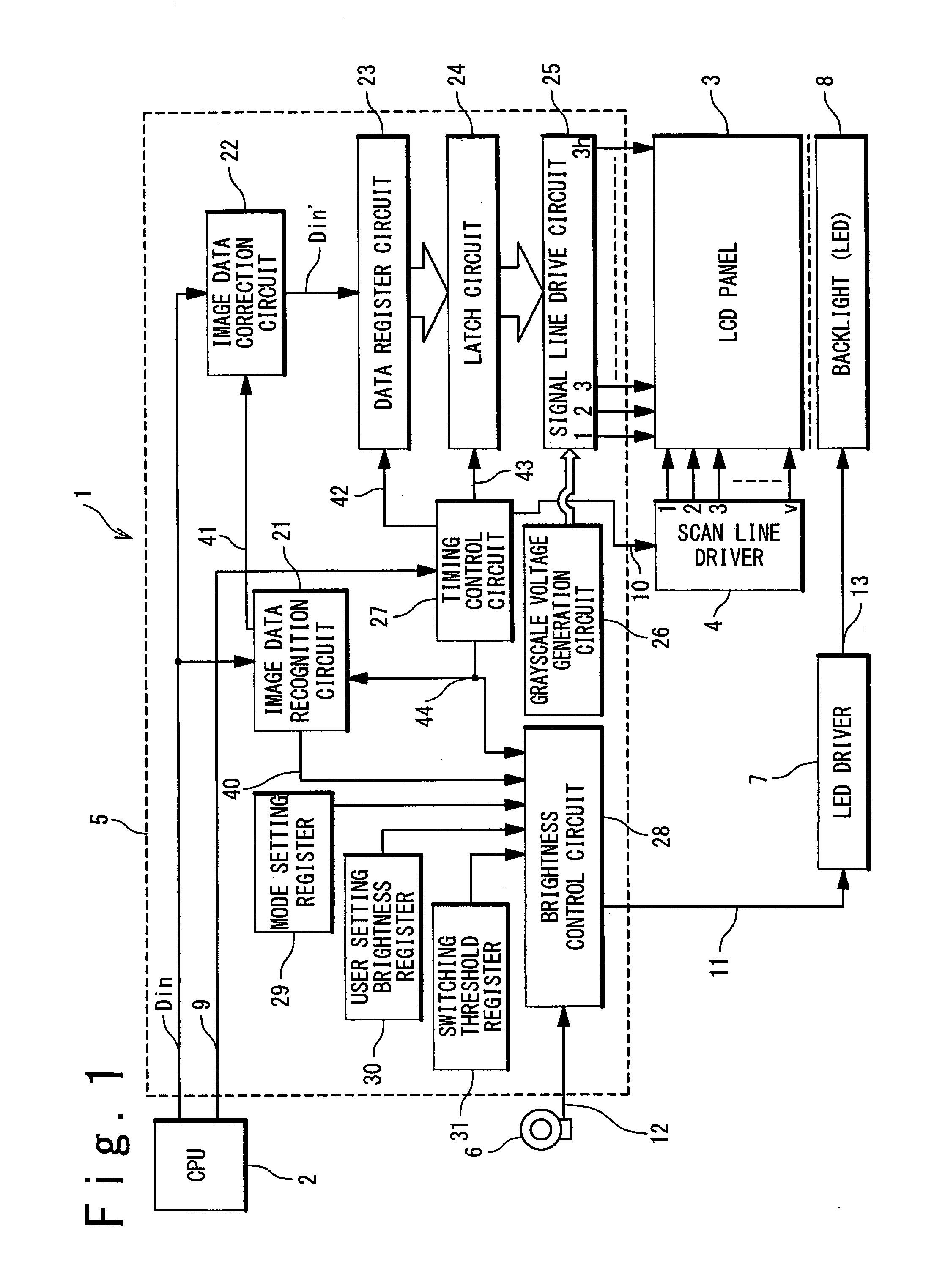

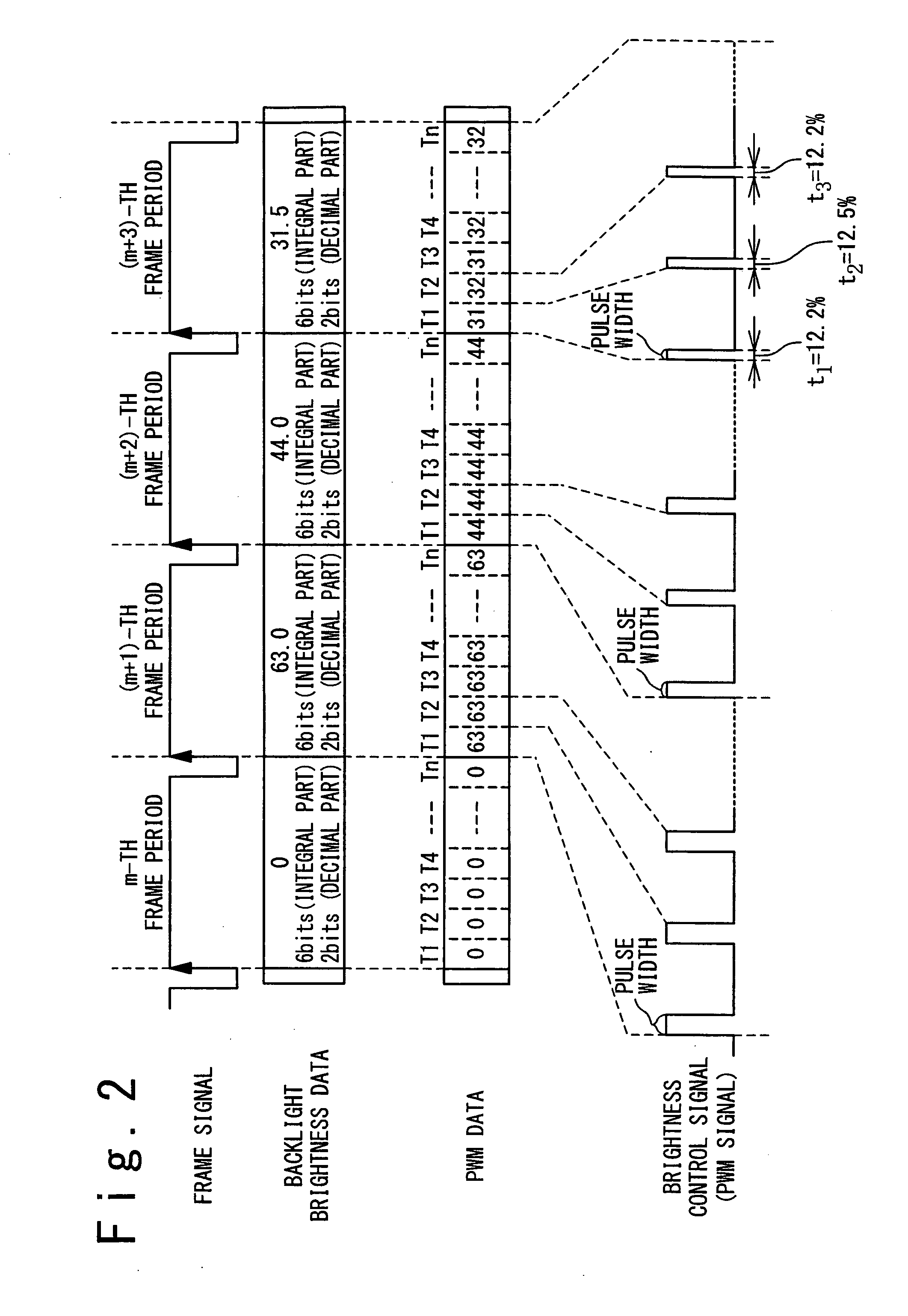

Backlight brightness control for panel display device

ActiveUS20100164922A1Increase the number ofReduce circuit sizeElectrical apparatusElectroluminescent light sourcesDisplay deviceComputer science

A display device is provided with a display panel; a backlight which illuminates the display panel; and a backlight brightness controller controlling a brightness of the backlight so that the brightness of the brightness is variable in the middle of each frame period.

Owner:SYNAPTICS JAPAN GK

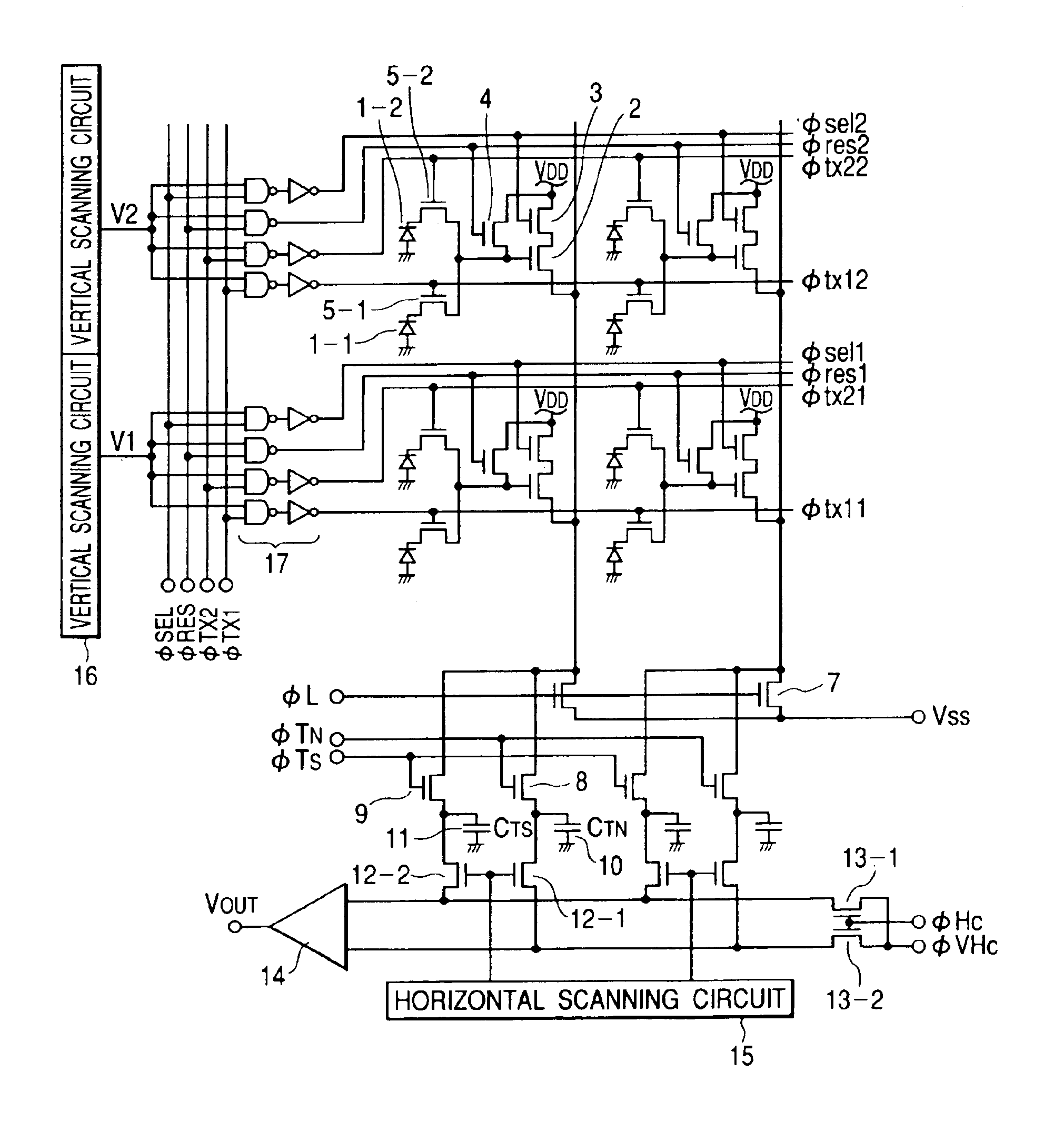

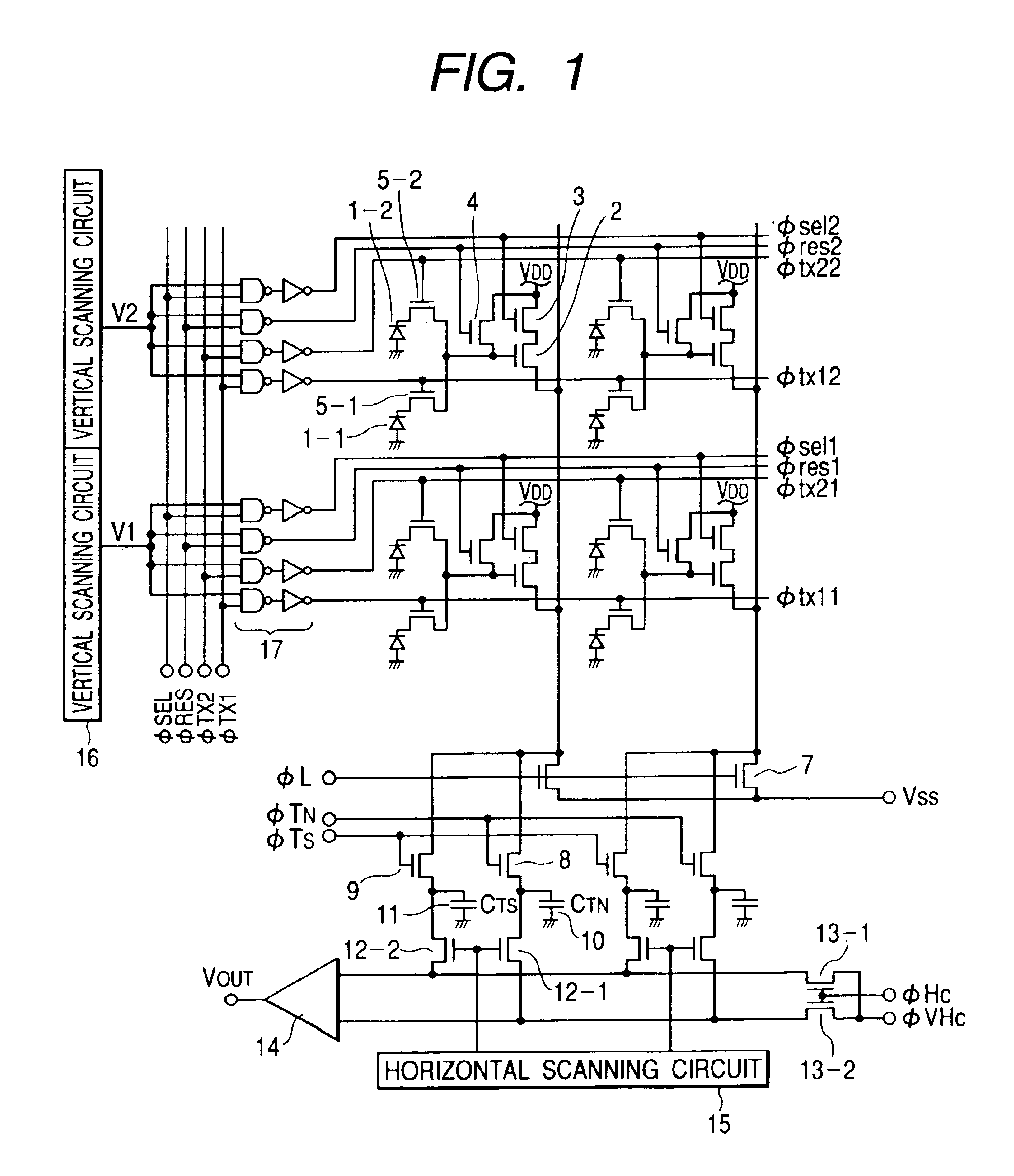

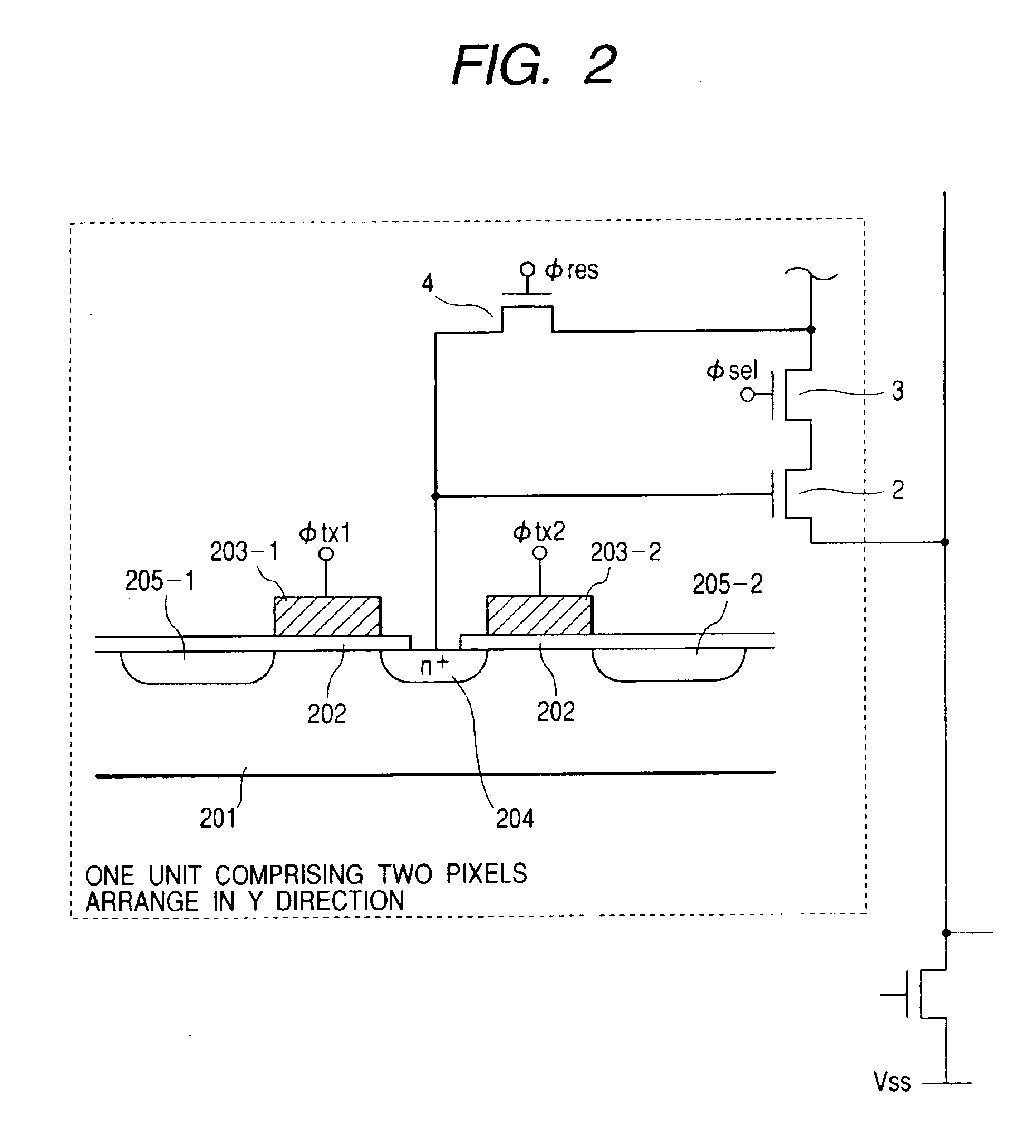

Image pickup apparatus having a common amplifier

InactiveUS6947088B2Reduce areaReduce circuit sizeTelevision system detailsTelevision system scanning detailsAudio power amplifierTransfer switch

To implement a solid-state image pickup element in which the peripheral circuit is downsized, there is provided a solid-state image pickup element including a plurality of pixel blocks each having a plurality of photoelectric conversion elements, a plurality of transfer switches each having one terminal connected to a corresponding photoelectric conversion element, a signal input portion commonly connected to the other terminal of each of the plurality of transfer switches, and an amplifier connected to the signal input portion, and a scanning circuit for outputting a scanning clock for each pixel block.

Owner:CANON KK

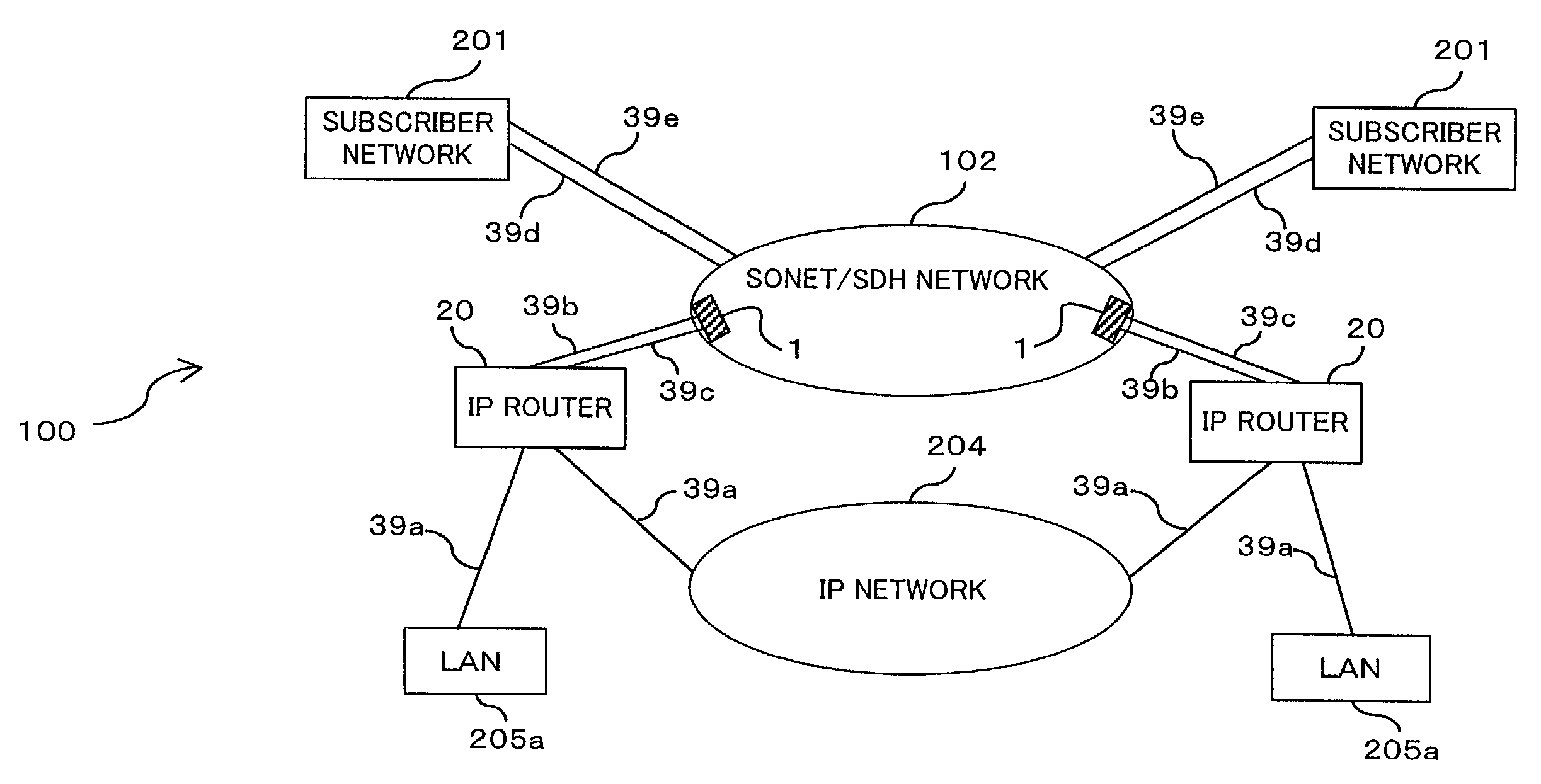

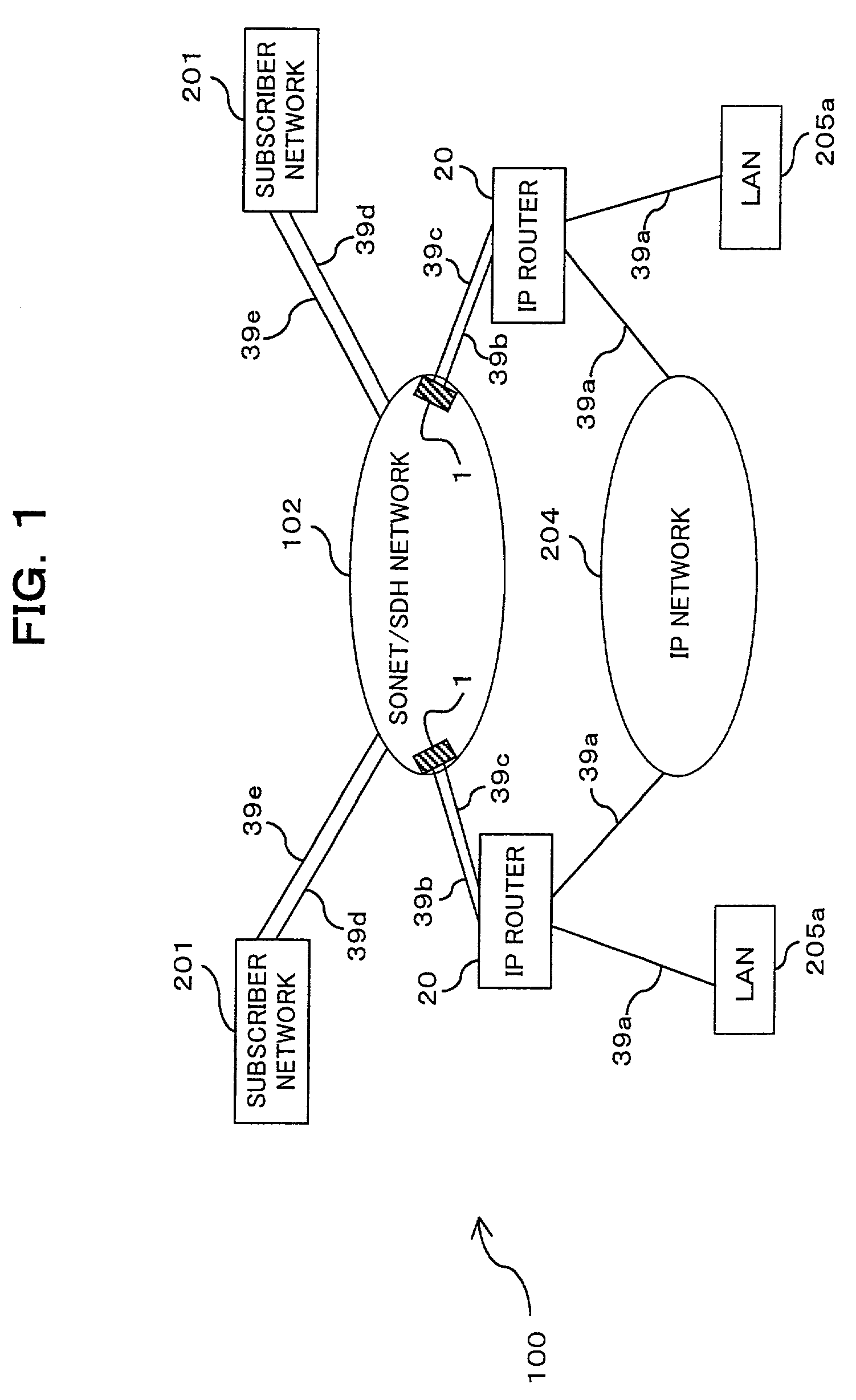

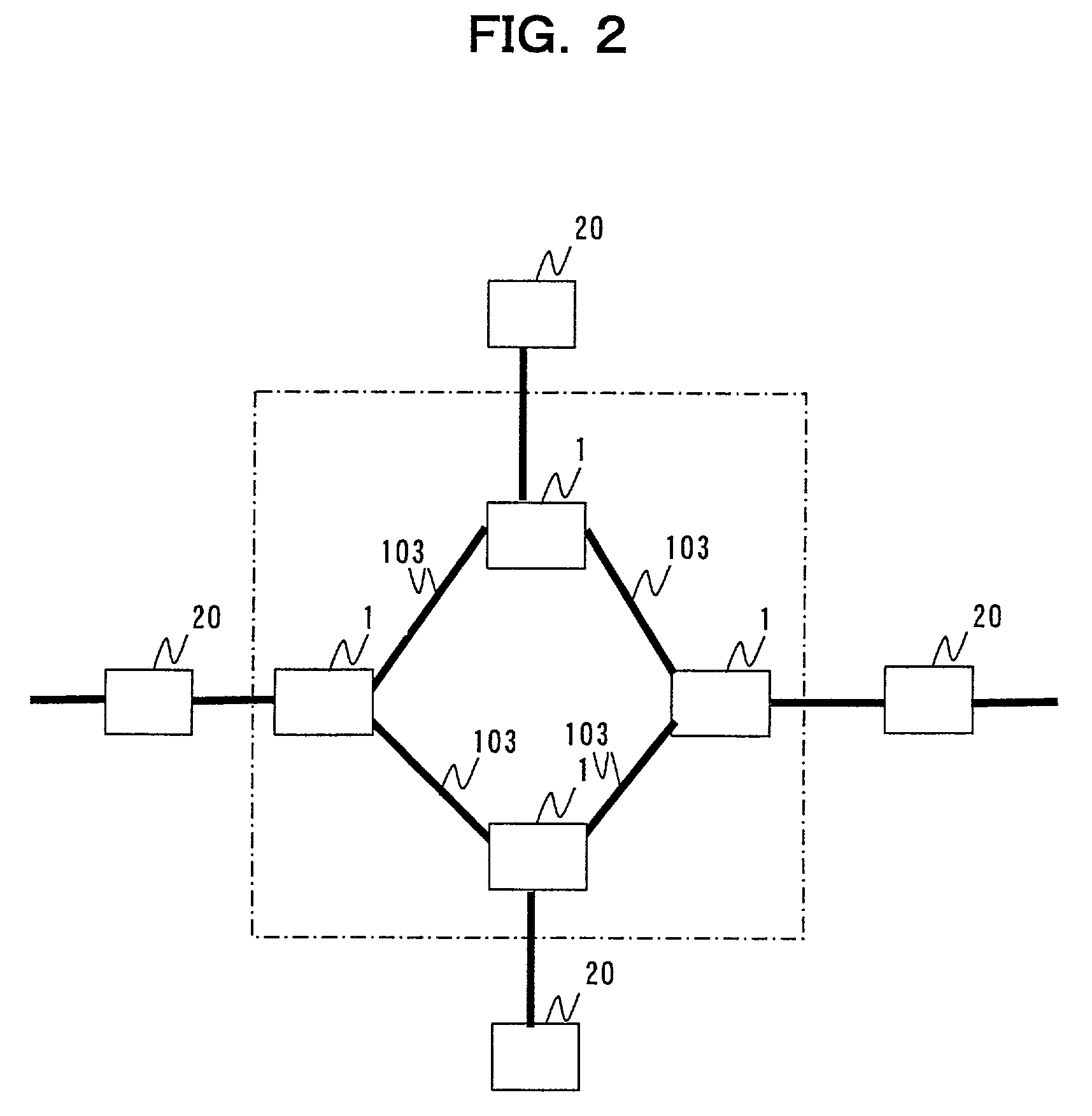

Transmitter, SONET/SDH transmitter, and transmission system

InactiveUS7315511B2Easy to handleSmooth switchingError preventionTransmission systemsEngineeringLine switching

Disclosed herein is a SONET / SDH transmitter provided in a transmission system in which a SONET / SDH network and an IP network are connected with optical LAN-IF. The SONET / SDH transmitter has a redundancy transmission line structure consisting of two transmission lines, a K-packet processing section, and a transmitting section. The K-packet processing section is used for generating a specific byte (SONET K1 / K2 byte) of data representing transmission-line switching control information about the transmission lines, packetizing the generated data, and outputting a packet. The transmitting section is used for transmitting the packet to the transmitter provided opposite through the transmission lines. This SONET / SDH transmitter further has a redundancy line switching section. The redundancy line switching section is capable of selecting a transmission line, where a transmission signal with information data is transmitted, according to a status in which a packetized specific byte of data from the transmitter opposite is received.

Owner:FUJITSU LTD

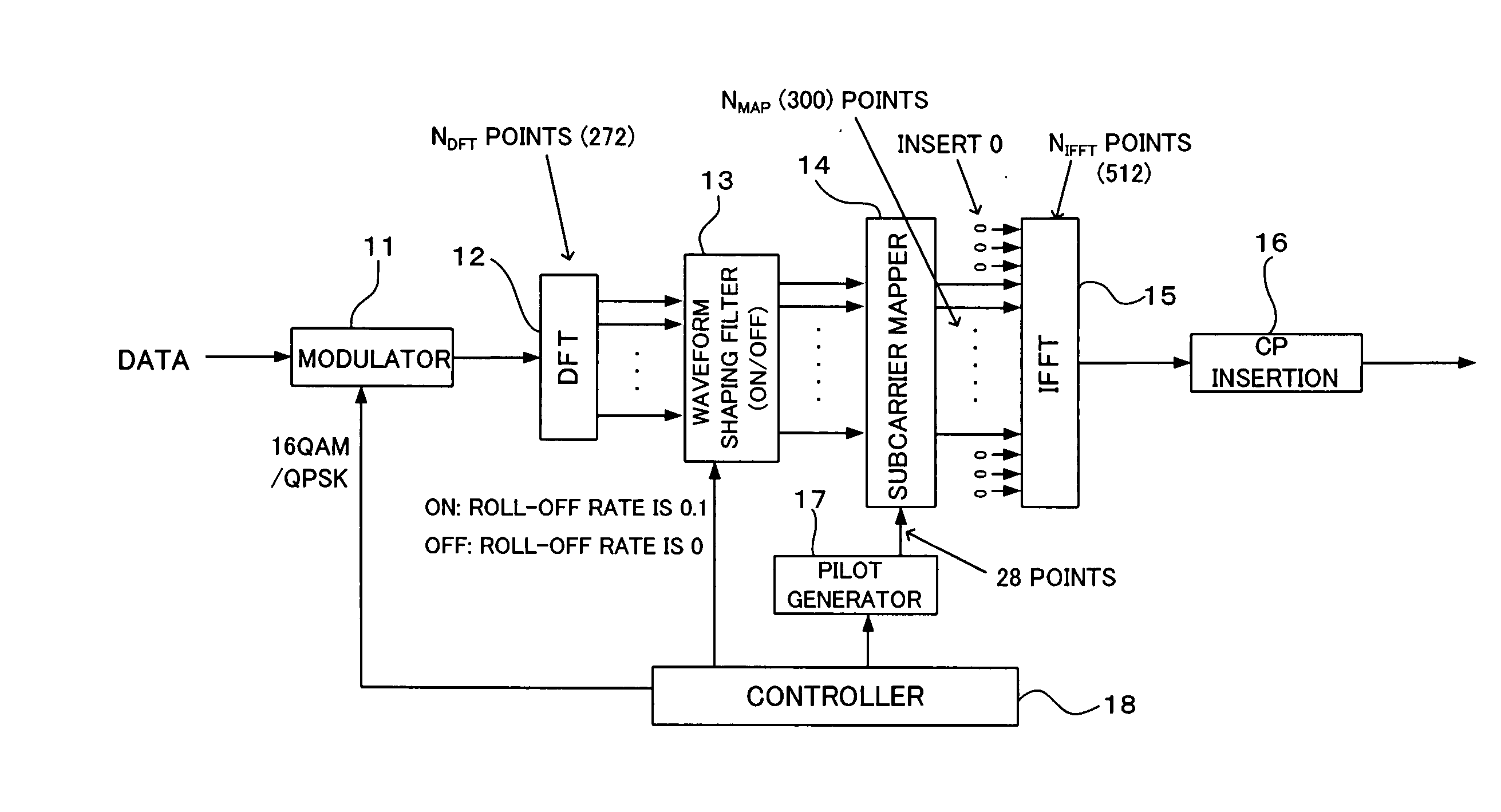

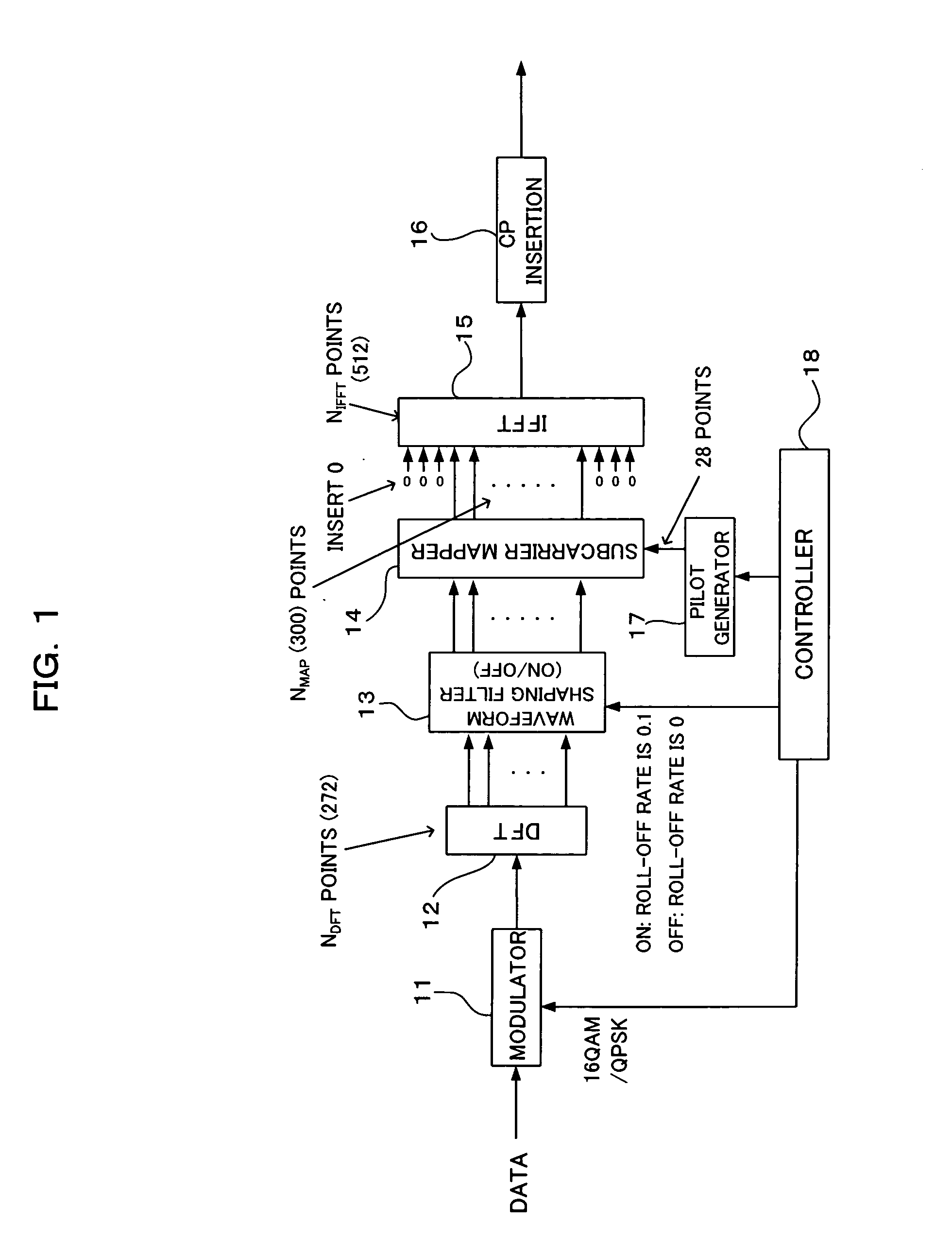

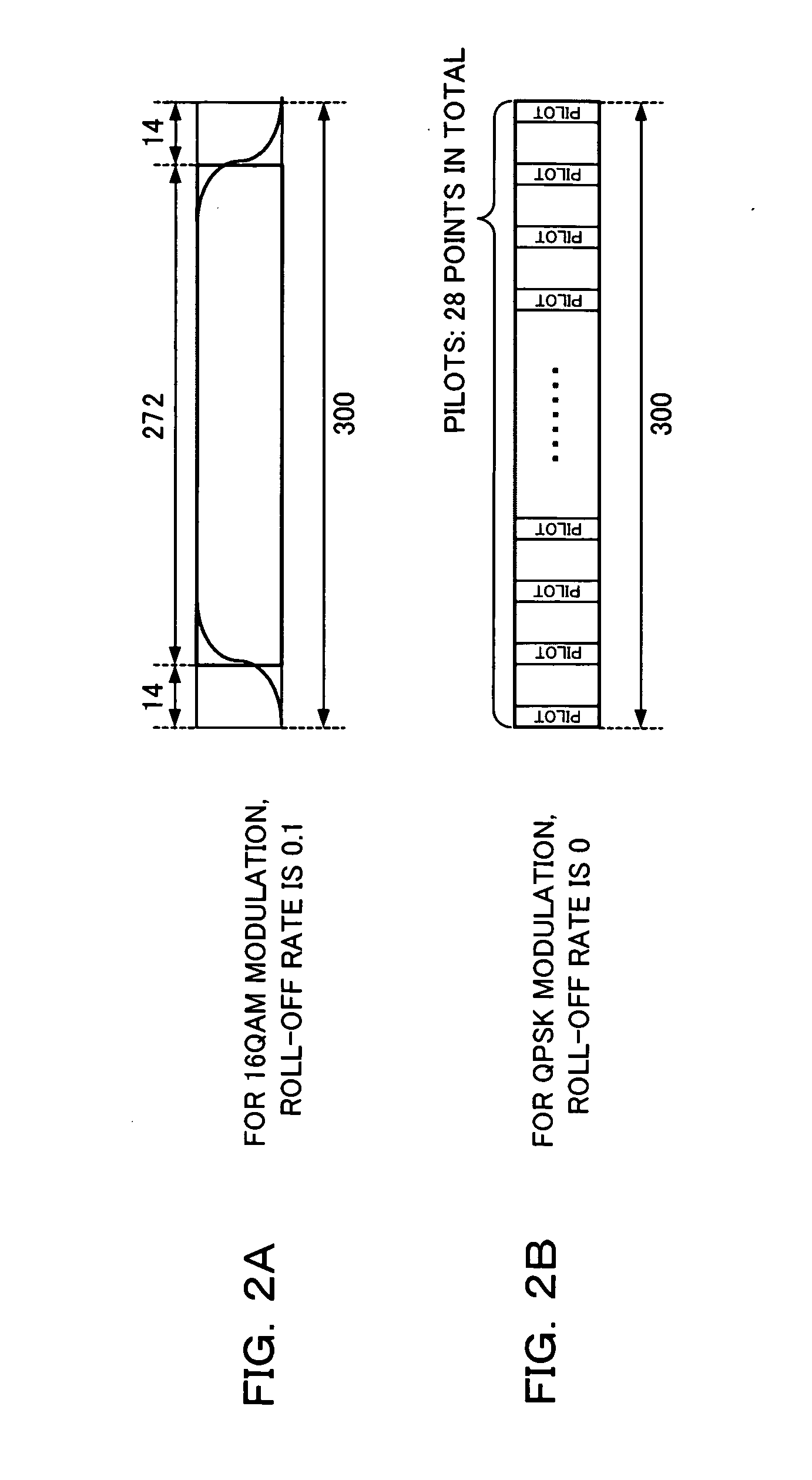

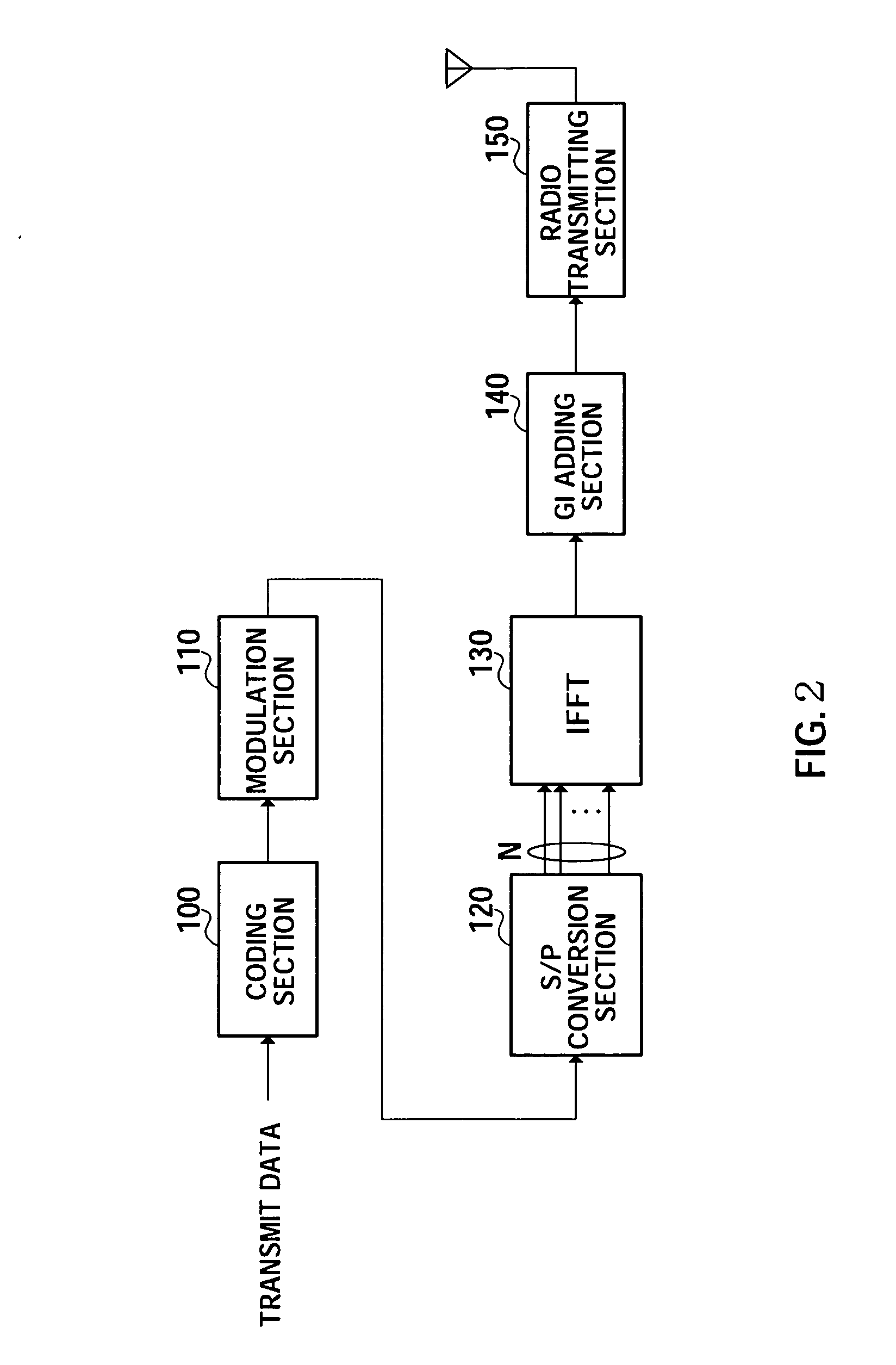

Transmitter and transmission method

InactiveUS20070280365A1Frequency utilization efficiency can be improvedSmall sizeTransmission path divisionSecret communicationTime domainCarrier signal

A transmitter includes a time / frequency-domain converter that converts a time-domain data signal to a frequency-domain data signal of a fixed number; a subcarrier allocator that allocates the obtained frequency-domain data signal to any of subcarriers, the number of which exceeds the fixed number, the subcarriers being allocated in a predetermined transmission frequency band; and a controller that controls the subcarrier allocator to allocate signals other than the data signal to subcarriers in an idle band to which the data signal is not allocated. By this, without the need for a plurality of time / frequency-domain conversion circuits with a large size, such as DFTs, frequency utilization efficiency (data transmission efficiency) is improved.

Owner:FUJITSU LTD

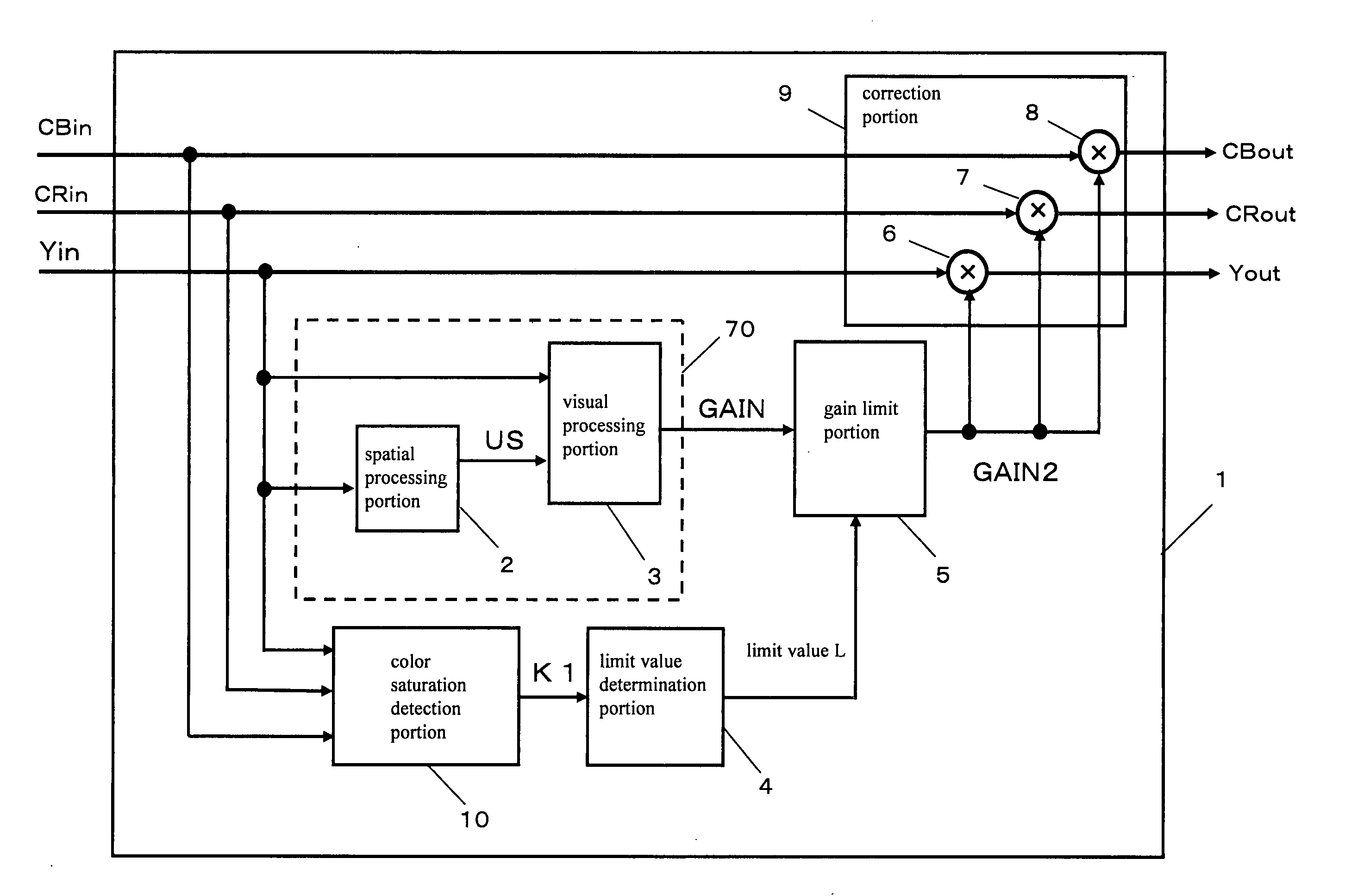

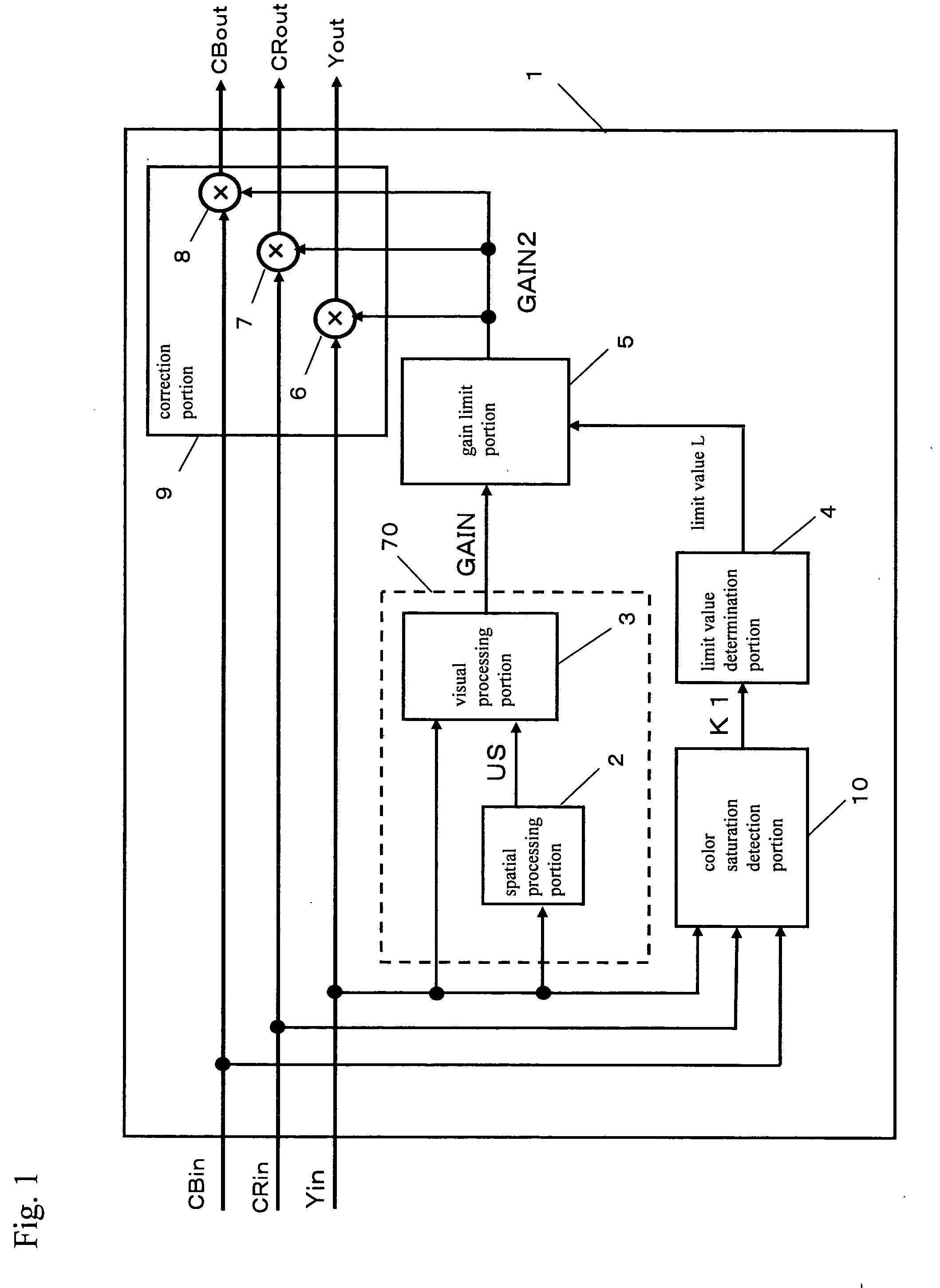

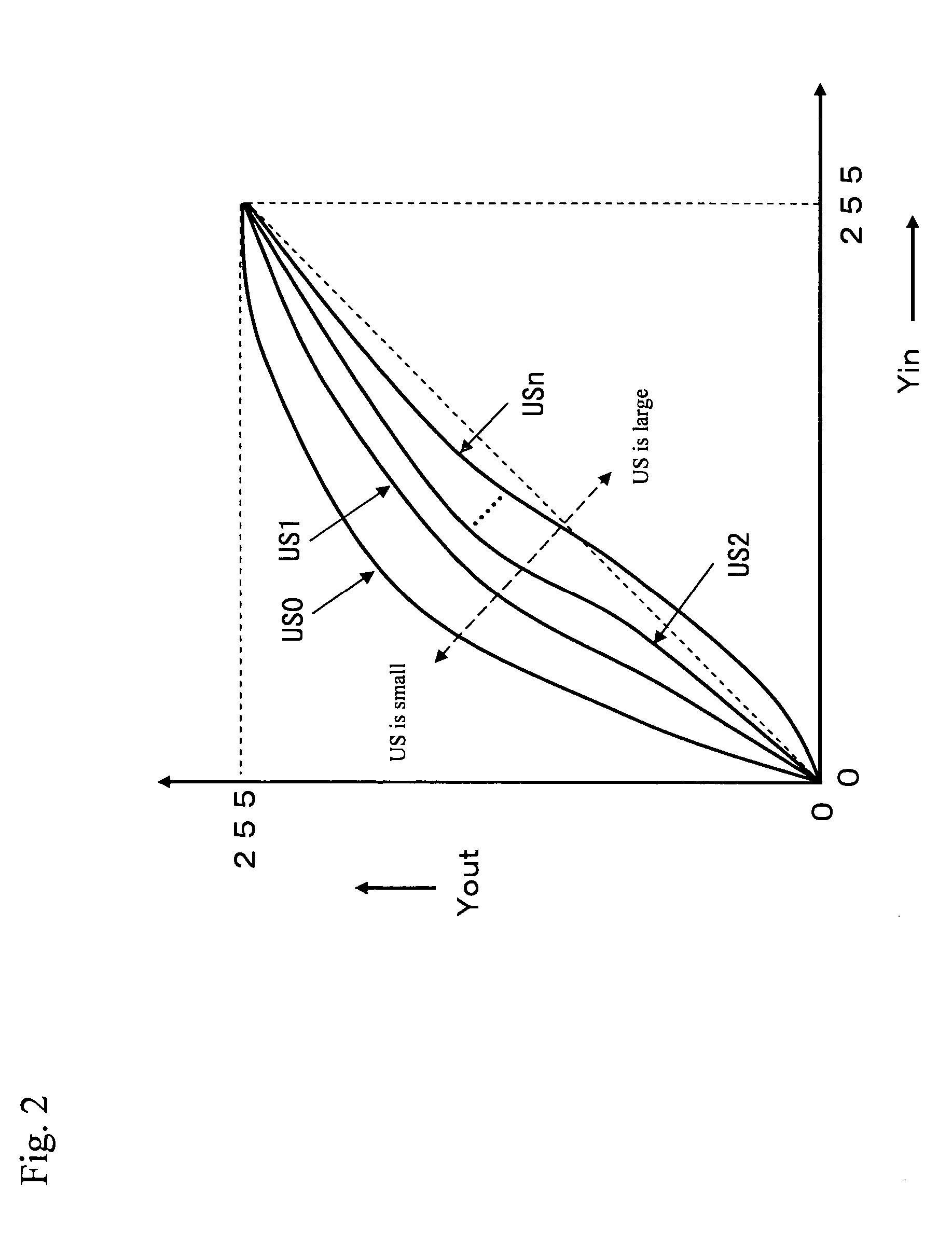

Visual processing device, display device, and integrated circuit

ActiveUS20070080975A1Precise processingSimple structureTelevision system detailsImage enhancementPattern recognitionDisplay device

The invention achieves a visual processing device that can execute precise contrast adjustment on image signals that have been input and that does not cause discrepancies in the output timing of the image signals that are output. The visual processing device is provided with a gain-type visual processing portion that outputs a first gain signal having predetermined gain characteristics with respect to the input image signal, and a correction portion that corrects the input image signal based on the first gain signal.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

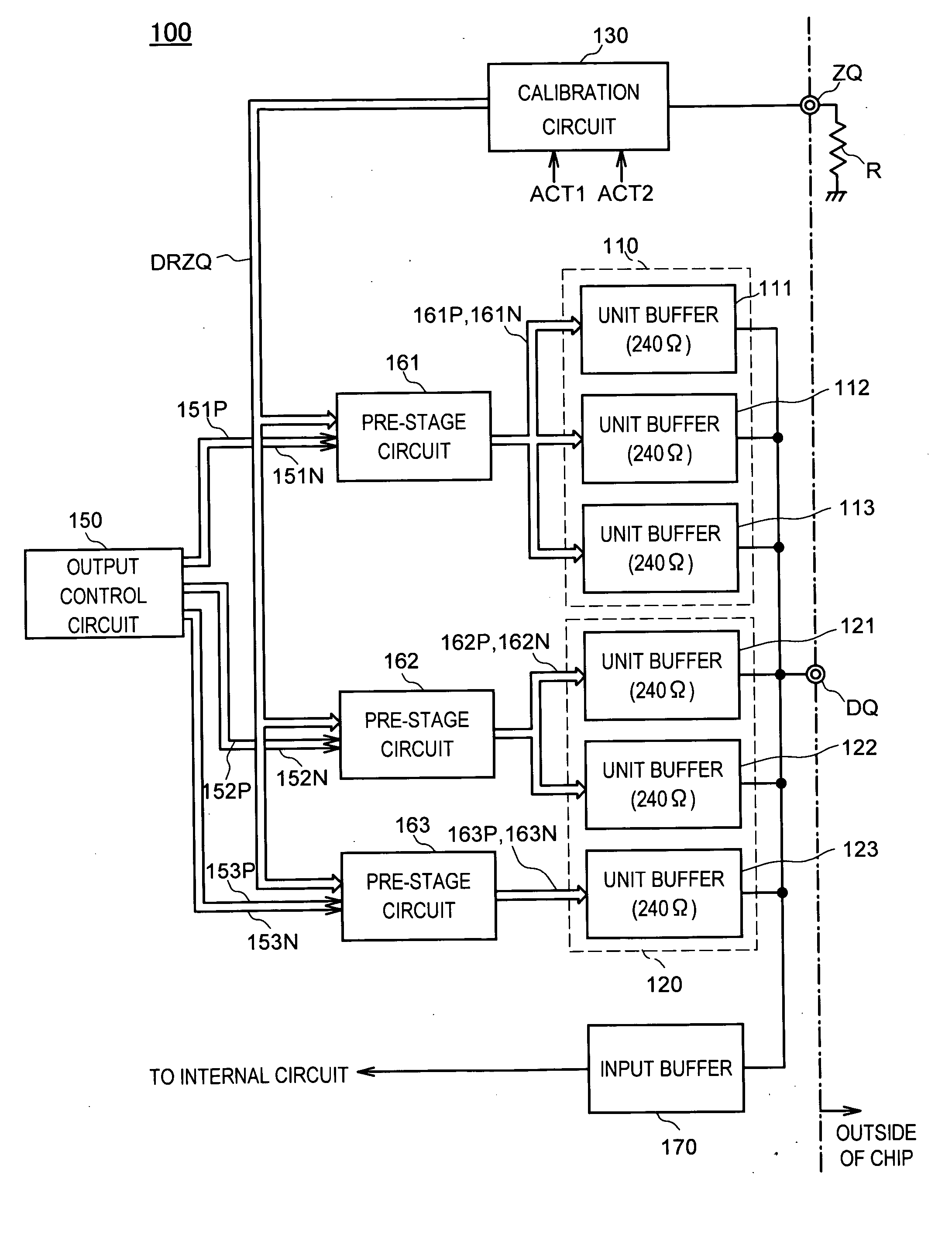

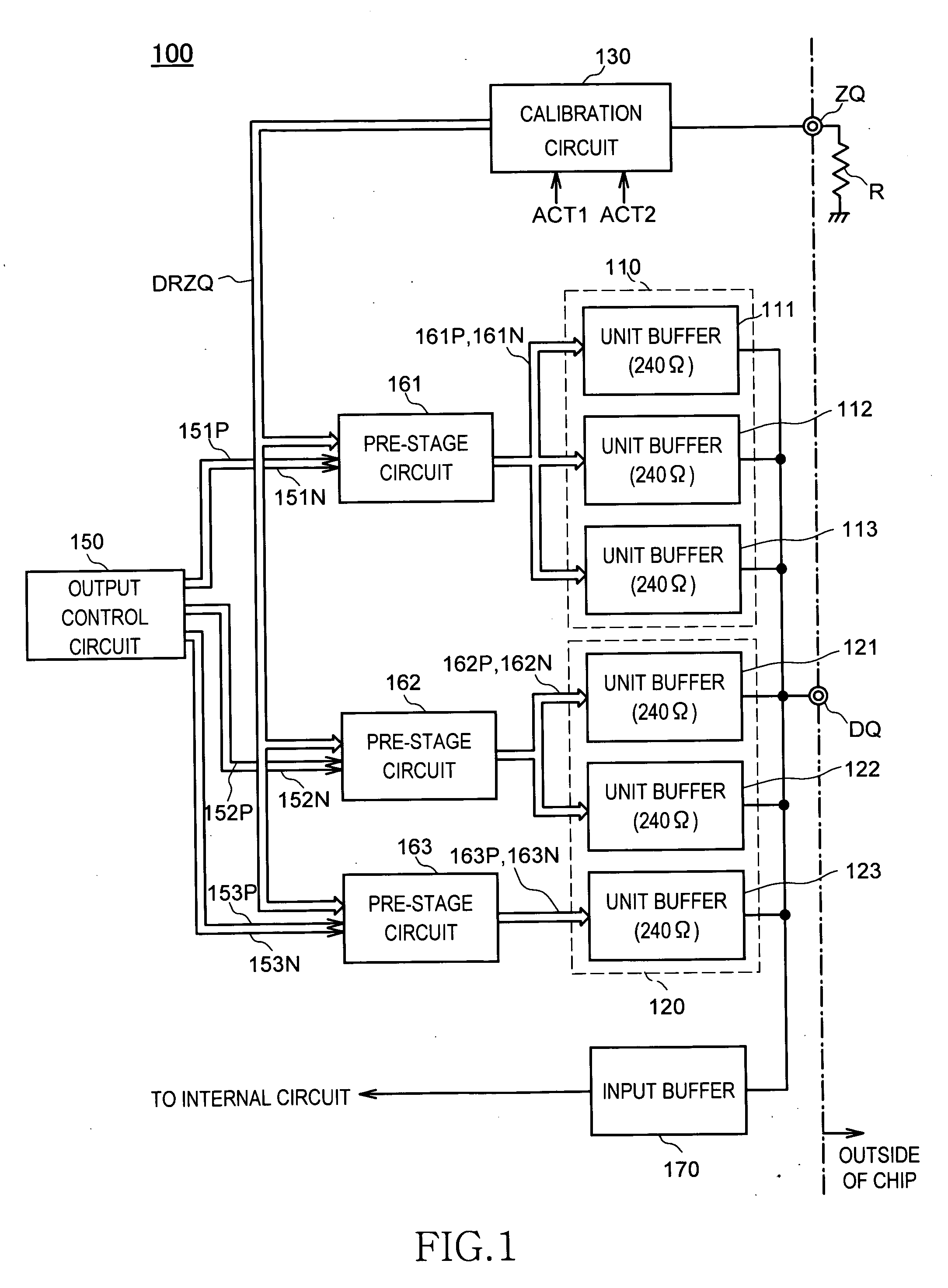

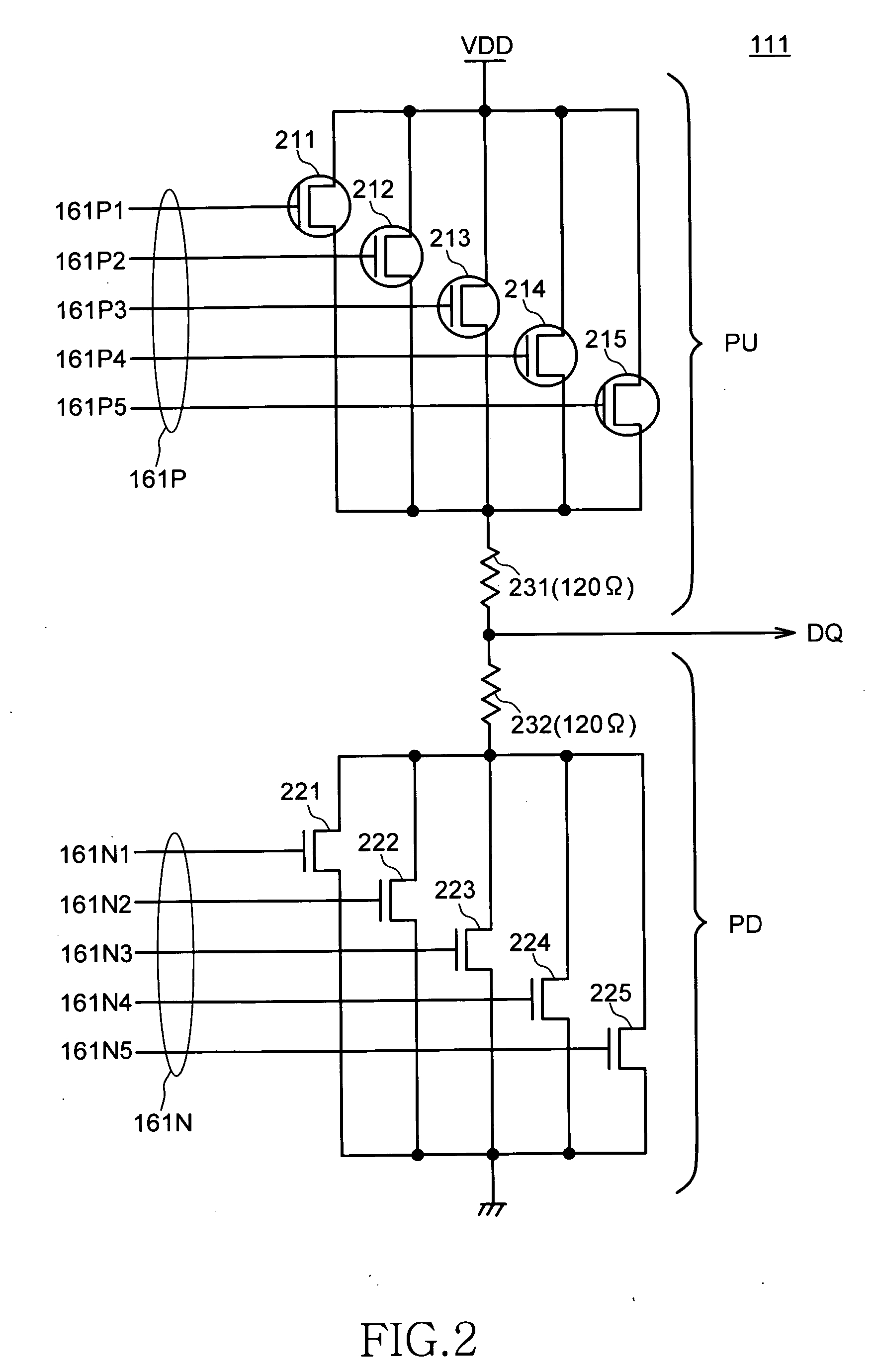

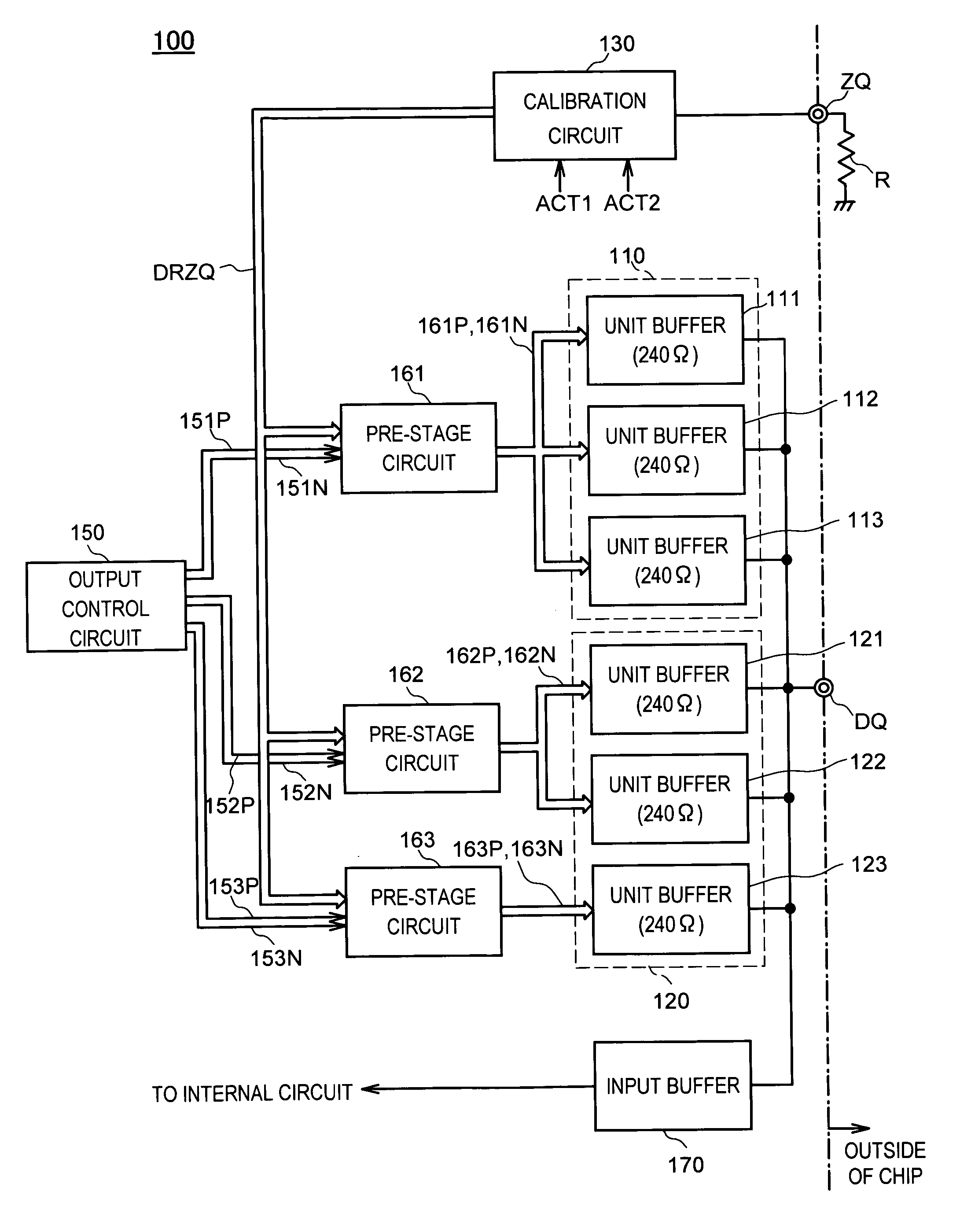

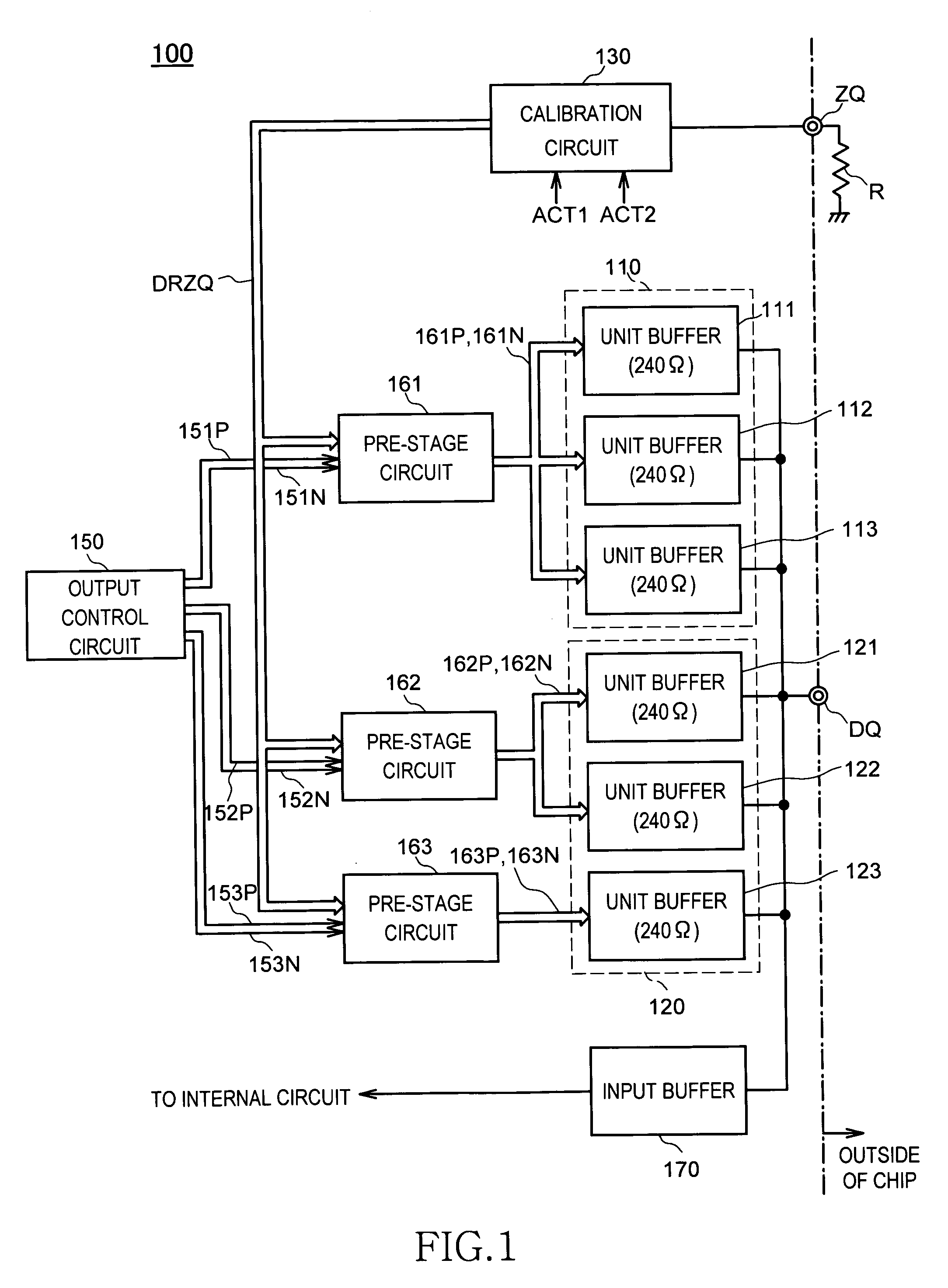

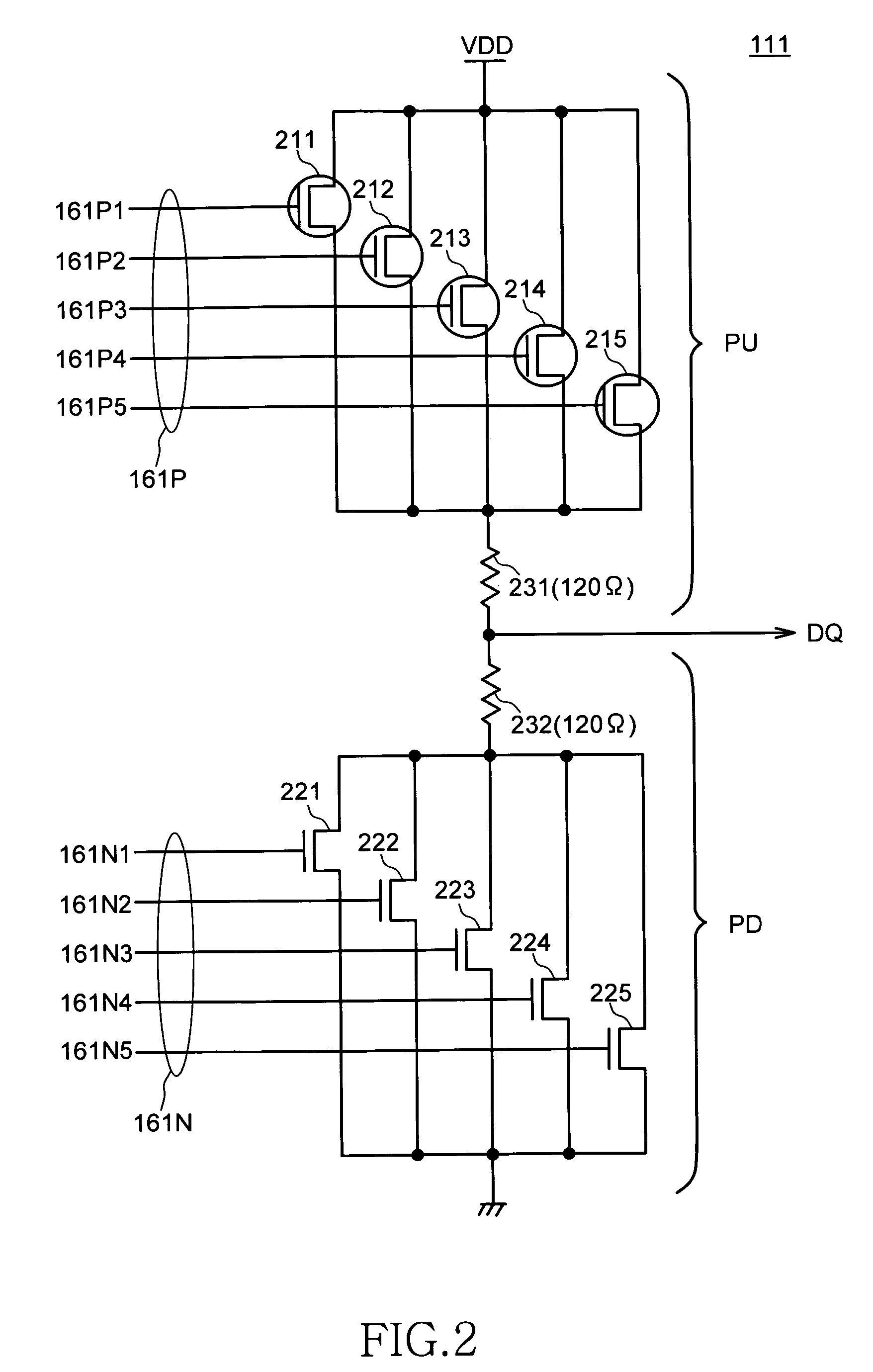

Output circuit for semiconductor device, semiconductor device having output circuit, and method of adjusting characteristics of output circuit

ActiveUS20060158198A1Reduce calibration timeReduce circuit sizeInput/output impedence modificationImpedence matching networksEngineeringSemiconductor

Owner:LONGITUDE LICENSING LTD

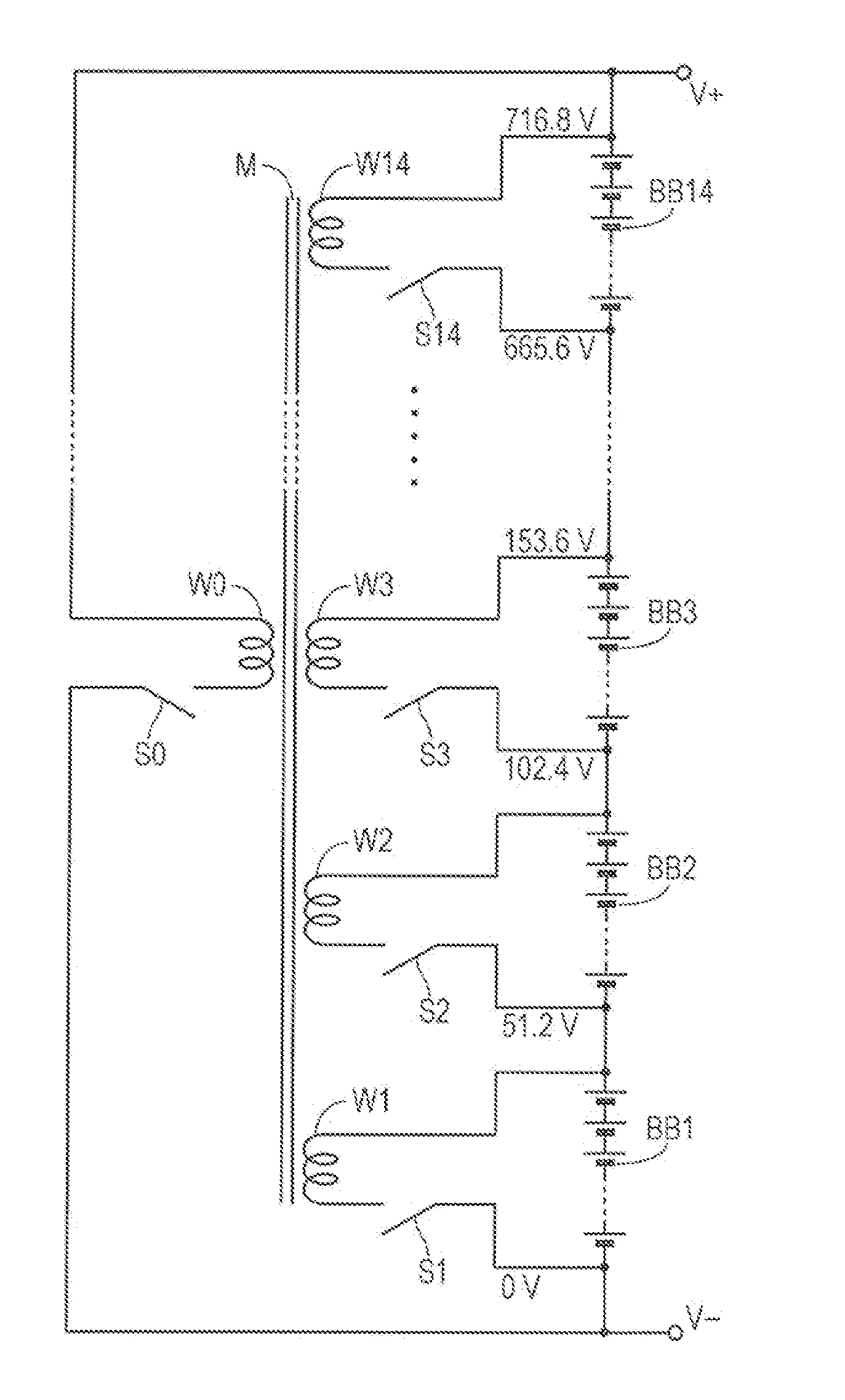

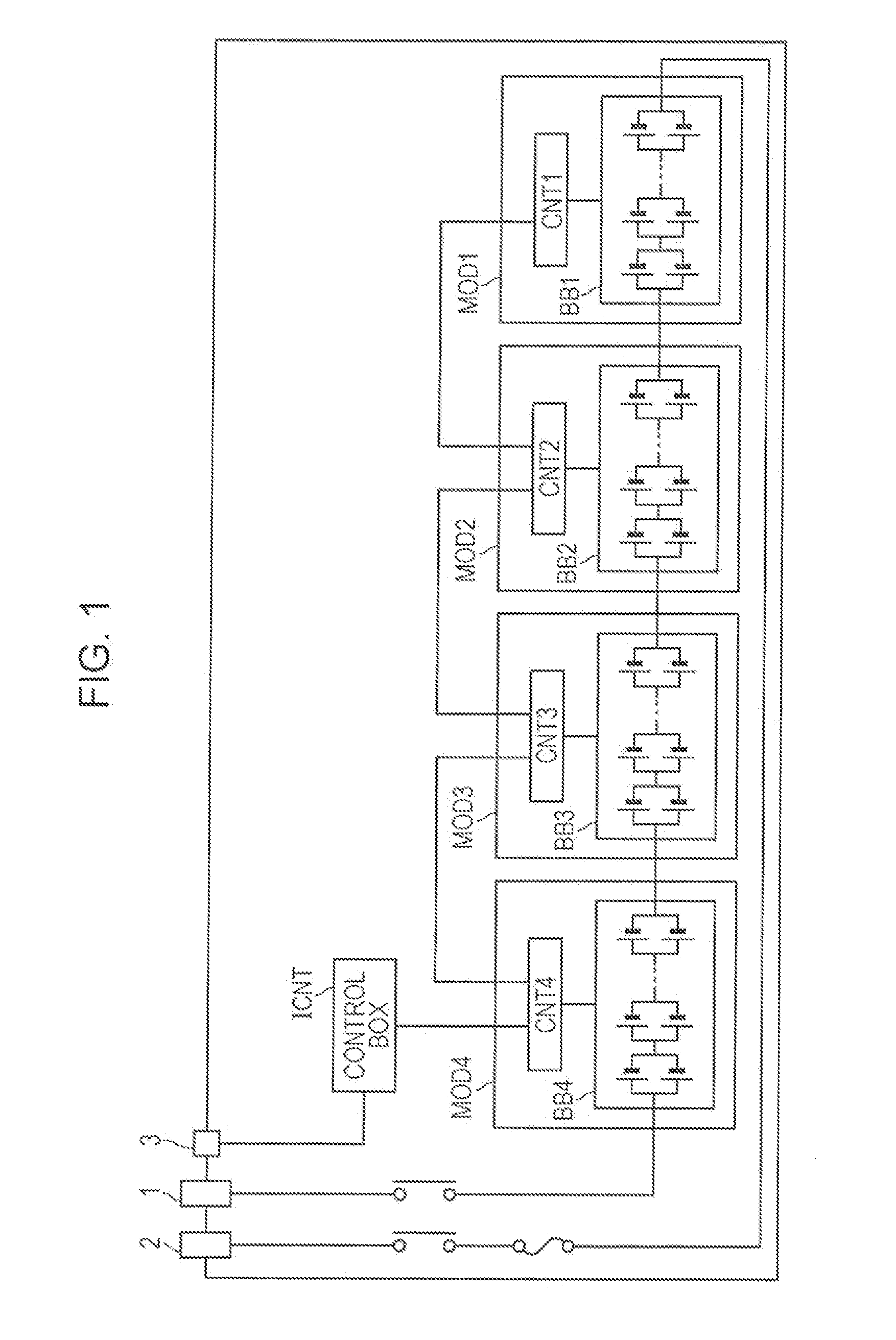

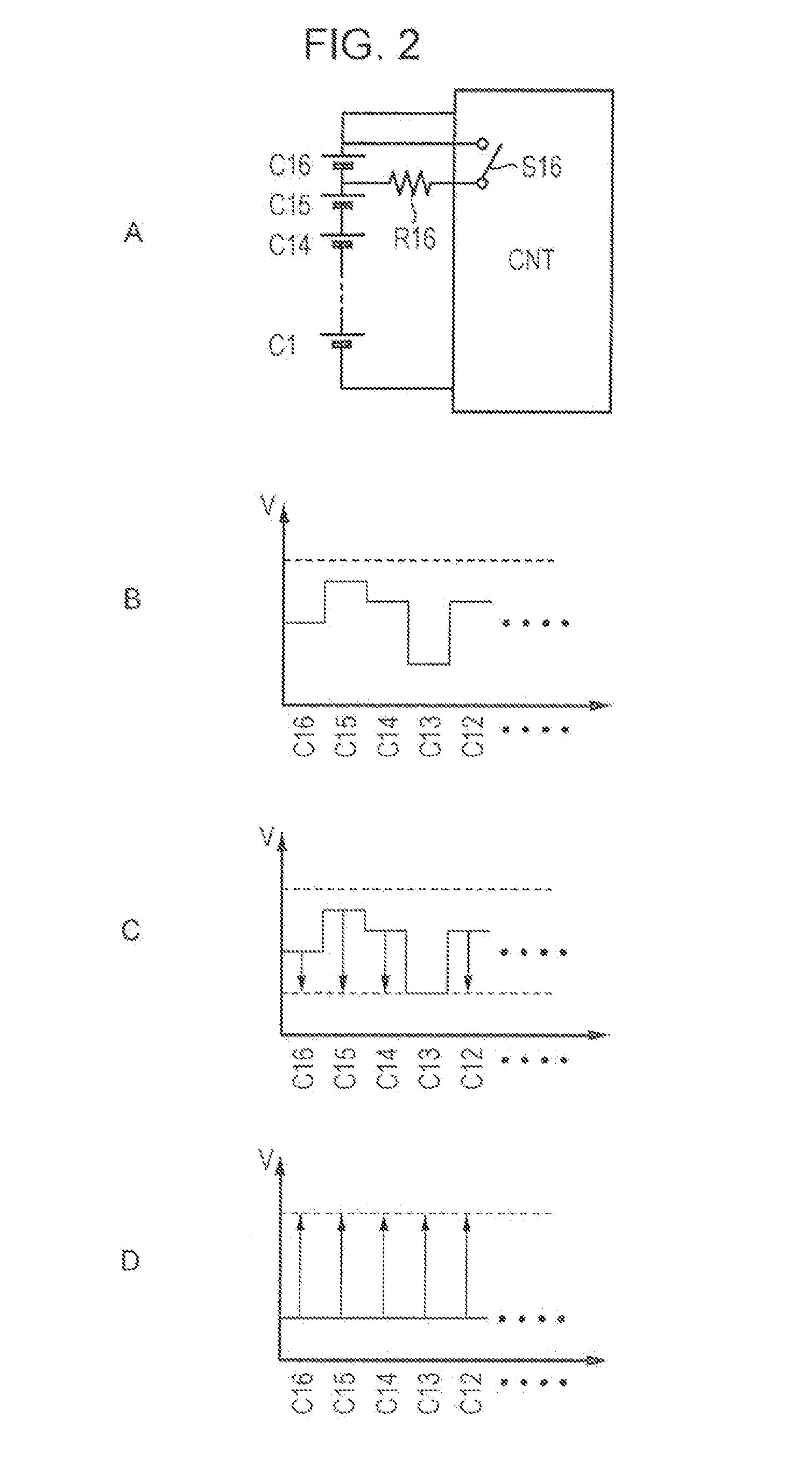

Power reserve apparatus, power system, and electric vehicle

ActiveUS20140354212A1Reduce circuit sizePrevent overall voltage from decreasingCharge equalisation circuitElectric devicesElectrical batteryComputer module

A power reserve apparatus is disclosed. In one embodiment, the power reserve apparatus comprises a first module including a first set of battery cells and a first inter-cell balance adjustment unit configured to use passive balancing to reduce voltage variance among the first set of battery cells. The power reserve apparatus also comprises a second module including a second set of battery cells and a second inter-cell balance adjustment unit configured to use passive balancing to reduce voltage variance among the second set of battery cells. The power reserve apparatus further comprises an inter-module balance adjustment unit configured to use active balancing to reduce voltage variance among the first and second modules.

Owner:MURATA MFG CO LTD

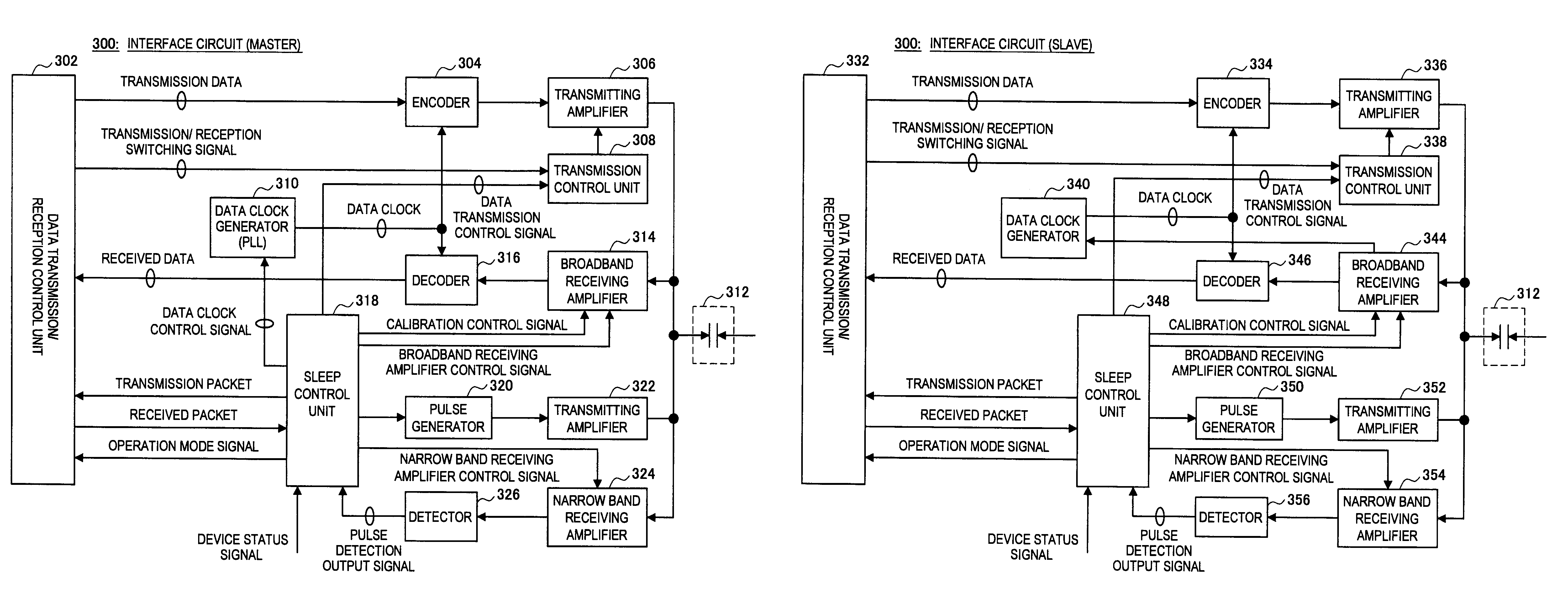

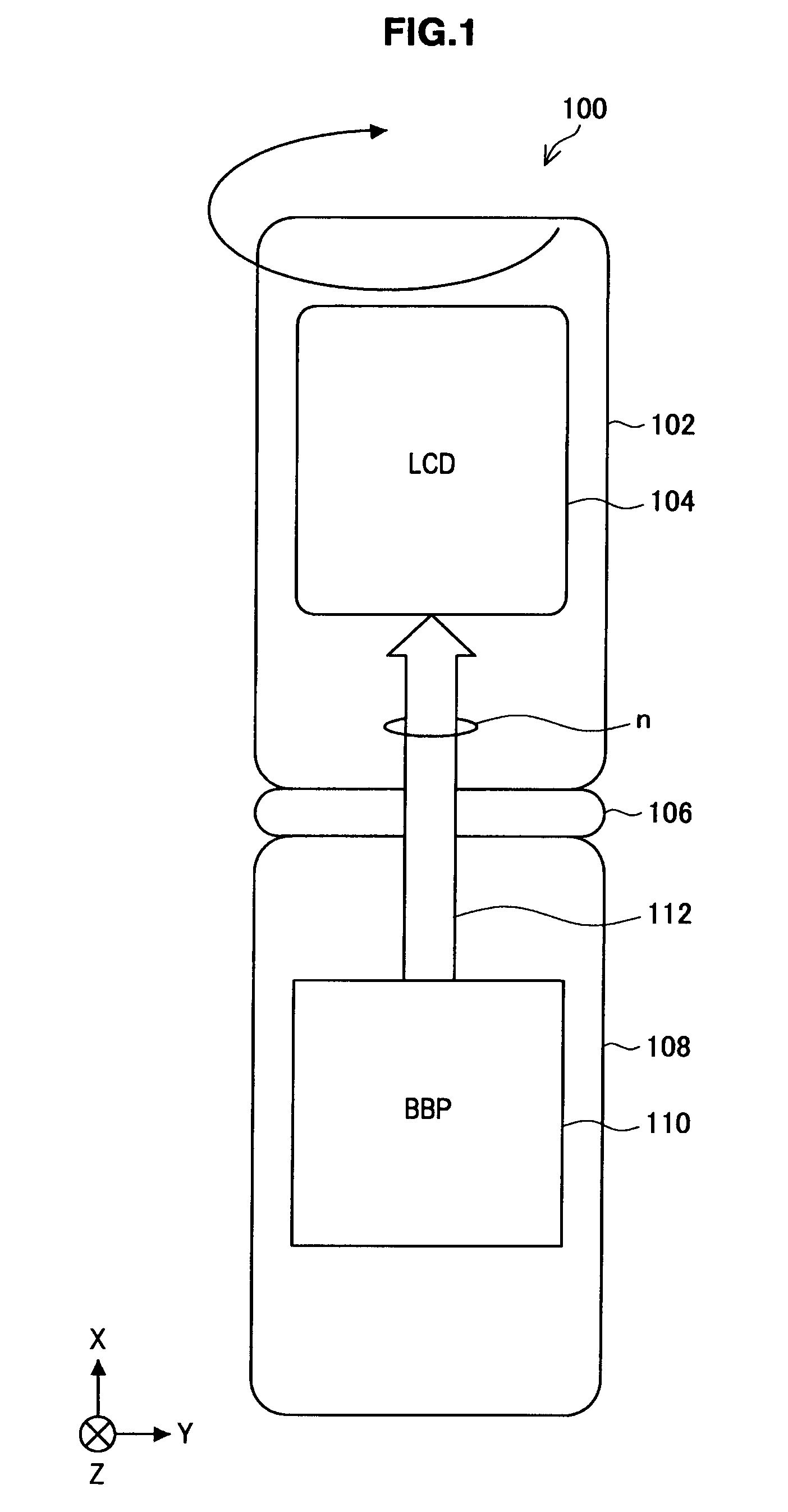

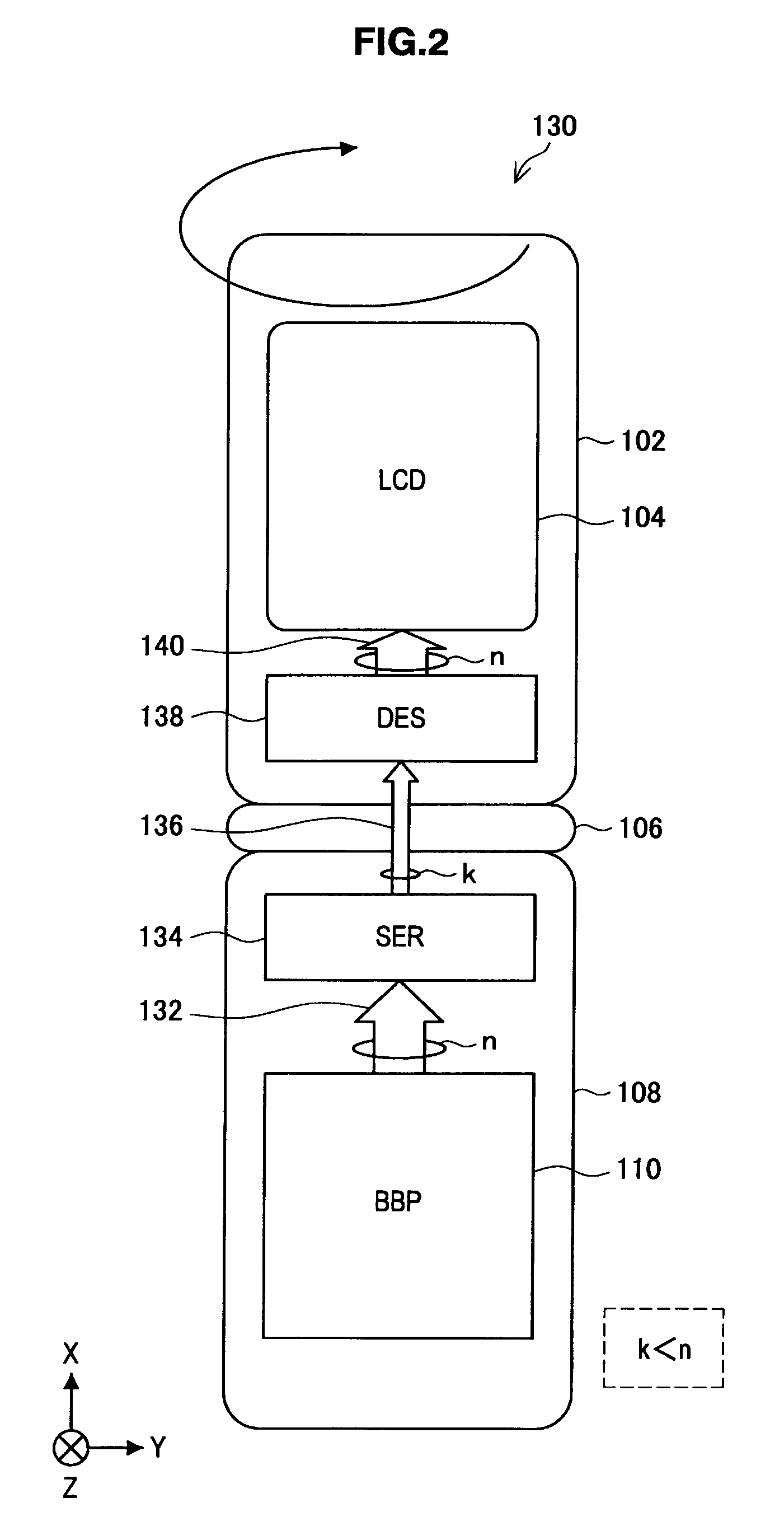

Information processing apparatus and mode switching method

InactiveUS8406316B2Reduce in quantityEasy to receive signalEnergy efficient ICTError preventionInformation processingEngineering

Provided is an information processing apparatus which includes a first-module including a first narrow-band communicator for performing narrow band communication with a second-module, a first broadband-communicator for performing broadband communication with the second-module, and a first controller for controlling an operation state of the first broadband-communicator according to an operation mode, and a second-module including a second narrow-band communicator for performing narrow-band communication with the first-module, a second broadband-communicator for performing broadband communication with the first-module, and a second controller for controlling an operation state of the second broadband-communicator according to an operation mode. The first controller places the first broadband-communicator in an operation state in a first mode, and places the first broadband-communicator in a standby state in a second mode. The second controller places the second broadband-communicator in an operation state in the first mode, and places the second broadband-communicator in a standby state in the second mode.

Owner:SONY CORP

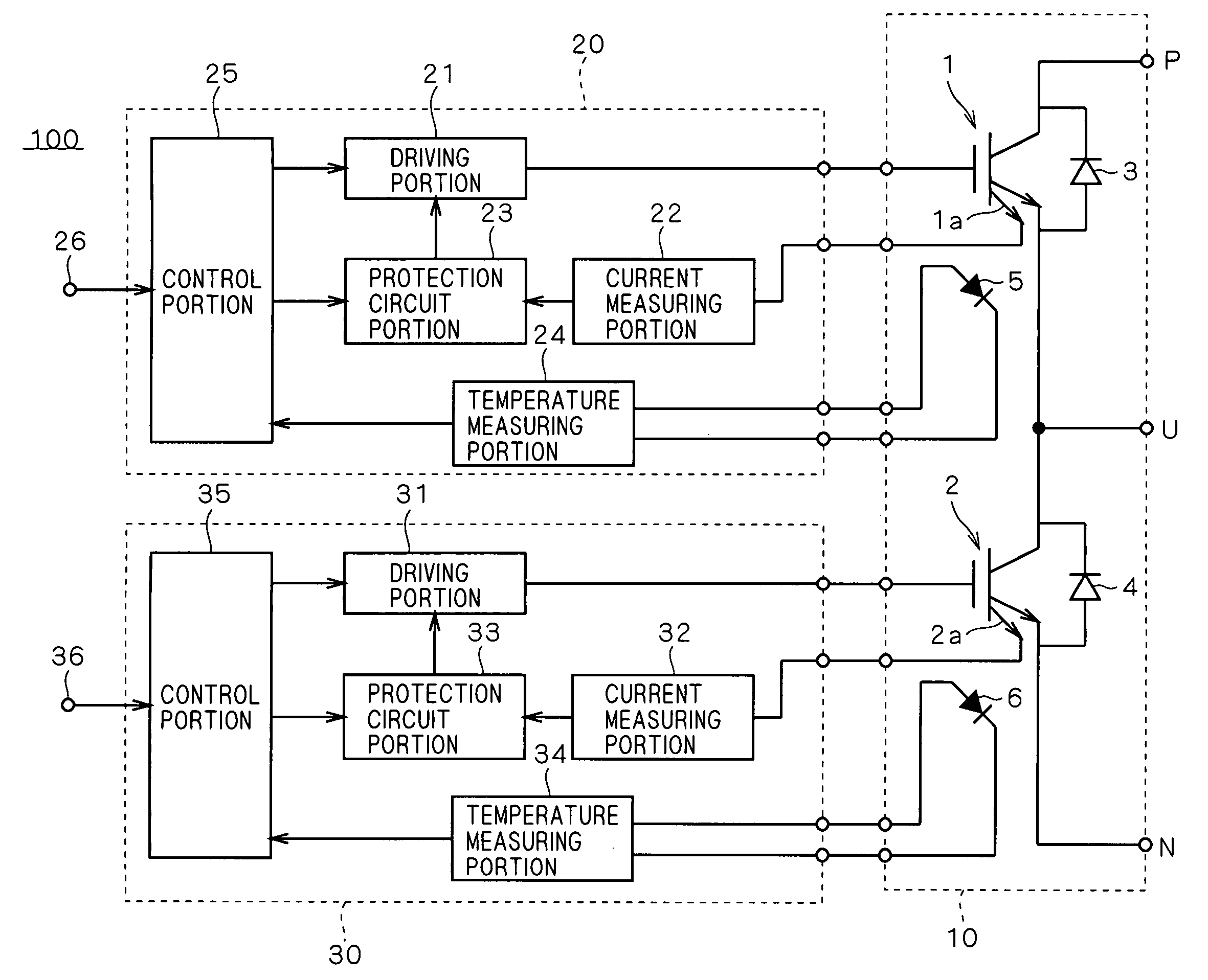

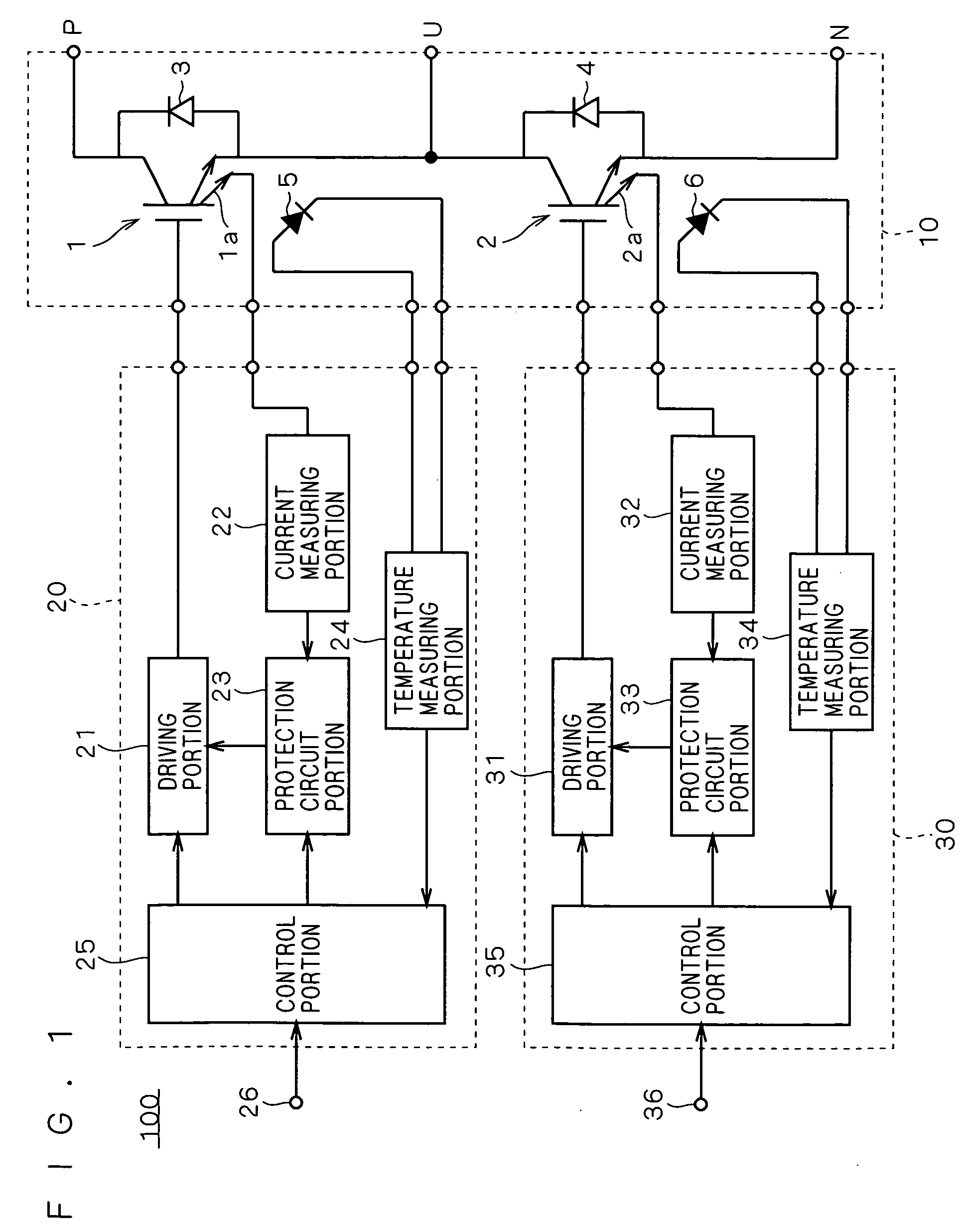

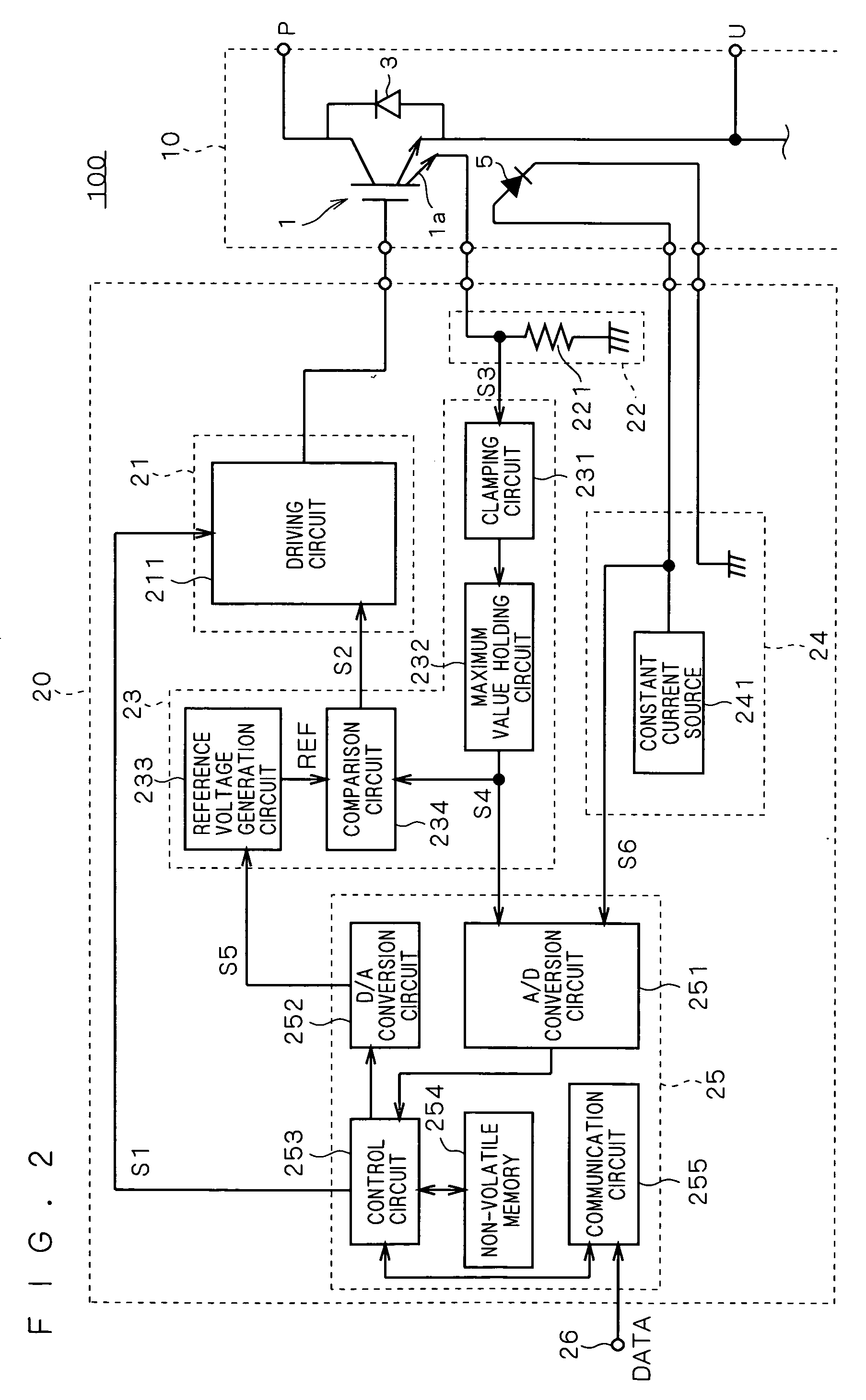

Semiconductor device having overcurrent protection function and data setting method thereof

InactiveUS20050099751A1Easy to changeReduce circuit sizeElectronic switchingArrangements responsive to excess currentPower semiconductor deviceDevice material

In a driving device (20) for driving an IGBT (1), a current measuring portion (22) measures a main current amount flowing through the IGBT (1). When the main current amount measured by the current measuring portion (22) reaches a predetermined reference level, a protection circuit portion (23) limits the main current at the IGBT (1) to protect it. A temperature measuring portion (24) measures the temperature of the IGBT (1). The control portion (25) adjusts the aforementioned reference level based on the temperature of the IGBT (1) measured by the temperature measuring portion (24). A control portion (35) stores setting values of the reference level as data.

Owner:MITSUBISHI ELECTRIC CORP

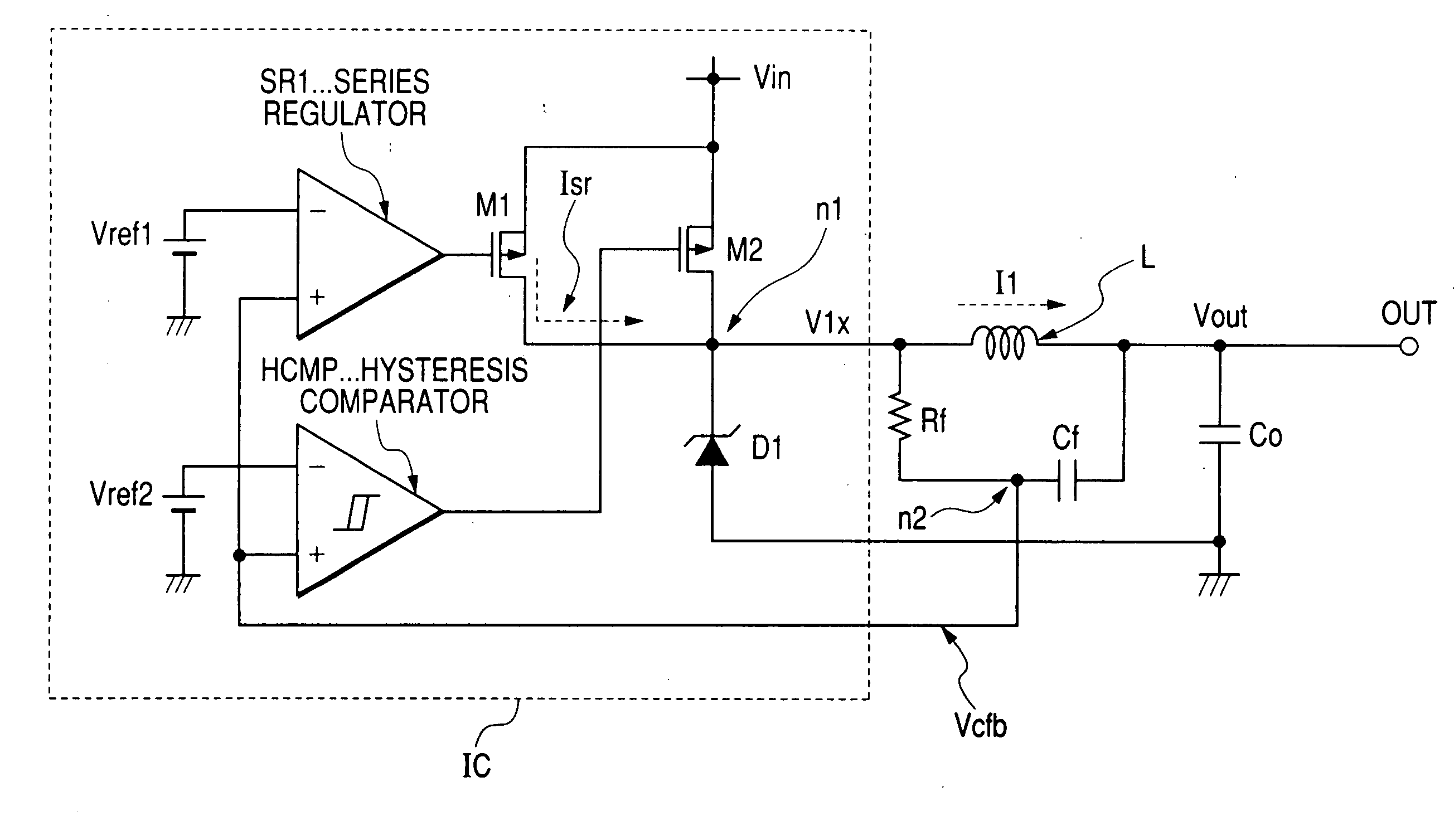

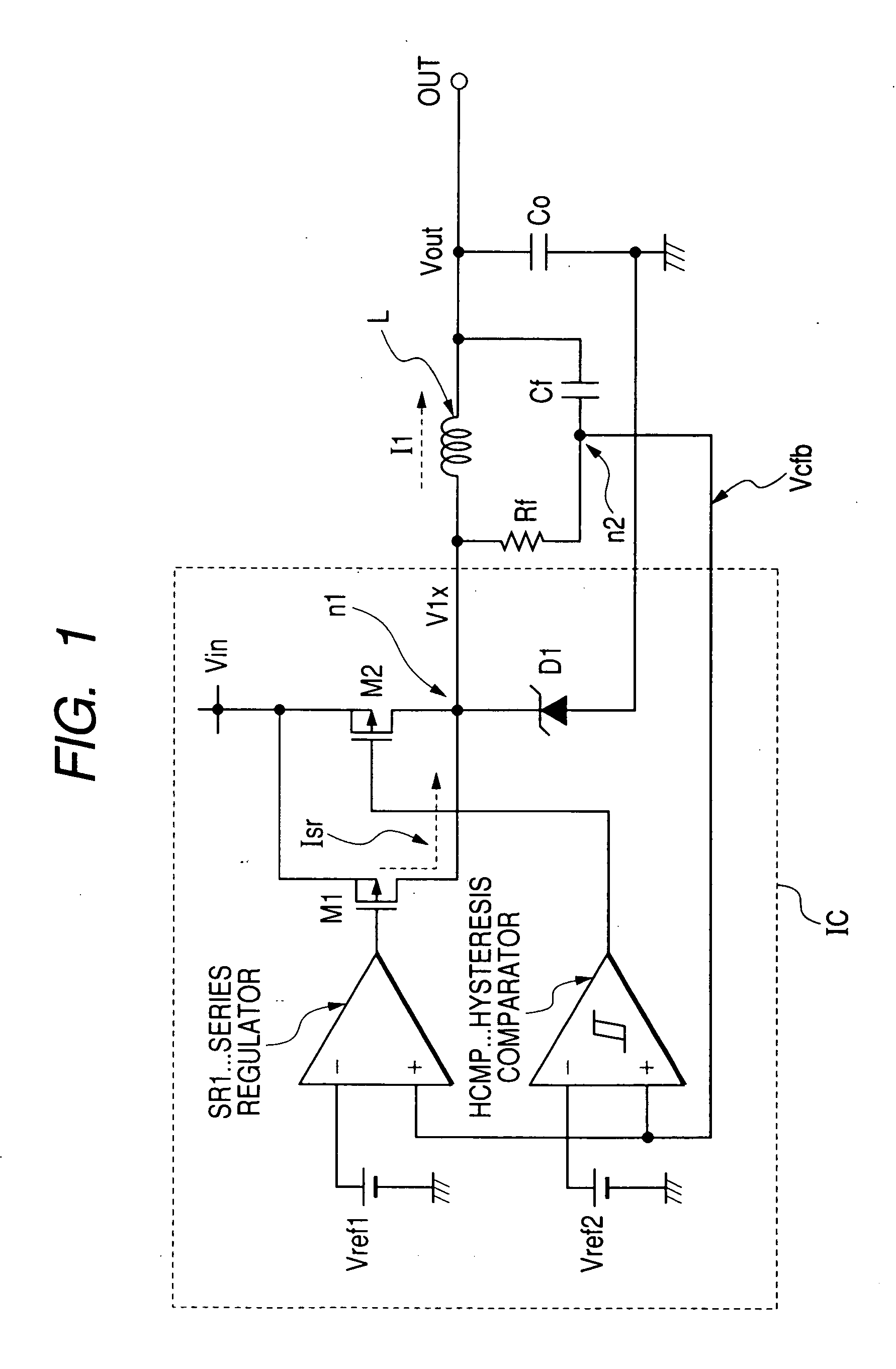

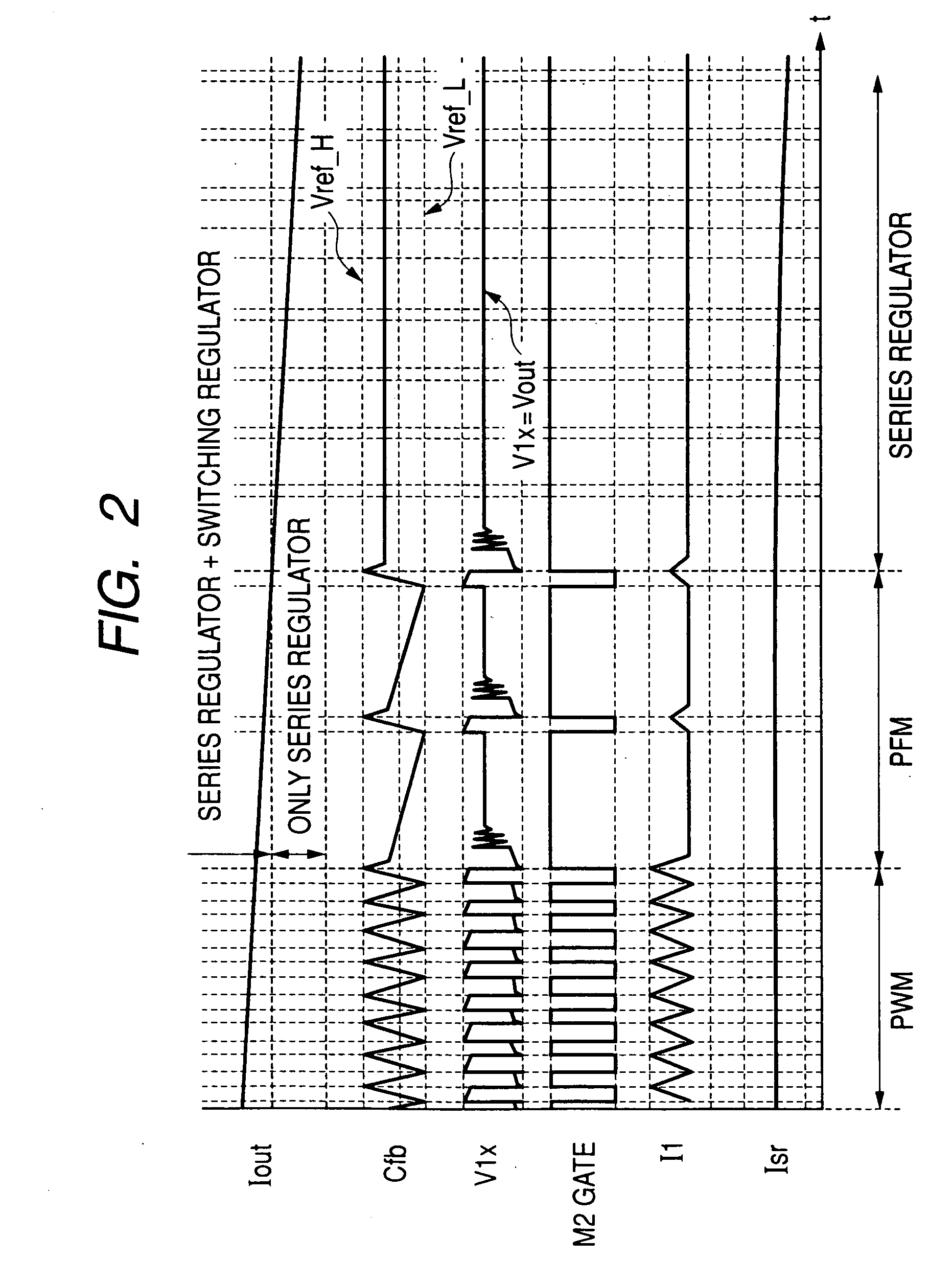

Switching power supply device and semiconductor integrated circuit

ActiveUS20050052168A1Reduce power lossReduce circuit sizeDc network circuit arrangementsEfficient power electronics conversionLoad circuitElectrical resistance and conductance

A switching power supply circuit in which a series circuit comprising a resistive element and a capacitive element is provided in a parallel configuration with an inductor which supplies a load current to a load circuit, a voltage comparator having first and second threshold voltages discriminates a voltage obtained from a mutual connecting point of the series circuit therefrom and controls a switch element for supplying a current to the inductor, thereby varying the current supplied to the inductor in accordance with a variation in the load current is combined with a series power supply circuit which shares the load current of the load circuit.

Owner:RENESAS ELECTRONICS CORP

Wireless communication system, wireless communication apparatus, and wireless communication method

ActiveUS8260198B2Without deteriorating beamforming characteristicImprove process capabilityMultiplex communicationNetwork topologiesCommunications systemComputer terminal

Owner:SONY CORP

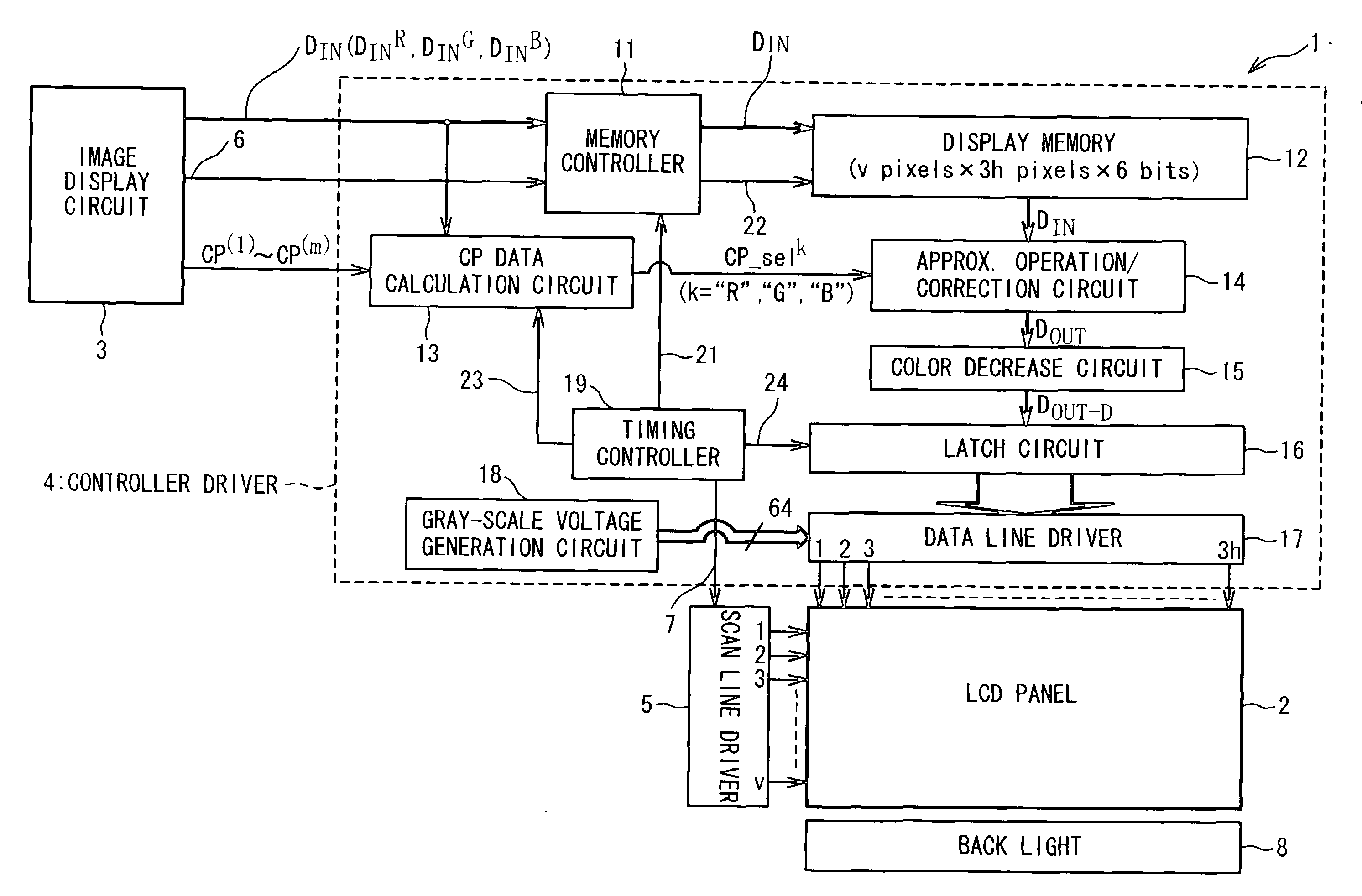

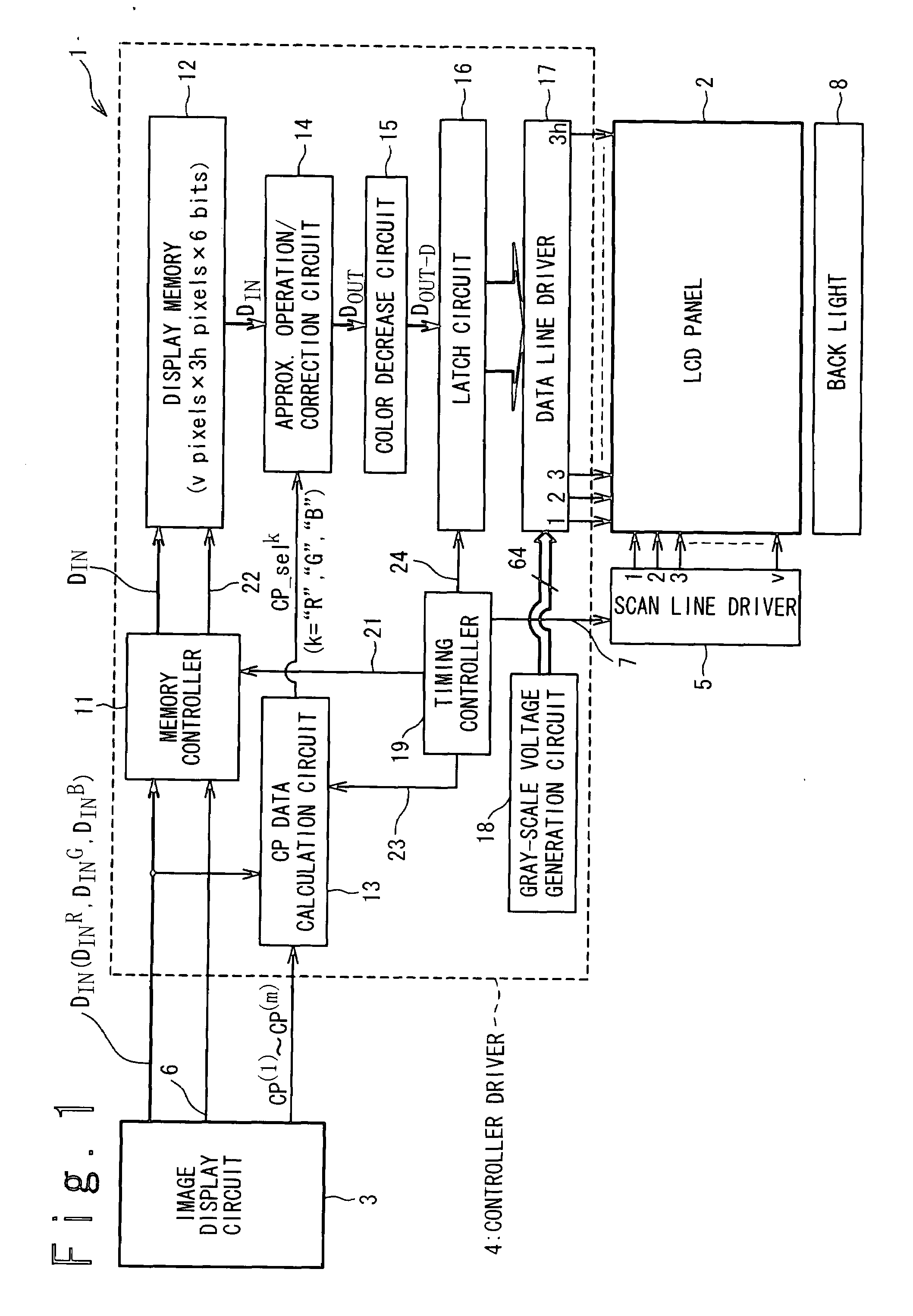

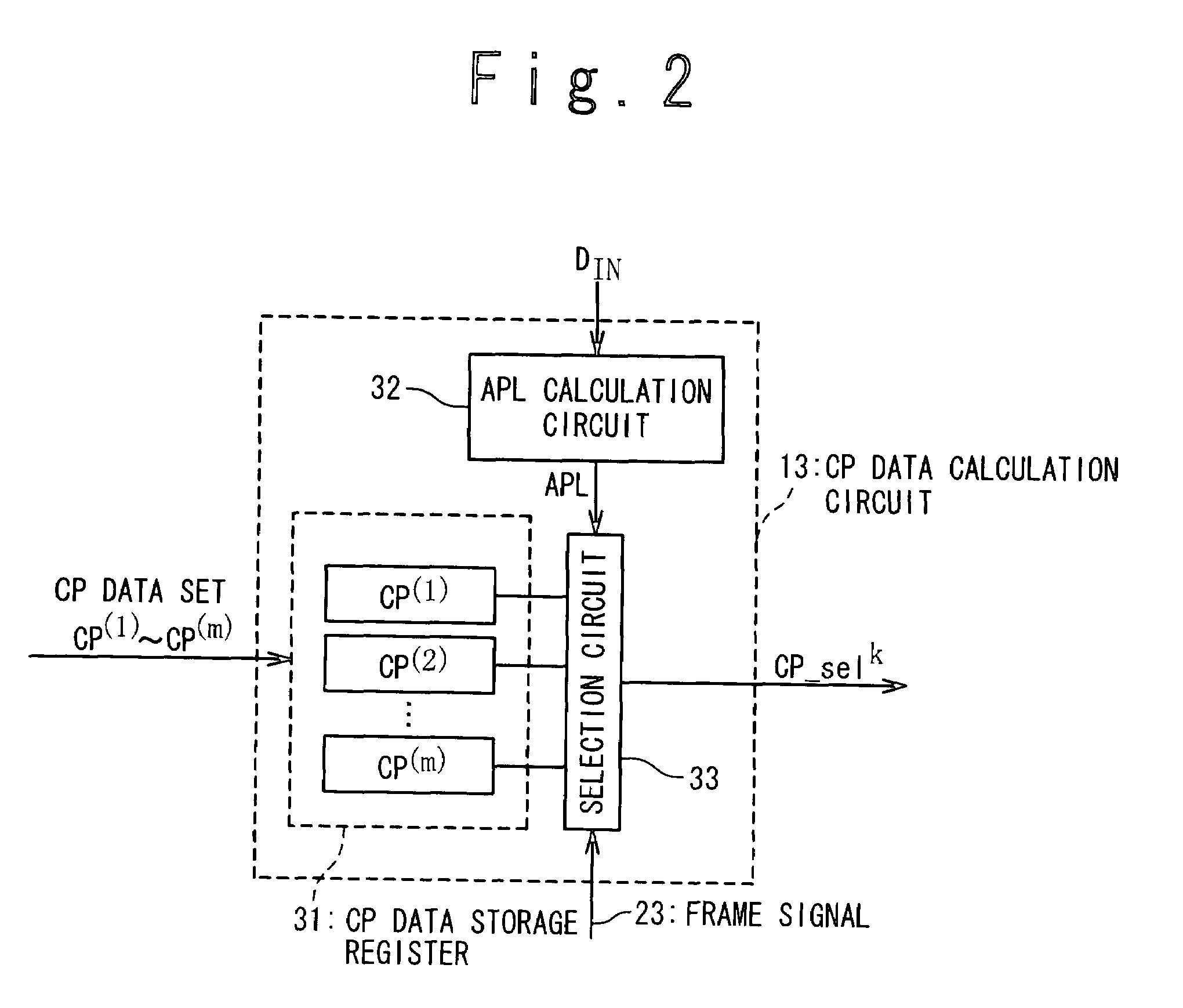

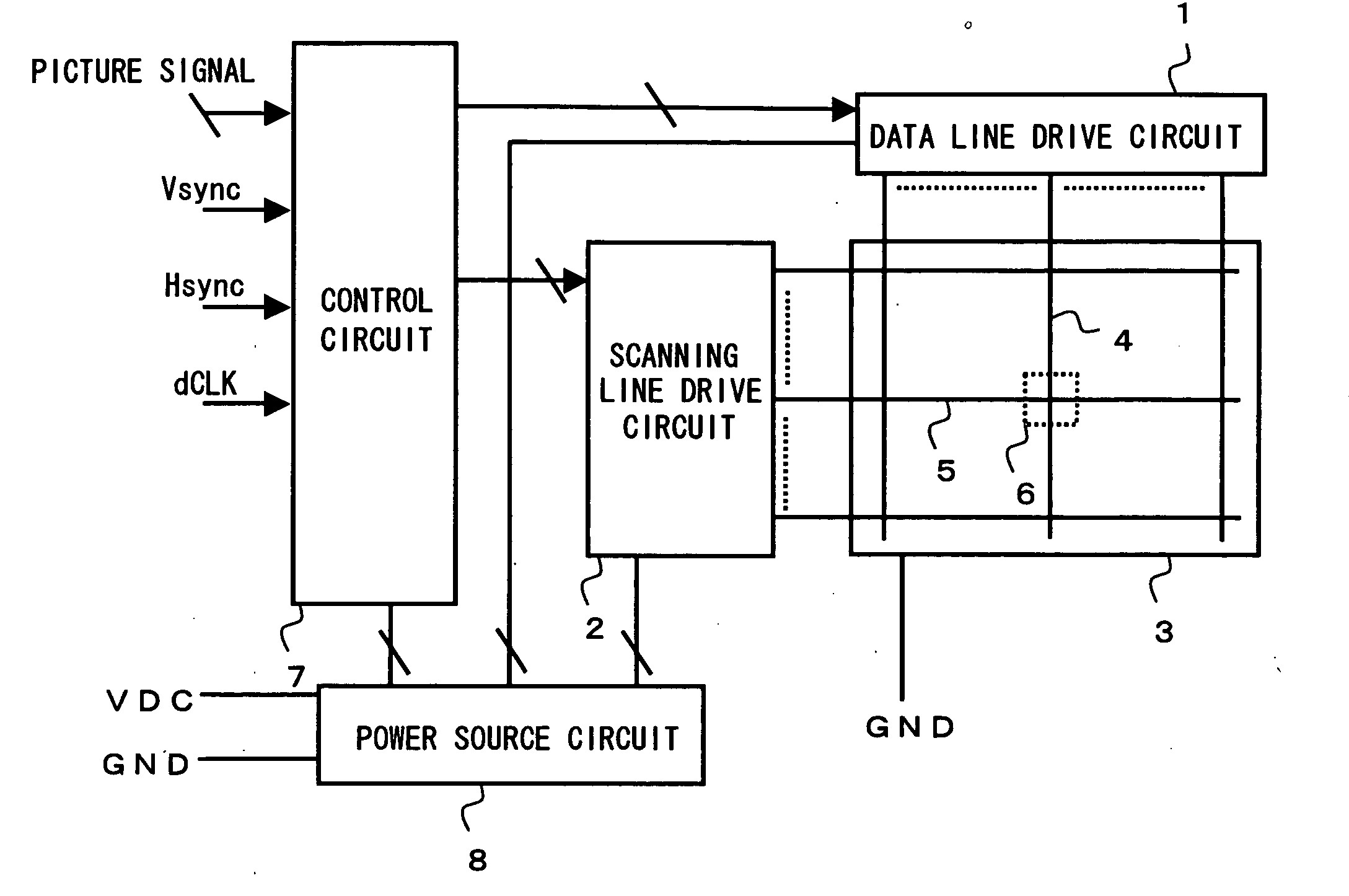

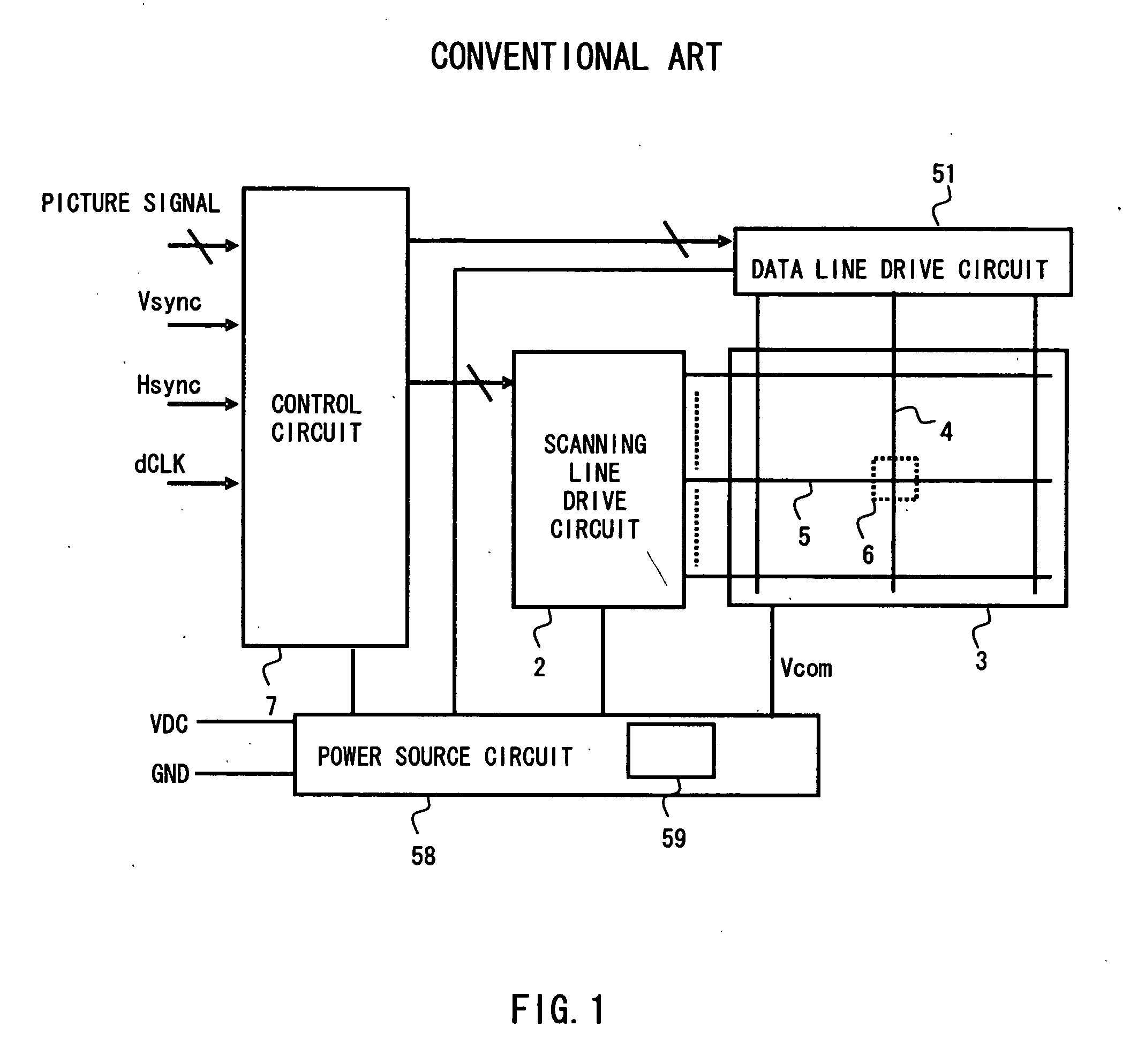

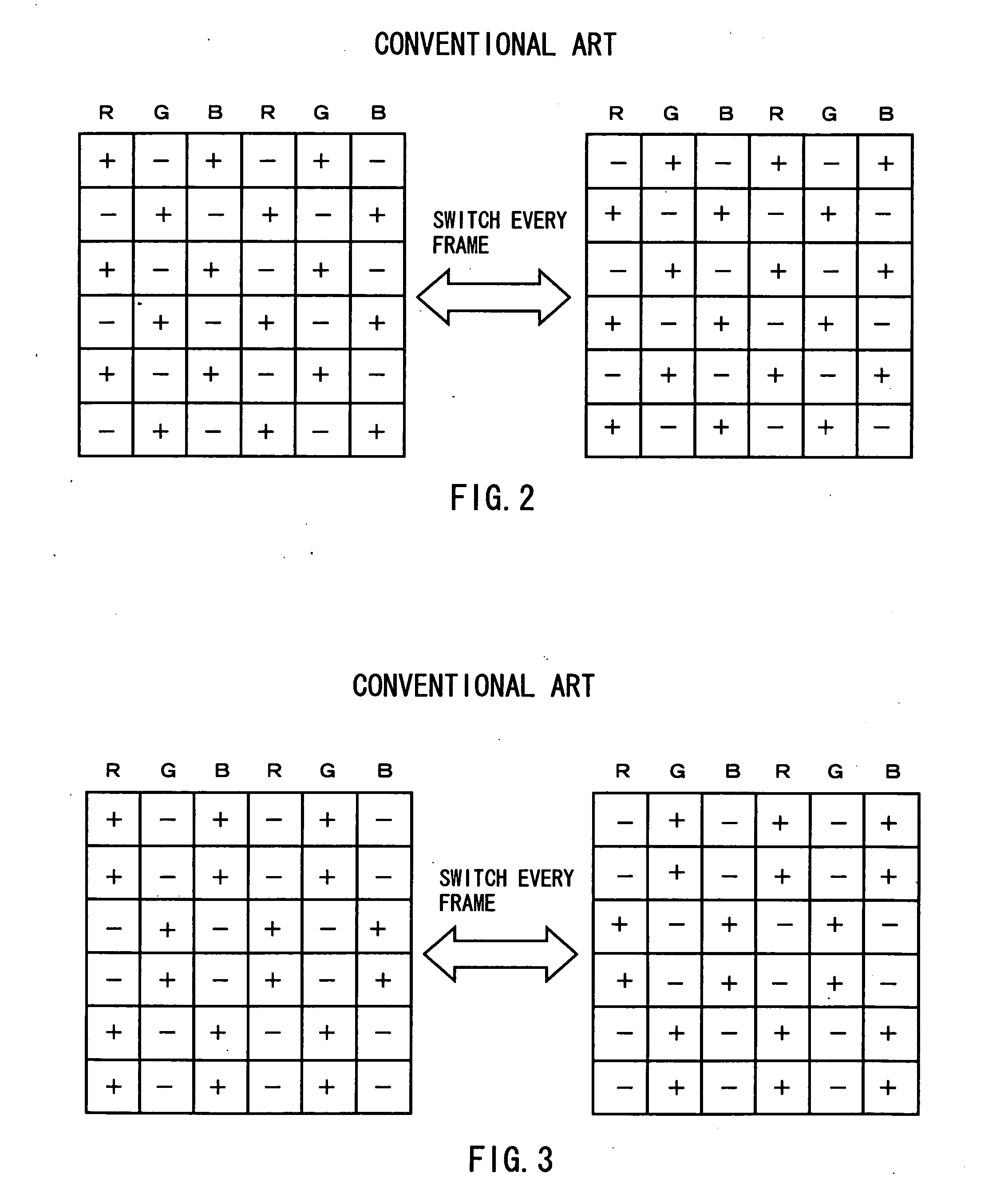

Display device, display panel driver and method of driving display panel

ActiveUS20070268524A1Reduce circuit sizeReduce power consumptionDigitally marking record carriersColor signal processing circuitsDisplay deviceLine driver

An LCD device according to the present invention has: an LCD panel; an operation and correction circuit configured to perform a correction operation with respect to an input gray-scale data of a target frame image by using an arithmetic expression to generate an output gray-scale data; a data line driver configured to drive the LCD panel in accordance with the output gray-scale data; and a correction data calculation circuit configured to generate a correction data that specifies a relationship between the input gray-scale data and the output gray-scale data of the target frame image, depending on the input gray-scale data of the target frame image or an input gray-scale data of a precedent frame image followed by the target frame image. The operation and correction circuit determines coefficients of the arithmetic expression from the correction data.

Owner:SYNAPTICS JAPAN GK

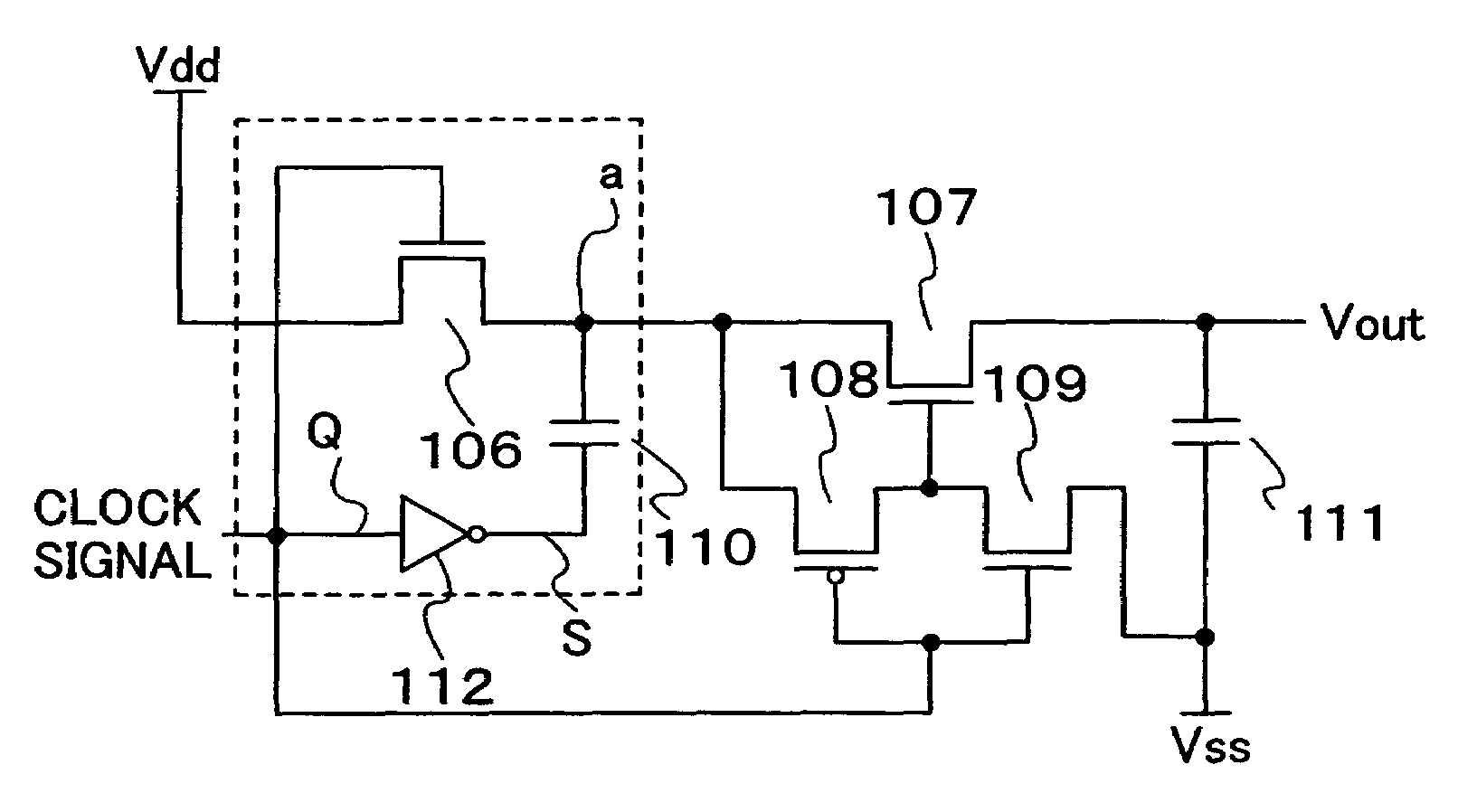

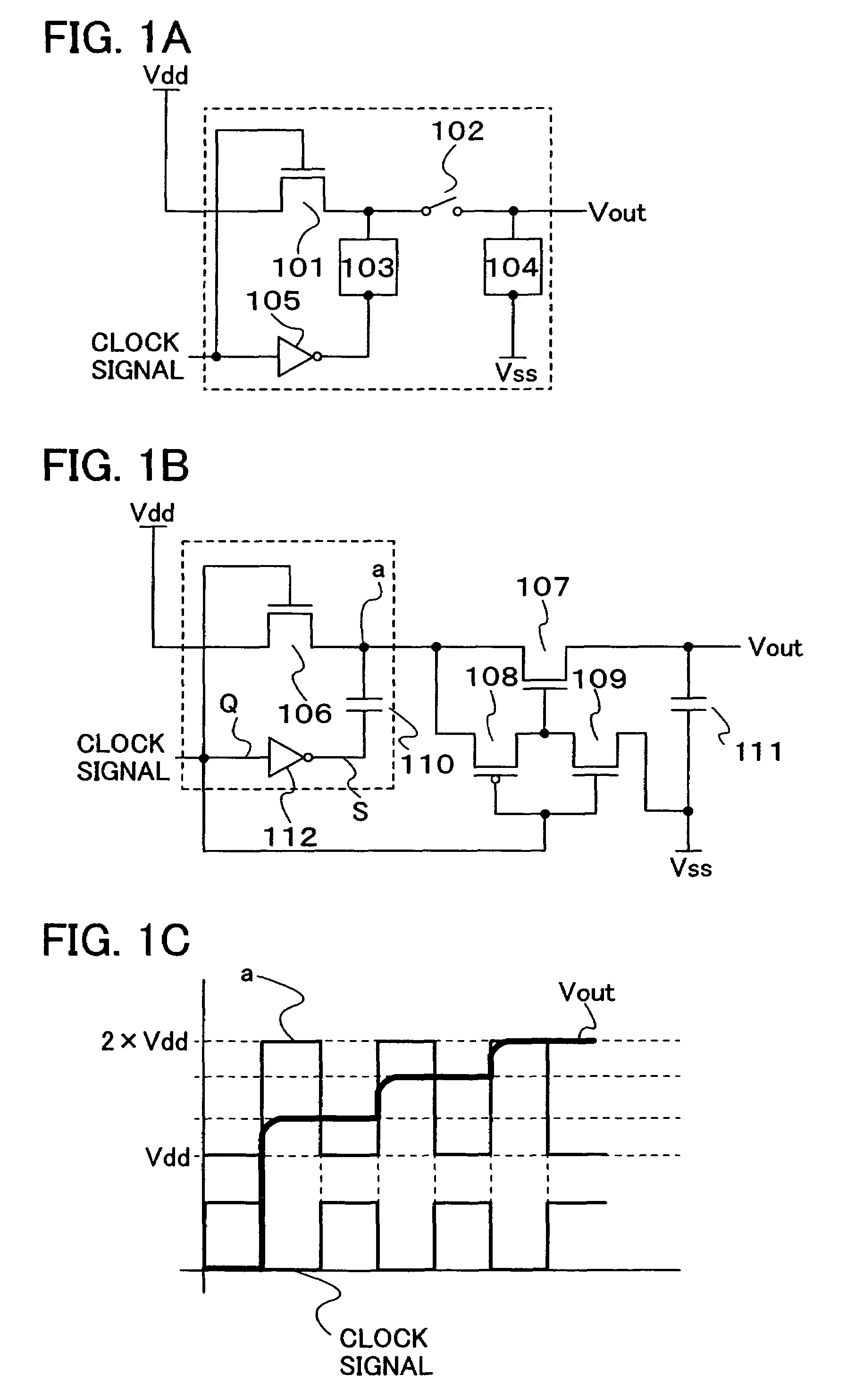

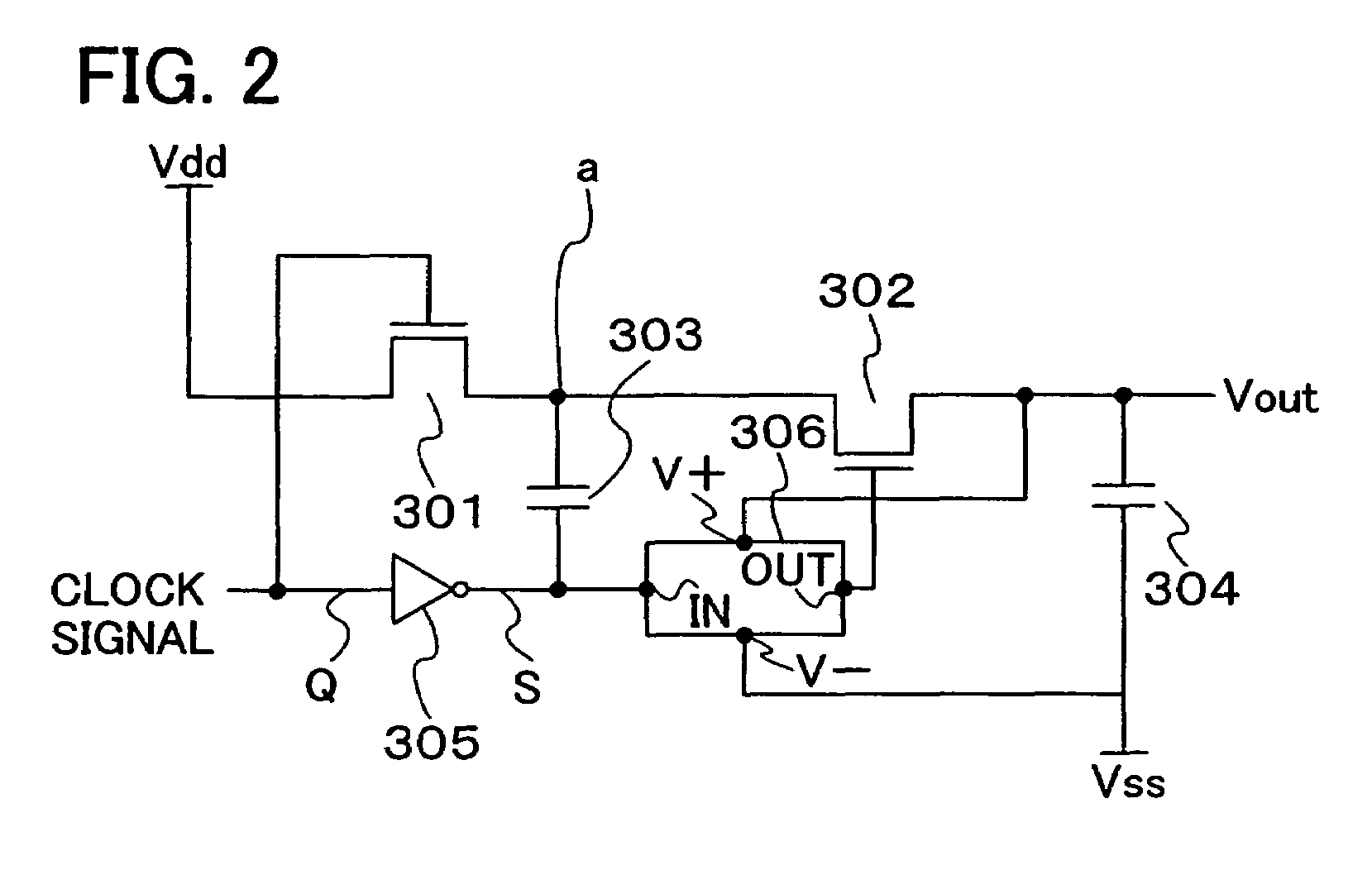

Charge pump circuit and semiconductor device having the same

InactiveUS7495501B2Reduce power consumptionIncrease currentAc-dc conversionApparatus without intermediate ac conversionEngineeringSemiconductor

A conventional charge pump circuit requires a step-up circuit or the like for turning on or off a transistor. Therefore, it has a problem of an increase in circuit scale, which leads to increases in circuit area and power consumption. One feature is to provide a charge pump circuit including a first transistor, a switch, a first capacitor, a second capacitor, and an inverter, in which one electrode of the first transistor is connected to a first potential, an output side of the inverter is connected to the other electrode of the first transistor and one side of the switch through the first capacitor, the other side of the switch is connected to a second potential through the second capacitor.

Owner:SEMICON ENERGY LAB CO LTD

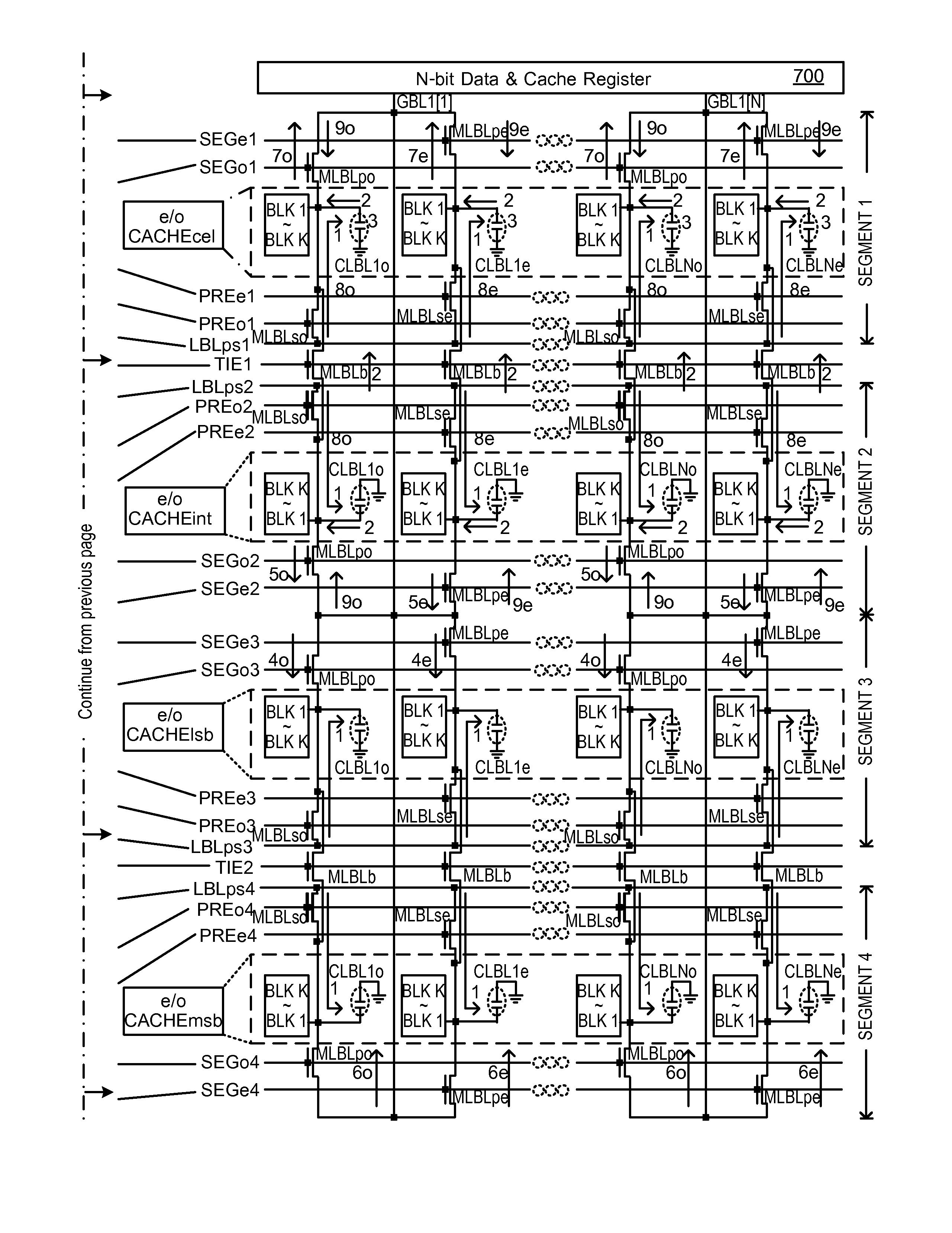

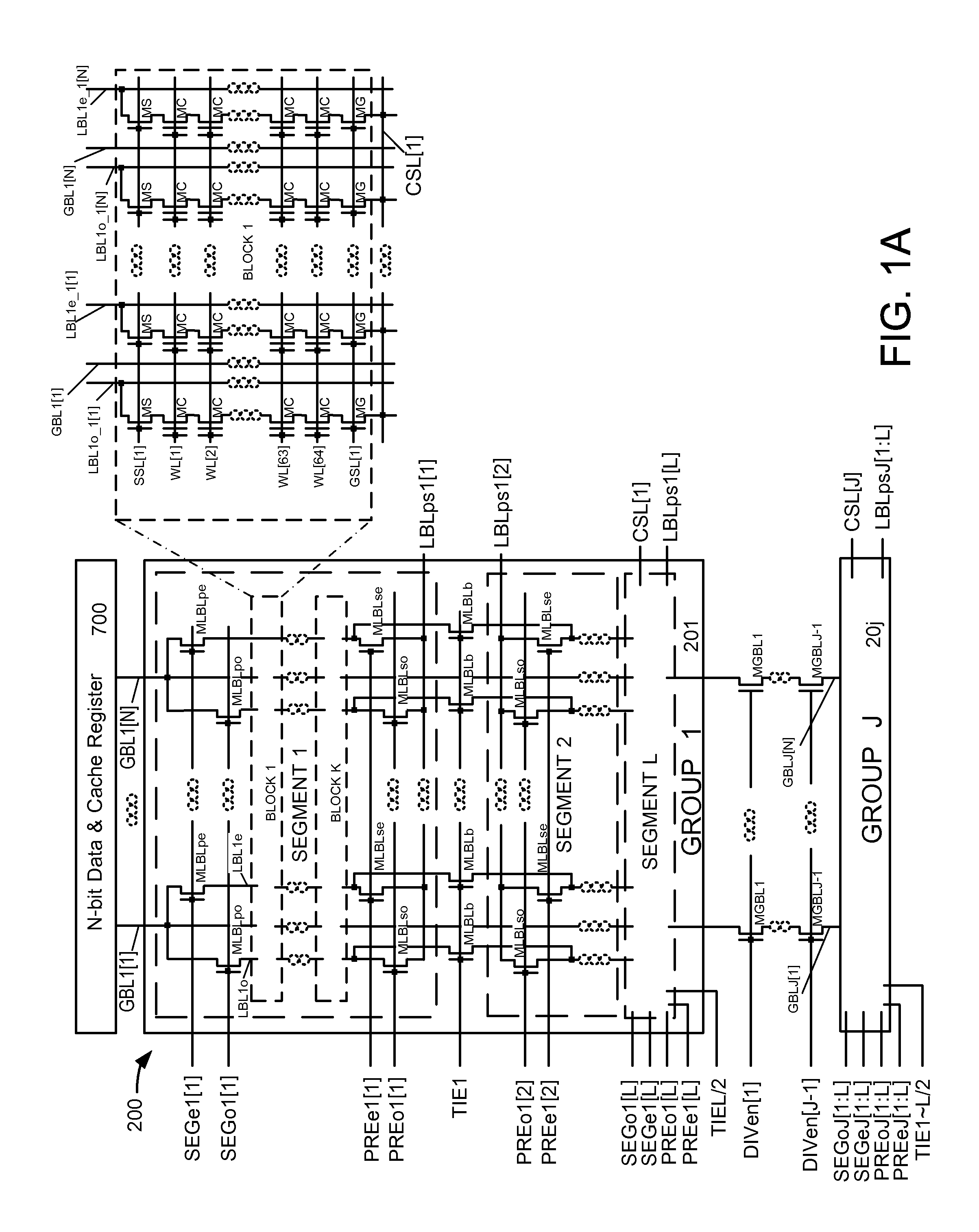

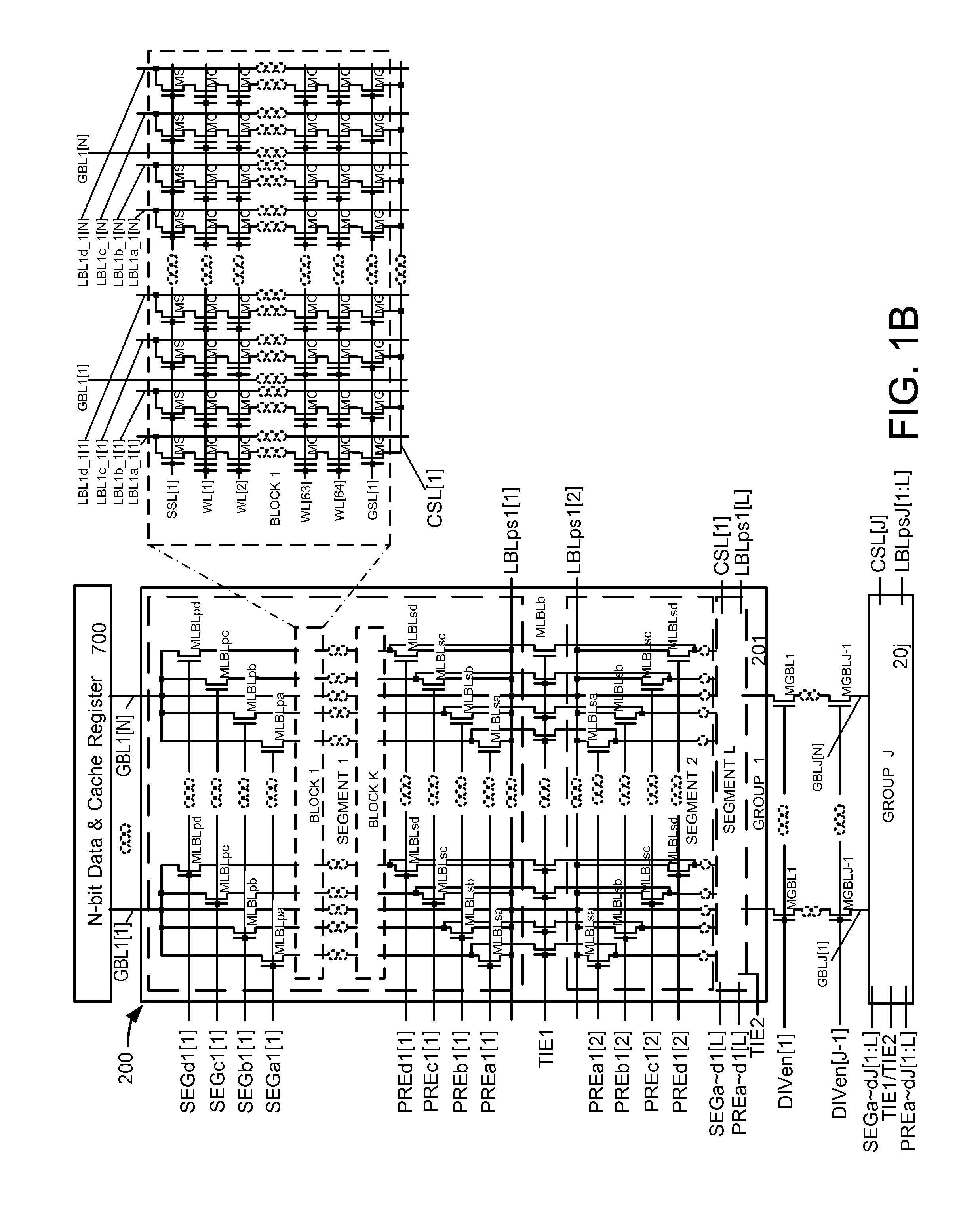

HYBRID NAND WITH ALL-BL m-PAGE OPERATION SCHEME

ActiveUS20150179269A1Reduce circuit sizeFlexible and effectiveRead-only memoriesDigital storageBit lineComputer architecture

This invention discloses 2D or 3D NAND flash array in two-level BL-hierarchical structure with flexible multi-page or random-page-based concurrent, mixed SLC and MLC Read, Program or Program-Verify operations including bit-flipping for each program state or any combinations of above operations. Tracking techniques of self-timed control and algorithm of programming, read and local-bit line (LBL) voltage generations are proposed for enhancing automatic controls over charging and discharging of a plurality of WLs and LBLs in one or more randomly selected Blocks in one or more Segments of one or more Groups in a NAND plane for m-page concurrent operations using Vdd / Vss to Vinh / Vss Program page data conversion, multiple pseudo CACHEs based on LBL capacitors for storing raw SLC and MSB / LSB loaded page data, writing back or reading from Sense-Amplifier, Program / Read Buffer, real CHCHE, and multiple pseudo CACHEs with M-fold reduction in latency and power consumption.

Owner:APLUS FLASH TECH

Output circuit for semiconductor device, semiconductor device having output circuit, and method of adjusting characteristics of output circuit

ActiveUS7215128B2Reduce calibration timeReduce circuit sizeInput/output impedence modificationImpedence matching networksEngineeringSemiconductor

Owner:LONGITUDE LICENSING LTD

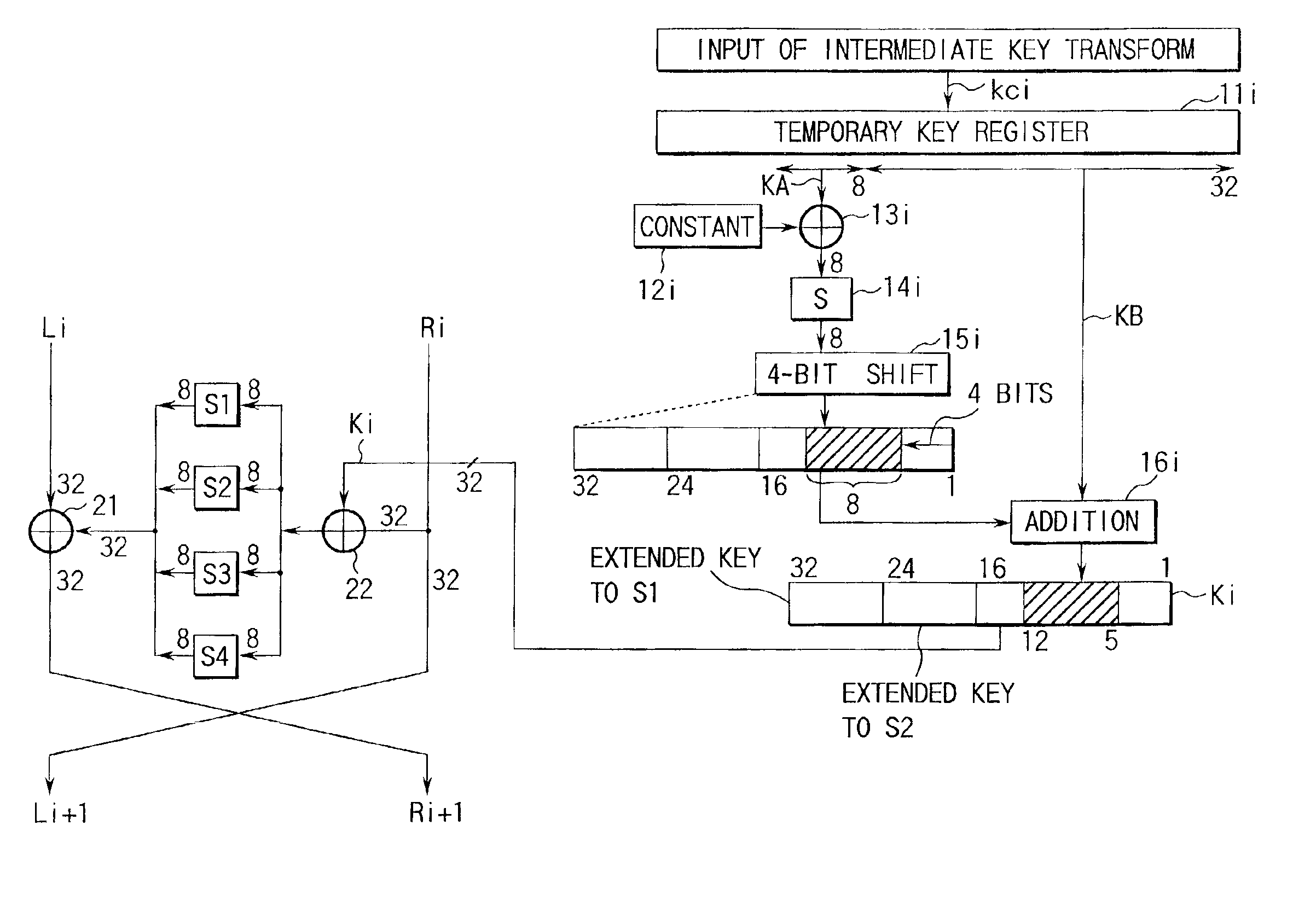

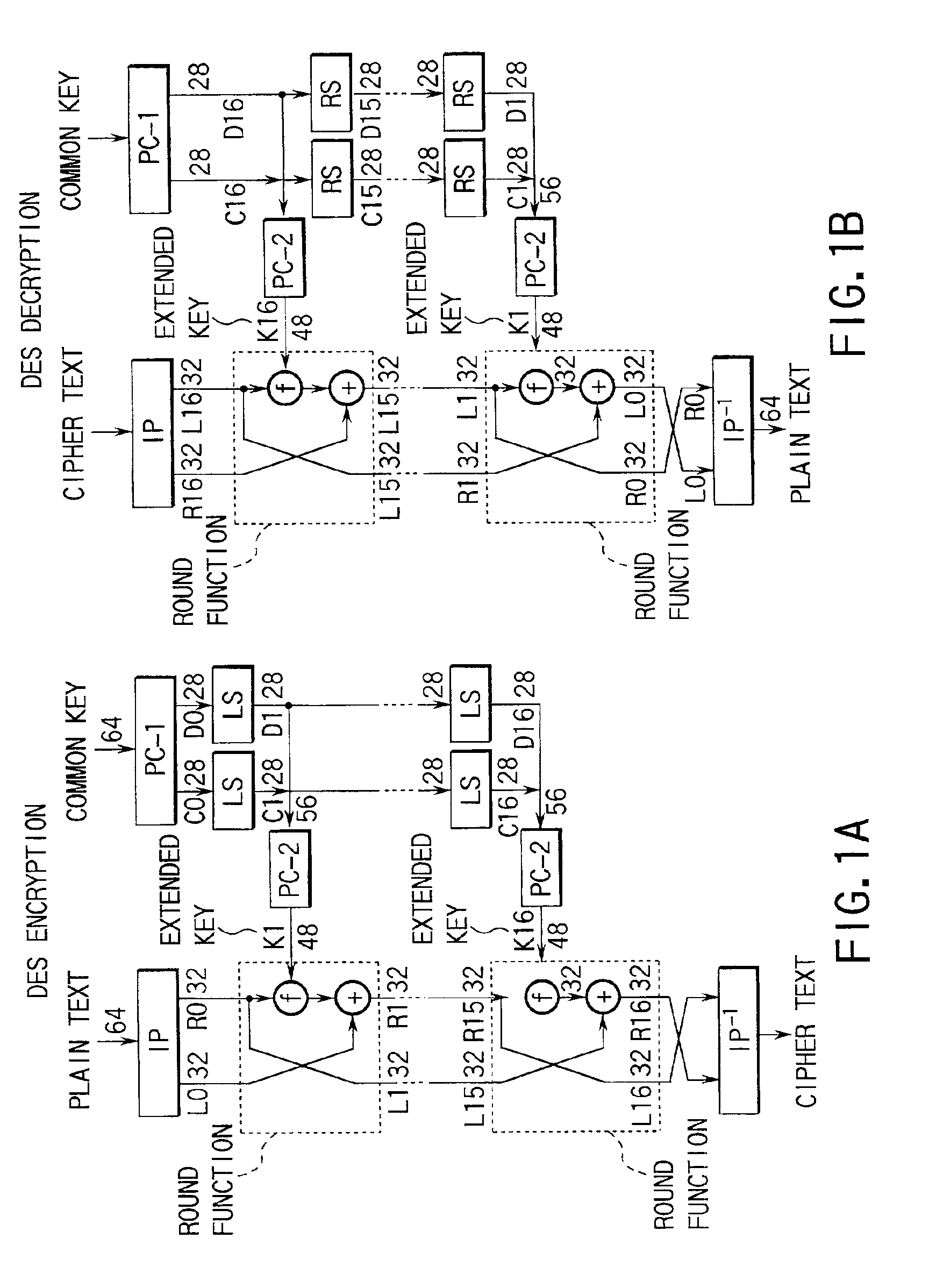

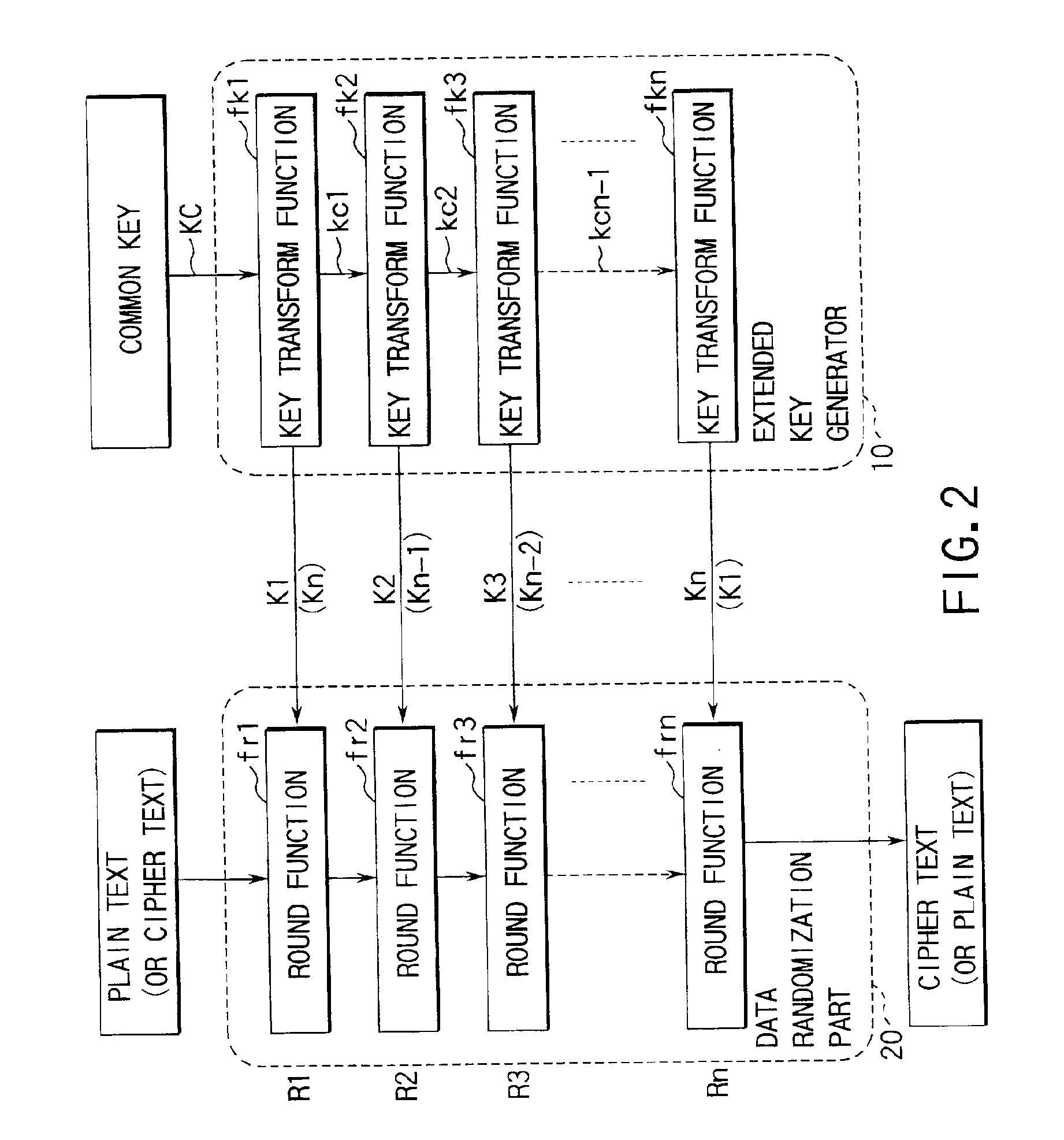

Extended key generator, encryption/decryption unit, extended key generation method, and storage medium

InactiveUS6891950B1Avoid it happening againImproving cryptological robustnessEncryption apparatus with shift registers/memoriesDigital data processing detailsComputer hardwareS-box

There are disclosed an extended key generator, encryption / decryption unit, and storage medium, in which as each of key transform functions, a transform process is done by an S box (substitution table) on the basis of a first key obtained from the inputted key, and an adder computes a corresponding one of extended keys on the basis of a value obtained by shifting the transformed result of the S box to the left, and a second key obtained from the inputted key.

Owner:KK TOSHIBA +1

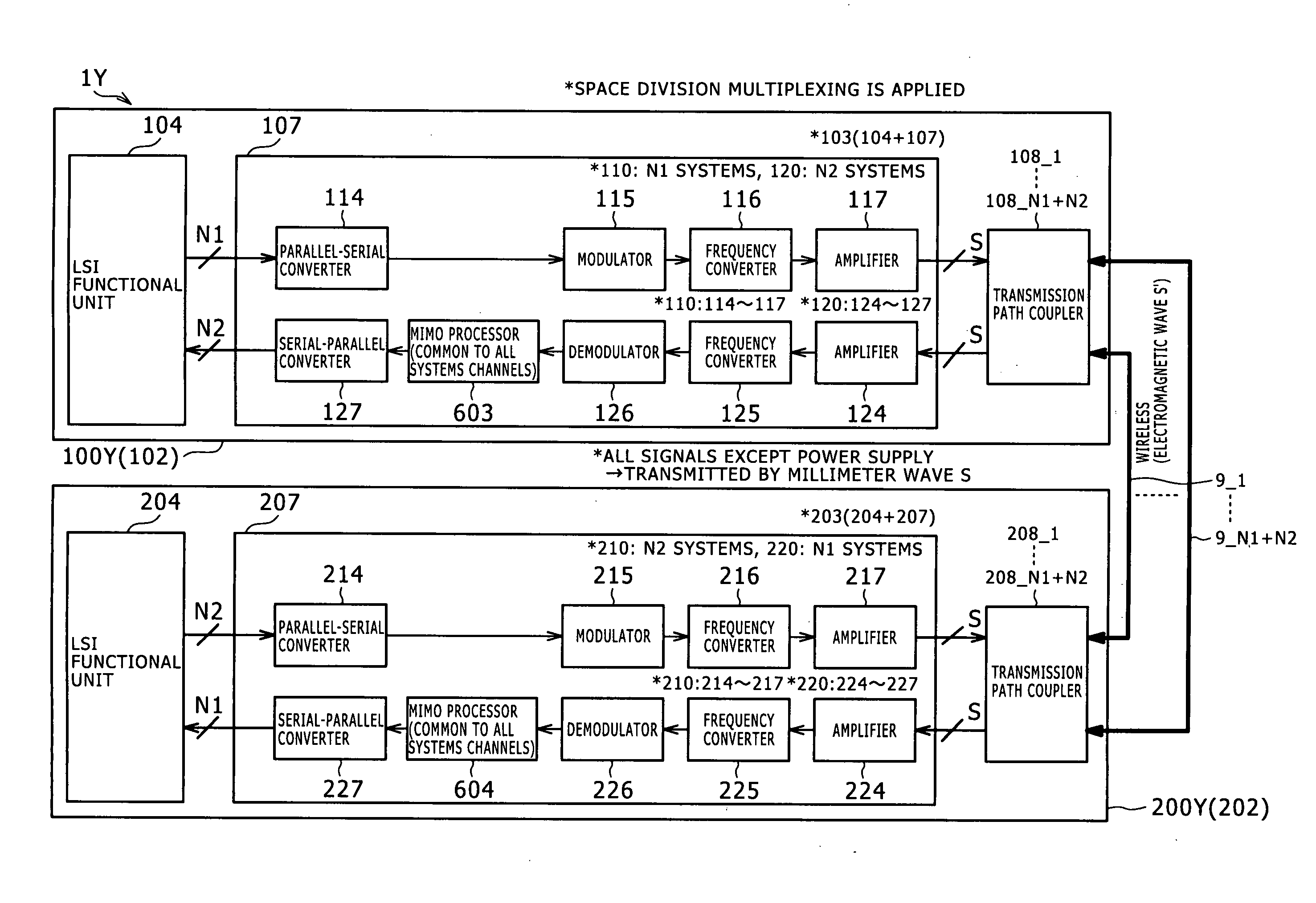

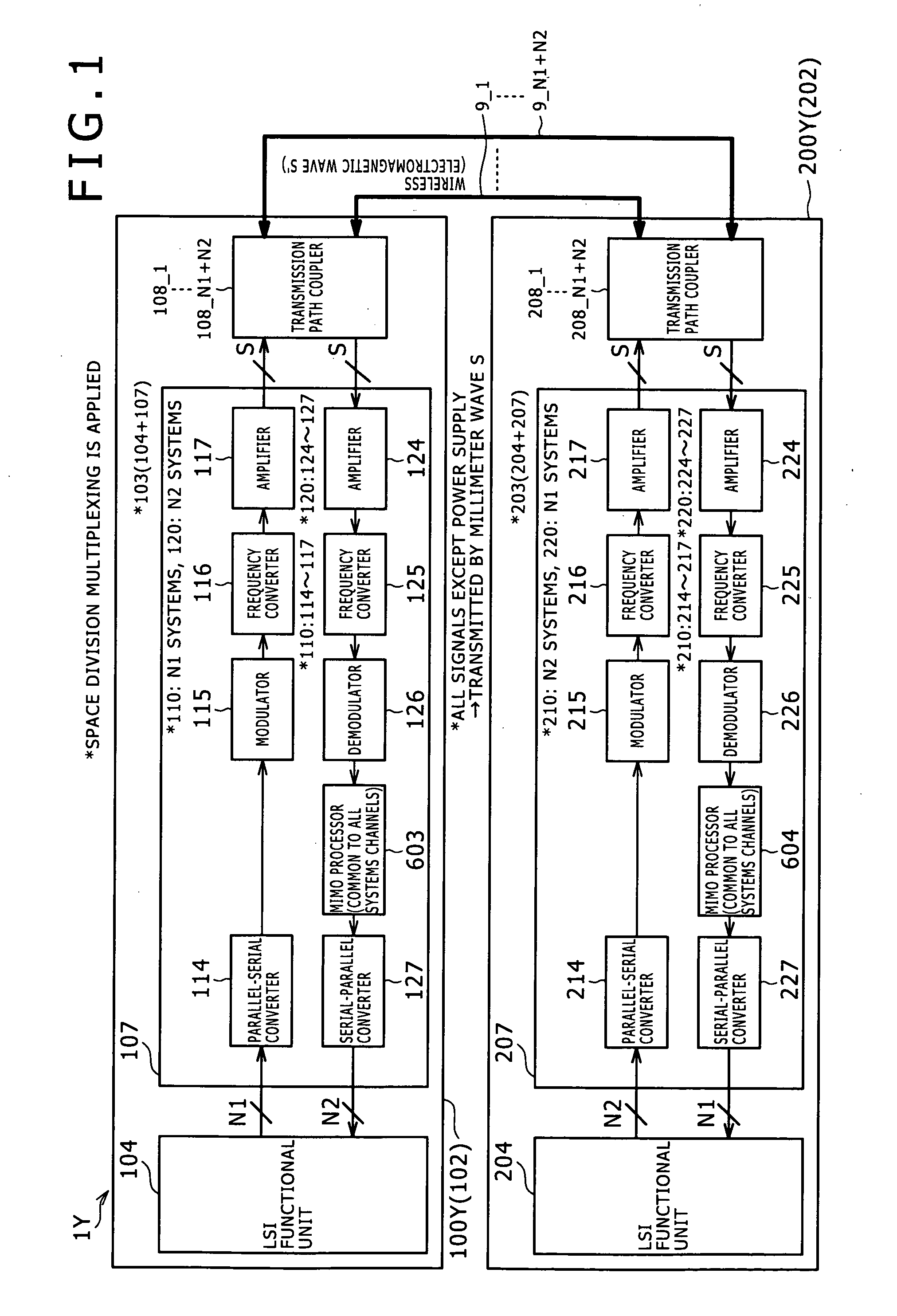

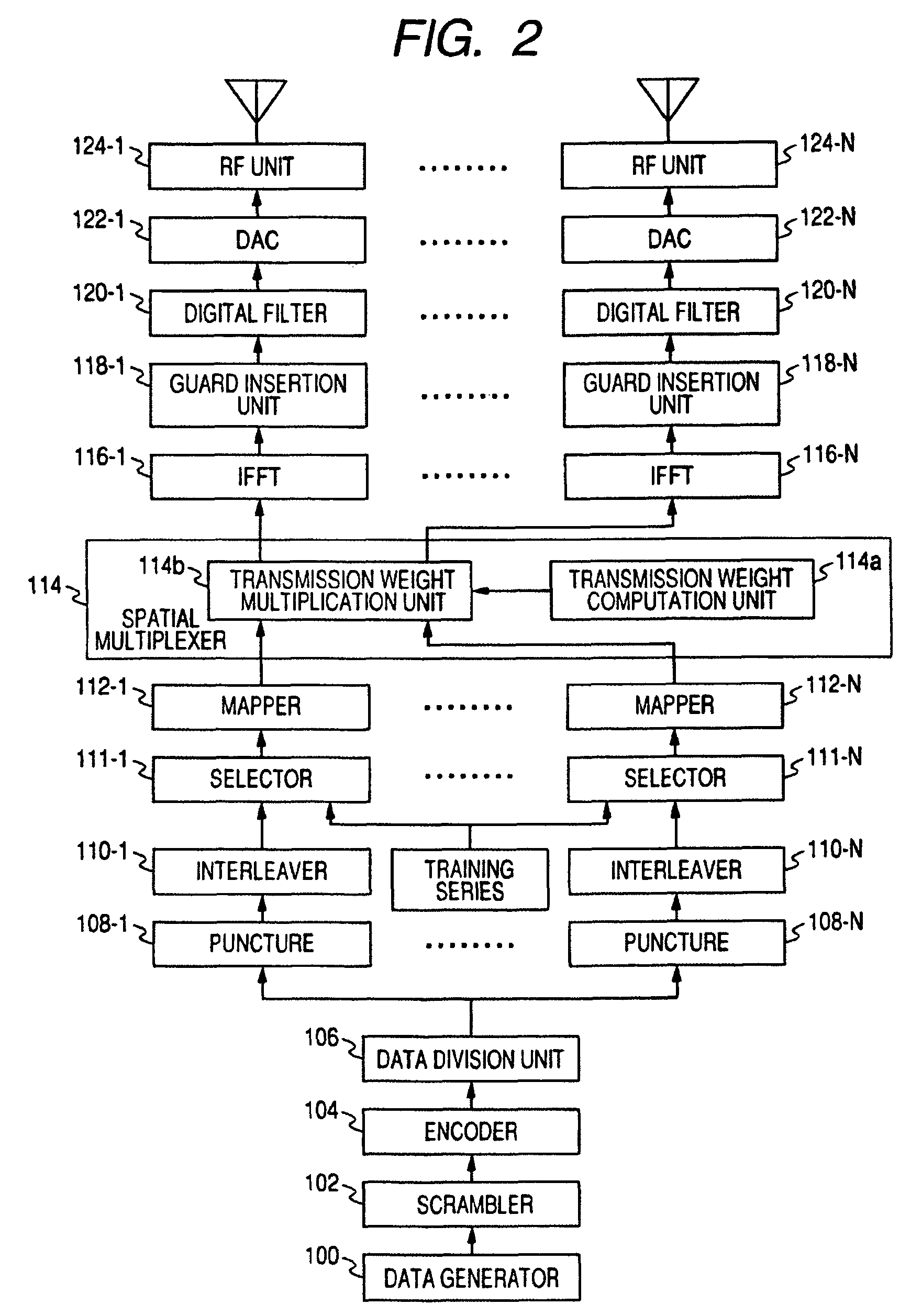

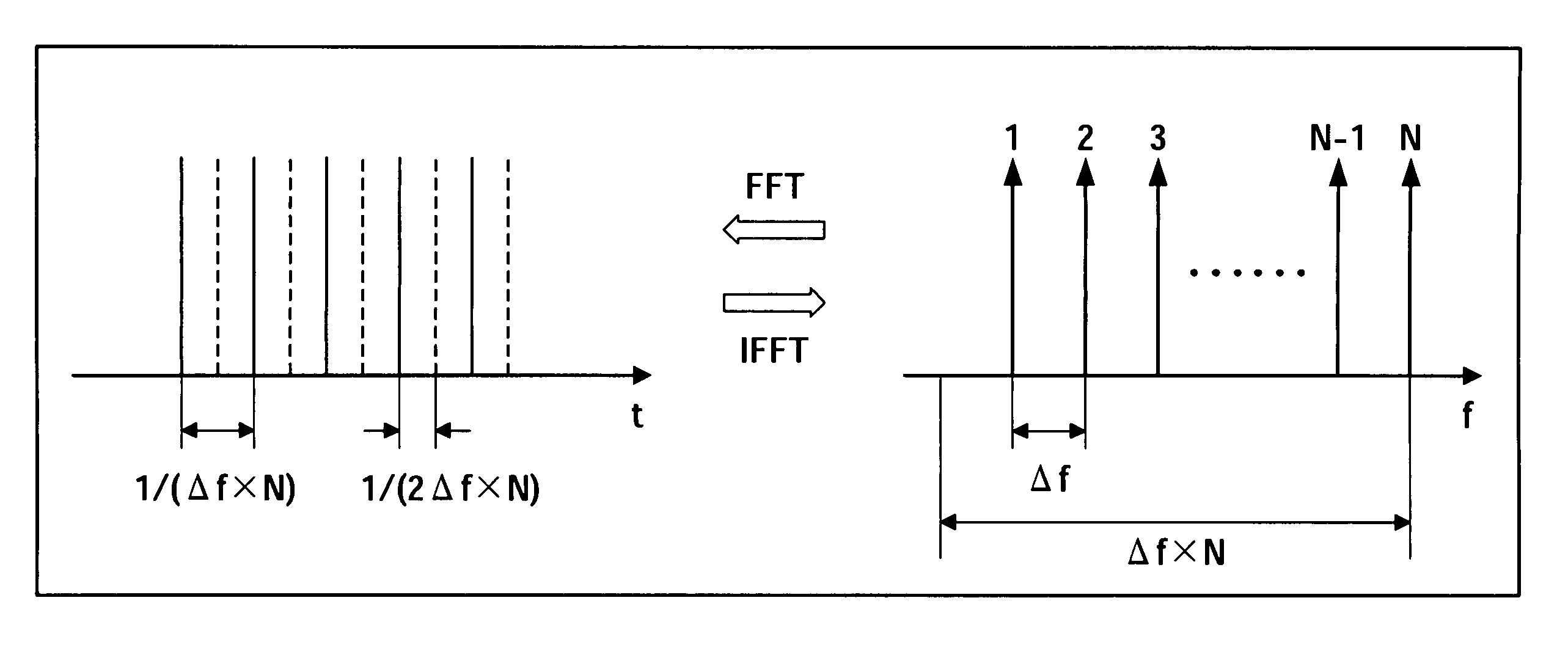

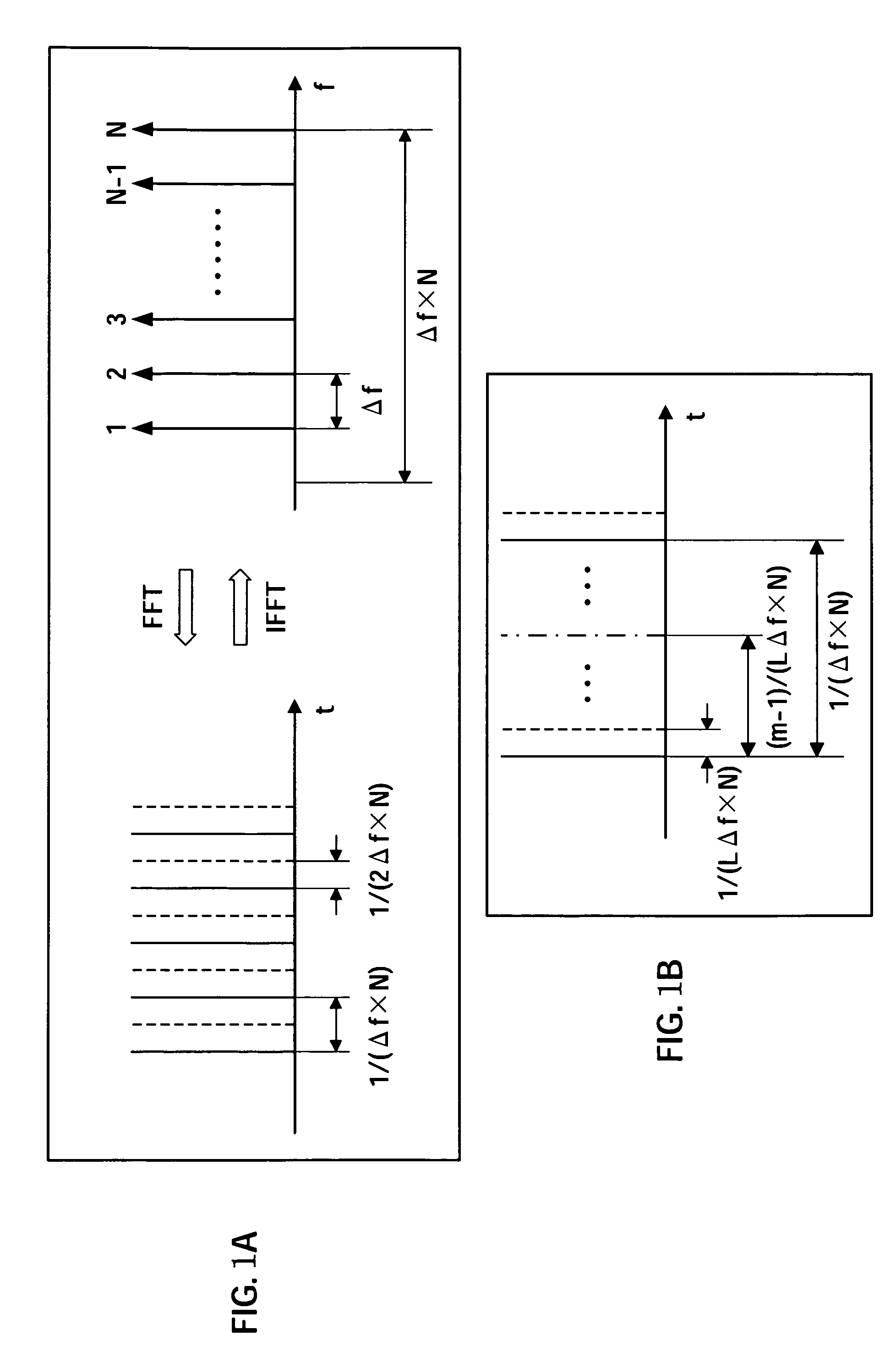

Wireless transmission system, wireless communication device and wireless transmission method

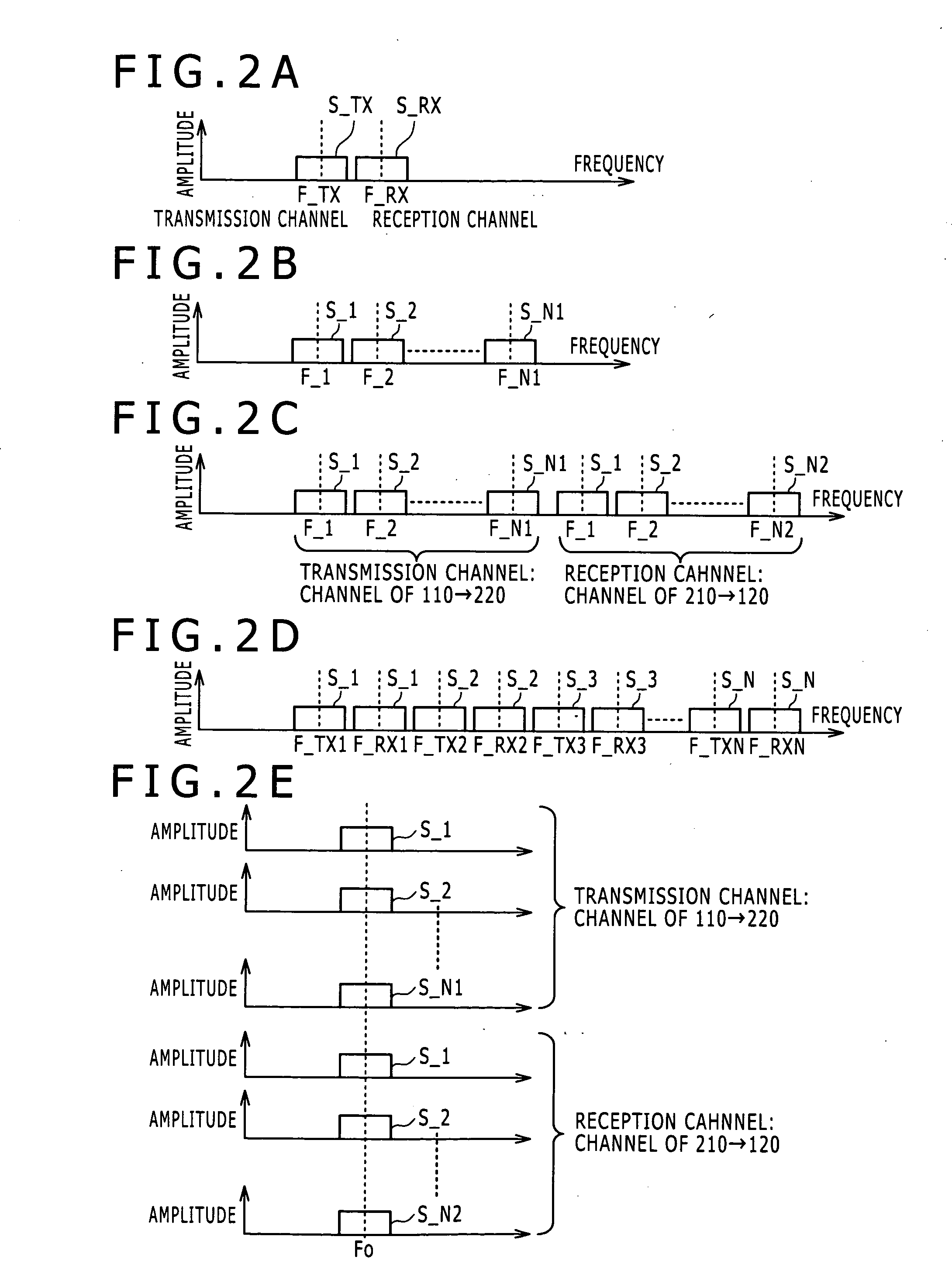

ActiveUS20110075581A1Reduce distanceEasy to processFrequency-division multiplex detailsTransmission systemsVIT signalsEngineering

Disclosed herein is a wireless transmission system including a plurality of antenna pairs; a demodulation functional unit; and a transmission characteristic correction unit. The plurality of antenna pairs each including a transmission antenna and a reception antenna. A wireless signal transmitted from a transmission antenna directly arrives as a desired wave at a corresponding reception antenna. Meanwhile, a wireless signal transmitted from a different transmission antenna directly arrives as an unnecessary wave at the reception antenna. The demodulation functional unit corresponding to each antenna pair demodulates a modulation signal received by the reception antenna. The transmission characteristic correction unit carries out correction calculation based on a transmission characteristic of a transmission space between the transmission and reception antennae based on demodulation signals demodulated by the demodulation functional units to acquire an output signal corresponding to a transmission subject signal.

Owner:SONY CORP

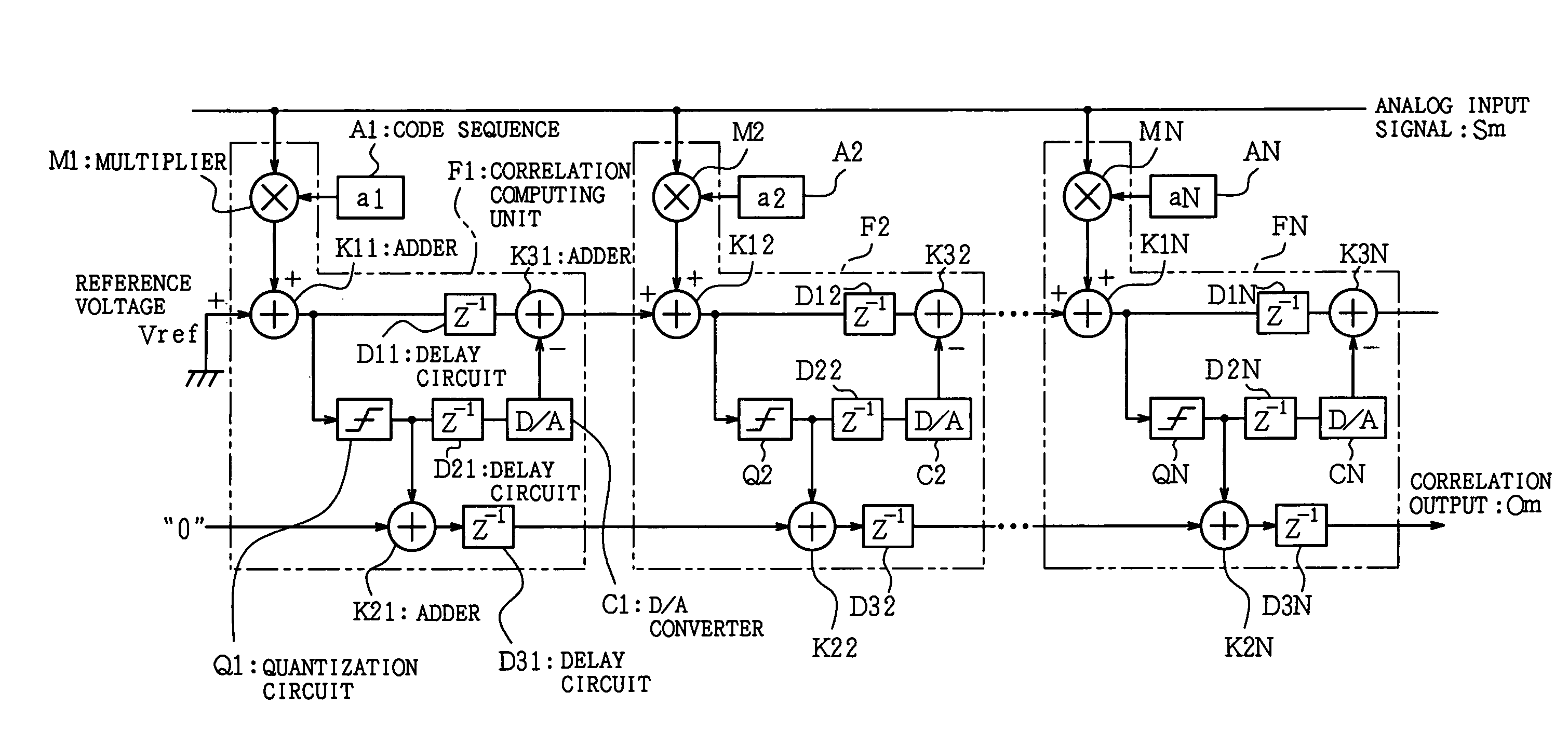

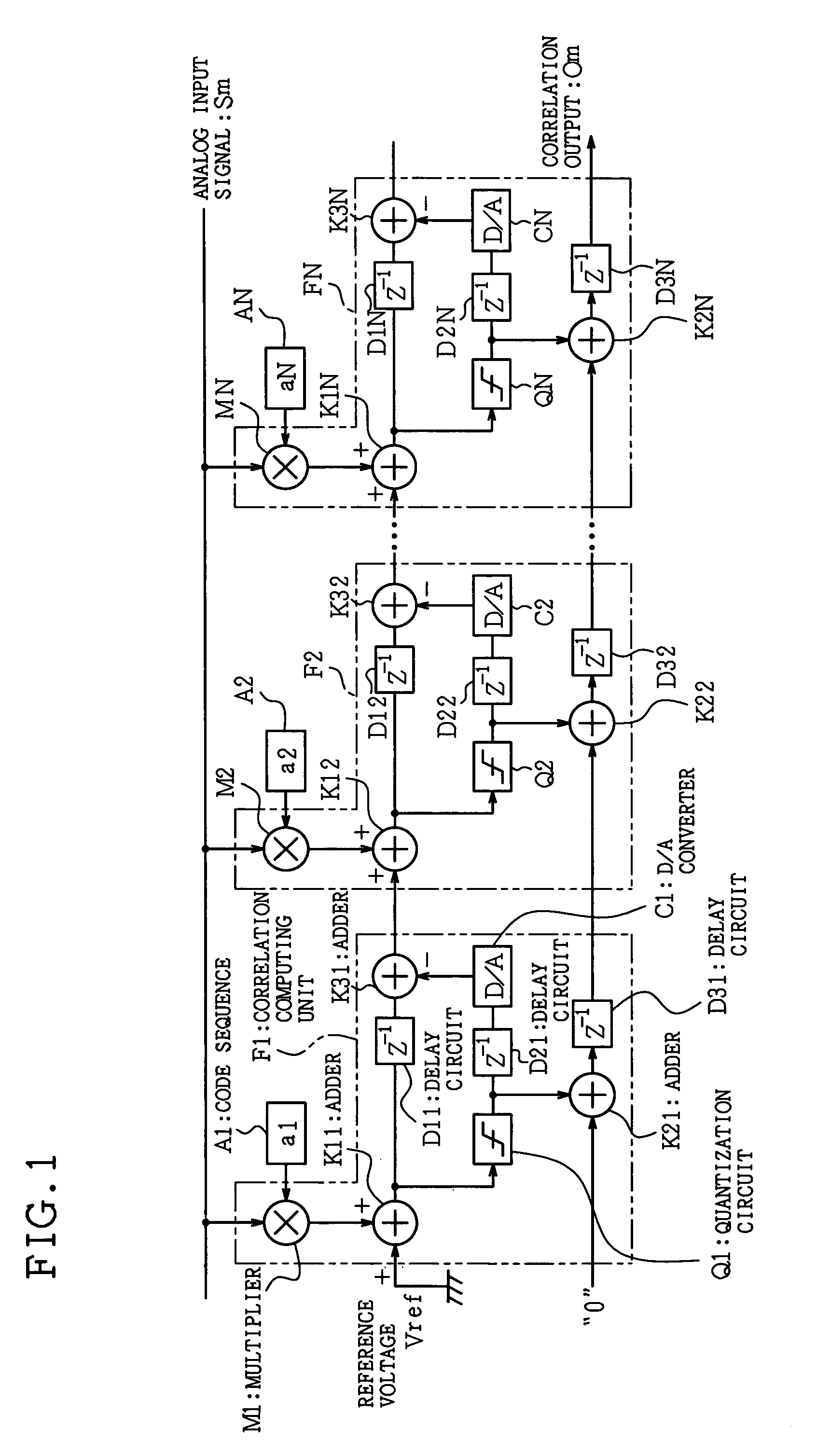

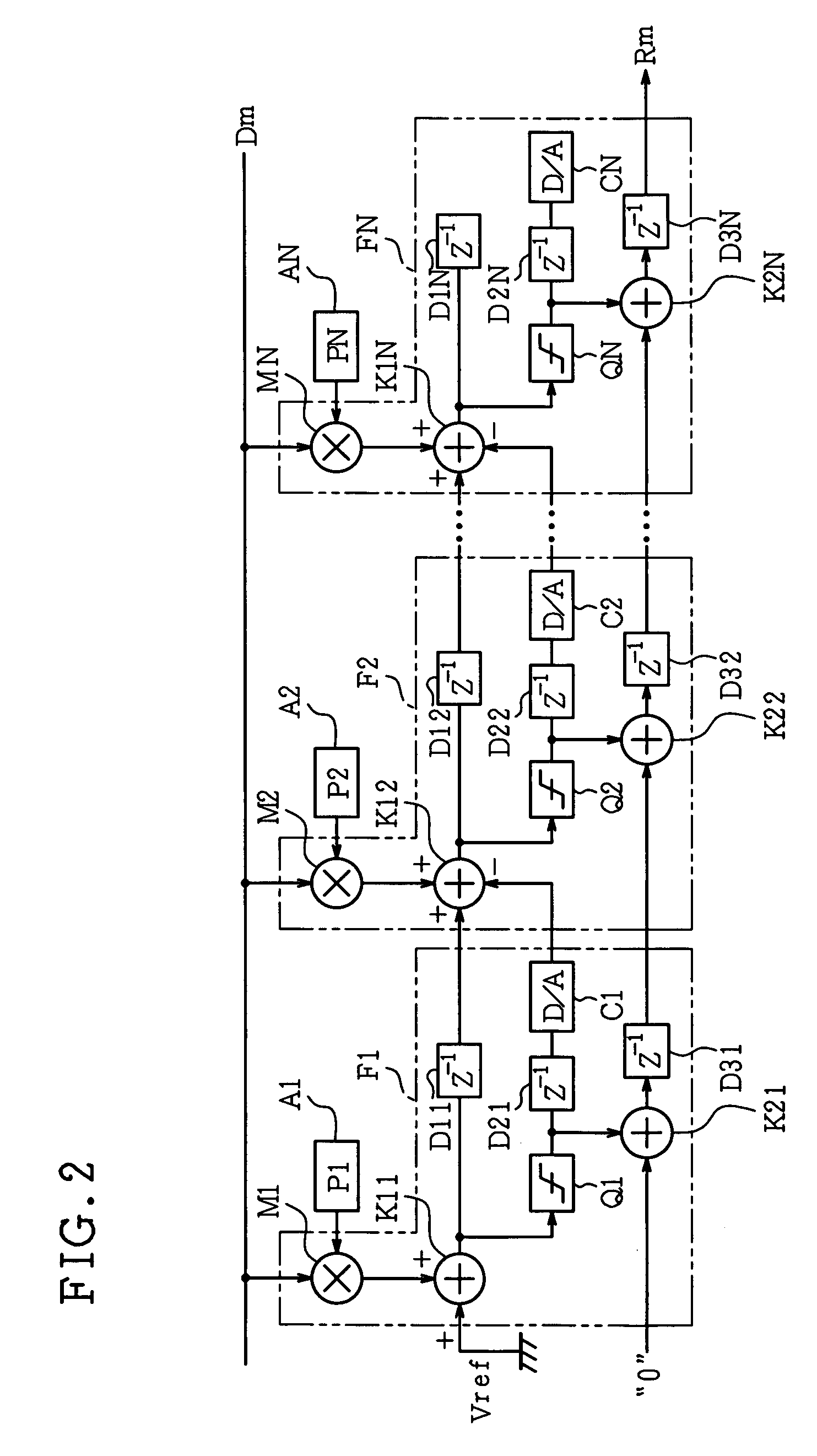

Filter circuit

InactiveUS6983011B1Reduce circuit sizeReduce power consumptionMultiple-port networksPower saving provisionsComputer scienceDynamic range

In a filter circuit of the present invention, a partial quantization value is computed by a quantization circuit according to a spread code and others in a unit at an arbitrary stage, where an integrating value is increased. The partial quantization value is successively added by an adder formed by a counter and is transmitted to a unit of the following stage. In an adder of the following stage, an analog residual is computed by subtracting an analog converted value of the partial quantization value, that is obtained by a D / A converter, from the integrating value so as to suppress an increase in the analog cumulative value. With this arrangement, the cumulative value is increased according to an increase in the number of taps, so that an analog adder can reduce power consumption, which is caused by expansion of a dynamic range at the following stage.

Owner:SHARP KK

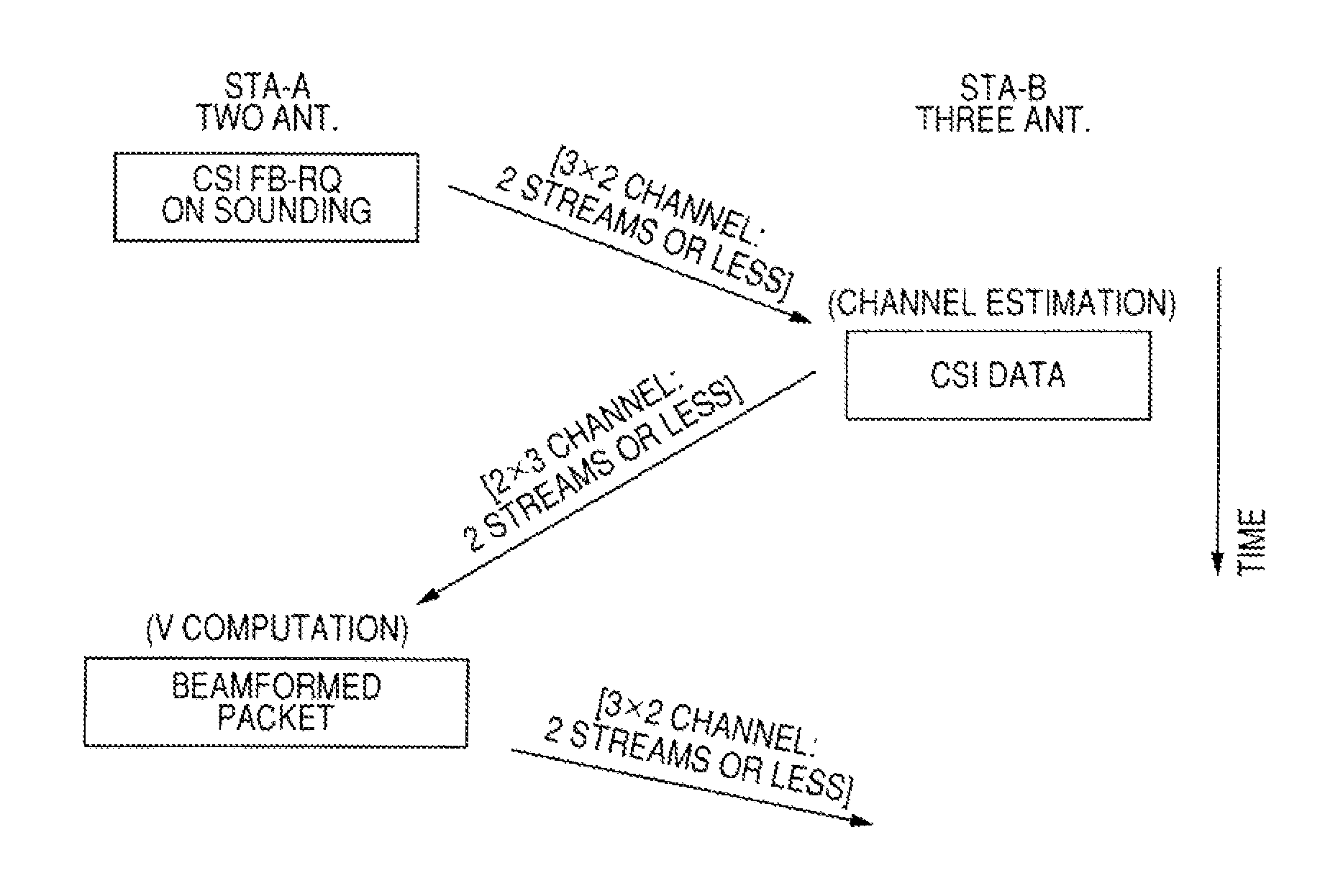

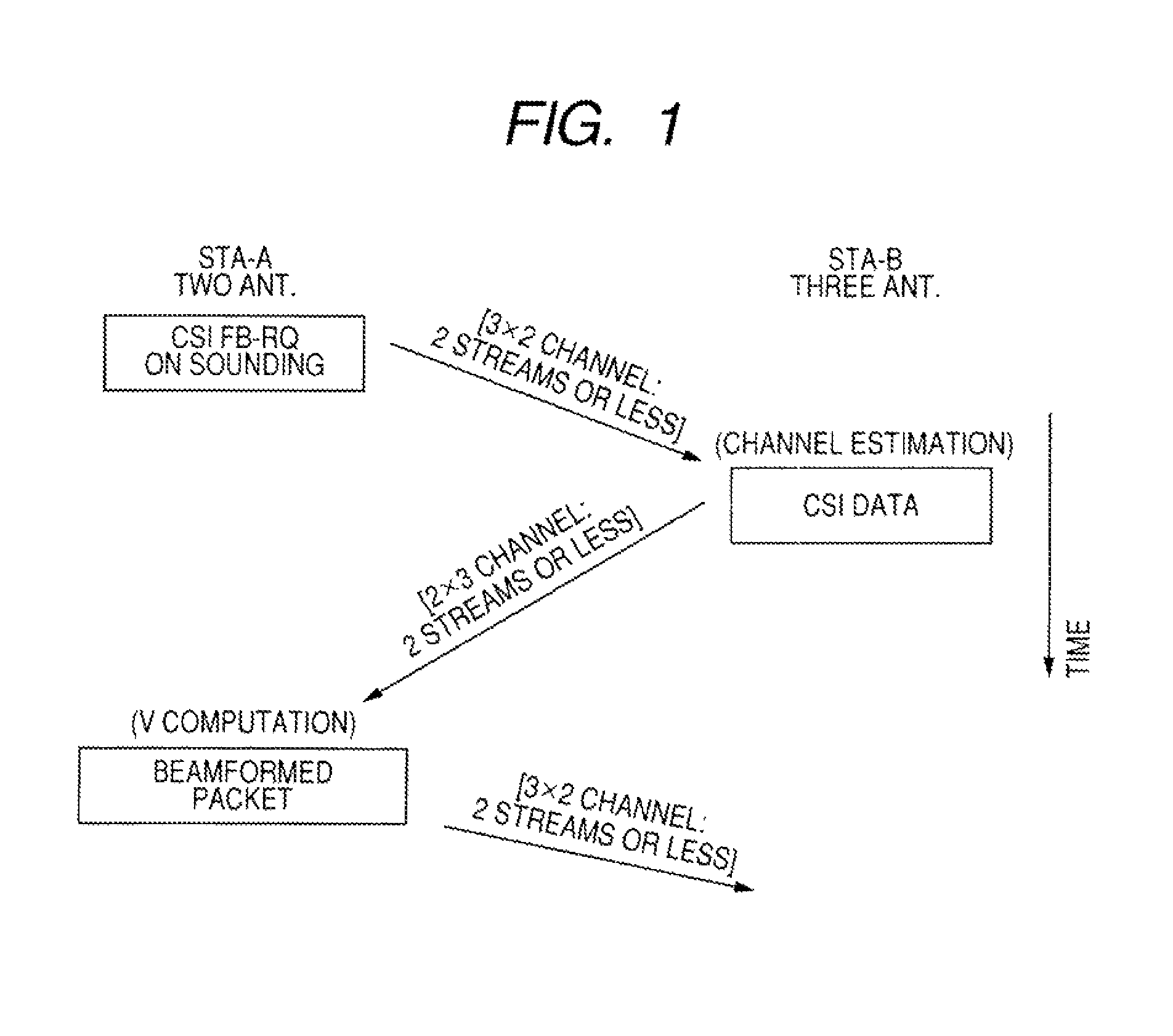

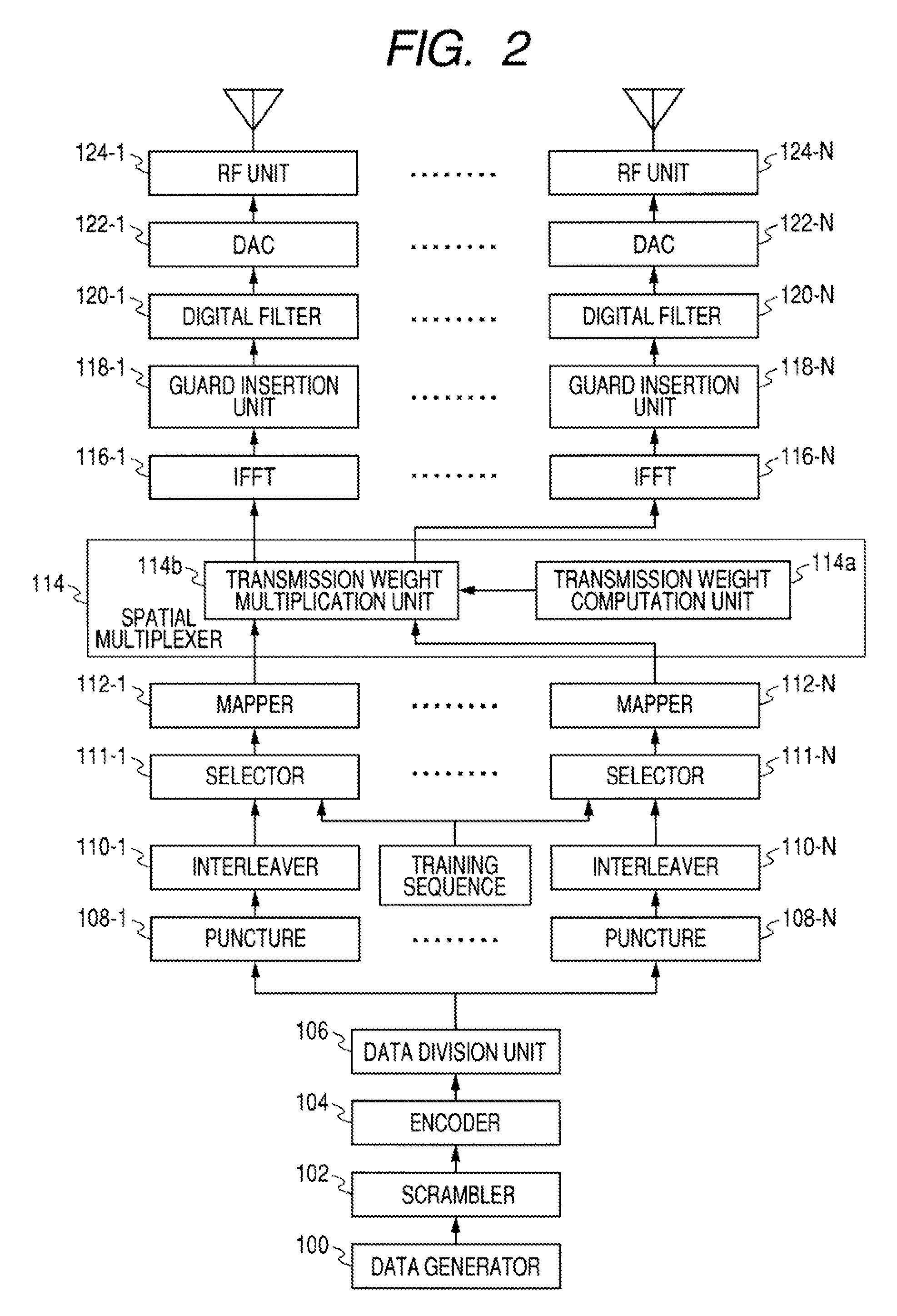

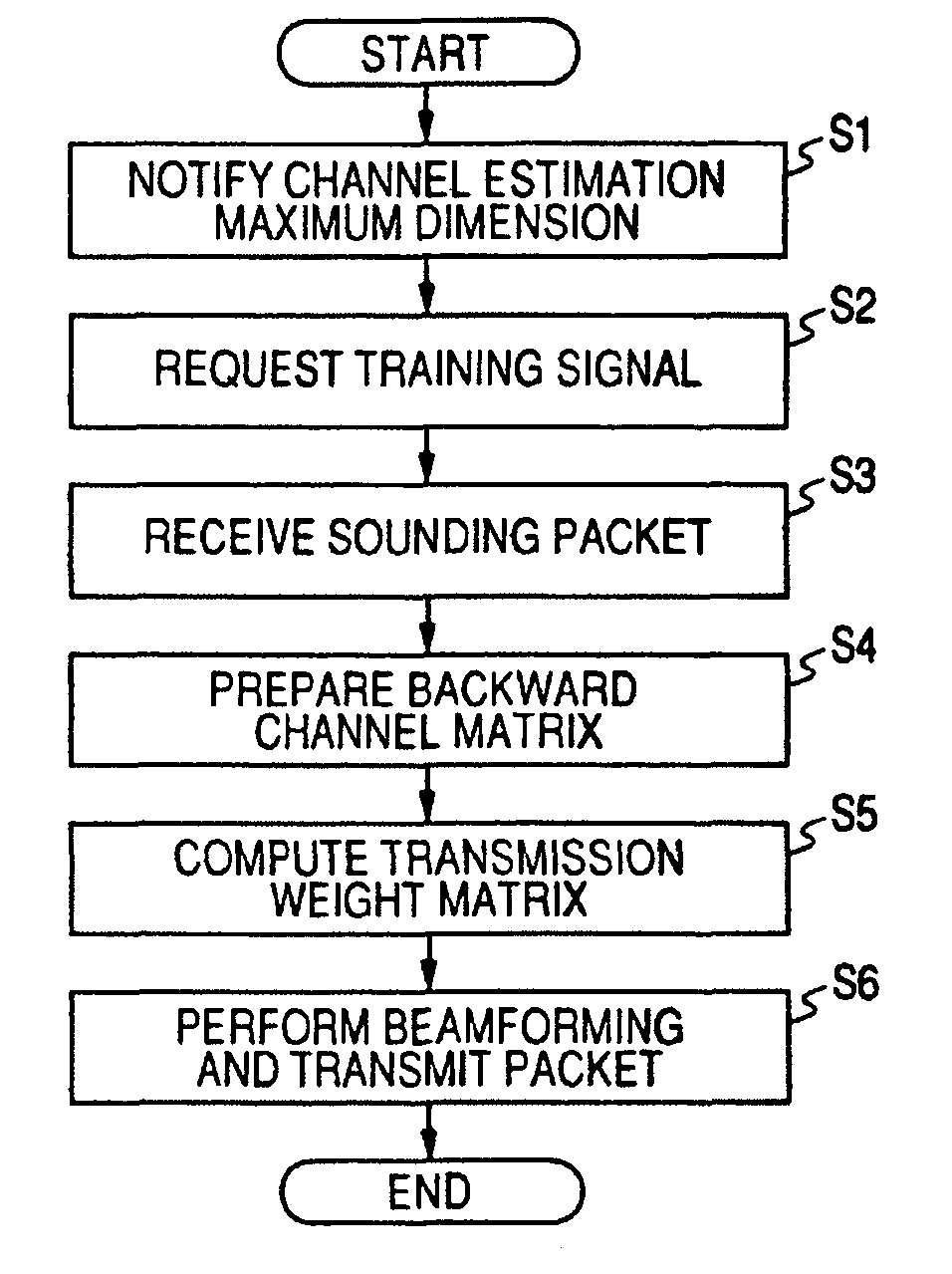

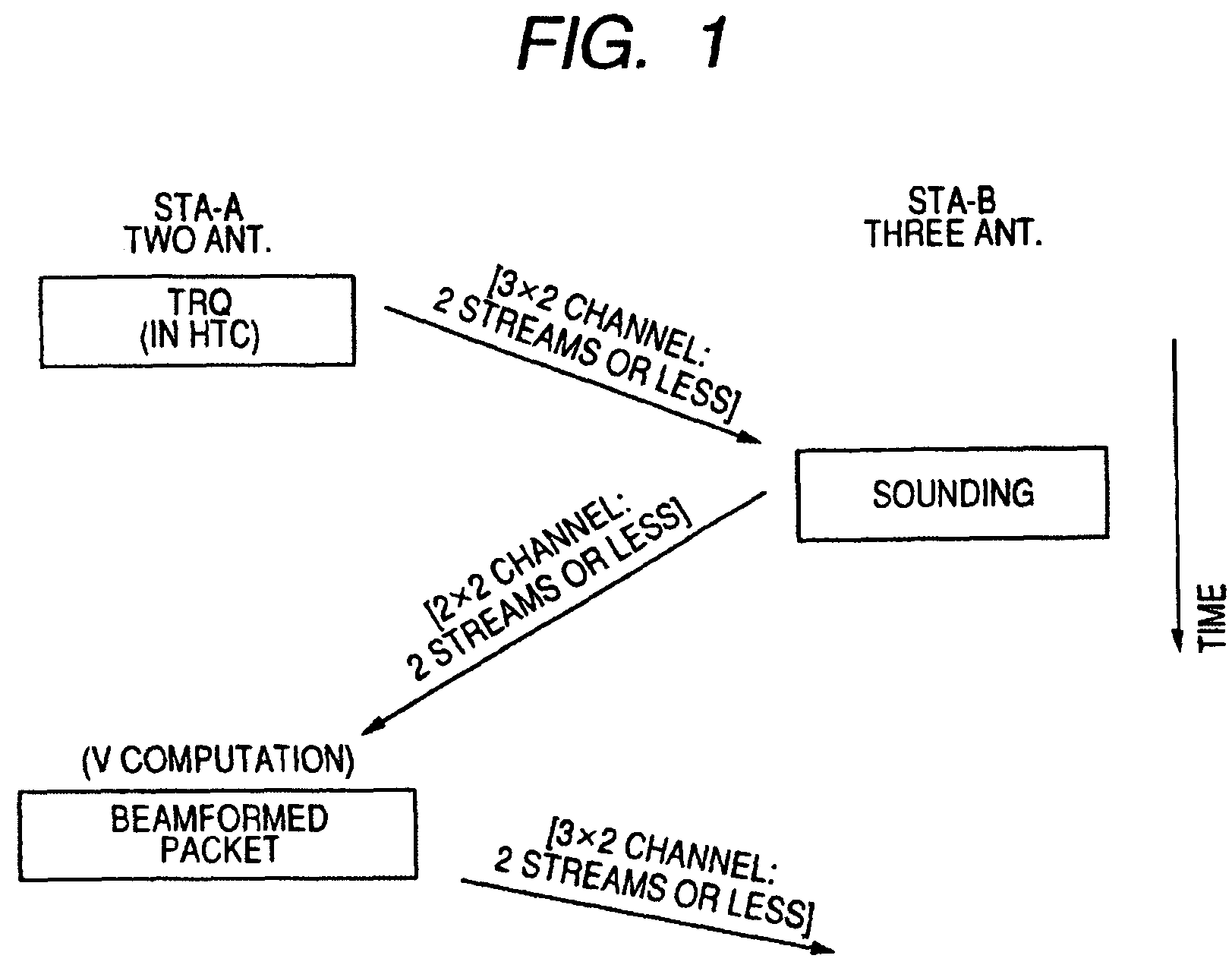

Wireless communication system, wireless communication apparatus, and wireless communication method

ActiveUS7848444B2Without deteriorating beamforming characteristicImprove process capabilityPolarisation/directional diversityMultiplex communicationCommunications systemData transmission

A wireless communication system is disclosed. The system performs data transmission from a first terminal including N antennas to a second terminal including M antennas using spatially multiplexed streams (N and M are integers larger than or equal to 2).

Owner:SONY CORP

Radio receiving apparatus, mobile station appartus, base station apparatus, and radio receiving method

InactiveUS20060274854A1Small apparatus sizeLow apparatus costSpatial transmit diversityAngle modulationRadio receptionCarrier signal

A radio receiving apparatus and radio receiving method are provided that enable the overall apparatus circuit scale to be reduced, and small apparatus size and low apparatus cost to be achieved, without increasing the processing load, together with a mobile station apparatus and base station apparatus equipped with this radio receiving apparatus. A phase control section (290) holds a phase rotation amount of each subcarrier signal due to the delay in the sampling timing of the second antenna with respect to the first antenna, decided in advance according to the number of antennas of the radio receiving apparatus and the subcarrier frequencies. The phase control section (290) performs phase rotation by the held phase rotation amount of each of N subcarrier signals output from an FFT section (240-2) corresponding to the second antenna.

Owner:PANASONIC CORP

Drive circuit for display apparatus and display apparatus

InactiveUS20050206635A1Reduce circuit sizeReduce chip sizeVibration massageCathode-ray tube indicatorsDisplay deviceEngineering

A drive circuit that is an example of the present invention is a drive circuit of a display device for outputting in parallel the analog picture signals generated based on the digital picture signals inputted in serial. This circuit comprises a level shift circuit for converting the voltage level of the digital picture signals that were inputted in serial, a D / A conversion circuit for generating analog picture signals based on the digital picture signals that were subjected to level conversion with the level shift circuit, and an expansion circuit connected to the output side of the D / A conversion circuit or between the level shift circuit and the D / A conversion circuit and serving to expand and hold the inputted serial picture signals in parallel and output the picture signals in parallel. The level shift circuit is thus formed in the front stage of the picture signal register circuit.

Owner:RENESAS ELECTRONICS CORP

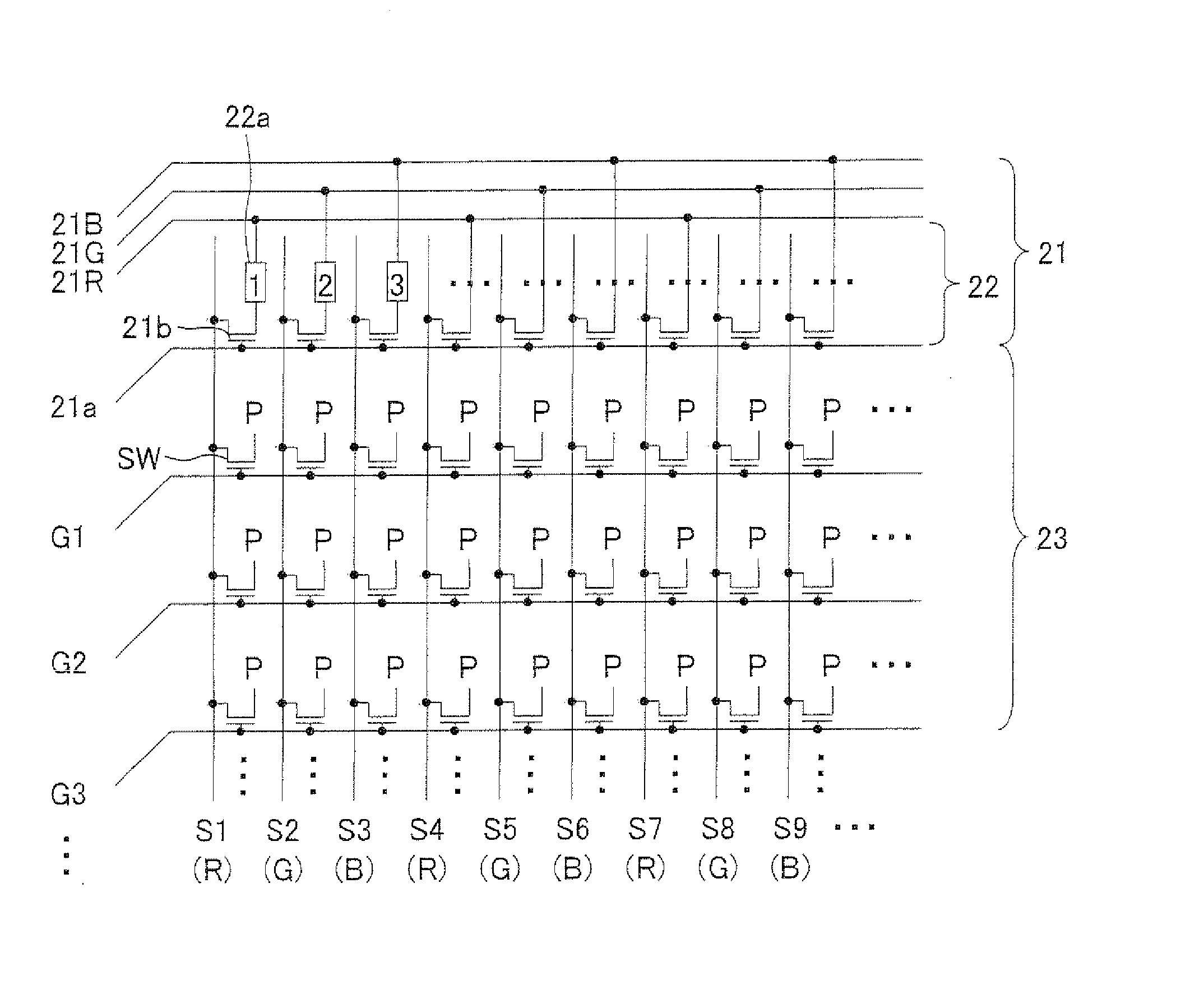

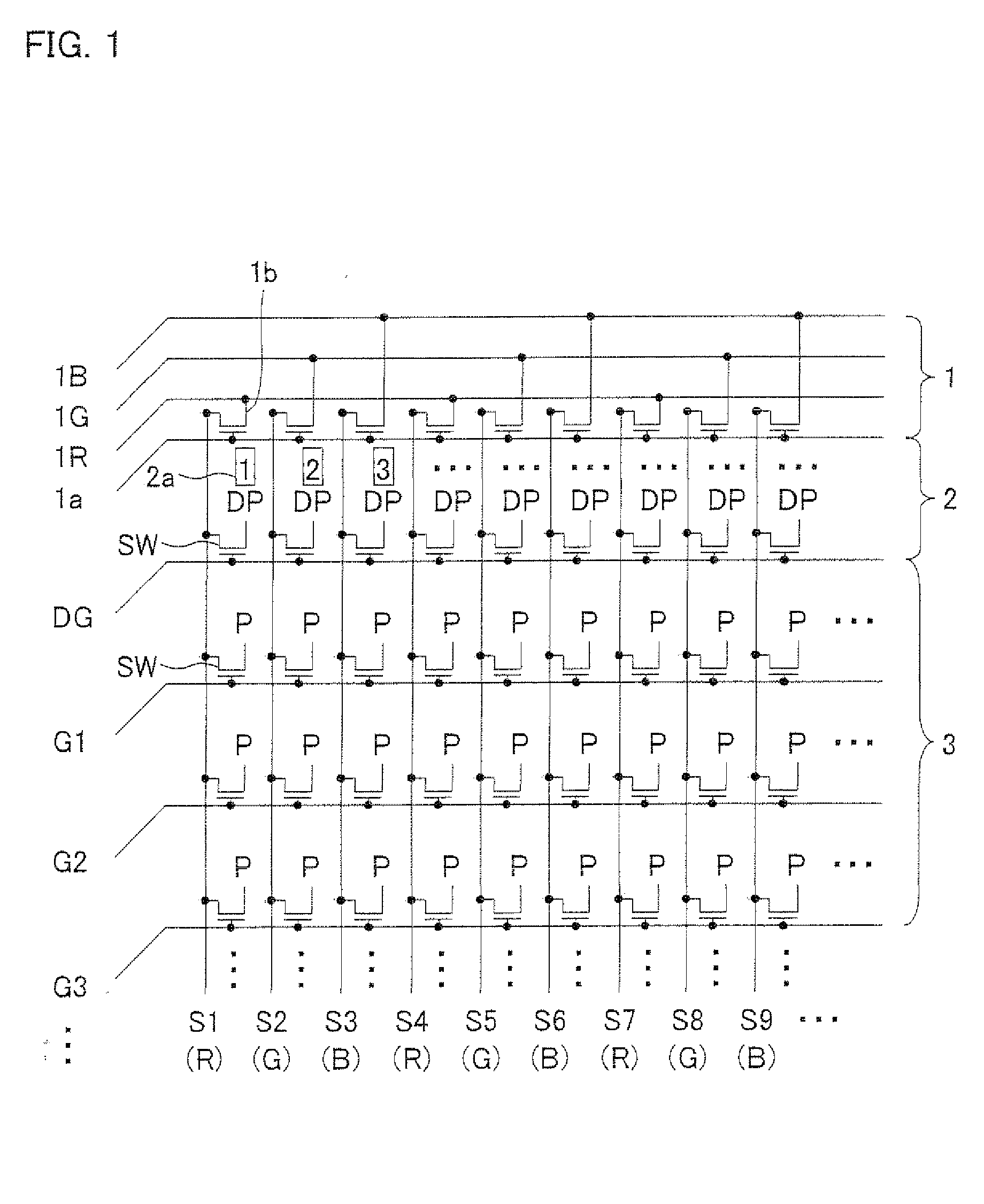

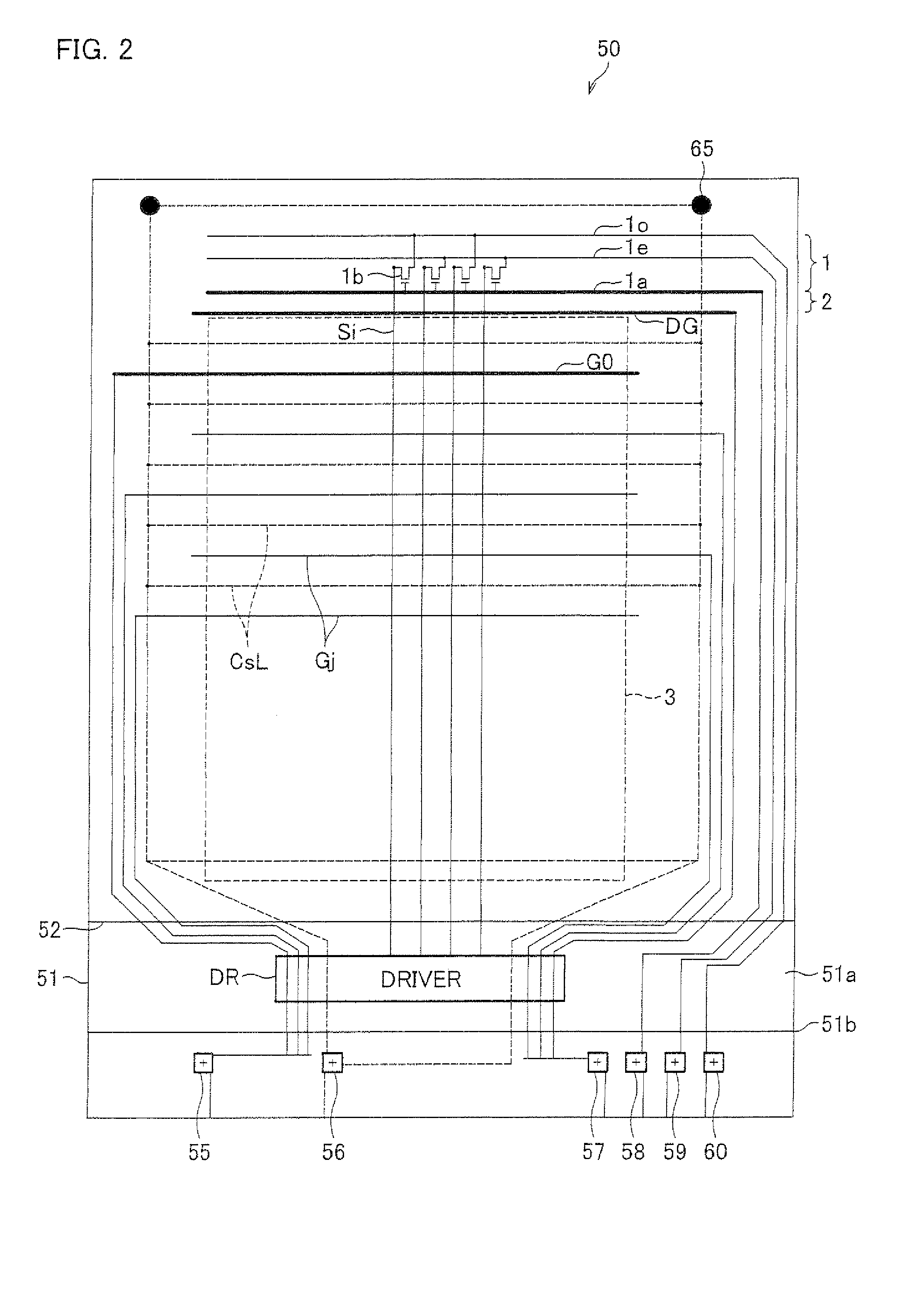

Display panel and display device having the panel

ActiveUS20090231255A1Simple processReduce areaStatic indicating devicesNon-linear opticsParasitic capacitanceDisplay device

A dummy line, which is disposed in a dummy pixel region (2) on the side of a test wiring region (1) and which has a parasitic capacitance effect like that of an adjacent scanning line (Gj) in an effective display region (3), is commonly used as a test switch line (1a). This test switch line (1a) is provided away from a dummy scanning line (DG) by intervals at which the scanning lines (Gj) are provided in the effective display region (3). As a result, it is possible to realize a display panel capable of reducing a frame area while keeping a test circuit region and the dummy pixel region in the frame area, and a display device having the display panel.

Owner:SHARP KK

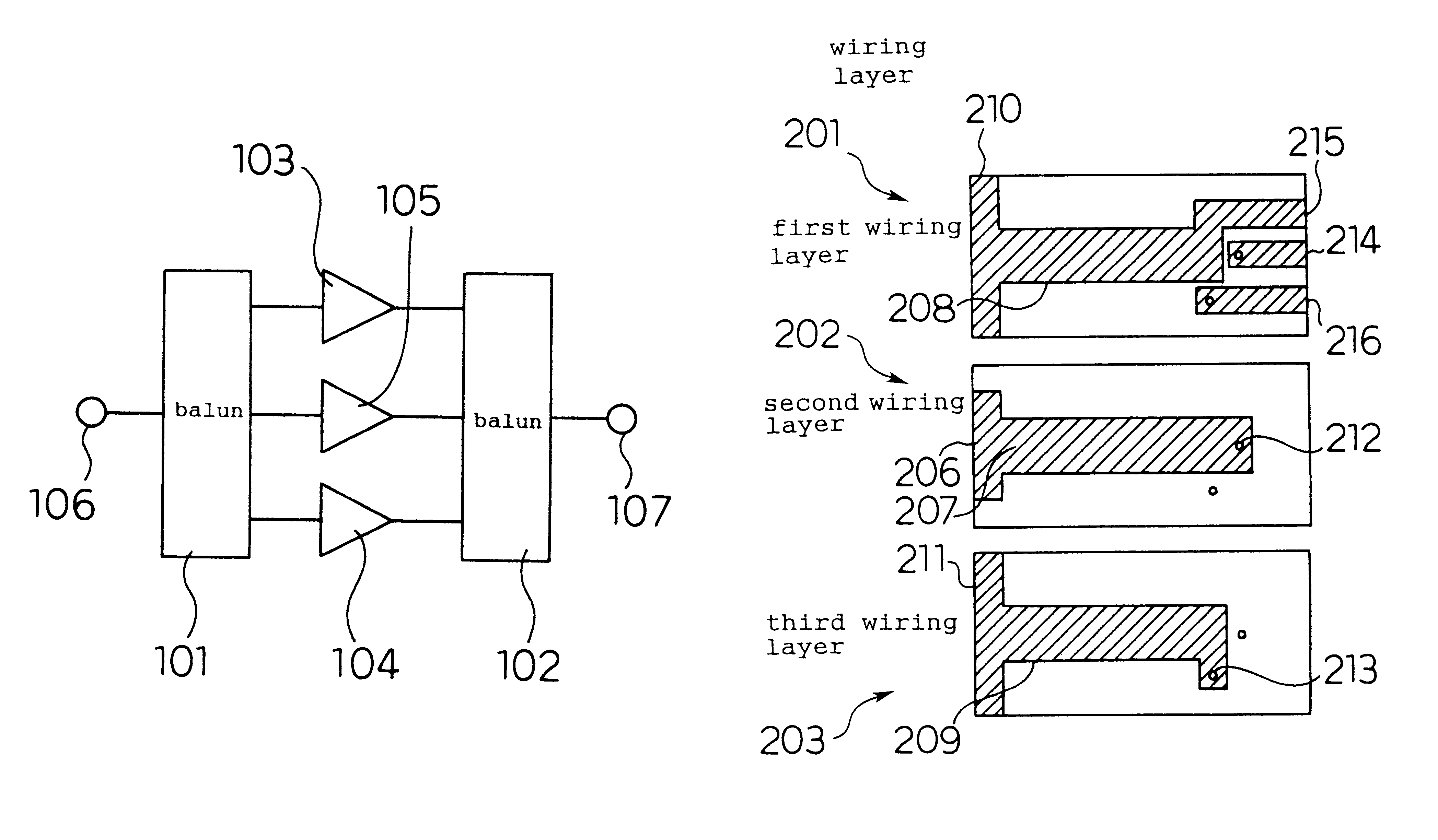

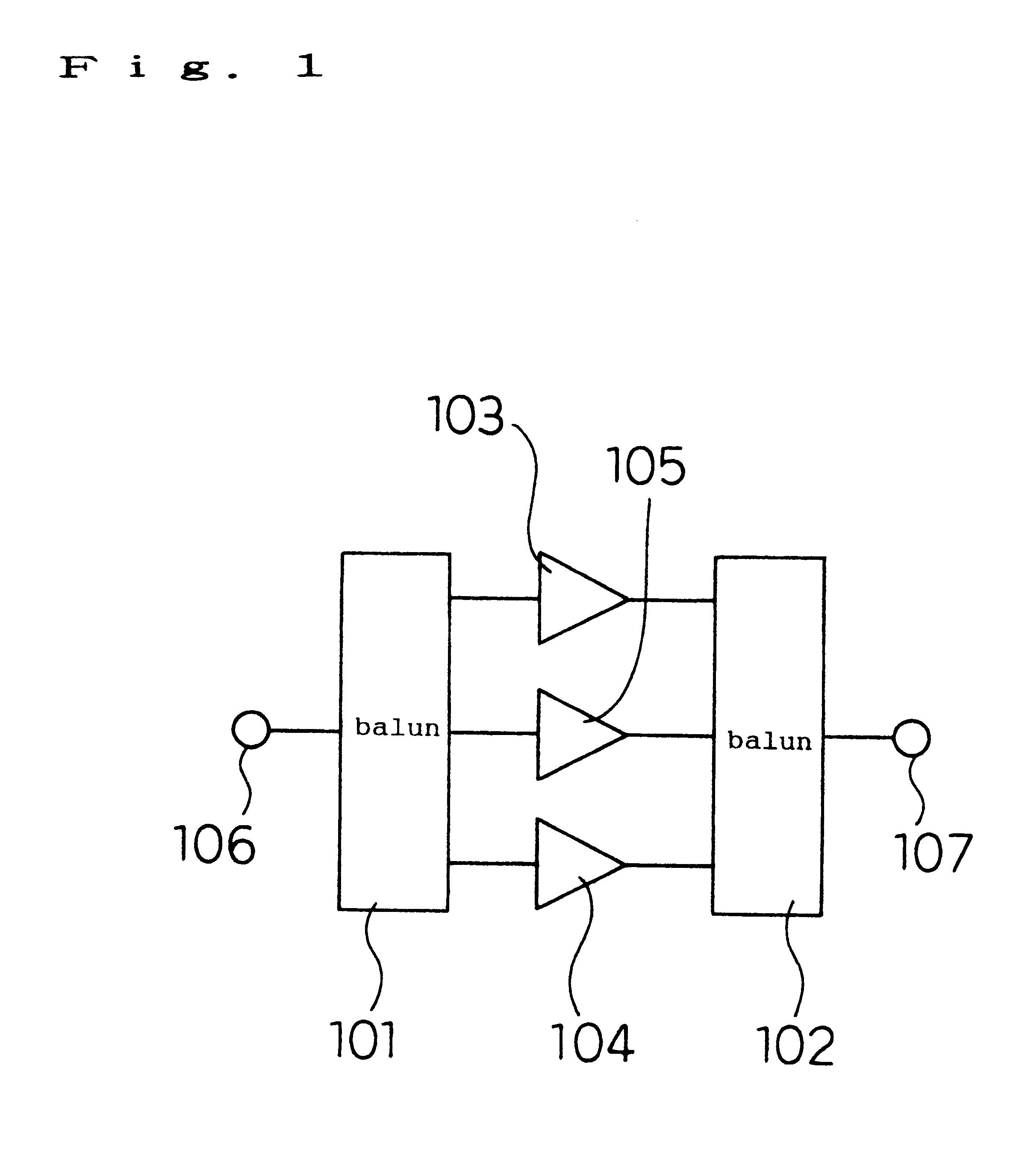

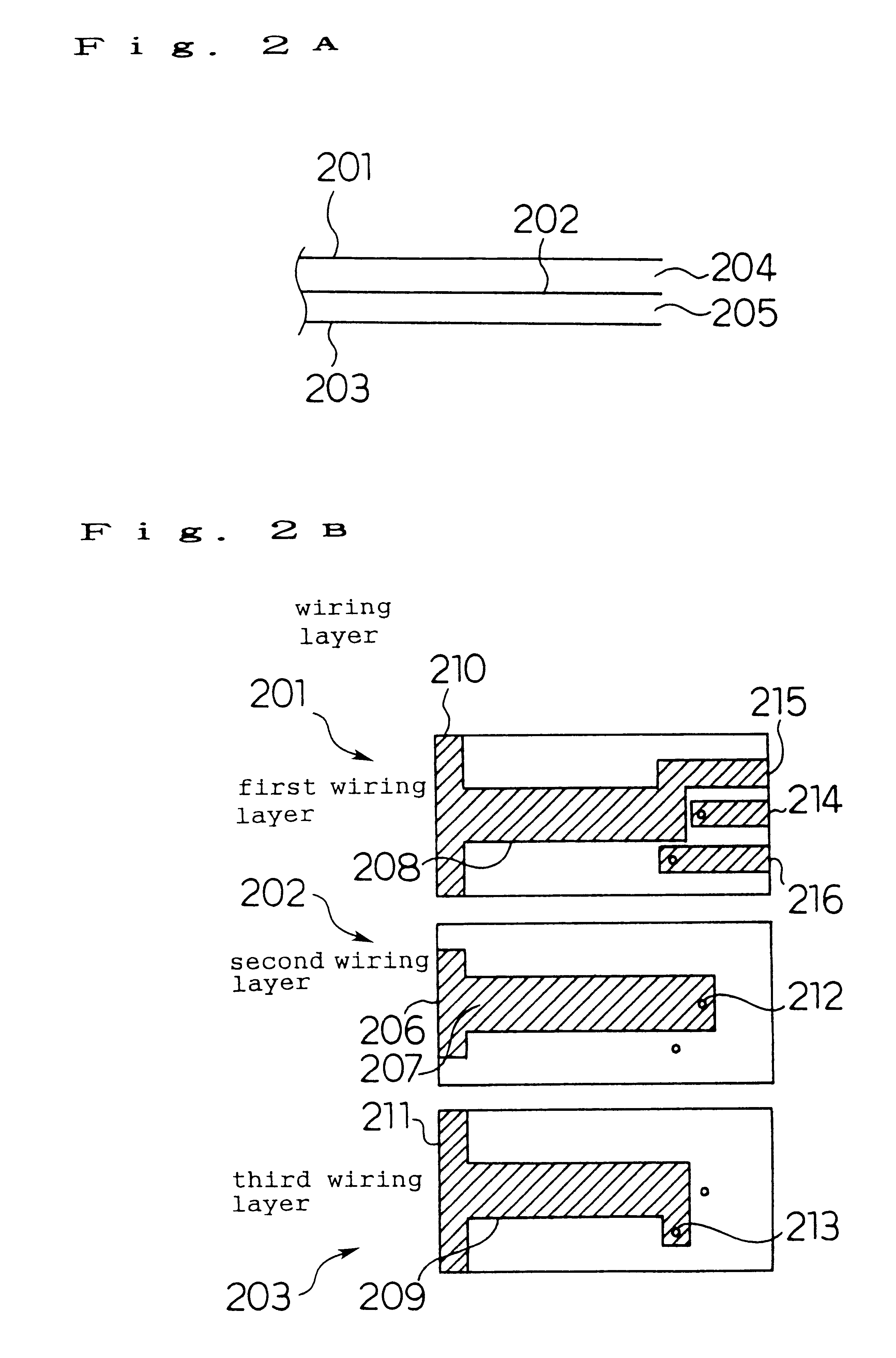

Power splitter/ combiner circuit, high power amplifier and balun circuit

InactiveUS6201439B1Reduce circuit sizePush-pull amplifiersPhase-splittersAudio power amplifierHigh power amplifier

A high power amplifier has a first balun propagating a half of an input signal to an in-phase output terminal, and also propagating a fourth of the input signal to first and second opposite-phase output terminals, the signal propagated to the first and second opposite-phase output terminals lagging 180 degrees behind the signal propagated to the in-phase output terminal; first and second power amplifier circuits connected to the first and second opposite-phase output terminals of the first balun and having the same characteristics; a third power amplifier circuit connected to the in-phase output terminal of the first balun and having output power substantially twice as much as the output power of the first or second power amplifier circuit; and a second balun having first and second opposite-phase input terminals for receiving the outputs of the first and second power amplifier circuits, having an in-phase input terminal for receiving the output of the third power amplifier circuit, combining the outputs of the first, second and third power amplifier circuits, and propagating combined output.

Owner:PANASONIC CORP

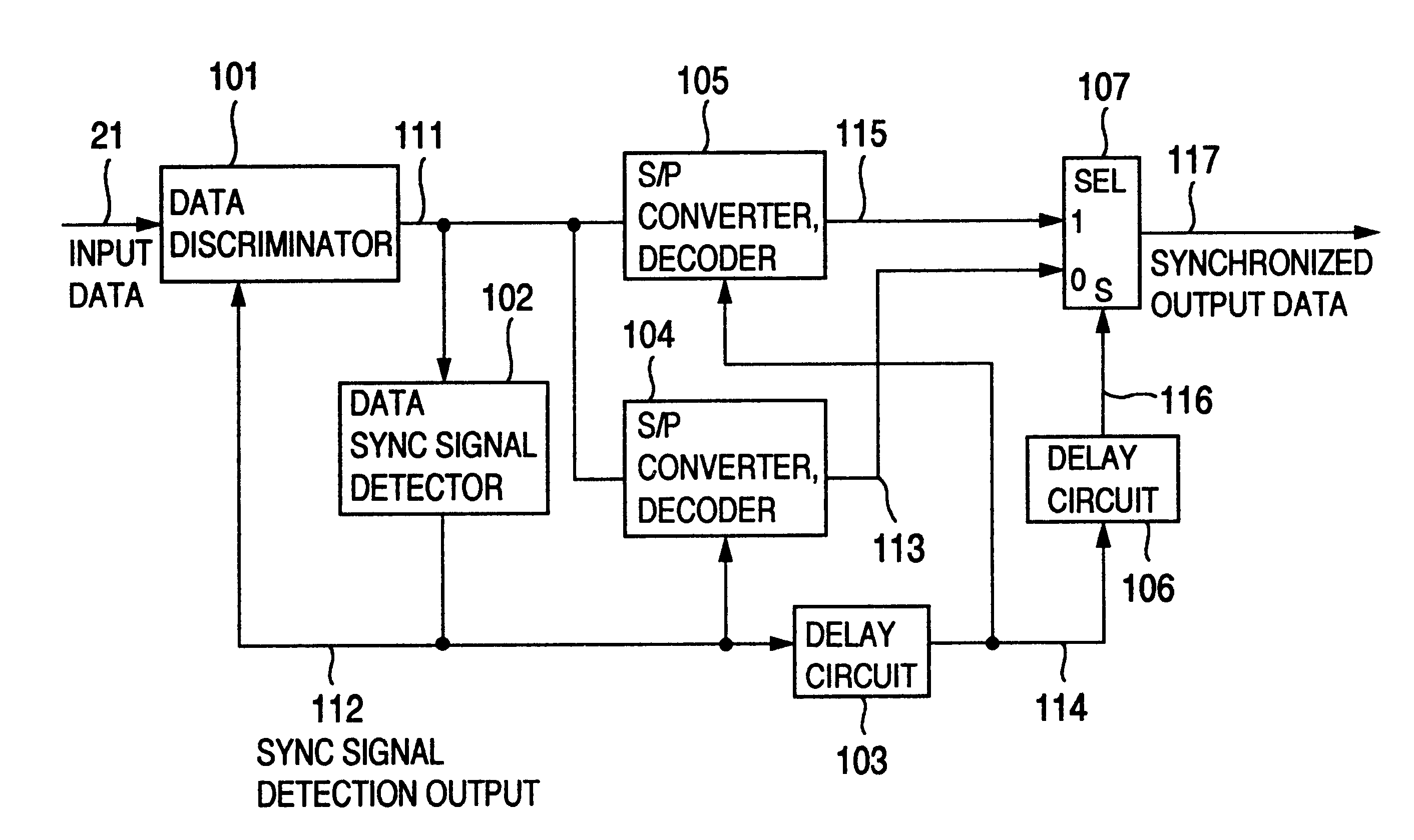

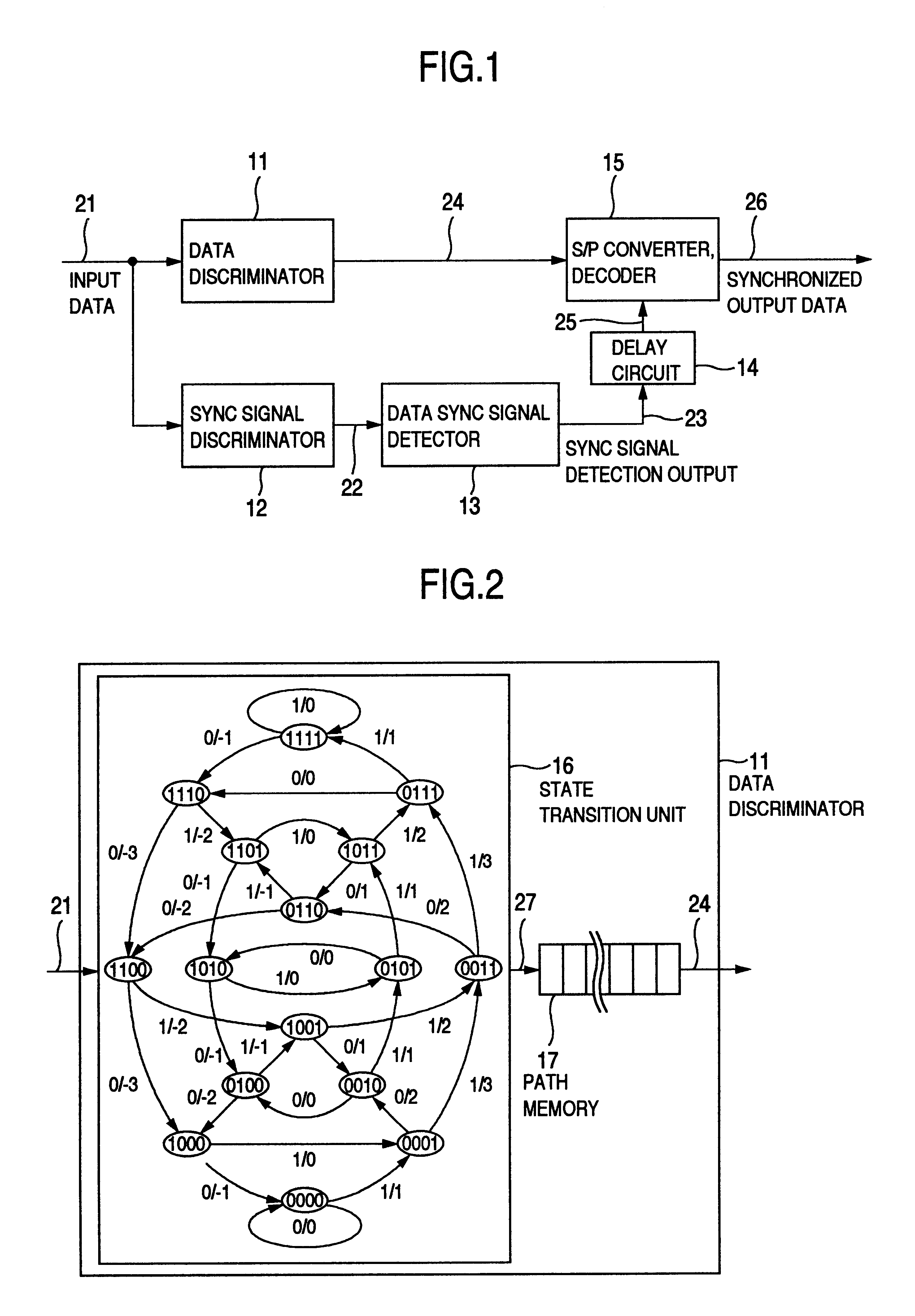

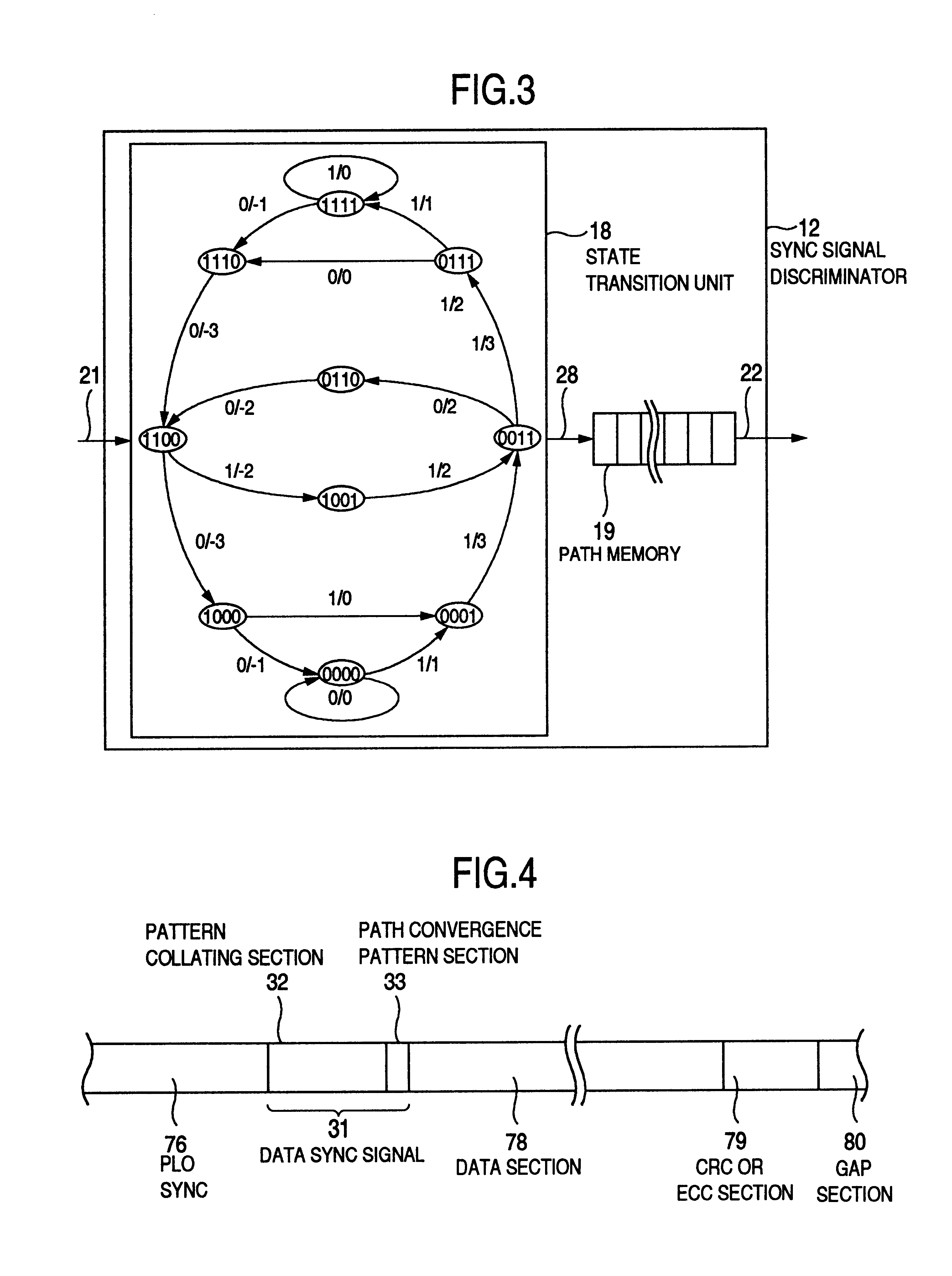

Data synchronizing signal detector, signal processing device using the detector, information recording and reproducing apparatus having the detector and the device, data synchronizing signal detecting method, and information recording medium for using in the method

InactiveUS6791777B2Improve accuracyImprove the detection rateModification of read/write signalsSynchronisation information channelsDiscriminatorData synchronization

A data discriminating unit includes a data discriminator and a sync signal discriminator. A data sync signal is detected for the bit string discriminated from the output of the sync signal discriminator, and the data is demodulated for the bit string discriminated from the output of the data discriminator, thereby optimizing the signal to a form suitable for discrimination and detection of the data sync signal and demodulation for data reproduction. As a result, the detection performance of the data sync signal can be improved while maintaining the data discrimination performance. A Viterbi decoder is used for discrimination by the data discriminator and the sync signal discriminator for the optimization thereby to optimize the number of states, the number of paths for state transition and the path memory length. A signal having no continuous inversions of the recording data is used as the data sync signal.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD +1