Patents

Literature

25963results about "Pulse automatic control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

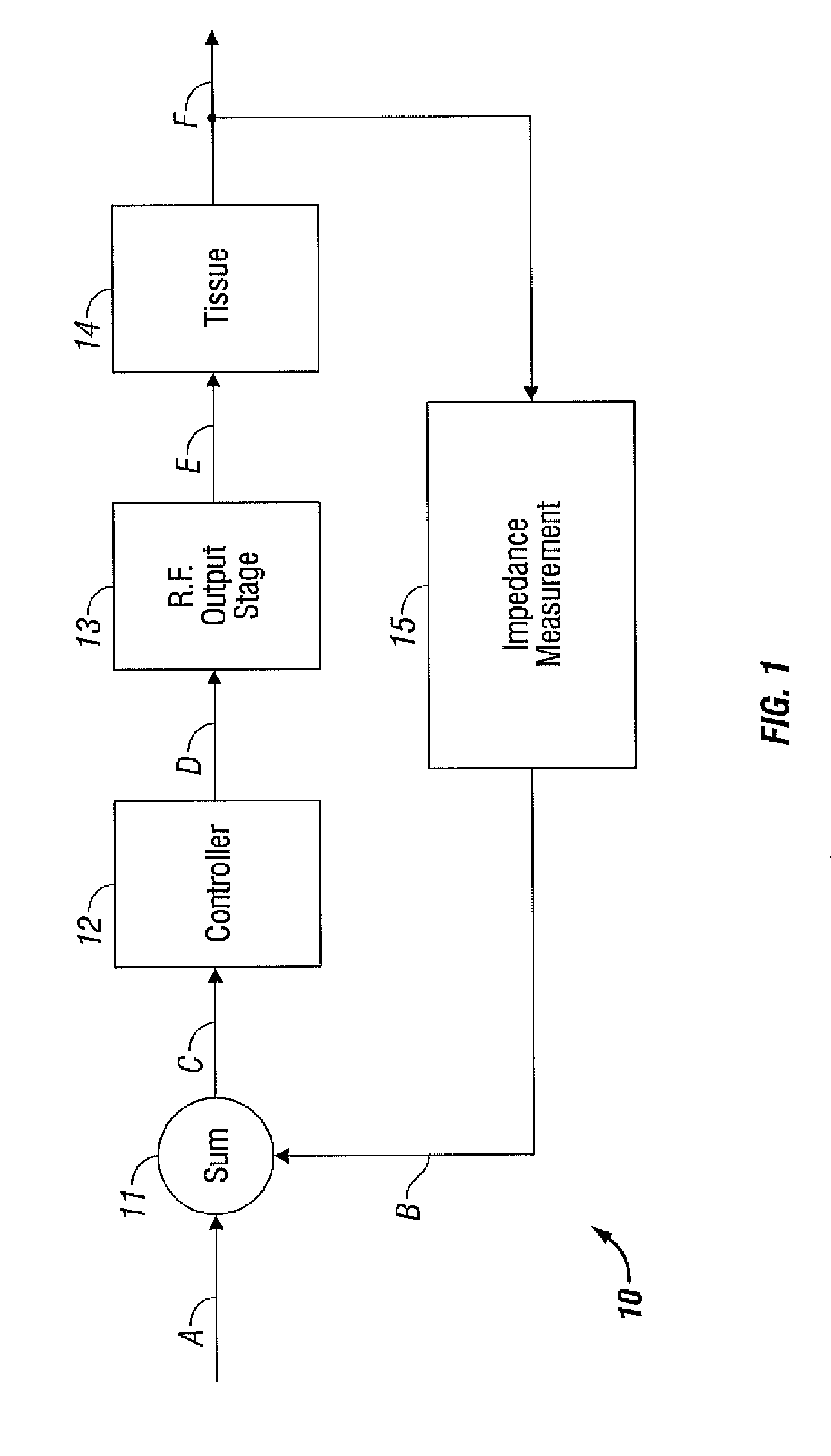

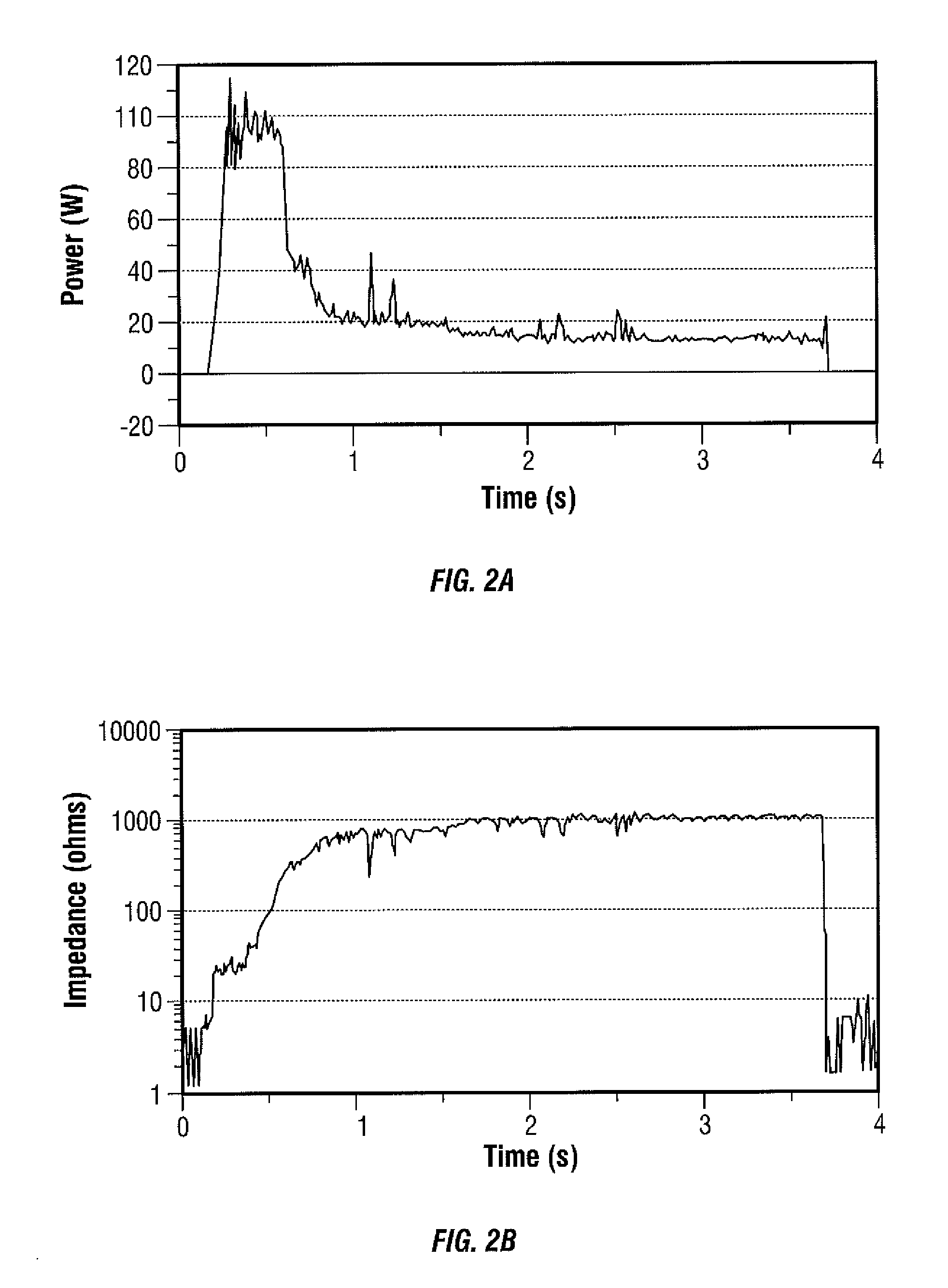

Electrosurgical generator with adaptive power control

InactiveUSRE40388E1Lower Level RequirementsImproved tissue sealing characteristicPulse automatic controlSurgical instruments for heatingThermal energyVessel sealing

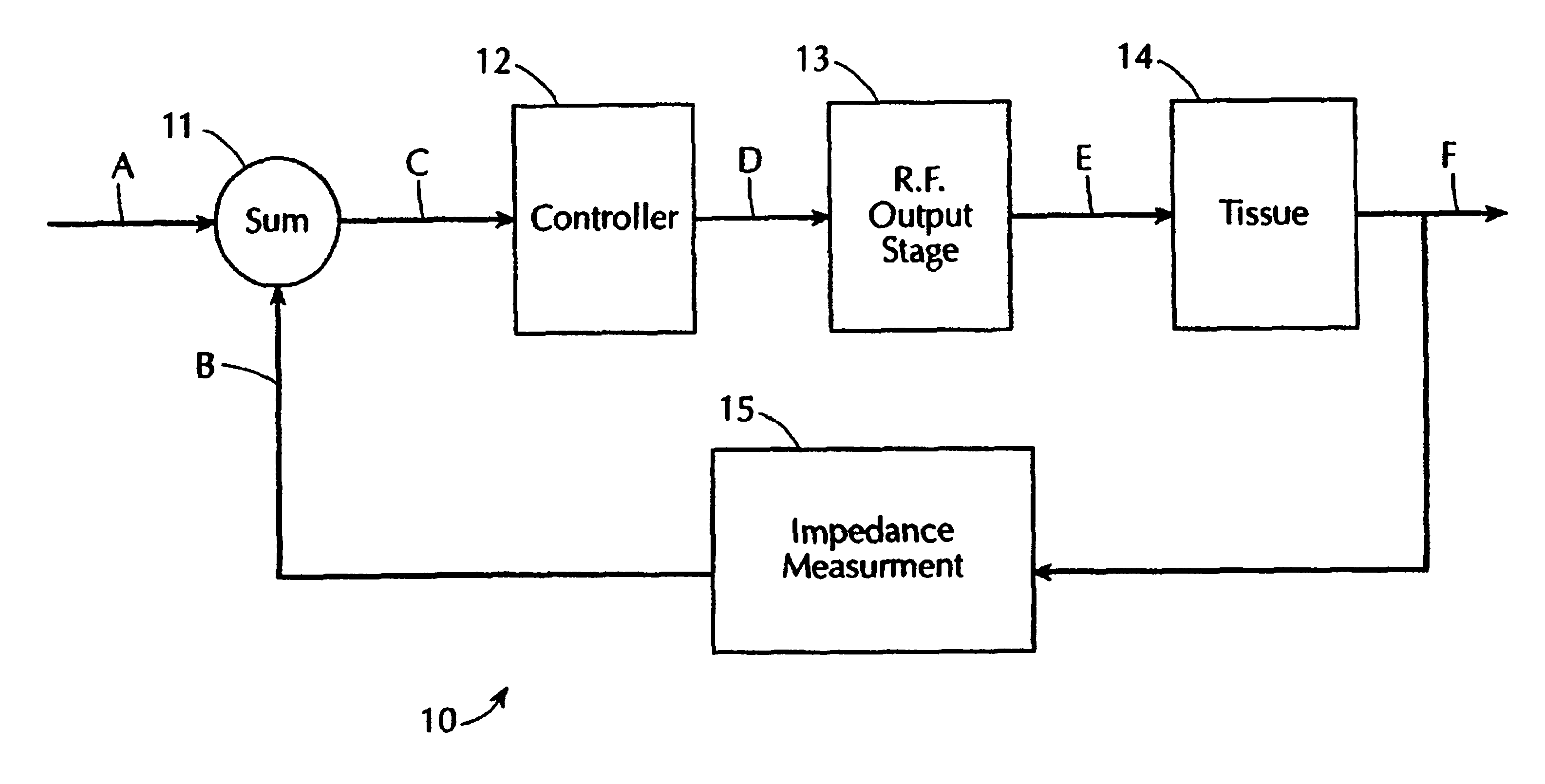

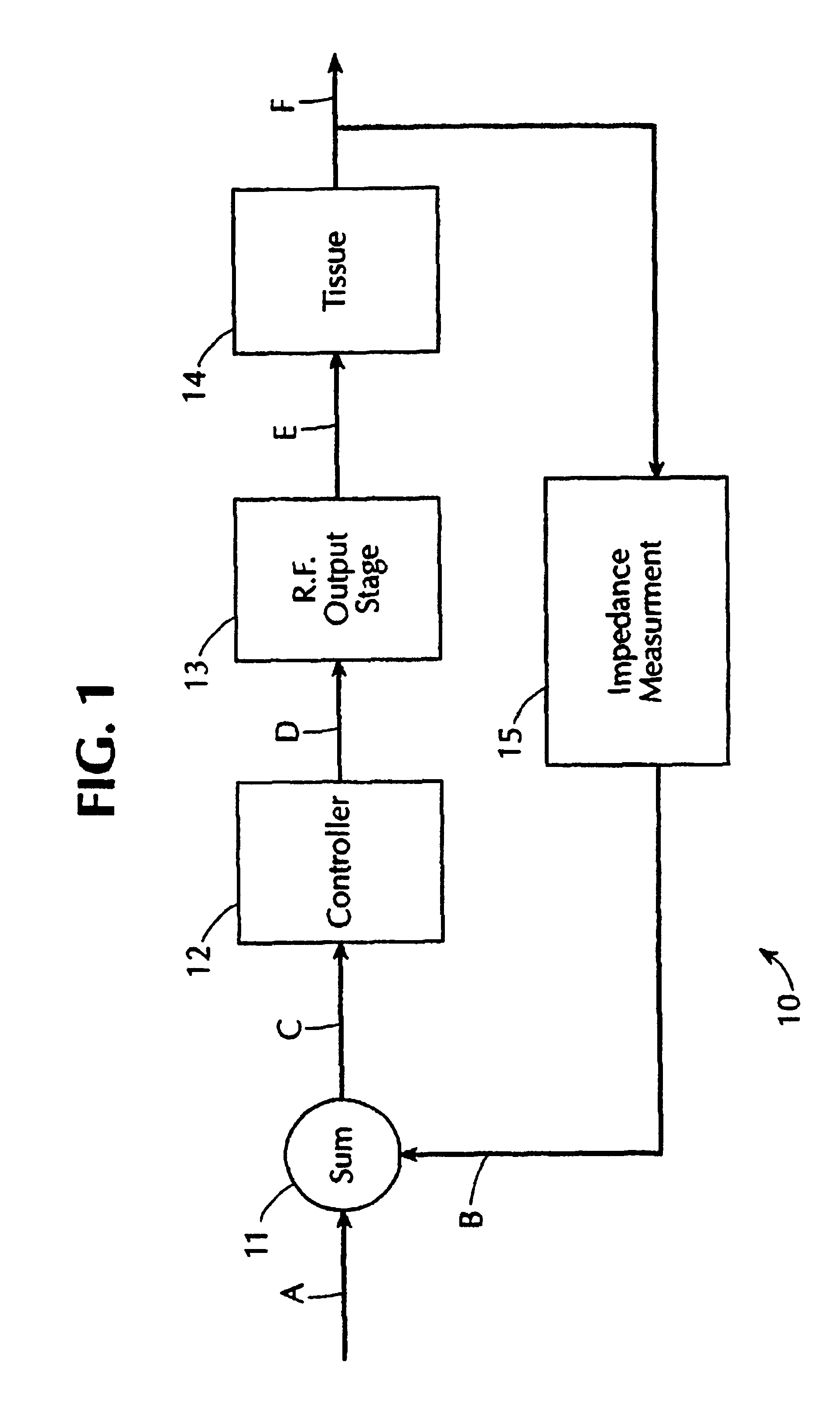

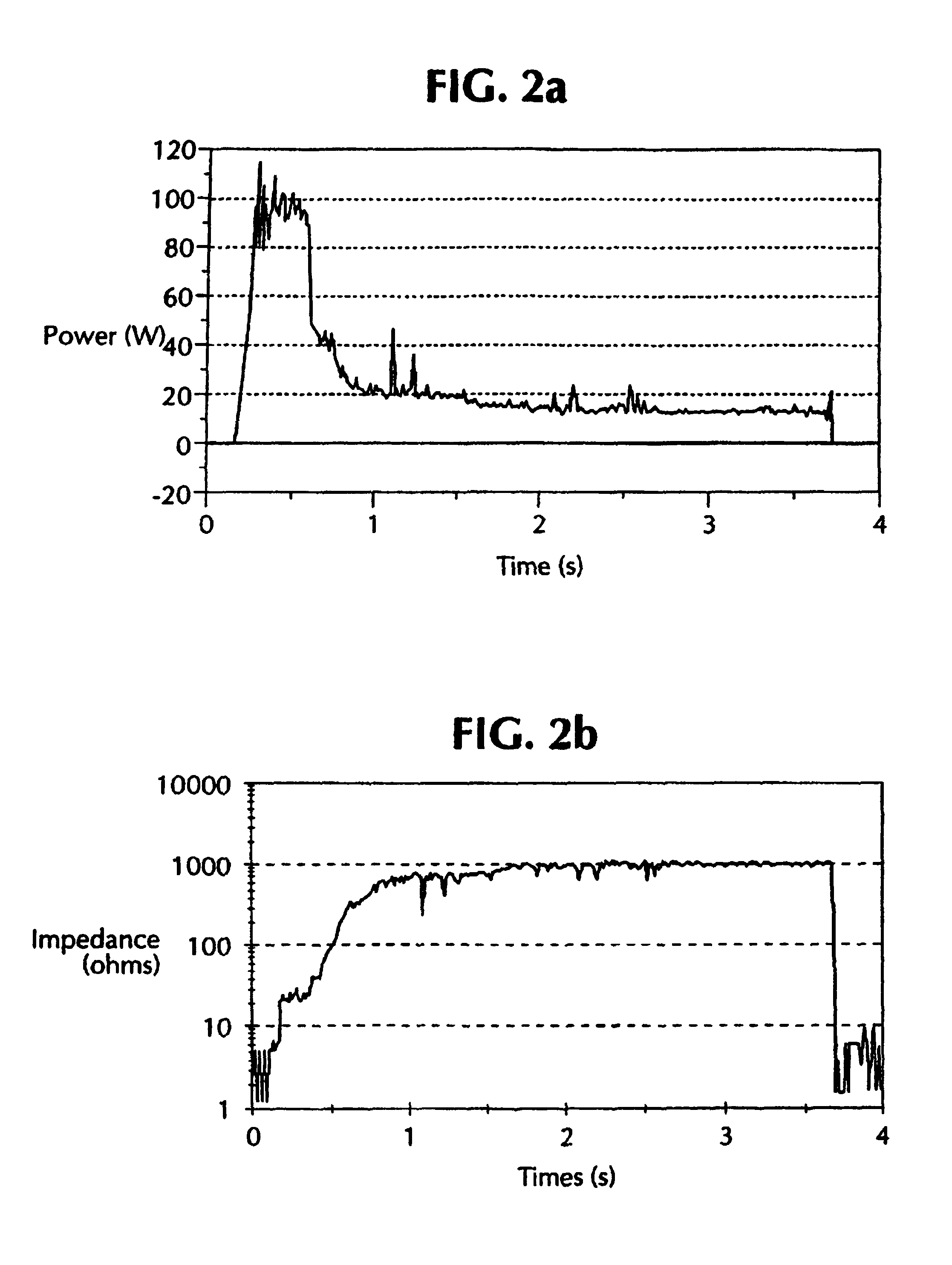

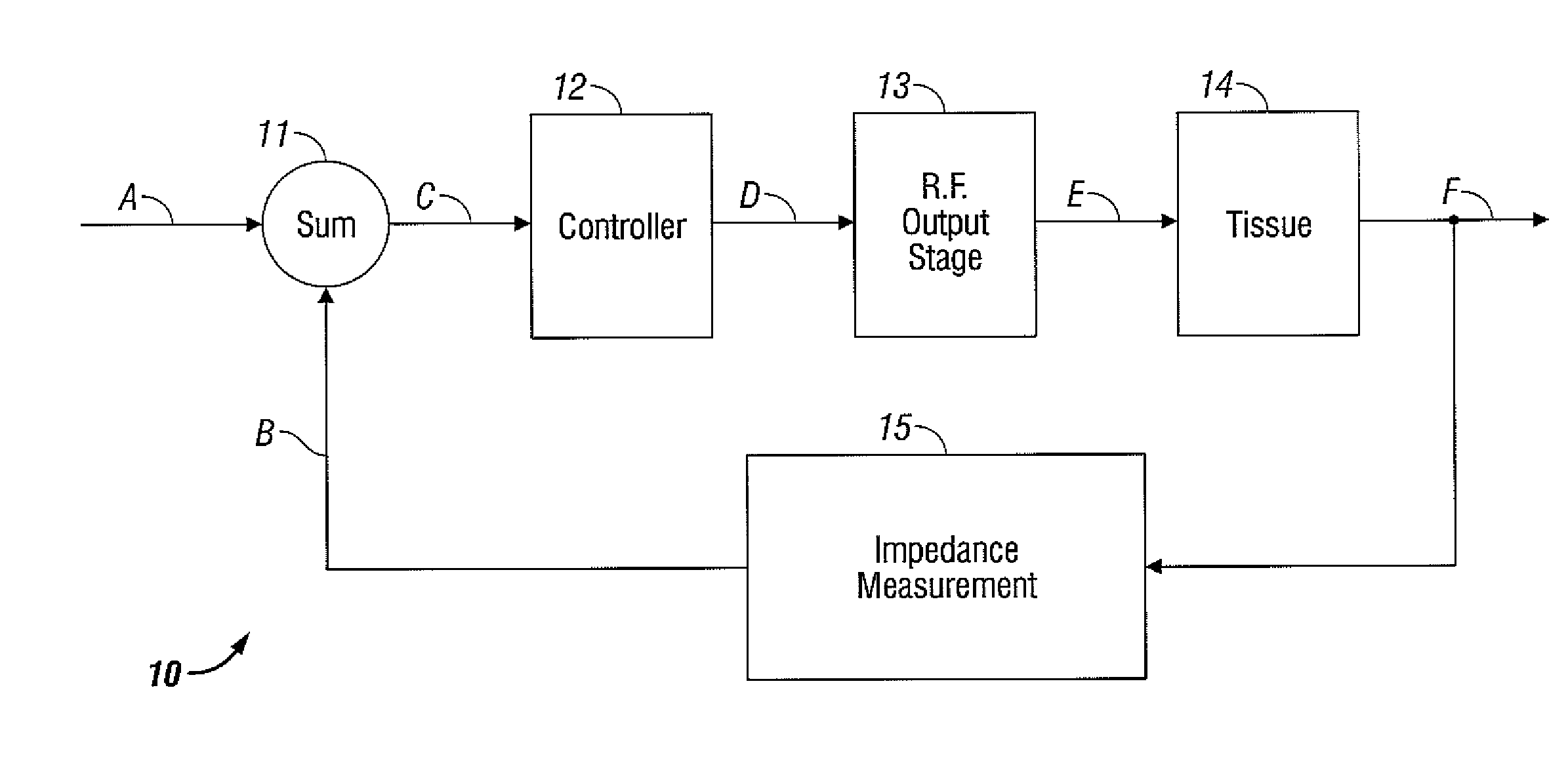

An electrosurgical generator has an output power control system that causes the impedance of tissue to rise and fall in a cyclic pattern until the tissue is desiccated. The advantage of the power control system is that thermal spread and charring are reduced. In addition, the power control system offers improved performance for electrosurgical vessel sealing and tissue welding. The output power is applied cyclically by a control system with tissue impedance feedback. The impedance of the tissue follows the cyclic pattern of the output power several times, depending on the state of the tissue, until the tissue becomes fully desiccated. High power is applied to cause the tissue to reach a high impedance, and then the power is reduced to allow the impedance to fall. Thermal energy is allowed to dissipate during the low power cycle. The control system is adaptive to tissue in the sense that output power is modulated in response to the impedance of the tissue.

Owner:COVIDIEN AG

Electrosurgical Generator With Adaptive Power Control

InactiveUS20080281315A1Pulse automatic controlSurgical instruments for heatingThermal energyVessel sealing

Owner:COVIDIEN AG

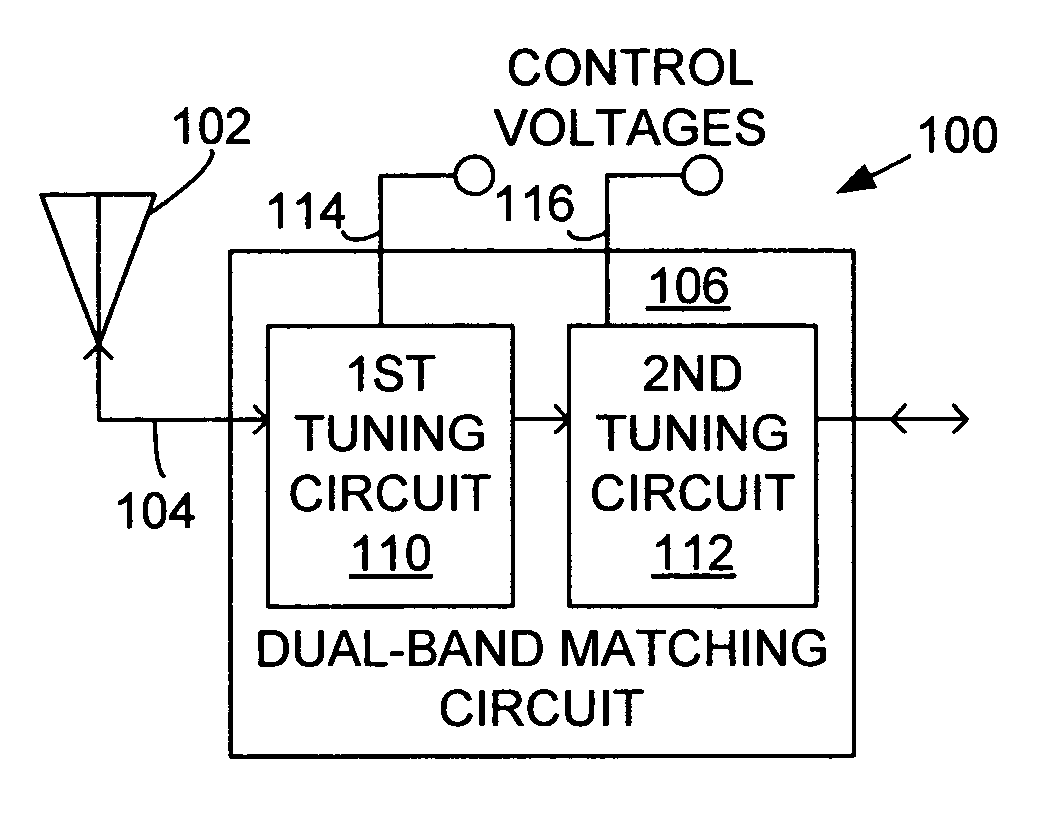

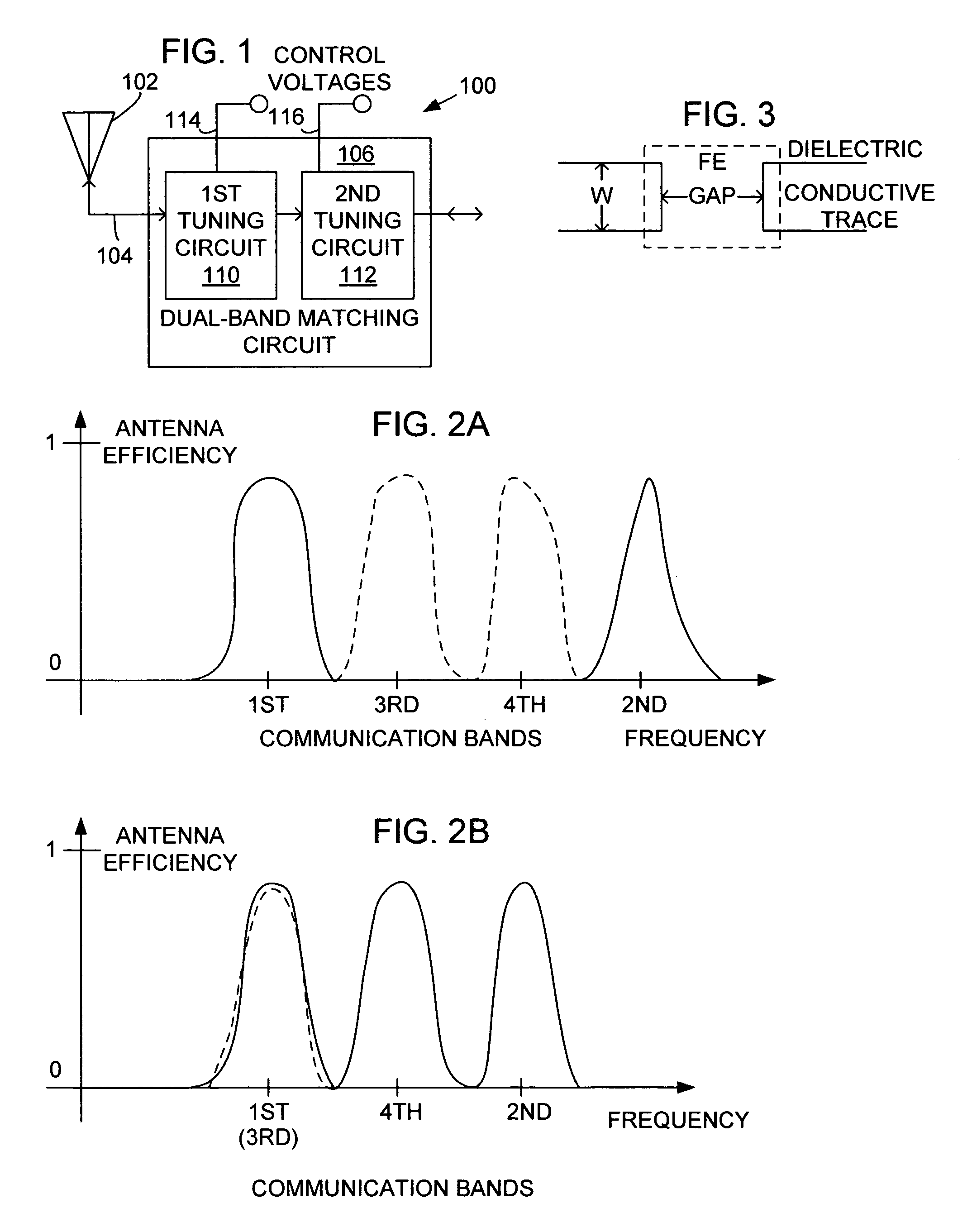

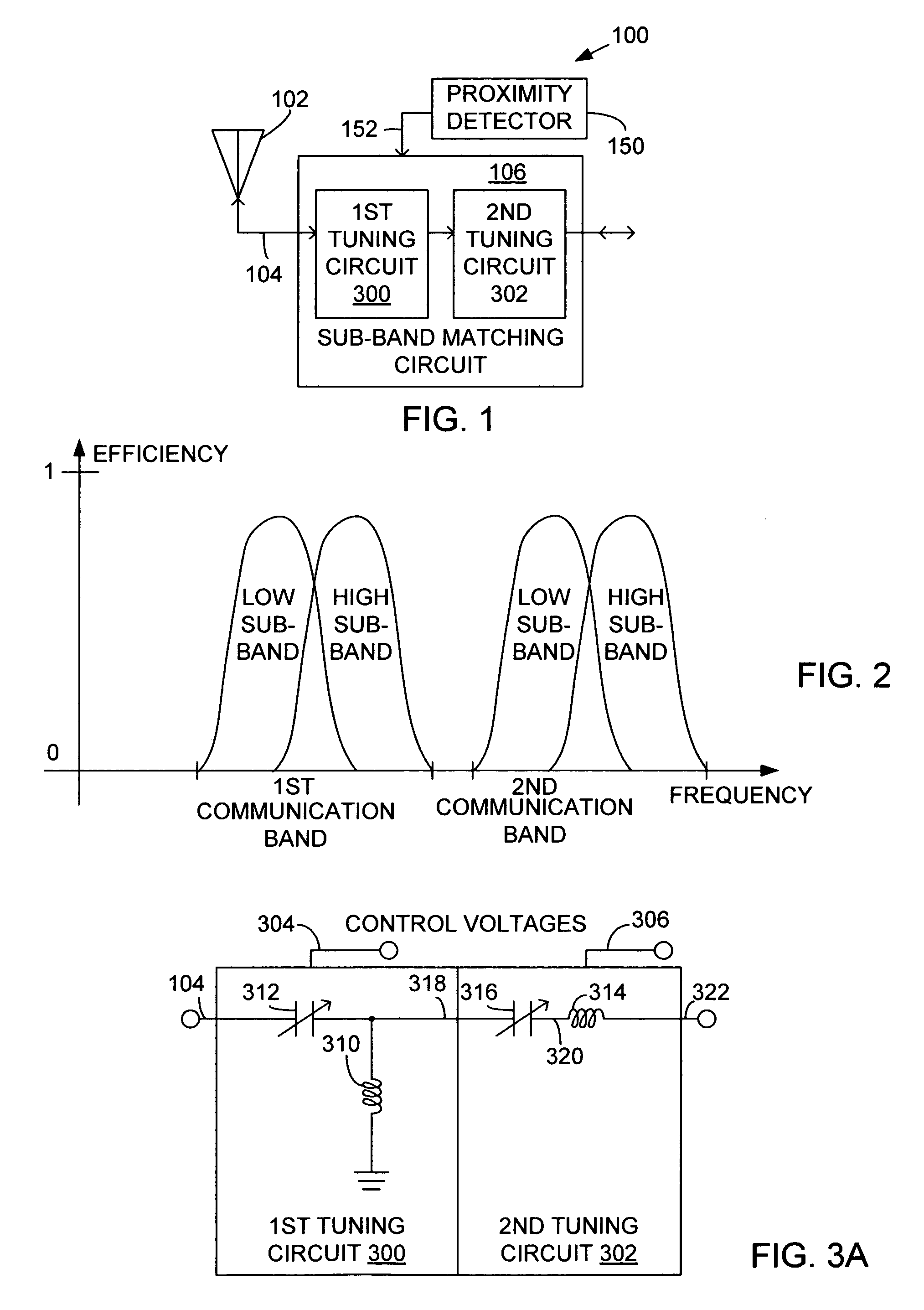

System and method for dual-band antenna matching

A dual-band antenna matching system and a method for dual-band impedance matching are provided. The method comprises: accepting a frequency-dependent impedance from an antenna; and, selectively supplying a conjugate impedance match for the antenna at either a first and a second communication band, or a third and a fourth communication band. More specifically, the method comprises: tuning a first tuning circuit to a first frequency; and, simultaneously tuning a second tuning circuit to a second frequency. In response, a conjugate match is supplied to the antenna in the first communication band in response to the first frequency. Simultaneously, the antenna is matched in the second communication band in response to the second frequency. When the first tuning circuit is tuned to a third frequency, and the second tuning circuit is tuned to a fourth frequency, then conjugate matches are supplied for the third and fourth communication bands, responsive to the third and fourth frequencies, respectively.

Owner:KYOCERA CORP

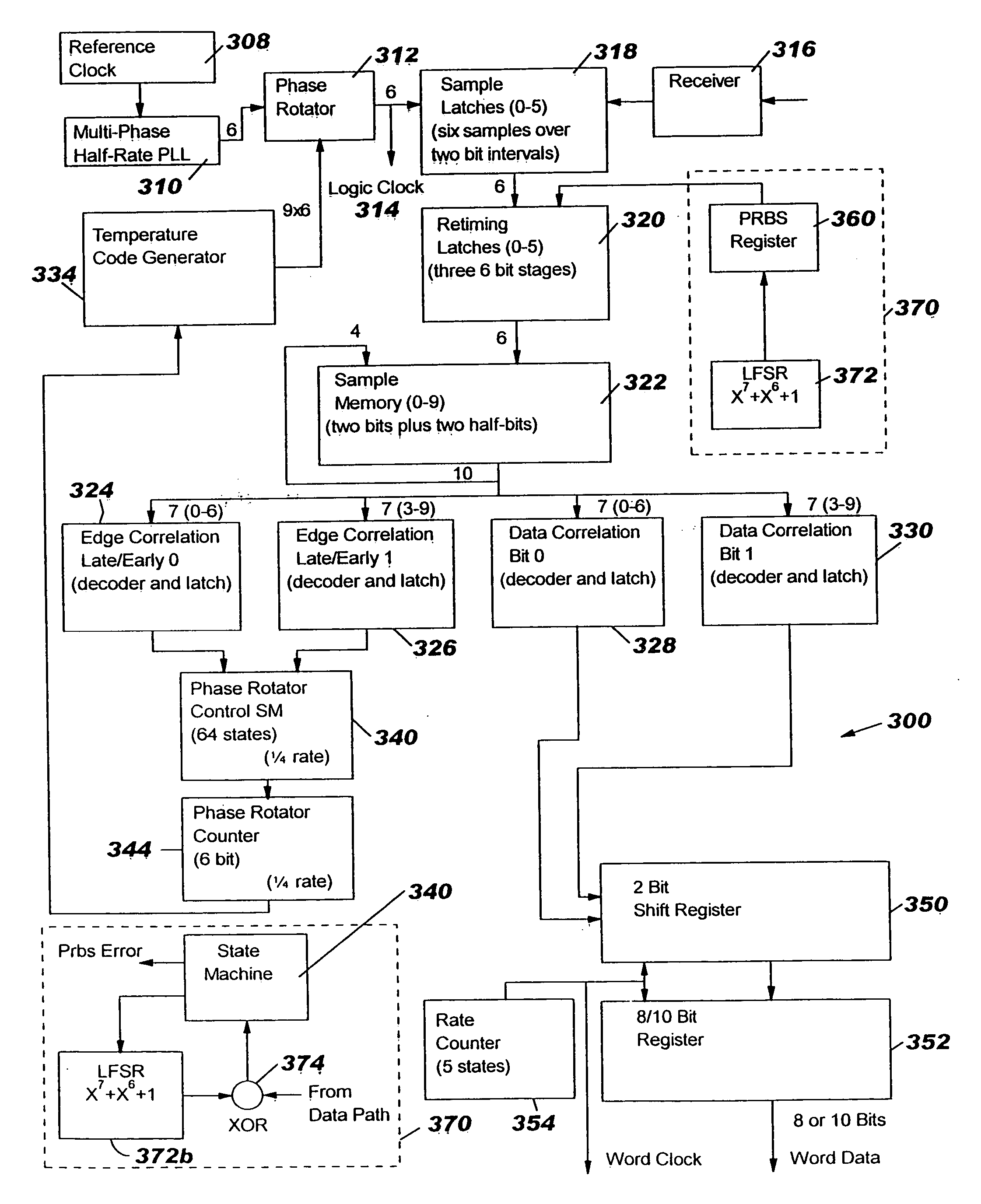

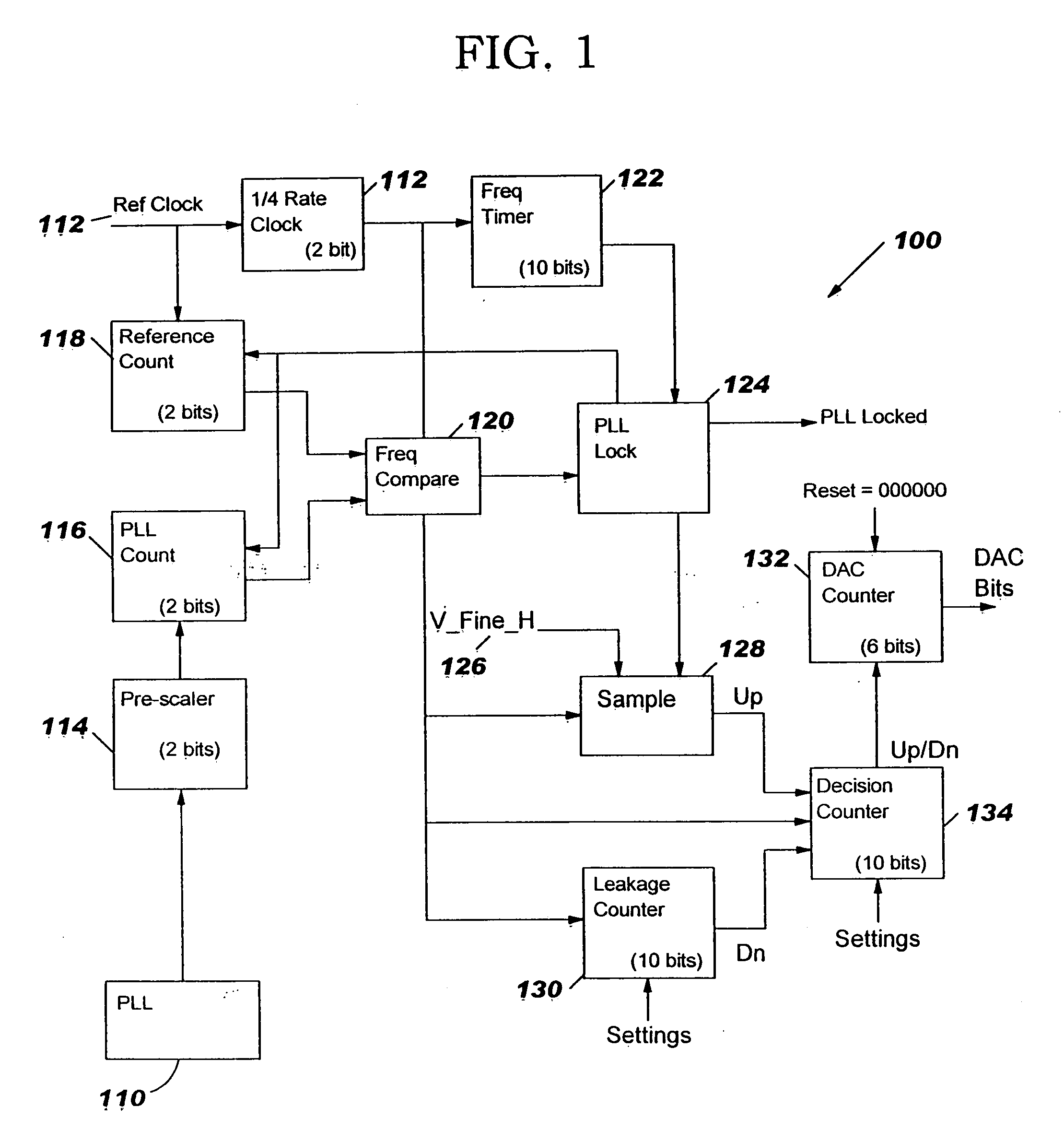

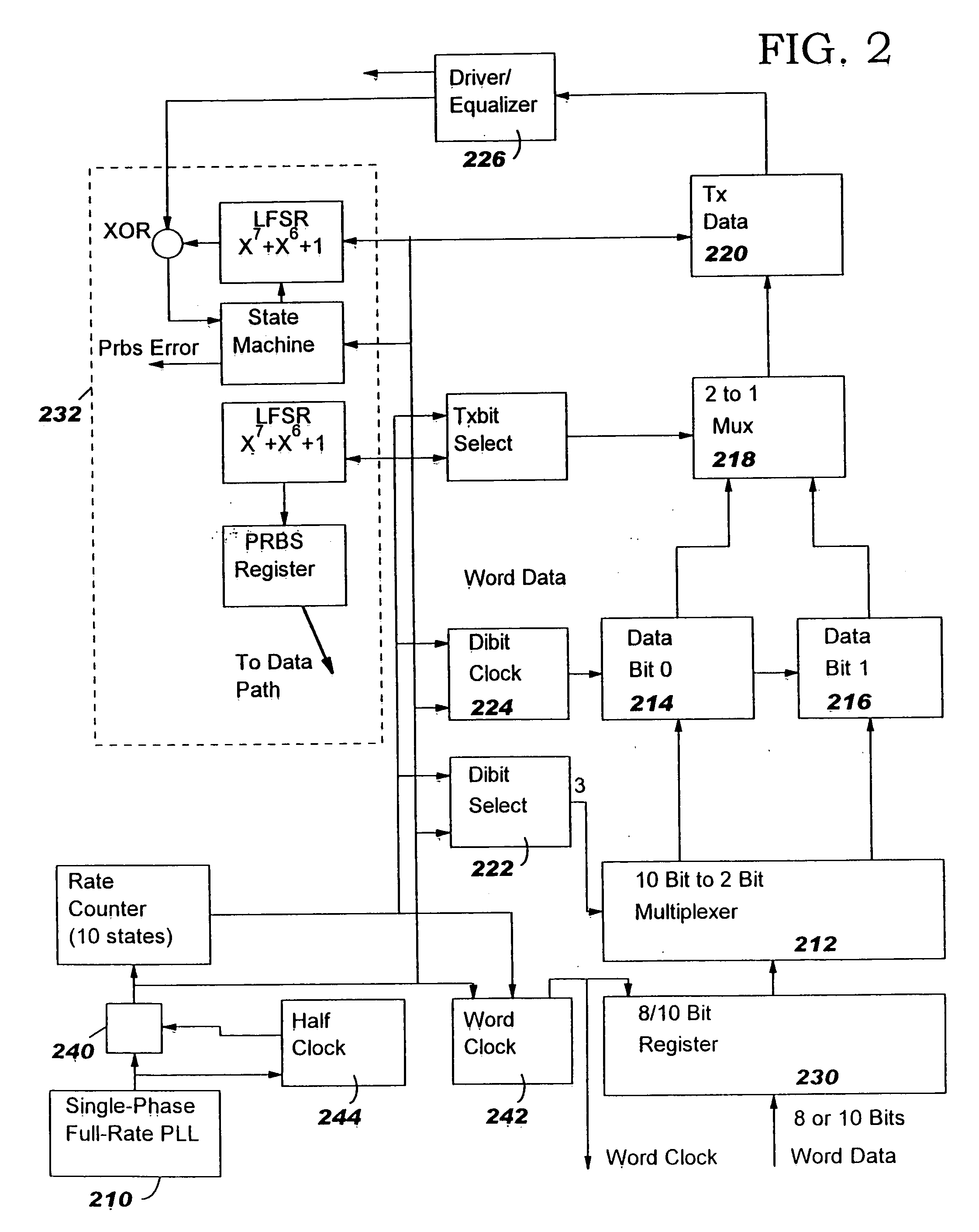

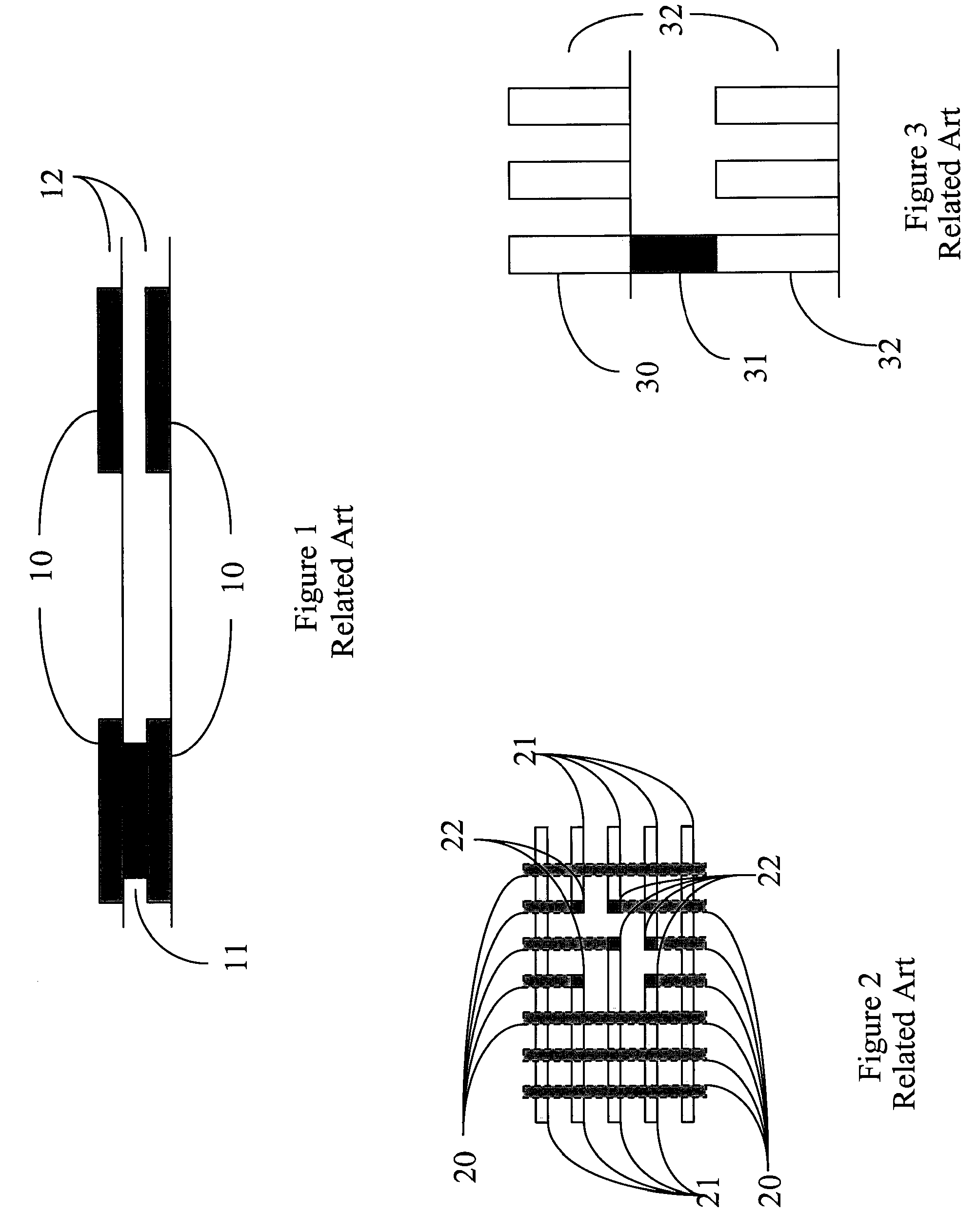

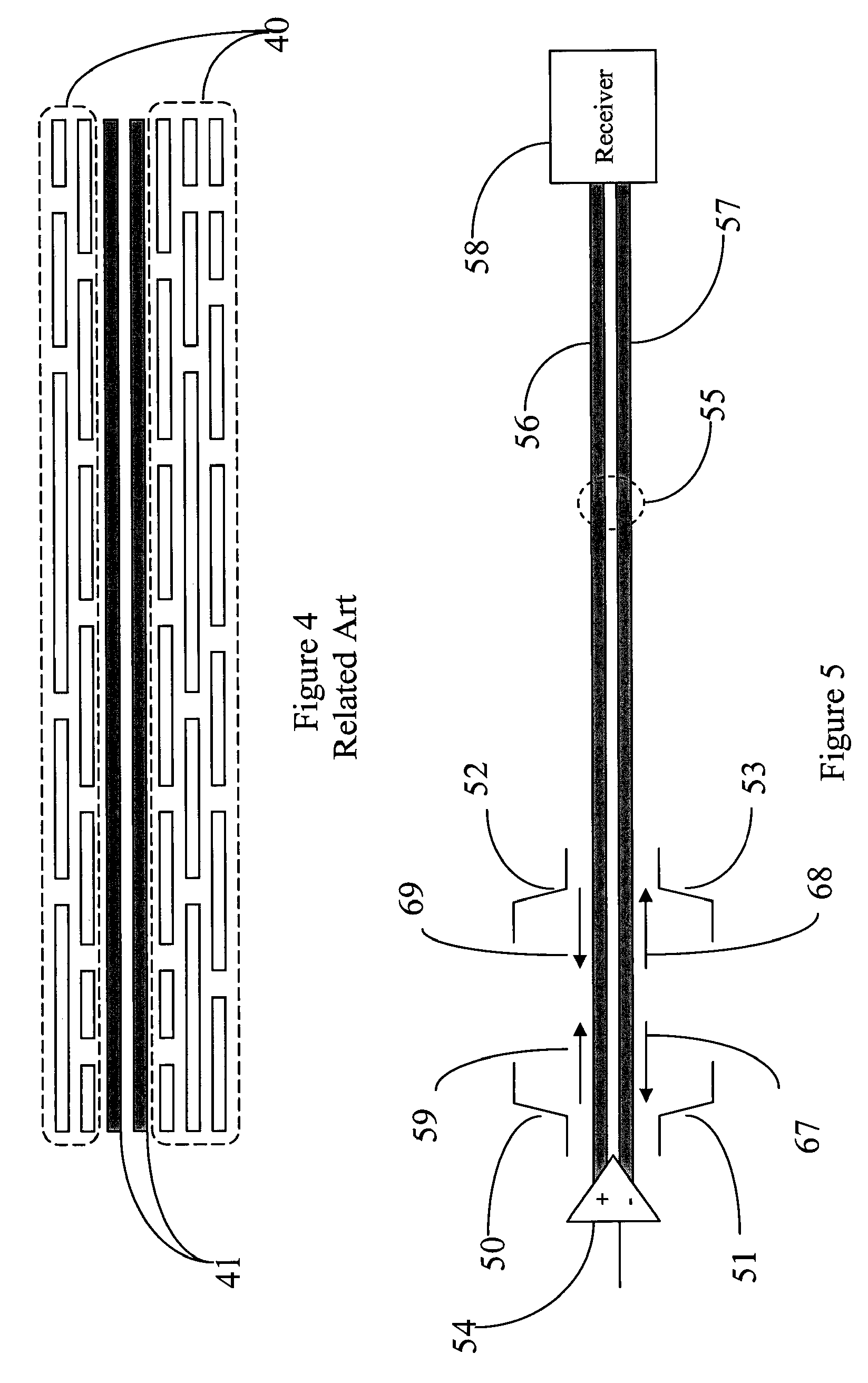

Unified digital architecture

InactiveUS20060029177A1Pulse automatic controlModulated-carrier systemsFinite impulse responseComputer science

A unified, unidirectional serial link is described for providing data across wired media, such as a chip-to chip or a card-to-card interconnect. It consists of a transmit section and a receive section that are operated as pairs to allow the serial data communication. The serial link is implemented as part of a VLSI ASIC module and derives its power, data and clocking requirements from the host modules. The logic transmitter portion contains a phase locked loop (PLL), a dibit data register, a finite impulse response (FIR) filter and a transmit data register. The phase locked loop comprises both a digital coarse loop and an analog fine loop. The digital receiver portion contains a PLL, an FIR phase rotator, a phase rotator control state machine, and a clock buffer. The transmitter and the receiver each preferably utilize a pseudo-random bit stream (PRBS) generator and checker.

Owner:IBM CORP

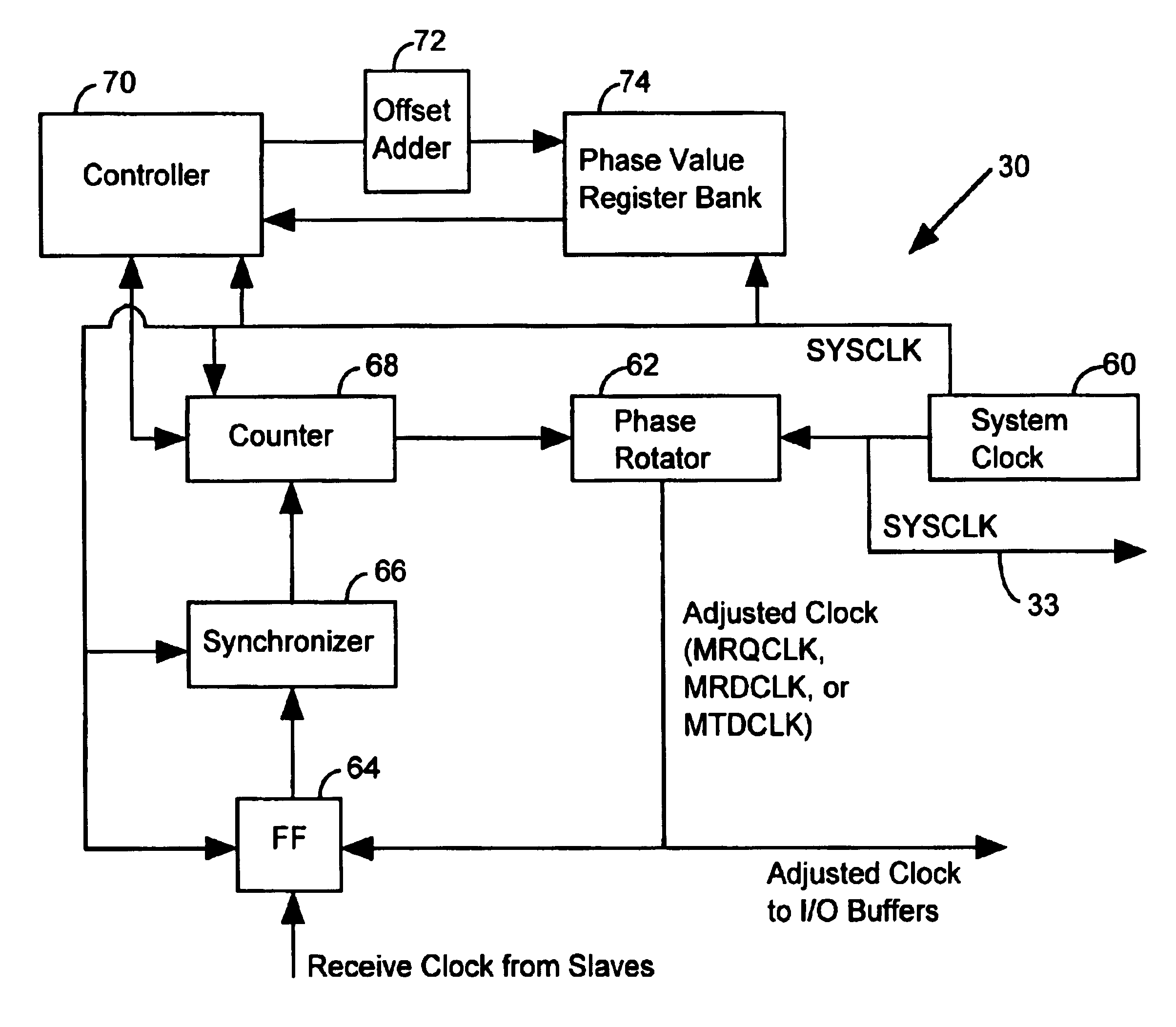

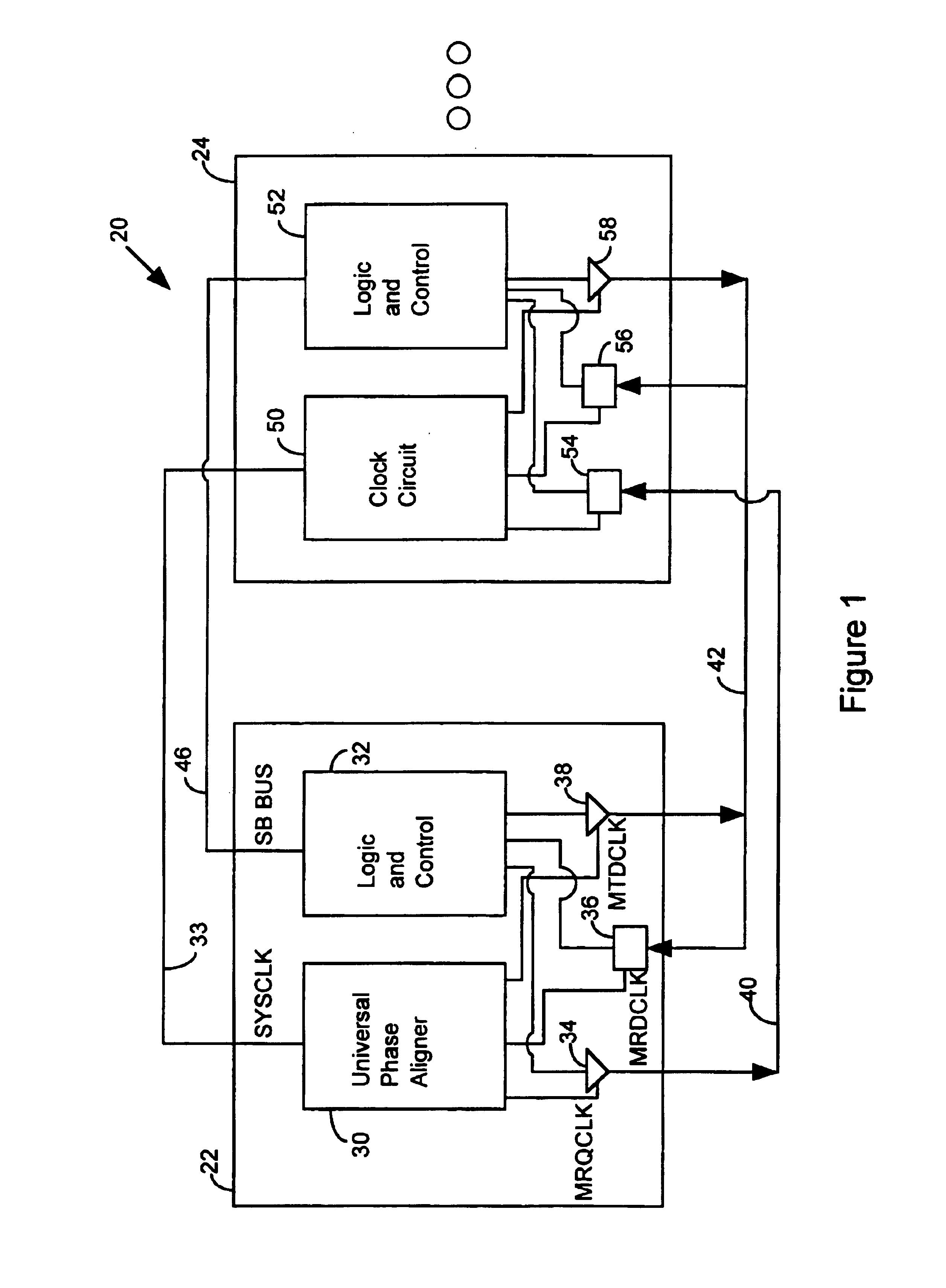

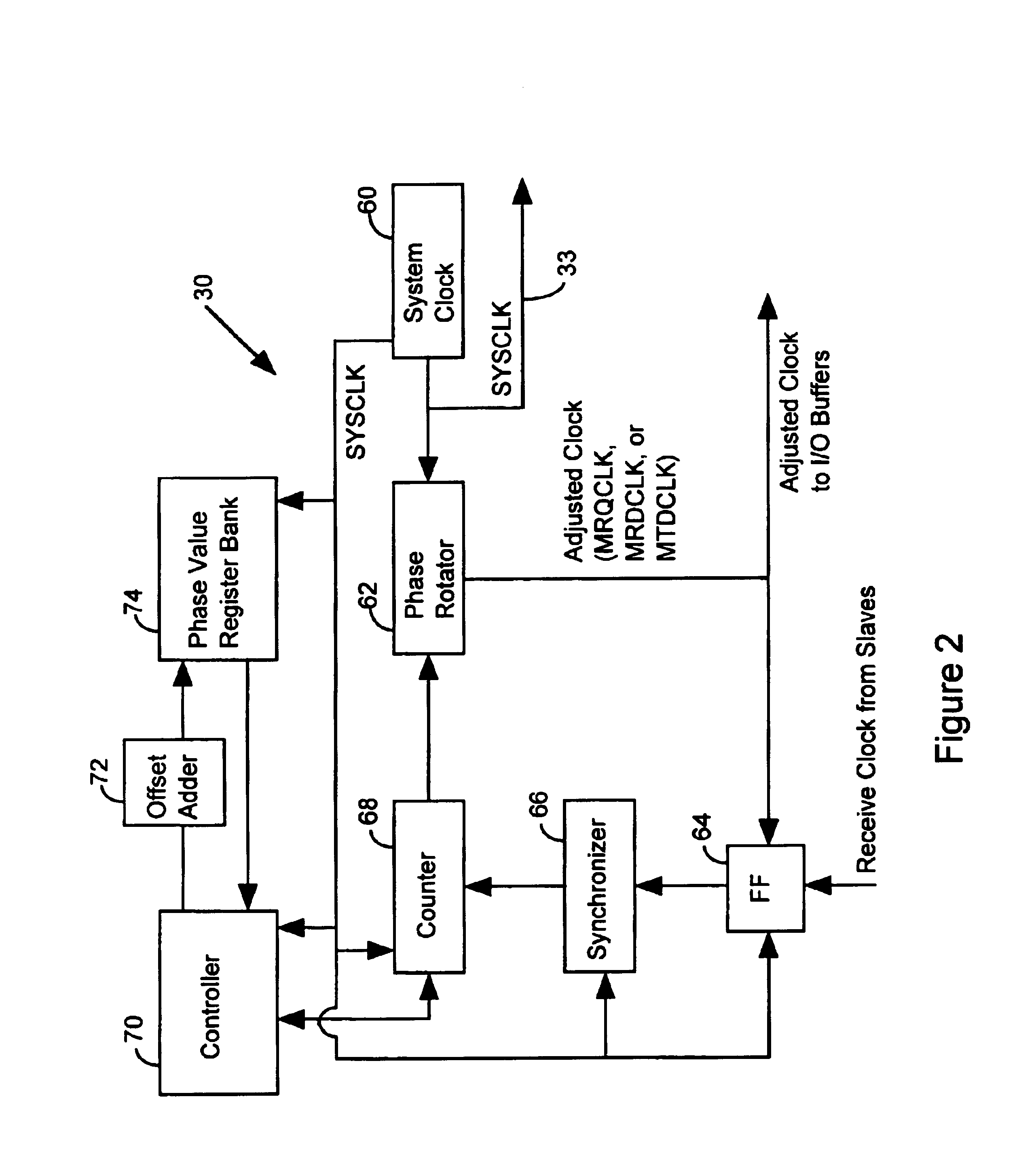

Apparatus and method for controlling a master/slave system via master device synchronization

InactiveUS6839393B1Reduce power consumptionImprove throughputEnergy efficient ICTPulse automatic controlComputer hardwareData shipping

A method of operating a master / slave system includes the step of identifying a master receive data phase value to coordinate the transfer of data from a slave device without phase alignment circuitry to a master device with a universal phase aligner. Data is transferred from the slave device to the master device in accordance with the master receive data phase value. The master device characterizes a master transmit data phase value to coordinate the transfer of data from the master device to the slave device. Subsequently, the master device routes data to the slave device in accordance with the master transmit data phase value.

Owner:RAMBUS INC

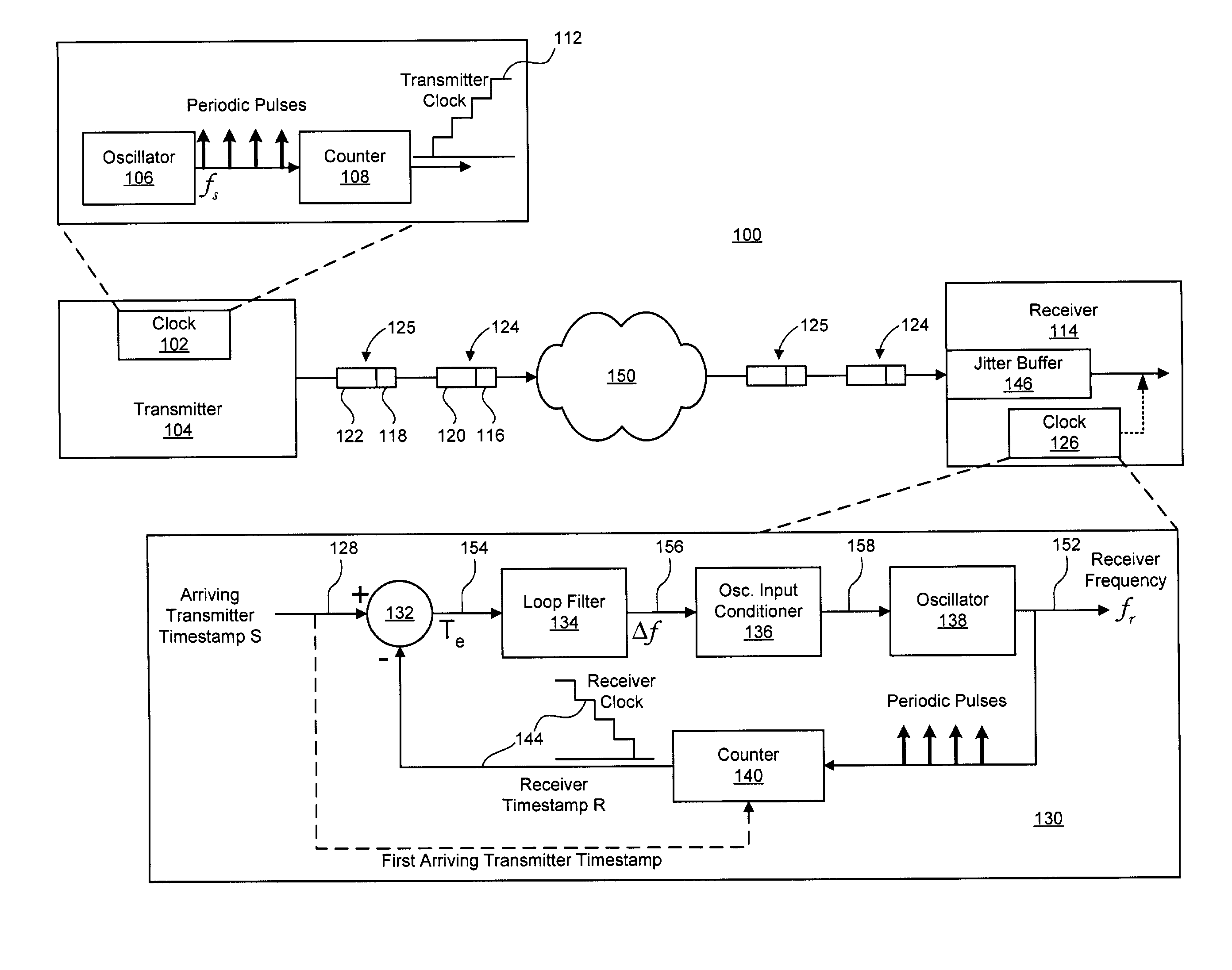

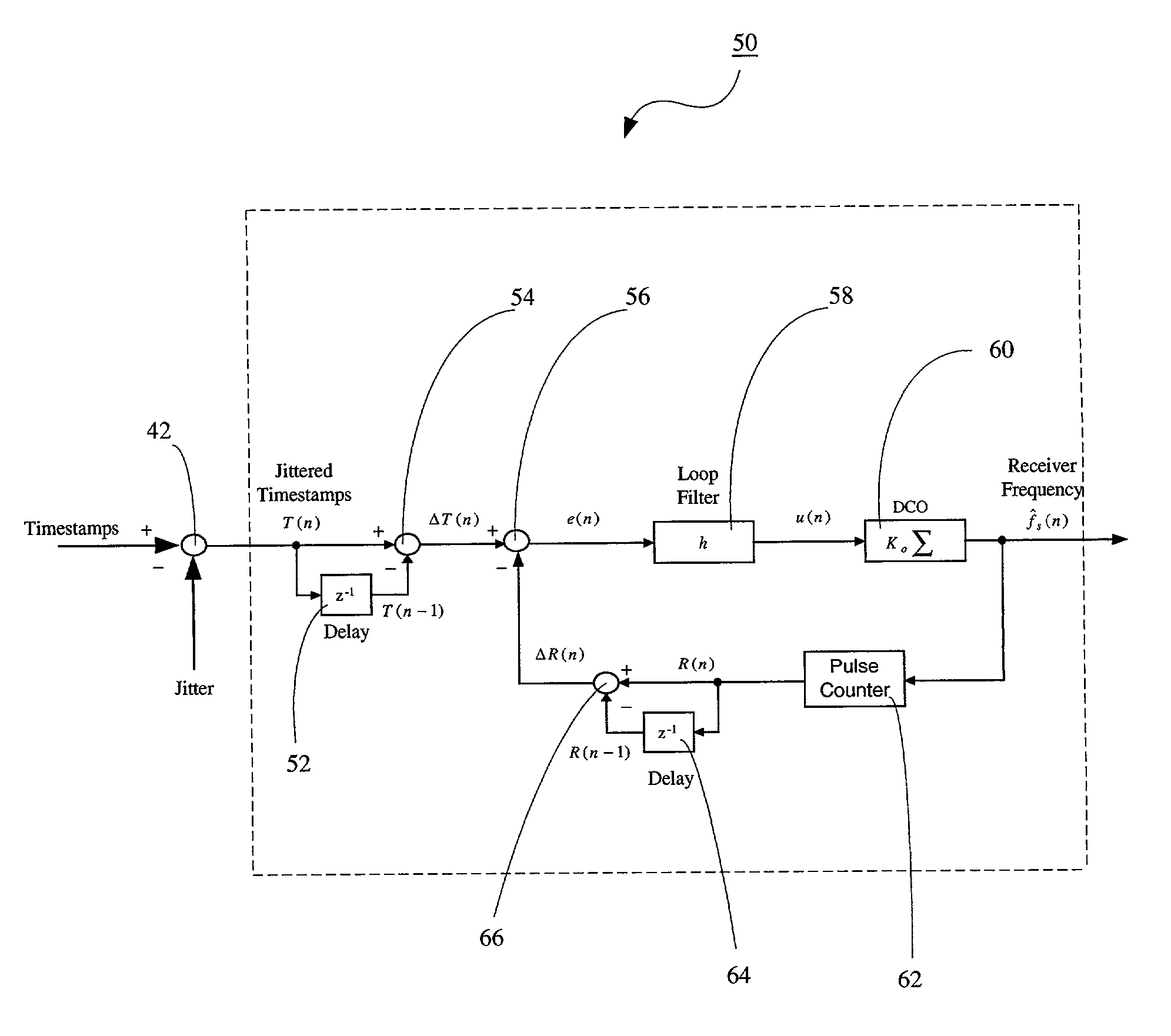

Clock recovery using a double-exponential smoothing process

A system and method for synchronizing a local clock to a reference clock using a linear model of the clock error between the local clock and the reference clock is disclosed. In one embodiment, a double-exponential smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the double-exponential smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:RPX CLEARINGHOUSE

Clock recovery using a direct smoothing process

ActiveUS7130368B1Guaranteed maximum utilizationPulse automatic controlModulated-carrier systemsClock recoveryLinear model

A system and method for synchronizing a local clock to a reference clock using a linear model of the error between the local clock and the reference clock is disclosed. In one embodiment, a direct smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the direct smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:CIENA

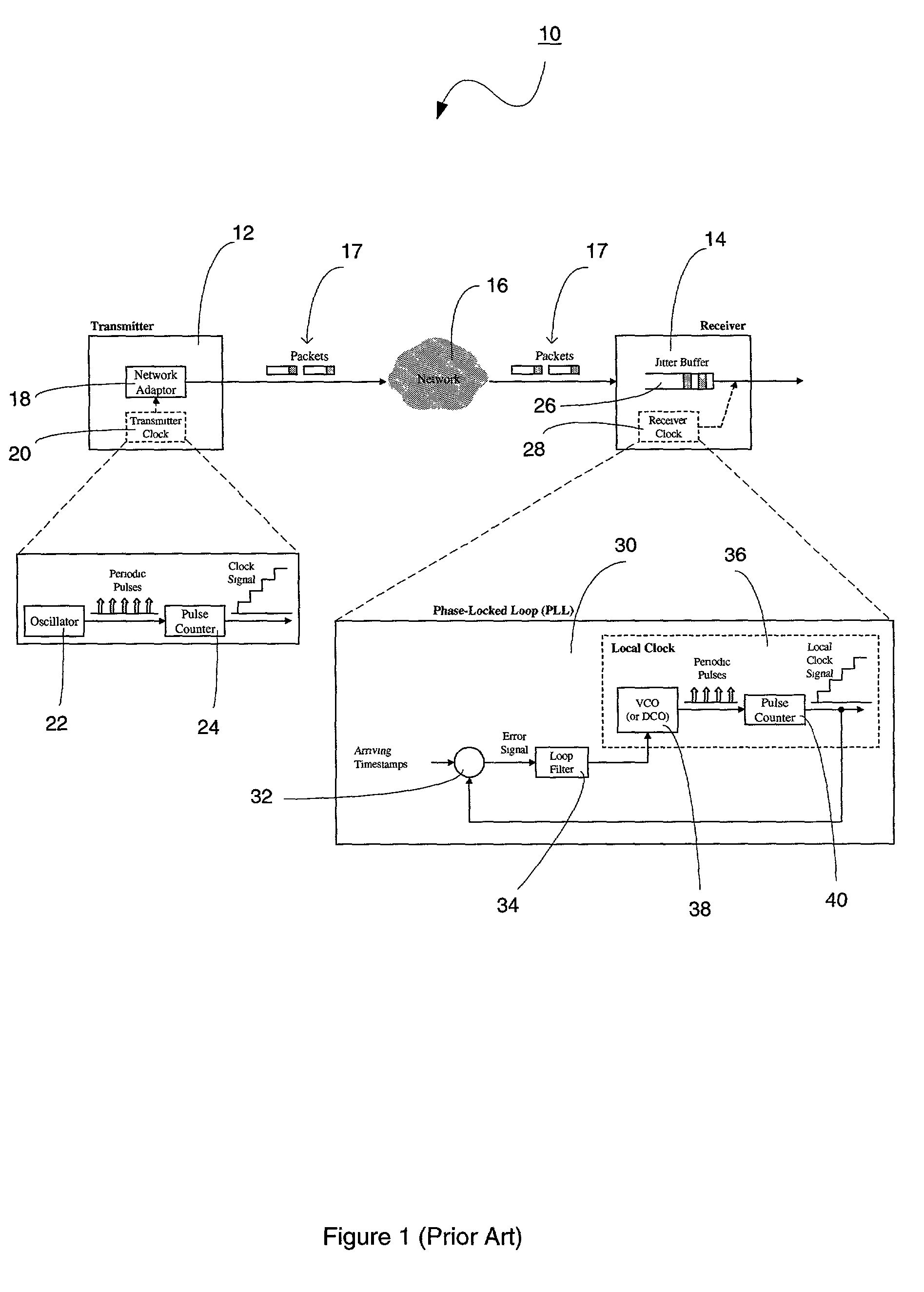

Technique for synchronizing clocks in a network

A technique for synchronizing clocks in a network is disclosed. In one exemplary embodiment, the technique may be realized as a method for synchronizing clocks in a network. The method comprises receiving a first timestamp and a second timestamp, each indicating a respective time instance as determined by a first clock signal within the network. The method also comprises measuring a first time interval between the first timestamp and the second timestamp. The method further comprises generating a difference signal representing a difference between the first time interval and a second time interval, and generating a second clock signal based upon the difference signal such that the second clock signal is synchronized with the first clock signal.

Owner:RPX CLEARINGHOUSE

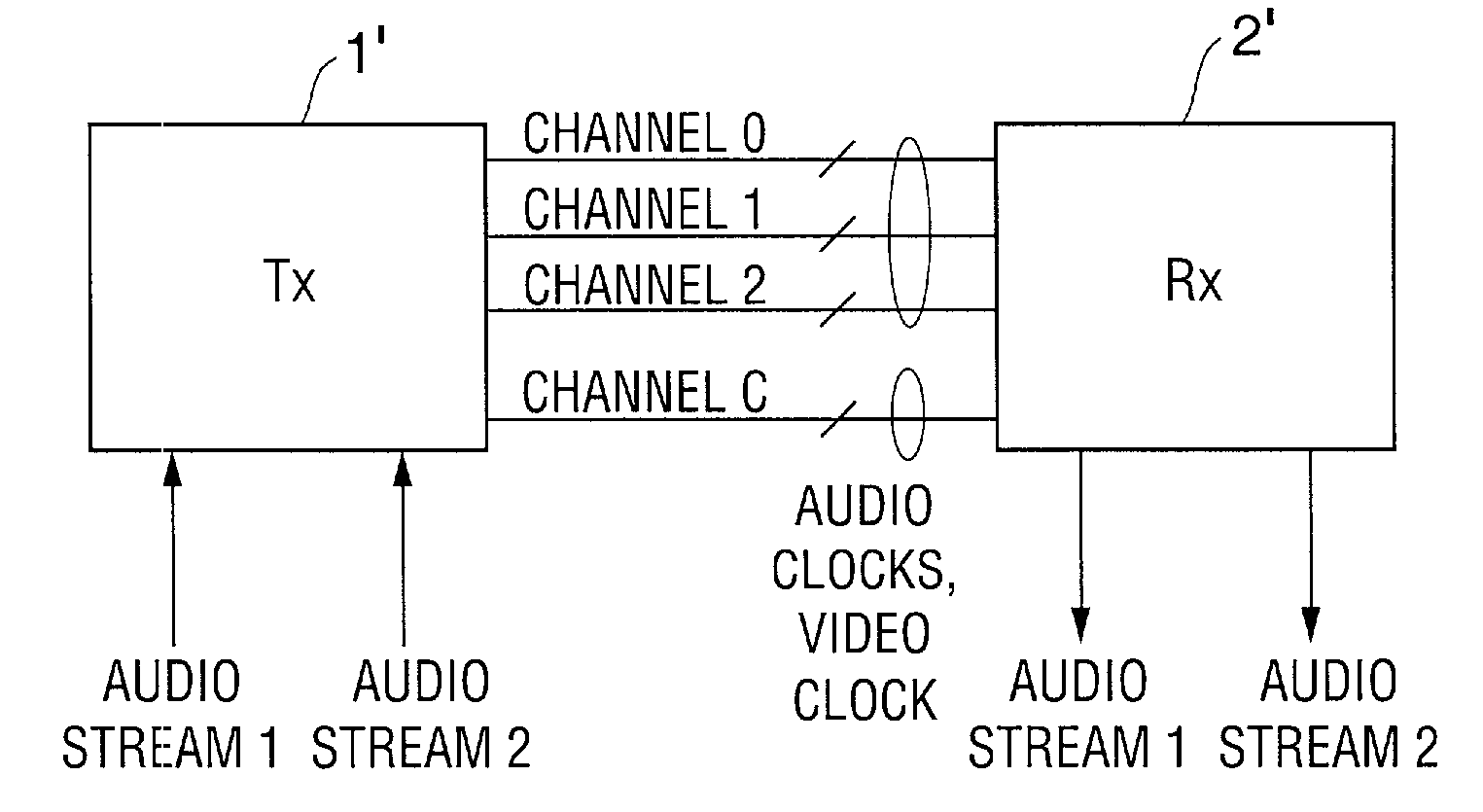

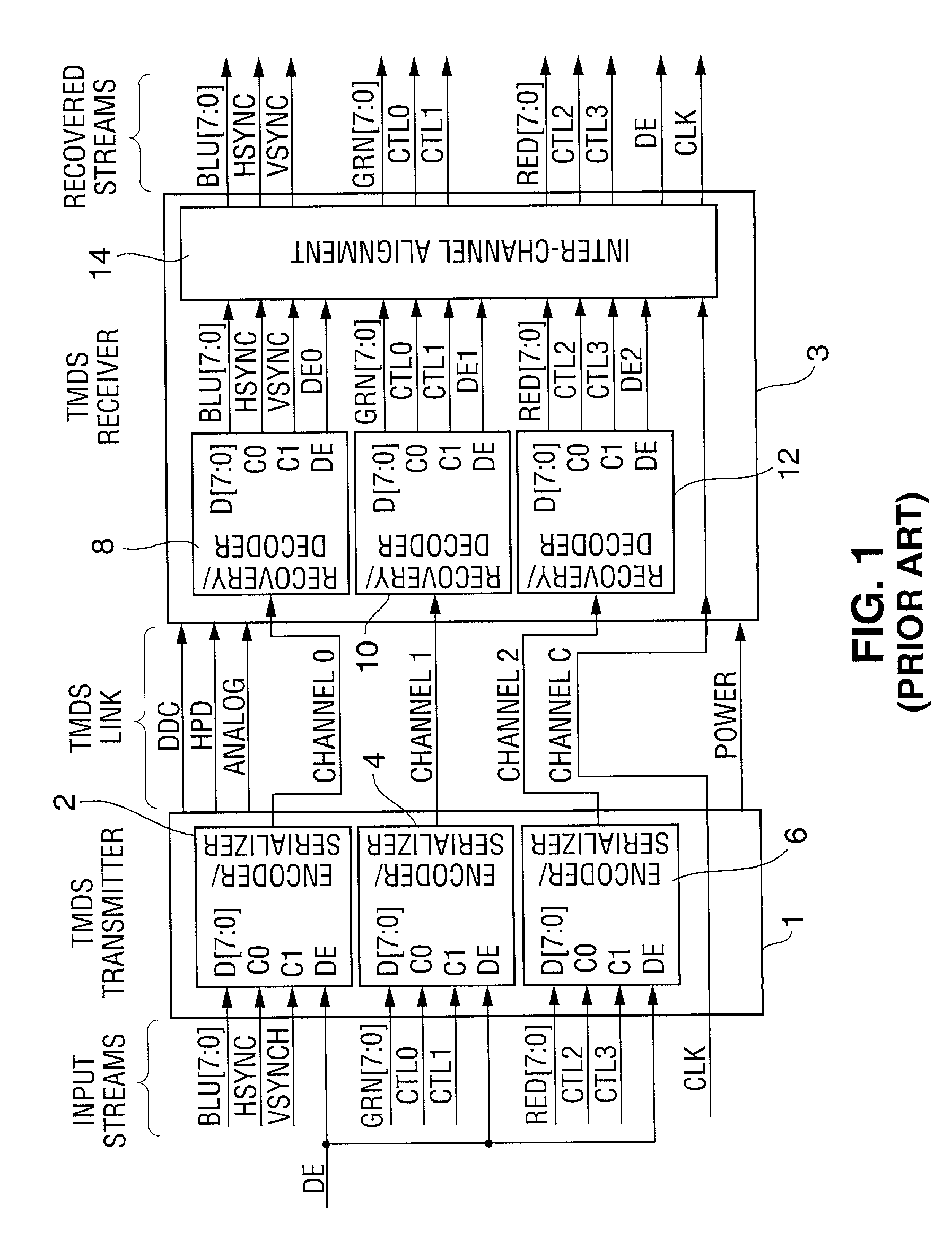

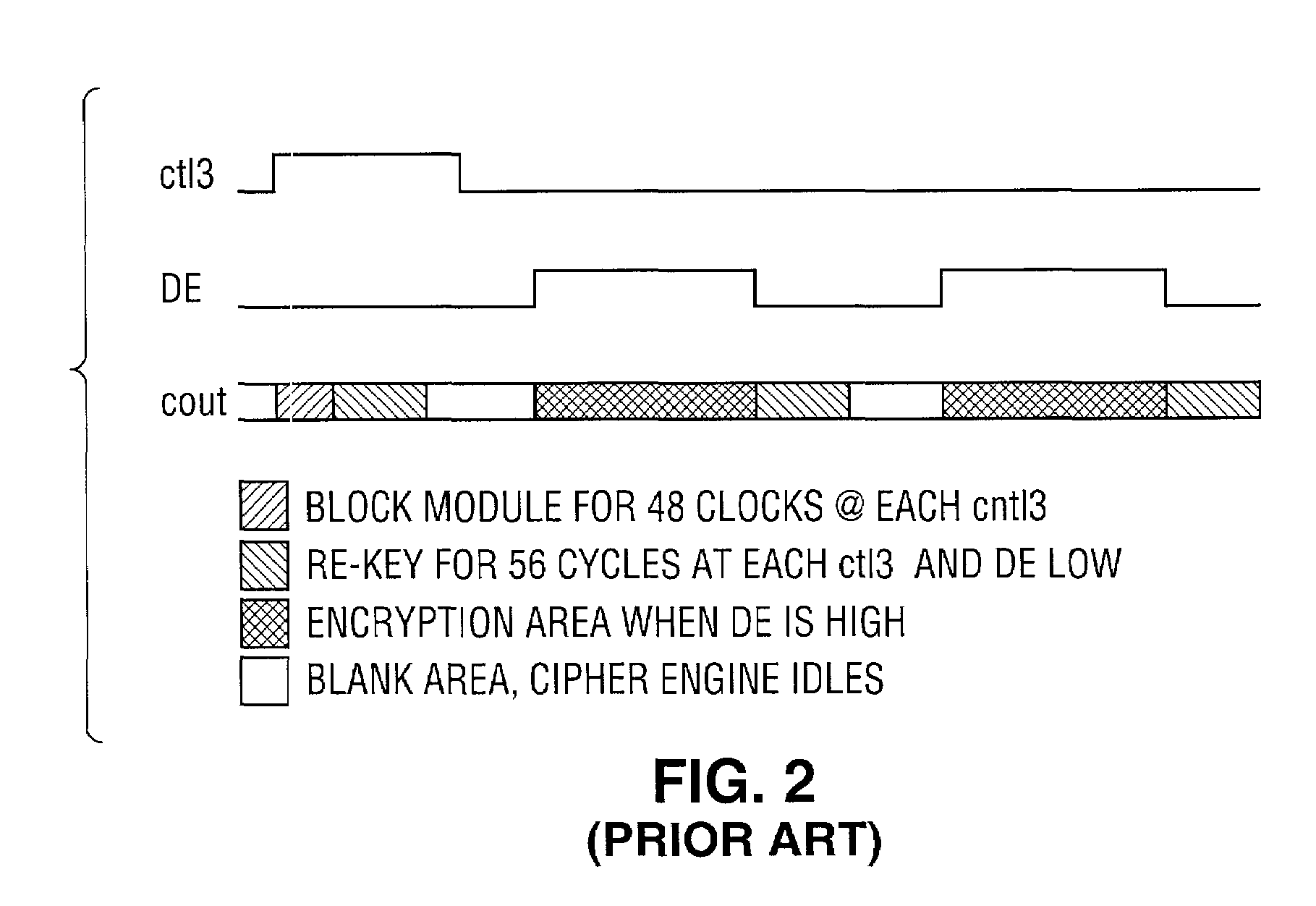

Method and apparatus for synchronizing auxiliary data and video data transmitted over a TMDS-like link

InactiveUS7295578B1Synchronisation information channelsPulse automatic controlData synchronizationCommunications system

A communication system including a transmitter, a receiver, and a TMDS-like link, in which video data and auxiliary data are transmitted from the transmitter to the receiver, or in which video data are transmitted over the link from the transmitter to the receiver and auxiliary data are transmitted from the receiver to the transmitter (or from the transmitter to the receiver and also from receiver to the transmitter), a transmitter or receiver for use in such a system, and methods for sending auxiliary data and video data over such a link, synchronizing such auxiliary data with such video data, and generating clocks having frequency closely matching the rate at which the auxiliary data are transmitted. Typically, the auxiliary data include one or more streams of audio data. In some embodiments the transmitter transmits a video clock to the receiver over a video clock channel, at least one of the transmitter and receiver transmits at least one stream of auxiliary data to the other one of the transmitter and the receiver, and at least one of the transmitter and the receiver transmits over the video clock channel at least one auxiliary clock for the auxiliary data.

Owner:LATTICE SEMICON CORP

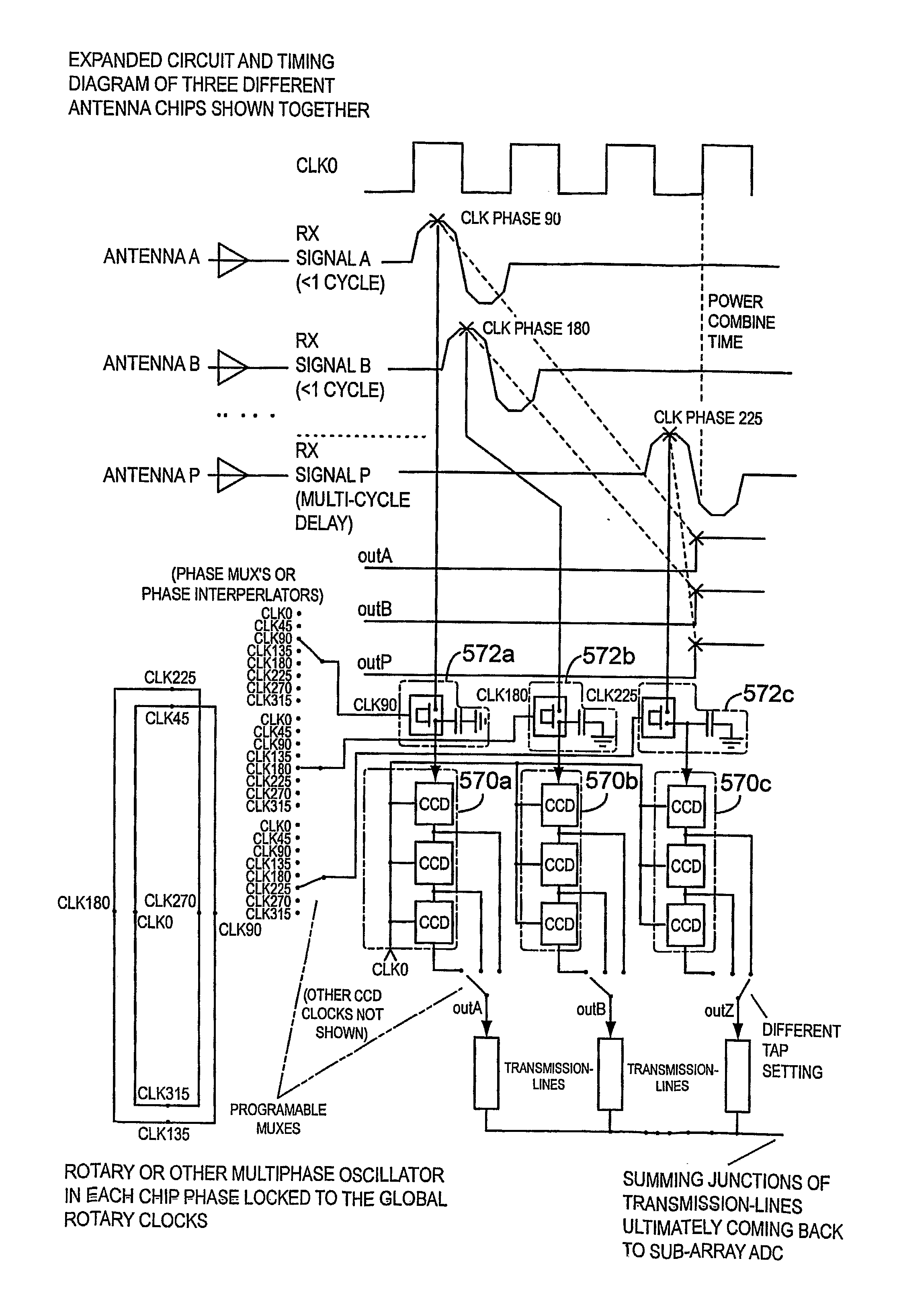

True time delay phase array radar using rotary clocks and electronic delay lines

ActiveUS20120039366A1Forming accuratelyEasy to moveAntenna arraysPulse automatic controlTime delaysAnalog delay line

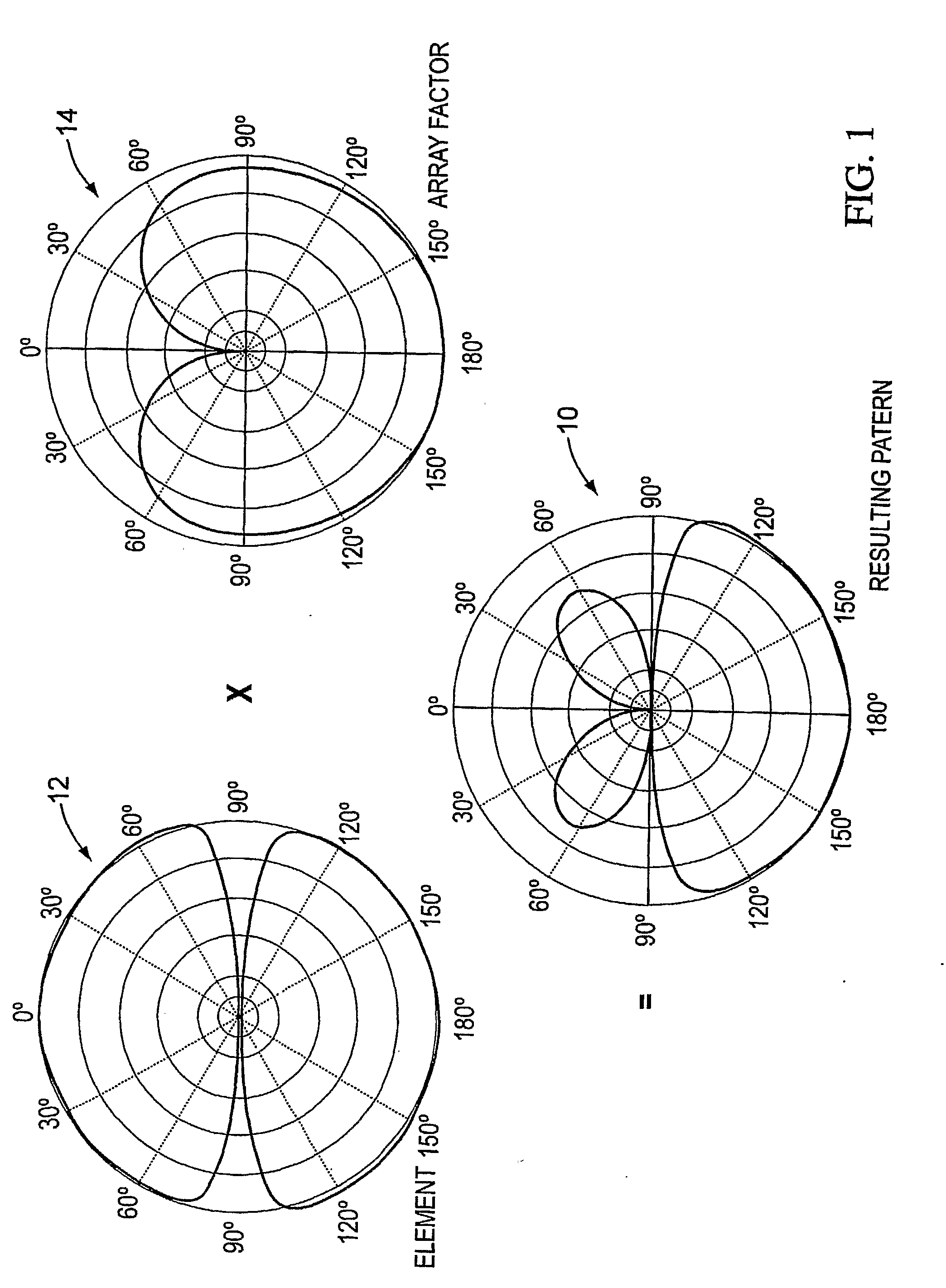

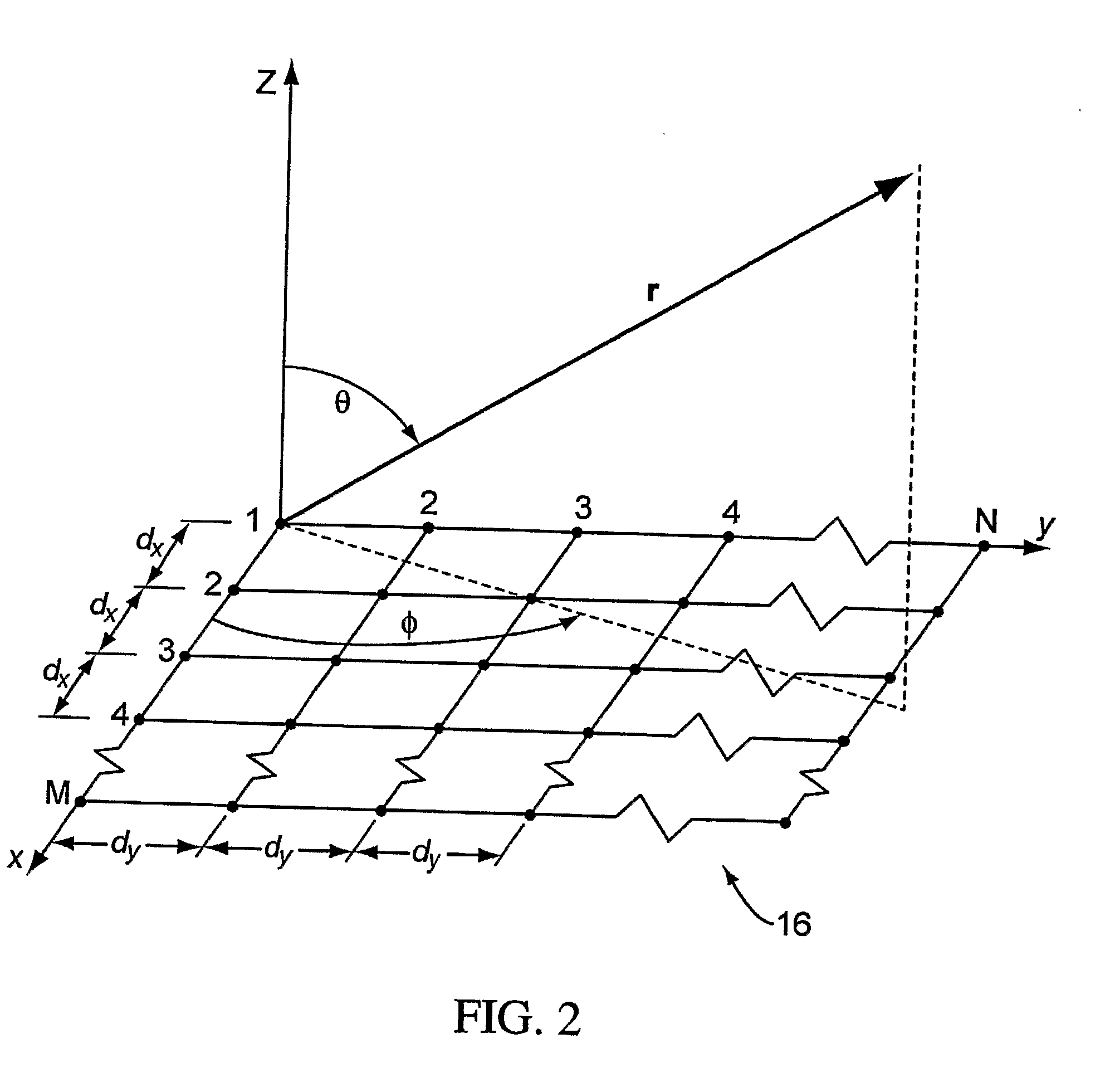

Local oscillator circuitry for an antenna array is disclosed. The circuitry includes an array of rotary traveling wave oscillators which are arranged in a pattern over an area and coupled so as to make them coherent. This provides for a set of phase synchronous local oscillators distributed over a large area. The array also includes a plurality of phase shifters each of which is connected to one of the rotary oscillators to provide a phase shifted local oscillator for the array. The phase shifter optionally includes a cycle counter that is configured to count cycles of the rotary oscillator to which it is connected and control circuitry that is then operative to provide a shifted rotary oscillator output based on the count from the cycle counter. A system and method for operating a true-time delay phased array antenna system. The system includes a plurality of antenna element circuits for driving or receiving an rf signal from the elements of the array. Each element circuit has a transmit and a receive path and a local multiphase oscillator, such as a rotary traveling wave oscillator. Each path has an analog delay line for providing a true-time delay for the antenna element. Preferably, the analog delay line is a charge coupled device whose control nodes are connected to phases of the local multiphase oscillator to implement a delay that is an integer number local multiphase oscillator periods. A fractional delay is also included in the path by using a sample and hold circuit connected to a particular phase of the oscillator. By delaying each antenna element by a true time delay, broadband operation of the array is possible.

Owner:ANALOG DEVICES INC

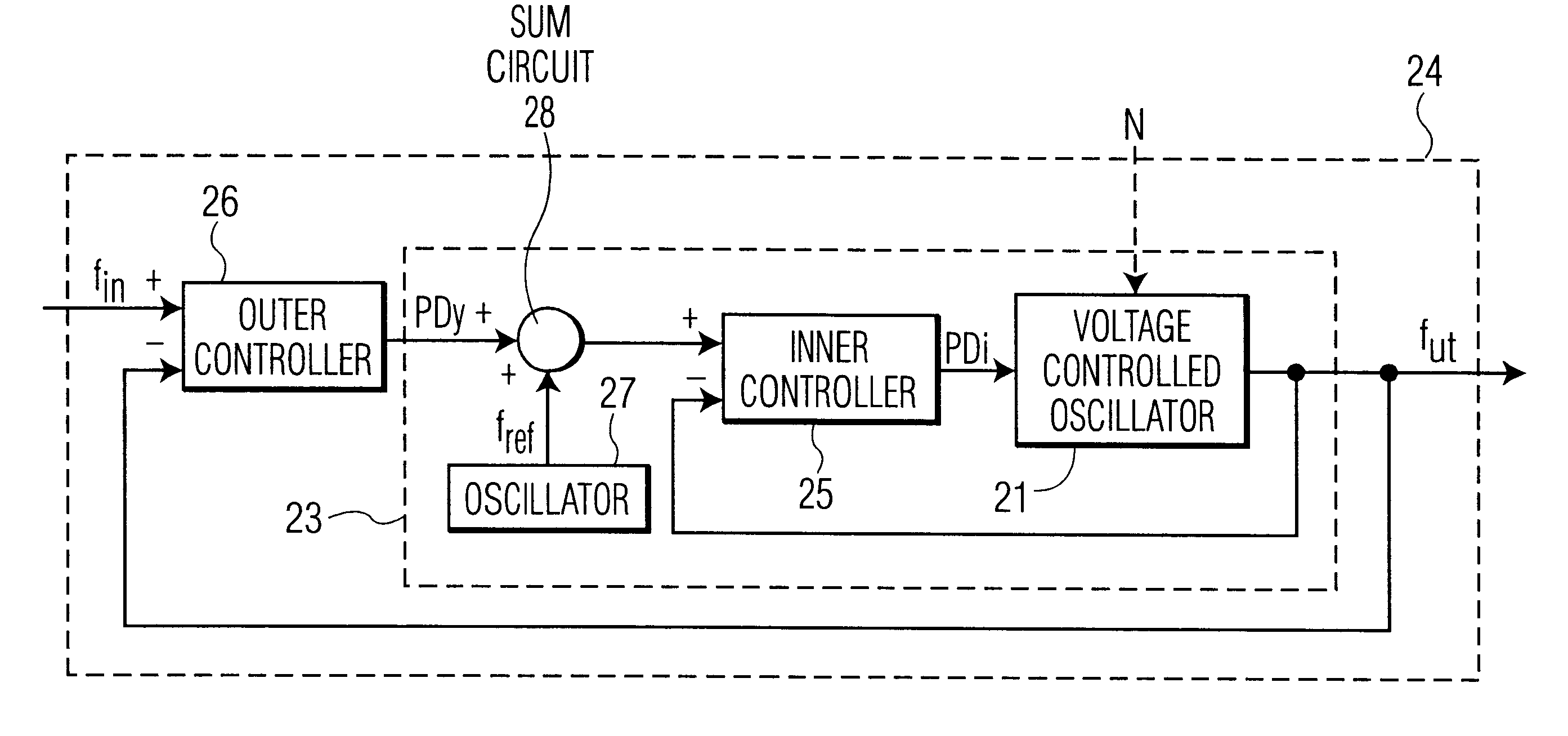

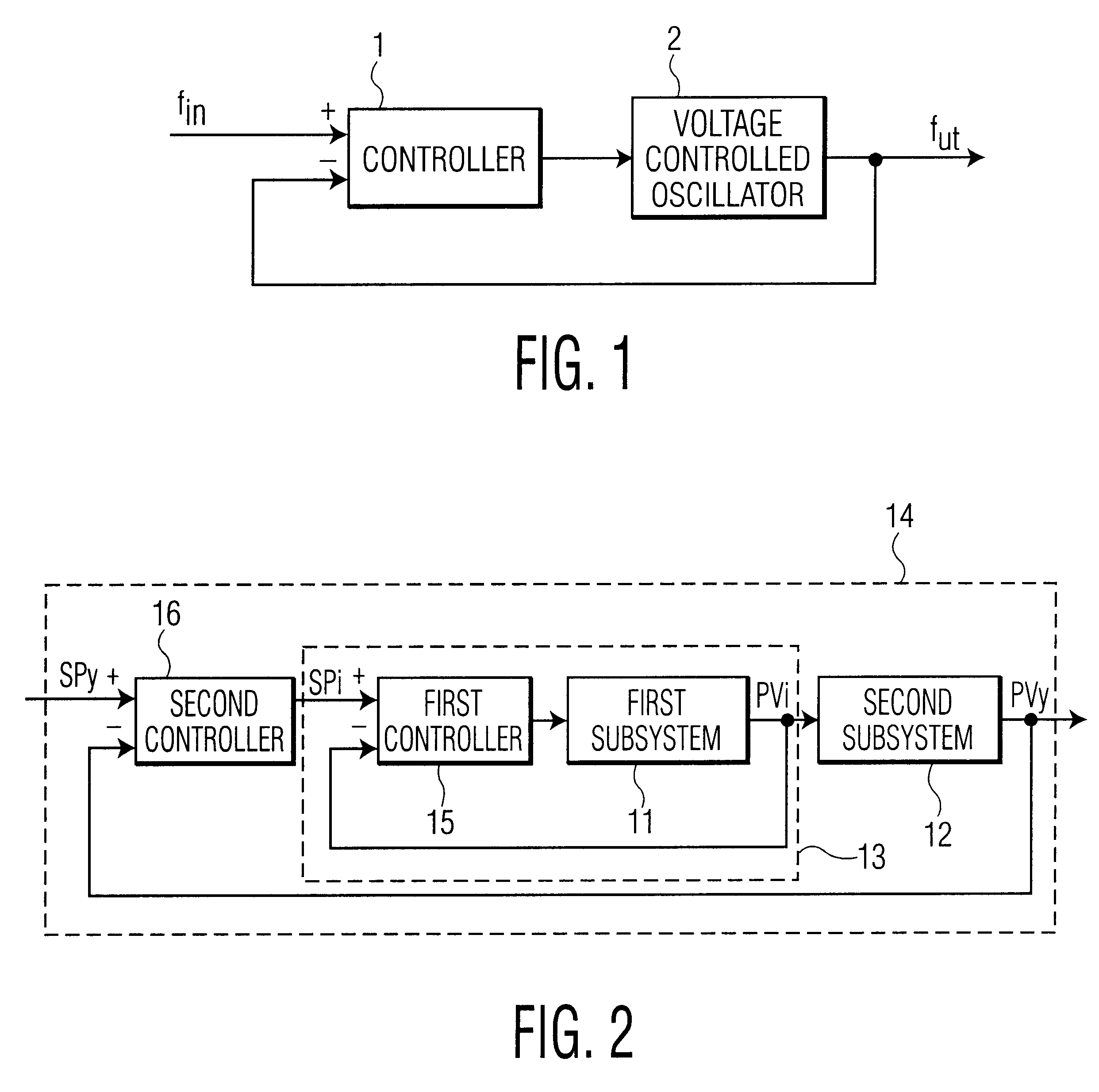

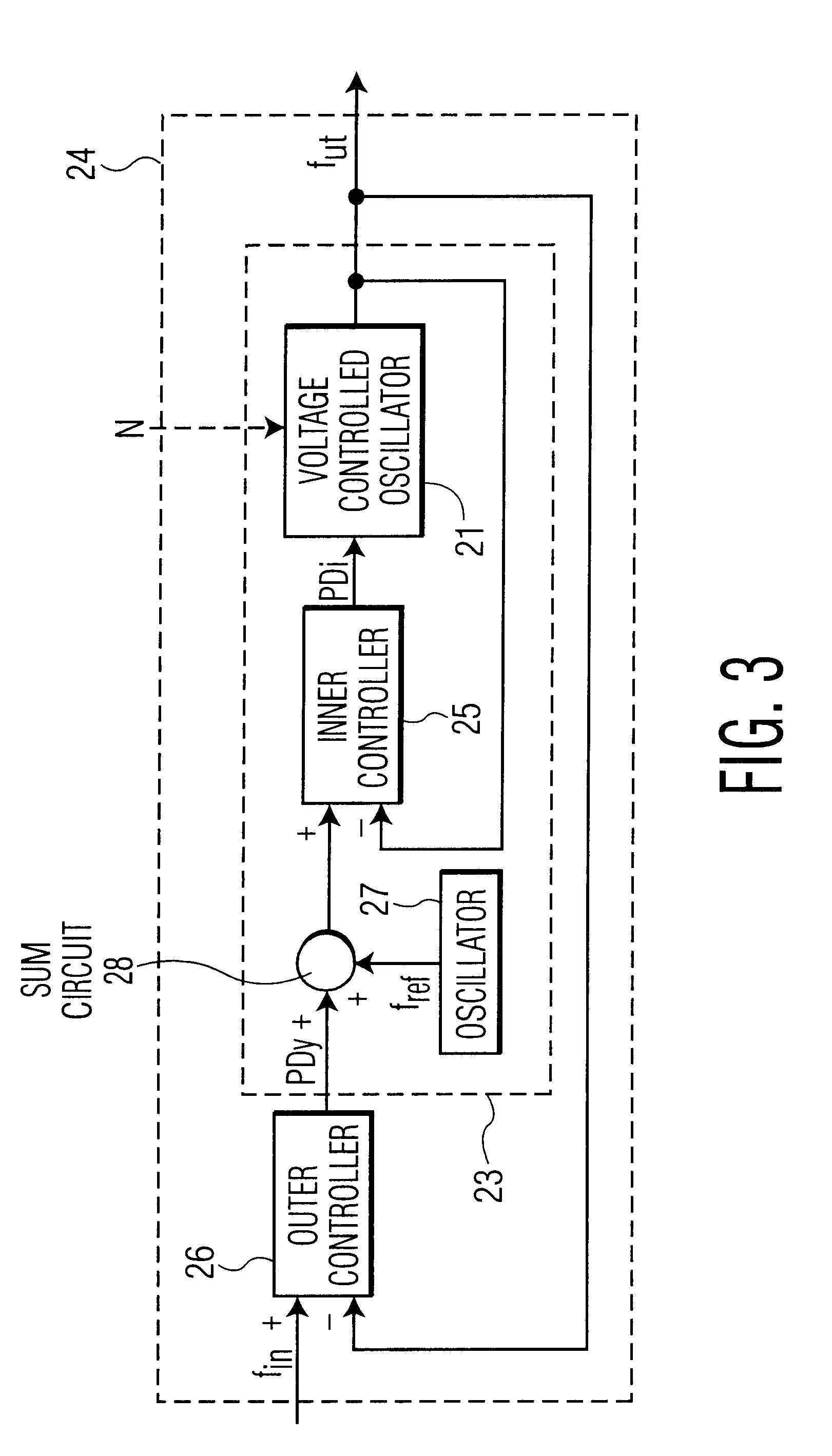

Phase locked loop control via inner and outer feedback control circuits

InactiveUS6384690B1Reduce inputGood frequencyPulse automatic controlNegative feedbackControl circuit

A phase locked loop includes at least one control circuit, where a voltage-controlled oscillator provides an output frequency which is arranged to strive to follow an input frequency. The phase locked loop also includes an outer, slow, negative feedback control circuit, having the input frequency as a setpoint, the output frequency as a process value and an outer output signal. The phase locked loop also includes an inner, fast, negative feedback control circuit, having the sum of a reference frequency from a stable oscillator and the outer output signal as a setpoint, the output frequency as the process value and an inner output signal for controlling the voltage controlled oscillator.

Owner:TELEFON AB LM ERICSSON (PUBL)

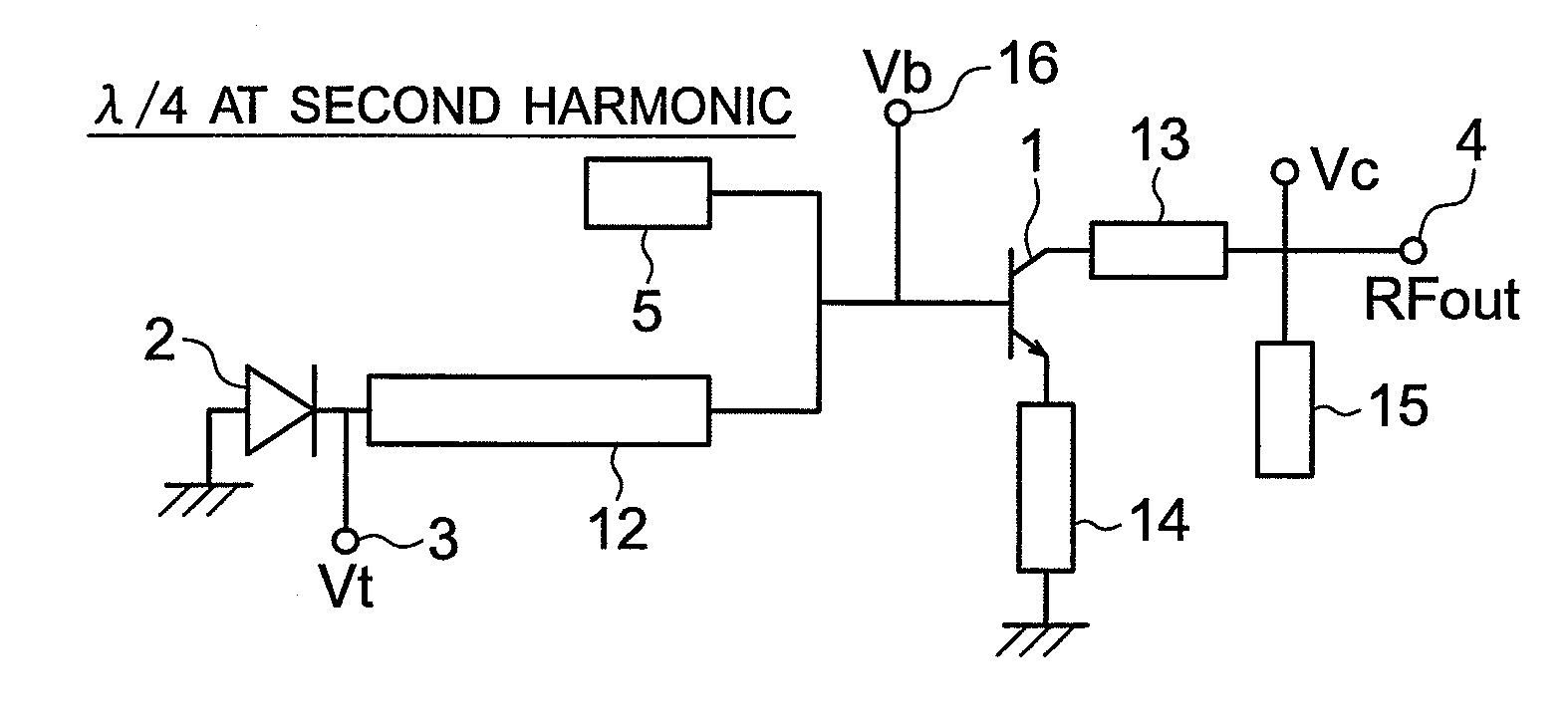

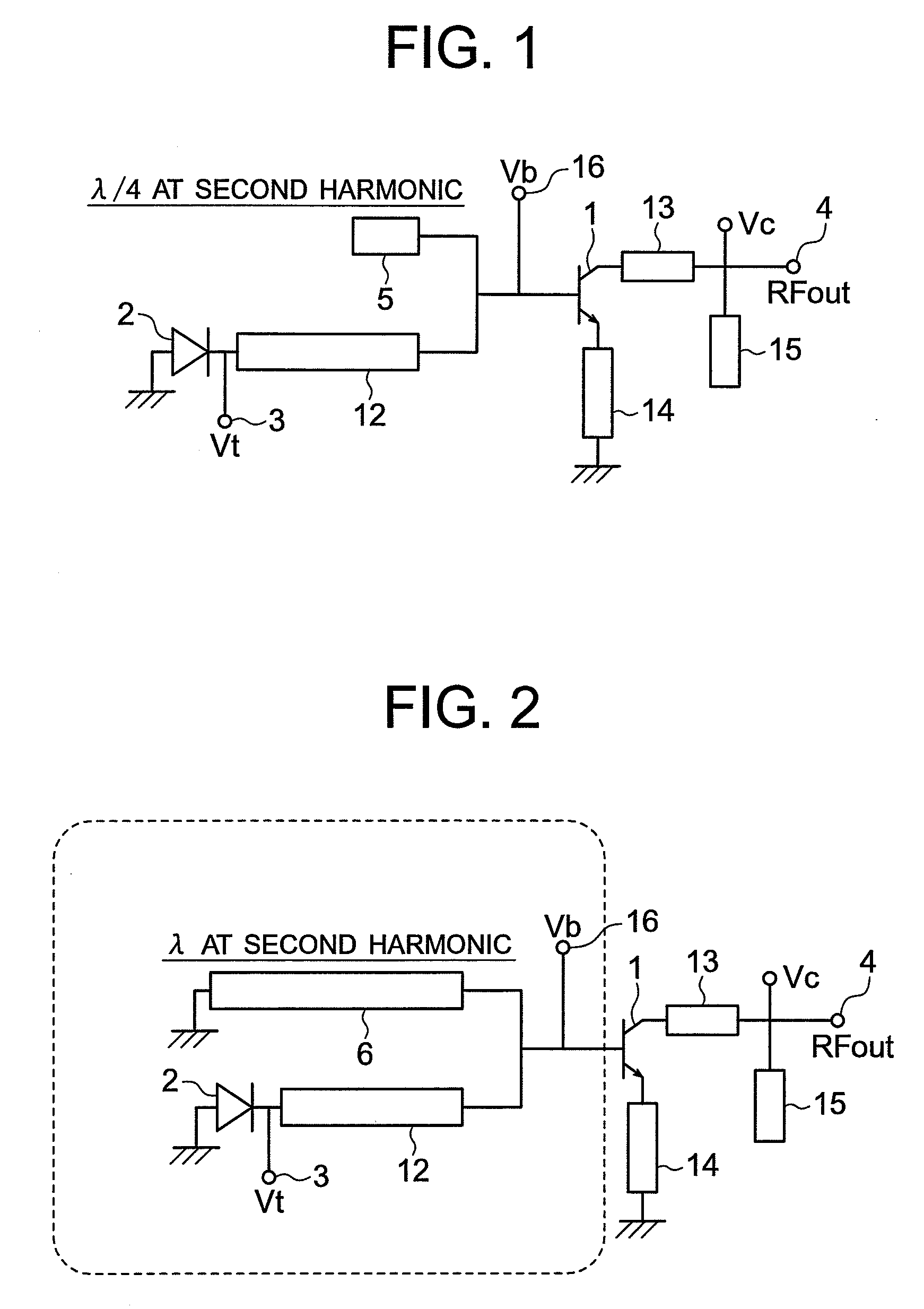

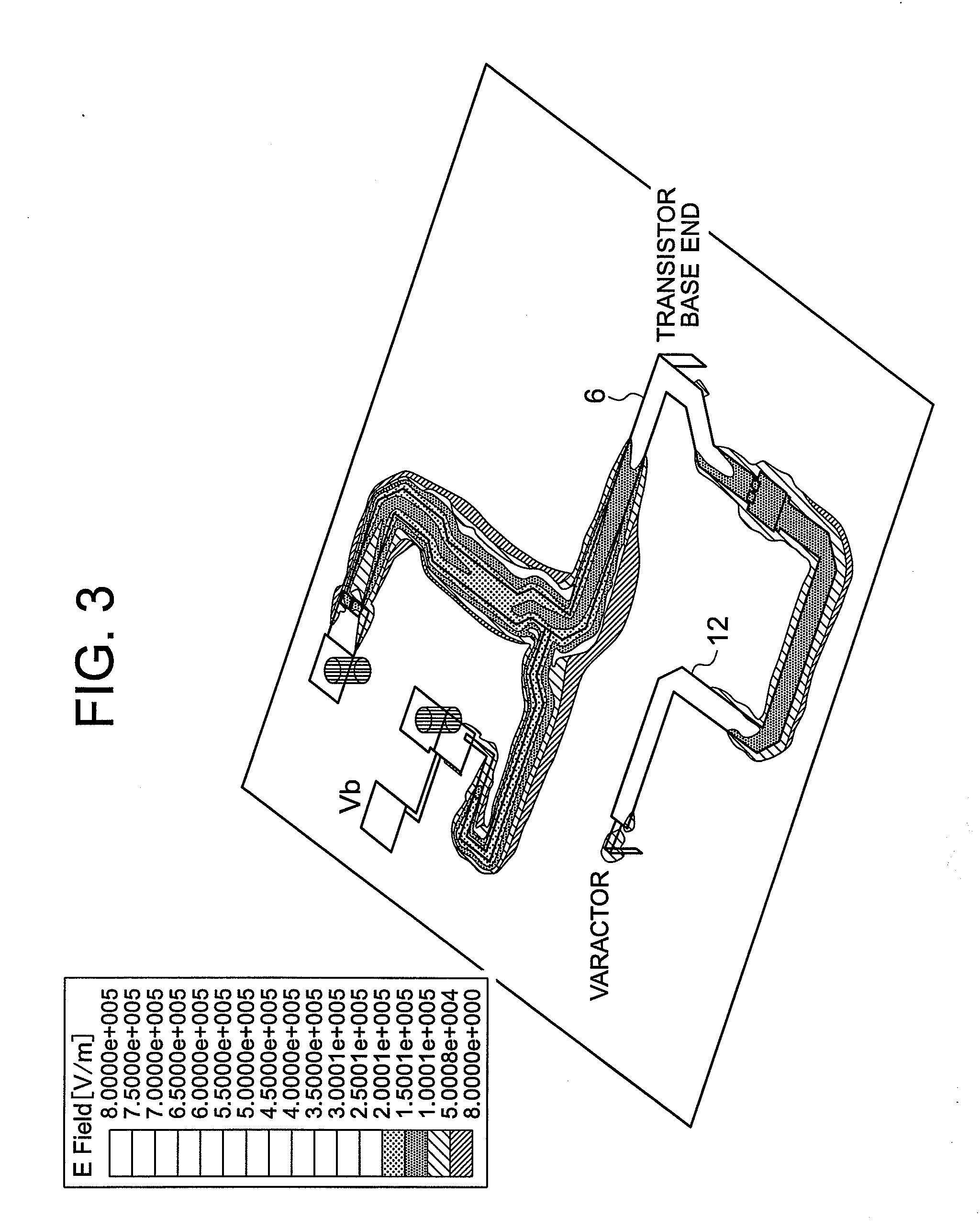

Voltage controlled oscillator, mmic, and high frequency wireless device

InactiveUS20100052799A1Low phase noise characteristicReduce noisePulse automatic controlOscillations generatorsPhase noiseHarmonic

A voltage controlled oscillator having low phase noise and including: a variable resonator including a varactor and a control voltage terminal; and an open-end stub connected in parallel to the variable resonator, the open-end stub having a length shorter than or equal to an odd multiple of one quarter of a wavelength of a harmonic signal plus one sixteenth of the wavelength of the harmonic signal, and longer than or equal to an odd multiple of one quarter of the wavelength of the harmonic signal minus one sixteenth of the wavelength of the harmonic signal. In this structure, a high Q value is realized for a fundamental wave frequency. Fluctuation in a control voltage due to a harmonic signal is controlled.

Owner:MITSUBISHI ELECTRIC CORP

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

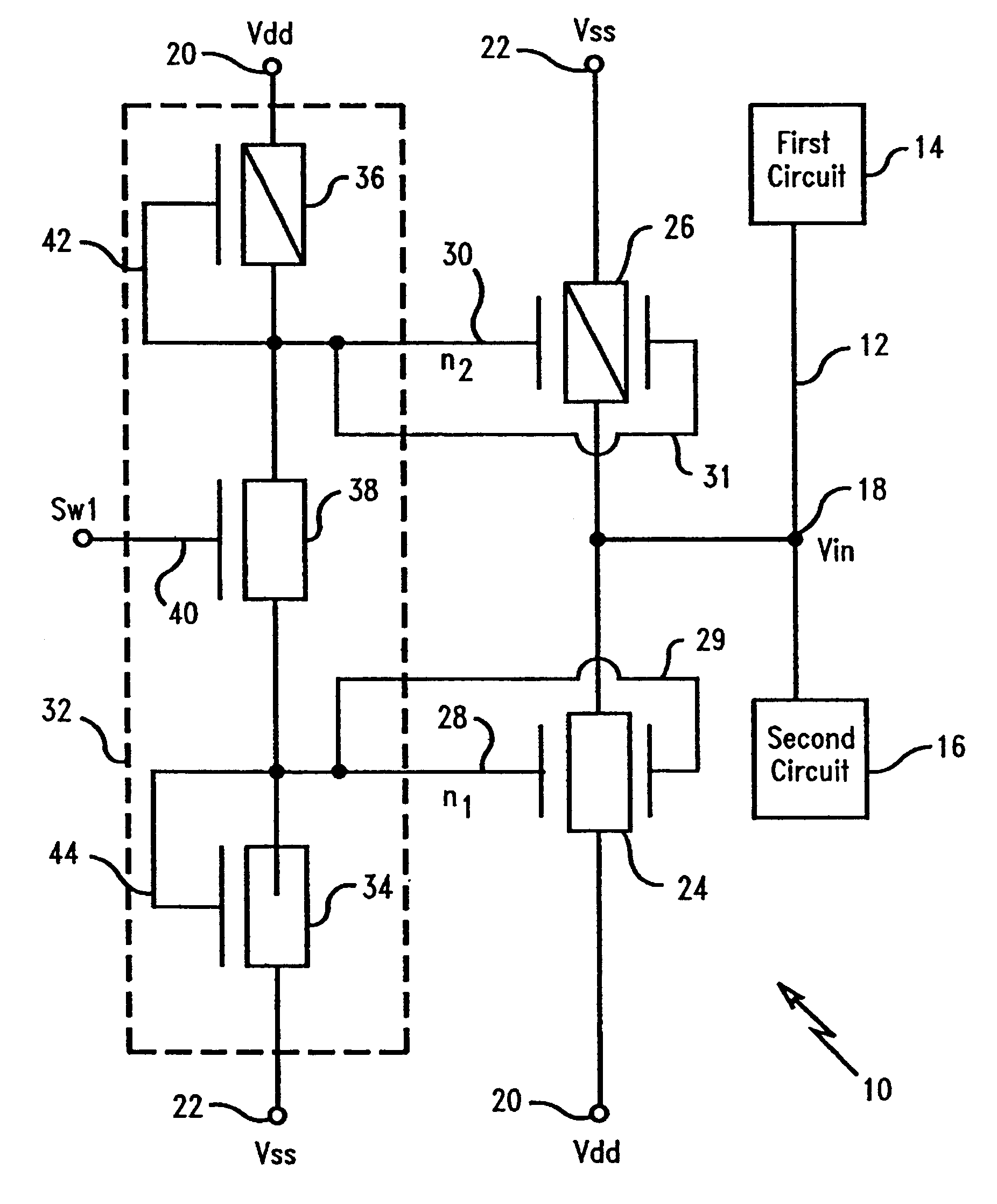

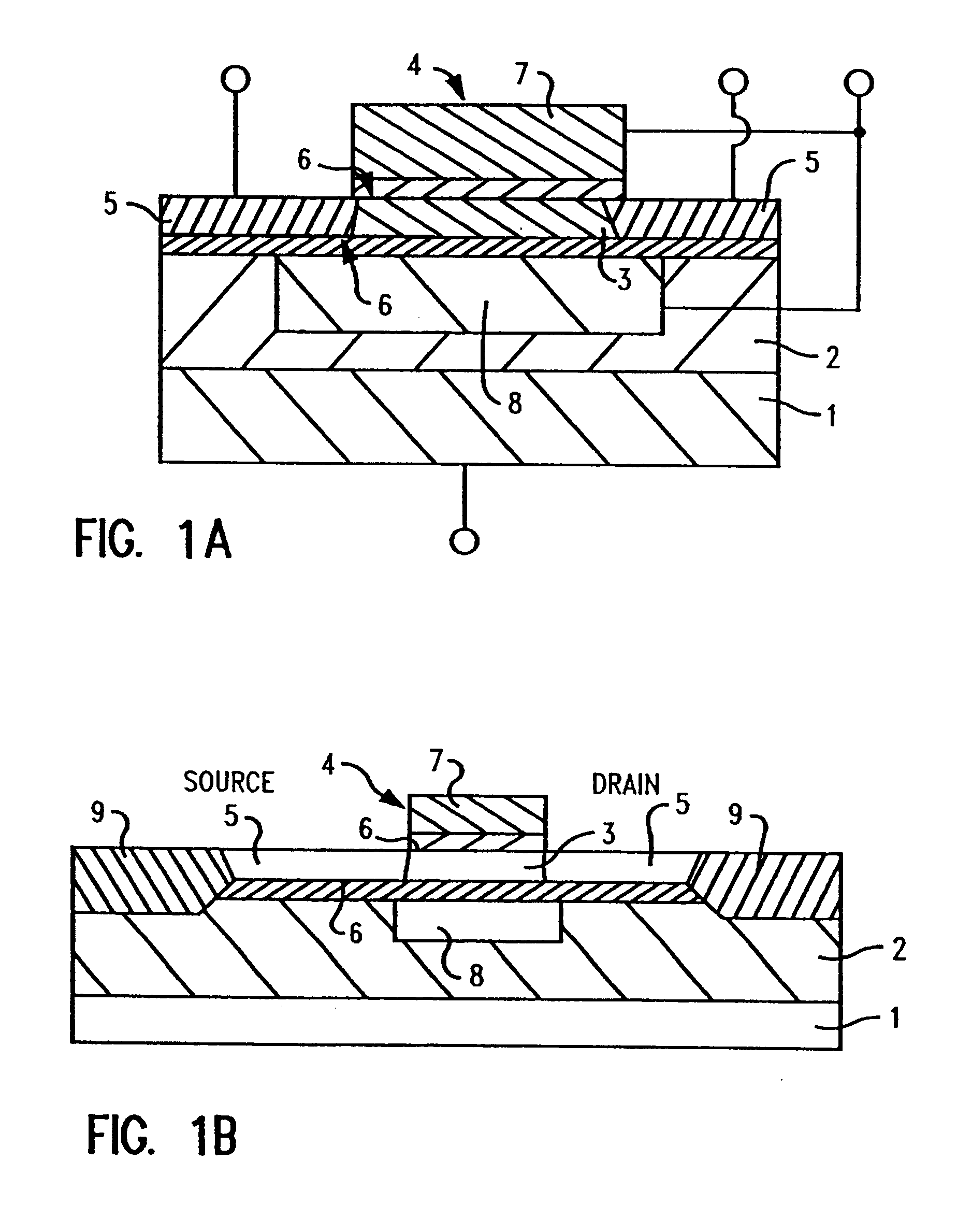

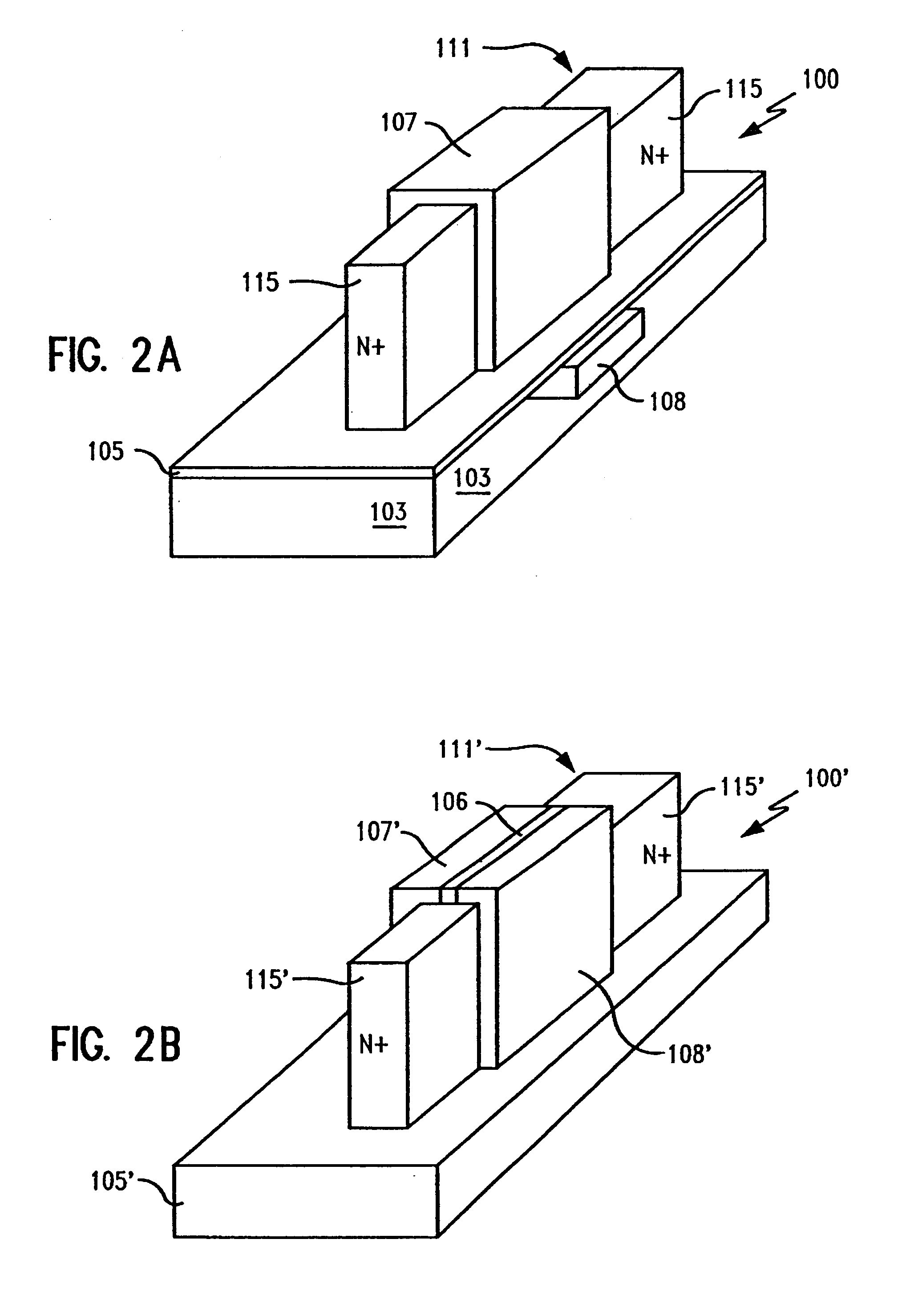

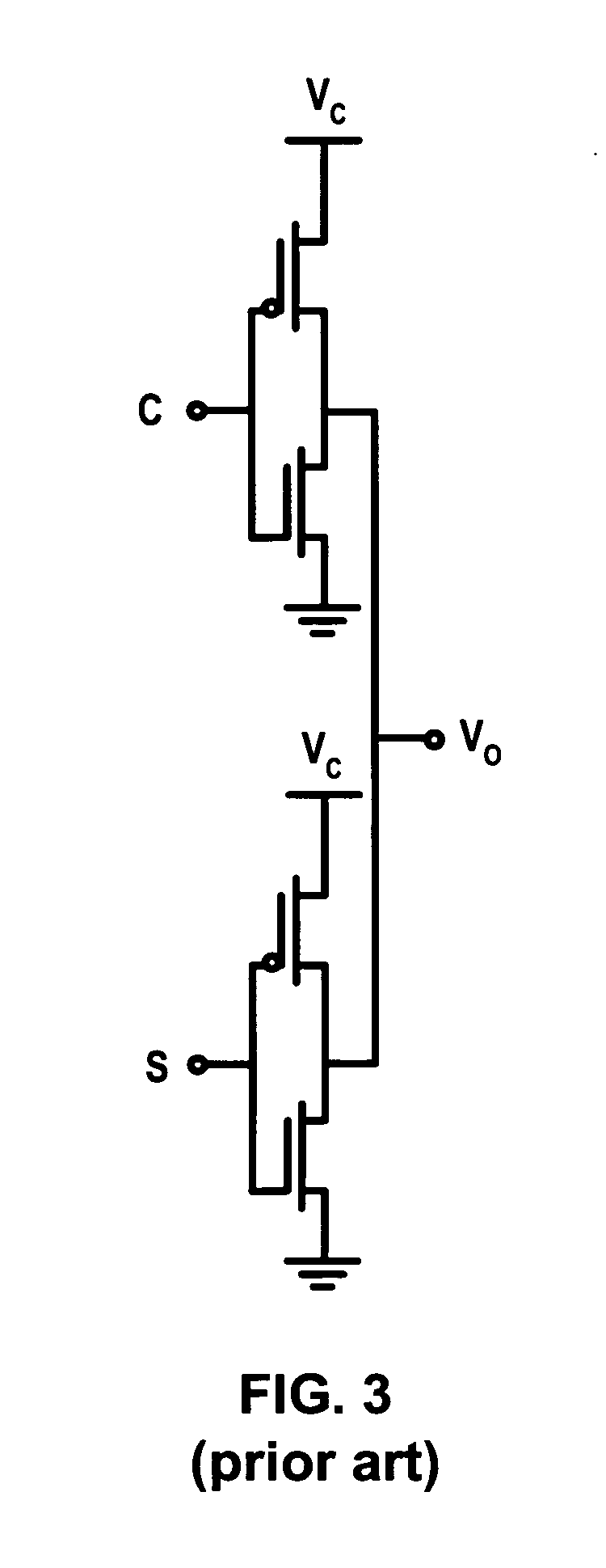

Double-gate low power SOI active clamp network for single power supply and multiple power supply applications

InactiveUS6433609B1Improve performanceReduce power consumptionTransistorPulse automatic controlActive clampLow voltage

A double-gated low power active clamp circuit for digital circuits includes a first double-gated MOSFET serially connected between an upper power supply voltage and an input terminal to be clamped, and a second double-gated MOSFET serially connected between a lower voltage power supply and the input terminal. The voltages at the gates of the first and second double-gated MOSFETs are held at constant reference voltages by a single or double reference circuits. The clamping action can be switched on or off. The double-gated active clamping network can be implemented with a single power supply voltage, or with multiple power supply voltages. The use of the back gates of the double-gated active clamping network enables additional clamping and ESD protection for smaller generations of transistors, such as, those having dimensions below 0.1 micron. The device is particularly suited for use with dynamic threshold double-gated silicon-on-insulator, FINFET, and bulk triple well technologies.

Owner:GLOBALFOUNDRIES US INC

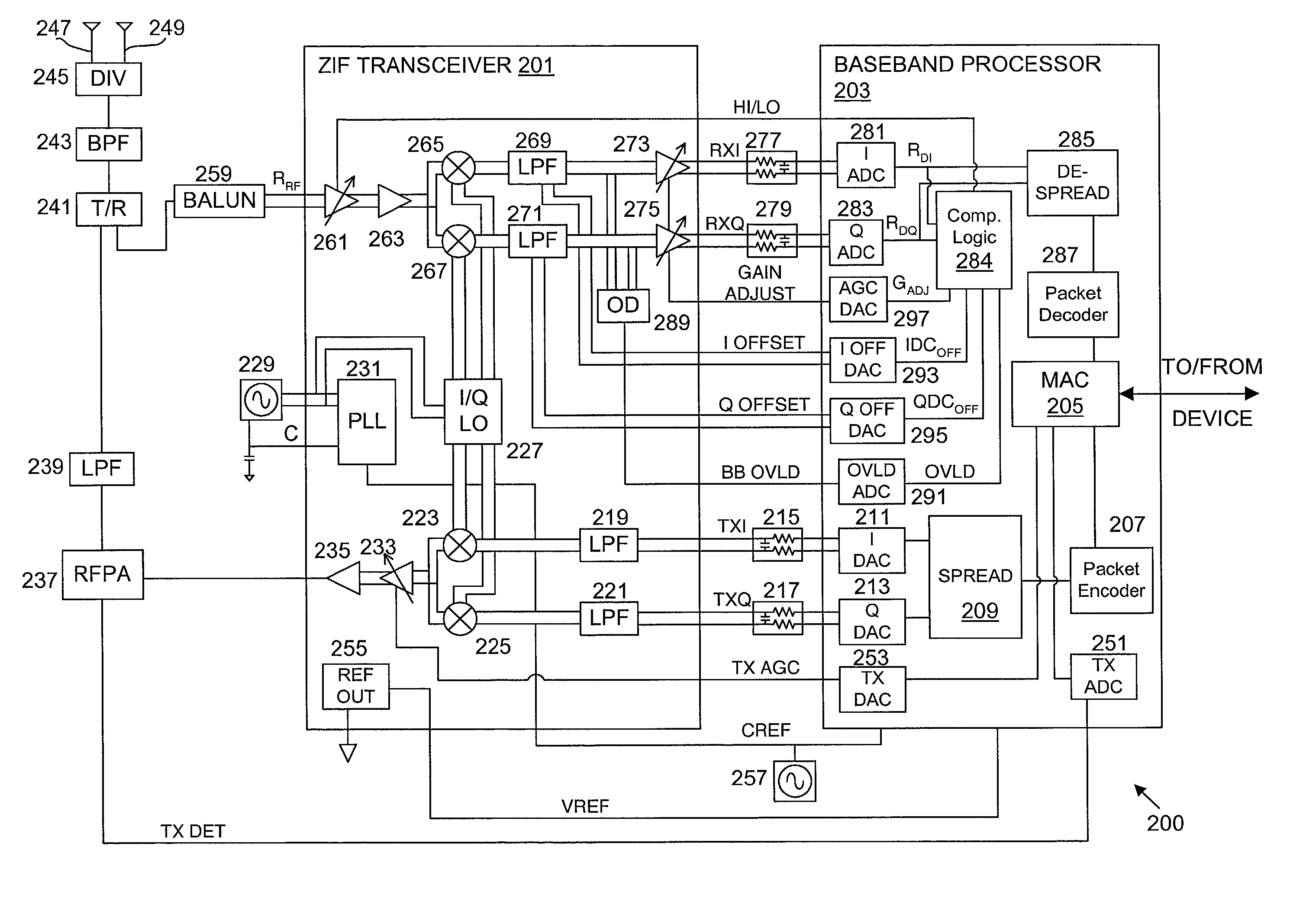

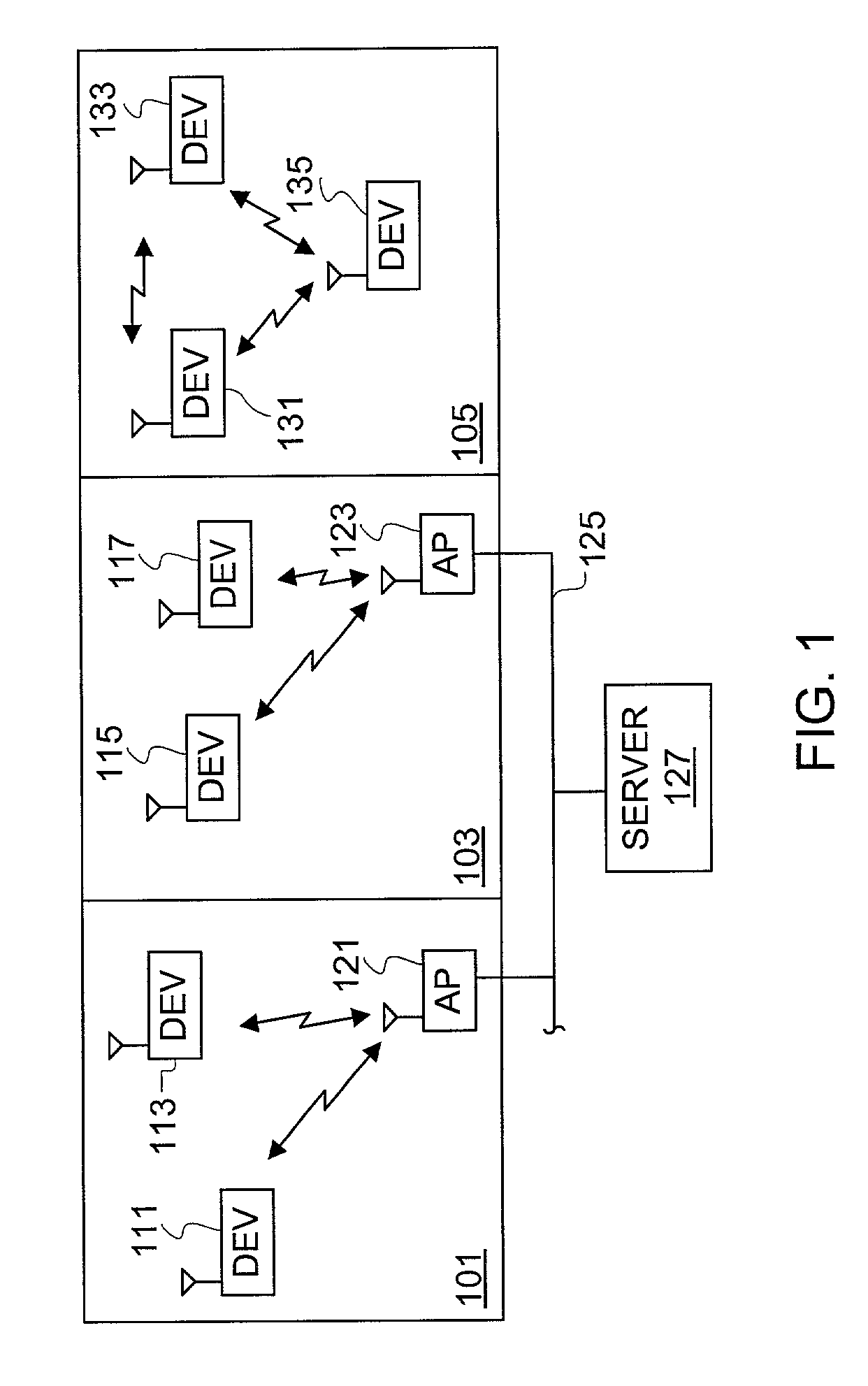

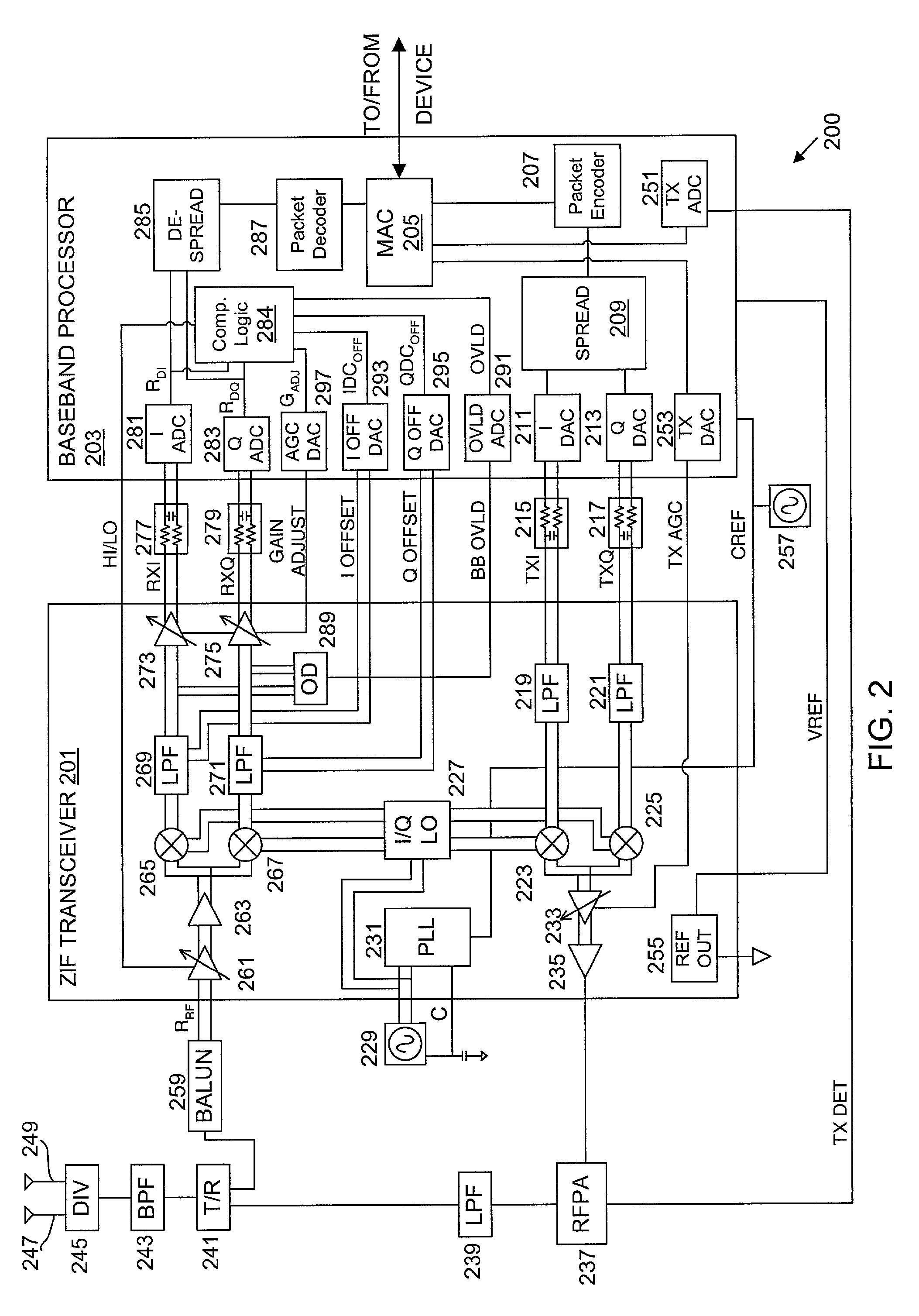

Packet acquisition and channel tracking for a wireless communication device configured in a zero intermediate frequency architecture

A method of controlling operation of a wireless device configured in a zero intermediate frequency architecture including a DC loop and a gain loop. The method includes processing energy in a wireless medium to generate a corresponding receive signal, monitoring the receive signal via a predetermined measurement window, detecting a changed condition in the channel, holding the gain feedback control loop at a constant gain level, and operating the DC loop in an attempt to search a stable DC value for the receive signal while the gain loop is held constant. A first case is DC saturation, where the gain is held constant until DC is controlled. A second case is clear channel assessment, where a prior stored gain setting is applied to the gain loop after detecting the end of the packet. A third case is preparation for receiving an expected acknowledgement packet after transmitting a packet, where again a prior stored gain setting is applied to the gain loop and DC is searched.

Owner:INTELLECTUAL VENTURES I LLC

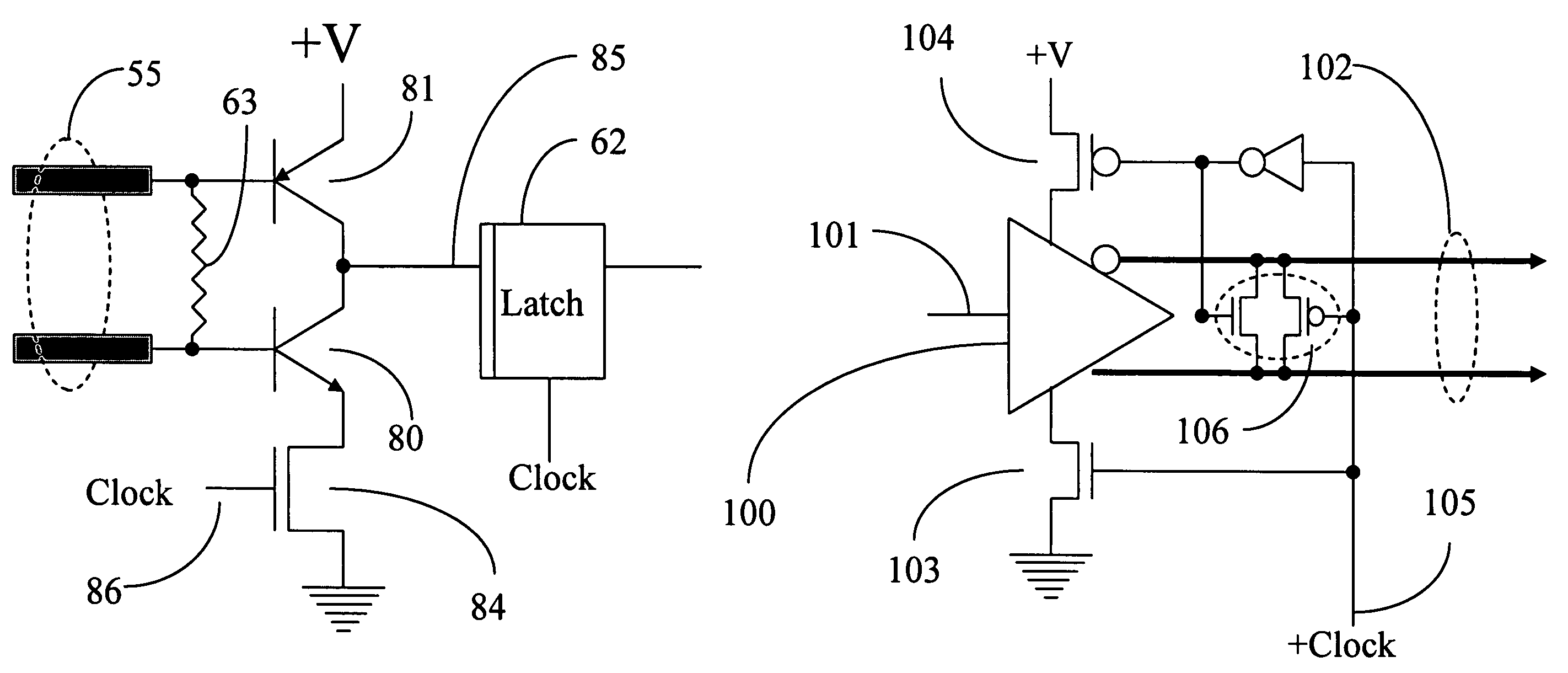

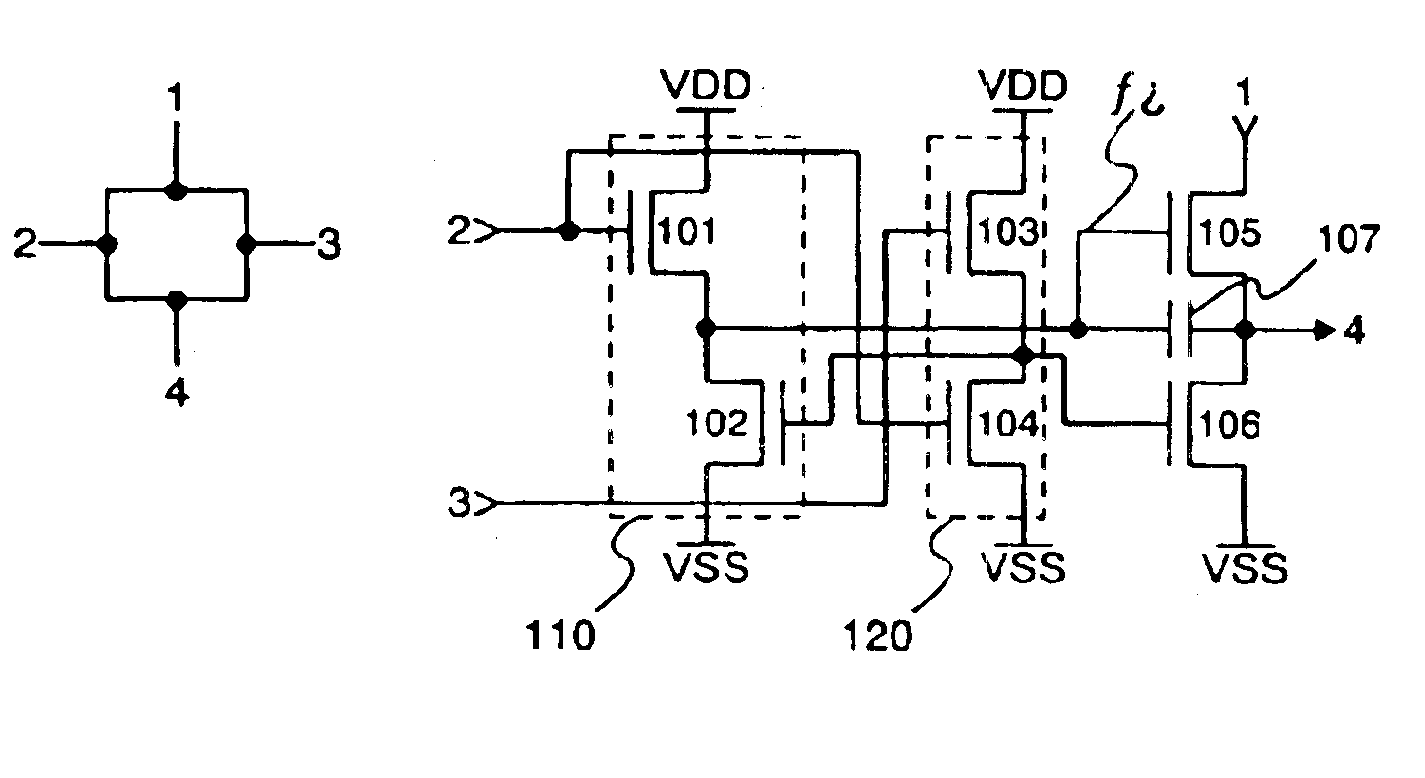

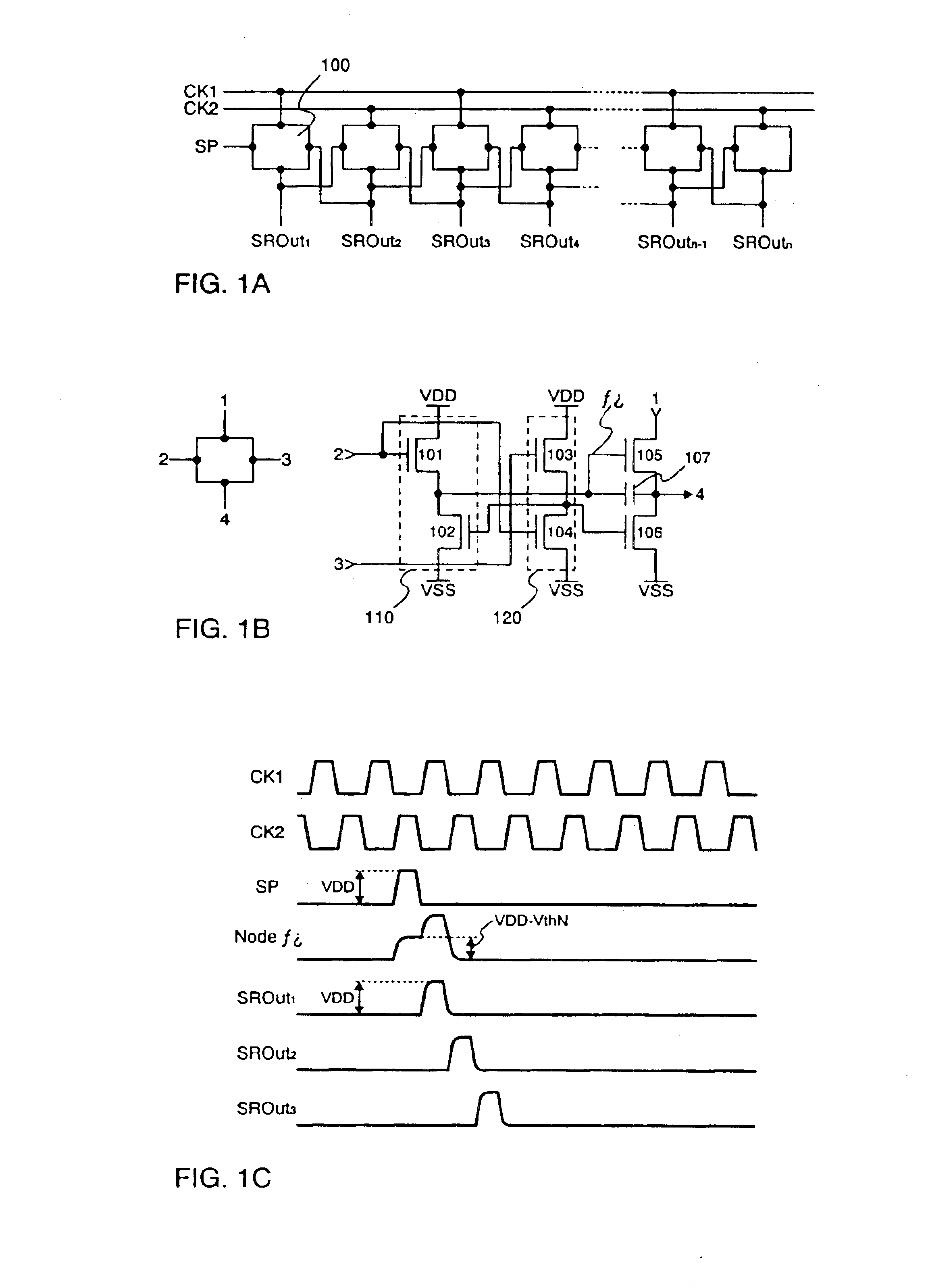

Pulse output circuit, shift register and electronic equipment

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 On, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

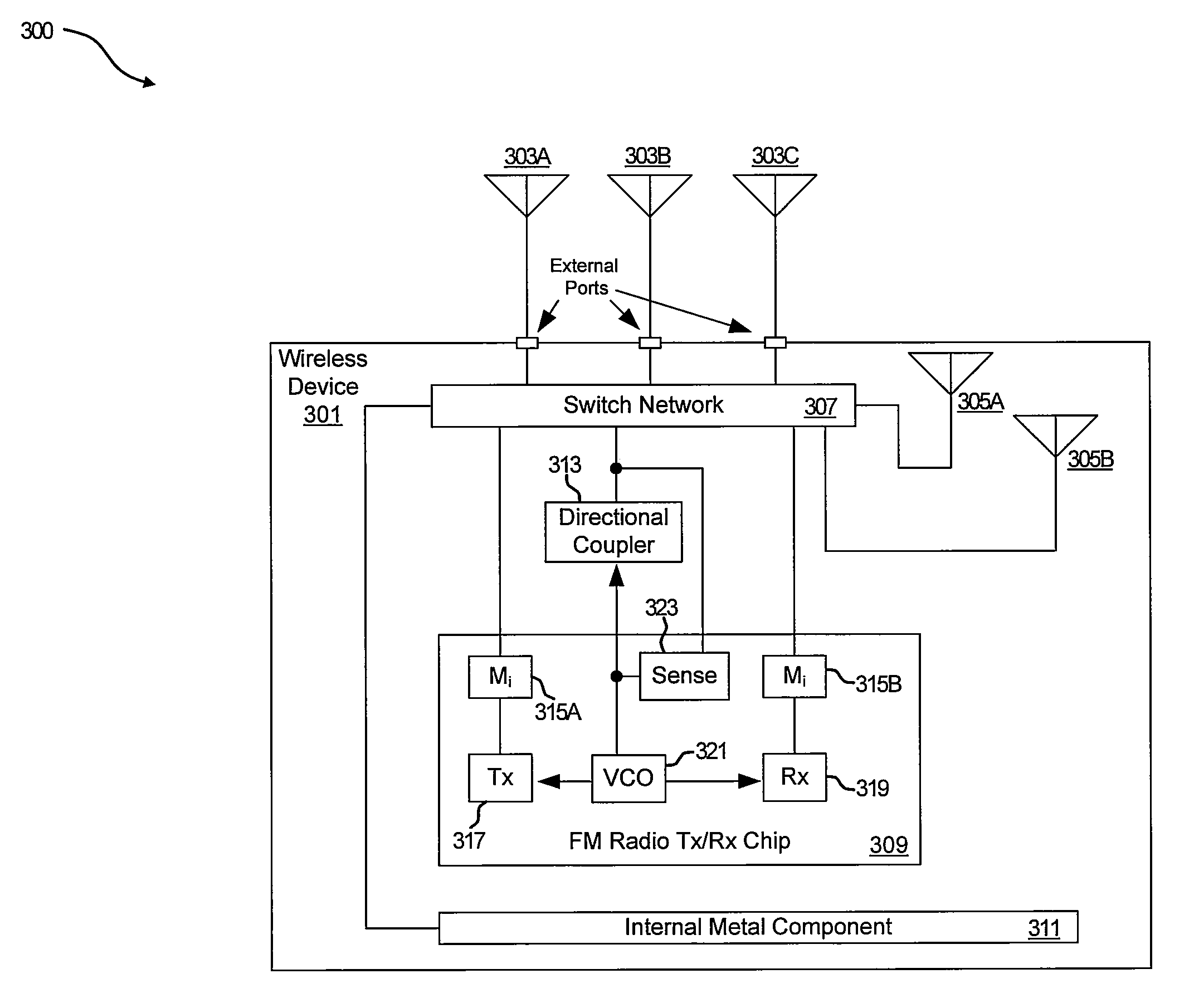

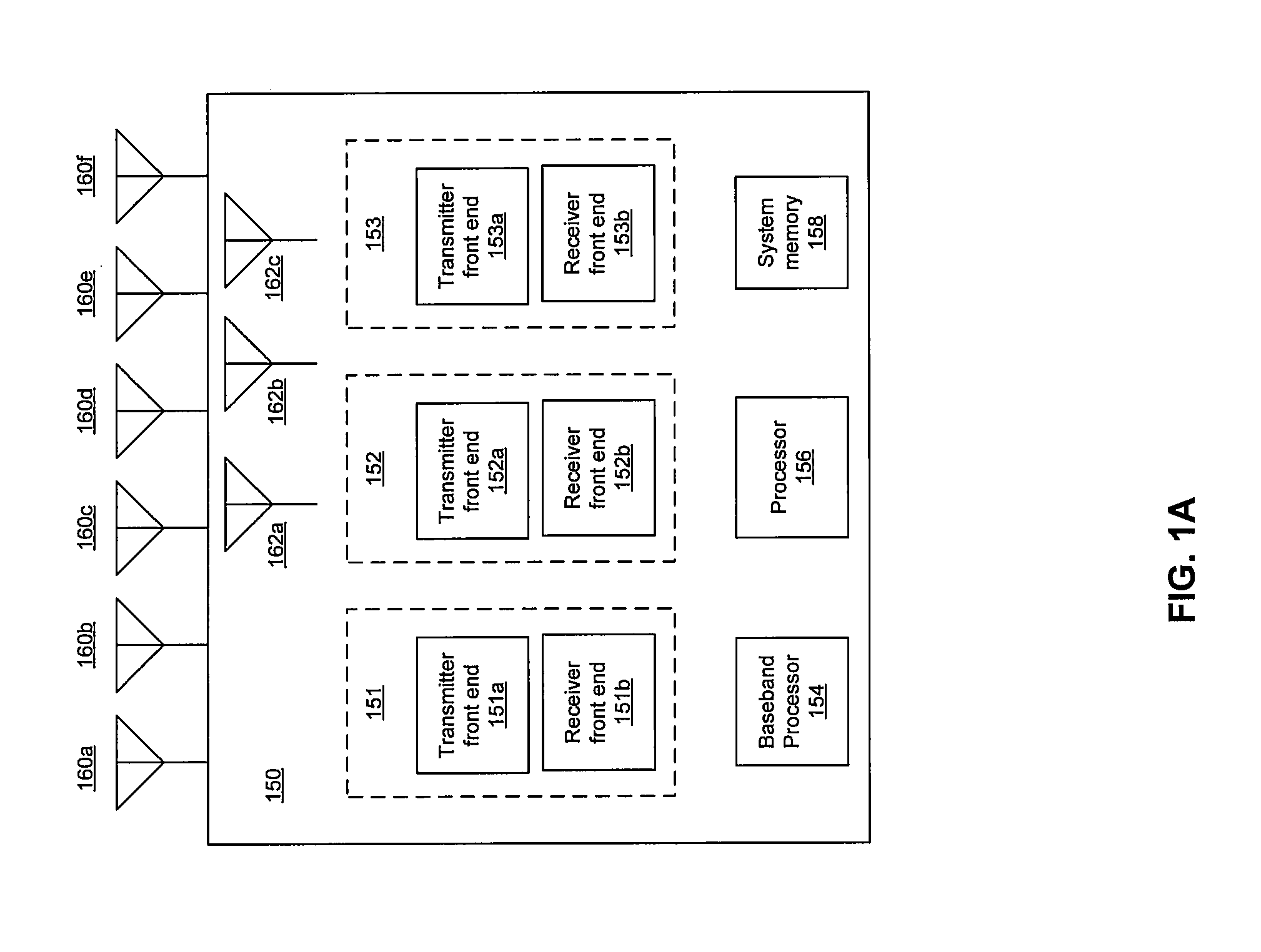

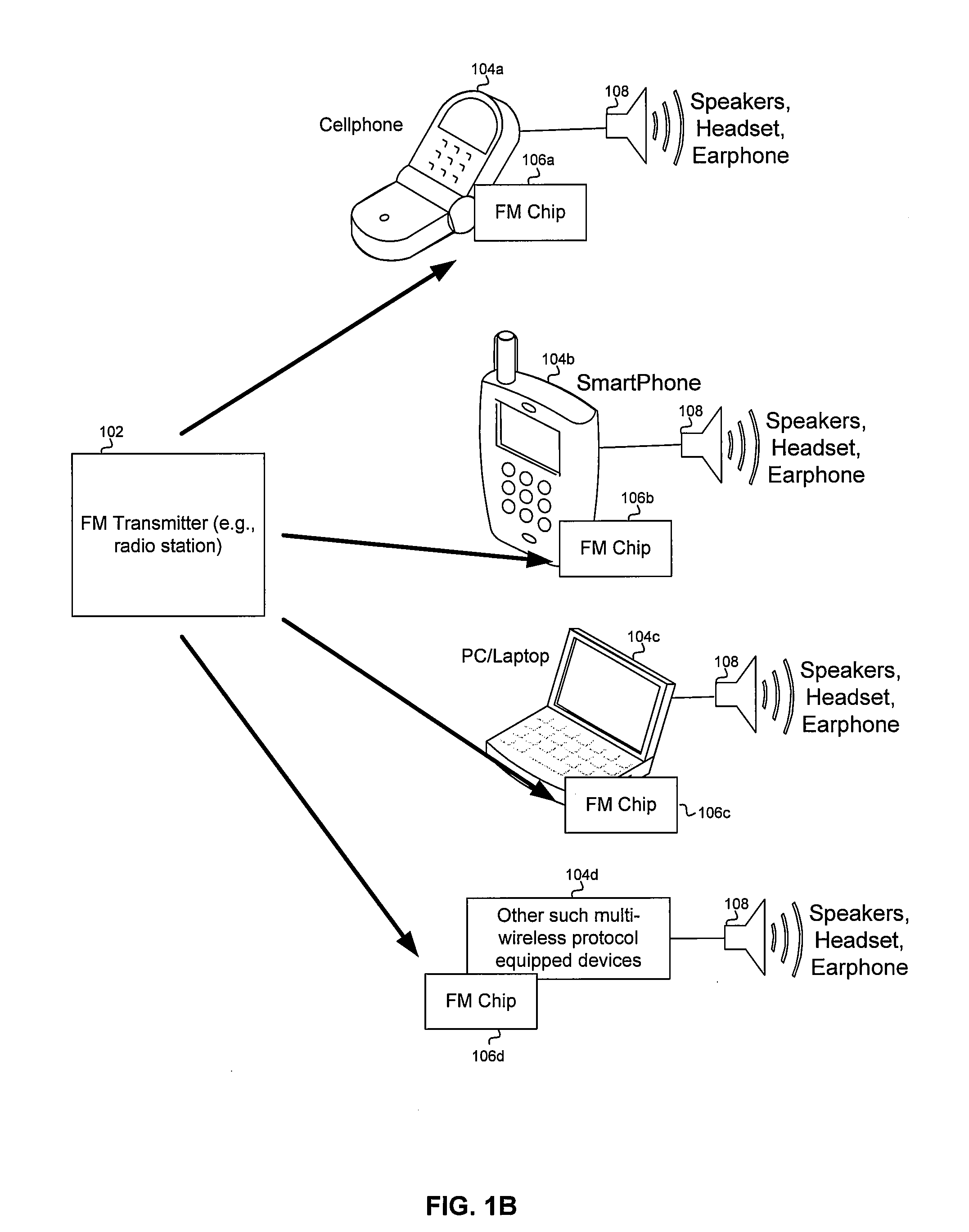

Method and system for auto detecting and auto switching antennas in a multi-antenna FM transmit/receive system

Methods and systems for auto detecting and auto switching antennas in a multi-antenna FM transmit / receive system are disclosed and may include detecting when an external antenna may be coupled to an external port of the wireless device and utilizing the external antenna for transmitting and / or receiving FM signals. The decoupling of an external antenna from an external port may be detected, which may cause the FM radio transmitter / receiver to be configured to transmit and / or receive FM signals utilizing antennas internal to the wireless device. One or more test signals, which may include AC signals, may be generated within the chip for detecting whether an external antenna may be coupled to an external port. A reflected signal from an external port may be measured and compared to a prestored value corresponding to a reflection due to an open circuit at the one or more external ports of the wireless device.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

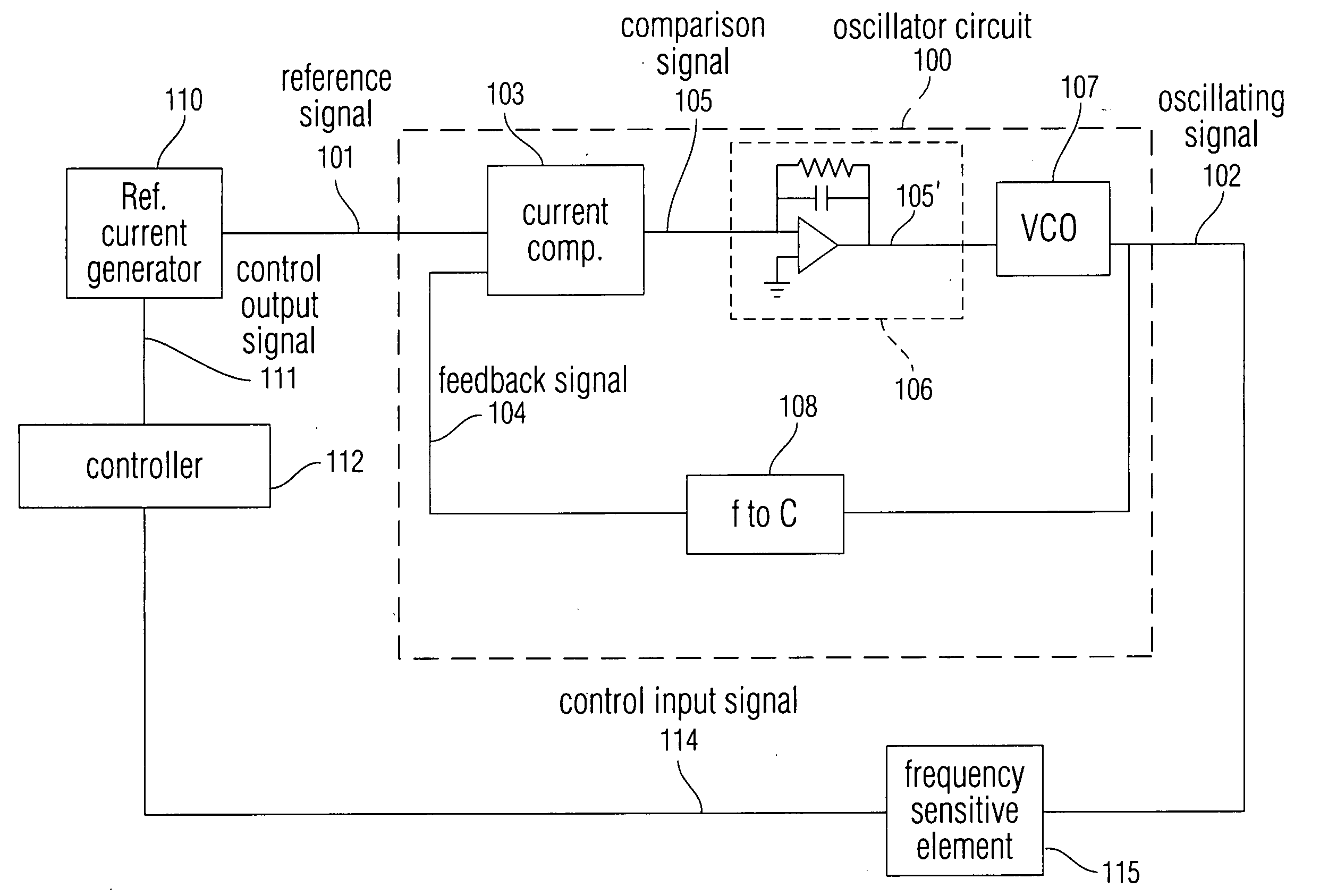

Noise reduction within an electronic device using automatic frequency modulation

ActiveUS20080157893A1High frequencyLimitation to input signalPulse automatic controlFrequency analysisEngineeringNoise reduction

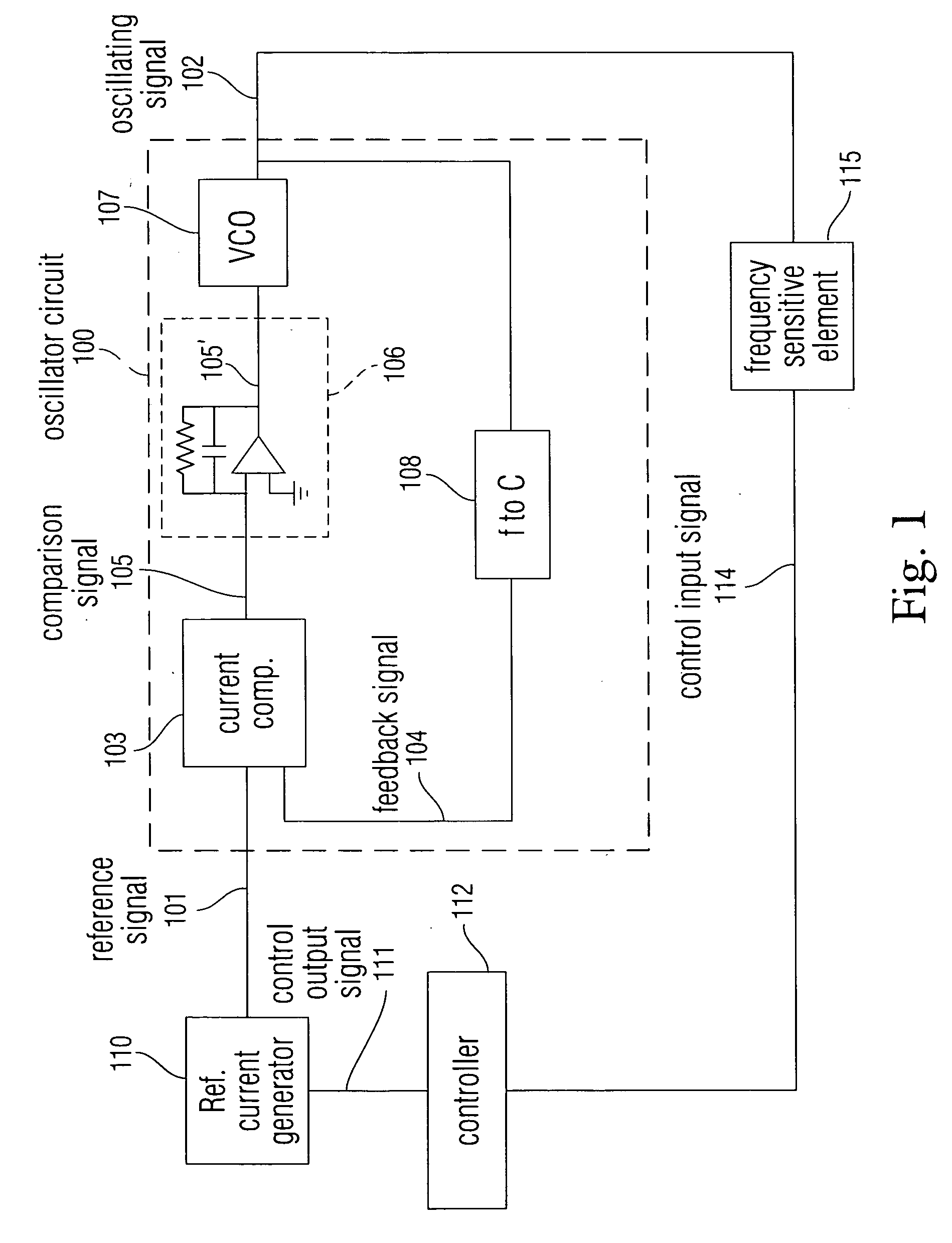

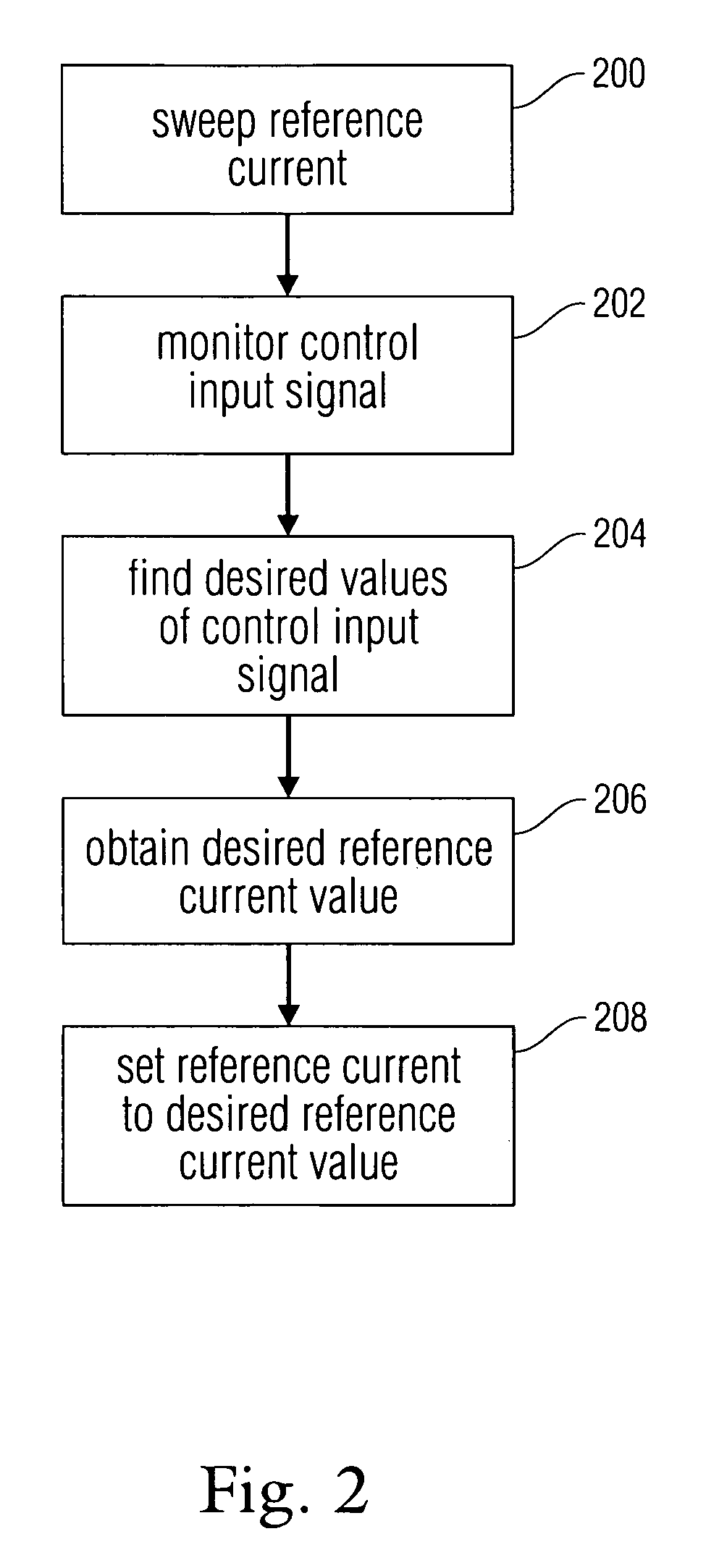

Disclosed is a system and method for providing an oscillating signal of relatively precise frequency without using a signal provided by a crystal as a reference. Disclosed is a feedback oscillator circuit configured to output an oscillating signal having a frequency defined by a reference signal. The oscillating signal can be sent to one or more circuits including at least one frequency sensitive element. The frequency sensitive element produces an output signal which depends on the frequency of the oscillating signal. A controller controls the reference signal in order to cause an attribute of the output signal to have a value within a desired range.

Owner:APPLE INC

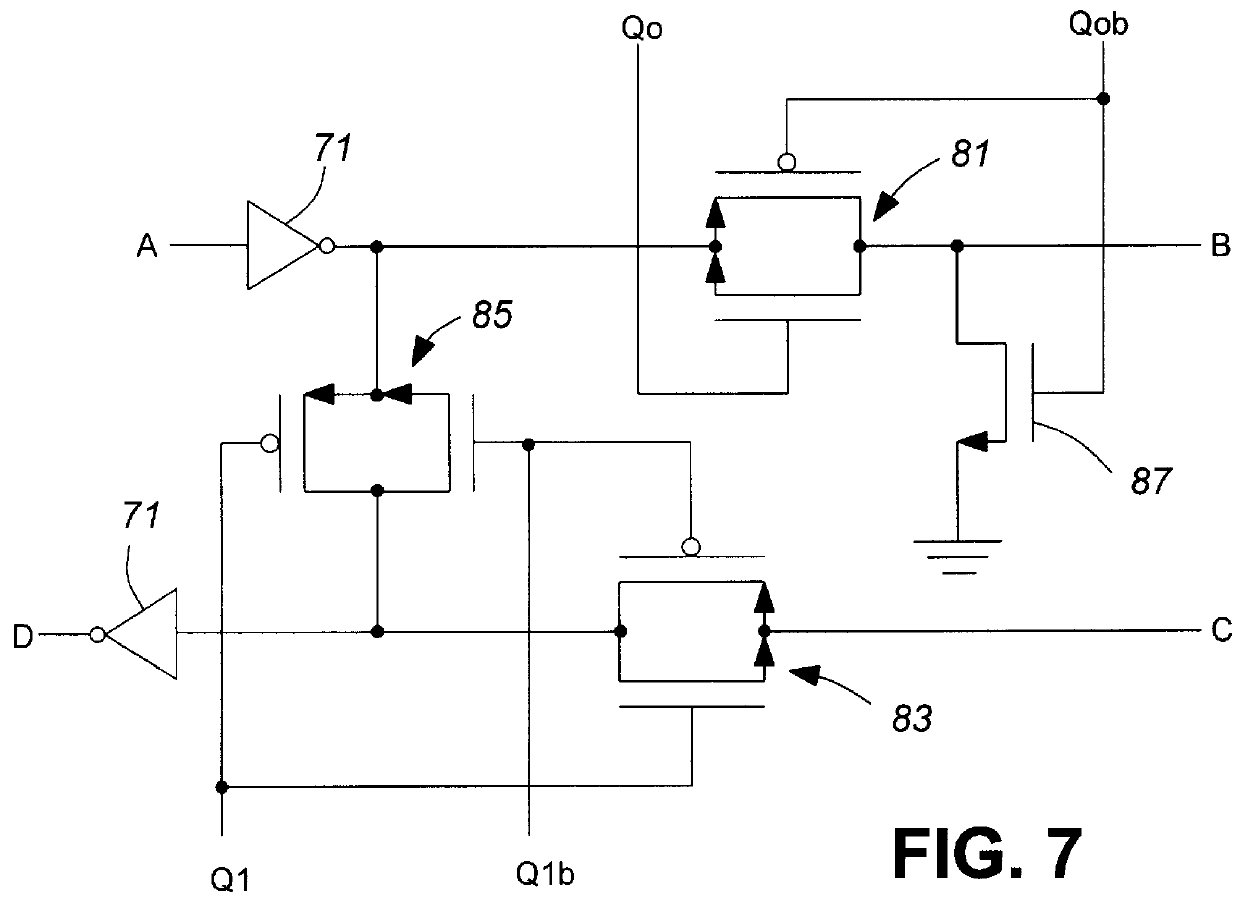

Array oscillator and polyphase clock generator

InactiveUS20060001496A1Increase speedReduce jitterPulse automatic controlPulse generation by logic circuitsMOSFETMultiplexing

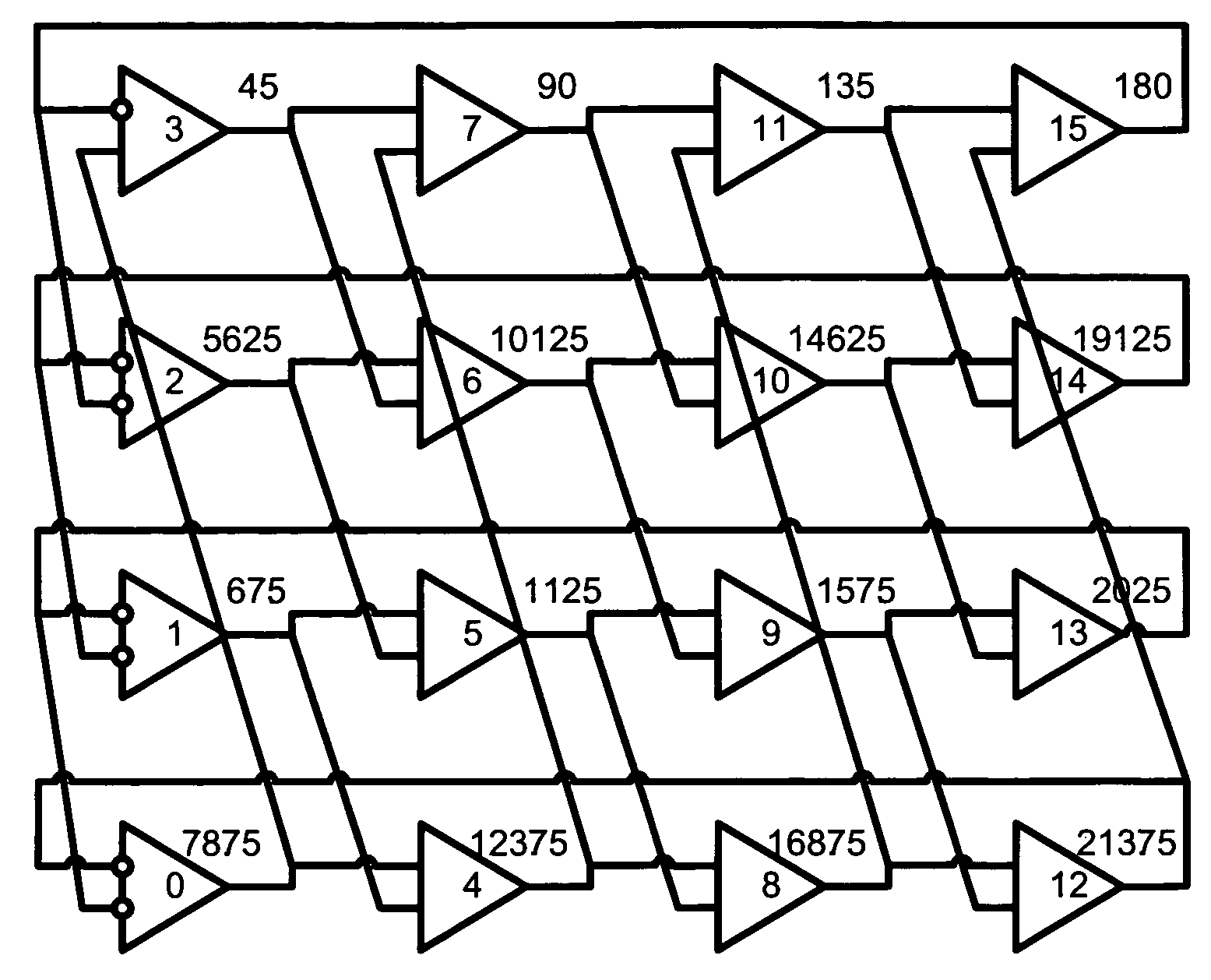

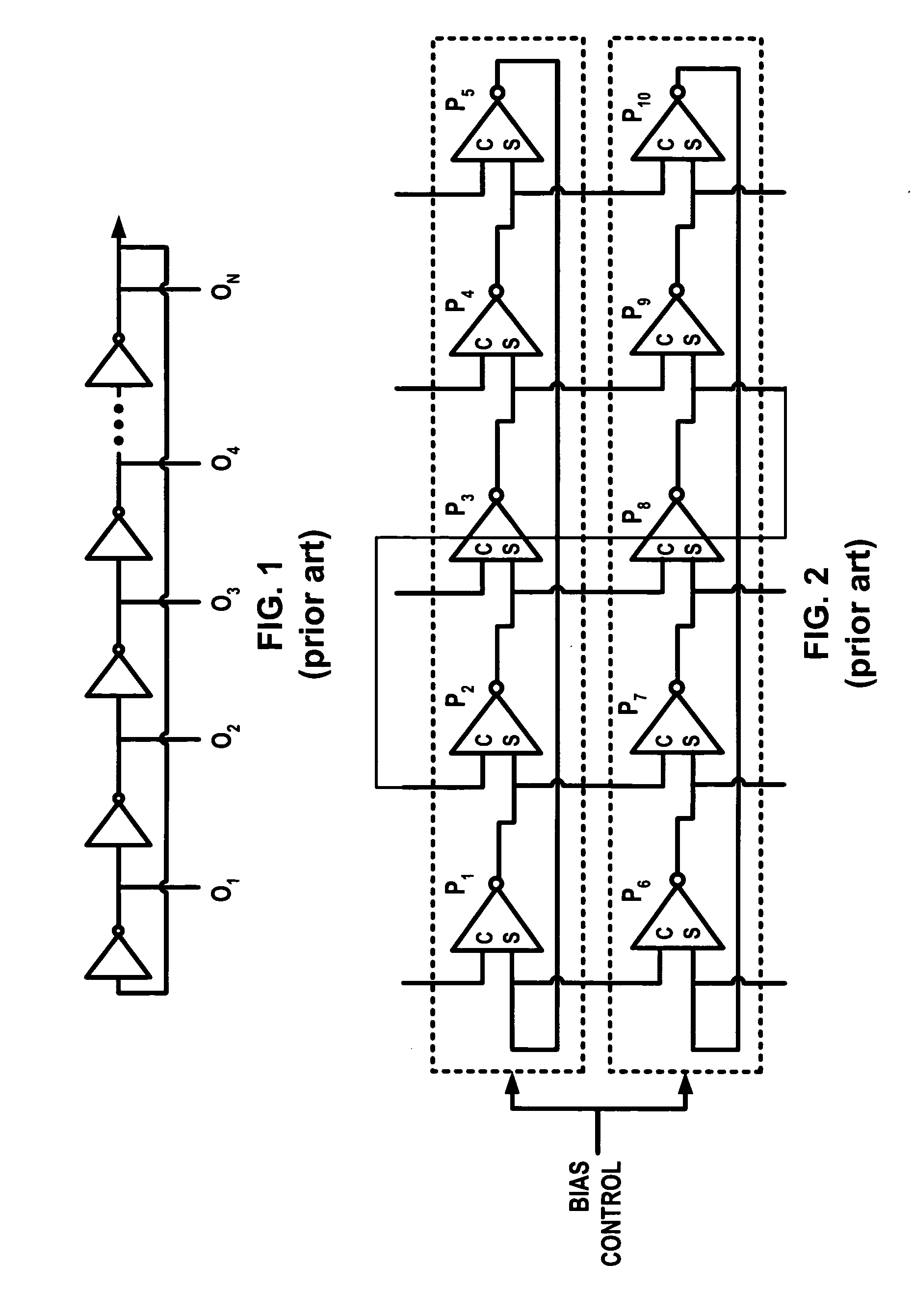

The present invention relates generally to array oscillator circuits for use as phase delay generators. More particularly, the present invention relates to a novel array oscillator for providing a plurality of phases which have stable phase relationships. The present invention is particularly applicable to the generation of poly-phase clocks for receivers of very high speed interfaces which employ an over-sampling technique, or multiplexing, and for high speed logic. The array oscillator according to the invention comprises at least one ring oscillator having a plurality of at least two interconnected buffer stages including at least one, or any integer odd number of inverting stages and a series of non-inverting stages, wherein the buffer stages are formed of N-type MOSFET transistors.

Owner:ACUID +1

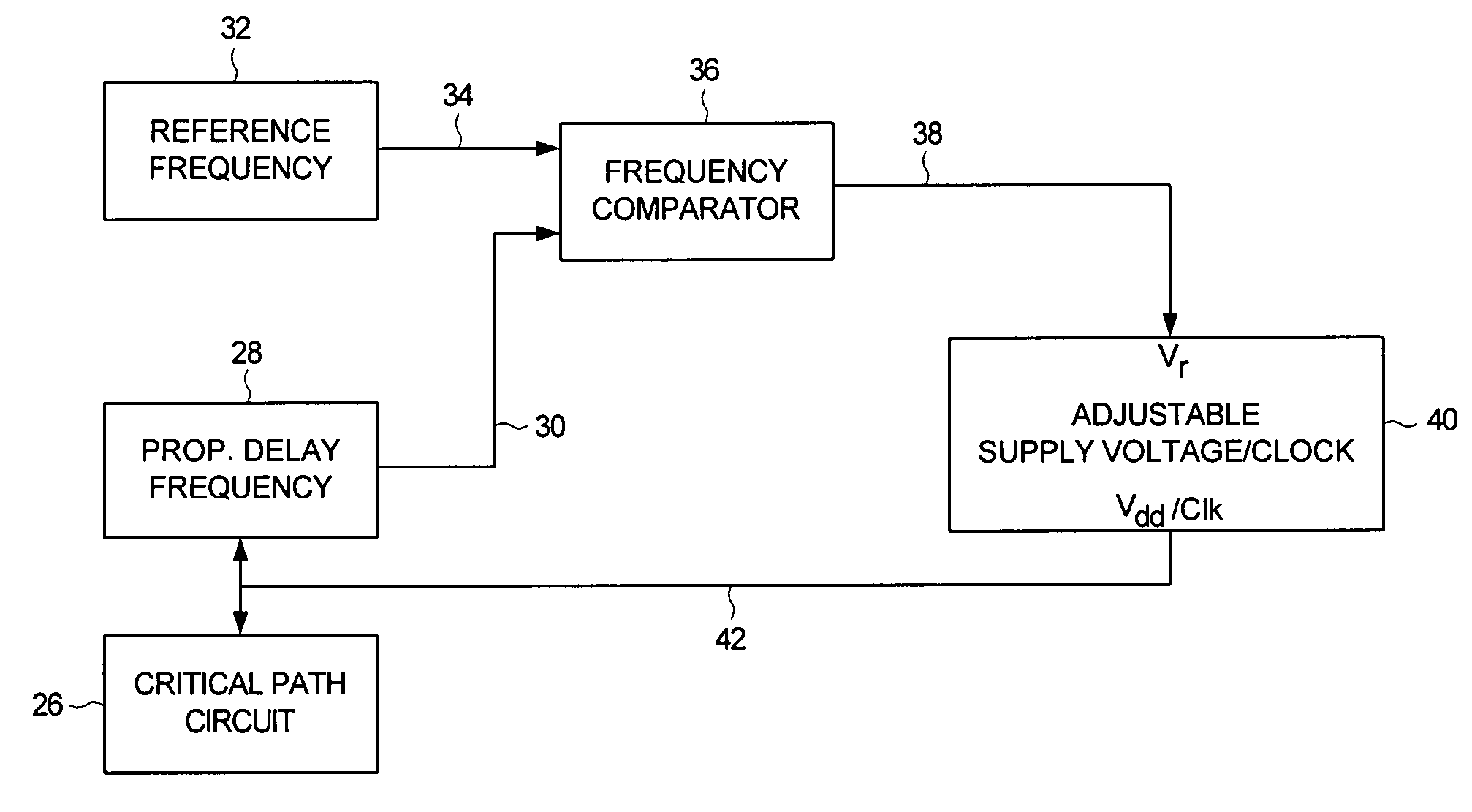

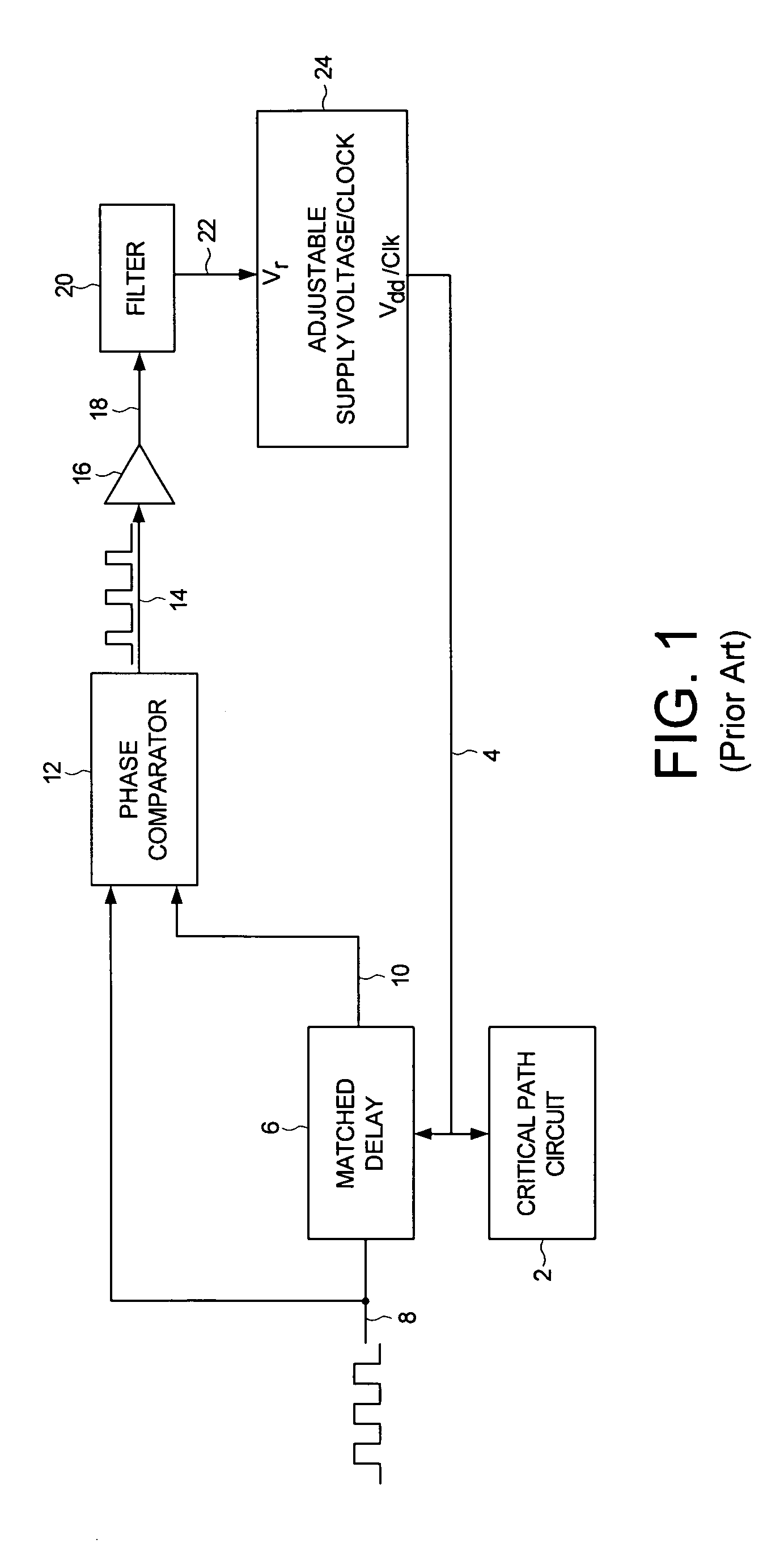

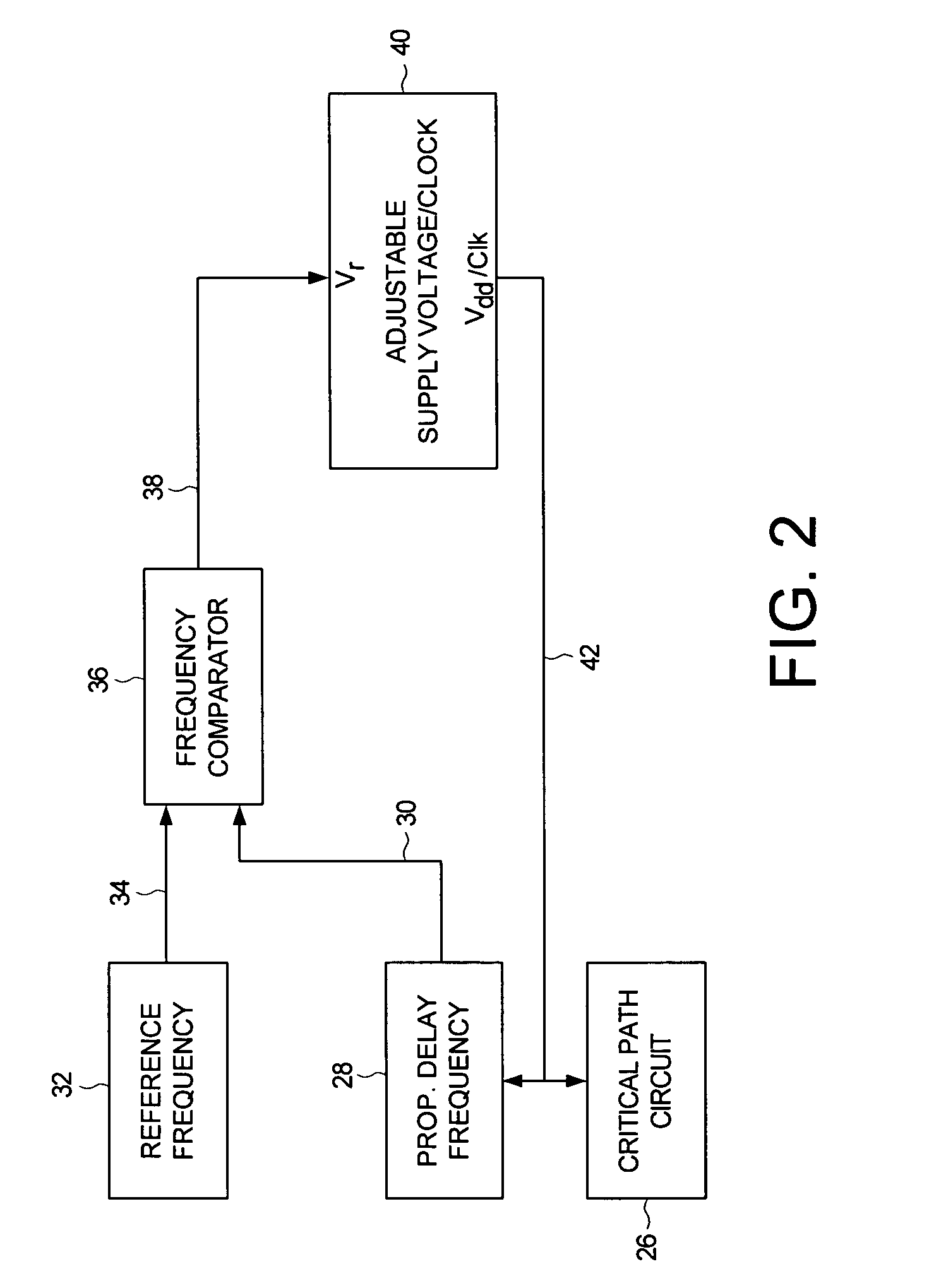

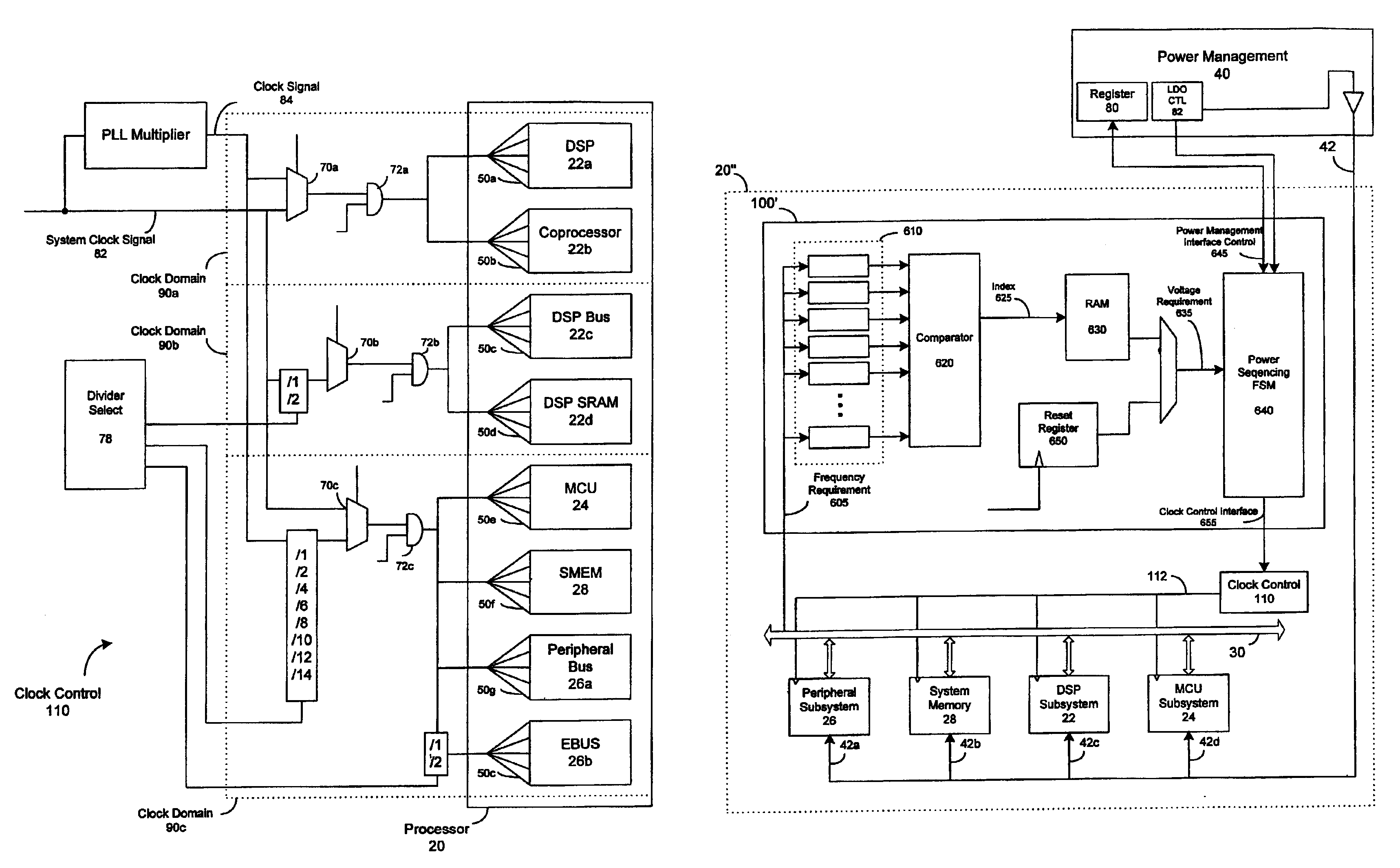

Adjusting power consumption of digital circuitry by generating frequency error representing error in propagation delay

A method and apparatus is disclosed for adjusting at least one of a supply voltage and a clocking frequency applied to digital circuitry of a computing device, wherein the digital circuitry comprises a critical path circuit. A propagation delay frequency representing a propagation delay of the critical path circuit is generated, and a frequency error signal is generated representing a difference between a reference frequency and the propagation delay frequency. At least one of the supply voltage and the clocking frequency is adjusted in response to the frequency error signal.

Owner:WESTERN DIGITAL TECH INC

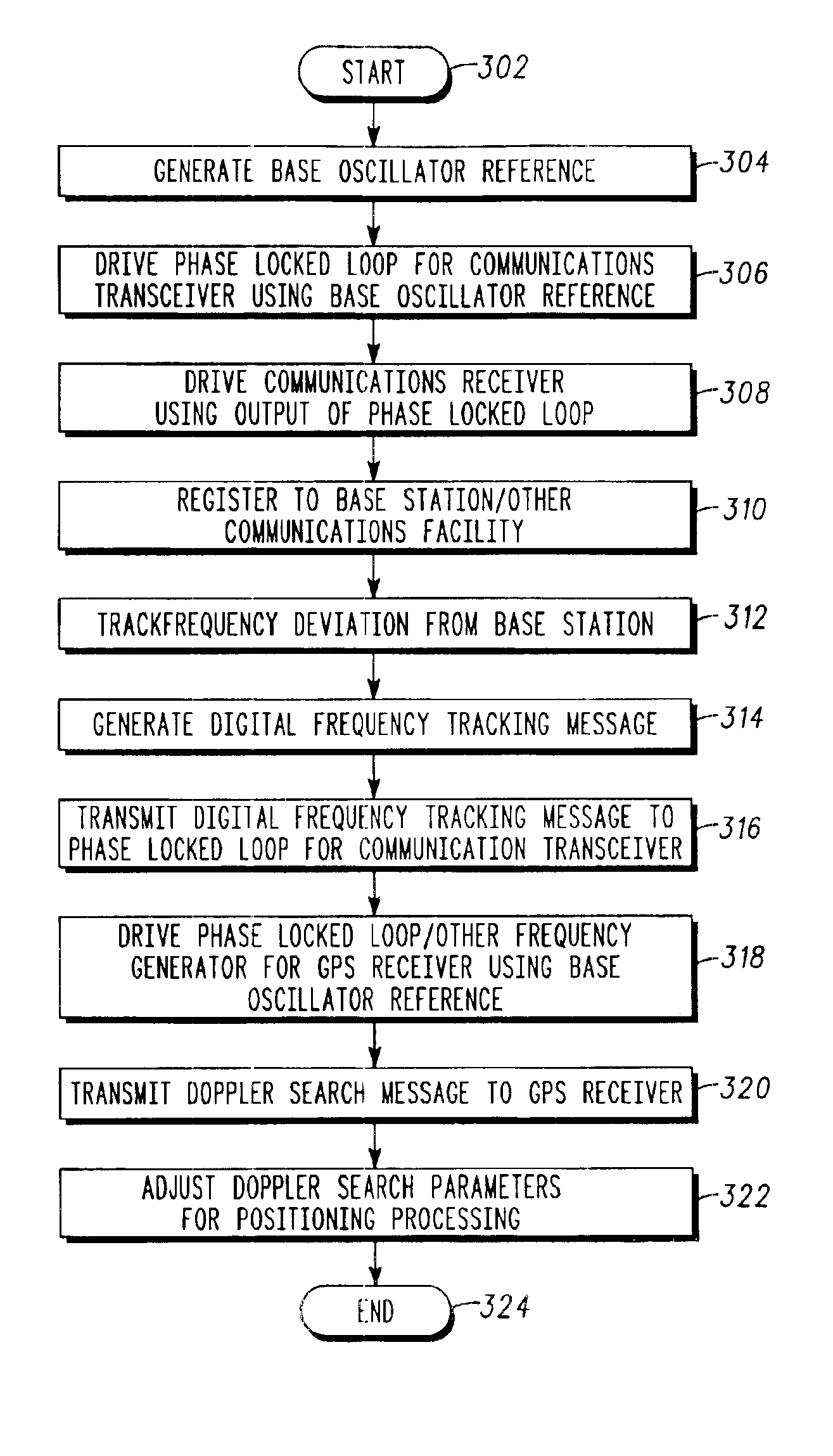

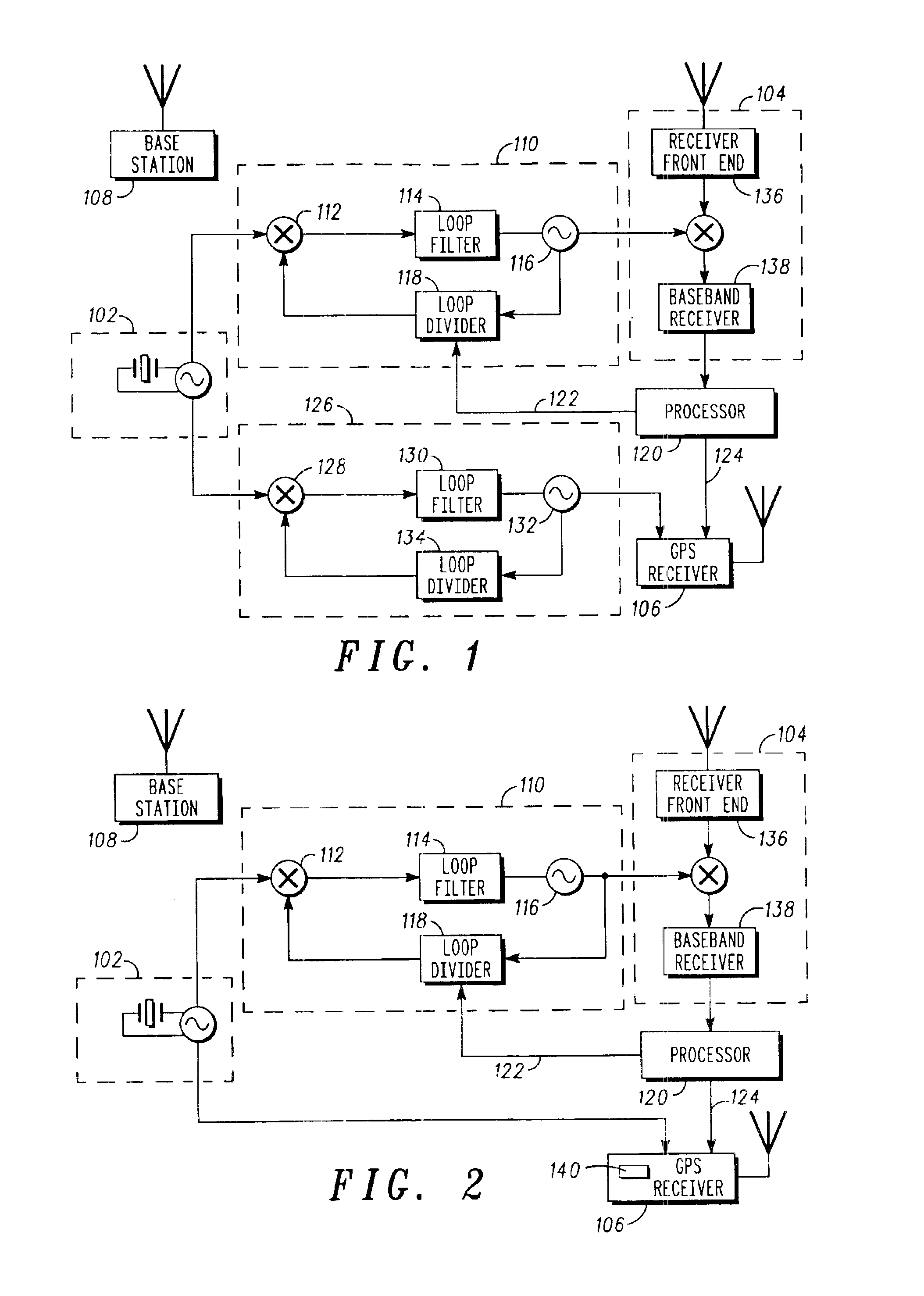

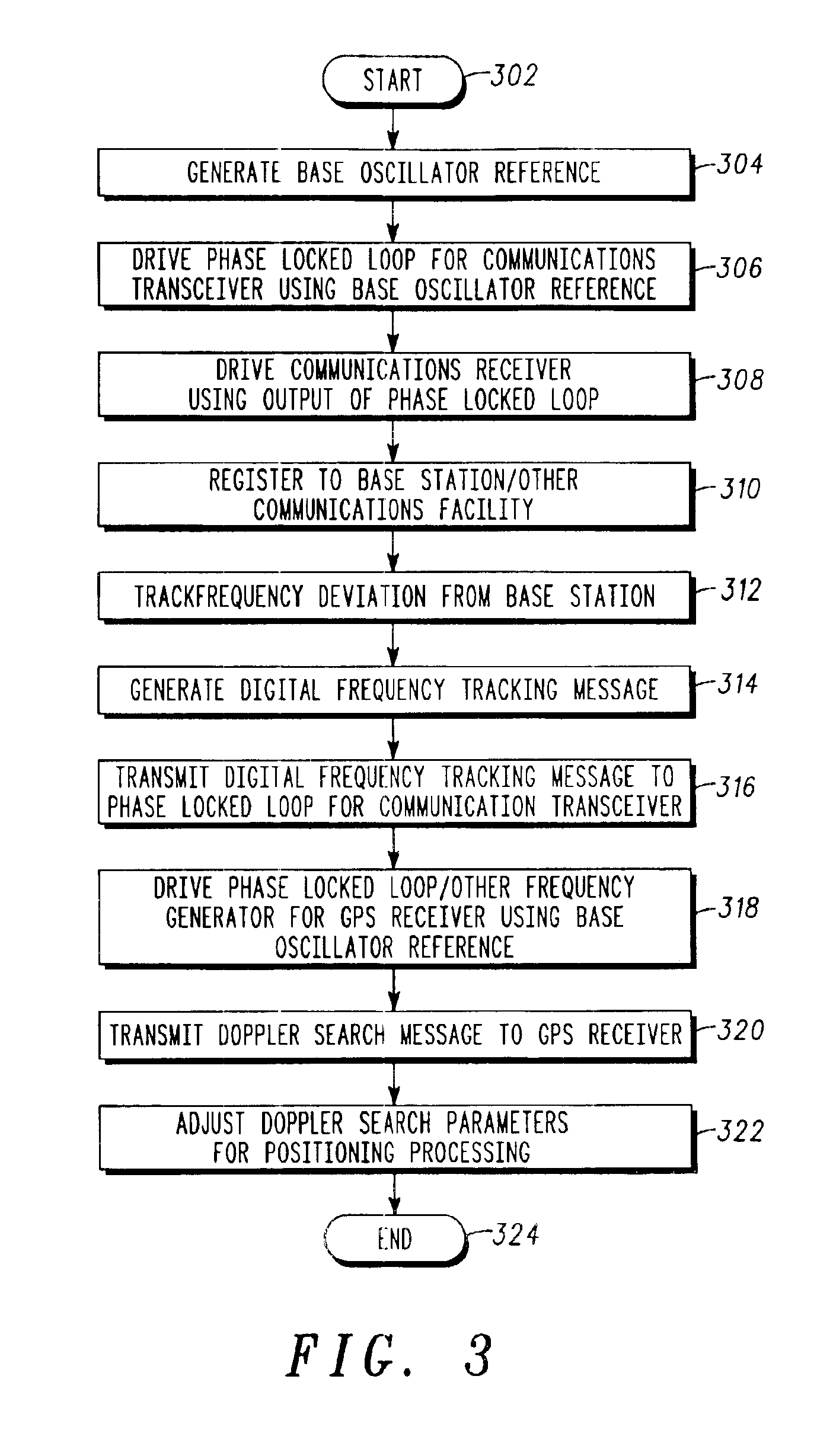

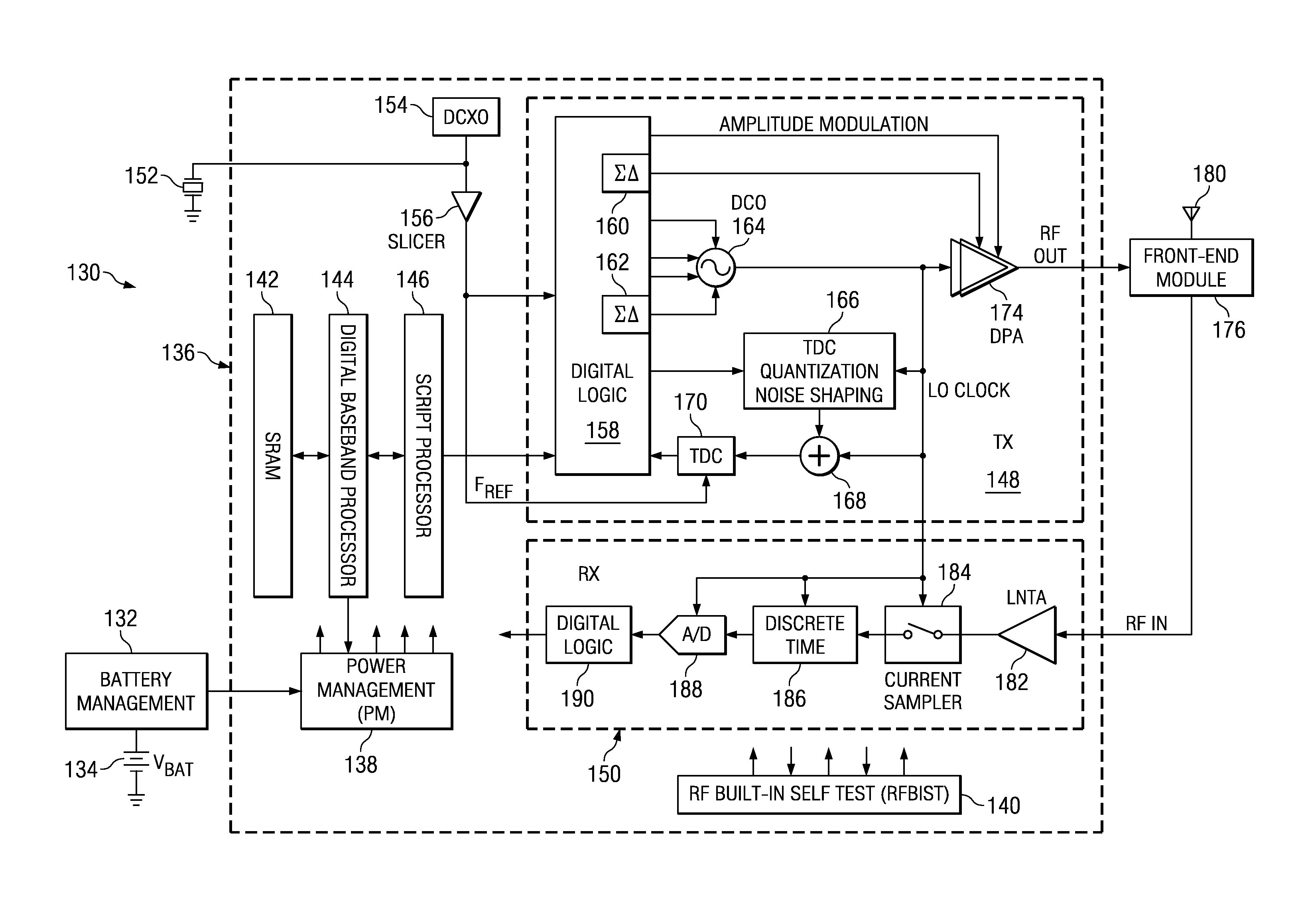

System and method for frequency management in a communications positioning device

InactiveUS6867734B2High positioning accuracySufficient GPS performanceSynchronisation arrangementPulse automatic controlTime to first fixTransceiver

A frequency management scheme for a hybrid communications / positioning device, such as a cellular / GPS or other combined device, generates a local clock signal for the communications portion of the device, using a crystal oscillator or other part. The oscillator output may be delivered to a phase locked loop to drive a high-frequency clock for the cellular or other communications portion of the hybrid device. A processor may determine frequency error between the phase locked loop and base station or other reference, to derive a digital frequency tracking message. A Doppler search or other logical control message may likewise be communicated from the processor to a GPS or other positioning receiver. The GPS receiver circuitry may consequently adjust Doppler center, window width or other parameters to enhance time to first fix or other performance. The architecture eliminates the need for a second crystal or other direct oscillator in the GPS receiver portion of the hybrid device, while still maintaining GPS performance. The architecture of the design also eliminates the need for frequency correcting elements in the crystal oscillator or other base reference oscillator or clock. The invention can furthermore be used in any system, radio, modem, transceiver, or receiver that has two or more receivers that share one reference or base oscillator or clock.

Owner:GOOGLE TECH HLDG LLC

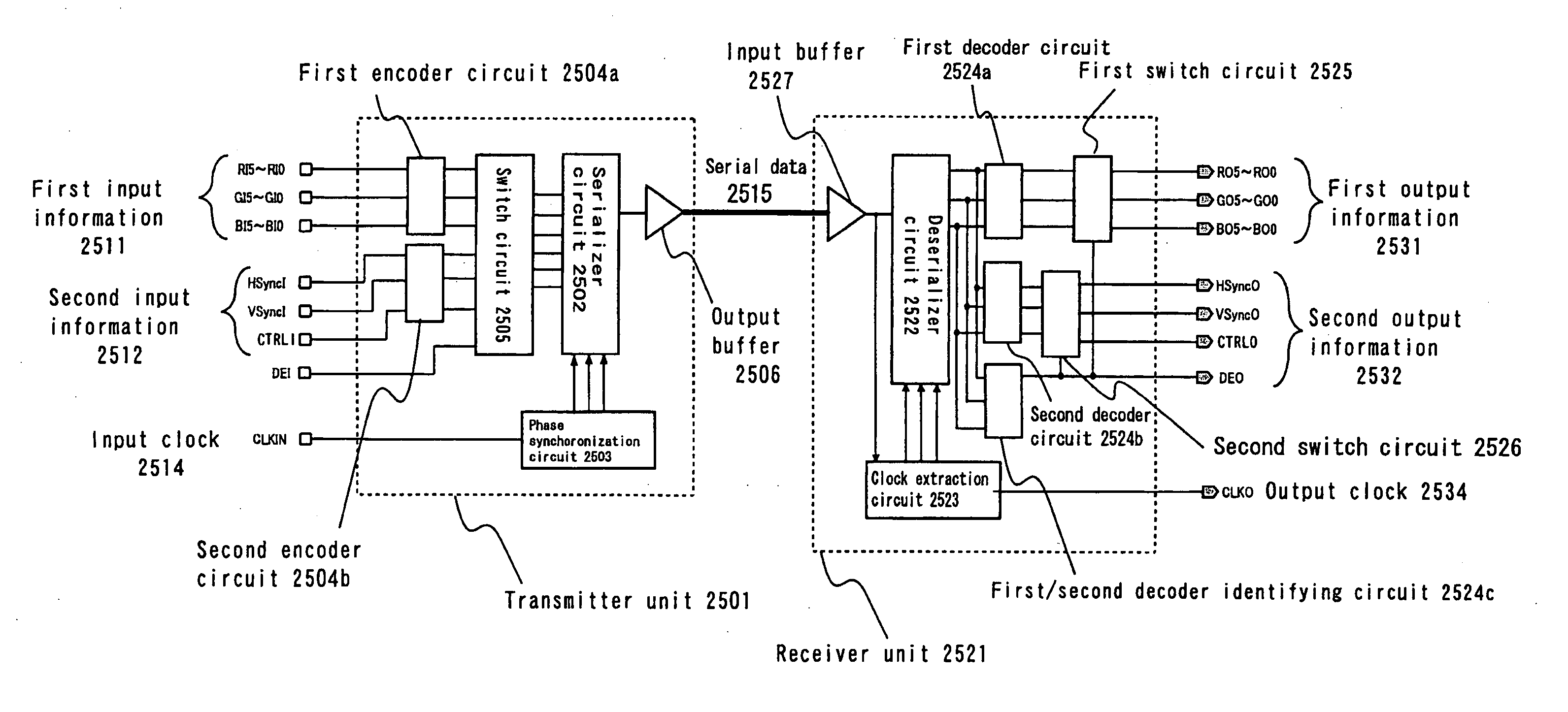

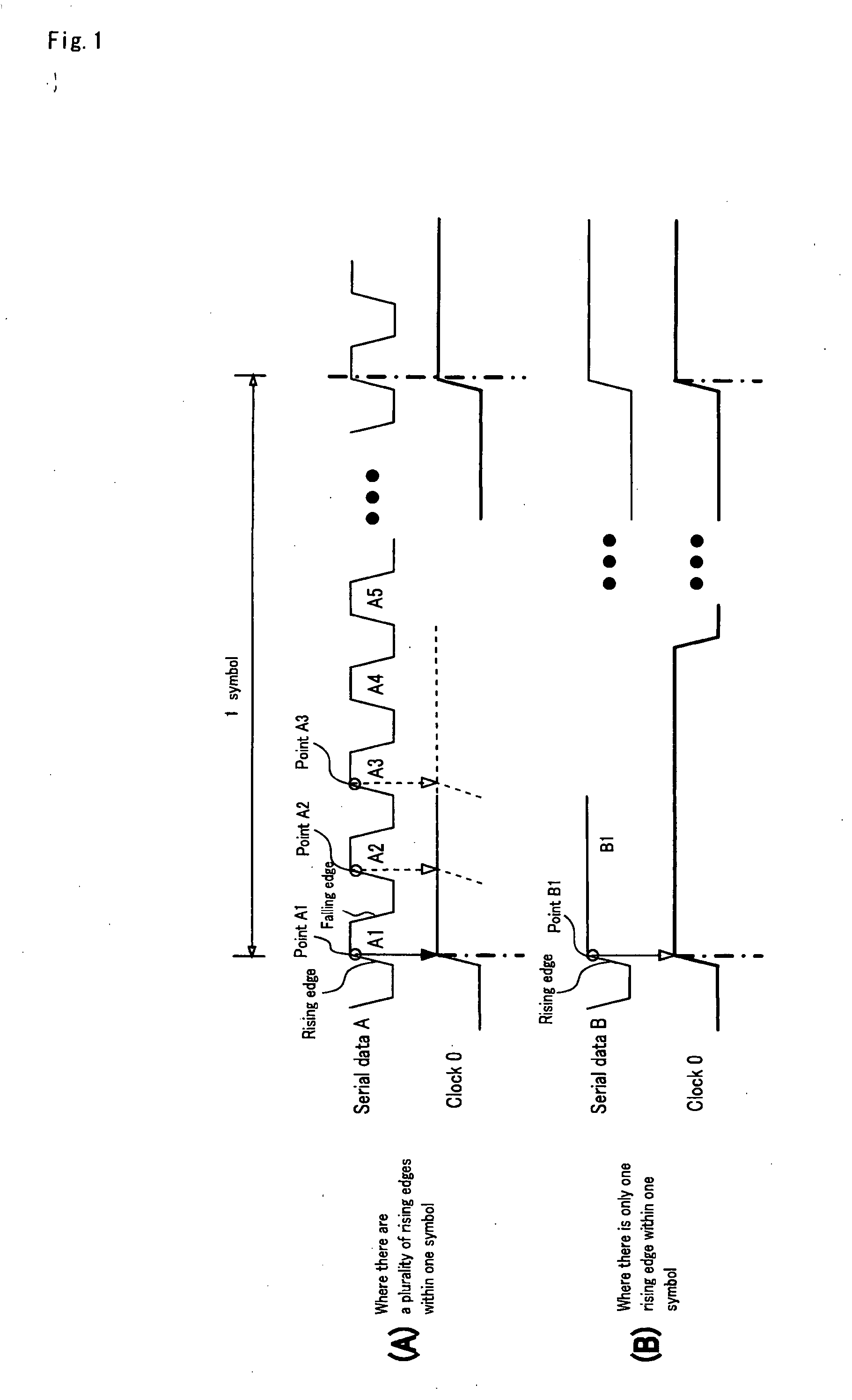

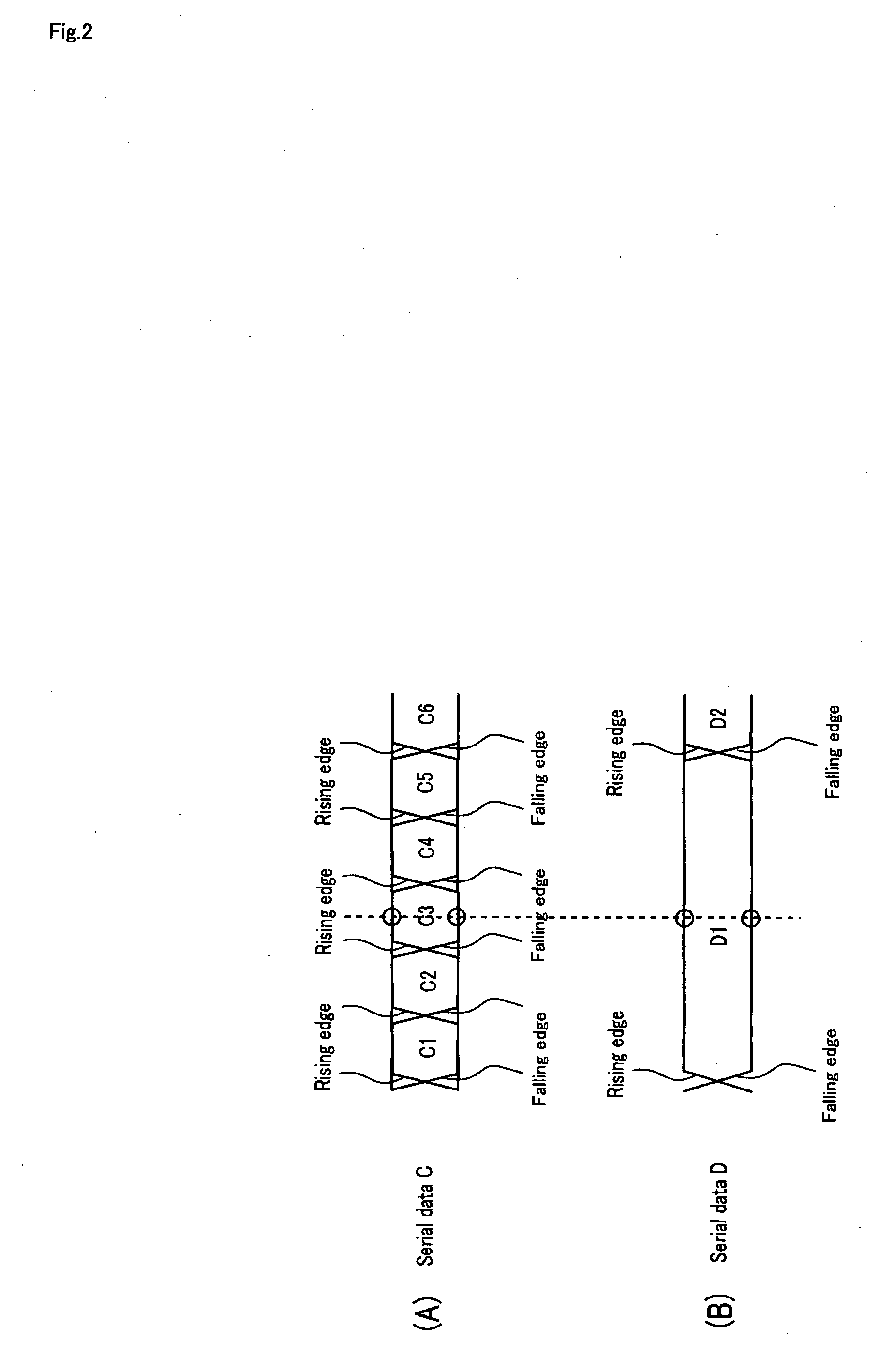

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS20050286643A1Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation. [Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

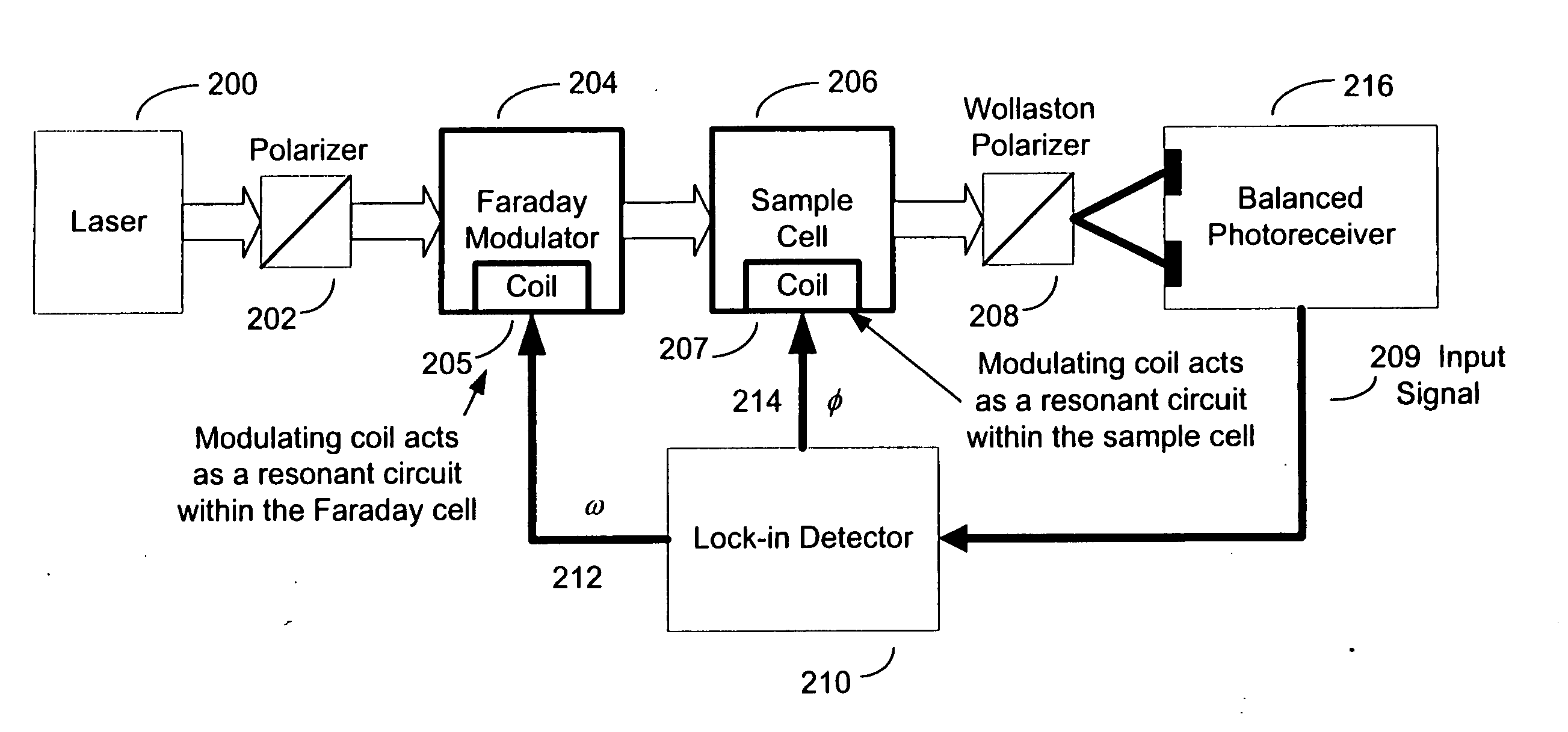

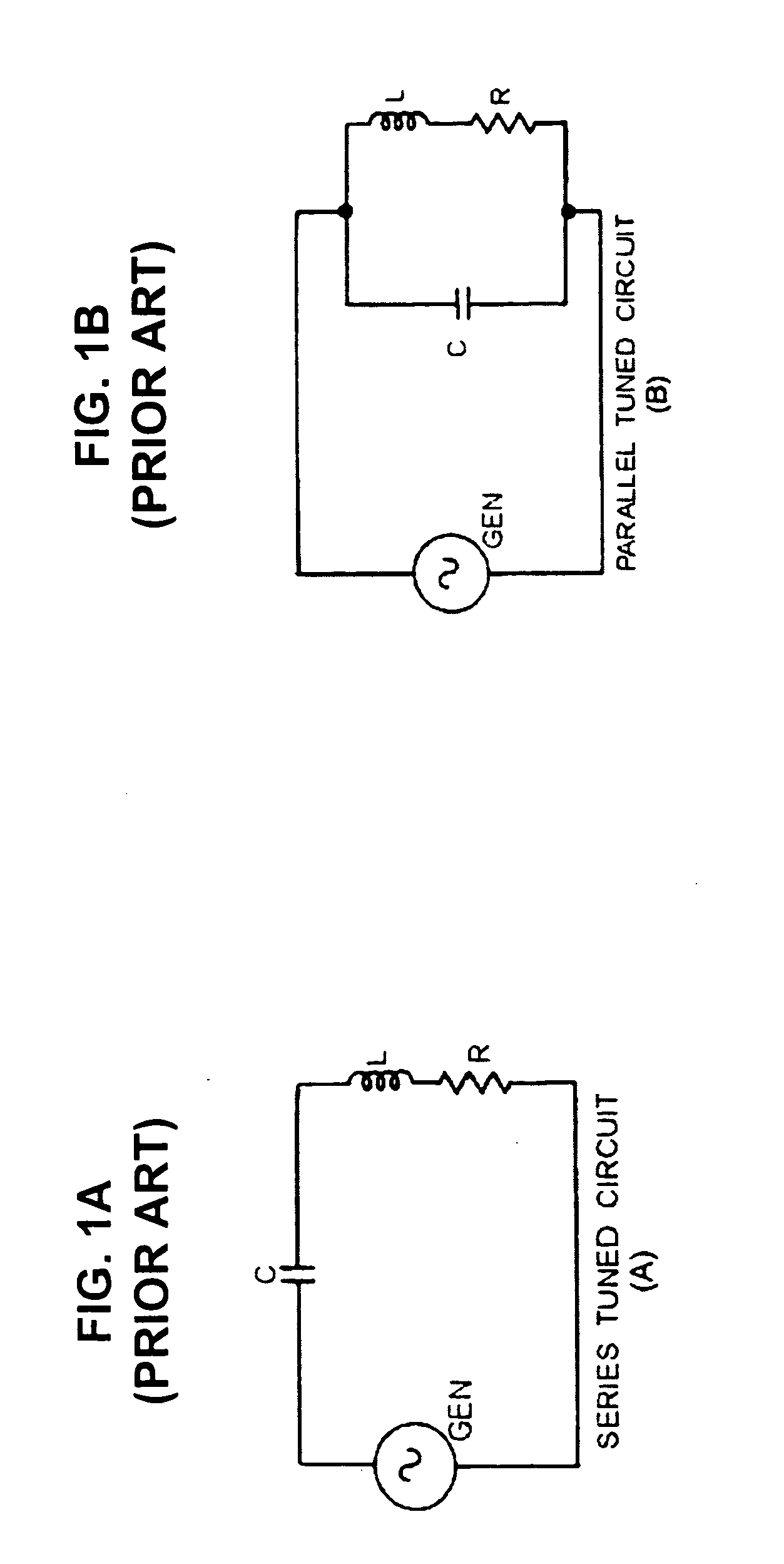

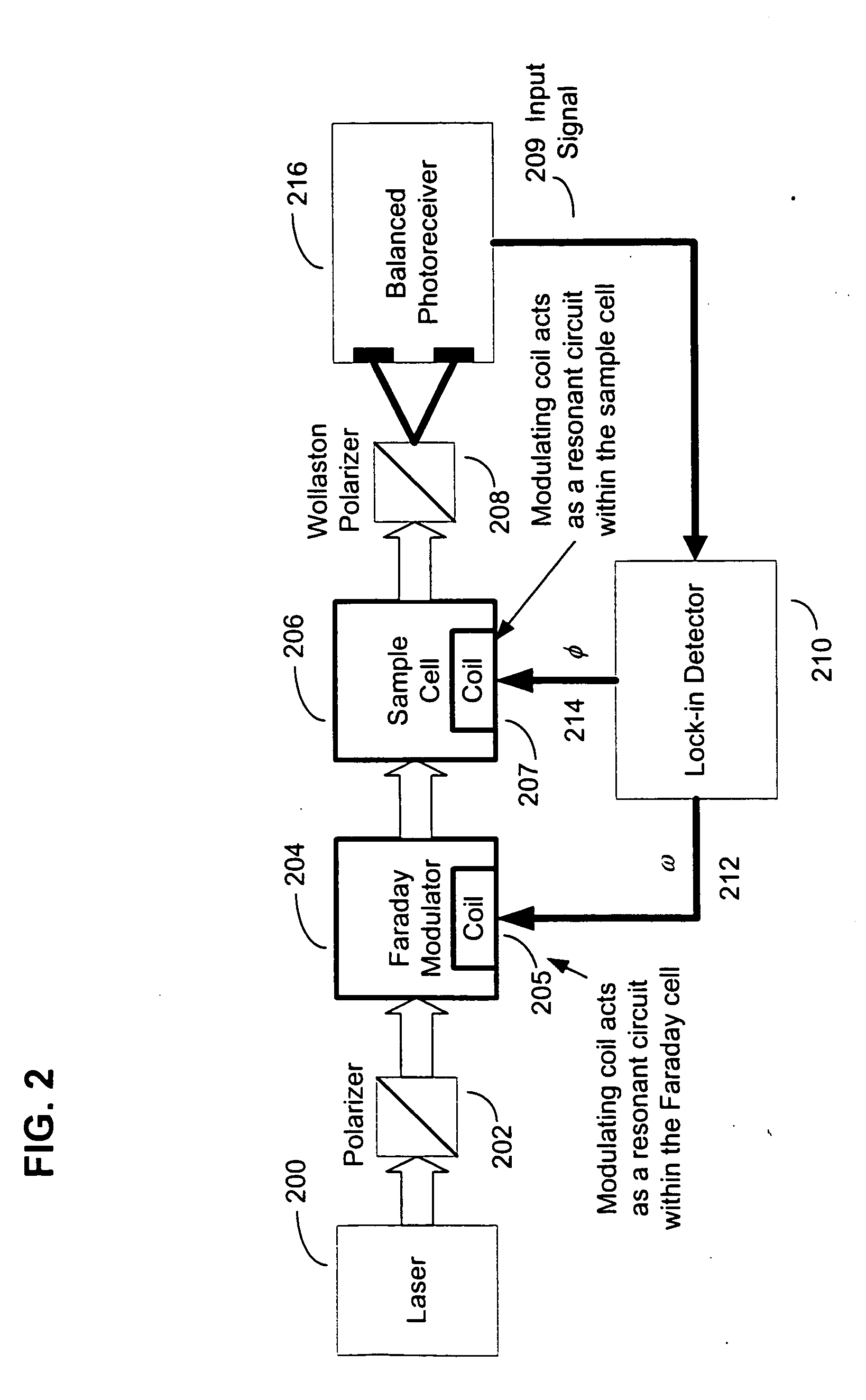

Systems and methods for automated resonant circuit tuning

An apparatus and method for automatically tuning a resonant circuit in a chiroptical measurement system. A sample cell holds a sample being measured for a chiroptical property as the sample is modulated by the resonant circuit. A signal source coupled to the resonant circuit generates a driving signal at one of a plurality of frequencies to modulate the resonant circuit. The frequencies are within a range of expected resonant frequencies for the resonant circuit. A feedback loop circuit coupled to the signal source is used to adjust the frequency of the driving signal to another of the frequencies in response to a feedback signal associated with a measured parameter of the driving signal. In this way, the frequency of the driving signal is adjusted to create a resonant condition. The driving signal may also be applied at a reduced power level so that the resonant circuit can be driven at off-resonant frequencies within the range of frequencies.

Owner:GIBBS PHILLIP R

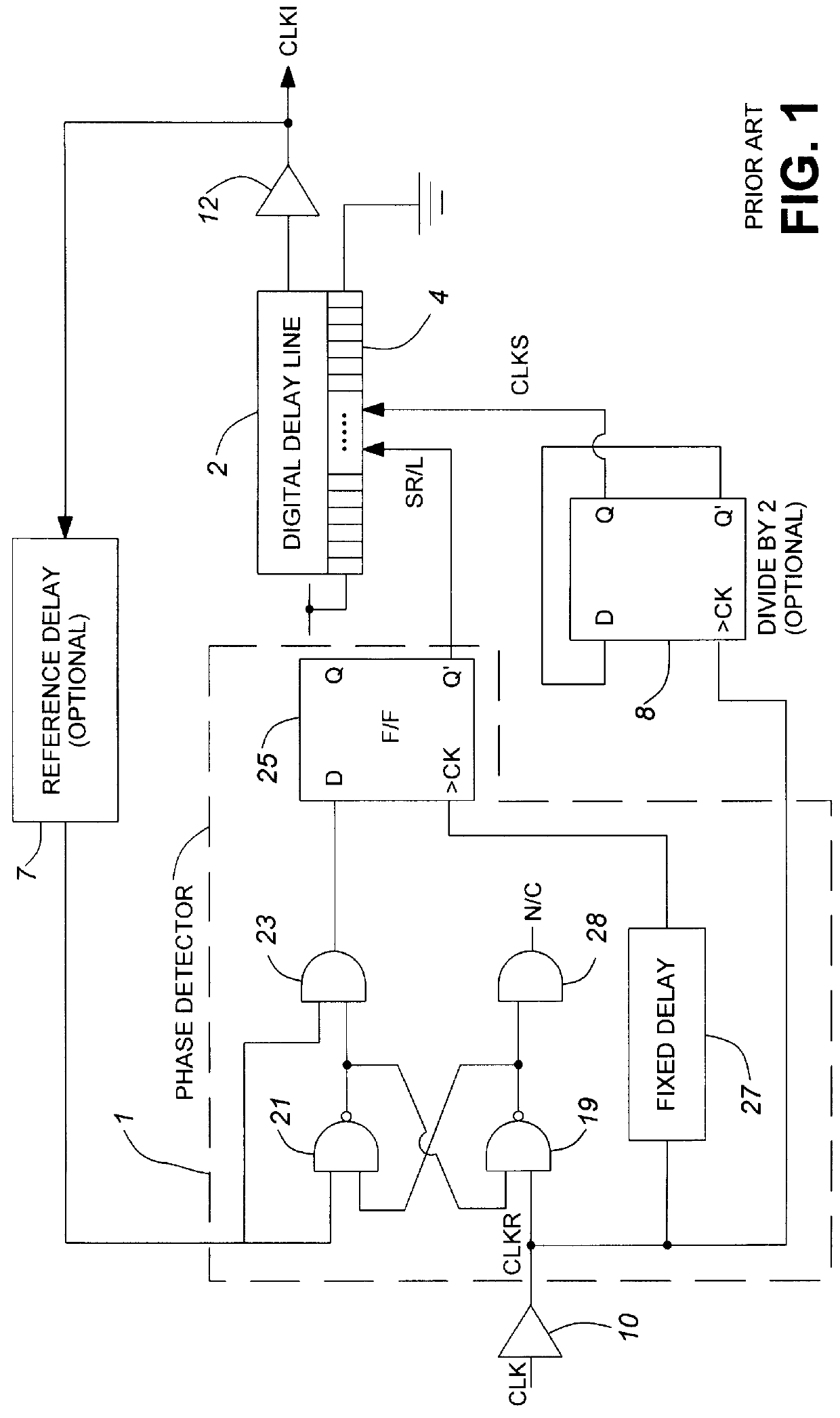

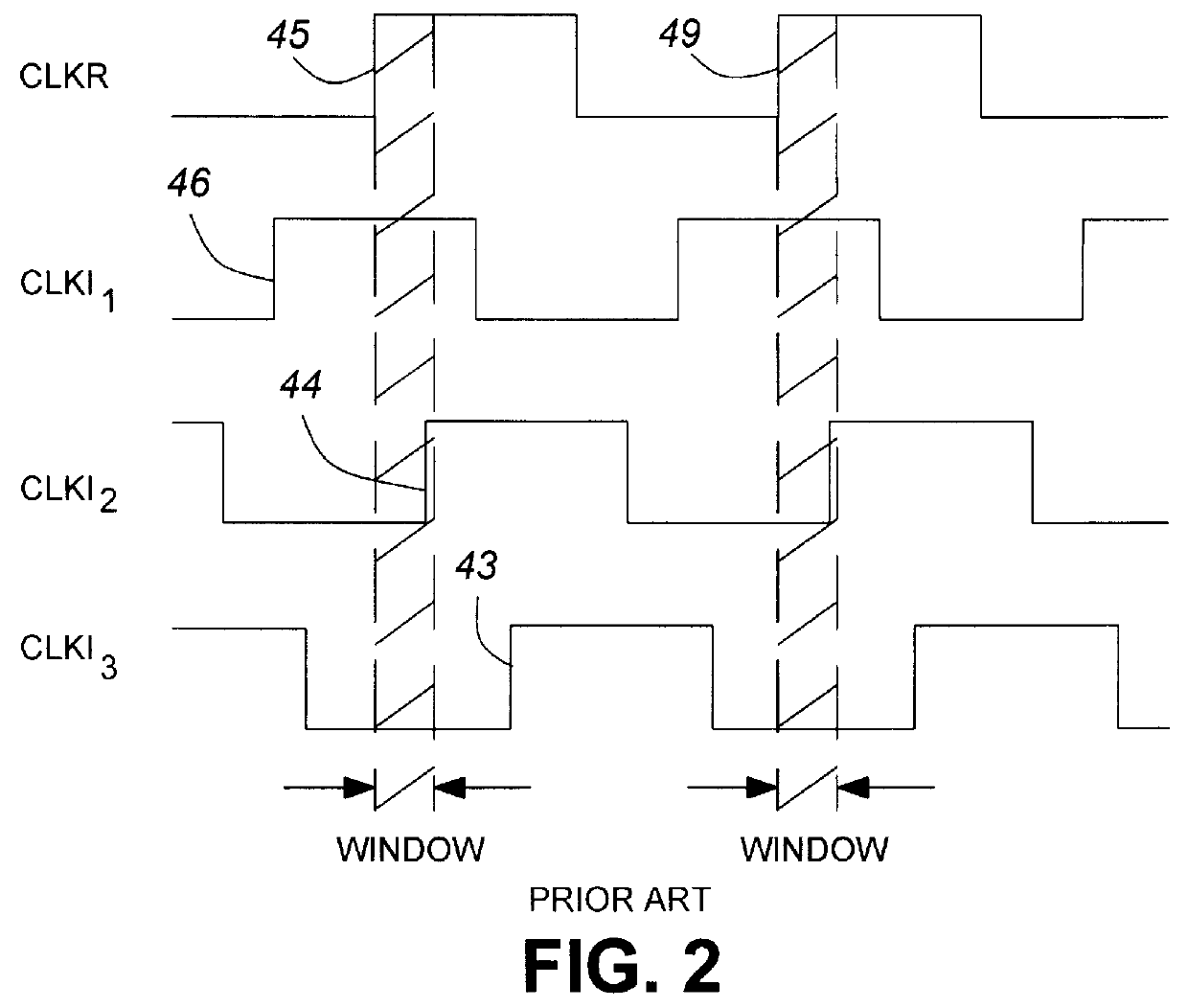

Digital delay locked loop

An improved edge-triggered fully digital delay locked loop (DLL), which maintains reliable synchronization from startup and in spite of system clock jitter is described. An internal clock signal is synchronized with a reference clock signal by propagating the reference clock signal through a variable digital delay path. A wide phase detection region surrounds a selected rising edge of the internal clock signal. The DLL loop is open as long as the internal clock signal and a target edge of the reference clock signal are not simultaneously within the phase detection region. To achieve a DLL locked condition, the variable delay is increased from a minimum setting until the edge of the phase detection region is shifted in time just past the target edge of the reference clock. Once the DLL loop has been closed, a clock jitter filter is enabled to reject reference clock jitter effects on the DLL locked condition. A digital phase detector controls the delay line propagation delay to establish synchronization between the internal clock and the reference clock. Unused delay elements within the variable delay path are deactivated to save power.

Owner:CONVERSANT INTPROP MANAGEMENT INC

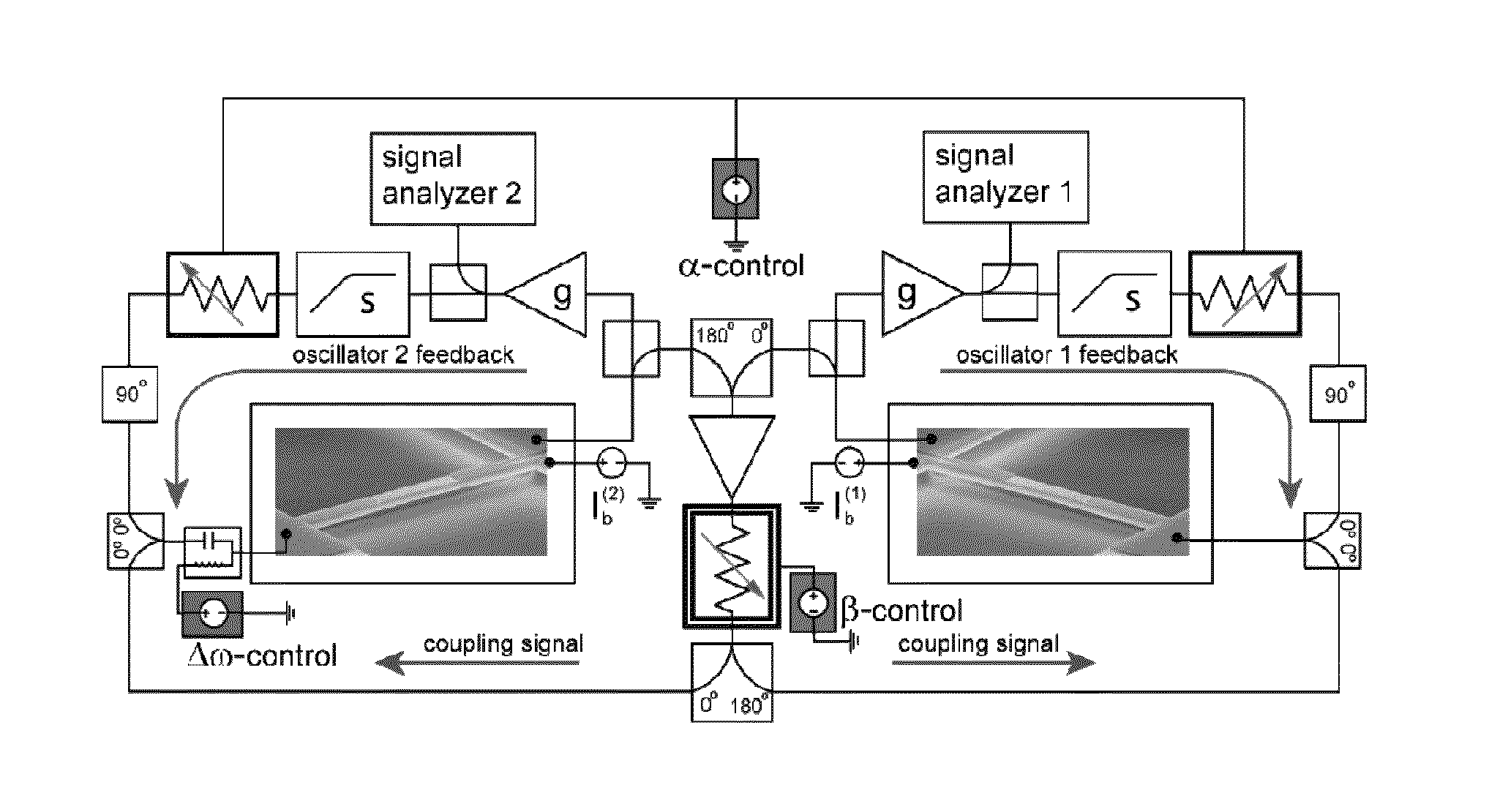

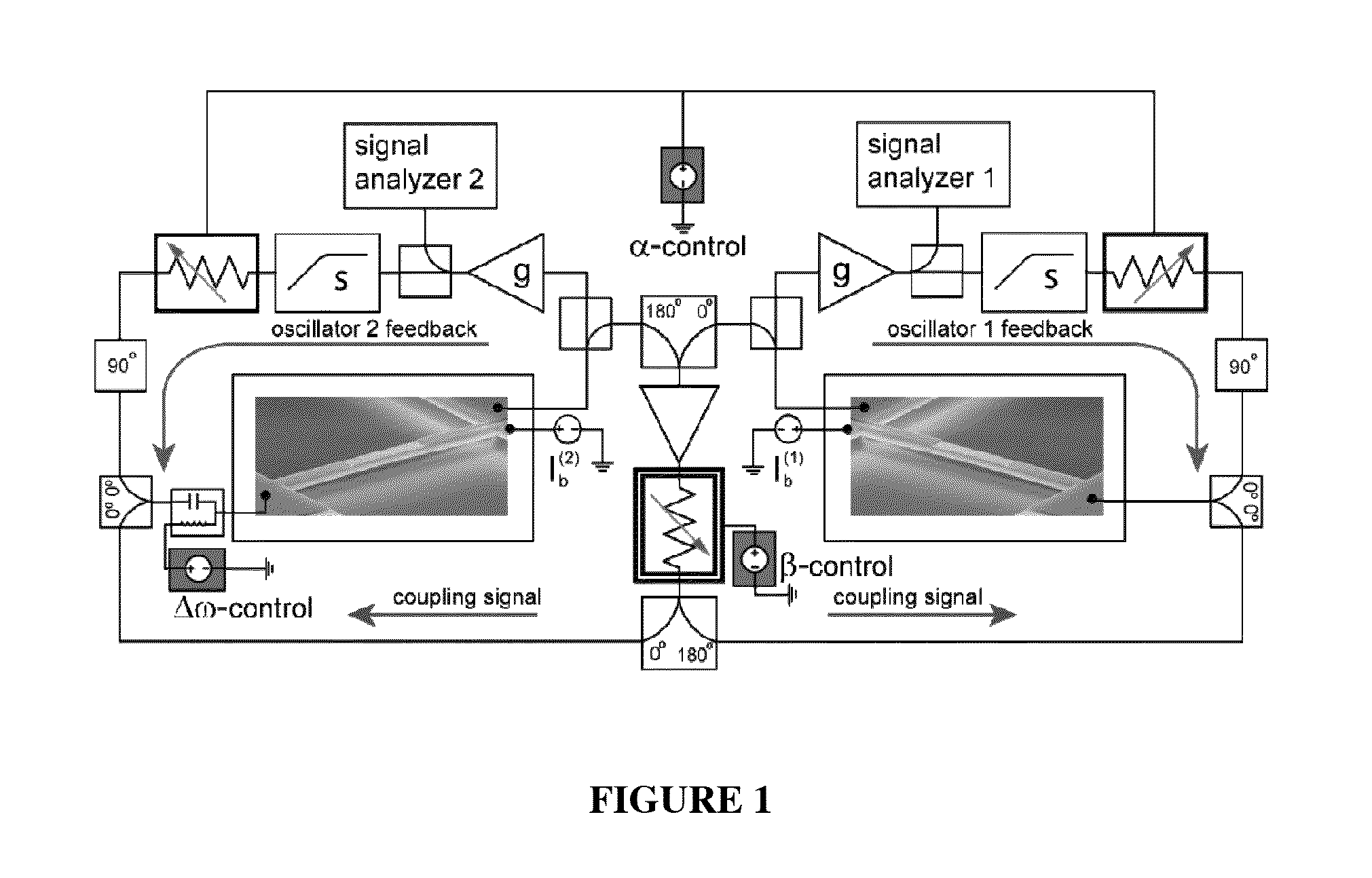

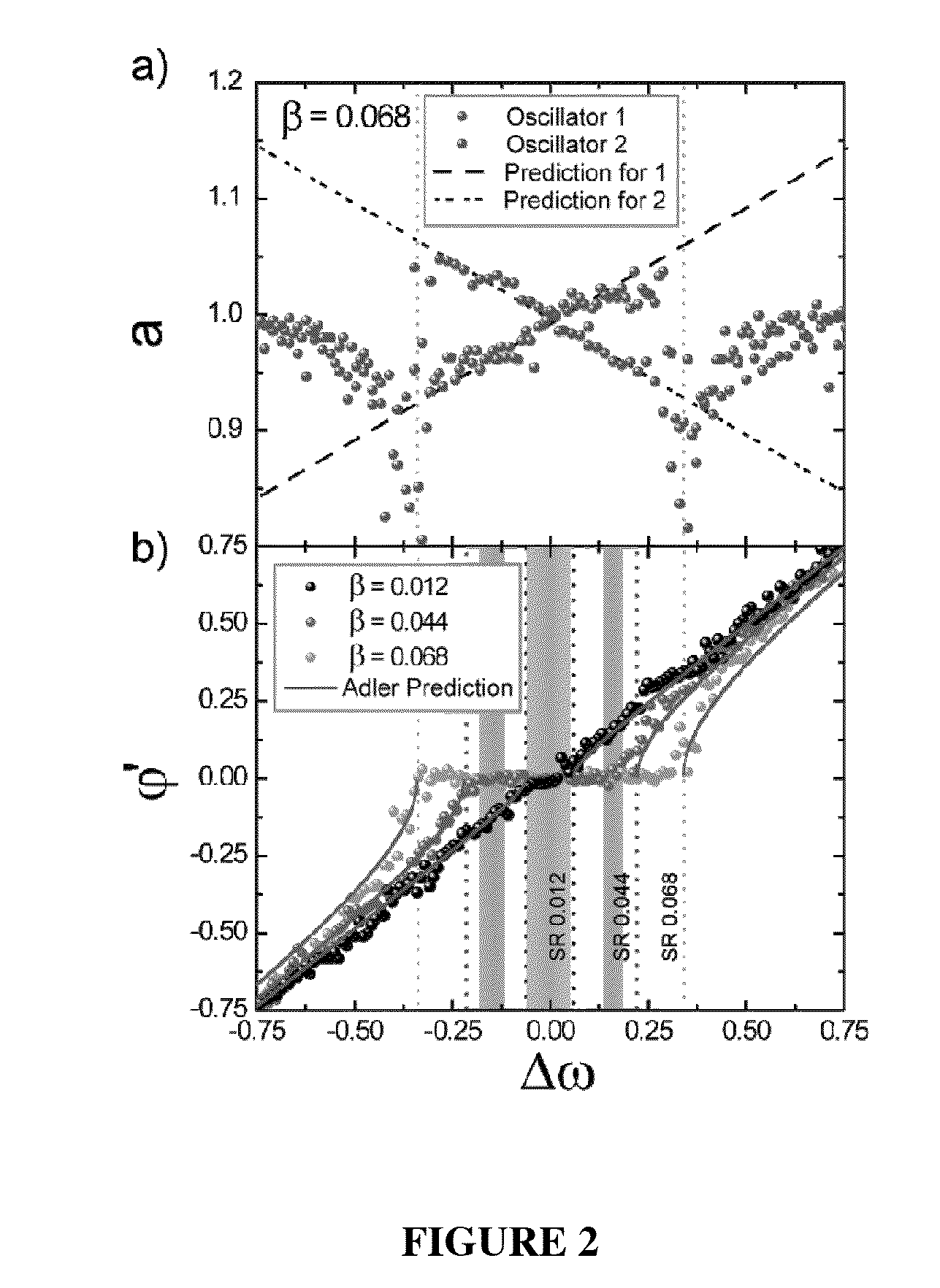

Synchronization of nanomechanical oscillators

ActiveUS20140176203A1Good for observationEasy to controlAnalysing solids using sonic/ultrasonic/infrasonic wavesPulse automatic controlPhase noiseOscillator network

Synchronization of oscillators based on anharmonic nanoelectromechanical resonators. Experimental implimentation allows for unprecedented observation and control of parameters governing the dynamics of synchronization. Close quantitative agreement is found between experimental data and theory describing reactively coupled Duffing resonators with fully saturated feedback gain. In the synchonized state, a significant reduction in the phase noise of the oscillators is demonstrated, which is key for applications such as sensors and clocks. Oscillator networks constructed from nanomechanical resonators form an important laboratory to commercialize and study synchronization—given their high-quality factors, small footprint, and ease of co-integration with modern electronic signal processing technologies. Networks can be made including one-, two-, and three-dimensional networks. Triangular and square lattices can be made.

Owner:CALIFORNIA INST OF TECH

Dynamic voltage control method and apparatus

Owner:MEDIATEK INC

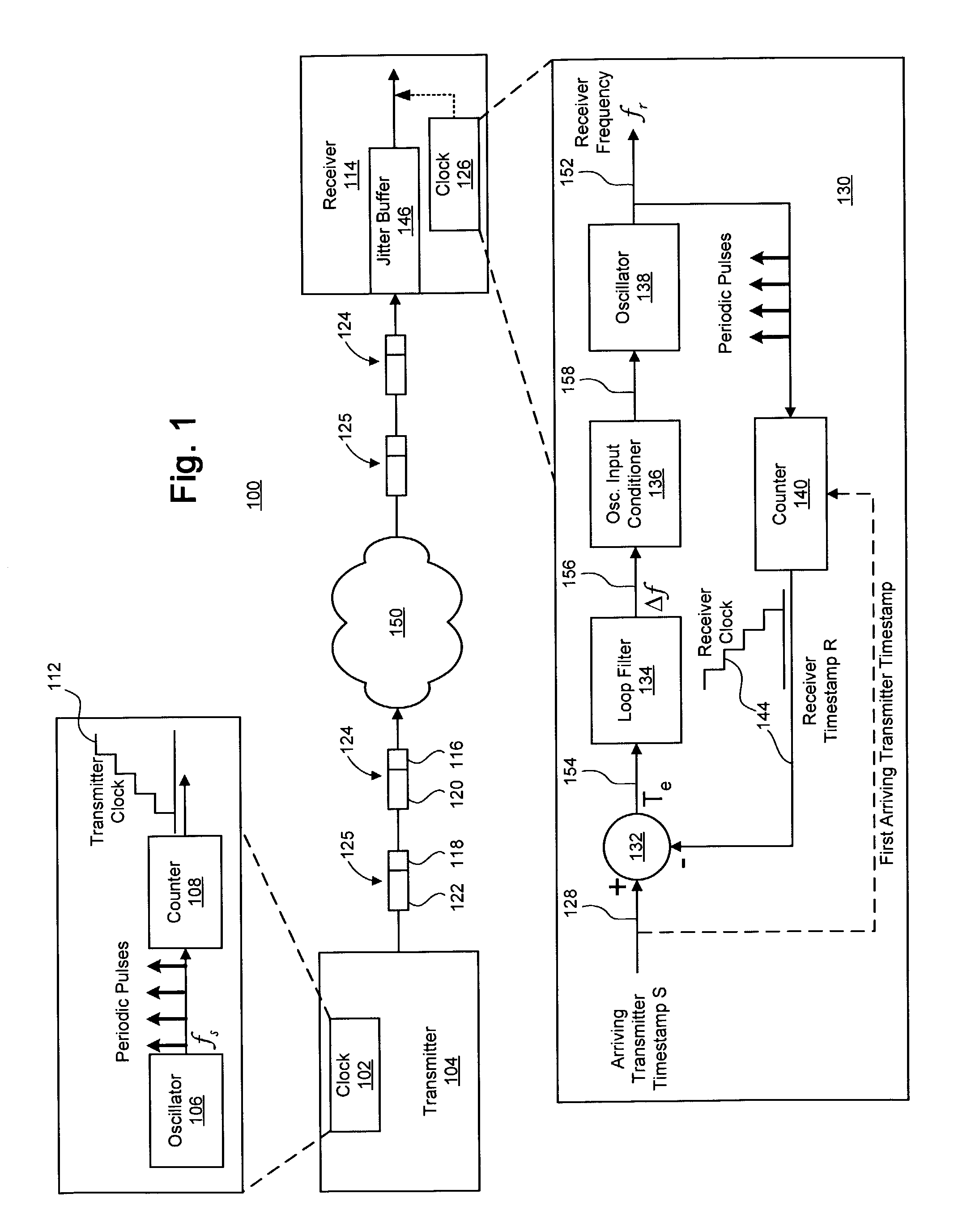

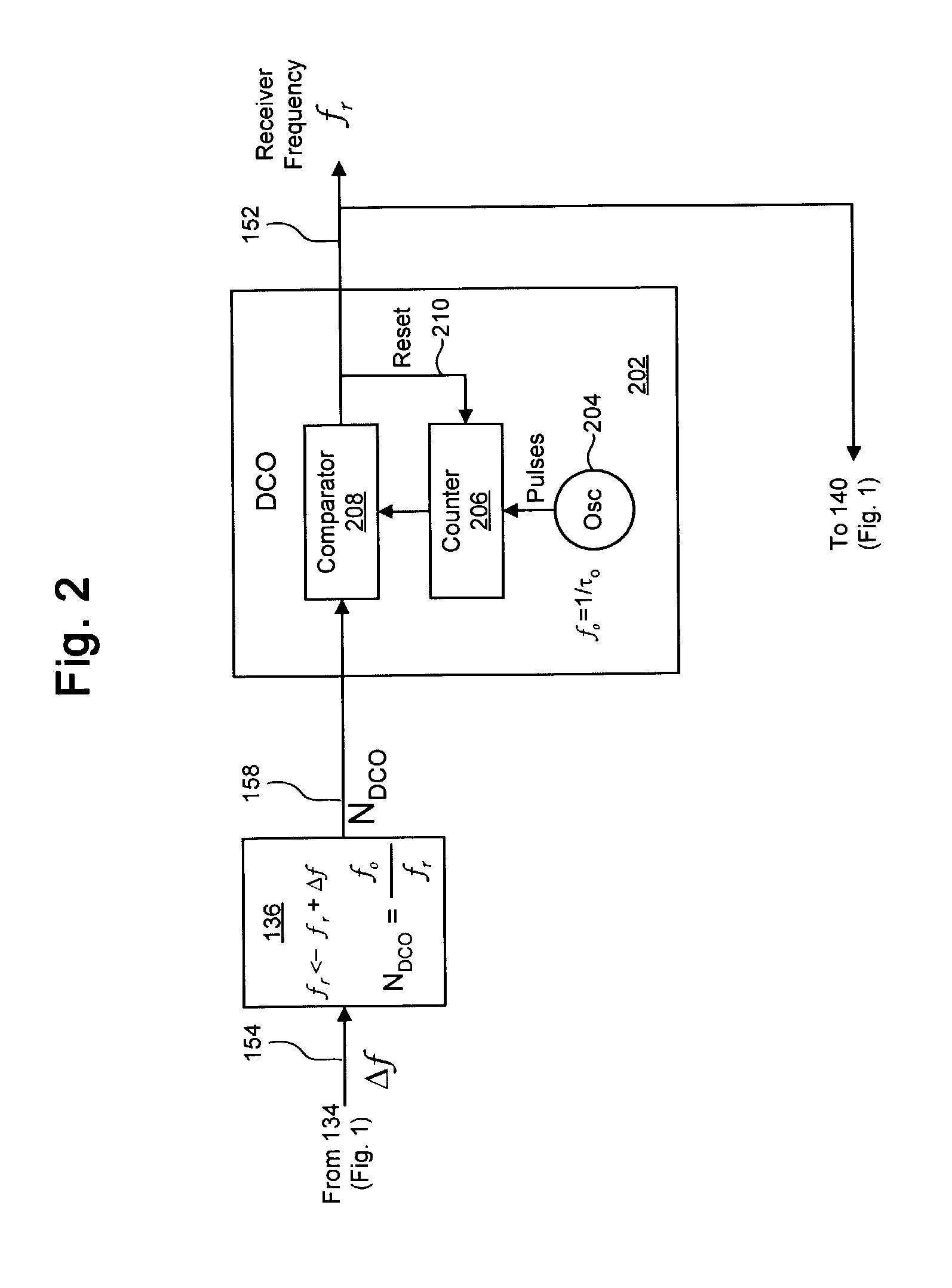

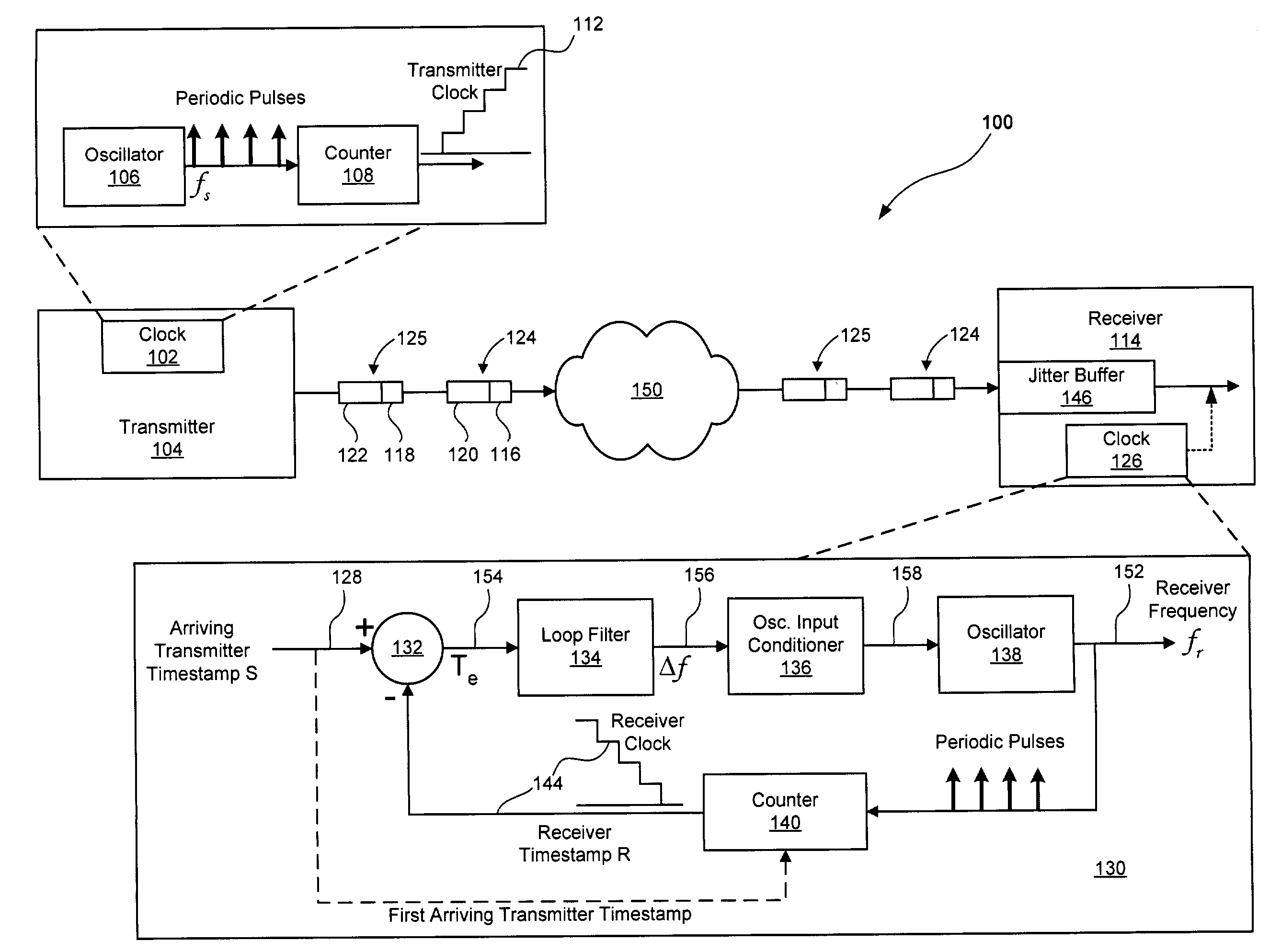

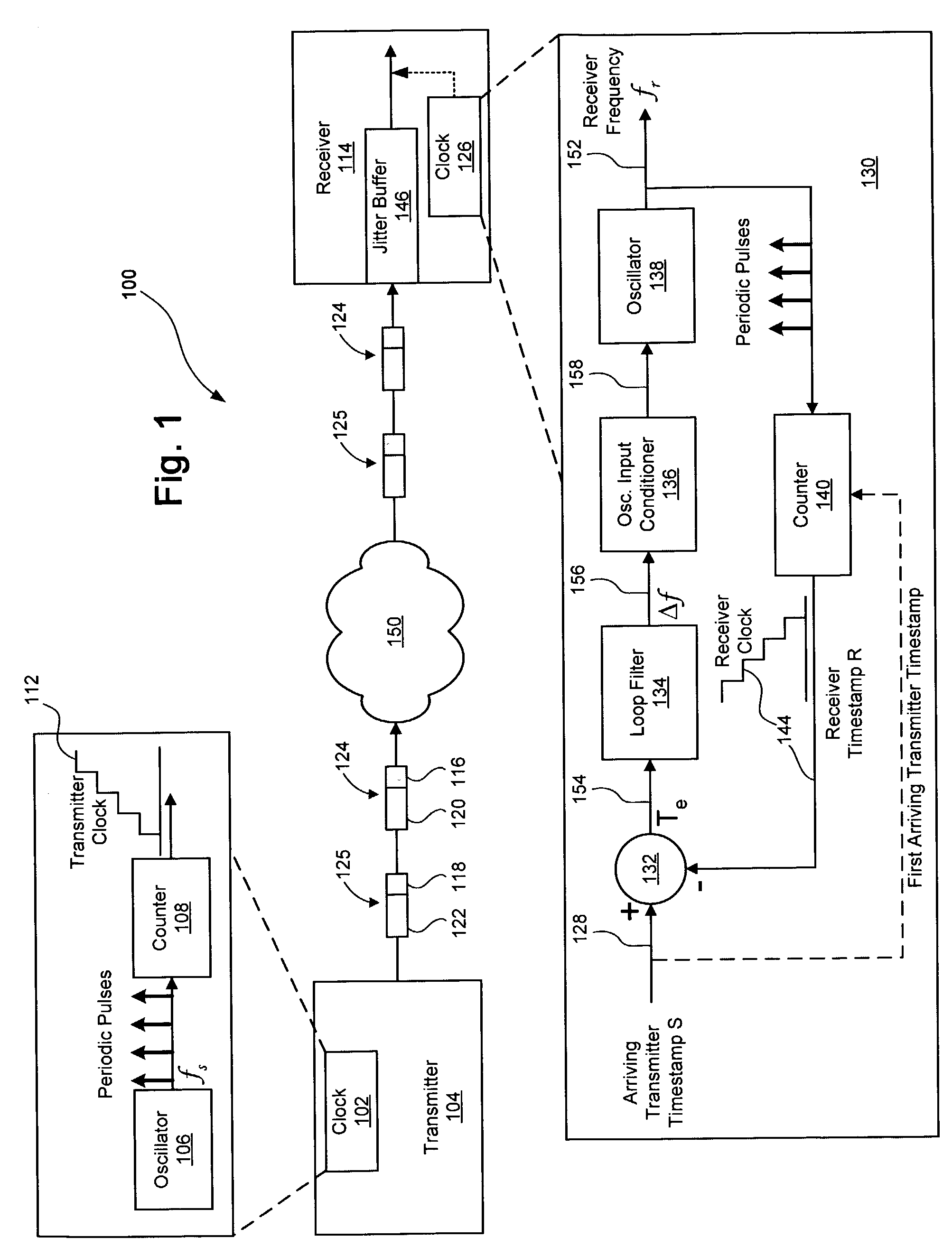

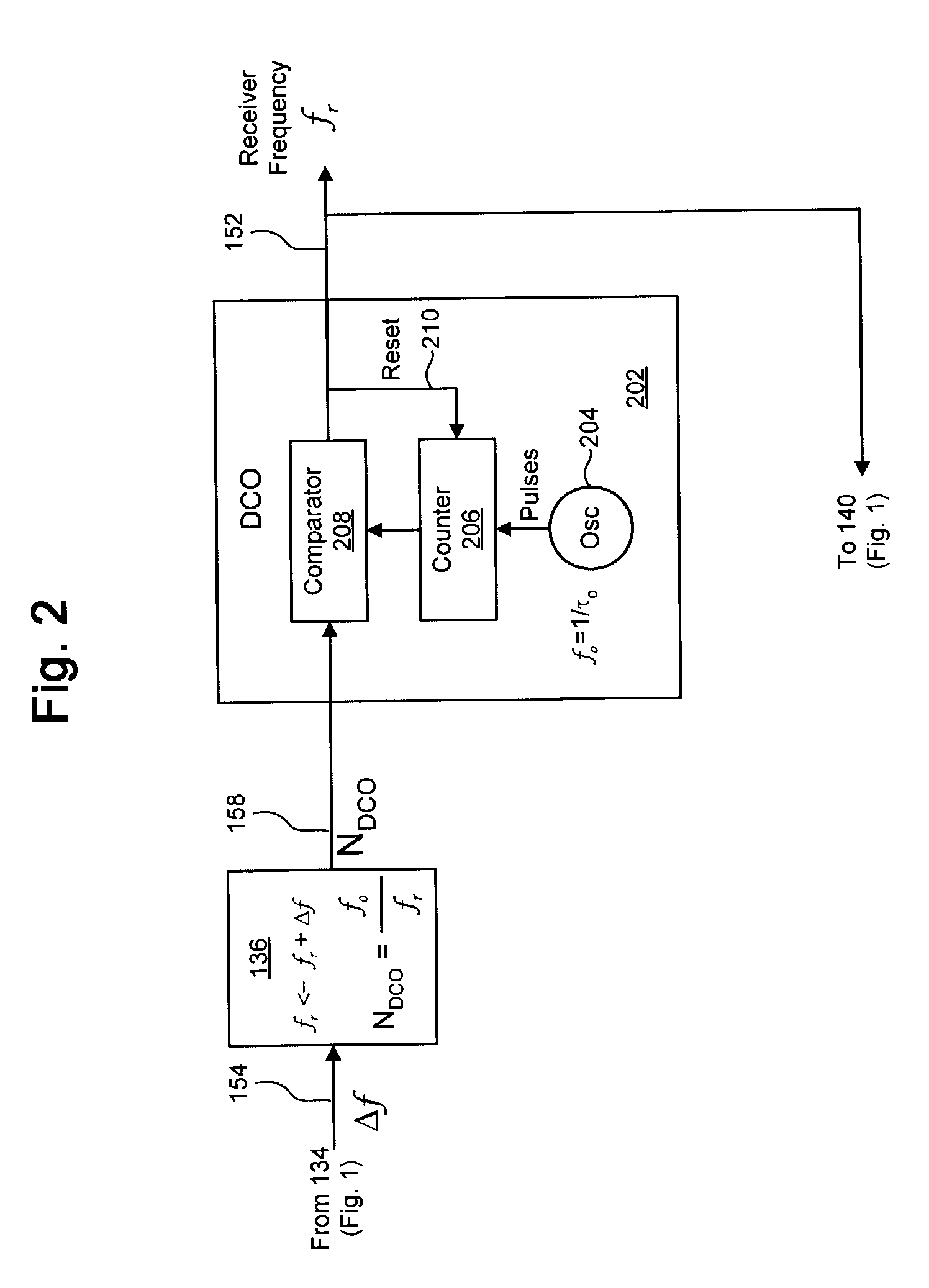

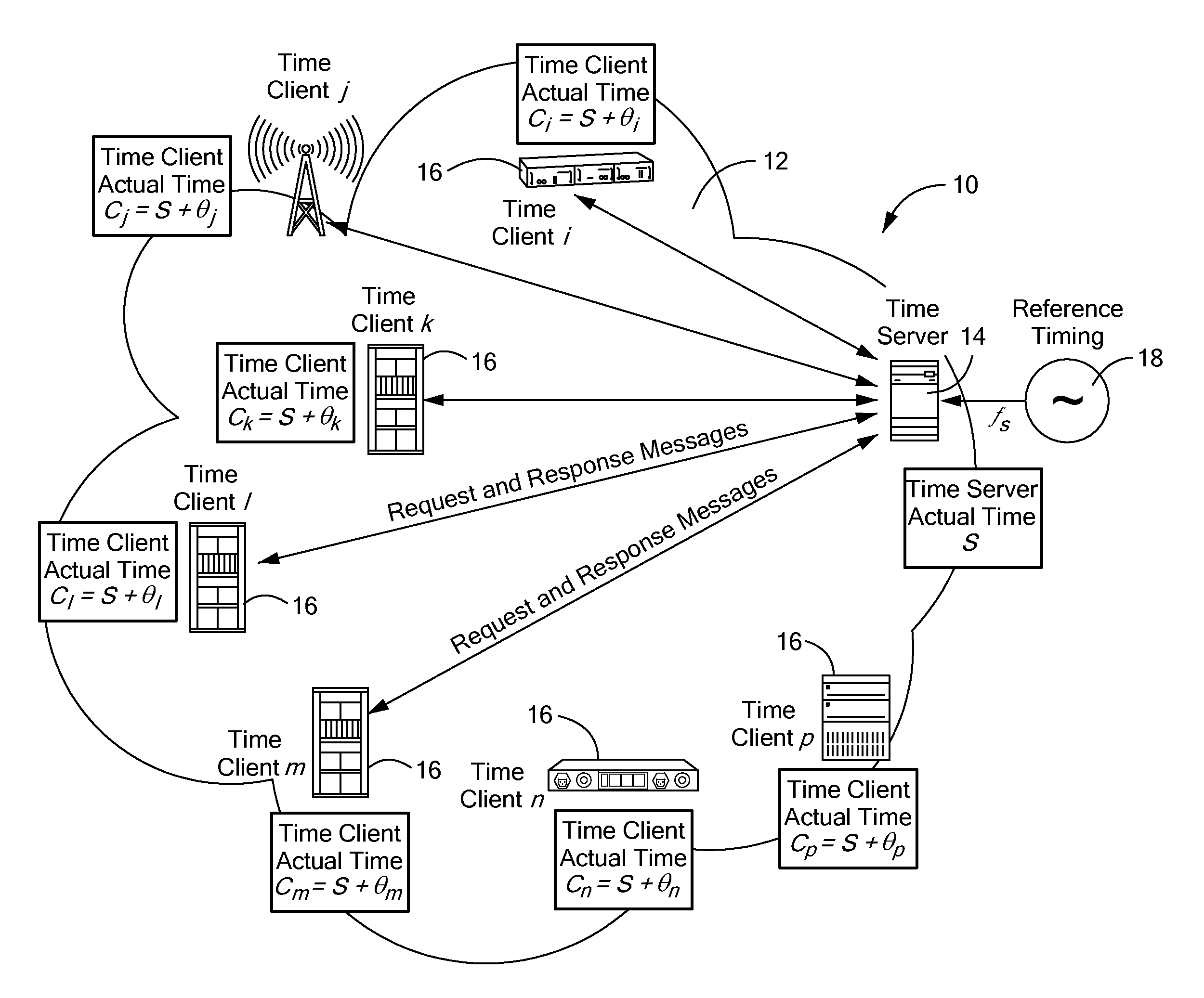

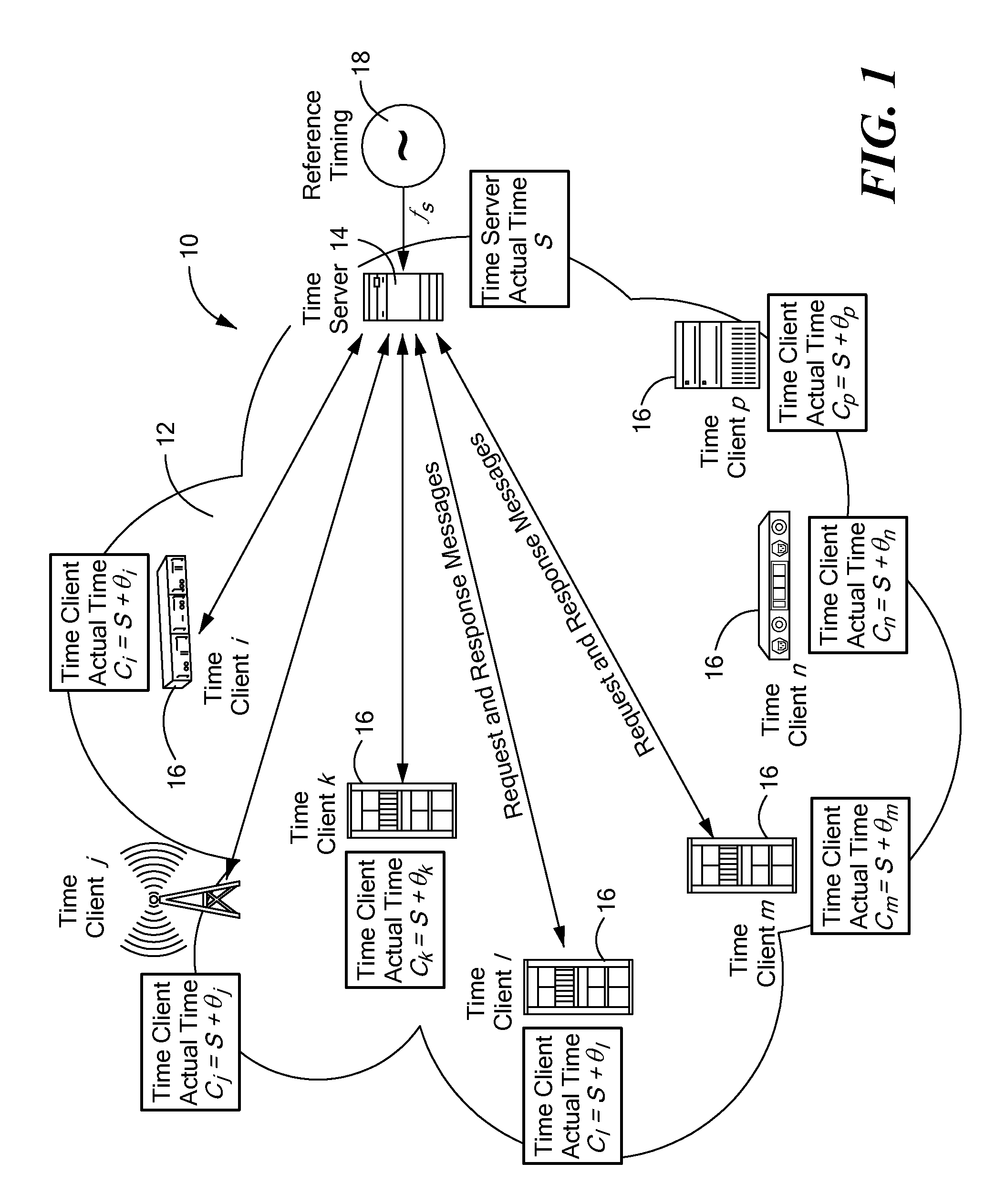

Method and apparatus for time and frequency transfer in communication networks

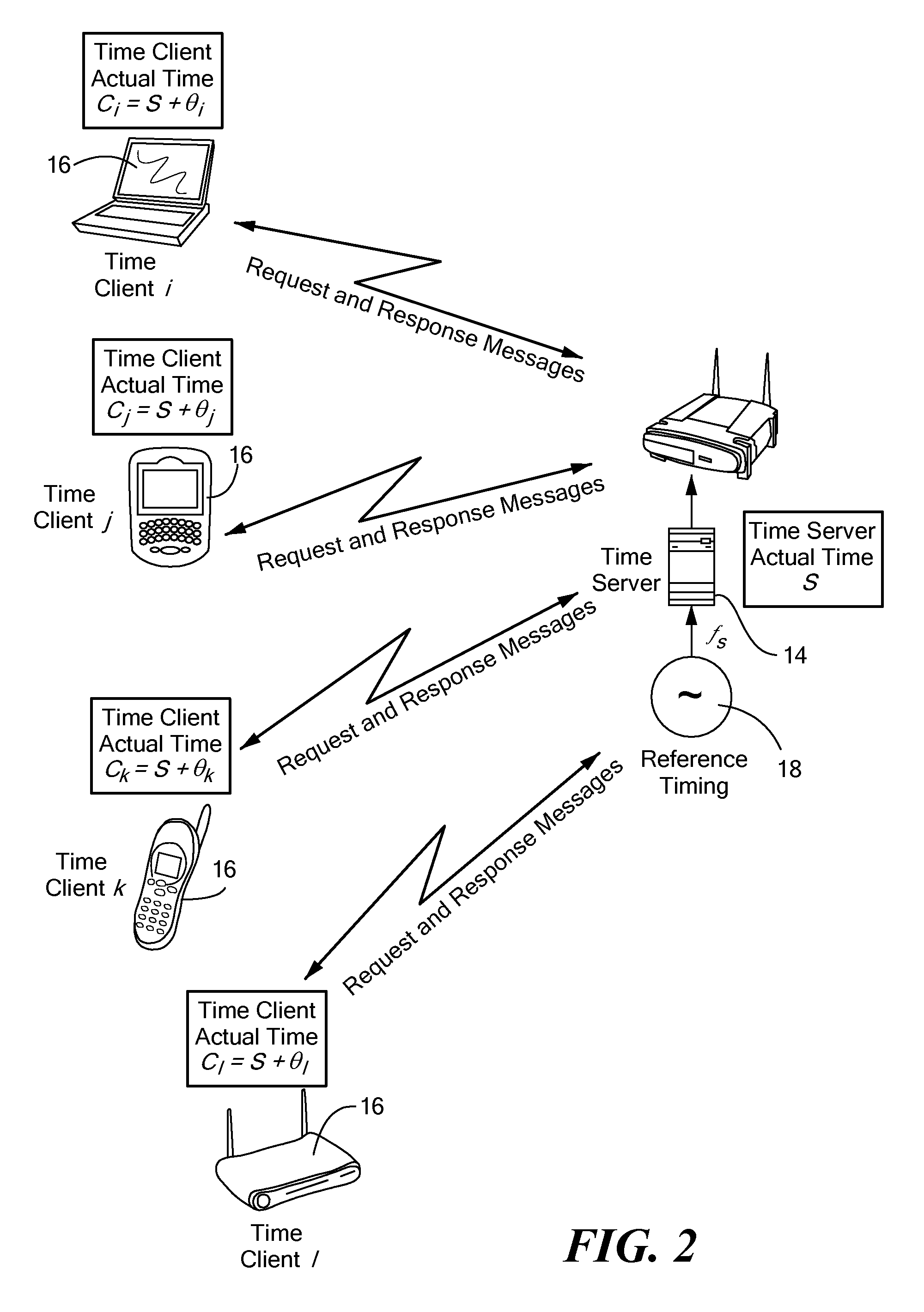

A timing system for time synchronization between a time server and a time client over a packet network. The timing system includes a time server for generating current timestamp information and a time client having a phase-locked loop driven client clock counter. The time client periodically exchanges time transfer protocol messages with the time server over the packet network, and calculates an estimated client time based on the timestamp information. The phase-locked loop in the time client receives periodic signals representing the estimated server time as its input and calculates a signal which represents the error difference between the estimated server time and the time indicated by the time client clock counter. The error difference eventually converges to zero or a given error range indicating the time presented by the client clock counter, which is driven by the phase-locked loop having locked onto the time of the time server.

Owner:RPX CLEARINGHOUSE +1

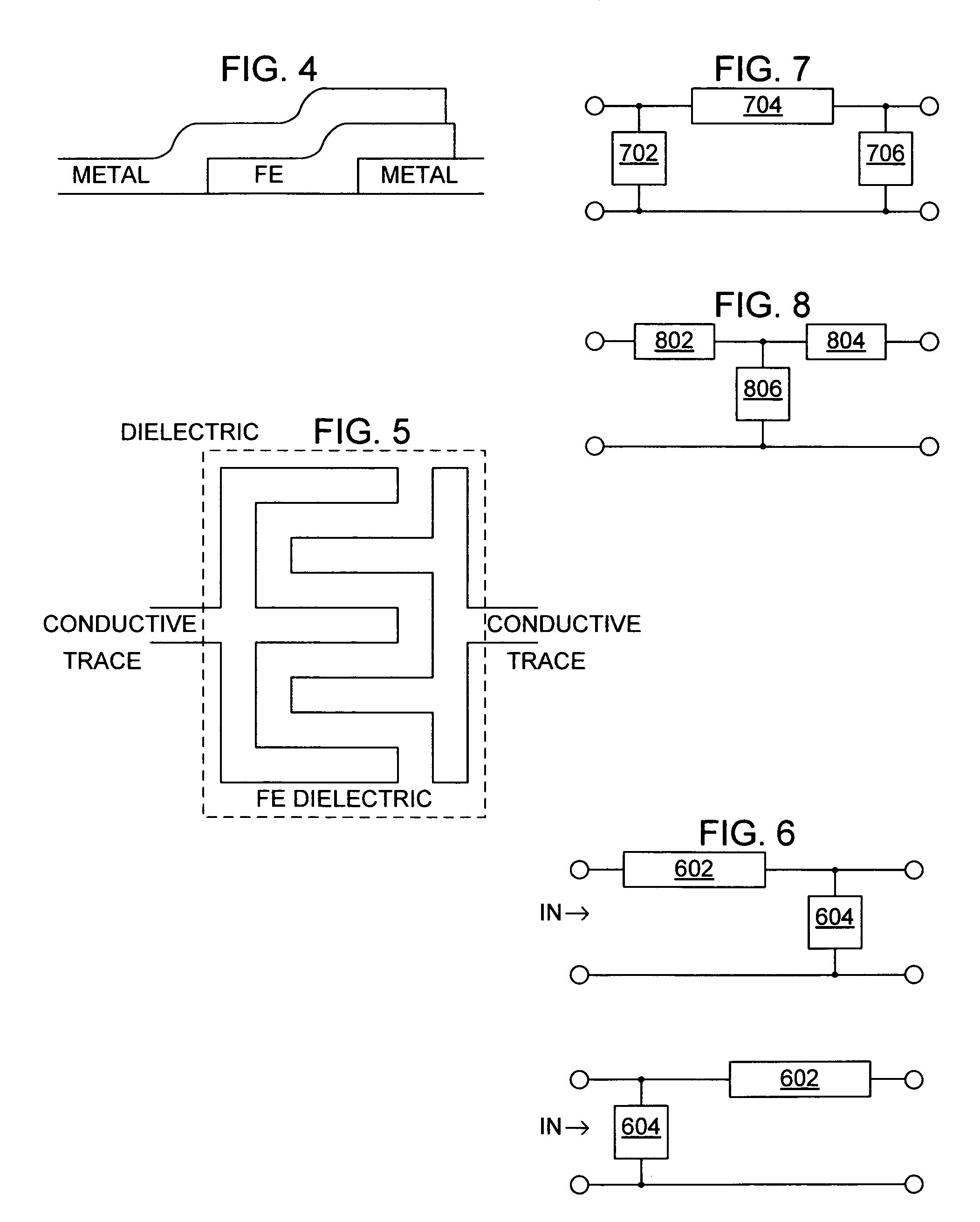

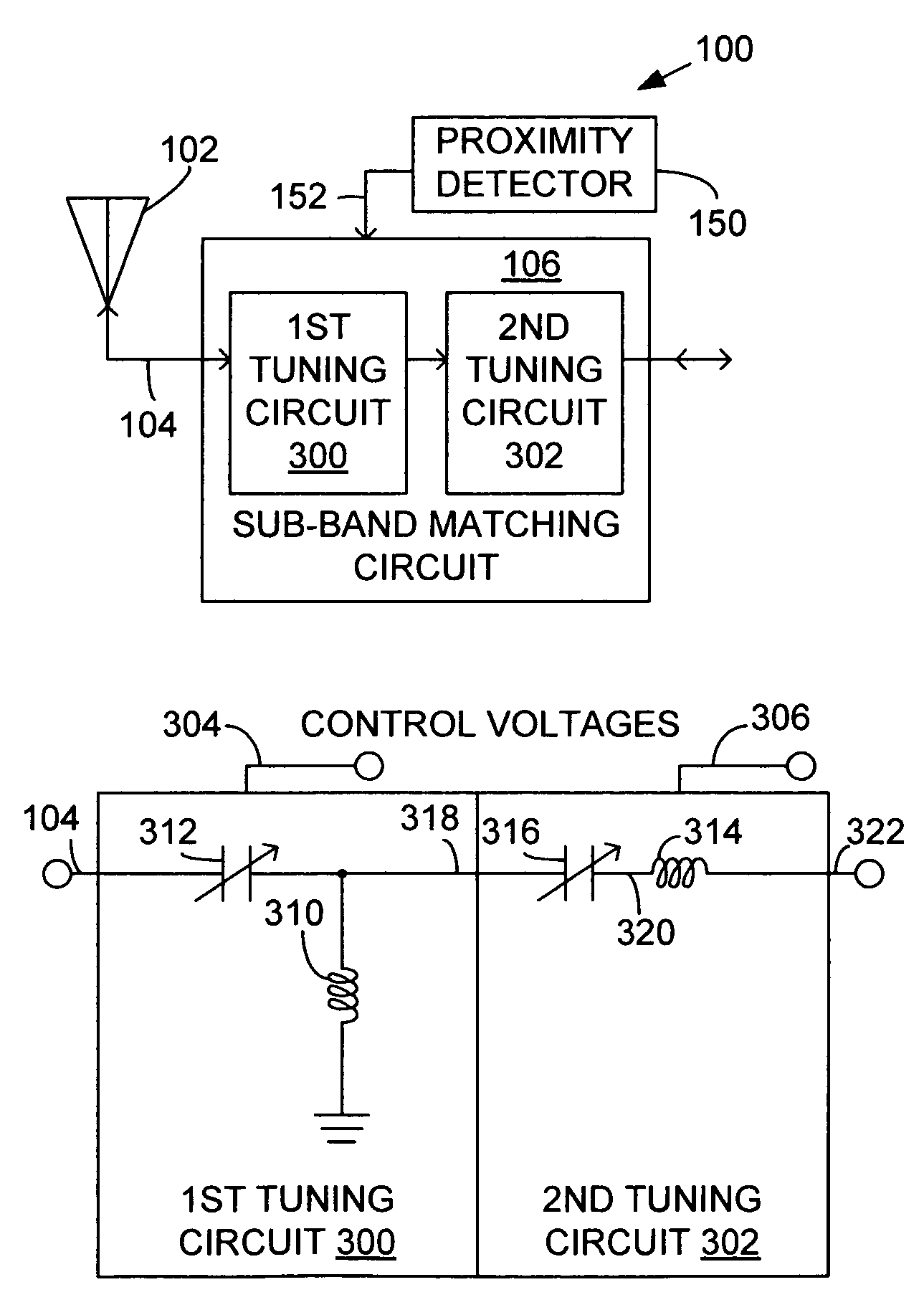

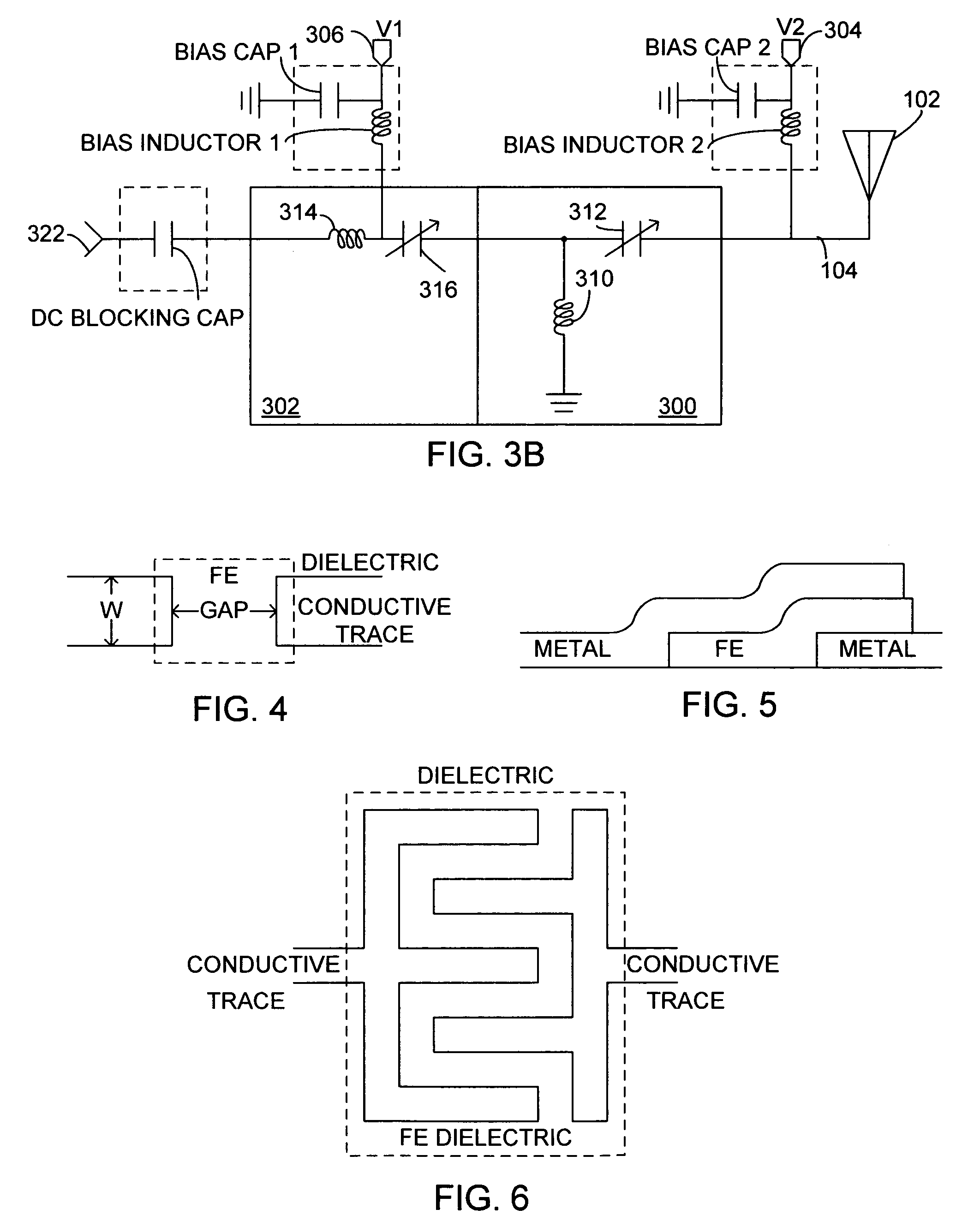

System and method for impedance matching an antenna to sub-bands in a communication band

InactiveUS7176845B2Improve efficiencyReduce noiseMultiple-port networksAntenna supports/mountingsAntenna impedanceMethod selection

A sub-band antenna matching method and an antenna matching system for selectively matching a communication bandwidth segment impedance have been provided. The method comprises: accepting a frequency-dependent impedance from an antenna; and, selectively supplying a conjugate impedance match for the antenna at a sub-band of a first communication band. In some aspects, the method selectively supplies a conjugate impedance match for the antenna at a sub-band of a second communication band. More specifically, the method comprises: tuning a first tuning circuit to a first frequency; simultaneously tuning a second tuning circuit to a second frequency to match the antenna at a low end of the first communication band. Likewise, the first tuning circuit is tuned to a third frequency and the second tuning circuit is tuned to a fourth frequency to match the antenna at a high end of the first communication band in response to the third and fourth frequencies.

Owner:KYOCERA CORP

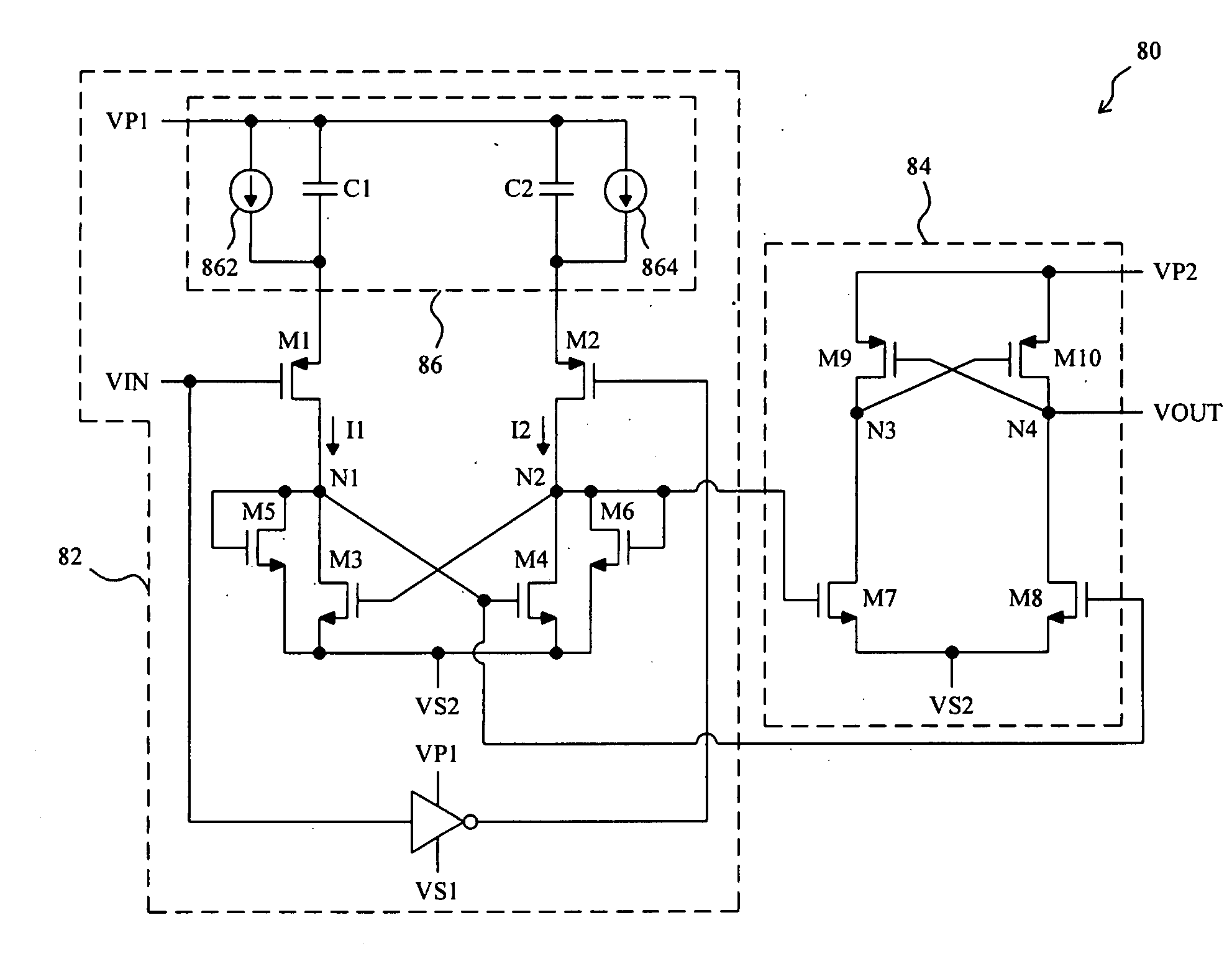

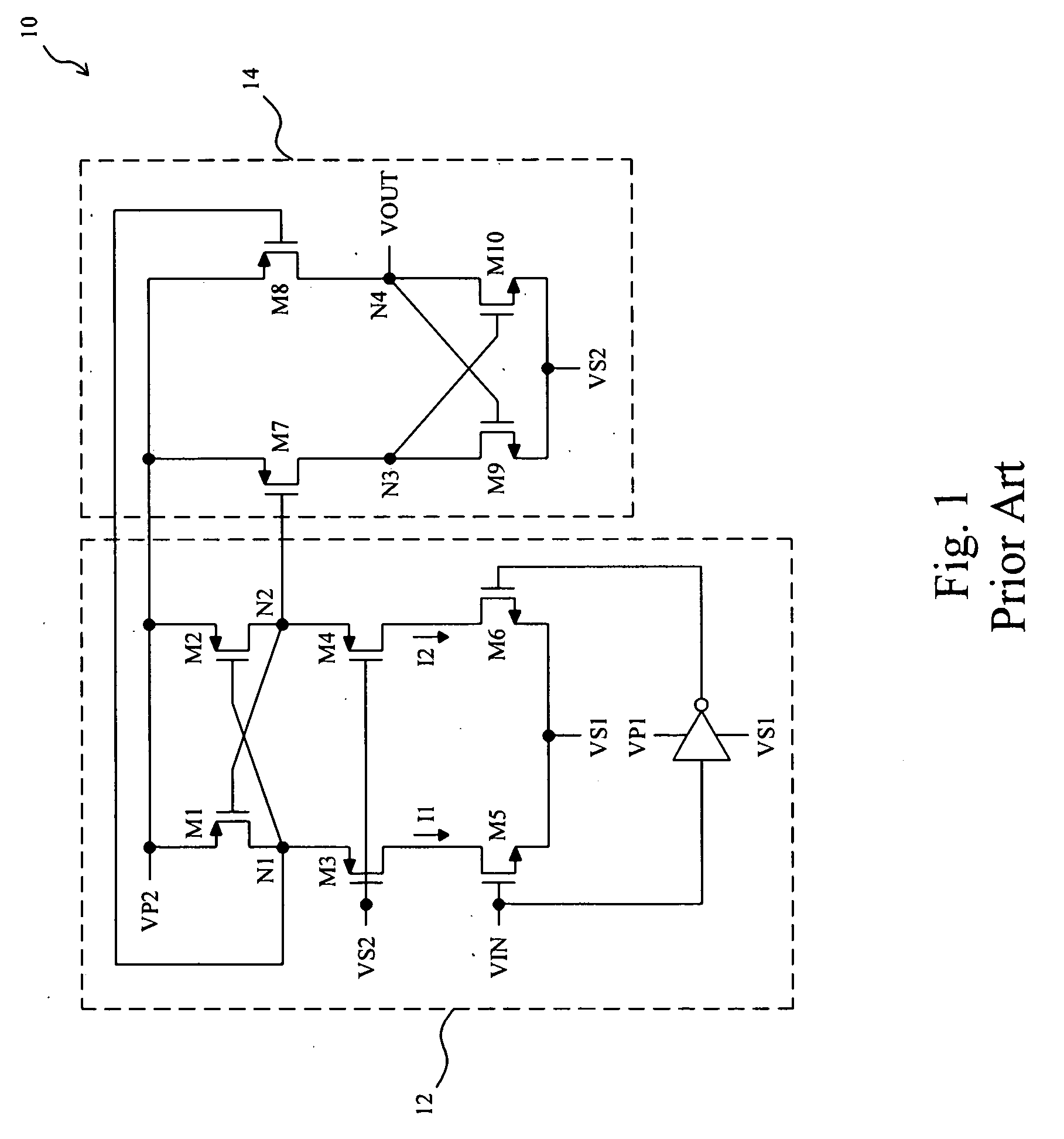

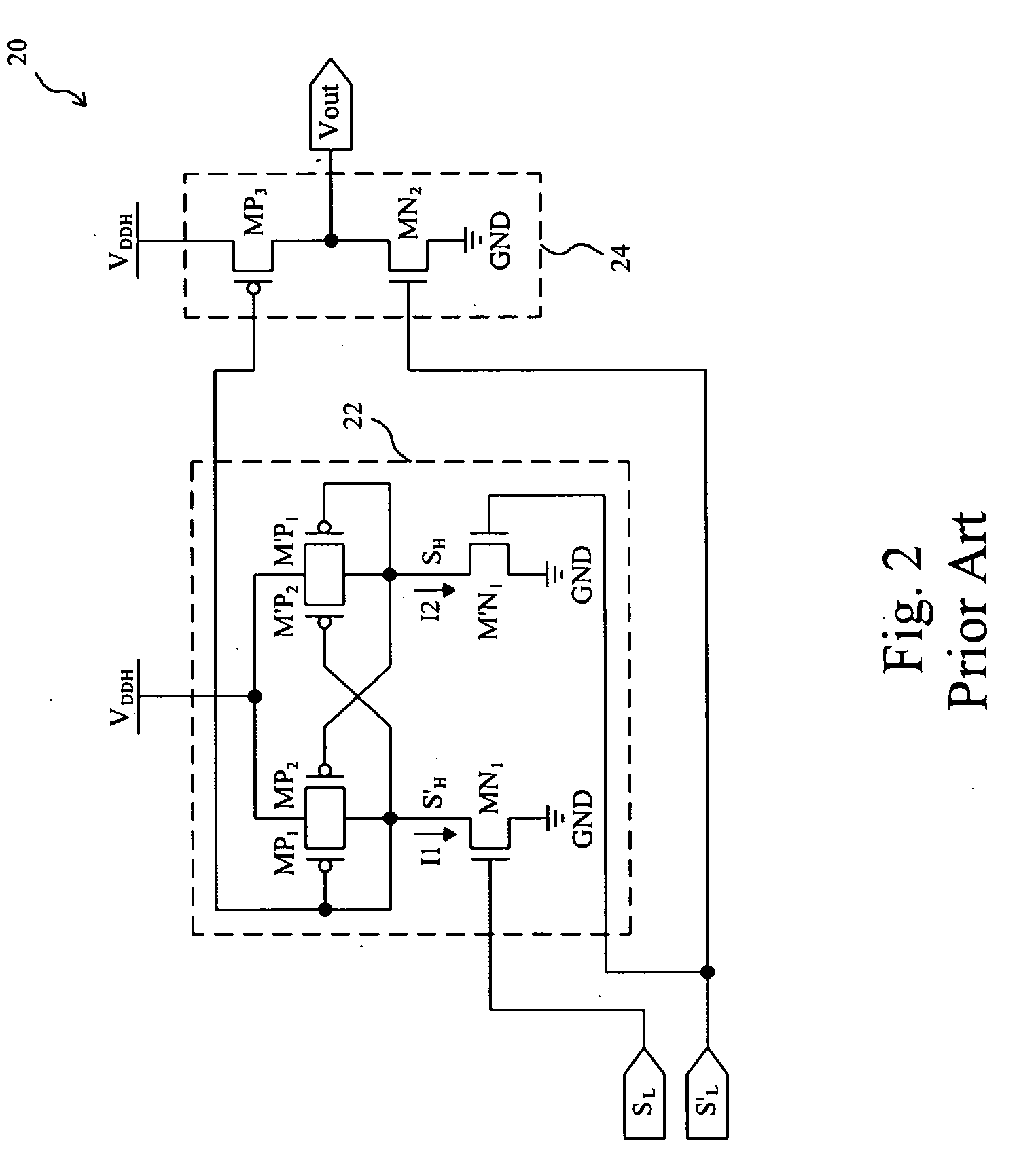

Level shift circuit

ActiveUS20090066399A1Fast processReduce layoutPulse automatic controlElectric pulse generatorLevel shiftingStable status

A level shift circuit includes an input stage and an output stage coupled to each other by two nodes. The input stage changes the voltages on the nodes according to an input signal, and the output stage determines an output signal according to the voltages on the two nodes. In a transition state, the input stage provides a large current to charge or discharge the first node or the second node so as to quickly change the voltage thereon. In a steady state, the input stage lowers the current so as to reduce power consumption.

Owner:RICHTEK TECH

Digital Phase Locked Loop with Integer Channel Mitigation

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal with a plurality of phases. A switch is coupled to receive the RF clock, and is operative to select one of the plurality of phases. A phase detection circuit is coupled to the switch and is operable to receive a selected phase and to provide digital phase error samples indicative of a time difference between the reference clock and the selected phase.

Owner:TEXAS INSTR INC

Popular searches

Discontinuous tuning by electric means Substation equipment Capacitor with voltage varied dielectric Antennas earthing switches association Amplifier input/output impedence modification Leaky-waveguide antennas Waveguide horns Dielectric property measurements Waveguide mouths Generator stabilization