Patents

Literature

1829results about "Pulse generation by logic circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

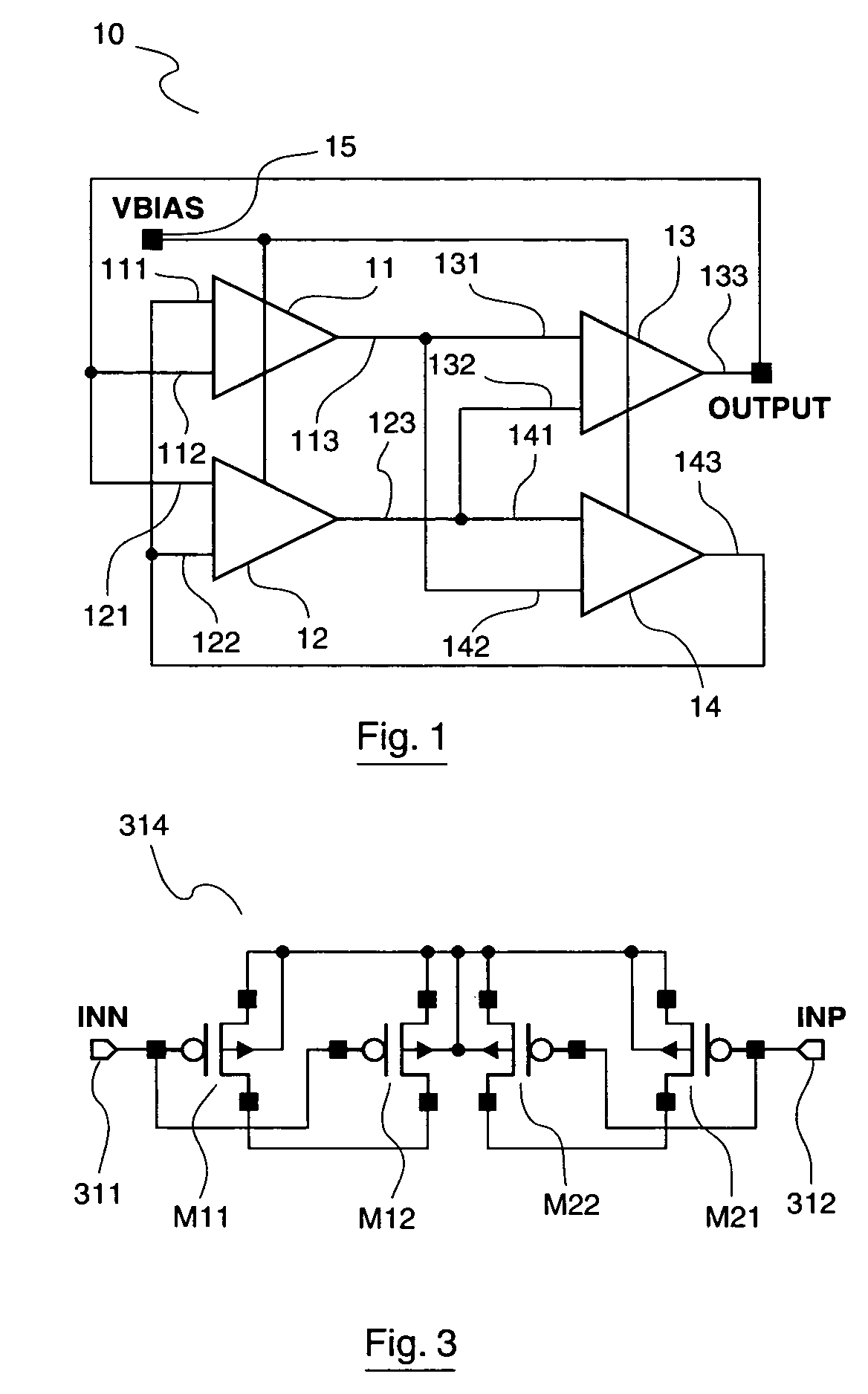

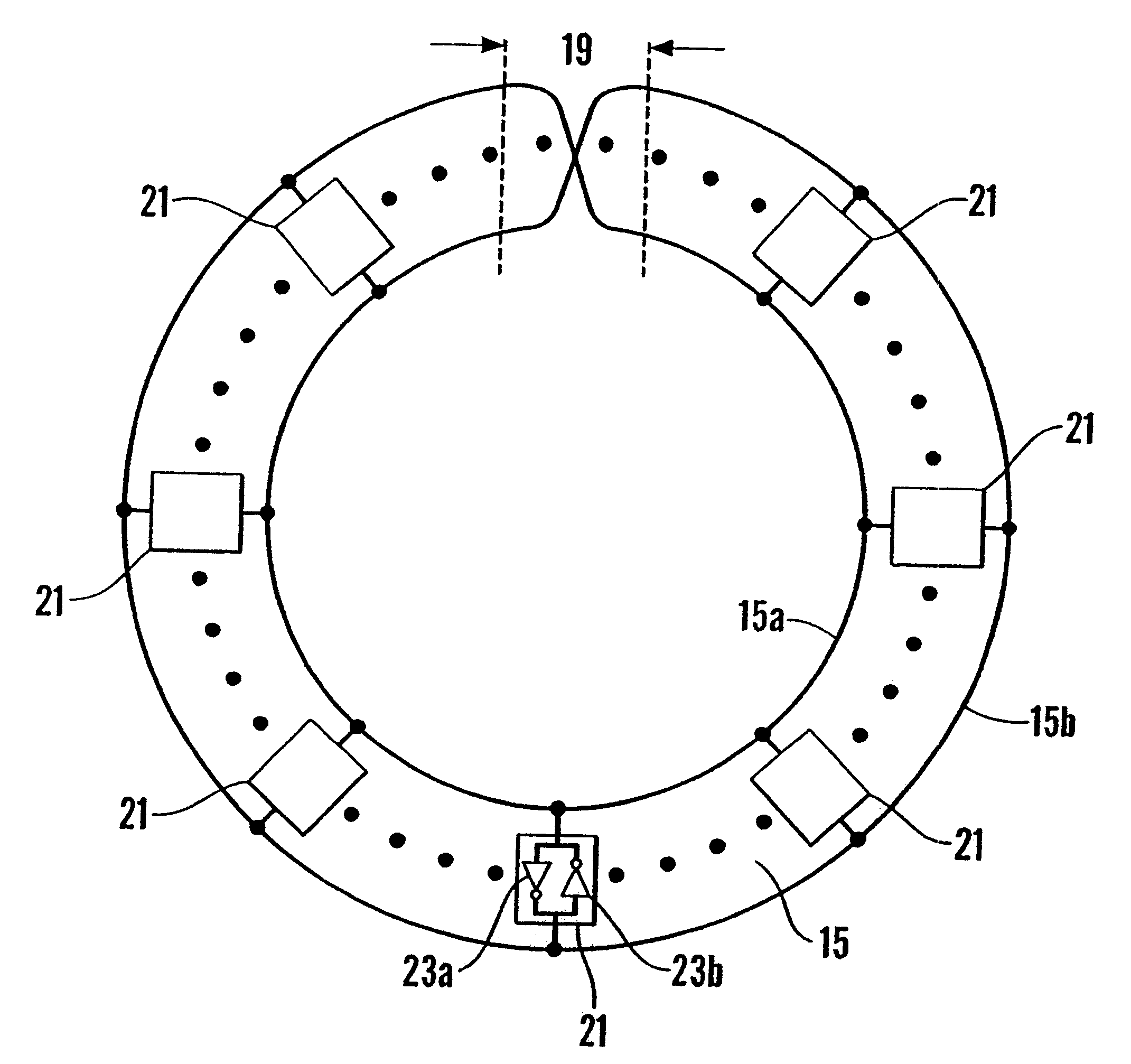

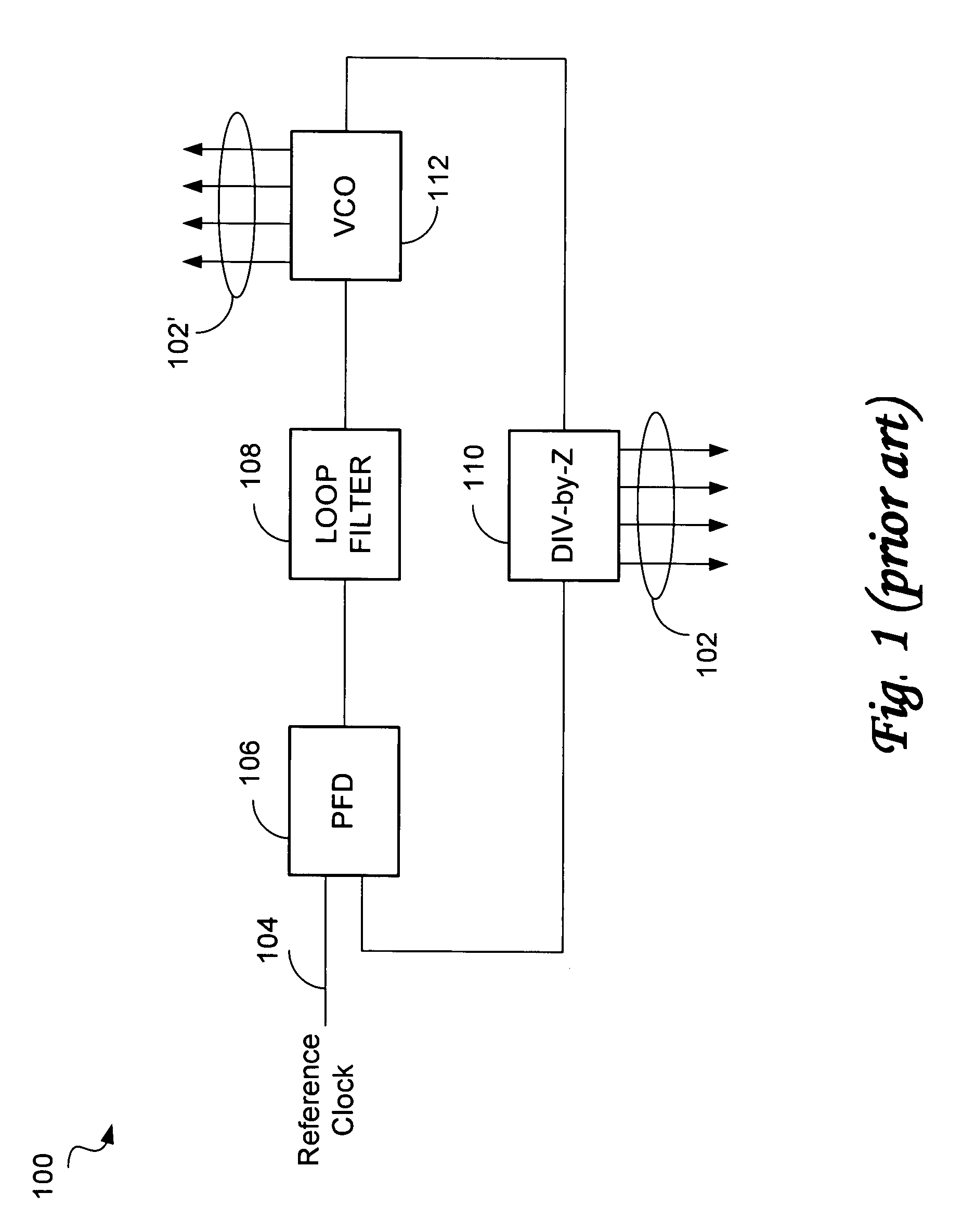

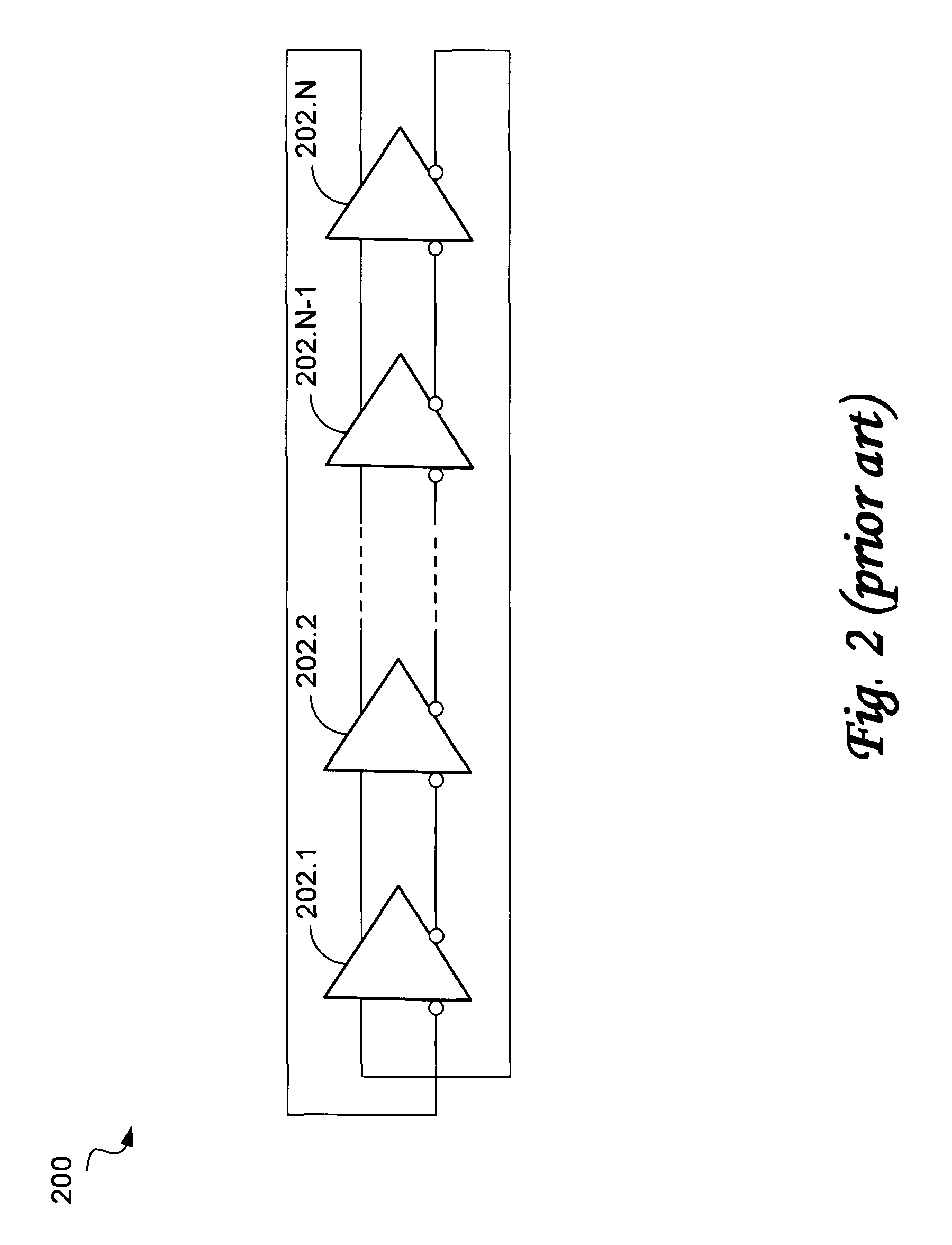

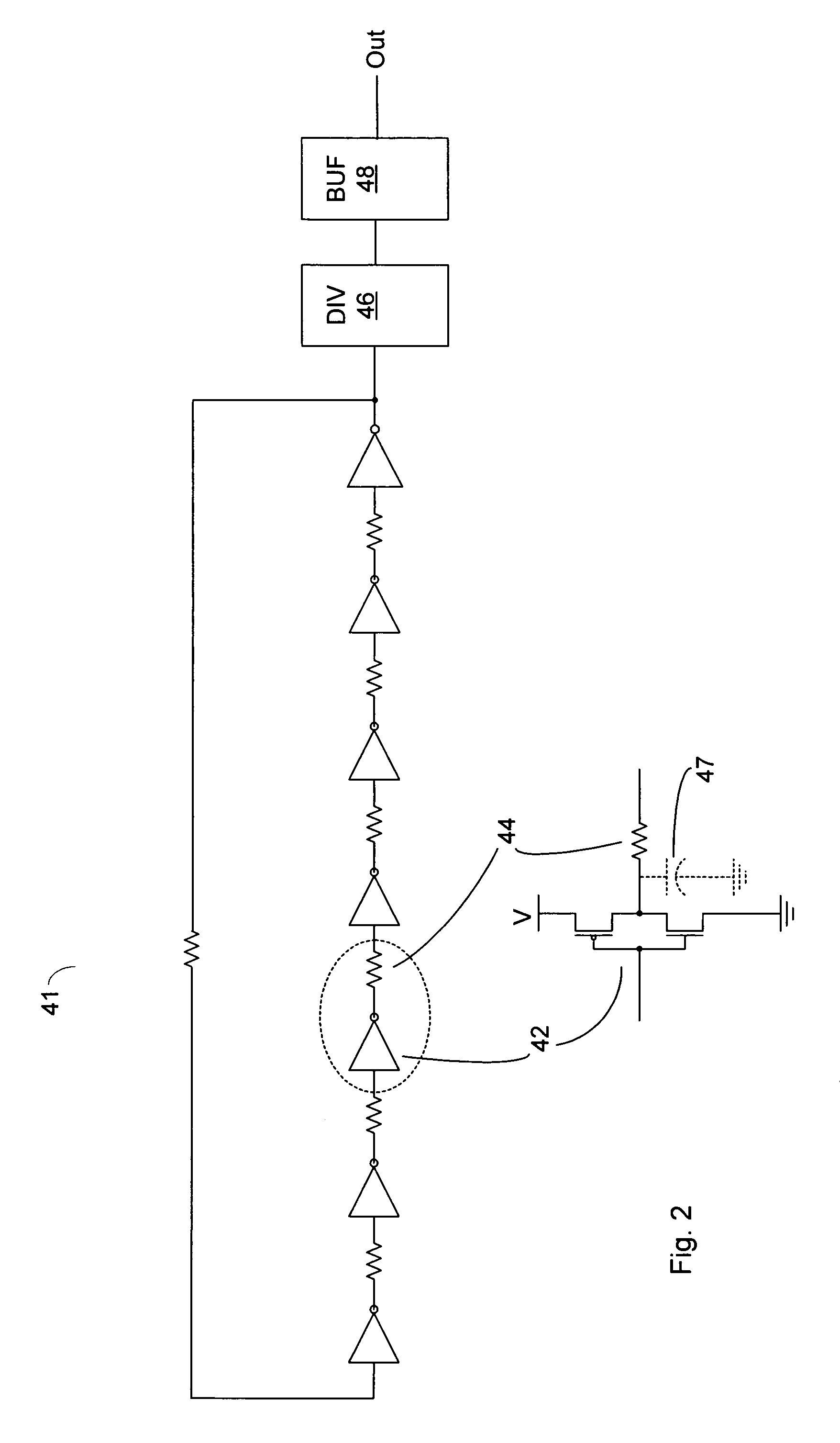

Array oscillator and polyphase clock generator

InactiveUS20060001496A1Increase speedReduce jitterPulse automatic controlPulse generation by logic circuitsMOSFETMultiplexing

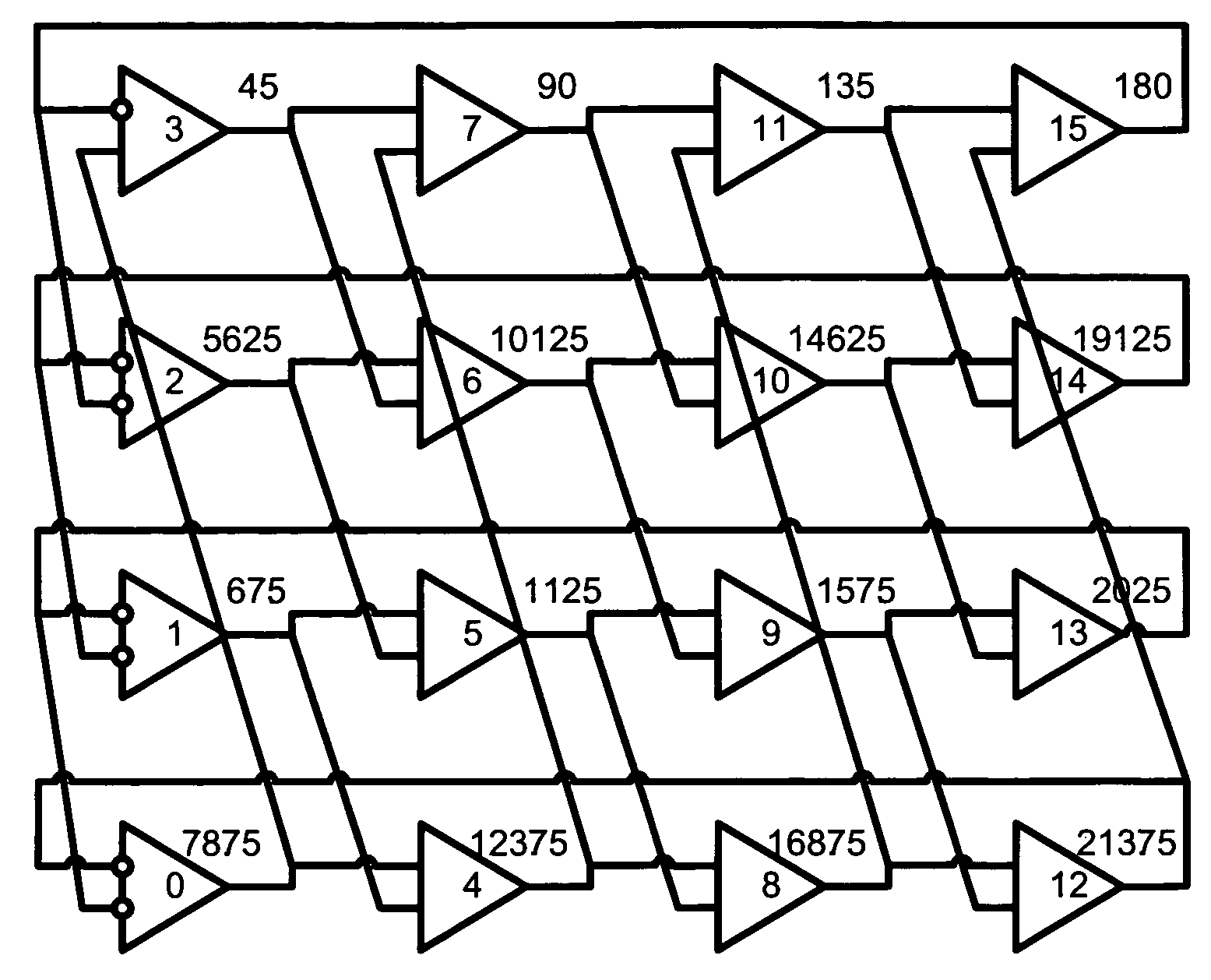

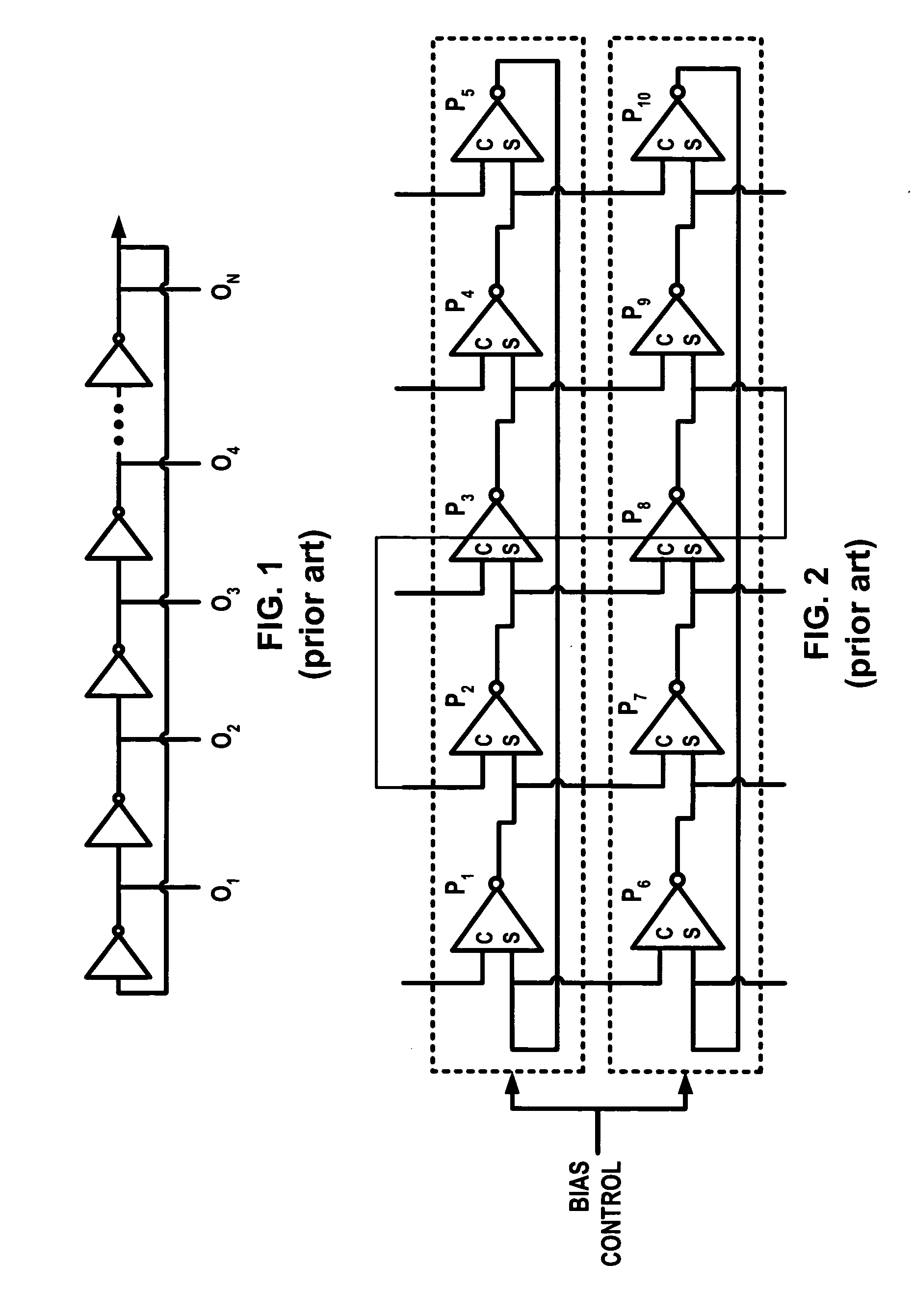

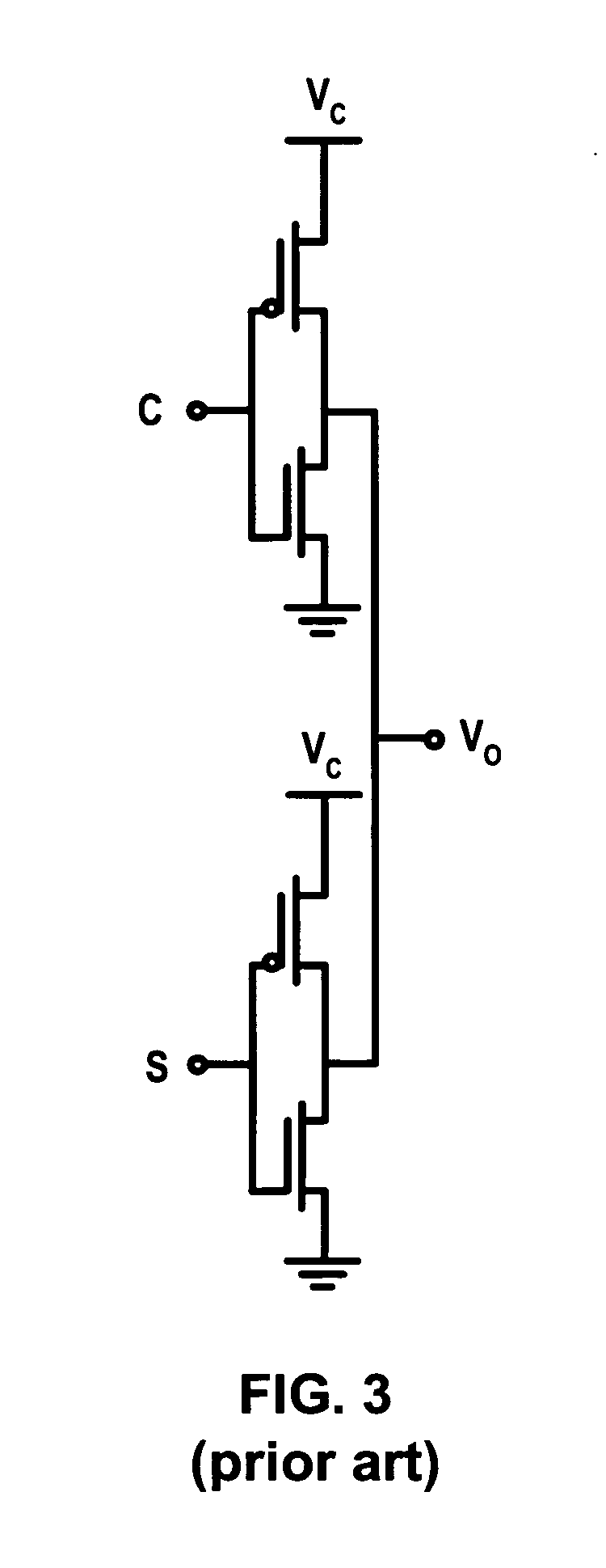

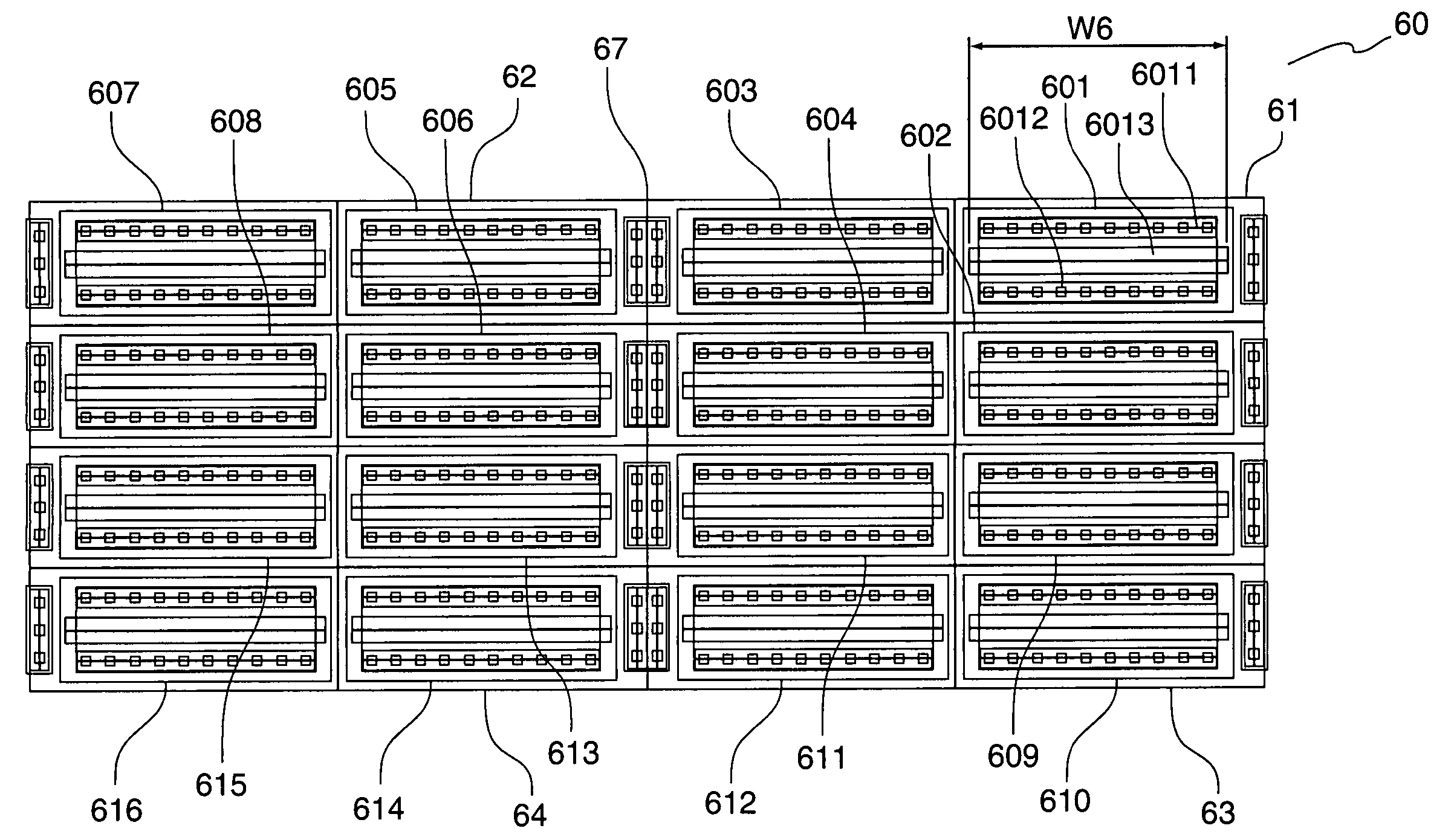

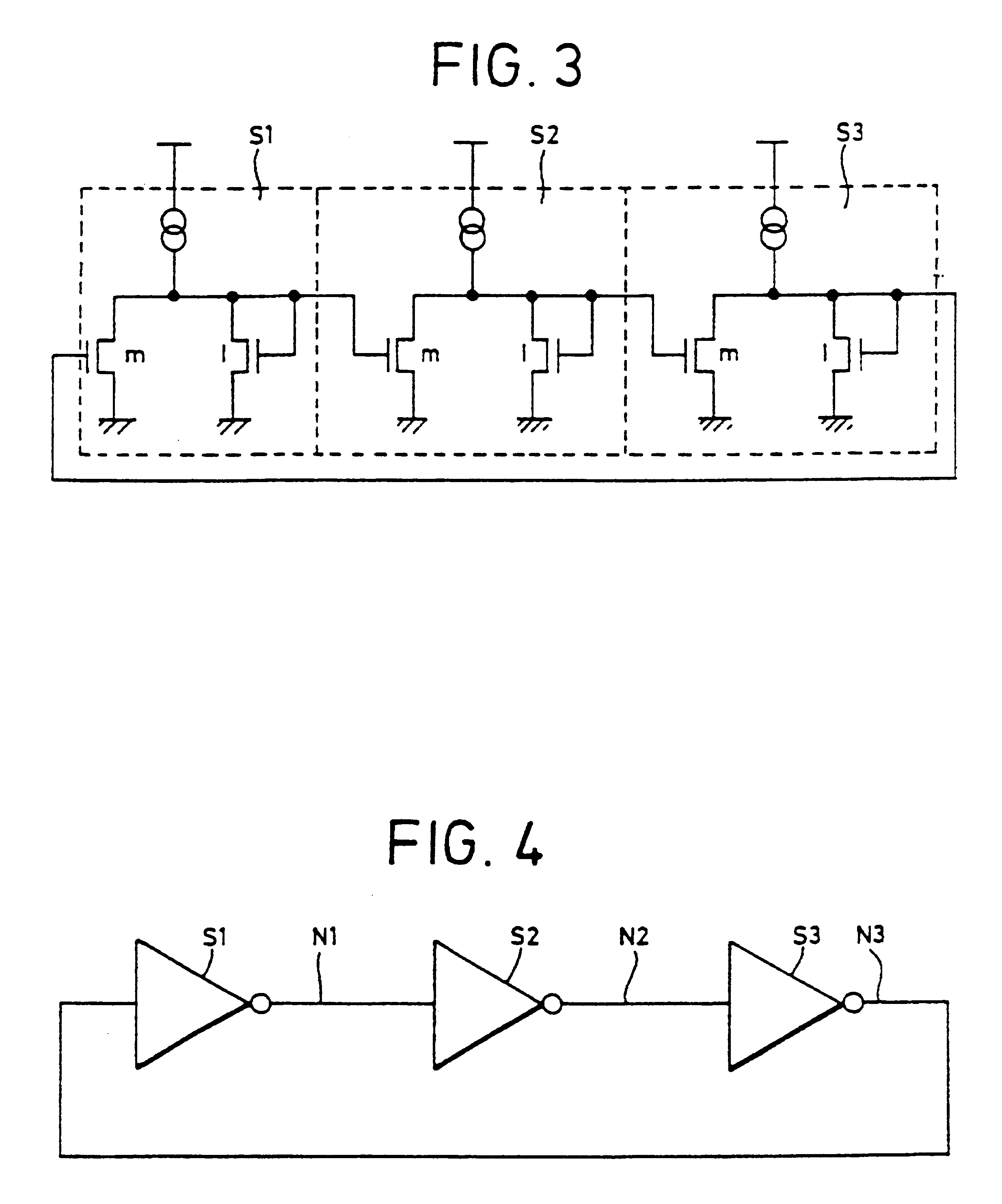

The present invention relates generally to array oscillator circuits for use as phase delay generators. More particularly, the present invention relates to a novel array oscillator for providing a plurality of phases which have stable phase relationships. The present invention is particularly applicable to the generation of poly-phase clocks for receivers of very high speed interfaces which employ an over-sampling technique, or multiplexing, and for high speed logic. The array oscillator according to the invention comprises at least one ring oscillator having a plurality of at least two interconnected buffer stages including at least one, or any integer odd number of inverting stages and a series of non-inverting stages, wherein the buffer stages are formed of N-type MOSFET transistors.

Owner:ACUID +1

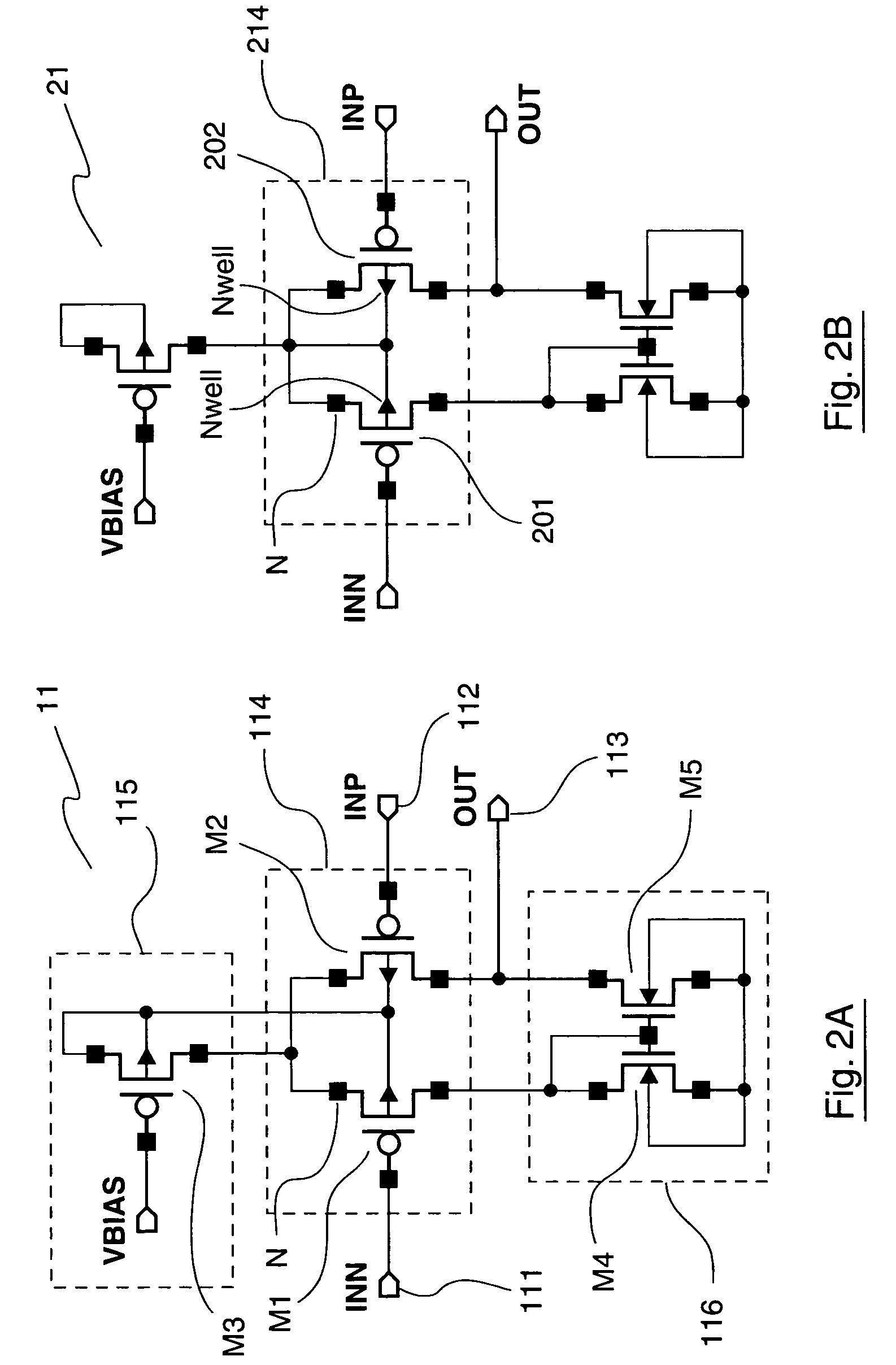

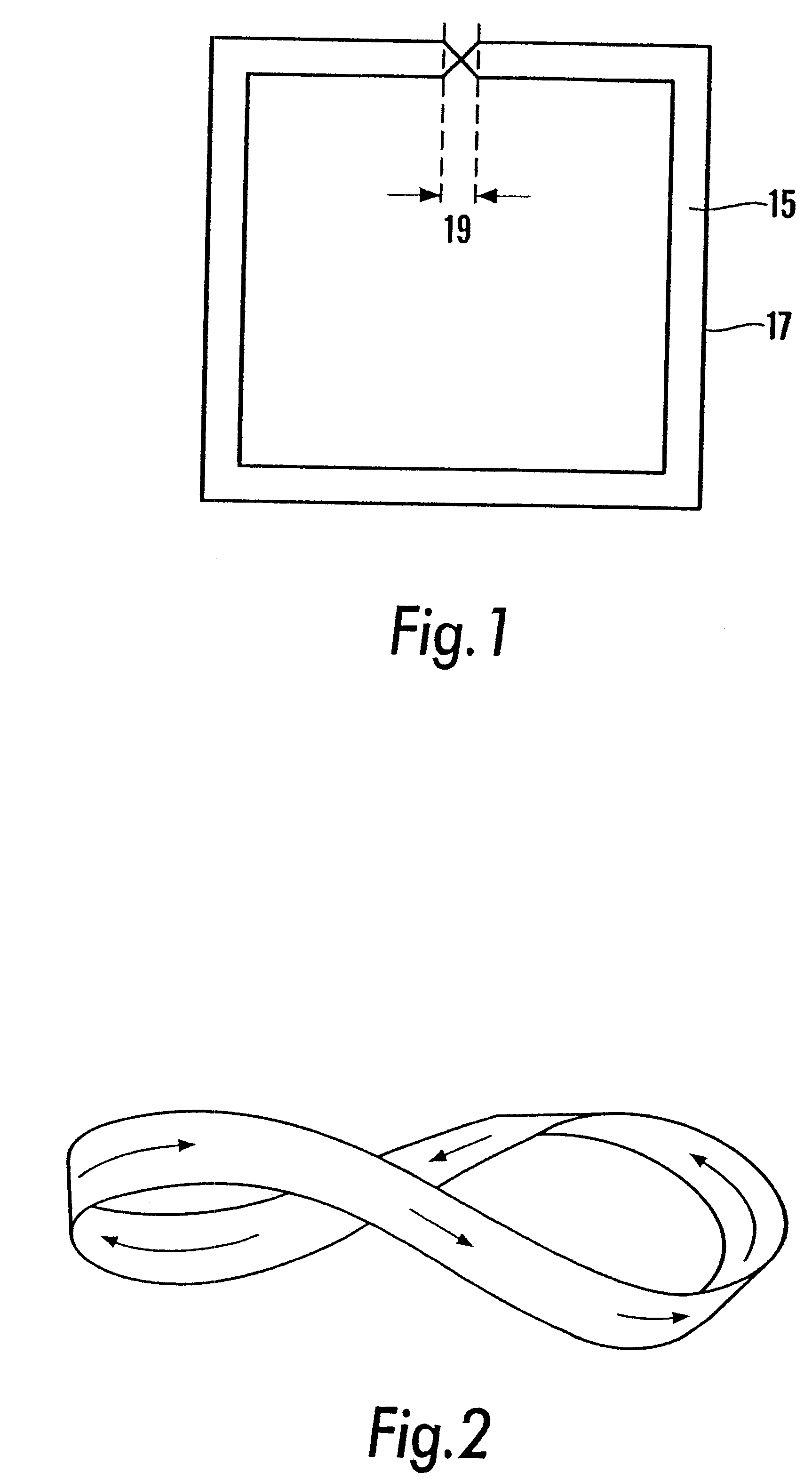

Electronic circuit including at least one first and one second differential pair with the transistors sharing one and the same well

ActiveUS20060158270A1Reduce capacitanceReduce surfaceSolid-state devicesAmplifier with semiconductor-devices/discharge-tubesEngineeringTransistor

The disclosure relates to an electronic circuit including at least one first and one second differential pair each including a plurality of transistors. All the transistors of said first and second differential pair are included in a single well.

Owner:ATMEL CORP

Electronic circuitry

InactiveUS6556089B2Short fallShort riseDelay lines pulse generationPulse automatic controlCMOSBipolar signal

Timing signal generation and distribution are combined in operation of a signal path exhibiting endless electromagnetic continuity affording signal phase inversion and having associated regenerative active means. Two-or more-phases of substantially square-wave bipolar signals arise directly in travelling wave transmission-line embodiments compatible with semiconductor fabrication including CMOS. Coordination by attainable frequency synchronism with phase coherence for several such oscillating signal paths has intra-IC inter-IC and printed circuit board impact.

Owner:ANALOG DEVICES INC

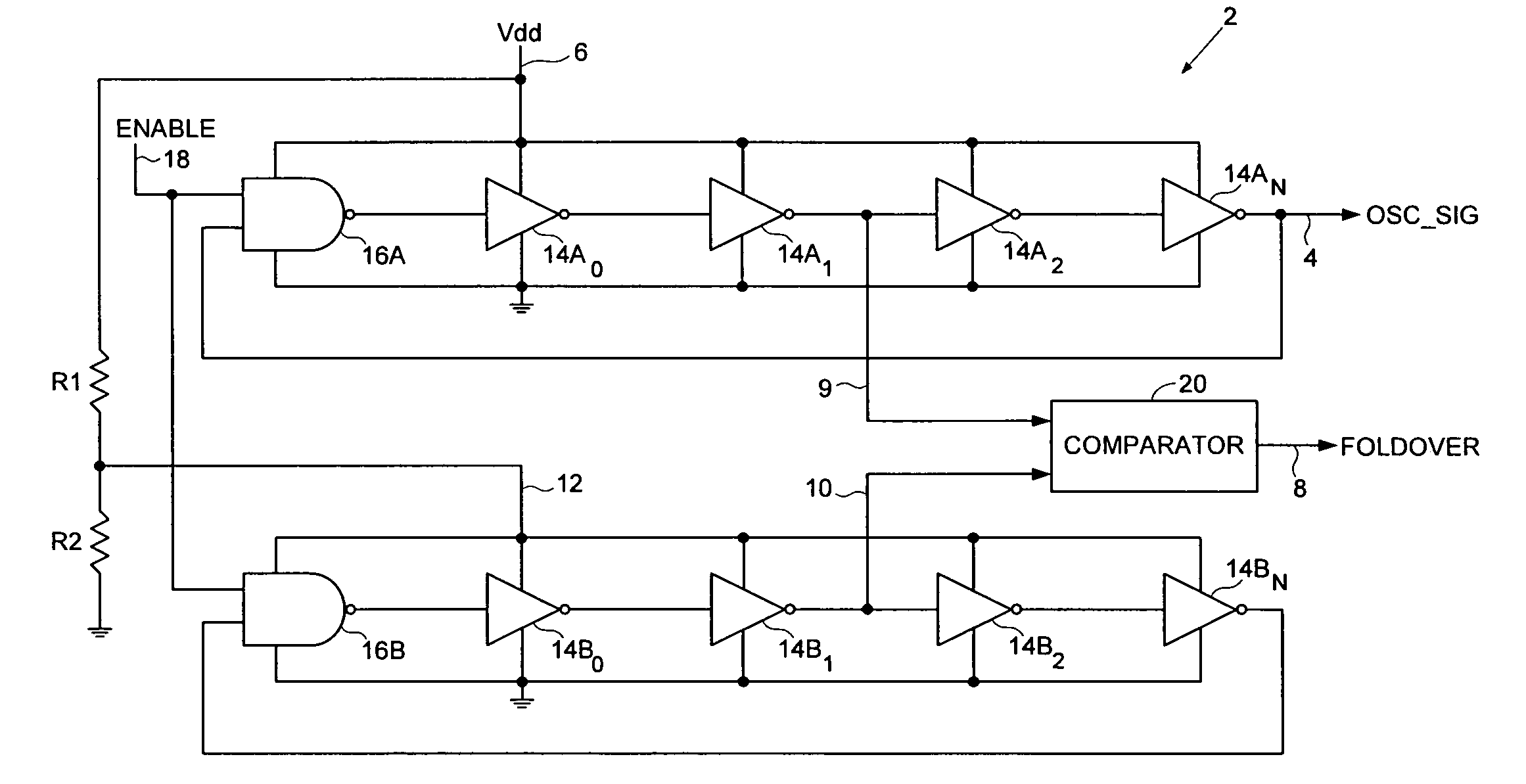

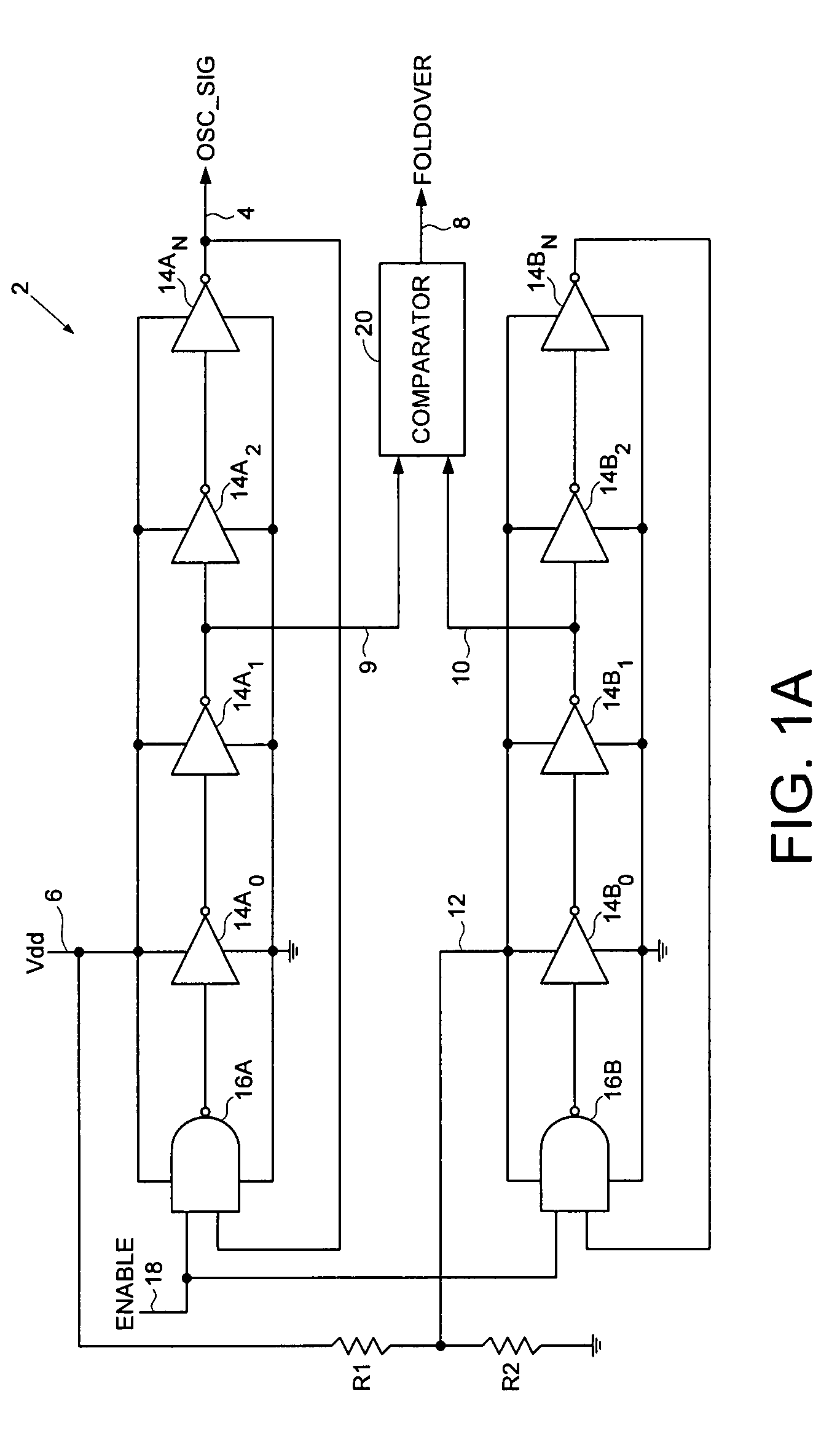

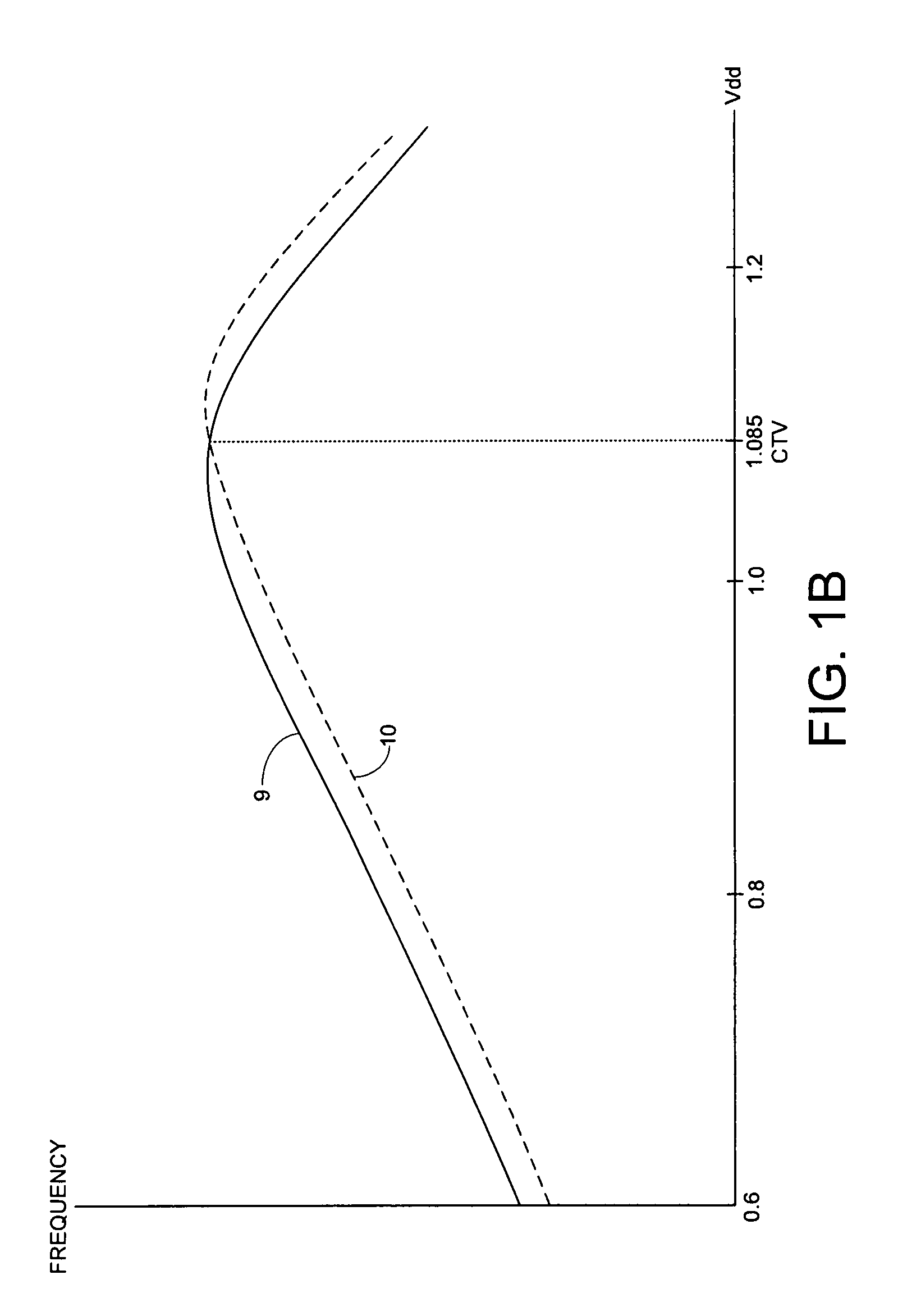

Oscillator comprising foldover detection

ActiveUS7733189B1High frequencyReduce frequencyElectrotherapyPulse automatic controlControl circuitVoltage

Control circuitry is disclosed including an oscillator operable to generate an oscillator signal. A frequency of the oscillator signal increases as an amplitude of a first voltage increases up to a threshold, and the frequency of the oscillator signal decreases as an amplitude of the first voltage exceeds the threshold. The oscillator is operable to generate a foldover signal indicating when the frequency of the oscillator signal is decreasing due to the first voltage exceeding the threshold.

Owner:WESTERN DIGITAL TECH INC

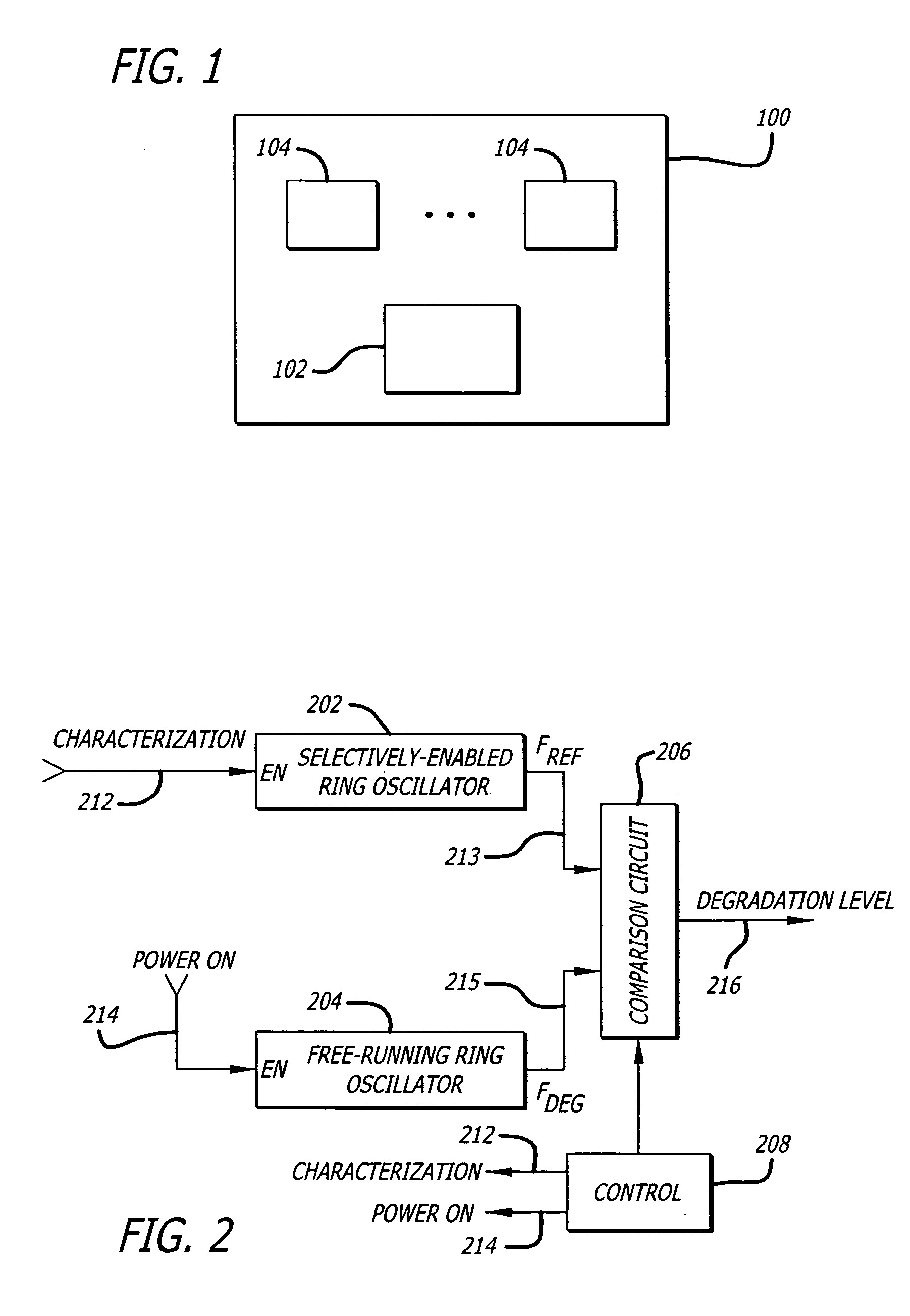

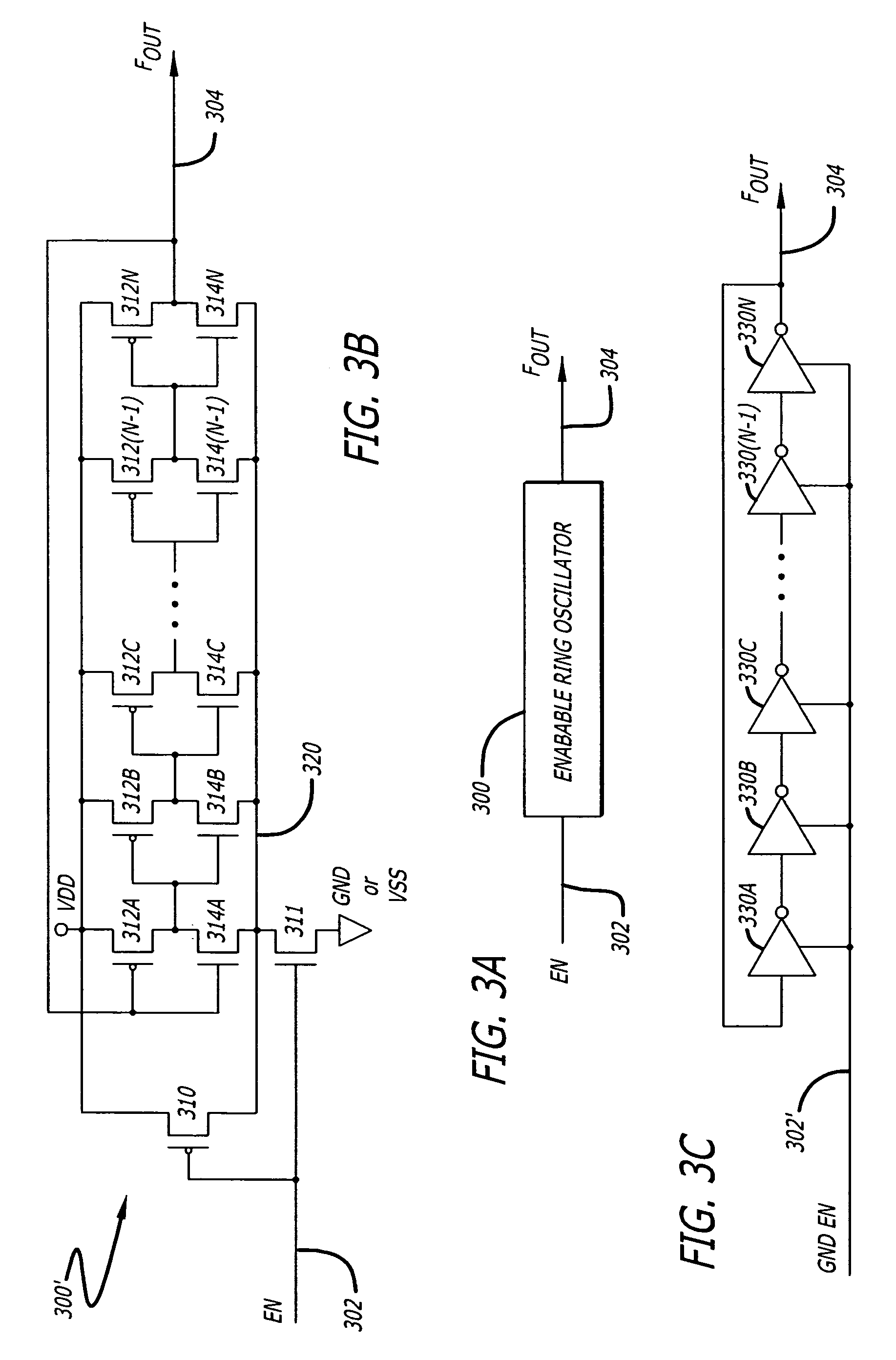

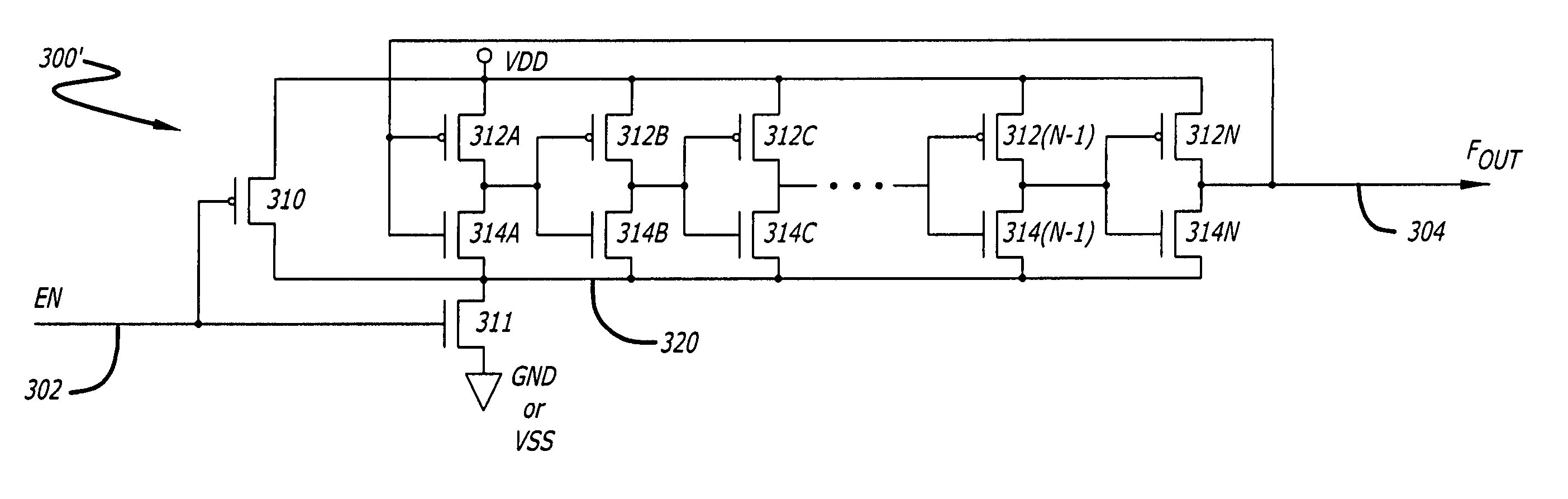

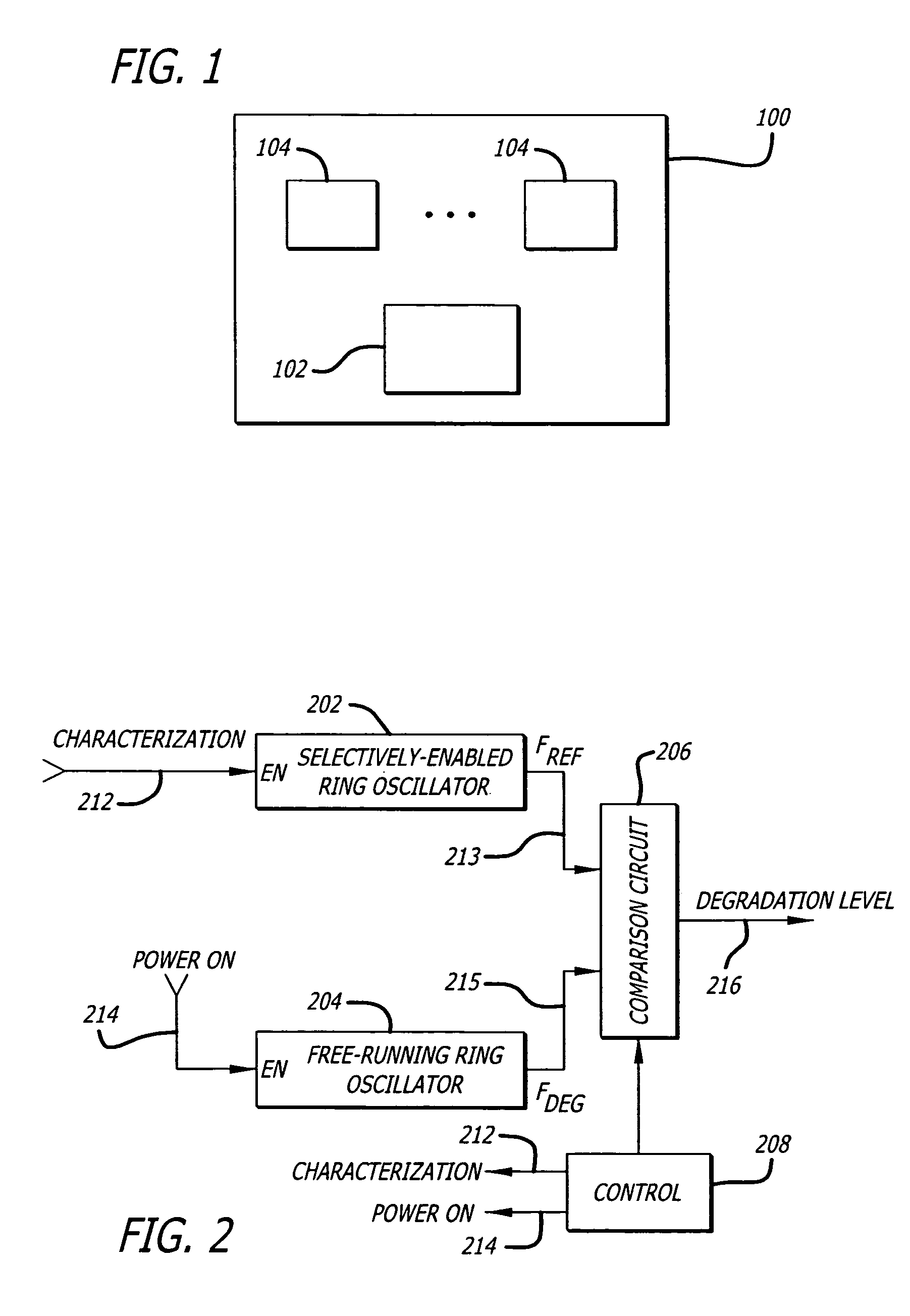

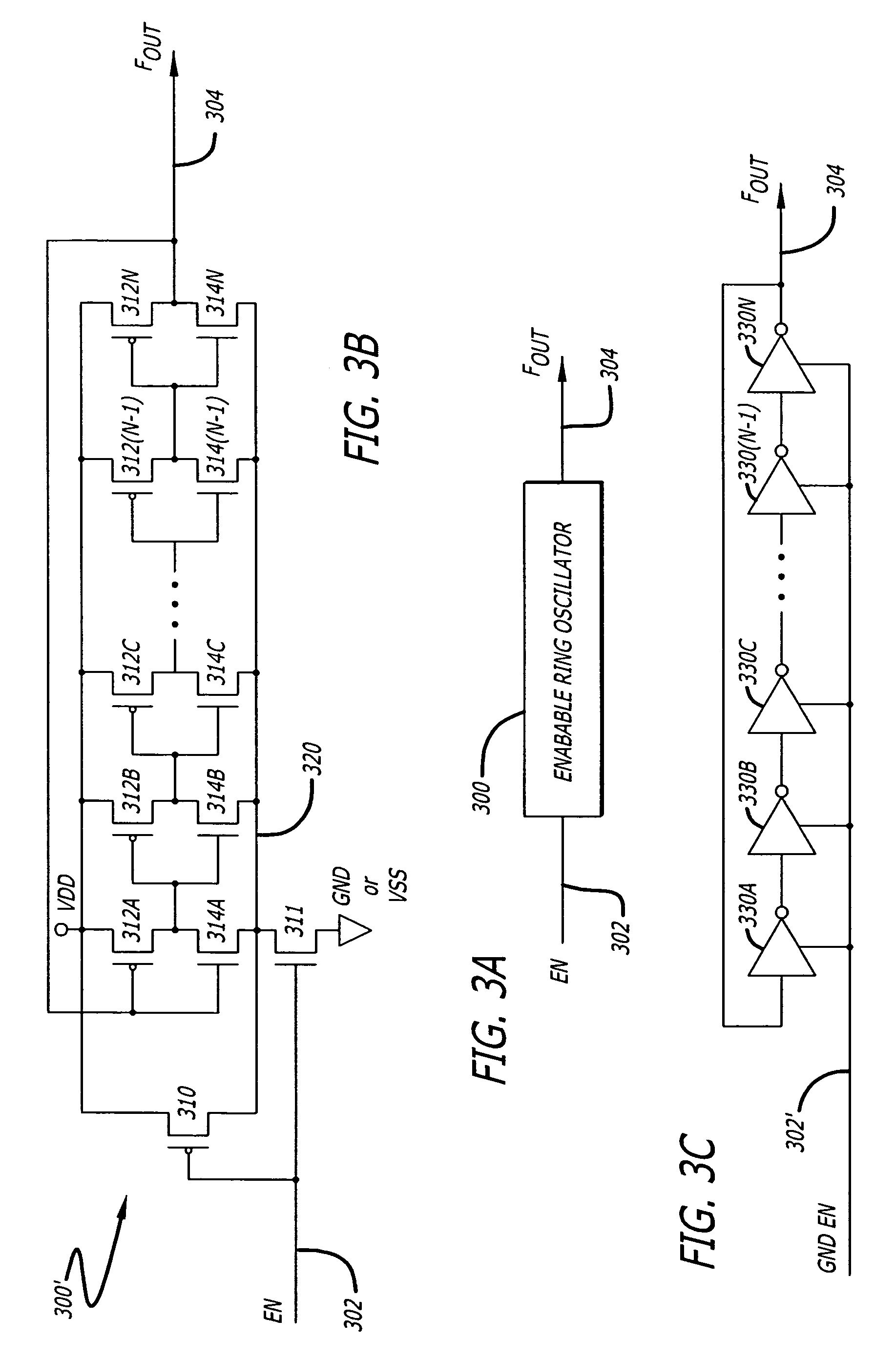

On-chip transistor degradation monitoring

InactiveUS20050134394A1Digital circuit testingPulse generation by logic circuitsEngineeringRing oscillator

Embodiments of the invention include on-chip characterization of transistor degradation. In one embodiment, includes one or more functional blocks to perform one or more functions and an integrated on-chip characterization circuit to perform on-chip characterization of transistor degradation. The integrated on-chip characterization circuit includes a selectively enabled ring oscillator to generate a reference oscillating signal, a free-running ring oscillator to generate a free-running oscillating signal, and a comparison circuit coupled to the selectively enabled ring oscillator and the free-running ring oscillator. From the reference oscillating signal and the free-running oscillating signal, the comparison circuit determine a measure of transistor degradation.

Owner:INTEL CORP

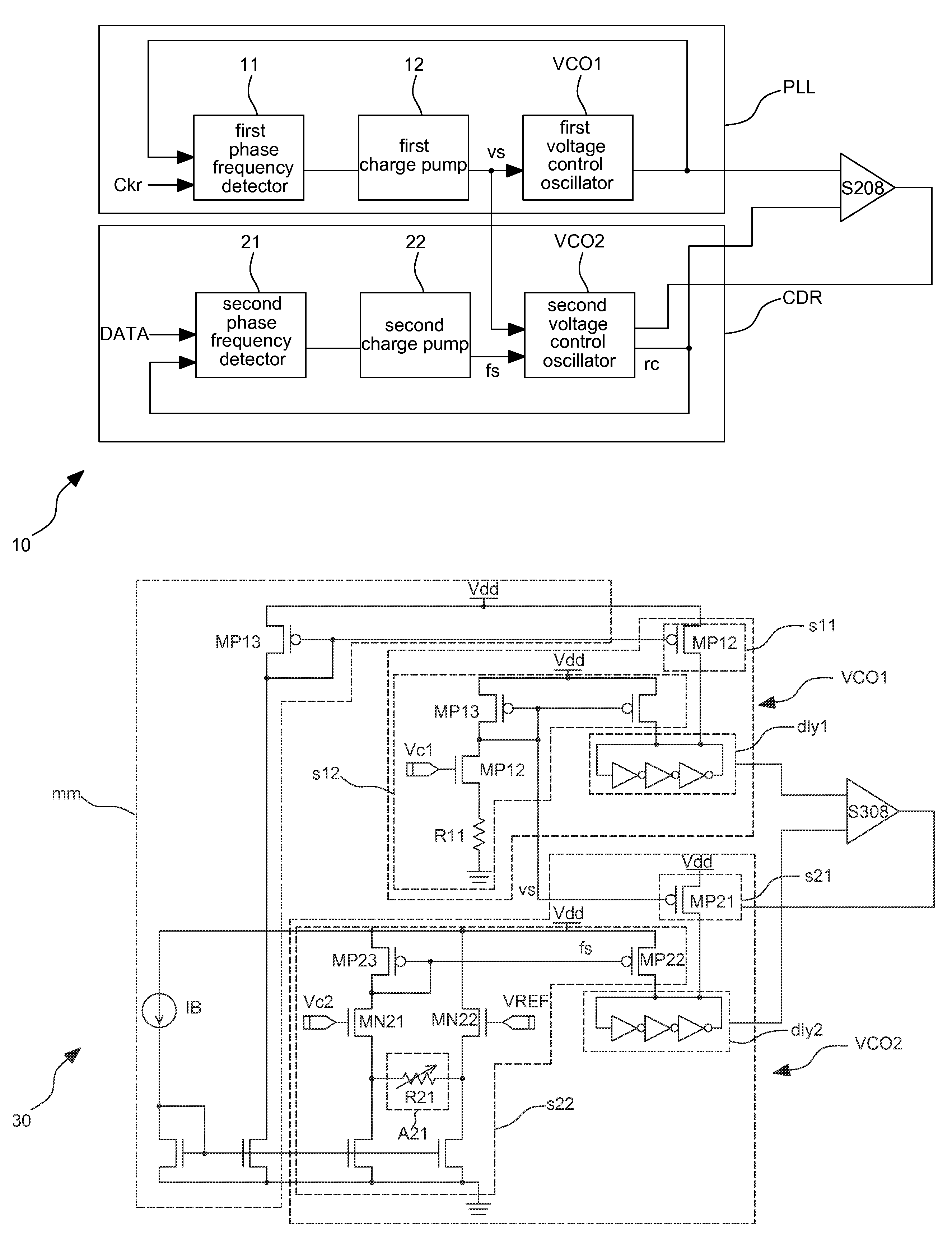

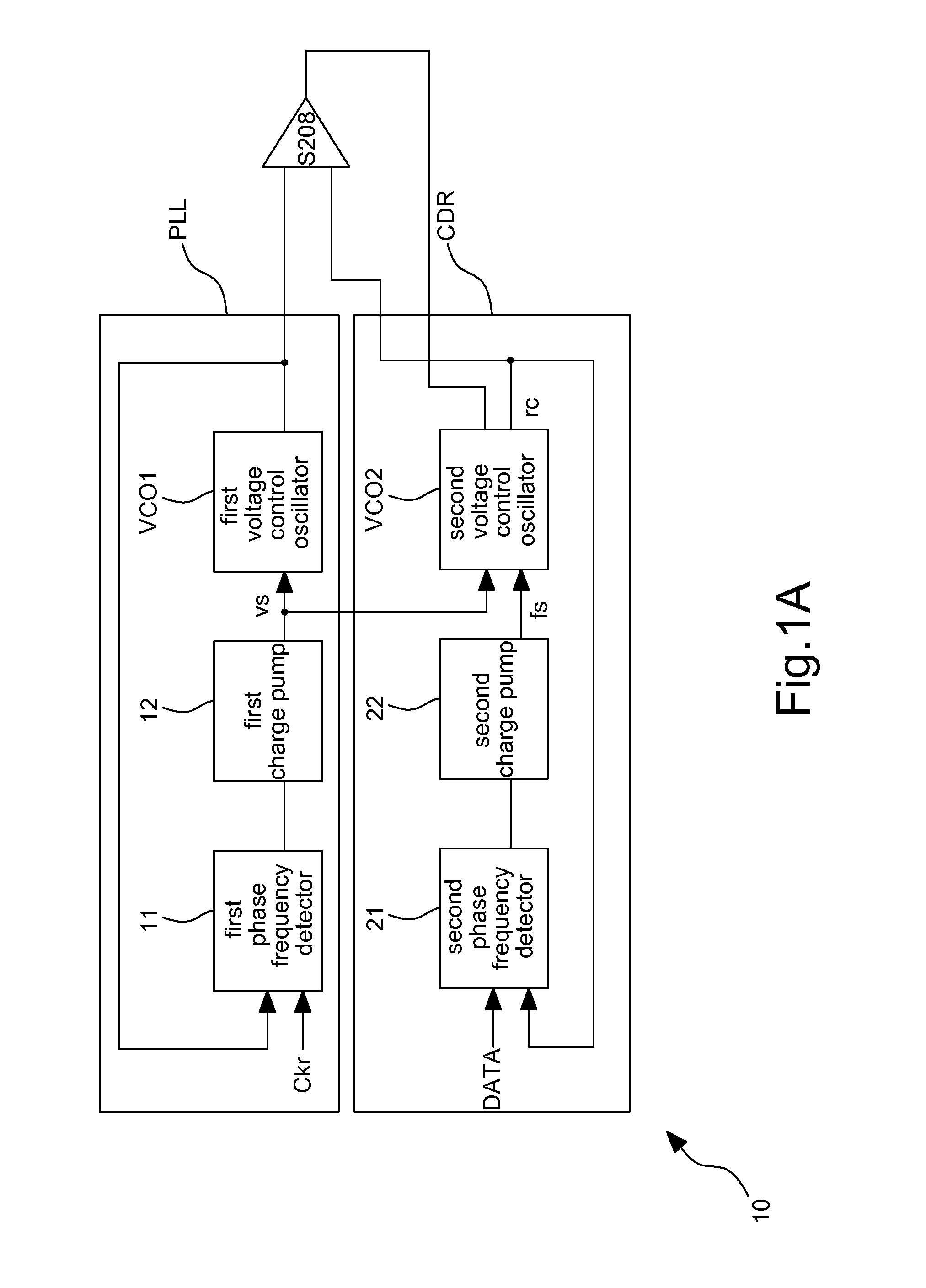

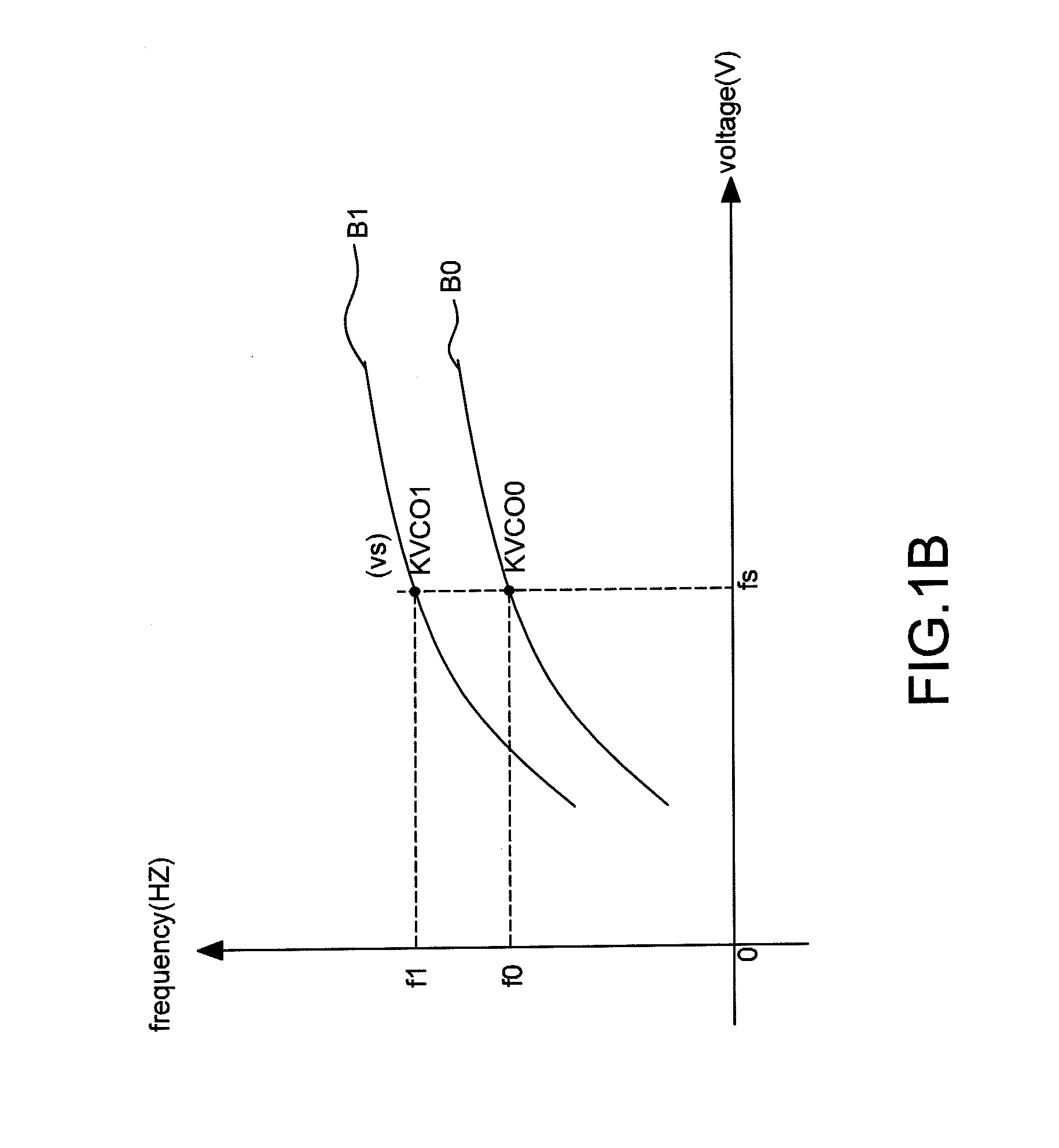

Transceiver, voltage control oscillator thereof and control method thereof

ActiveUS8928416B2Smaller VCO gainLarge rangePulse automatic controlPulse generation by logic circuitsTransceiverControl signal

A transceiver includes a phase lock loop (PLL) and a clock data recovery circuit (CDR). The phase lock loop generates a first level control signal. The clock data recovery circuit, coupled to the phase lock loop, locks an incoming data signal to generate a data recovery clock according to a second level control signal. Wherein the clock data recovery circuit receives the first level control signal to further control a frequency range of the data recovery clock.

Owner:REALTEK SEMICON CORP

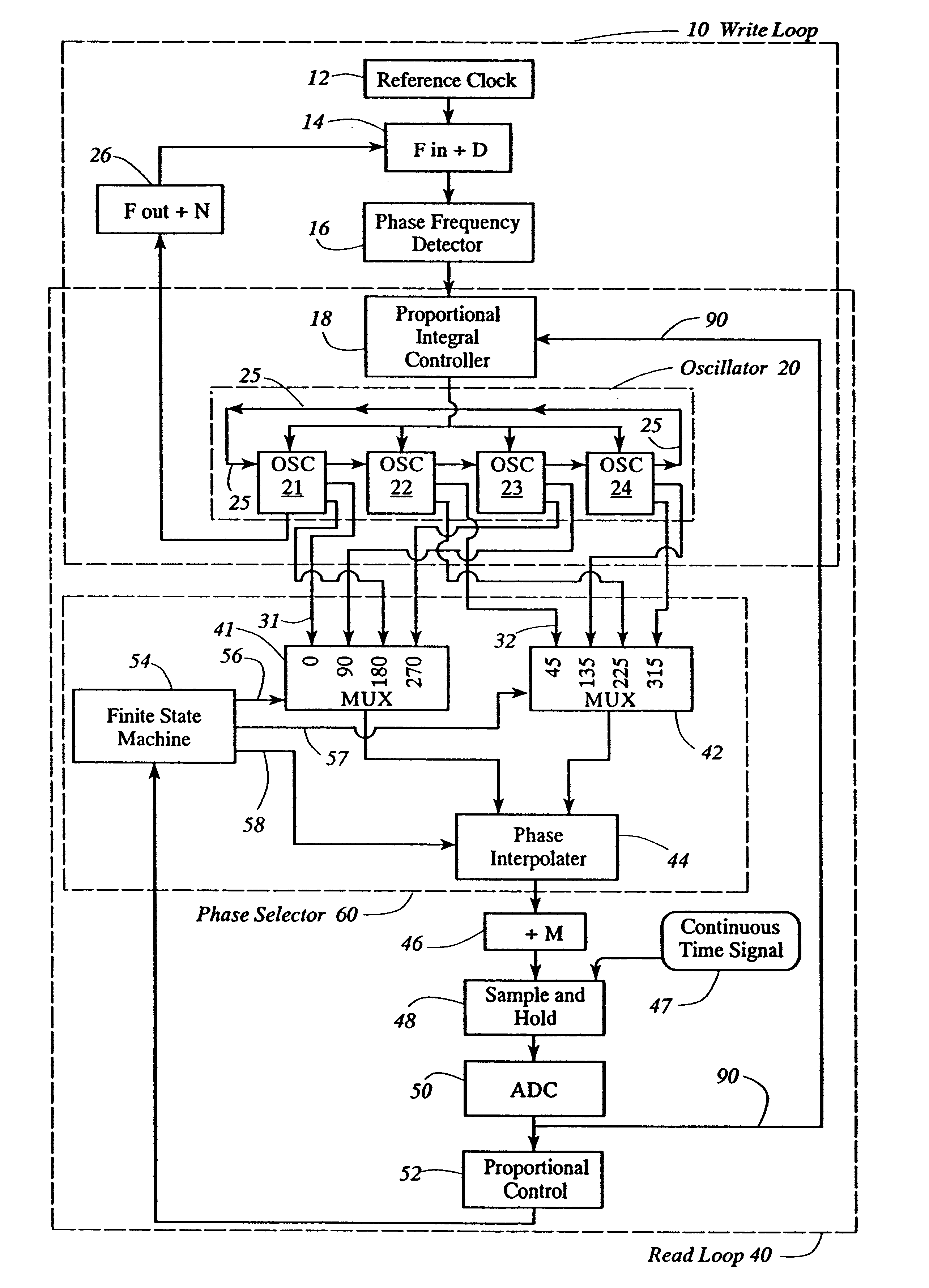

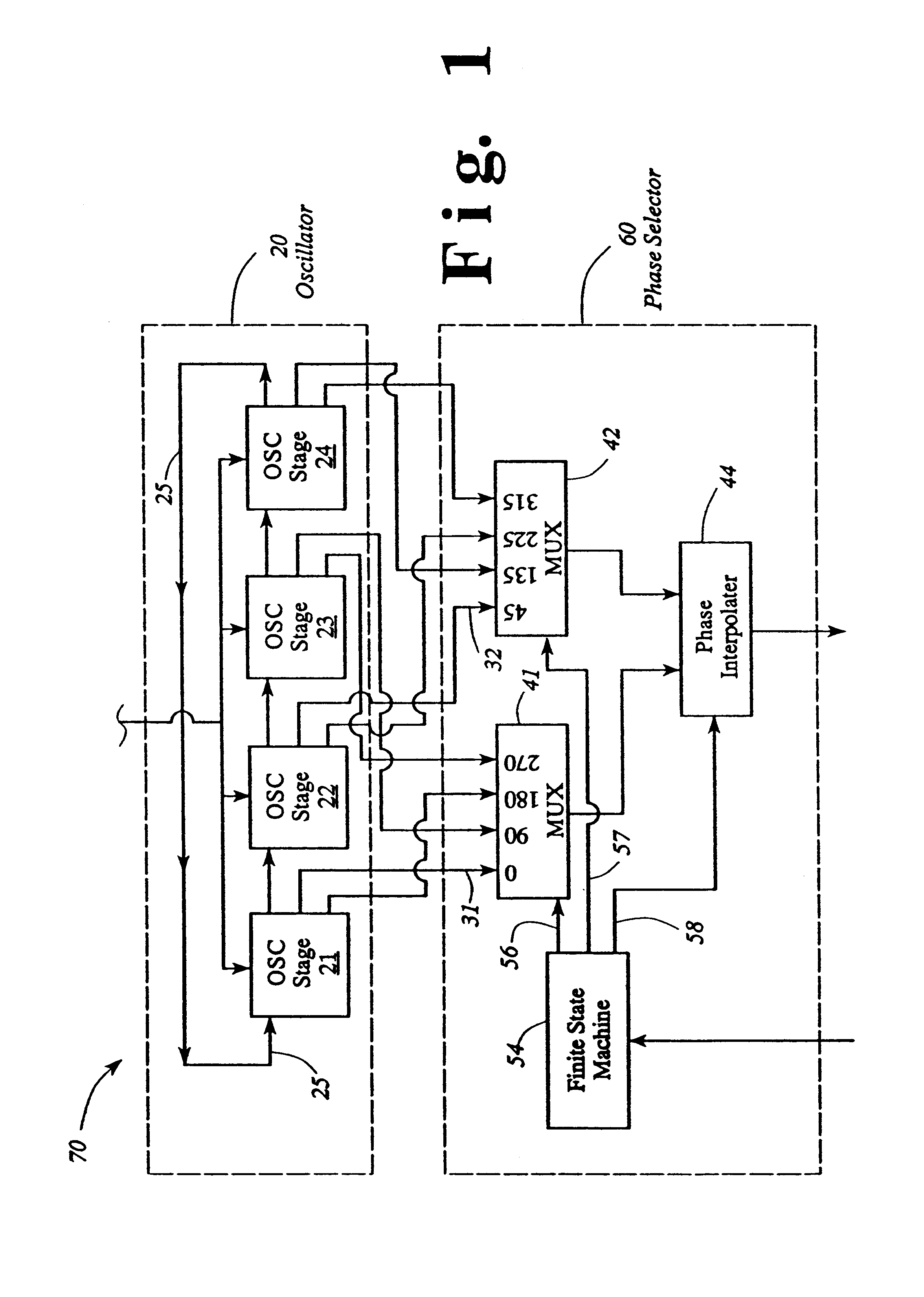

Oscillator with digitally variable phase for a phase-locked loop

InactiveUS6525615B1Disposition/mounting of recording headsPulse automatic controlMultiplexerImproved method

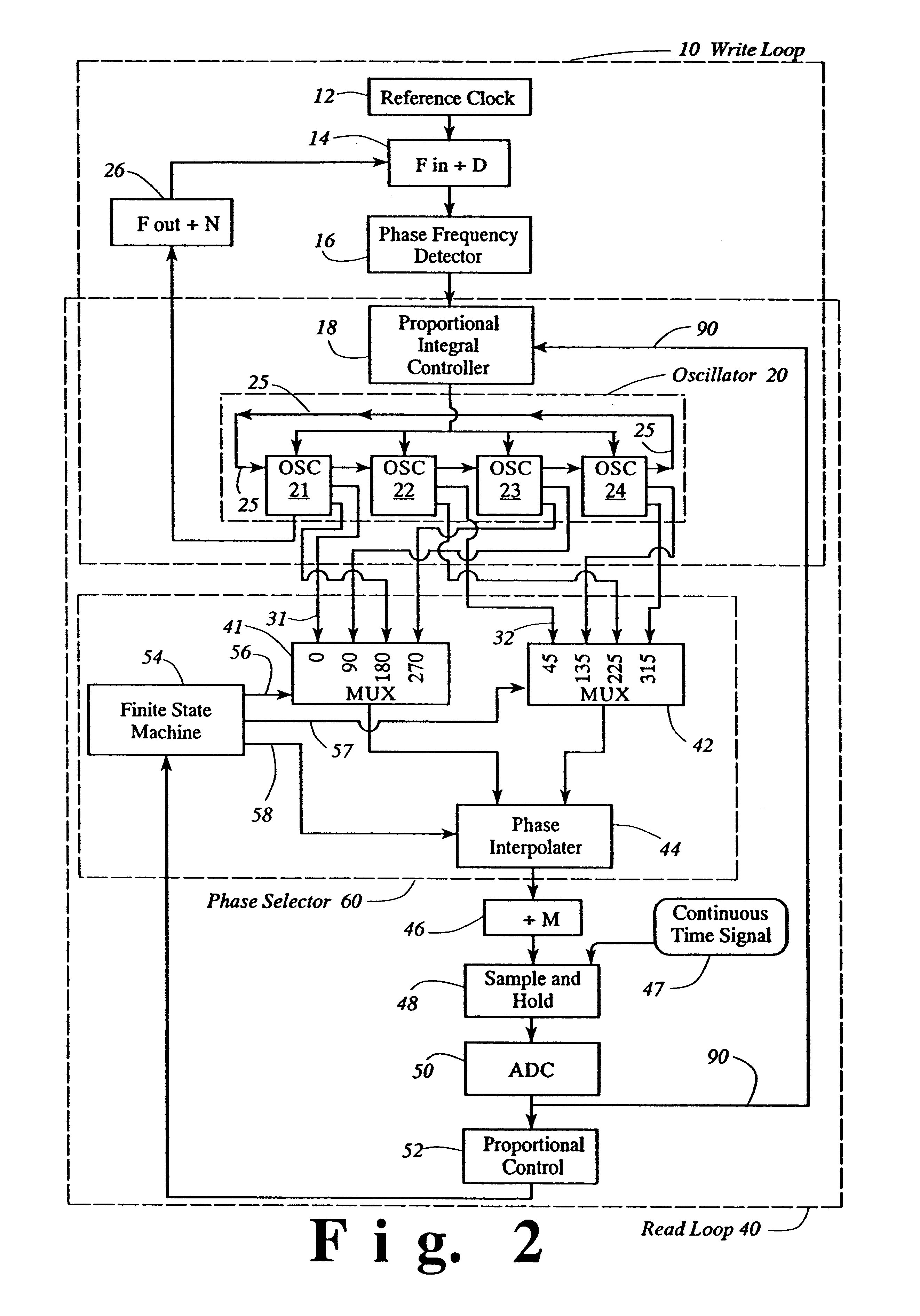

The present invention provides an improved method and apparatus for independently controlling phase and frequency using an oscillator having a plurality of stages in combination with a phase selector within a digitally controlled phase-locked loop, preferably, a read phase locked loop. The present invention provides a digitally controlled variable phase of the read timing loop in read channel integrated circuits associated with data storage devices. The phase selector has a digitally controlled fine interpolator with 12 states for further fine interpolation between at least two multiplexer phase outputs to provide a single phase output selected from a range comprising at least 2pi in selectable variable phase increments of 2pi / 96 radian. The combined oscillator with the phase selector within a phase locked loop controls phase by exact fractional increments of equally space phases of the operating frequency within the phase locked loop, therein controlling phase at all operating frequencies.

Owner:GLOBALFOUNDRIES INC

Nanomechanical Oscillator

ActiveUS20090294638A1Easy to detectHigh-frequency oscillationSolid-state devicesMaterial analysis by optical meansResonanceFrequency oscillation

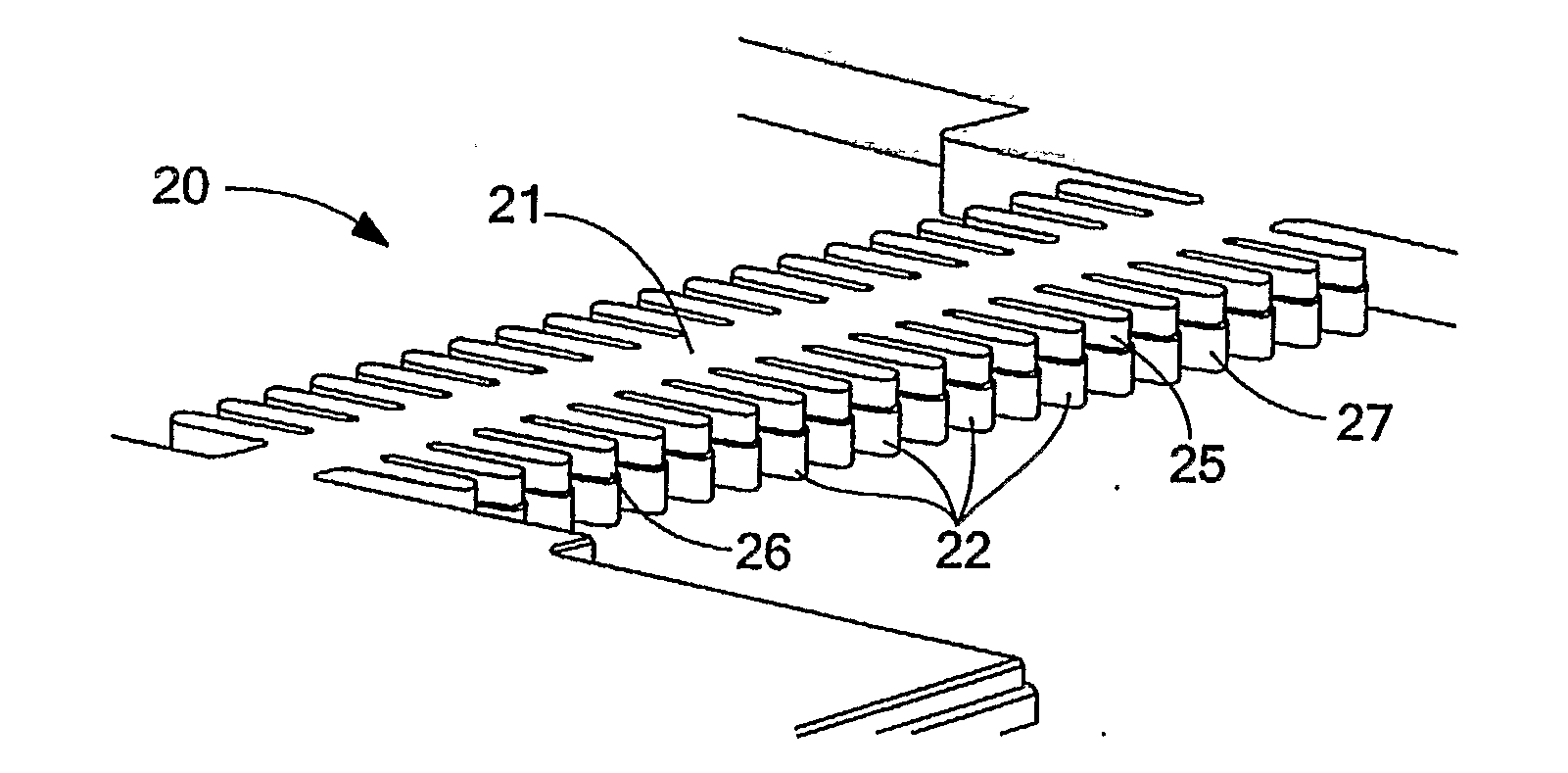

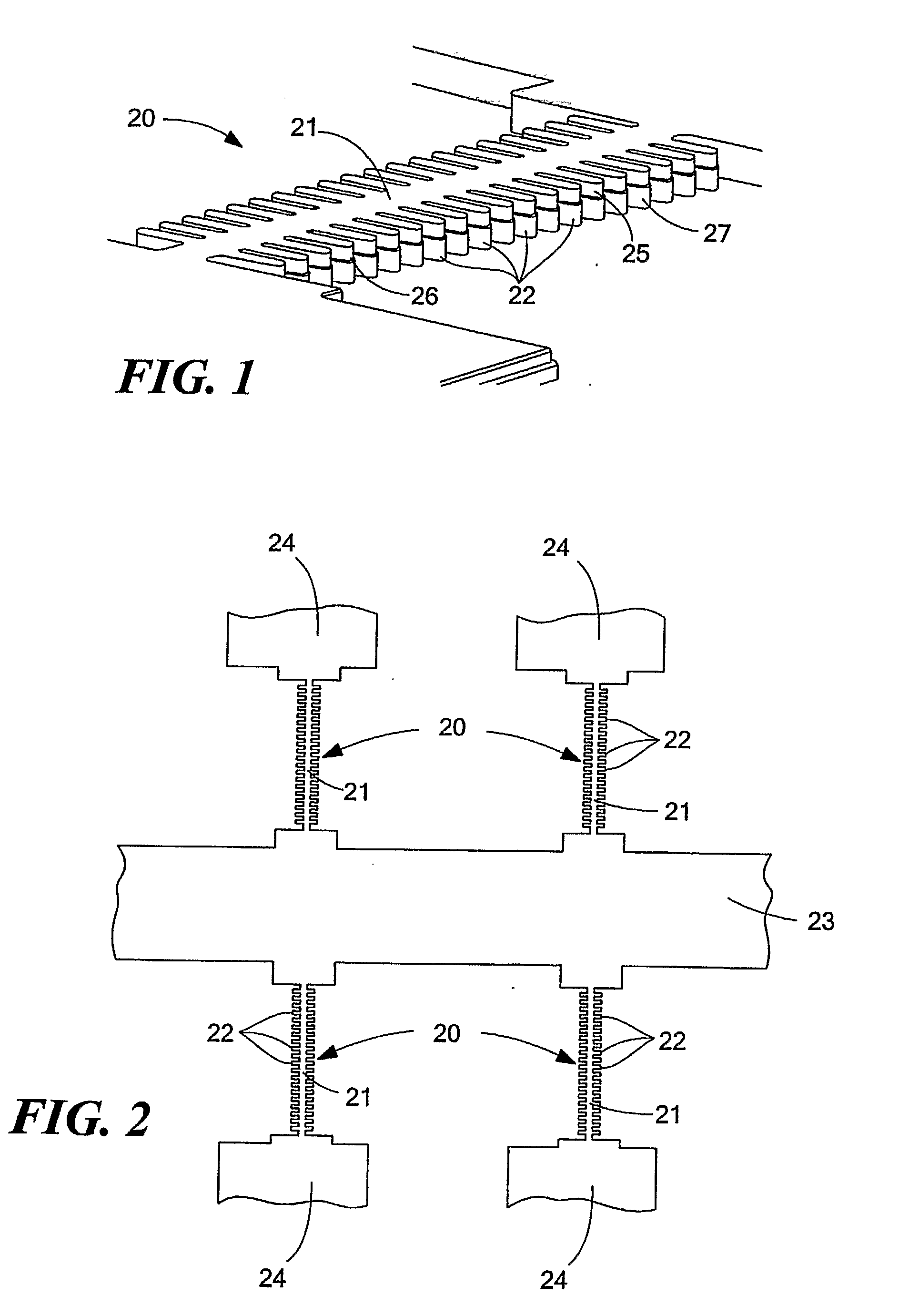

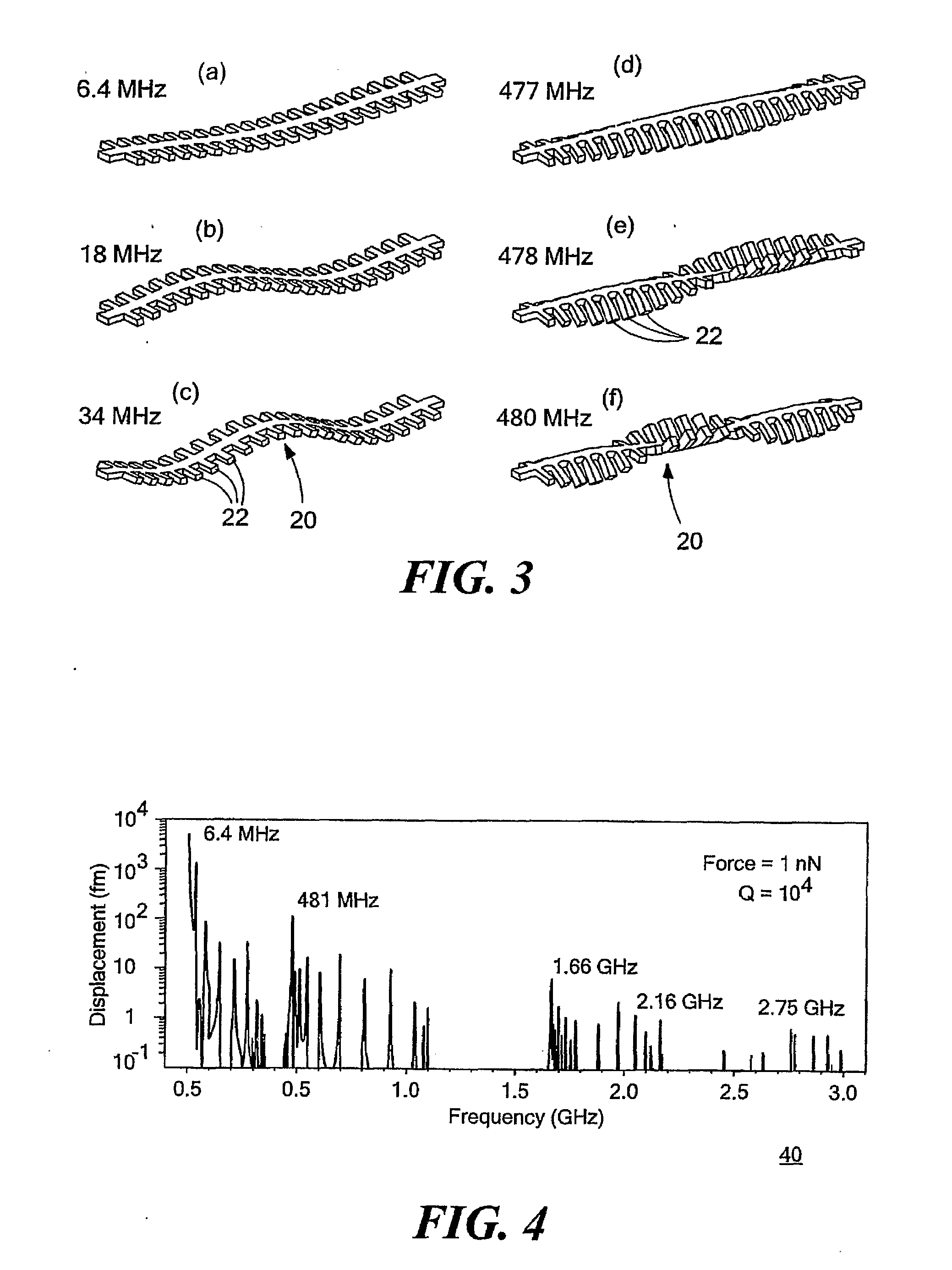

A mechanical oscillator has components with dimensions in a sub-micron range to produce resonance mode oscillations in a gigahertz range. A major element is coupled to a minor, sub-micron element to produce large amplitude gigahertz frequency oscillation that is detected with readily available techniques. The mechanical structure can be formed according to a number of geometries including beams and rings and is excited with electrostatic, magnetic and thermal related forces, as well as other excitation techniques. The mechanical structure can be arranged in arrays for applications such as amplification and mixing and is less sensitive to shock and radiative environments than electrical or optical counterparts.

Owner:TRUSTEES OF BOSTON UNIV

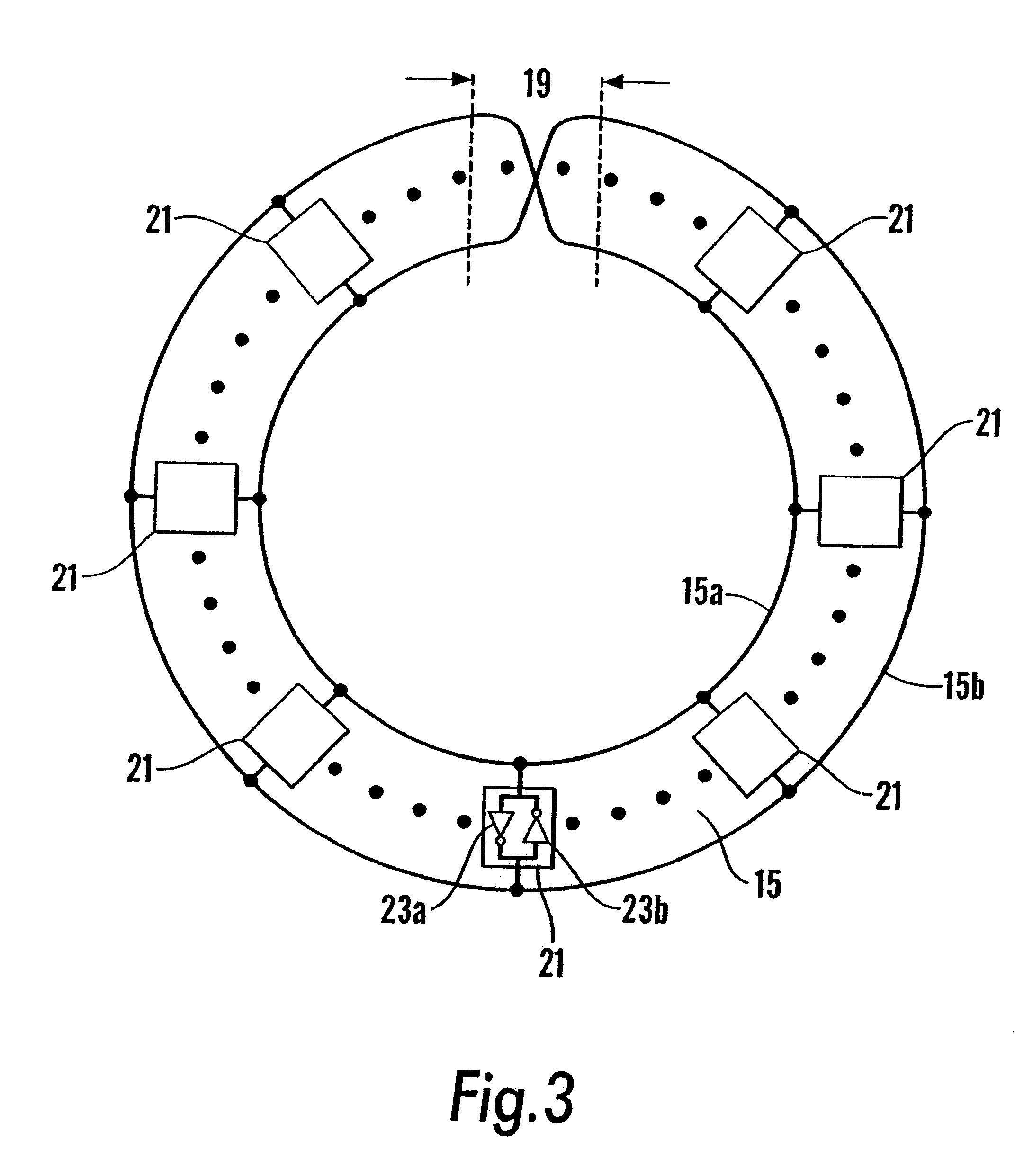

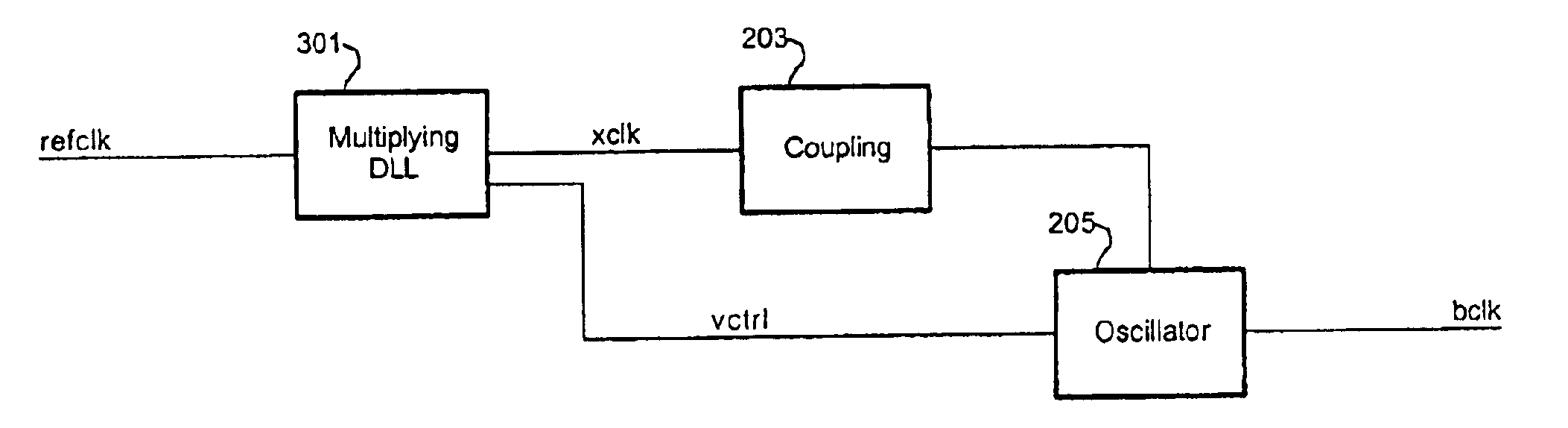

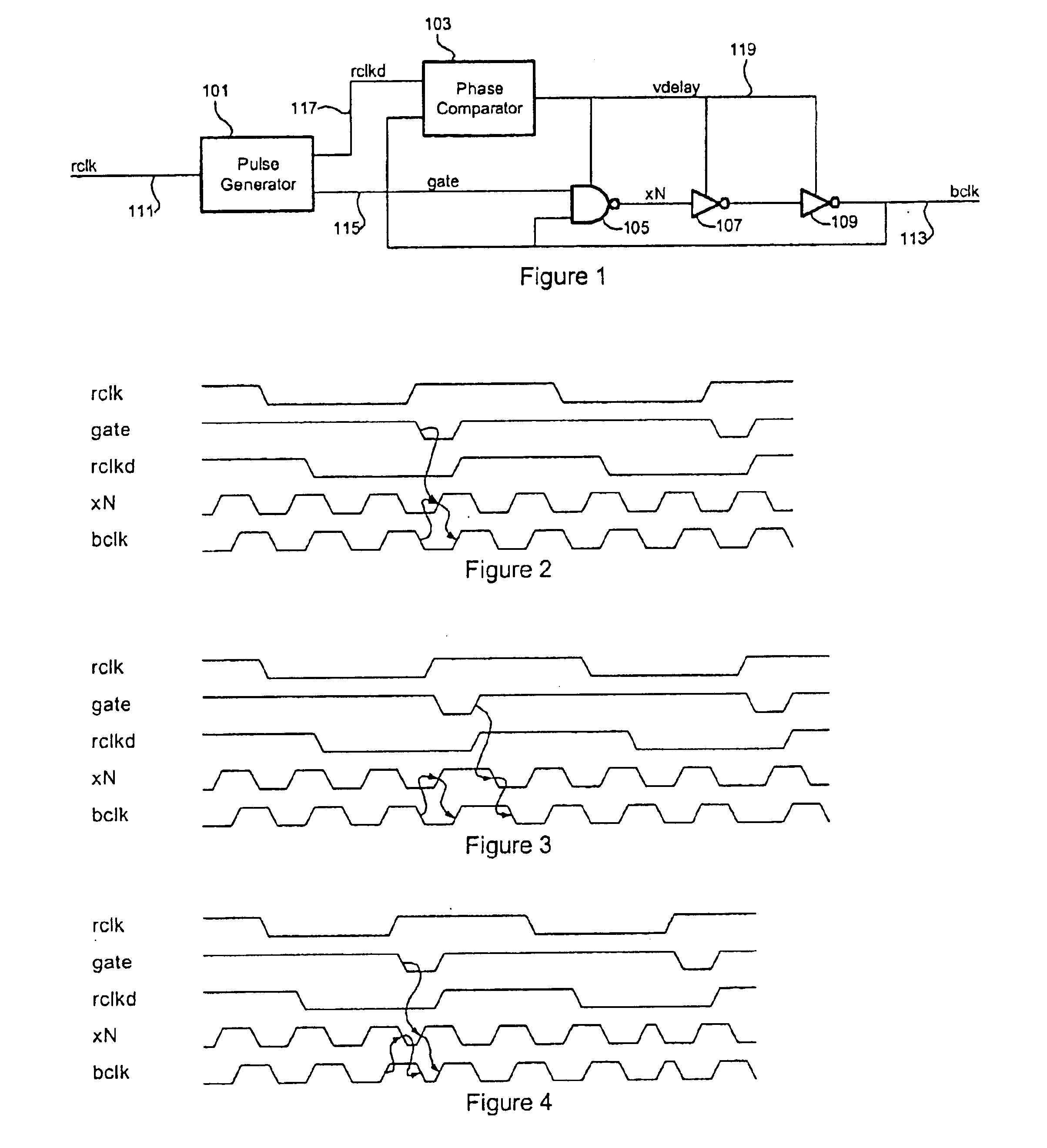

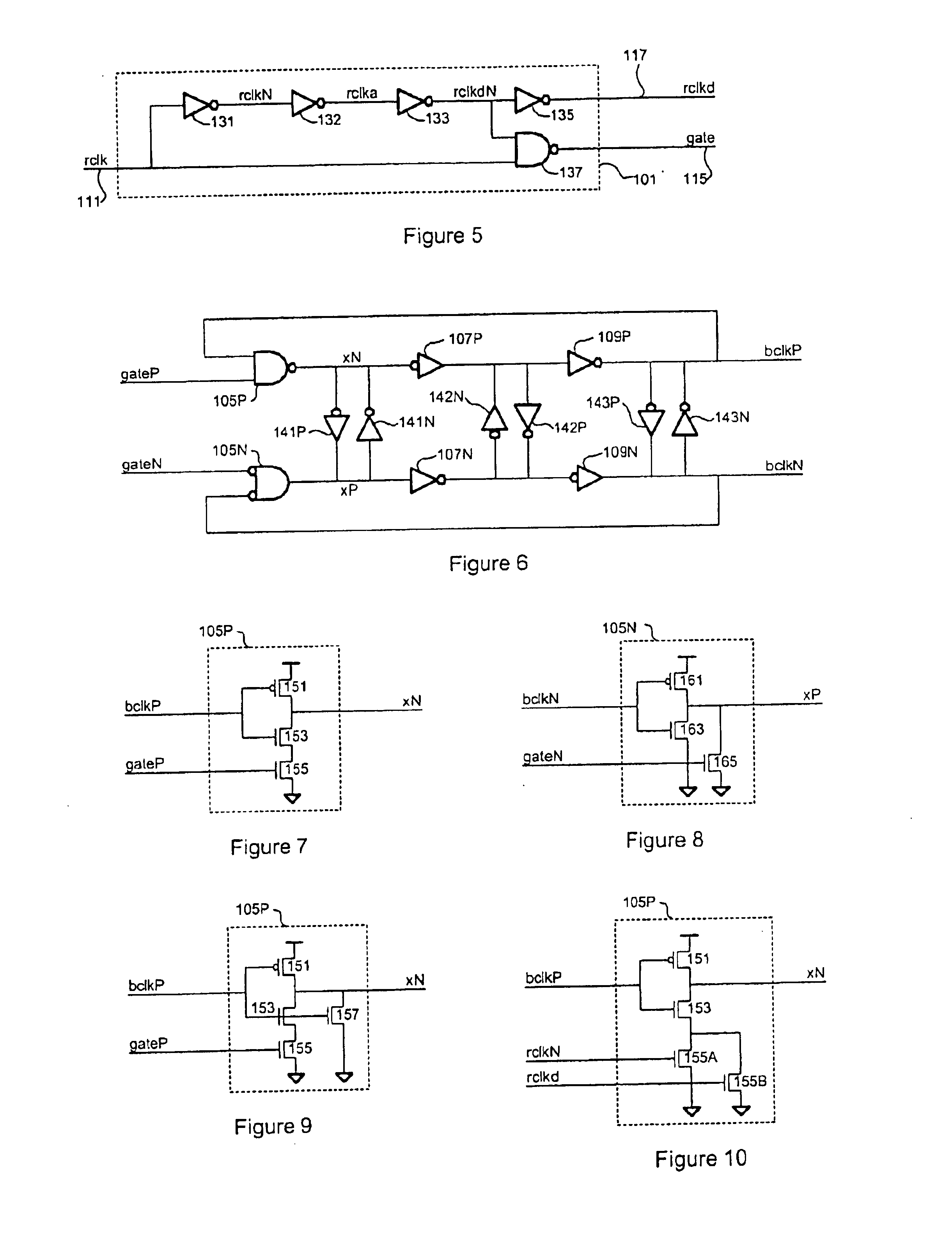

Phase controlled oscillator circuit with input signal coupler

An oscillating signal in an oscillator is caused to phase shift toward the phase of an input signal coupled to the oscillating signal. The resonant frequency of the oscillator is about equal to an integer multiple of the frequency of the input signal. The input signal may be generated in a pulse generator to have an input pulse duration less than or equal to that of the oscillating signal. The oscillator circuit may be used as a filter to filter pulse width variations or to filter jitter from a reference clock. The oscillator circuit may also serve as a buffer by amplifying the input signal. Phase interpolation can be obtained by coupling at least one input signal with at least one oscillating signal.

Owner:RAMBUS INC

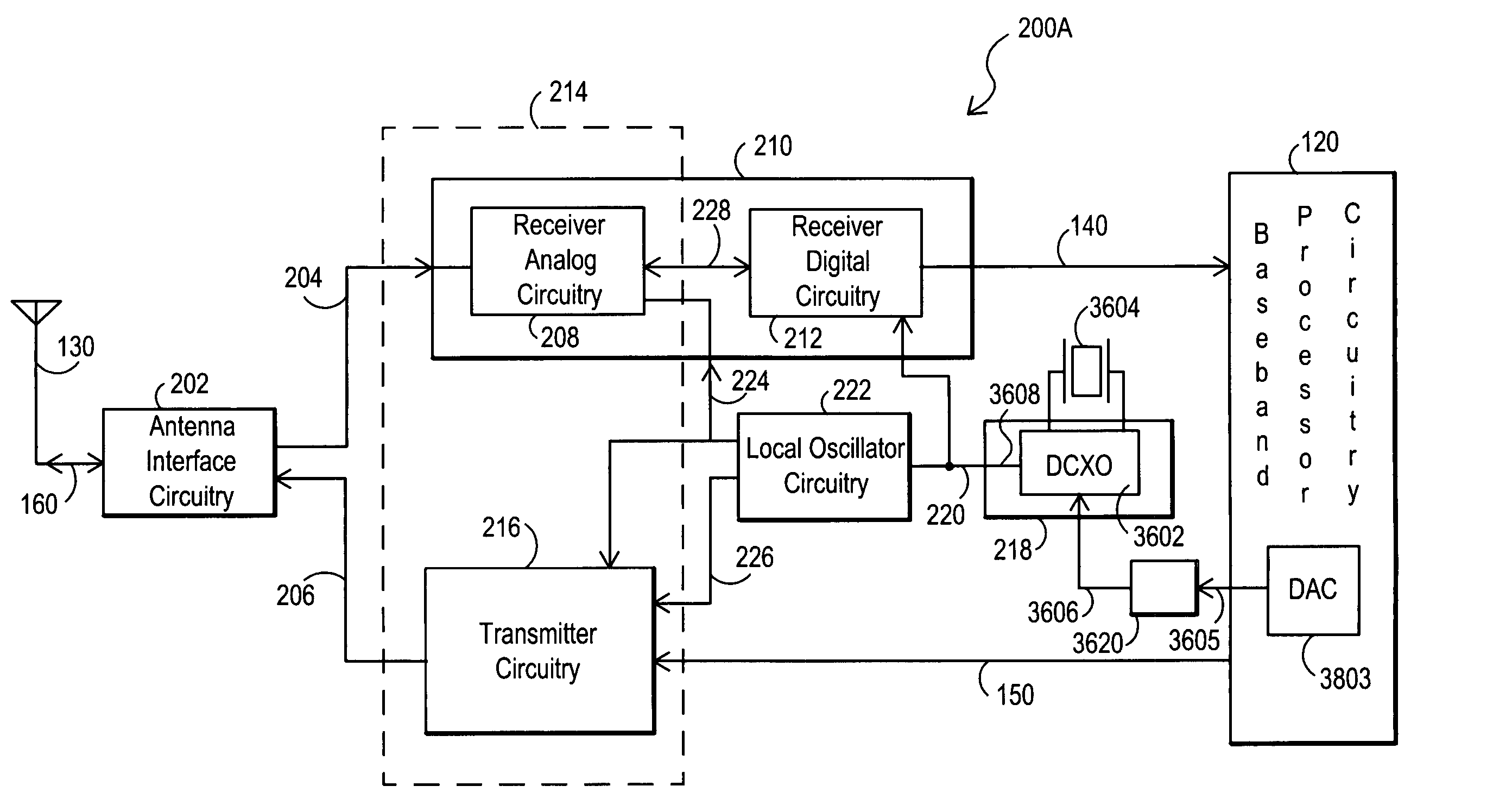

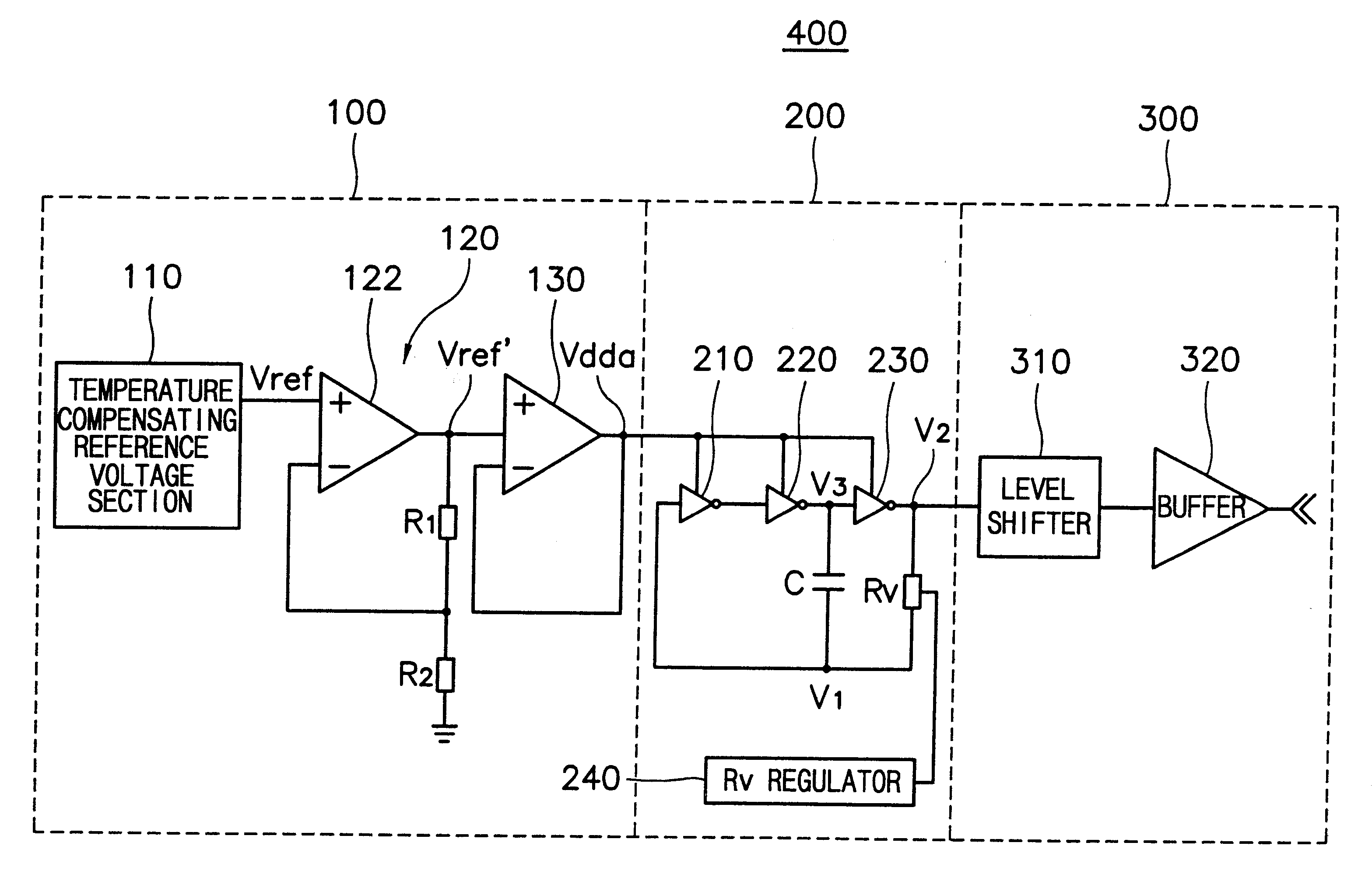

Systems and methods for providing an adjustable reference signal to RF circuitry

InactiveUS7035607B2Guaranteed interference effectReduce the impact of interferenceAutomatic scanning with simultaneous frequency displayPulse automatic controlControl signalEngineering

Frequency modification circuitry may be employed as part of a crystal oscillator circuit to generate a reference signal with adjustable frequency. The frequency modification circuitry may be implemented as part of a crystal oscillator circuit that includes digitally controlled crystal oscillator (“DCXO”) circuitry and a crystal. The frequency modification circuitry may adjust the frequency of the reference signal in response to one or more frequency control signals. In one example, the frequency modification circuitry may include variable capacitors such as one or more continuously variable and / or discretely variable capacitors for providing coarse and / or fine adjustment of the reference signal frequency.

Owner:SILICON LAB INC

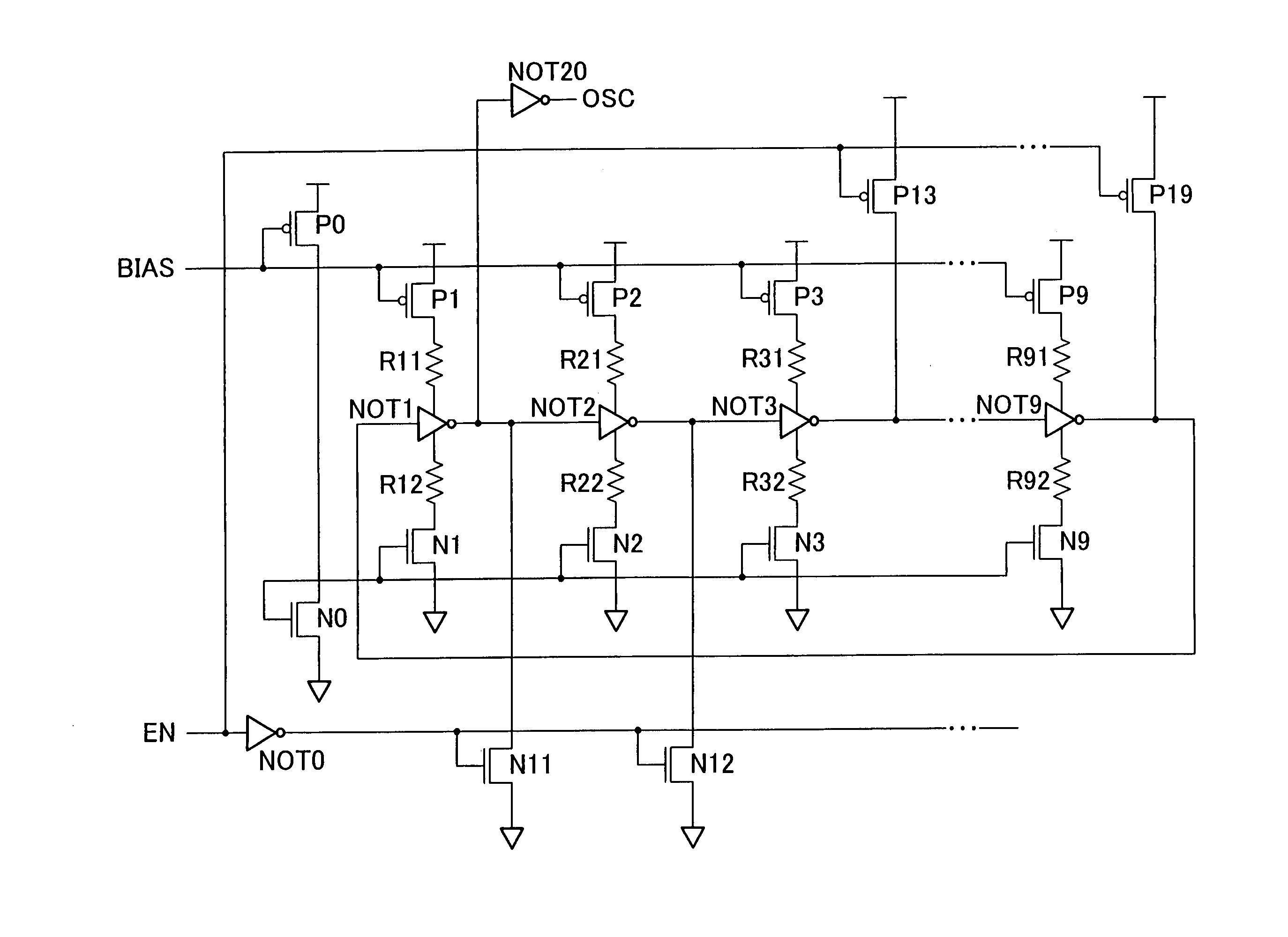

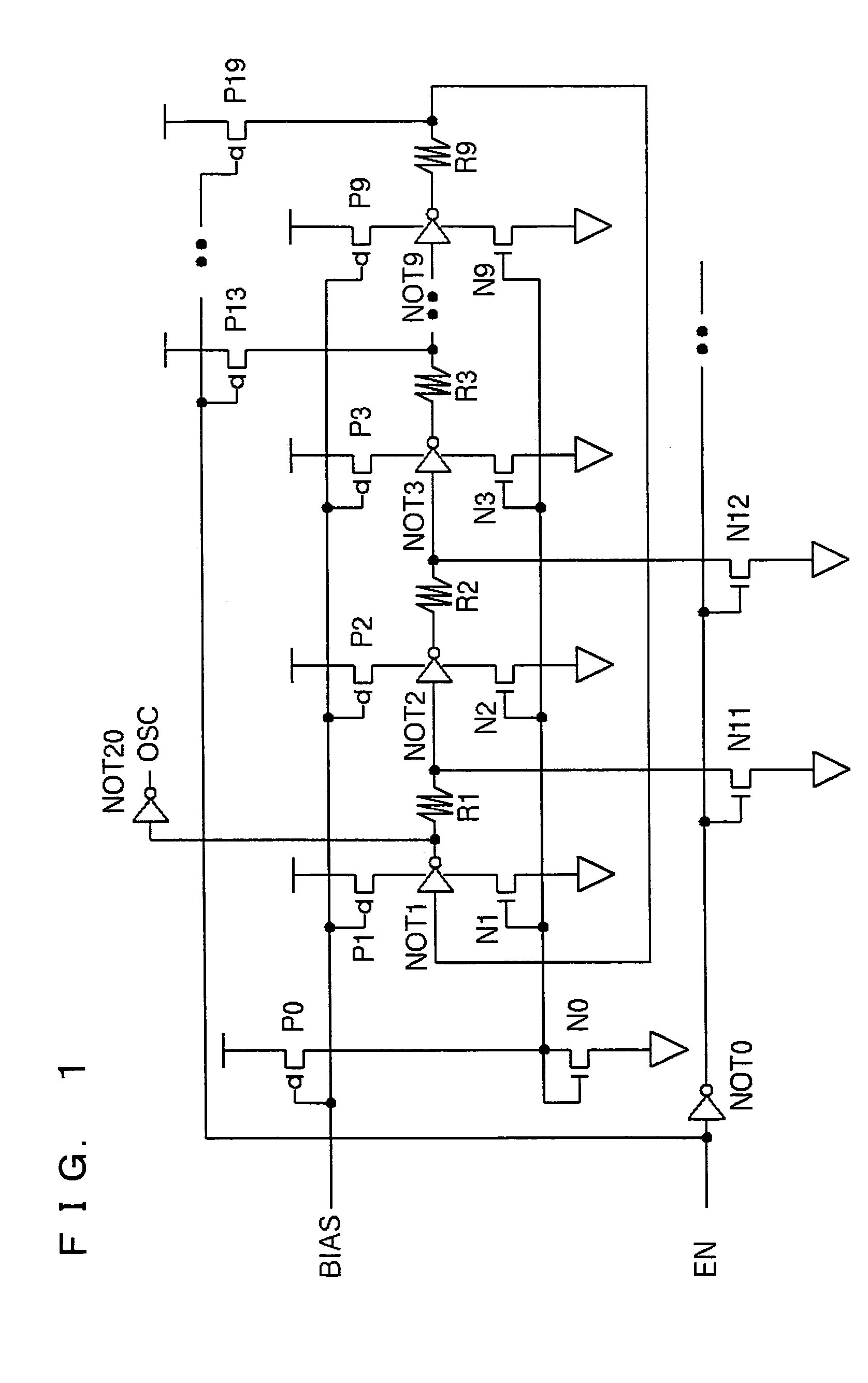

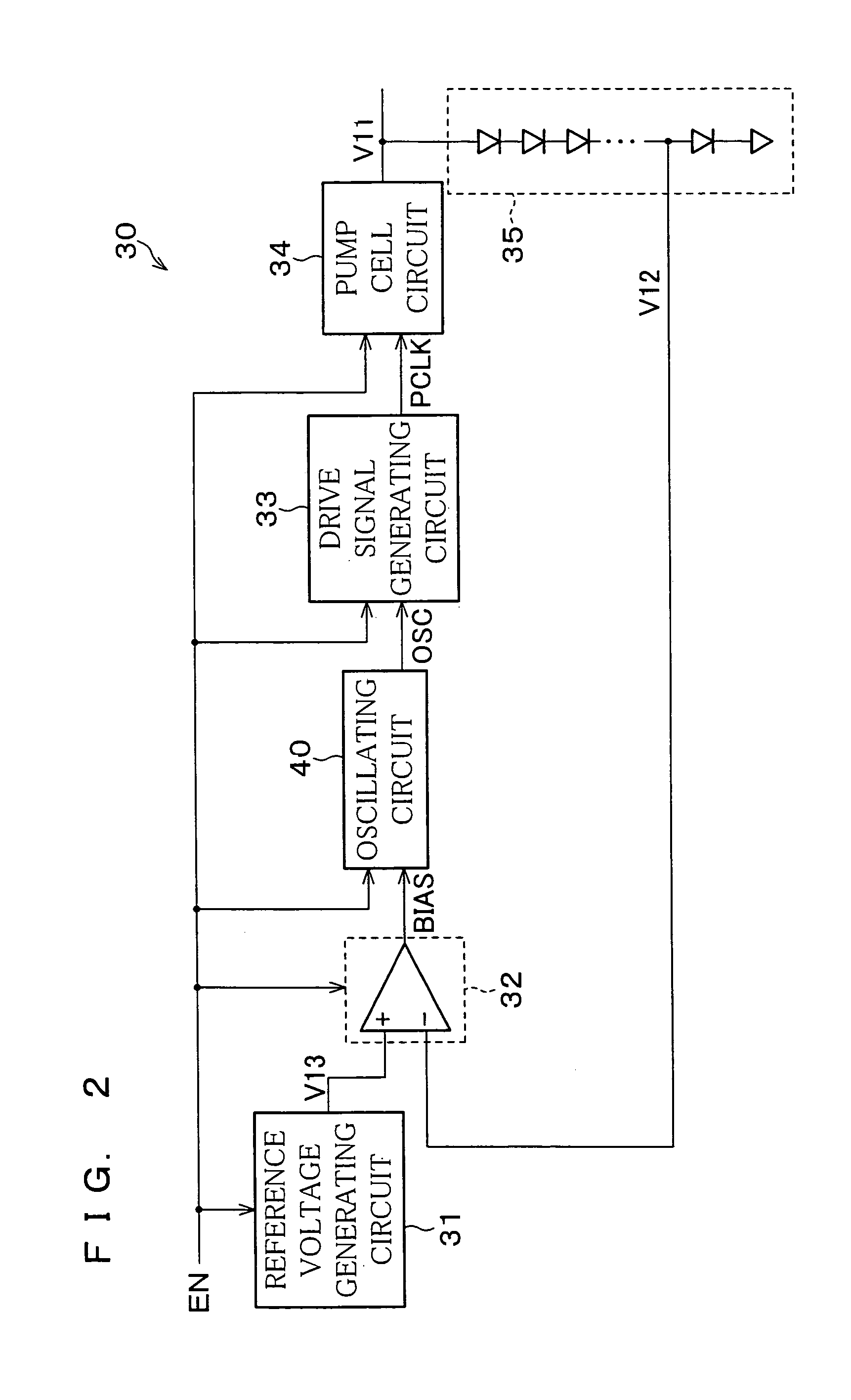

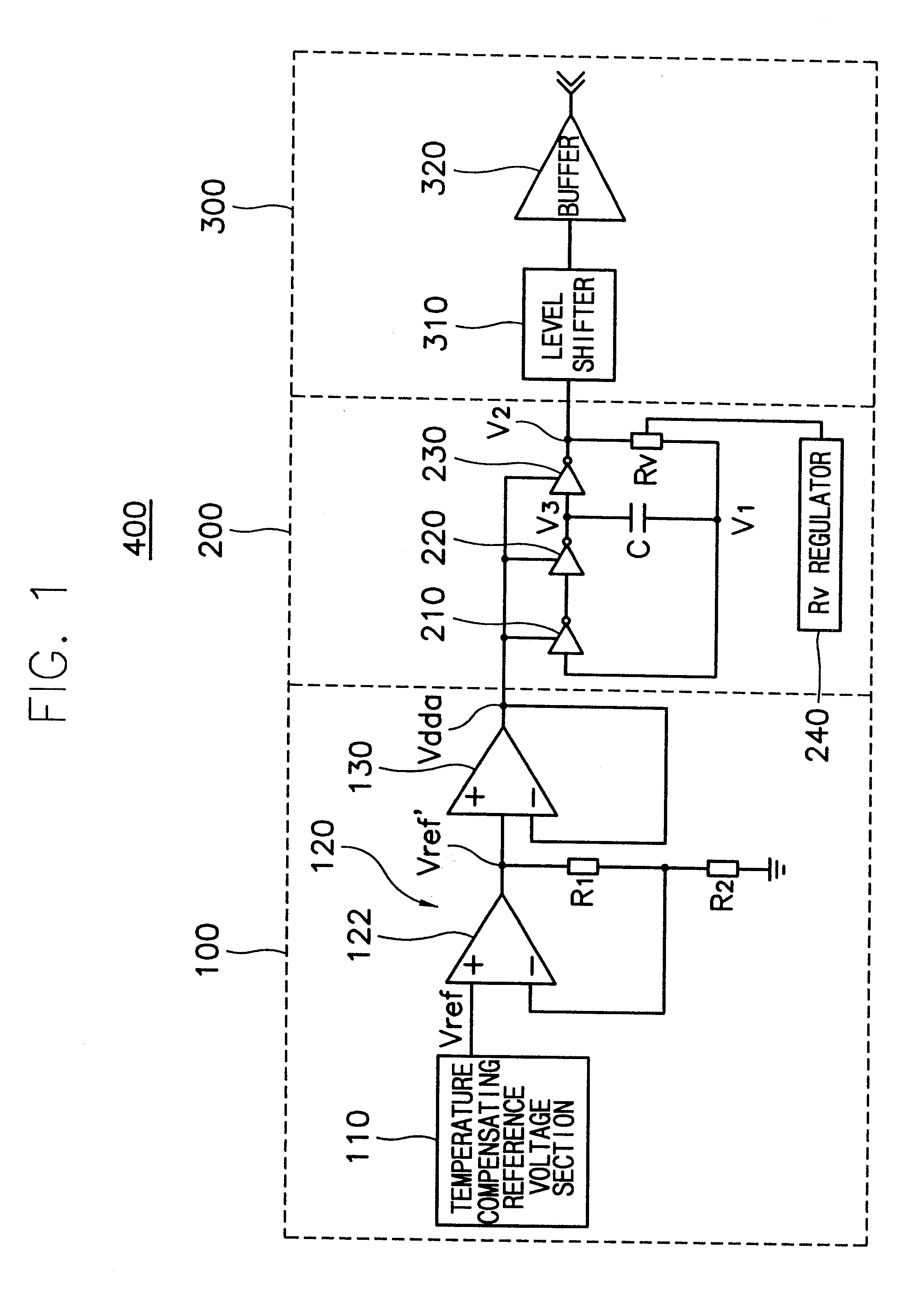

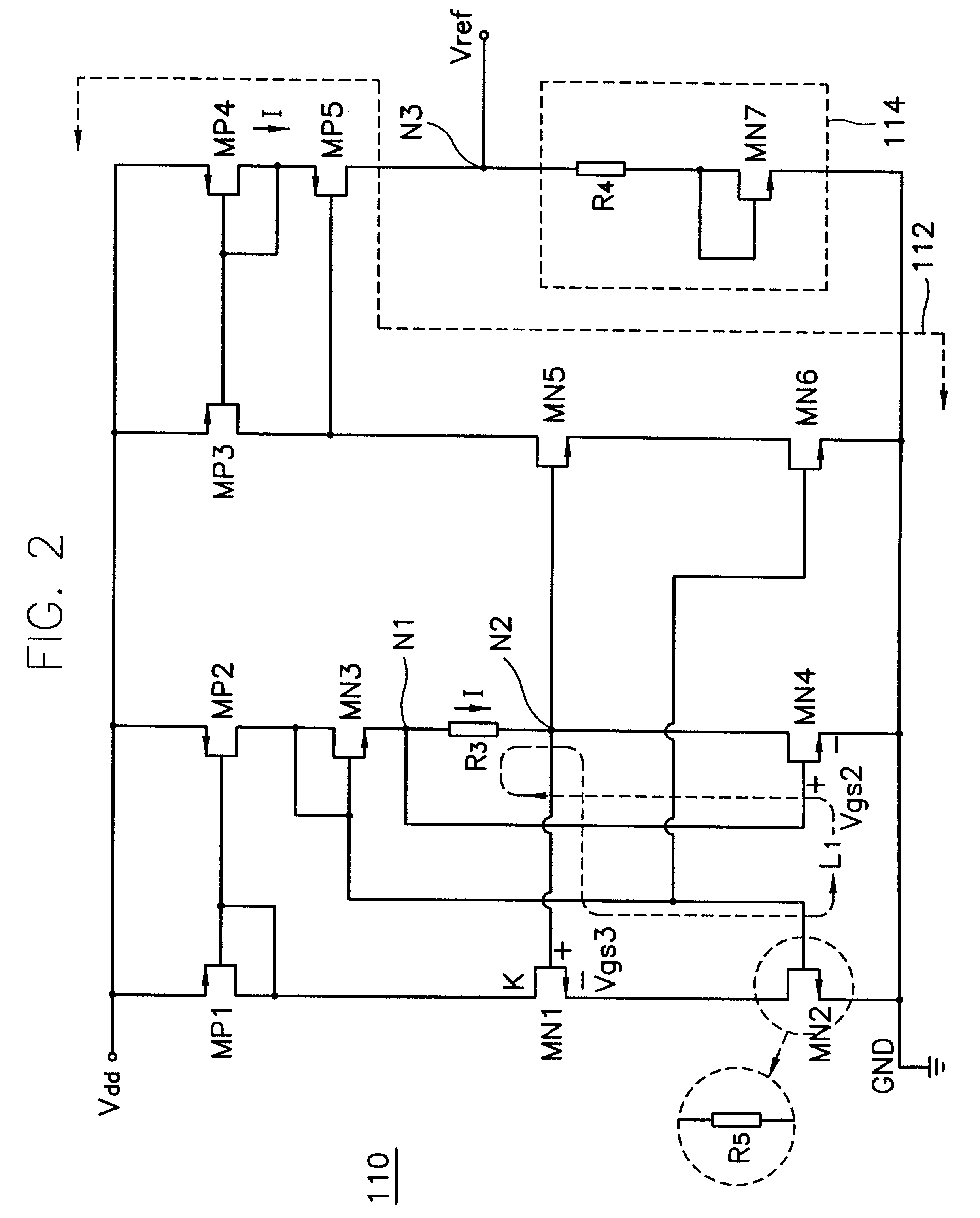

Oscillating circuit, booster circuit, nonvolatile memory device, and semiconductor device

InactiveUS7180794B2Suppress the variation in the oscillating frequencies of an output signalChange in resistancesSolid-state devicesRead-only memoriesPower inverterEngineering

In a ring oscillator constituting an oscillating circuit, resistor circuits are used as delay circuits to be connected to respective inverters. That is, the inverters and the resistors are connected in series so that the resistor is provided between the adjacent inverters. With the arrangement, it is possible to provide an oscillating circuit which is less dependent on any of power supply voltages, temperatures, and manufacturing variations, while maintaining a characteristic in which the oscillating frequency decreases as an output voltage of a booster circuit increases.

Owner:TAMIRAS PER PTE LTD LLC

On-chip transistor degradation monitoring

InactiveUS7205854B2Digital circuit testingPulse generation by logic circuitsEngineeringSelf excited oscillation

Embodiments of the invention include on-chip characterization of transistor degradation. In one embodiment, includes one or more functional blocks to perform one or more functions and an integrated on-chip characterization circuit to perform on-chip characterization of transistor degradation. The integrated on-chip characterization circuit includes a selectively enabled ring oscillator to generate a reference oscillating signal, a free-running ring oscillator to generate a free-running oscillating signal, and a comparison circuit coupled to the selectively enabled ring oscillator and the free-running ring oscillator. From the reference oscillating signal and the free-running oscillating signal, the comparison circuit determine a measure of transistor degradation.

Owner:INTEL CORP

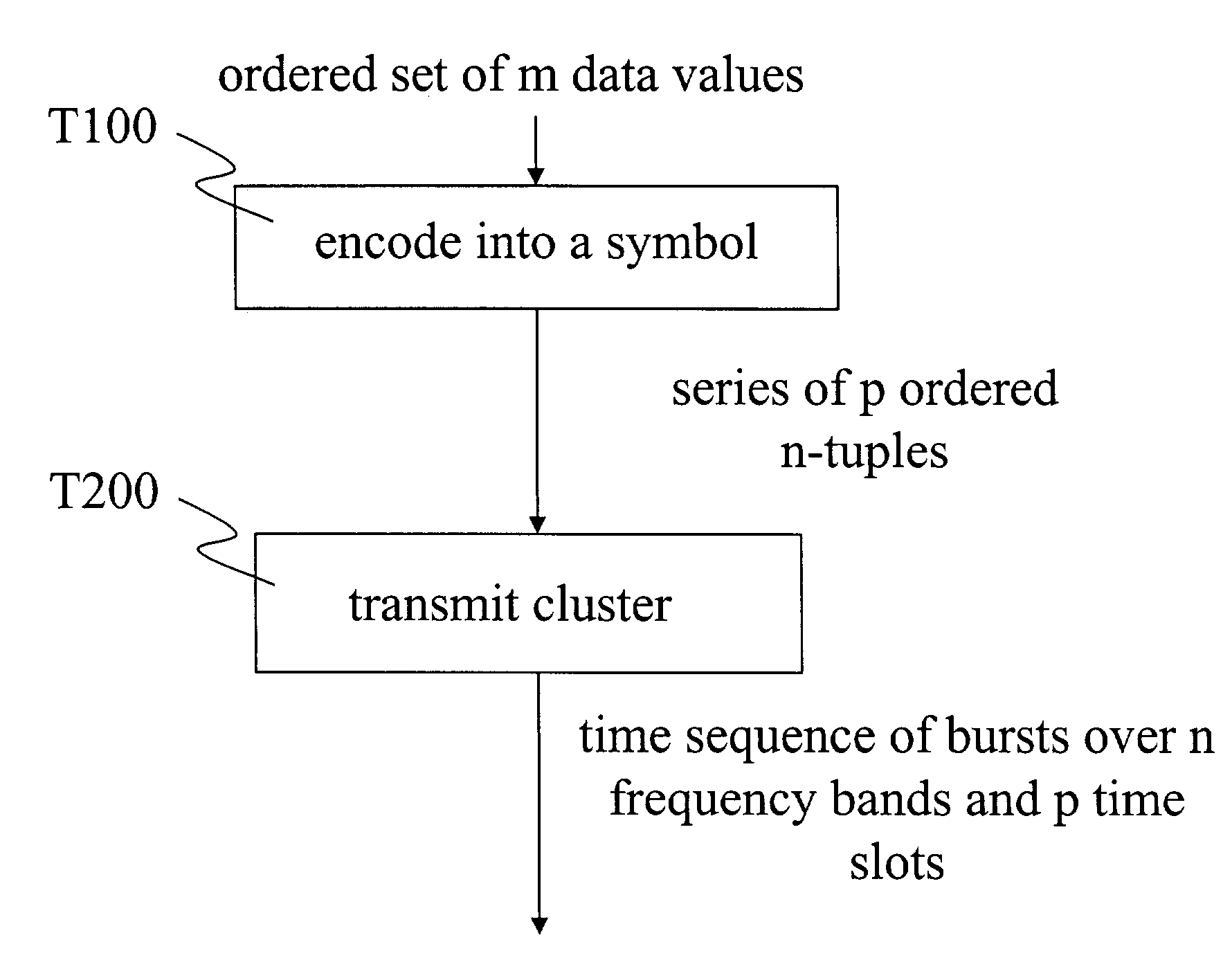

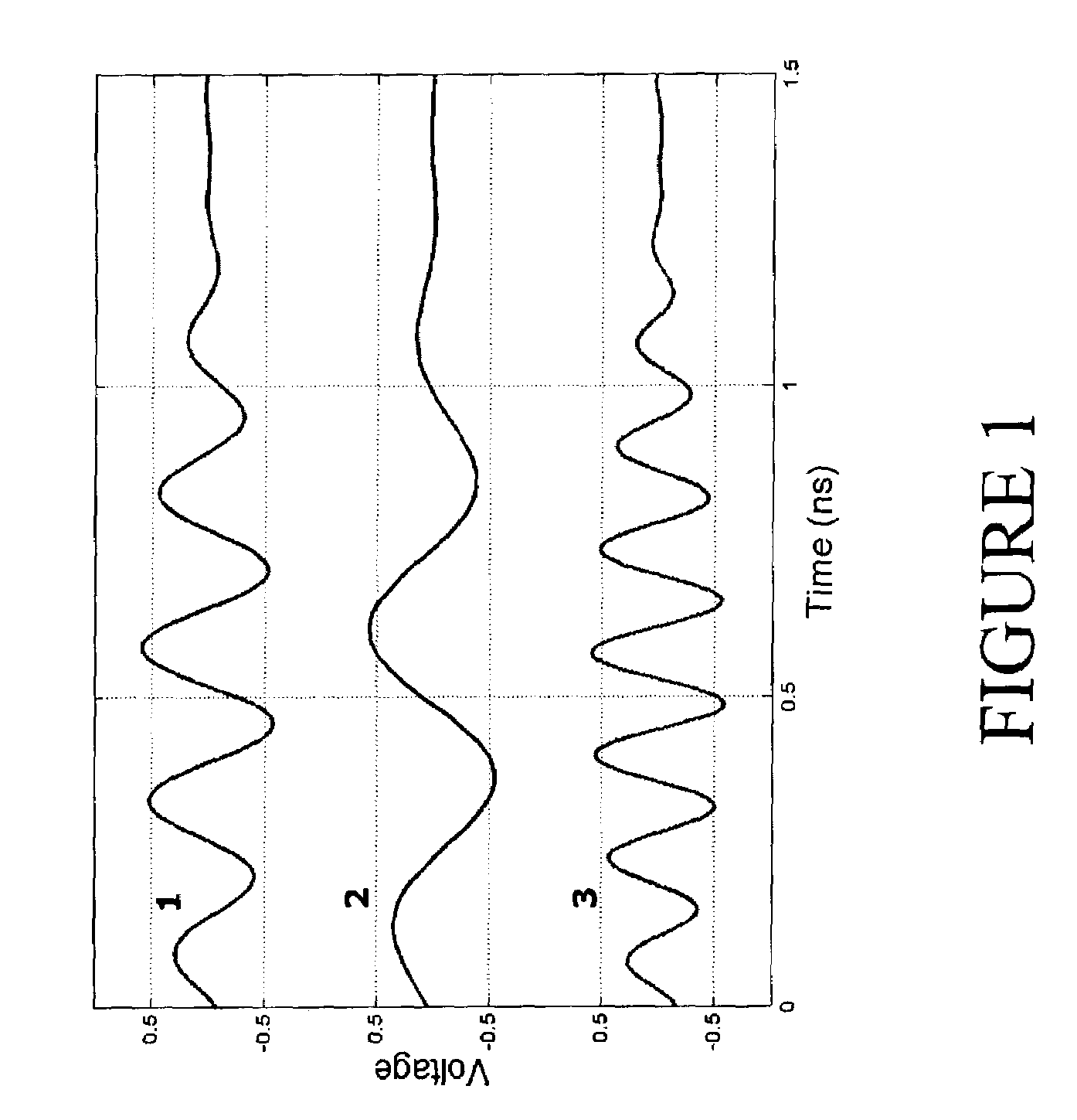

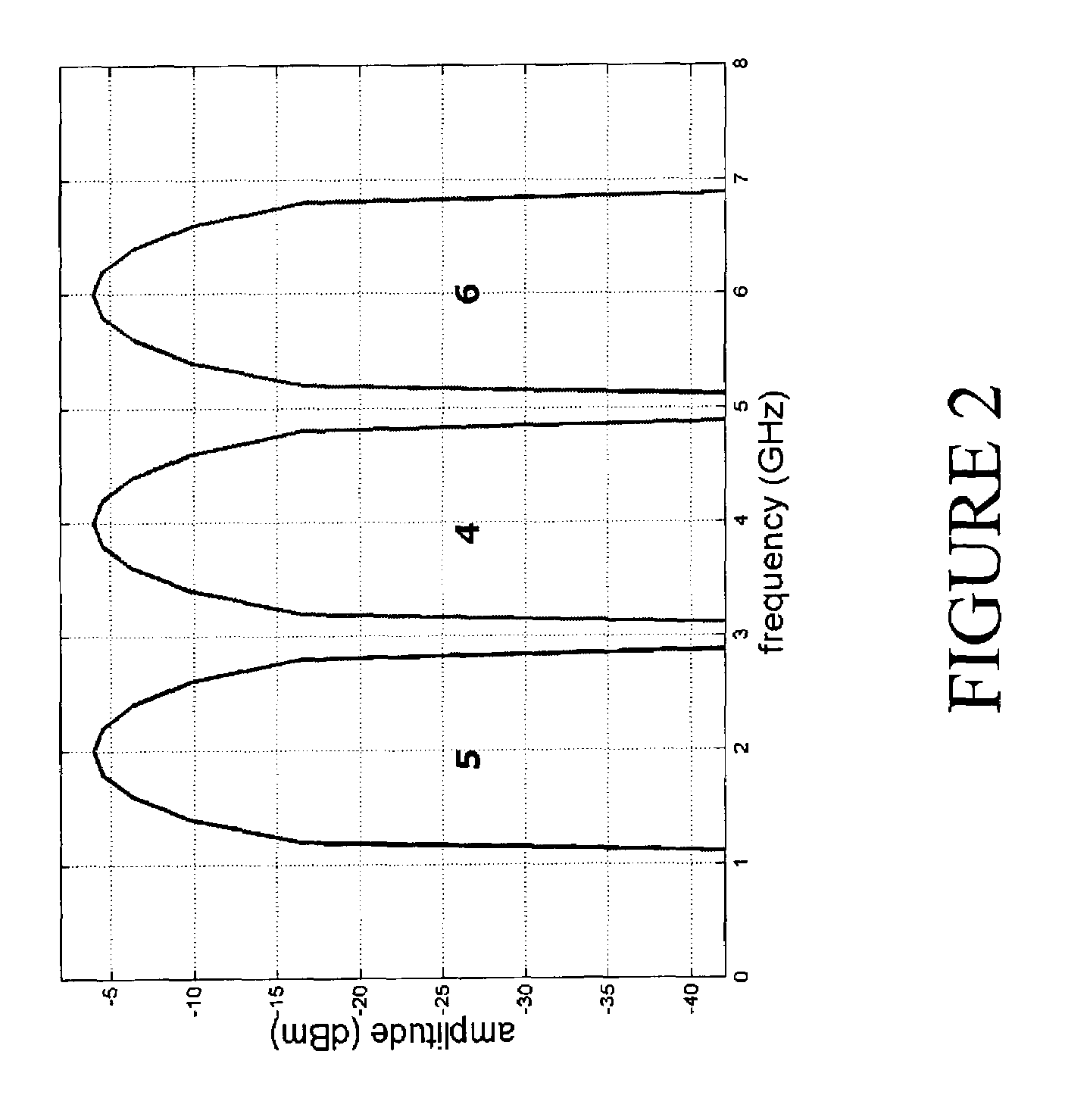

Method and apparatus for data transfer using a time division multiple frequency scheme supplemented with polarity modulation

A method of data transmission according to one embodiment of the invention includes encoding a set of data values to produce a corresponding series of ordered n-tuples. The method also includes transmitting, according to the series of ordered n-tuples, a plurality of bursts over a plurality n of frequency bands. Specifically, for each of the plurality of bursts, a frequency band occupied by the burst is indicated by the order within its n-tuple of an element corresponding to the burst. A bandwidth of at least one of the plurality of bursts is at least two percent of the center frequency of the burst. Information is encoded into a polarity of at least one of the plurality of bursts.

Owner:GENERAL ATOMICS

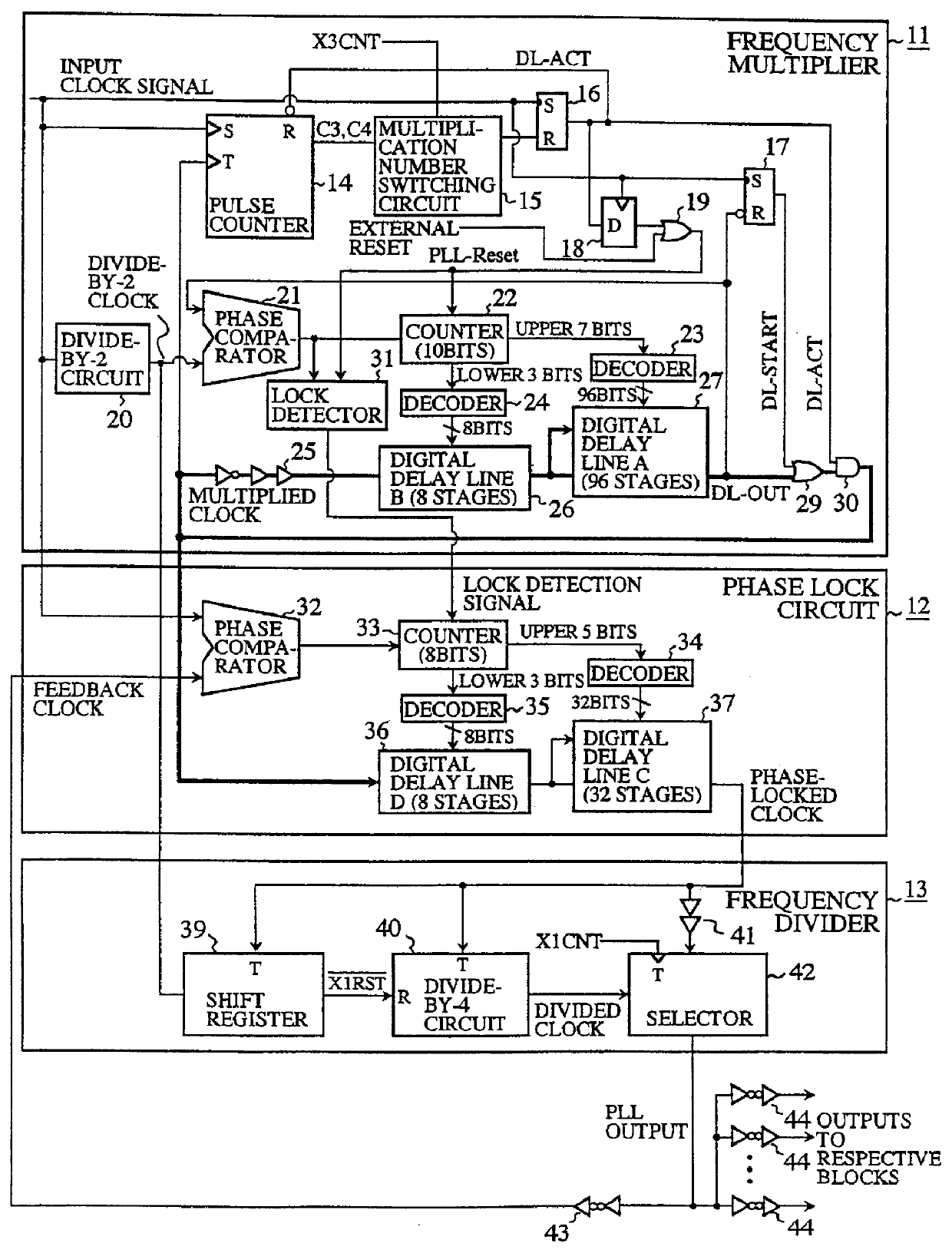

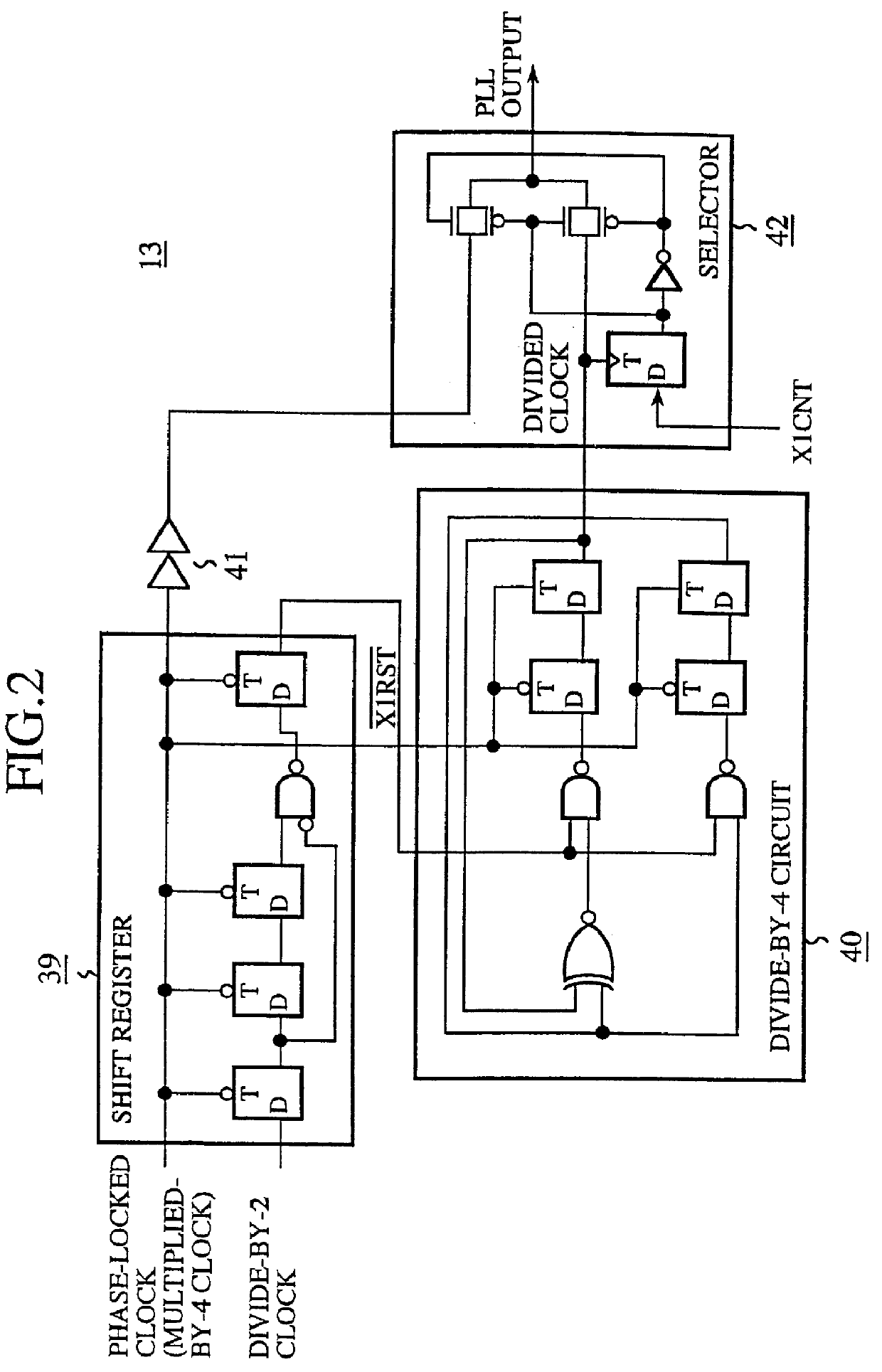

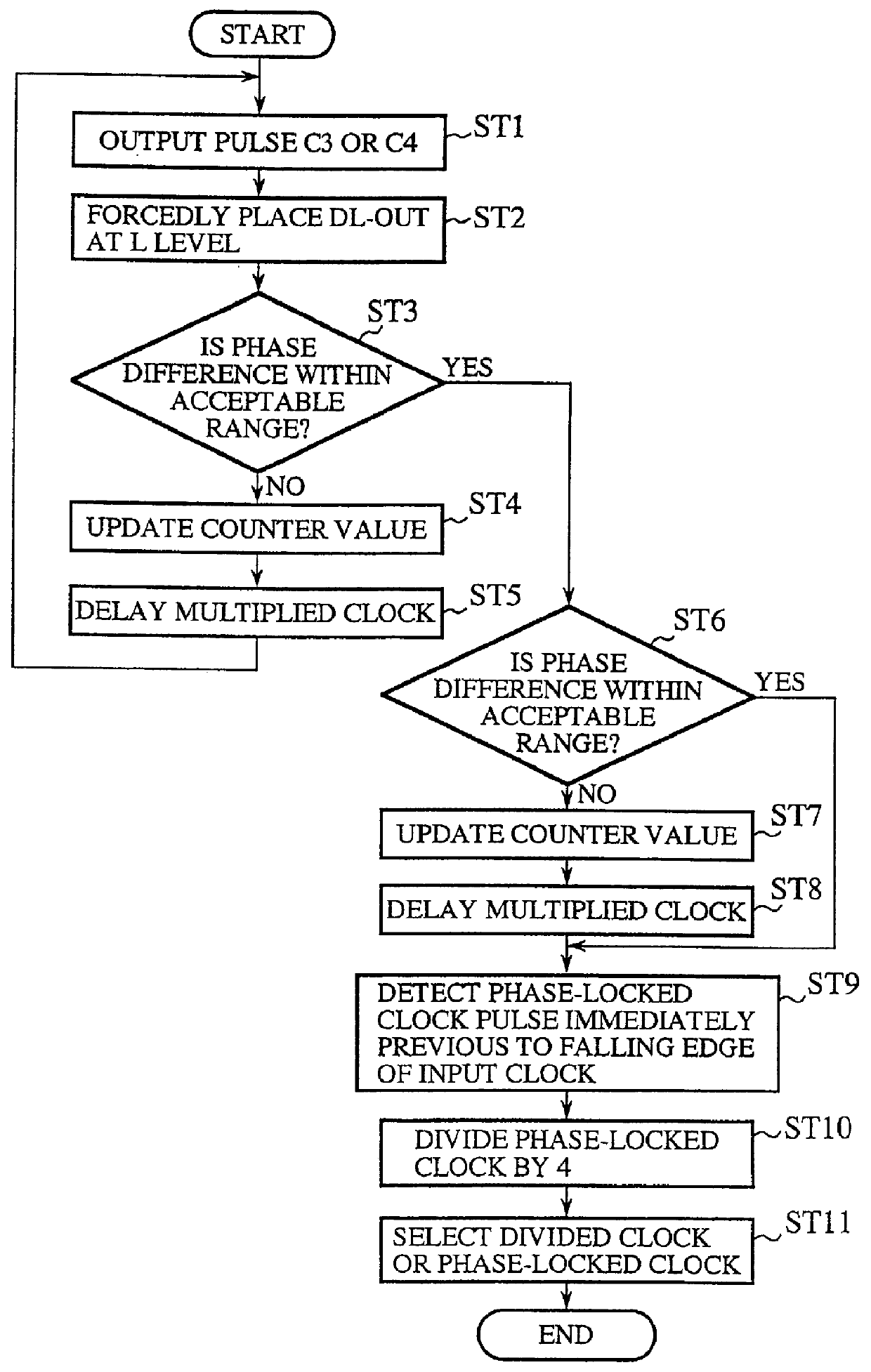

Clock generator and clock generating method capable of varying clock frequency without increasing the number of delay elements

InactiveUS6049238AReduce frequencyDelay lines pulse generationPulse automatic controlPhase differenceDelayed time

A clock generator including a frequency multiplier, a phase lock circuit and a frequency divider. The frequency multiplier generates a frequency multiplied clock by multiplying the frequency of an input clock. The phase lock circuit detects a phase difference between the input clock and a frequency divided clock, and generates, by delaying the frequency multiplied clock by an amount corresponding to the phase difference, a phase-locked clock with its phase locked with the input clock. The frequency divider detects in every fixed cycle a particular pulse of the phase-locked clock, and generates the frequency divided clock by dividing the phase-locked clock with reference to the particular pulse of the phase-locked clock. In particular, the frequency divider detects the particular pulse immediately previous to a falling edge of the input clock. This can reduce the phase difference between the input clock and the phase-locked clock, and hence to solve a problem of a conventional clock generator in that a delay time of a digital delay line in a phase lock circuit must be lengthened with a reduction in the multiplication number of the frequency multiplied clock, which requires a greater number of delay elements because of a large occupying area of the delay elements and a decoder, thereby increasing the circuit scale and cost of a chip to reduce the multiplication number of the frequency multiplied clock.

Owner:RENESAS ELECTRONICS CORP

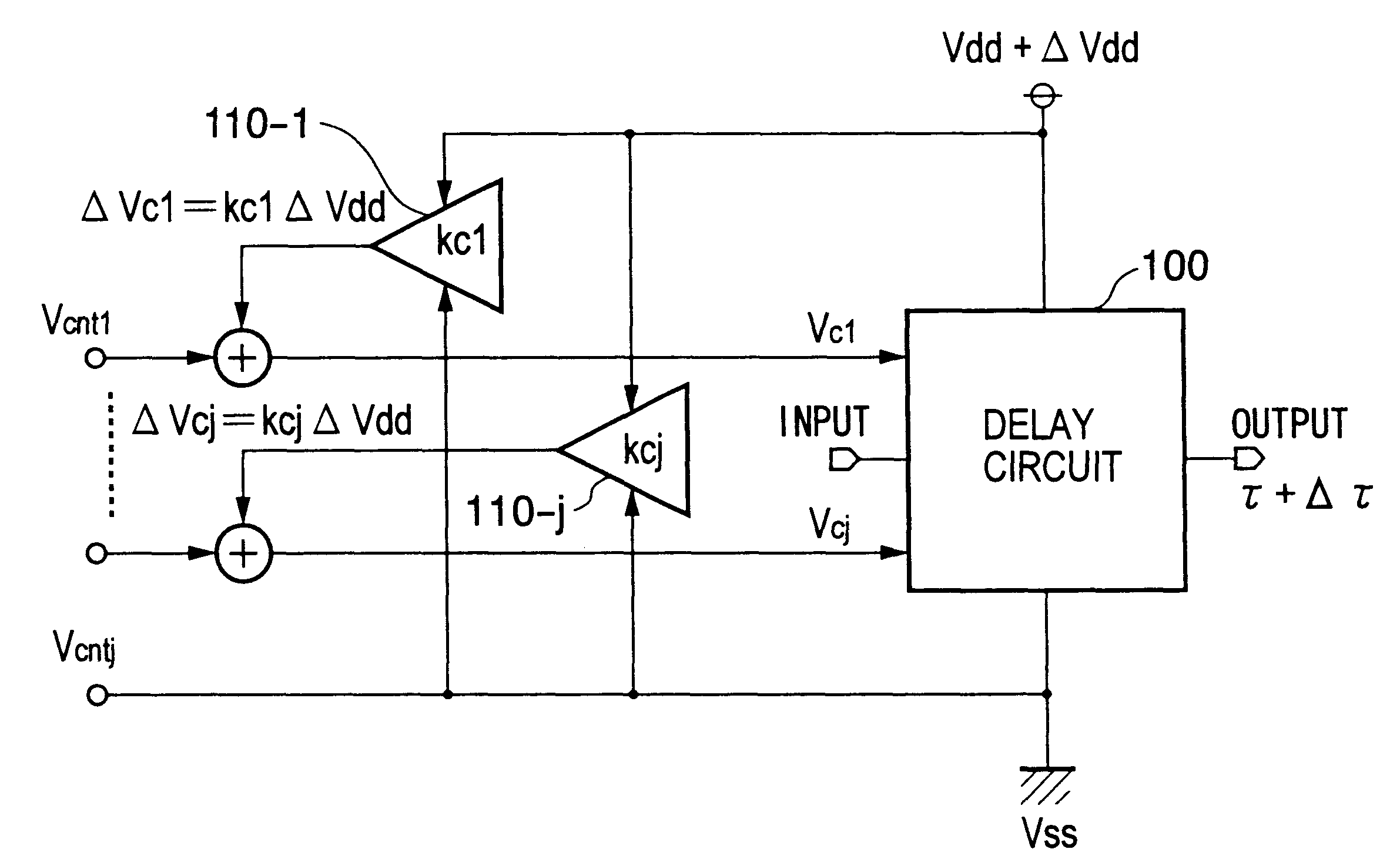

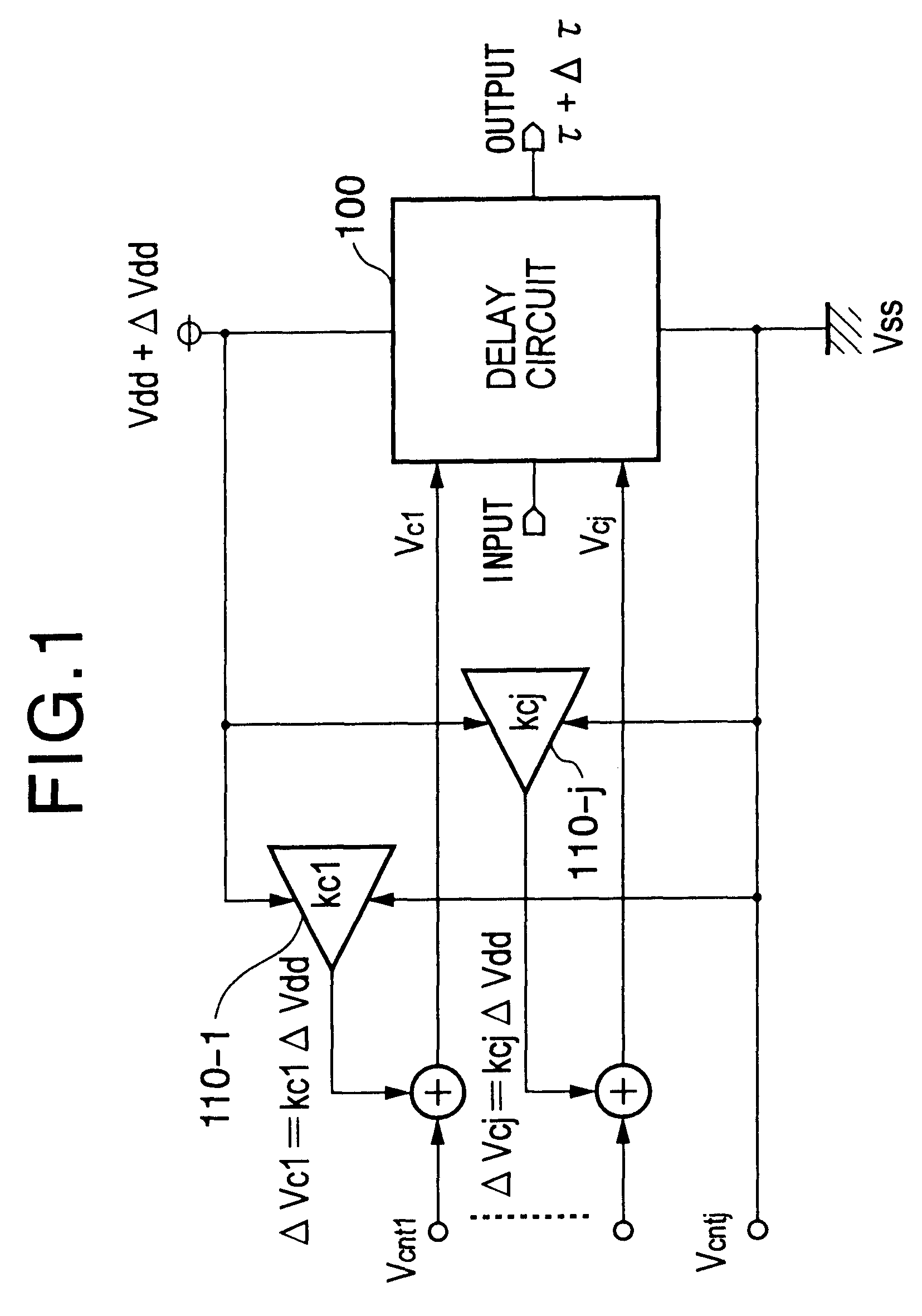

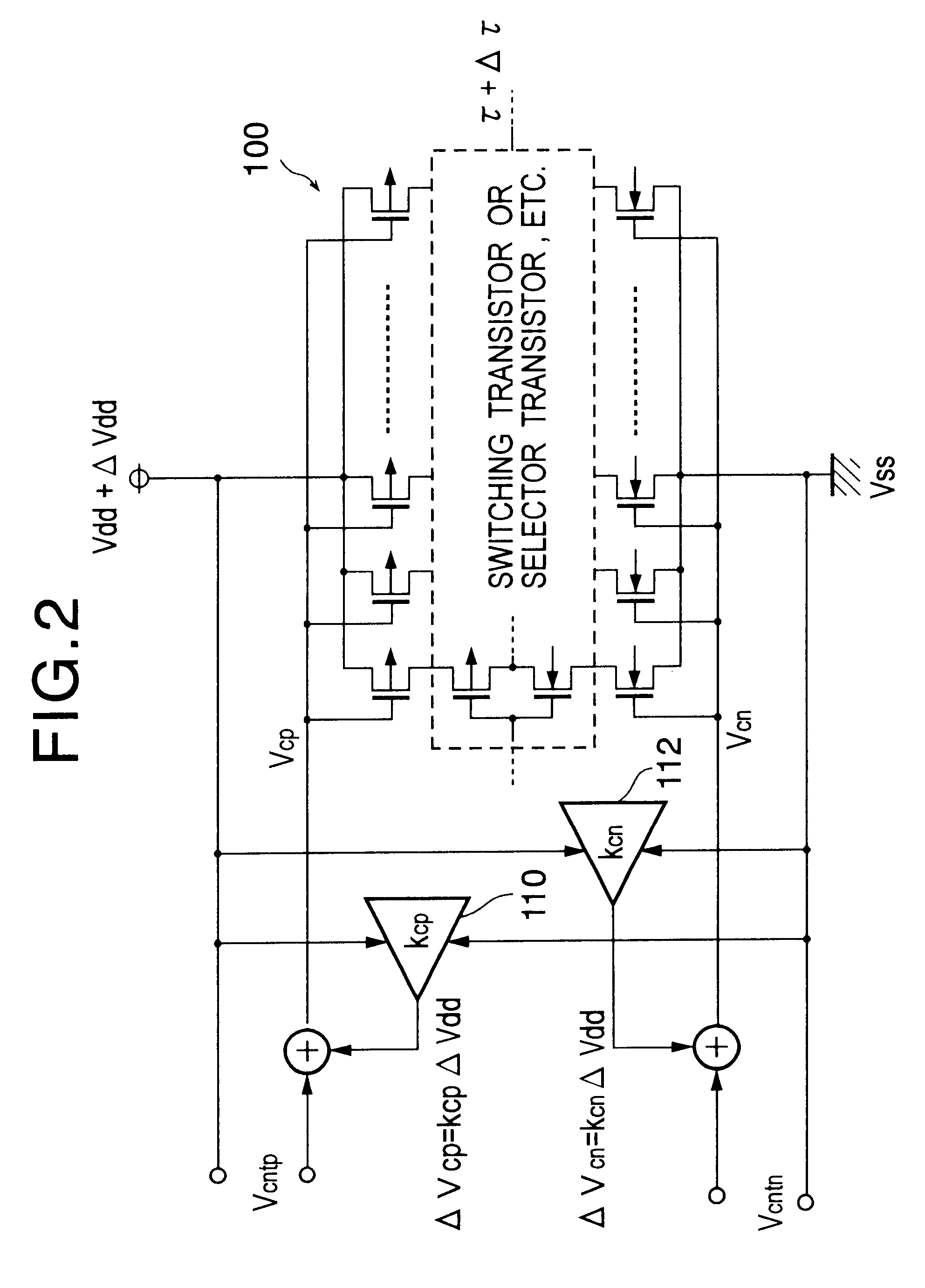

Delay circuit, voltage-controlled delay circuit, voltage-controlled oscillation circuit, delay adjustment circuit, DLL circuit, and PLL circuit

An inverter type delay circuit, voltage-controlled oscillation circuit, and voltage-controlled delay circuit capable of realizing simplification of circuit configuration, reduction of an effect of power source noise, and reduction of jitter, wherein a delay circuit, voltage-controlled oscillation circuit, and voltage-controlled delay circuit comprised of a plurality of delay stages controlled in drive current in accordance with a bias voltage or a control voltage and determined in delay time by the drive current, adding a change of a power source voltage to the above bias voltage or control voltage by a predetermined ratio and supplying a result of the addition to the above delay stages to suppress the power source voltage dependencies of the delay times of the delay stages, or connecting by a predetermined ratio a plurality of delay stages having different power source voltage dependencies, for example, power source voltage dependencies of opposite delay times, to suppress the power source voltage dependencies of delay times of the delay stages are realized.

Owner:SONY CORP

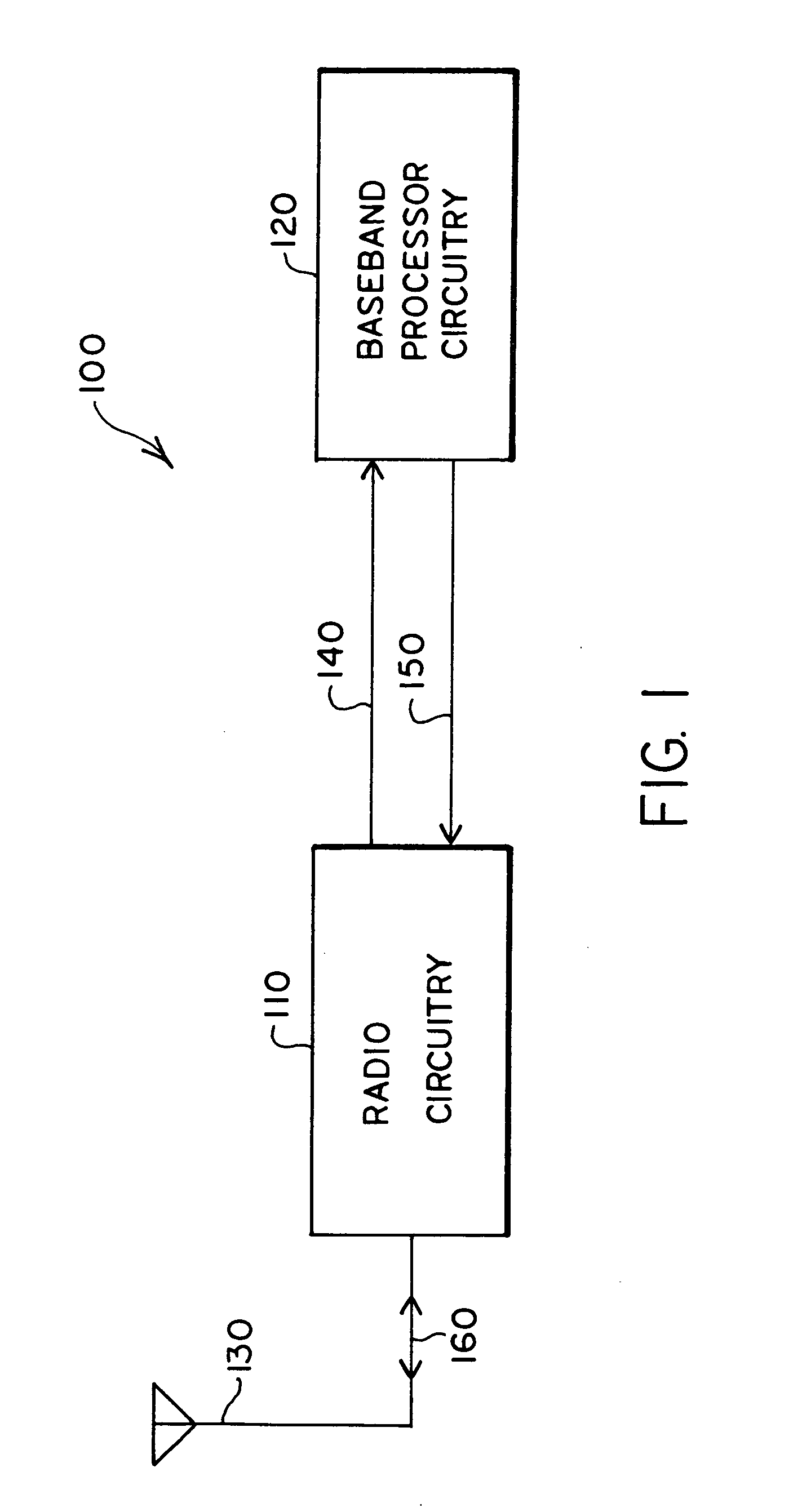

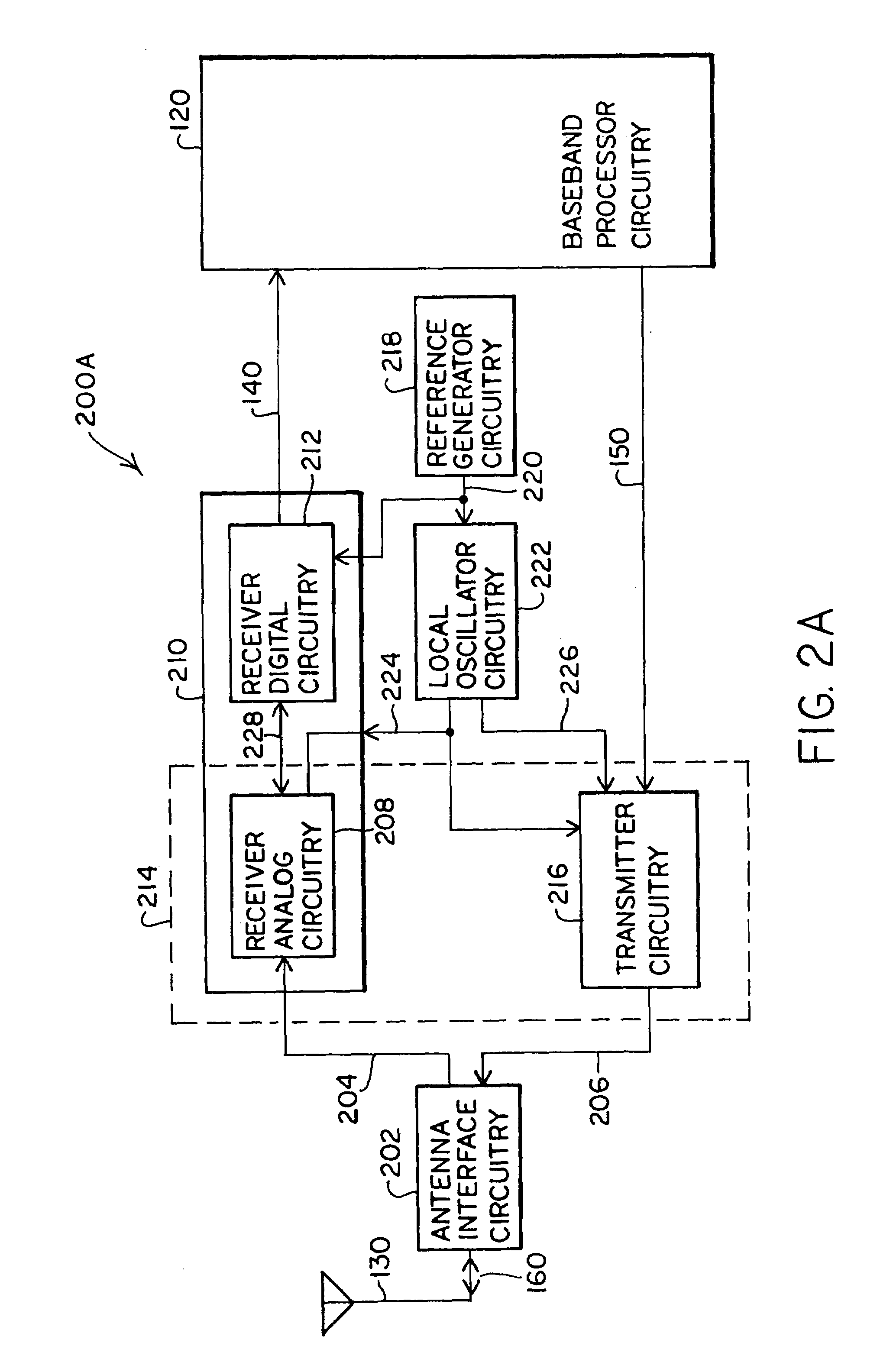

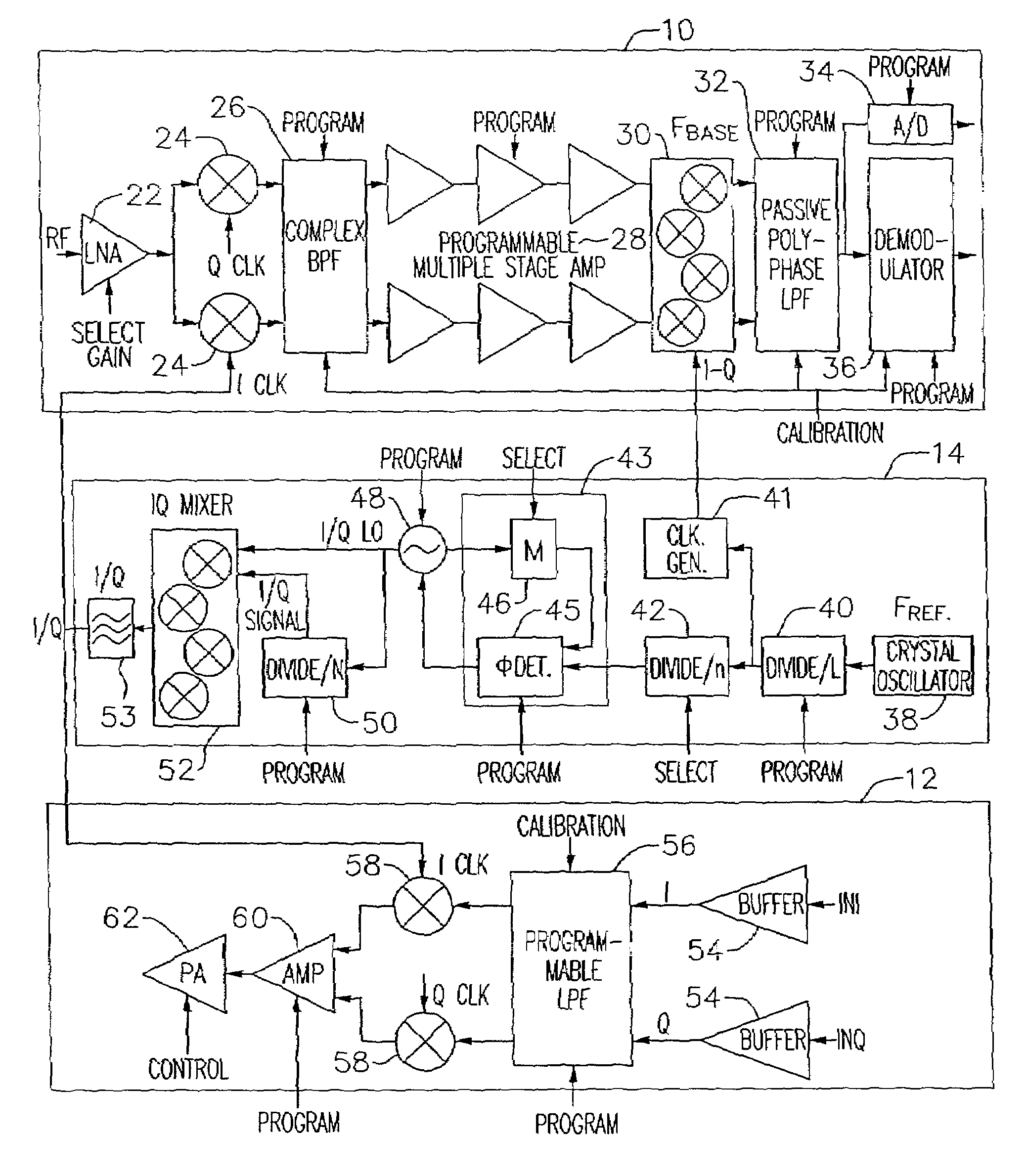

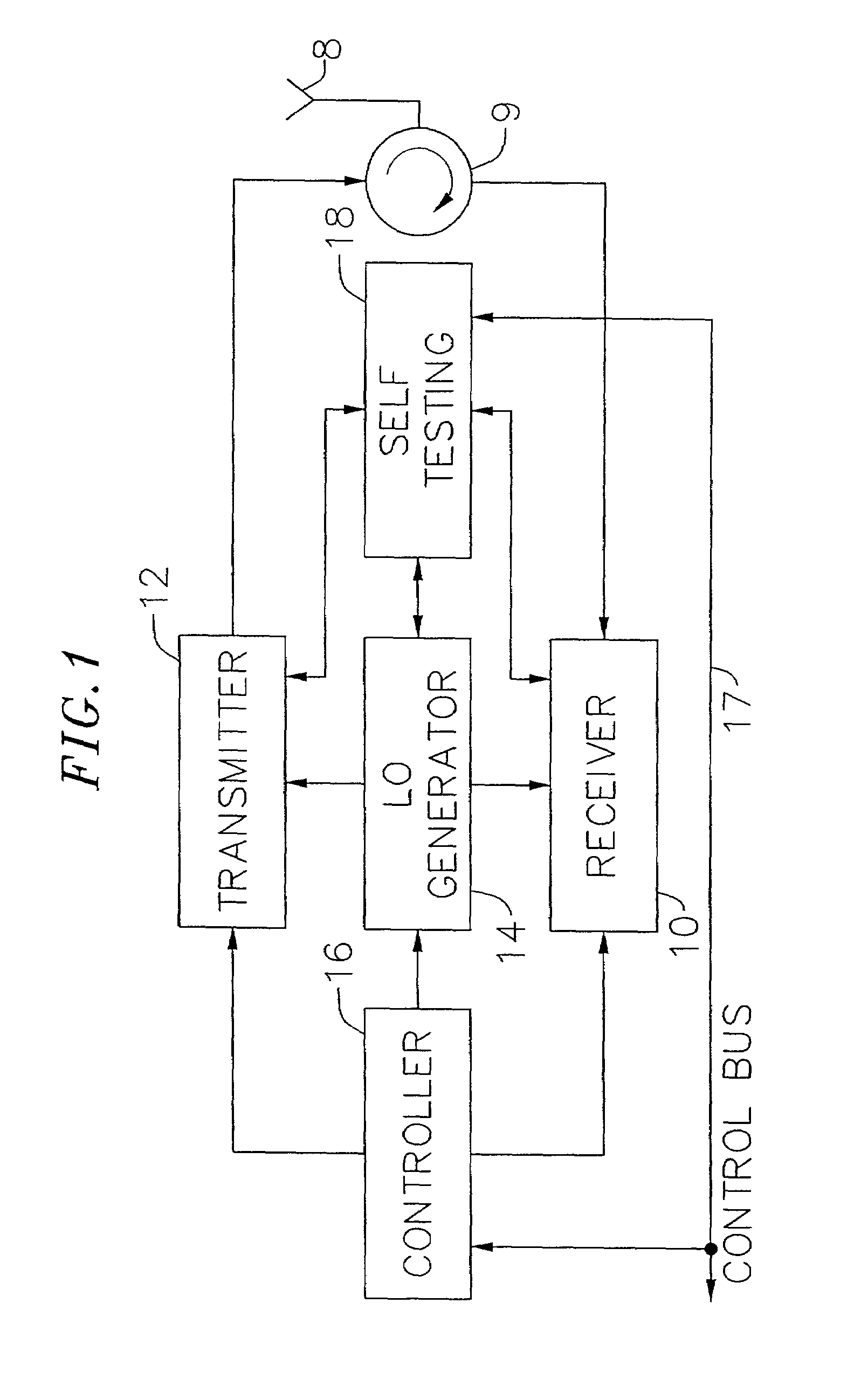

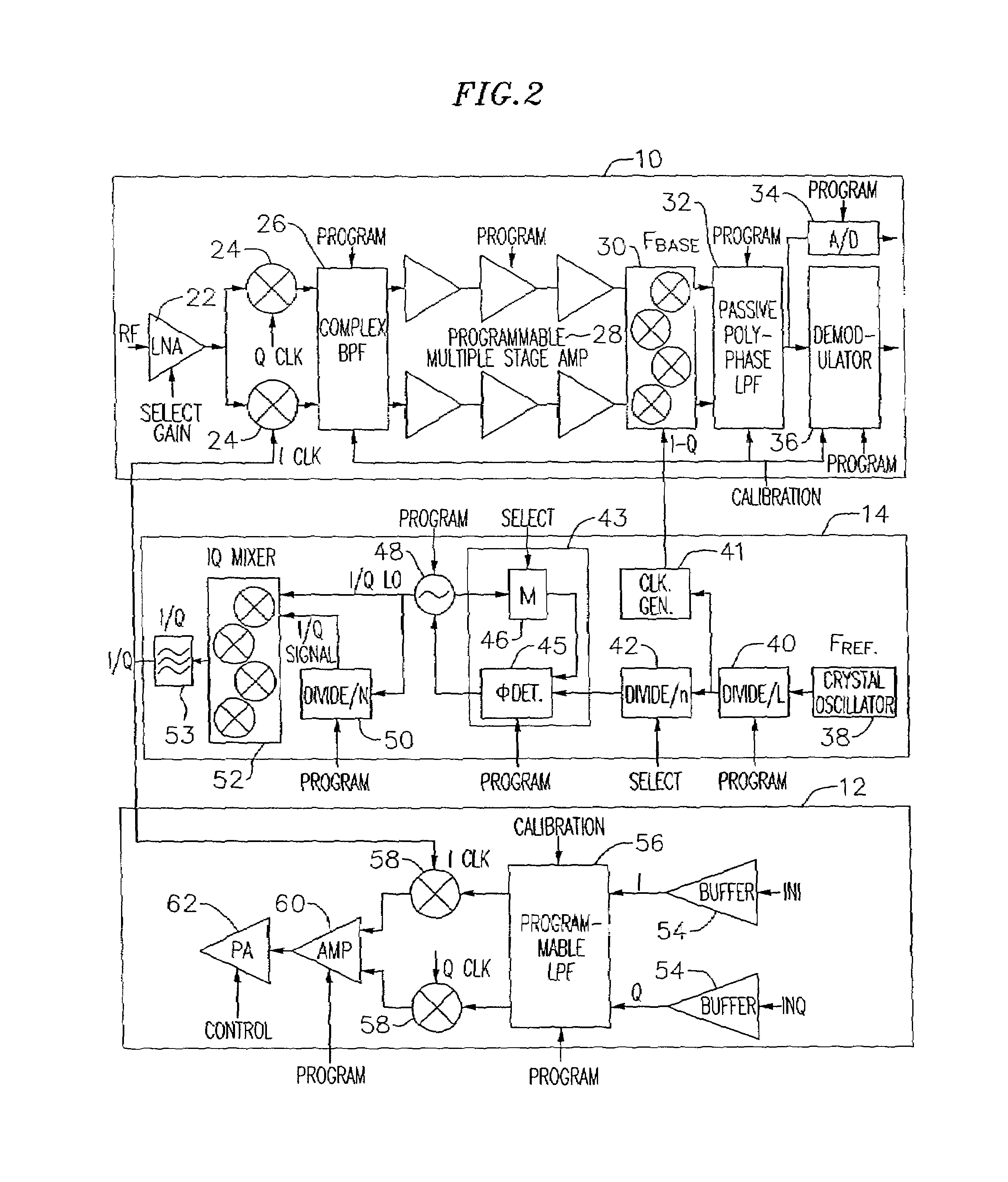

Adaptive radio transceiver with a local oscillator

InactiveUS7031668B2Increase data rateIncrease costTransmitters monitoringResonant circuit tuningTransceiverAdaptive programming

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

Voltage Controlled Oscillator (VCO) with a wide tuning range and substantially constant voltage swing over the tuning range

A wide tuning range and constant swing VCO is described that is based on a multipass Ring Oscillator enhanced with feed-backward connections. This VCO is designed to overcome tuning range limitations of prior-art “feed-forward” ring oscillators. The Feedback multipass Ring Oscillator of the invention provides decreasing frequency when tuned by increasing the feedback, thus covering a much wider tuning range irrespective of the speed limit of the technology while at the same time providing almost constant amplitude.

Owner:RAMBUS INC

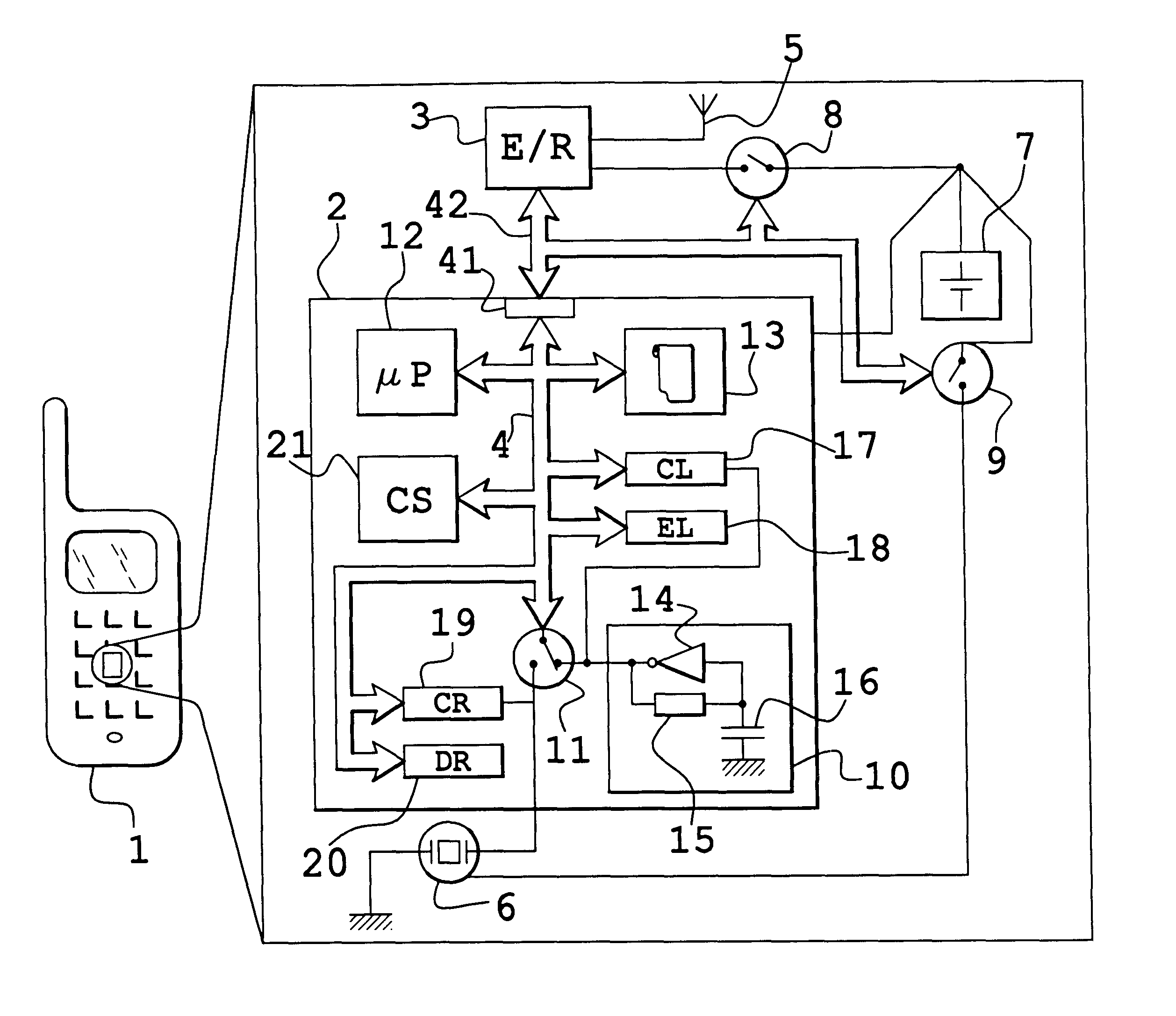

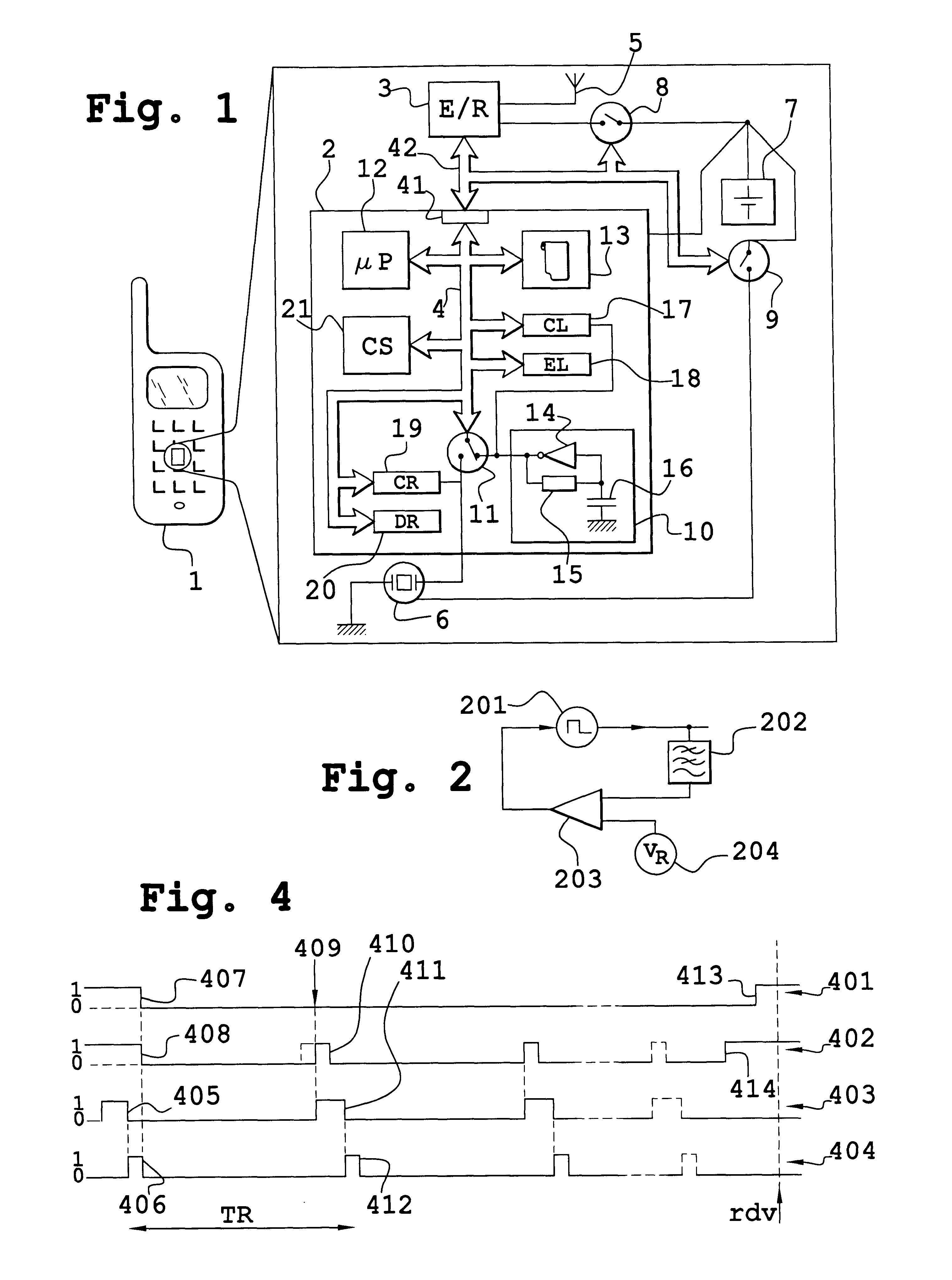

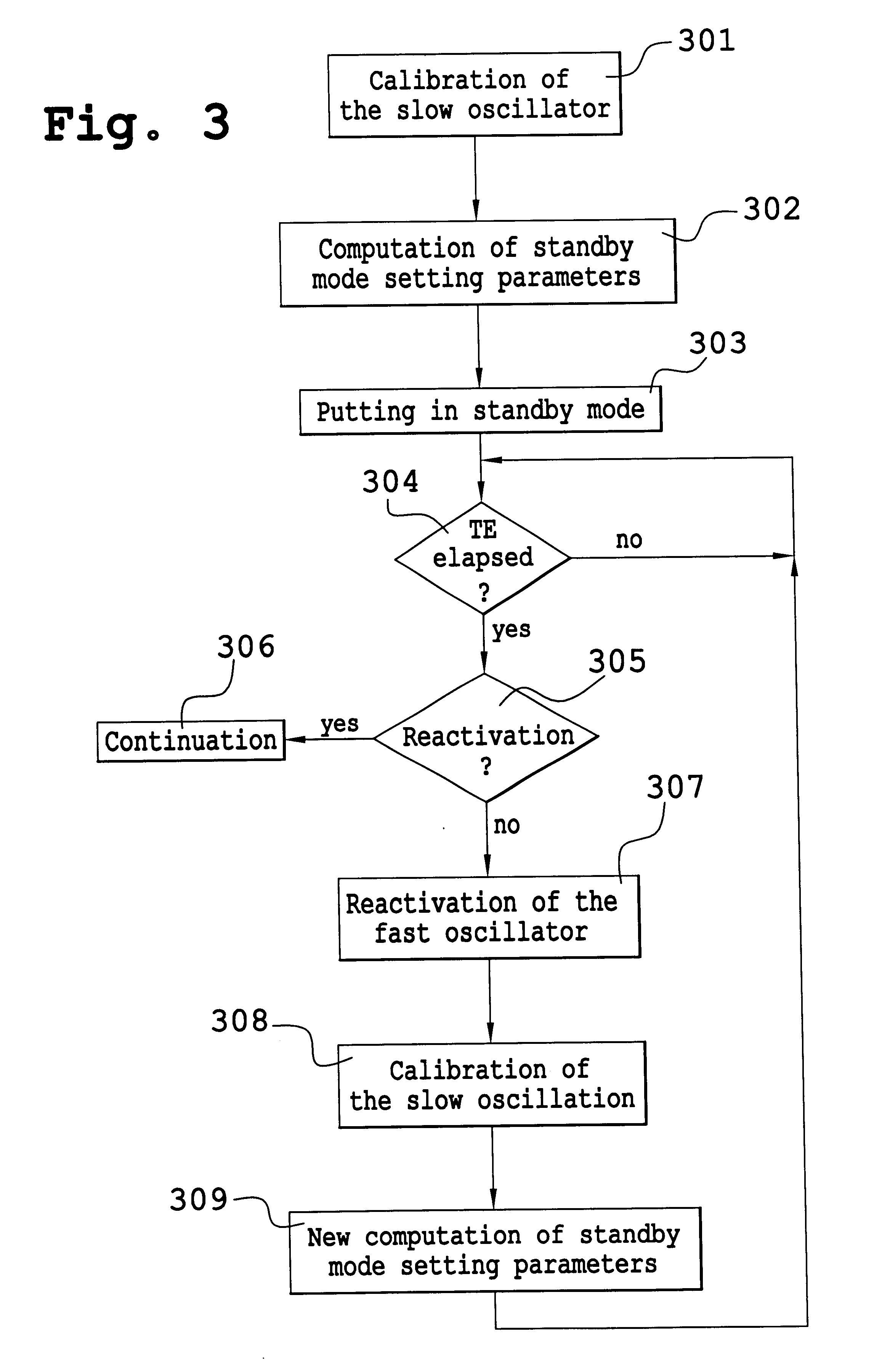

Mobile device and method for the management of a standby mode in a mobile device of this kind

An RC type oscillator (10) is integrated into a processor circuit (2) of a mobile device (1). This oscillator is used to set the pace of the activity of the processor circuit during periods when the mobile device is on standby. The frequency drift due to the temperature variations of the oscillator is concerted by a regular calibration of the oscillator by a faster oscillator recognized to be stable. This embodiment gives gain in space and a reduction in cost.

Owner:SAGEM SA

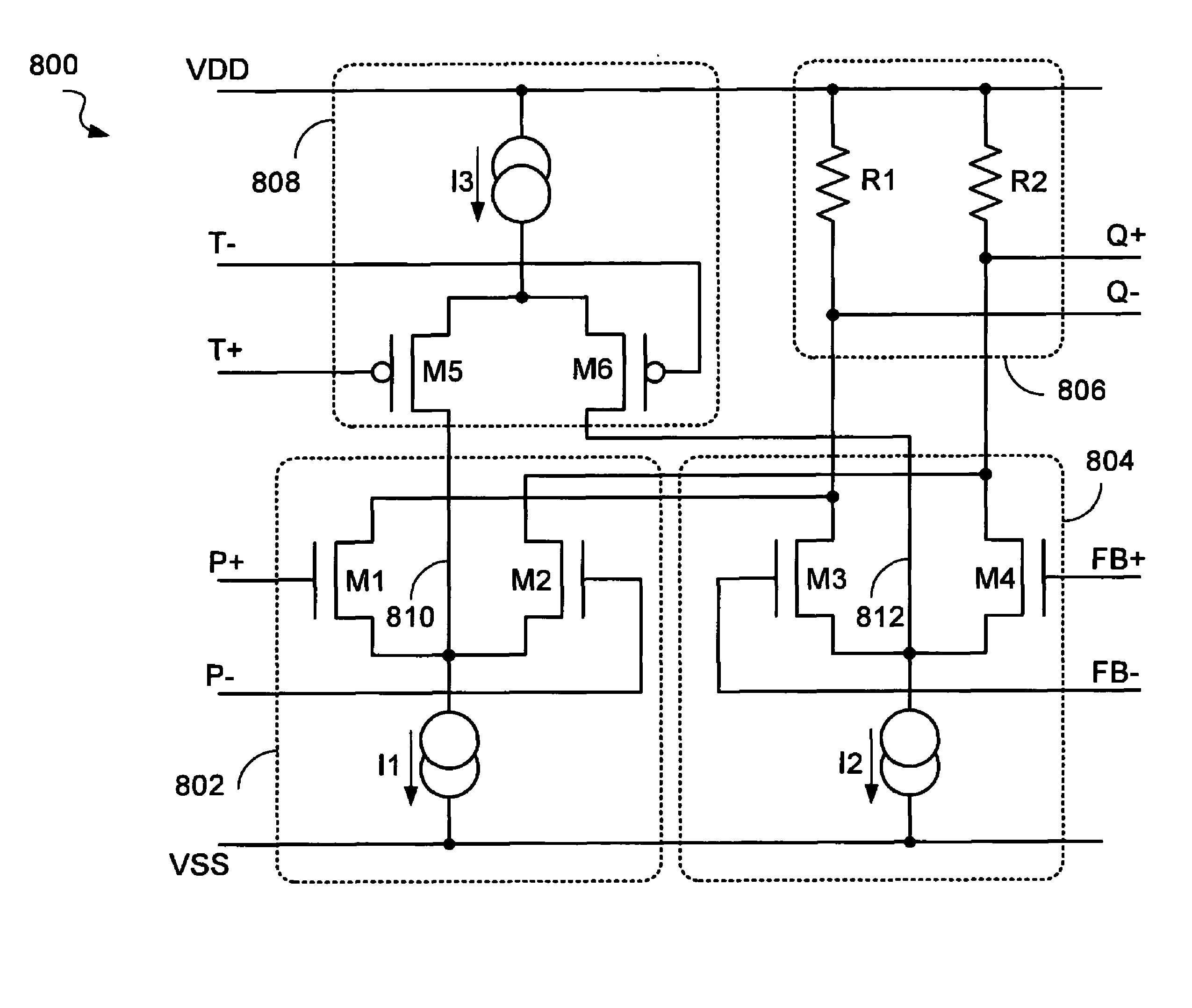

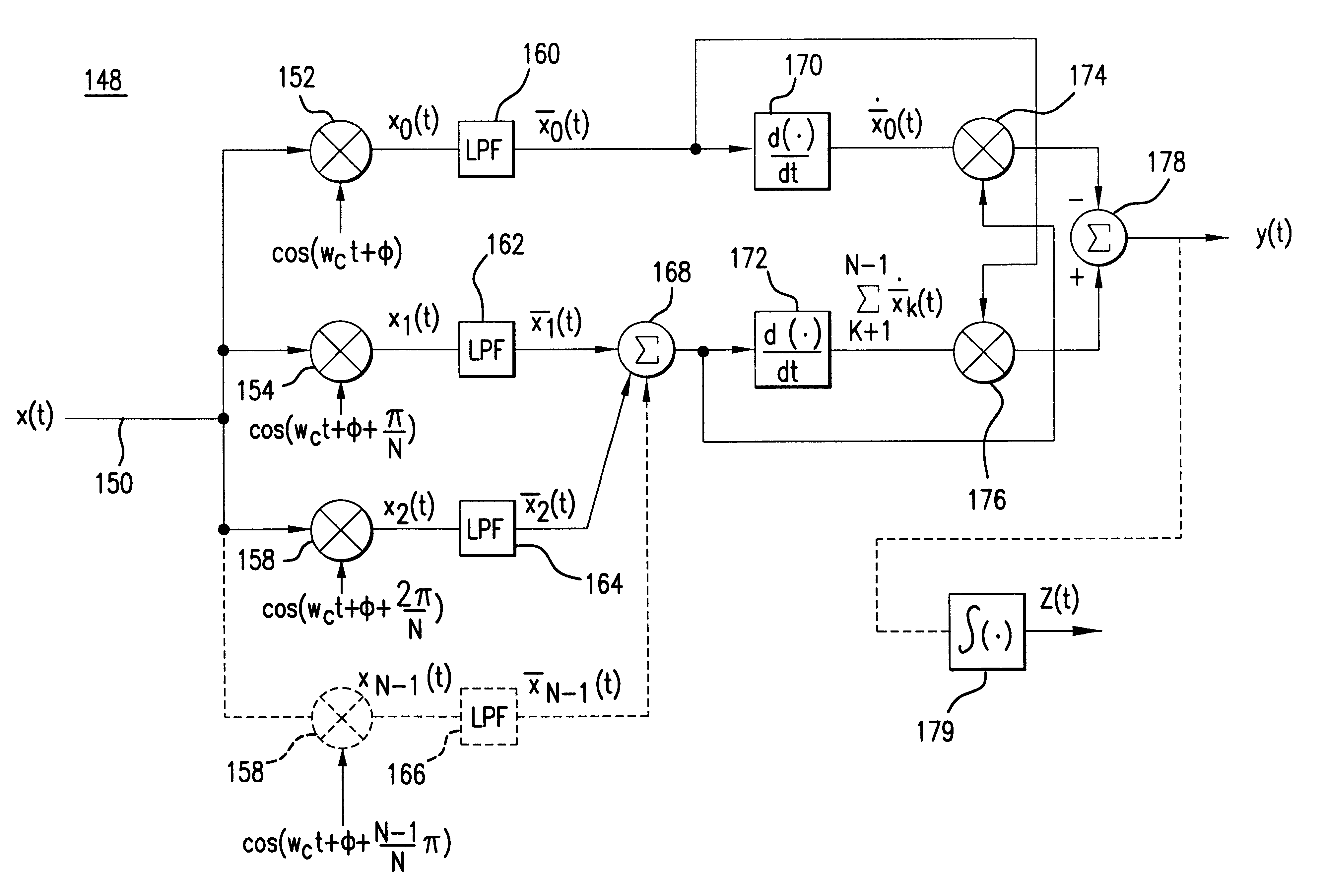

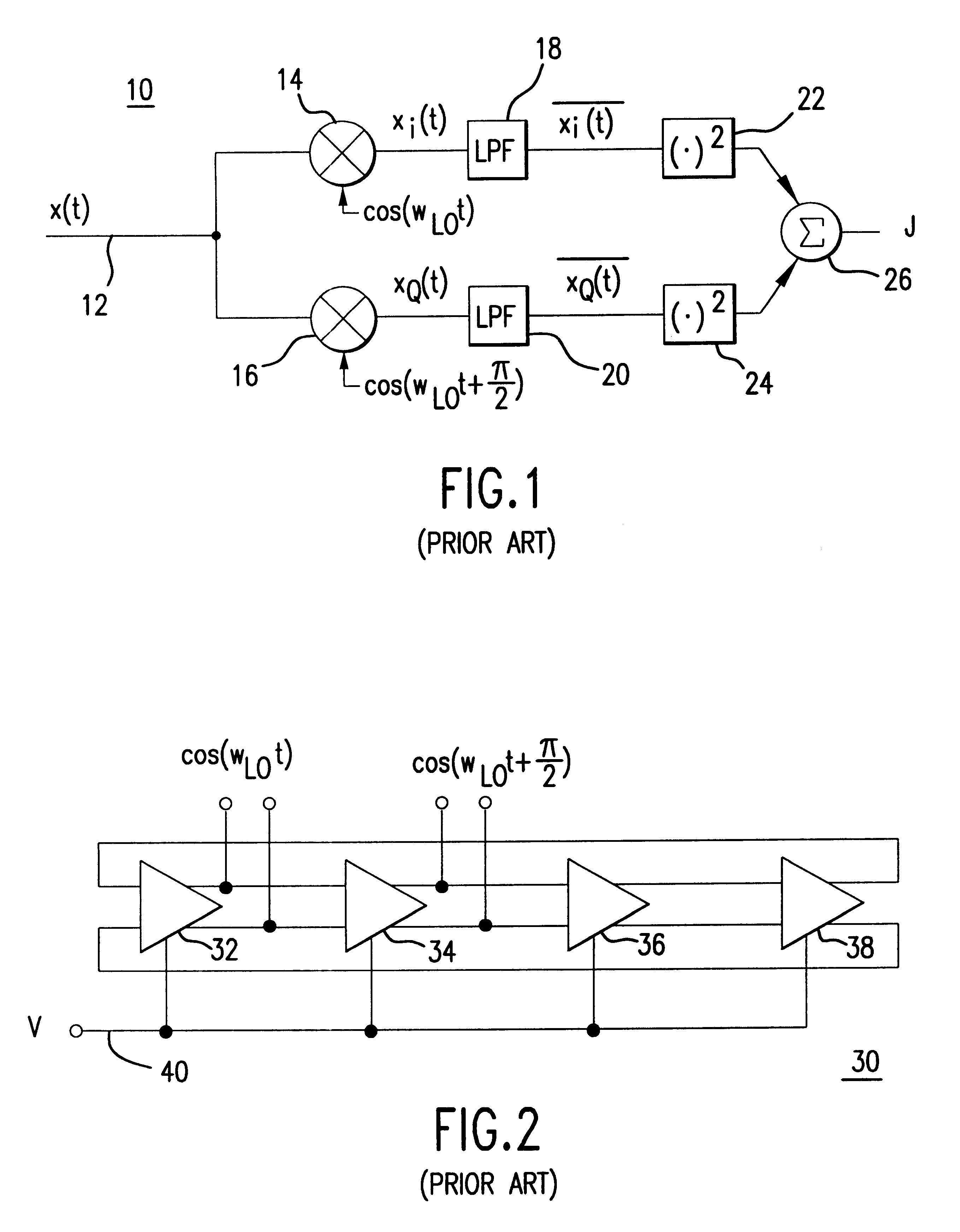

Multiphase receiver and oscillator

InactiveUS6385442B1Single output arrangementsPulse generation by logic circuitsLocal oscillator signalEngineering

A differential ring oscillator is provided with three differential amplifiers and provides three-phase output signals which can be used for synchronous detection of a received multi-phase modulated signal in a multi-phase receiver, wherein the phase of the local oscillator signals may be in other-than-quadrature relation. Two of the phase outputs of the local oscillator can be combined to provide a signal that is in quadrature with the remaining output. The oscillator is preferably controlled in coarse frequency control steps and using a fine voltage control signal responsive to a phase-locked loop to reduce frequency modulation of the oscillator signal arising out of leakage signals.

Owner:EXTREME NETWORKS INC

Automatic frequency correction PLL circuit

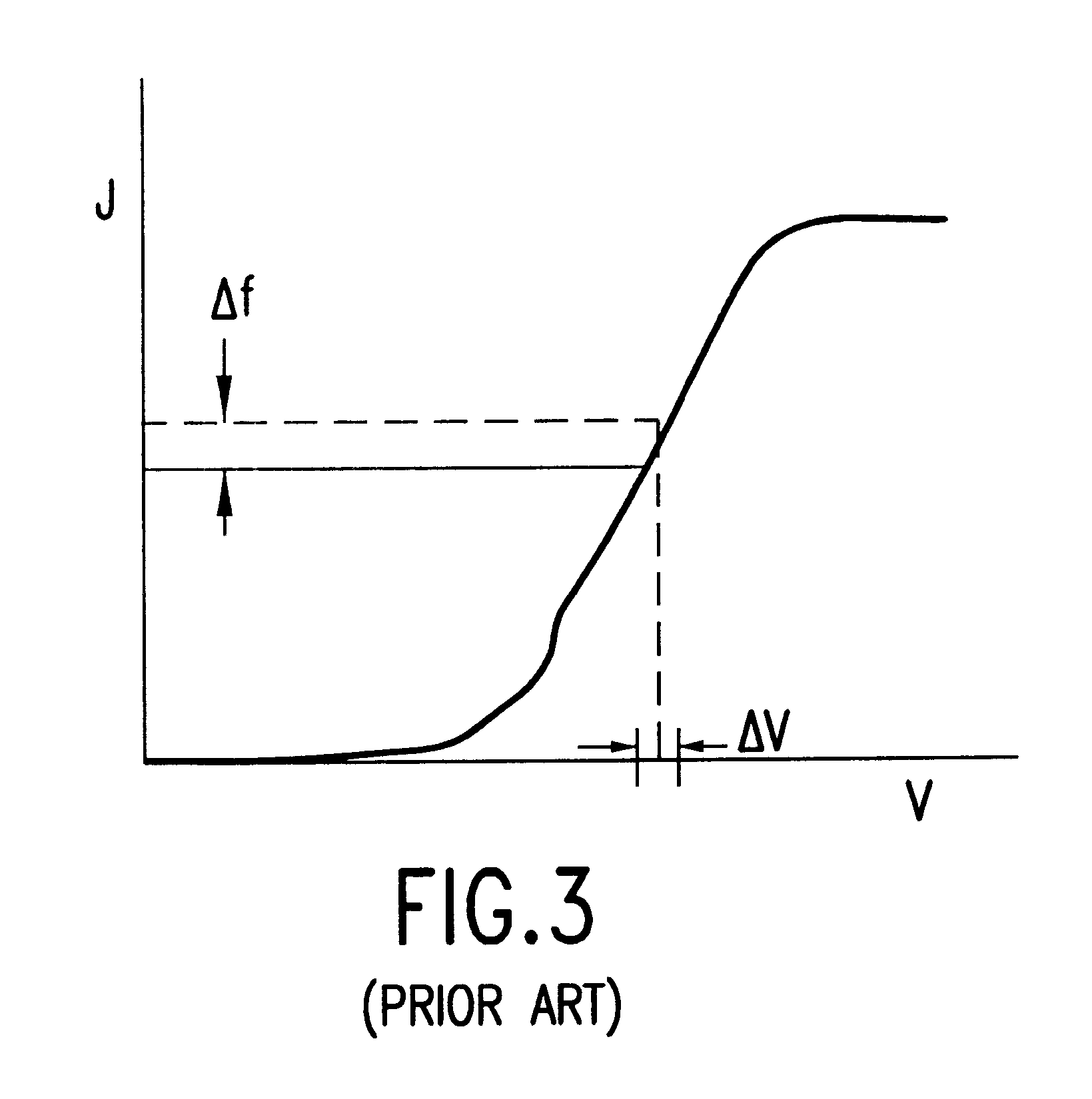

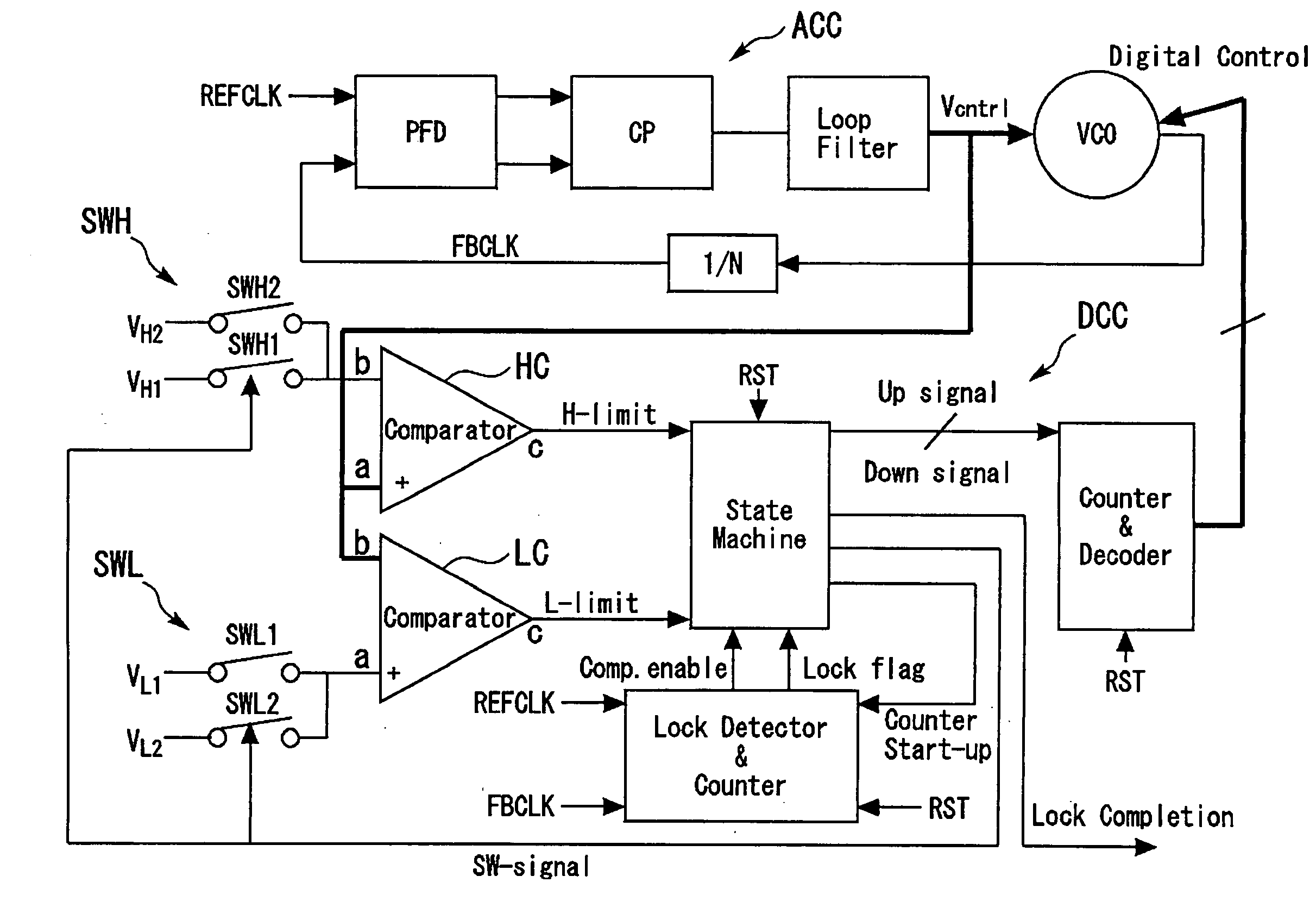

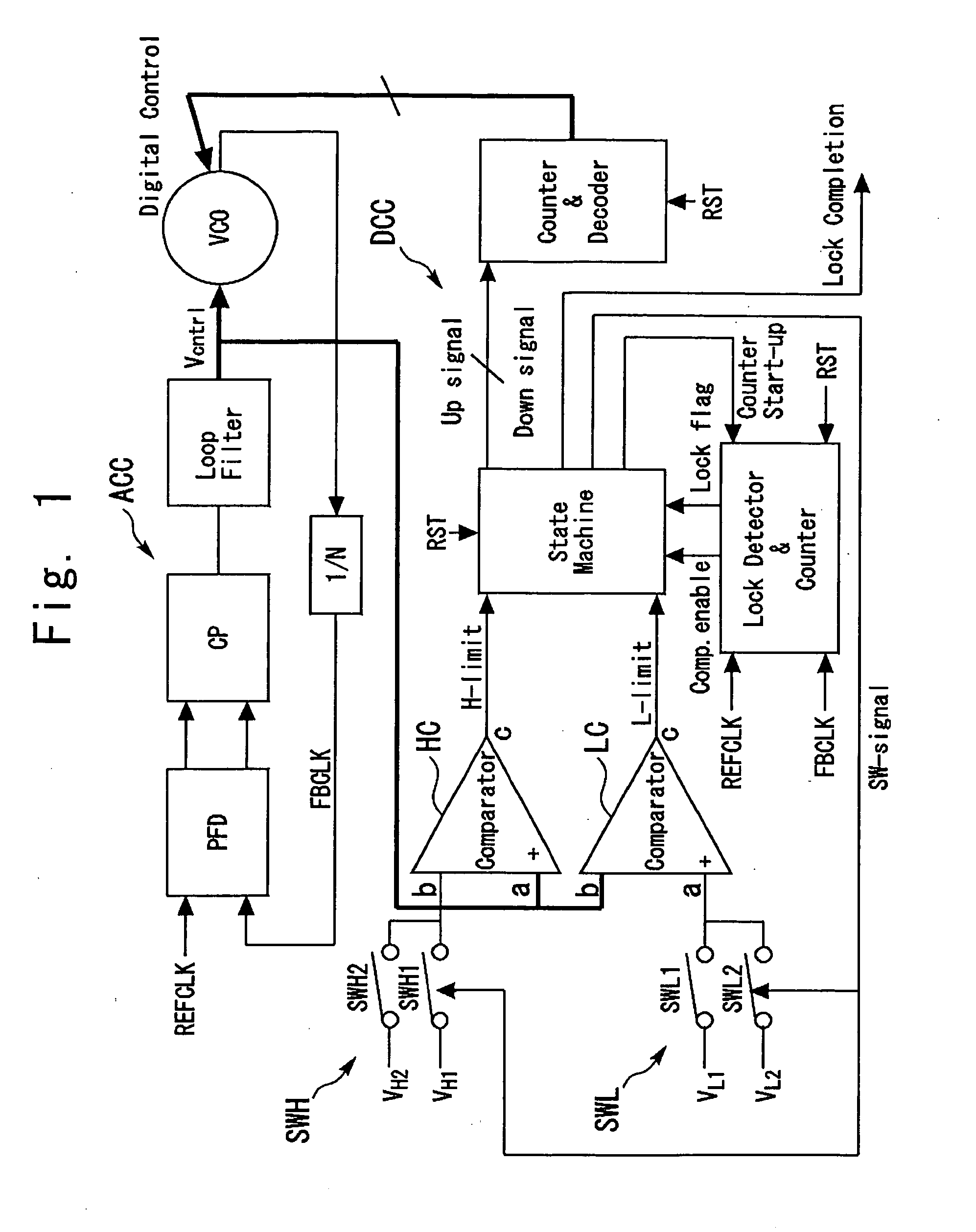

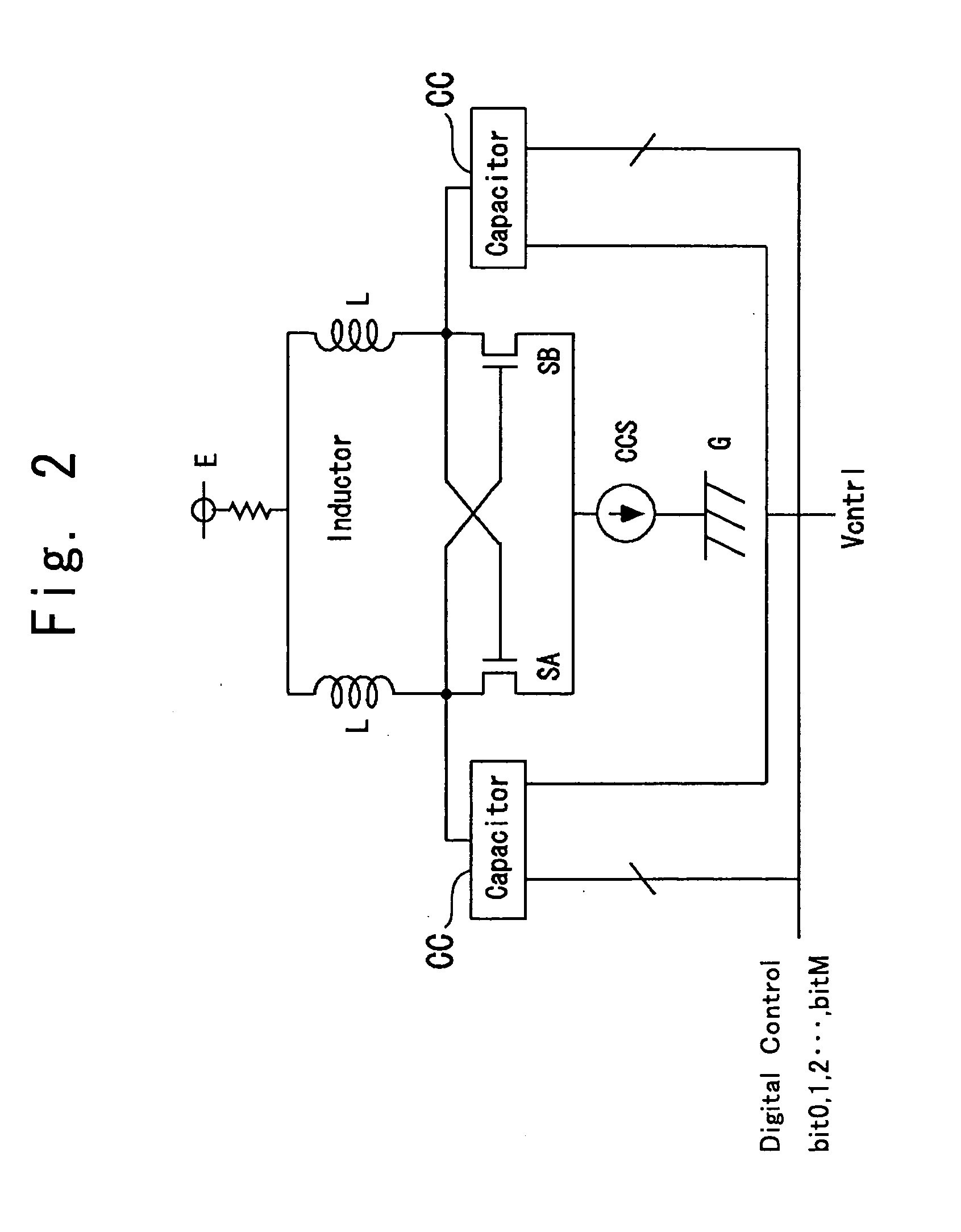

ActiveUS20050226357A1Prevent unnecessary switchingAvoid switchingPulse automatic controlPulse generation by logic circuitsEngineeringComparator

An automatic frequency correction phase-locked loop (PLL) circuit includes an analog control circuit and a digital control circuit. The digital control circuit includes a High-side comparator and a Low-side comparator which receive an analog control voltage, a state monitor circuit, and a counter and decoder circuit. At least one of the High-side comparator and the Low-side comparator includes a threshold switching circuit which selectively gives a first threshold and a second threshold having different. When the analog control voltage remains between the High-side threshold and the Low-side threshold in a state in which the threshold switching circuit gives the first threshold, the threshold switching circuit switches the first threshold to the second threshold and expands the interval between the High-side threshold and the Low-side threshold.

Owner:MITSUBISHI ELECTRIC CORP

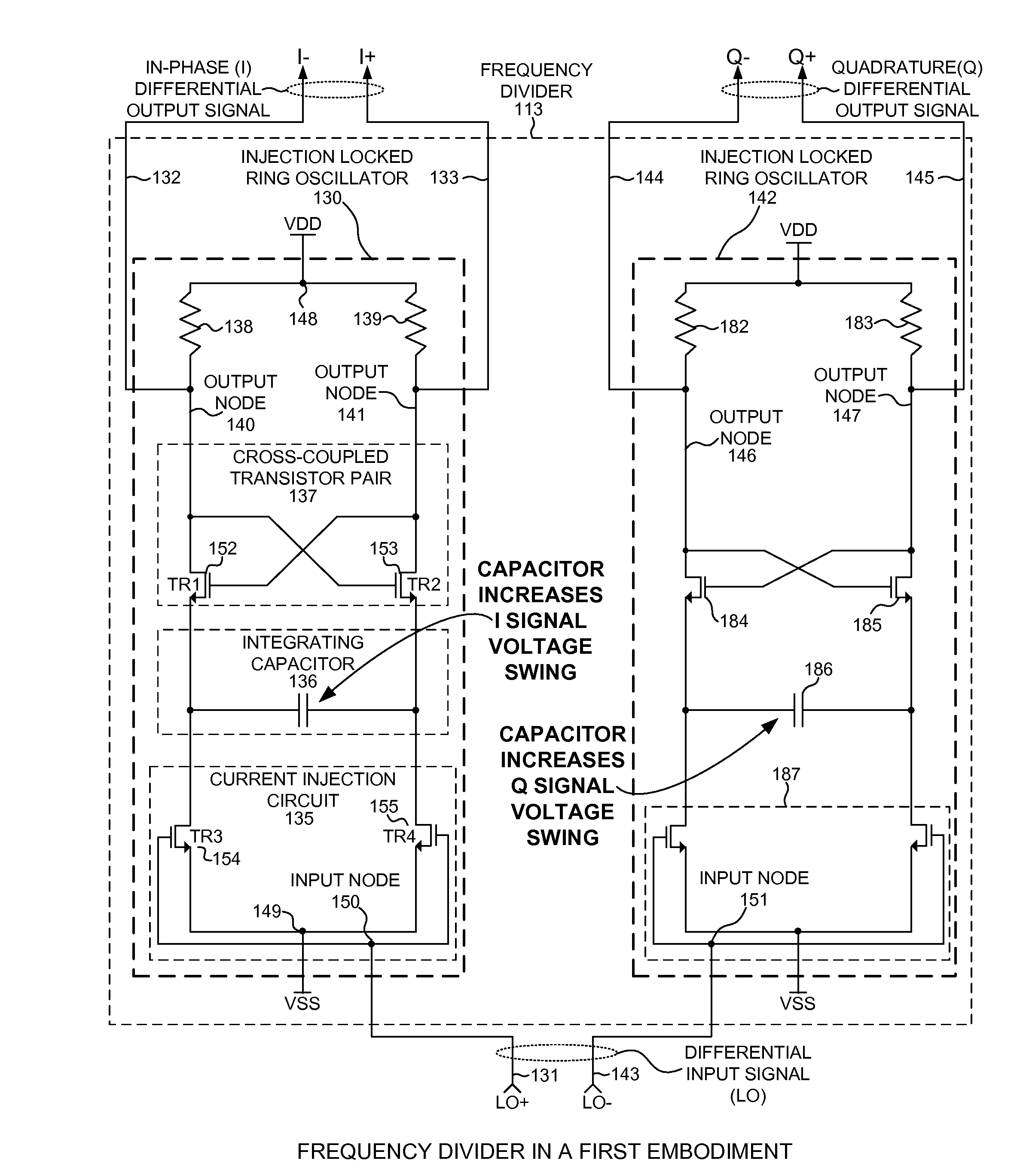

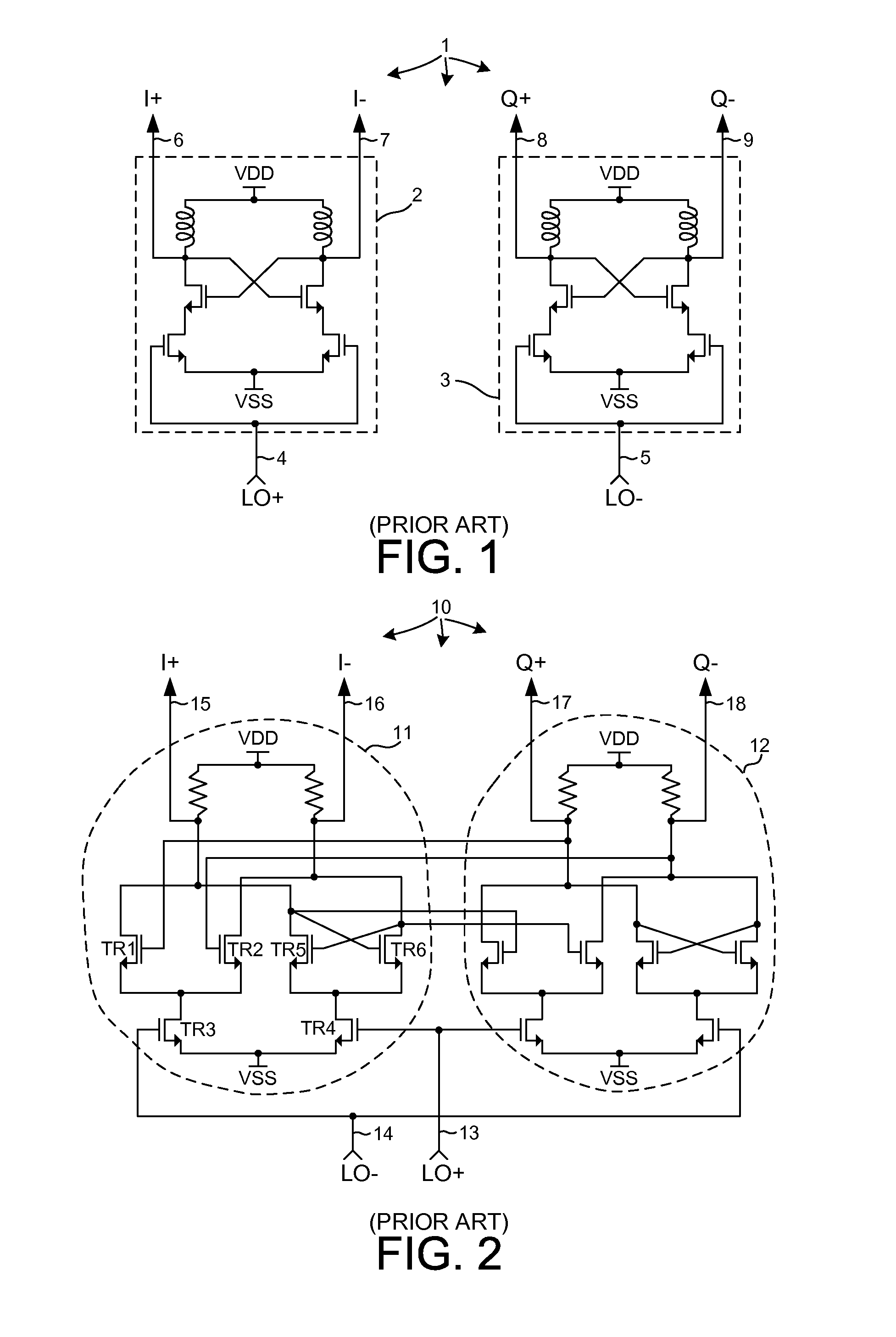

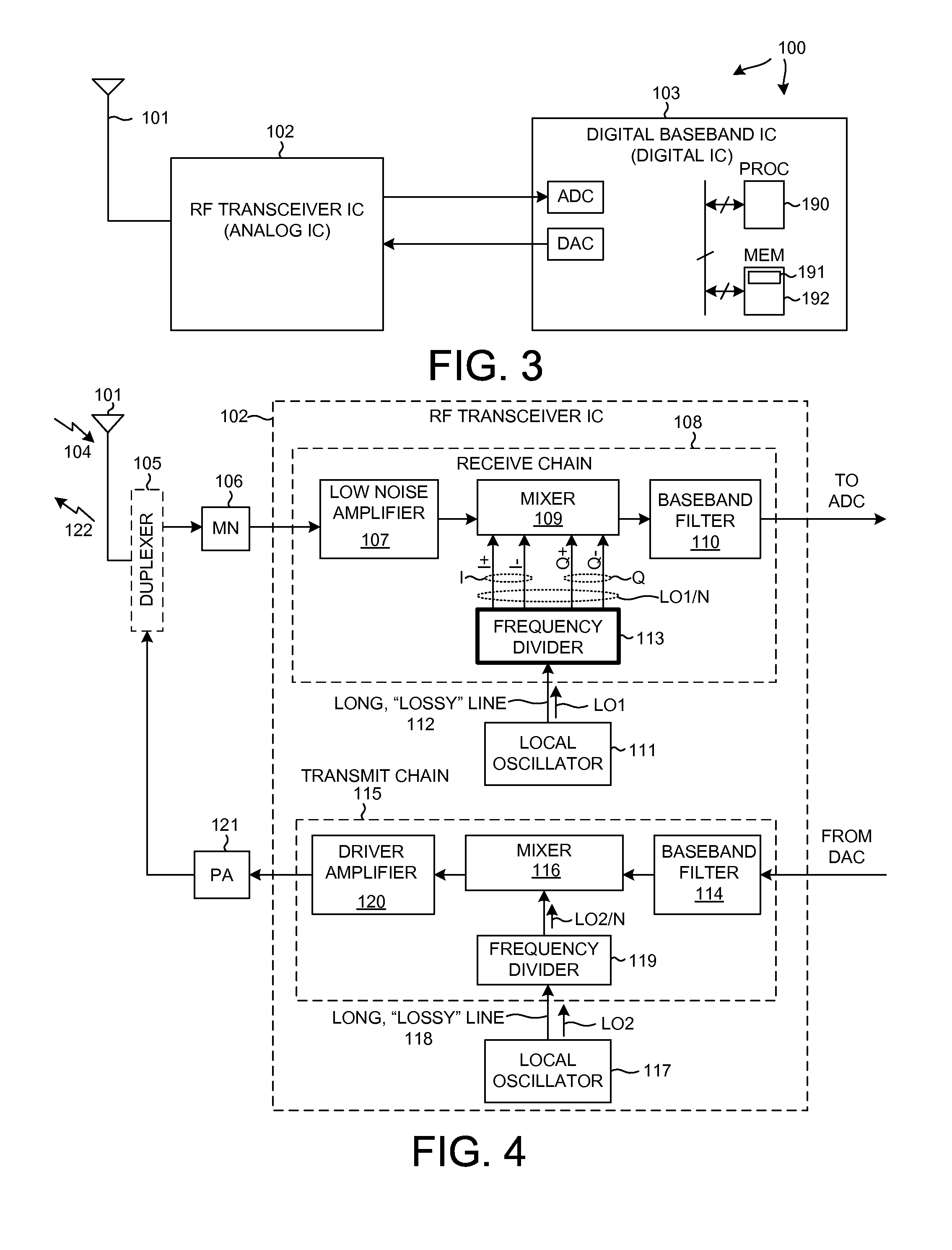

Divide-by-two injection-locked ring oscillator circuit

InactiveUS20110050296A1Improved output signal slew rateIncrease productivityPulse generation by logic circuitsOscillations generatorsInjection lockedLoad resistance

A frequency divider involves a plurality of Injection-locked Ring Oscillators (ILRO). A first ILRO includes a pair of cross-coupled N-channel transistors, a pair of load resistors, an integrating capacitor, and a current injection circuit. The drain of each transistor is coupled to the gate of the other transistor. Each load resistor couples the drain of each transistor to a circuit voltage source. The integrating capacitor couples the sources of each transistor. The current injection circuit alternately opens and closes a path from the source of each transistor to circuit ground in response to an oscillatory input signal of a first frequency. In response, the voltage state at the drain of each transistor is alternately latched and toggled, generating a differential pair of oscillating signals frequency divided by two. A first and second ILRO driven in antiphase generate two differential output signals in phase quadrature.

Owner:QUALCOMM INC

Micropower RC oscillator

InactiveUS6462625B2Logic circuits coupling/interface using field-effect transistorsGenerator stabilizationElectrical resistance and conductanceClosed loop

Owner:SAMSUNG ELECTRONICS CO LTD

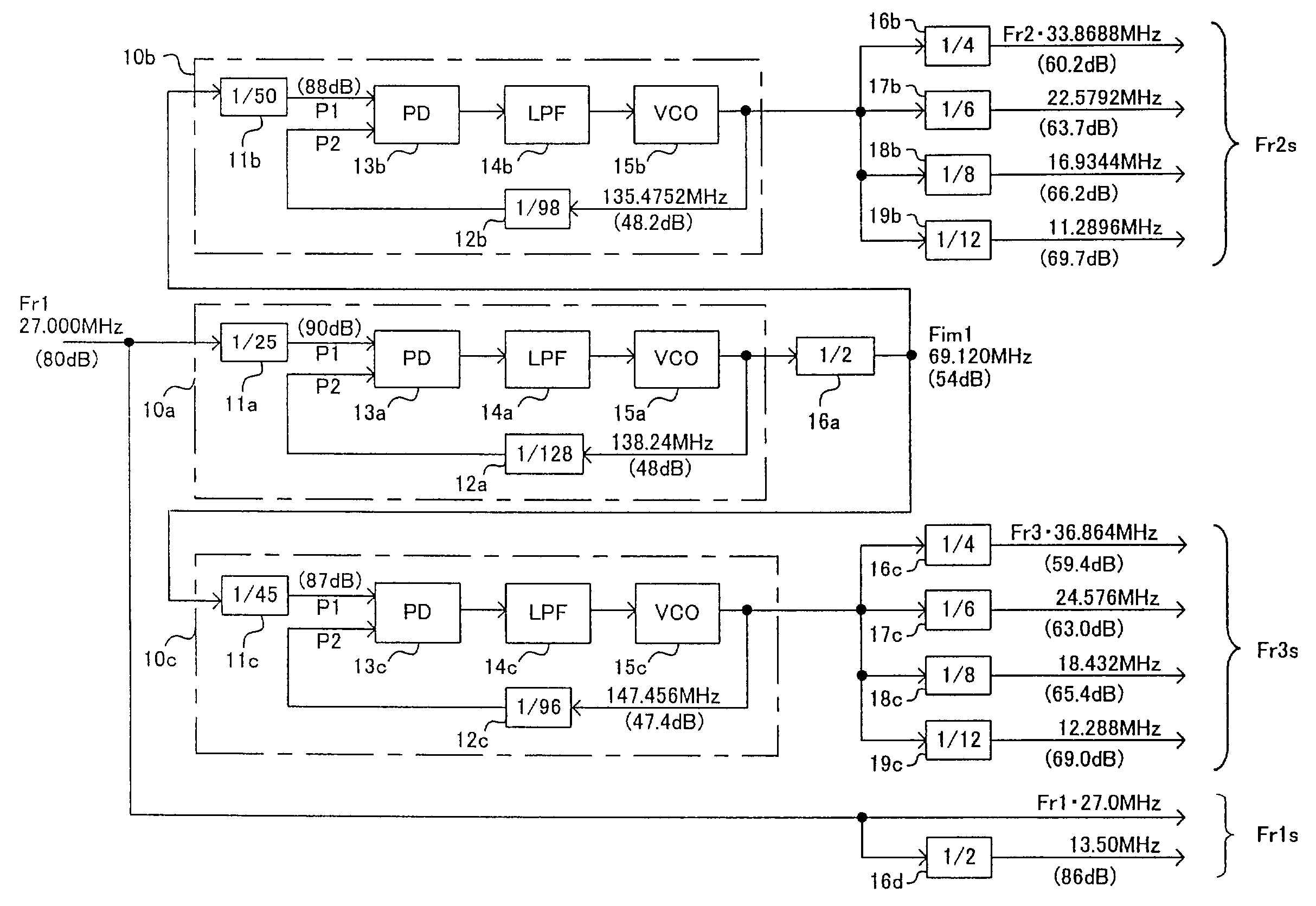

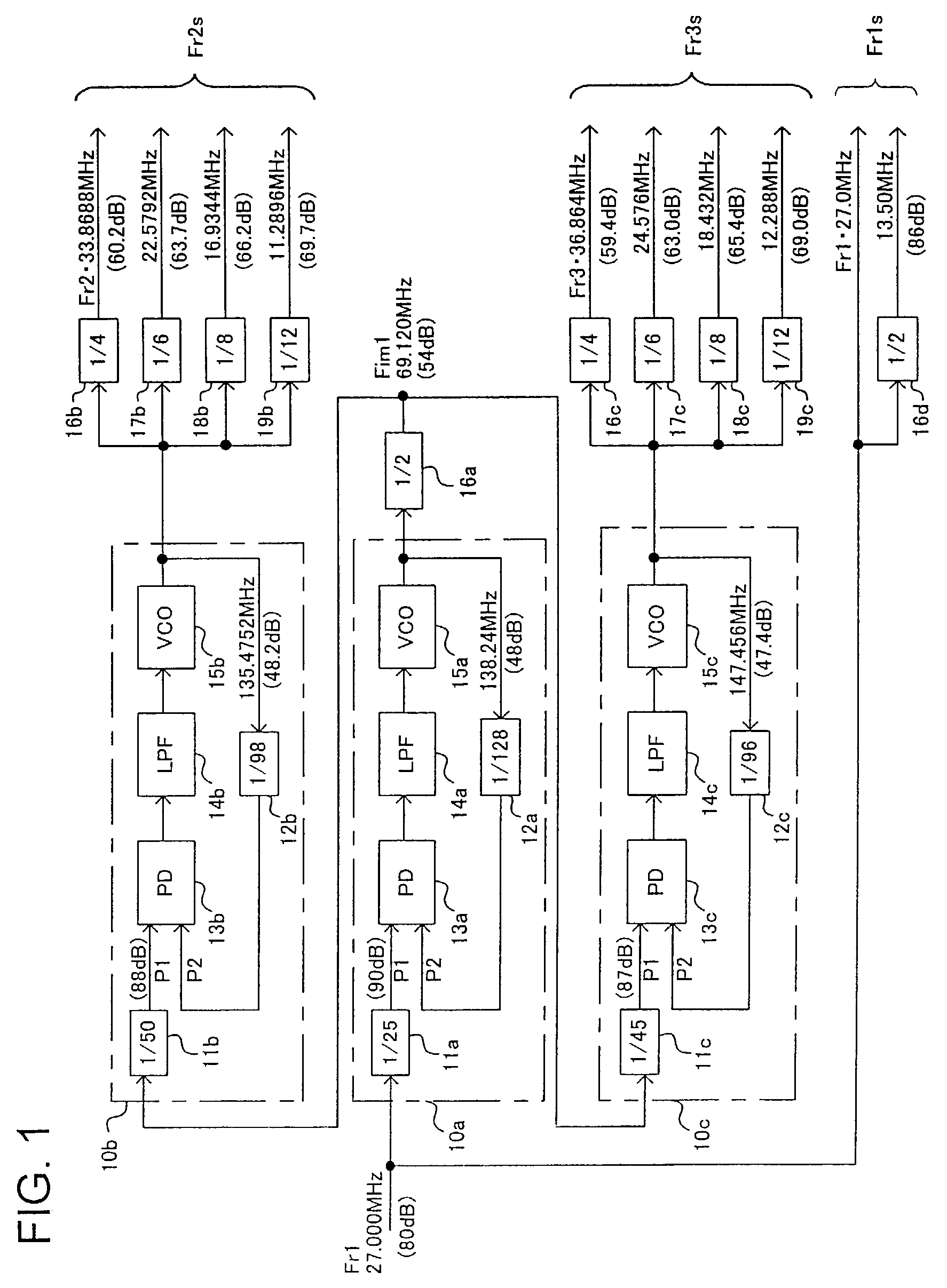

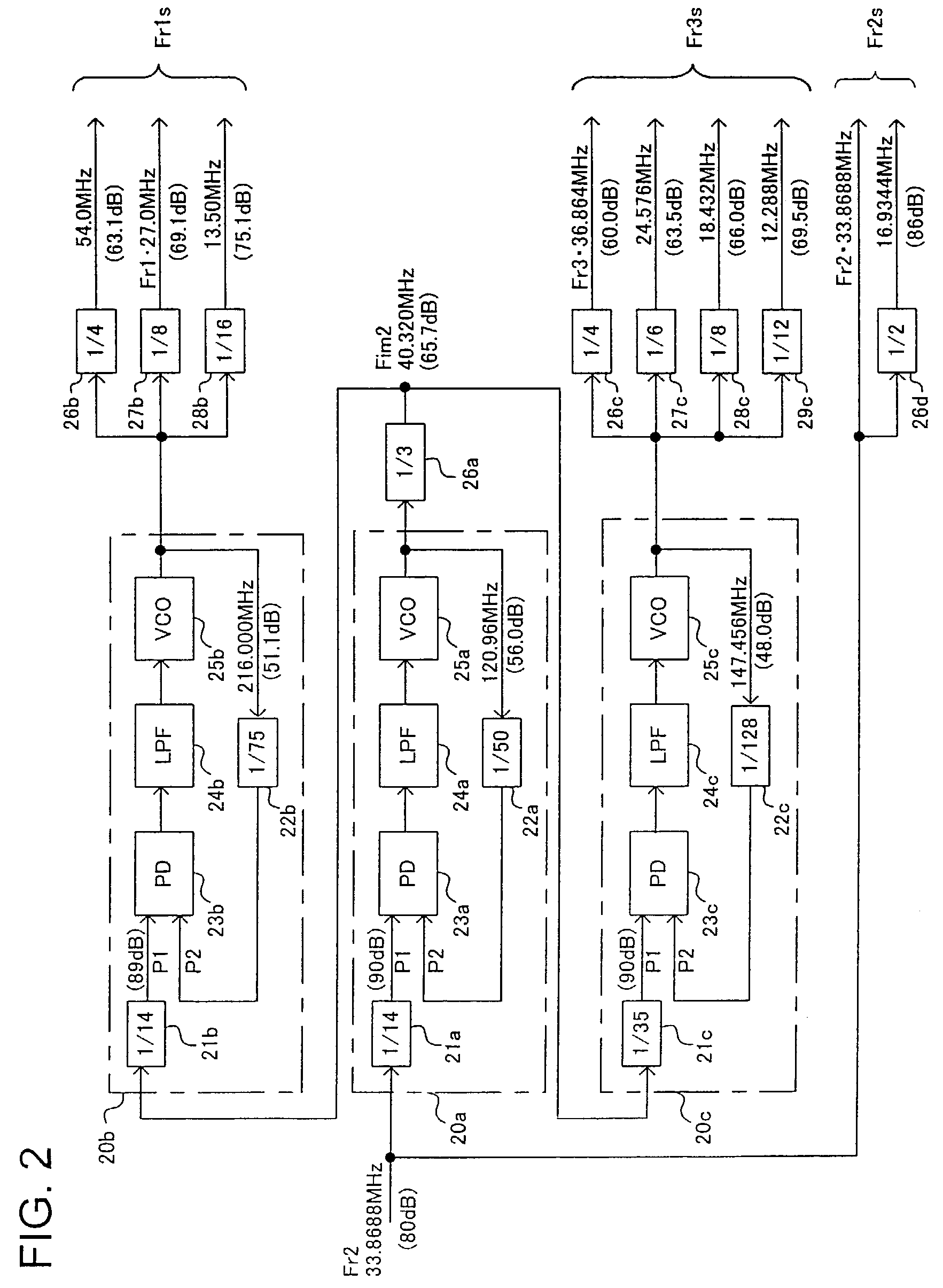

Clock generation system

ActiveUS7216249B2Elimination of the limitation,Weaken influencePulse automatic controlError detection/correctionIntermediate frequencyNoise floor

A clock generation system for generating a first-, a second-, and a third-reference frequency clocks having respective frequencies having predetermined ratios to the reference frequency of a reference clock, using PL circuits in such a way that the clocks have sufficient S / N ratios in spite of the S / N ratio limitation by the noise floor. A first reference frequency clock is supplied to a first PLL circuit to generate an intermediate-frequency clock having an intermediate frequency having a predetermined ratio to the reference clock. The intermediate-frequency clock is supplied to a second and a third PLL circuits to generate a second and a third reference frequency clocks having frequencies respectively having a second and a third ratios to the intermediate frequency, respectively.

Owner:ROHM CO LTD

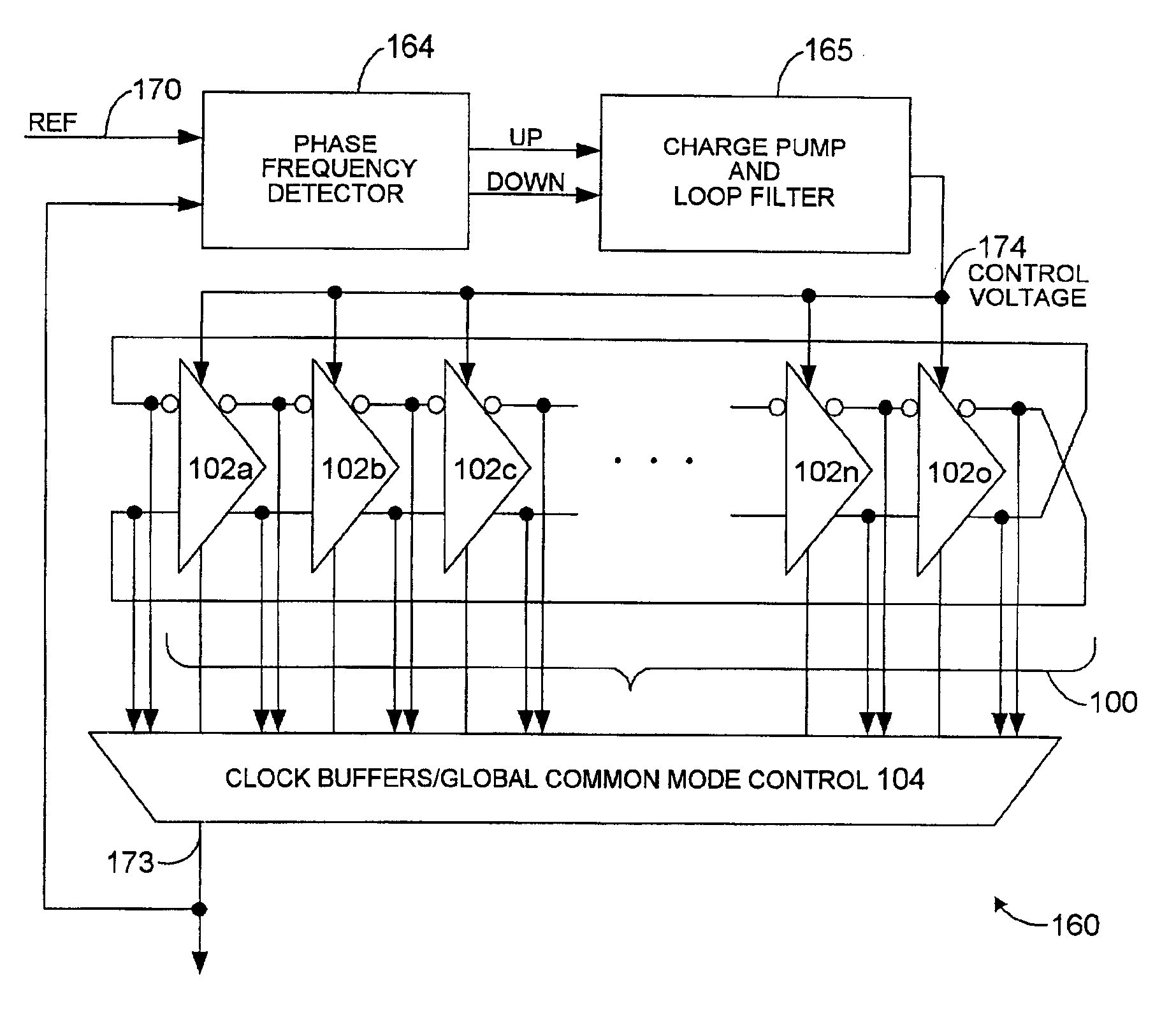

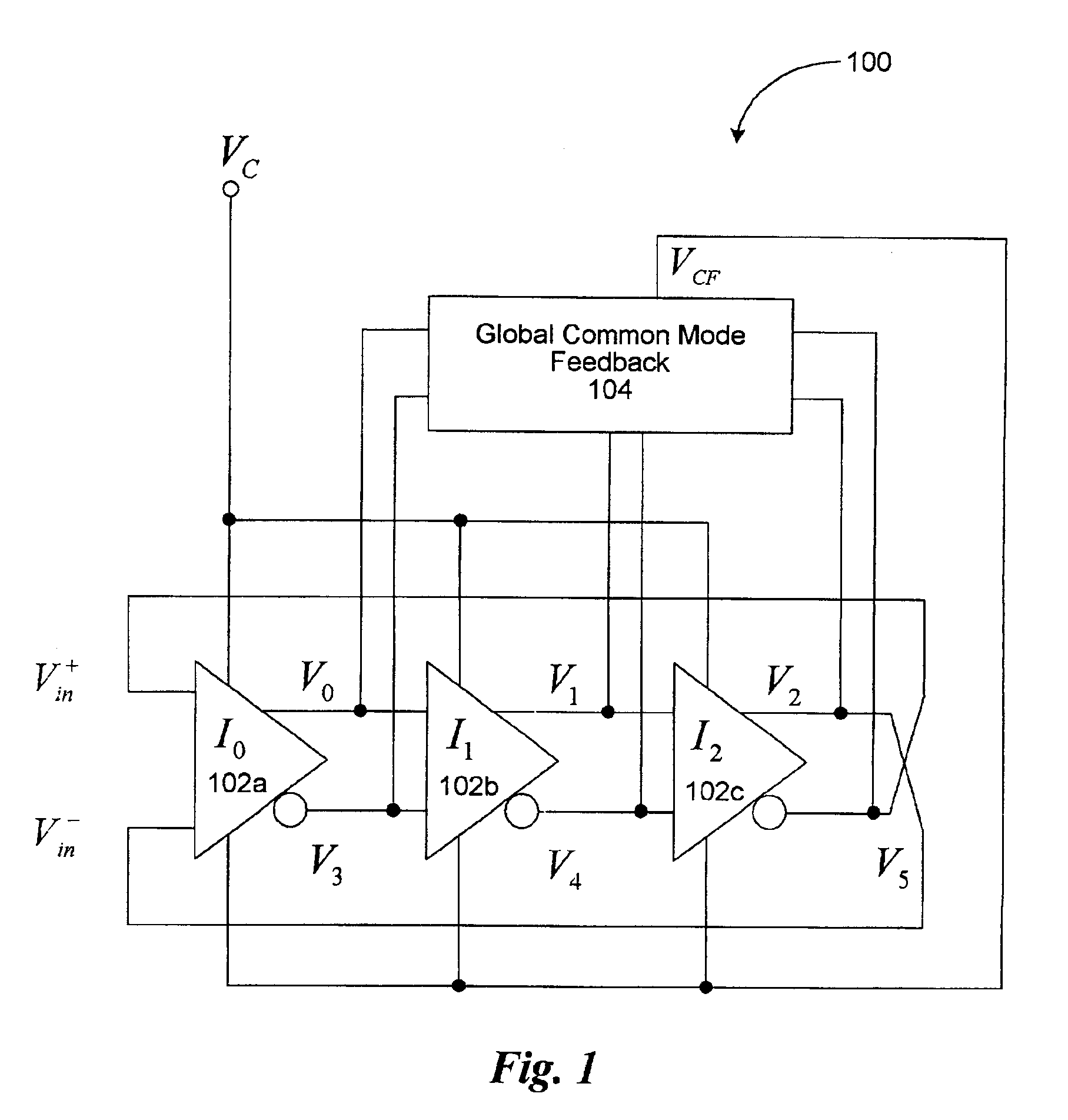

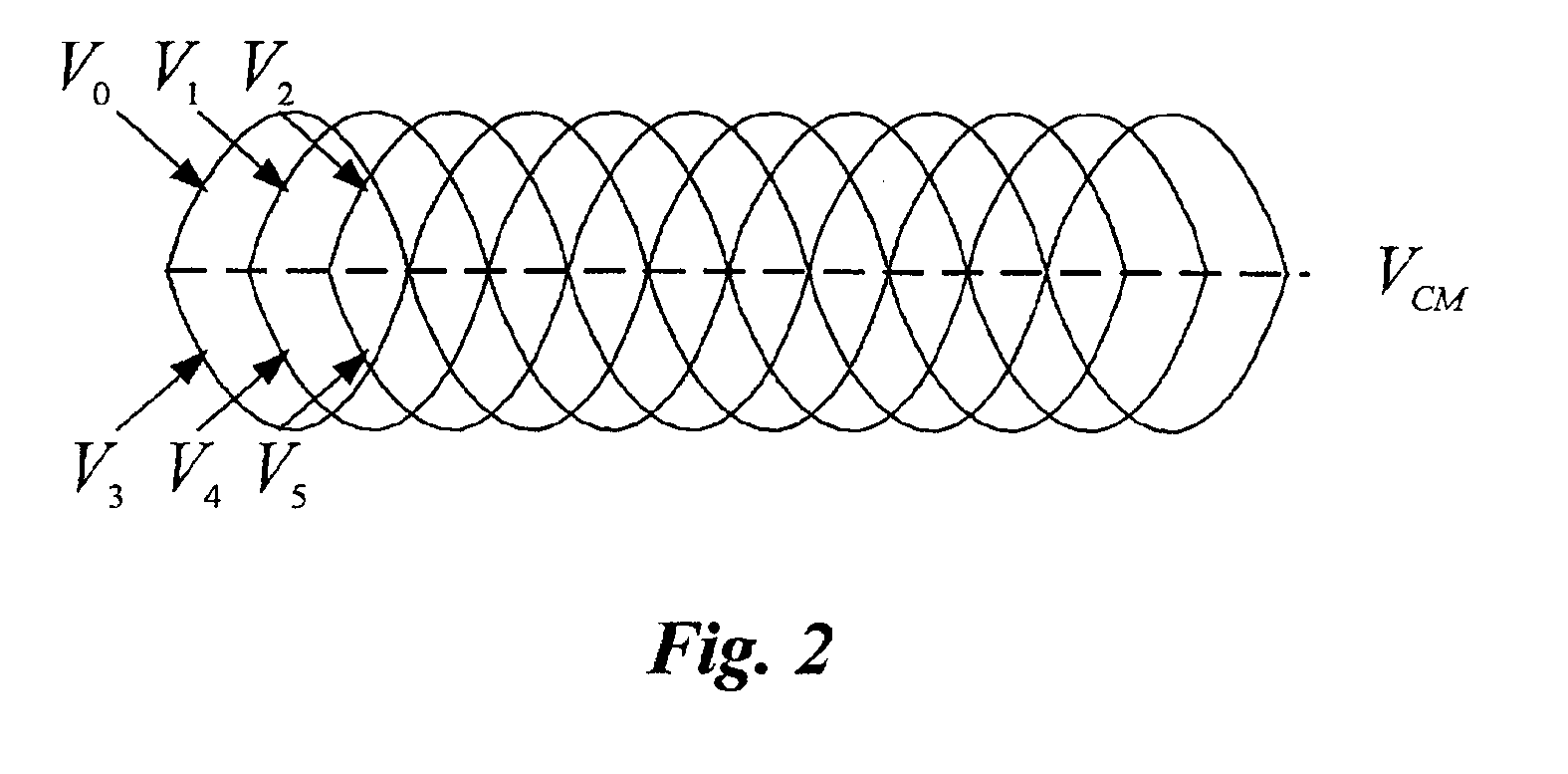

Multi-phase voltage controlled oscillator (VCO) with common mode control

A voltage controlled oscillator ("VCO") circuit capable of generating signals with reduced jitter and / or low-phase noise is provided. One embodiment provides a plurality of cascaded VCO cells, where each VCO cell can include a source coupled differential pair, a bias transistor connected to the differential pair for biasing the differential pair, a resistive load pair connected to the differential pair, and a voltage controlled capacitor pair or varactor pair connected to the differential pair. The varactors provide control over the frequency of the oscillations produced by the VCO circuit in combination with a control voltage. A phase frequency detector combined with a charge pump and loop filter provide the control voltage.

Owner:UNIVERSAL CONNECTIVITY TECH INC

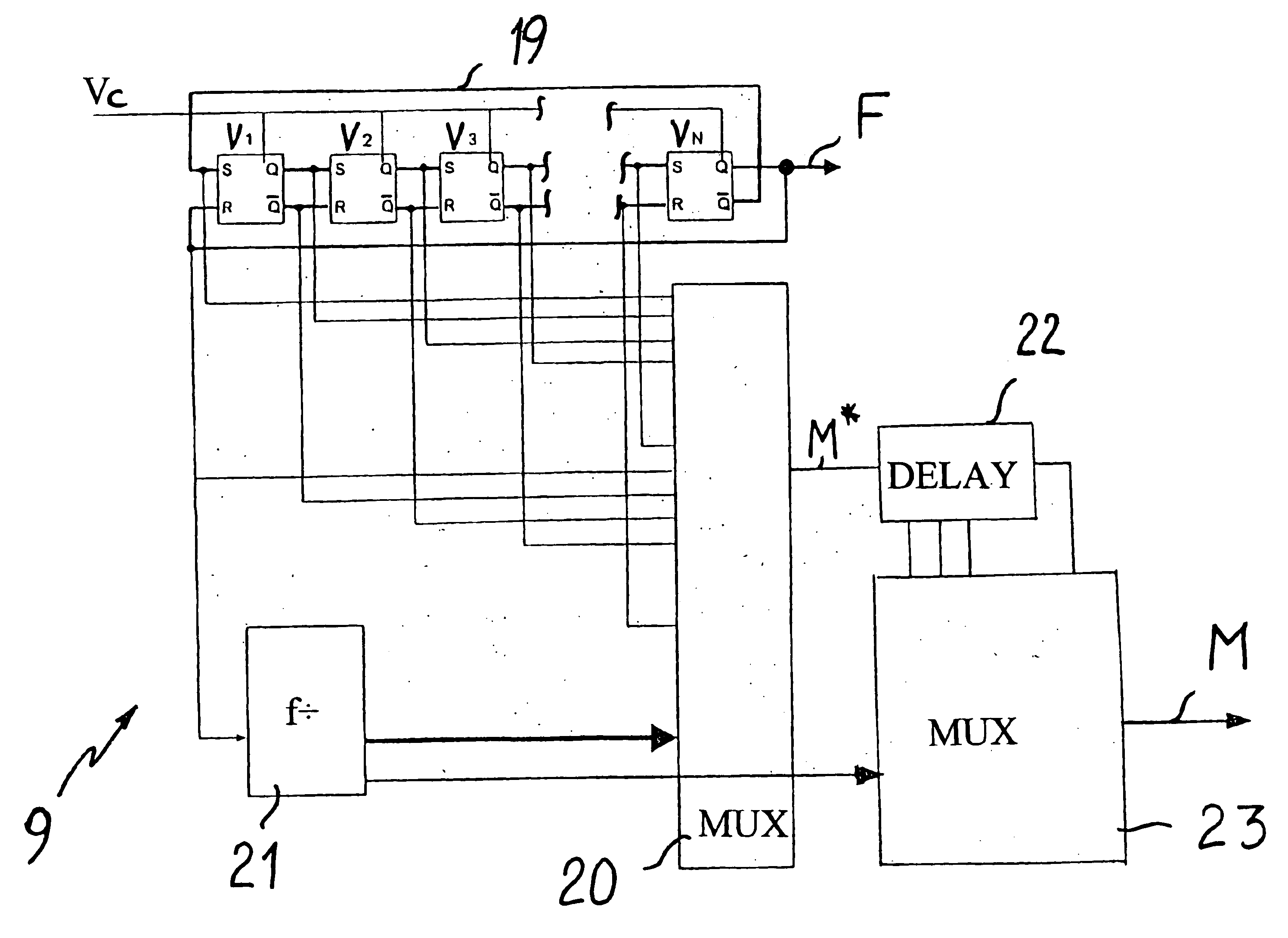

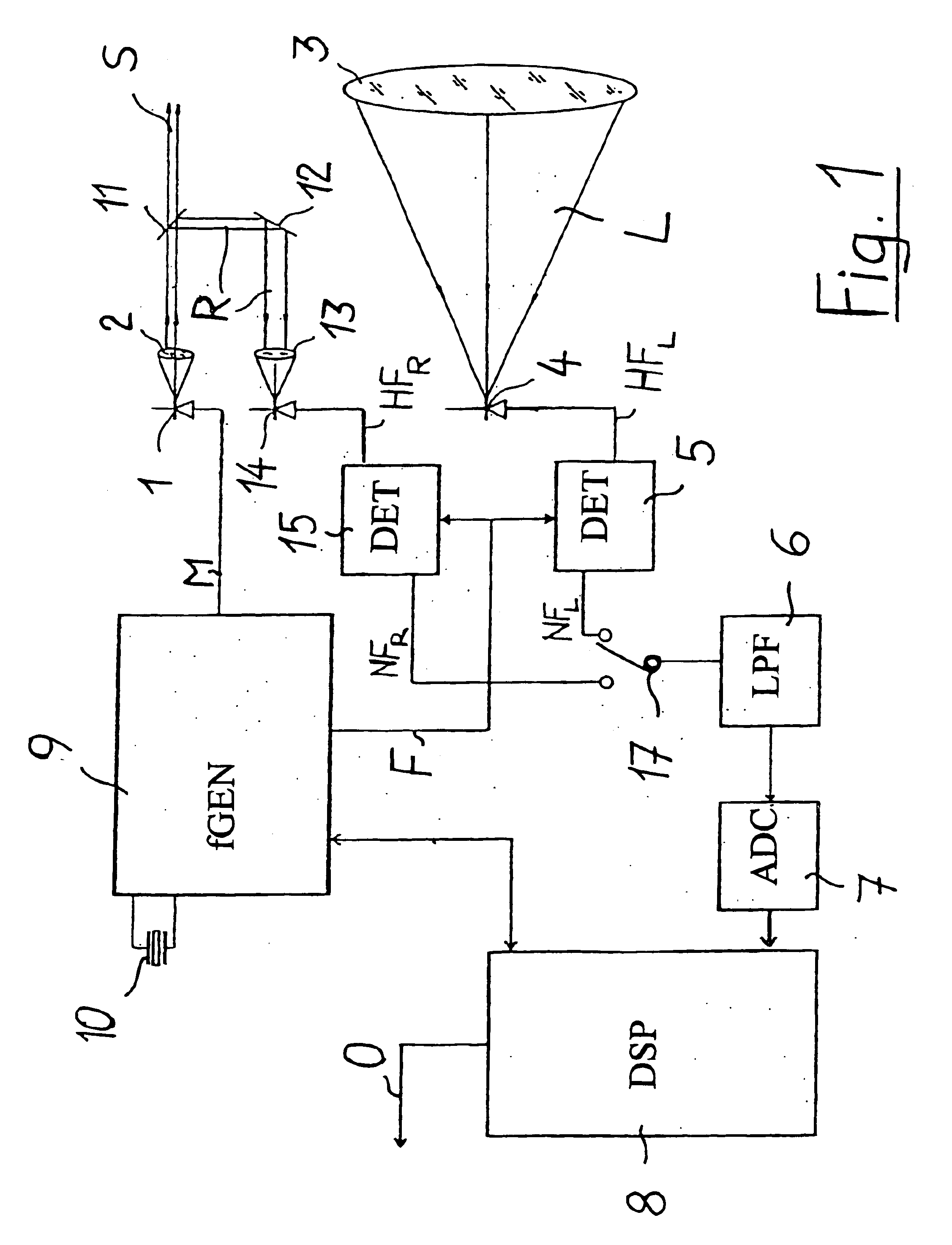

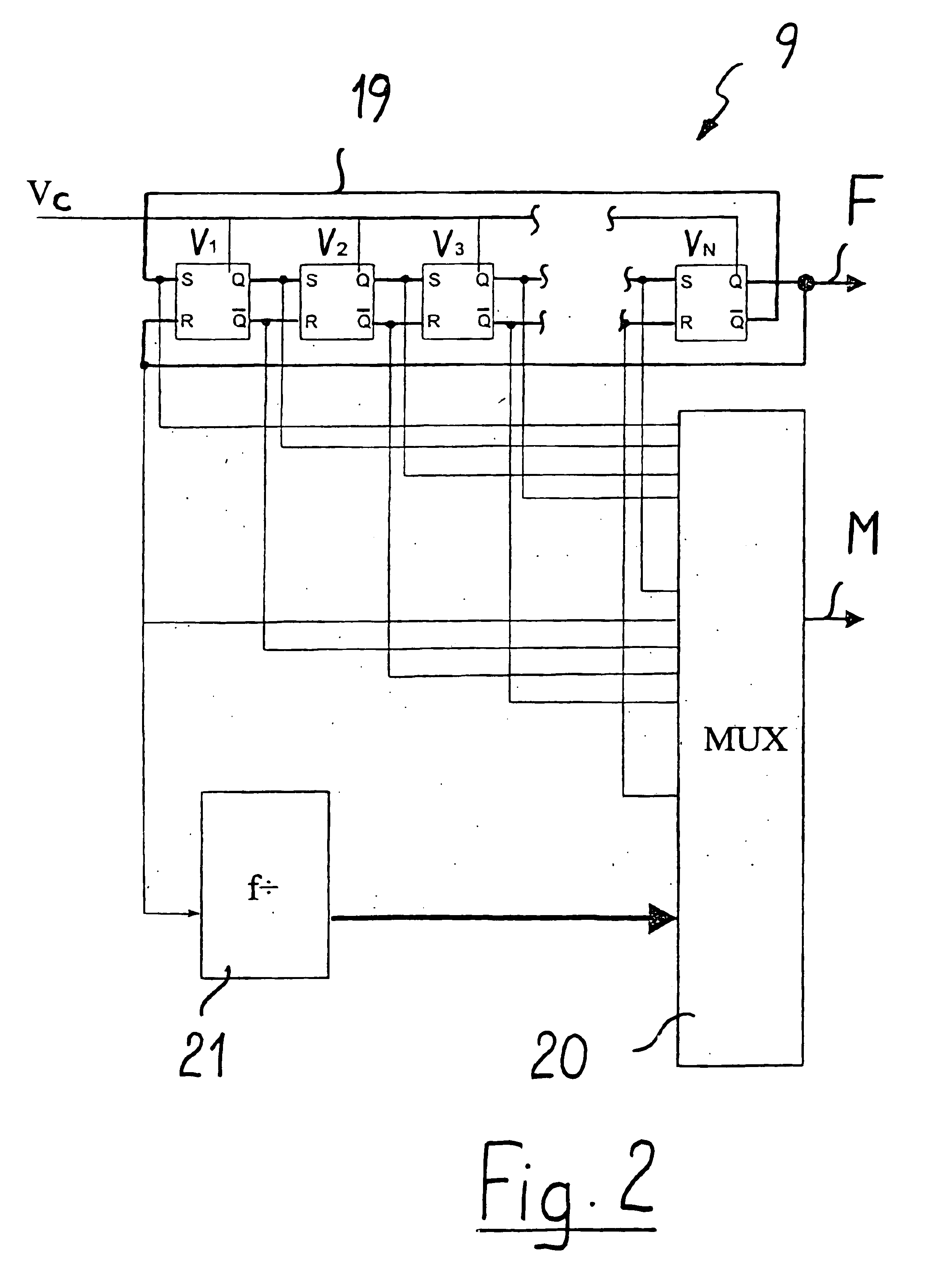

Method and device for carrying out frequency synthesis in a distance measuring device

InactiveUS6859744B2Reduce phase noiseReduce energy consumptionDigital computer detailsMechanical clearance measurementsMultiplexerElectromagnetic radiation

In a method and a device for carrying frequency synthesis, in particular in a distance measuring device based on the principle of evaluating the change over time in the phase of an electromagnetic radiation emitted by a radiation source and remitted by an object aimed at, a frequency, which is preferably furnished by a quartz oscillator, is regulated in a ring oscillator with N delay elements (V1, V2, V3, . . . , VN) to a desired first high frequency (F), which is used as a mixer frequency or as a modulation frequency. The signals at the N delay elements (V1, V2, V3, . . . , VN) are delivered to a multiplexer, which is switched over with a cadence that is equivalent to 2*N times the frequency of the low-frequency measurement signal to be evaluated to produce a modulation frequency or mixer frequency.

Owner:LEICA GEOSYSTEMS AG

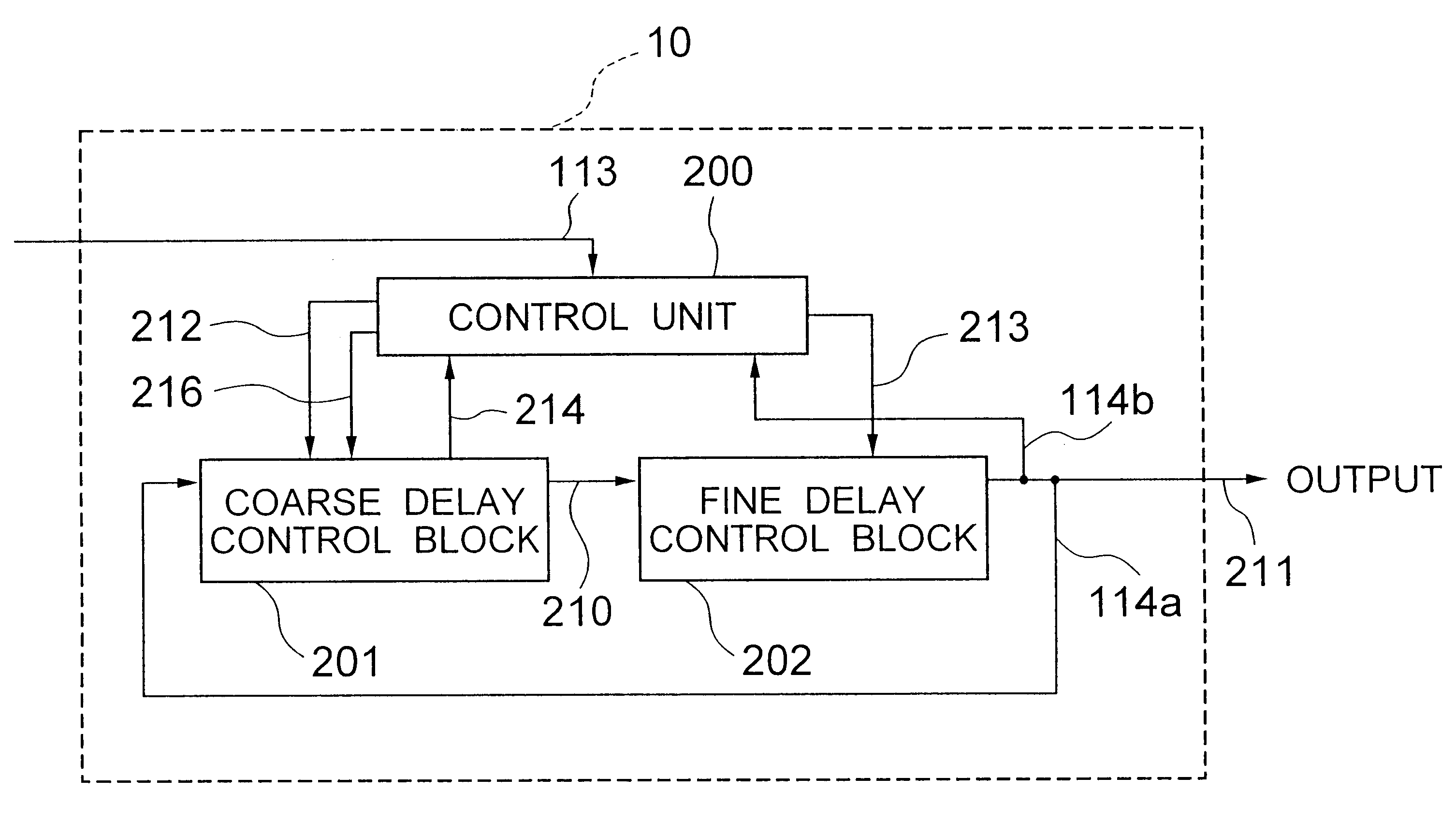

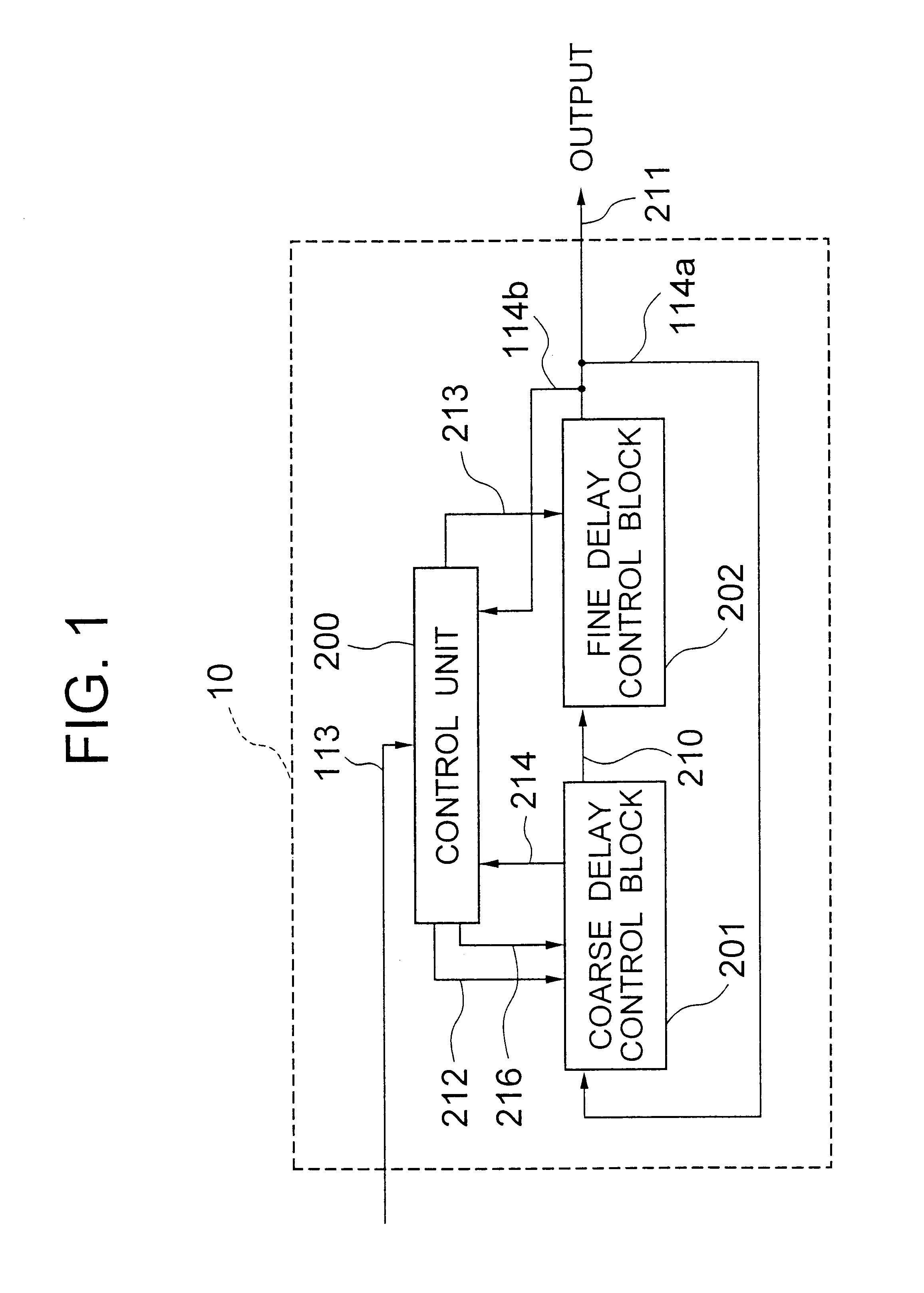

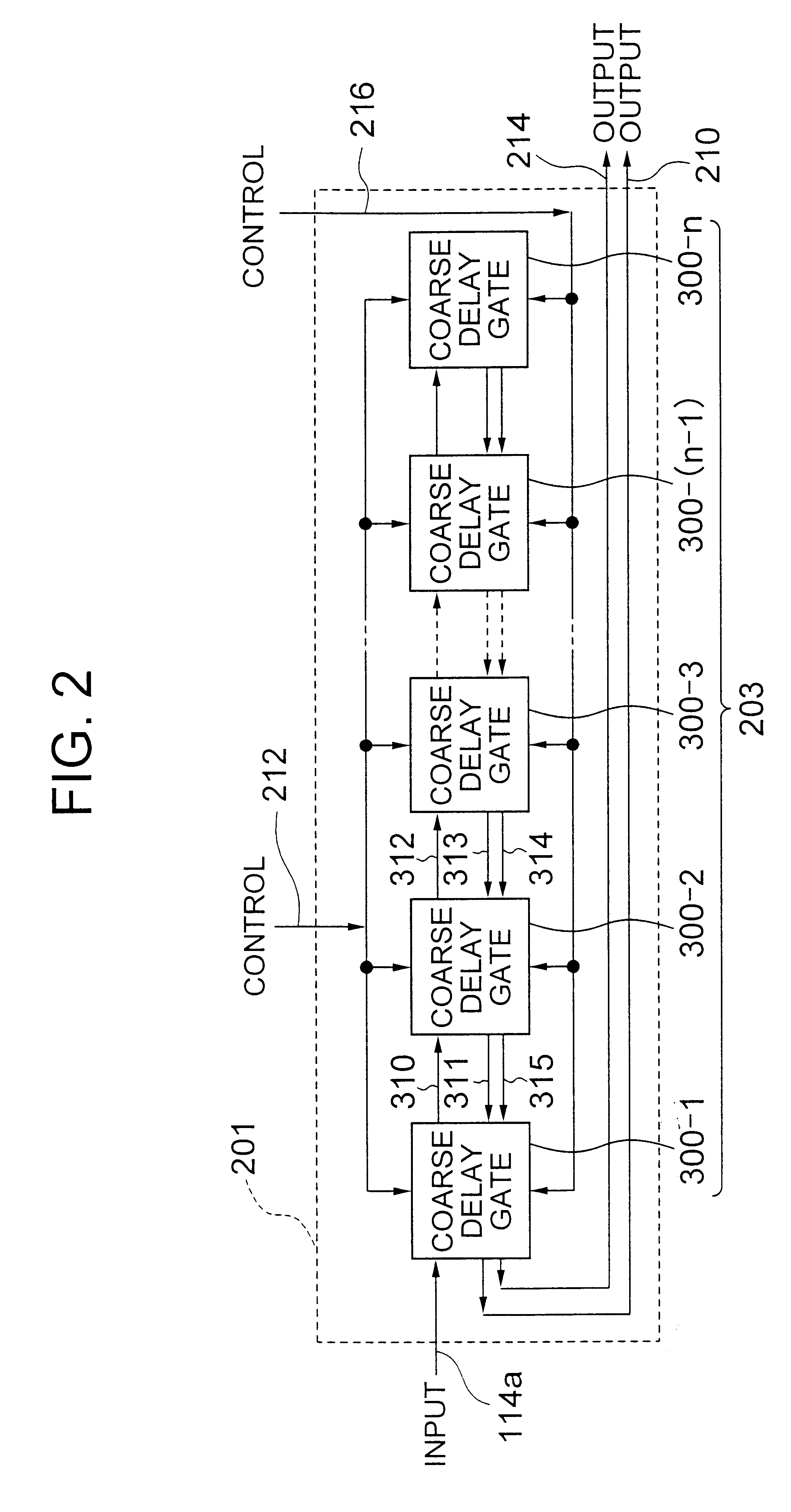

Ring oscillator having variable coarse and fine delays

A ring oscillator includes a coarse delay control block including a plurality of coarse delay gates, and a fine delay control block including a plurality of fine delay gates. The total delay of the fine delay control block is larger than a single delay step of the coarse delay control block, whereby variations of the delay step do not cause an adverse effect on the jitter characteristic of a PLL circuit having the ring oscillator. In a normal operation, the coarse delay control block increments the delay step after the total of the delay steps of the fine delay control block exceeds the delay step of the coarse delay control block.

Owner:RENESAS ELECTRONICS CORP

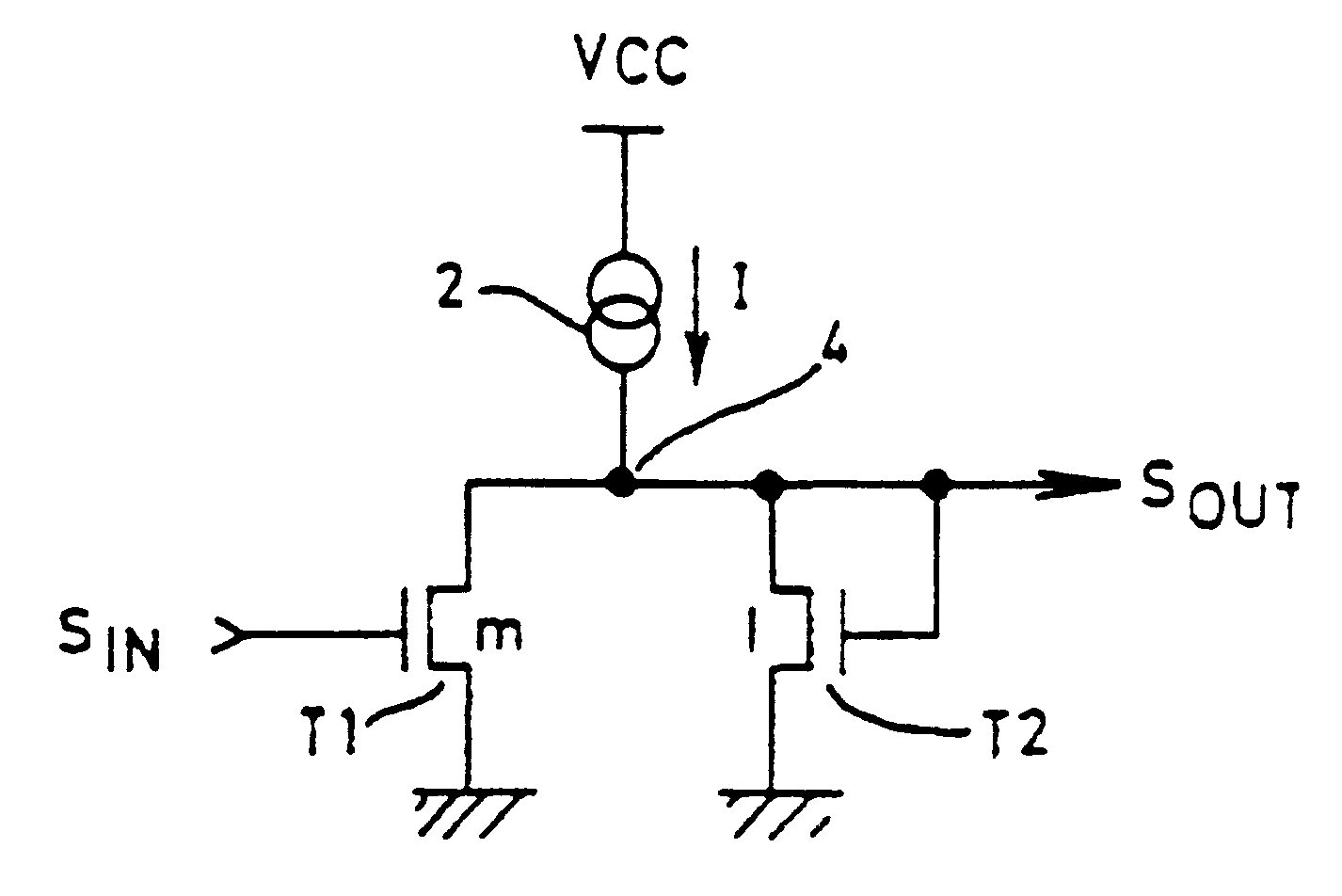

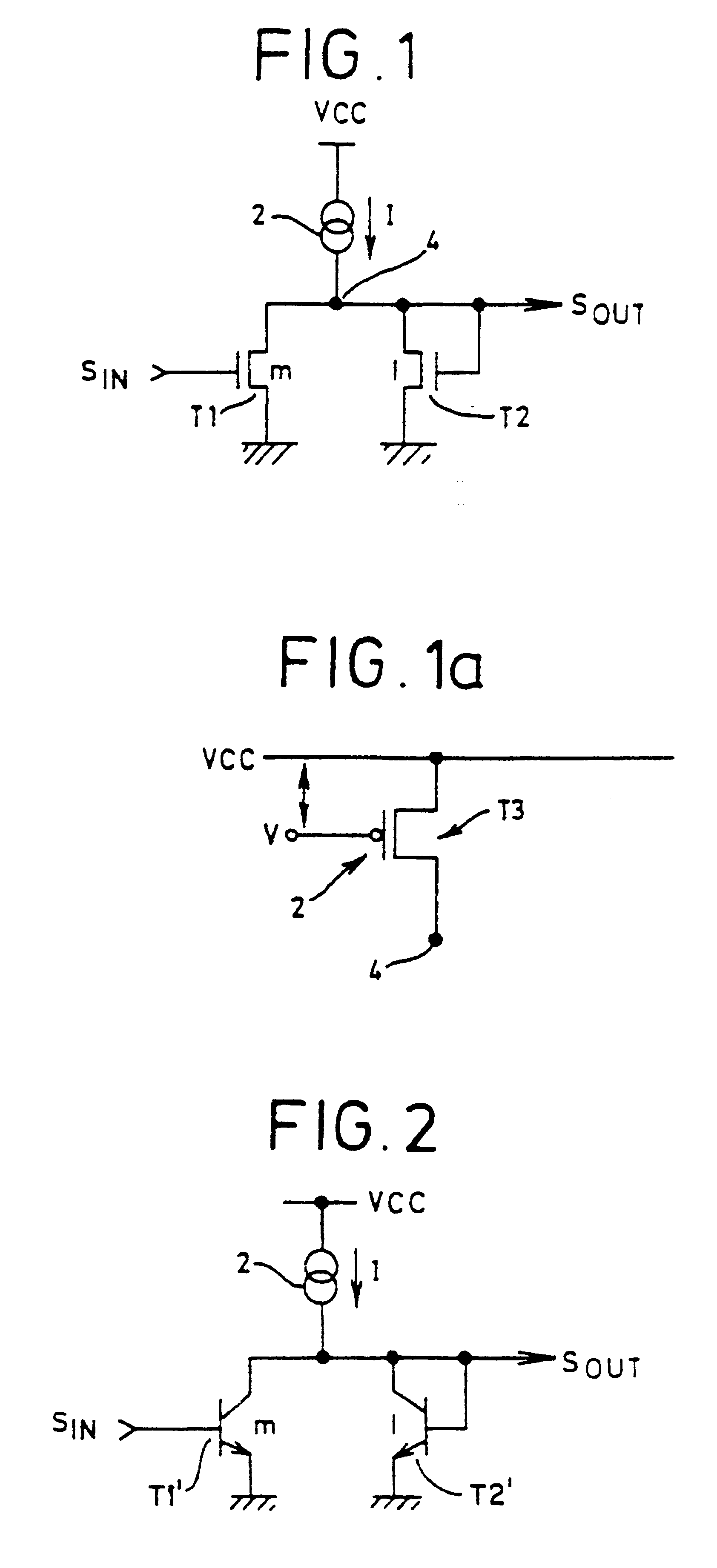

Ring oscillator using current mirror inverter stages

InactiveUSRE37124E1Limit maximum frequencyPulse automatic controlPulse generation by logic circuitsLow voltageEngineering

A ring oscillator having an odd number of single ended stages, each stage including two transistors connected as a current mirror. The stage provides for low-voltage performance and improved process tolerance characteristics.

Owner:STMICROELECTRONICS SRL

Monolithic clock generator and timing/frequency reference

ActiveUS7227423B2High frequencyLoud noiseResonant circuit tuningPulse automatic controlAudio power amplifierPulsed mode

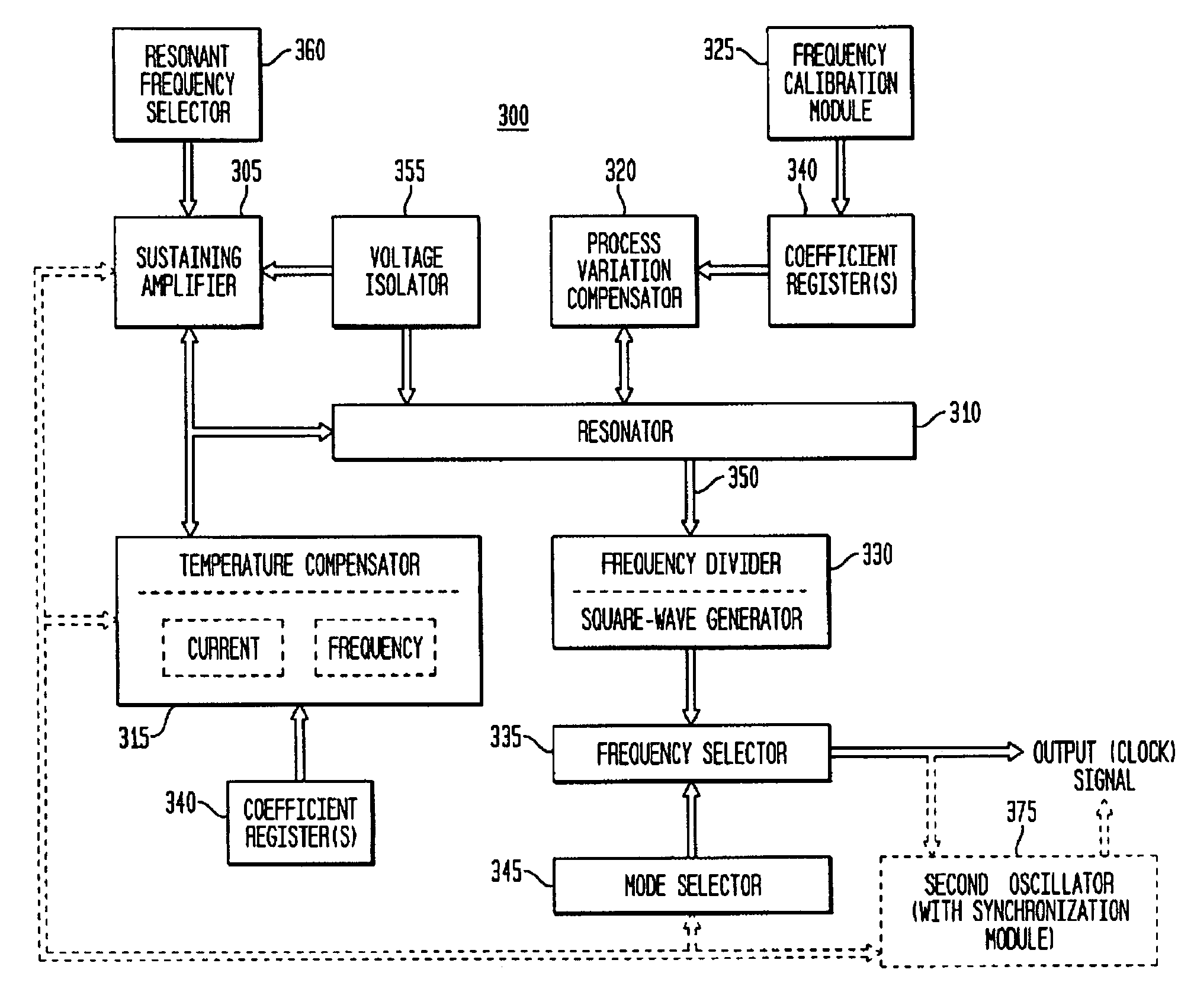

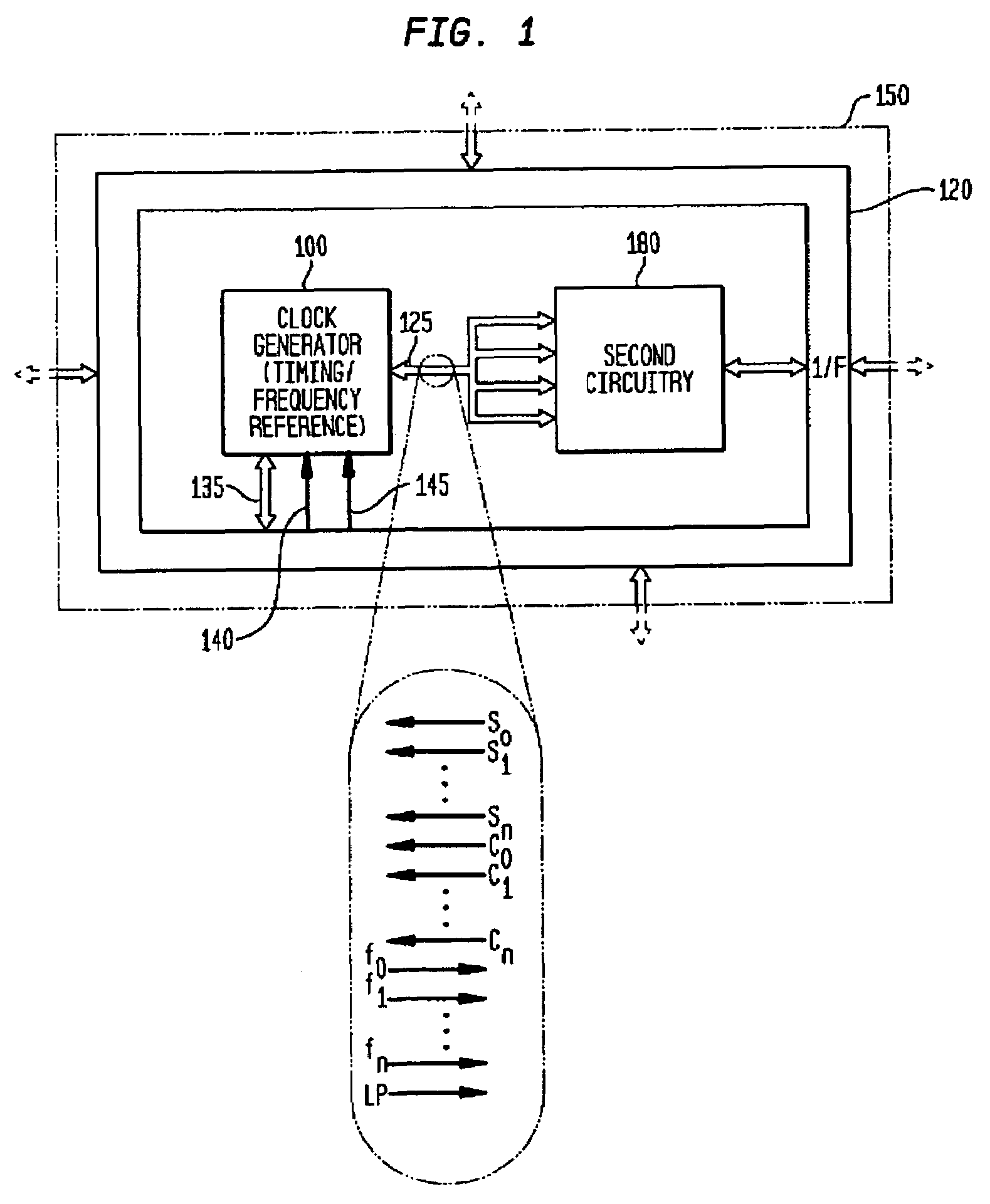

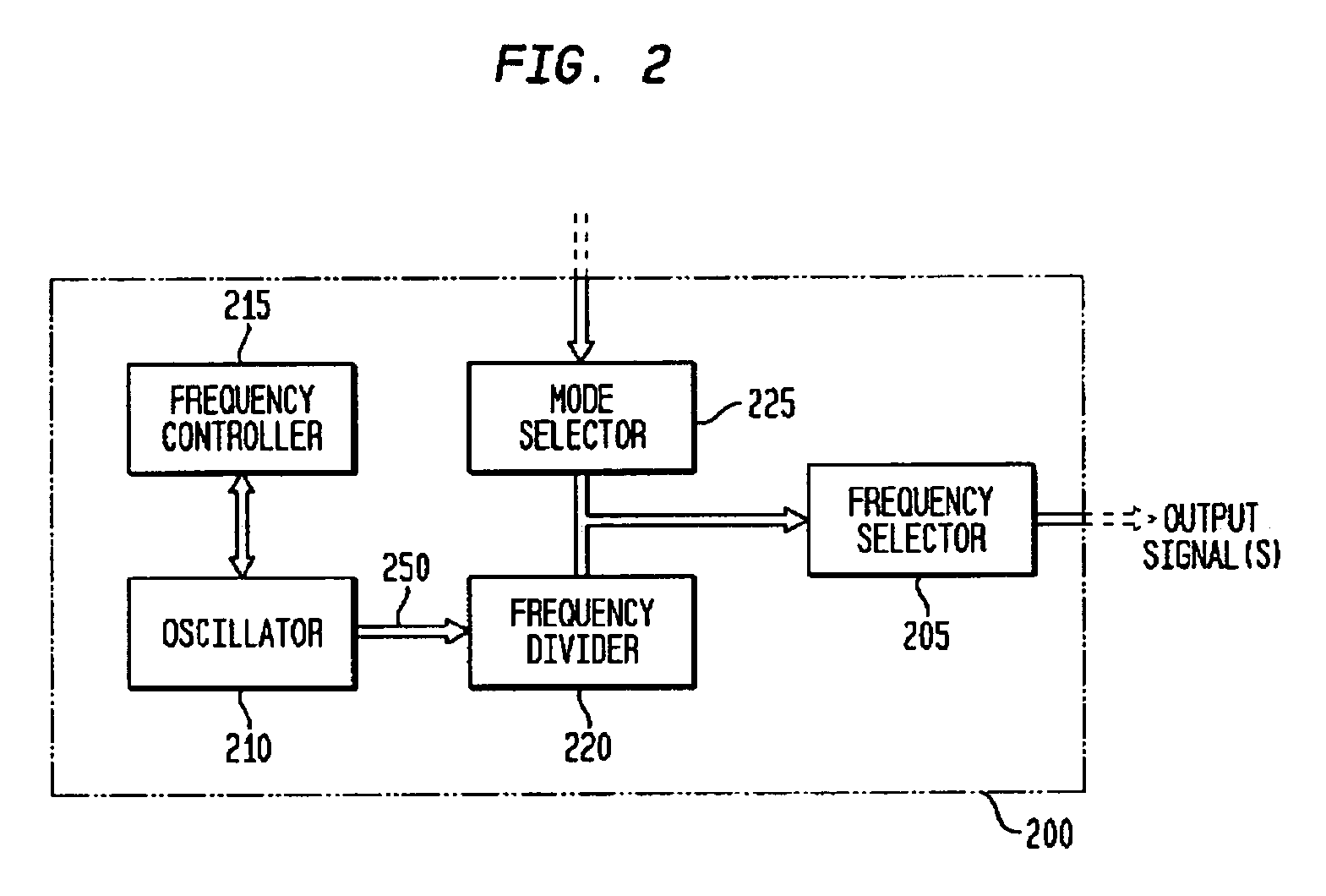

In various embodiments, the invention provides a clock generator and / or a timing and frequency reference, with multiple operating modes, such power conservation, clock, reference, and pulsed modes. The various apparatus embodiments include a resonator adapted to provide a first signal having a resonant frequency; an amplifier; a temperature compensator adapted to modify the resonant frequency in response to temperature; and a process variation compensator adapted to modify the resonant frequency in response to fabrication process variation. In addition, the various embodiments may also include a frequency divider adapted to divide the first signal having the resonant frequency into a plurality of second signals having a corresponding plurality of frequencies substantially equal to or lower than the resonant frequency; and a frequency selector adapted to provide an output signal from the plurality of second signals. The output signal may be provided in any of various forms, such as differential or single-ended, and substantially square-wave or sinusoidal.

Owner:INTEGRATED DEVICE TECH INC

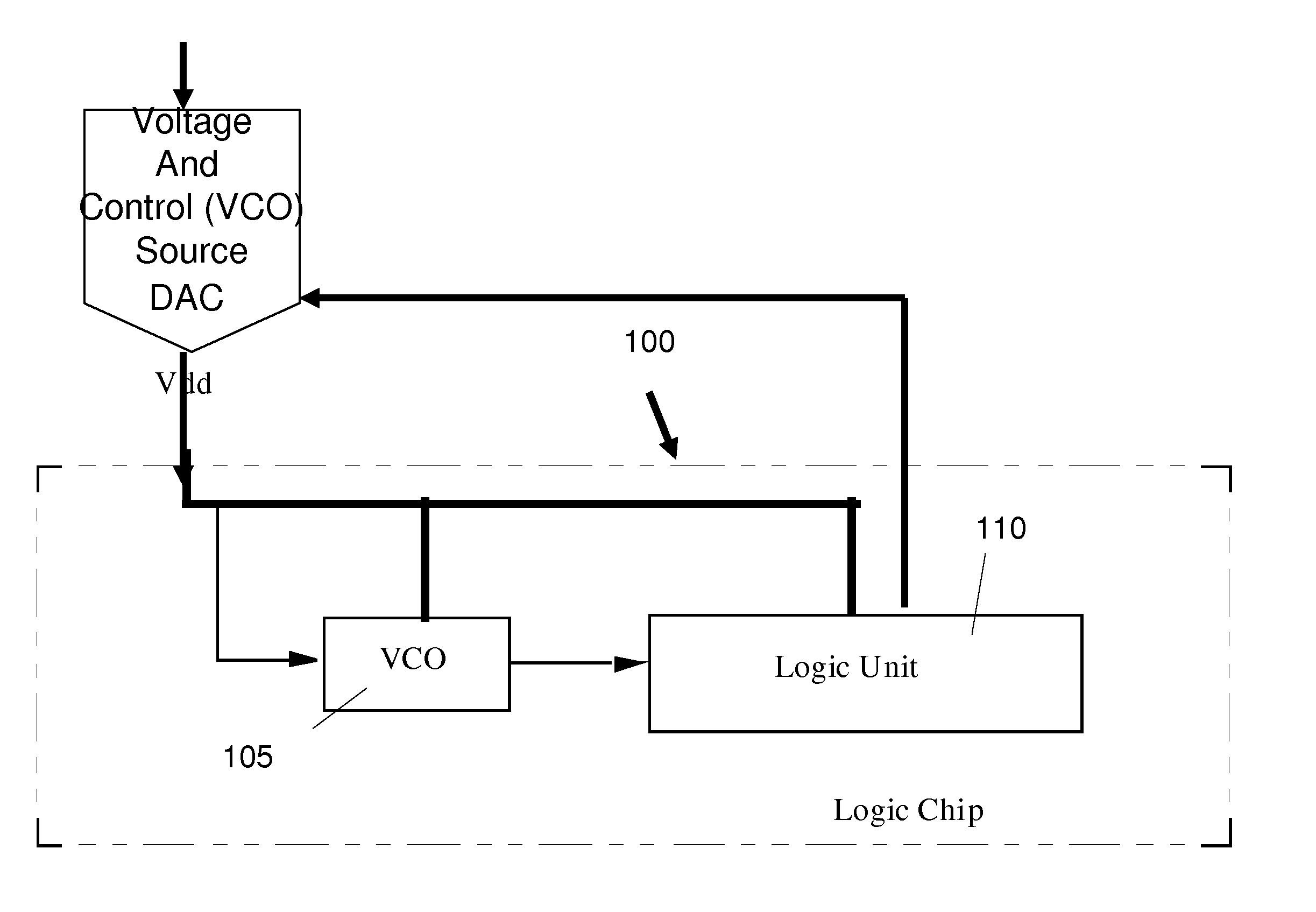

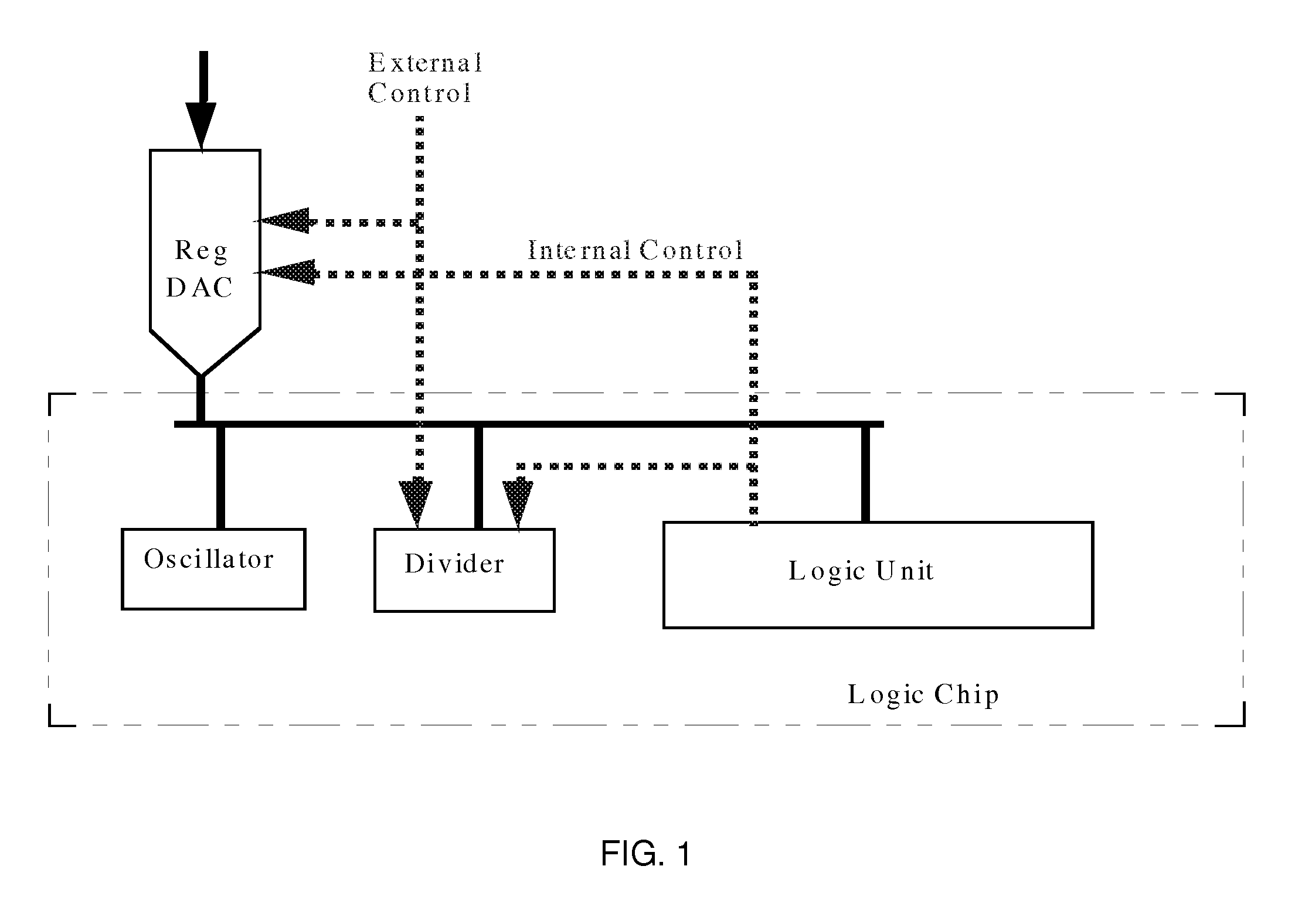

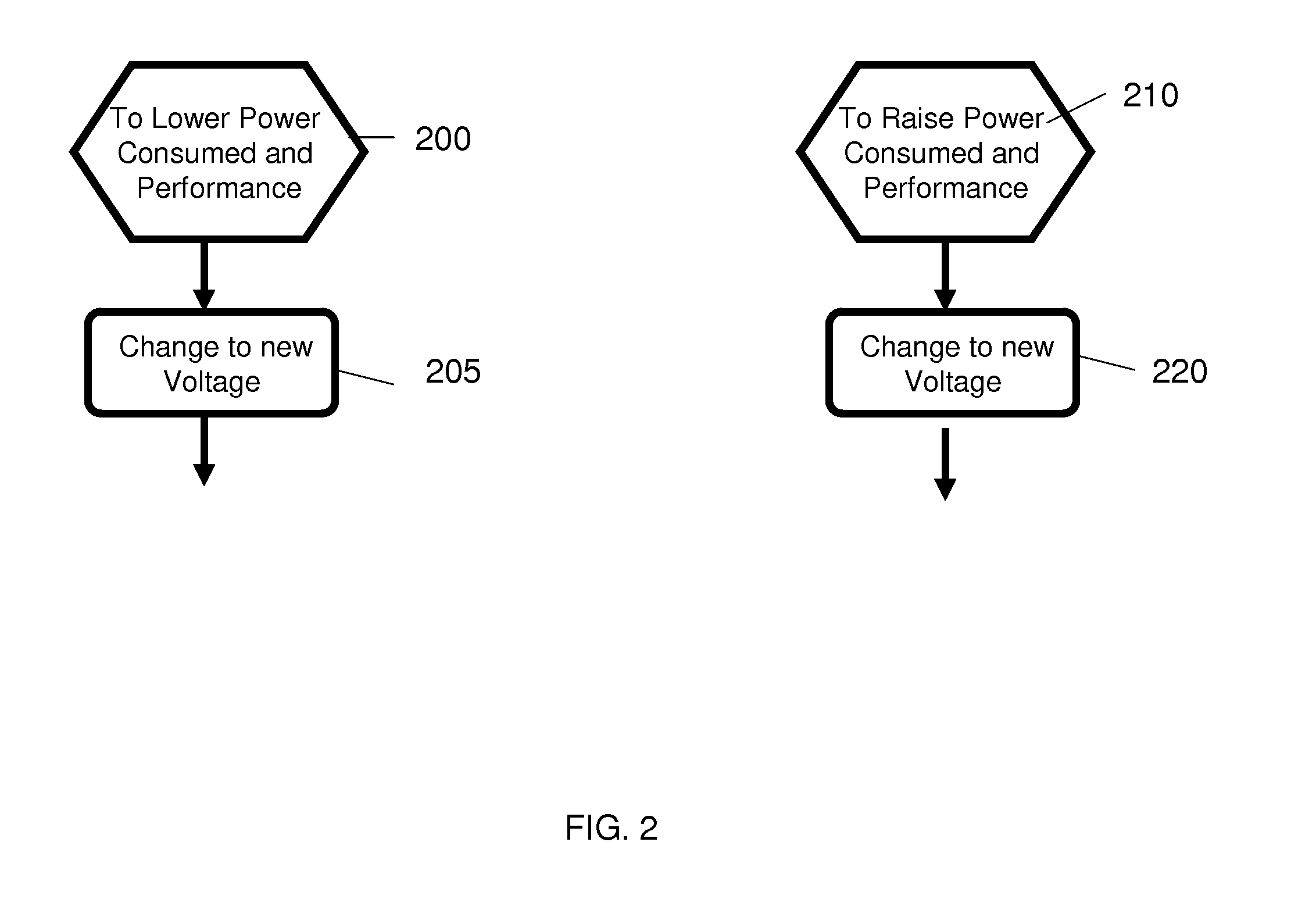

Power management architecture and method of modulating oscillator frequency based on voltage supply

A method and system for modulating logic clock oscillator frequency based on voltage supply. The system comprises a logic unit having a logic operation and a device to produce self-adjusting clocks to match the logic operation. The device is configured to use supply voltage as an independent variable to optimize device parameters for voltage variations.

Owner:GLOBALFOUNDRIES INC

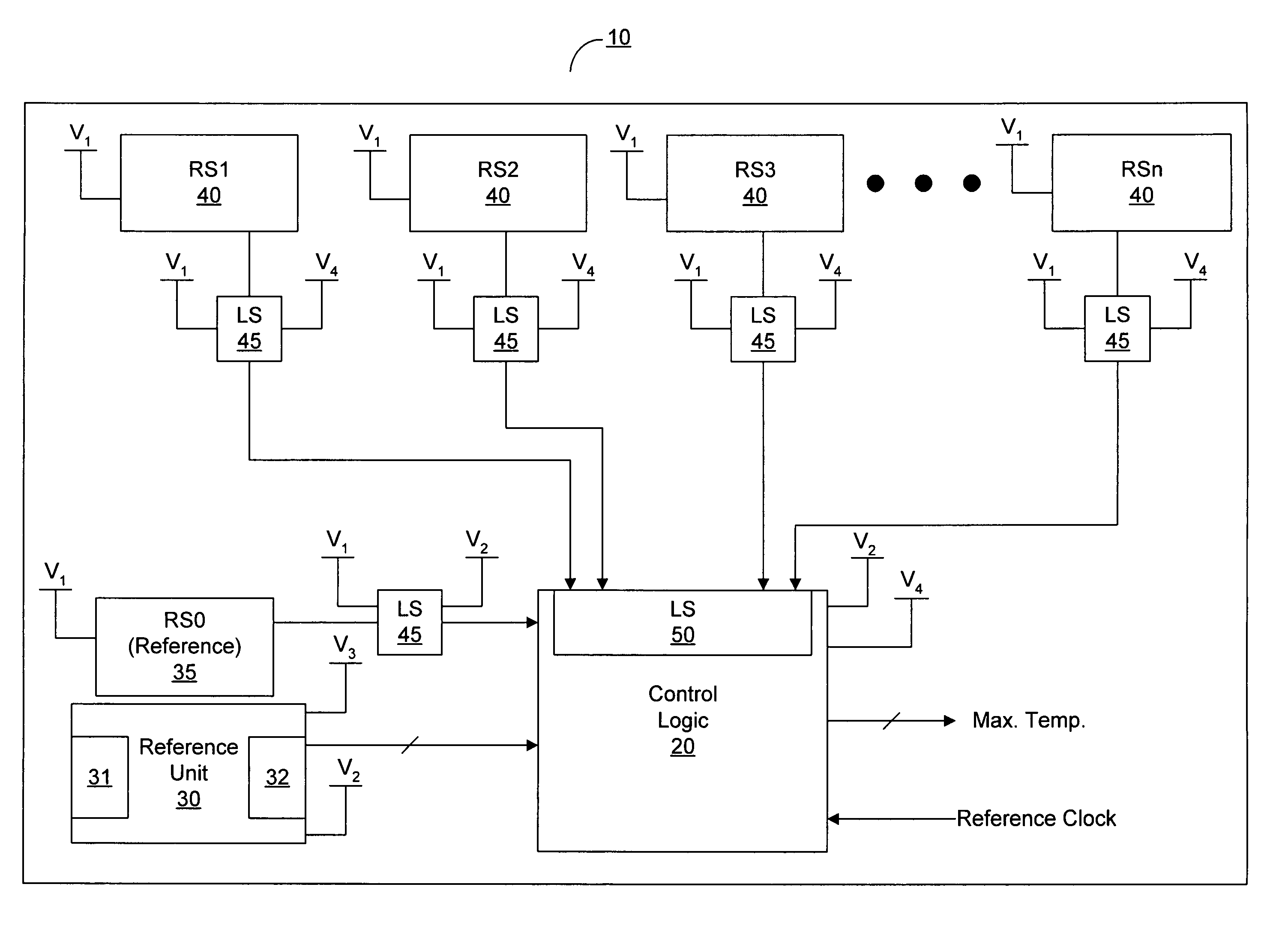

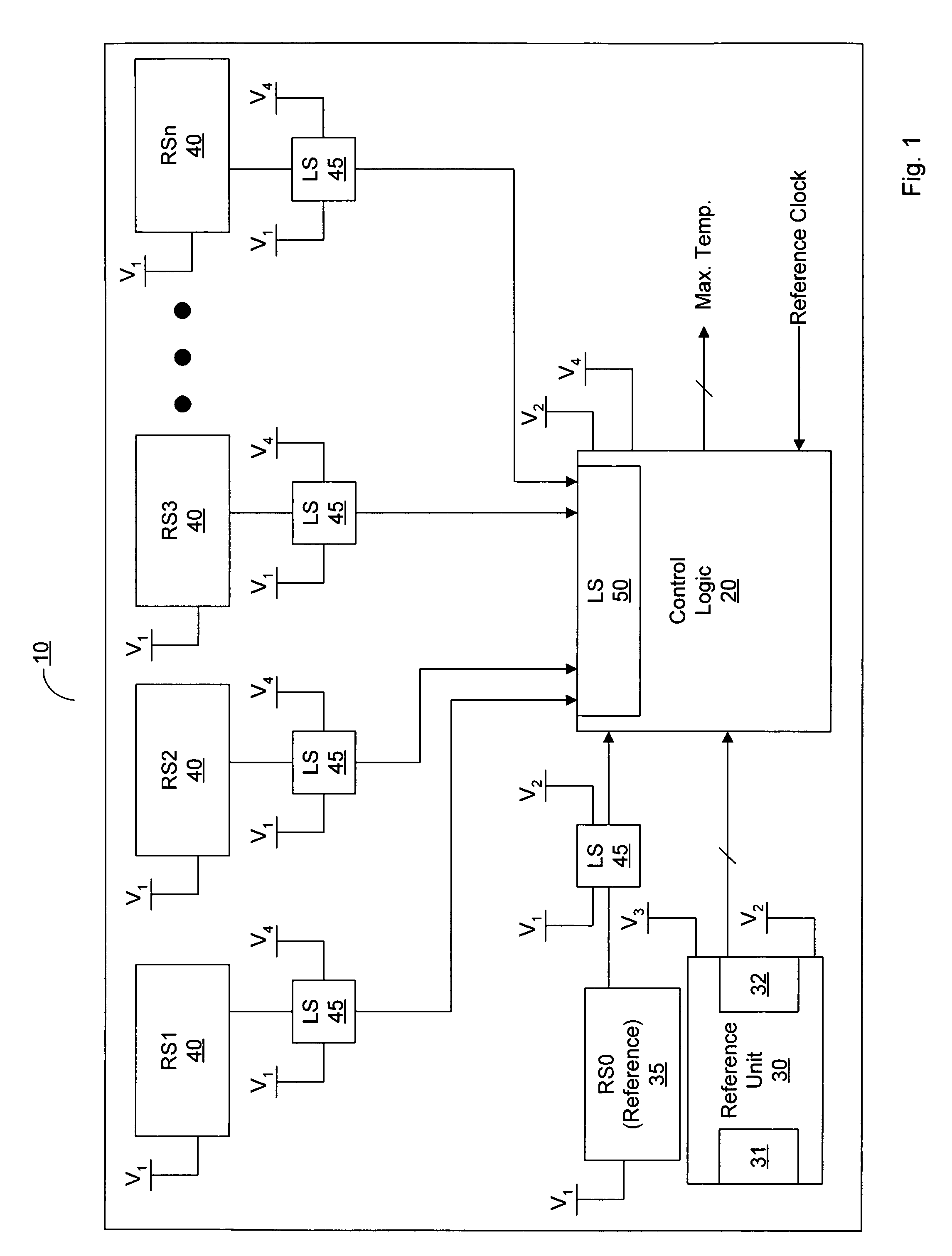

Method and apparatus for temperature sensing in integrated circuits

InactiveUS7455450B2Easy wiringSave extra spaceThermometer detailsThermometers using material expansion/contactionEngineeringMaximum temperature

A method and apparatus for temperature sensing in an IC. The IC includes a plurality of remote temperature sensors each coupled to a control logic unit. The plurality of remote temperature sensors may be distributed throughout the integrated circuit. The integrated circuit includes a reference unit coupled to provide a reference temperature to the control logic unit and a reference sensor coupled to provide a signal having a reference frequency to the control logic unit. The reference unit and the reference sensor are located near each other. The control logic unit is configured to correlate the reference frequency received from the reference sensor with the reference temperature received from the reference unit. The control logic unit is further configured to determine the temperature of each of the remote temperature sensors based on this correlation, and also configured to determine the maximum temperature of all of the temperature sensors.

Owner:ADVANCED MICRO DEVICES INC

Popular searches

Pulse manipulation Semiconductor/solid-state device manufacturing Semiconductor devices Generating/distributing signals Oscillations comparator circuits Electric variable regulation Electrial characteristics varying frequency control Angle demodulation by phase difference detection Record information storage Digital recording