Patents

Literature

494 results about "RC oscillator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

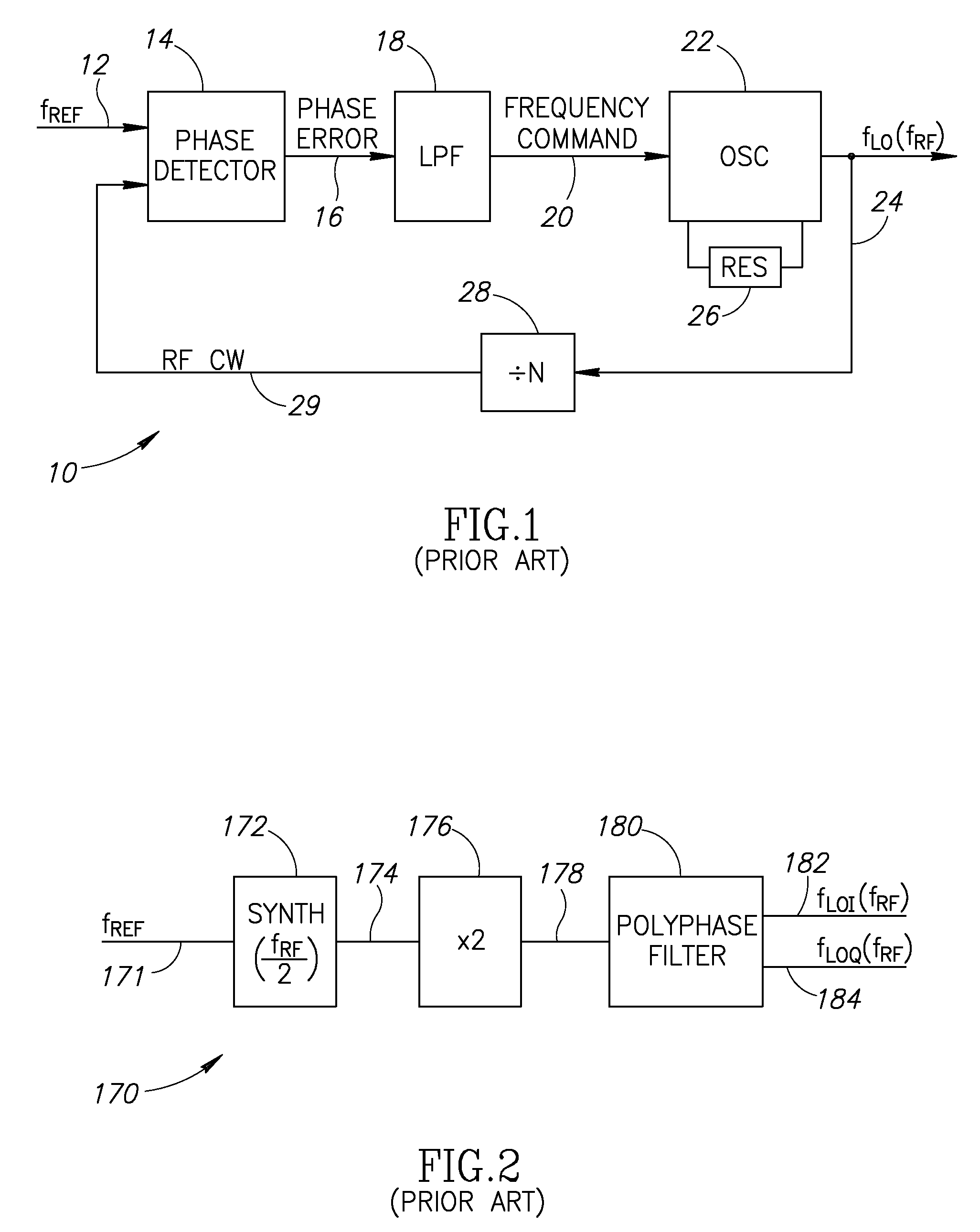

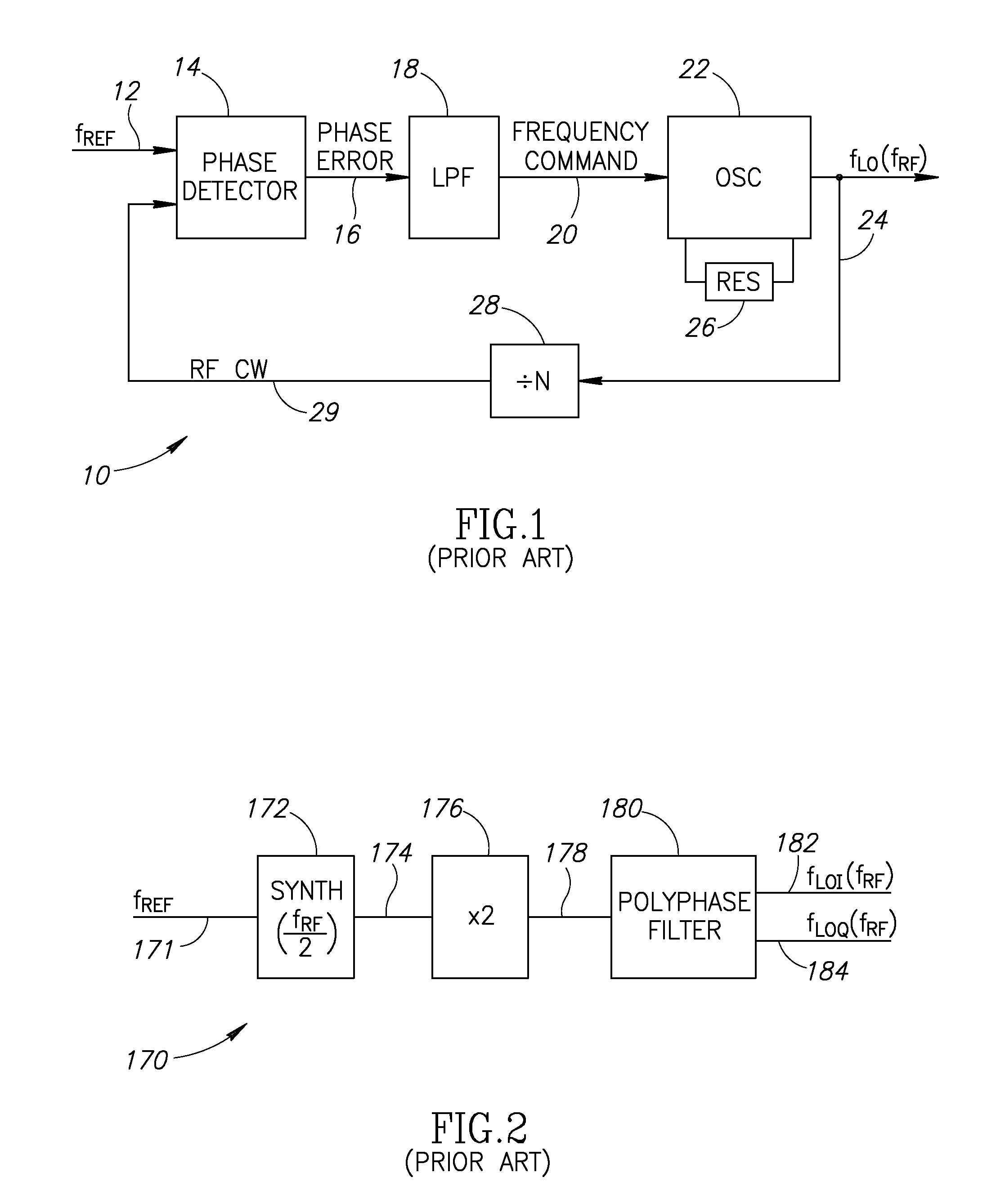

Linear electronic oscillator circuits, which generate a sinusoidal output signal, are composed of an amplifier and a frequency selective element, a filter. A linear oscillator circuit which uses an RC network, a combination of resistors and capacitors, for its frequency selective part is called an RC oscillator.

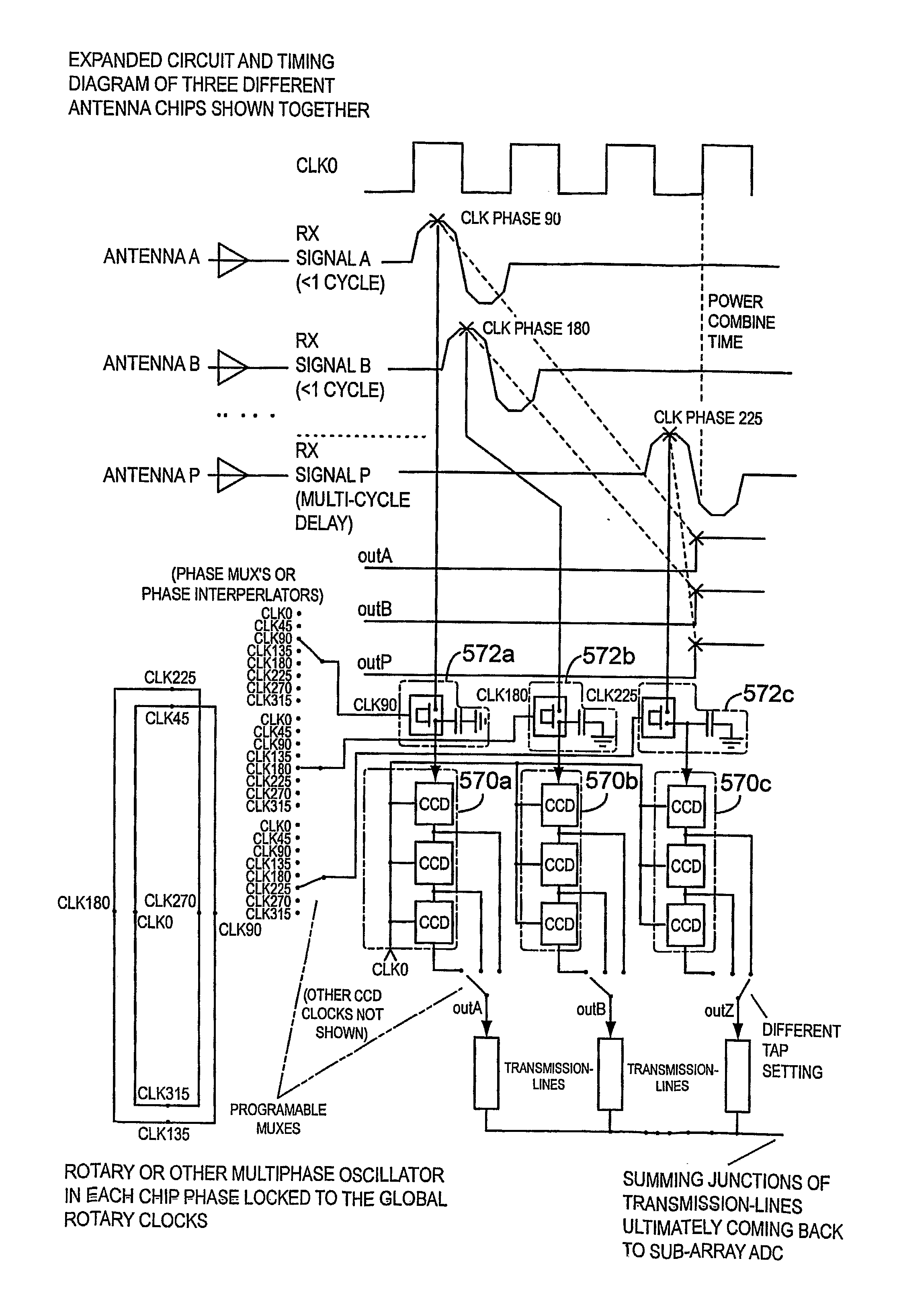

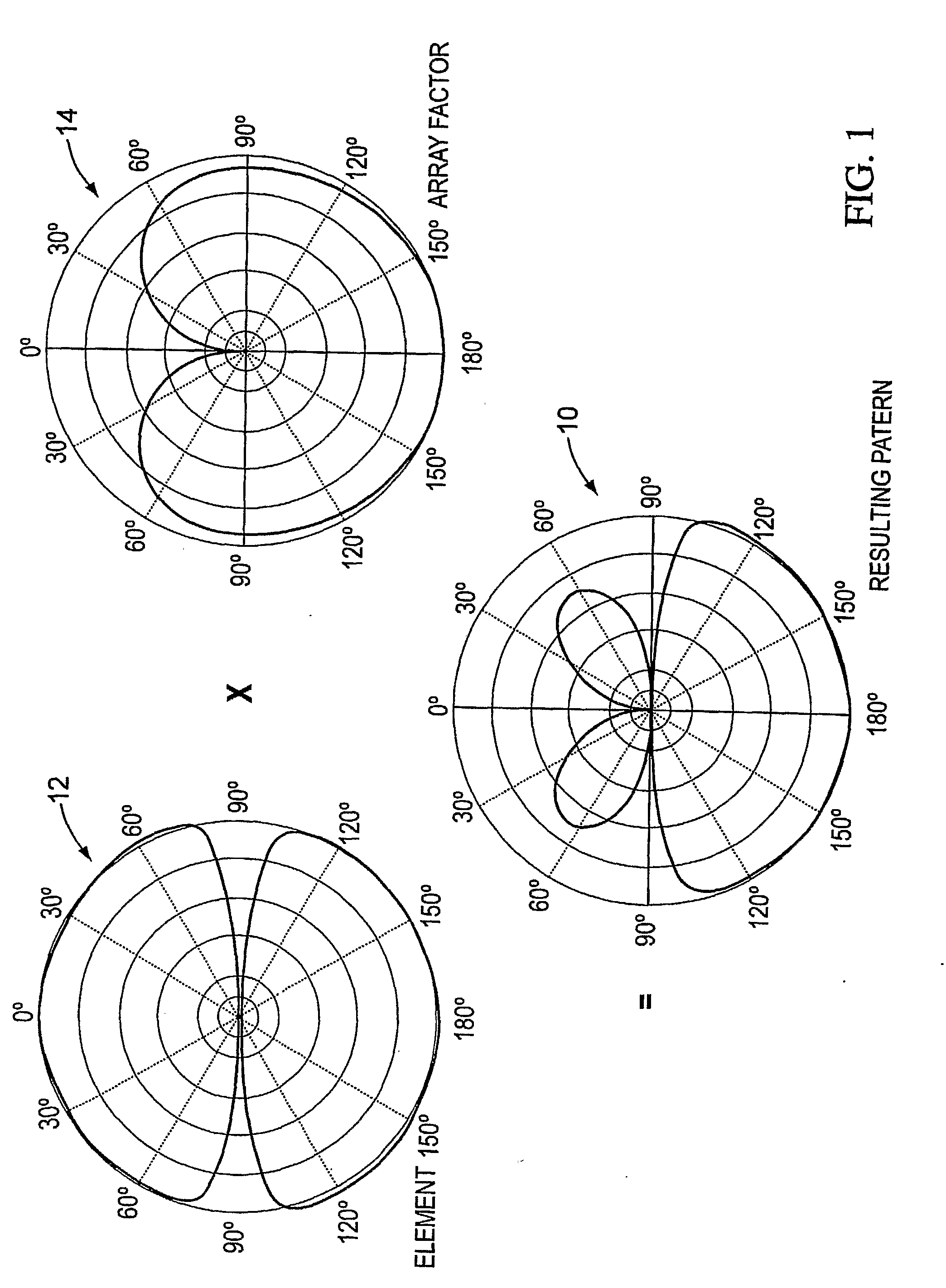

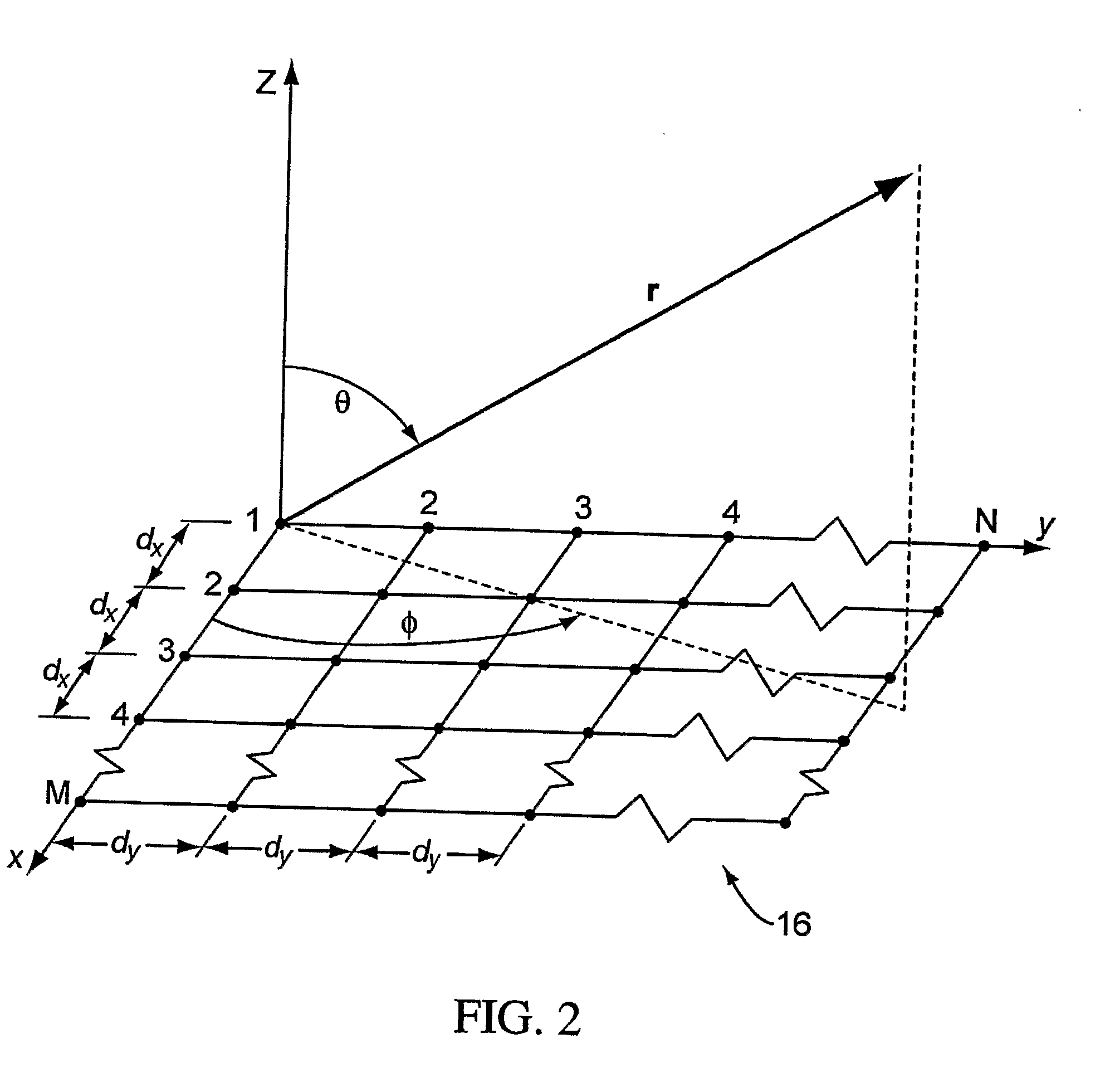

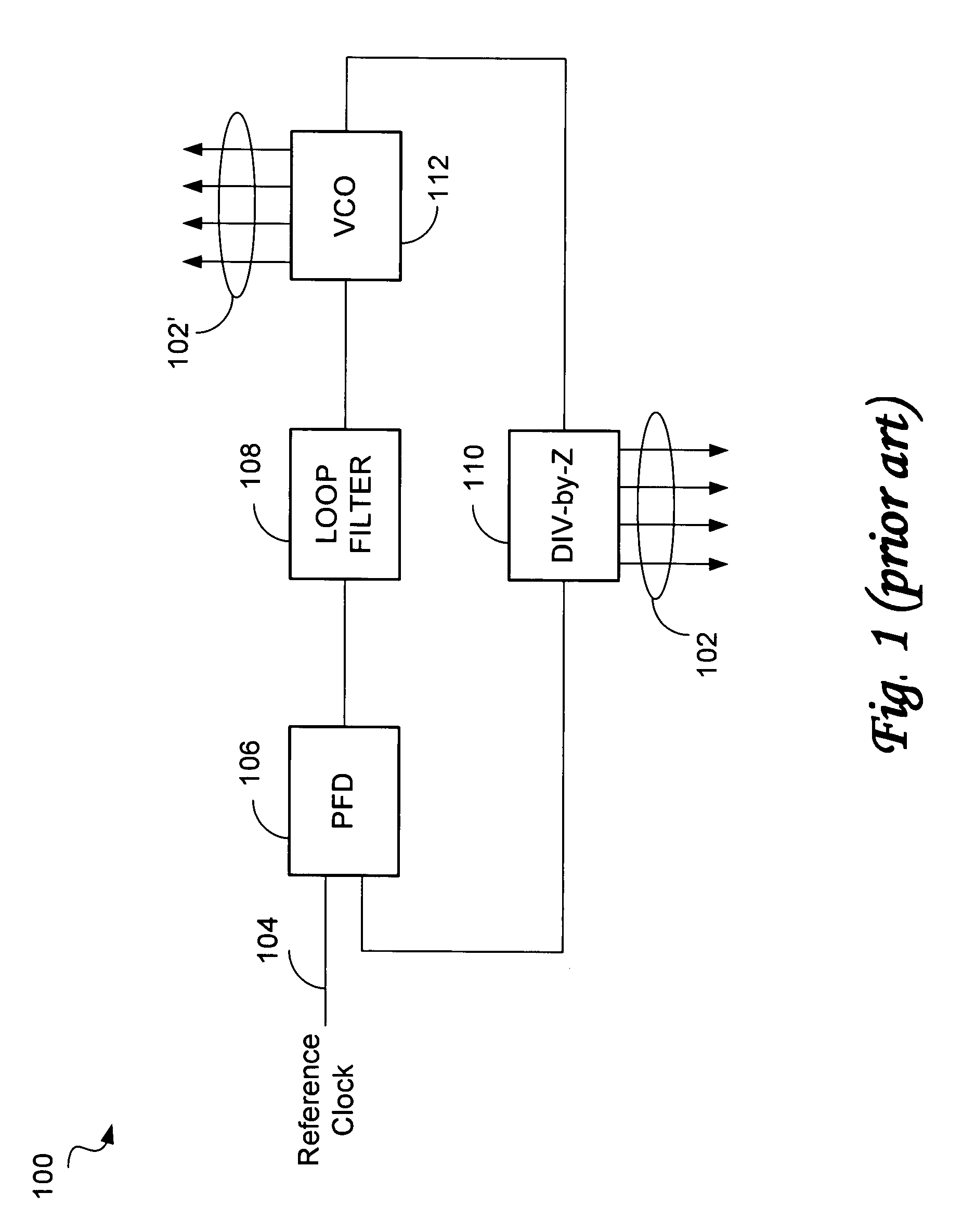

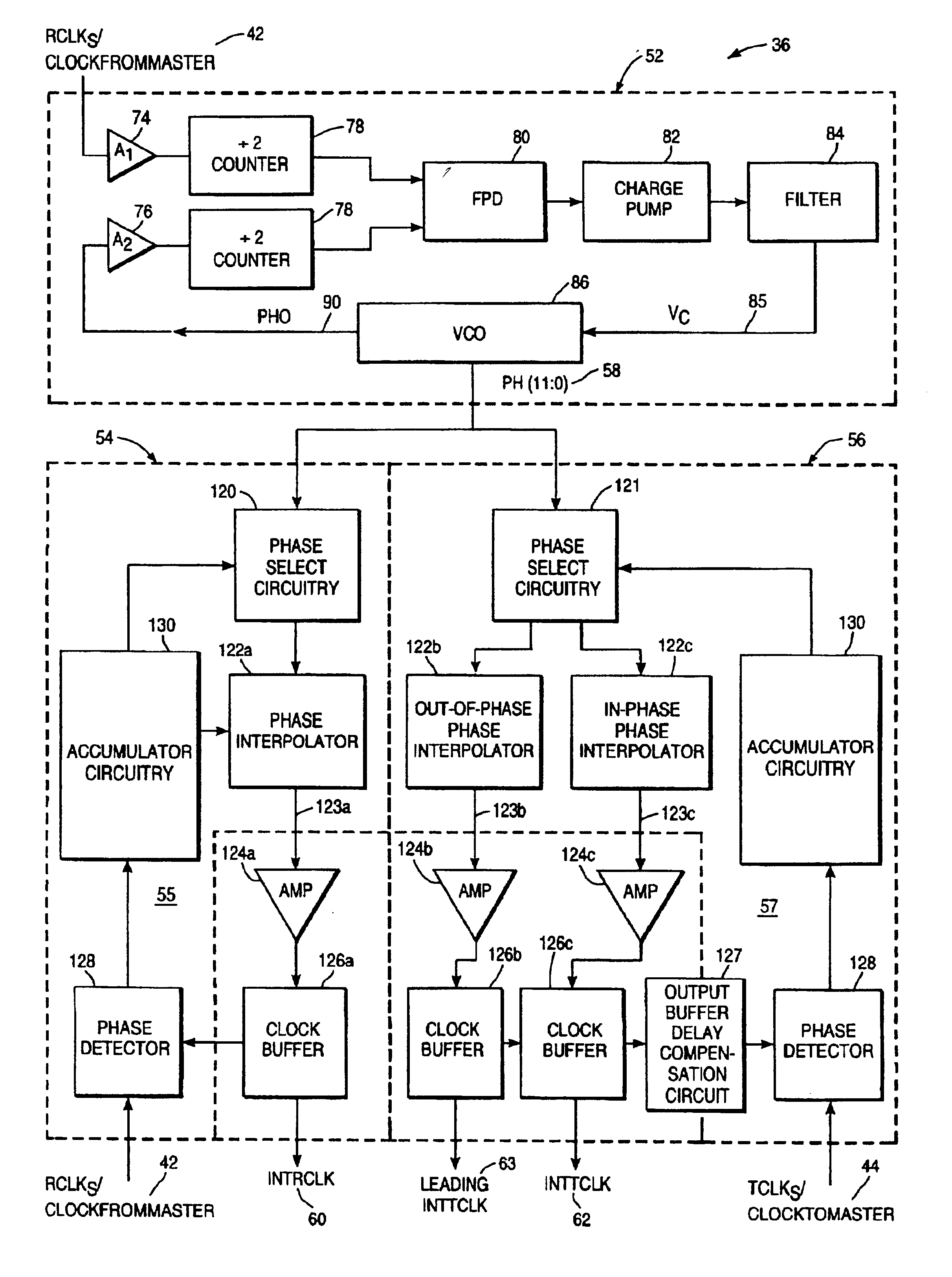

True time delay phase array radar using rotary clocks and electronic delay lines

ActiveUS20120039366A1Forming accuratelyEasy to moveAntenna arraysPulse automatic controlTime delaysAnalog delay line

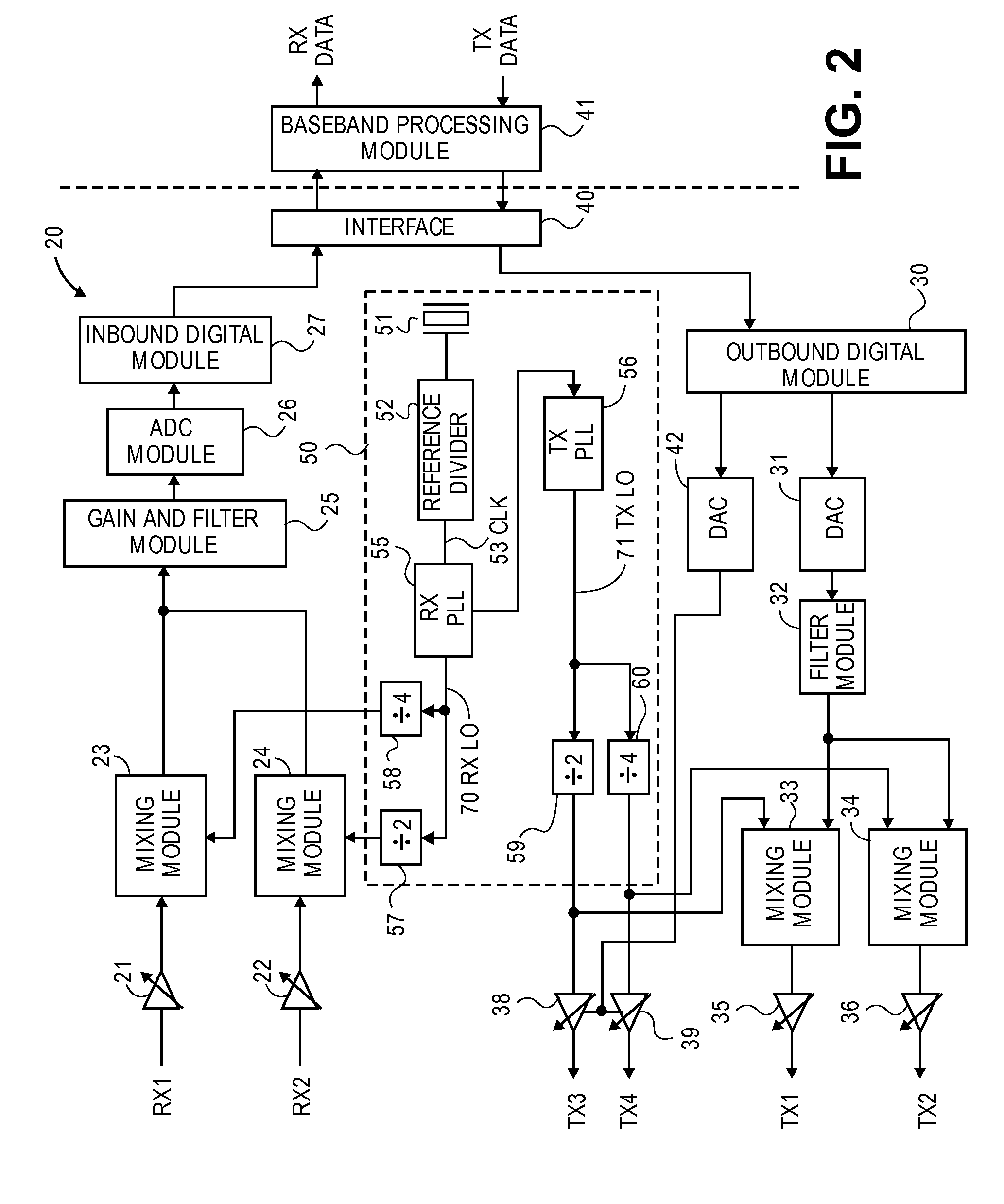

Local oscillator circuitry for an antenna array is disclosed. The circuitry includes an array of rotary traveling wave oscillators which are arranged in a pattern over an area and coupled so as to make them coherent. This provides for a set of phase synchronous local oscillators distributed over a large area. The array also includes a plurality of phase shifters each of which is connected to one of the rotary oscillators to provide a phase shifted local oscillator for the array. The phase shifter optionally includes a cycle counter that is configured to count cycles of the rotary oscillator to which it is connected and control circuitry that is then operative to provide a shifted rotary oscillator output based on the count from the cycle counter. A system and method for operating a true-time delay phased array antenna system. The system includes a plurality of antenna element circuits for driving or receiving an rf signal from the elements of the array. Each element circuit has a transmit and a receive path and a local multiphase oscillator, such as a rotary traveling wave oscillator. Each path has an analog delay line for providing a true-time delay for the antenna element. Preferably, the analog delay line is a charge coupled device whose control nodes are connected to phases of the local multiphase oscillator to implement a delay that is an integer number local multiphase oscillator periods. A fractional delay is also included in the path by using a sample and hold circuit connected to a particular phase of the oscillator. By delaying each antenna element by a true time delay, broadband operation of the array is possible.

Owner:ANALOG DEVICES INC

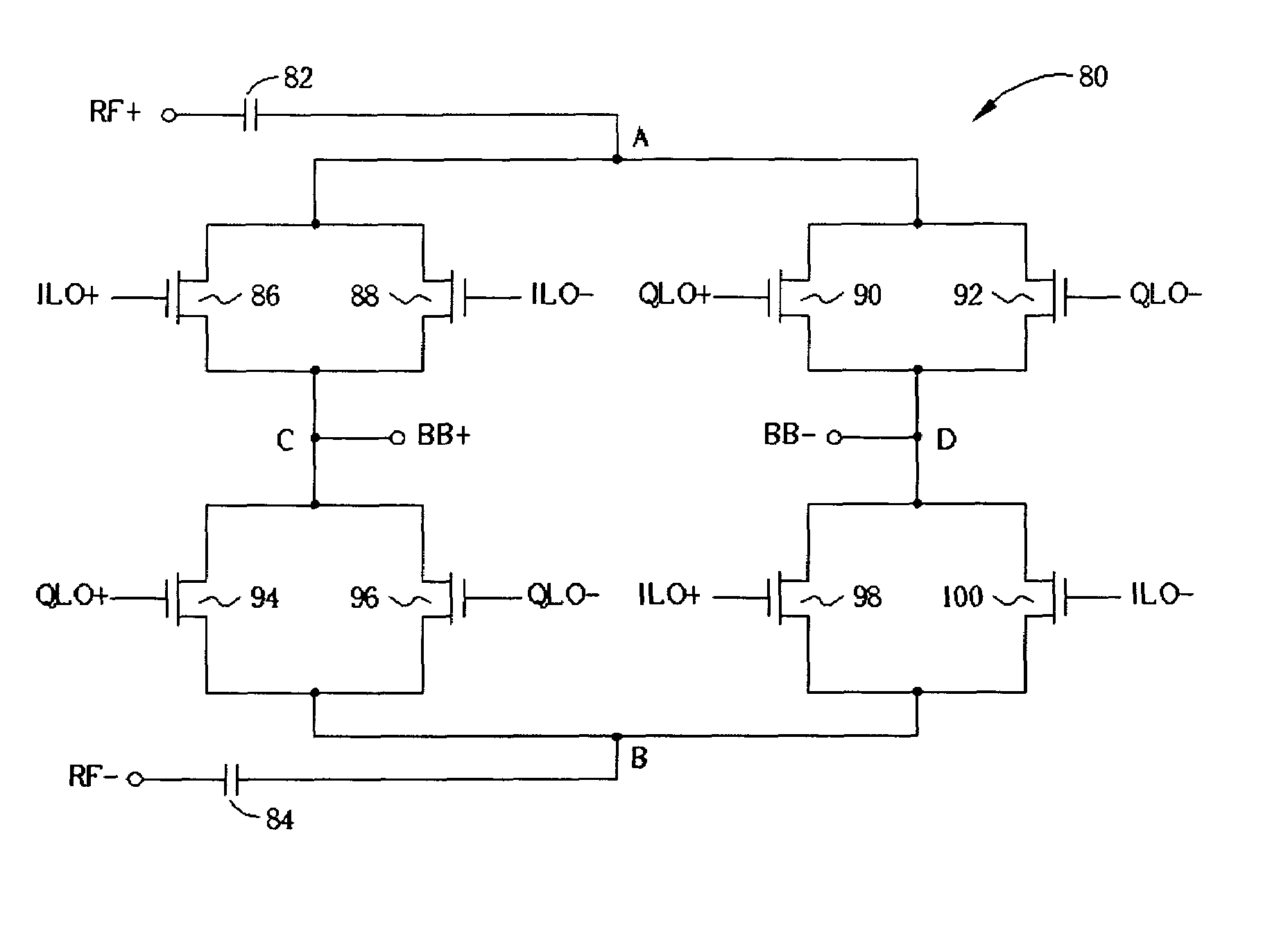

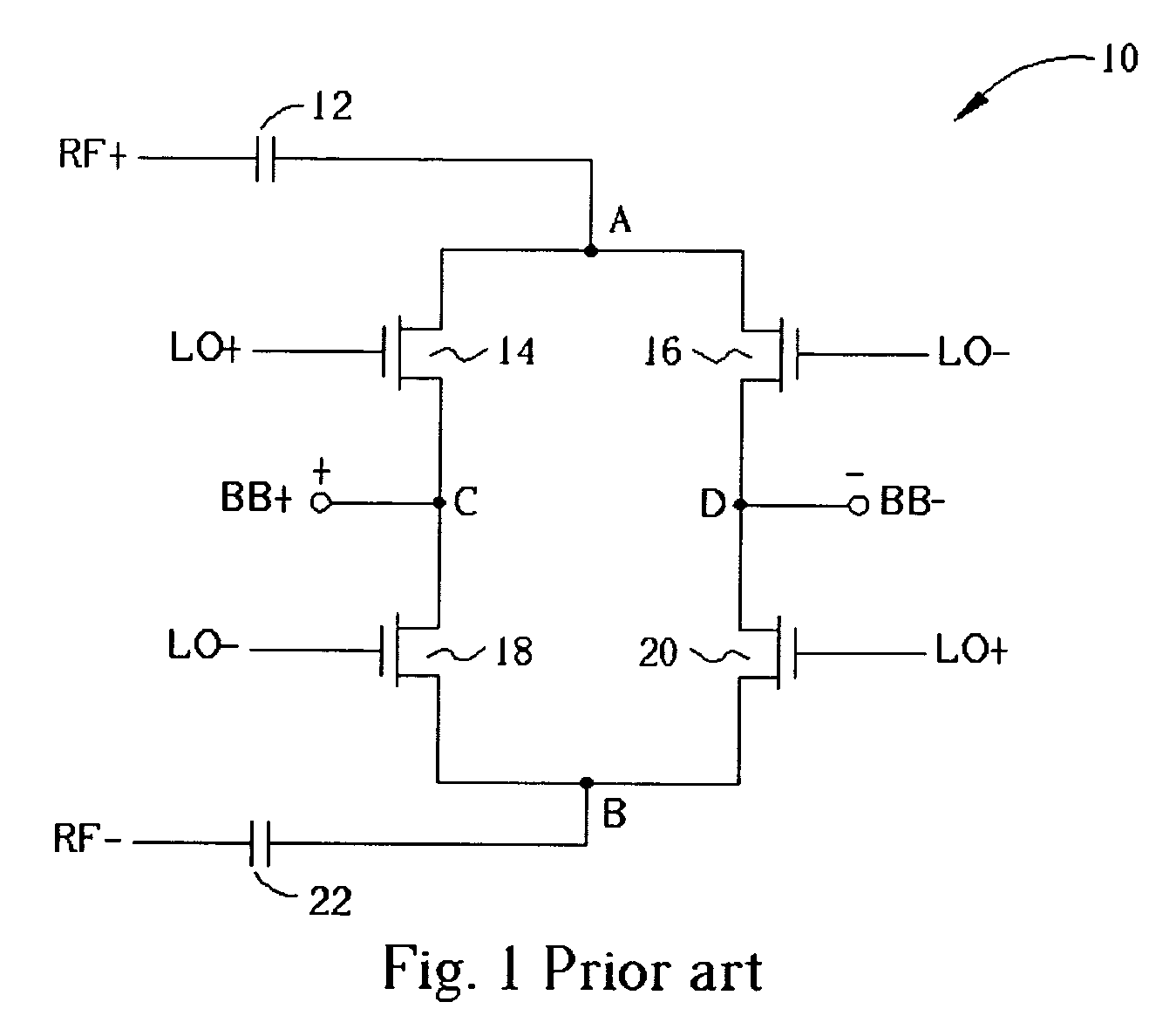

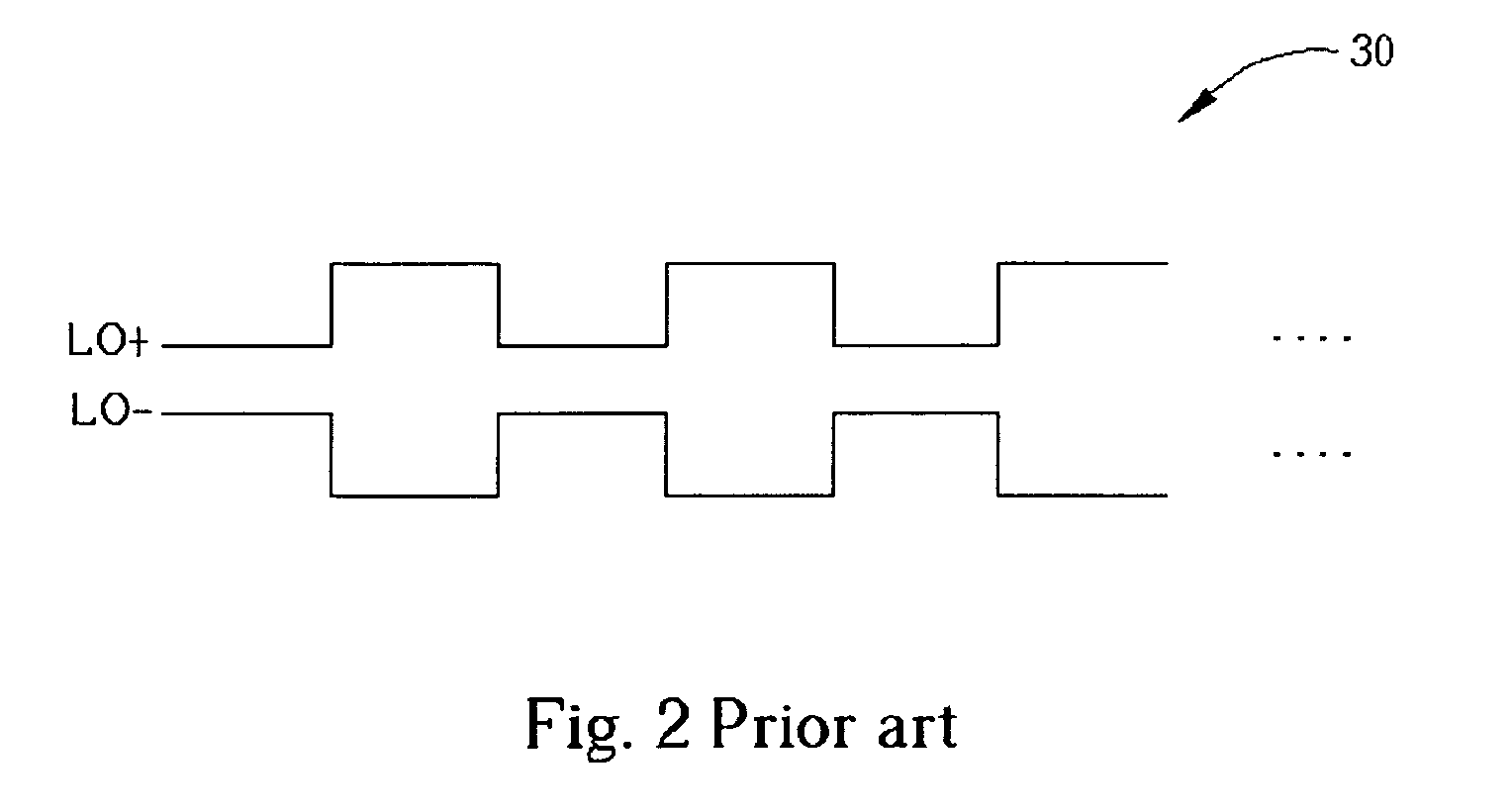

Passive harmonic switch mixer

A passive harmonic switch mixer is shown that is immune to self mixing of the local oscillator greatly reducing leakage noise, pulling noise, and flicker noise when used in a direct conversion receiver or direct conversion transmitter circuit. The passive harmonic switch mixermixes an input signal received on an input port with an in-phase oscillator signal and a quadrature-phase oscillator signal and outputs an output signal on an output port. Because the quadrature-phase oscillator signal is the in-phase oscillator signal phase shifted by 90 °, the passive harmonic switch mixer operates with a local oscillator running at half the frequency of the carrier frequency of an RF signal. Additionally, because the passive harmonic switch mixer has no active components, the DC current passing through each switch device is reduced and the associated flicker noise of the mixer is also greatly reduced.

Owner:REALTEK SEMICON CORP

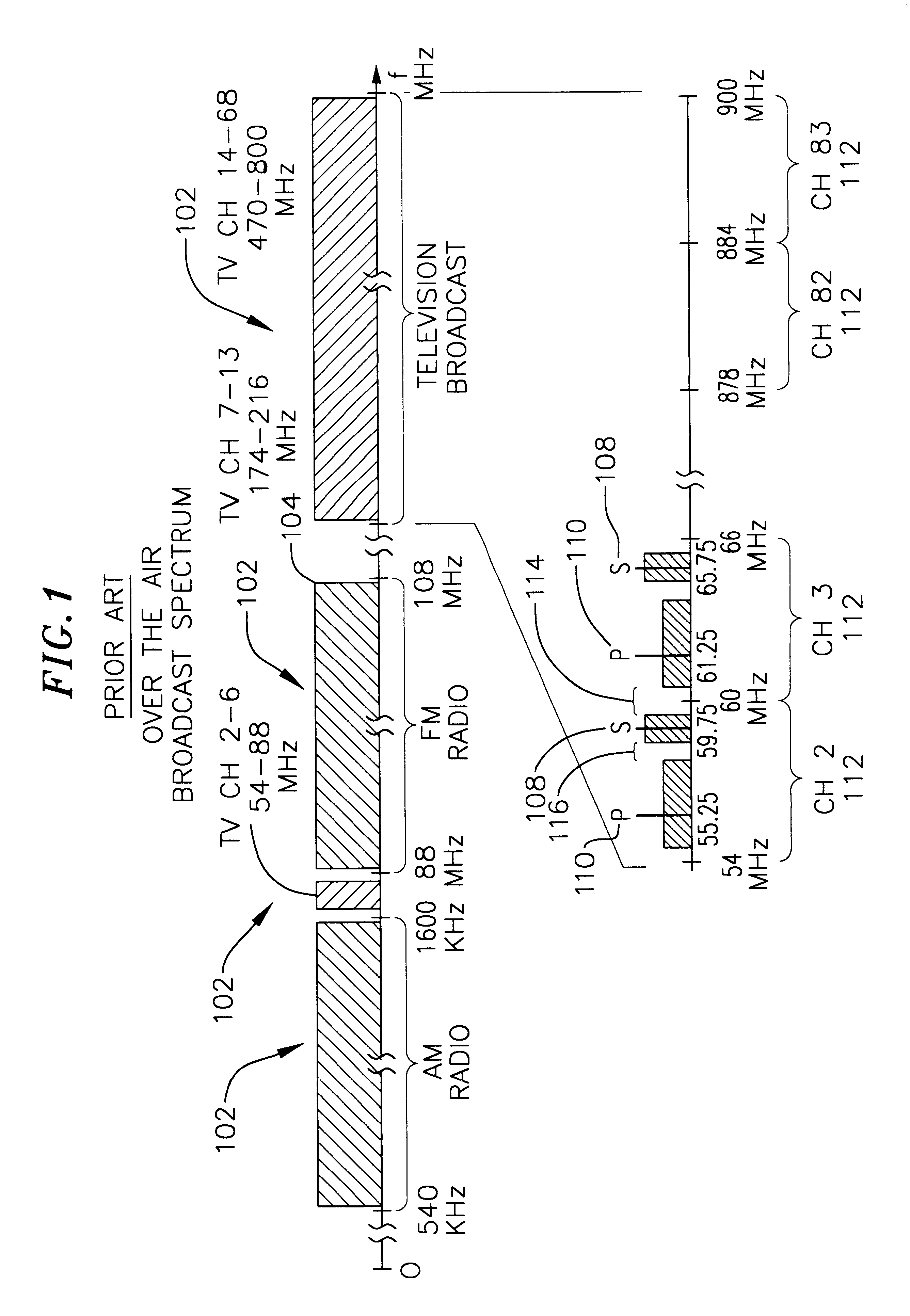

Integrated switchless programmable attenuator and low noise amplifier

InactiveUS6879816B2Multiple-port active networksSwitched capacitor networksCapacitanceLocal oscillator signal

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

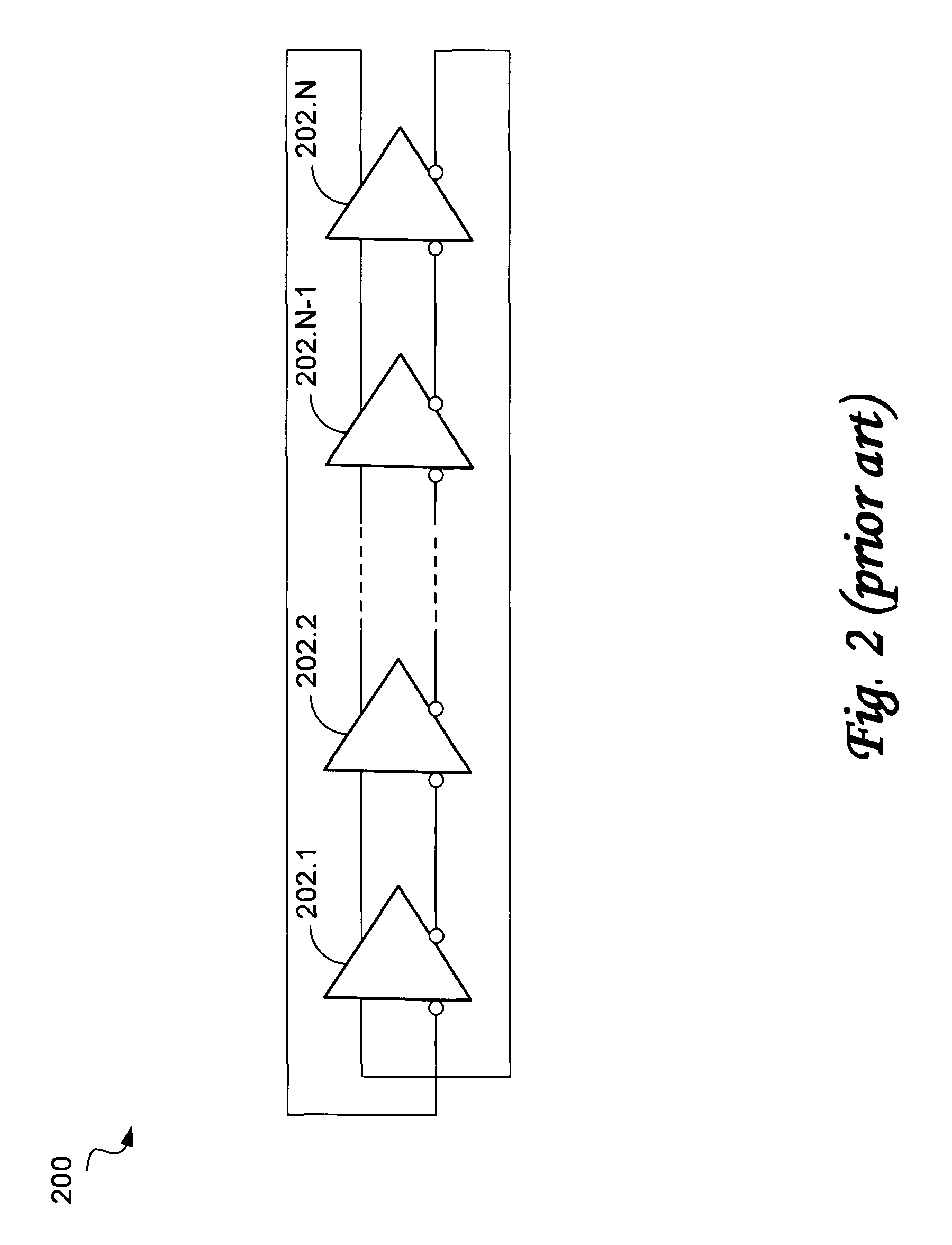

Voltage Controlled Oscillator (VCO) with a wide tuning range and substantially constant voltage swing over the tuning range

A wide tuning range and constant swing VCO is described that is based on a multipass Ring Oscillator enhanced with feed-backward connections. This VCO is designed to overcome tuning range limitations of prior-art “feed-forward” ring oscillators. The Feedback multipass Ring Oscillator of the invention provides decreasing frequency when tuned by increasing the feedback, thus covering a much wider tuning range irrespective of the speed limit of the technology while at the same time providing almost constant amplitude.

Owner:RAMBUS INC

Micropower RC oscillator

InactiveUS6462625B2Logic circuits coupling/interface using field-effect transistorsGenerator stabilizationElectrical resistance and conductanceClosed loop

Owner:SAMSUNG ELECTRONICS CO LTD

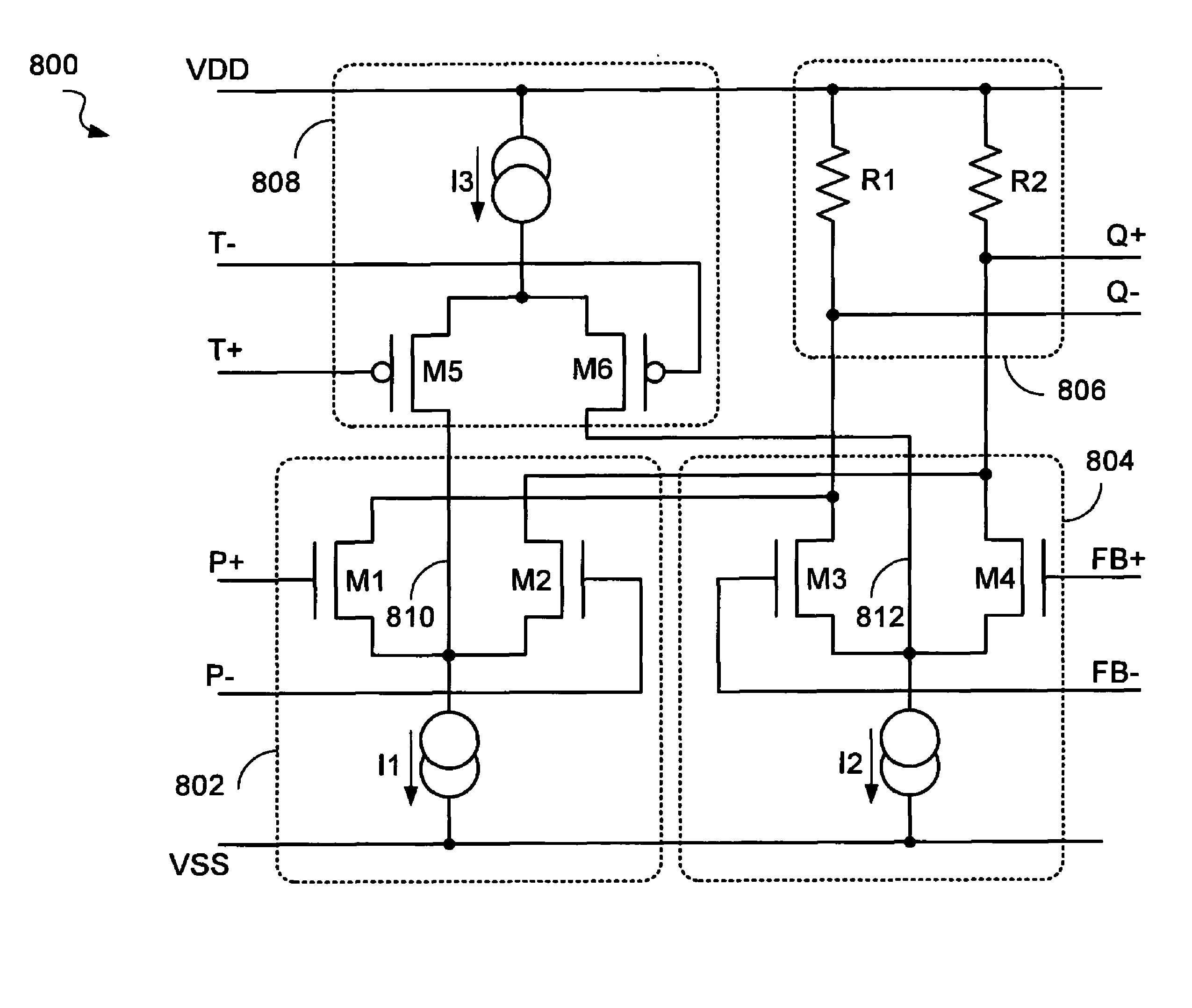

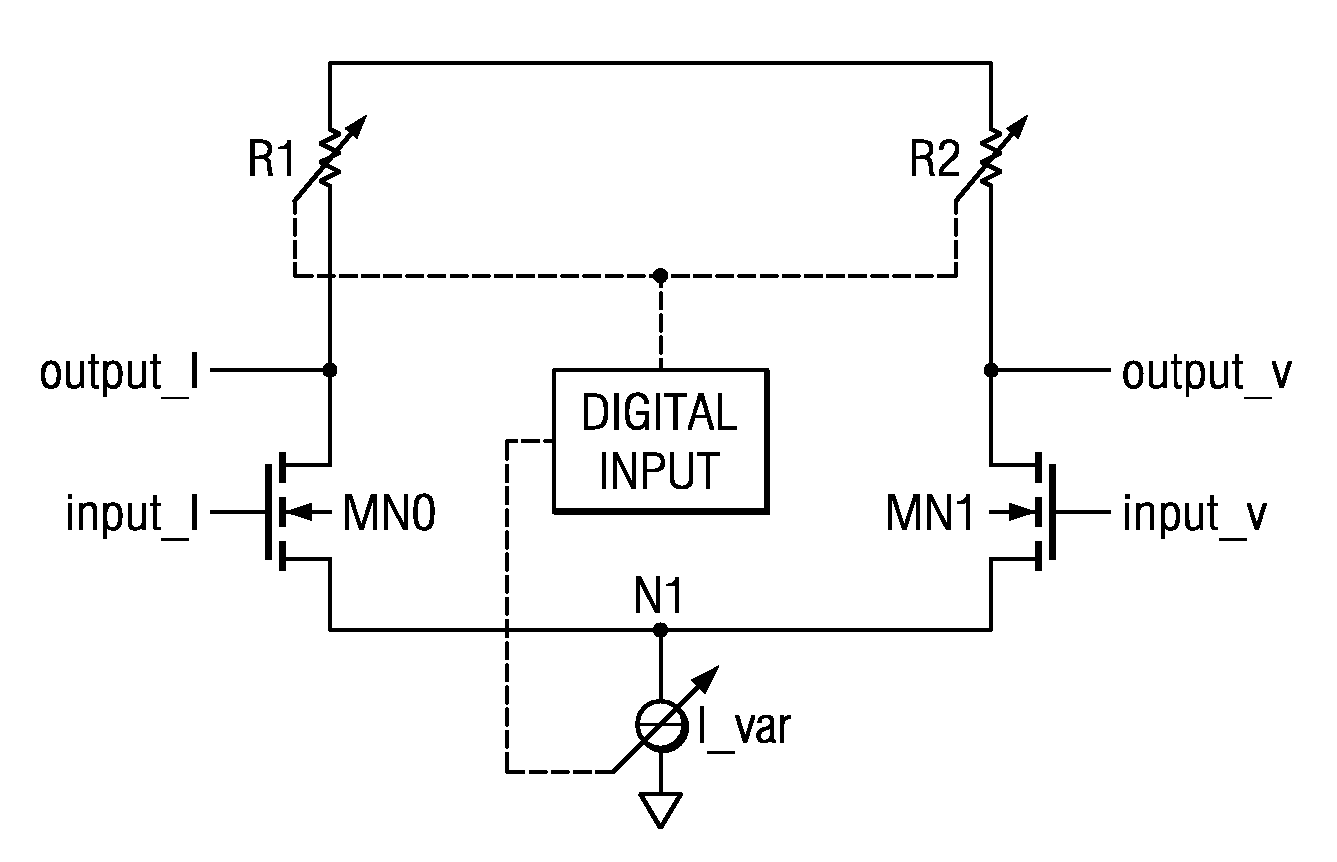

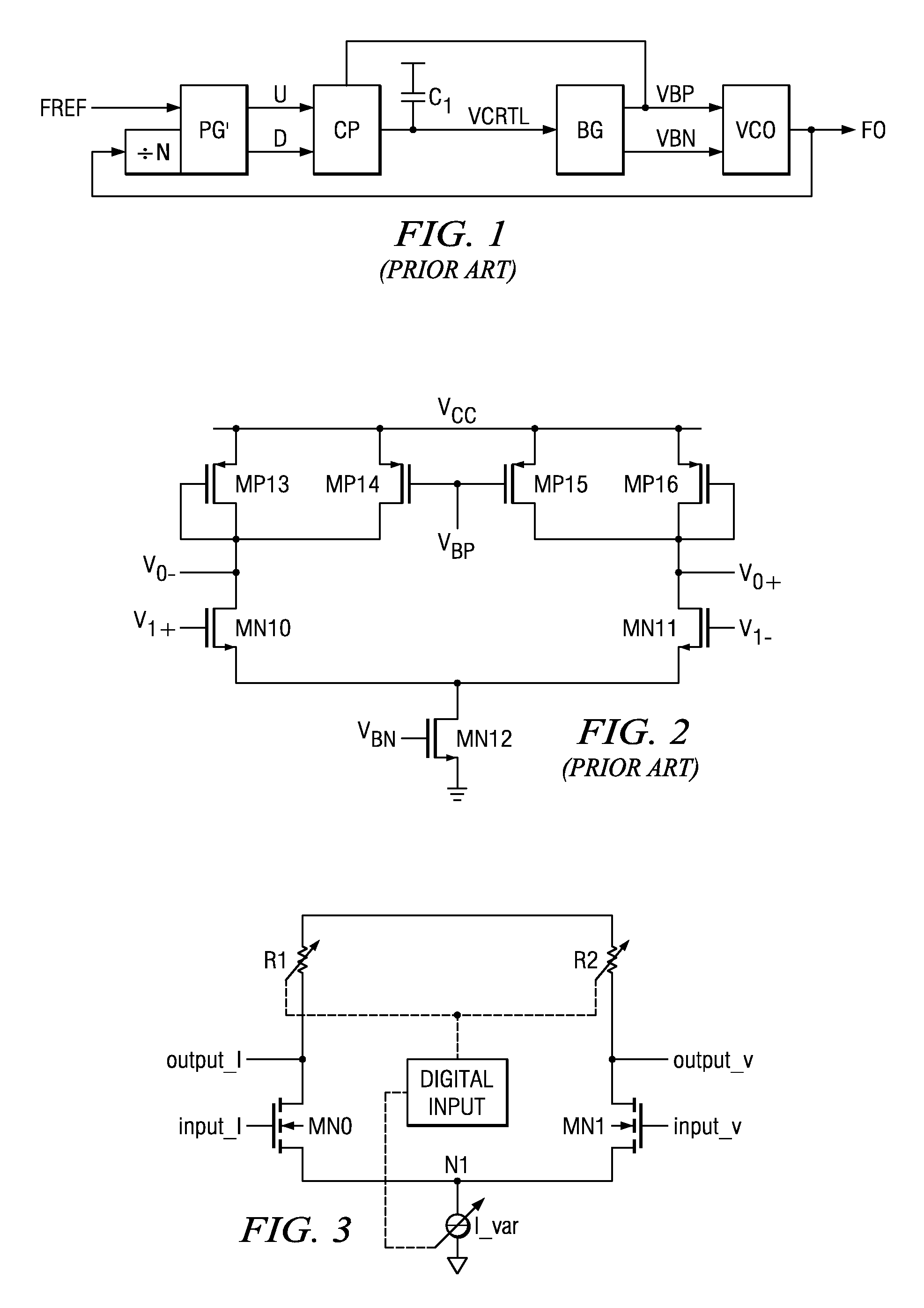

Delay stage circuitry for a ring oscillator

InactiveUSRE38482E1Easy to optimizePulse automatic controlTime-division multiplexEngineeringVoltage clamp

A ring oscillator includes an even-numbered plurality of ring coupled delay stages. Each delay stage includes a differential amplifier, a voltage clamping circuit, and a current source. The differential amplifier receives first and second input signals from a preceding delay stage. The differential amplifier provides a first output signal and a complementary second output signal at first and second nodes, respectively. The voltage clamping circuit is coupled between the first and second nodes to limit a peak-to-peak voltage swing of each of the first and second output signals. The current source is coupled to the differential amplifier and varies a bias current in accordance with a delay bias voltage.

Owner:RAMBUS INC

Method and apparatus of a ring oscillator for phase locked loop (PLL)

InactiveUS20080284529A1Pulse generation by logic circuitsOscillations generatorsResistive loadRC oscillator

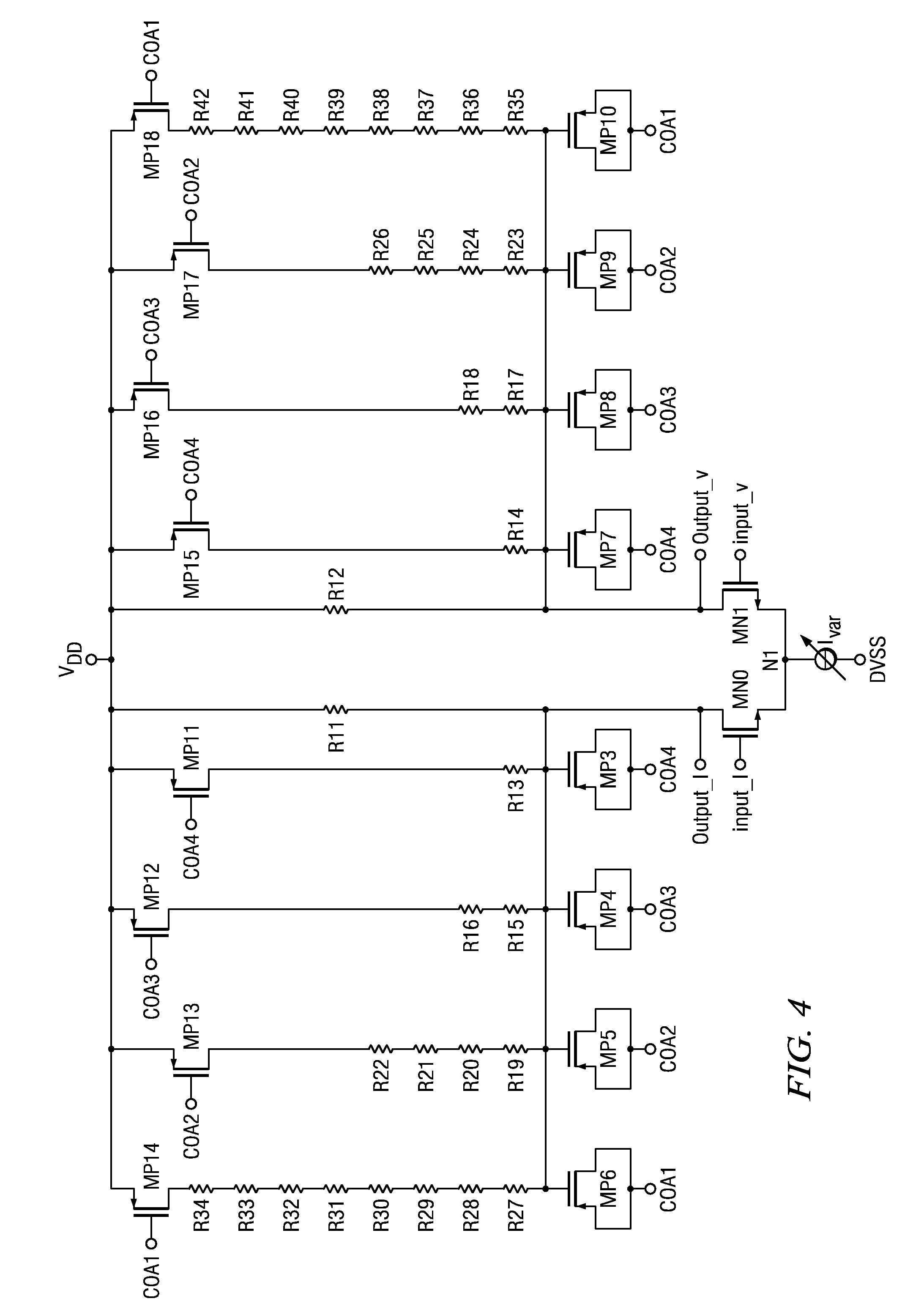

The present invention relates to a ring oscillator including a delay stage, the delay stage includes a differential pair of input transistor, a variable resistive load coupled to the transistor, a differential output between the variable resistive load and the corresponding input transistor, a variable current source coupled to the differential pair of transistors for variably setting a bias current through the differential pair of transistors, and an input coupled to the variable resistive load and the variable current source for receiving an configuration signal, wherein the variable resistive load and the variable current source are changed in response to the configuration signal, wherein the bias current of the variable current source increases and the variable resistive load decreases, and vice versa.

Owner:TEXAS INSTR INC

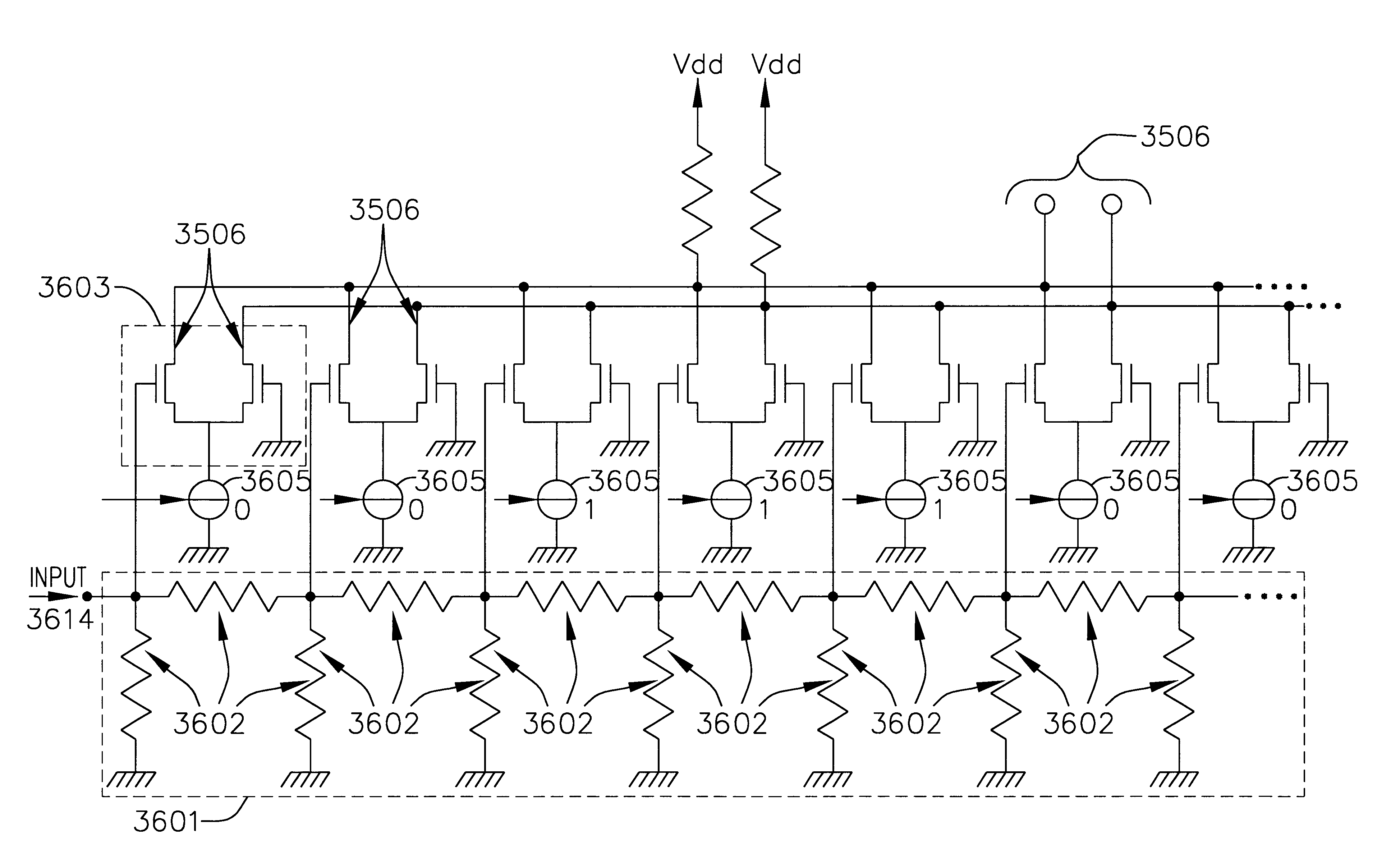

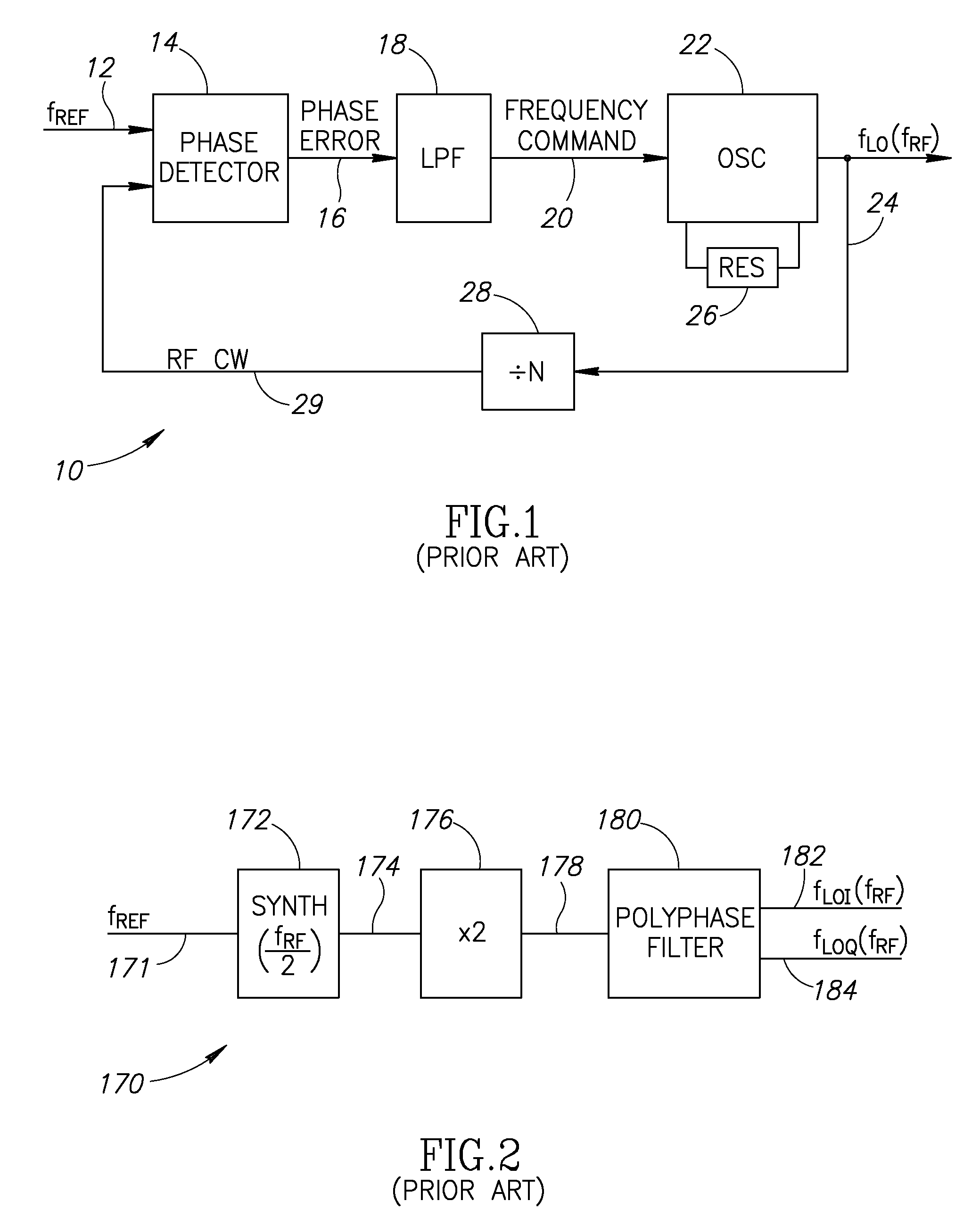

Local oscillator with non-harmonic ratio between oscillator and RF frequencies using pulse generation and selection

ActiveUS20080055010A1Avoid serious problemsEasy to implementModulated-carrier systemsElectrical testingHarmonicLocal oscillator

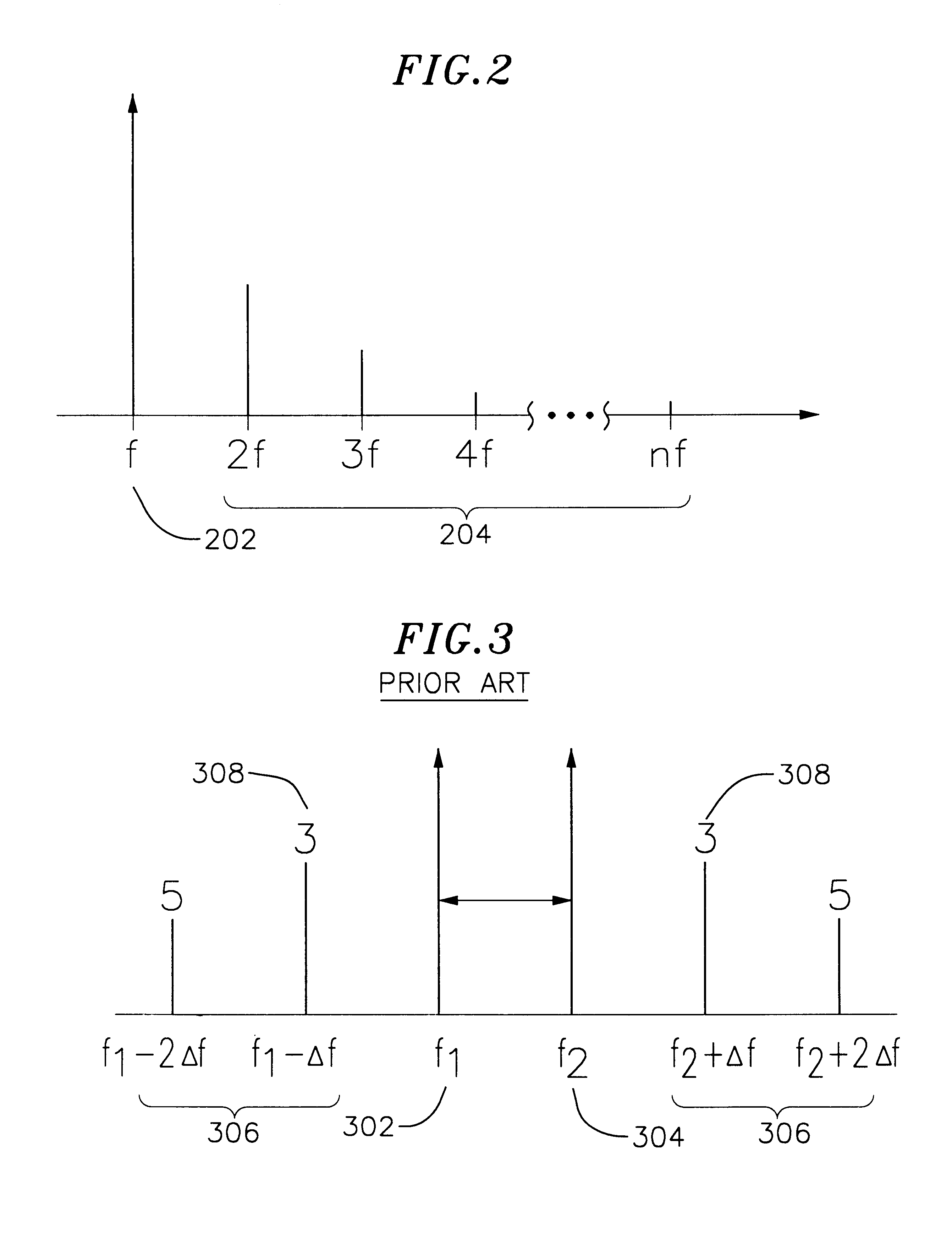

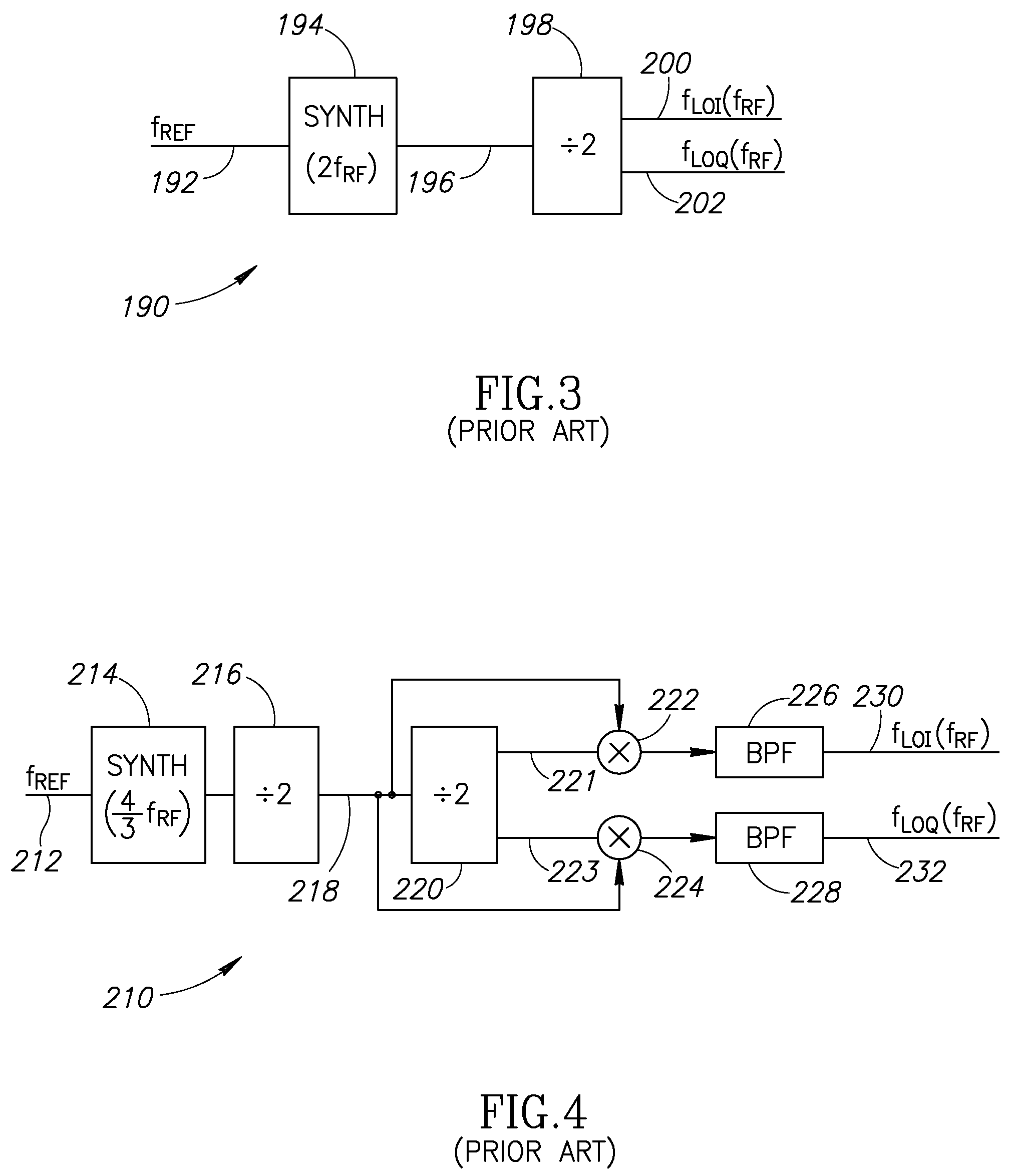

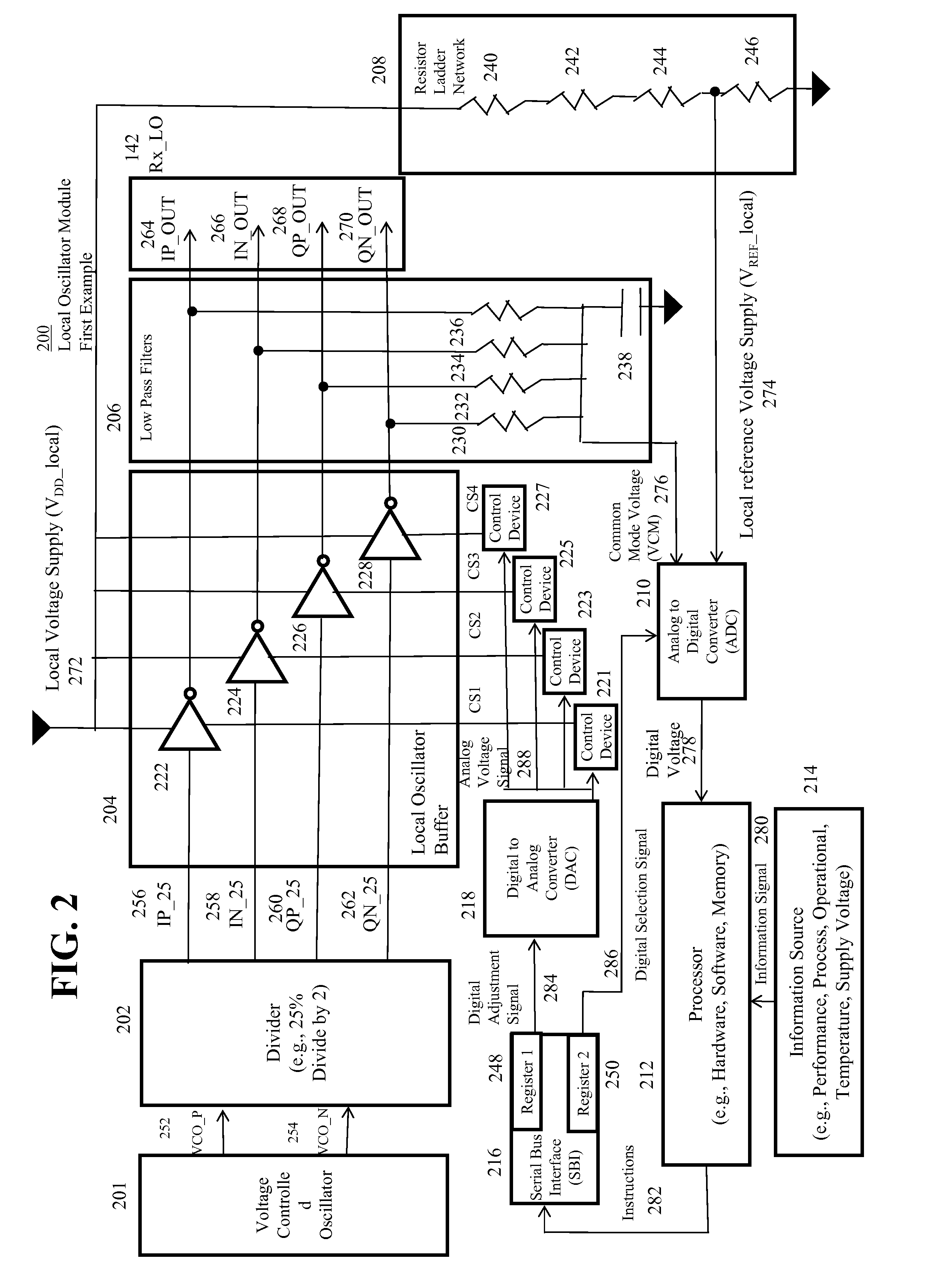

A novel and useful apparatus for and method of local oscillator (LO) generation with non-integer multiplication ratio between the local oscillator and RF frequencies. The LO generation schemes presented are operative to generate I and Q square waves at a designated frequency while avoiding the well known issue of harmonic pulling. The input signal is fed to a synthesizer timed to a rational multiplier of the RF frequency L / N fRF. The clock signal generated is divided by a factor Q to form 2Q phases of the clock at a frequency of L(N*Q) fRF, wherein each phase undergoes division by L. The phase signals are input to a pulse generator which outputs a plurality of pulses. The pulses are input to a selector which selects which signal to output at any point in time. By controlling the selector, the output clock is generated as a TDM based signal. Any spurs are removed by an optional filter.

Owner:TEXAS INSTR INC

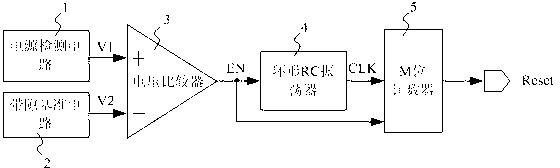

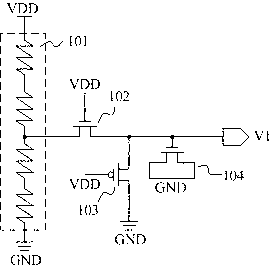

Automatic reset detection circuit for power up and power failure

ActiveCN103095265AAutomatically correct and fast outputEfficient outputElectronic switchingPower-on resetLow voltage

The invention discloses an automatic reset detection circuit for power up and power failure. The circuit comprises a power supply detection circuit (1), a band-gap reference circuit (2), a voltage comparator (3), a ring-shaped RC (remote control) oscillator (4) and an M-bit counter (5), wherein the power supply detection circuit (1) is used for detecting change of power supply voltage, when the power supply voltage is higher than preset threshold voltage, the voltage comparator (3) outputs a high voltage level, the ring-shaped RC oscillator (4) and the M-bit counter (5) begin to work, after 2M periods, an output Reset signal is changed to the high voltage level, and the power up reset detection is completed; when the power supply voltage is lower than the preset threshold voltage, the voltage comparator (3) outputs a low voltage level, the ring-shaped RC oscillator (4) and the M-bit counter (5) stop working, the output Reset signal is changed to the low voltage level, and the power failure reset detection is completed. The automatic reset detection circuit is simple in structure and easy to implement, and further has the power up and power failure reset detection functions simultaneously.

Owner:CHANGSHA JINGJIA MICROELECTRONICS

Clock generator including a ring oscillator with precise frequency control

InactiveUS20080298455A1Duration/width modulated pulse demodulationElectric pulse generatorEngineeringReference device

A clock generator for providing a desired system clock signal in accordance with an embodiment of the present application includes a ring oscillator operable to provide an oscillator output signal having a first frequency, a divider operable to divide the oscillator output signal by a predetermined divisor and to output the divided signal as the desired system clock signal, a reference device operable to provide a reference signal with a known second frequency and a ratio device operable to provide a ratio value indicative of a relationship between the oscillator output signal and the reference signal, wherein the predetermined divisor of the divider is determined based on the ratio value such that the desired system clock signal has a desired frequency.

Owner:INTERNATIONAL RECTIFIER COEP

Local oscillator with non-harmonic ratio between oscillator and RF frequencies using pulse generation and selection

ActiveUS7756487B2Avoid serious problemsEasy to implementModulated-carrier systemsElectrical testingHarmonicLocal oscillator

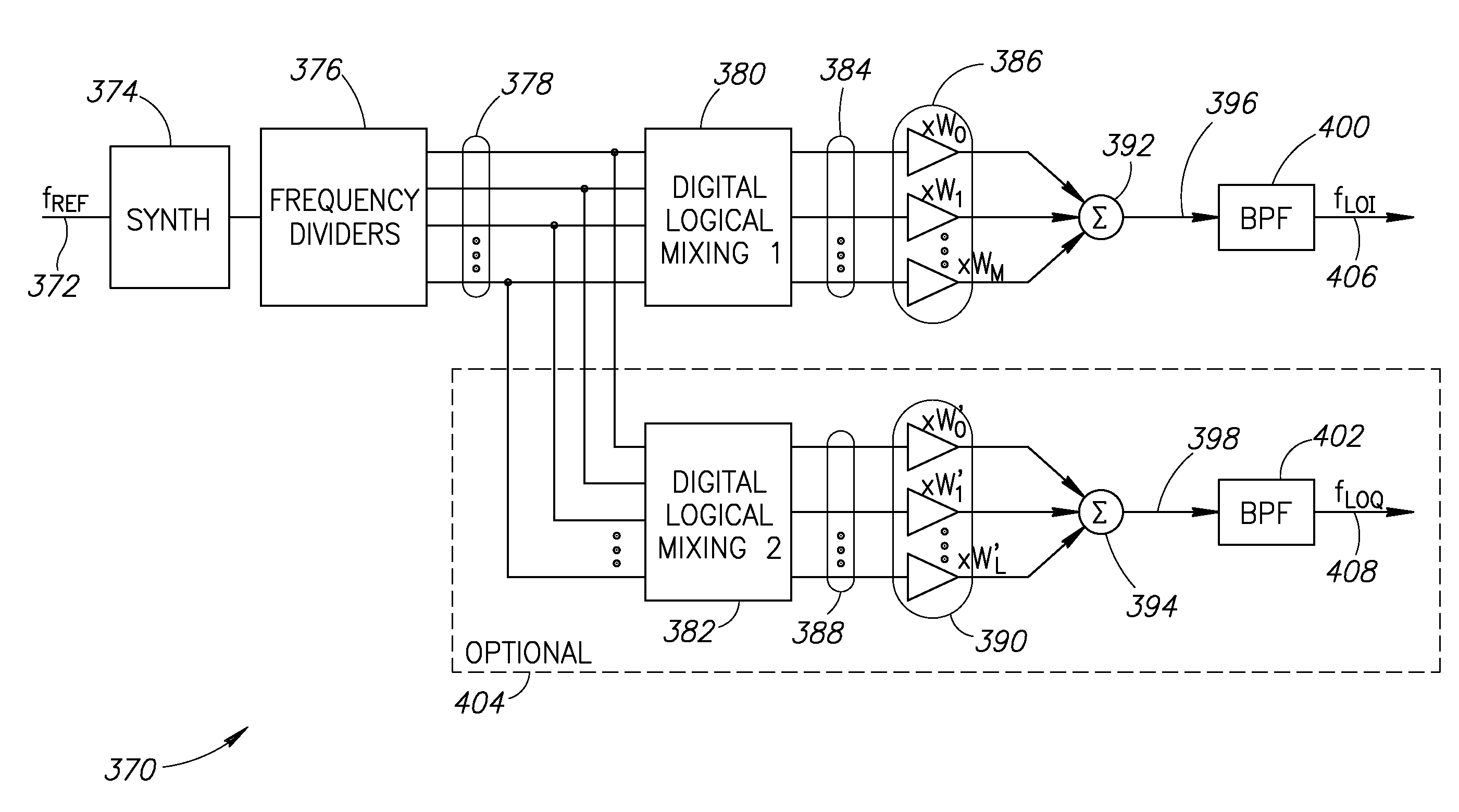

A novel and useful apparatus for and method of local oscillator (LO) generation with non-integer multiplication ratio between the local oscillator and RF frequencies. The LO generation schemes presented are operative to generate I and Q square waves at a designated frequency while avoiding the well known issue of harmonic pulling. The input signal is fed to a synthesizer timed to a rational multiplier of the RF frequency L / N fRF. The clock signal generated is divided by a factor Q to form 2Q phases of the clock at a frequency of L(N*Q)fRF, wherein each phase undergoes division by L. The phase signals are input to a pulse generator which outputs a plurality of pulses. The pulses are input to a selector which selects which signal to output at any point in time. By controlling the selector, the output clock is generated as a TDM based signal. Any spurs are removed by an optional filter.

Owner:TEXAS INSTR INC

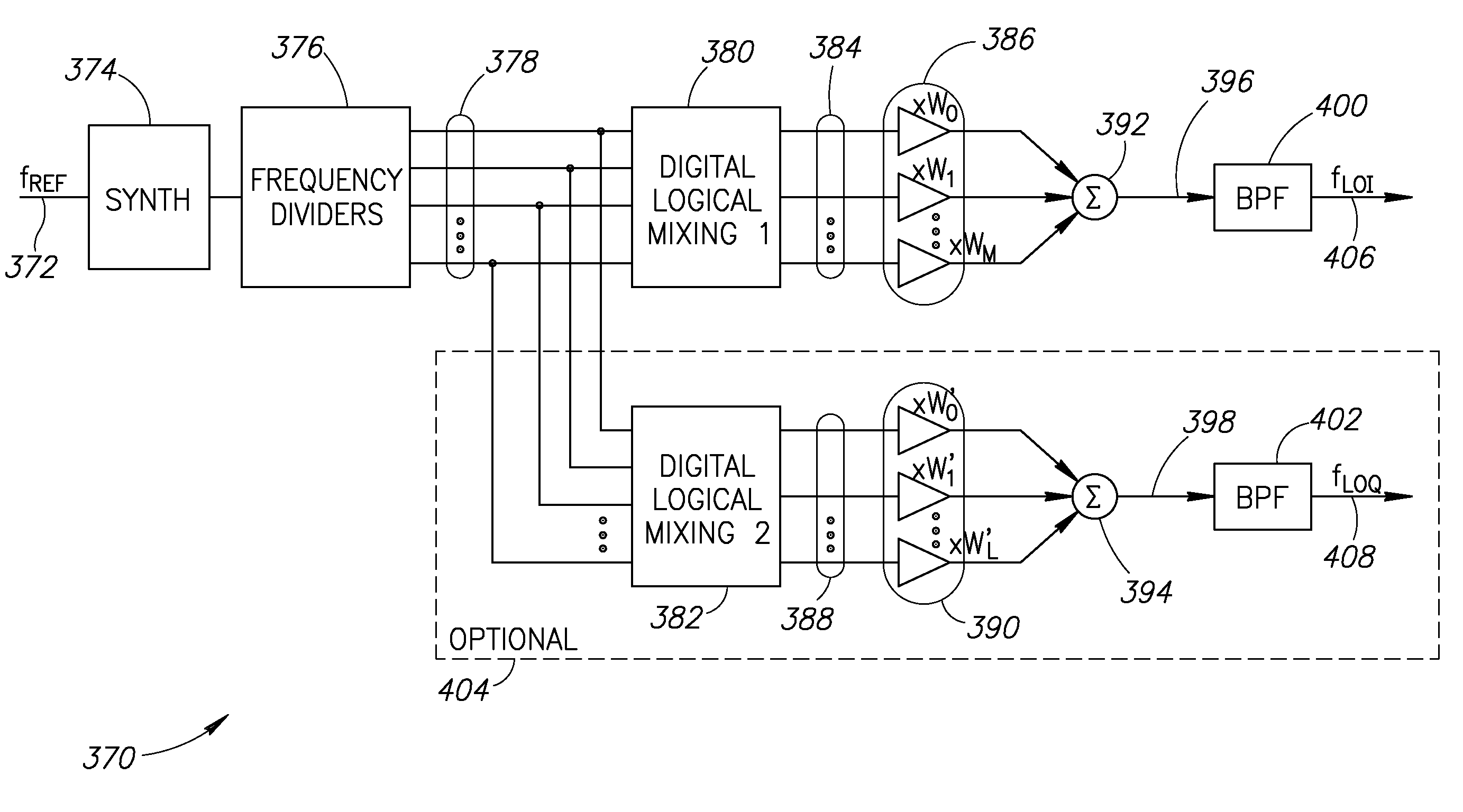

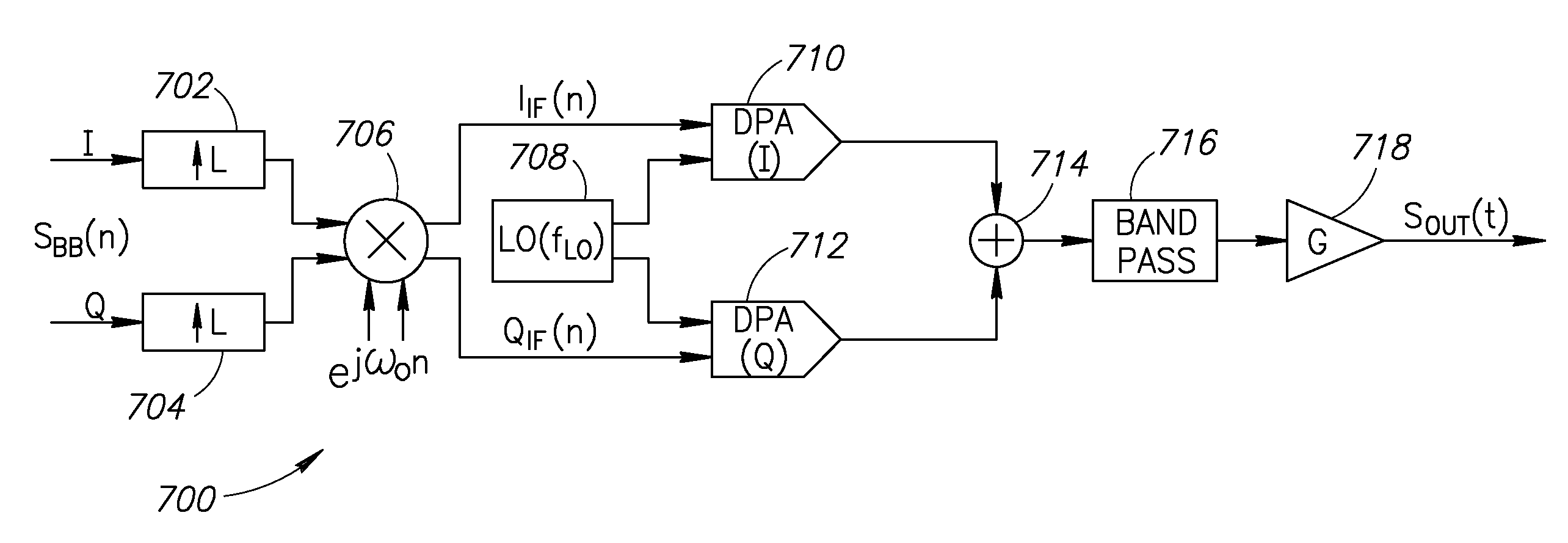

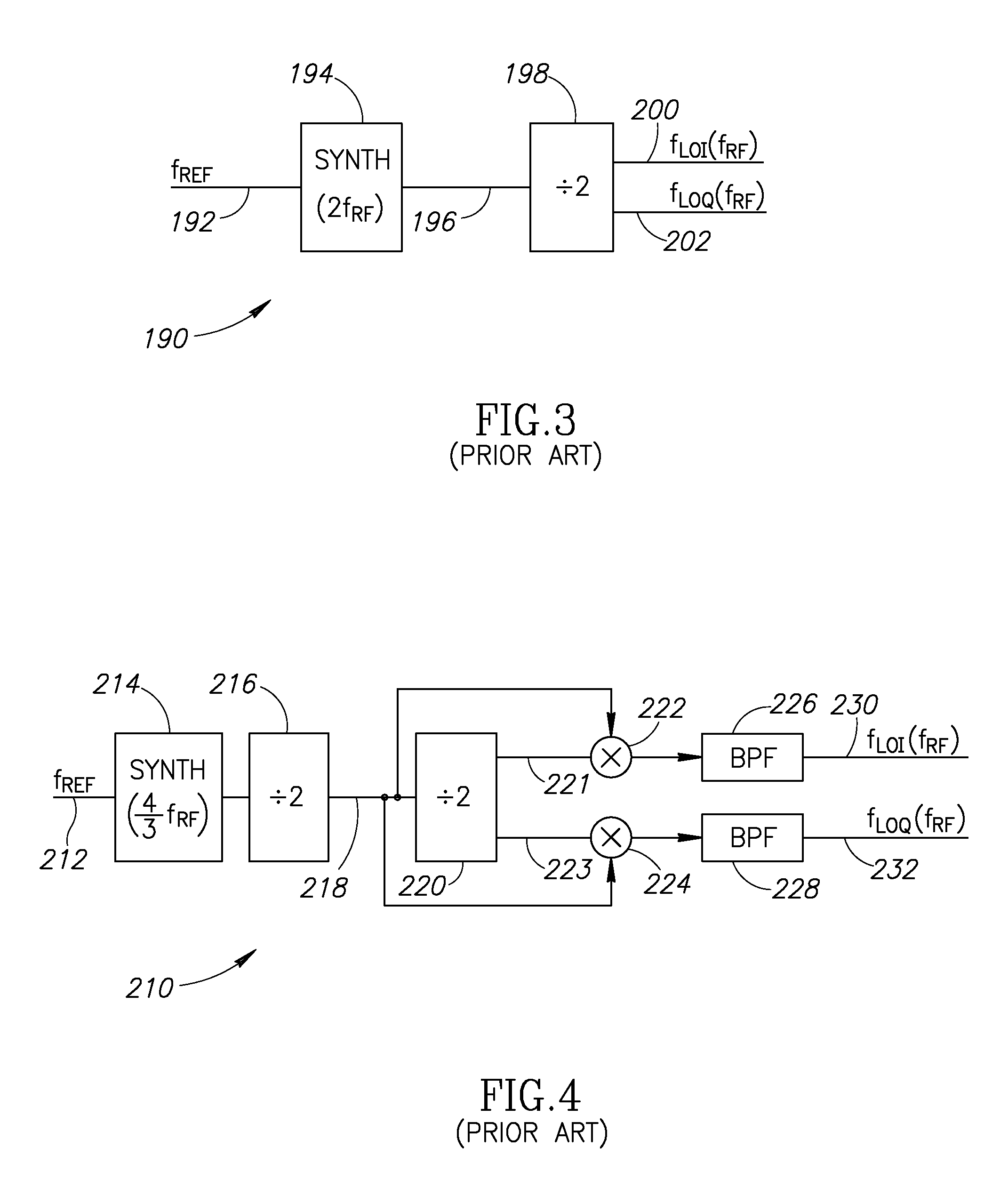

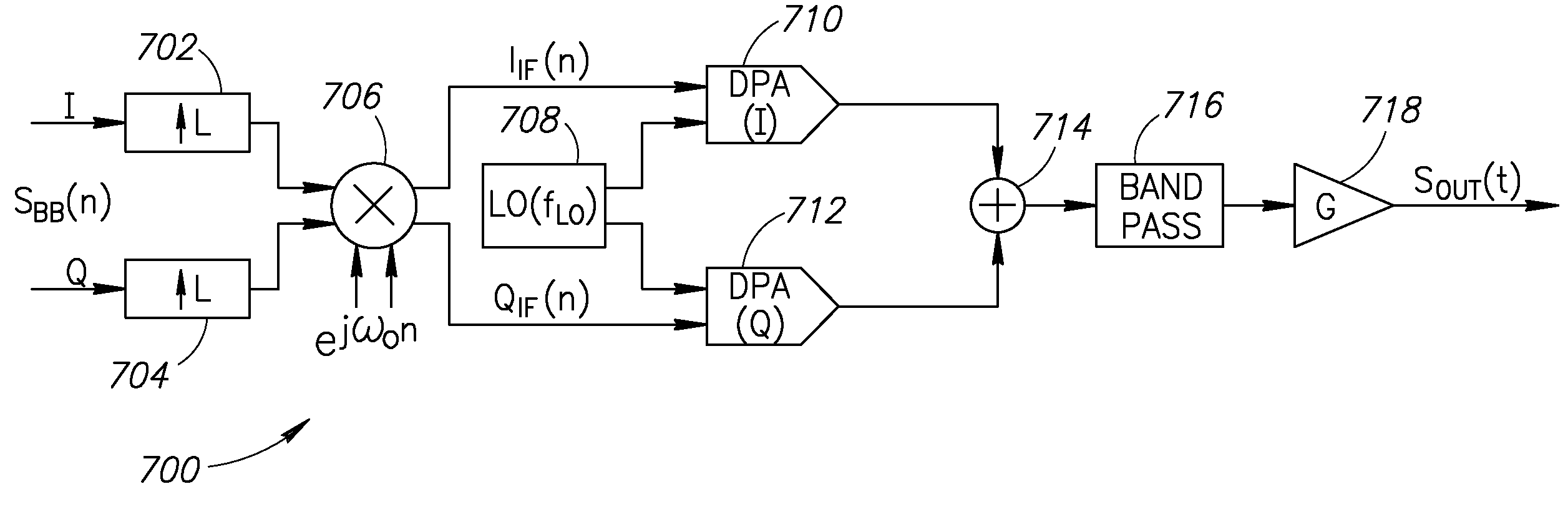

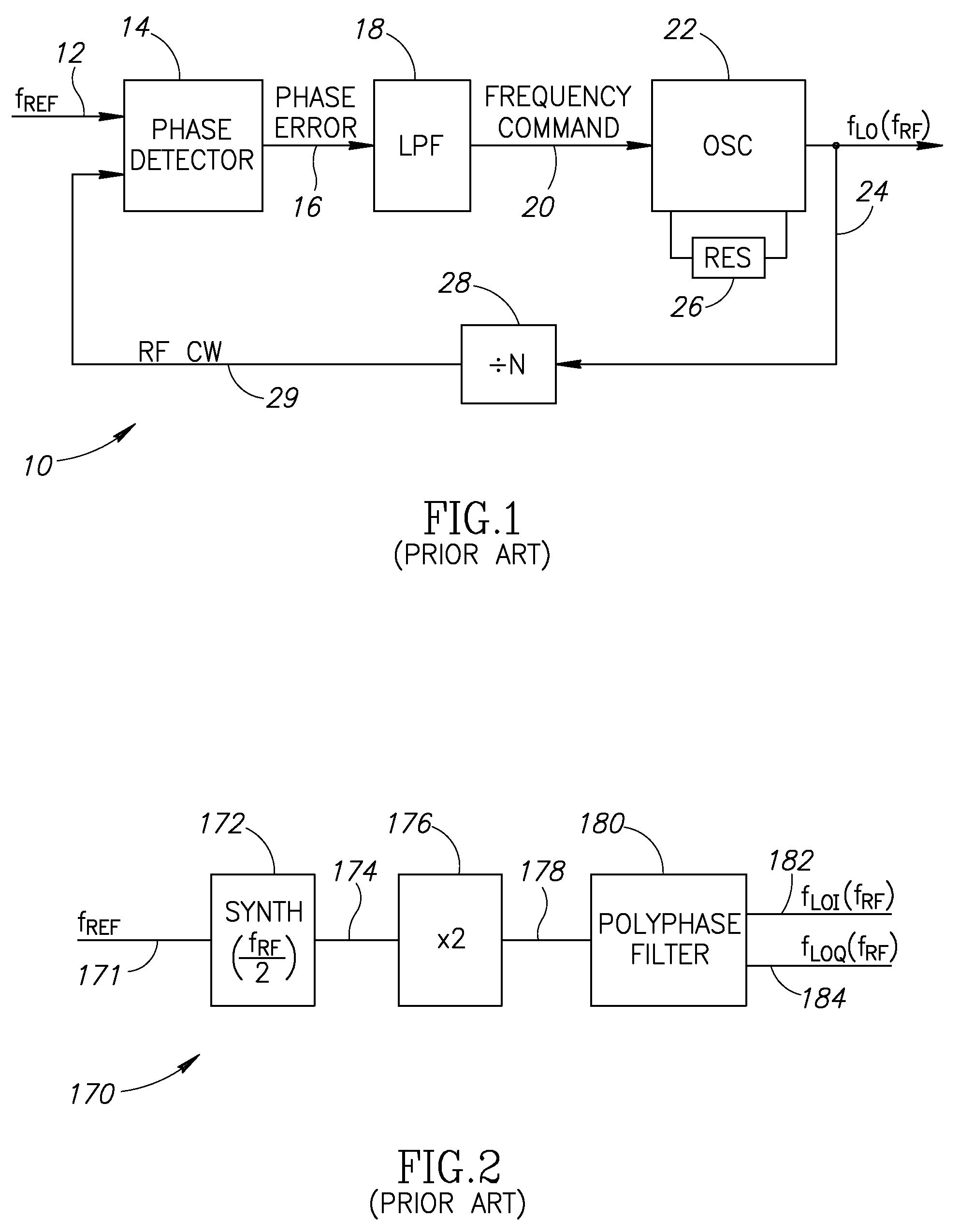

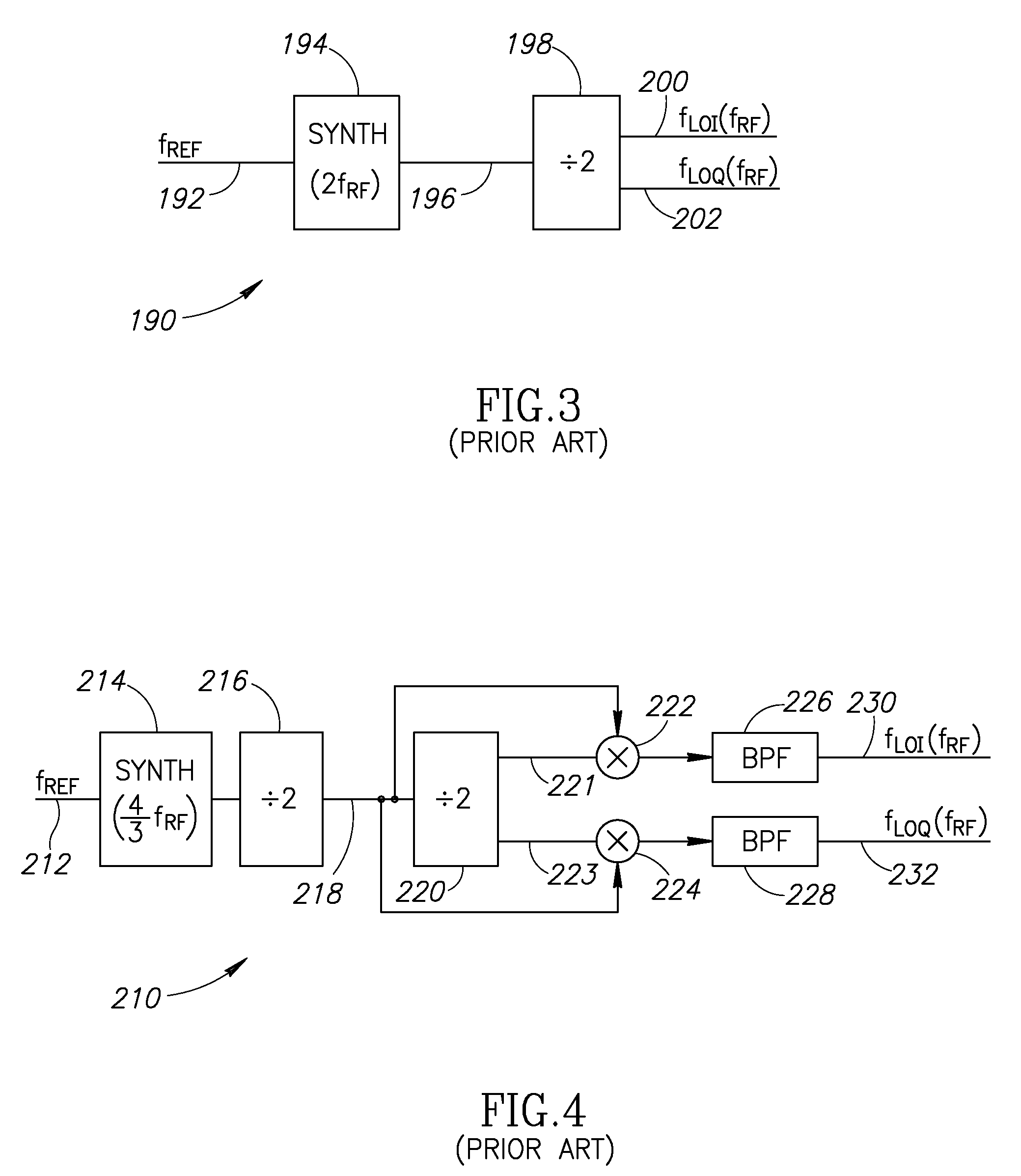

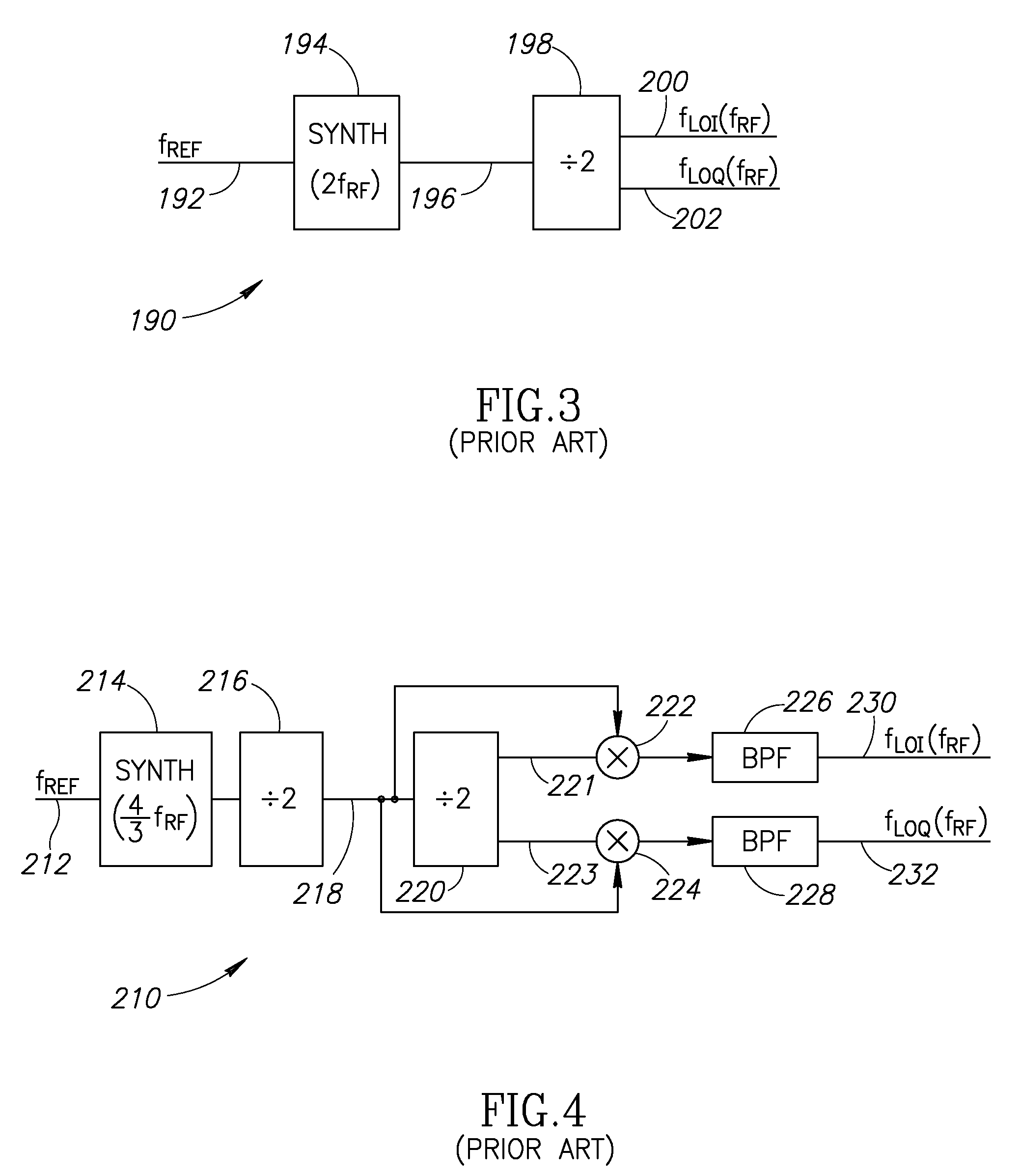

Local oscillator with non-harmonic ratio between oscillator and RF frequencies using wideband modulation spectral replicas

ActiveUS20080055014A1Easy to implementAvoid serious problemsModulation transferencePulse automatic controlBandpass filteringFrequency spectrum

A novel and useful apparatus for and method of local oscillator (LO) generation with non-integer multiplication ratio between the local oscillator and RF frequencies. The LO generation schemes presented are operative to generate I and Q square waves at a designated frequency while avoiding the well known issue of harmonic pulling. An input baseband signal is interpolated and upconverted in the digital domain to an IF. The LO operates at a frequency which is a n / m division of the target RF frequency fRF. The IF frequency is configured to ½ of the LO frequency. The upconverted IF signal is then converted to the analog domain via digital power amplifiers followed by voltage combiners. The output of the combiners is band pass filtered to extract the desired replica.

Owner:TEXAS INSTR INC

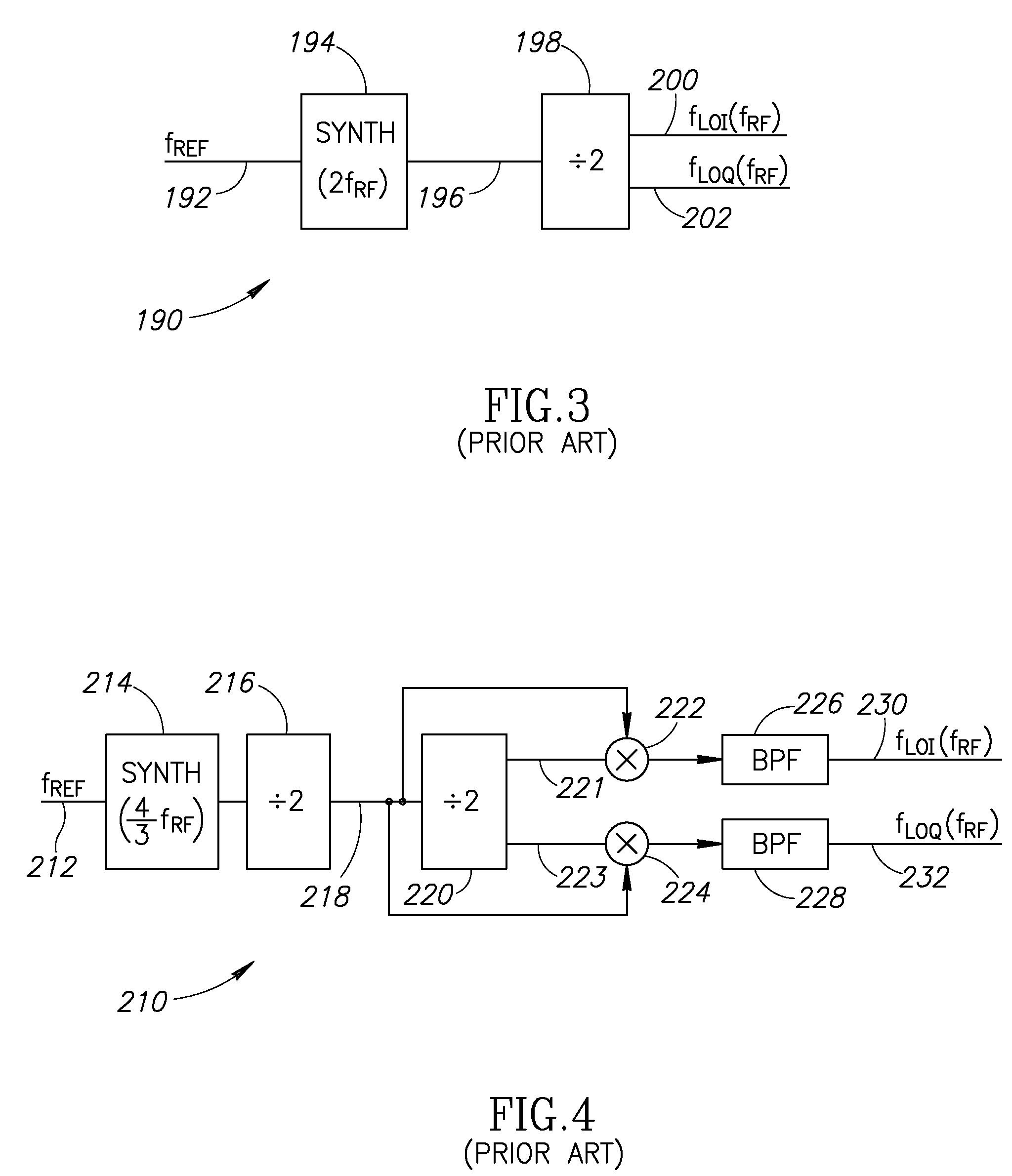

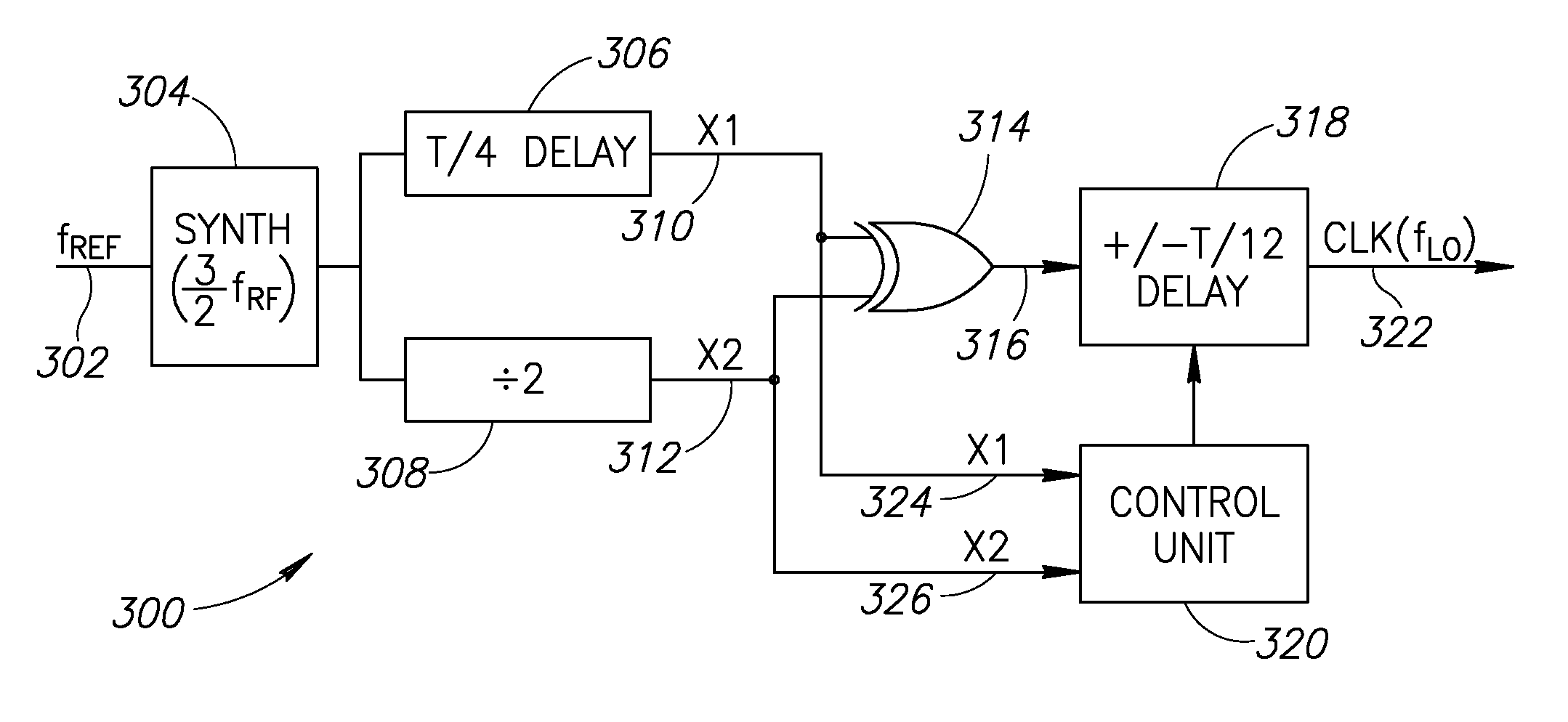

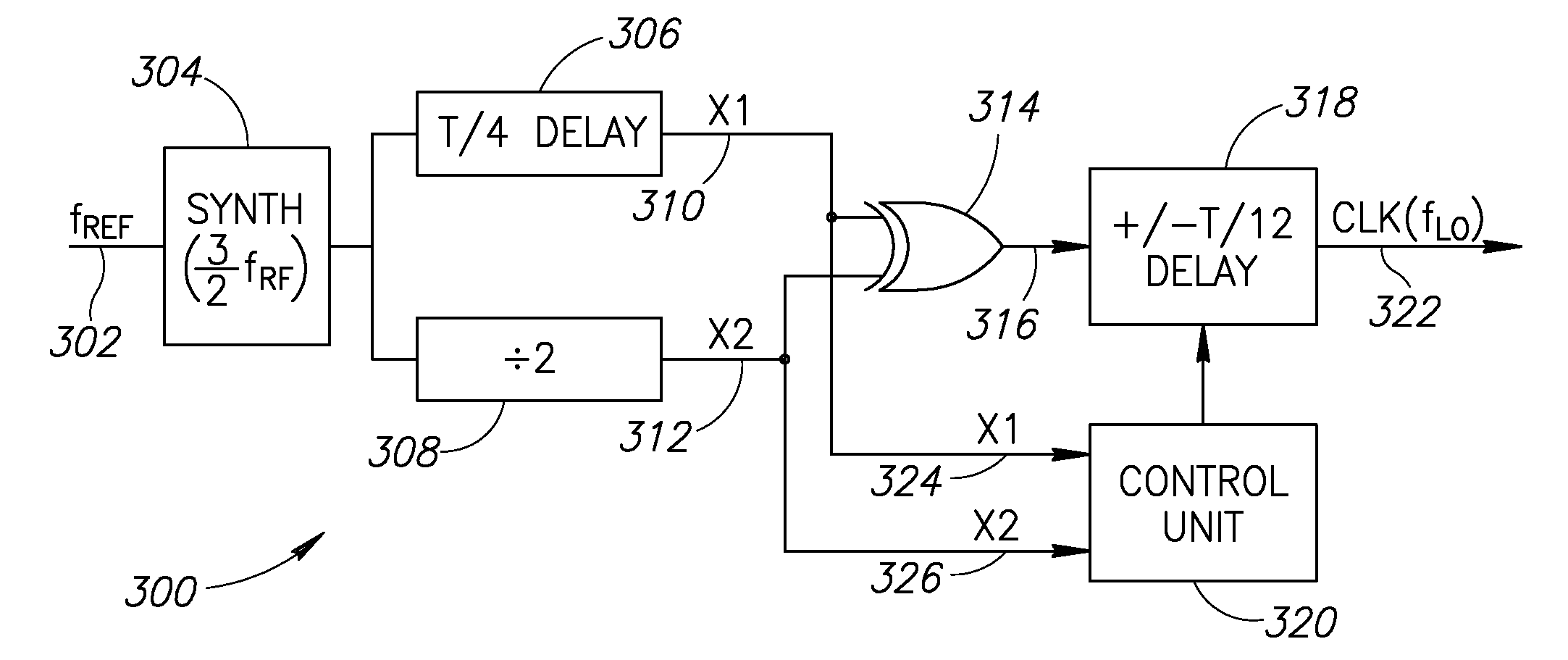

Local oscillator with non-harmonic ratio between oscillator and RF frequencies using XOR operation

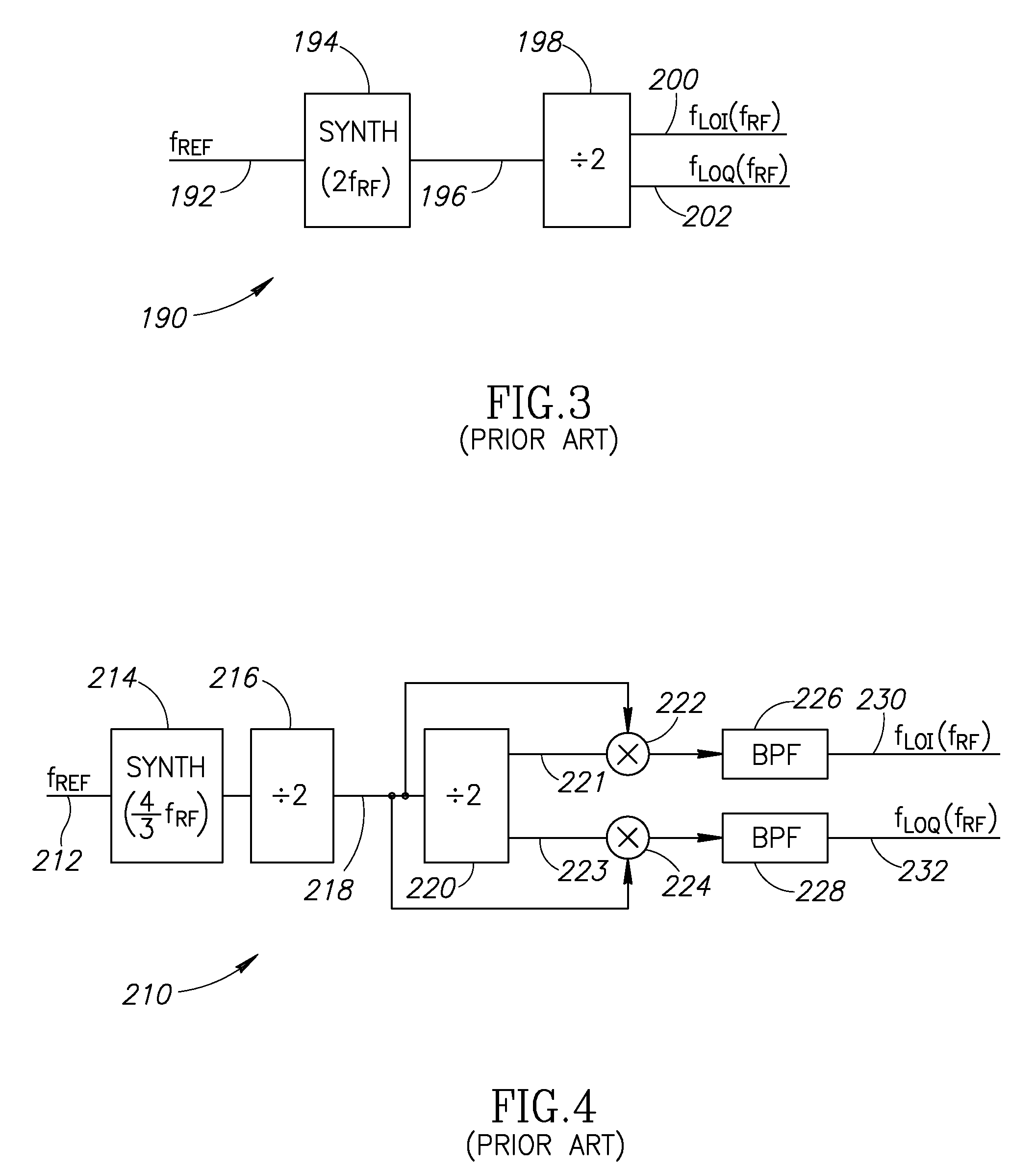

ActiveUS20080056337A1Easy to implementAvoid serious problemsFrequency/rate-modulated pulse demodulationData switching by path configurationFrequency spectrumHarmonic

A novel and useful apparatus for and method of local oscillator (LO) generation with non-integer multiplication ratio between the local oscillator and RF frequencies. The LO generation schemes presented are operative to generate I and Q square waves at a designated frequency while avoiding the well known issue of harmonic pulling. A synthesizer provides 4 / 3 the desired frequency fRF. This frequency is divided by two to obtain in-phase and quadrature square waves at ⅔ fRF. The in-phase signal is divided by two again to obtain in-phase and quadrature square waves at ⅓ fRF. The signals are then logically combined using XOR operations to obtain I and Q branch signals containing spectral spurs. Since the spurs are located in non-disturbing bands, they can be filtered out resulting in the desired output signal.

Owner:TEXAS INSTR INC

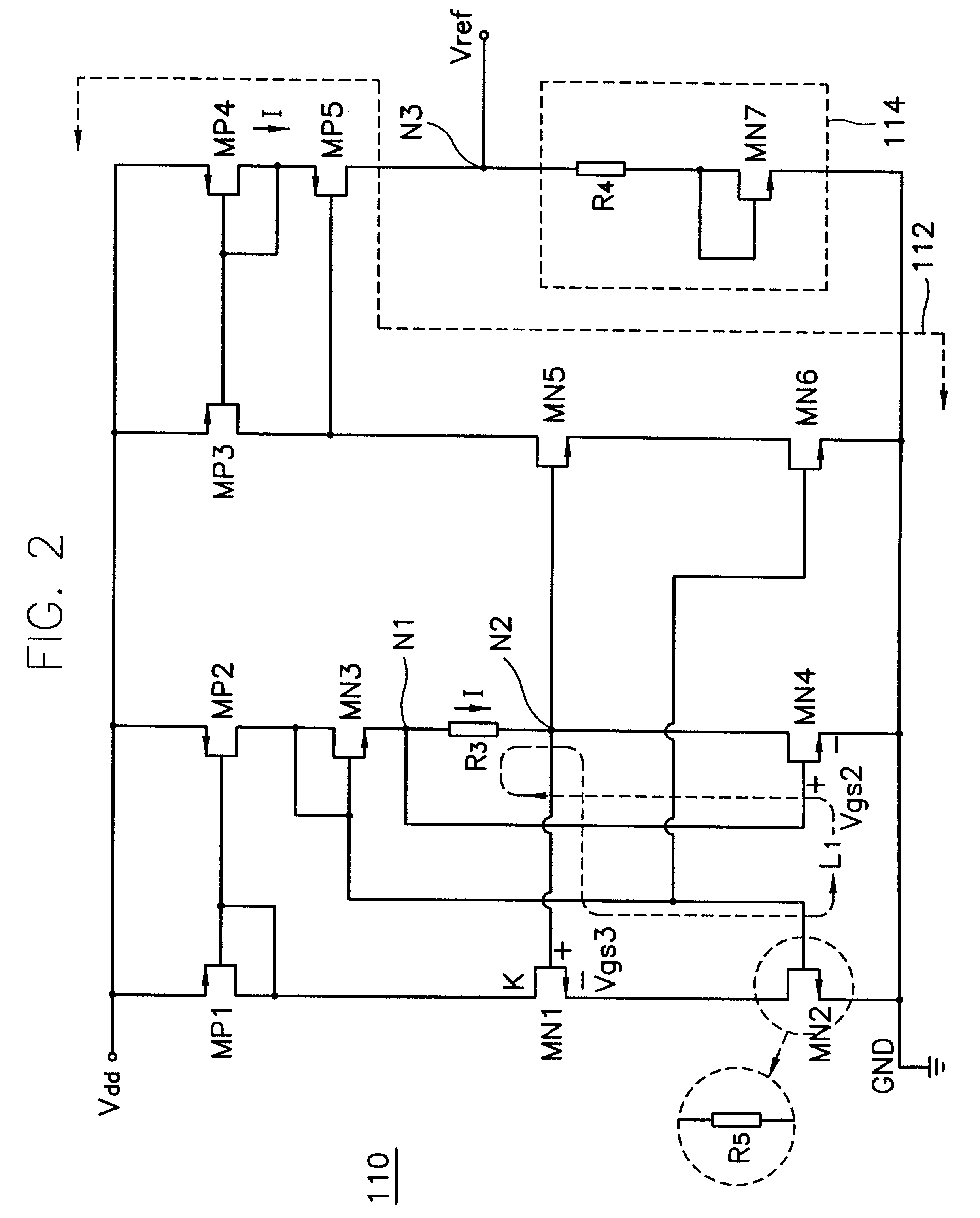

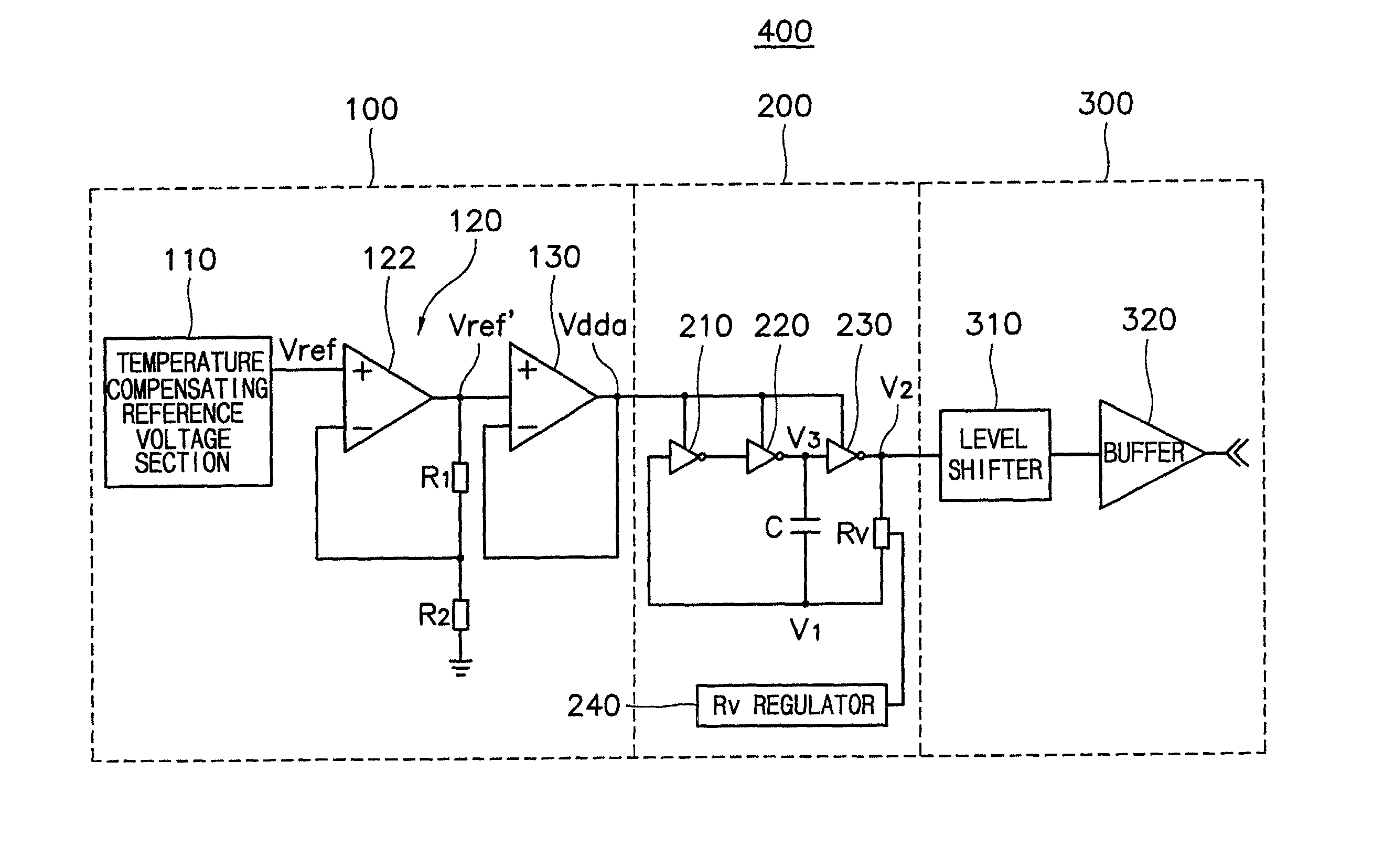

Resistor-capacitor oscillation circuit capable of adjusting oscillation frequency and method of the same

InactiveUS20080100391A1Angle modulation by variable impedencePulse automatic controlCapacitanceRC oscillator

There is provided an RC oscillation circuit capable of adjusting an oscillation frequency, and an oscillation method thereof. The RC oscillation circuit including: an RC oscillator including a variable resistor and a variable capacitor, the RC oscillator generating an RC oscillating signal having a frequency determined by a resistance of the variable resistor and a capacitance of the variable capacitor; a counter counting a clock number of a reference oscillating signal corresponding to one period of the RC oscillating signal to generate a first count value, the reference oscillating signal having a preset frequency; and a frequency controller controlling a frequency of the RC oscillating signal by determining the resistance of the variable resistor and the capacitance of the variable capacitor such that a difference between the first count value and a preset second count value is smaller than a preset first critical value.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Local oscillator with non-harmonic ratio between oscillator and RF frequencies using wideband modulation spectral replicas

ActiveUS7809338B2Avoid serious problemsEasy to implementModulation transferencePulse automatic controlBandpass filteringFrequency spectrum

A novel and useful apparatus for and method of local oscillator (LO) generation with non-integer multiplication ratio between the local oscillator and RF frequencies. The LO generation schemes presented are operative to generate I and Q square waves at a designated frequency while avoiding the well known issue of harmonic pulling. An input baseband signal is interpolated and upconverted in the digital domain to an IF. The LO operates at a frequency which is a n / m division of the target RF frequency fRF. The IF frequency is configured to ½ of the LO frequency. The upconverted IF signal is then converted to the analog domain via digital power amplifiers followed by voltage combiners. The output of the combiners is band pass filtered to extract the desired replica.

Owner:TEXAS INSTR INC

Duty cycle adjustment for a local oscillator signal

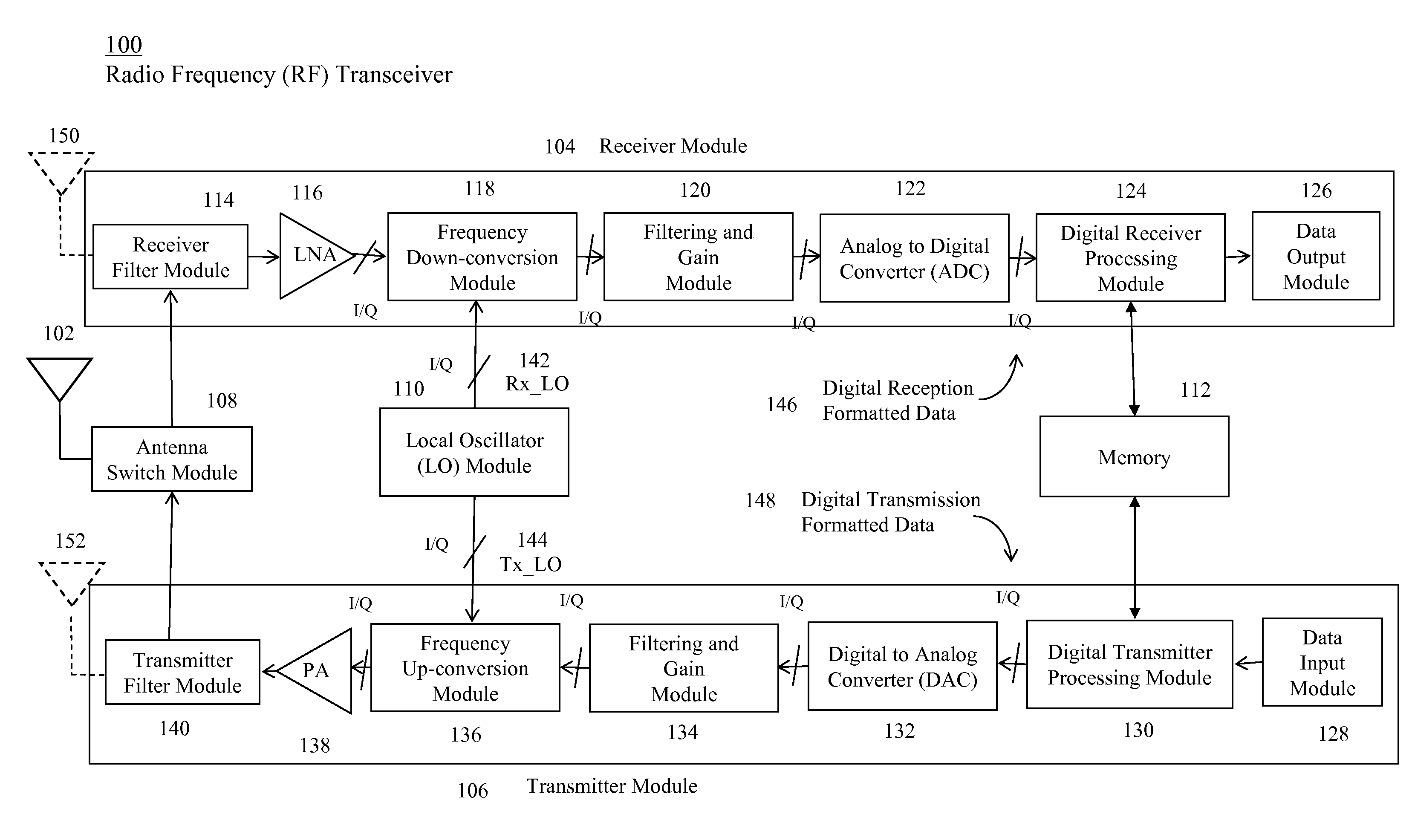

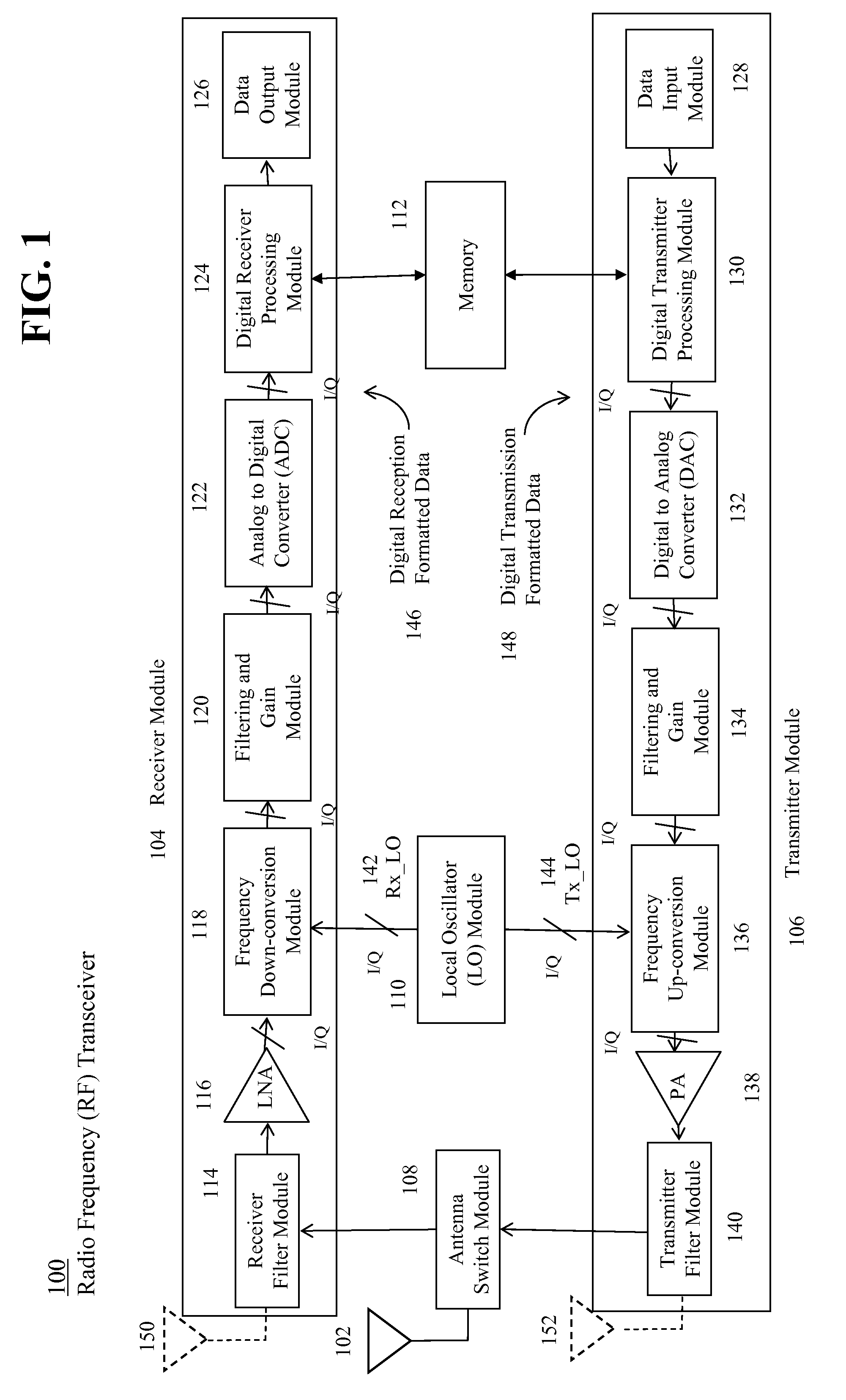

ActiveUS20100130139A1Pulse automatic controlContinuous to patterned pulse manipulationLocal oscillator signalEngineering

A local oscillator (LO) module comprises a local oscillator and a feedback circuit. The local oscillator, biased at a supply voltage, generates a local oscillator signal having a duty cycle. The feedback circuit makes an absolute adjustment of the duty cycle of the local oscillator signal in response to a difference between a first voltage signal, representing a voltage level of the local oscillator signal, and a second voltage signal, representing a voltage level of a portion of the supply voltage corresponding to a desired duty cycle for the local oscillator signal.

Owner:QUALCOMM INC

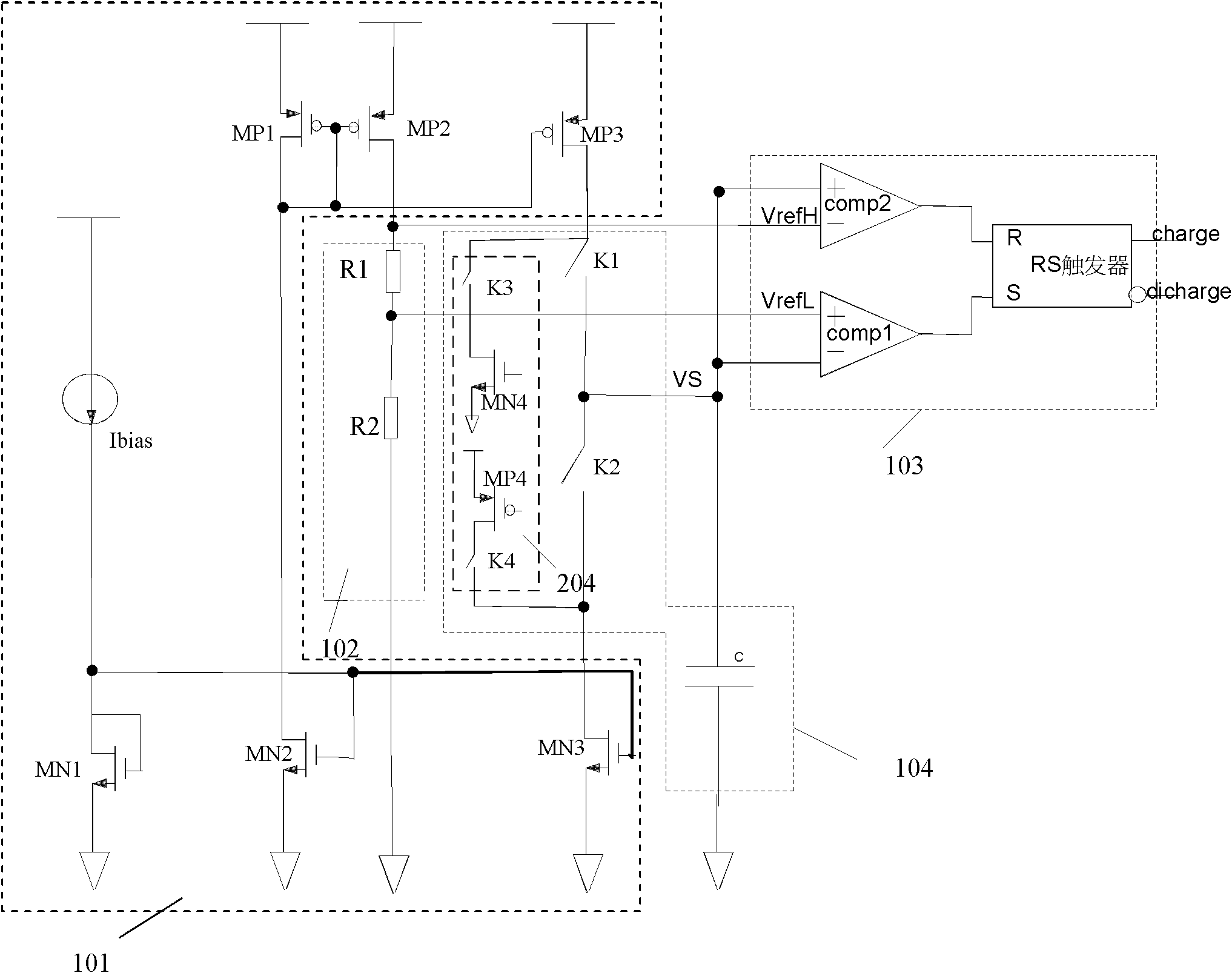

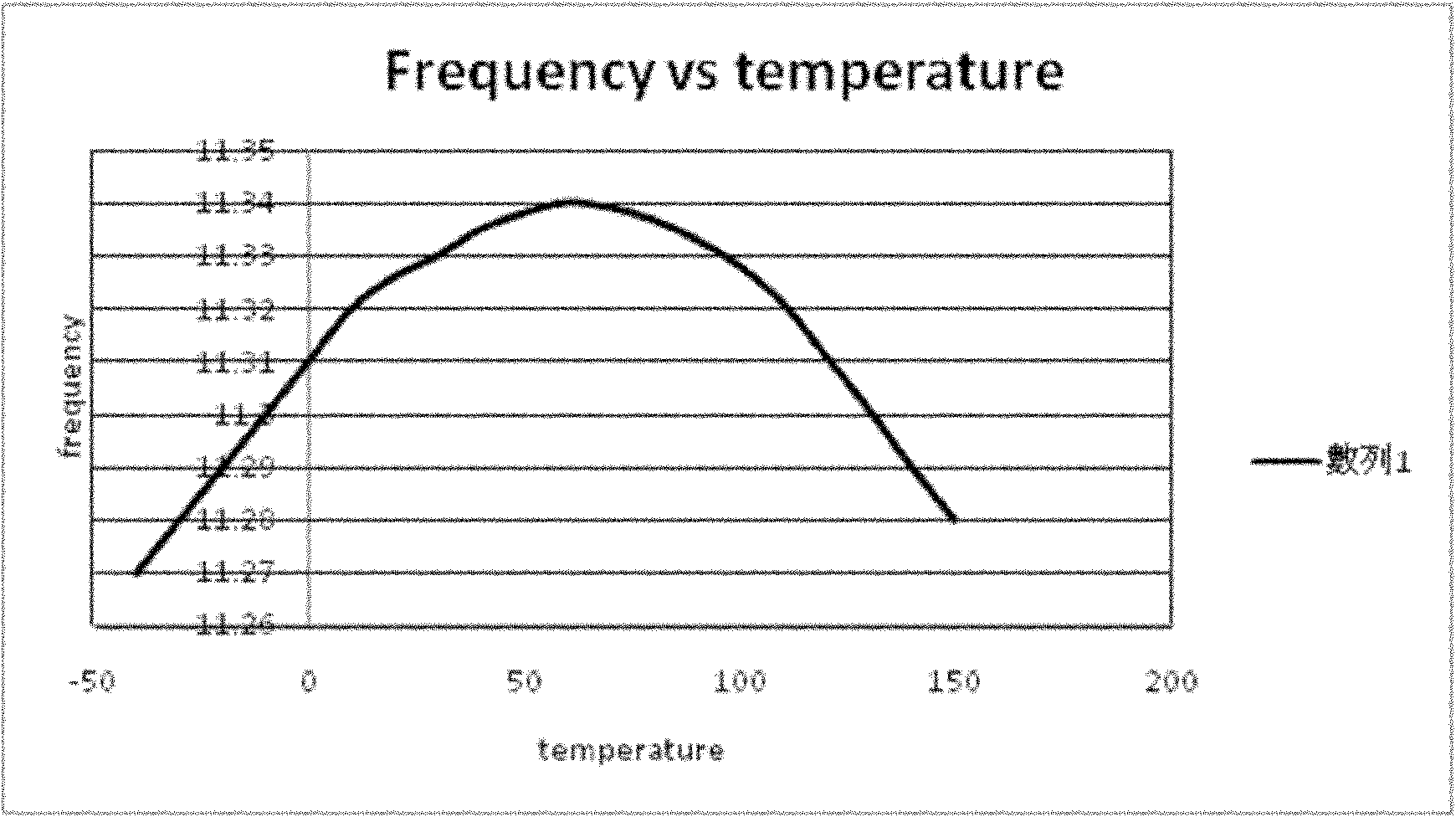

Resistance-capacitance (RC) oscillator and realization method thereof

The invention provides a resistance-capacitance (RC) oscillator and a realization method thereof. According to the invention, a reference voltage generating circuit is used for obtaining charge upper limit voltage and a discharge lower limit voltage, and a comparison shaping circuit is used for comparing the charge upper limit voltage and discharge lower limit voltage with the charge and discharge voltages to generate a charge control signal and a discharge control signal to control a charge and discharge capacitor in a charge and discharge circuit to carry out charge and discharge so as to obtain the RC oscillator with more accurate oscillation frequency. The oscillation frequency of the RC oscillator does not depend on the reference offset current but depends on the resistance and the capacitance of the charge and discharge capacitor, therefore, the RC oscillator which does not depend on temperature and power supply voltage can be obtained by using the resistor and the capacitor with low temperature coefficients and low voltage drifts.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

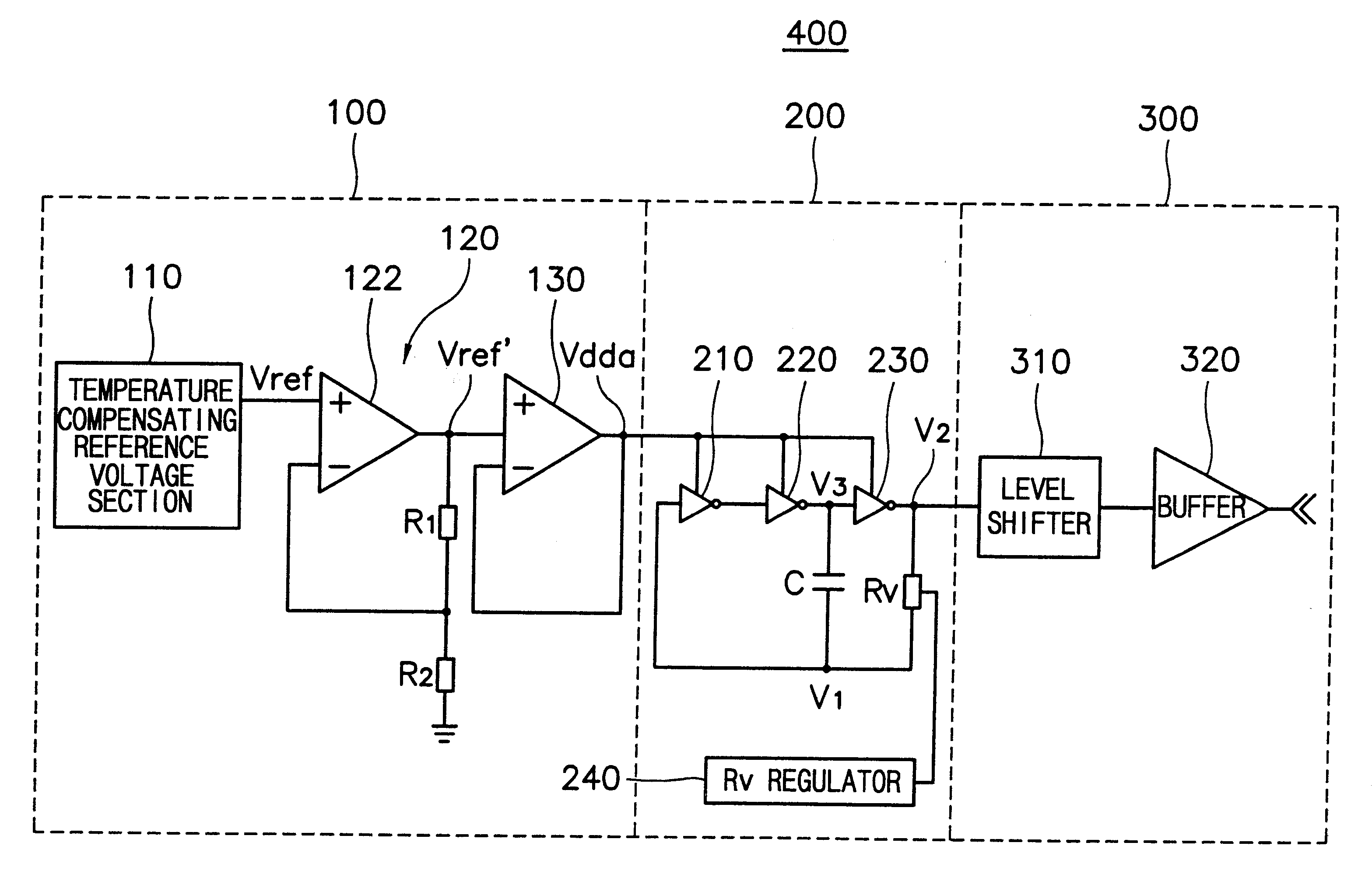

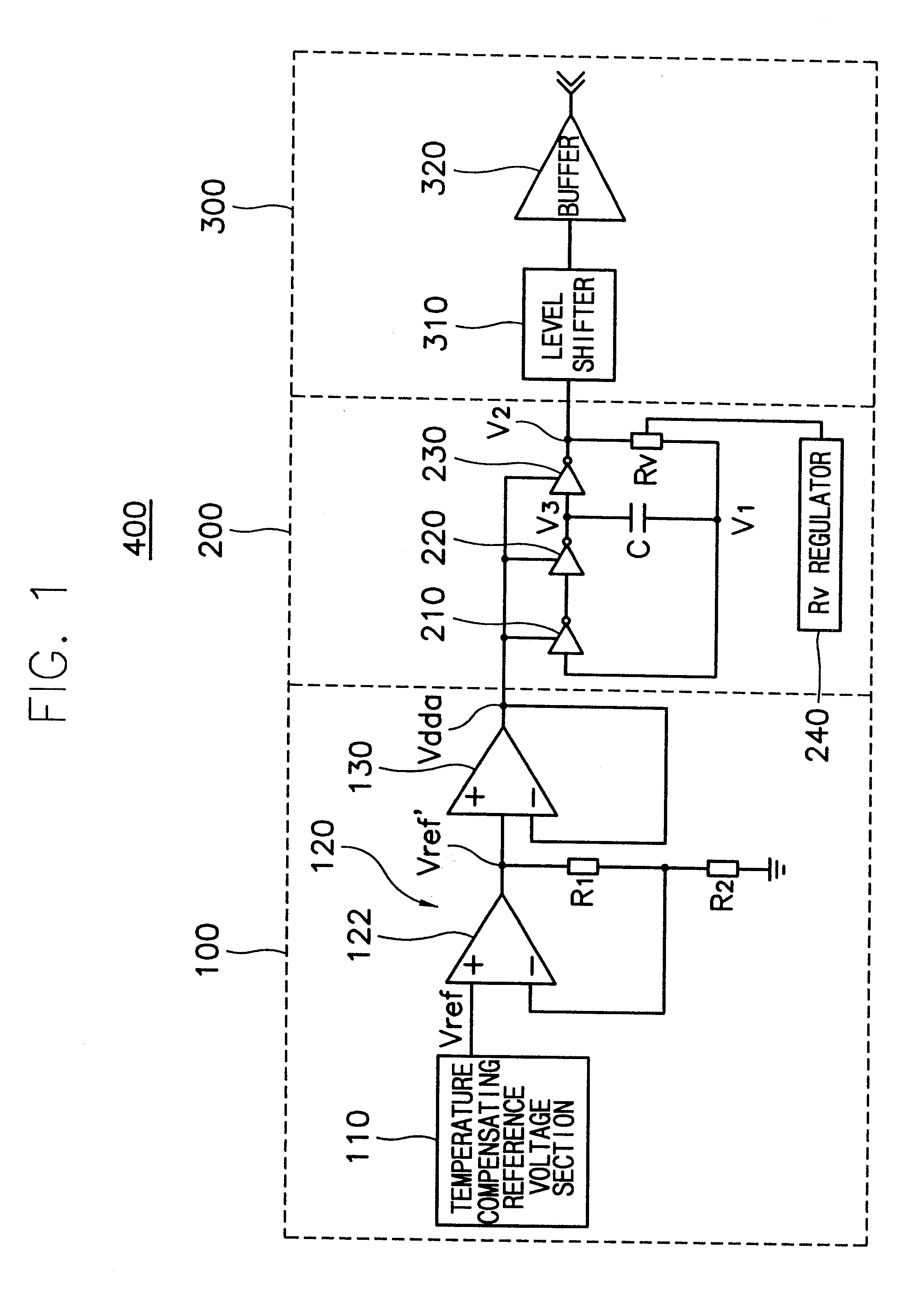

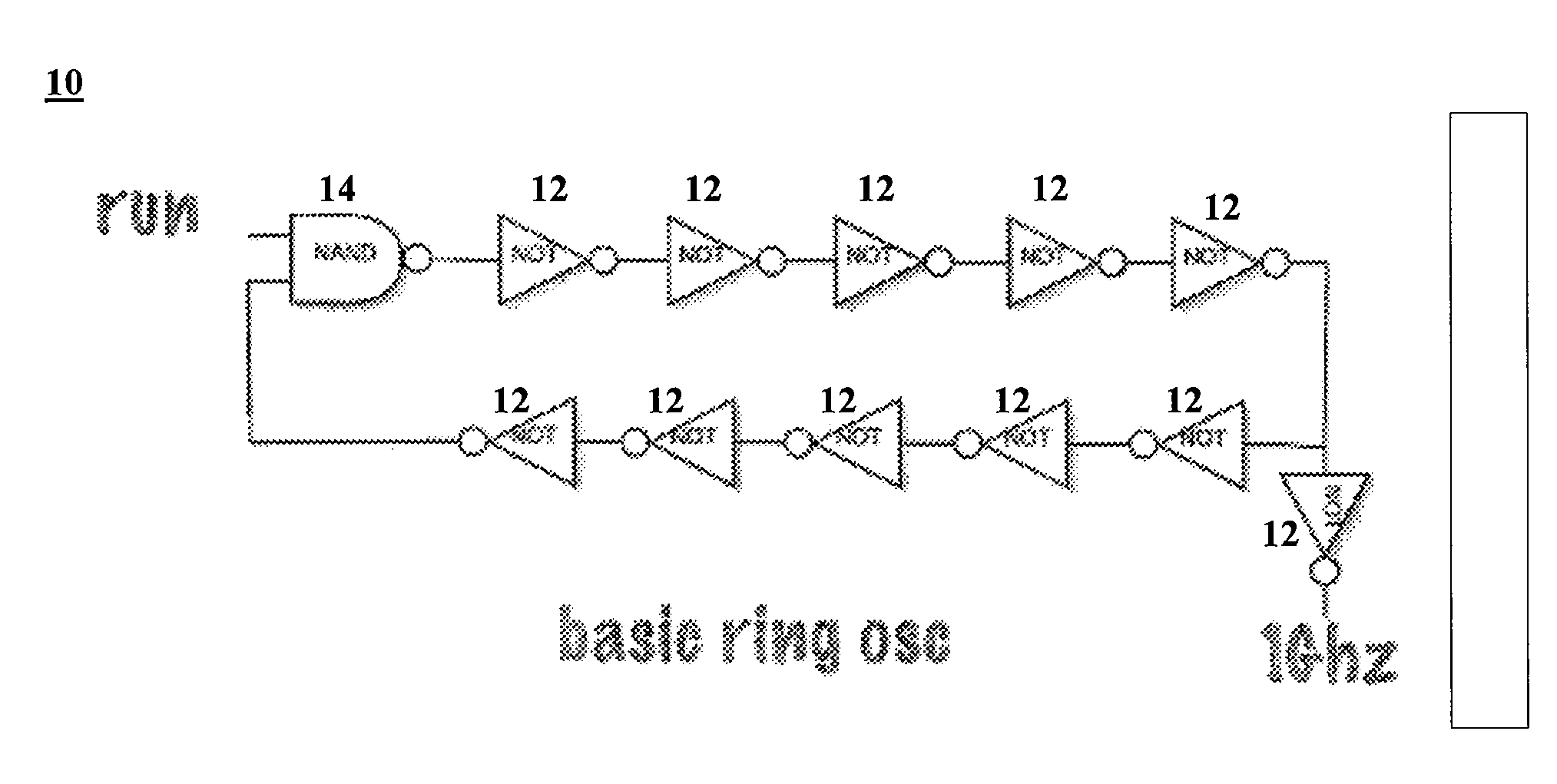

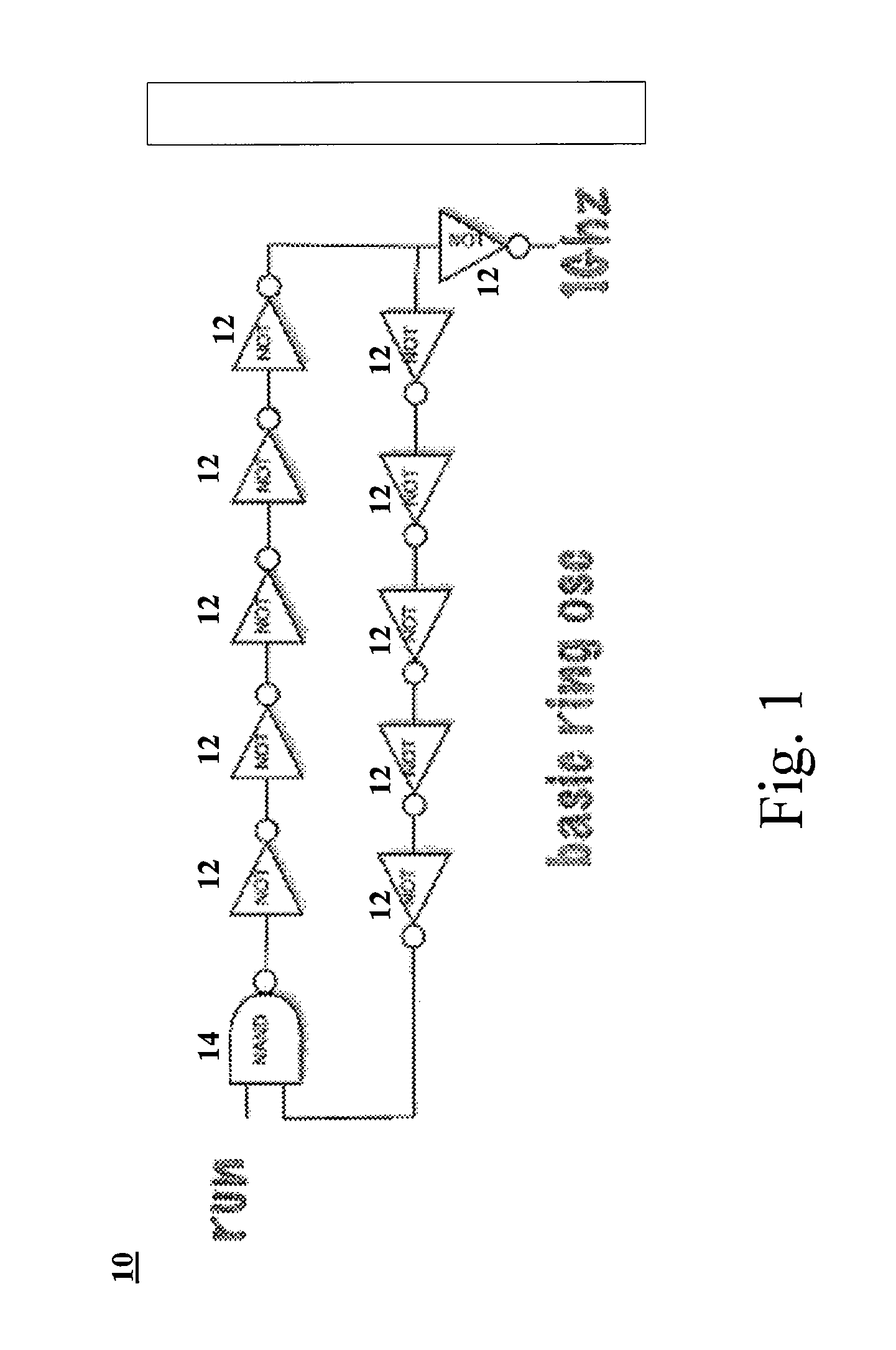

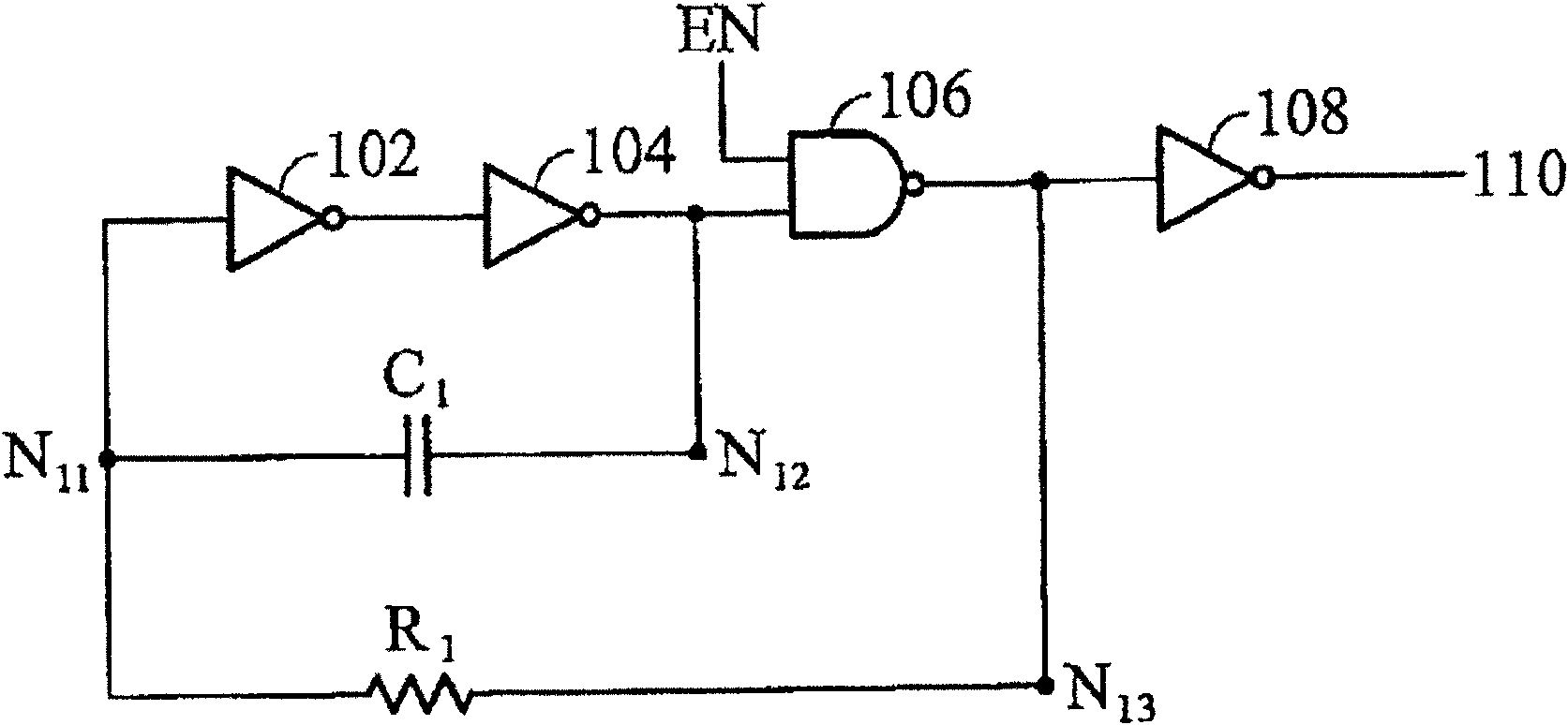

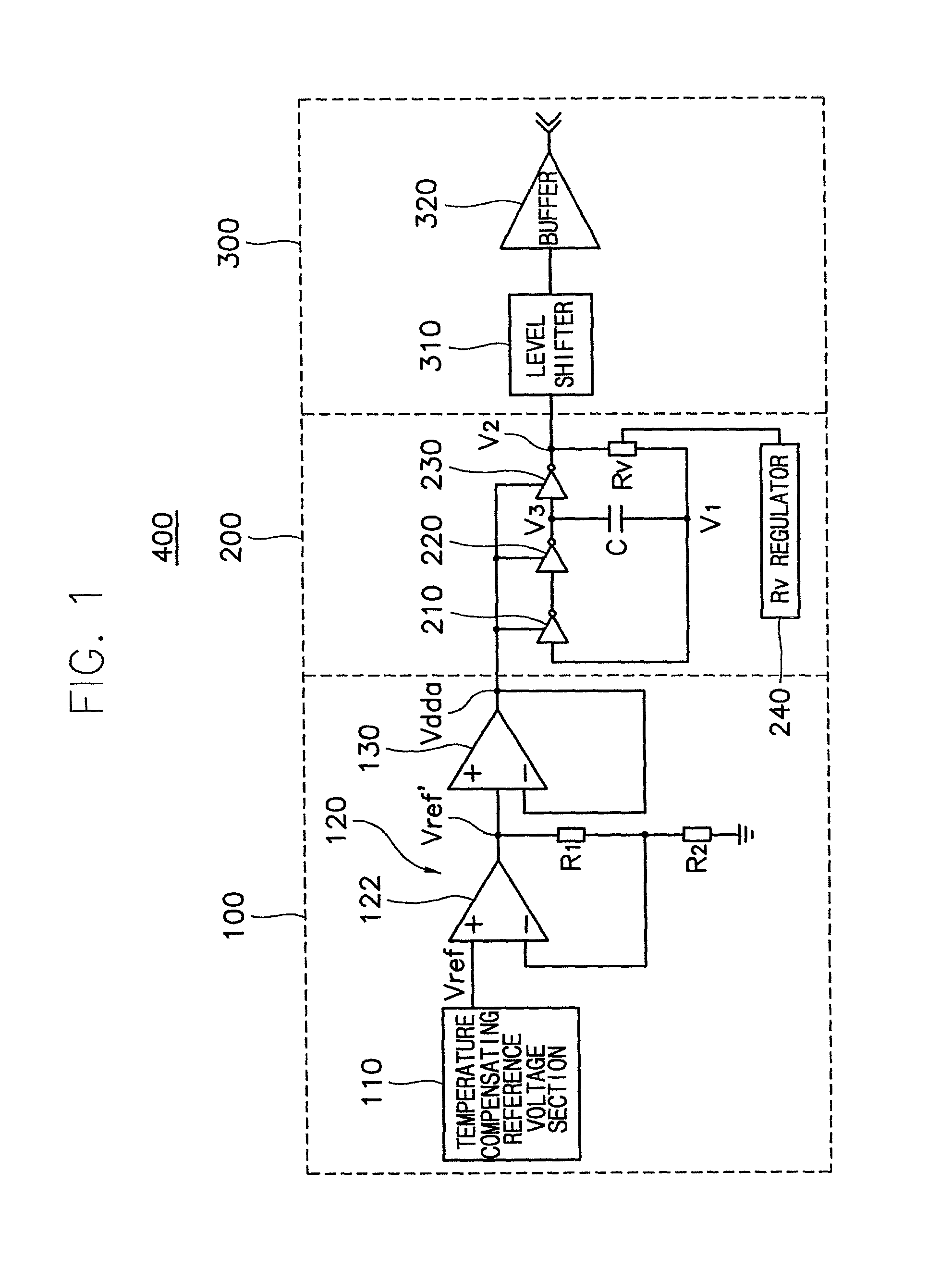

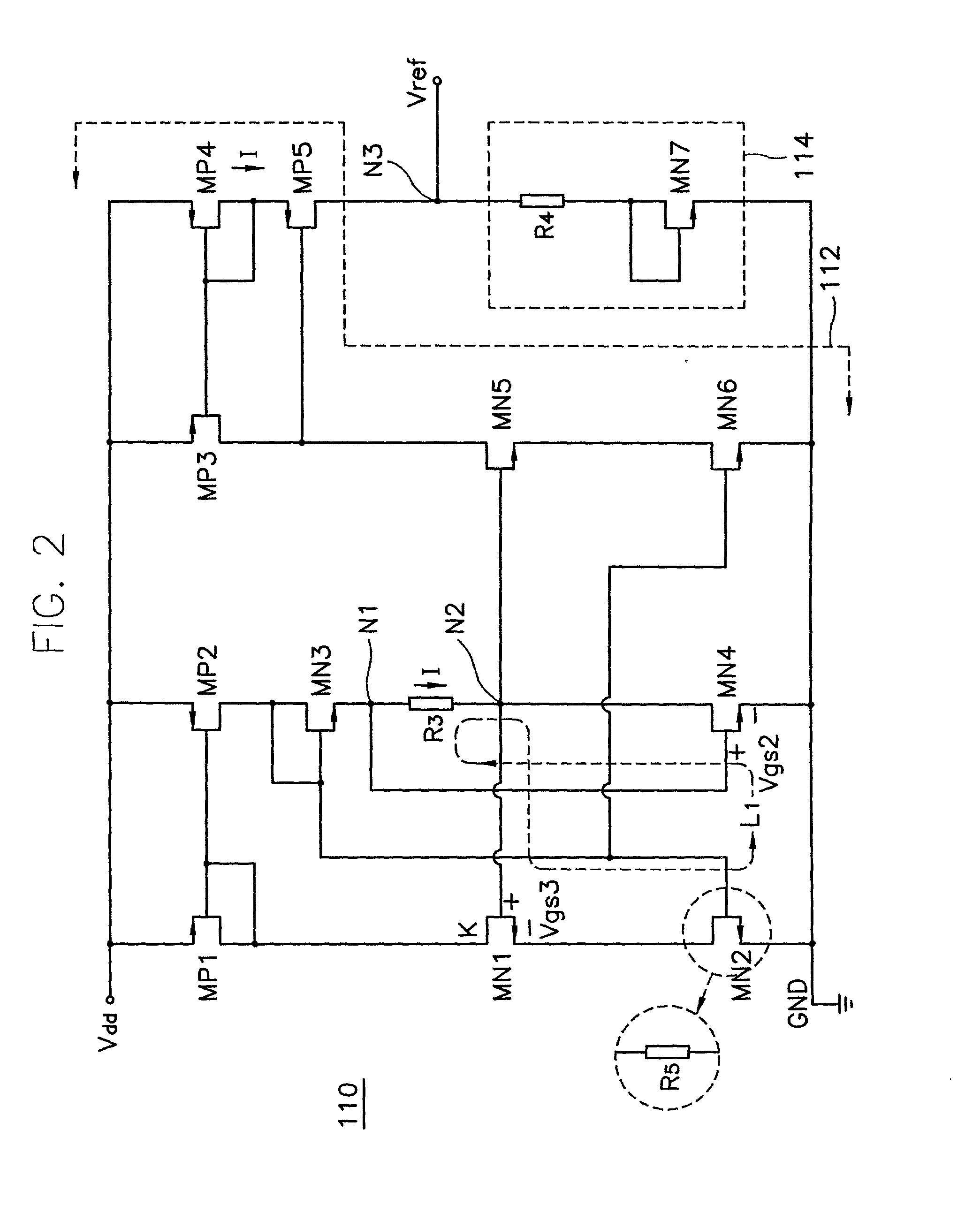

Micropower RC oscillator

InactiveUS20020000889A1Pulse automatic controlLogic circuits coupling/interface using field-effect transistorsLevel shiftingElectrical resistance and conductance

A micropower RC oscillator having stable frequency characteristics with varying temperature includes a number of inverting circuits which are driven by an external driving voltage and connected in series with each other and an RC circuit having a resistor disposed in between a head-inverter and a tail inverter to form a closed loop and a capacitor disposed between the tail-inverter and the head-inverter. The resistor comprises a plurality of unit resistors constituting of a P+ diffusion resistor and a polysilicon resistor having opposing characteristics with respect to temperature variation at a predetermined ratio. A resistance regulator controls the resistance of the resistor by decoding an external resistance setting data to select a unit resistor that determines the oscillation frequency effectively. A driving voltage circuit receives a reference signal having the voltage level which is stable against the temperature variation by using a current source and a load having opposing characteristics with respect to the temperature variation and provides as a driving voltage of the RC oscillating circuit after increasing a fan-out capacity of the reference signal. An output level shifting circuit can be added to the rear side of the RC oscillating circuit to adjust the voltage level of the oscillation signal with the appropriate standard required at a receiving end.

Owner:SAMSUNG ELECTRONICS CO LTD

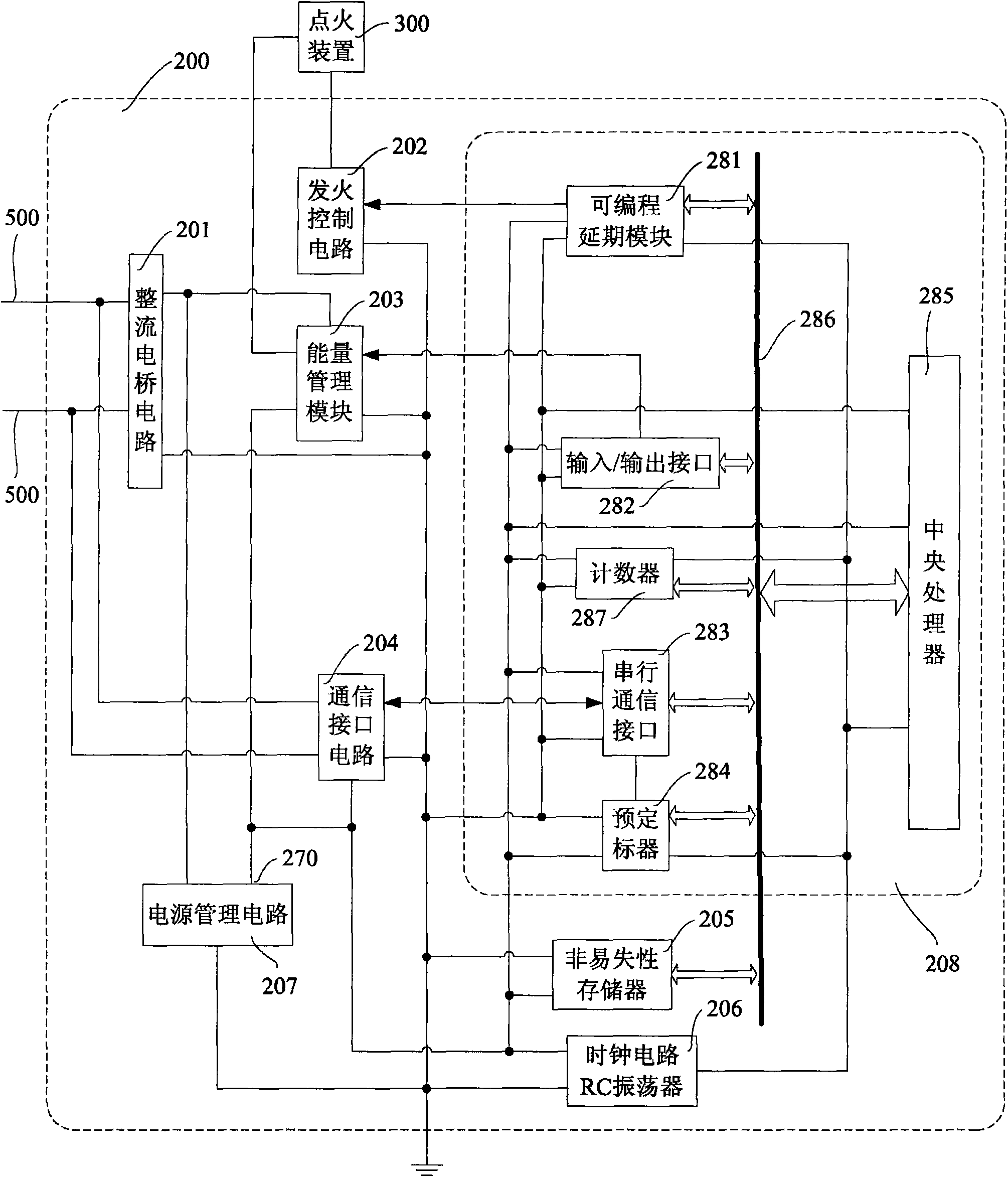

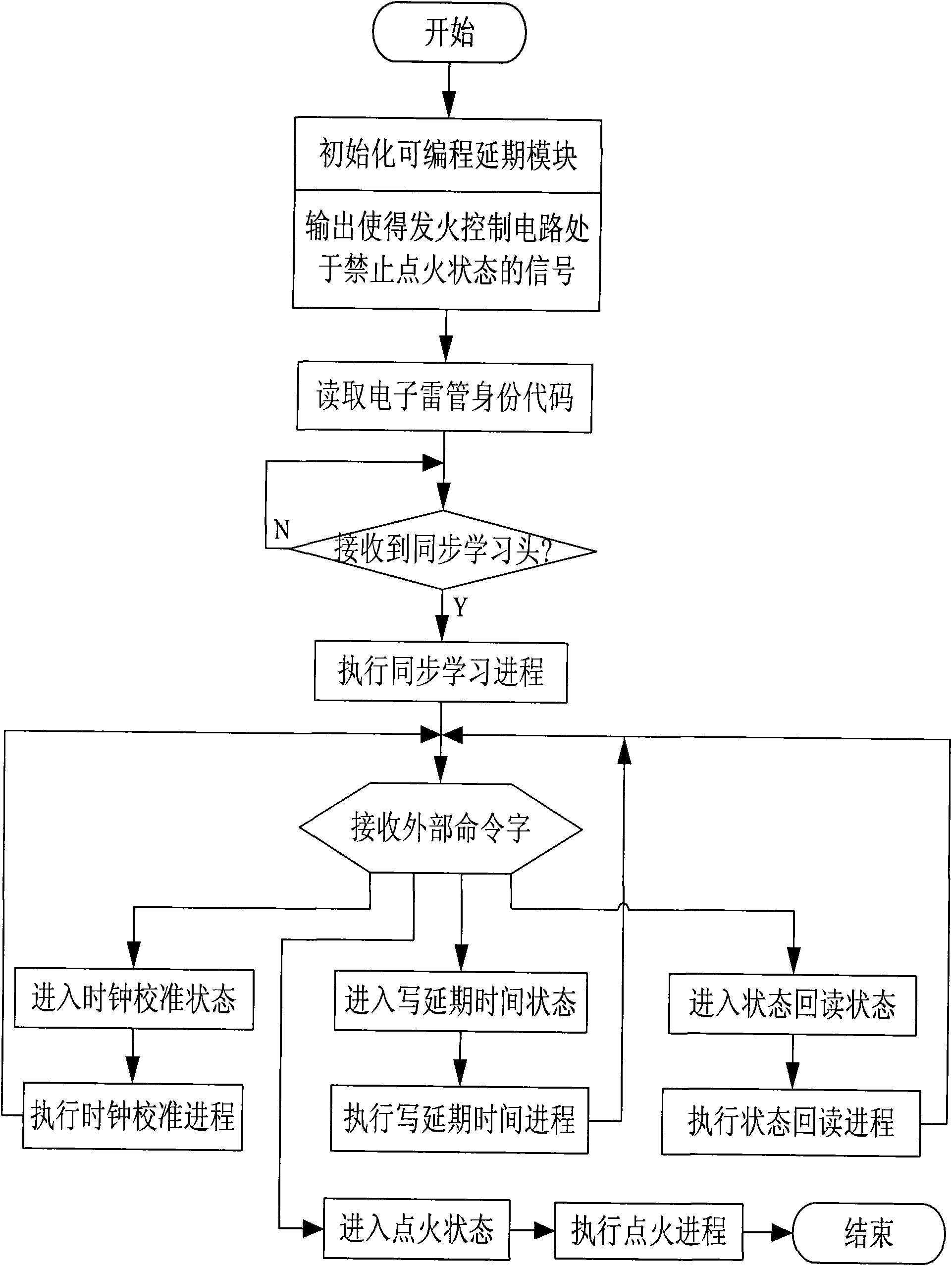

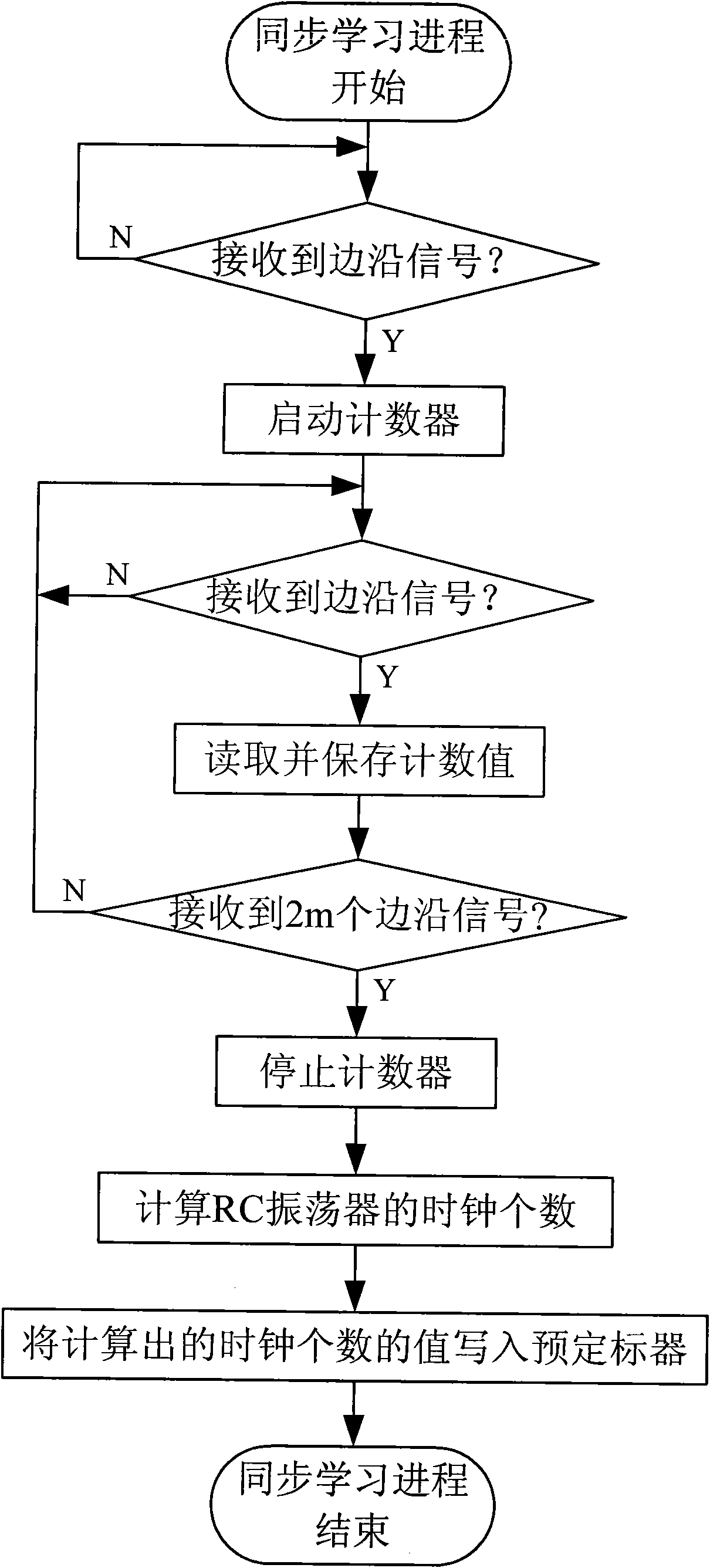

Adjustable electronic detonator control chip and flow for controlling same

The invention provides an adjustable electronic detonator control chip. A clock circuit of the chip is a RC oscillator; and a logic control circuit comprises a programmable delay module, an input / output interface, a serial communication interface, a prescaler, a central processor, and a counter. One end of the counter is connected with the power output end of a power management circuit; one end isearthed; one end is connected with the central processor through an internal bus; and the other end and the central processor, the programmable extension module and the prescaler are connected and are connected with the RC oscillator together. The invention also provides a chip controlling flow which comprises a plurality of implementing proposals including a synchronous learning course, a clockadjusting course, a state re-reading course, a writing delay time course, an ignition course and other sub-flows. The technical proposal realizes the electronic detonator control chip with good shockresistance and integratability and enough time delay precision, thereby realizing an electronic detonator with high time delay precision.

Owner:南通炜天电子科技有限公司

Local oscillator with non-harmonic ratio between oscillator and RF frequencies using XOR operation with jitter estimation and correction

ActiveUS7778610B2Avoid serious problemsEasy to implementPulse automatic controlPulse generation by logic circuitsHarmonicLocal oscillator

Owner:TEXAS INSTR INC

Current reused stacked ring oscillator and injection locked divider, injection locked multiplier

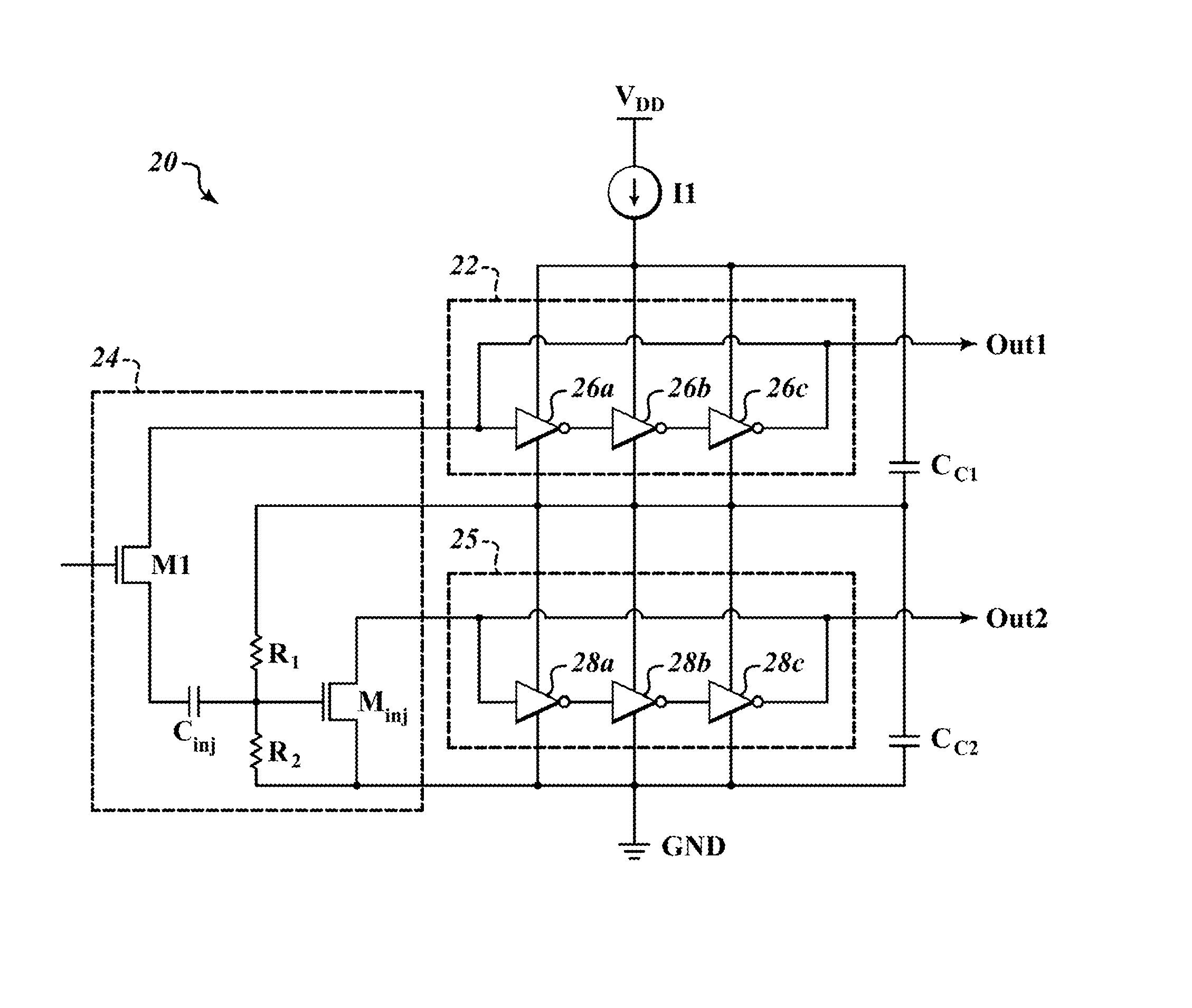

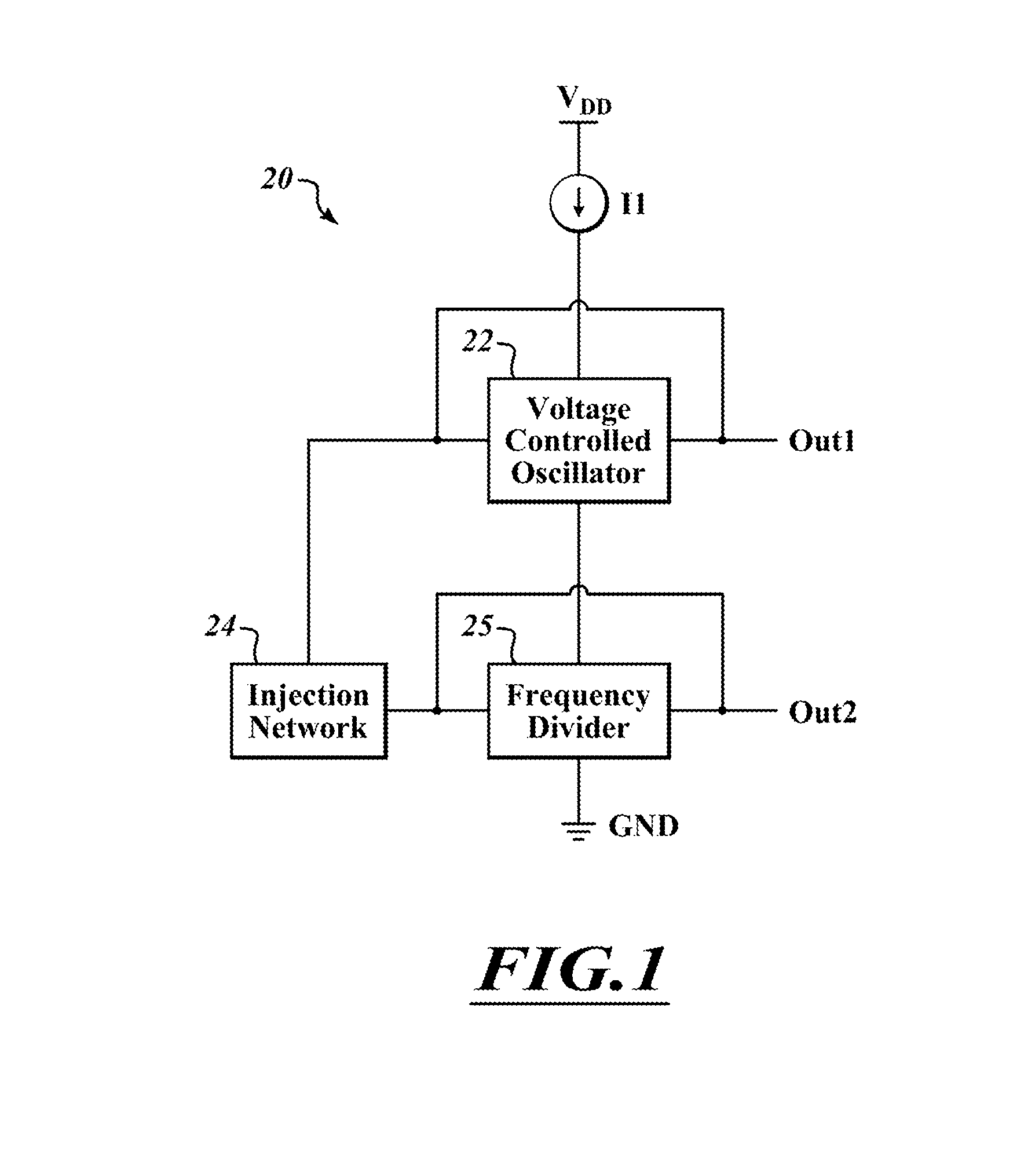

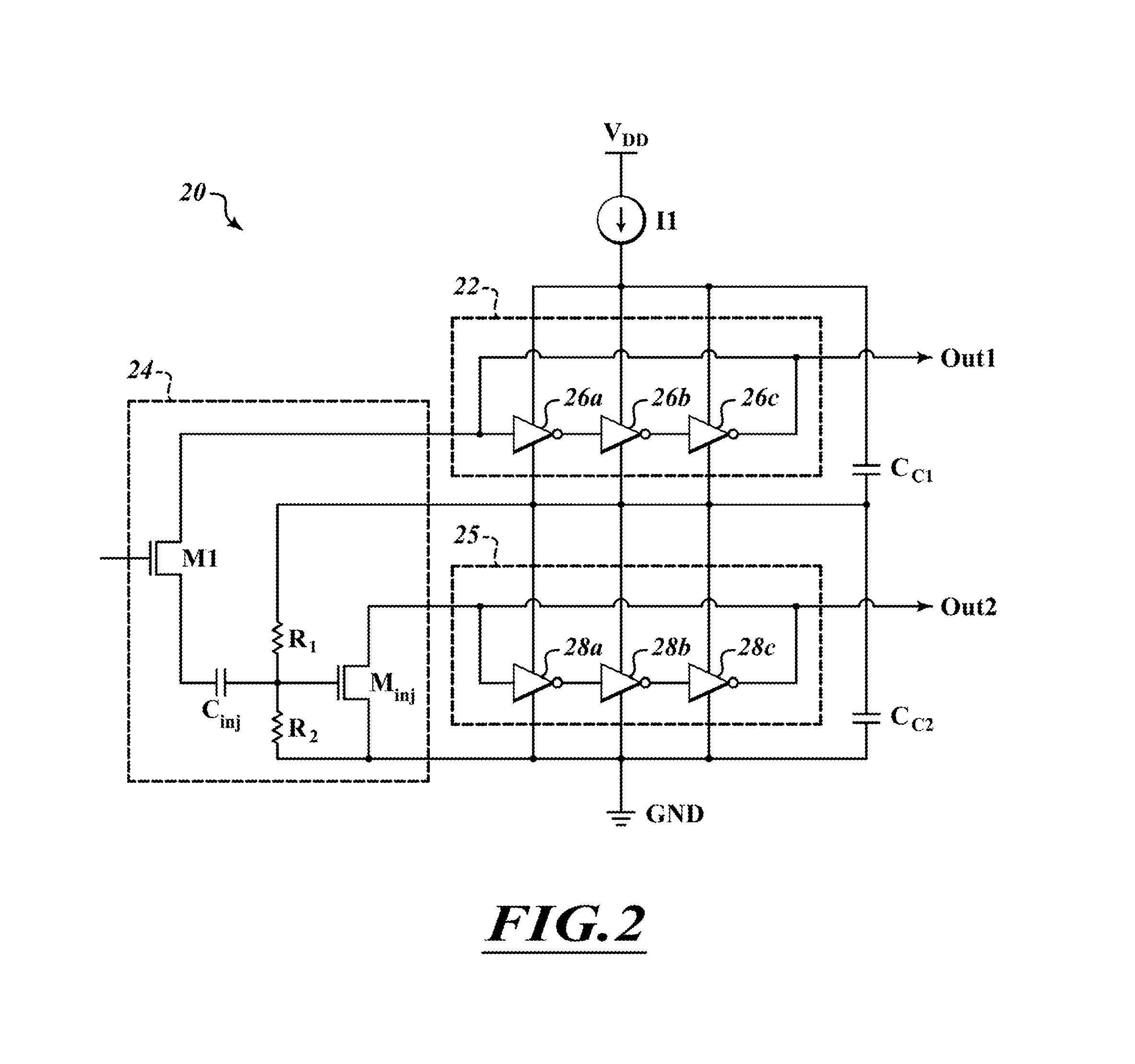

ActiveUS9018987B1Reduce power consumptionContinuously circulated pulse countersPulse automatic controlDriving currentInjection locked

A phase locked loop includes a voltage controlled oscillator and a frequency divider or frequency multiplier. The voltage controlled oscillator and the frequency divider / multiplier are coupled together in a stacked configuration. A drive current is supplied to the voltage controlled oscillator. The drive current passes from the voltage controlled oscillator to the frequency divider / multiplier, thereby driving the frequency divider / multiplier with the same drive current that was supplied to the voltage controlled oscillator.

Owner:STMICROELECTRONICS INT NV

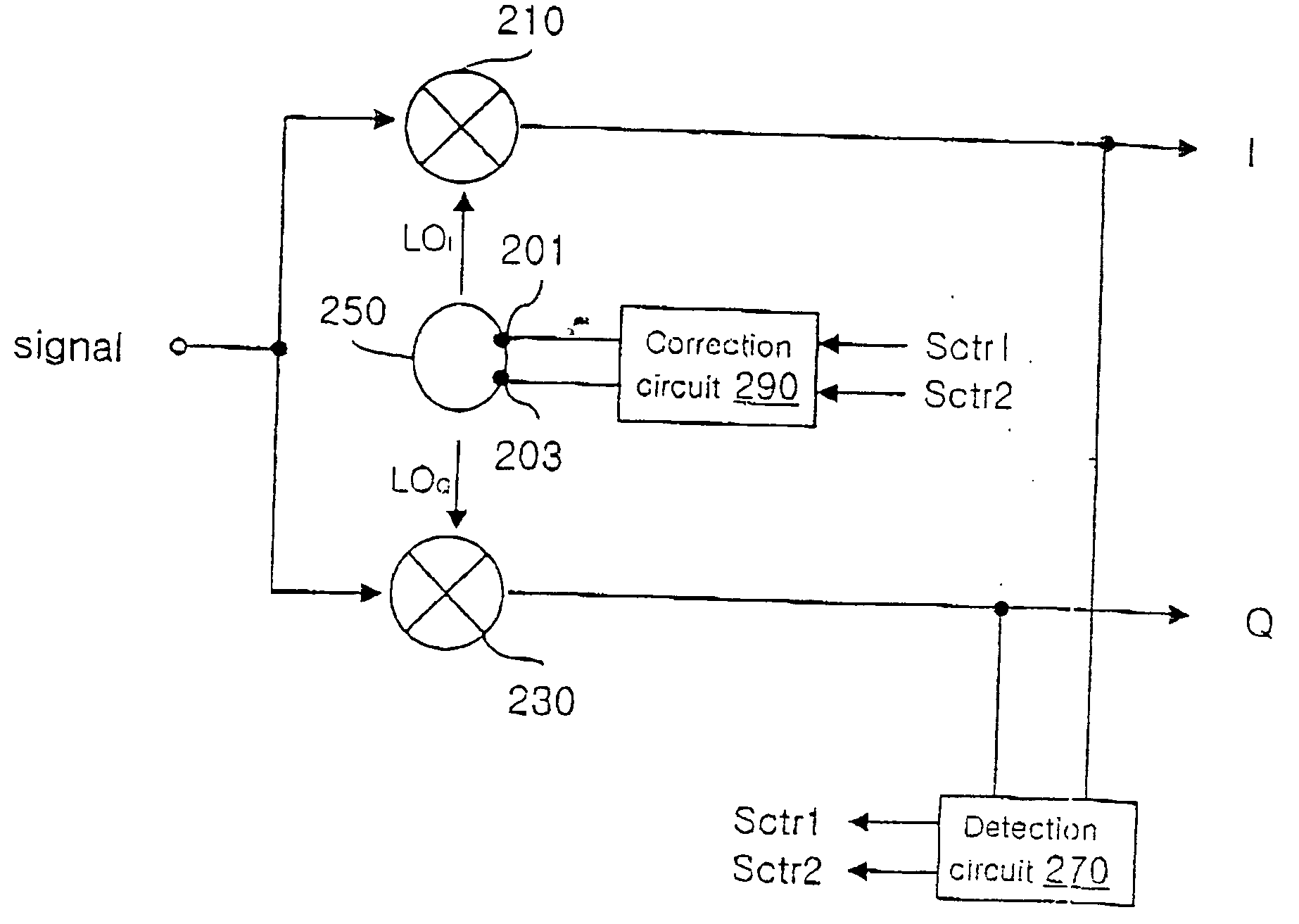

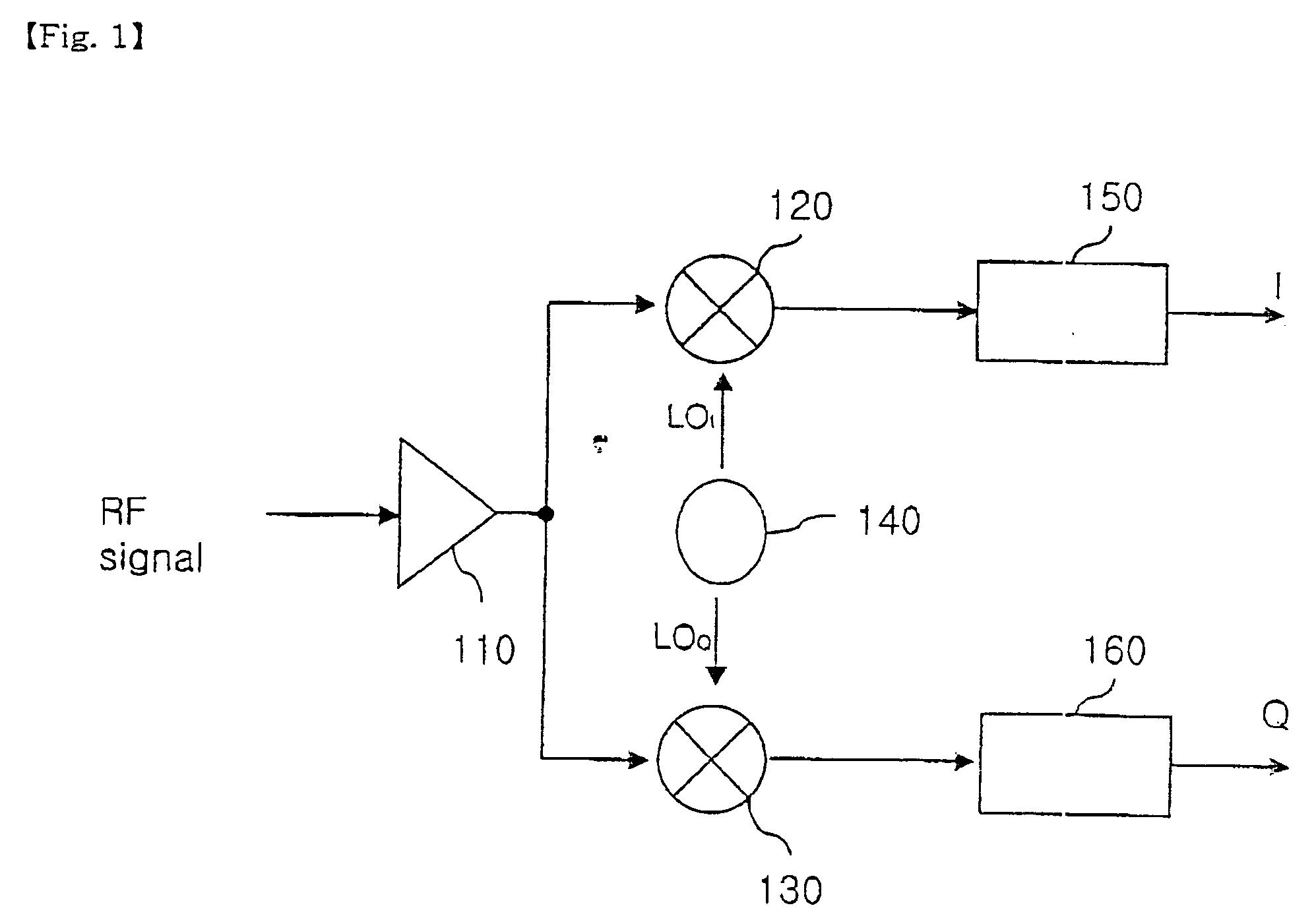

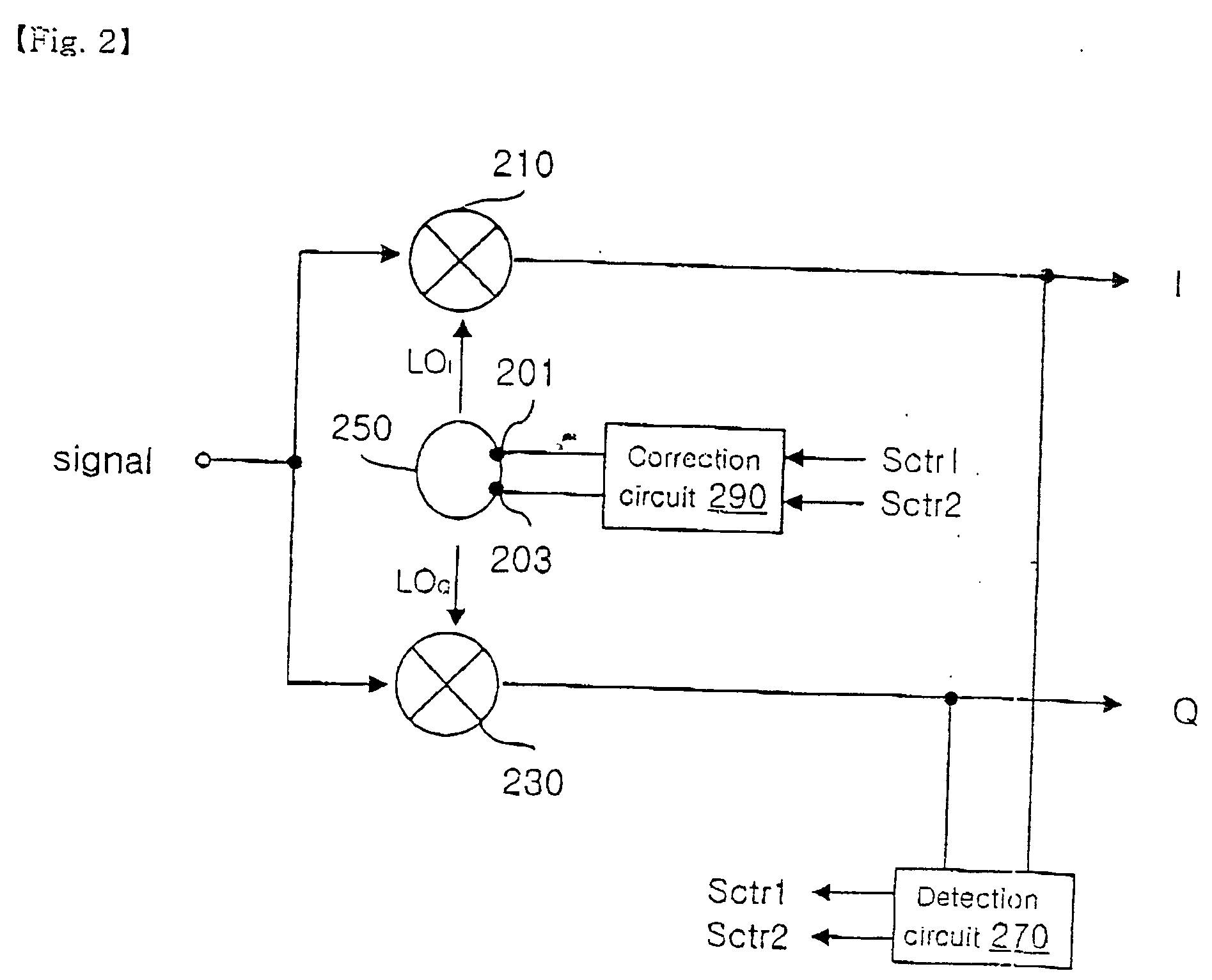

Local oscillator using I/Q mismatch compensating circuit through LO path receiver using thereof

InactiveUS20040092241A1Efficient use ofAutomatic scanning with simultaneous frequency displayModulated-carrier systemsFrequency mixerLocal oscillator

This invention relates to a local oscillator using a correction circuit for correcting I / Q mismatch through LO path and a receiver using the same. The local oscillator provides in-phase local oscillating signal and quadrature-phase signal to first and second mixers outputting input signal with mixing in-phase local oscillating signal and quadrature-phase local oscillating signal, respectively. The oscillator comprises a local oscillator having first and second delay cells and outputting said in-phase local oscillating signal and said quadrature-phase local oscillating signal; and a correction circuit for controlling phase matching characteristic between said in-phase local oscillating signal and said quadrature-phase local oscillating signal outputted from said local oscillator, said correction circuit setting bias current flowing in said first and second delay cells of said local oscillator as being different. In another embodiments, the phase matching characteristic is controlled by setting bias voltage applied to the first and second delay cells as being different, by setting width of active device included in the first and second delay dells as being different, or by setting impedance of passive device as being different.

Owner:INTEGRANT TECH

Local oscillator with non-harmonic ratio between oscillator and RF frequencies using XOR operation with jitter estimation and correction

ActiveUS20080055008A1Easy to implementAvoid serious problemsPulse automatic controlPulse generation by logic circuitsHarmonicLocal oscillator

A novel and useful apparatus for and method of local oscillator (LO) generation with non-integer multiplication ratio between the local oscillator and RF frequencies. The LO generation schemes presented are operative to generate I and Q square waves at a designated frequency while avoiding the well known issue of harmonic pulling. The use of analog mixers of the prior art is avoided and replaced with an XOR gate configured to generate the correct average frequency. The edges are dynamically adjusted by ±T / 12 or zero based on the state of the controlled oscillator down-divided clock.

Owner:TEXAS INSTR INC

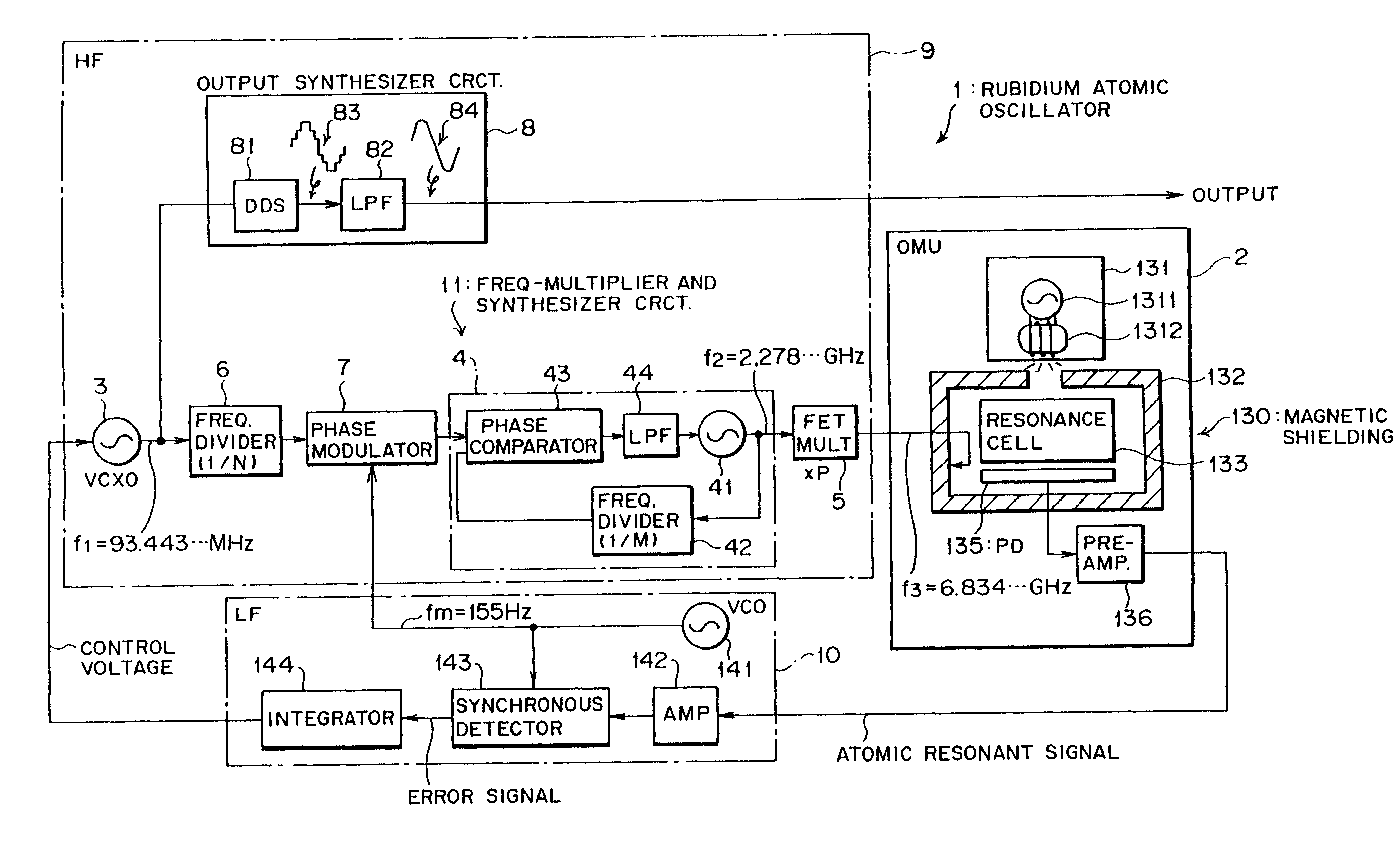

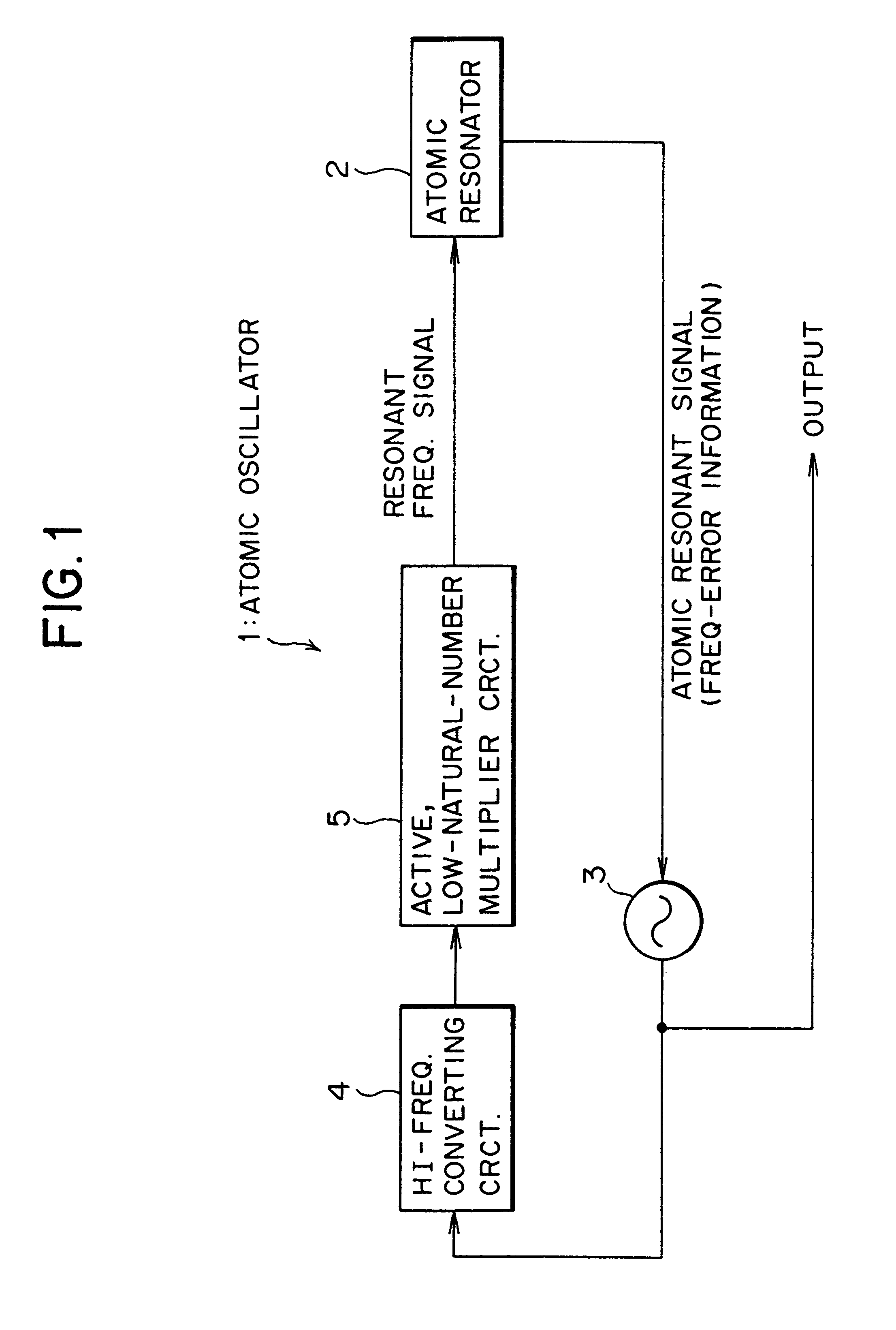

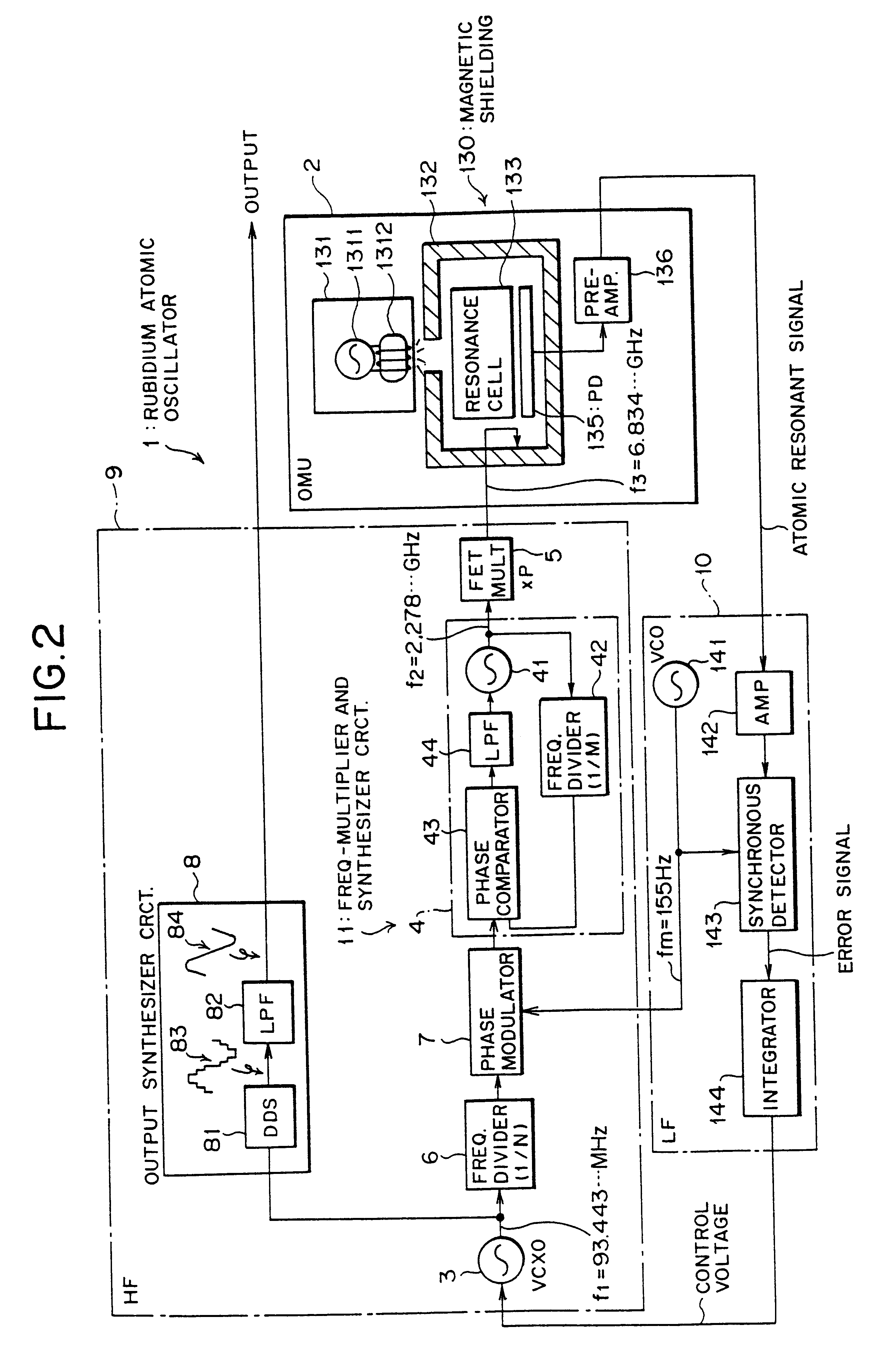

Atomic oscillator utilizing a high frequency converting circuit and an active, low-integral-number multiplier

InactiveUS6300841B1Highly stable low-frequency modulation signalImprove performancePulse automatic controlGaseous masersRC oscillatorRubidium atom

In an atomic oscillator, a high-frequency converting circuit converts the output of a standard oscillator into a high frequency signal such that the frequency of the high frequency signal multiplied by a low natural number equals an atomic resonant frequency signal. The high frequency signal is then multiplied by a low natural number in an active, low-natural-number multiplier circuit to convert the output frequency of the standard oscillator into a resonant frequency to be input to the atomic oscillator. The result is that, without using a passive, high-natural-number multiplier circuit, such as a varactor diode, which is expensive, it is possible to convert the output frequency of the standard oscillator into a resonant frequency signal of a rubidium atom, thus downsizing the circuits of the atomic oscillator and reducing the term and cost of manufacture.

Owner:FUJITSU LTD

Oscillator circuit

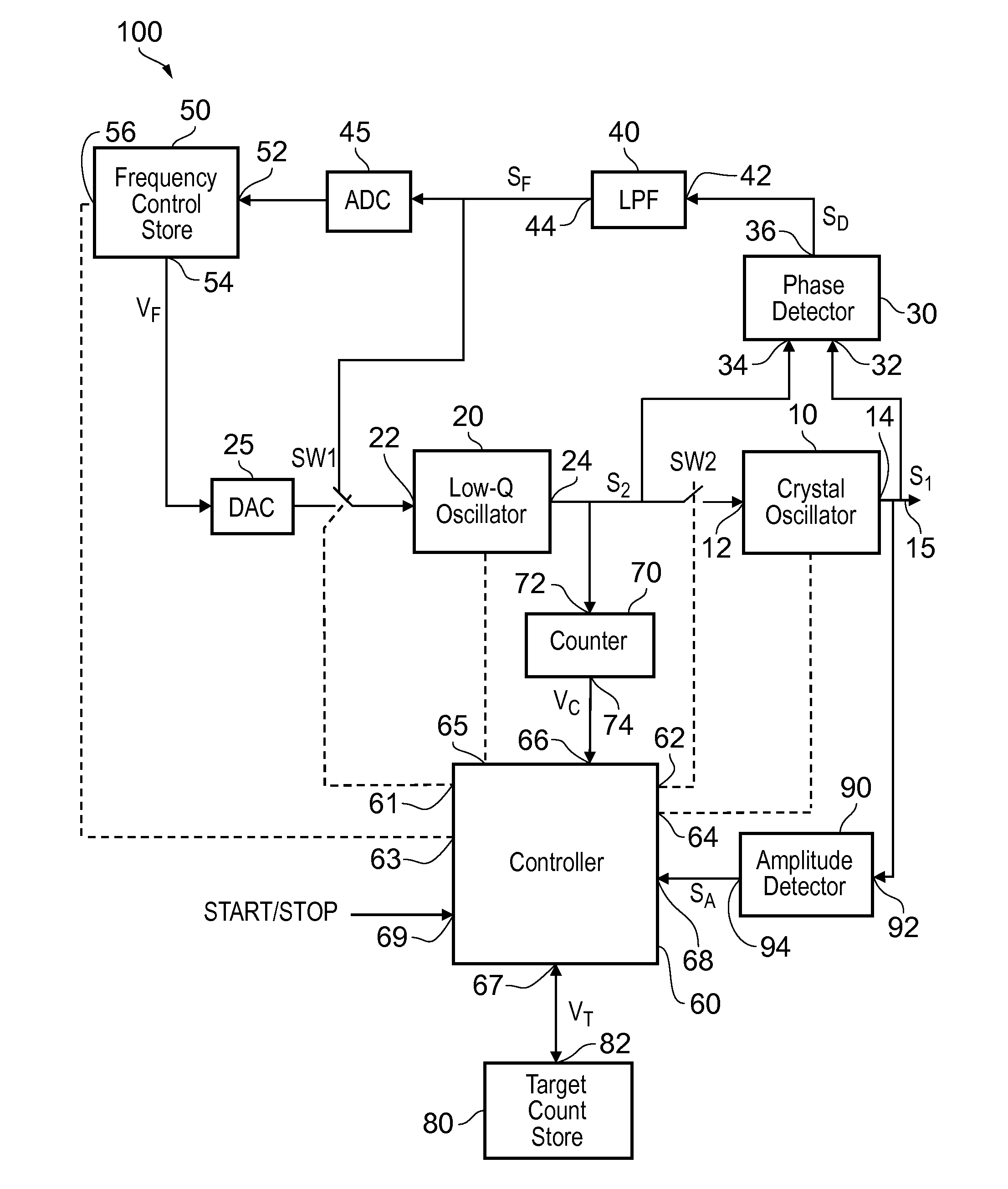

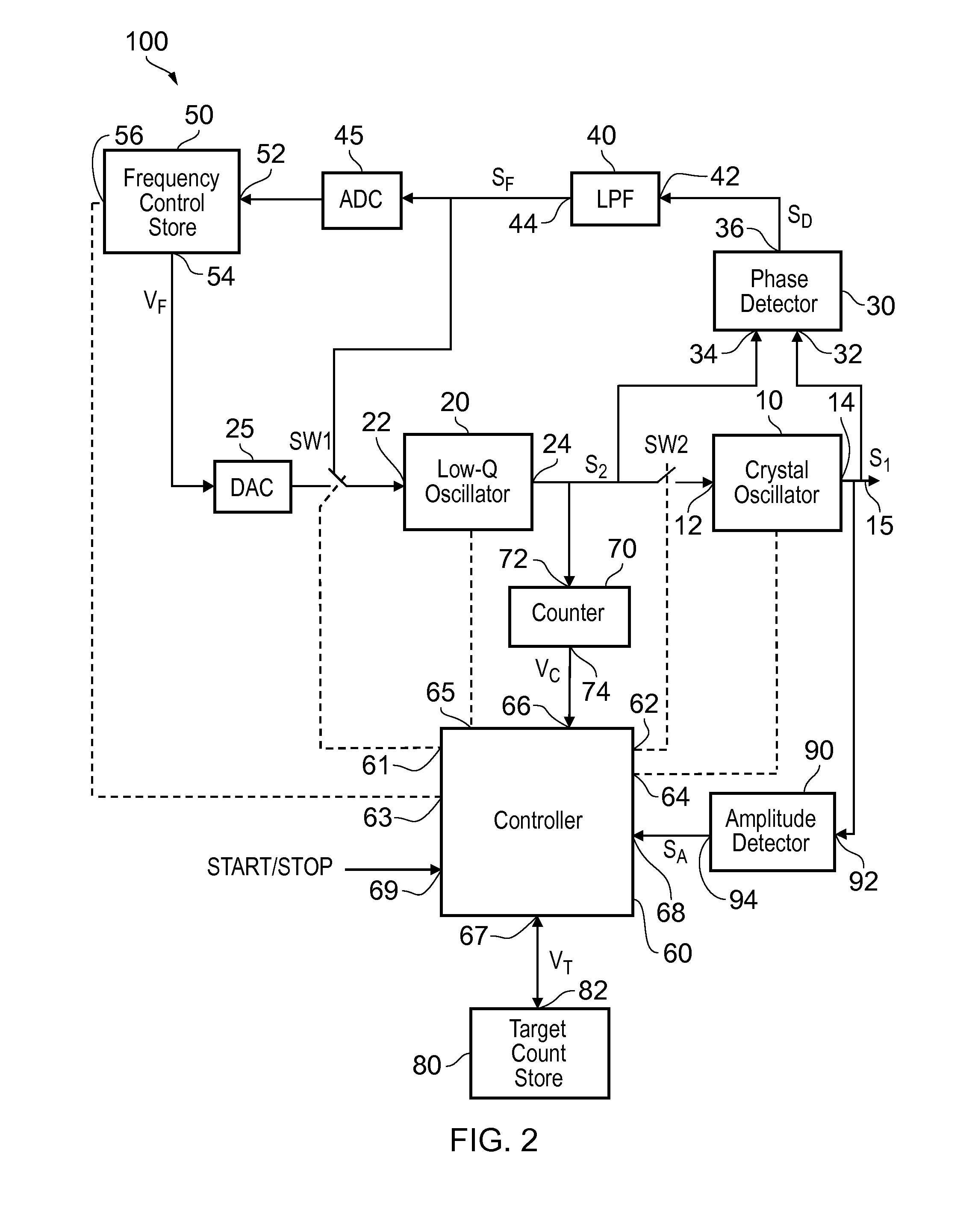

ActiveUS20160308491A1Reduce startup timeStart up more quicklyPulse automatic controlGenerator starterRC oscillatorQuantum electrodynamics

An oscillator circuit comprises a first, high-Q crystal oscillator and a second, low-Q oscillator arranged for kick-starting the crystal oscillator at switch-on by coupling the second oscillator to the first oscillator for a time period. The oscillator circuit is arranged to select the frequency of the second oscillator by placing the second oscillator in a phase locked loop with the first oscillator providing a reference frequency, and adjusting the frequency of the second oscillator towards the frequency of the first oscillator.

Owner:TELEFON AB LM ERICSSON (PUBL)

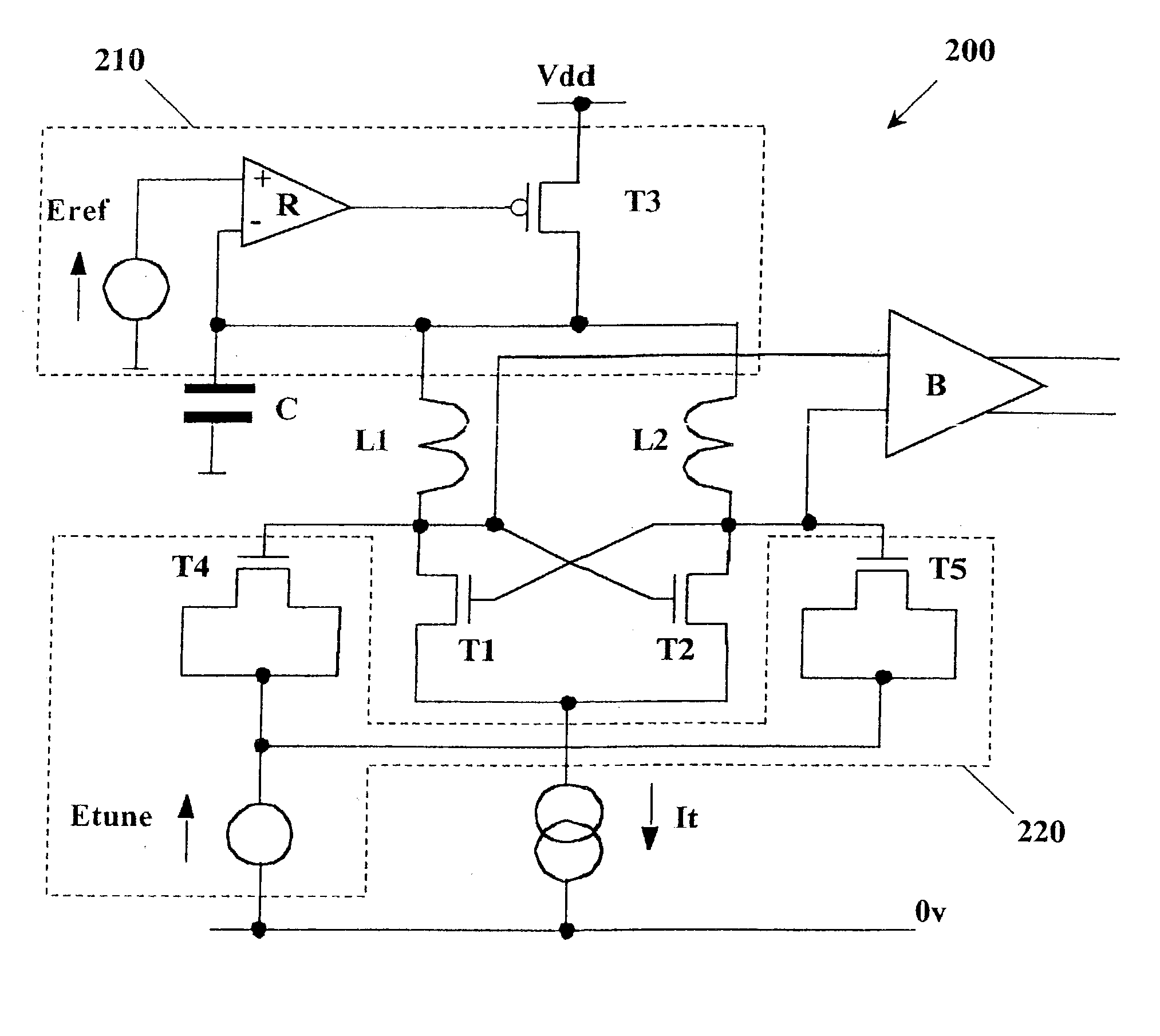

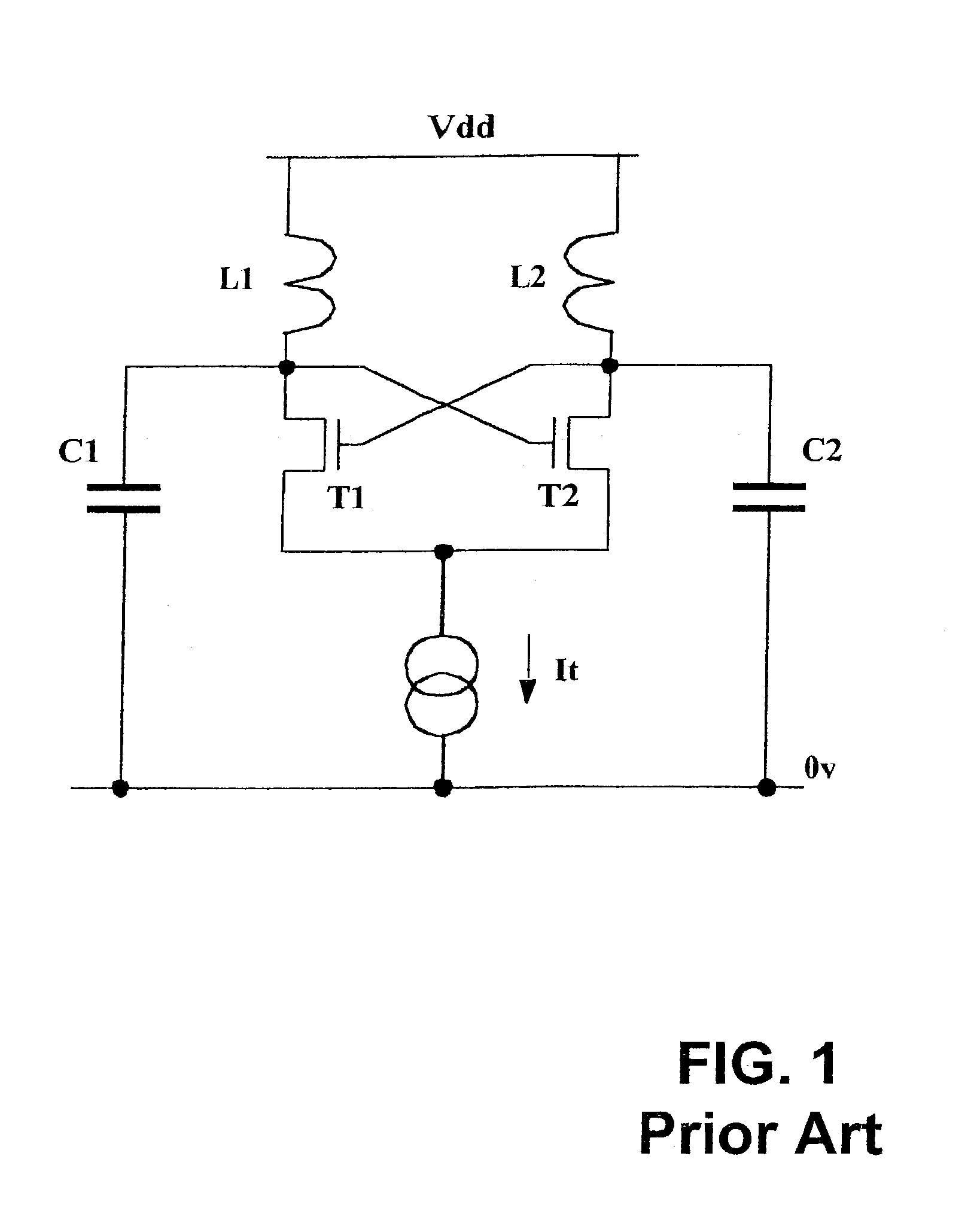

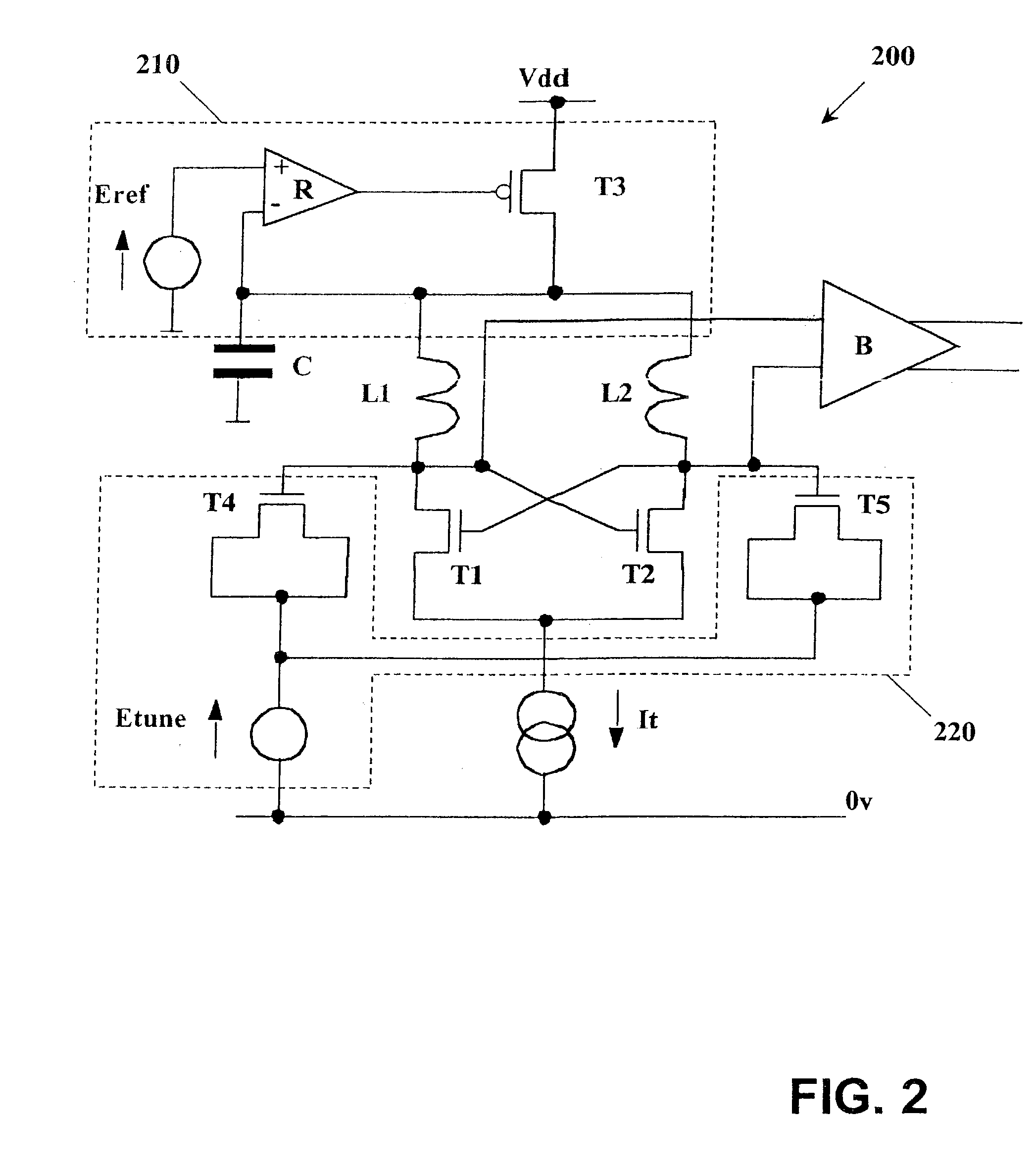

Voltage controlled oscillator circuit and method

A voltage controlled oscillator circuit and method comprising: a harmonic oscillator having a cross-coupled NFET devices (T1, T2) and an LC tank circuit (L1, L2, C) performing oscillation; a series voltage regulator (210) regulating voltage applied to the harmonic oscillator via a PFET device (T3) and differential amplifier (R); and a tuning circuit (220) having voltage controlled capacitance 'Zero-Vt' NFET devices (T4, T5) controlling oscillation of the harmonic oscillator. A differential output buffer (B) provides output buffering to a subsequent stage. This provides advantages that: operation at low supply voltages is facilitated and the sensitive oscillator cell is decoupled from the main supply noise offering improved phase noise performance; the output swing of the oscillator has a well controlled common-mode value which can be selected to most efficiently drive a following stage; and using 'Zero-Vt' NFETs facilitates the use of a lower supply voltage.

Owner:IBM CORP

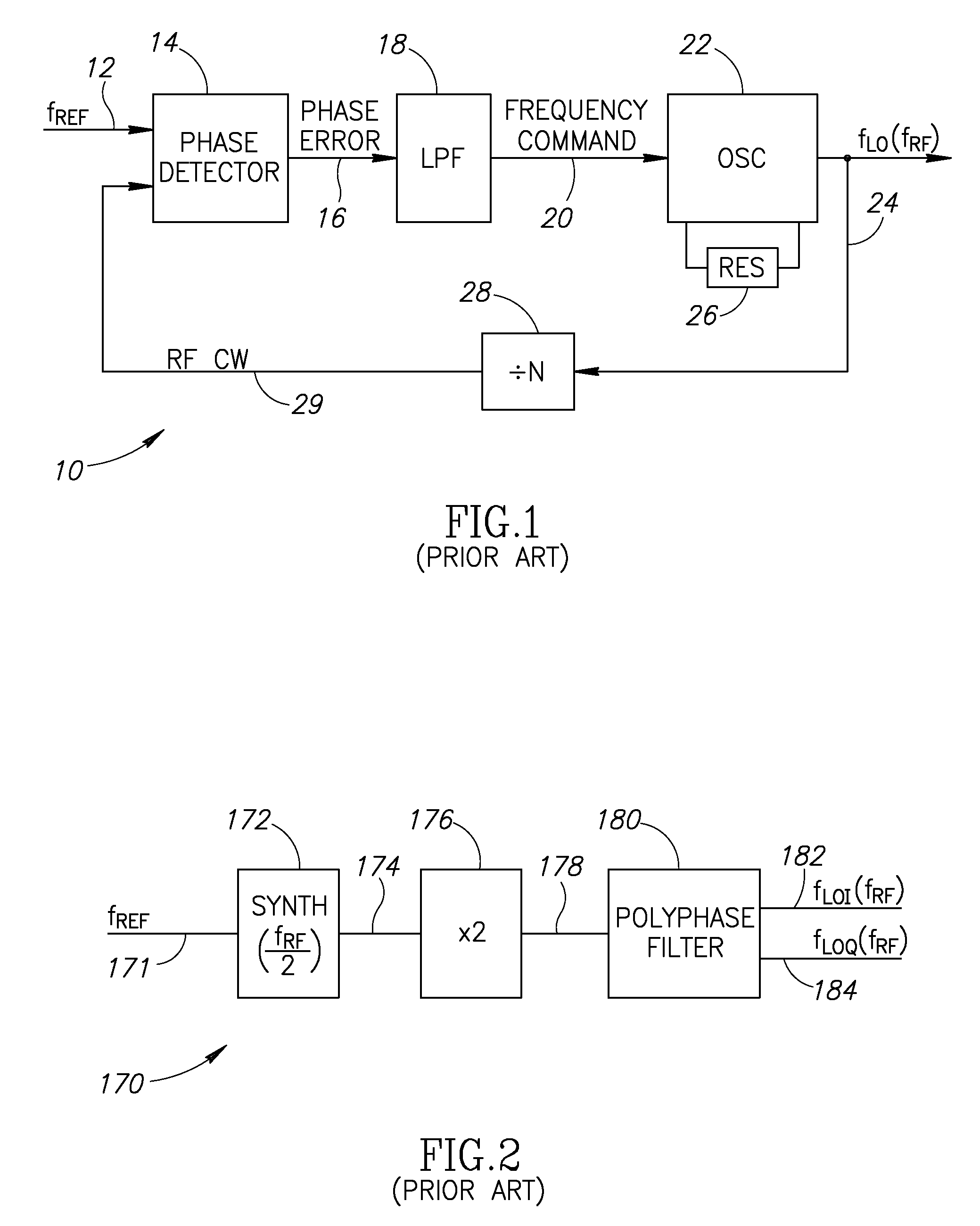

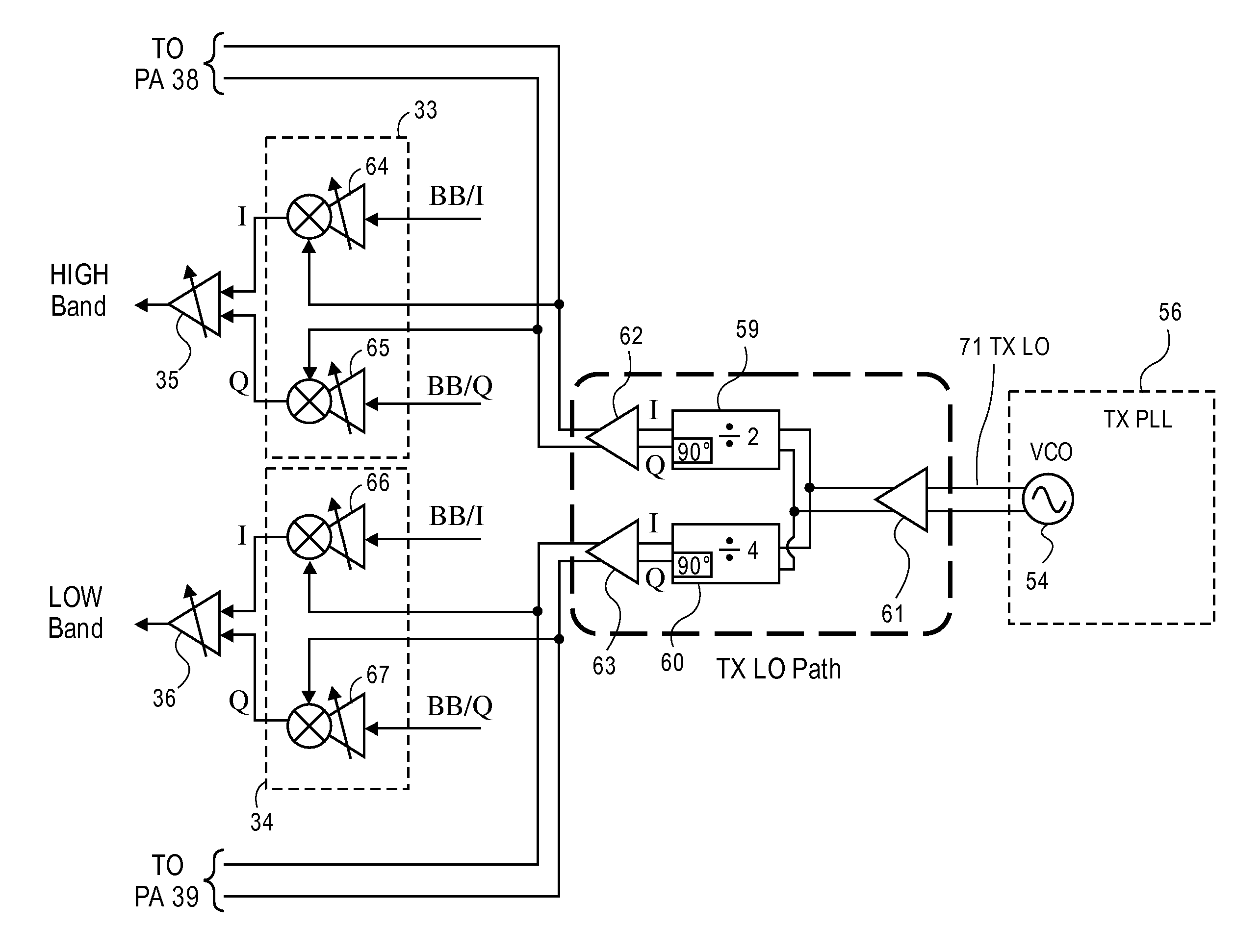

Low power frequency division and local oscillator generation

A plurality of inverters are arranged serially to form a ring oscillator and coupled to receive a reference clock signal. The reference clock signal is used to switch the inverters on and off so that not all of the inverters are on at a same time. The ring oscillator circuit is used as a divider circuit to divide the frequency of the reference clock signal to produce a local oscillator signal at a second frequency.

Owner:AVAGO TECH INT SALES PTE LTD

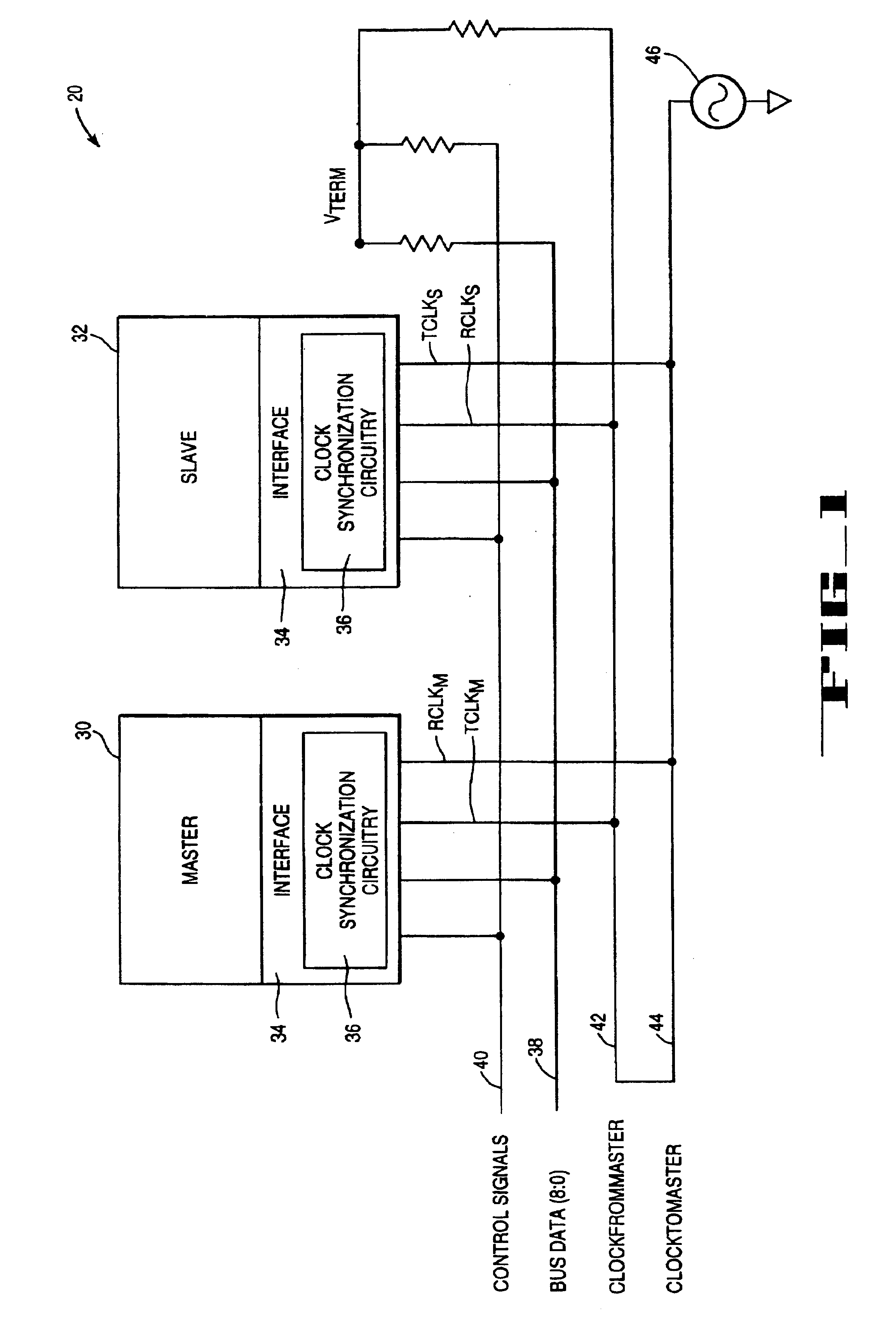

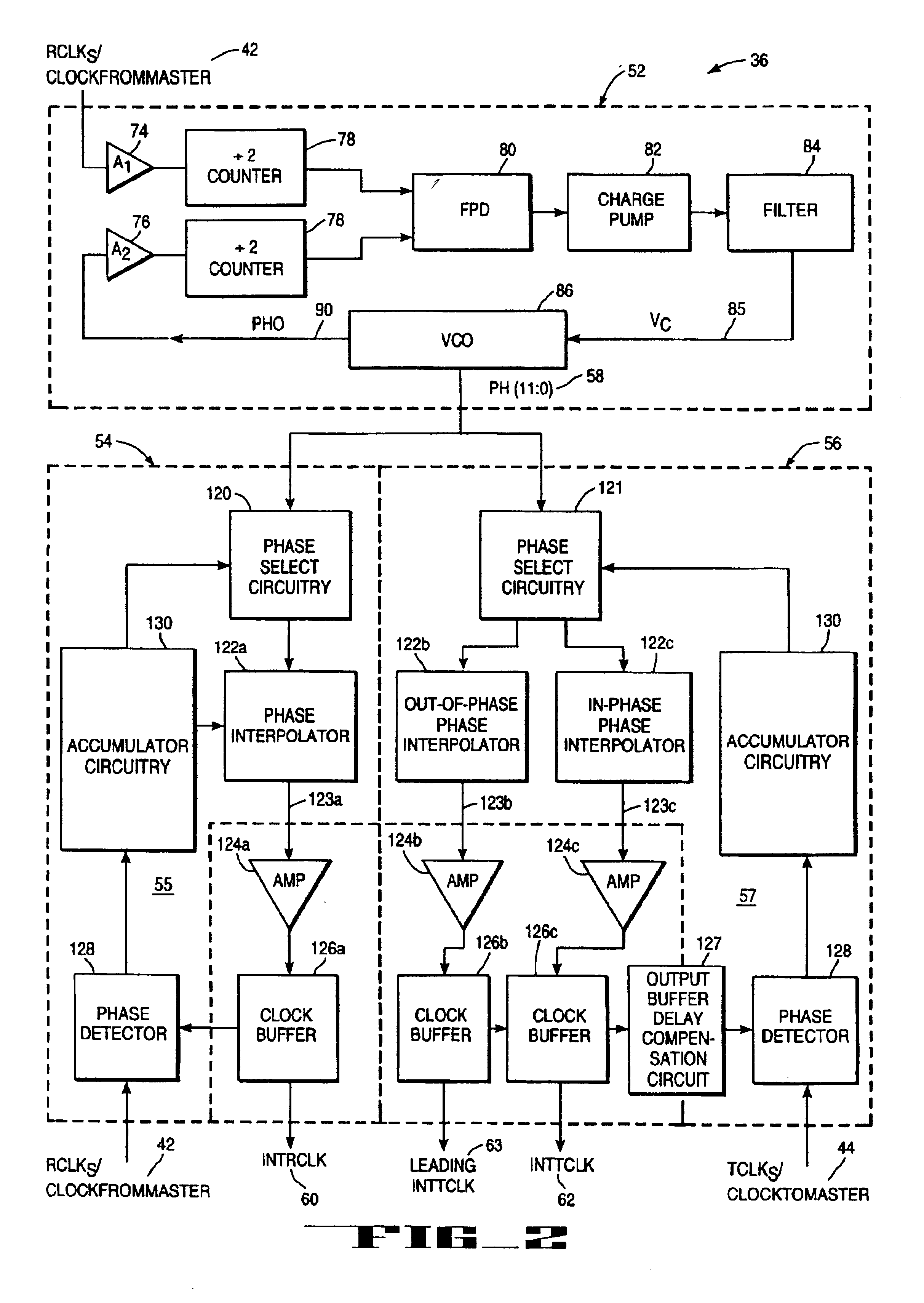

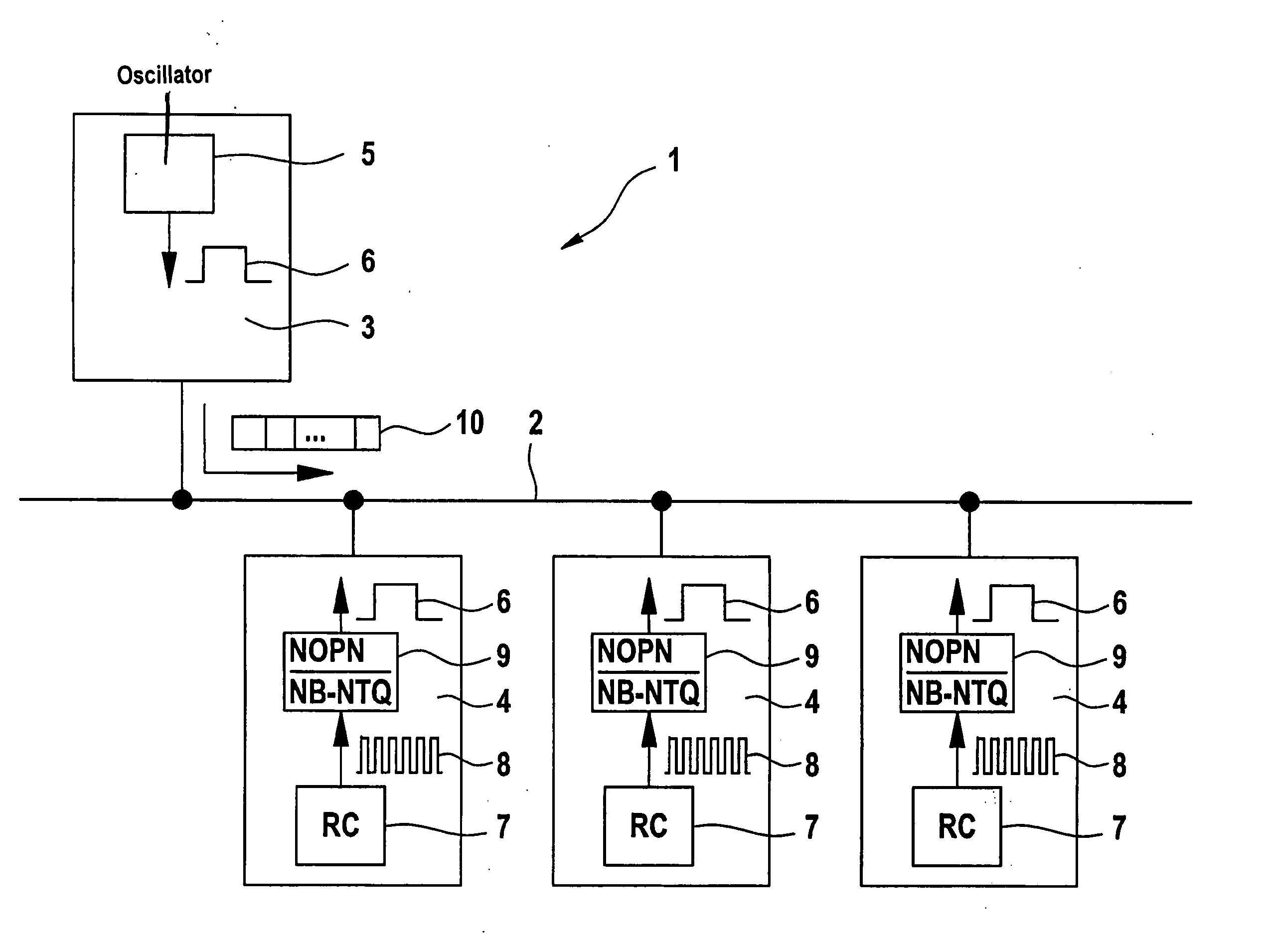

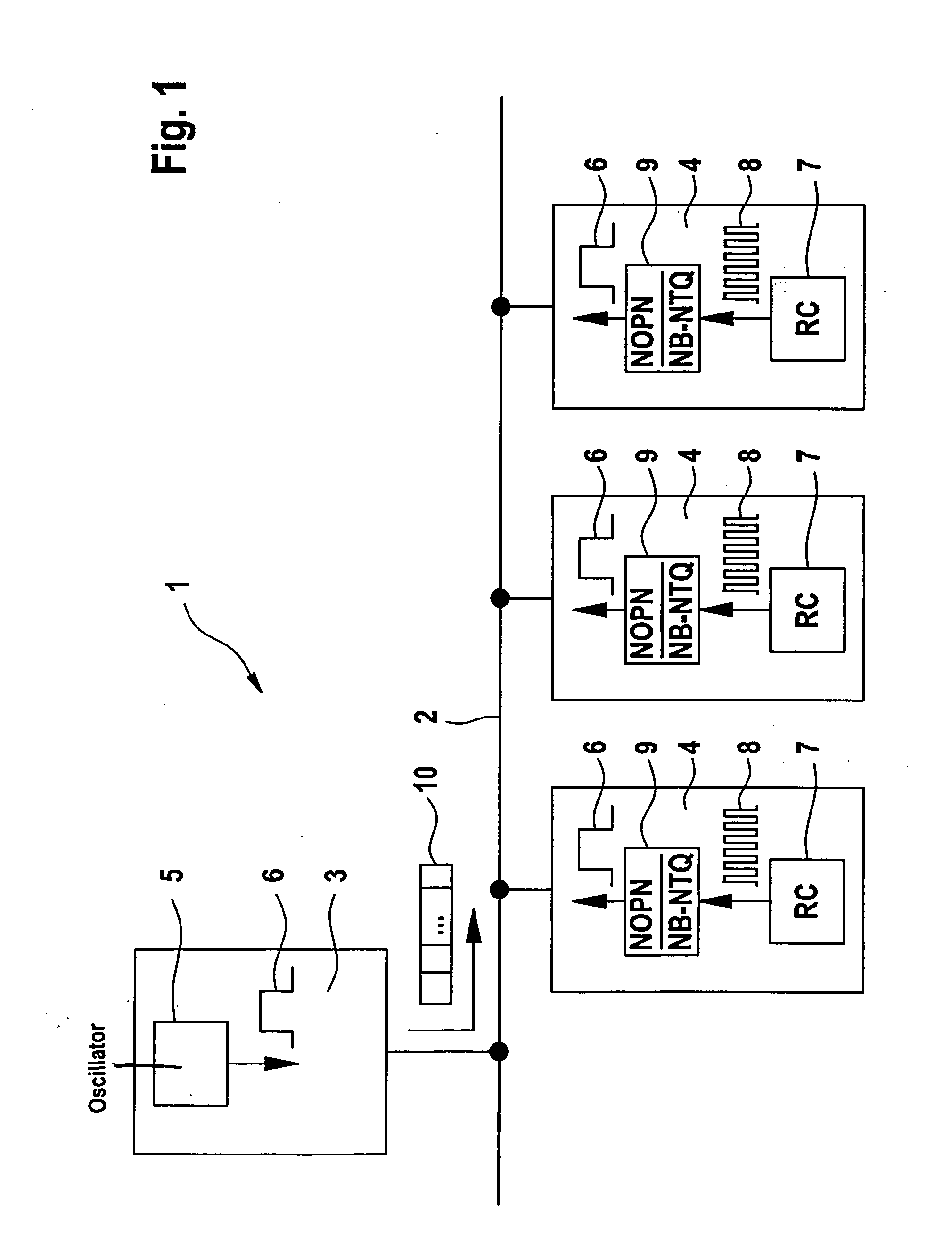

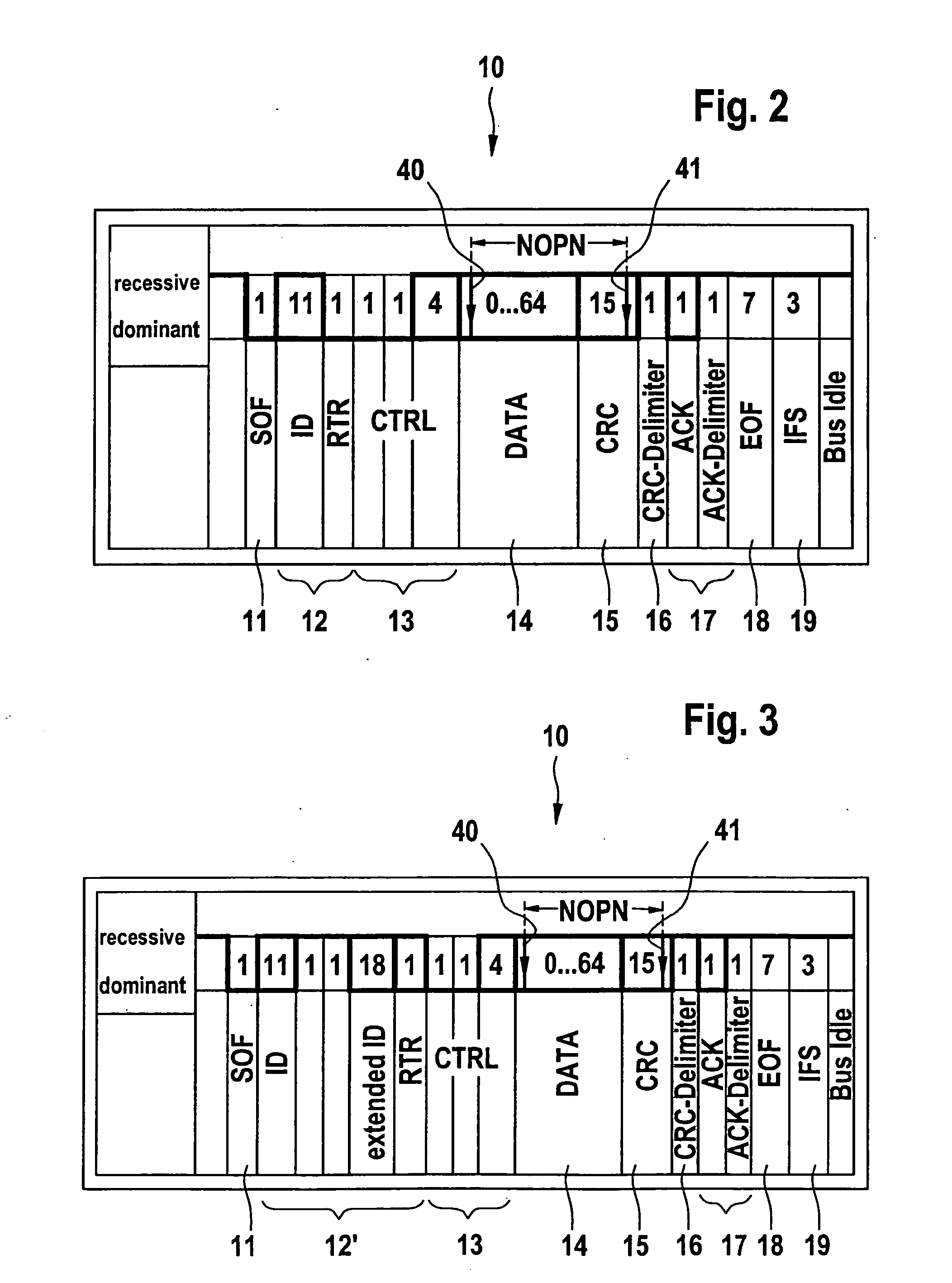

Communication system including a data bus and multiple user nodes connected thereto, and method for operating such a communication system

ActiveUS20110038388A1Improve calibration accuracyReduce measurement errorTime-division multiplexGenerating/distributing signalsCommunications systemControl system

A communication system is described that includes a data bus and multiple user nodes connected to the data bus. Also described is a method for operating such a communication system. Data frames for data transmission each include a data field and / or a control field and a check sum field. One user has a high-precision clock generator (for example, precise quartz, MEMS resonator, etc.), and the remaining users have a clock generator (for example, an RC oscillator or imprecise quartz) having a lower precision. During operation of the communication system calibration messages are present on the data bus, and the users having the imprecise clock generator receive a calibration message. The users having the imprecise clock generator calibrate the imprecise clock generator to a system clock signal of the data bus, taking into account information contained in the received calibration message. To expedite the calibration of such a communication system and at the same time conserve bandwidth on the data bus, any given messages transmitted via the data bus are used as calibration messages for calibrating the system. For the calibration, a distance (NOPN) between an edge in the data field or in the control field of a received data frame and another edge in a field of the received data frame is measured in oscillator periods. The number (NB) of bits between these two edges is counted, and a clock divider which generates a system clock signal of a data bus protocol control system of the user to be calibrated is to be set so that a system clock signal period has a length of NOPN / NB·NTQ oscillator periods.

Owner:ROBERT BOSCH GMBH

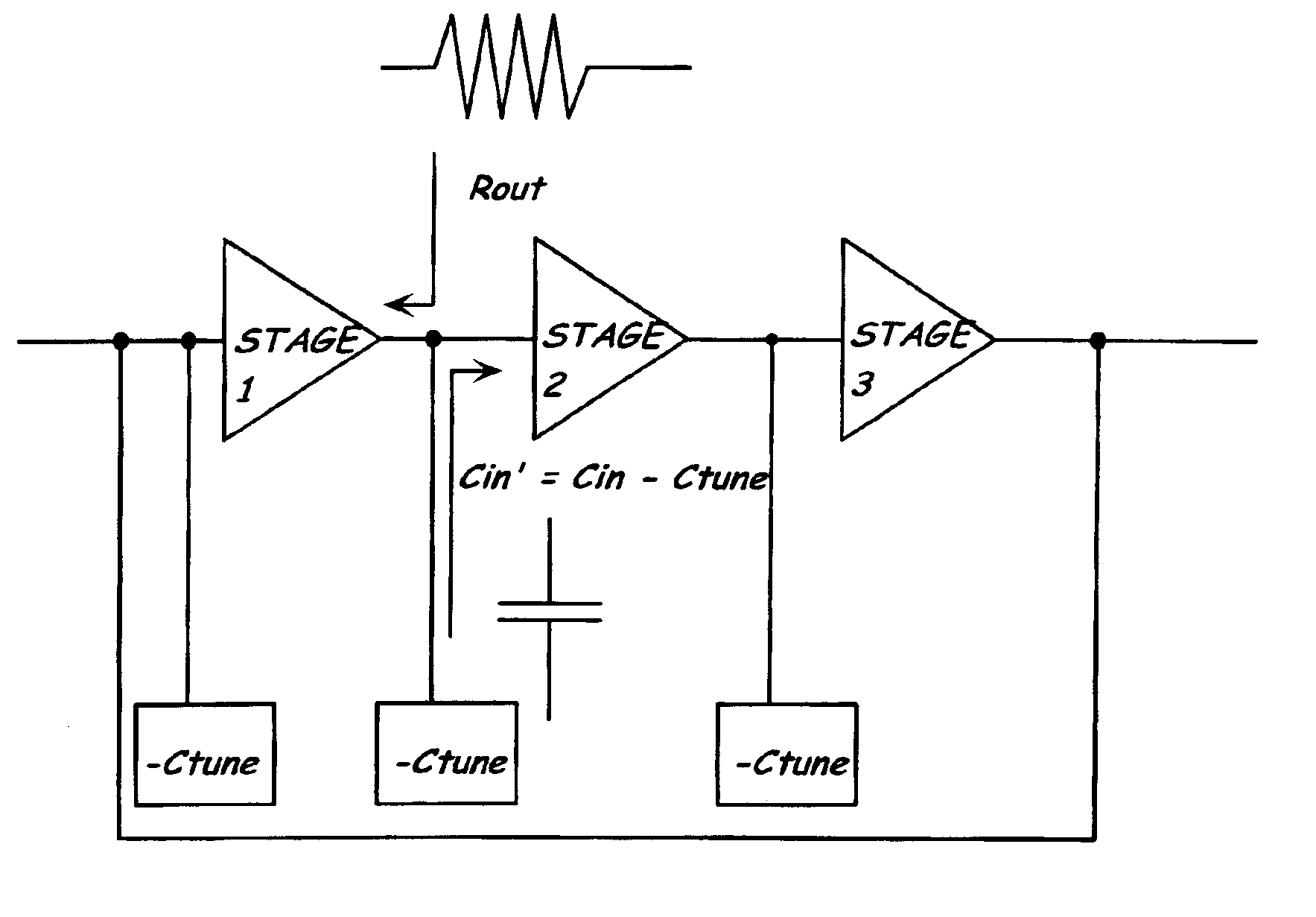

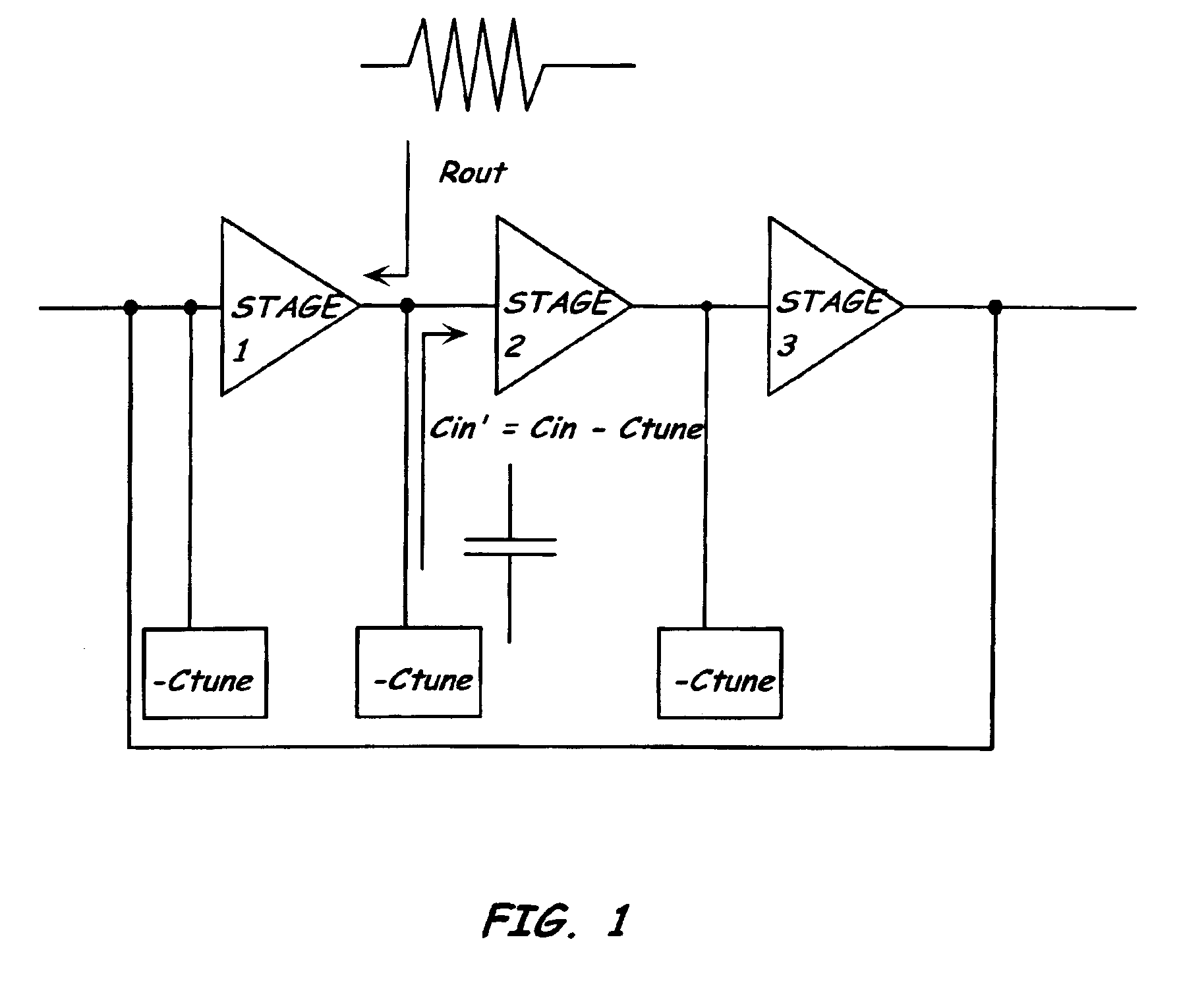

Widely tunable ring oscillator utilizing active negative capacitance

ActiveUS6943633B2Increase the oscillation frequencyNot waste layout areaPulse generation by logic circuitsOscillations generatorsCapacitanceRC oscillator

A ring oscillator that uses active negative capacitance at one or more stages of the ring oscillator to adjust the frequency of oscillation. By using a negative capacitance generator, negative capacitance may be placed in shunt with each stage of the ring, thereby reducing the effective input capacitance. Tuning of the ring oscillation frequency is accomplished without changing the bias point of each stage. The ring oscillation frequency may be increased, rather than reduced as in current approaches.

Owner:AVAGO TECH INT SALES PTE LTD

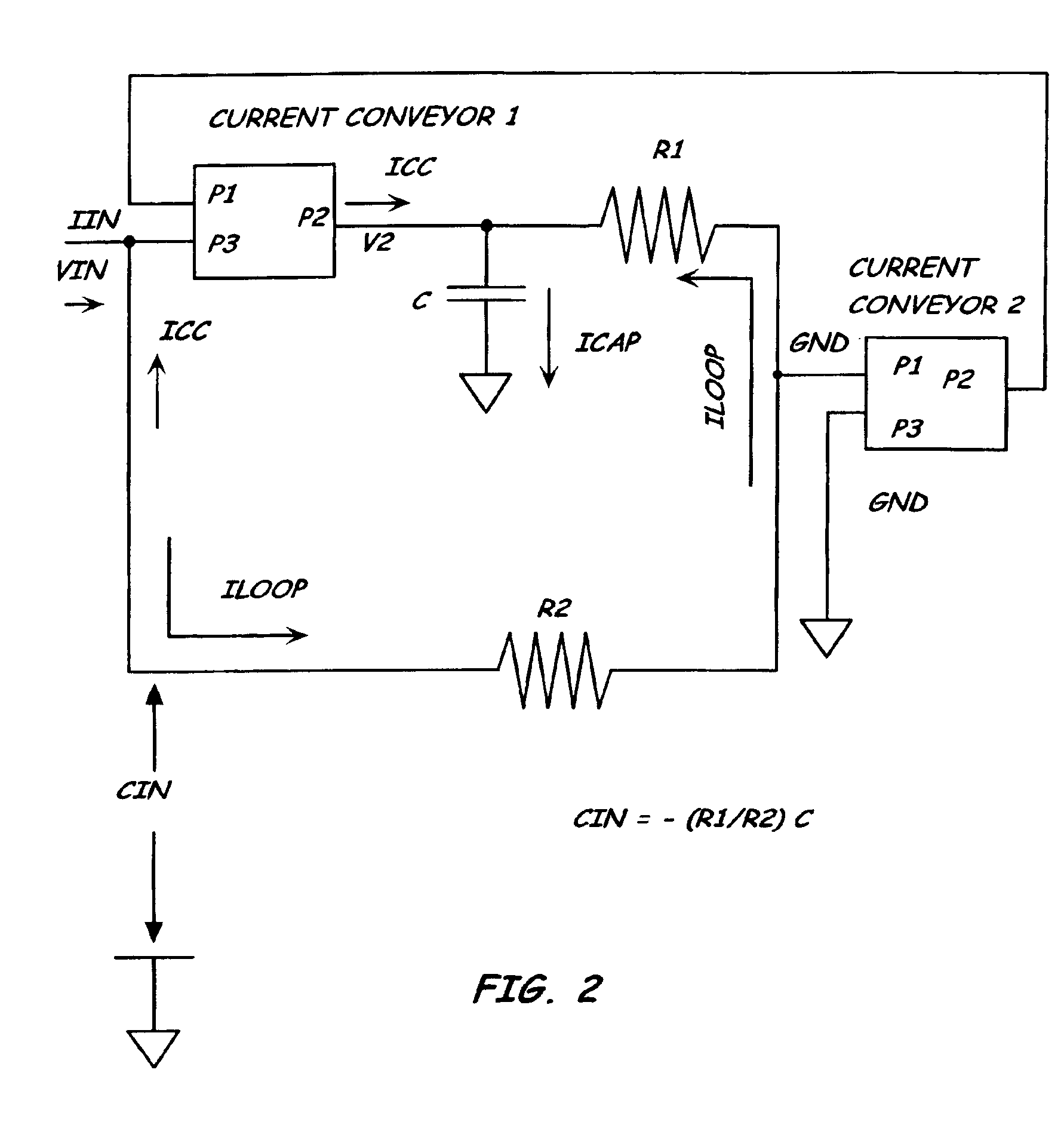

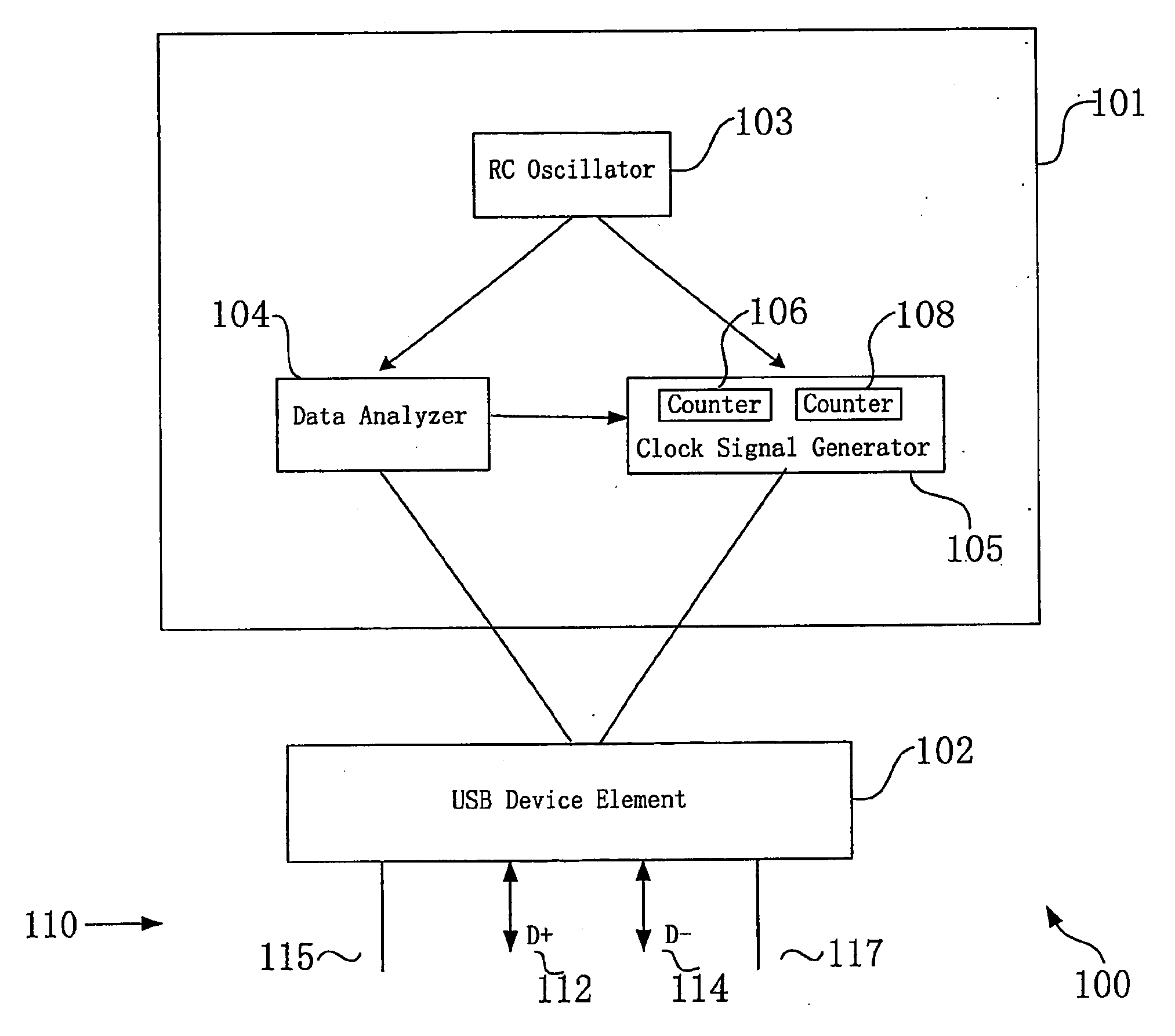

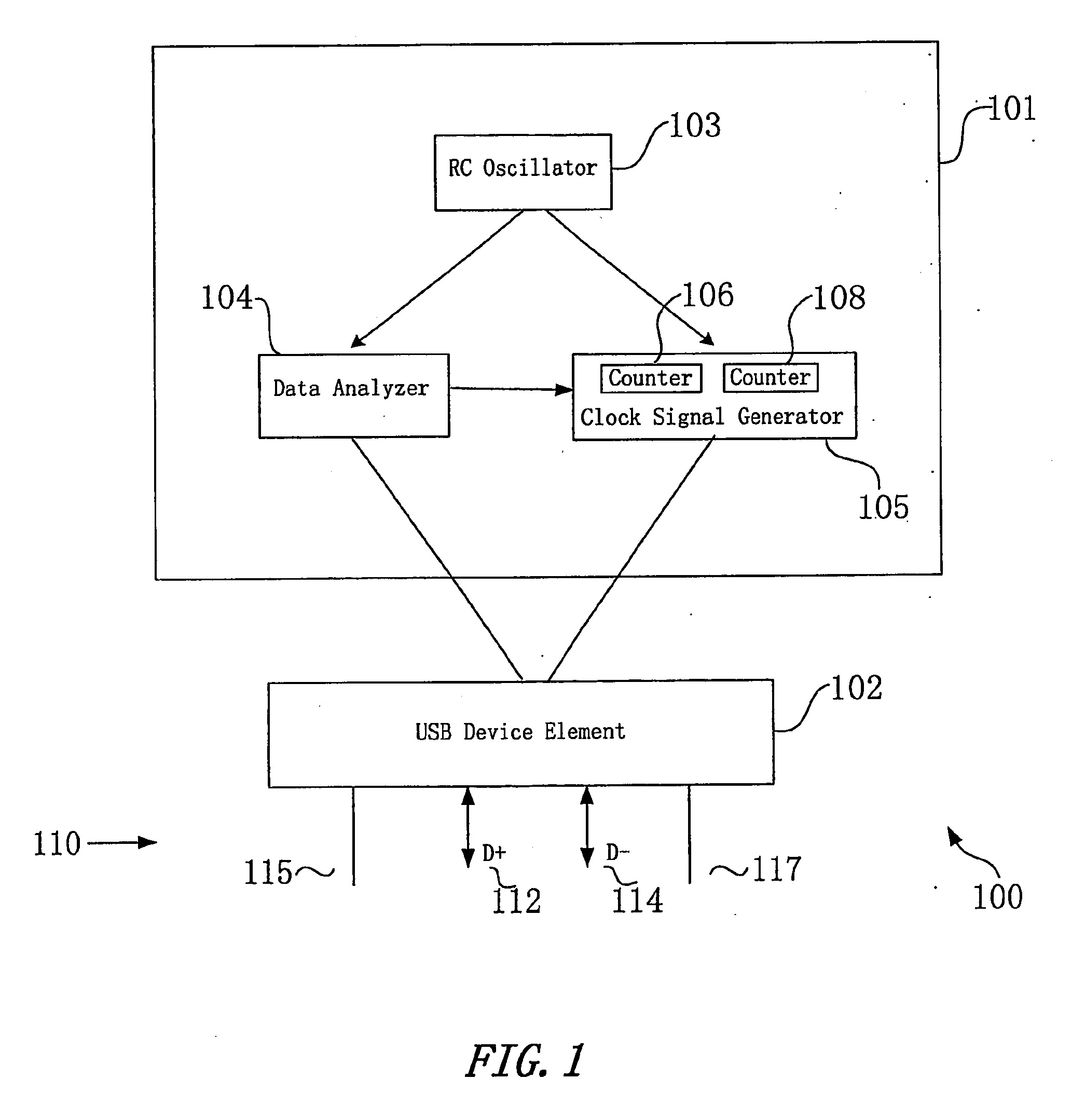

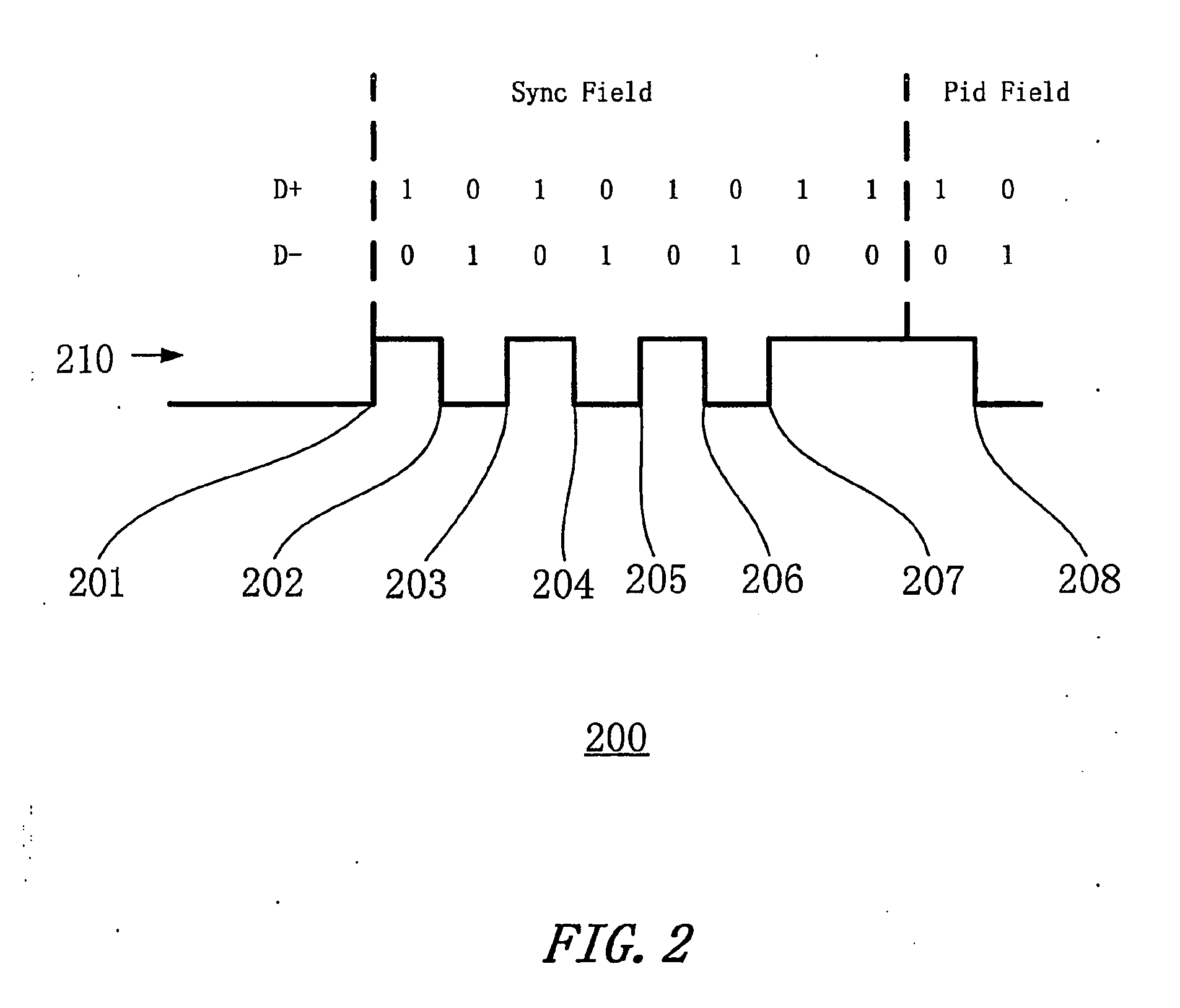

System and method for clock signal synchronization

InactiveUS20070159221A1Small sizeGuaranteed uptimePulse automatic controlGenerating/distributing signalsRC oscillatorDigital control

A system (101) for clock signal synchronization includes a data analyzer (104) and a synchronized clock signal generator (105) coupled to an RC oscillator (103). The data analyzer (104) generates a digital control signal representing the number of cycles of a reference signal of the RC oscillator (103) during an eight-bit period of an incoming token packet. The synchronized signal clock generator (105) uses the digital control signal to lock a clock signal to packets that have the same bit rate as the token packet.

Owner:APEXONE MICROELECTRONICS