Patents

Literature

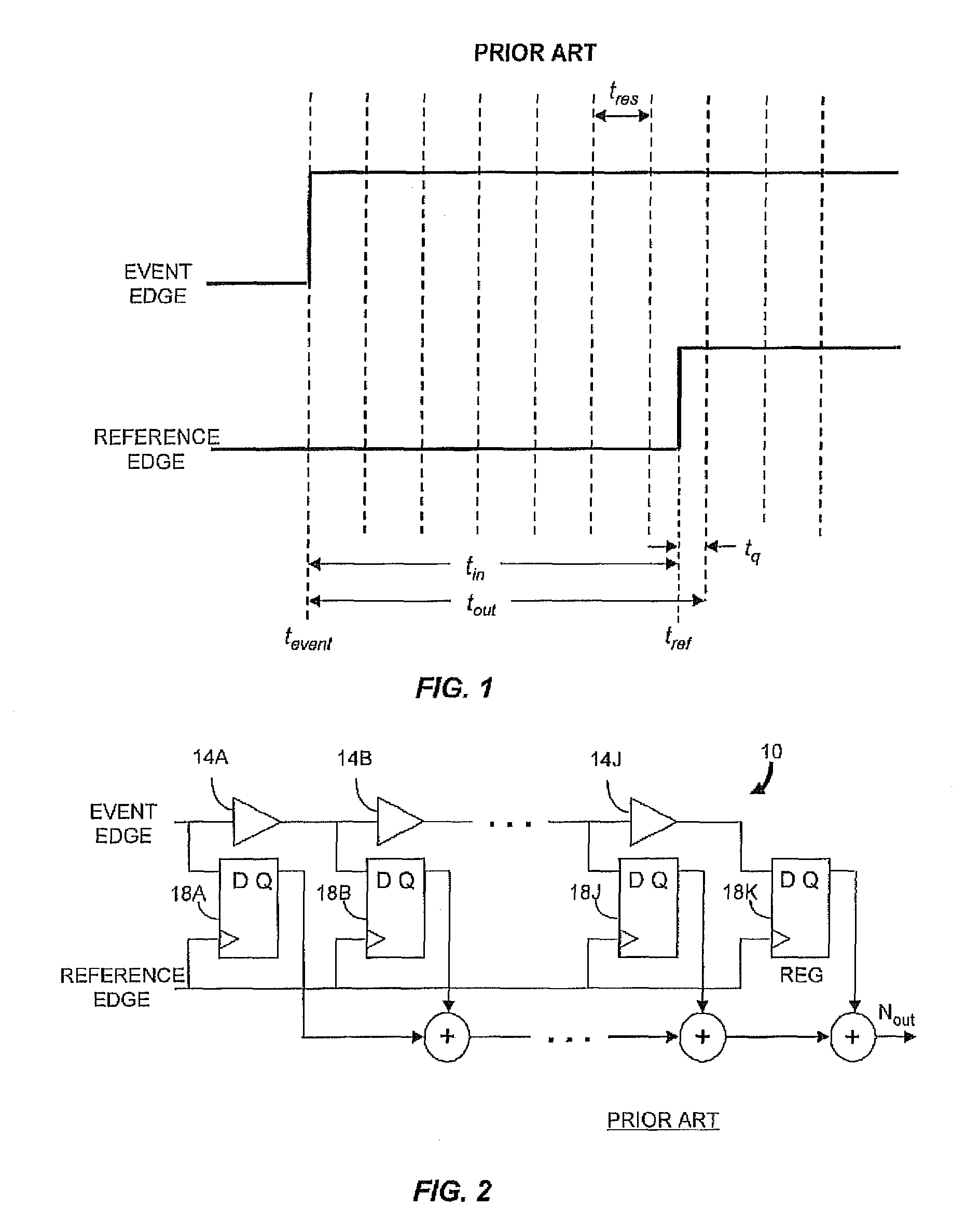

111results about "Continuously circulated pulse counters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

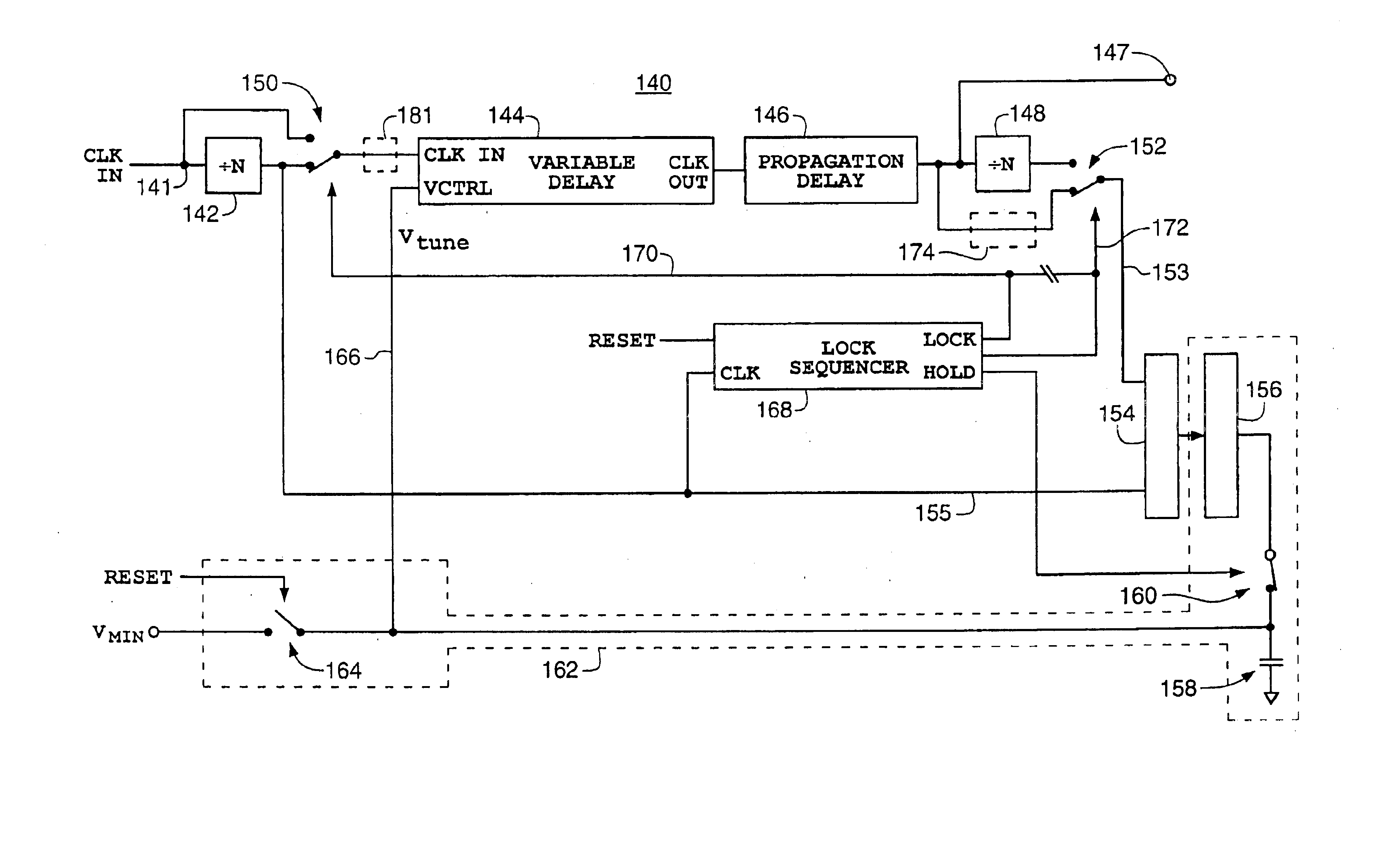

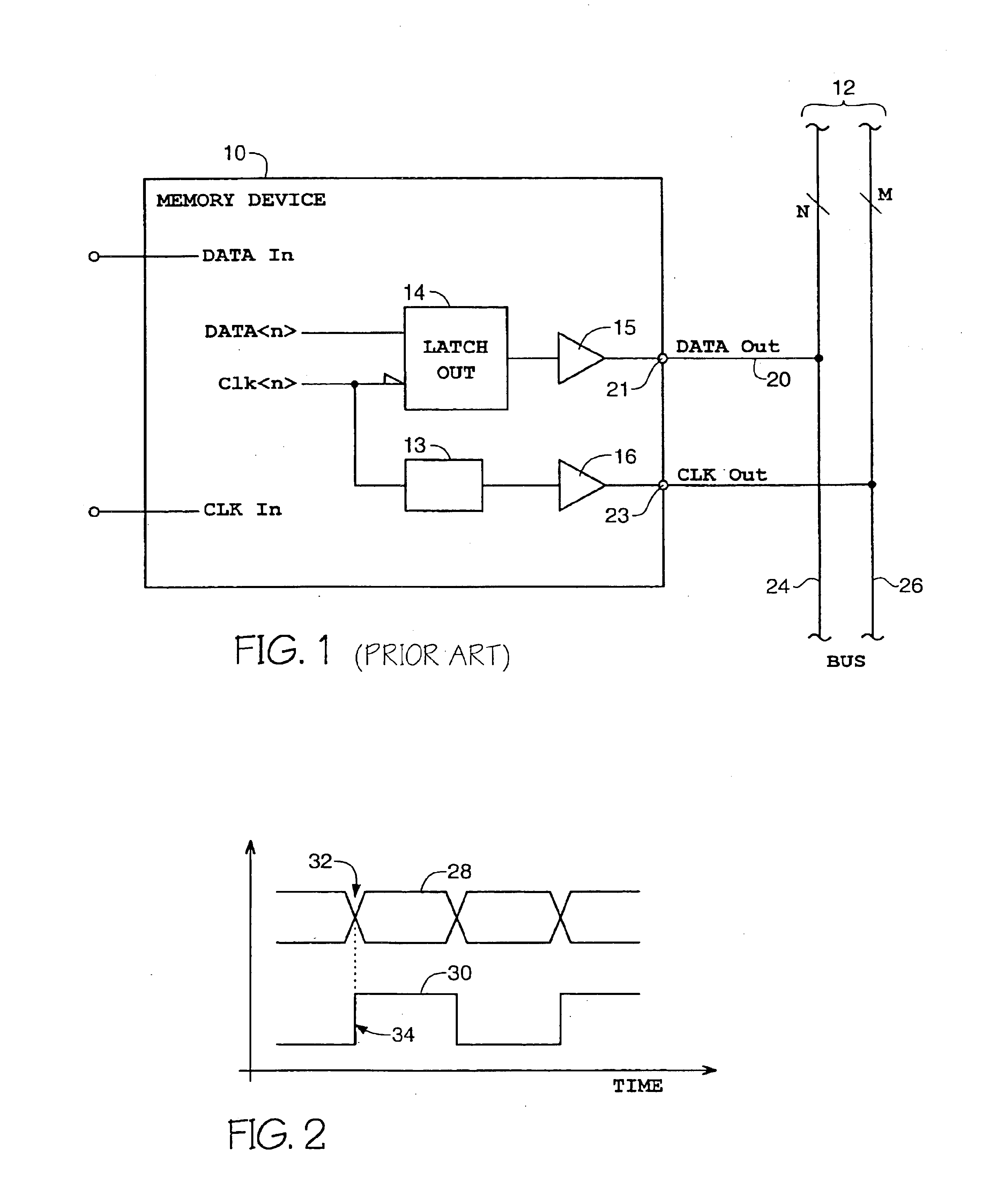

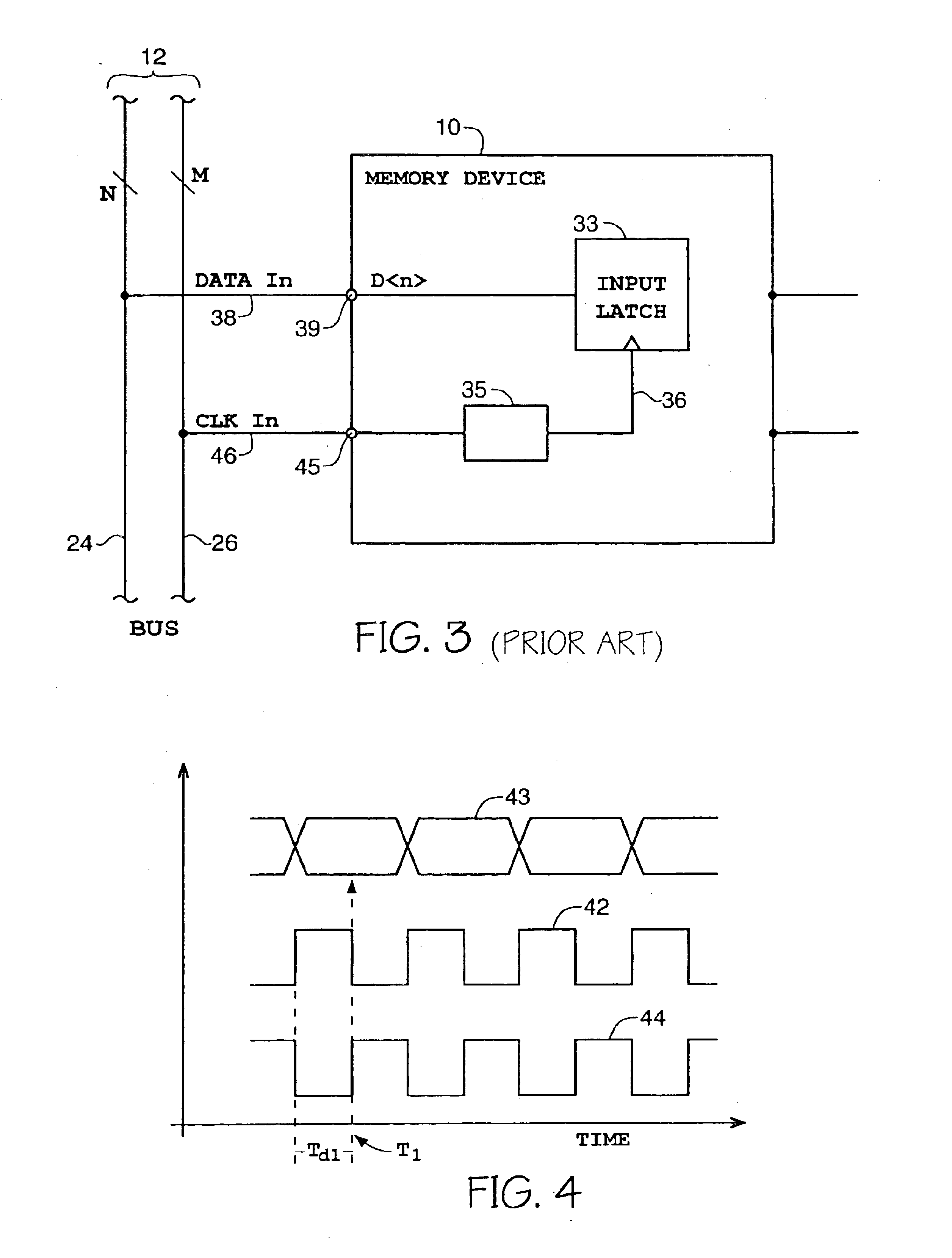

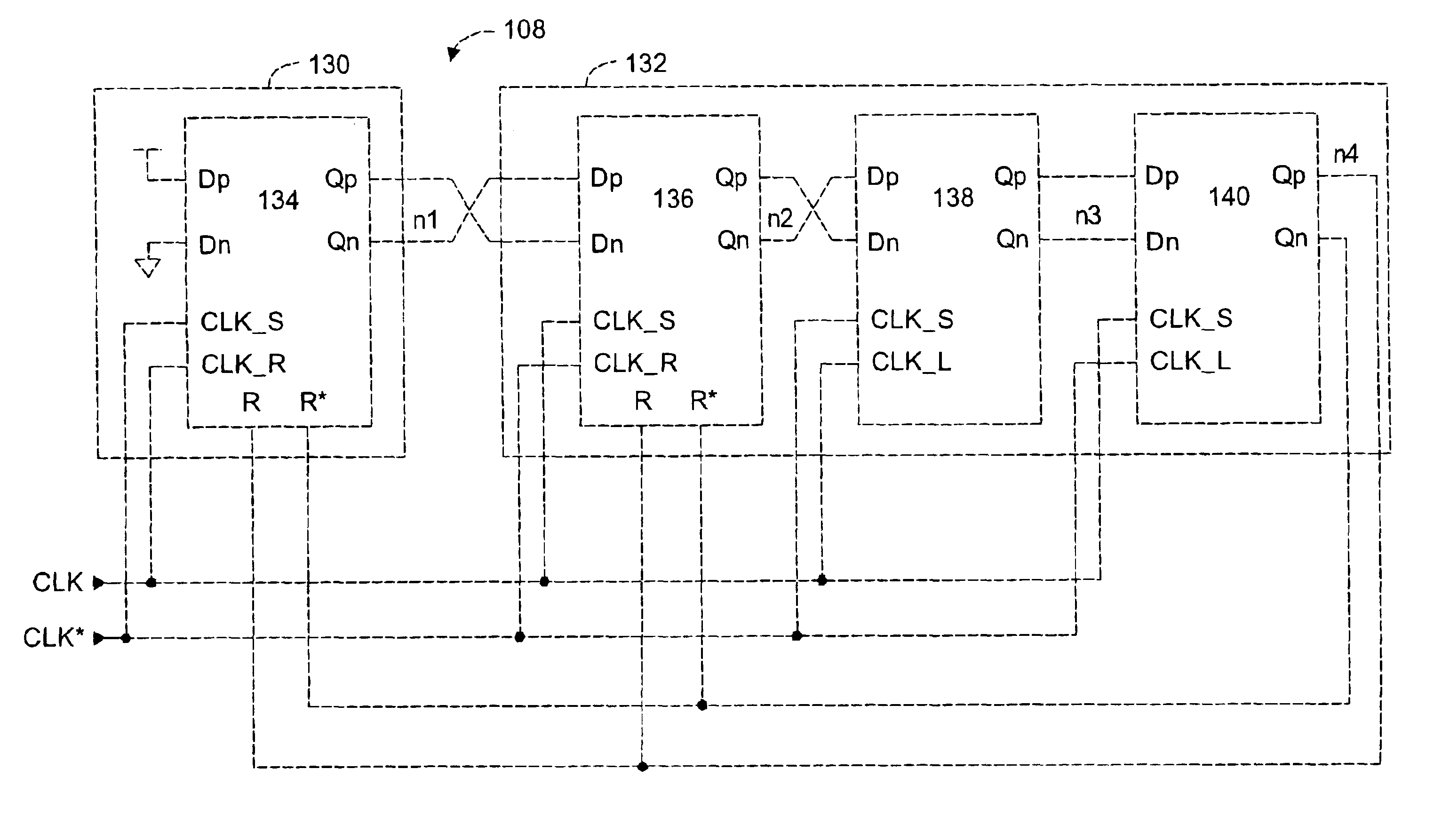

Delay lock loop circuit useful in a synchronous system and associated methods

InactiveUS6842399B2Continuously circulated pulse countersPulse automatic controlPhase detectorControl signal

A method and circuitry for a delay lock loop useful in synchronizing the accessing of a memory array with a system clock is disclosed. In a preferred embodiment, the delay lock loop includes a variable delay element. The delay of the variable delay element is initially set to a minimum delay value. The system clock is then frequency divided and sent to the variable delay element, the output of which will ultimately be used to access the memory array in a synchronized manner with the system clock. The frequency divided clock and the output of the variable delay element are input to a phase detector, which creates a control signal for adjusting the delay of the variable delay element. After the signals are determined to be locked by the phase detector, an undivided clock signal version of the clock signal is sent to the variable delay element, and a frequency divided version of the output of the variable delay element is sent to the phase detector in lieu of the previous output of the variable delay element.

Owner:ROUND ROCK RES LLC

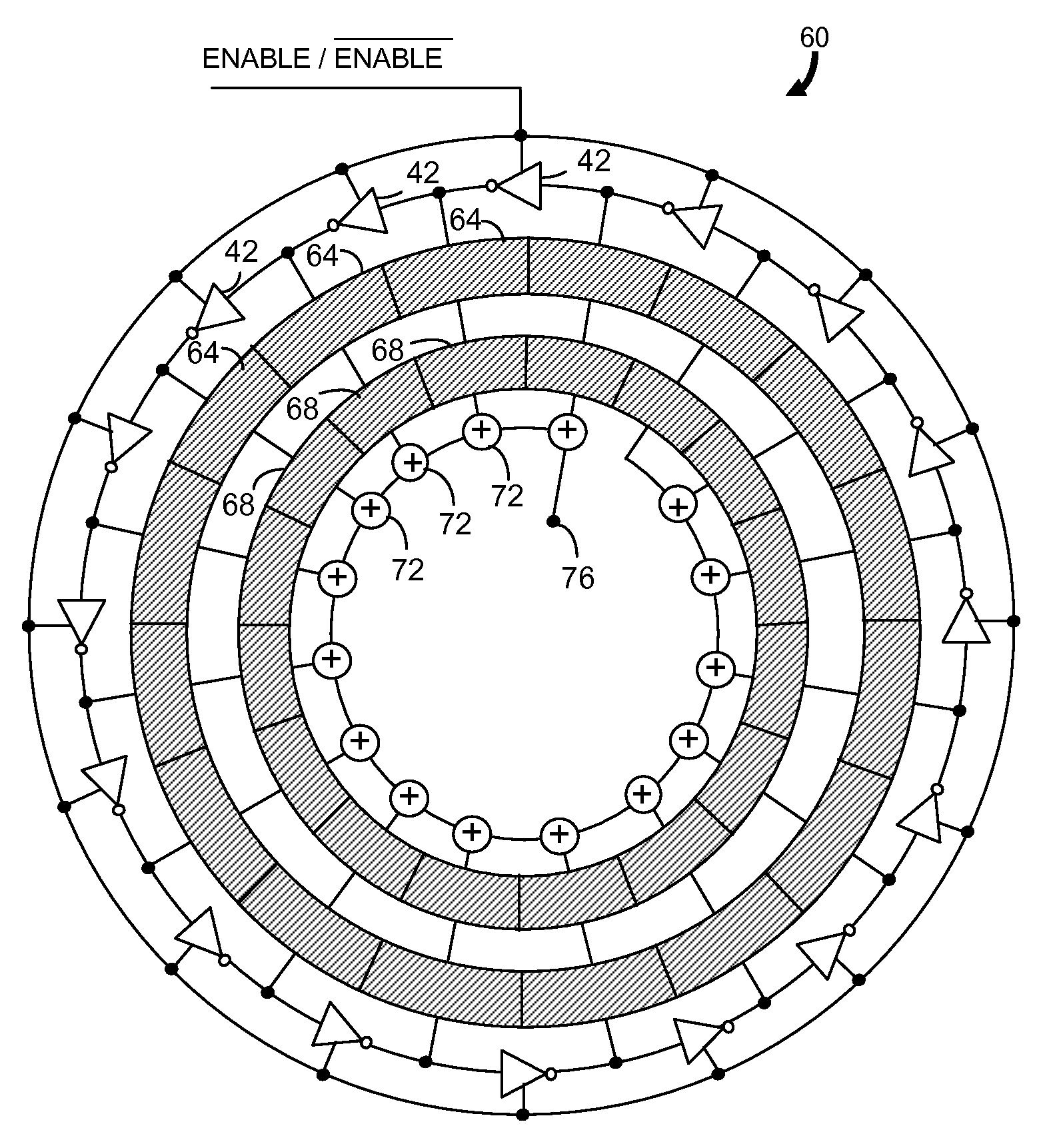

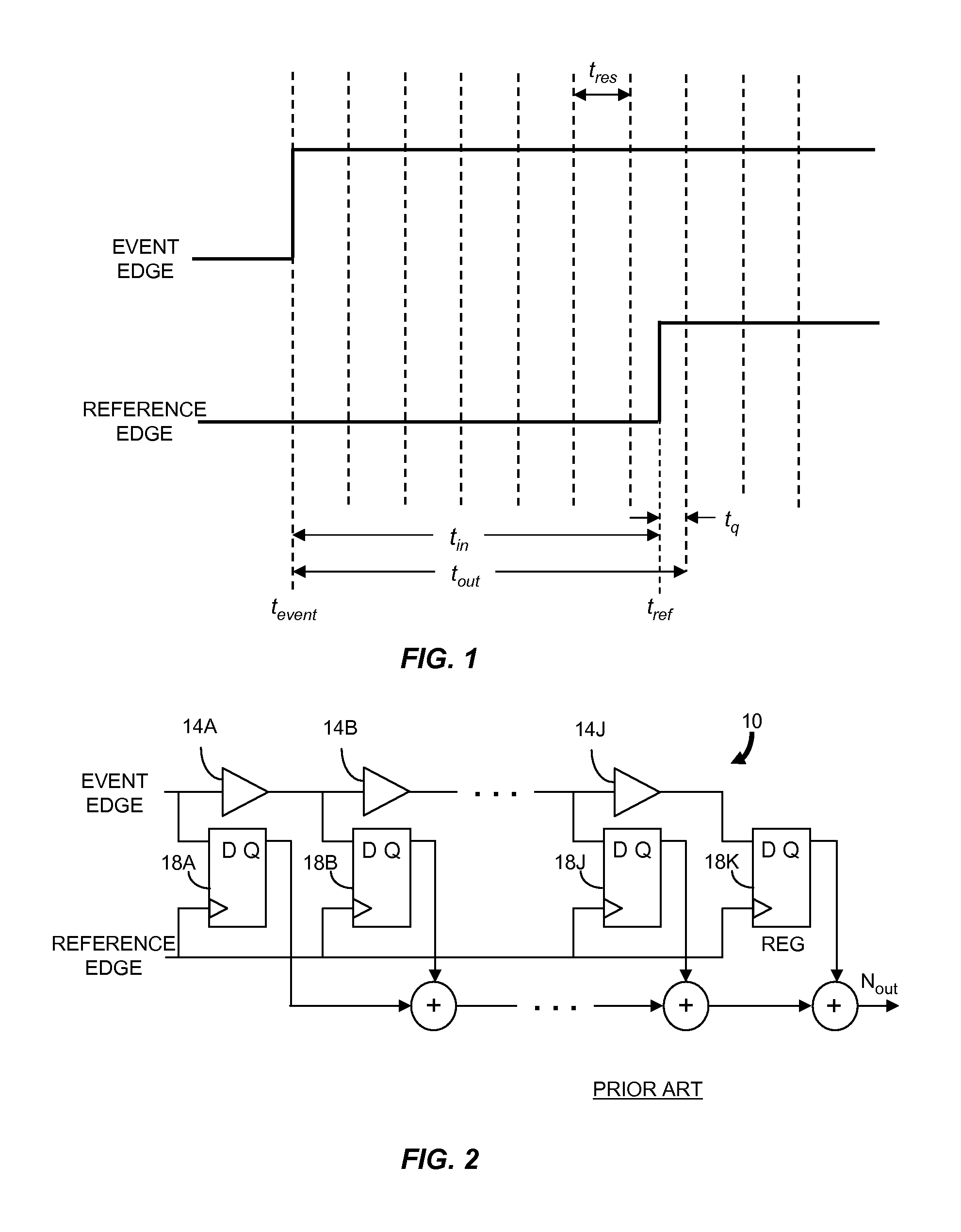

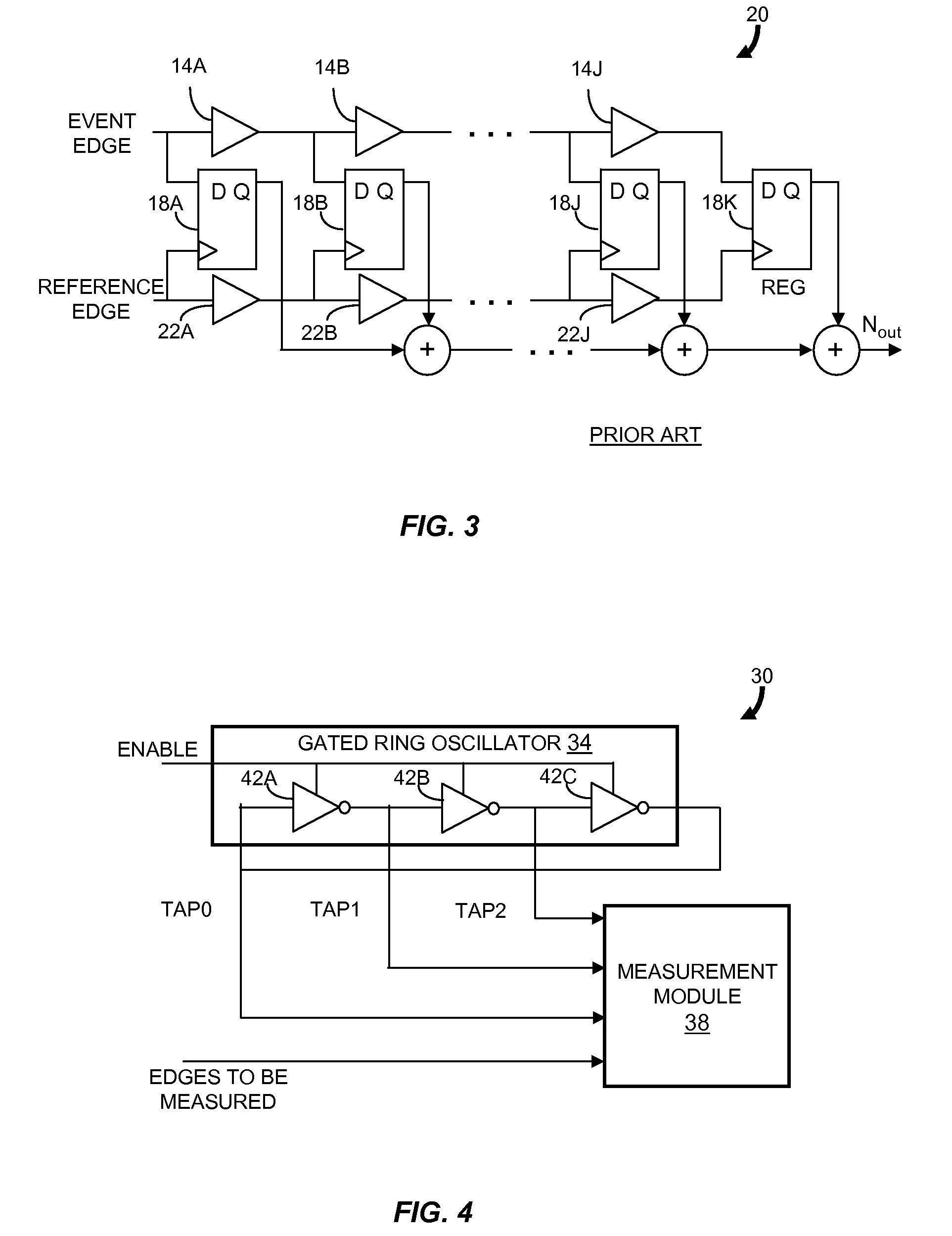

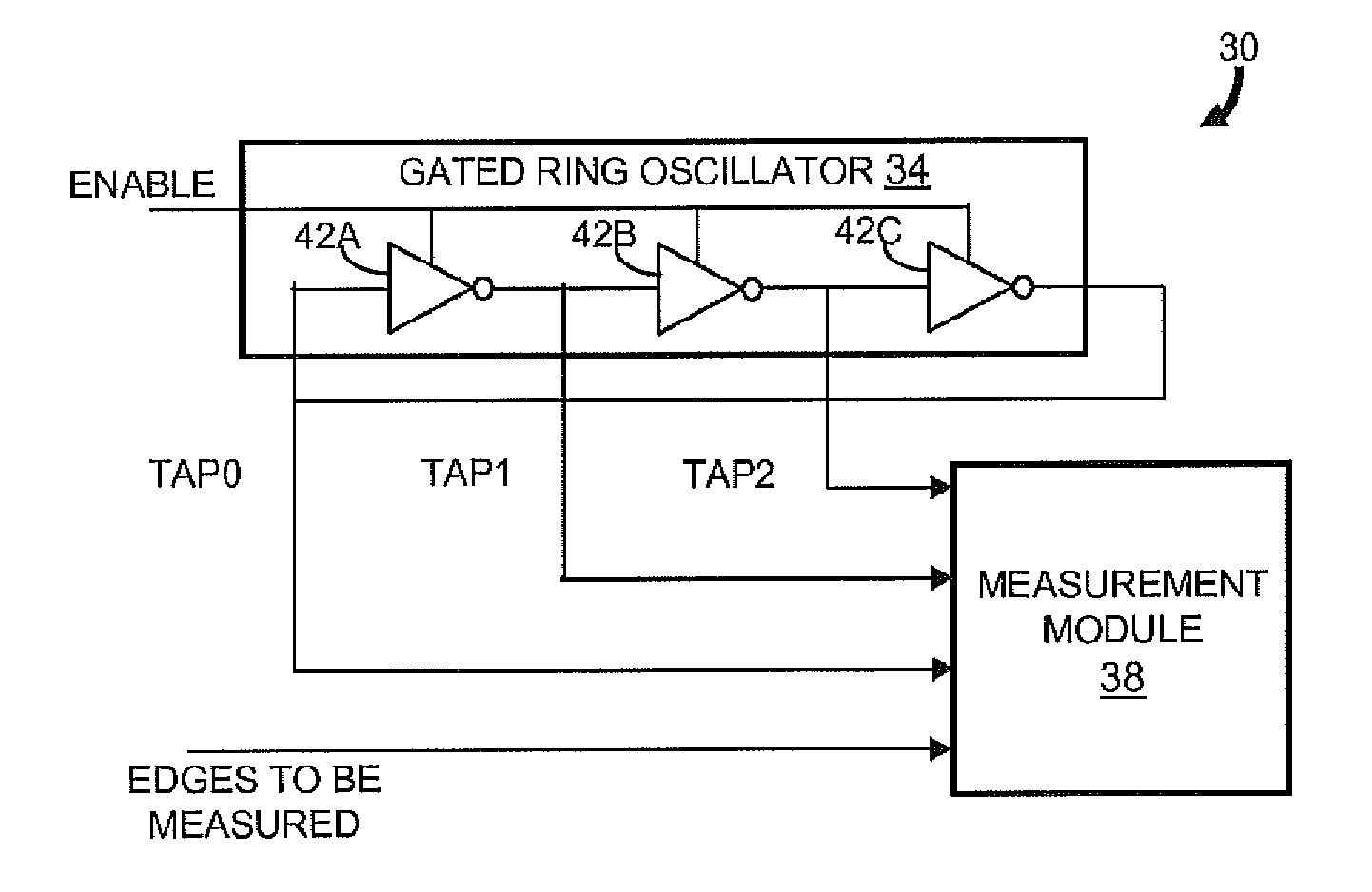

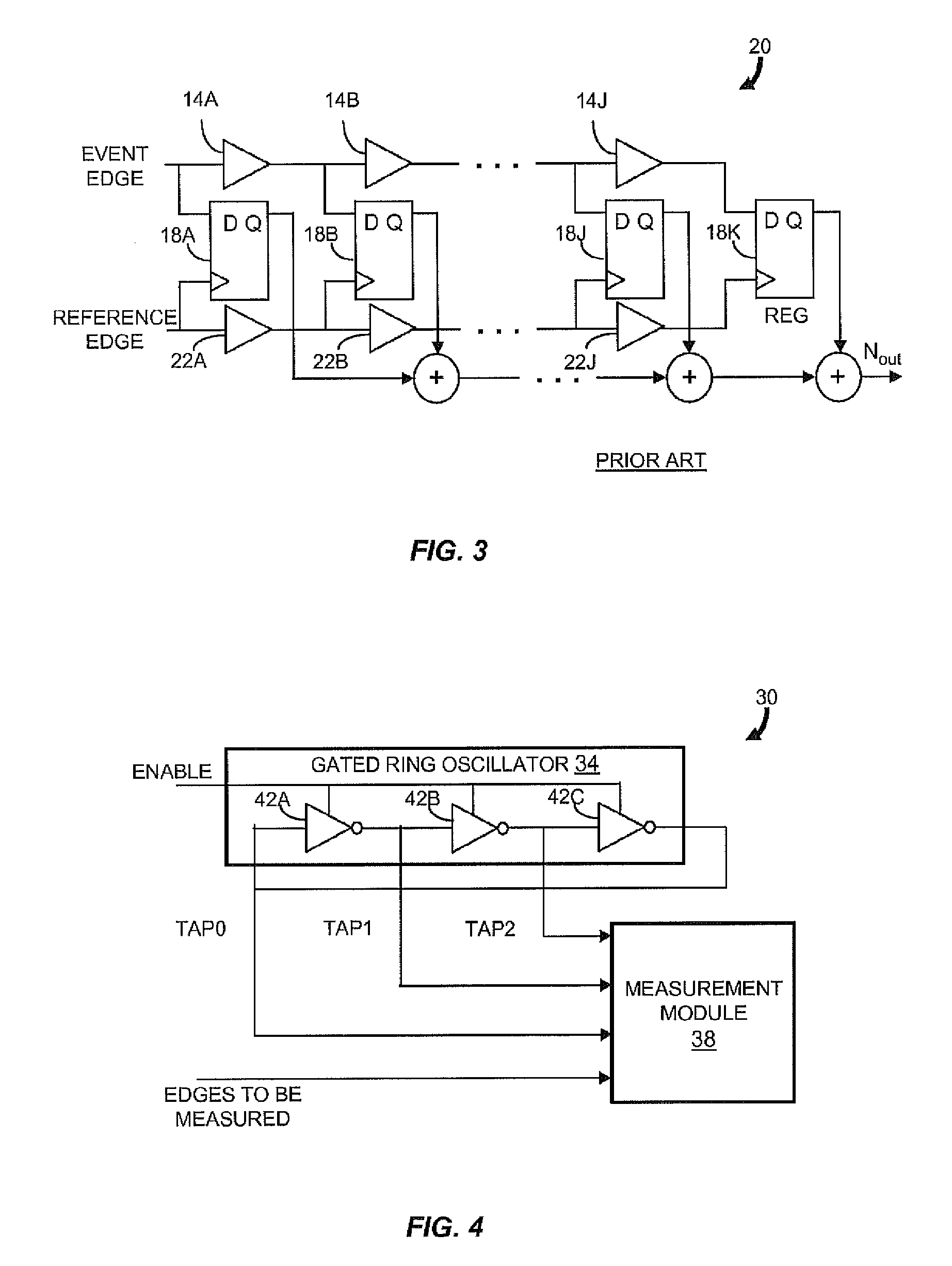

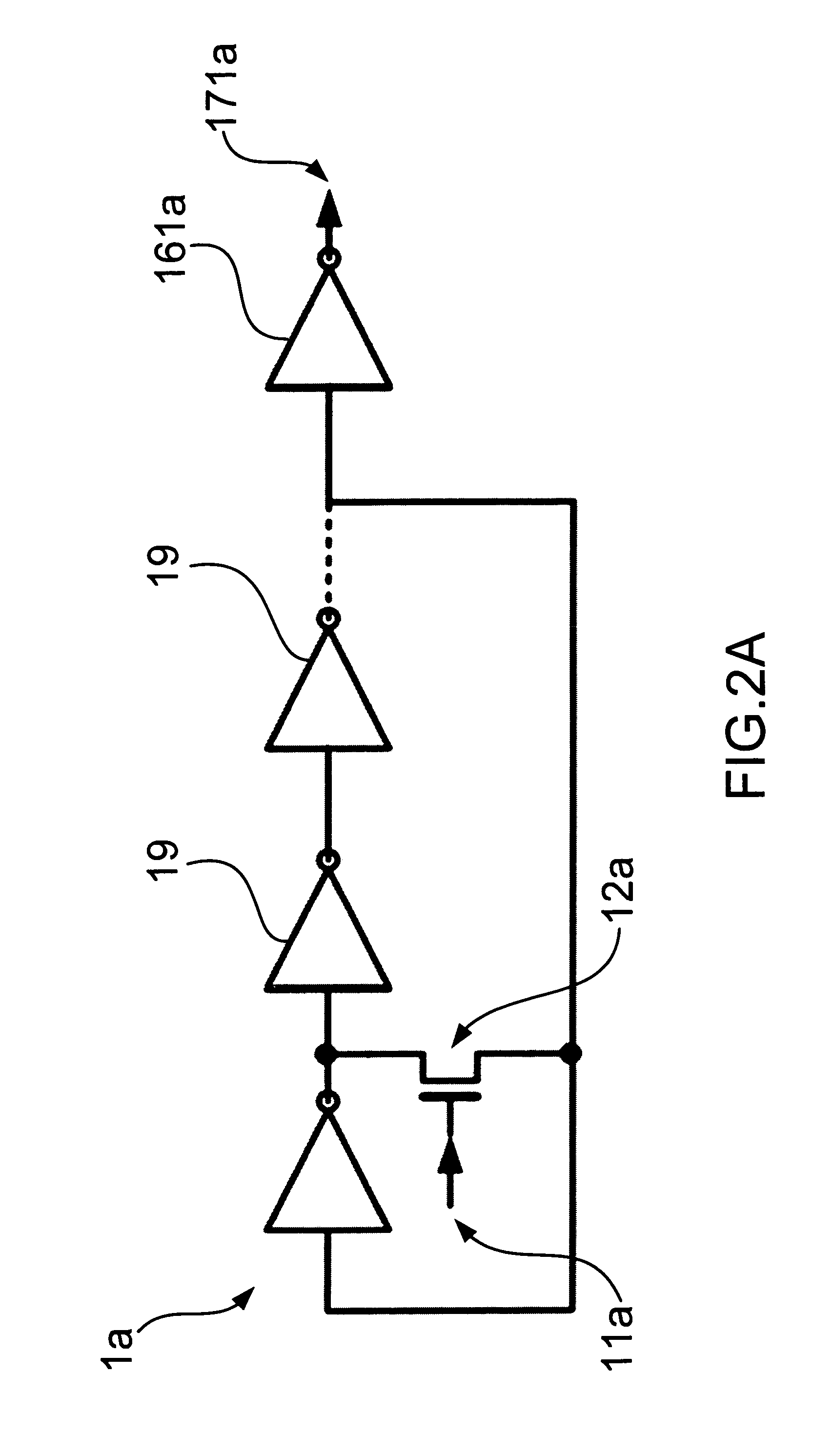

Gated ring oscillator for a time-to-digital converter with shaped quantization noise

ActiveUS20080069292A1Resolution timeContinuously circulated pulse countersCounting chain synchronous pulse countersImage resolutionNoise shaping

Described is a compact, lower power gated ring oscillator time-to-digital converter that achieves first order noise shaping of quantization noise using a digital implementation. The gated ring oscillator time-to-digital converter includes a plurality of delay stages configured to enable propagation of a transitioning signal through the delay stages during an enabled state and configured to inhibit propagation of the transitioning signal through the delay stages during a disabled state. Delay stages are interconnected to allow sustained transitions to propagate through the delay stages during the enabled state and to preserve a state of the gated ring oscillator time-to-digital converter during the disabled state. The state represents a time resolution that is finer than the delay of at least one of the delay stages. A measurement module determines the number of transitions of the delay stages.

Owner:MASSACHUSETTS INST OF TECH

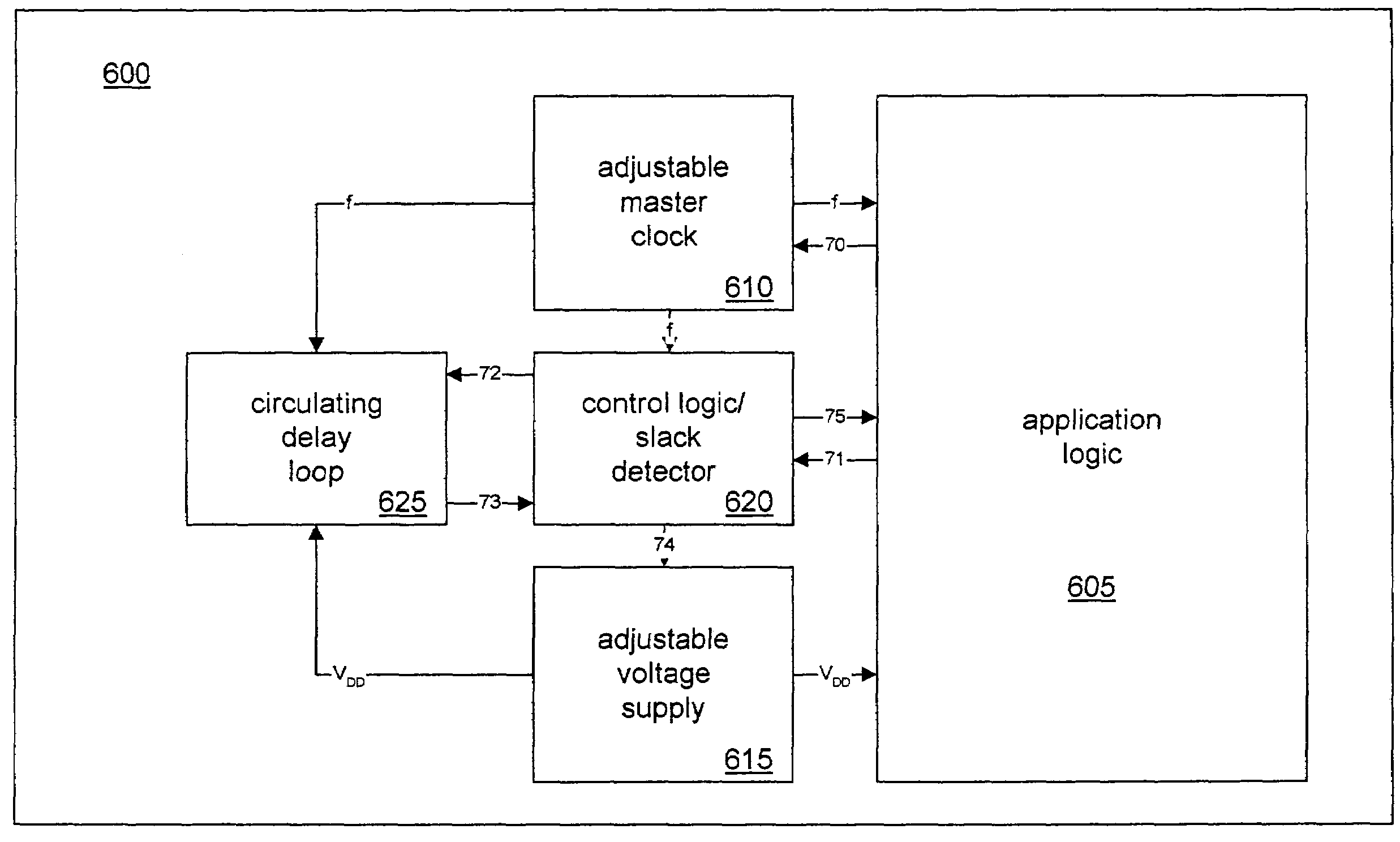

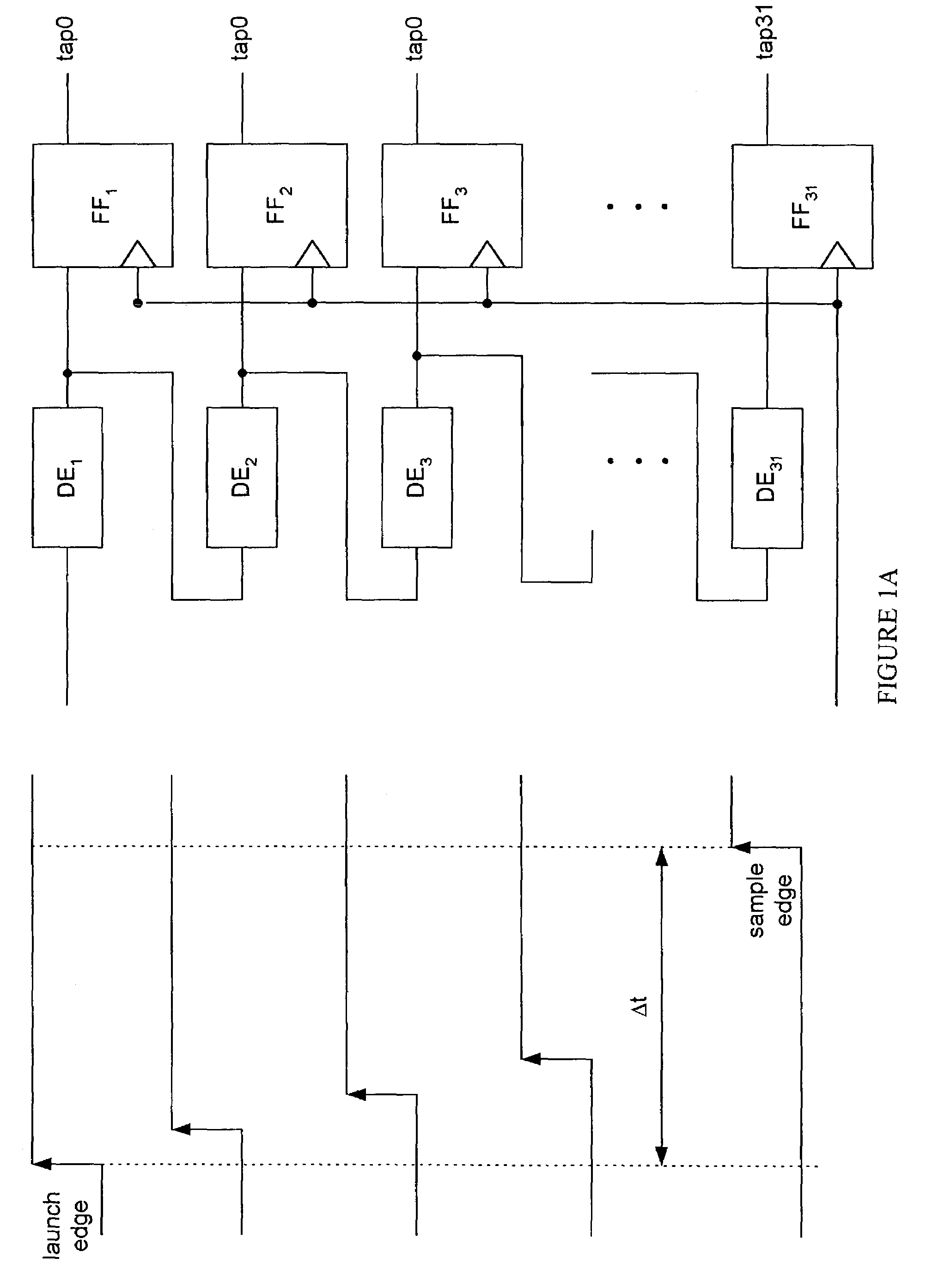

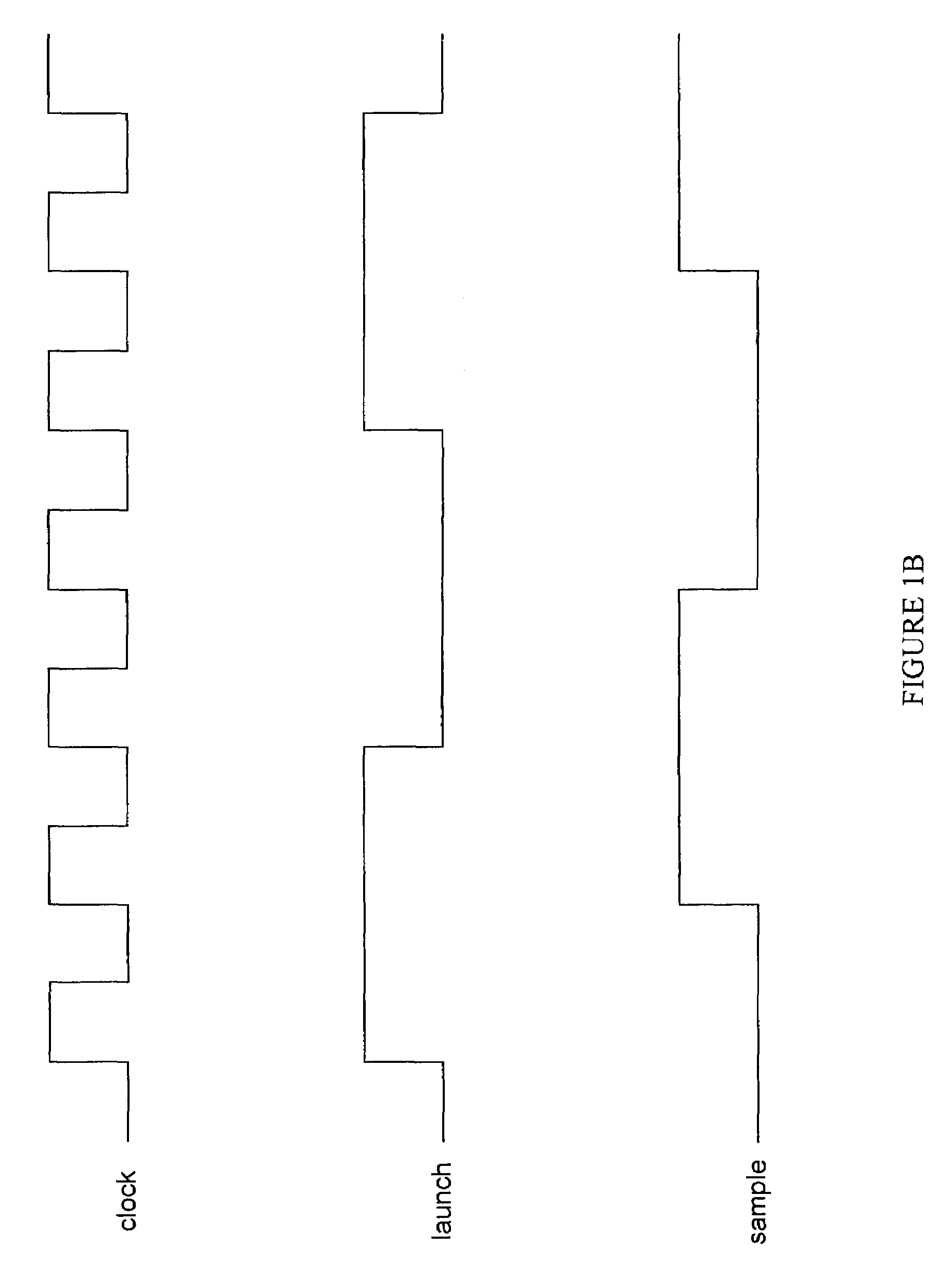

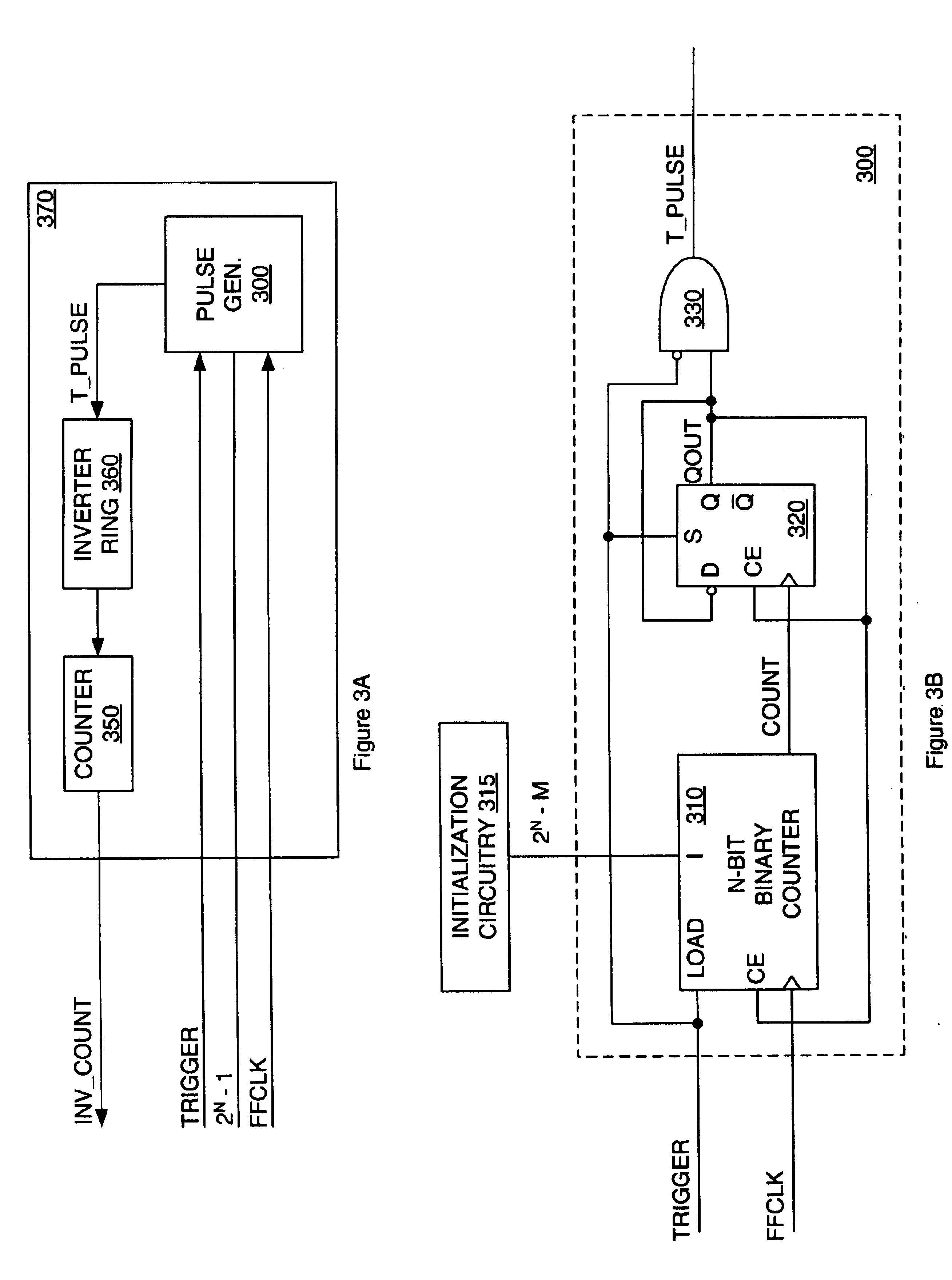

System and method for signal delay in an adaptive voltage scaling slack detector

ActiveUS7149903B1Easy maintenanceContinuously circulated pulse countersVolume/mass flow measurementLeading edgeSelf adaptive

A system and method for slack determination in a logic integrated circuit. A launch pulse is input to a circular delay loop circuit. The leading edge of the launch pulse causes a pulse to circulate around the circular delay loop. The number of passes made through the loop by the circulating pulse is counted by a latch / counter circuit. A sample pulse is input to the latch / counter circuit to latch the number of pulse circulations at the leading edge of the sample pulse. The pulse circulation count provides delay information in the circuit that may subsequently be used to adjust a supply voltage in the integrated circuit.

Owner:NAT SEMICON CORP

Gated ring oscillator for a time-to-digital converter with shaped quantization noise

ActiveUS8138843B2Continuously circulated pulse countersCounting chain synchronous pulse countersDigital down converterImage resolution

Described is a compact, lower power gated ring oscillator time-to-digital converter that achieves first order noise shaping of quantization noise using a digital implementation. The gated ring oscillator time-to-digital converter includes a plurality of delay stages configured to enable propagation of a transitioning signal through the delay stages during an enabled state and configured to inhibit propagation of the transitioning signal through the delay stages during a disabled state. Delay stages are interconnected to allow sustained transitions to propagate through the delay stages during the enabled state and to preserve a state of the gated ring oscillator time-to-digital converter during the disabled state. The state represents a time resolution that is finer than the delay of at least one of the delay stages. A measurement module determines the number of transitions of the delay stages.

Owner:MASSACHUSETTS INST OF TECH

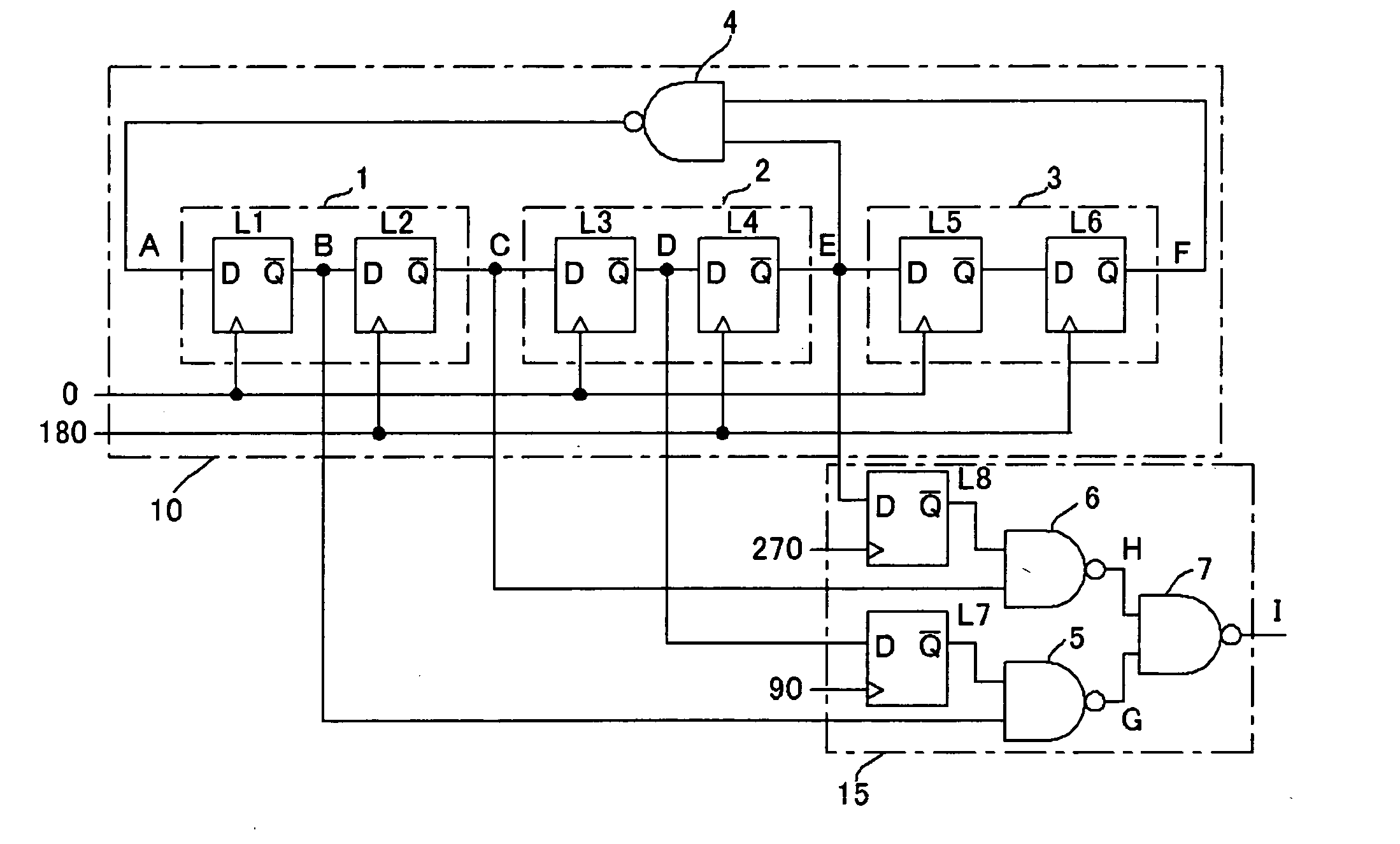

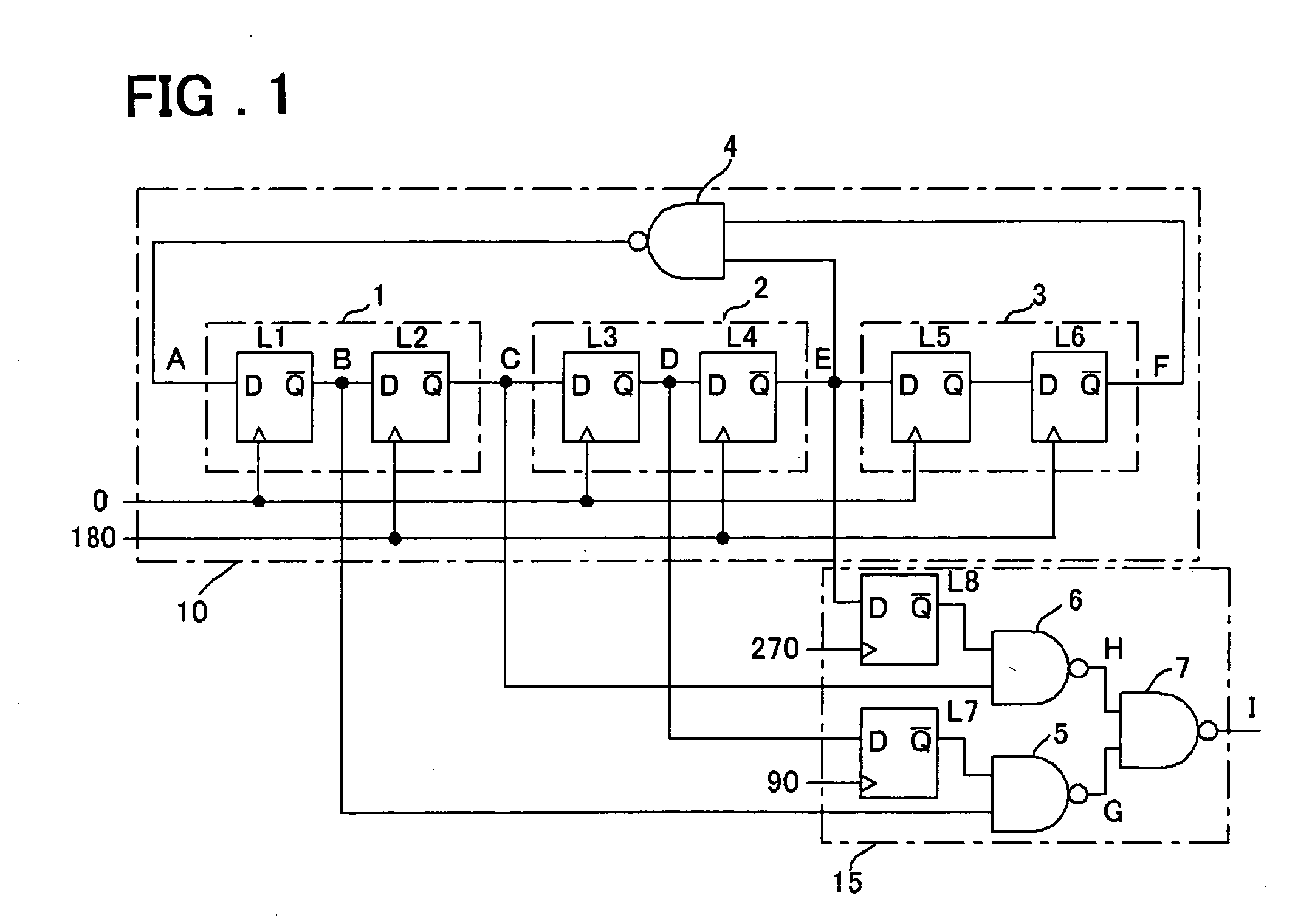

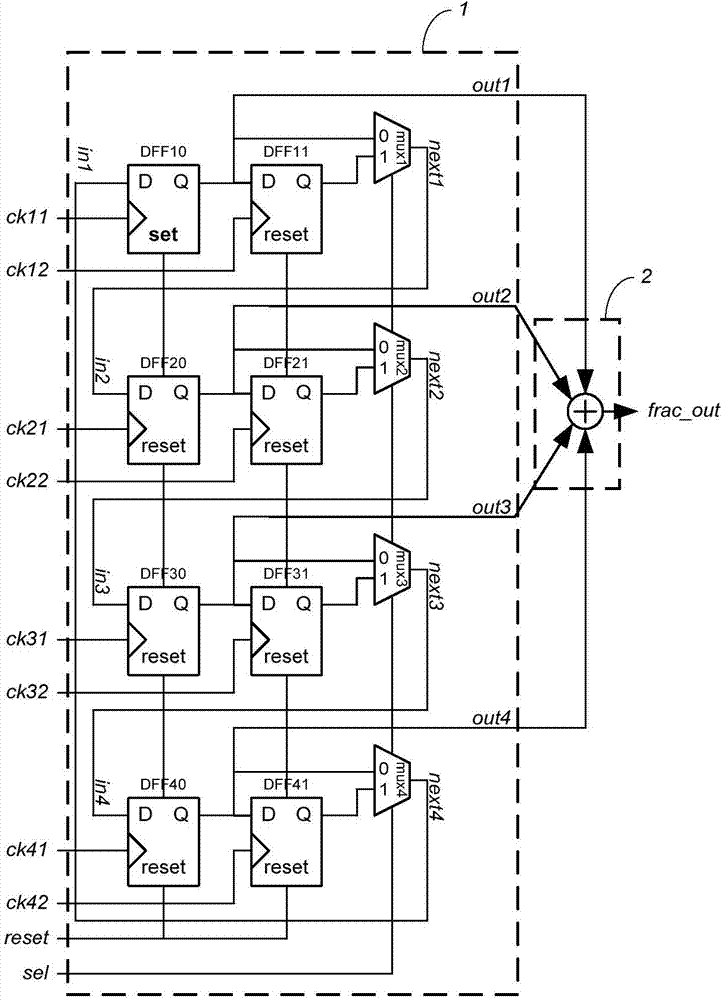

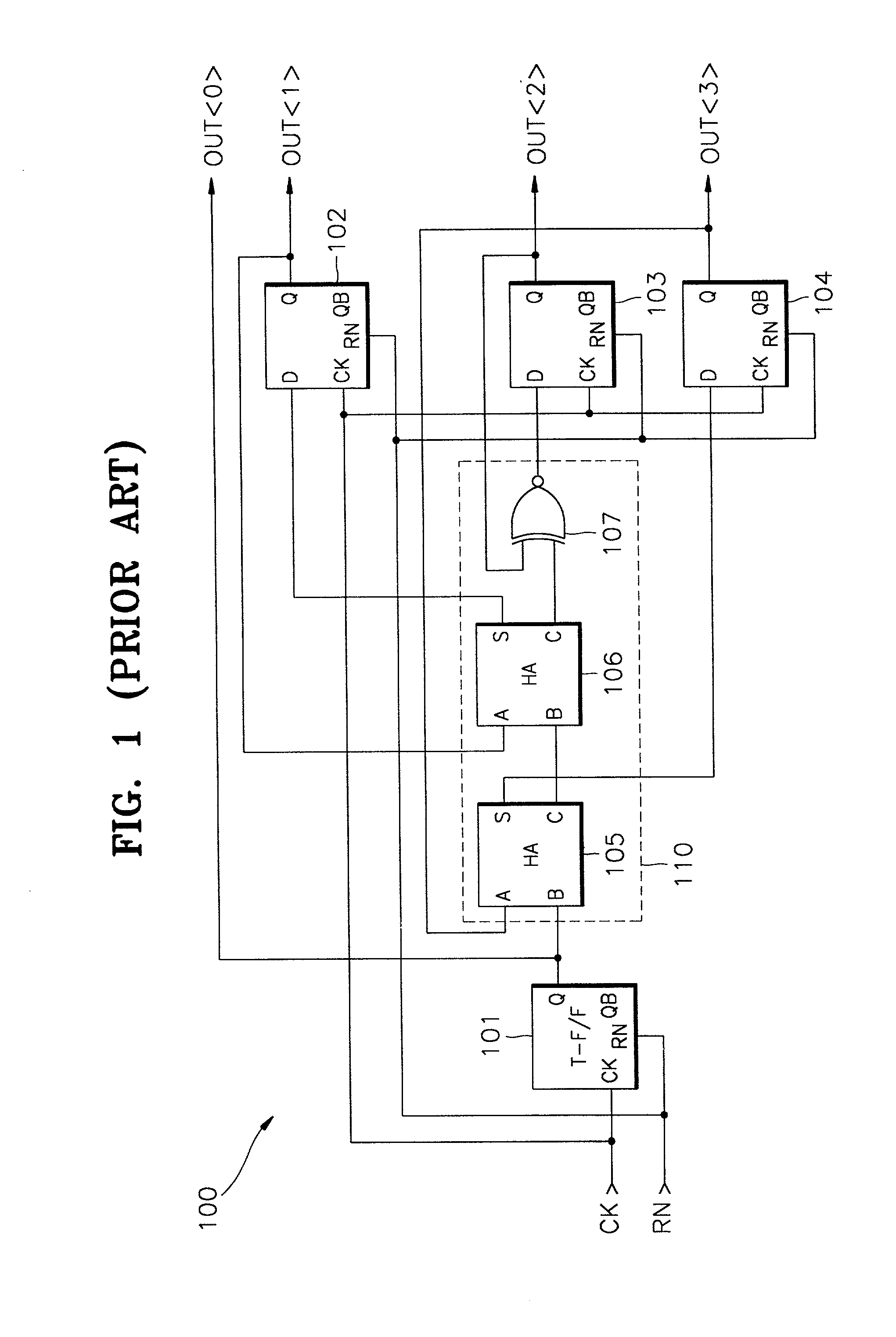

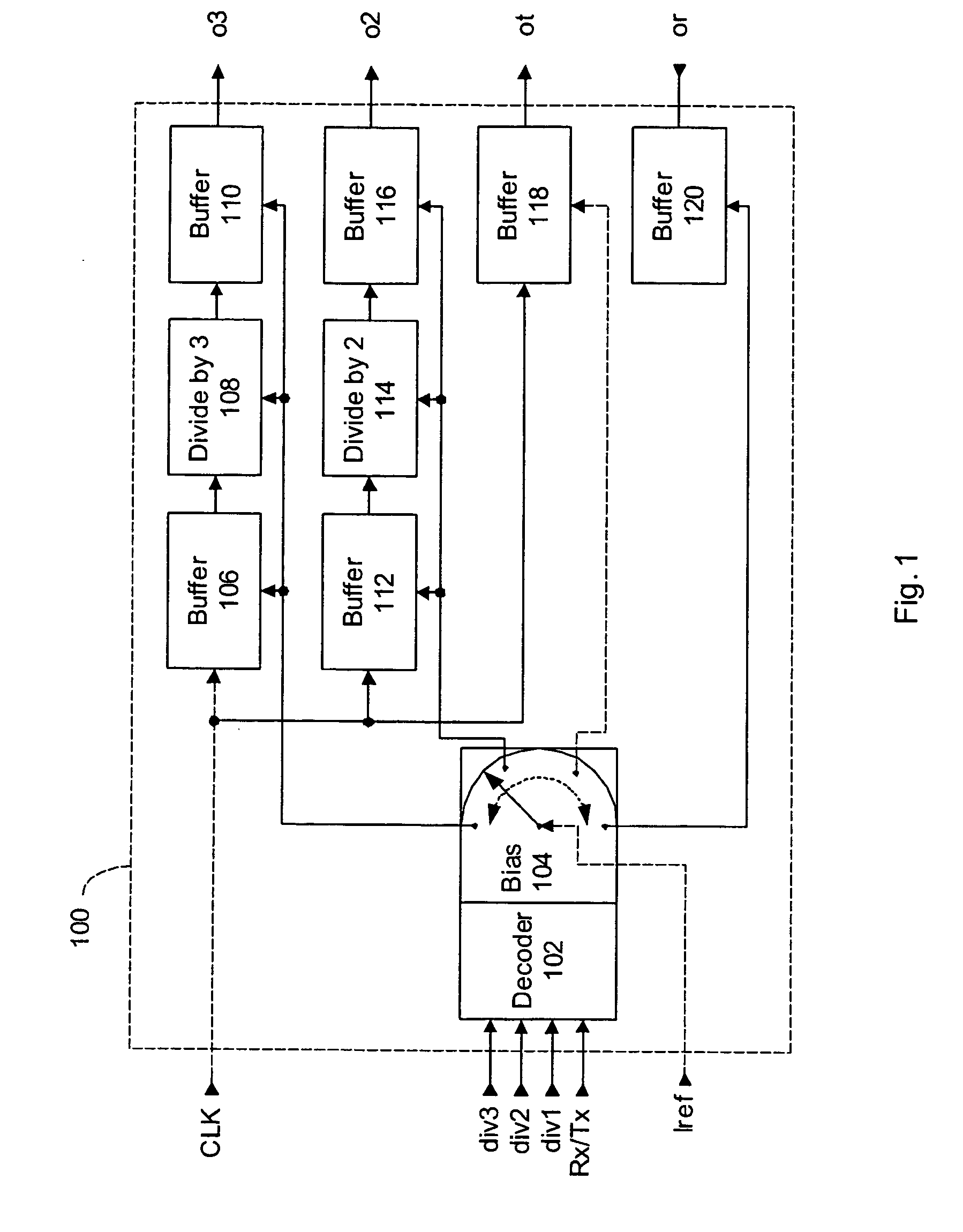

Fractional frequency divider circuit and data transmission apparatus using the same

InactiveUS20050174153A1Small sizeReduce power consumptionContinuously circulated pulse countersPulse automatic controlEngineeringData transmission

A fractional frequency divider circuit with a small circuit scale that outputs a clock with a duty ratio of 50%, and a data transmission apparatus comprising same. The fractional frequency divider circuit is constituted by multiple master-slave flip-flops, and comprises an integer frequency divider circuit that frequency-divides a clock signal with a frequency-division ratio of 1 / N(N is an integer), and a logic circuit into which multiple signals outputted from master stages and slave stages of the master-slave flip-flops are inputted and that outputs a signal with a duty ratio of 50% obtained by frequency-dividing the clock signal with a frequency-division ratio of 2 / N. The data transmission apparatus is constituted such that it is possible to switch over between a frequency-multiplied clock outputted by a PLL and a clock obtained by frequency-dividing the frequency-multiplied clock with the fractional frequency divider circuit for each channel.

Owner:RENESAS ELECTRONICS CORP

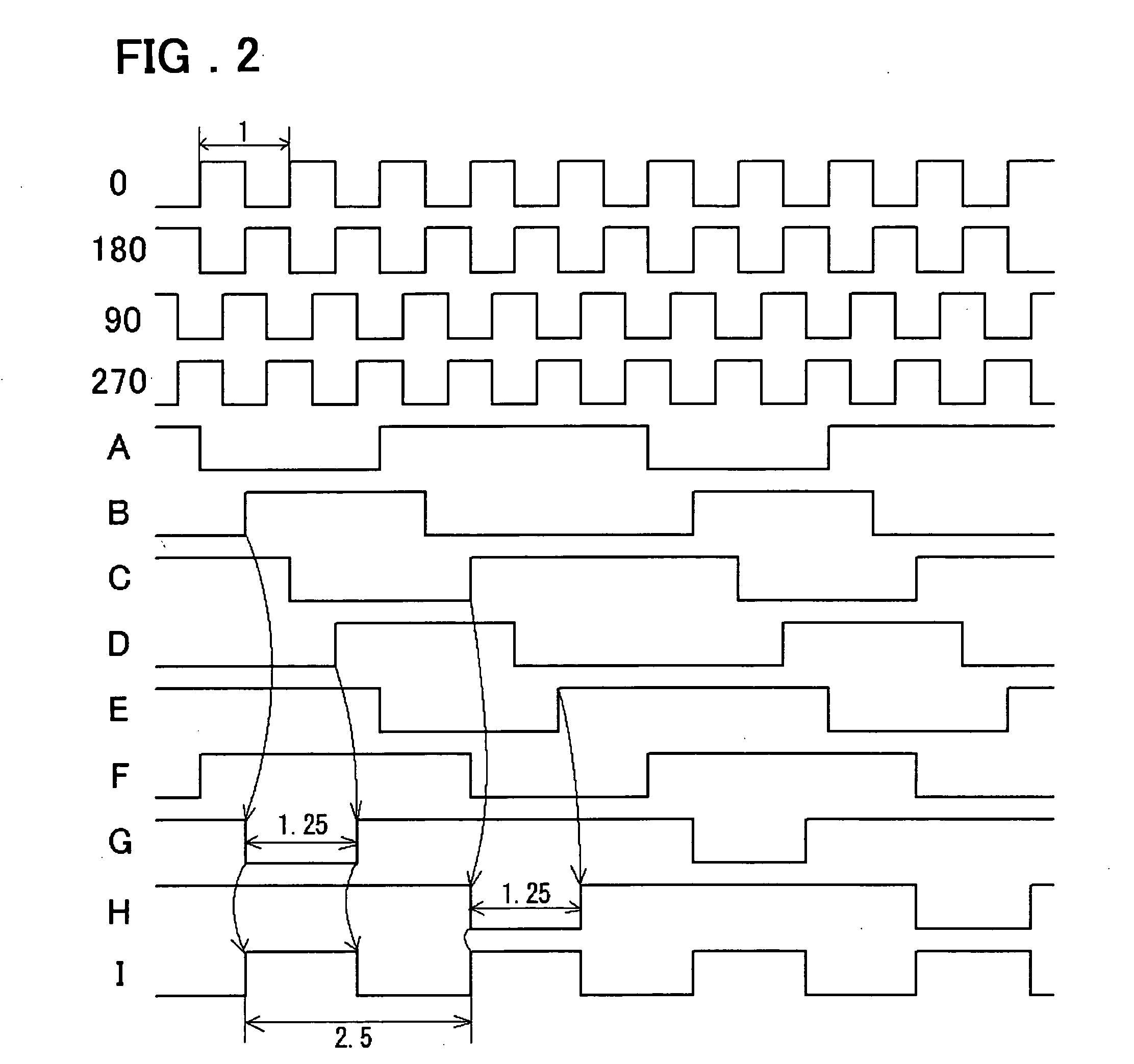

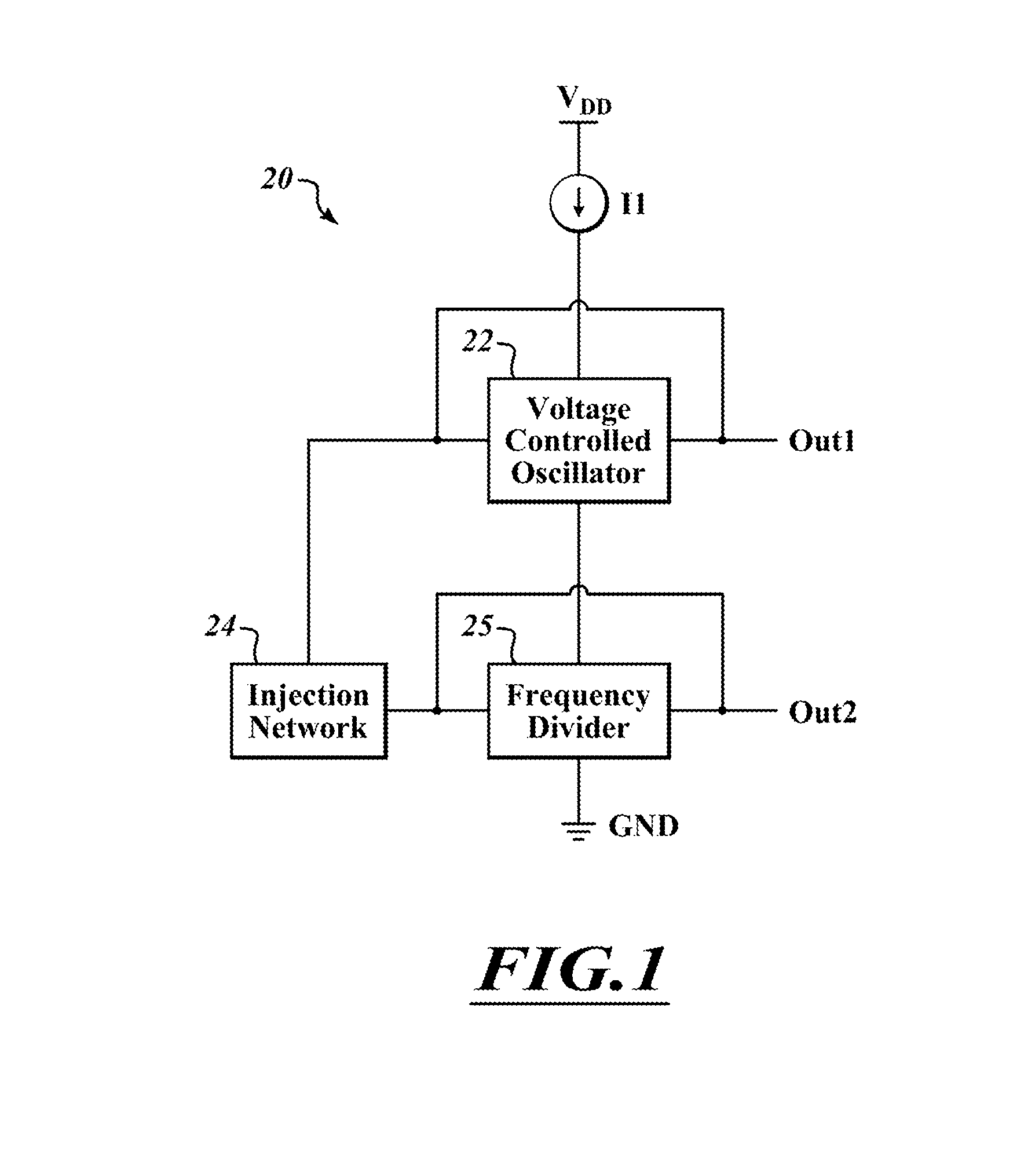

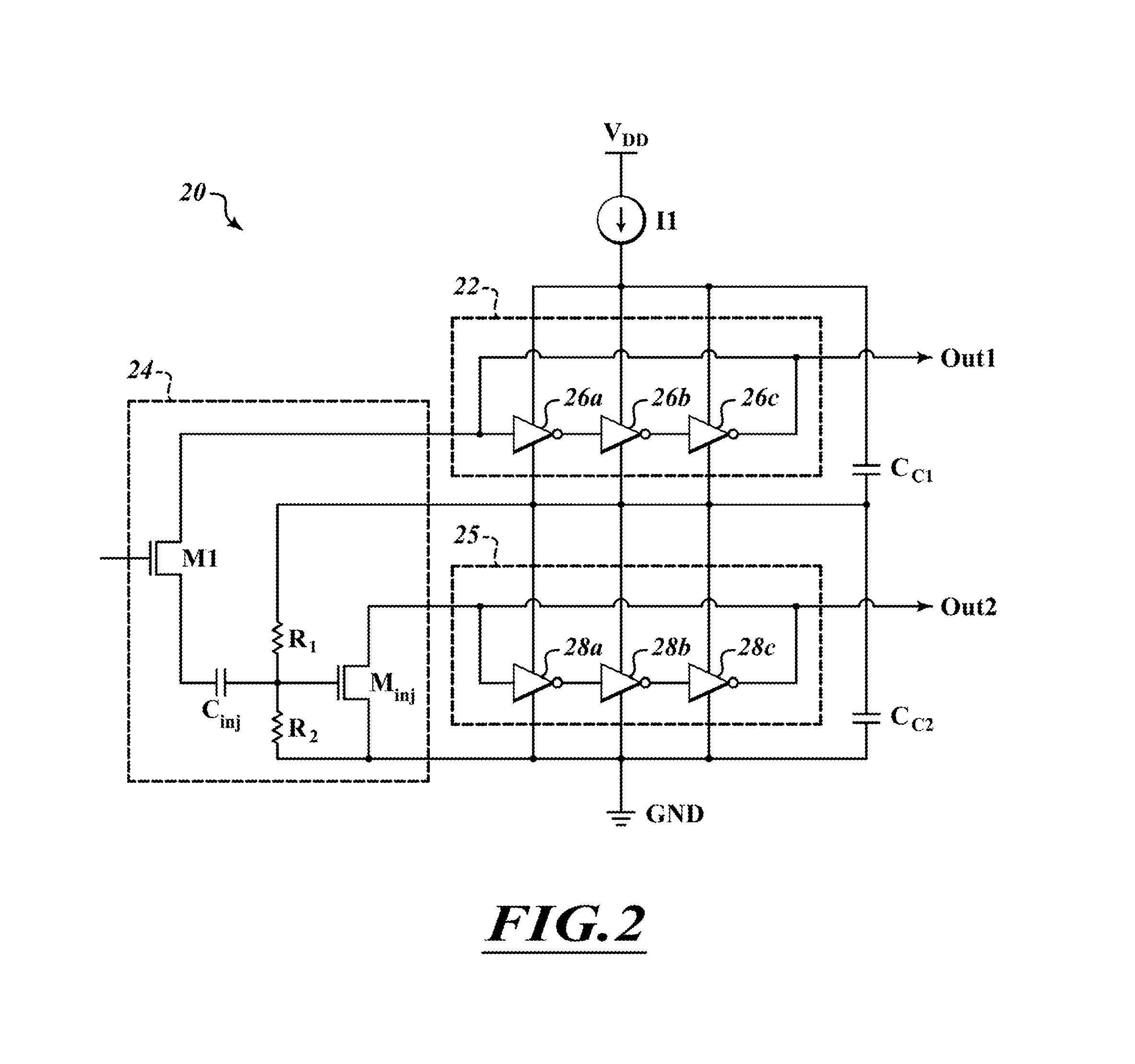

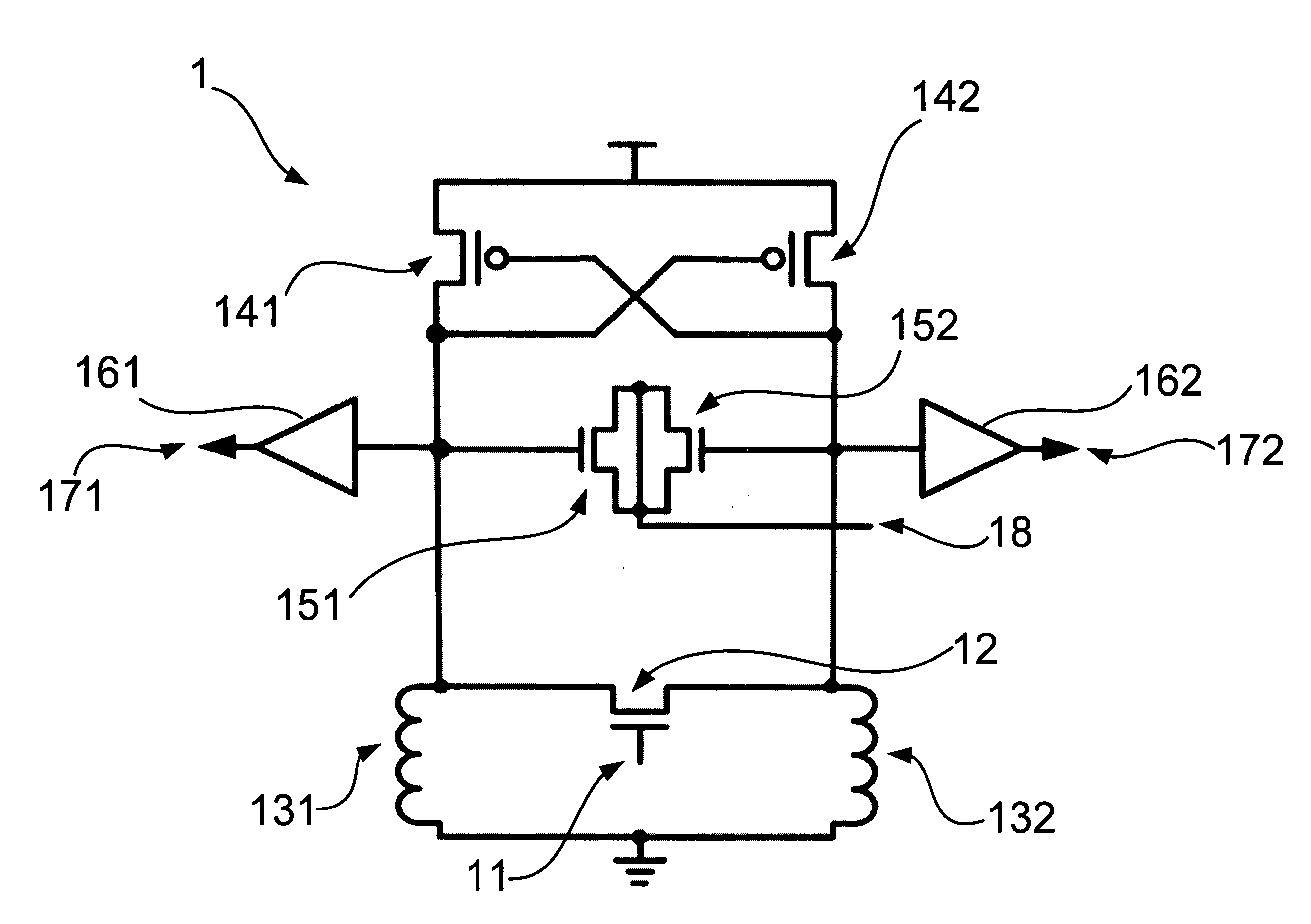

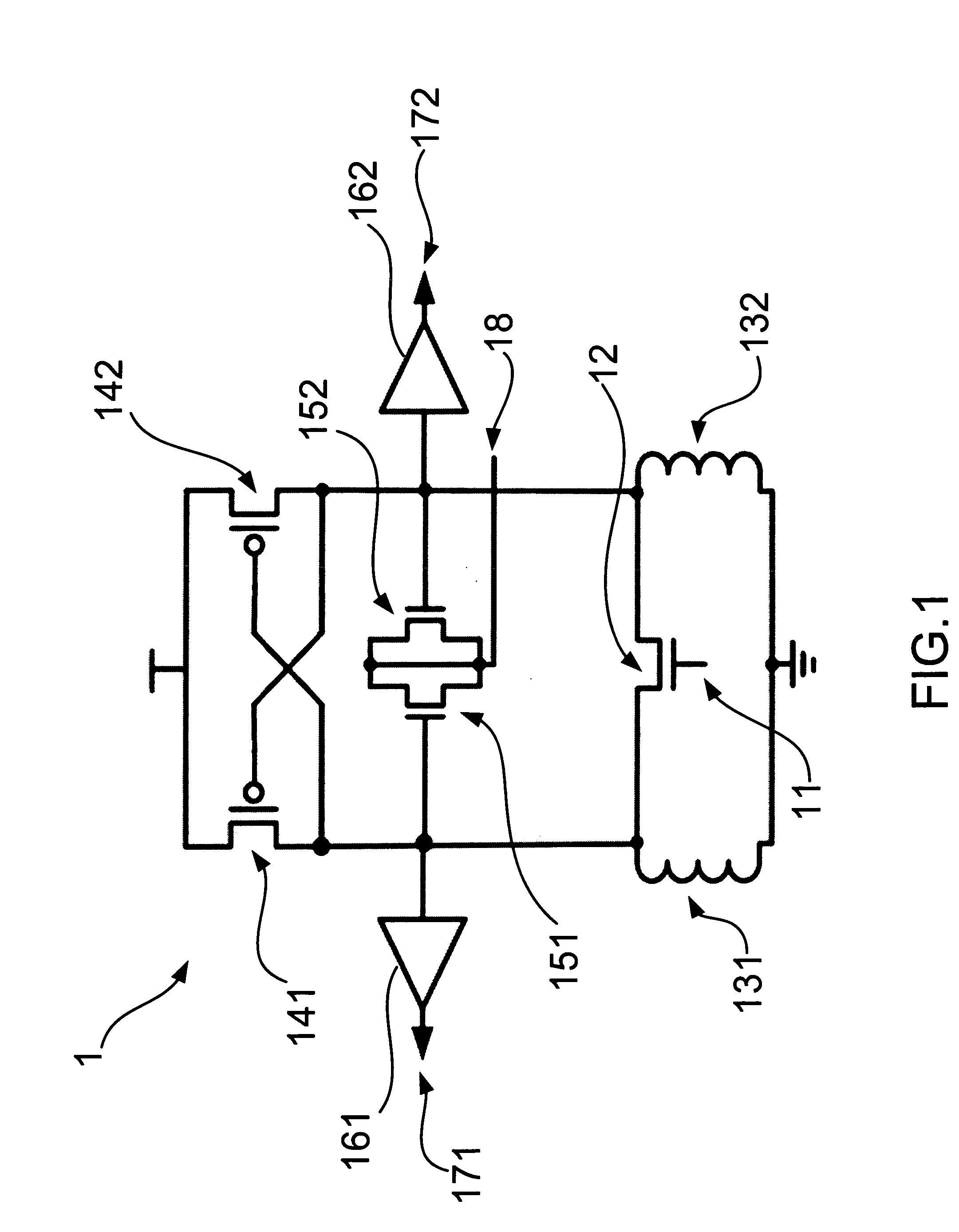

Current reused stacked ring oscillator and injection locked divider, injection locked multiplier

ActiveUS9018987B1Reduce power consumptionContinuously circulated pulse countersPulse automatic controlDriving currentInjection locked

A phase locked loop includes a voltage controlled oscillator and a frequency divider or frequency multiplier. The voltage controlled oscillator and the frequency divider / multiplier are coupled together in a stacked configuration. A drive current is supplied to the voltage controlled oscillator. The drive current passes from the voltage controlled oscillator to the frequency divider / multiplier, thereby driving the frequency divider / multiplier with the same drive current that was supplied to the voltage controlled oscillator.

Owner:STMICROELECTRONICS INT NV

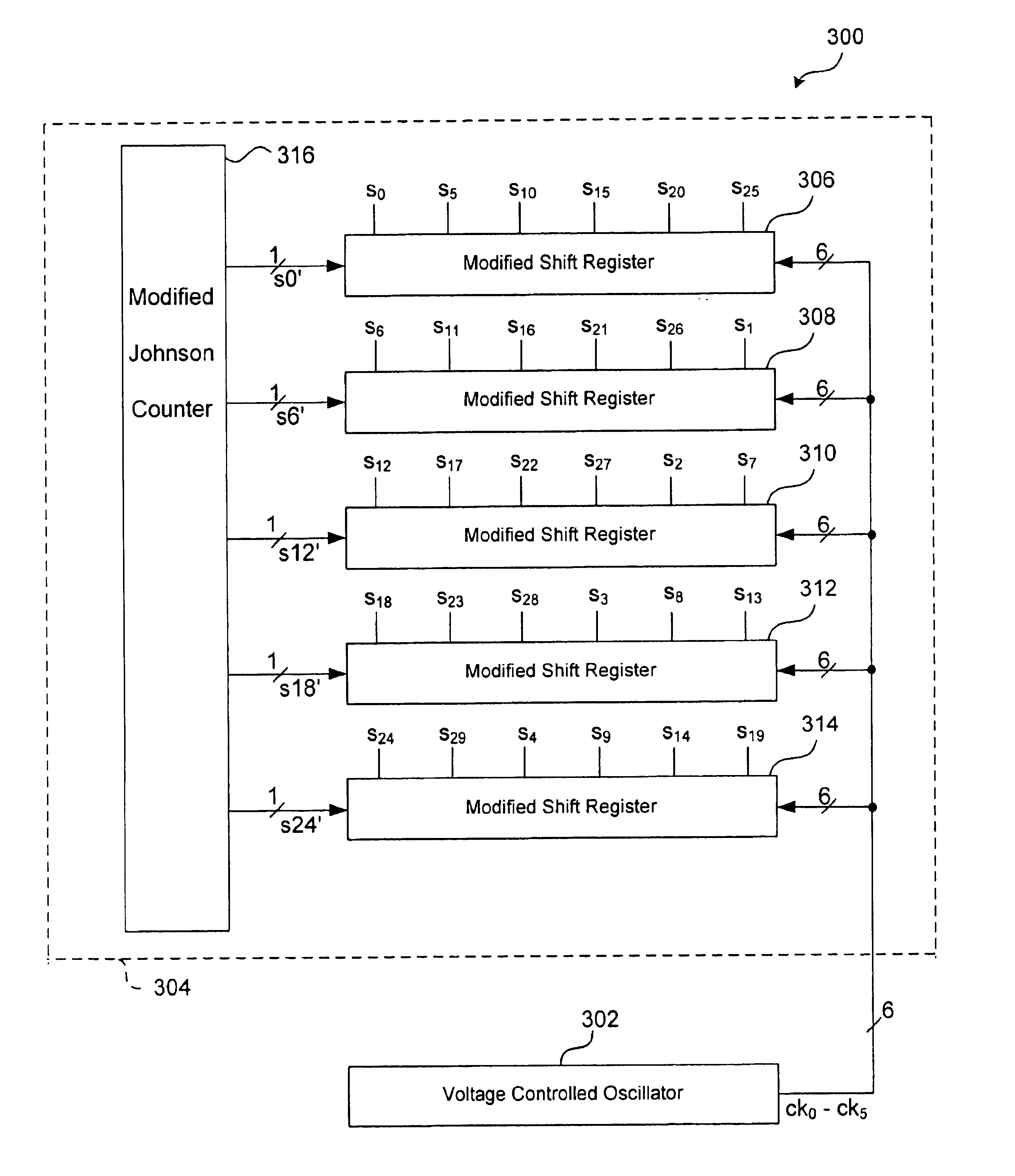

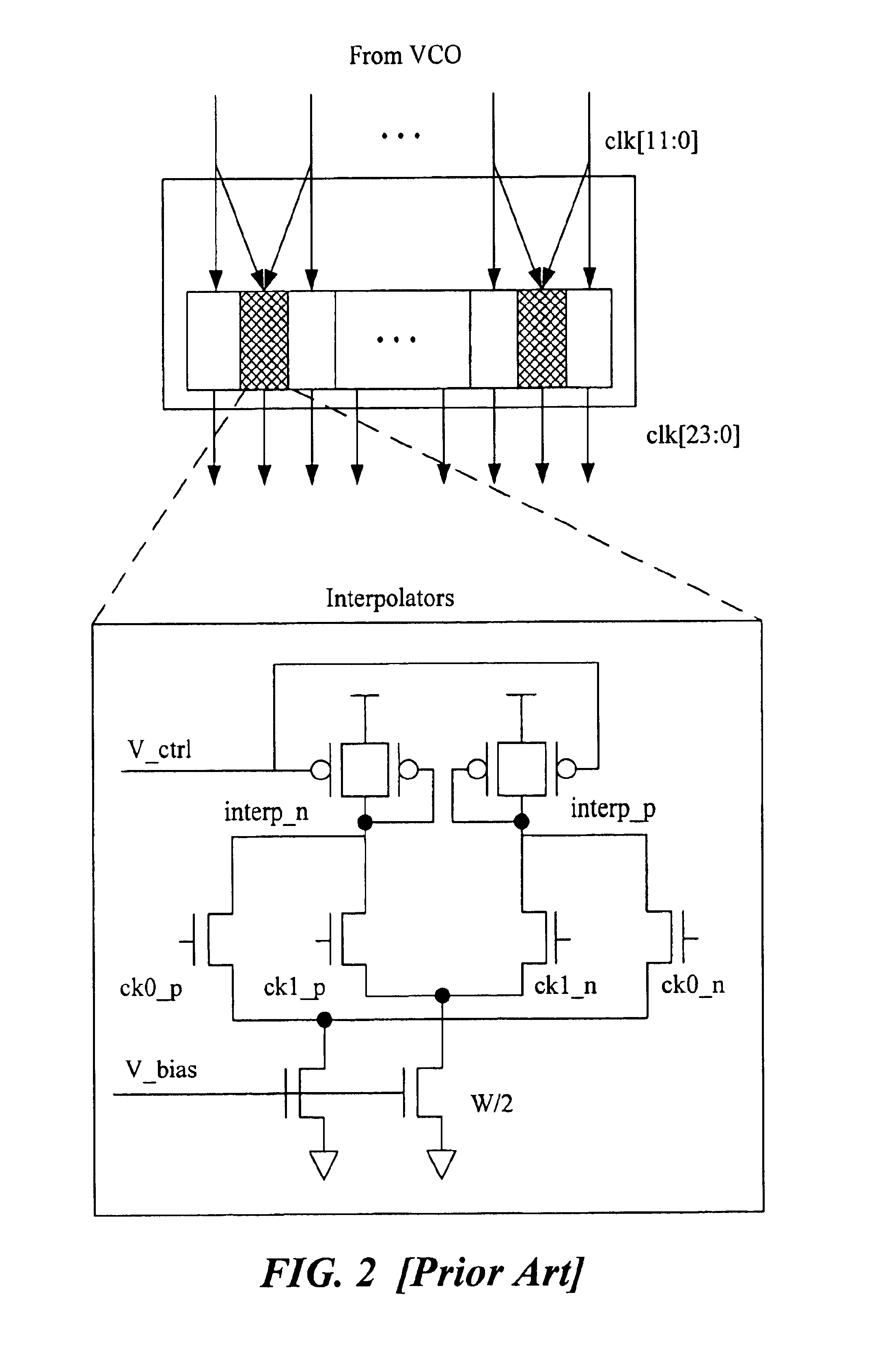

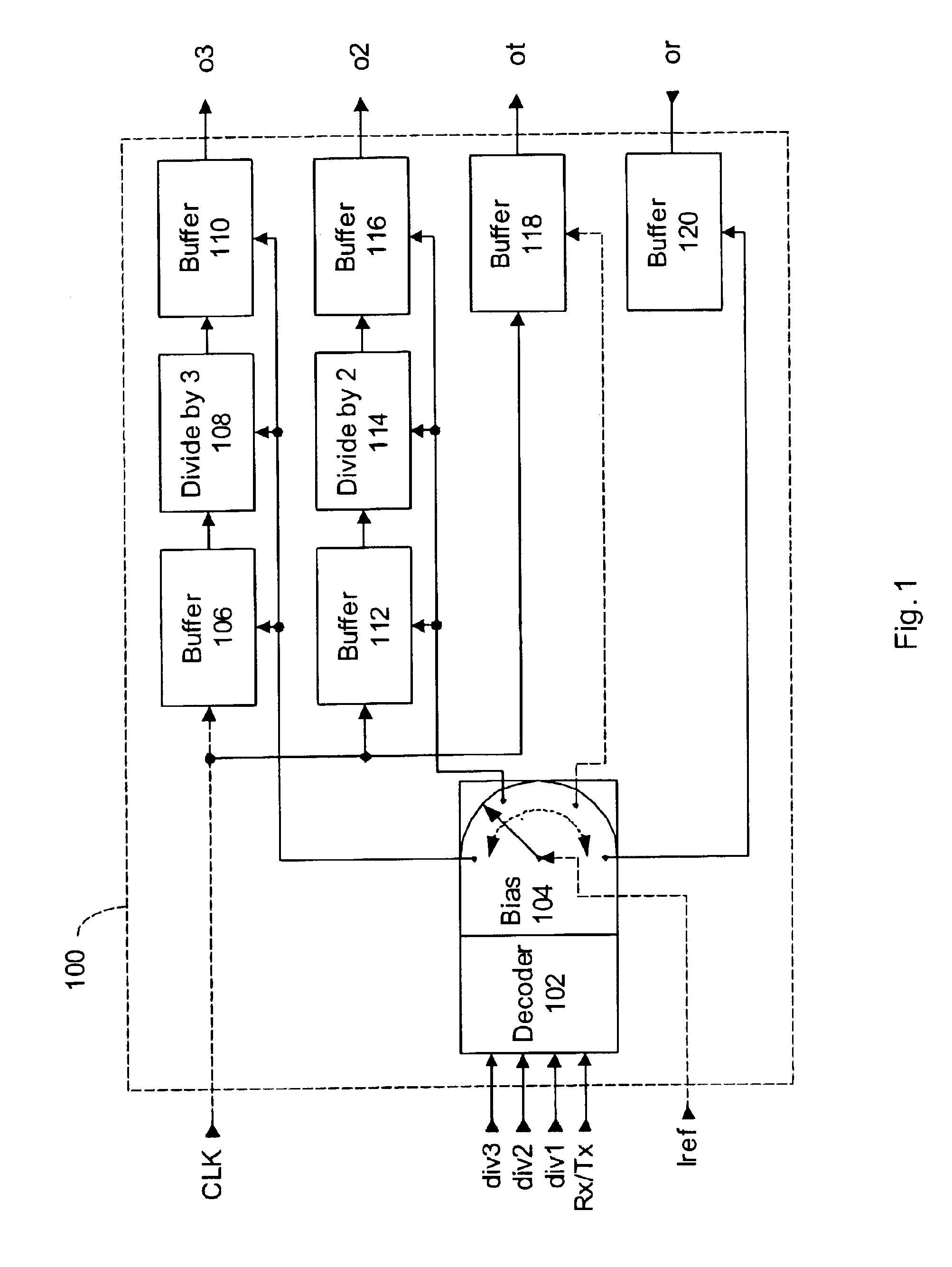

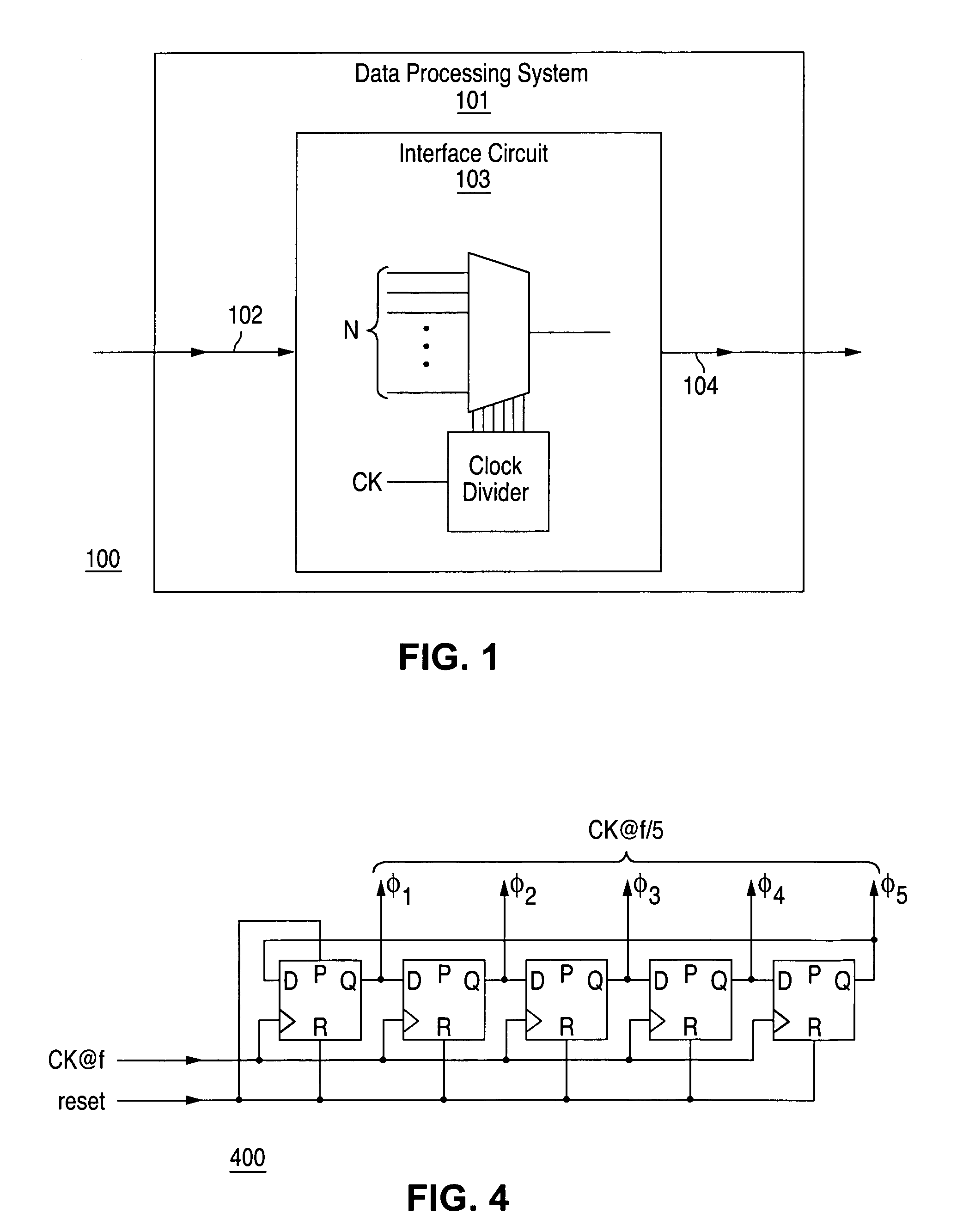

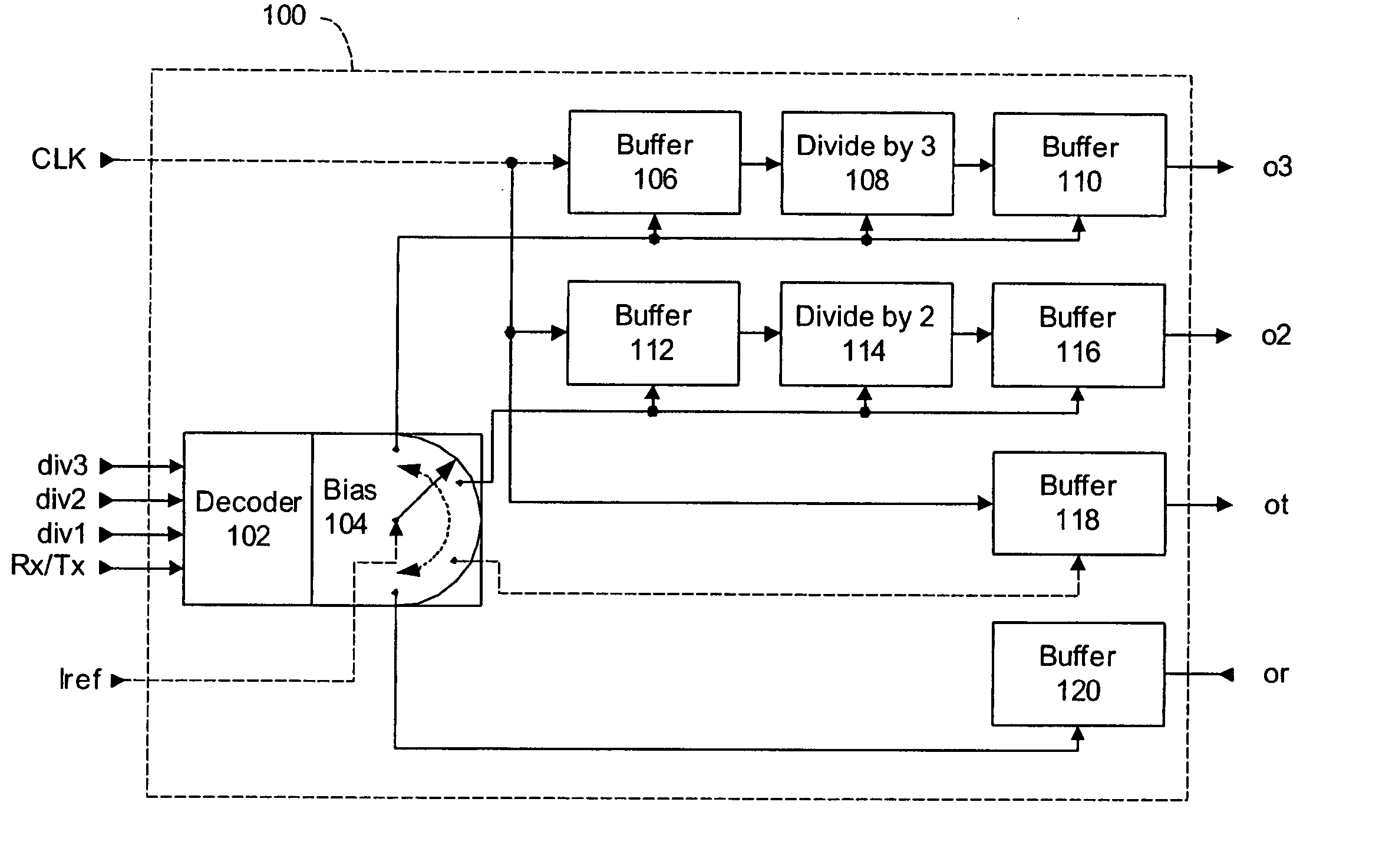

System and method for multiple-phase clock generation

InactiveUS6809567B1Continuously circulated pulse countersPulse automatic controlShift registerEngineering

A system and method for multiple-phase clock generation is disclosed. In one embodiment, a multiple-stage voltage controlled oscillator ("VCO") transmits a plurality of clock phases to a clock divider circuit which produces the desired number of clock phase outputs. The clock divider circuit in this embodiment includes a state machine, e.g., a modified Johnson counter, that provides a plurality of divided down clock phases, each of which is connected to a separate modified shift register. Each modified shift register contains D-type flip-flops and each D-type flip-flop provides a separate clock phase output. In one embodiment the number of clock phase outputs of the multiple-phase clock is a function of the number of VCO clock phases times the number of desired states in the modified Johnson counter.

Owner:UNIVERSAL CONNECTIVITY TECH INC

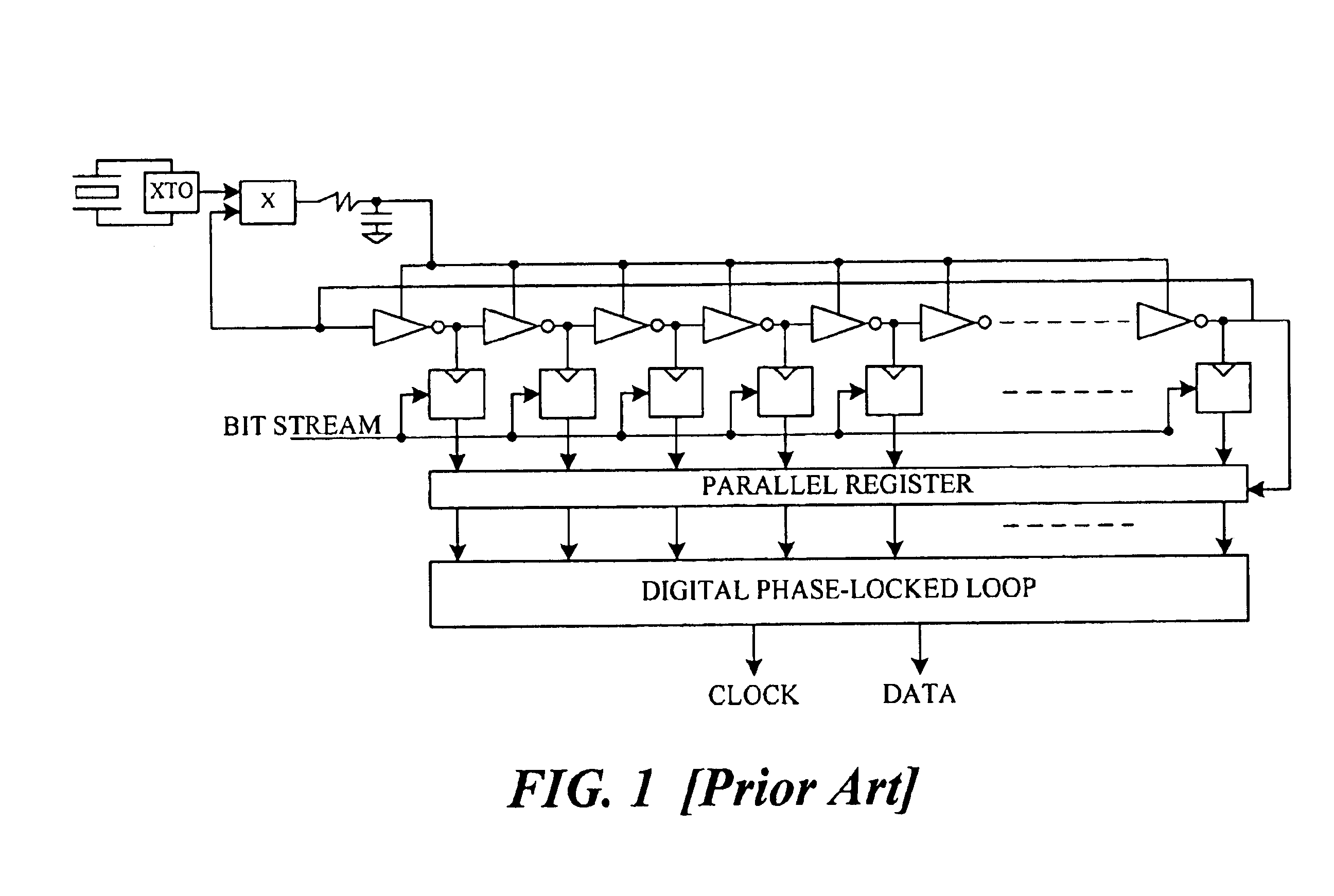

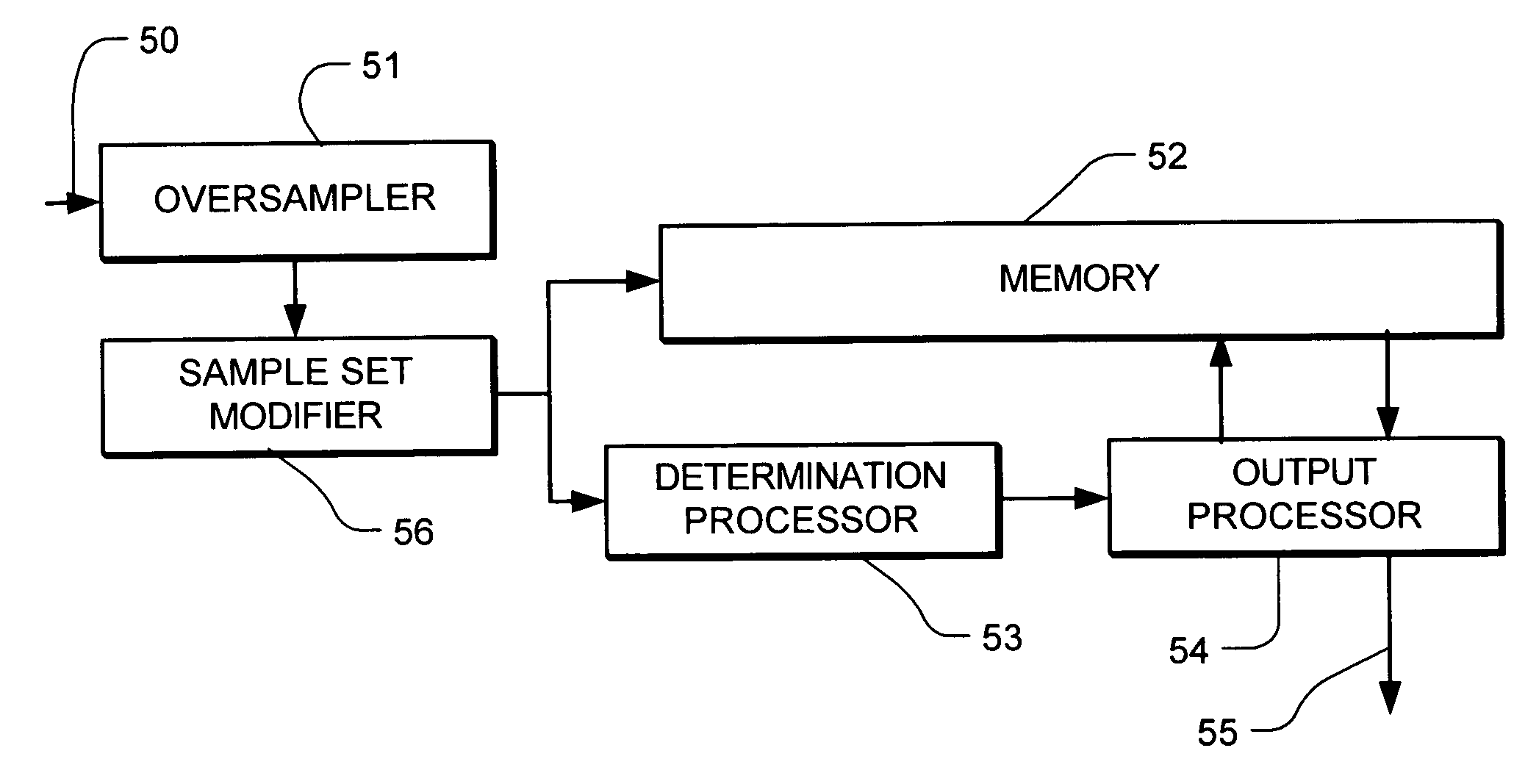

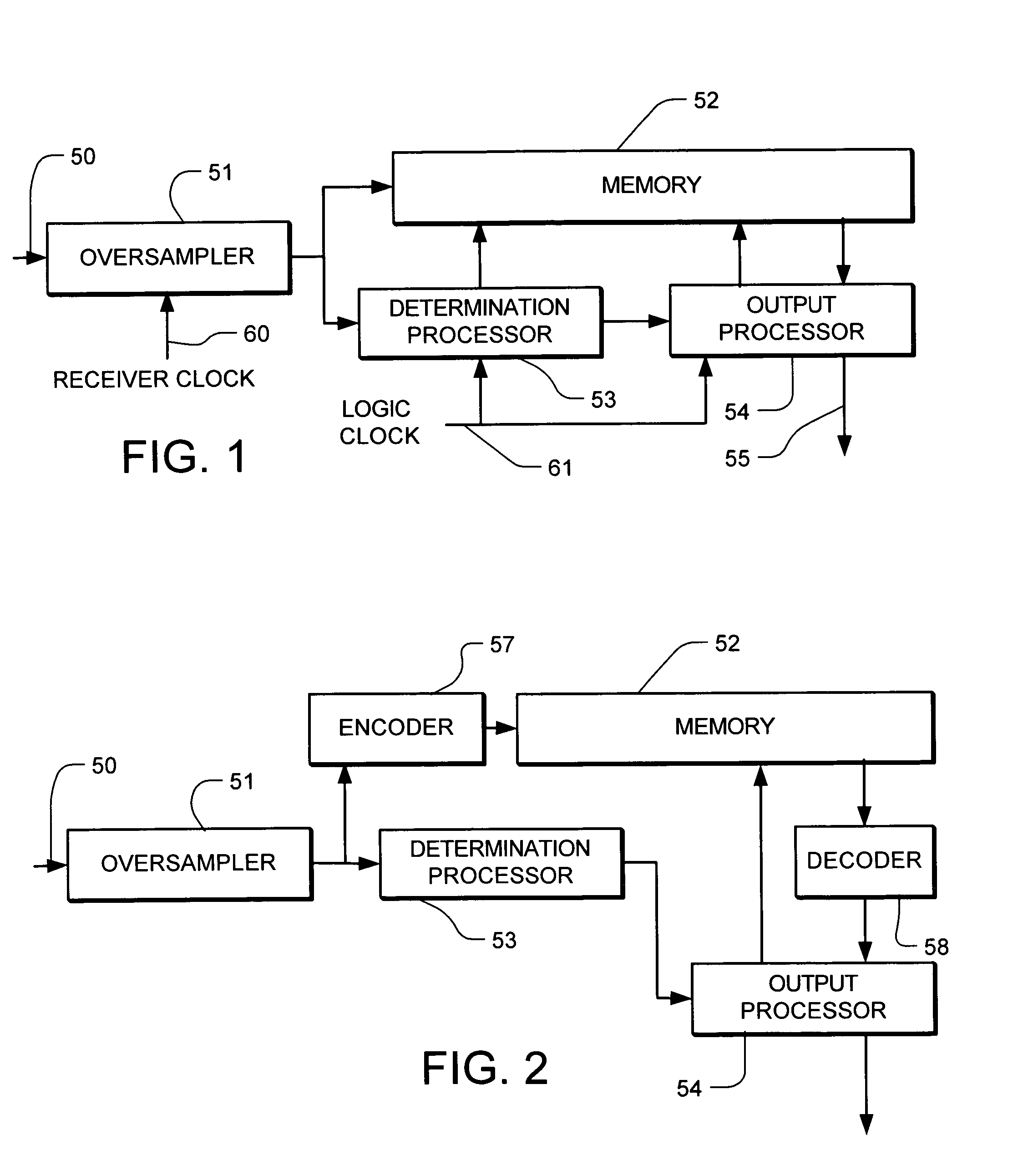

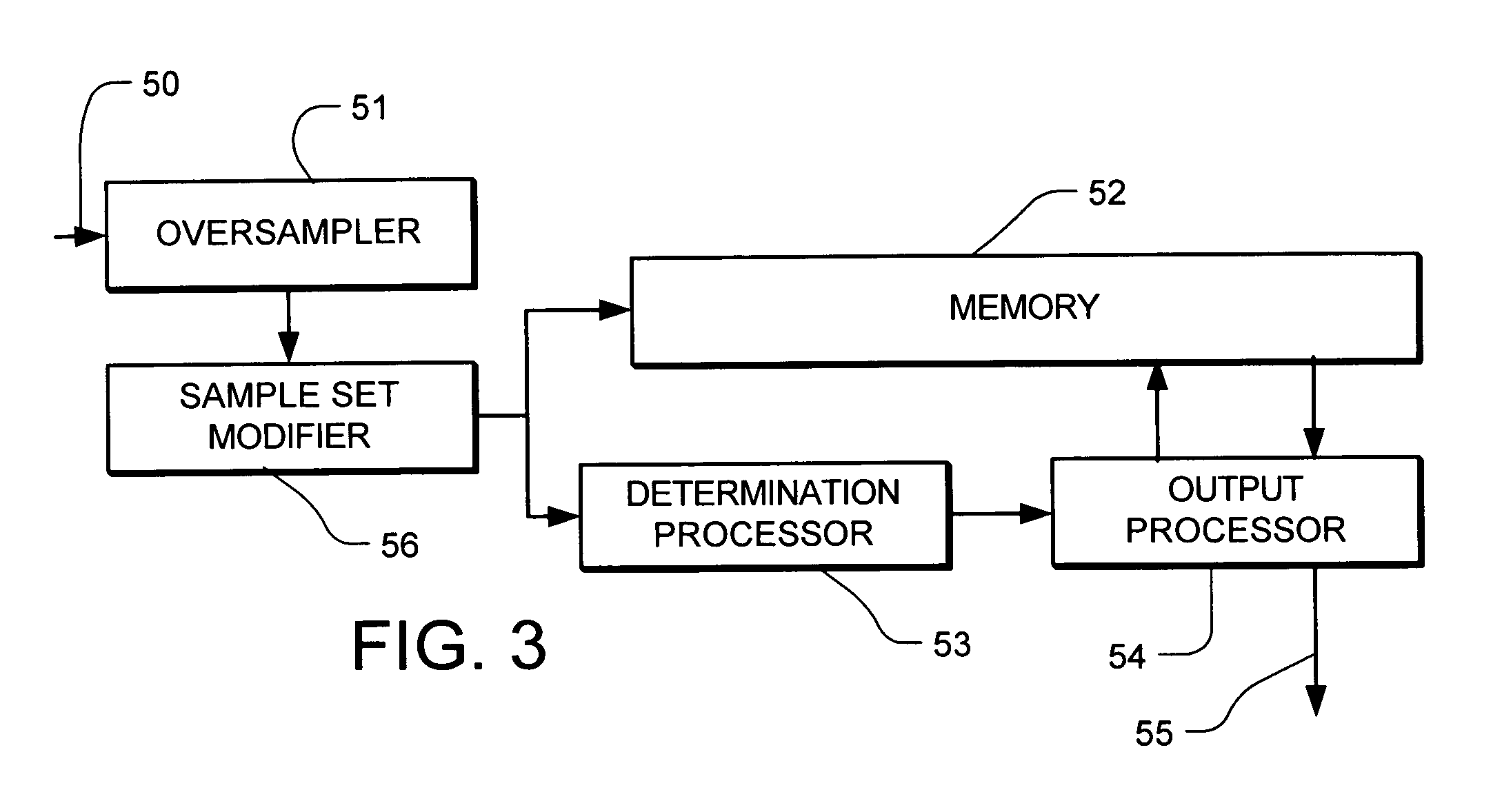

Method and apparatus for data recovery

ActiveUS7489739B2Continuously circulated pulse countersModulated-carrier systemsData compressionData signal

A method for recovering data includes oversampling an input data signal to provide sample sets, and storing a plurality of sample sets in addressable memory. The sample sets are processed, using sequential logic to make determinations of respective samples suitable for use in data recovery from corresponding sample sets. One function applied for the determination, includes taking a first mean transition position in a first group of sample sets, taking a second mean transition position in a second group of sample sets, computing a slope value for change in transition position, and making the determination based on the order of the plurality of samples, the first and second means, and the slope. The determined samples are obtained and data recovery is achieved. Sample sets can be modified according to equalization functions. Other modifications include encoding the sample sets for data compression.

Owner:RAMBUS INC

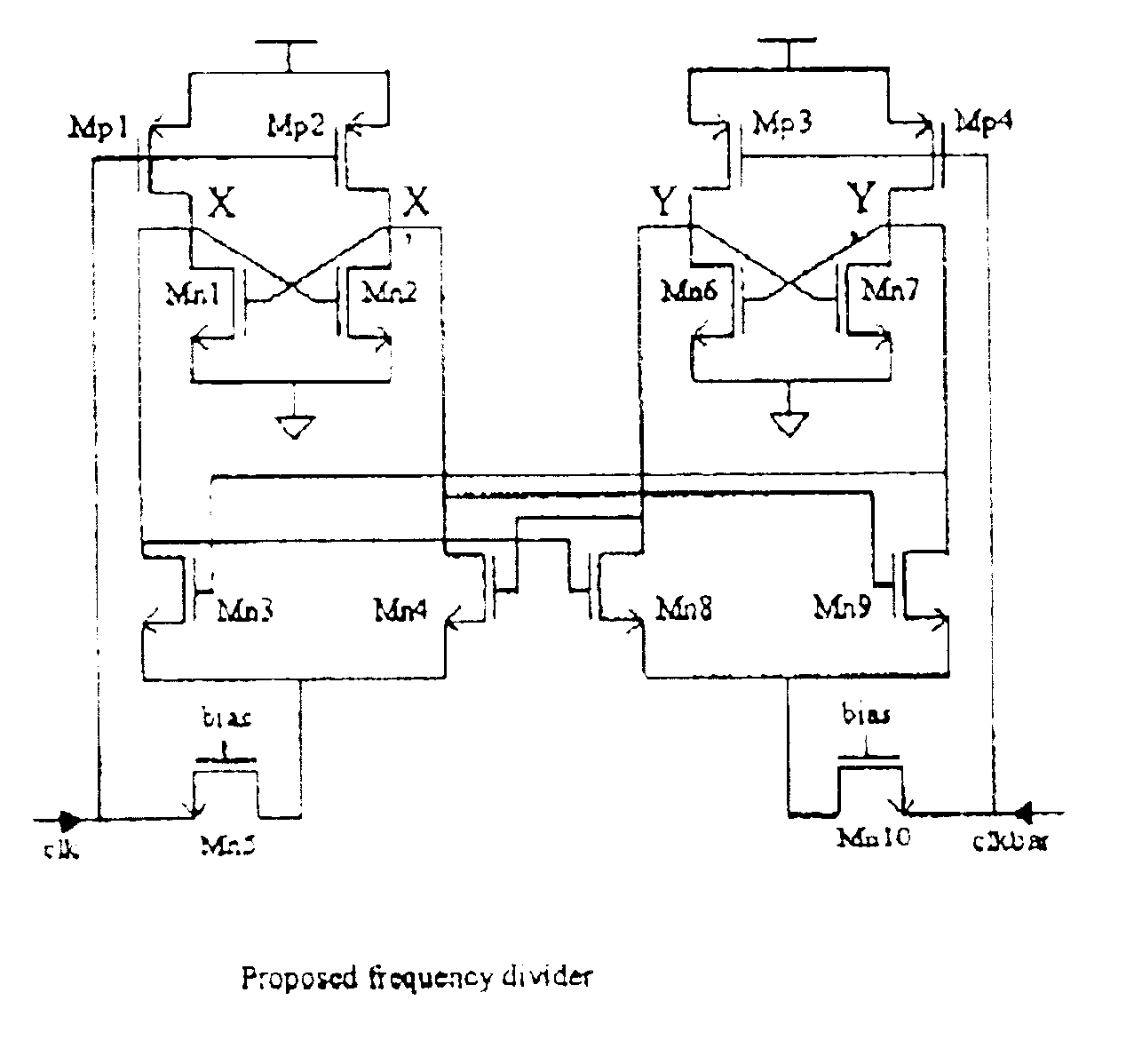

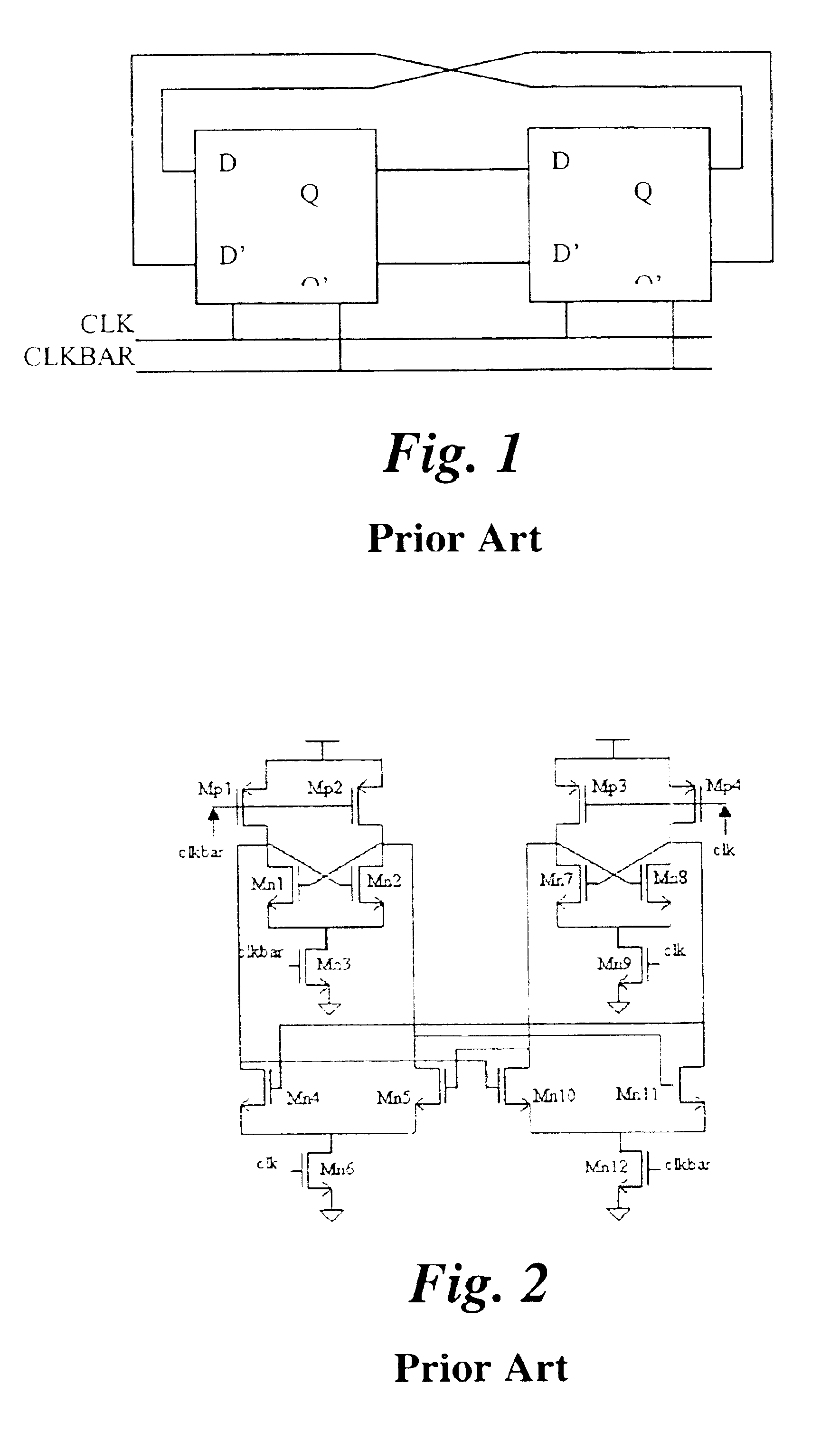

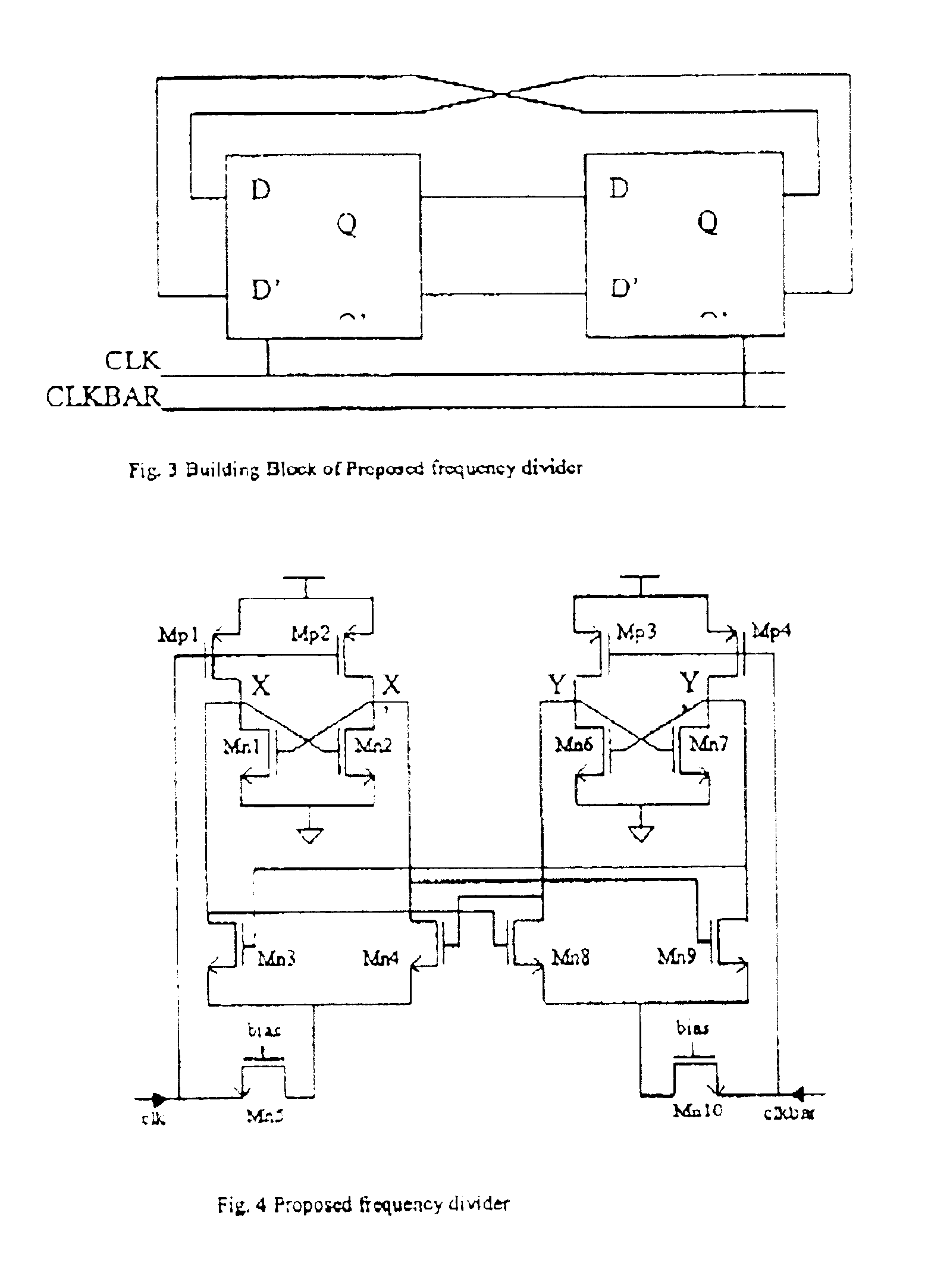

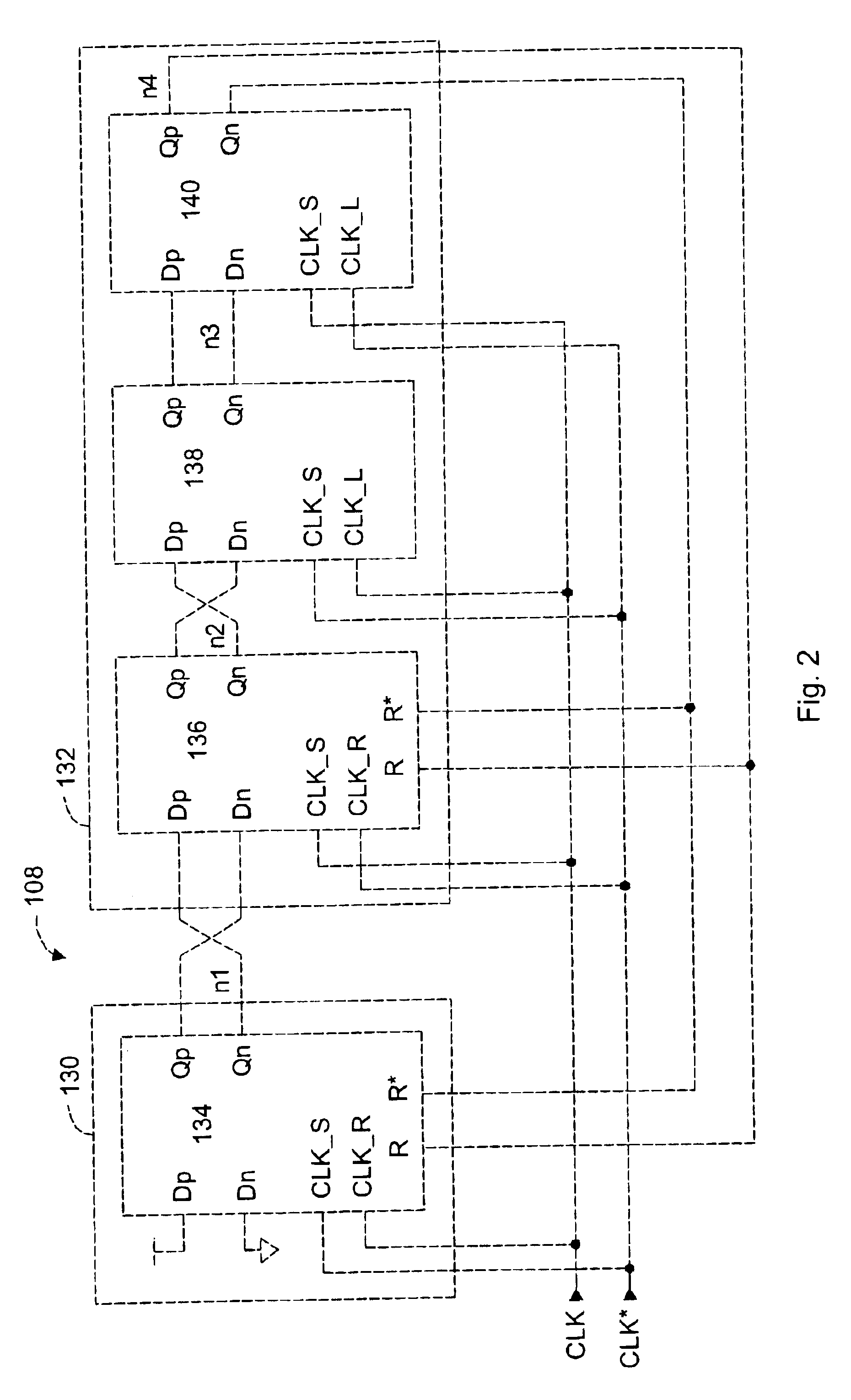

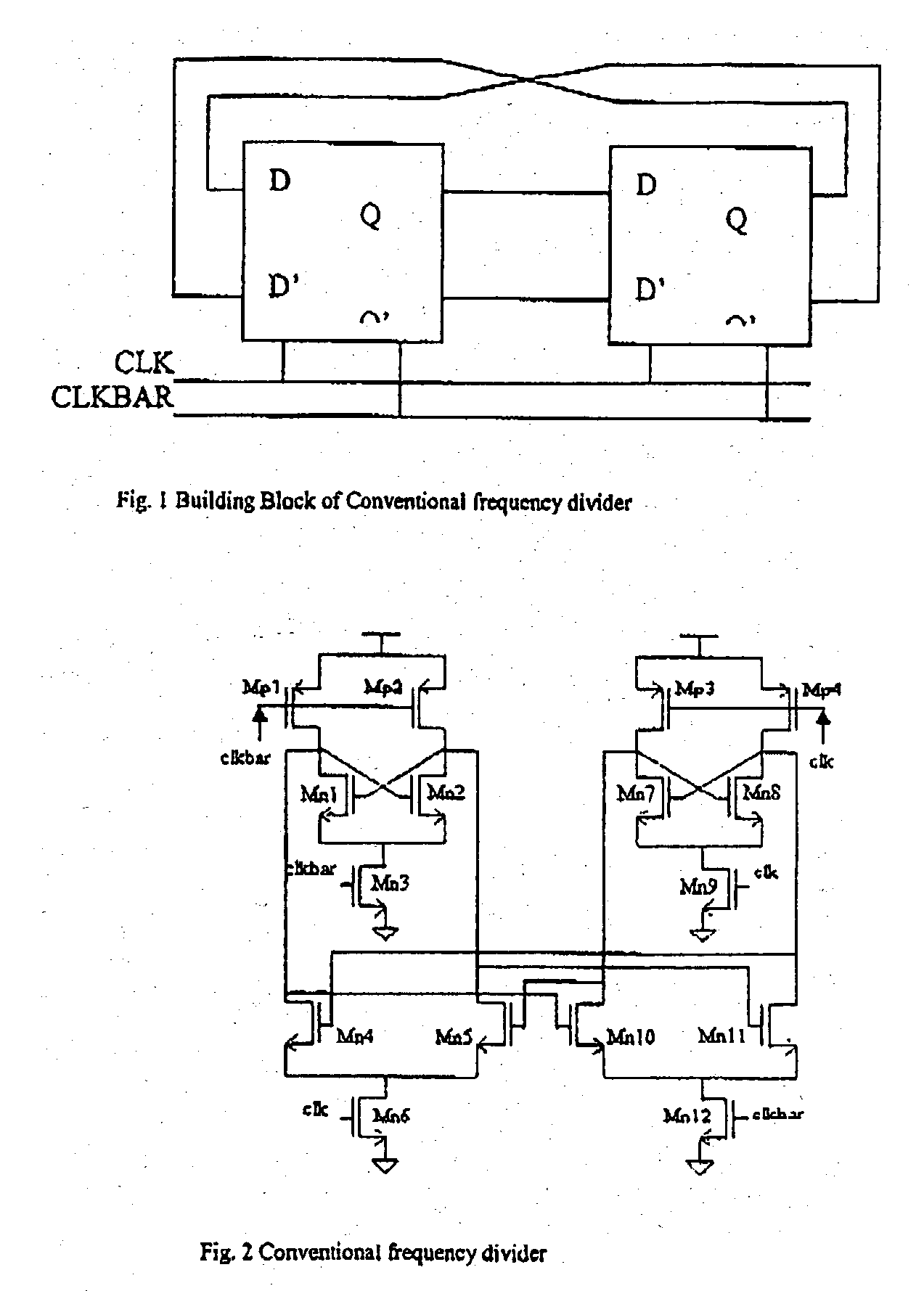

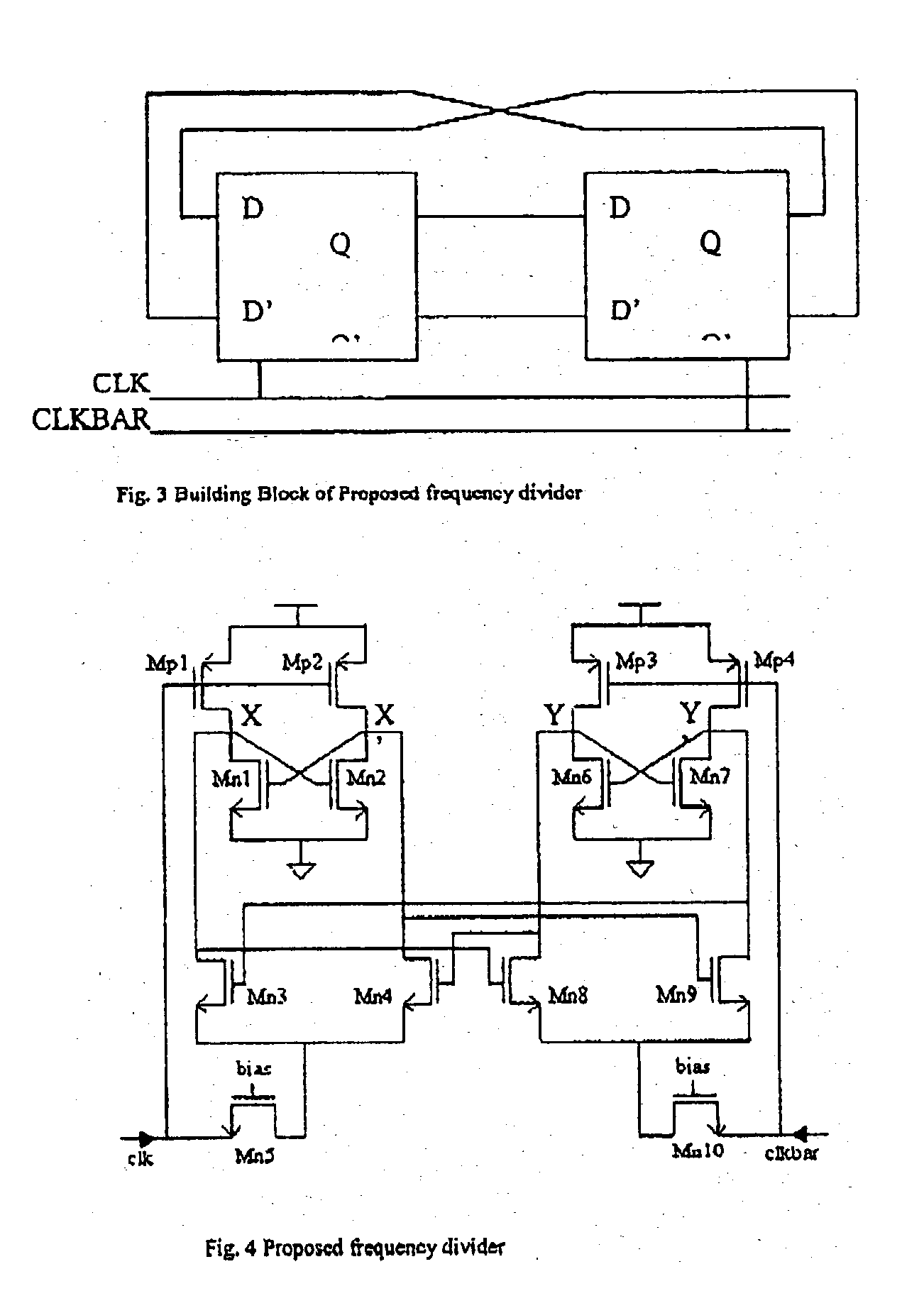

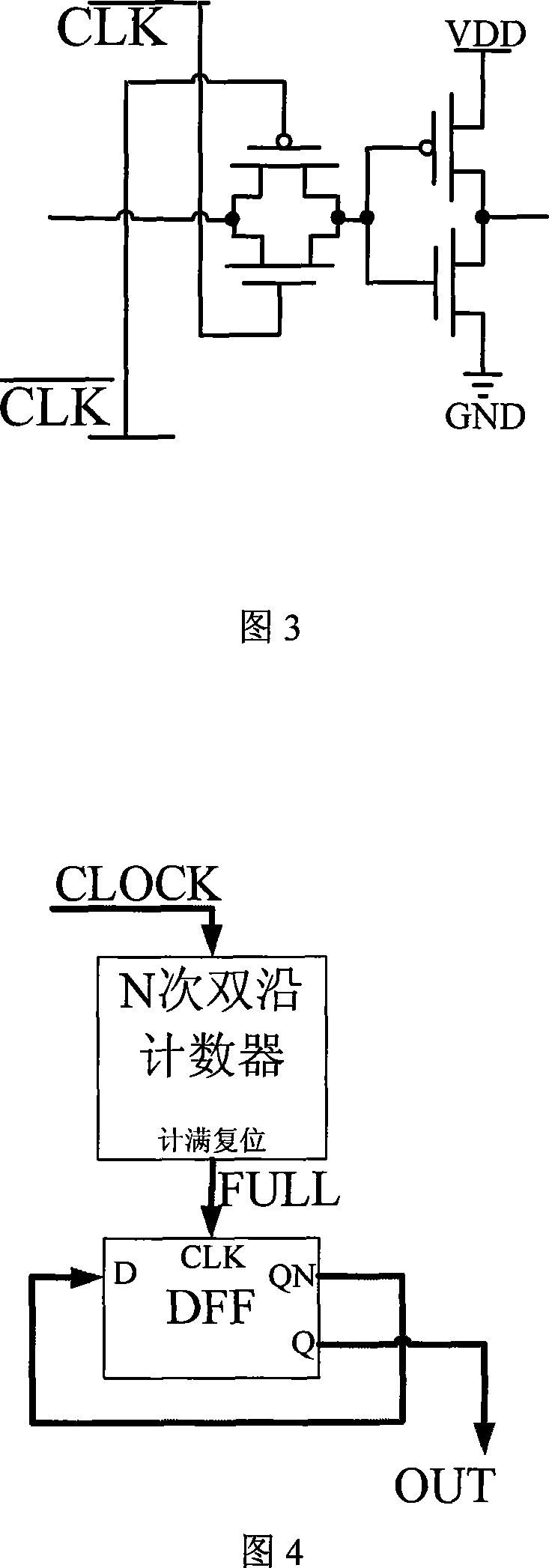

Low-voltage high-speed frequency-divider circuit

InactiveUS6831489B2Continuously circulated pulse countersCounting chain synchronous pulse countersLow voltageEngineering

A frequency divider circuit is disclosed that generates output signals having a frequency substantially half of the frequency of the input signal. The circuit comprises two D-Flip-Flop circuits wherein one employs the said input signal and the other one employs the complement of the said input signal, and each of the two D-Flip-Flop circuits consists of a pair of loading transistors, two regenerative pairs coupled with each others, and two common-gate switches.

Owner:THE HONG KONG UNIV OF SCI & TECH

Frequency divider system

InactiveUS6847239B2Logic circuits characterised by logic functionContinuously circulated pulse countersSignal frequencyActive phase

A frequency divider circuit for providing a divided clock signal having a frequency that is an odd integer factor less than the frequency of an incoming system clock signal. The frequency divider includes a clock generator circuit coupled to a delay circuit which operates in an active and a reset phase to provide a divided clock signal from the system clock signal. In the active phase, the clock generator circuit drives the divided clock signal to a first logic state until a reset signal is received. The delay circuit then generates the reset signal at a predetermined number of system clock edges after the divided clock signal is driven to the first logic state. In the reset phase, both the clock generator circuit and the delay circuit are reset in response to the reset signal such that the clock generator circuit immediately drives the divided clock signal to a second logic state, and the delay circuit disables the reset signal within the predetermined number of system clock edges. The delay circuit maintains a 50% duty cycle for the divided clock signal.

Owner:BLACKBERRY LTD

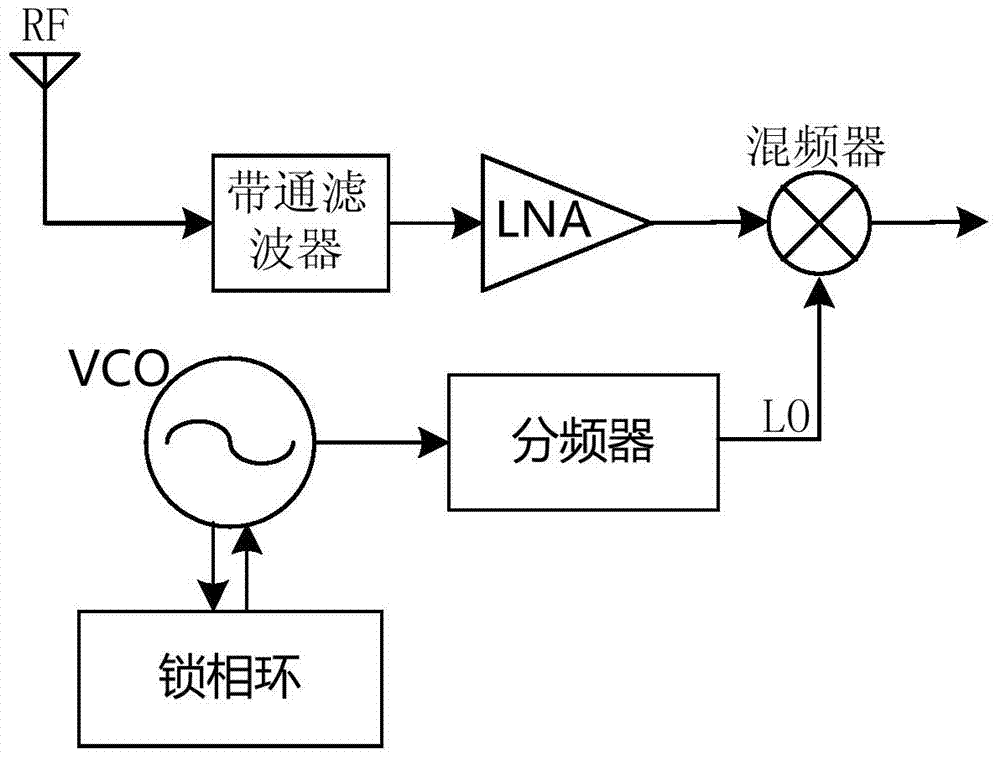

Frequency divider and wireless communication device

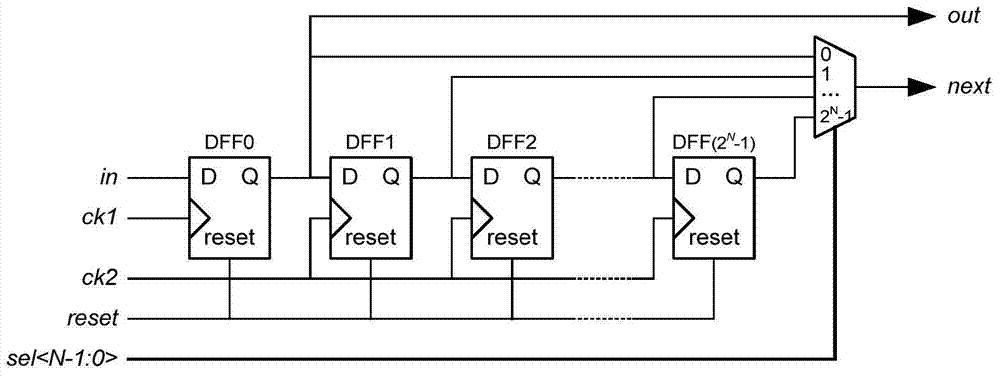

ActiveCN103929173ASimple structureSuitable for high frequency workContinuously circulated pulse countersPulse automatic controlShift registerProcessor register

The embodiment of the invention discloses a frequency divider and a wireless communication device. The frequency divider comprises a shifting register unit and an output frequency synthesis unit, wherein the shifting register unit comprises multiple basic units cascaded circularly; each basic unit comprises 2N D flip-flops connected in series and a multi-path gating device, output of the 2N D flip-flops connected in series is connected into the multi-path gating device, and the output of the multi-path gating device is connected with input of the basic unit at a next level; the phase of clock signals connected into other 2N-1 D flip-flops except the first D flip-flop at the signal input end of the basic unit at each level is lagged than that of clock signals connected into the first D flip-flop by a M / 2 clock period; the phase of clock signals connected to the first D flip-flop in the basic unit at the next level is lagged than that of clock signals connected into other 2N-1 D flip-flops in the basis unit at the previous level by three fourths clock period; output signals of the first D flip-flops in the basic units at all the levels are superposed through the output frequency synthesis unit to generate fractional frequency output signals.

Owner:HUAWEI TECH CO LTD

Frequency changer and tuner

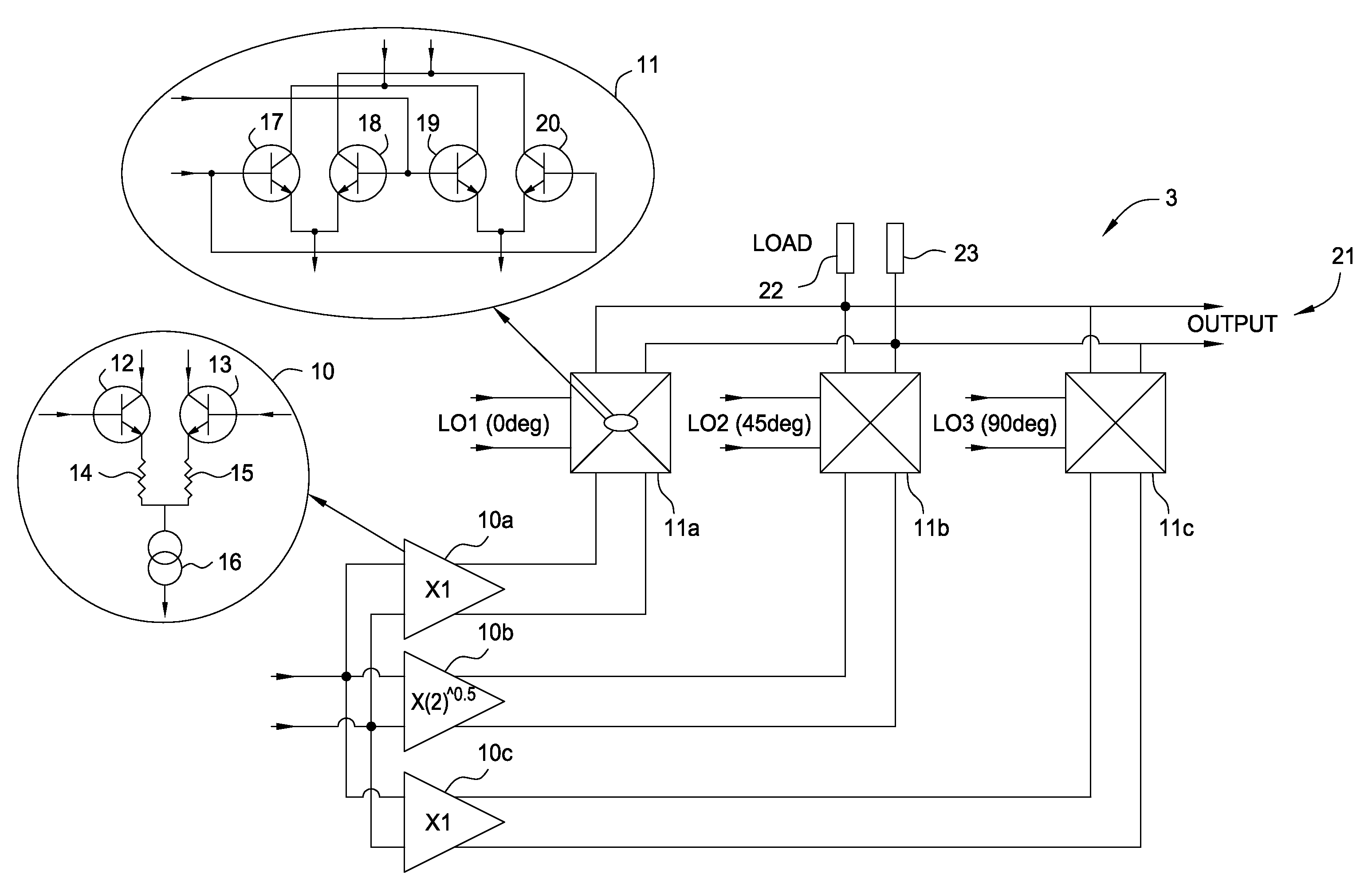

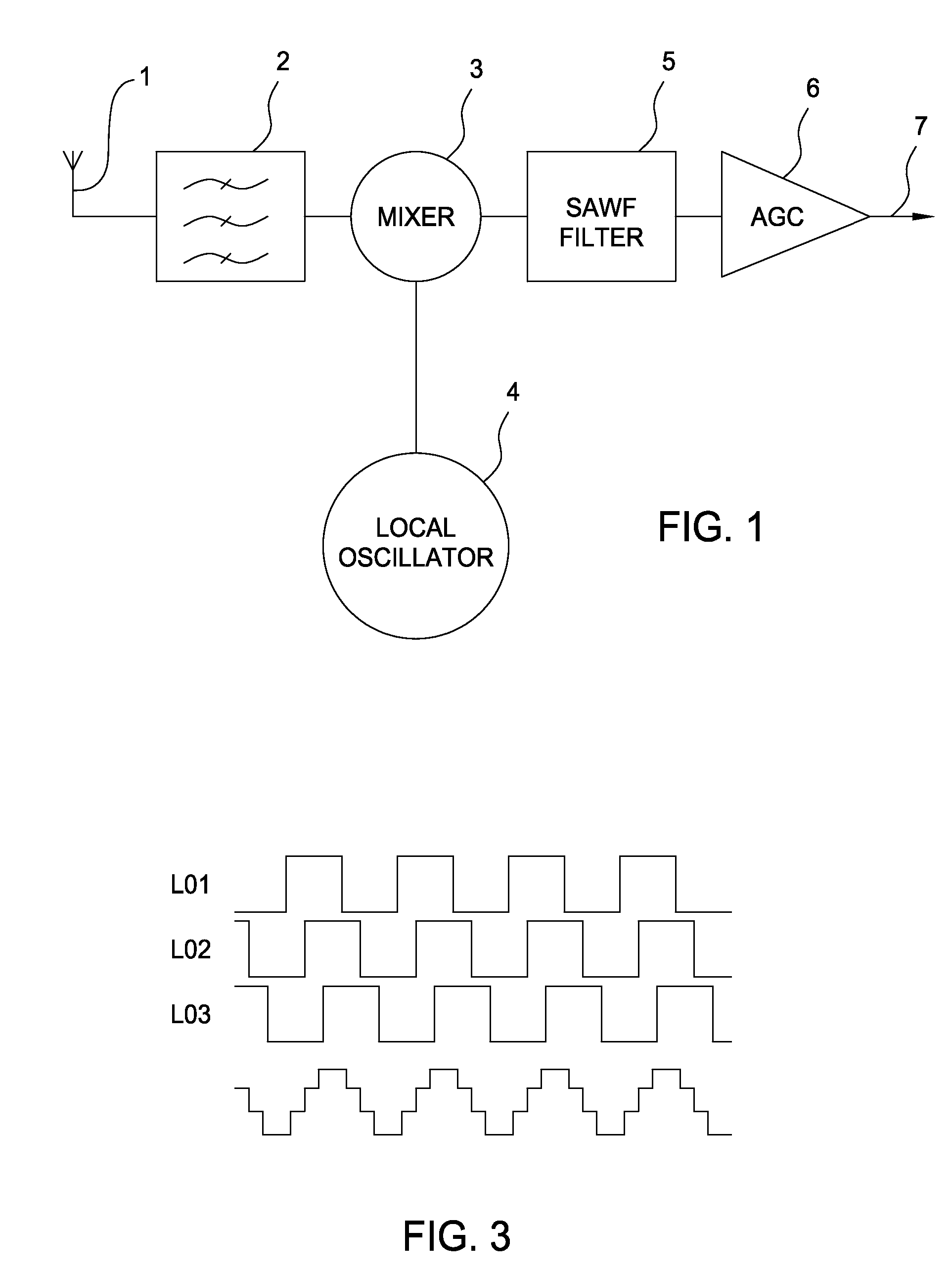

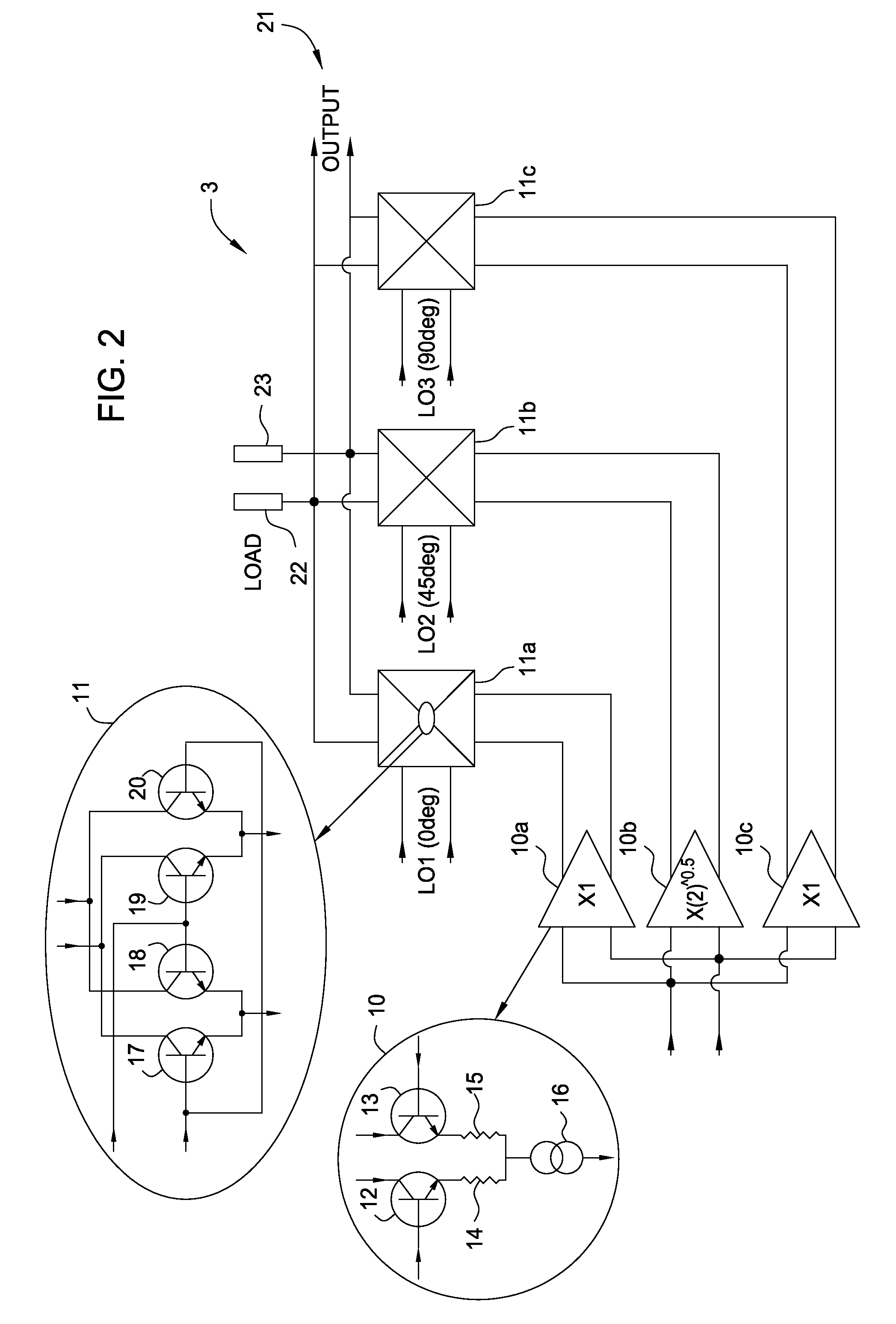

InactiveUS20070042743A1Contamination or interference caused by harmonic mixing isEasy to manufactureContinuously circulated pulse countersCounting chain synchronous pulse countersFrequency changerFrequency mixer

A frequency changer for a radio frequency tuner and a tuner incorporating such a frequency changer are provided. The frequency changer comprises a mixer comprising a plurality of mixing stages. The output signals of these stages are supplied without relative phase shift to a summer, for example, in the form of a common load arrangement. The inputs of the stages are connected together to form a signal input of the mixer. Commutating signal inputs of the mixing stages received from the local oscillator are of the same frequency, but of different phases. The commutating signals are square or rectangular waves.

Owner:INTEL CORP

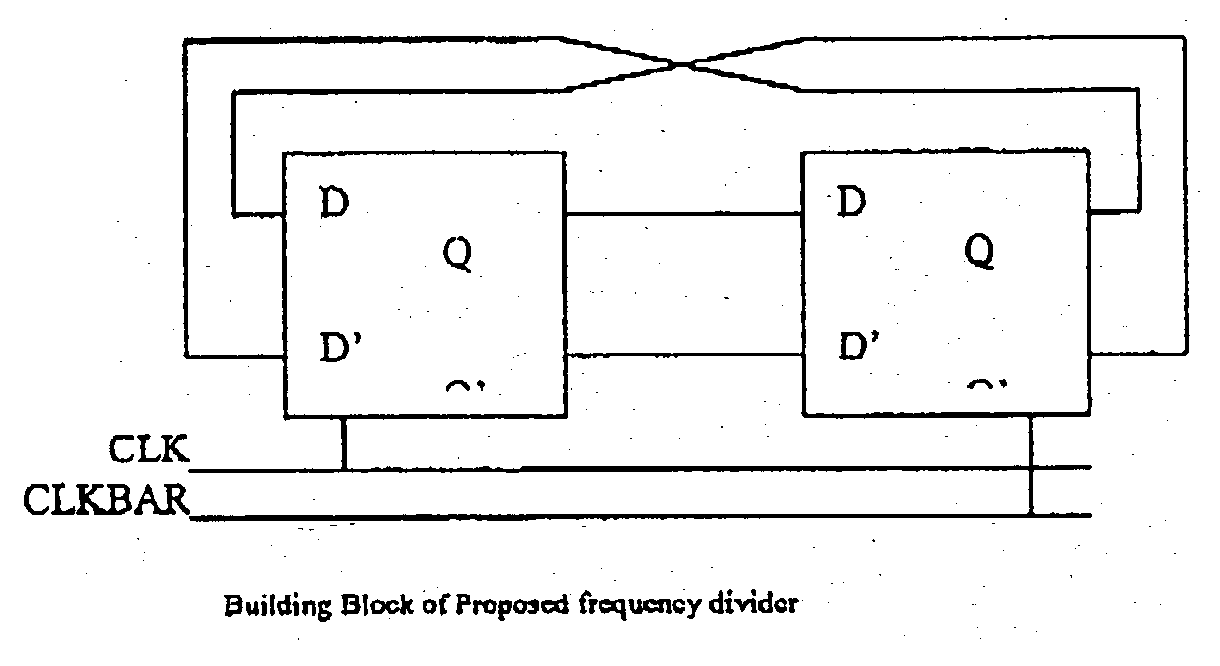

Low-voltage high-speed frequency-divider circuit

InactiveUS20040012416A1Continuously circulated pulse countersCounting chain synchronous pulse countersLow voltageEngineering

A frequency divider circuit is disclosed that generates output signals having a frequency substantially half of the frequency of the input signal. The circuit comprises two D-Flip-Flop circuits wherein one employs the said input signal and the other one employs the complement of the said input signal, and each of the two D-Flip-Flop circuits consists of a pair of loading transistors, two regenerative pairs coupled with each others, and two common-gate switches.

Owner:THE HONG KONG UNIV OF SCI & TECH

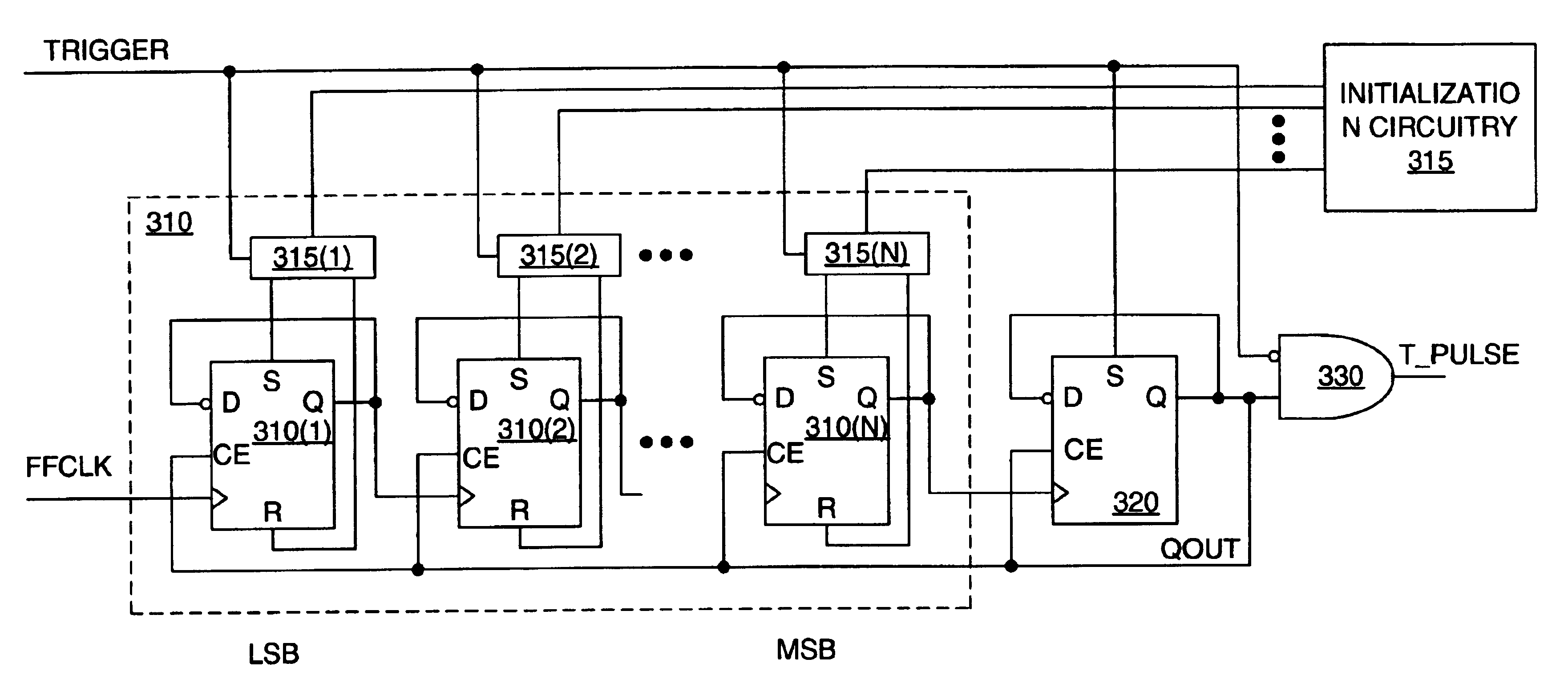

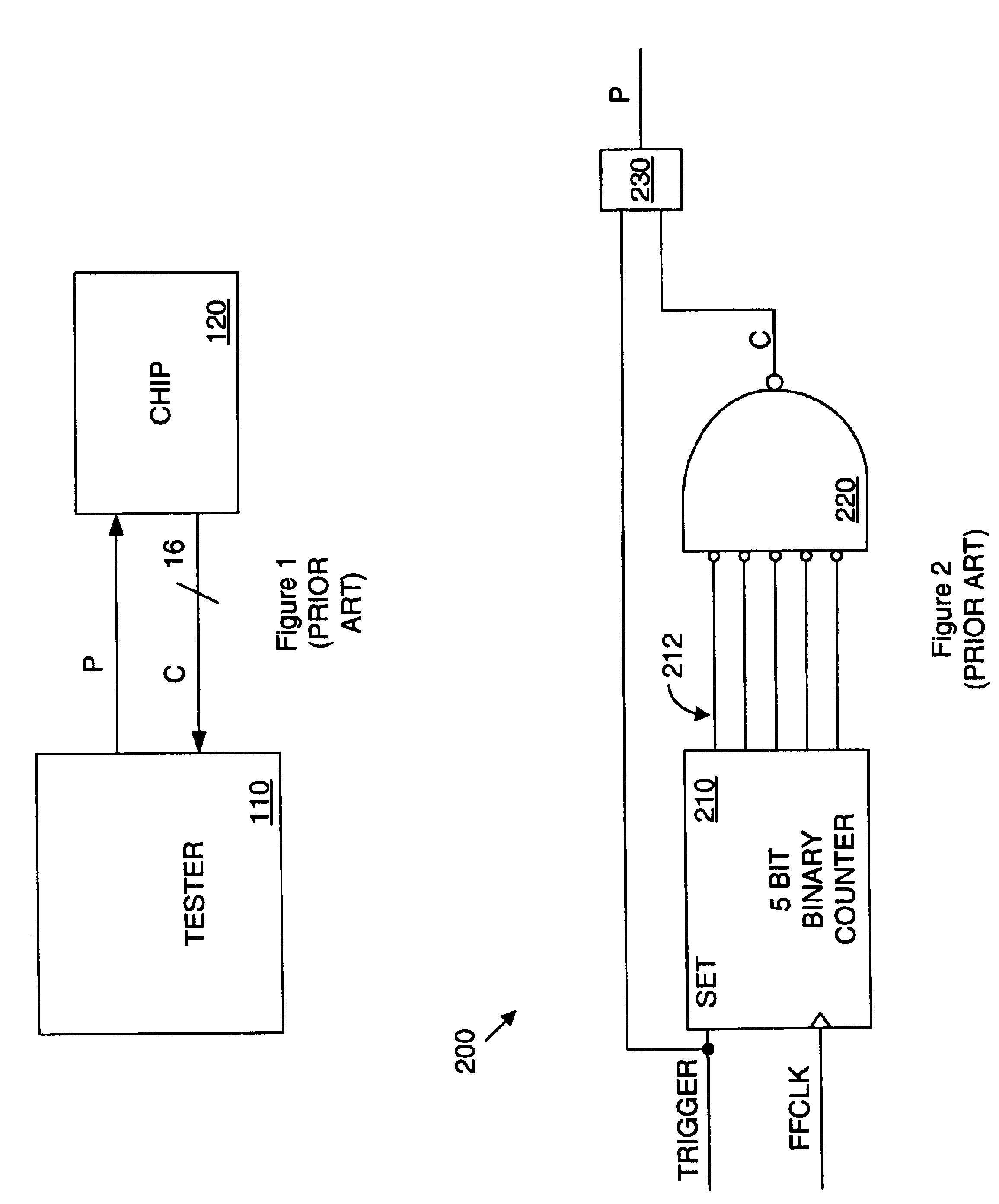

Glitchless pulse generator

InactiveUS6879201B1Reduce errorsOccupies spaceContinuously circulated pulse countersCounting chain synchronous pulse countersGlitchDuration time

A glitchless T length pulse is generated by coupling a trigger signal and the latched output of a counter. The trigger signal initiates the start of the T length pulse, and the latched output of the counter initiates the end of the T length pulse after counting up a duration of T from a number of clock cycles of a clock signal. Latching the output of the counter prior to terminating the T length pulse eliminates glitches. Accuracy of the count determining the length of the T length pulse may be increased by latching the trigger signal with the clock signal to generated a synchronized trigger signal, and using the synchronized trigger signal to initiate the T length pulse.

Owner:XILINX INC

High frequency divider circuit

InactiveUS6130564AContinuously circulated pulse countersCounting chain synchronous pulse countersTransistorHigh frequency

A frequency divider circuit operable at high frequencies for producing an output signal having a frequency value equal to substantially half the frequency value of a clock signal from which the circuit operates. The circuit includes a first transistor branch, an inventor and a second transistor branch. The first transistor branch is connected to an input of the inventor and the second transistor branch is connected to an output of the inventor. The first transistor branch receives a plurality of input signals including the clock signal, a compliment of the clock signal, and the circuit output signal and produces an input signal which is provided to the inventor. The second transistor branch receives a plurality of inputs including the compliment of the clock signal, the clock signal and the inventor output signal, and produces the circuit output signal. The circuit is configured such that the next inventor state is always available for conveyance to the output signal upon a change in the clock signal.

Owner:LUCENT TECH INC

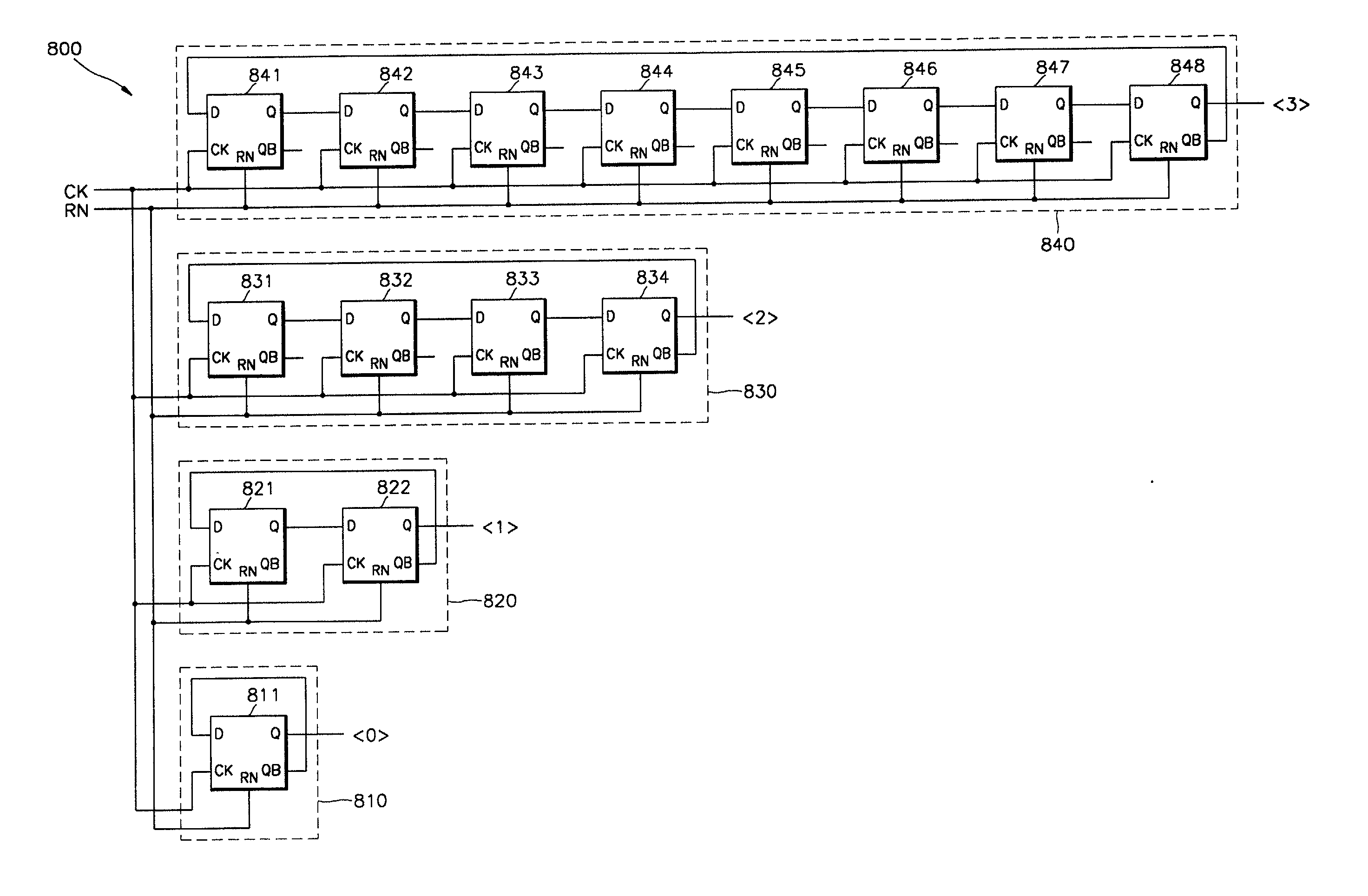

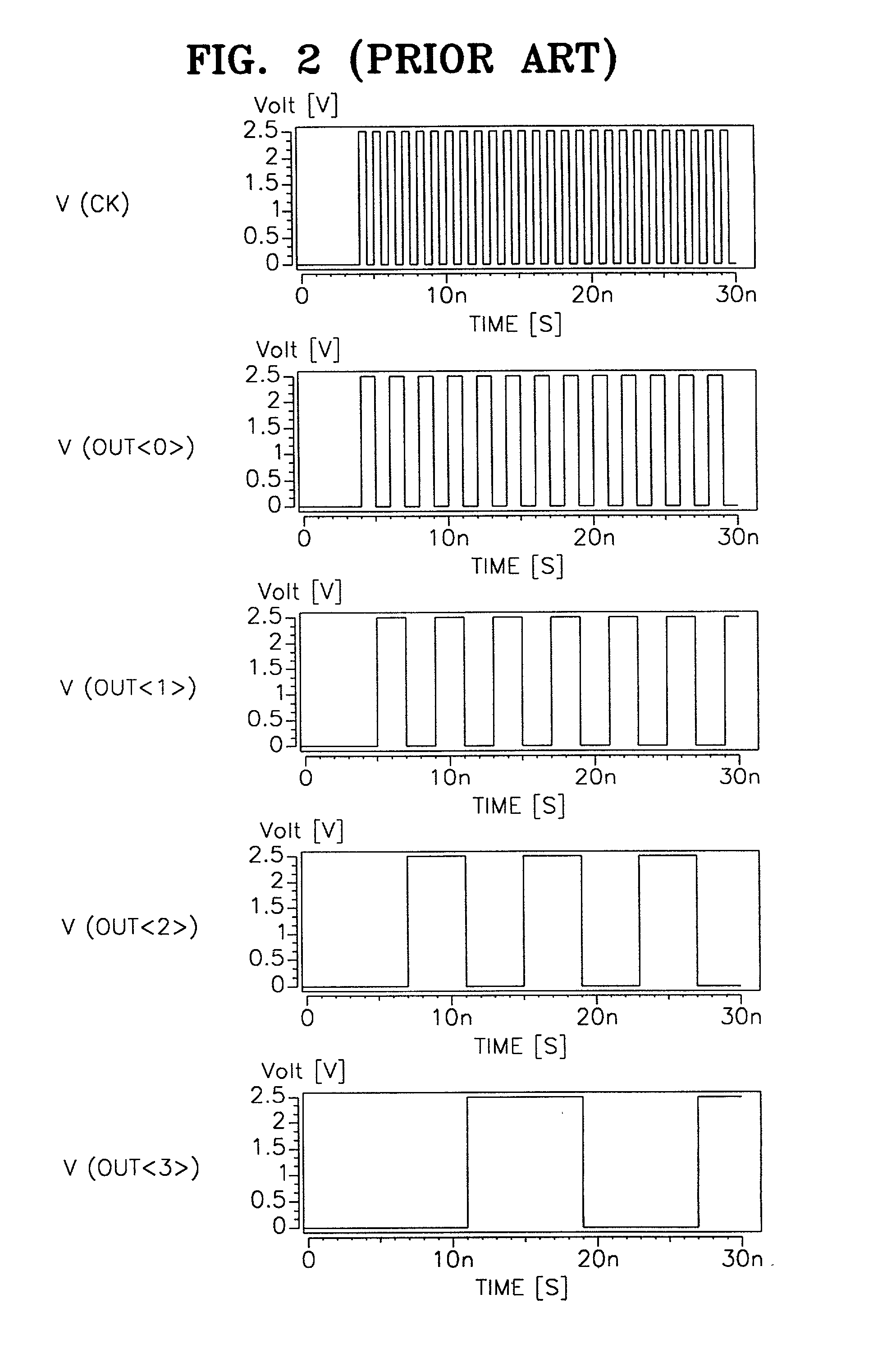

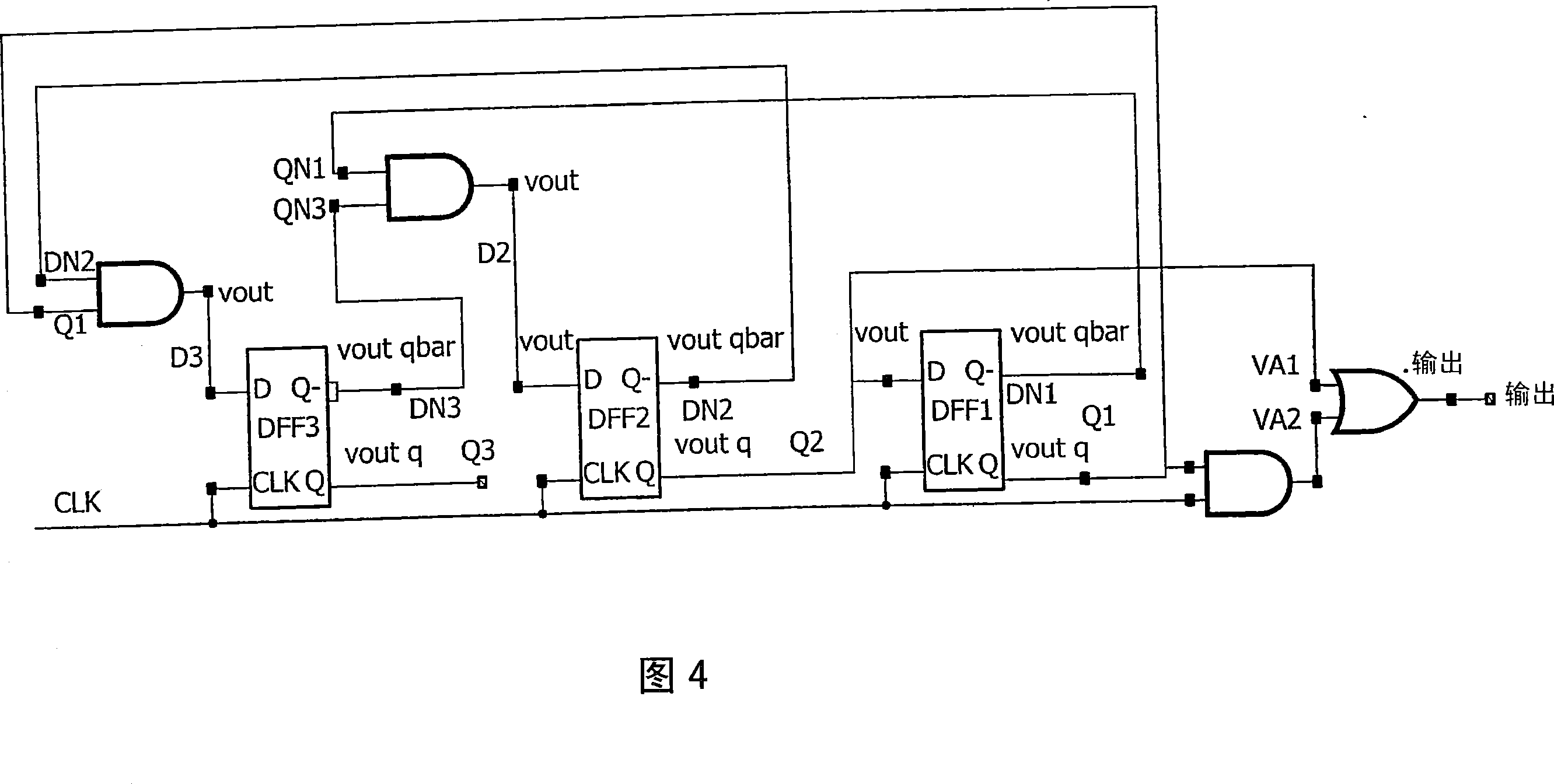

High-speed counter with sequential binary count order and method thereof

InactiveUS20020075989A1Continuously circulated pulse countersStatic indicating devicesComputer scienceFLOPS

A counter circuit, which is capable of operating at high speed and realizing a sequential binary count order, and a counting method thereof are provided. The counter circuit includes a first bit generation circuit, a second bit generation circuit, a third bit generation circuit, and a fourth bit generation circuit. The first bit generation circuit includes a D-flip-flop, inverts its output value every cycle of the clock signal, and generates a first bit output. The second bit generation circuit includes two D-flip-flops, inverts its output value every two cycles of the clock signal, and generates a second bit output. The third bit generation circuit includes four D-flip-flops, inverts its output value every four cycles of the clock signal, and generates a third bit output. The fourth bit generation circuit includes eight D-flip-flops, inverts its output value every eight cycles of the clock signal, and generates a fourth bit output. According to the counter circuit, bit outputs are generated with almost the same delay time within one cycle of a clock signal in a sequential binary count order. Thus, the operation of a system can be prevented from being delayed, and the performance of the system can be improved.

Owner:SAMSUNG ELECTRONICS CO LTD

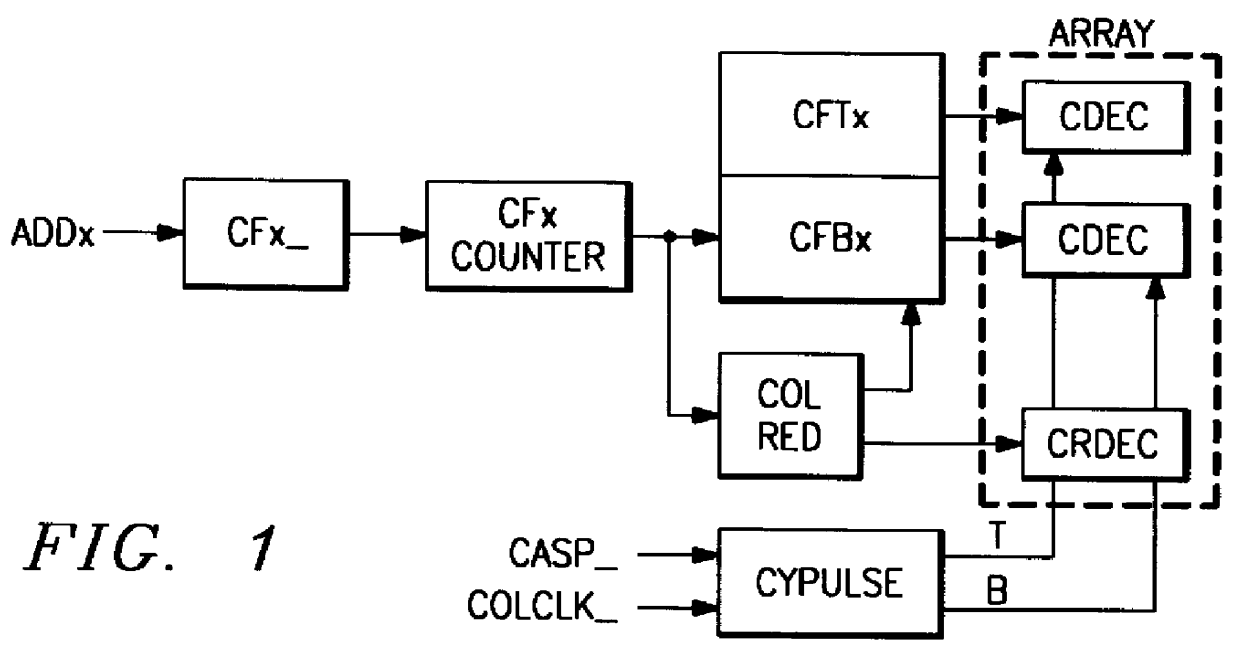

Synchronous random access memory having column factor counter for both serial and interleave counting

InactiveUS6091665AContinuously circulated pulse countersCounting chain synchronous pulse countersAccess timeRandom access memory

A synchronous dynamic random access memory (SDRAM) improves memory access time by incorporating into the column address path a bidirectional column factor counter.

Owner:TEXAS INSTR INC

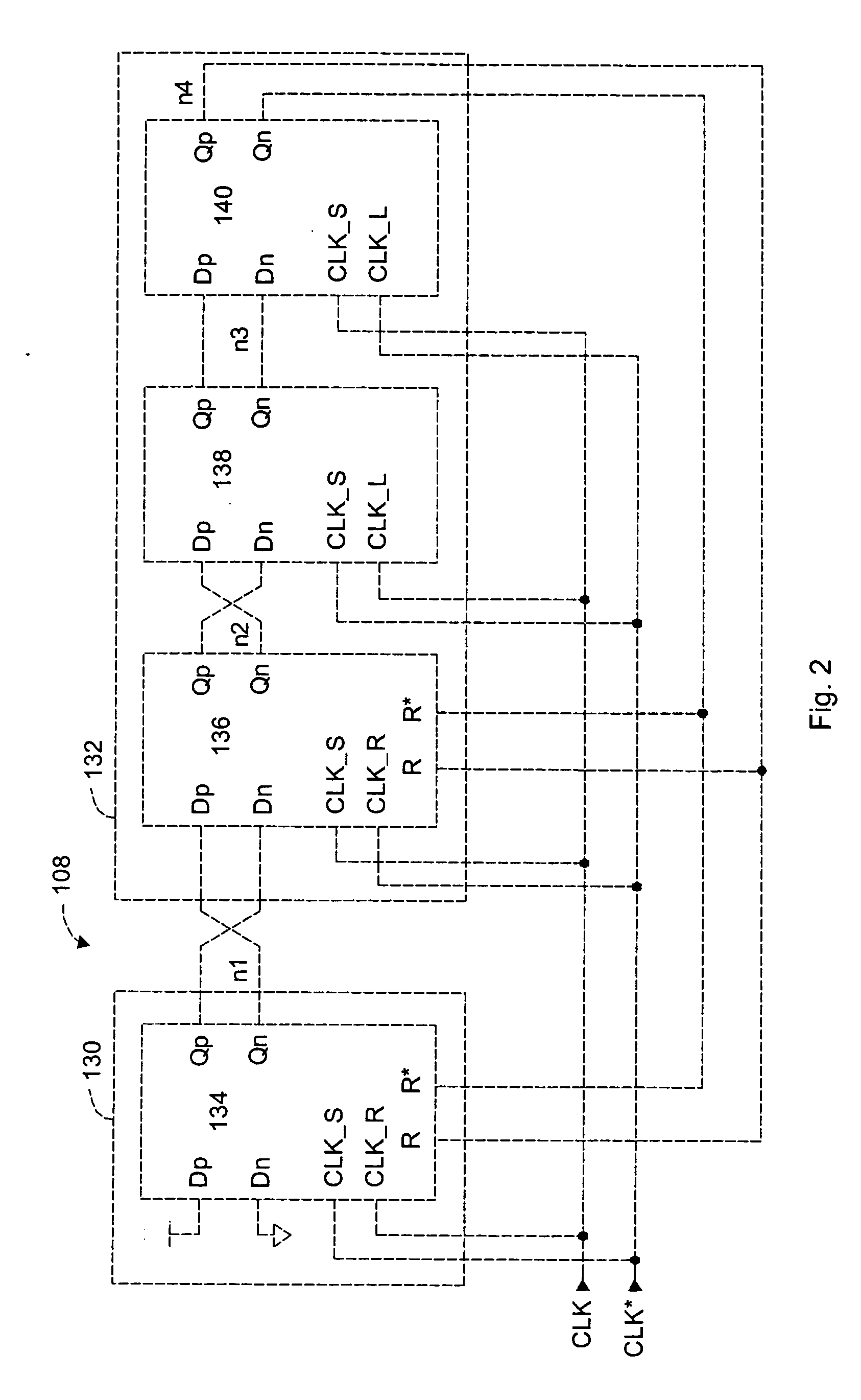

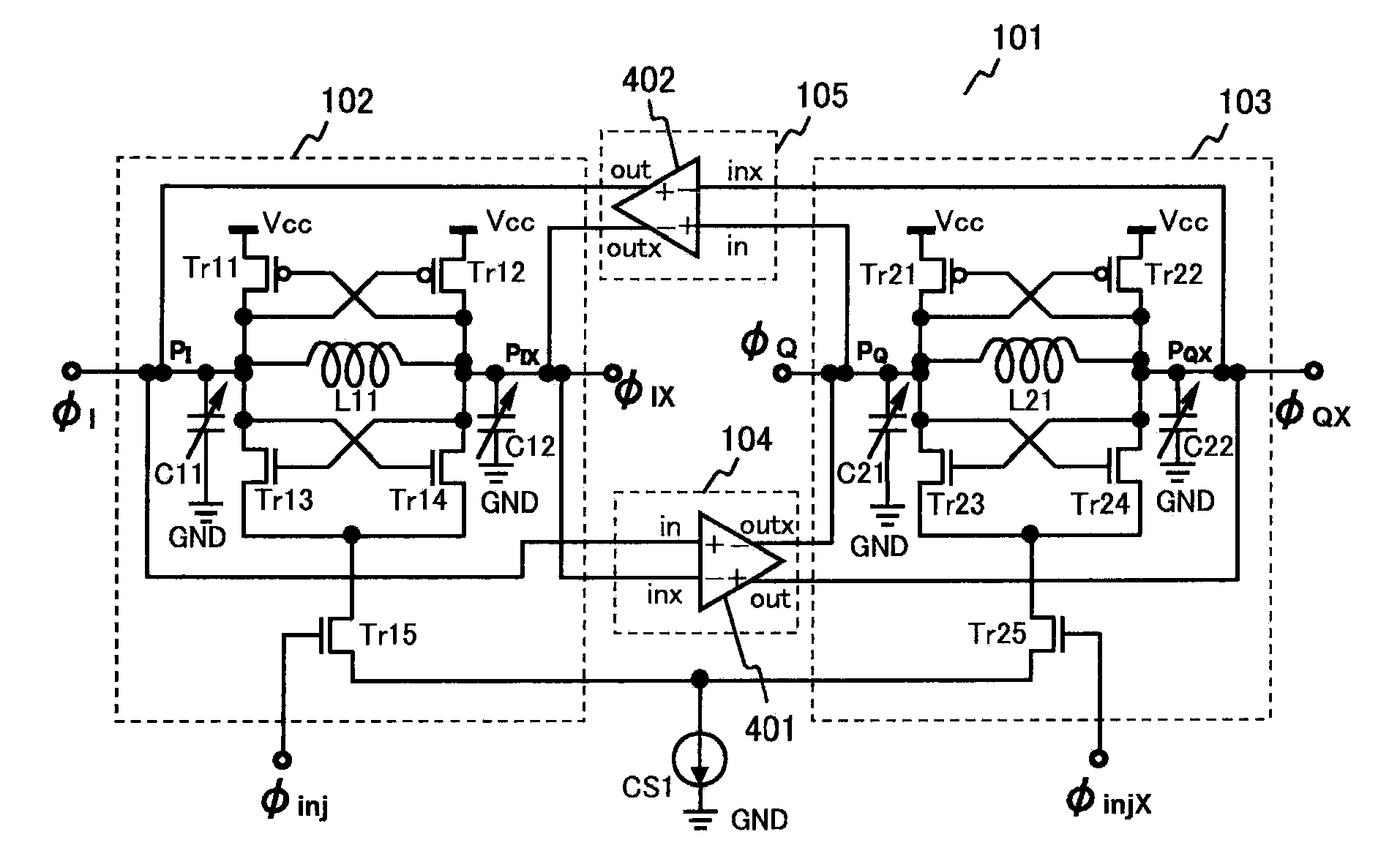

High frequency divider with input-sensitivity compensation

InactiveUS20070257735A1Reduce power intensityReduce power consumptionContinuously circulated pulse countersPulse automatic controlCapacitanceEngineering

A frequency divider, which has a cross-coupled inductor-capacitor (LC) structure or a ring structure, is inputted with a direct current (DC) control voltage from an input terminal. By doing so, the frequency divider can adjust an oscillation frequency; and further compensate the input power sensitivity, lower the power consumption and increase the division range. The frequency divider can be used in high-band / high-speed digital or analog communication systems.

Owner:NAT CENT UNIV

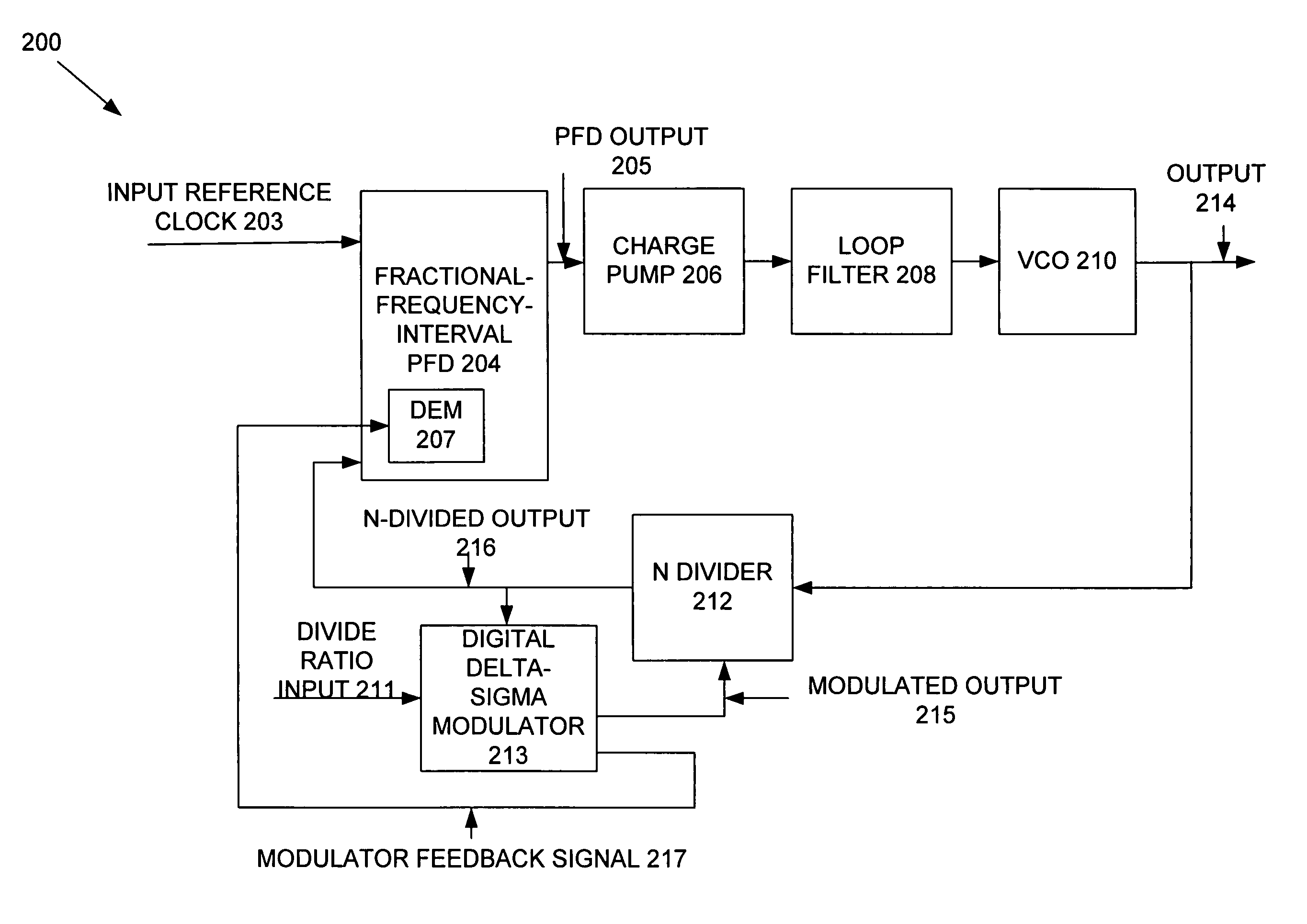

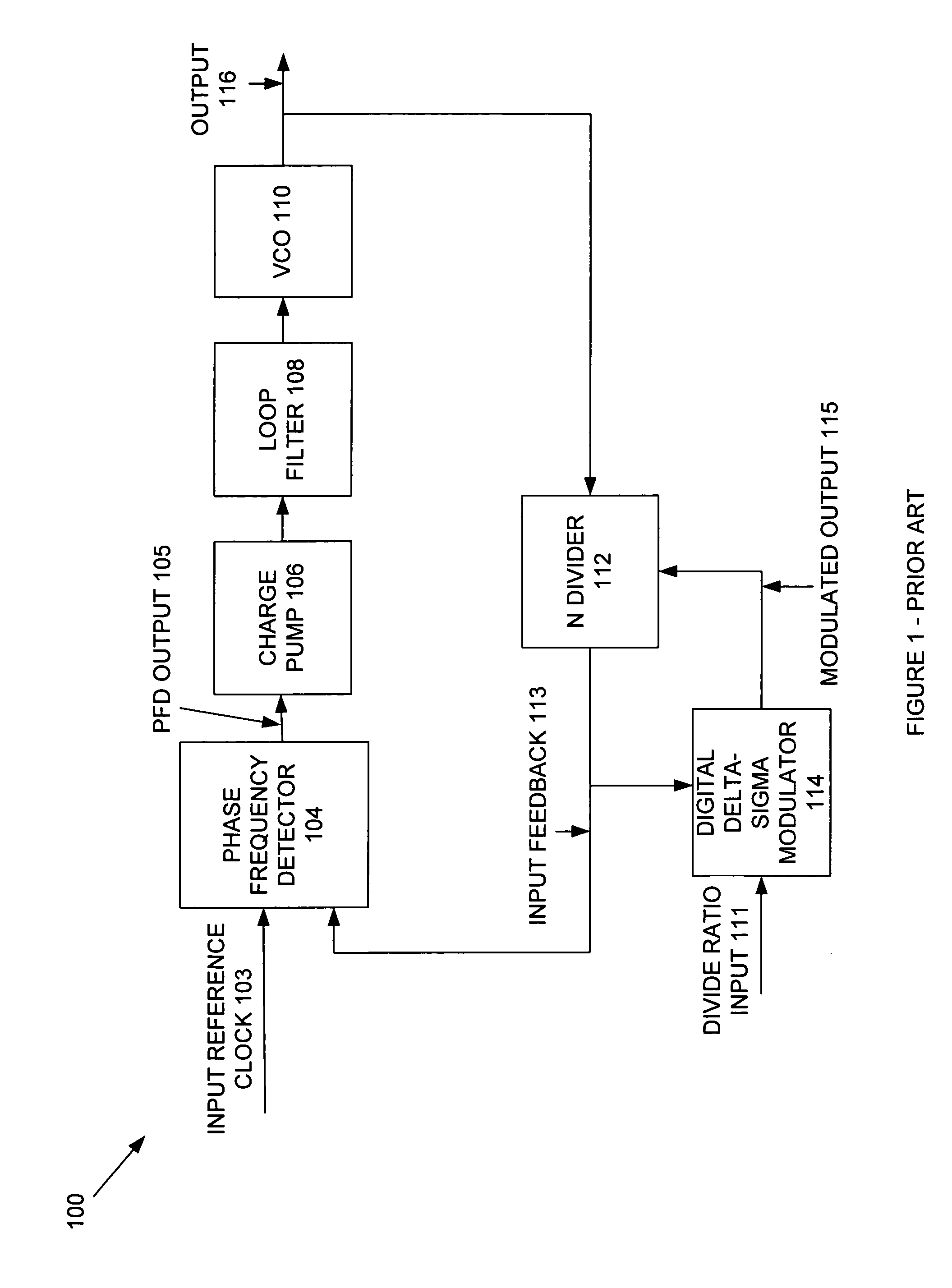

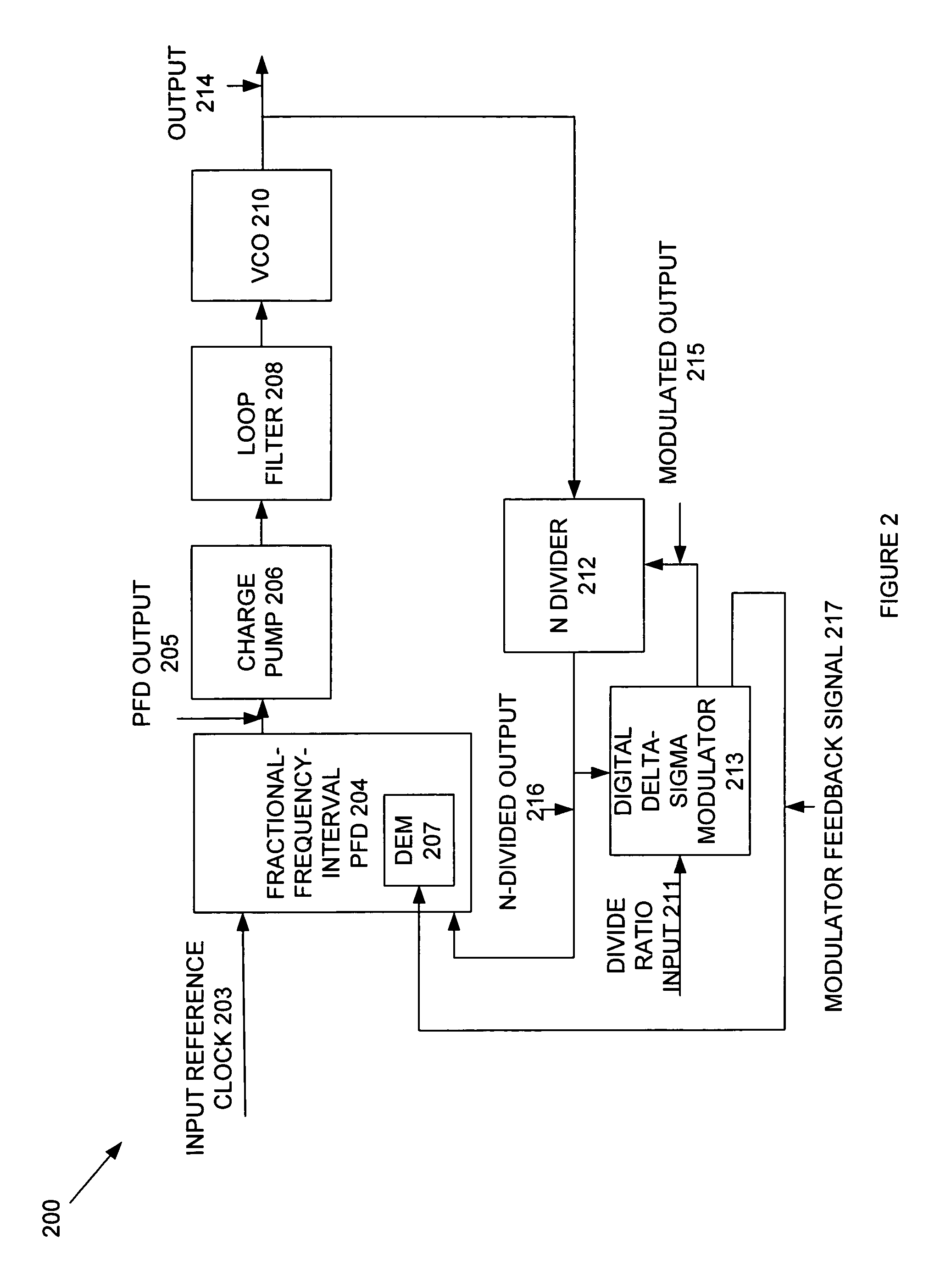

Fractional-integer phase-locked loop system with a fractional-frequency-interval phase frequency detector

ActiveUS7049852B2Continuously circulated pulse countersPulse automatic controlPhase locked loop circuitPhase frequency detector

A phase-locked loop circuit has a fractional-frequency-interval phase frequency detector, a charge pump, an oscillator, and a divider. The fractional-frequency-interval phase frequency detector has a phase frequency detector unit that is utilized as or comprises a plurality of phase frequency detector units. The divider is responsive to the oscillator and provides divider values for dividing an oscillator frequency by the divider values to provide a feedback frequency of a feedback loop signal of the phase-locked loop circuit. A reference input frequency is input as a first input into the phase frequency detector unit. The feedback frequency is input and selectively delayed as second inputs into the phase frequency detector unit so that the second inputs are aligned for input according to the reference input frequency and an oscillator frequency is, in effect, responsive to the phase frequency detector units and allowed to be divided by a fractional-integer divider value.

Owner:CIRRUS LOGIC INC

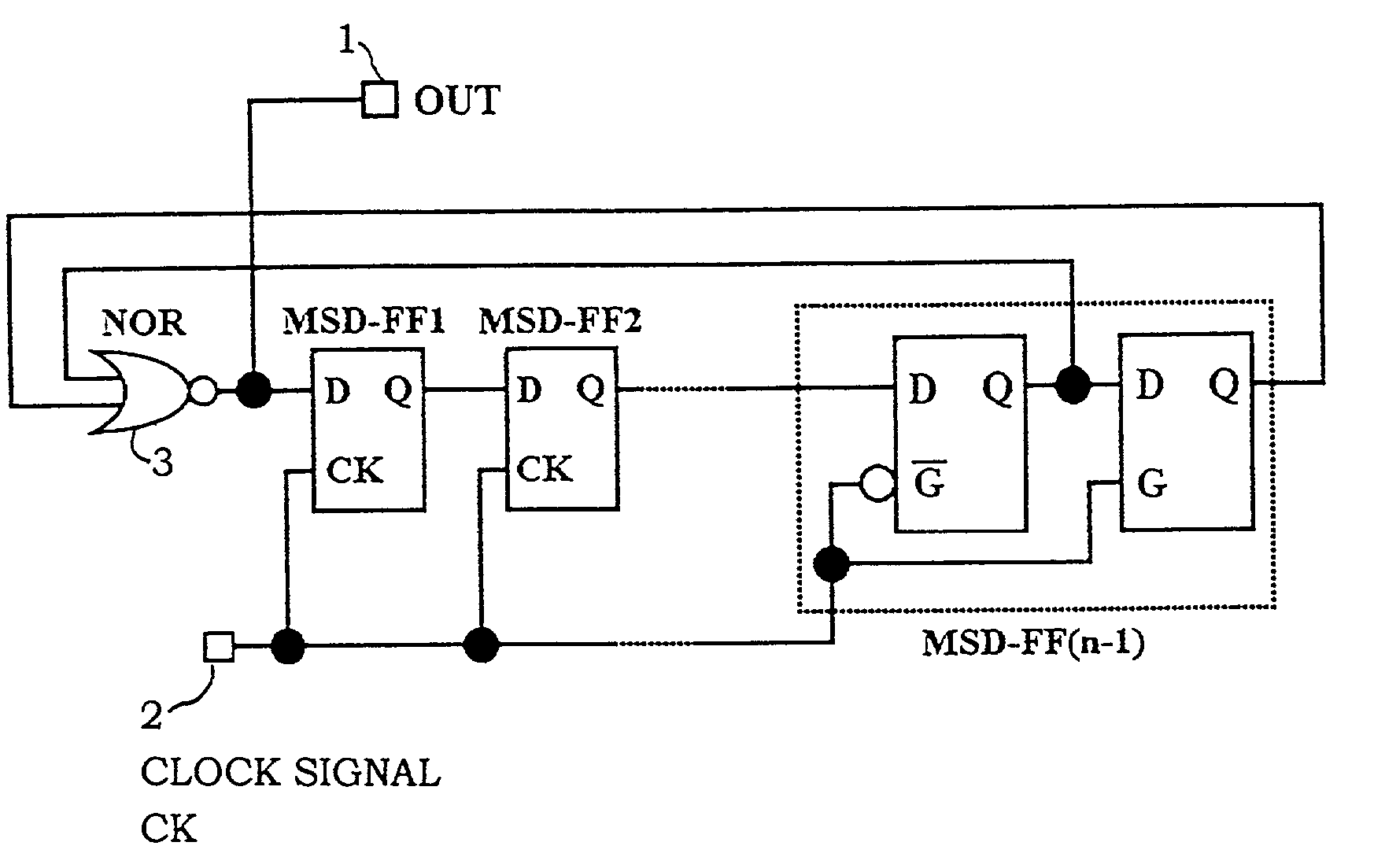

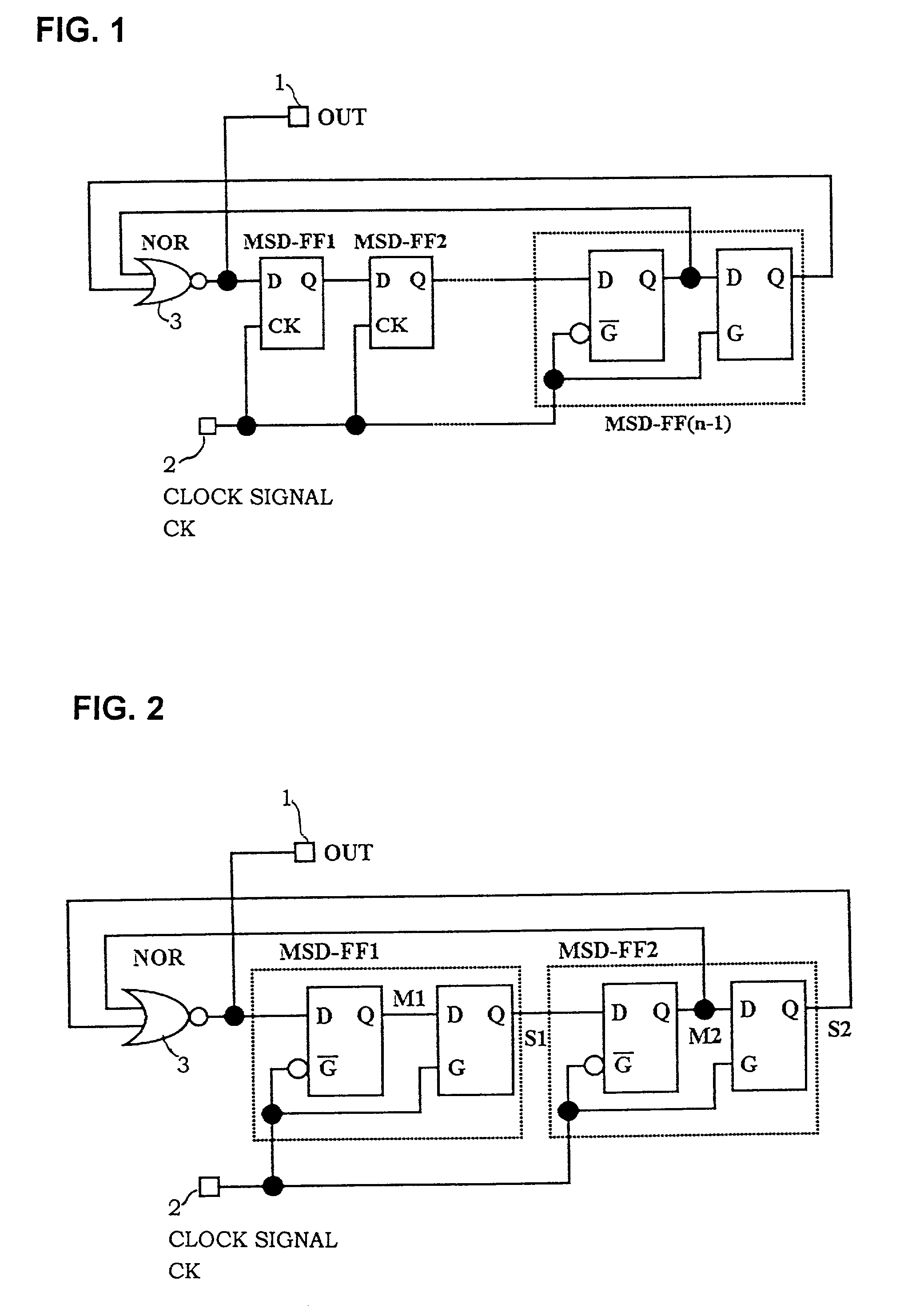

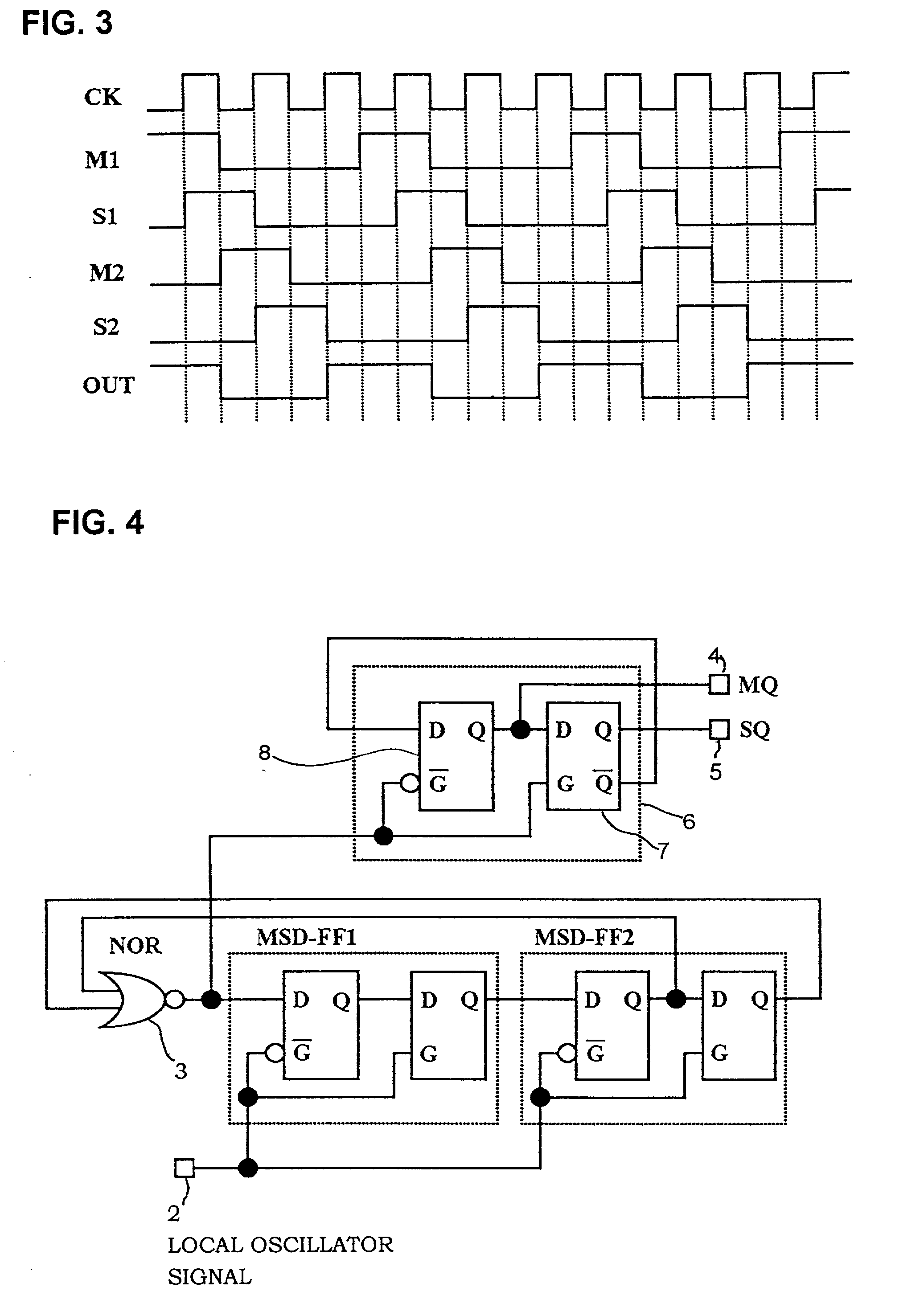

Odd -number factor frequency divider and 90o phase splitter which operates from output signal of the frequency divider

InactiveUS20020171458A1Small scaleLower average currentContinuously circulated pulse countersCounting chain synchronous pulse countersNOR gatePhase splitter

An odd number factor frequency divider which generates a final output signal having a duty ratio of 1 / 2 is formed of a plurality of cascade-connected MSD-FFs (master-slave D-type flip-flops), operating from a common clock signal, with a single NOR gate being used to derive a signal expressing the negated logic sum of the respective Q-terminal logic outputs from the master D-type latch and the slave D-type latch which constitute the final-stage MSD-FF of the plurality of cascade-connected MSD-FFs, with that output signal from the NOR gate being applied to the D input terminal of the first-stage MSD-FF, while also being supplied to an output terminal as the final output signal from the frequency divider. Since a minimum number of circuit elements are employed, the overall circuit scale can be small, and current consumption low.

Owner:PANASONIC CORP

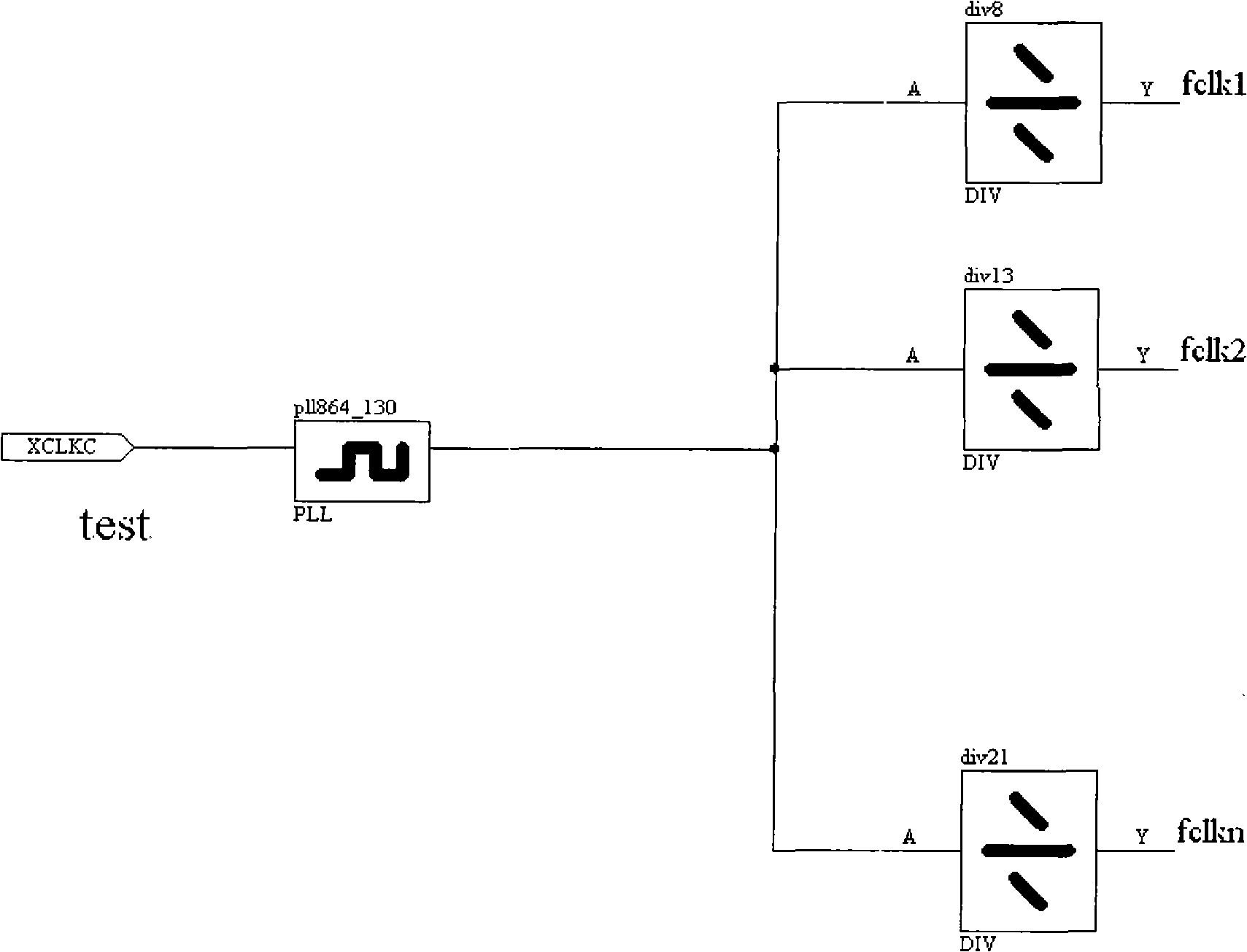

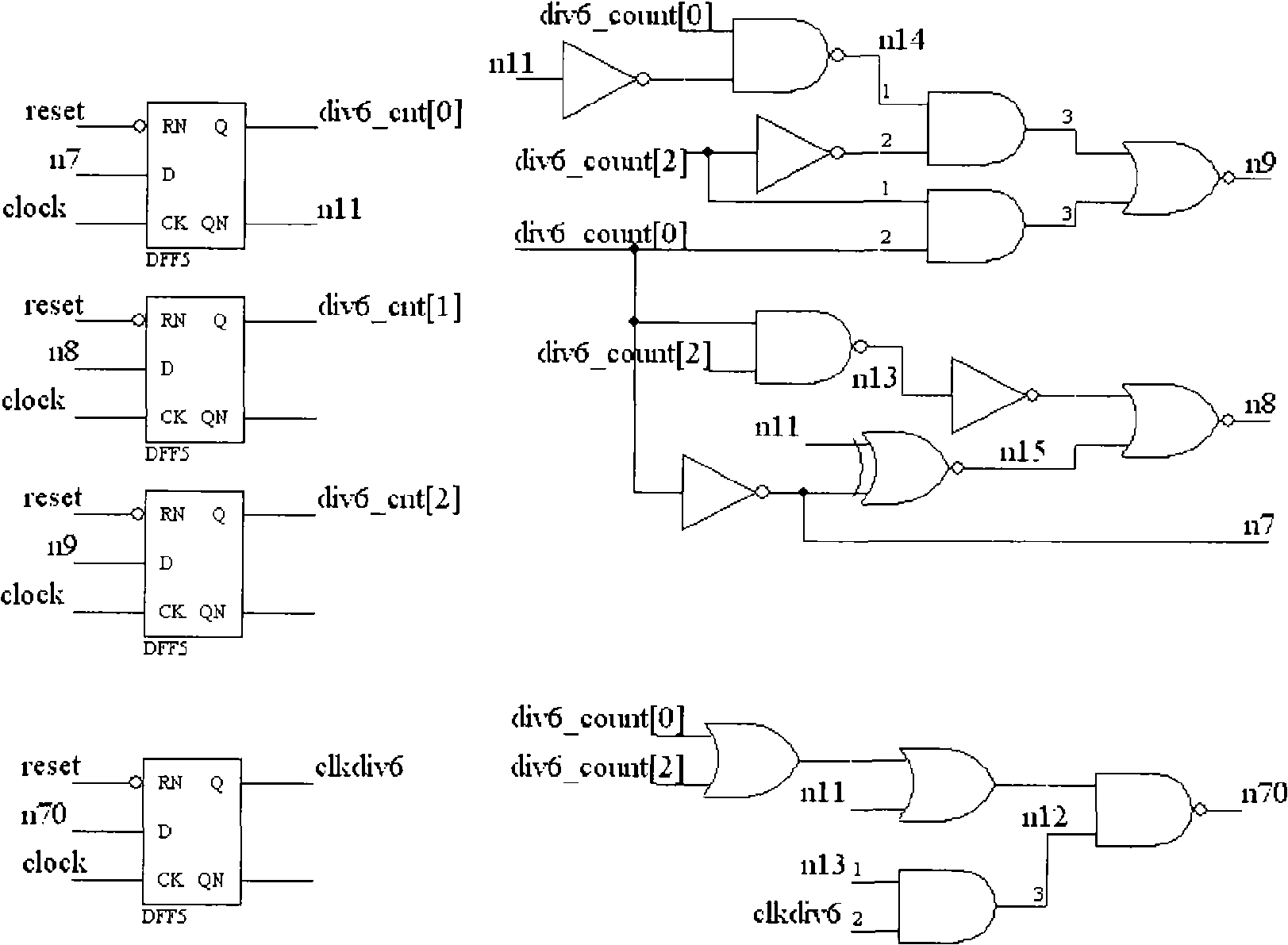

Clock frequency dividing method based on trigger ring and clock frequency dividing circuit thereof

InactiveCN101291149ASmall scaleLower latencyContinuously circulated pulse countersCounting chain synchronous pulse countersRing circuitClock rate

The present invention relates to a clock frequency division technology for an integrated circuit, in particular to a clock frequency division method based on a trigger ring and a clock frequency division circuit thereof. The method is to orderly connect data input ends and data output ends of a plurality of triggers to form a trigger ring circuit. The number of the triggers with set ends and reset ends in the trigger ring is selected according to the requirement of the frequency division circuit for a duty ratio. The positions of the triggers with set ends and reset ends are determined according to the requirement of a clock waveform. The trigger ring circuit accesses a system frequency division circuit, and a spare data output end of the last trigger is used as an output end of the trigger ring circuit so as to realize clock frequency division. The number of the frequency division of the method and the circuit structure thereof do not influence the highest frequency of the working circuit. The normal work of the frequency division circuit can be at a comparatively high clock frequency, and the clock frequency division can be realized in the manner of cascade connection of the frequency division circuit so that the scale of the circuit realization can be properly reduced.

Owner:VIMICRO CORP

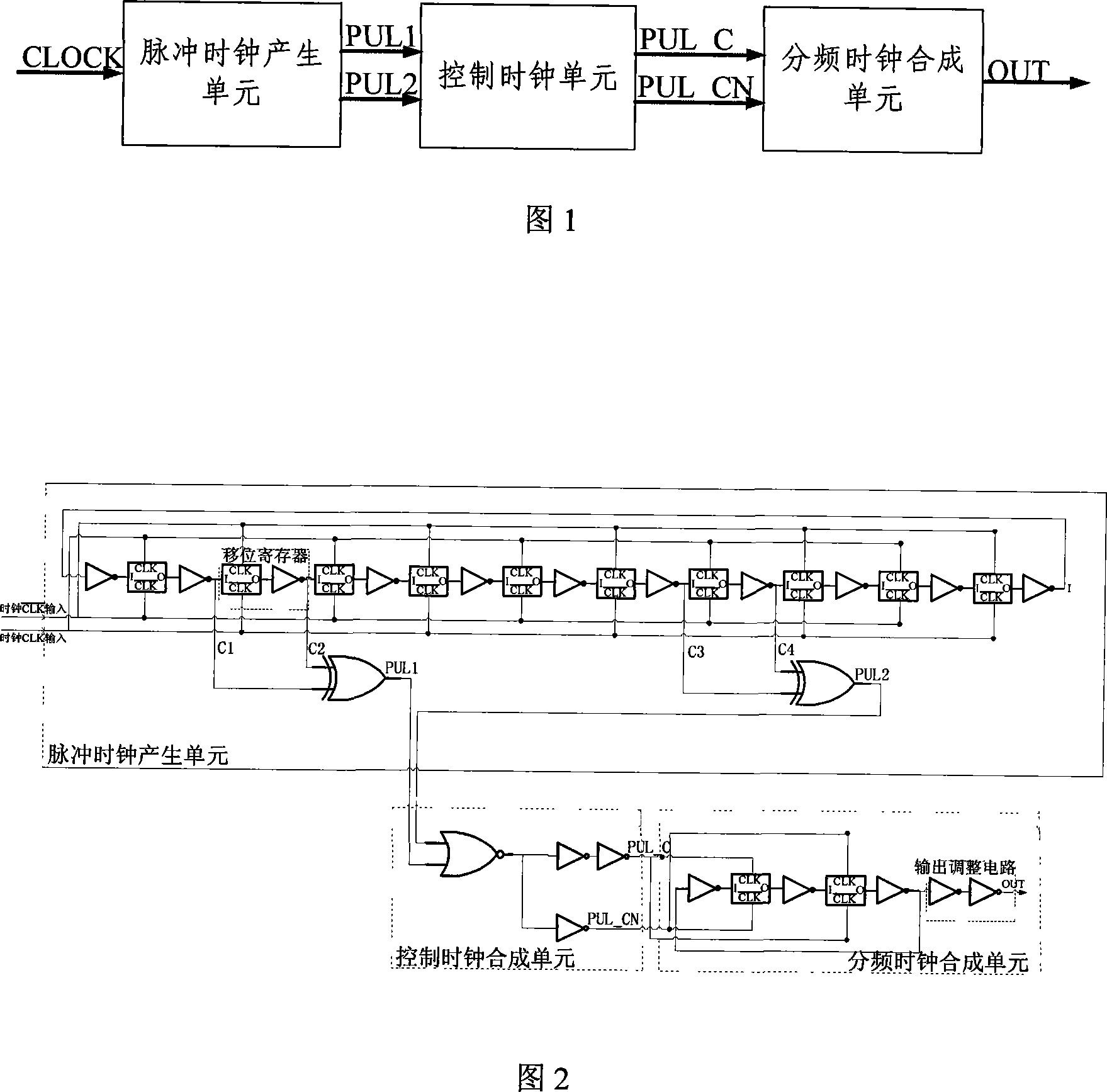

Idle percent adjustable N-time frequency division circuit of pulse mixing mode

InactiveCN101087141AImprove stabilityStrong resistance to PVT changesContinuously circulated pulse countersPulse automatic controlShift registerDividing circuits

The invention discloses dutycycle adjustable N order frequency dividing circuit of pulse synthesizing method, which includes: generating unit of pulse clock which consists of shift register with cascaded N dynamic lock memorizers, and the N is the frequency dividing ratio of input clock, the control clock of odd shift register is connected with the control clock of even shift register reversely, and the output of the last shift register feeds back to the input end of first shift register by inverter; the synthesis unit of control clock consists of NOT-OR gate and three drive inverters; the synthesis unit of frequency dividing clock consists of two shift registers and the adjusting unit of input information, two shift registers controlled by reversed clock control form a dynamic trigger, and feeds back to input by inverter. The invention is dutycycle adjustable N order frequency dividing circuit of pulse synthesizing method with simple structure, adopting pulse synthesizing method, and the dutycycle adjustable random order frequency dividing.

Owner:NAT UNIV OF DEFENSE TECH

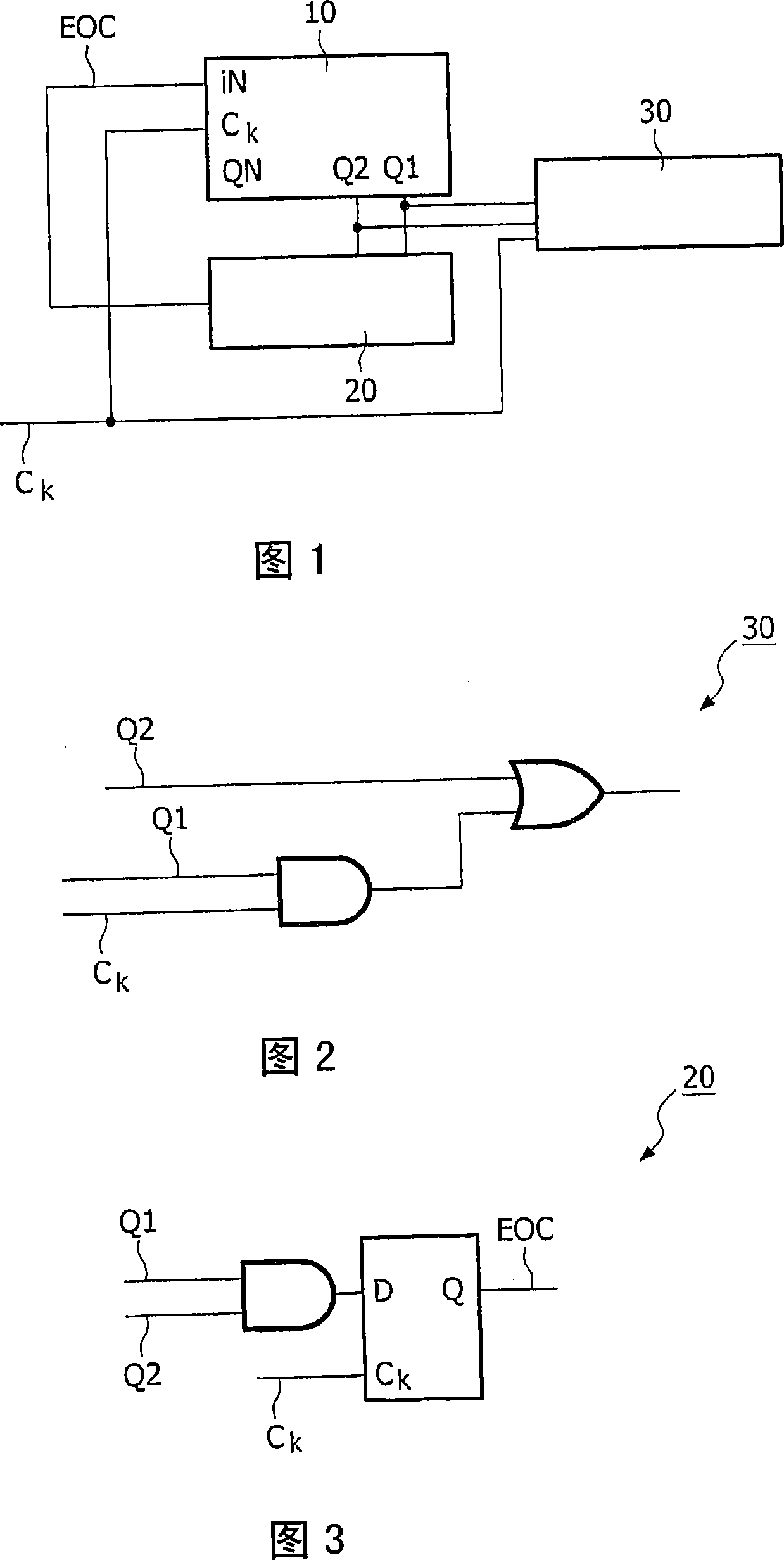

Frequency divider

ActiveCN101006645AContinuously circulated pulse countersCounting chain synchronous pulse countersEngineeringClock signal

A frequency divider providing an odd integer division factor comprising a binary counter (10) providing an even integer division factor, which is the first even number smaller than the odd division factor, the binary counter having a clock input for receiving a periodical clock signal (Ck) having a frequency. The circuit further comprises an end of count circuit (20) coupled to the binary counter and generating an End Of Count signal (EOC) for a clock (Ck) period after every even integer number periods of the clock signal (Ck), the end of count signal (EOC) being inputted to an input (IN) of the counter (10). The circuit further includes an output generator (30) coupled to the binary counter and to the clock signal (Ck), the output generator (30) generating an output signal (OUT) having a frequency which is substantially equal with the frequency of the frequency signal (Ck) divided by the odd division factor.

Owner:NXP BV

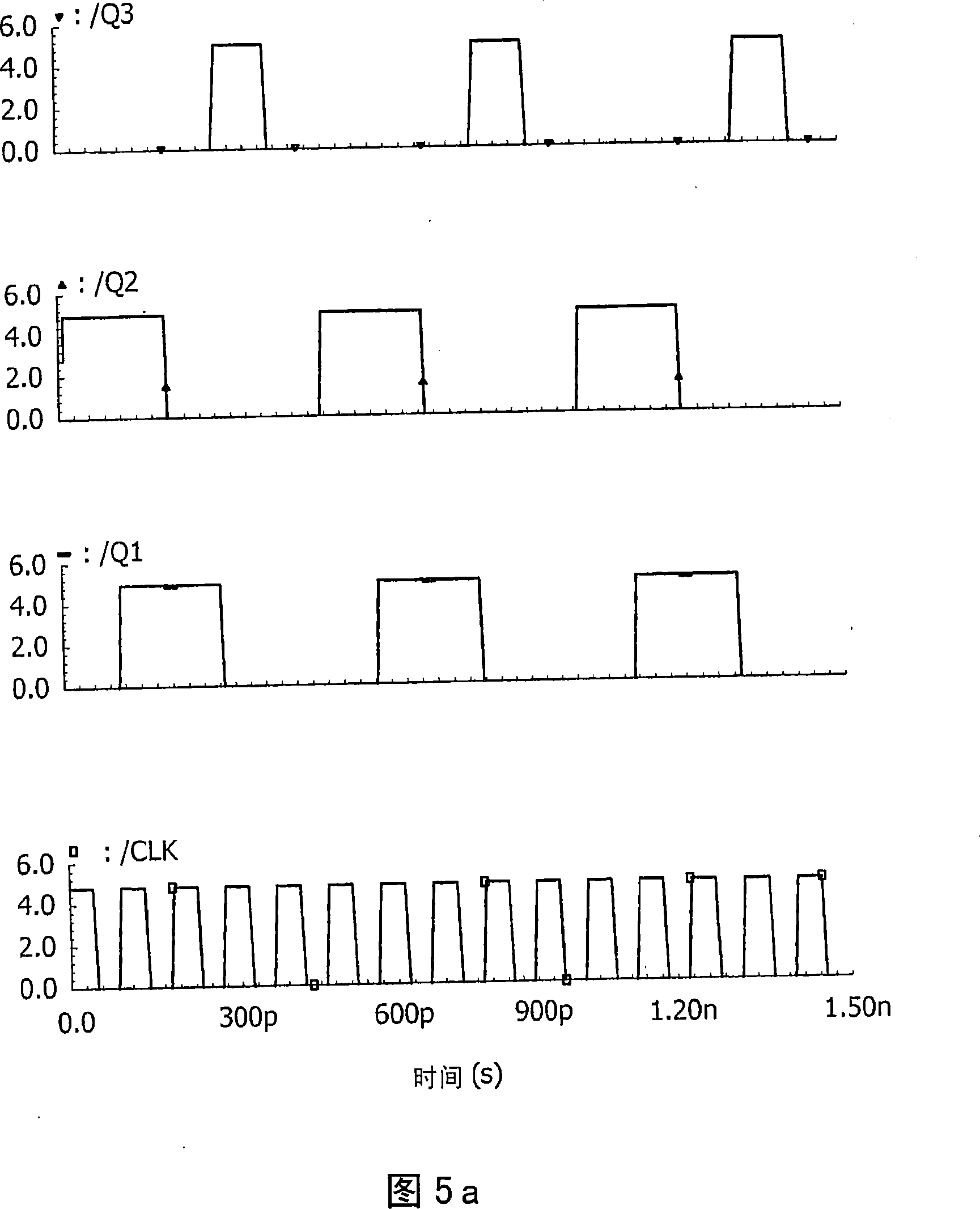

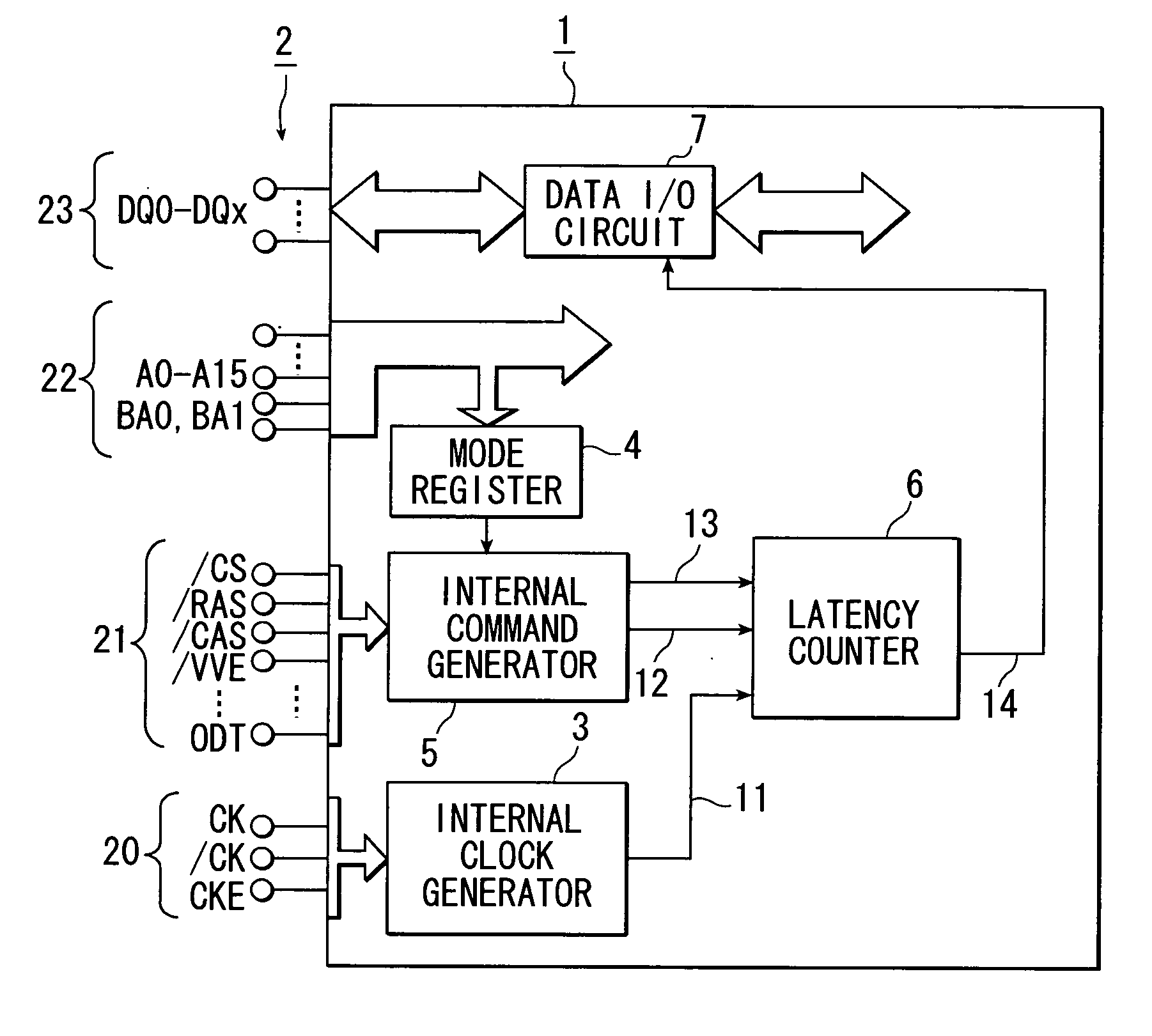

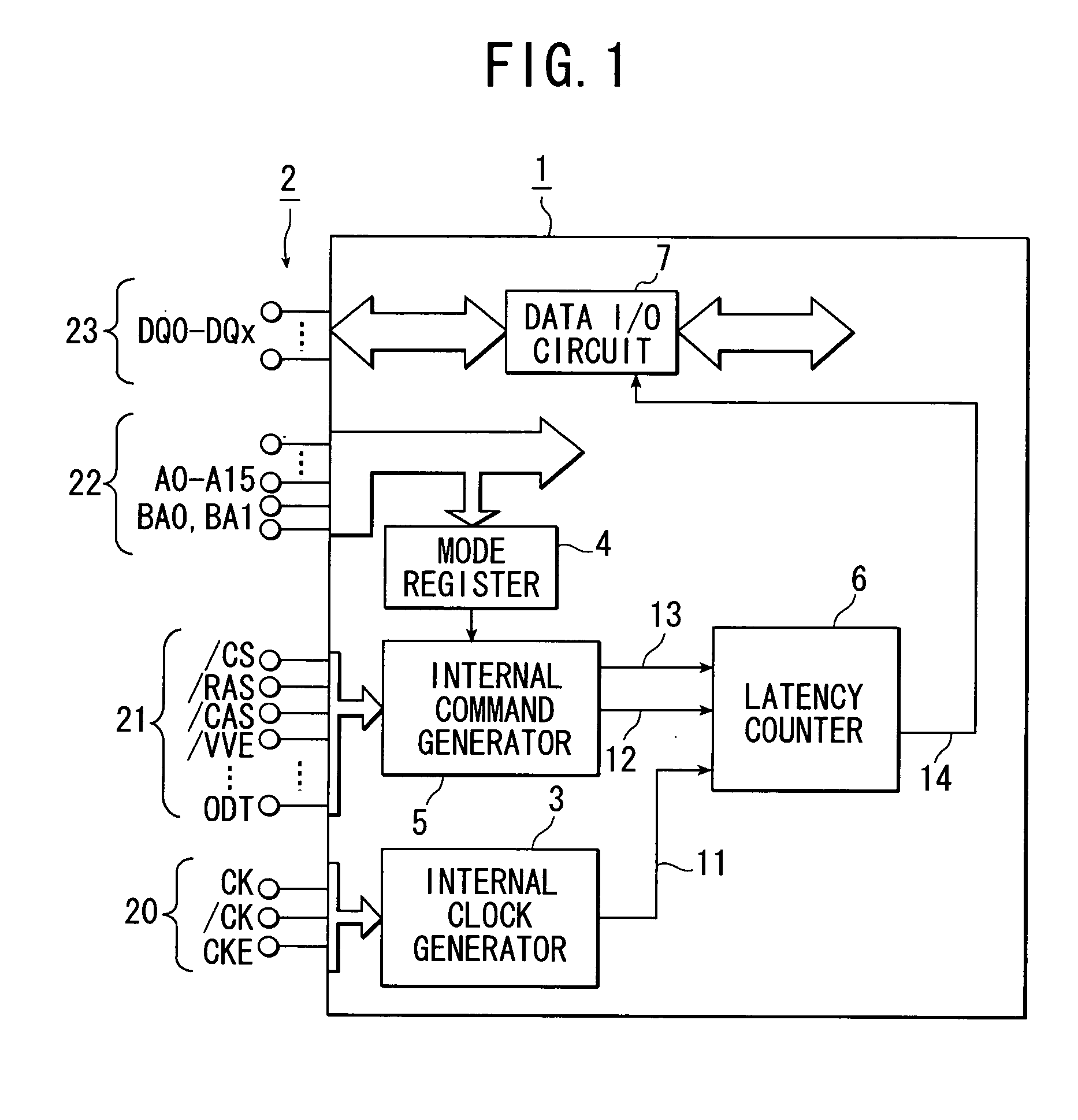

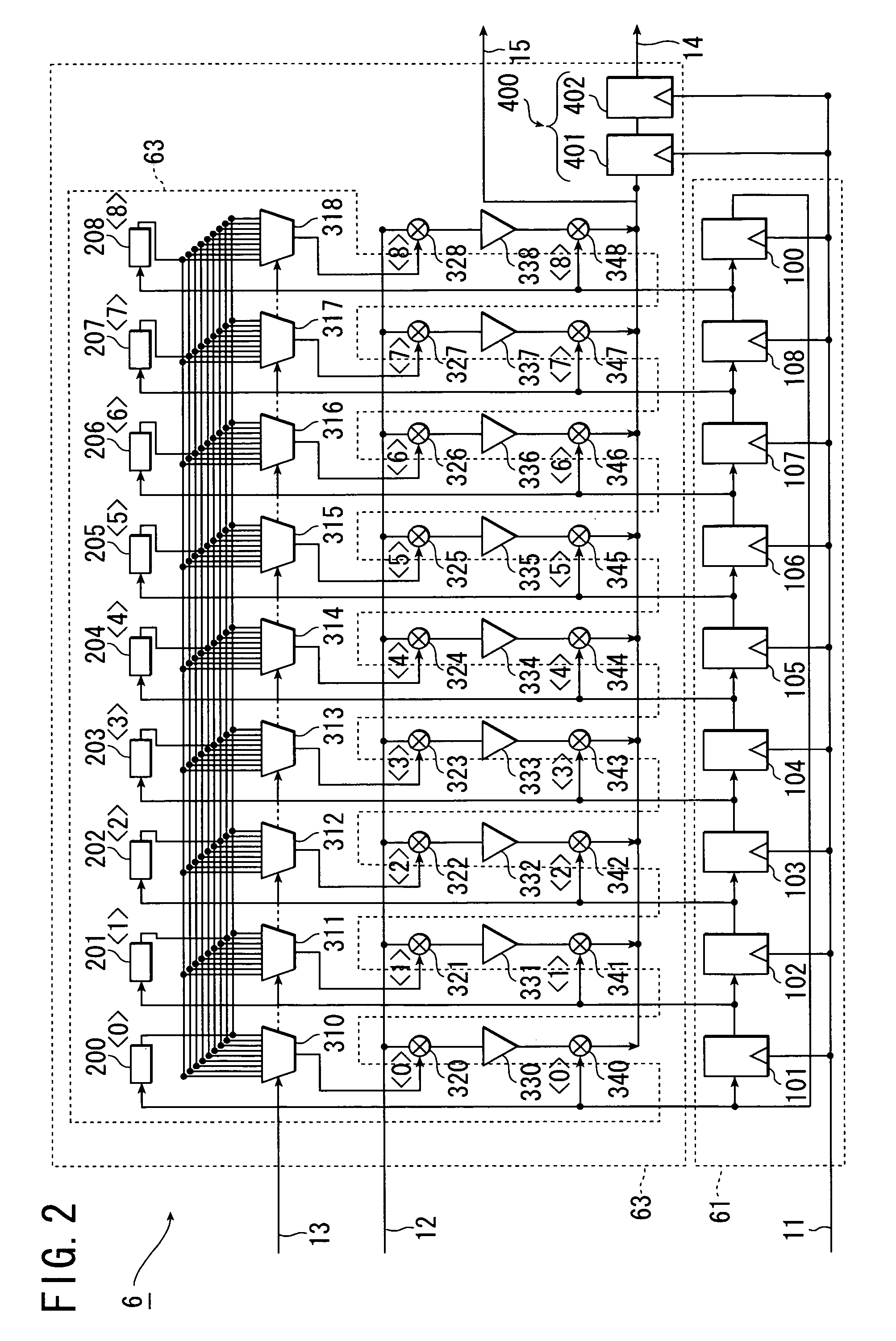

Semiconductor device with latency counter

InactiveUS20070076516A1Reduce power consumptionContinuously circulated pulse countersCounting chain synchronous pulse countersSignal generatorComputer science

A latency counter of a semiconductor device comprises a single cyclic signal generator and a command delay circuit. The single cyclic signal generator cyclically produces 0-th to n-th base signals based on an internal clock signal. The command delay circuit comprises 0-th to n-th latch elements and latches an internal command by means of a p-th latch element (p is an integer; 0≦p≦n) in response to a q-th base signal (q is an integer; 0≦q≦n) and to output the latched internal command corresponding to the latency timeout signal therefrom in response to a r-th base signal (r is an integer; 0≦r≦n), where r=q+s if q+s≦n, while r=q+s−(n+1) if q+s>n, s being a natural number equal to or less than n.

Owner:LONGITUDE LICENSING LTD

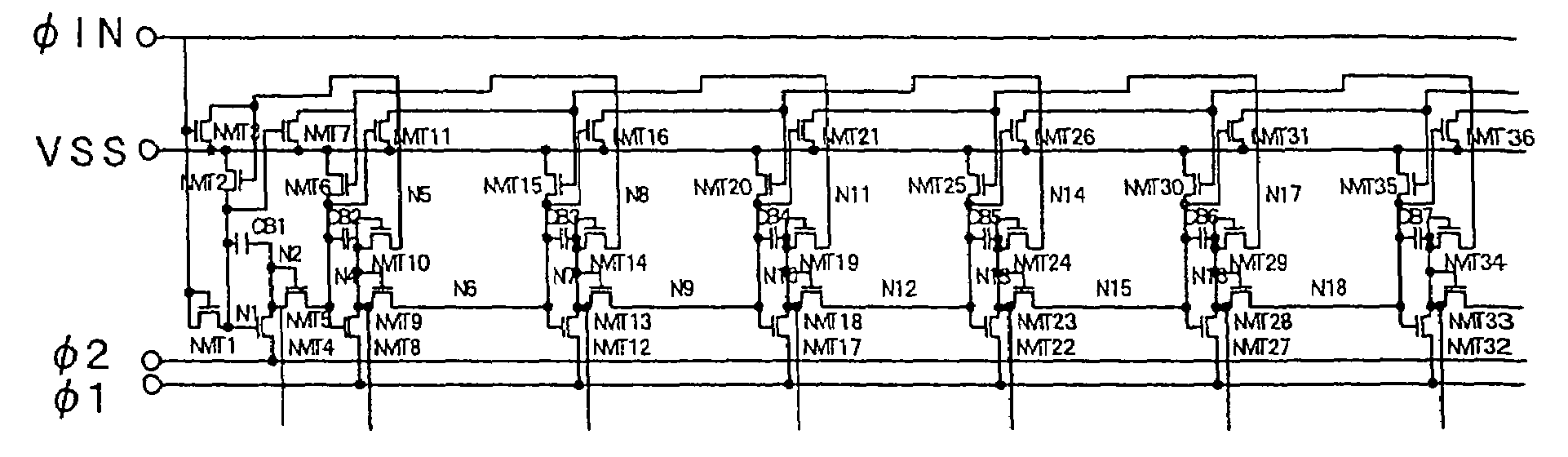

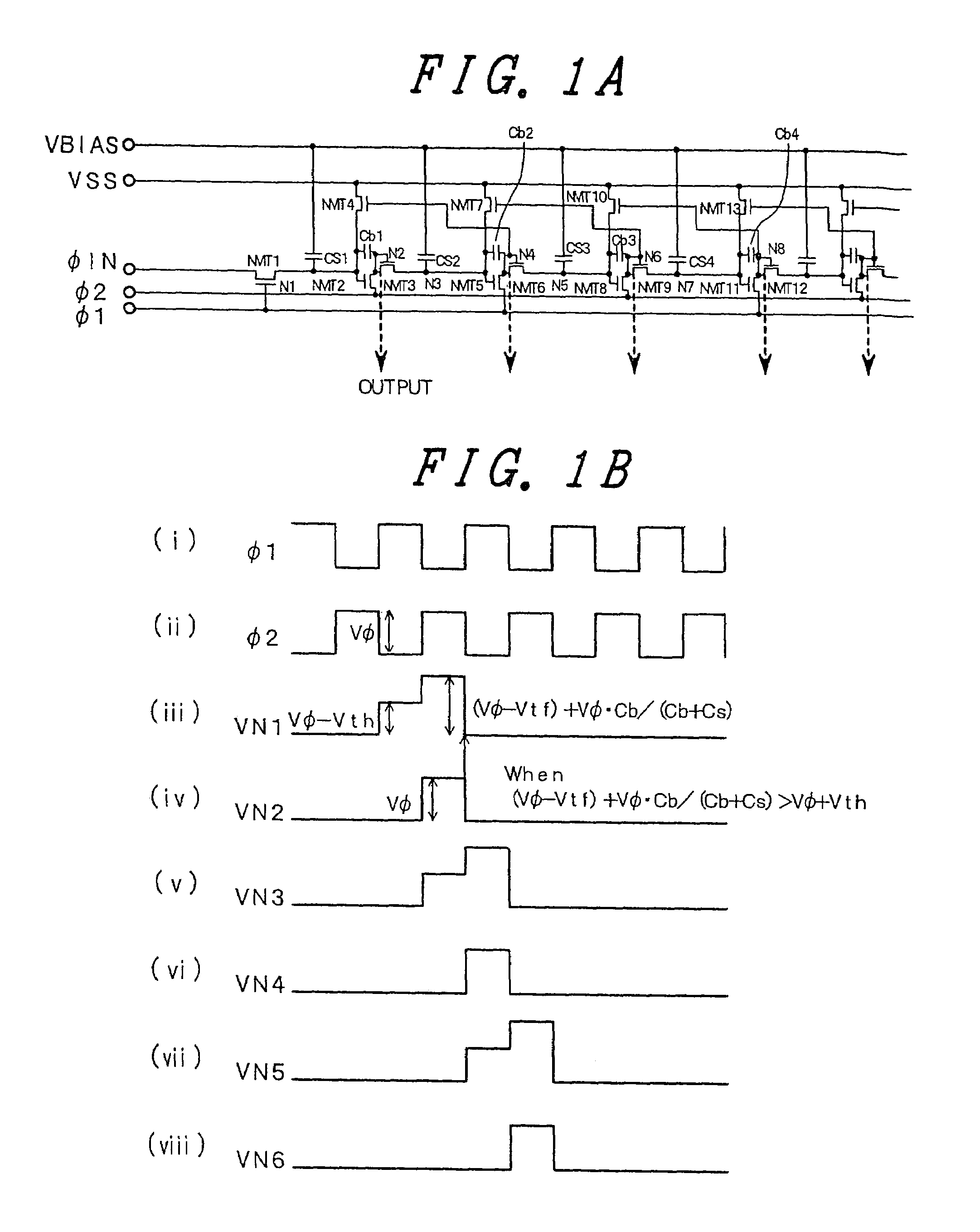

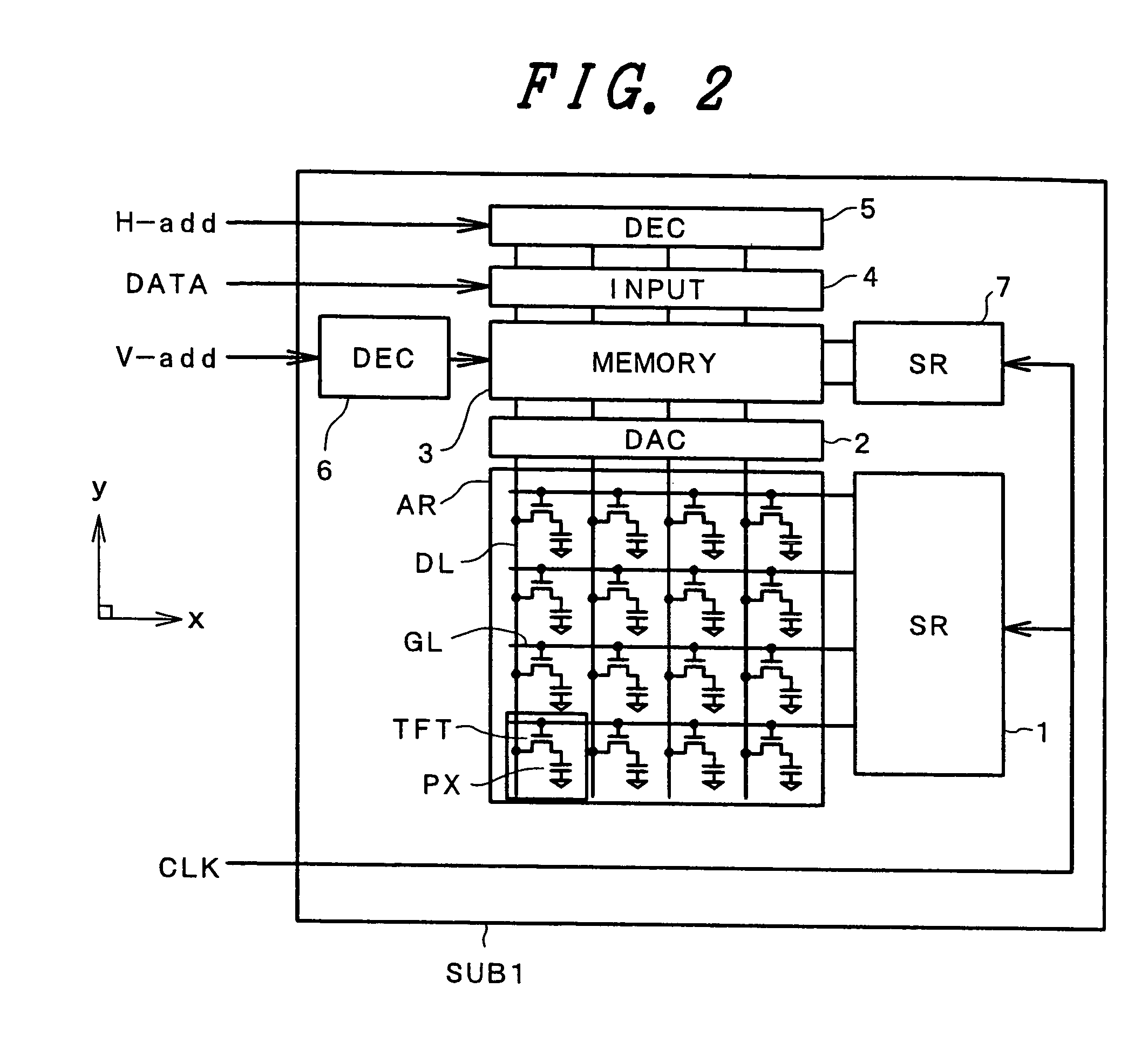

Active matrix display device

InactiveUS7274362B2Continuously circulated pulse countersCounting chain synchronous pulse countersCapacitanceShift register

A display device includes a dynamic ratioless shift register which is operated in a stable manner and can expand the degree of freedom of design. In the dynamic ratioless shift register which is provided with thin film transistors having semiconductor layers made of p-Si on a substrate surface, a node which becomes the floating state is connected to a fixed potential through a capacitance element.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

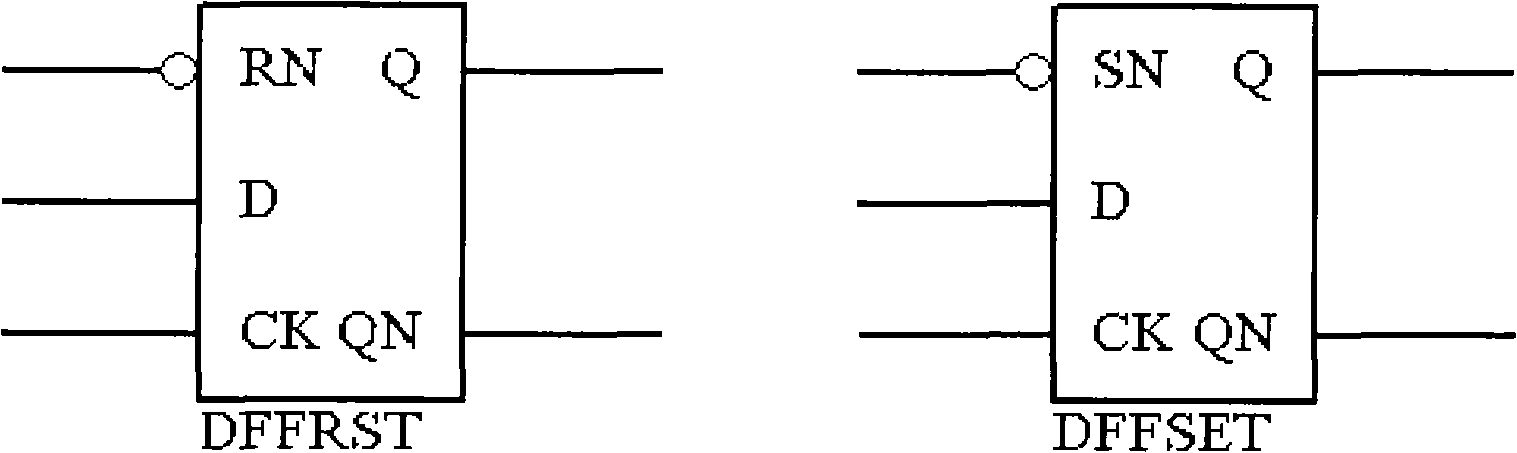

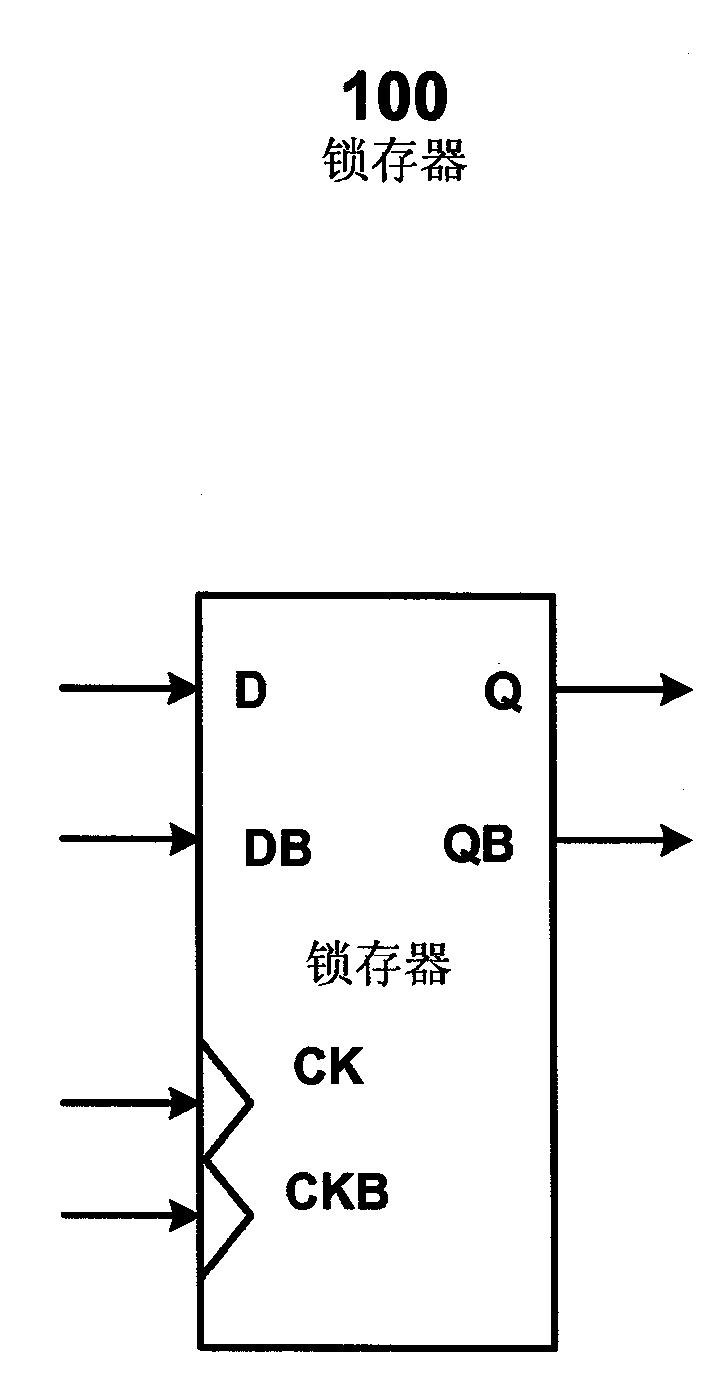

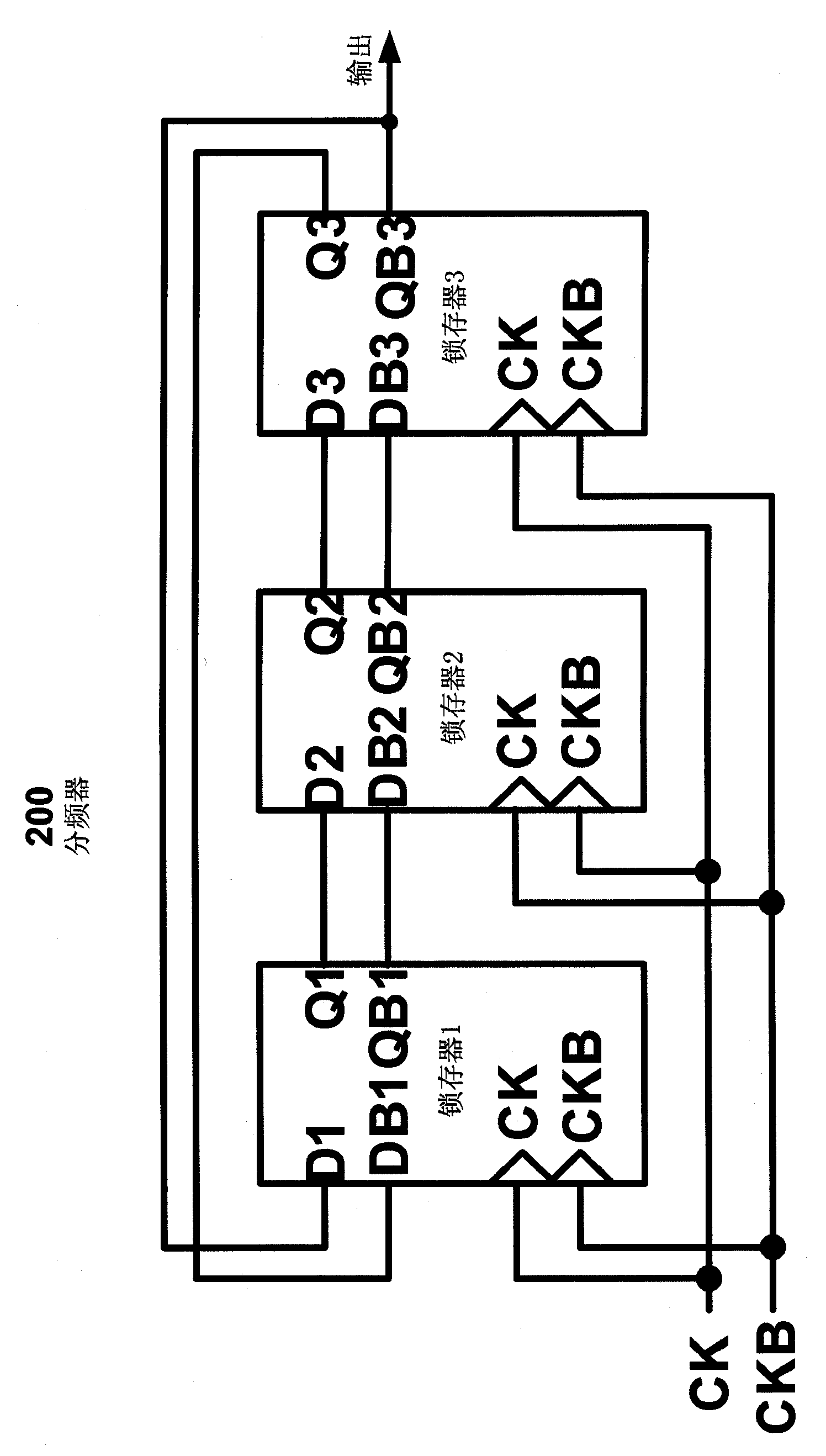

Latch structure, frequency divider, and methods for operating same

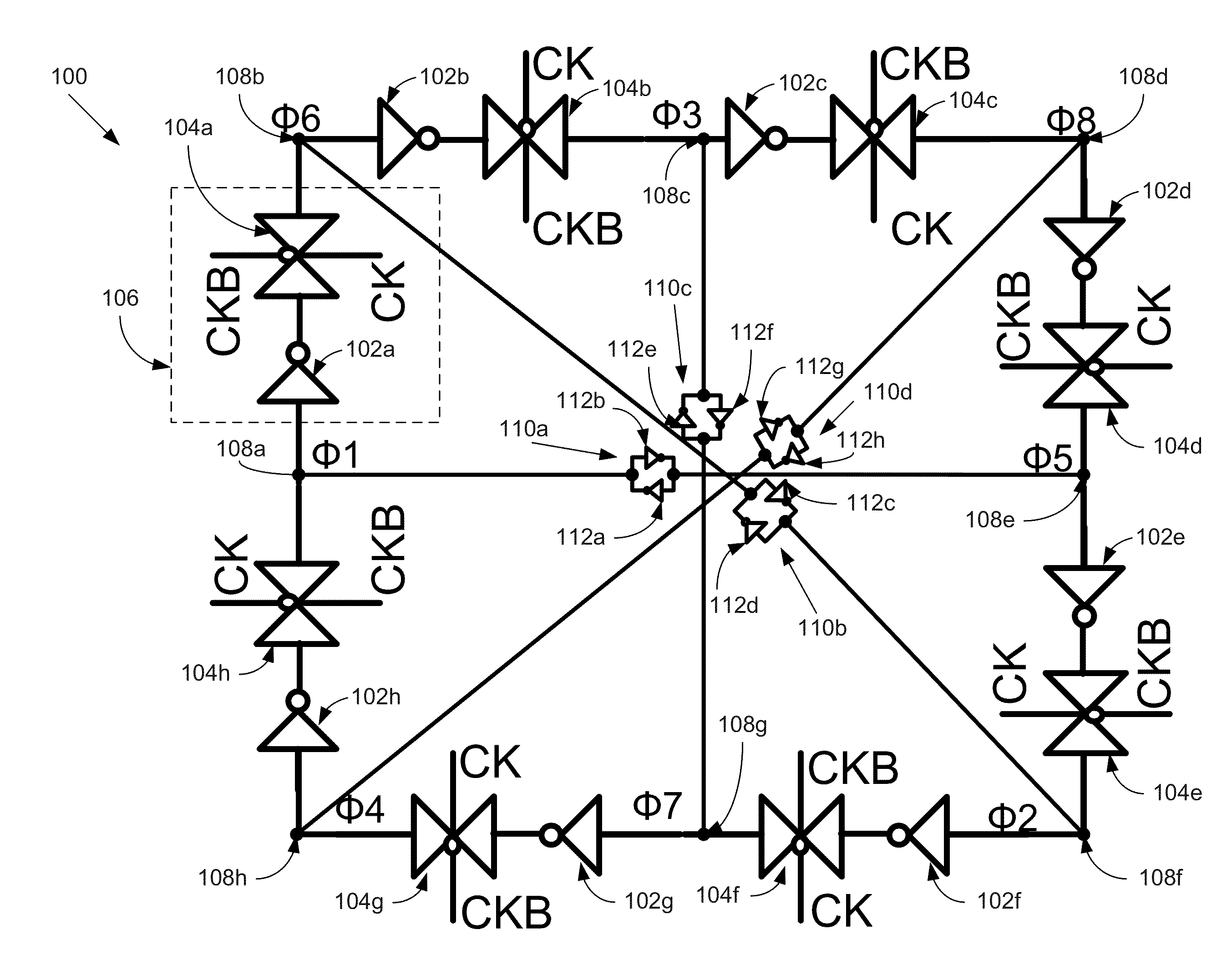

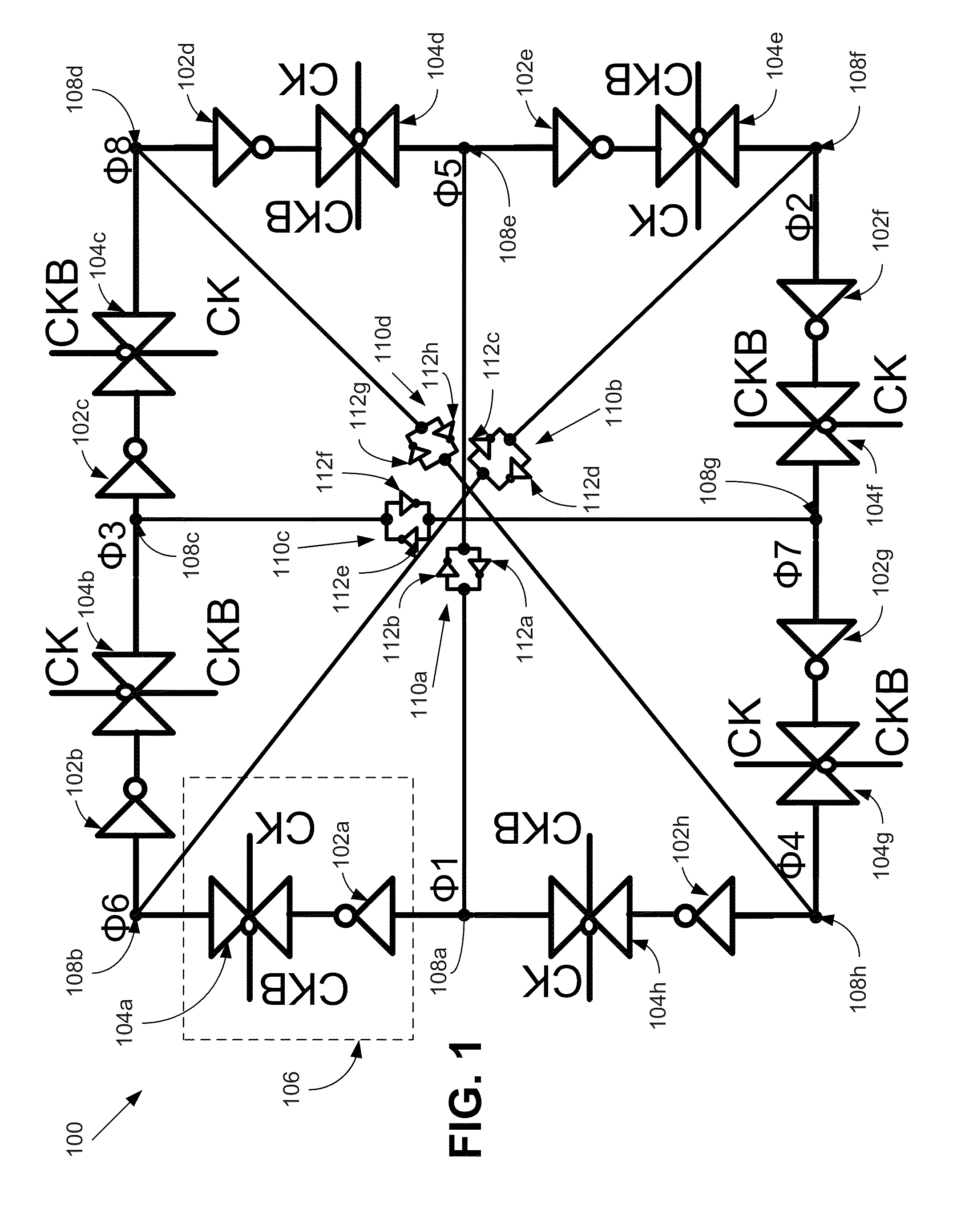

ActiveCN102160289AContinuously circulated pulse countersCounting chain synchronous pulse countersClock phaseHigh impedance

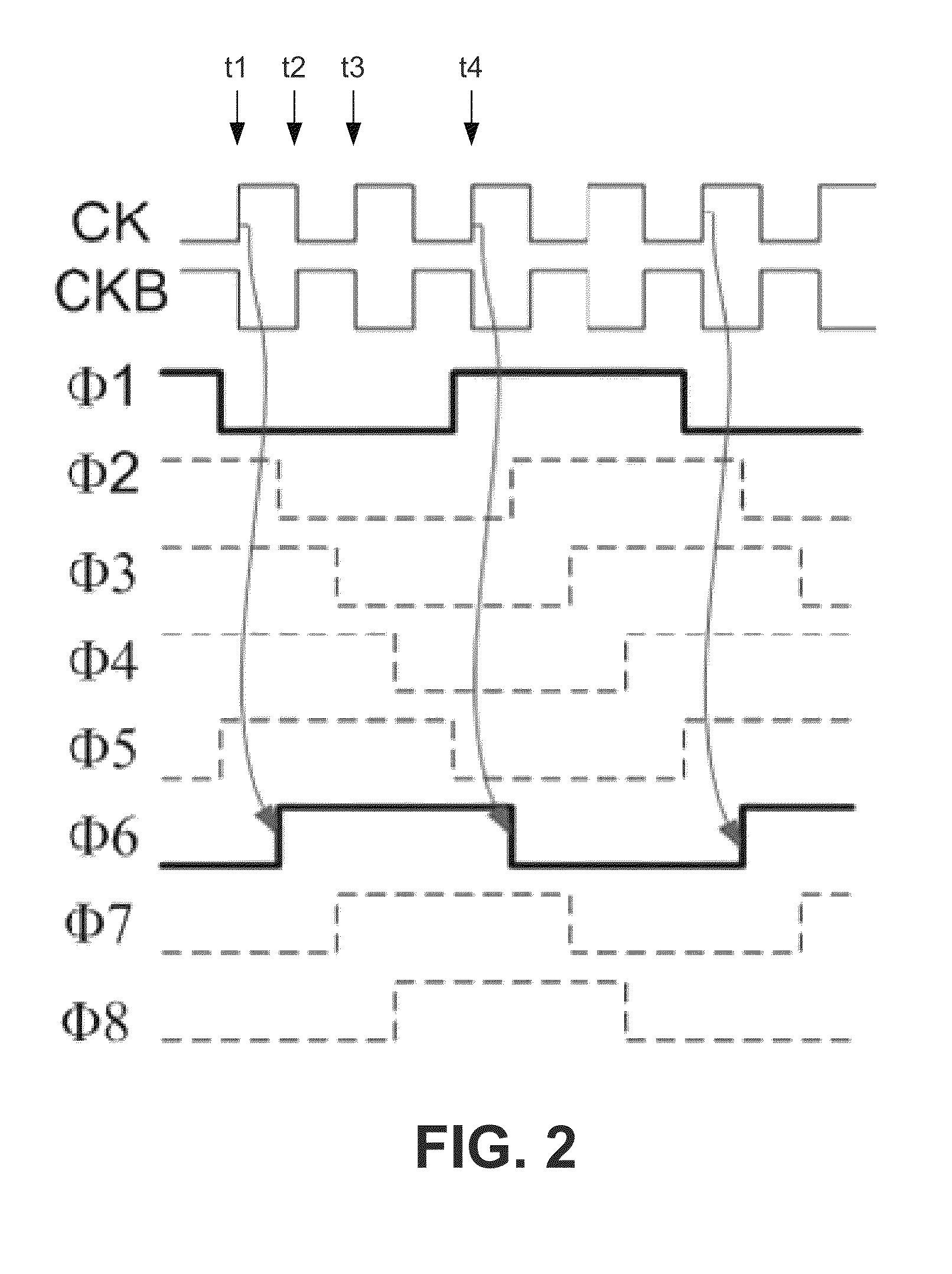

A latch includes three circuits. The first circuit drives a first output (QB) to a first level when a first input (D) and a first clock phase (CK) are both low, to a second level when D and CK are both high, and provides high impedance (HI-Z) when different logic levels are applied to D and CK. The second circuit drives a second output (Q) to the first level when a third input (DB) and a complimentary clock phase (CKB) are both low, to the second level when DB and CKB are both high, and provides HI-Z when different logic levels are applied to DB and CKB. The third circuit maintains voltages of Q and QB when the first and second circuits provide HI-Z at Q and QB. Odd-number dividers constructed with such latches produce 50% duty cycle operation without restricting output pulse widths to integer multiples of input periods.

Owner:QUALCOMM INC

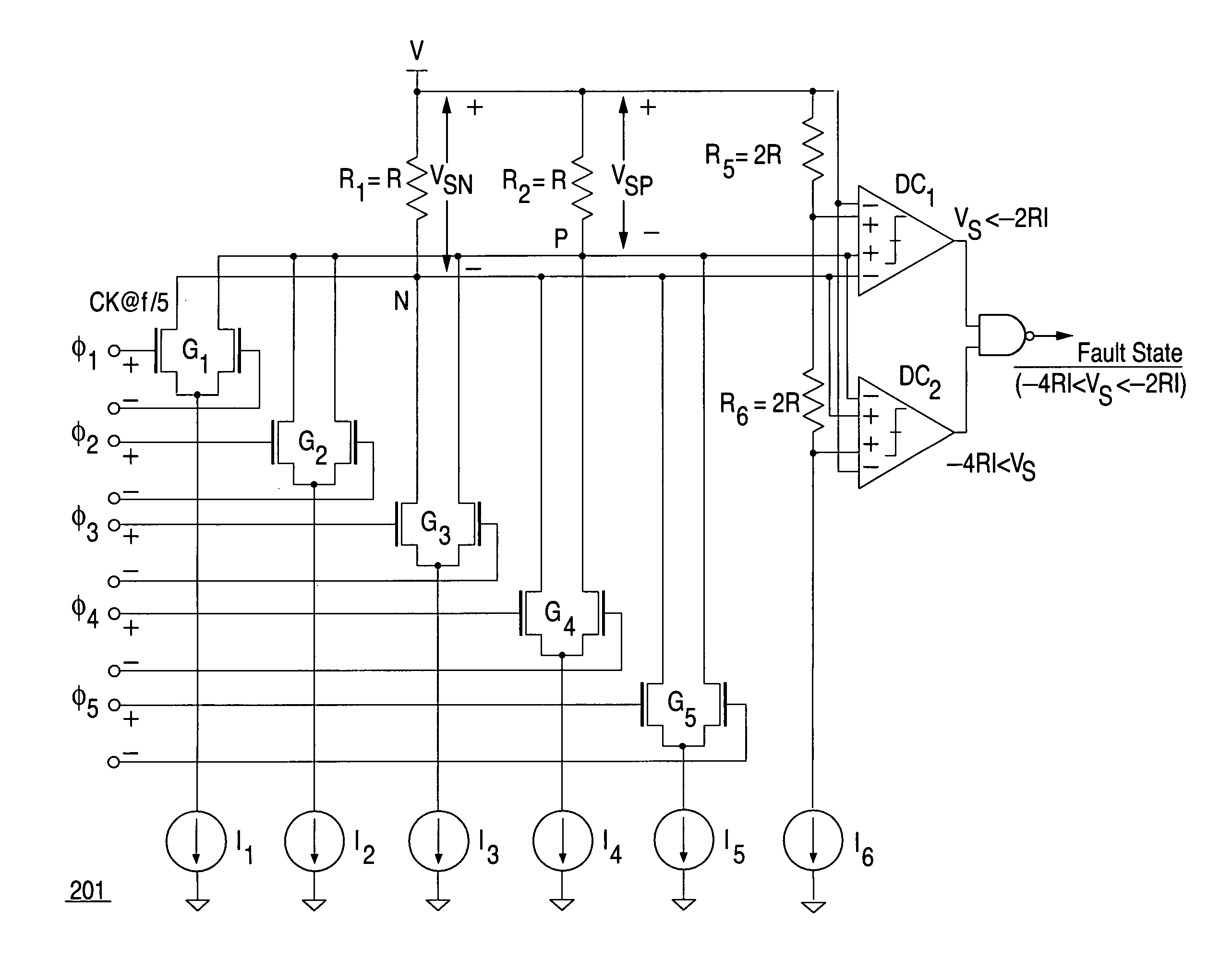

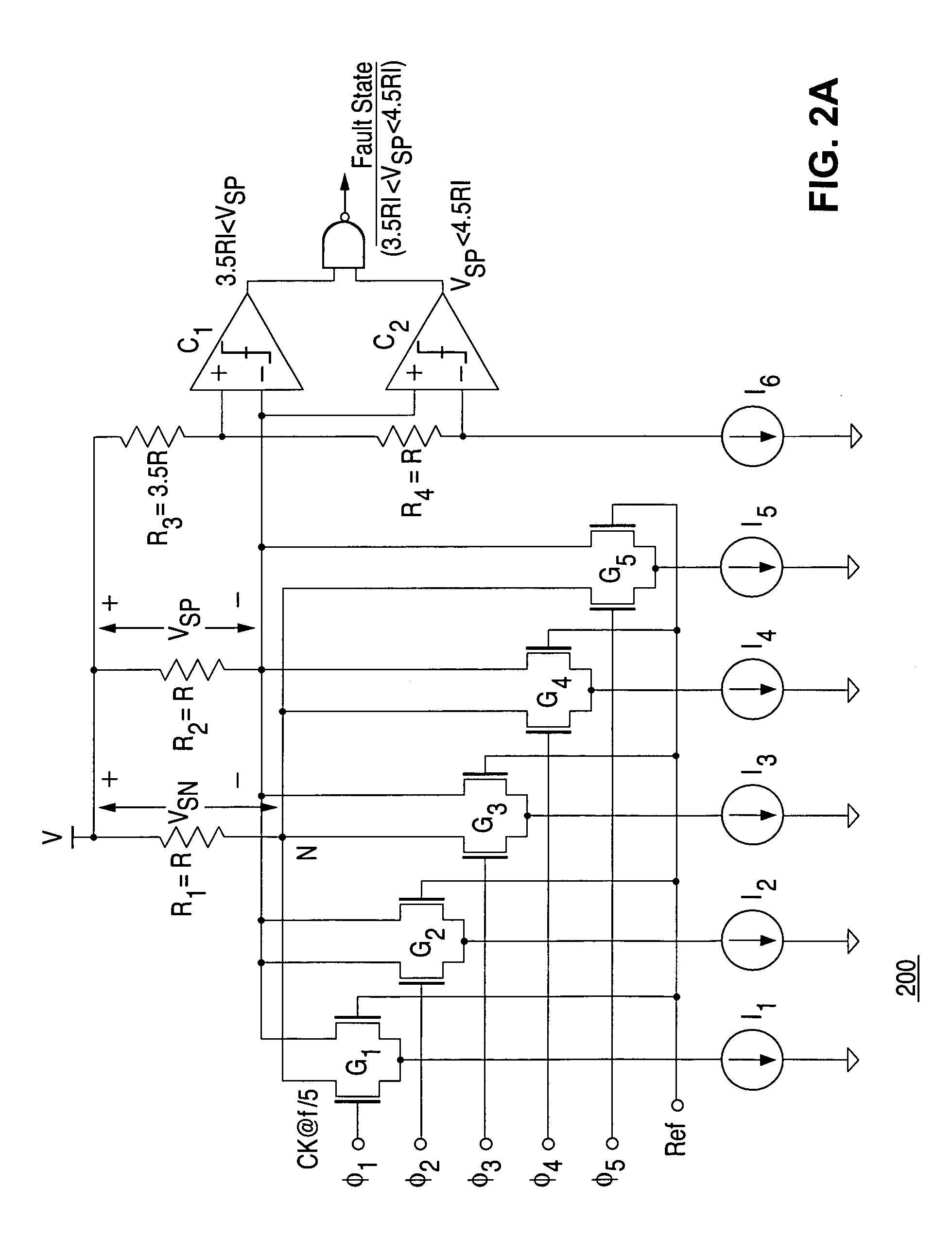

Fault state detection mechanism for a ring-counter-based frequency divider-by-N that generates non-overlapping N-phases of divide-by-N clocks with 1/N duty ratio

ActiveUS6950490B1Continuously circulated pulse countersCounting chain synchronous pulse countersRing counterEngineering

A fault state detector for a ring counter is formed from unit current sources each switched under the control of a different one of the outputs of the ring counter. The currents switched in that manner are passed through a unit resistance to generate a voltage signal proportional to the number of asserted outputs from the ring counter. The voltage signal is compared to boundary reference values for valid states of the ring counter outputs and, if the voltage signal is not between the boundary reference values, a fault state is indicated.

Owner:NAT SEMICON CORP

Frequency divider system

InactiveUS20050127959A1Logic circuits characterised by logic functionContinuously circulated pulse countersEngineeringActive phase

A frequency divider circuit for providing a divided clock signal having a frequency that is an odd integer factor less than the frequency of an incoming system clock signal. The frequency divider includes a clock generator circuit coupled to a delay circuit which operates in an active and a reset phase to provide a divided clock signal from the system clock signal. In the active phase, the clock generator circuit drives the divided clock signal to a first logic state until a reset signal is received. The delay circuit then generates the reset signal at a predetermined number of system clock edges after the divided clock signal is driven to the first logic state. In the reset phase, both the clock generator circuit and the delay circuit are reset in response to the reset signal such that the clock generator circuit immediately drives the divided clock signal to a second logic state, and the delay circuit disables the reset signal within the predetermined number of system clock edges. The delay circuit maintains a 50% duty cycle for the divided clock signal.

Owner:MALIKIE INNOVATIONS LTD

Clock frequency dividing circuit

InactiveUS20090027091A1Continuously circulated pulse countersCounting chain pulse countersCouplingDividing circuits

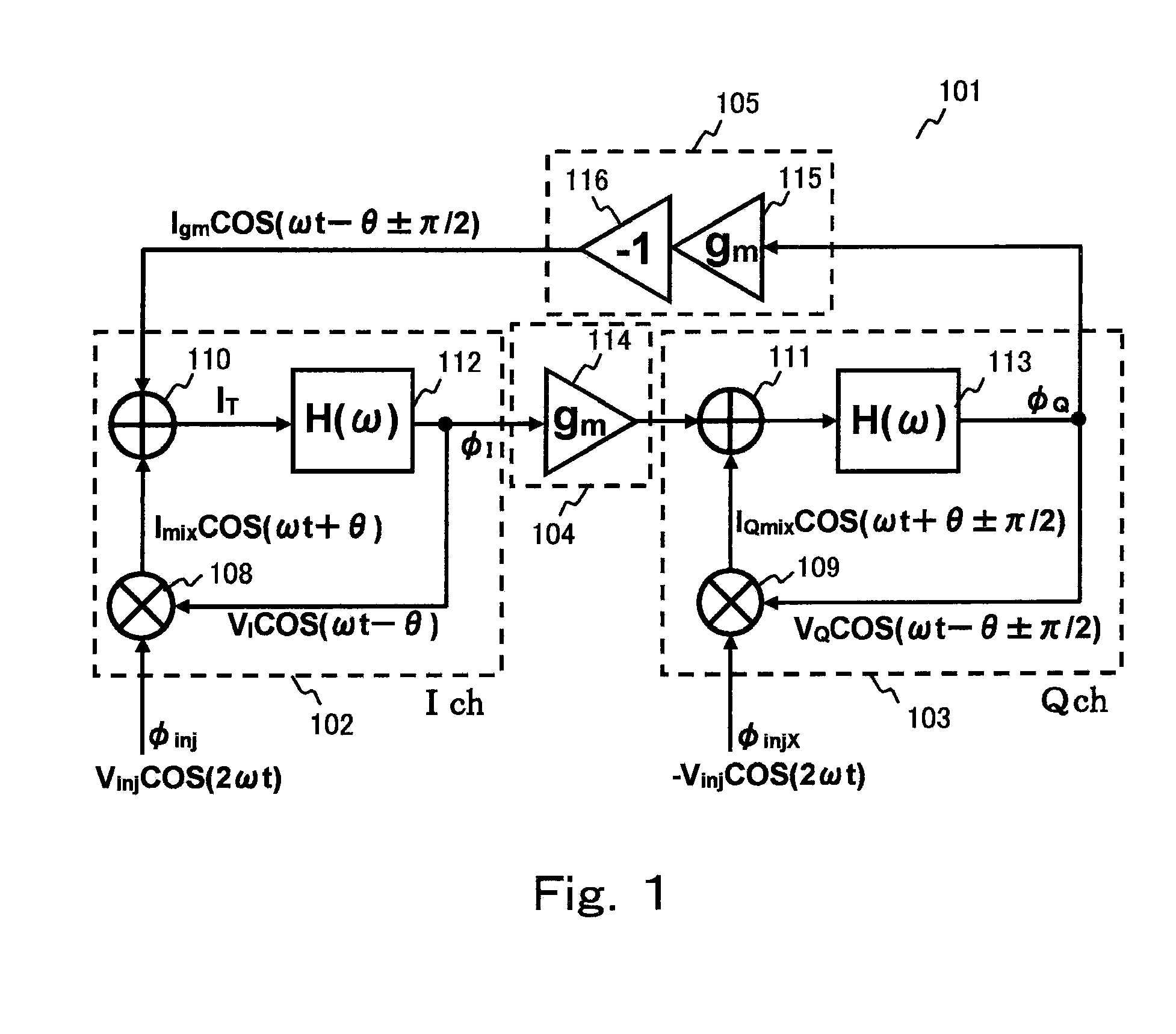

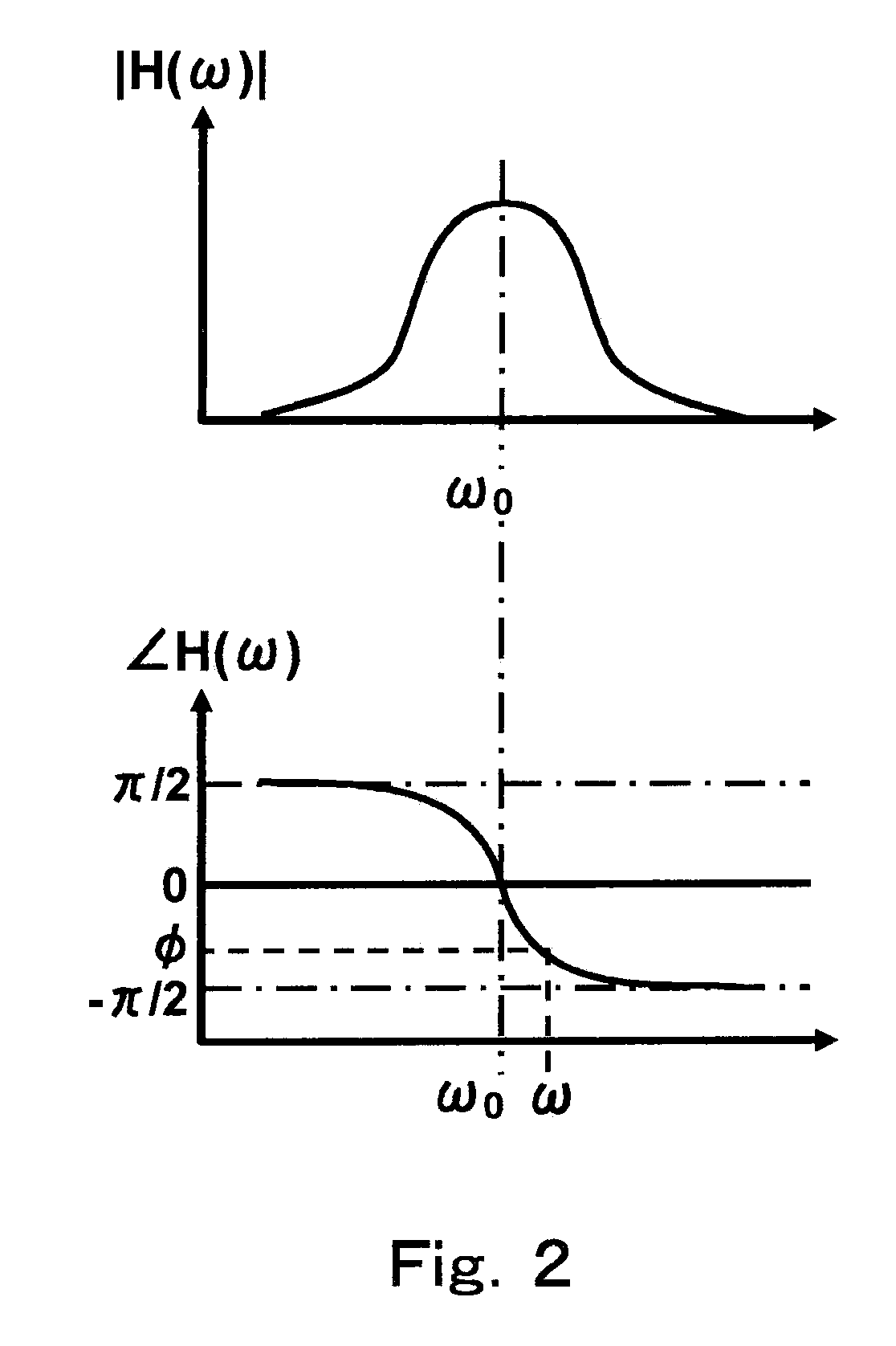

A first frequency dividing circuit and a second frequency dividing circuit are provided, and these circuits frequency-divide two-phase external clocks injected from an external part, to output four-phase clocks with phase guarantee. Each of the frequency dividing circuits includes a mixer, an adding circuit, and a phase circuit. The first frequency dividing circuit and the second frequency dividing circuit are coupled in loop shape via a first coupling circuit and a second coupling circuit. The first coupling circuit receives a first output signal of the first frequency dividing circuit to output a second external input signal to the second frequency dividing circuit, and the second coupling circuit receives a second output signal of the second frequency dividing circuit to output a first external input signal to the first frequency dividing circuit, and a clock frequency dividing circuit with a high loop gain and a wide lock range can be realized.

Owner:FUJITSU LTD

Multi-phase clock generation apparatus and method

InactiveUS8749289B2Continuously circulated pulse countersPulse automatic controlEngineeringClock generator

A multi-phase clock generator may receive an input clock signal as an input. The clock generator may also receive an inverse of the input clock signal. The clock generator may produce a plurality of output clock signals having different phases. The phases of the output clock signals may be evenly spaced. The output clock signals may have a similar waveform to the input clock signal, with a frequency that is lower than the input clock signal by a division factor.

Owner:INTEL CORP

Popular searches

Digital storage Electromechanical unknown time interval measurement Counters with additional facilities Pulse generation by logic circuits Frequency analysis Time-to-digital converters Power supply for data processing Oscillations generators Angle demodulation by phase difference detection Pulse counters with static storage